Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2198 results about "Electron mobility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In solid-state physics, the electron mobility characterises how quickly an electron can move through a metal or semiconductor, when pulled by an electric field. There is an analogous quantity for holes, called hole mobility. The term carrier mobility refers in general to both electron and hole mobility. Electron and hole mobility are special cases of electrical mobility of charged particles in a fluid under an applied electric field.

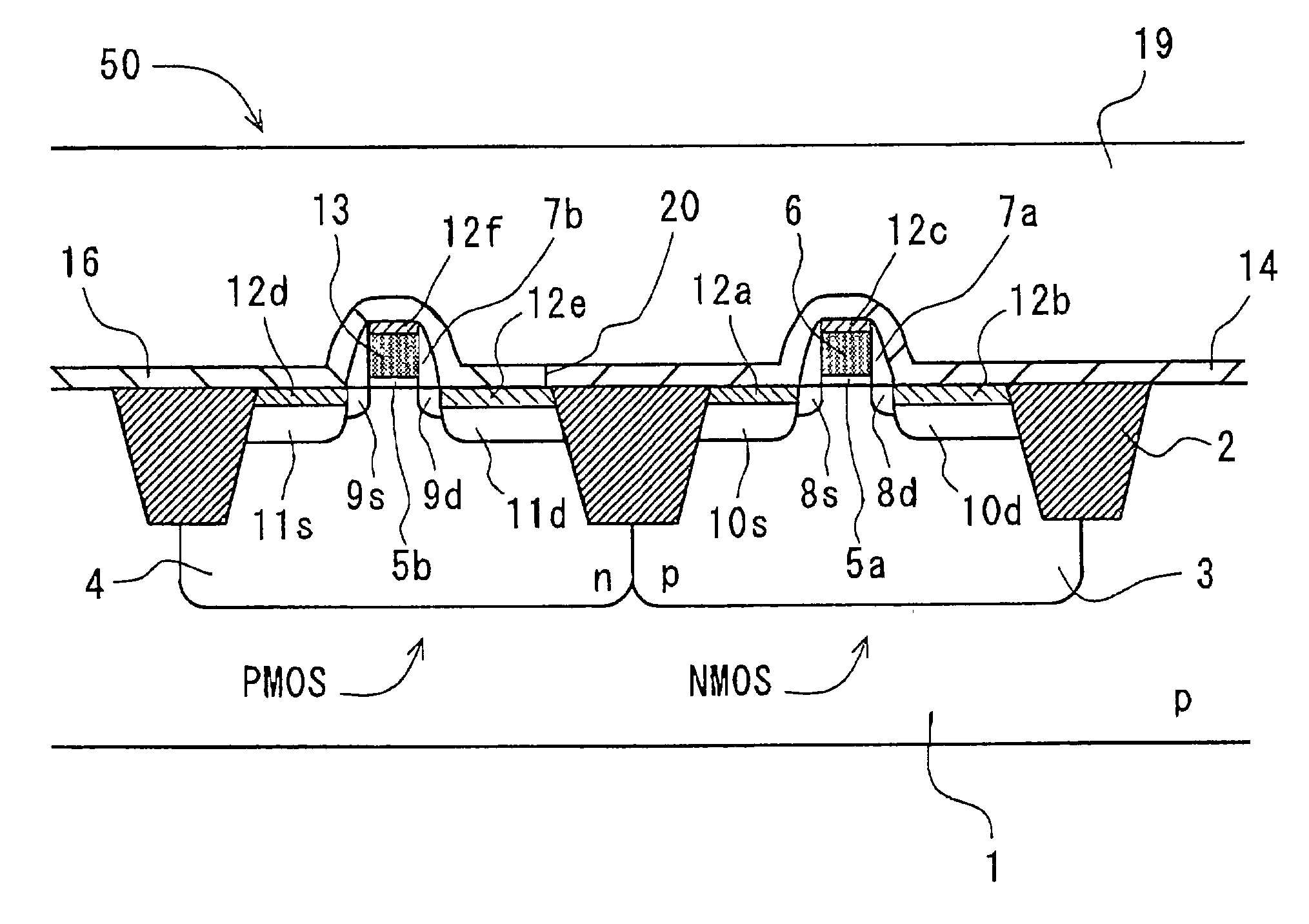

Semiconductor device and method of fabricating the same

InactiveUS20030040158A1TransistorSemiconductor/solid-state device manufacturingMOSFETElectron mobility

A semiconductor device improves the electron mobility in the n-channel MOSFET and reduces the bend or warp of the semiconductor substrate or wafer. The fist nitride layer having a tensile stress is formed on the substrate to cover the n-channel MOSFET. The tensile stress of the first nitride layer serves to relax a compressive stress existing in the channel region. The second nitride layer having an actual compressive stress is formed on the substrate to cover the p-channel MOSFET. The first and second nitride layers serve to decrease bend or warp of the substrate. Preferably, the first nitride layer is a nitride layer of Si formed by a LPCVD process, and the second nitride layer is a nitride layer of Si formed by a PECVD process.

Owner:NEC ELECTRONICS CORP

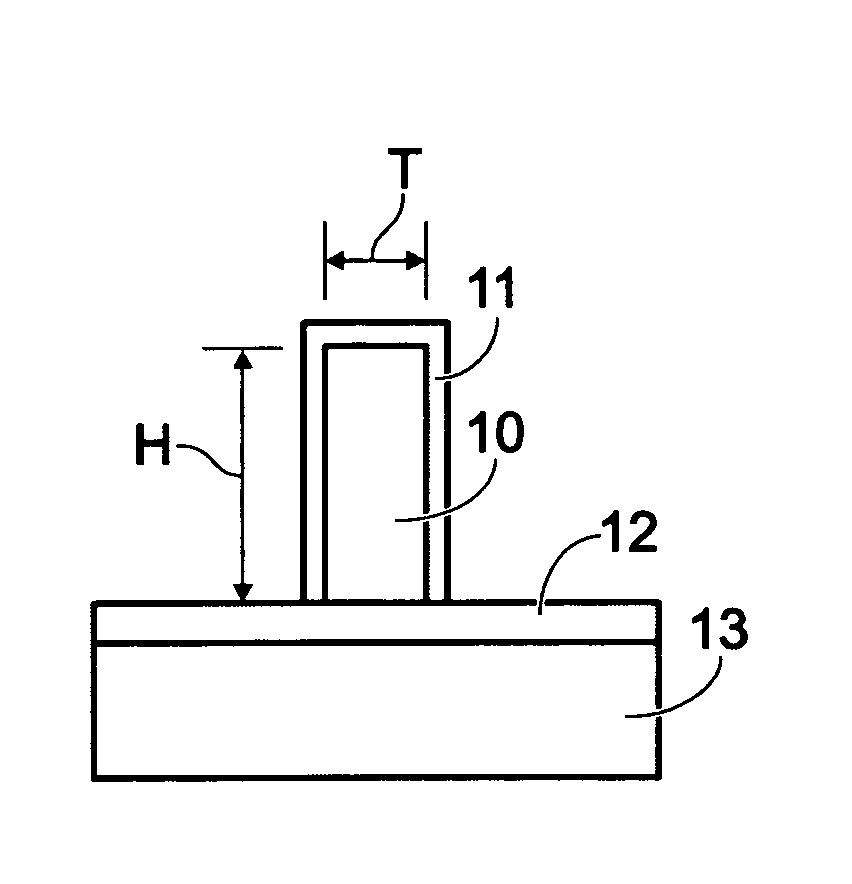

Strained silicon fin structure

InactiveUS20060113522A1Suppression of short channel effectsIncrease currentTransistorSemiconductor/solid-state device manufacturingDriving currentLattice mismatch

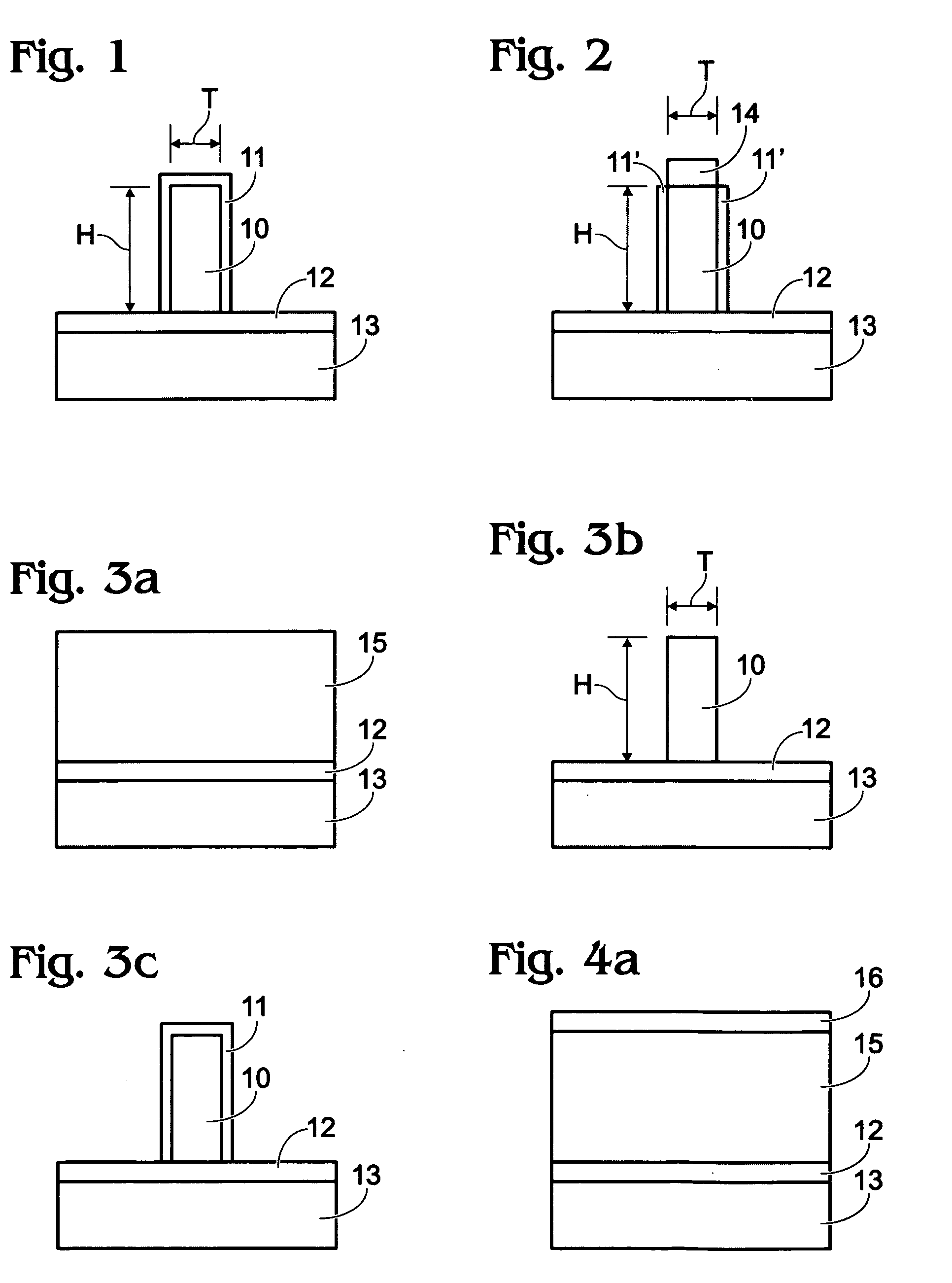

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

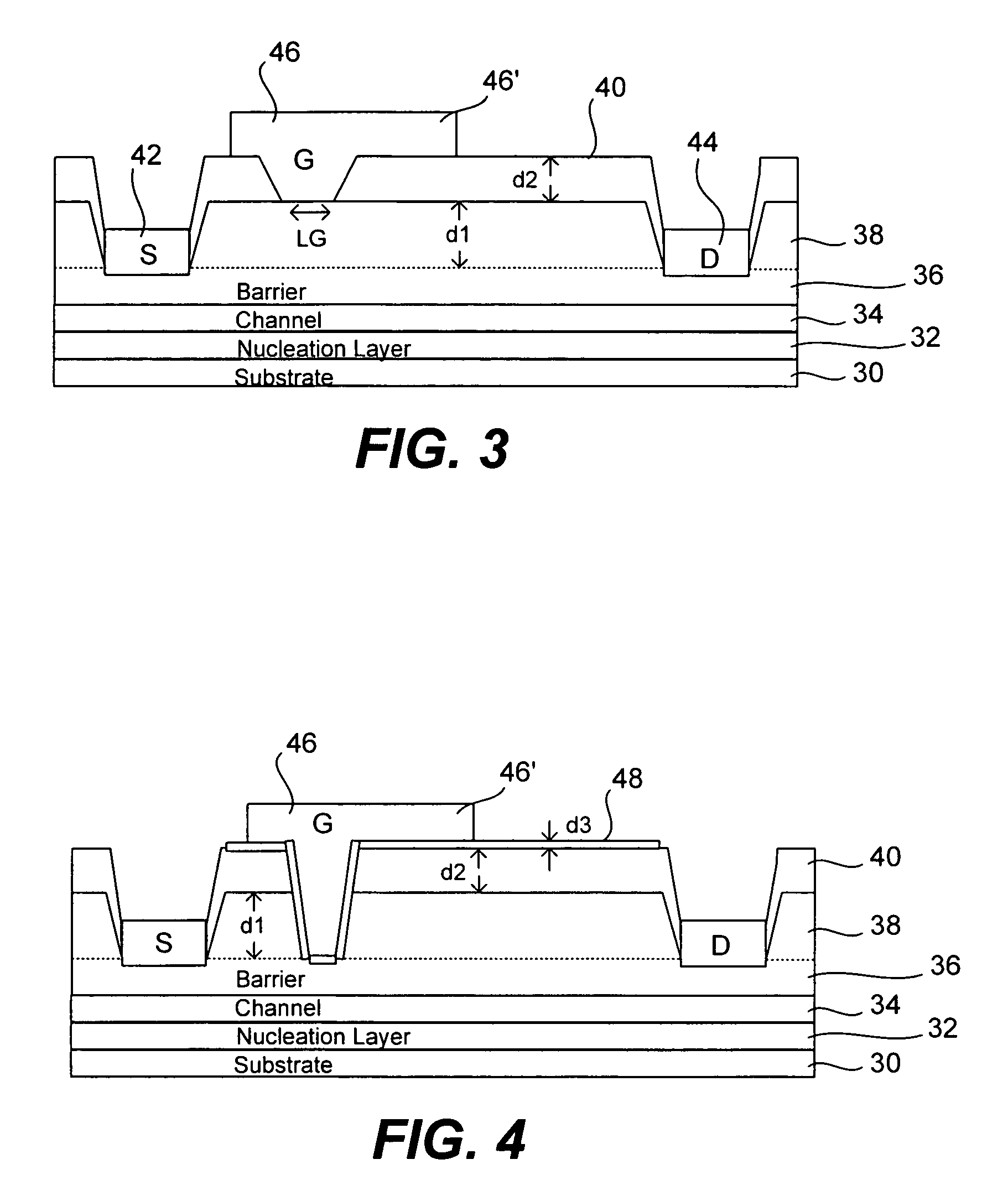

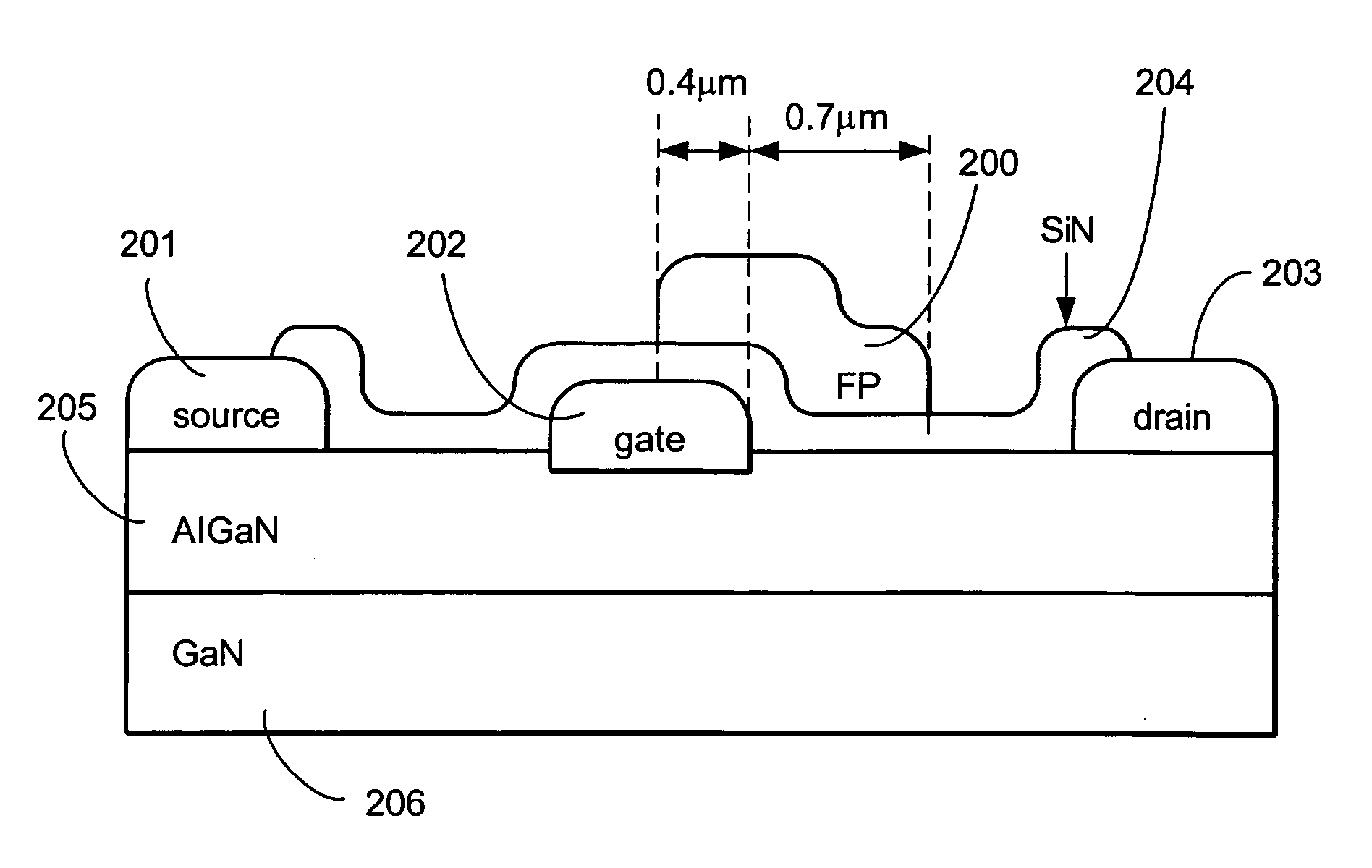

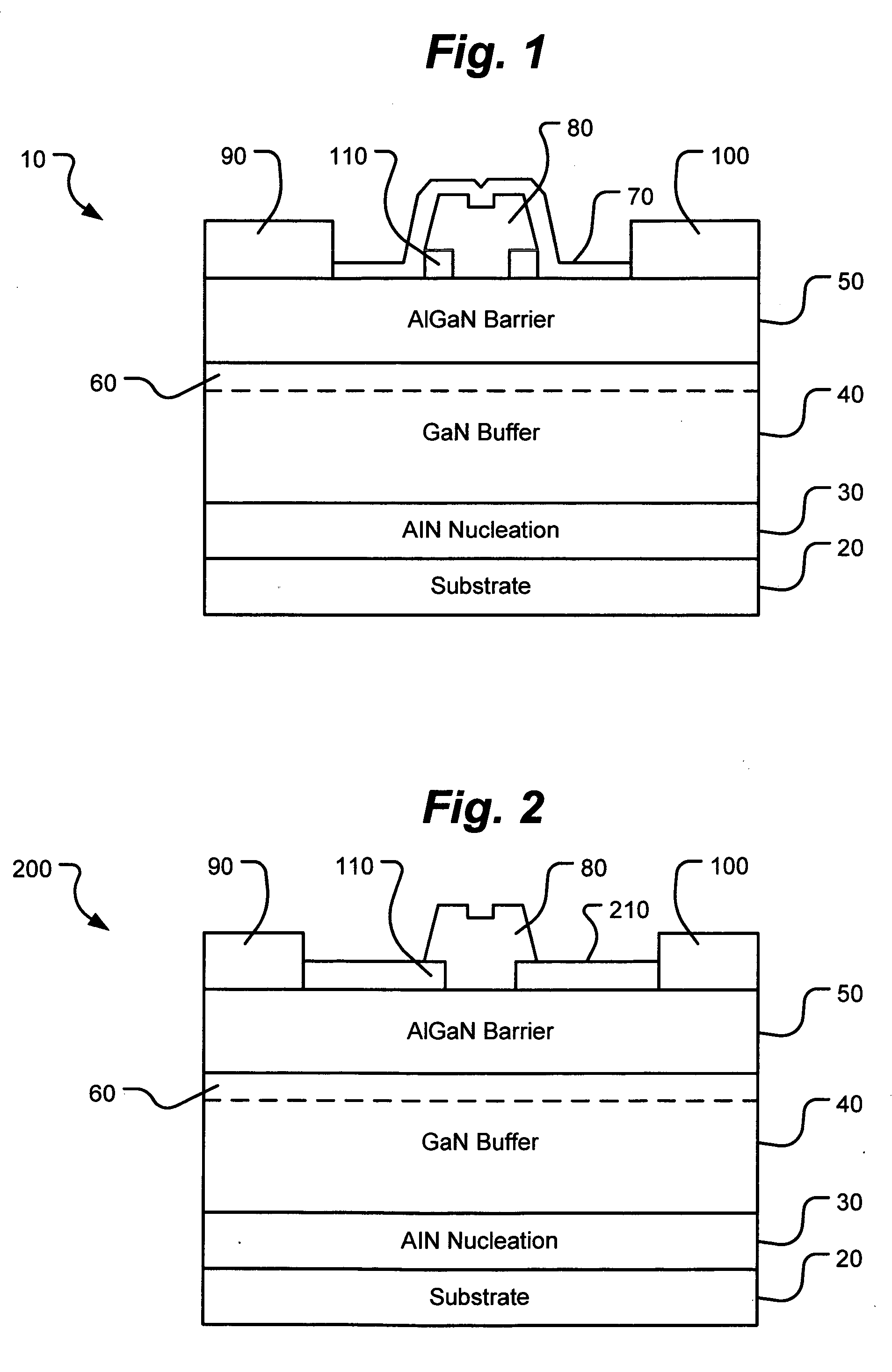

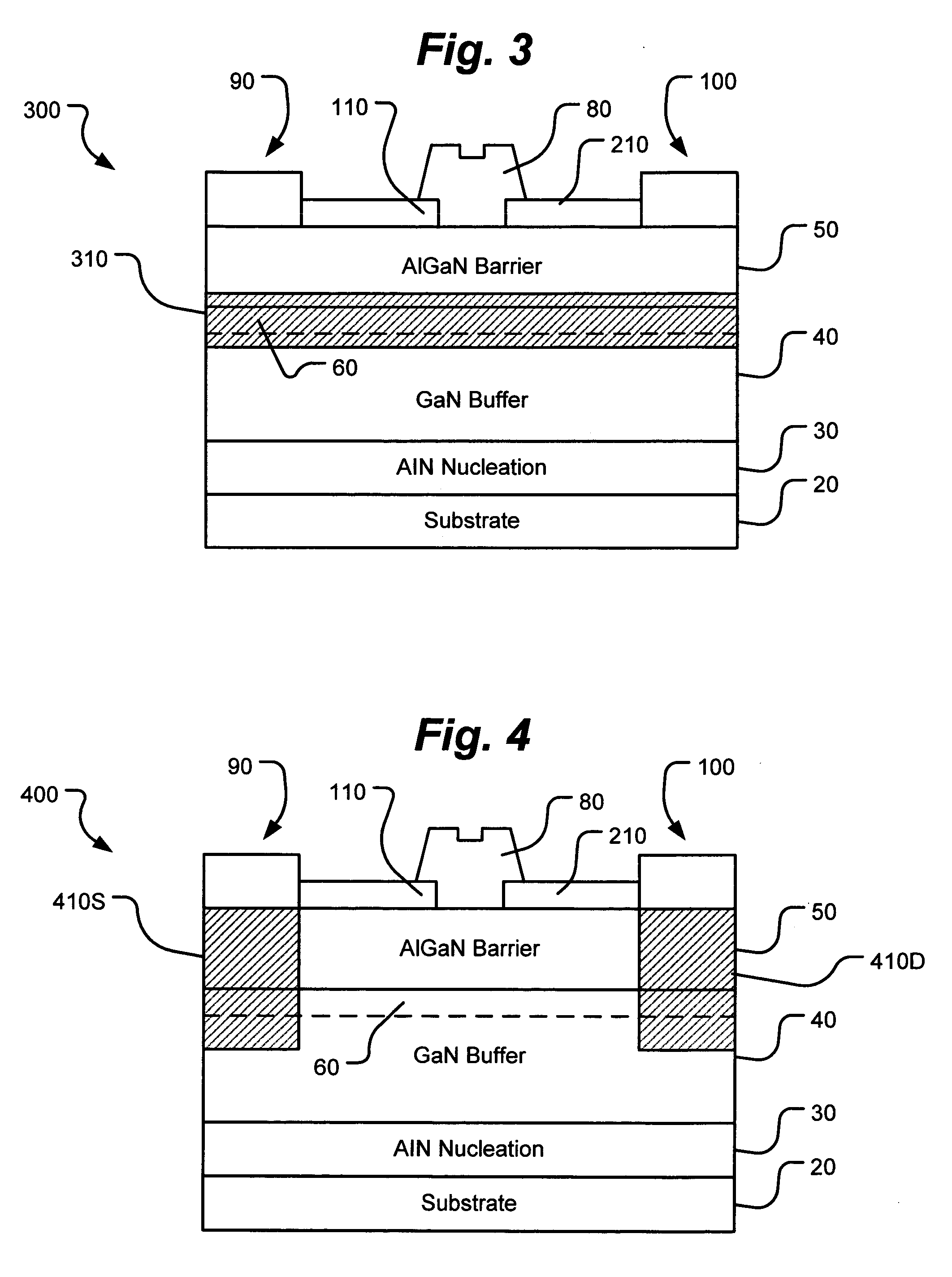

Switch mode power amplifier using MIS-HEMT with field plate extension

ActiveUS7548112B2Guaranteed uptimeIncrease heightTransistorHigh frequency amplifiersAudio power amplifierSilicon oxide

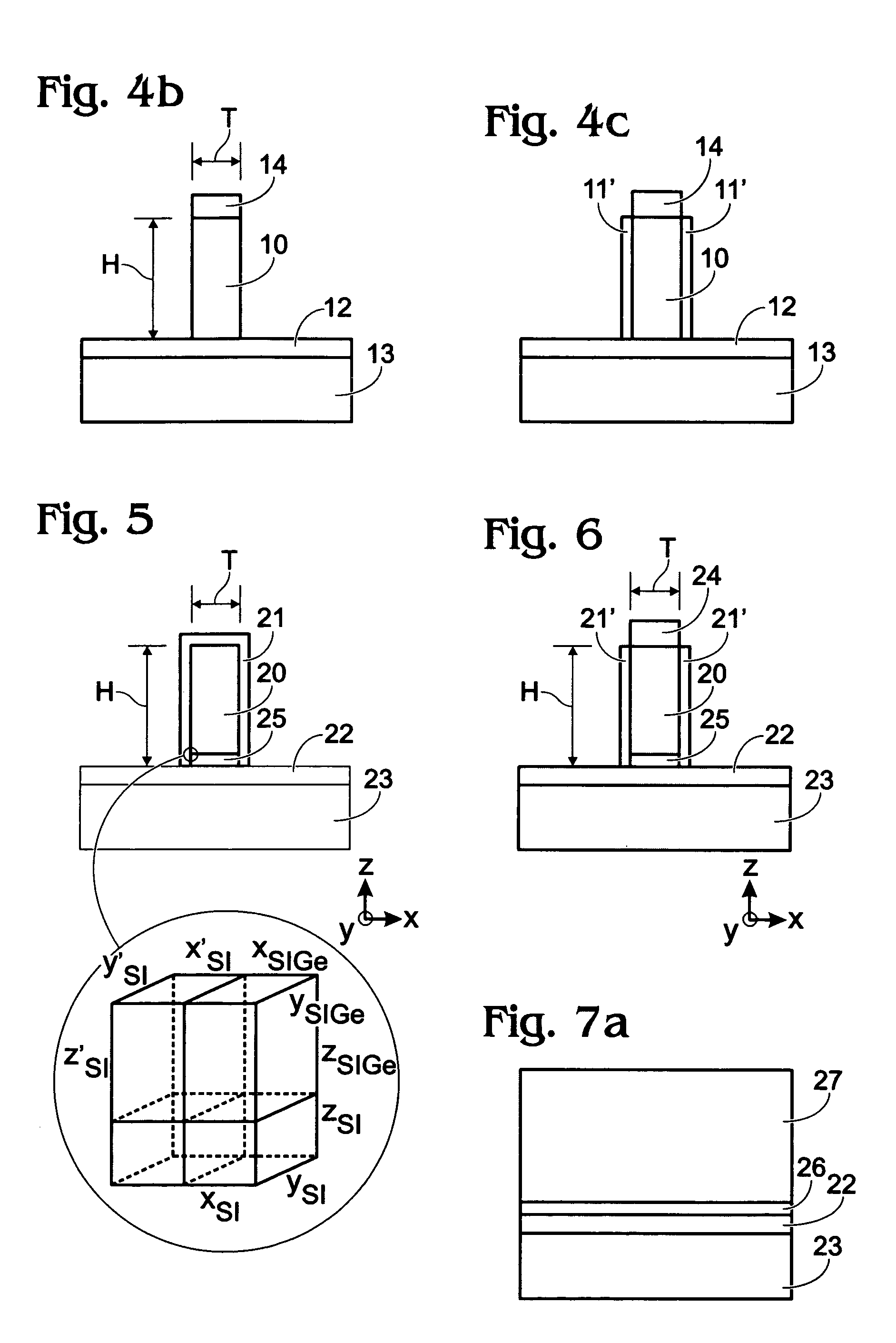

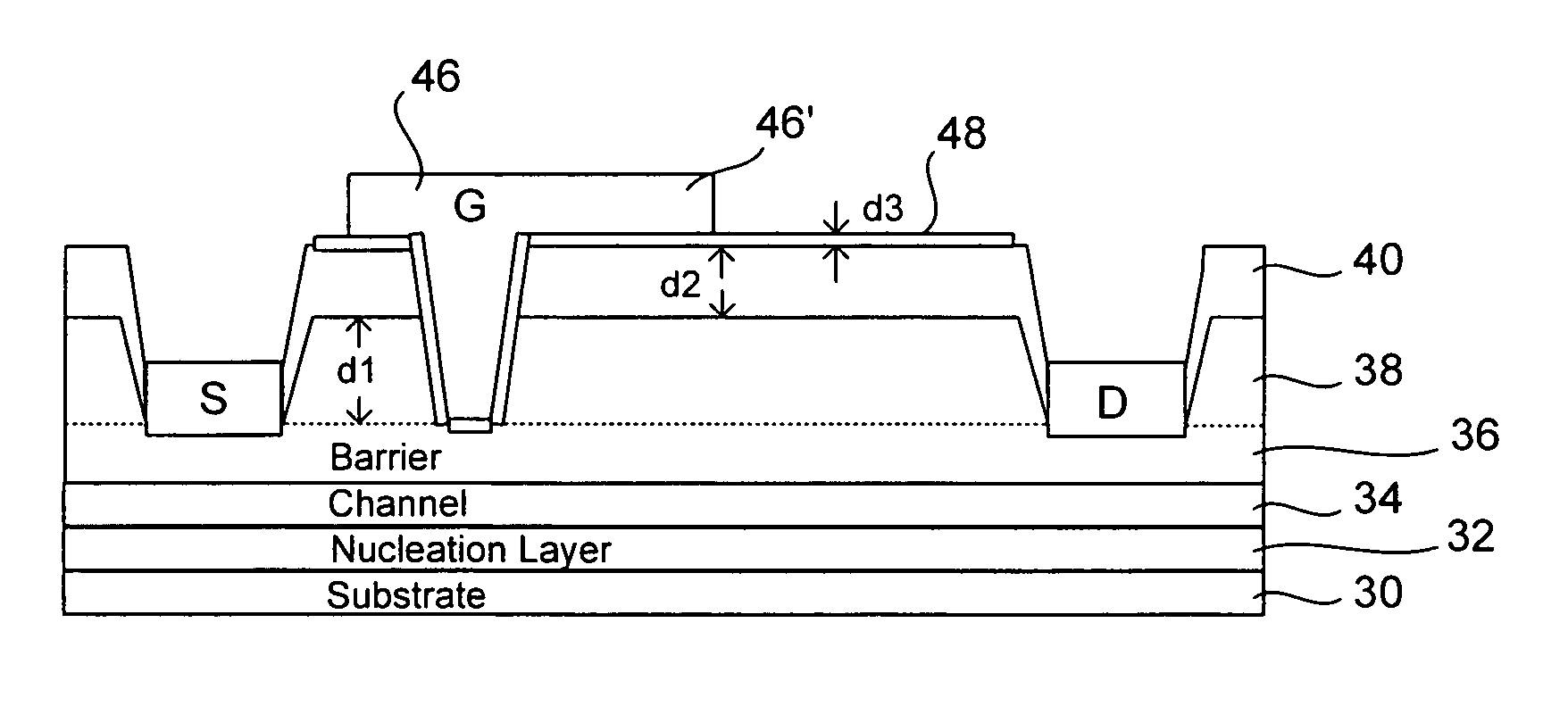

Disclosed are a switch mode power amplifier and a field effect transistor especially suitable for use in a switch mode power amplifier. The transistor is preferably a compound high electron mobility transistor (HEMT) having a source terminal and a drain terminal with a gate terminal therebetween and positioned on a dielectric material. A field plate extends from the gate terminal over at least two layers of dielectric material towards the drain. The dielectric layers preferably comprise silicon oxide and silicon nitride. A third layer of silicon oxide can be provided with the layer of silicon nitride being positioned between layers of silicon oxide. Etch selectivity is utilized in etching recesses for the gate terminal.

Owner:WOLFSPEED INC

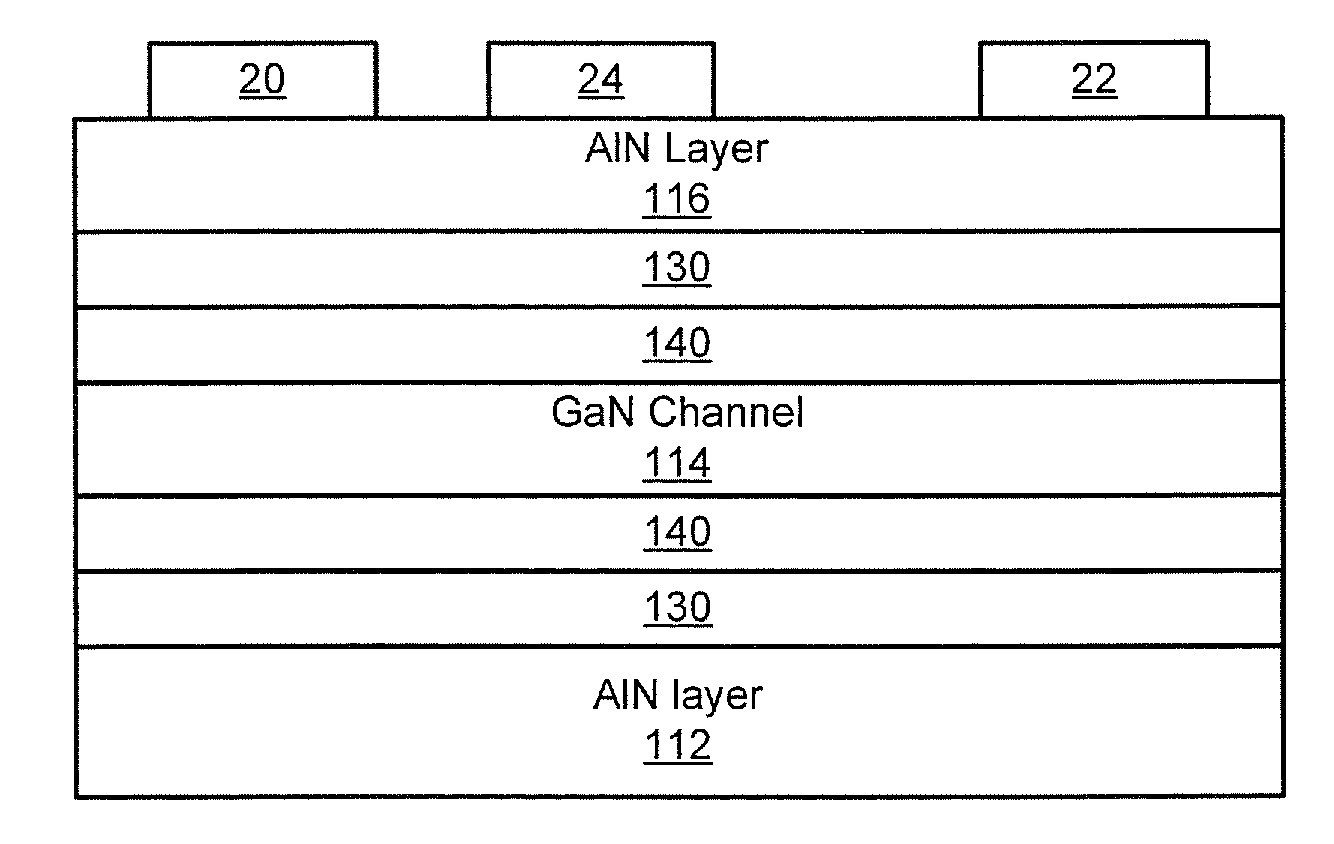

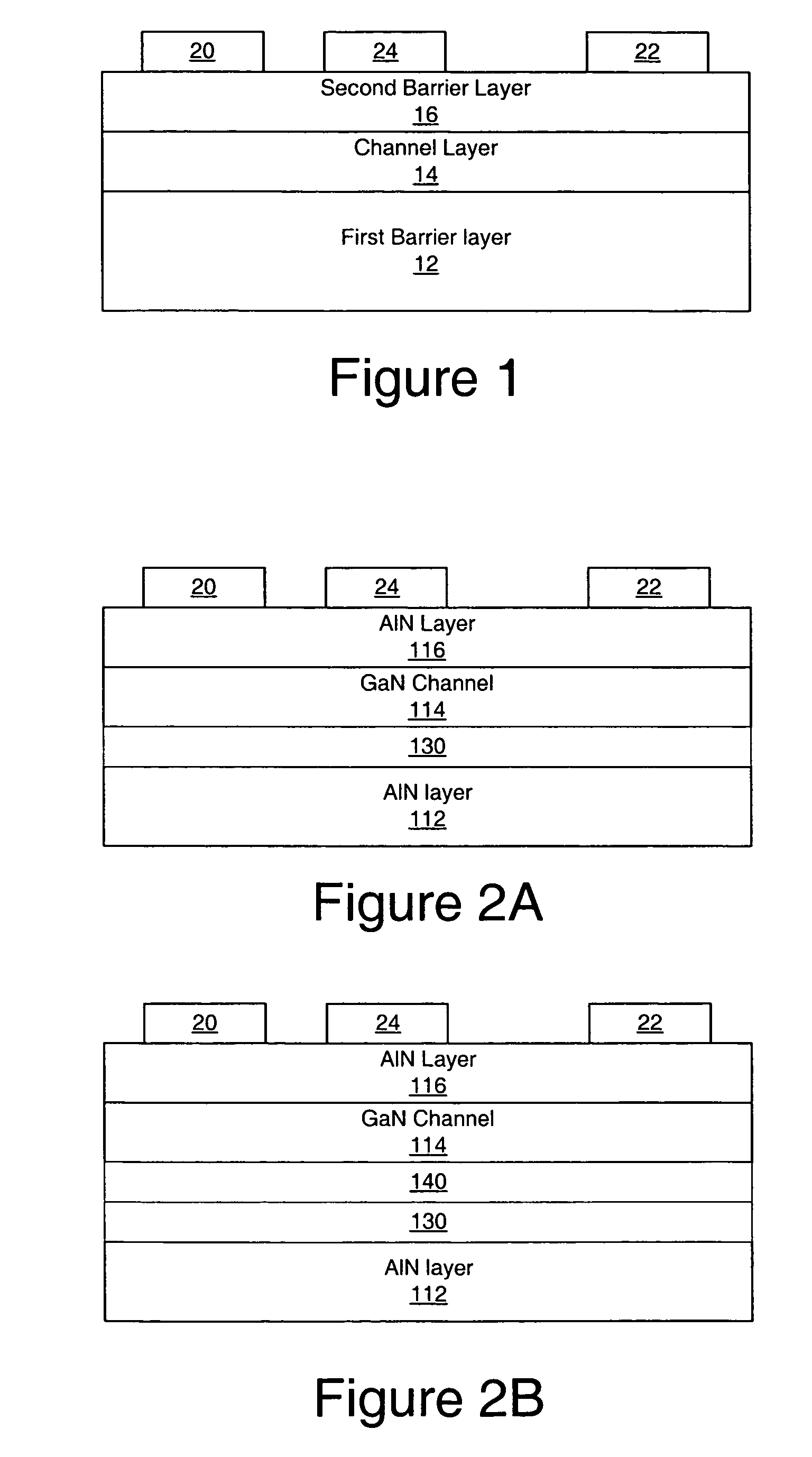

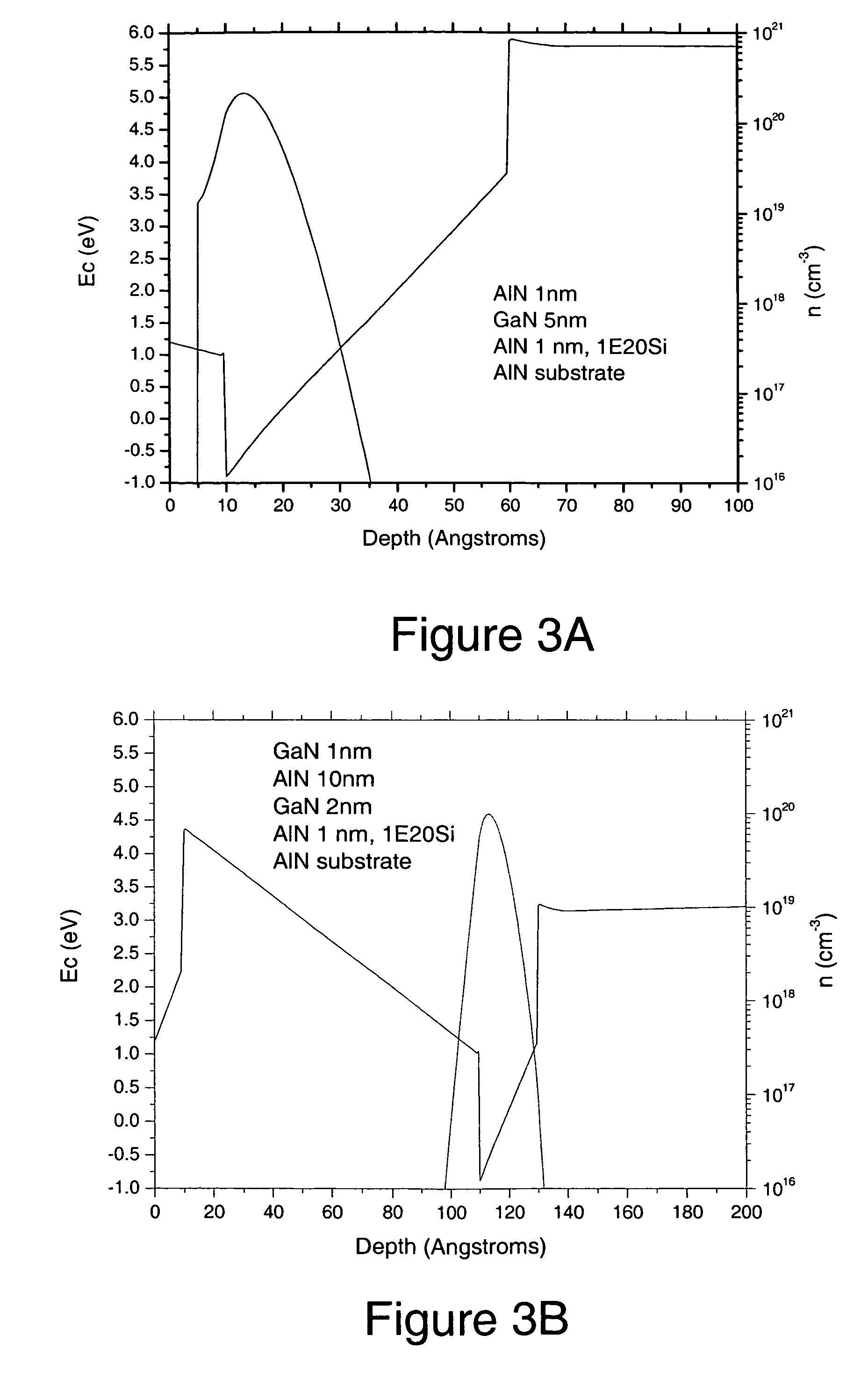

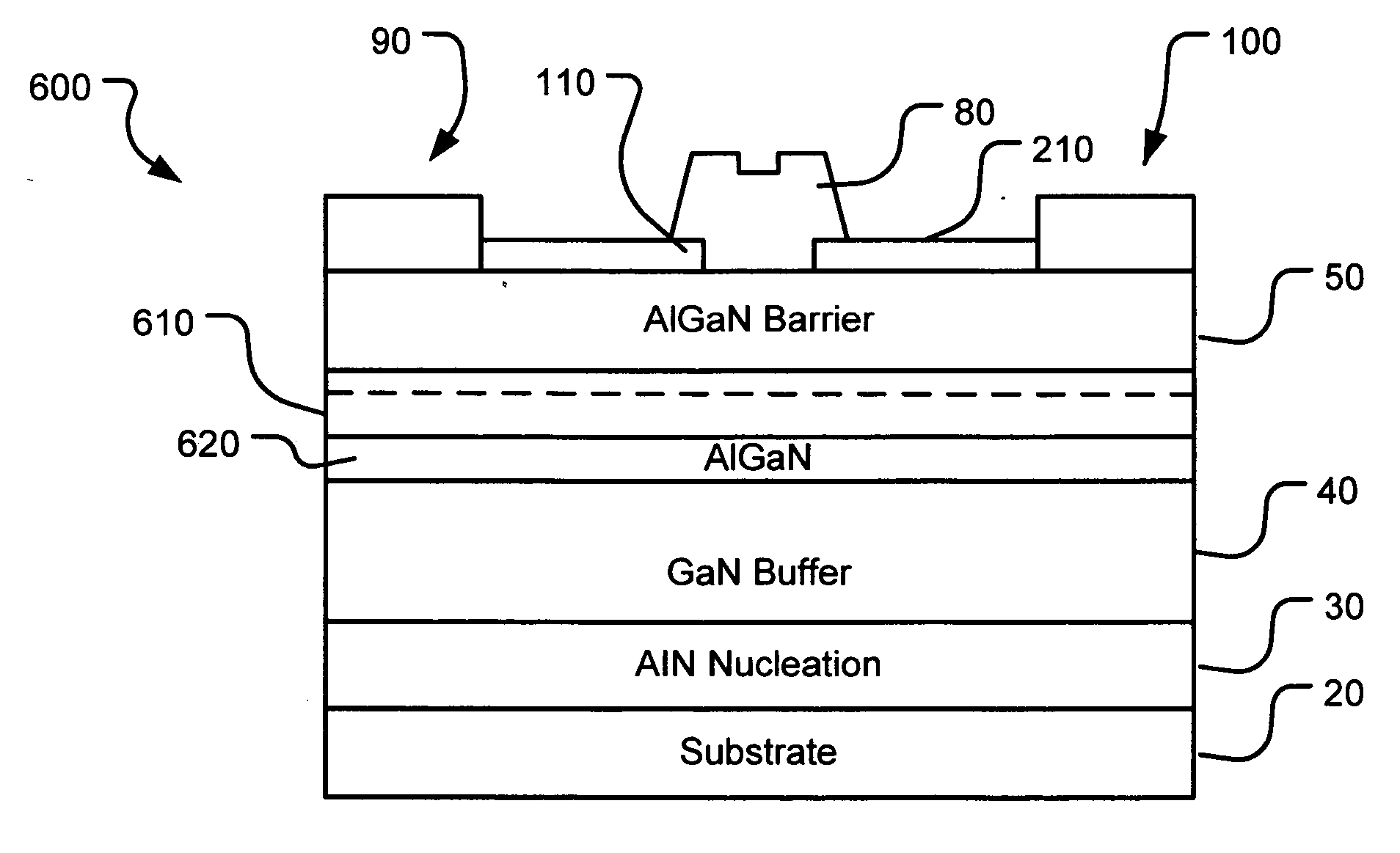

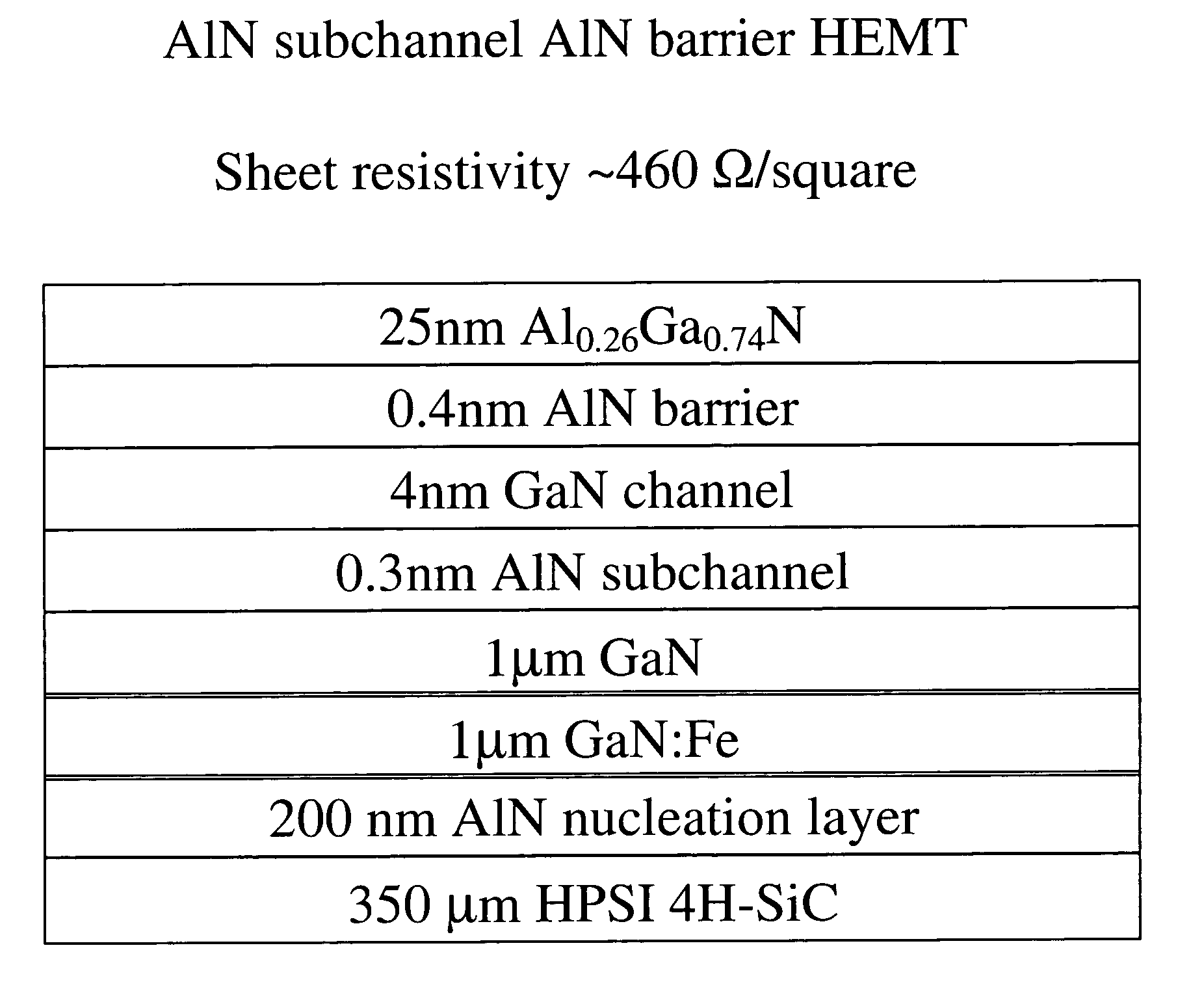

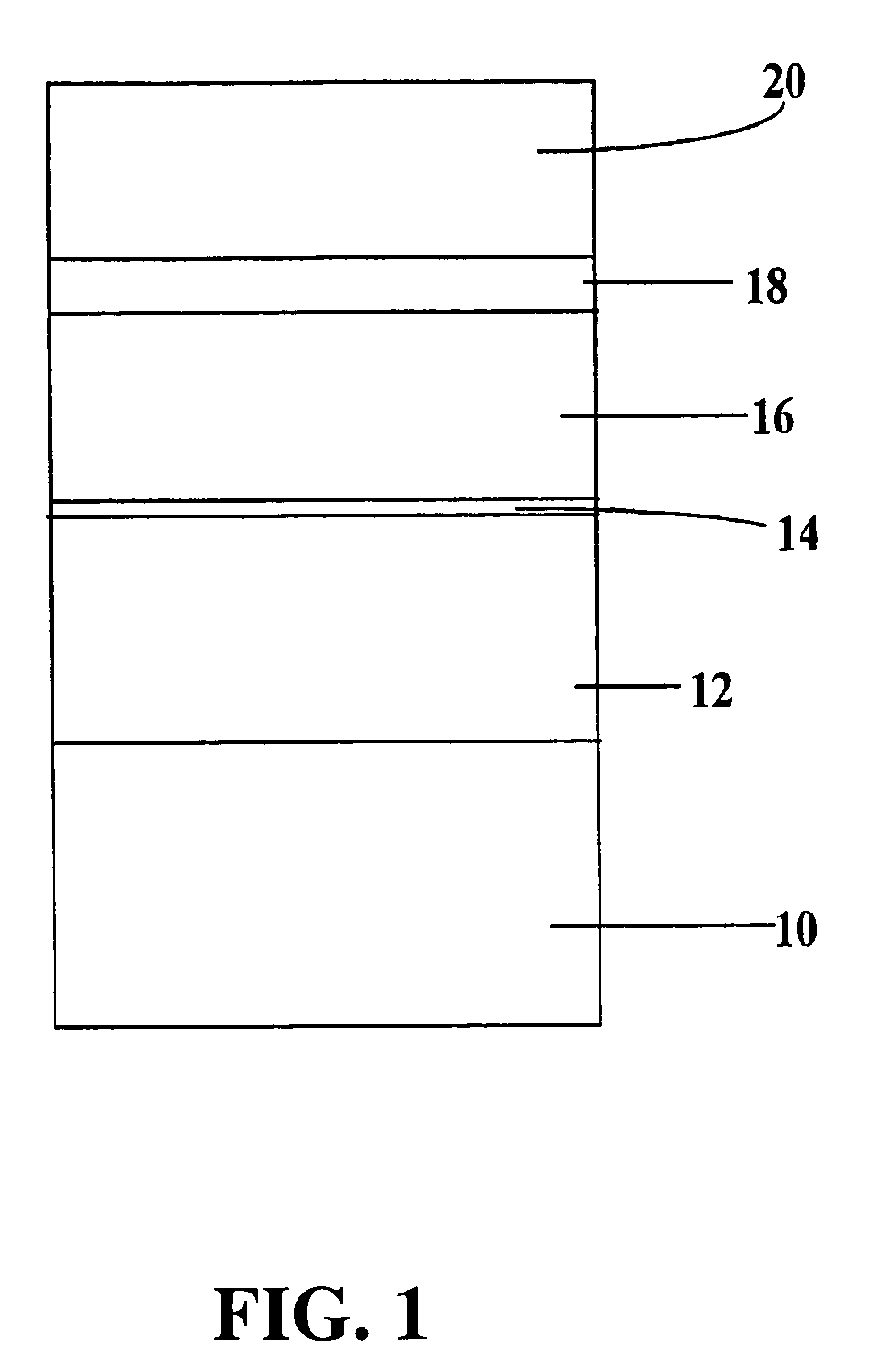

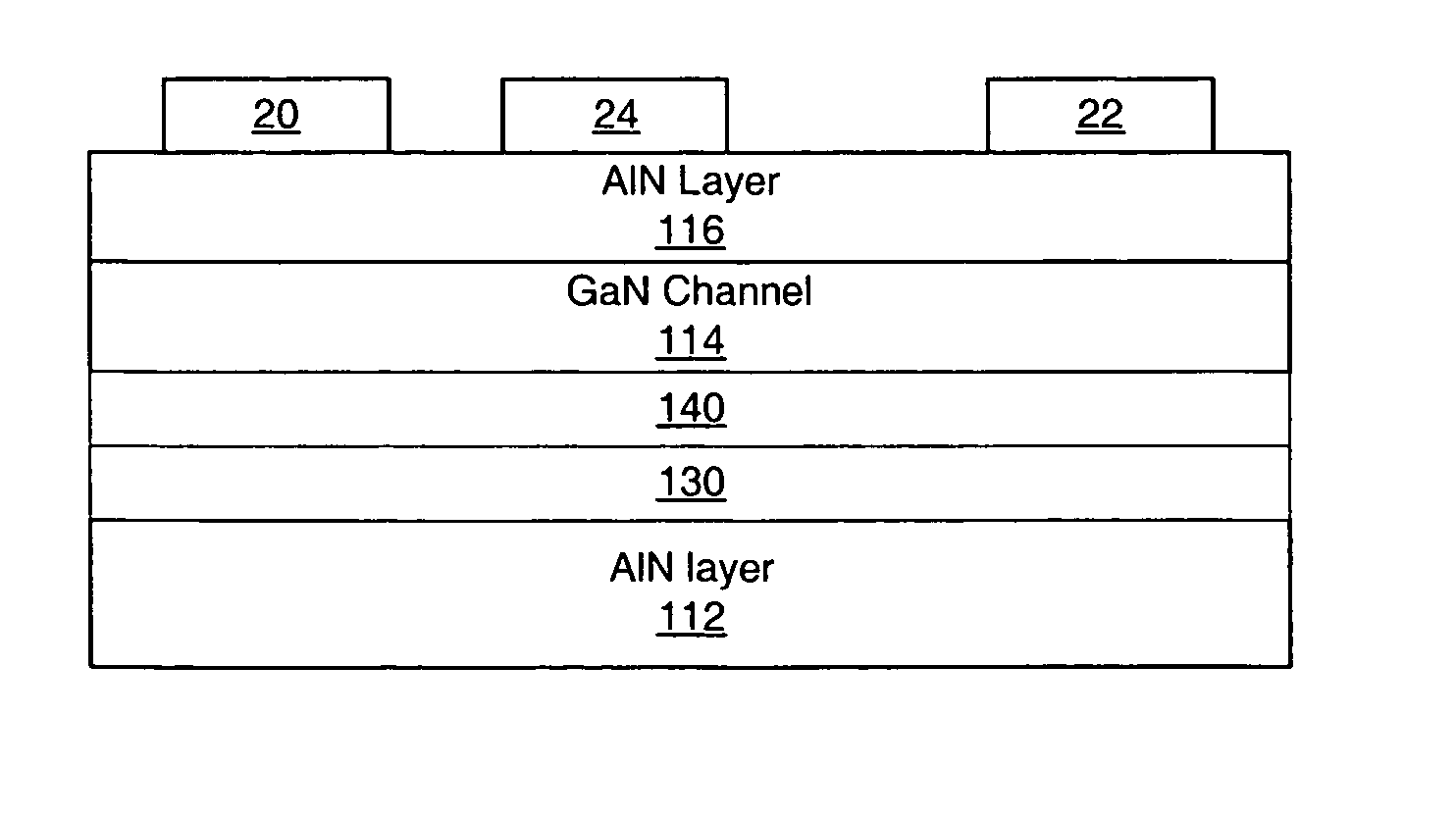

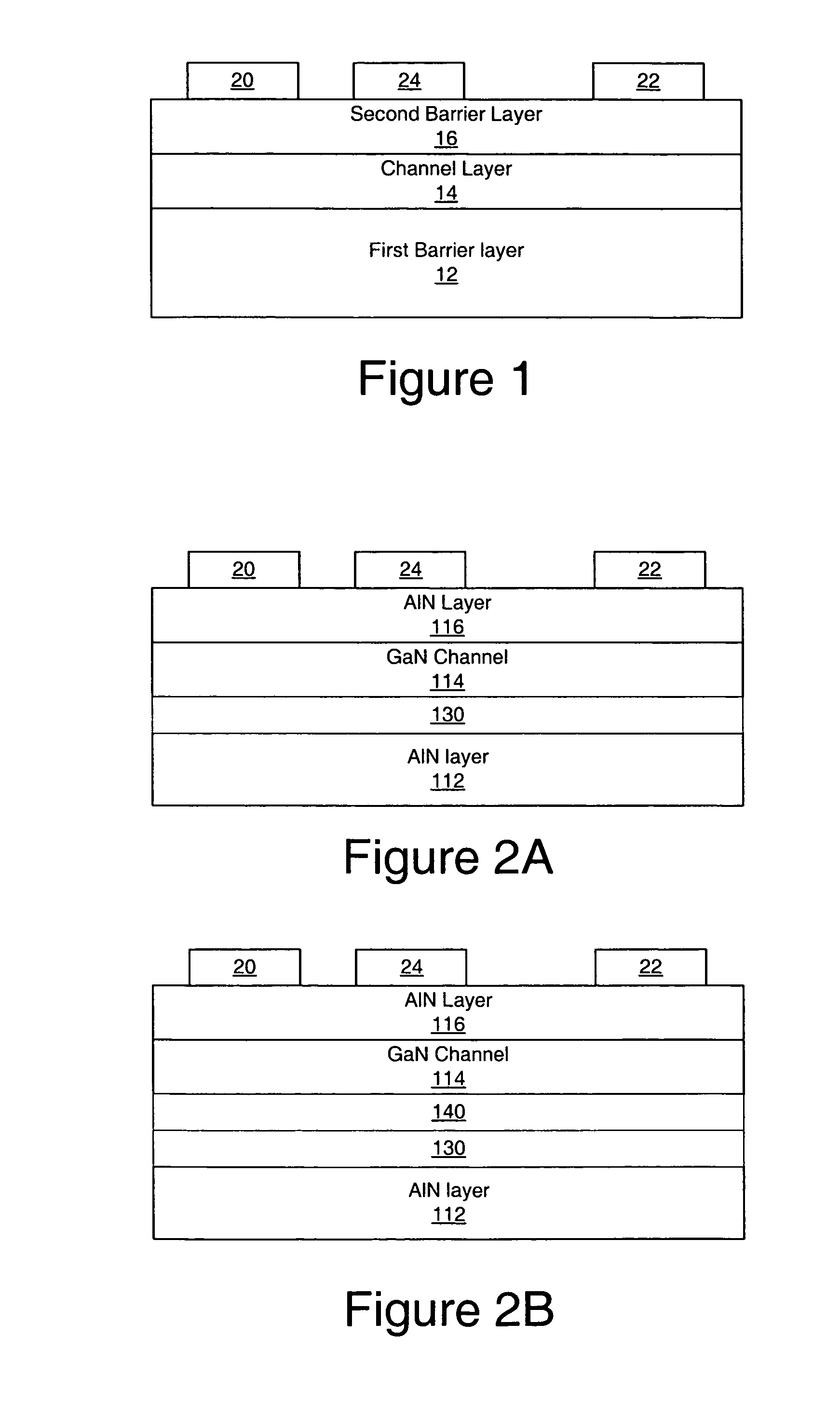

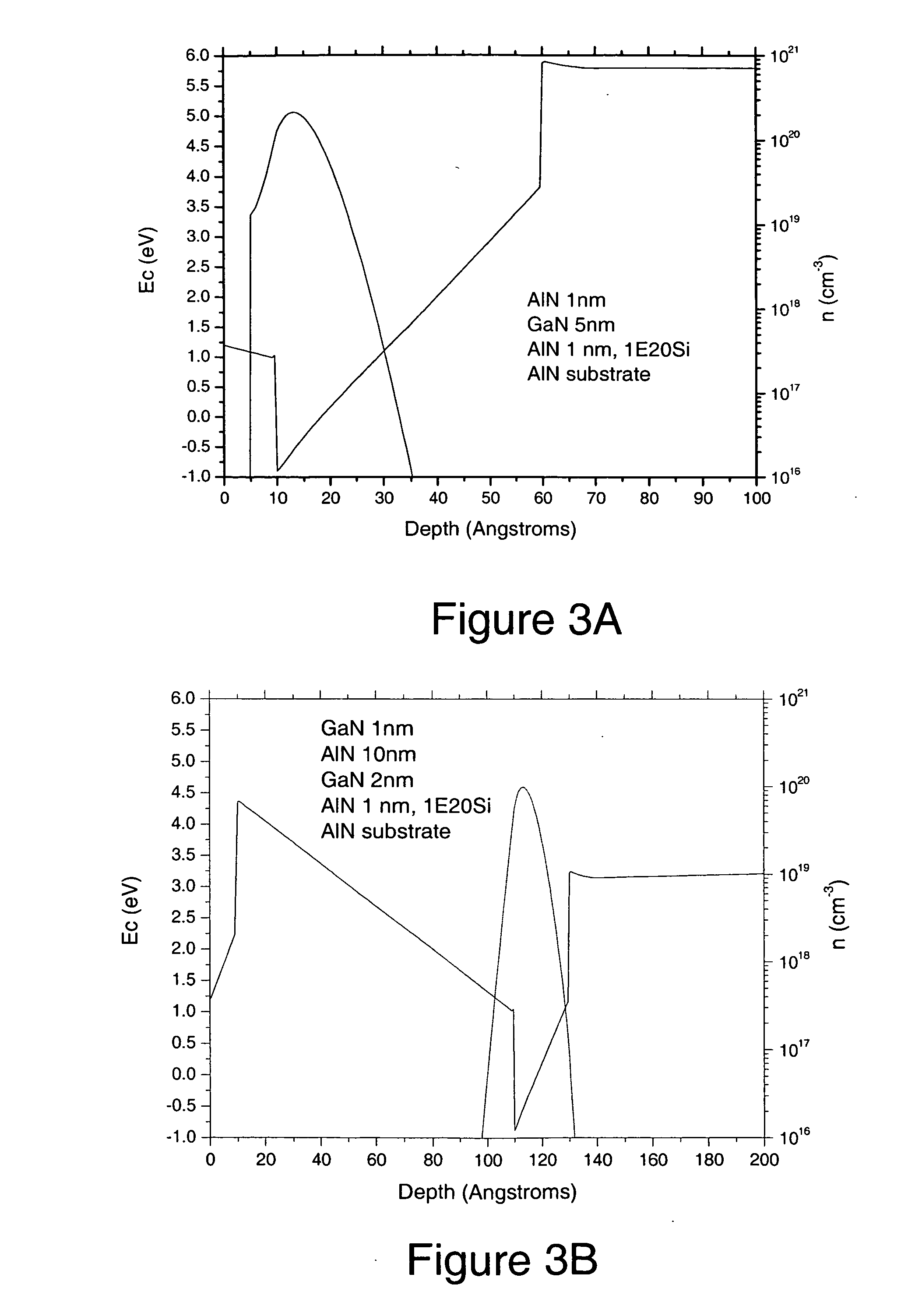

Binary group III-nitride based high electron mobility transistors

Binary Group III-nitride high electron mobility transistors (HEMTs) and methods of fabricating binary Group III-nitride HEMTs are provided. In some embodiments, the binary Group III-nitride HEMTs include a first binary Group III-nitride barrier layer, a binary Group III-nitride channel layer on the first barrier layer; and a second binary Group III-nitride barrier layer on the channel layer. In some embodiments, the binary Group III-nitride HEMTs include a first AIN barrier layer, a GaN channel layer and a second AIN barrier layer.

Owner:CREE INC

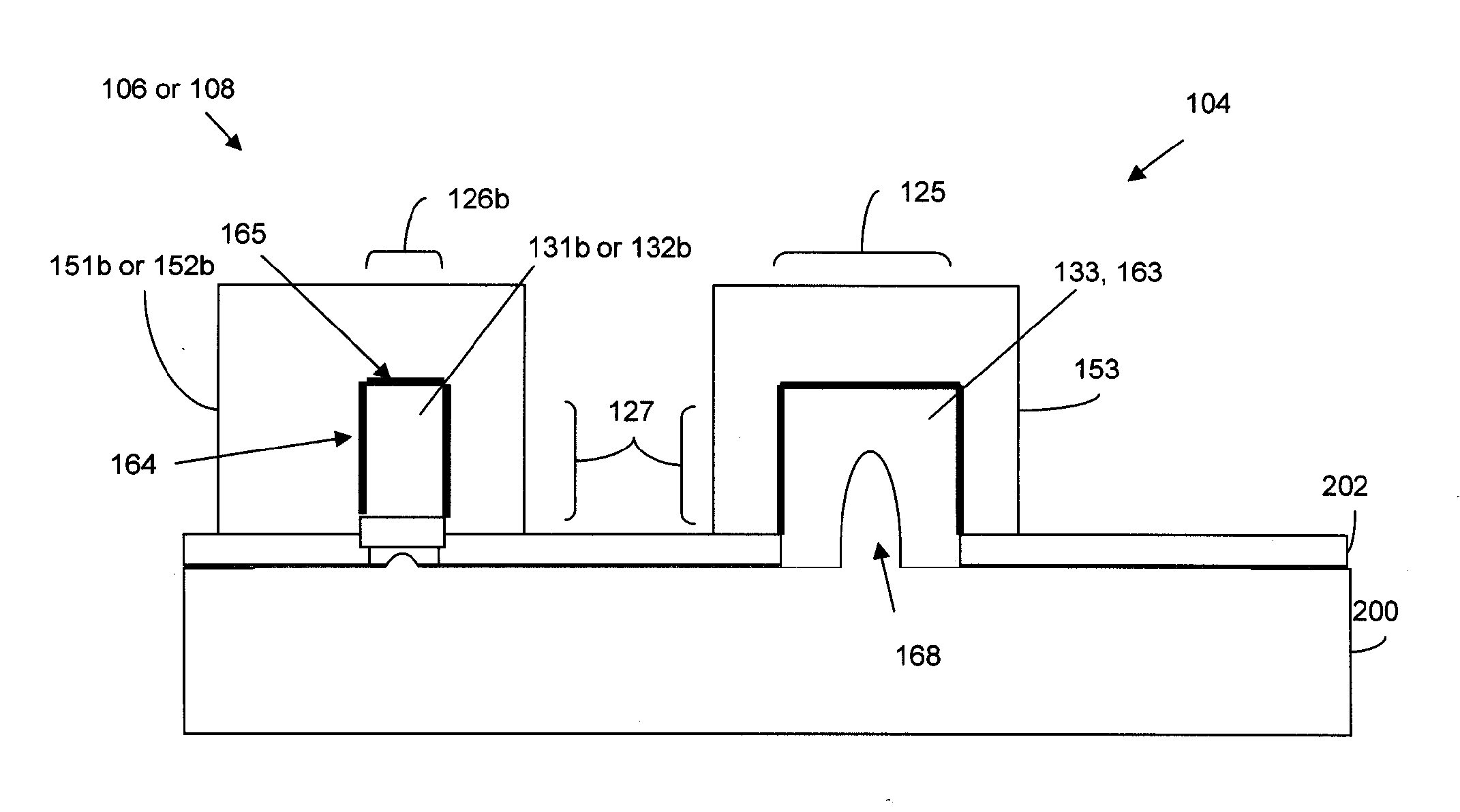

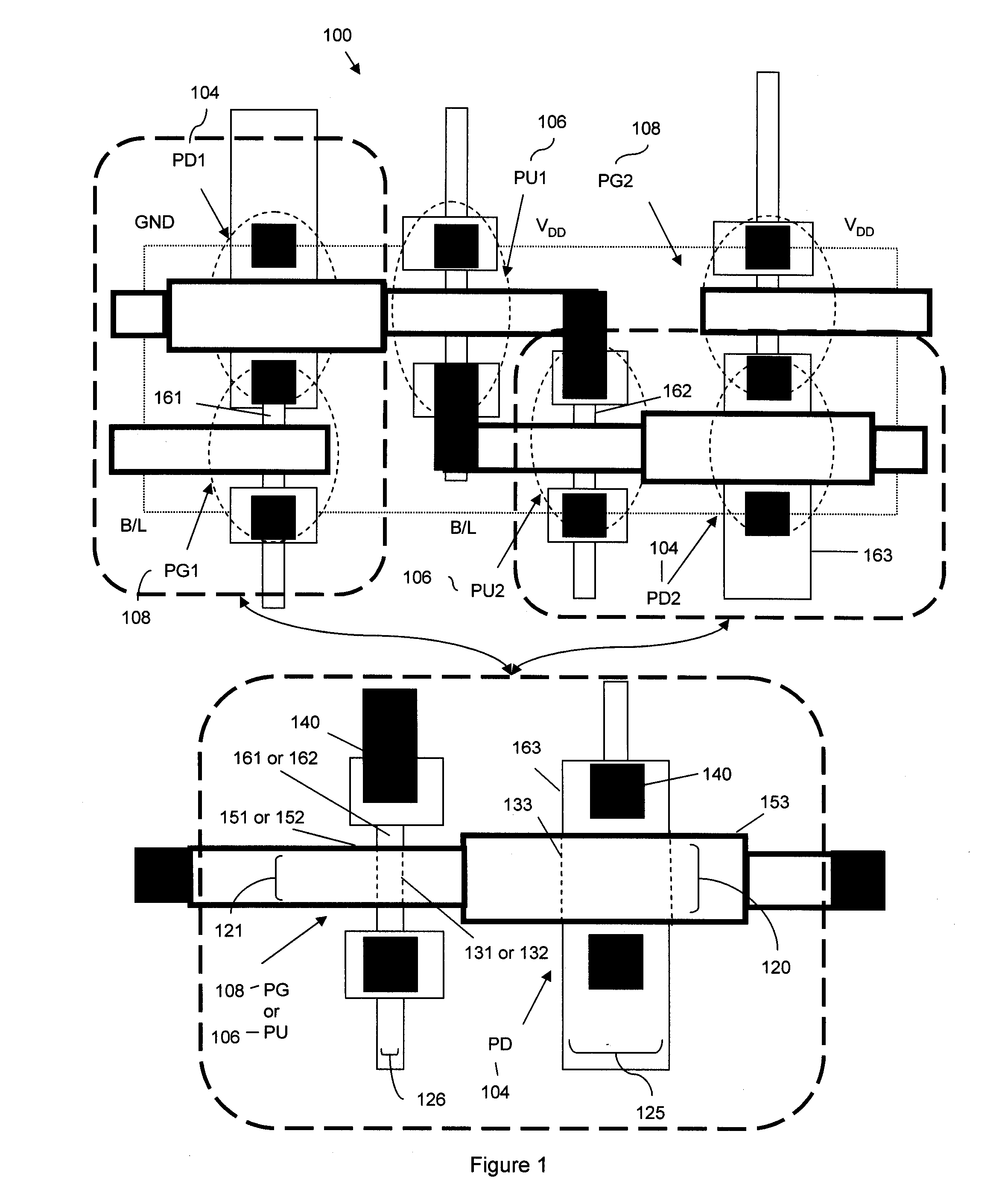

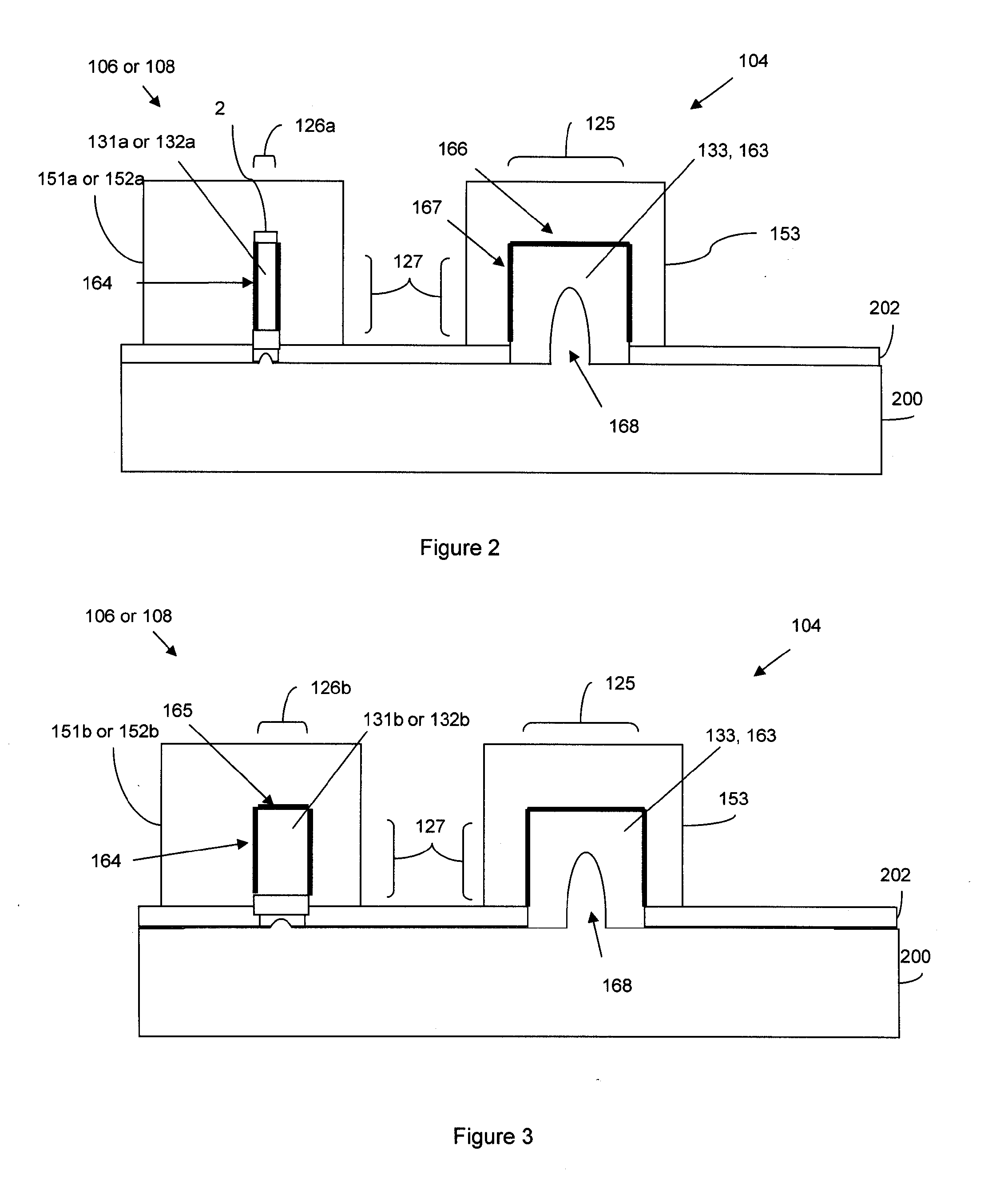

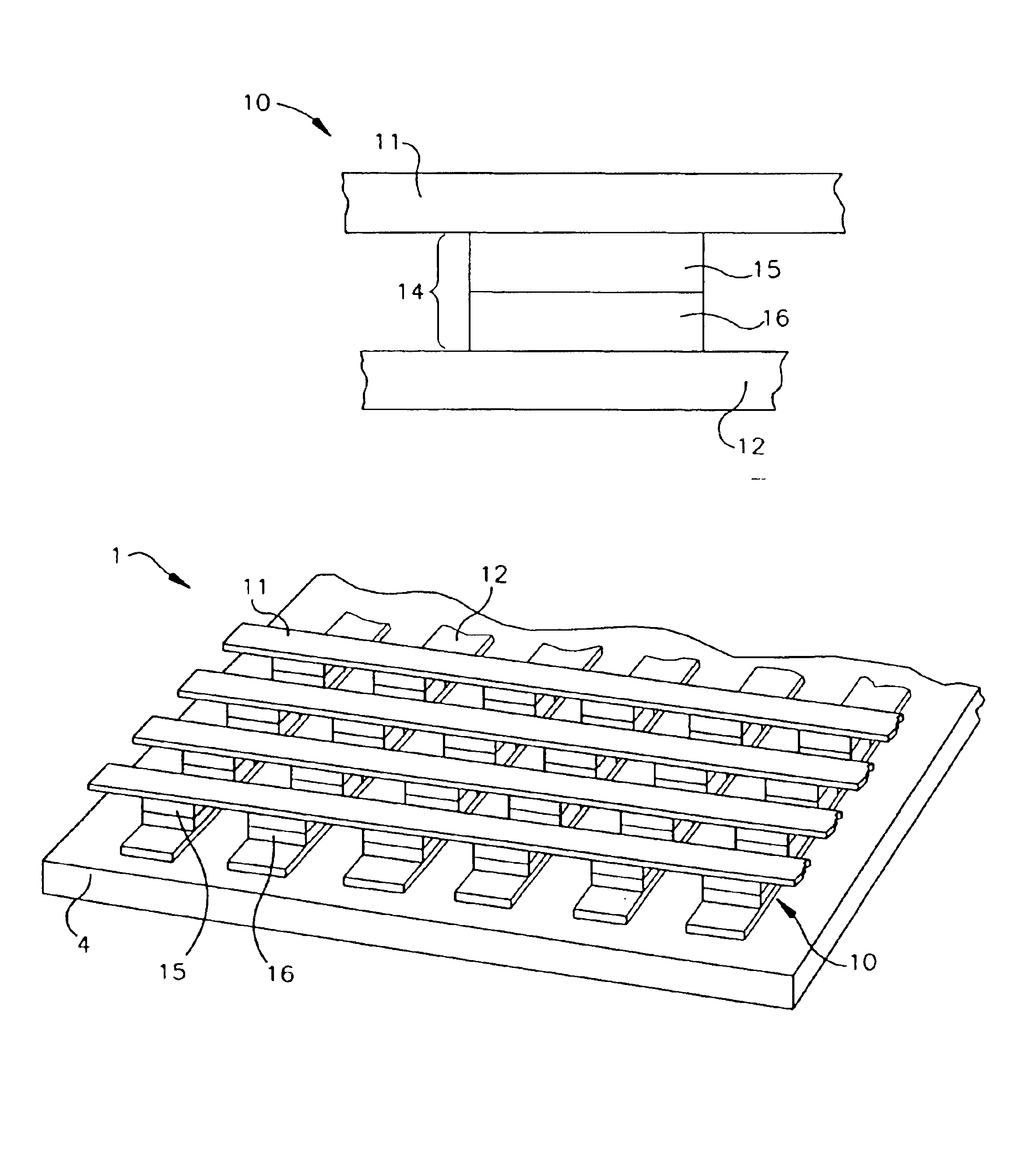

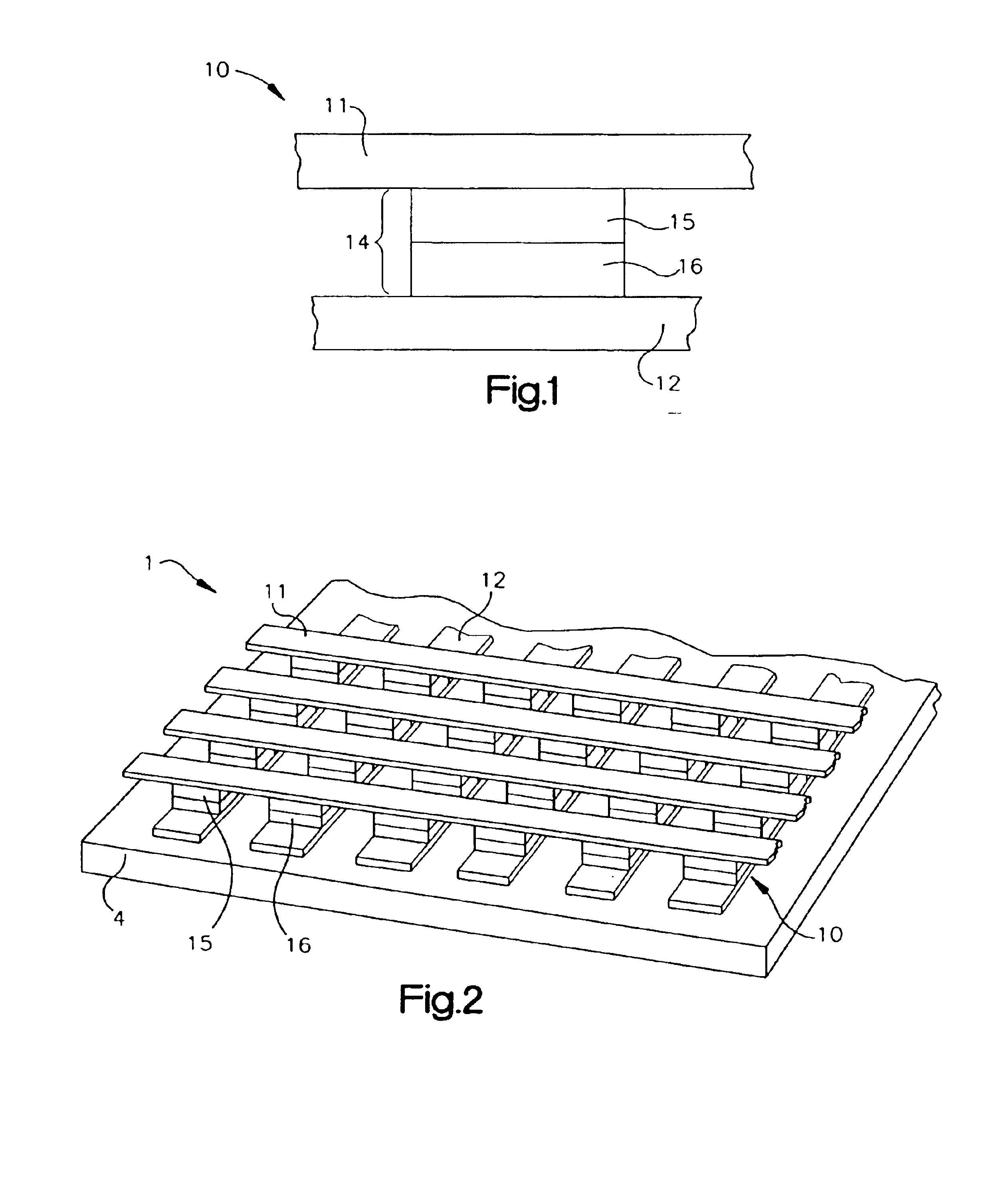

SRAM cell

InactiveUS20070108528A1Increase effective widthImprove carrying capacityTransistorSolid-state devicesDriving currentEngineering

Disclosed is an SRAM cell on an SOI, bulk or HOT wafer with two pass-gate n-FETs, two pull-up p-FETs and two pull-down n-FETs and the associated methods of making the SRAM cell. The pass-gate FETs and pull-down FETs are non-planar fully depleted finFETs or trigate FETs. The pull-down FETs comprise non-planar partially depleted three-gated FETs having a greater channel width and a greater gate length and, thus, a greater drive current relative to the pass-gate and pull-up FETs. Additionally, for optimal electron mobility and hole mobility, respectively, the channels of the n-FETs and p-FETs can comprise semiconductors with different crystalline orientations.

Owner:IBM CORP

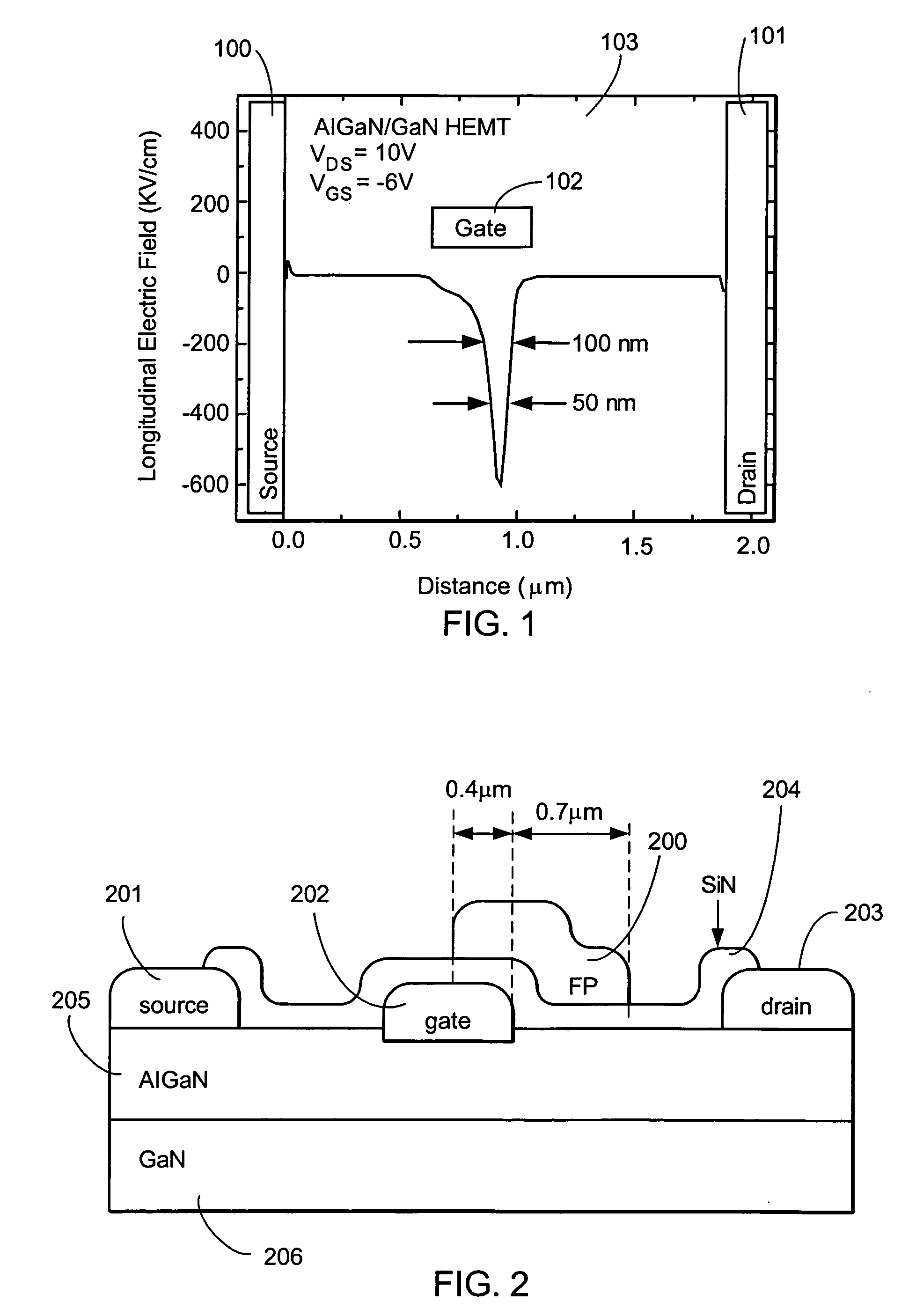

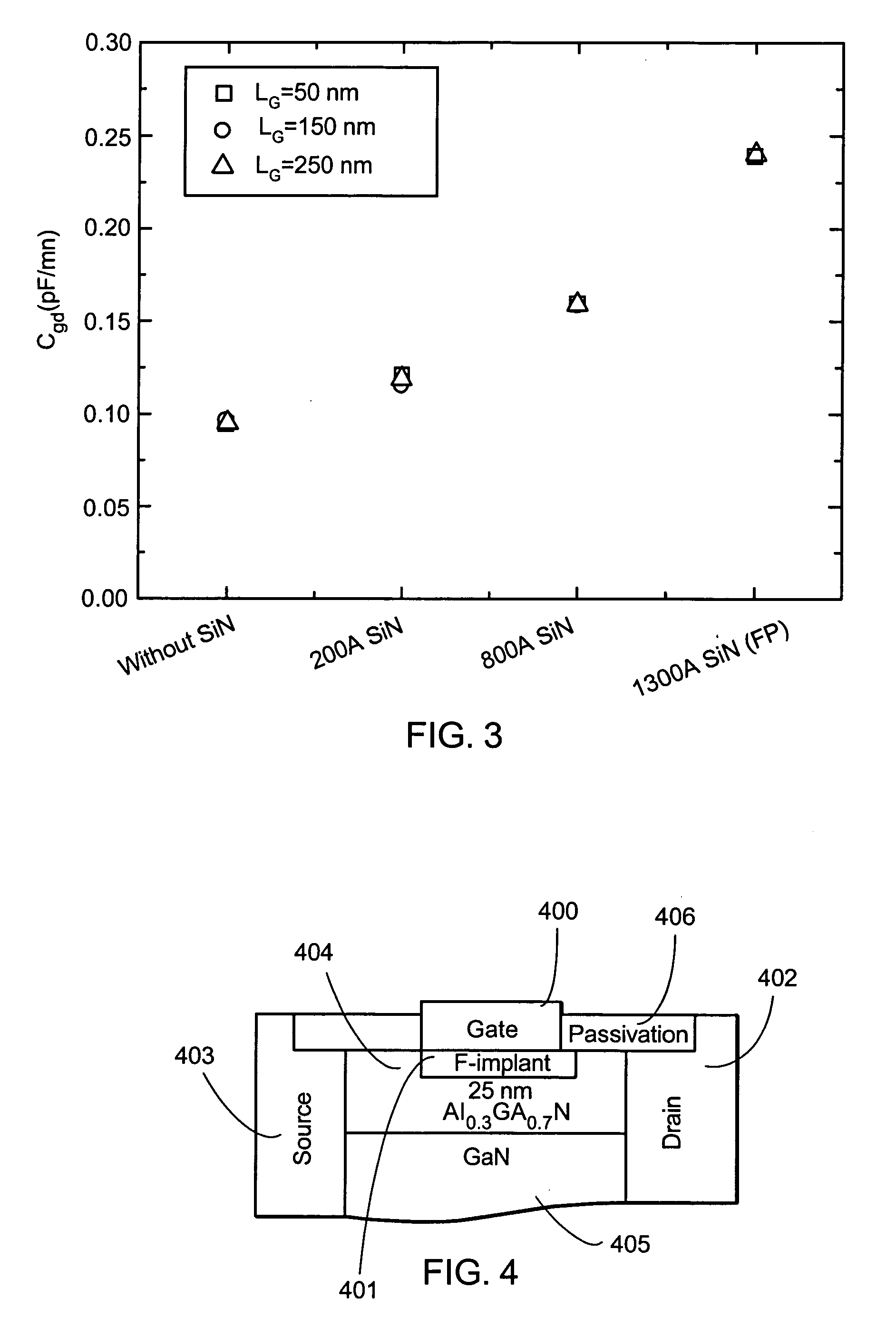

Methods to shape the electric field in electron devices, passivate dislocations and point defects, and enhance the luminescence efficiency of optical devices

ActiveUS20070224710A1Increase output powerReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueDislocation

A fluorine treatment that can shape the electric field profile in electronic devices in 1, 2, or 3 dimensions is disclosed. A method to increase the breakdown voltage of AlGaN / GaN high electron mobility transistors, by the introduction of a controlled amount of dispersion into the device, is also disclosed. This dispersion is large enough to reduce the peak electric field in the channel, but low enough in order not to cause a significant decrease in the output power of the device. In this design, the whole transistor is passivated against dispersion with the exception of a small region 50 to 100 nm wide right next to the drain side of the gate. In that region, surface traps cause limited amounts of dispersion, that will spread the high electric field under the gate edge, therefore increasing the breakdown voltage. Three different methods to introduce dispersion in the 50 nm closest to the gate are described: (1) introduction of a small gap between the passivation and the gate metal, (2) gradually reducing the thickness of the passivation, and (3) gradually reducing the thickness of the AlGaN cap layer in the region close the gate.

Owner:RGT UNIV OF CALIFORNIA

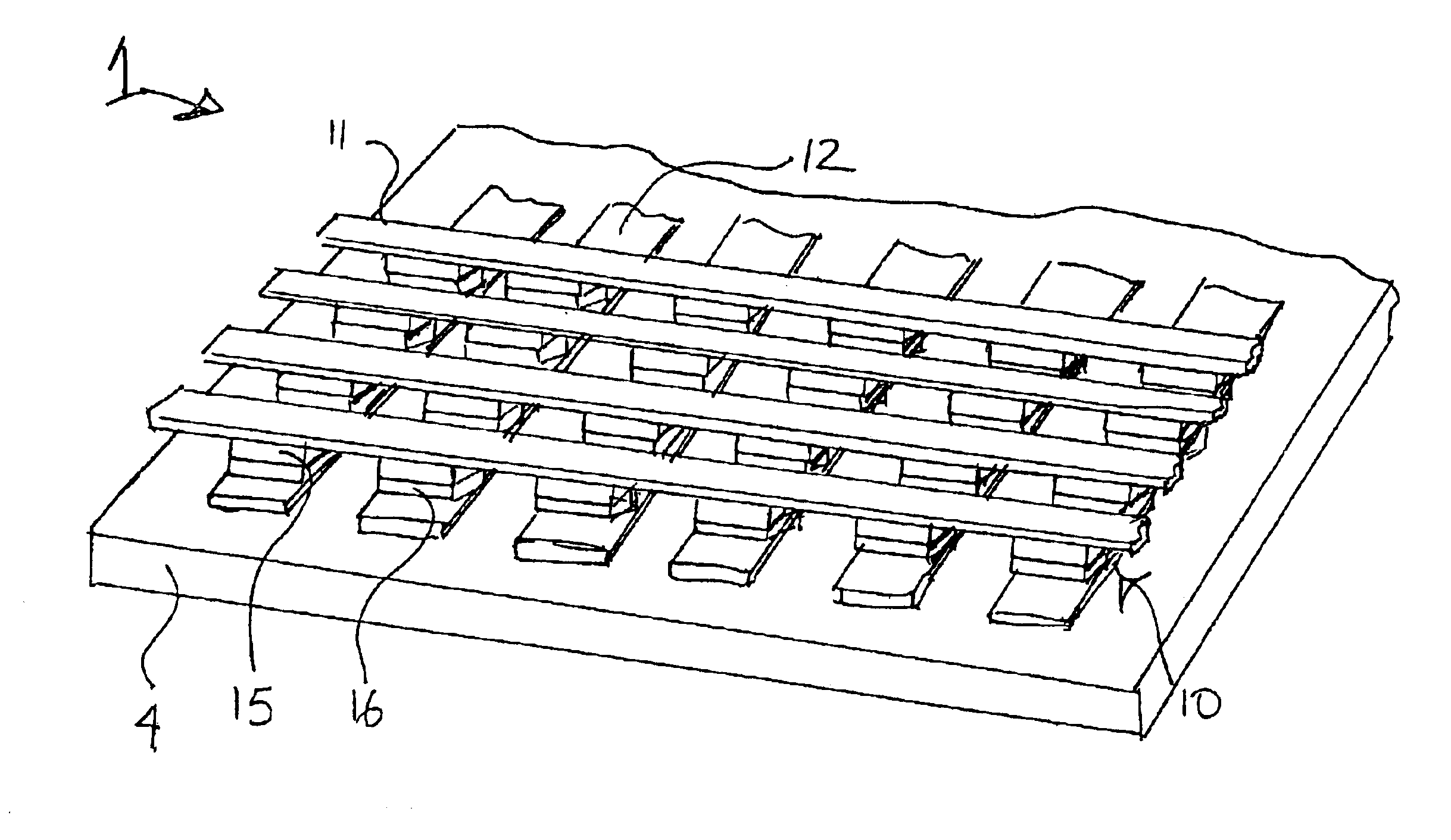

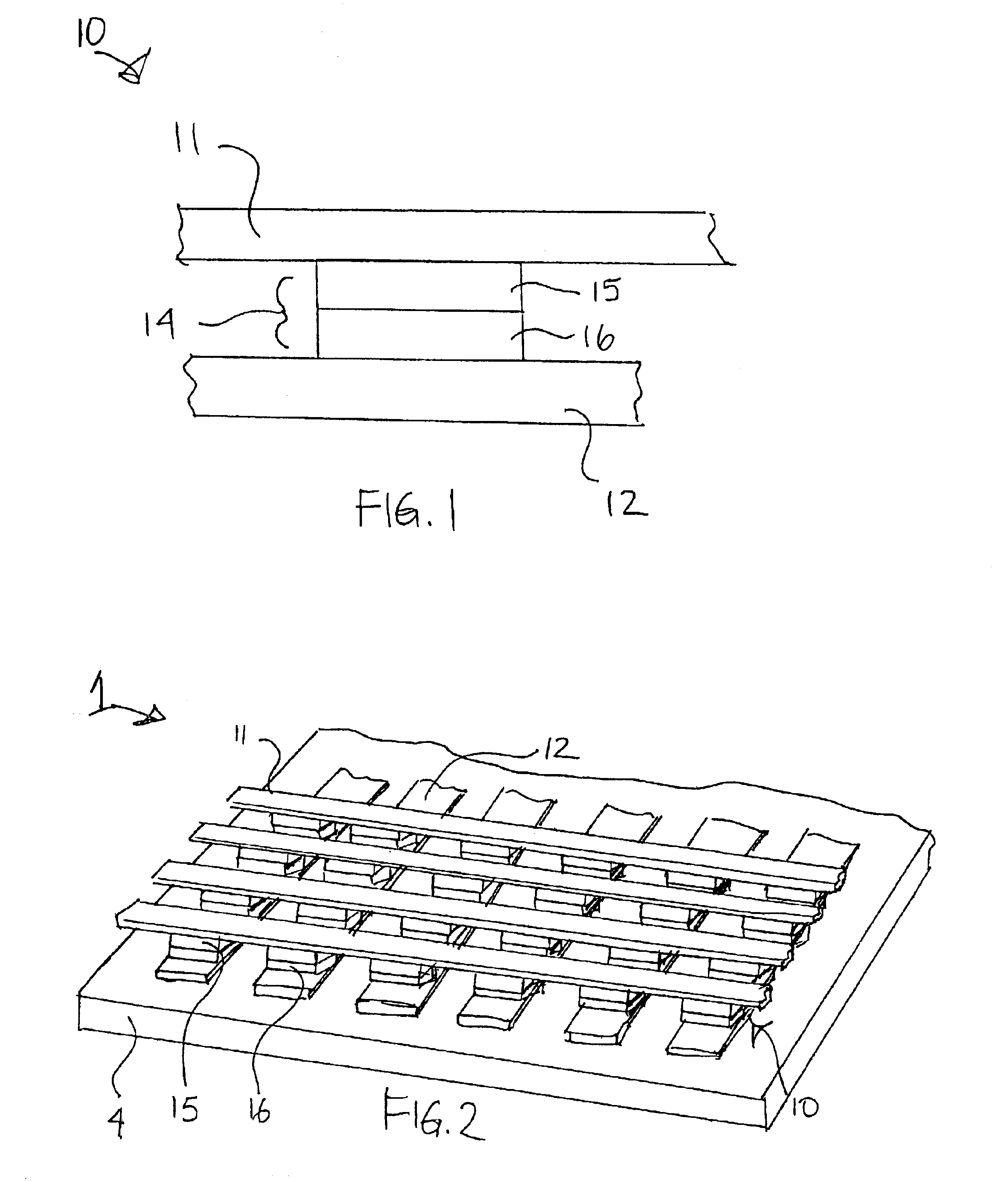

Memory device with active and passive layers

InactiveUS6858481B2Improve reading speedIncrease write speedNanoinformaticsSolid-state devicesAmount of substanceElectron mobility

A memory including memory cells having active and passive layers may store multiple information bits. The active layer may include an organic polymer that has a variable resistance based on the movement of charged species (ions or ions and electrons) between the passive layer and the active layer. The passive layer may be a super-ionic material that has high ion and electron mobility. The active layer may be self-assembled from a monomer in a liquid or gas.

Owner:SPANSION LLC

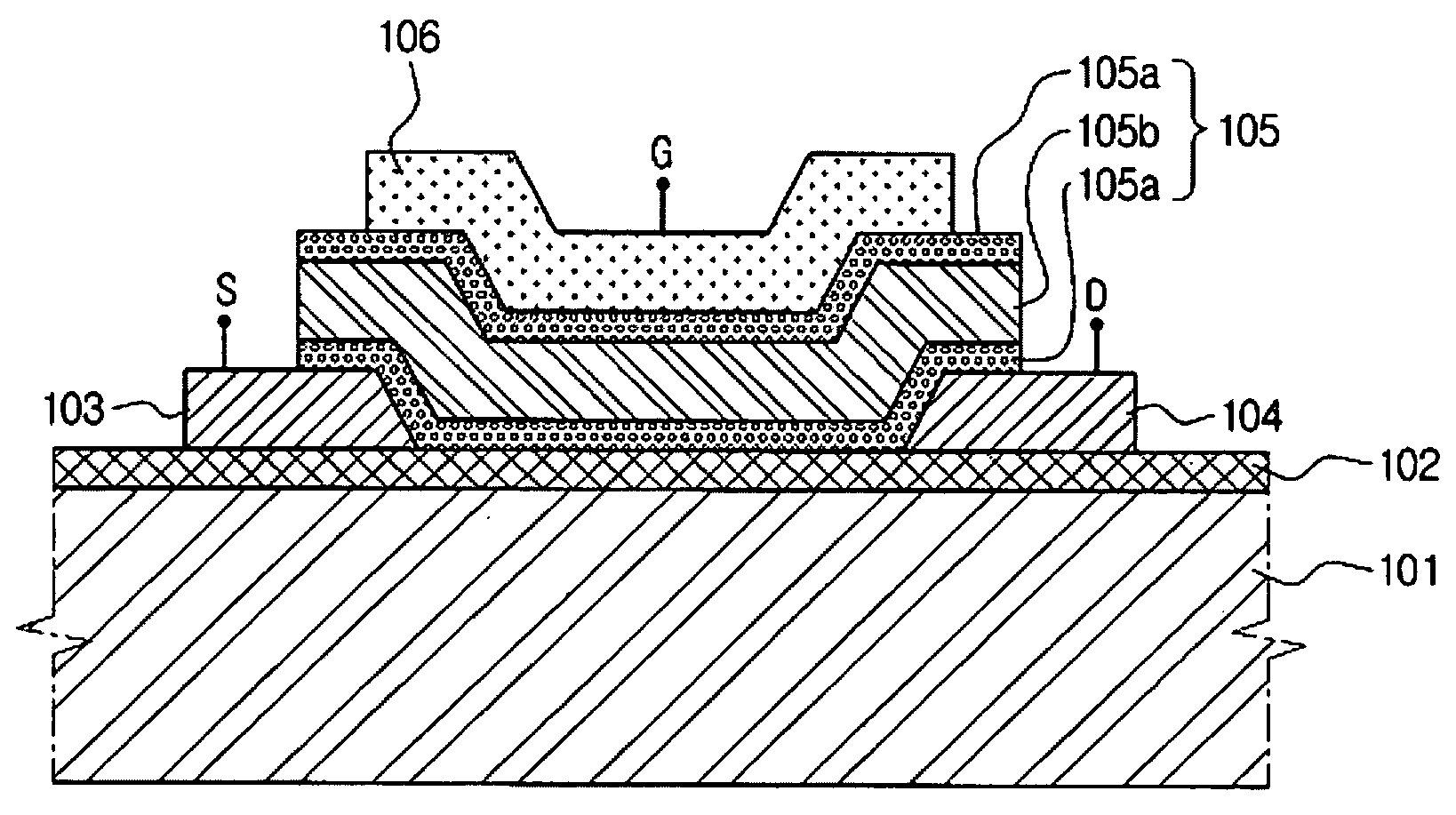

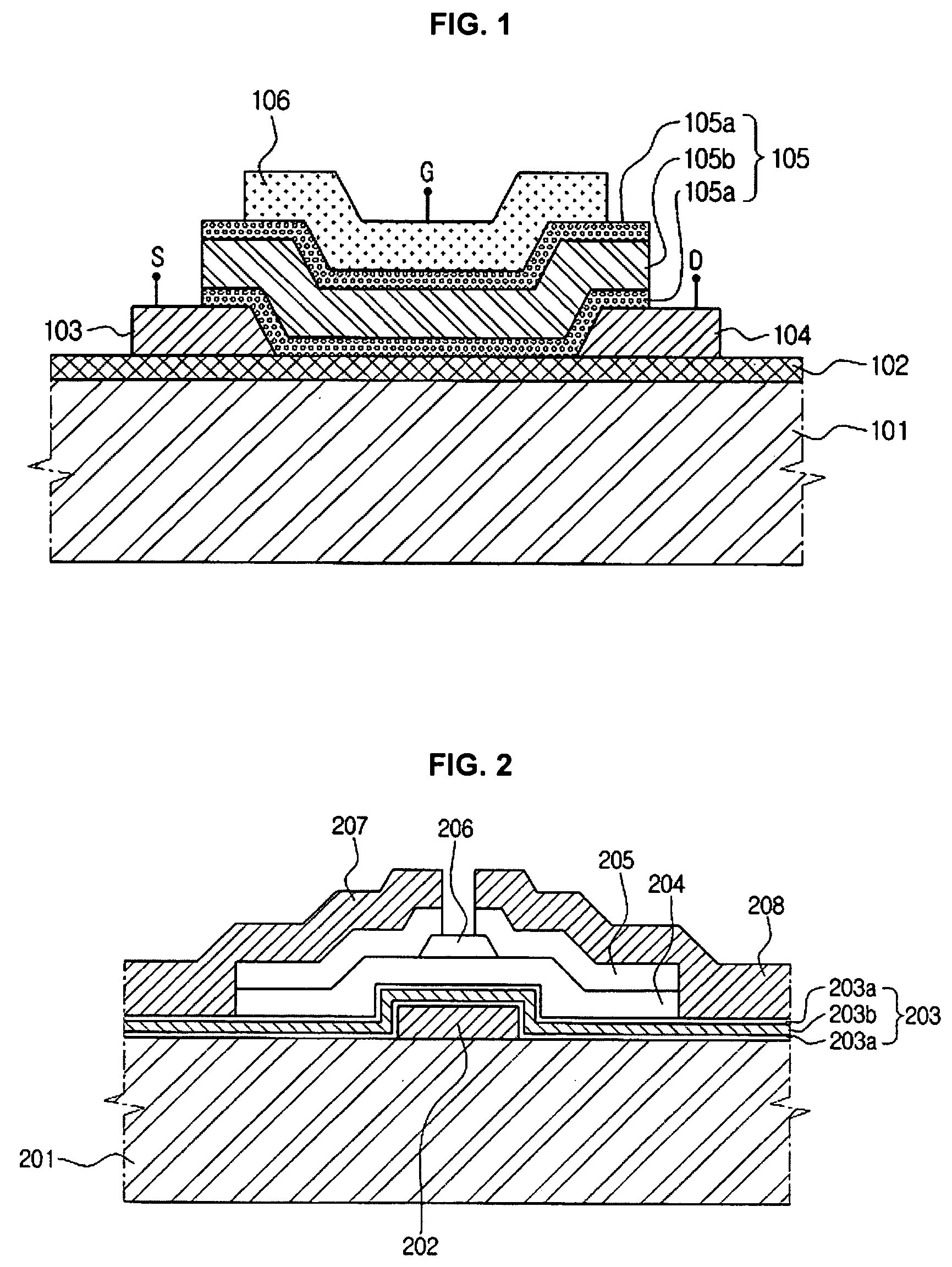

Thin Film Transistor

InactiveUS20090278120A1High electron mobilityMinimize occurrenceTransistorHysteresisElectron mobility

There is provided a thin film transistor (TFT) capable of improving electron mobility and minimizing the occurrence of hysteresis due to traps. The TFT includes a channel layer and a gate insulating layer, wherein the channel layer is made of an oxide semiconductor. In the TFT, the gate insulating layer includes one or more first dielectric layer and a second dielectric layer, and the first dielectric layer has a dielectric constant different from that of the second dielectric layer.

Owner:KOREA INST OF SCI & TECH

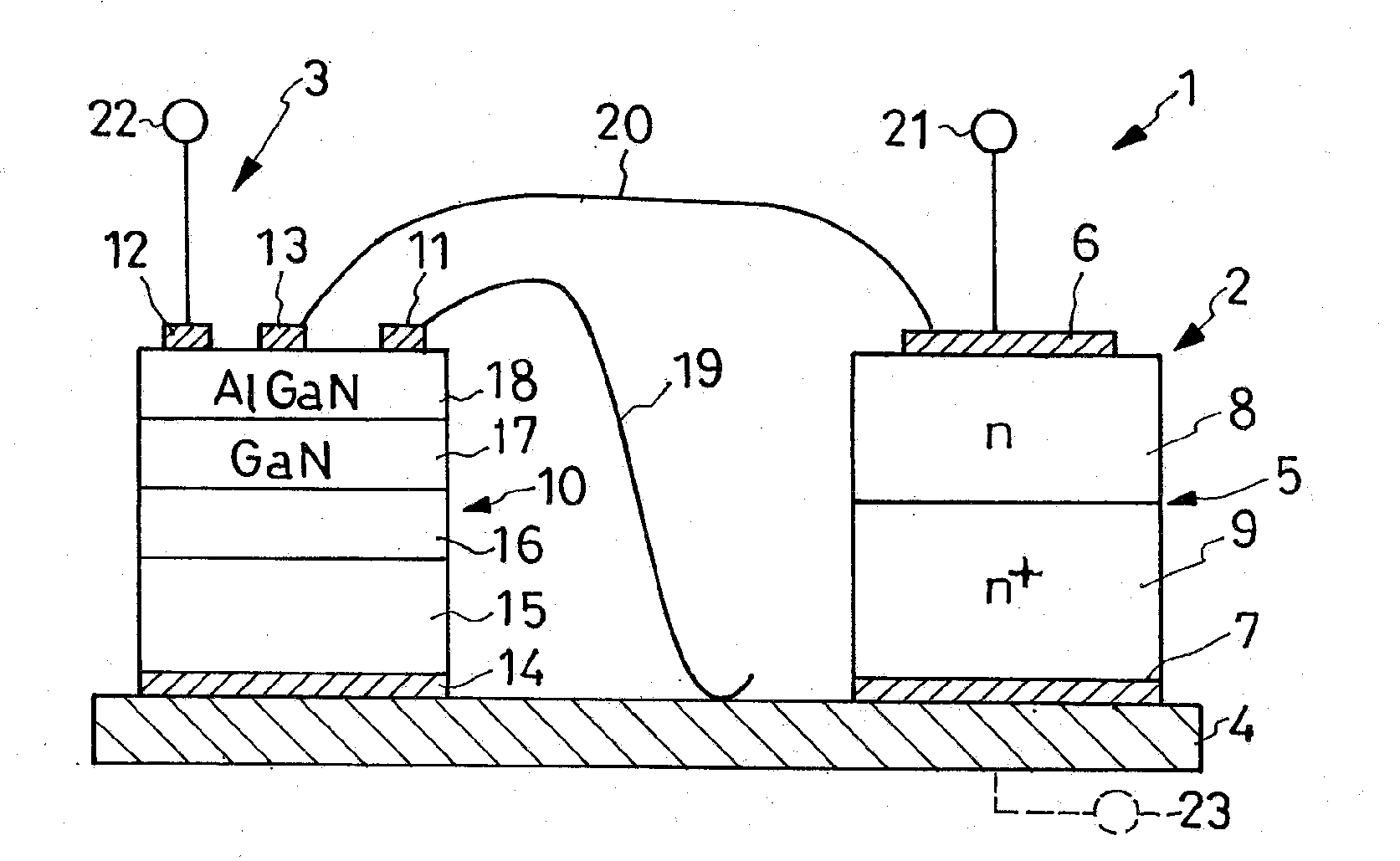

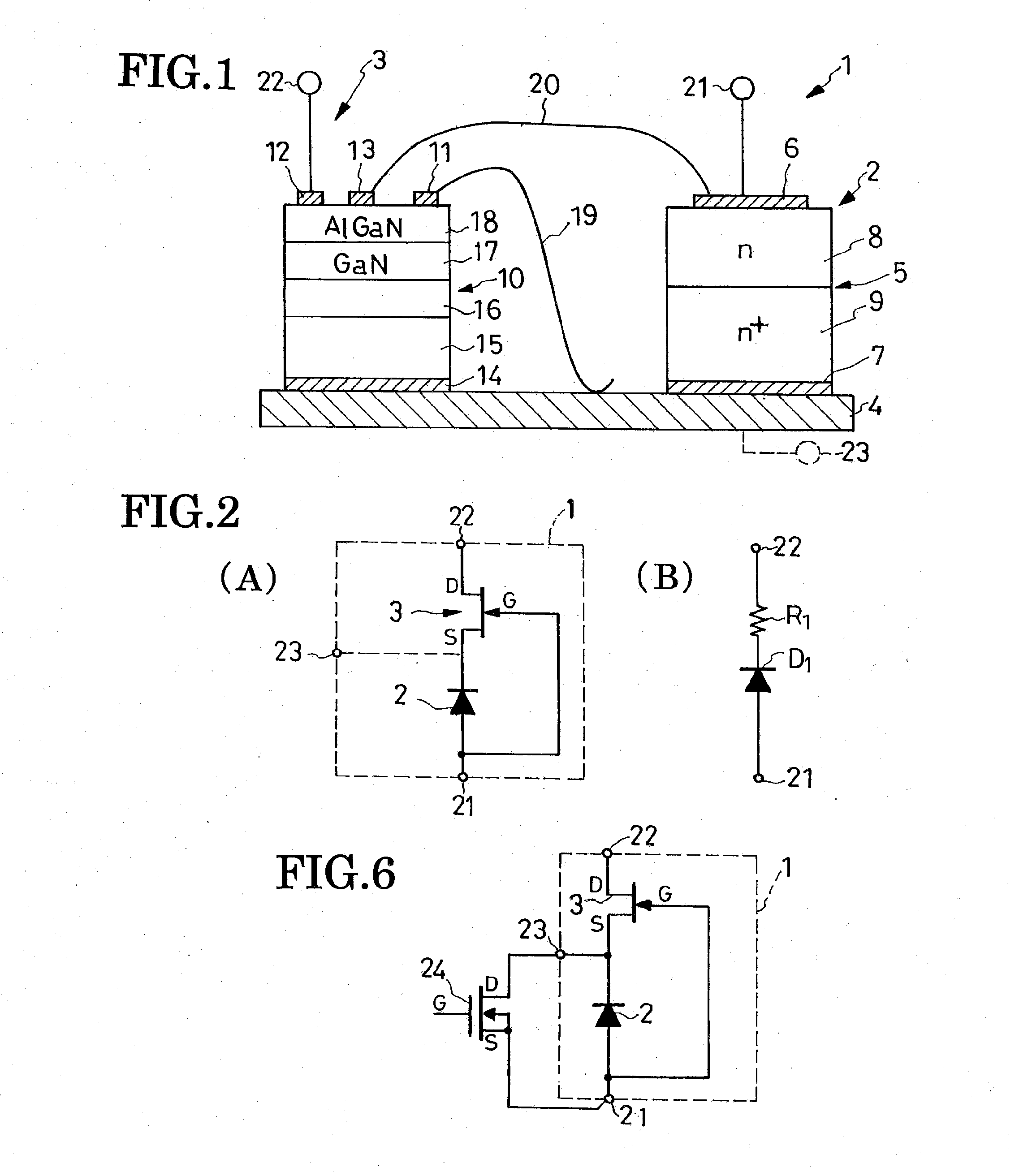

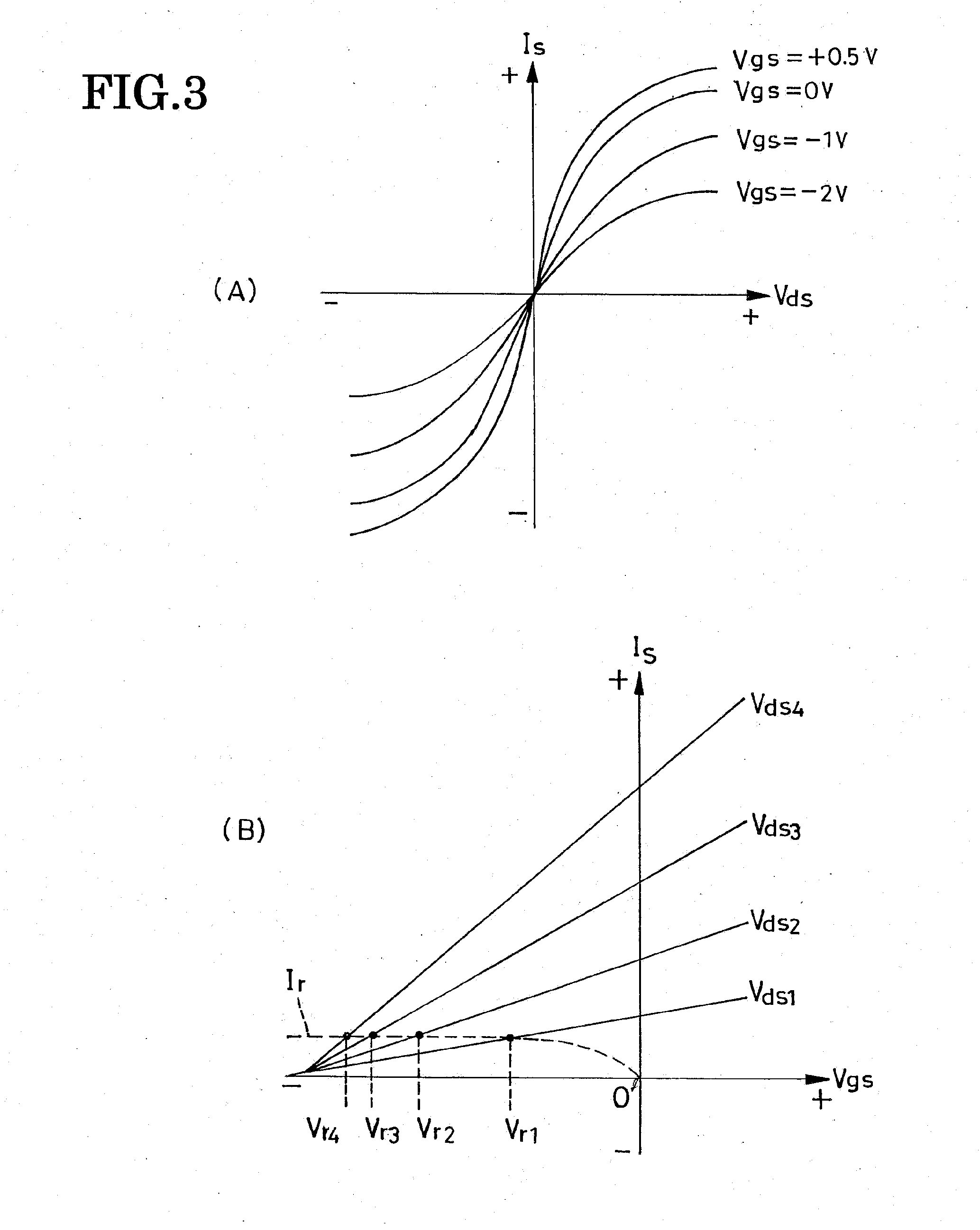

Diode-Like Composite Semiconductor Device

ActiveUS20080191216A1Minimal current capacityPrevent excess flowSolid-state devicesElectronic switchingSchottky barrierCompressive strength

A silicon-made low-forward-voltage Schottky barrier diode is serially combined with a high-antivoltage-strength high-electron-mobility transistor made from a nitride semiconductor that is wider in bandgap than silicon. The Schottky barrier diode has its anode connected to the gate, and its cathode to the source, of the HEMT. This HEMT is normally on. The reverse voltage withstanding capability of the complete device depends upon that between the drain and gate of the HEMT.

Owner:SANKEN ELECTRIC CO LTD

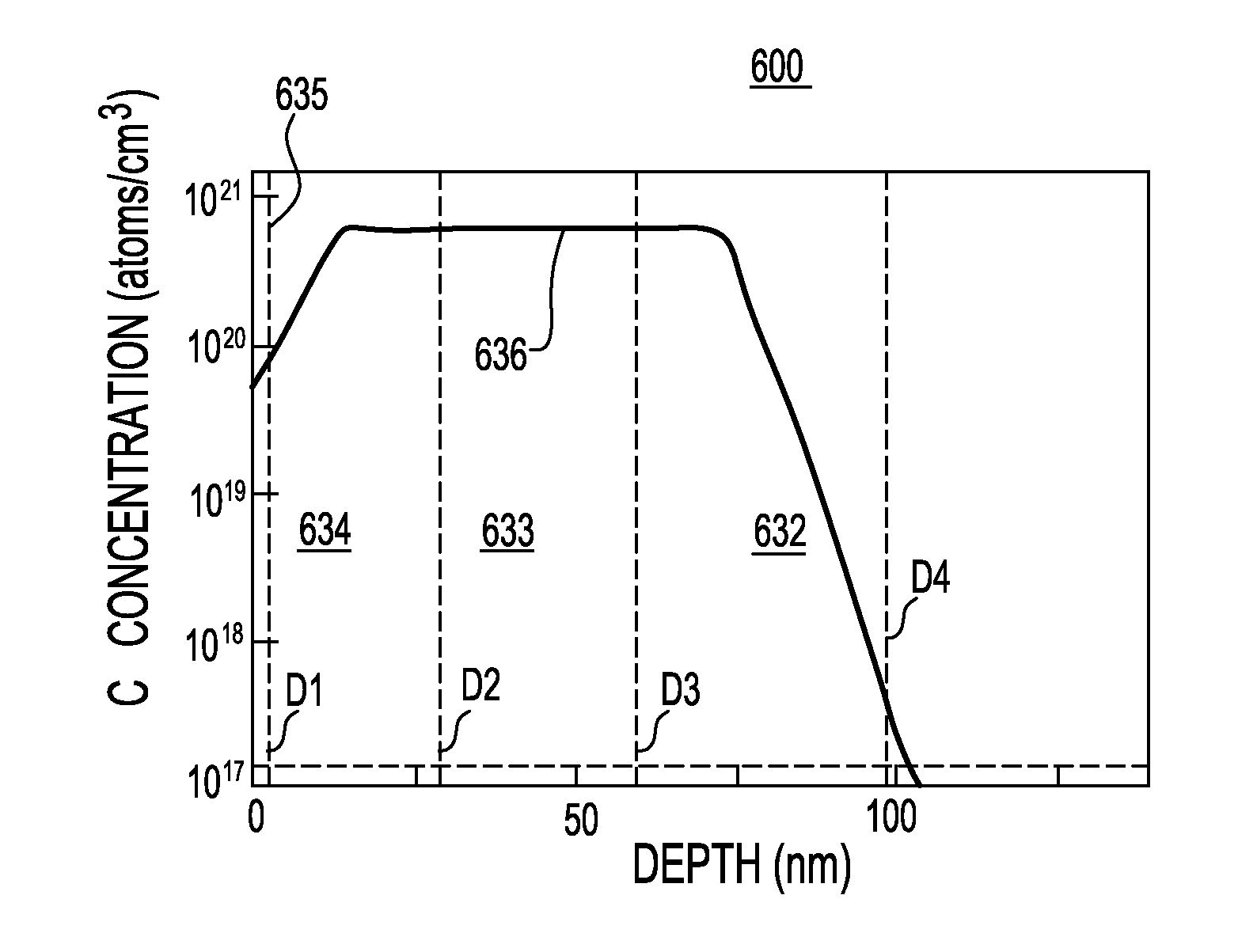

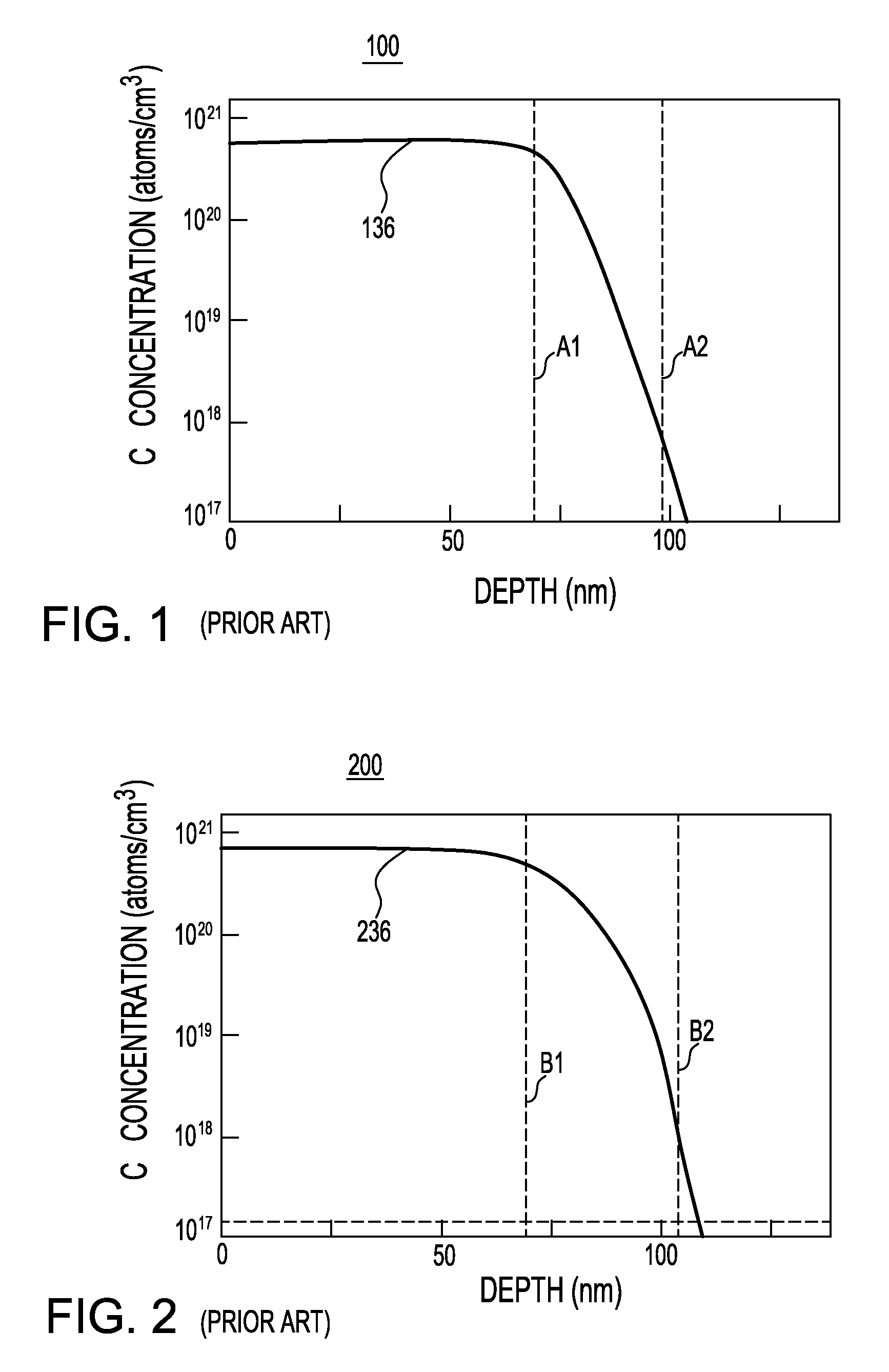

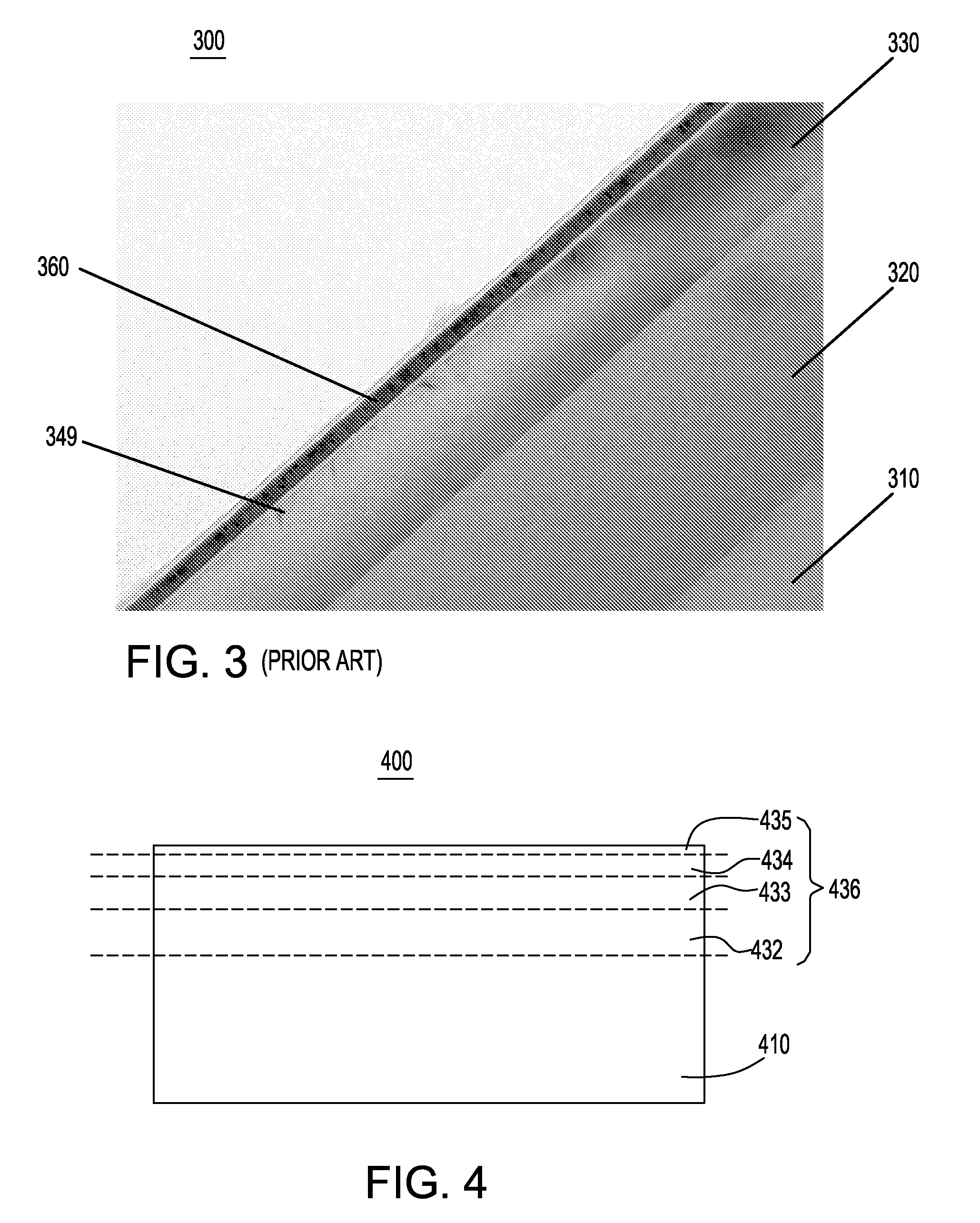

Low defect Si:C layer with retrograde carbon profile

ActiveUS7696000B2High bulk carbon concentrationReduce defect densitySolid-state devicesSemiconductor/solid-state device manufacturingHigh concentrationSemiconductor structure

Formation of carbon-substituted single crystal silicon layer is prone to generation of large number of defects especially at high carbon concentration. The present invention provides structures and methods for providing low defect carbon-substituted single crystal silicon layer even for high concentration of carbon in the silicon. According to the present invention, the active retrograde profile in the carbon implantation reduces the defect density in the carbon-substituted single crystal silicon layer obtained after a solid phase epitaxy. This enables the formation of semiconductor structures with compressive stress and low defect density. When applied to semiconductor transistors, the present invention enables N-type field effect transistors with enhanced electron mobility through the tensile stress that is present into the channel.

Owner:GLOBALFOUNDRIES U S INC

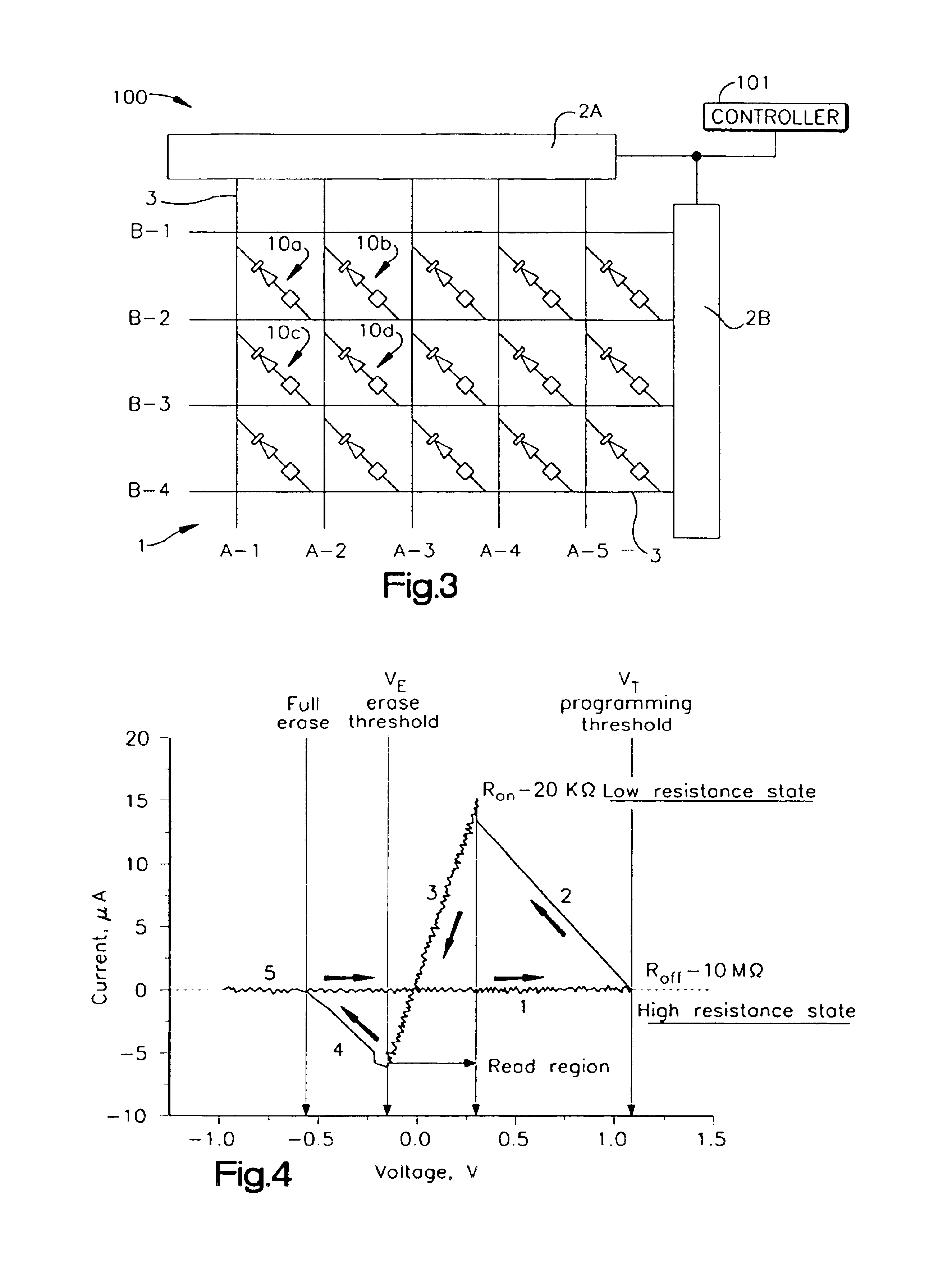

Memory device with active passive layers

InactiveUS6838720B2Improve read and write speedLong-term data retentionTransistorNanoinformaticsActive layerElectron mobility

A memory including memory cells having active and passive layers may store multiple information bits. The active layer may include an organic polymer that has a variable resistance based on the movement of charged species (ions or ions and electrons) between the passive layer and the active layer. The passive layer may be a super-ionic material that has high ion and electron mobility. The active layer may be self-assembled from a monomer in a liquid or gas.

Owner:SPANSION LLC

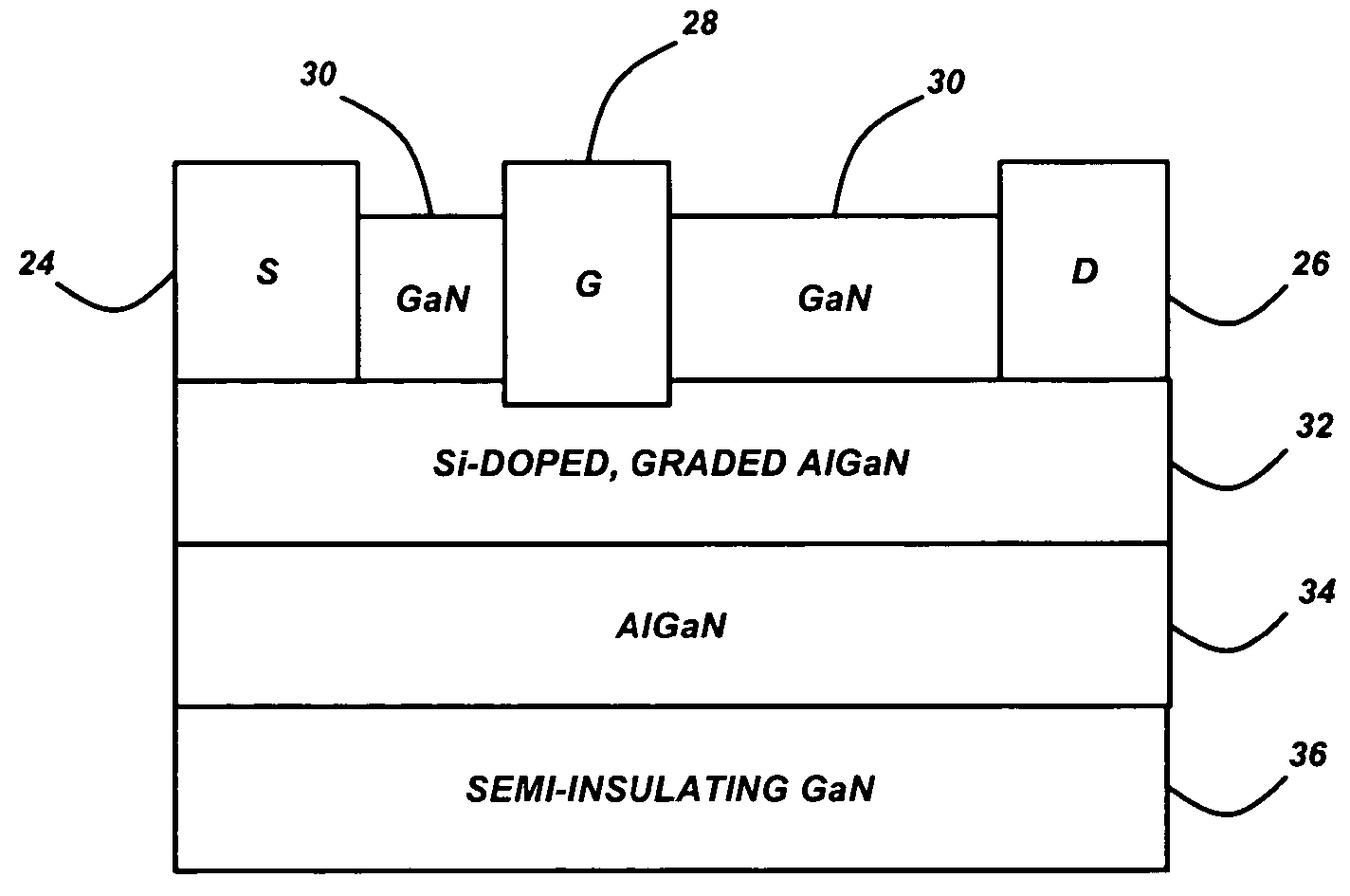

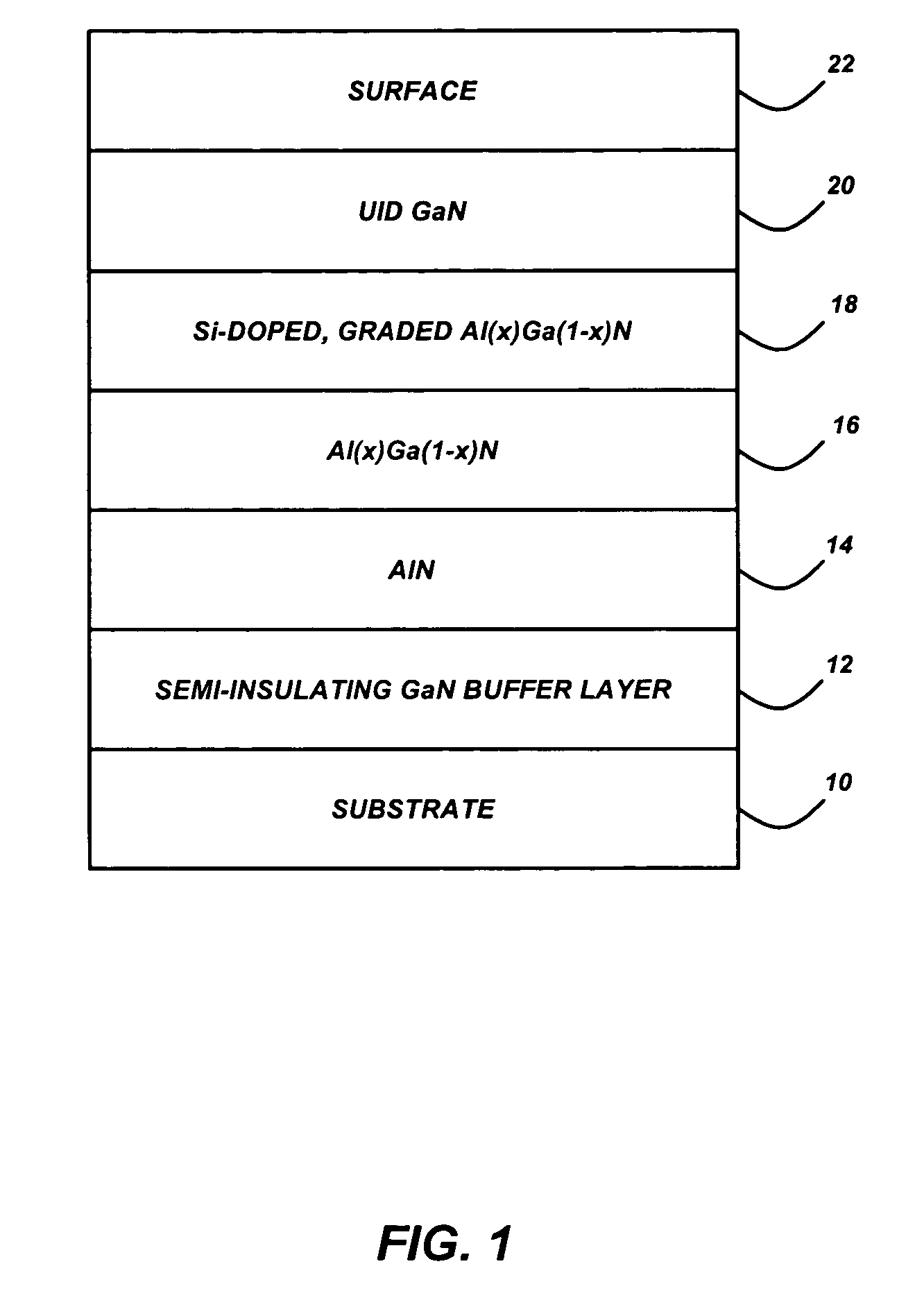

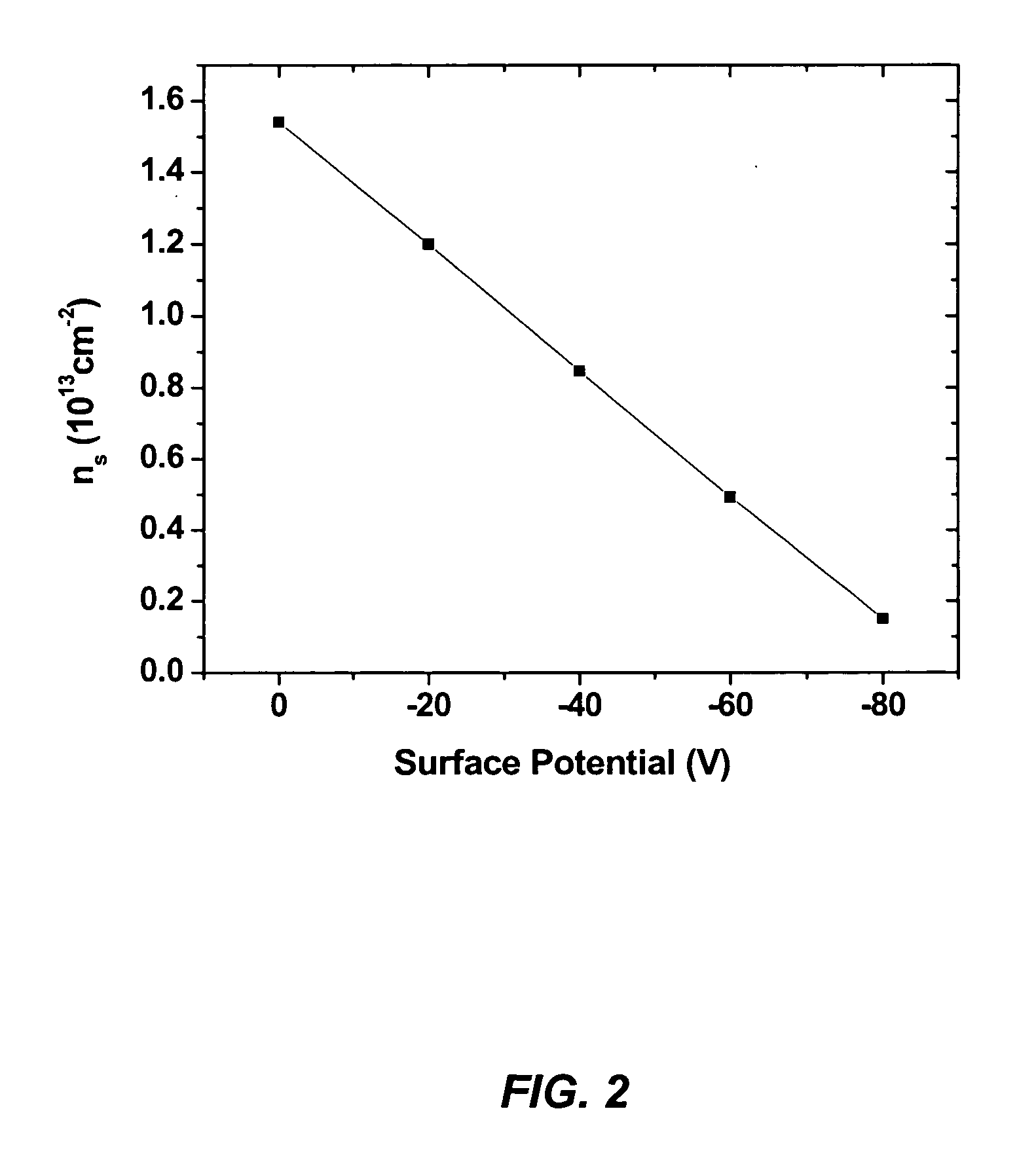

GaN/AIGaN/GaN dispersion-free high electron mobility transistors

InactiveUS20050077541A1High electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh electronGallium nitride

A dispersion-free high electron mobility transistor (HEMT), comprised of a substrate; a semi-insulating buffer layer, comprised of gallium nitride (GaN) or aluminum gallium nitride (AlGaN), deposited on the substrate, an AlGaN barrier layer, with an aluminum (Al) mole fraction larger than that of the semi-insulating buffer layer, deposited on the semi-insulating buffer layer, an n-type doped graded AlGaN layer deposited on the AlGaN barrier layer, wherein an Al mole fraction is decreased from a bottom of the n-type doped graded AlGaN layer to a top of the n-type doped graded AlGaN layer, and a cap layer, comprised of GaN or AlGaN with an Al mole fraction smaller than that of the AlGaN barrier layer, deposited on the n-type doped graded AlGaN layer.

Owner:RGT UNIV OF CALIFORNIA

GaN-based high electron mobility transistor and method for making the same

A high electron mobility transistor including: a GaN material system based heterostructure; a passivating nitride layer over the heterostructure and defining a plurality of openings; and a plurality of electrical contacts for the heterostructure and formed through the openings.

Owner:LOCKHEED MARTIN CORP

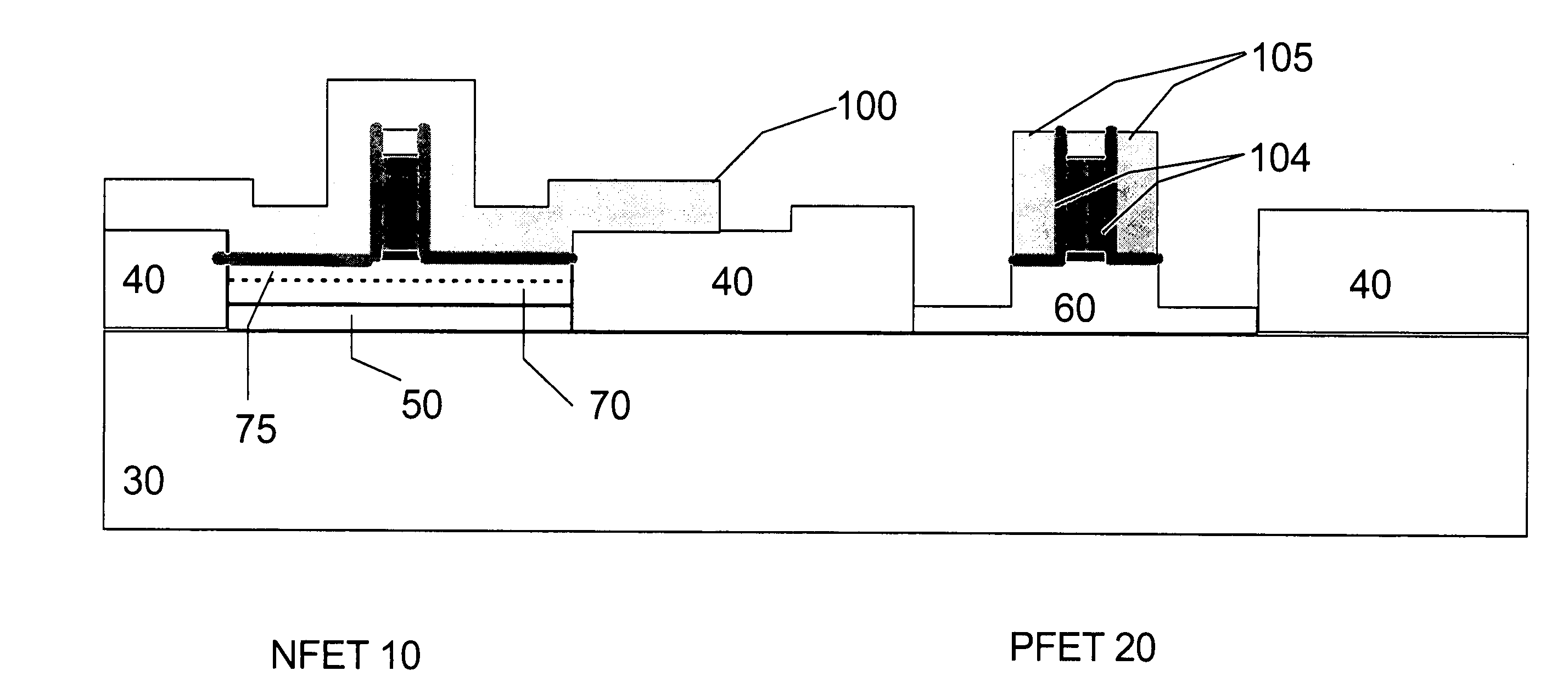

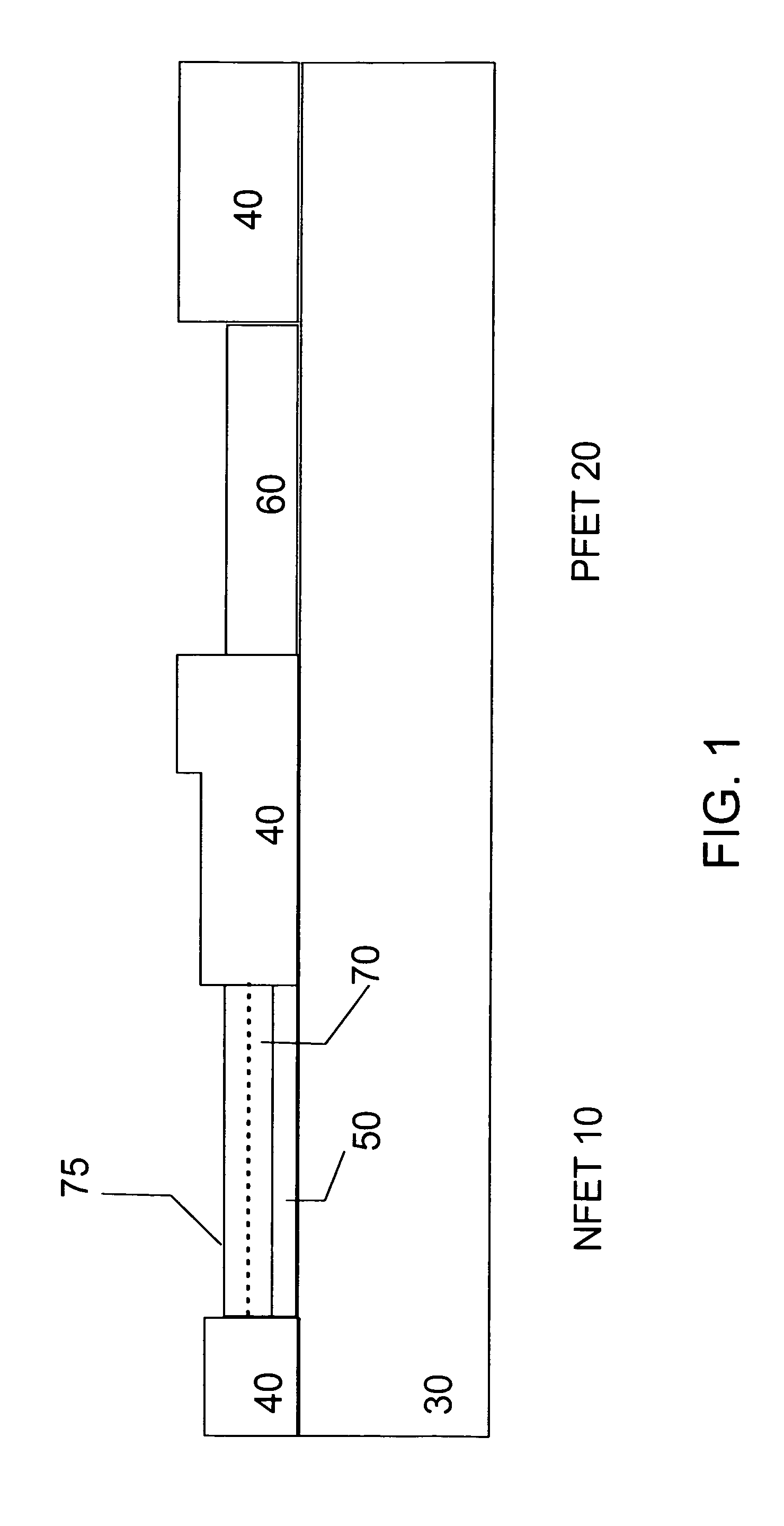

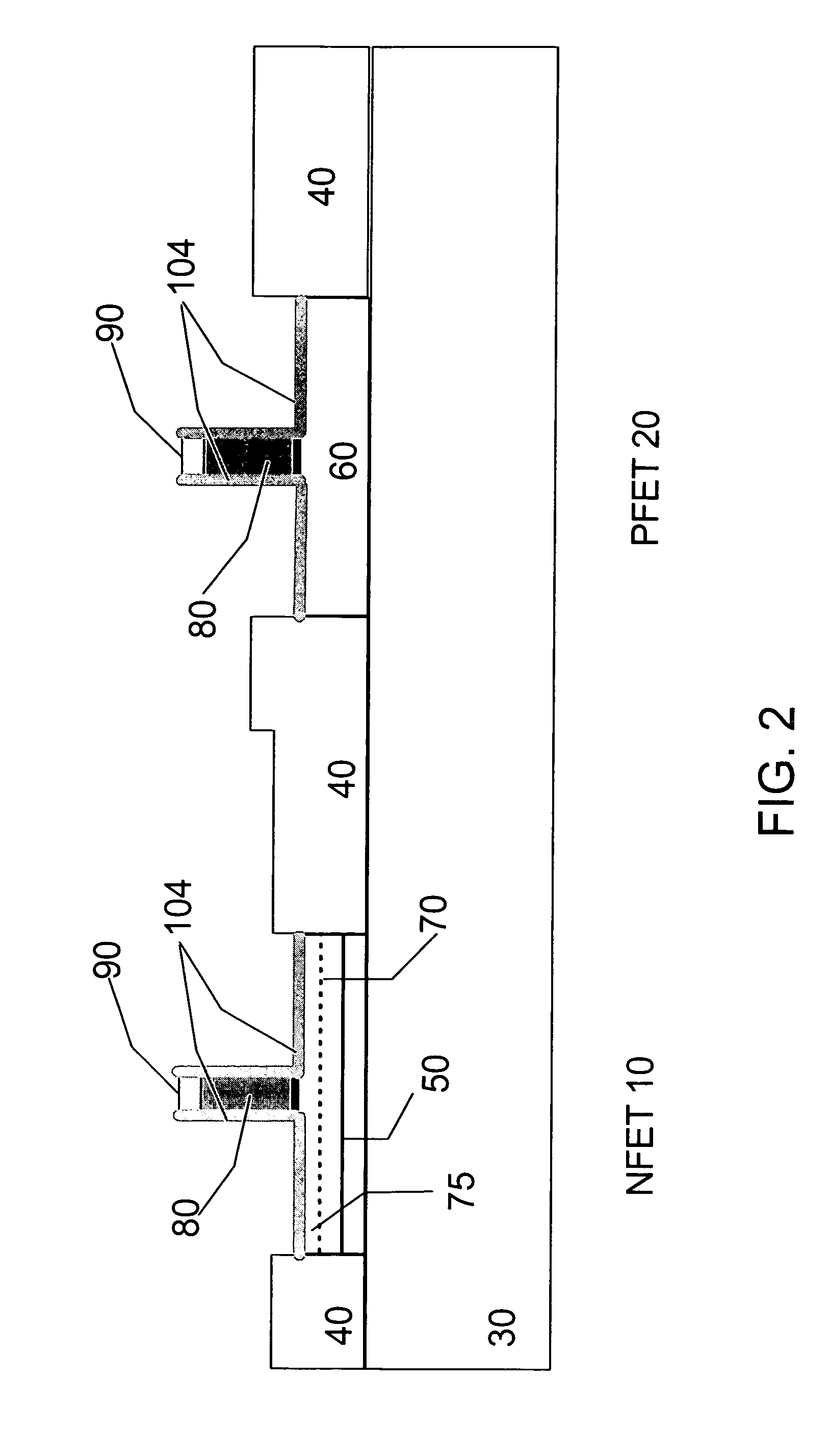

Pseudomorphic Si/SiGe/Si body device with embedded SiGe source/drain

InactiveUS20070196987A1Solid-state devicesSemiconductor/solid-state device manufacturingCMOSSemiconductor structure

The invention relates to a semiconductor structure and method of manufacturing and more particularly to a CMOS device with at least one embedded SiGe layer in the source / drain region of the PFET, and at least one embedded SiGe layer in the channel region of the NFET. In one embodiment, the structure of the invention enhances the electron mobility in the NFET device, and further enhances the hole mobility in the PFET device. Additionally, by using the fabrication methods and hence achieving the final structure of the invention, it is also possible to construct a PFET and NFET each with embedded SiGe layers on the same substrate.

Owner:IBM CORP

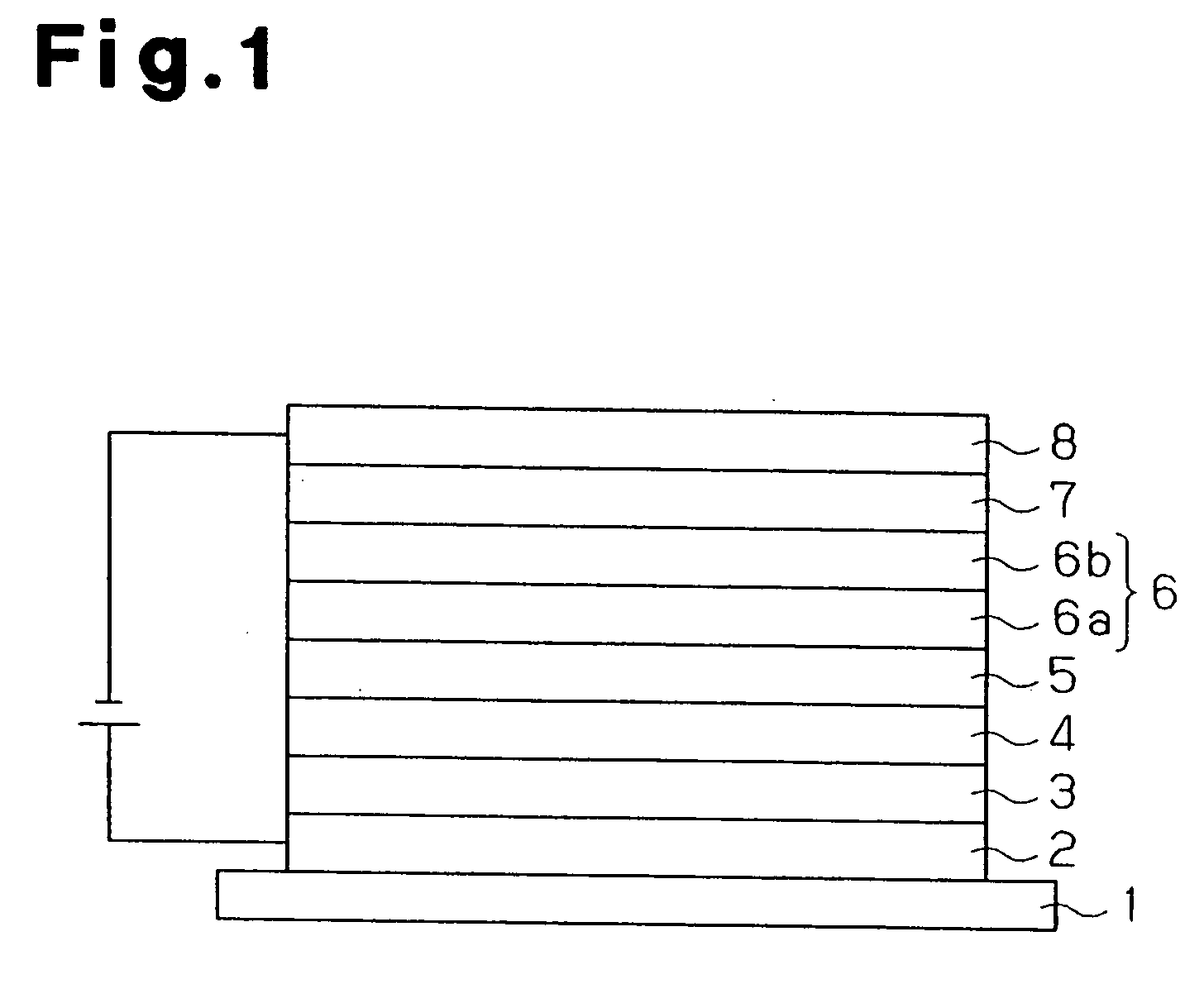

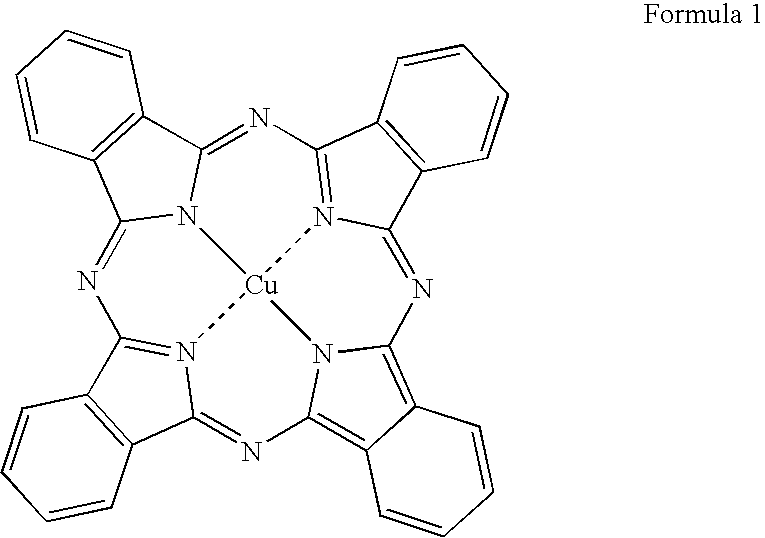

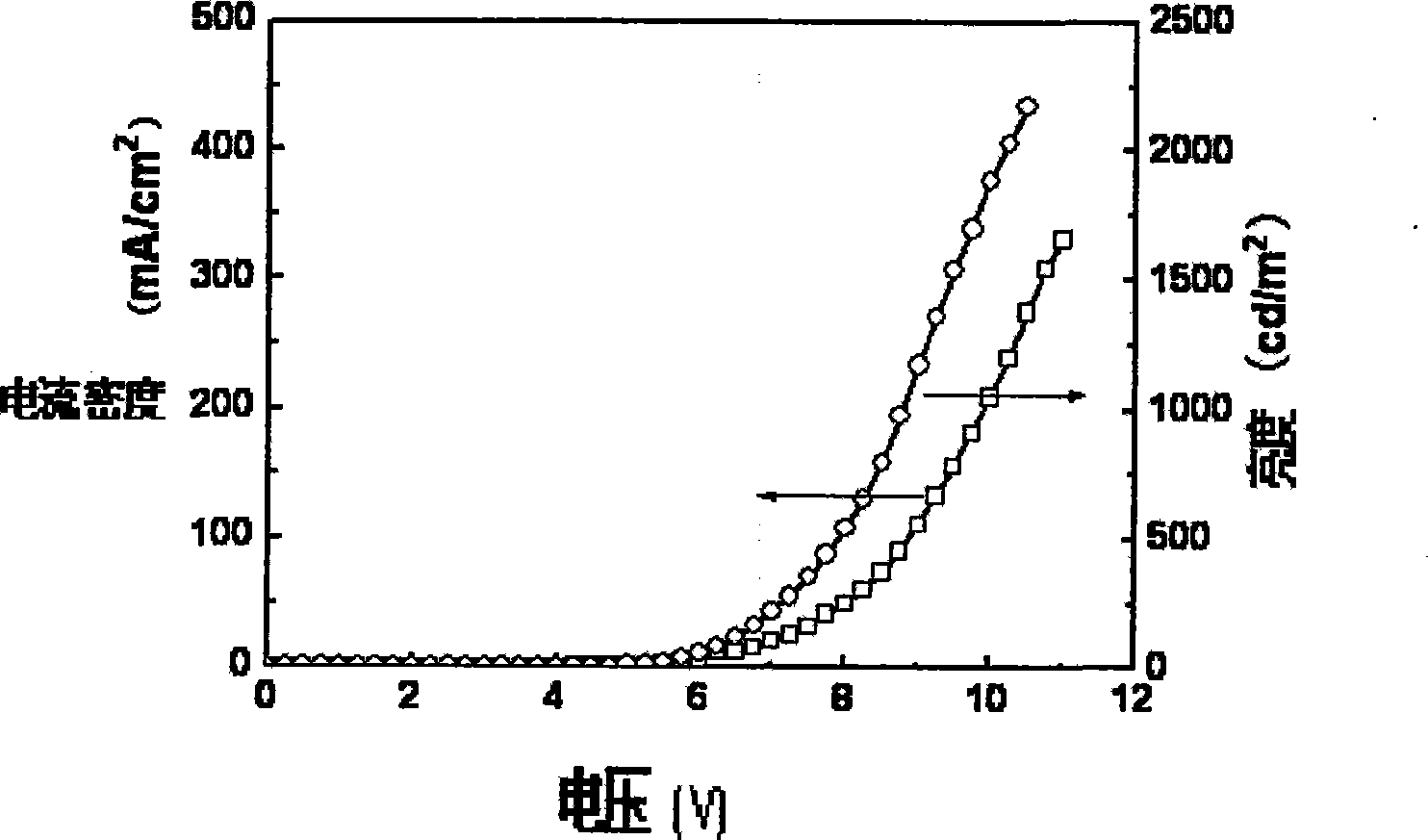

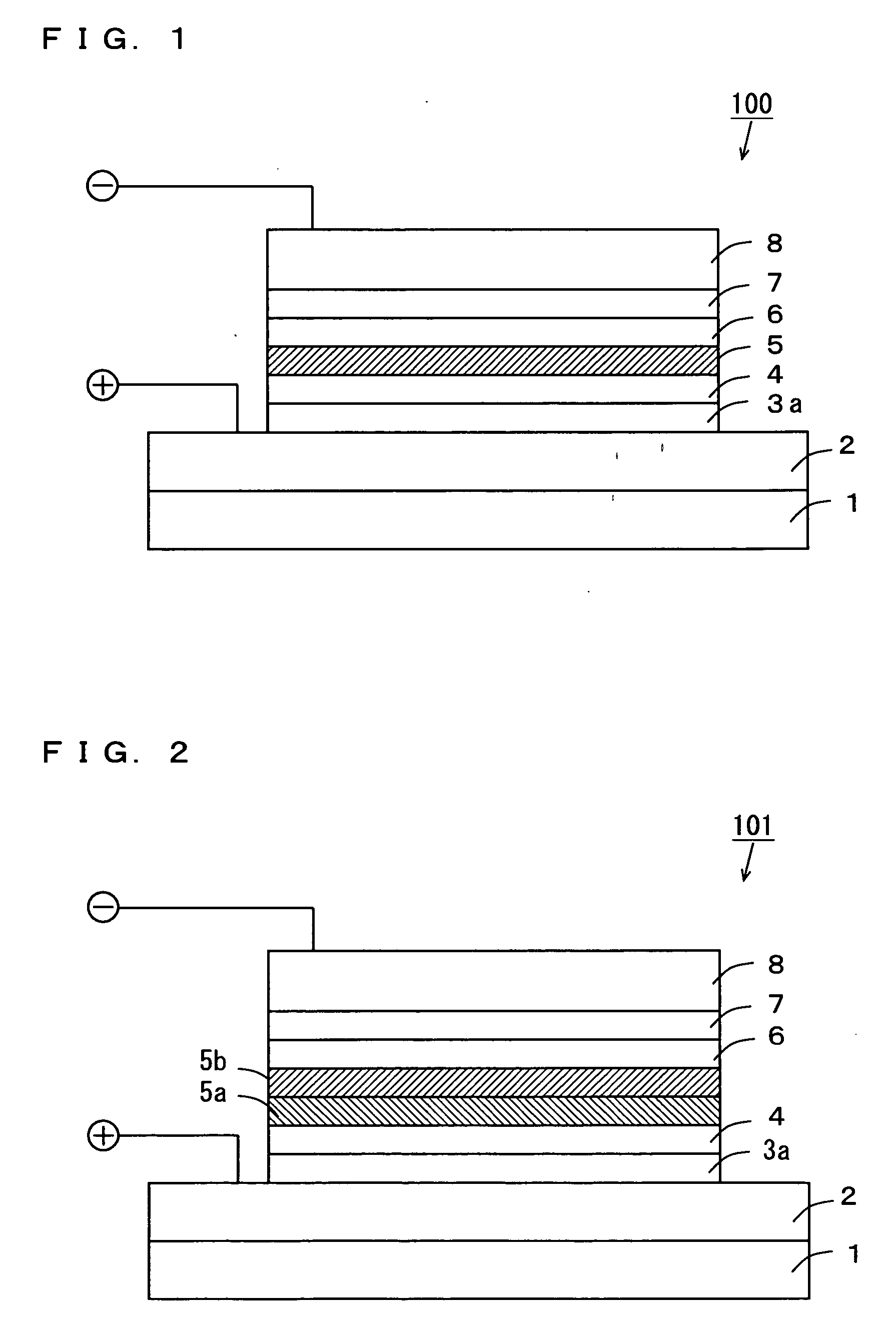

Organic electroluminescent device

InactiveUS20060228577A1Solve low luminous efficiencyLong half-lifeDischarge tube luminescnet screensElectroluminescent light sourcesCompound (substance)Organic electroluminescence

The organic EL device of the present invention includes a plurality of organic compound-containing layers provided between a cathode and an anode. Of two of the organic compound-containing layers adjacent to each other, one layer positioned nearer the anode has electron mobility lower than that of the other layer positioned nearer the cathode. Accordingly, the organic EL device of the present invention has a high luminous efficiency and a long half-life of the initial luminance.

Owner:TOYOTA IND CORP

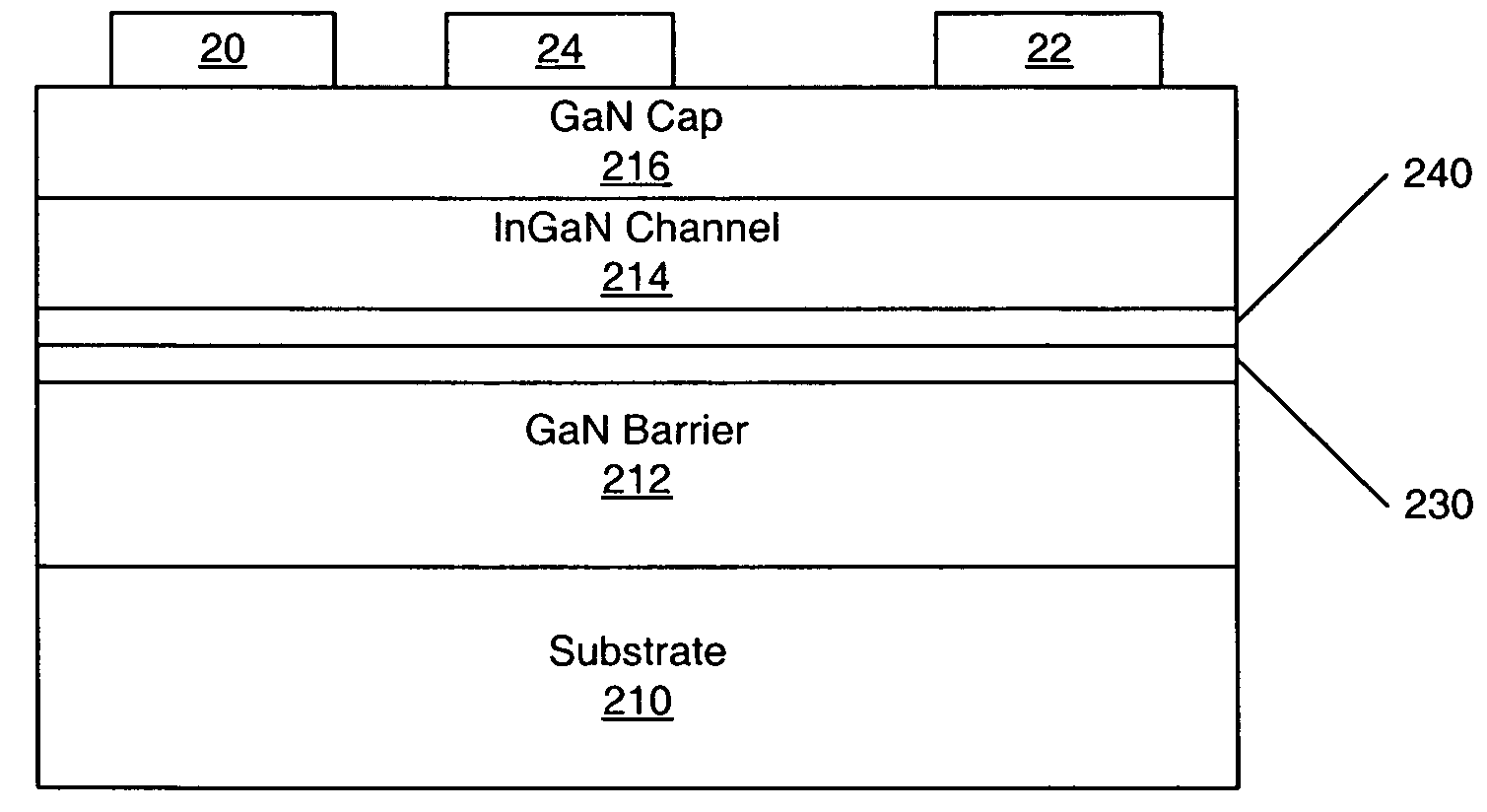

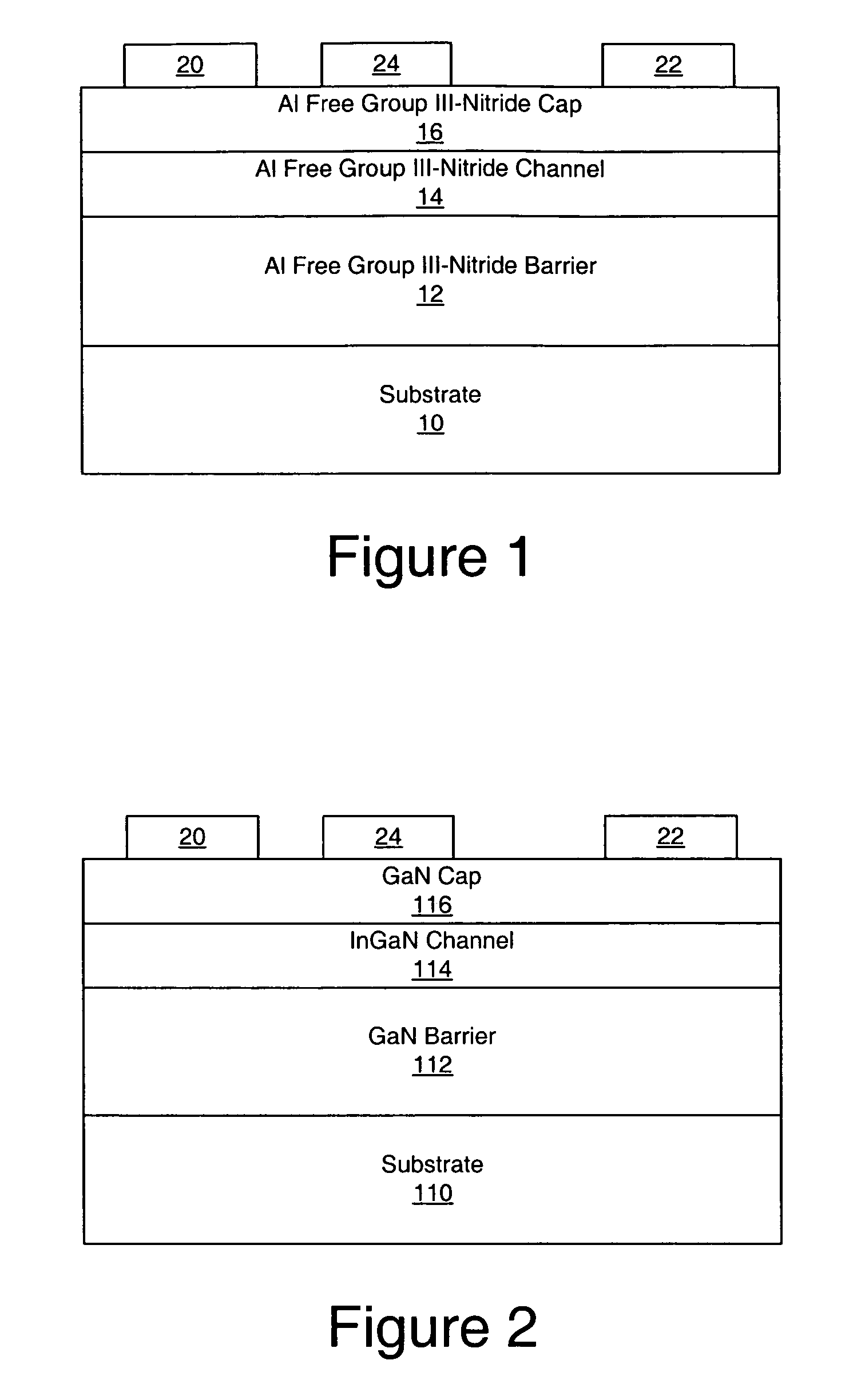

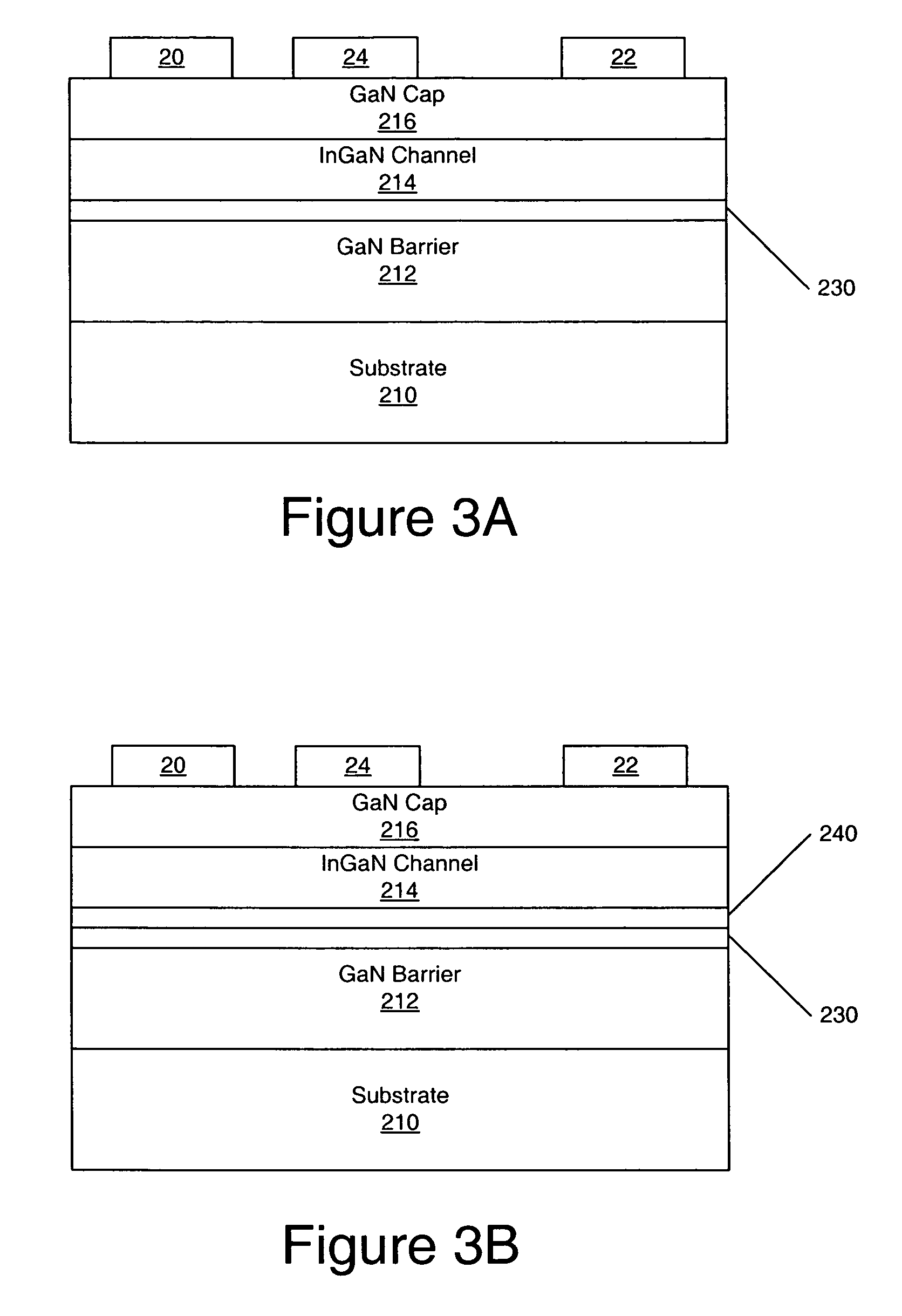

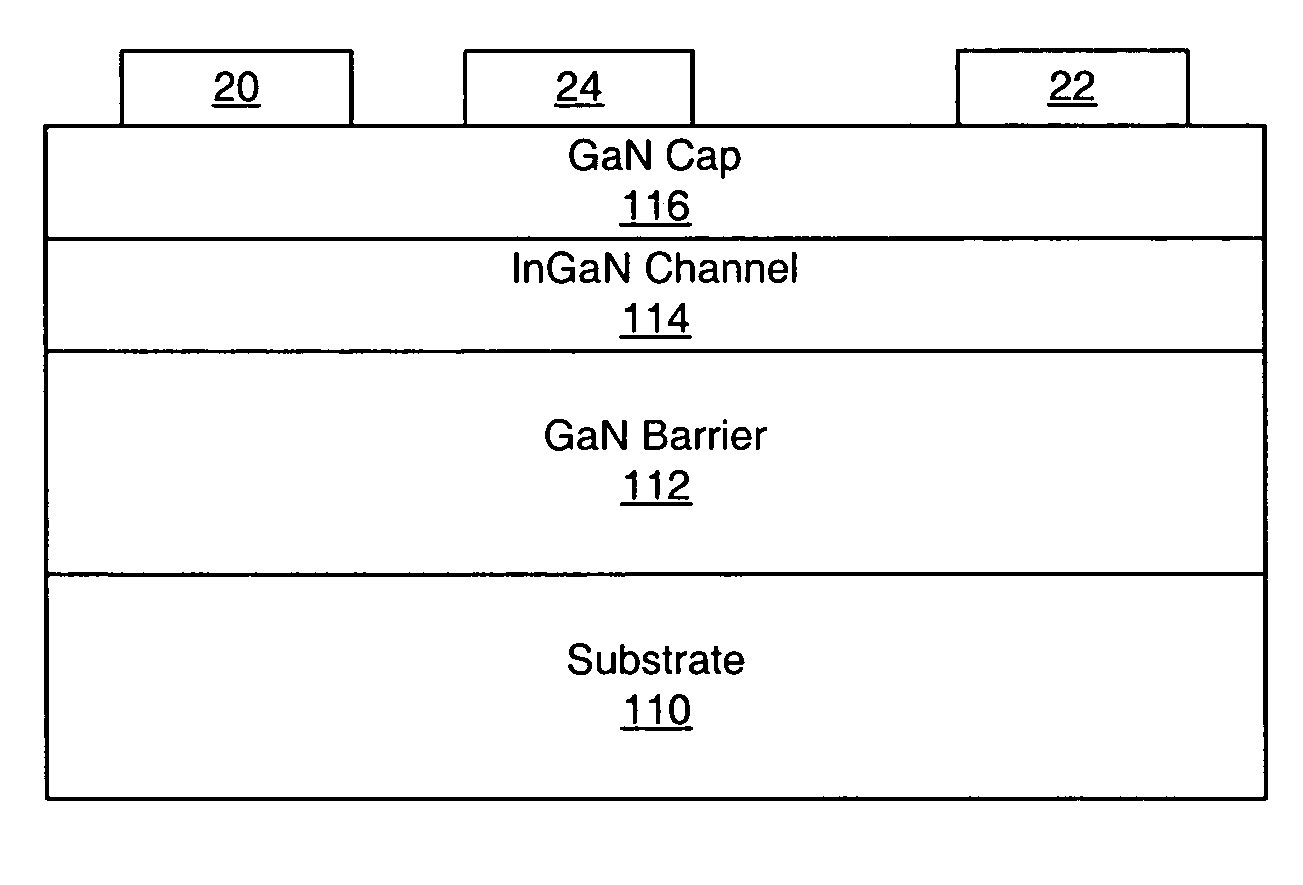

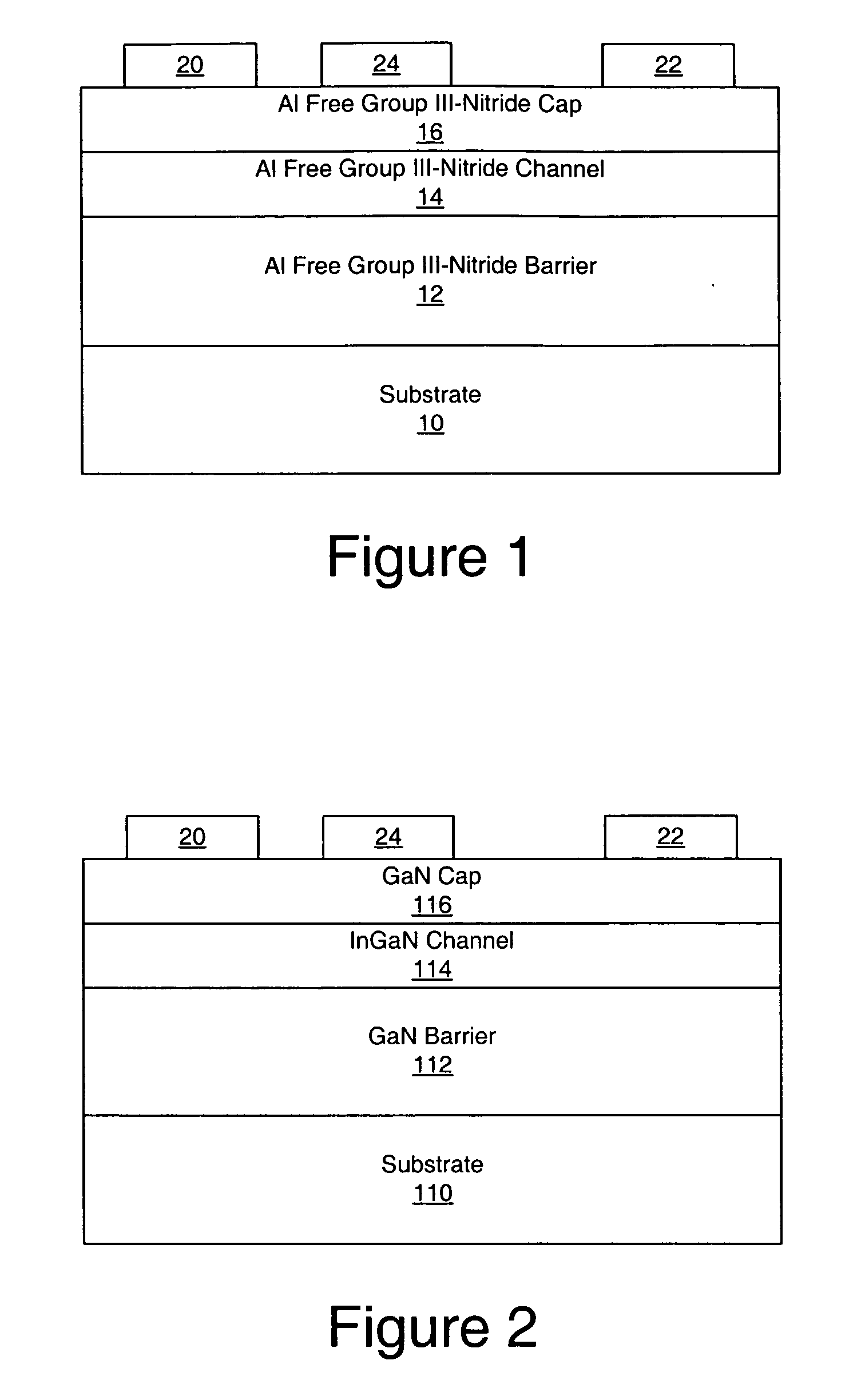

Aluminum free group III-nitride based high electron mobility transistors

Aluminum free high electron mobility transistors (HEMTs) and methods of fabricating aluminum free HEMTs are provided. In some embodiments, the aluminum free HEMTs include an aluminum free Group III-nitride barrier layer, an aluminum free Group III-nitride channel layer on the barrier layer and an aluminum free Group III-nitride cap layer on the channel layer.

Owner:WOLFSPEED INC

CMOS Transistors With Silicon Germanium Channel and Dual Embedded Stressors

ActiveUS20100224938A1High hole mobilityHigh electron mobilityTransistorSolid-state devicesHigh concentrationMOSFET

A p-type MOSFET of a CMOS structure has a silicon-germanium alloy channel to which a longitudinal compressive stress is applied by embedded epitaxial silicon-germanium alloy source and drain regions comprising a silicon-germanium alloy having a higher concentration of germanium than the channel of the p-type MOSFET. An n-type MOSFET of the CMOS structure has a silicon-germanium alloy channel to which a longitudinal tensile stress is applied by embedded epitaxial silicon source and drain regions comprising silicon. The silicon-germanium alloy channel in the p-type MOSFET provides enhanced hole mobility, while the silicon-germanium alloy channel in the n-type MOSFET provides enhanced electron mobility, thereby providing performance improvement to both the p-type MOSFET and the n-type MOSFET.

Owner:GLOBALFOUNDRIES US INC

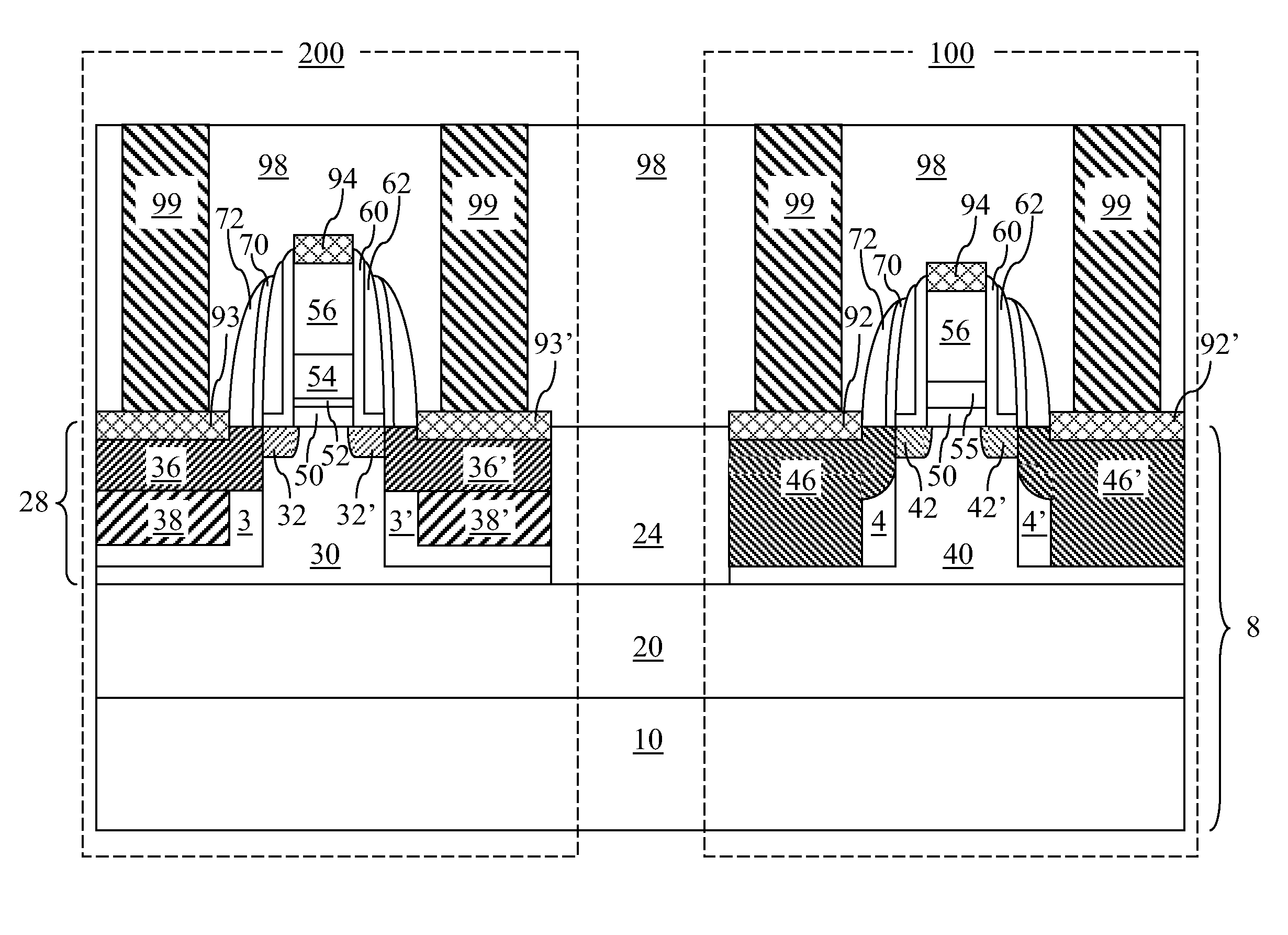

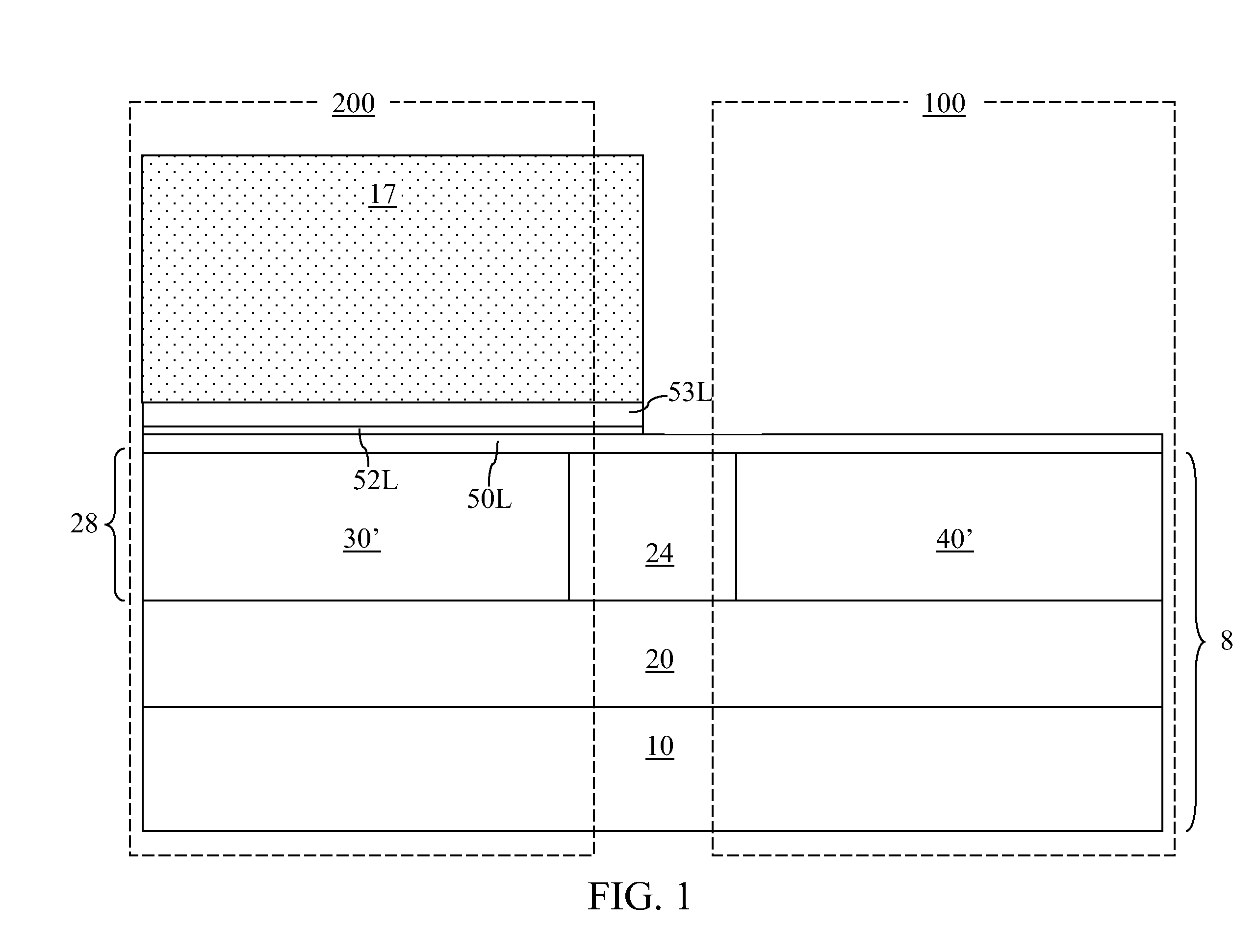

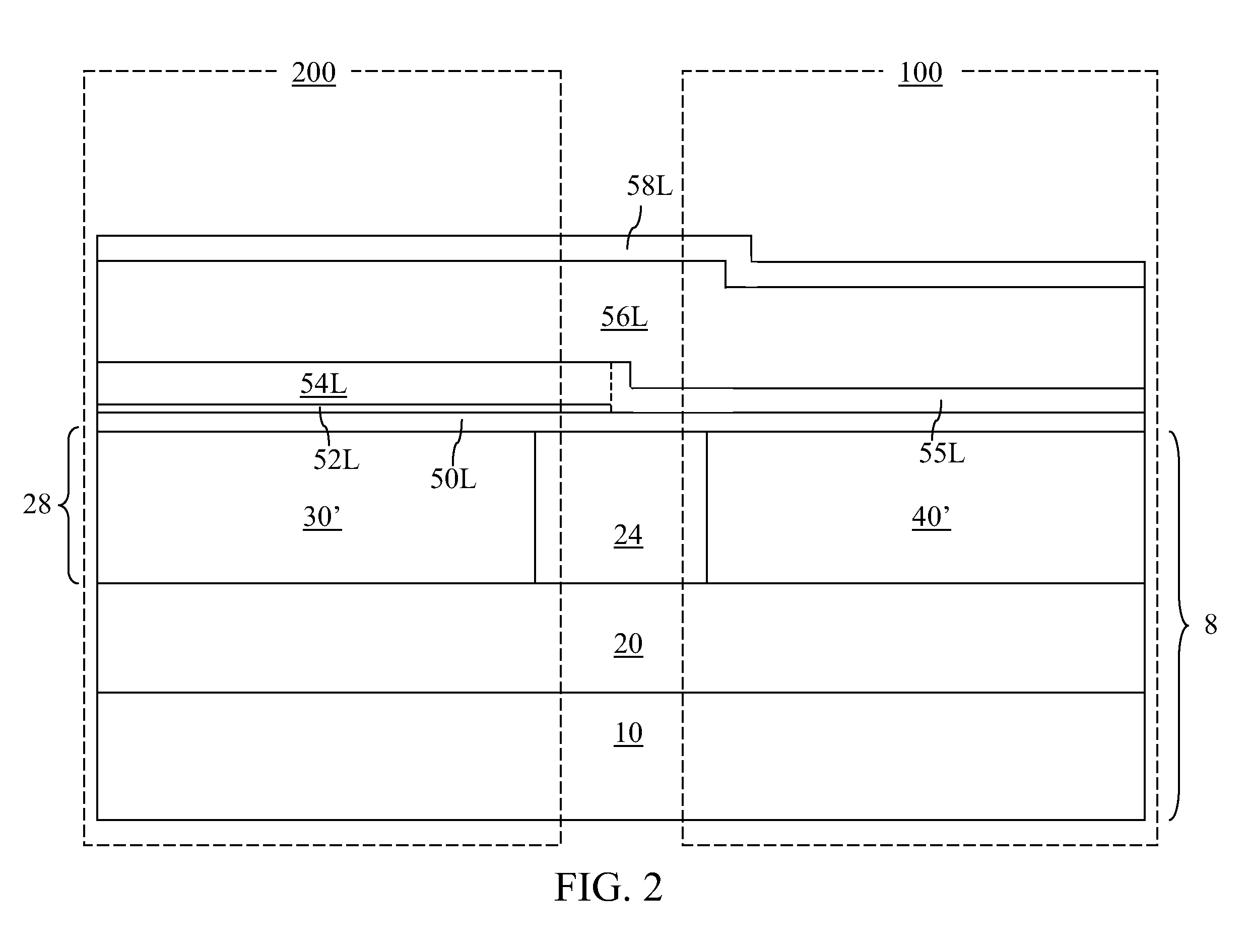

Aluminum free group III-nitride based high electron mobility transistors and methods of fabricating same

Aluminum free high electron mobility transistors (HEMTs) and methods of fabricating aluminum free HEMTs are provided. In some embodiments, the aluminum free HEMTs include an aluminum free Group III-nitride barrier layer, an aluminum free Group III-nitride channel layer on the barrier layer and an aluminum free Group III-nitride cap layer on the channel layer.

Owner:WOLFSPEED INC

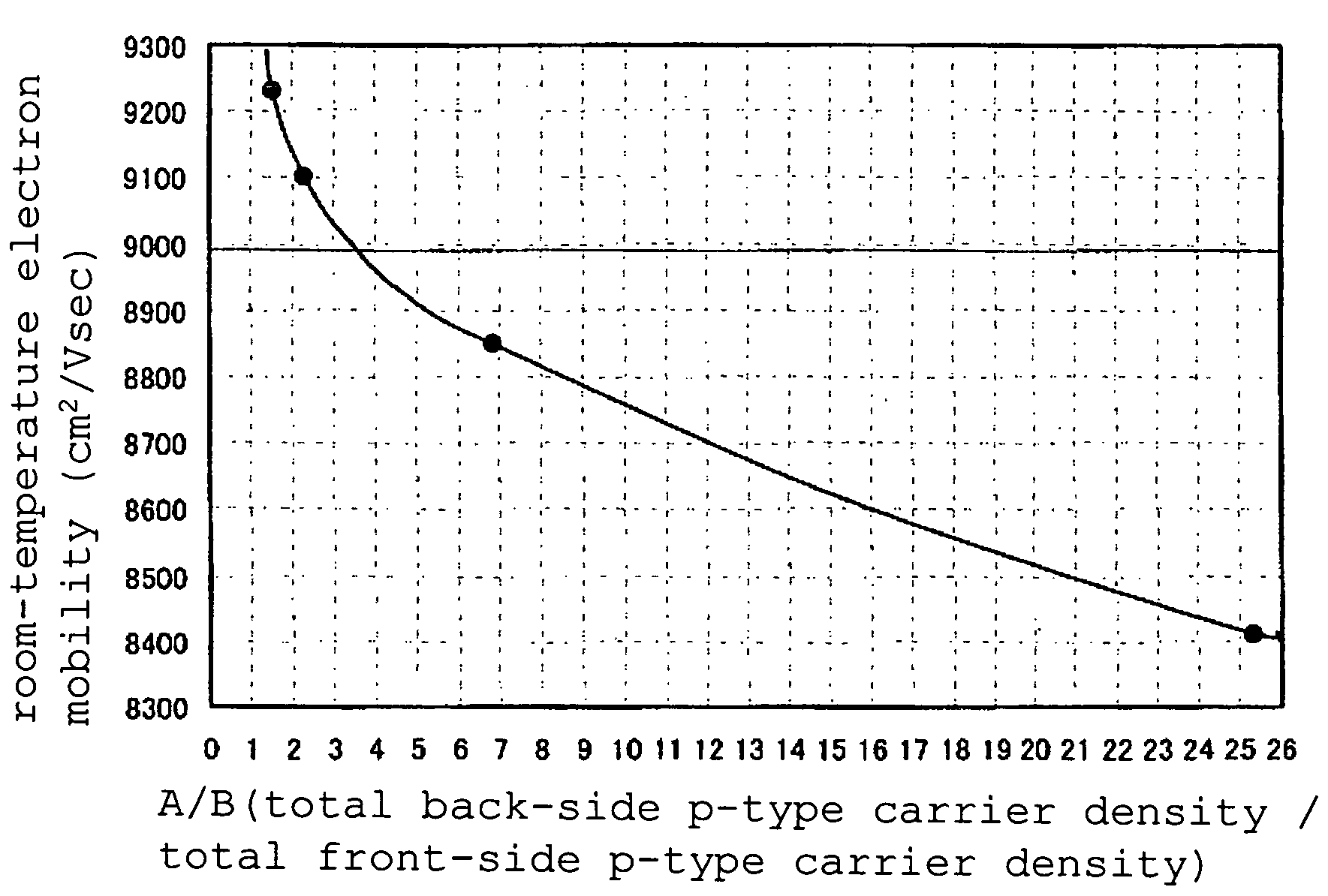

Compound semiconductor epitaxial substrate and method for producing the same

InactiveUS7935984B2Improved electron mobility characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesAcceptor impurityElectron mobility

Owner:SUMITOMO CHEM CO LTD

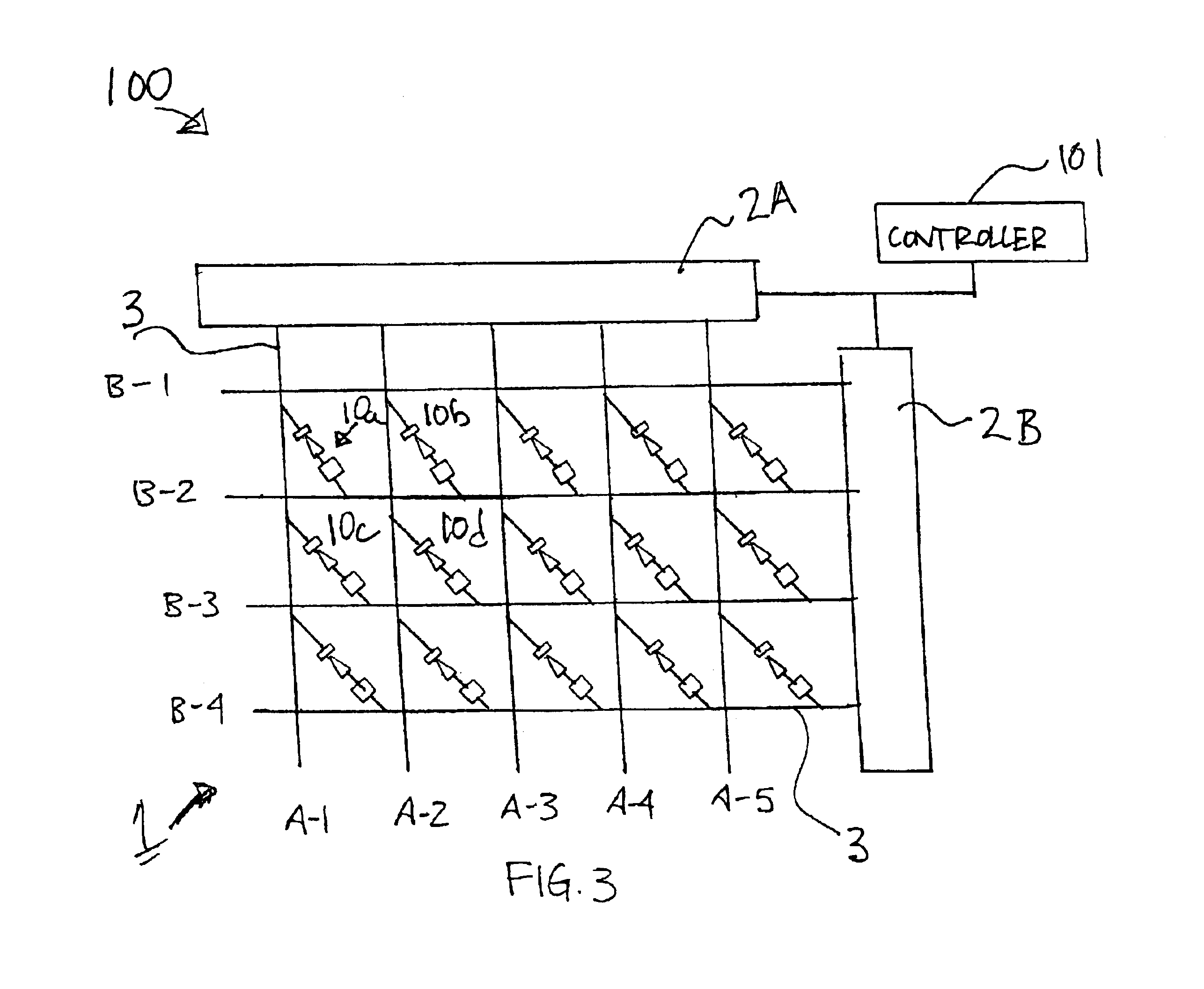

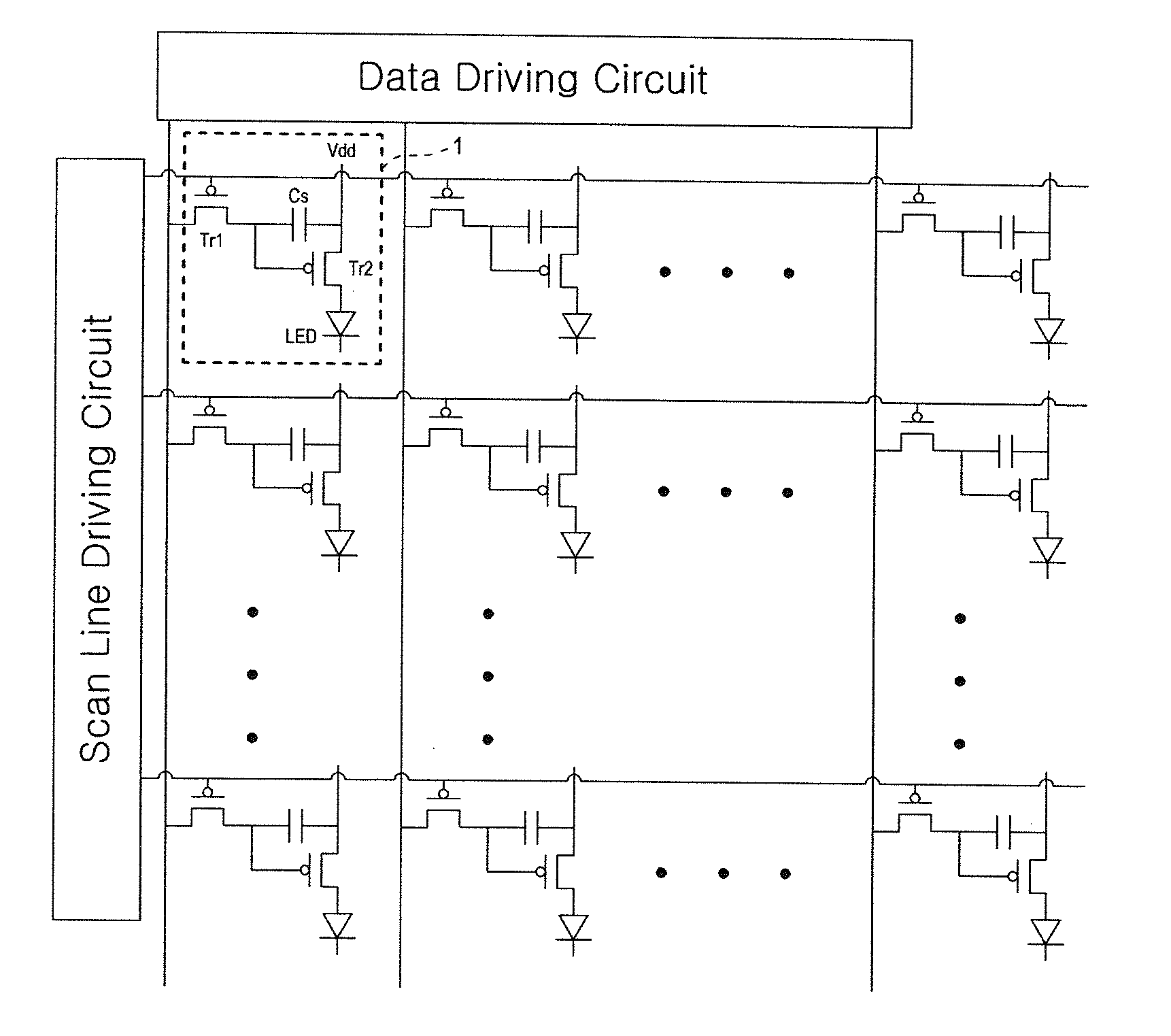

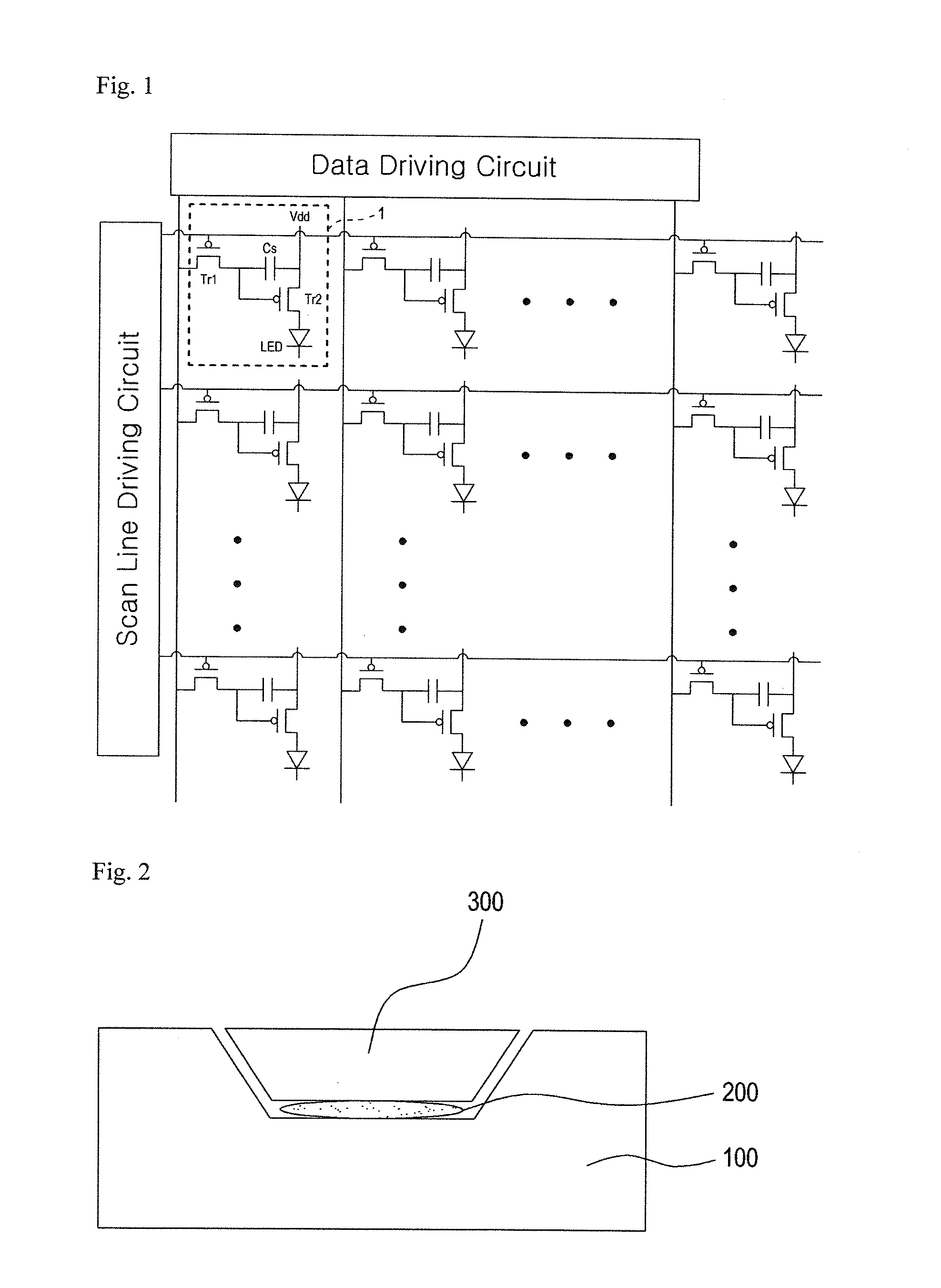

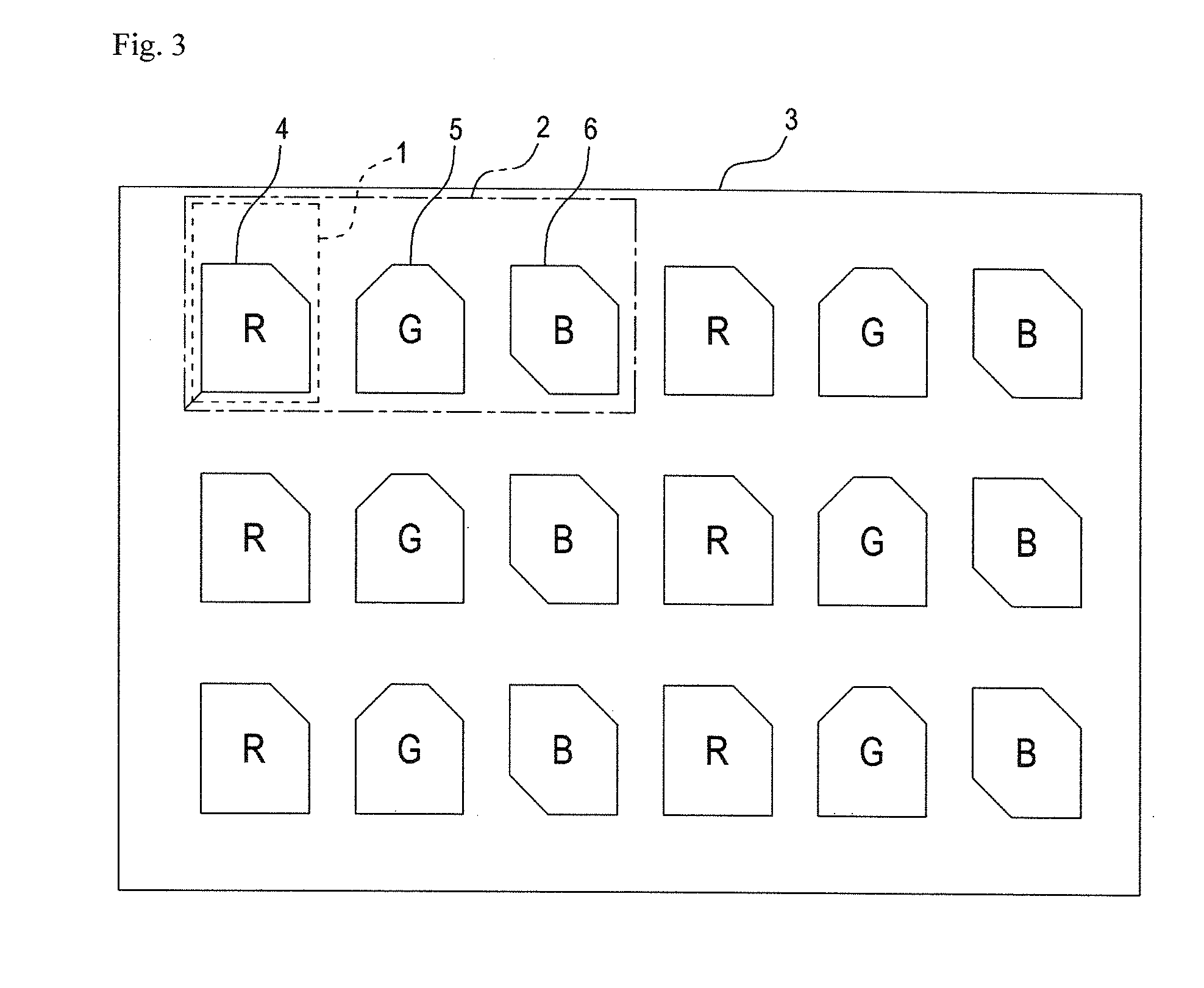

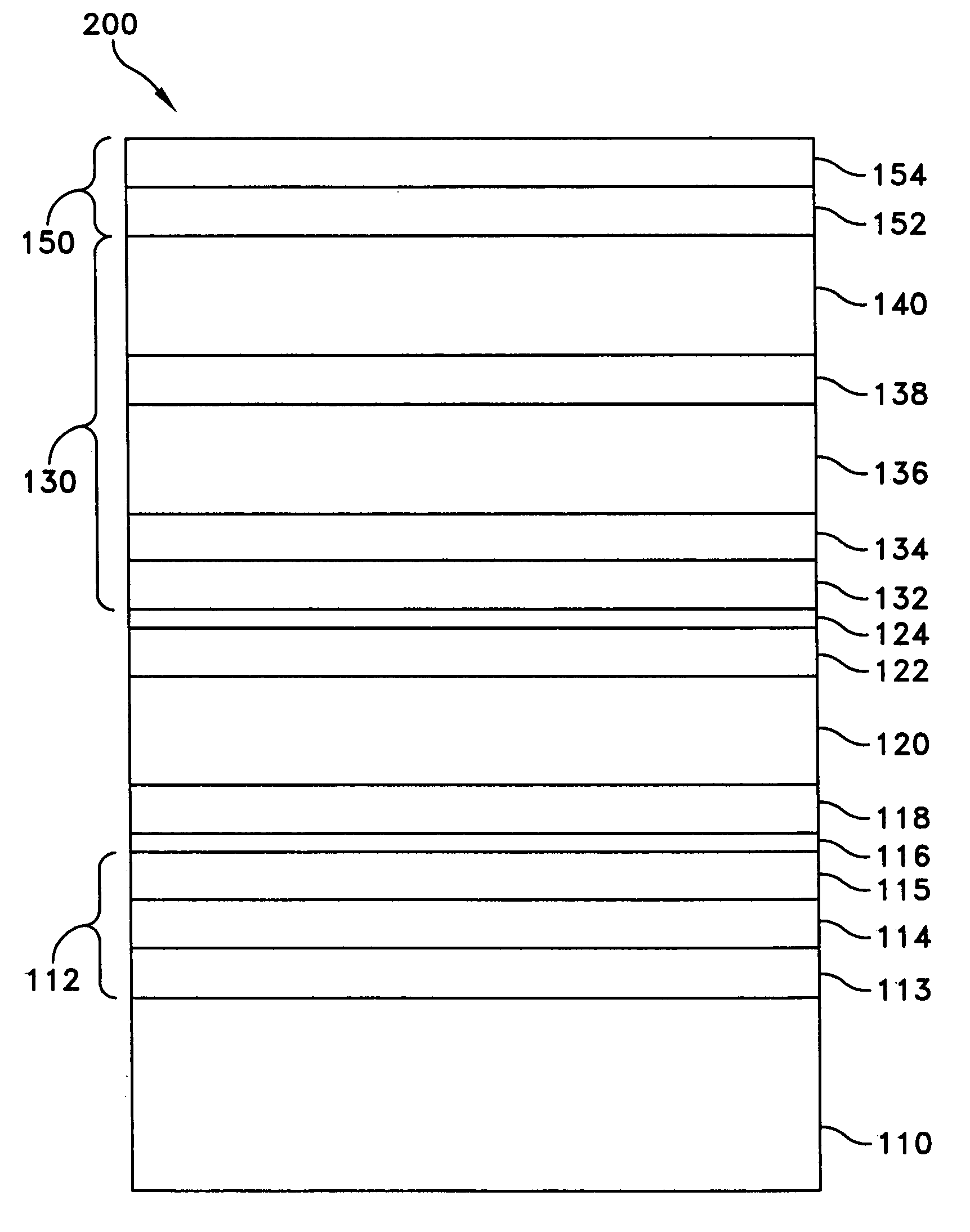

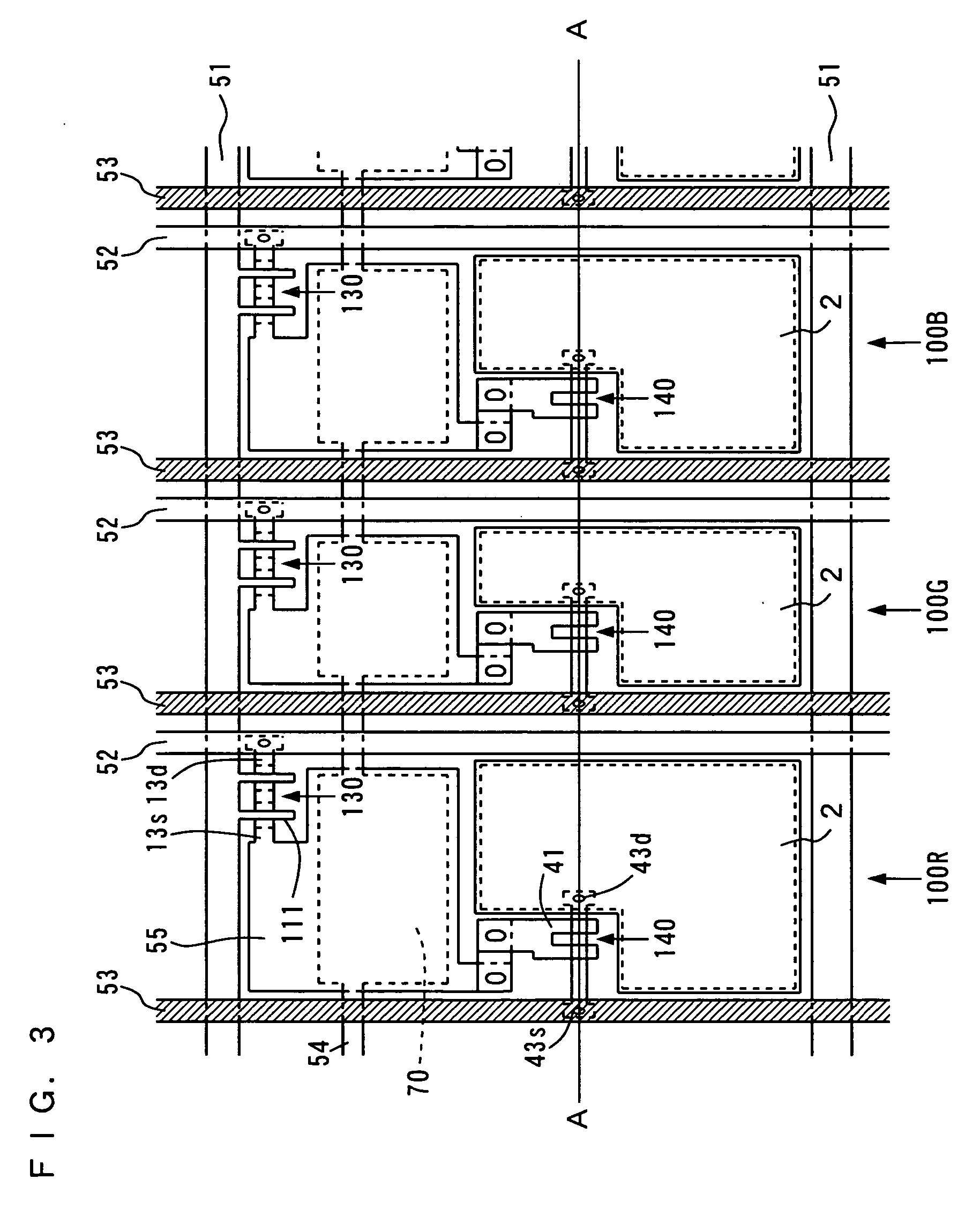

LED display apparatus having active devices and fabrication method thereof

ActiveUS20110273410A1Increase brightnessReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingOptical propertyLED display

An active matrix LED display apparatus and a fabrication method thereof are provided. The active matrix LED display apparatus enables to miniaturize pixel by a formation of wiring on bottom layer and an assembly of each block through each eutectic layer into each transistor block receptor and / or each LED block receptor formed according to each color element unit, and to be embodied with high luminance, low power consumption, high reliability and superior optical property by assembling a transistor block having high electron mobility. And the fabricating method of the present invention enables to make efficiently an AM-LED display apparatus at room temperature in a short time by using different shapes of receptor and block depending on the function of a transistor and / or on the color of an LED.

Owner:SEOUL NAT UNIV R&DB FOUND

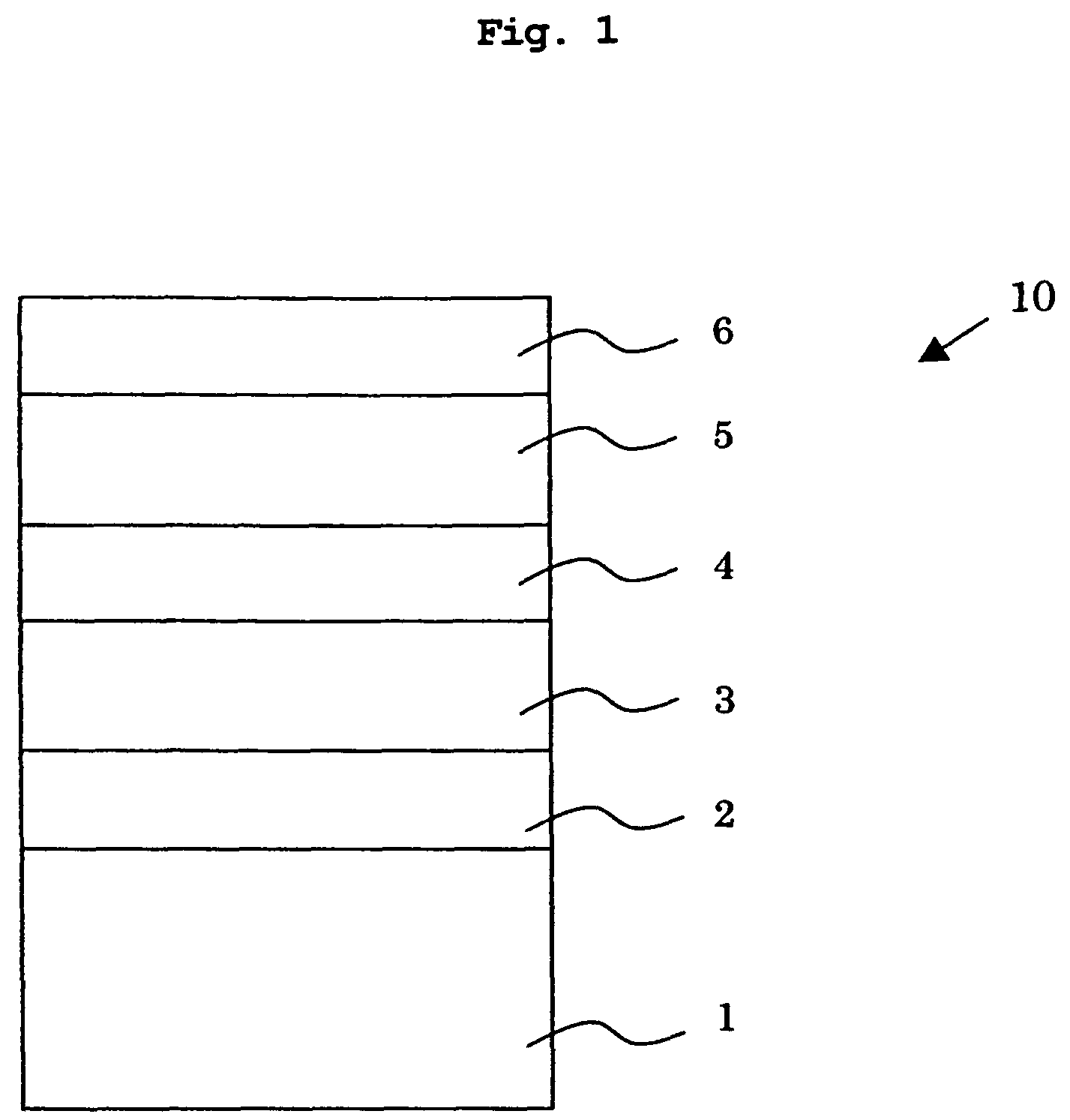

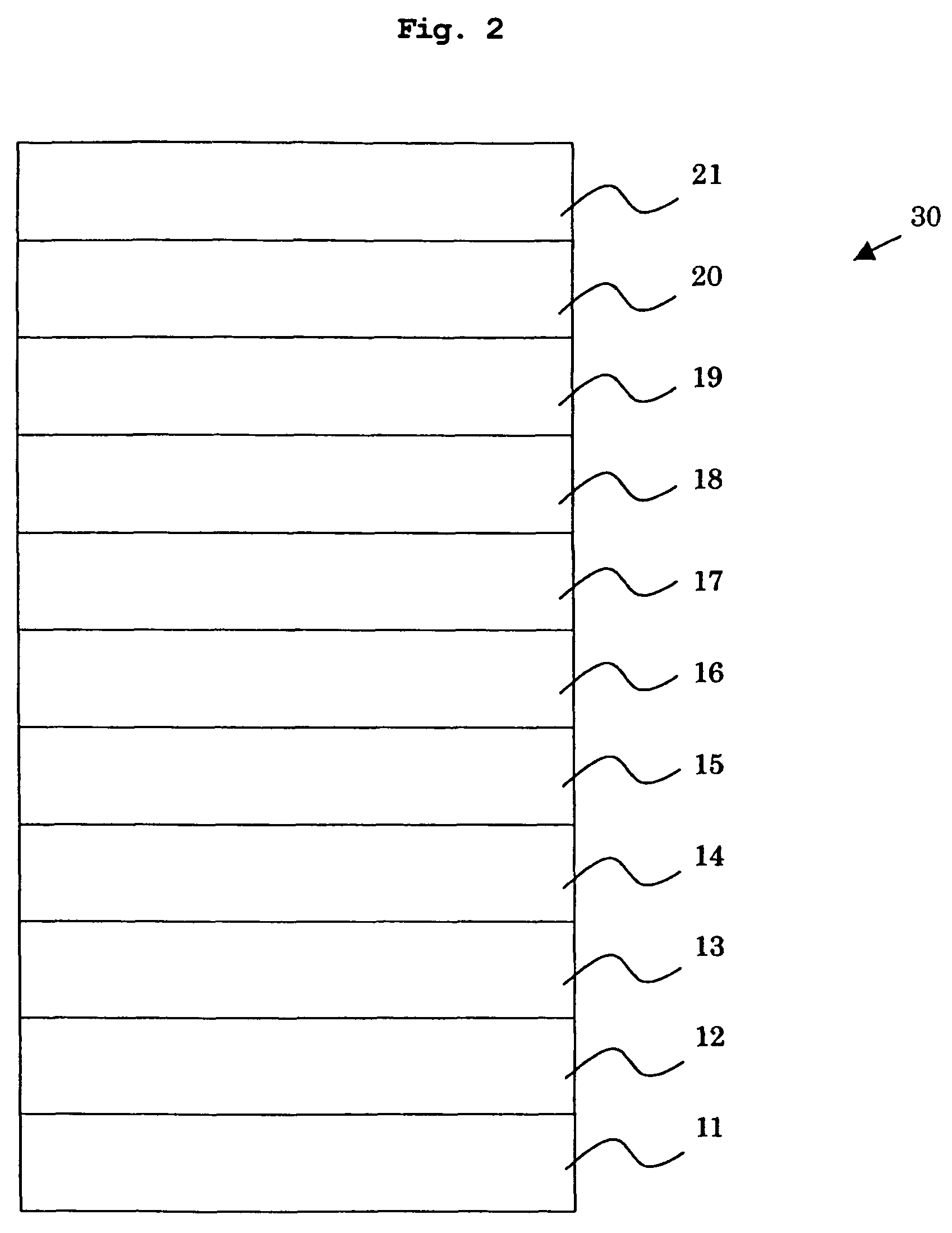

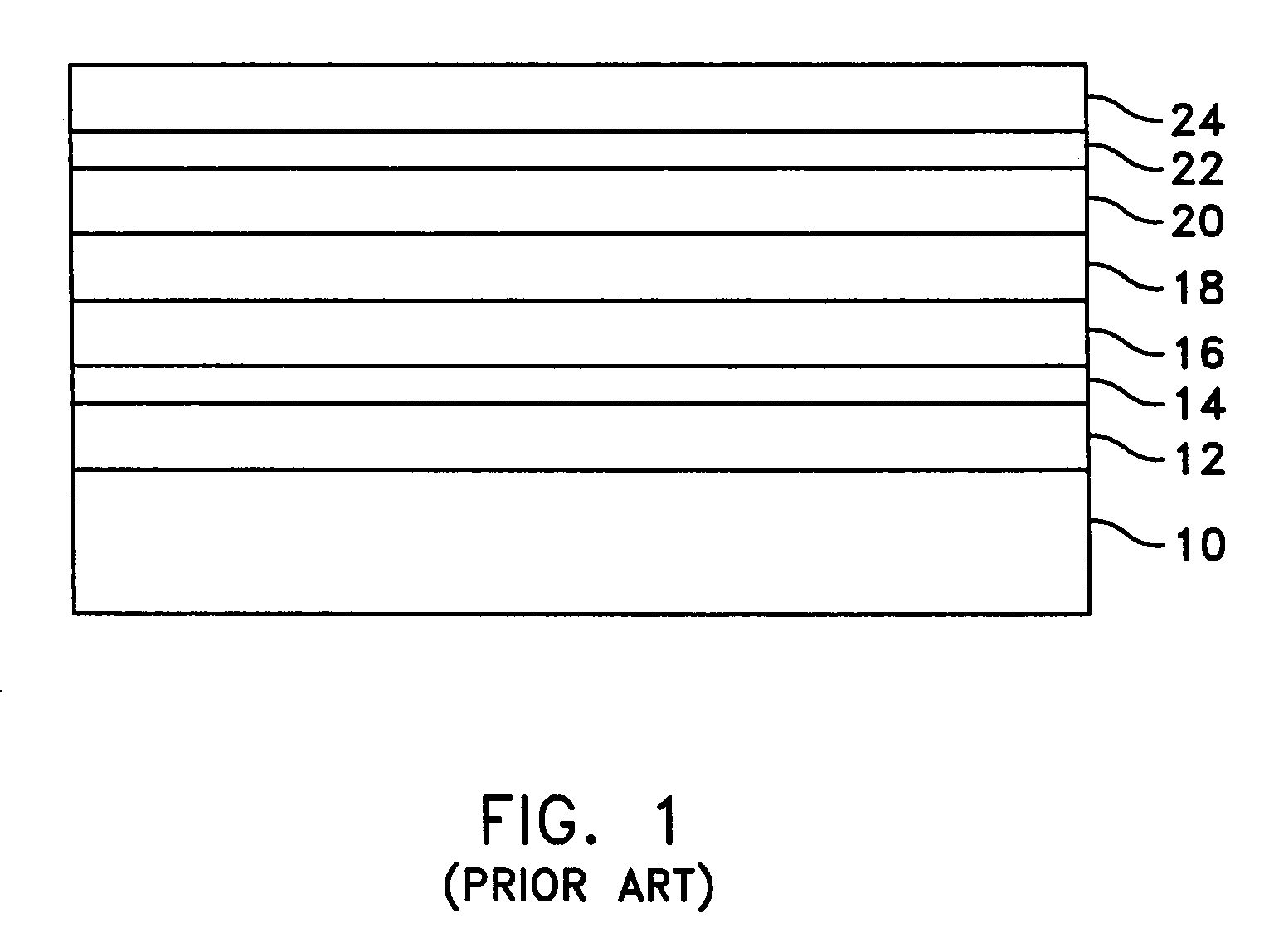

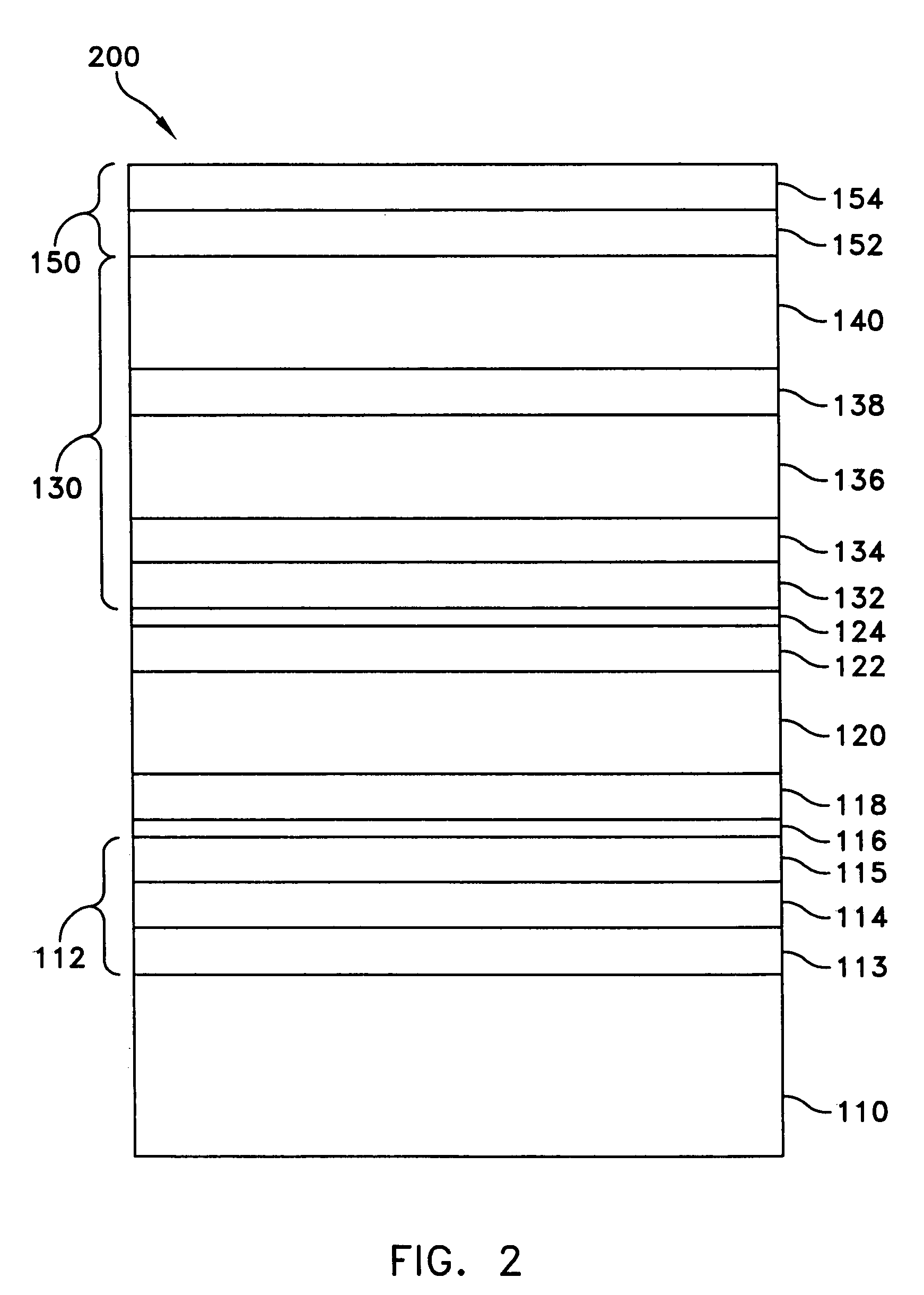

Multi-layer structure for use in the fabrication of integrated circuit devices and methods for fabrication of same

InactiveUS7321132B2Semiconductor/solid-state device manufacturingSemiconductor devicesHigh electronContact layer

A multi-layer structure for use in the fabrication of integrated circuit devices is adapted for the formation of enhancement mode high electron mobility transistors, depletion mode high electron mobility transistors, and power high electron mobility transistors. The structure has, on a substrate, a channel layer, spacer layer on the channel layer, a first Schottky layer, a second Schottky layer on the first Schottky layer, and a third Schottky layer on the second Schottky layer, and a contact layer on the third Schottky layer. Etch stops are defined intermediate the first and second Schottky layers, intermediate the second and third Schottky layers, and intermediate the third Schottky layer and the contact layer.

Owner:LOCKHEED MARTIN CORP +1

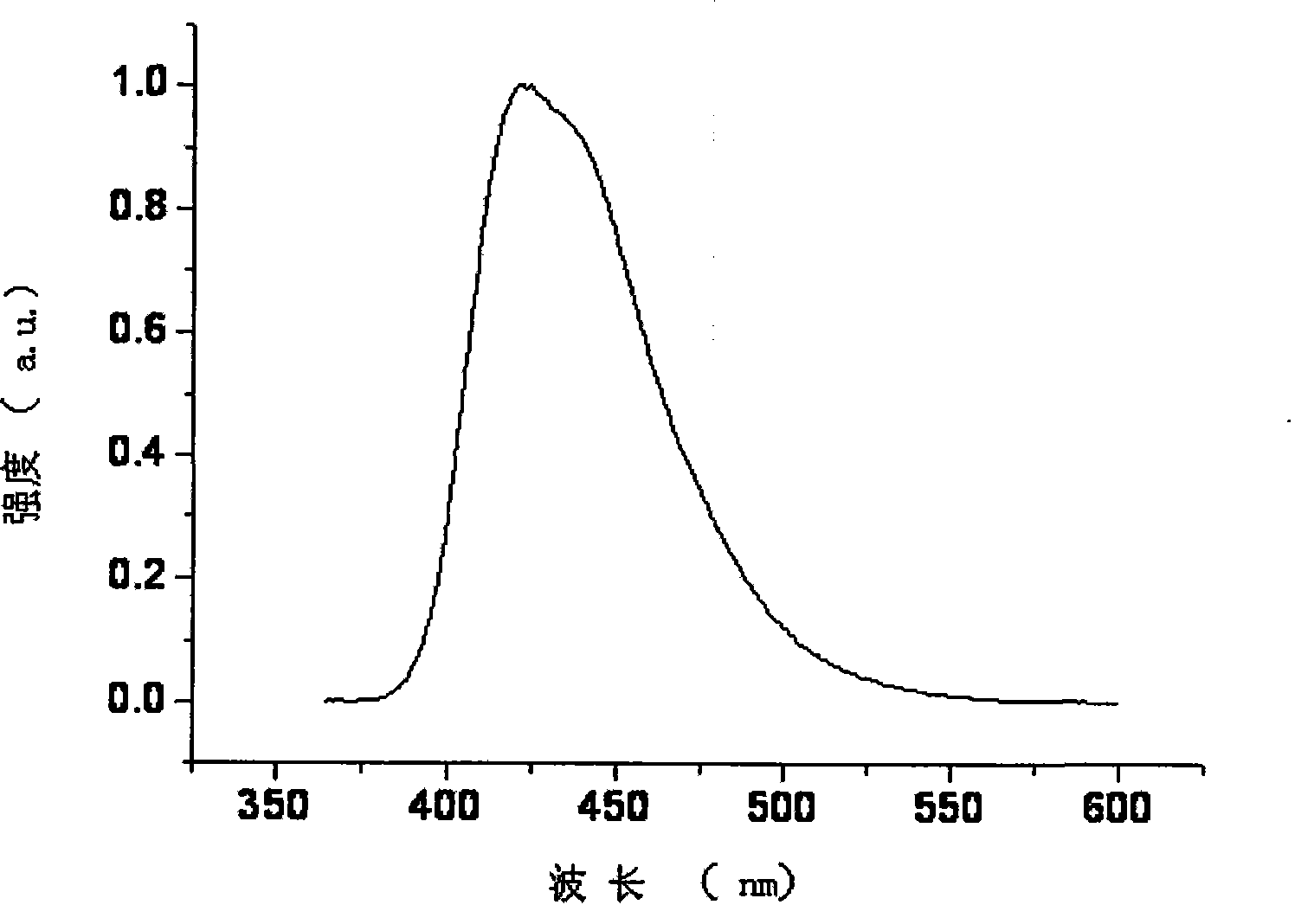

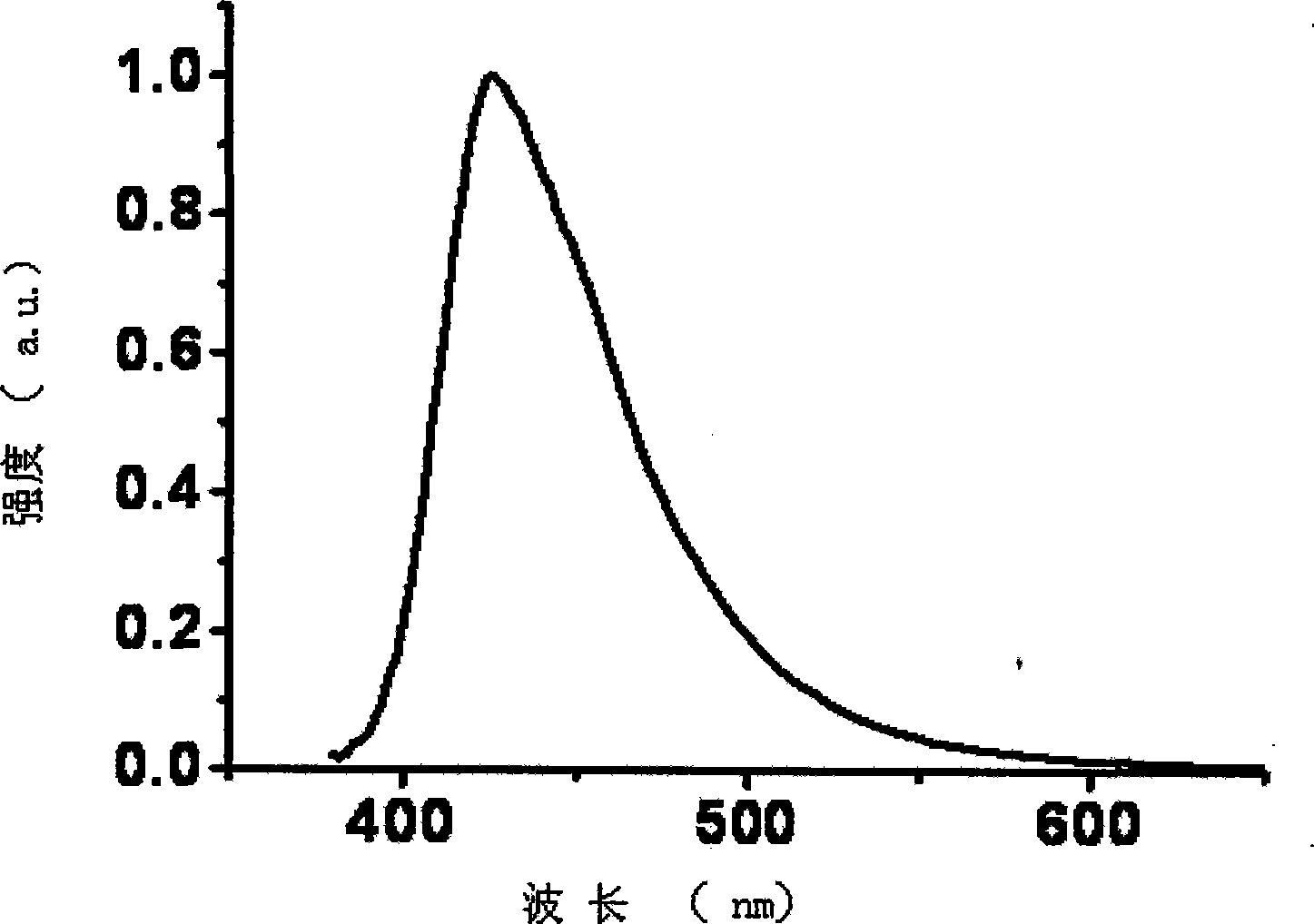

Spirofluorene xanthene material, and preparation and use thereof

InactiveCN101440082ATest thermal stabilityThe synthesis steps are simpleOrganic chemistrySolid-state devicesVitrificationNonlinear optics

The invention discloses a spirofluorene xanthene material and a preparation method and an application method thereof, and relates to application of the material in the fields such as organic electroluminescence, photovoltaic cell, organic electrical storage, organic nonlinear optics, chemical and biological sensing, organic laser and so on. The material has the following structure. The material has the advantages that (1) the material is prepared through a one pot process and has simple steps and mild conditions; (2) the material has the advantages of spirobifluorene materials, and shows high thermal stability and vitrification temperature; and (3) the material has high hole or electron mobility and so on. An electroluminescent device prepared by utilizing the material achieves satisfactory results in aspects such as illumination, luminous efficiency, voltage withstand stability and so on.

Owner:NANJING UNIV OF POSTS & TELECOMM

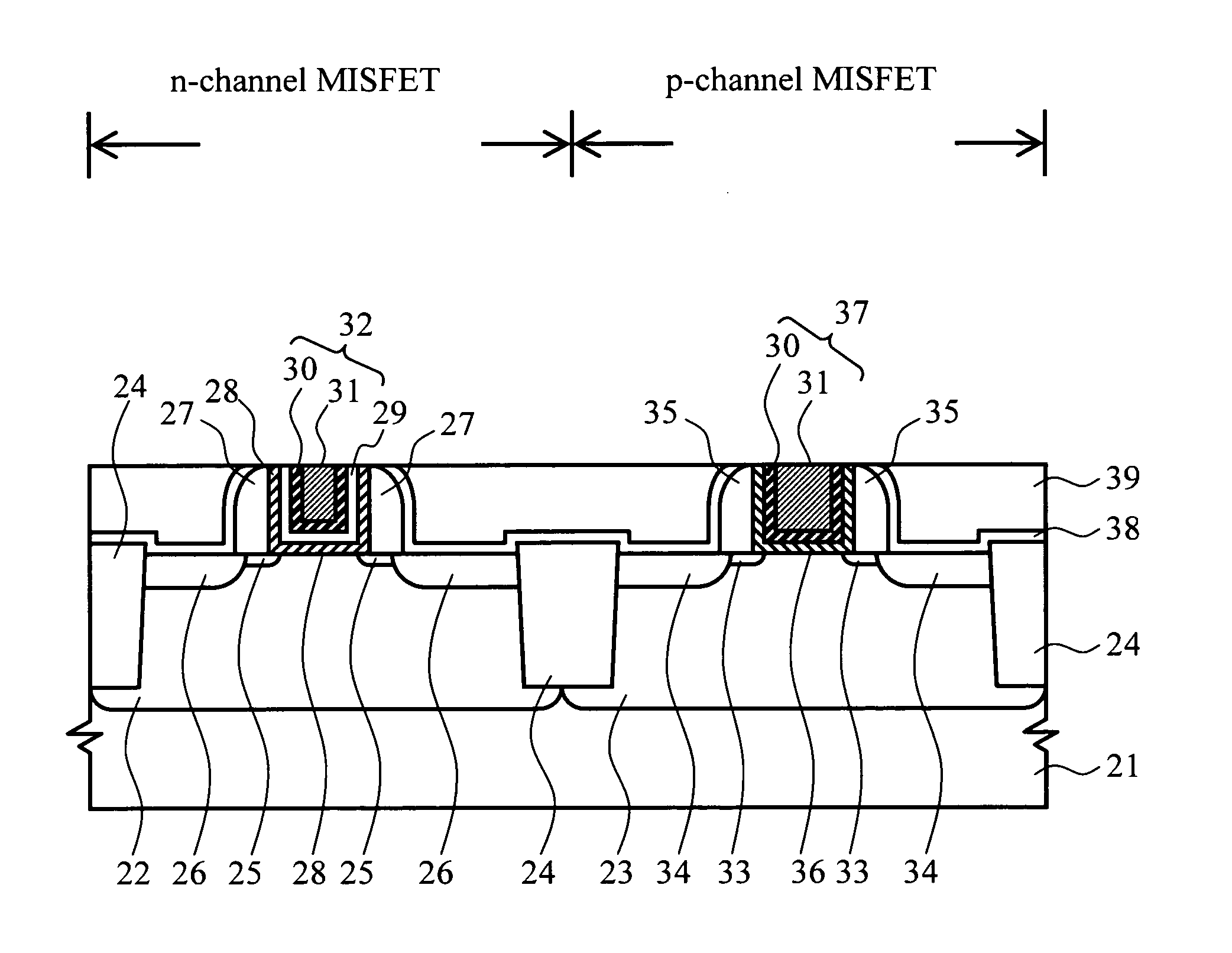

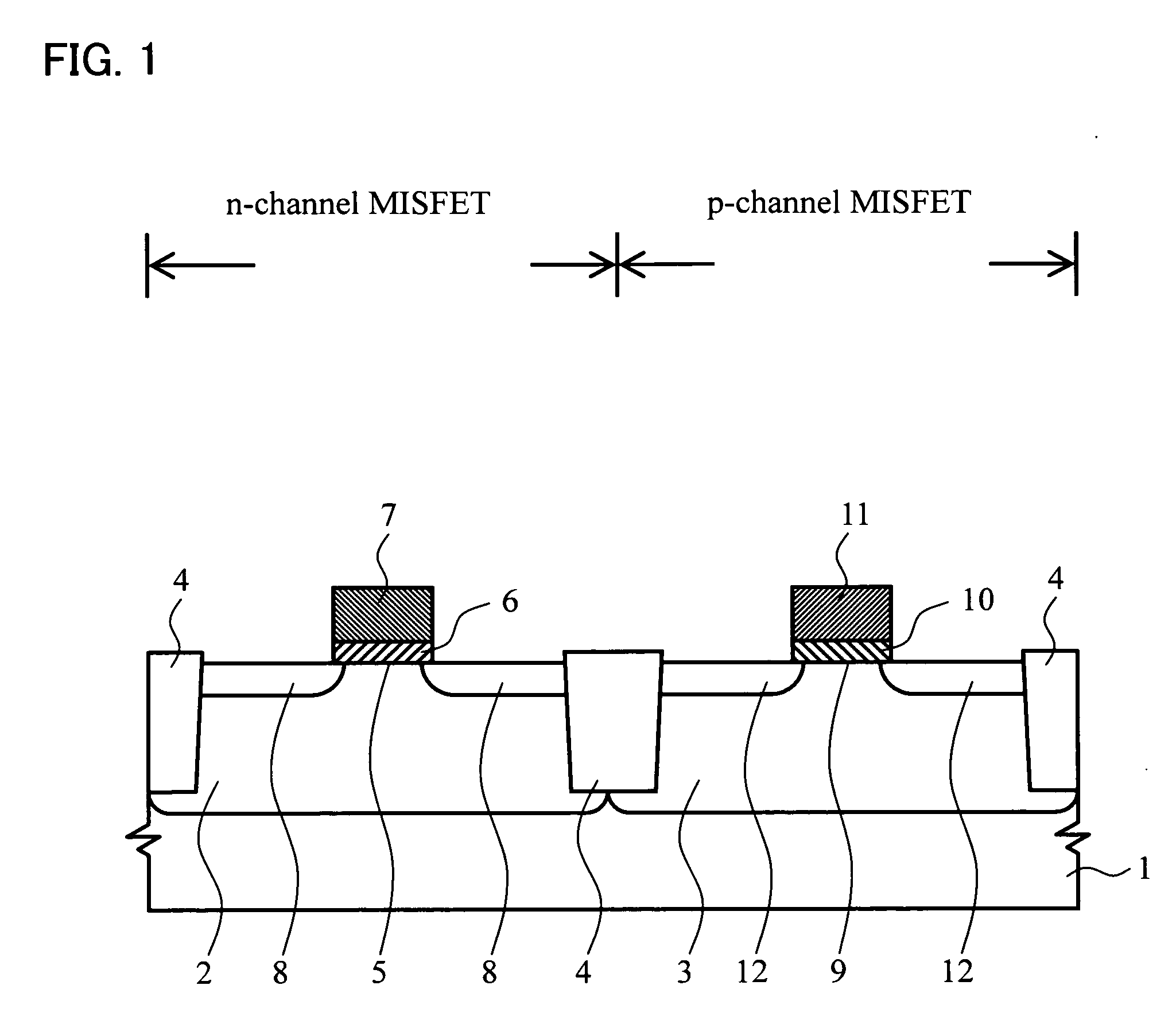

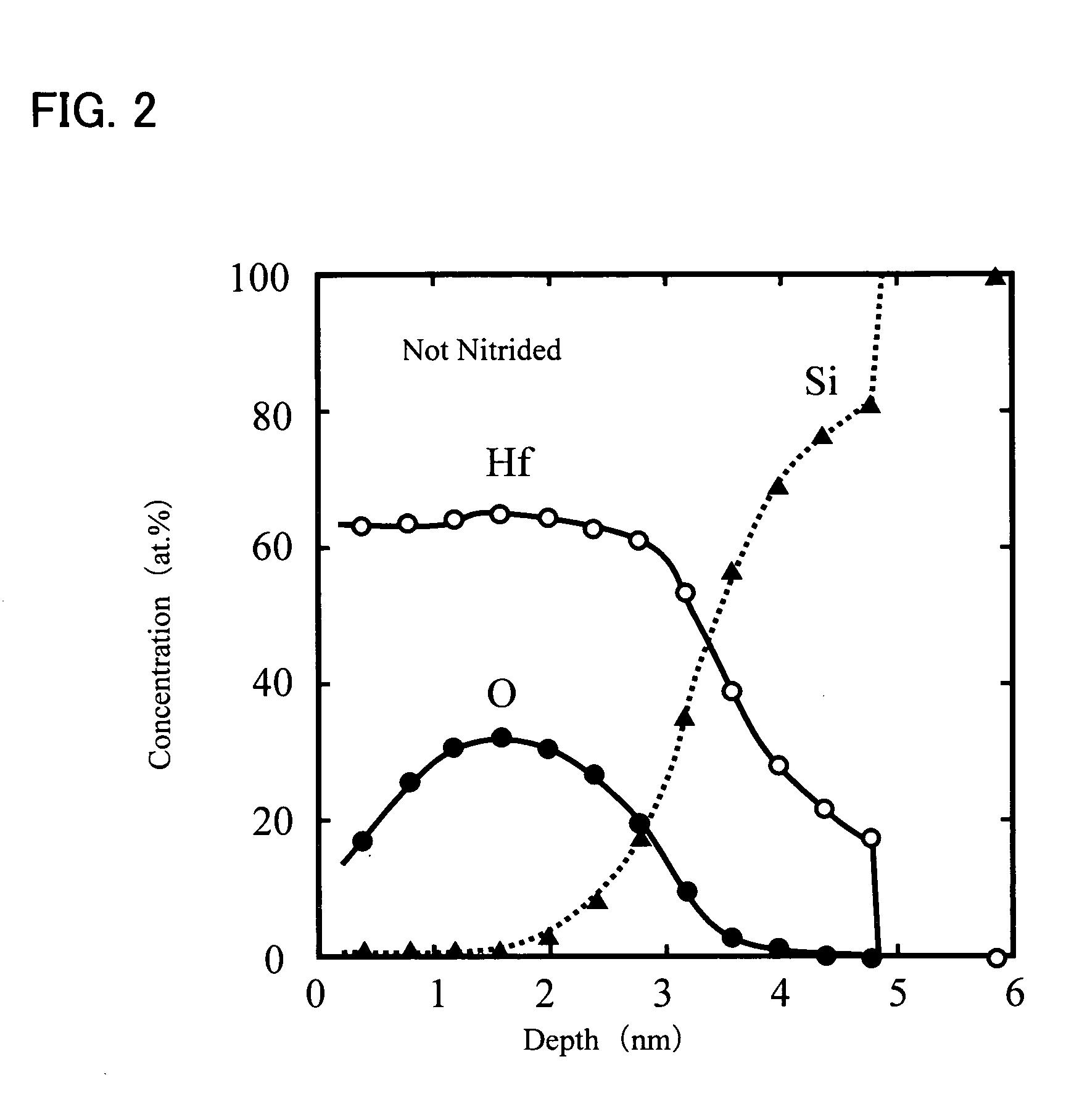

Semiconductor device having misfet using high dielectric constant gate insulation film and method for fabricating the same

A semiconductor device having a metal insulator semiconductor field effect transistor (MISFET) with increased electron mobility and enhanced hole mobility is disclosed. In this semiconductor device, a p-type well layer and an n-type well layer are formed in a surface portion of a silicon substrate. A nitrogen-nondoped n-channel interface layer and a nitrogen-free n-channel high dielectric constant gate insulation film plus an n-channel gate electrode are formed in an n-channel MISFET as partitioned by an element isolation region. And, n-type source / drain diffusion layers are provided. In a p-channel MISFET, a nitrogen-doped p-channel interface layer, a nitrogen-added p-channel high dielectric gate insulation film and a p-channel gate electrode are formed along with p-channel source / drain diffusion layers as provided therein. A method of fabricating this semiconductor device is also disclosed.

Owner:KK TOSHIBA

AlGaN/GaN high electron mobility transistor devices

ActiveUS20060006414A1Avoid crackingReduce the appearance of cracksSolid-state devicesSemiconductor/solid-state device manufacturingMESFETCooling down

The present invention recites a new method for manufacturing Group III-N field-effect devices, such as HEMT, MOSHFET, MISHFET devices or MESFET devices, grown by Metal-Organic Vapor Phase Expitaxy, with higher performance (power), by covering the surface with a thin SiN layer on the top AlGaN layer, in the reactor where the growth takes place at high temperature, prior cooling down the structure and loading the sample out of the reactor, as well as a method to produce some HEMT transistors on those heterostructures, by depositing the contact on the surface without any removal of the SiN layer by MOCVD. The present invention recites also a device.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

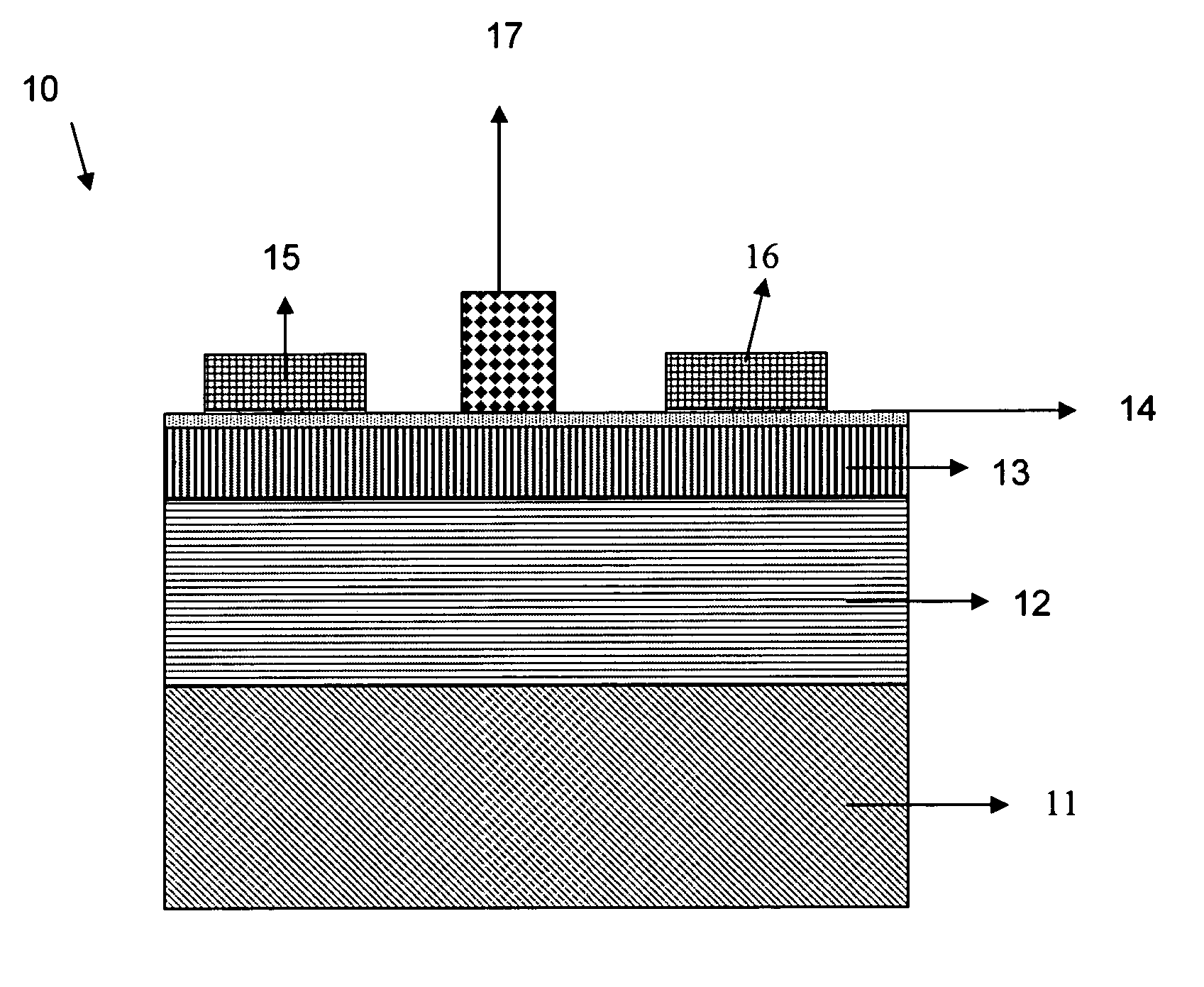

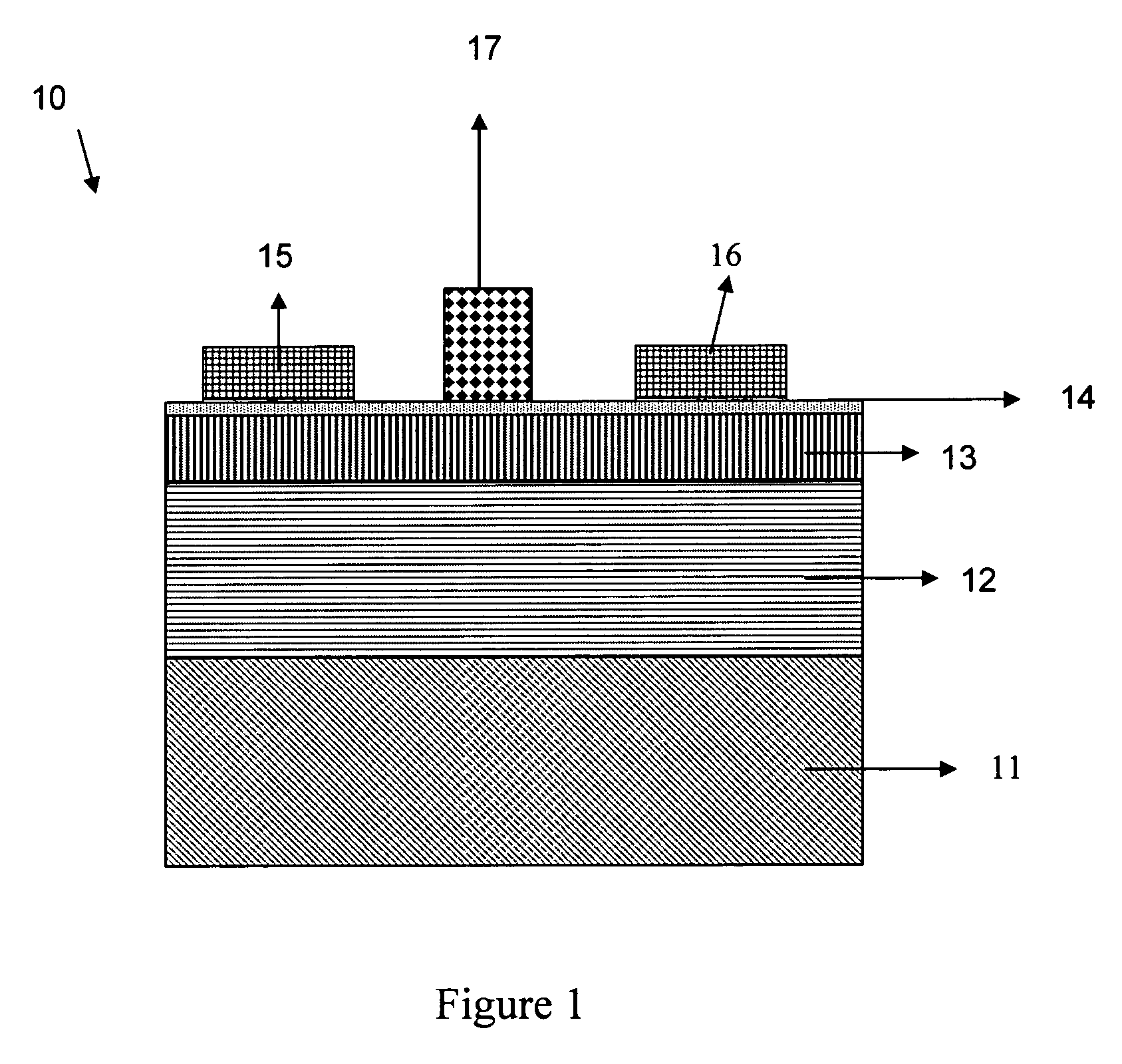

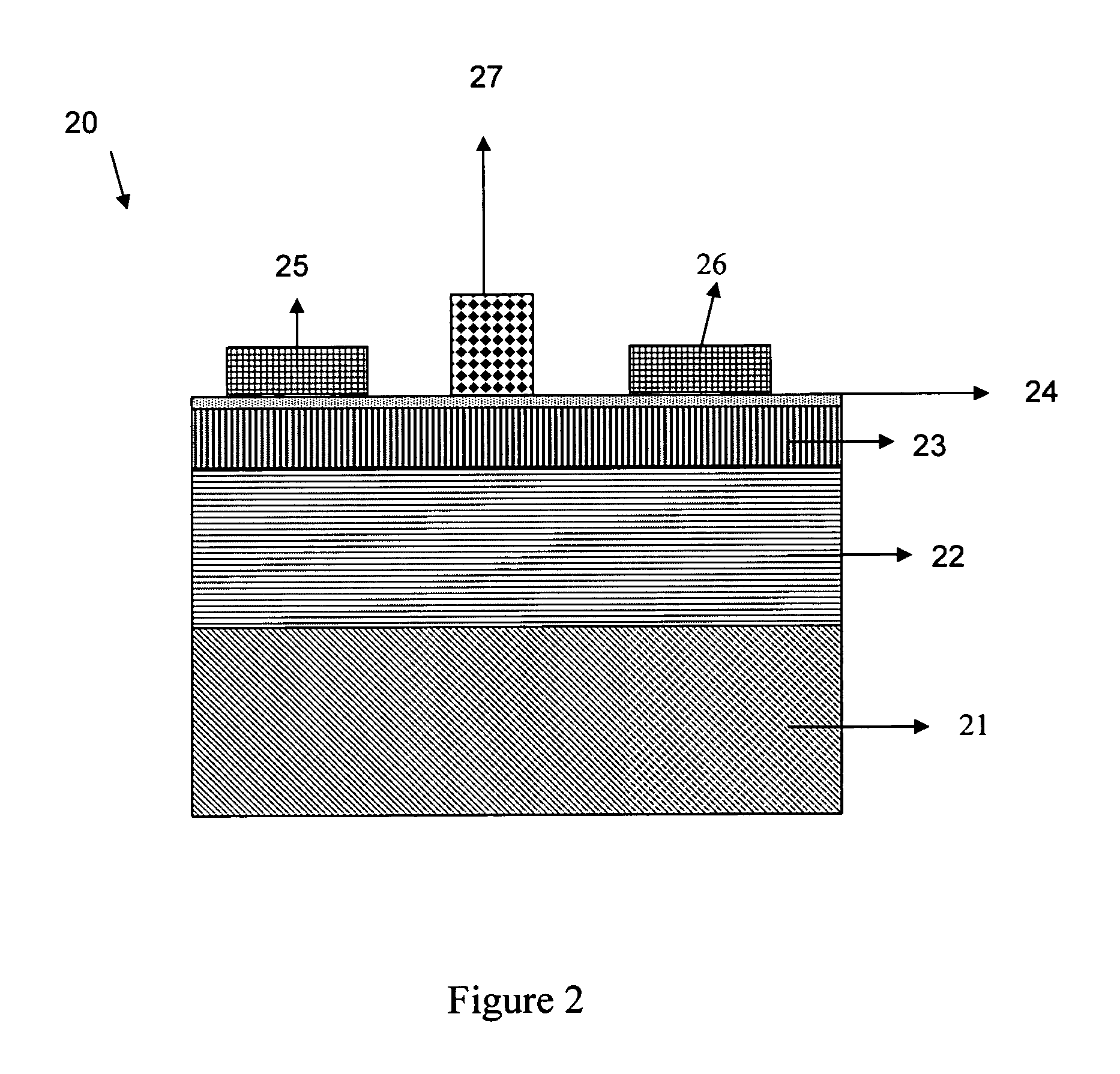

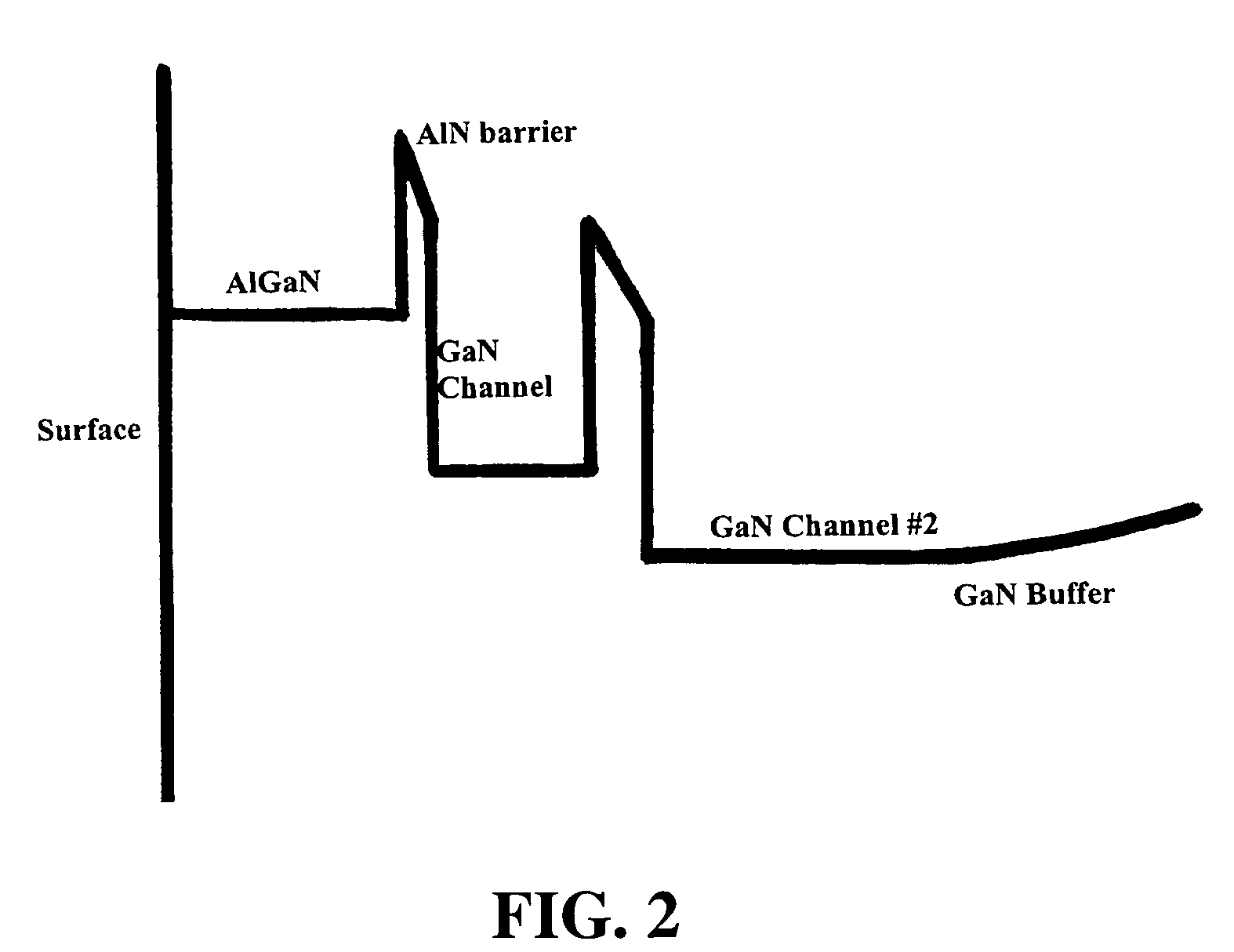

High electron mobility transistor

ActiveUS7253454B2Improving linearity without substantial loss of electron mobilityTransistorBand bendingElectron mobility

A HEMT device including a GaN channel structure including a very thin (Al,In,Ga)N subchannel layer that is disposed between a first GaN channel layer and a second GaN channel layer, to effect band bending induced from the piezoelectric and spontaneous charges associated with the (Al,In,Ga)N subchannel layer. This GaN channel / (Al,In,Ga)N subchannel arrangement effectively disperses the 2DEG throughout the channel of the device, thereby rendering the device more linear in character (relative to a corresponding device lacking the subchannel (Al,In,Ga)N sub-layer), without substantial loss of electron mobility.

Owner:WOLFSPEED INC

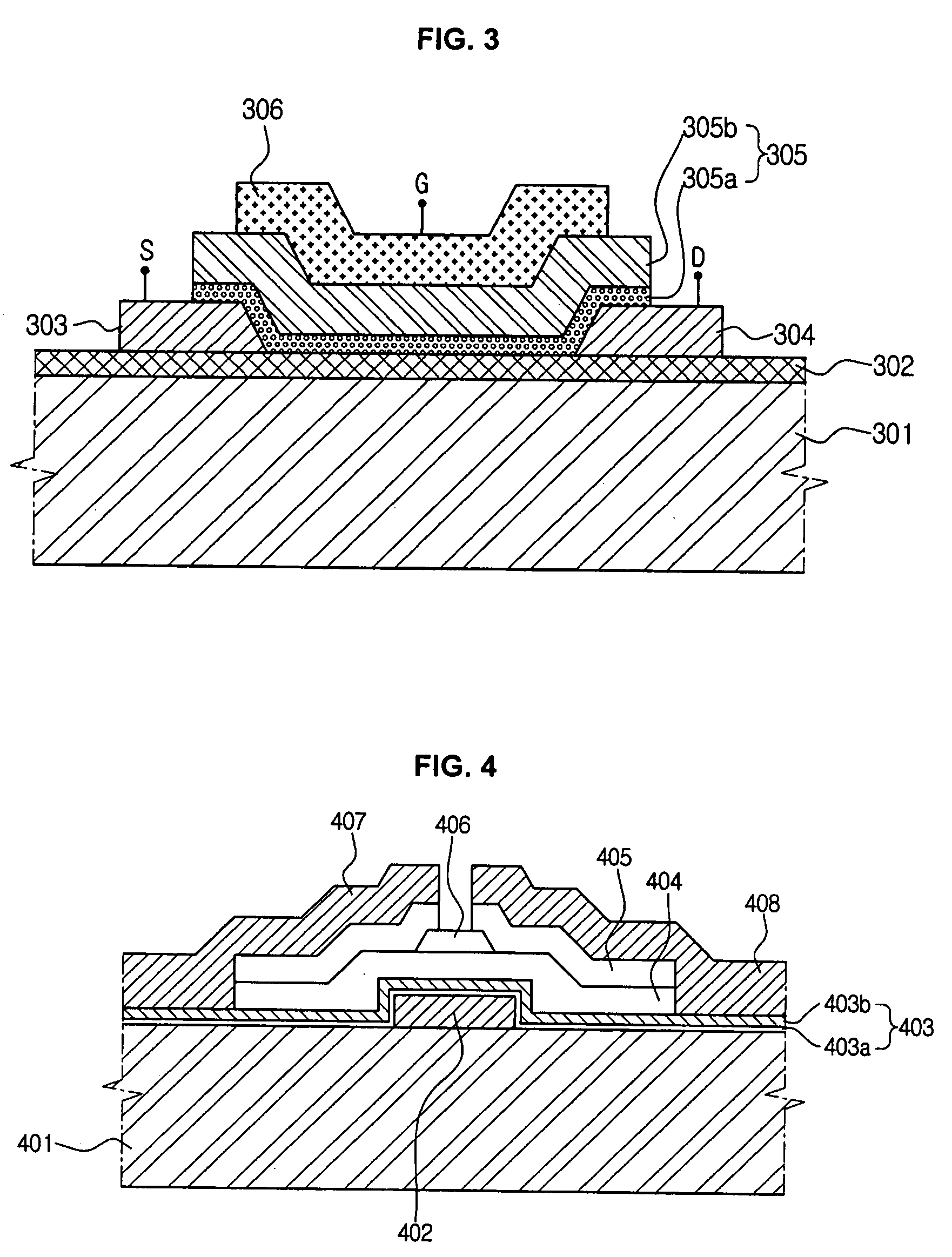

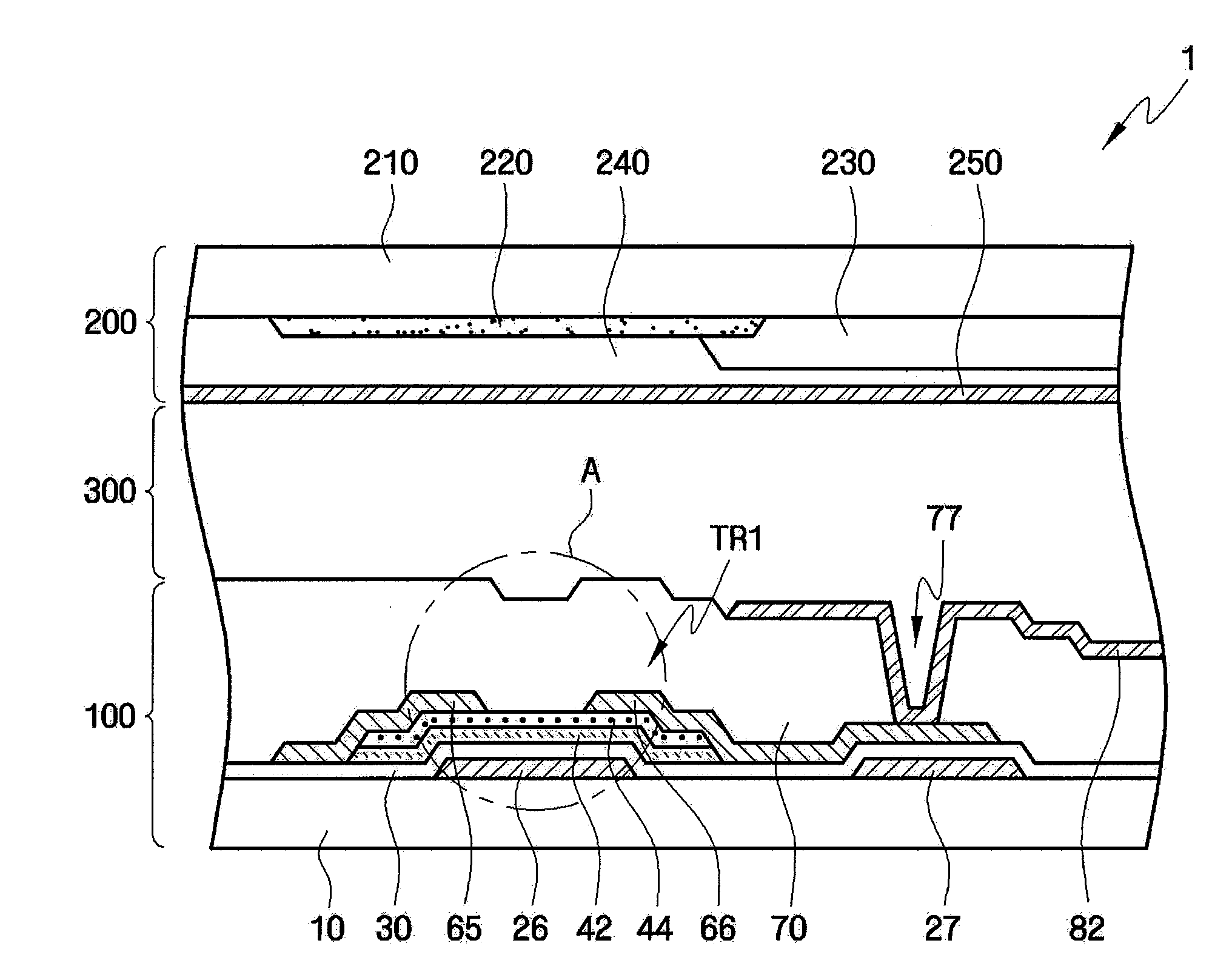

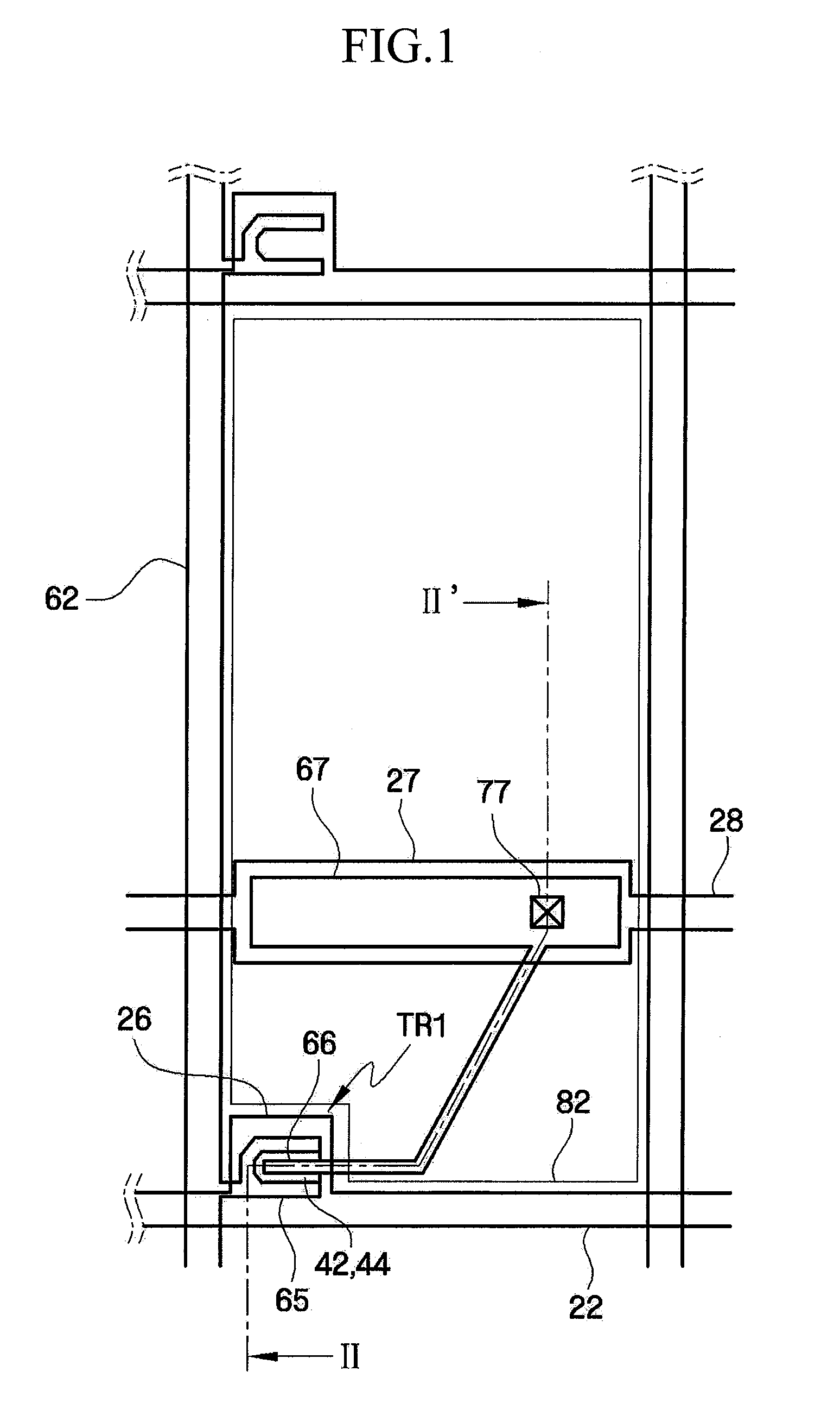

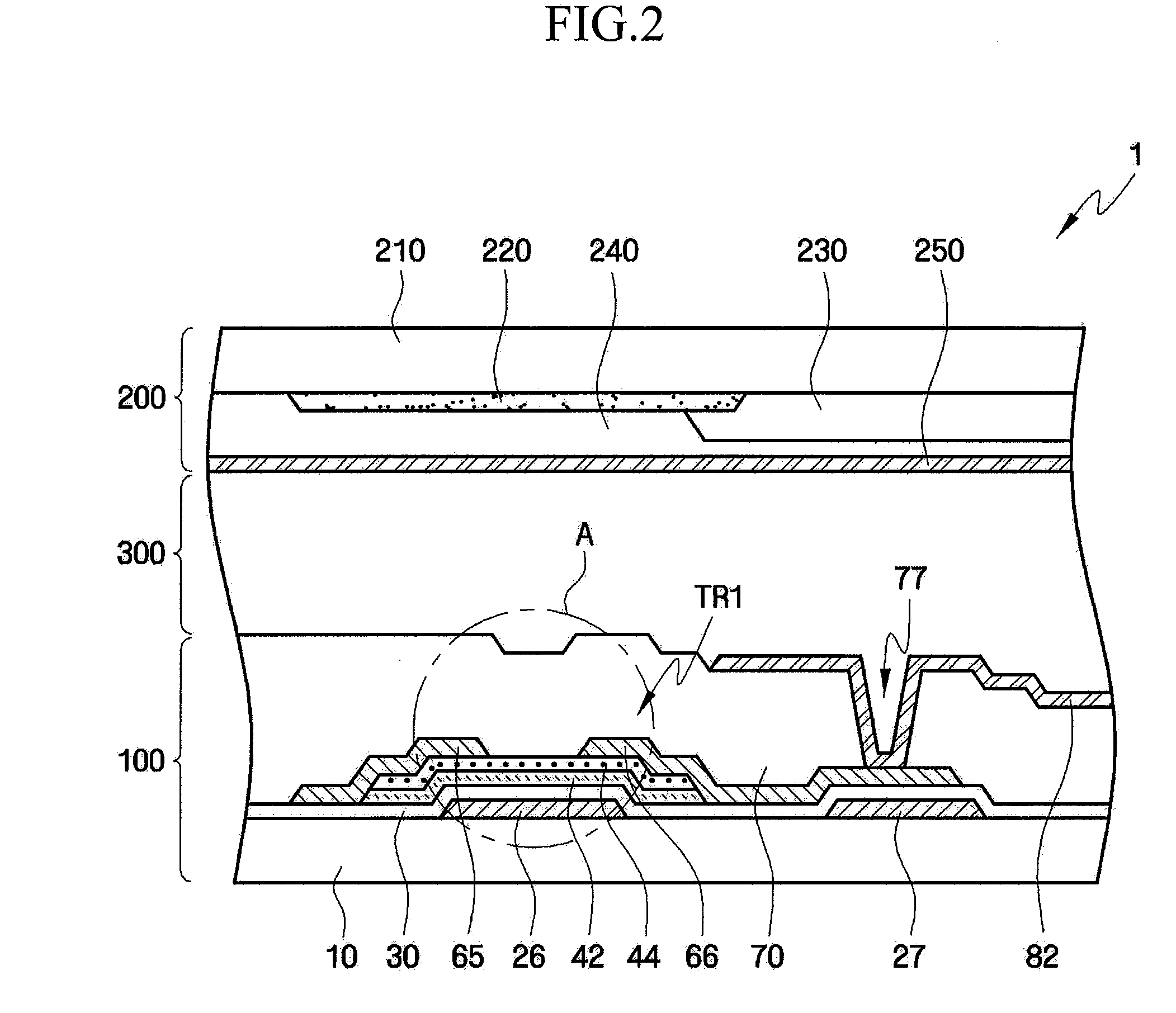

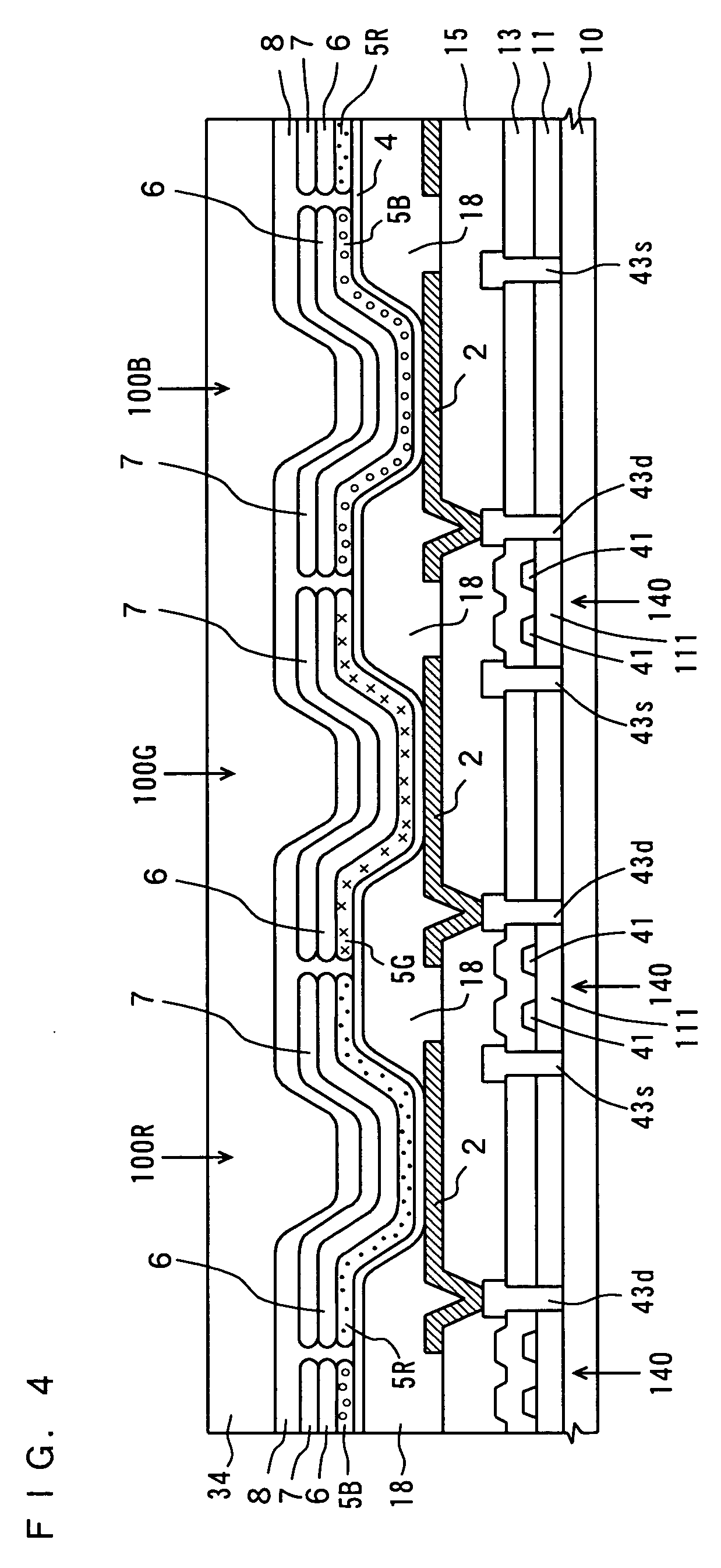

Display substrate having quantum well for improved electron mobility and display device including the same

ActiveUS20090180045A1Improve operating characteristicsImprove display qualitySolid-state devicesNon-linear opticsQuantum wellDisplay device

Provided are a display substrate and a display device including the same. The display substrate includes: gate wiring; a first semiconductor pattern formed on the gate wiring and having a first energy bandgap; a second semiconductor pattern formed on the first semiconductor pattern and having a second energy bandgap which is greater than the first energy bandgap; data wiring formed on the first semiconductor pattern; and a pixel electrode electrically connected to the data wiring. Because the second energy bandgap is larger than the first energy bandgap, a quantum well is formed in the first semiconductor pattern, enhancing electron mobility therein.

Owner:SAMSUNG DISPLAY CO LTD

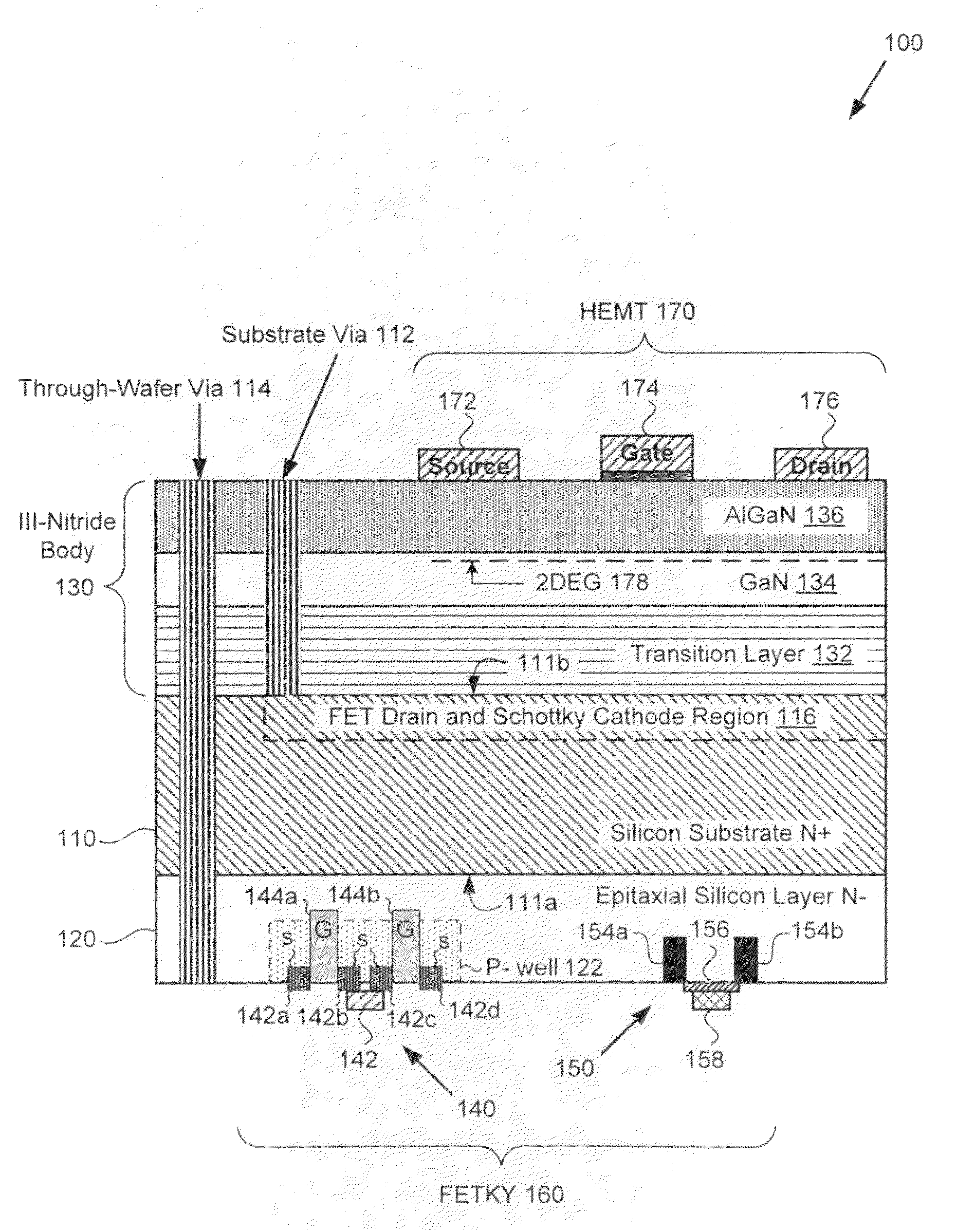

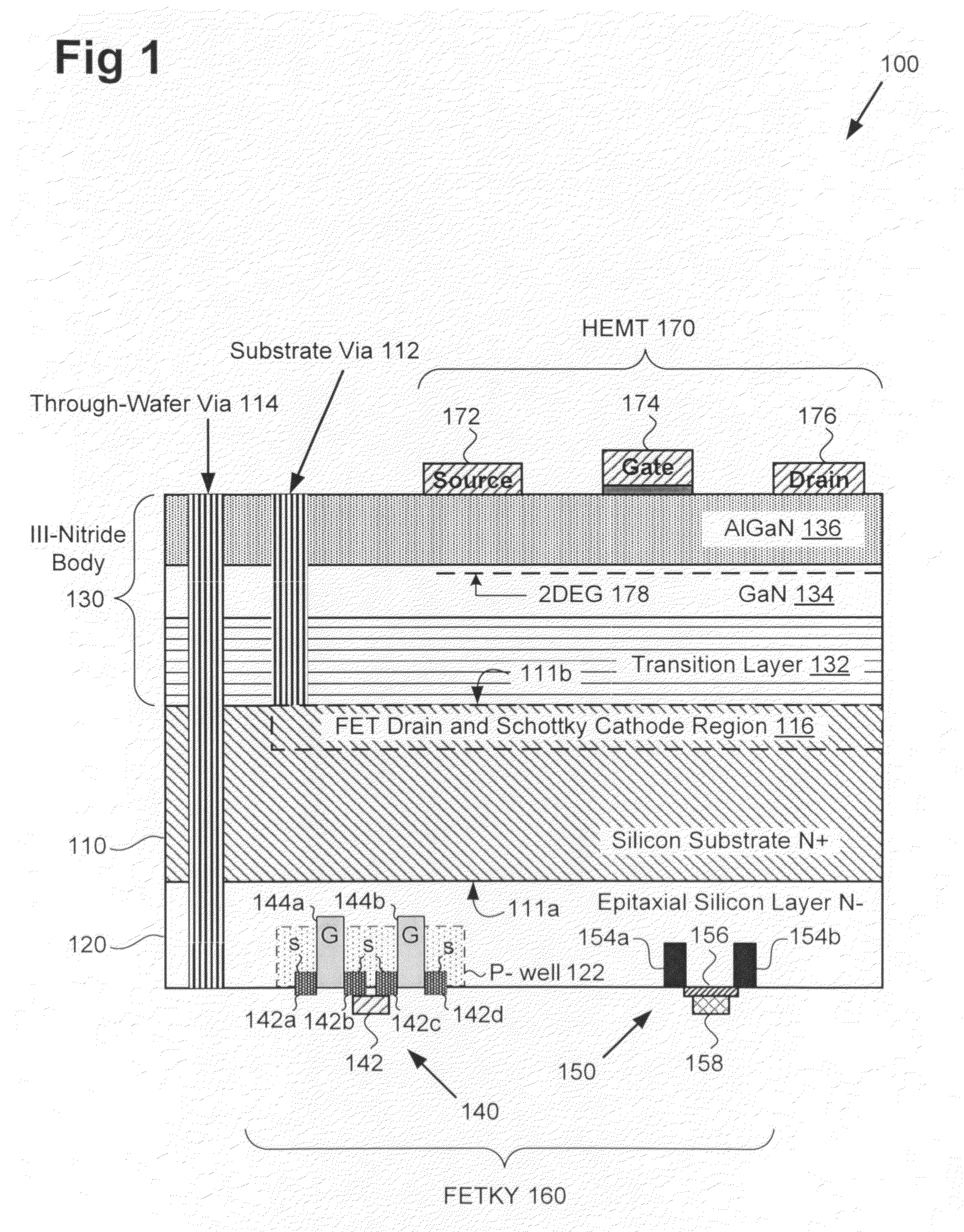

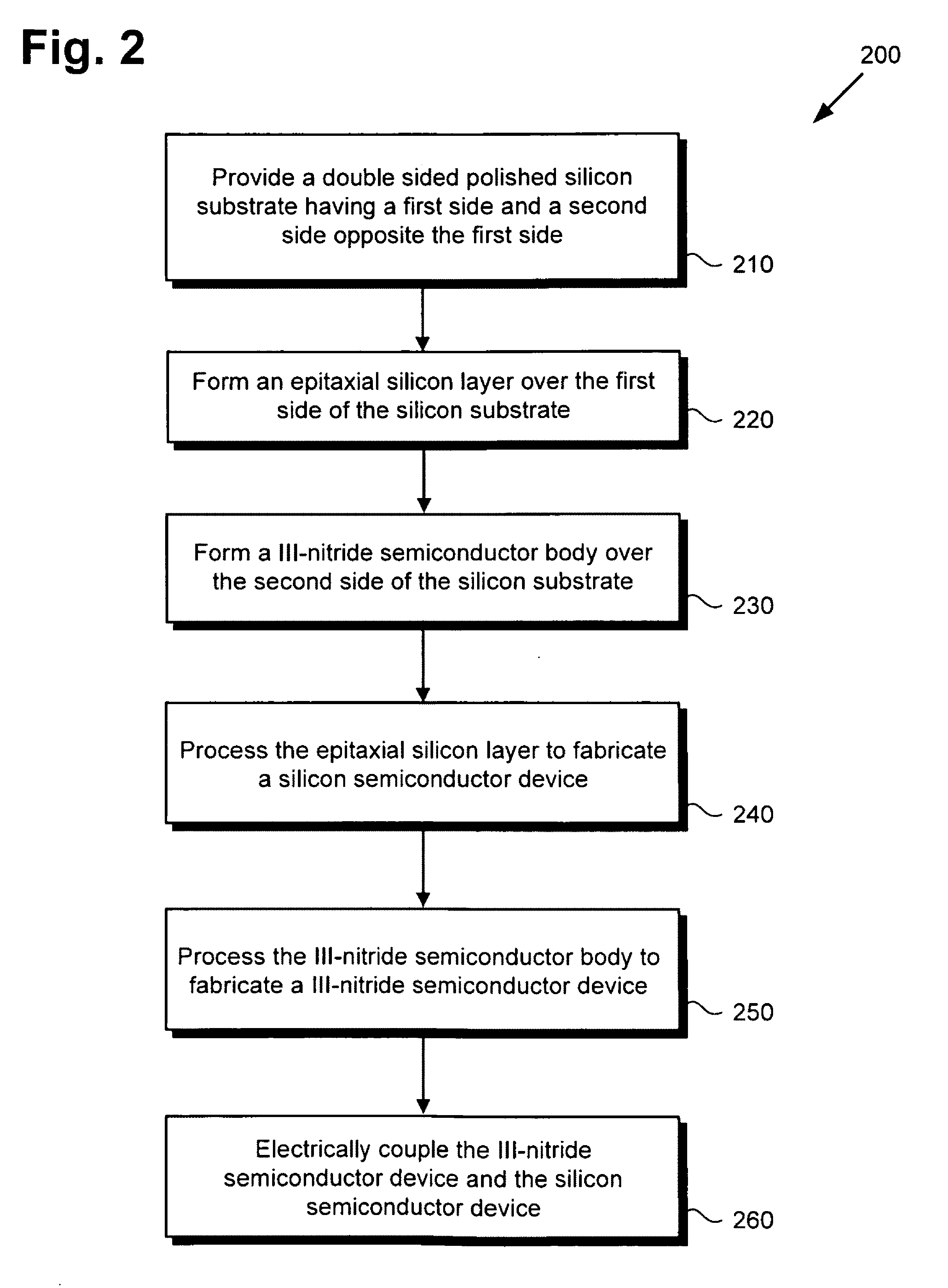

Monolithic vertically integrated composite group III-V and group IV semiconductor device and method for fabricating same

InactiveUS7915645B2TransistorSemiconductor/solid-state device detailsPower semiconductor deviceEngineering

According to one disclosed embodiment, a monolithic vertically integrated composite device comprises a double sided semiconductor substrate having first and second sides, a group IV semiconductor layer formed over the first side and comprising at least one group IV semiconductor device, and a group III-V semiconductor body formed over the second side and comprising at least one group III-V semiconductor device electrically coupled to the at least one group IV semiconductor device. The composite device may further comprise a substrate via and / or a through-wafer via providing electric coupling. In one embodiment, the group IV semiconductor layer may comprise an epitaxial silicon layer, and the at least one group IV semiconductor device may be a combined FET and Schottky diode (FETKY) fabricated on the epitaxial silicon layer. In one embodiment, the at least one group III-V semiconductor device may be a III-nitride high electron mobility transistor (HEMT).

Owner:INFINEON TECH AMERICAS CORP

Binary group III-nitride based high electron mobility transistors and methods of fabricating same

Binary Group III-nitride high electron mobility transistors (HEMTs) and methods of fabricating binary Group III-nitride HEMTs are provided. In some embodiments, the binary Group III-nitride HEMTs include a first binary Group III-nitride barrier layer, a binary Group III-nitride channel layer on the first barrier layer; and a second binary Group III-nitride barrier layer on the channel layer. In some embodiments, the binary Group III-nitride HEMTs include a first AIN barrier layer, a GaN channel layer and a second AlN barrier layer.

Owner:CREE INC

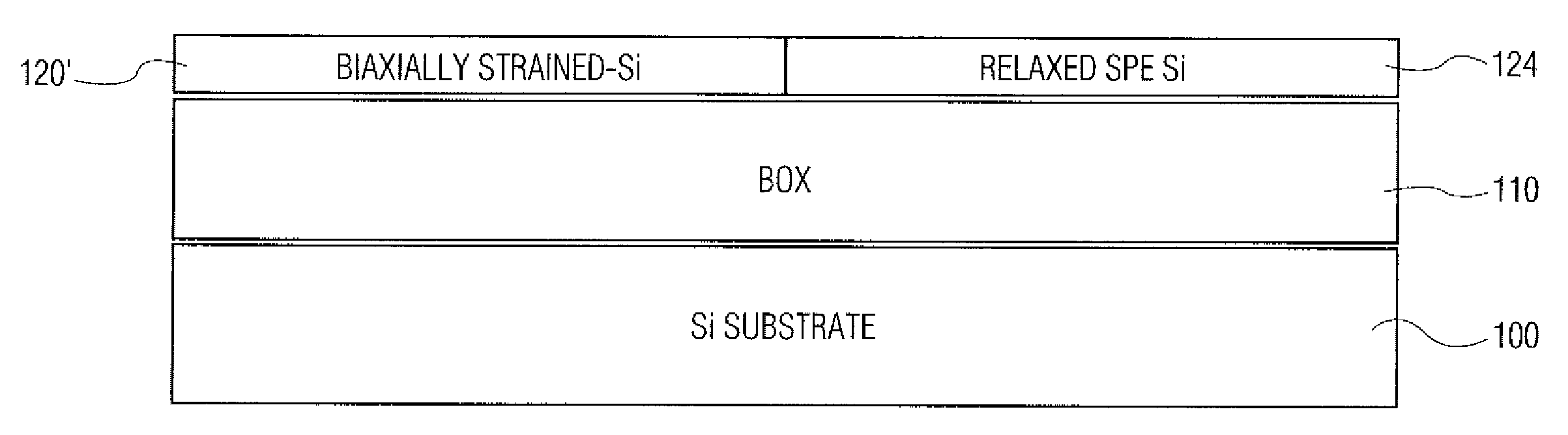

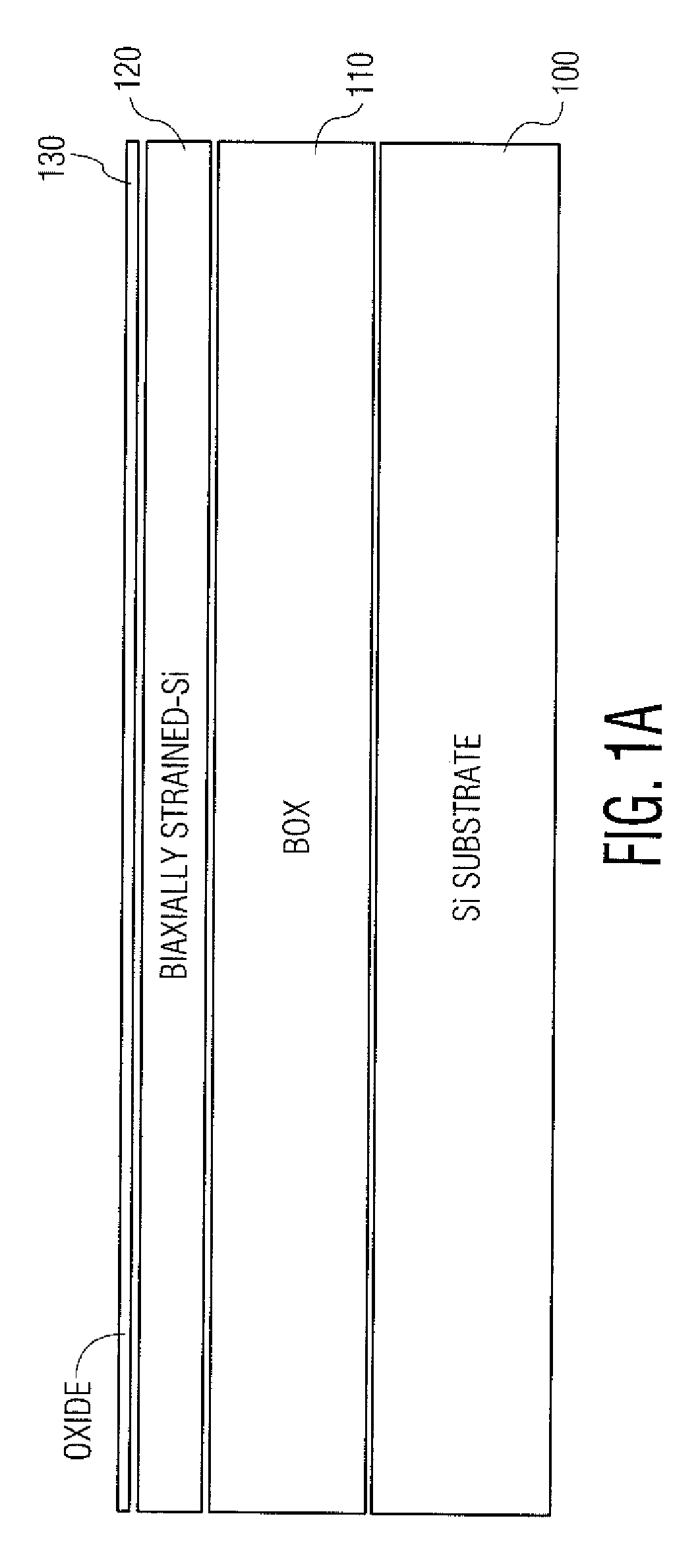

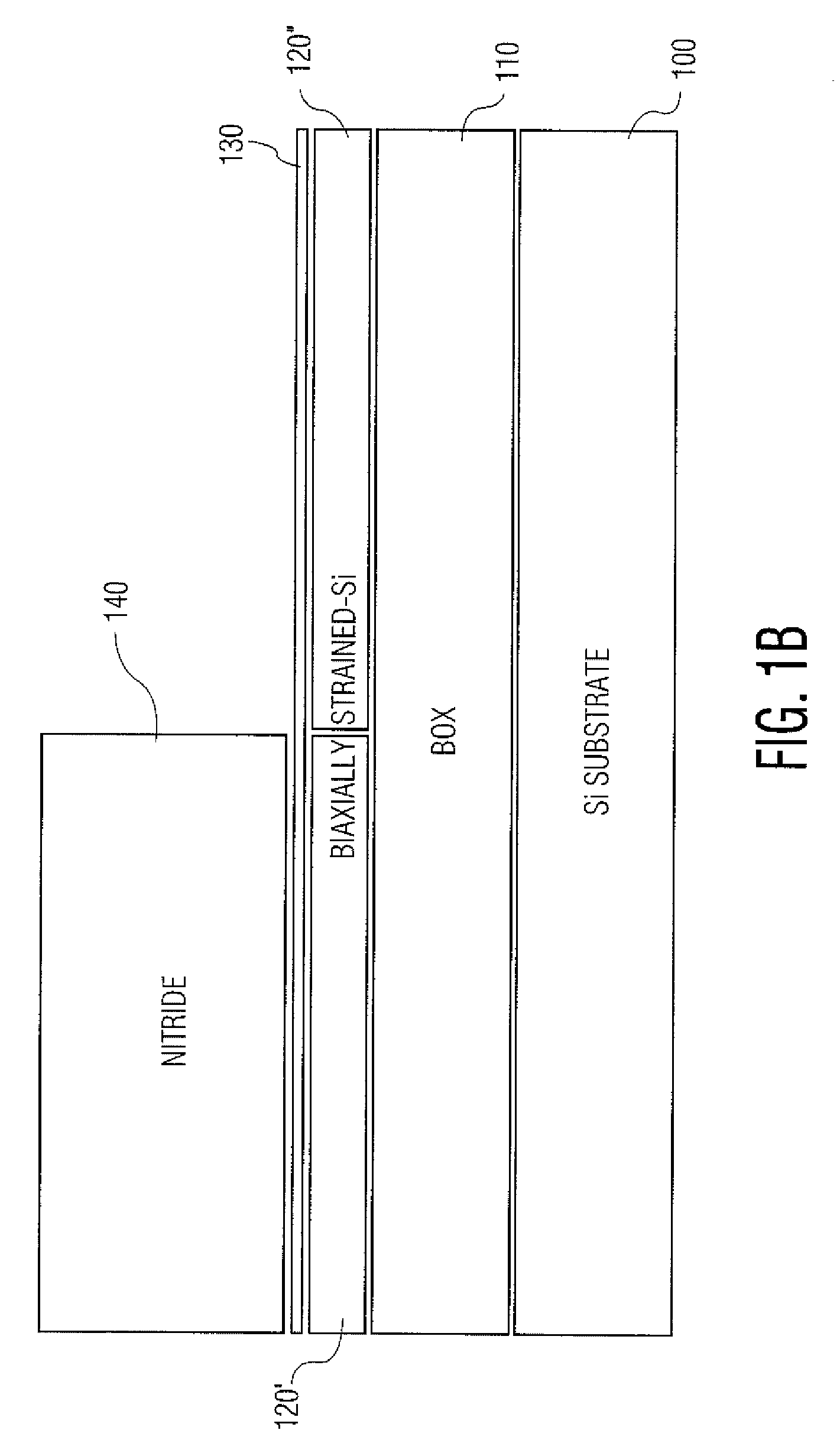

Localized strain relaxation for strained Si directly on insulator

InactiveUS7524740B1Semiconductor/solid-state device manufacturingSemiconductor devicesElectron mobilityNitride

A method of forming a localized region of relaxed Si in a layer of strained Si arranged within a strained silicon directly on insulator (SSDOI) semiconductor substrate is provided by the invention. The strained Si layer is formed on a buried oxide (BOX) layer disposed on a Si substrate base. The method includes depositing a nitride hard mask pattern above a region of the strained Si layer in which enhanced electron mobility is desired, leaving an unmasked region within the strained Si layer, and carrying out various other processing steps to modify and relax the unmasked portion of the strained region. The method includes growing an EPI SiGe region upon the unmasked region using pre-amorphization implantation, and forming a buried amorphous SiGe region in a portion of the EPI SiGe region, and an amorphous Si region, below the amorphous SiGe region. Then, using SPE regrowth, modifying the amorphous SiGe and amorphous Si regions to realize an SPE SiGe region and relaxed SPE Si layer. The SiGe region and the SPE SiGe region are etched, leaving the relaxed SPE Si region above the buried oxide layer. The nitride pattern is stripped.

Owner:IBM CORP

Organic electroluminescent device

InactiveUS20060029828A1Reduce the driving voltageLong lastingDischarge tube luminescnet screensConstructionsMolecular orbital energyElectron hole

An organic EL device has a structure that includes a hole injecting electrode, hole injecting layer, hole transporting layer, light emitting layer, electron restricting layer, electron transporting layer, and electron injecting electrode, in sequence, on a substrate. For the electron restricting layer, a material having an electron mobility lower than that of the electron transporting layer or a material having a low LUMO (lowest unoccupied molecular orbital) energy level is used.

Owner:SANYO ELECTRIC CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com