Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

635results about How to "Improve read and write speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

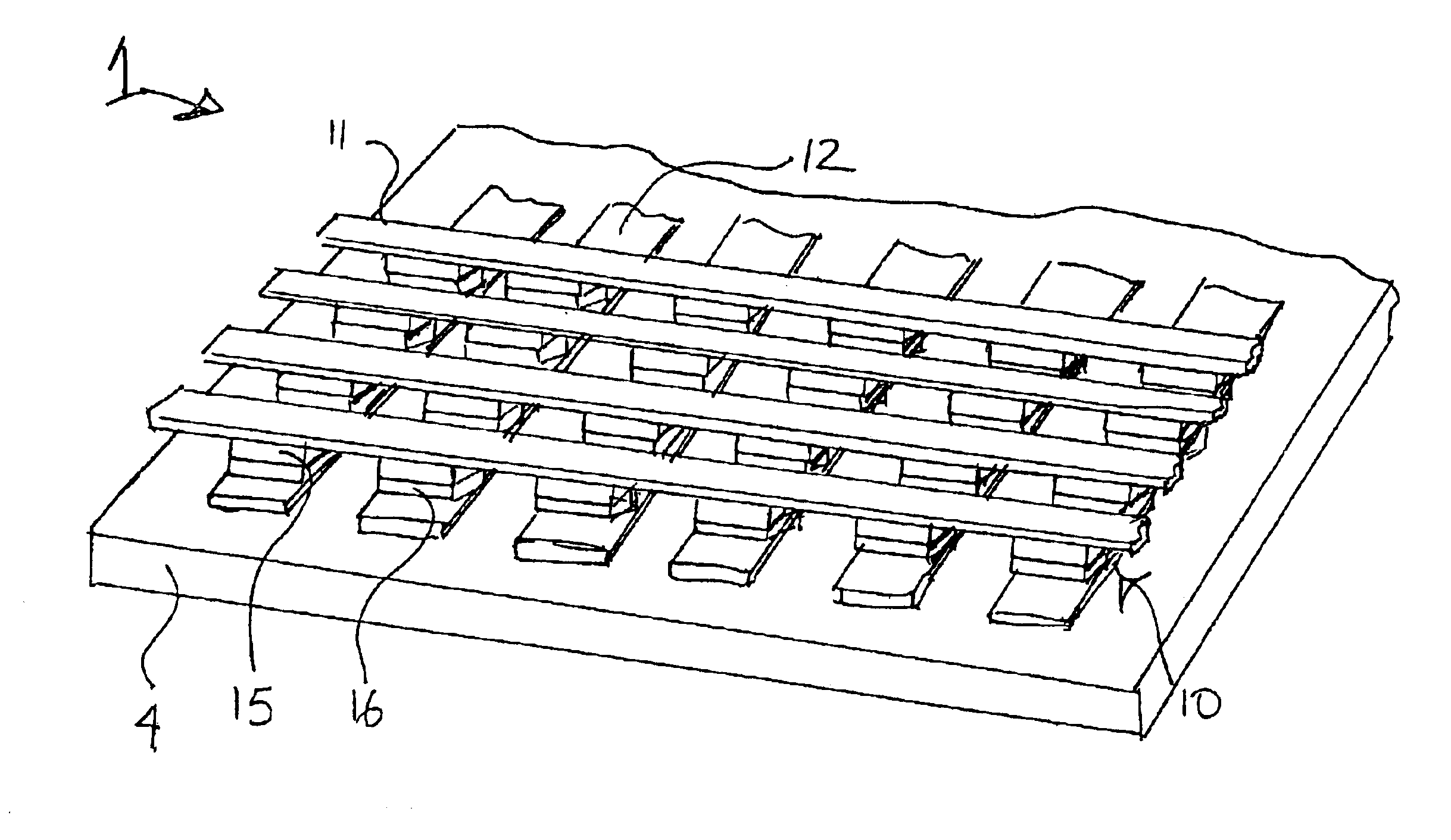

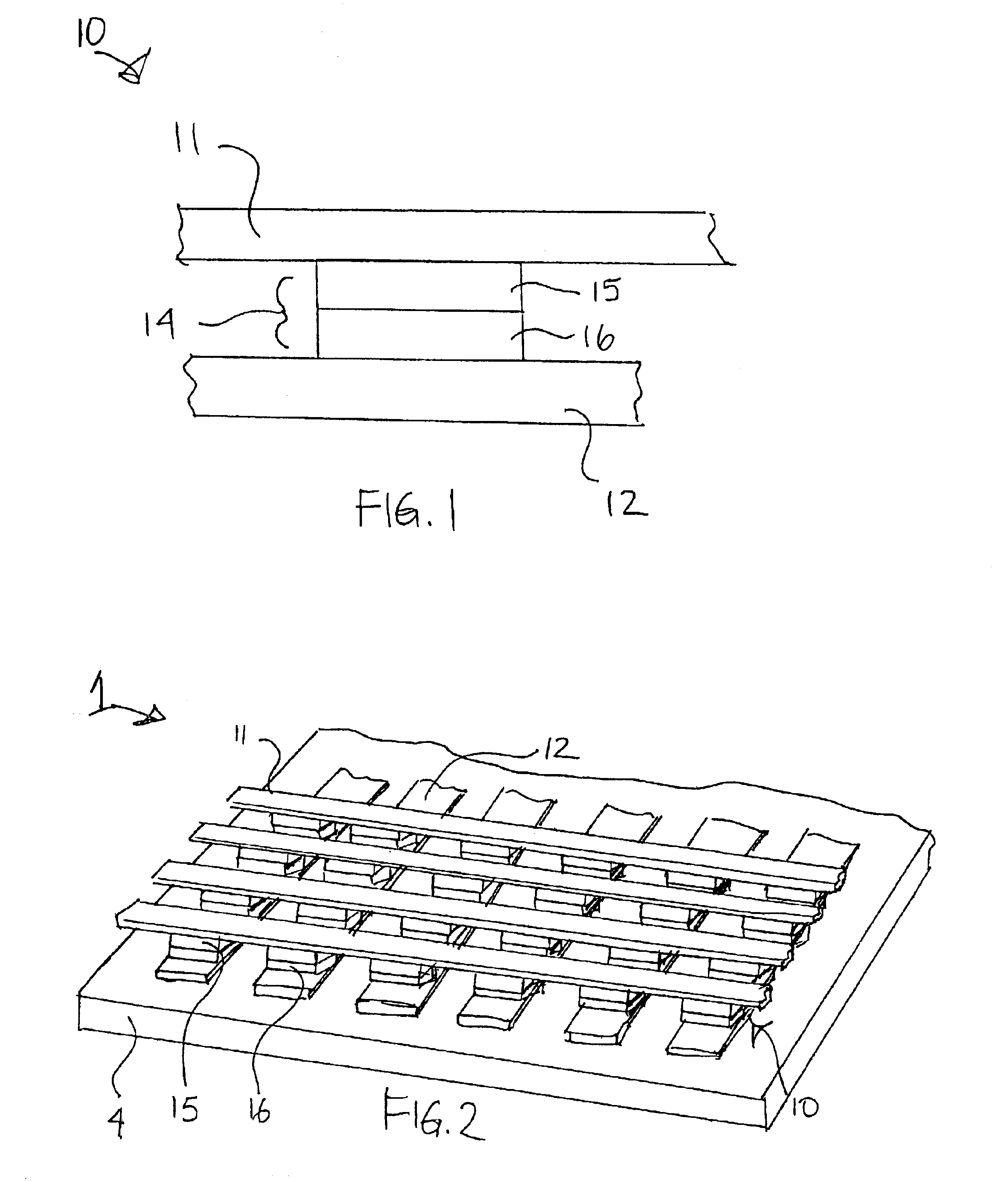

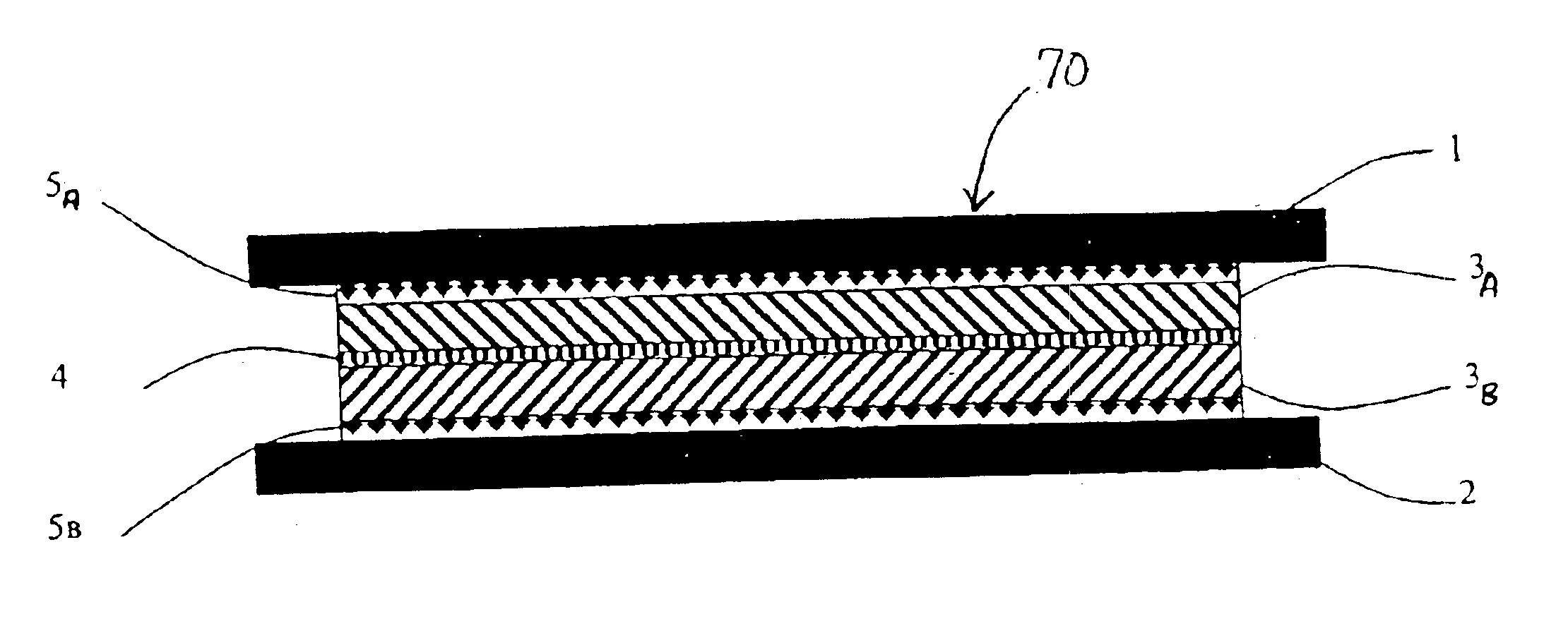

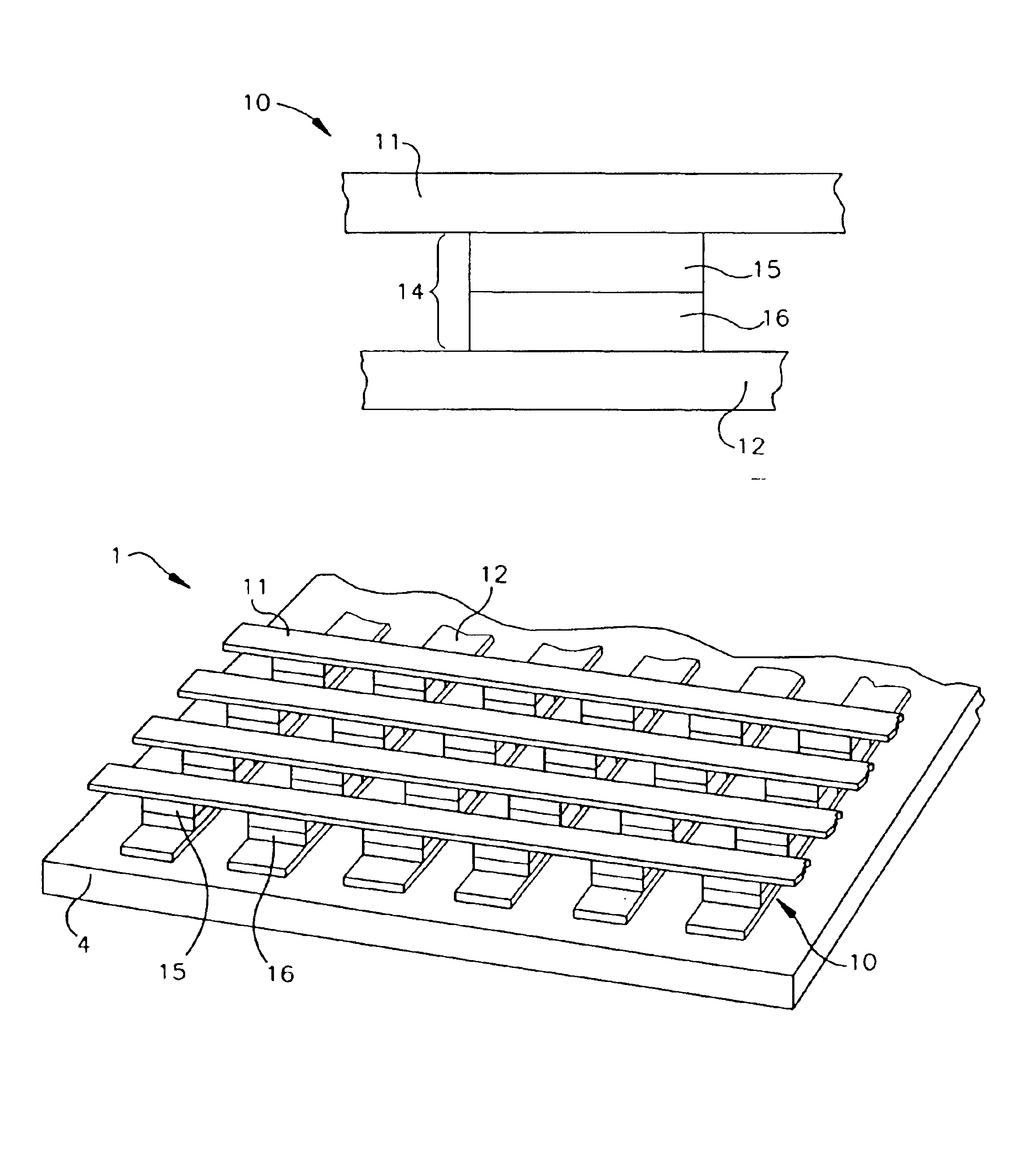

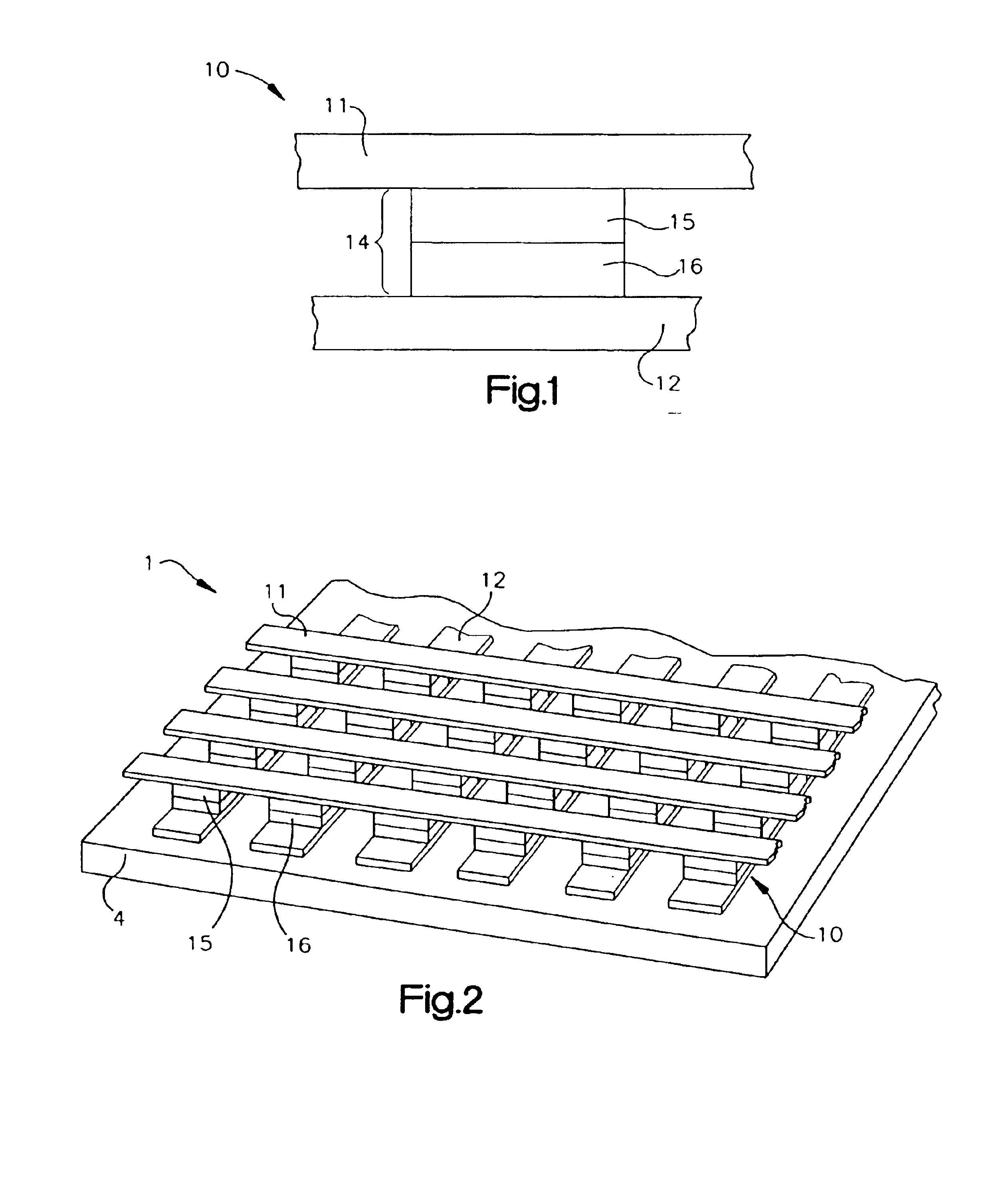

Memory device with active and passive layers

InactiveUS6858481B2Improve reading speedIncrease write speedNanoinformaticsSolid-state devicesAmount of substanceElectron mobility

A memory including memory cells having active and passive layers may store multiple information bits. The active layer may include an organic polymer that has a variable resistance based on the movement of charged species (ions or ions and electrons) between the passive layer and the active layer. The passive layer may be a super-ionic material that has high ion and electron mobility. The active layer may be self-assembled from a monomer in a liquid or gas.

Owner:SPANSION LLC

Memory device

A memory storage and retrieval device containing (a) an electrically conductive first electrode; (b) an electrically conductive second electrode; (c) a layer stack intermediate the first and second electrodes containing (d) at least one active layer with variable electrical conductivity; and (e) at least one passive layer containing a source material for varying the electrical conductivity of the at least one active layer upon application of an electrical potential difference between the first and second electrodes.

Owner:SPANSION LLC

Memory device with active passive layers

InactiveUS6838720B2Improve read and write speedLong-term data retentionTransistorNanoinformaticsActive layerElectron mobility

A memory including memory cells having active and passive layers may store multiple information bits. The active layer may include an organic polymer that has a variable resistance based on the movement of charged species (ions or ions and electrons) between the passive layer and the active layer. The passive layer may be a super-ionic material that has high ion and electron mobility. The active layer may be self-assembled from a monomer in a liquid or gas.

Owner:SPANSION LLC

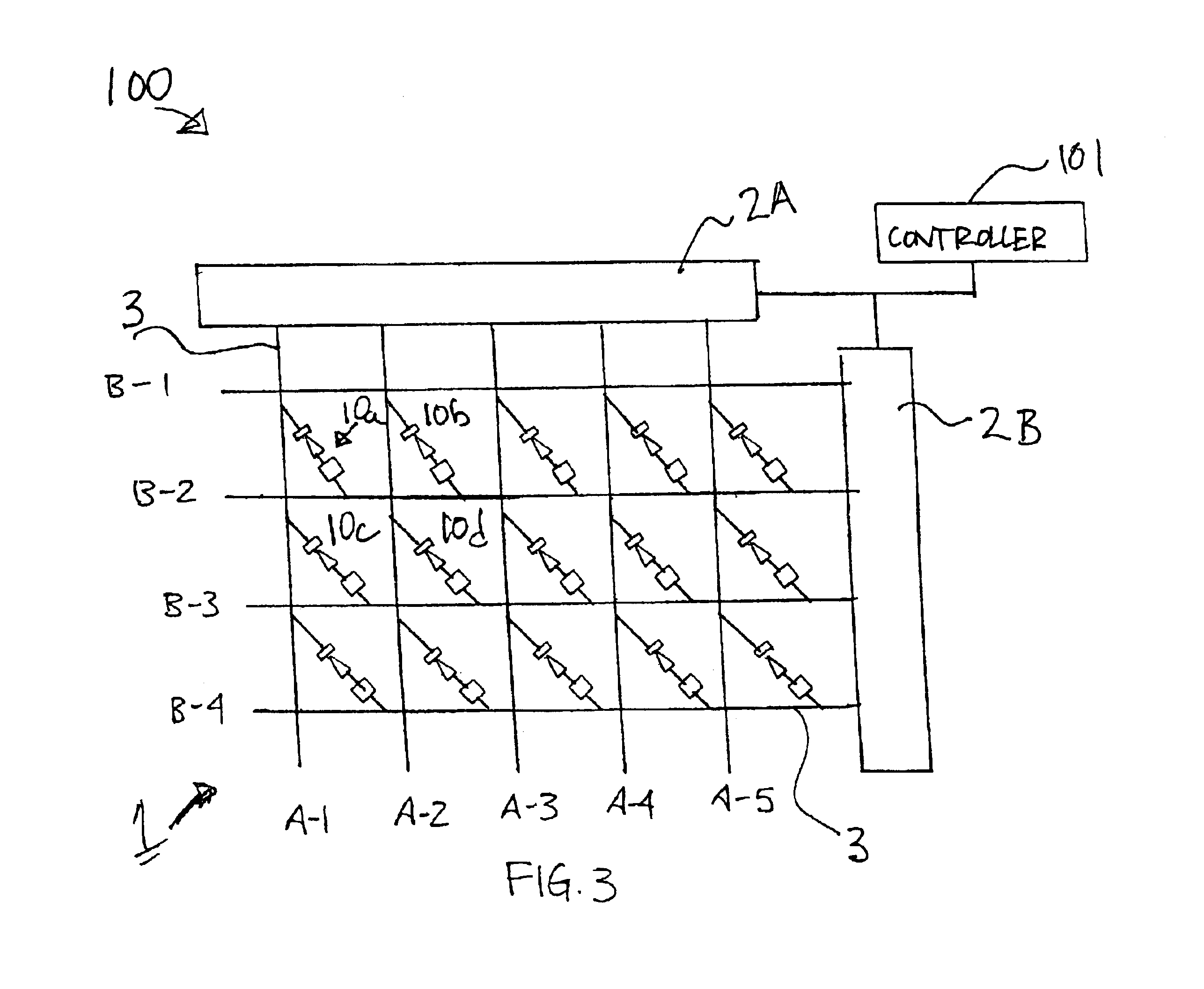

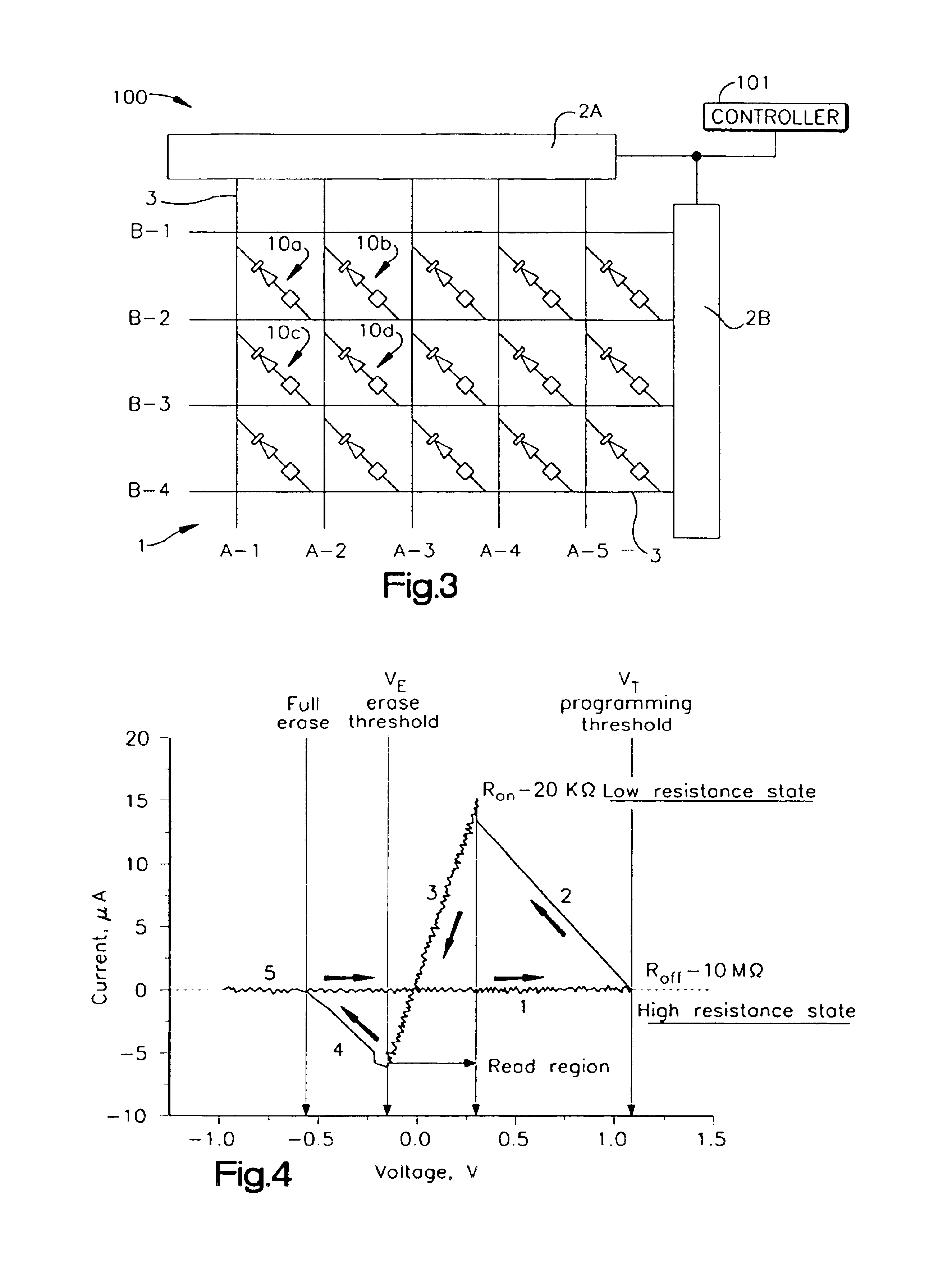

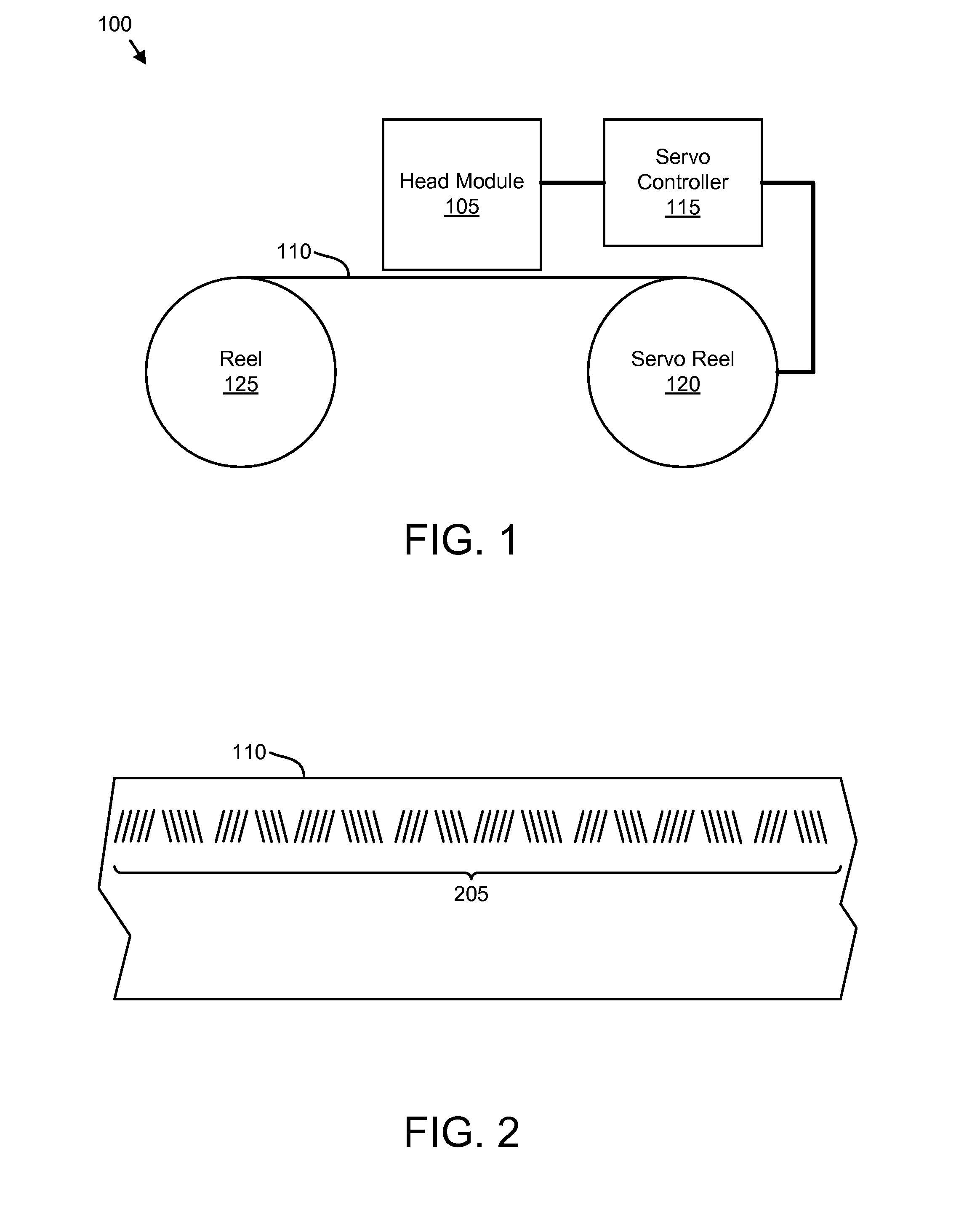

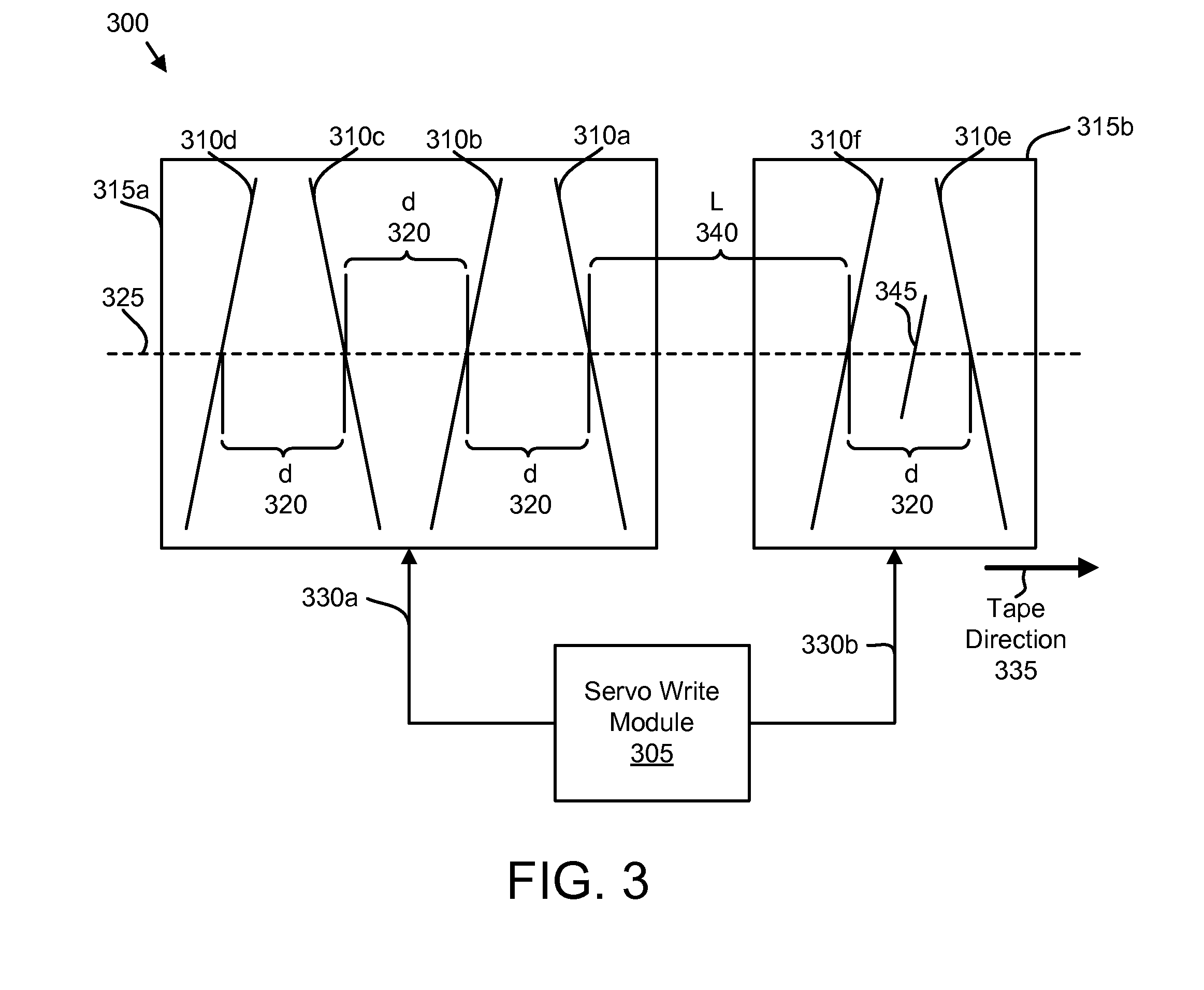

Apparatus, system, and method for timing based servo tape formating

InactiveUS20080174897A1Reduce readReduce write errorDriving/moving recording headsAlignment for track following on tapesMagnetic tapeComputer science

An apparatus, system, and method are disclosed for formatting a timing-based servo pattern on a magnetic tape. A first write head concurrently writes a base number of stripes to a plurality of first stripe patterns with a first and third element and writes the base number of stripes to a plurality of second stripe patterns with a second and fourth element of a first write head in response to at least one first write signal. A second write head concurrently writes an incremental number of stripes to a specified first stripe pattern to form a first incremental stripe pattern with a fifth write element and writes the incremental number of stripes to a specified second stripe pattern to form a second incremental stripe pattern with a sixth write element.

Owner:IBM CORP

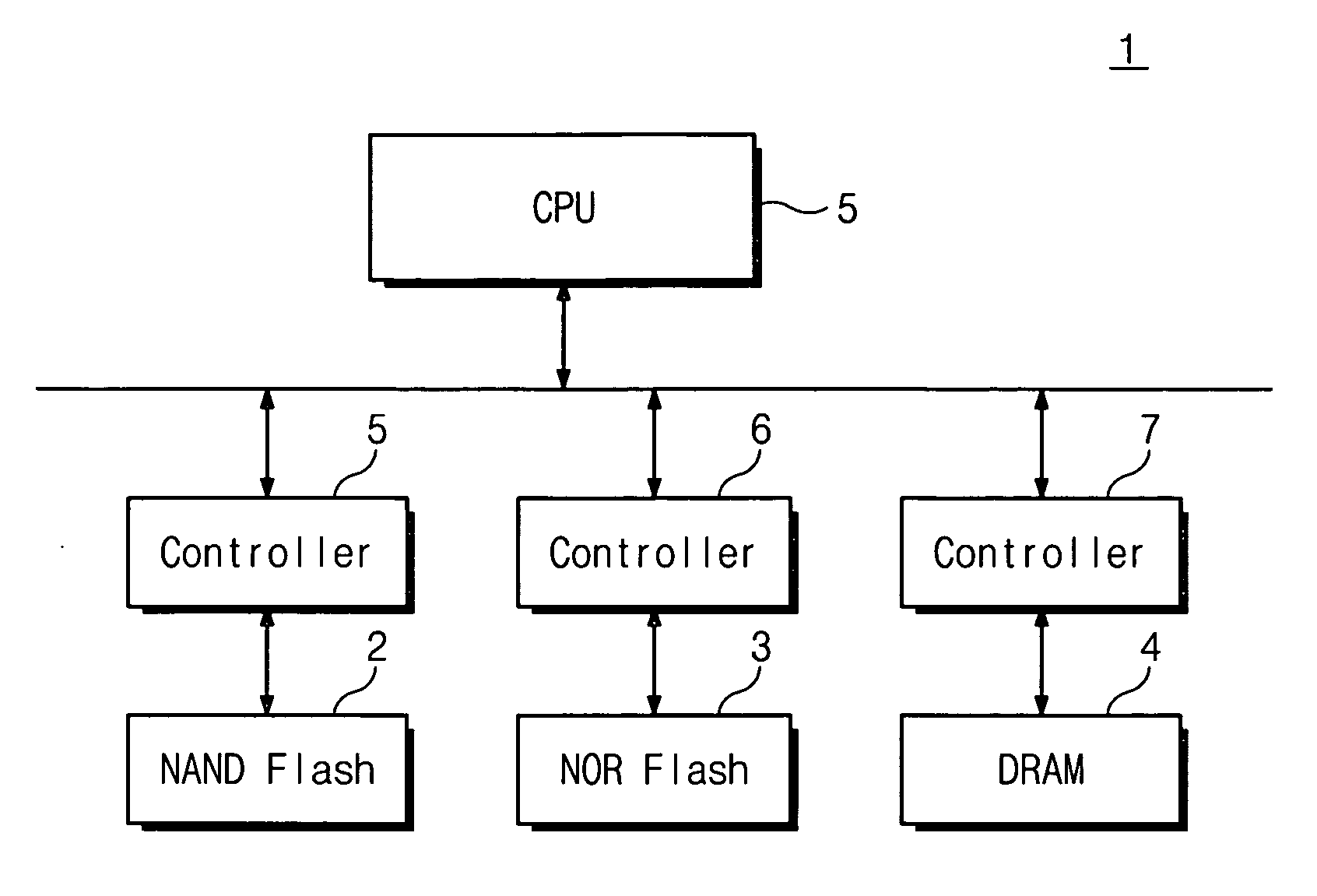

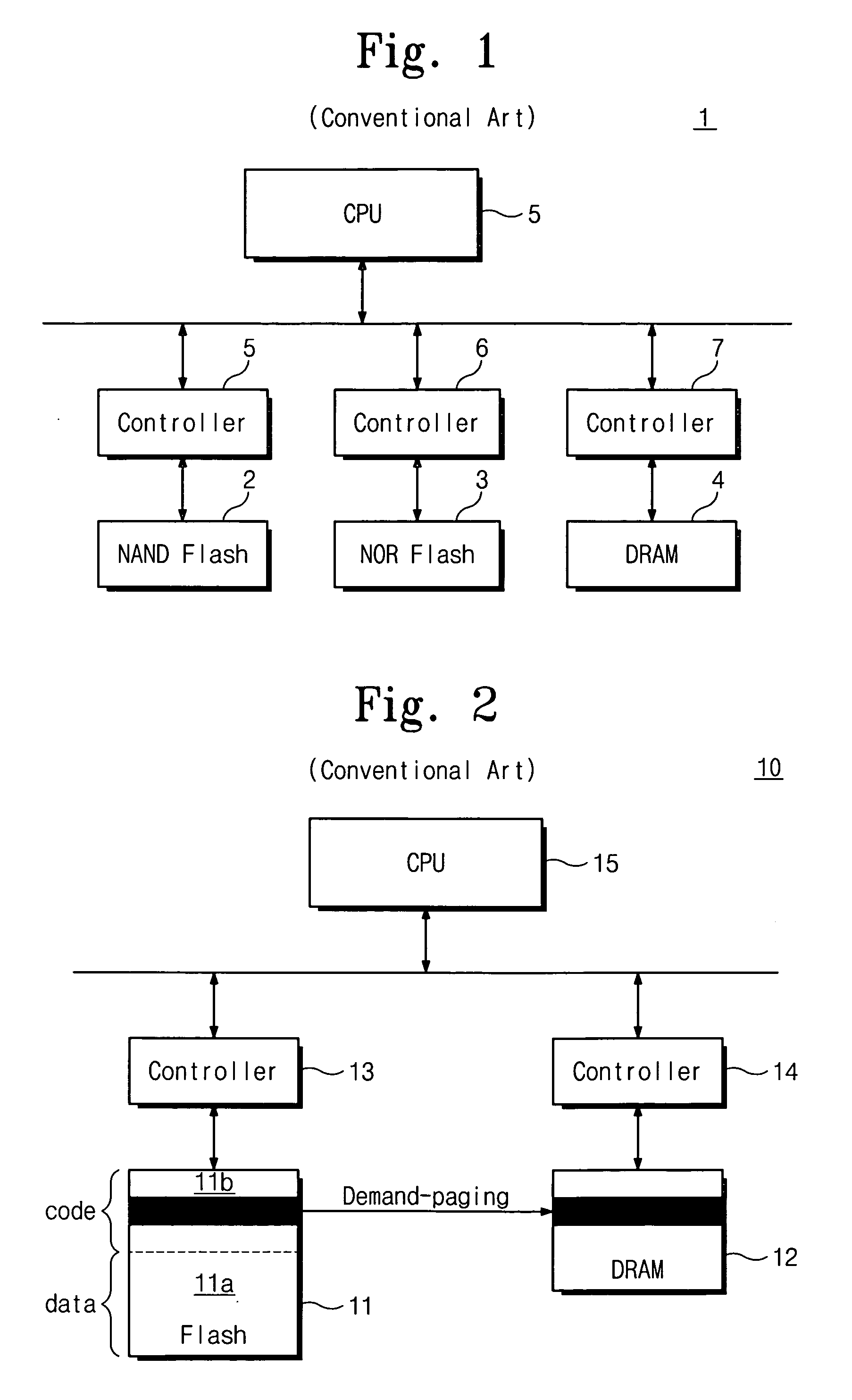

Flash memories and processing systems including the same

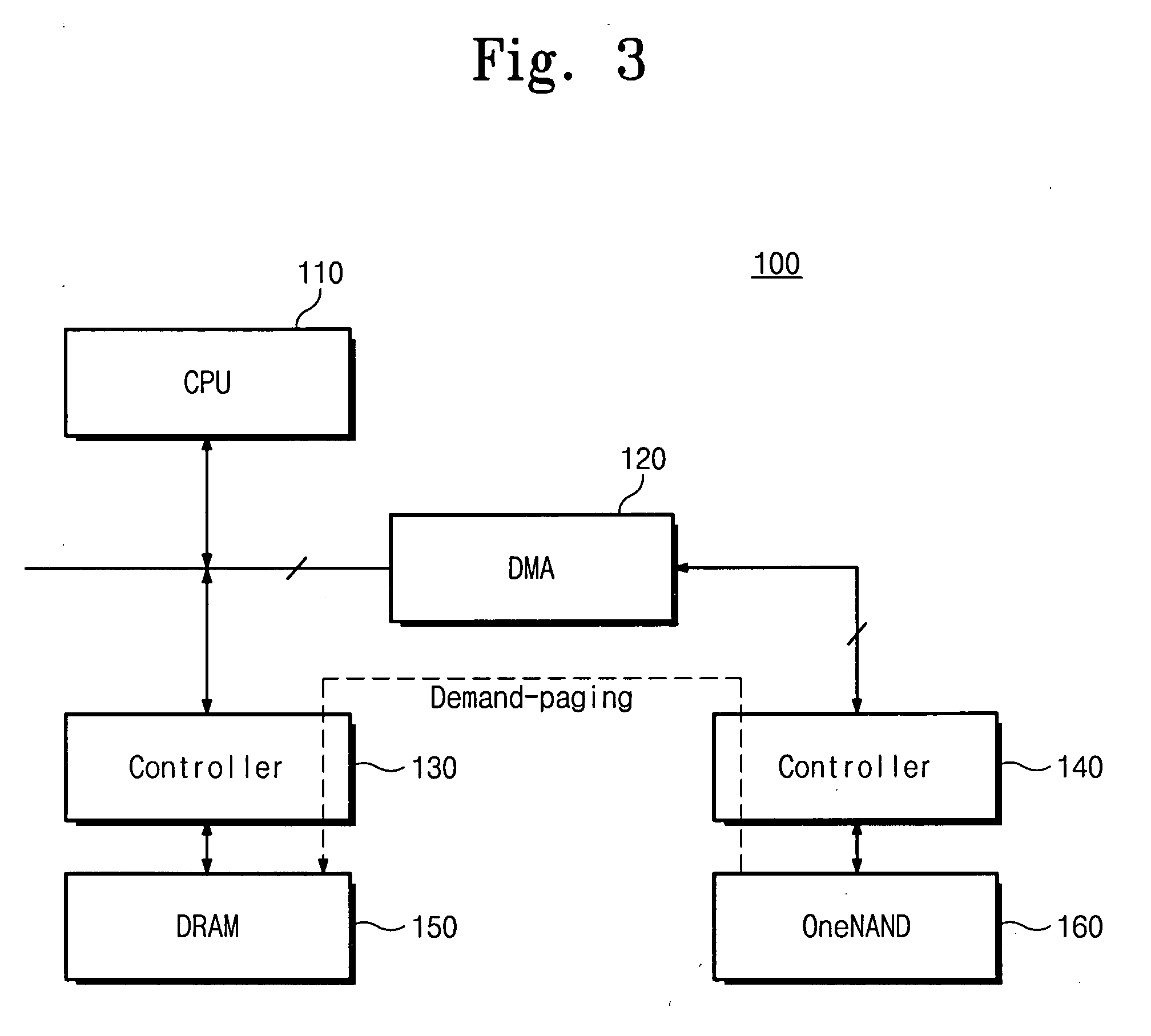

InactiveUS20060224789A1Improve reading speedIncrease write speedRead-only memoriesDigital storageExternal storageData shipping

A memory may include first and second buffer memories and a memory core. The memory core may include memory blocks each having a plurality of pages and a page buffer for reading data from a selected memory block. A control logic may control the first and second buffer memories and the memory core. The control logic may have a register for storing address and command information of the memory core. The control logic may control the memory core so that data read periods for pages of the selected memory block are carried out according to the stored address and command information. The control logic may control the first and second buffer memories and the memory core so that data in the page buffer may be transferred to the first and / or second buffer memories during the data read periods. The control logic may deactivate an interrupt signal when data in the page buffer is transferred to the first and / or second buffer memory and may activate the interrupt signal when data in the first and / or second buffer memory is transferred to an external storage.

Owner:SAMSUNG ELECTRONICS CO LTD

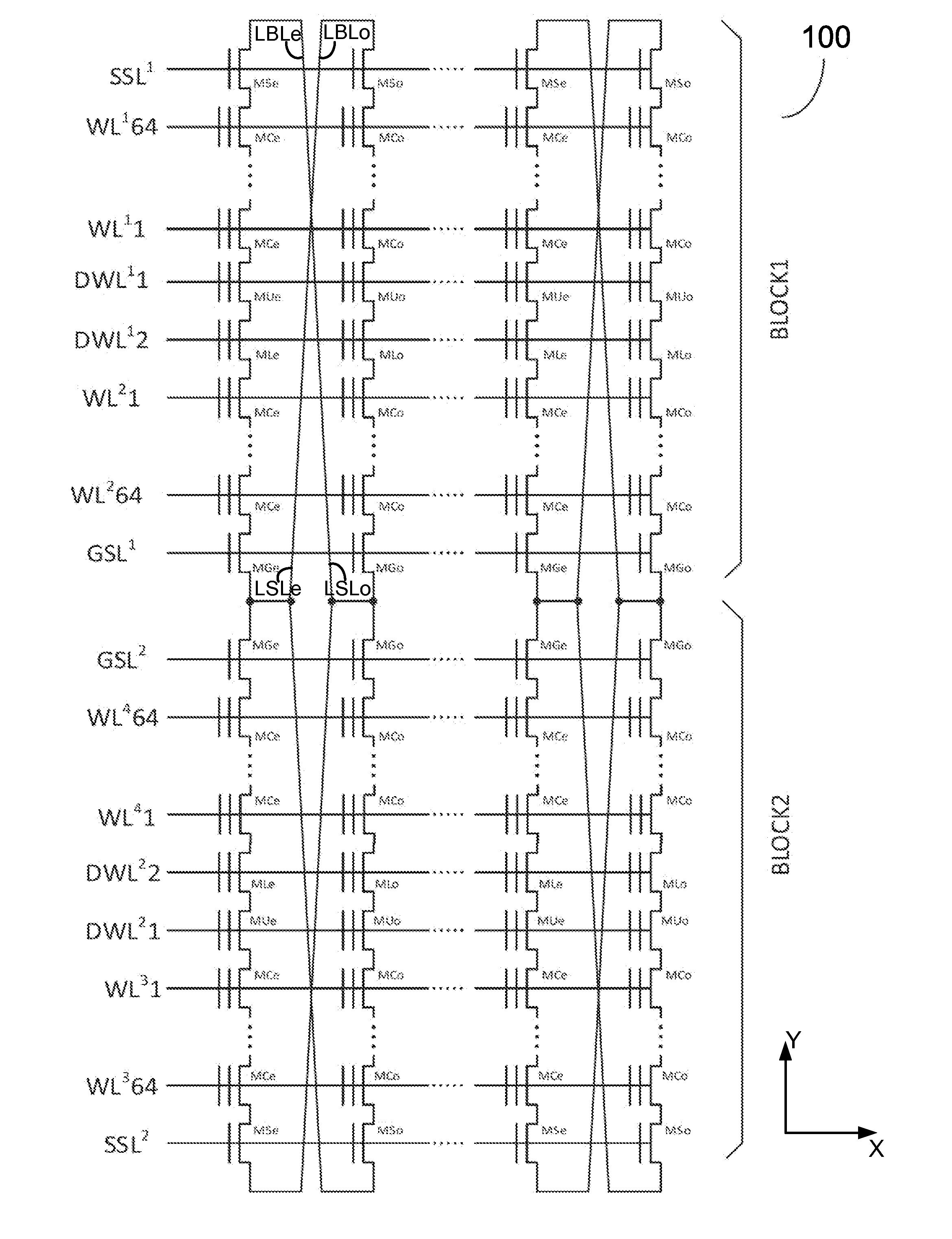

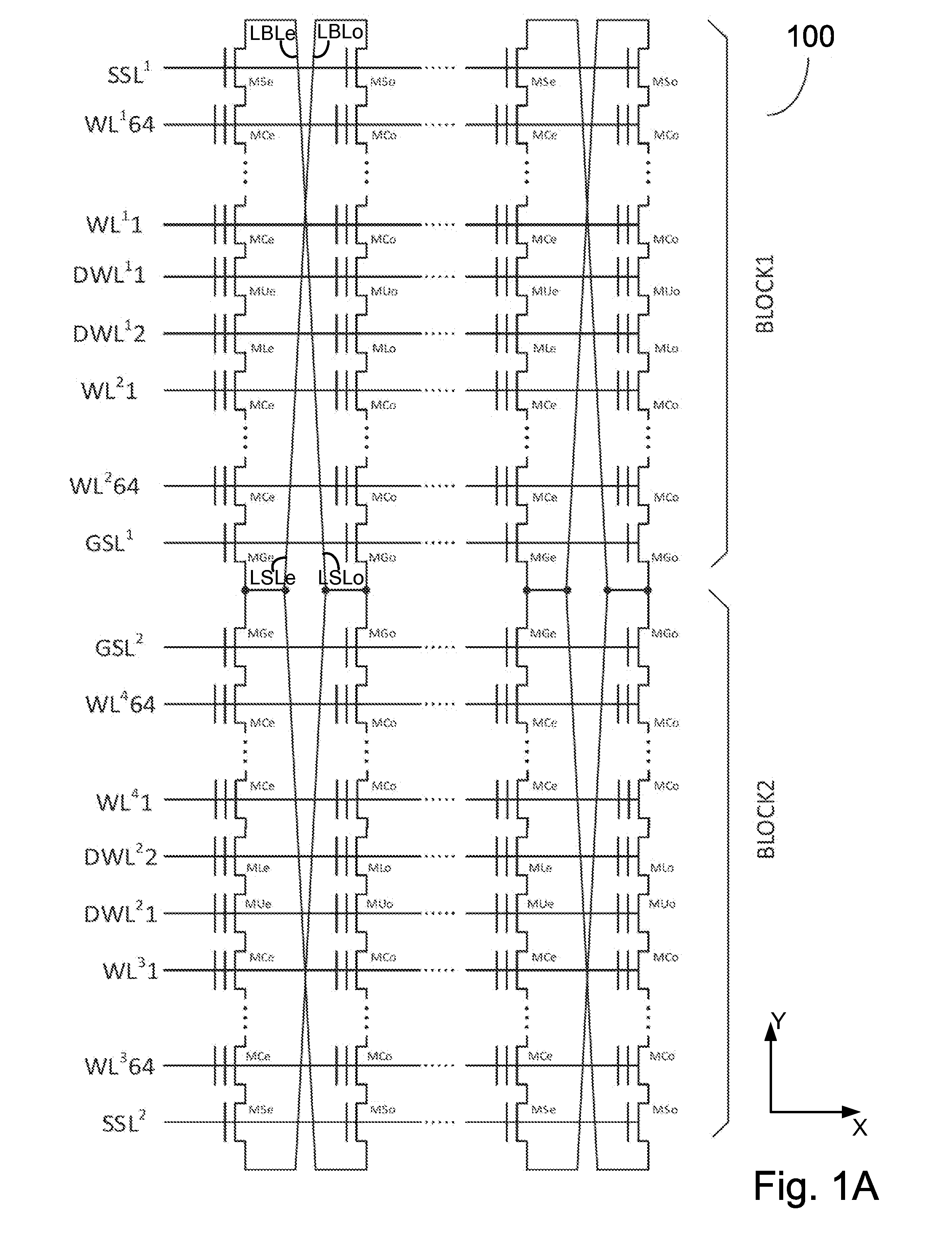

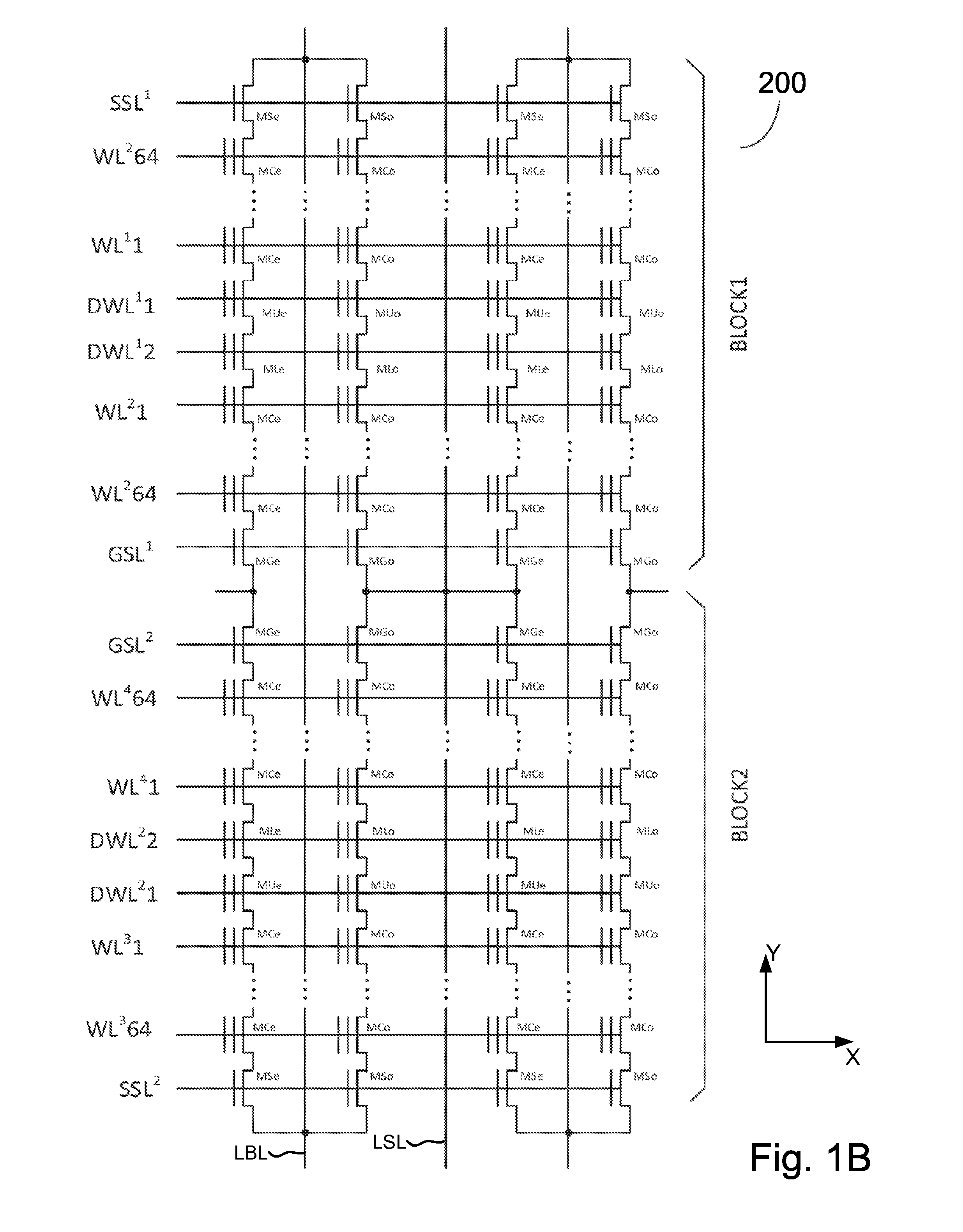

YUKAI VSL-BASED Vt-COMPENSATION FOR NAND MEMORY

ActiveUS20160027504A1Less Yupin coupling effectLess capacitanceRead-only memoriesDigital storageVirtual cellBatch processing

A YUKAI NAND array comprising multiple strings associated with hierarchical global / local bit lines (GBL / LBL) and each string being associated with one LBL and having adjacent LBL as a dedicated local source line (LSL) without a common source line to connect all strings. Each of the LBLs is interleavingly associated with either an Odd or Even string selected via one pair of dummy cells inserted in each string and is used as one on-chip PCACHE register with full BL-shielding without wasting extra silicon area to allow batch-based multiple concurrent MLC All-BL, All-Vtn-Program and Alternative-WL program, Odd / Even read and verify operations with options of providing individual and common VSL-based Vt-compensation and VLBL compensations to mitigate high WL-WL and BL-BL coupling effects. Bias conditions in each string are provided to correctly sense highly-negative erase-verify voltage, multiple negative program-verify voltages and without VDS punch-through, breakdown and body-effect in both boundary and non-boundary WLs cells.

Owner:LEE PETER WUNG

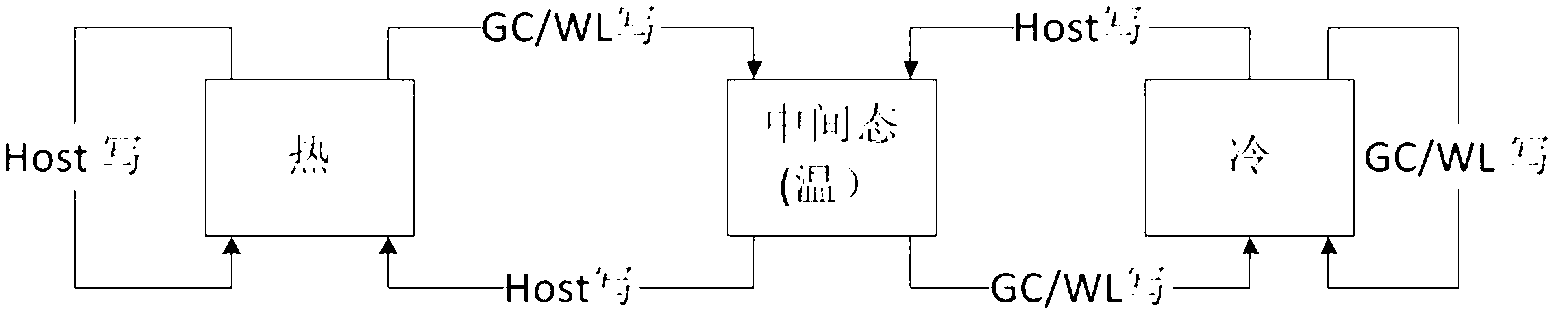

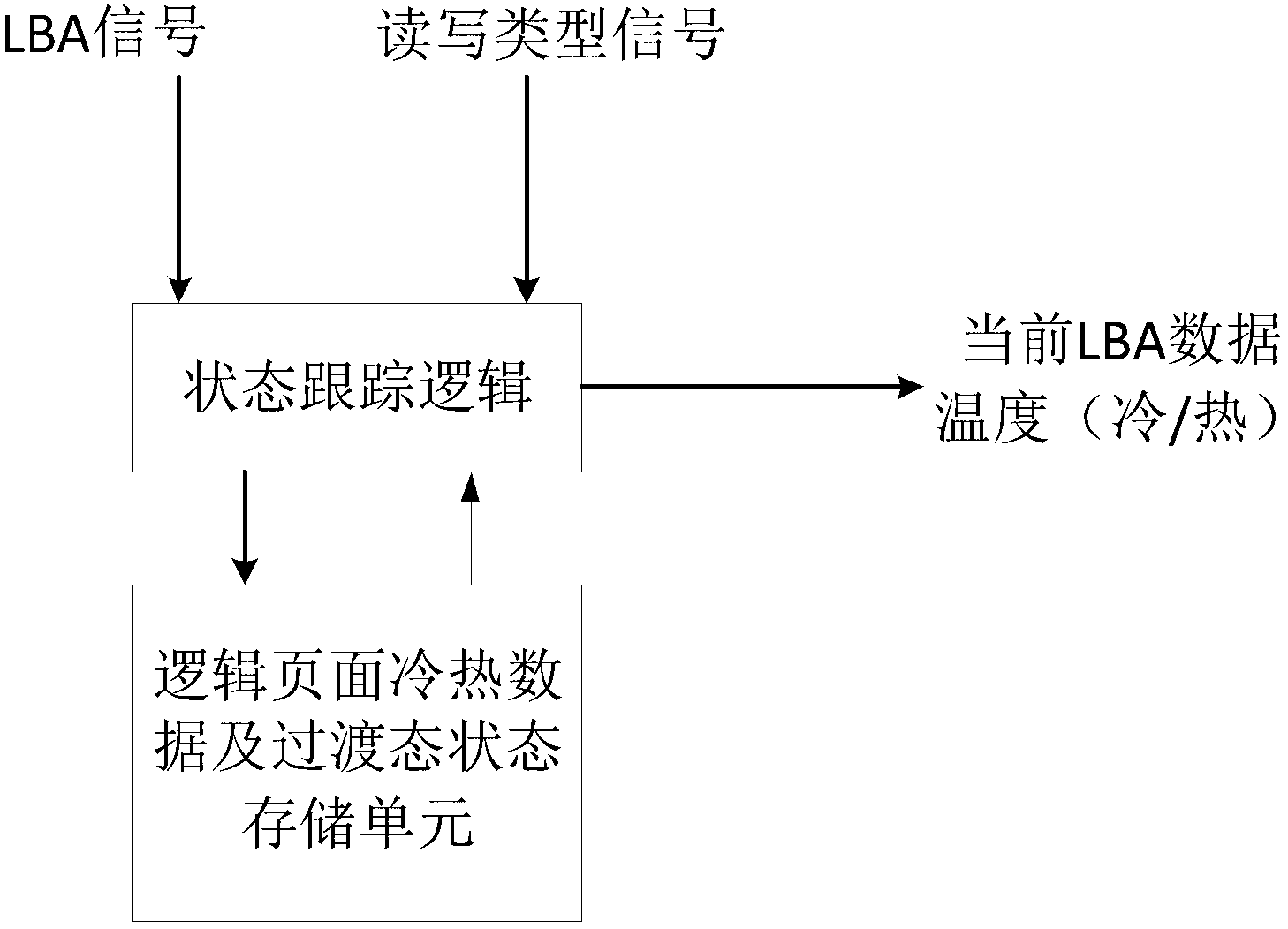

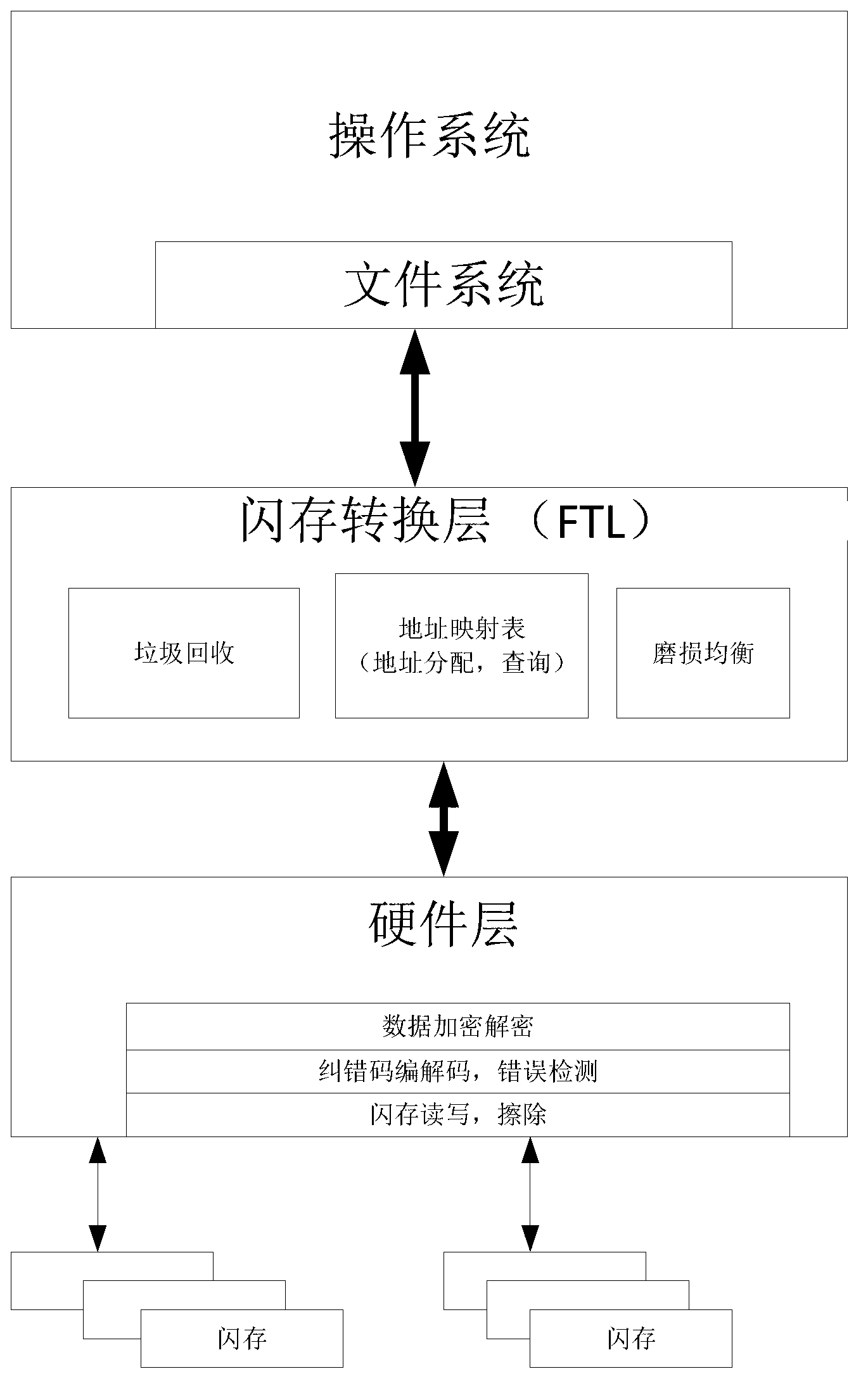

Storage system and method based on solid state medium and cold-hot data identification method

ActiveCN102799534AThe identification method is simpleGood for dynamic identificationMemory architecture accessing/allocationMemory adressing/allocation/relocationSolid-state storagePhysical address

The invention discloses a storage system and a method based on a solid state medium. The storage system comprises at least one identification method of cold-hot data, the identification method is used for identifying the state of a logic page, and the state at least comprises a cold data state and a hot data state; the identification method comprises the following steps: if the logic page is updated for one or multiple times by a host in a preset time, judging that the logic page is in the hot data state; otherwise, if the logic page is not updated by the host for a long time, and the updating is carried out for one or multiple times to the storage physical address of the logic page by the action of a garbage recycle and abrasion balancing unit, judging that the logic page is in the cold data stage. According to the storage system and the method based on the solid state medium, the performances (reading and writing speeds and bandwidth) of the solid state storage can be improved, and the purpose of achieving maximal service life of the solid state storage system is realized by the reduction of the written data.

Owner:SHANNON SYST

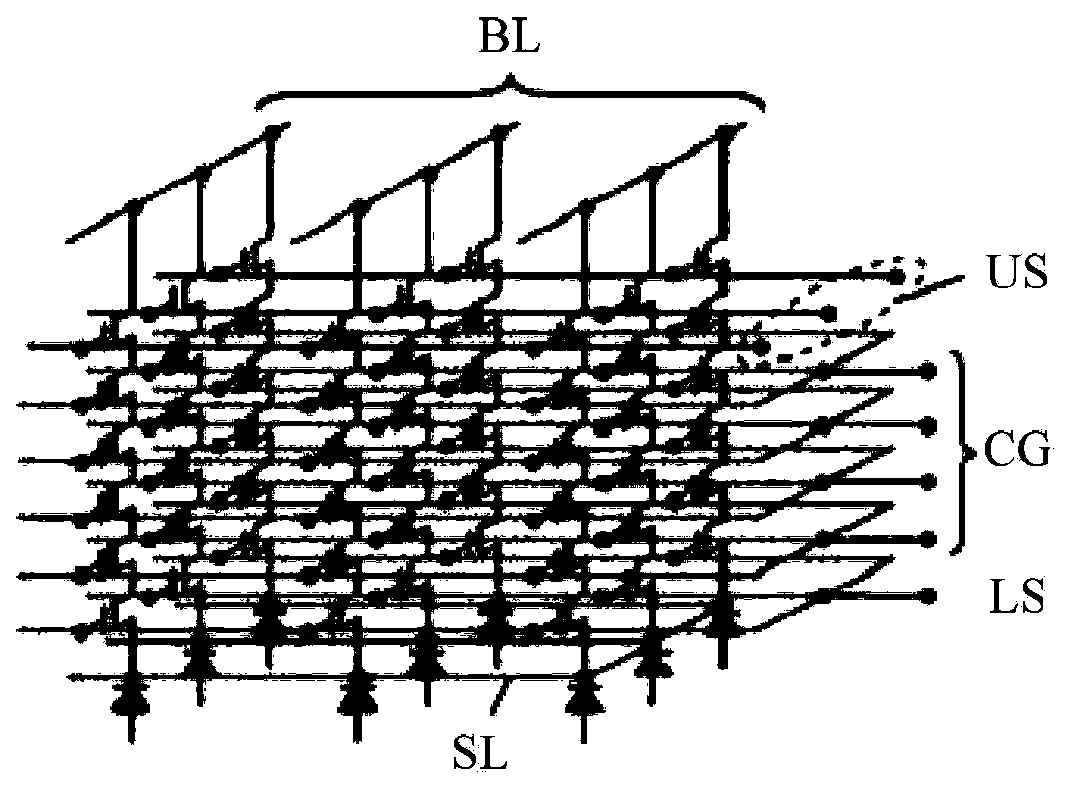

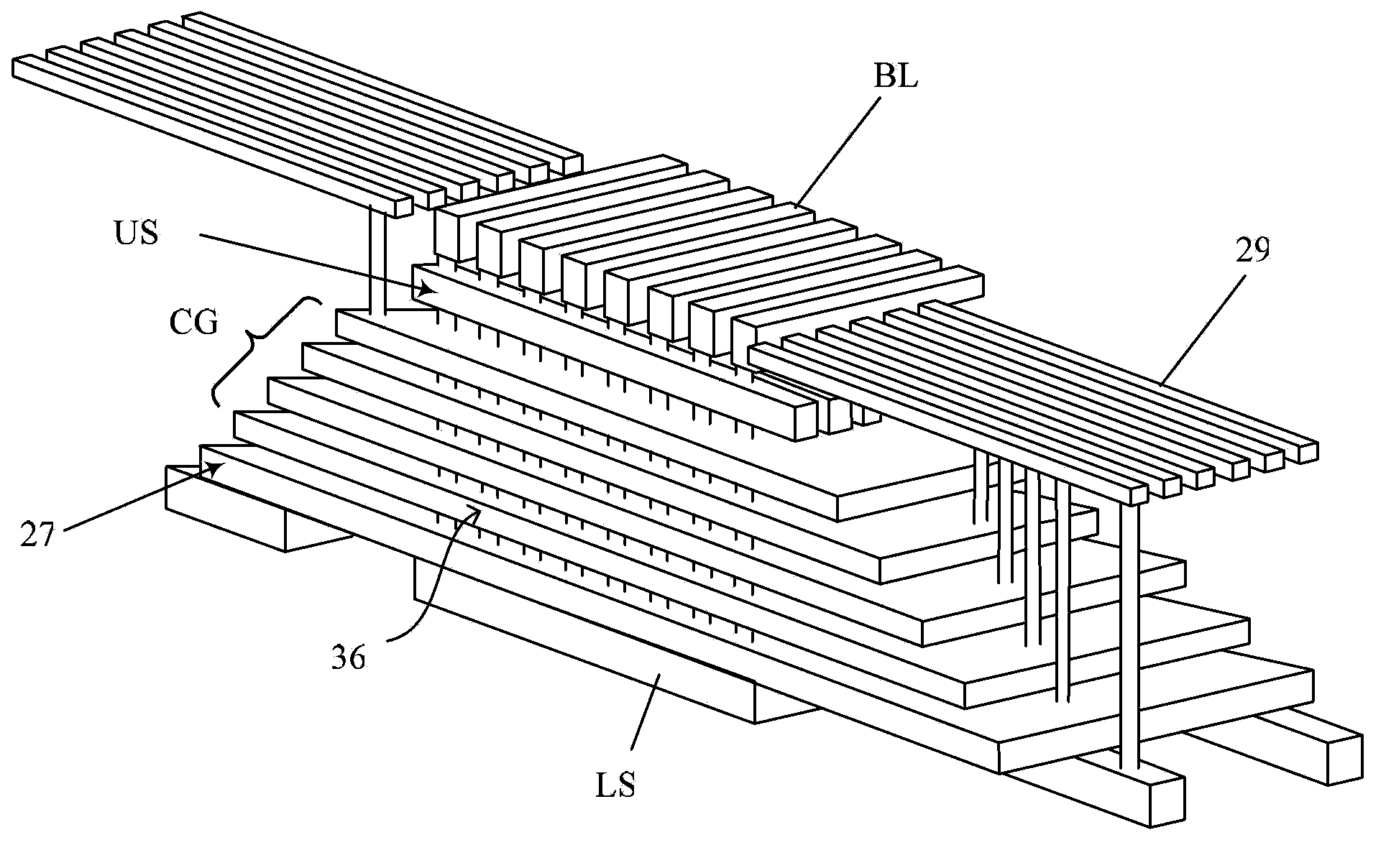

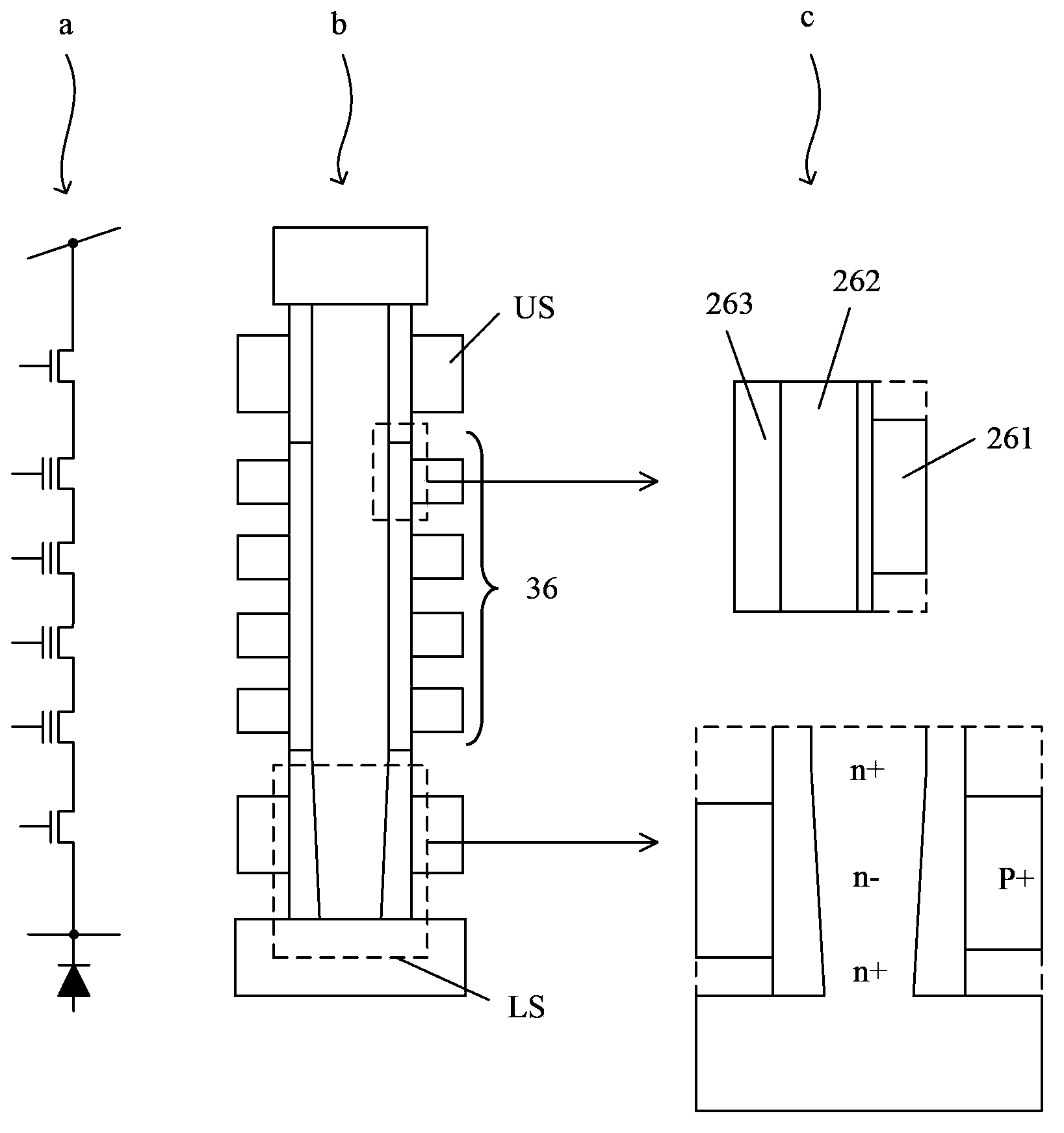

3D (three-dimensional) NAND memory and manufacturing method thereof

ActiveCN103680611AImprove controlReduce parasitic parametersSolid-state devicesRead-only memoriesInput controlComputer science

The invention discloses a 3D (three-dimensional) NAND memory and a manufacturing method of the 3D NAND memory. The 3D NAND memory comprises multiple layers of storage arrays and multiple layers of control grid circuits, wherein each layer of the control grid circuit is electrically connected to the same layer of the storage array, so that selection of each layer of the storage array is realized; each layer of the control grid circuit is obtained by cascading a same number of transistors; grids of all the transistors of the control grid circuits are electrically connected to control wires; the number of the control wires is as the same as that of the transistors comprised in each layer of the control grid circuit; the grids of different transistors positioned on the same layer of the control grid circuit are electrically connected to different control wires. According to the 3D NAND memory, a small number of input control wires SSL select a large number of control grid layers through the control grid circuits, so that the area and the volume of the whole memory cannot be enlarged due to the increase of the number of the required layers of control grids when the storage capacity of the memory is improved due to the increase of the number of storage unit layers.

Owner:SEMICON MFG INT (SHANGHAI) CORP

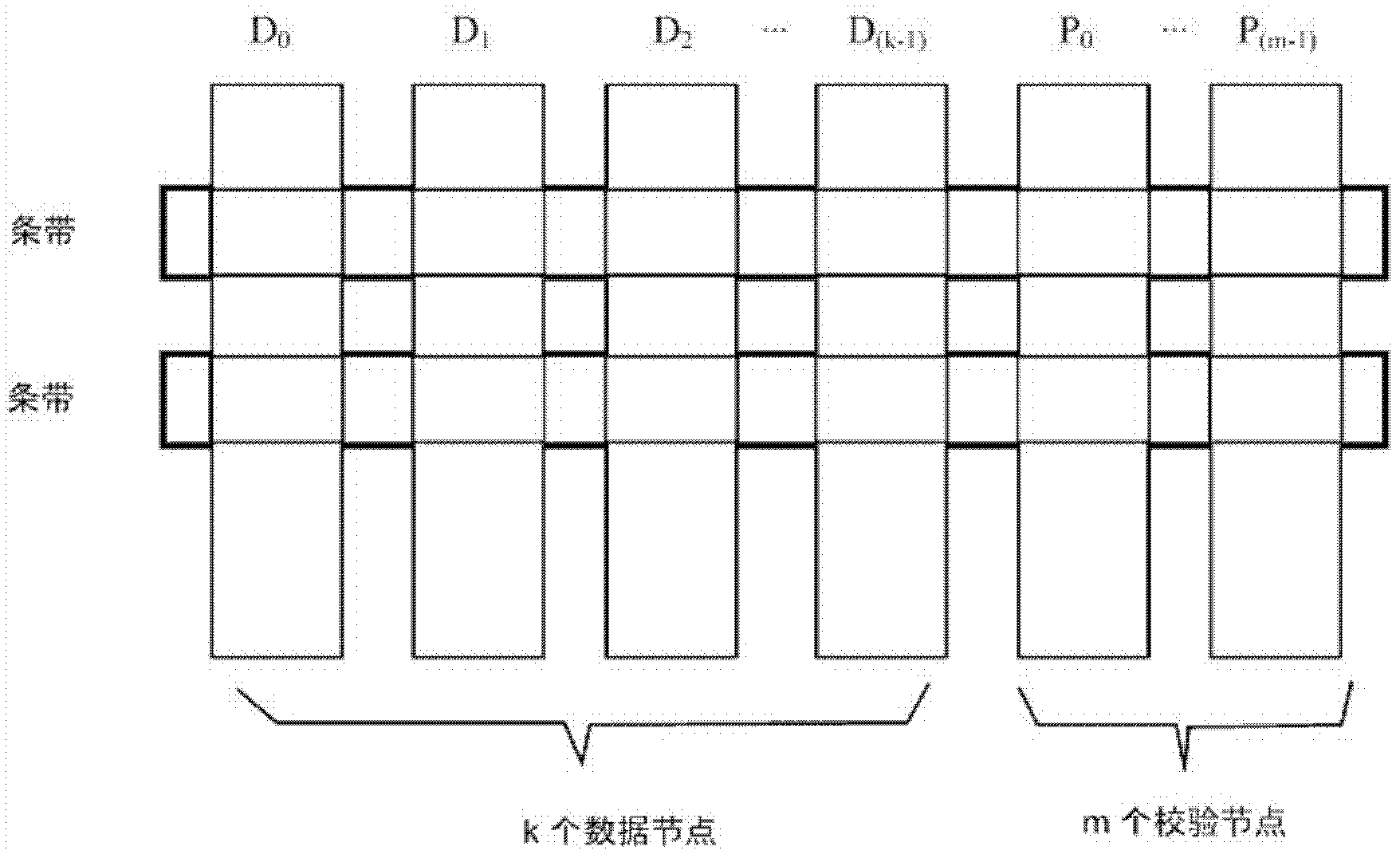

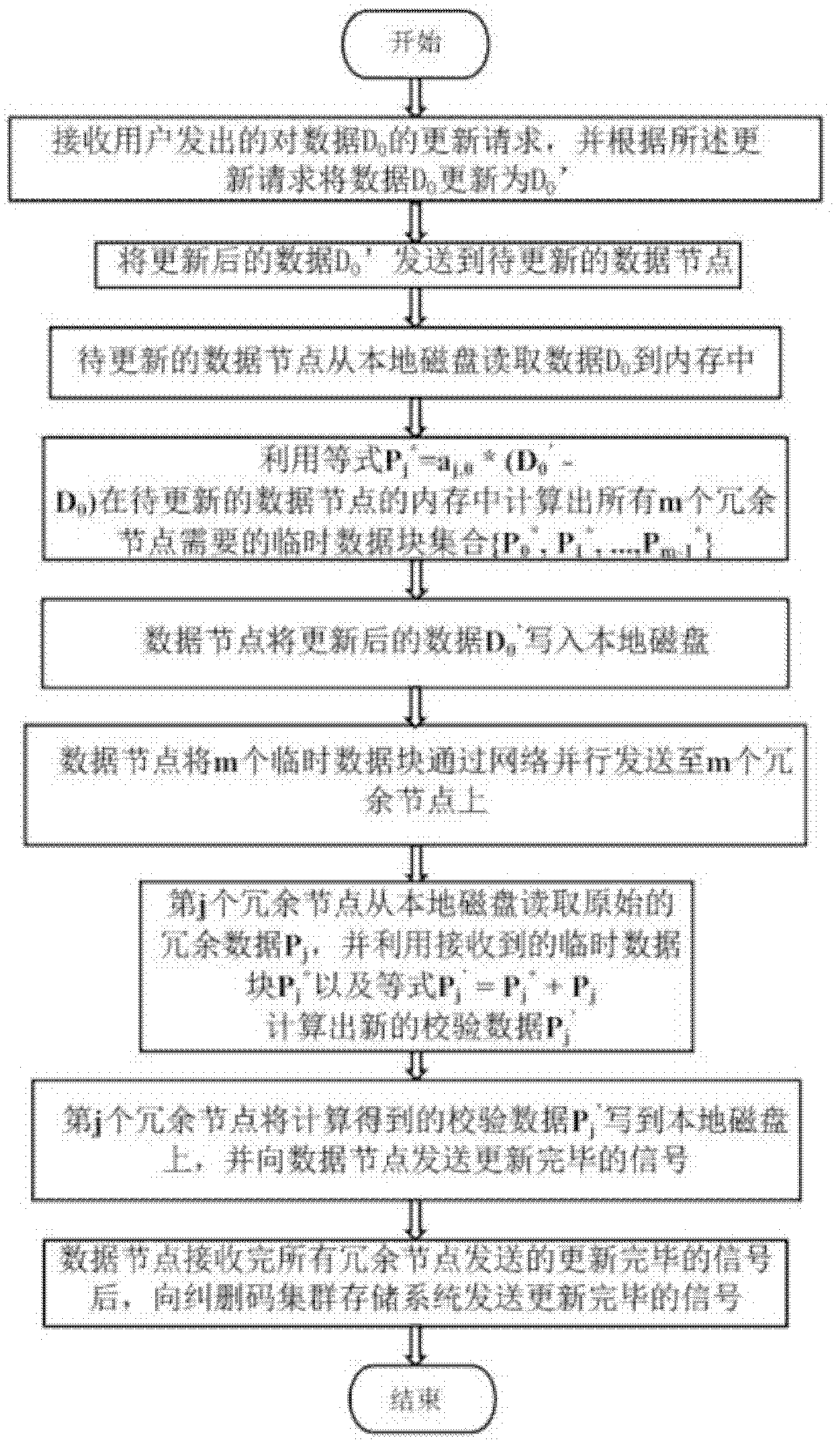

Local data updating method based on erasure code cluster storage system

InactiveCN102681793ASave bandwidthReduce transmissionInput/output to record carriersRedundant data error correctionOperating systemData node

The invention discloses a local data updating method based on an erasure code cluster storage system, which comprises the following steps: receiving a data D0 updating request sent by a user; updating a data D0 into a data D0'; sending the data D0' to a data node to be updated; reading the data D0' from a local disc to a memory by the data node to be updated; calculating a provisional data block set needed by m redundant nodes in the memory of the data node to be updated; writing the data D0' into the local disc by the data node to be updated; sending m provisional data blocks onto the m redundant nodes by the data node to be updated through the network at the same time; reading an original redundant data Pj by the j redundant node from the local disc, and calculating to obtain a new check data Pj'; and writing the check data block Pj' obtained through calculating into the local disc by the redundant node. Due to the adoption of the local data updating method based on the erasure code cluster storage system, the consumption of the bandwidth can be reduced effectively, the load pressure of the update server can be decreased, and the data updating performance can be improved.

Owner:HUAZHONG UNIV OF SCI & TECH

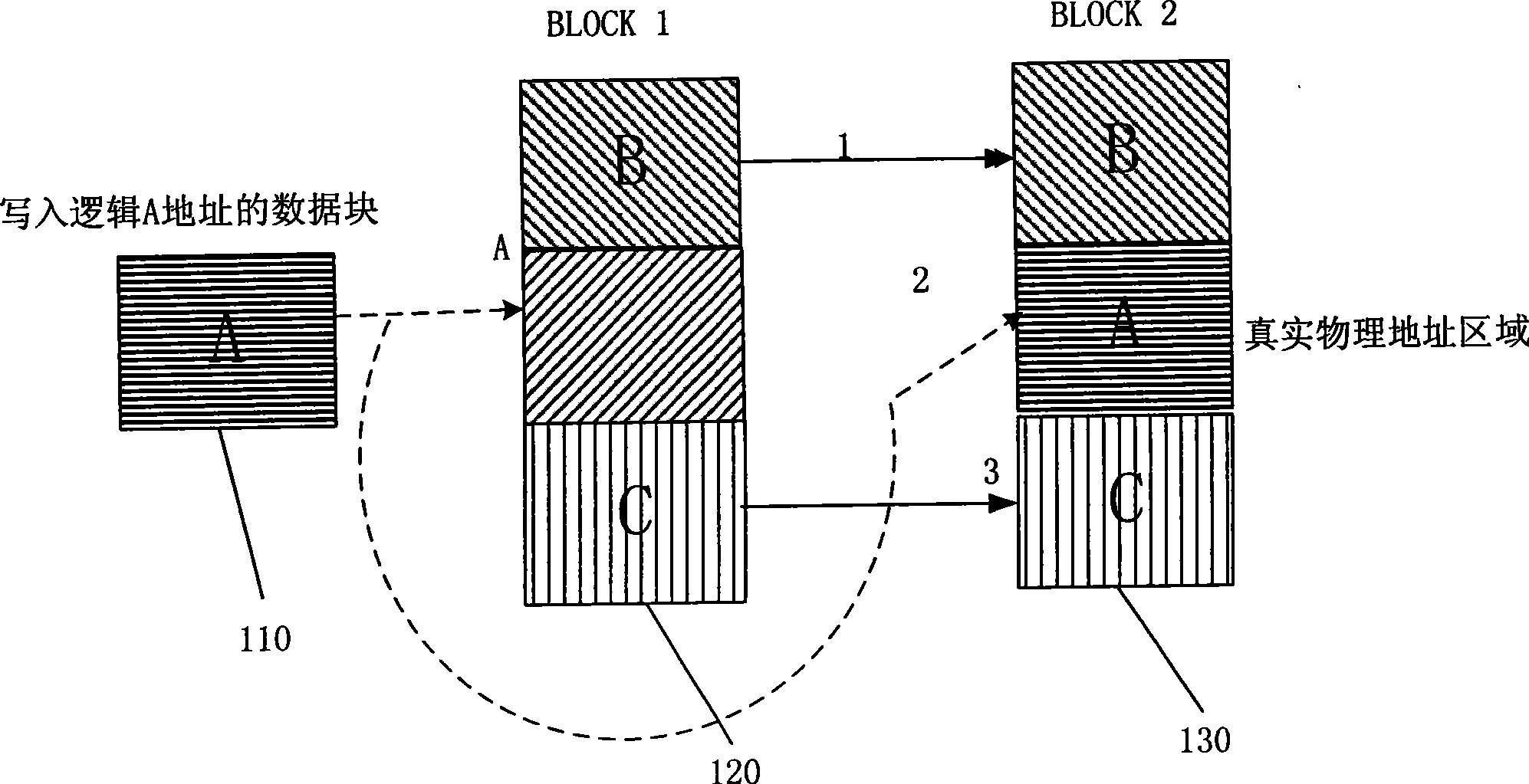

NAND flash memory optimizing and managing method based on data interchange zone

ActiveCN101382918AExtended service lifeImprove read and write speedMemory adressing/allocation/relocationFlash memory controllerMemory controller

The invention discloses a NAND Flash memory optimization management method based on a data exchange zone, which comprises the following steps: at least 2 blocks are set on the NAND Flash as the data exchange zone; a dynamic data effectiveness identification item is added for recording the aging degree of the data blocks in the data exchange zone; and the data block, before being modified during the setting period, is written into the real physical address of the flash memory after a logical address is re-mapped. By the management method, through the data exchange zone of a plurality of blocks set in the NAND Flash chip by a flash memory controller, the mid-process data during the read-write is stored by buffering, thus reducing the write-in frequency in the system document zone of the NAND Flash chip, increasing the read-write speed of the chip, as well as balancing the abrasion of the chip and prolonging the service life of the NAND Flash.

Owner:SLICONGO MICROELECTRONICS INC

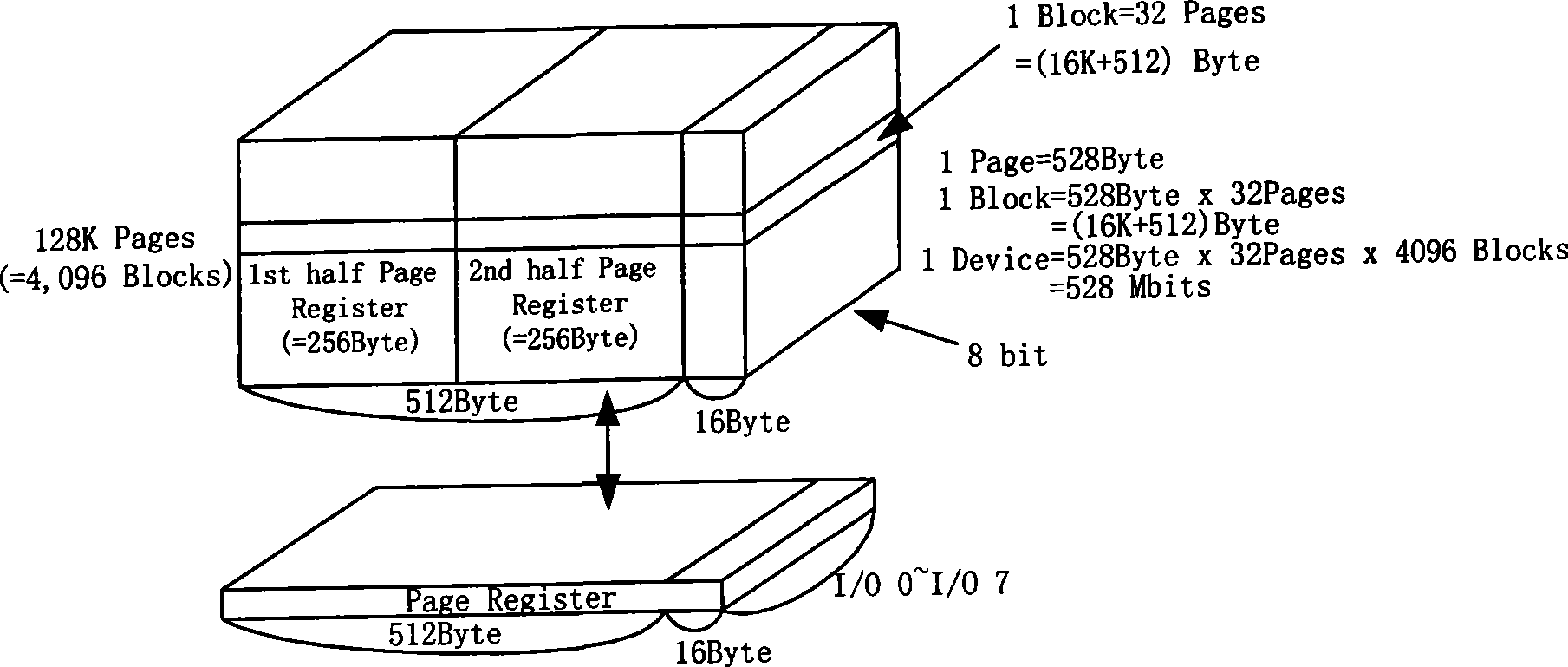

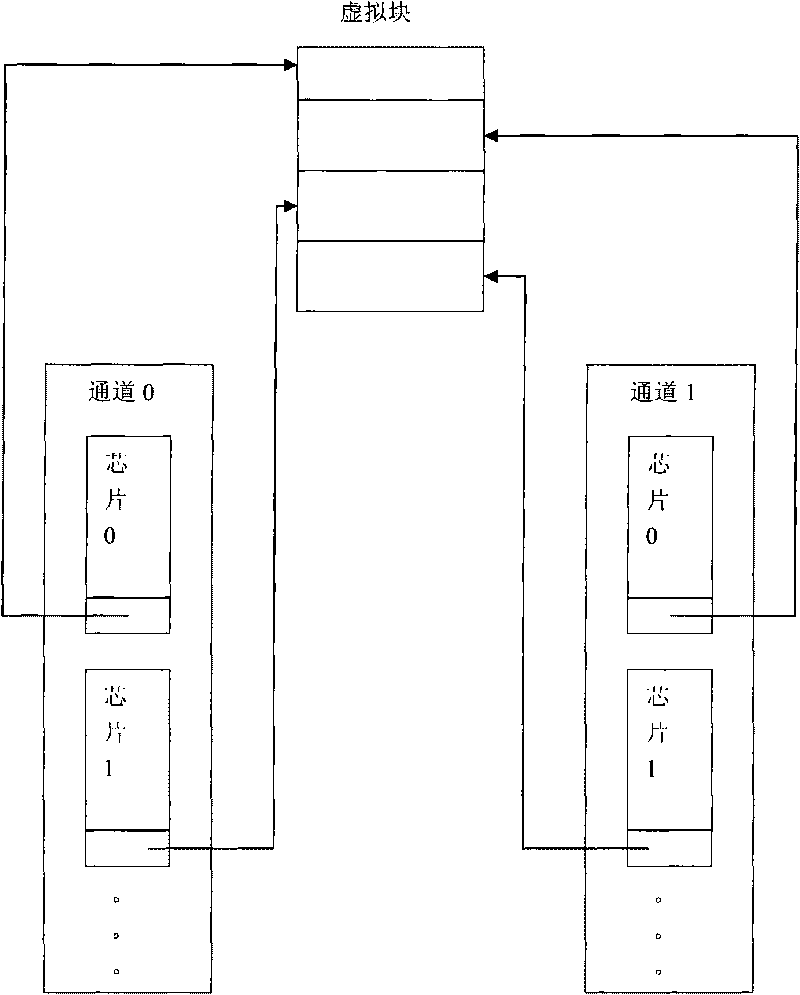

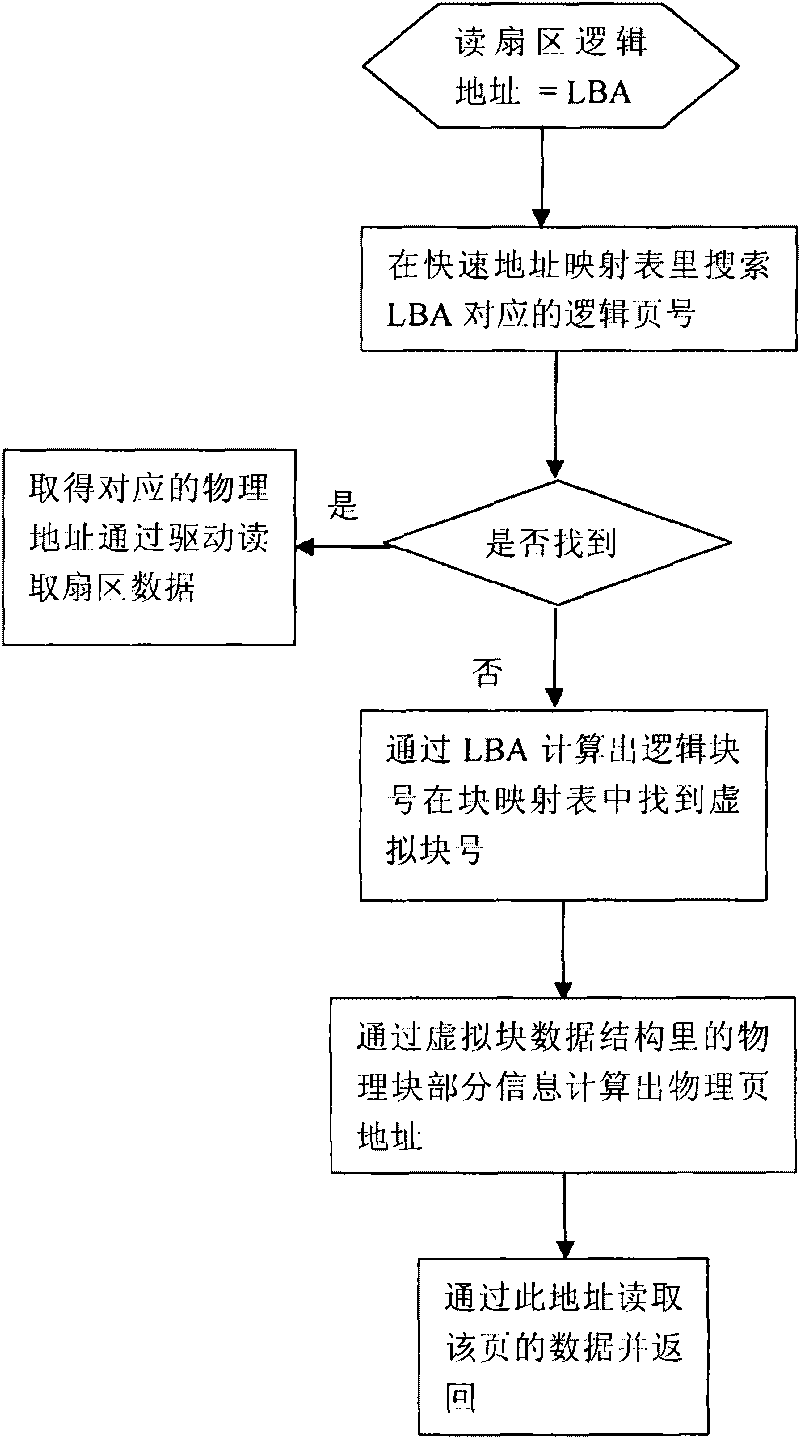

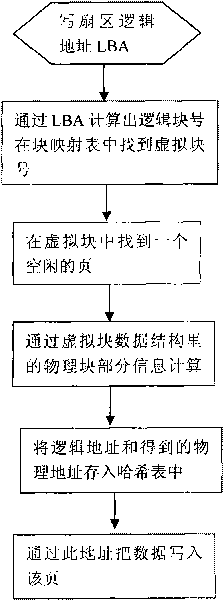

Method for writing in and reading out data based on virtual block flash memory address mapping

InactiveCN101727295AIncrease profitExtend your lifeInput/output to record carriersMemory adressing/allocation/relocationParallel computingAddress mapping

The invention relates to a method for writing in and reading out data based on virtual block flash memory address mapping. The method is characterized by comprising the following steps of: building a virtual block, building an initial address mapping table, writing in data and reading out the data. The method solves the technical problem on increasing the speed without utilizing the parallel advantages in a passage, has the advantage of mapping the data in a plurality of chips in a plurality of passages so as to simultaneously carry out the parallel operations of the passages and the parallel operations in the passages for increasing the read-write speed under the circumstance of continuous logic addresses of user data. Meanwhile, the invention can be used for building a virtual block under the circumstance of idleness of a physical block, thereby increasing the utilization rate of the physical block and prolonging the service life of the flash memory chip.

Owner:XIAN KEYWAY TECH

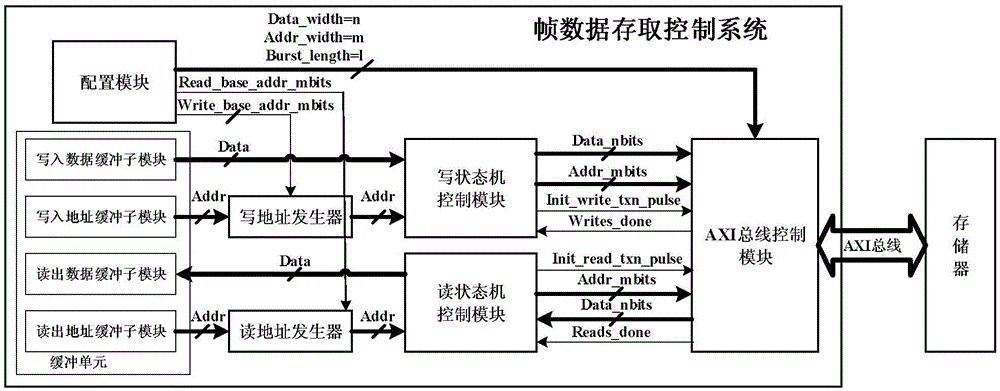

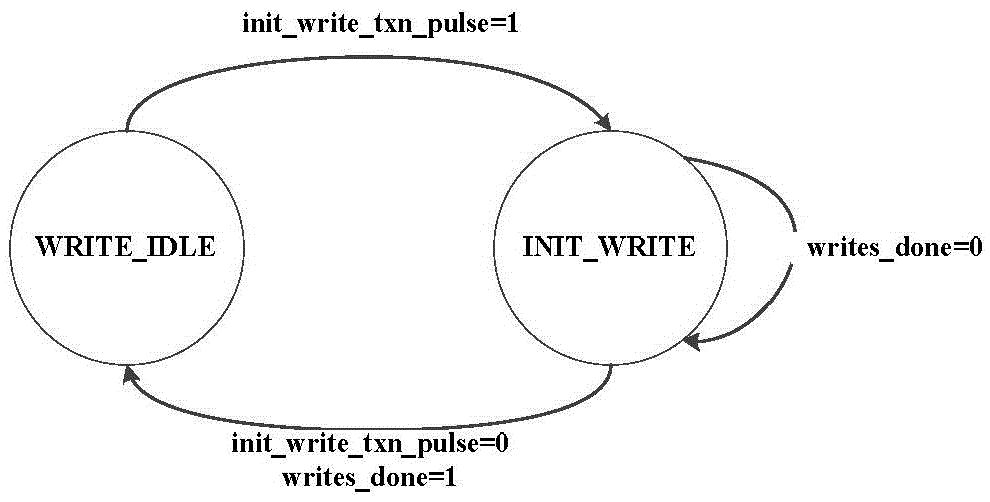

AXI bus based convenient configurable frame data access control system

ActiveCN105468547AIncrease transfer rateFast transmissionElectric digital data processingMachine controlData access control

The invention relates to an AXI bus based convenient configurable frame data access control system, aiming to solve problems that existing methods are complex to operate and the systems in the prior art have low overall performance. The system comprises a configuration module, a buffer module, a write address generator module, a read address generator module, a read state machine control module, a write state machine control module and an AXI bus control module. The buffer module comprises a write data buffer submodule, a write address buffer submodule, a read data buffer submodule, and a read address buffer submodule. The system is applied to the field of data access.

Owner:HARBIN INST OF TECH

Multi-channel flash memory transmission controller, chip and storage device

InactiveCN1790308AImprove read and write speedElectric digital data processingControl signalBus mastering

The invention discloses a multichannel flash memory transmission controller and chip with the controller and storage equipment, which comprises the following parts: main control state set, bus control unit and data bus control unit, wherein the bus control unit sends control signal to several flash memories through a group of multiplying control bus, which returns the state signal to main control state set; the state signal of several flash memories is input in the bus control unit at line pattern through multiplying control bus; several groups of individual data bus transmits data to the data bus control unit simultaneously. The invention improves the reading and writing speed of flash memory greatly.

Owner:VIMICRO CORP

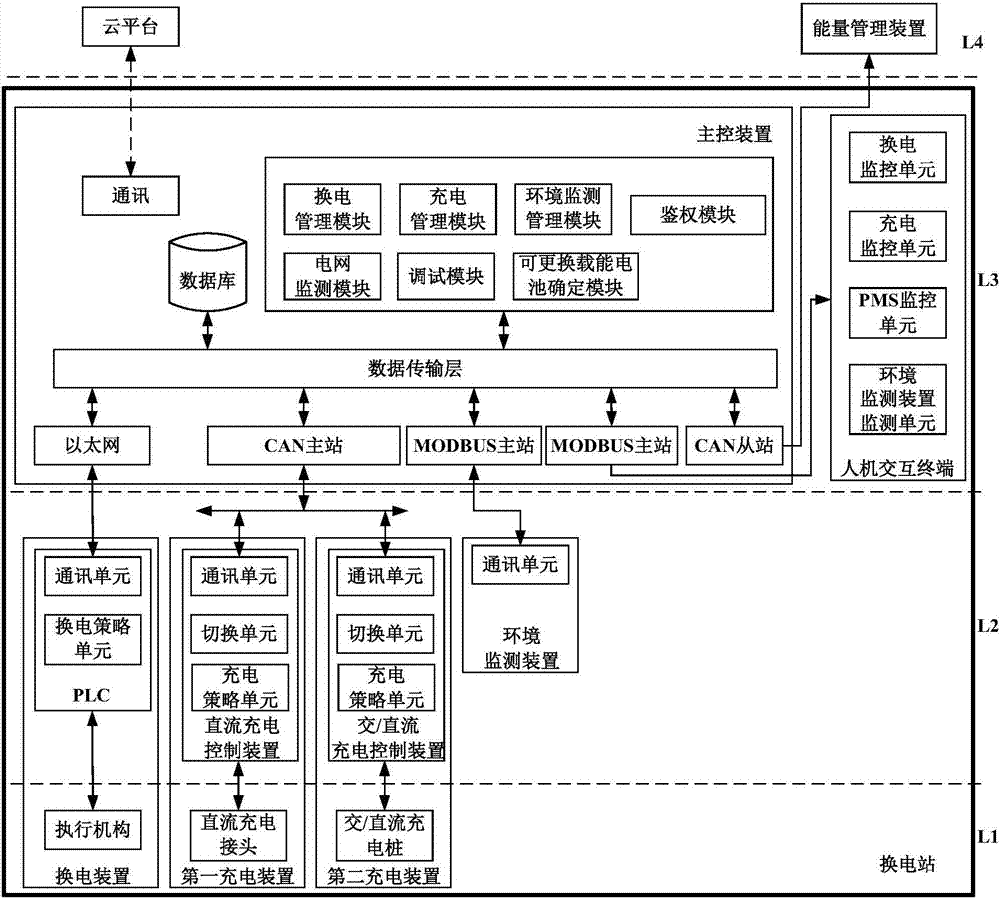

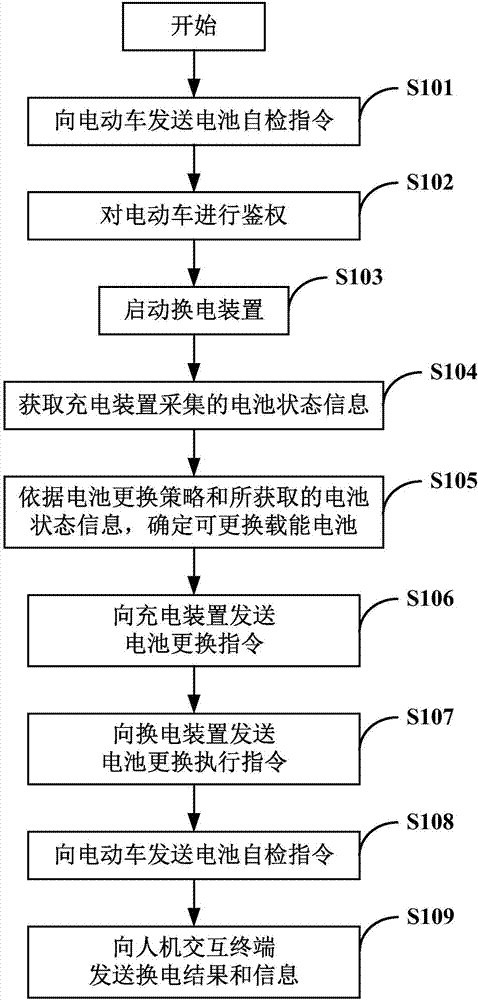

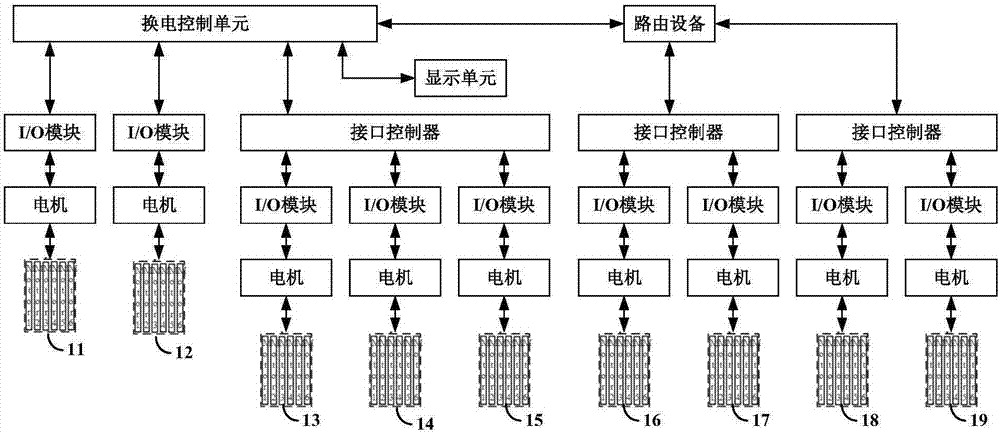

Charging and battery replacement station and charging and battery replacement control system

ActiveCN107161020AExpandable and flexibleQuick RechargeCharging stationsElectric propulsion mountingBattery state of chargeElectricity

The invention relates to a charging and battery replacement station and a charging and battery replacement system. Bay level equipment of the system comprises a battery replacement device and a charging device. Station control level equipment comprises a master control device. The master control device communicates with the battery replacement device through a first type bus and communicates with the charging device through a second type bus. The master control device is configured to control the charging device to charge an energy loaded battery and / or an electric automobile according to a received charging instruction, and / or to determine a replaceable energy loaded battery of the electric automobile according to energy loaded battery charging state information fed back by the charging device and to control the battery replacement device to replace the determined replaceable energy loaded battery to the electric automobile. The charging and battery replacement station comprises the charging and battery replacement control system. Compared with the prior art, by adoption of the charging and battery replacement control system, flexibility extension of charging and battery replacement of the charging and battery replacement station is facilitated, and electric automobile charging and battery replacement demands increasing day by day are met.

Owner:NIO CO LTD

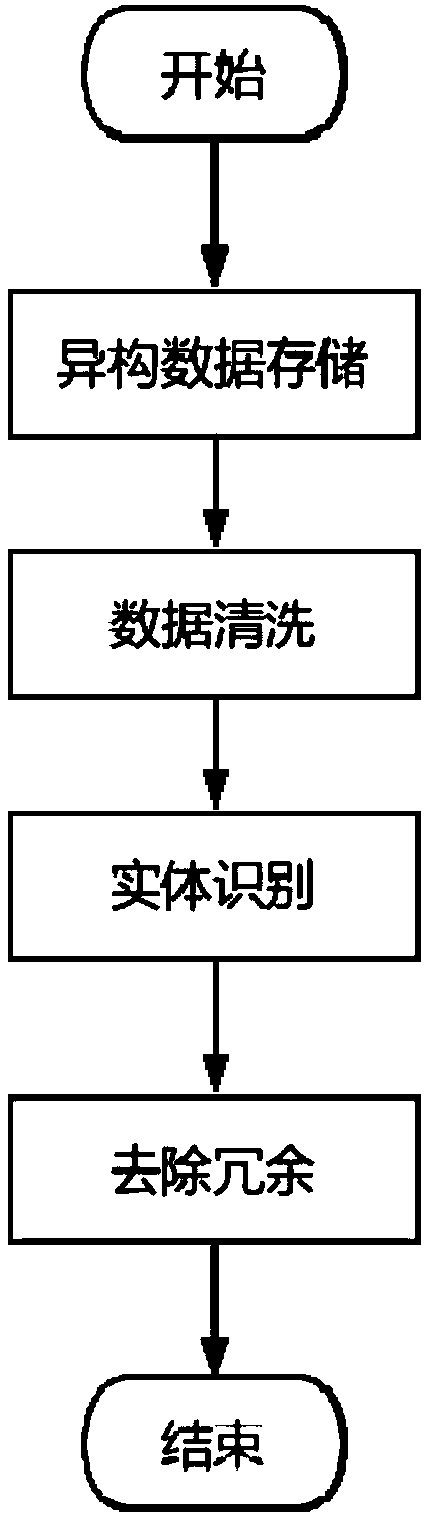

A preprocessing method of multi-source heterogeneous big data

InactiveCN109165202AEfficient preprocessingImprove storage efficiencyDatabase management systemsDatabase modelsPretreatment methodDistributed File System

The invention discloses a preprocessing method of multi-source heterogeneous big data, comprising the following steps: 1, heterogeneous data storage: extracting data from heterogeneous data sources according to preset conditions and uploading the data to a distributed file system HDFS for storage; 2, data cleaning: loading the data in the distributed file system HDFS into the memory through a Spark frame, removing the duplicate data and noise data, and transforming the format; 3, entity identification: identifying different representations of the same entity for the cleaned data, correctly identifying all the different entities, and merging the data of the same entity; 4, removal of redundancy: using hash-based duplicate data removal technology to remove redundant data. The method of the invention can reduce the storage resource and the network bandwidth, improve the data storage efficiency, and improve the quality of the subsequent data analysis work.

Owner:SOUTH CHINA UNIV OF TECH

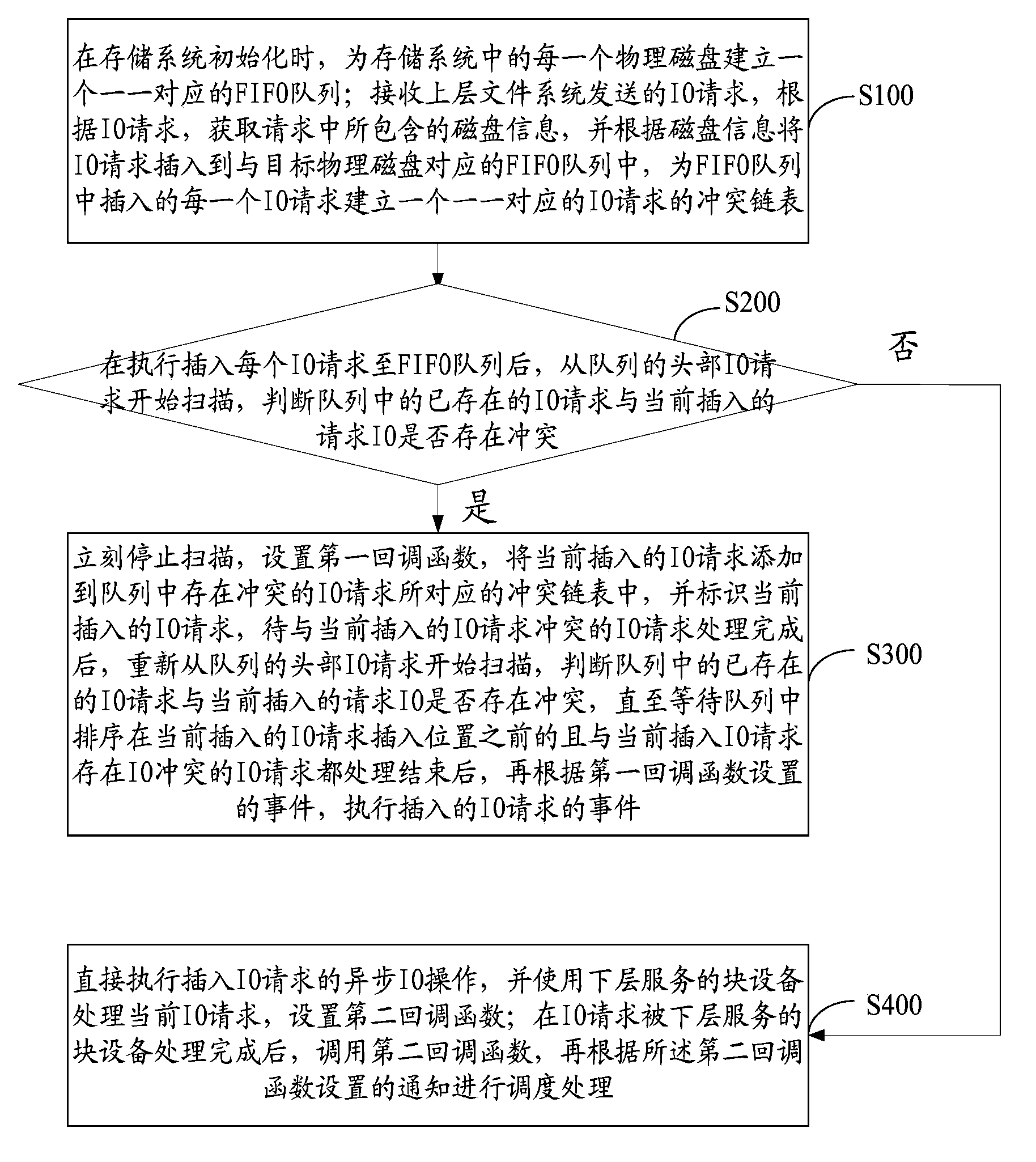

IO (input output) scheduling method and IO scheduling device

ActiveCN103823636AEasy to handleImprove read and write speedInput/output to record carriersSolid-state driveFifo queue

The invention discloses an IO (input output) scheduling method and IO scheduling device. The IO scheduling method includes steps of creating an FIFO (first input first output) queue for each physical disk in a storage system when the storage system is initialized; creating an IO request conflict link table for each IO request inserted into the corresponding FIFO queue; starting scanning head IO requests of the queues after each IO request inserted into the corresponding FIFO queue is executed, judging queue conflicts, recording the IO request conflict link tables, preparing to-be-processed events and transmitting notification by the aid of the conflict link tables. The FIFO queues are in one-to-one correspondence with the physical disks. The IO request conflict link tables are in one-to-one correspondence with the IO requests. The notification indicates that other IO request conflicts in the link tables are relieved. The IO scheduling method and the IO scheduling device have the advantages that large quantities of IO conflicts caused when solid state disks are used as caches and are processed can be prevented, and I / O reading and writing rates and transmission rates can be effectively increased.

Owner:常熟它思清源科技有限公司

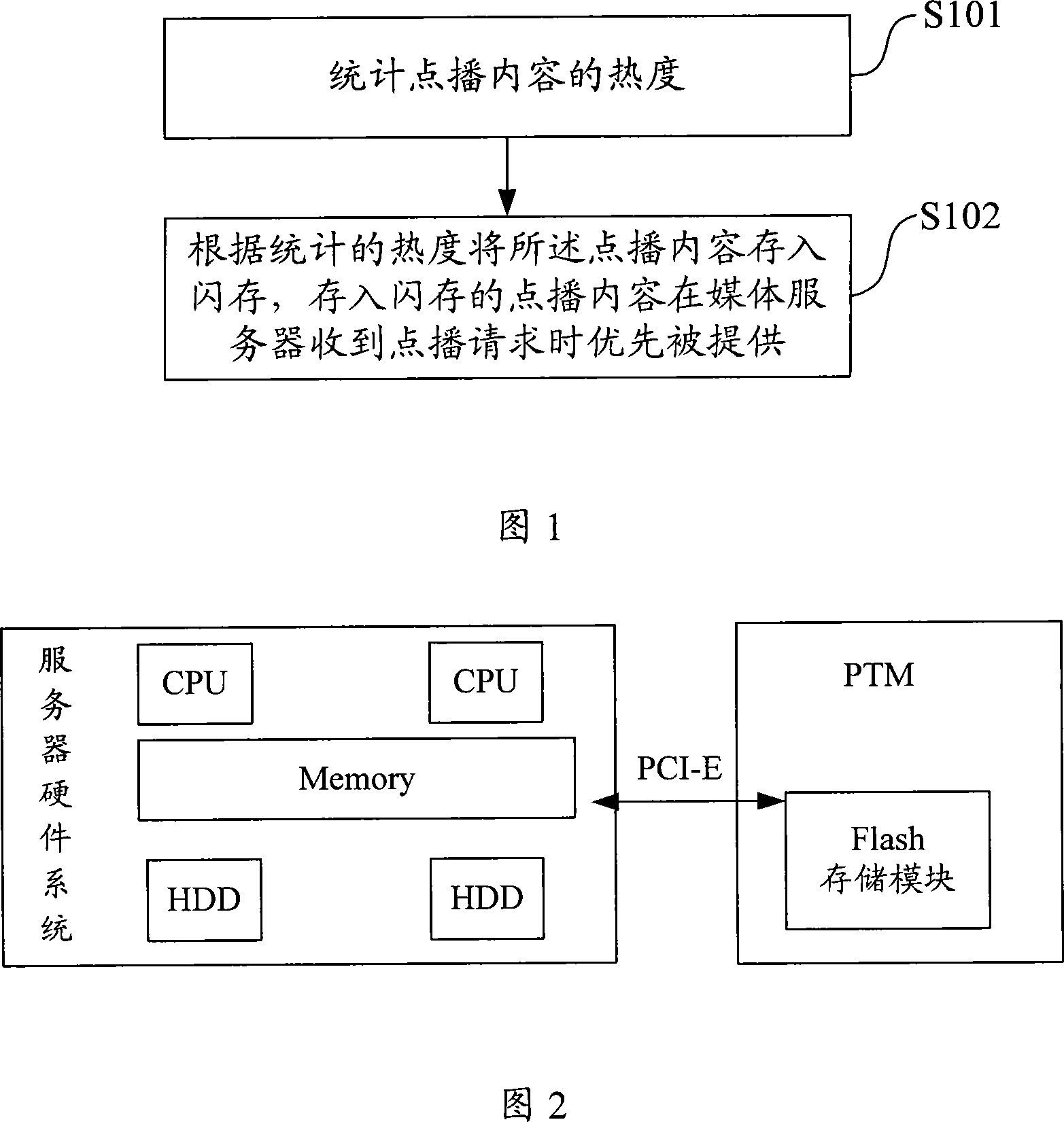

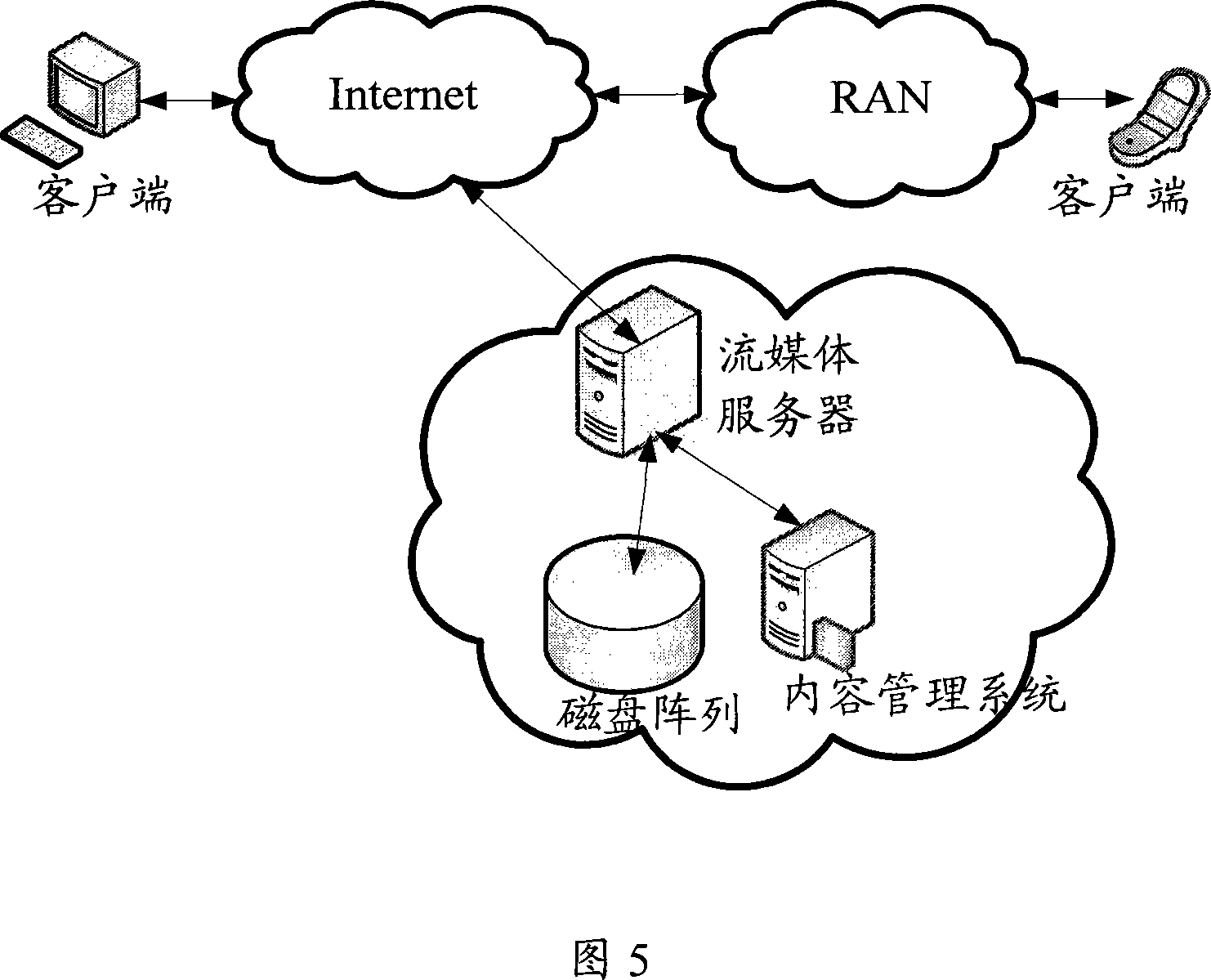

Device, system and method for providing order program contents

InactiveCN101232600AImprove performanceImprove read and write speedTelevision system detailsPulse modulation television signal transmissionMedia serverStart up

The embodiment of the invention discloses a method, a system and an apparatus for providing ordered contents, wherein the method for providing ordered contents comprises: calculating the heat of ordered contents and saving the request contents into a flash disk according to the calculated heat, so when a media server receives the ordering request, priority will be given to the ordered content saved in the flash disk. Through saving the hot movies into the flash disk inside the stream media server, the execution example of the invention can increase I / O read / write speed, and therefore improve the performance of unit stream media servers. Moreover, the flash disk is characterized in that no data are lost in power-off status; therefore, it is not necessary to read data of hot movies from hard drives into the flash disk even in a restart process, so as to improve the start-up speed.

Owner:HUAWEI TECH CO LTD

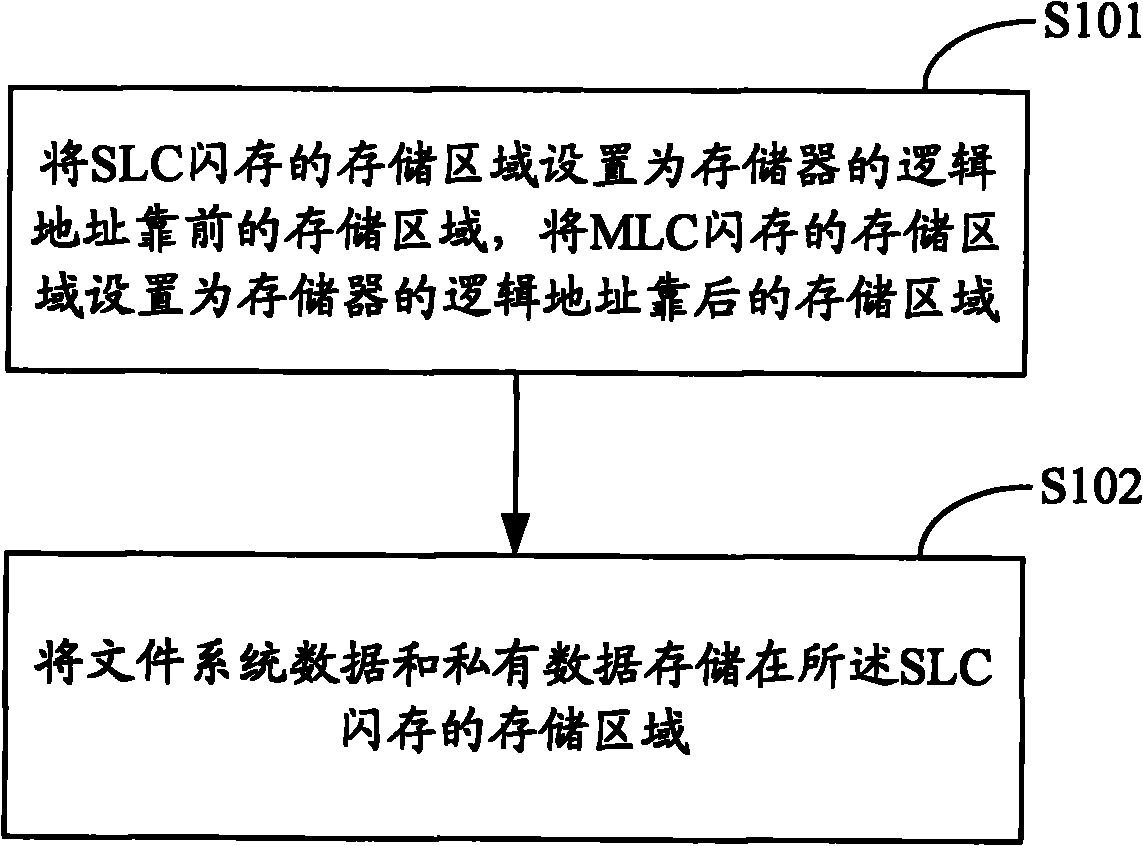

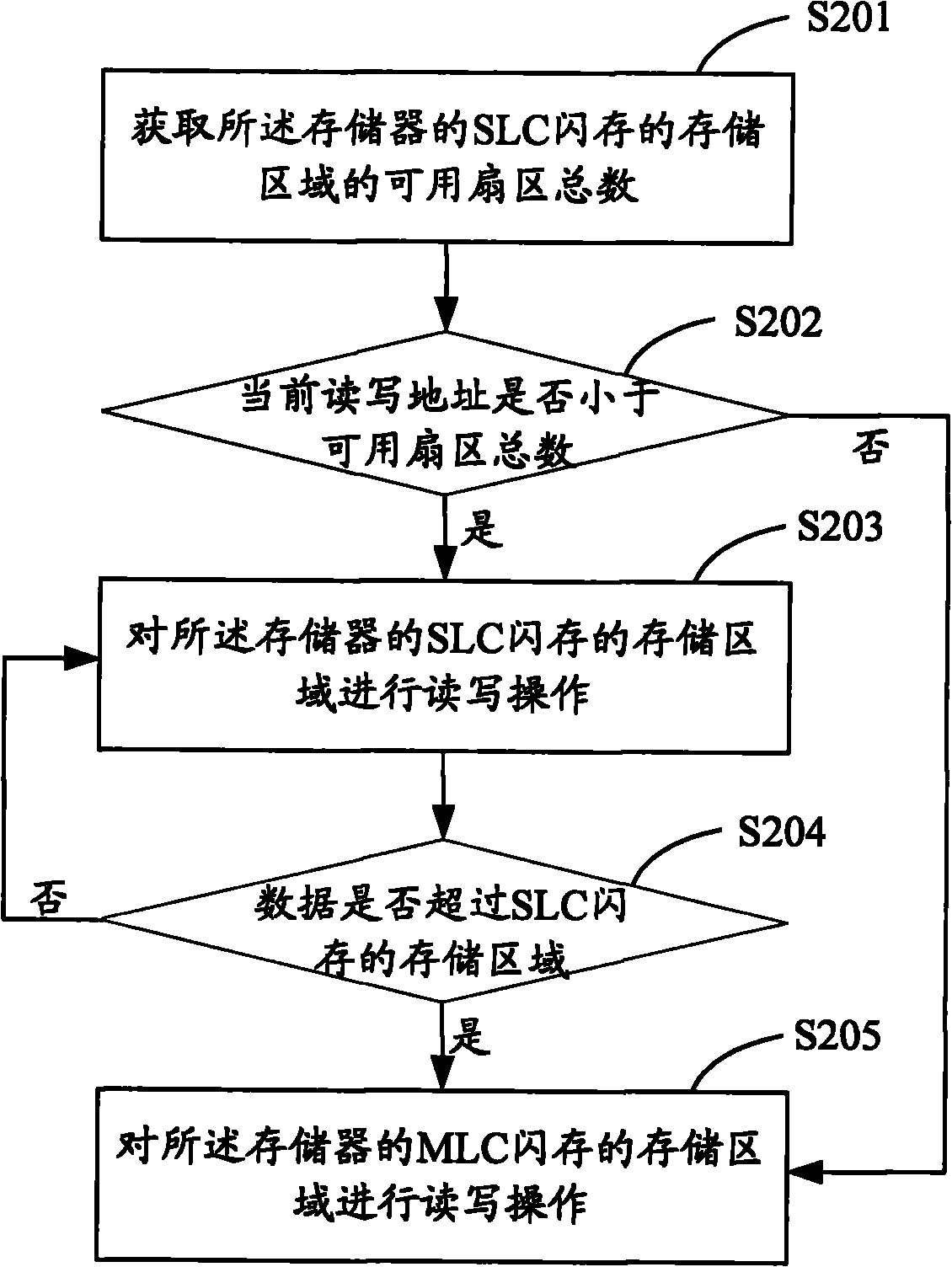

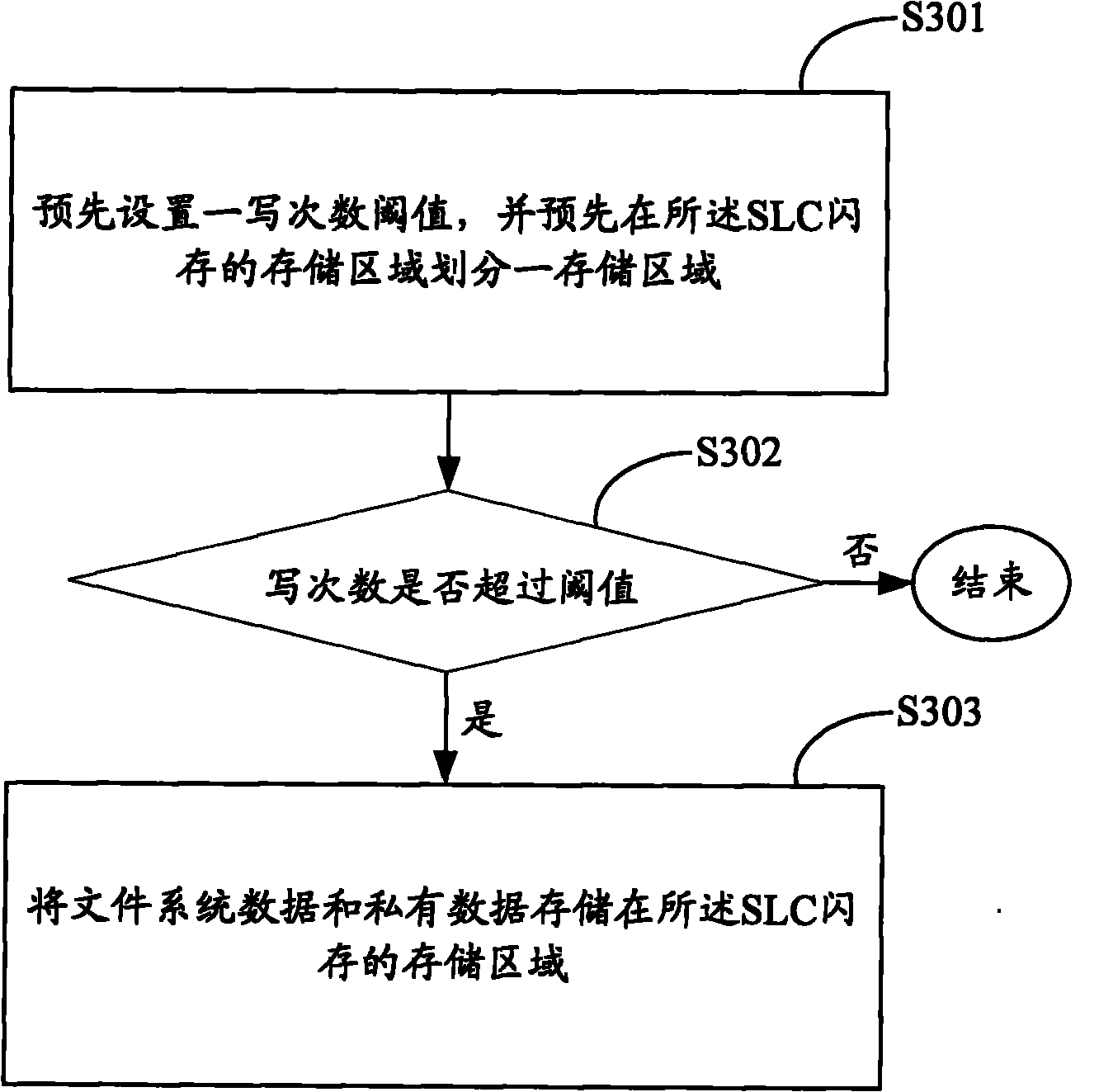

Memory and memory read-write control method and system

InactiveCN102142277AImprove read and write speedEasy to useMemory adressing/allocation/relocationDigital storageLogical addressSingle level

The invention is applied in the technical field of storage, and provides a memory, a memory read-write control method and a memory read-write control system. The memory comprises at least one single-level cell (SLC) flash memory and at least one multi-level cell (MLC) flash memory, wherein the storage region of the SLC flash memory is set as a logic address forward storage region of the memory, and the storage region of the MLC flash memory is set as a logic address backward storage region of the memory. According to the embodiment, perfect combination of respective advantages of the SLC flash memory and the MLC flash memory is realized, the data read-write speed of the memory is improved by fully using the respective advantages of the SLC flash memory and the MLC flash memory, and convenience is brought to a user in use.

Owner:SHENZHEN NETCOM ELECTRONICS CO LTD

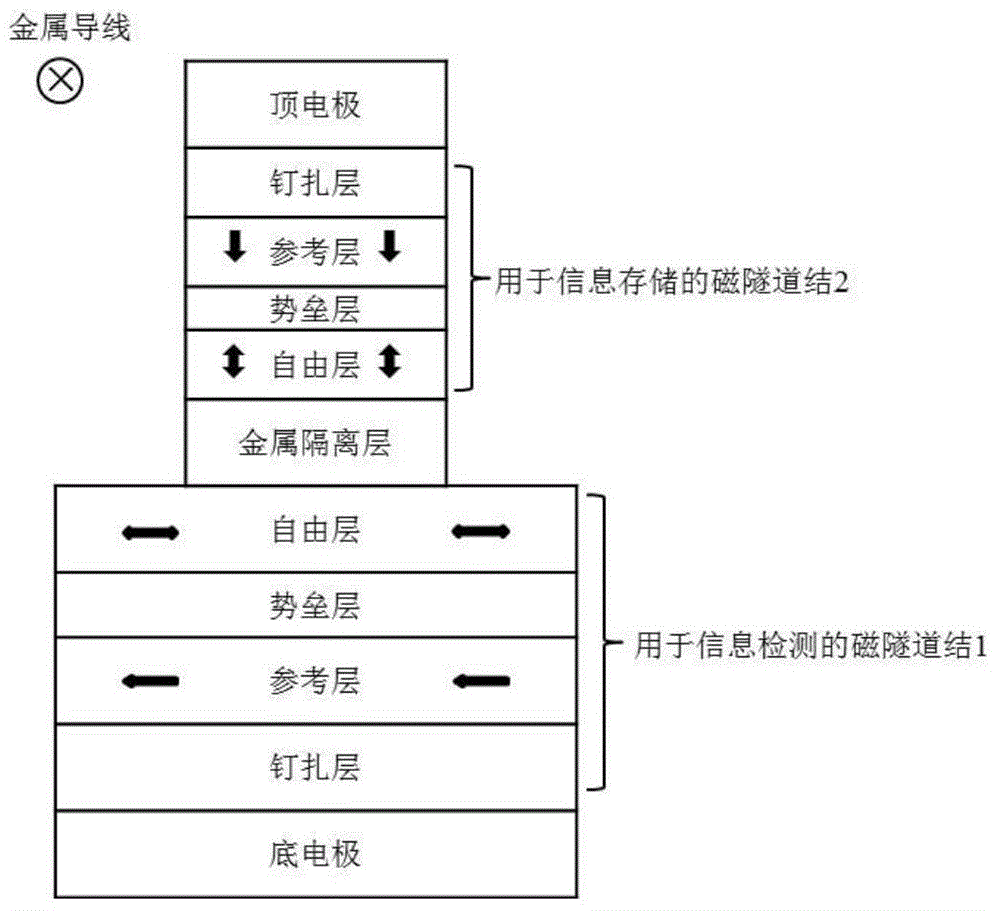

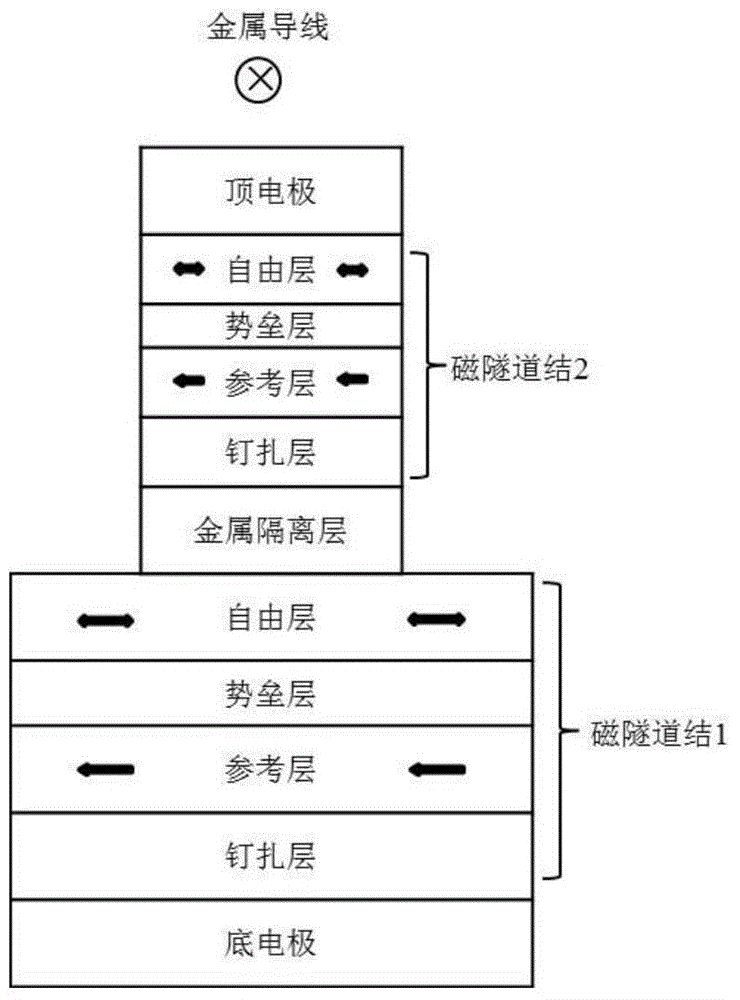

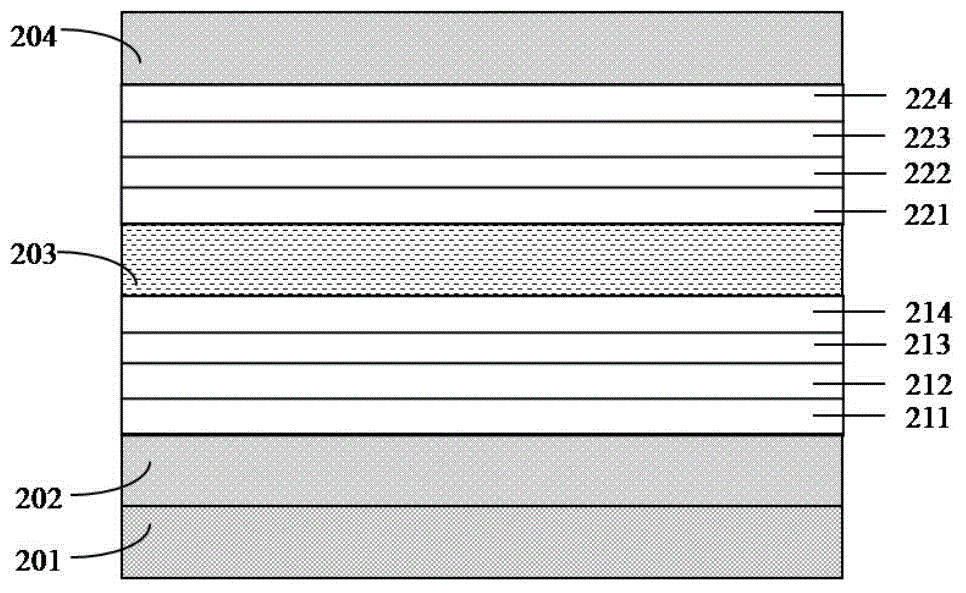

Information sensing and storing device and fabrication method thereof

ActiveCN104134748ARealize the detection functionRealize the storage functionMagnetic-field-controlled resistorsGalvano-magnetic device manufacture/treatmentSputteringMetallic electrode

An information sensing and storing device has a dual-MTJ (Magnetic Tunnel Junction) structure, and comprises a bottom electrode, an MTJ 1, a non-ferromagnetic metal isolation layer, an MTJ 2 and a top electrode sequentially from bottom to top, wherein a metal wire is arranged at one side of the device. A fabrication method of the information sensing and storing device comprises the five steps of: 1, depositing a magnetic multi-layer film material on a substrate; 2, performing annealing through an ultrahigh magnetic field vacuum annealing apparatus to fix the magnetization direction of a reference layer; 3, finishing shape fabrication of the dual-MTJ structure by using traditional nanometer device processing technologies such as photoetching, etching and magnetron sputtering; 4, depositing an isolation layer at the outer side of the dual-MTJ structure, and configuring the metal wire near the dual-MTJ structure through the technologies such as photoetching, etching and inlaying; and 5, forming a metal electrode at the top of the dual-MTJ structure by using the processing technologies such as photoetching, etching and inlaying for subsequent integration or test.

Owner:BEIHANG UNIV

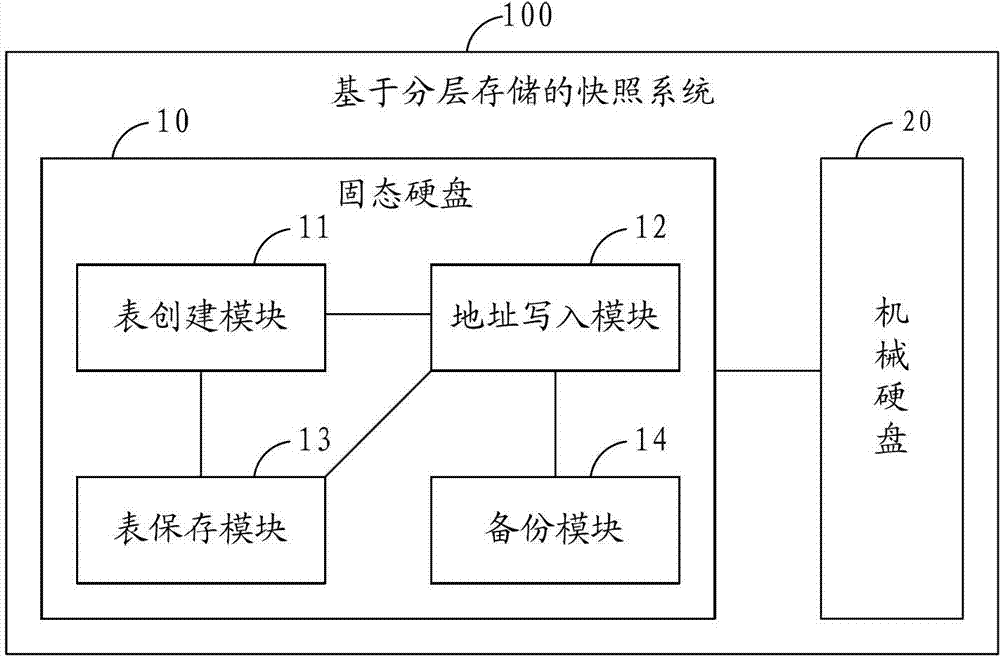

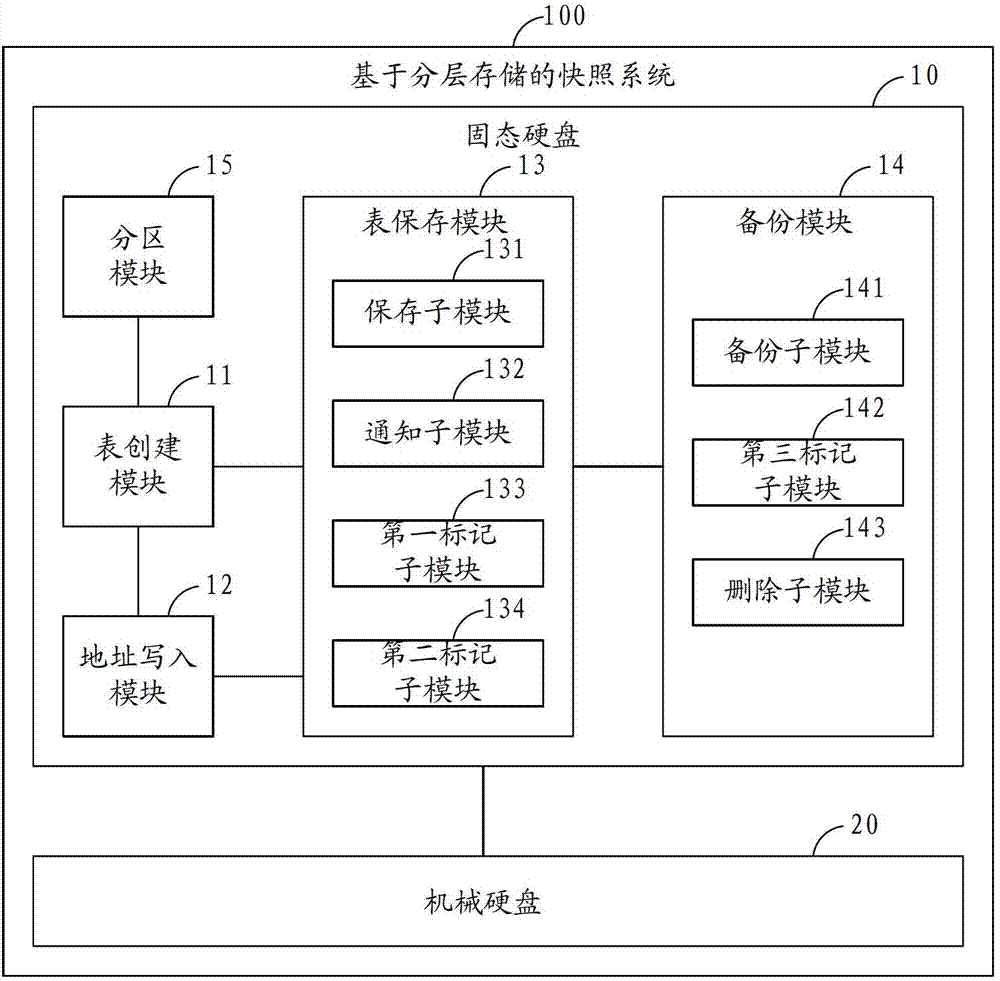

Snapshot method and system based on tiered storage

ActiveCN103049349AImprove efficiencyImprove read and write speedInput/output to record carriersRedundant operation error correctionLogical addressAddress mapping

The invention provides a snapshot method and a system based on tiered storage. The snapshot method is applied to a snapshot system which comprises at least one solid-state disk and at least one hard disk drive. The snapshot method includes the following steps: (a) creating a snapshot address mapping table, (b) writing mapping relations between the logic address and physical address of updated data in the created snapshot address mapping table when data are updated in the solid-state disk, (c) storing the written snapshot address mapping table when the scheduled time point comes and creating a new snapshot address mapping table; (d) backing up the corresponding snapshot data of the stored snapshot address mapping table in the hard disk drive according to the scheduled backup strategy when an scheduled backup opportunity comes. According to the snapshot method and system based on tiered storage, at latest current data are stored in a high-speed solid-state disk so that the read-write speed of data is improved, meanwhile, snapshot data are stored in a low-speed hard disk drive so that the use efficiency of the solid-state disk is improved.

Owner:RAMAXEL TECH SHENZHEN

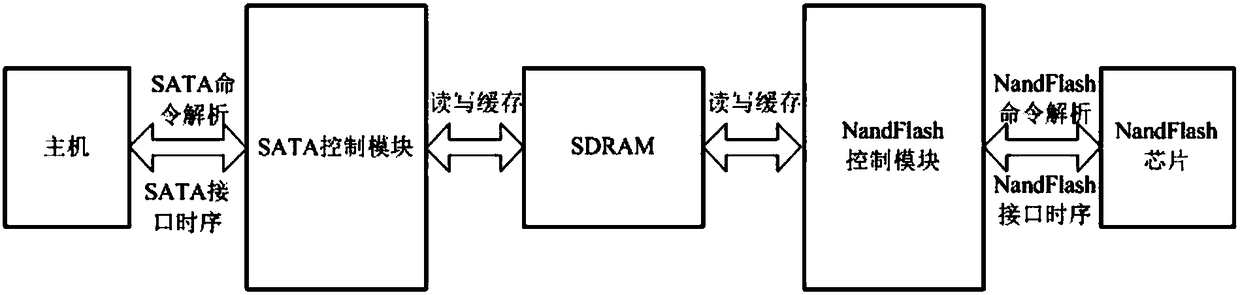

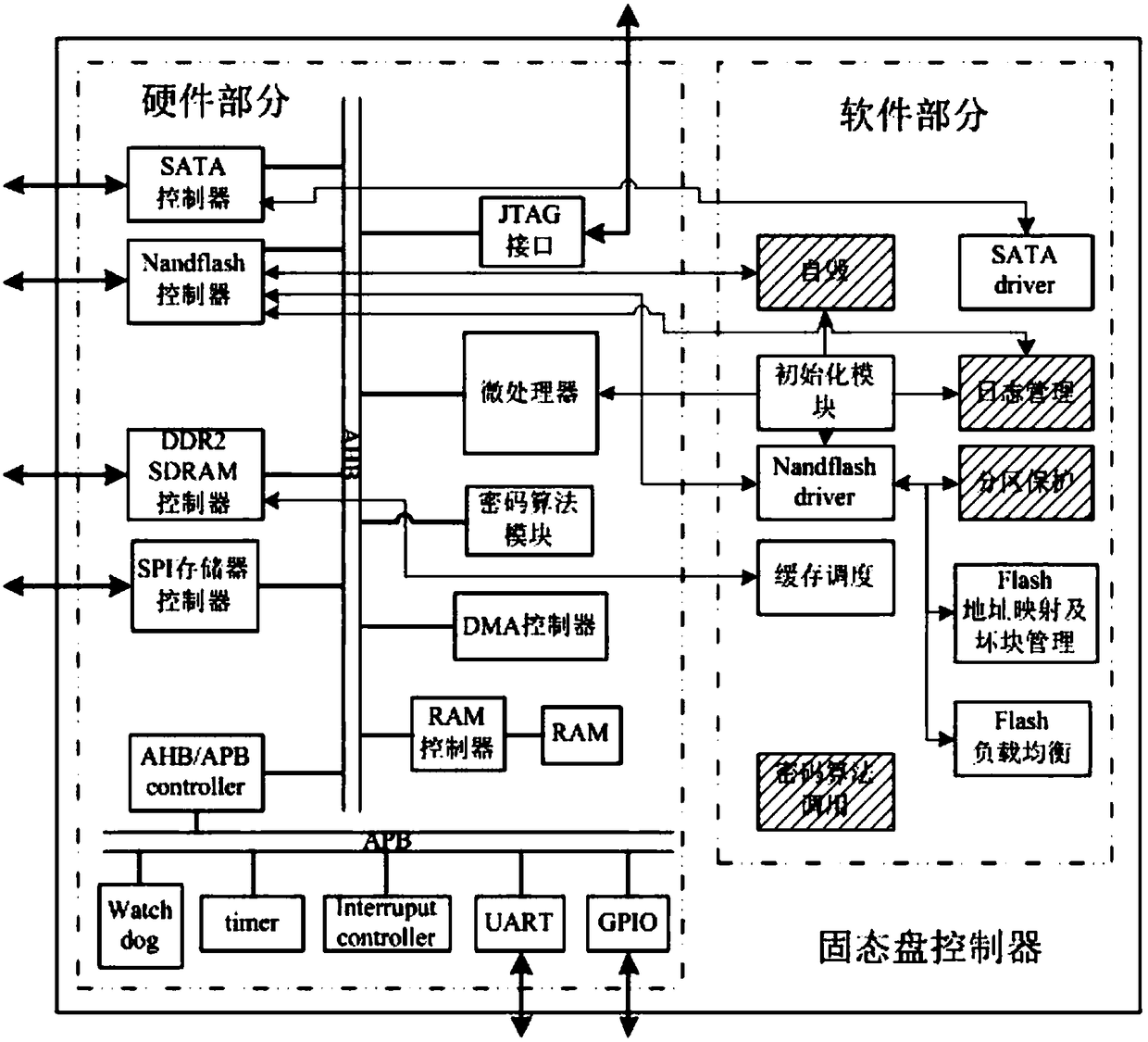

Storage array control method and device based on multiple channels of NandFlash memory

PendingCN108121672AIncrease capacityImprove data transfer rateEnergy efficient computingElectric digital data processingComputer moduleJoint Test Action Group

The invention provides a storage array control method and device based on multiple channels of a NandFlash memory. The device includes an embedded-type microprocessor, and the embedded-type microprocessor is connected with each external module through an in-chip high-speed intercommunication bus; the external modules include the SATA controller, the Nandflash controller, the DDR2 SDRAM controller,the JTAG debugging interface, the AHB / APB bridge, the code algorithm module, the DMA controller, the on-chip RAM controller and the SPI flash controller. The AHB / APB bridge connects the in-chip high-speed intercommunication bus with an in-chip low-power-consumption intercommunication bus, the in-chip low-power-consumption intercommunication bus is connected with an interrupt controller, a timer,a watchdog, a serial port and a GPIO, and therefore a complete on-chip system is constructed. The control method is designed on the basis of an assembly line framework and a fully-connected parallel framework, parallel running of the channels and an assembly line operation are achieved, the access bandwidth of a Flash interface is fully utilized, and the system performance is further improved.

Owner:HONGQIN (BEIJING) TECHNOLOGY CO LTD

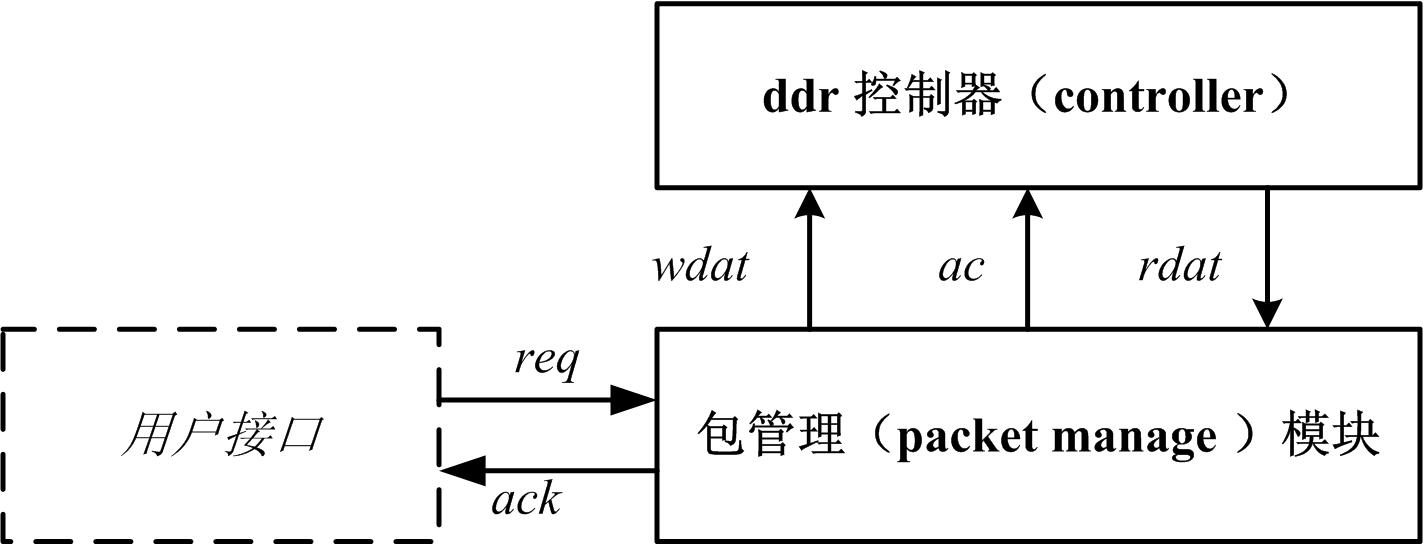

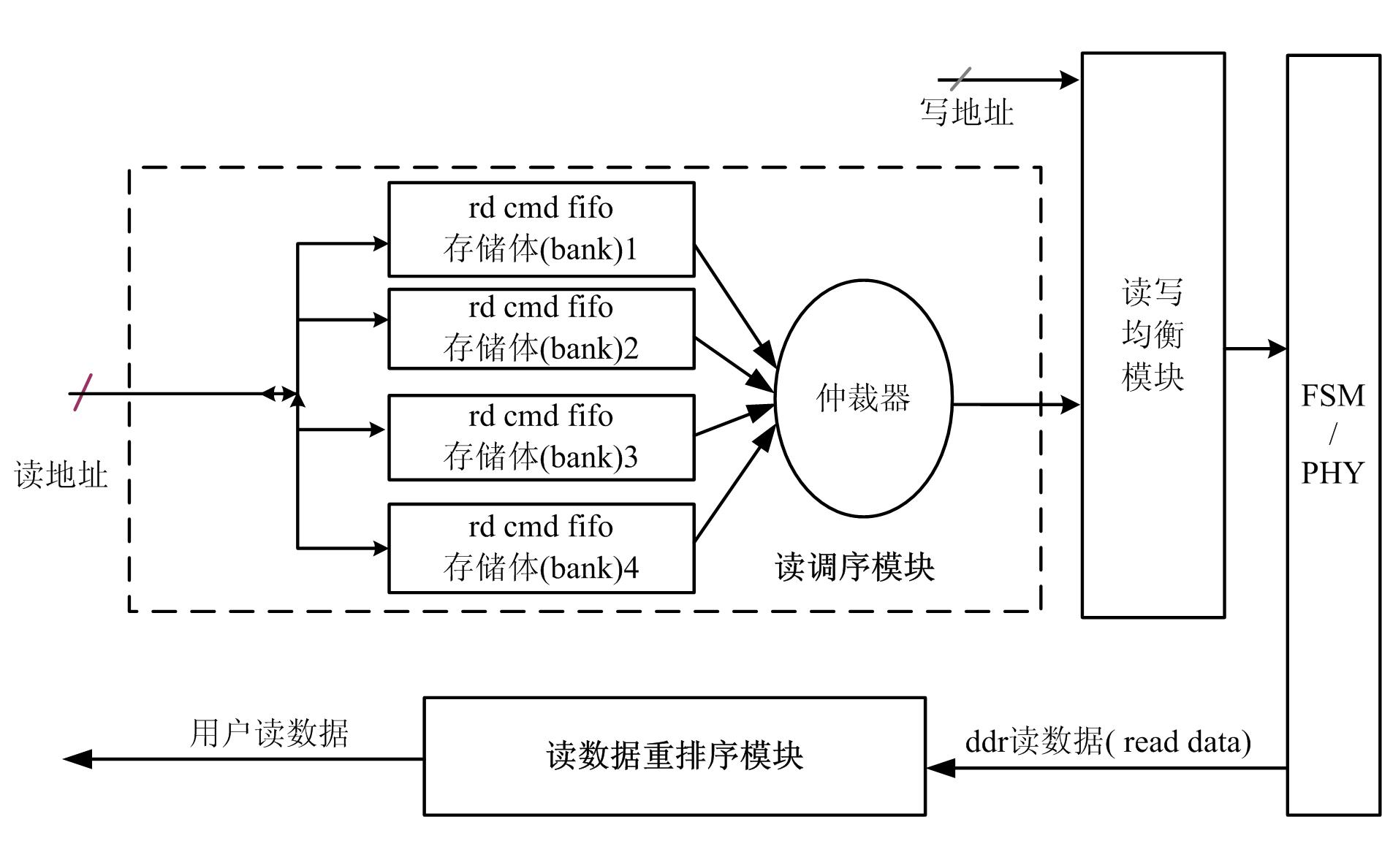

Method and device for increasing read-write rate of double data rate synchronous dynamic random access memory

InactiveCN102103548AImprove read and write speedImprove realizabilityMemory adressing/allocation/relocationLimited resourcesDouble data rate

The invention provides a method and a device for increasing the read-write rate of a double data rate synchronous dynamic random access memory (DDRSDRAM). The method comprises the following steps of: receiving a read address corresponding to a read request of a packet; caching the read address in a corresponding first first-in first-out queue (FIFO) according to a bank number; reading the read address out from a first FIFO in the first FIFO for the first time; if the next read address in the first FIFO and the read address read out for the first time belong to same-line addresses, continuously reading the first FIFO; and if the next read address in the first FIFO and the read address read out for the first time belong to different-line addresses, reading the next first FIFO in a polling mode. By the method and the device for increasing the read-write rate of the DDRSDRAM, realization difficulties are reduced, the realizability and the adjustment force of a field programmable gate array (FPGA) project are improved, and the read-write efficiency of the DDRSDRAM is greatly improved by limited resources.

Owner:ZTE CORP +1

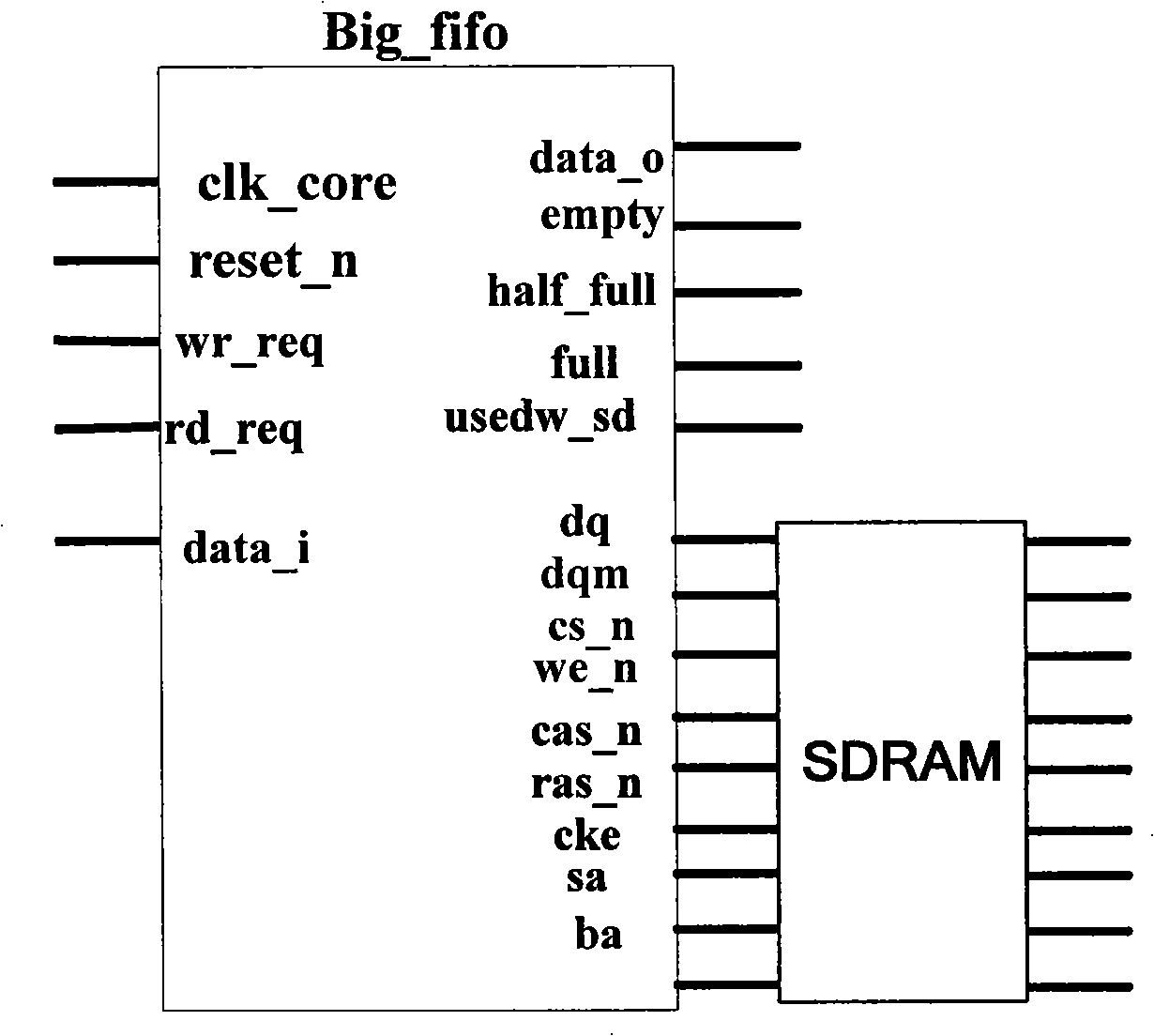

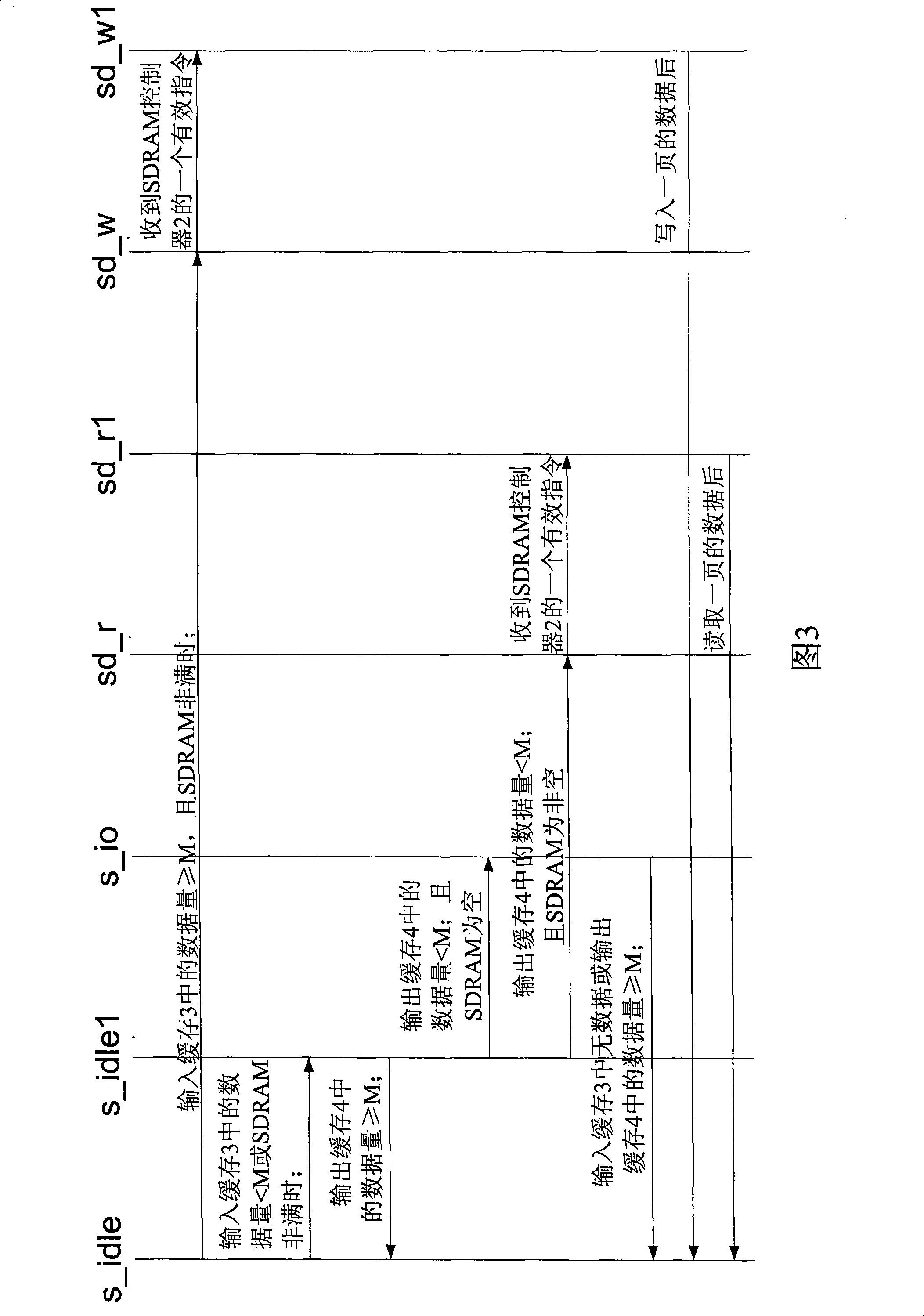

FIFO burst buffer with large capacity based on SDRAM and data storage method

InactiveCN101308697AImprove read and write speedReduce occupancyDigital storageData conversionMaster controllerData store

A FIFO burst buffer memory with large capacity based on SDRAM and a data storage method are disclosed, relating to burst buffer memory, solving the problems of small capacity and high cost on FIFO burst buffer memories and avoiding the defect on SDRAM storages that reading and writing operations can not be done at the same time and the defect of low operation efficiency. The SDRAM controller of the invention is a module used to control the SDRAM storage; the master controller is the control center of the whole system, with the responsibility for attempering the whole system; the input buffer memory and the output buffer memory, two FIFOs with small capacity, are respectively used as cushions for input date and output data; the input data first enter the input buffer memory and when the data in the input buffer memory are added up to certain number, the master controller transmits part of the data in the input buffer memory to the SDRAM storage. When the output buffer memory is in deficiency of data, the master controller transmits part of the data in the SDRAM storage to the output buffer memory. The FIFO burst buffer memory is low in cost and has a data read-write speed of 75MHz.

Owner:HARBIN INST OF TECH

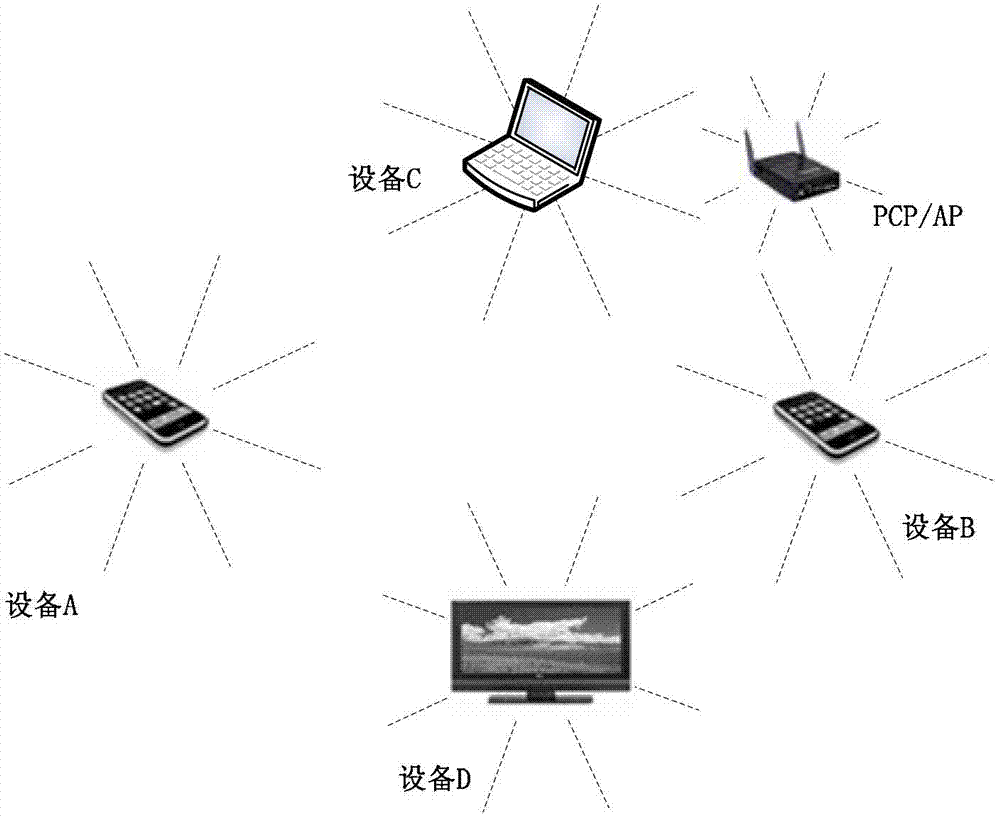

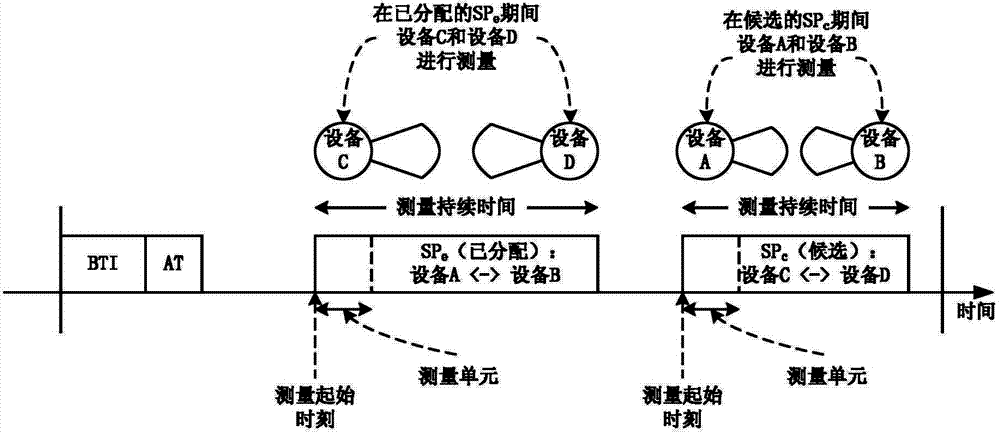

Spatial multiplexing method for intercepting millimeter wave high speed communication system wave beam sectors

InactiveCN103199906AImprove throughputImprove communication efficiencySpatial transmit diversityWireless communicationOmnidirectional antennaCommunications system

The invention discloses a spatial multiplexing method for intercepting millimeter wave high speed communication system wave beam sectors. When a device participating wave beam forming transmits a training sequence, other devices intercept signals in an omnidirectional antenna mode, and a list is built according to interception results of all sectors of a transmitting device, when the devices request SP, interception lists of optimum transmitting sectors obtained by self wave beam forming and local sectors are reported to a PCP / AP. The PCP / AP stores the information, thereby having all the sector interception lists of the devices needing to communicate in the SP, and under the condition that the devices are not indicated to carry out spatial multiplexing measurement, the PCP / AP can obtain disturbed conditions among links, so that the links are effectively selected for carrying out spatial multiplexing.

Owner:SOUTHEAST UNIV

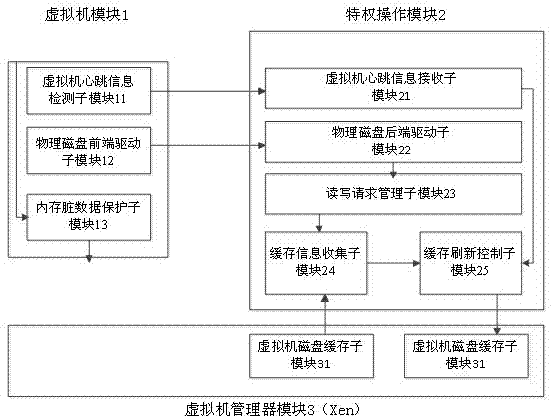

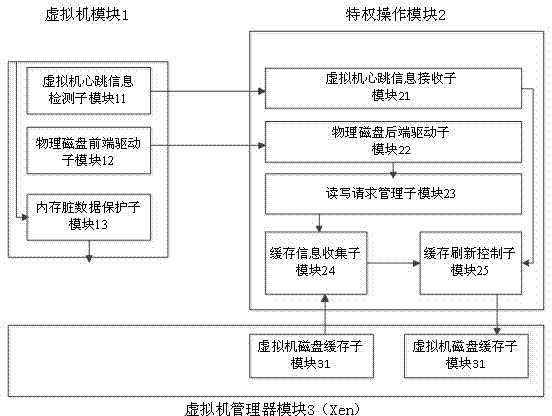

Dirty data write-back system in virtual environment

InactiveCN102541468AImprove read and write speedIncrease profitInput/output to record carriersSoftware simulation/interpretation/emulationVirtualizationFile system

The invention discloses a dirty data write-back system in a virtual environment. The dirty data write-back system comprises a virtual machine module, a privileged operation module and a virtual machine manager module, wherein the virtual machine module is used for sending a physical disk read-write request and dirty data from a user application program to the privileged operation module; and the privileged operation module is used for storing the physical disk read-write request and the dirty data in a virtual machine cache of the virtual machine manager module, and processing the physical disk read-write request when the utilization rate of the virtual machine cache reaches a predefined threshold value, and transmitting the dirty data to a physical disk. According to the dirty data write-back system disclosed by the invention, the read-write speed of the physical disk in the virtual machine and the utilization rate of the bandwidth of the physical disk in the virtual machine can be increased, the reliability of a file system in the virtual machine can be enhanced, the interferences of read-write operations of the physical disks among different virtual machines on the same physical platform can be reduced, and the transparency on application programs in the virtual machine and an operating system in the virtual machine and the expandability on a virtual platform are realized.

Owner:HUAZHONG UNIV OF SCI & TECH

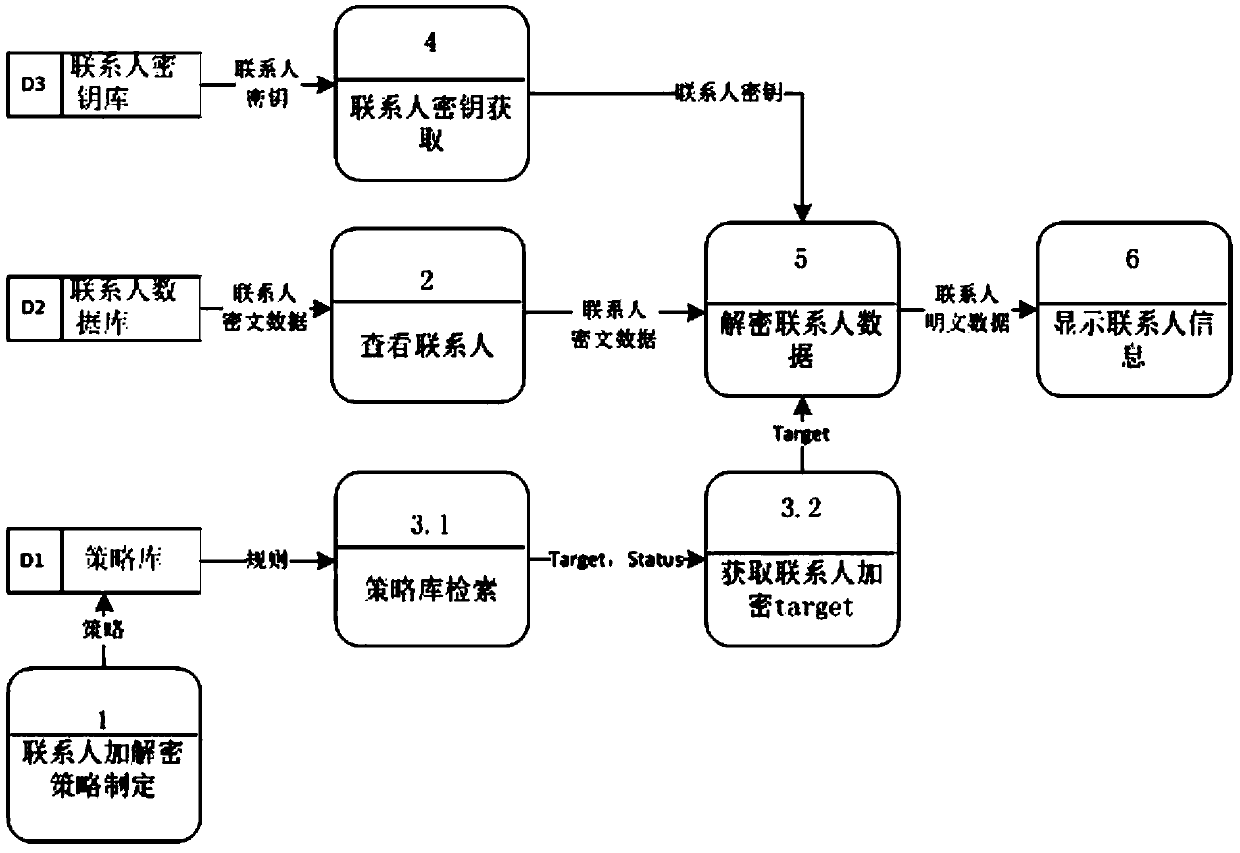

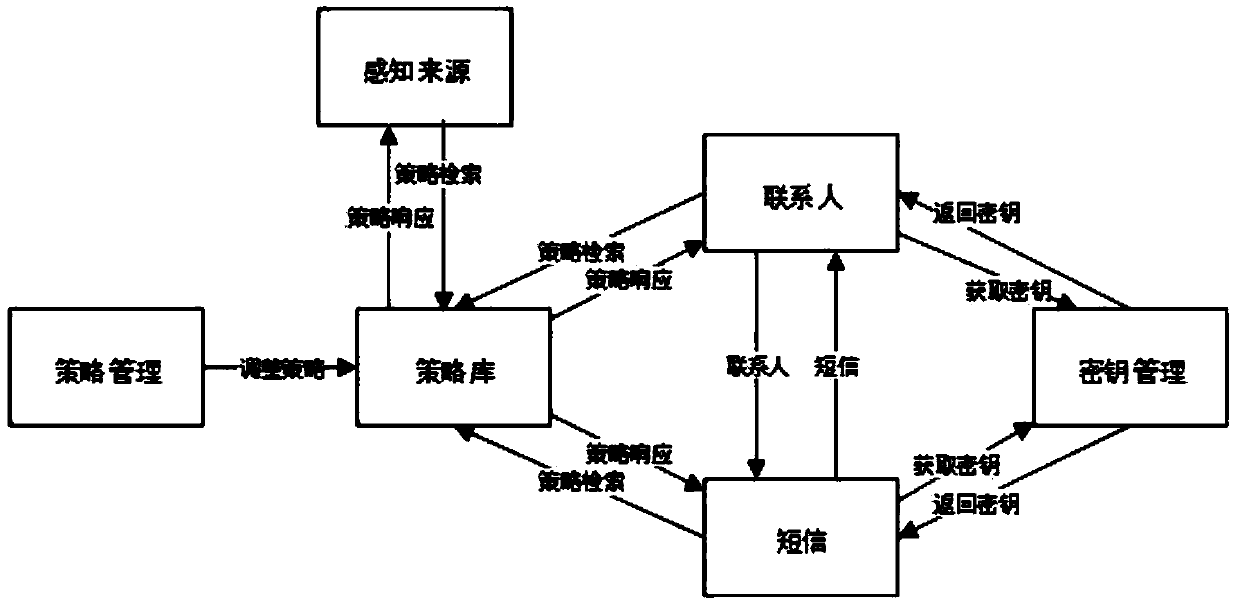

Android access control system for enhancing confidentiality and integrality

InactiveCN103686716AAddress storage securityTroubleshoot backup issuesSecurity arrangementOperational systemControl system

The invention belongs to the technical field of mobile communication equipment, and particularly relates to an Android access control system for enhancing confidentiality and integrality on the basis of cryptography and policy driven. In order to promote system confidentiality and integrality protection, the Android is improved, and the Android access control system based on existing safety mechanisms is realized. The improved Android access control system comprises a contact management module, a short message management module, an induction source control module, a strategy management module and a key management module. All the modules cooperate with one another, and finally safety of Android user data access and induction module access can be achieved. In addition, the improved Android access control system can be used for operation systems of Android users so that different protection settings on personal data and induction sources under different scenes can be achieved, and complexity of safe strategy management can be simplified beneficially.

Owner:FUDAN UNIV

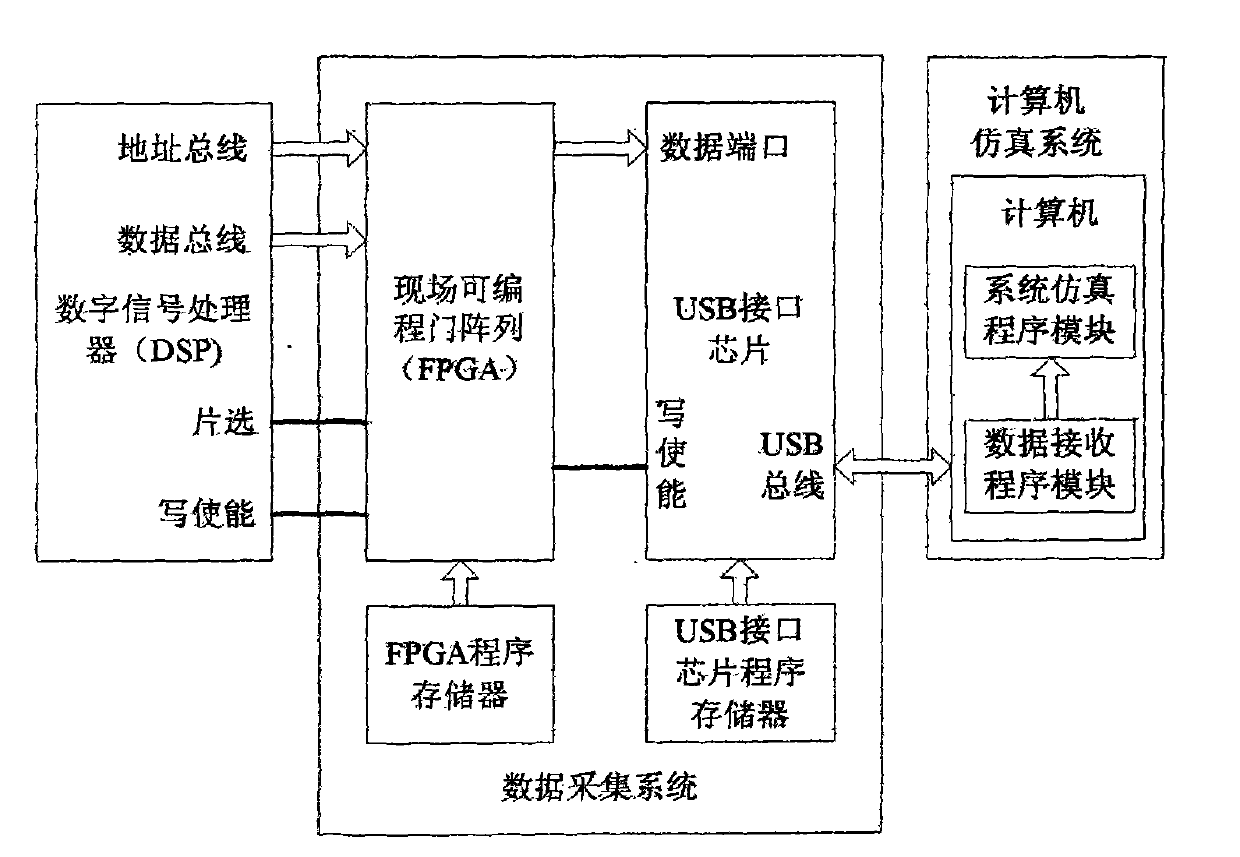

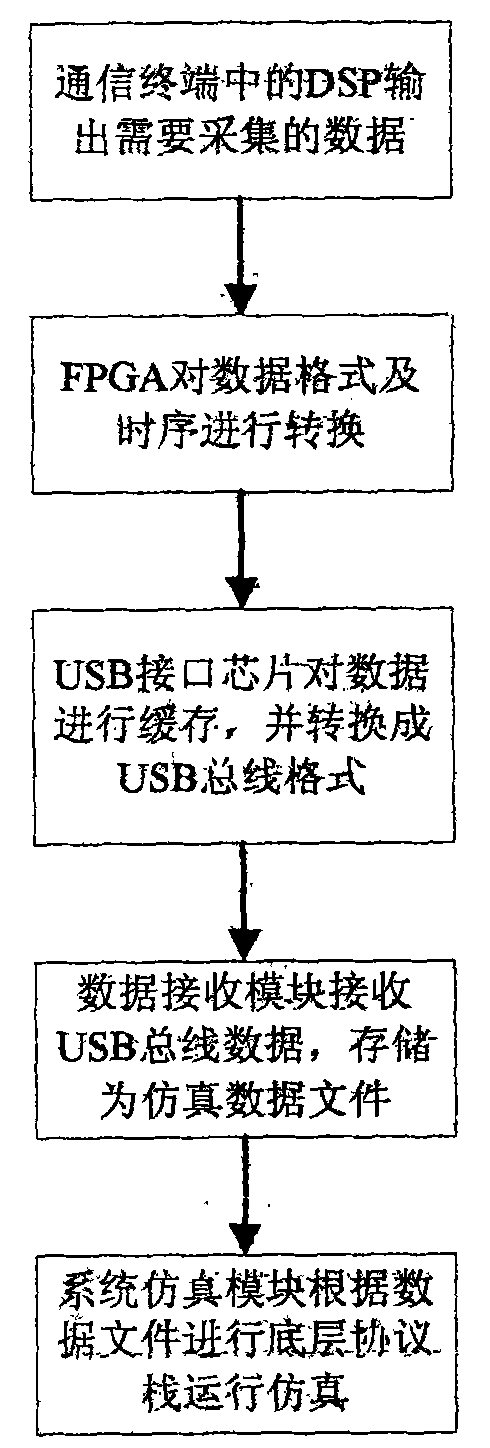

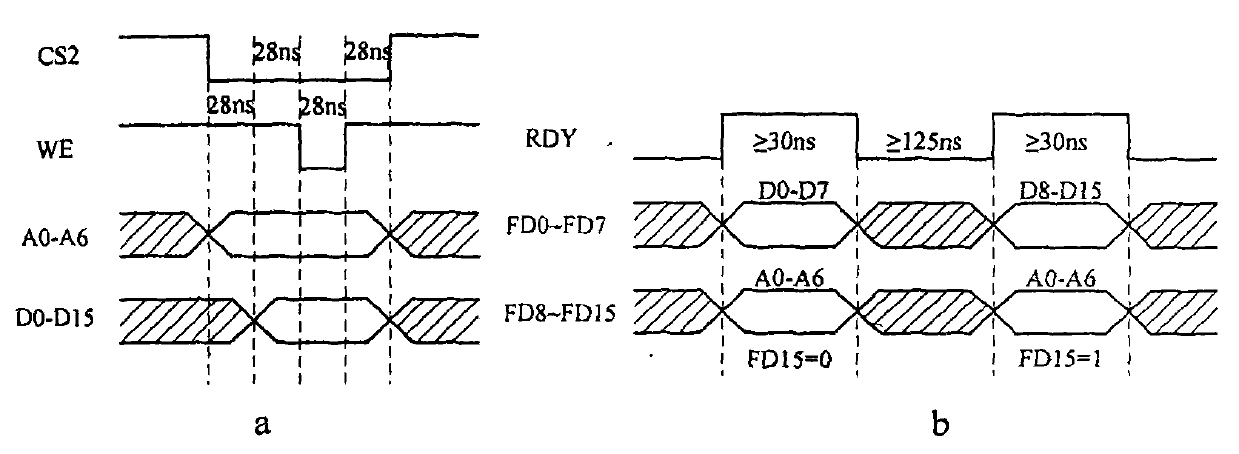

Data acquisition and emulation system suitable for underlying protocol stack of digital communication terminal

ActiveCN101770424AOperation impactImprove read and write speedSoftware testing/debuggingData acquisitionAddress bus

The invention relates to a data acquisition and emulation system suitable for an underlying protocol stack of a digital communication terminal. The system comprises a digital signal processor (DSP), a data acquisition system, and a computer emulation system, wherein the data acquisition system comprises a field-programmable gate array (FPGA), a universal serial bus (USB) interface chip, and a memory corresponding to the FPGA and the USB interface chip; the computer emulation system comprises a computer, and a data receiving program module and a system emulation program module operated on the computer; the DSP is connected to the FPGA through an address bus, a data bus, a chip selection, and a write enable respectively; and the acquisition output end of the FPGA is connected to the data input end of the USB interface chip; and the USB interface chip is connected to the computer through a USB bus. The data acquisition and emulation system has the advantages that: the acquired data and the data input by the underlying protocol stack can be ensured to be completely consistent by directly connecting the data acquisition system with the DSP high-speed data bus; the data bus has high read and write rate and low time consumption, so that the operation of the underlying protocol stack cannot be affected; the system is suitable for the development and debugging of the underlying protocol stack so as to track and find out problems and search program defects.

Owner:TIANJIN 712 COMM & BROADCASTING CO LTD

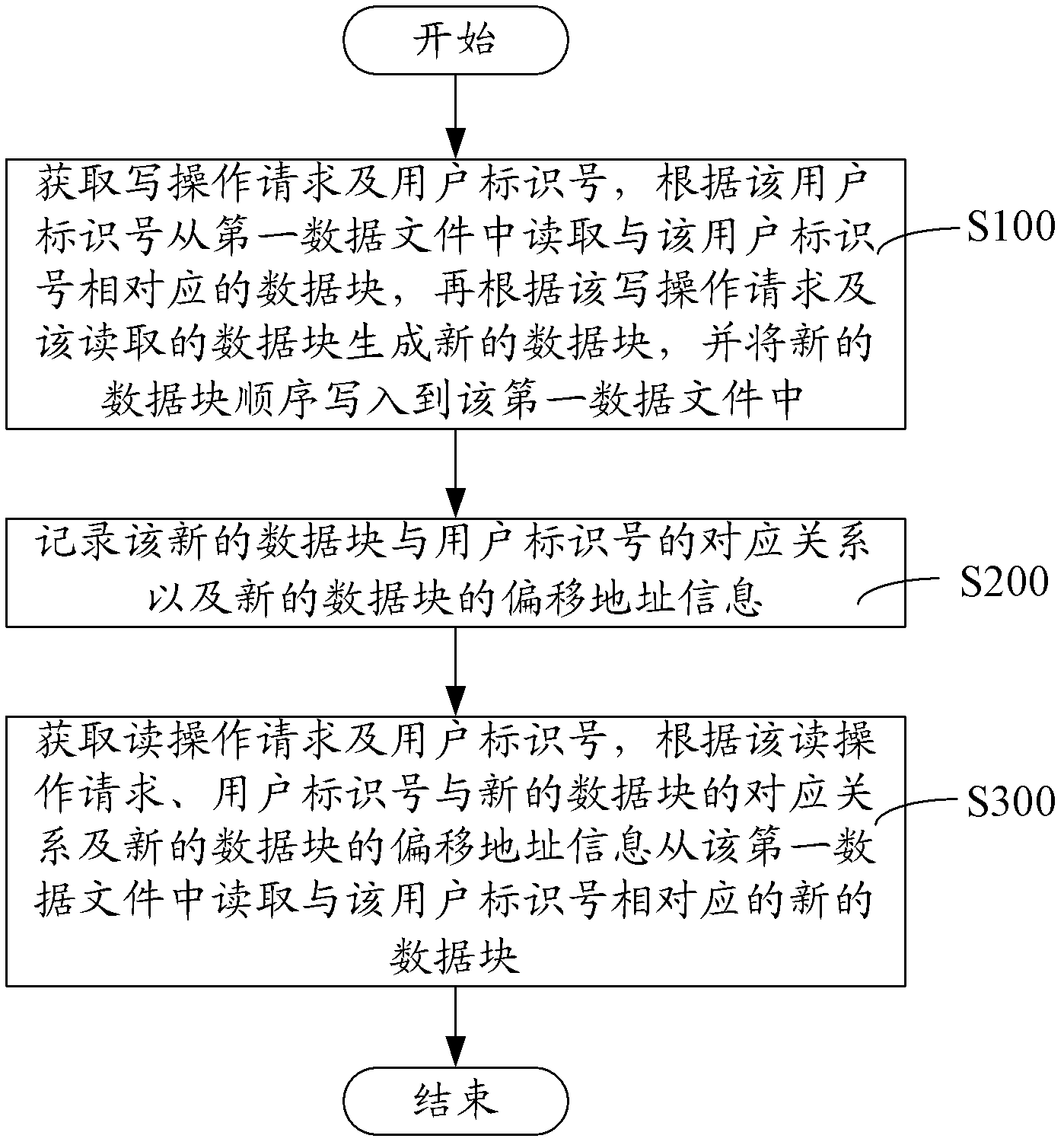

Data read-write method and system

ActiveCN102810092AFast read and writeImprove read and write speedSpecial data processing applicationsData file

The invention relates to a data read-write method and a system. The data read-write method comprises the steps as follows: a write operation request and a user identifying number are acquired; a data block corresponding to the user identifying number is read from a first data file according to the user identifying number; then a new data block is generated according to the write operation request and the read data block; the new data block is written in the first data file in sequence; the corresponding relation between the new data block and the user identifying number and the deflection address information of the new data block are recorded; and a read operation request and the user identifying number are obtained, and a new data block corresponding to the user identifying number is read from the first data file according to the corresponding relation among the read operation request, the user identifying number and the new data block as well as the deflection address information of the new data block. The data read-write method and the system can achieve quick read-write of multiuser data and can improve the read-write speed.

Owner:TENCENT TECH (SHENZHEN) CO LTD +1

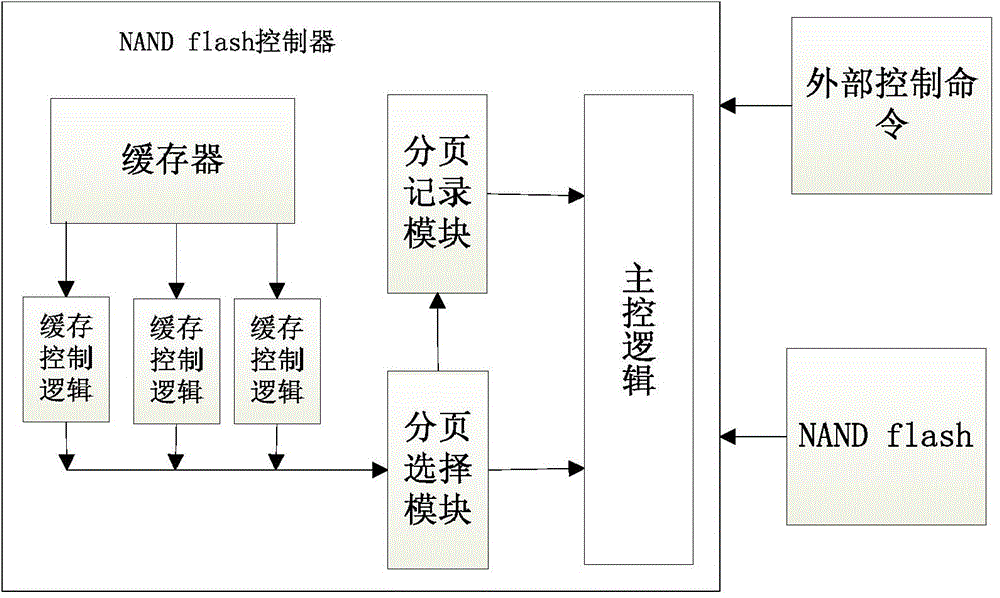

Method for increasing reading and writing speeds of NAND flash controller

ActiveCN103559146AImprove read and write speedFlexible cache operation modeMemory adressing/allocation/relocationCache pagePaging

The invention discloses a method for increasing the reading and writing speeds of an NAND flash controller, and belongs to the technical field of integrated circuit design. One end of the NAND flash controller is connected to a system bus, and the other end of the NAND flash controller is directly connected with a NAND flash. The method comprises the following steps: reading the parameter of a page size from the NAND flash; dynamically allocating cache inside the NAND flash controller to generate a plurality of cache sub-pages adapting to the page size of the NAND flash; selecting a current cache sub-page via an external control command; selecting a current cache page to allow the external control command to directly operate the current cache page. The method has the advantages that the controller can well adapt to different models of NAND flash, the own limited cache resources are utilized to the maximum extent, a more flexible cache operating way is provided for the external control command, and the reading and writing speeds of the NAND flash are increased.

Owner:SHANDONG UNIV

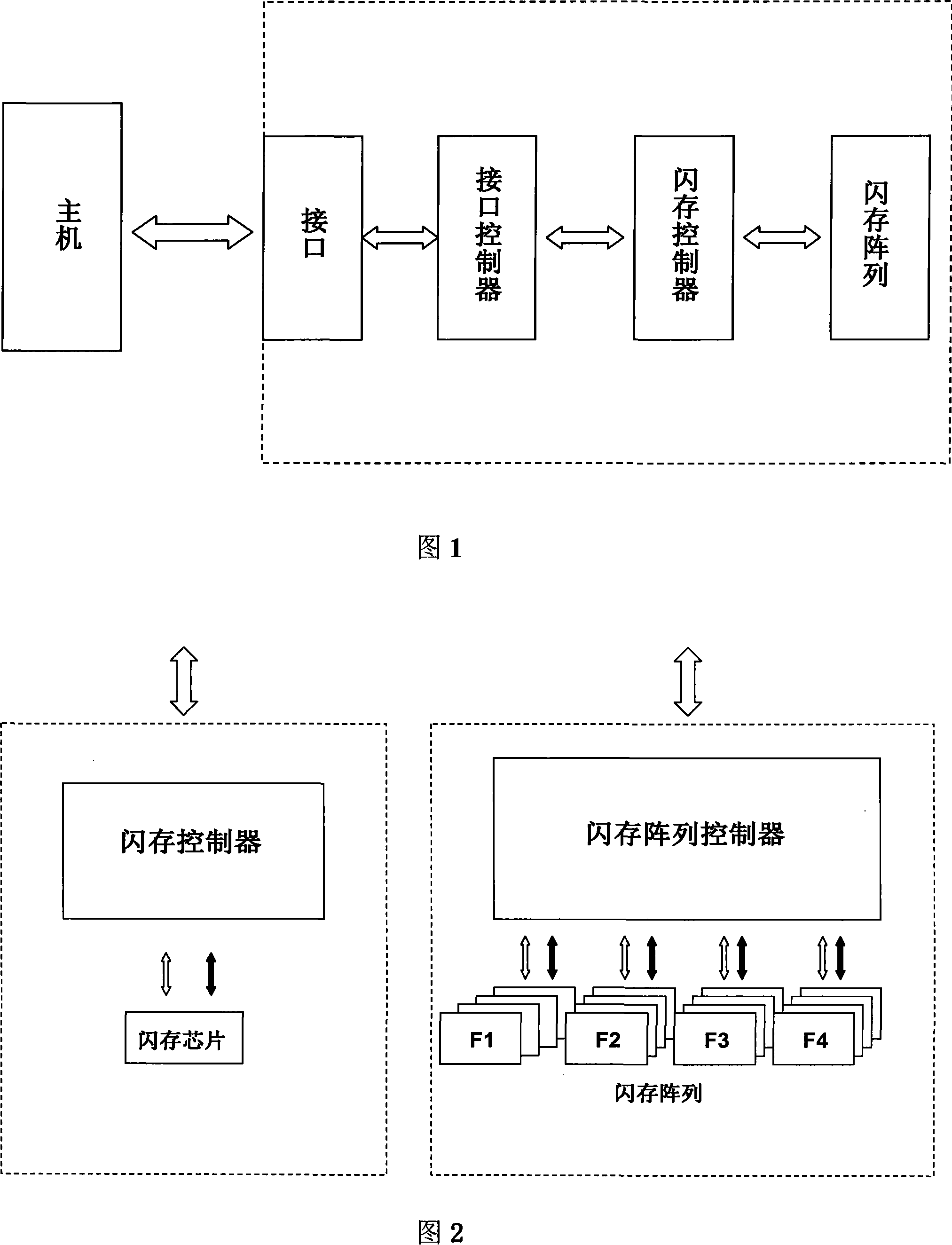

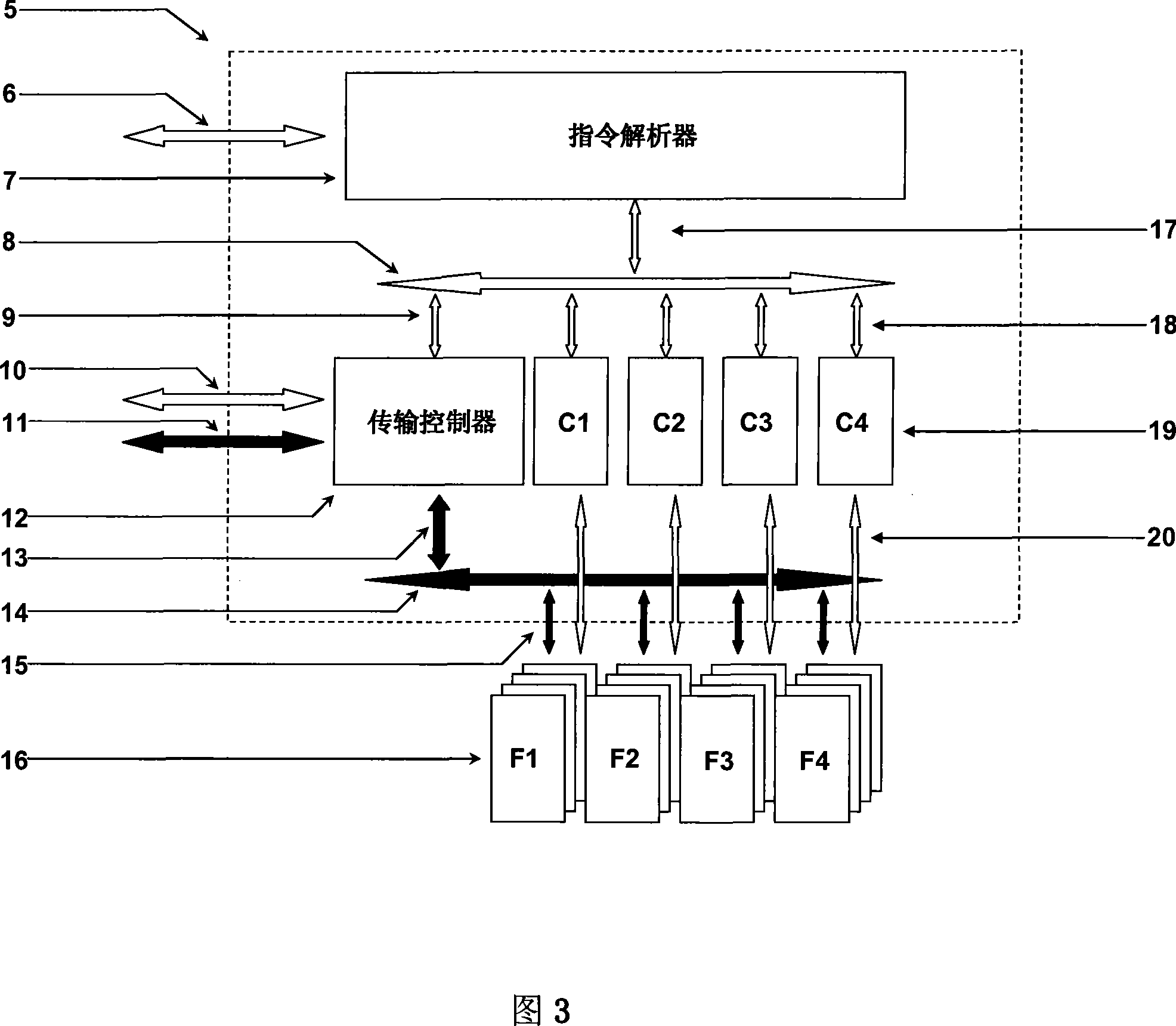

Flash controller

ActiveCN101046725ASolve bottlenecksImprove read and write speedInput/output to record carriersControl signalFlash memory controller

The present invention discloses a flash storage controller. Said flash storage controller includes the following several portions: instruction resolver, transmission controller and several on-chip flash storage control units. Said invention also provides the concrete function and action of above-mentioned every portion, and also provides the working principle of said flash storage controller and its concrete operation method. The flash memory made up by adopting the invented flash storage controller can greatly raise read / write speed.

Owner:MEMORIGHT (WUHAN) CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com