Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1614 results about "Control grid" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The control grid is an electrode used in amplifying thermionic valves (vacuum tubes) such as the triode, tetrode and pentode, used to control the flow of electrons from the cathode to the anode (plate) electrode. The control grid usually consists of a cylindrical screen or helix of fine wire surrounding the cathode, and is surrounded in turn by the anode. The control grid was invented by Lee De Forest, who in 1906 added a grid to the Fleming valve (thermionic diode) to create the first amplifying vacuum tube, the Audion (triode).

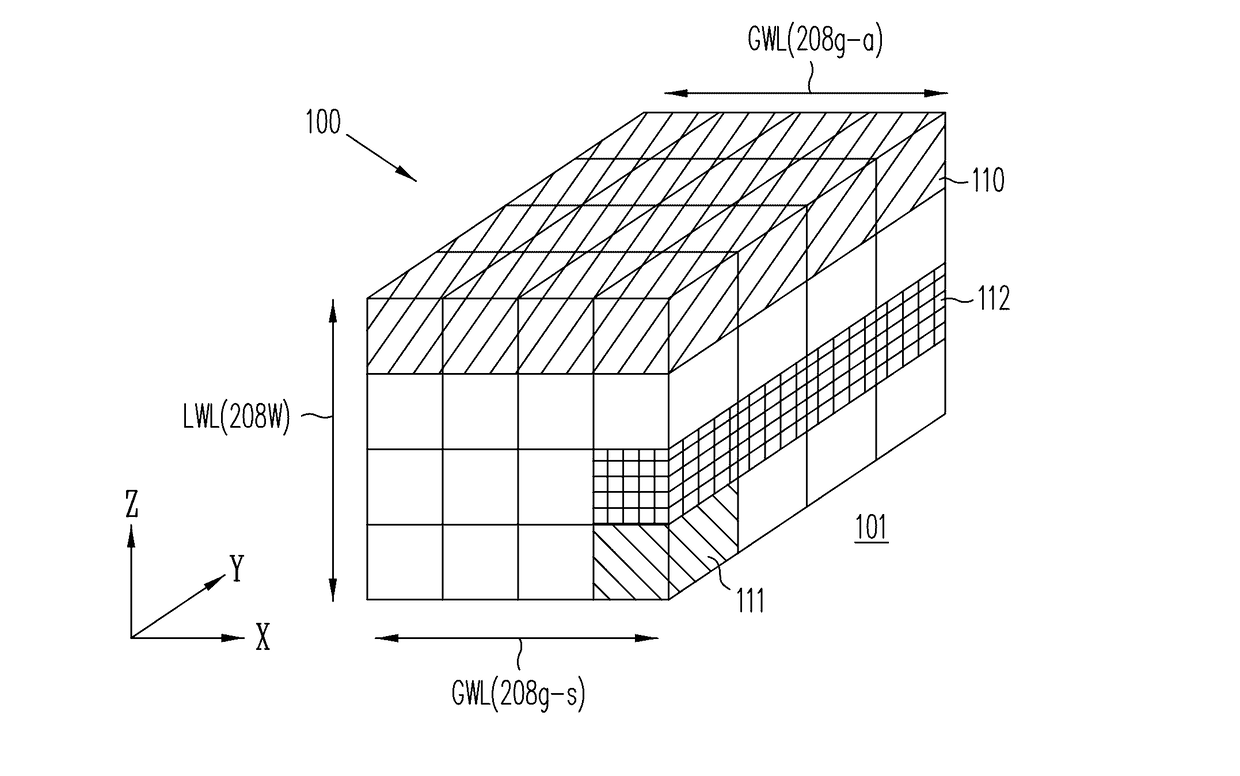

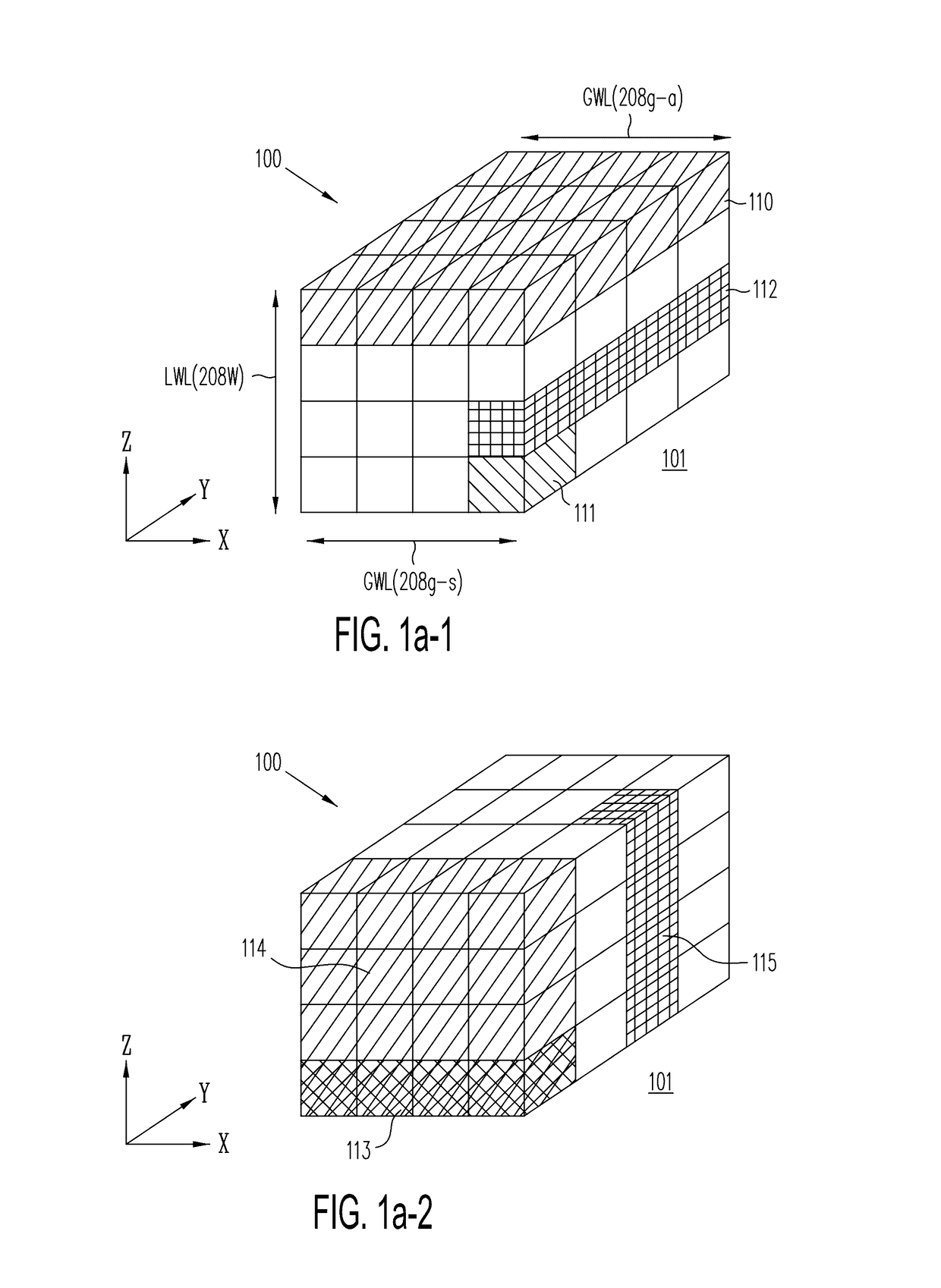

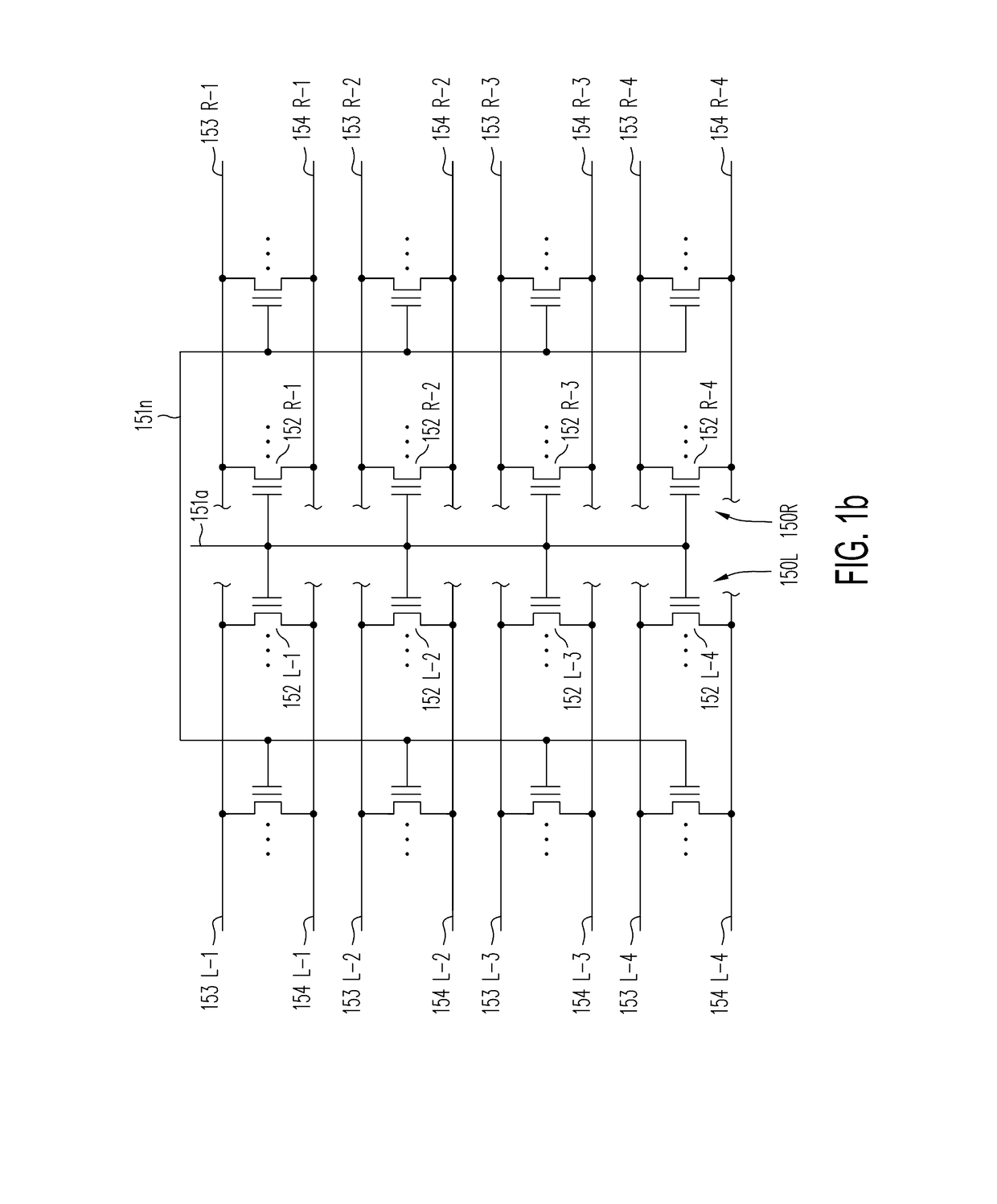

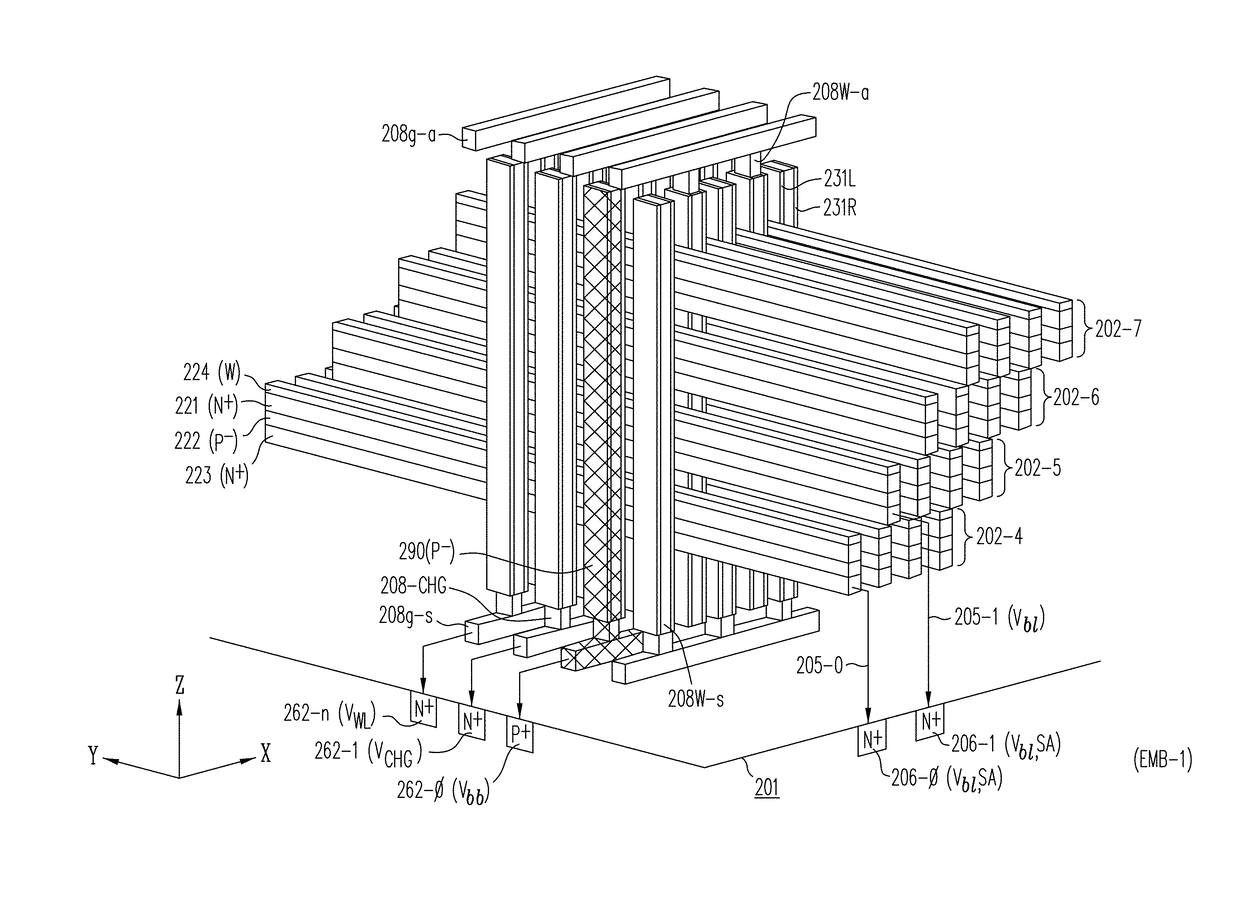

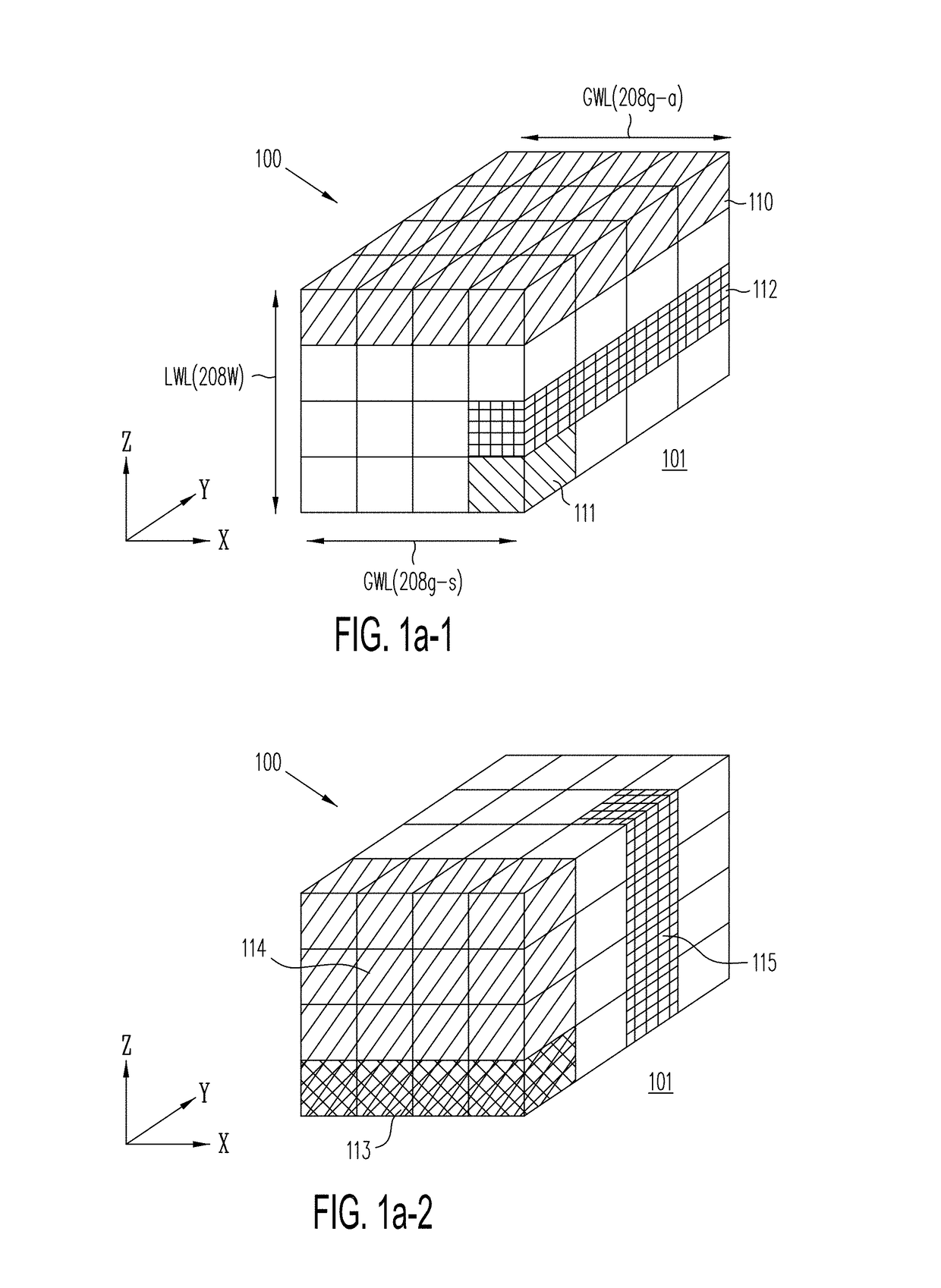

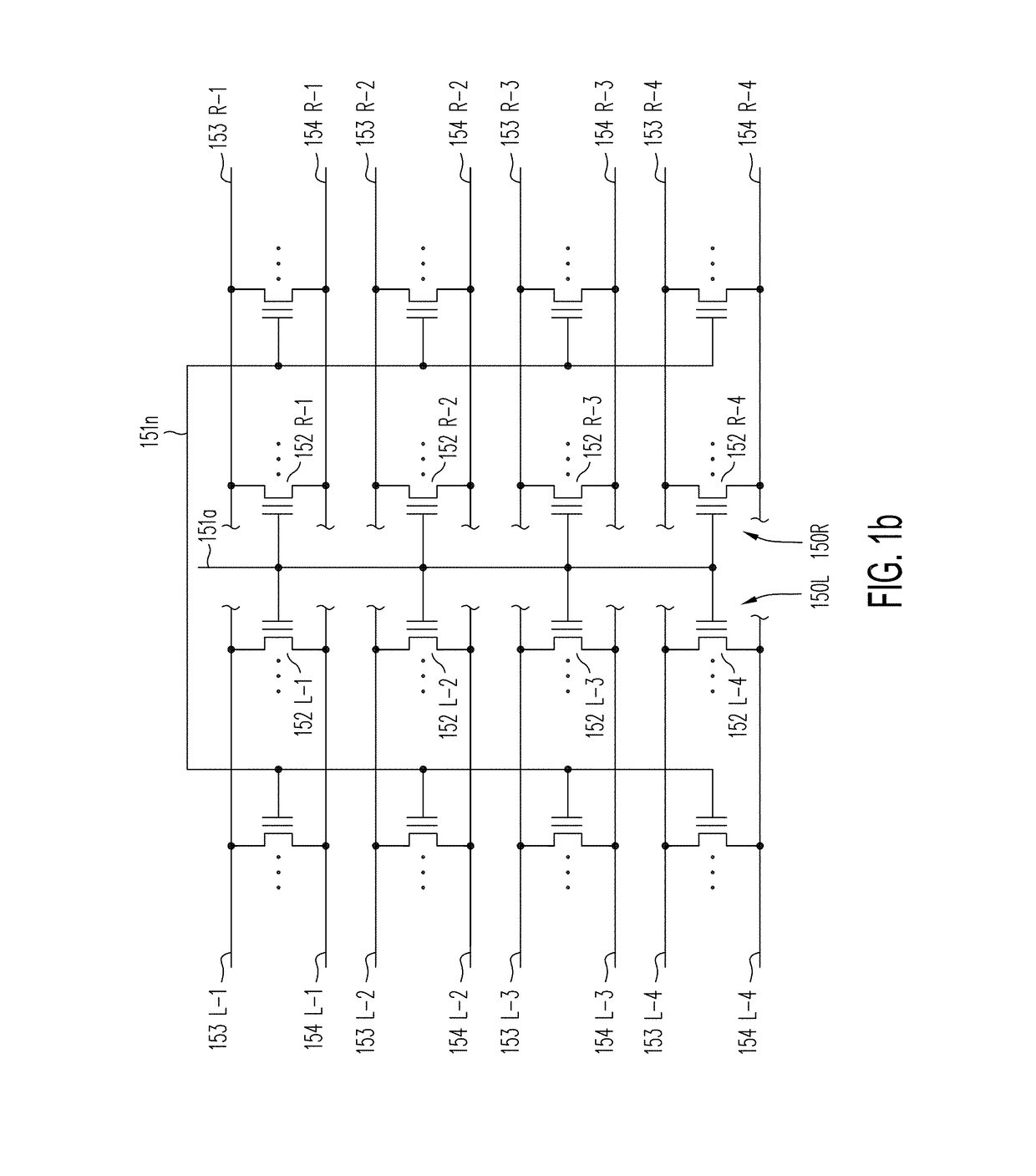

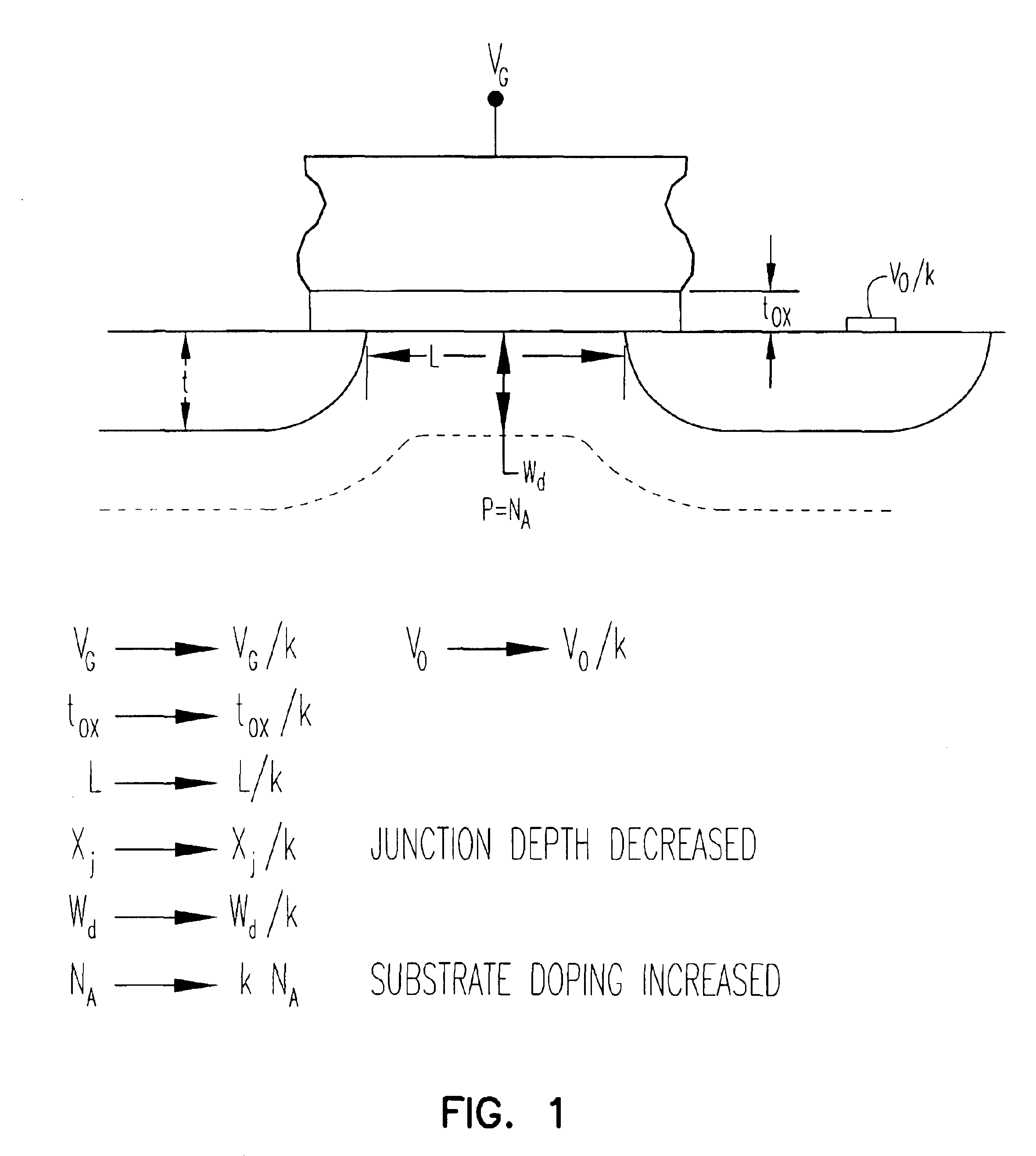

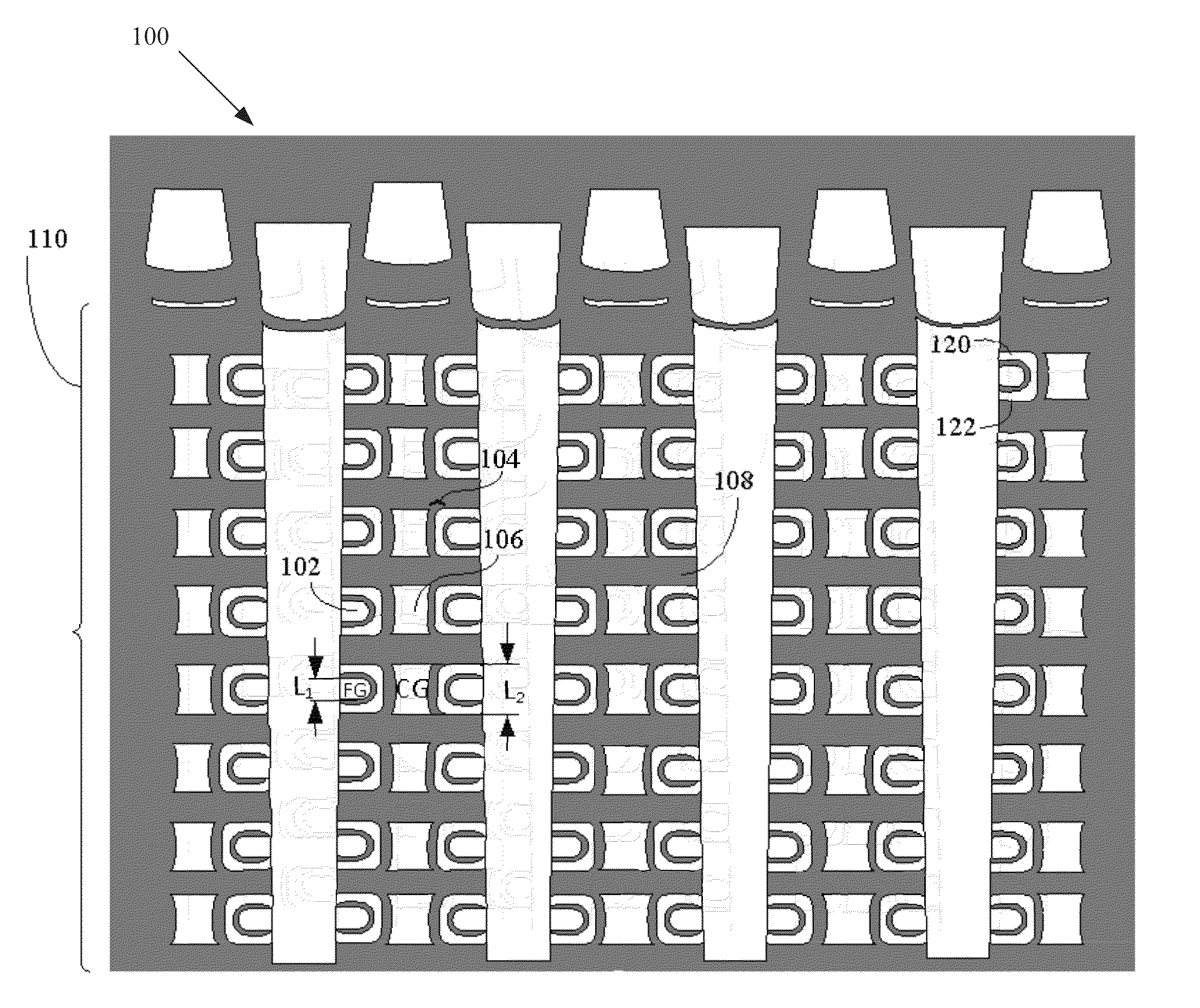

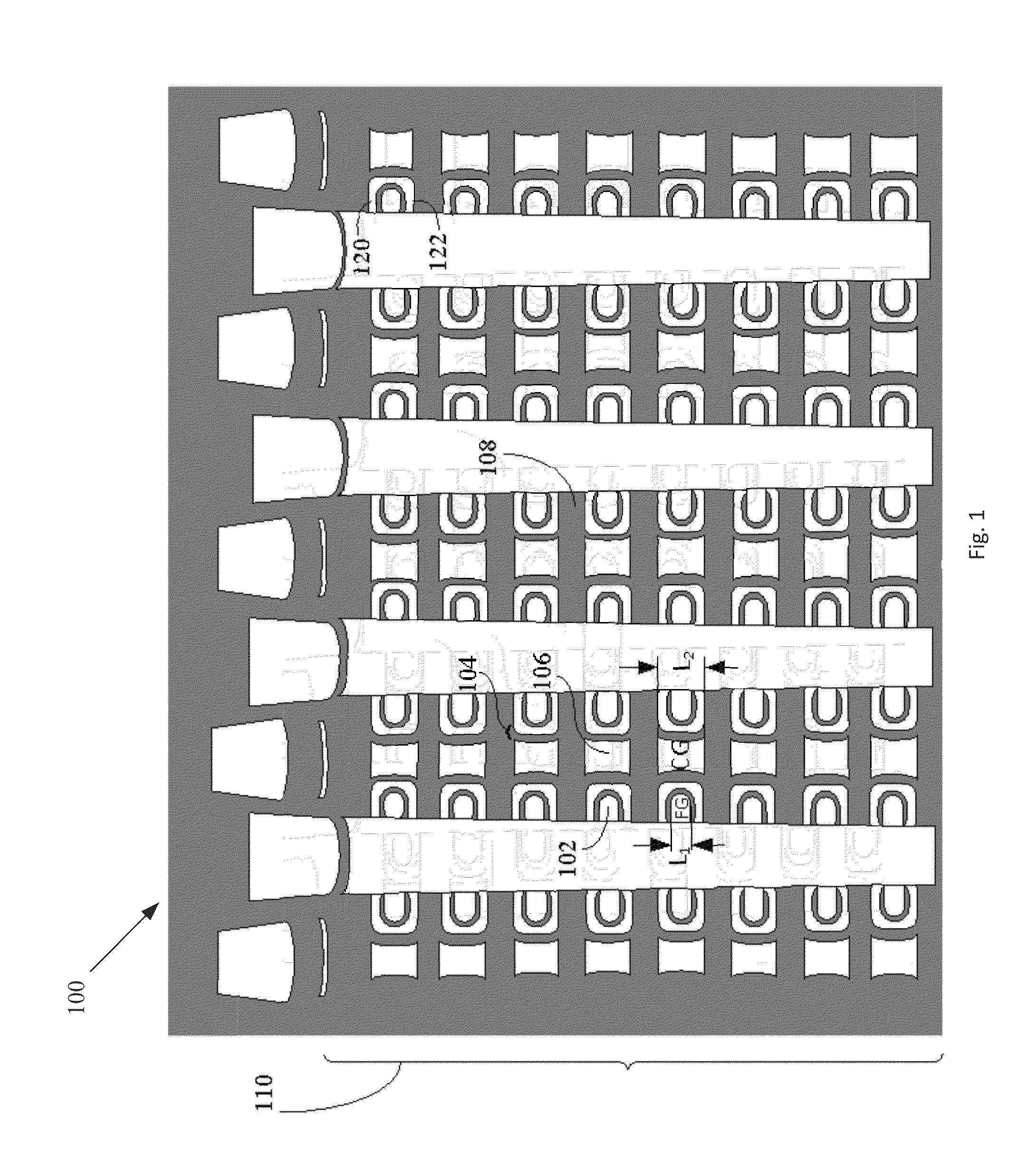

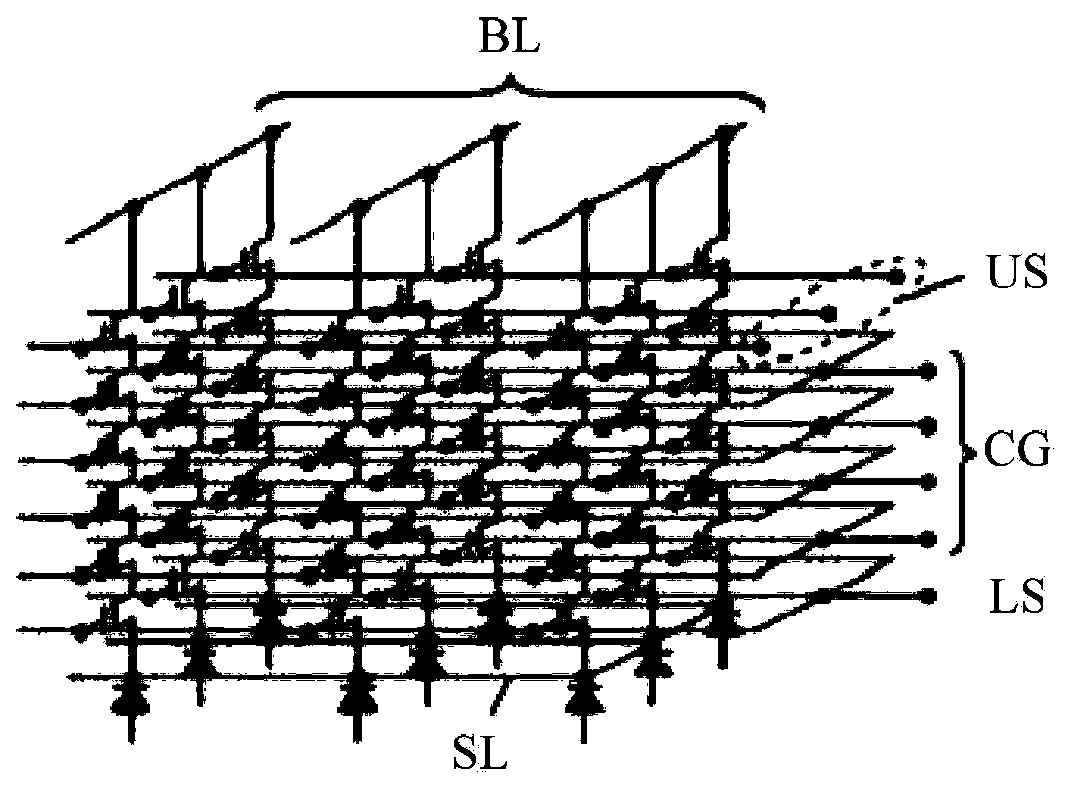

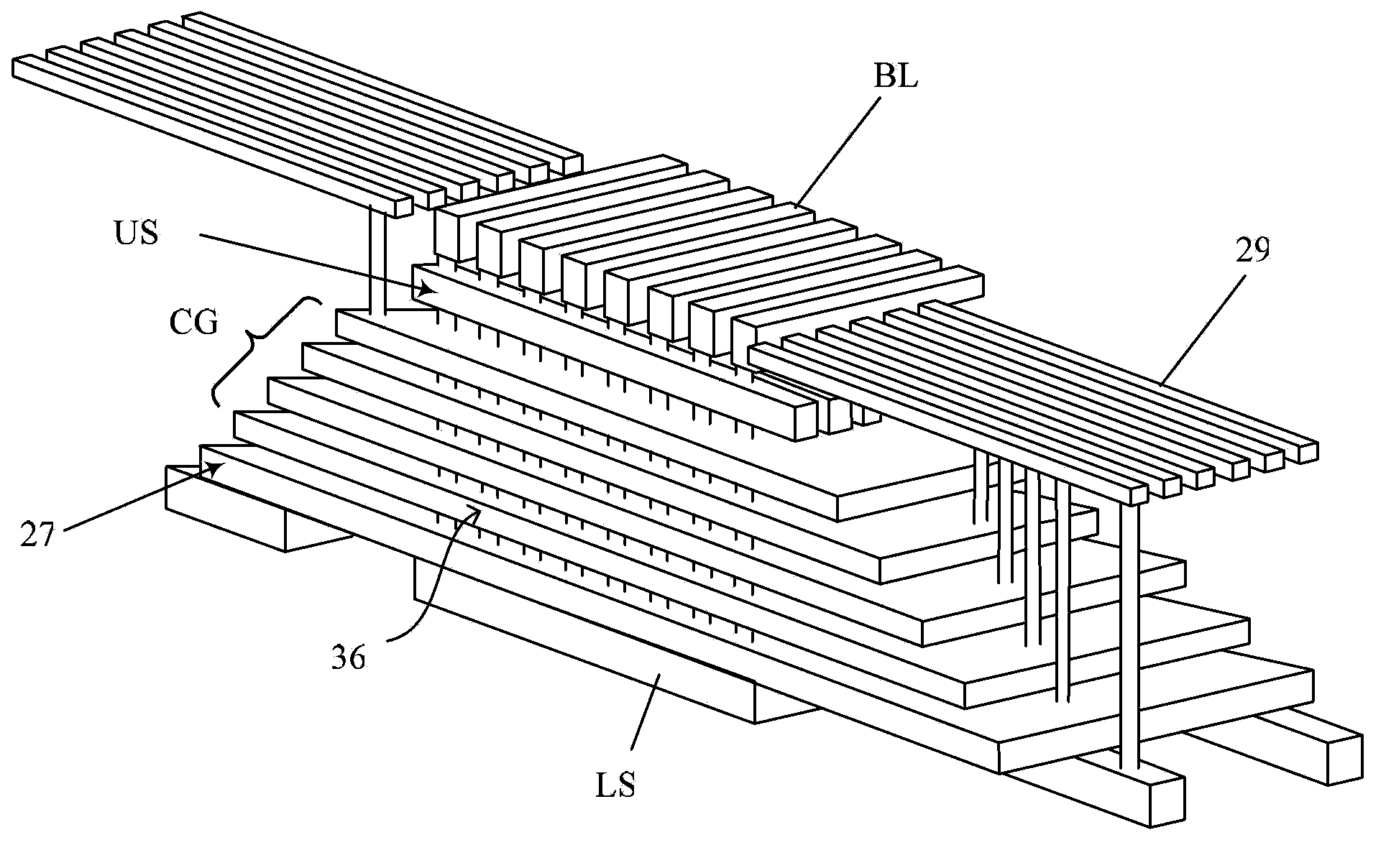

Capacitive-coupled non-volatile thin-film transistor strings in three dimensional arrays

ActiveUS20170092371A1Improve storage densityLower read latencyTransistorSolid-state devicesCapacitive couplingParasitic capacitance

Multi-gate NOR flash thin-film transistor (TFT) string arrays are organized as three dimensional stacks of active strips. Each active strip includes a shared source sublayer and a shared drain sublayer that is connected to substrate circuits. Data storage in the active strip is provided by charge-storage elements between the active strip and a multiplicity of control gates provided by adjacent local word-lines. The parasitic capacitance of each active strip is used to eliminate hard-wire ground connection to the shared source making it a semi-floating, or virtual source. Pre-charge voltages temporarily supplied from the substrate through a single port per active strip provide the appropriate voltages on the source and drain required during read, program, program-inhibit and erase operations. TFTs on multiple active strips can be pre-charged separately and then read, programmed or erased together in a massively parallel operation.

Owner:SUNRISE MEMORY CORP

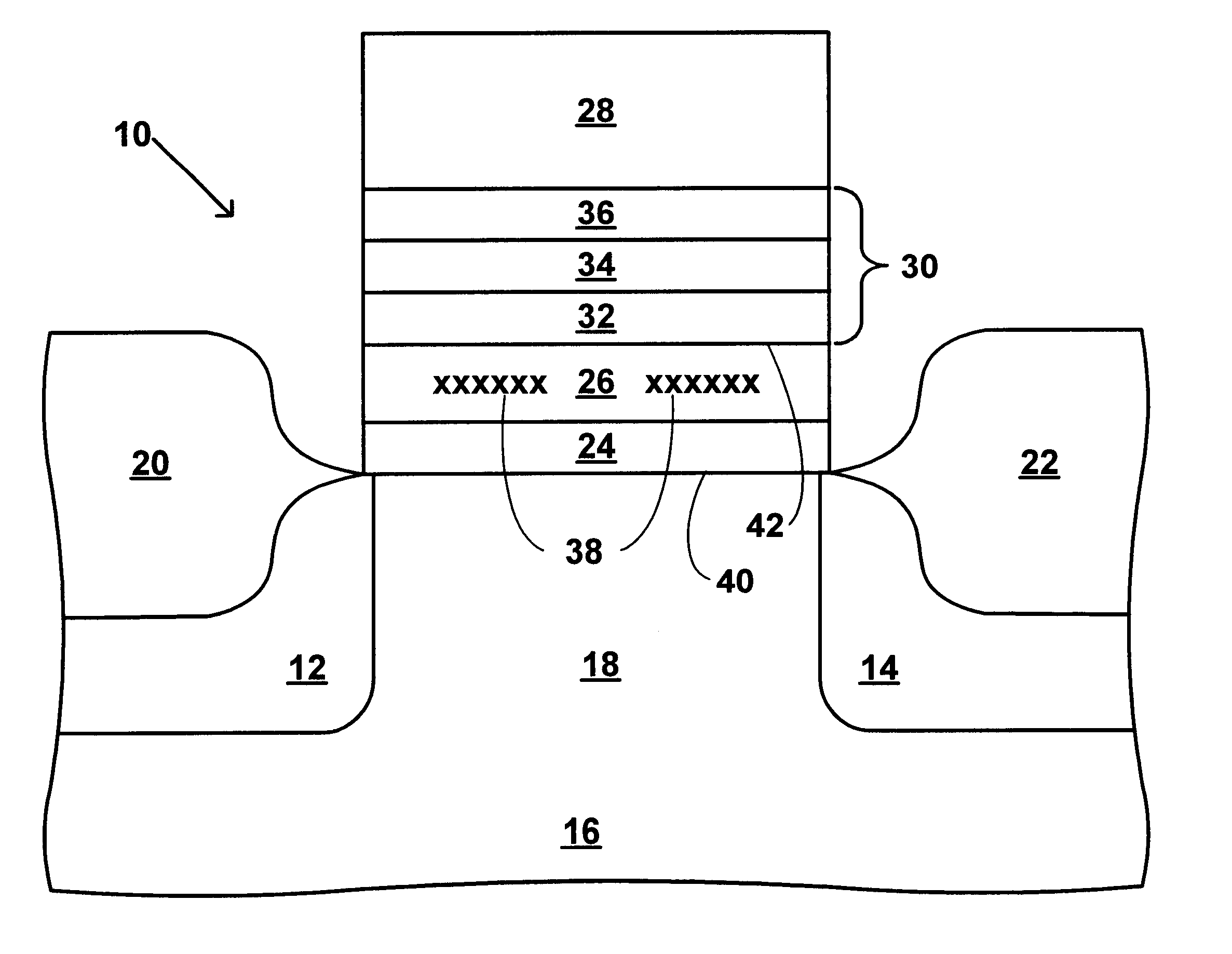

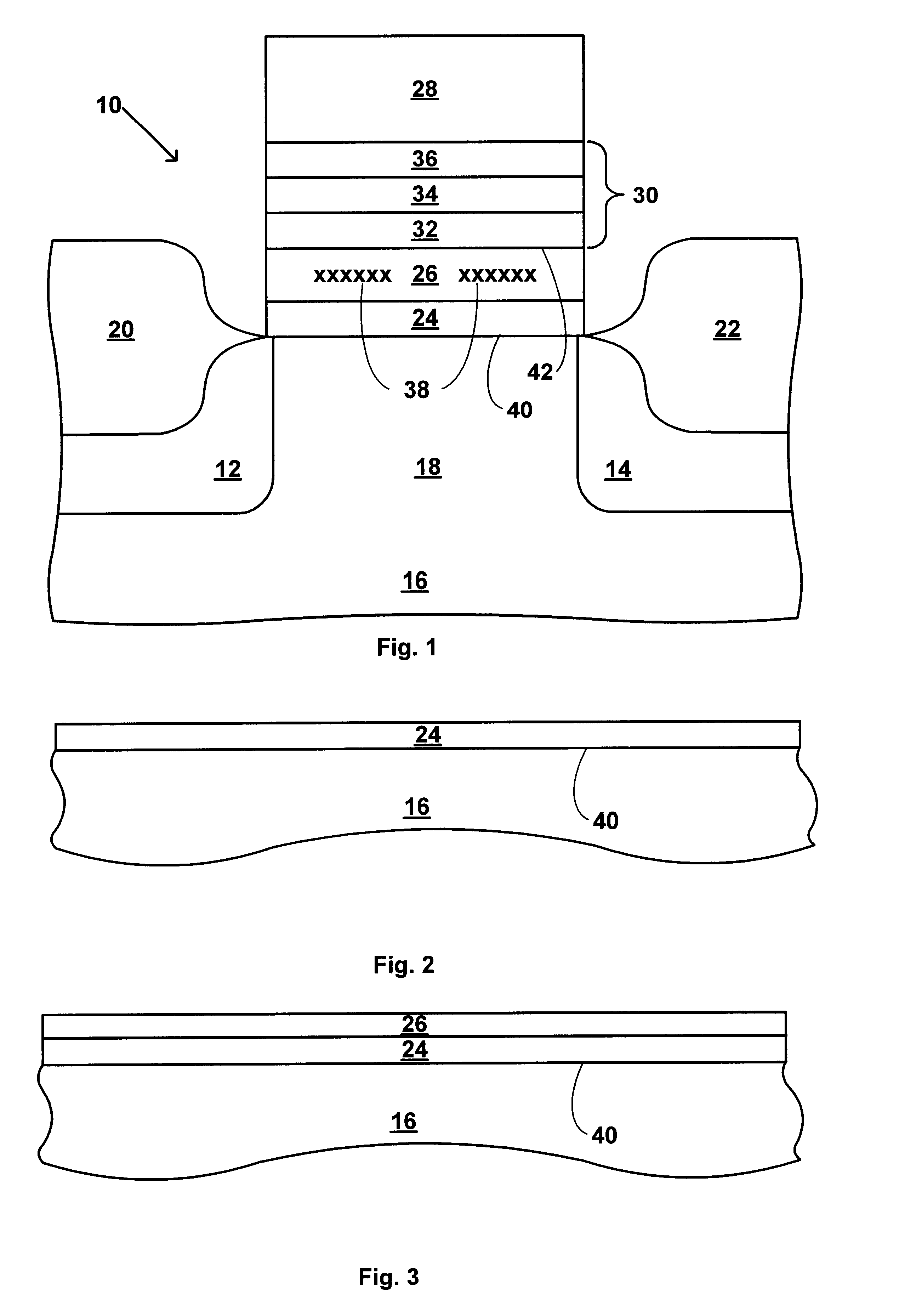

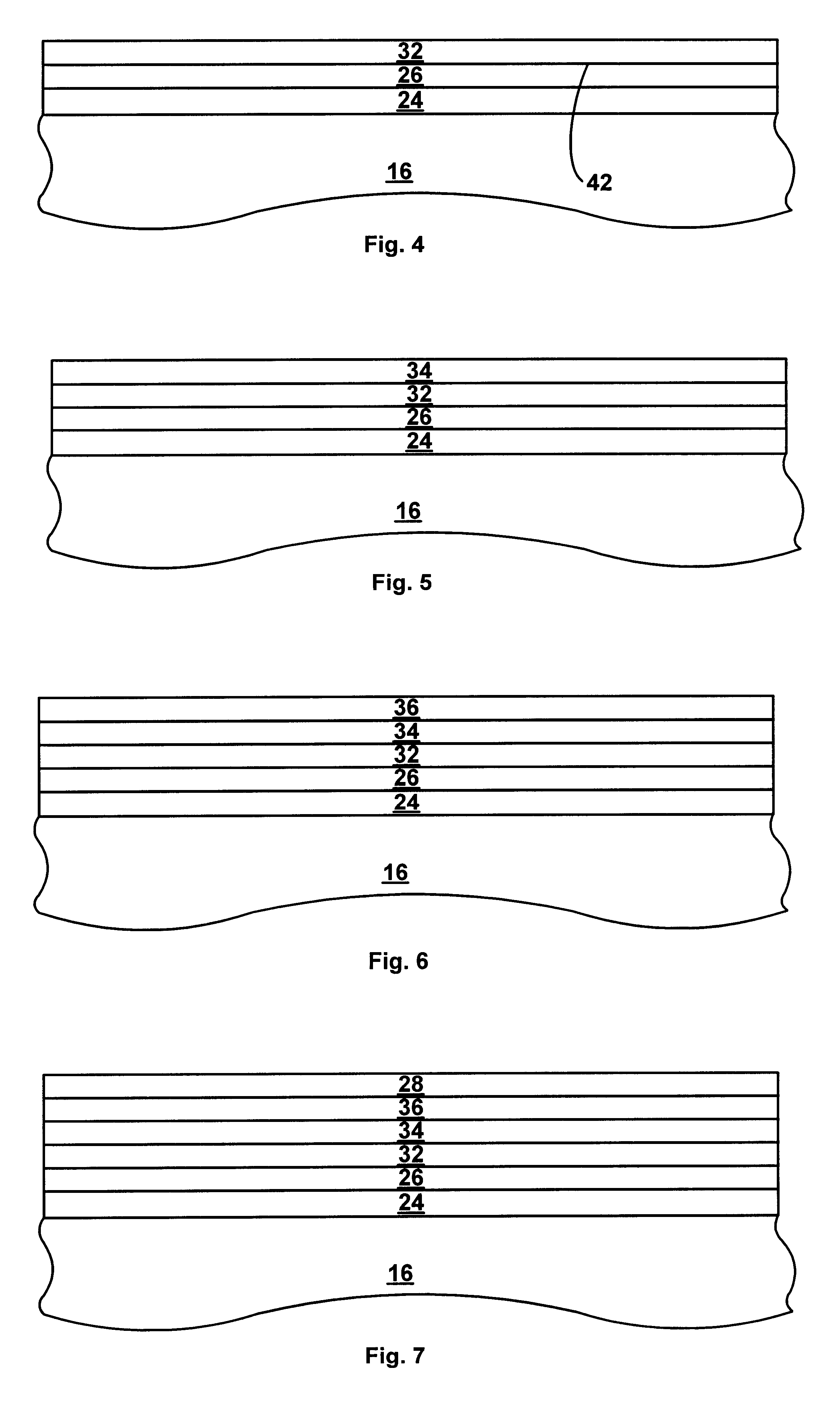

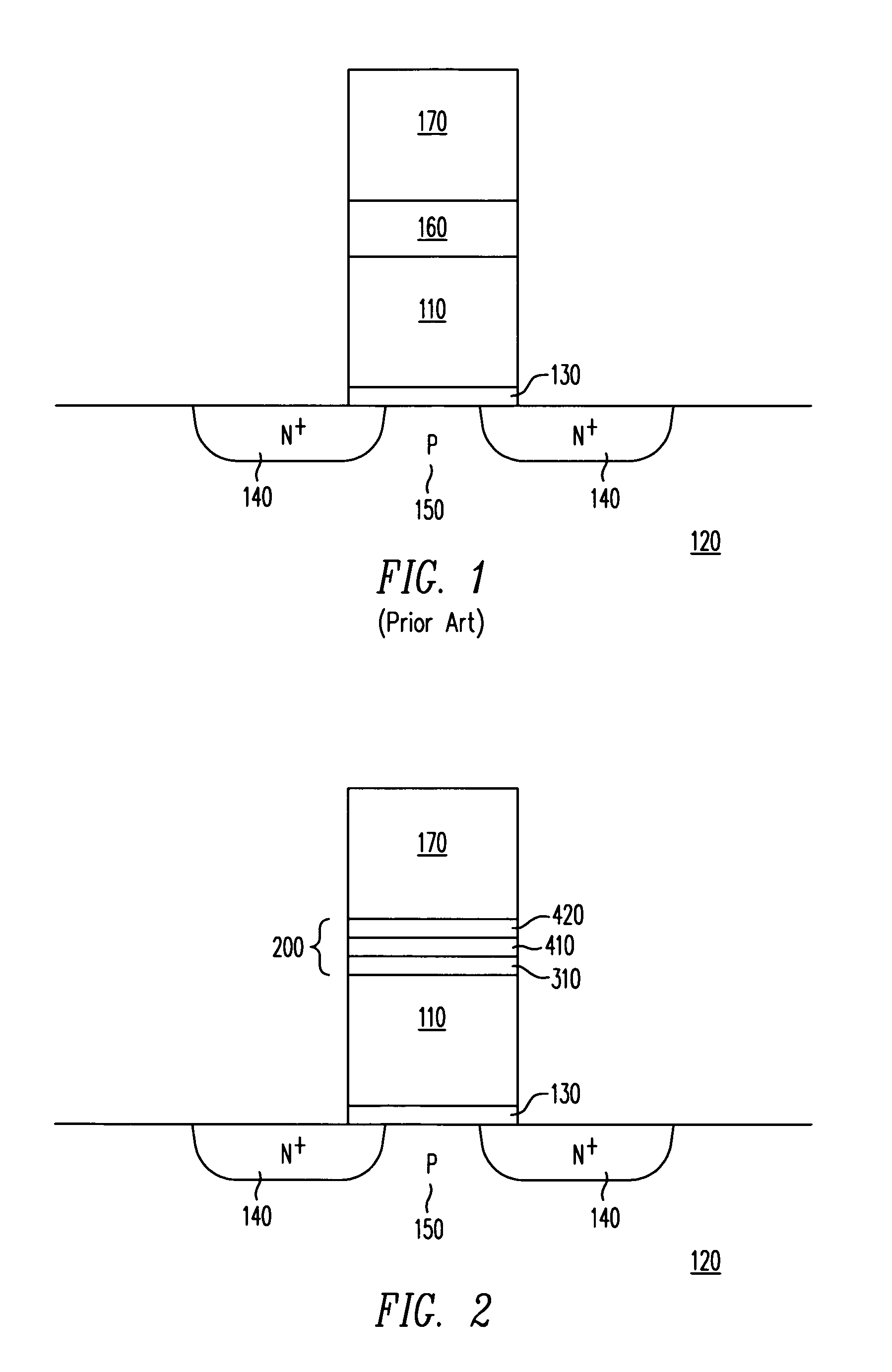

Use of high-K dielectric material for ONO and tunnel oxide to improve floating gate flash memory coupling

InactiveUS6617639B1Enhanced couplingReduce equivalent oxide thicknessTransistorSemiconductor/solid-state device manufacturingCouplingDielectric layer

A floating gate flash memory device including a substrate comprising a source region, a drain region, and a channel region positioned therebetween; a floating gate electrode positioned above the channel region and separated from the channel region by a tunnel dielectric material layer; and a control gate electrode positioned above the floating gate electrode and separated from the floating gate electrode by an interpoly dielectric layer, the interpoly dielectric layer comprising a modified ONO structure having a bottom dielectric material layer adjacent to the floating gate electrode, a top dielectric material layer adjacent to the control gate electrode, and a center layer comprising a nitride and positioned between the bottom dielectric material layer and the top dielectric material layer, in which the tunnel dielectric material layer, and at least one of the bottom dielectric material layer and the top dielectric material layer, comprise a high-K dielectric material.

Owner:MONTEREY RES LLC

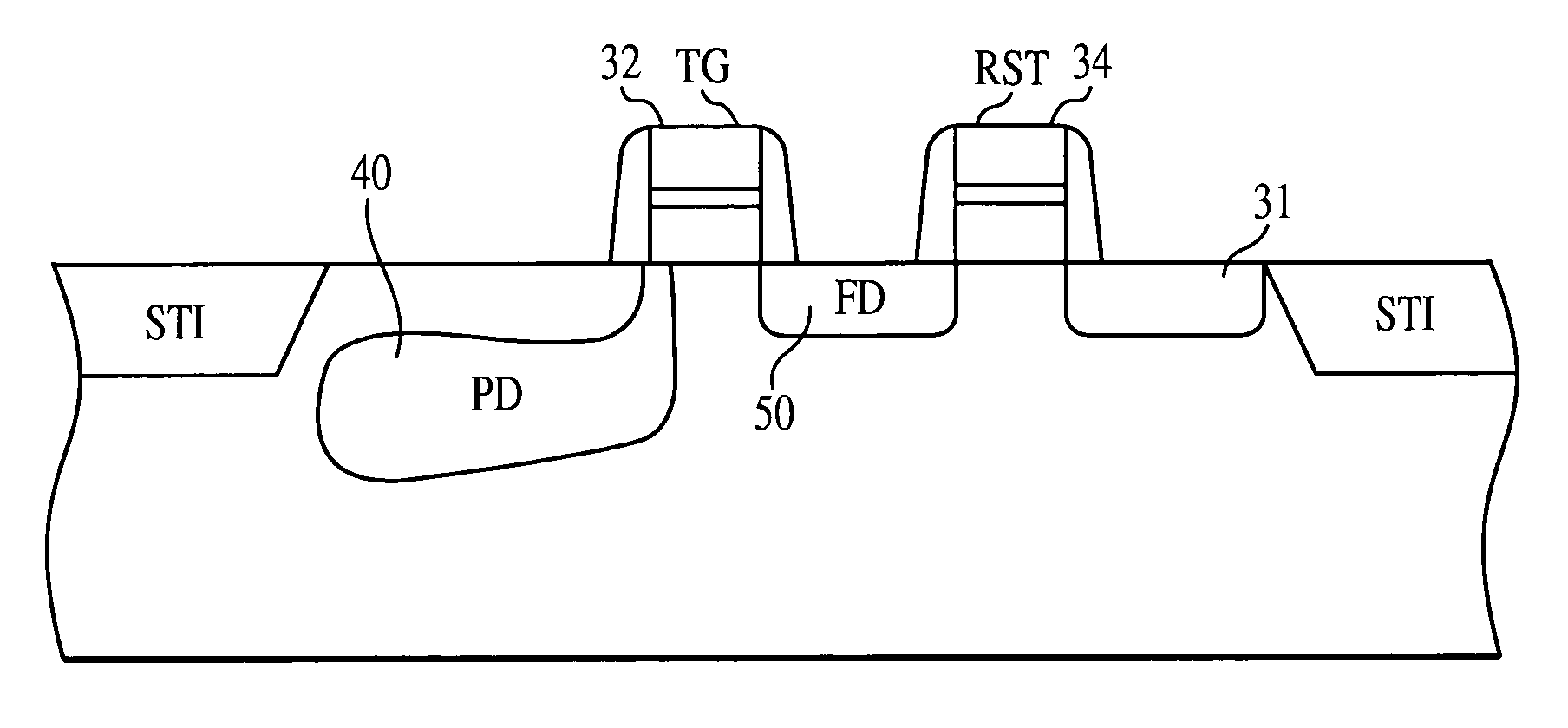

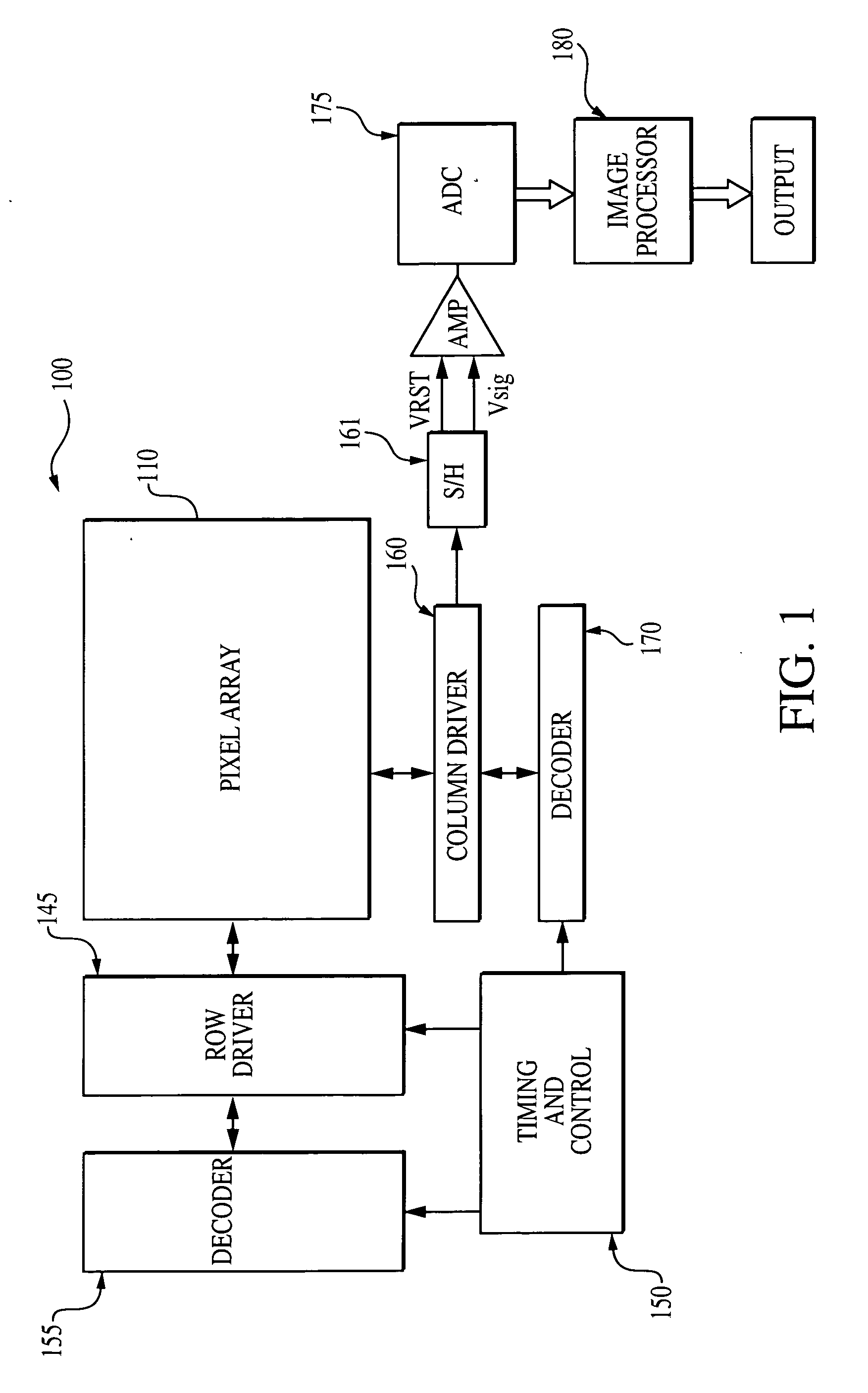

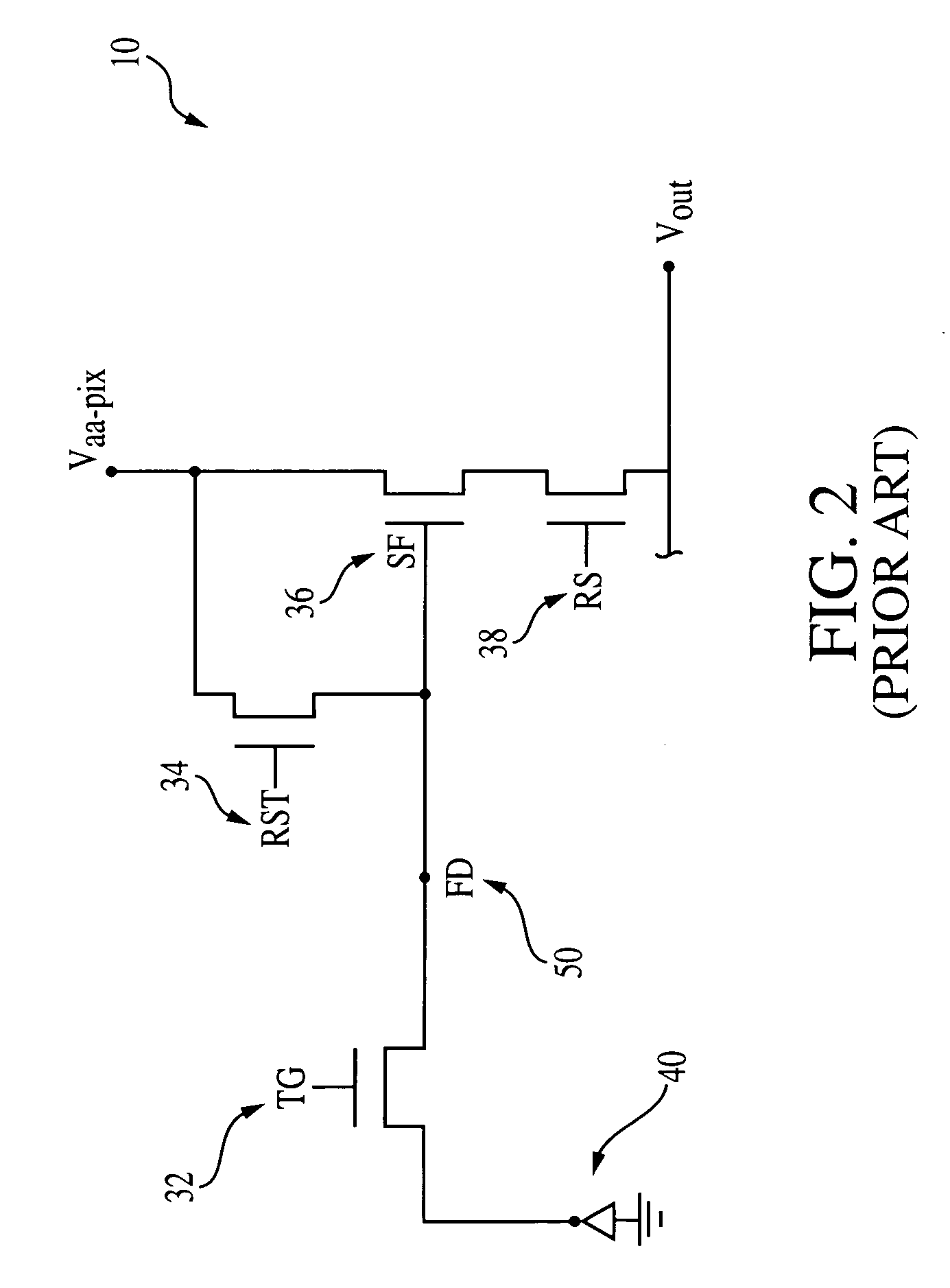

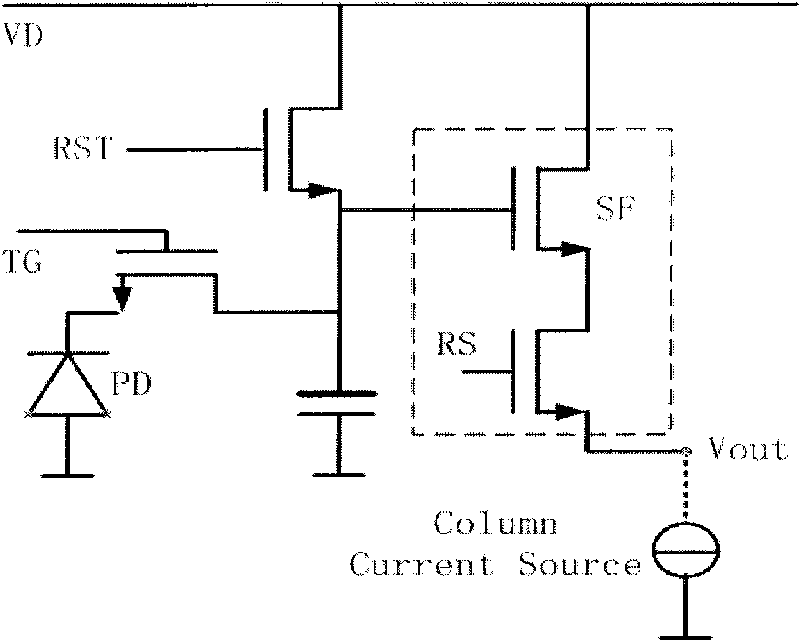

High dynamic range pixel amplifier

ActiveUS20050224843A1Increase capacitanceReduce capacitanceTelevision system detailsTelevision system scanning detailsCapacitanceEngineering

A pixel cell with increased dynamic range is formed by providing a floating diffusion region having a variable capacitance, controlled by at least one gate having source and drain regions commonly connected to the floating diffusion region. The gate has an intrinsic capacitance which, when the gate is activated, is added to the capacitance of the floating diffusion region, providing a low conversion gain readout. When the gate is off, the floating diffusion region capacitance is minimized, providing a high conversion gain readout. The gate may also be selectively switched to mid-level. At mid-level, a mid-level conversion gain, which is between the high and low conversion gains, readout is provided, but the gate still provides some capacitance to prevent the floating diffusion region from saturating.

Owner:APTINA IMAGING CORP

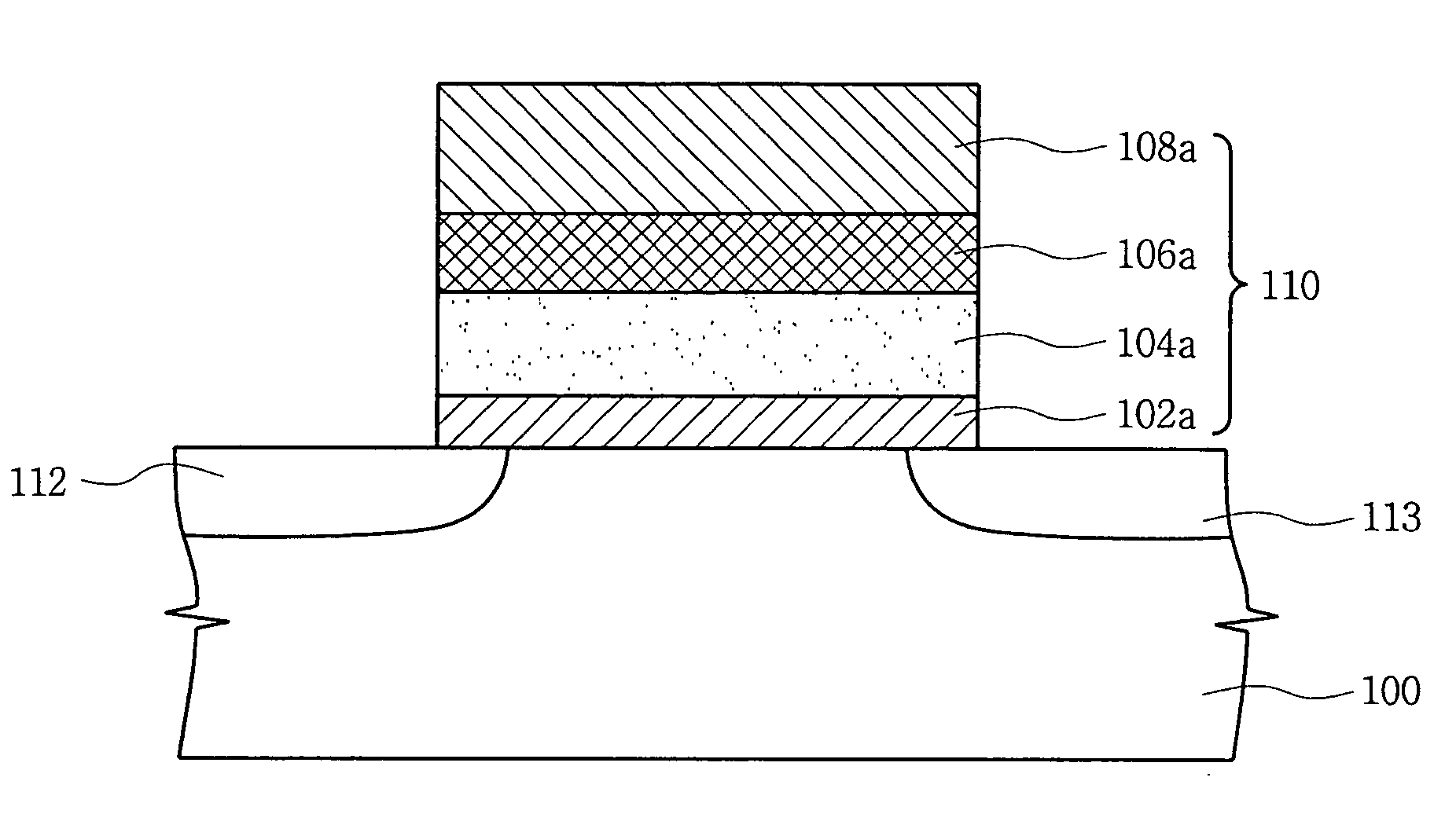

Nonvolatile memory device and method of fabricating the same

There are provided a nonvolatile memory device and a method of fabricating the same. A gate region of the nonvolatile memory device is formed as a stack structure including a tunnel oxide layer, a trapping layer, a blocking layer and a control gate electrode. The trapping layer is formed of a high-k dielectric having a higher dielectric constant than that of the tunnel oxide layer. When the trapping layer is formed of high-k dielectric, an EOT in a same thickness can be reduced, and excitation of electrons of the control gate electrode to the tunnel oxide layer due to a high potential barrier relative to the tunnel oxide layer is prevented so that program and erase voltages can be further reduced. As such, a problem that the tunnel oxide layer is damaged due to the conventional high program and erase voltages can be solved by reducing the program and erase voltages, and program and erase speeds of the transistor can be further improved.

Owner:SAMSUNG ELECTRONICS CO LTD

Capacitive-coupled non-volatile thin-film transistor NOR strings in three-dimensional arrays

ActiveUS10121553B2High densityLower read latencyTransistorSolid-state devicesCapacitive couplingParasitic capacitance

Owner:SUNRISE MEMORY CORP

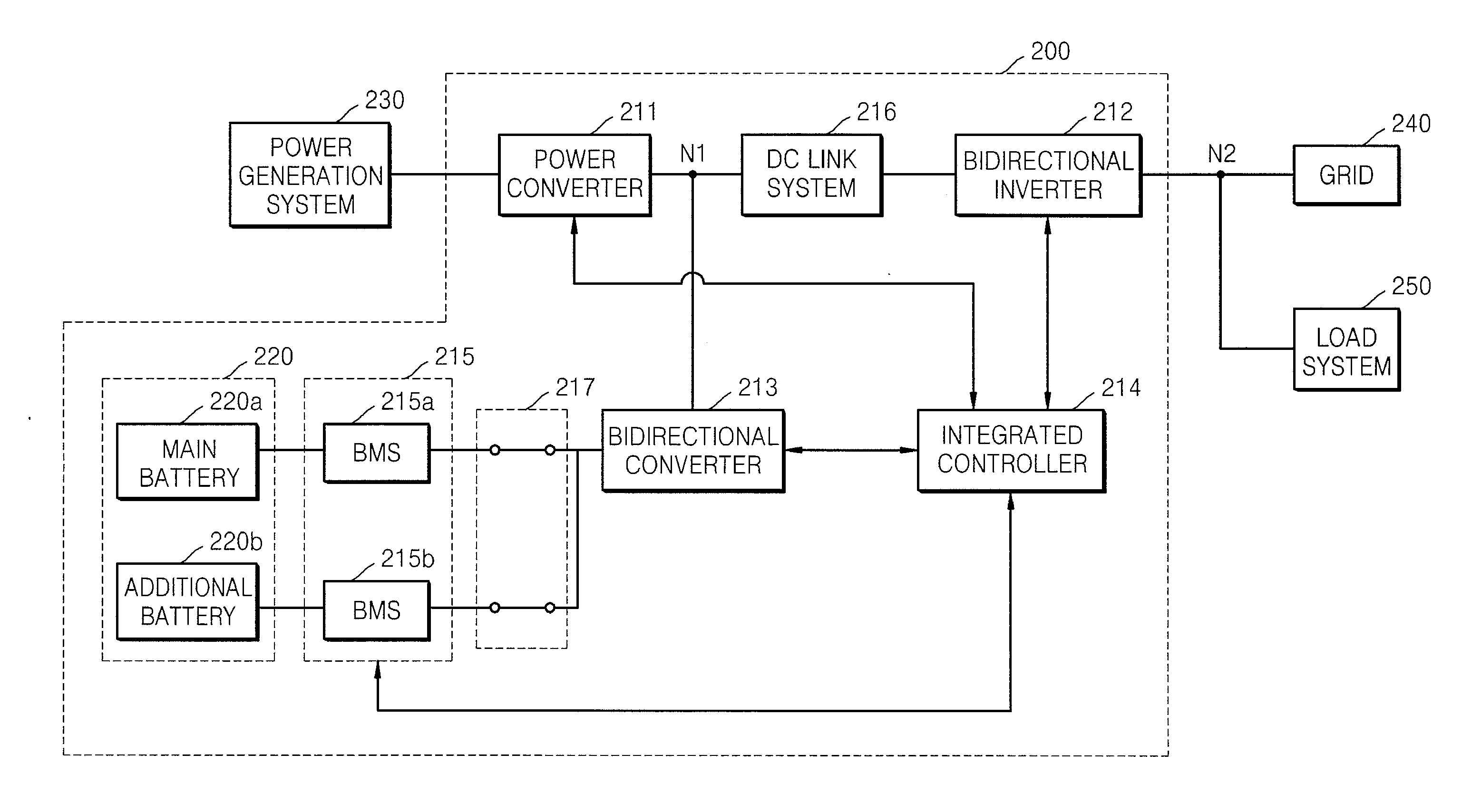

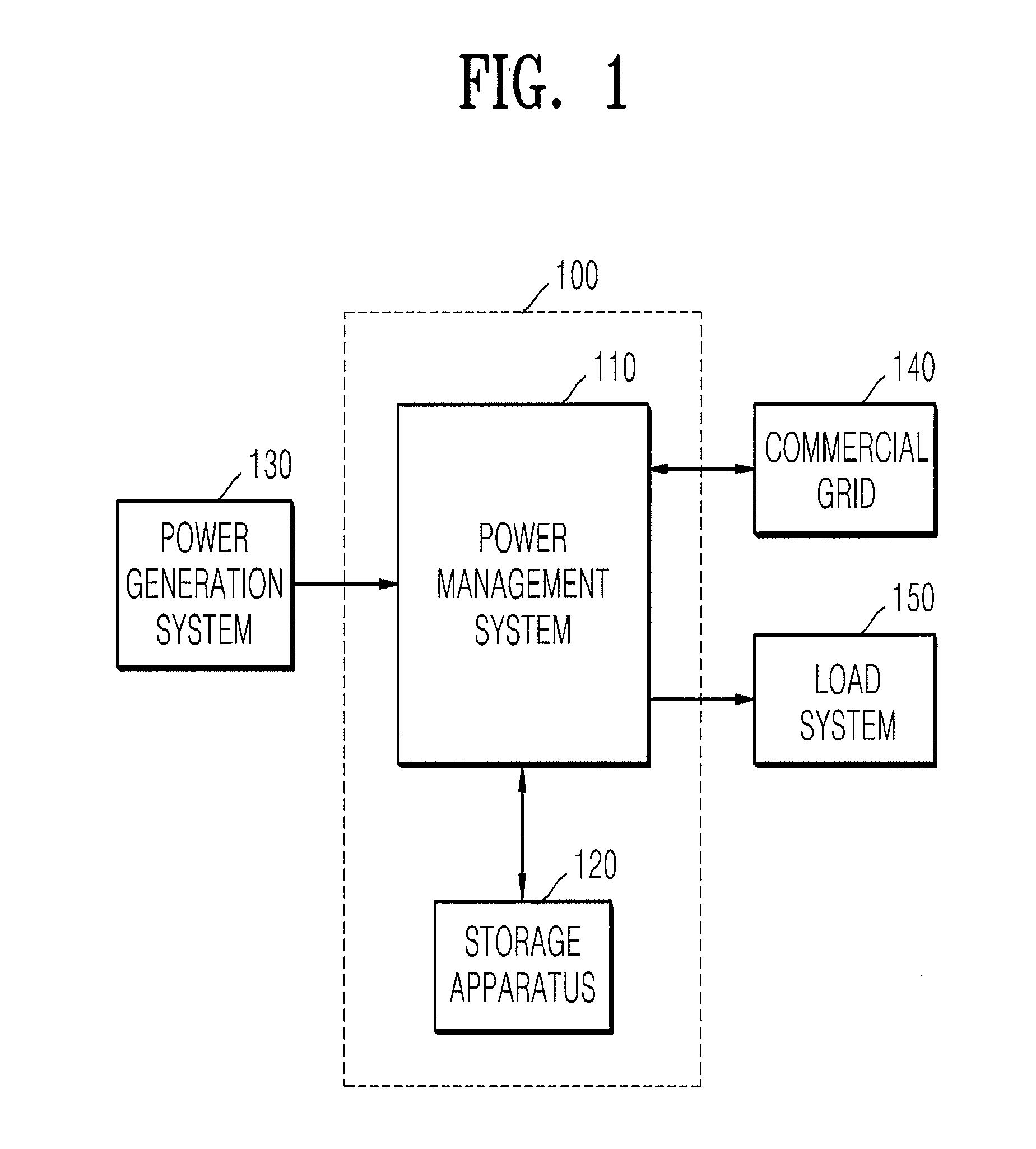

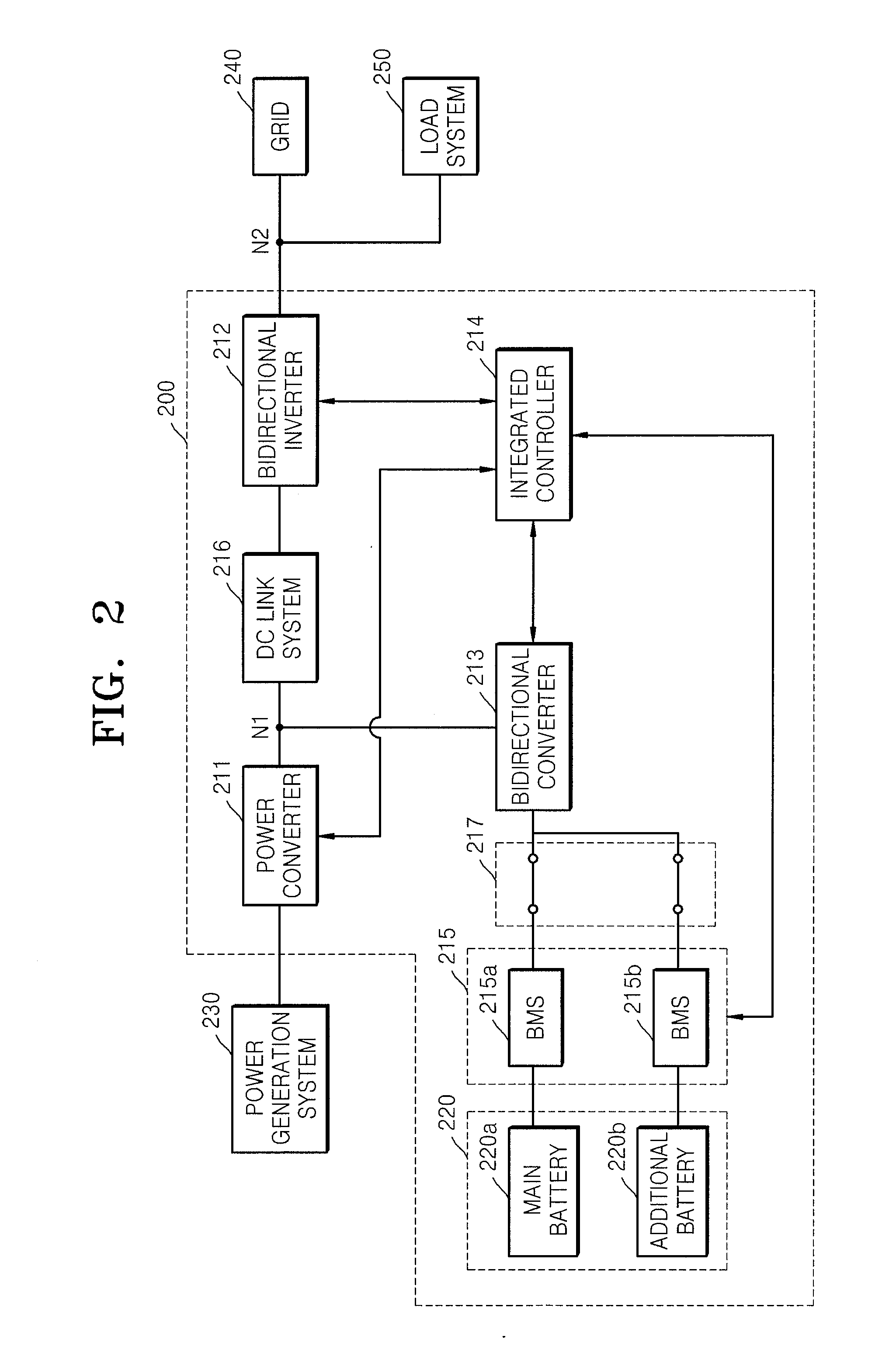

Grid-connected power storage system and method for controlling grid-connected power storage system

ActiveUS20110133558A1Reduce spacingIncreased power consumptionBatteries circuit arrangementsSingle network parallel feeding arrangementsElectrical batteryPower grid

A grid-connected power storage system for coupling a power generation system to a grid, including: a main battery for discharging stored power to the load system; at least one additional battery coupled to the main battery for discharging stored power to the load system; a bidirectional converter coupled to the main and additional batteries, and including a plurality of switches for performing a conversion between a DC link voltage, between the power generation system and the grid, and a battery voltage, a first switch of the plurality of switches corresponding to the main battery and a second switch of the plurality of switches corresponding to the additional battery, wherein the first and second switches are connected to each other in parallel; and an integrated controller for selectively controlling operations of the first switch and the second switch based on an amount of power used by the load system.

Owner:HANWHA SOLUTIONS CORP

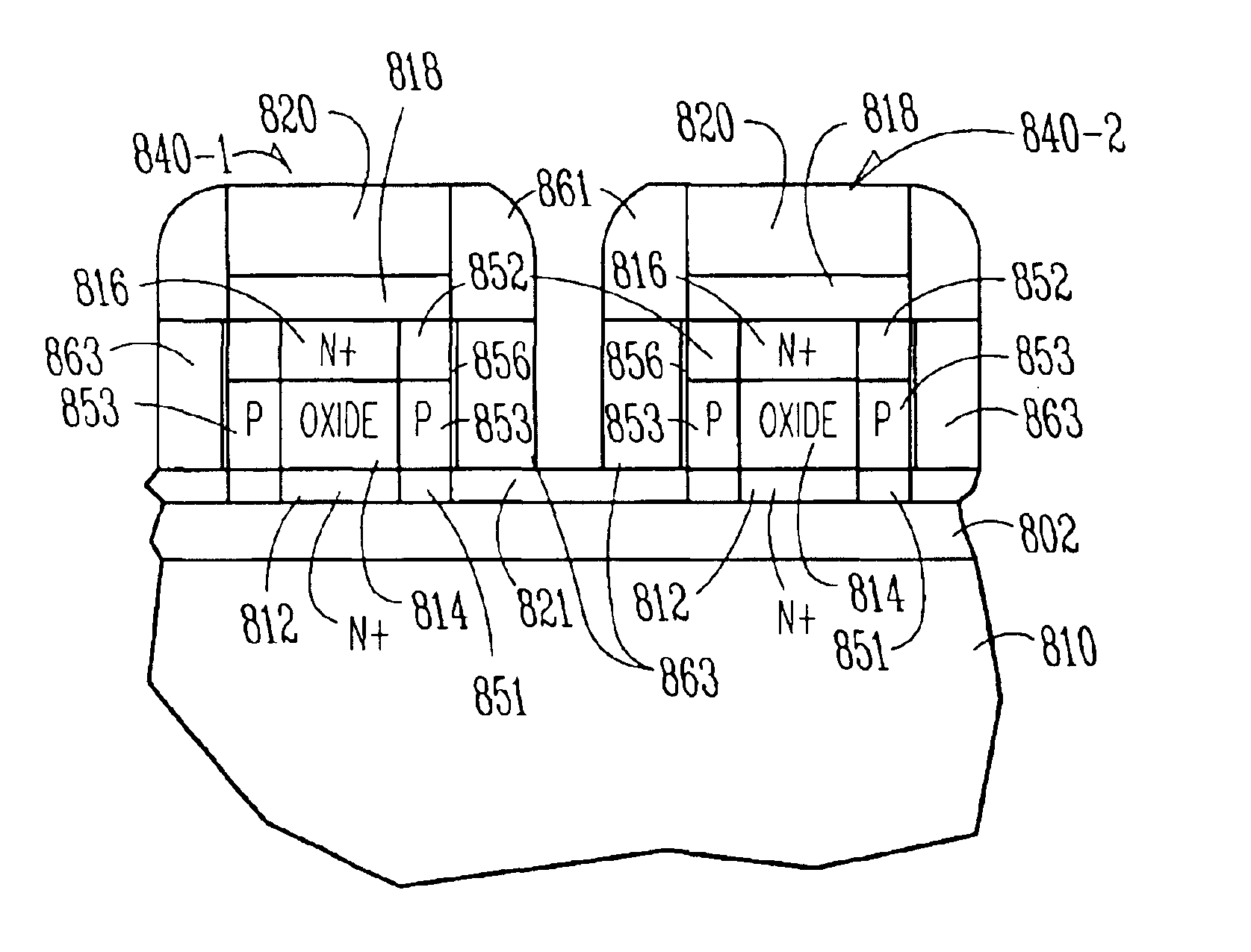

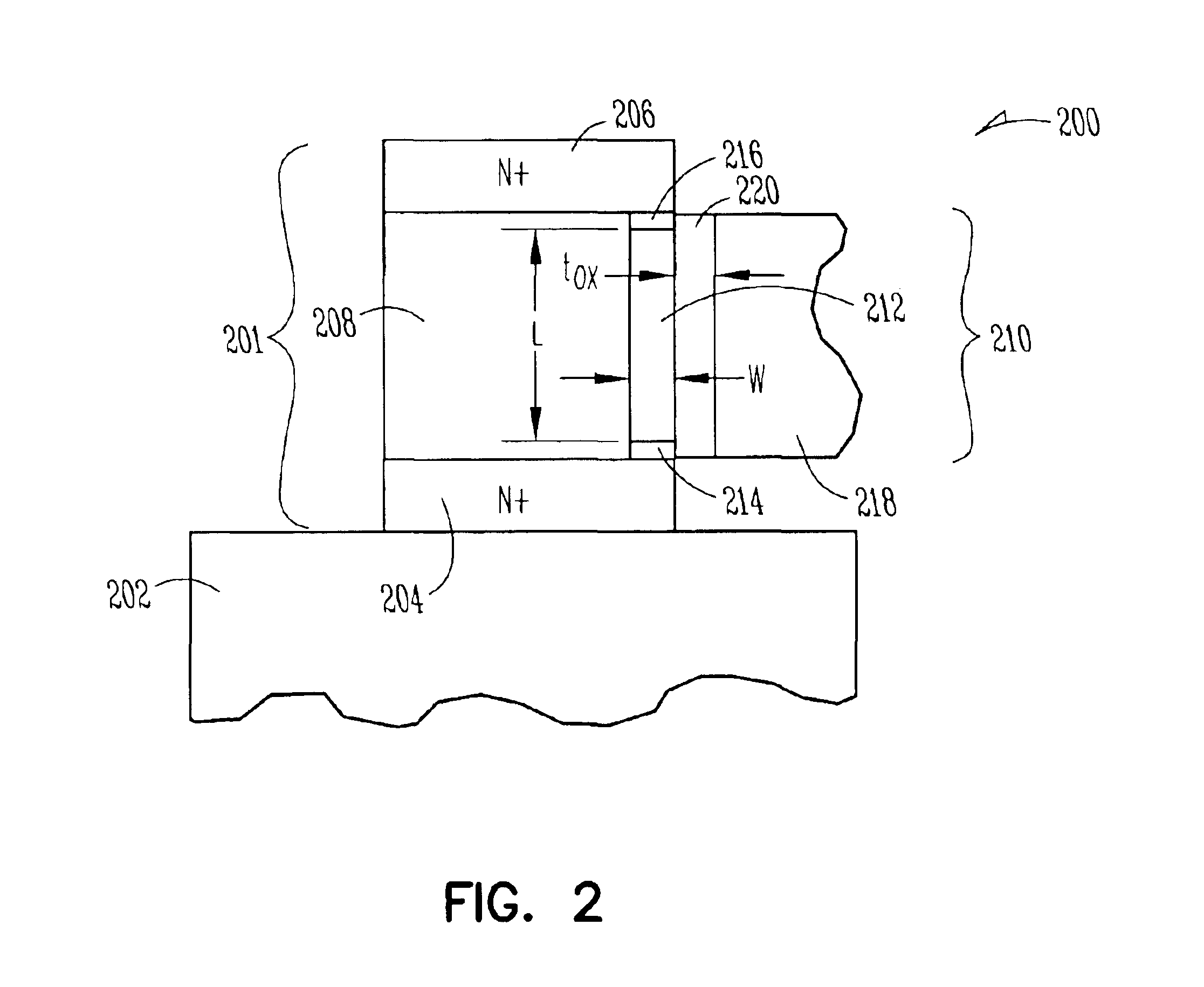

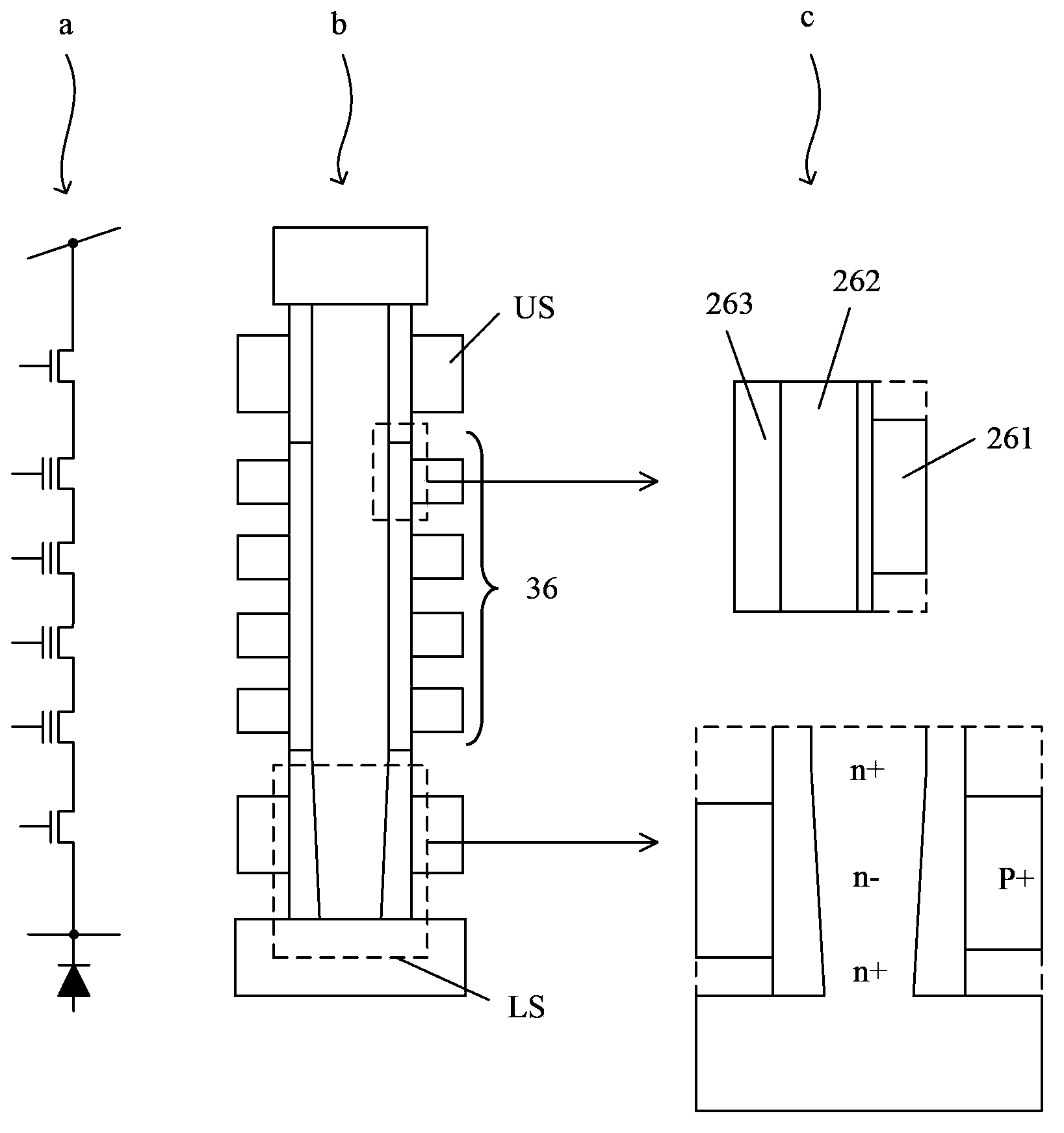

Programmable memory address and decode circuits with vertical body transistors

Various embodiments provide a decoder for a memory array, comprising an array of address and output lines, vertical pillars, vertical floating gate transistors, and buried source lines. Each pillar includes single crystalline first and second contact layers separated by an oxide layer. Each floating gate transistor is formed in a single crystalline layer, having a thickness less than 10 nanometers, selectively disposed on a side of one of the pillars. Each transistor includes first and second source / drain regions in contact with the first and second contact layers, respectively, a body region opposing the oxide layer and contacting the first and second source / drain regions, and a floating gate opposing the body region. The source lines are disposed below the pillars and interconnect the first contact layer of pillars. Each of the address lines is disposed between rows of pillars and serves as a control gate.

Owner:MICRON TECH INC

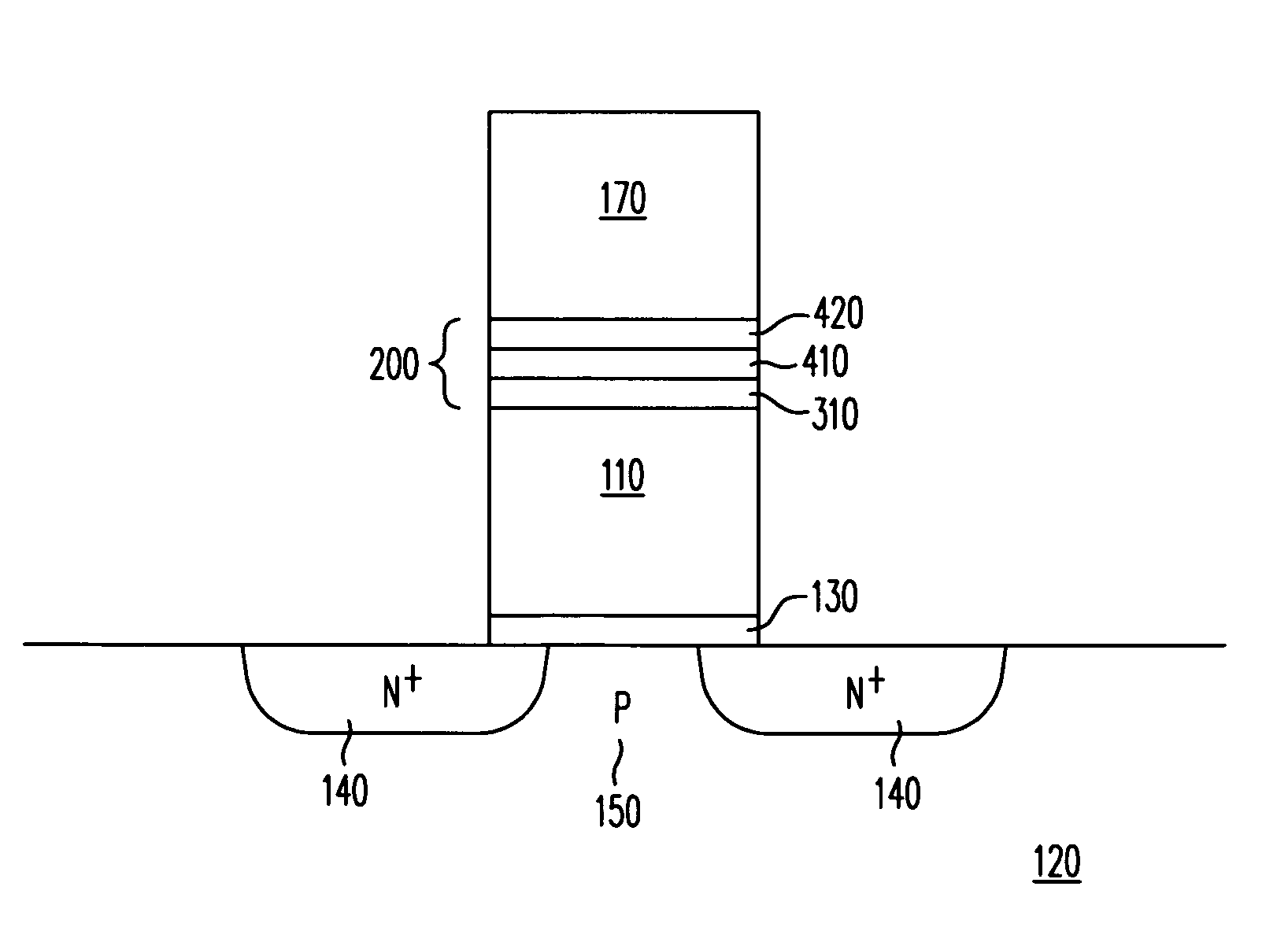

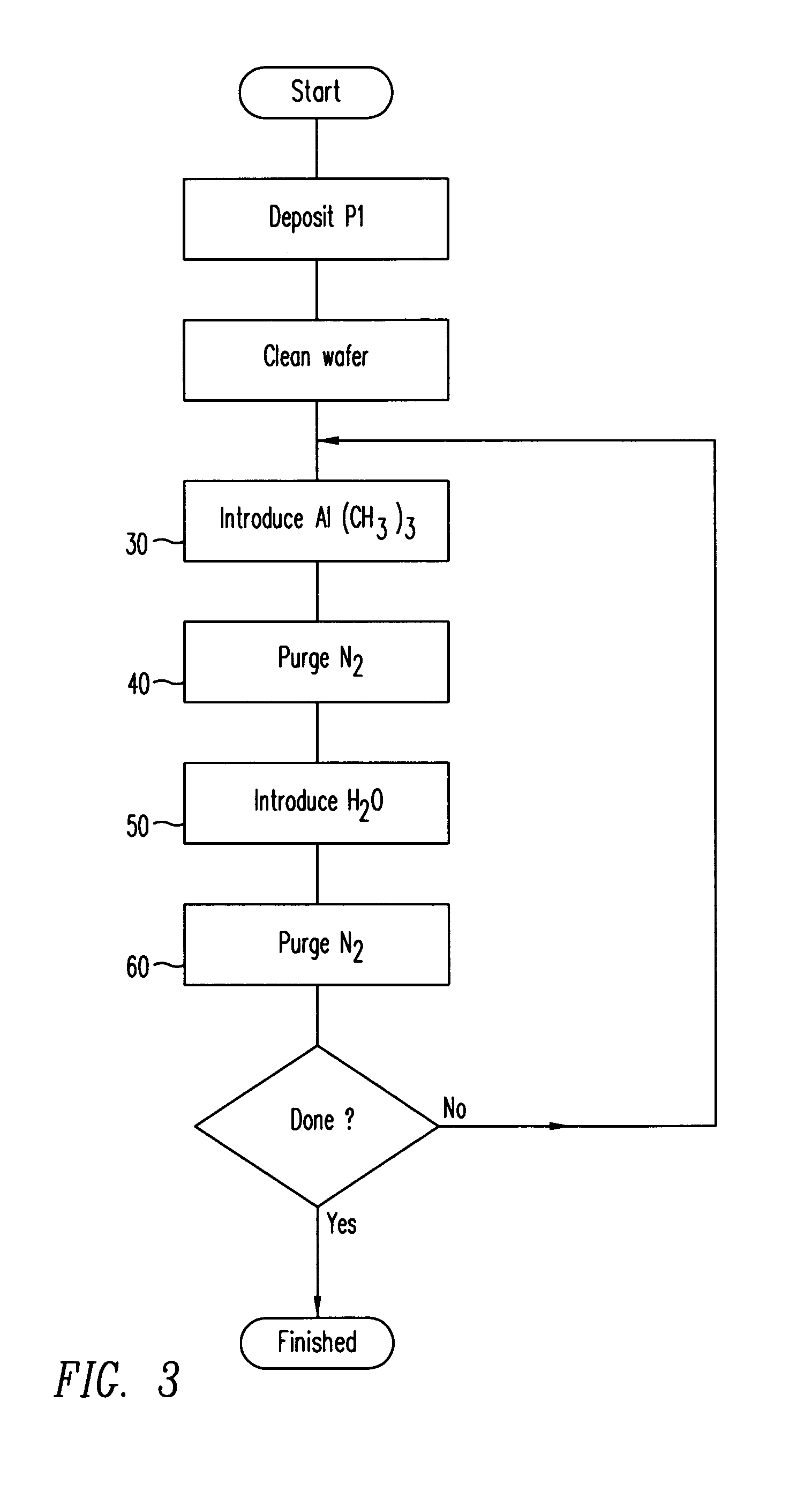

Atomic layer deposition of interpoly oxides in a non-volatile memory device

InactiveUS7122415B2Reduce in quantityFewer crystal defects or pin holesSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceMemory cell

Aluminum oxide is deposited by atomic layer deposition to form a high-k dielectric for the interpoly dielectric layer of a non-volatile memory device. The increased capacitive coupling can allow a thicker oxide layer to be used between the floating gate and the control gate, resulting in improved reliability and longer lifetime of the memory cells fabricated according to this invention.

Owner:PROMOS TECH INC

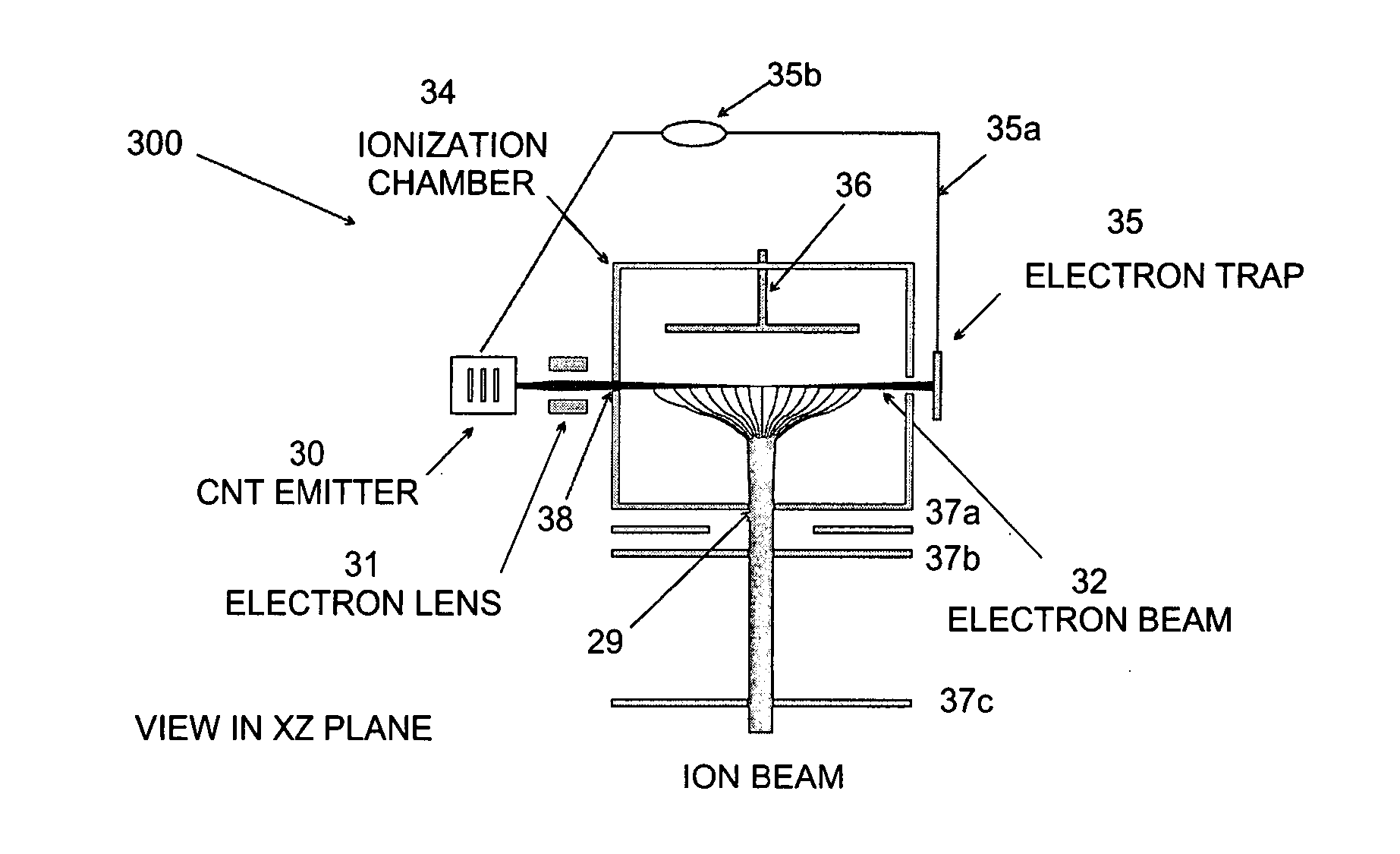

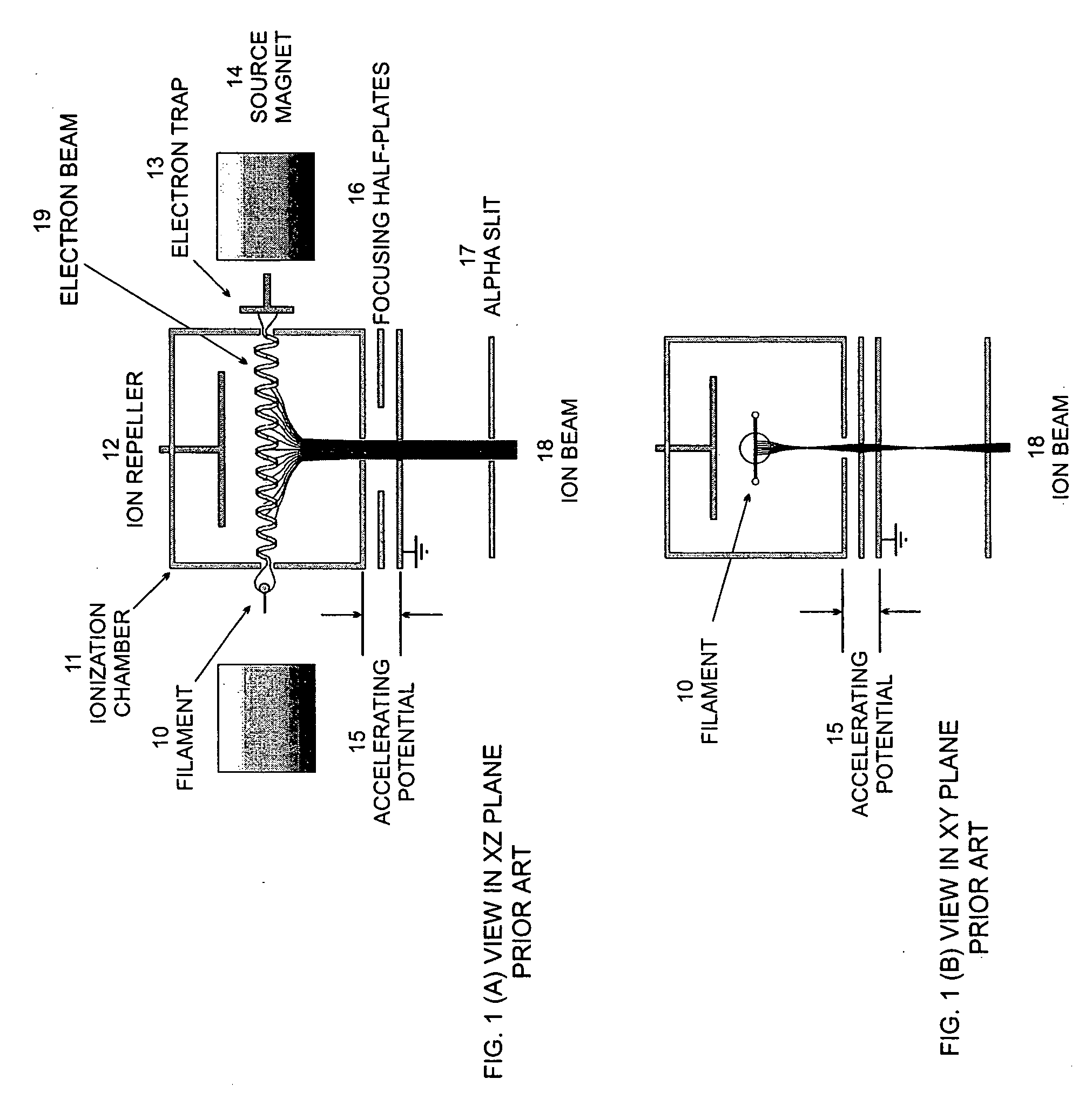

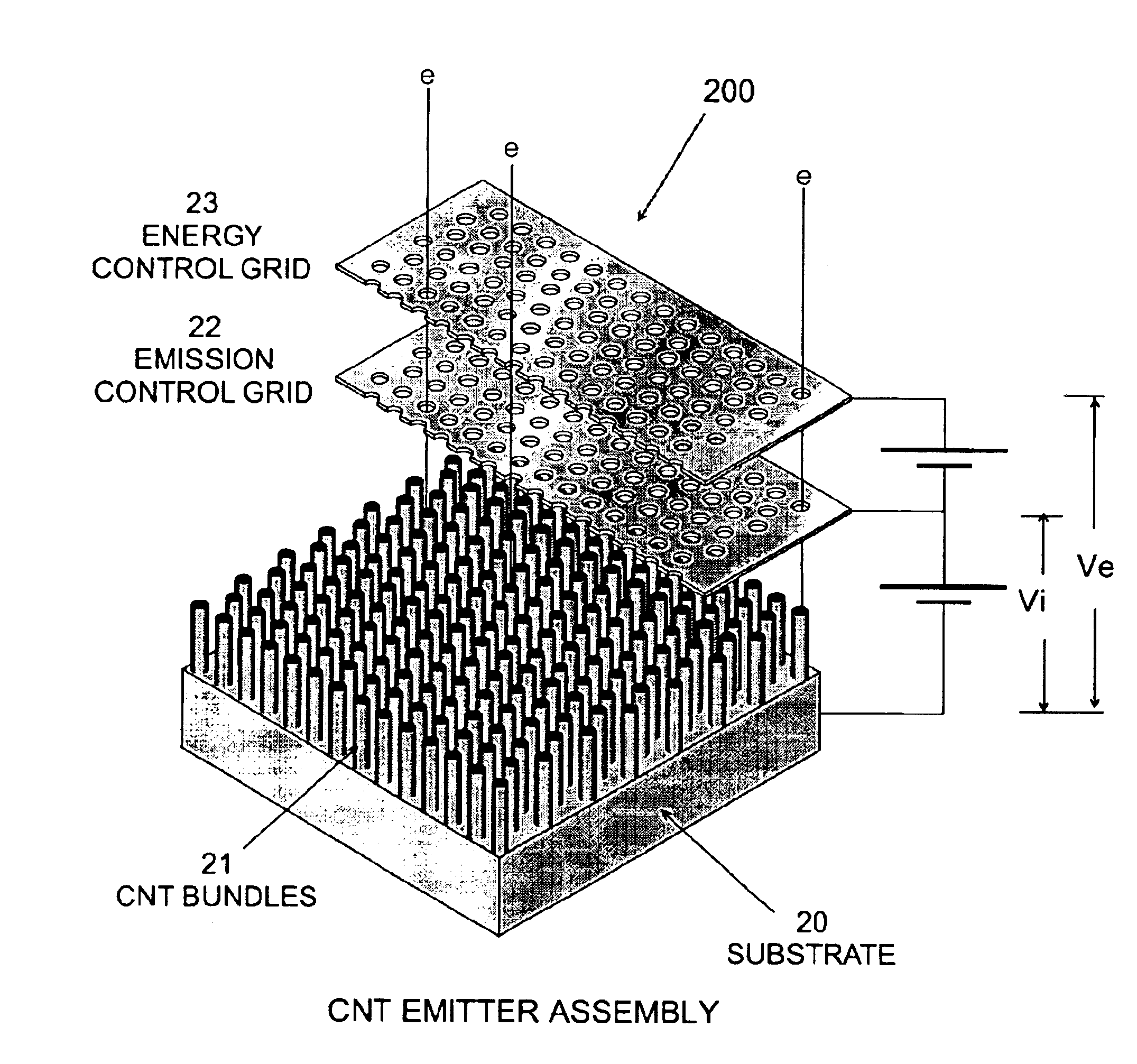

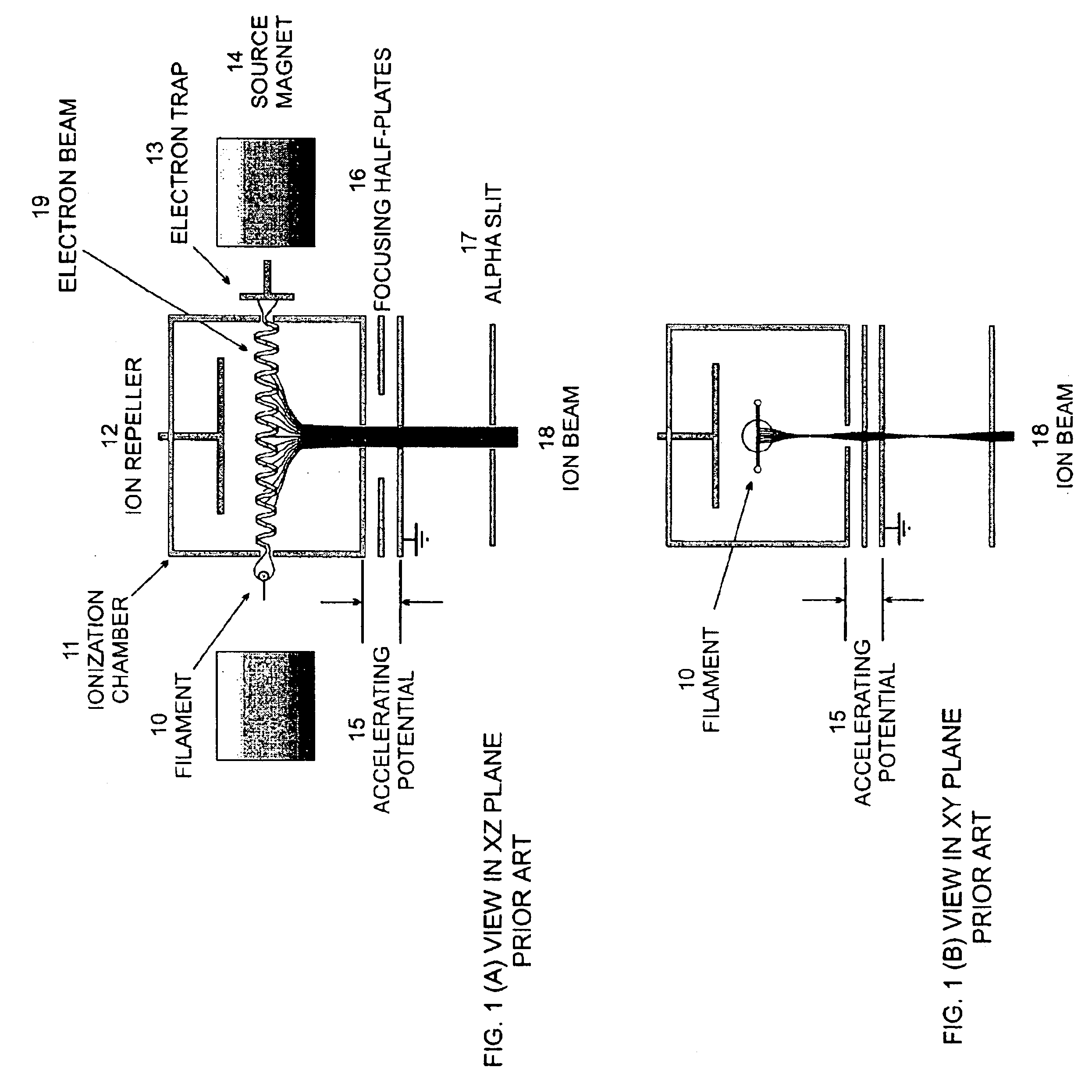

Carbon nanotube electron ionization sources

InactiveUS20050098720A1Reduce in quantityEasy CalibrationMaterial nanotechnologyNanoinformaticsCarbon nanotubeIonization chamber

Owner:THERMO ELECTRON A DE

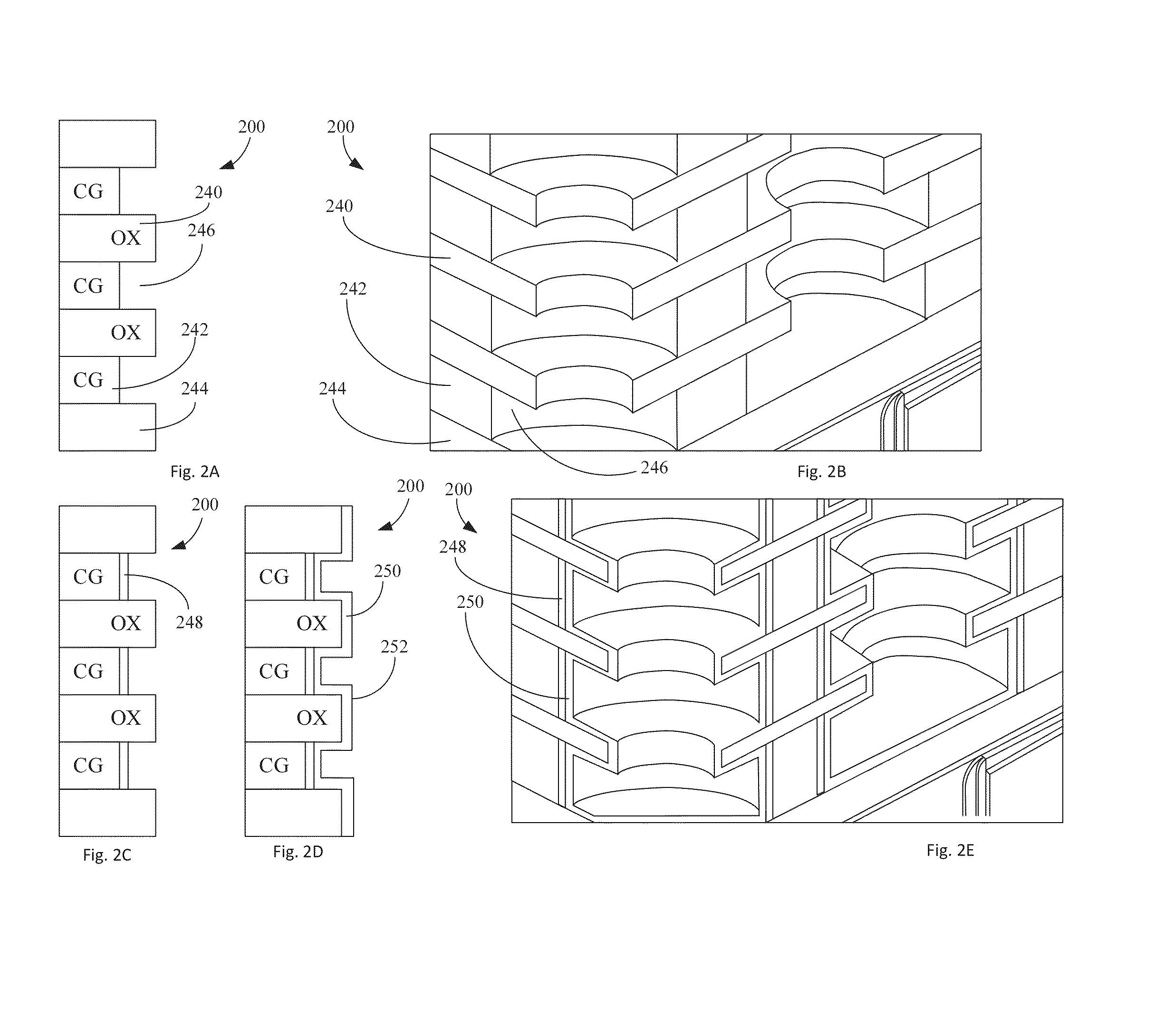

Floating gate memory cells in vertical memory

Floating gate memory cells in vertical memory. A control gate is formed between a first tier of dielectric material and a second tier of dielectric material. A floating gate is formed between the first tier of dielectric material and the second tier of dielectric material, wherein the floating gate includes a protrusion extending towards the control gate. A charge blocking structure is formed between the floating gate and the control gate, wherein at least a portion of the charge blocking structure wraps around the protrusion.

Owner:MICRON TECH INC

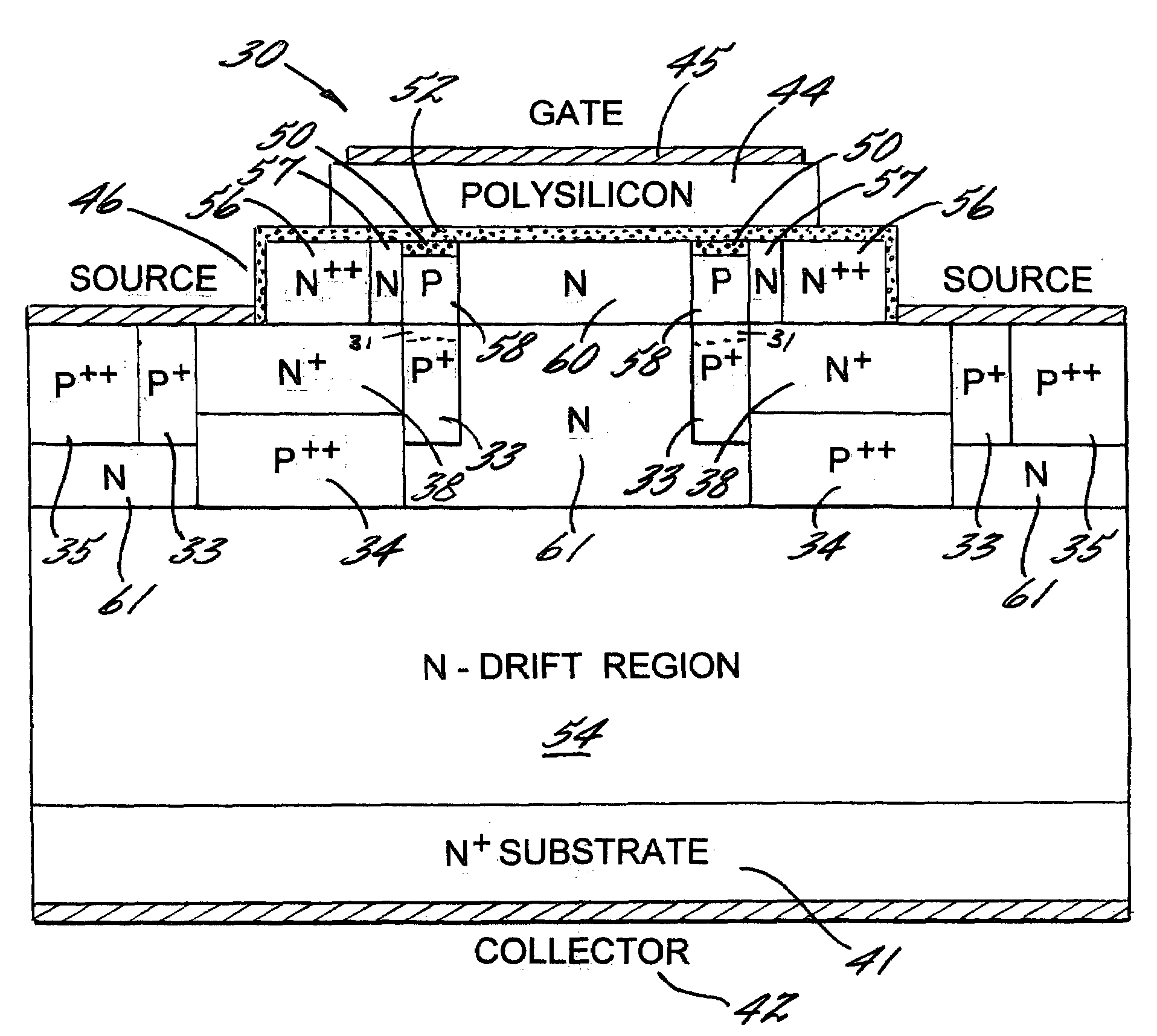

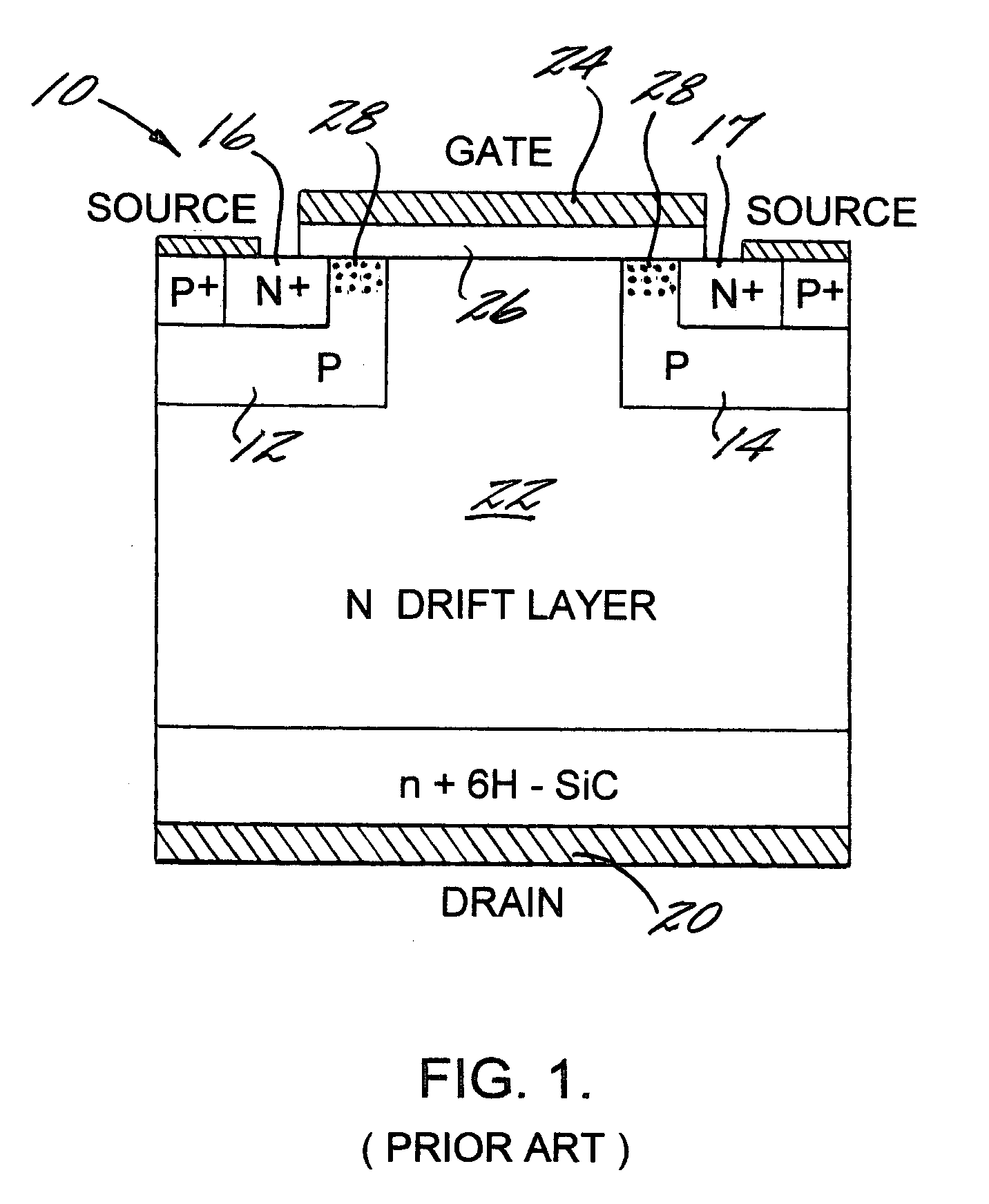

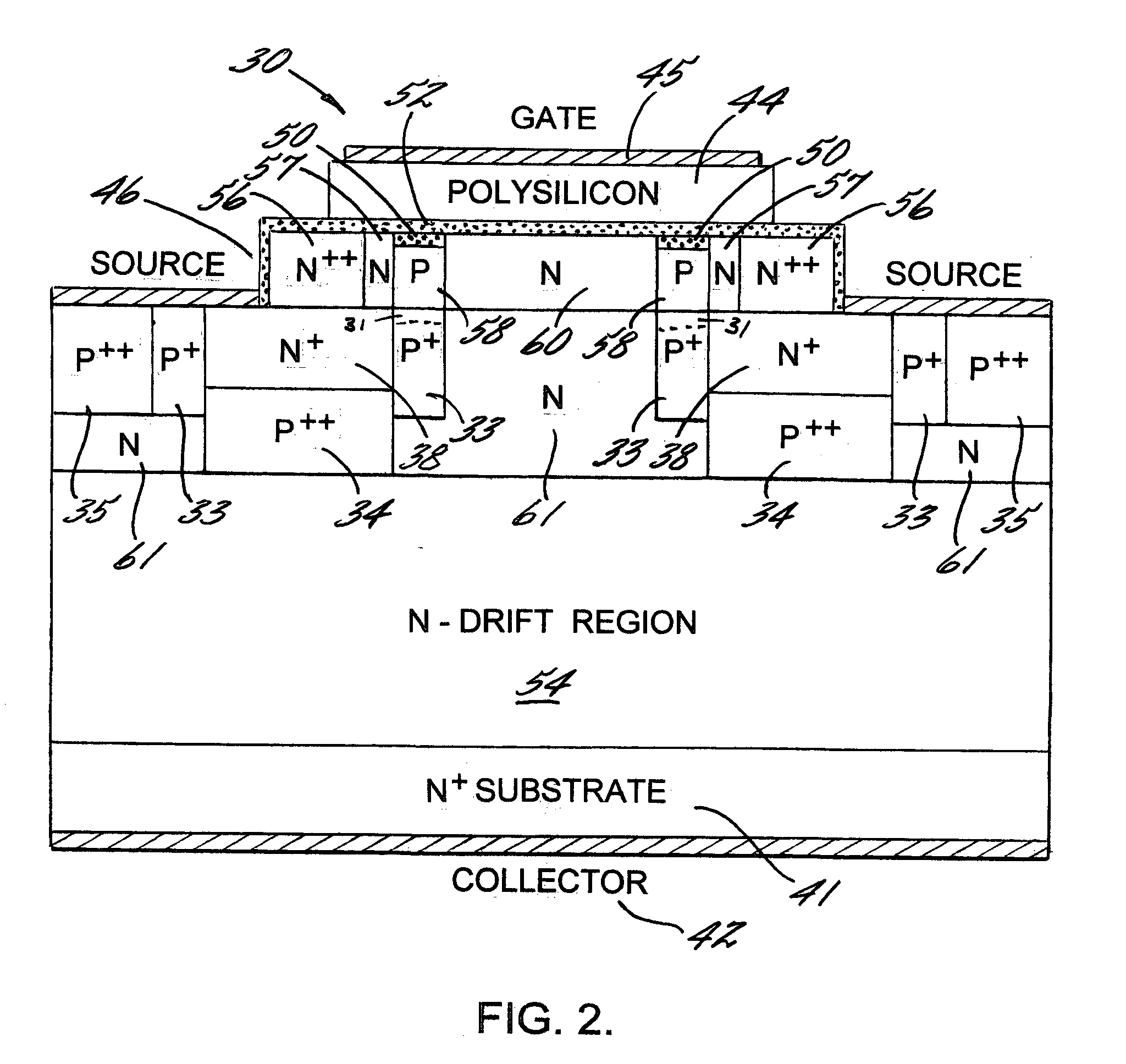

Semiconductor transistor with p type re-grown channel layer

ActiveUS20090189228A1Easy to controlTransistorSemiconductor/solid-state device manufacturingMOSFETEngineering

The invention is a device for controlling conduction across a semiconductor body with a P type channel layer between active semiconductor regions of the device and the controlling gate contact. The device, often a MOSFET or an IGBT, includes at least one source, well, and drift region. The P type channel layer may be divided into sections, or divided regions, that have been doped to exhibit N type conductivity. By dividing the channel layer into regions of different conductivity, the channel layer allows better control over the threshold voltage that regulates current through the device. Accordingly, one of the divided regions in the channel layer is a threshold voltage regulating region. The threshold-voltage regulating region maintains its original P type conductivity and is available in the transistor for a gate voltage to invert a conductive zone therein. The conductive zone becomes the voltage regulated conductive channel within the device.

Owner:WOLFSPEED INC

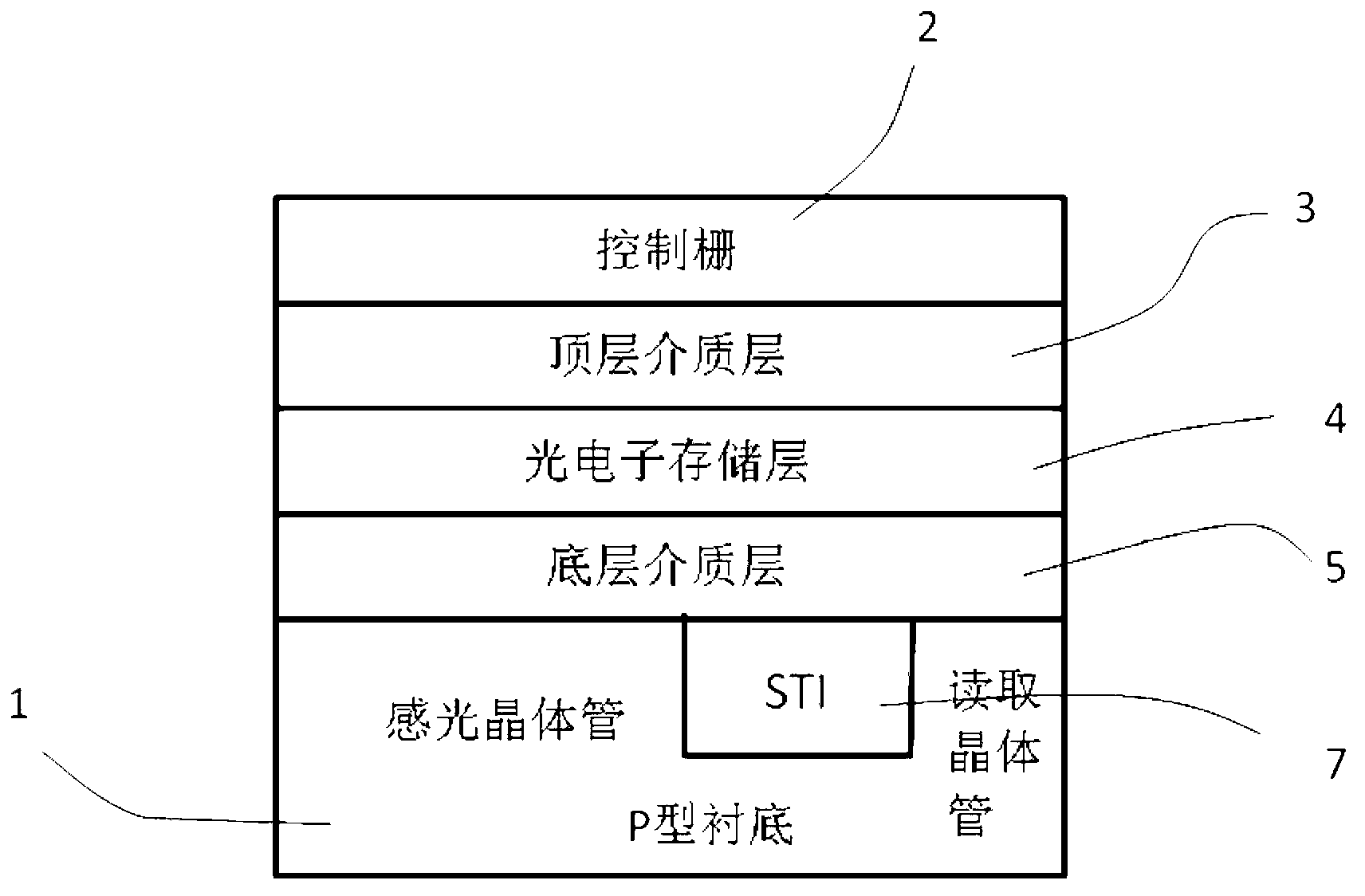

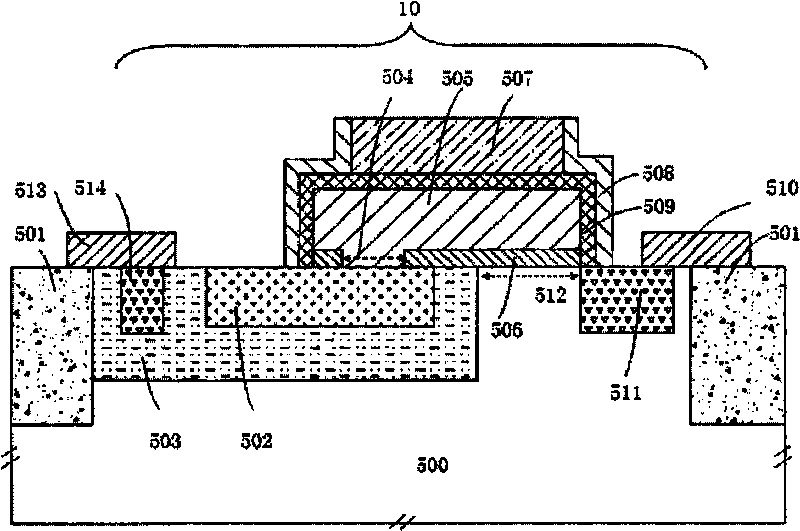

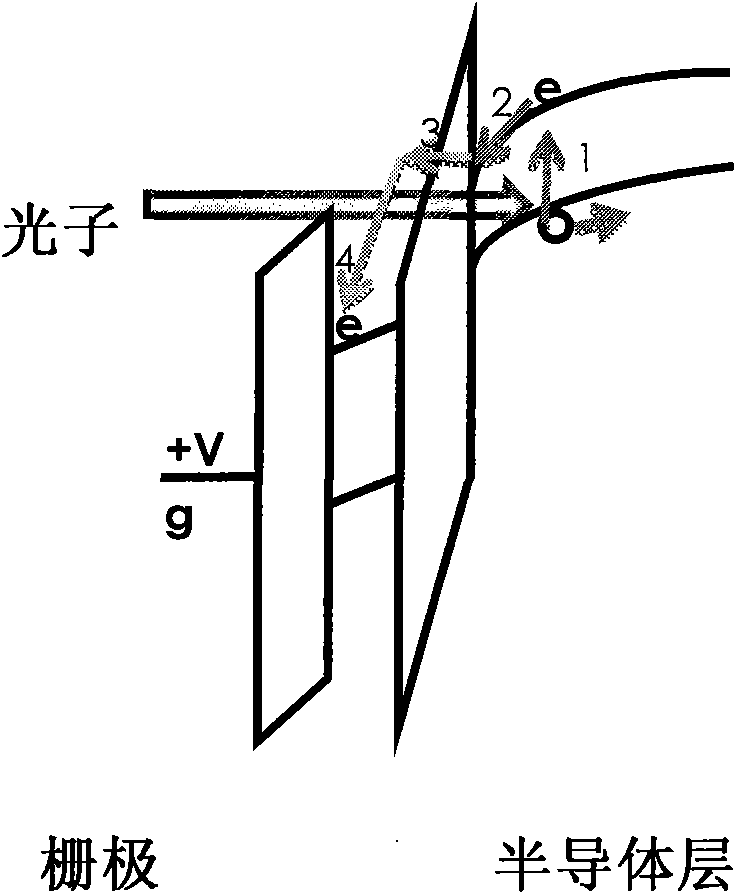

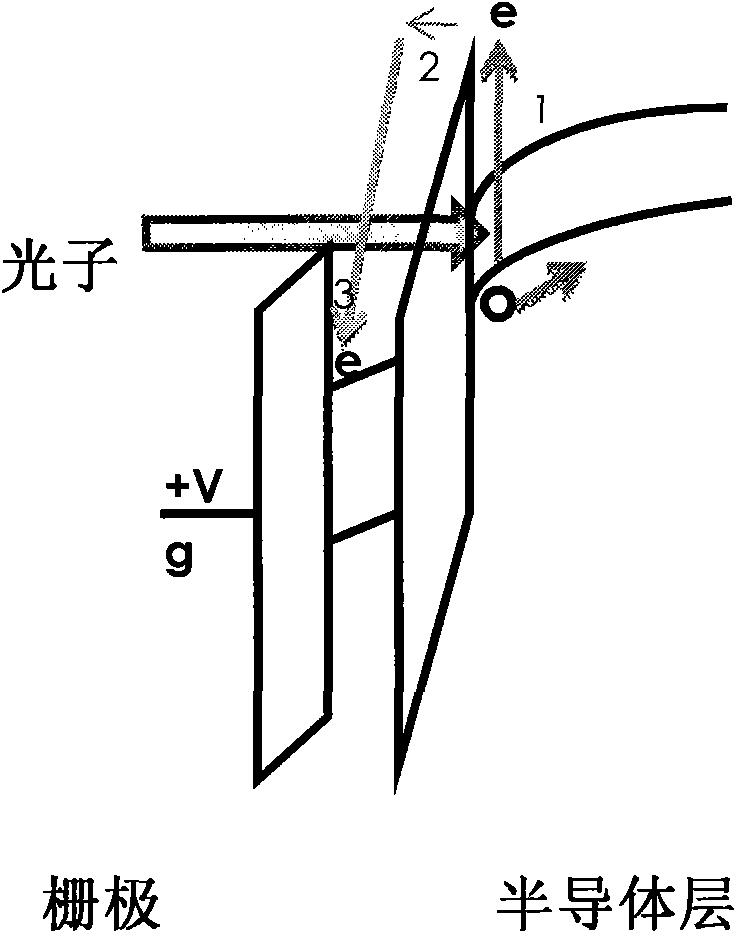

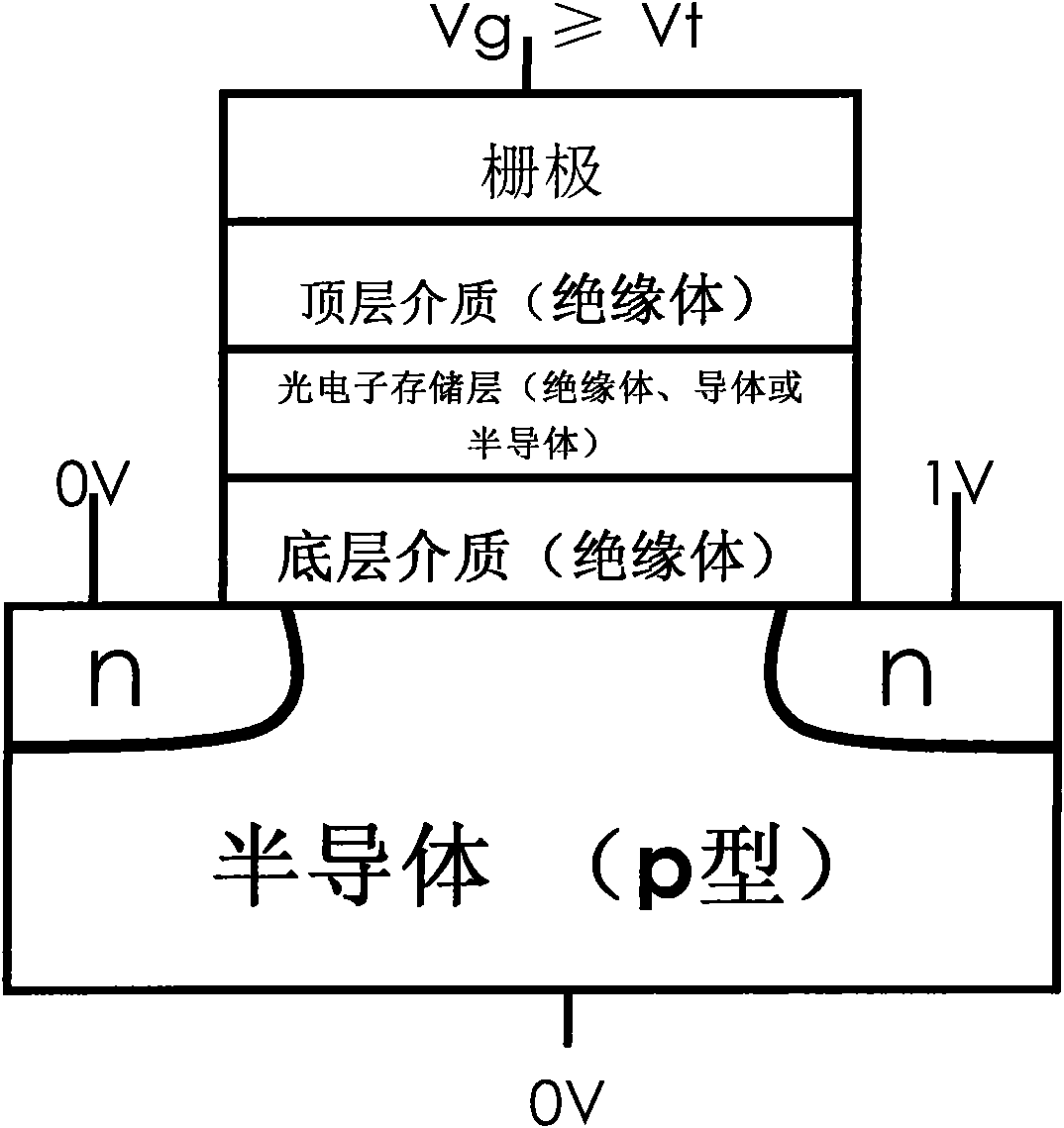

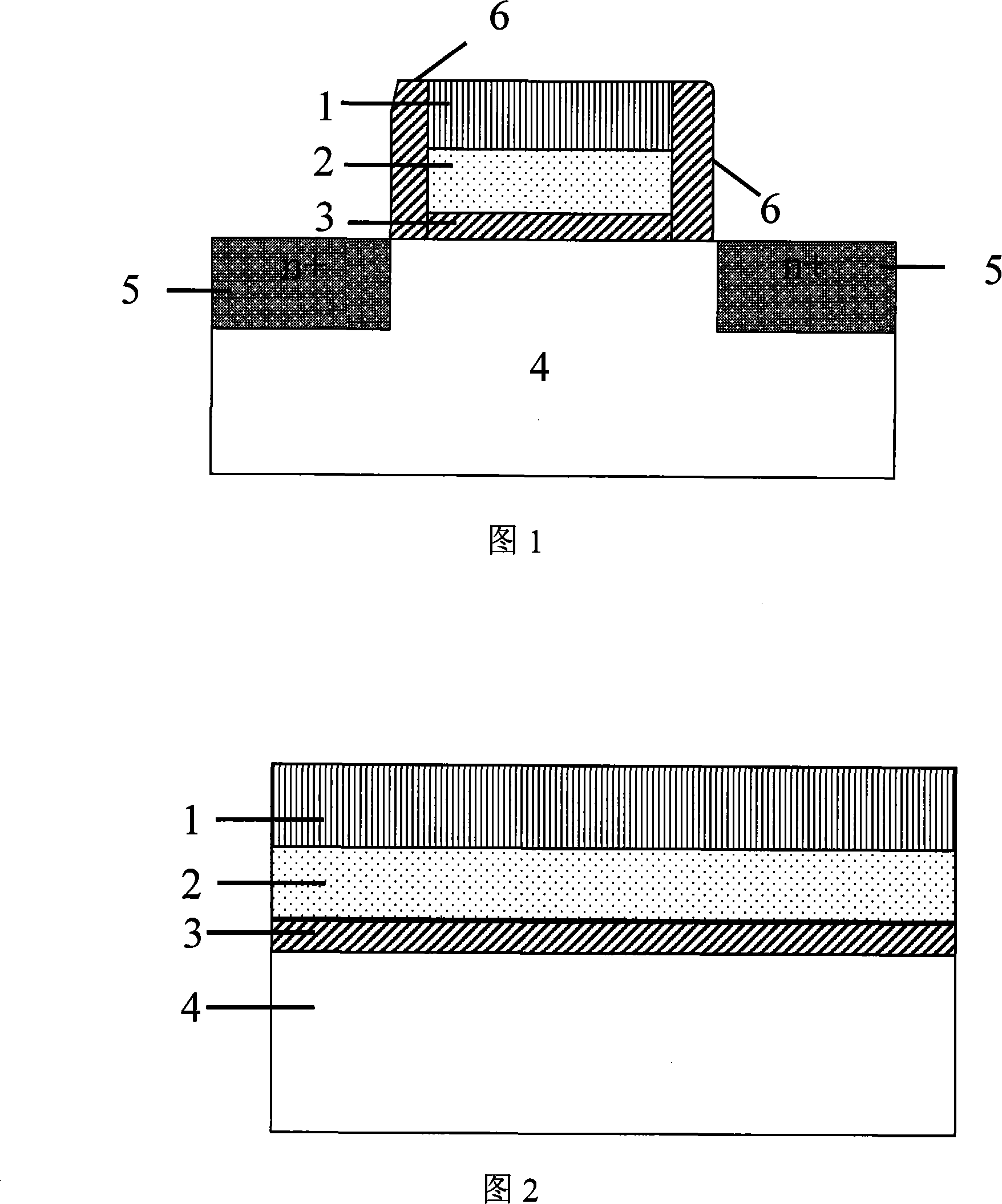

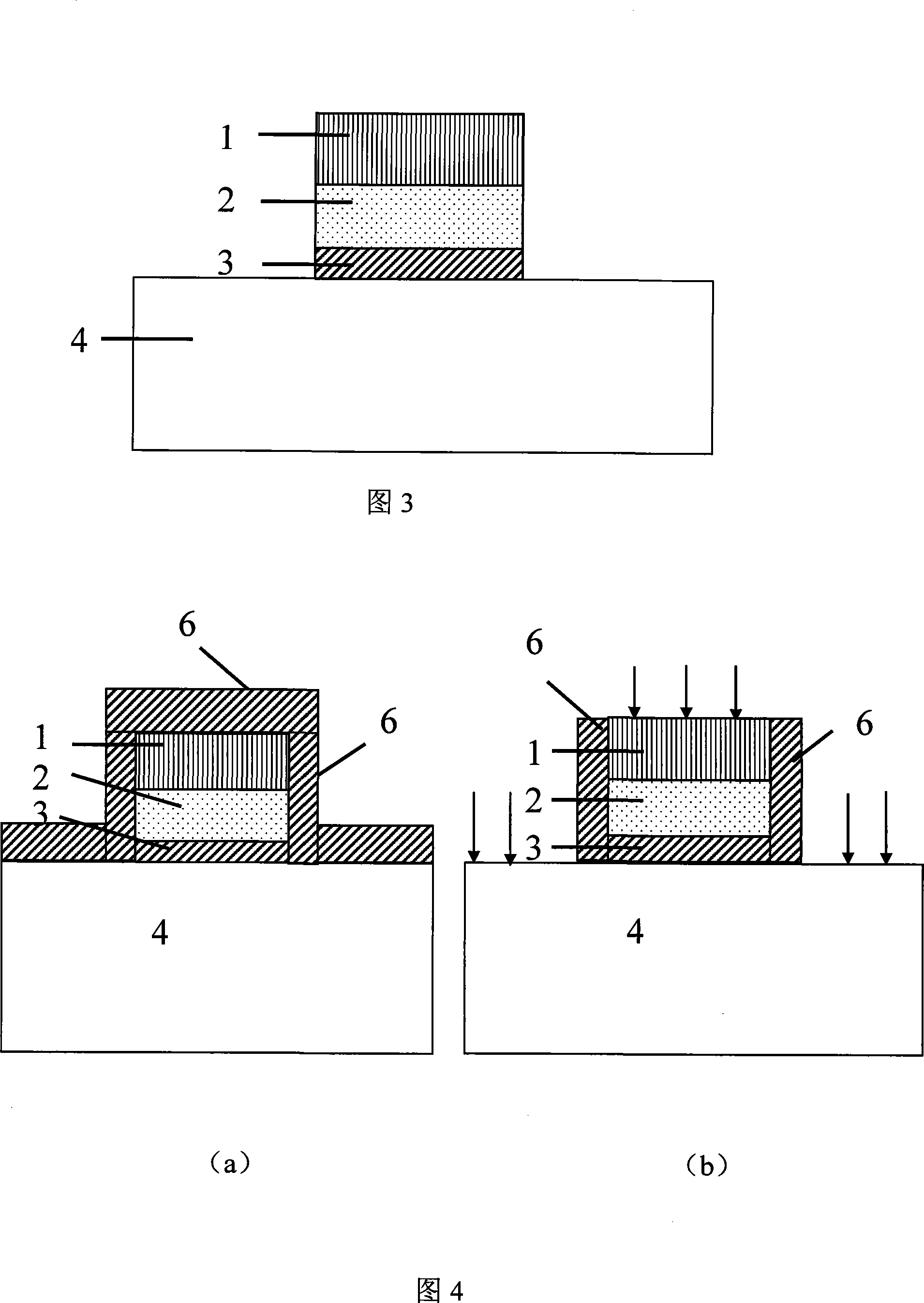

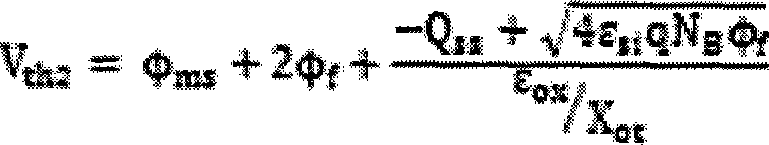

Composite dielectric grating metal-oxide-semiconductor field effect transistor (MOSFET) based dual-transistor light-sensitive detector and signal reading method thereof

ActiveCN102938409APhotosensitiveRealize functionTelevision system detailsColor television detailsMOSFETSemiconductor materials

The invention discloses a composite dielectric grating MOSFET based dual-transistor light-sensitive detector. Each of the unit detectors comprises two transistors, wherein the two transistors comprise a photoreceptive transistor and a reading transistor which are used for implementing the photoreceptive function and the reading function respectively, both of the two transistors are formed above a composite dielectric grating MOSFET substrate P-type semiconductor material (1) and are separated through shallow trench isolation (STI), a bottom layer of an insulating dielectric material, a top layer of the insulating dielectric material and a control grid (2) are arranged above the substrate P-type semiconductor material respectively, a photoelectron storage layer (4) is arranged between the two layers of insulating dielectric materials, a source / drain electrode is arranged on the reading transistor to read signals, and the two transistors are connected through the photoelectron storage layer, so that the reading transistor can read photoelectrons which are stored by the photoreceptive transistor in the photoelectron storage layer through sensitization.

Owner:南京威派视半导体技术有限公司

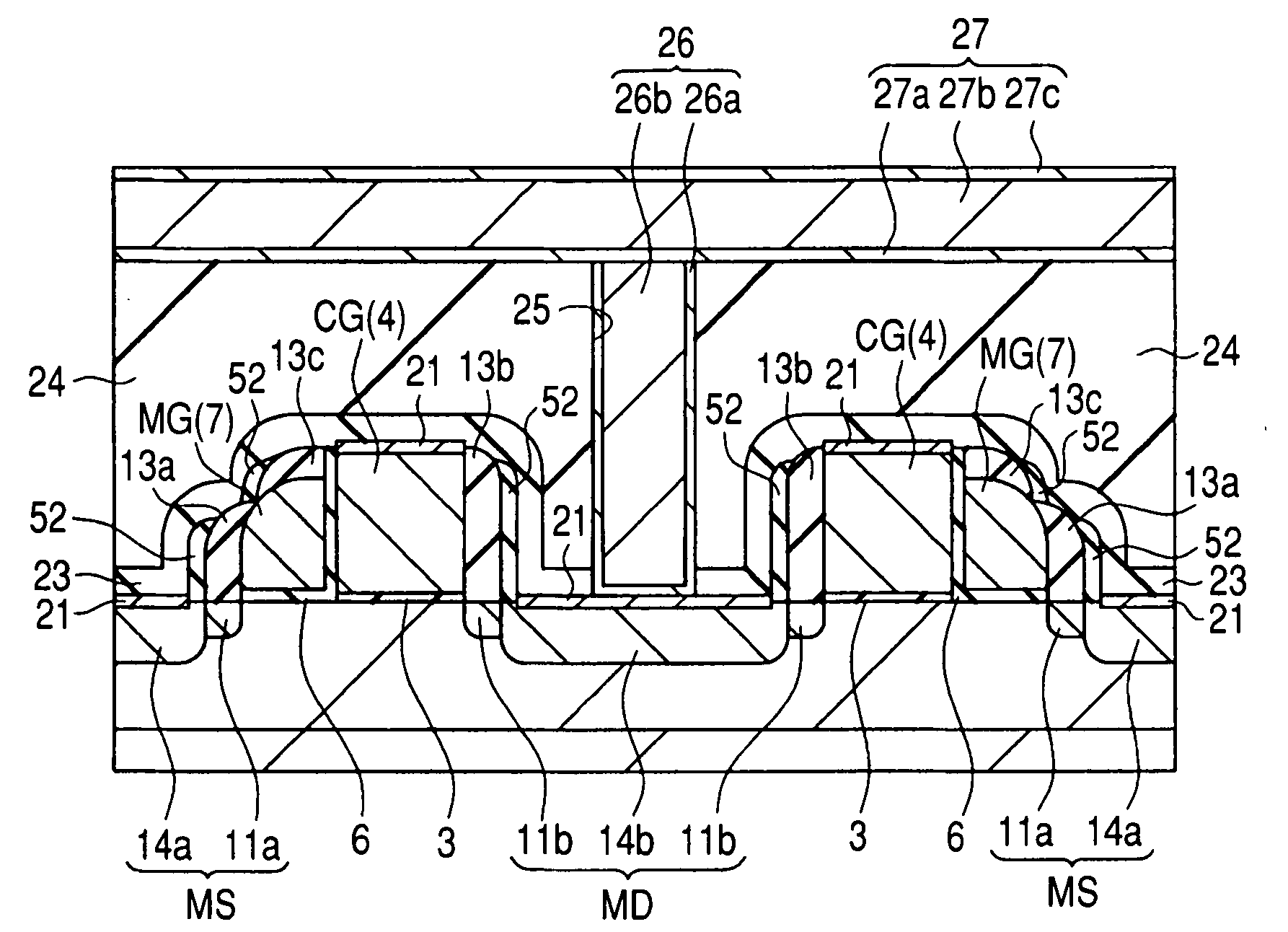

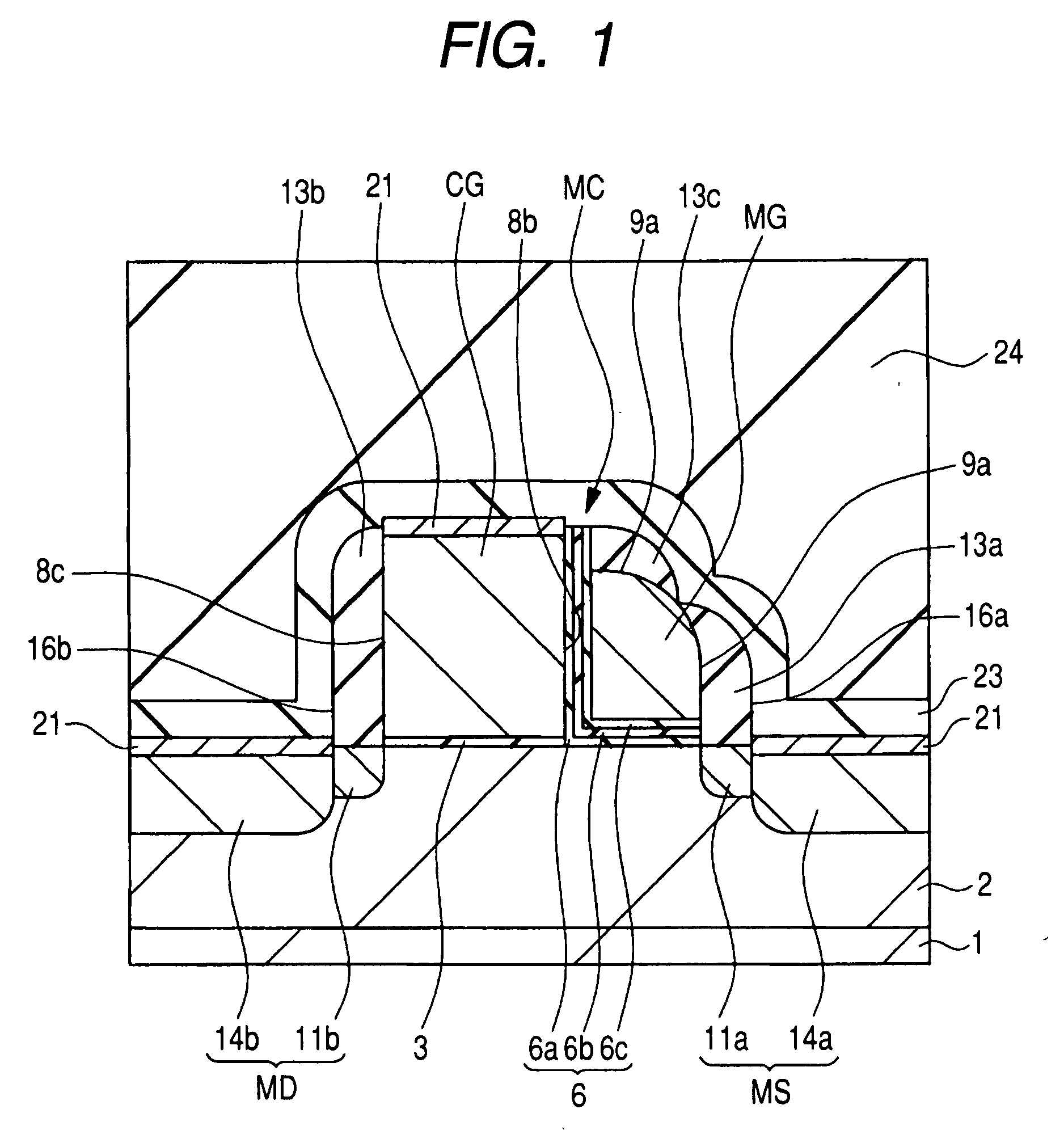

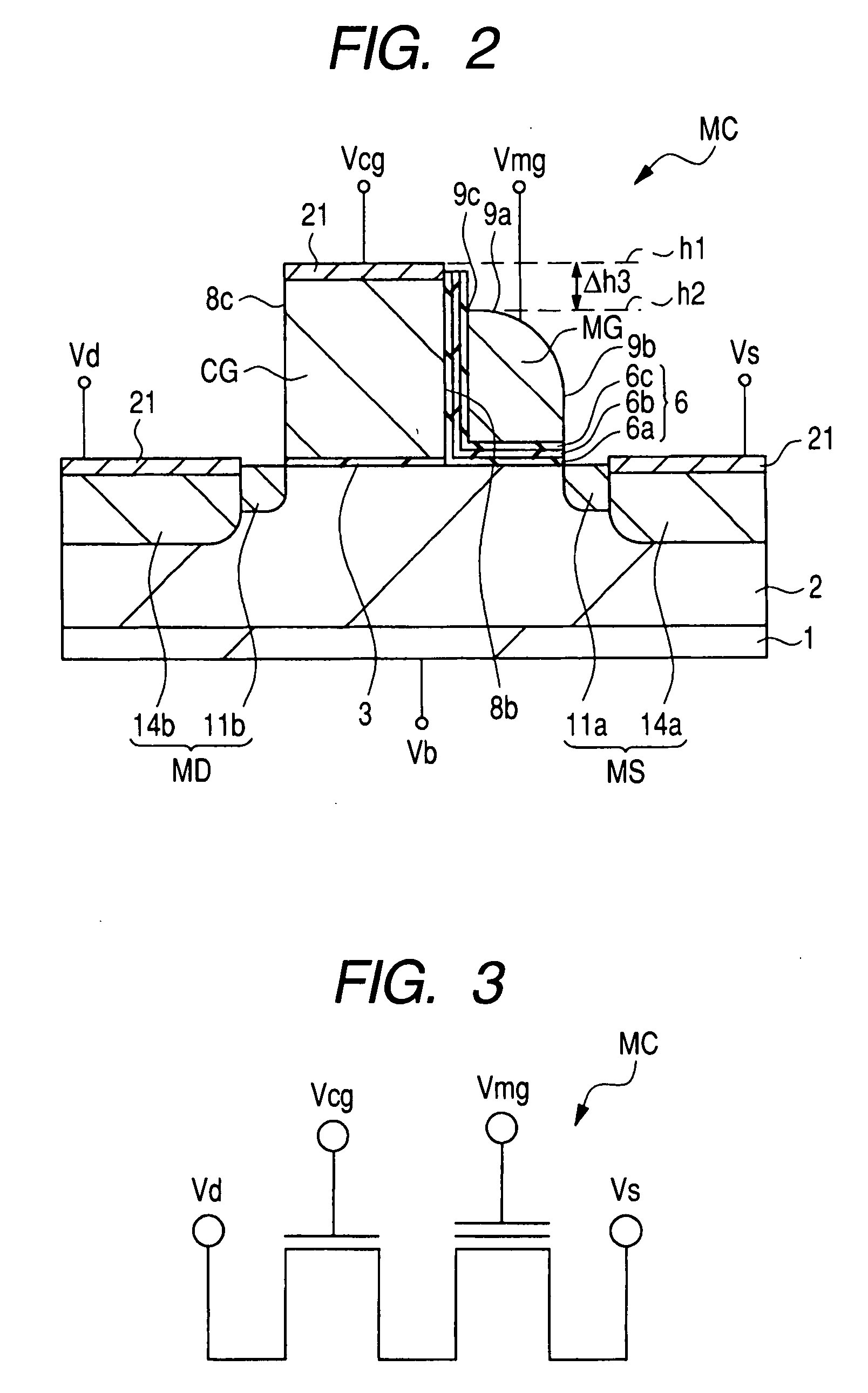

Semiconductor device and a method of manufacturing the same

ActiveUS20070228498A1Improve production yieldImprove semiconductor device performanceSolid-state devicesSemiconductor/solid-state device manufacturingSalicideMetal silicide

Provided is a semiconductor device having, over a semiconductor substrate, a control gate electrode and a memory gate electrode which are adjacent to each other and constitute a nonvolatile memory. The height of the memory gate electrode is lower than the height of the control gate electrode. A metal silicide film is formed over the upper surface of the control gate electrode, but not formed over the upper surface of the memory gate electrode. The memory gate electrode has, over the upper surface thereof, a sidewall insulating film made of silicon oxide. This sidewall insulating film is formed in the same step as that for the formation of respective sidewall insulating films over the sidewalls of the memory gate electrode and the control gate electrode. The present invention makes it possible to improve the production yield and performance of the semiconductor device having a nonvolatile memory.

Owner:RENESAS ELECTRONICS CORP

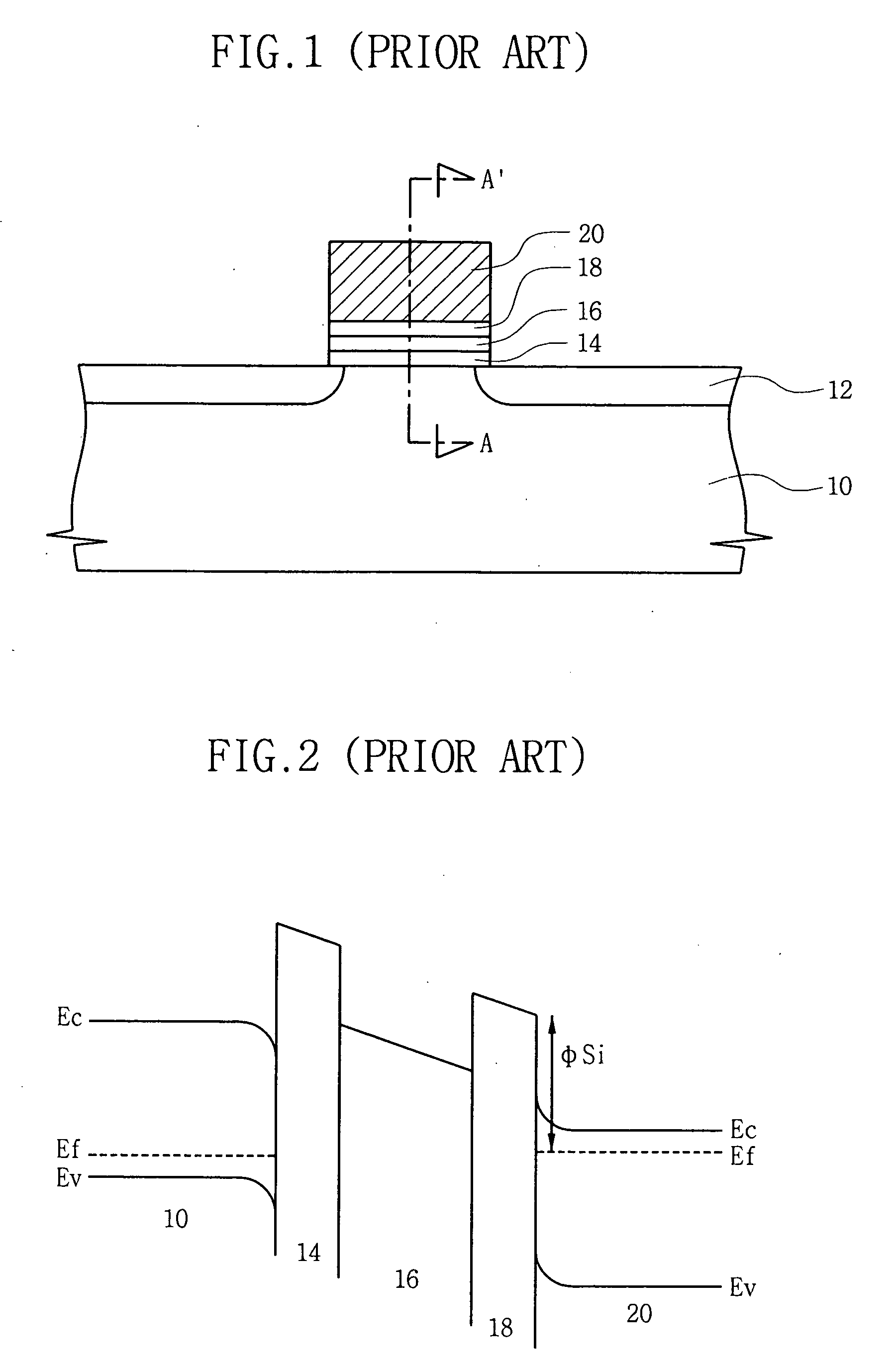

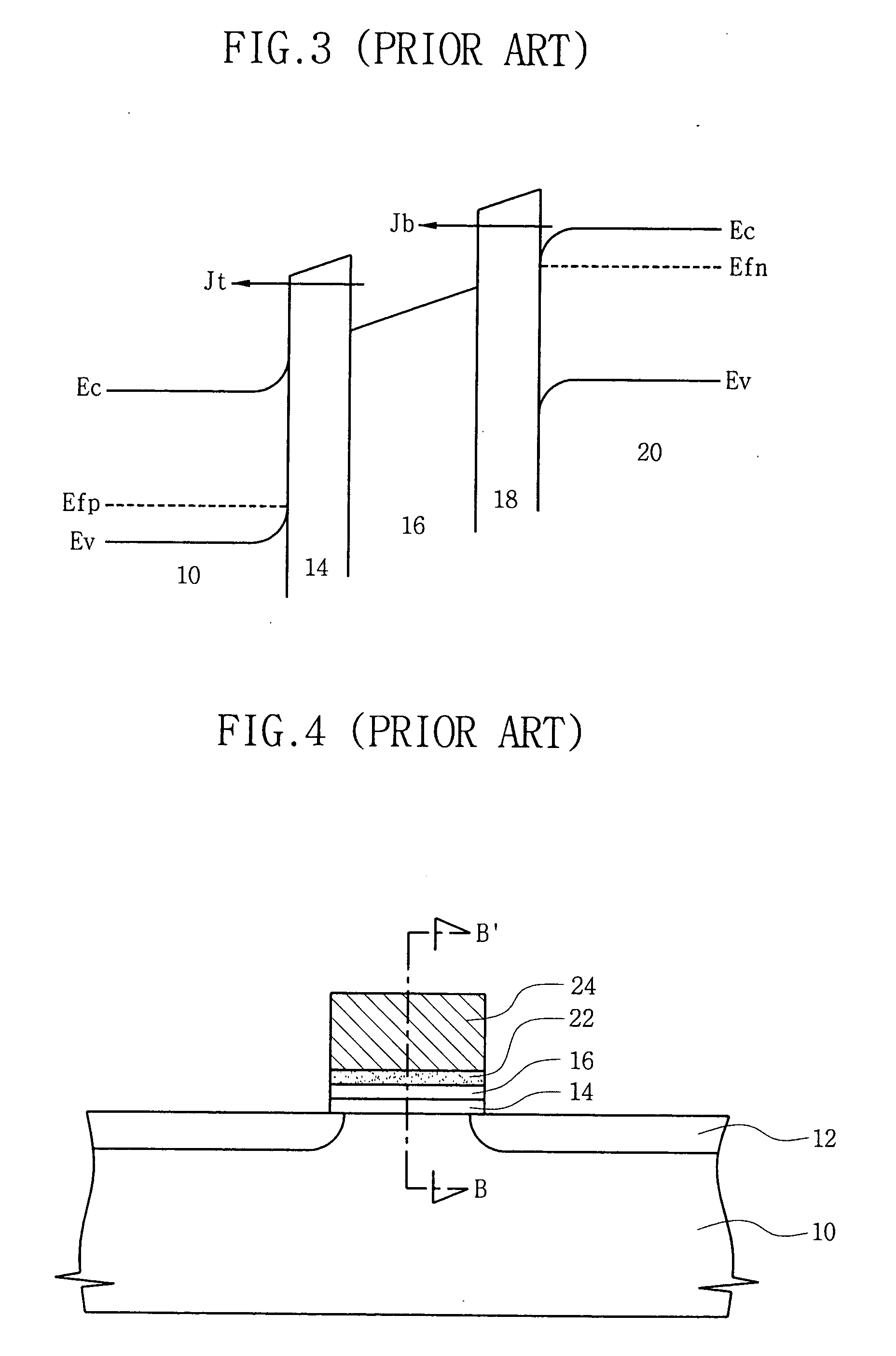

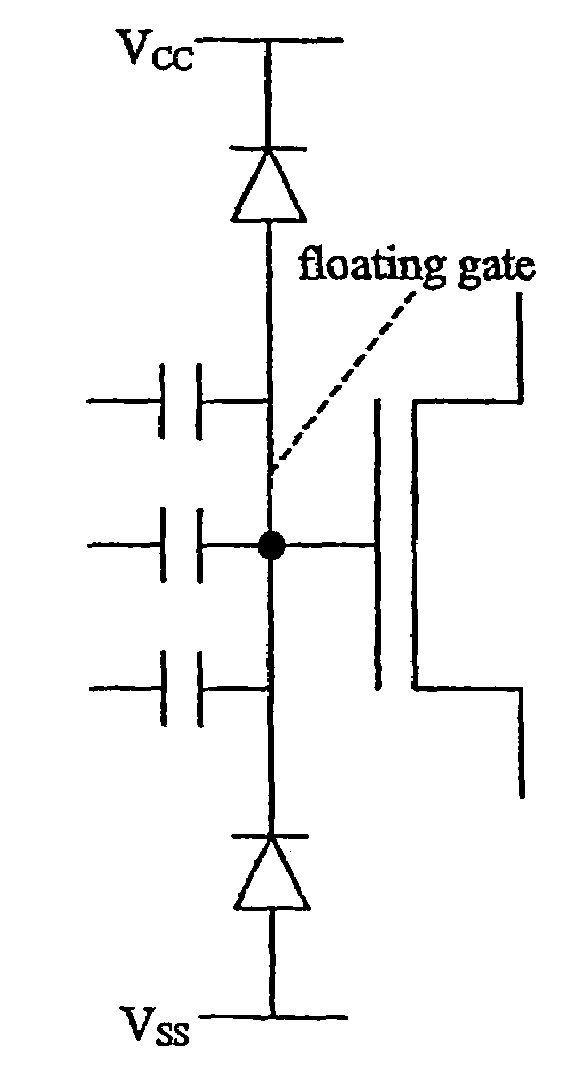

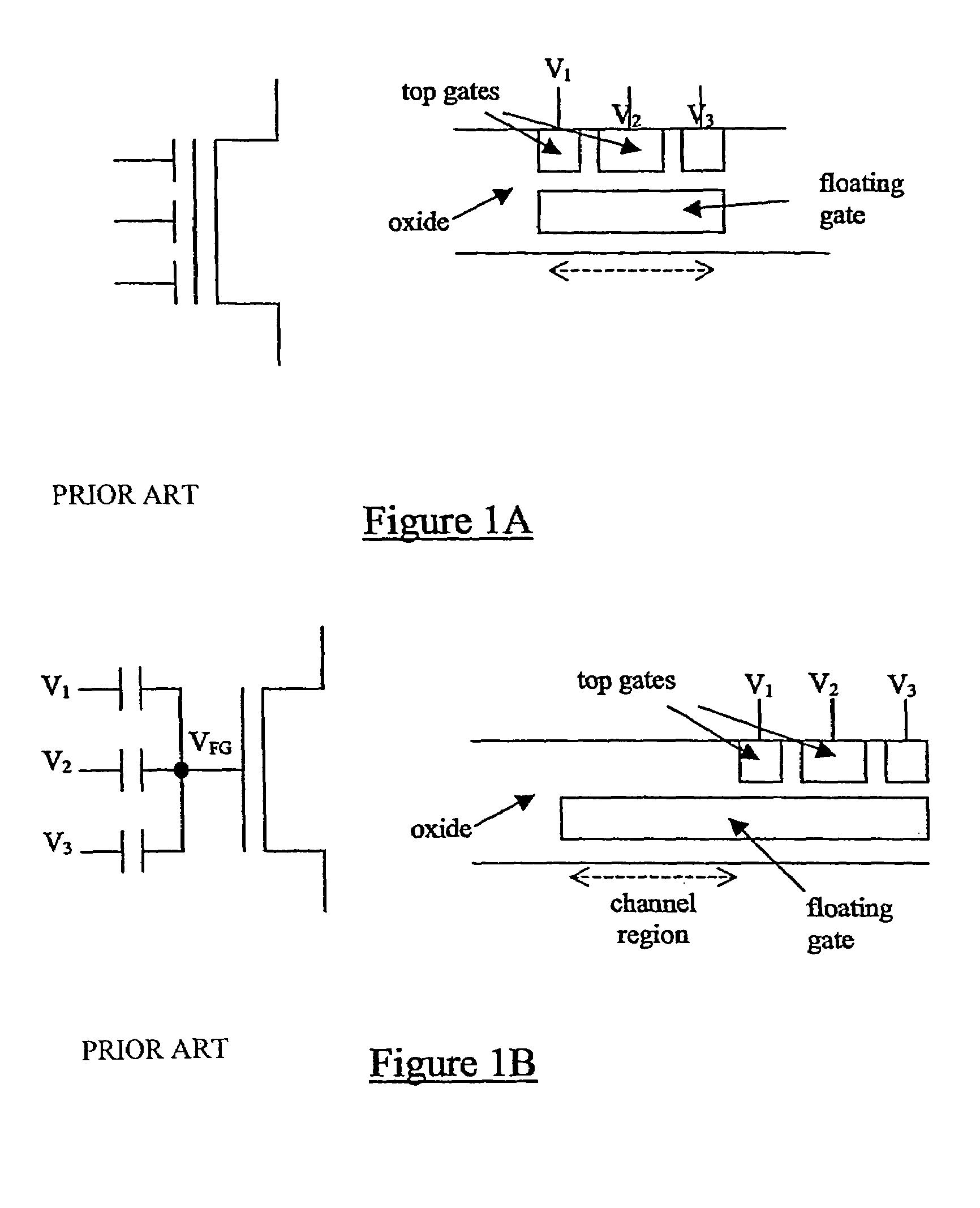

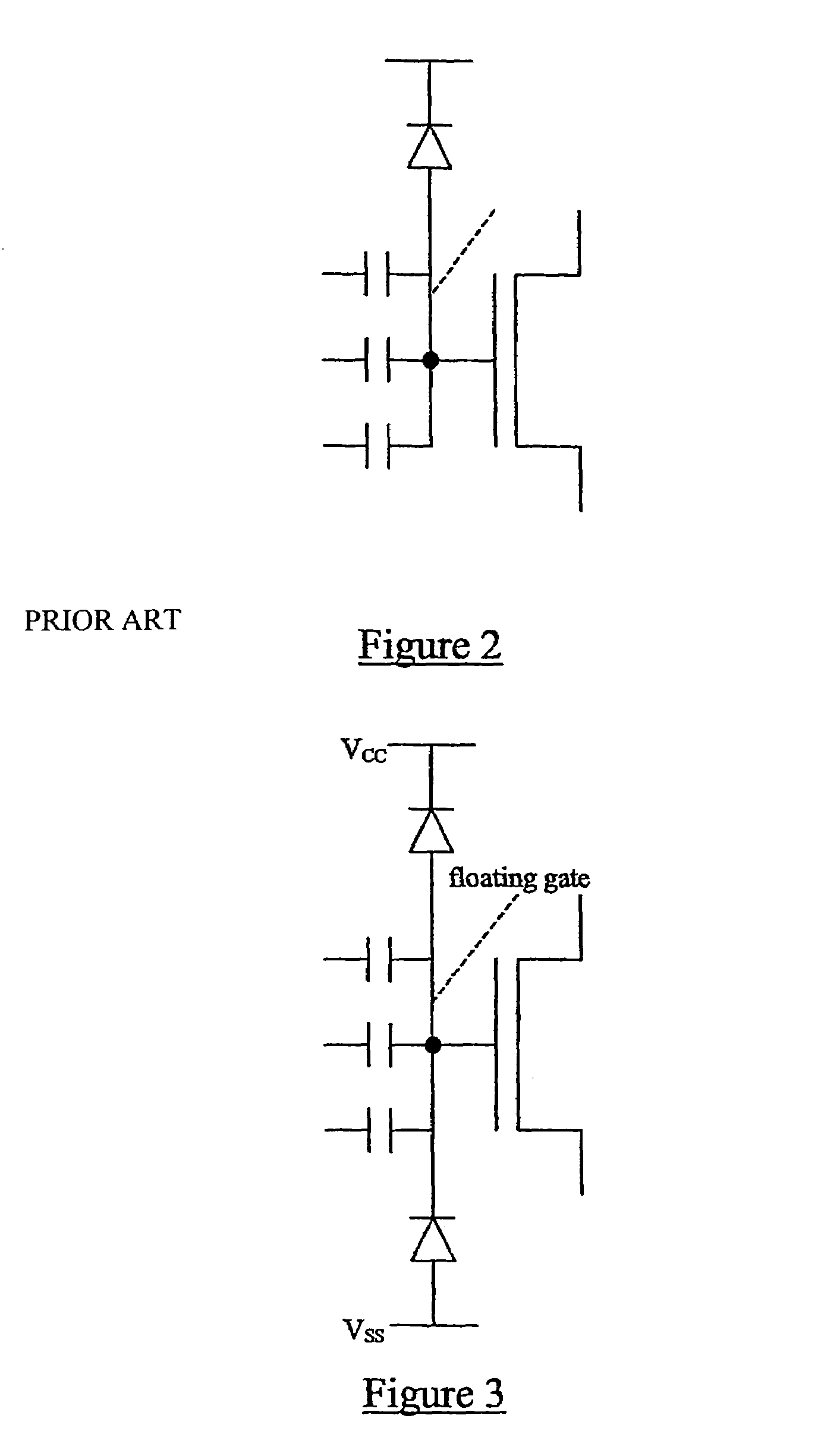

Floating gate transistors

InactiveUS7193264B2Enhance layeringImprove leakageTransistorSolid-state devicesElectrical resistance and conductanceNonlinear resistor

A floating gate MOS transistor comprises one or more control gates, an active channel, and at least one floating gate disposed between the control gate(s) and the active channel. First and second non-linear resistances couple the floating gate to first and second control voltage sources respectively, the non-linear resistances forming a voltage divider network which sets the operating voltage of the floating gate.

Owner:TOUMAZ TECH

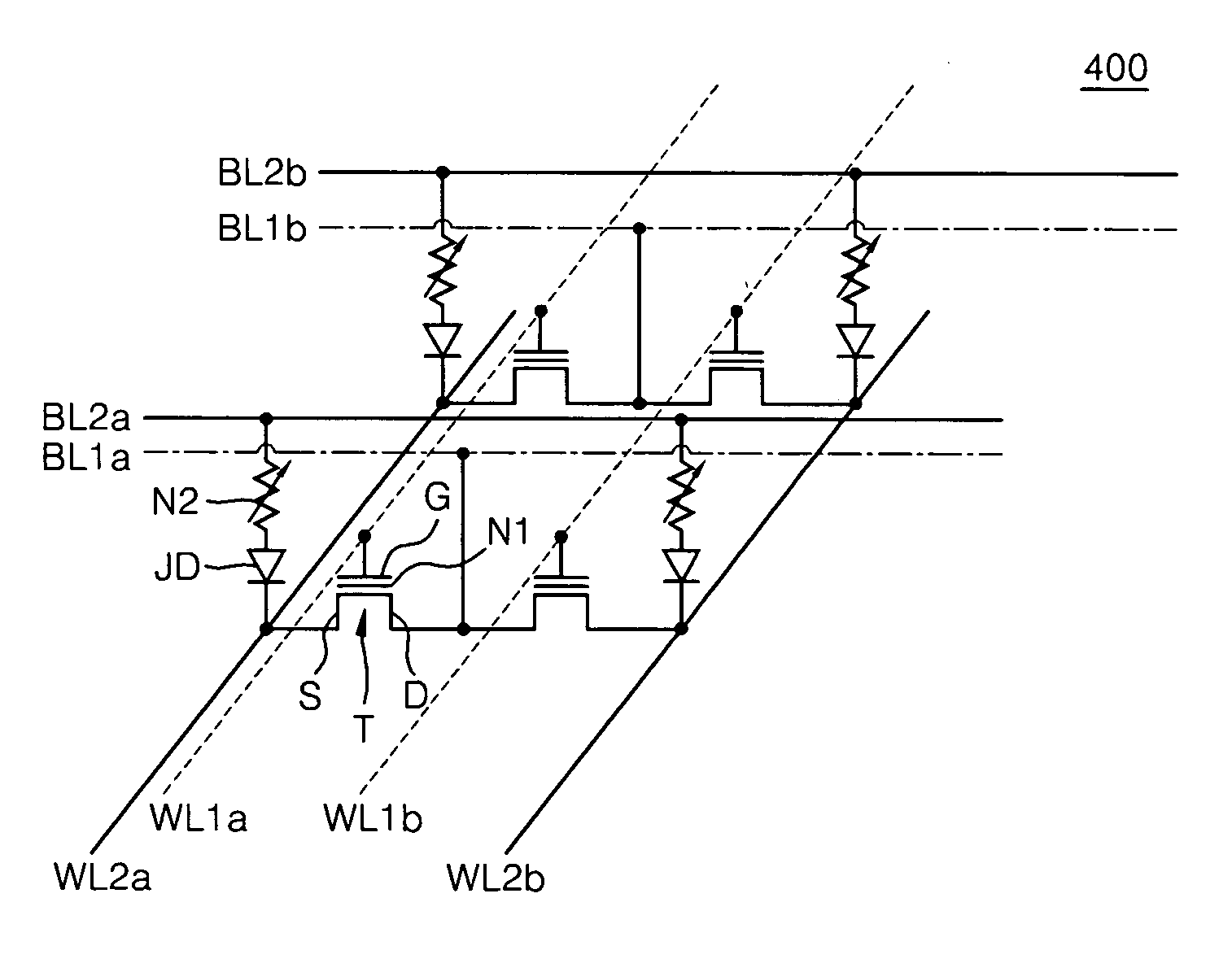

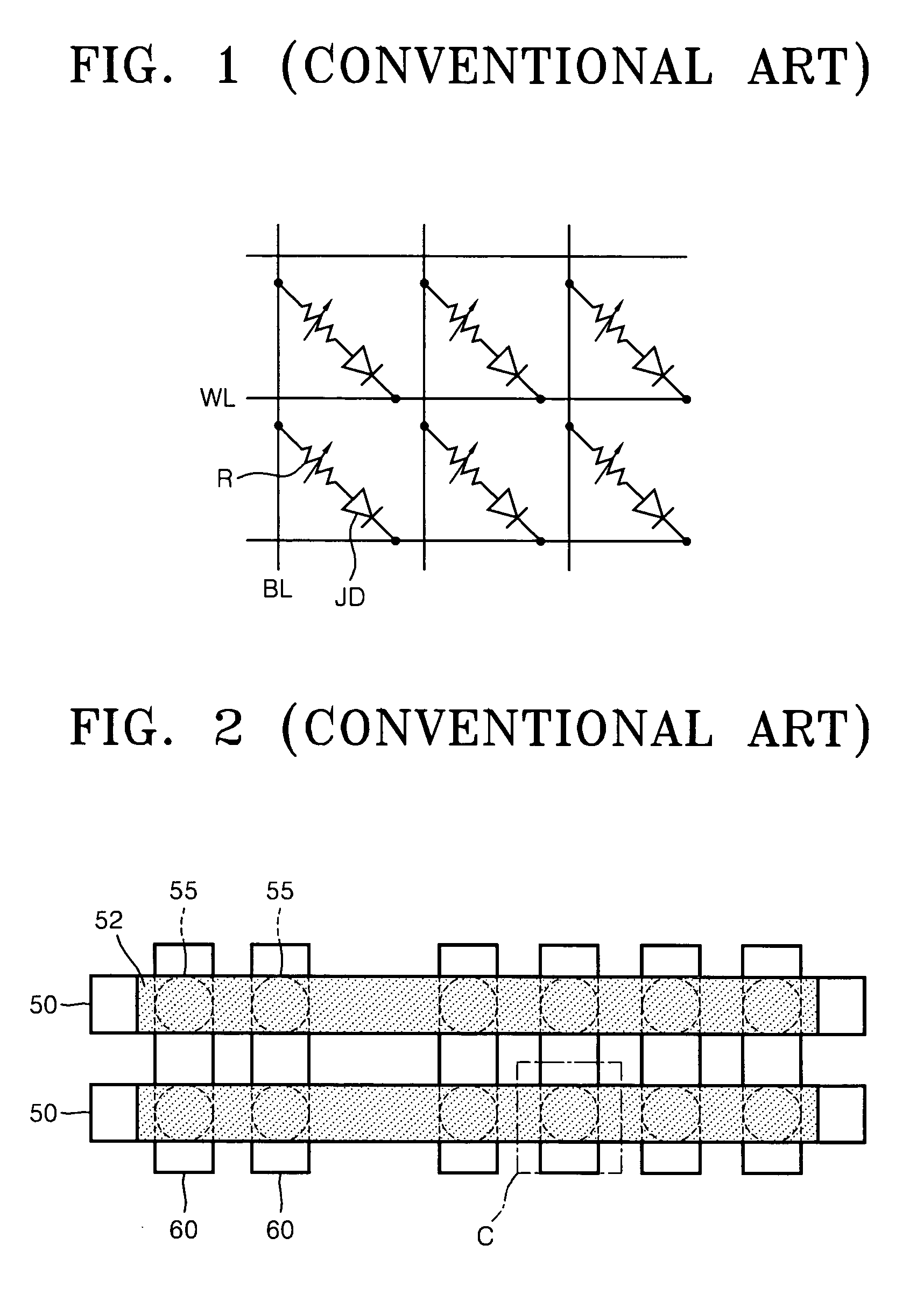

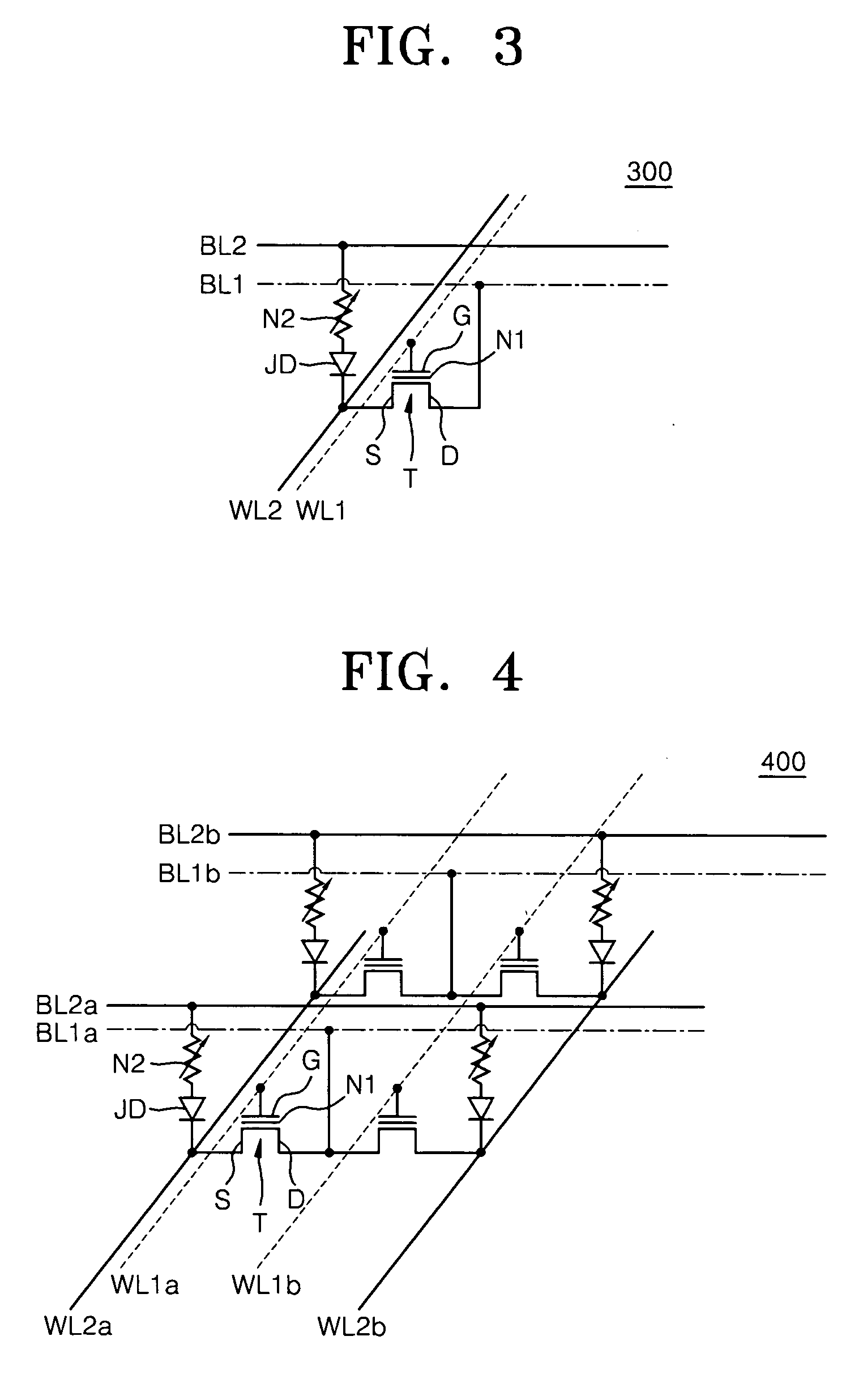

Non-volatile memory devices and method thereof

ActiveUS20070103963A1High capacitanceSolid-state devicesRead-only memoriesSemiconductorVolatile memory

Non-volatile memory devices and a method thereof are provided. A non-volatile memory device according to an example embodiment of the present invention may include a first transistor including a source, a drain, and a control gate, a first storage node coupled to the first transistor, the first storage node configured to store information in a first manner, a first diode having a first end connected to the source of the transistor, the first diode configured to rectify a flow of current from the source of the transistor and a second storage node connected to a second end of the first diode, the second storage node configured to store information in a second manner. Another non-volatile memory device according to another example embodiment of the present invention may include a semiconductor substrate having a first conductivity type including an active region defined by a device isolating layer, a source region and a drain region formed by doping an impurity having a second conductivity type in the active region, a control gate electrode insulated from the active region, the control gate electrode extending across the active region disposed between the source region and the drain region, a first storage node layer interposed between the active region and the control gate electrode configured to store information in a first manner, a second storage node layer disposed on the source region configured to store information in a second manner and a diode interposed between the source region and the second storage node layer to rectify a flow of current to the source region. The example method may be directed to obtaining a higher storage capacity per cell area in either of the above-described example non-volatile memory devices.

Owner:SAMSUNG ELECTRONICS CO LTD

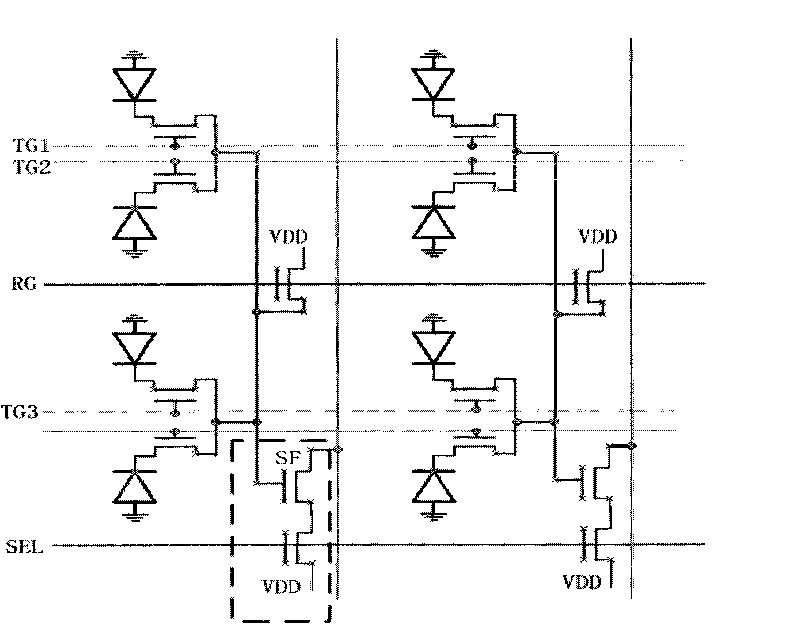

Semiconductor photosensitization device, production method and application thereof

ActiveCN101707202AReduce manufacturing costHigh image resolutionTelevision system detailsSemiconductor/solid-state device manufacturingManufacturing cost reductionPixel density

The invention discloses a semiconductor photosensitization device which comprises a source electrode, a drain electrode, a control grid, a floating grate region, a substrate, and a p-n node diode for connecting a floating gate region and a drain electrode. The floating grate region of the semiconductor photosensitization device is used for storing charges, and the floating grate potential of the semiconductor photosensitization device is related to light exposure intensity and time, thus, the invention can be used as a semiconductor photosensitization device. The invention also discloses production methods of the semiconductor photosensitization device and an image sensor, as well as an image sensor formed by arrays formed by the semiconductor photosensitization device. The semiconductor photosensitization device can simplify the design of a single pixel unit in a traditional image sensor and reduce the area occupied by the single pixel unit, thereby improving the pixel density of the image sensor, increasing the resolution of the image sensor and reducing the production cost of the image sensor.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

Non volatile charge trapping dielectric memory cell structure with gate hole injection erase

A dielectric memory cell comprises a substrate which includes a source region, a drain region, and a channel region positioned there between. A multilevel charge trapping dielectric is positioned on the surface of the substrate and a control gate is positioned on the surface of the dielectric and is positioned over and aligned with the channel region. The multilevel charge trapping dielectric includes a tunneling dielectric layer, a charge trapping dielectric layer, and a top dielectric layer. The tunneling dielectric layer comprises a first dielectric material having a wide band gap between a tunneling dielectric layer valance band Fermi level and a tunneling dielectric layer conduction band Fermi level. The top dielectric layer comprises a second dielectric material having a valance band Fermi level approximately equal to the tunneling dielectric layer valance band Fermi level and having a conduction band Fermi level greater than the tunneling dielectric layer conduction band Fermi level. The charge trapping layer is positioned between the bottom layer and the top layer of a third dielectric with charge trapping properties.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

Grid storage system and method of operating thereof

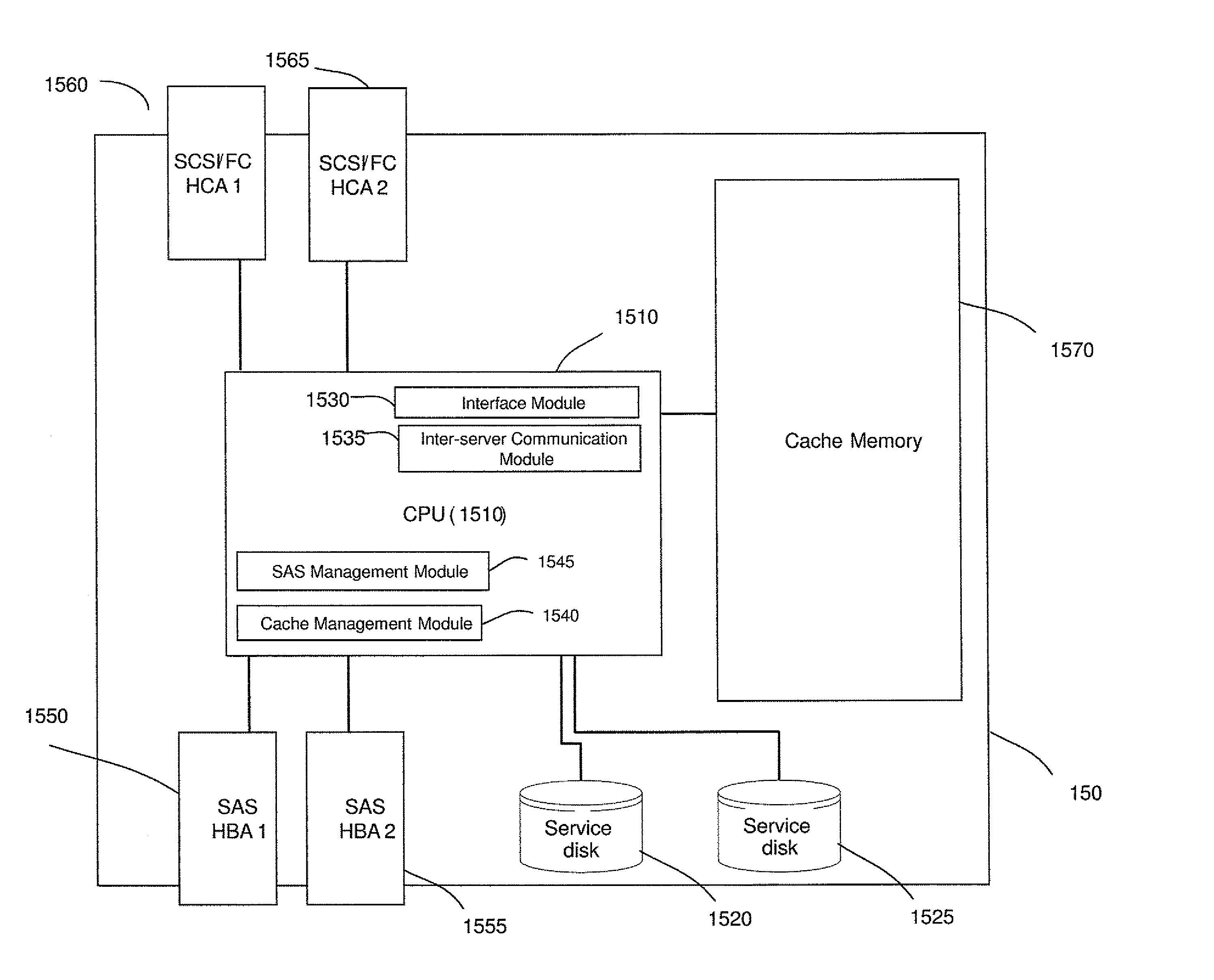

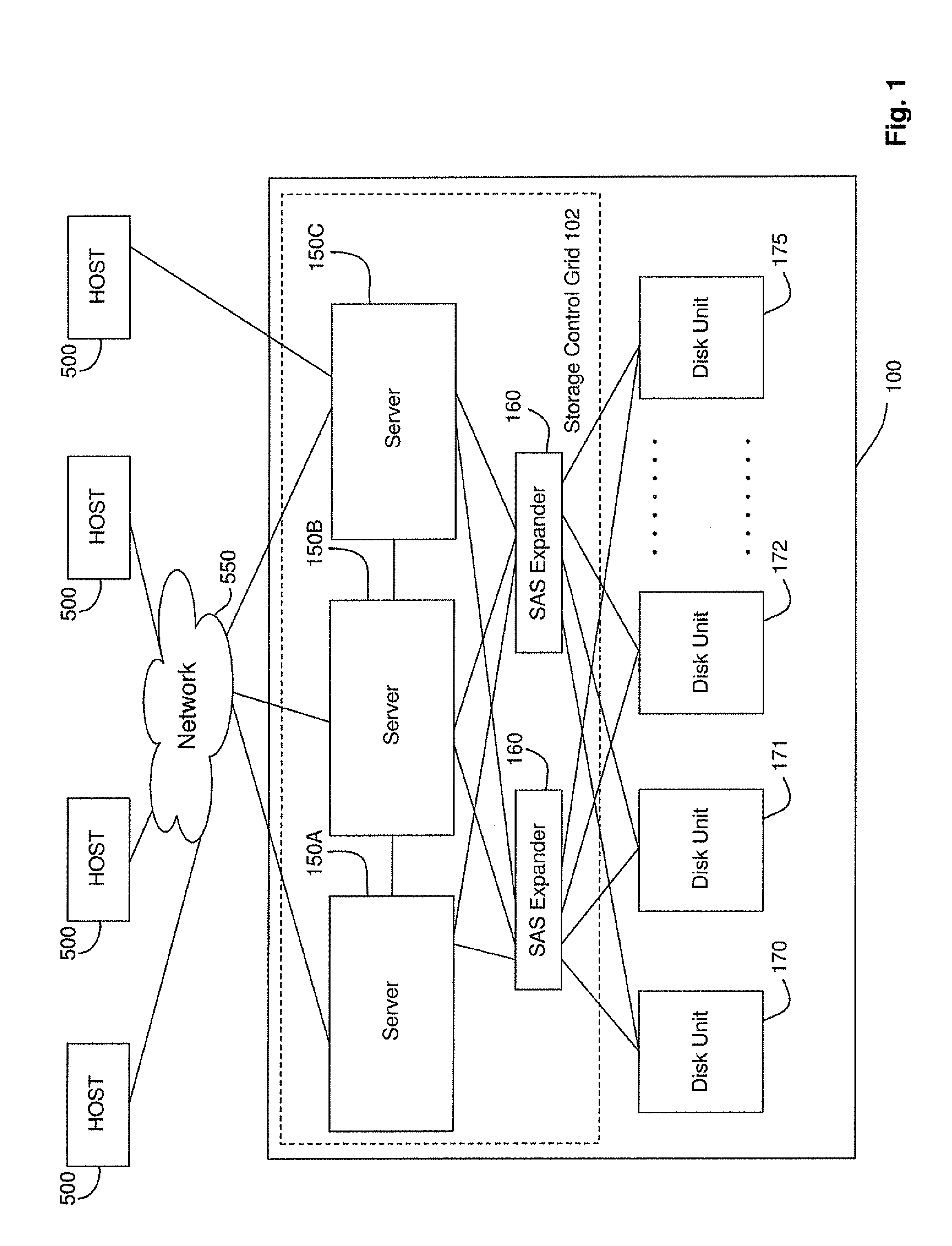

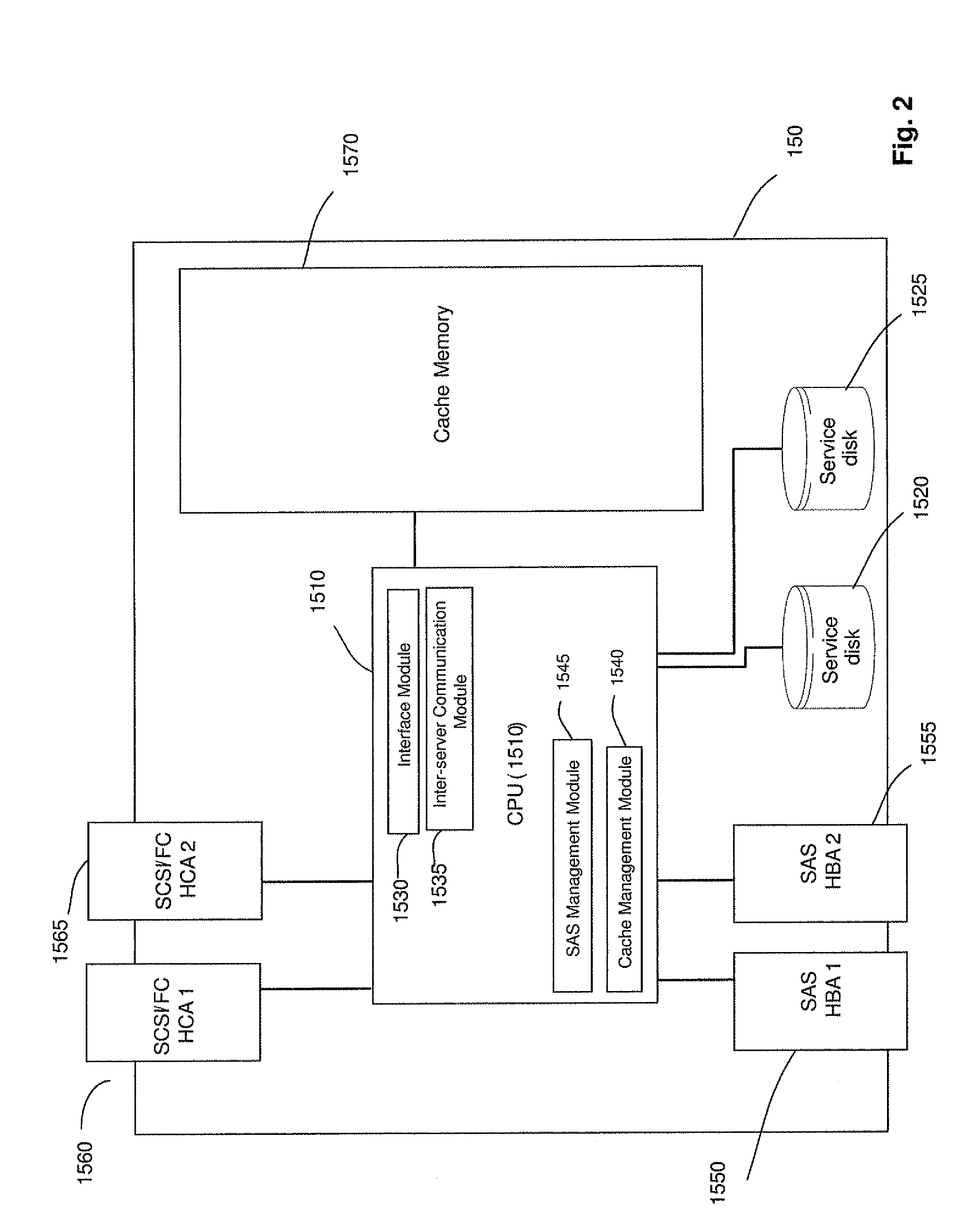

ActiveUS20100153638A1Improve availabilityImprove protectionFault responseMemory adressing/allocation/relocationLogical block addressingAddress space

There is provided a storage system and method of operating thereof. The storage system comprises a plurality of disk units adapted to store data at respective ranges of logical block addresses (LBAs), said addresses constituting an entire address space divided between a plurality of virtual partitions (VP), and a storage control grid operatively connected to the plurality of disk units and comprising a plurality of data servers, each server having direct or indirect access to the entire address space. Each certain virtual partition is configured to be controlled by at least two data servers among said plurality of data servers, a primary data server configured to have a primary responsibility for handling requests directed to any range of LBAs corresponding to said certain virtual partition and a secondary data server configured to have a secondary responsibility for handling requests directed to any range of LBAs corresponding to said certain virtual partition and to overtake the primary responsibility for handling respective requests if the primary server fails. Respectively, each data server is configured to have primary responsibility over all LBAs corresponding to at least two virtual partitions and to have secondary responsibility over all LBAs corresponding to at least two other virtual partitions.

Owner:INFINIDAT

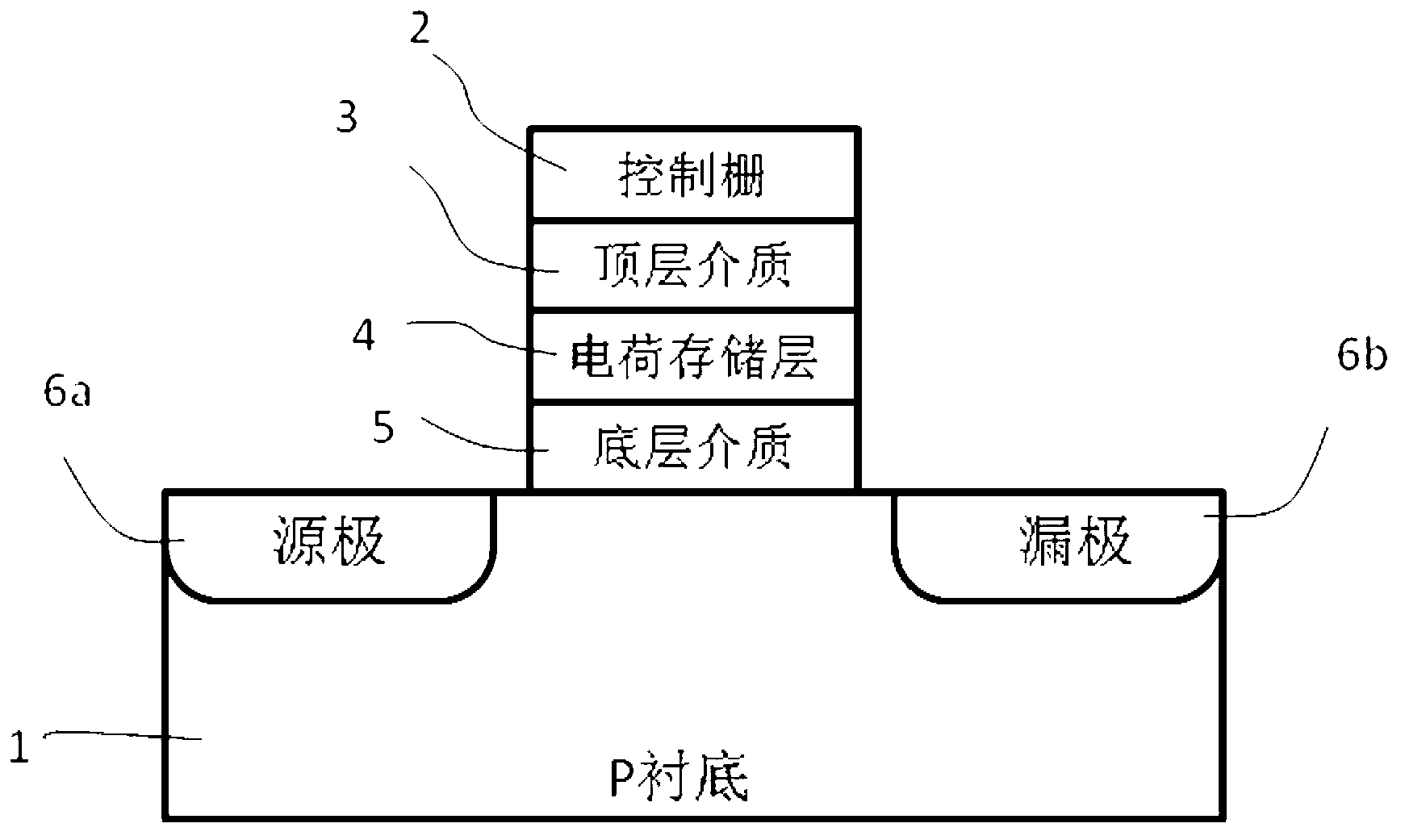

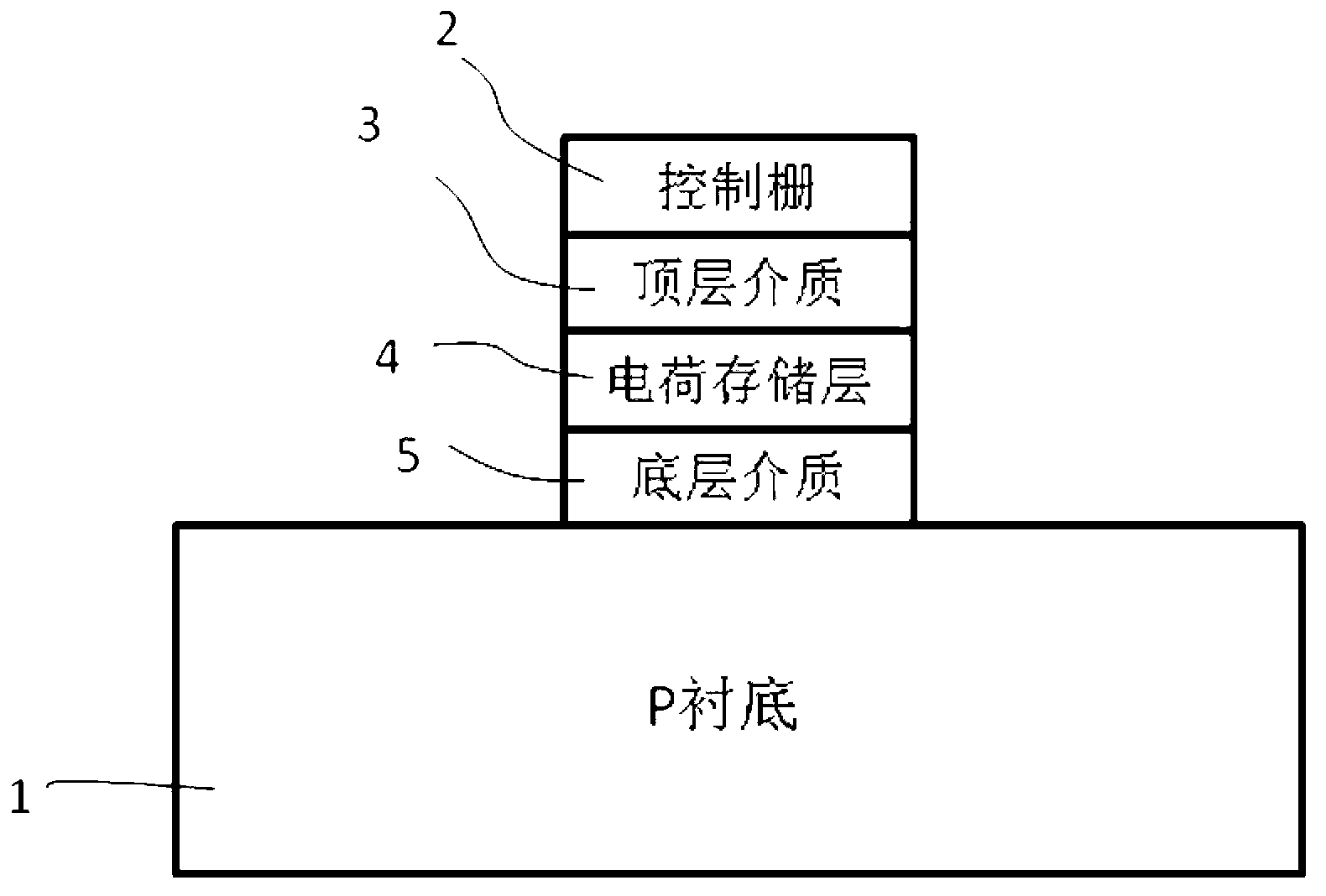

Photosensitive composite dielectric gate MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) detector

ActiveCN101807547ARealize terrain matching functionImprove scalabilitySolid-state devicesSemiconductor/solid-state device manufacturingMOSFETSemiconductor materials

The invention relates to an arrangement method of a photosensitive composite dielectric gate MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) detector. Each unit detector has a structure that N-shaped semiconductor regions are respectively arranged at both upper sides of a P-shaped semiconductor material of a substrate, two insulated dielectric material layers and a control grid electrode are respectively arranged over the substrate, a photoelectron storage layer is arranged between the two insulated dielectric material layers, the second insulated dielectric in contact with the control grid is made of a material preventing charges stored in the photoelectron storage layer from flowing into the grid electrode, a source electrode and a drain electrode are in suspended structures when photoelectrons are collected and stored to the photoelectron storage layer, the first insulated dielectric is a bottom dielectric and adopts silica, SiON or other dielectric materials with high dielectric constants, the second insulated dielectric layer is made from a top dielectric and adopts silica / silicon nitride / silica, silica, alumina or other dielectric materials with high dielectric constants, and the substrate layer or the grid electrode surface is provided with at least one transparent or semi-transparent window for detecting the wavelength of the detector.

Owner:NANJING UNIV +1

3D (three-dimensional) NAND memory and manufacturing method thereof

ActiveCN103680611AImprove controlReduce parasitic parametersSolid-state devicesRead-only memoriesInput controlComputer science

The invention discloses a 3D (three-dimensional) NAND memory and a manufacturing method of the 3D NAND memory. The 3D NAND memory comprises multiple layers of storage arrays and multiple layers of control grid circuits, wherein each layer of the control grid circuit is electrically connected to the same layer of the storage array, so that selection of each layer of the storage array is realized; each layer of the control grid circuit is obtained by cascading a same number of transistors; grids of all the transistors of the control grid circuits are electrically connected to control wires; the number of the control wires is as the same as that of the transistors comprised in each layer of the control grid circuit; the grids of different transistors positioned on the same layer of the control grid circuit are electrically connected to different control wires. According to the 3D NAND memory, a small number of input control wires SSL select a large number of control grid layers through the control grid circuits, so that the area and the volume of the whole memory cannot be enlarged due to the increase of the number of the required layers of control grids when the storage capacity of the memory is improved due to the increase of the number of storage unit layers.

Owner:SEMICON MFG INT (SHANGHAI) CORP

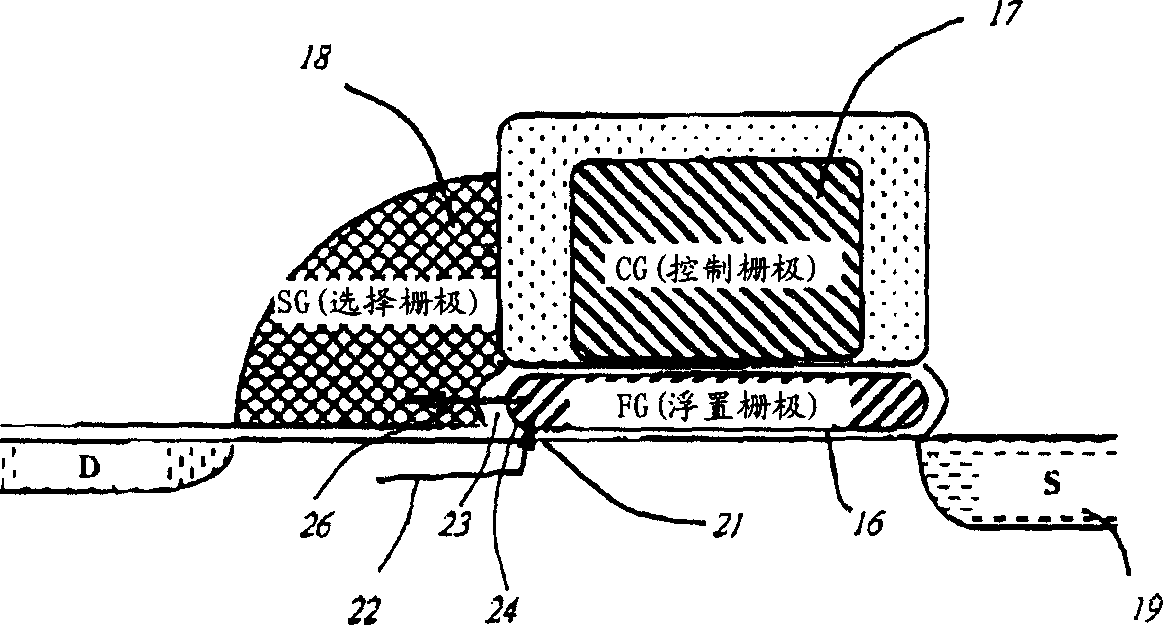

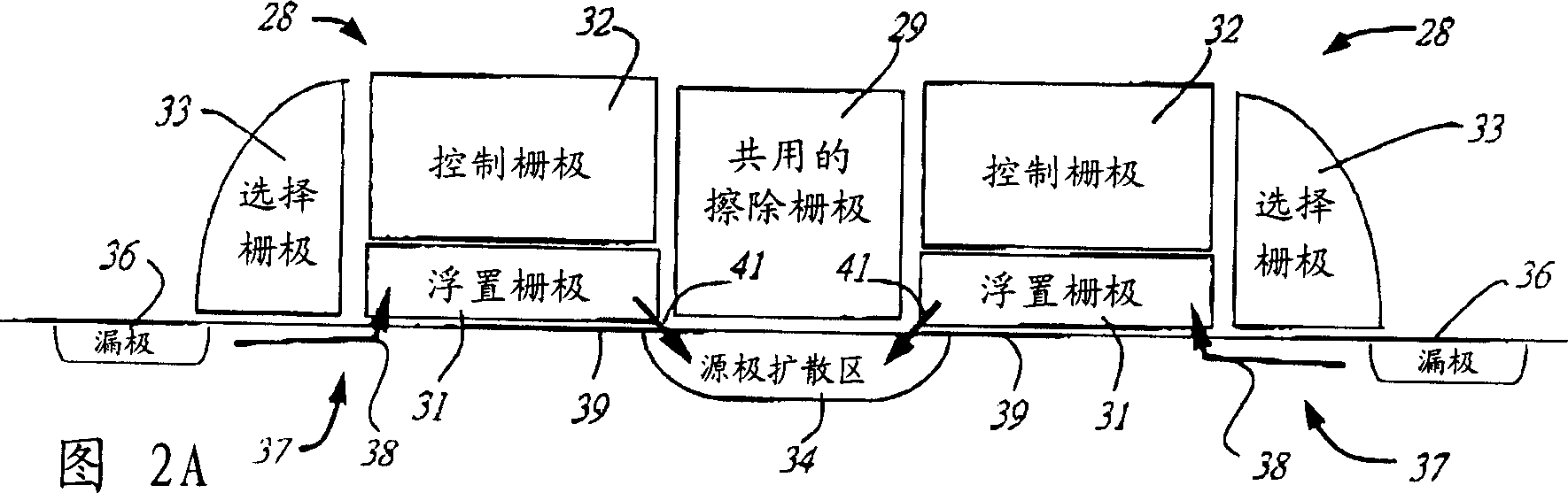

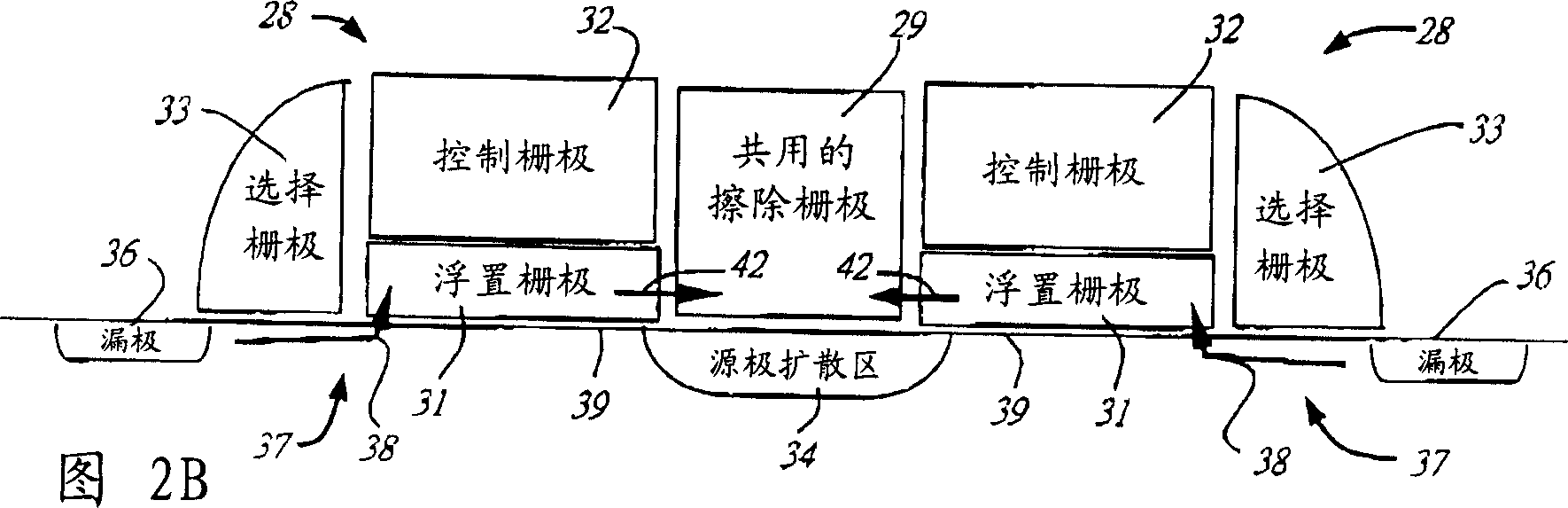

Flash memory cells and fabrication process thereof

Vertical contraposed pair of floating grid and control grid is formed at side opposite to source diffusion zone in substrate. Erasing grid is formed between above source diffusion zone and contraposed grid. Selecting grid is formed is formed at side opposite to contraposed grid and erasing grid. Programming channel is extended from intermediate channel region on substrate to peripheral part of the selecting grid faced to the floating grid. Erasing channel is extended from peripheral part of the erasing grid faced to the floating grid to the source diffusion zone and the erasing grid. In some instances, the source diffusion zone is connected to the erasing grid electrically. In other instances, the floating grid stands out one or two sides of the control grid laterally. Comparing with prior art, the invention provides better programming and erasing performances with very small size of storage cell.

Owner:SILICON STORAGE TECHNOLOGY

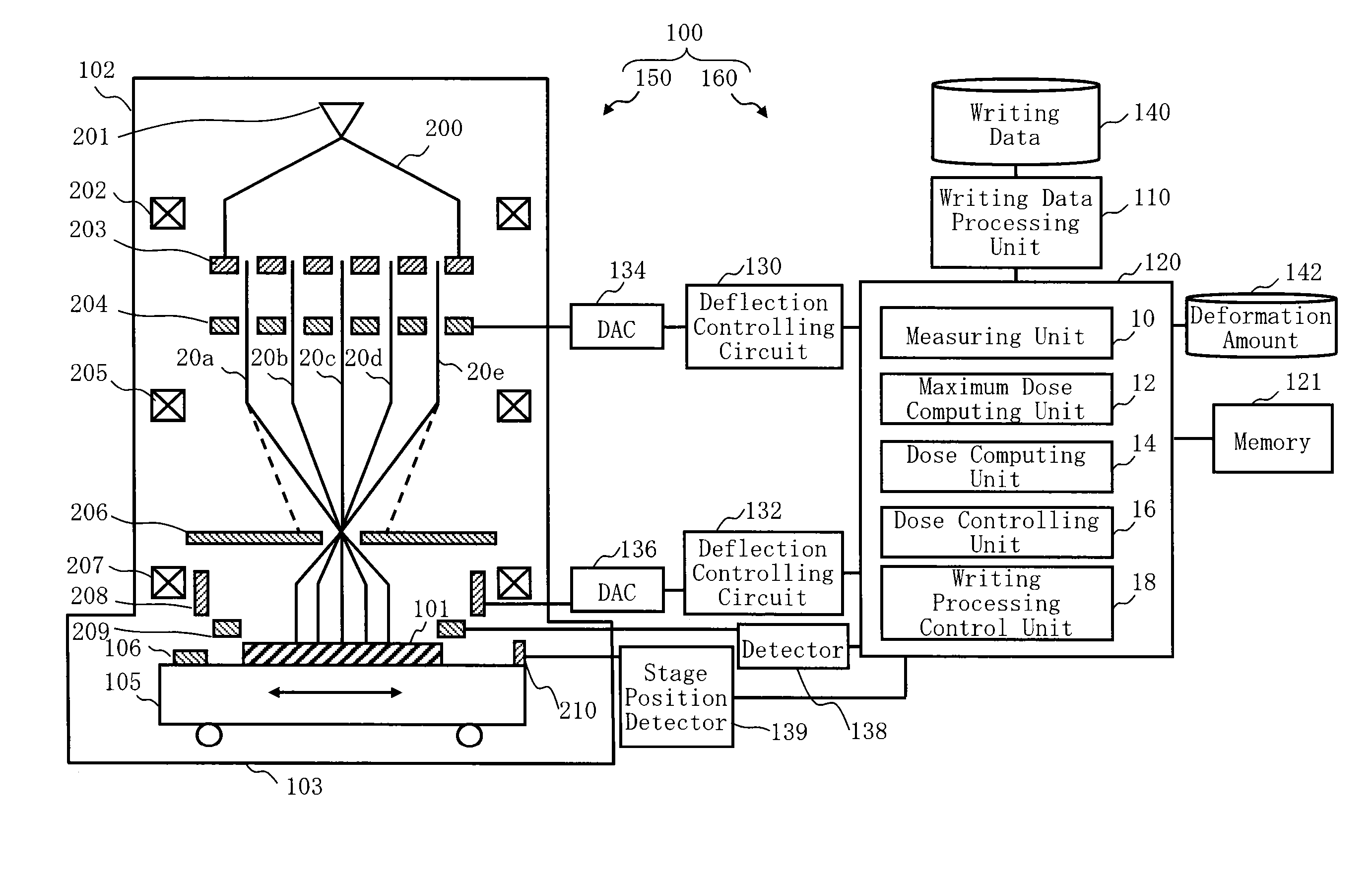

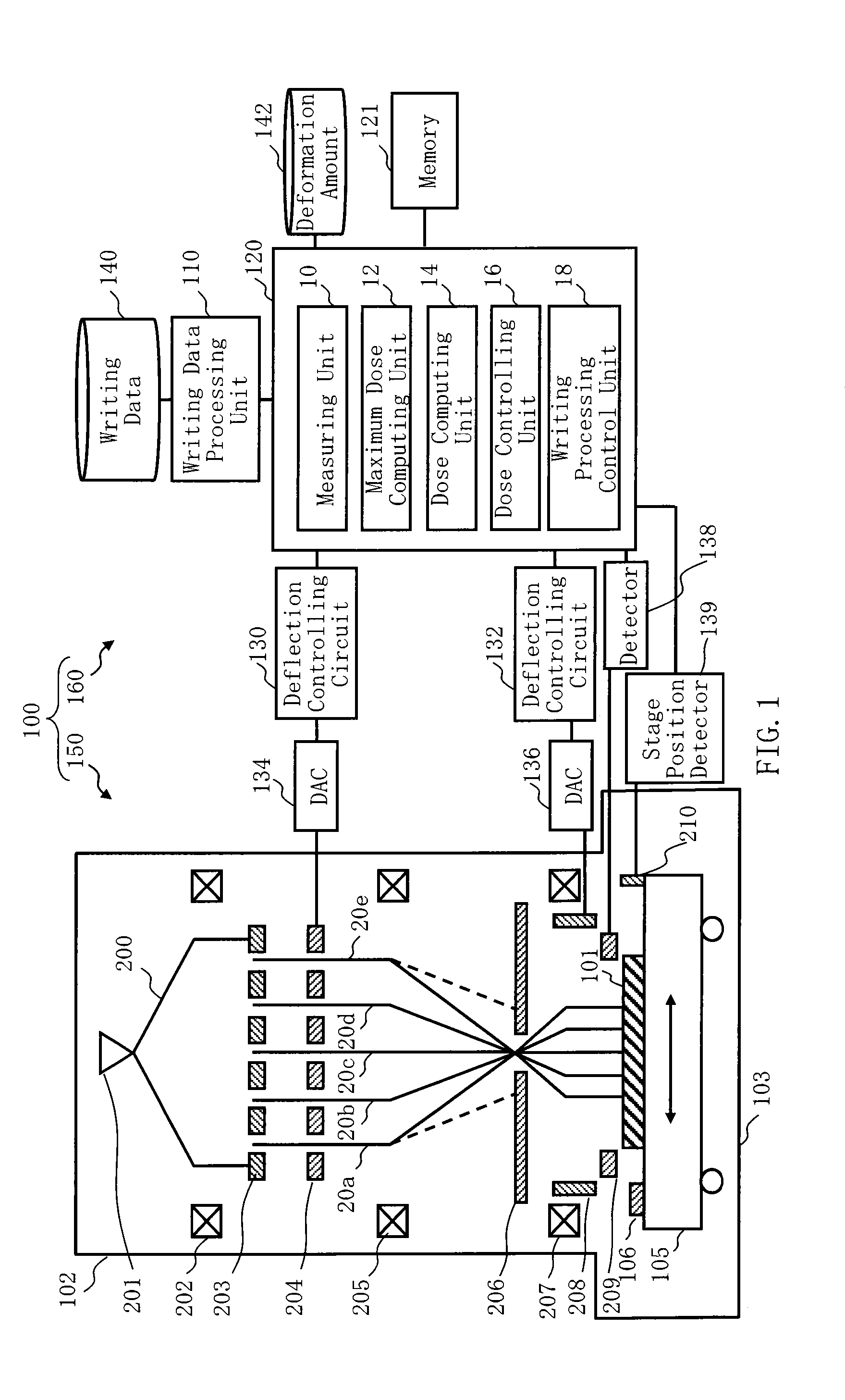

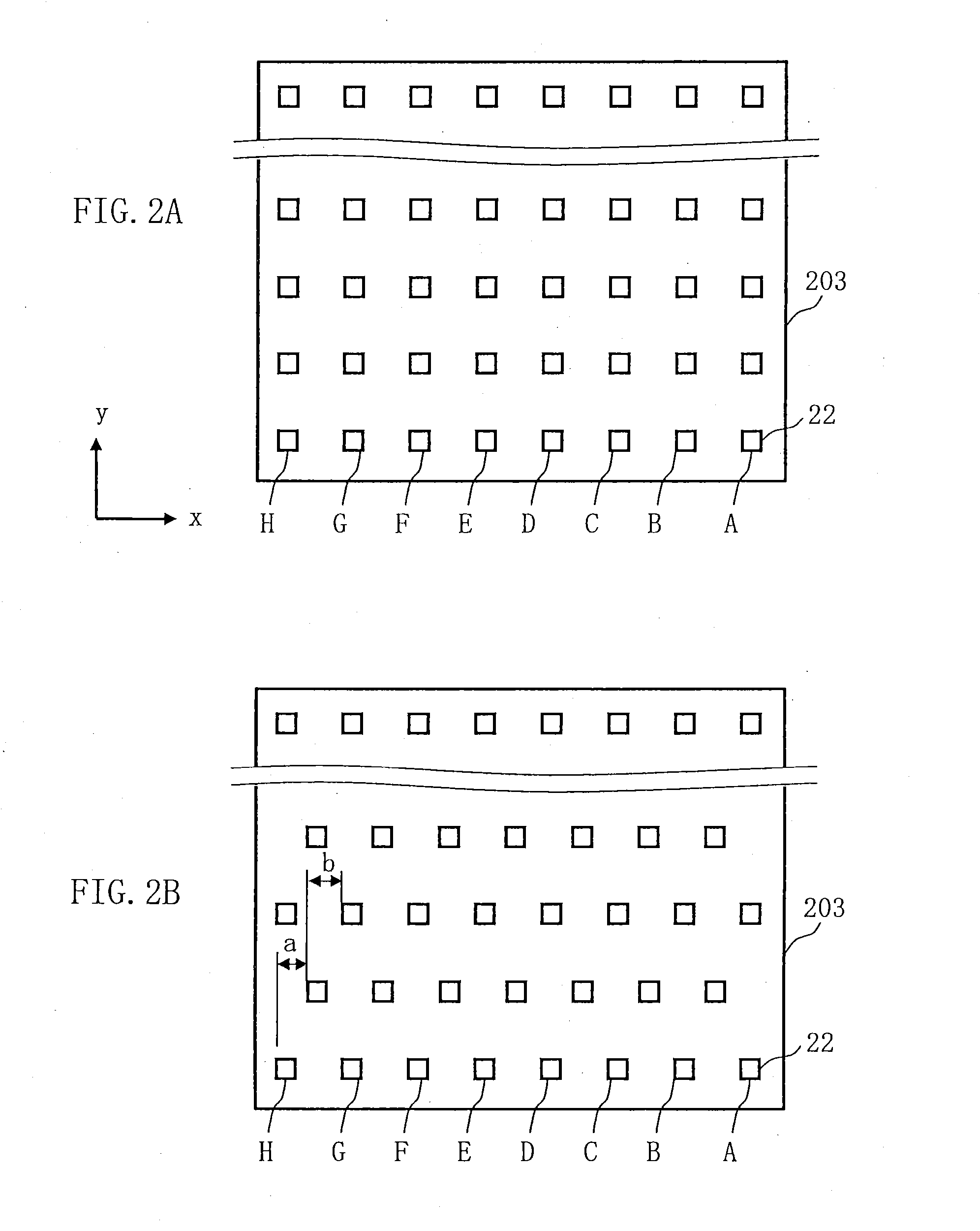

Multi charged particle beam writing apparatus and multi charged particle beam writing method

ActiveUS20130056647A1Thermometer detailsBeam/ray focussing/reflecting arrangementsLight beamMulti beam

In accordance with one aspect of this invention, a multi charged particle beam writing apparatus includes an aperture member, in which a plurality of openings are formed, configured to form multi-beams by making portions of the charged particle beam pass through the plurality of openings; a plurality of blankers configured to perform blanking-deflect regarding beams corresponding to the multi-beams; a writing processing control unit configured to control writing processing with a plurality of beams having passed through different openings among the plurality of openings being irradiated on the target object at a predetermined control grid interval; and a dose controlling unit configured to variably control a dose of a beam associated with deviation according to a deviation amount when an interval between the plurality of beams irradiated is deviated from the control grid interval.

Owner:NUFLARE TECH INC

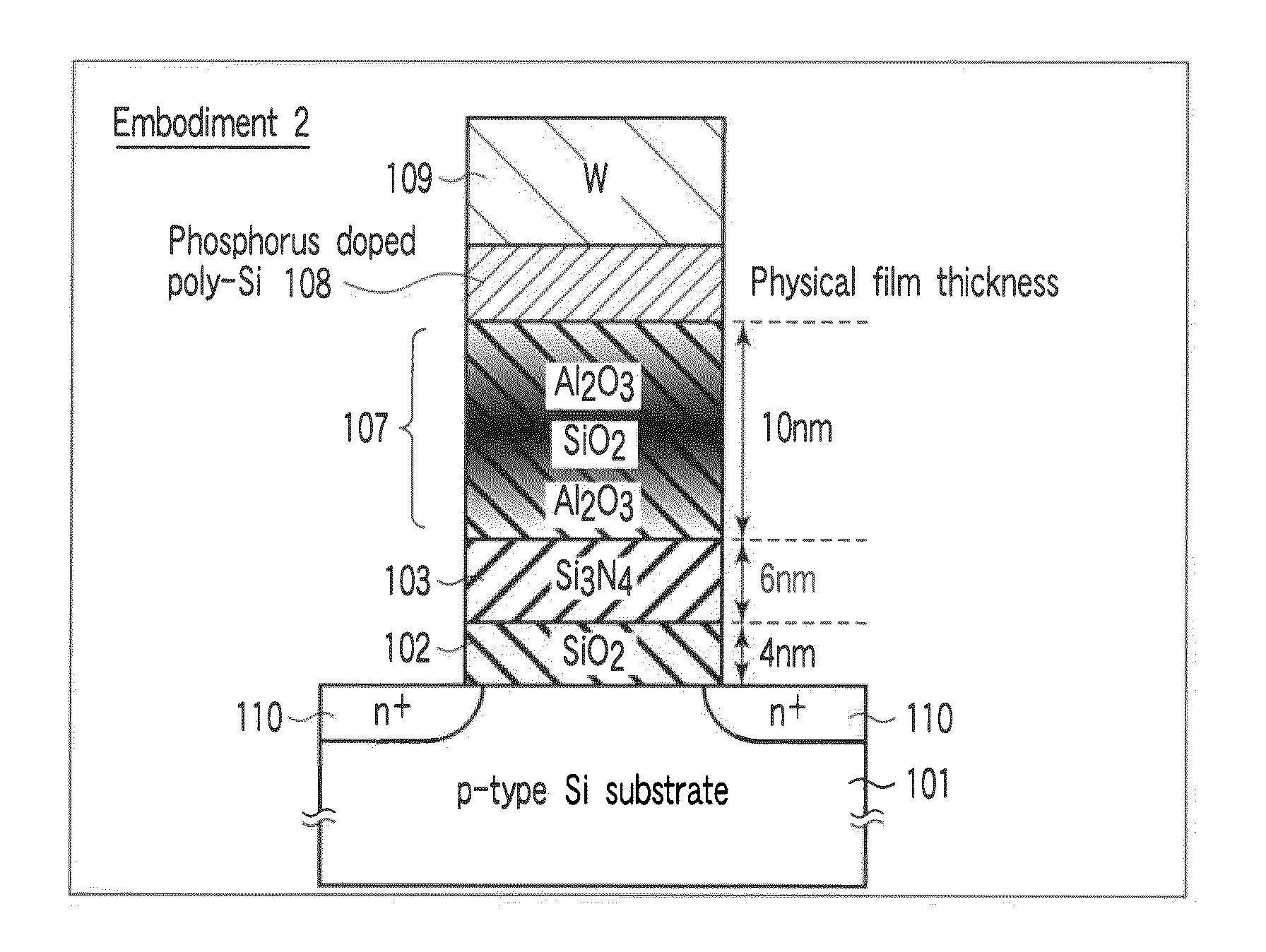

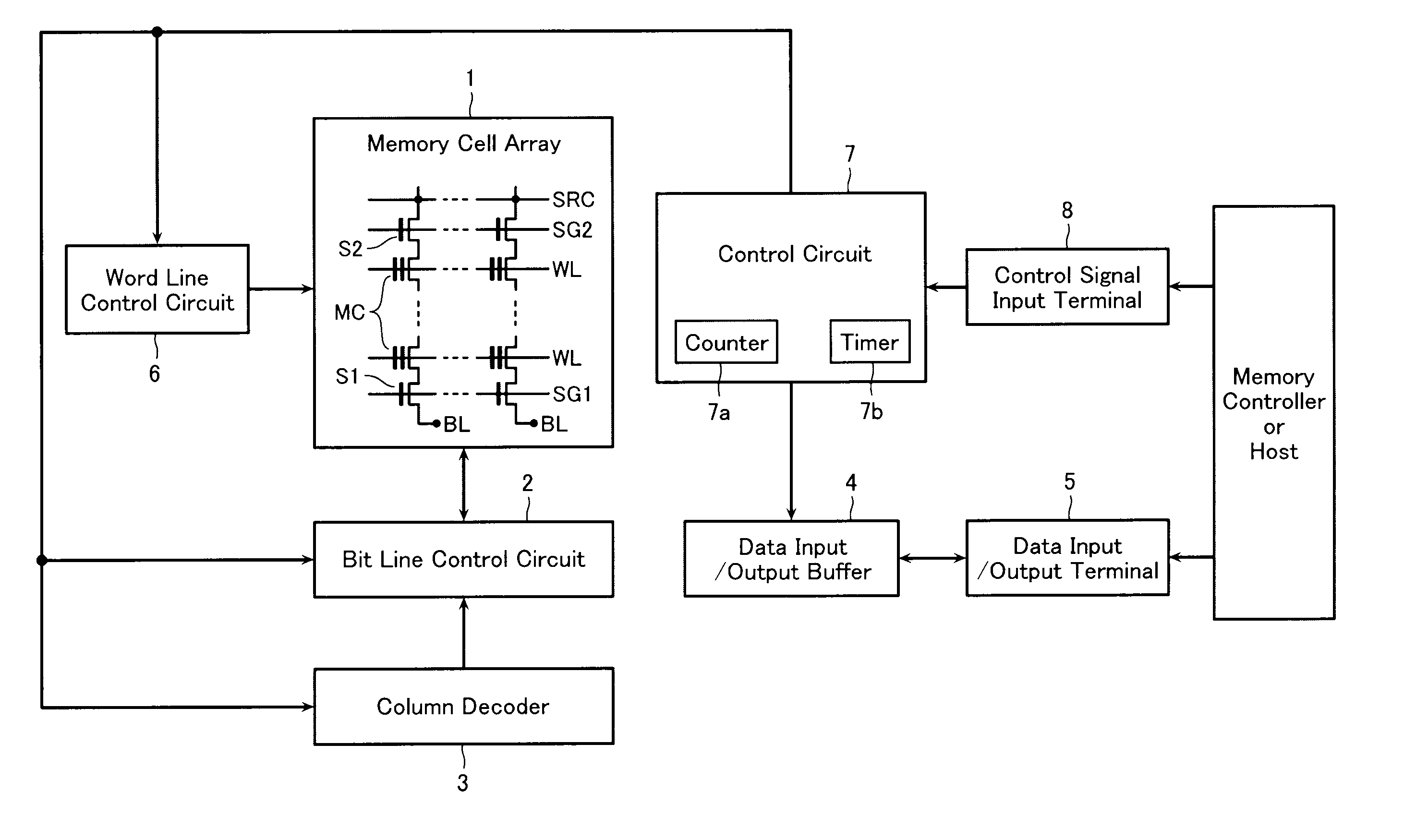

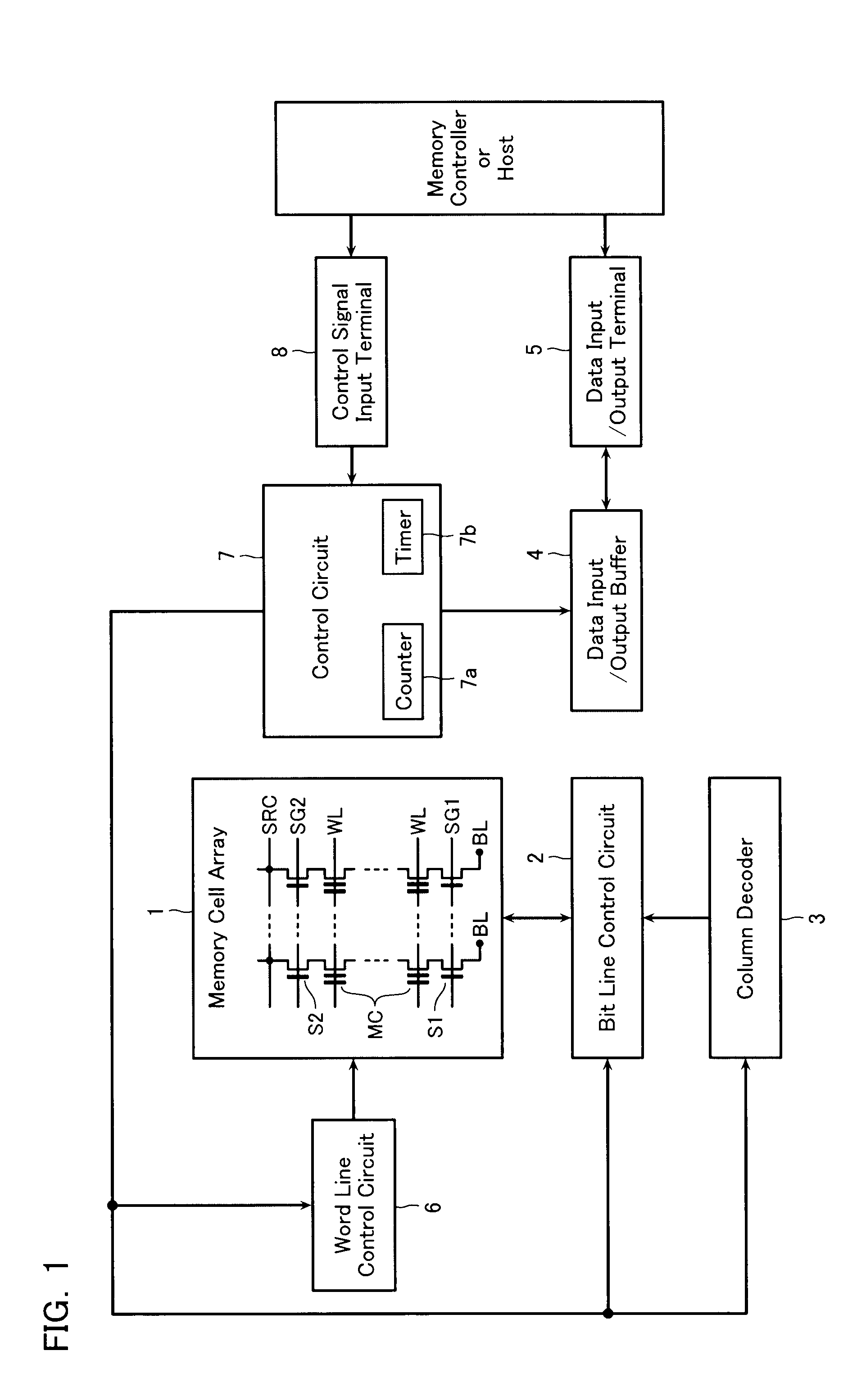

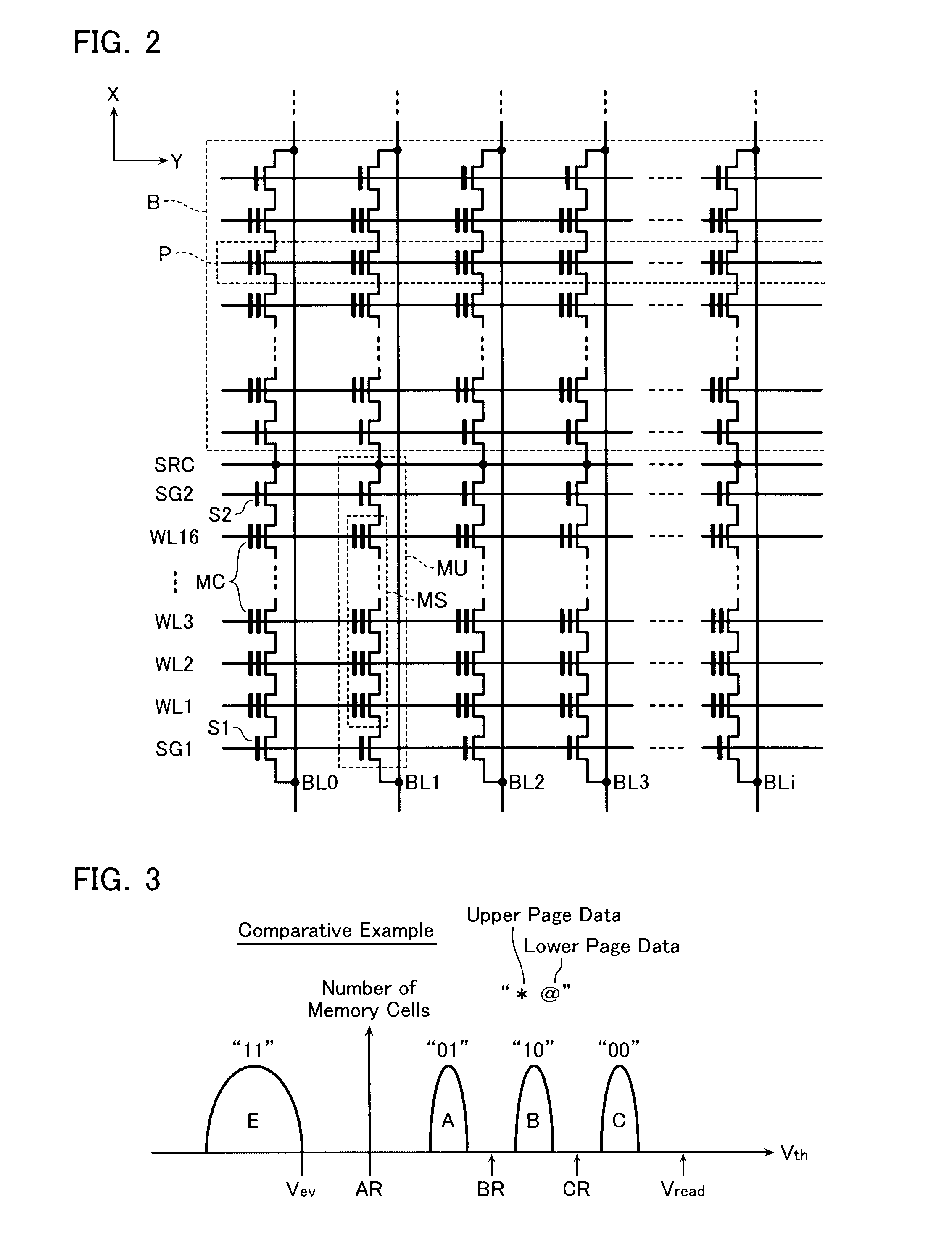

Nonvolatile semiconductor memory device

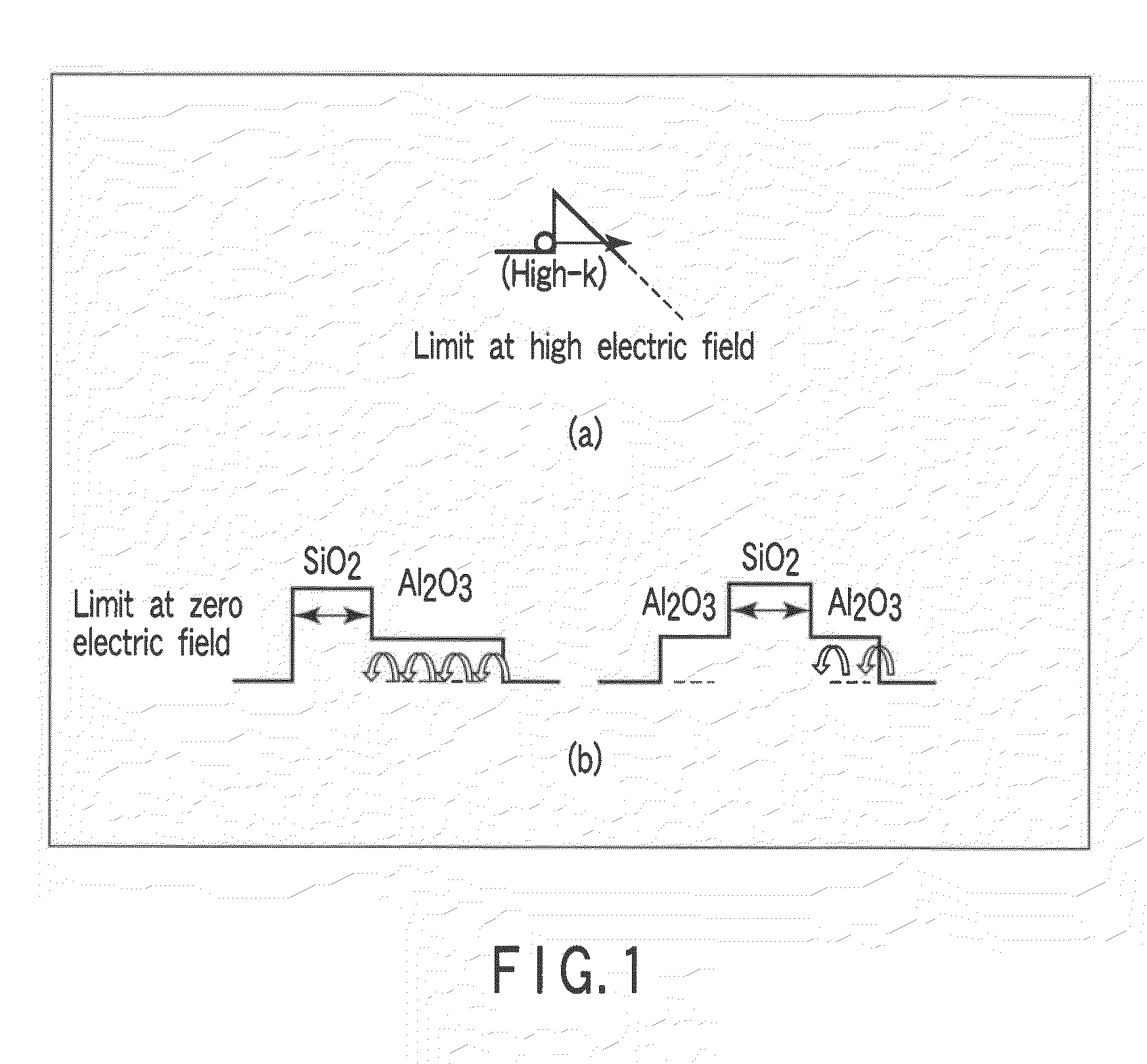

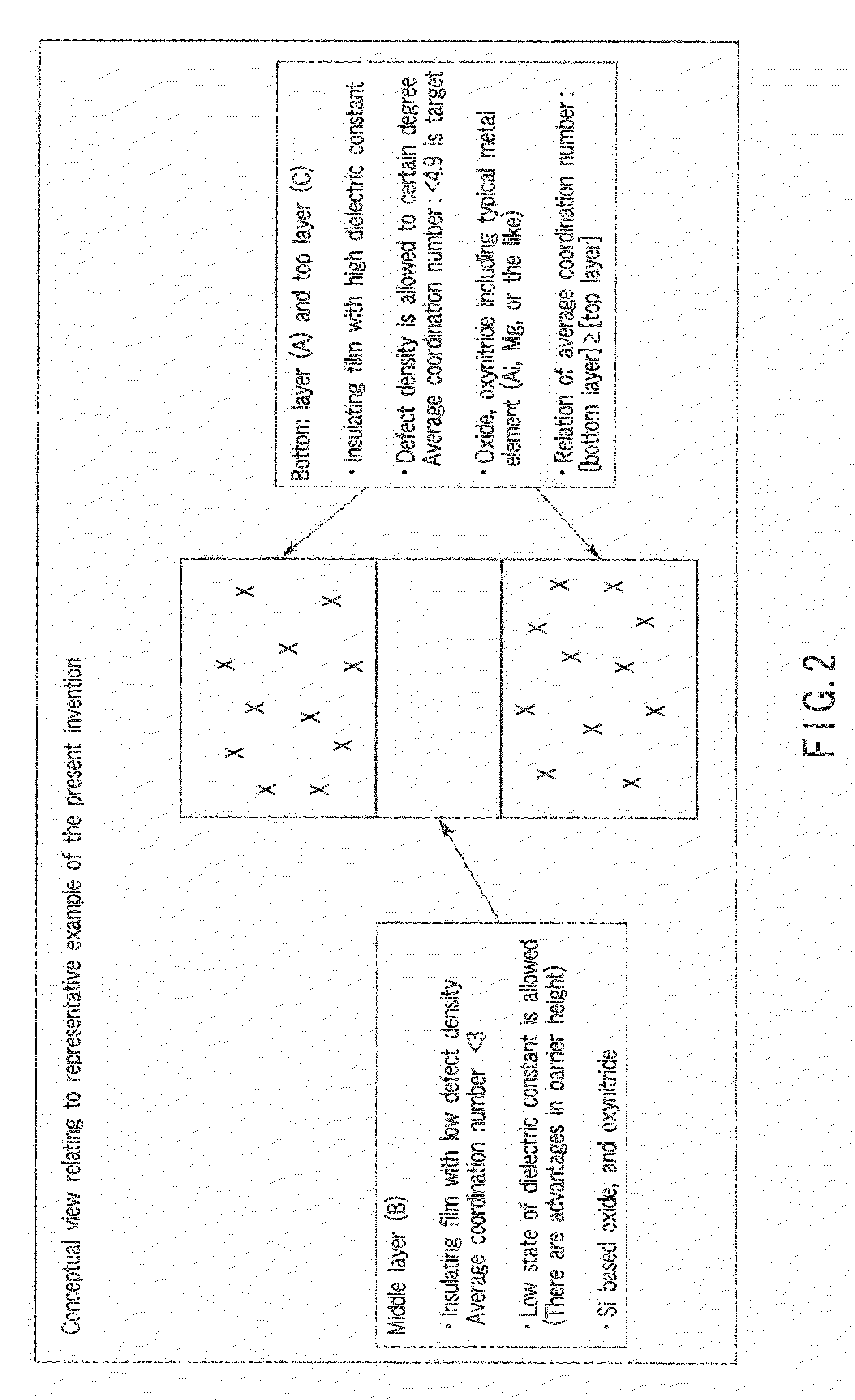

ActiveUS7956406B2TransistorSemiconductor/solid-state device detailsEngineeringDielectric permittivity

A nonvolatile semiconductor memory device includes a charge storage layer on a first insulating film, a second insulating film which is provided on the charge storage layer, formed of layers, and a control gate electrode on the second insulating film. The second insulating film includes a bottom layer (A) provided just above the charge storage layer, a top layer (C) provided just below the control gate electrode, and a middle layer (B) provided between the bottom layer (A) and the top layer (C). The middle layer (B) has higher barrier height and lower dielectric constant than both the bottom layer (A) and the top layer (C). The average coordination number of the middle layer (B) is smaller than both the average coordination number of the top layer (C) and the average coordination number of the bottom layer (A).

Owner:KIOXIA CORP

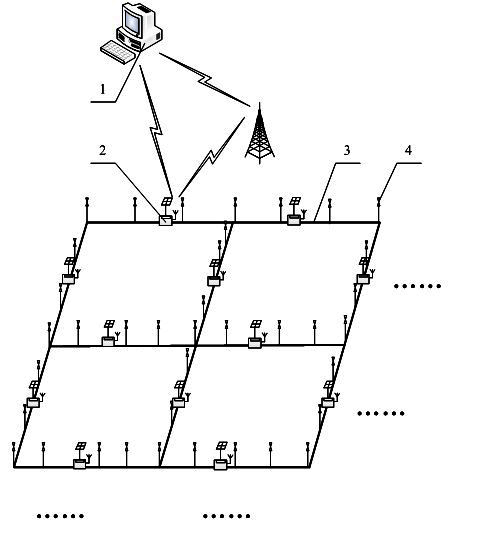

Forest fire monitoring and preventing and controlling system and control method thereof

InactiveCN101968912AEnable early monitoringRealize prevention and controlClimate change adaptationFire rescueControl gridEngineering

The invention provides a forest fire monitoring and preventing and controlling system and a control method thereof, the forest fire monitoring and preventing and controlling system divides a forest cover region into a plurality of independent preventing and controlling grids via a grid form distribution, once there is fire in the grids, the fire can be detected in time and controlled by spraying water, so that the fire is isolated within a grid range, fire spreading is effectively prevented, and the fire is completely monitored by a central supervisory control computer, so that workers can take corresponding fire protection measures according to fire situation, and early monitoring and preventing and controlling for the forest fire are implemented; simultaneously, the method of the invention is used for controlling fire, fire protection in each grid of the system is automatically detected and controlled by a monitoring terminal, even in bad communication environment or communication breakdown, fire spreading is preferably controlled, increase of fire damage caused by delayed fire protection measures in bad communication situation is avoided, and emergency handling capability of the system is enhanced.

Owner:CHONGQING ACADEMY OF SCI & TECH

Field-effect tranisistor realizing memory function and method of producing the same

InactiveCN101179095AImprove reliabilityMeet functional applicationsSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing technologyField-effect transistor

The invention provides a field effect transistor that achieves the storage function and the preparation method, which belongs to the filed of semiconductor integrated circuit and manufacturing technology. The transistor comprises a source region, a drain region and a control grid, wherein the control grid utilizes a grid stepped construction which comprises a bottom layer of a tunneling oxidizing layer, an interface layer of a resistance-varying material layer and a top layer of a conductive electrode layer. The field effect transistor obtains an electrically programmable multi-threshold function, the source and drain currents of which are different when a same reading voltage is imposed on the grid, thereby achieving the information storage on two different states or other functions. Utilizing the invention, a plurality of devices and circuits with new functions, high performance and high reliability can be composed, thereby meeting the application of different circuit functions. Meanwhile the invention can adopt the compatibility with the CMOS technology of the conventional PN source or drain junction structure, and can also adopt the compatibility with the CMOS technology of the Schottky source or drain junction structure, with a greater flexibility in technology selection.

Owner:PEKING UNIV

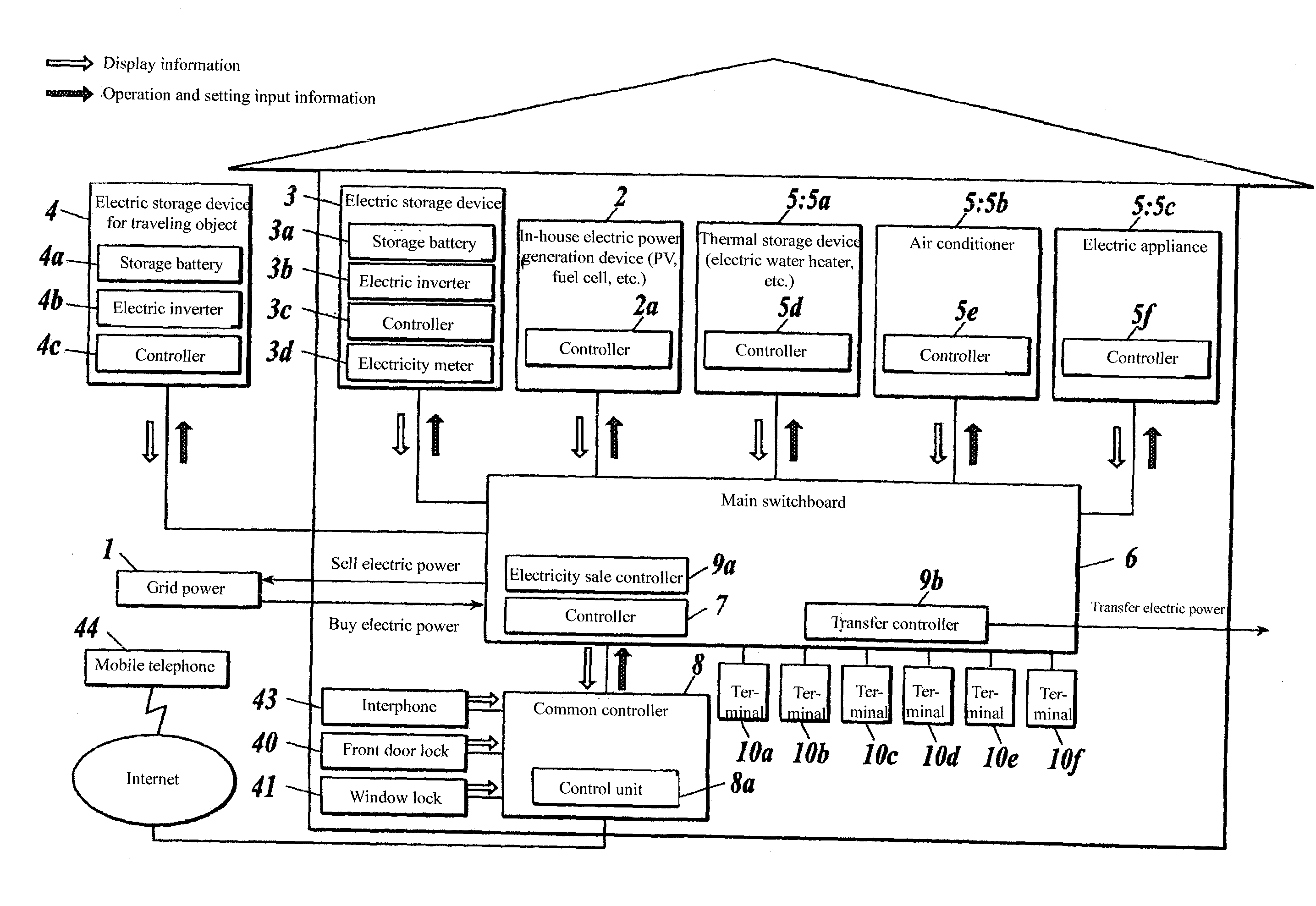

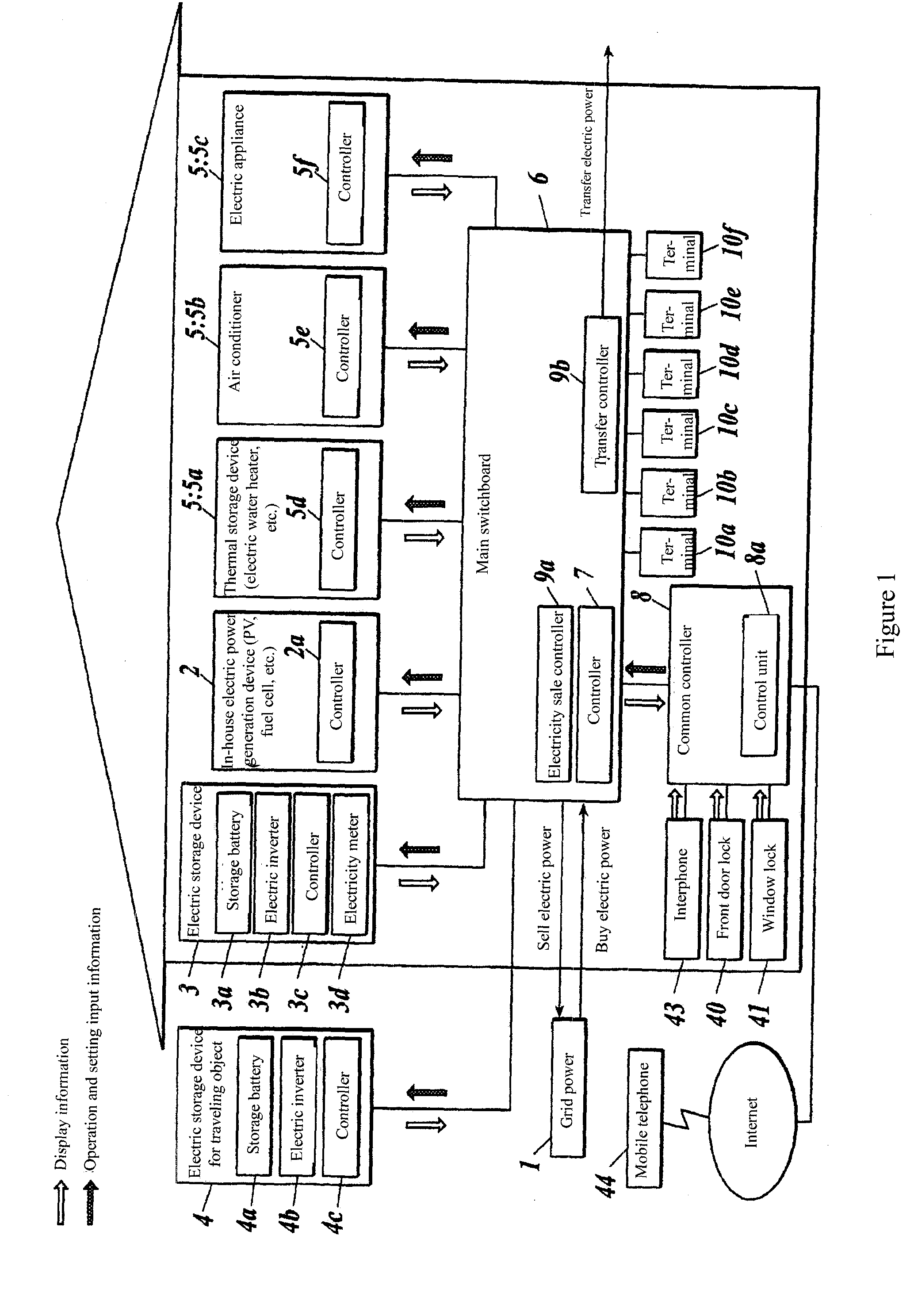

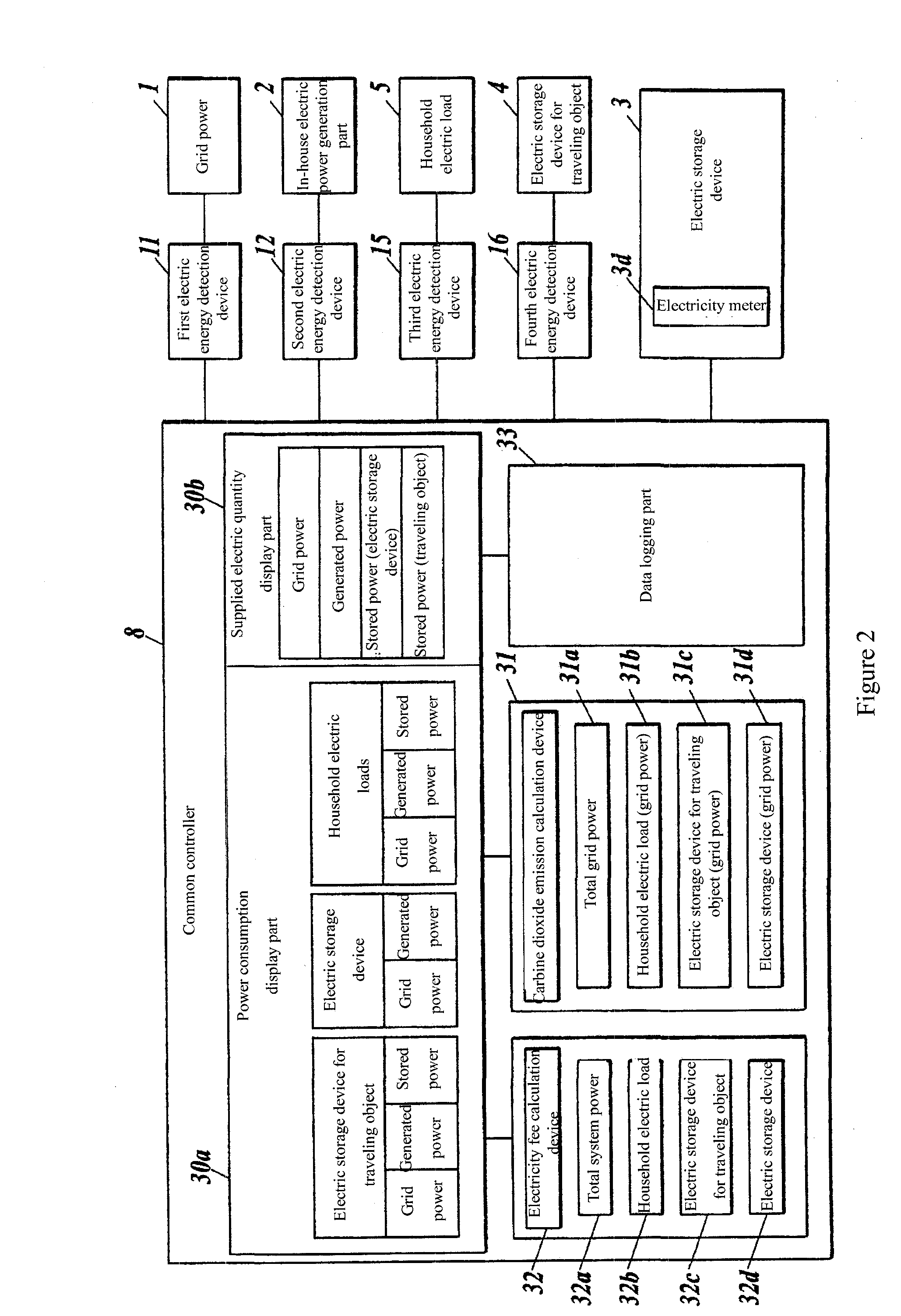

Energy management system for houses

InactiveUS20130013123A1Easy to buildBuildLevel controlVolume/mass flow measurementPower gridControl theory

A household energy management system, which comprises a common controller connected with a controller for controlling grid power, a controller for controlling an in-house electric power generation device, a controller for controlling an electric storage device, a controller for controlling an electric storage device for traveling object, controllers for controlling household electric loads, and manage the energy consumption and supply by controlling the respective controllers, so that the overall energy consumption and supply in the house can be managed centrally, and the respective machines can be controlled with a single controller centrally.

Owner:MISAWA HOMES CO LTD

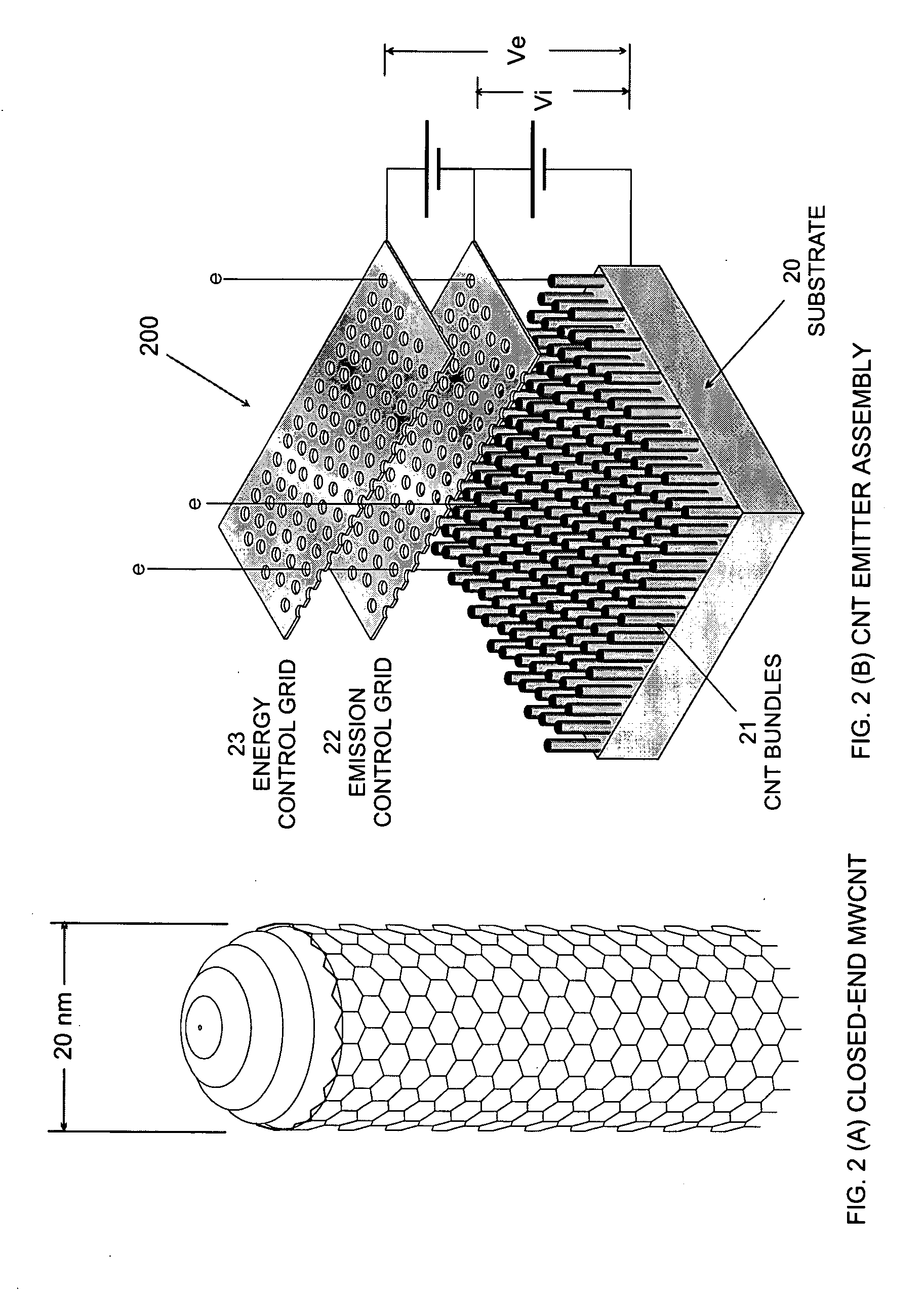

Carbon nanotube electron ionization sources

ActiveUS6885010B1Reduce in quantityEasy CalibrationMaterial nanotechnologyLamp incadescent bodiesLight beamIonization chamber

An ion source for use in a mass spectrometer includes an electron emitter assembly configured to emit electron beams, wherein the electron emitter assembly comprises carbon nanotube bundles fixed to a substrate for emitting the electron beams, a first control grid configured to control emission of the electron beams, and a second control grid configured to control energies of the electron beams; an ionization chamber having an electron-beam inlet to allow the electron beams to enter the ionization chamber, a sample inlet for sample introduction, and an ion-beam outlet to provide an exit for ionized sample molecules; an electron lens disposed between the electron emitter assembly and the ionization chamber to focus the electron beams; and at least one electrode disposed proximate the ion-beam outlet to focus the ionized sample molecules exiting the ionization chamber.

Owner:THERMO ELECTRON A DE

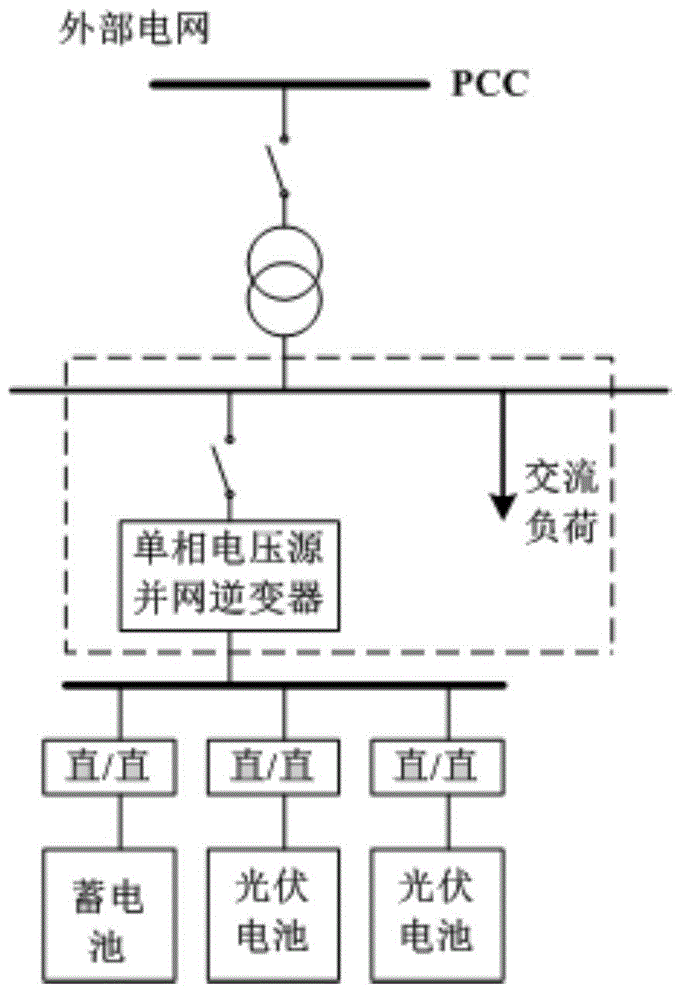

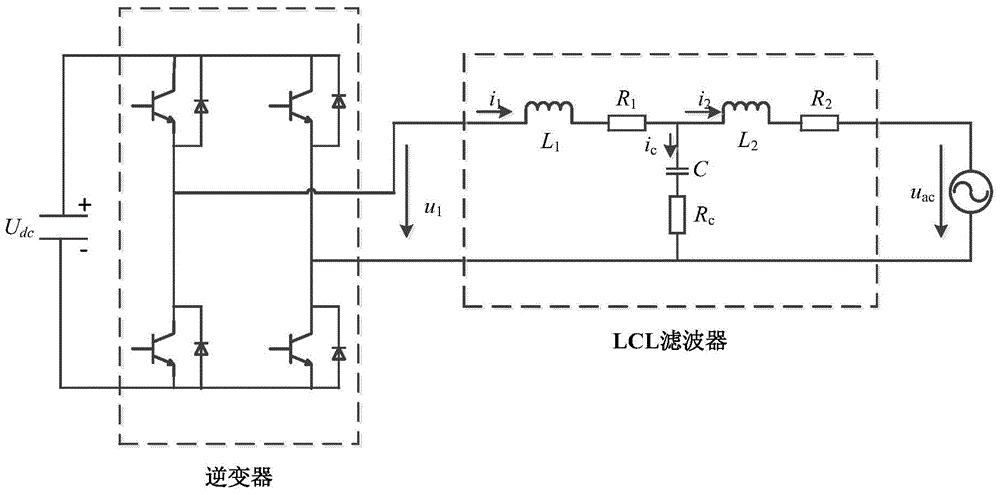

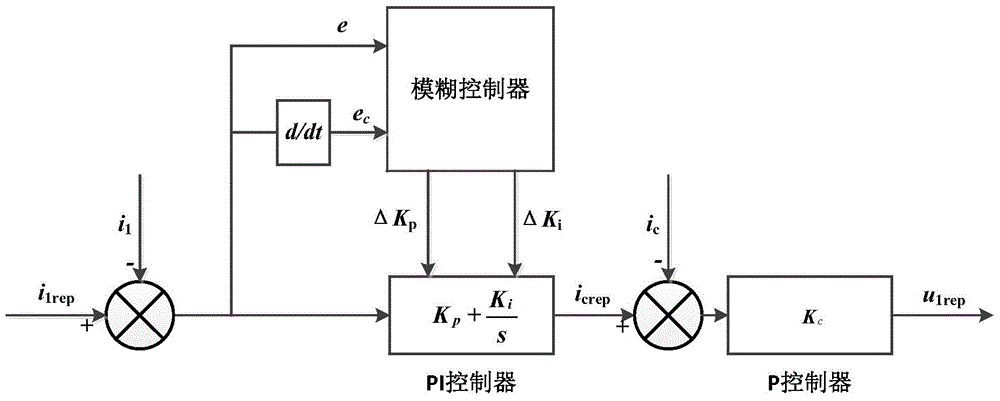

Method for controlling grid-connected inverter of micro grid based on fuzzy PI algorithm

ActiveCN103956769AIncrease the damping ratioGuaranteed uptimeEfficient power electronics conversionAc-dc conversionControl signalFuzzy pi

The invention discloses a method for controlling a grid-connected inverter of a micro grid based on the fuzzy PI algorithm. The method comprises the steps that (1) the voltage of the current power grid, the output current of the current grid-connected inverter and the capacitive current of a current filter are sampled; (2) the command value of a grid-connected current is determined; (3) the proportionality coefficient and the integral coefficient of a PI controller are adjusted; (4) the command value of the capacitive current of the filter is acquired through the adjusted PI controller; (5) the command value of the output voltage of the grid-connected inverter is acquired through the PI controller; (6) a control signal is generated to control switch-on or switch-off of a switching tube of the grid-connected inverter, and an expected output voltage is generated at the power output end of the grid-connected inverter; (7) the step (1) to the step (6) are repeatedly executed to make the output current of the grid-connected inverter trace the command values all the time. According to the method, by adjusting the control parameter of the PI controller in an on-line mode through the fuzzy algorithm, the output current of the grid-connected inverter can trace a current command signal quickly and accurately.

Owner:HUAZHONG UNIV OF SCI & TECH

Shifting register unit, driving method thereof, grid drive circuit and display device

ActiveCN105513524AImprove noise reductionStatic indicating devicesDigital storageShift registerControl signal

The invention provides a shifting register unit, a driving method thereof, a grid drive circuit and a display device. The shifting register unit comprises a pull-up node control module, a pull-down node control module, a grid drive signal output end and a grid drive signal output module. The grid drive signal output module is connected with a pull-up node, a pull-down node, a normal phase clock signal input end and the grid drive signal output end. The pull-down node control module is connected with the pull-down node and an inverse phase clock signal input end. The shifting register unit further comprises a noise reduction module which is connected with a noise reduction control signal output end and the grid drive signal output end. The noise reduction module controlled by a noise reduction control signal is adopted with the existing grid drive signal output module to control grid drive signal denoising, and the noise reduction effect is improved.

Owner:BOE TECH GRP CO LTD +1

Nonvolatile semiconductor memory device

A nonvolatile semiconductor memory device according to one embodiment of the present invention includes: a memory cell array and a control circuit. The control circuit executes a first reading operation and a second reading operation. The first reading operation is an operation of reading a threshold voltage set in the selected memory cell by setting a voltage between a control gate electrode and source of the selected memory cell to a first value. The second reading operation is an operation of reading a threshold voltage set in the selected memory cell by setting a voltage between the control gate electrode and source of the selected memory cell to a second value lower than the first value. When executing the second reading operation, the control circuit keeps a voltage of the control gate electrode of the selected memory cell to 0 or a positive value.

Owner:KIOXIA CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com