Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

90 results about "Acceptor impurity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

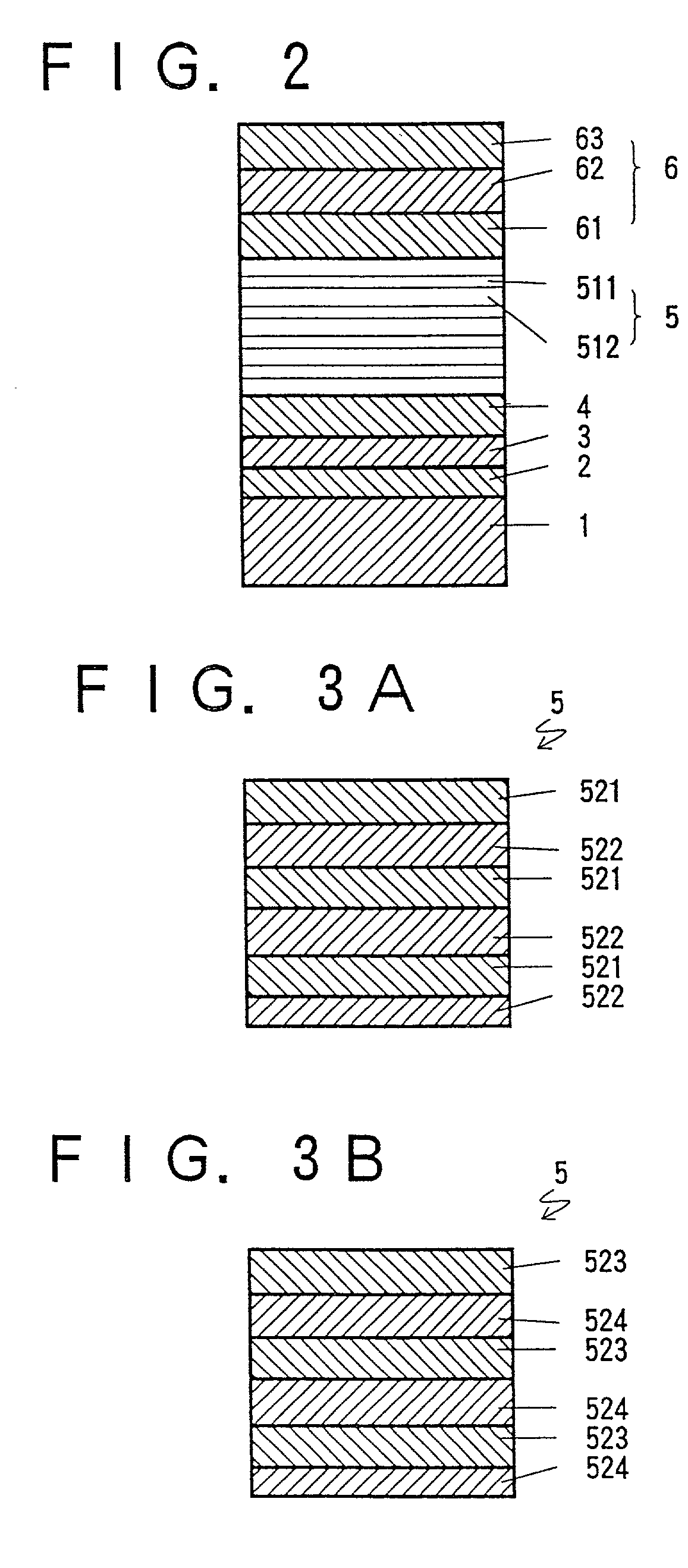

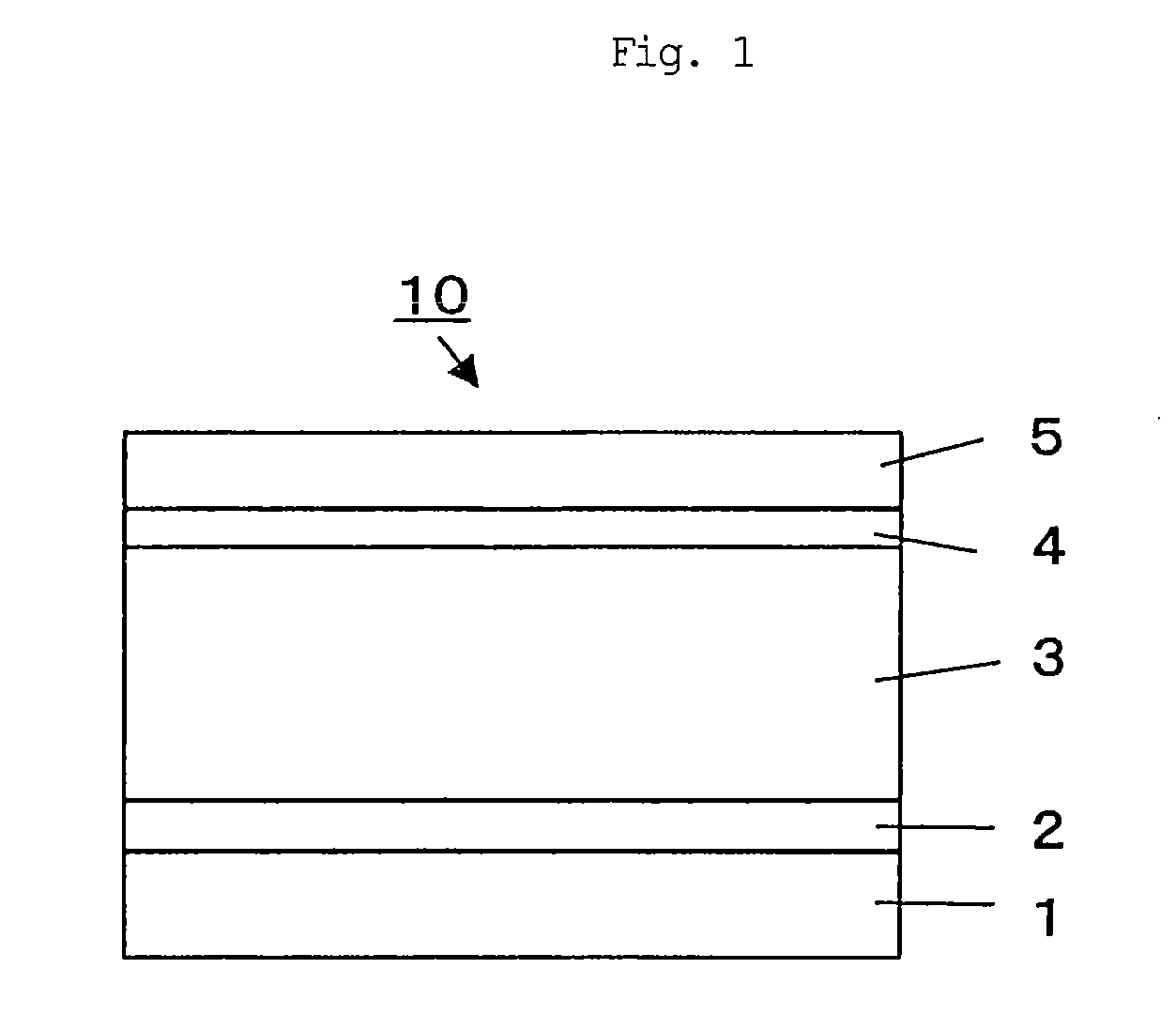

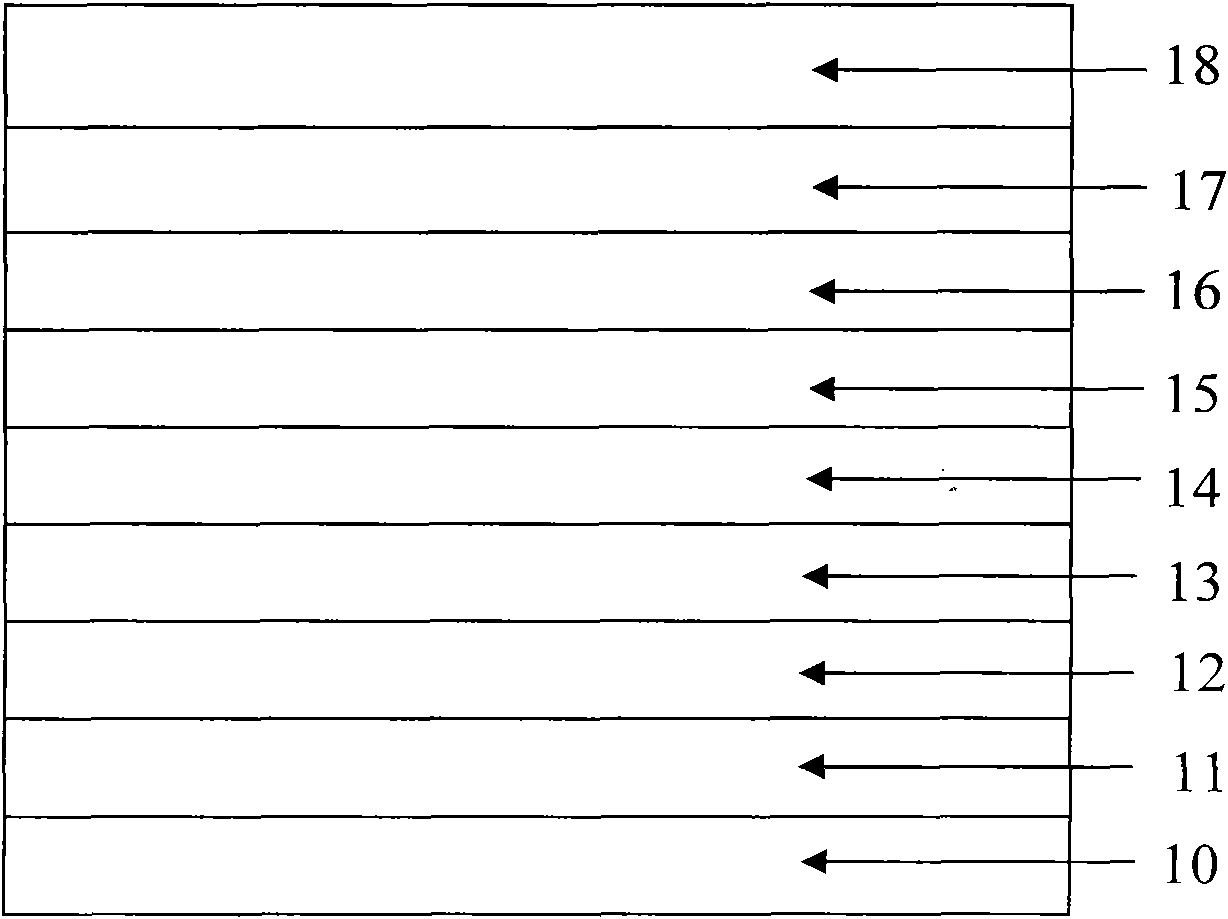

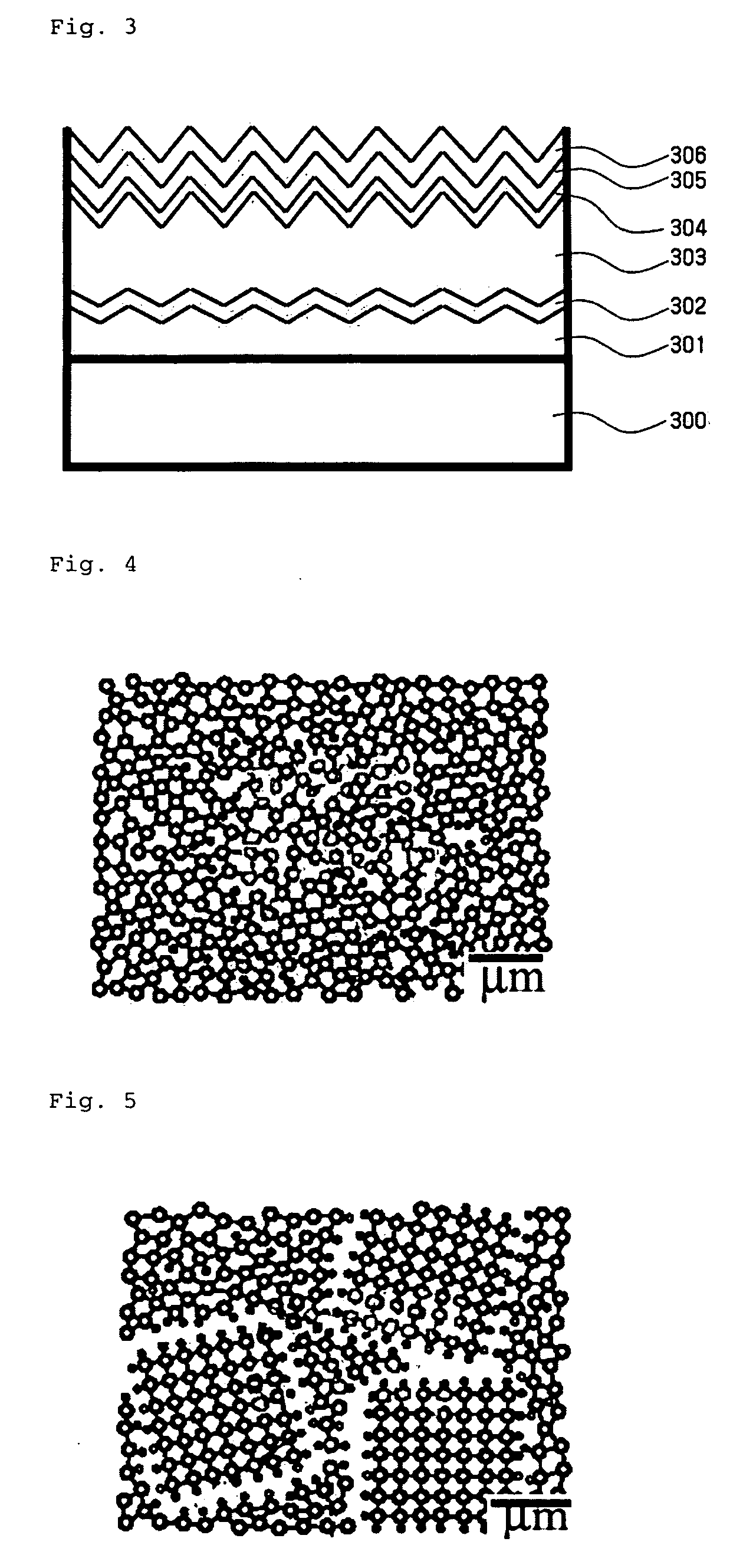

Compound semiconductor epitaxial substrate and method for producing the same

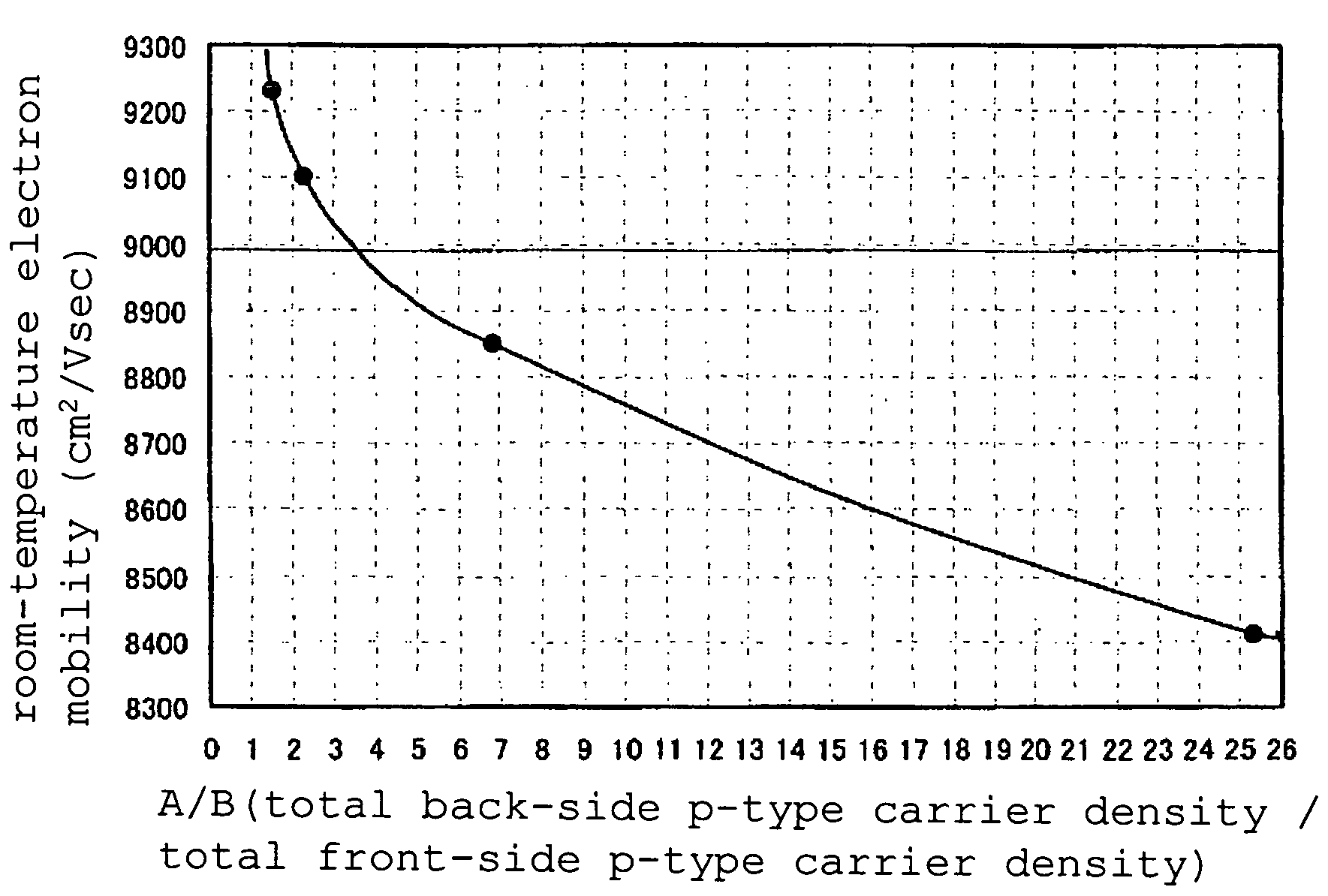

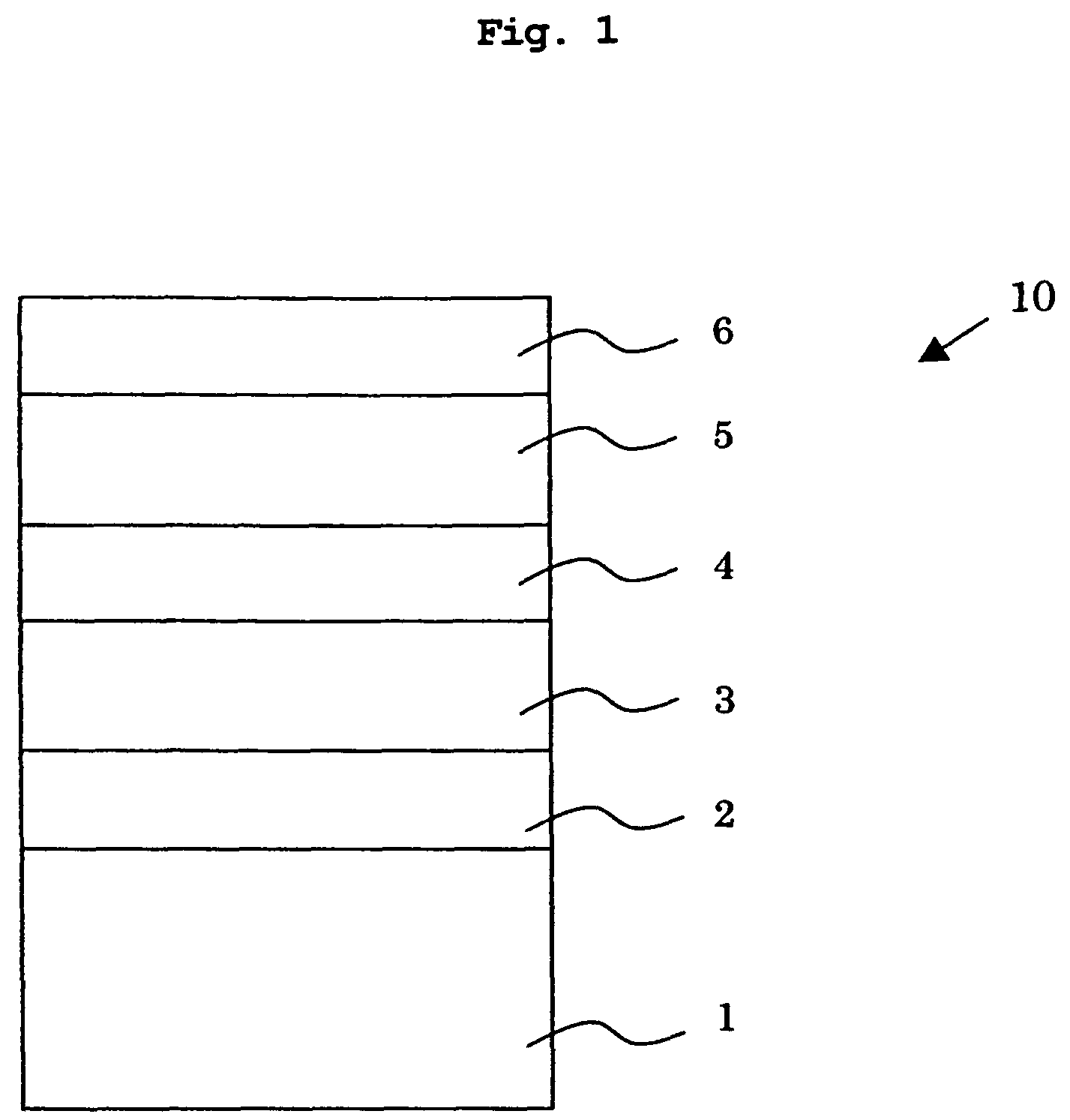

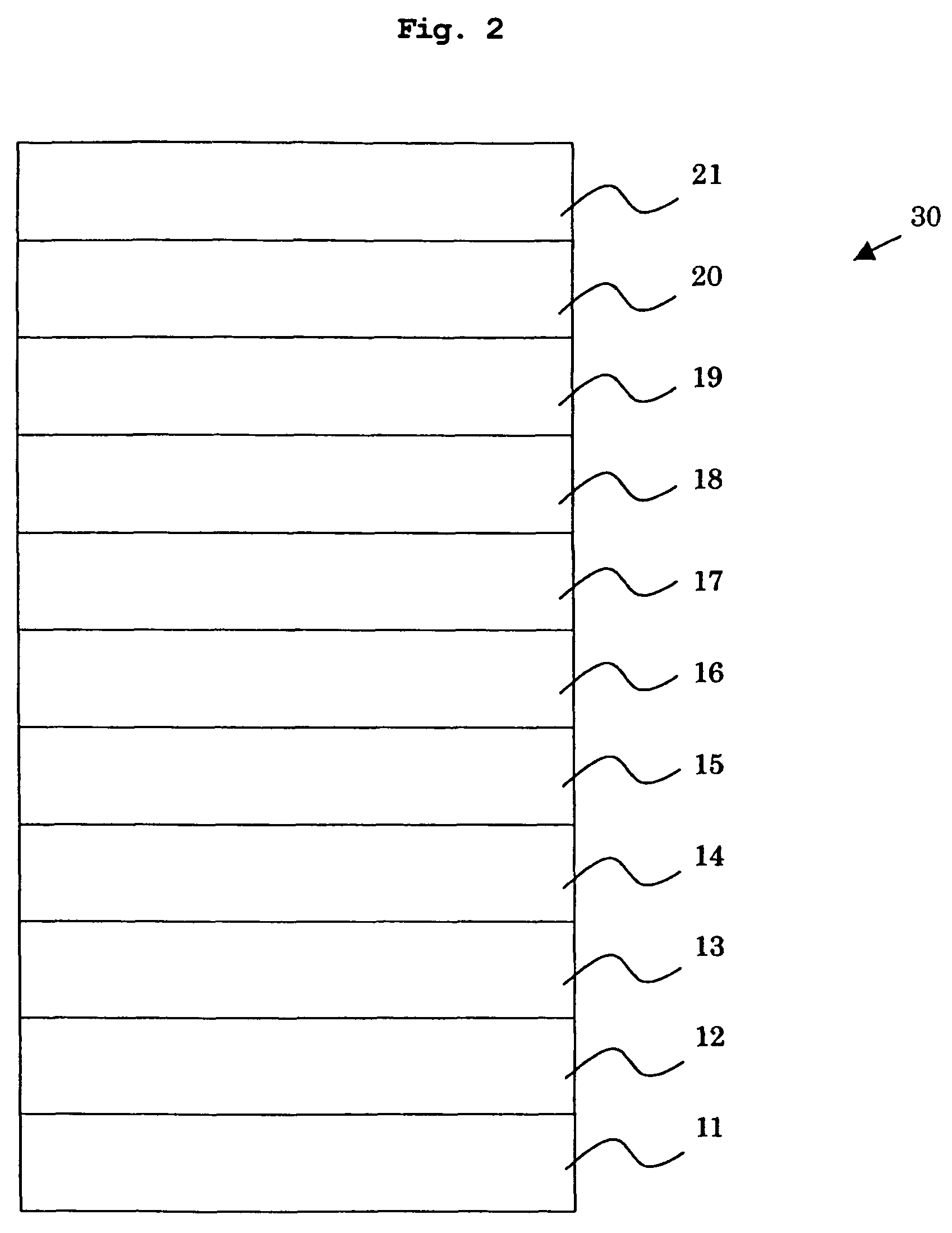

InactiveUS7935984B2Improved electron mobility characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesAcceptor impurityElectron mobility

Owner:SUMITOMO CHEM CO LTD

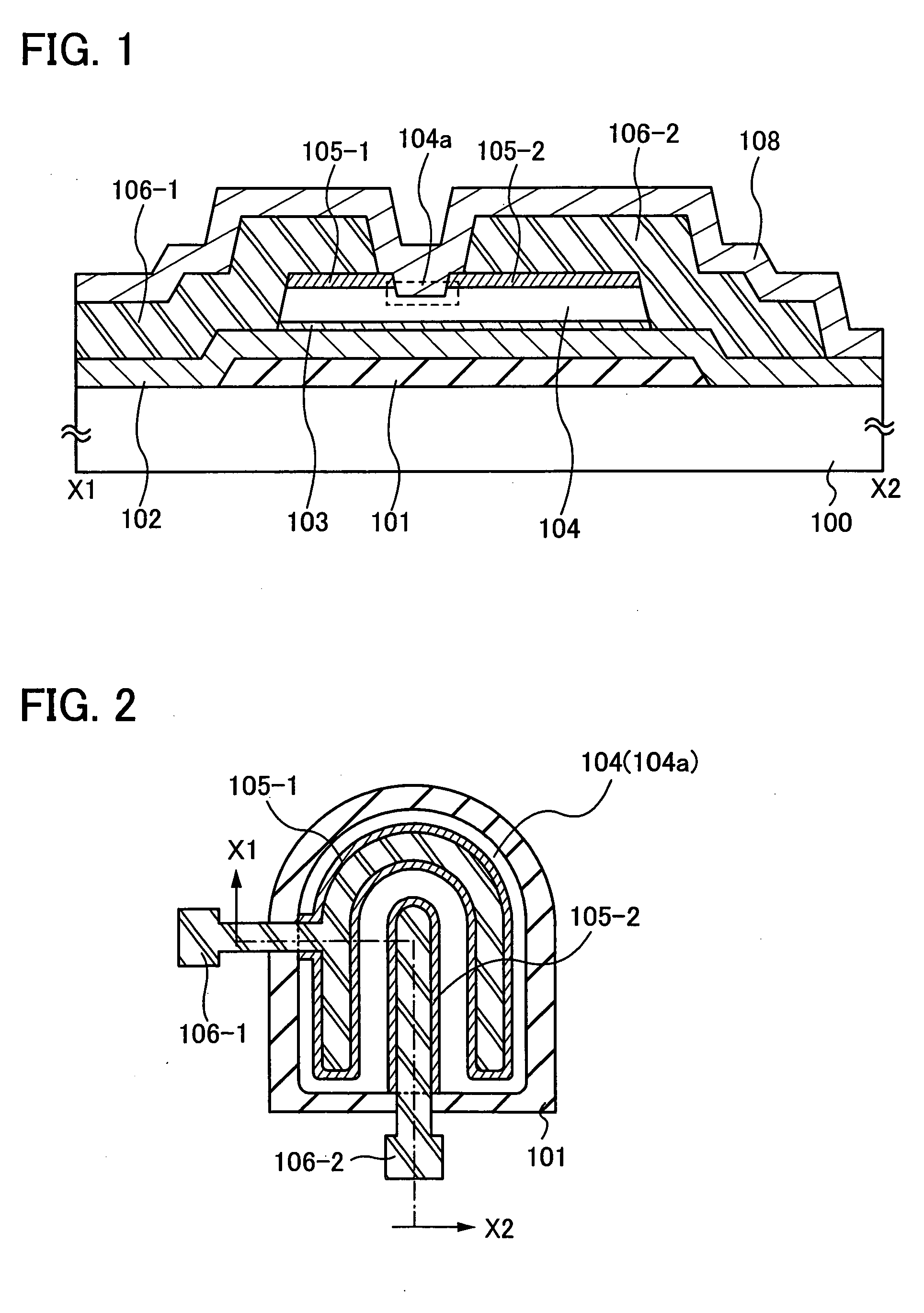

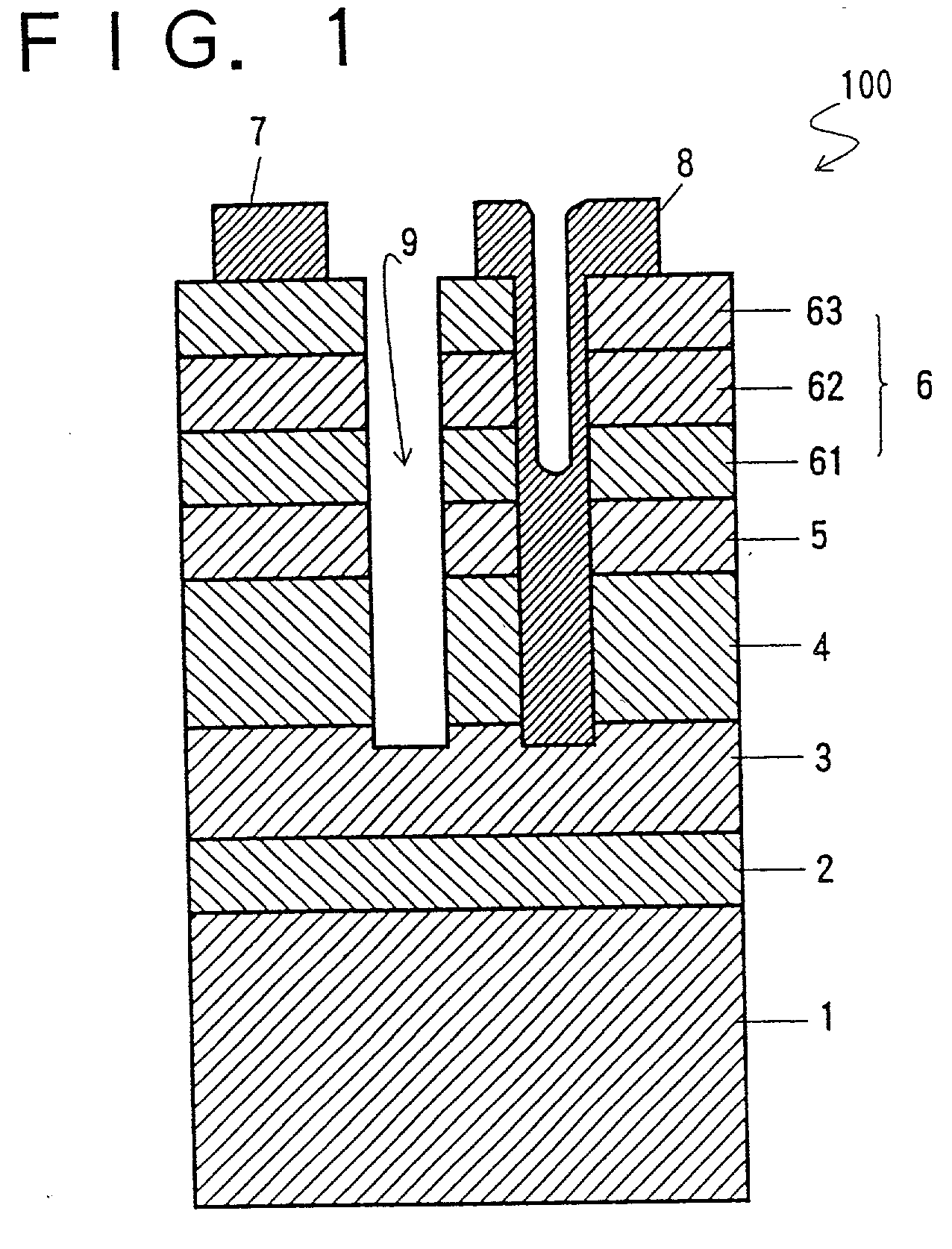

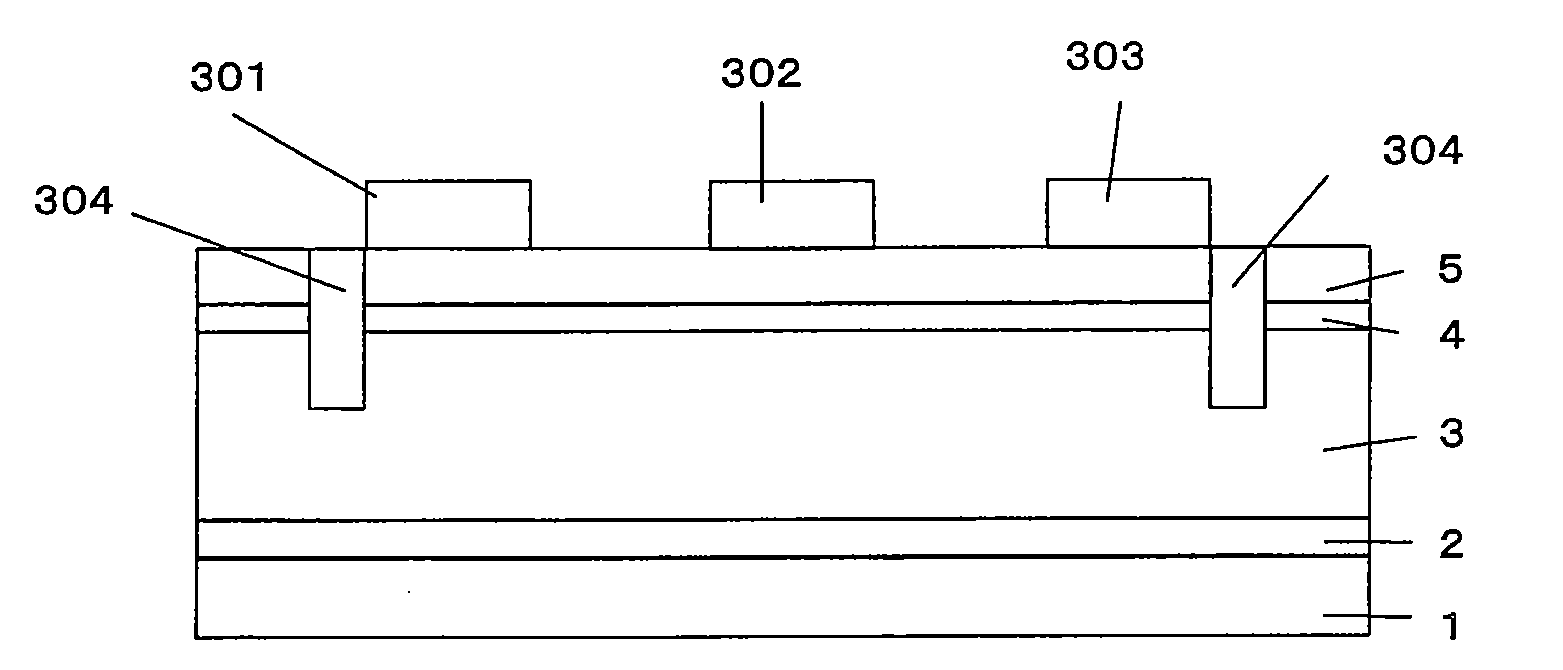

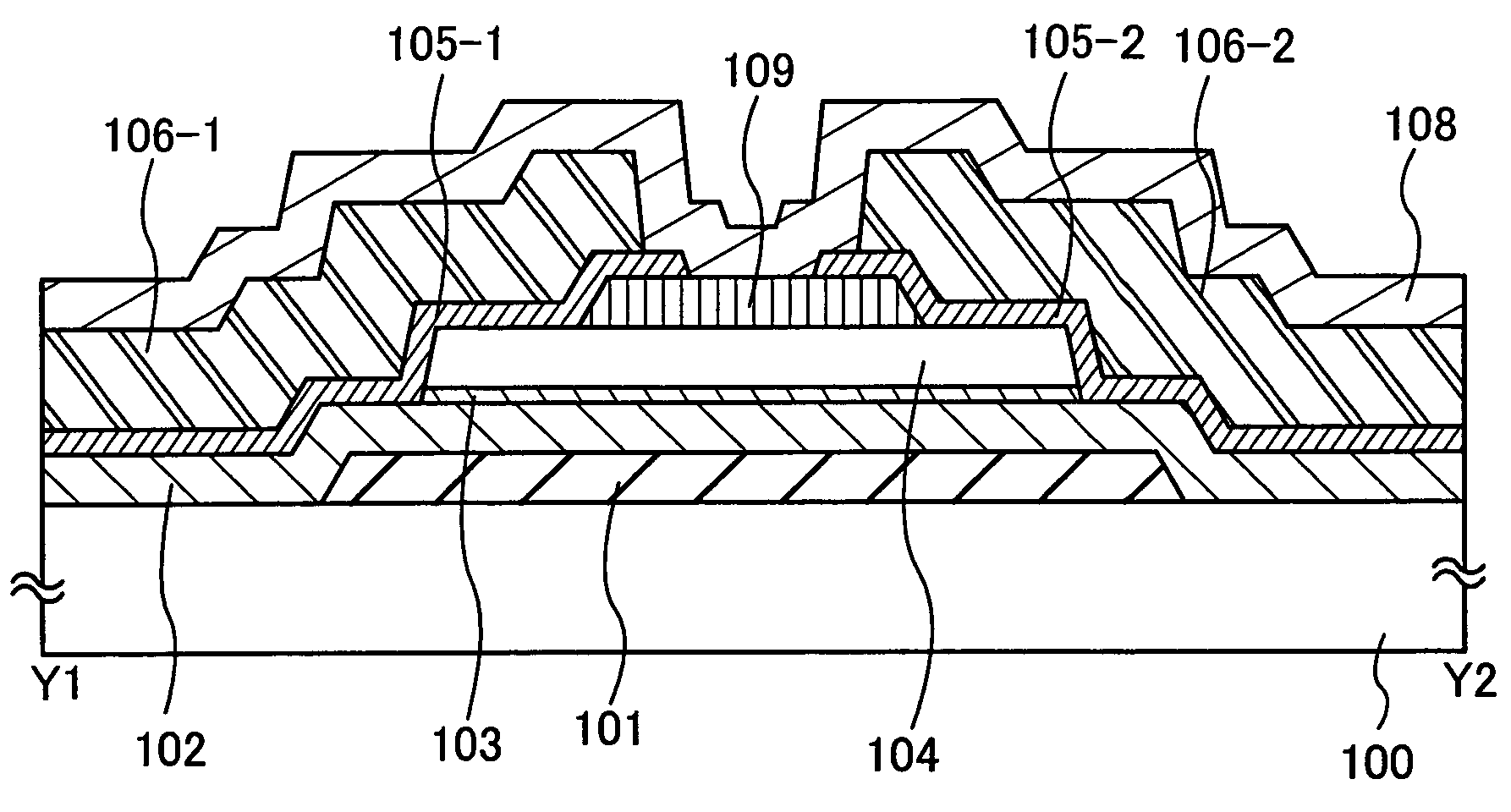

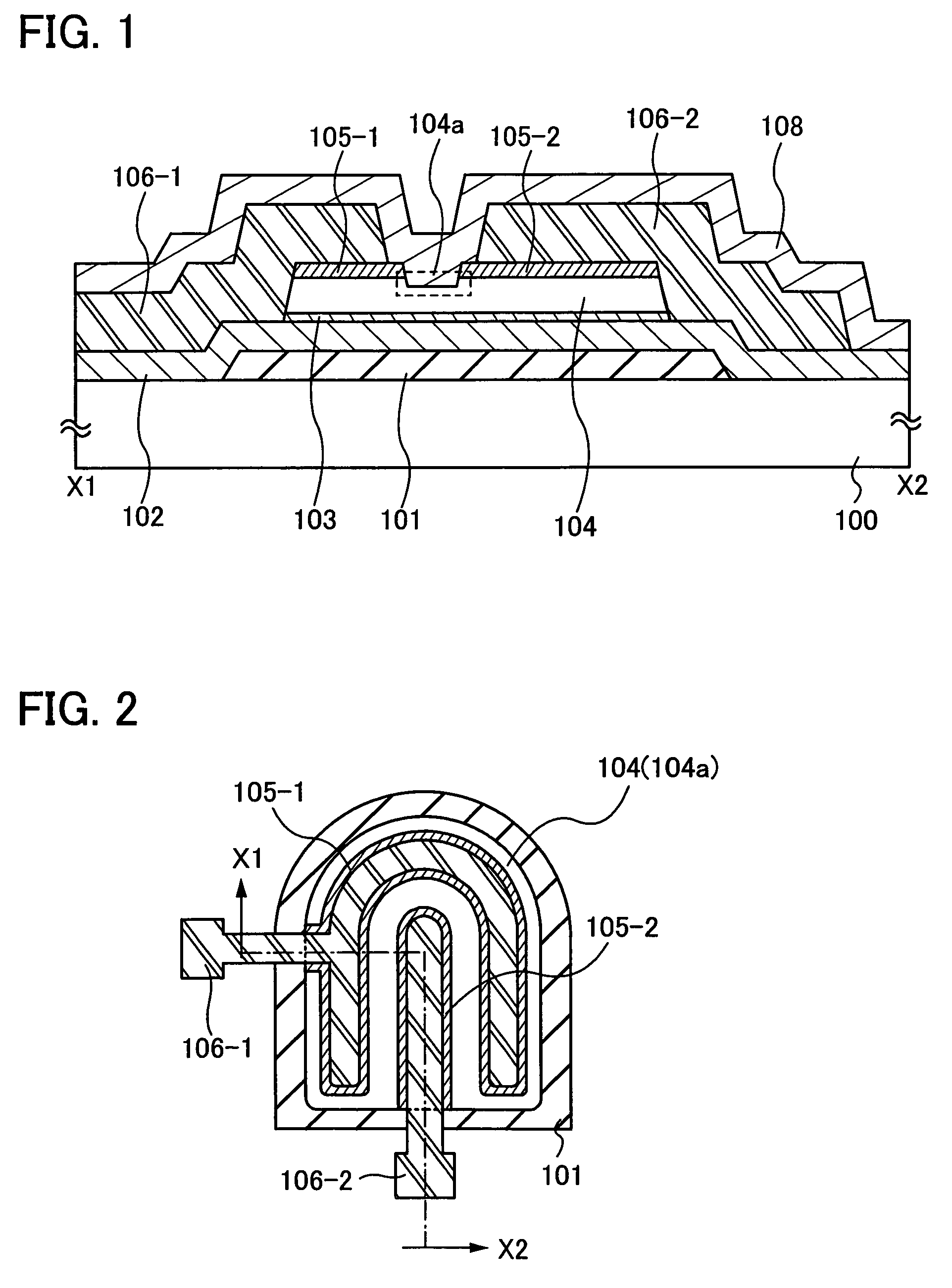

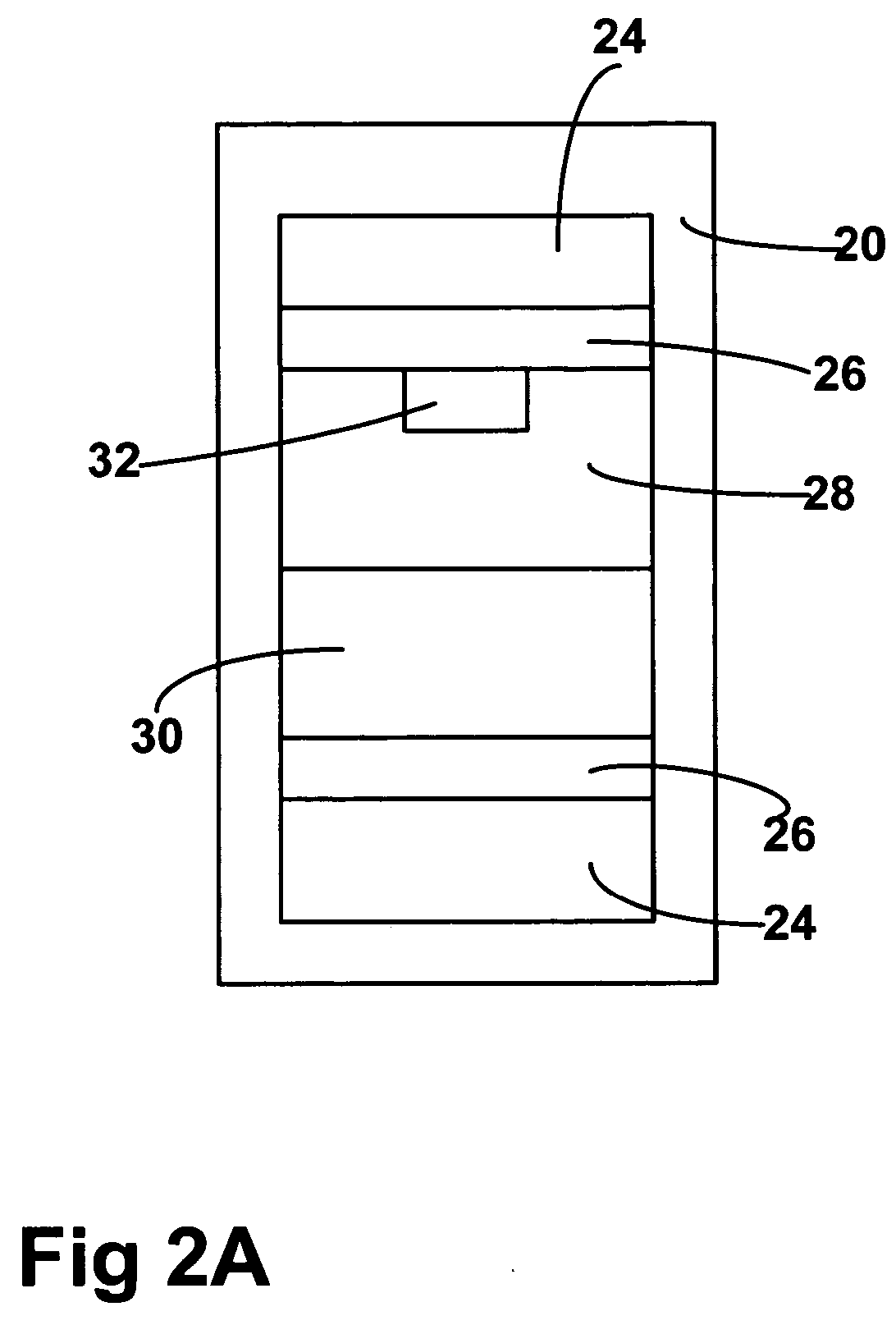

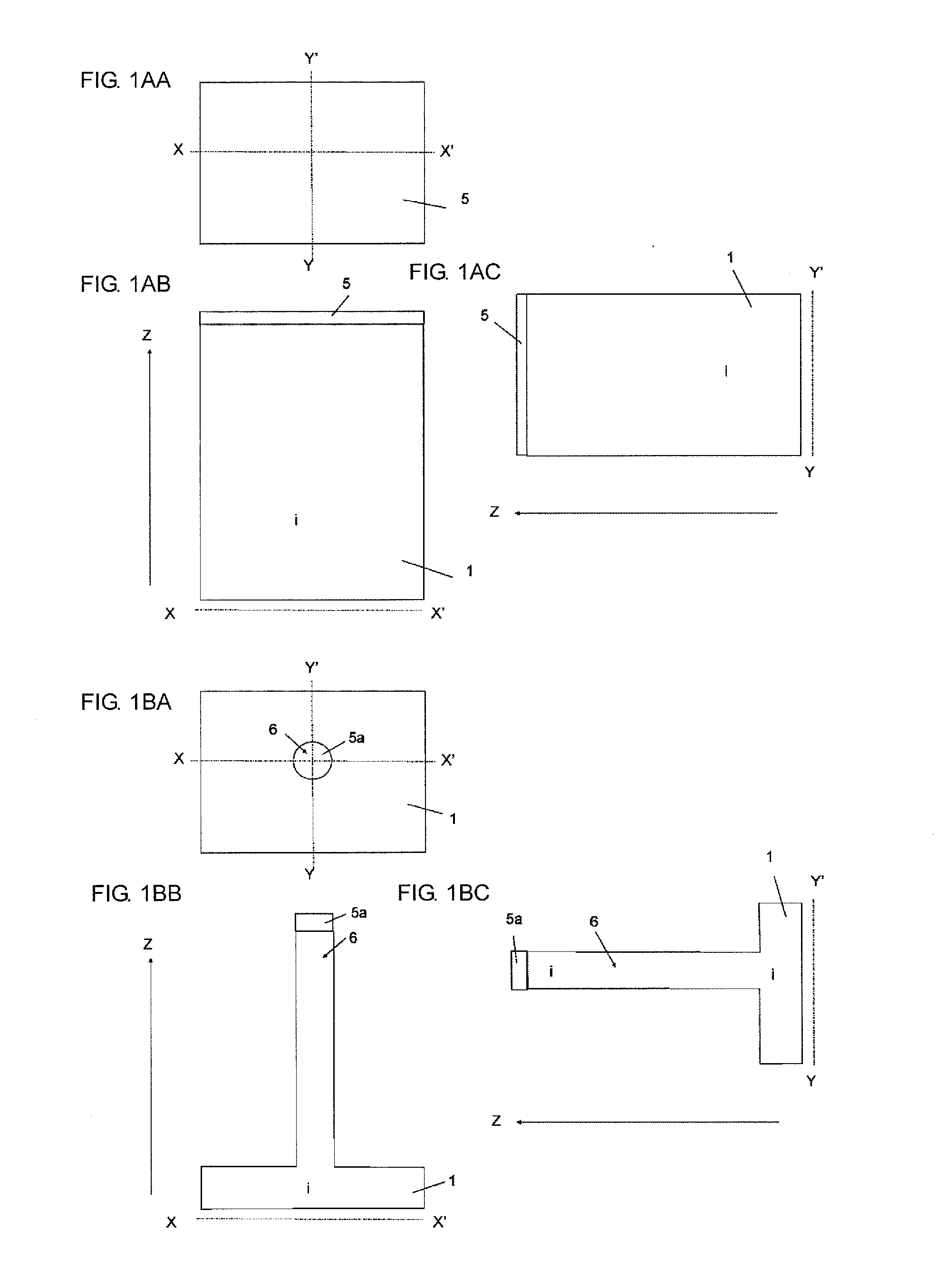

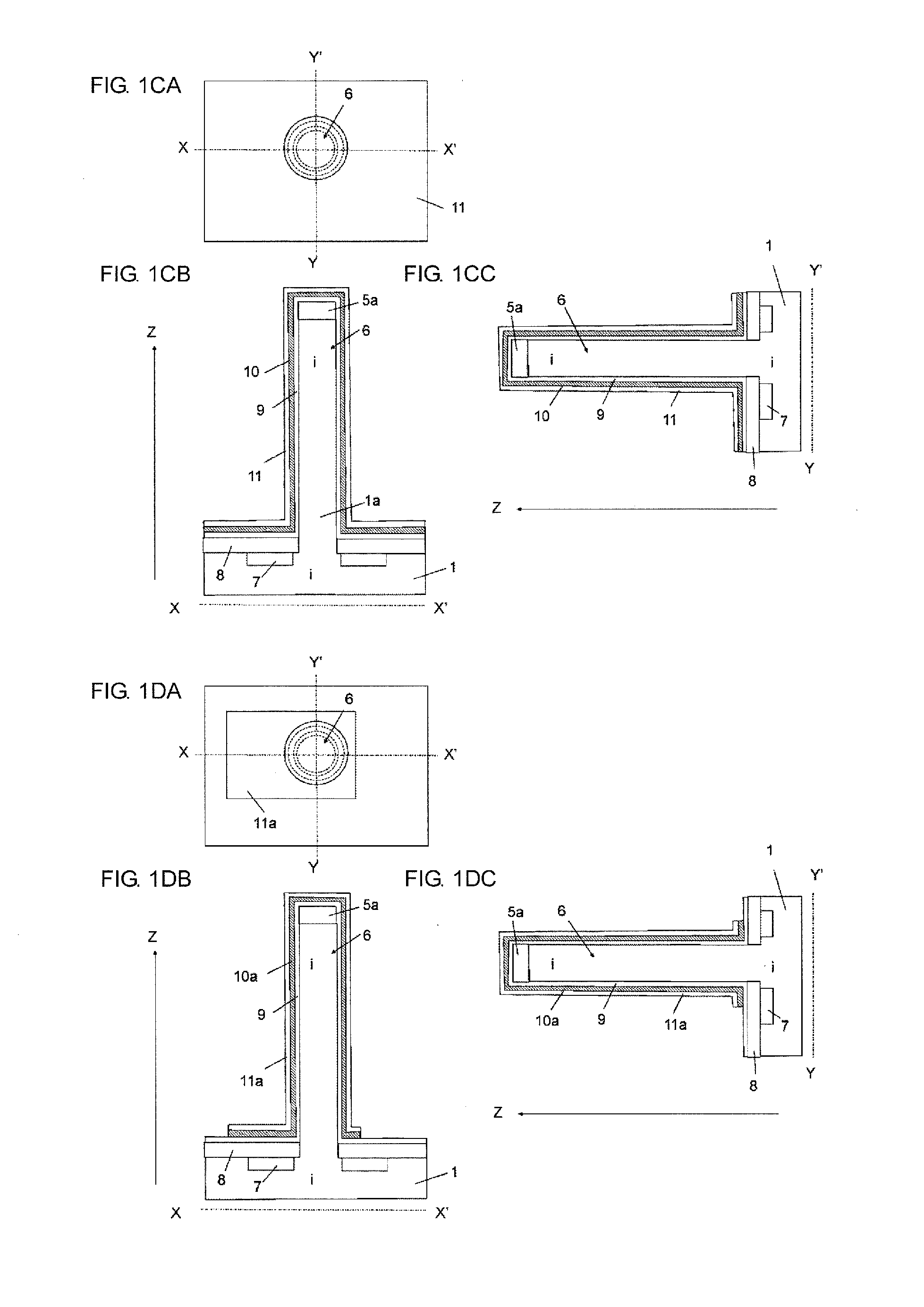

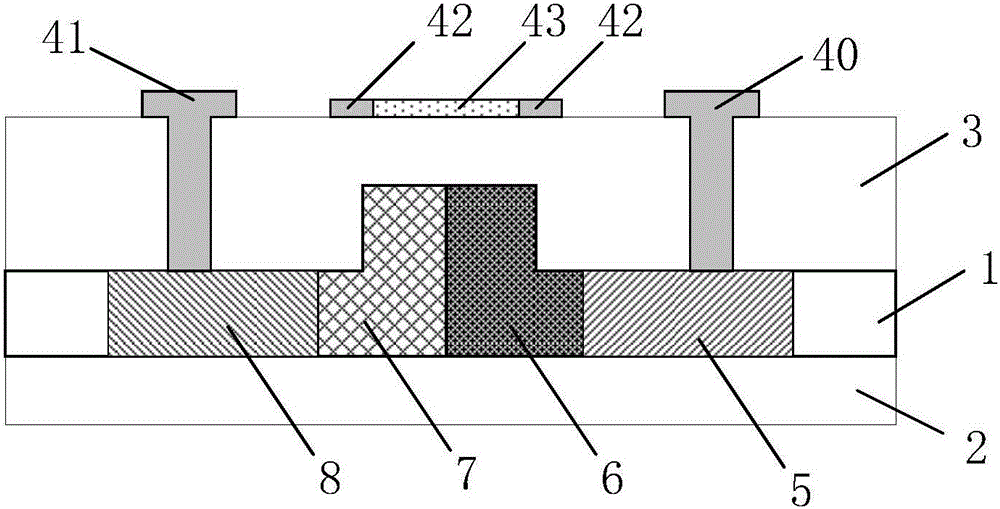

Semiconductor device, its manufacturing method, and electronic device

InactiveCN1806322ATransistorSemiconductor/solid-state device manufacturingIntrinsic resistanceGate voltage

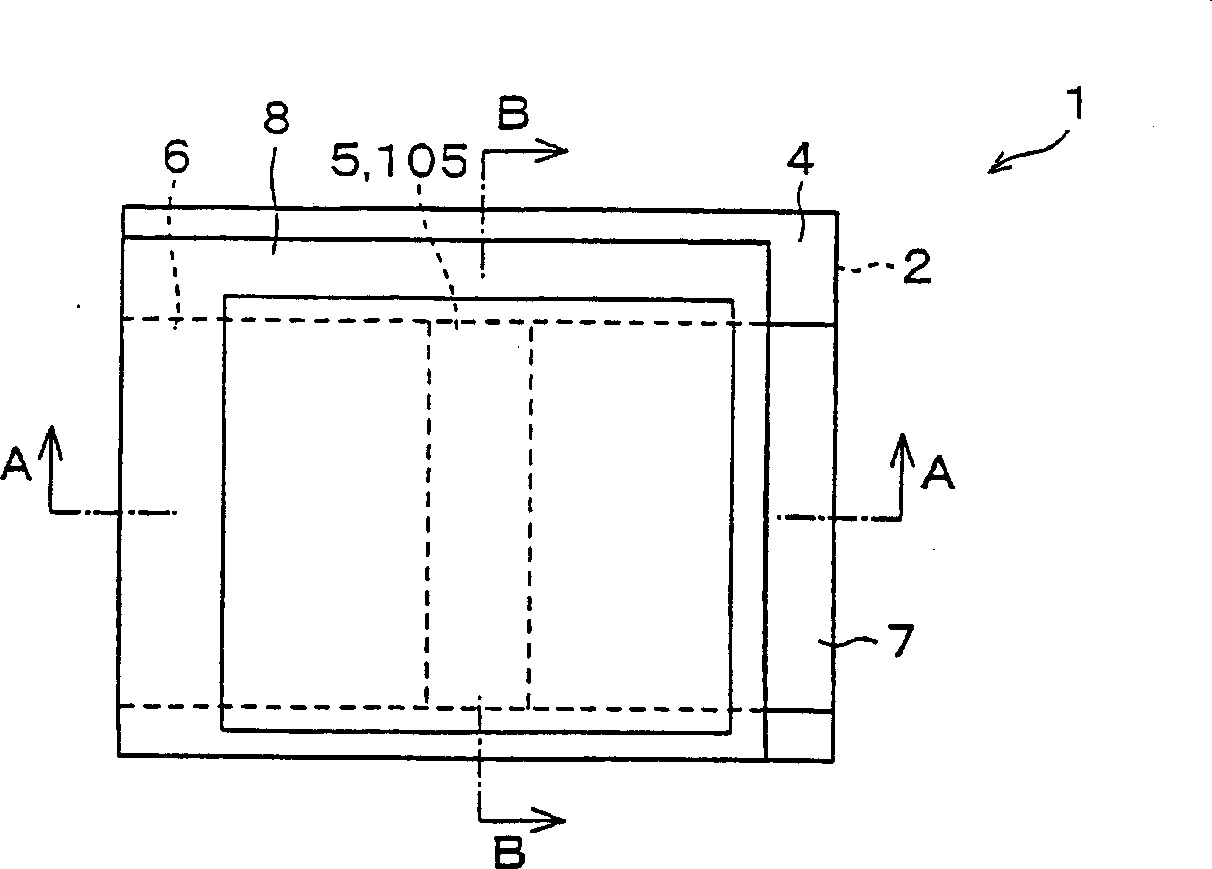

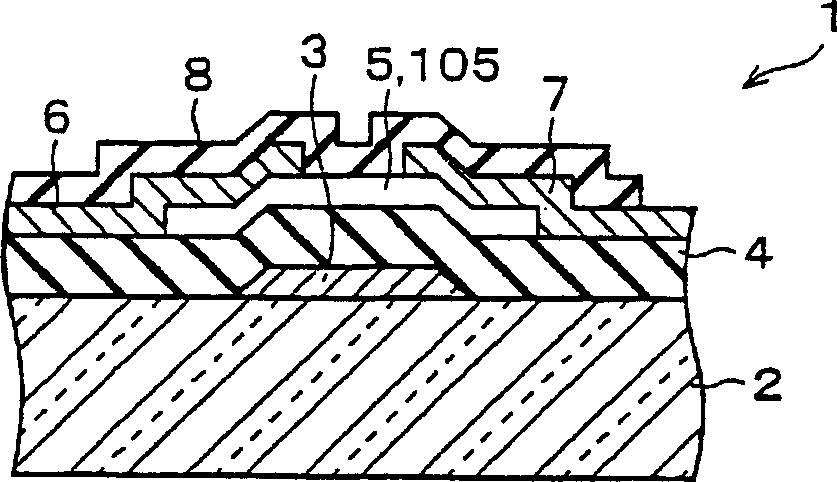

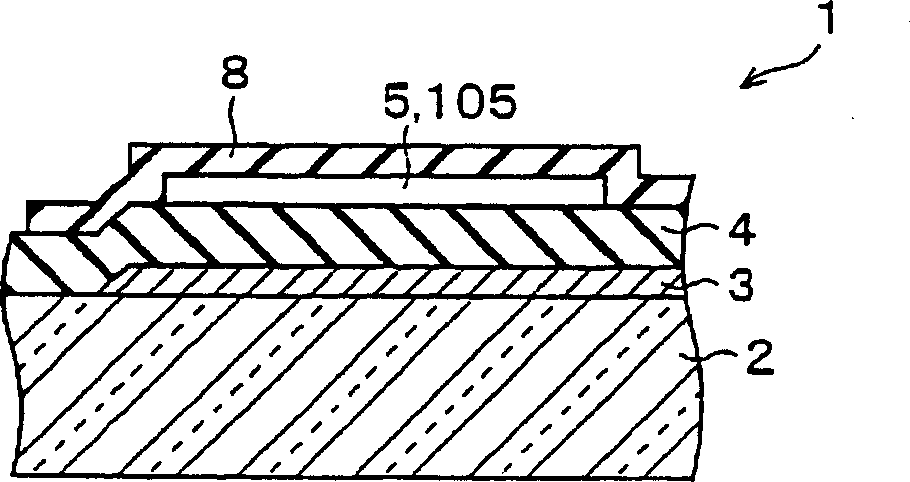

A thin film transistor (1) wherein a gate electrode (3) is formed on an insulative substrate (2), a gate insulating layer (4) is formed on the gate electrode (3), a semiconductor layer (5) is formed on the gate insulating layer (4), a source electrode (6) and a drain electrode (7) are formed on the semiconductor layer (5), and a protective layer (8) covering them are formed. The semiconductor layer (5) is isolated from the atmosphere. The semiconductor layer (5) (active layer) is formed of a ZnO polycrystalline semiconductor doped with, for example, a group V element. Since the surface state of the ZnO semiconductor is reduced thanks to the protective layer (8) and inward expansion of the depletion layer is prevented, the ZnO semiconductor is of an n-type showing its intrinsic resistance value and contains excessive free electrons. The added element acts as acceptor impurities in the ZnO semiconductor, decreasing the excessive electrons. Thus the gate voltage to eliminate the excessive free electrons lowers, thereby making the threshold voltage around 0 V. A semiconductor device using a zinc oxide for an active layer and having a protective layer for isolating the active layer from the atmosphere can be actually used.

Owner:SHARP KK +2

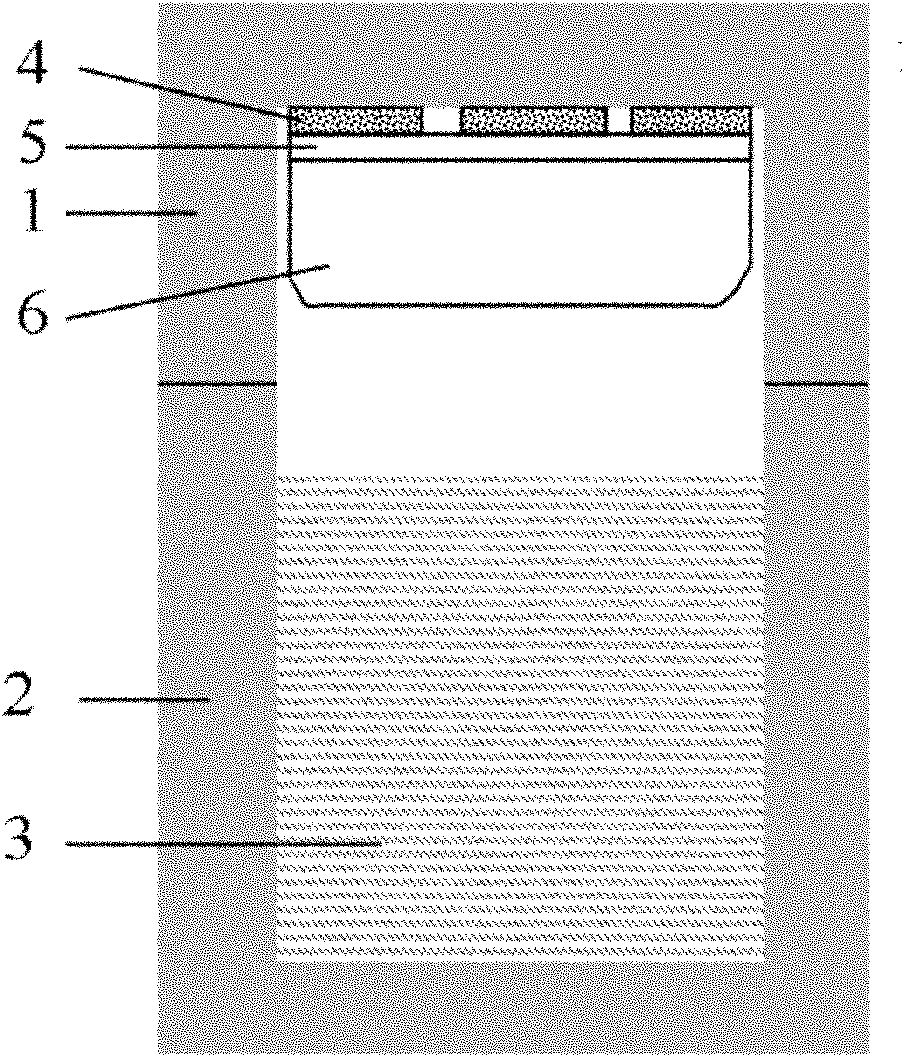

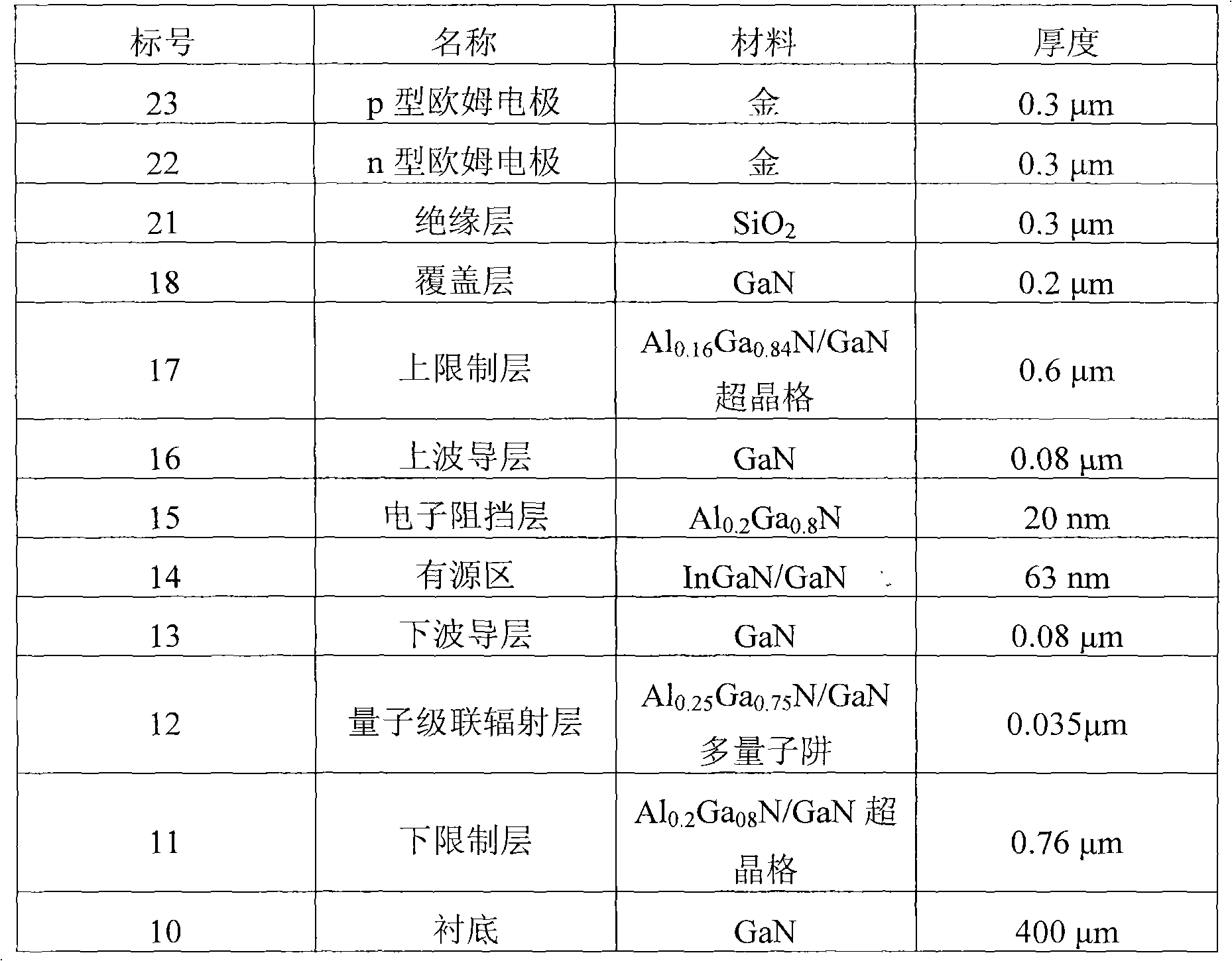

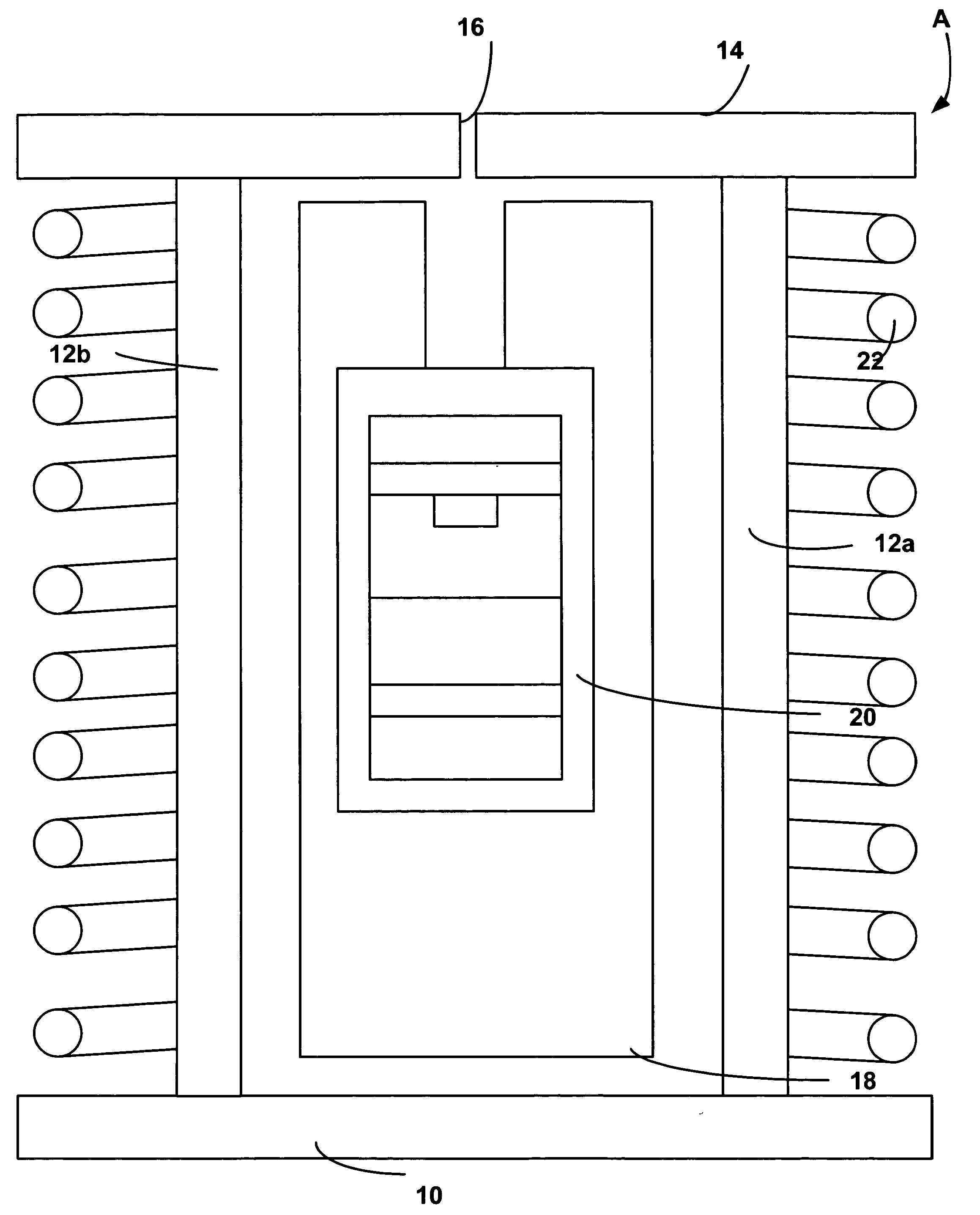

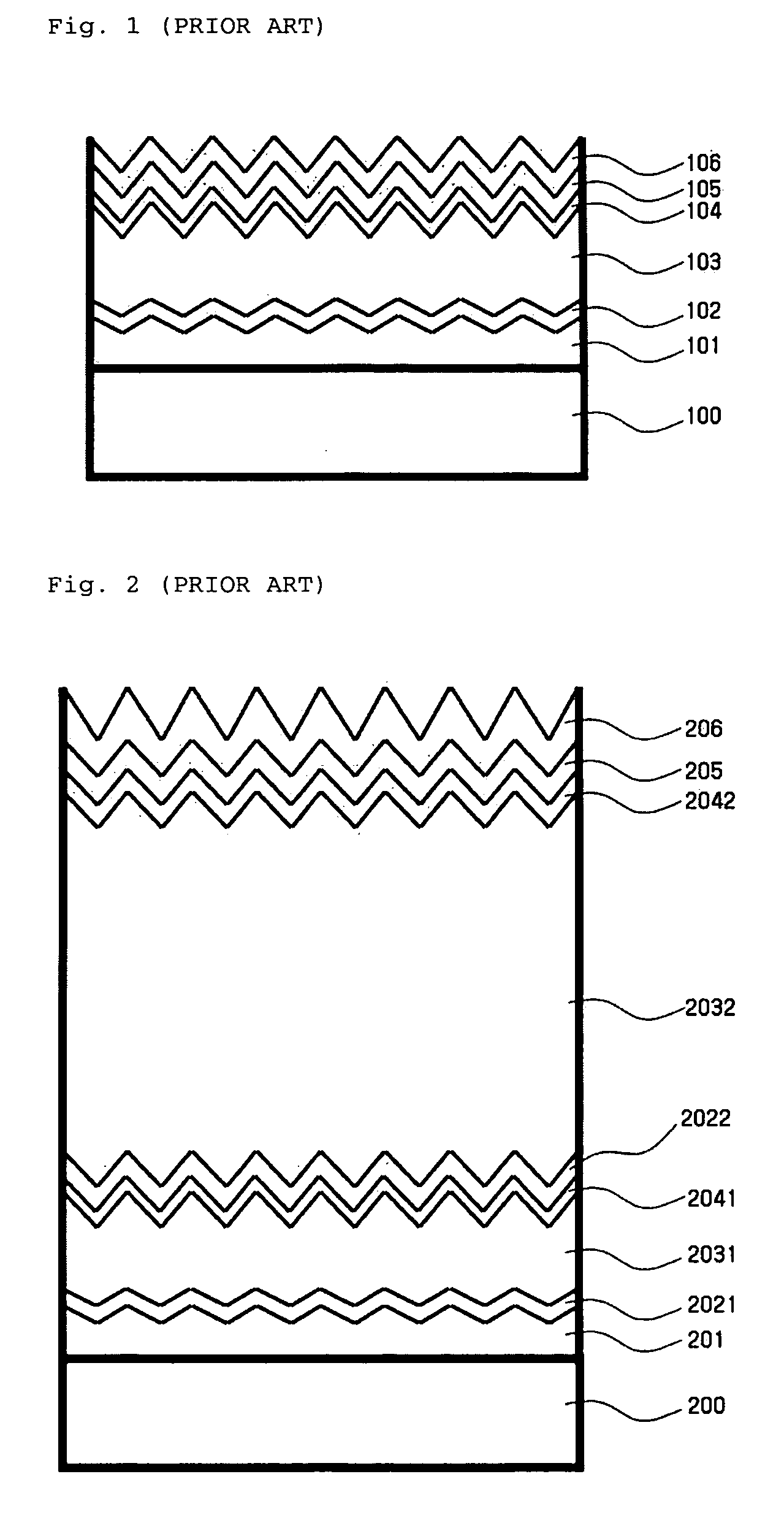

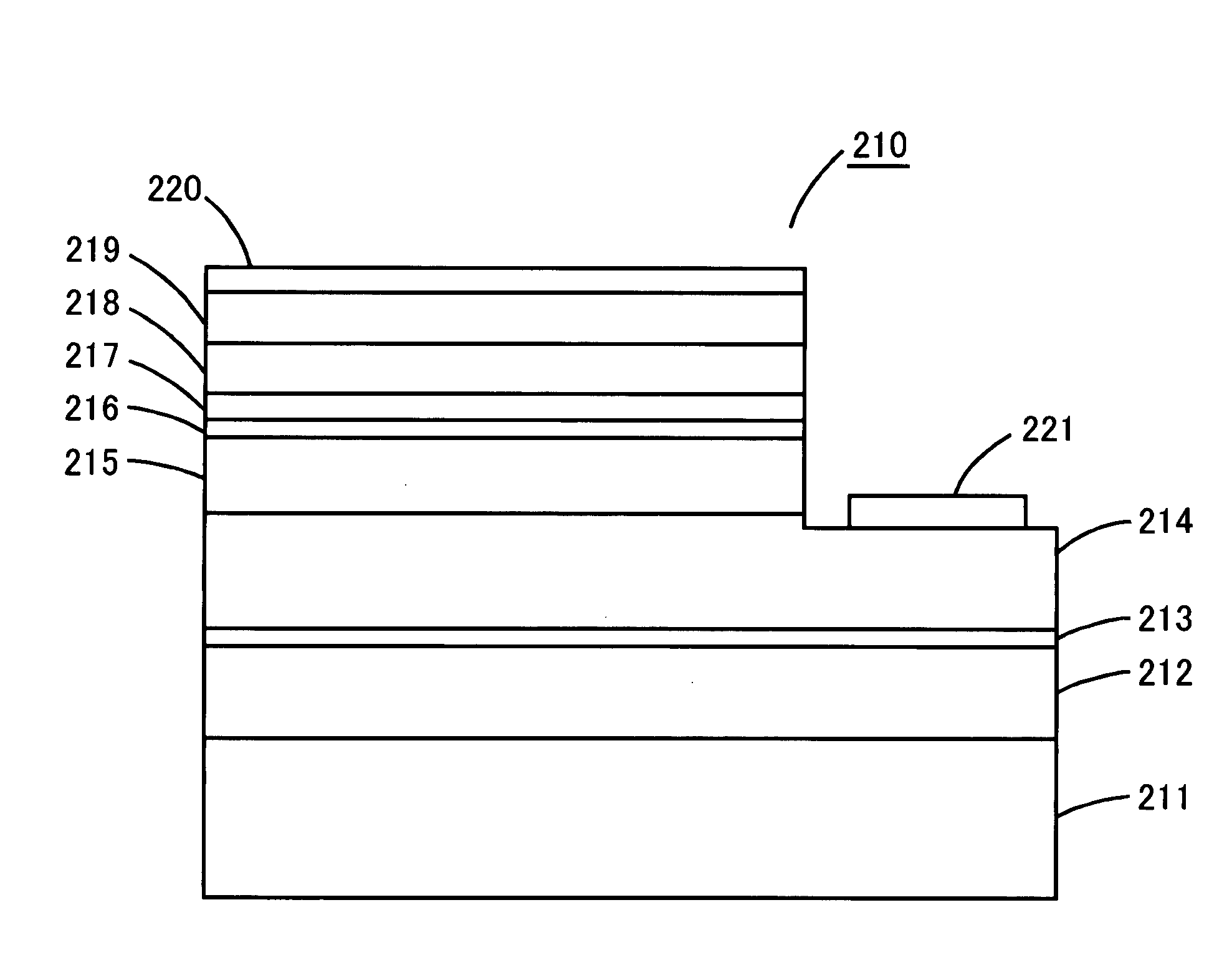

GaN based optoelectronic device and method for manufacturing the same

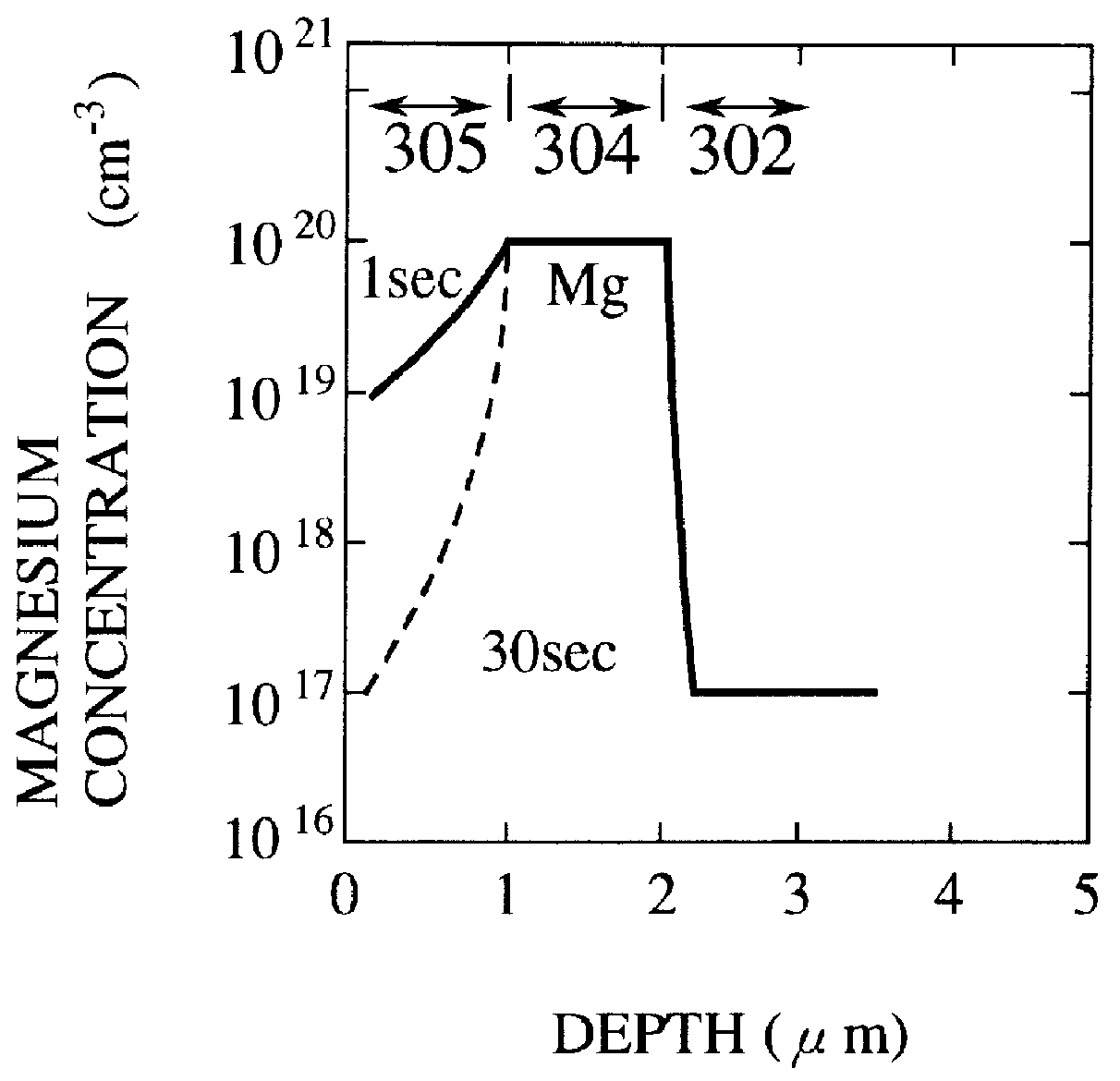

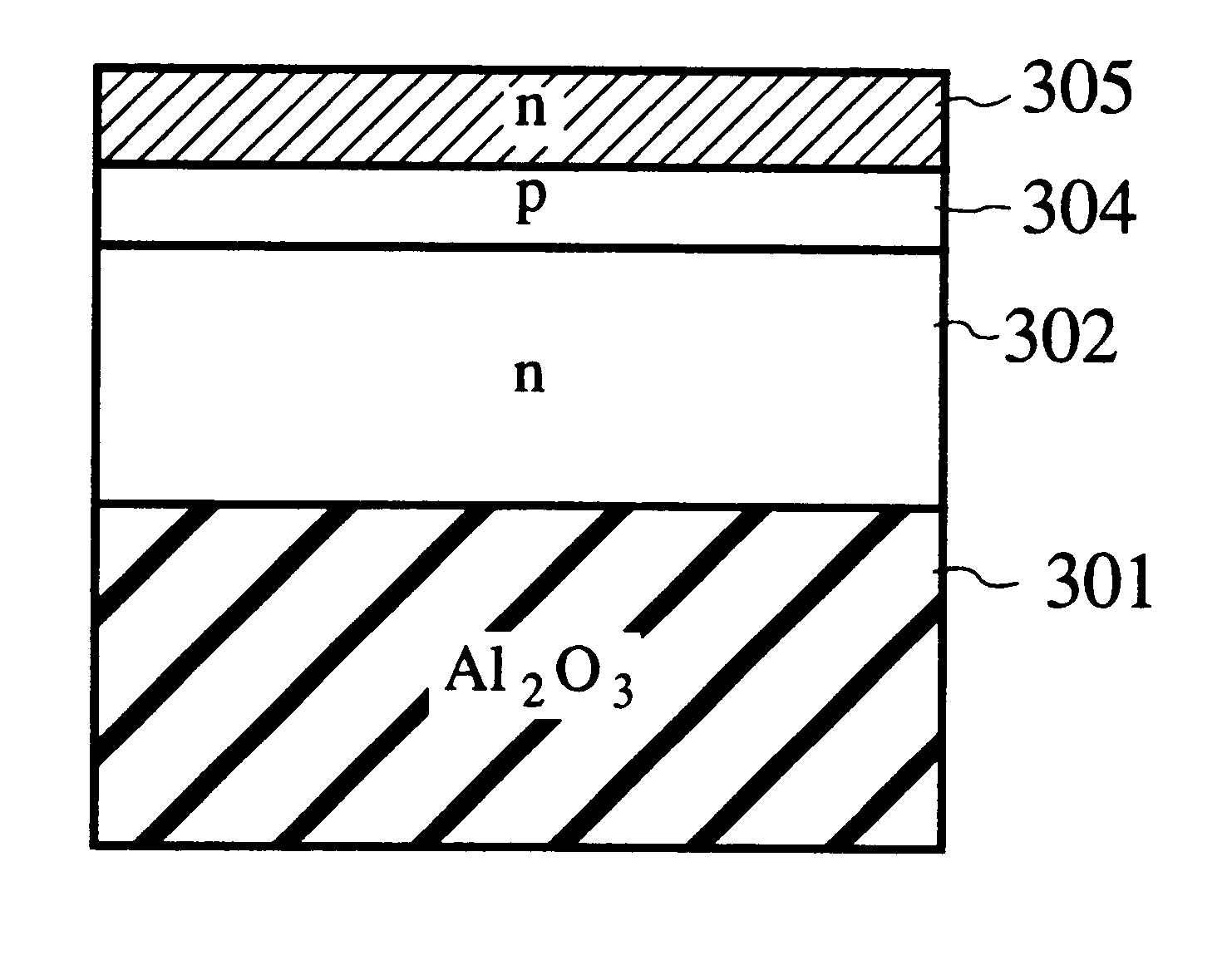

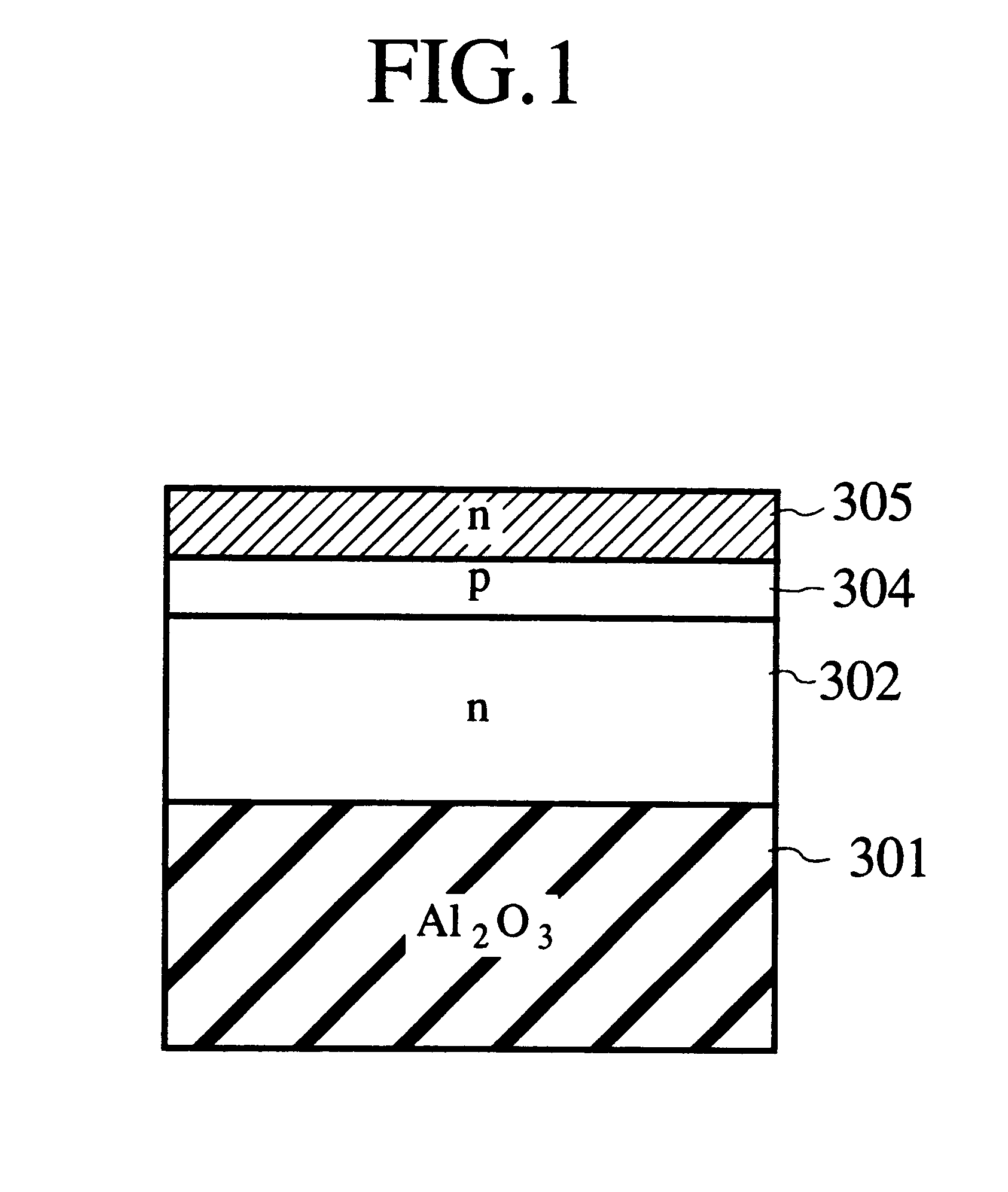

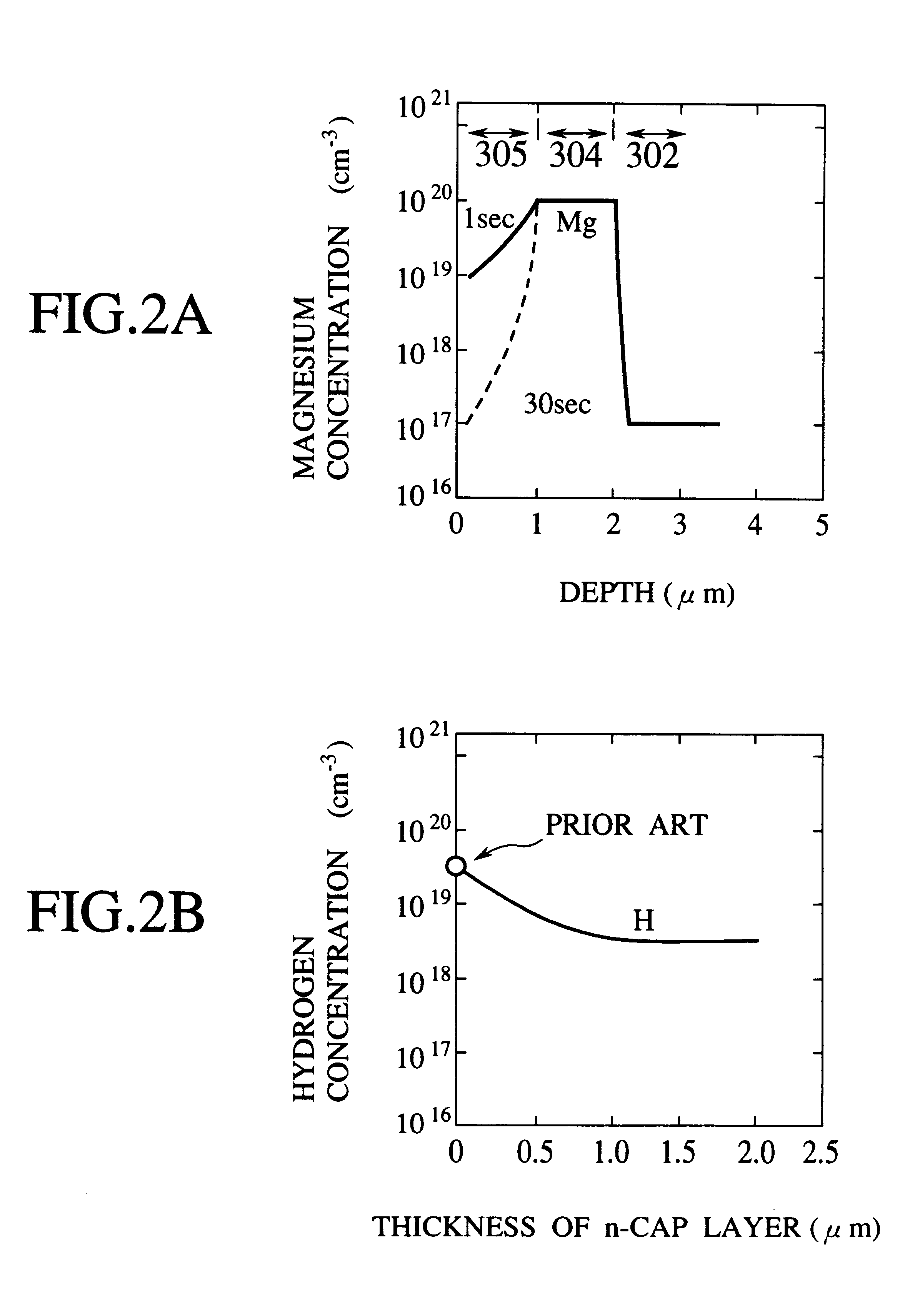

InactiveUS6020602AImprove extraction efficiencyImprove luminous performanceLaser detailsLaser active region structureCharge carrierAcceptor impurity

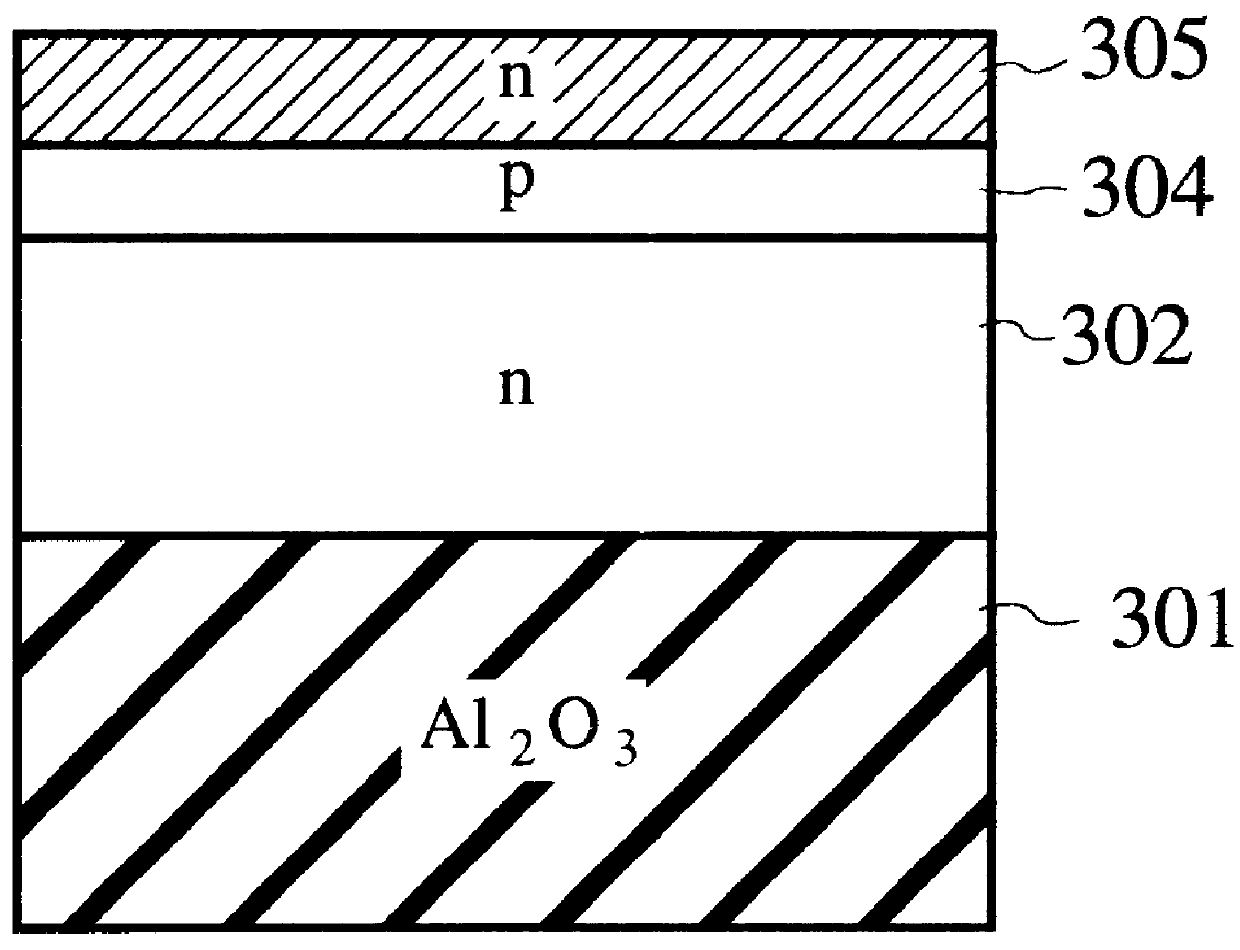

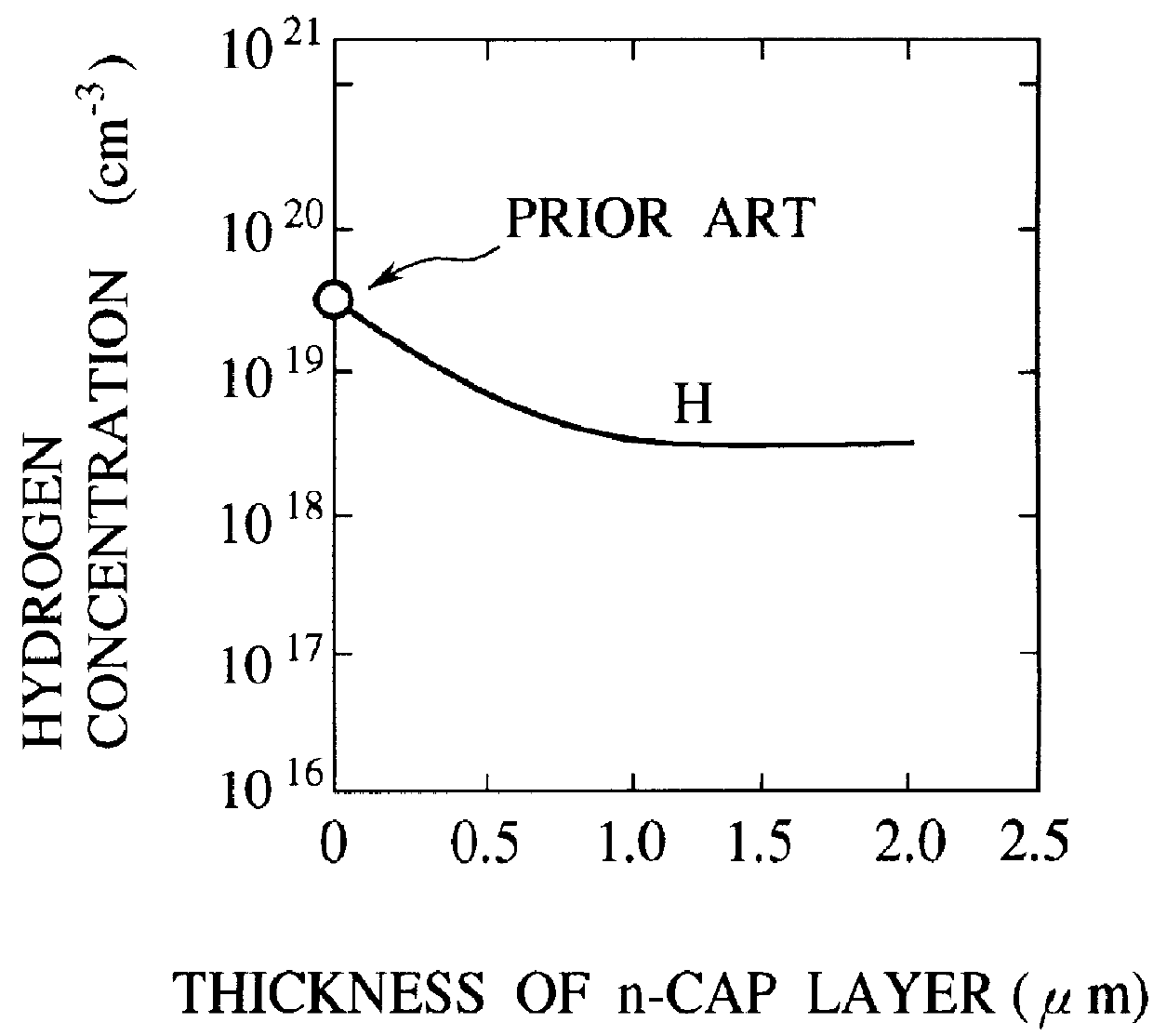

An n-cap layer is formed on a top surface of p-type clad layers, the p-type clad layer is a top layer of a stacked structure having a pn-junction for emitting carriers into light-emitting region of a GaN based light-emitting device, thus increasing the activation ratio of acceptor impurities in the p-type clad layers. The n-cap layer is used also as a current blocking layer, thereby constructing a current-blocked structure. The n-cap layer should preferably be made of InuAlvGa1-u-vN (0<u, v<1) deposited as thick as 1.0 micron or more. The present invention will easily provide a high luminous efficiency GaN based semiconductor light-emitting device without using any complicated processes such as electron-beam irradiation or thermal annealing.

Owner:KK TOSHIBA

GaN based optoelectronic device and method for manufacturing the same

InactiveUS6221684B1Improve extraction efficiencyImprove luminous performanceLaser active region structureSemiconductor/solid-state device manufacturingCharge carrierAcceptor impurity

An n-cap layer is formed on a top surface of p-type clad layers, the p-type clad layer is a top layer of a stacked structure having a pn-junction for emitting carriers into light-emitting region of a GaN based light-emitting device, thus increasing the activation ratio of acceptor impurities in the p-type clad layers. The n-cap layer is used also as a current blocking layer, thereby constructing a current-blocked structure. The n-cap layer should preferably be made of InuAlvGa1-u-vN (0<u, v<1) deposited as thick as 1.0 micron or more. The present invention will easily provide a high luminous efficiency GaN based semiconductor light-emitting device without using any complicated processes such as electron-beam irradiation or thermal annealing.

Owner:KK TOSHIBA

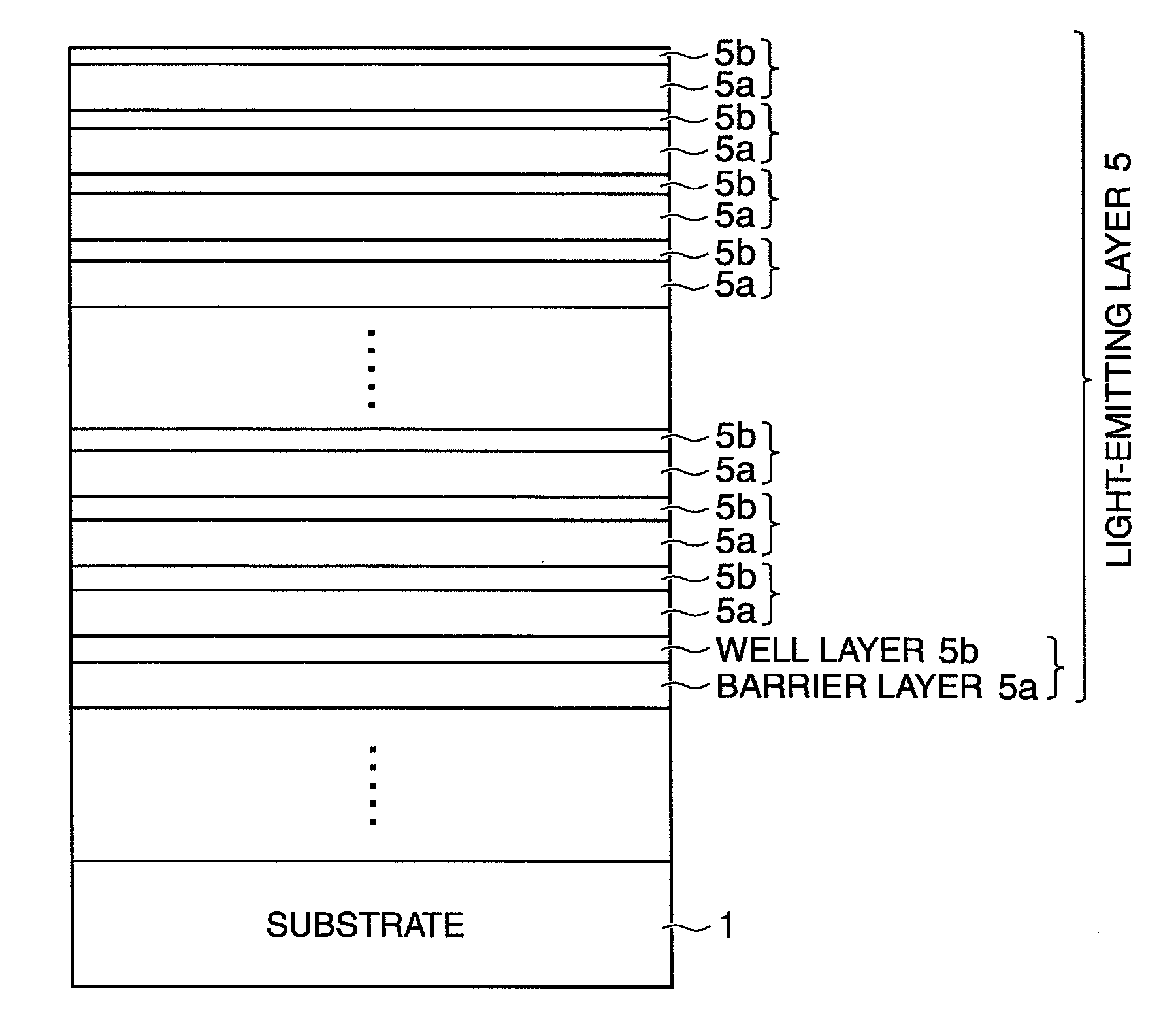

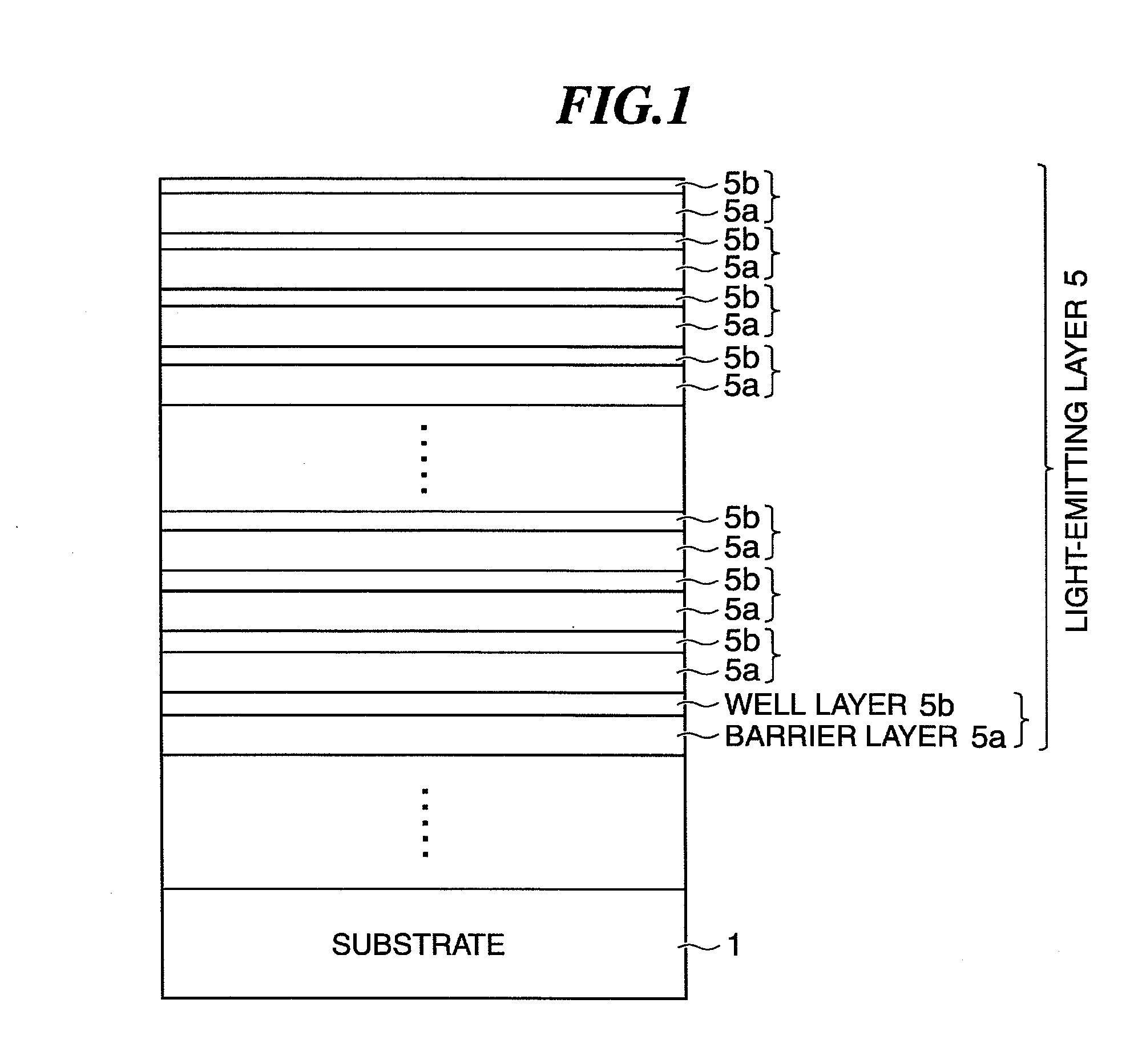

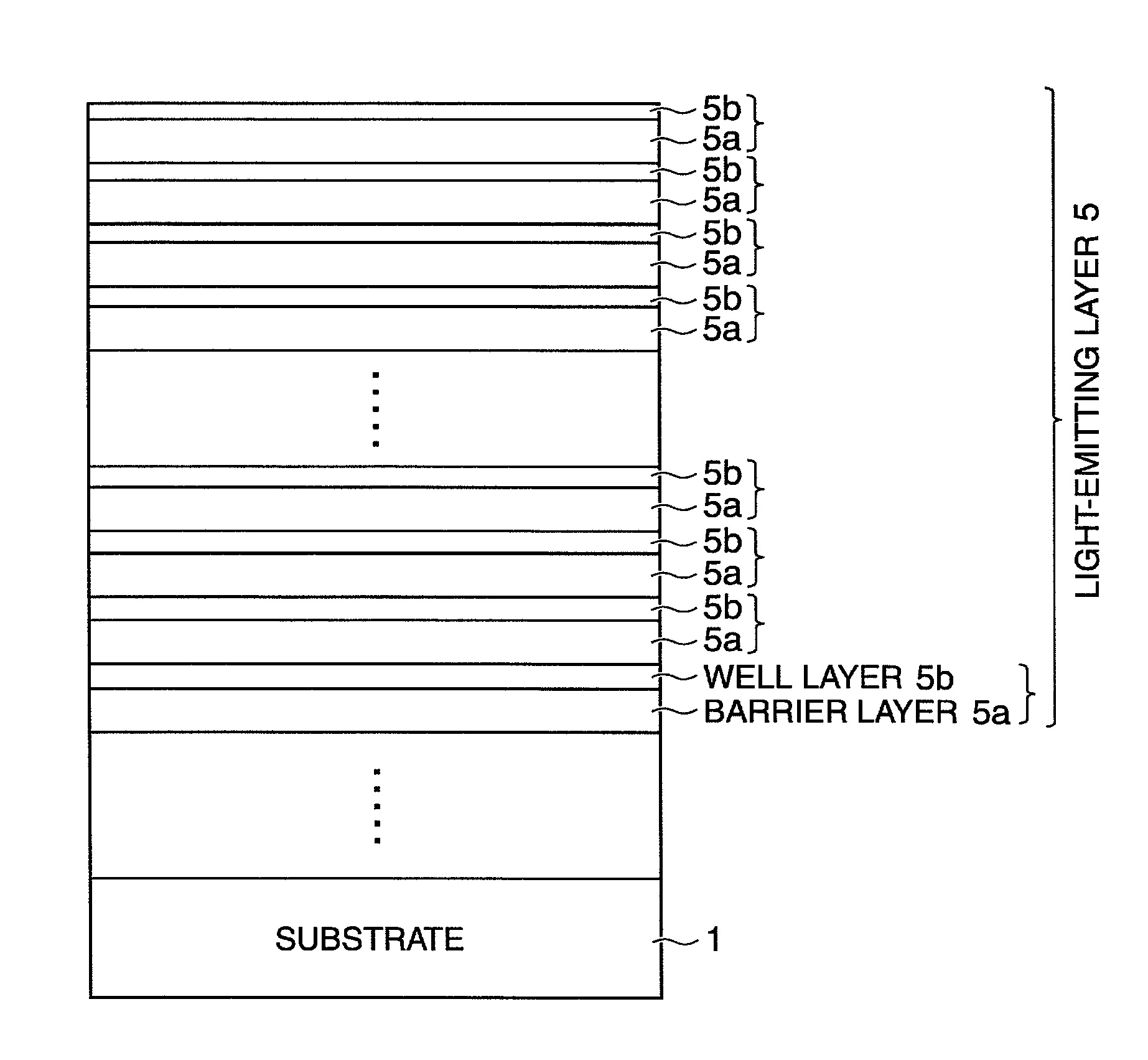

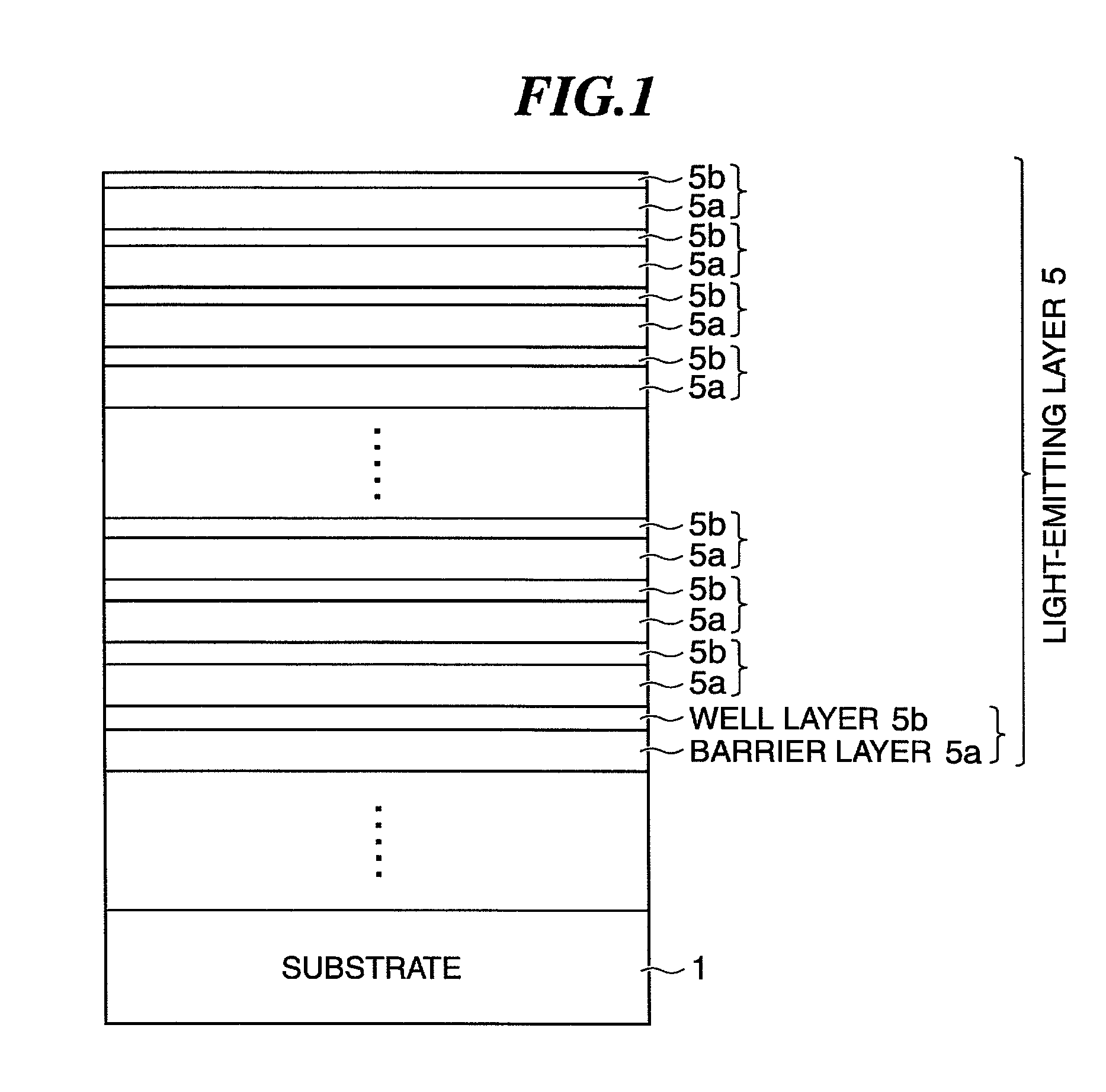

Group iii nitride semiconductor light-emitting device

A Group III nitride semiconductor light-emitting device comprises a substrate (1) and a light-emitting layer (5) having the multiple quantum well structure that comprises barrier layers (5a) and well layers (5b) formed of a gallium-containing Group III nitride semiconductor material provided on the substrate. Each of the well layers constituting the multiple quantum well structure is made of a Group III nitride semiconductor layer to which acceptor impurities are added, and which has thicknesses different from one another and the same conductivity type as that of the barrier layer. The present invention can provide a Group III nitride semiconductor white light-emitting device which can enhance luminous intensity, can obtain high color rendering properties has a simple structure that can be easily formed without fine adjustment of a composition of a phosphor.

Owner:SHOWA DENKO KK

Semi-insulating silicon carbide mono-crystal

ActiveCN102560671AAvoid crystalline massImprove crystal qualityPolycrystalline material growthSemiconductor/solid-state device manufacturingShallow donorDopant

Disclosed is a semi-insulating silicon carbide mono-crystal, which comprises intrinsic point defects, deep level dopants, background shallow donors, and acceptor impurities; wherein the concentration sum of the deep level dopants and the intrinsic point defects is larger than the difference between the shallow donors and the acceptor impurities, and the concentration of the intrinsic point defects is smaller than that of the deep level dopants. Resistivity of the semi-insulating silicon carbide mono-crystal is larger than 1x105 omega.cm at the room temperature, and electric properties and crystal quality meet the producing requirements of corresponding microwave devices. According to the mono-crystal, shallow level impurities are compensated through the combined action of the deep level dopants and the intrinsic point defects to obtain high-quality semi-insulating mono-crystals; resistivity is not obviously decreased and maintains over 1x105 omega.cm after annealing the mono-crystals at a temperature of 1800 DEG C.

Owner:BEIJING TIANKE HEDA SEMICON CO LTD

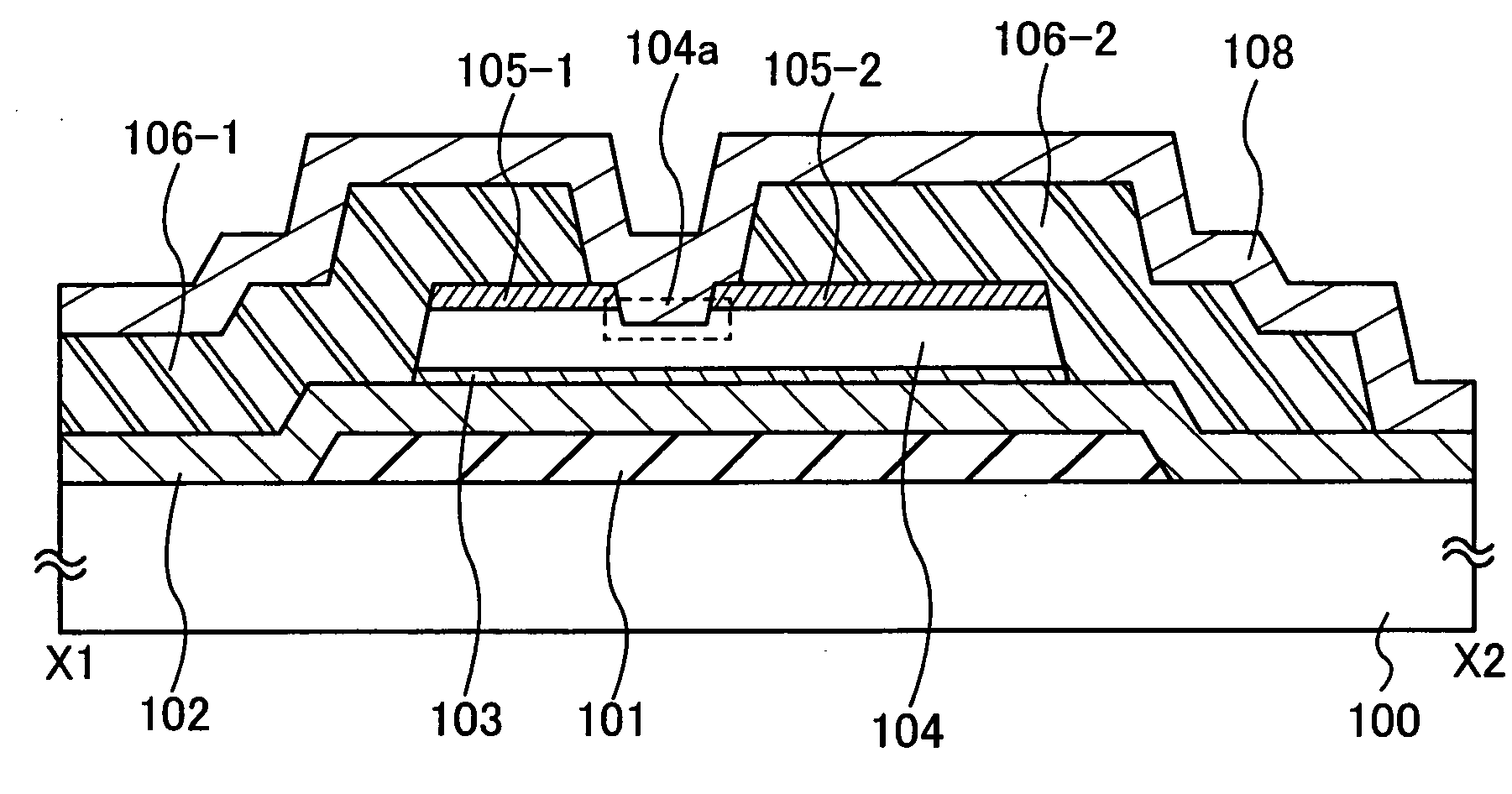

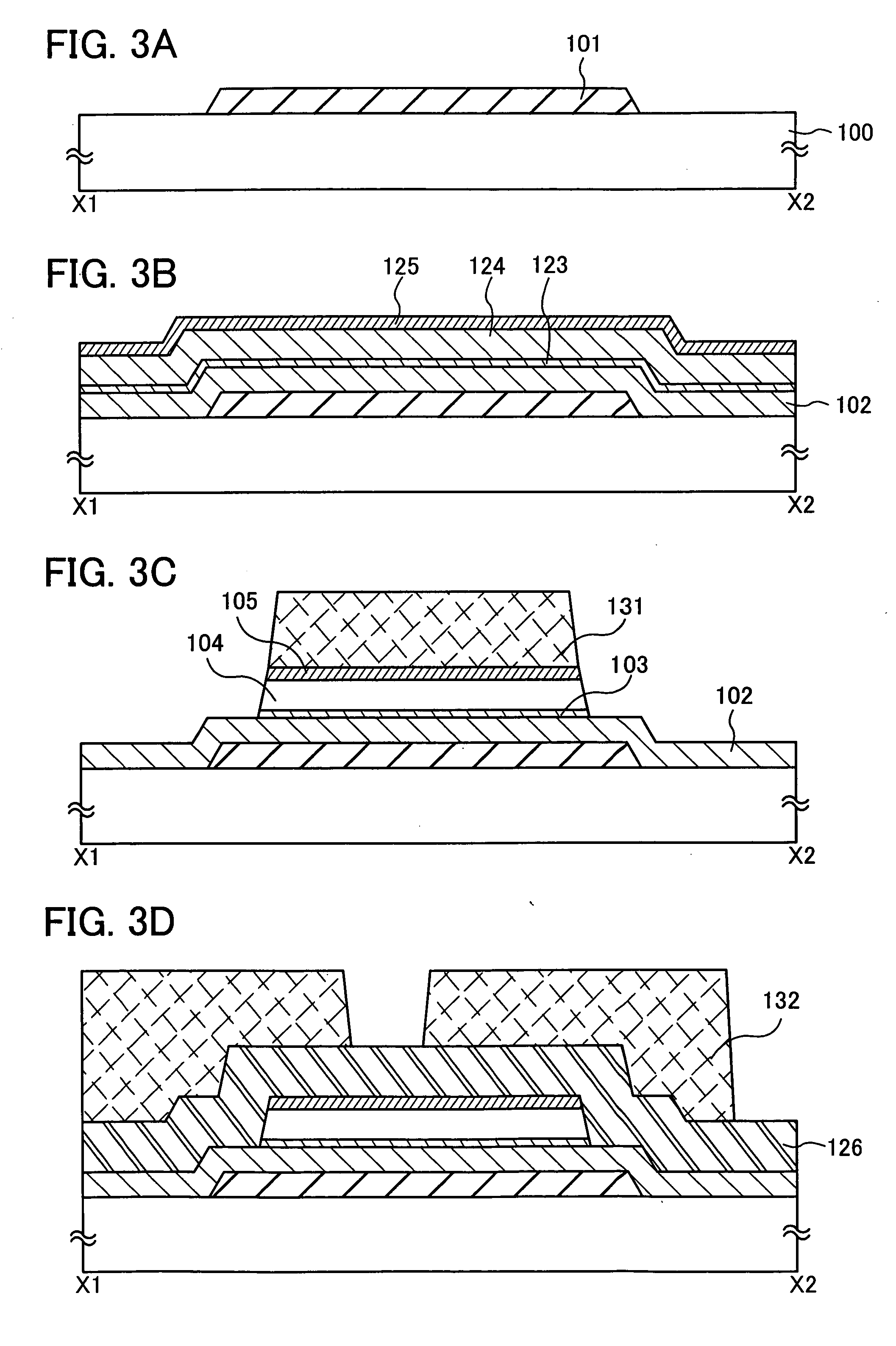

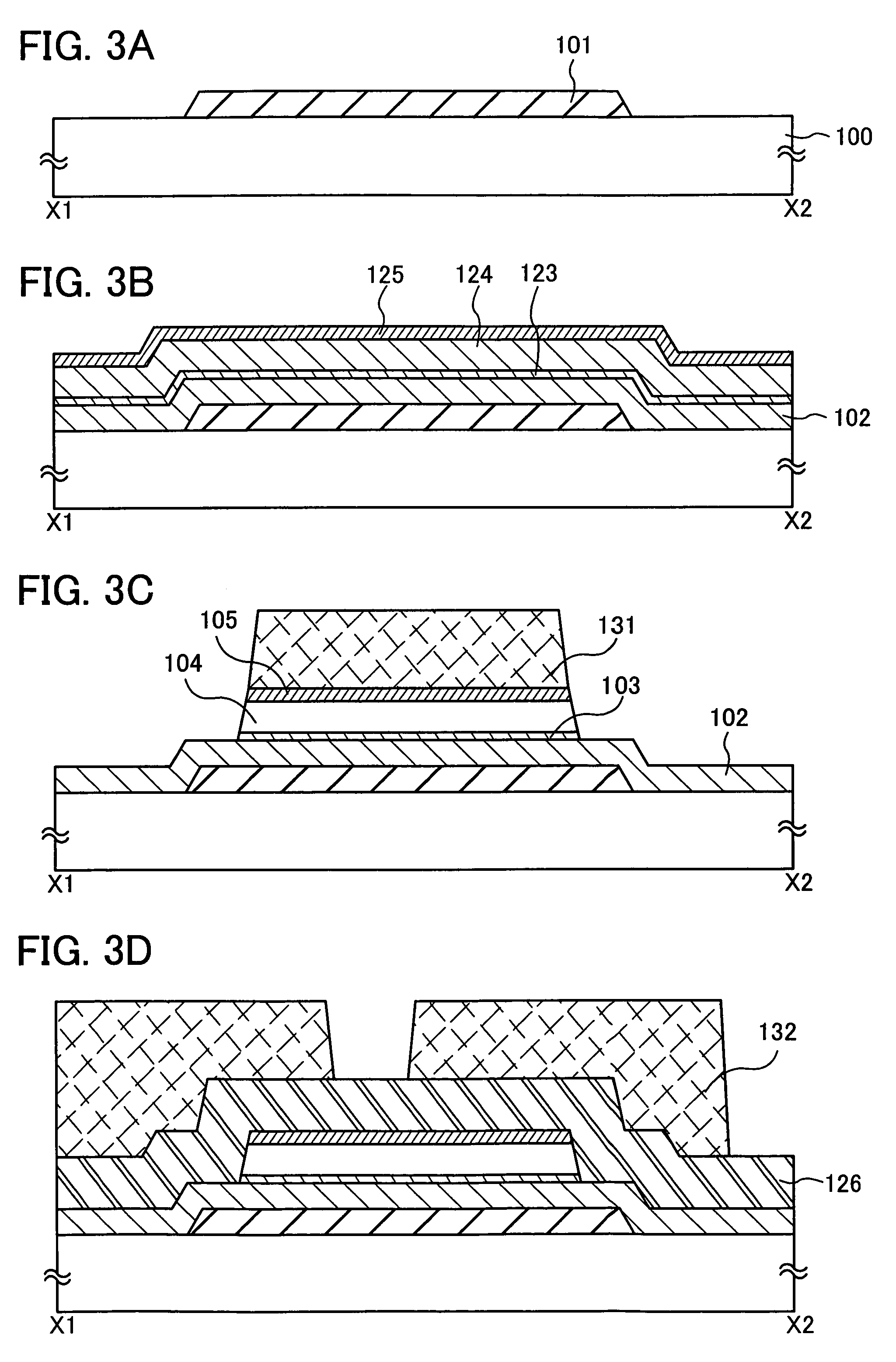

Semiconductor device and manufacturing method thereof

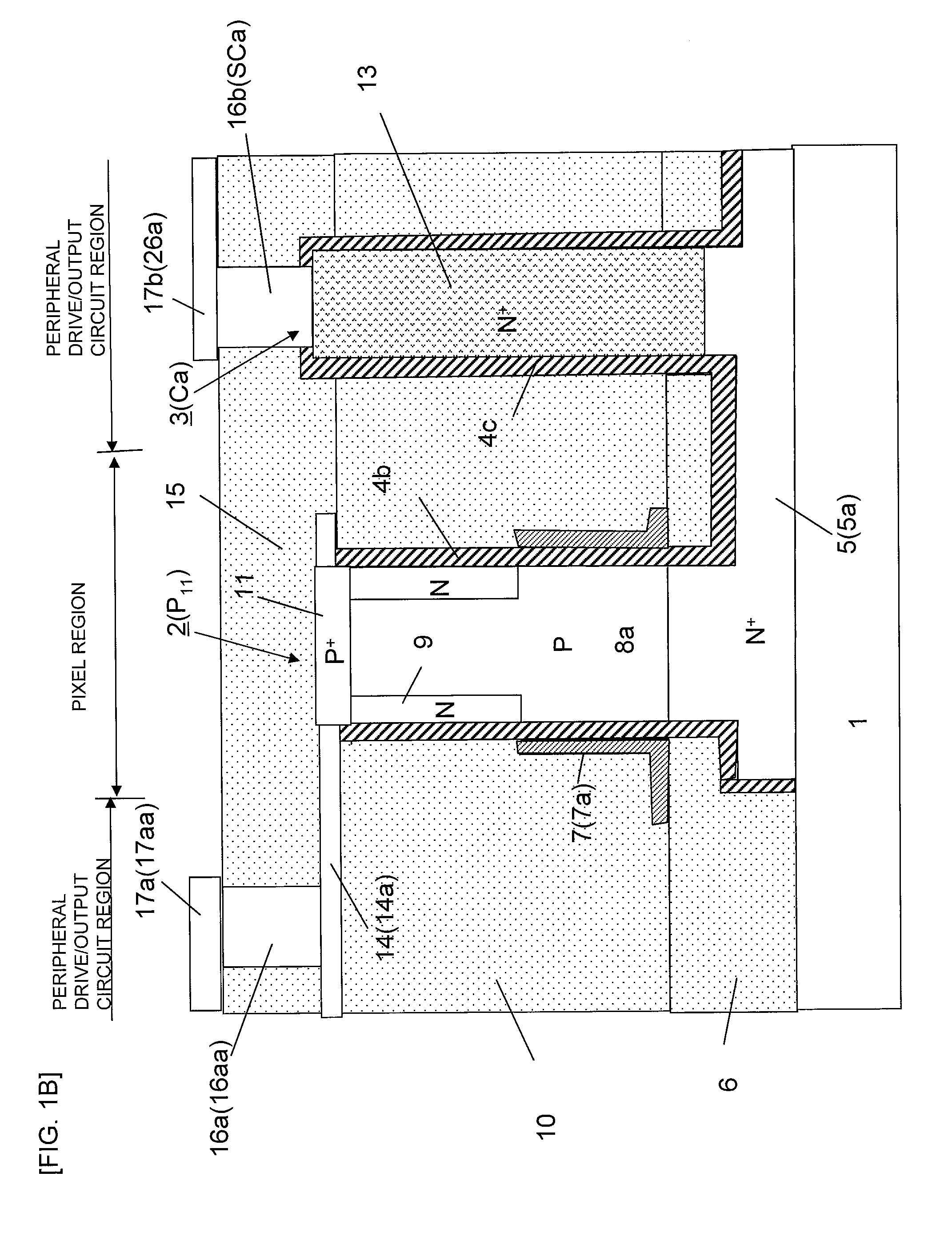

InactiveUS20090045401A1Efficient additionExcellent electrical propertiesSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorAcceptor impurity

The present invention relates to a semiconductor device including a thin film transistor comprising a microcrystalline semiconductor which forms a channel formation region and includes an acceptor impurity element, and to a manufacturing method thereof. A gate electrode, a gate insulating film formed over the gate electrode, a first semiconductor layer which is formed over the gate insulating film and is formed of a microcrystalline semiconductor, a second semiconductor layer which is formed over the first semiconductor layer and includes an amorphous semiconductor, and a source region and a drain region which are formed over the second semiconductor layer are provided in the thin film transistor. A channel is formed in the first semiconductor layer when the thin film transistor is placed in an on state.

Owner:SEMICON ENERGY LAB CO LTD

Group III nitride semiconductor light-emitting device

A Group III nitride semiconductor light-emitting device comprises a substrate (1) and a light-emitting layer (5) having the multiple quantum well structure that comprises barrier layers (5a) and well layers (5b) formed of a gallium-containing Group III nitride semiconductor material provided on the substrate. Each of the well layers constituting the multiple quantum well structure is made of a Group III nitride semiconductor layer to which acceptor impurities are added, and which has thicknesses different from one another and the same conductivity type as that of the barrier layer. The present invention can provide a Group III nitride semiconductor white light-emitting device which can enhance luminous intensity, can obtain high color rendering properties has a simple structure that can be easily formed without fine adjustment of a composition of a phosphor.

Owner:RESONAC HOLDINGS CORPORATION

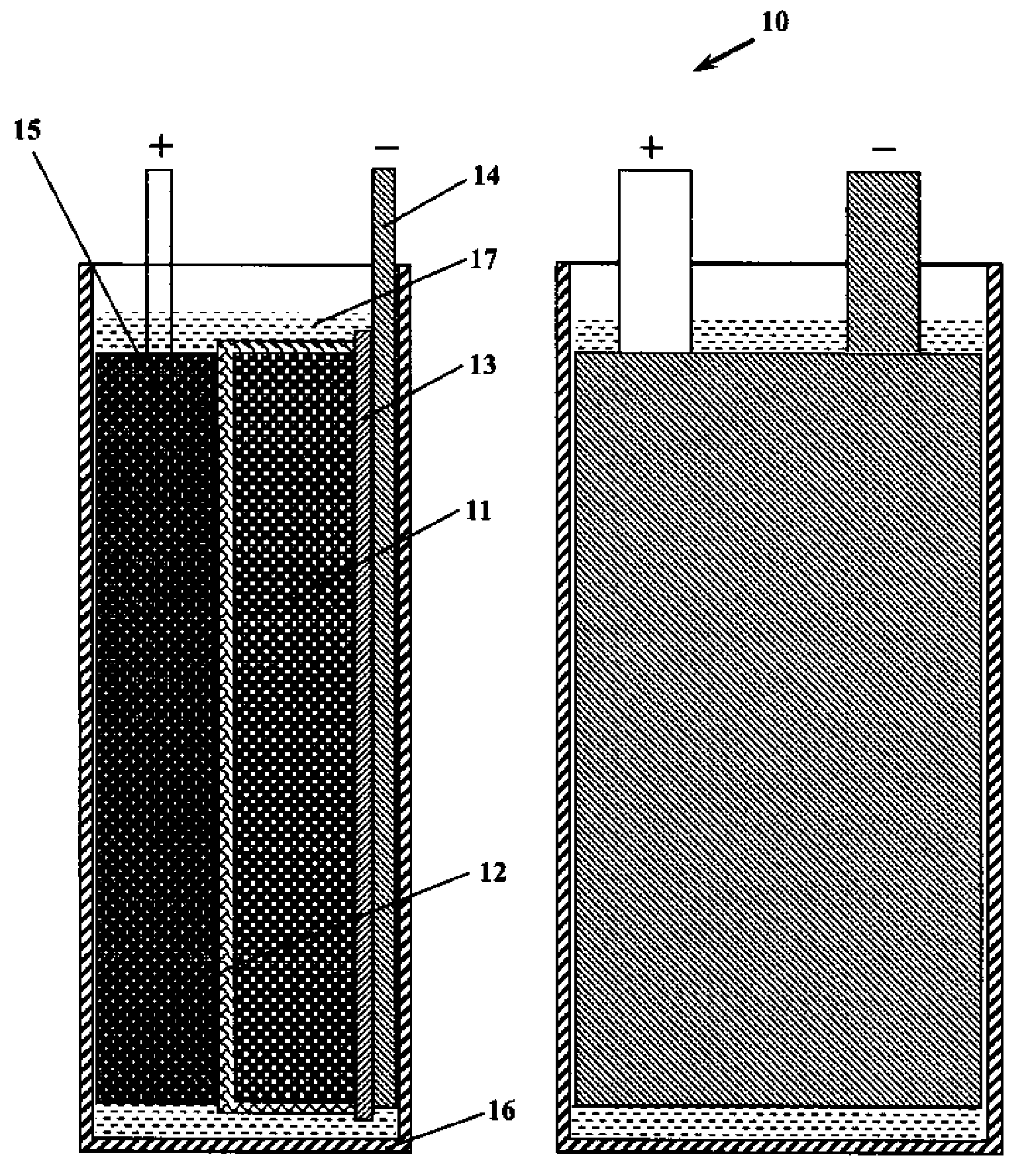

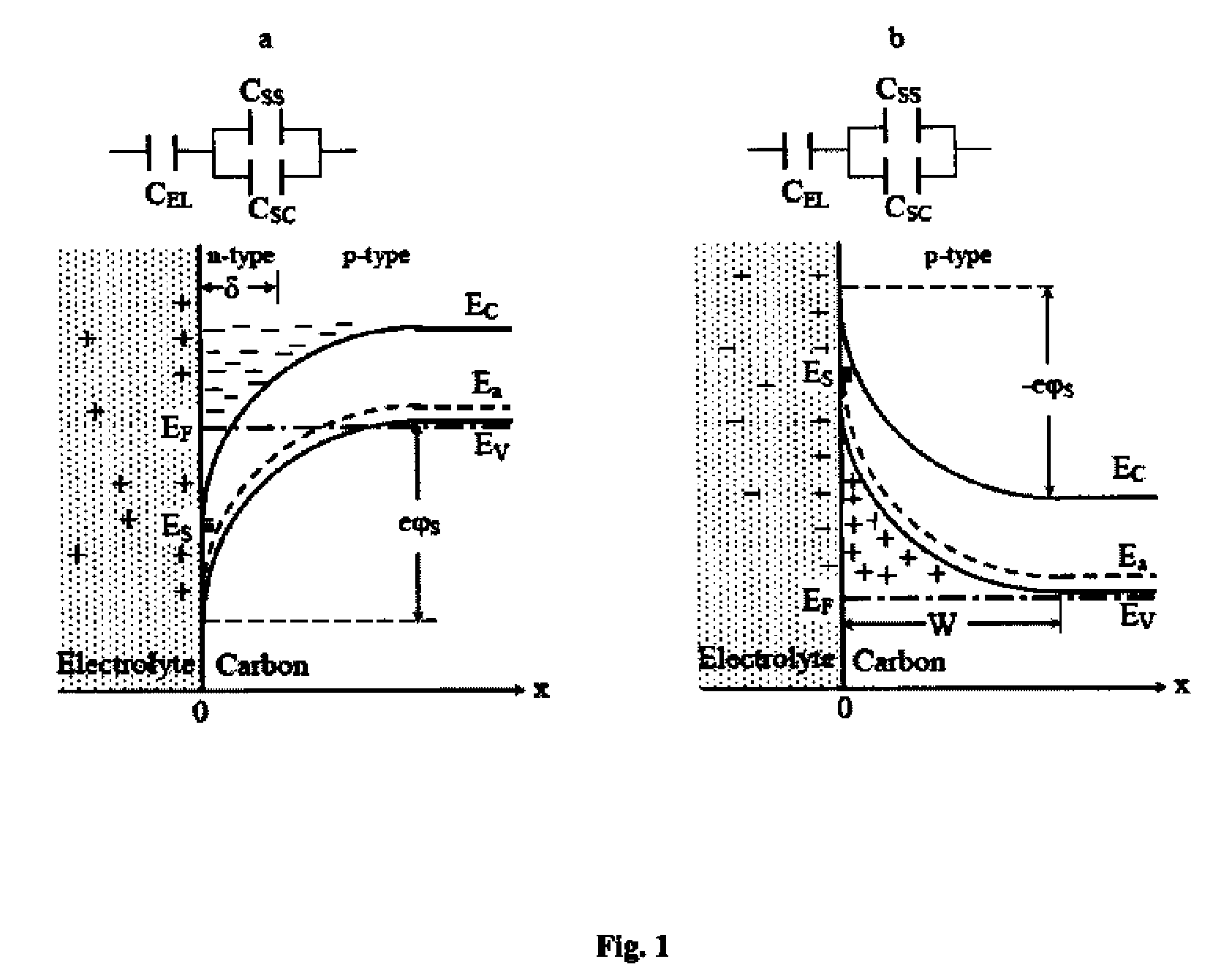

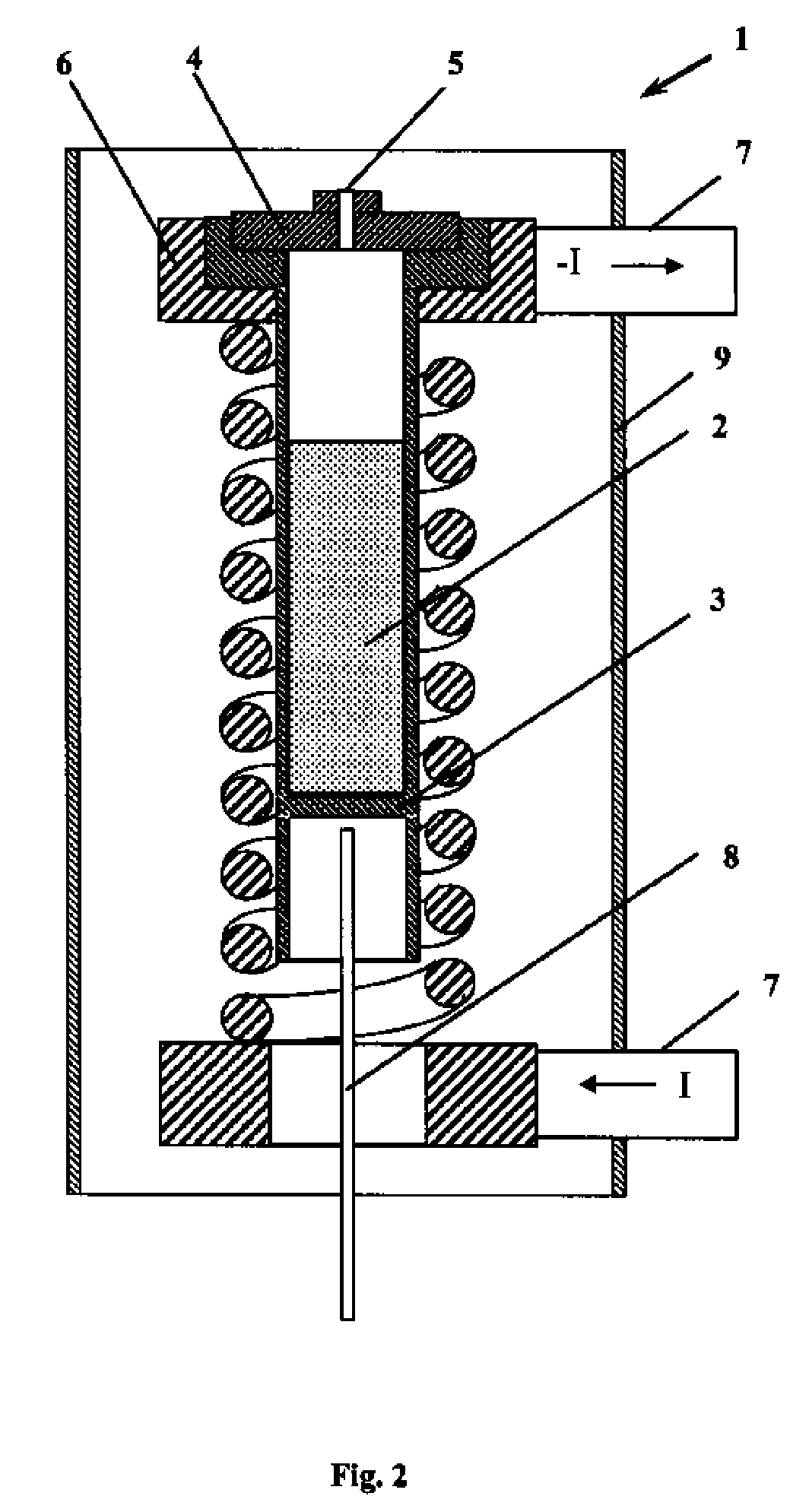

Electrode for use with double electric layer electrochemical capacitors having high specific parameters

InactiveUS20080266754A1Improve and optimize specific energyImprove and optimize and power parameterHybrid capacitor electrodesLiquid electrolytic capacitorsHigh concentrationHigh energy

The present invention relates to the production of electrochemical capacitors with a DEL. The proposed electrodes with DEL are based on non-metal conducting materials, including porous carbon materials, and are capable of providing for high specific energy, capacity and power parameters of electrochemical capacitors. P-type conductivity and high concentration of holes in electrode materials may be provided by thermal, ionic or electrochemical doping by acceptor impurities; irradiating by high-energy fast particles or quantums; or chemical, electrochemical and / or thermal treatment. The present invention allows for an increase in specific energy, capacity and power parameters, as well as a reduction in the cost of various electrochemical capacitors with DEL. The proposed electrodes with DEL can be used as positive and / or negative electrodes of symmetric and asymmetric electrochemical capacitors with aqueous and non-aqueous electrolytes.

Owner:UNIVERSAL SUPERCAPACITORS LLC

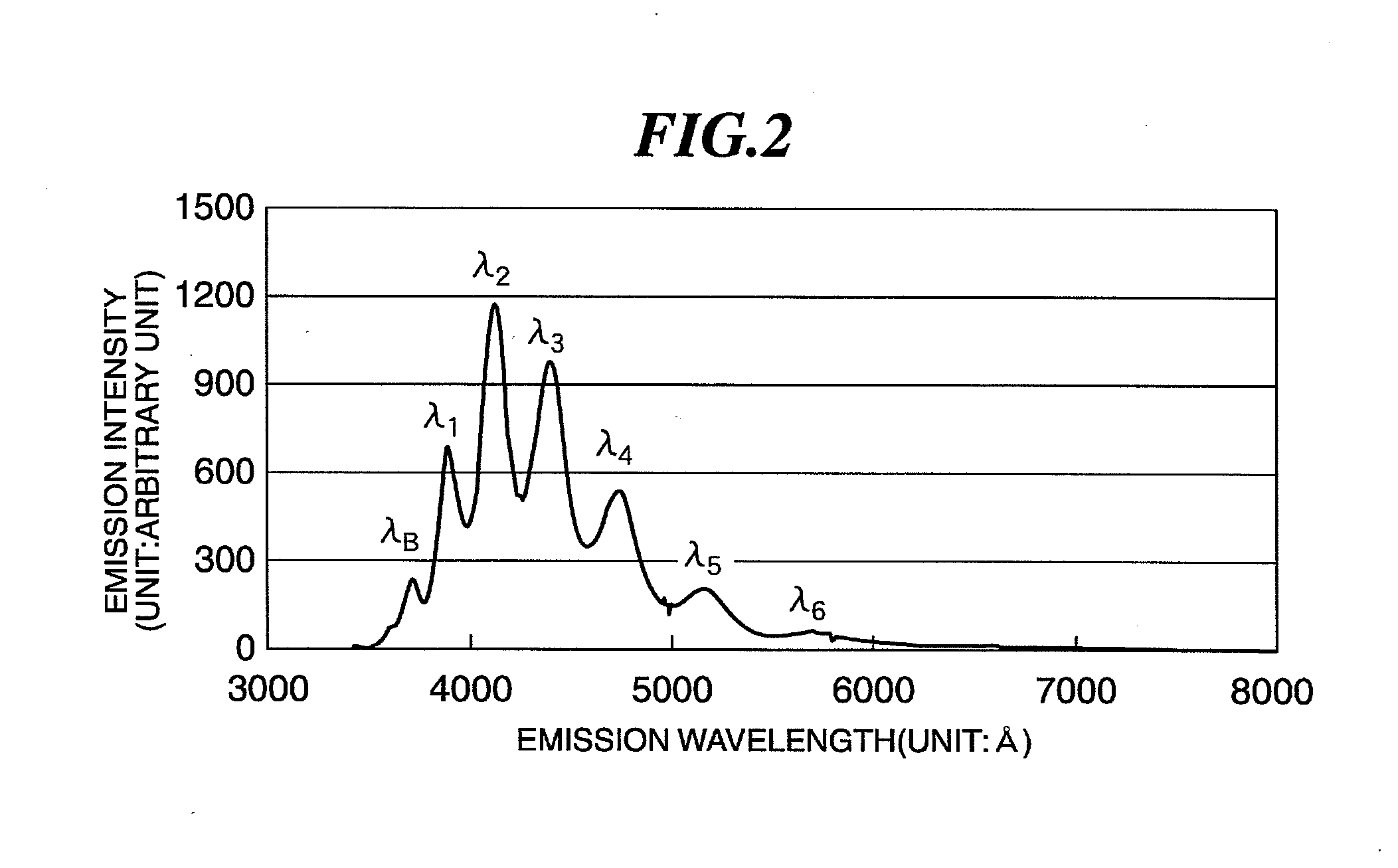

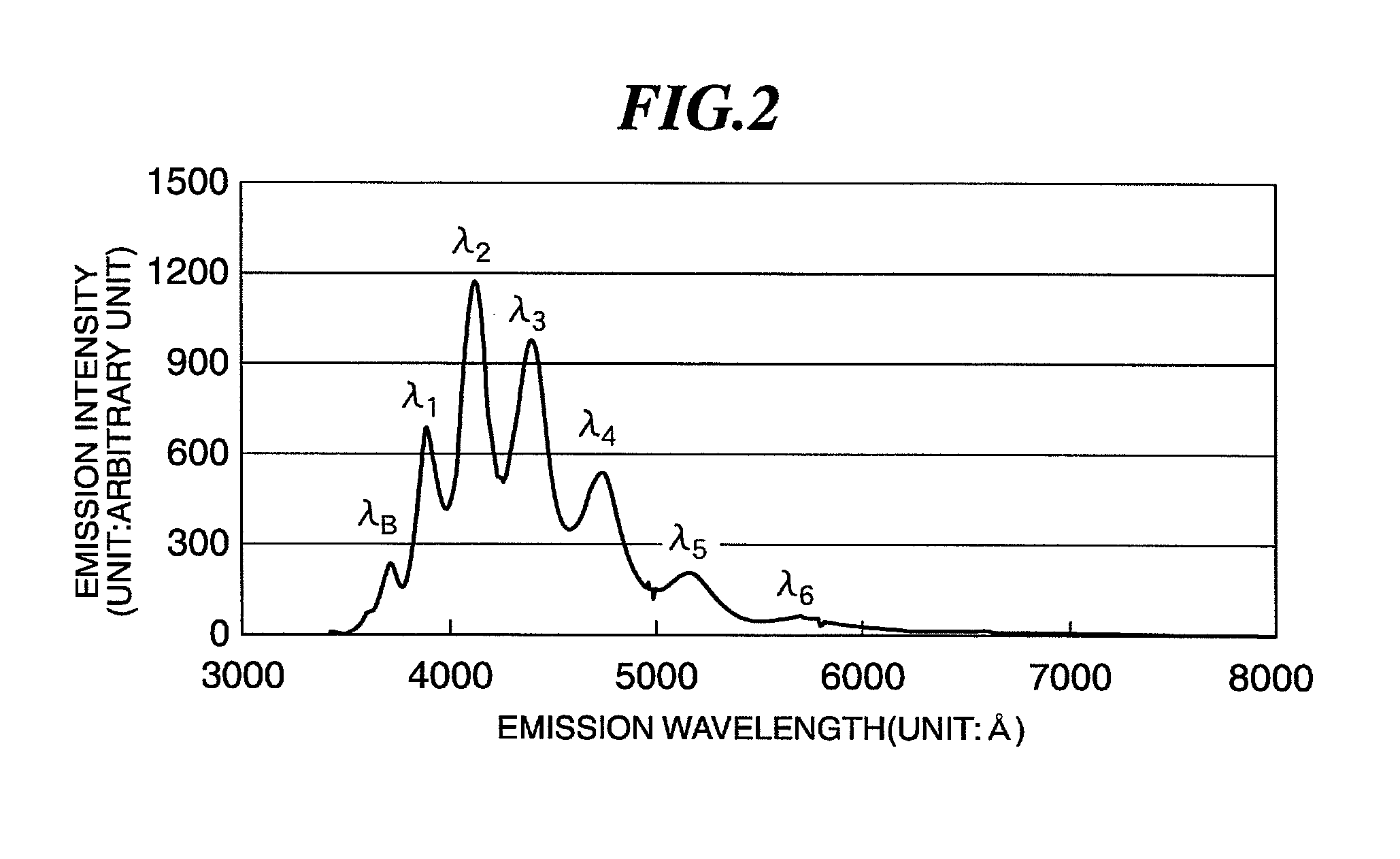

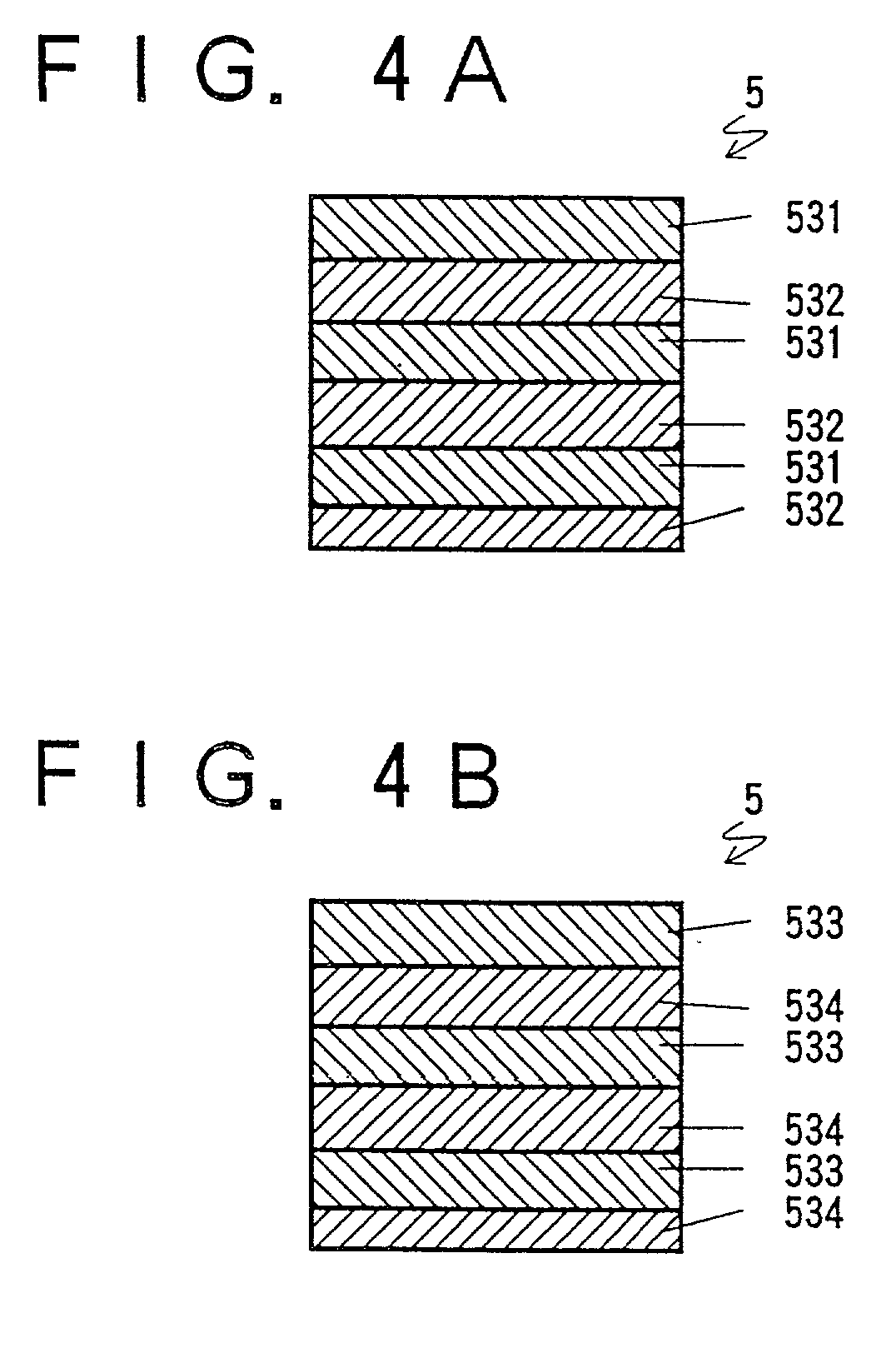

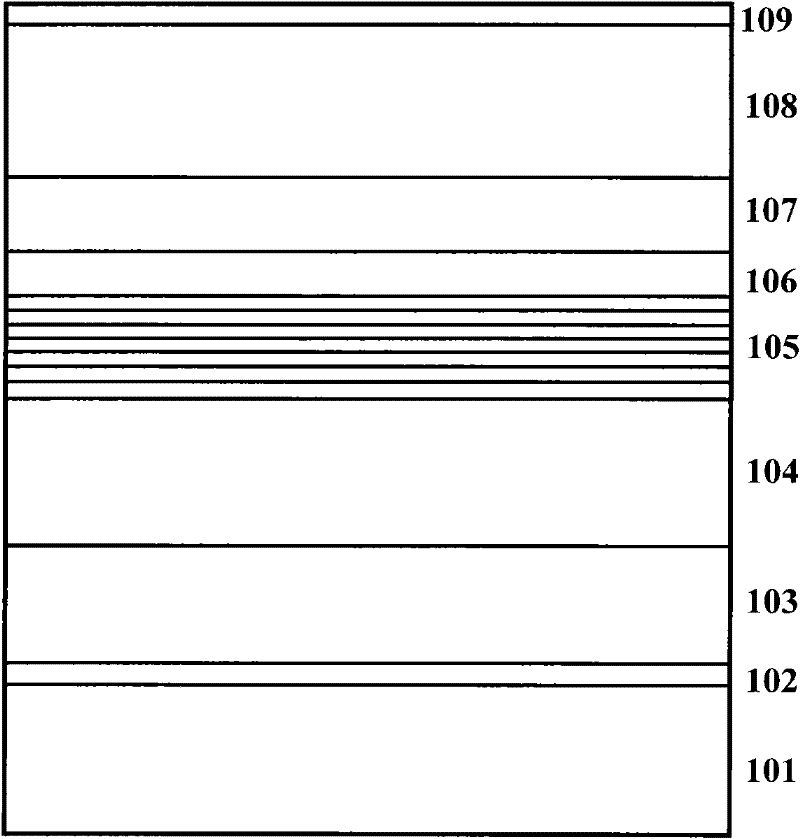

Light-emitting semiconductor device using group III nitride compound

InactiveUS20010045564A1Semiconductor/solid-state device manufacturingNanoopticsLuminous intensityQuantum well

An emission layer (5) for a light source device is formed to have a multi-layer structure, doped with an acceptor and a donor impurity. The multi-layer structure may include a quantum well (QW) structure or a multi quantum well (MQW) structure (50). With such a structure, a peak wavelength of the light source can be controlled, because the distances between atoms of the acceptor and the donor impurities are widened. Several arrangements can be made by, e.g., altering the thickness of each composite layer of the multi-layer structure, altering their composition ratio, forming undoped layer 5 between the impurity doped layers, and so forth. Further, luminous intensity of ultra violet color can be improved, because doping the donor impurity and the acceptor impurity realizes a donor-acceptor emission mechanism and abundant carriers. Several arrangements can be made by, e.g., optimizing the materials of the composite layers, optimizing their composition ratios, optimizing their lattice constants, and so forth to further enhance the luminous intensity of the light source.

Owner:TOYODA GOSEI CO LTD

Gallium-nitride-based light-emitting diode (LED) epitaxial wafer and growth method thereof

InactiveCN102208505AImprove growth qualityImprove performanceSemiconductor devicesGallium nitrideLight-emitting diode

The invention discloses a growth method of a gallium-nitride-based epitaxial wafer. In the epitaxial wafer, triethyl gallium used as a metal organic source of gallium and di (cyclopentadienyl) magnesium used as an acceptor impurity growth p-type cavity injection layer are adopted between a multiple quantum well layer and a p-type AlGaN layer; and according to the growth structure, the bulk resistance of the p-type layer is reduced, the effective concentration of the injected cavity is improved, the effective compound of the cavity and an electron in an active region is enlarged, and the luminous efficiency of a light-emitting diode (LED) is improved. According to a standard chip process, a chip which has a size of 300*200 mu m<2> and uses Indium tin oxide (ITO) as a transparent electrode is manufactured, the forward voltage of the chip can be reduced by 0.15V, and the light transmission efficiency is improved by above 17%.

Owner:DALIAN MEIMING EPITAXIAL WAFER TECH

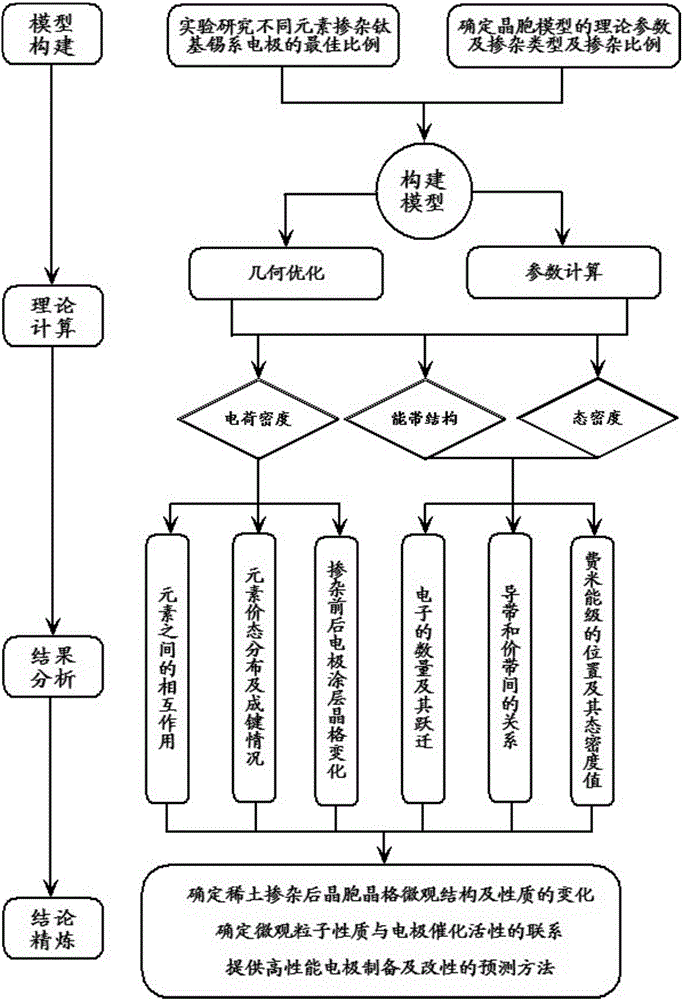

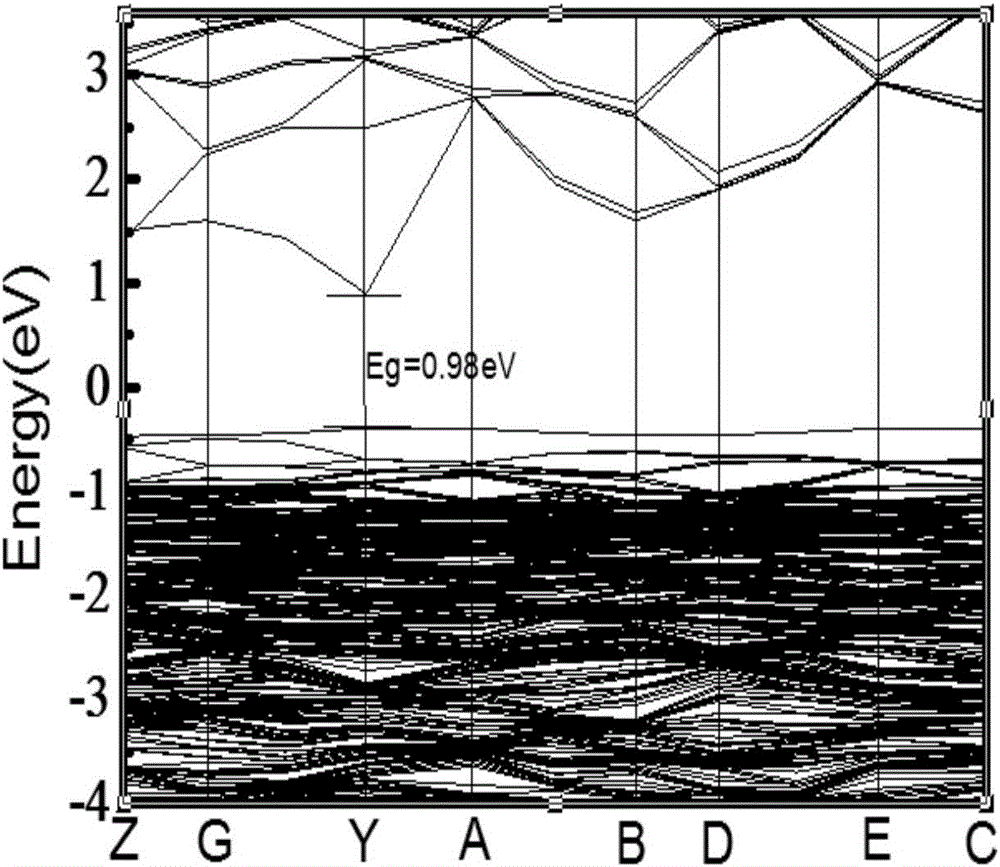

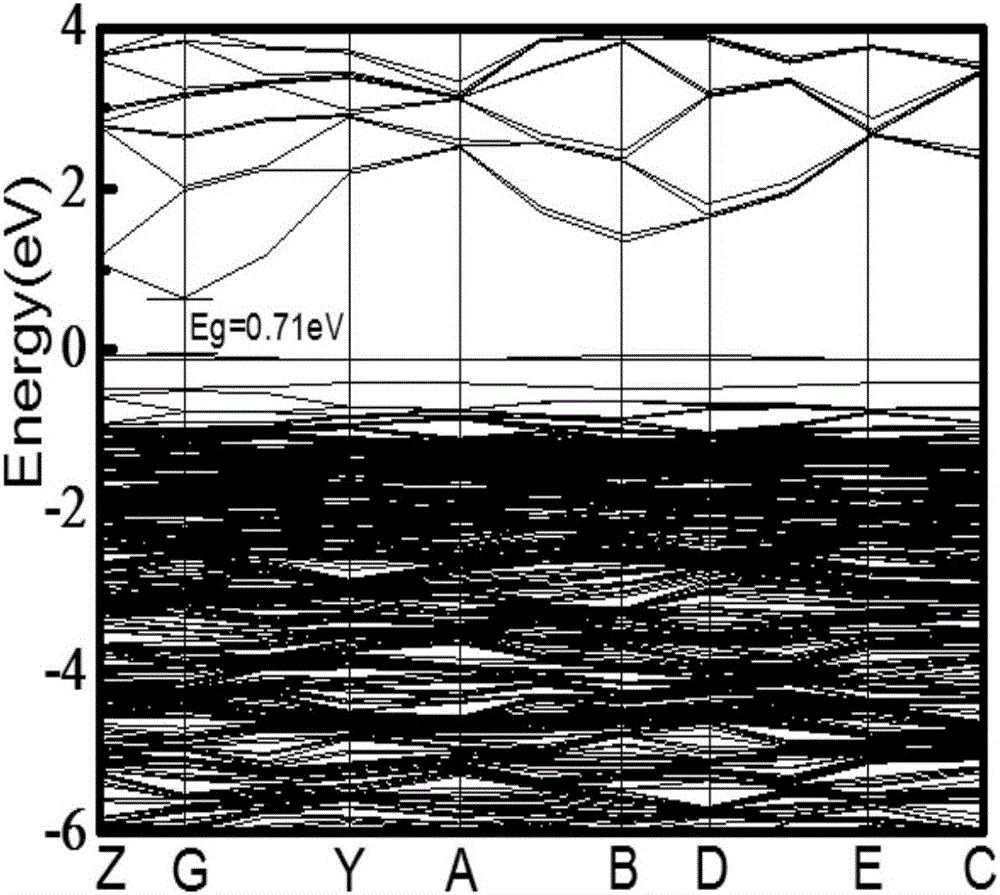

Prediction method for performance of rare-earth-doped modified titanium-based stannic oxide electrode

The invention provides a prediction method for the performance of a rare-earth-doped modified titanium-based stannic oxide electrode. The modified performance is predicted by calculating changes of stannic oxide crystal structure parameters before and after rare earth doping on the basis of a density functional theory of the first principles; the crystal geometric structures of SnO2 doped with La with the different concentrations are optimized by taking lanthanum as a doping agent, the lattice constant, the energy band structure, the state density and the formation energy of crystal cells of SnO2 with the different lanthanum doping quantities are calculated, and it shows that doped SnO2 has the higher electric conductivity and the good electro-catalytic property, energy band degeneration is intensified and the acceptor impurity energy level moves towards the direction away from the valence band maximum along with increasing of the doping concentration, the formation energy is lowest when the doping concentration is 1.39%, the electronic structure of SnO2 is most stable at the moment, and experiments verify that when the actual adding amount is 1.5%, the catalytic performance is best. According to the method, the performance of different systems of oxide electrodes doped with other rare earth or elements can be effectively predicted and analyzed according to the difference of doping elements and the different doped electrode systems.

Owner:XI'AN UNIVERSITY OF ARCHITECTURE AND TECHNOLOGY

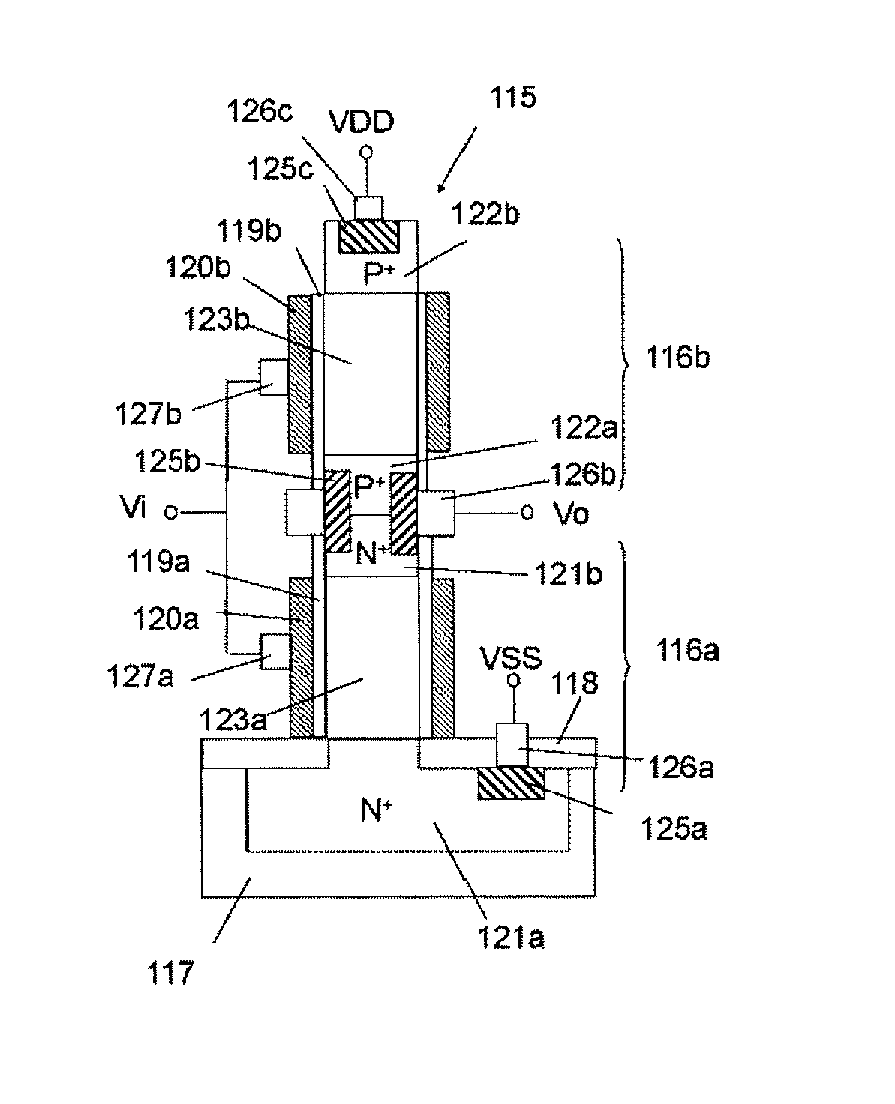

Method for producing semiconductor device and semiconductor device

ActiveUS20130069149A1Easy to integrateGuaranteed uptimeSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorDevice material

A method for producing a semiconductor device includes the steps of forming first and second pillar-shaped semiconductors on a substrate at the same time so as to have the same height; forming a first semiconductor layer by doping a bottom region of the first pillar-shaped semiconductor with a donor or acceptor impurity to connect the first semiconductor layer to the second pillar-shaped semiconductor; forming a circuit element including an upper semiconductor region formed by doping an upper region of the first pillar-shaped semiconductor with a donor or acceptor impurity; forming a first conductor layer in the second pillar-shaped semiconductor; forming first and second contact holes that are respectively connected to the first and second pillar-shaped semiconductors; and forming a wiring metal layer that is connected to the upper semiconductor region and the first conductor layer through the first and second contact holes, respectively.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

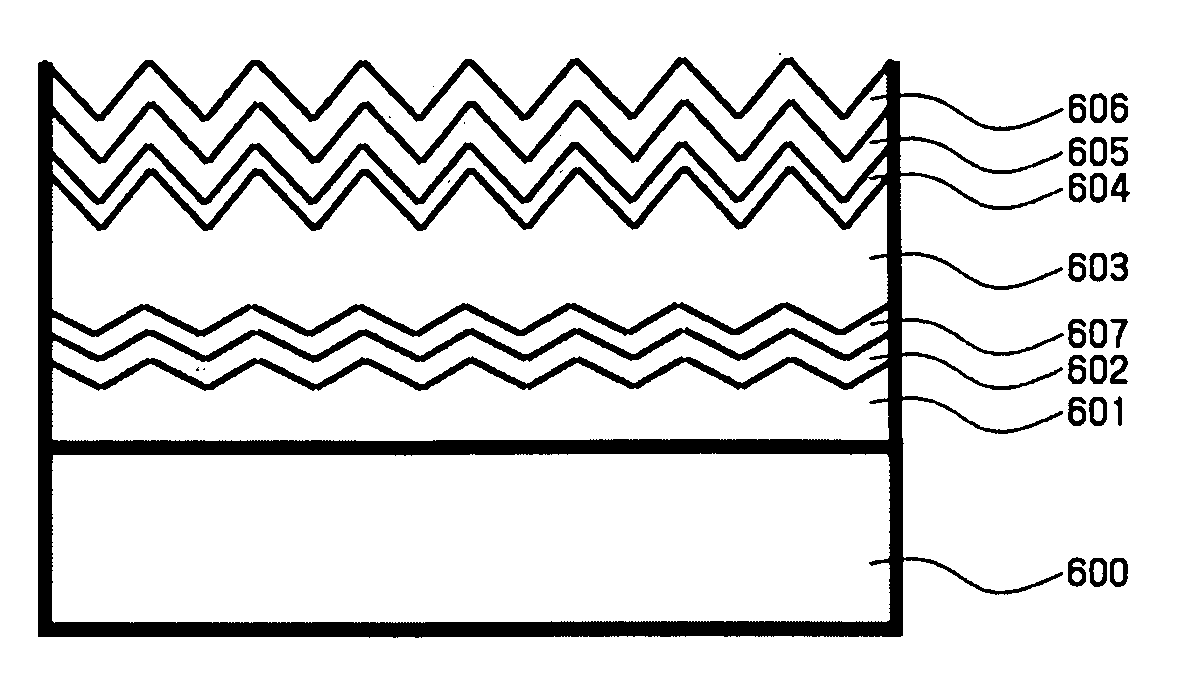

Epitaxial substrate for field effect transistor

InactiveUS20100019277A1Semiconductor/solid-state device manufacturingSemiconductor devicesAcceptor impurityHigh resistivity

The present invention provides an epitaxial substrate for field effect transistor. In the epitaxial substrate for field effect transistor, a nitride-based Group III-V semiconductor epitaxial crystal containing Ga is interposed between the ground layer and the operating layer, and the nitride-based Group III-V semiconductor epitaxial crystal comprises the following (i), (ii) and (iii). (i) a first buffer layer containing Ga or Al and containing a high resistivity crystal layer having added thereto compensation impurity element present in the same period as Ga in the periodic table and having small atomic number; (ii) a second buffer layer containing Ga or Al, laminated on the operating layer side of the first buffer layer; and (iii) a high purity epitaxial crystal layer containing acceptor impurities in a slight amount such that non-addition or depletion state can be maintained, provided between the high resistivity layer and the operating layer.

Owner:SUMITOMO CHEM CO LTD

Method for producing semiconductor device and semiconductor device having pillar-shaped semiconductor

ActiveUS8669601B2Increase the number ofDecrease degree is preventedSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceElectrical conductor

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

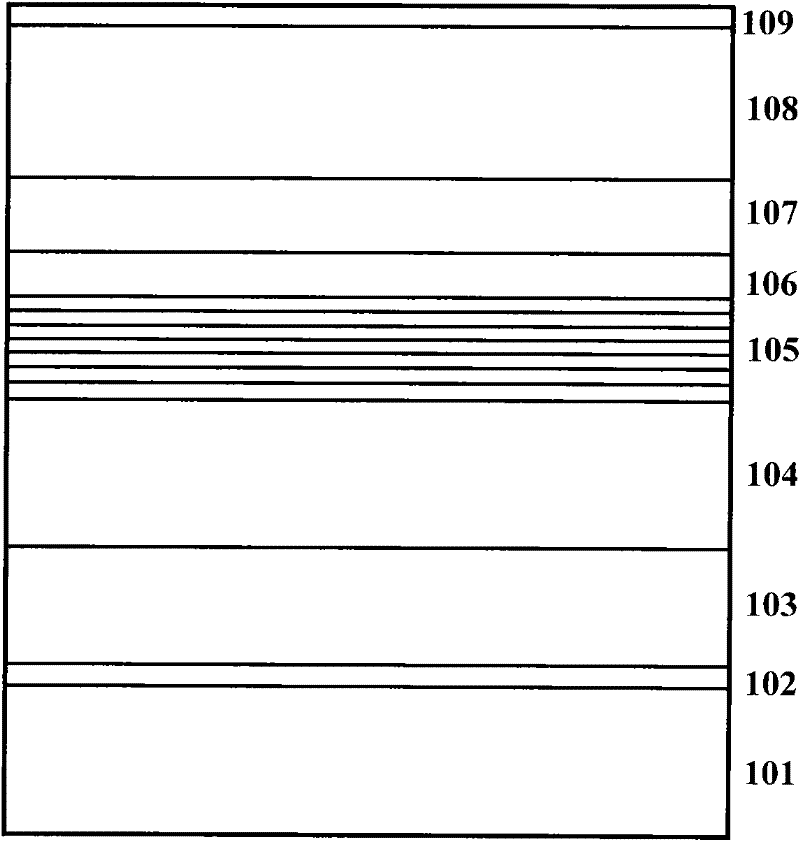

Thin film transistor having microcrystalline semiconductor layer and amorphous semiconductor layer

InactiveUS8017946B2Excellent electrical propertiesSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorOxide thin-film transistor

Owner:SEMICON ENERGY LAB CO LTD

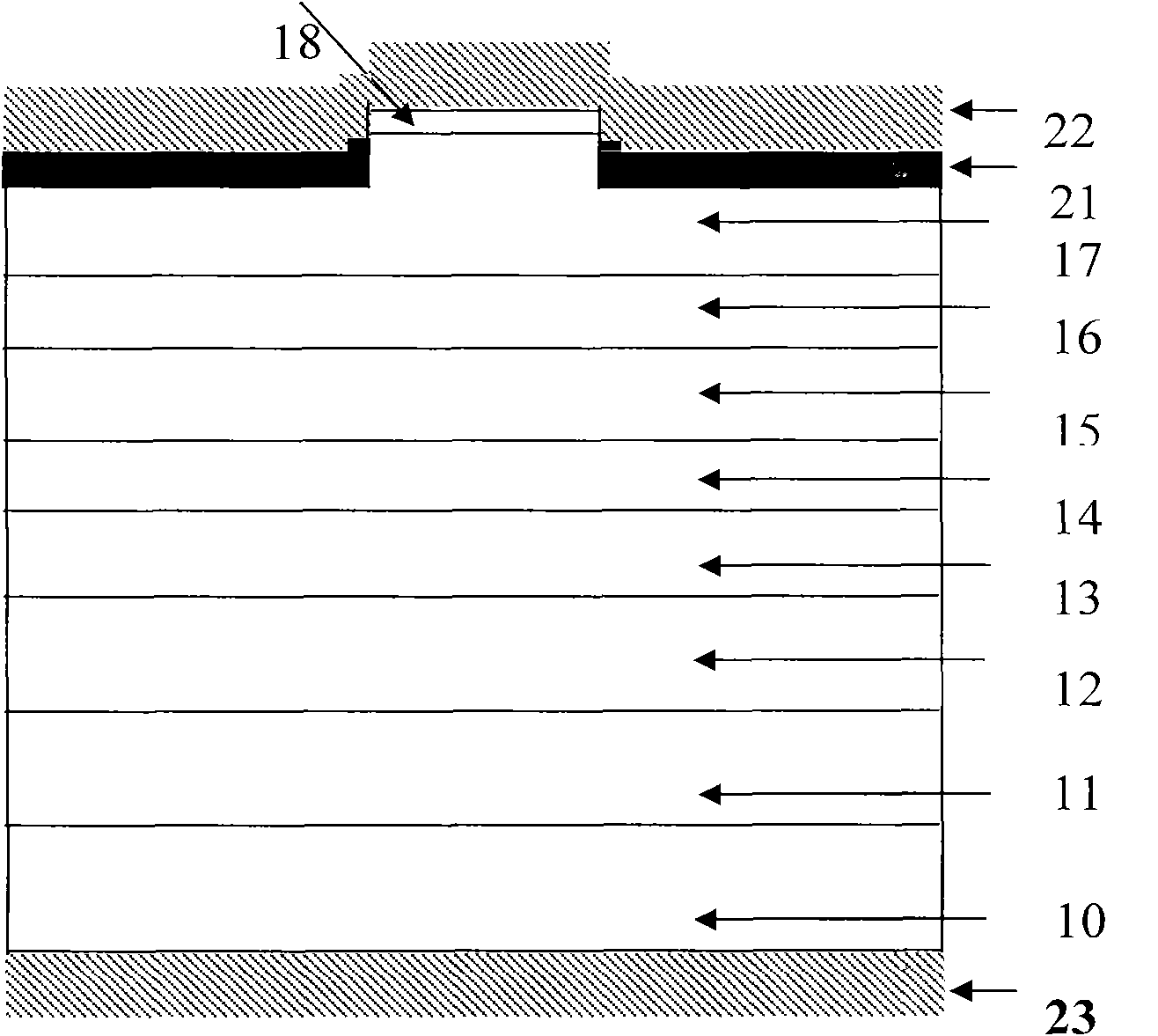

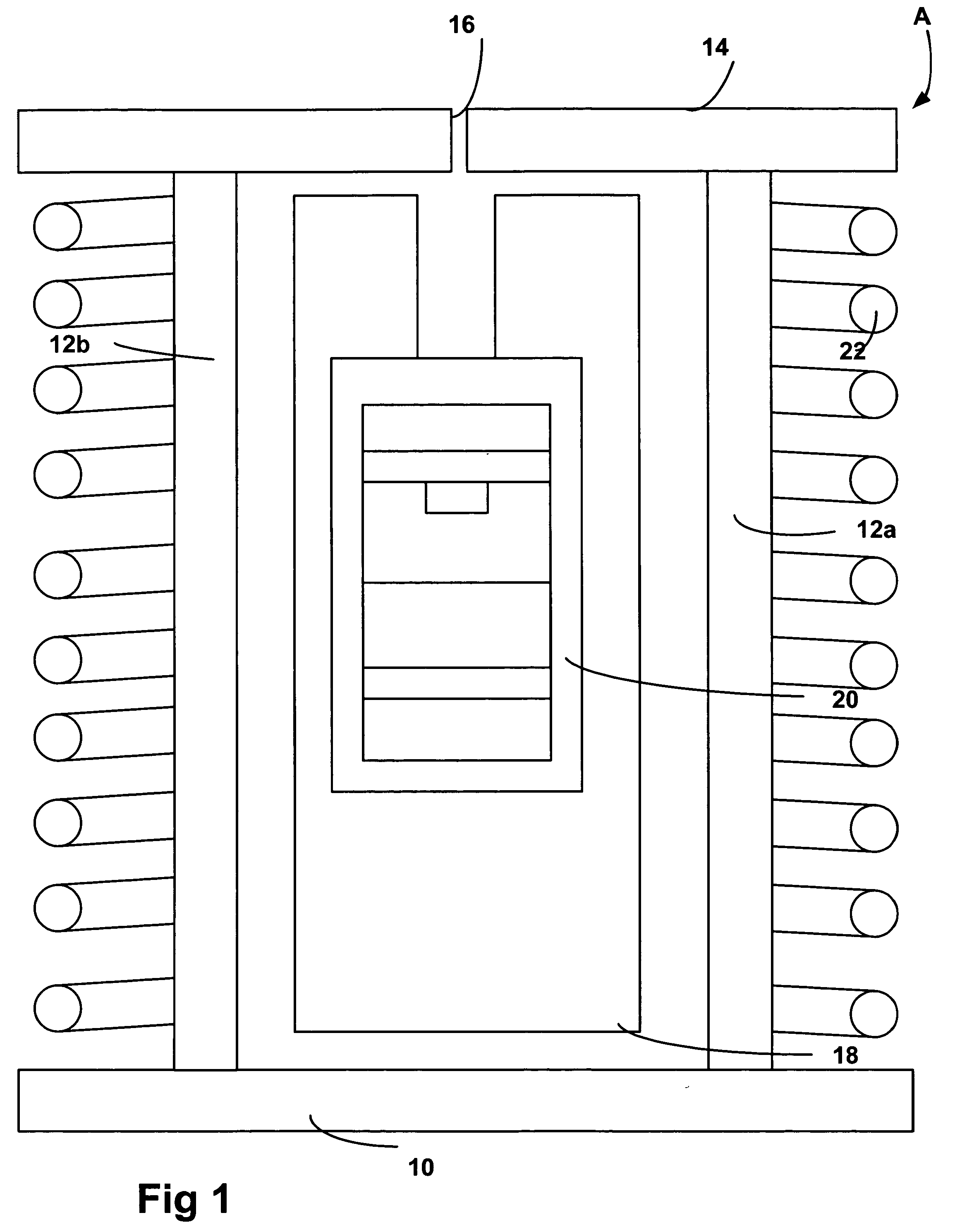

GaN-based semiconductor laser and manufacturing method thereof

The invention relates to a GaN-based semiconductor laser and a manufacturing method thereof, belonging to the field of semiconductor lasers. The device has the structure that a quantum cascade radiation layer is introduced between an n-type optical confinement layer and an n-type waveguide layer of the laser. By applying infrared radiation generated by the quantum cascade radiation layer when the laser works, the ionization of magnesium acceptor impurities in a p-type GaN waveguide layer, a p-type AlGaN optical confinement layer and a p-type GaN covering layer is realized, the carrier concentration of each p-type layer is increased, and the working voltage of the laser is reduced. The average Al component of the quantum cascade radiation layer is close to that of an n-type AlGaN optical confinement layer, thus the optical confinement factor of the laser has no obvious change. Although the voltage drop of the n-type layers can be increased when the laser works, the laser can still work at a lower voltage because the voltage drop of the p-type layers is greatly reduced. By applying the structure of the laser, the series resistance of the laser can be reduced to further reduce the working voltage of the laser and prolong the service life of the laser.

Owner:BEIJING UNIV OF CHEM TECH

System and method for fabricating diodes

InactiveUS20050184296A1Semiconductor/solid-state device manufacturingSemiconductor devicesAcceptor impurityLinearity

This invention is directed to a system and method of fabricating PN and PiN diodes by diffusing an acceptor impurity into a substrate. This invention is particularly advantageous for fabricating SiC diodes having linearly graded, deep pn junctions. One method that this invention uses to achieve its advantages is by diffusing an acceptor impurity into a substrate using a crucible, acceptor source, substrate, and furnace.

Owner:SUDARSHAN T S +2

Photoelectric conversion device and fabrication method thereof

InactiveUS20080245415A1Improve mechanical propertiesGood physical propertiesSemiconductor/solid-state device manufacturingPhotovoltaic energy generationCarbon filmDiamond-like carbon

A photoelectric conversion device includes at least one p-type semiconductor layer made of amorphous like hydrogenated carbon film or diamond like carbon (DLC) film doped with acceptor impurities such as boron (B). In a solar cell having a photoelectric conversion region, hydrogenated carbon is used as substances forming a p-type semiconductor layer, making it possible to provide a solar cell with high photoelectric conversion efficiency.

Owner:LG ELECTRONICS INC

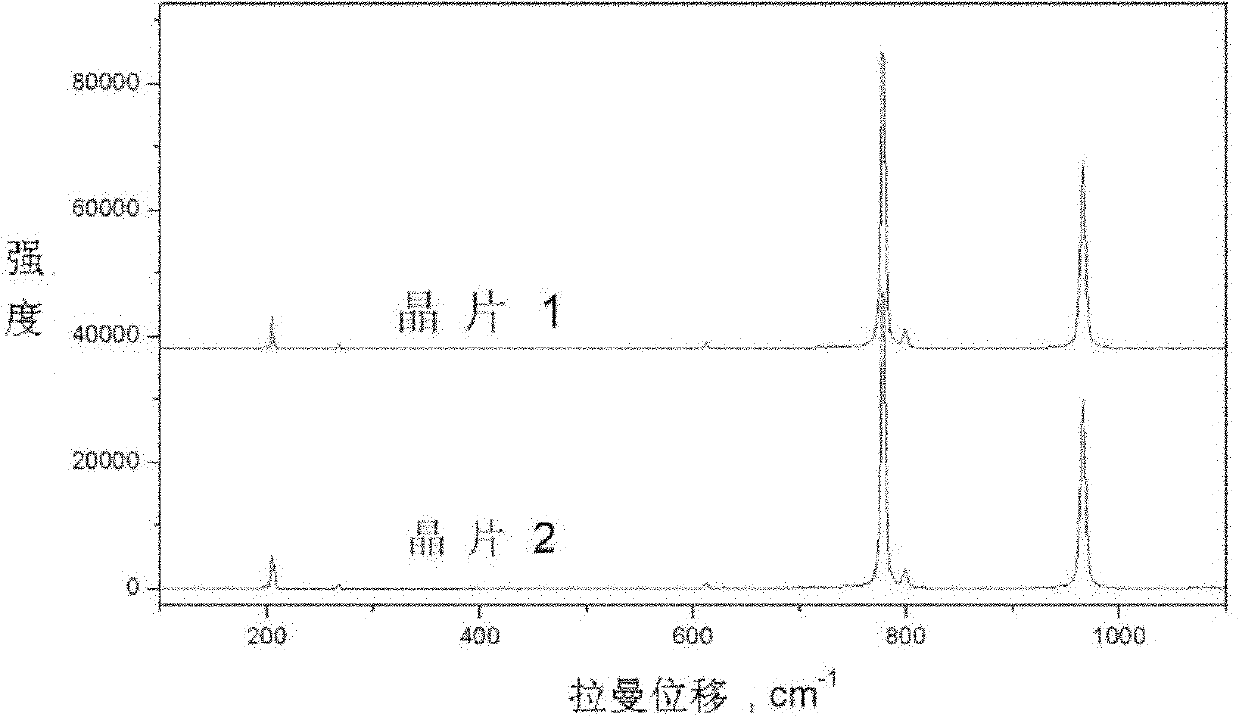

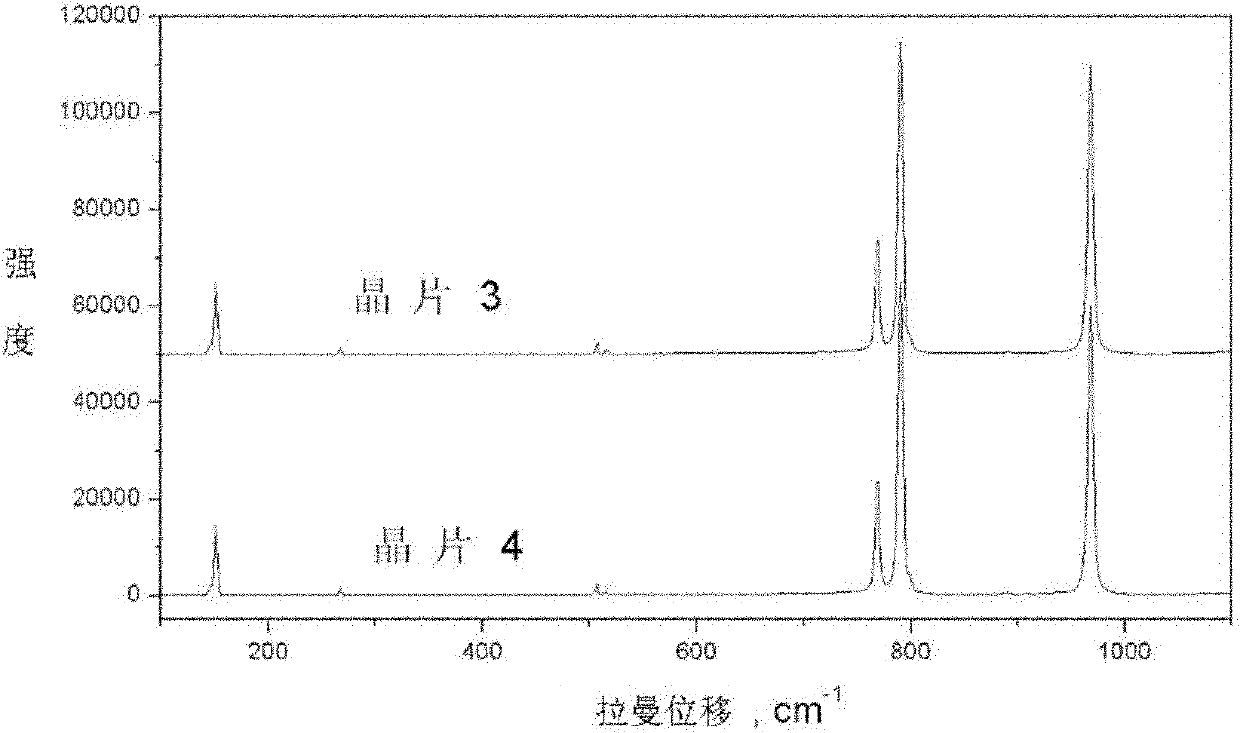

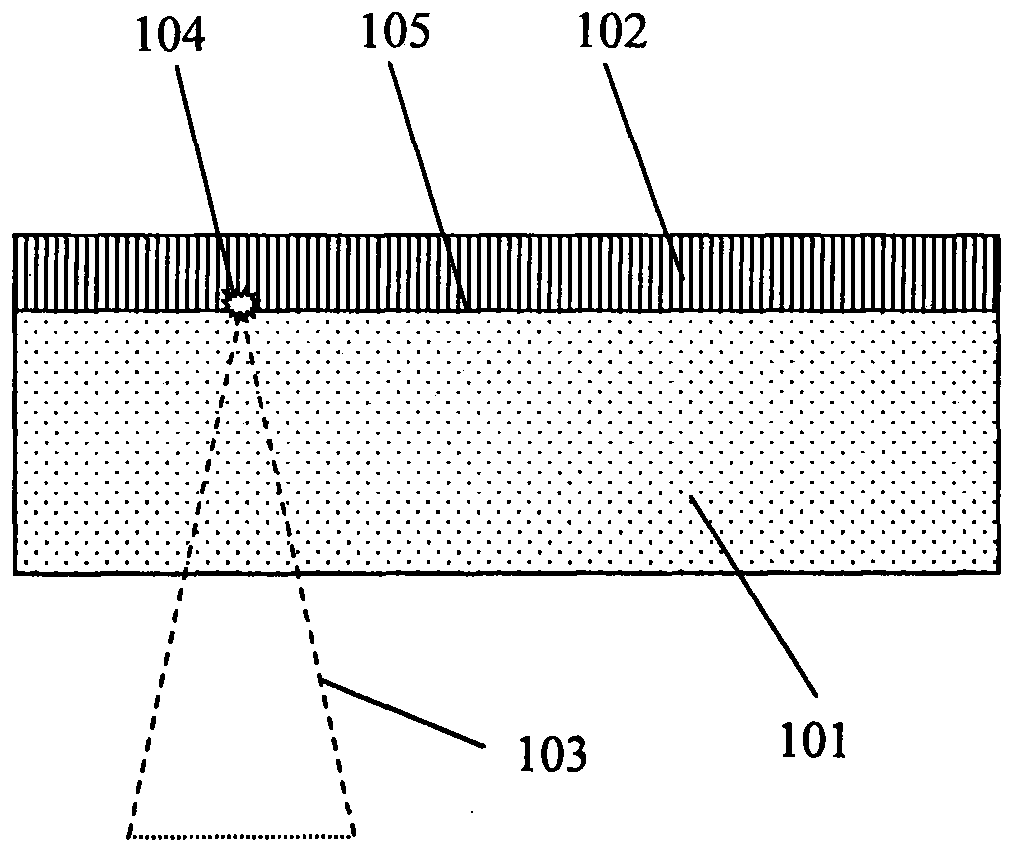

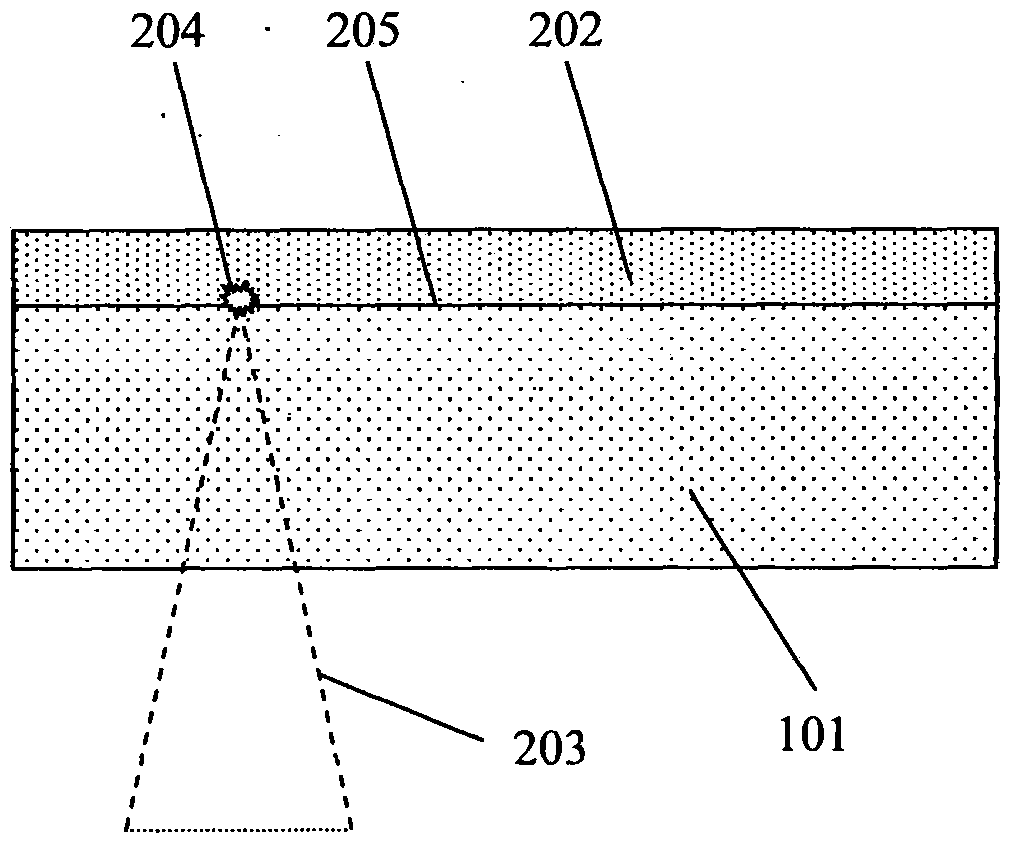

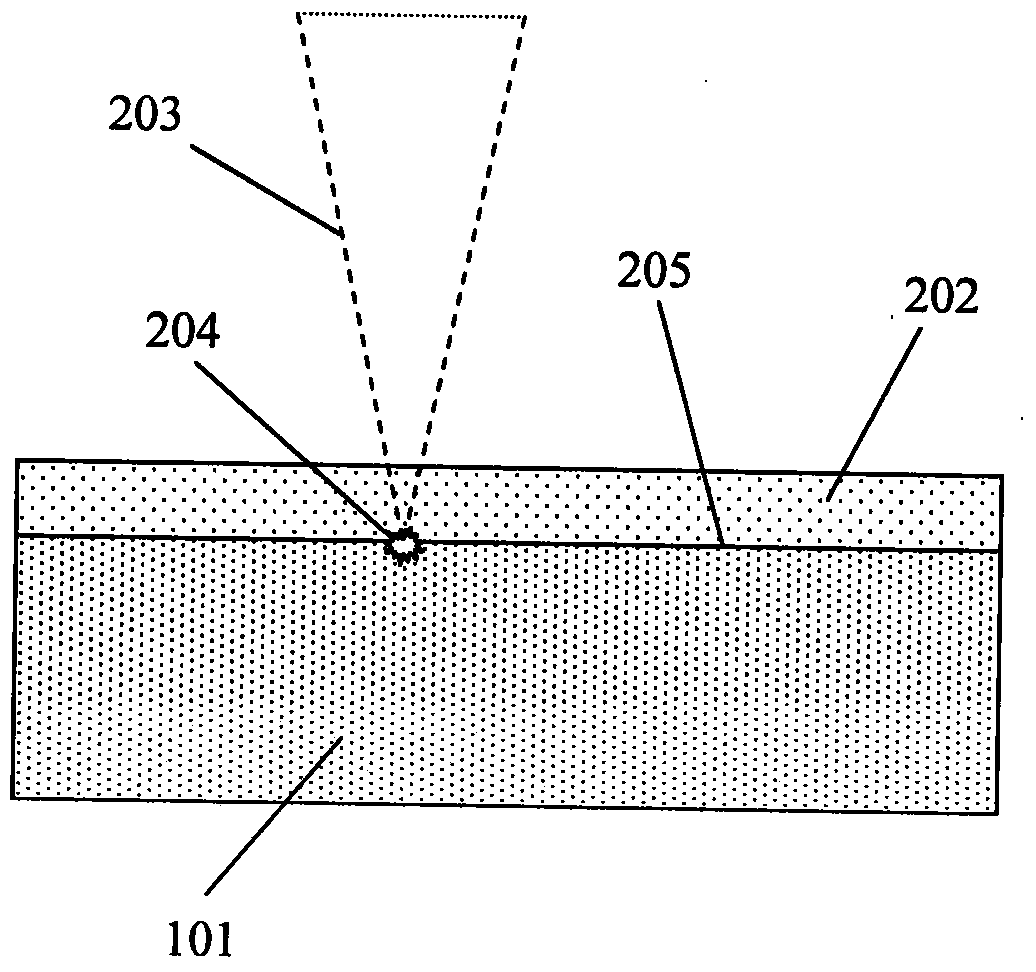

Method of laser separation of the epitaxial film or of the epitaxial film layer from the growth substrate of the epitaxial semiconductor structure (variations)

ActiveCN103703552ASolid-state devicesSemiconductor/solid-state device manufacturingAbsorption factorSemiconductor structure

The present invention proposes variations of the laser separation method allowing separating homoepitaxial films from the substrates made from the same crystalline material as the epitaxial film. This new method of laser separation is based on using the selective doping of the substrate and epitaxial film with fine donor and acceptor impurities. In selective doping,, concentration of free carries in the epitaxial film and substrate may essentially differ and this can lead to strong difference between the light absorption factors in the infrared region near the residual beams region where free carriers and phonon-plasmon interaction of the optical phonons with free carriers make an essential contribution to infrared absorption of the optical phonons. With the appropriate selection of the doping levels and frequency of infrared laser radiation it is possible to achieve that laser radiation is absorbed in general in the region of strong doping near the interface substrate- homoepitaxial film. When scanning the interface substrate- homoepitaxial film with the focused laser beam of sufficient power, thermal decomposition of the semiconductor crystal takes place with subsequent separation of the homoepitaxial film. The advantage of the proposed variations of the method for laser separation of epitaxial films in comparison with the known ones is in that it allows to separate homoepitaxial films from the substrates, i.e., homoepitaxial films having the same width of the forbidden gap as the initial semiconductor substrate has. The proposed variations of the method can be used for separation of the epitaxial films. Besides, the proposed method allows using the high-effective and inexpensive infrared gas silicon dioxide CO2 or silicon oxide CO lasers for separation of the epitaxial films.

Owner:尤里·杰奥尔杰维奇·施赖特尔 +2

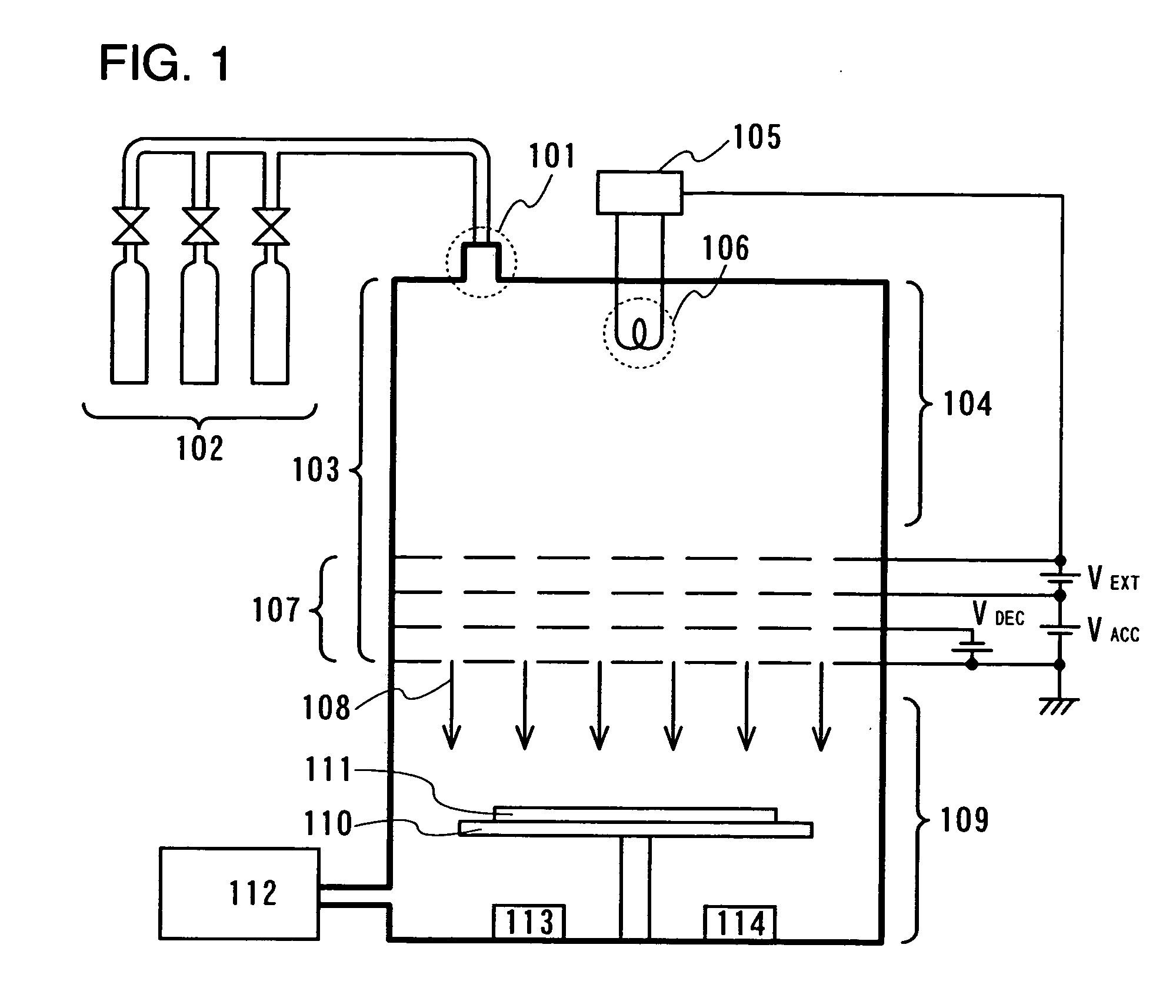

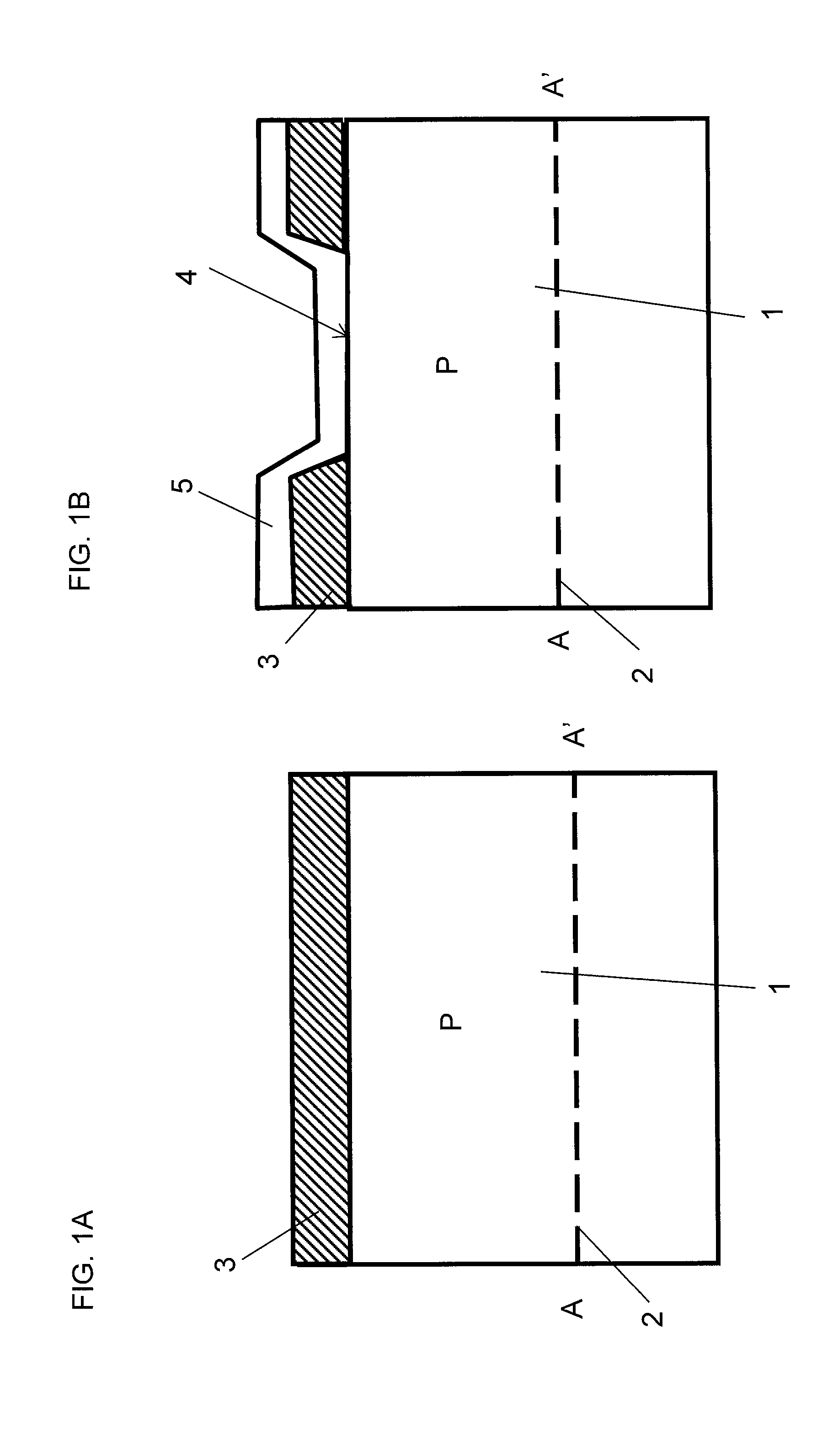

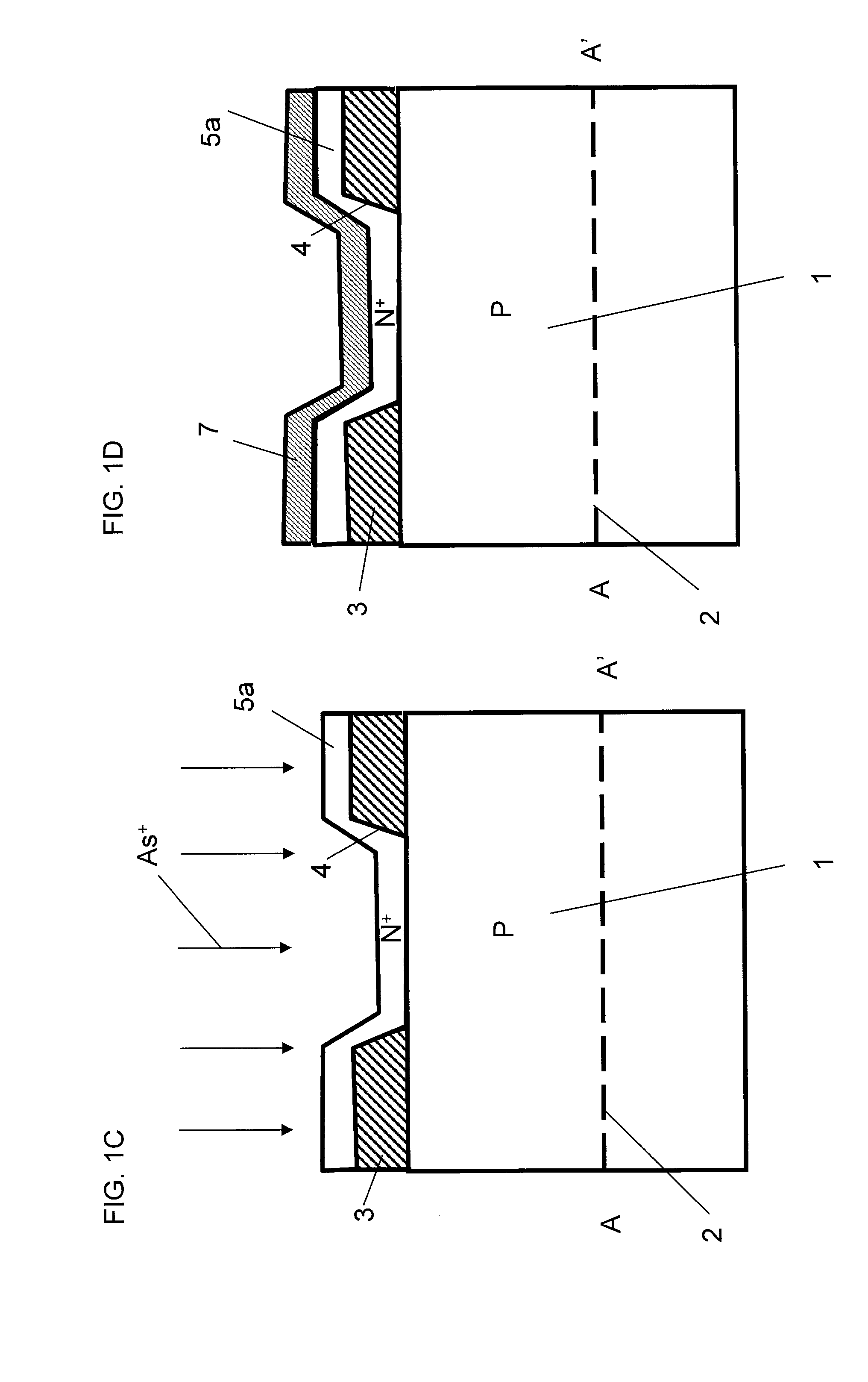

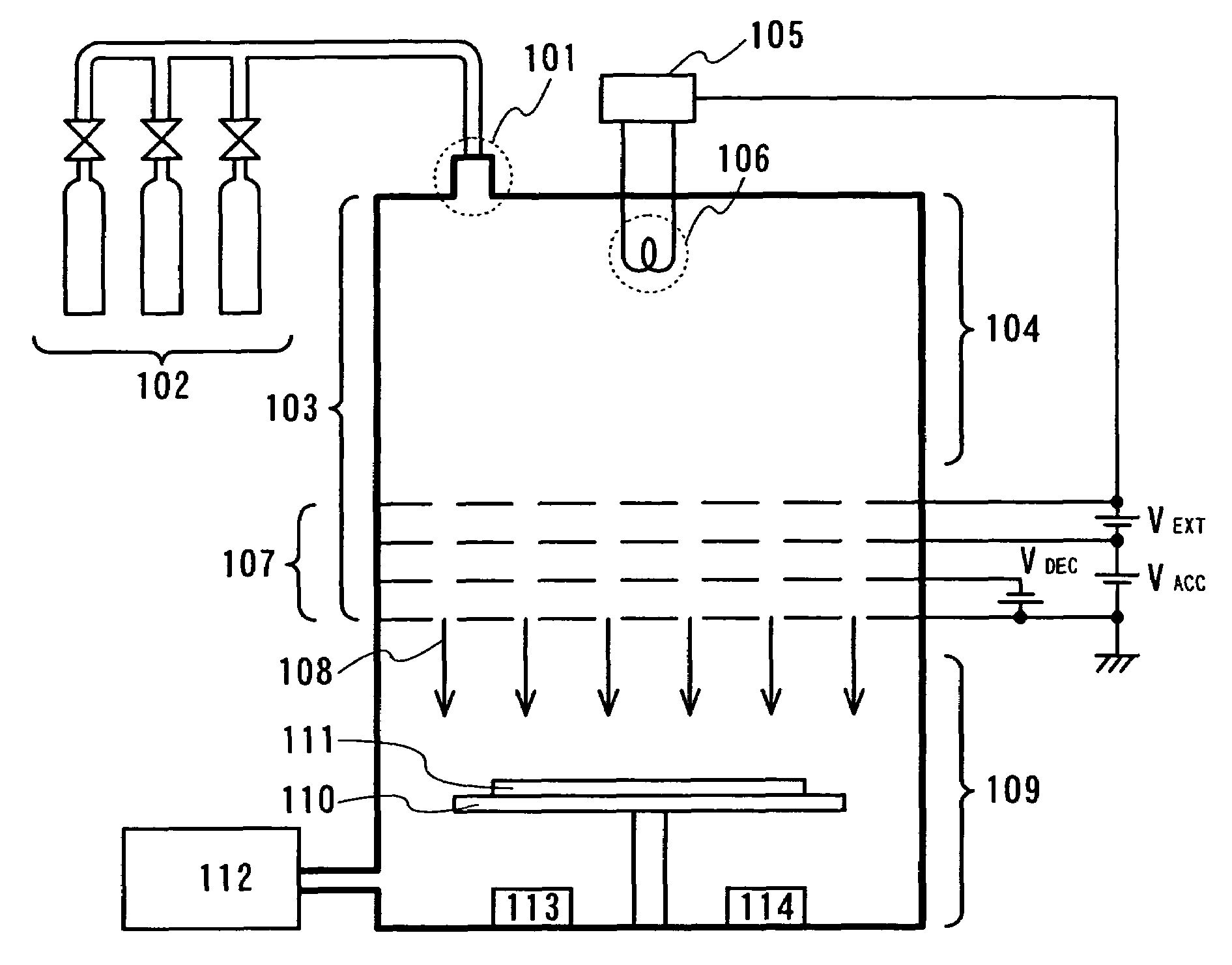

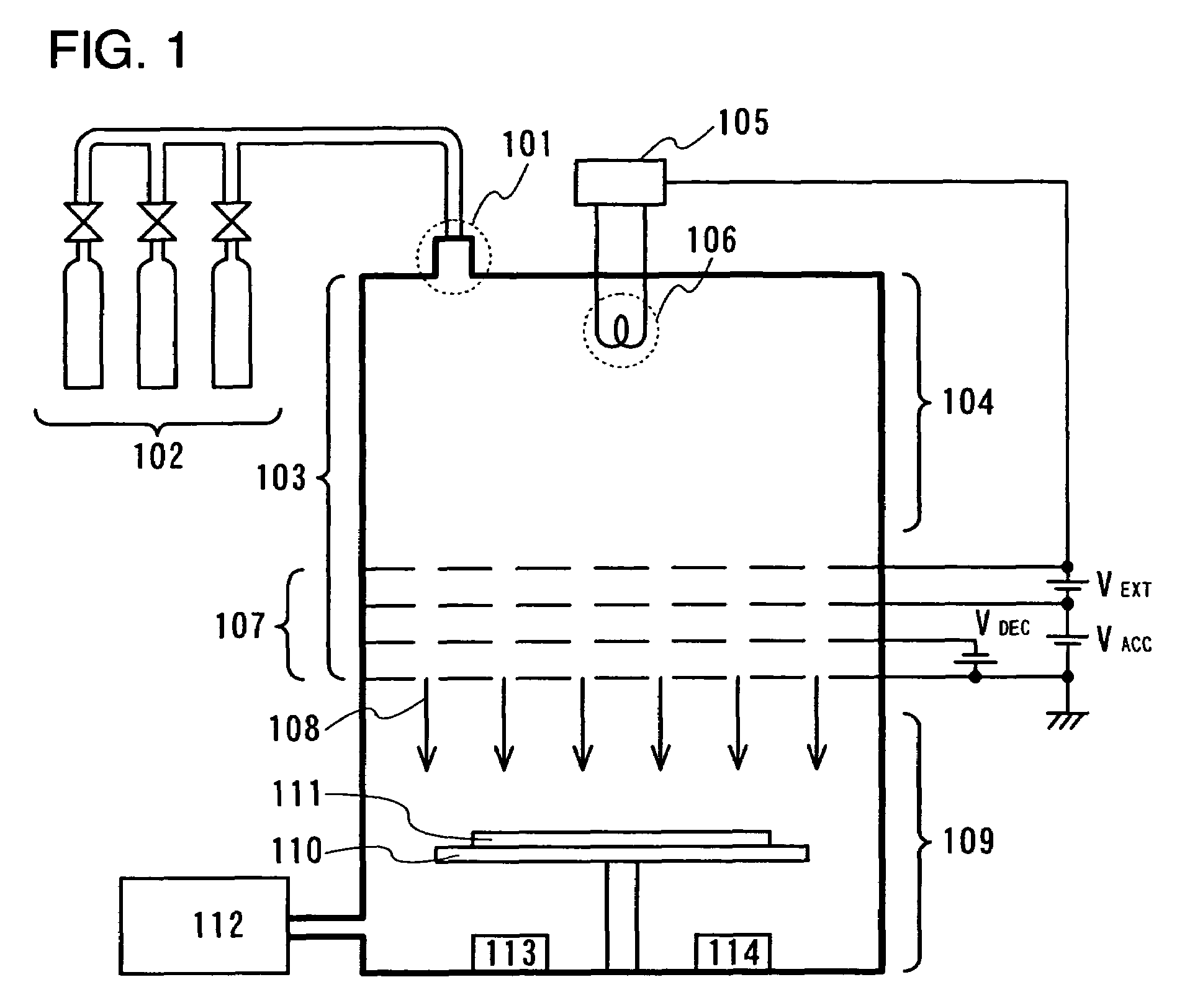

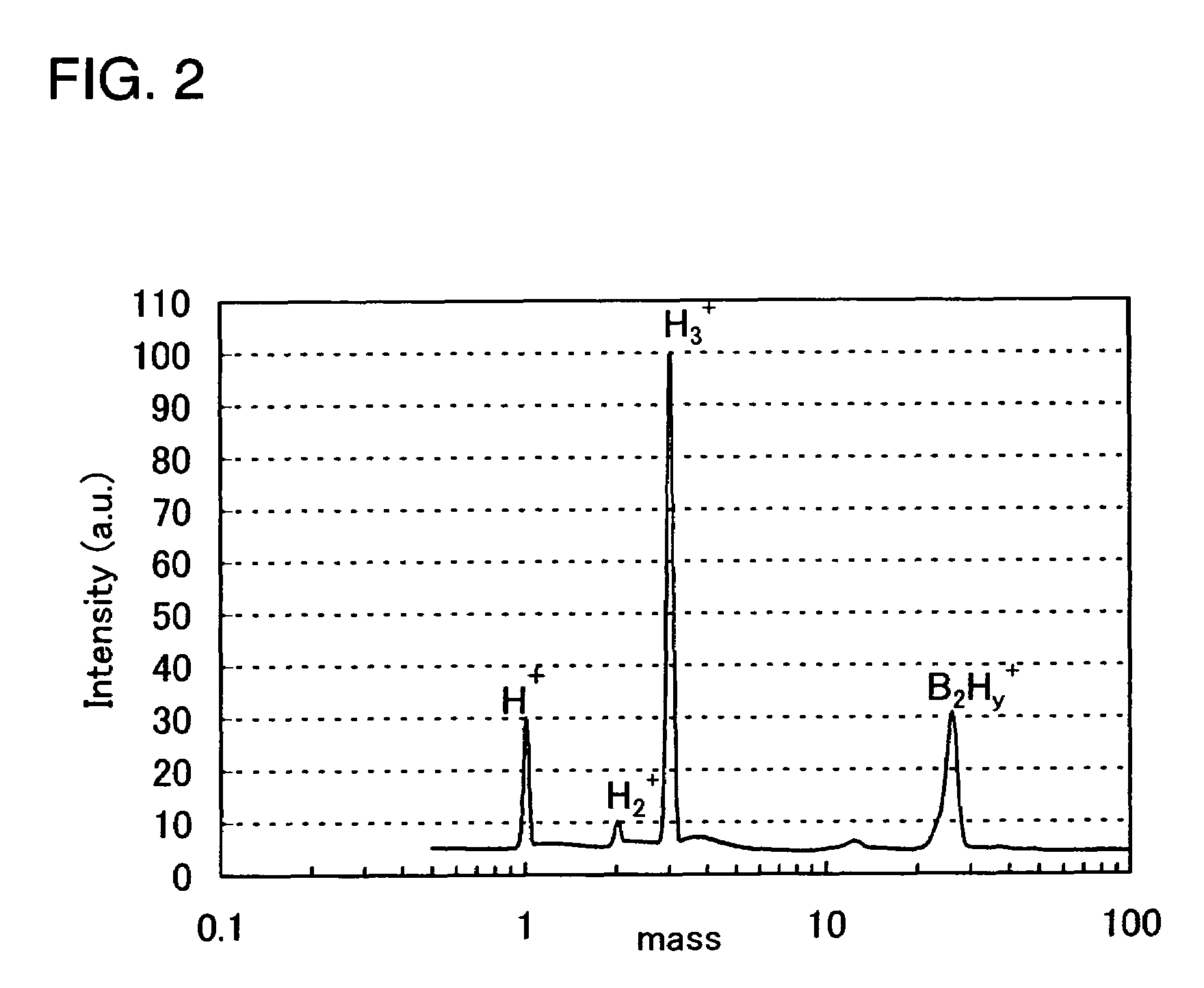

Doping method and method of manufacturing field effect transistor

InactiveUS20060177996A1Reduce variationReduce variation of threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesCompound (substance)Acceptor impurity

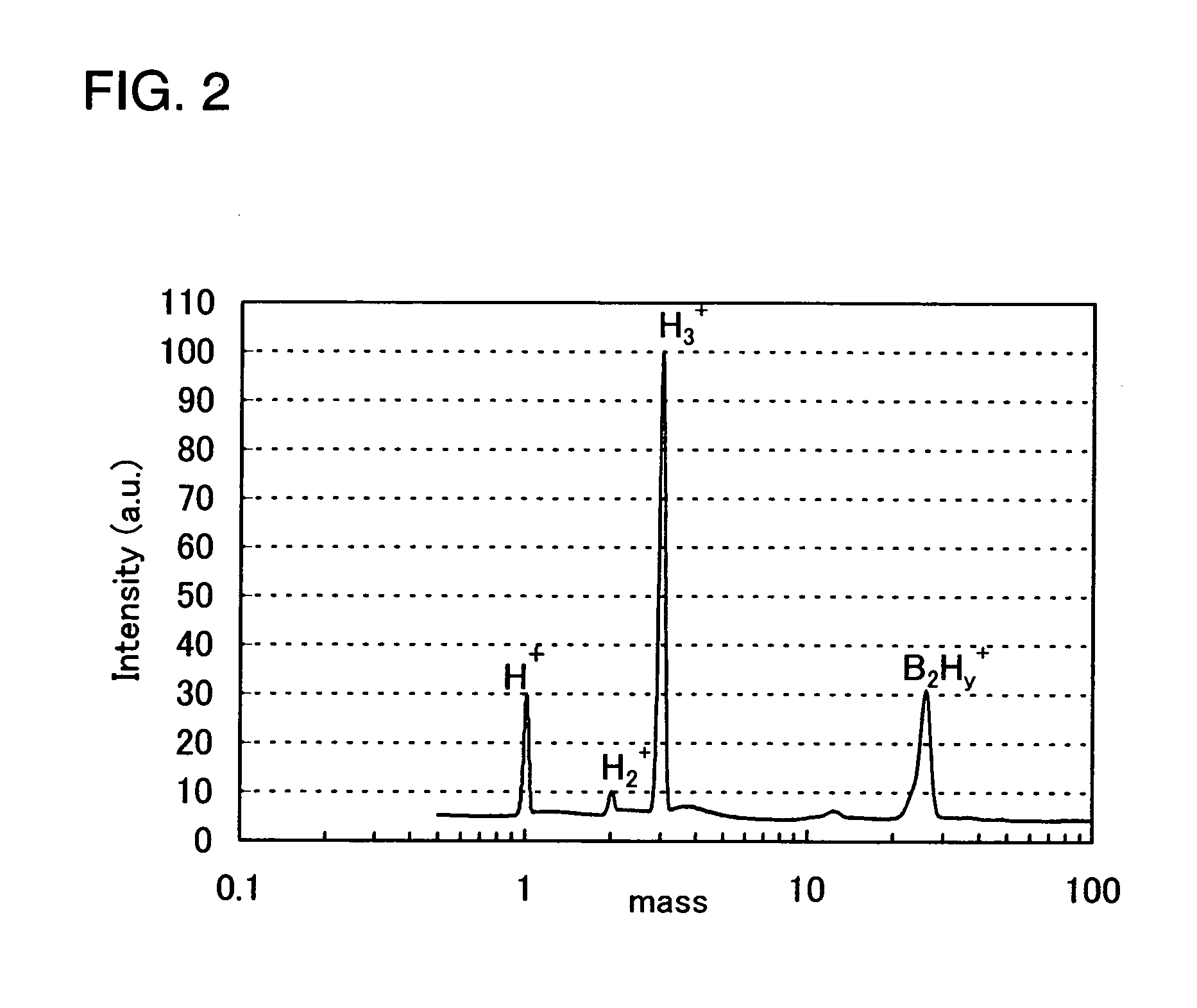

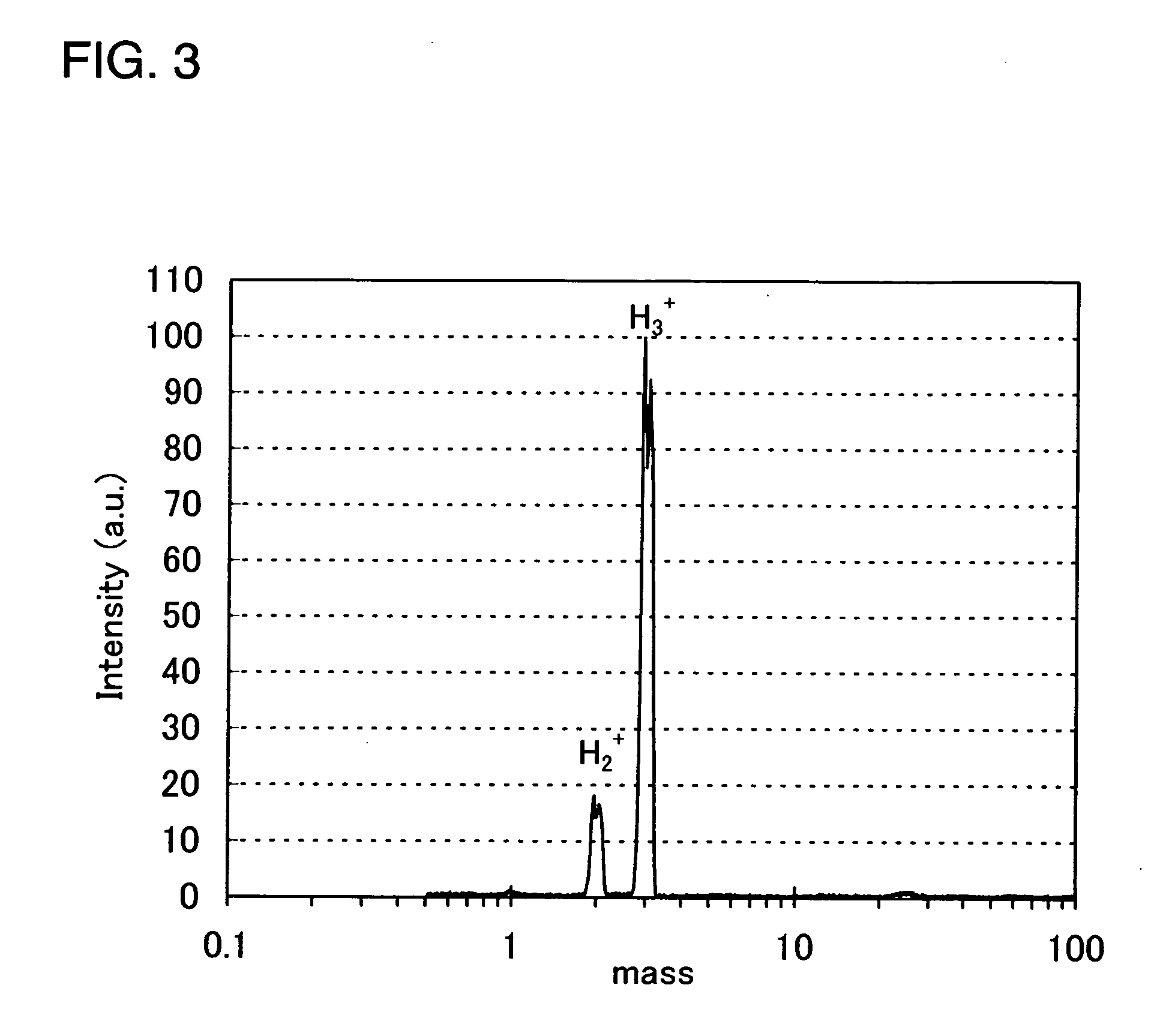

A doping method comprising the steps of; obtaining a proportion X of ions of a compound including a donor or an acceptor impurity in total ions from mass spectrum by using a first source gas of a first concentration; analyzing a peak concentration Y of the compound in a first processing object which is doped by using a second source gas of a second concentration equal to or lower than the first concentration, referring to a dose amount of total ions as Do and setting an acceleration voltage at a value, obtaining a dose amount D1 of total ions from a expression, Y=(D1 / D0)(aX+b), and doping a second processing object with the donor or the acceptor impurity by a ion doping apparatus using a third source gas, wherein a dose amount of total ions is set at D1, and an acceleration voltage is set at the value.

Owner:SEMICON ENERGY LAB CO LTD

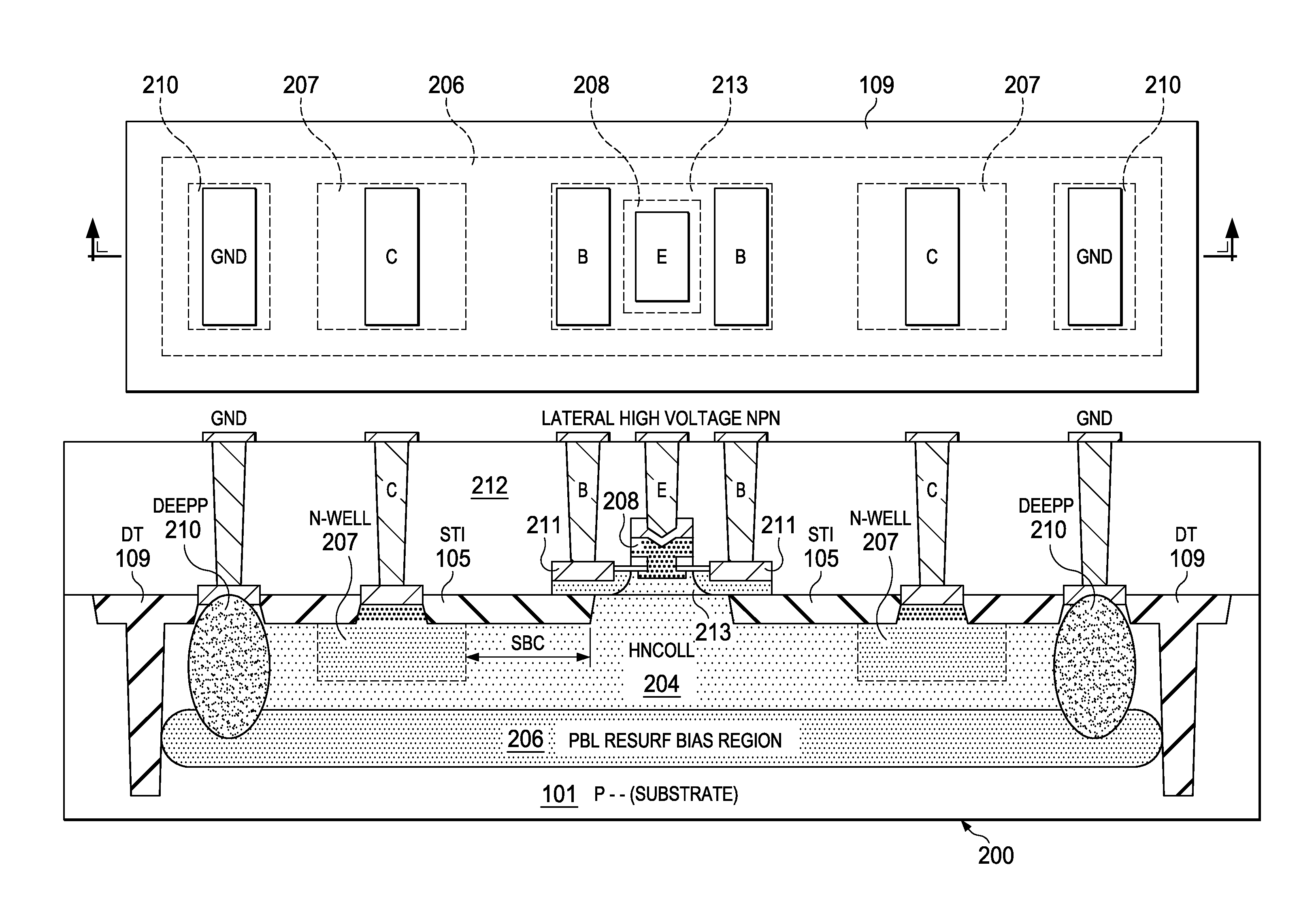

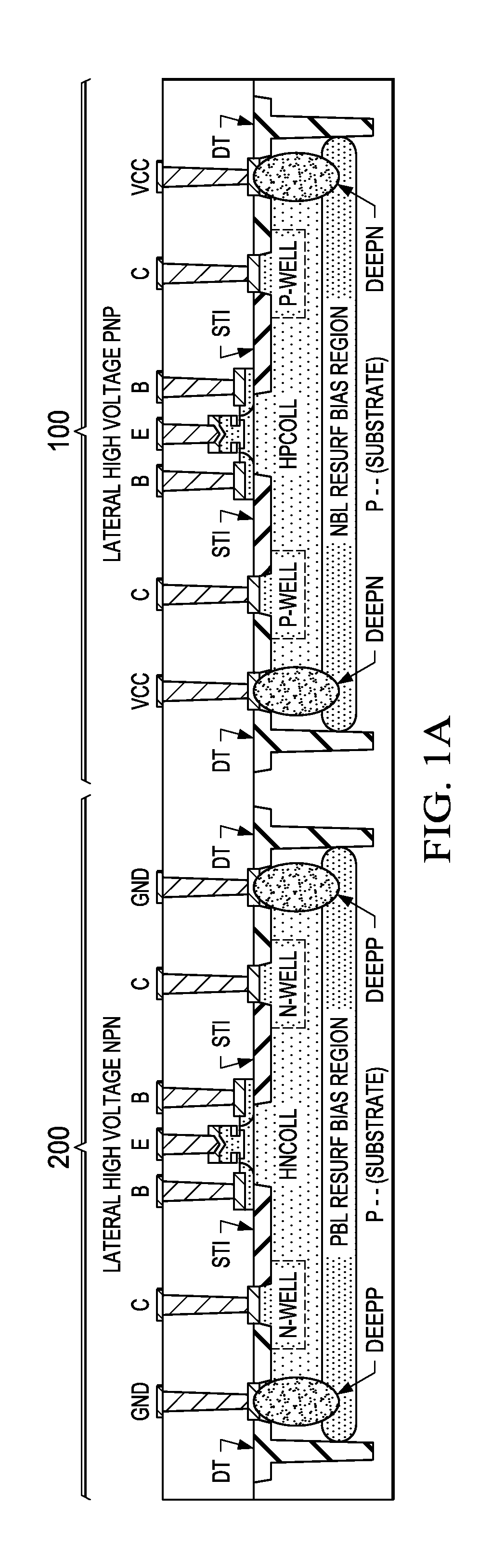

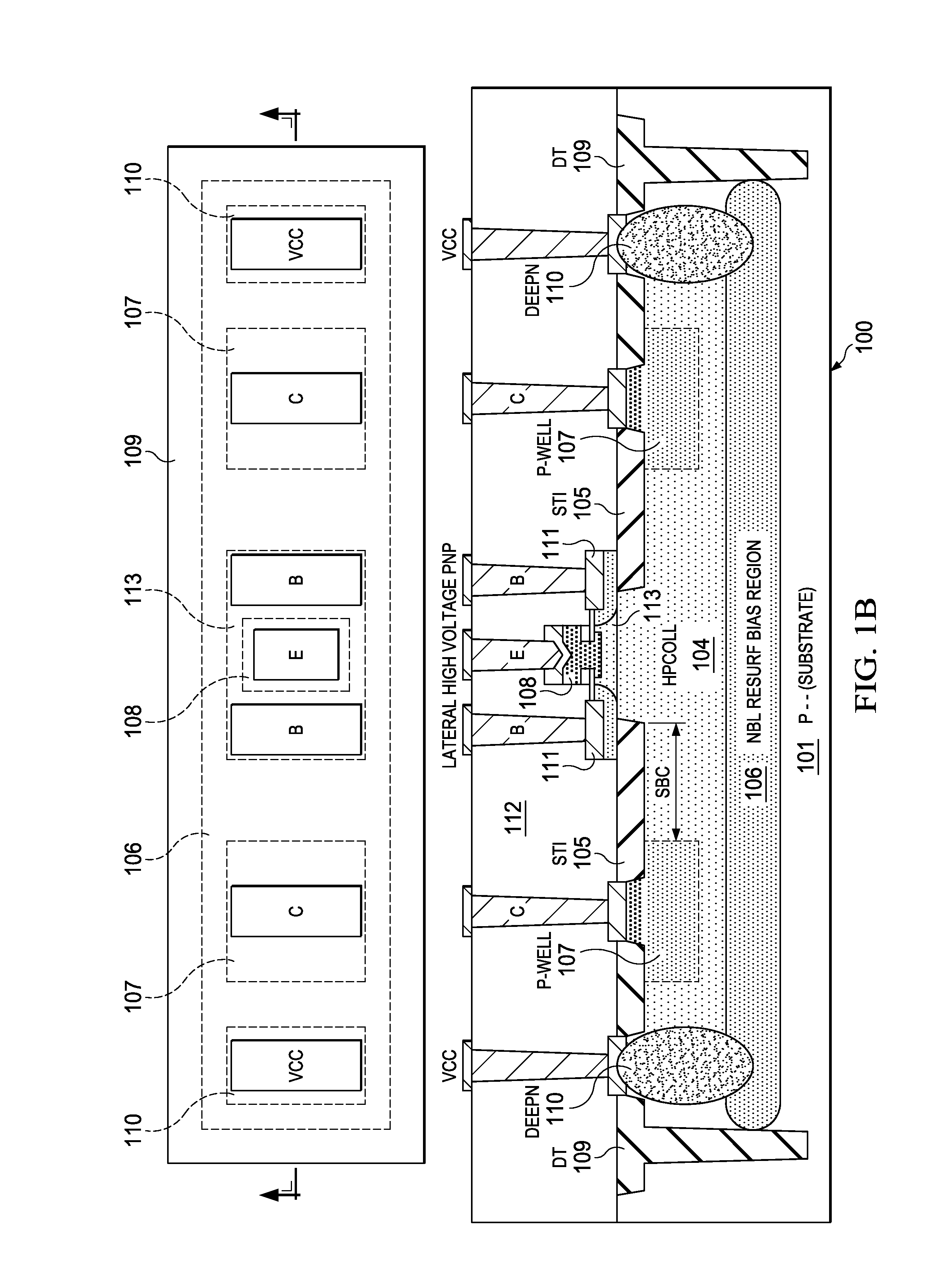

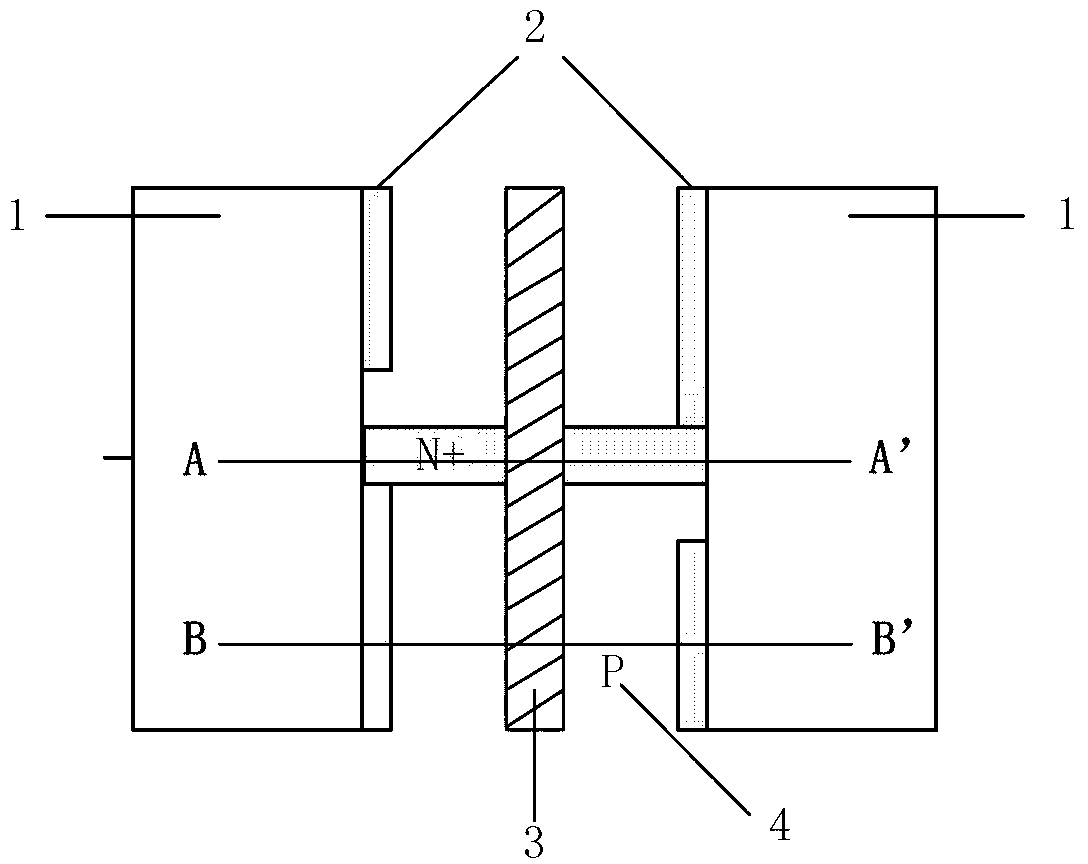

Method for creating the high voltage complementary bjt with lateral collector on bulk substrate with resurf effect

Complementary high-voltage bipolar transistors formed in standard bulk silicon integrated circuits are disclosed. In one disclosed embodiment, collector regions are formed in an epitaxial silicon layer. Base regions and emitters are disposed over the collector region. An n-type region is formed under collector region by implanting donor impurities into a p-substrate for the PNP transistor and implanting acceptor impurities into the p-substrate for the NPN transistor prior to depositing the collector epitaxial regions. Later in the process flow these n-type and p-type regions are connected to the top of the die by a deep n+ and p+ wells respectively. The n-type well is then coupled to VCC while the p-type well is coupled to GND, providing laterally depleted portions of the PNP and NPN collector regions and hence, increasing their BVs.

Owner:TEXAS INSTR INC

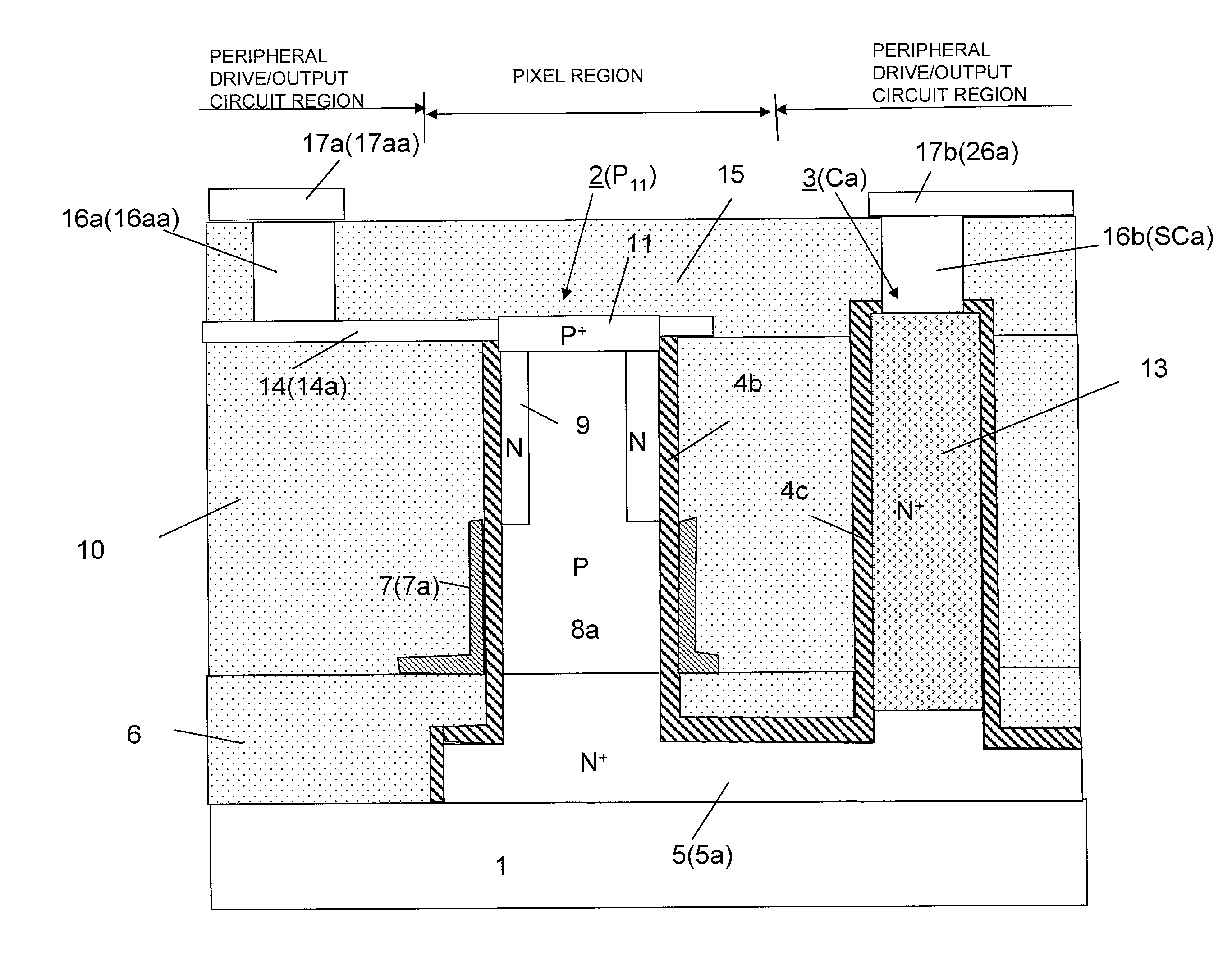

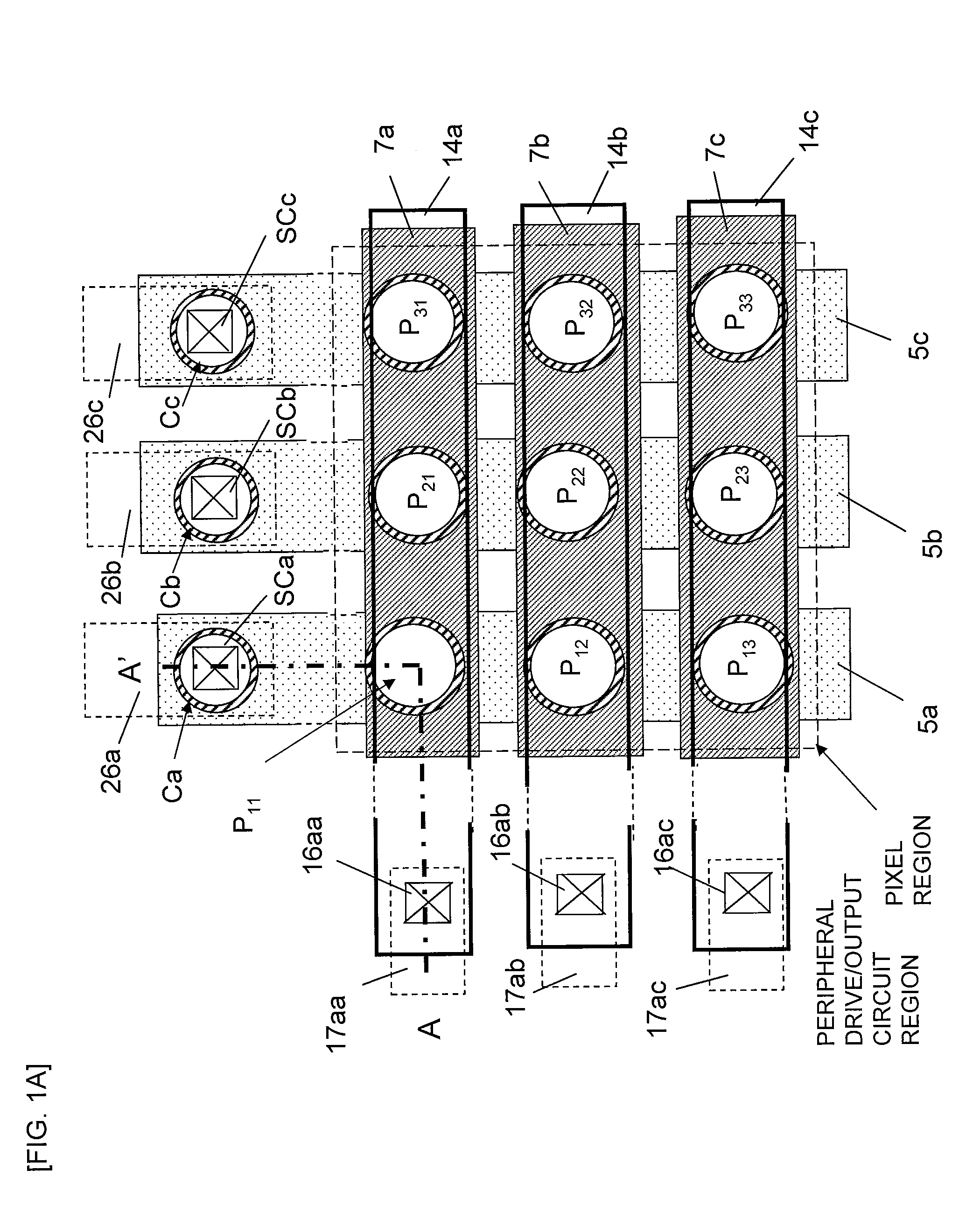

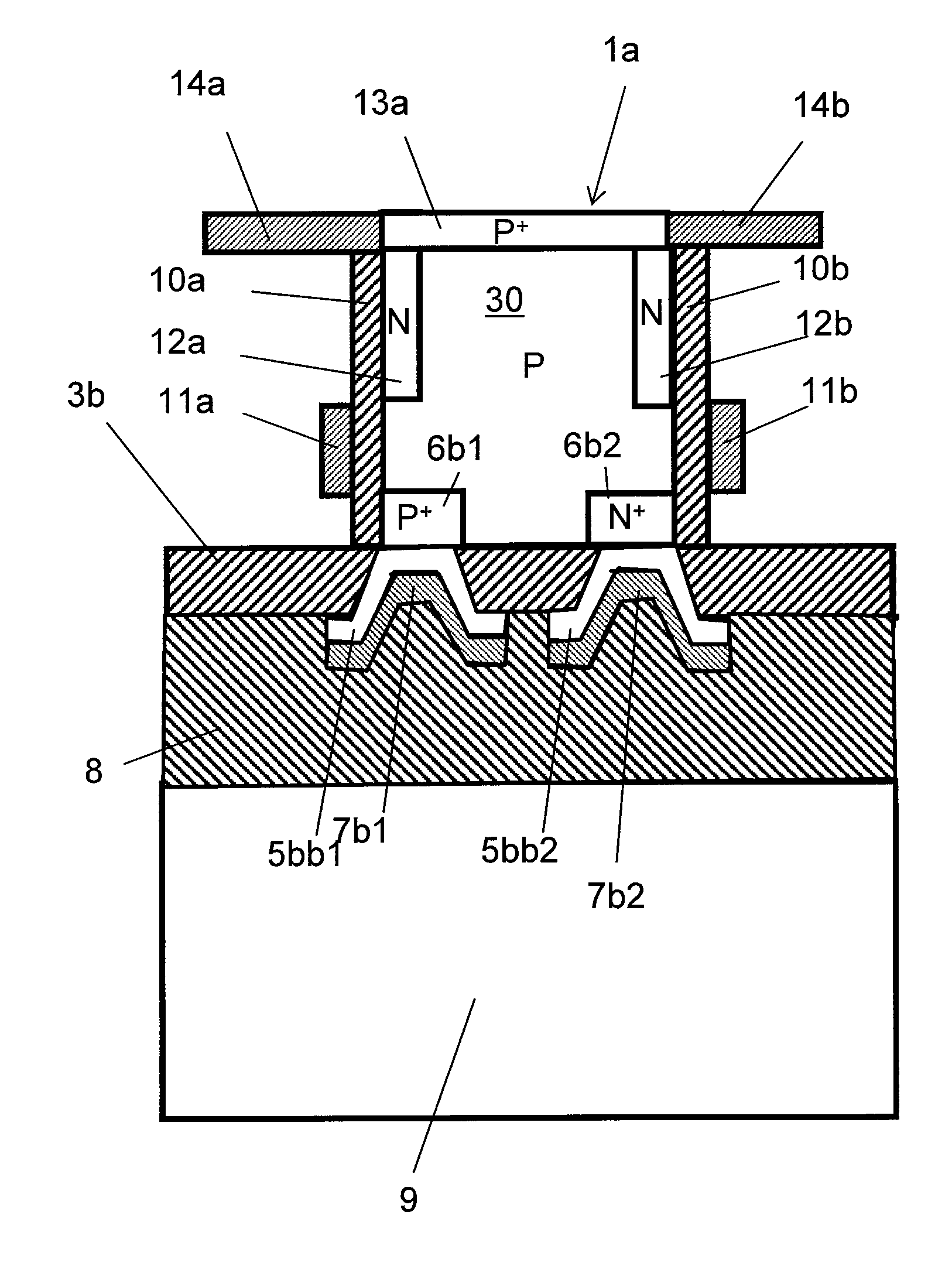

Method for producing semiconductor device and semiconductor device

ActiveUS20120228677A1Guaranteed high speed operationRun at high speedTransistorSolid-state devicesPower semiconductor deviceElectrical conductor

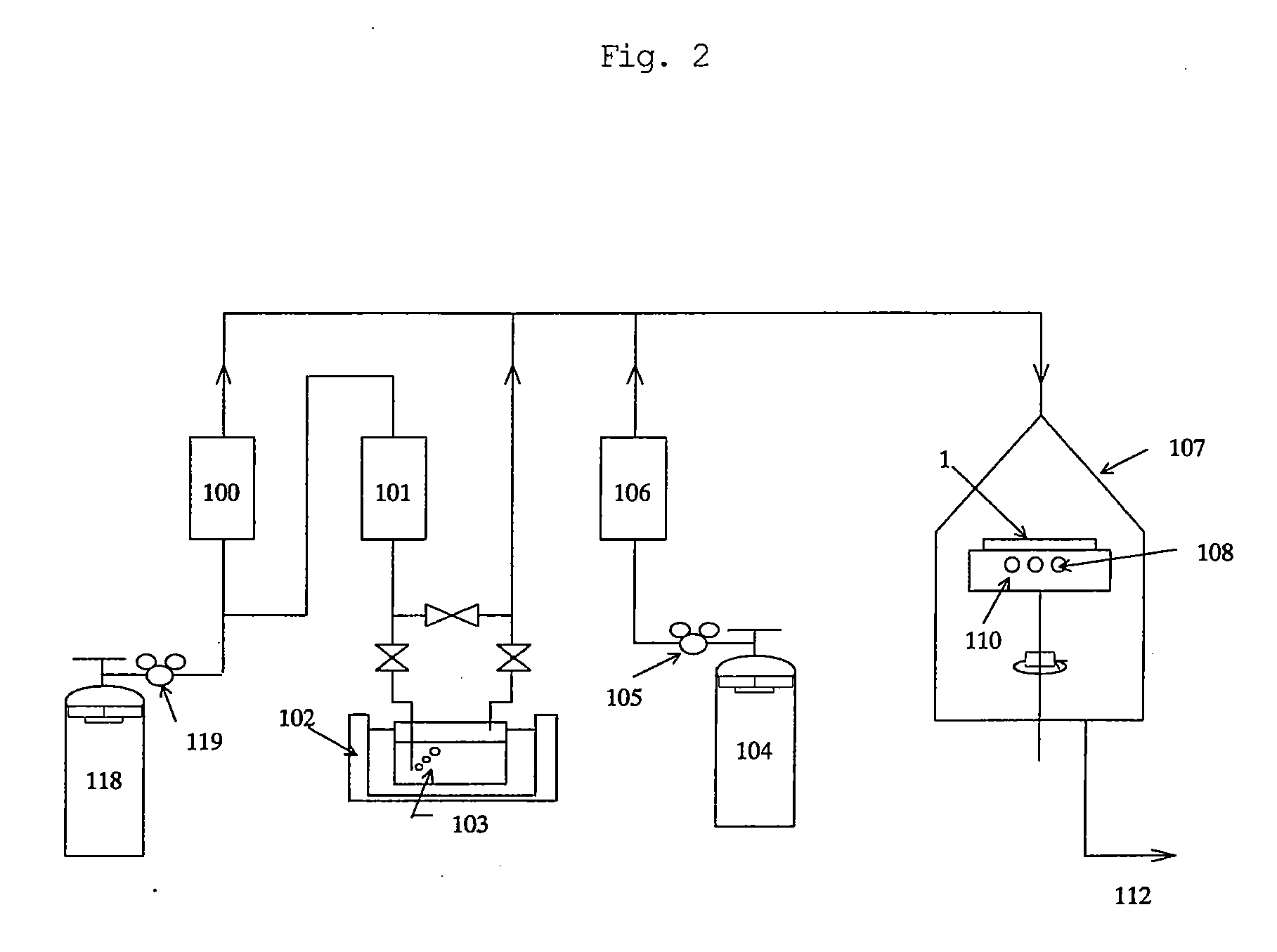

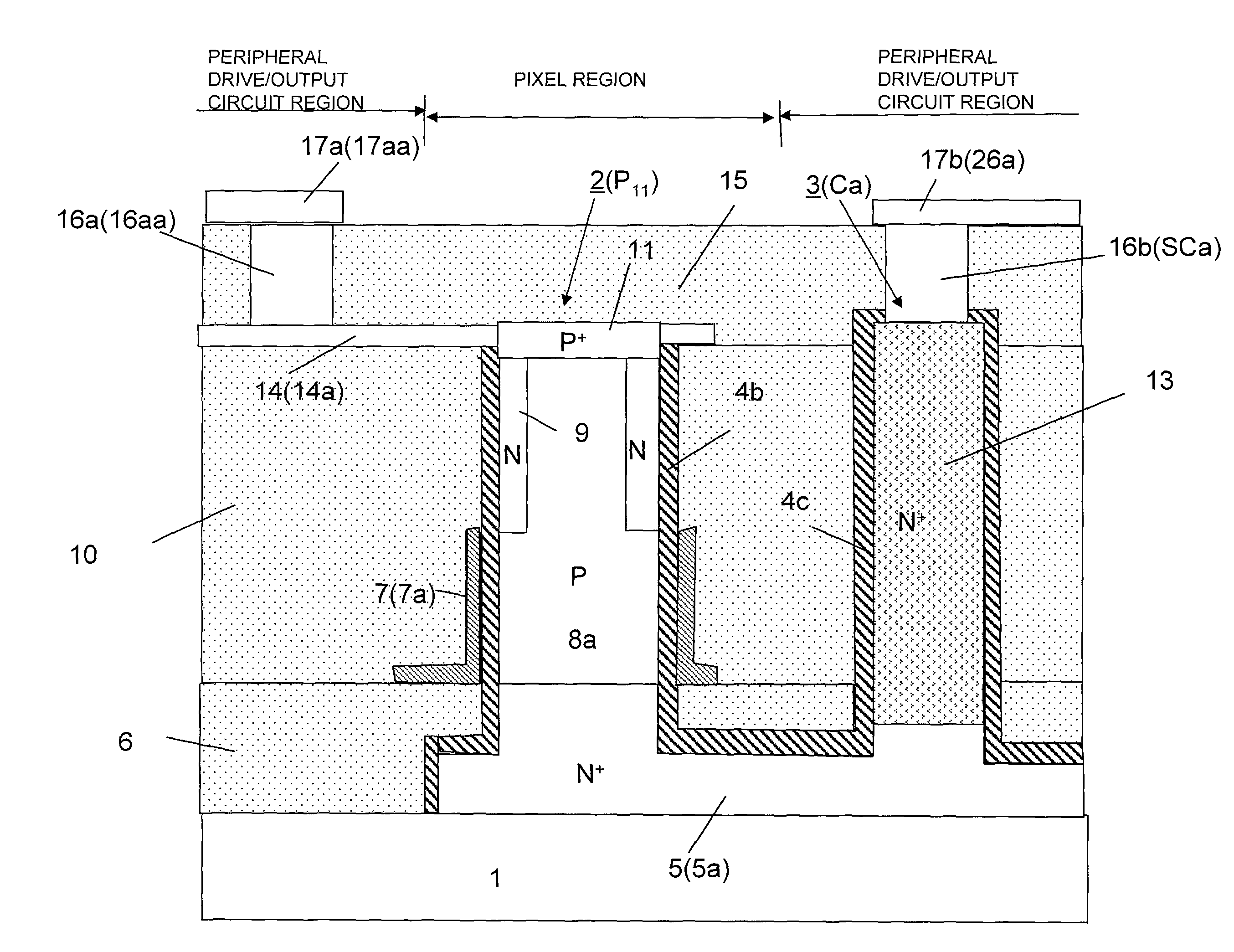

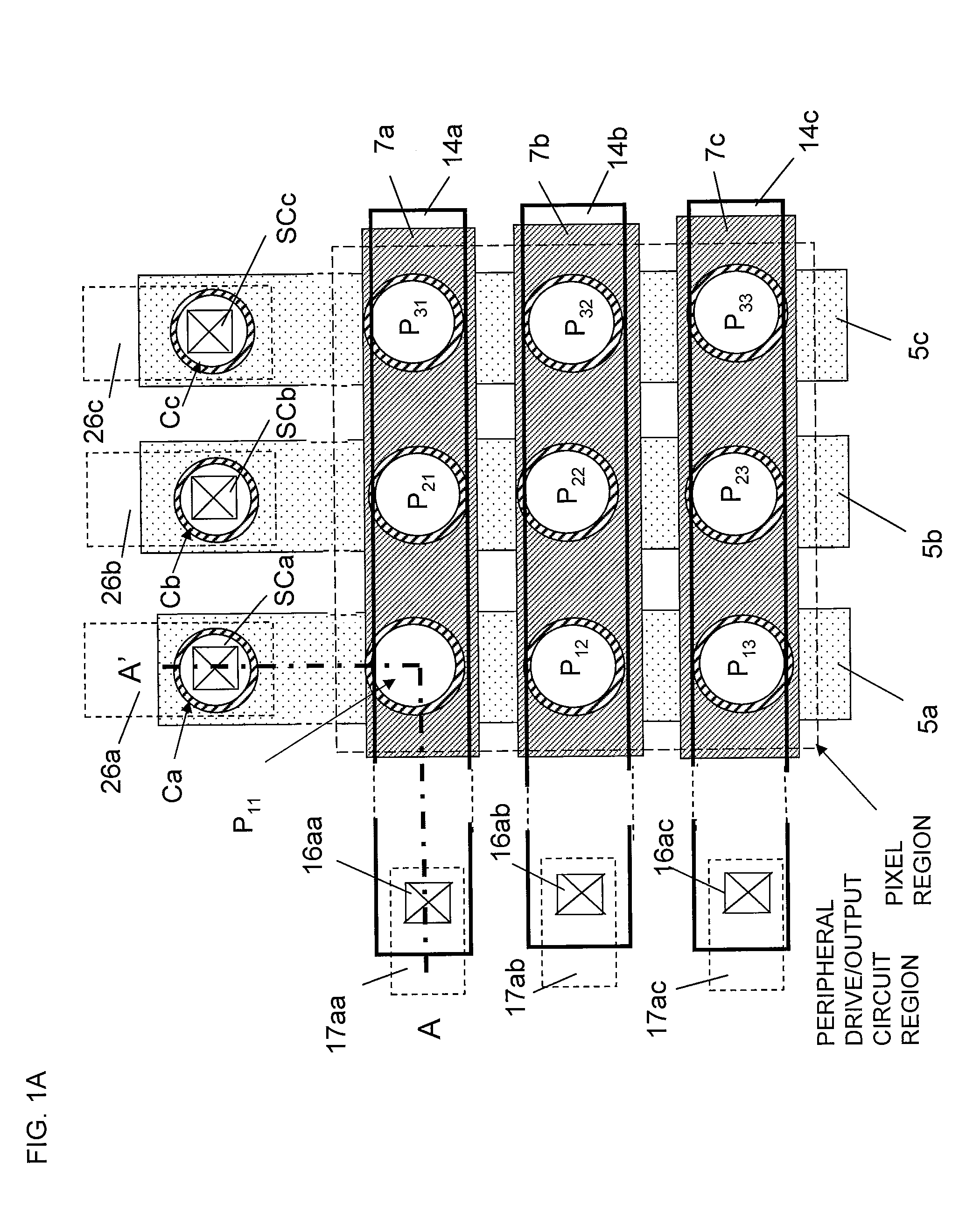

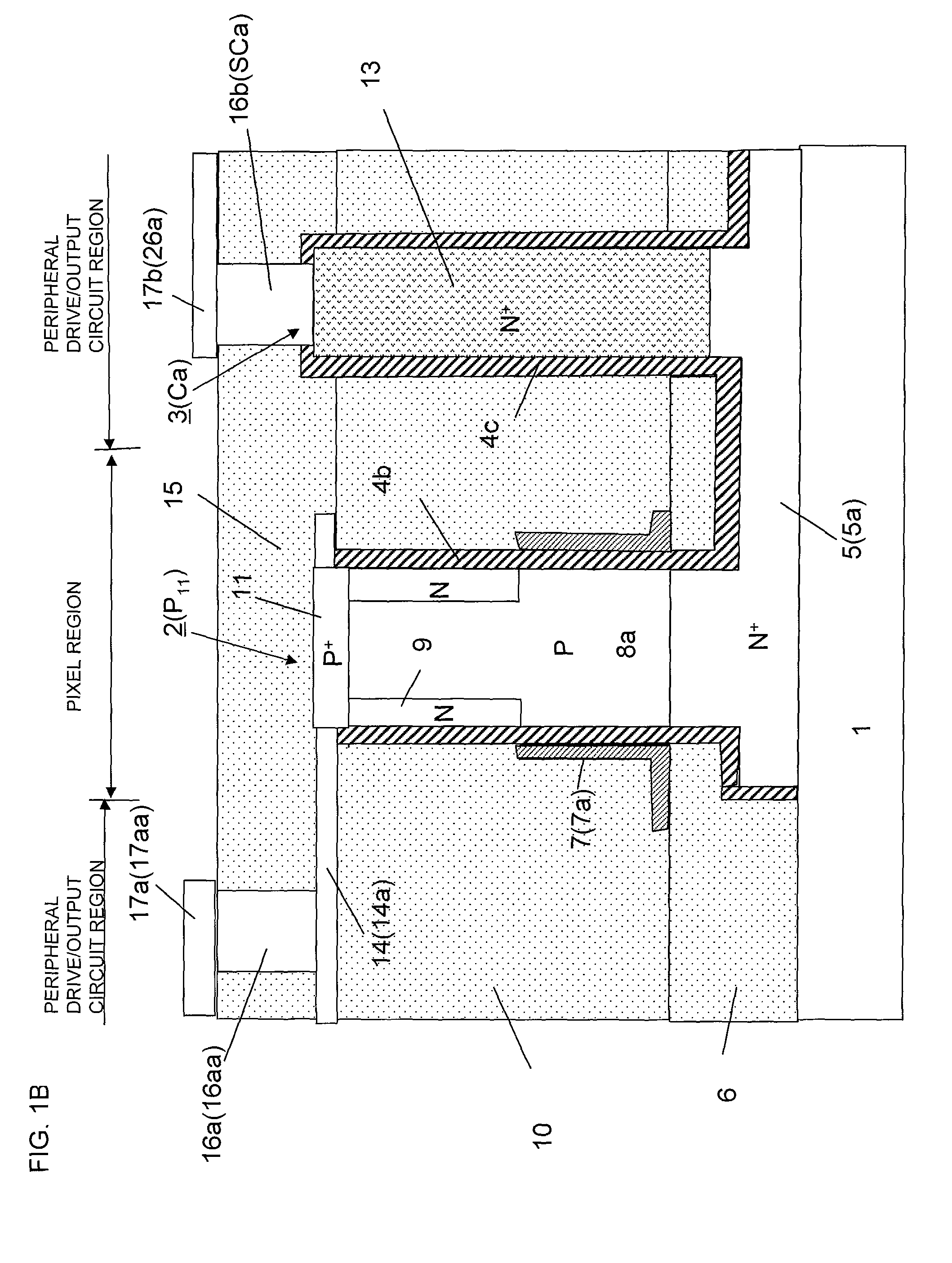

A method for producing a semiconductor device includes a step of forming a conductor layer and a first semiconductor layer containing a donor impurity or an acceptor impurity on a first semiconductor substrate; a step of forming a second insulating layer so as to cover the first semiconductor layer; a step of thinning the first semiconductor substrate to a predetermined thickness; a step of forming, from the first semiconductor substrate, a pillar-shaped semiconductor having a pillar-shaped structure on the first semiconductor layer; a step of forming a first semiconductor region in the pillar-shaped semiconductor by diffusing the impurity from the first semiconductor layer; and a step of forming a pixel of a solid-state imaging device with the pillar-shaped semiconductor into which the impurity has been diffused.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

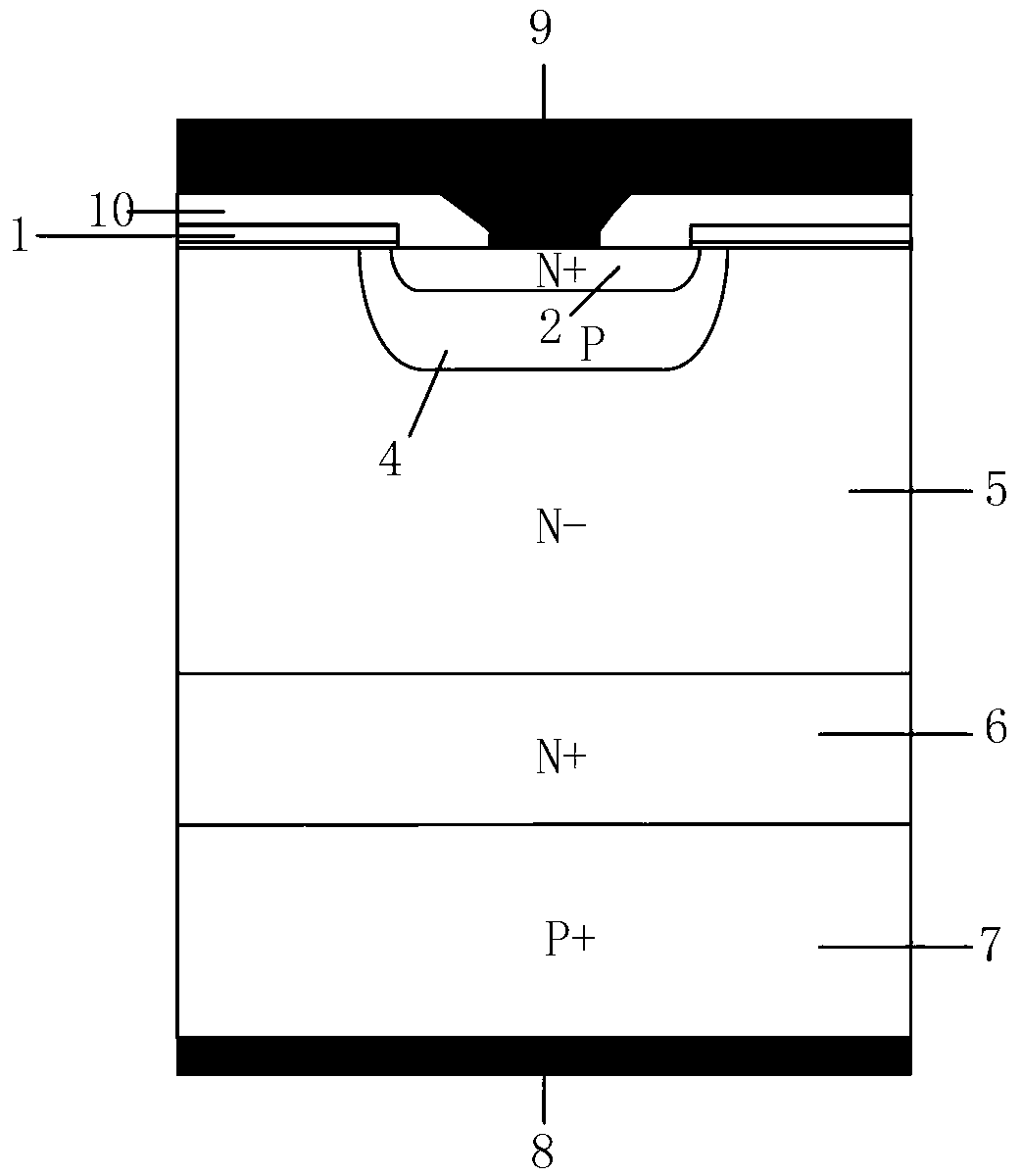

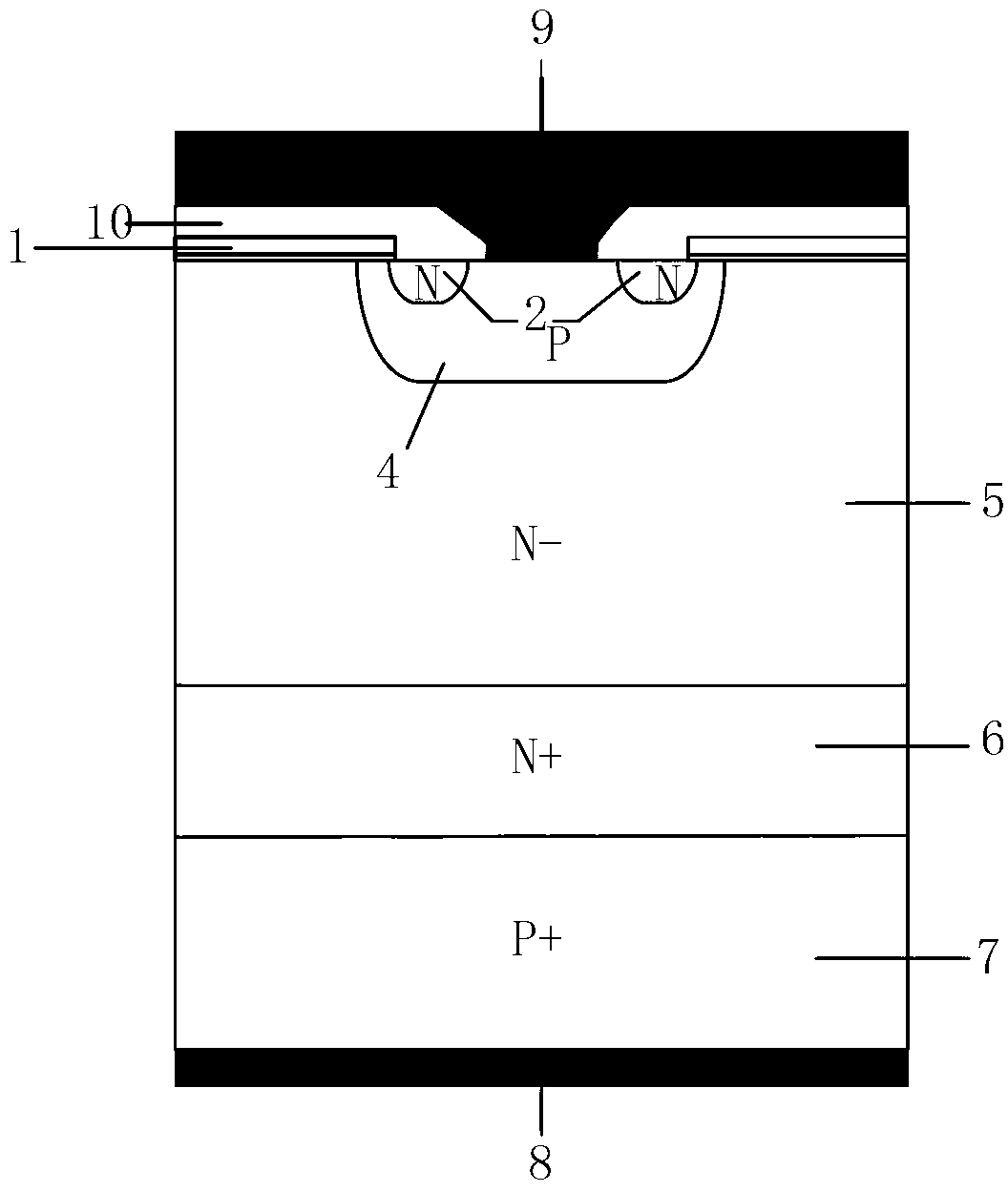

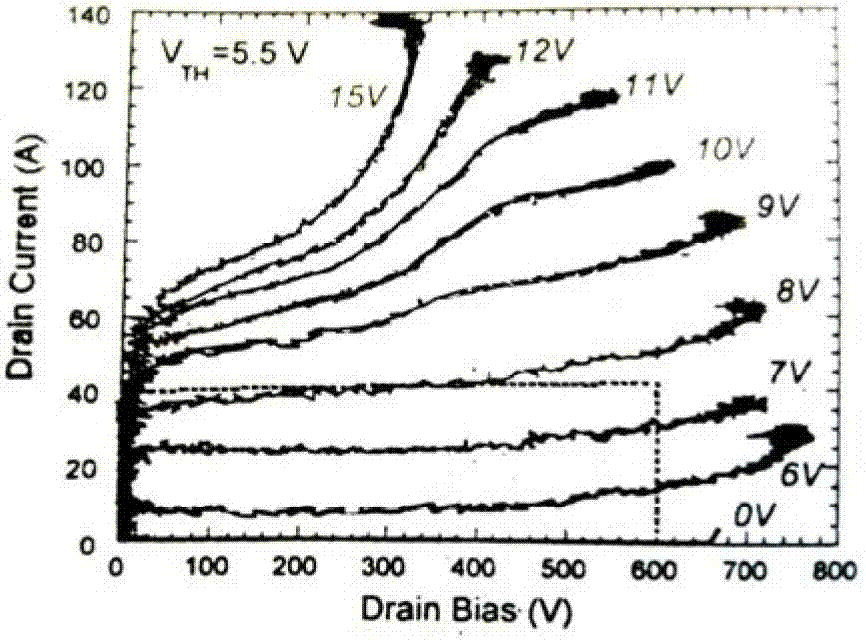

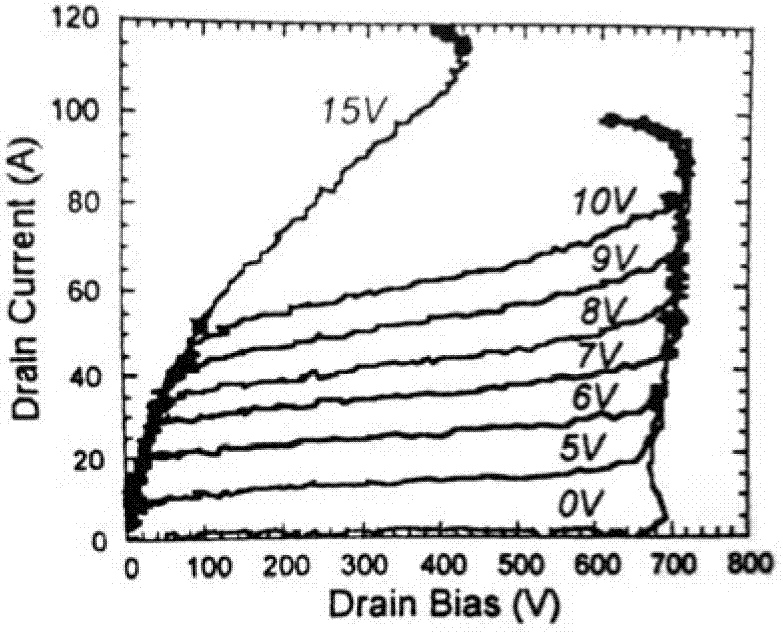

Insulated gate bipolar transistor (IGBT) device with positive temperature coefficient emitter ballast resistance

InactiveCN103258848AImprove short circuit performanceImproves latch-up resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCompensation effectEngineering

The invention discloses an insulated gate bipolar transistor (IGBT) device with positive temperature coefficient emitter ballast resistance (EBR), and belongs to the technical field of power semiconductor devices. In a conventional IGBT device of an EBR structure, the EBR is composed of a strip-shaped N<+> emitter region strip, the resistance value of the EBR generally represents a negative-temperature coefficient, namely, the higher the temperature is, the smaller the resistance value is, saturation current of the IGBT is increased, and the short-circuit capacity of the IGBT device with the positive temperature coefficient EBR will be remarkably reduced in high-temperature environments. According to the IGBT device with the positive temperature coefficient EBR, deep energy level acceptor impurities, including In or Ti or Co or Ni, are doped into the N<+> emitter region, holes produced after ionization of the deep energy level acceptor impurities have a certain compensation effect on N-type impurities, positive temperature coefficient EBR is achieved, thus the resistance value of the EBR is increased along with rise of the temperature of the IGBT device, and the short circuit capacity and latch resistant capacity of the IGBT are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Doping method and method of manufacturing field effect transistor

InactiveUS7442631B2Reduce variationSemiconductor/solid-state device manufacturingSemiconductor devicesAcceptor impurityMass spectrometry

A doping method comprising the steps of; obtaining a proportion X of ions of a compound including a donor or an acceptor impurity in total ions from mass spectrum by using a first source gas of a first concentration; analyzing a peak concentration Y of the compound in a first processing object which is doped by using a second source gas of a second concentration equal to or lower than the first concentration, referring to a dose amount of total ions as D0 and setting an acceleration voltage at a value, obtaining a dose amount D1 of total ions from a expression, Y=(D1 / D0)(aX+b), and doping a second processing object with the donor or the acceptor impurity by a ion doping apparatus using a third source gas, wherein a dose amount of total ions is set at D1, and an acceleration voltage is set at the value.

Owner:SEMICON ENERGY LAB CO LTD

SiC crystal and semiconductor device

InactiveUS20080277670A1Conductive materialWelding/cutting media/materialsAcceptor impurityLight emission

The present invention discloses a SiC crystal, comprising: acceptor impurities that are in a concentration greater than 5×1017 cm−3; donor impurities that are in a concentration less than 1×1019 cm−3 and greater than the concentration of the acceptor impurities. The present invention discloses a semiconductor device, comprising: a SiC fluorescent layer having acceptor impurities that are in a concentration greater than 5×1017 cm−3 and donor impurities that are in a concentration less than 1×1019 cm−3 and greater than the concentration of the acceptor impurities; and a light emission layer that is layered on the SiC fluorescent layer and emits excitation light for the SiC fluorescent layer.

Owner:EL SEED CORP

Pillar-shaped semiconductor device and method for producing the same

ActiveUS20160155842A1Accurate and easy formationSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideElectrical conductor

An opening extending through a gate insulating layer and a gate conductor layer is formed in the circumferential portion of a Si pillar at an intermediate height of the Si pillar. A laminated structure including two sets each including a Ni film, a poly-Si layer containing donor or acceptor impurity atoms, and a SiO2 layer is formed so as to surround the opening. A heat treatment is carried out to form silicide from the poly-Si layers and this silicide formation causes the resultant NiSi layers to protrude and come into contact with the side surface of the Si pillar. The donor or acceptor impurity atoms diffuse from the NiSi layers into the Si pillar to thereby form an N+ region and a P+ region serving as a source or a drain of SGTs.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

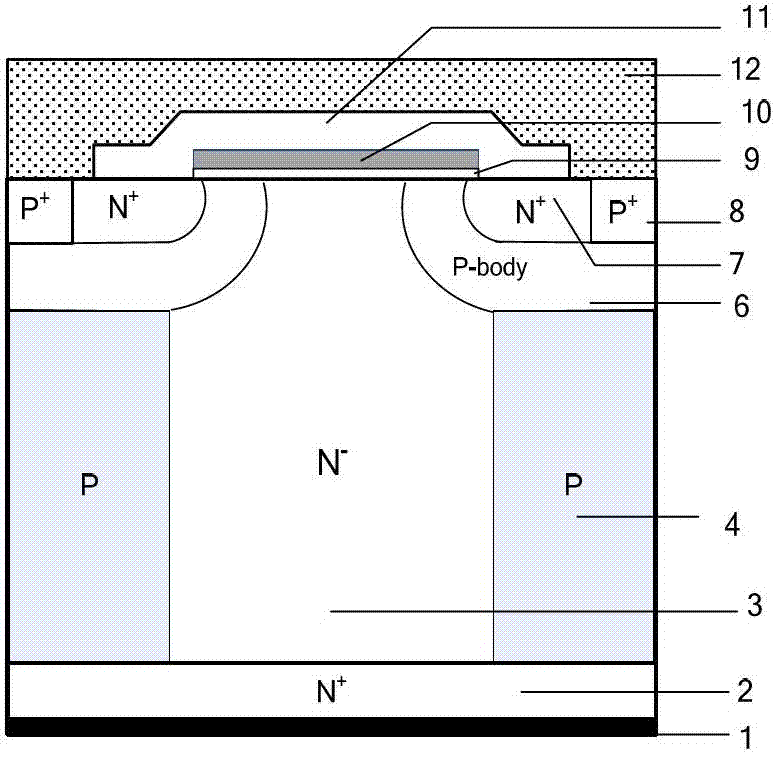

Super-junction vertical double-diffused metal oxide semiconductor (VDMOS) capable of effectively preventing charge imbalance

InactiveCN102738214AImprove breakdown voltageImprove safe work areaSemiconductor devicesCurrent rangeElectron avalanche

The invention discloses a super-junction vertical double-diffused metal oxide semiconductor (VDMOS) capable of effectively preventing charge imbalance and belongs to the field of power semiconductor devices. Deep energy level impurities are doped in the conventional super-junction VDMOS structure and a columnar region (4) of which the conductive type is opposite to that of an epitaxial region (3), wherein donor impurities such as S, Se or Te are doped in an N-channel device, and acceptor impurities such as In, Ti or Zn are doped in a P-channel device. The deep energy level donor impurities are low in ionization rate at normal temperature, the contribution of the deep energy level donor impurities on the doping concentration of the columnar region (4) can be ignored, and the static load balance of the device is not influenced. When the device is positively conducted and operates under high current, the ionization rate of the deep energy level impurities can be greatly improved along with increase of the temperature of the device, the doping level of the columnar region (4) is relatively reduced, the phenomenon that the avalanche breakdown voltage of the device is reduced caused by load imbalance of the super-junction structure because carriers flow through the epitaxial region (3) is effectively avoided, the operative current range of the device is widened, and the positive safety working area of the device is enlarged.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

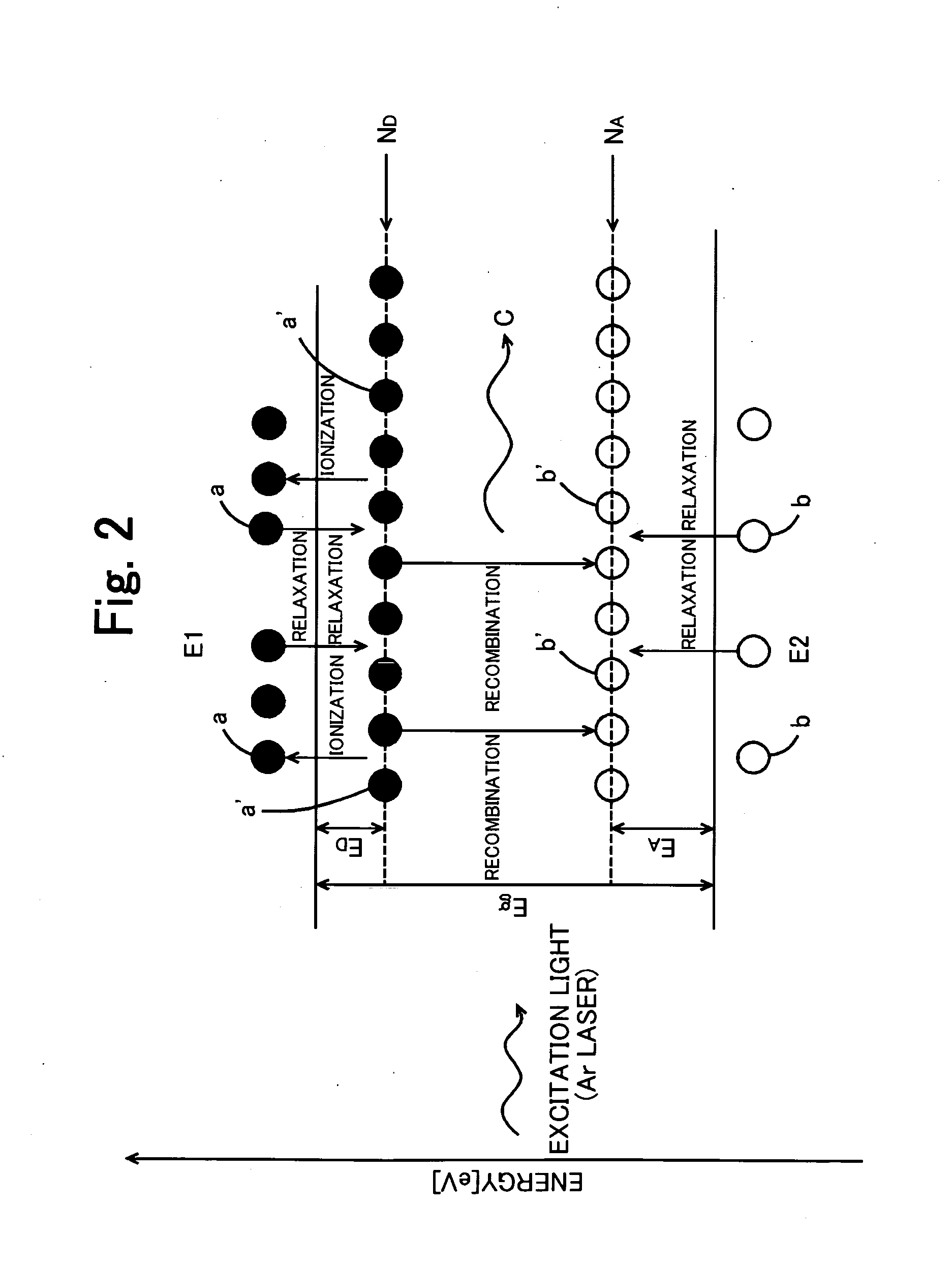

Silicon infrared optical detector structure and manufacturing method therefor

InactiveCN105932077AProcess compatibleFinal product manufacturePhotovoltaic energy generationSingle crystalAcceptor doping

The invention relates to a silicon infrared optical detector structure and a manufacturing method therefor. A super-heavy doped silicon single crystal material with weight compensation is taken as an infrared photoelectric conversion material; a super-heavy donor doped silicon single crystal material with weight acceptor compensation or a super-heavy acceptor doped silicon single crystal material with weight donor compensation is singly adopted for absorbing infrared light to generate electron-hole pairs; or the super-heavy donor doped silicon single crystal material with weight acceptor compensation and the super-heavy acceptor doped silicon single crystal material with weight donor compensation are adopted concurrently to form a PN junction for absorbing infrared light to generate the electron-hole pairs. According to the silicon infrared optical detector structure, the donor impurity and the acceptor impurity are heavily doped in the silicon single crystal material concurrently, so that a donor impurity energy band and an acceptor impurity energy band are formed in a forbidden band at the same time; meanwhile, an energy band tail connected with a conduction band and an energy band tail connected with a valence band are formed as well, so that the energy levels of the impurities participate in the infrared photon absorption and electron and hole jumps; and therefore, the photoelectric conversion efficiency of the silicon material at the near infrared communication waveband is improved.

Owner:NAT CENT FOR ADVANCED PACKAGING

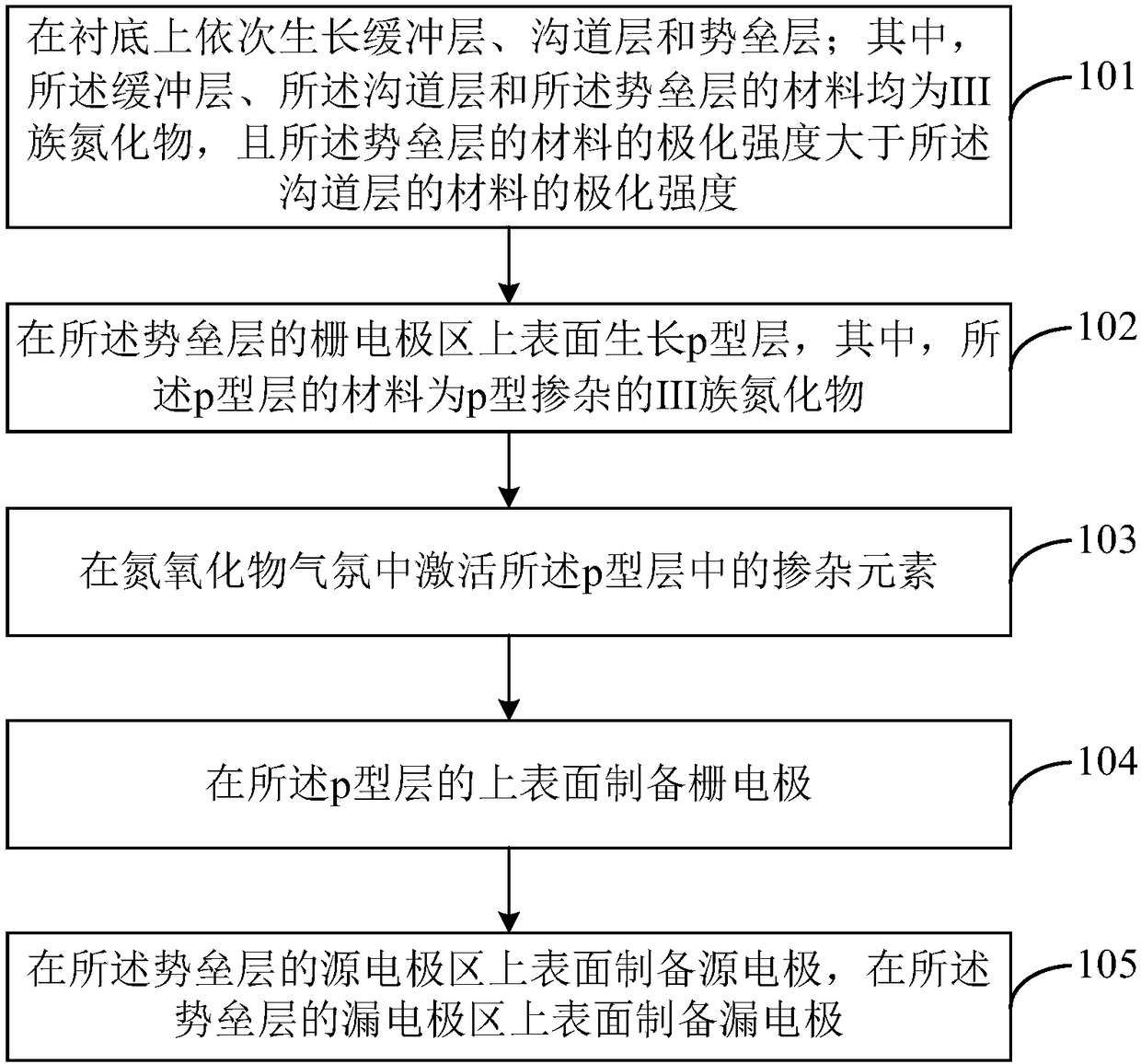

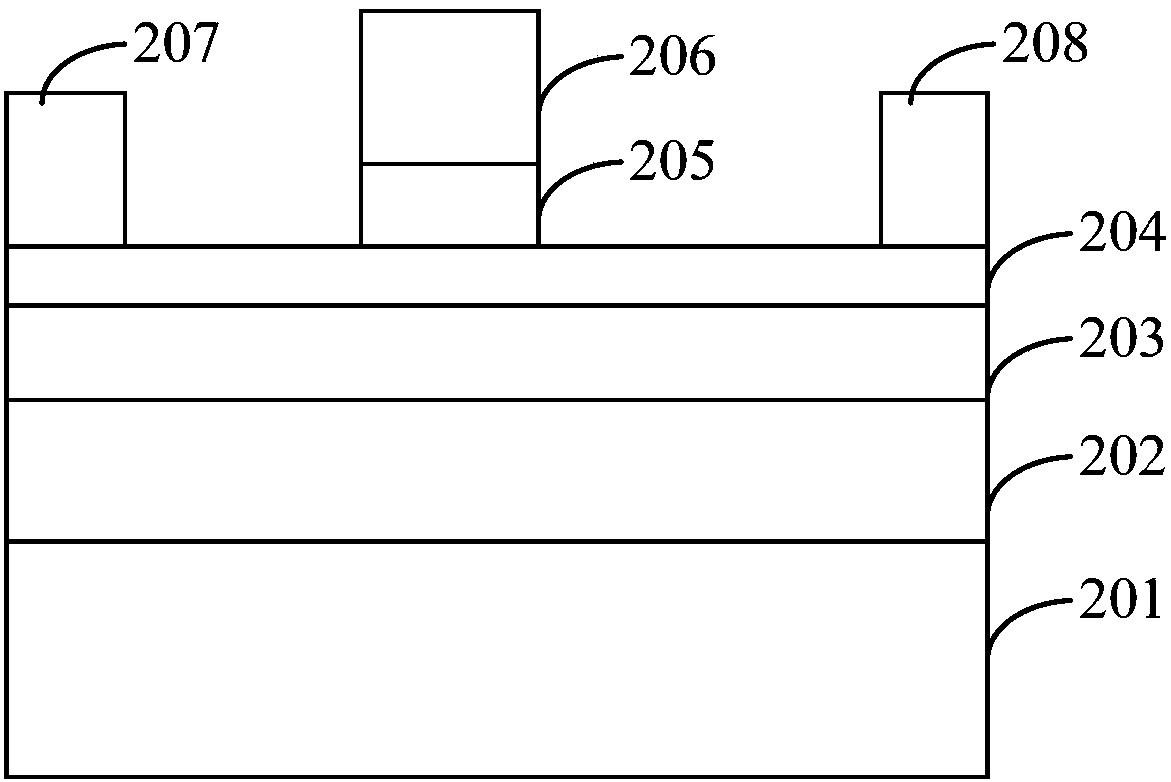

Preparation method of enhanced high-electron-mobility transistor

ActiveCN108447788AIncrease the carrier concentrationReduce self-compensation effectSemiconductor/solid-state device manufacturingSemiconductor devicesNitrogen oxidesAcceptor impurity

The invention is suitable for the technical field of semiconductors, and provides a preparation method of an enhanced high-electron-mobility transistor. The method comprises the steps that a buffer layer, a channel layer and a barrier layer are grown on a substrate in turn, wherein the material of the buffer layer, the channel layer and the barrier layer is the III-nitride, and the intensity of polarization of the material of the barrier layer is greater than that of the material of the channel layer; a p-type doped III-nitride p-type layer is grown on the upper surface of the gate electrode region of the barrier layer; the doping element in the p-type layer is activated in the atmosphere of the nitrogen oxide; a gate electrode is formed on the upper surface of the p-type layer; and a source electrode is formed on the upper surface of the source electrode region of the barrier layer, and a drain electrode is formed on the upper surface of the drain electrode region of the barrier layer. The ionization rate of the acceptor impurities can be enhanced and thus the carrier concentration of the p-type layer can be enhanced.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com