Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

73results about How to "Improve safe work area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

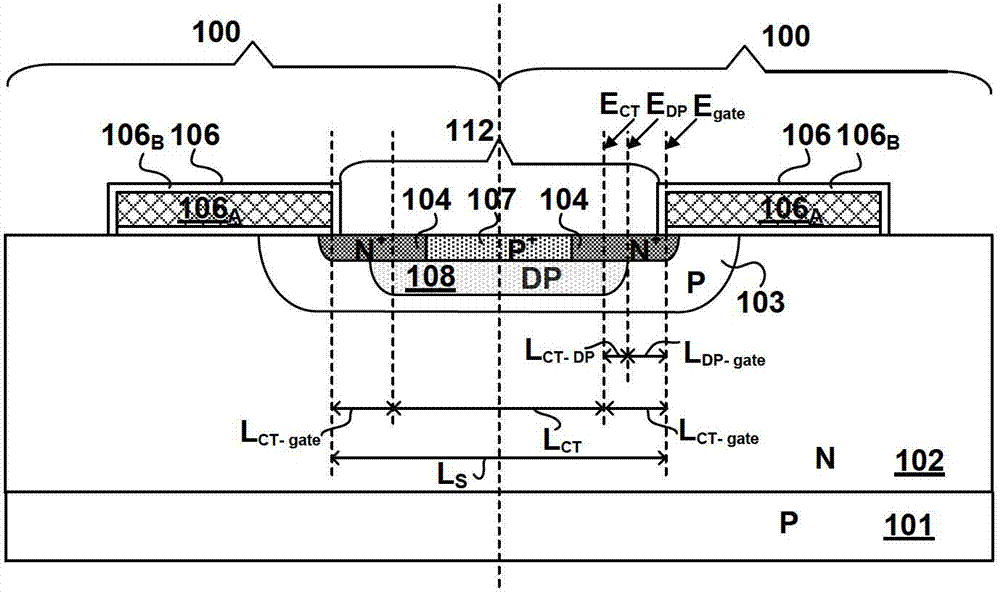

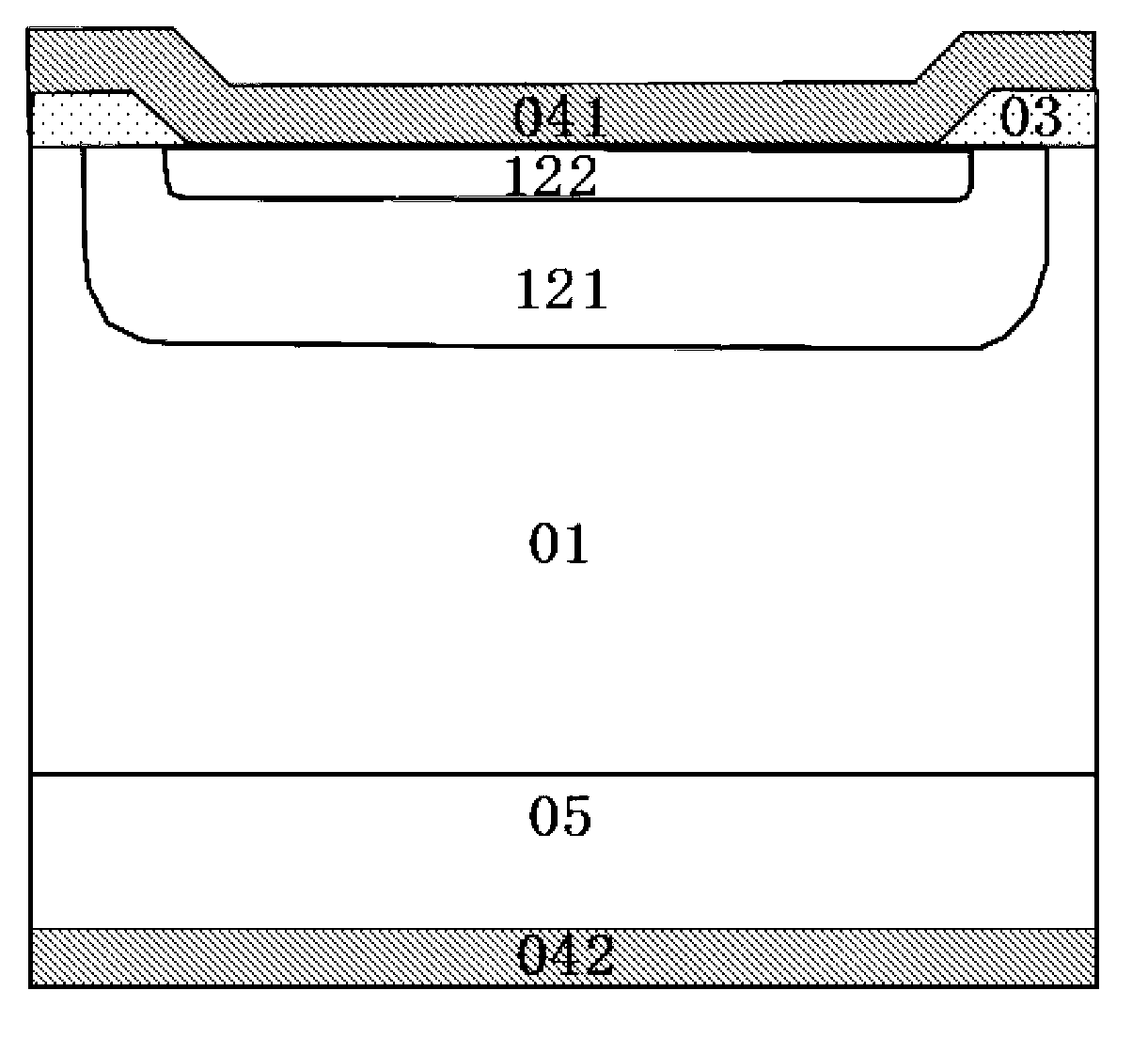

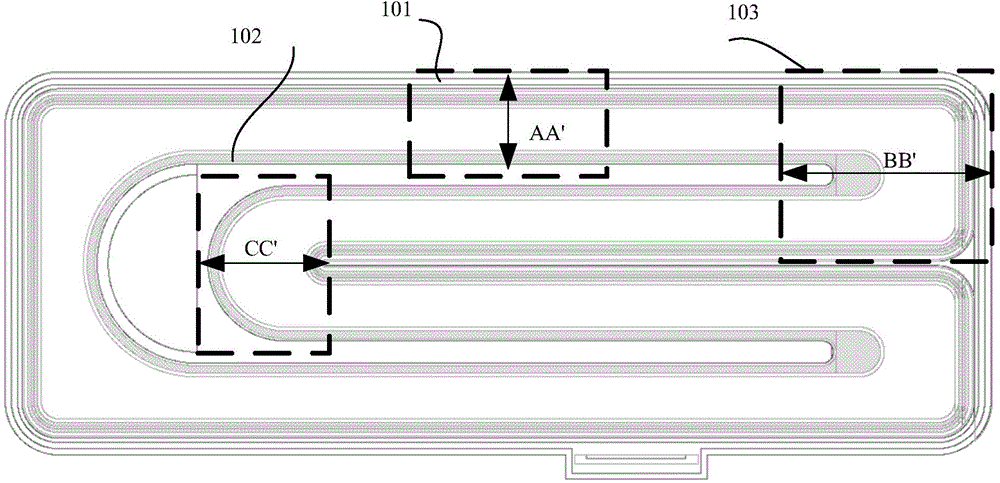

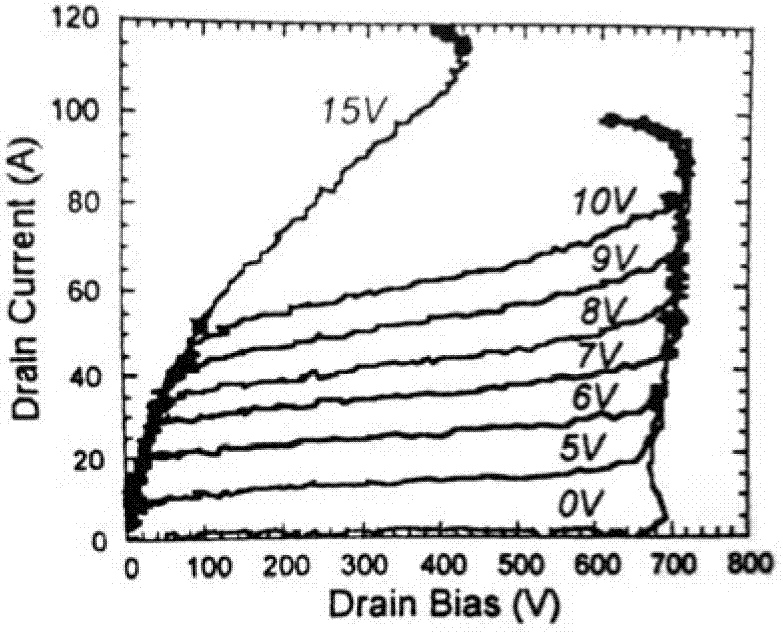

Large-current silicon on insulator lateral insulated gate bipolar transistor device

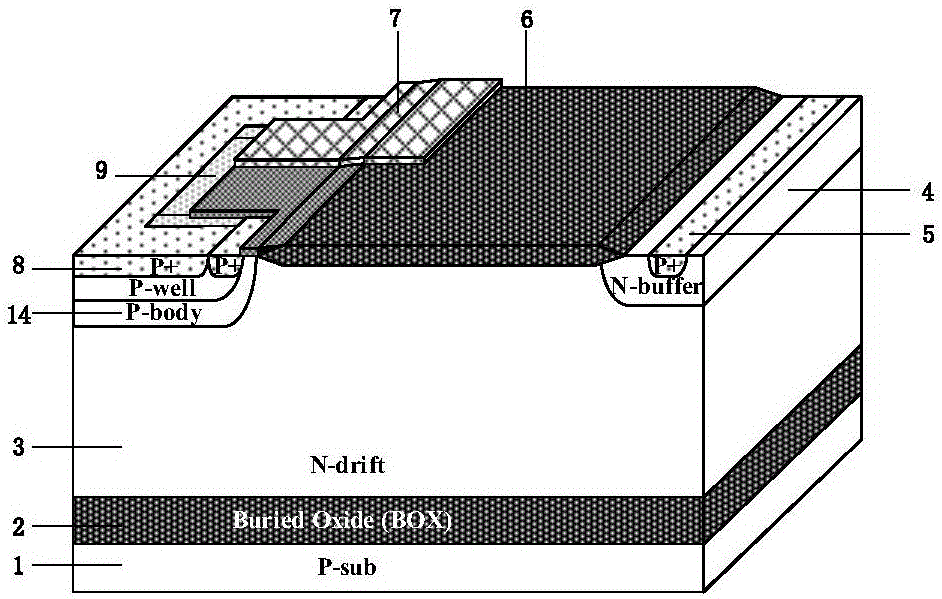

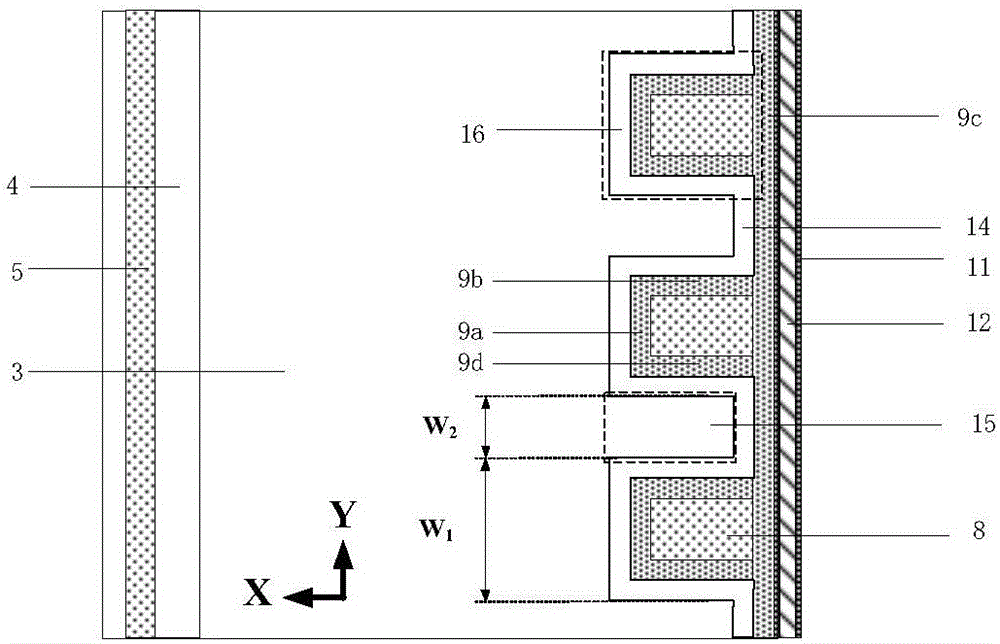

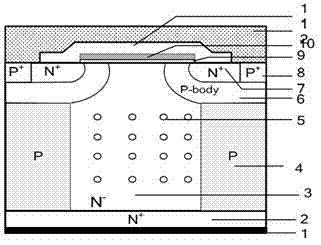

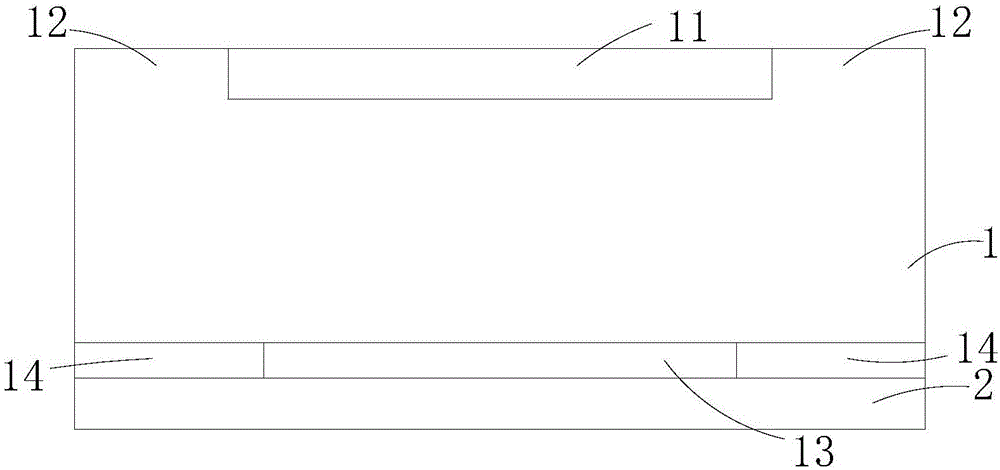

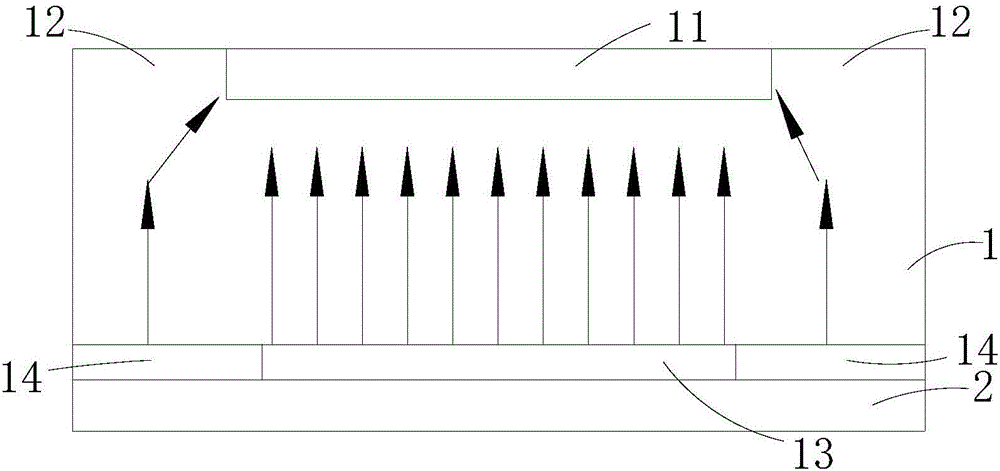

The invention discloses a novel large-current silicon on insulator lateral insulated gate bipolar transistor. According to the semiconductor, a buried oxide is arranged on a P-type substrate, an N-type drift region is arranged on the buried oxide, a P-type body region and an N-type buffer region are arranged on the N-type drift region, the N-type buffer region is internally provided with a P-type collector region, a collector metal is connected onto the P-type collector region, a field oxygen layer is arranged above the N-type drift region, the P-type body region is internally provided with a P-type emitter region, an N-type emitter region is arranged around, an emitter metal is connected onto the N-type emitter region and the P-type emitter region, a gate oxide is arranged between the field oxygen layer and the N-type emitter region, a first polysilicon layer is arranged on the surface of the gate oxide, a first gate metal is connected onto the surface of the first polysilicon layer, a longitudinal groove is arranged outside the P-type body region, the longitudinal groove is internally provided with silicon dioxide and a second polysilicon layer coated by other medium, and a second gate metal is connected onto the second polysilicon layer.

Owner:SOUTHEAST UNIV

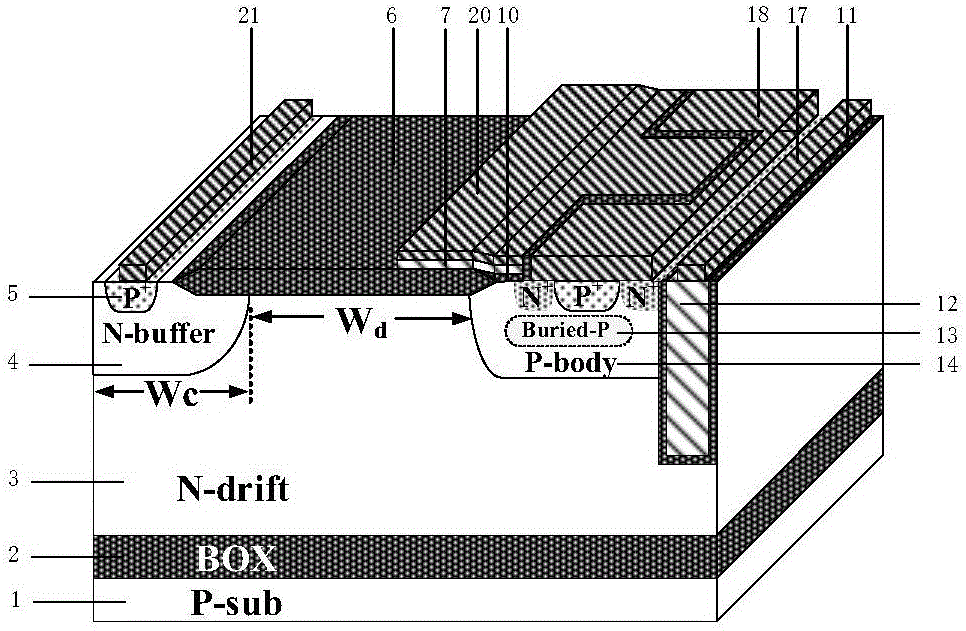

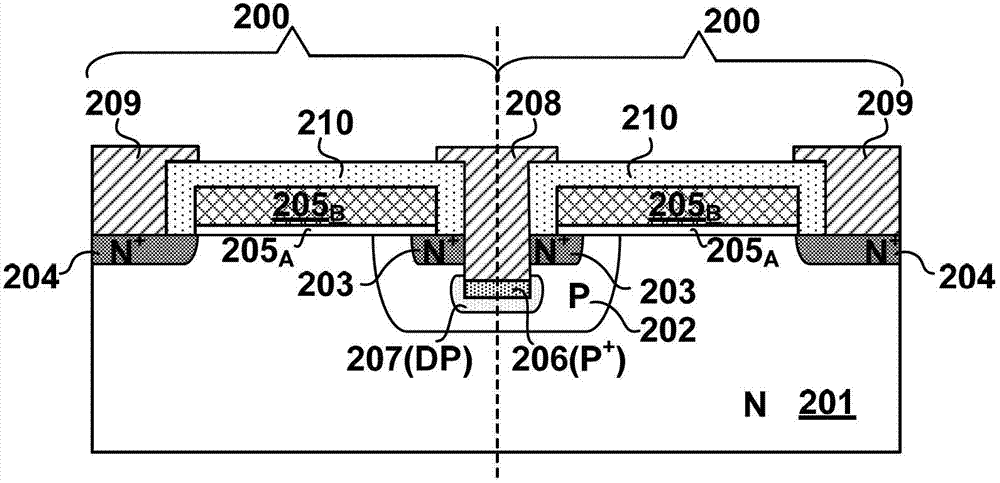

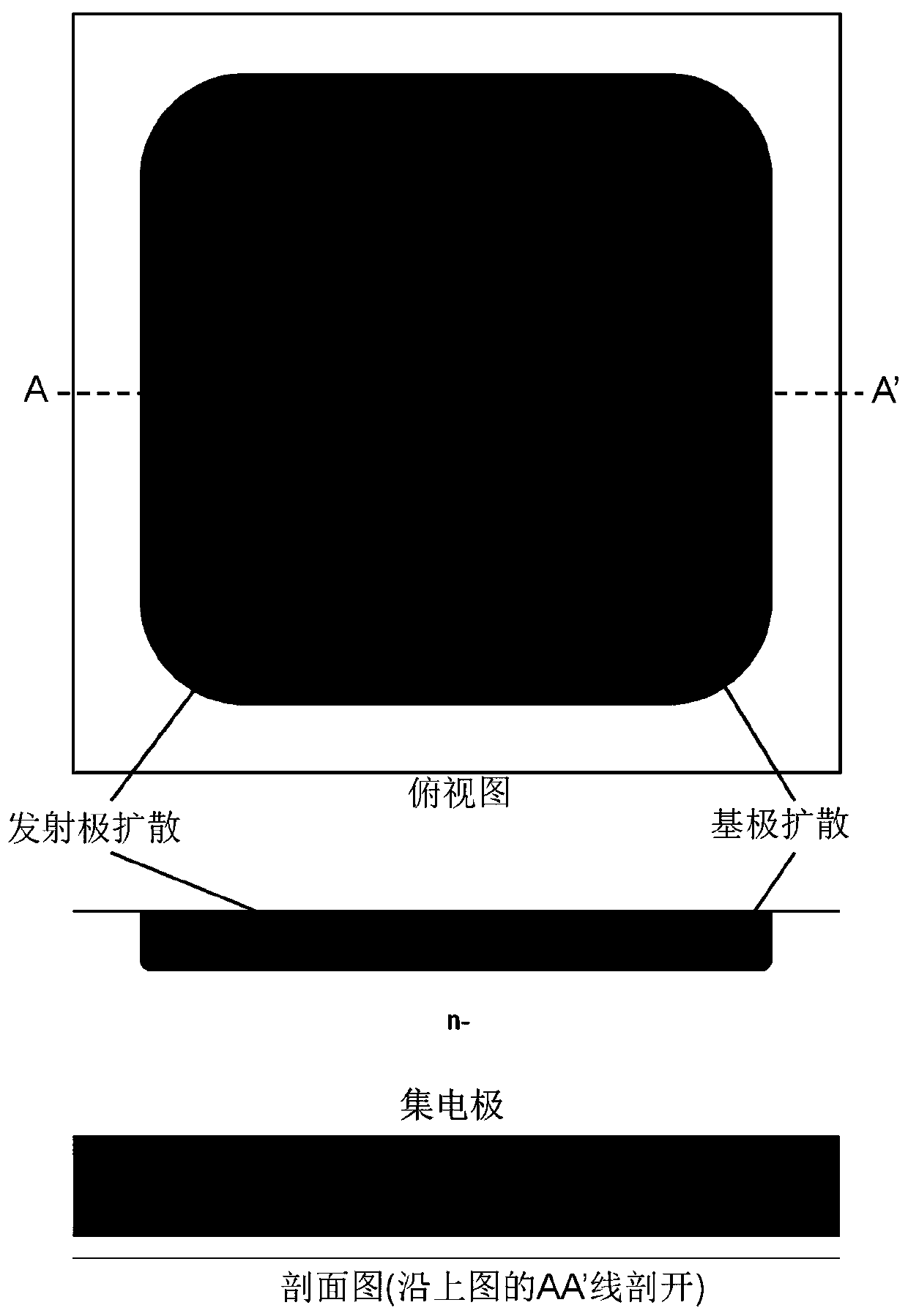

crosswise double diffusion MOFET and manufacturing method thereof

ActiveCN102738215ALower base resistanceImprove stabilityTransistorSemiconductor/solid-state device manufacturingDouble diffusionBody area

The invention provides a crosswise DMOS with cupped source electrode contact and a method for forming the crosswise DMOS. The crosswise DMOS comprises a cupped source electrode contact, wherein the cupped source electrode contact comprises a cupped part which longitudinally extends and penetrates the source area of the crosswise DMOS and contacts the body area,and the cupped part is electrically coupled with the source area and the body area. The crosswise DMOS not only has smaller size, but also is low in production cost.

Owner:CHENGDU MONOLITHIC POWER SYST

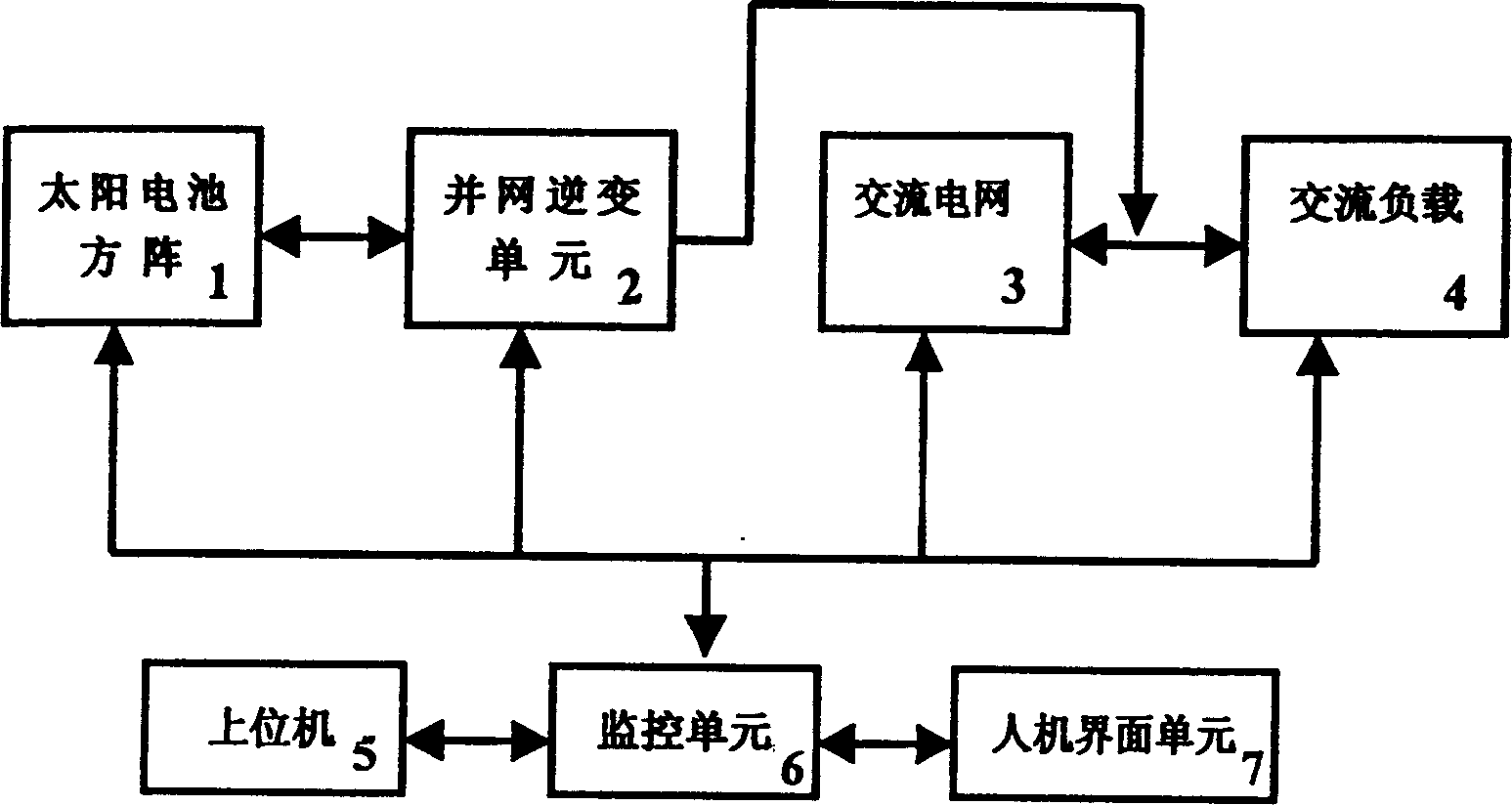

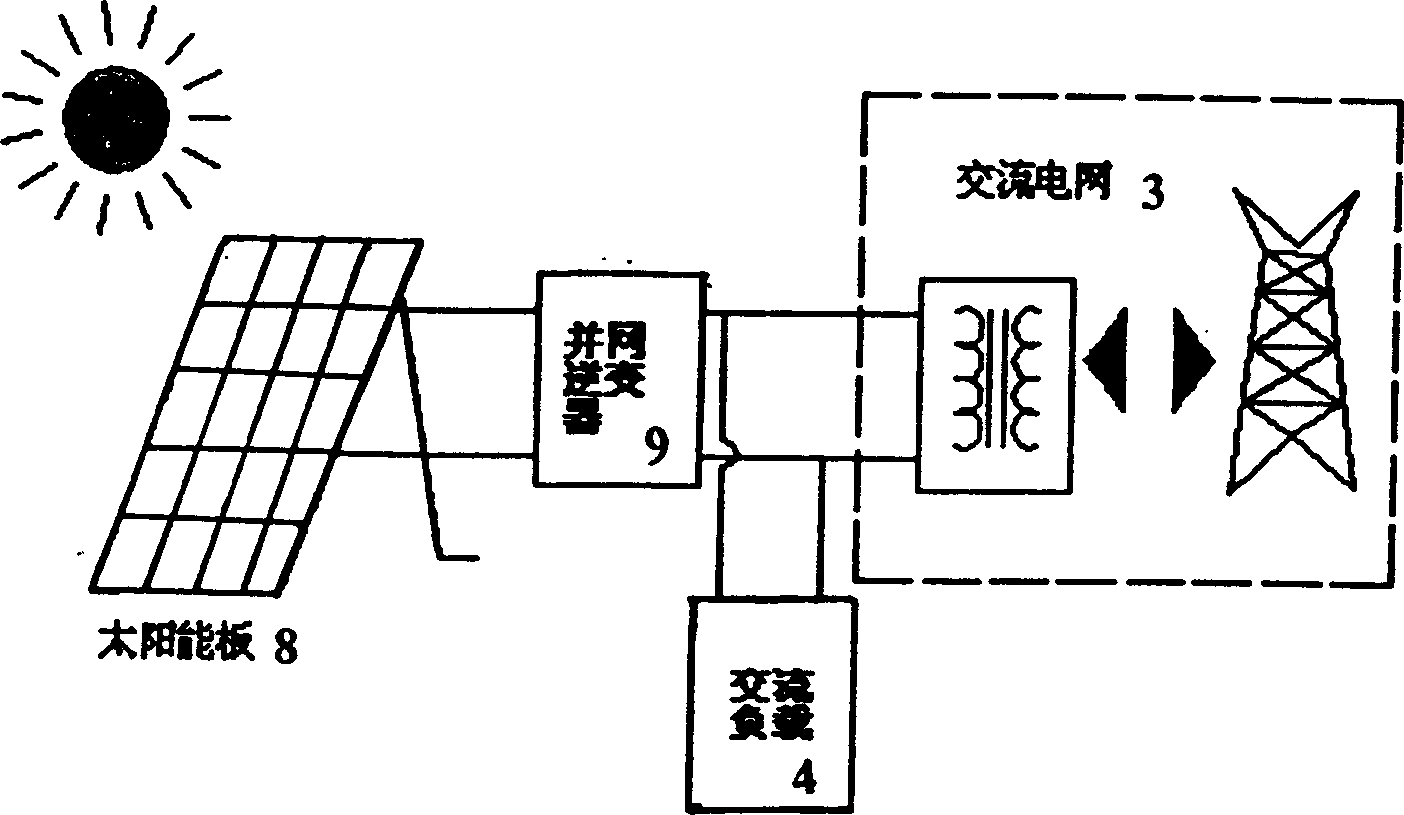

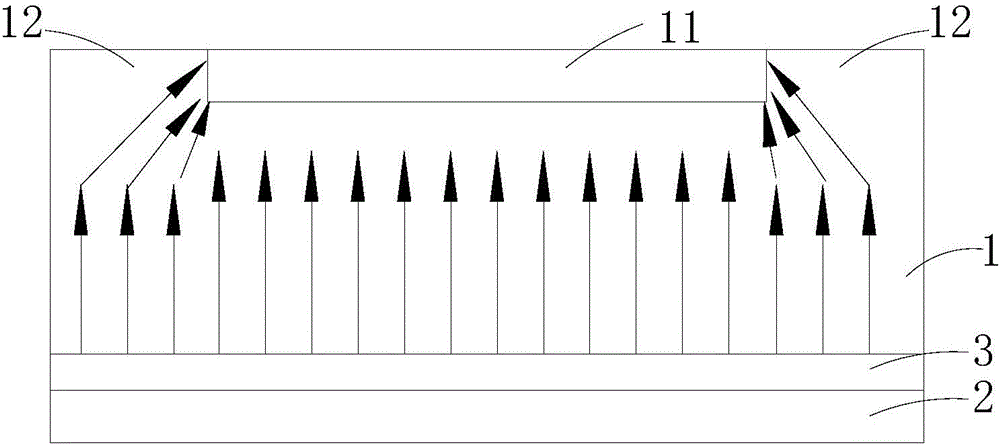

Solar photovoltaic integrally incoporating controller and method

InactiveCN1554913AReduce harmonic interferenceReduce electromagnetic interferenceSolar heat devicesSingle network parallel feeding arrangementsHuman–machine interfaceStructure of Management Information

The present invention relates to control device and method for solar photovoltaic electricity generating system. The apparatus of the present invention consists of solar plates, control device, monitor, AC load, AC power network, etc. The system has square solar cell matrix connected to networking inverter unit, AC power network connected to AC load, the networking inverter unit with output connected between AC power network and AC load, upper computer connected to the monitor, the monitor connected to man-computer interface unit, and RS232 interface for the connection between man-computer interface unit and the upper computer. The present invention has the advantages of simple circuit, great voltage and current capacity, high work frequency, low switch loss, etc.

Owner:SHANGHAI CHENGYI ELECTRIC CO LTD +1

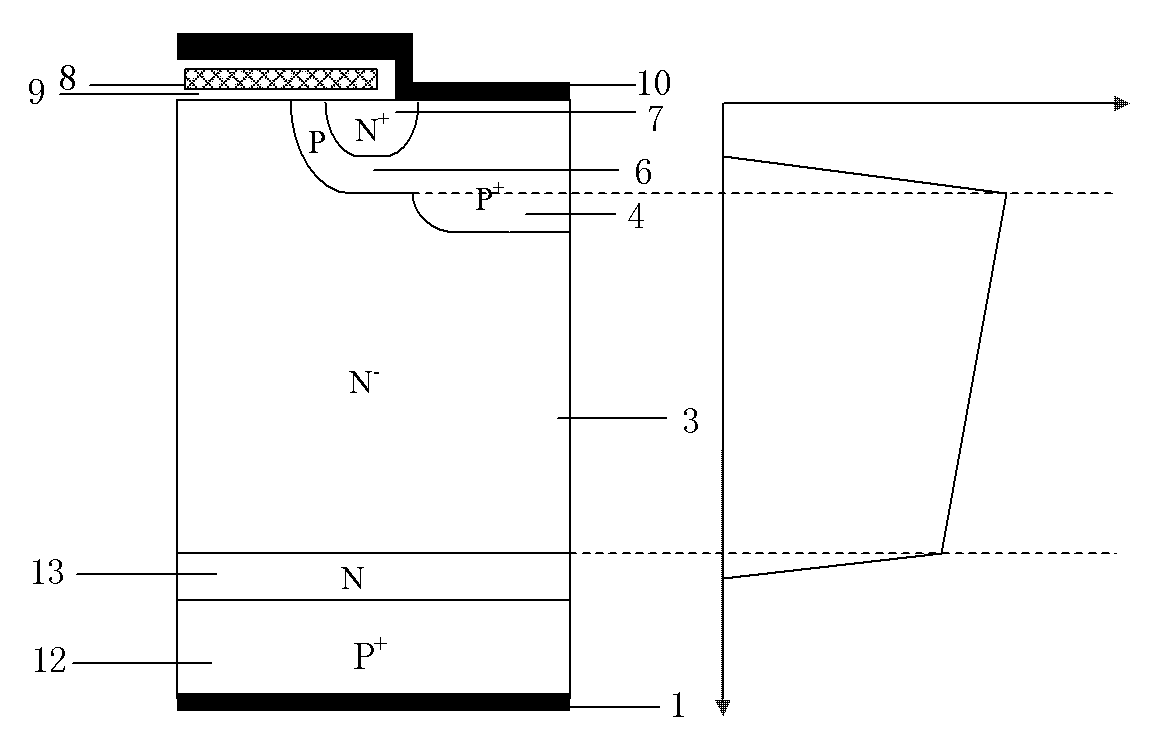

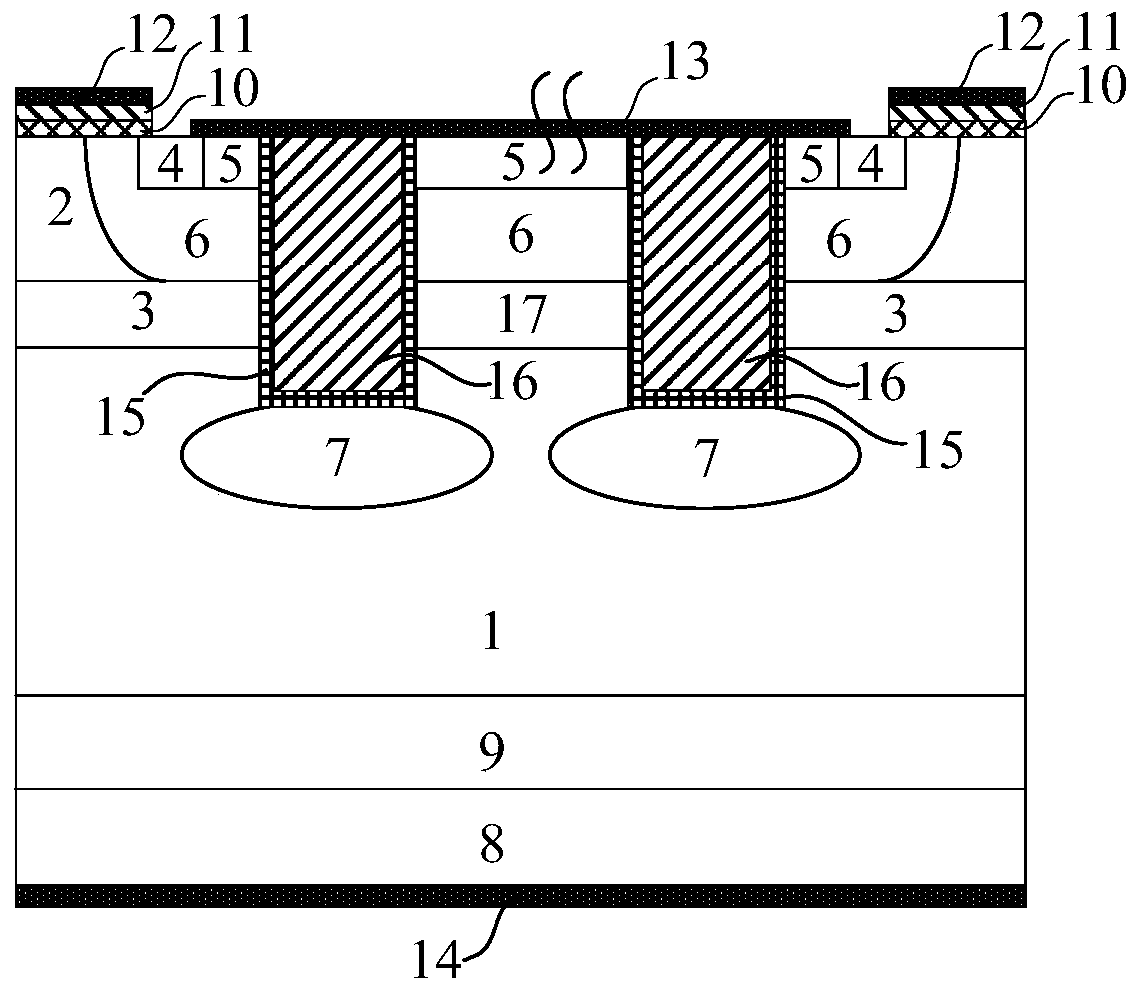

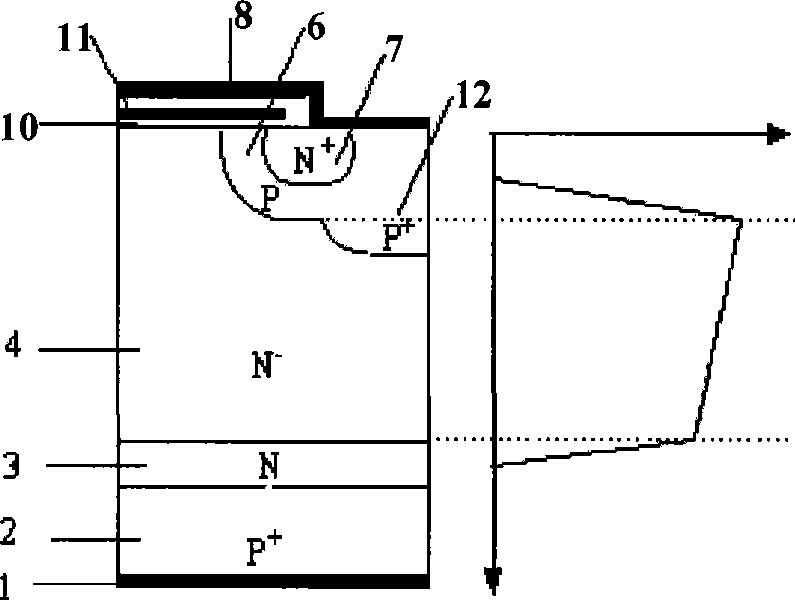

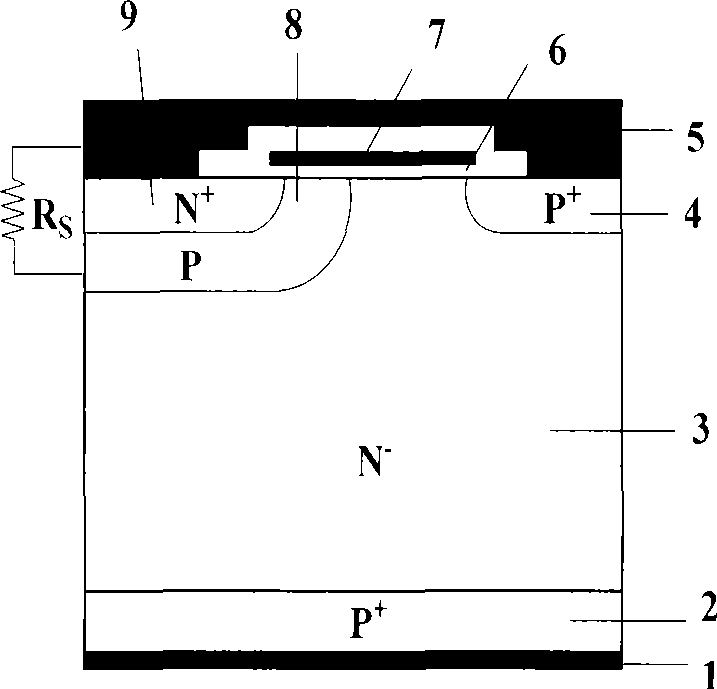

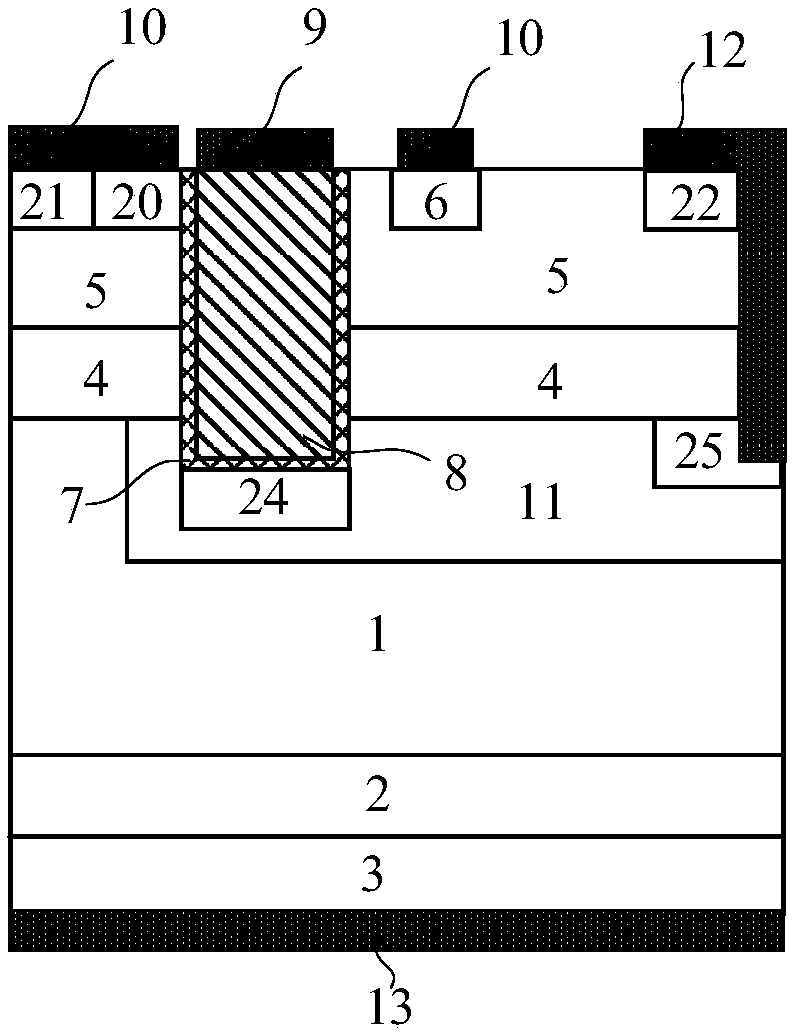

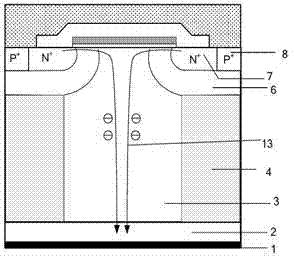

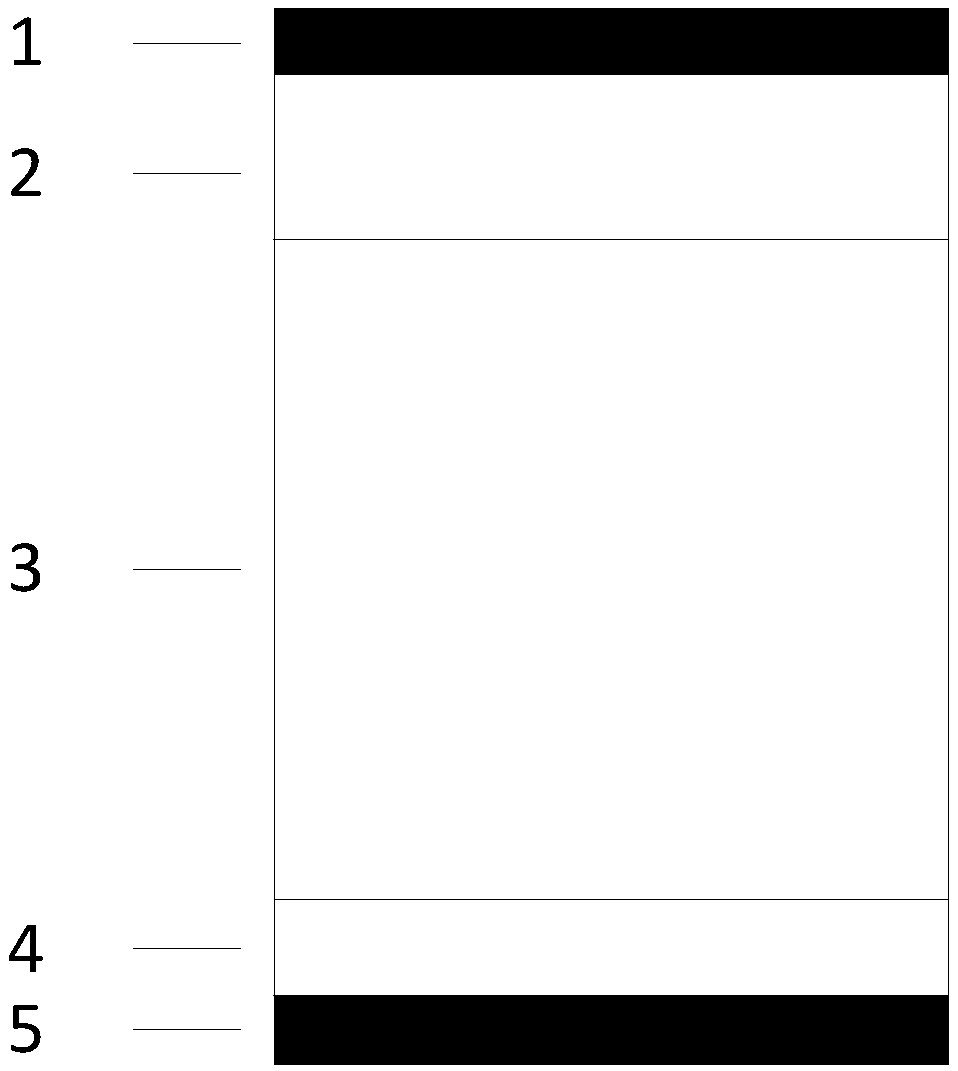

IGBT with current carrier storage layer and additional hole passage

InactiveCN102157551AIncrease the minority carrier concentrationPrevent openingSemiconductor devicesCharge carrierConductivity modulation

The invention discloses an insulate gate bipolar transistor (IGBT) with a current carrier storage layer and an additional hole passage, and belongs to the technical field of semiconductor power devices. In the IGBT, an N-type current carrier storage layer (5) and a large P<+> tagma (4) structure are introduced on the basis of a conventional planar non-pouch-through IGBT. The N-type current carrier storage layer (5) improves a conductivity modulation effect close to an emitter and the large P<+> tagma (4) structure plays a role in providing an additional passage for a hole so that the latch-up resistance is improved. Due to the design of the N-type current carrier storage layer (5) and the large P<+> tagma (4), the flow path of a hole current of the conventional IGBT is optimized, so that a safety operation area of a device is enlarged and the sensitivity of latch current density to a temperature is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

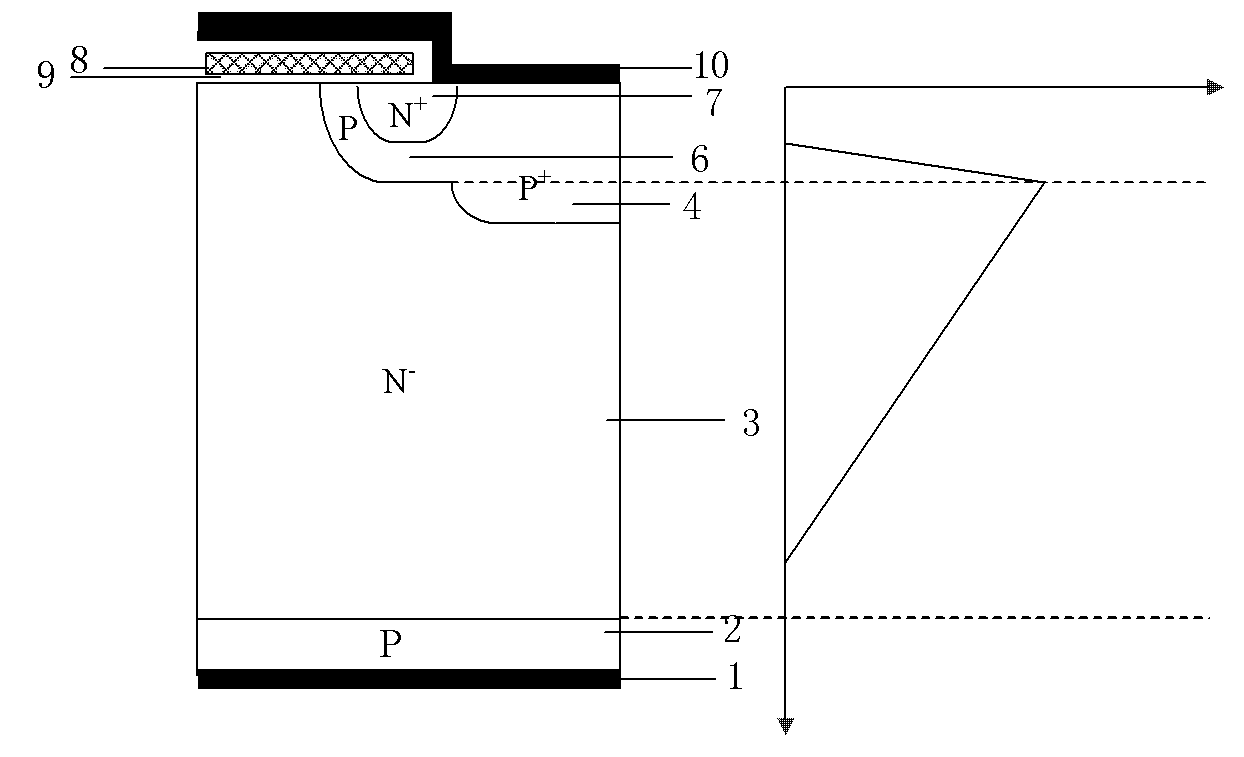

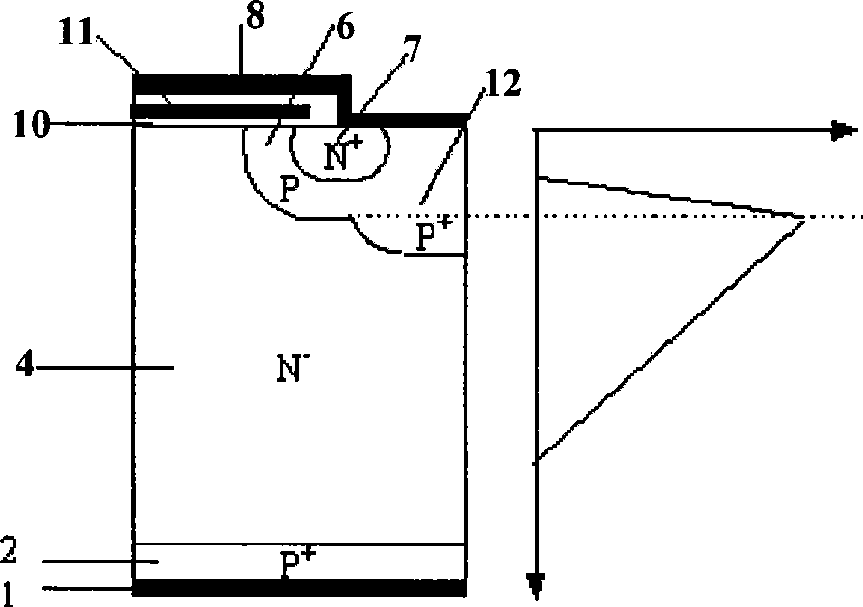

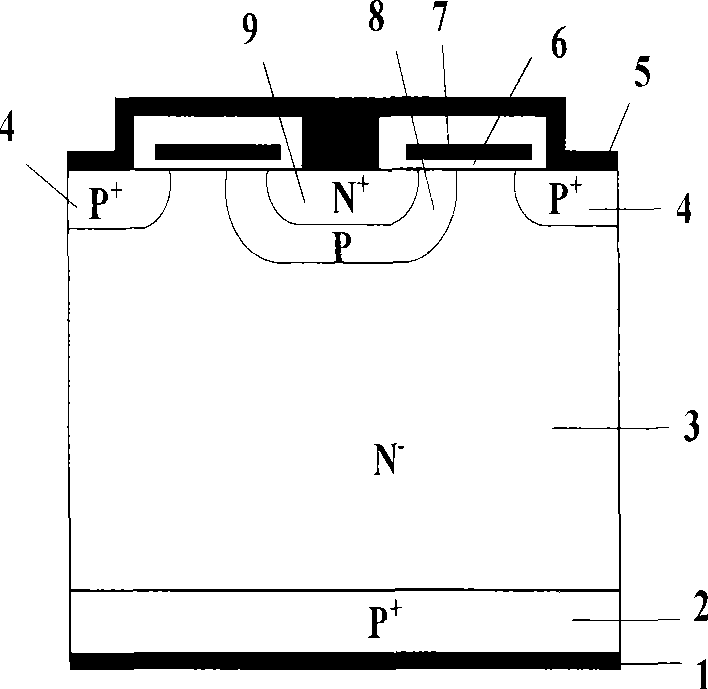

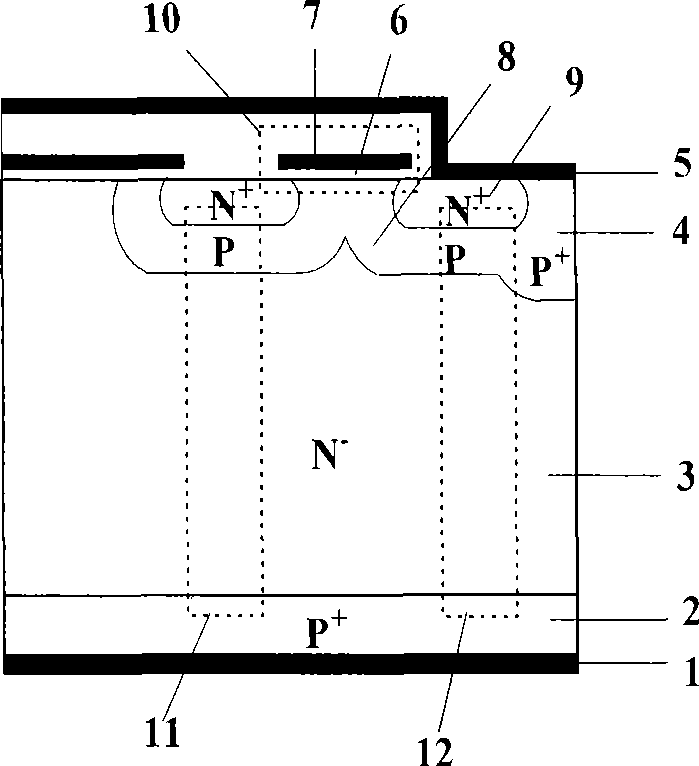

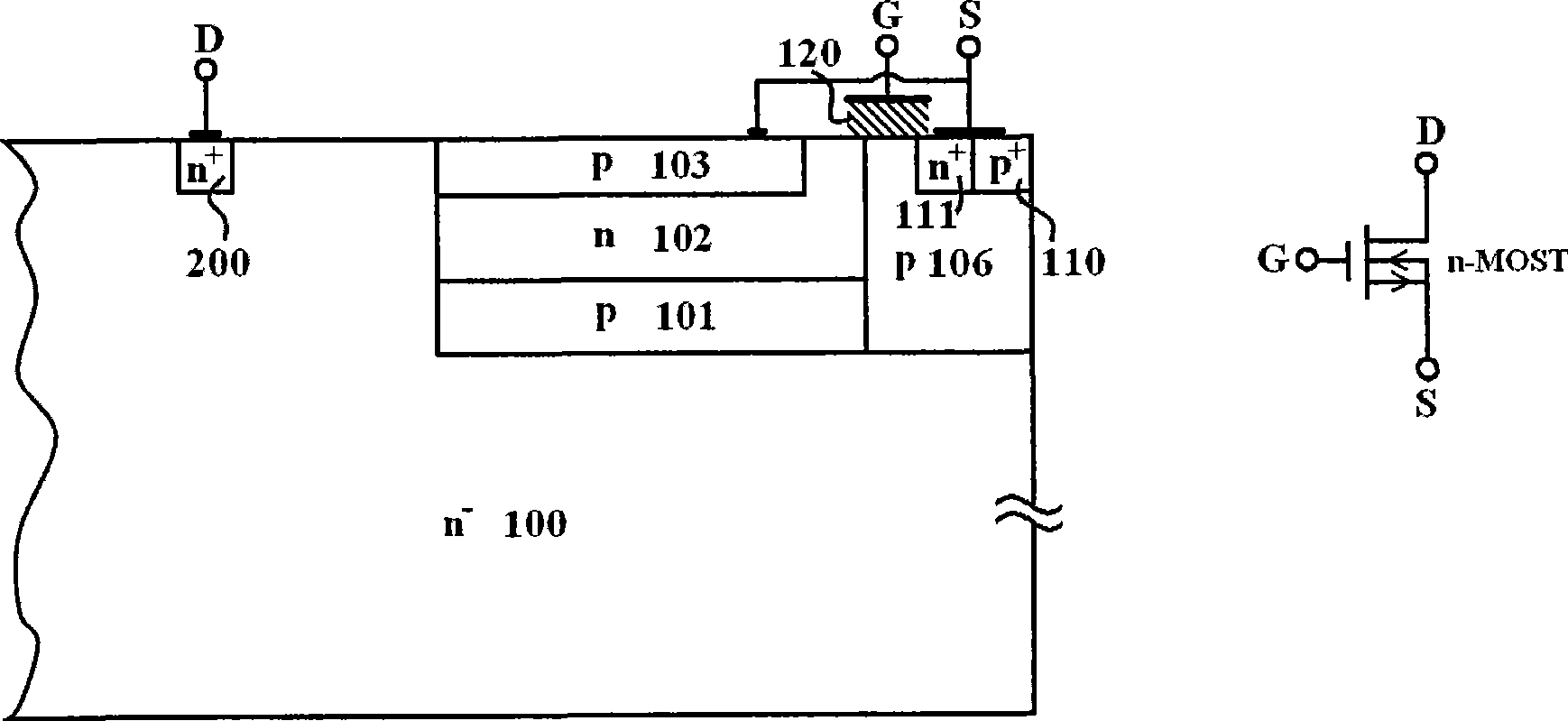

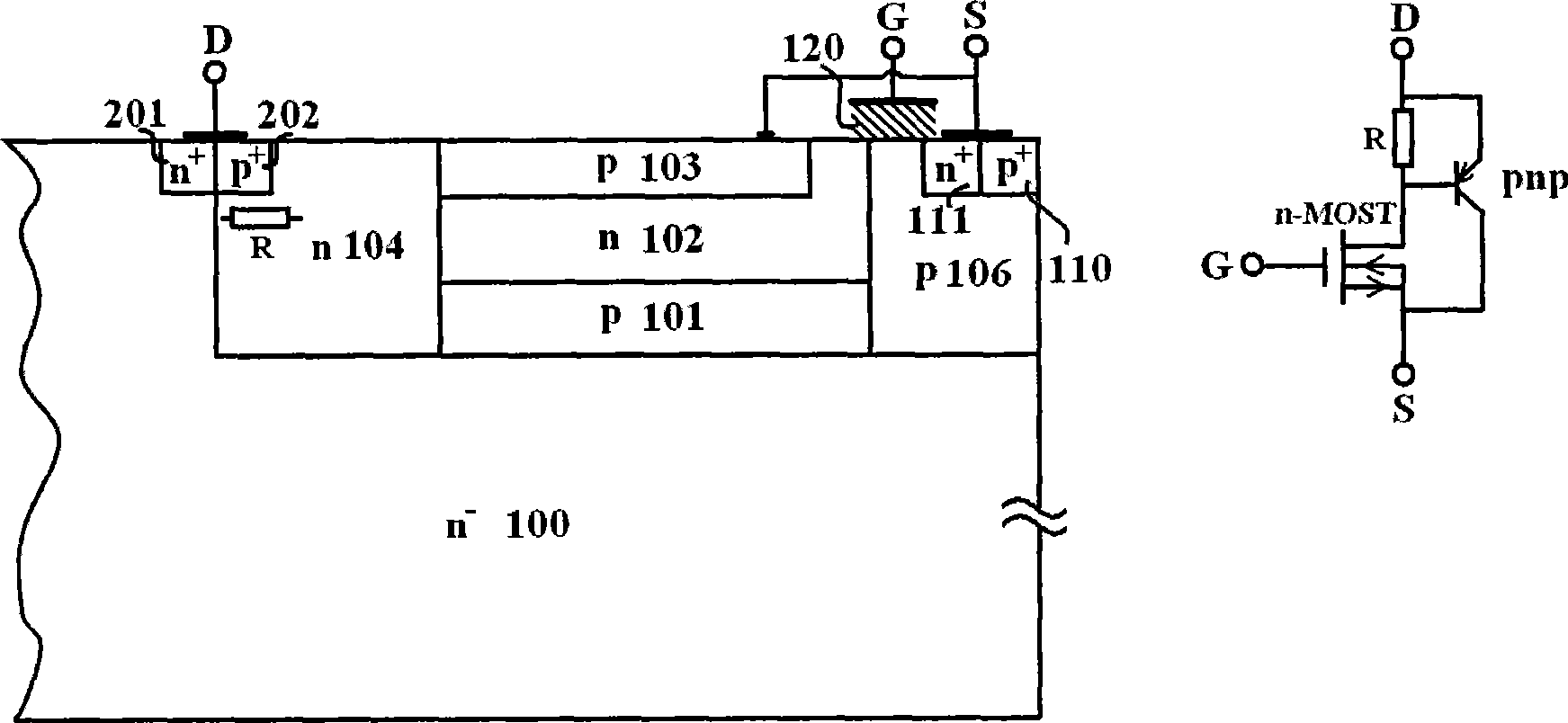

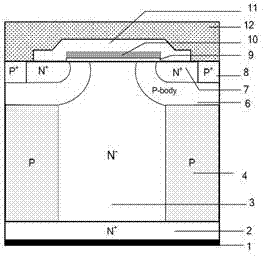

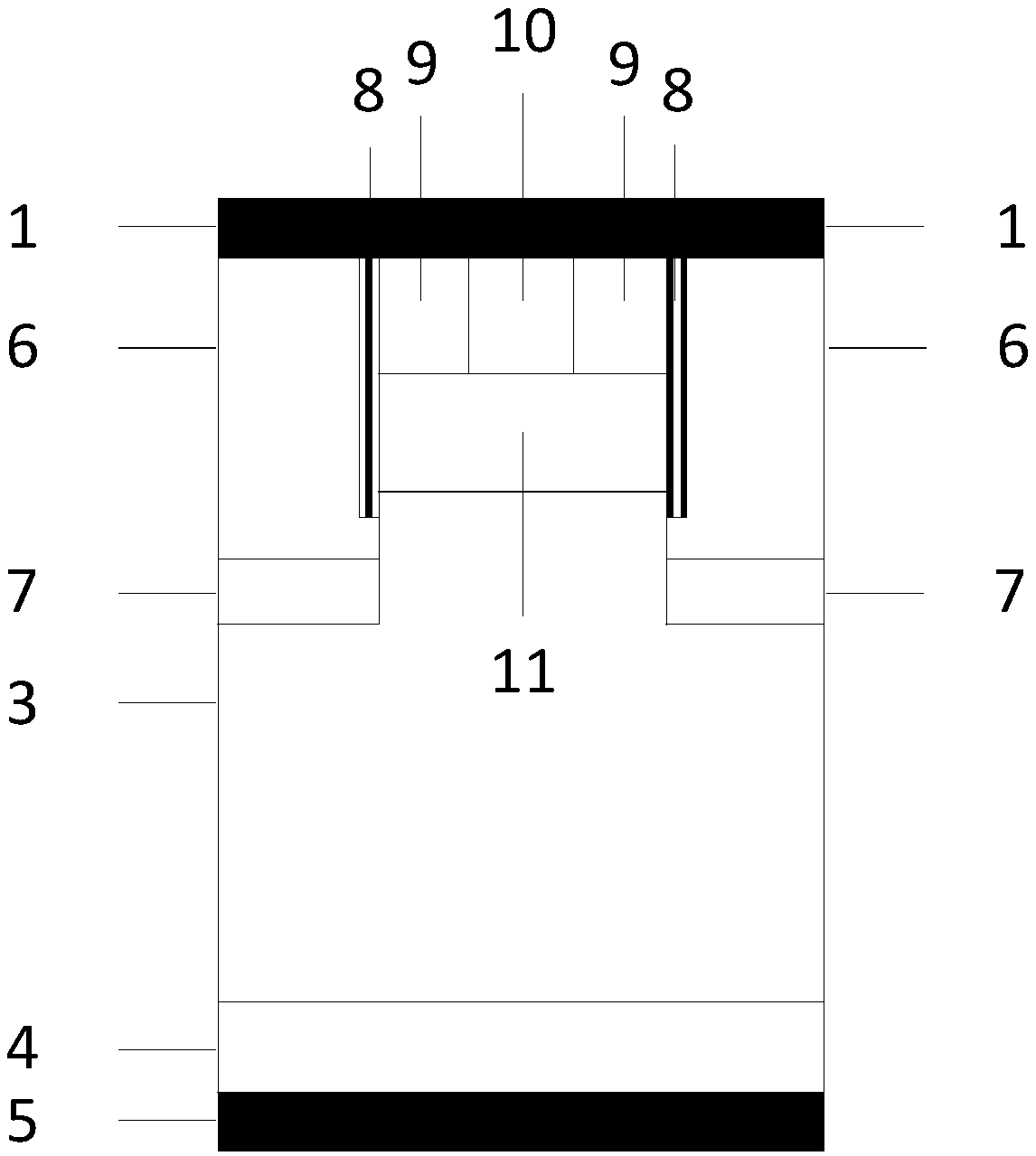

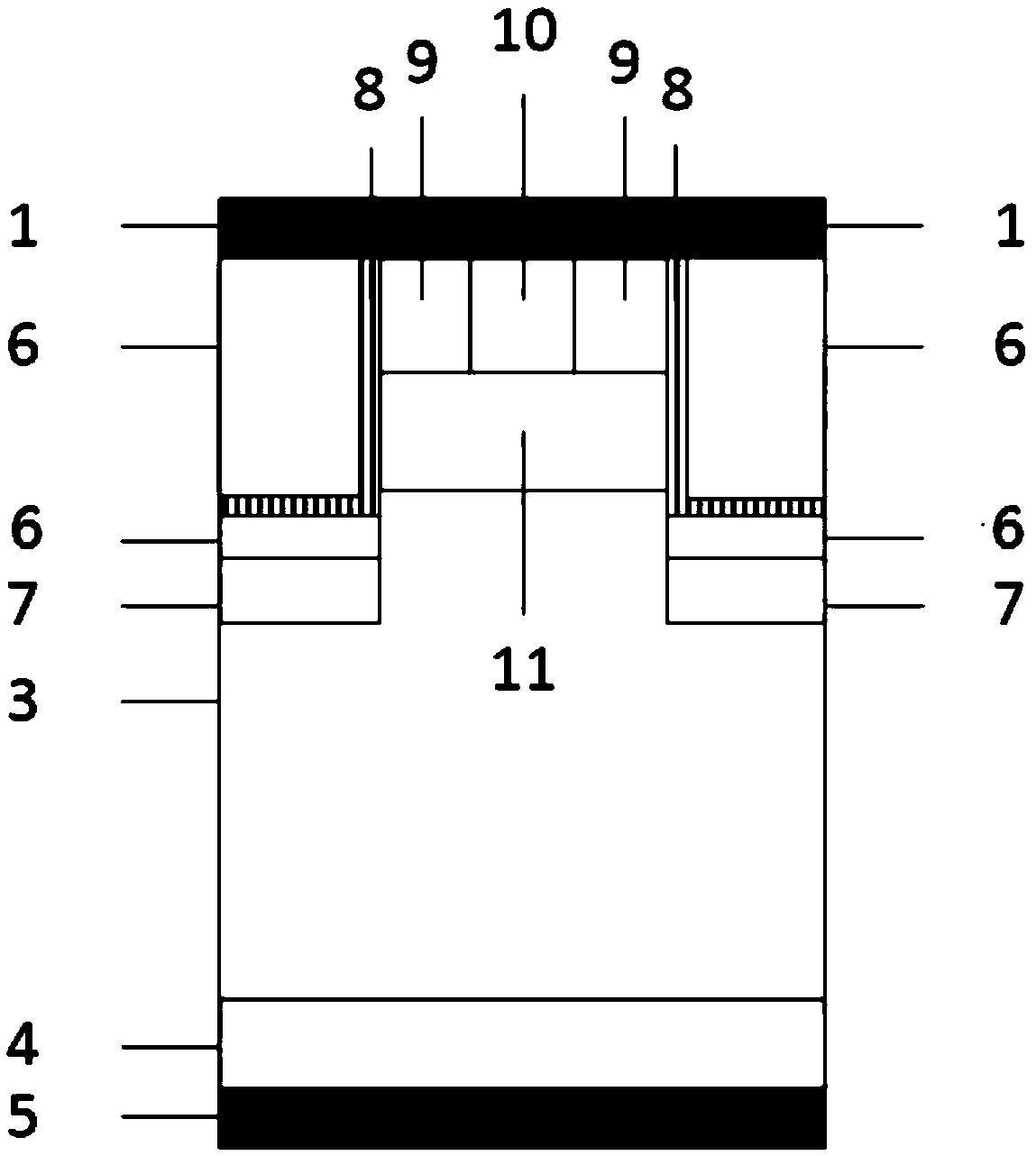

Accumulation layer controlled insulation gate type bipolar transistor

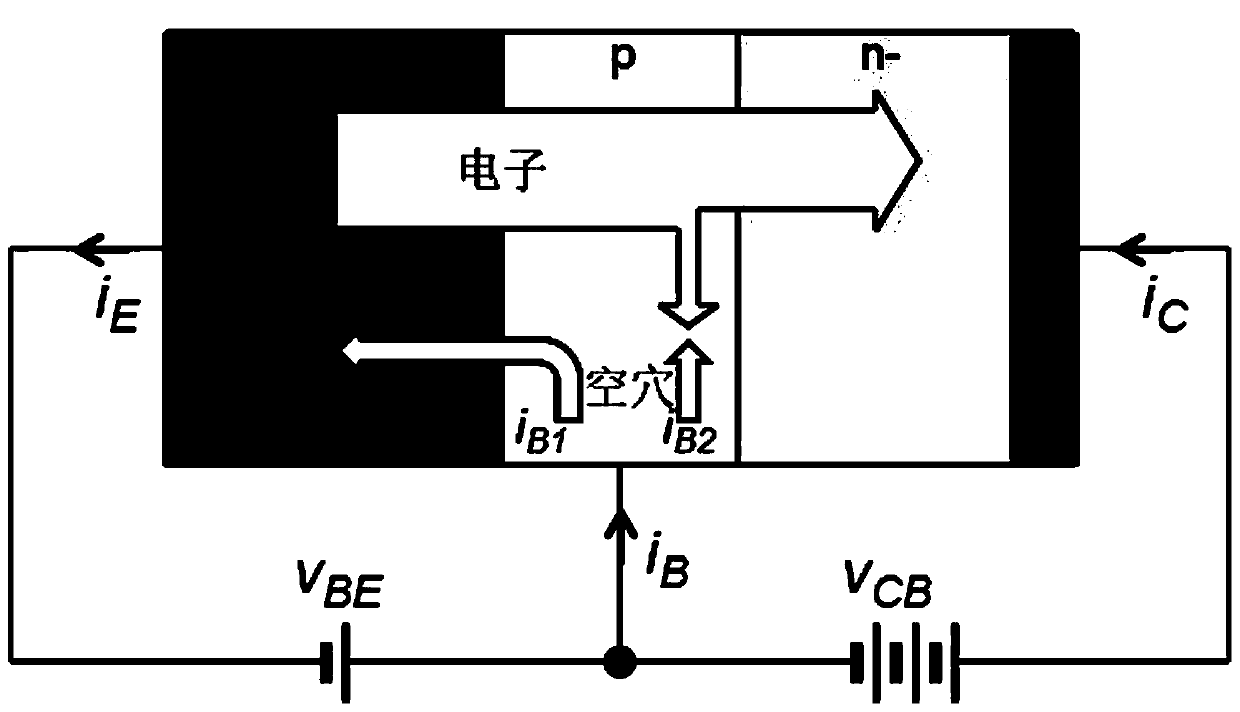

InactiveCN101393927AIncreased saturation current densityElimination of parasitic thyristor effectsSemiconductor devicesElectron flowParasitic bipolar transistor

Insulated gate bipolar transistors controlled by an accumulation layer belong to the technical field of semiconductor power devices. The transistors include a channel insulated gate bipolar transistor, a plane insulated gate bipolar transistor and a transverse insulated gate bipolar transistor. According to the invention, when a device is in the blocking state, a built-in electric field formed by a P body region (10) and an N base region (4) forms part of an electron barrier which stops electrons flowing from an N source region (9) into the N base region(4) with the voltage-resistance of the device improved; when the device is in the conductive state, the accumulation layer is formed between the N source region (4) and a gate oxide layer (5), and the electrons can flow from the N source region (9) to the N base region (4) through the accumulation layer so as to control the normal operation of the device. With the accumulation layer rather than a P-type base region and an MOS inversion channel of a traditional insulated gate bipolar transistor, the invention can achieve lower conductive voltage drop and greater saturation current density, thereby avoiding parasitic thyristor effect, and ensuring that the safe operating area, the reliability and the high-temperature working characteristics of the device can be greatly promoted.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

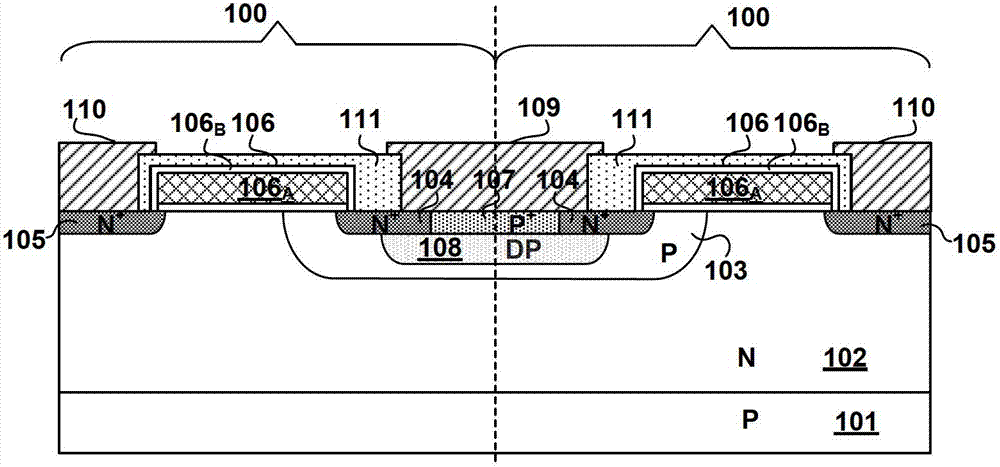

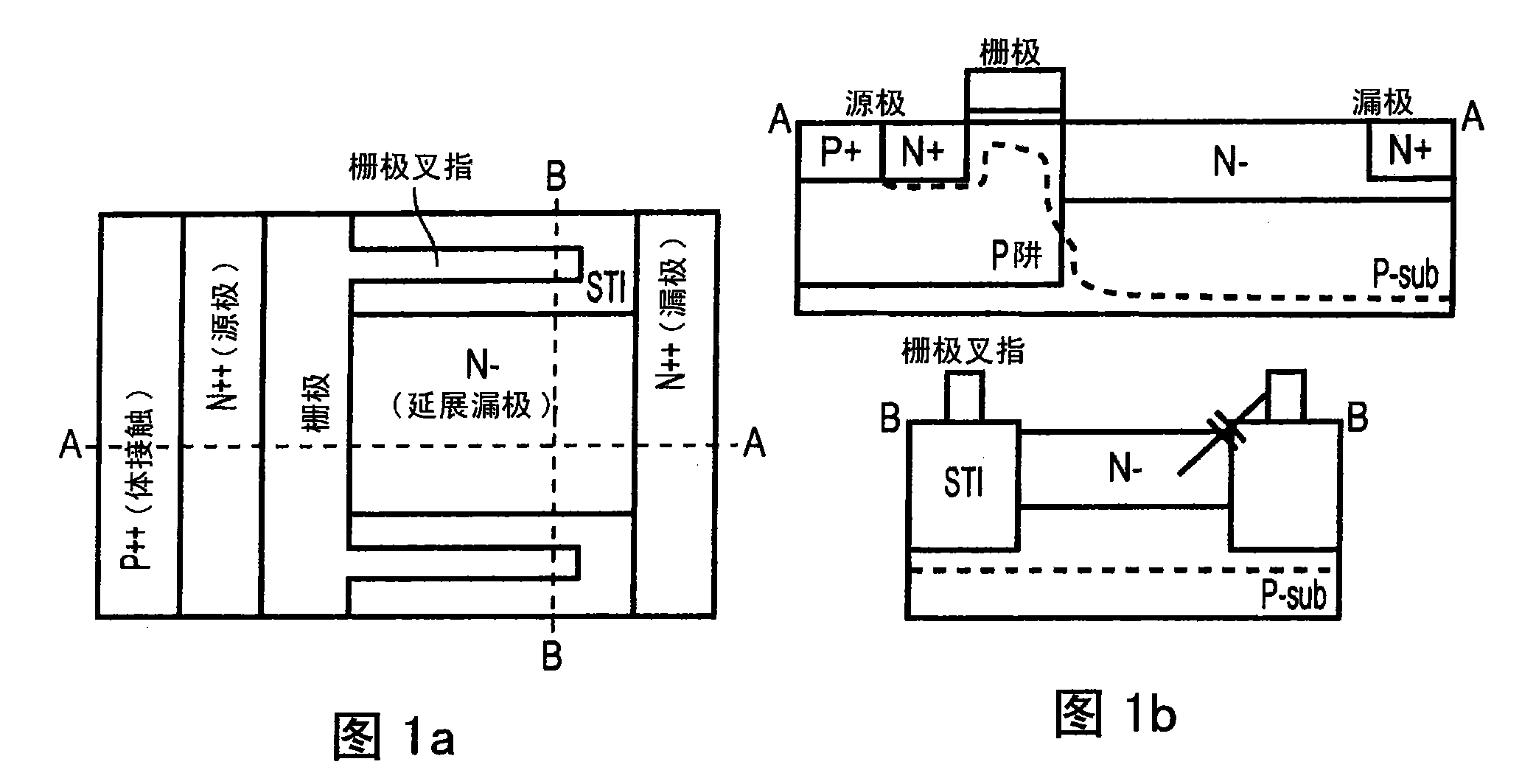

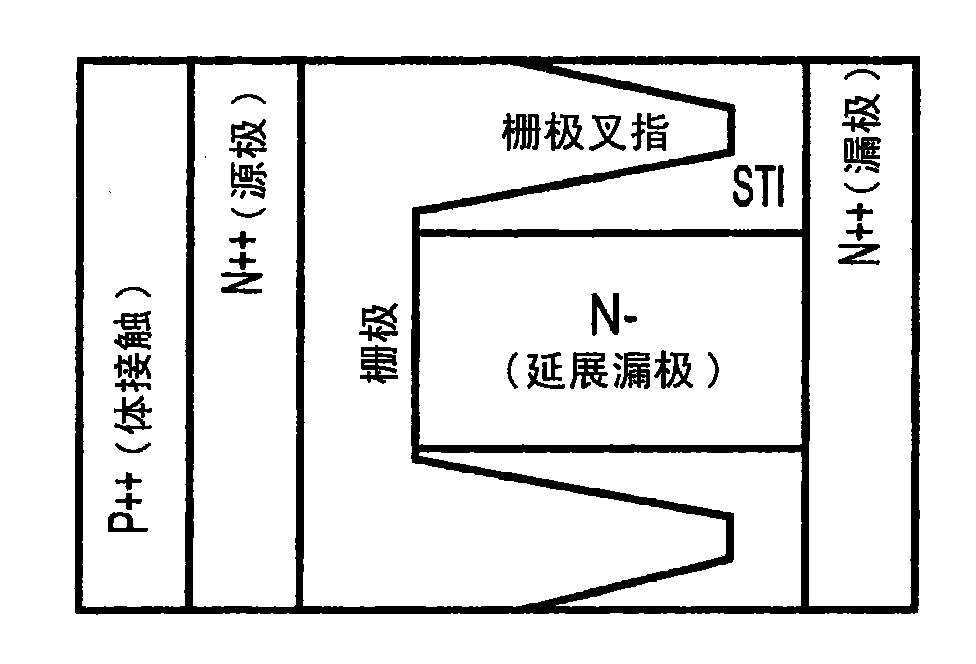

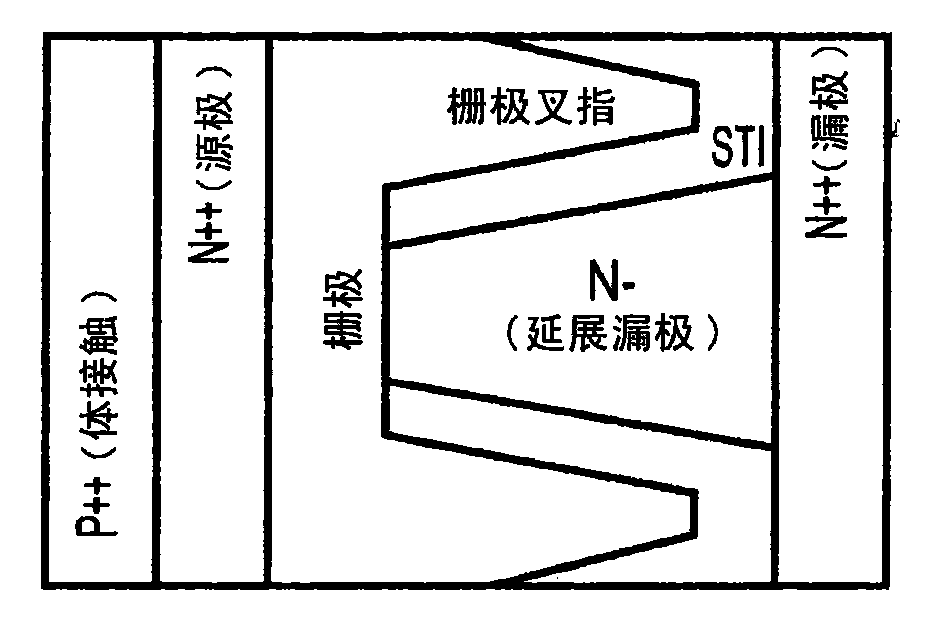

High voltage semiconductor device

InactiveCN101828253AImprove safe work areaImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesCMOSElectrical resistance and conductance

This invention describes implementation of medium / high voltage semiconductor devices with a better voltage-blocking capability versus specific on-resistance trade off. This approach can be implemented in baseline and submicron CMOS without any additional process steps. CMOS semiconductor devices, such as transistors, are known. Typically these 5 devices have only limited applicability in high voltage (HV) due to for instance breakdown of voltage. Many IC (Integrated Circuit) applications require for instance power management units for DC:DC down-or up-conversion of the supply voltage. Typically NMOS and PMOS semiconductor devices, such as transistors, with capability from10 V up 10 to 25 V are required for such applications.

Owner:NXP BV

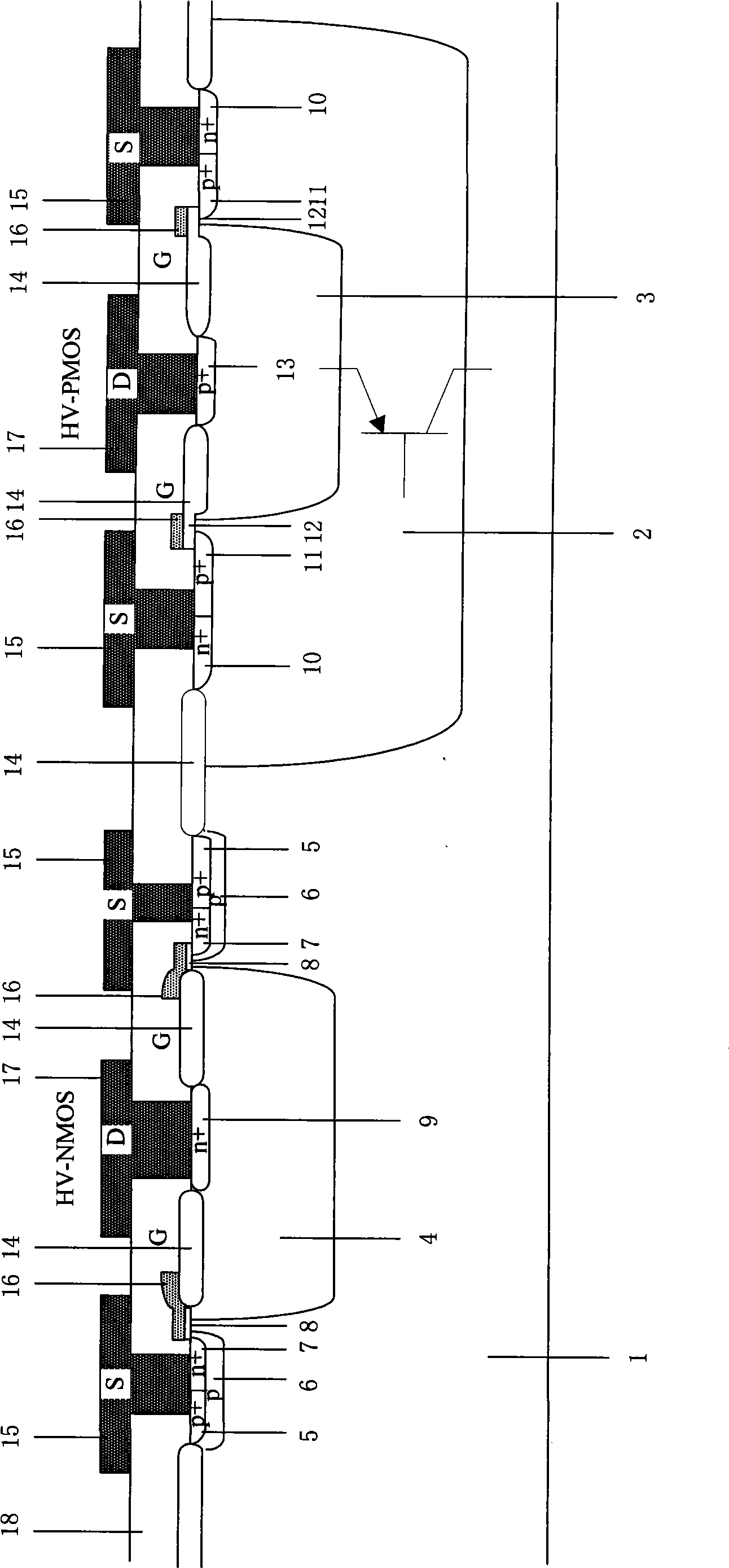

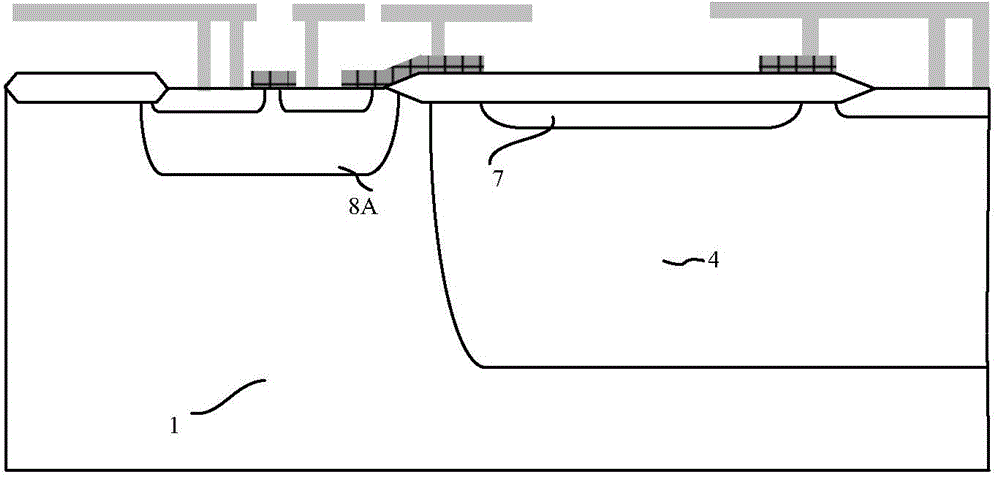

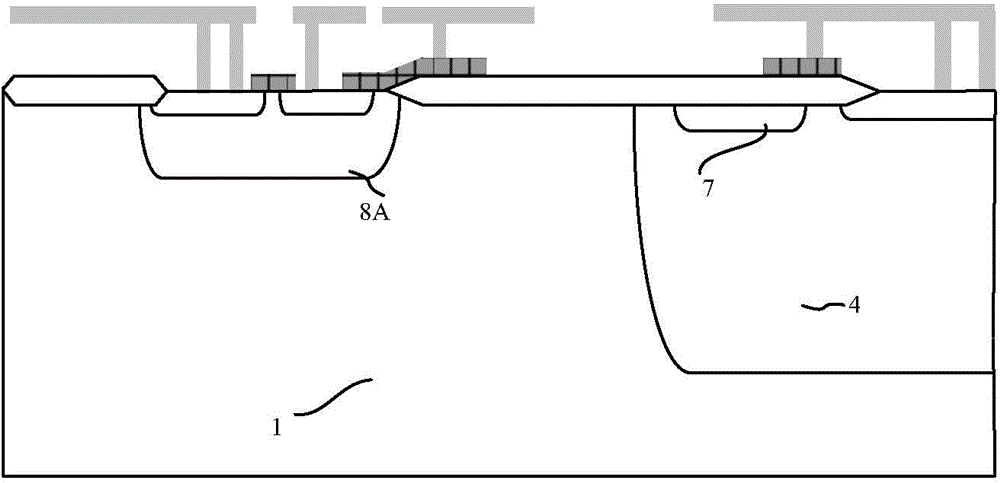

High voltage device for drive chip of plasma flat-panel display

InactiveCN101510551AIncrease load capacityImprove safe work areaSolid-state devicesSemiconductor devicesHigh densityLow voltage

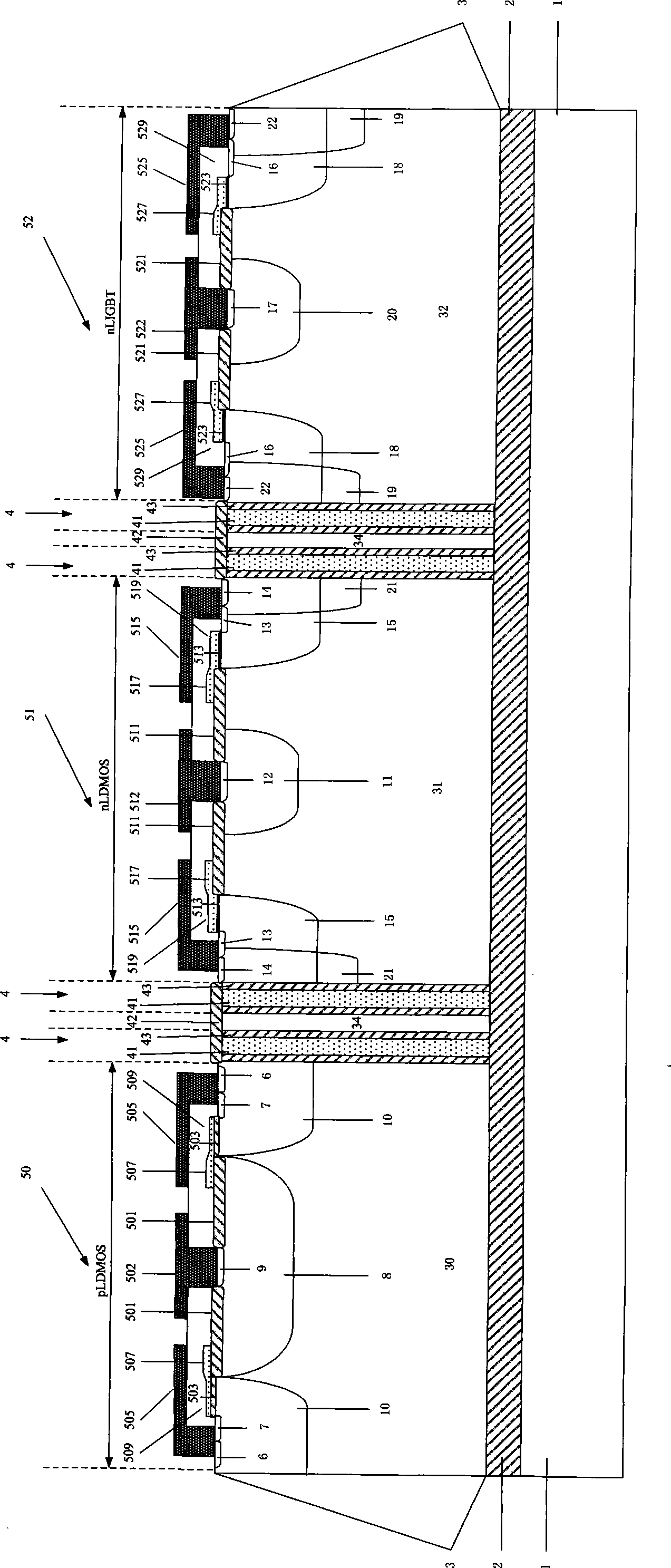

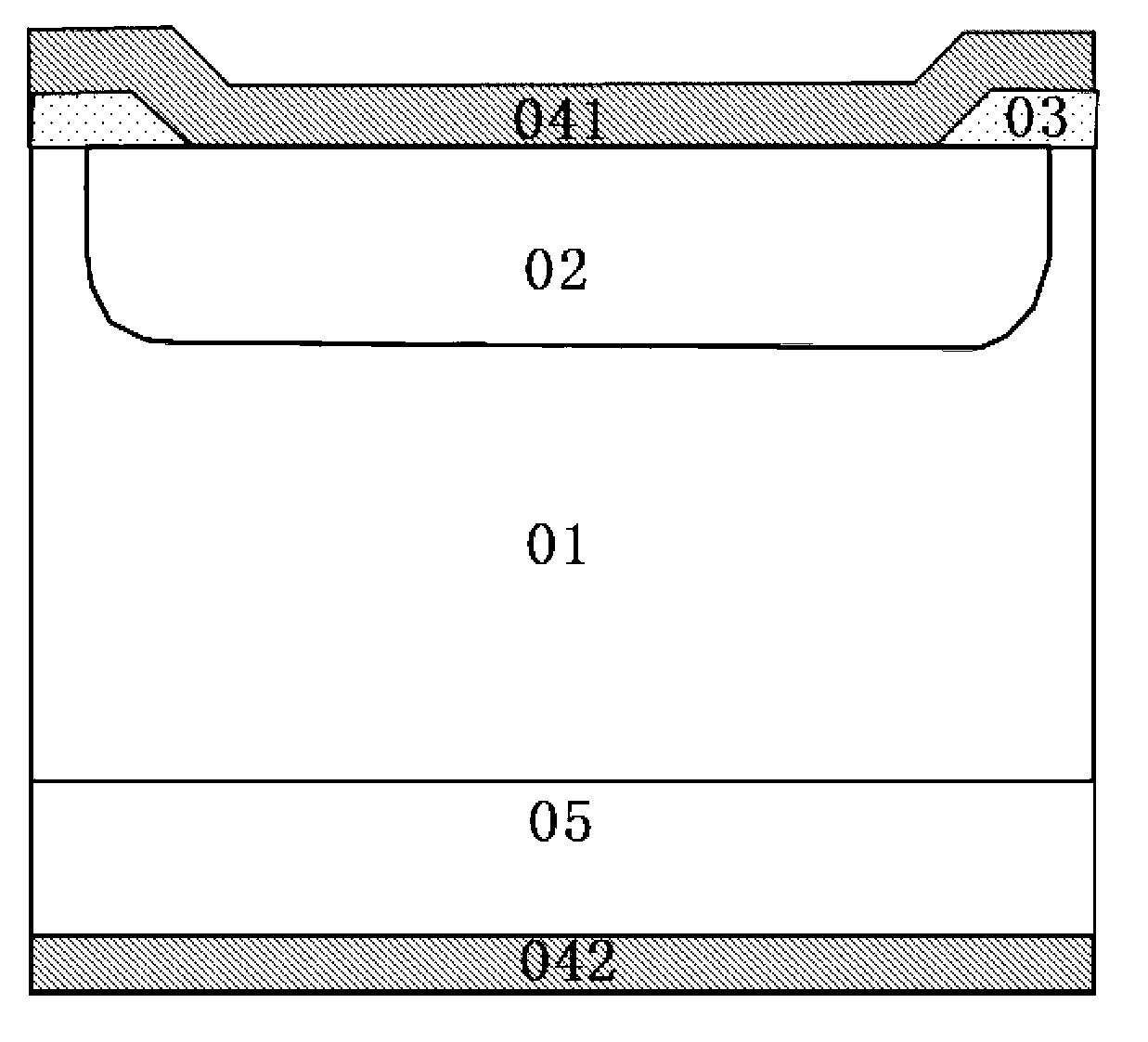

The invention provides a high-voltage device for a drive chip of a plasma flat-panel display, pertaining to the field of a semi-conductor power device. A high-voltage pLDMOS device, a high-voltage nLDMOS device and a high-voltage nLIGBT device are established on a substrate, an oxygen burying layer and an SOI layer and separated by deep-slot medium isolation areas. The oxygen burying layer and the deep-slot medium isolation areas positioned between the substrate and the SOI layer realize the full medium isolation of the device and low-voltage logic circuits. The thickness of the SOI layer is 8 micrometers and can meet the requirements of the device for high-voltage resistance. Compared with the thin SOI technology, the self-heating effect is relieved obviously and the nLIGBT device has low conduction resistance. The group of the high-voltage device for the drive chip of the plasma flat-panel display based on the thick SOI layer fully utilizes the characteristics of the SOI technology, such as low leak, small chip occupying area, high speed, high density of integration and low power consumption, thus meeting the development requirements of the large-sized plasma flat-panel display.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

High voltage MOS device

InactiveCN101217160AImprove breakdown voltageSpeed is not affectedSemiconductor devicesElectrical resistance and conductanceBreakdown voltage

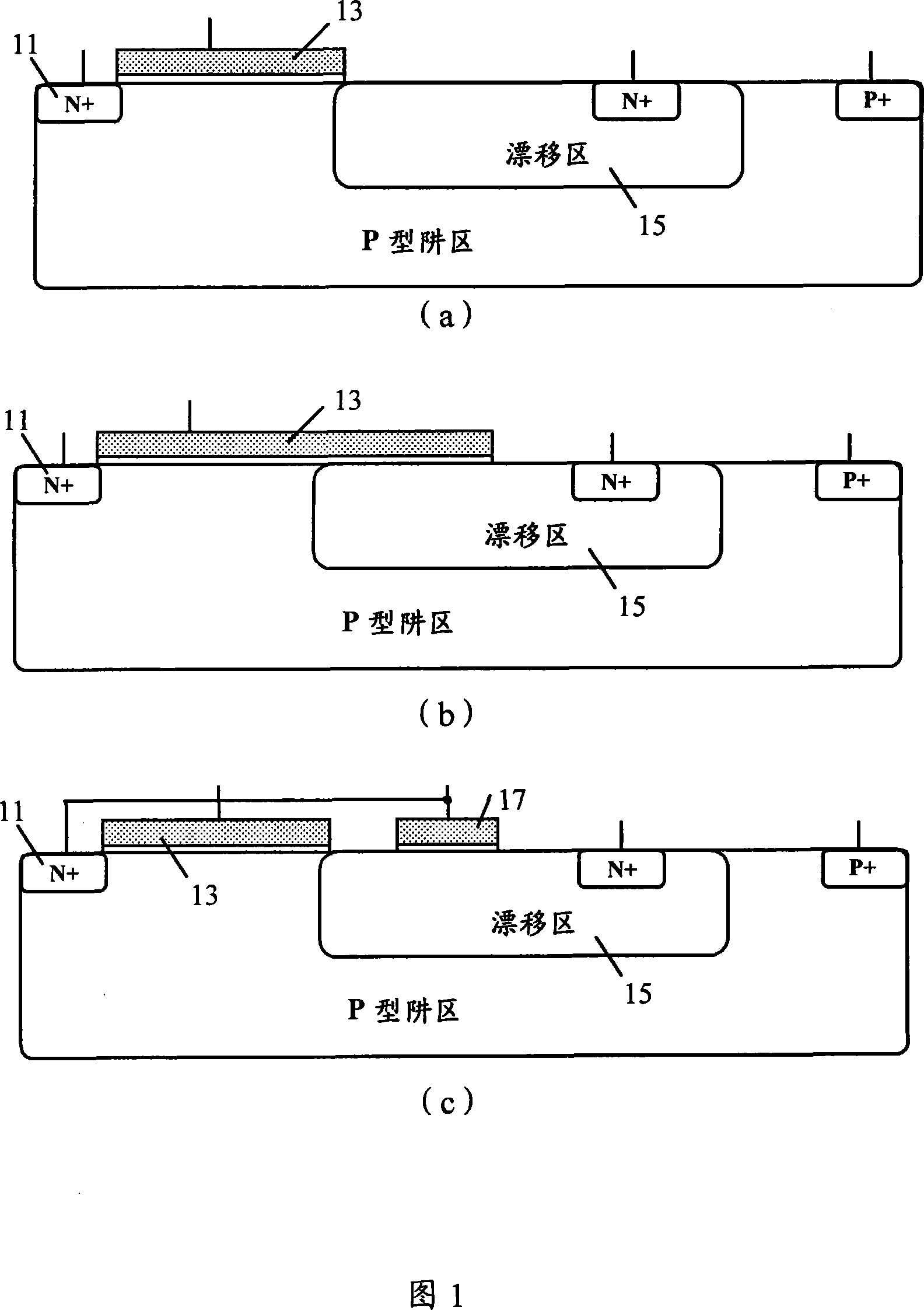

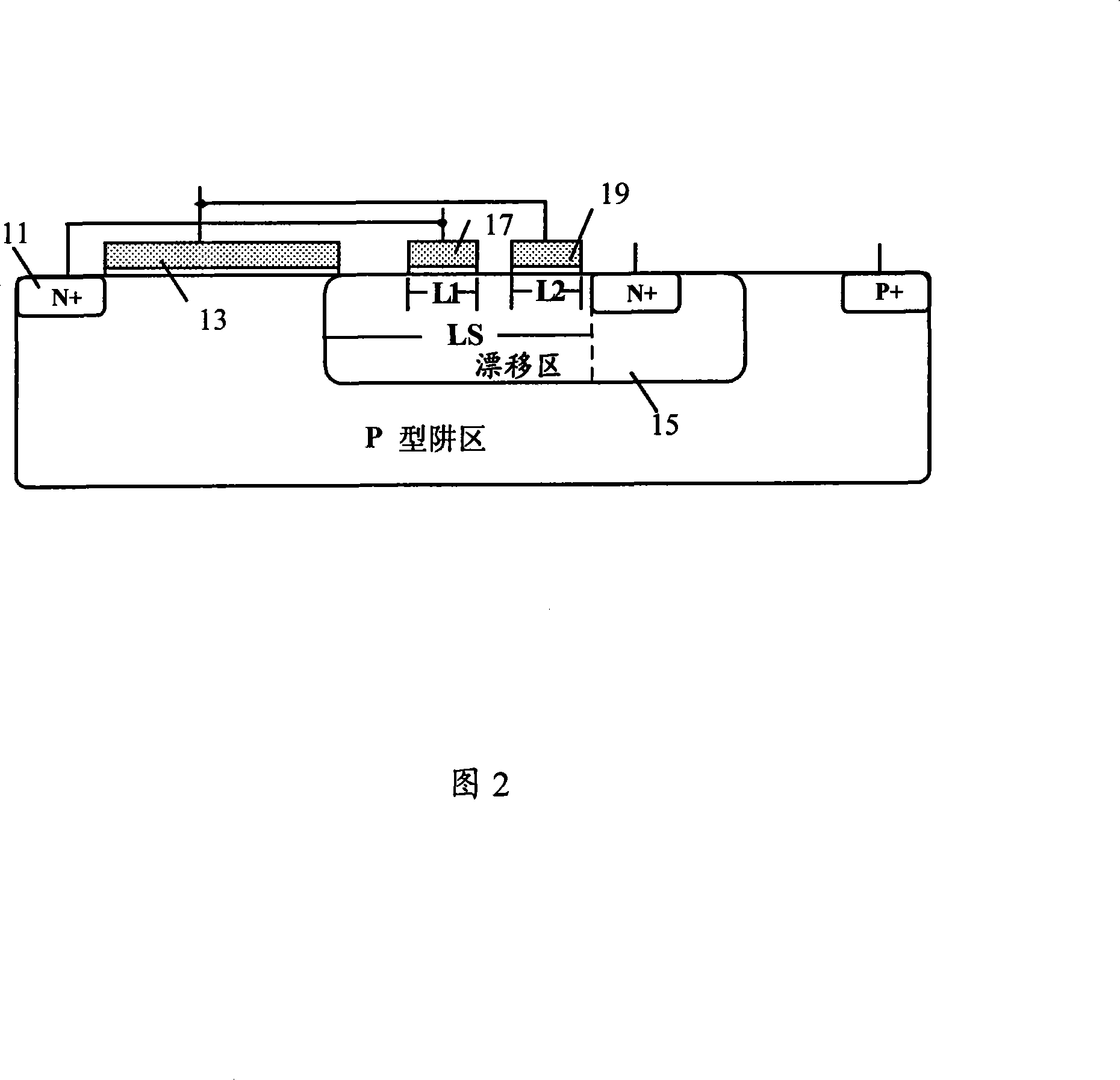

The invention provides a high-voltage MOS device, which at least includes a grid, a source and a drift region, wherein, the device further includes at least two field plates which are mutually separated with certain distance and are distributed at the upper surface of the drift region, the field plate which is nearest to the grid is connected with the source, and the other field plate is connected with the grid. The two field plates are both composed of polysilicon layers, and the thickness is the same as the thickness of the polysilicon layers. The lengths of the two filed plates can be same or different. The length of the field plate is decided by the doping level of the drift area, the lower the doping level of the drift area is, the longer the filed plate is, and the length of the filed plate is not more than one third of the length of the drift region. The length of the field plate is more than one sixth and less than one fourth of the length of the drift region. Compared with the prior art, the device of the invention can improve breakdown voltage and reduce on-resistance, the speed of the device is not affected and safe working area is larger.

Owner:GRACE SEMICON MFG CORP

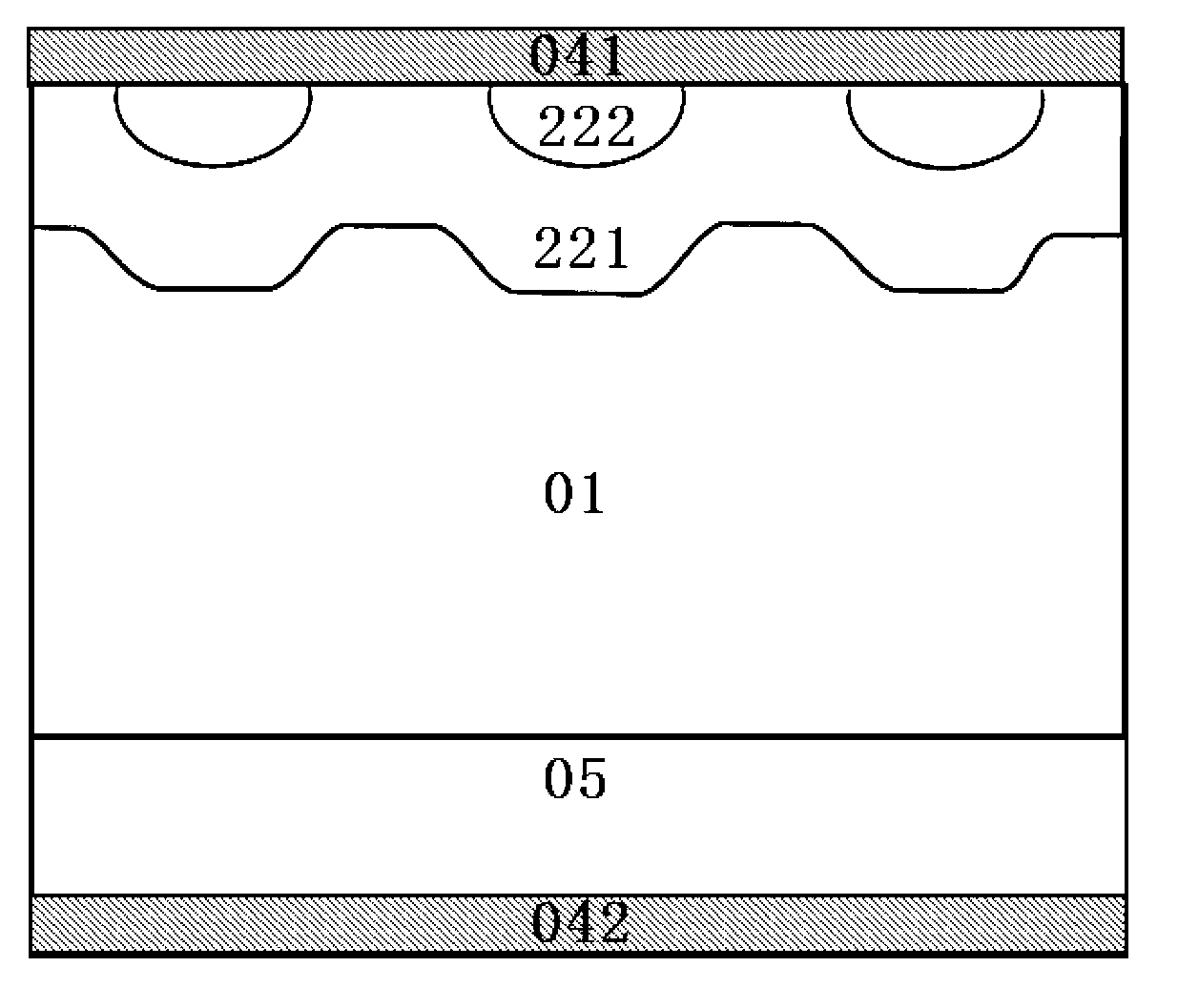

Fast recovery diode and manufacturing method thereof

ActiveCN103022154AReduce shockImprove safe work areaSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryIntrinsics

The invention discloses a fast recovery diode and a manufacturing method of the fast recovery diode. The diode disclosed by the invention comprises an anodic diffusion P-type doped region, an evenly-doped intrinsic region, a cathodic diffusion N-type region, anode and cathode metal layers, wherein the anodic diffusion P-type doped region is a P-type doped region provided with alternated high and low concentrations and formed by locally pouring through a mask plate. Compared with the prior art, the diode disclosed by the invention has the characteristics of low inverse peak current IRRM, short reverse recovery time trr and high reverse recovery softness.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +1

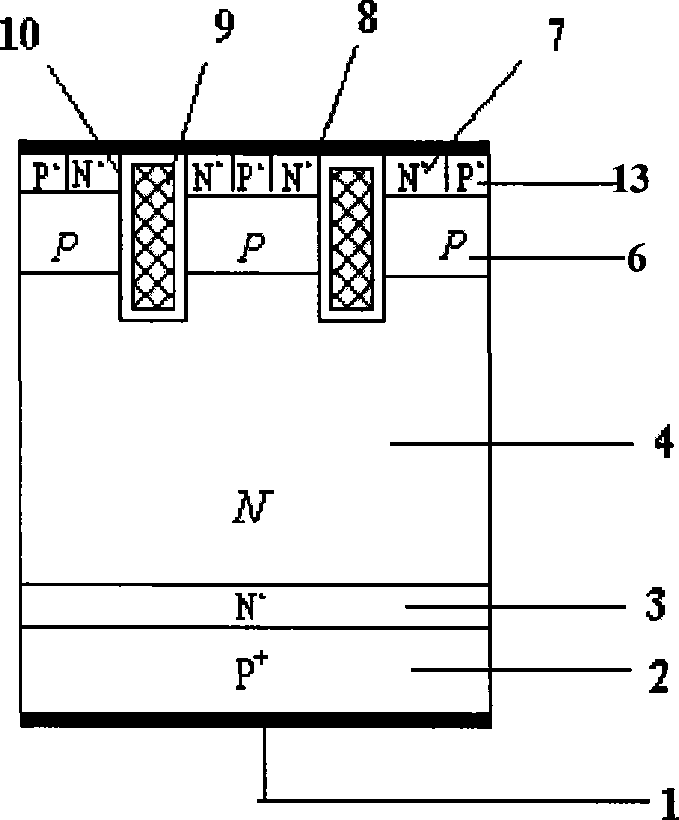

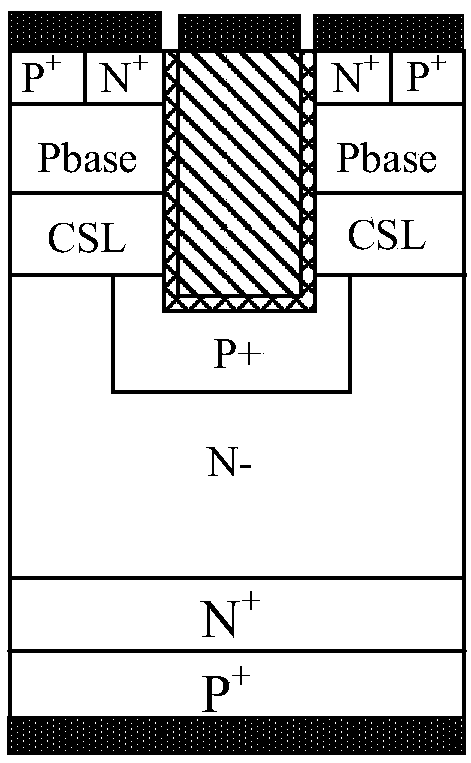

Planar gate IGBT device with deep trench electric field shielding structure

ActiveCN109728084AImprove safe work areaIncrease concentrationSemiconductor devicesCharge carrierEngineering

The invention relates to the field of power semiconductors, and provides a planar gate IGBT device with a deep trench electric field shielding structure, which is used for overcoming the problems thata current groove-gate IGBT gate with a carrier storage layer is too large in drive charges and small in short-circuit safety working region and is limited in the concentration of the CSL layer. The deep groove used for manufacturing the groove-gate IGBT channel traditionally and a P-type buried layer at the bottom portion of the groove are combined to form an electric field shielding structure toachieve clamping of the potential of the carrier storage layer; one IGBT cell is internally provided with a plurality of deep grooves to improve the concentration of the carrier storage layer of theIGBT compared to a traditional IGBT, have the higher cathode injection efficiency, and obtain the better trade-off relation of the on-state voltage and the turn-off loss. A planar gate and an electricfield shielding structure are employed, the IGBT has lower gate drive power consumption and lower saturation current density so as to improve the safety working region of the IGBT.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

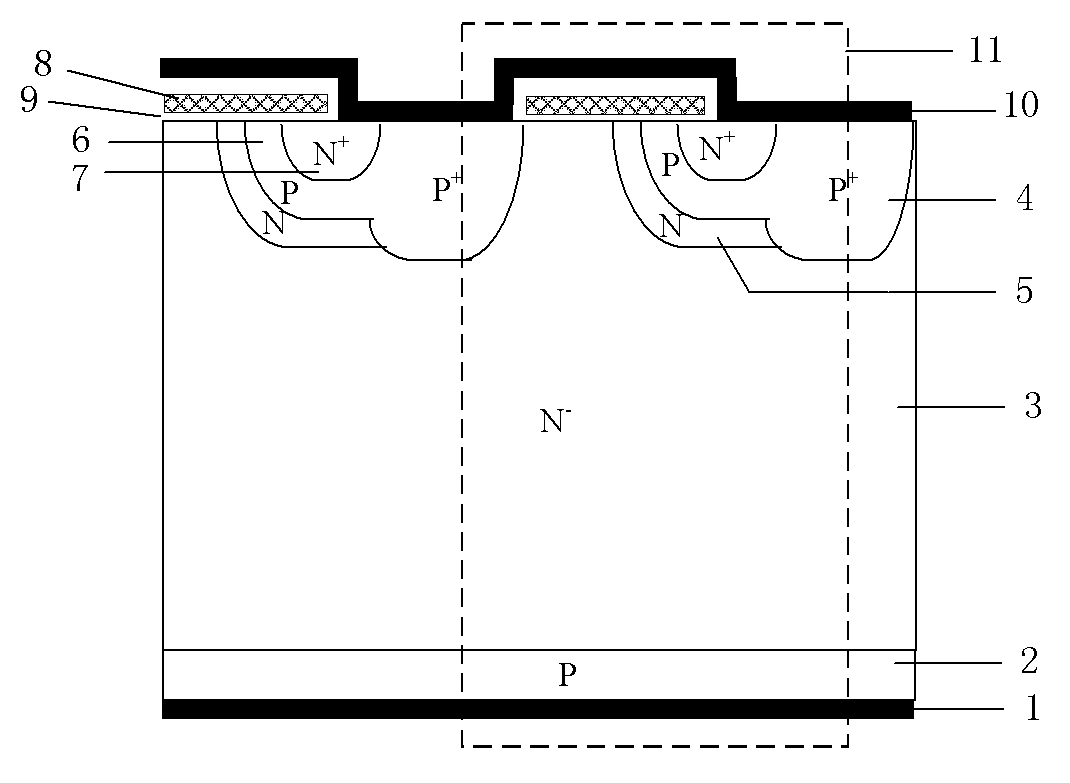

Insulated trench gate electrode bipolar type transistor

InactiveCN101452952AChange the circulation pathCirculation path to avoidSemiconductor devicesElectrical resistance and conductanceEngineering

The invention provides a slot simulated gate bipolar transistor, which belongs to the technical field of semiconductor power devices. Based on the prior slot simulated gate bipolar transistor, the invention is additionally provided with a P<+> hole collecting zone (5), to avoid holes entering a P type zone (6) and achieve good action of bypassing the holes, thereby greatly weakening the parasitic thyristor effect, improving the safety operation zone of the device and particularly improving the high-temperature latching resistance of the device. Simultaneously, a metal emitter (8) of the invention is made into a slot metal electrode. Besides the reduction of the contact resistance of the device, the device can dissipate heat more easily and reduces temperature rise, thereby achieving excellent high-temperature operating characteristics. Furthermore, During the injection of the P<+> hole collecting zone(5) and an N<+> source(7) of the slot simulated gate bipolar transistor, an additional masking plate is needed, thereby properly lowering production cost.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

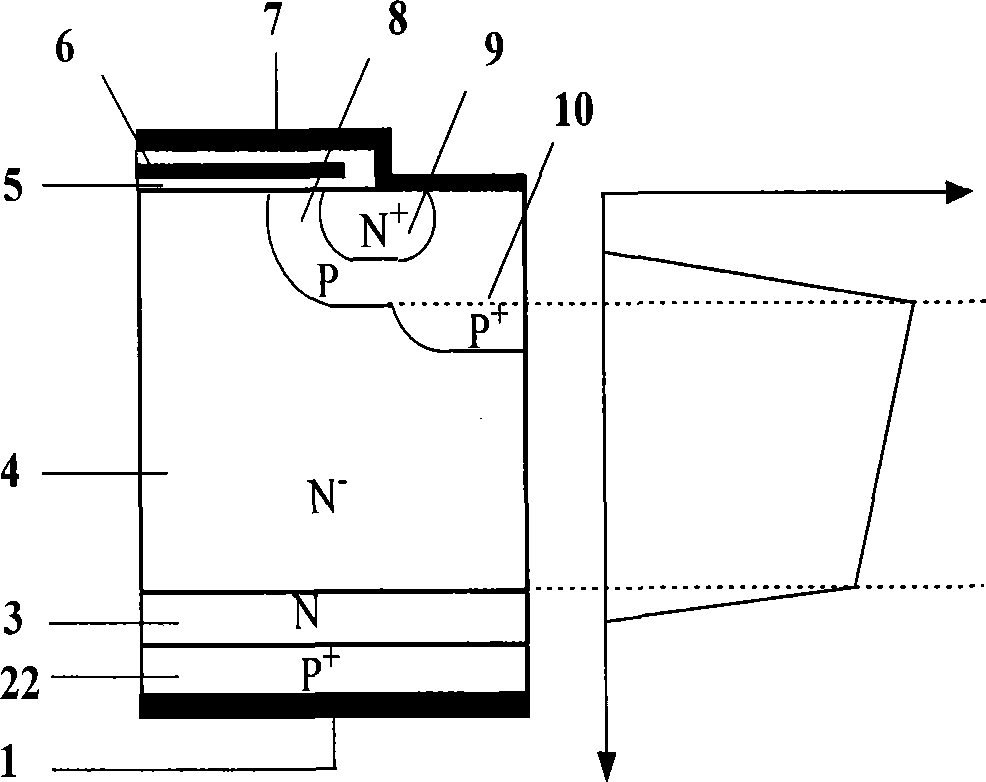

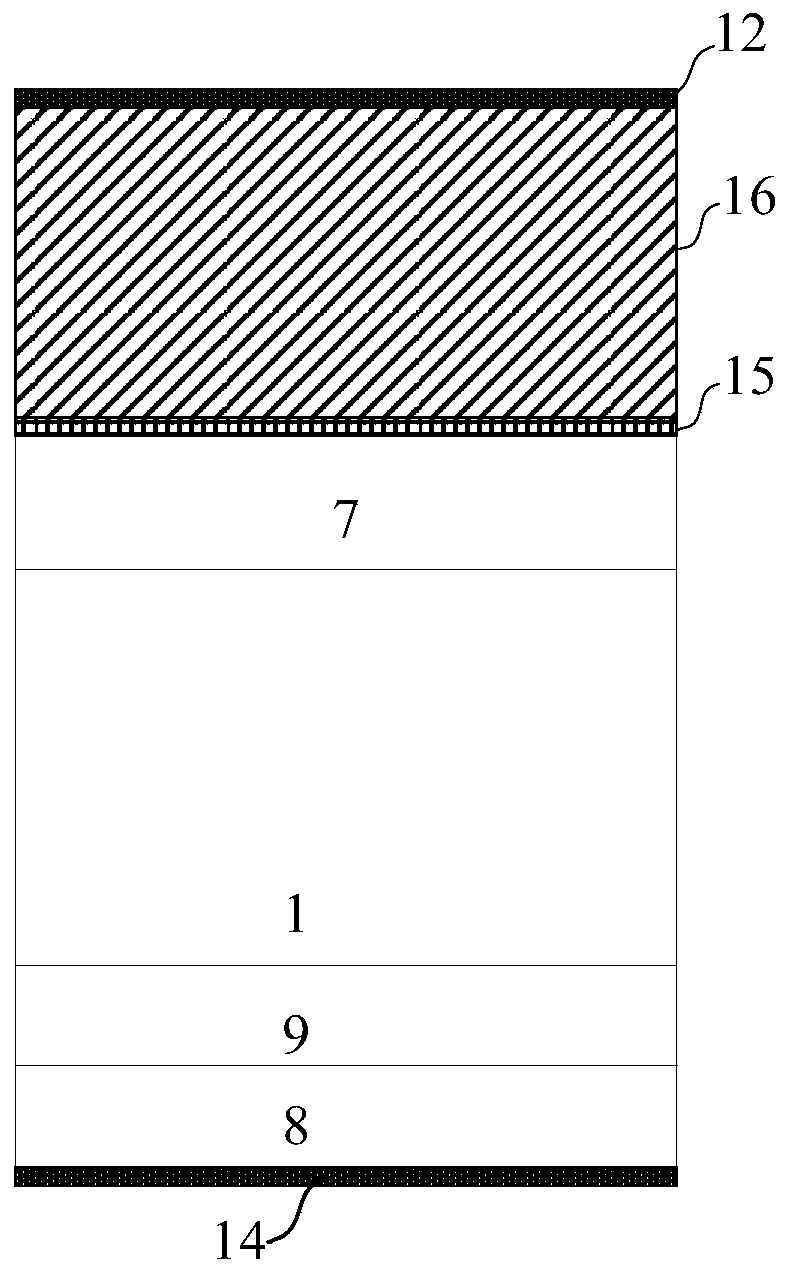

Insulated gate bipolar transistor (IGBT) device and manufacture process method thereof

ActiveCN103035519AFully activatedImprove safe work areaSemiconductor/solid-state device manufacturingSemiconductor devicesImpurity diffusionPhysical chemistry

The invention discloses a manufacture process method for an insulated gate bipolar transistor (IGBT). Double-sided N type impurity diffusion is carried out on an N base zone to form a double-sided N type mixed zone which comprises a front N type mixed zone and a back N type mixed zone. The front N type mixed zone is thinned, and the remained front N type zone serves as a carrier storage layer. The back N type mixed zone is thinned, and the remained back N type zone serves as an N type buffer layer. Thus, a front carrier storage layer is formed to improve a safe working zone of the device. Simultaneously, the deep N type buffer layer is formed at the back to furthest optimize voltage resistance and drop voltage of a device. The invention simultaneously discloses a device manufactured with the method.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

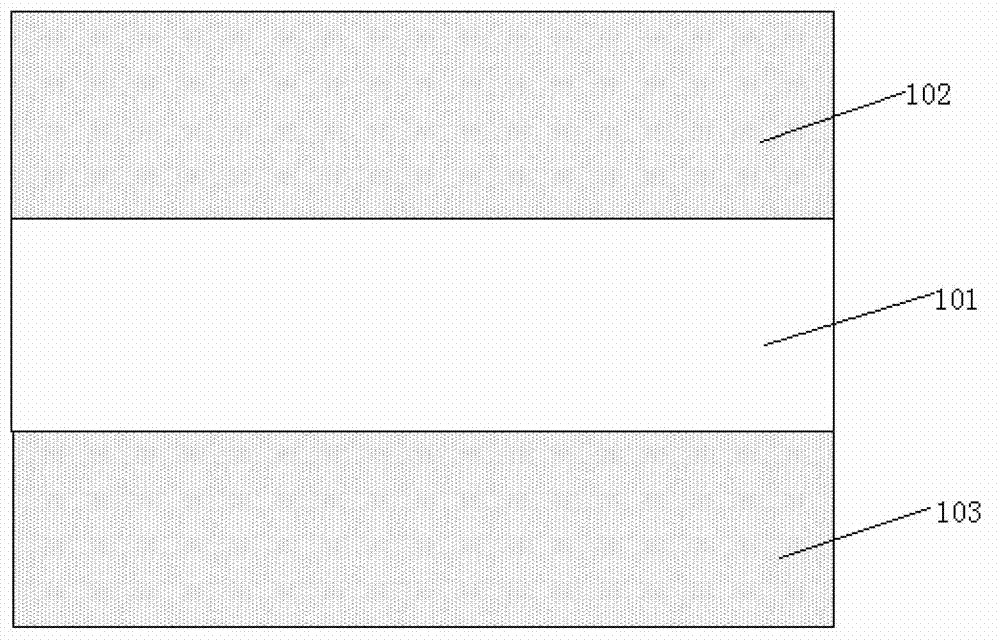

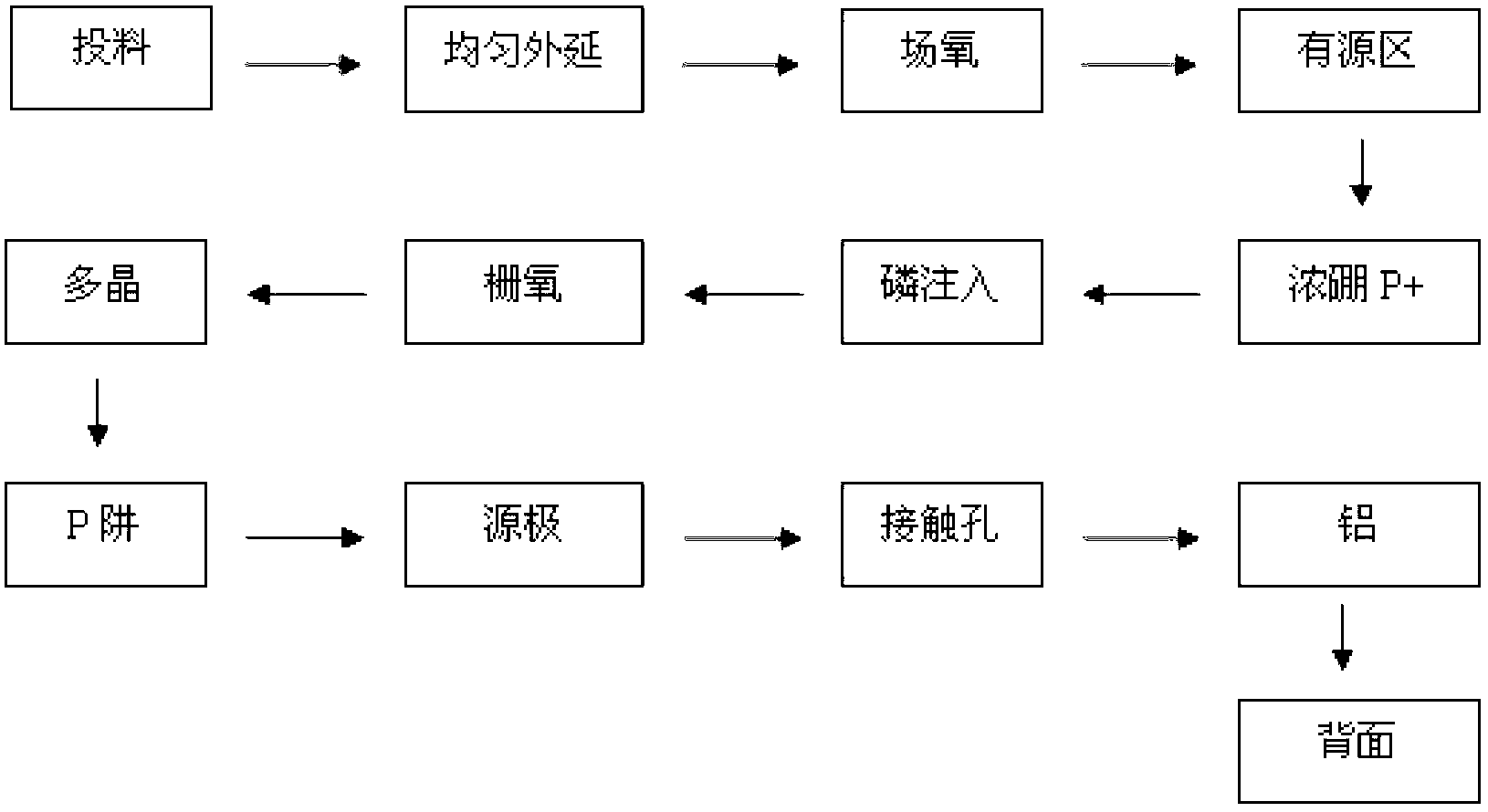

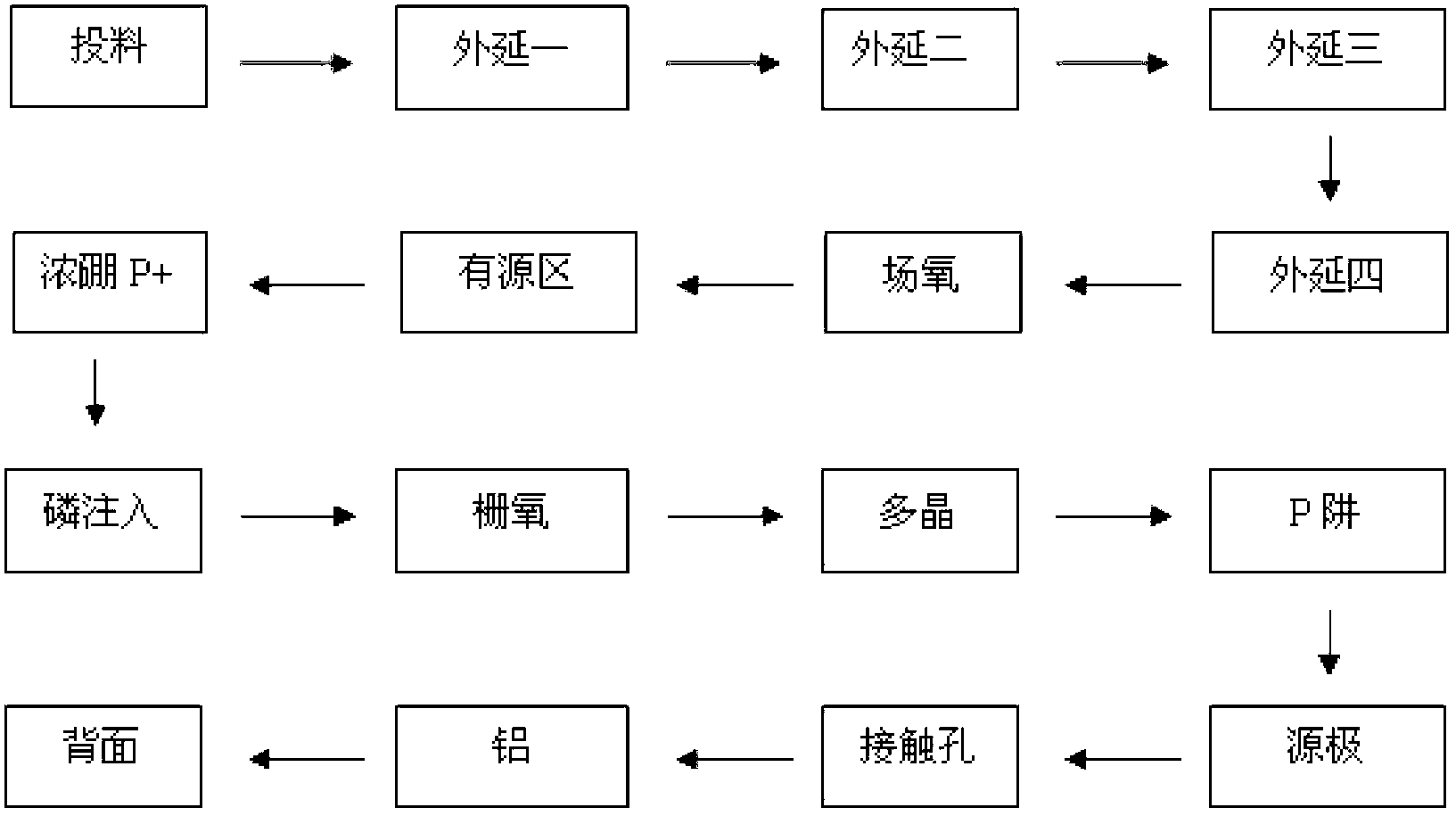

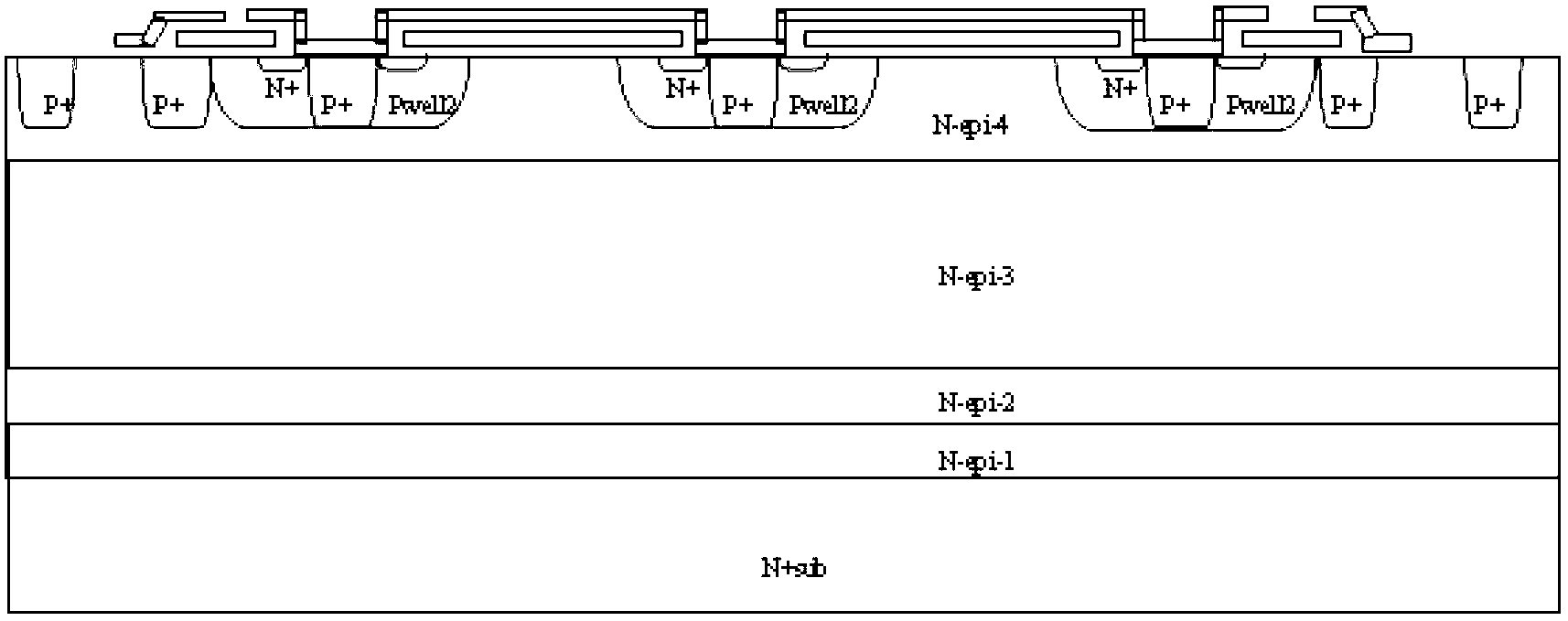

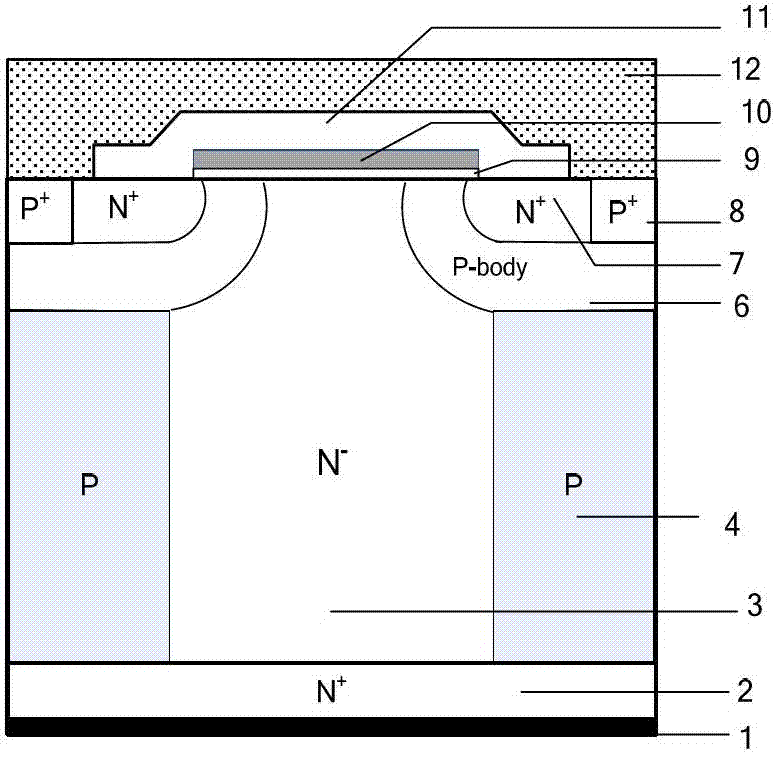

Process for manufacturing series of intermediate-voltage N-type vertical conduction double-diffused metal oxide semiconductor transistors by using composite epitaxy

InactiveCN102709191AImprove safe work areaImprove reliabilitySemiconductor/solid-state device manufacturingHigh concentrationEtching

The invention discloses a process for manufacturing series of intermediate-voltage N-type vertical conduction double-diffused metal oxide semiconductor (VDMOS) transistors by using composite epitaxy. The process comprises the steps of: batch feeding, first-step epitaxy, second-step epitaxy, third-step epitaxy, fourth-step epitaxy, field oxidation, etching of an active area, high-concentration boron injection and junction depth increasing, phosphorus injection and junction depth increasing, gate oxidation, polycrystalline silicon gate deposition and doping, PWELL boron injection and junction depth increasing, source N+ arsenic injection and junction depth increasing, contact hole etching, aluminum evaporation and corrosion, back thinning evaporation and the like. By a process platform, any additional procedure and operation is avoided, and on-resistance can be lowered by 10 percent on the basis of ensuring withstand voltage; by the VDMOS transistor manufactured by the process, a high-current intense-electric field effect can be effectively suppressed, and the safety working area of a device is enlarged to a certain extent; and the on-resistance is lowered, so that power consumption is greatly reduced, energy sources are saved, and the reliability of a circuit is greatly improved.

Owner:WUXI CRYSTAL SOURCE MICROELECTRONICS CO LTD

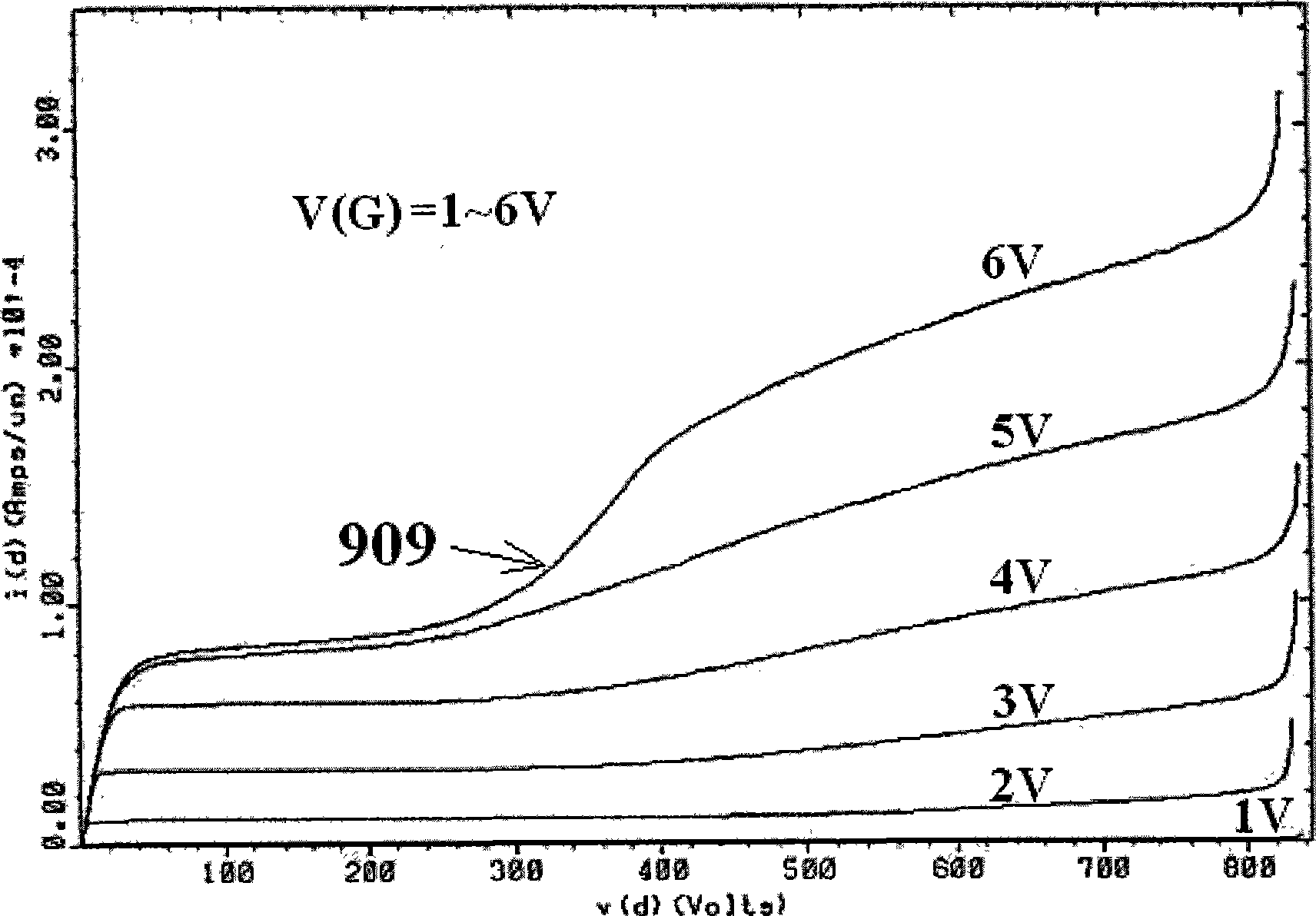

Thyristor controlled by accumulation layer

An accumulation layer controlled thyristor, which belongs to the technical field of semiconductor power devices, is characterized in that the on / off of the thyristor can be controlled by stopping electron circulation through an electron barrier of an internal electric field formed in a P bypass region and an N depletion region. When a positive voltage is applied on a gate, an accumulation layer is formed at the interface between the N depletion region (33) and a gate oxide layer (6); an electron inversion channel is formed in a P-type base region (8); and electrons pass through an N active region (9), the accumulation layer, an N layer (200), and the electron inversion channel to the an N base region (3), thereby controlling the normal operation of the device. The accumulation layer controlled thyristor as the substitute of the conventional gate controlled thyristors, such as MOS controlled thyristors, has the advantages of lower conduction voltage drop, larger saturation current density, no parasitic effect, and greatly improved safety operation area, and can overcome the disadvantages of the conventional gate-controlled thyristors, such as the deficiency of current saturation characteristic and poor turn-off capability.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

High voltage semiconductor device and manufacture method thereof

ActiveCN104835837AReduce sensitivityOptimizing Surface Field DistributionSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactHigh pressure

The invention provides a high voltage semiconductor device and a manufacture method thereof; the device comprises a first dope type semiconductor substrate, a second dope type epitaxial layer arranged on the semiconductor substrate, a second dope type high voltage well positioned in the epitaxial layer, a second dope type deep well positioned in the high voltage well, a first dope type reduced-field layer positioned on the surface of the epitaxial layer and / or in the epitaxial layer (wherein at least a part of the reduced-field layer is positioned in the deep well), a first dope type first well parallel to the high voltage well and positioned in the epitaxial layer, a second dope type source electrode ohmic contact zone arranged in the first well, a drain electrode ohmic contact zone arranged in the deep well, a grid electrode close to the source electrode ohmic contact zone and at least covering the epitaxial layer between the source electrode ohmic contact zone and the high voltage well. The high voltage semiconductor device and the manufacture method thereof can effectively reduce technical manufacture difficulty, improve device parameter characteristics, and improve device reliability.

Owner:HANGZHOU SILAN MICROELECTRONICS

Super-junction vertical double-diffused metal oxide semiconductor (VDMOS) capable of effectively preventing charge imbalance

InactiveCN102738214AImprove breakdown voltageImprove safe work areaSemiconductor devicesCurrent rangeElectron avalanche

The invention discloses a super-junction vertical double-diffused metal oxide semiconductor (VDMOS) capable of effectively preventing charge imbalance and belongs to the field of power semiconductor devices. Deep energy level impurities are doped in the conventional super-junction VDMOS structure and a columnar region (4) of which the conductive type is opposite to that of an epitaxial region (3), wherein donor impurities such as S, Se or Te are doped in an N-channel device, and acceptor impurities such as In, Ti or Zn are doped in a P-channel device. The deep energy level donor impurities are low in ionization rate at normal temperature, the contribution of the deep energy level donor impurities on the doping concentration of the columnar region (4) can be ignored, and the static load balance of the device is not influenced. When the device is positively conducted and operates under high current, the ionization rate of the deep energy level impurities can be greatly improved along with increase of the temperature of the device, the doping level of the columnar region (4) is relatively reduced, the phenomenon that the avalanche breakdown voltage of the device is reduced caused by load imbalance of the super-junction structure because carriers flow through the epitaxial region (3) is effectively avoided, the operative current range of the device is widened, and the positive safety working area of the device is enlarged.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Semiconductor transverse device and high-voltage device

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

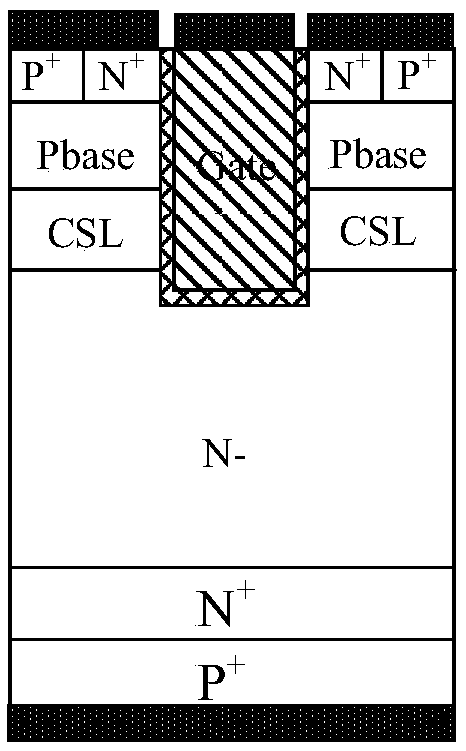

Trench gate IGBT device with carrier storage layer

This invention relates to the power semiconductor field, providing a trench gate IGBT device with carrier storage which is used for solving the problems of high saturation voltage, small short circuitsafe working area and limited concentration of the existing trench gate IGBT device with carrier storage layer, and put forward a novel trench gate IGBT device with carrier storage layer. The trenchgate IGBT device with carrier storage layer directly integrates a plurality of series diodes on the surface of silicon wafers to clamp the potential of the electric field shielding layer in the P region, thereby breaking the concentration limit of CSL on the basis of trench gate IGBT process, greatly improving the injection efficiency of IGBT emitter and greatly improving the trade-off relation between forward voltage drop and turn-off loss of IGBT. Meanwhile, due to the clamping effect of the diode, the drain near the IGBT nMOS channel is clamped at a lower voltage under high voltage and large current, thereby greatly reducing the saturation current of the novel IGBT and improving the short circuit safe working area of IGBT.

Owner:杭州朋声科技有限公司

IGBT device with carrier storage layer using diode clamping

ActiveCN109686787AInhibit onPrevent breakdownTransistorSolid-state devicesSaturation voltageSemiconductor

The invention relates to the field of power semiconductors, provides an IGBT device with a carrier storage layer using diode clamping, and solves the problems that the saturation voltage of an existing groove gate IGBT with the carrier storage layer (CSL) is high, a short circuit safe working area is smaller, and the CSL concentration is limited. The IGBT device with the carrier storage layer using diode clamping has the advantages that the IGBT directly integrates one or more series diodes on the surface of a silicon wafer through a groove gate IGBT process for clamping electric potential ofan electric field shielding layer of a P region, on the basis of the groove gate IGBT process, the limitation of the CSL concentration is broken through, the injection efficiency of an IGBT emitting electrode is greatly improved, thereby greatly improving the tradeoff relationship between conduction voltage drop and turn-off loss of the IGBT; due to the clamping action of a diode, a drain electrode near an nMOS channel of the IGBT is clamped at a lower voltage under the high voltage and large current, so that saturation current of the novel IGBT is reduced to a great extent, thereby enlargingthe short circuit safe working area of the IGBT.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

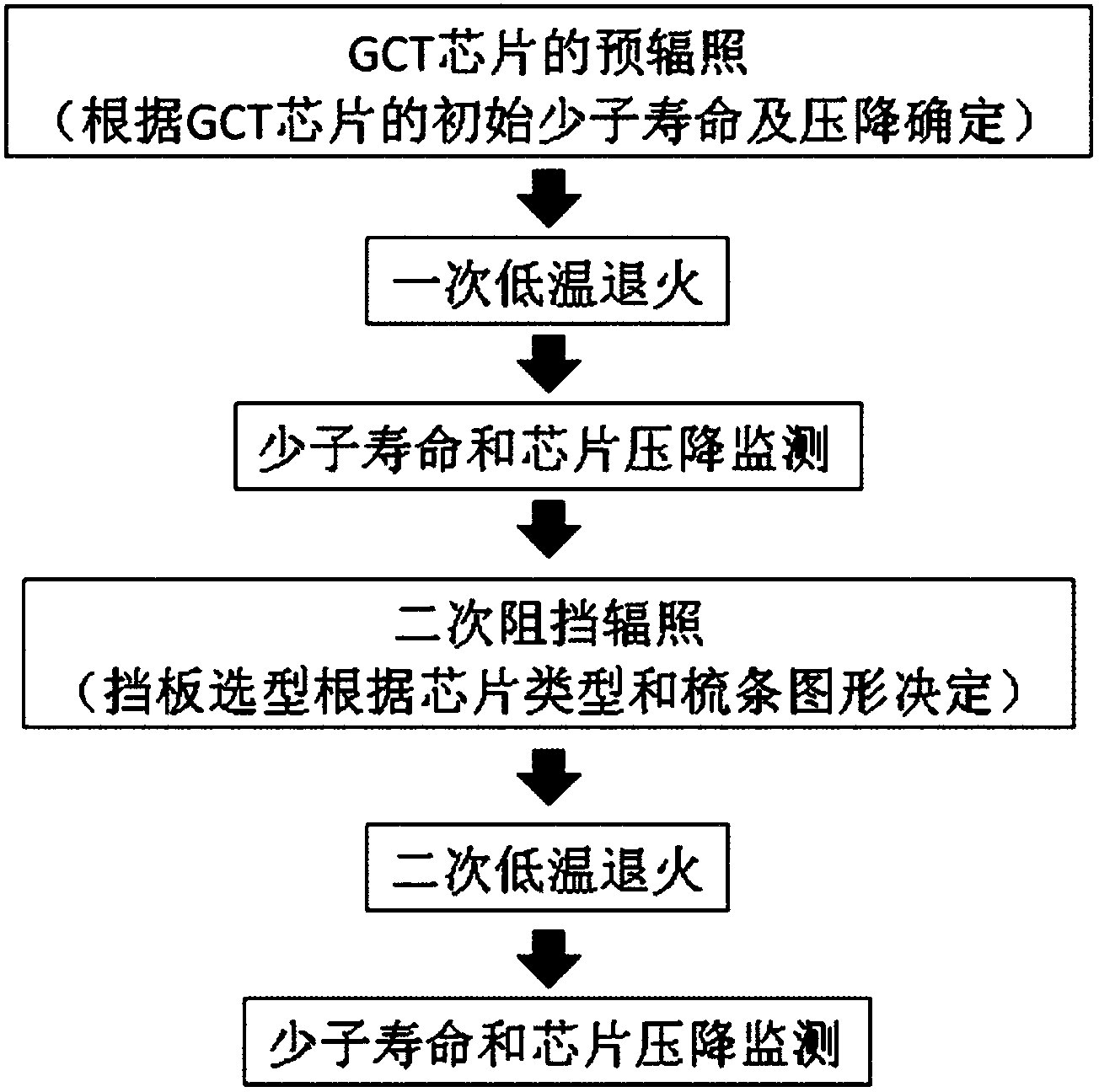

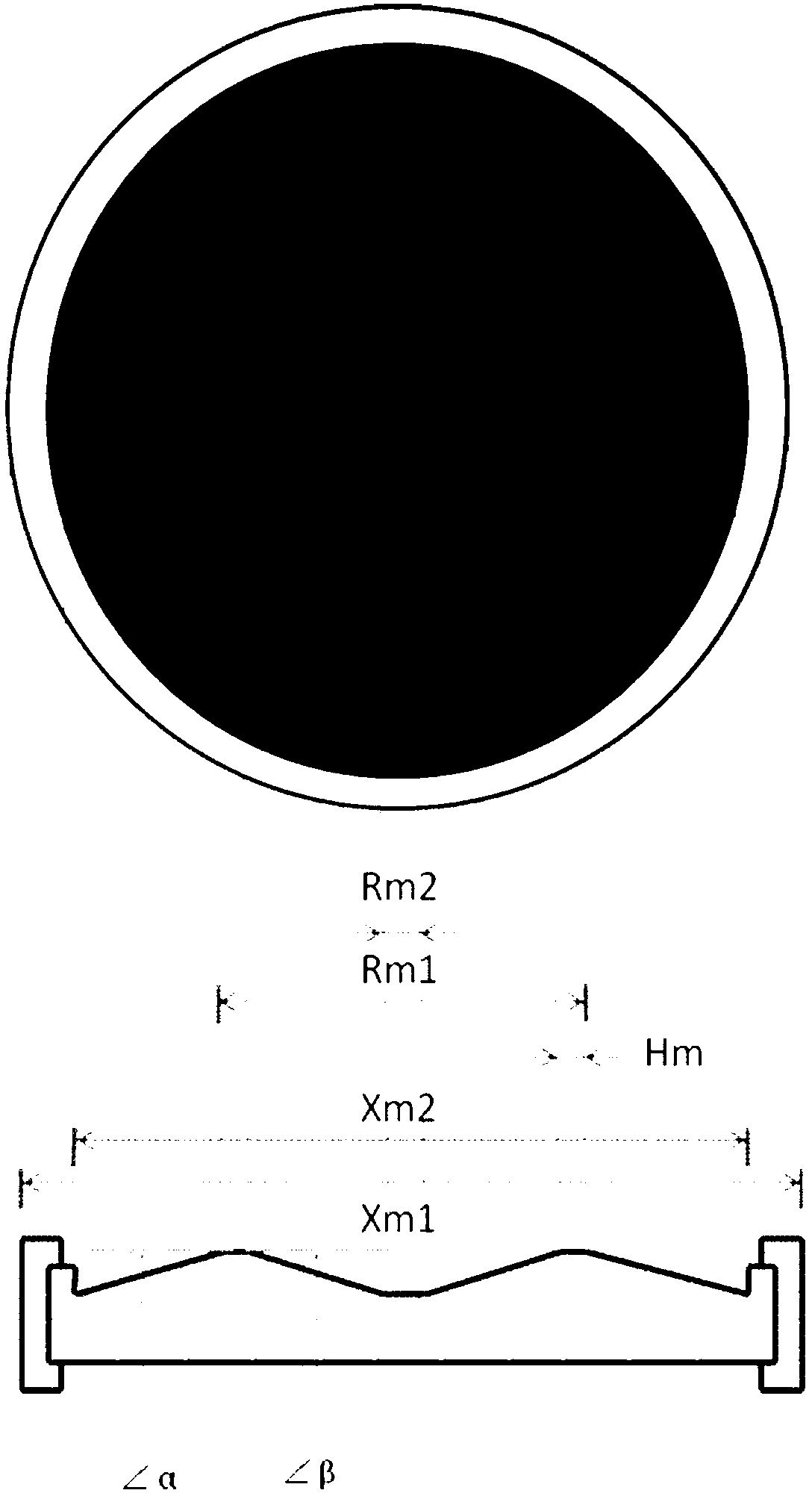

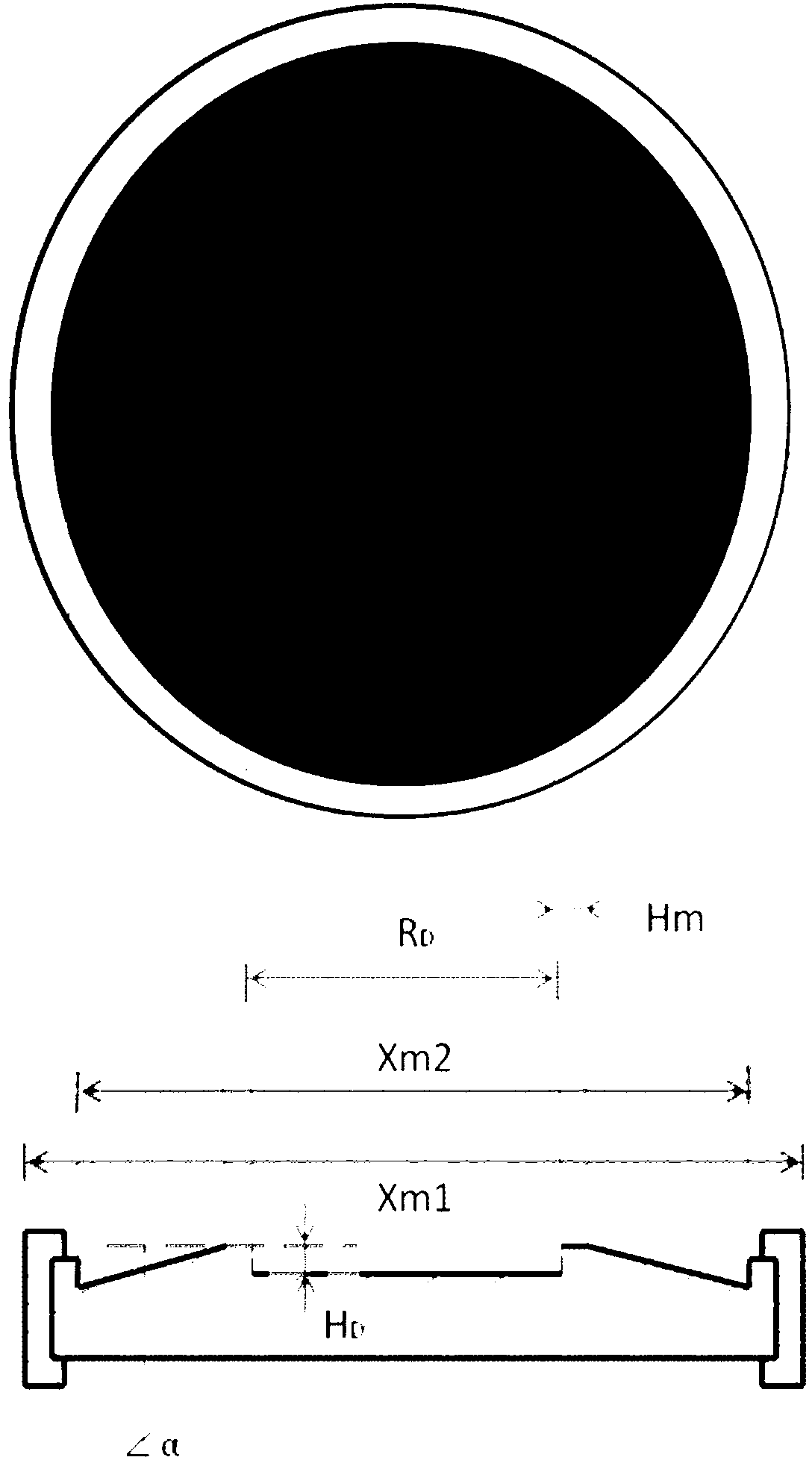

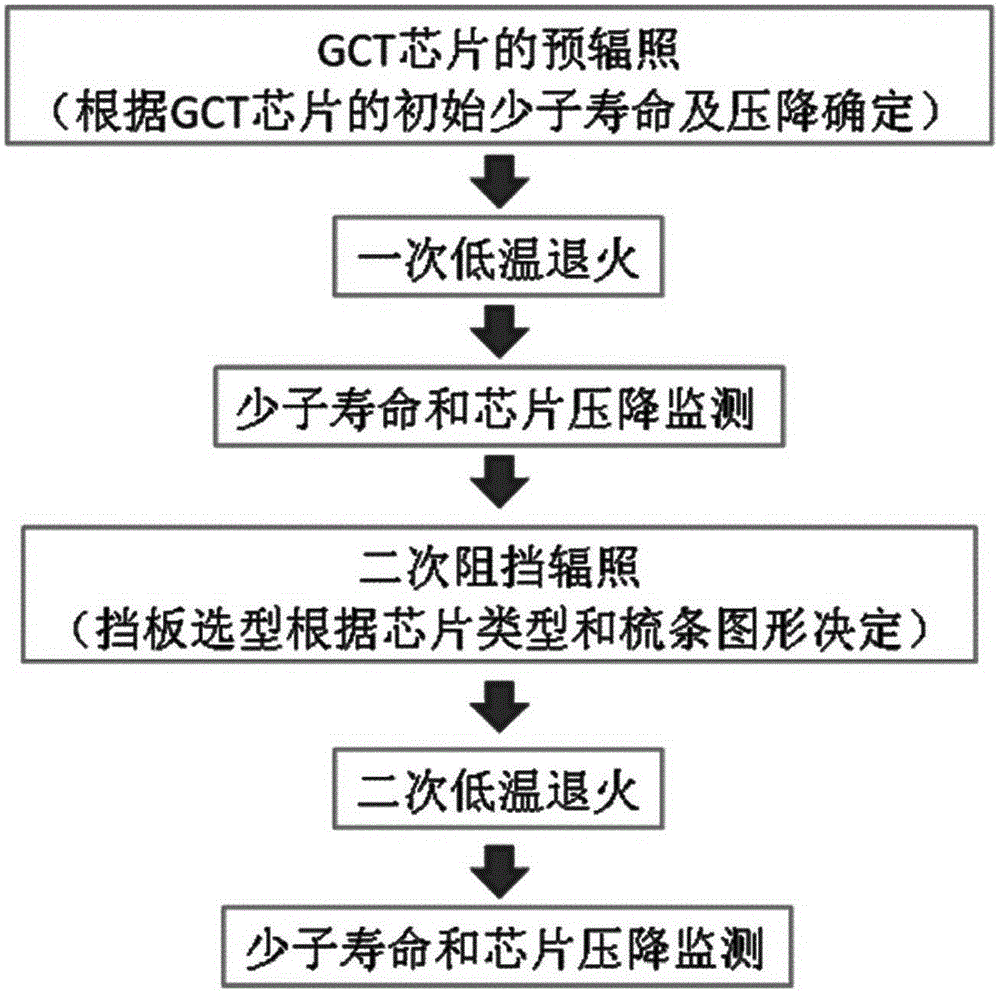

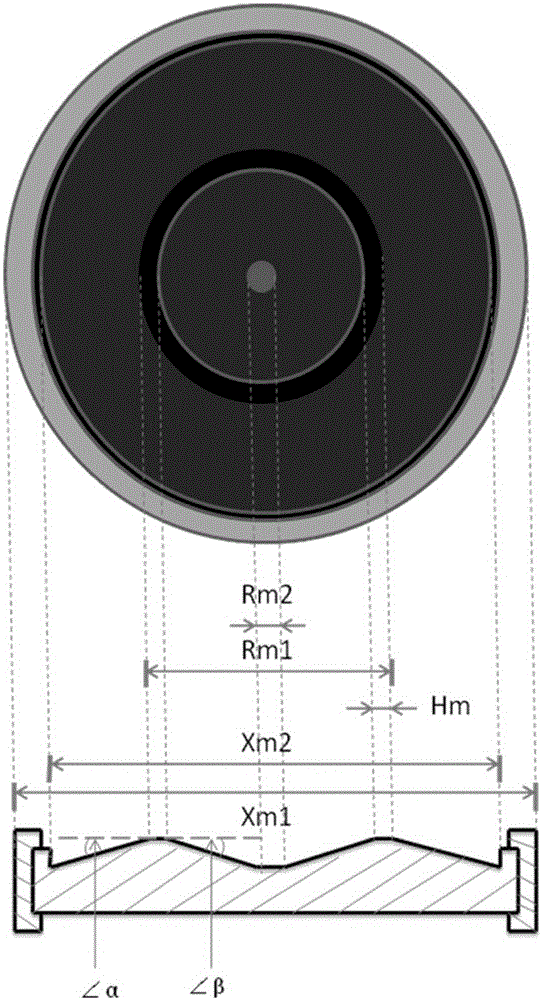

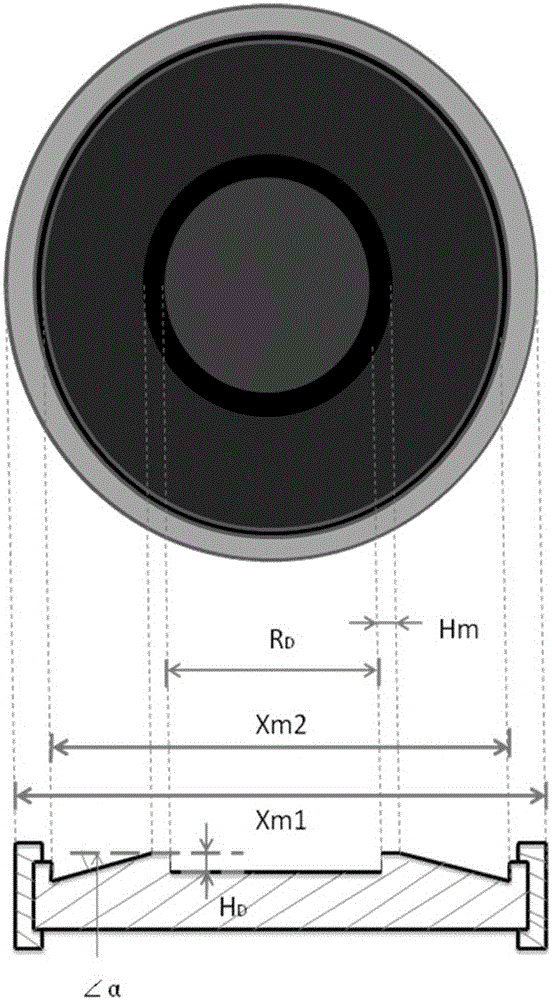

Crosswise heterogeneous electron irradiation method of improving global completion table (GCT) chip safe working area

ActiveCN103065950AMethod for Improving Transverse Non-uniform Electron IrradiationReduce redistribution effectsSemiconductor/solid-state device manufacturingPre irradiationAlloy

Provided is a crosswise heterogeneous electron irradiation method of improving a global completion table (GCT) chip safe working area. The crosswise heterogeneous electron irradiation method of improving the GCT chip safe working area comprises the following steps: (1) carrying out pre-radiation of a GCT chip, and carrying out a primary pre-irradiation to the GCT chip through methods of controlling minority carrier lifetime and pressure drop of the GCT chip, (2) carrying out monitoring of the minority carrier lifetime and pressure drop of the GCT chip after a primary annealing, (3) adopting composite alloy baffles, carrying out a second irradiation and a second annealing to the GCT chip by using heterogeneity of electron irradiation penetrating through the composite alloy baffles, and (4) carrying out the monitoring of the minority carrier lifetime and pressure drop of the GCT chip again. The crosswise heterogeneous electron irradiation method of improving the GCT chip safe working area has the advantages of being simple in principle, and simple and convenient to operate, achieving control of the minority carrier lifetime of parts of the GCT chip, reducing redistribution effect of an electric current in the process of cutoff of GCT by reducing the minority carrier lifetime of far from gate pole slivers, and improving a whole safe working area of the GCT chip and the like.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Super-junction vertical double-diffusion metal-oxide-semiconductor (VDMOS) device with dynamic charge balance

InactiveCN102810567AImprove breakdown voltageImprove safe work areaSemiconductor devicesCurrent rangeEngineering

The invention discloses a super-junction vertical double-diffusion metal-oxide-semiconductor (VDMOS) device with dynamic charge balance and belongs to the field of power semiconductor devices. Deep-energy level impurities (for an N-channel device, a main impurity S, Se or Te; and for a P-channel device, a main impurity In, Ti or Zn) is doped into an epitaxial region (3) of a super junction structure of the conventional super junction VDMOS device. Ionization rates of the deep-energy level impurities are low at room temperature, and the contribution to the dosage concentration of a super-junction center pillar column (4) can be neglected, so that static charge balance of the device is not influenced; when the device is switched in the forward direction and operated under high current, the ionization rates of the deep-energy level impurities are greatly improved along with the raise of the temperature of the device, and equivalently, the doping level of the epitaxial region (3) is improved, so that a phenomenon that avalanche breakdown voltage of the device is dropped caused by the charge unbalance of the super-junction structure when a charge carrier flows by the epitaxial region (3) is avoided; and therefore, the operative current range of the device is widened, and a forward direction safe operation zone of the device is enlarged.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

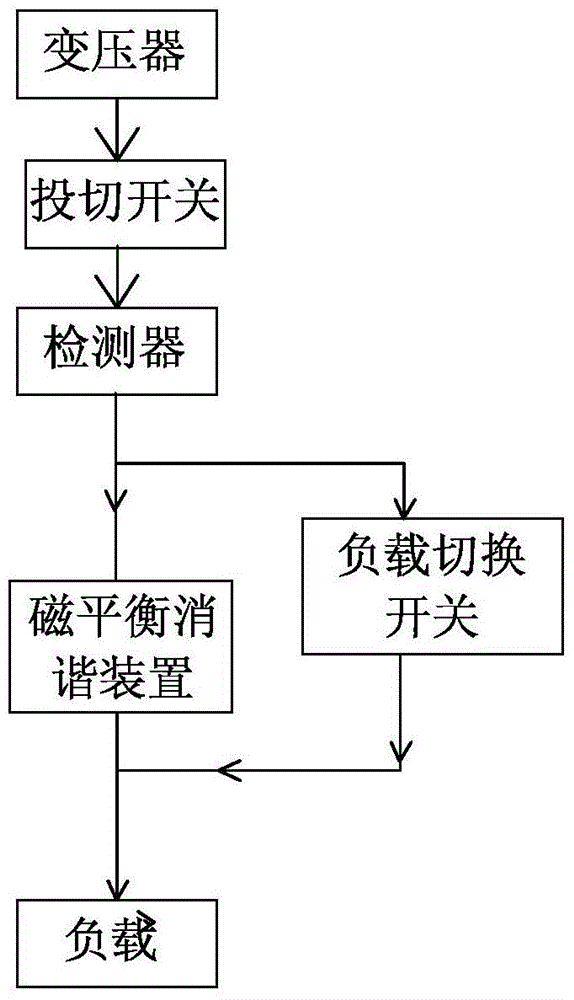

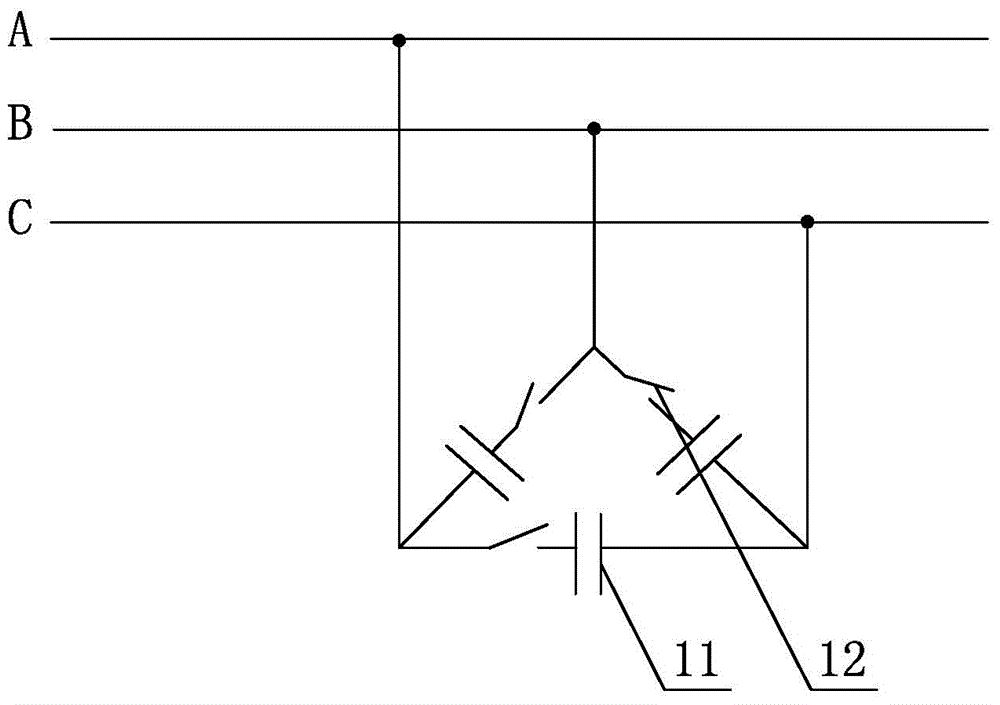

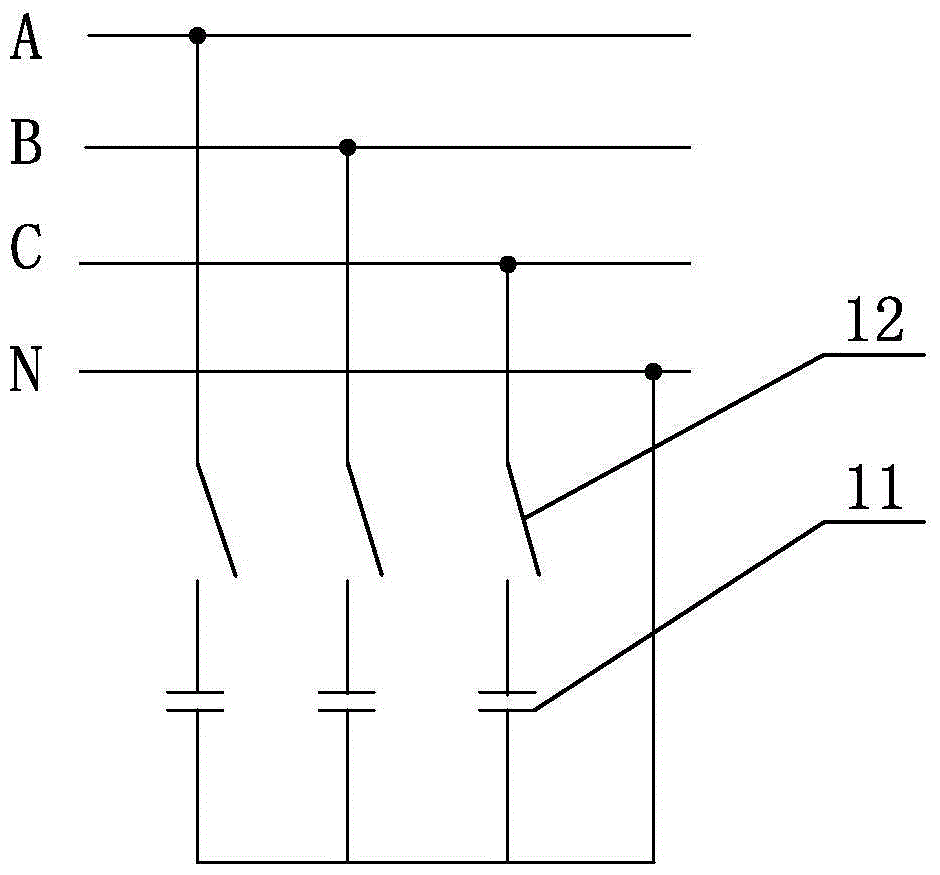

Magnetic balanced harmonic elimination reactive compensation device and method

ActiveCN105048464ANo pollution in the processImprove thermal stabilityPolyphase network asymmetry elimination/reductionReactive power adjustment/elimination/compensationPower qualityLoad circuit

The invention belongs to the field of an intelligent power device and a control device, in particular relates to a magnetic balanced harmonic elimination reactive compensation device and a method. According to the device and the method, three-phase unbalanced data of a circuit is acquired by a detector and is also stored and processed, the state of a load diverter switch on a load circuit is controlled so as to control access states of two branches connected with the detector, wherein one branch is provided with a magnetic balanced harmonic elimination device, the detector controls the load diverter switch to have access to the magnetic balanced harmonic elimination device according to power quality on a detection circuit of the detector when an exception occurs, and the original branch is cut off so as to perform magnetic balanced harmonic elimination. The method and the device have the following advantages that: 1, power supply quality is timely and accurately detected to reach economic operation, and operation loss of the original electromagnetic balanced power saver is effectively reduced; 2, switching in and switching out are convenient so as to guarantee power supply; 3, no-load loss can be effectively reduced; and 4, the device and the method are applicable for a place where a load condition is complicated and harmonic wave of a power grid is high, and power supply reliability is increased.

Owner:山东计保电气有限公司

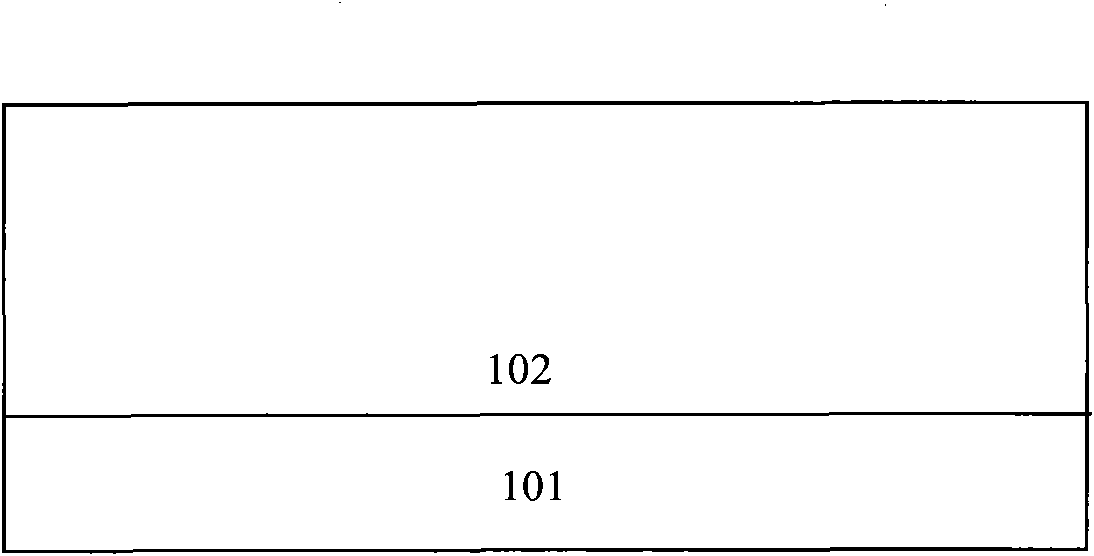

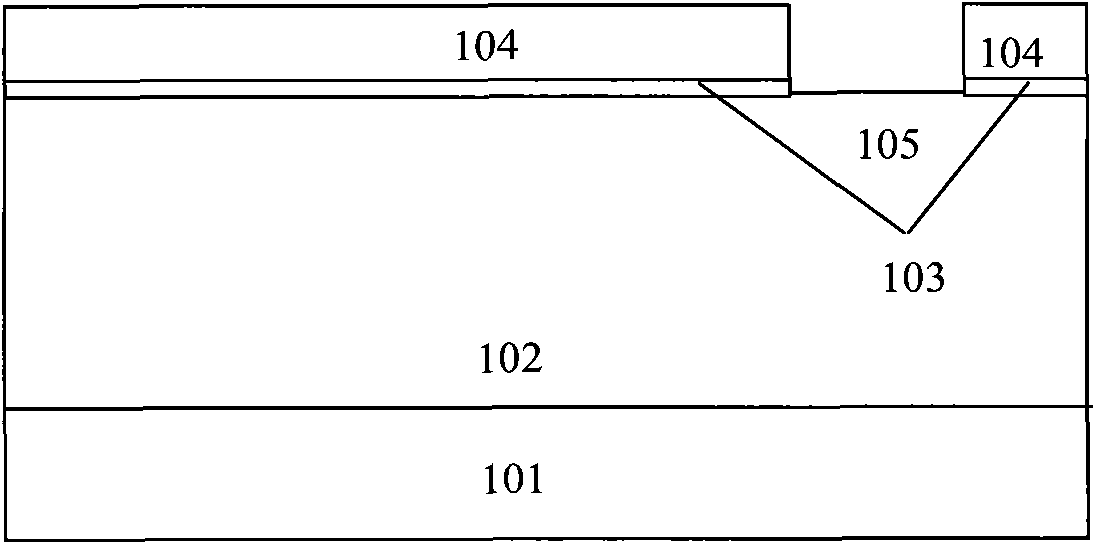

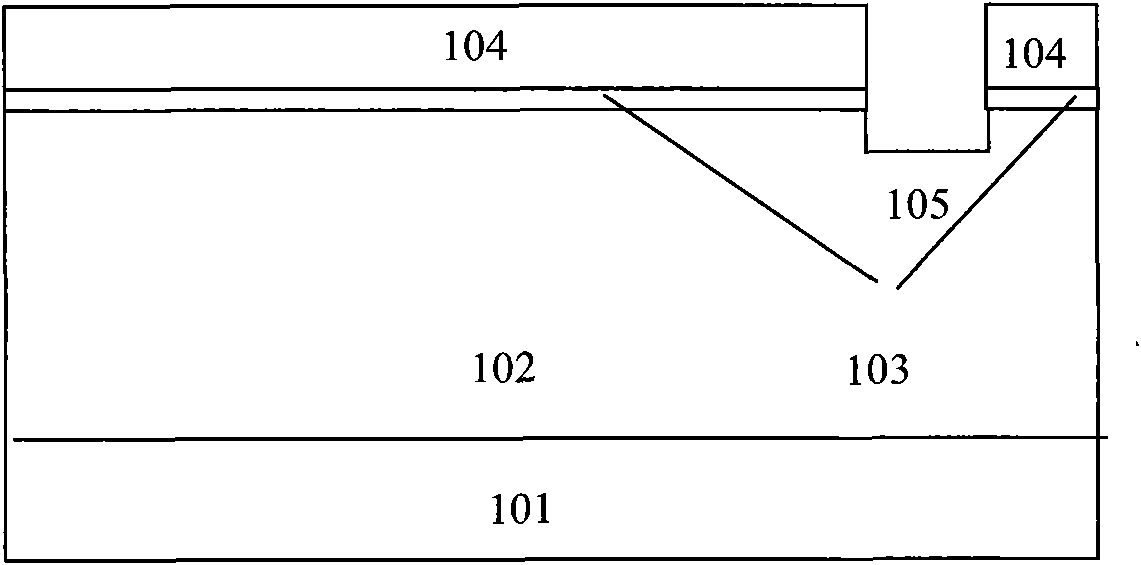

DMOS device and manufacturing methods thereof

ActiveCN102339857AImprove the conduction breakdown voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh energySilicon etching

The invention discloses a DMOS device. Lateral impurities in a drift region distribute nonuniformly and drift region impurity concentration of an active region is greater than the drift region impurity concentration under an isolated oxidation layer. The invention discloses a manufacturing method of the DMOS device. The method comprises the following steps: carrying out several times of ion implantation from high energy to low energy in an area of forming the drift region; carrying out silicon etching in the area of forming the isolated oxidation layer; forming the isolated oxidation layer and carrying out heat propulsion to the drift region. The invention discloses another manufacturing method of the DMOS device. The method comprises the following steps: carrying out first ion implantation so as to form a lightly doped drift region and the isolated oxidation layer, and then carrying out the heat propulsion to the lightly doped drift region; carrying out the second ion implantation, wherein injection energy of the second ion implantation is less than the injection energy of the first ion implantation; carrying out impurity heat propulsion. By using the device and the methods of the invention, on-resistance can be reduced; a high injection effect can be decreased; a conduction breakdown voltage can be increased; a cut-off breakdown voltage of the device can be maintained or raised.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

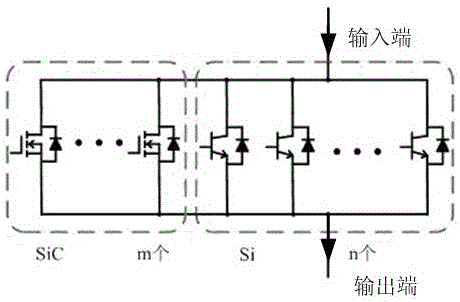

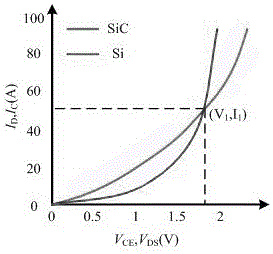

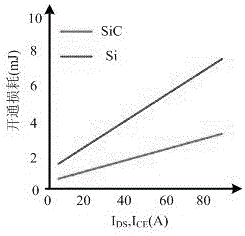

SiC/Si hybrid parallel switch device and optimization control method thereof

InactiveCN105958804AImprove safe work areaReduce lossEfficient power electronics conversionPower conversion systemsPower processingEngineering

The invention discloses an SiC / Si hybrid parallel switch device and an optimization control method thereof. The device comprises an SiC device group connected between the input end and the output end of the switch device and an Si device group connected between the two ends of the SiC device group in parallel. The SiC device group is formed by the parallel connection of m SiC devices, and m is a positive integer larger than 1. The Si device group is formed by the parallel connection of n Si devices, and n is a positive integer larger than 1. According to the load current between the input end and the output end of the switch device, the switch-on or switch-off of the SiC device group and the Si device group is controlled. According to the method, the loss of a power converter can be reduced to the maximum degree, the overload working ability is improved, the safe working area of a hybrid parallel device is enlarger, in addition, while the power processing ability of the power converter is improved, the loss of the power device is reduced as much as possible, at the same time, the loss and cost of a system are reduced, and the overload requirement of the power converter is satisfied.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Switching power-semiconductor device and manufacturing method thereof

PendingCN106684118AReduce functionImprove safe work areaSemiconductor/solid-state device manufacturingSemiconductor devicesEdge cellSwitching power

The invention relates to the technical filed of a power semiconductor device, in particular to a switching power semiconductor and a manufacturing method thereof. The device comprises a silicon layer and a metal layer connected with the silicon layer, wherein the silicon lay comprises a relative first surface and a second surface on the opposite side, and the first surface comprises an active area and a junction termination area, and the active area is surrounded by the junction termination area. The second surface comprises a first ion doping region according to the junction termination area and a second ion doping region according to the junction termination area which ion doping concentration is lower than the first ion doping region, the second ion doping region is surrounded by the first ion doping region. The switching power semiconductor and a manufacturing method thereof has the advantages that the free carrier concentration and current density in the device junction termination area is reduced, the collision ionization and dynamic avalanche breakdown is cut down, the edge cell latch-up damage due to the concentration of the current is decreased and the integral safety area of the device is expanded.

Owner:CR TECH PINGTAN CO LTD

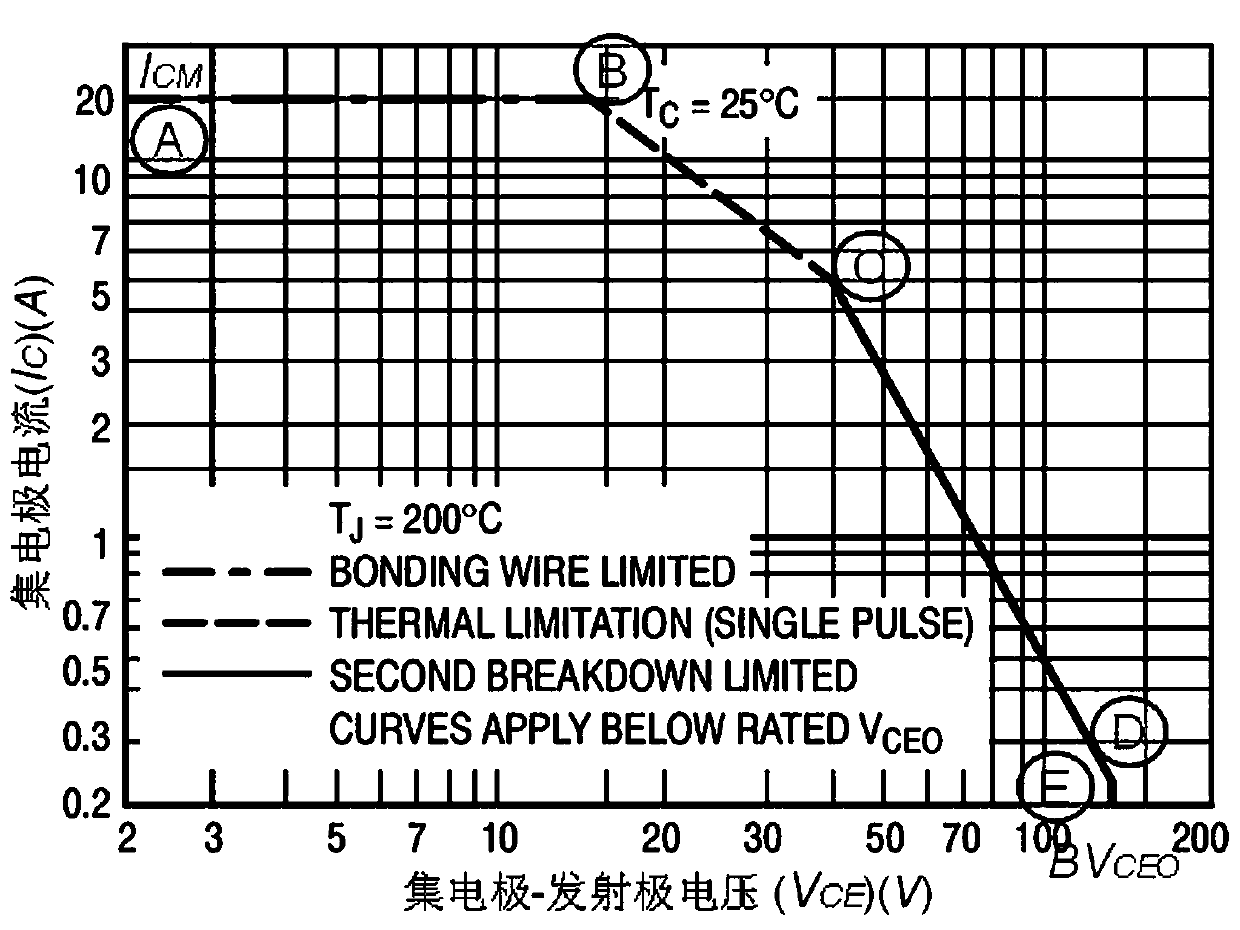

Transistor with high performance, wide safety operation area and high reliability

InactiveCN110600544AIncrease the effective chip areaImprove current magnificationTransistorSolid-state devicesPower flowLocal current

The invention discloses a transistor with high performance, wide safety operation area and high reliability. The transistor comprises multiple mutually independent sub-transistors, and the sub-transistors are formed by entirely segmenting and spacing the original big transistor; the segmentation of the total current of the entire transistor is realized at each sub-transistor, so that the temperatures at multiple parts of the entire transistor are uniform, the excessive increasing of the local current of the transistor is effectively inhibited, and multiple sub-transistors are arranged on one monocrystalline silicon wafer. The transistor disclosed by the invention has the advantages of improving the secondary breakdown tolerance of the power transistor, broadening the safety operation arearange, reinforcing the reliability of the device and the electronic product, prolonging the service life of the transistor and the complete machine, and expanding the application field of the power transistor.

Owner:SHANDONG AOTIAN ELECTRONICS & TECH CO LTD

Diode and manufacturing method thereof

ActiveCN108735823AImproved reverse recovery characteristicsImprove compromise propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryBody region

The invention discloses a diode device and a manufacturing method thereof, and belongs to the technical field of power semiconductor devices. A cellular structure of the device comprises a metal negative electrode, an N+ substrate and an N- epitaxial layer; a trench structure is arranged on the two sides of the top layer of the epitaxial layer; the trench structure comprises a P-type semiconductorregion and a heterogeneous semiconductor from the bottom up; the top layer of the N-epitaxial layer is also provided with a P-type body region, an N+ source region and a P+ contact region; the N+ source region, the P-type body region, a part of the N- epitaxial layer and the heterogeneous semiconductor are in contact through a dielectric layer of the side wall of the trench; the surface of the device is covered with a metal positive electrode; and the heterogeneous semiconductor, the dielectric layer, the source region, the body region and the epitaxial layer form an ultra-potential barrier structure. By virtue of the diode device and the manufacturing method thereof, the problems of high forward opening voltage, poor reverse recovery capability and the like existing in the existing PIN diode device can be solved; and in addition, lower electric leakage and a larger safe working region are achieved on the premise that the withstand voltage is not affected, and the reliability of the device is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A lateral non-uniform electron irradiation method to improve the safe working area of GCT chips

ActiveCN103065950BMethod for Improving Transverse Non-uniform Electron IrradiationReduce redistribution effectsSemiconductor/solid-state device manufacturingPre irradiationAlloy

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

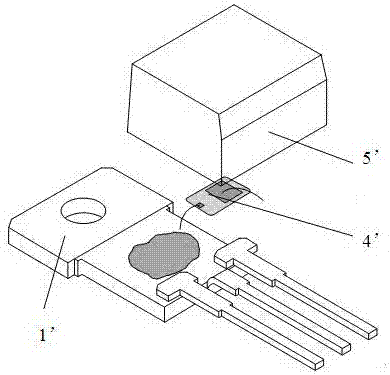

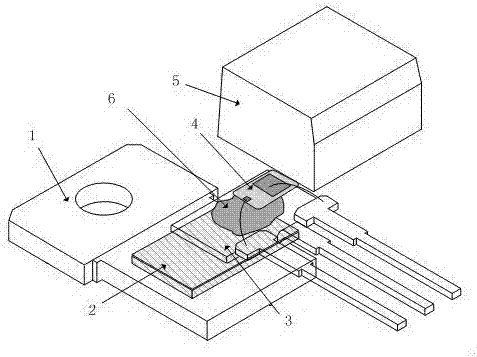

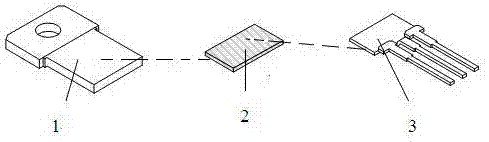

Novel plastic packaging structure for power MOS

PendingCN106887391AEasy to assembleLower package thermal resistanceSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

The invention relates to a novel plastic packaging structure for a power MOS. The novel plastic packaging structure comprises a frame, a chip, and a packaging body. The frame is a copper frame having two parts; one part of the copper frame is used as a piece of slide glass and is connected with a back electrode of a device and a pin is led out to form electrical connection; and the other part of the copper frame is a cooling back panel for realizing a heat radiation function; and the two parts are isolated from each other by a high-thermal-conduction isolation layer, so that the two parts of the copper frame are in physical connection. According to the invention, because the slide glass and the cooling panel are independent parts isolated from each other and the slide glass is used for electrical connection and the cooling panel is used for providing a cooling channel, PCB assembling becomes convenient and the packaging thermal resistance of the power MOS can be reduced, and the security working zone at an application terminal is enhanced; and advantages of high power and low power consumption of the power MOS are fully realized.

Owner:SHANGHAI CHANGYUAN WAYON MICROELECTRONICS

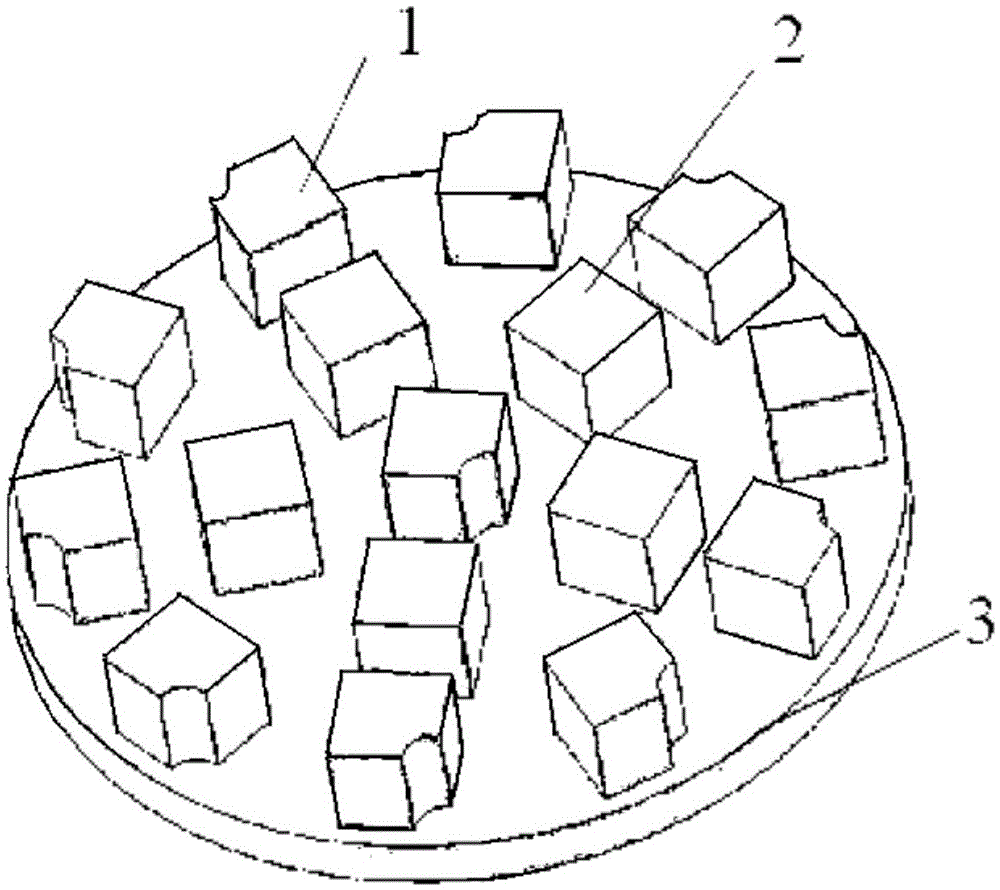

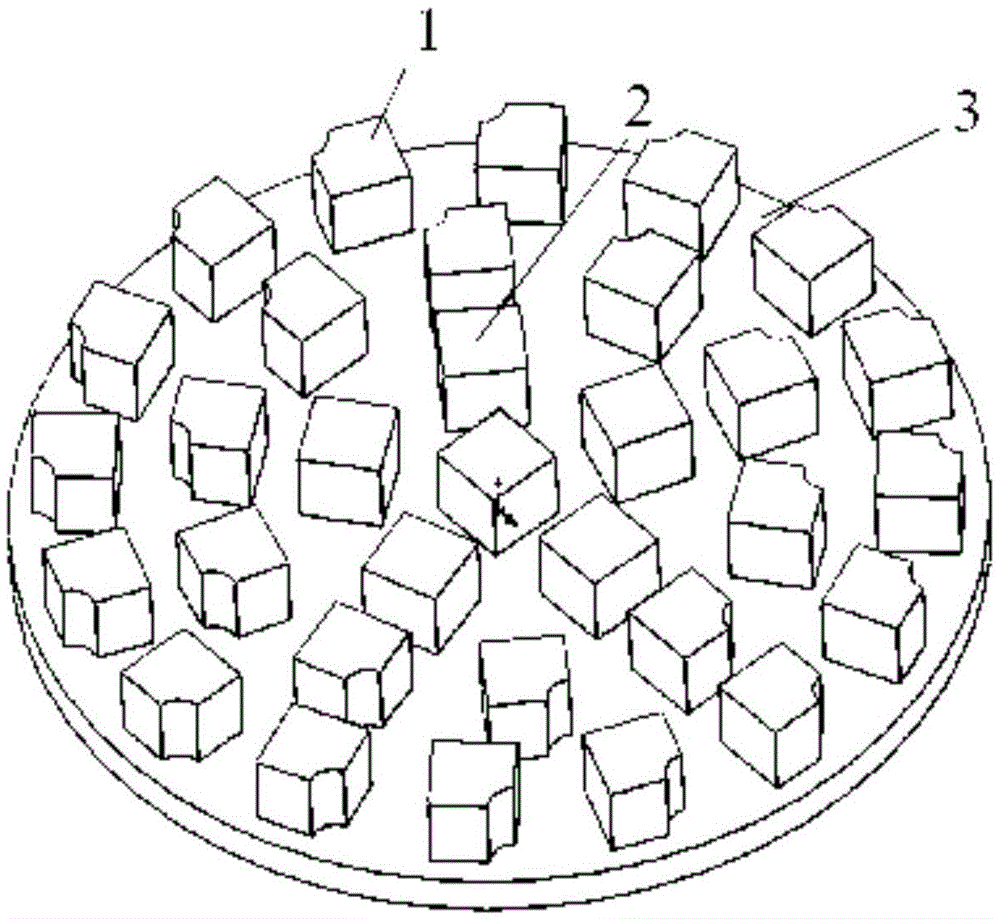

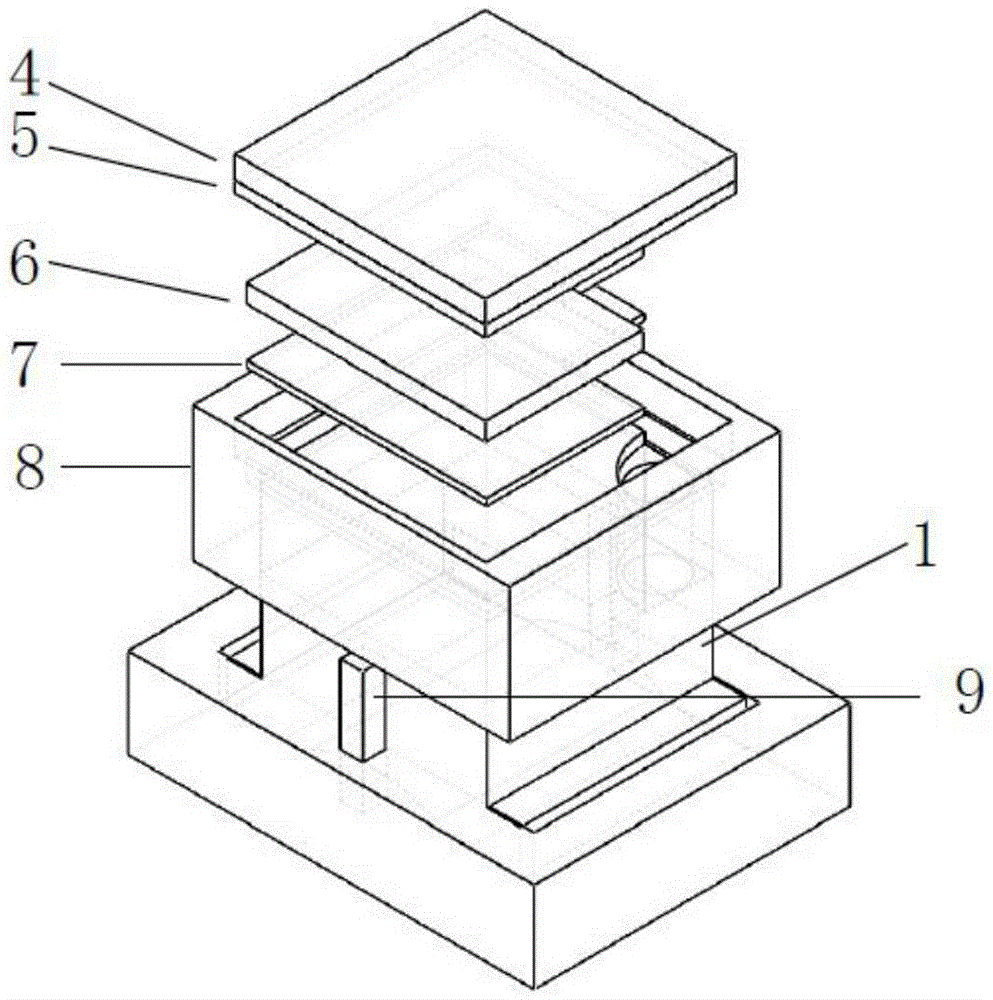

Novel crimping type IGBT module

ActiveCN105552037ASignificant progressImprove the problem of too much current overshootSemiconductor/solid-state device detailsSolid-state devicesTransient statePower flow

The invention provides a novel crimping type IGBT module. The novel crimping type IGBT module comprises a tube shell, and platy metal electrodes coaxially arranged at the upper and lower ends of the tube shell, wherein lug bosses are fixed on the inner side face of the metal electrode at the lower end; power sub modules are crimped between the lug bosses and the metal electrode at the upper end; the lug bosses are arranged by taking the center of the metal electrode at the lower end as the center of a circle; and the lug bosses are distributed on the inner side face of the metal electrode at the lower end circumferentially from the inner layer to the outer layer at an equidistributed manner in sequence. According to the technical scheme of the novel crimping type IGBT module provided by the invention, the problem of overhigh overshoot of partial current when transient state current passes through the lug bosses of the crimping type IGBT module is solved; and the reliability of the crimping type IGBT module is improved, and the safety operation area of the crimping type IGBT module is enlarged.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com