Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1538 results about "Trench gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Trench-gate field effect transistors and methods of forming the same

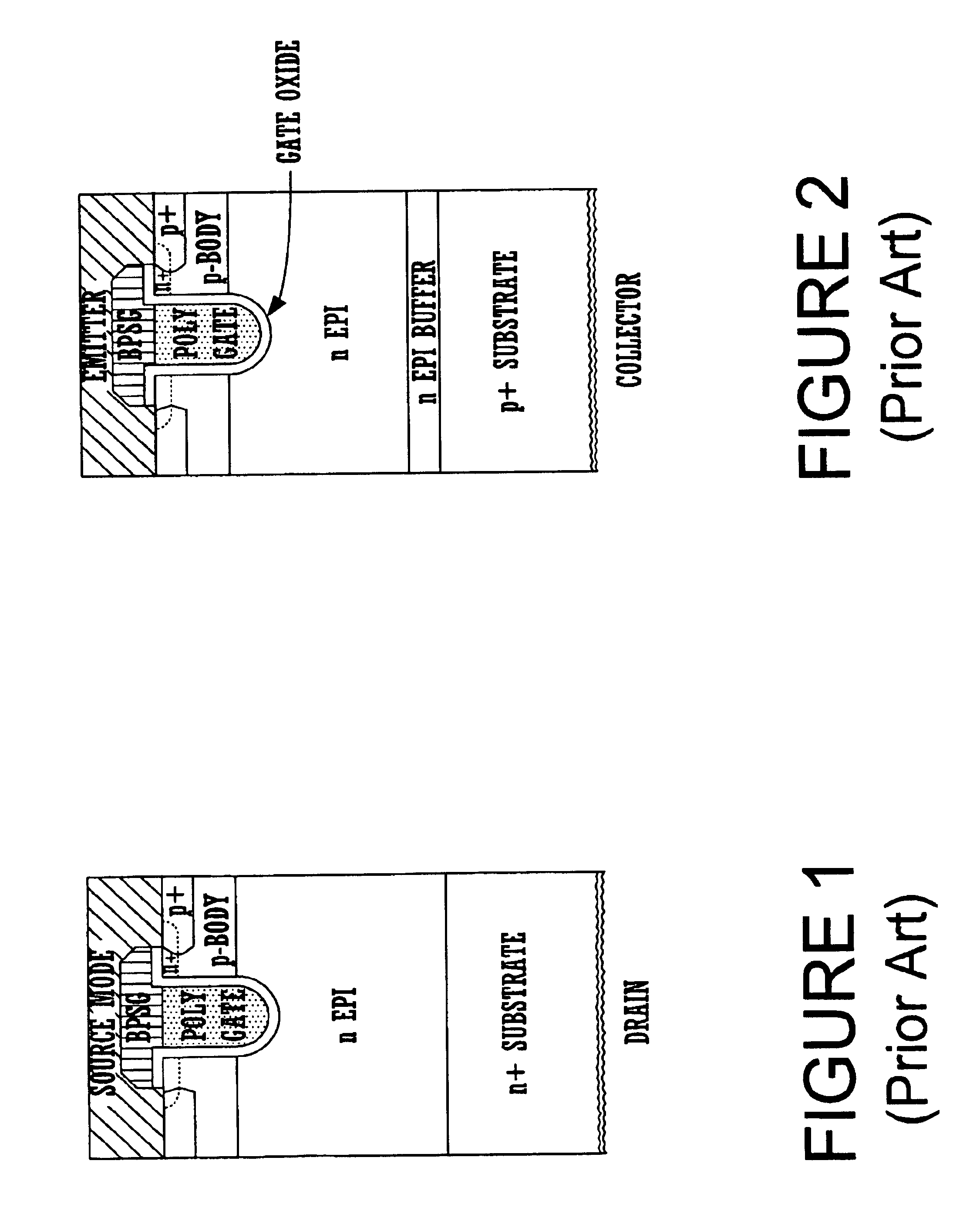

InactiveUS20060273386A1Reduce channel resistanceSemiconductor/solid-state device manufacturingDiodeGate dielectricField-effect transistor

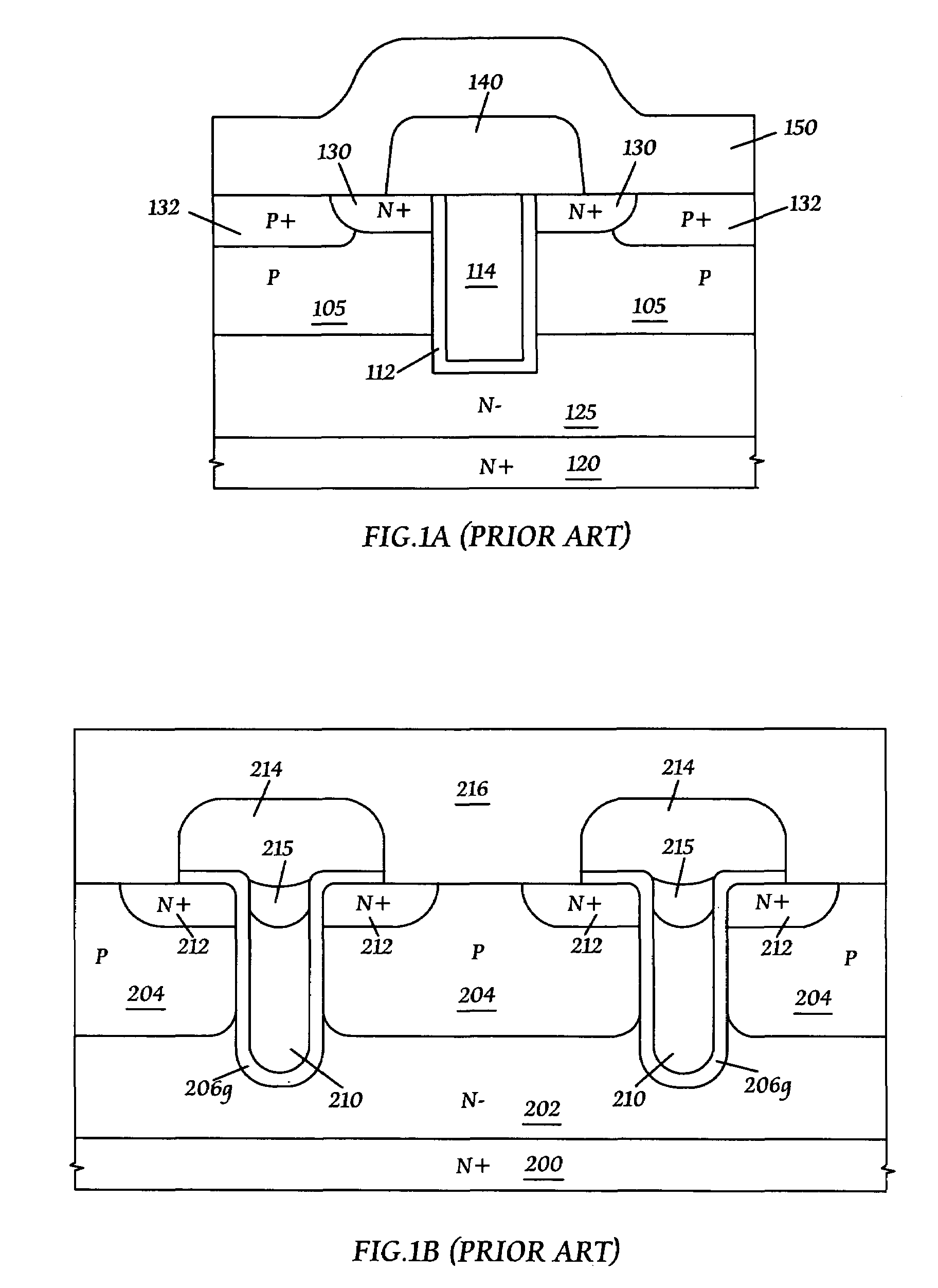

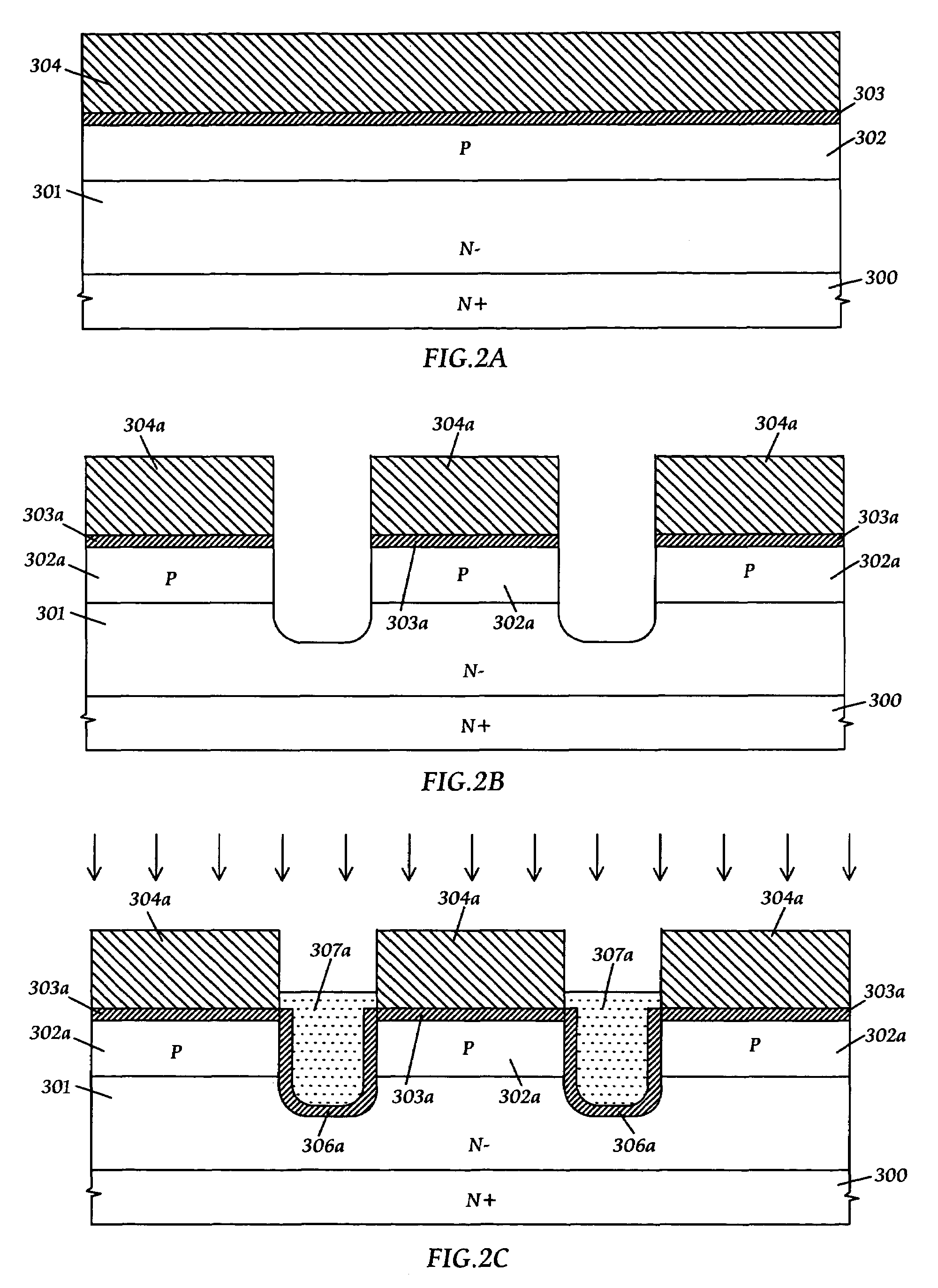

A field effect transistor includes a body region of a first conductivity type over a semiconductor region of a second conductivity type. A gate trench extends through the body region and terminates within the semiconductor region. At least one conductive shield electrode is disposed in the gate trench. A gate electrode is disposed in the gate trench over but insulated from the at least one conductive shield electrode. A shield dielectric layer insulates the at lease one conductive shield electrode from the semiconductor region. A gate dielectric layer insulates the gate electrode from the body region. The shield dielectric layer is formed such that it flares out and extends directly under the body region.

Owner:SEMICON COMPONENTS IND LLC

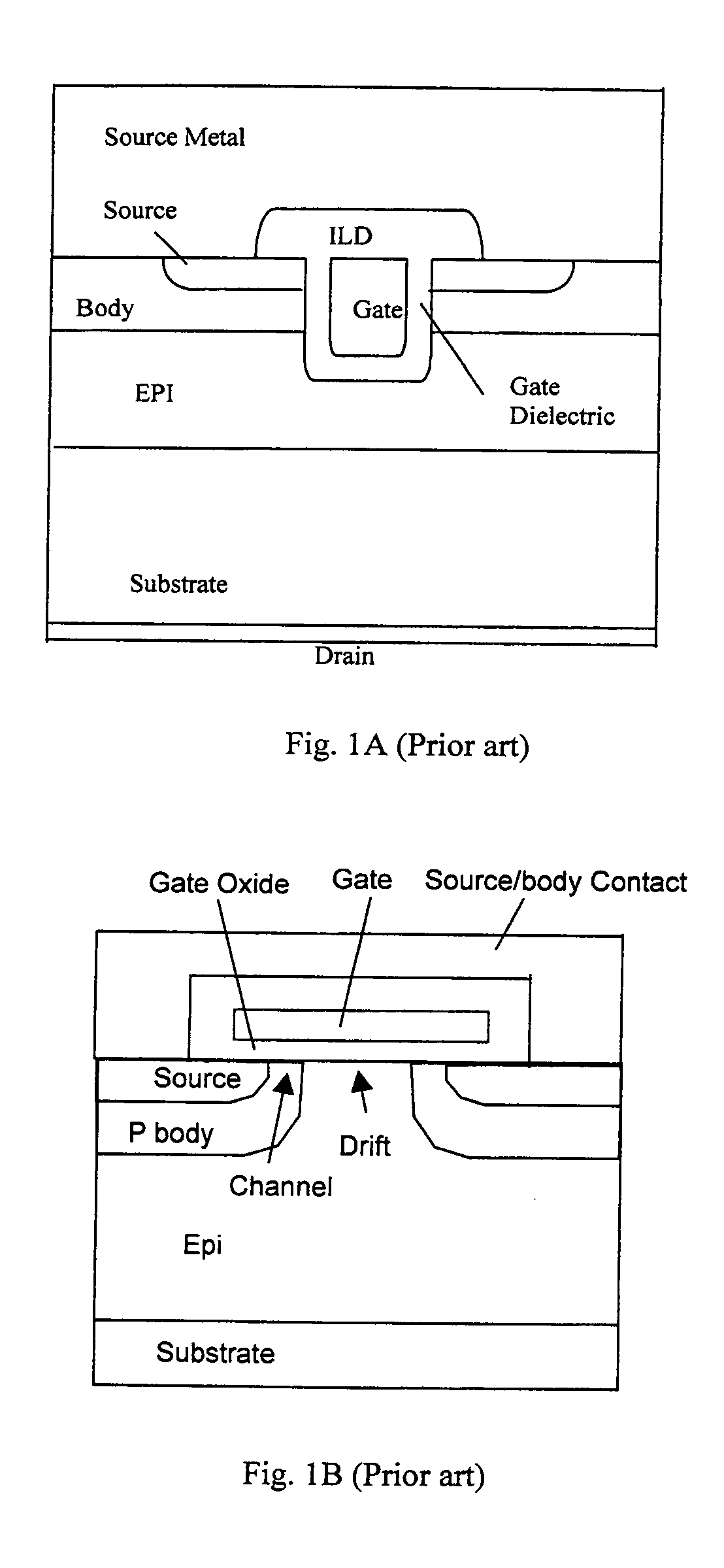

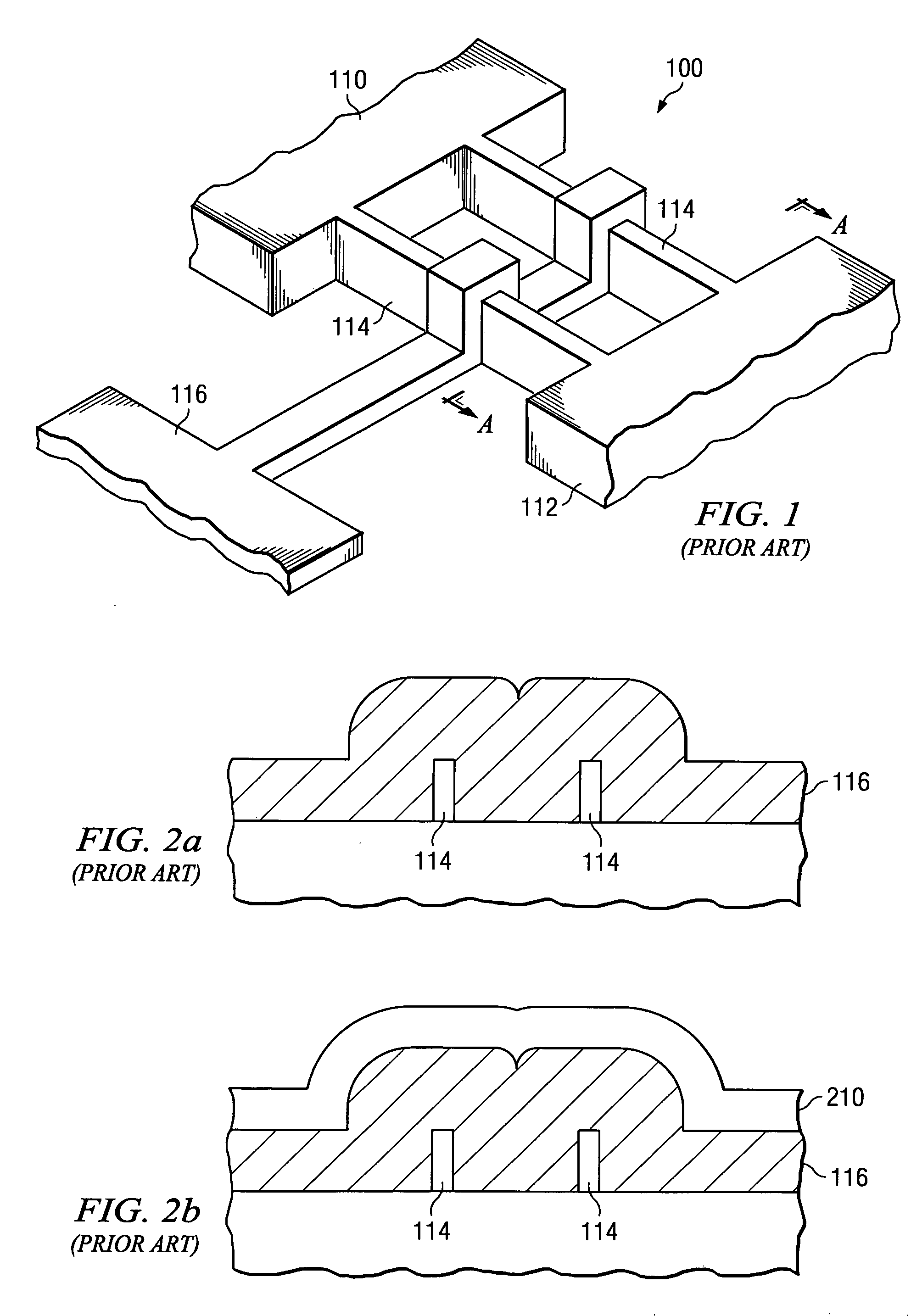

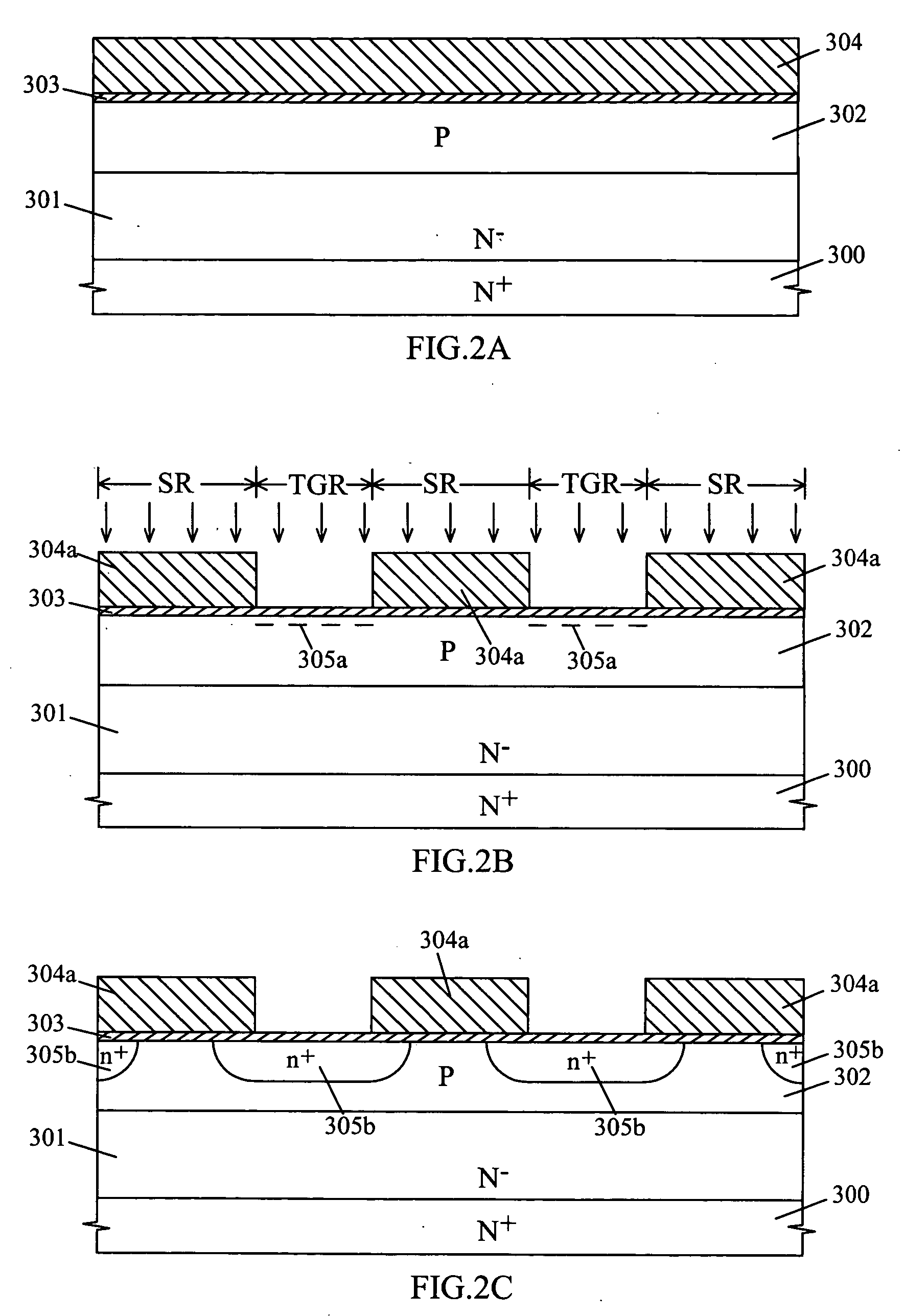

Power device utilizing chemical mechanical planarization

InactiveUS20070155104A1Semiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorTrench gate

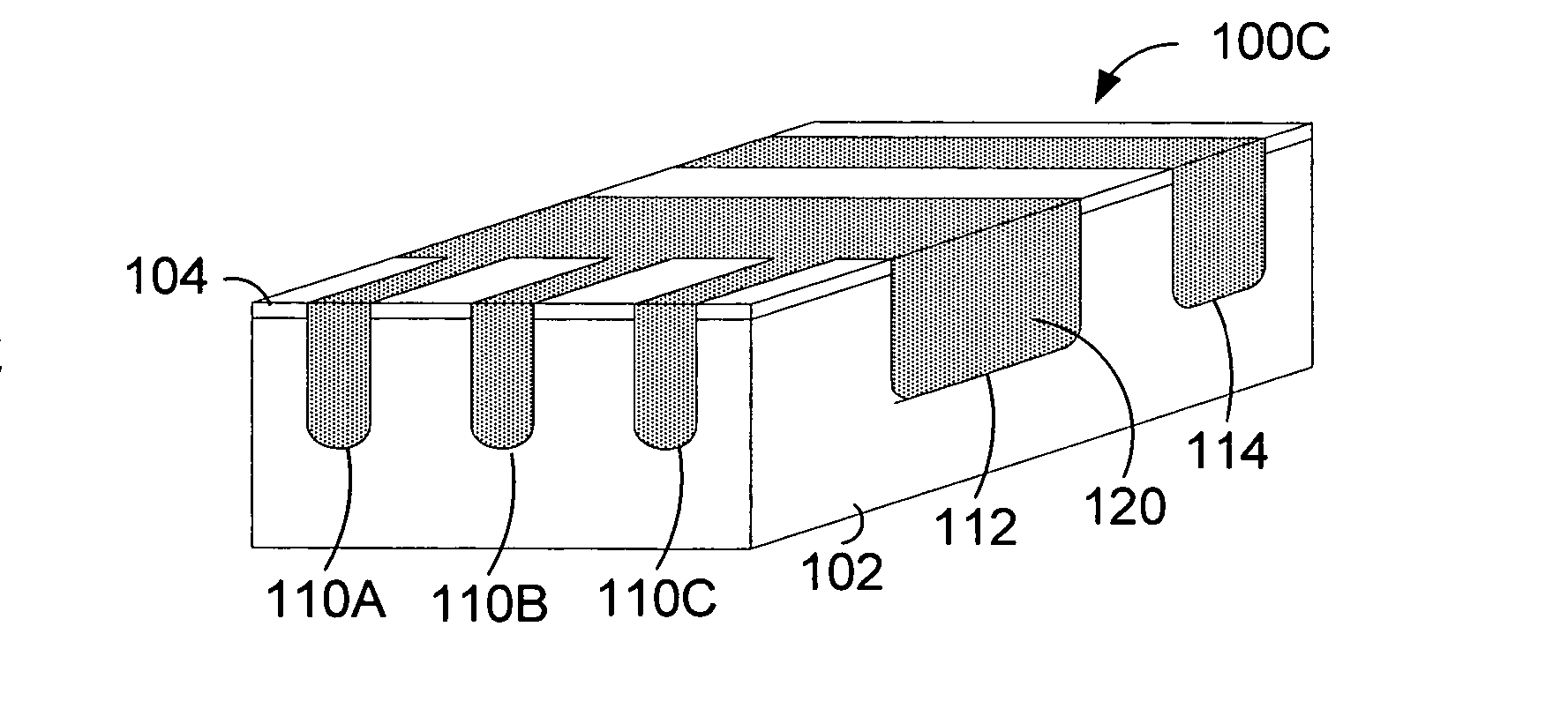

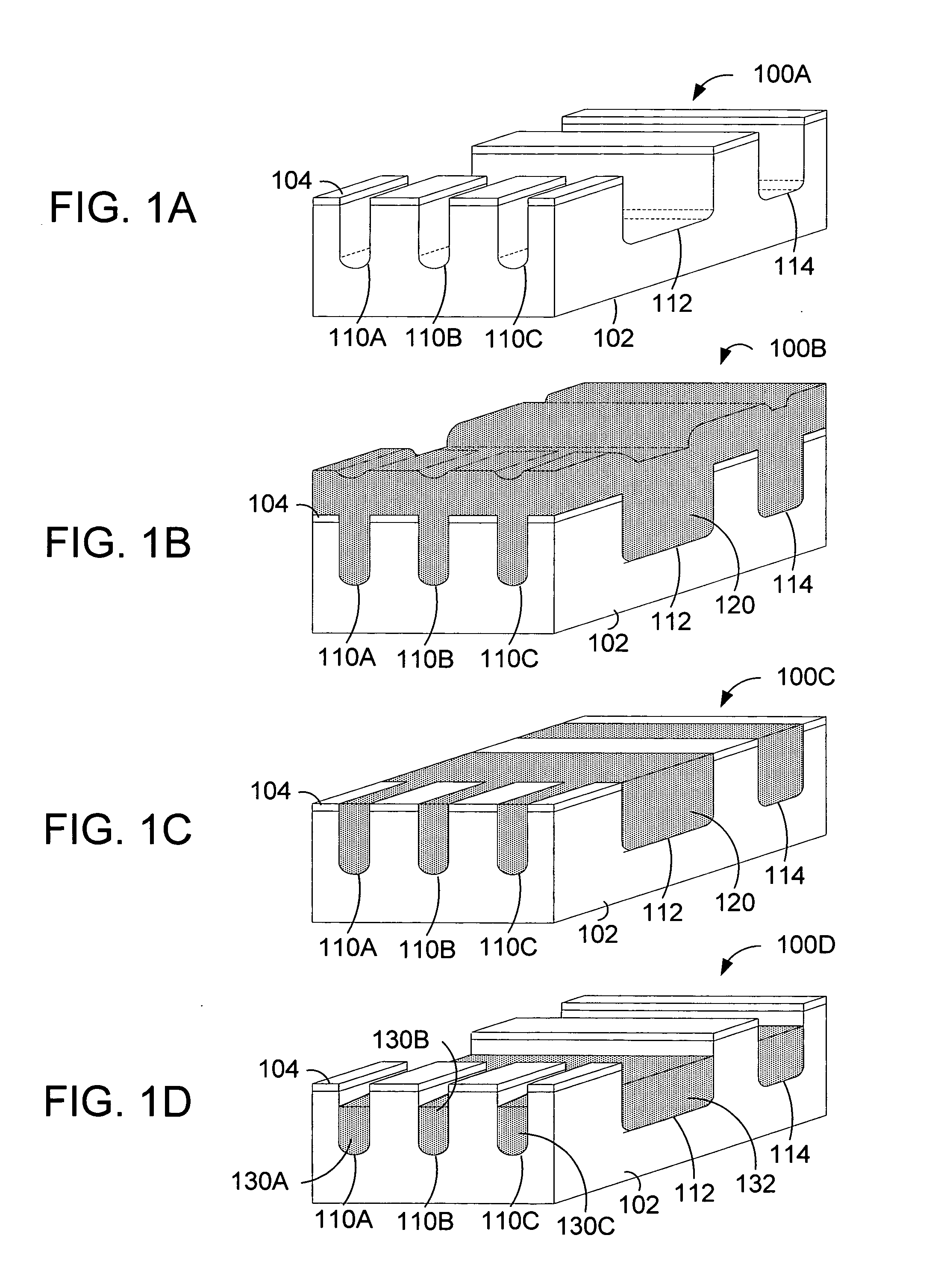

A trench-gated field effect transistor (FET) is formed as follows. Using one mask, a plurality of active gate trenches and at least one gate runner trench are defined and simultaneously formed in a silicon region such that (i) the at least one gate runner trench has a width greater than a width of each of the plurality of active gate trenches, and (ii) the plurality of active gate trenches are contiguous with the at least one gate runner trench.

Owner:SEMICON COMPONENTS IND LLC

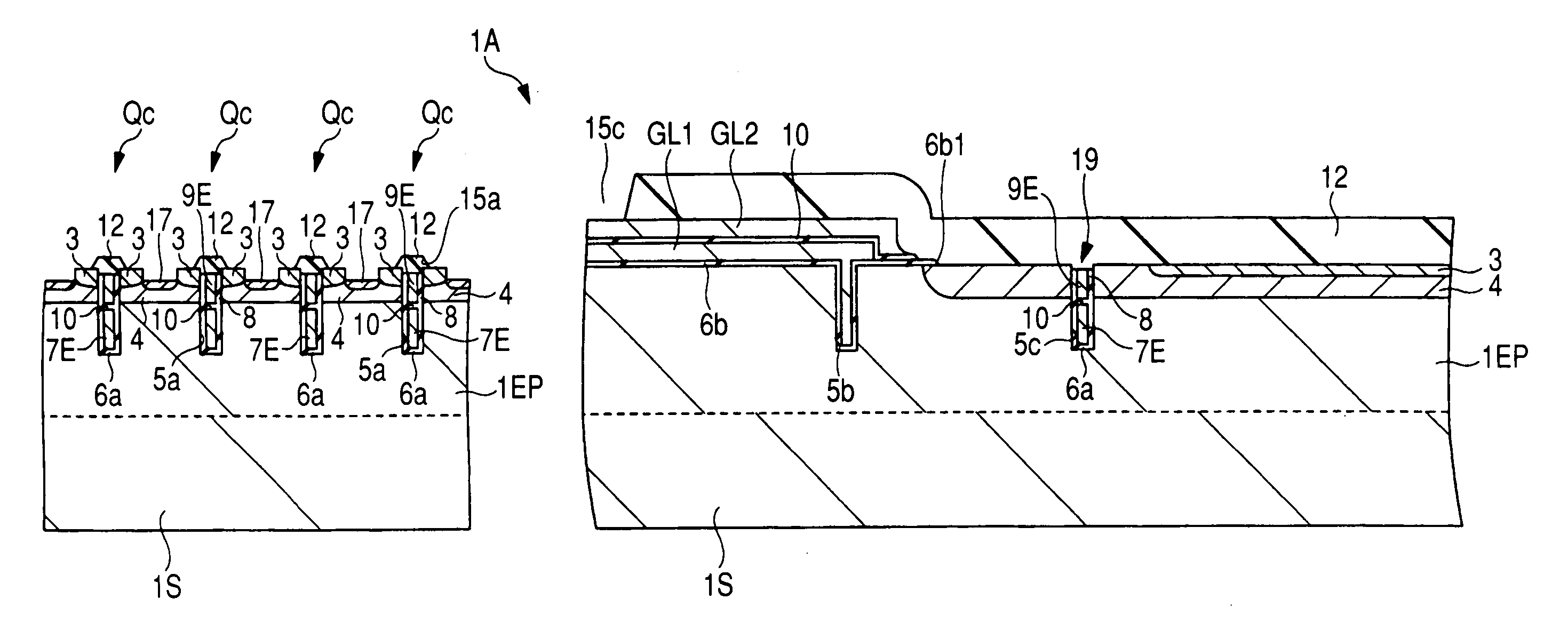

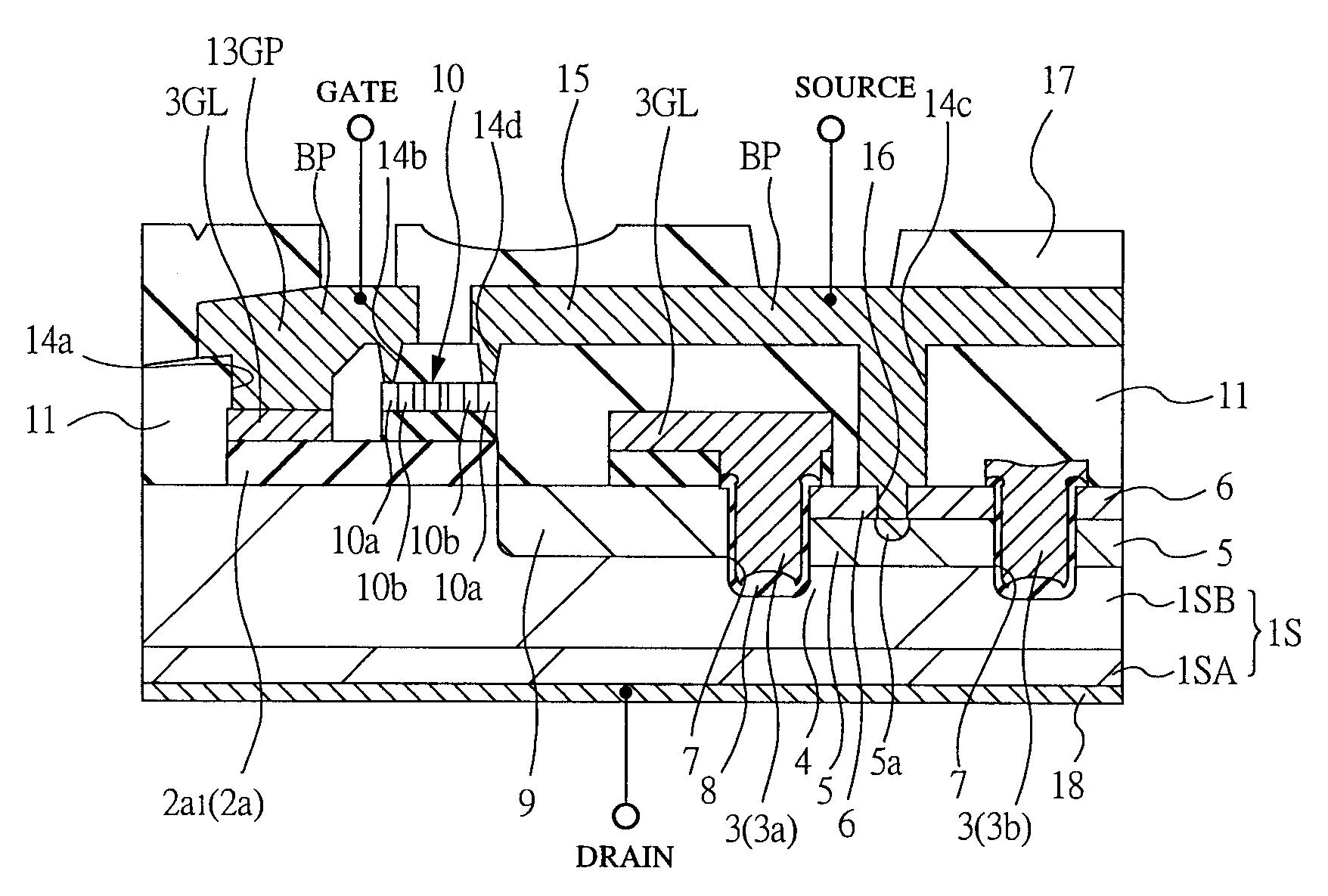

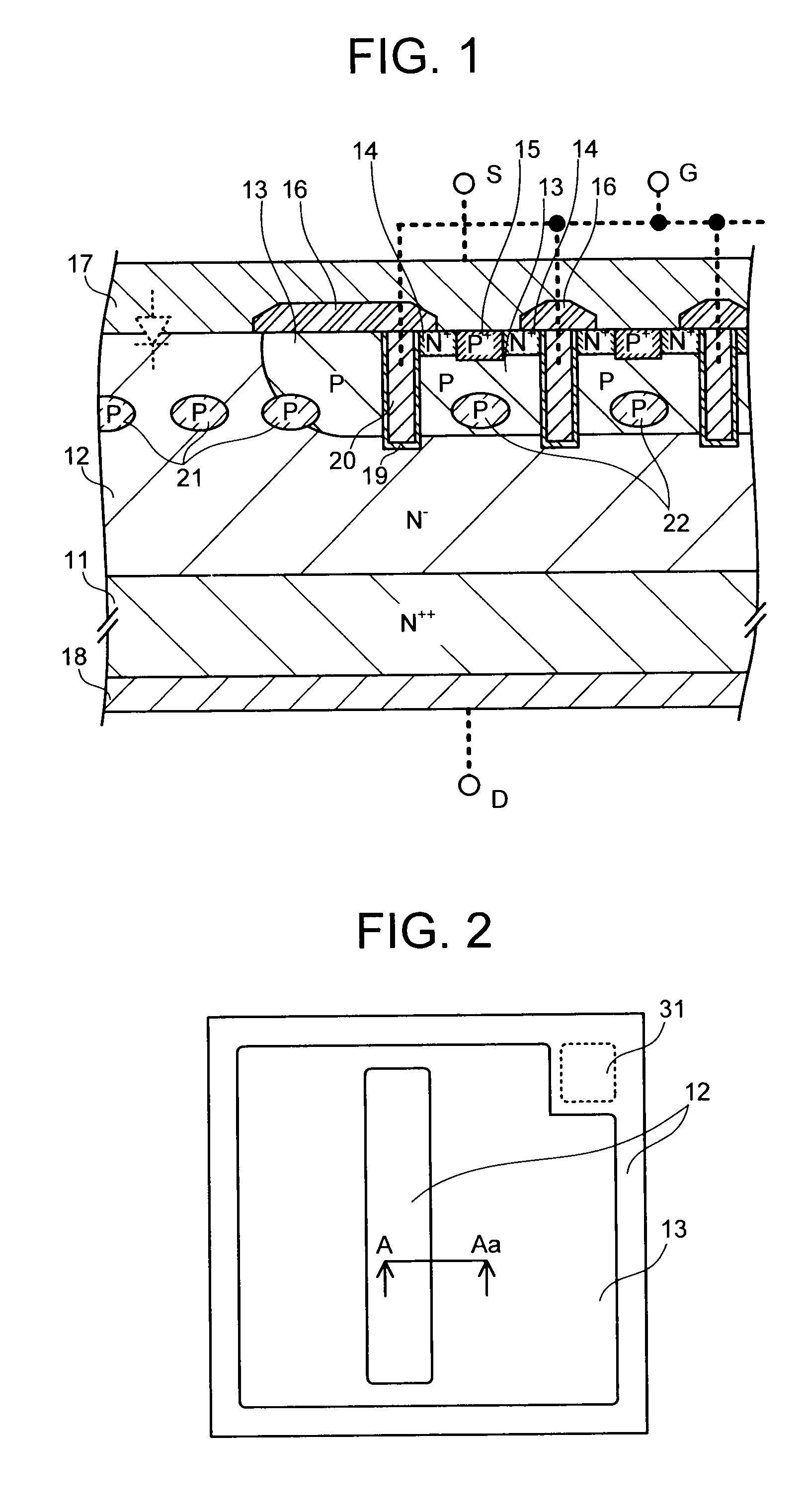

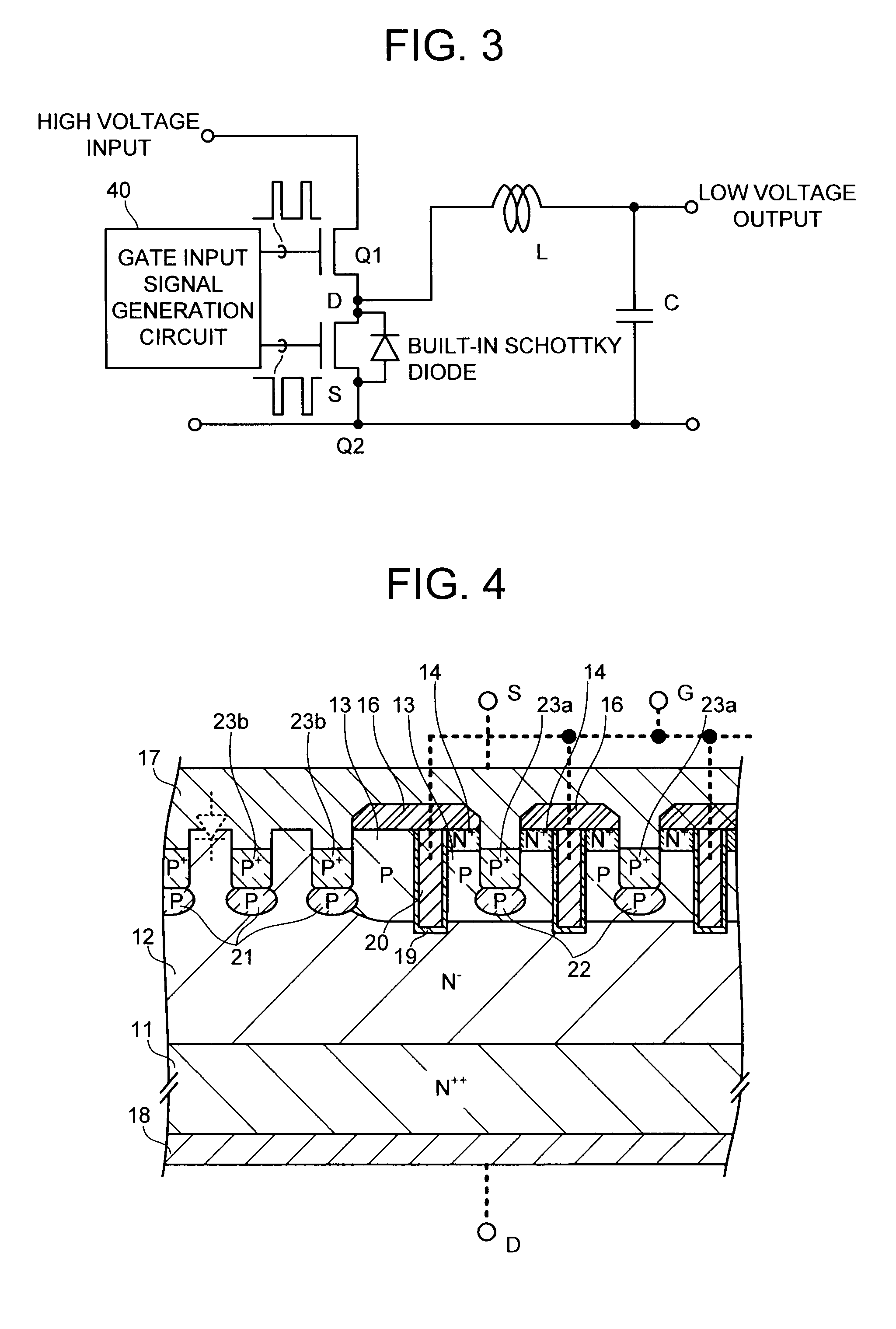

Trench gate type semiconductor device and method of producing the same

InactiveUS20090272982A1Good ohmic contactExcessive electric field is preventedTransistorSemiconductor/solid-state device manufacturingMOSFETOhmic contact

A method of producing a trench gate type MOSFET is provided in which each intersection trench is formed as a two-stage trench structure. A gate trench is backfilled with a mask material and the mask material is then patterned to form a mask used for forming each intersection trench. The intersection trench intersecting the gate trench is provided so as to be deeper than the gate trench. A Schottky electrode is provided in the bottom of each intersection trench 10p. In this manner, there is provided a trench gate type semiconductor device and a method of producing the same, in which: the cell pitch can be reduced even when a wide band gap semiconductor is used as a main semiconductor substrate; good ohmic contacts can be obtained; and an excessive electric field is prevented from being applied to an insulating film in the bottom of each trench.

Owner:FUJI ELECTRIC CO LTD

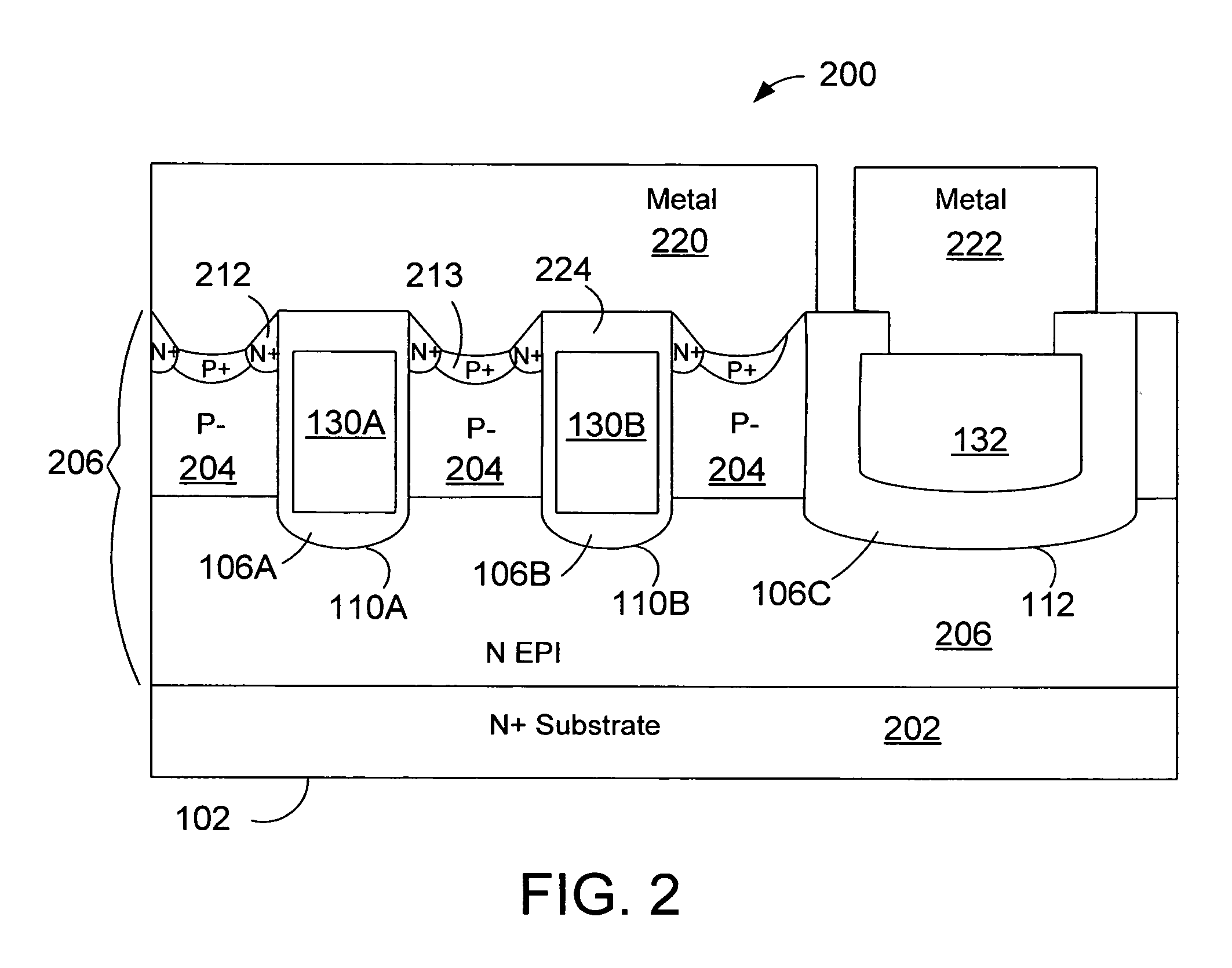

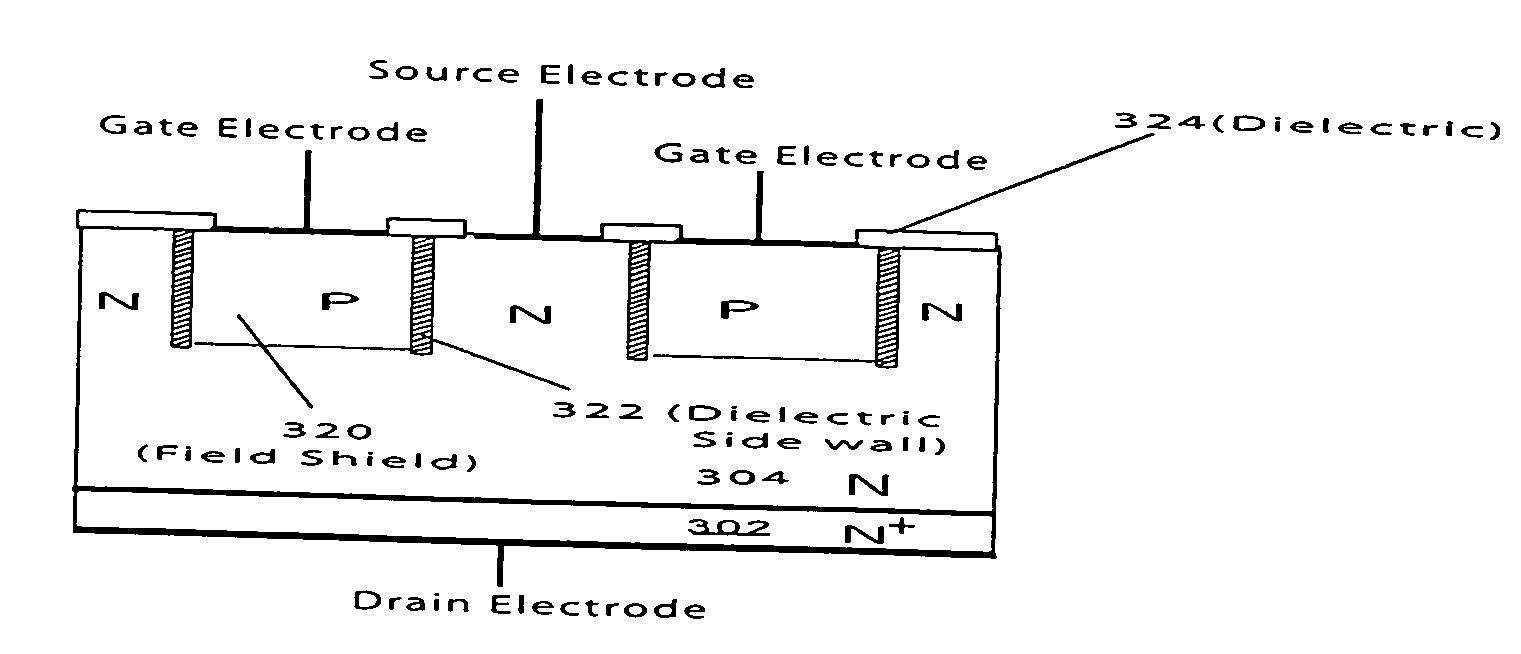

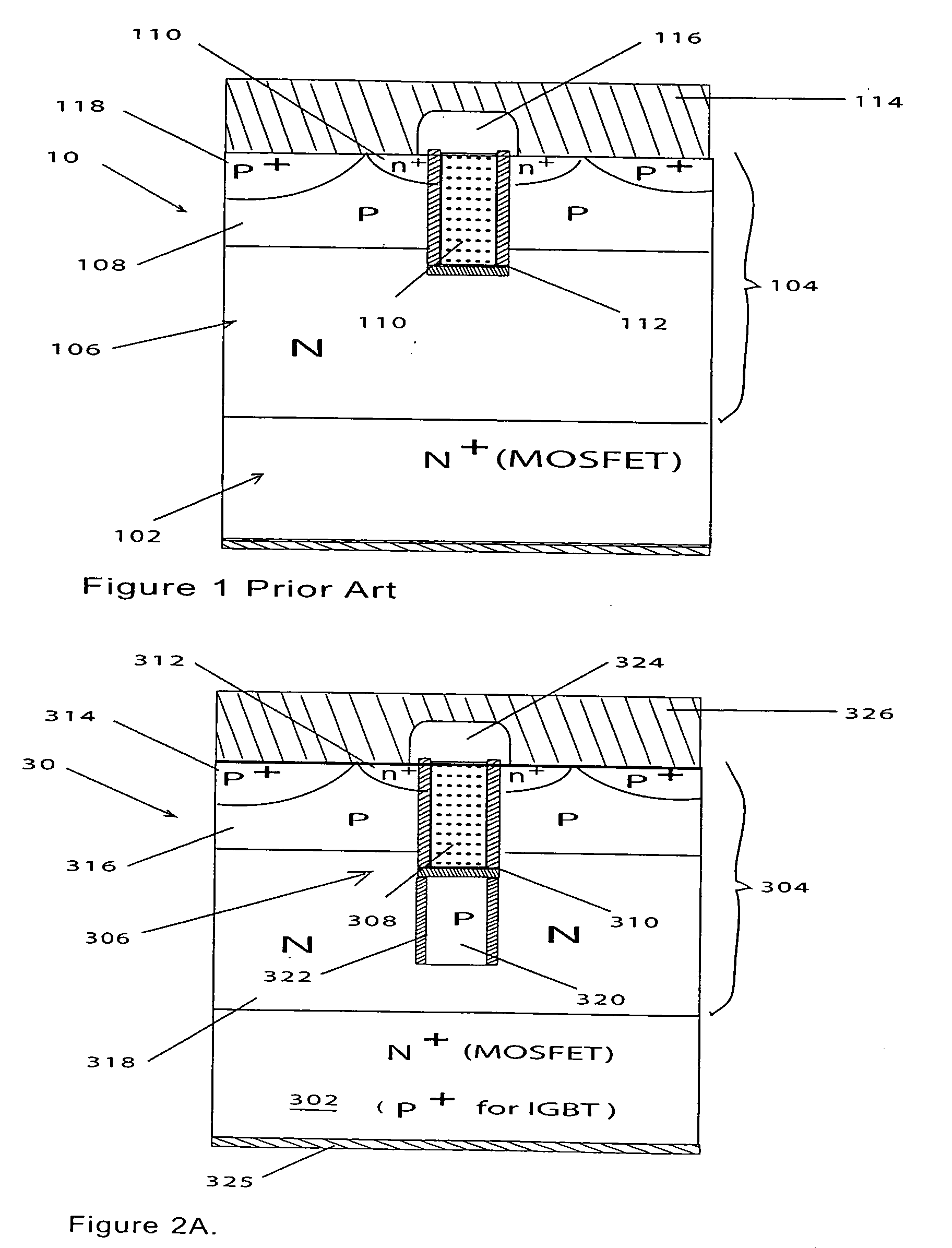

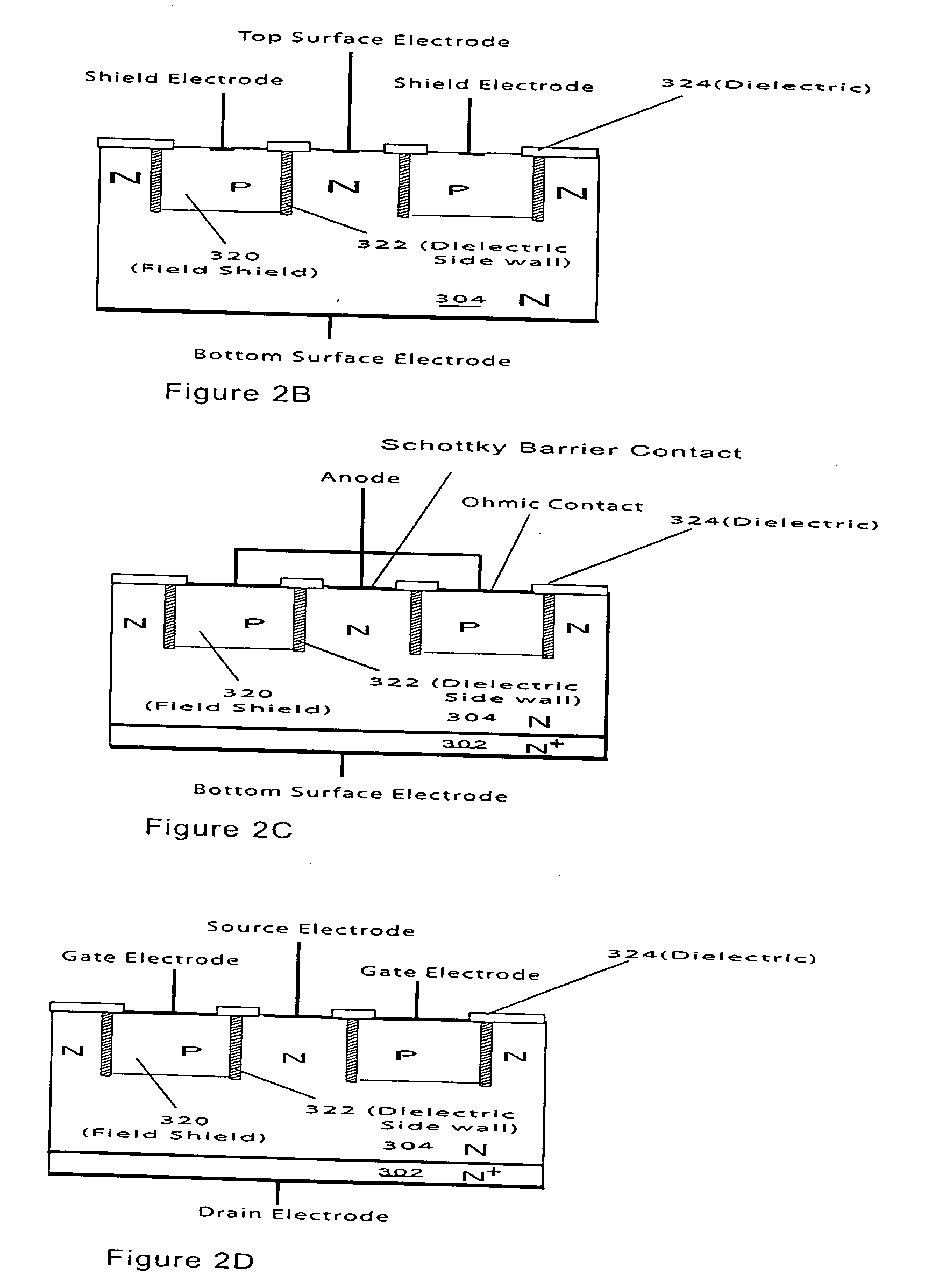

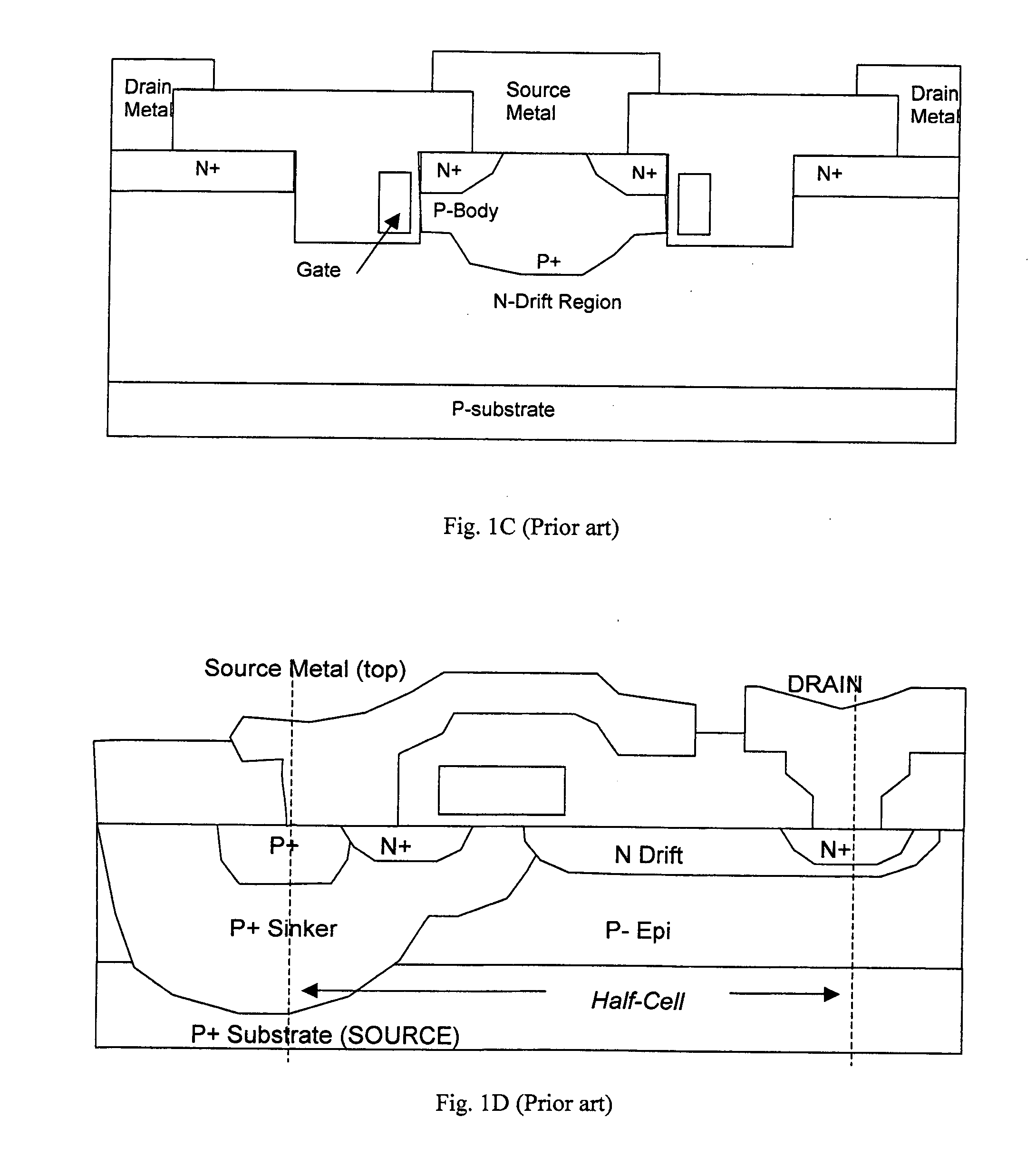

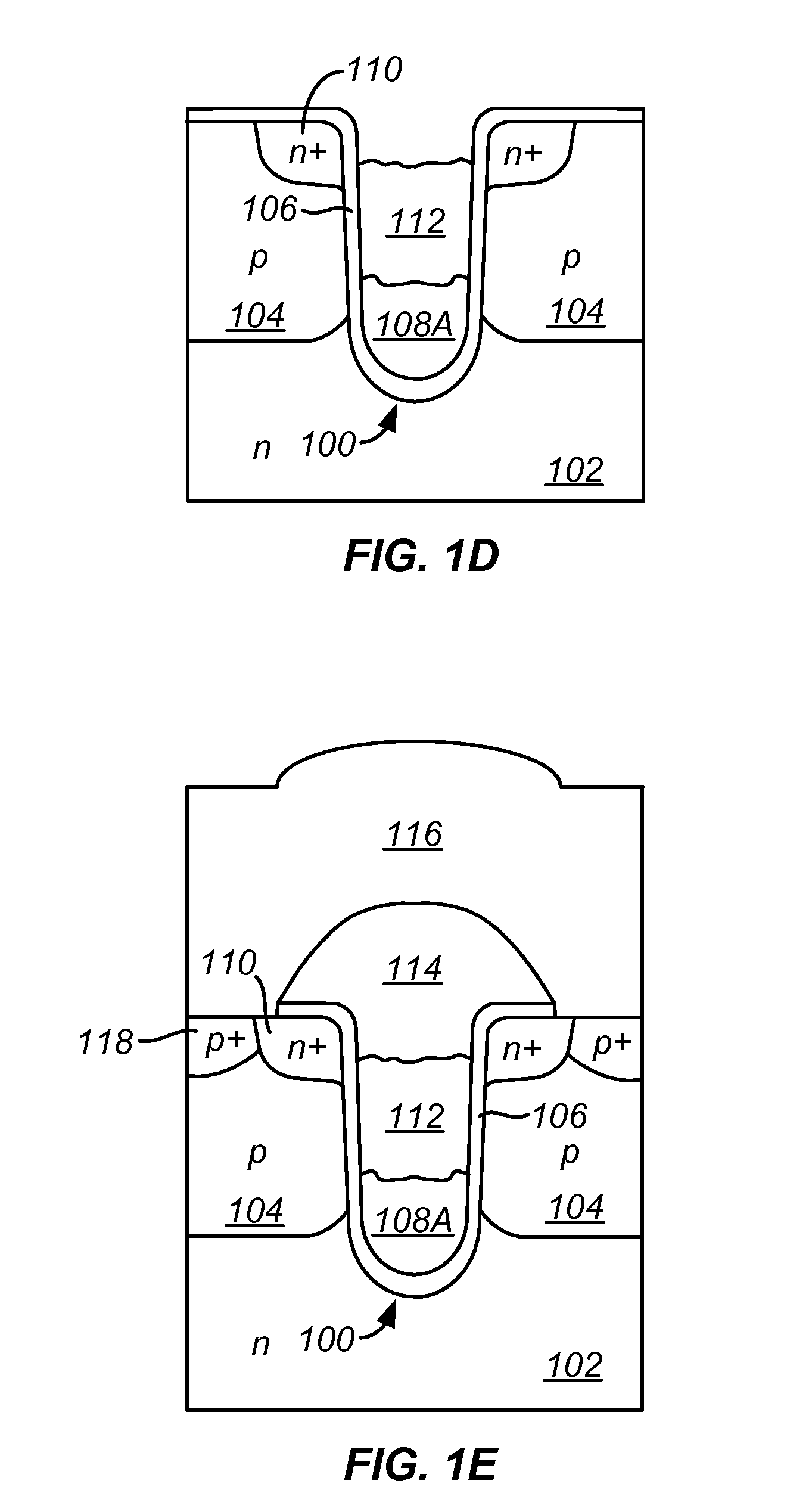

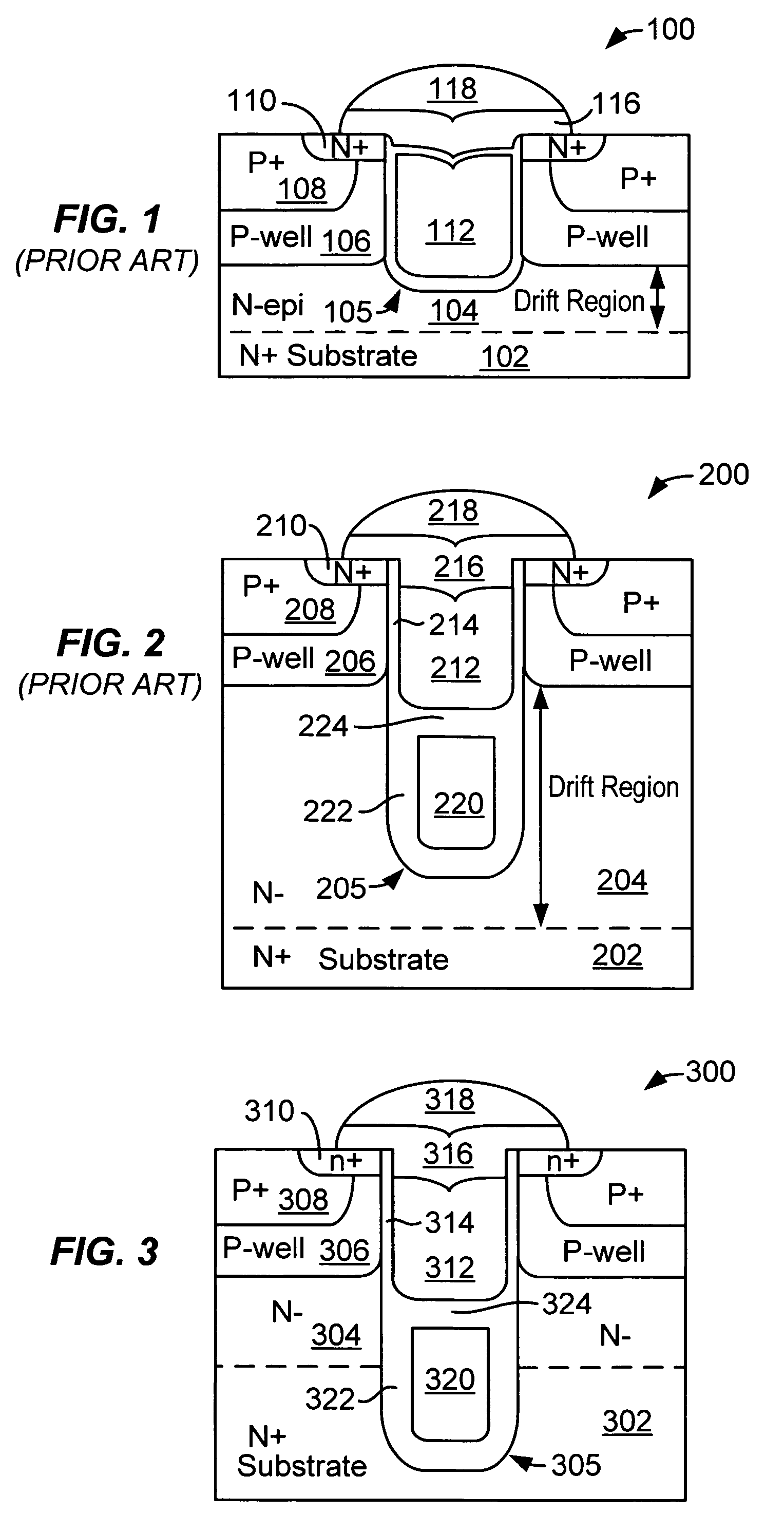

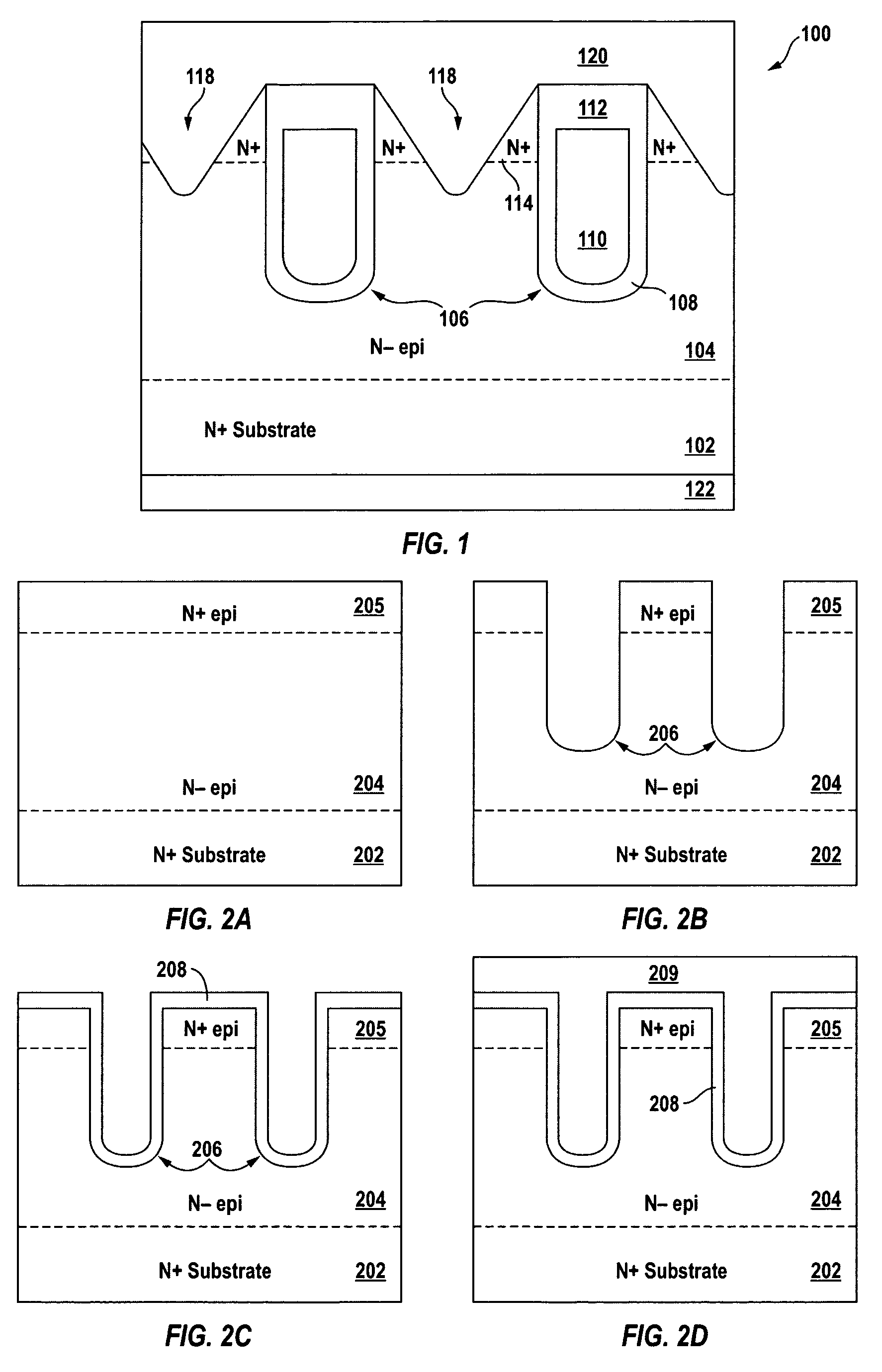

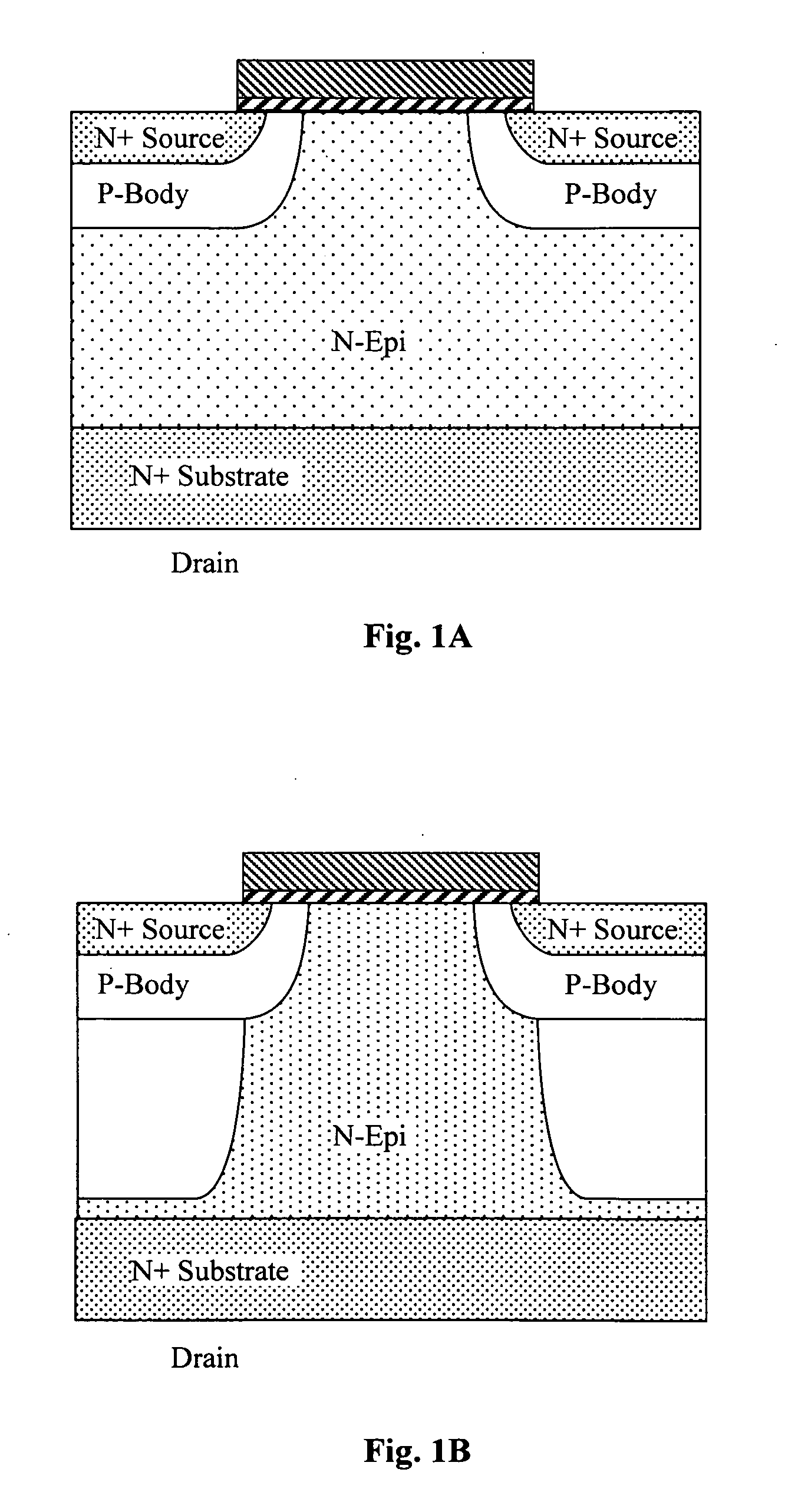

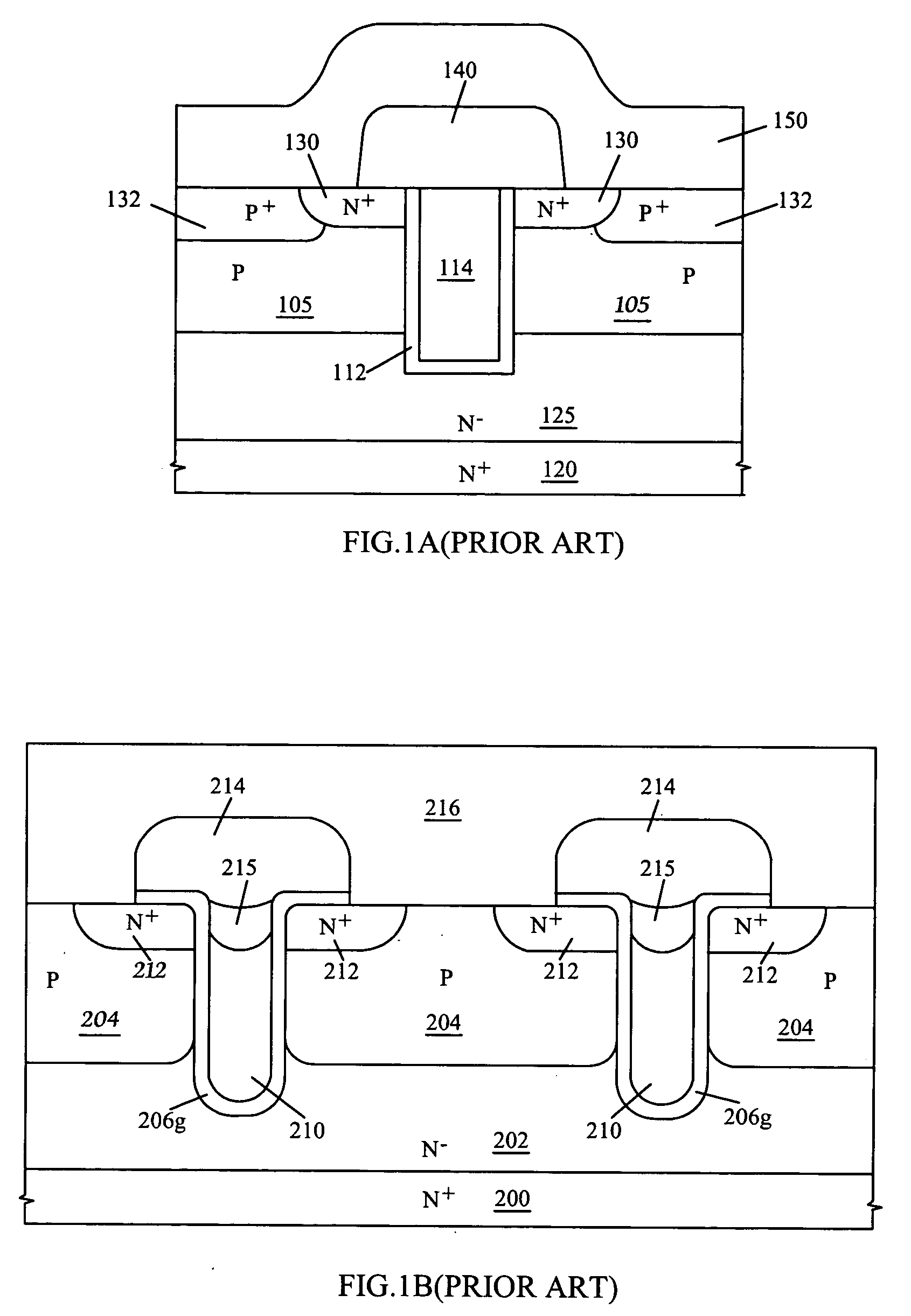

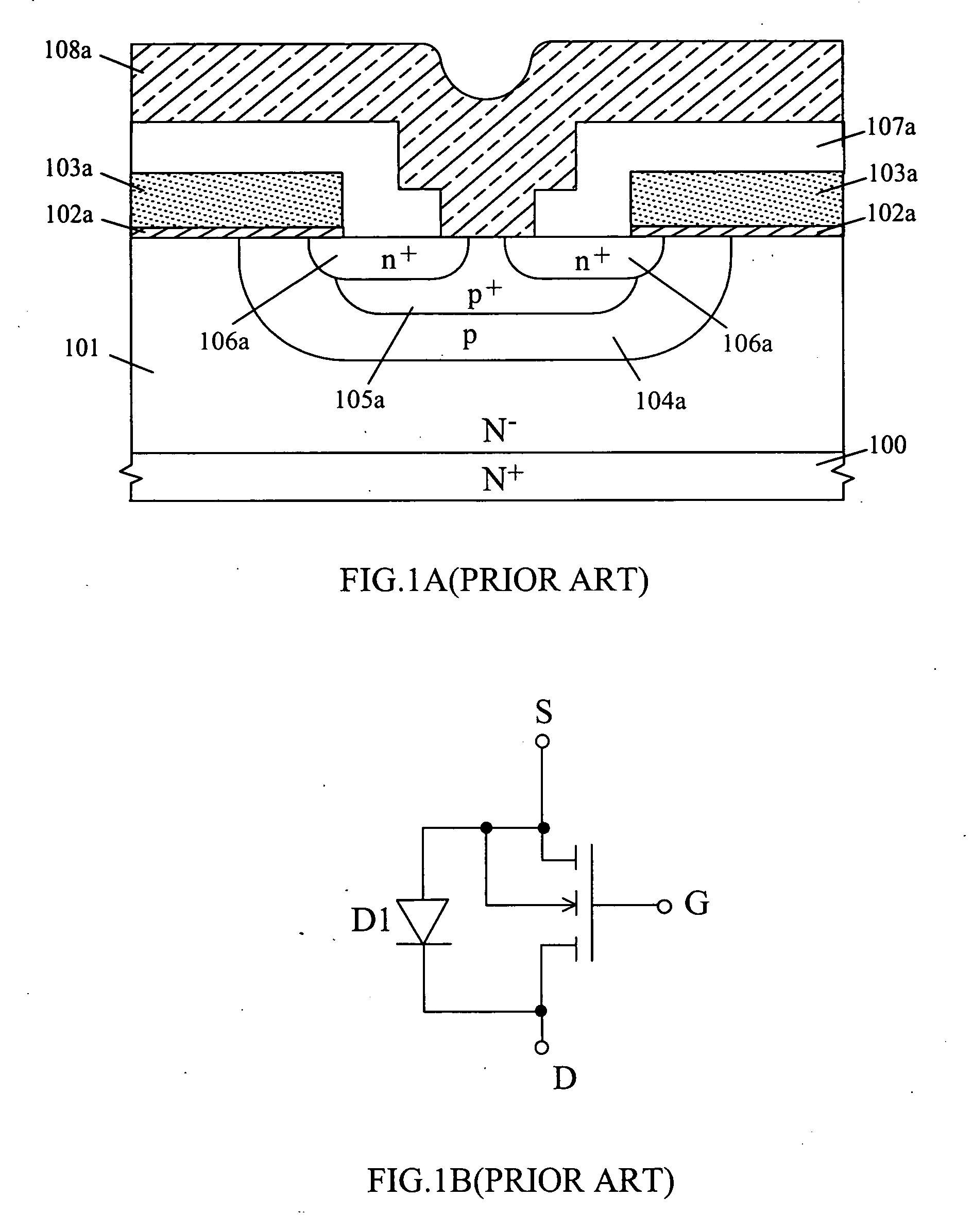

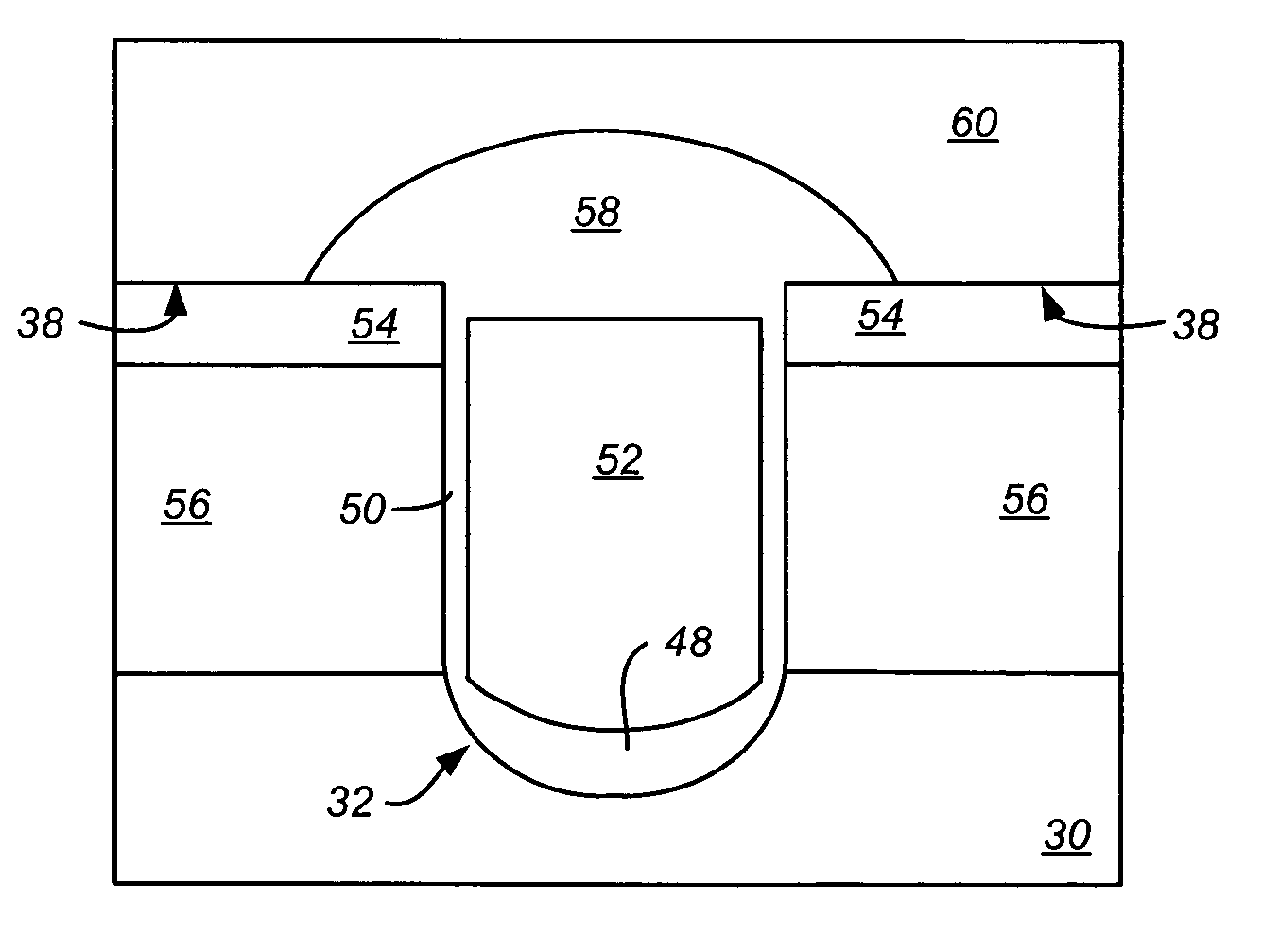

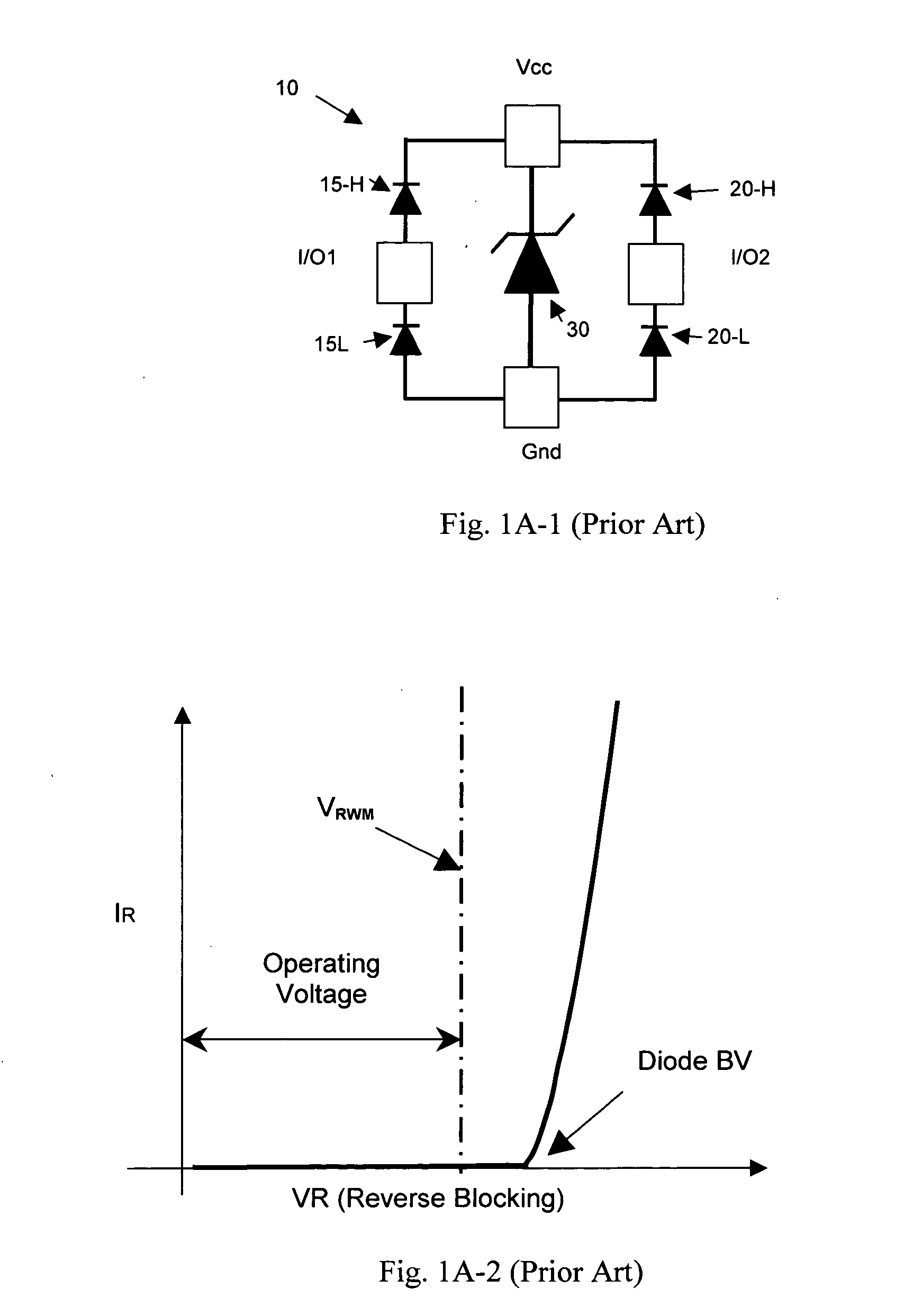

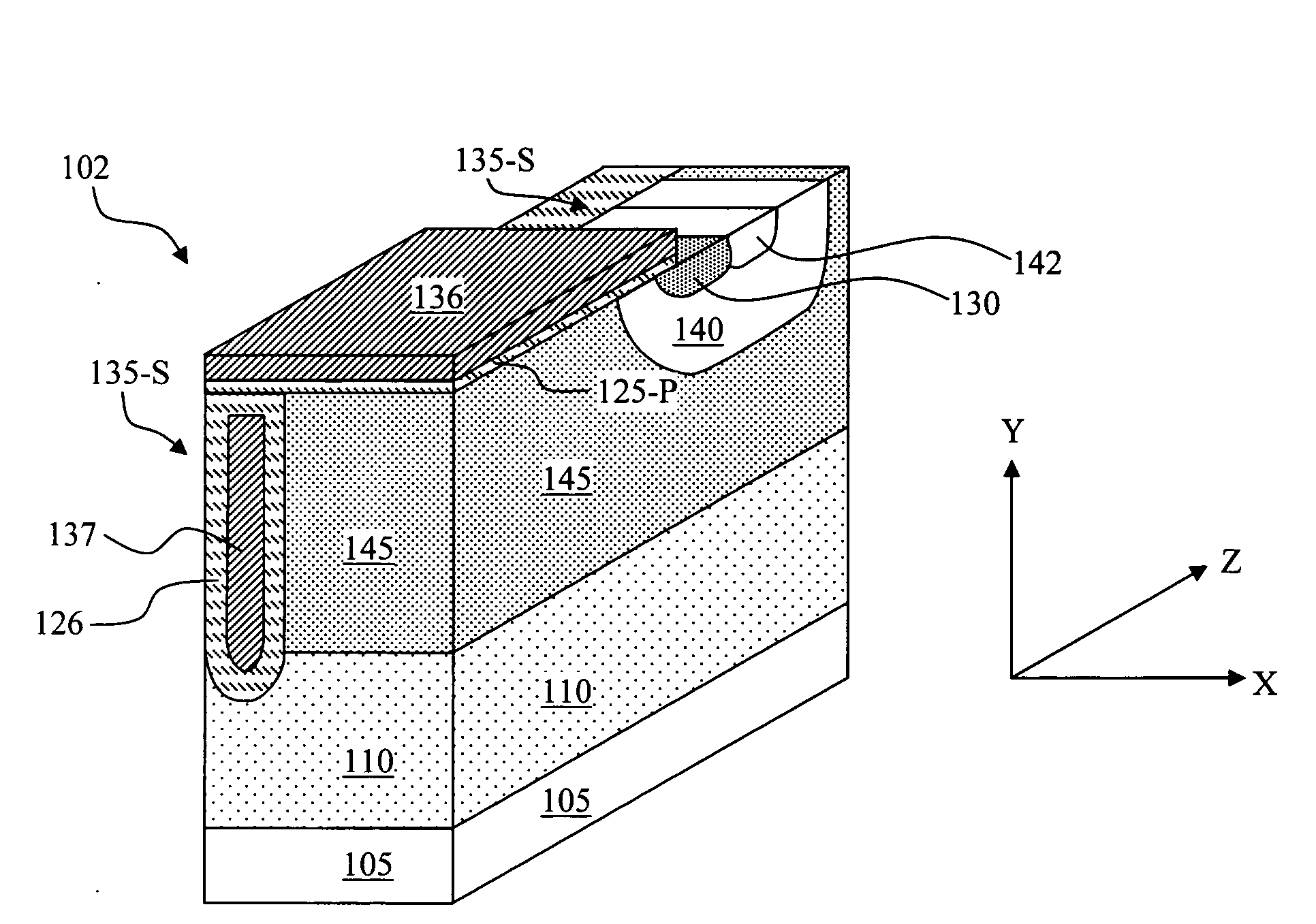

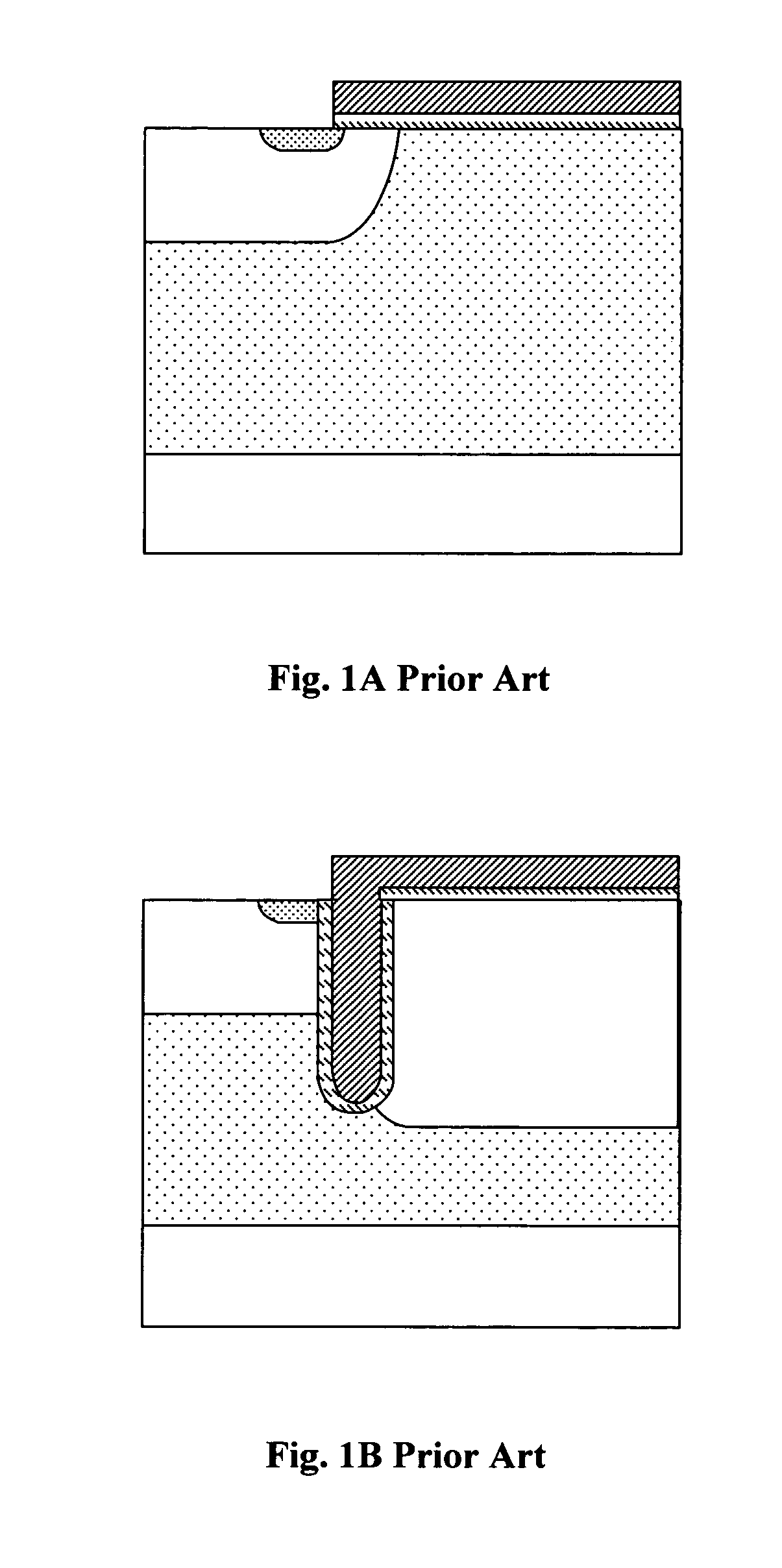

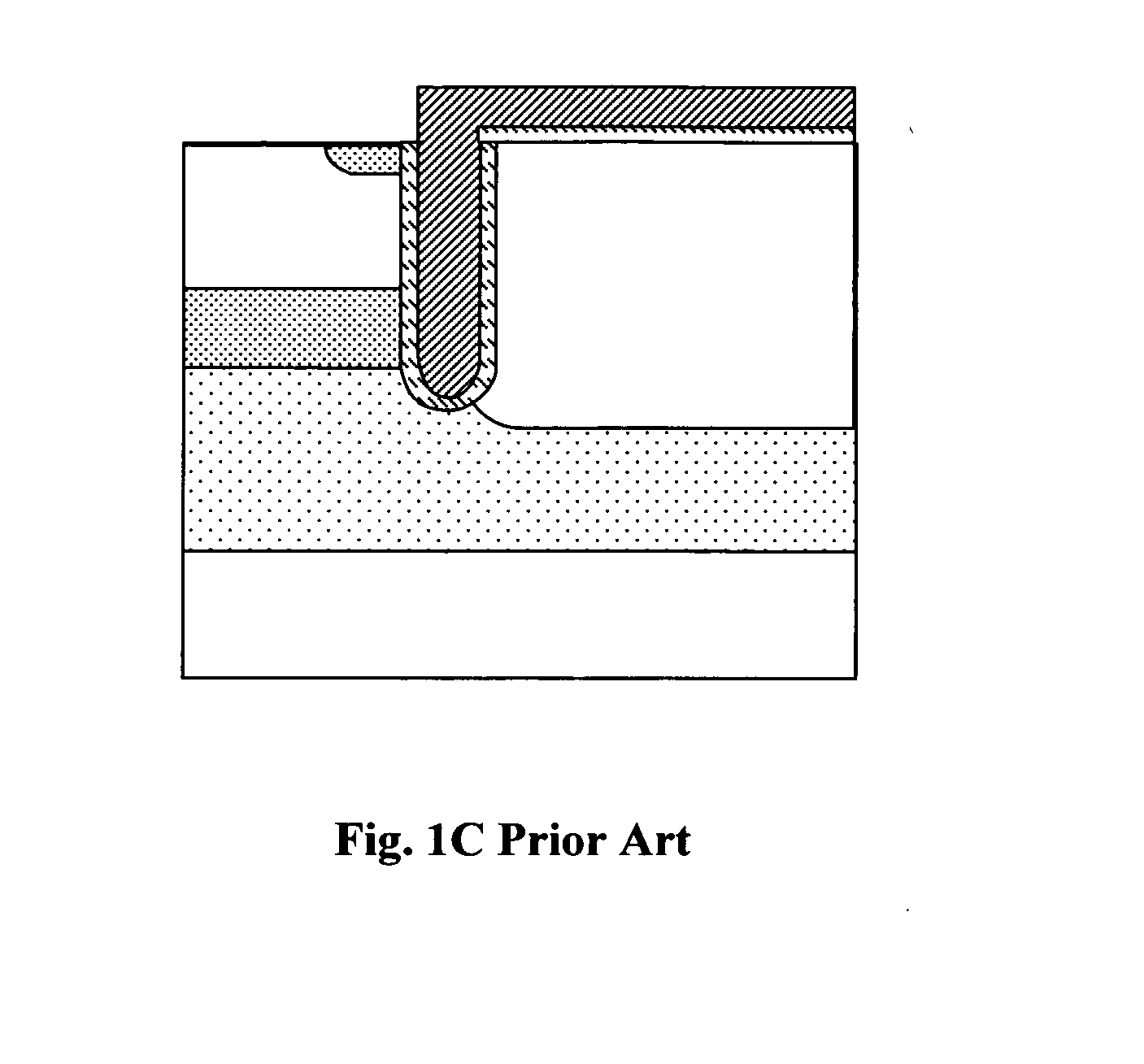

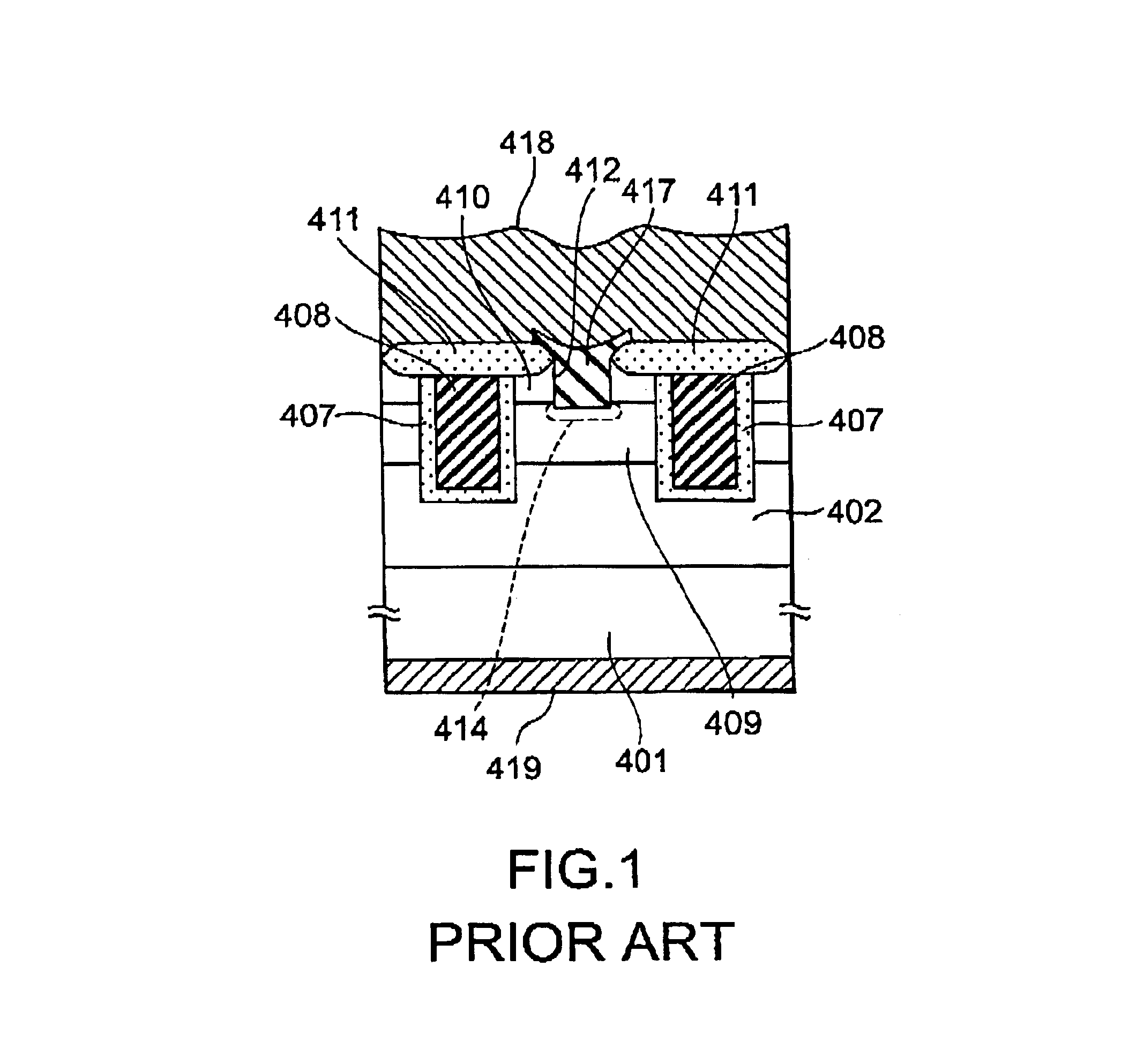

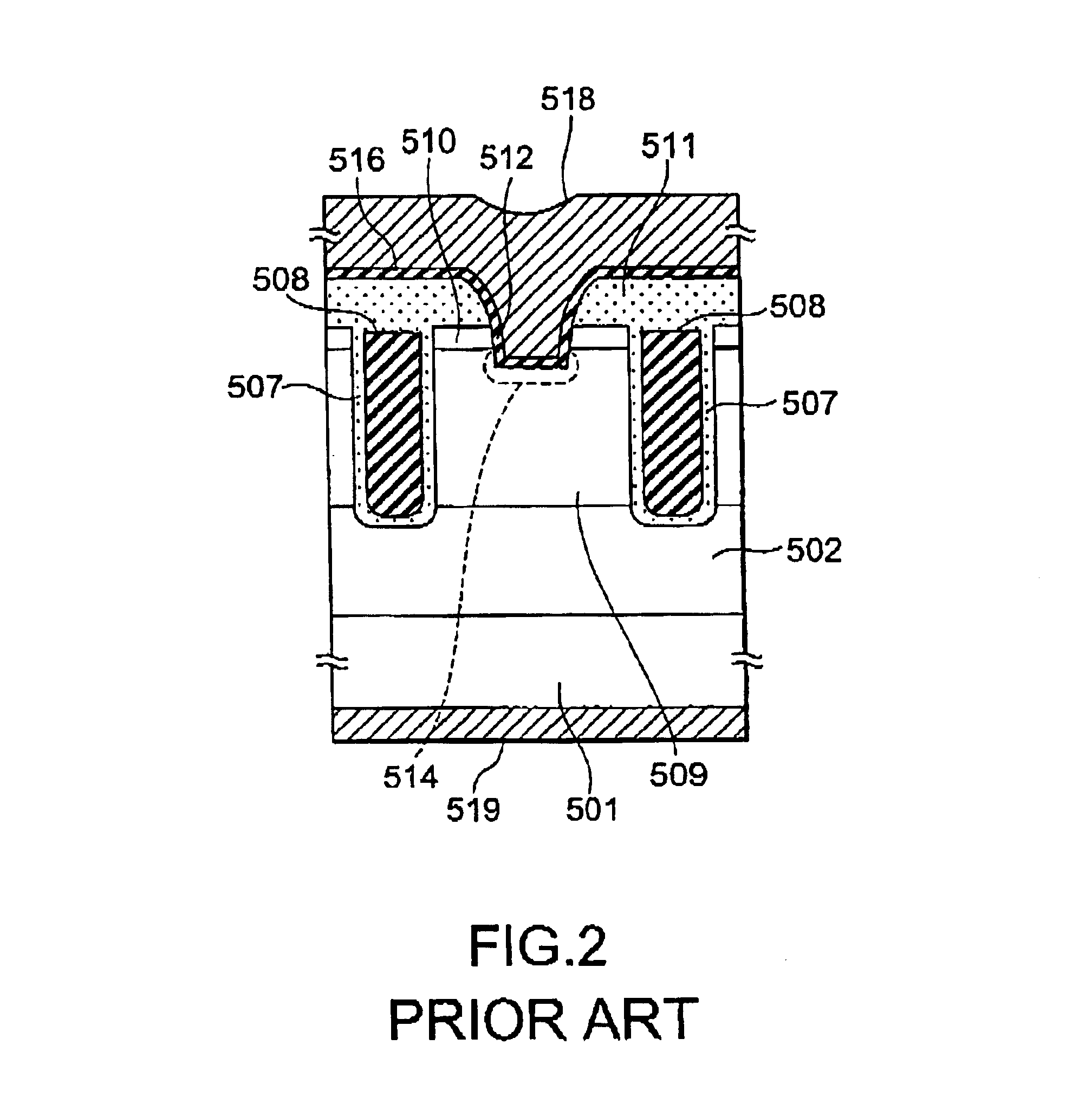

Semiconductor device containing dielectrically isolated pn junction for enhanced breakdown characteristics

InactiveUS20050167695A1Increased avalanche breakdown voltageLower on-resistanceThyristorSemiconductor/solid-state device manufacturingDevice materialPower MOSFET

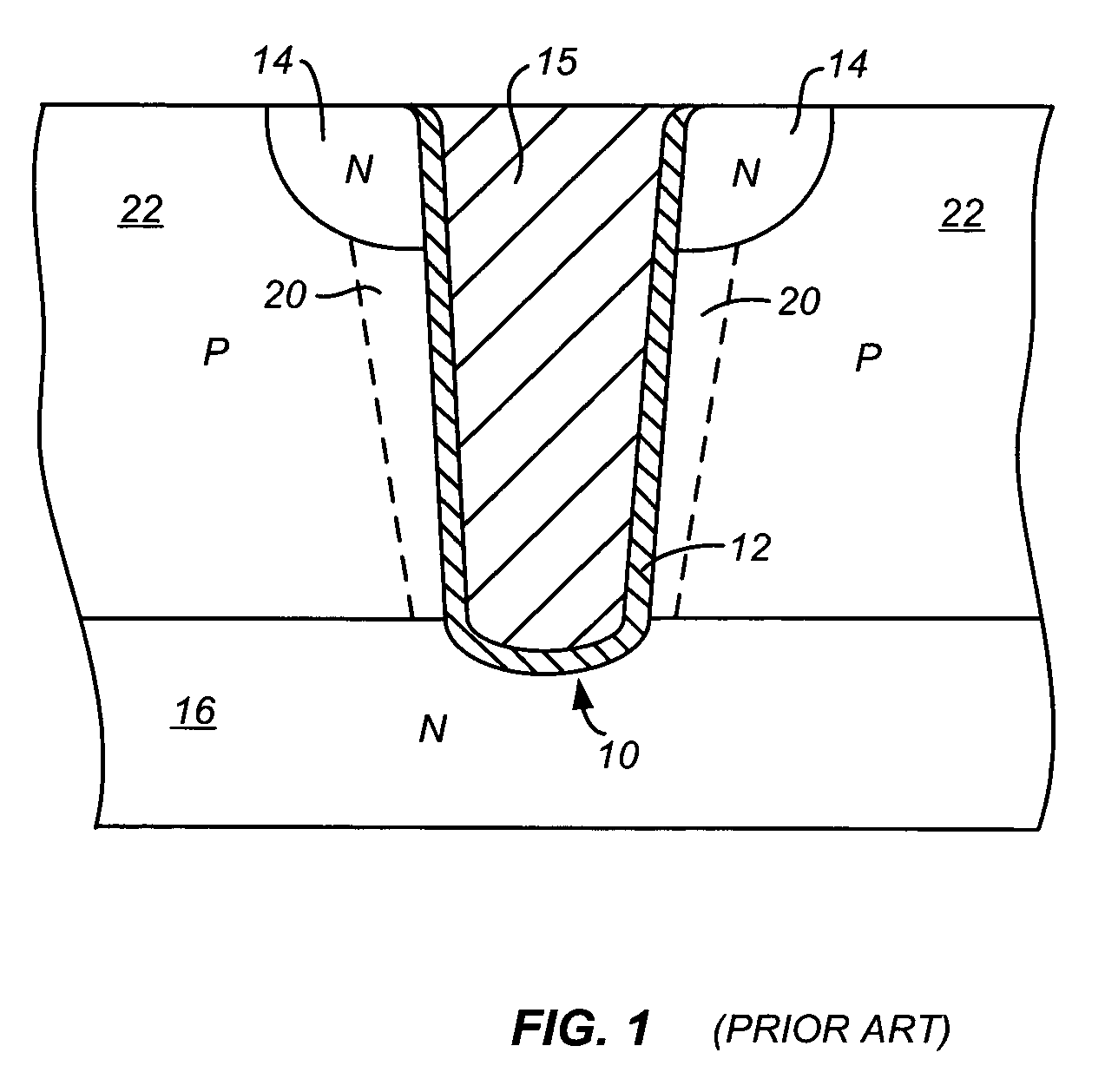

A semiconductor device includes a field shield region that is doped opposite to the conductivity of the substrate and is bounded laterally by dielectric sidewall spacers and from below by a PN junction. For example, in a trench-gated MOSFET the field shield region may be located beneath the trench and may be electrically connected to the source region. When the MOSFET is reverse-biased, depletion regions extend from the dielectric sidewall spacers into the “drift” region, shielding the gate oxide from high electric fields and increasing the avalanche breakdown voltage of the device. This permits the drift region to be more heavily doped and reduces the on-resistance of the device. It also allows the use of a thin, 20 Å gate oxide for a power MOSFET that is to be switched with a 1V signal applied to its gate while being able to block over 30V applied across its drain and source electrodes, for example.

Owner:ALPHA & OMEGA SEMICON INC

Dynamic deep depletion field effect transistor

Owner:INFINEON TECH AMERICAS CORP

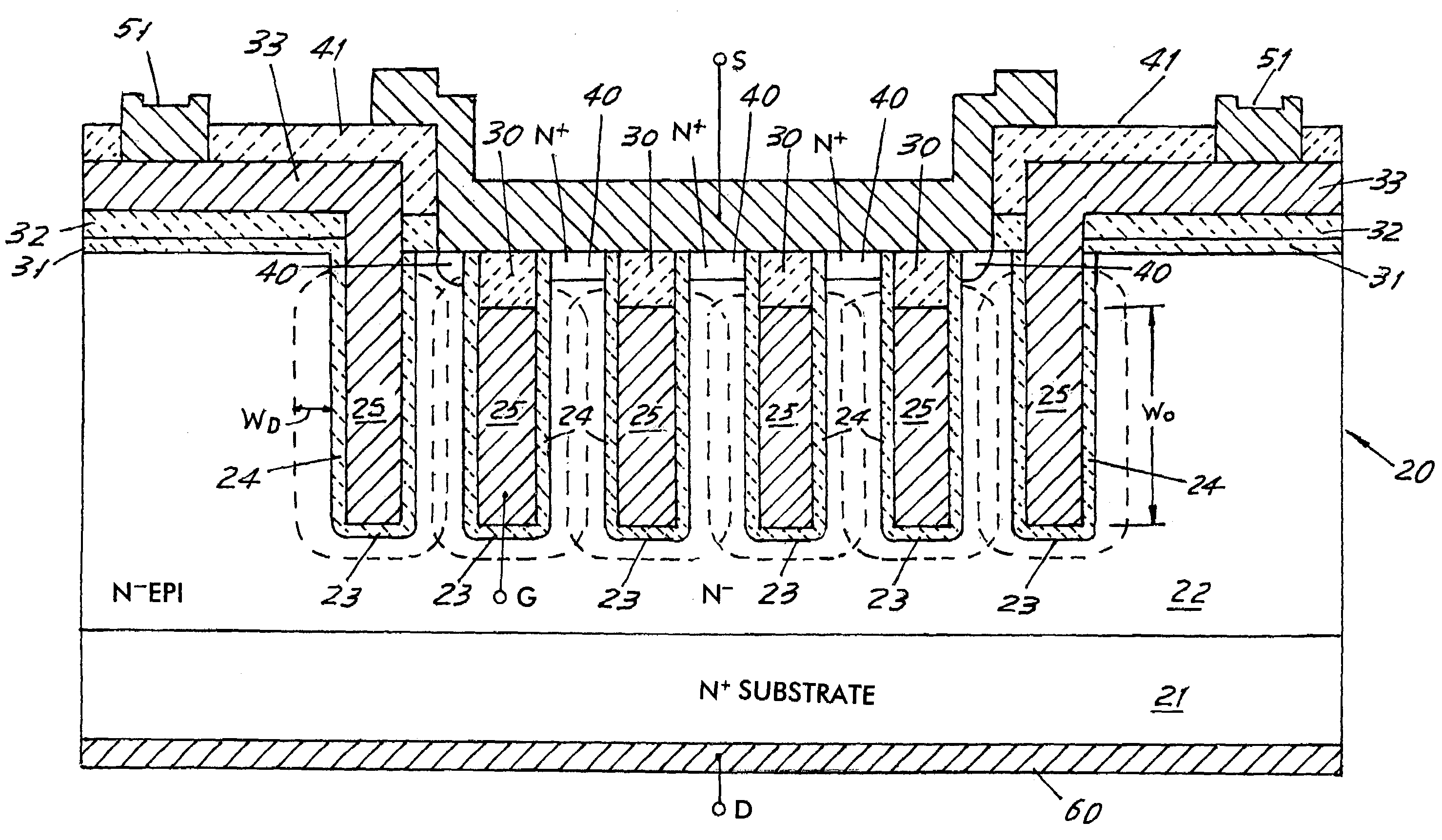

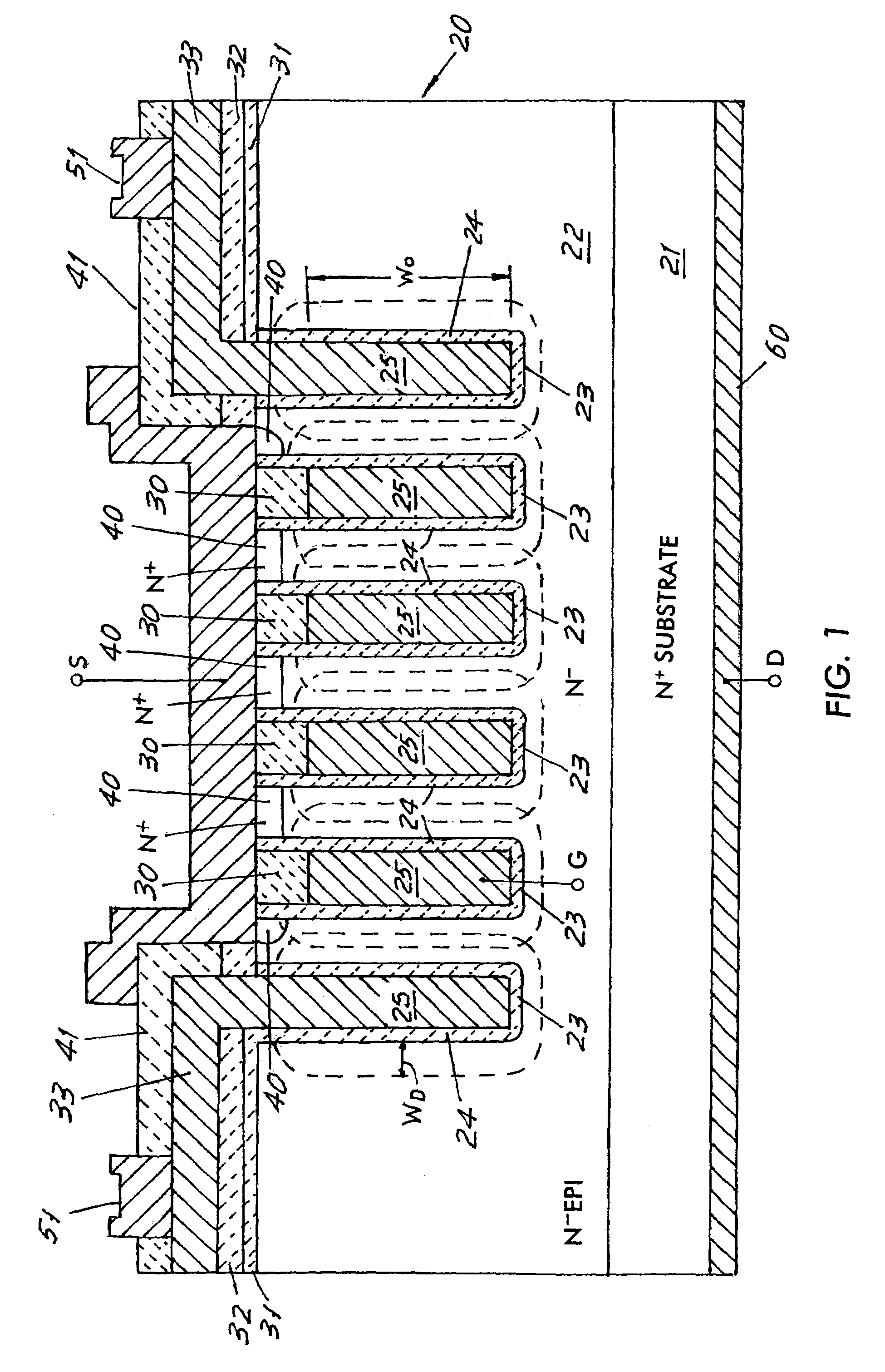

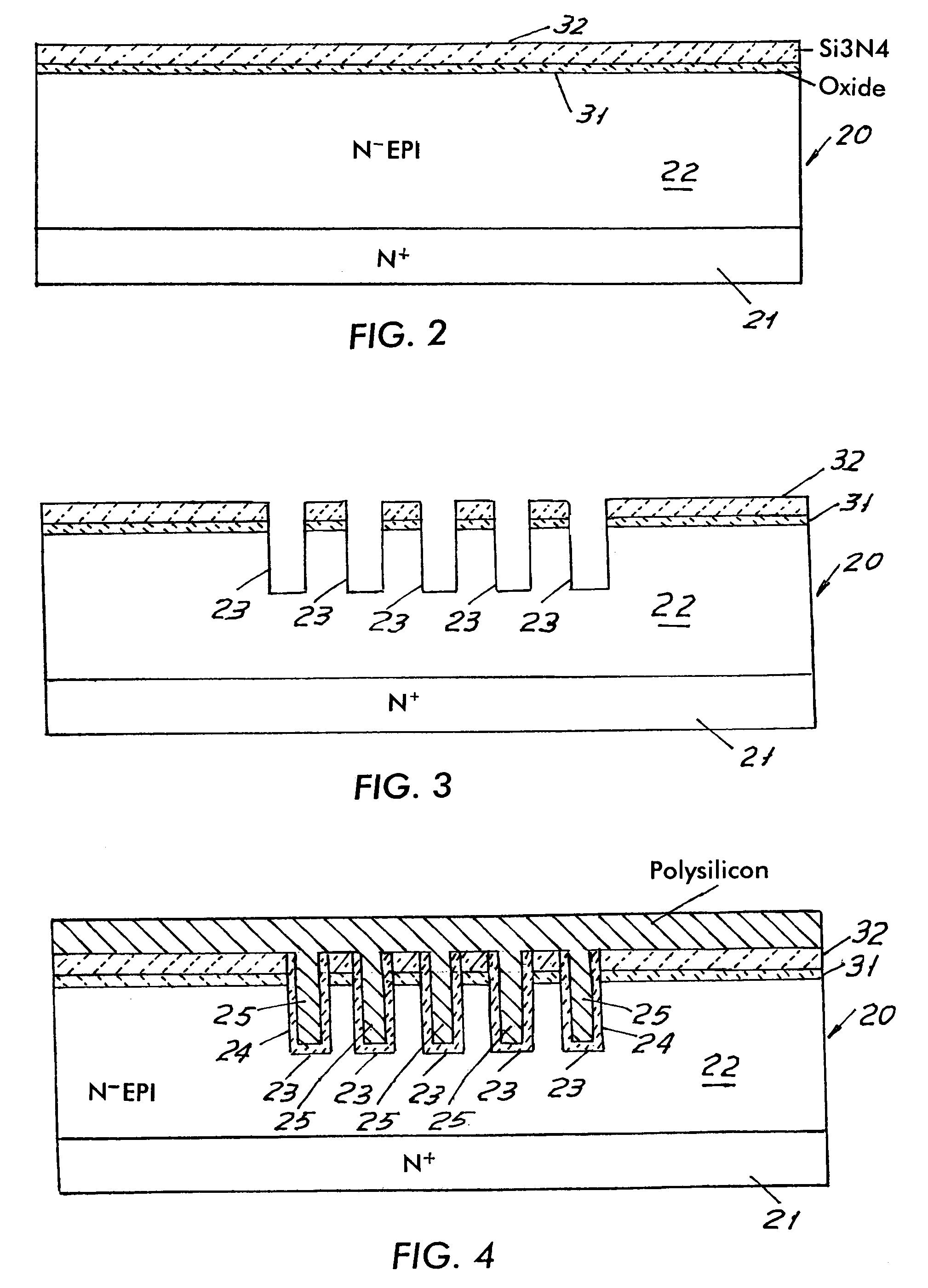

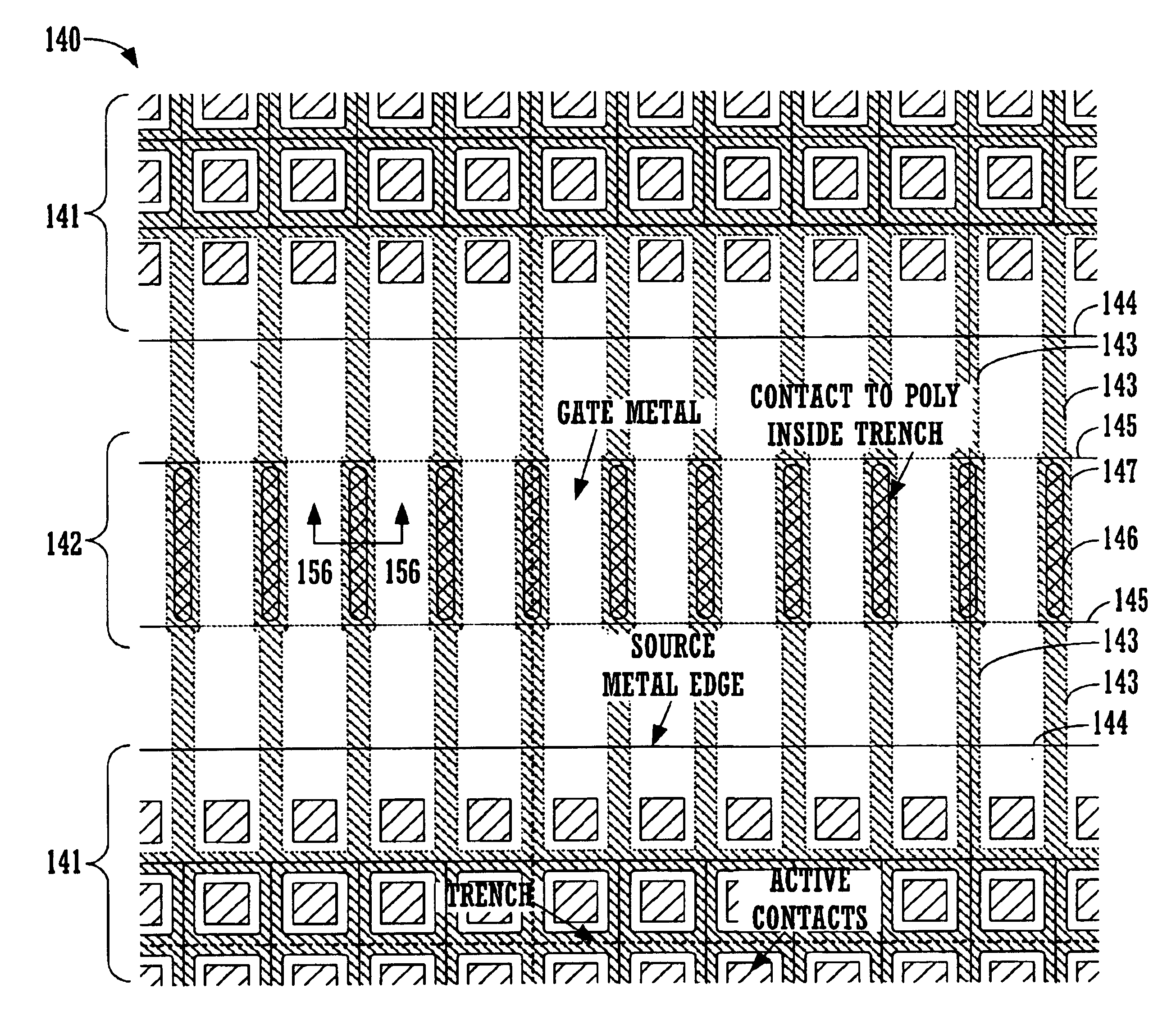

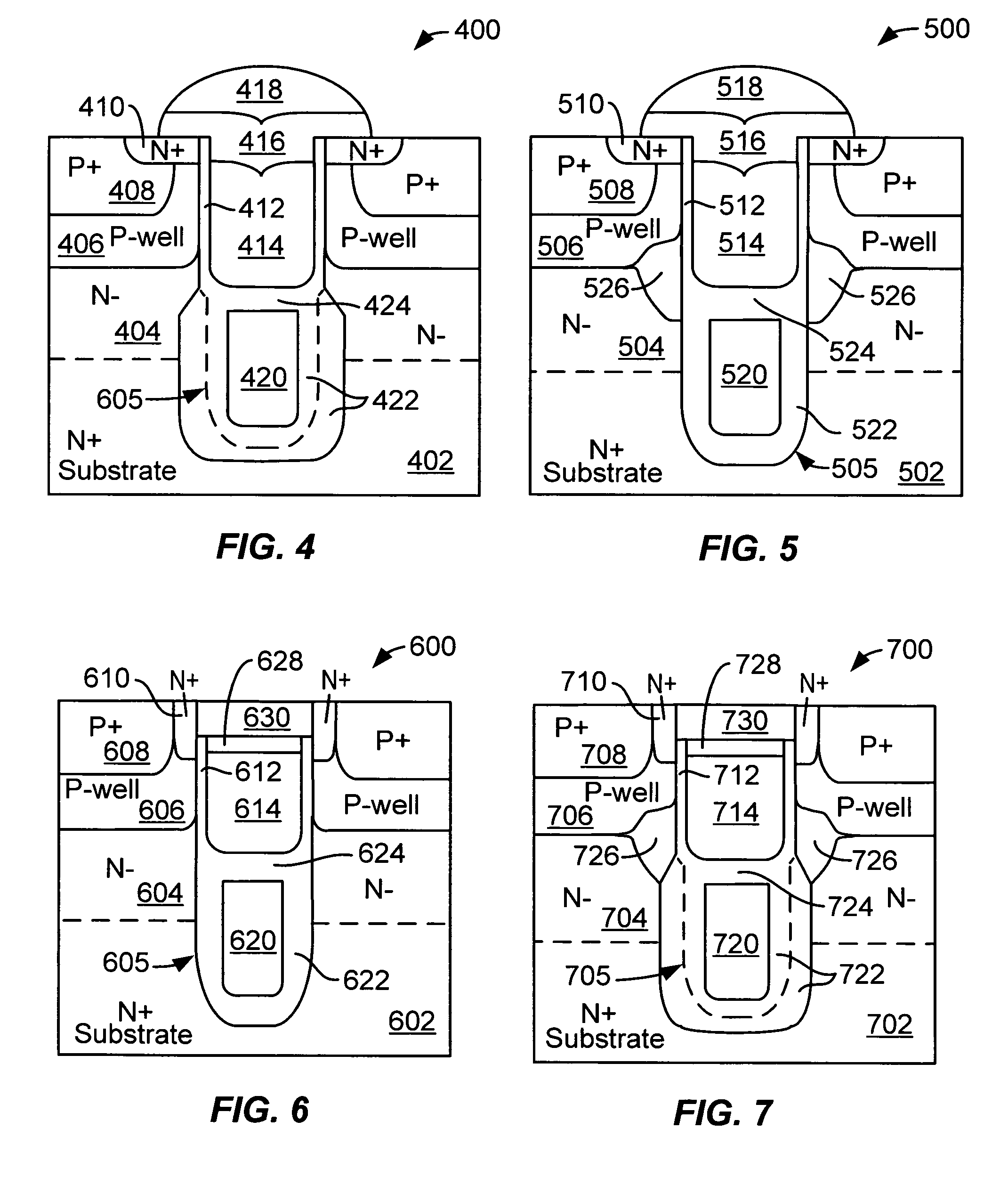

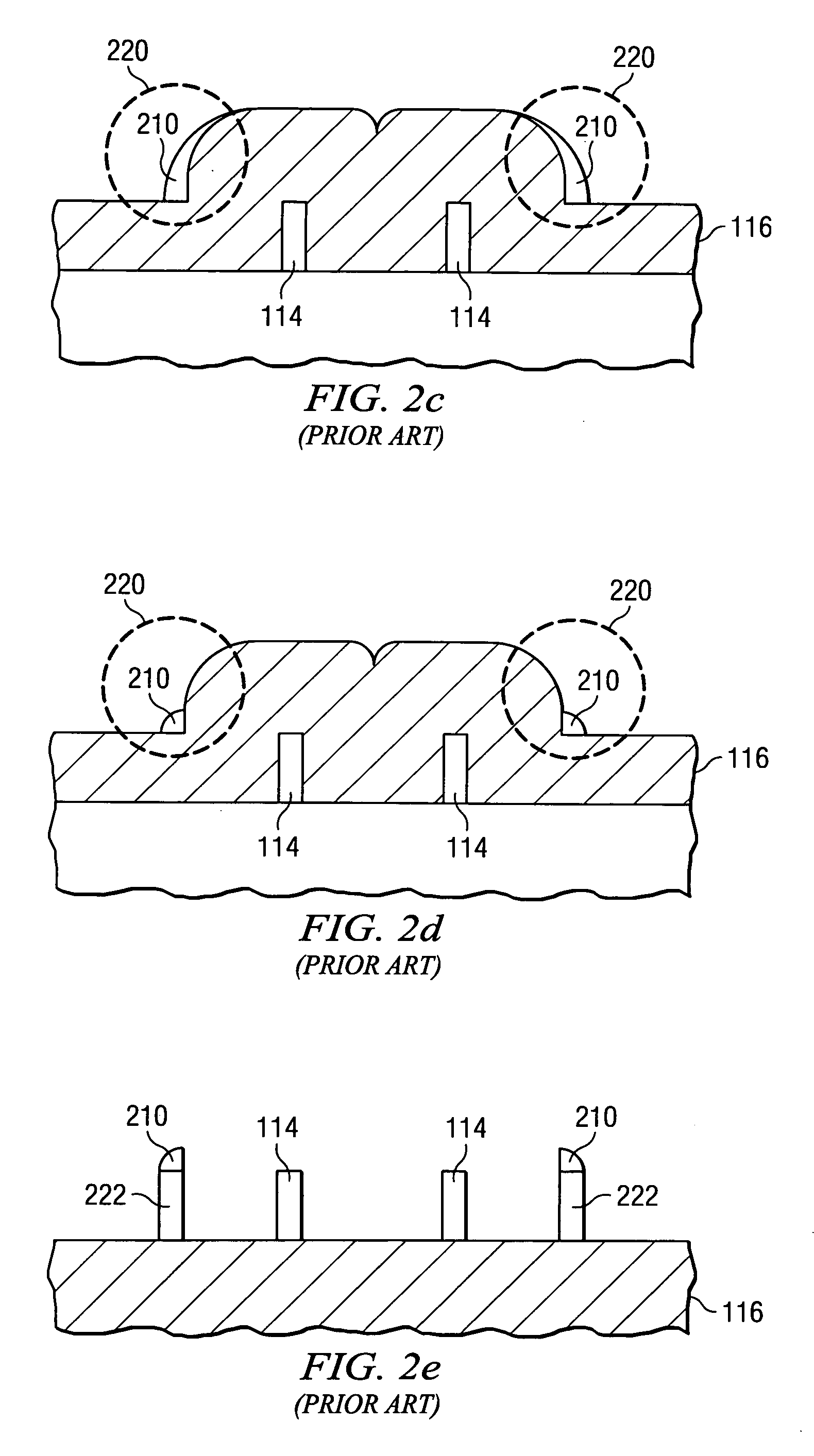

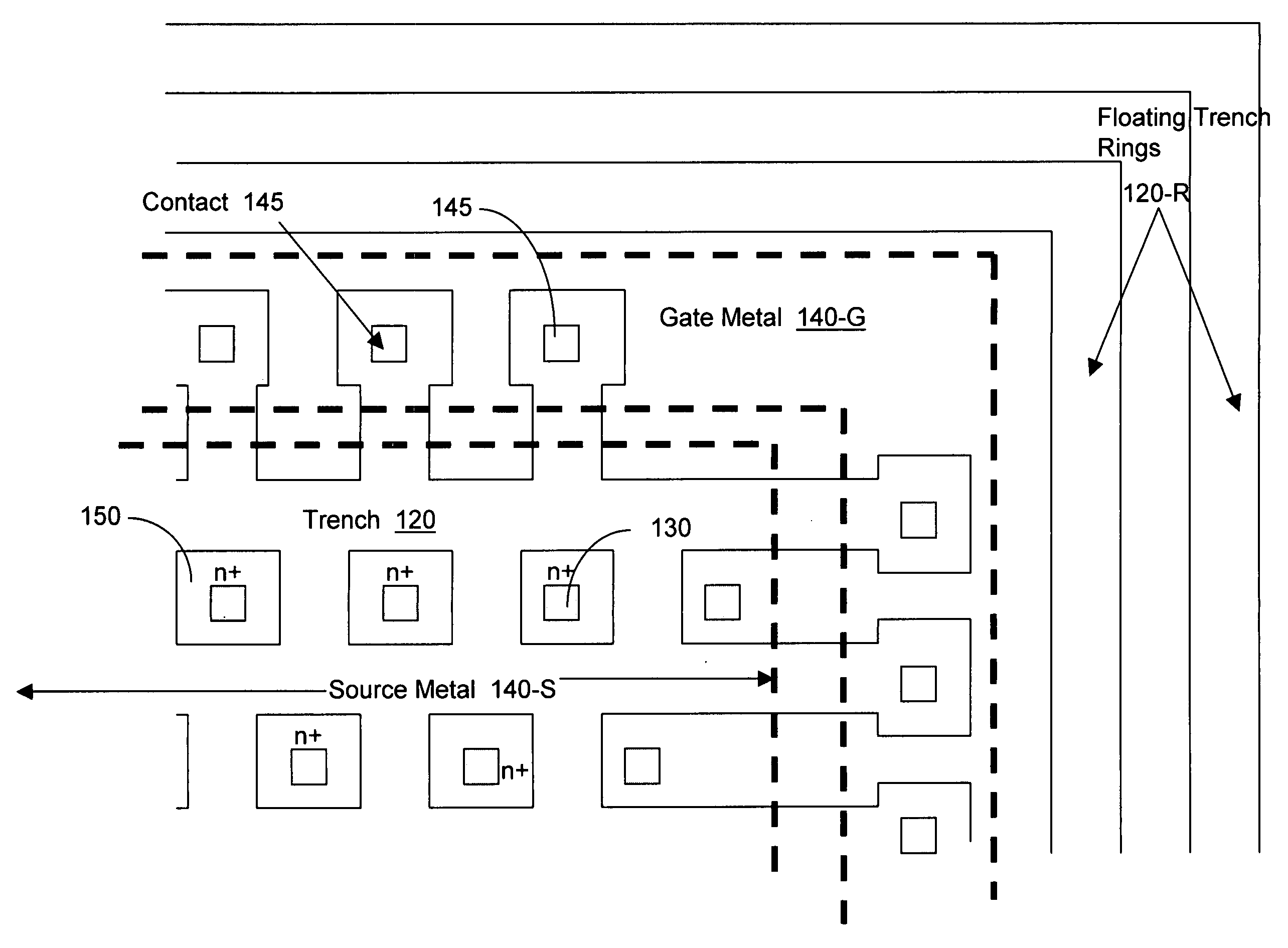

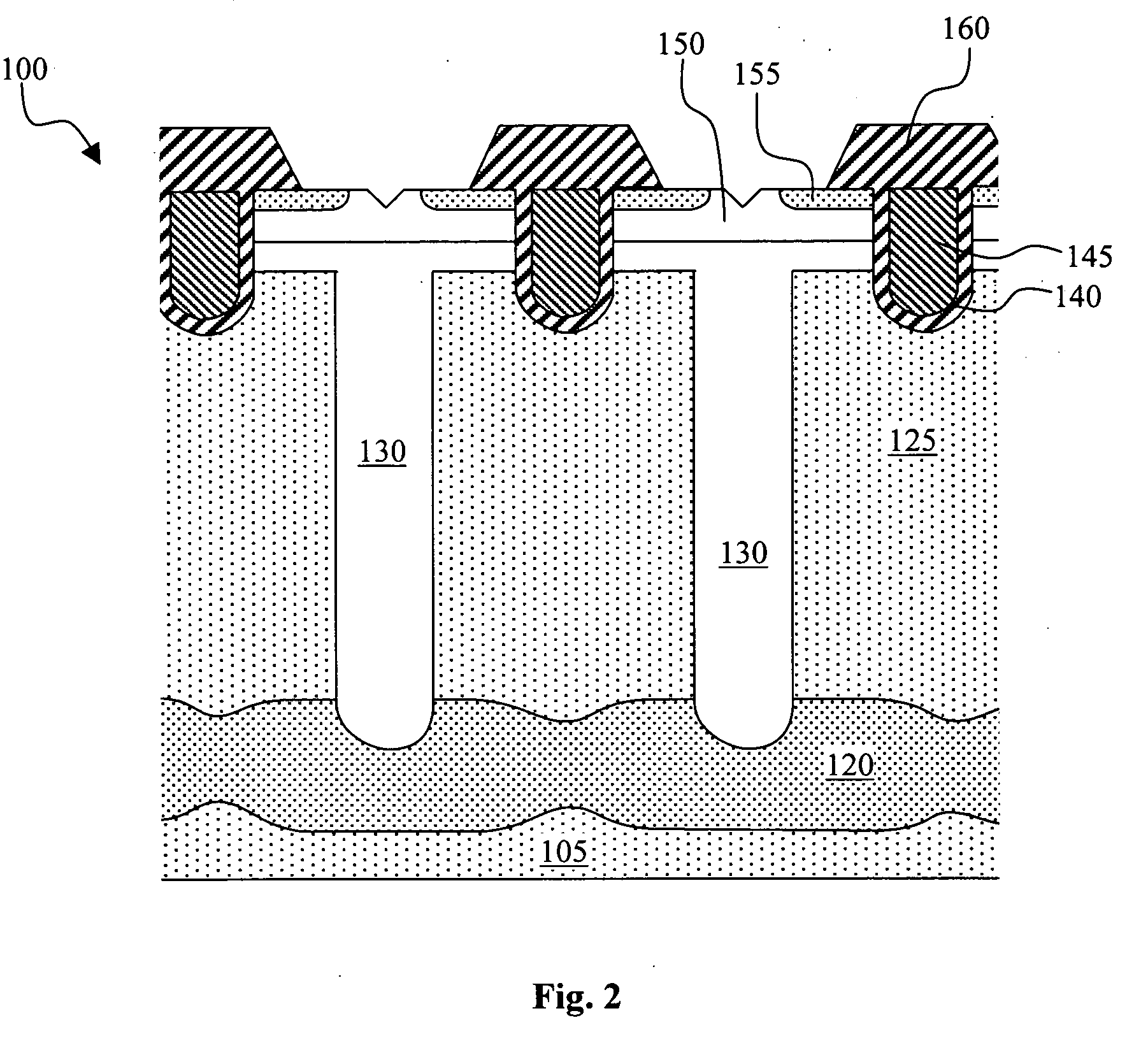

Structures of and methods of fabricating trench-gated MIS devices

In a trench-gated MIS device contact is made to the gate within the trench, thereby eliminating the need to have the gate material, typically polysilicon, extend outside of the trench. This avoids the problem of stress at the upper corners of the trench. Contact between the gate metal and the polysilicon is normally made in a gate metal region that is outside the active region of the device. Various configurations for making the contact between the gate metal and the polysilicon are described, including embodiments wherein the trench is widened in the area of contact. Since the polysilicon is etched back below the top surface of the silicon throughout the device, there is normally no need for a polysilicon mask, thereby saving fabrication costs.

Owner:SILICONIX

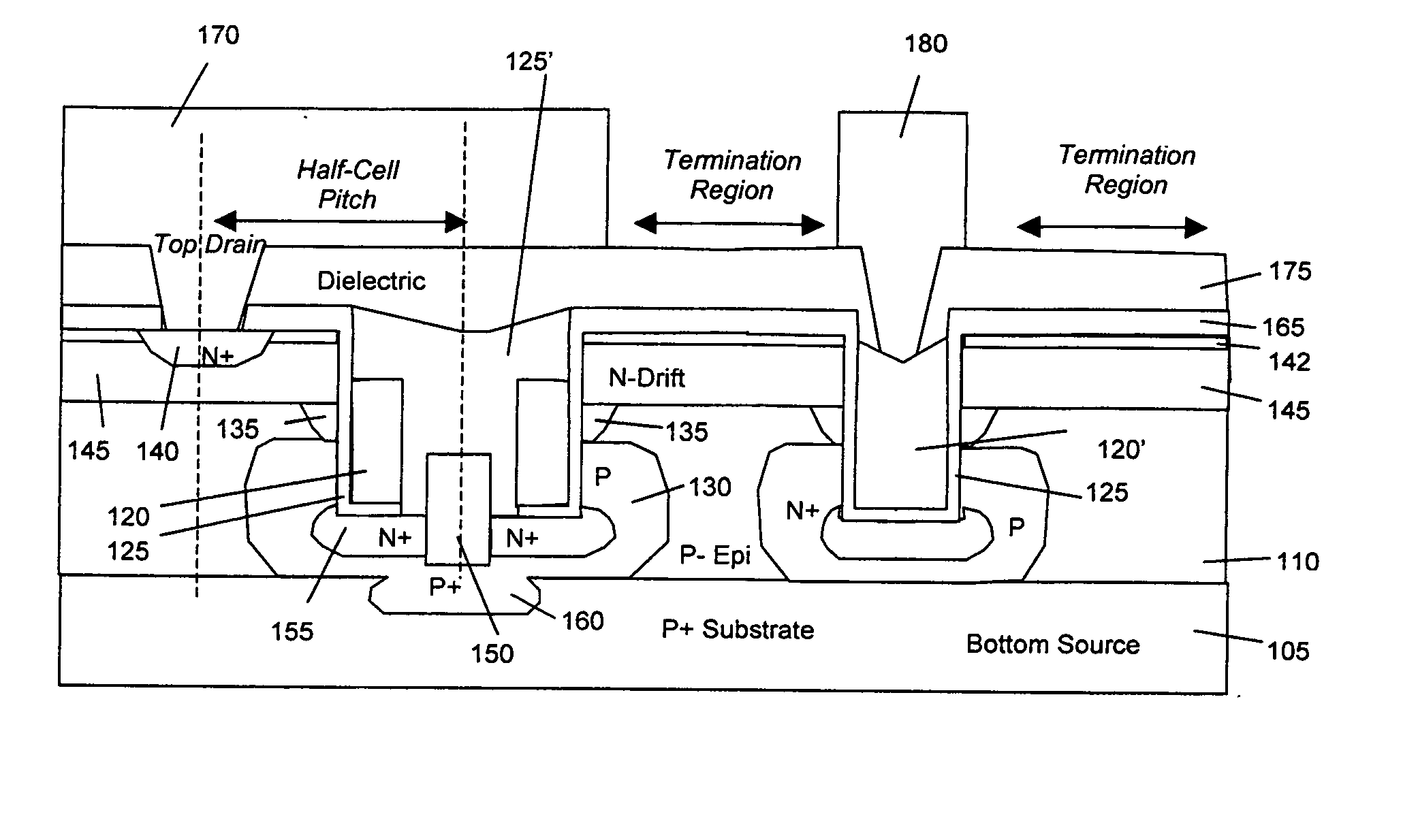

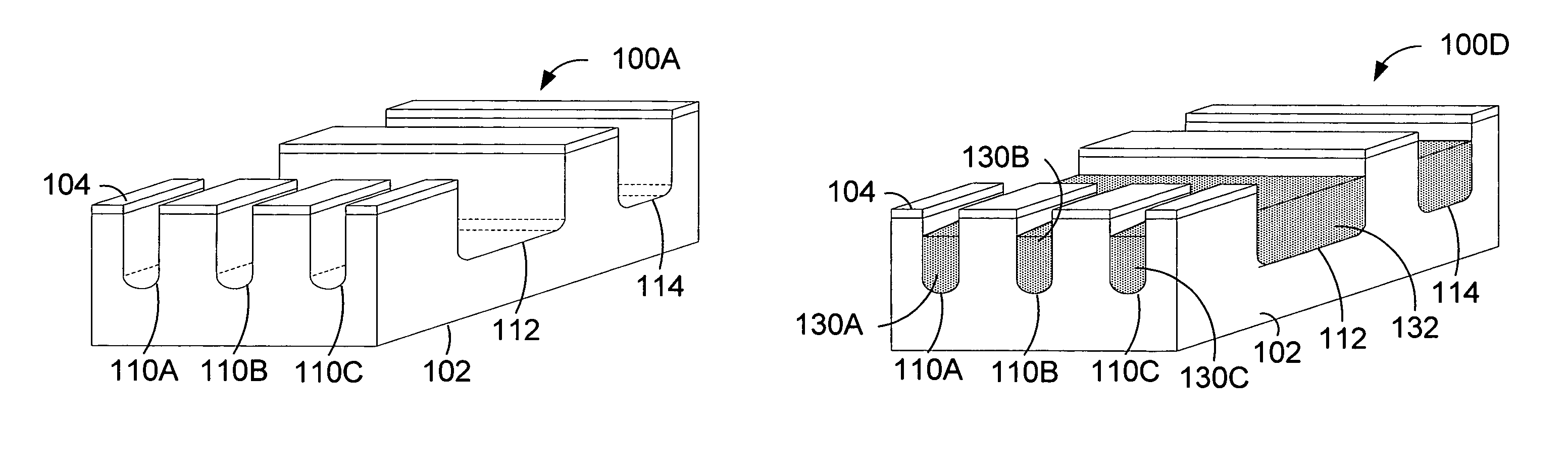

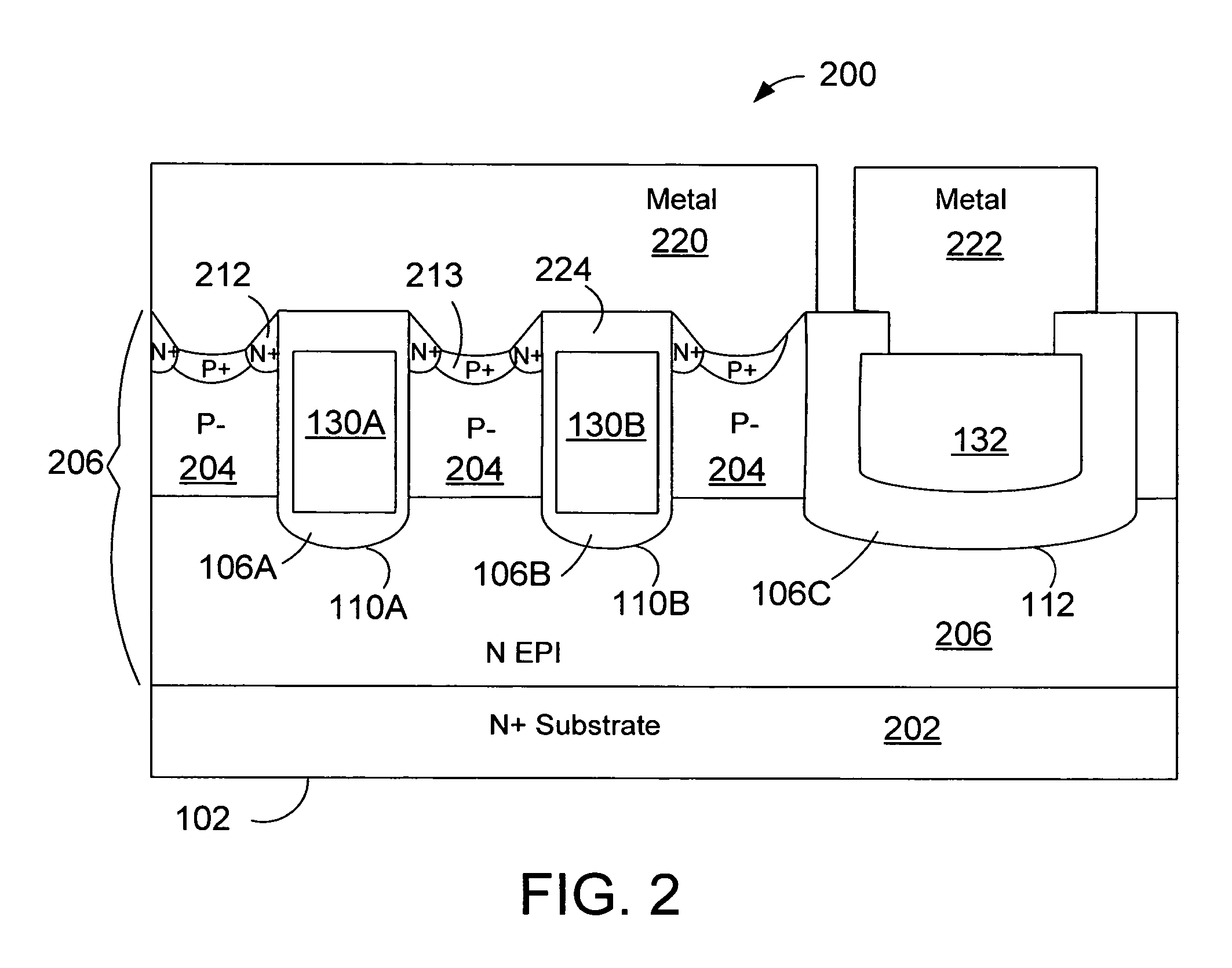

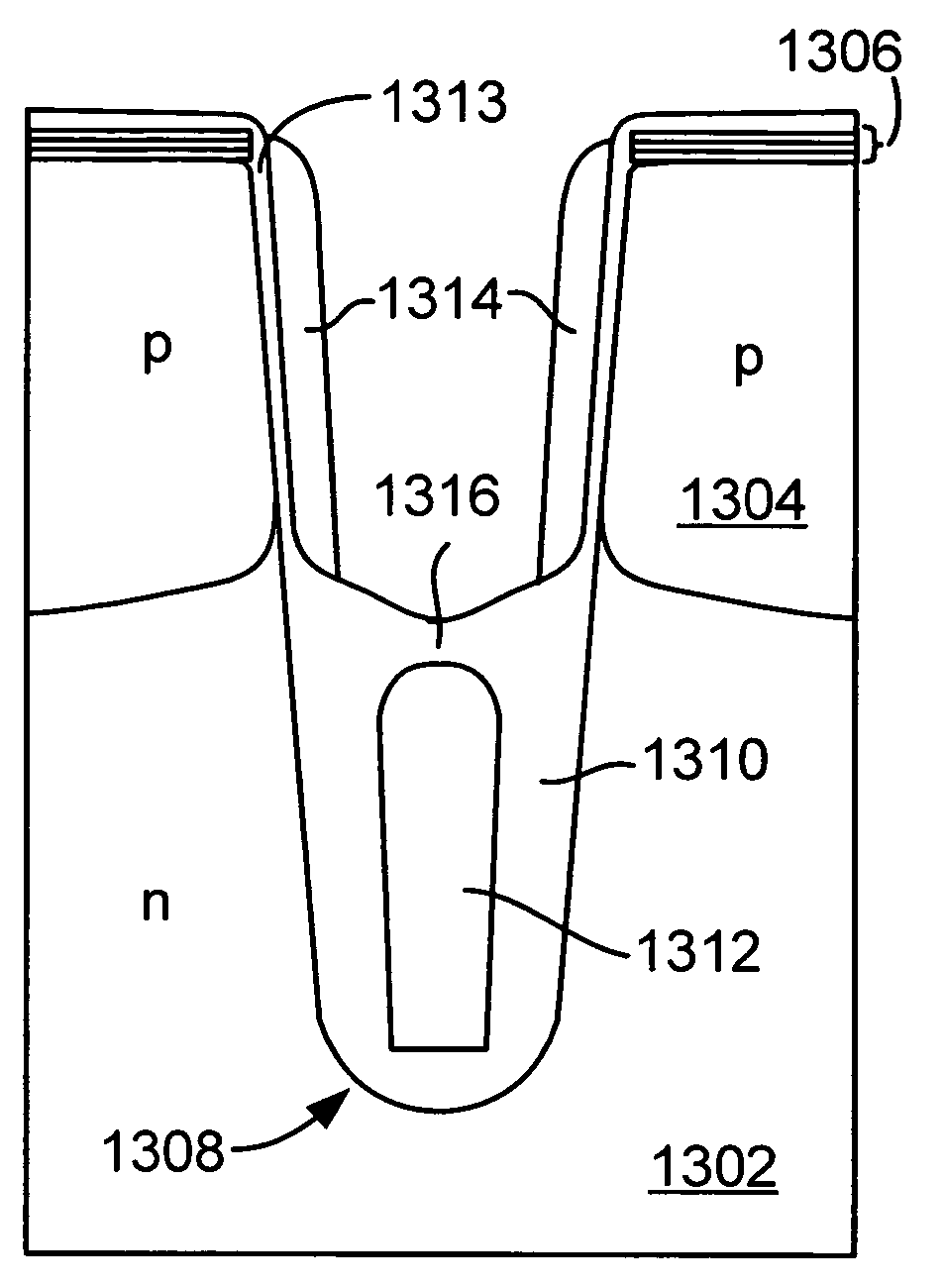

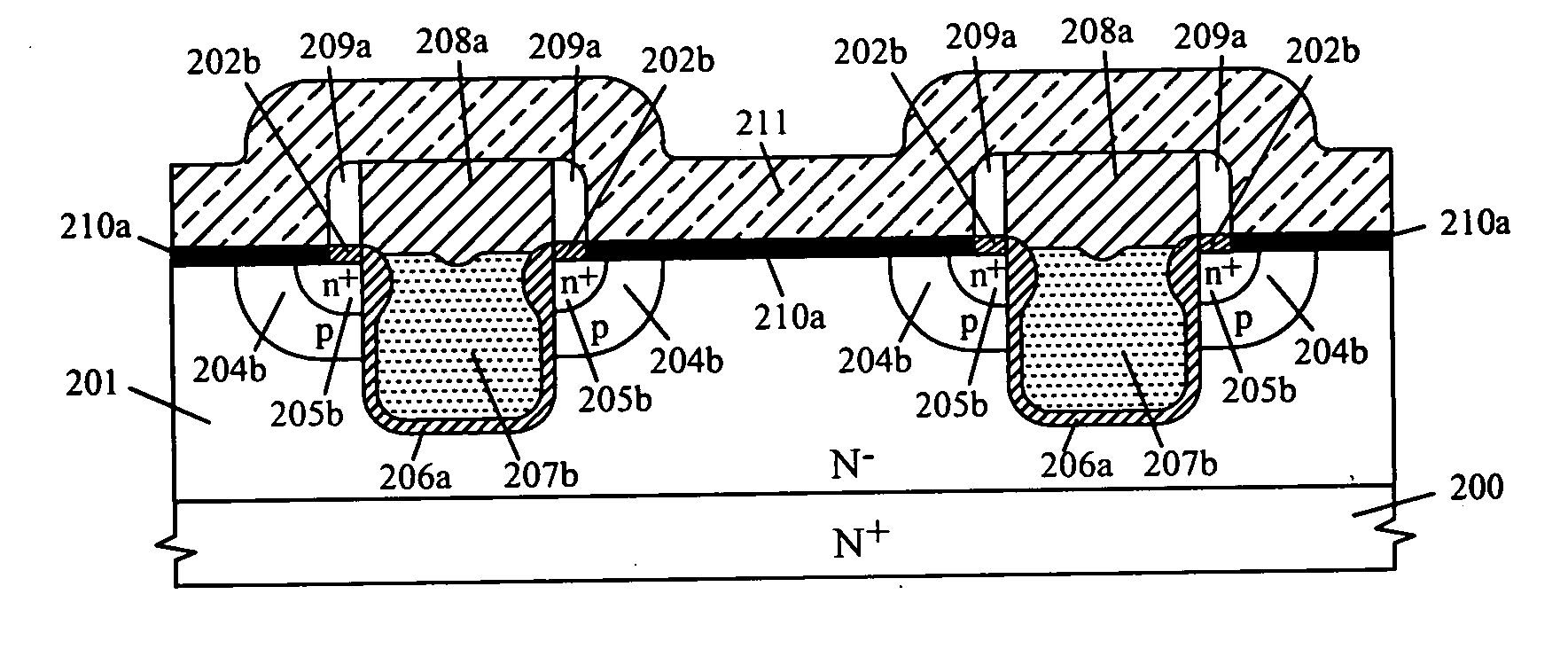

Inverted-trench grounded-source fet structure using conductive substrates, with highly doped substrates

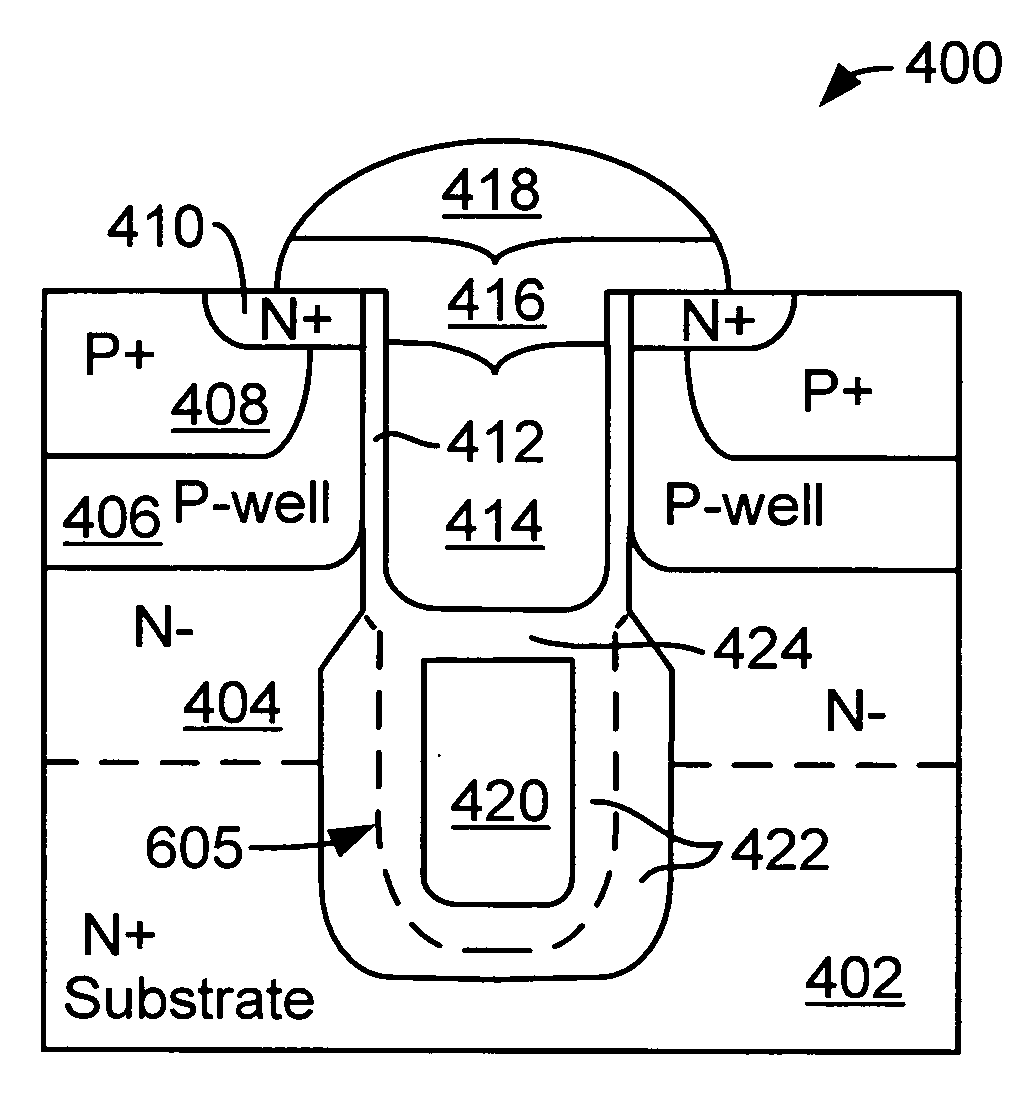

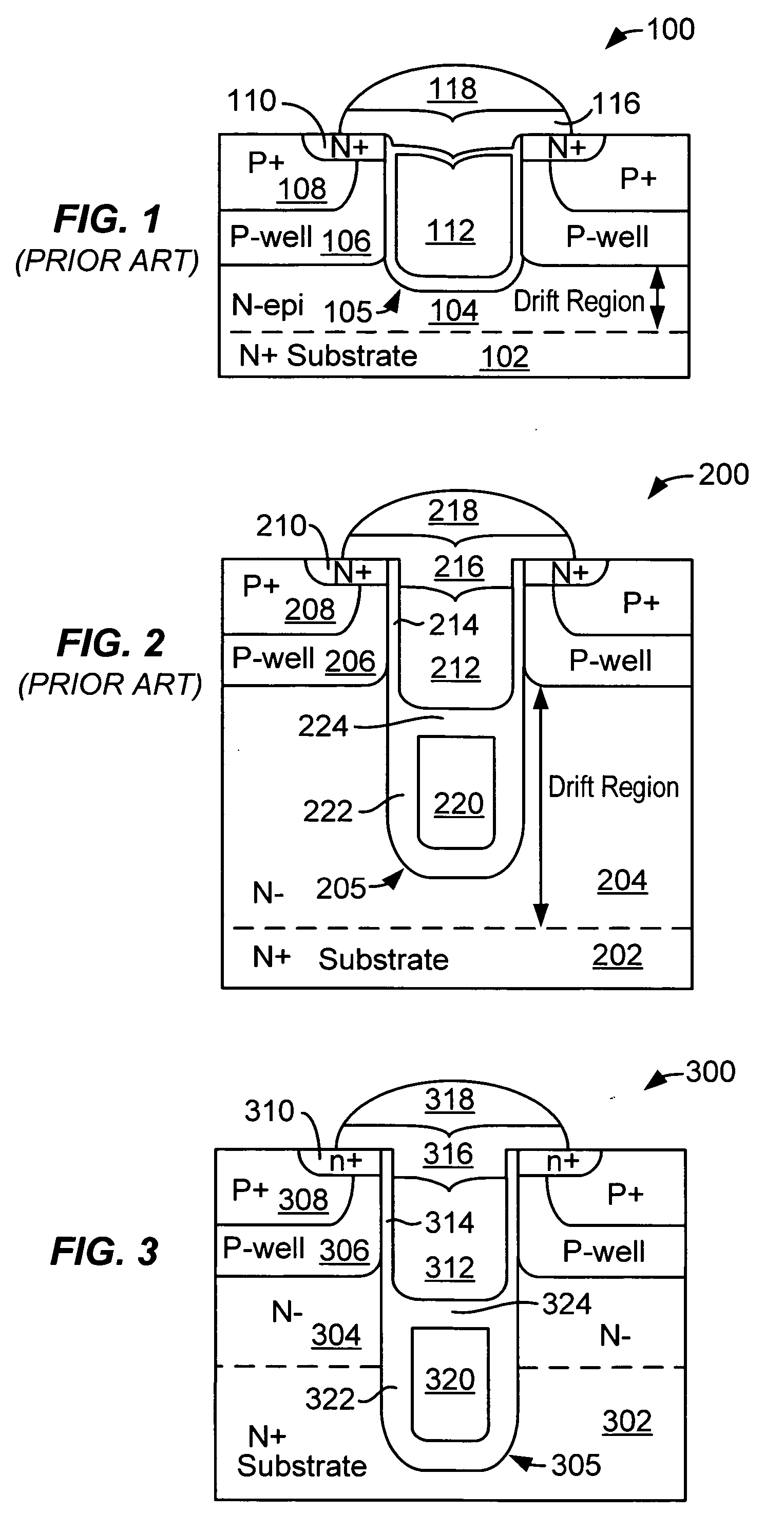

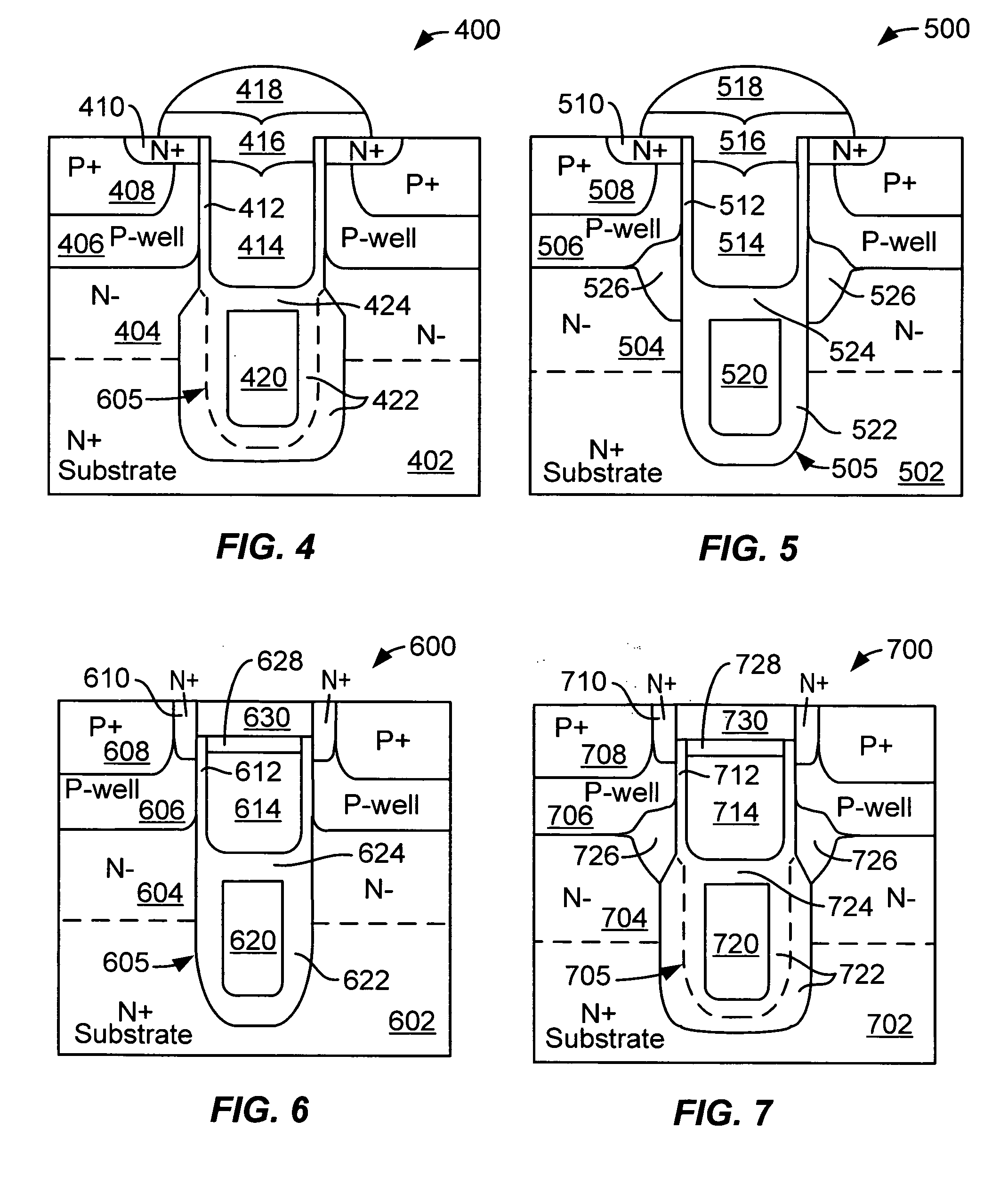

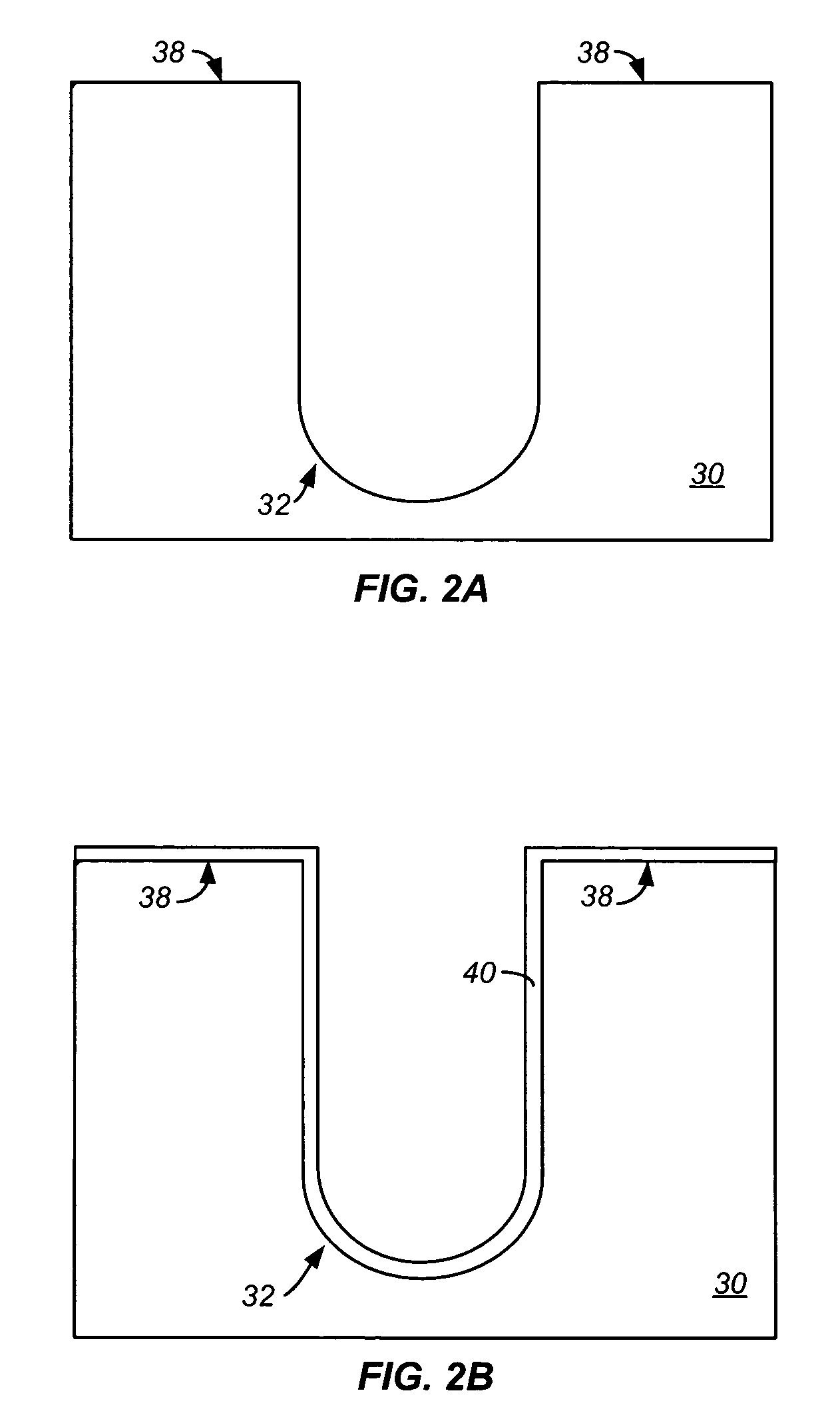

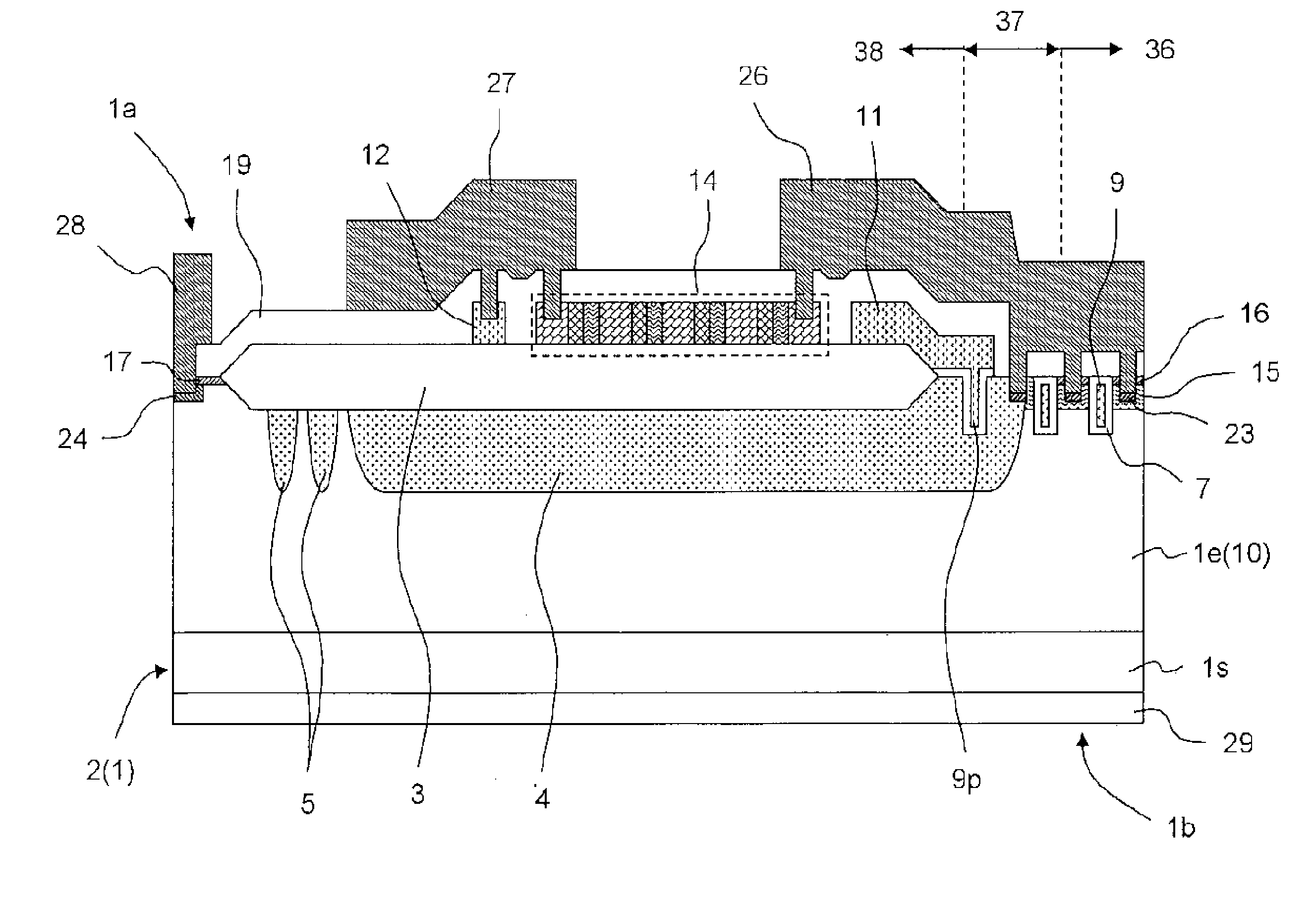

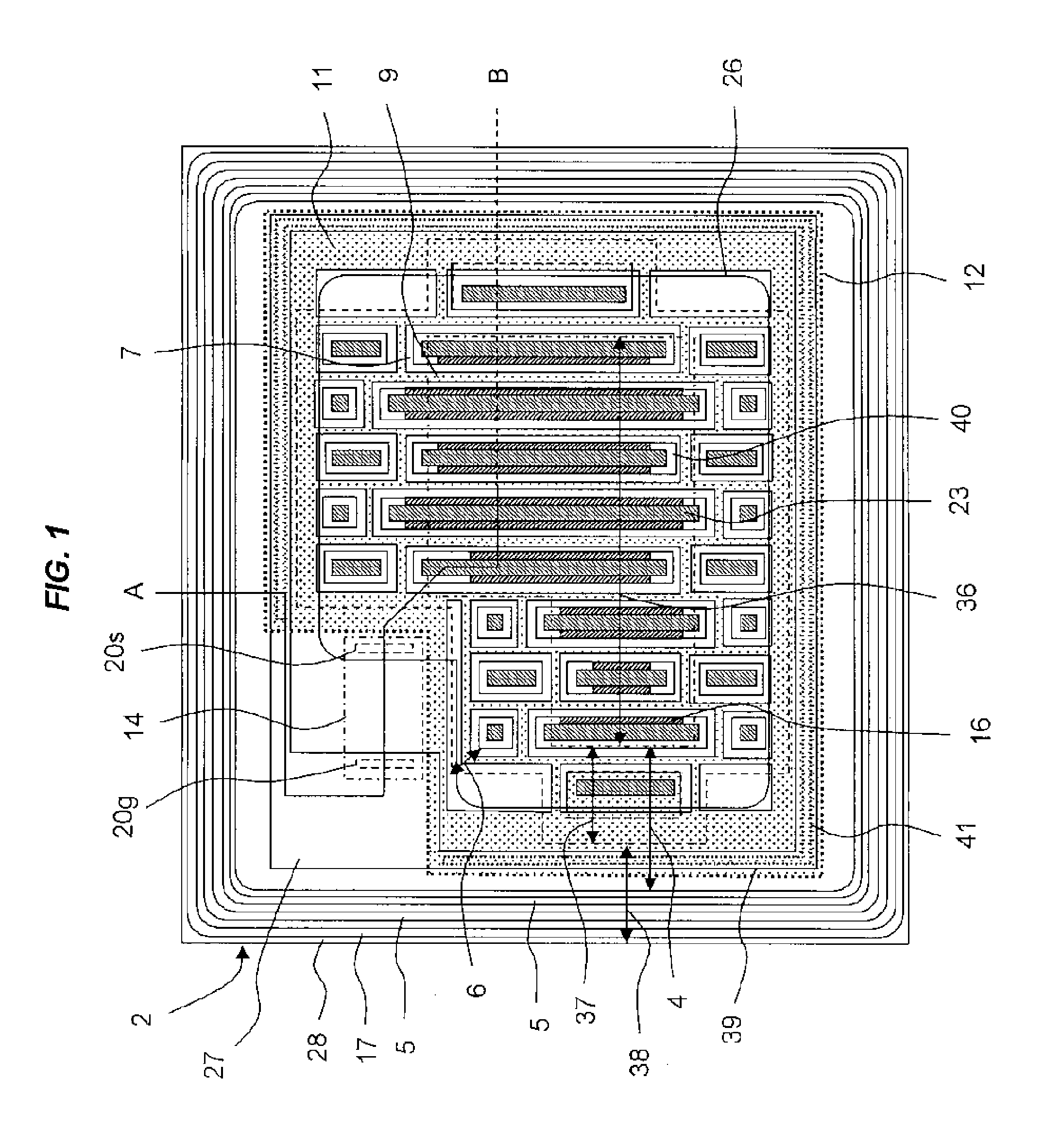

ActiveUS20080035987A1Reduced cell pitchReduce manufacturing costTransistorSemiconductor/solid-state device manufacturingMOSFETCapacitance

This invention discloses an improved trenched metal oxide semiconductor field effect transistor (MOSFET) device that includes a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The MOSFET cell further includes a shielded gate trench (SGT) structure below and insulated from the trenched gate. The SGT structure is formed substantially as a round hole having a lateral expansion extended beyond the trench gate and covered by a dielectric linen layer filled with a trenched gate material. The round hole is formed by an isotropic etch at the bottom of the trenched gate and is insulated from the trenched gate by an oxide insulation layer. The round hole has a lateral expansion beyond the trench walls and the lateral expansion serves as a vertical alignment landmark for controlling the depth of the trenched gate. The MOSFET device has a reduced gate to drain capacitance Cgd depending on the controllable depth of the trenched gate disposed above the SGT structure formed as a round hole below the trenched gate.

Owner:ALPHA & OMEGA SEMICON LTD

Power device utilizing chemical mechanical planarization

InactiveUS7449354B2Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

Owner:SEMICON COMPONENTS IND LLC

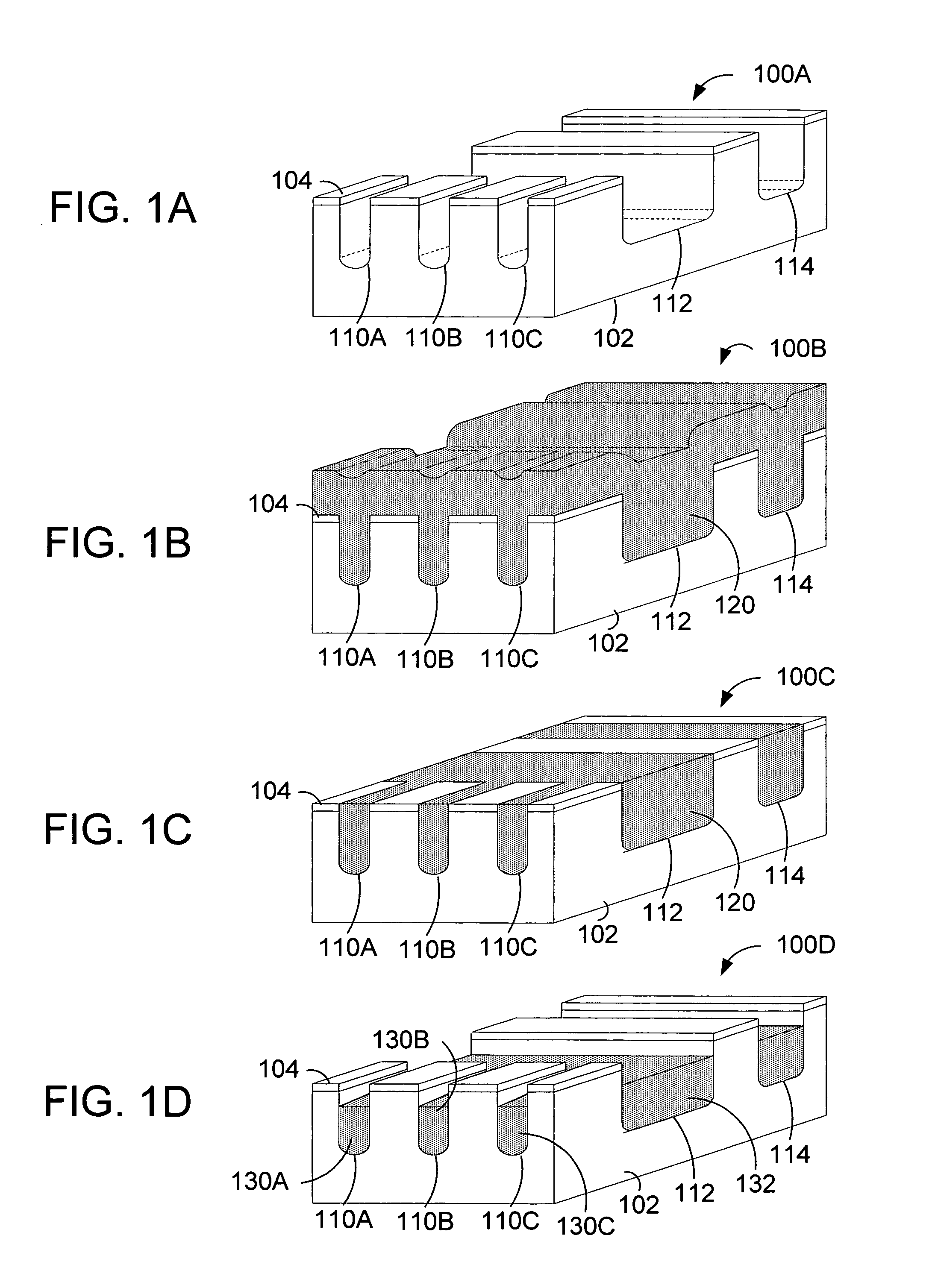

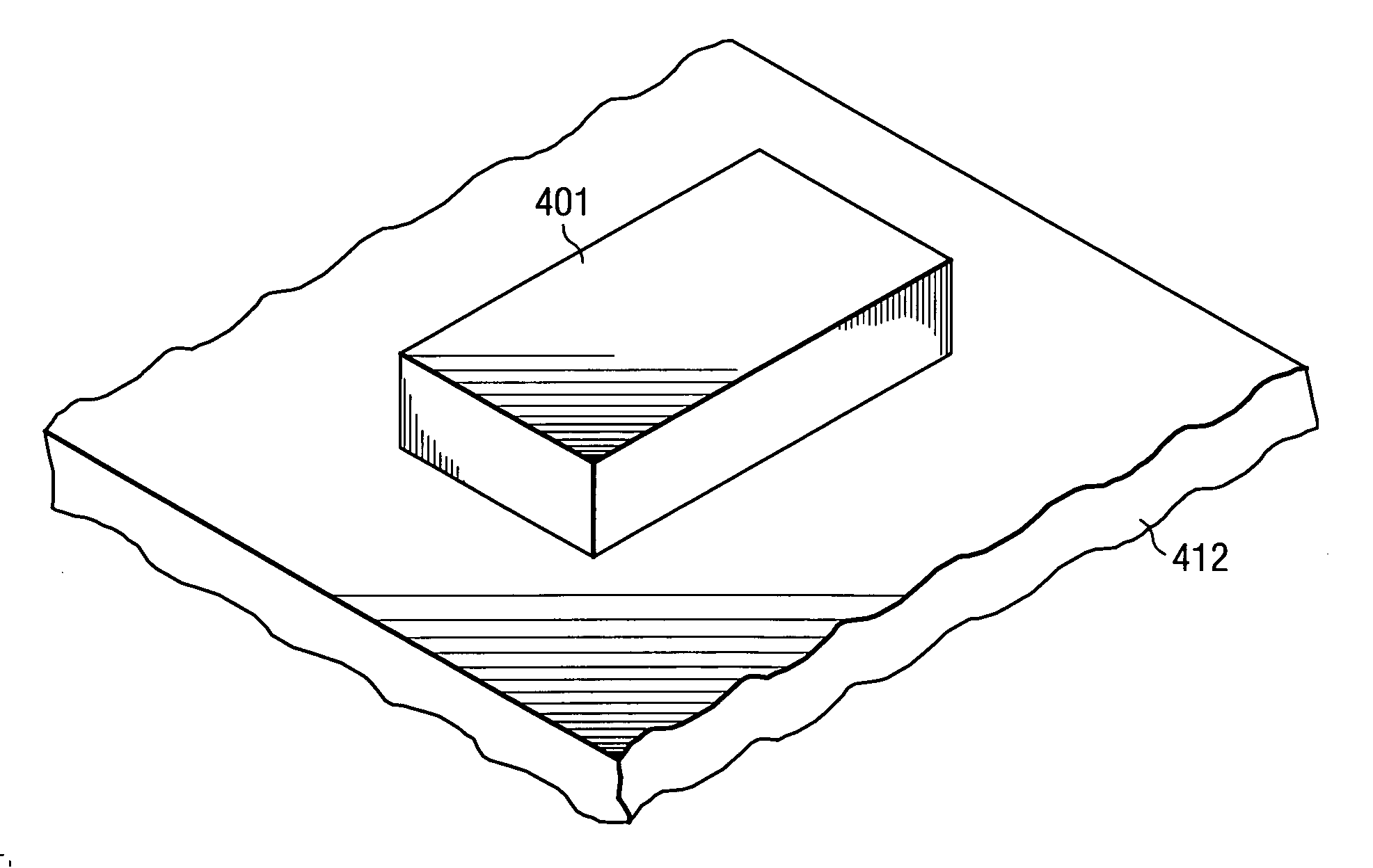

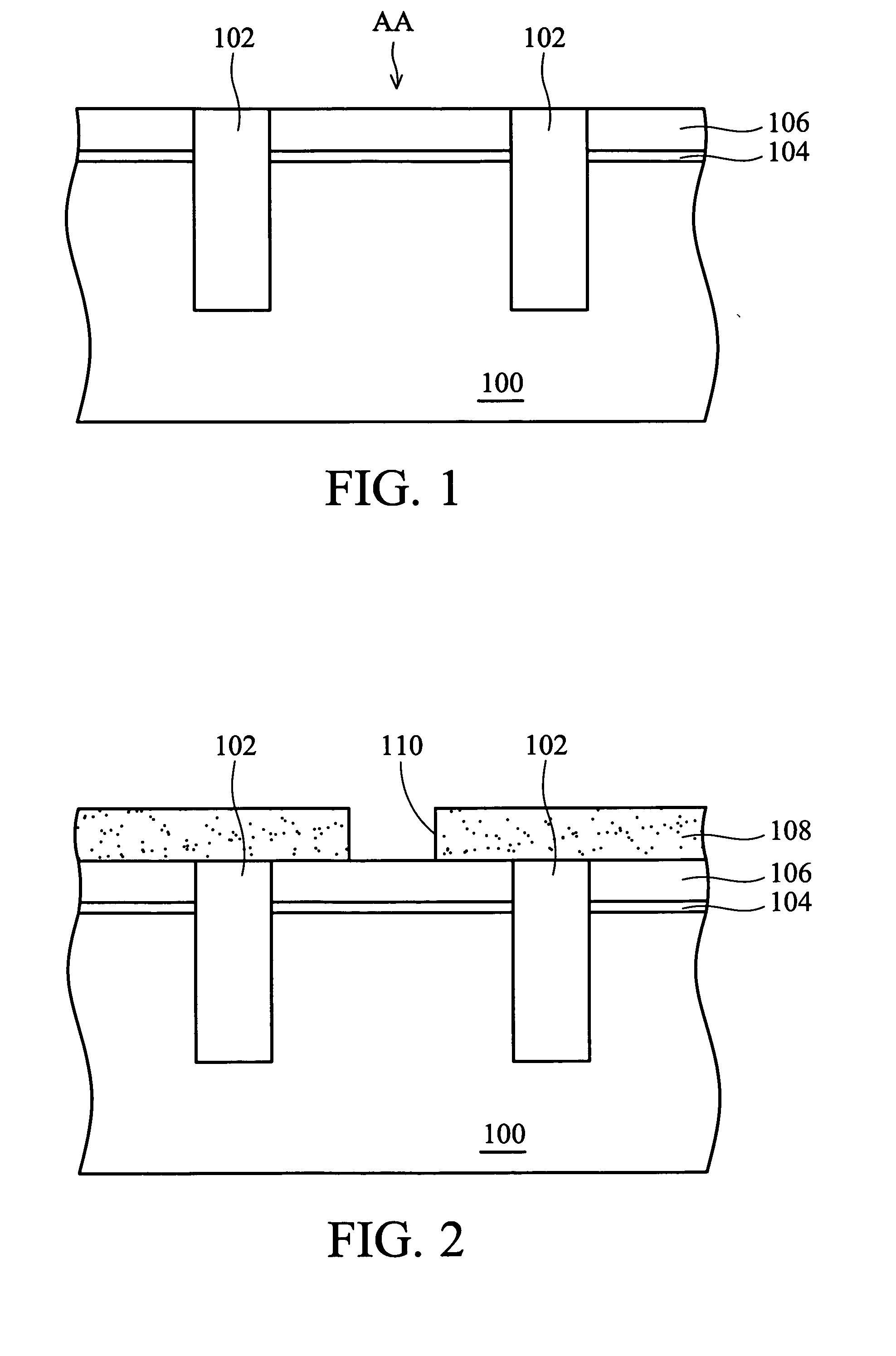

Low resistance gate for power mosfet applications and method of manufacture

ActiveUS20070190728A1Semiconductor/solid-state device manufacturingSemiconductor devicesPower MOSFETField-effect transistor

A trench gate field effect transistor is formed as follows. A trench is formed in a semiconductor region, followed by a dielectric layer lining sidewalls and bottom of the trench and extending over mesa regions adjacent the trench. A conductive seed layer is formed in a bottom portion of the trench over the dielectric layer. A low resistance material is grown over the conductive seed layer, wherein the low resistance material is selective to the conductive seed layer.

Owner:SEMICON COMPONENTS IND LLC +1

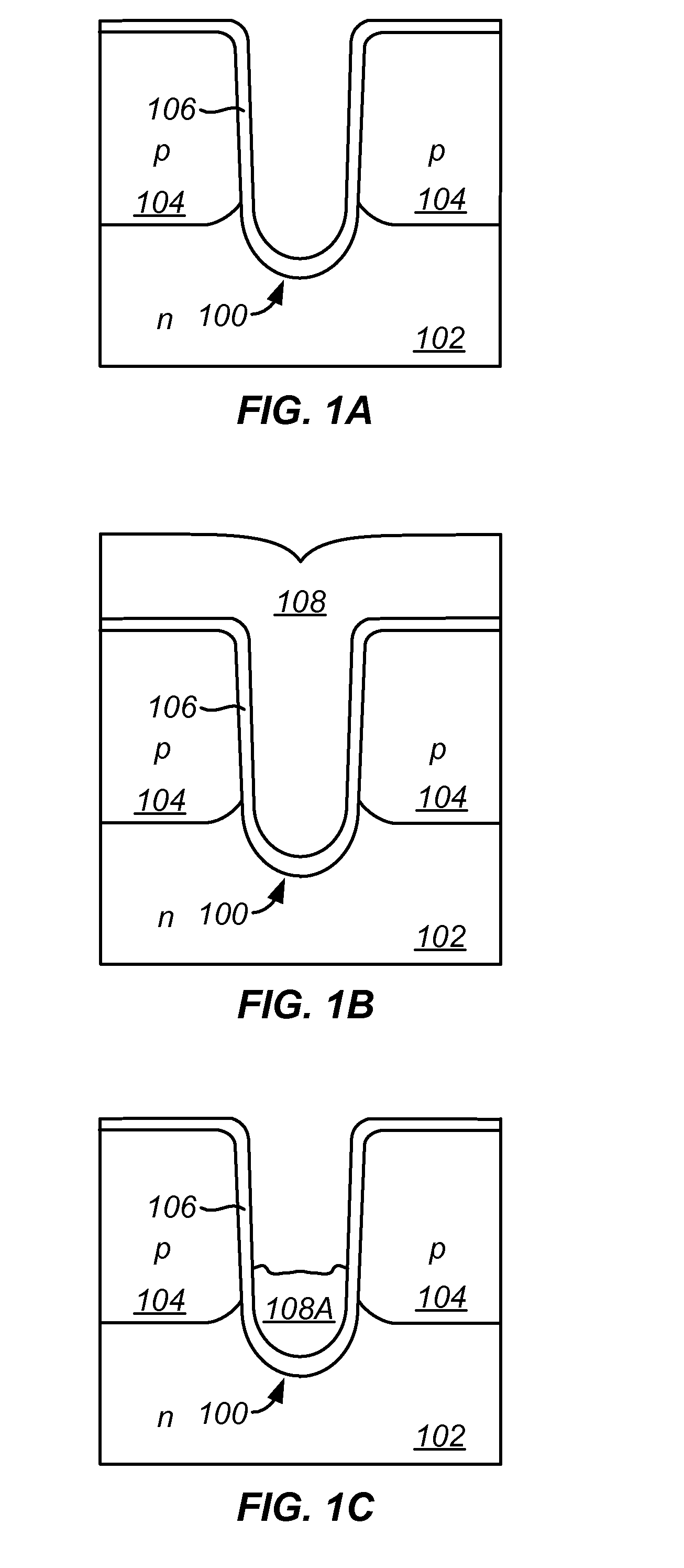

Trench-gate field effect transistors and methods of forming the same

InactiveUS7504303B2Reduce channel resistanceSemiconductor/solid-state device manufacturingDiodeEngineeringField-effect transistor

A method for forming a shielded gate field effect transistor includes the following steps. Trenches extending into a silicon region are formed using a mask that includes a protective layer. A shield dielectric layer lining sidewalls and bottom of each trench is formed. A shield electrode is formed in a bottom portion of each trench. Protective spacers are formed along upper sidewalls of each trench. An inter-electrode dielectric is formed over the shield electrode. The protective spacers and the protective layer of the mask prevent formation of inter-electrode dielectric along the upper sidewalls of each trench and over mesa surfaces adjacent each trench. A gate electrode is formed in each trench over the inter-electrode dielectric.

Owner:SEMICON COMPONENTS IND LLC

Trench-gate electrode for FinFET device

InactiveUS20060189043A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

A FinFET device having a trench-gate electrode, and a method of manufacture, is provided. The trench-gate electrode may be fabricated by forming a mask layer on a substrate having a semiconductor layer, e.g., silicon, formed thereon. A trench is formed in the mask layer and fins are formed in the exposed region of the underlying semiconductor layer. A gate electrode may be formed in the trench by, for example, depositing a gate electrode material such that the trench is filled, planarizing the surface to the surface of the mask layer, and optionally forming a recess in the surface of the gate electrode. Spacers may be formed in the trench and an optional gate dielectric layer may be formed over the fins prior to depositing the gate electrode material. Raised source and drain regions may be used by using selective epitaxial growth processes.

Owner:INFINEON TECH AG

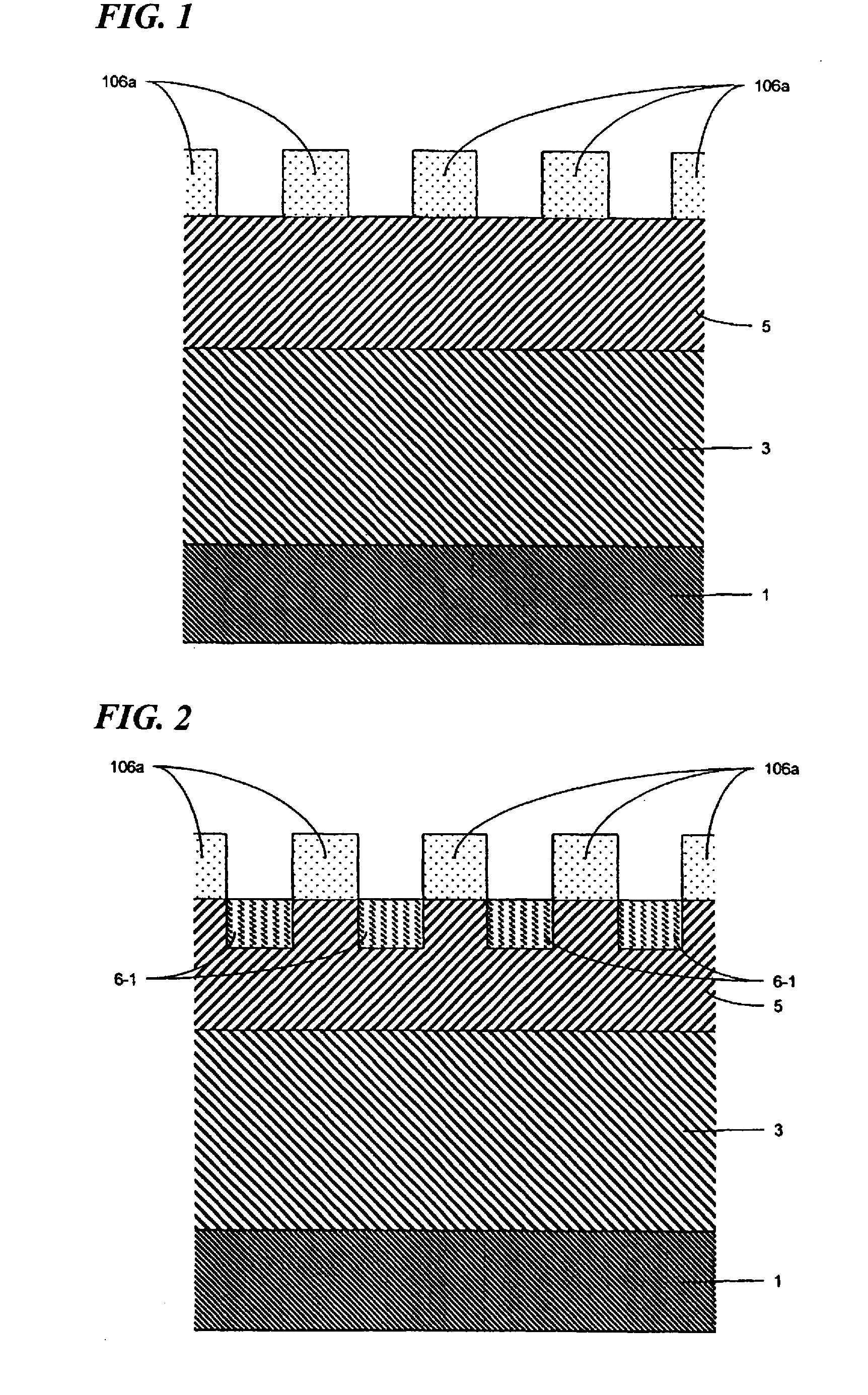

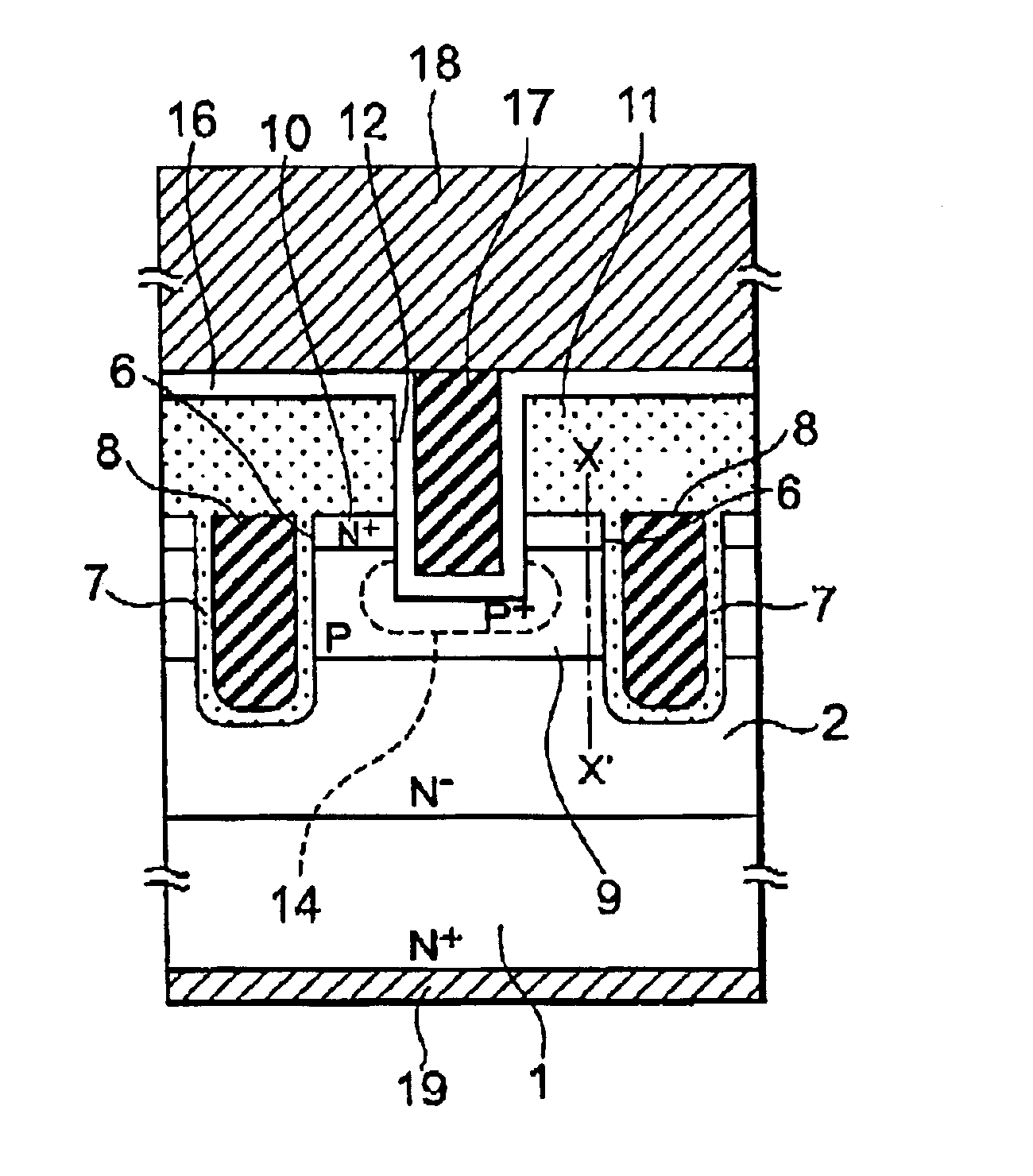

Semiconductor device and a method of manufacturing the same

InactiveUS20050029584A1Easy to integrateReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceFeedback capacitance

A technology is provided to reduce ON-resistance, and the prevention of punch through is achieved with respect to a trench gate type power MISFET. Input capacitance and a feedback capacitance are reduced by forming a groove in which a gate electrode is formed so as to have a depth as shallow as about 1 μm or less, a p−type semiconductor region is formed to a depth so as not to cover the bottom of the groove, and a p-type semiconductor region higher in impurity concentration than the p−type semiconductor region is formed under a n+type semiconductor region serving as a source region of the trench gate type power MISFET, causing the p-type semiconductor region to serve as a punch-through stopper layer of the trench gate type power MISFET.

Owner:RENESAS TECH CORP

Semiconductor device and manufacturing method of the same

ActiveUS20060157779A1Lower on-resistanceSuppress and prevent operation of parasiticSolid-state devicesSemiconductor devicesElectrical resistance and conductanceDevice material

The on-resistance of a semiconductor device having a power transistor with a trench gate structure is reduced. A power MIS-FET with a trench gate structure is so formed that the relation expressed as 0≦b≦a holds, where a is the distance between an end of an interlayer insulating layer over the upper face of a semiconductor region for source and the end (position on the periphery of a trench) of the upper face of the semiconductor region for source farther from the gate electrode; and b is the length of the overlap between the interlayer insulating layer and the upper face of the semiconductor region for source. (b is the distance between the position of the end of the interlayer insulating layer over the upper face of the semiconductor region for source and position on the periphery of a trench). As a result, the area of contact between source pads and the semiconductor regions for source is increased, and further the distance between the source pads and a channel forming region can be shortened. Therefore, the on-resistance of the power MIS-FET with a trench gate structure can be reduced.

Owner:RENESAS ELECTRONICS CORP

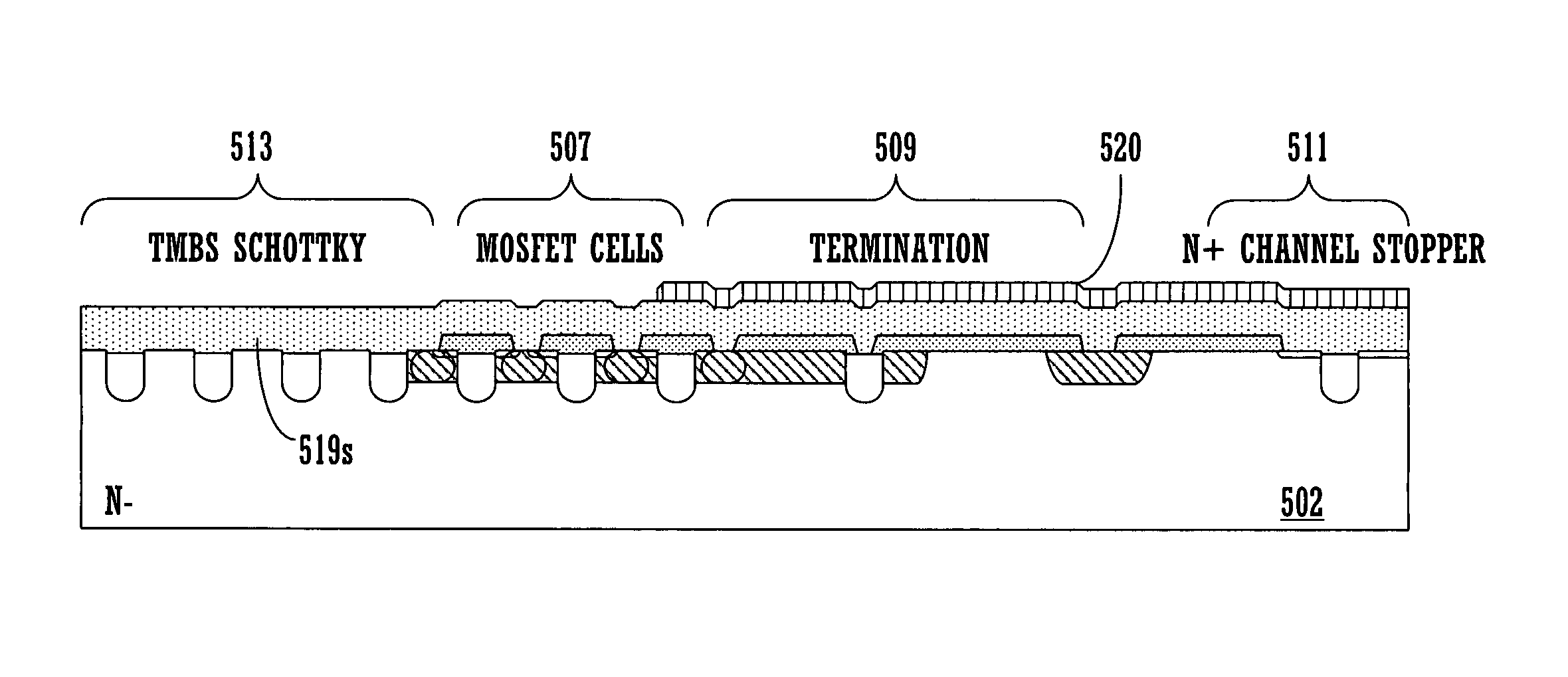

Method of forming trench gate field effect transistor with recessed mesas

A monolithically integrated field effect transistor and Schottky diode includes gate trenches extending into a semiconductor region. Source regions having a substantially triangular shape flank each side of the gate trenches. A contact opening extends into the semiconductor region between adjacent gate trenches. A conductor layer fills the contact opening to electrically contact: (a) the source regions along at least a portion of a slanted sidewall of each source region, and (b) the semiconductor region along a bottom portion of the contact opening, wherein the conductor layer forms a Schottky contact with the semiconductor region.

Owner:SEMICON COMPONENTS IND LLC

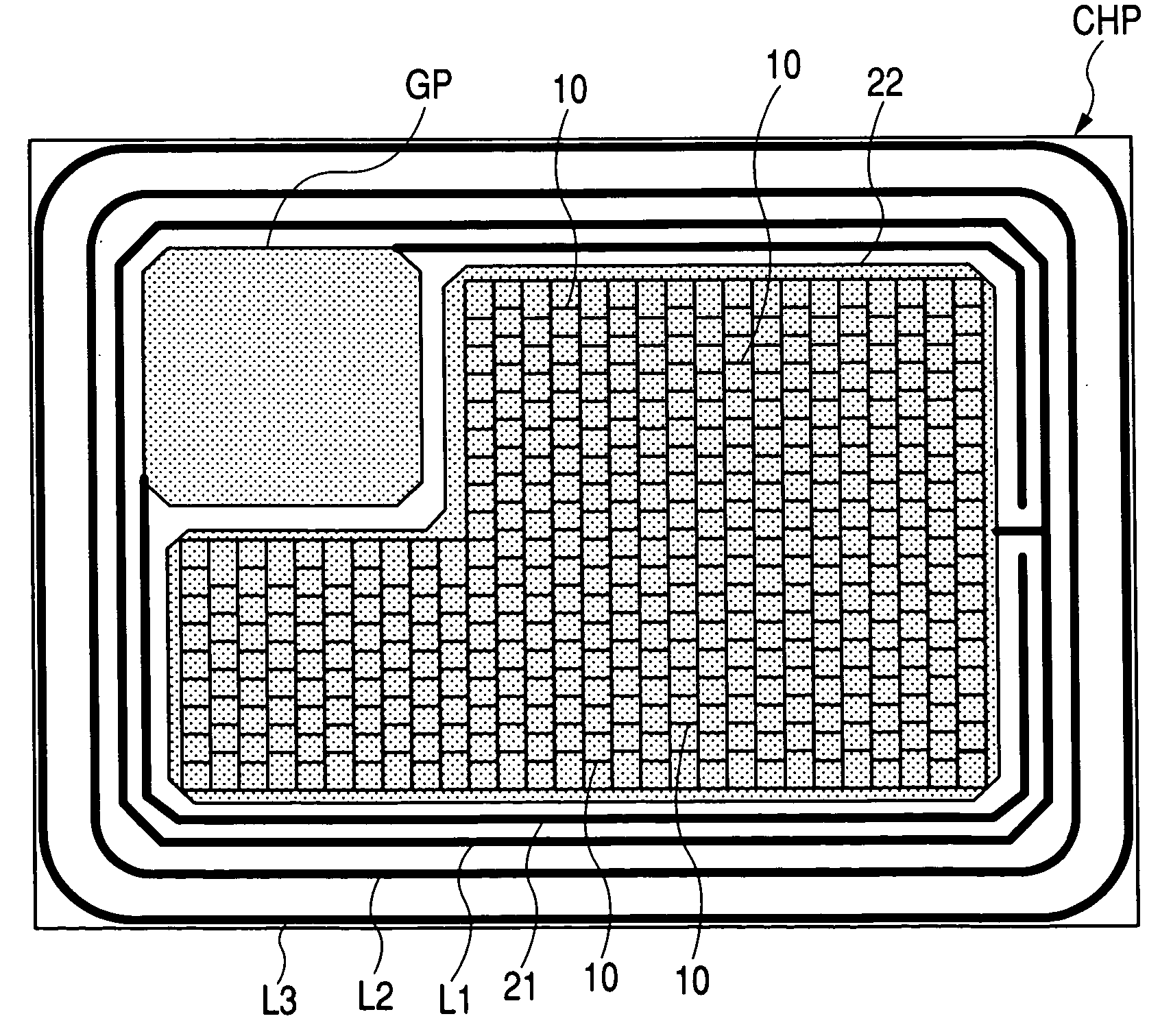

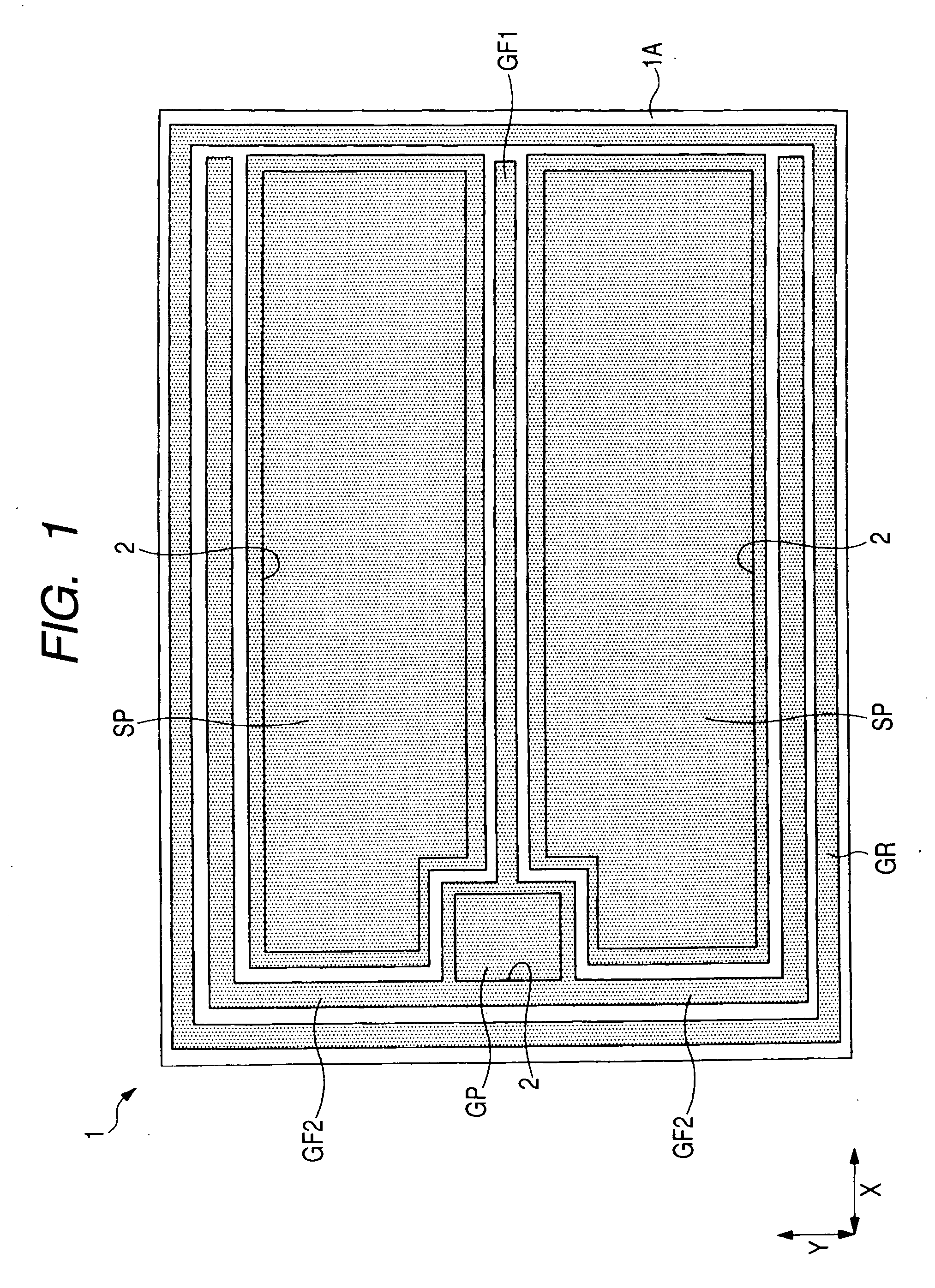

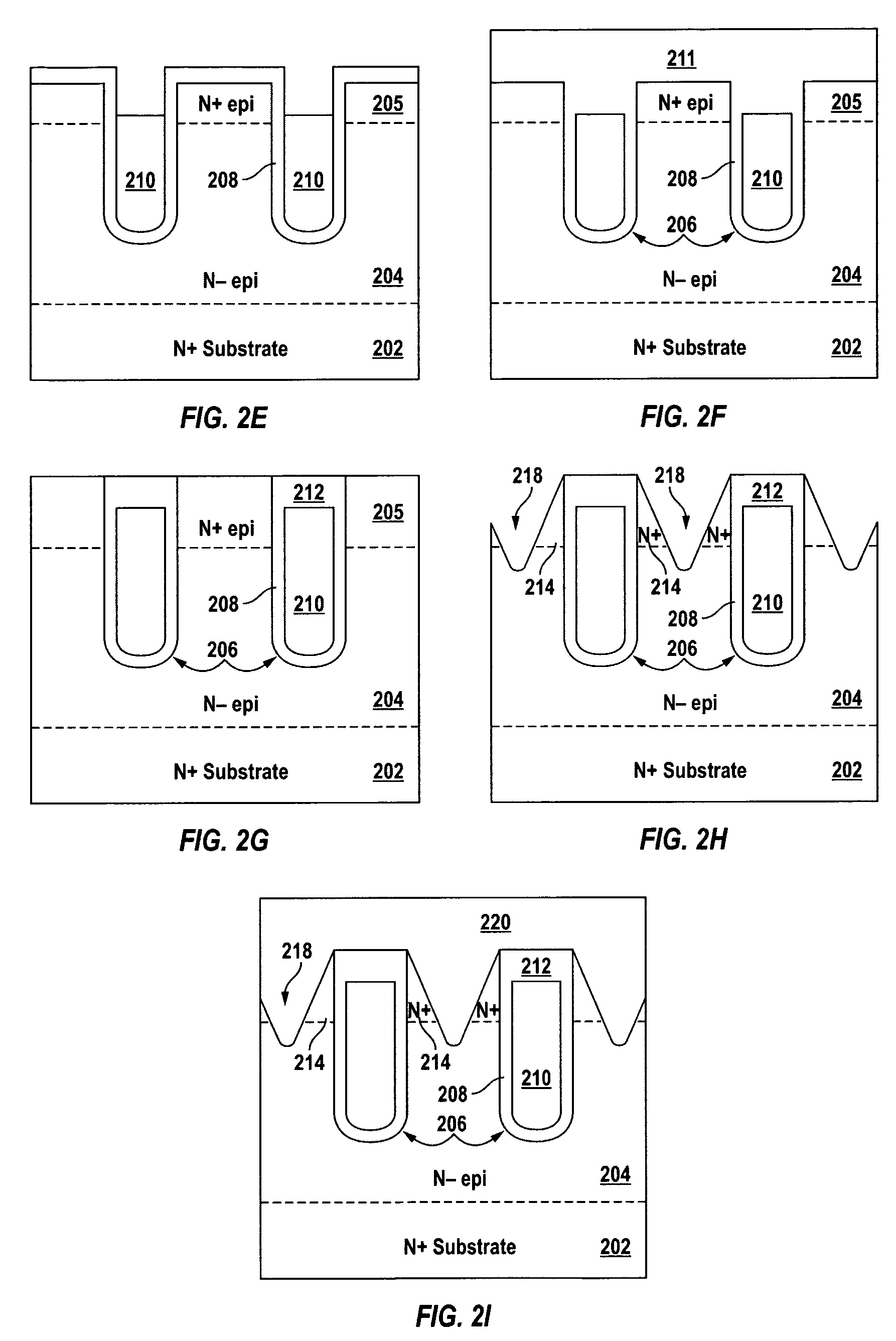

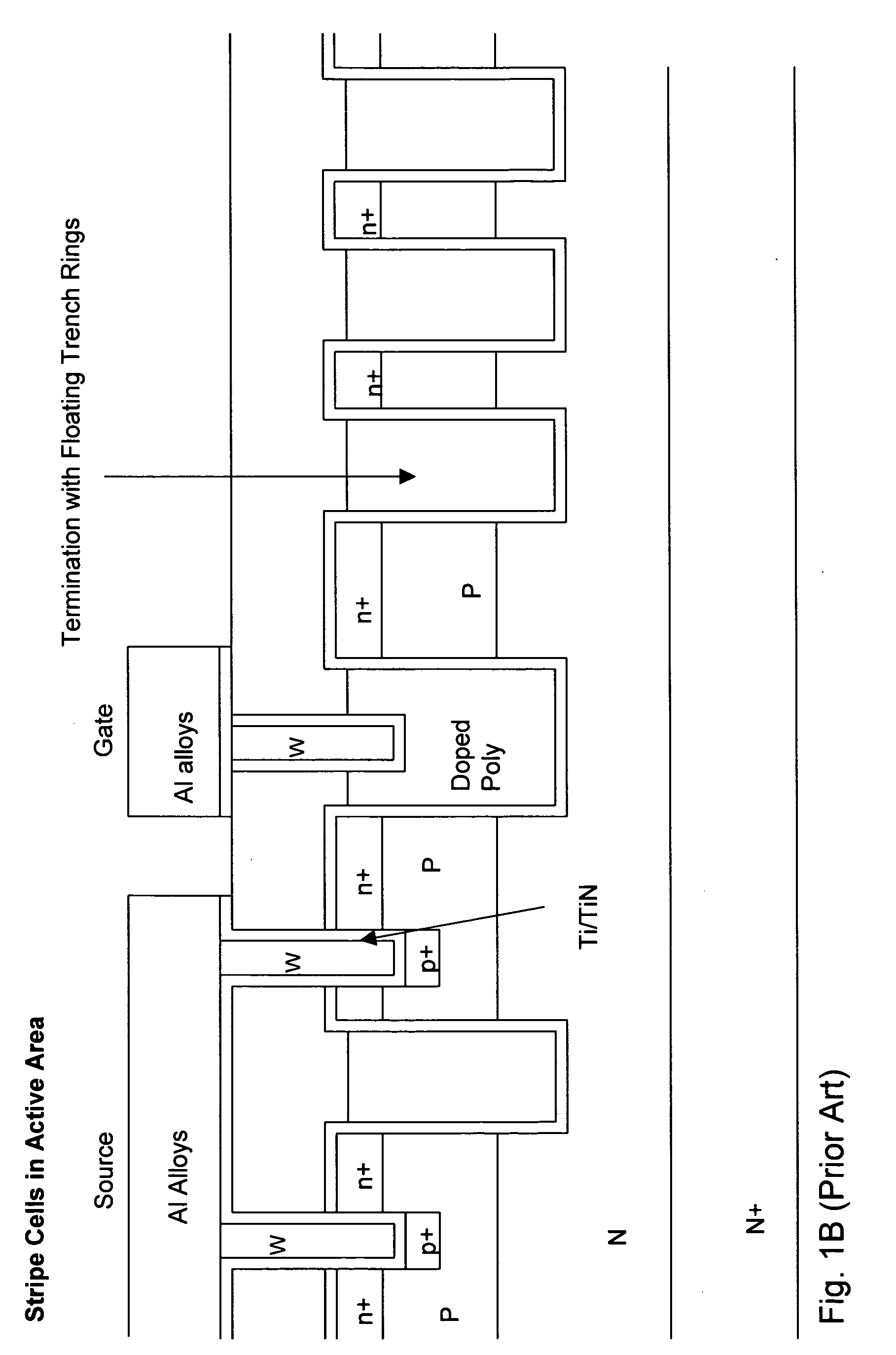

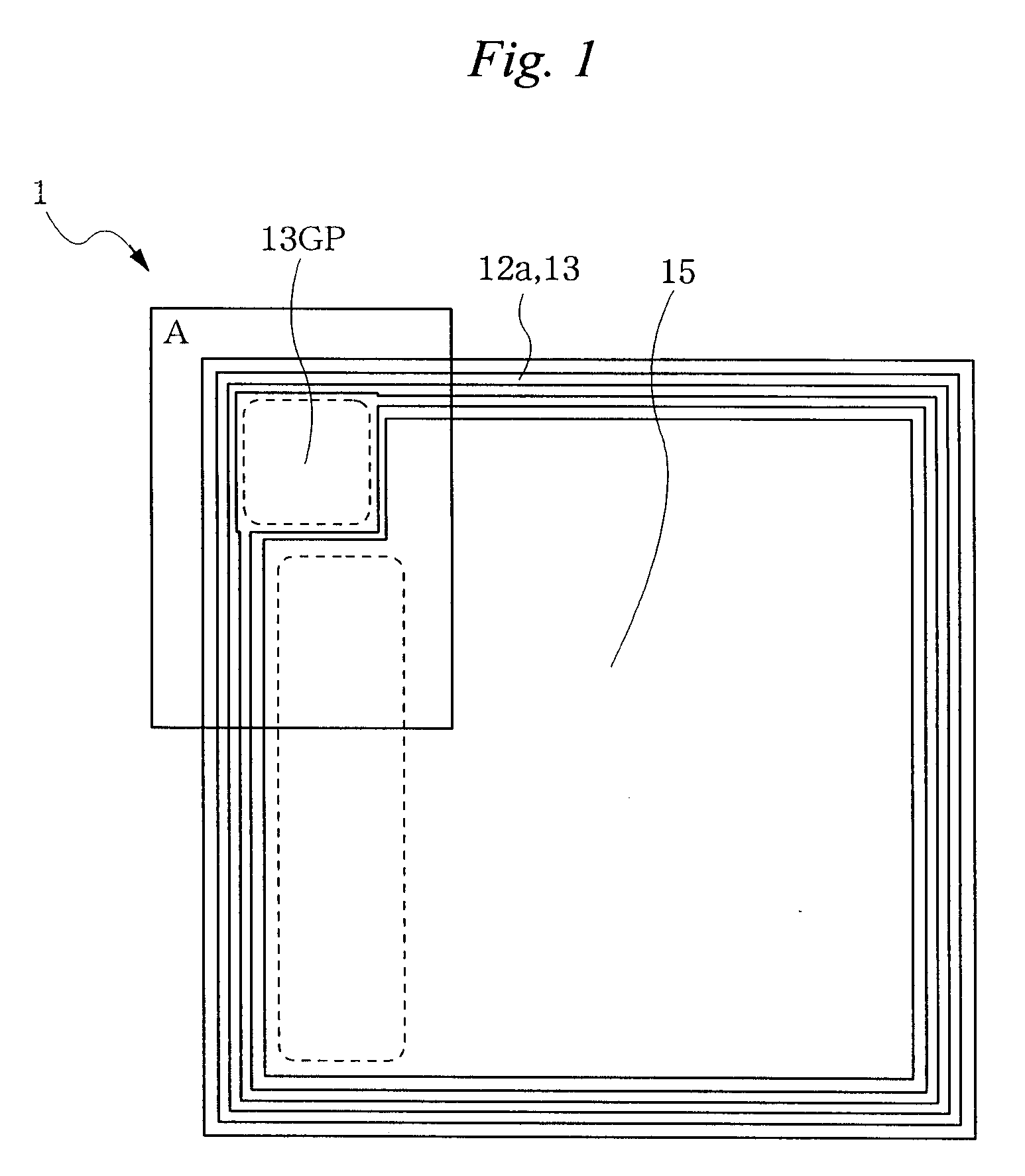

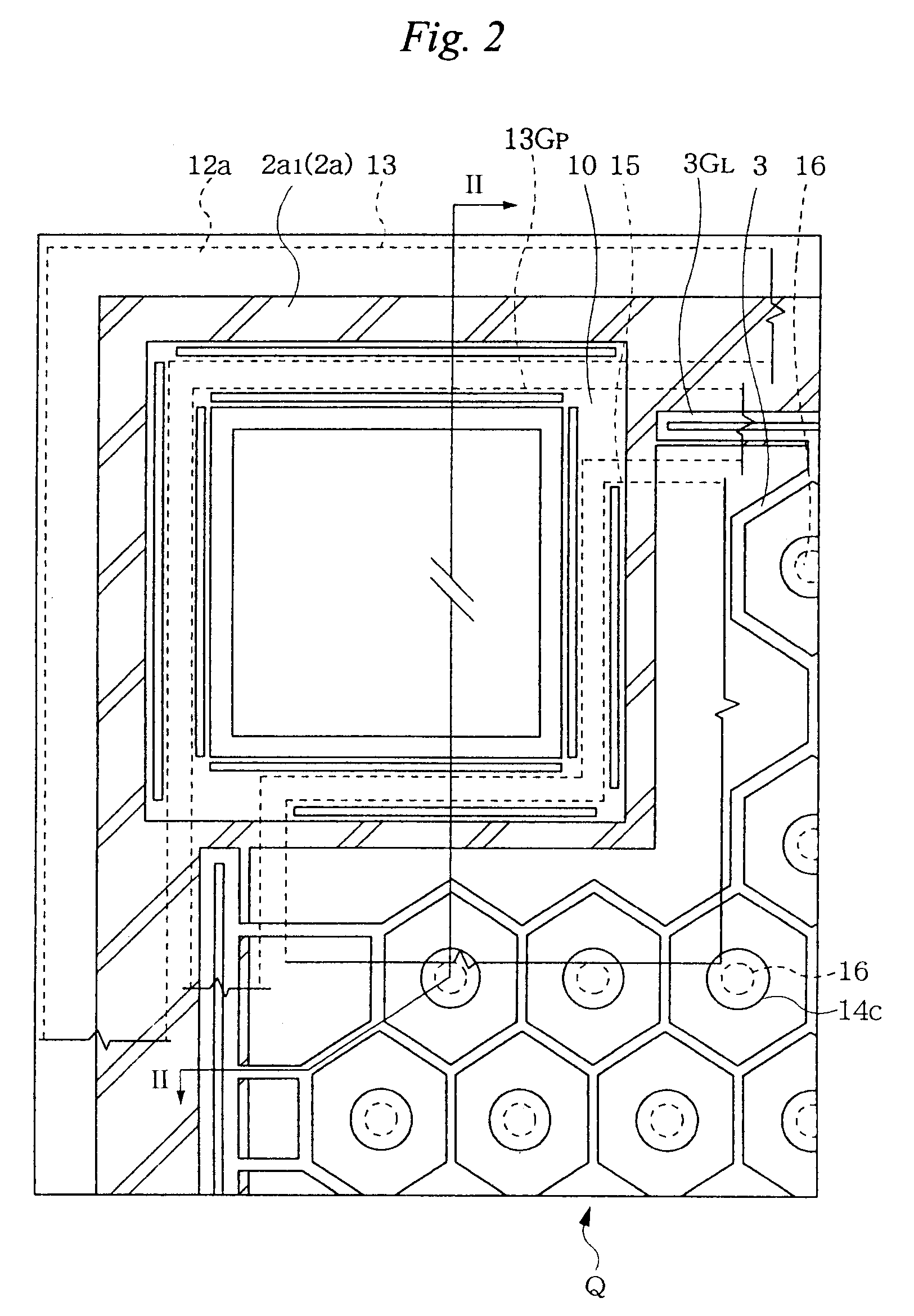

Closed trench MOSFET with floating trench rings as termination

ActiveUS20080179662A1Increased durabilityImprove breakdown voltageTransistorSolid-state devicesTrench mosfetTrench gate

A semiconductor power device includes a plurality of closed N-channel MOSFET cells surrounded by trenched gates constituting substantially a square or rectangular cell. The trenched gates are further extended to a gate contact area and having greater width as wider trenched gates for electrically contacting a gate pad wherein the semiconductor power device further includes a source region disposed only in regions near the trenched gates in the closed N-channel MOSFET cells and away from regions near the wider trenched gate whereby a device ruggedness is improved. The source region is further disposed at a distance away from a corner or an edge of the semiconductor power device and away from a termination area. The semiconductor device further includes multiple trenched rings disposed in a termination area opposite the active area and the trenched rings having a floating voltage. The closed N-channel MOSFET cells are further supported on a red phosphorous substrate.

Owner:FORCE MOS TECH CO LTD

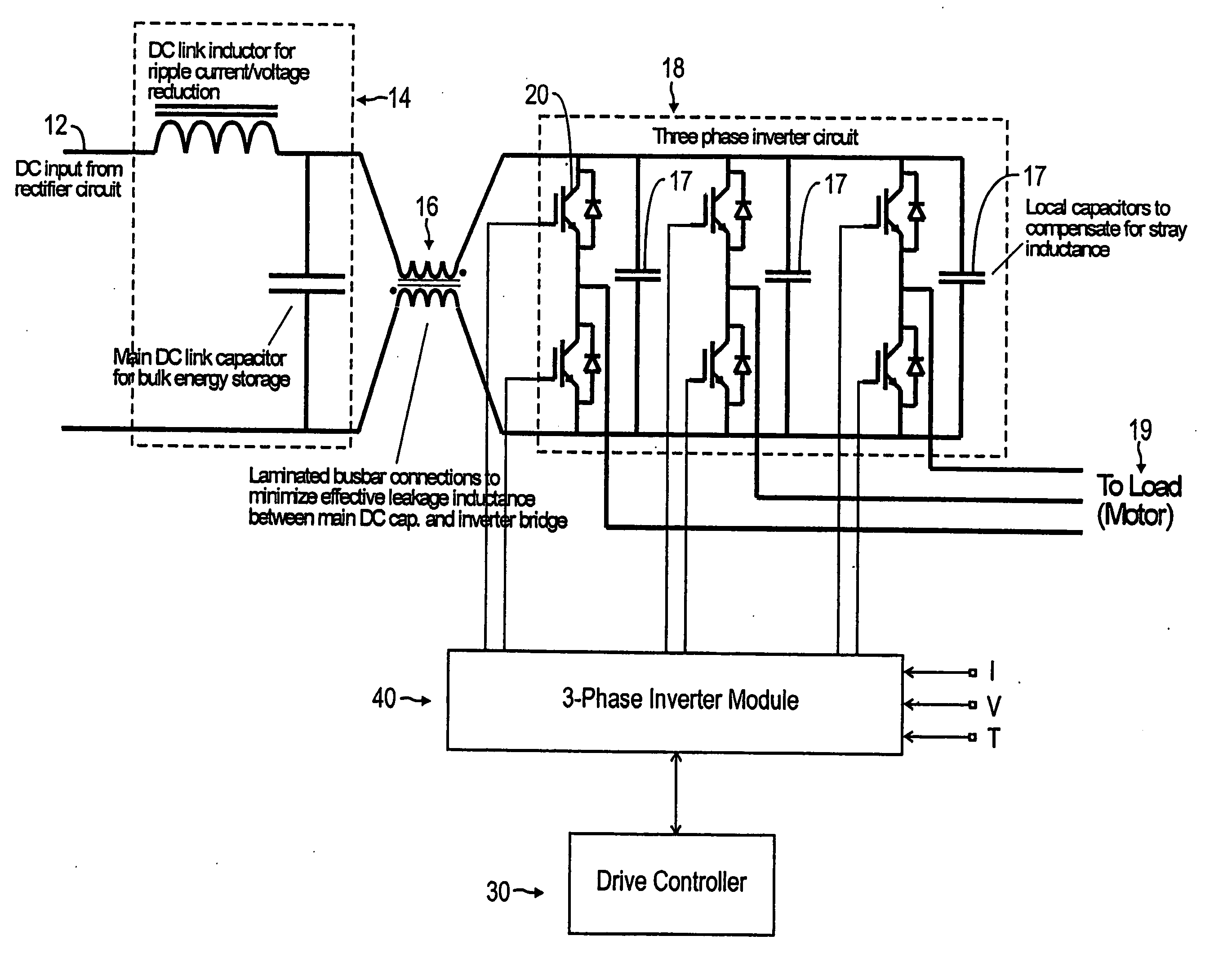

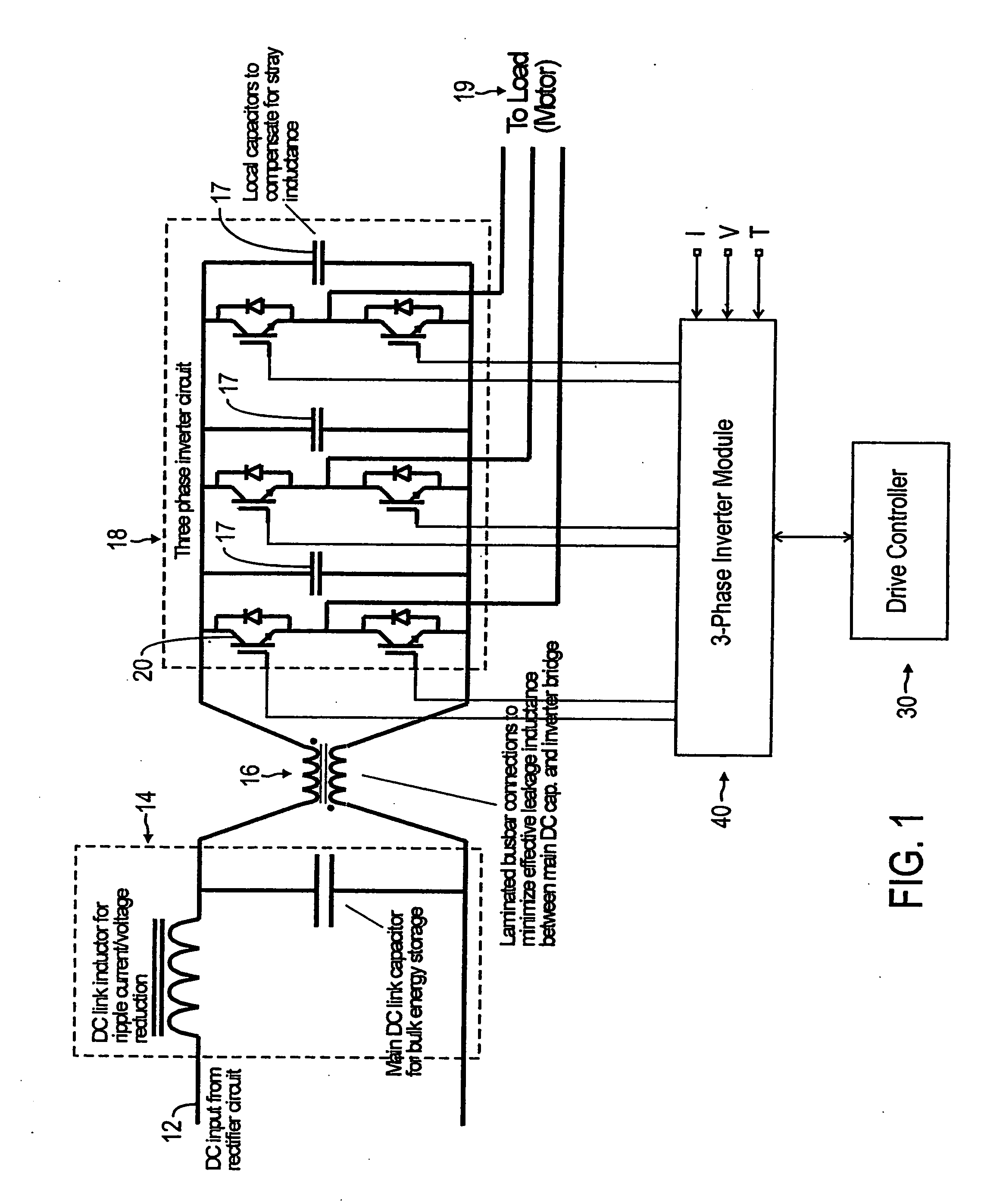

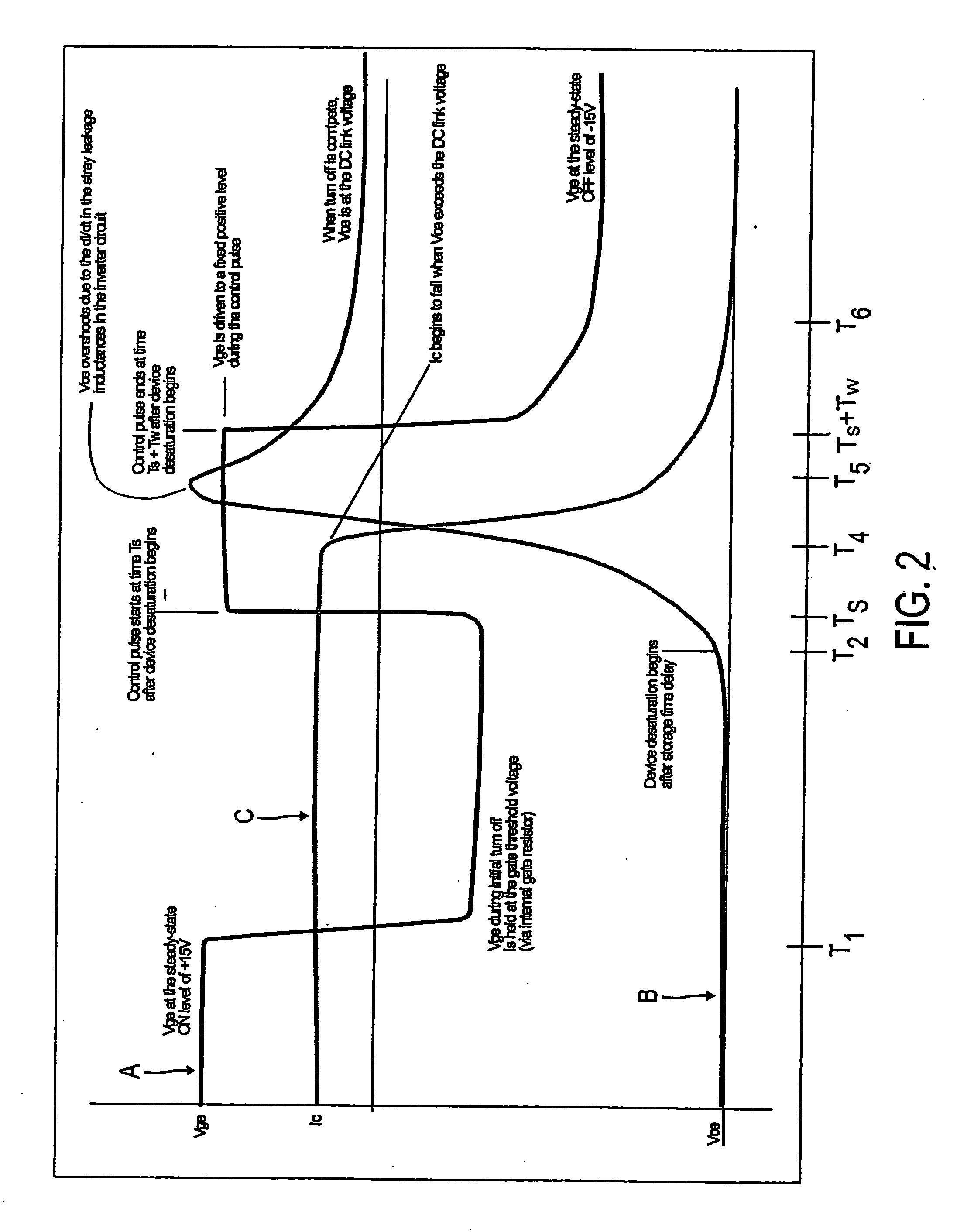

Adaptive gate drive for switching devices of inverter

An adaptive gate drive for an inverter includes control circuitry having a Field Programmable Gate Array (FPGA) and includes power circuitry having a plurality of FETs for operating a switching device, such as a Trench Gate Insulated Gate Bipolar Transistor (IGBT device). The control circuitry provides switching signals for operating the switching device. In addition, the control circuitry receives signals of output current of the IGBT device, temperature of the IGBT device, and DC link voltage. The FPGA has a plurality of operating points stored therein. Each operating point has corresponding parameters for a control signal that is used to control the turn-on or turn-off behavior of the IGBT device. During operation, the control circuitry compares the measured current, voltage and temperature operating points stored in the FPGA and sends the corresponding parameters to the gate drive circuit. The gate drive modifies the signal on the gate of the IGBT accordingly and thereby optimizes the turn-on and / or turn-off behavior of the device based on actual operating conditions.

Owner:LETOURNEAU TECH DRILLING SYST

Configurations and methods for manufacturing charge balanced devices

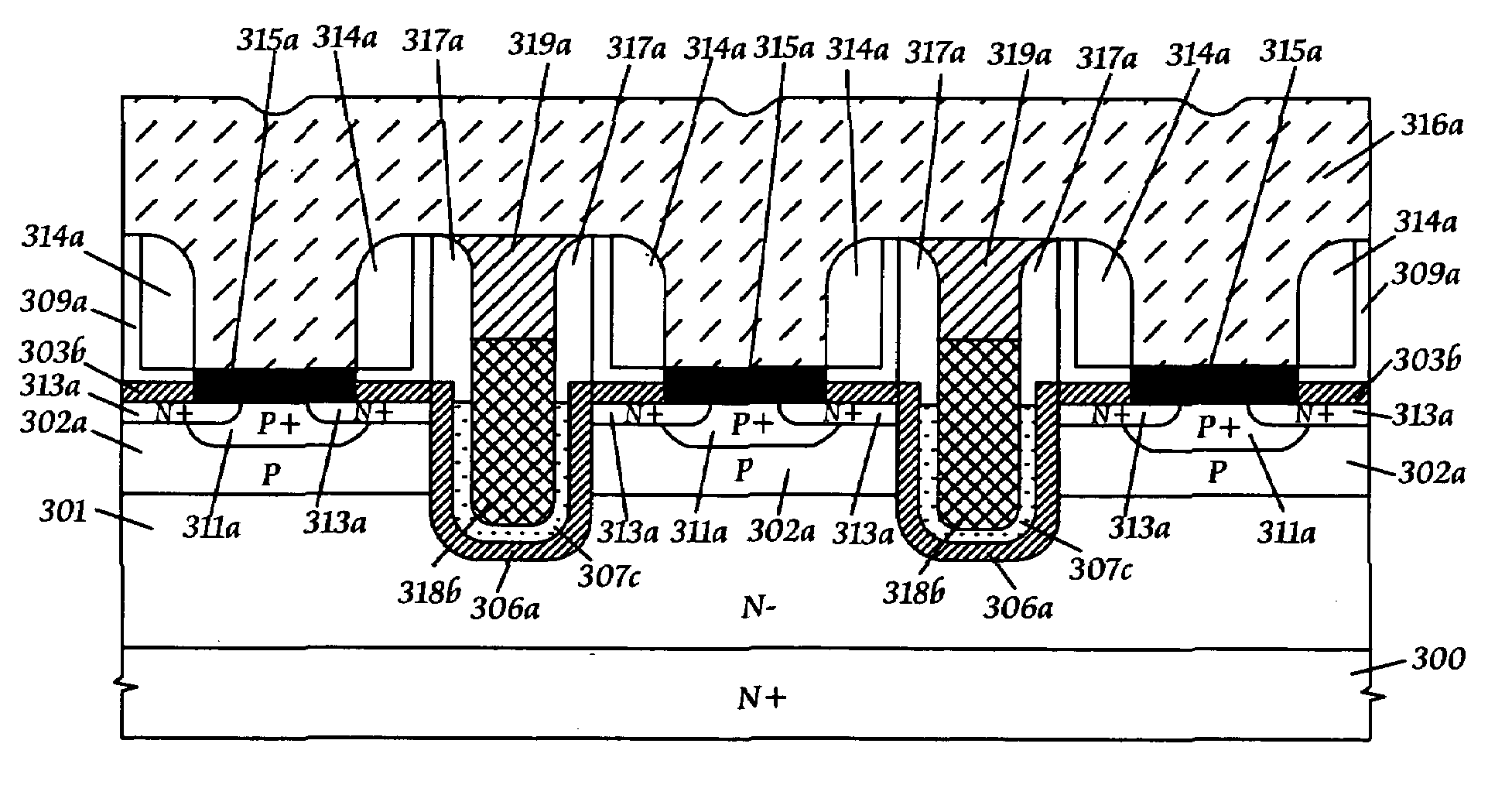

ActiveUS20100044791A1Simple and convenient processing stepReduce processing stepsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricTrench gate

This invention discloses a semiconductor power device disposed in a semiconductor substrate and the semiconductor substrate has a plurality of deep trenches. The deep trenches are filled with an epitaxial layer thus forming a top epitaxial layer covering areas above a top surface of the deep trenches covering over the semiconductor substrate. The semiconductor power device further includes a plurality of transistor cells disposed in the top epitaxial layer whereby a device performance of the semiconductor power device is dependent on a depth of the deep trenches and not dependent on a thickness of the top epitaxial layer. Each of the plurality of transistor cells includes a trench DMOS transistor cell having a trench gate opened through the top epitaxial layer and filled with a gate dielectric material.

Owner:ALPHA & OMEGA SEMICON LTD

Self-aligned trench-type DMOS transistor structure and its manufacturing methods

InactiveUS20060113588A1Increase resistanceIncreased durabilitySemiconductor devicesDielectricGate dielectric

The self-aligned trench-type DMOS transistor structure comprises a self-aligned source region being surrounded by a trench gate region. The self-aligned source region comprises a moderately-doped p-base diffusion region formed in a lightly-doped epitaxial semiconductor substrate, a self-aligned heavily-doped n+ source diffusion ring formed in a side surface portion of the moderately-doped p-base diffusion region, a heavily-doped p+ contact diffusion region formed in a surface portion of the moderately-doped p-base diffusion region surrounded by the heavily-doped n+ source diffusion ring, and a self-aligned source contact window formed by a semiconductor surface surrounded by a sidewall dielectric spacer. The trench gate region comprises a gate dielectric layer being lined over a trenched semiconductor surface with or without a thicker isolation dielectric layer formed on a bottom trenched semiconductor surface and a self-aligned highly conductive gate layer being formed at least over the gate dielectric layer.

Owner:SILICON BASED TECH

Structures of and methods of fabricating trench-gated MIS devices

In a trench-gated MIS device contact is made to the gate within the trench, thereby eliminating the need to have the gate material, typically polysilicon, extend outside of the trench. This avoids the problem of stress at the upper corners of the trench. Contact between the gate metal and the polysilicon is normally made in a gate metal region that is outside the active region of the device. Various configurations for making the contact between the gate metal and the polysilicon are described, including embodiments wherein the trench is widened in the area of contact. Since the polysilicon is etched back below the top surface of the silicon throughout the device, there is normally no need for a polysilicon mask, thereby saving fabrication costs.

Owner:VISHAY SILICONIX LLC

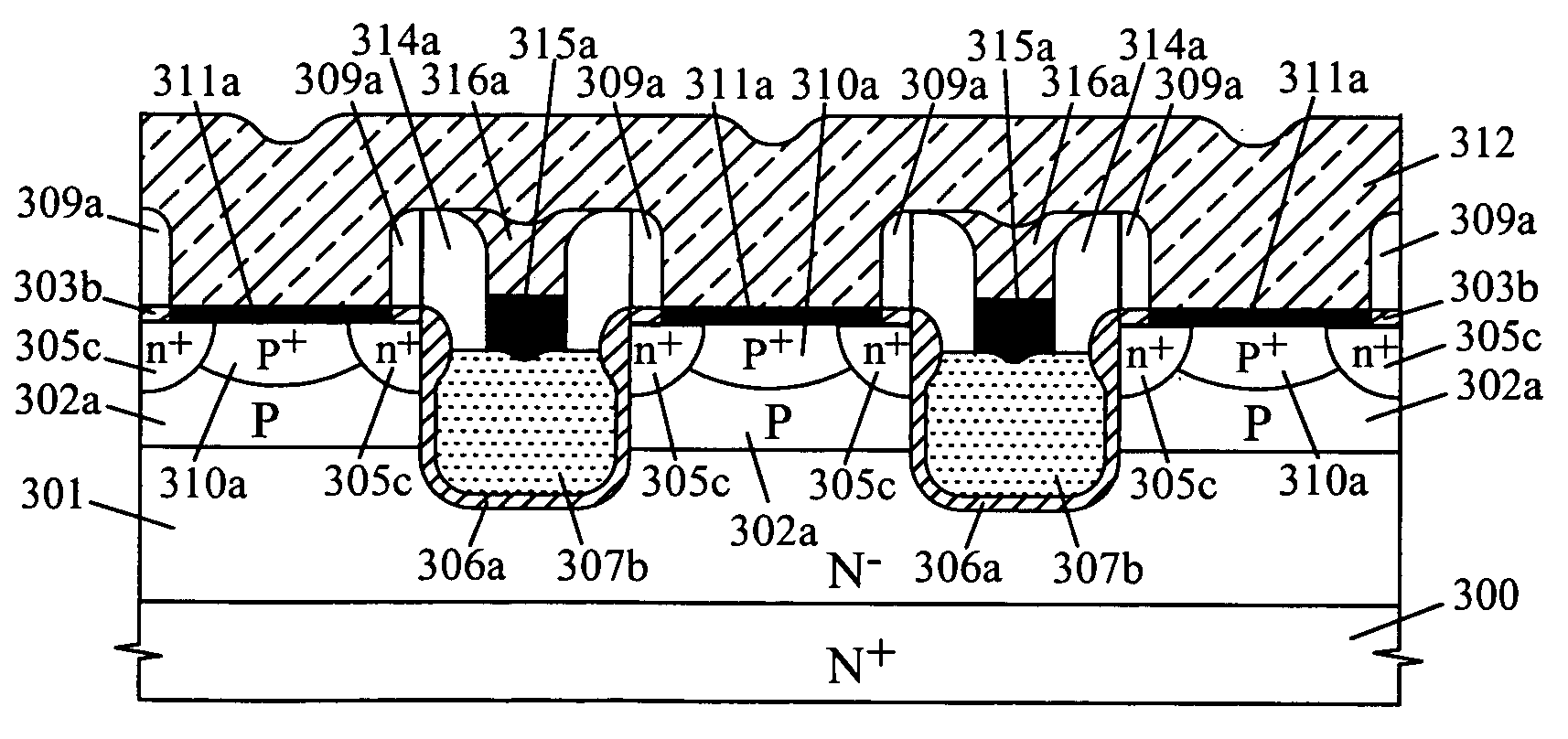

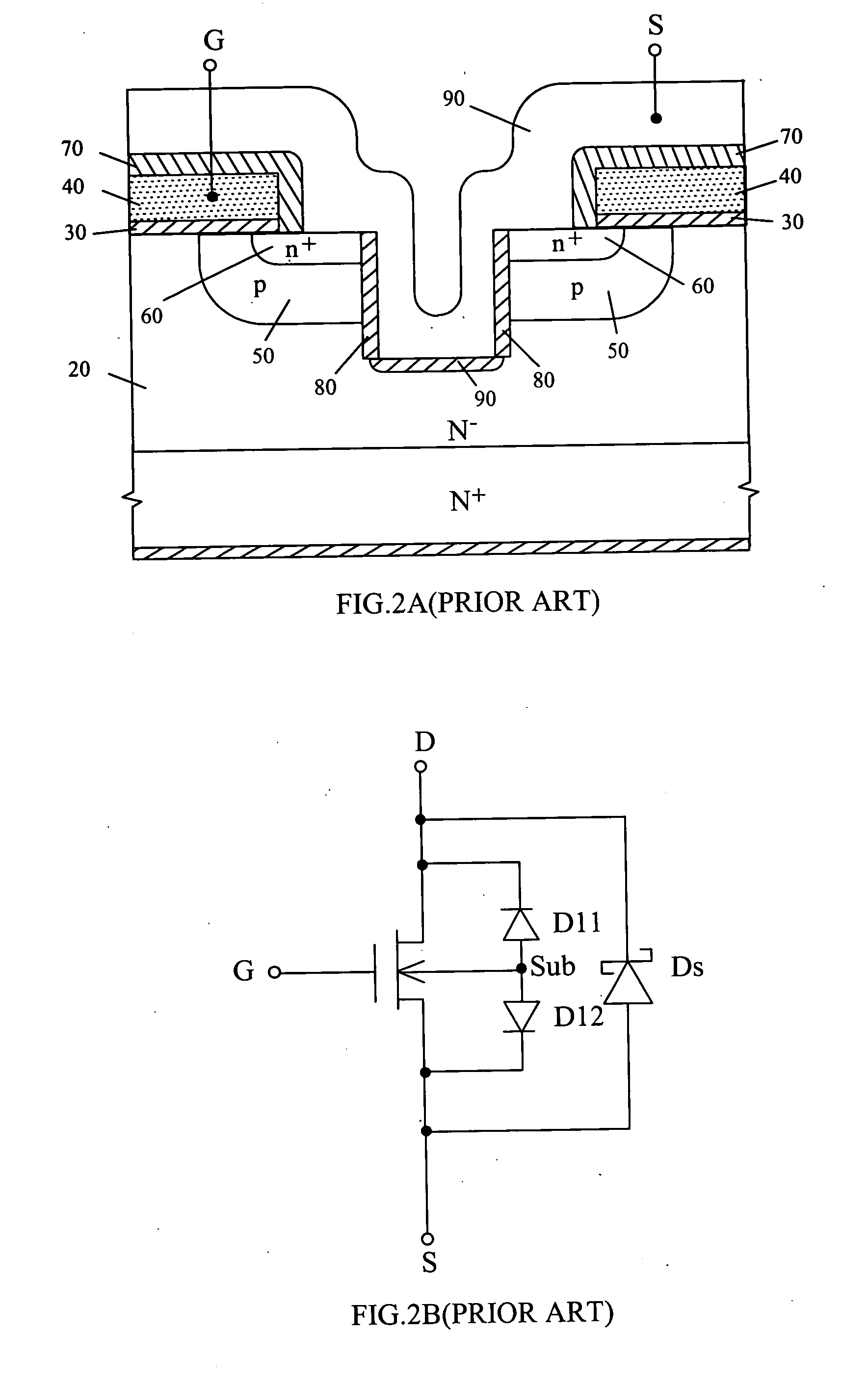

Self-aligned schottky-barrier clamped trench DMOS transistor structure and its manufacturing methods

The self-aligned Schottky-barrier clamped trench DMOS transistor structure of the present invention comprises a Schottky-barrier diode being formed in a middle semiconductor portion of a self-aligned source region. The self-aligned source region comprises a lightly-doped epitaxial semiconductor layer, a moderately-doped base diffusion ring being formed in a surface portion of the lightly-doped epitaxial semiconductor layer surrounded by a trench gate region, a heavily-doped source diffusion ring being formed in a side surface portion of the moderately-doped base diffusion ring, and a self-aligned source contact being formed on a semiconductor surface of the self-aligned source region surrounded by a sidewall dielectric spacer. The trench gate region comprises a self-aligned conductive gate layer being formed over a gate dielectric layer lined over a trenched semiconductor surface in a shallow trench with or without a thicker isolation dielectric layer being formed on a bottom surface of the shallow trench.

Owner:SILICON BASED TECH

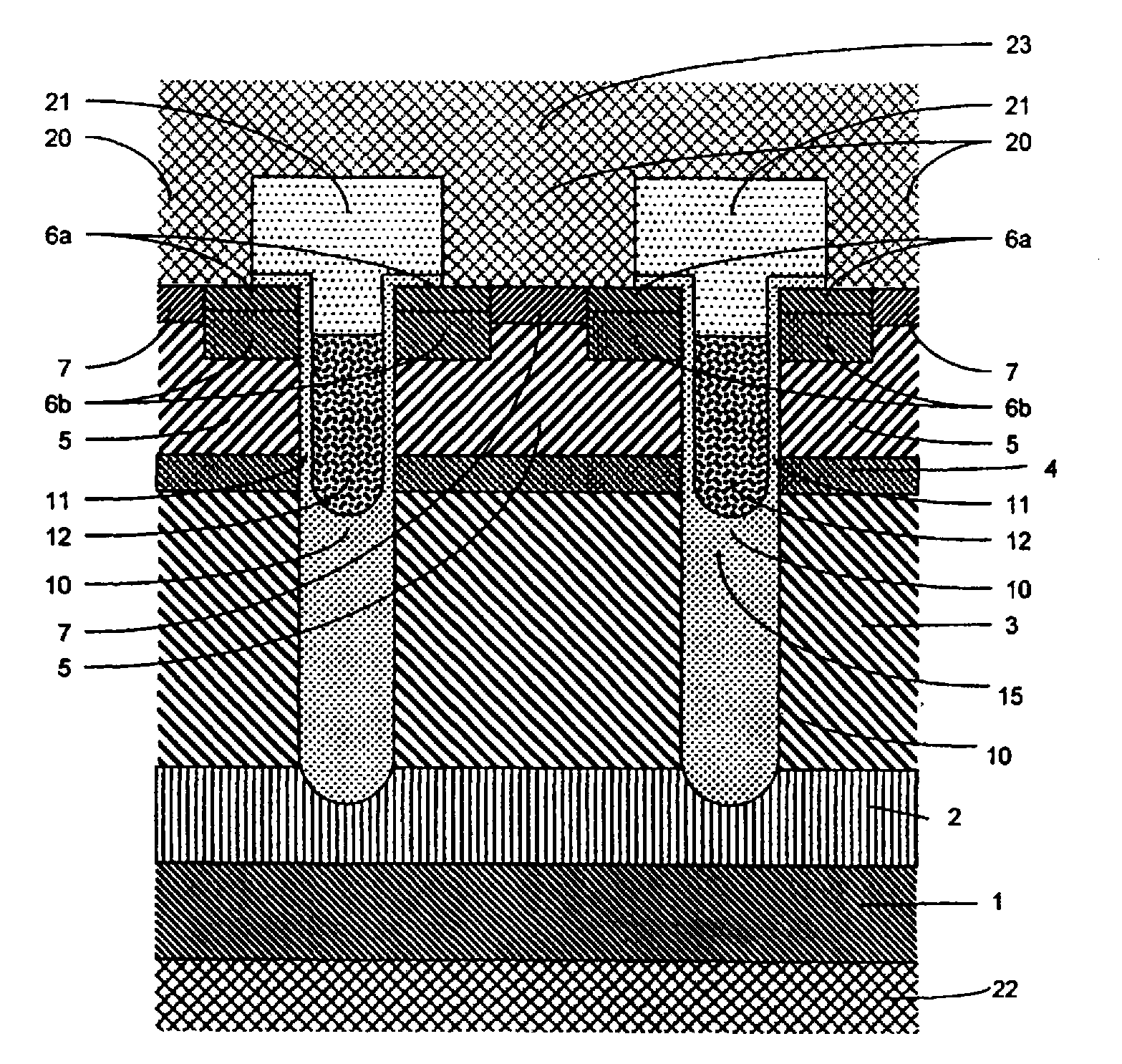

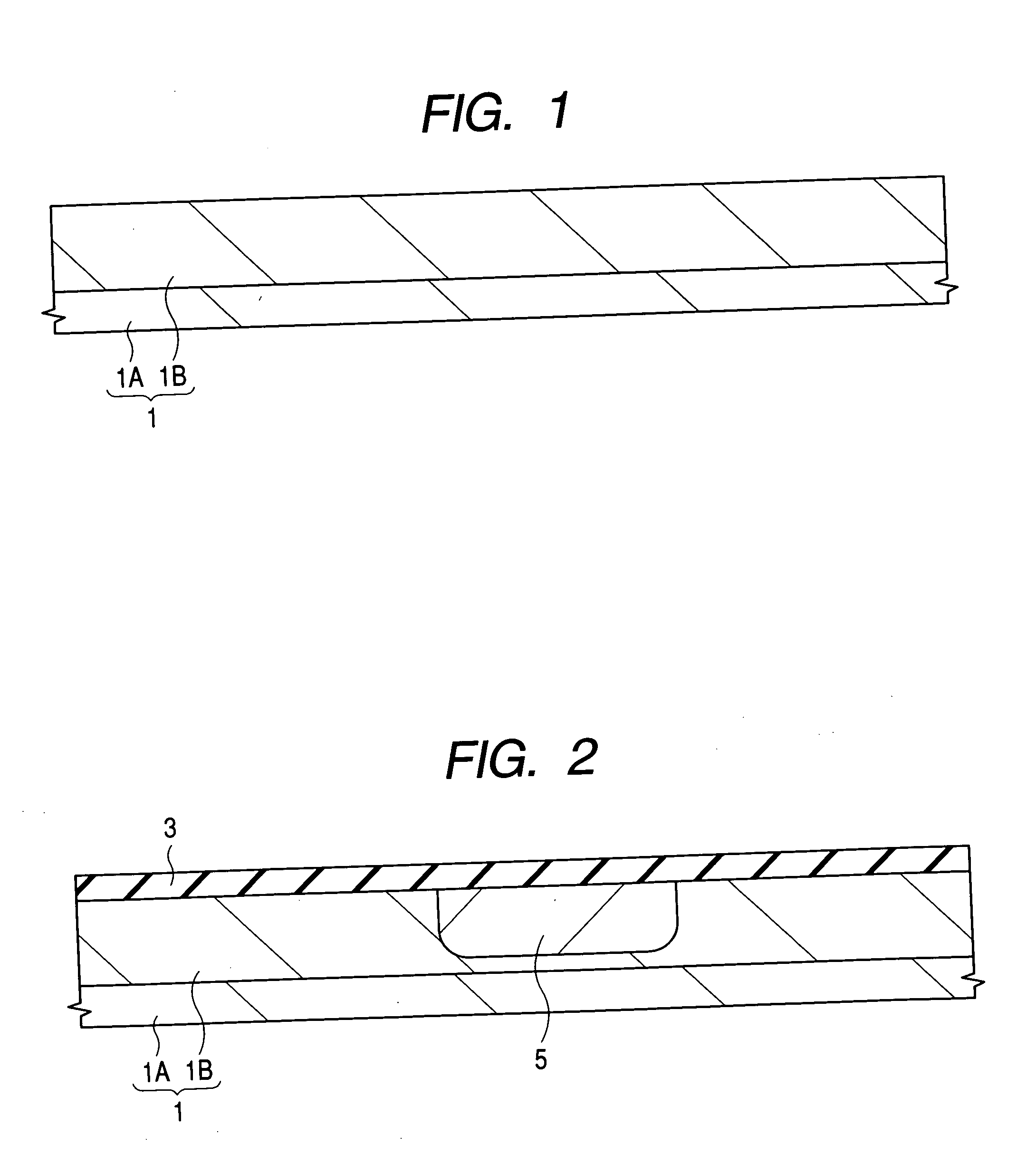

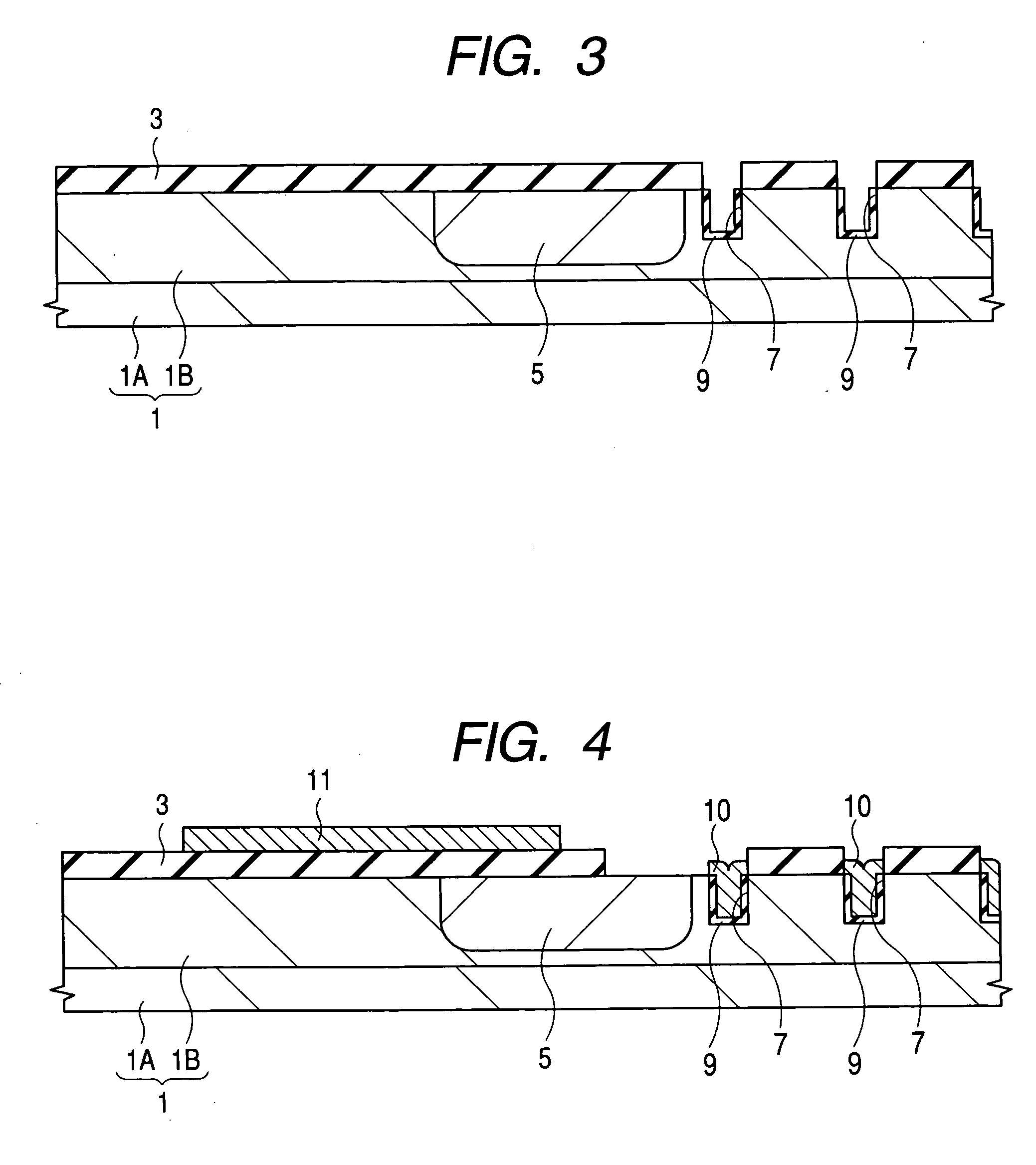

Method of manufacturing a trench gate power transistor with a thick bottom insulator

InactiveUS6455378B1Reduce capacityImprove rendering capabilitiesSemiconductor/solid-state device manufacturingDiodeGate insulatorEngineering physics

There are formed a gate insulator 8 and a gate 3 of a power transistor Q having a trench-gate structure. There are then formed a channel region 5 and a source region 6 of the power transistor Q.

Owner:HITACHI LTD +1

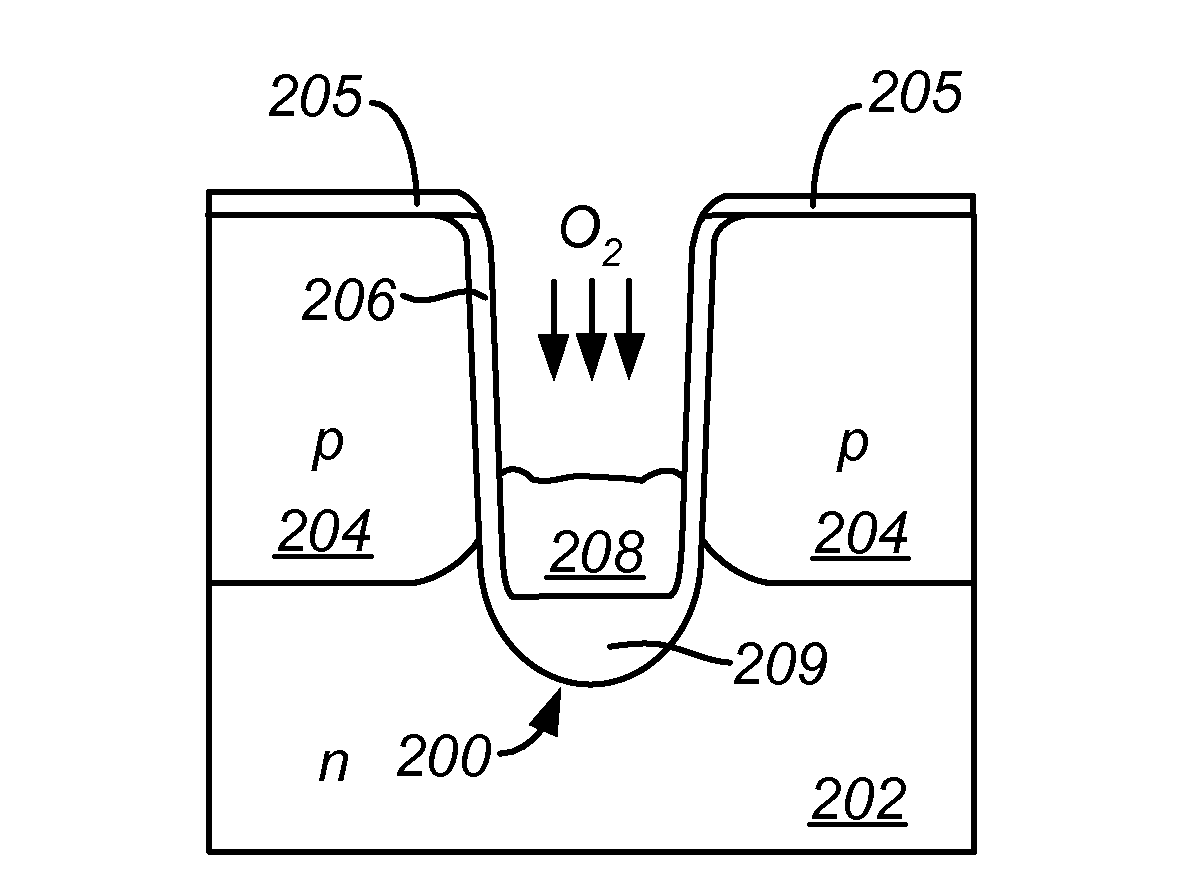

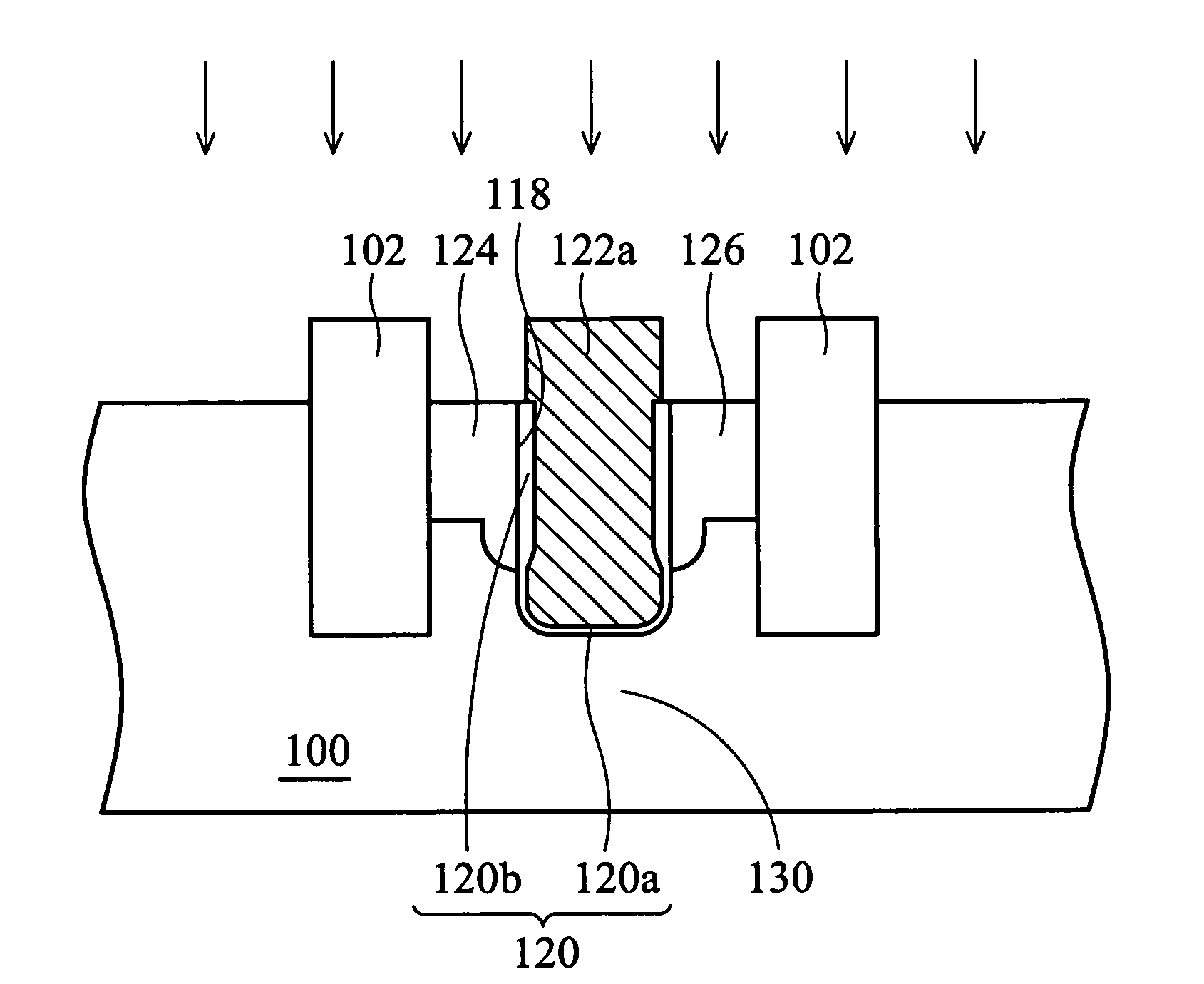

Structure and method for forming laterally extending dielectric layer in a trench-gate FET

ActiveUS20060289929A1Semiconductor/solid-state device detailsSolid-state devicesPartial oxidationField-effect transistor

A field effect transistor (FET) is formed as follows. A trench is formed in a silicon region. An oxidation barrier layer is formed over a surface of the silicon region adjacent the trench and along the trench sidewalls and bottom. A protective layer is formed over the oxidation barrier layer inside and outside the trench. The protective layer is partially removed such that a portion of the oxidation barrier layer extending at least along the trench bottom becomes exposed and portions of the oxidation barrier layer extending over the surface of the silicon region adjacent the trench remain covered by remaining portions of the protective layer.

Owner:SEMICON COMPONENTS IND LLC

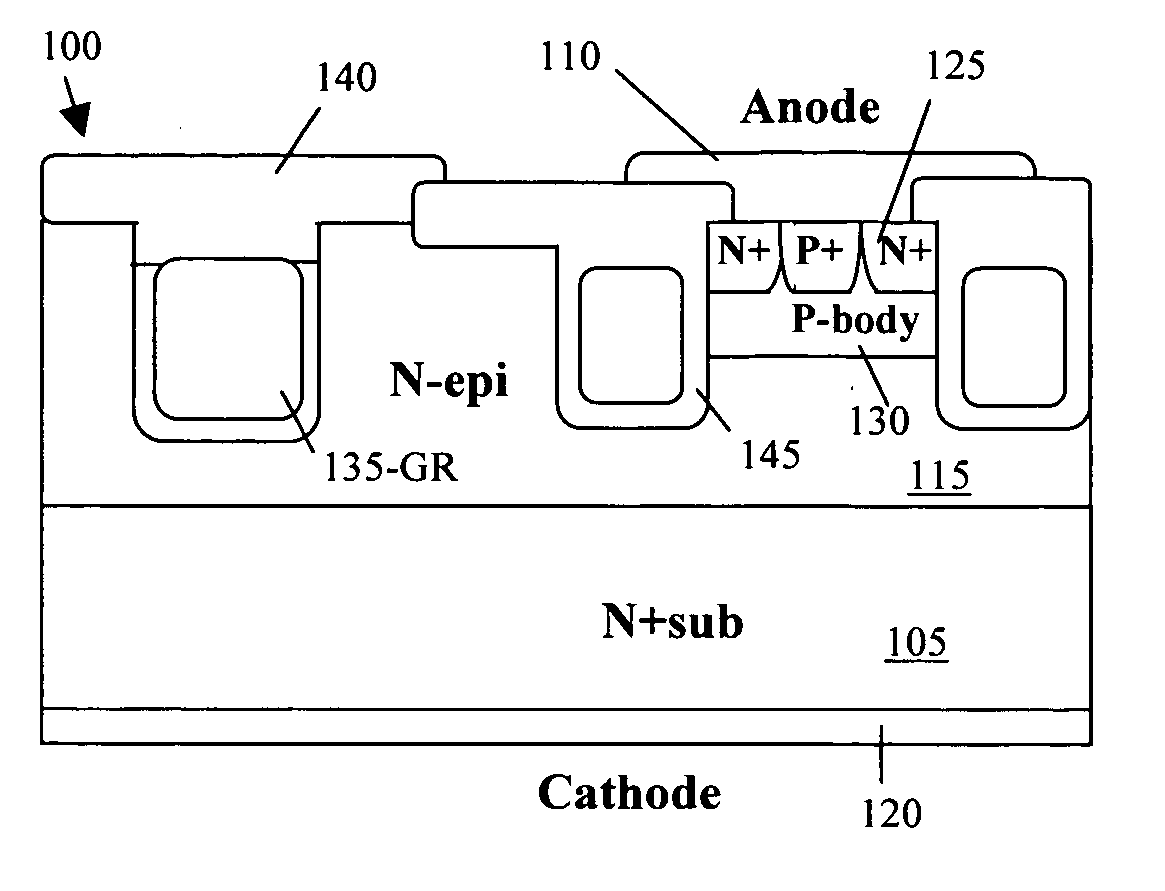

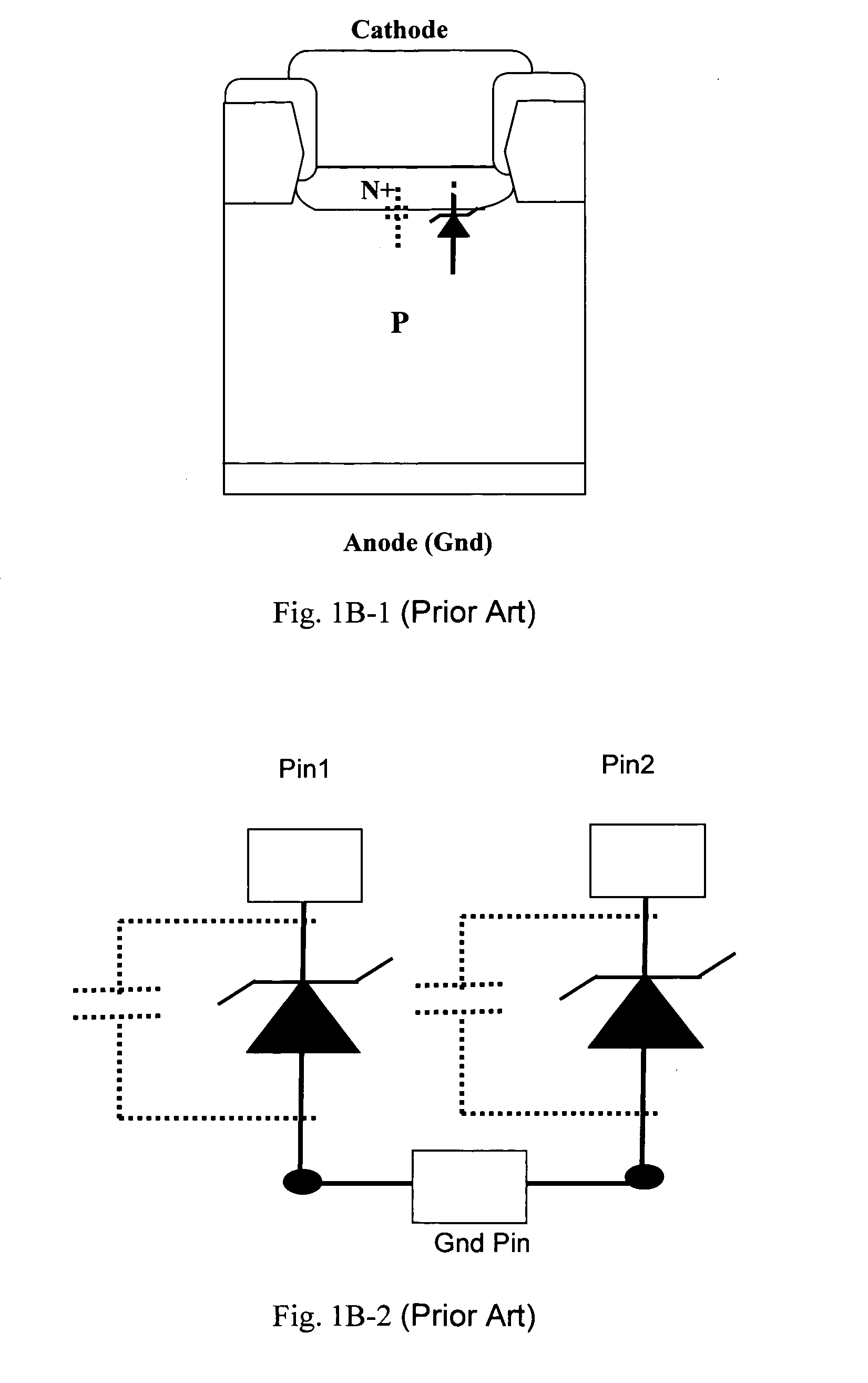

Circuit configuration and manufacturing processes for vertical transient voltage suppressor (TVS) and EMI filter

ActiveUS20080121988A1Small footprintLow costSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceTransient voltage suppressor

A vertical TVS (VTVS) circuit includes a semiconductor substrate for supporting the VTVS device thereon having a heavily doped layer extending to the bottom of substrate. Deep trenches are provided for isolation between multi-channel VTVS. Trench gates are also provided for increasing the capacitance of VTVS with integrated EMI filter.

Owner:ALPHA & OMEGA SEMICON LTD

Semiconductor device having a trench gate and method of fabricating the same

ActiveUS20070138545A1Easy to controlImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialOptoelectronics

A method of fabricating a semiconductor device having a trench gate is provided. First, a semiconductor substrate having a trench etch mask thereon is provided. The semiconductor substrate is etched to form a first trench having a first depth using the trench etch mask as a shield. Impurities are doped into the semiconductor substrate through the first trench to form a doped region. The doped region and the semiconductor substrate underlying the first trench are etched to form a second trench having a second depth greater than the first depth, wherein the second trench has a sidewall and a bottom. A gate insulating layer is formed on the sidewall and the bottom of the second trench. A trench gate is formed in the second trench.

Owner:NAN YA TECH

Trench gate semiconductor device and method of manufacturing the same

Disclosed is a trench gate semiconductor device including: a semiconductor layer having a first conductivity type; a first diffusion region having a second conductivity type having a planar structure on the semiconductor layer; a second diffusion region having the first conductivity type positioned selectively on the first diffusion region; a gate electrode provided via a gate insulation film in each first trench facing the second diffusion region and penetrating through the first diffusion region to reach the semiconductor layer; a first semiconductor region of the second conductivity type provided at a position, in the semiconductor layer, apart in a lateral direction from the first diffusion region; a second semiconductor region of the second conductivity type provided at a position, in the first diffusion region, between the adjacent first trenches; and a main electrode in contact with the semiconductor layer and the second diffusion region.

Owner:KK TOSHIBA

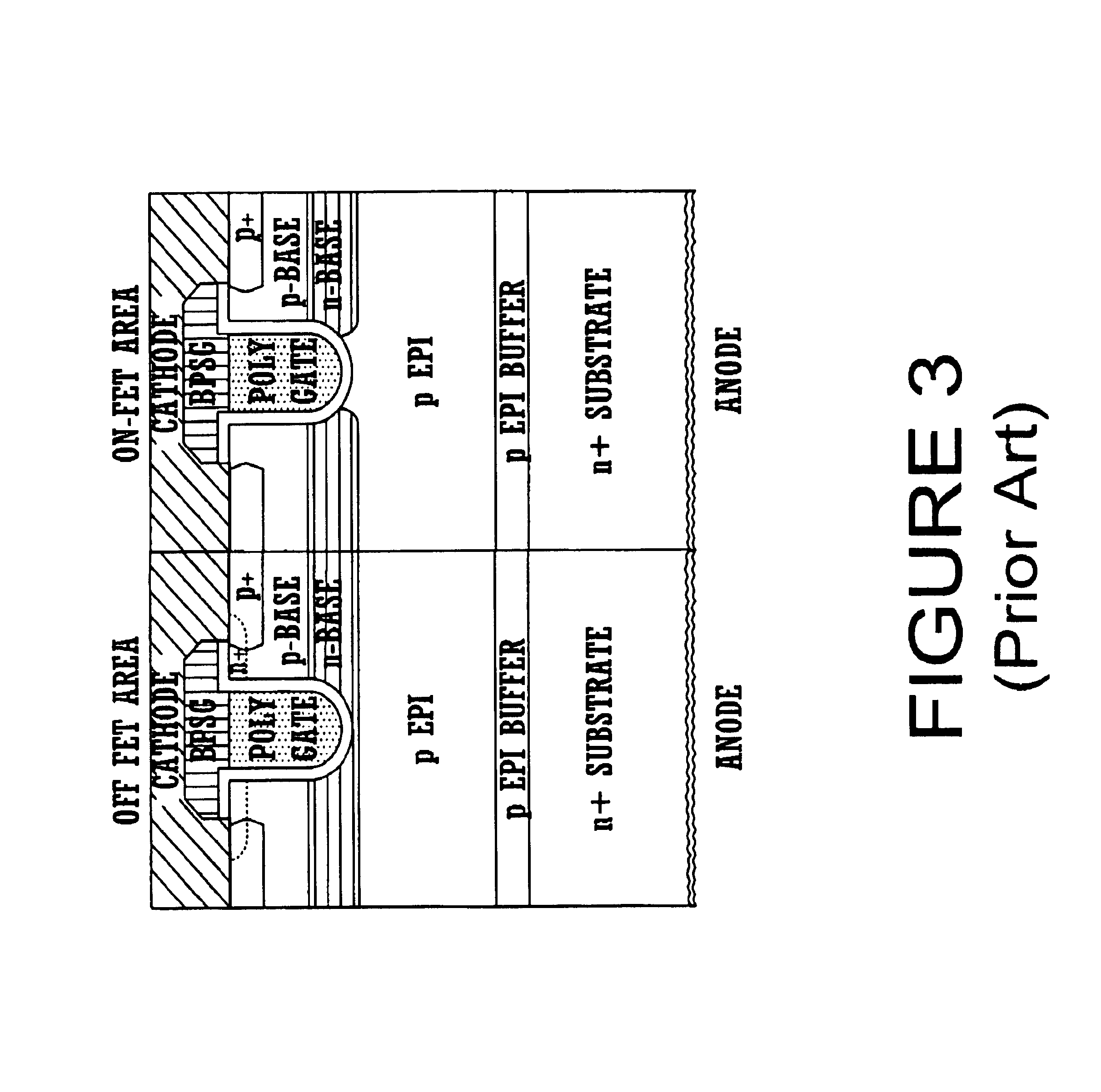

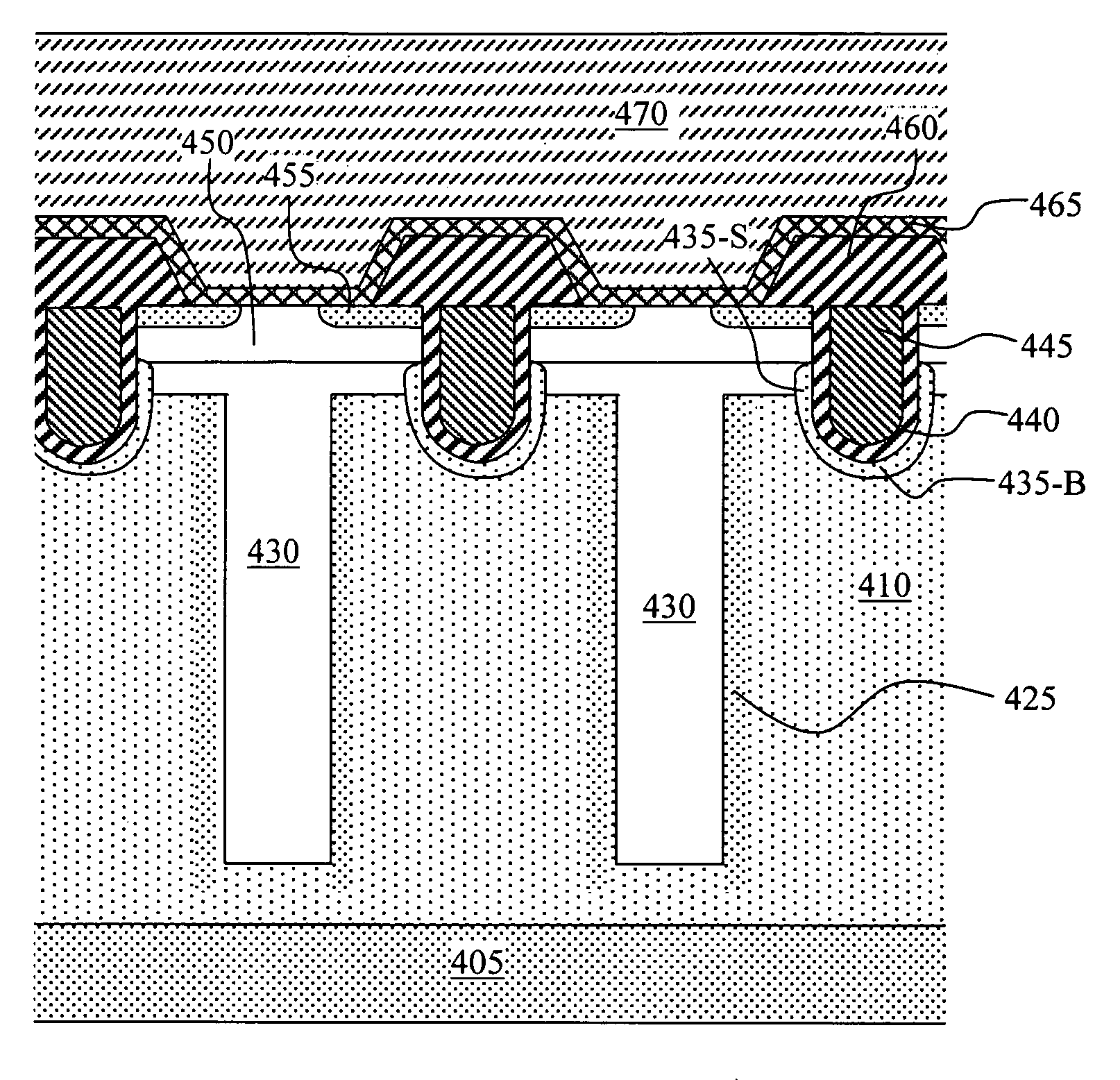

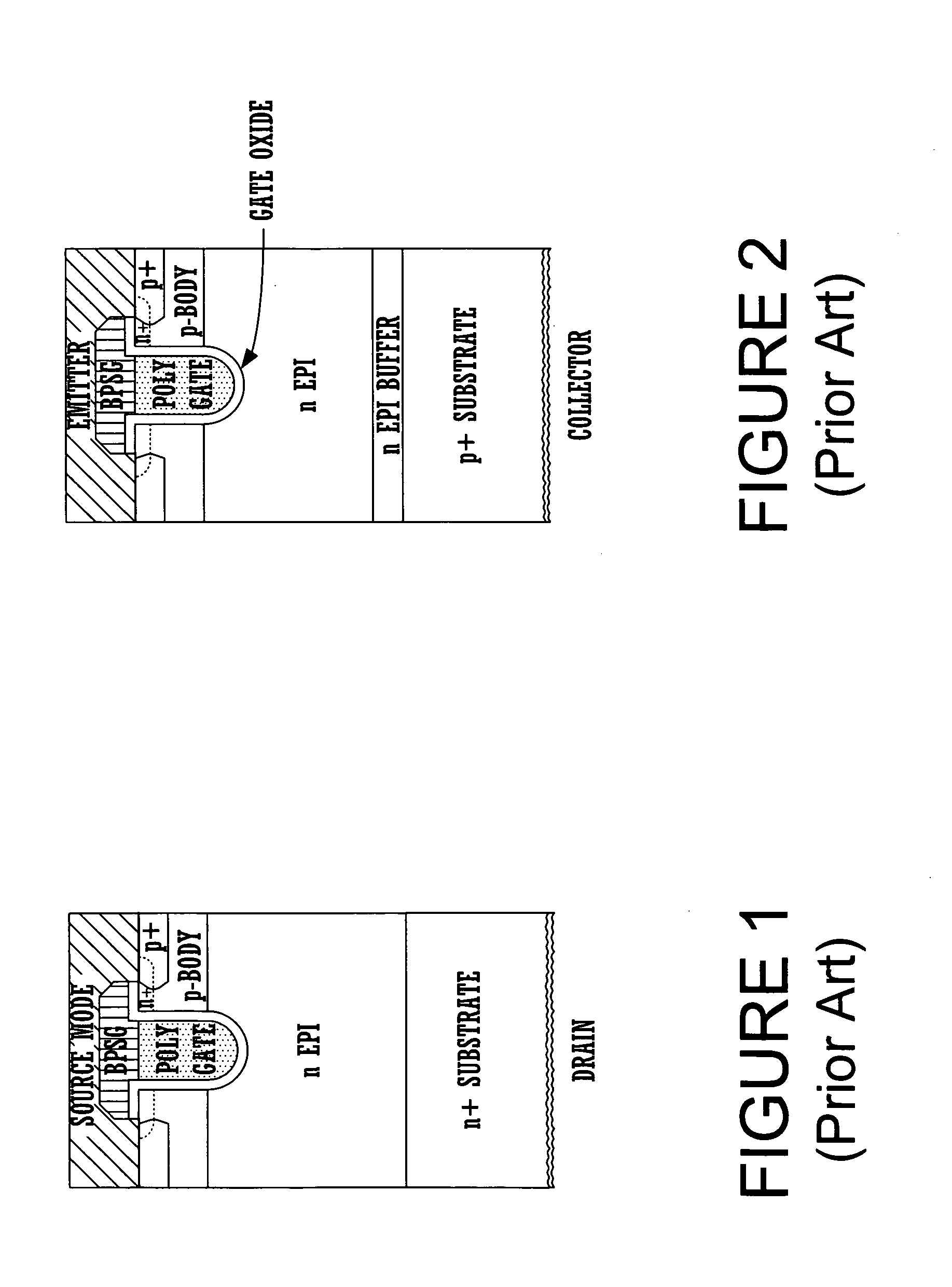

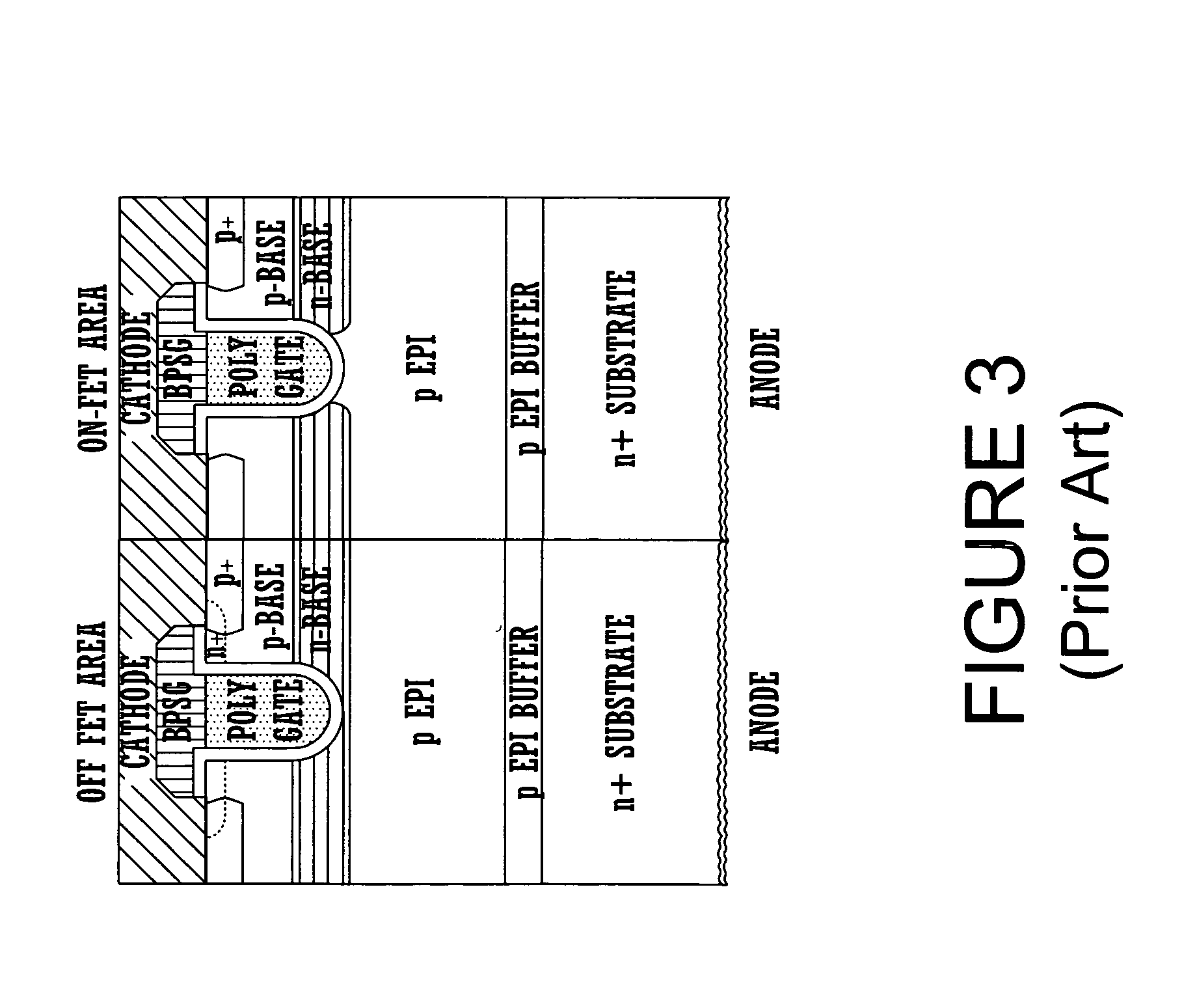

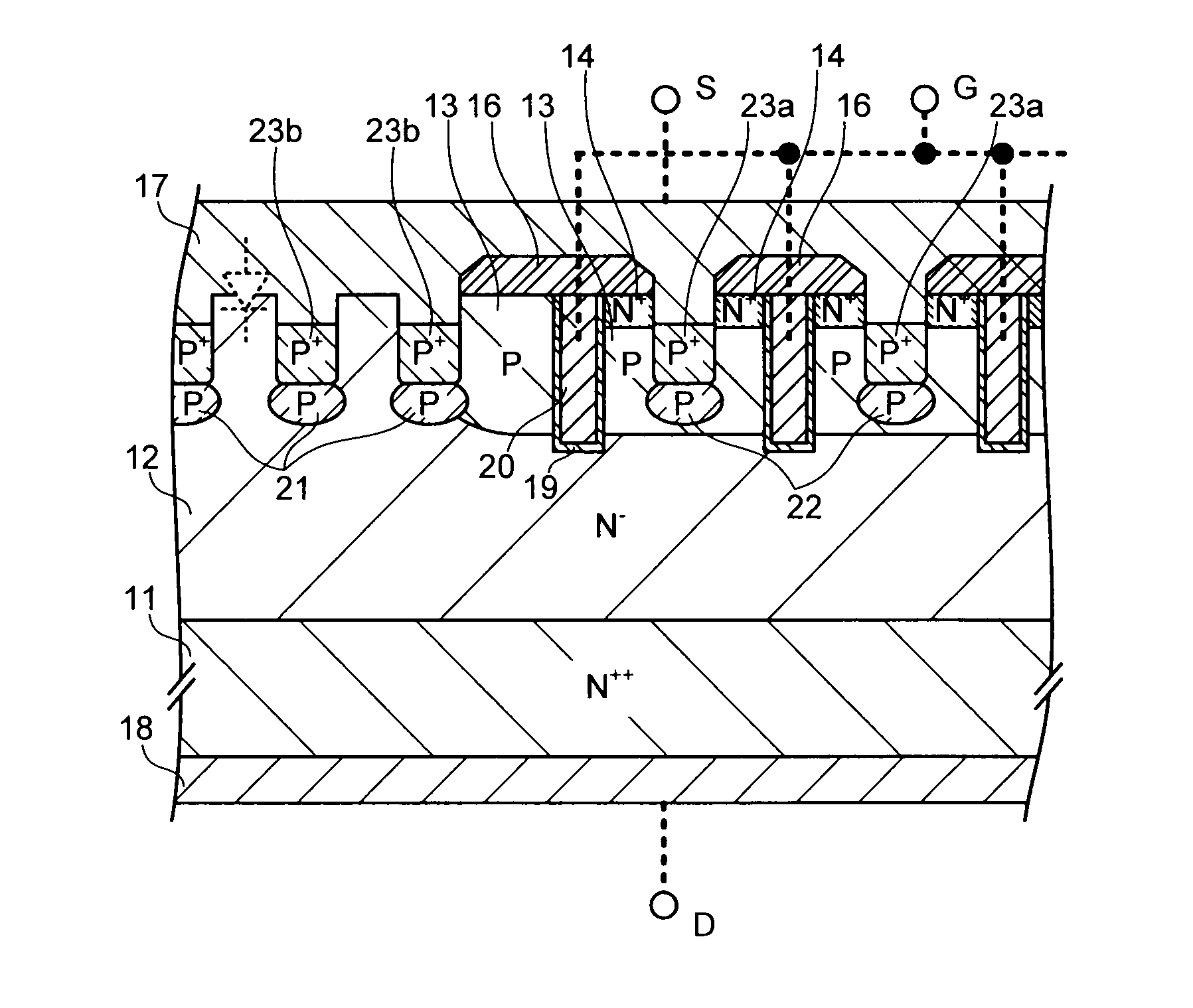

Topside structures for an insulated gate bipolar transistor (IGBT) device to achieve improved device performances

ActiveUS20120104555A1Easy injectionLower E-on and E-off lossesSemiconductor/solid-state device manufacturingSemiconductor devicesDopantEngineering

This invention discloses an insulated gate bipolar transistor (IGBT) device formed in a semiconductor substrate. The IGBT device has a split-shielded trench gate that includes an upper gate segment and a lower shield segment. The IGBT device may further include a dummy trench filled with a dielectric layer disposed at a distance away from the split-shielded trench gate. The IGBT device further includes a body region extended between the split-shielded trench gate and the dummy trench encompassing a source region surrounding the split-shielded trench gate near a top surface of the semiconductor substrate. The IGBT device further includes a heavily doped N region disposed below the body region and above a source-dopant drift region above a bottom body-dopant collector region at a bottom surface of the semiconductor substrate. In an alternative embodiment, the IGBT may include a planar gate with a trench shield electrode.

Owner:ALPHA & OMEGA SEMICON INC

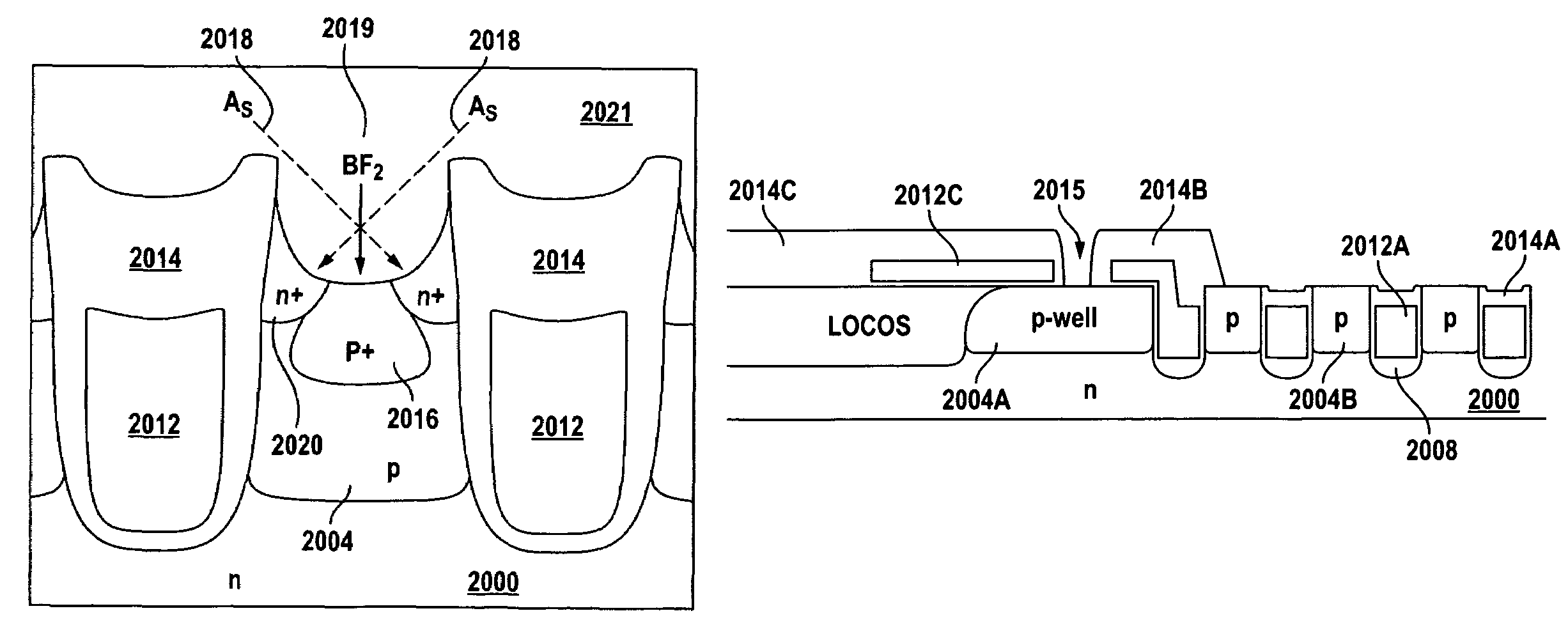

Manufacturing method of semiconductor device

InactiveUS7037788B2Suppress mutationDeterioration of characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesSub thresholdHigh acceleration

By improving profile of impurity concentration in a channel portion of an FET or an IGBT of a trench gate type, variation of threshold value is lessened, and a destruction caused by current concentration is prevented while suppressing deterioration of cut-off characteristics. An island of a base region of p-type is formed in a semiconductor substrate of n-type by carrying out high acceleration ion implantation twice followed by annealing, so that the impurity concentration profile in a channel portion changes gradually in a depth direction. Accordingly, it is possible to lessen variation of the threshold value and to reduce pinch resistance while at the same time improving sub-threshold voltage coefficient and conductance characteristics.

Owner:DENSO CORP

Self-aligned trench DMOS transistor structure and its manufacturing methods

A self-aligned trench DMOS transistor structure of the present invention comprises a self-aligned source structure and a self-aligned trench gate structure, in which the self-aligned source structure comprises a p-base diffusion region, a self-aligned n+ source diffusion ring, a self-aligned p+ contact diffusion region, and a self-aligned source contact window; the self-aligned trench gate structure comprises a self-aligned silicided conductive gate structure, a self-aligned polycided conductive gate structure or a self-aligned polycided trenched conductive gate structure. The self-aligned trench DMOS transistor structure as described is fabricated by using only one masking photoresist step and can be easily scaled down to obtain a high-density trench DMOS power transistor with ultra low on-resistance, low gate-interconnection parasitic resistance, and high device ruggedness.

Owner:SILICON BASED TECH

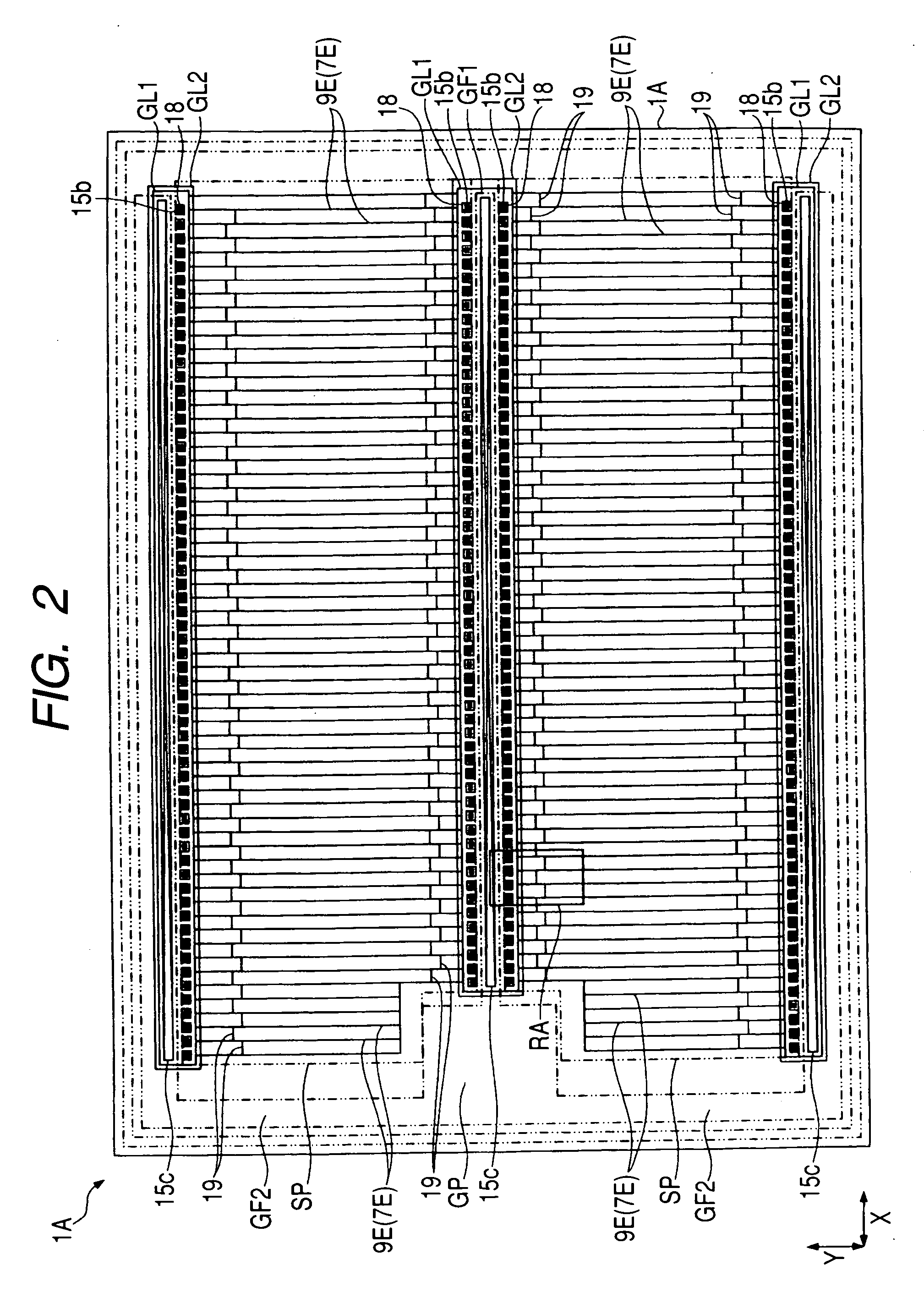

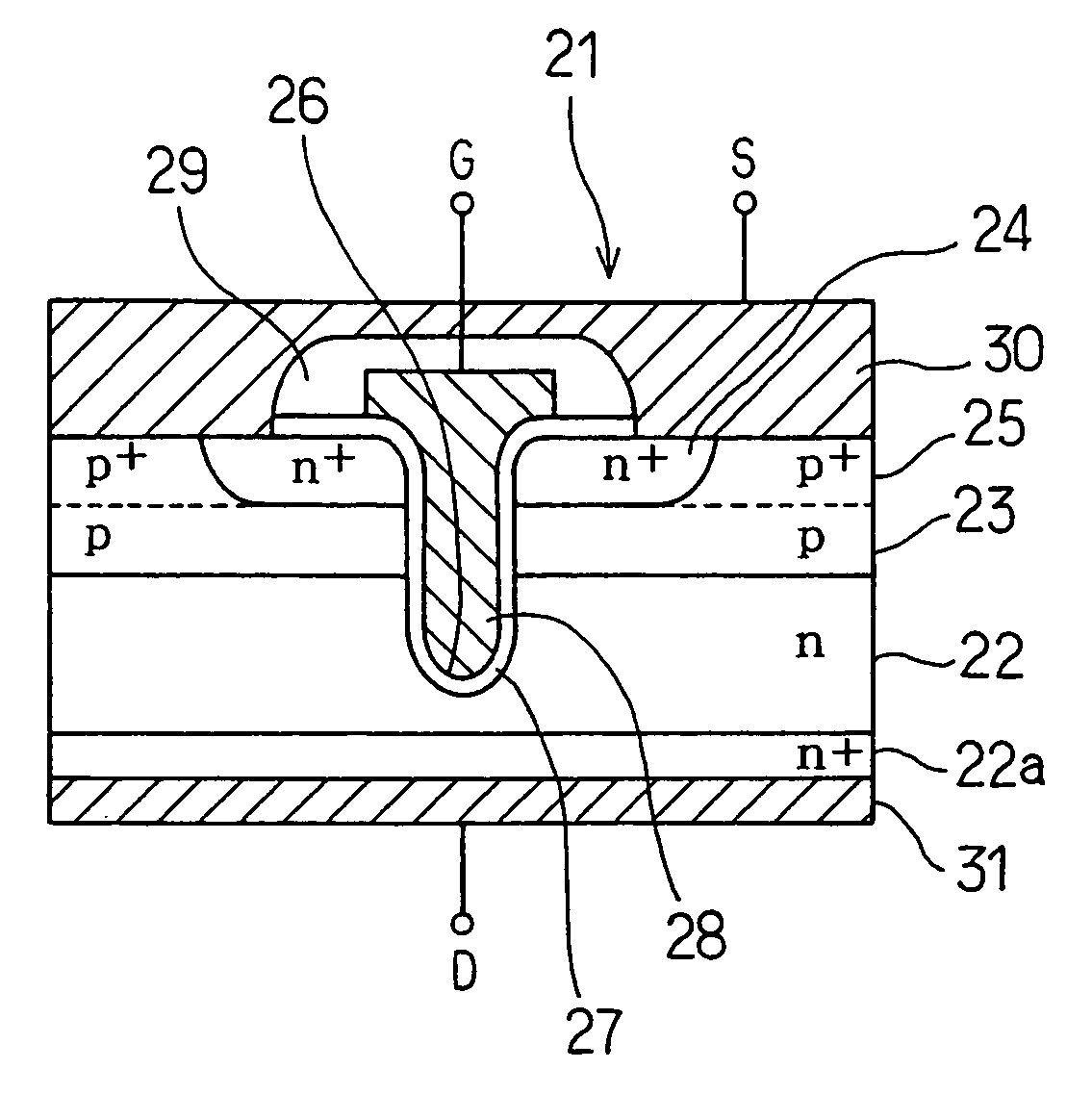

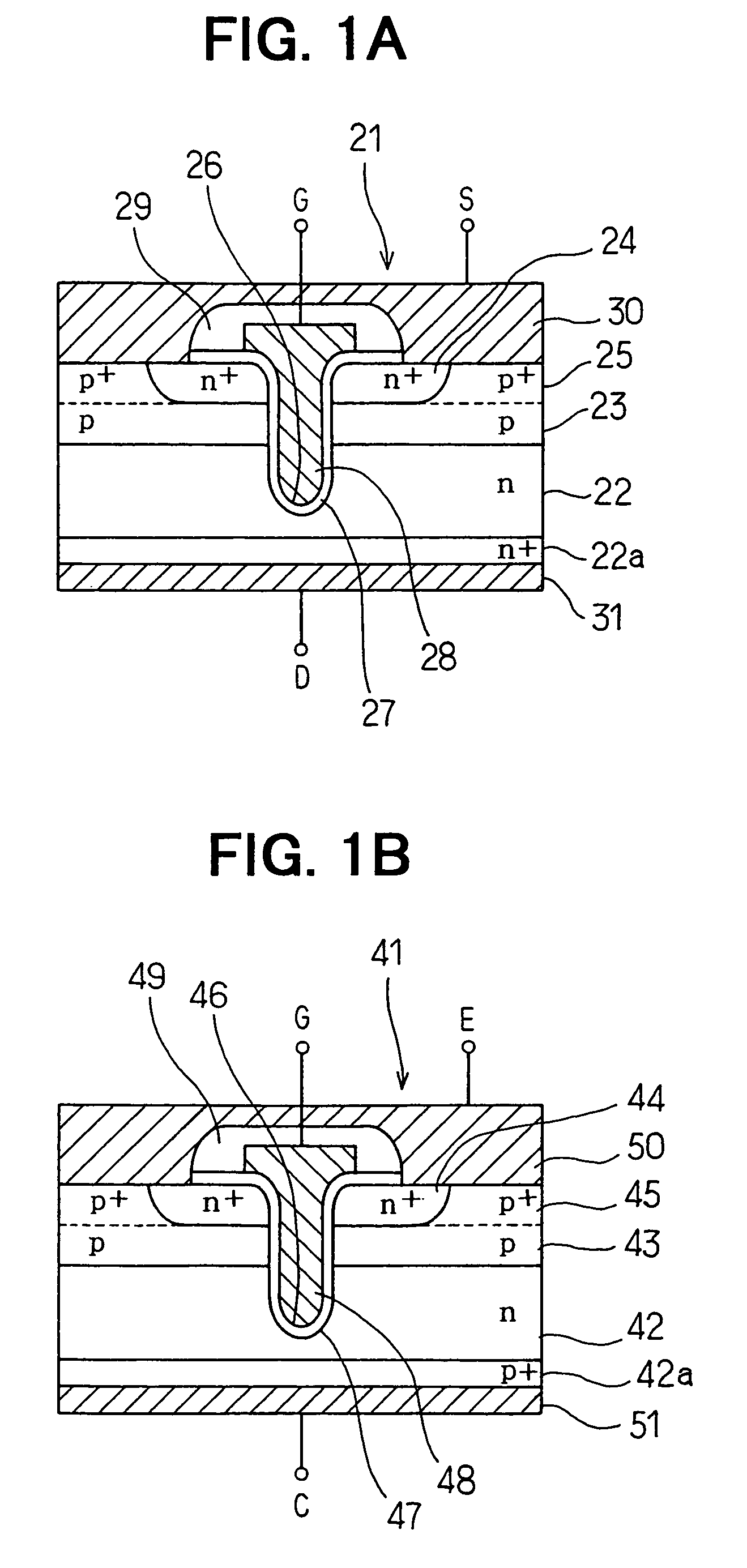

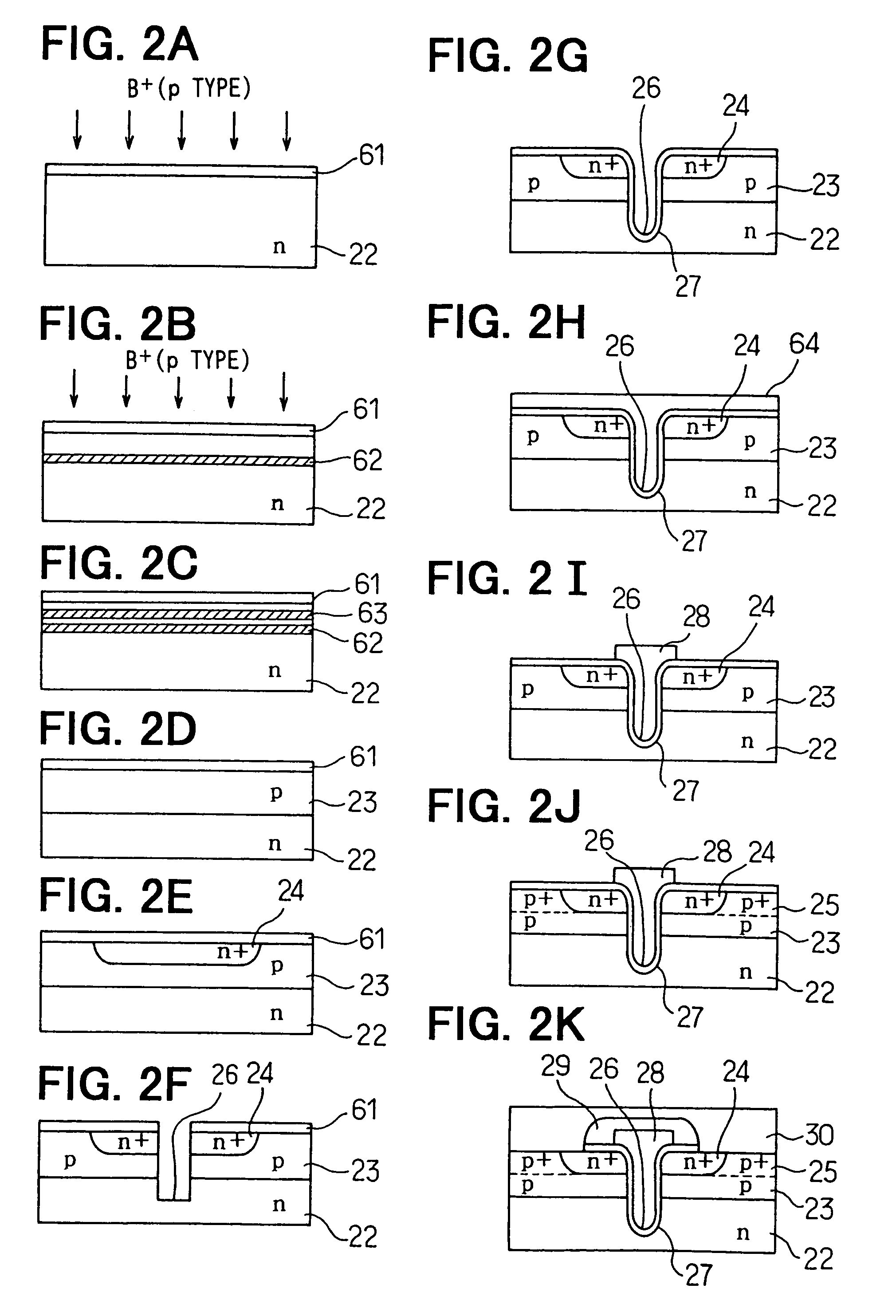

Vertical MOSFET reduced in cell size and method of producing the same

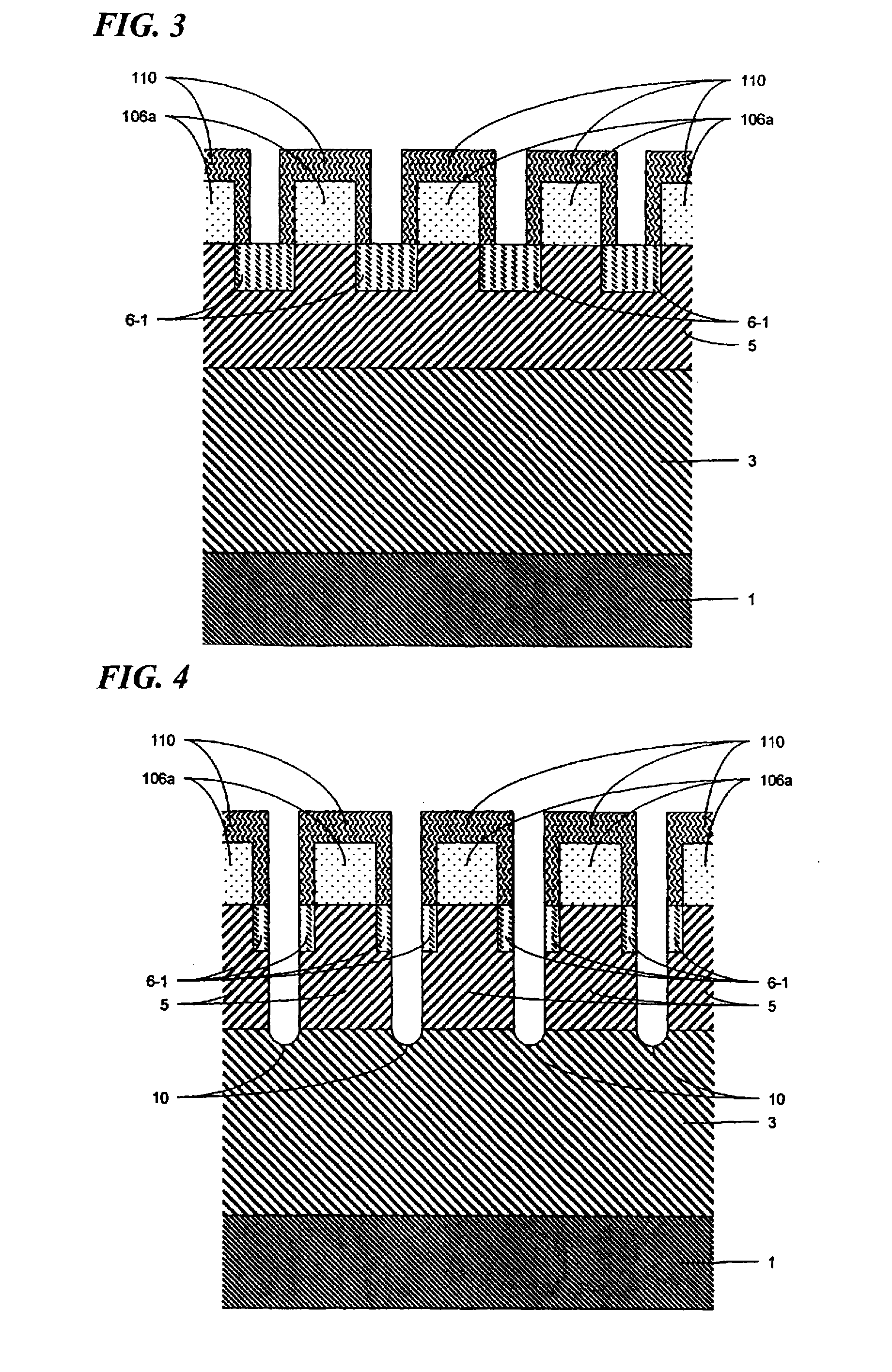

InactiveUS6888196B2Inhibition effectSmall sizeSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETContact formation

In a vertical MOSFET comprises: a semiconductor layer (1, 2, 9, 10) having first and second surfaces opposite to each other and trenches (6) formed on the first surface; trench gates (8) formed in the trenches; a unit cell formed in a region of the semiconductor layer surrounded by the trench gates, the unit cell comprising a base layer (9) and a source layer (10) formed on the base layer and having the first surface as a principal semiconductor surface, the unit cell having a contact hole (12) formed on a center of the principal semiconductor surface and extending from the principal semiconductor surface through the source layer to an inside of the base layer; a contact (17) formed in the contact hole; a source electrode (18) formed on the contact; and a drain electrode (19) formed on the second surface, the contact is formed to a depth different to a peak depth which is a position having a maximum impurity-concentration in a depth direction of the base layer. The unit call further comprises a base contact layer (14) formed within the base layer so as to enclose a bottom of the contact and to bring the base contact layer into contact with the bottom of the contact.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device

InactiveUS20120049187A1Reliable manufacturingEffectively prevent deteriorationSolid-state devicesDiodeZener diodeMiniaturization

Accompanying the miniaturization of a gate electrode of a trench gate power MOSFET, the curvature of the bottom part of the trench increases, and thereby, electric fields concentrate on the part and deterioration of a gate oxide film (insulating film) occurs. The deterioration of the gate insulating film is more likely to occur when the gate side bias is negative in the case of an N-channel type power MOSFET and when the gate side bias is positive in the case of a P-channel type power MOSFET.The present invention is a semiconductor device including an insulating gate power transistor etc. in a chip, wherein a gate protection element includes a bidirectional Zener diode and the bidirectional Zener diode has a plurality of P-type impurity regions (or a P-type impurity region) having different concentrations so that the withstand voltage with its gate side negatively biased and the withstand voltage with the gate side positively biased are different from each other.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com