Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

513 results about "Silicon etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

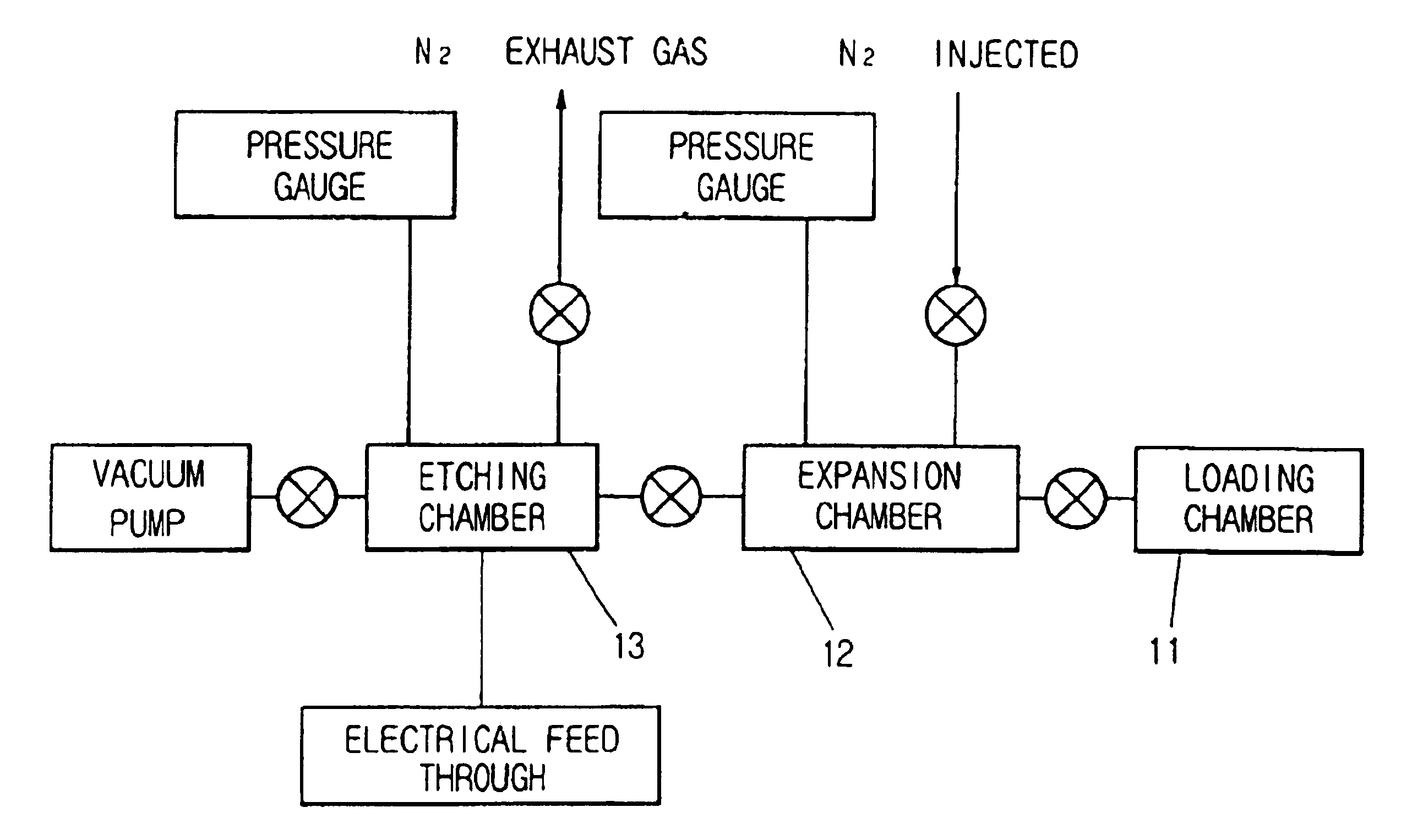

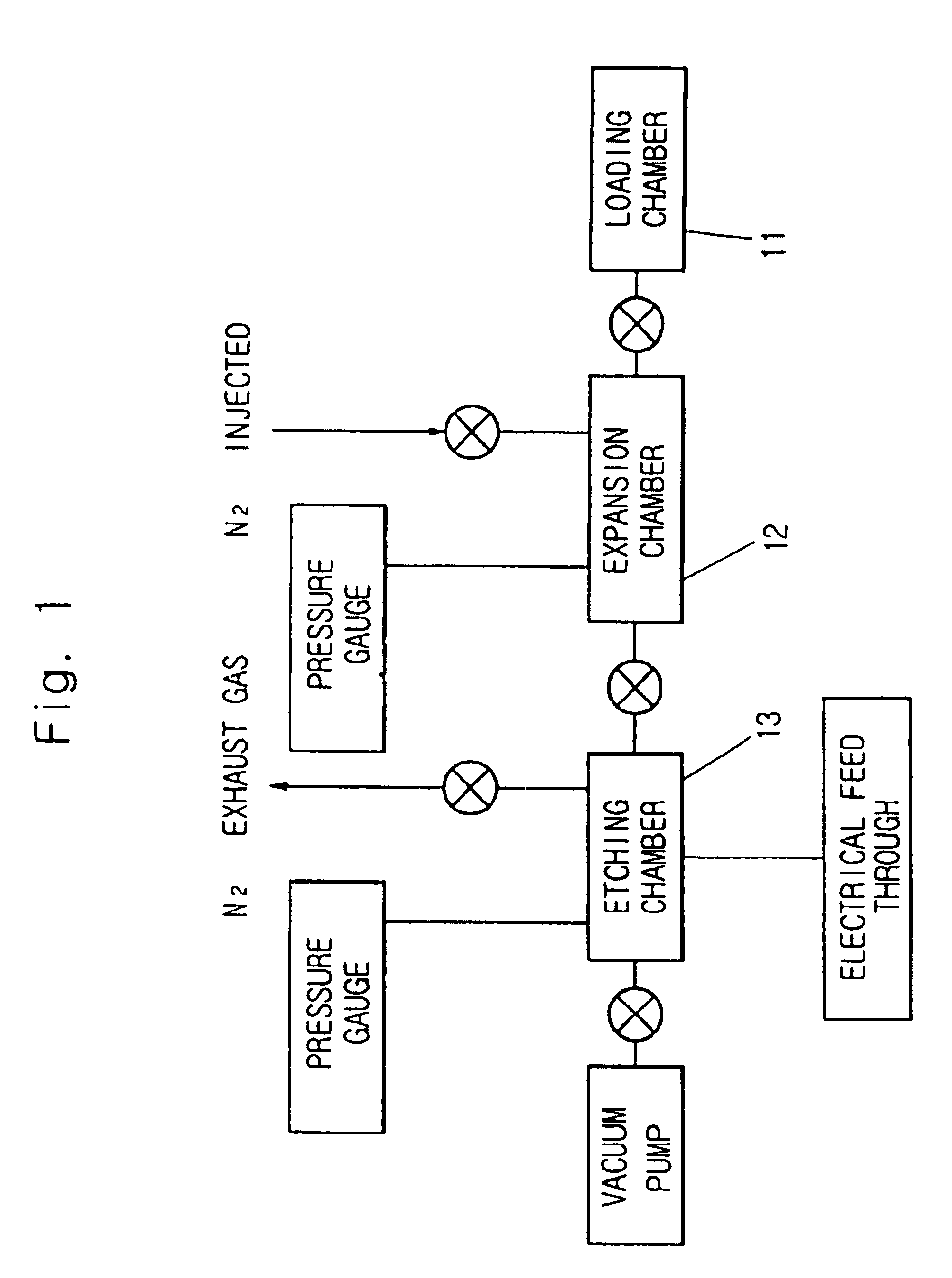

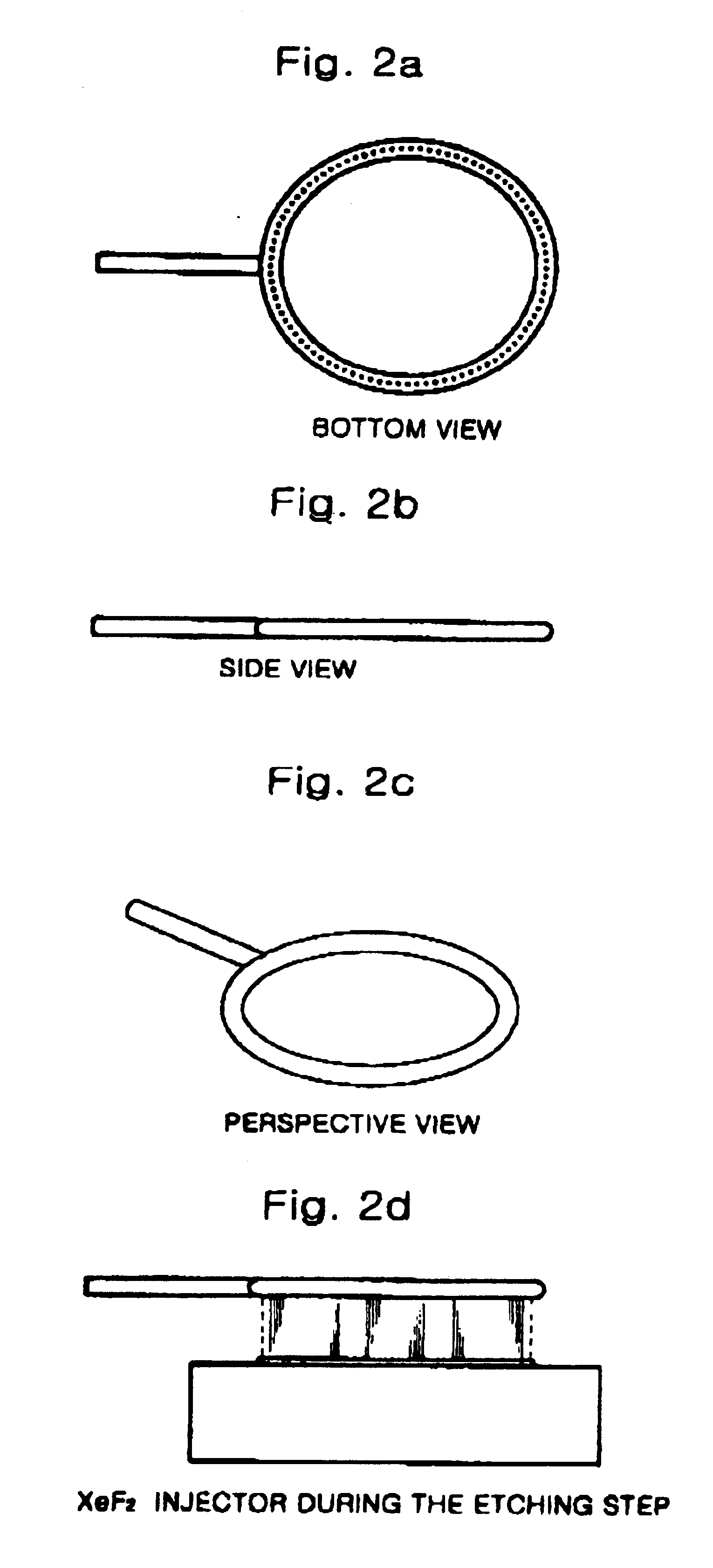

Silicon etching apparatus using XeF2

InactiveUS6736987B1Minimize damageUniform etchingVacuum gauge using ionisation effectsDecorative surface effectsInternal pressureFeedback controller

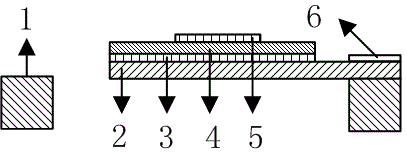

The silicon etching apparatus using XeF2 includes: a basic structure composed of a loading chamber tot loading XeF2, an expansion chamber for collecting sublimated XeF2 gas, and an etching chamber for performing an etching process; and a means for injecting nitrogen prior to the etching process to eliminate air moisture in the apparatus and thus preventing the formation of HF. The silicon etching apparatus using XeF2 further includes: an injector having a predefined shape provided in the etching chamber for uniformly injecting the XeF2 gas downward on to surface of a wafer; a feedback controller for feedback controlling the internal pressure of the loading chamber in order to prevent sublimation of the residual XeF2 in the loading chamber; and a weight scale for measuring the weight of XeF2 in the loading chamber.

Owner:TECHBANK

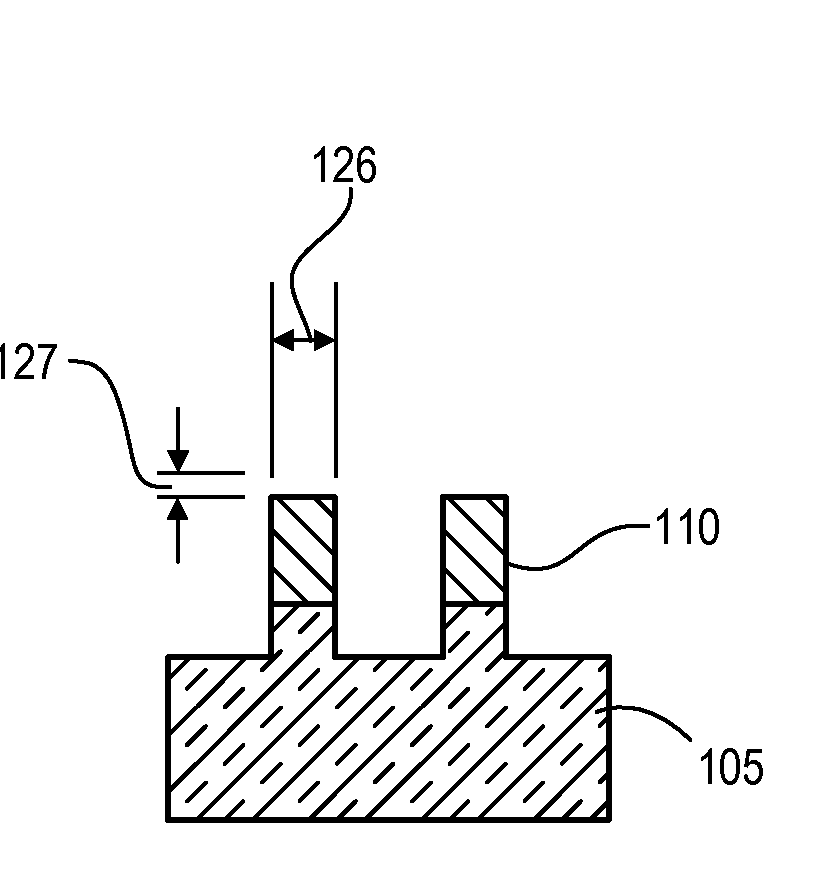

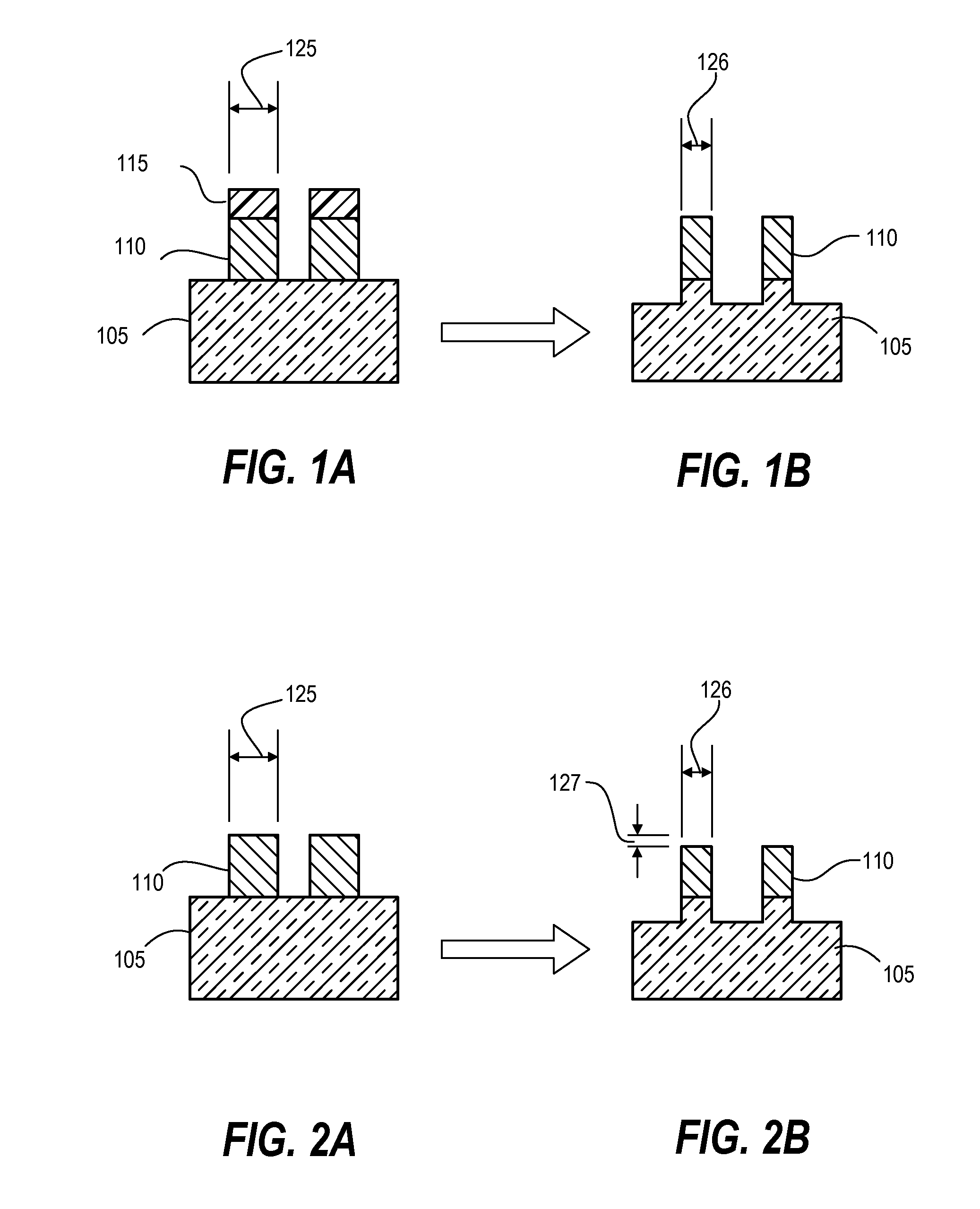

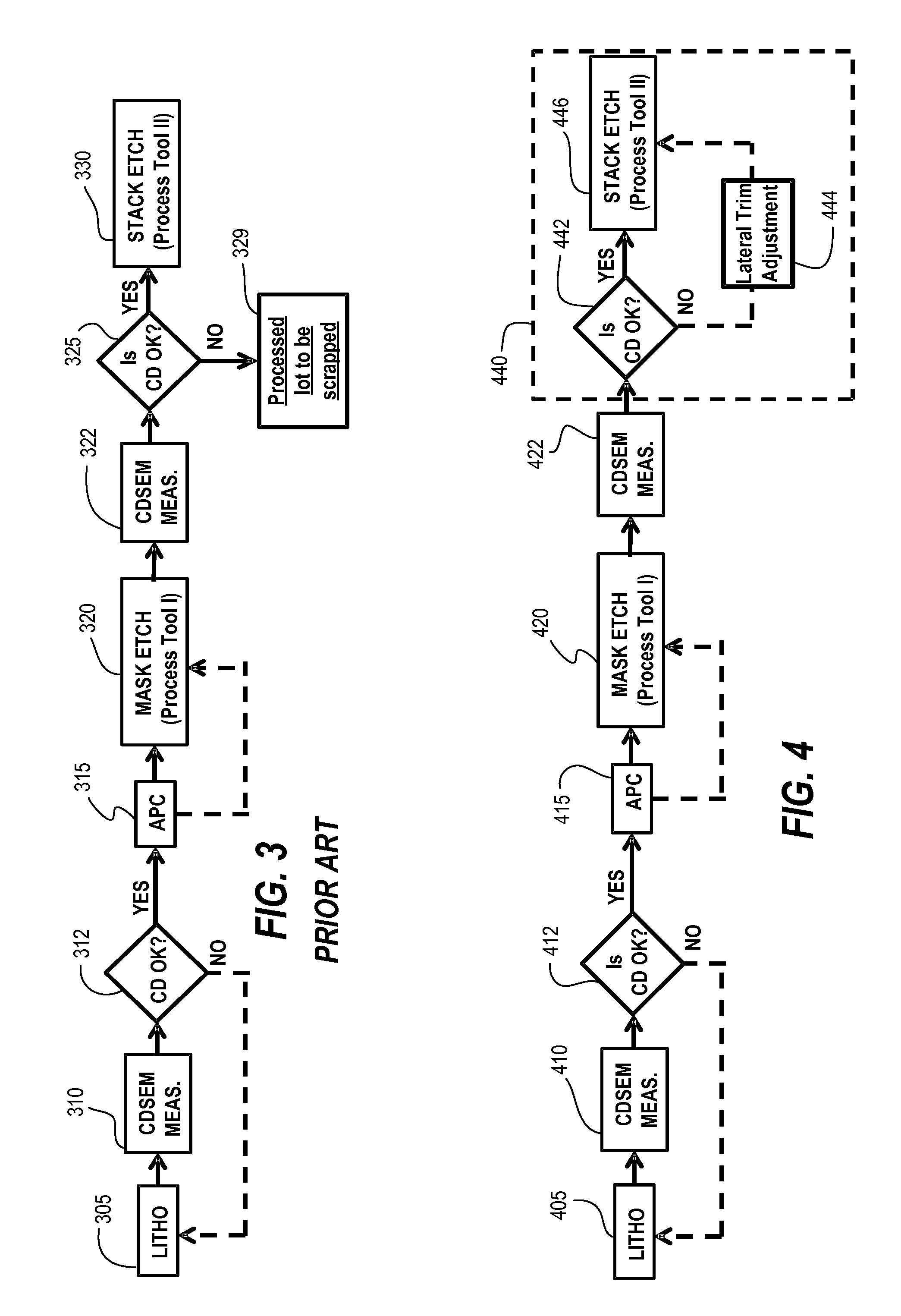

Method for Laterally Trimming a Hardmask

ActiveUS20150064918A1Reduce decreaseReduced dimensionSemiconductor/solid-state device manufacturingDielectricFluorocarbon

Techniques herein include methods for controllable lateral etching of dielectrics in polymerizing fluorocarbon plasmas. Methods can include dielectric stack etching that uses a mask trimming step as part of a silicon etching process. Using a fluorocarbon mixture for dielectric mask trimming provides several advantages, such as being straightforward to apply and providing additional flexibility to the process flow. Thus, techniques herein provide a method to correct or tune CDs on a hardmask. In general, this technique can include using a fluorine-based and a fluorocarbon-based, or fluorohydrocarbon-based, chemistry for creating a plasma, and controlling a ratio of the two chemistries. Without the hardmask trim method disclosed herein, if a hardmask CD is not on target, then a wafer is scrapped. With hard-mask trim capability in silicon etch as disclosed herein, a given CD can be re-targeted to eliminate wafer-scraps.

Owner:TOKYO ELECTRON LTD

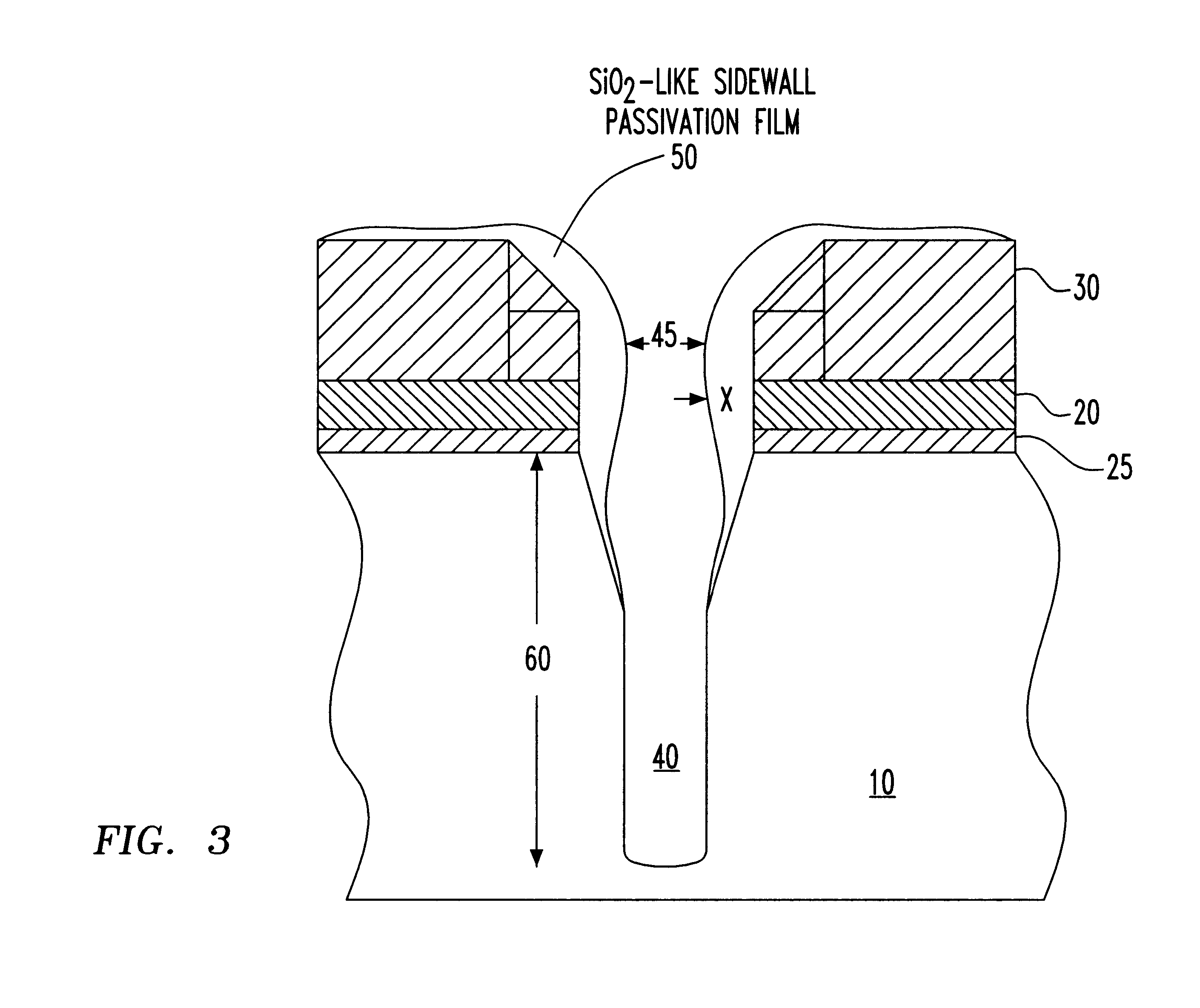

Method of reducing RIE lag for deep trench silicon etching

InactiveUS6284666B1Eliminating and at least minimizing RIE lagEliminating or at least minimizing RIE lagTransistorSemiconductor/solid-state device manufacturingHydrofluoric acidGas phase

A method of minimizing RIE lag (i.e., the neutral and ion fluxes at the bottom of a deep trench (DT) created during the construction of the trench opening using a side wall film deposition)) in DRAMs having a large aspect ratio (i.e., <30:1) is described. The method forms a passivation film to the extent necessary for preventing isotropic etching of the substrate, hence maintaining the required profile and the shape of the DT within the substrate. The RIE process described provides a partial DT etched into a substrate to achieve the predetermined depth. The passivation film is allowed to grow to a certain thickness still below the extent that it would close the opening of the deep trench. Alternatively, the passivation film is removed by a non-RIE etching process. The non-RIE process that removes the film can be wet etched with chemicals, such as hydrofluoric acid (buffered or non buffered) or, alternatively, using vapor phase and / or non-ionized chemicals, such as anhydrous hydrofluoric acid. The controlled thickness of the film allows achieving a predetermined DT depth for high aspect ratio structures.

Owner:INFINEON TECH AG +1

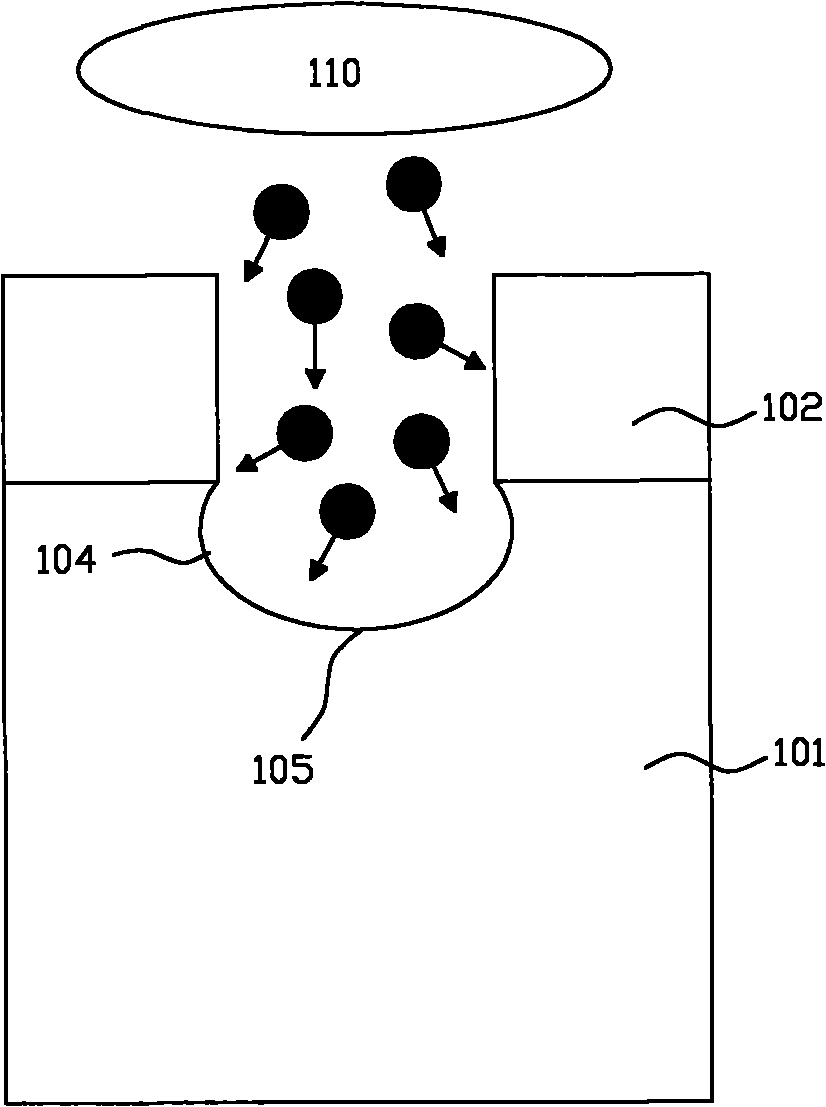

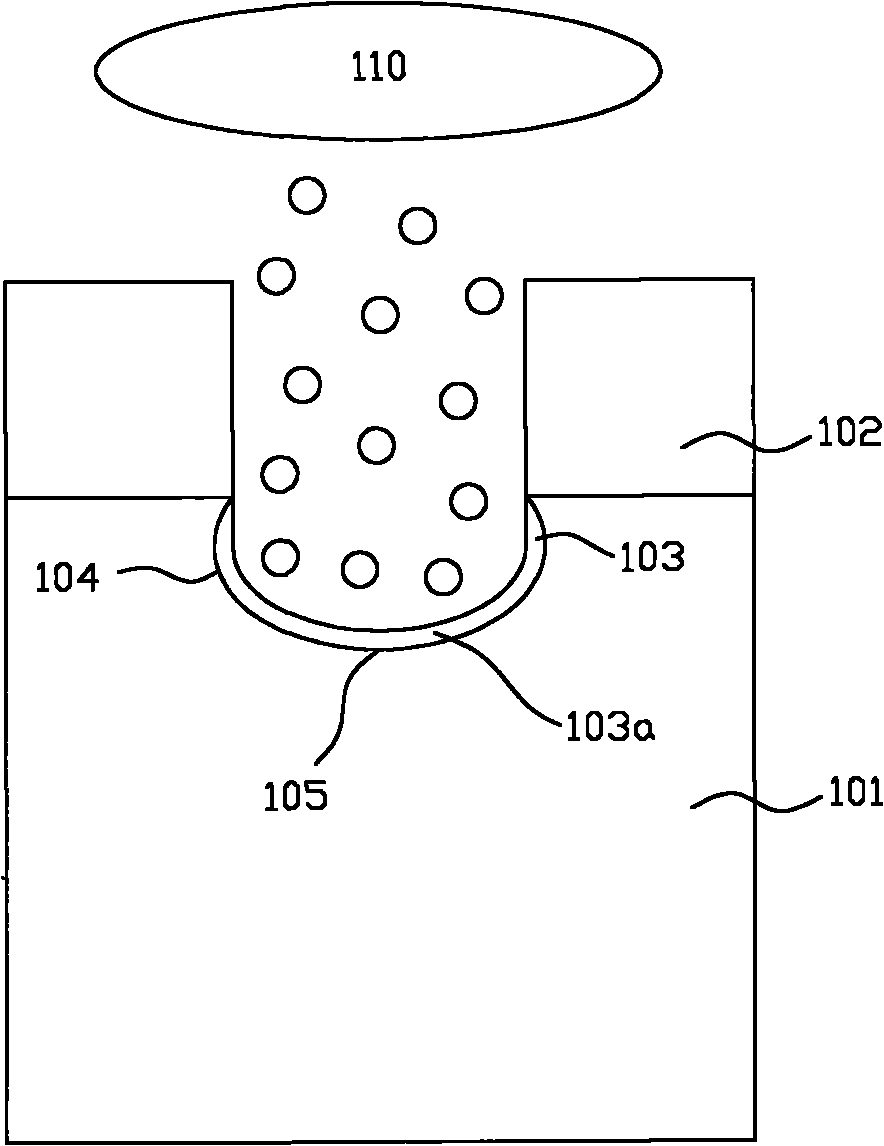

Silicon chip shallow plow groove isolation etching method

ActiveCN101179046ASimple processFew stepsSemiconductor/solid-state device manufacturingSilicon chipSilicon etching

The invention discloses a silicon chip shallow trench isolation etching method which is used for etch groove on silicon. The method comprises the following steps: A. upper layer silicon etching step; B. oxide layer etching step, which is used for etching the oxide layer between upper layer silicon and base silicon and is also used for etching partial base silicon for the top fillet etching preparation; C. base silicon etching step which is used for etching groove on silicon base and to form slippery top fillet at the junctional position of oxide layer and silicon base on the sidewall of groove. The etching process gas used in the Step B is mixed gas consisting of HBr gas and CHF3 gas. The etching process gas is ionized into active groups like Br*, CHF*, etc., and can form the top fillet during Step C. The method has the advantages of simple process with less steps, low cost and slippery top fillet formation of etching groove, and is applicable to shallow trench isolation etching and other etchings of various type of semiconductor silicon wafers.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

Deep silicon etching method

ActiveCN101962773AImprove the selection ratioFast etch rateSemiconductor/solid-state device manufacturingPulse power supplySilicon chip

The invention provides a deep silicon etching method. The method comprises a step of etching a silicon chip surface which is not covered by a photoresist layer first to form an etched surface and a side wall which is vertical to the etched surface basically; and the method also comprises the following steps of: a first depositing step, namely performing isotropic deposition for covering a barrierlayer on the etched surface, the side wall and the surface of the photoresist layer; a first etching step, namely performing anisotropic etching for removing the barrier layer covered on the etched surface so as to expose the etched surface, wherein the photoresist layer is prevented from being etched by the barrier layer covered on the photoresist layer; a second etching step, namely performing the isotropic etching for etching the exposed etched surface, wherein the side wall is prevented from being etched by the barrier layer covered on the side wall and the photoresist layer is not damaged in the isotropic etching; and repeating the depositing step, the first etching step and the second etching step circularly until reaching a predetermined etching depth. The method does not need complex equipment such as a low-frequency pulse power supply and the like, contributes to maintenance, and reduces equipment cost.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

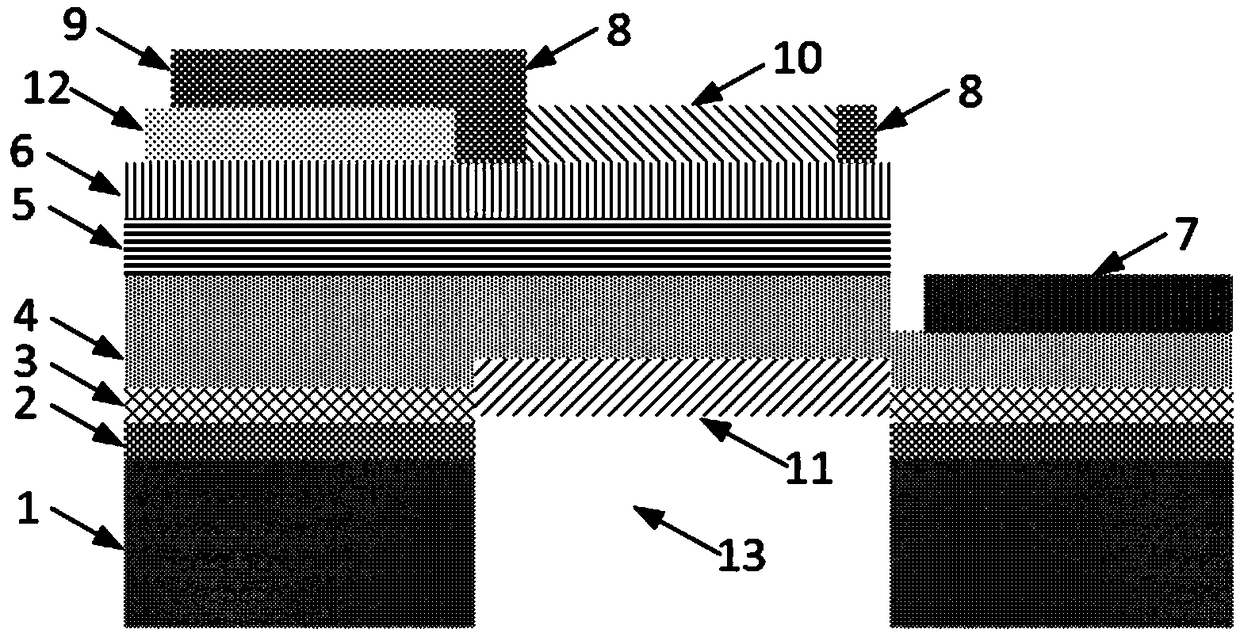

Superconducting nanowire single photon detector based on deep silicon etching process and preparation method

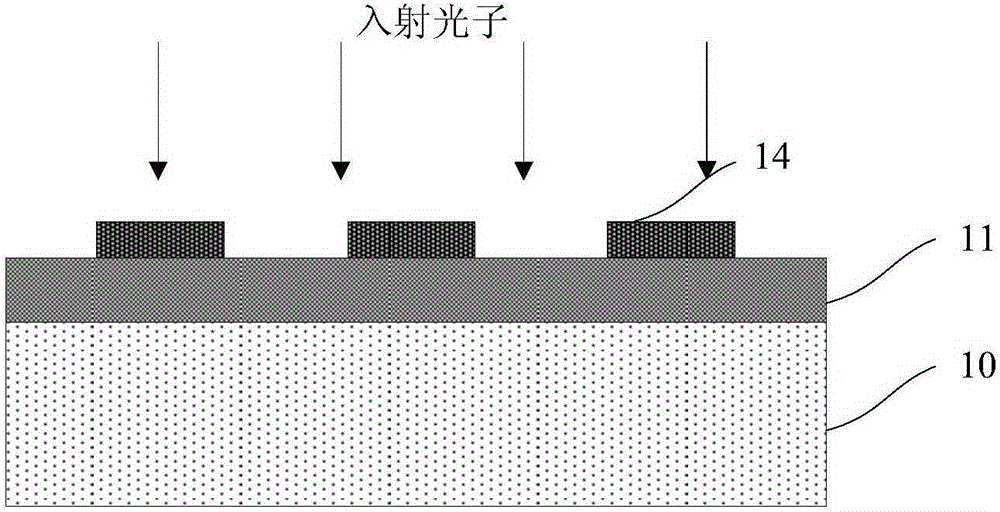

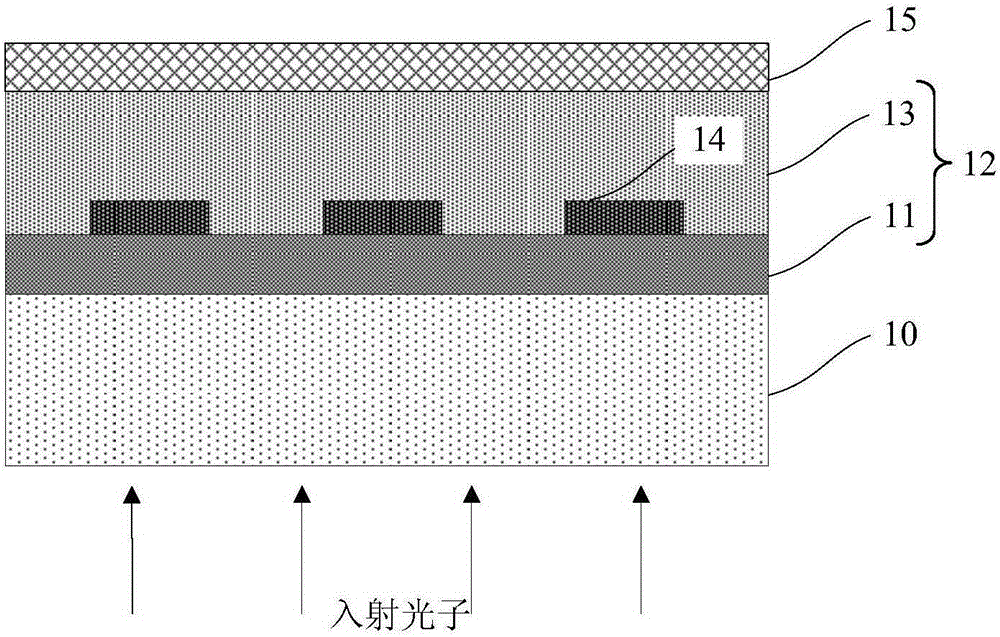

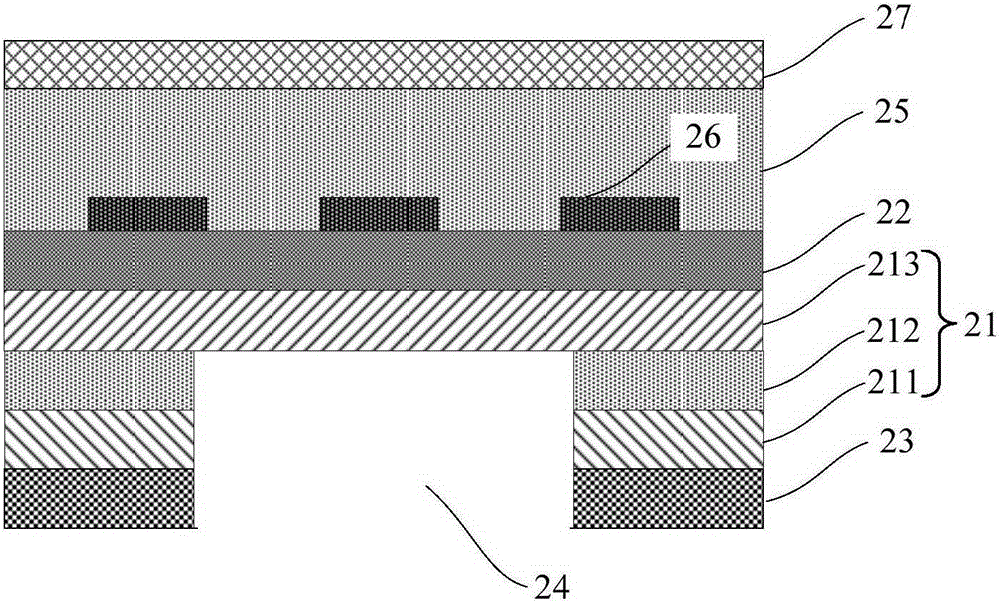

ActiveCN106549099AImprove absorption efficiencyReduce usageSuperconductor detailsSuperconductor device manufacture/treatmentLong-focus lensNanowire

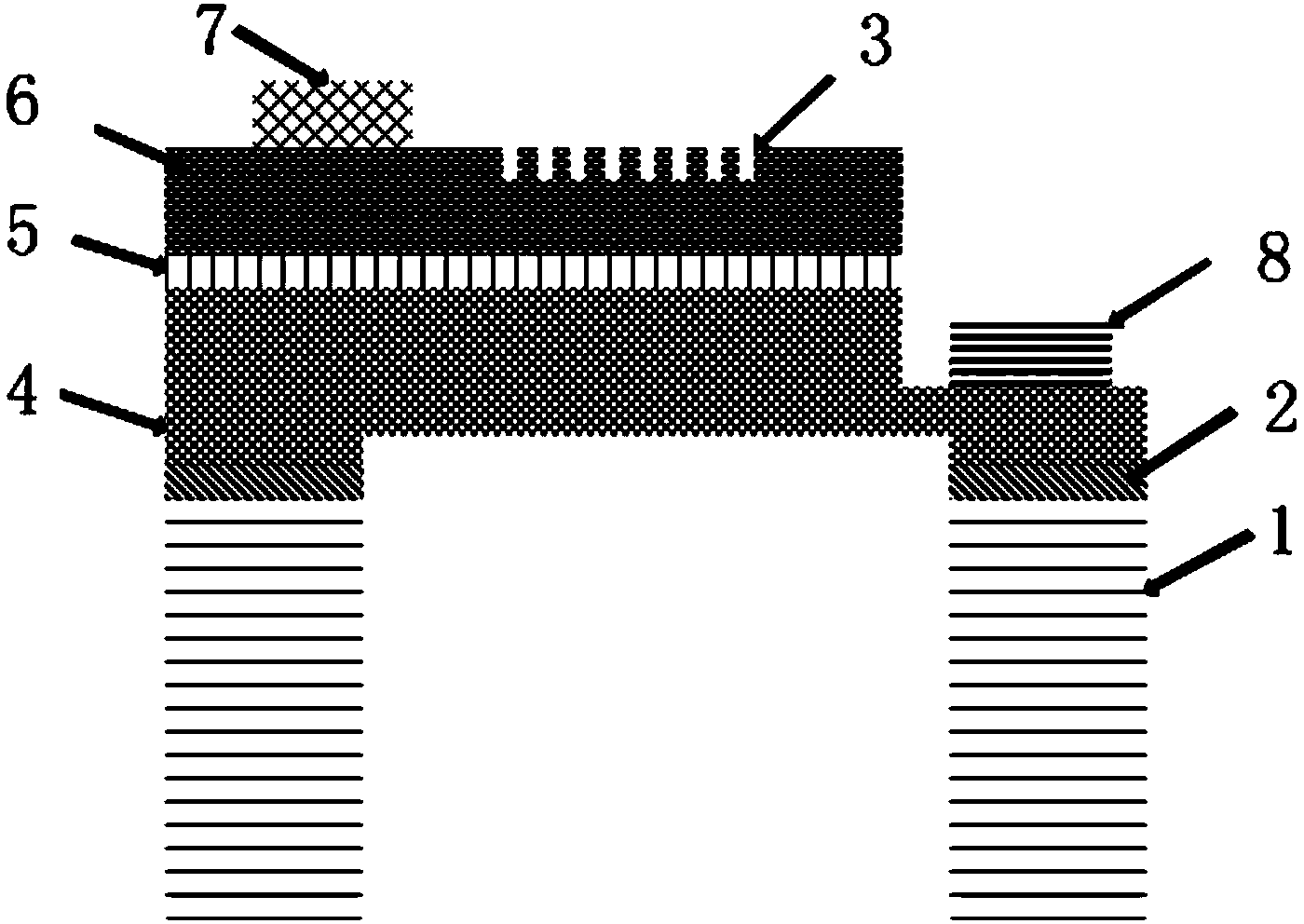

The invention provides a superconducting nanowire single photon detector based on a deep silicon etching process and a preparation method. The detector comprises an SOI base which is composed of a back substrate, a buried oxygen layer and top silicon in sequence from bottom to top, a first anti-reflection layer which is disposed on the surface of the top silicon, a second anti-reflection layer which is disposed on the surface of the back substrate, a deep groove which penetrates through the second anti-reflection layer, the back substrate and the buried oxygen layer, an optical cavity structure which is disposed on the surface of the first anti-reflection layer, superconducting nanowires which are disposed between the first anti-reflection layer and the optical cavity structure, and a mirror which is disposed on the surface of the optical cavity structure. By etching the deep groove on the substrate, the distance between a coupling optical fiber and the device is narrowed, the use of a long-focus lens in the traditional back-coupling superconducting nanowire single photon detector is avoided, and alignment coupling between the MU head of an optical fiber and the device is facilitated. The problem concerning long-distance focusing in the optical cavity structure and the influence of the Fabry-Perot cavity of the susbtrate on the absorption efficiency are avoided. The absorption efficiency of target wavelength is improved. The detection efficiency of the device is improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

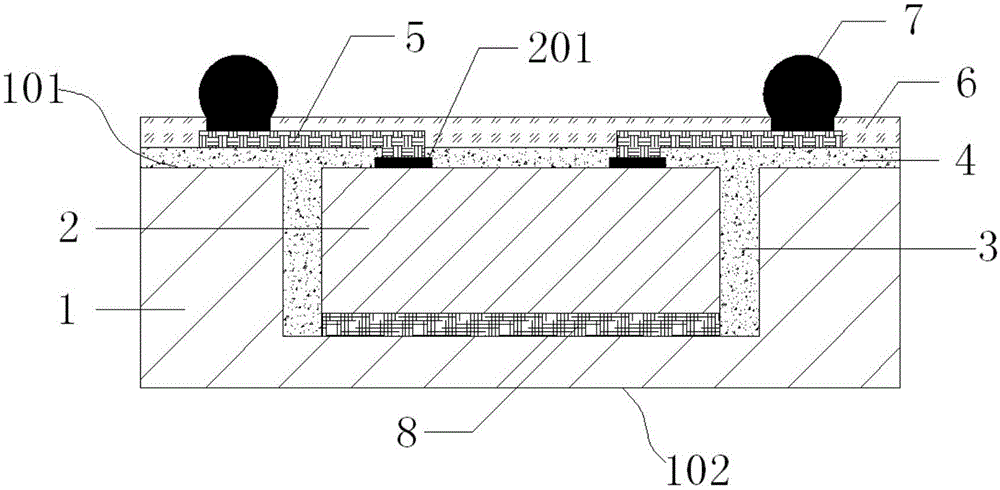

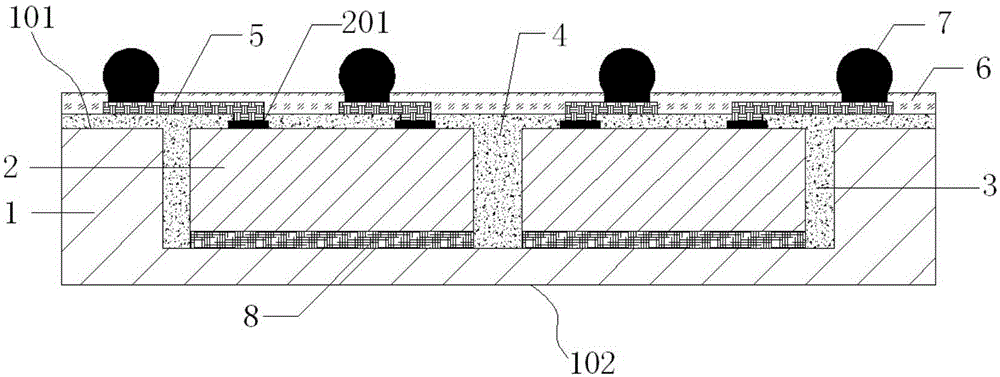

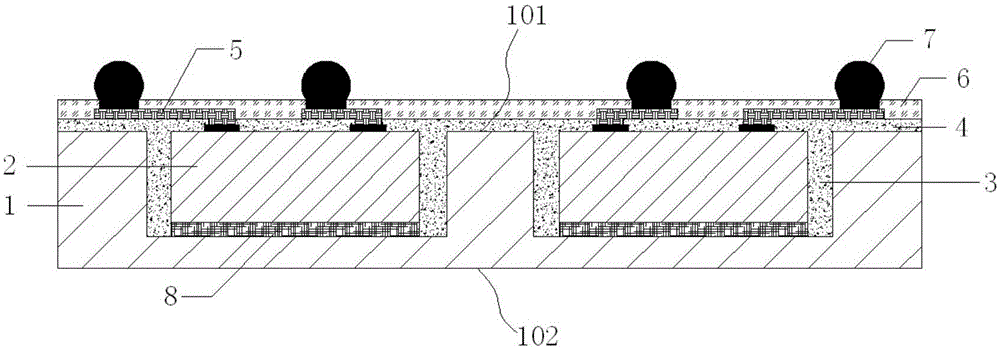

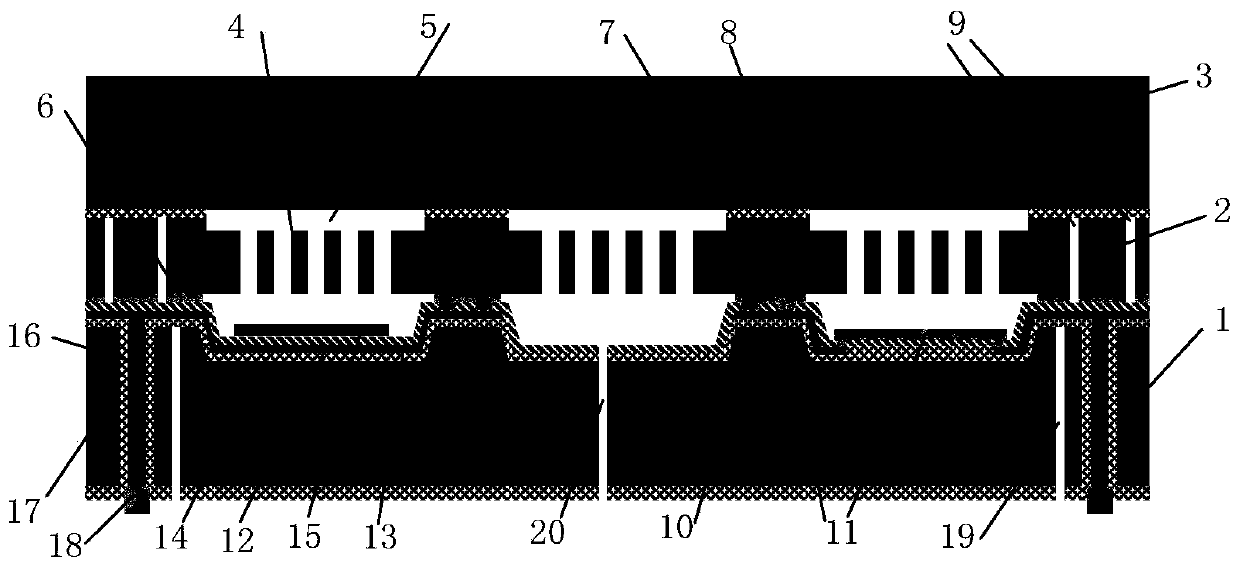

Embedded silicon substrate fan-out type packaging structure and manufacturing method thereof

InactiveCN105023900AImprove cooling effectAvoid offsetSemiconductor/solid-state device detailsSolid-state devicesSilicon matrixPolymer adhesive

The invention discloses an embedded silicon substrate fan-out type packaging structure and a manufacturing method thereof. A silicon matrix is adopted to replace molding material to act as a fan-out matrix, and fine wiring can be manufactured by fully utilizing the advantages of the silicon matrix. Holes, grooves and other structures can be accurately etched by utilizing a mature silicon etching technology. Chips are embedded in the grooves on the silicon matrix, the gaps between the chips and the side walls of the grooves are filled by polymer glue and partial welded balls are welded at the surface of the silicon matrix in a fan-out way so that packaging reliability can be enhanced, the technology is simple and cost is low. The silicon matrix has great heat radiation and lower warping so that enhancement of packaging heat radiation is facilitated, adverse warping can be overcome and smaller wiring line width can be acquired, and thus the structure is suitable for high-density packaging. `Wafer plastic packaging and the de-bonding technology can be eliminated as for the aspect of technology so that technology difficulty can be reduced, and thus cost can be substantially reduced and yield rate can be enhanced.

Owner:HUATIAN TECH KUNSHAN ELECTRONICS

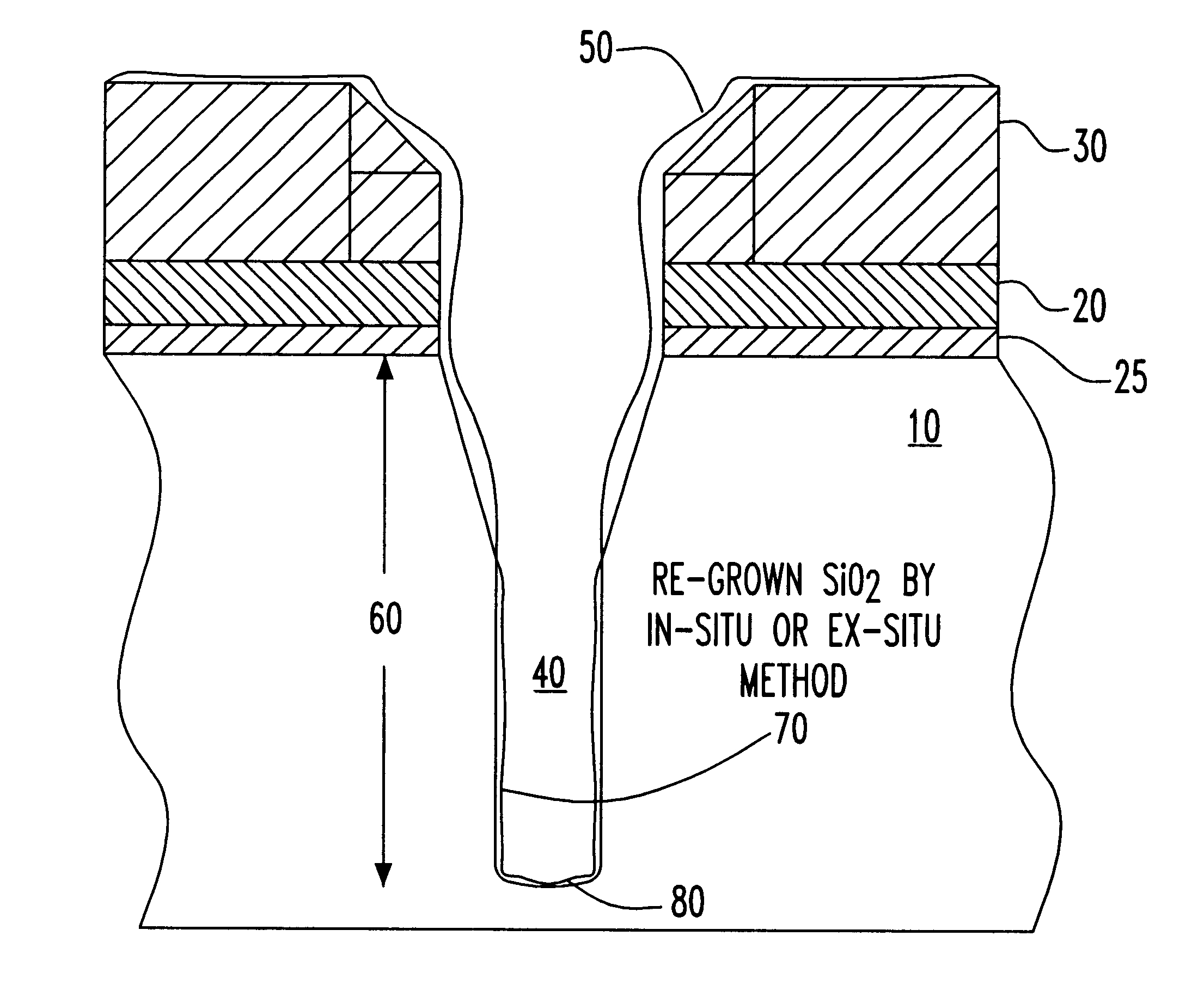

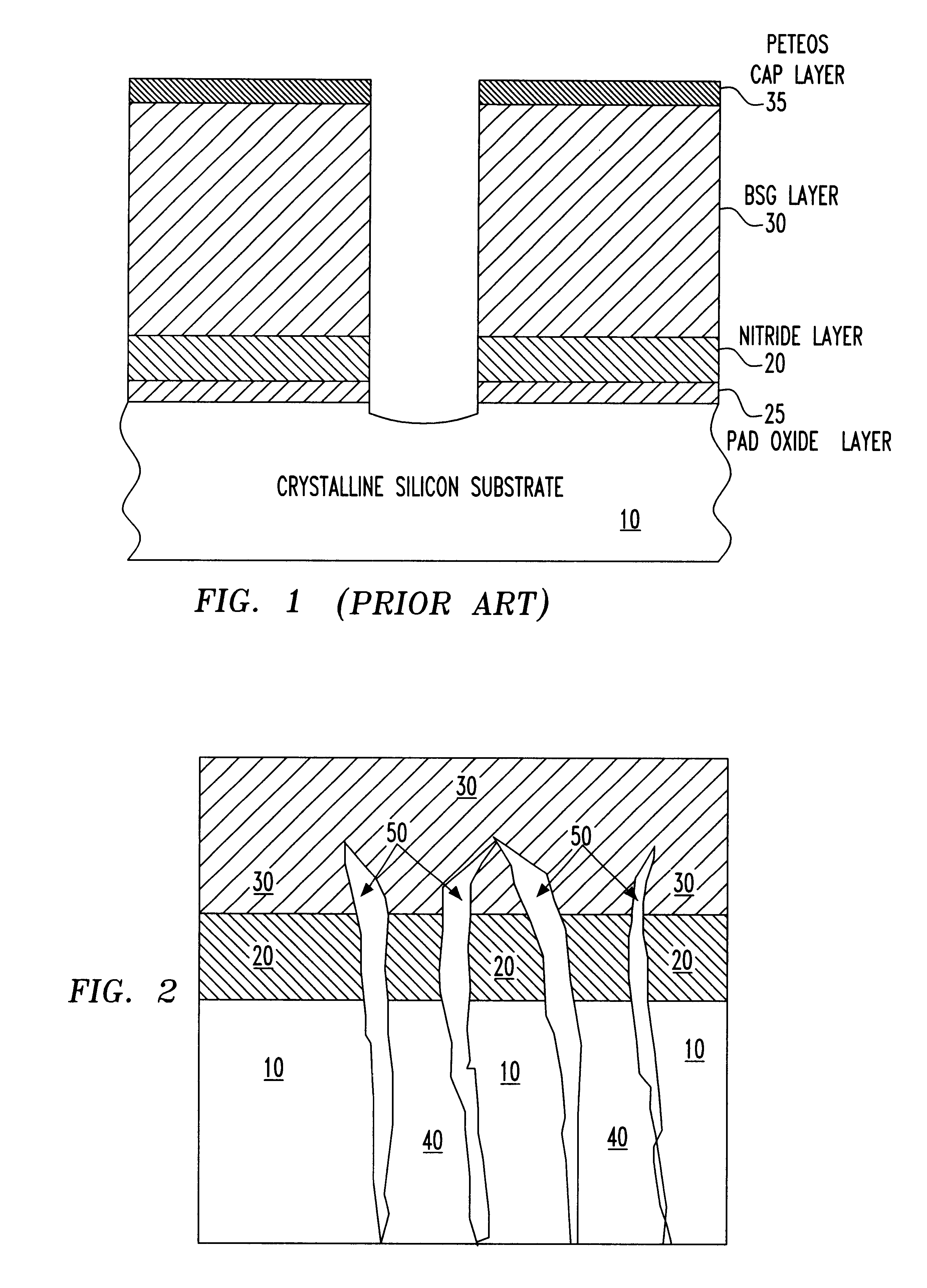

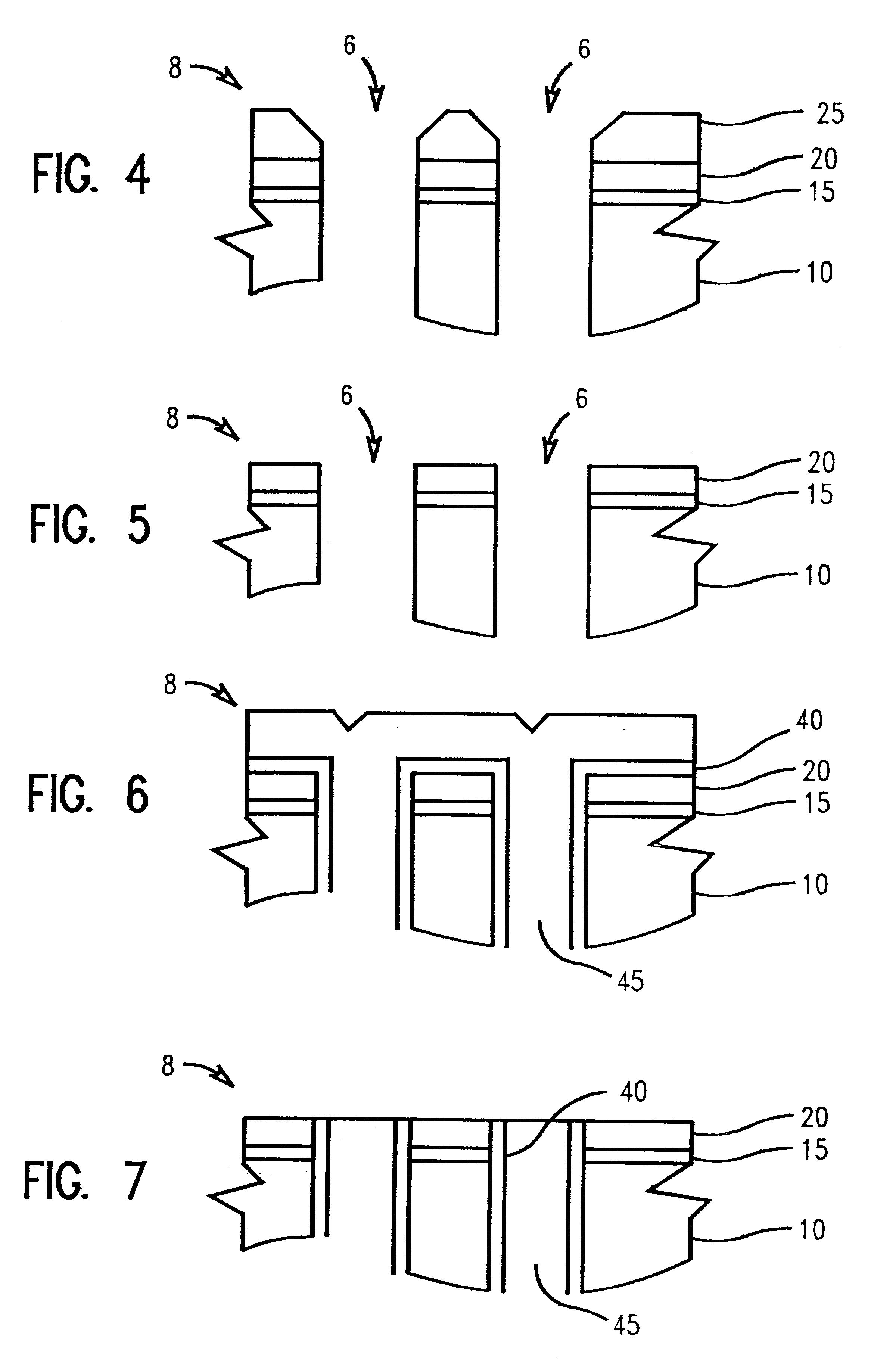

Multi-layer hard mask for deep trench silicon etch

InactiveUS6440858B1Minimize moisture sensitivityEnhanced vapor depositionSolid-state devicesSemiconductor/solid-state device manufacturingDielectricBi layer

A method of etching multiple films with a dual layer hard mask wherein one layer is totally removed and the other layer partially removed during deep trench etching of the silicon substrate. In particular, a method of deep trench etching silicon substrates comprising the steps of providing a semiconductor substrate capable of being etched, with HBr / NF3 / He / O2, having a layer of pad dielectric disposed depositing a layer of material capable of selective removability with respect to the pad dielectric, preferably BSG; depositing a layer of material having a slower etch rate than the semiconductor substrate and the layer of material capable of selective removability with respect to the pad dielectric, preferably, silicon oxide deposited by PECVD; patterning at least one of the layers, and etching the semiconductor substrate to form a trench and removing the layer of material having a slower etch rate than the semiconductor substrate, wherein trenches are of close proximity to each other.

Owner:IBM CORP

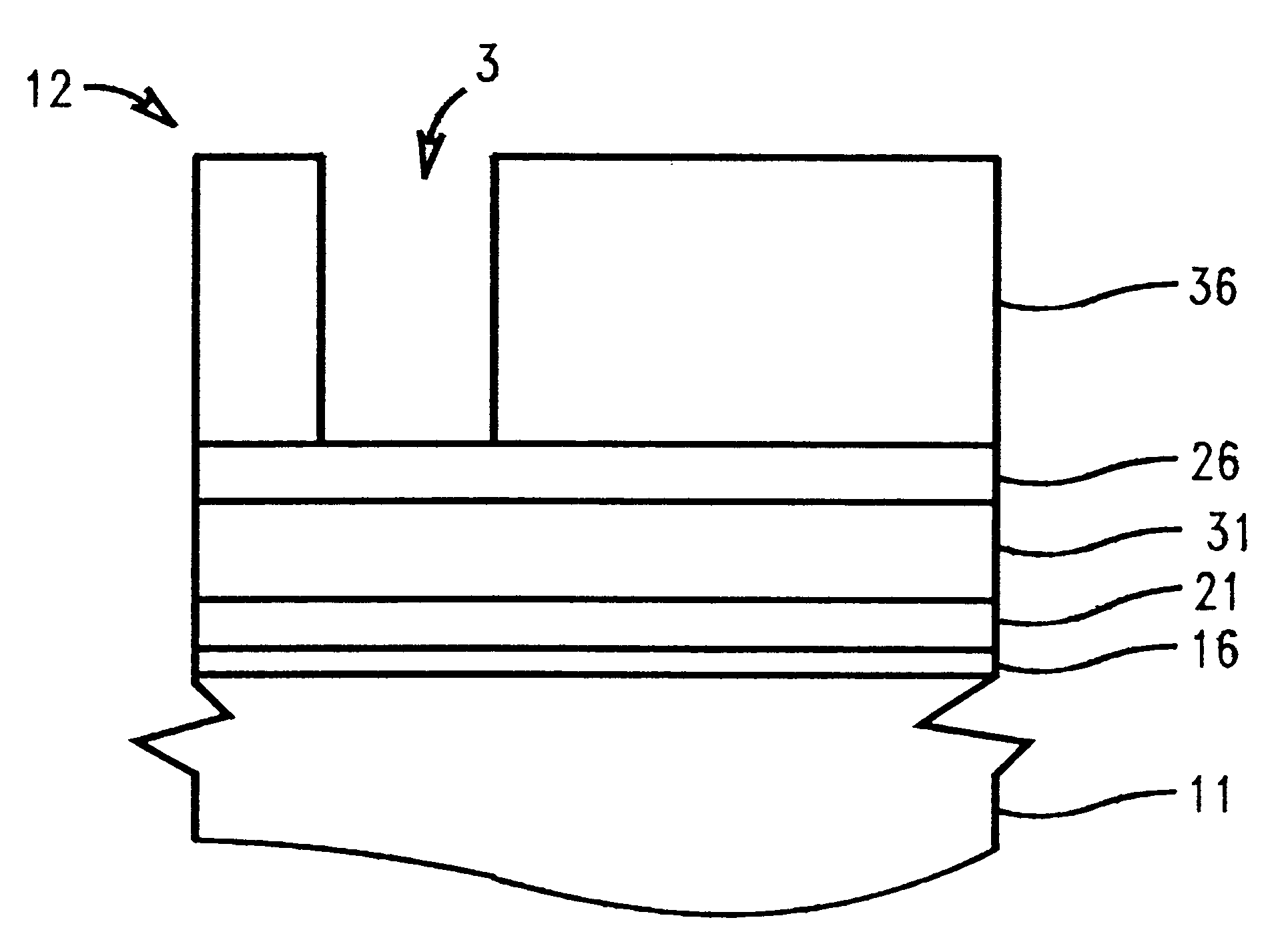

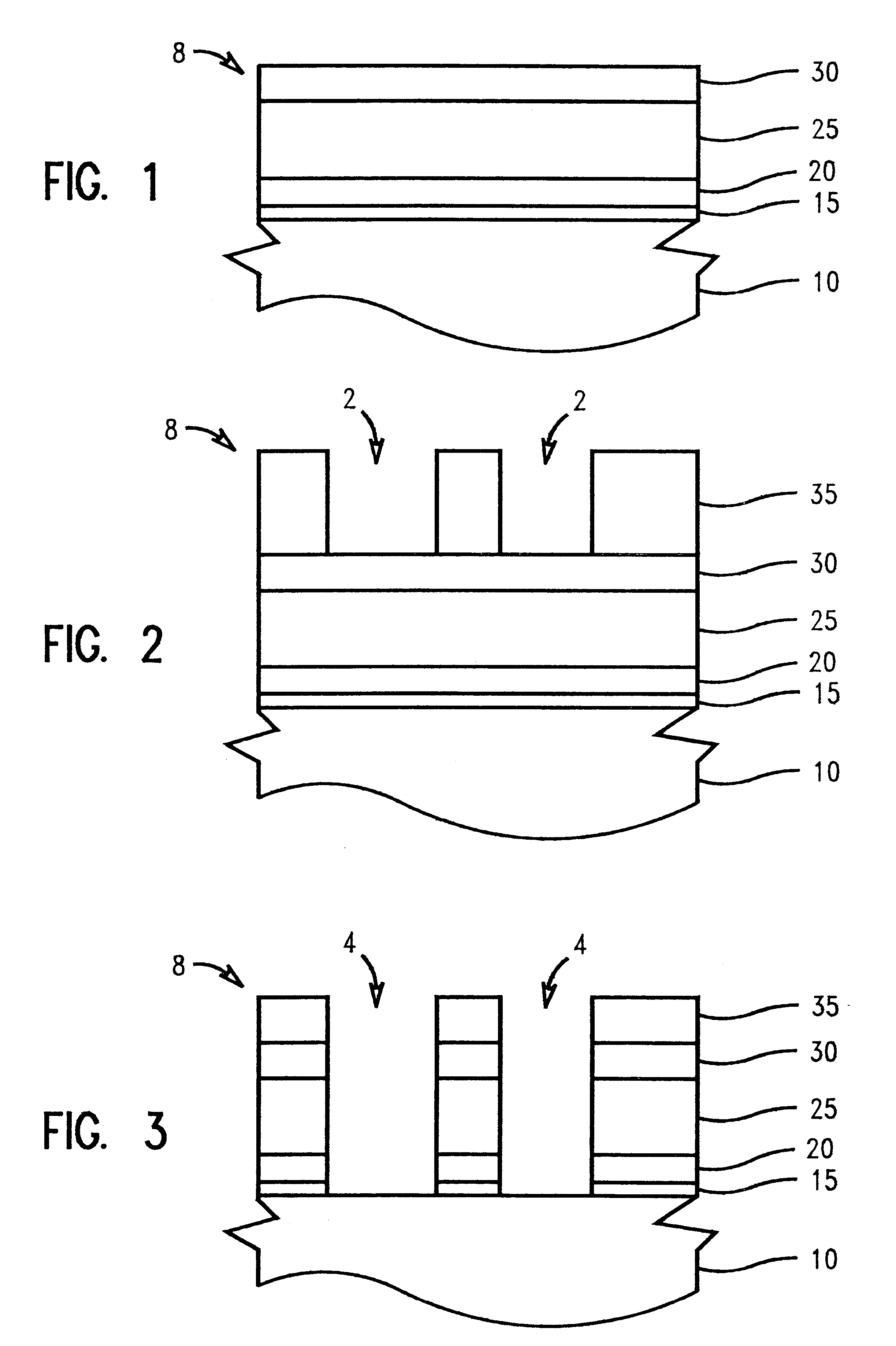

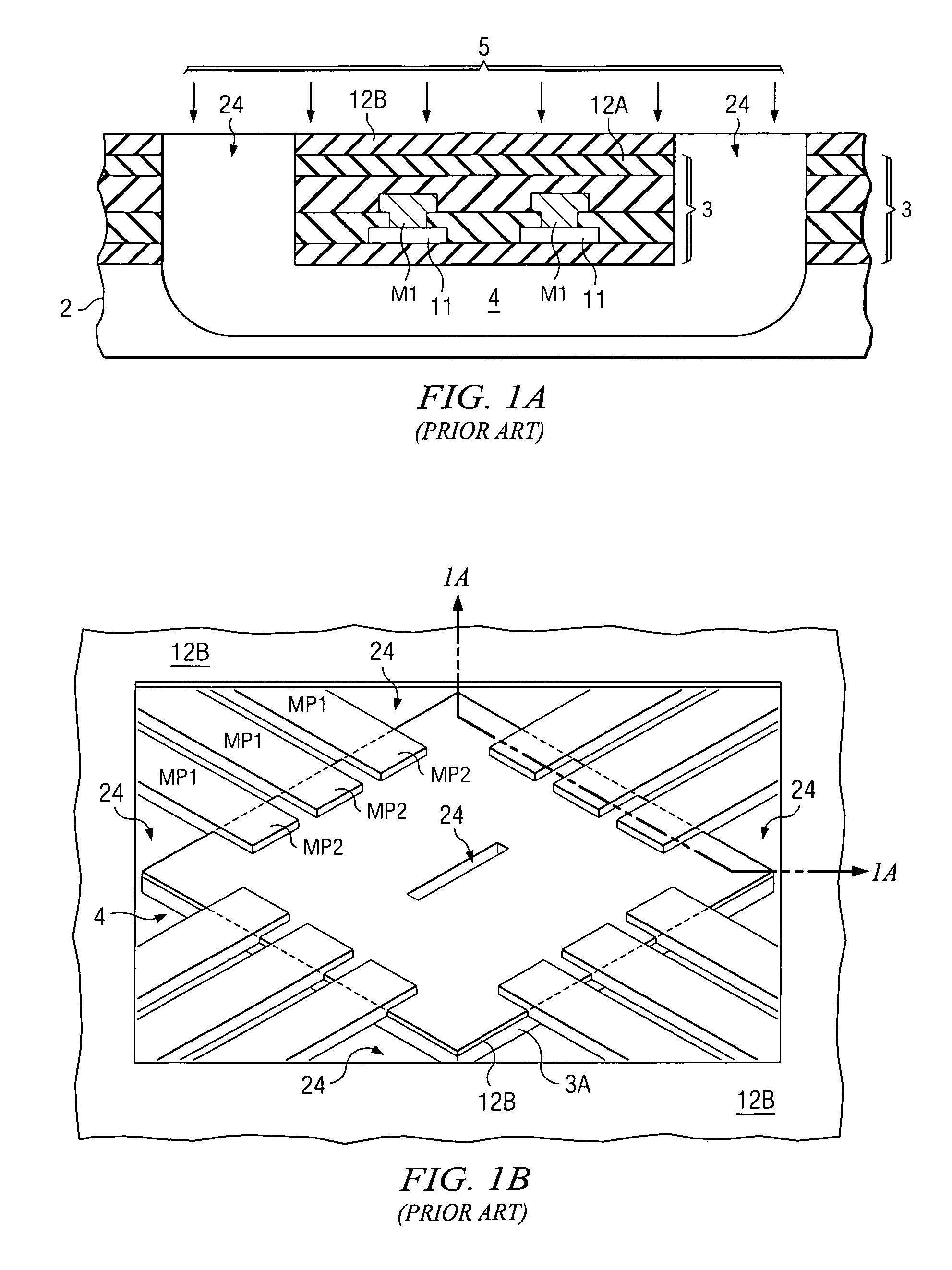

Silicon dioxide cantilever support and method for silicon etched structures

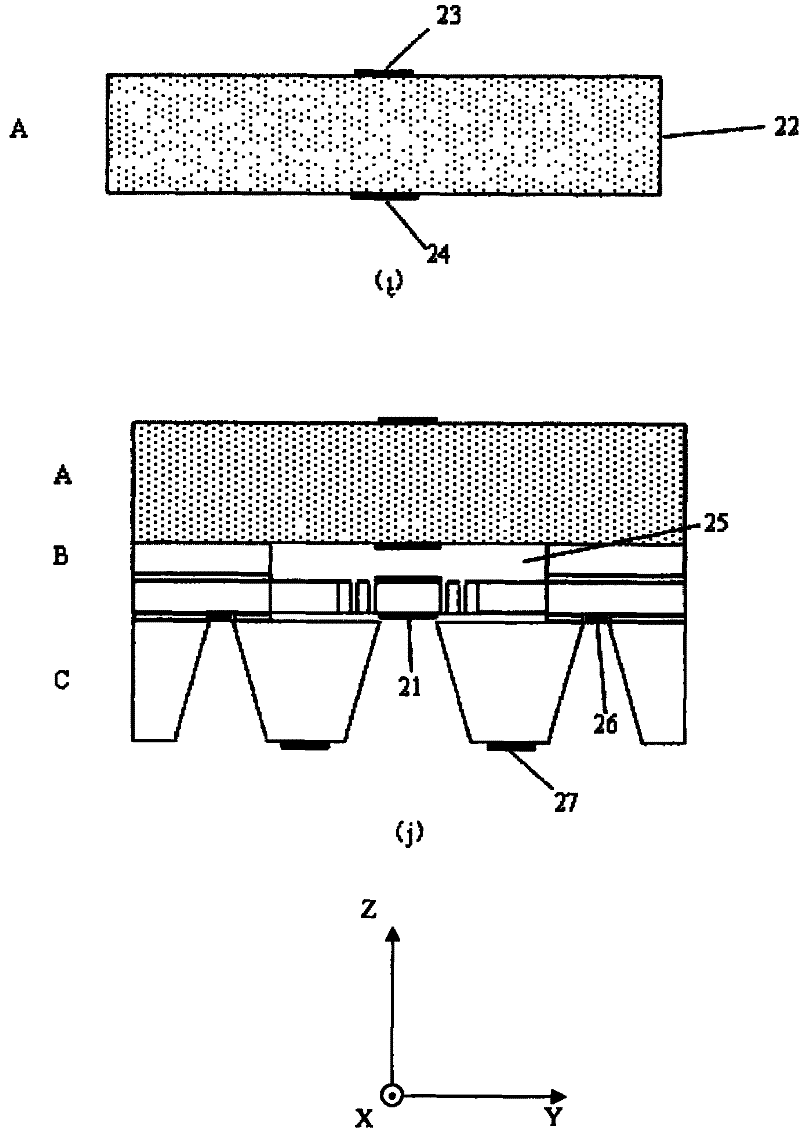

ActiveUS20100289108A1Robust and economicalImprove robustnessSolid-state devicesPhotovoltaicsSilicon dioxideCantilever

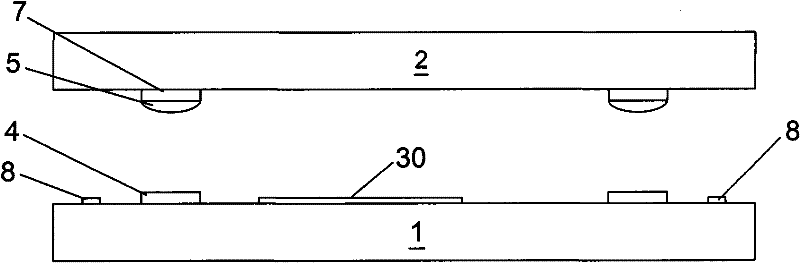

A semiconductor device includes a semiconductor layer (2) having therein a cavity (4). A dielectric layer (3) is formed on the semiconductor layer. A plurality of etchant openings (24) extend through the dielectric layer for passage of etchant for etching the cavity. An SiO2 pillar (25) extends from a bottom of the cavity to engage and support a portion of the dielectric layer extending over the cavity. In one embodiment, a cap layer (34) on the dielectric layer covers the etchant openings.

Owner:TEXAS INSTR INC

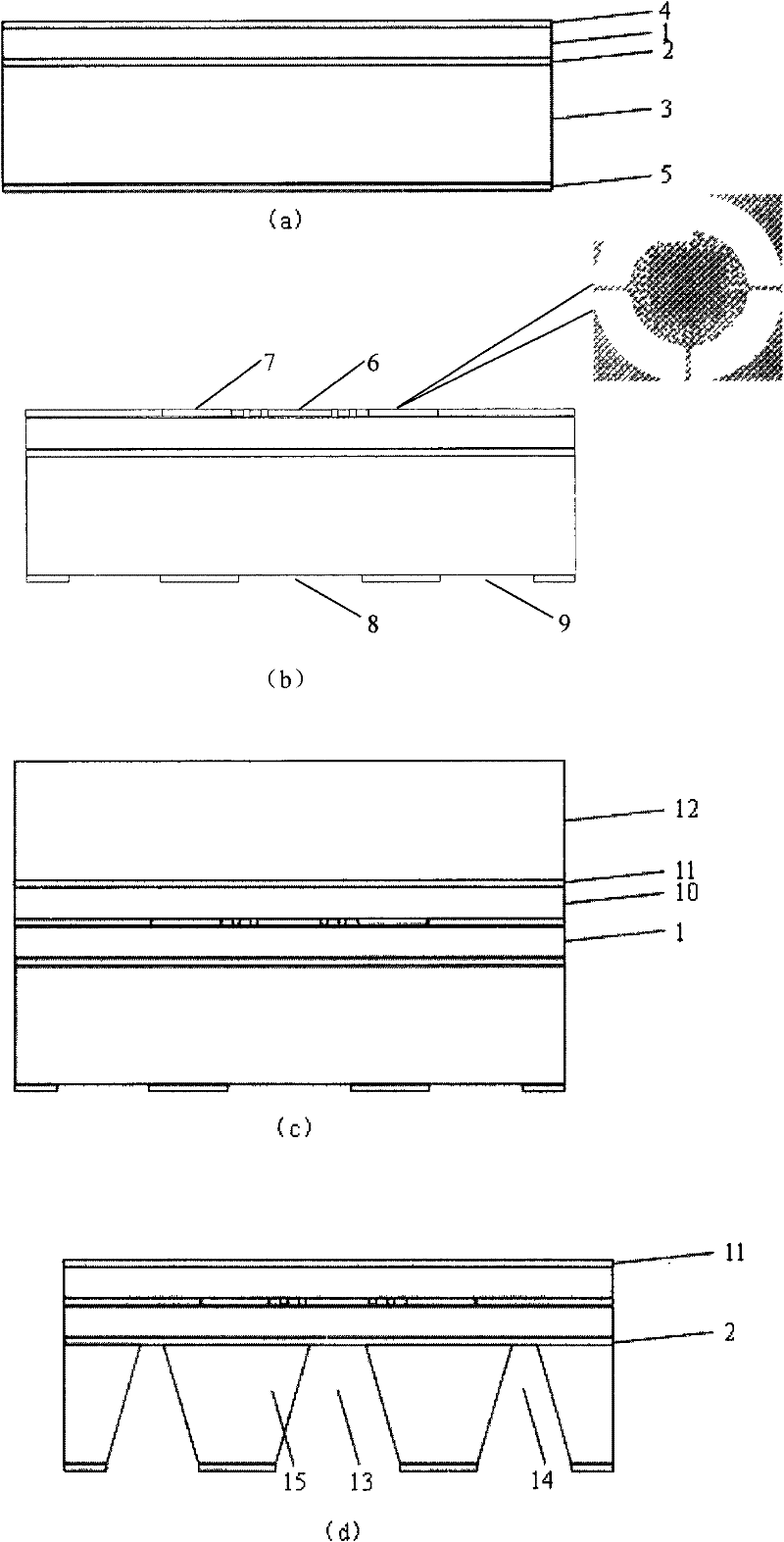

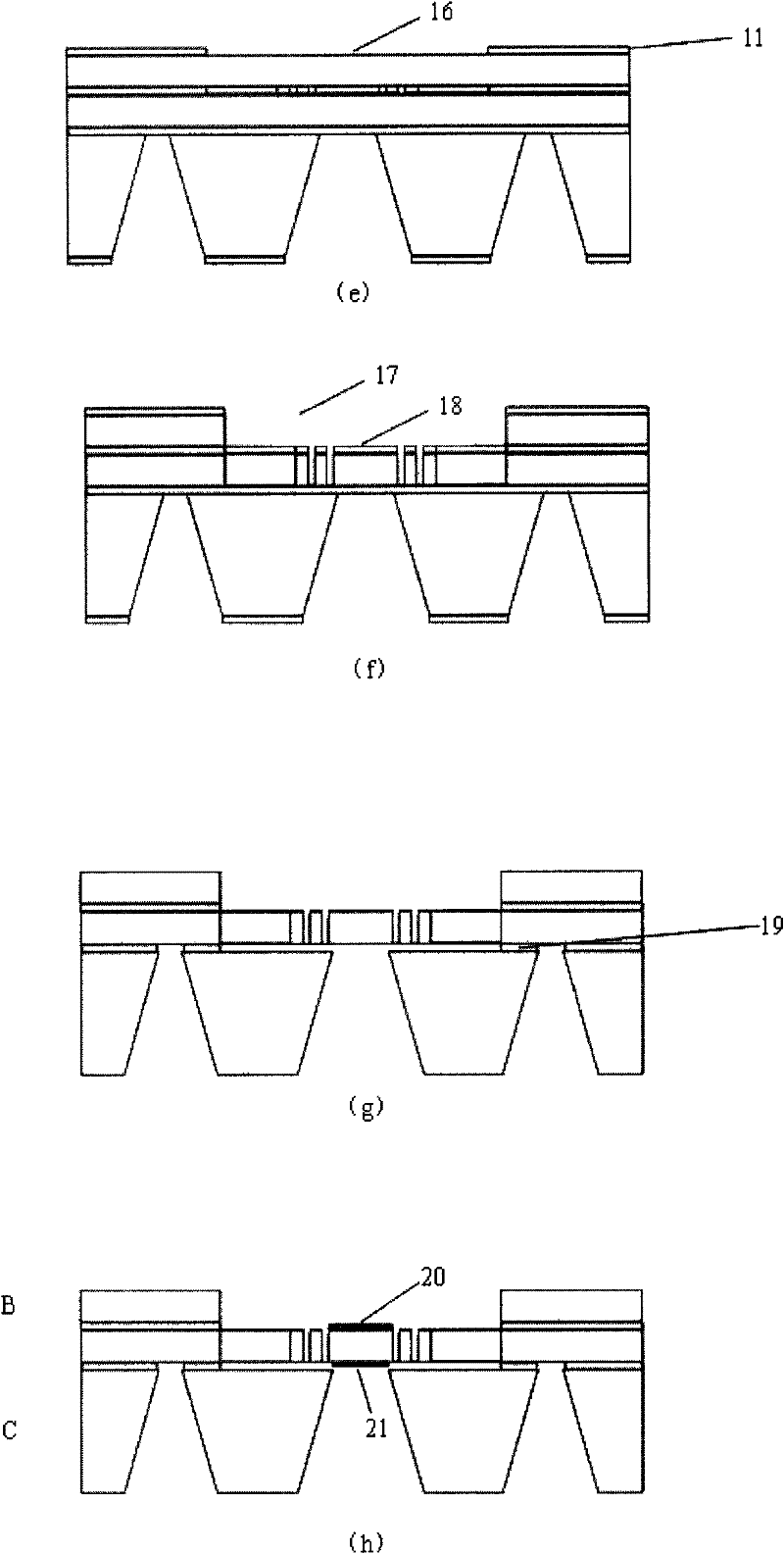

Wafer-level vacuum encapsulating method for micro-electromechanical device

ActiveCN101798054AAvoid contactWill not harmPrecision positioning equipmentSoldering apparatusEngineeringSilicon etching

The invention provides a wafer-level vacuum encapsulating method for a micro-electromechanical device, which comprises the following steps in turn: S1, preparing a seal cover wafer and a device wafer; S2, growing a seal ring on the fronts of the device wafer and the seal cover wafer respectively; S3, growing a solder on the seal ring on the front of the seal cover wafer; S4, performing deep silicon etching on the seal cover wafer to form a groove by using the seal ring as a mask; S5, growing a degasser film on the front of the seal cover wafer, wherein the pattern of the degasser film is directly obtained from the grown mask plate; S6, heating linkage equipment to activate the degasser film, and bonding the seal cover wafer and the device wafer together; S7, growing an anti-reflection film on the back of the seal cover wafer, wherein the pattern of the anti-reflection film is directly obtained from the grown mask plate; and S8, cutting flakes. The method avoids the influence of the post process on the previous process by adjusting the sequence of the processes, and is particularly suitable for encapsulating infrared devices.

Owner:北方广微科技有限公司

Preparation method of antifouling material having crossed regular microstructure on surface

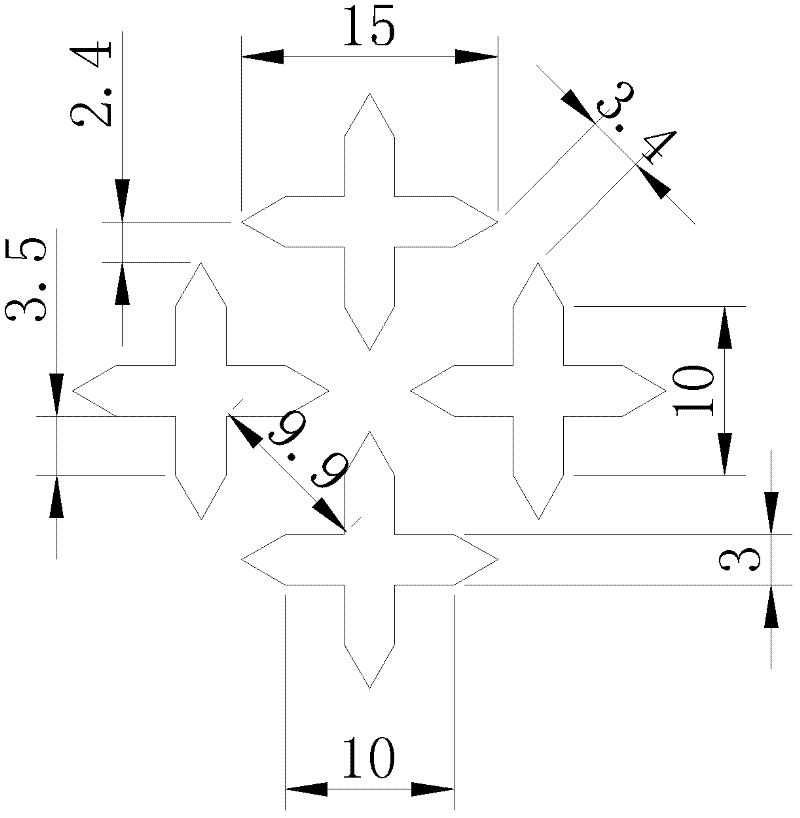

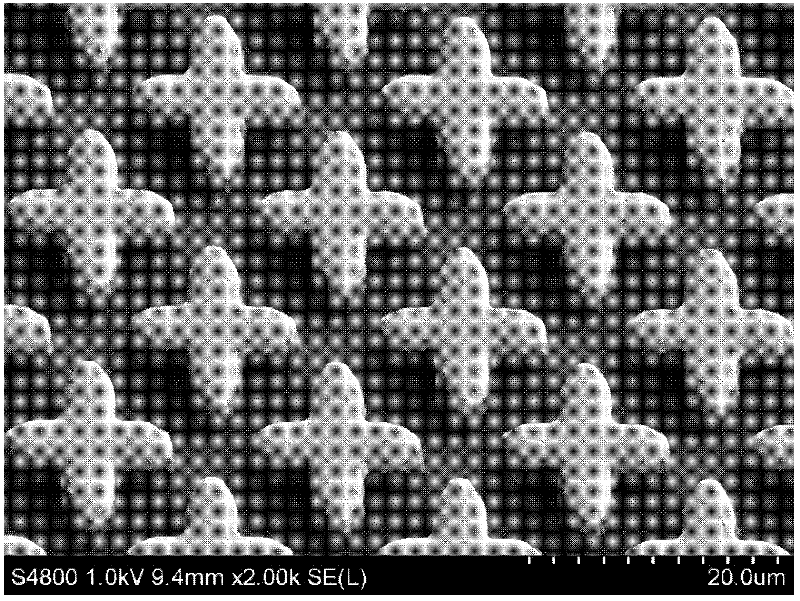

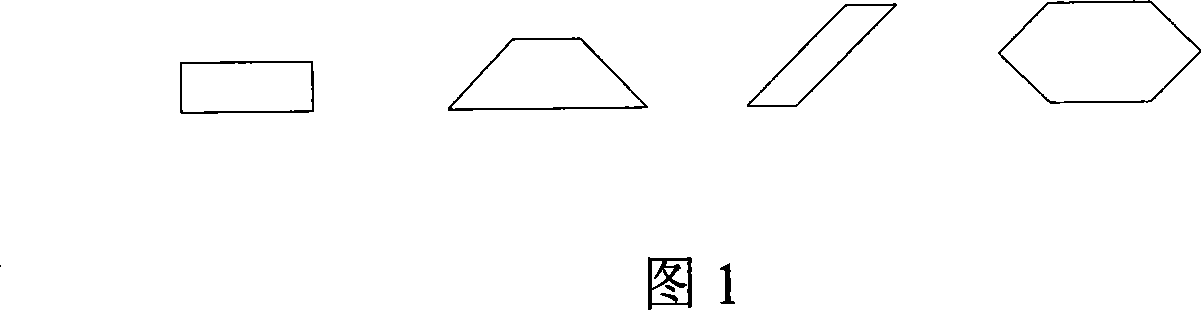

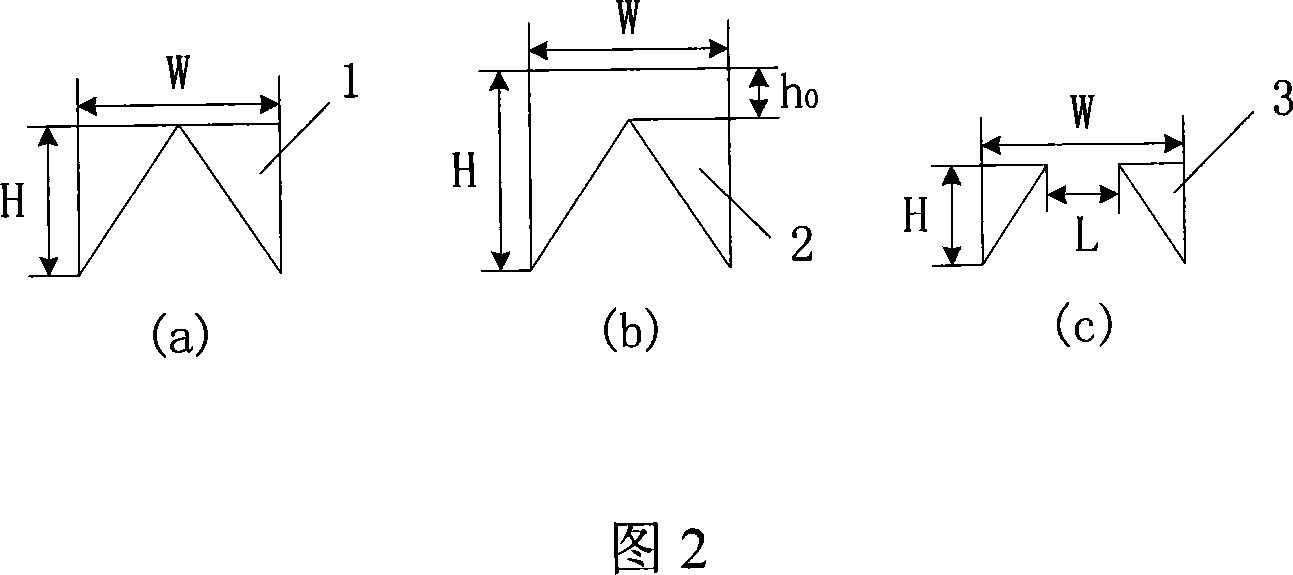

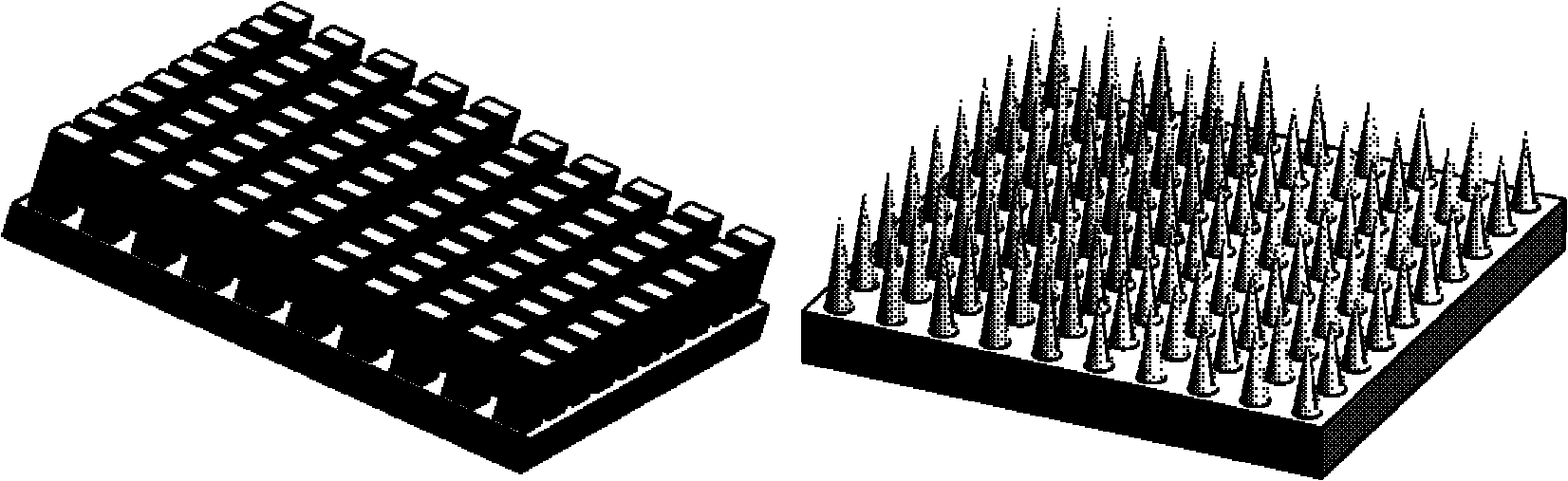

InactiveCN102417792AReduced attachment sitesGood adhesionAntifouling/underwater paintsPhotomechanical apparatusBiofoulingPhotomask

The invention relates to a preparation method of an antifouling material having a crossed regular microstructure on the surface. The method comprises the following steps of: etching a microstructure with a crossed pattern on a photomask, and arranging crossed cylindrical basic units with conical tail ends in a staggered way to form an array; forming a microstructure of a specified depth on the surface of a silicon chip by adopting a plasma deep silicon etching process; and preparing the antifouling material with themicrostructure by adopting a method for rolling over and copying polydimethylsiloxane. Due to the adoption of the crossed pattern of the microstructure and the arrangement mode, the contact area between a fouling organism and the material is reduced, the surface hydrophobicity of the material is enhanced, and adhesion of fouling organisms such as ulva spores, diatoms, barnacle larvae and the like can be effectively prevented. According to the material, an antifouling effectis achieved by using the microstructure on the surface, and loss is avoided; and moreover, the antifouling material can be self-cleaned under the action of water current erosion, is an environmentally-friendly antifouling material, and can be used for preventing and eliminating bio-fouling on the surfaces of ships and marine structural objects under marine environment.

Owner:725TH RES INST OF CHINA SHIPBUILDING INDAL CORP

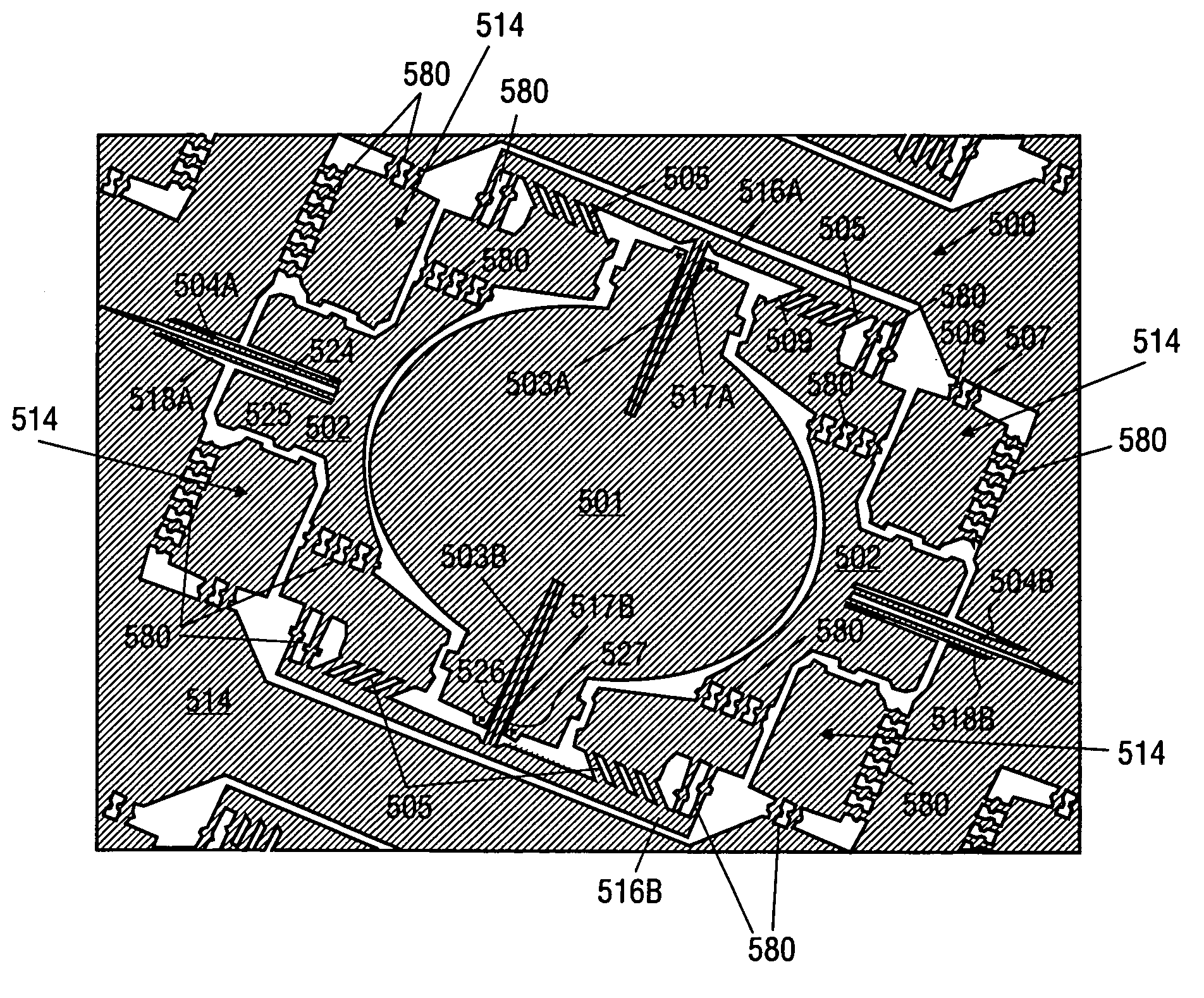

Electrostatic actuator for microelectromechanical systems and methods of fabrication

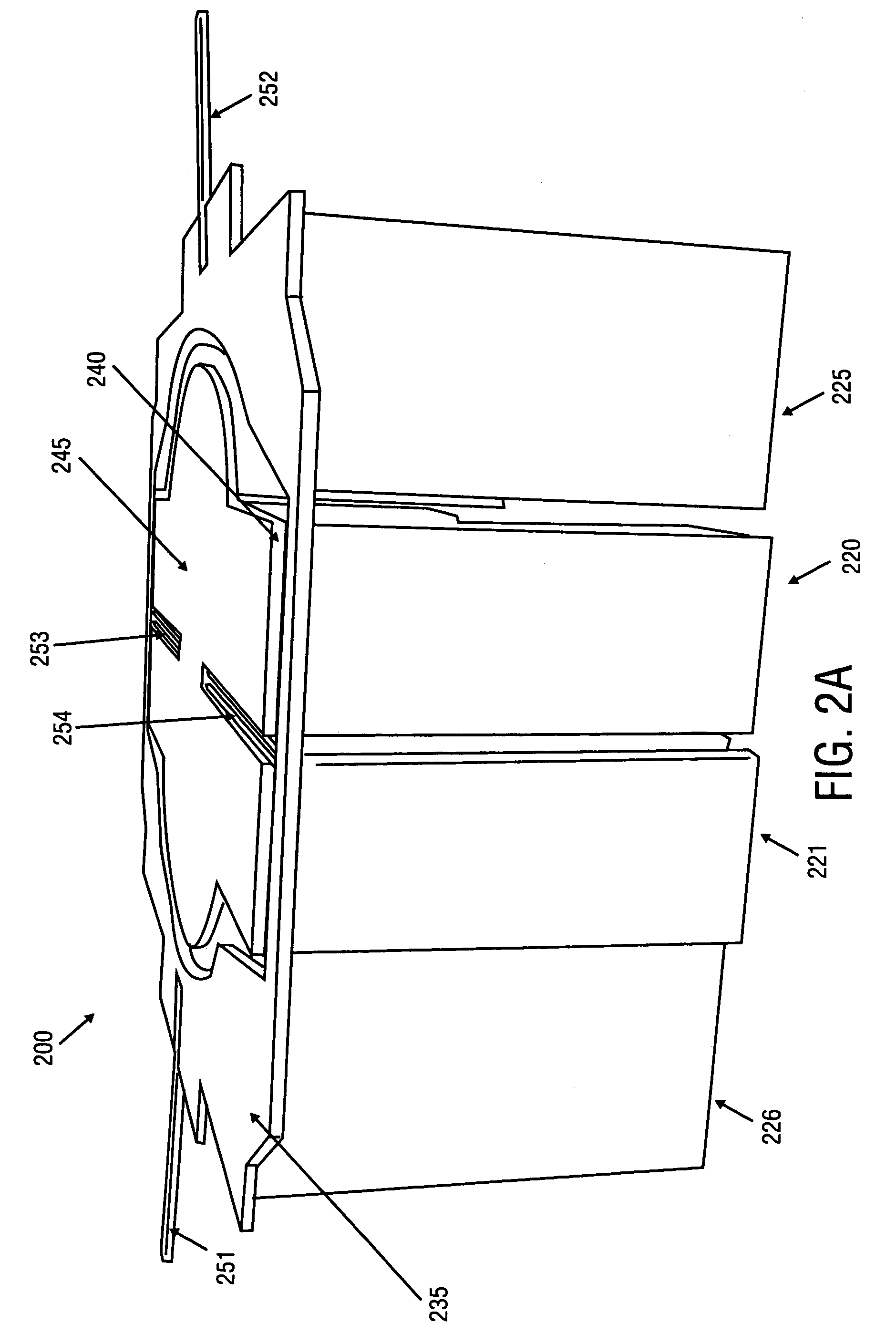

A method and apparatus are described that may be used to provide decoupled rotation of structures about different pivot points. The apparatus may include one or more fixed blades mounted to a frame or substrate, one or more movable blades mounted to each structure to be moved, and flexures on which the structures are suspended. Separate movable blades may be provided for each degree of freedom. When voltage is applied between the fixed and movable blades, the electrostatic attraction generates a force attracting movable blades toward blades that are fixed relative to the moveable blades, causing a structure to rotate about the flexures. The angle of rotation that results may be related to the size, number and spacing of the blades, the stiffness of the flexures and the magnitude of the voltage difference applied to the blades. The blades are fabricated using deep silicon etching.

Owner:CALIENT TECH

Wafer-level vacuum packaging method for MEMS devices

ActiveCN102275863AAvoid contactReduce infrared transmittanceDecorative surface effectsChemical vapor deposition coatingEngineeringSilicon etching

The invention provides a wafer-level vacuum encapsulating method for a micro-electromechanical device, which sequentially comprises the following steps of: 1, preparing a capping wafer and a device wafer, wherein the capping wafer is insulated silicon consisting of a front silicon layer, a back silicon layer and a middle silicon dioxide layer; 2, growing sealing rings on the front of the device wafer and the front of the capping wafer; 3, growing solder on the sealing ring on the front of the capping wafer; 4, performing deep silicon etching on the capping wafer by taking the sealing ring as a mask to obtain a groove; 5, growing a getter film on the front of the capping wafer, wherein the pattern of the getter film is obtained by a maskplate during growth; 6, heating to activate the getter film and bonding the capping wafer and the device wafer together by using bonding equipment; 7, growing an antireflection film on the back of the capping wafer, wherein the pattern of the antireflection film is obtained by the maskplate during growth; and 8, cutting the wafers. By adjusting process order, the influence of a next process on a result of a previous process is avoided, and the method is particularly suitable for encapsulating infrared devices.

Owner:北方广微科技有限公司

Suspended nitride film LED device and manufacturing method

ActiveCN103779452ASolve the problem of luminous efficiencyReduce internal lossesSemiconductor devicesRefractive indexSilicon etching

The invention discloses a suspended nitride film LED device and a manufacturing method thereof. A carrier can be a silicon substrate nitride wafer. The suspended nitride film LED device comprises a top nitride device layer and a silicon substrate layer. The method can achieve stripping of high-refractive-index silicon substrate layer and the nitride device layer, eliminate absorption of exciting light by the silicon substrate layer, and achieve manufacturing of the suspended nitride film LED device. A nanostructure is arranged on the upper surface of the top nitride device layer and used for improving the interface state of nitrides and improving the light emitting efficiency. With the back aligning and deep silicon etching technology, the silicon substrate layer under the LED device is removed, and the suspended nitride film LED device is obtained; the nitride back thinning etching technology is further adopted to obtain the ultrathin suspended nitride film LED device, internal loss of the LED device is lowered, and the light emitting efficiency is improved.

Owner:NANJING UNIV OF POSTS & TELECOMM

Method of etching silicon

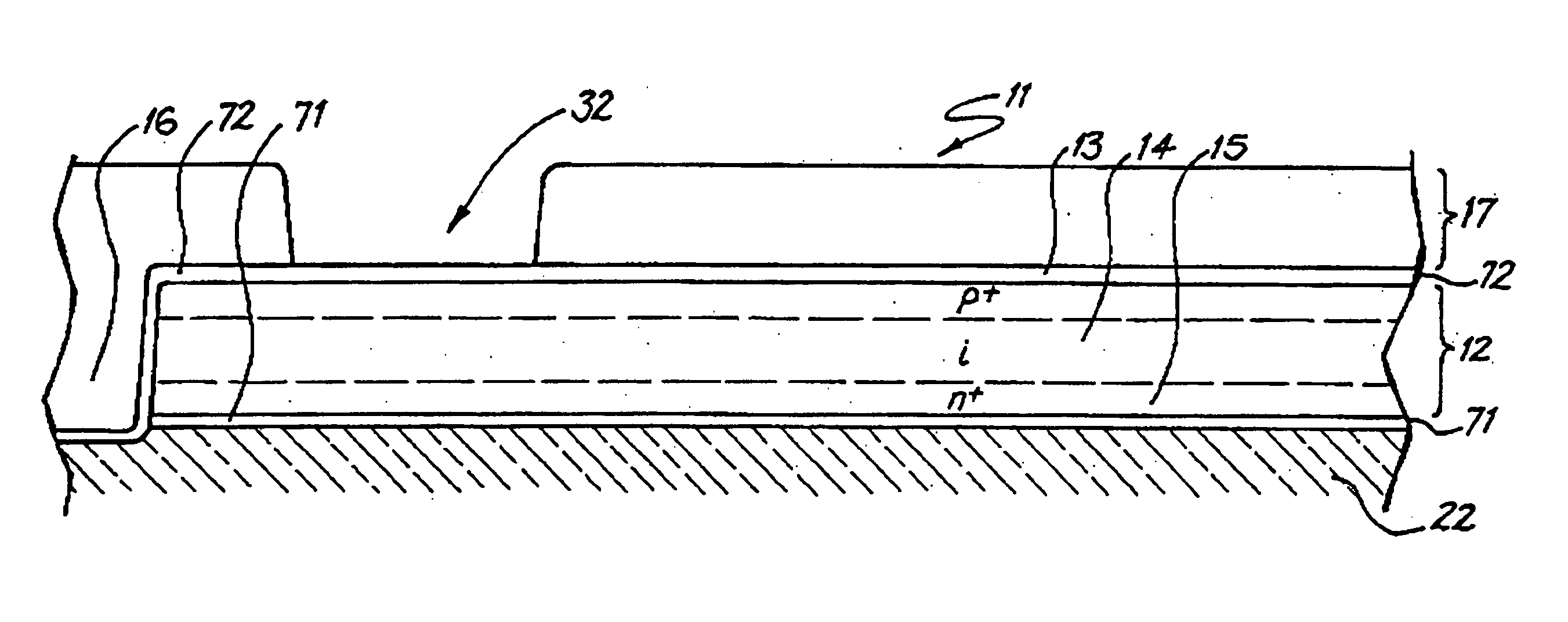

Silicon (12) is etched through a mask (11) comprising a layer of organic resin material (such as novolac) through which openings (32) are formed in the areas to be etched. The layer of organic resin is first deposited over a free surface of the device to be etched. The openings (32) are then formed by depositing droplets of a caustic etchant such as sodium hydroxide (NaOH) or potassium hydroxide (KOH) with an inkjet printer. The etchant reacts with the resin to expose the silicon surface in areas to be etched. The etching of the silicon surface is performed by applying a dilute solution of hydrofluoric acid (HF) and potassium permanganate (KMnO4) to the exposed surface through the openings in the mask to etch the silicon to a desired depth (83).

Owner:CSG SOLAR AG

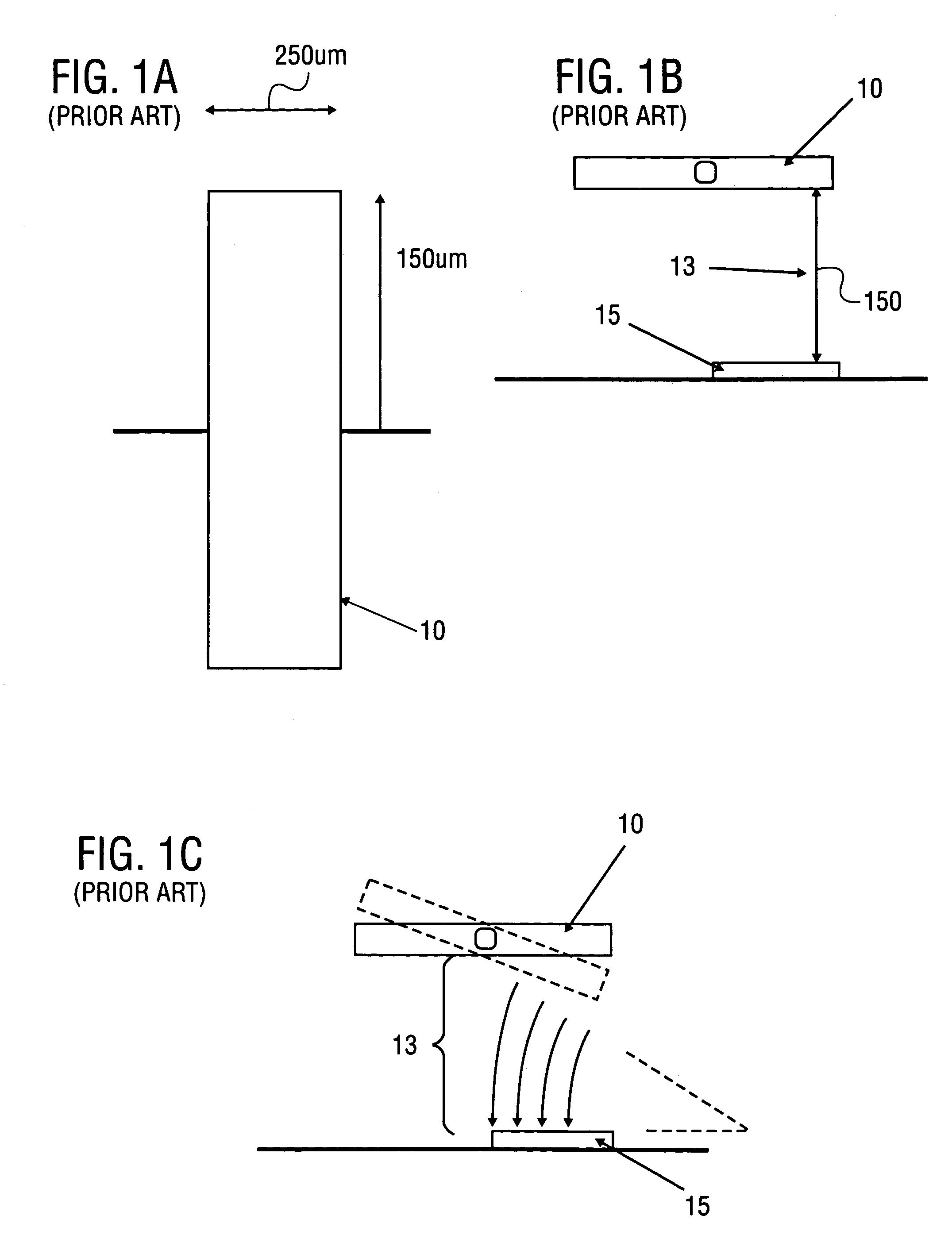

Scanning probe having integrated silicon tip with cantilever

ActiveUS20120060244A1Robust and economical processLamination ancillary operationsDecorative surface effectsAtomic force microscopyScanning probe microscopy

A cantilever-tip assembly for atomic force microscopy (AFM) or other scanning probe microscopy and its method of making based on micro-electromechanical systems (MEMS). Two crystalline silicon wafers and attached oxide and nitride layers are bonded together across an intermediate dielectric layer. A thin cantilever with a tetrahedral silicon probe tip at its distal end are formed in one wafer by anisotropic etching of silicon and a support structure is formed in the other wafer to support the proximal end of the cantilever preferably having an inclined face formed by anisotropic silicon etching. The cantilever may be silicon or silicon nitride.

Owner:APPLIED NANOSTRUCTURES INC

Silicon-based waveguide grating coupler on insulator and preparation method thereof

InactiveCN102253459AEfficient couplingReduce coupling lossCoupling light guidesFine structureLithographic artist

The invention relates to photonic device technical field, concretely providing a silicon-based waveguide grating coupler on an insulator and a preparation method thereof. The grating coupler comprises a Silicon-On-Insulator (SOI) chip. The SOI chip is characterized in that: the SOI chip is composed of a silicon substrate, a restriction layer and a top silicon layer, wherein the restriction layer is above the silicon substrate, the top silicon layer is above the restriction layer, a surface of the top silicon layer is provided with diffraction grating, a broad waveguide, a taper waveguide and a submicron waveguide connecting with the taper waveguide are provided at an opposite side of the diffraction grating, and a fiber used for receiving diffracted light is provided above the diffraction grating on the top silicon layer. The invention provides a preparation method of the grating coupler, electron beam exposure and common lithography are combined, which means that fine grating and the submicron waveguide structure are defined by the high precision electron beam exposure and a second silicon etching window is defined by the low precision common lithography, thus technology tolerance of production is substantially raised and integrity of a fine structure is guaranteed.

Owner:ZHEJIANG ORIENT CRYSTAL OPTICS

Cantilever structure and its making process and application

InactiveCN101066749AImprove manufacturing yieldImprove yieldDecorative surface effectsChemical vapor deposition coatingCapacitanceCantilever

The present invention relates to cantilever structure manufactured based on the anisotropic silicon etching and its making process, and belongs to the field of microelectronic mechanical system. The present invention features that the cantilever has pentagonal cross section, upper surface of (100) monocrystalline silicon face and lower surface of two (111) monocrystalline silicon faces. The cantilever structure is manufactured through anisotropic etching with the (111) faces as the automatic etching terminating face, and may be controlled precisely to result in high product quality. The present invention may be used in several MEMS devices, such as capacitance type acceleration sensor, resistance type acceleration sensor, micro mechanical gyro, etc for raised device manufacturing control level and device quality.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Selective silicon etch chemistries, methods of production and uses thereof

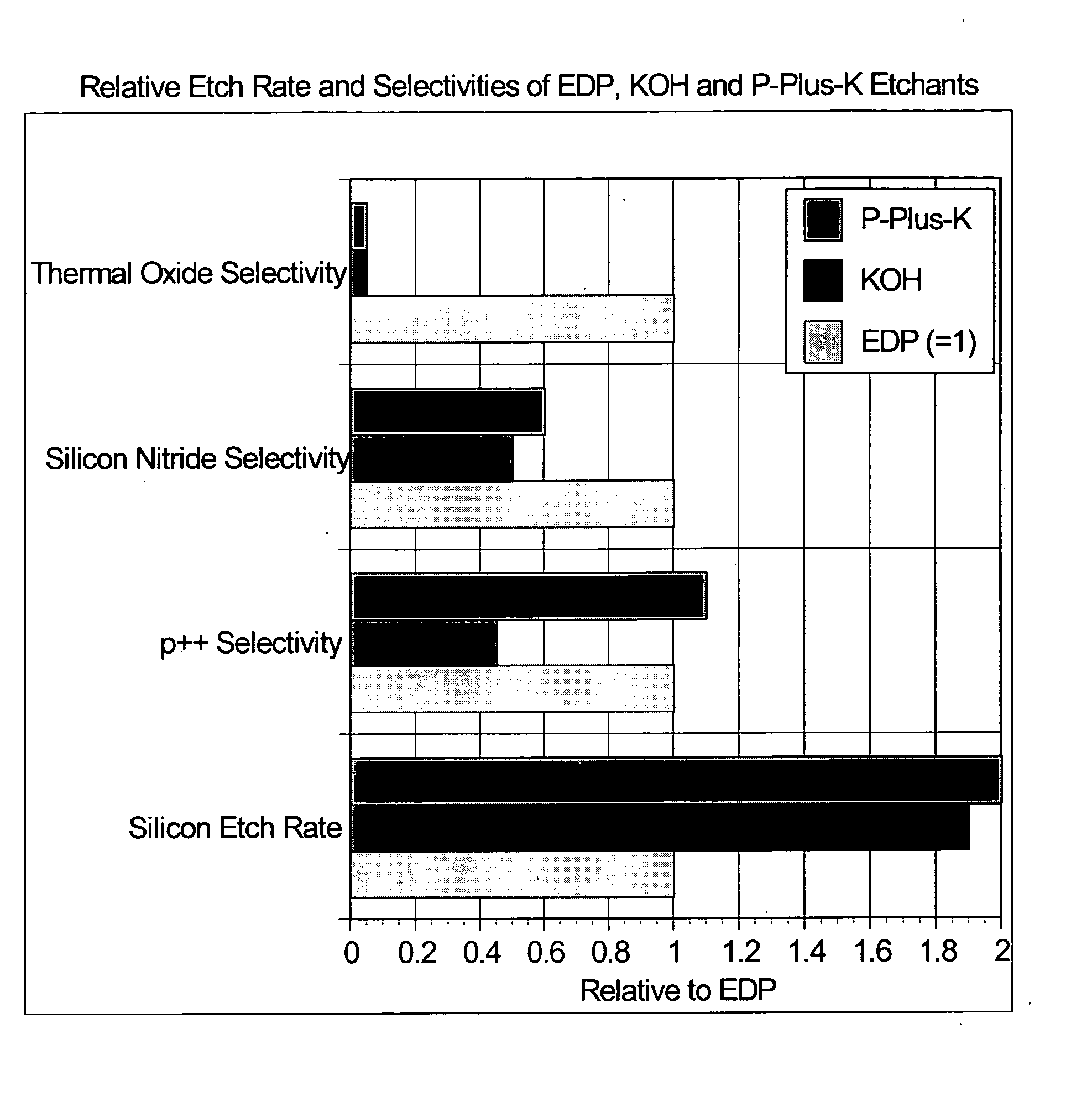

InactiveUS20050065050A1Surface-active detergent compositionsDetergent mixture composition preparationTetramethylammonium hydroxidePotassium hydroxide

Silicon etchants described herein are aqueous solutions that comprise at least one of potassium hydroxide or tetramethyl ammonium hydroxide; at least one additive, wherein the additive comprises at least two of the following physical properties: water-soluble, non-volatile and non-flammable; and an aqueous environment that comprises at least one solvent or solvent blend. Methods of producing a selective silicon etchant include: a) providing at least one of potassium hydroxide or tetramethyl ammonium hydroxide; b) providing at least one additive, wherein the additive comprises at least two of the following physical properties: water-soluble, non-volatile and non-flammable; c) providing an aqueous environment that comprises at least one solvent or solvent blend; and d) blending the at least one potassium hydroxide or tetramethyl ammonium hydroxide with the at least one additive in the aqueous environment in order to form a solution that can be utilized as a selective silicon etchant.

Owner:HONEYWELL INT INC

Silicon substrate suspended LED optical waveguide integrated photonic device and manufacturing method thereof

ActiveCN105445854ASolving integration challengesSimple manufacturing processOptical waveguide light guideNon-linear opticsPhotonicsWaveguide

The invention provides a silicon substrate suspended LED optical waveguide integrated photonic device and a manufacturing method thereof. The device is designed based on the anisotropic silicon etching technique, wherein the silicon substrate layer and the epitaxial buffer layer of the device are stripped to be removed and then a suspended nitride thin-film LED light waveguide integrated photonic device is obtained. Furthermore, based on the nitride backside thinning and etching technique, an ultra-thin silicon substrate suspended LED optical waveguide integrated photonic device is obtained. In this way, the internal loss of the LED device is lowered, and the light extraction efficiency is improved. According to the technical scheme of the invention, a light source and a light waveguide are integrated on the same piece of wafer. Therefore, the integration problem of a planar photonic single chip can be solved. At the same time, the light emitted from the LED is transmitted along the light waveguide. As a result, the light transmission problem inside the light waveguide can be solved, and the plane transmission function of the light is realized.

Owner:NANJING UNIV OF POSTS & TELECOMM

Dissociation of silicon clusters in a gas phase during chemical vapor deposition homo-epitaxial growth of silicon carbide

InactiveUS7247513B2Polycrystalline material growthSemiconductor/solid-state device detailsGas phaseProduct gas

A method of forming a layer of silicon carbide wherein silicon clusters are dissociated in a gas phase. Silicon clusters may be dissociated by a silicon-etching gas such as a group VII-containing component. A semiconductor device is also disclosed having a layer formed by the methods of the invention.

Owner:PRONOMIC IND

Photonic crystals splitter based on SOI and preparing method

InactiveCN1967298ALow insertion lossWide range of available bandwidthOptical waveguide light guidePhotonic crystalPhotonics

The invention involves a method based on SOI material photonic crystal splitter, including an SOI substrate material. In SOI silicon-etching produced the silicon column is the six-party or square lattice with the lattice. Silicon column height is the top of SOI silicon thickness, integrity in the lattice structure of silicon saving its column and forming splitter input waveguide, two output waveguide; input waveguide attached to the output waveguide two in the middle, with two output waveguide by a silicon-segregation. Front-end input waveguide also have at least one silicon column, the output waveguide also have at least the end of a silicon column. Connected with the outside, the SOI waveguide is placed in the input waveguide input, two output of the output waveguide. The SOI waveguide is of the same height of the silicon-contour. The splitter compact structure, its length than the conventional waveguide Y splitter narrow several times. By controlling the importation of isolation and the output waveguide, silicon waveguide column size can achieve different beam than the light output, therefore more flexibility and practicality.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Preparation method of hollow medical metal micro-needle

InactiveCN101623535AExcellent mechanical propertiesStrong penetrating powerMicroneedlesMedical devicesLithographic artistProcessing cost

The invention relates to a preparation method of a hollow medical metal micro-needle, which belongs to the technical field of biomedical engineering. The preparation method comprises the steps of firstly opening a silicon etching window on a double-throw oxide silicon wafer by lithography, wet-etching silicon in the window for obtaining a pyramid-shaped cavity, then throwing a negative photoresist on the silicon wafer for filling the pyramid-shaped cavity, adjusting the height of the micro-needle through the thickness of the negative photoresist, then selecting a specific mask for exposing and removing the negative photoresist in the pyramid-shaped cavity, obtaining a micro-needle cavity with different shape, sputtering a metal thin film in the micro-needle cavity as a conducting layer, electroplating a metal layer on the conducting layer, finally opening a micro-needle through hole in the micro-needle, removing the silicon and the negative photoresist, and further obtaining the hollow metal micro-needle with the different shape. The preparation method adopts the silicon and non-silicon compounding method for preparing the hollow metal micro-needle, and the processing cost is low. The shape of a needle tip of the micro-needle can be controlled by exposure, thereby improving the effect of inserting the micro-needle into skin, effectively controlling the height of the micro-needle and improving the strength of the micro-needle.

Owner:SHANGHAI JIAO TONG UNIV

Method for preparing step micro-needle array

InactiveCN101829394AEffective size controlReduce penetration resistanceMicroneedlesPhotomechanical apparatusSilicon chipSilicon etching

The invention discloses a method for preparing a step micro-needle array in the technical field of biomedical engineering. The method comprises the following steps of: gapping a silicon etching window on a silicon chip through photoetching and performing wet etching on the silicon in the silicon etching window; cutting the silicon chip to obtain a micro square column array by using a slicing machine, and further cutting the micro square column array to obtain micro square blocks; and finally performing the wet etching on the micro square column array to obtain the step micro-needle array. Micro-needle arrays with different heights are prepared by the method, and the micro-needle arrays puncture into the skin in a progressive mode. Meanwhile, the method has the advantage of simple preparation process, and the step micro-needle array is prepared by adopting the method of combining the wet etching with machining, so the cost is low and the method is convenient to popularize.

Owner:SHANGHAI JIAO TONG UNIV

Manufacturing method of adjustable FP (filter pass) optical filter based on MEMS (micro electro mechanical system) process

InactiveCN102225739AImprove yieldGood process compatibilityDecorative surface effectsChemical vapor deposition coatingAcid etchingEvaporation

The invention relates to a manufacturing method of an adjustable FP (filter pass) optical filter based on an MEMS (micro electro mechanical system) process, which is characterized in that the etching window of all graphs is manufactured by adopting the etching twice; the manufacturing of a middle FP air cavity and a movable reflector surface structure is finished by adopting the plasma silicon etching once; a movable silicon membrane reflector is manufactured by adopting the processes such as the silicon-silicon bonding, the plasma dry etching, the HF (hydrogen fluoride) acid etching and the silicon oxide layer releasing once; the high-reflection membrane and anti-reflection membrane of the two reflectors in the FP cavity are manufactured by adopting a method for selecting evaporation through a hard template; and a final FP cavity filter is formed by adopting the silicon-glass bonding once. In the manufacturing method provided by the invention, the process procedures are greatly simplified; the mirror finish and parallelism of the FP cavity are guaranteed; and the optical technical index and chip yield of the manufactured FP filter are improved. Compared with the existing like product manufacturing process, the manufacturing method provided by the invention has the advantages of good process compatibility and maneuverability, low driving voltage and good optical tuning repeatability and stability and can be widely applied to an optical communication WDM (wavelength division multiplex) system.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

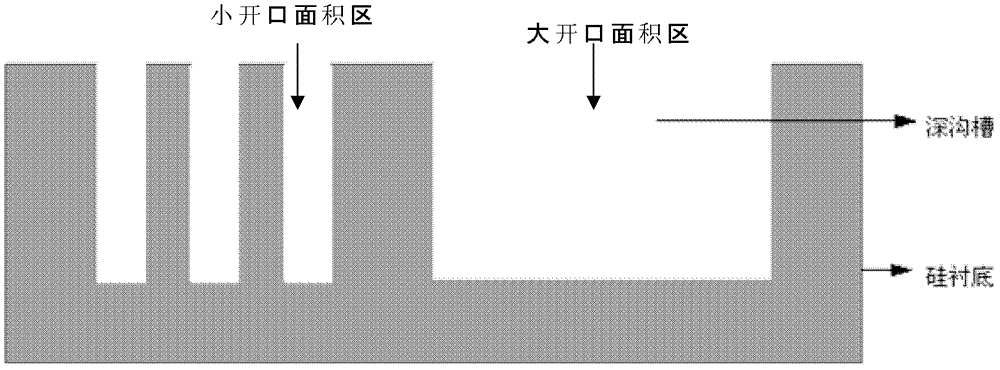

Method for reducing silicon etching loading effect

ActiveCN103065959ASolve the preparation processImprove etch loading effectSemiconductor/solid-state device manufacturingManufacturing technologySilicon oxide

The invention discloses a method for reducing a silicone etching loading effect. The method comprises the following steps of (1) forming a groove hard mask layer image, (2) enabling a silicon substrate to espouse in a zone with large opening area and keeping part of dielectric films in a zone with small opening area, (3) growing silicone in the zone with the large opening area and growing no silicon in the zone with the small opening area, and (4) conducting groove etching to form a final groove image. The dielectric films like silicon oxide and silicon nitride are kept in the zone (the zone with the small opening area) where etching speed is low, mono-crystalline silicon is exposed in the zone (the zone with the large opening area) where the etching speed is fast, the silicone is grown in the zone with the large opening area by the utilization of a selective epitaxial method, the compensation dosage of the grown silicon is worked out according to etching load to enable the final depths, in zones with different opening area, of groove structures to be the same so as to improve the etching loading effect, and therefore the problems of buried layer connection of bipolar transistors and manufacturing technology of optical branching devices are solved, and physical structures of grooves are realized.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Wafer level packaging MEMS chip structure and processing method thereof

ActiveCN110467148APrevent air leakageGood package sealingDecorative surface effectsSolid-state devicesThermal dilatationSignal processing circuits

The invention relates to a wafer level packaging MEMS chip structure and a processing method thereof, and the structure forms a cavity structure for the movement of a comb tooth microstructure of a device layer through the sequential bonding of a cap layer, the device layer and a substrate layer. Electrical signals in the packaging cavity are led out from the side surface of the structure by crossing a substrate bonding sealing ring by a first-layer lead of a double-layer metal lead arranged on the substrate layer; after metal eutectic bonding wafer-level vacuum packaging is completed, deep silicon etching is carried out at a position corresponding to a metal electrode on the back surface of a substrate wafer to form a through hole, a conductive material is used for filling the through hole or forming a conductive silicon column, and electrode leading-out is carried out on the back surface. The structure can be integrated with a signal processing circuit in a flip-chip bonding mode. Compared with a mode of manufacturing a TSV through hole in a packaging cavity for electrical lead-out, the problem of packaging air tightness caused by filling a cavity with an insulating medium is avoided, and the problems of temperature stability and reliability caused by mismatching of thermal expansion coefficients of a filling material and a silicon material are also avoided.

Owner:BEIJING INST OF AEROSPACE CONTROL DEVICES

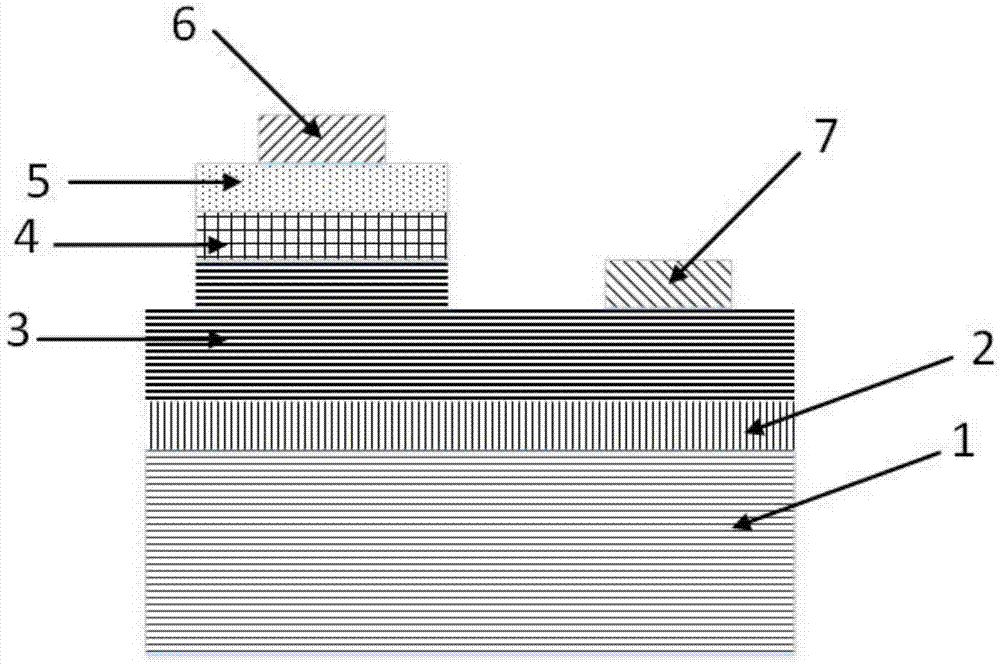

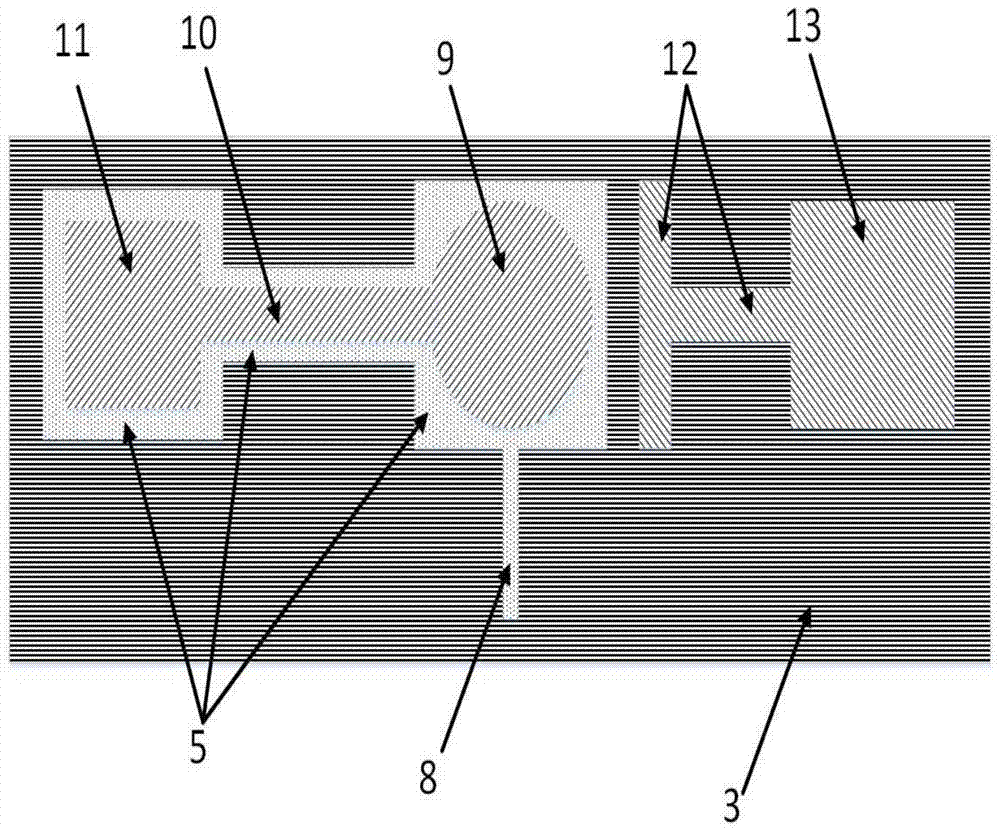

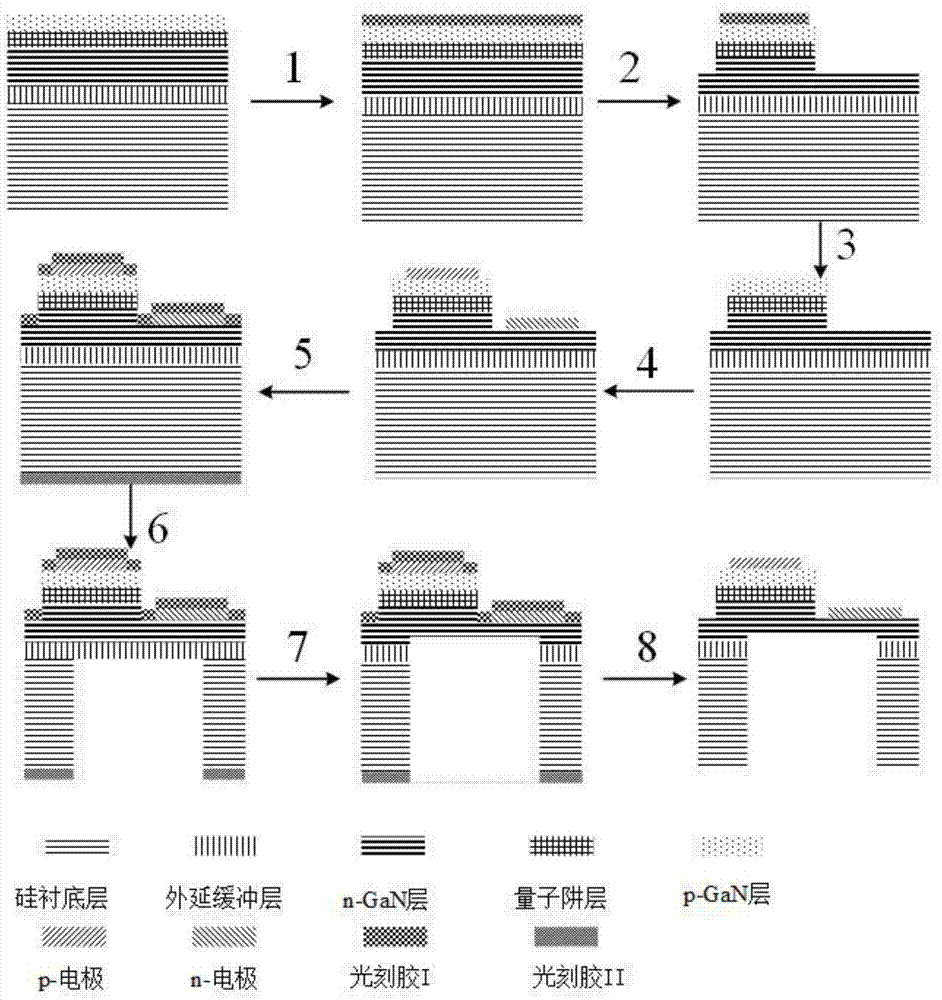

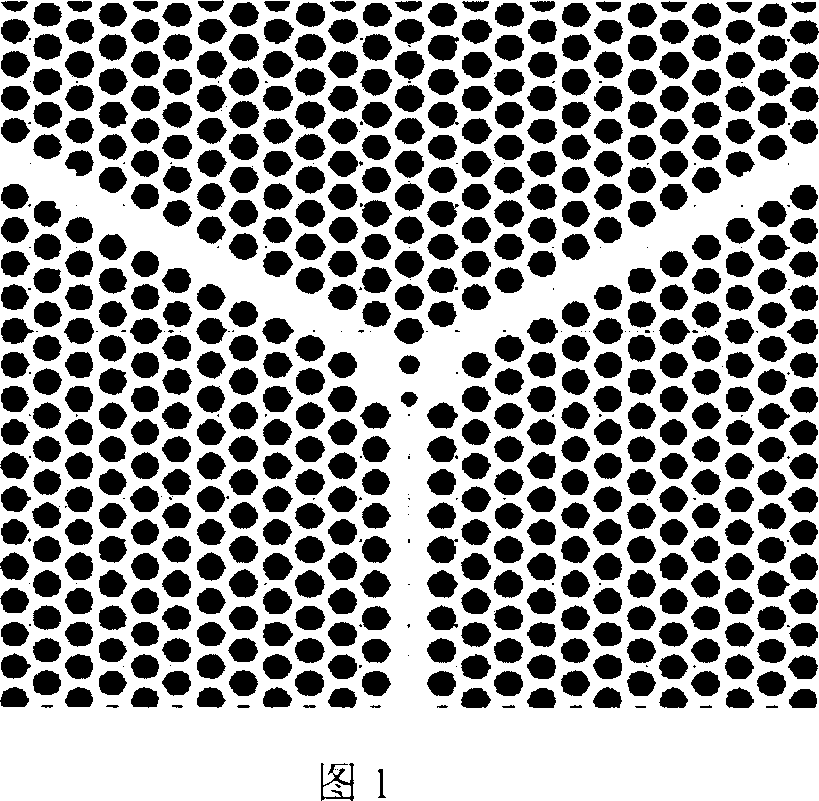

A vertical cavity surface emitting silicon substrate GaN laser based on a dielectric Bragg mirror and a preparation method thereof

InactiveCN109149361AGood thermal conductivityGood for mass productionLaser detailsSemiconductor lasersDielectricInsulation layer

The invention discloses a vertical cavity surface emitting silicon substrate GaN laser based on a dielectric Bragg mirror and a preparation method thereof, Using deep silicon etching technology, the silicon substrate on the bottom of the device is stripped completely, and then the AlN layer, AlGaN layer and part of n-GaN layer are etched off from the back by inductively coupled plasma reactive ionetching technology. GaN lay to regulate that length of the vertical resonant microcavity; The mirrors at the top and bottom of the vertical resonant microcavity are realized by electron beam evaporation technology to deposit dielectric Bragg mirrors. The insulating insulation layer and the top mirror located below the p-type electrode bonding region are simultaneously accomplished using a one-step electron beam evaporation process. During the fabrication process, tunable wavelength and controllable laser direction can be obtained by adjusting the related parameters to achieve the laser wavelength and emission direction selection, so as to obtain an electrically pumped GaN laser. The vertical cavity surface emitting silicon substrate GaN laser based on the dielectric Bragg mirror has low cost, simple preparation process and can be used in a plurality of fields.

Owner:NANJING INST OF TECH

Optical pumping nitride echo wall laser performing emission in single direction and preparation method thereof

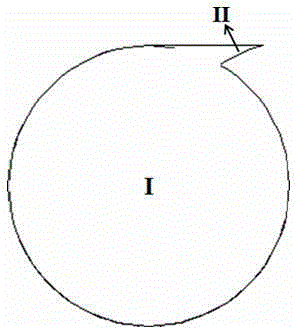

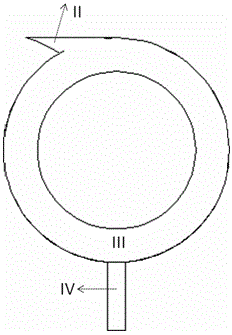

InactiveCN105337168AHigh precisionEtching deviation is smallLaser detailsLaser optical resonator constructionOptical pumpingErbium lasers

The invention discloses an optical pumping nitride echo wall laser performing emission in the single direction and a preparation method thereof. Asymmetric nitride suspension thin film microcavities are prepared in nitride materials on a silicon substrate via the photoetching technology and the deep silicon etching technology. Echo wall die laser emitting in the single direction is obtained in the proper optical pumping condition.

Owner:NANJING UNIV OF POSTS & TELECOMM

Electric pump gallium nitride micro laser capable of achieving single-direction emission and preparation method thereof

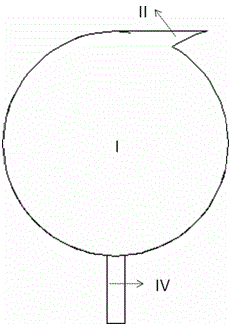

InactiveCN104009393AHigh optical gainReduce lossLaser detailsLaser optical resonator constructionWhispering galleryUltraviolet

The invention discloses an electric pump gallium nitride micro laser capable of achieving single-direction emission and a preparation method of the electric pump gallium nitride micro laser. The method comprises the steps of firstly utilizing silicon-based p-type gallium nitride / quantum well / n-type gallium nitride materials, utilizing the electron beam etching technology and the deep-silicon etching technology for preparing an asymmetric gallium nitride suspension thin film micro-cavity supported by a single cantilever beam, conducting vapor deposition of an Au / Ni electrode on the front face of a wafer, conducting vapor deposition of Au / Ti on the surface of the n-type gallium nitride, adopting the ultrasonic bonding technology, bonding a lead on the surface of the electrode, and finally preparing the complete laser. According to the electric pump gallium nitride micro laser and the preparation method of the electric pump gallium nitride micro laser, a proper current is exerted on the prepared laser, and whispering gallery mode ultraviolet laser with single-direction emission is obtained.

Owner:NANJING UNIV OF POSTS & TELECOMM

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com