Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2260results about How to "Improve manufacturing yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

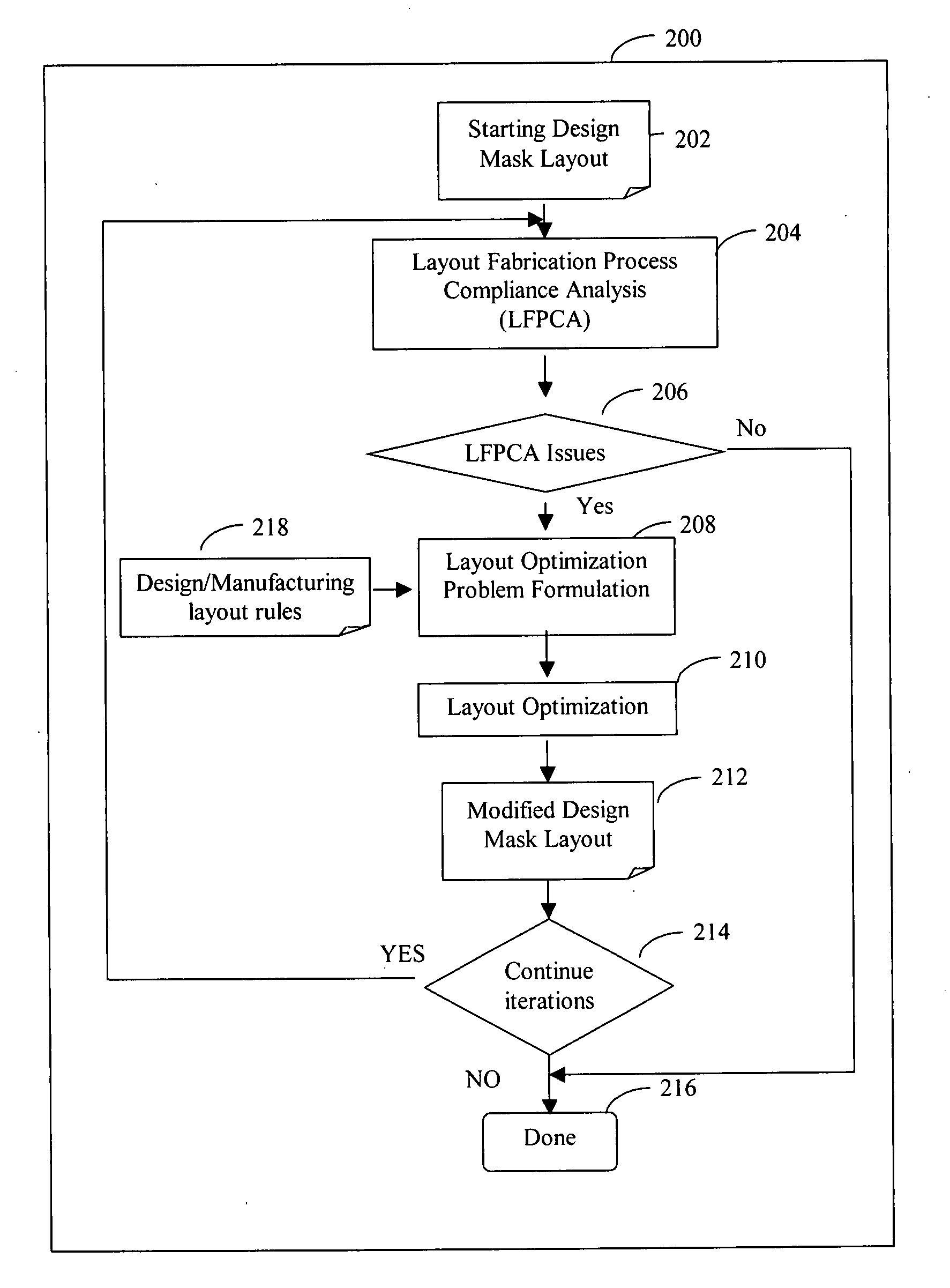

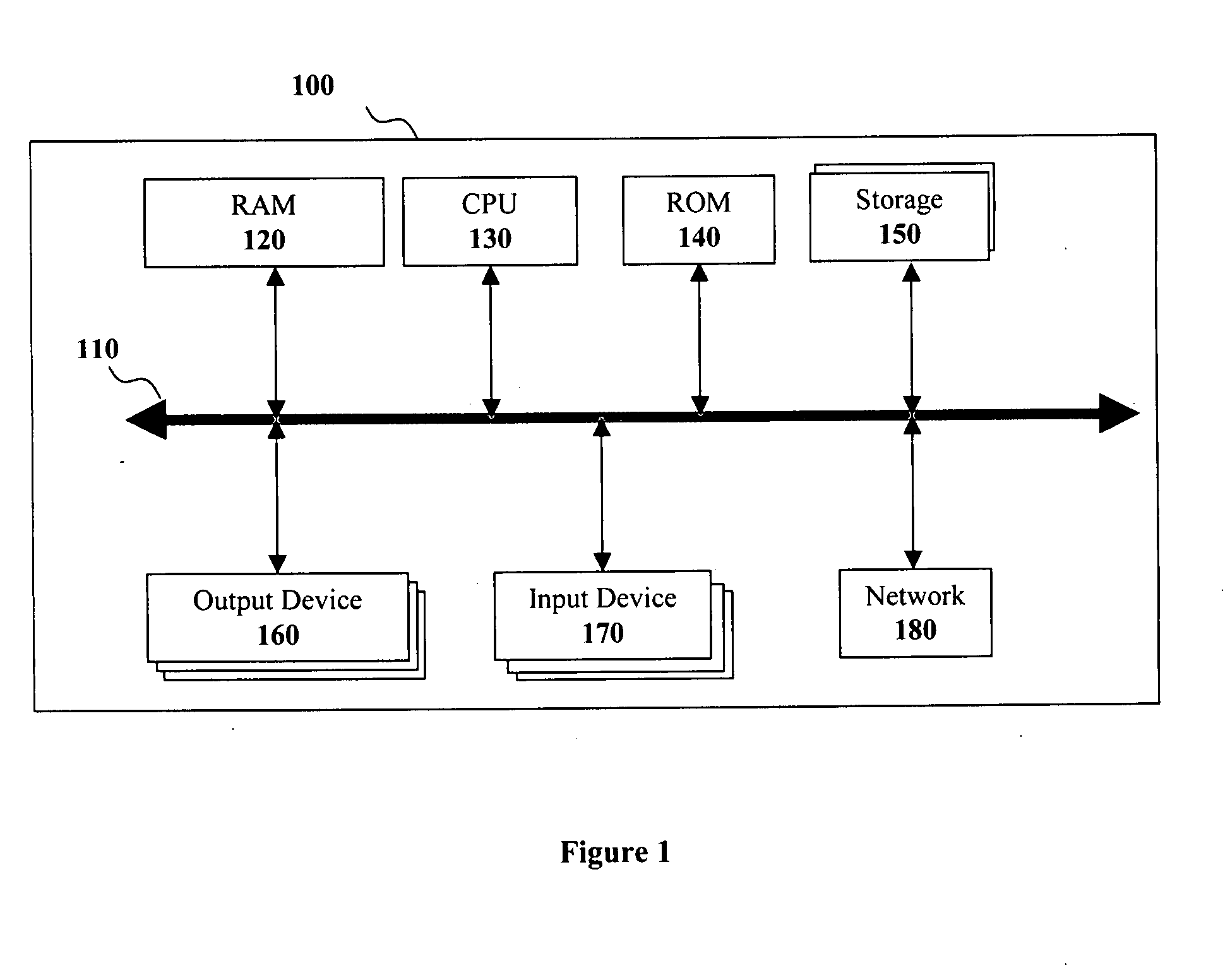

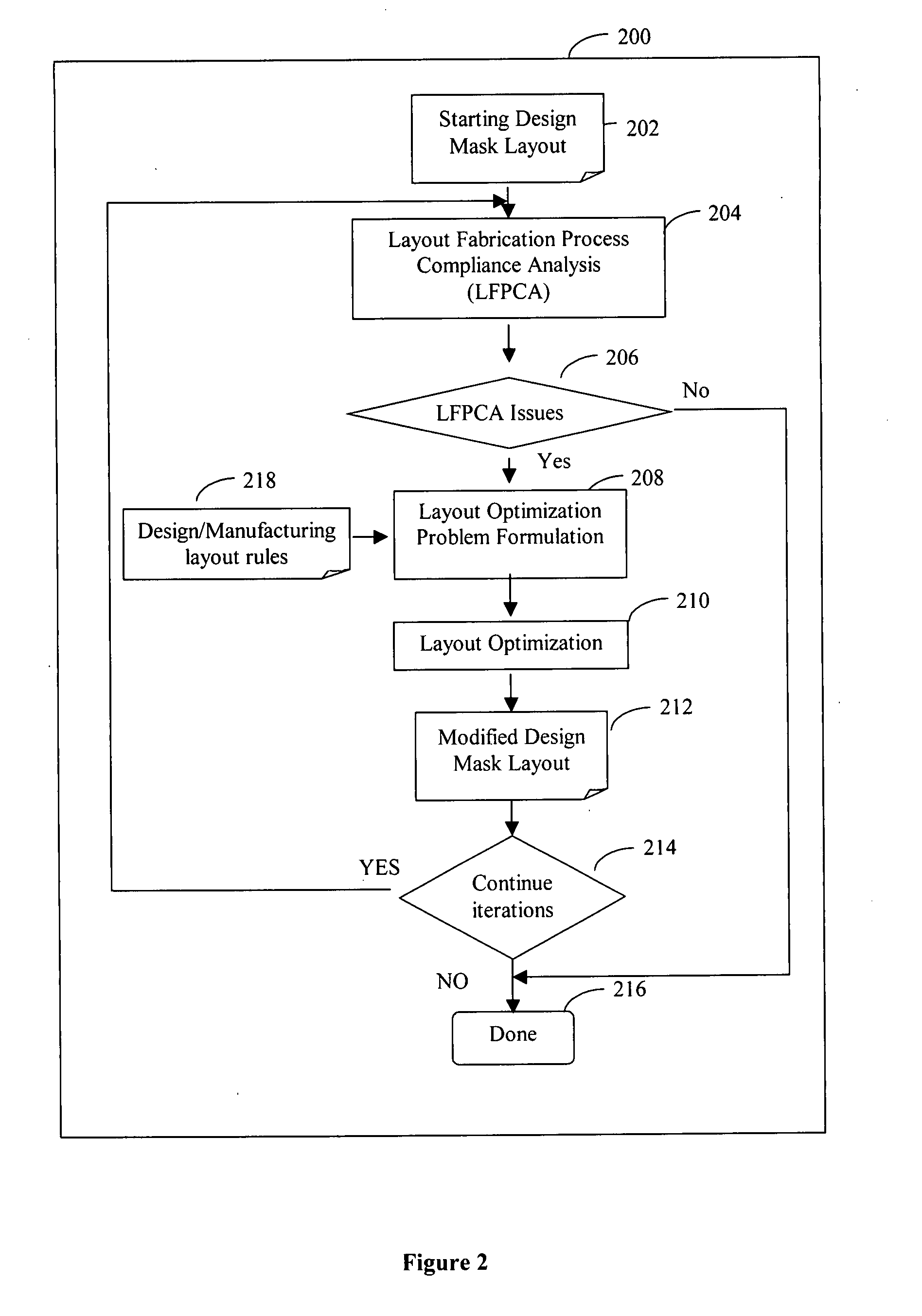

System and method of maximizing integrated circuit manufacturing yield with fabrication process simulation driven layout optimization

InactiveUS20080046846A1Maximizing manufacturing yieldYield maximizationCAD circuit designSoftware simulation/interpretation/emulationIntegrated circuit manufacturingEngineering

A system and a method of maximizing the manufacturing yield of integrated circuit (“IC”) design using IC fabrication process simulation driven layout optimization is described. An IC design layout is automatically modified through formulation of a layout optimization problem utilizing the results of layout fabrication process compliance analysis tools. The modification of layout is performed adaptively and iteratively to make an IC layout less susceptible to yield issues while maintaining design rule correctness and minimal circuit performance impact.

Owner:CHEW MARKO P +1

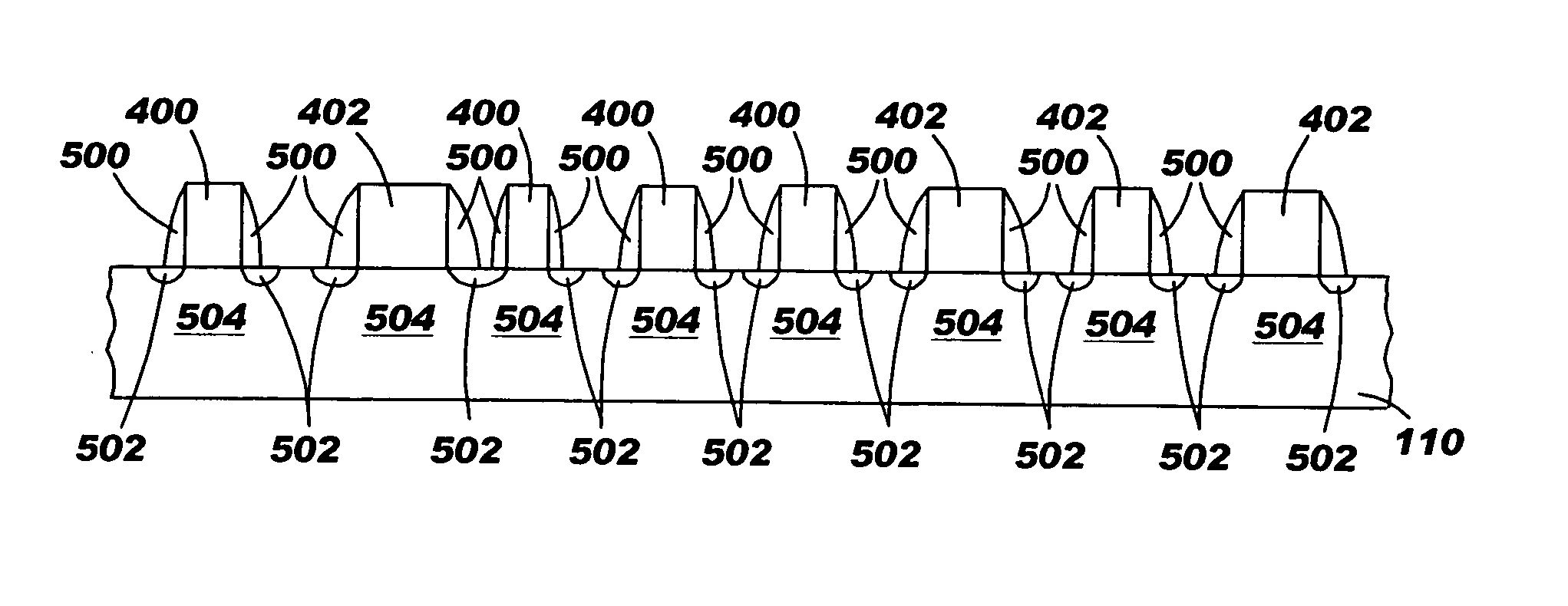

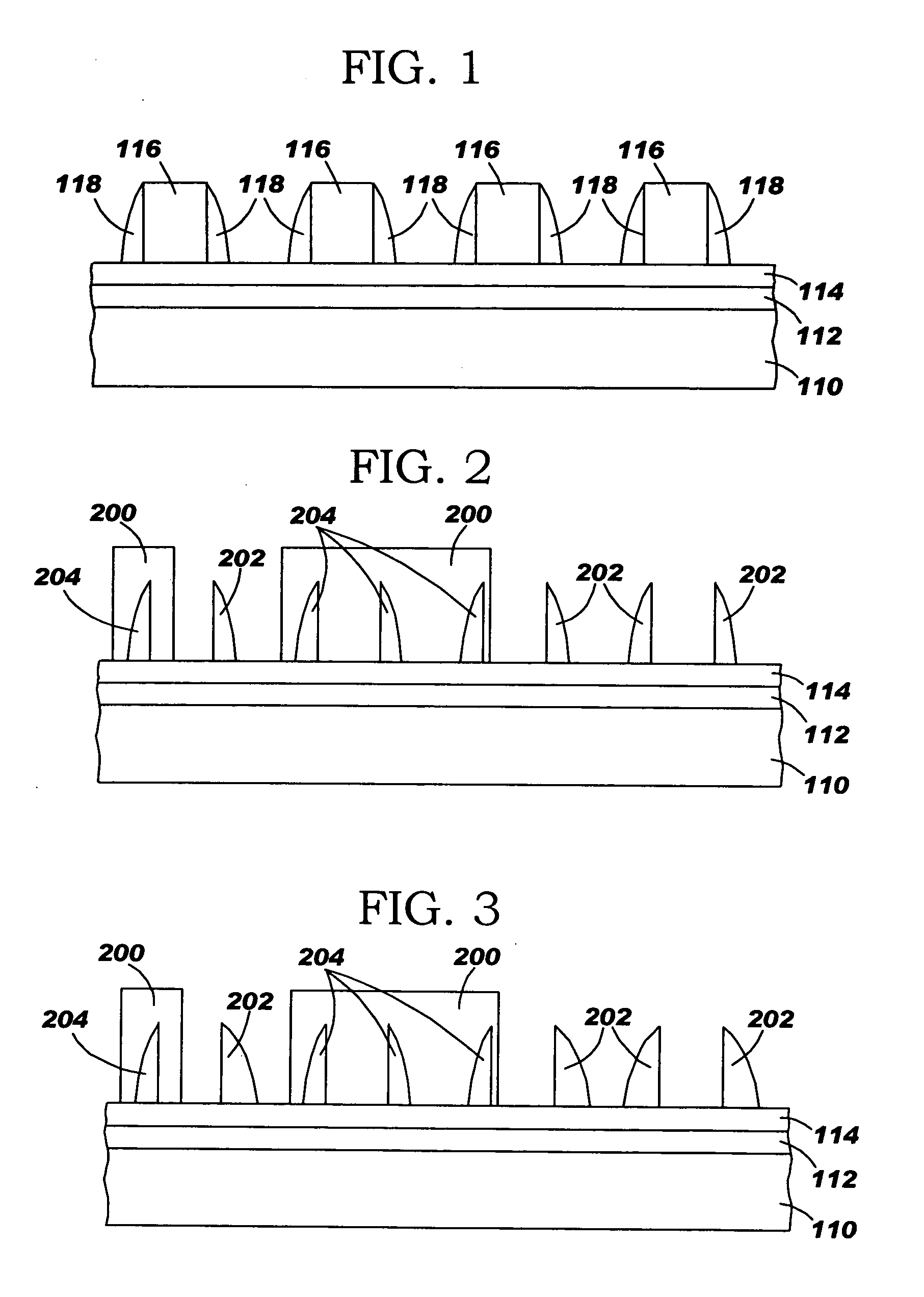

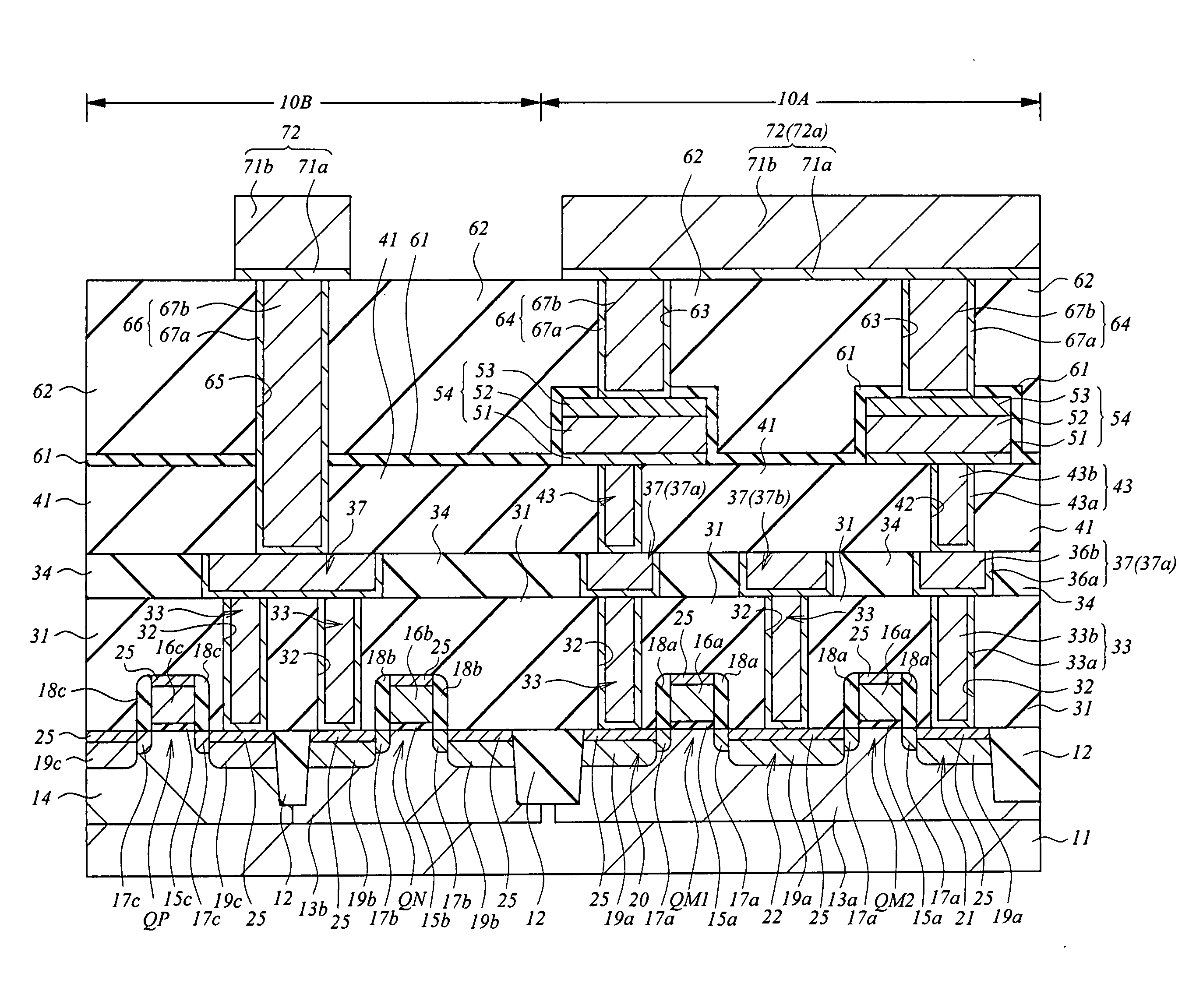

Method of independent P and N gate length control of FET device made by sidewall image transfer technique

InactiveUS20050153562A1Different sizeSelectively exposeSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectrical conductor

Disclosed is a method that forms a conductive layer on a substrate and patterns sacrificial structures above the conductive layer. Next, the invention forms sidewall spacers adjacent the sacrificial structures using a spacer material capable of undergoing dimensional change, after which the invention removes the sacrificial structures in processing that leaves the sidewall spacers in place. The invention then protects selected ones of the sidewall spacers using a sacrificial mask and leaves the other ones of the sidewall spacers unprotected. This allows the invention to selectively expose the unprotected sidewall spacers to processing that changes the size of the unprotected sidewall spacers. This causes the unprotected sidewall spacers have a different size than protected sidewall spacers. Then, the invention removes the sacrificial mask and patterns the conductive layer using the sidewall spacers as a gate conductor mask to create differently sized gate conductors on the substrate. Following this, the invention removes the sidewall spacers and forms the source, drain, and channel regions adjacent the gate conductors.

Owner:IBM CORP

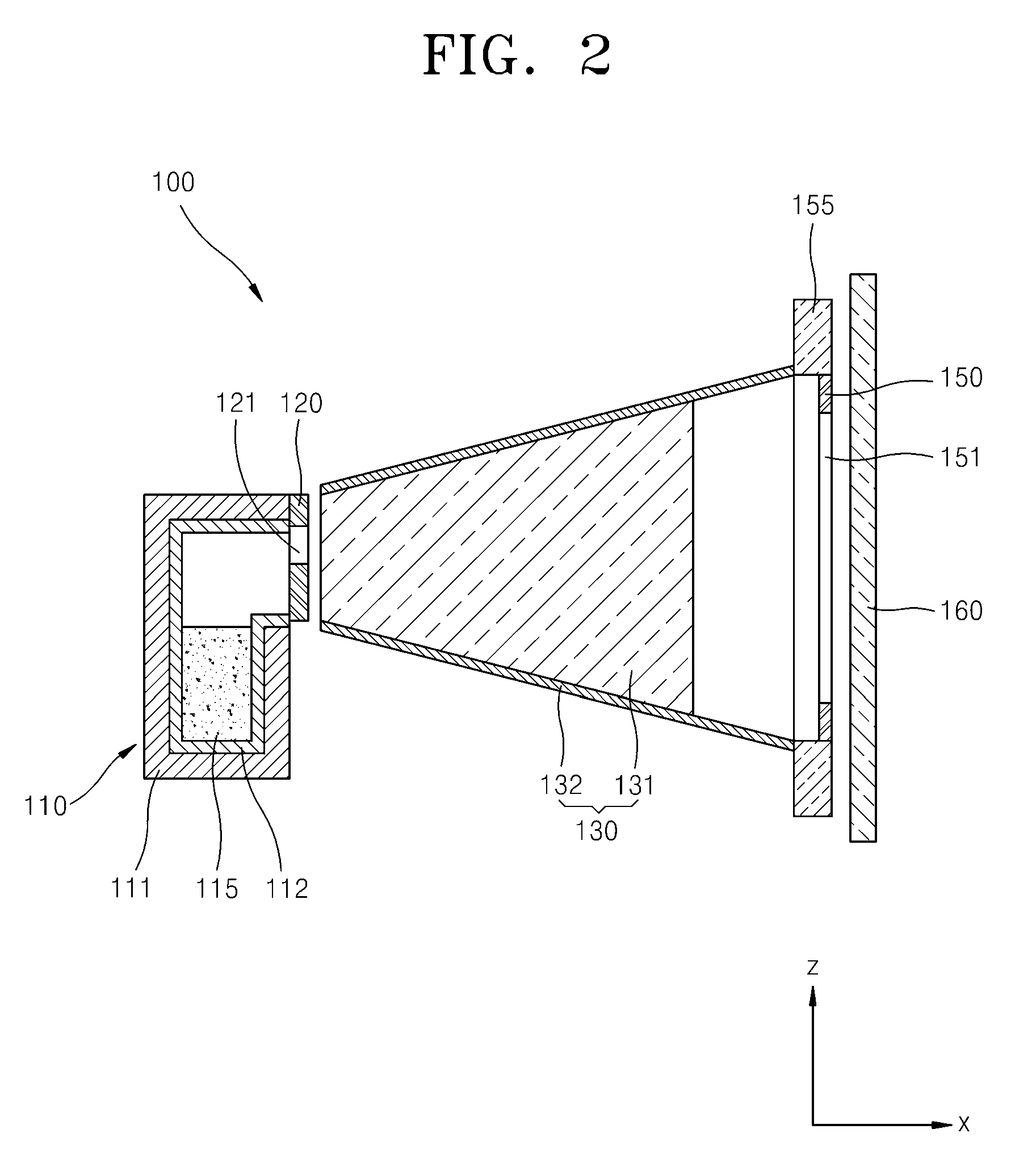

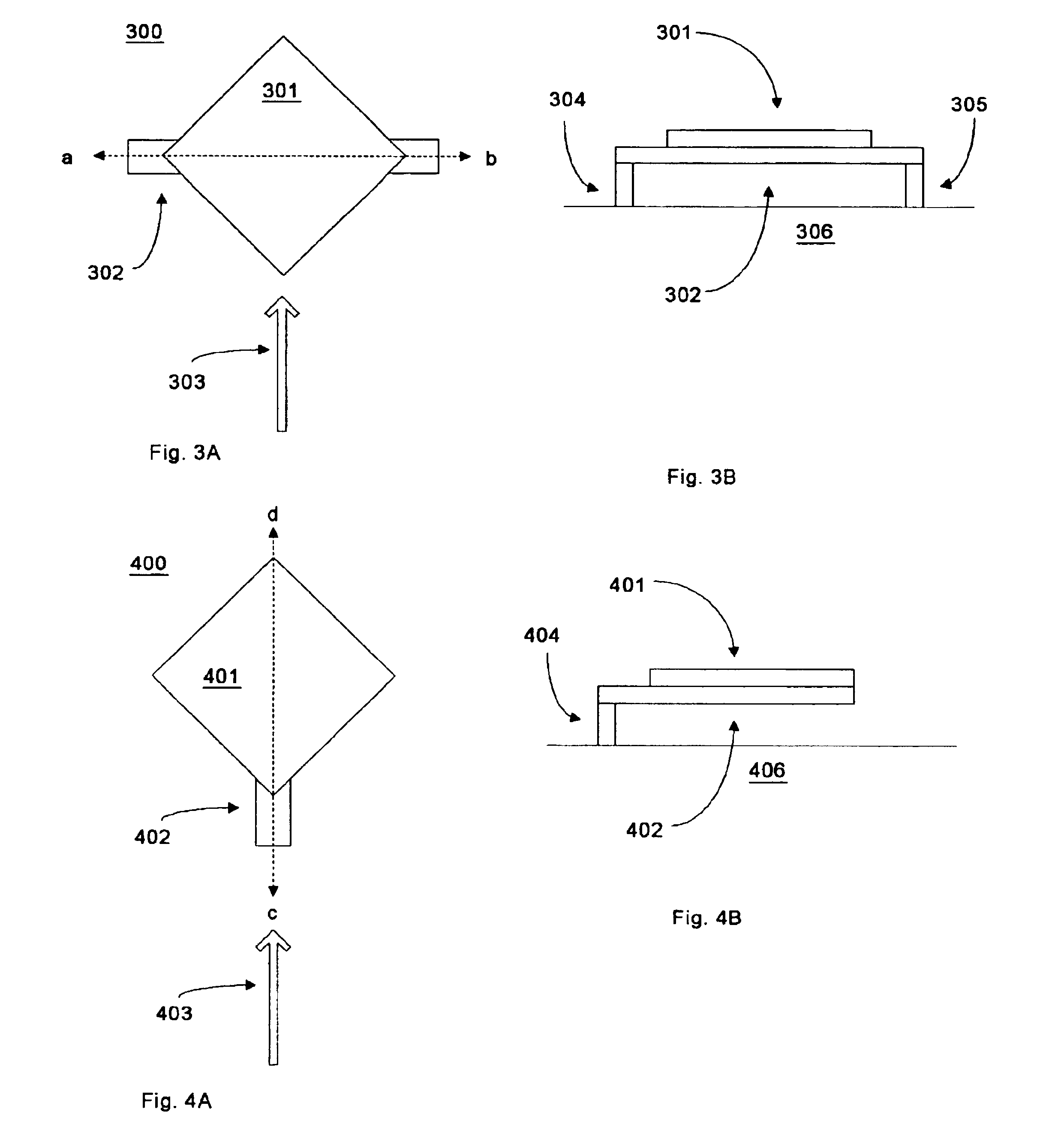

High performance micromirror arrays and methods of manufacturing the same

InactiveUS6862127B1Improved dielectric isolationImprove manufacturing yieldSemiconductor/solid-state device manufacturingPiezoelectric/electrostrictive devicesSpatial light modulatorEngineering

A 1 dimensional or 2 dimensional array of micromirror devices comprises a device substrate with a 1st surface and a 2nd surface, control circuitry disposed on said 1st surface and a plurality of micromirrors disposed on said 2nd surface. Each micromirror comprises a reflective surface that is substantially optically flat, with neither recesses nor protrusions. Such a 1 dimensional or 2 dimensional array of micromirror devices may be used as a spatial light modulator (SLM). Methods of fabricating arrays of micromirror devices are also disclosed. Such methods generally involve providing a device substrate with a 1st surface and a 2nd surface, fabricating control circuitry on the 1st surface, and fabricating micromirrors on the 2nd surface, such that the reflective surfaces of the micromirrors are substantially optically flat, with neither recesses nor protrusions.

Owner:IGNITE INC

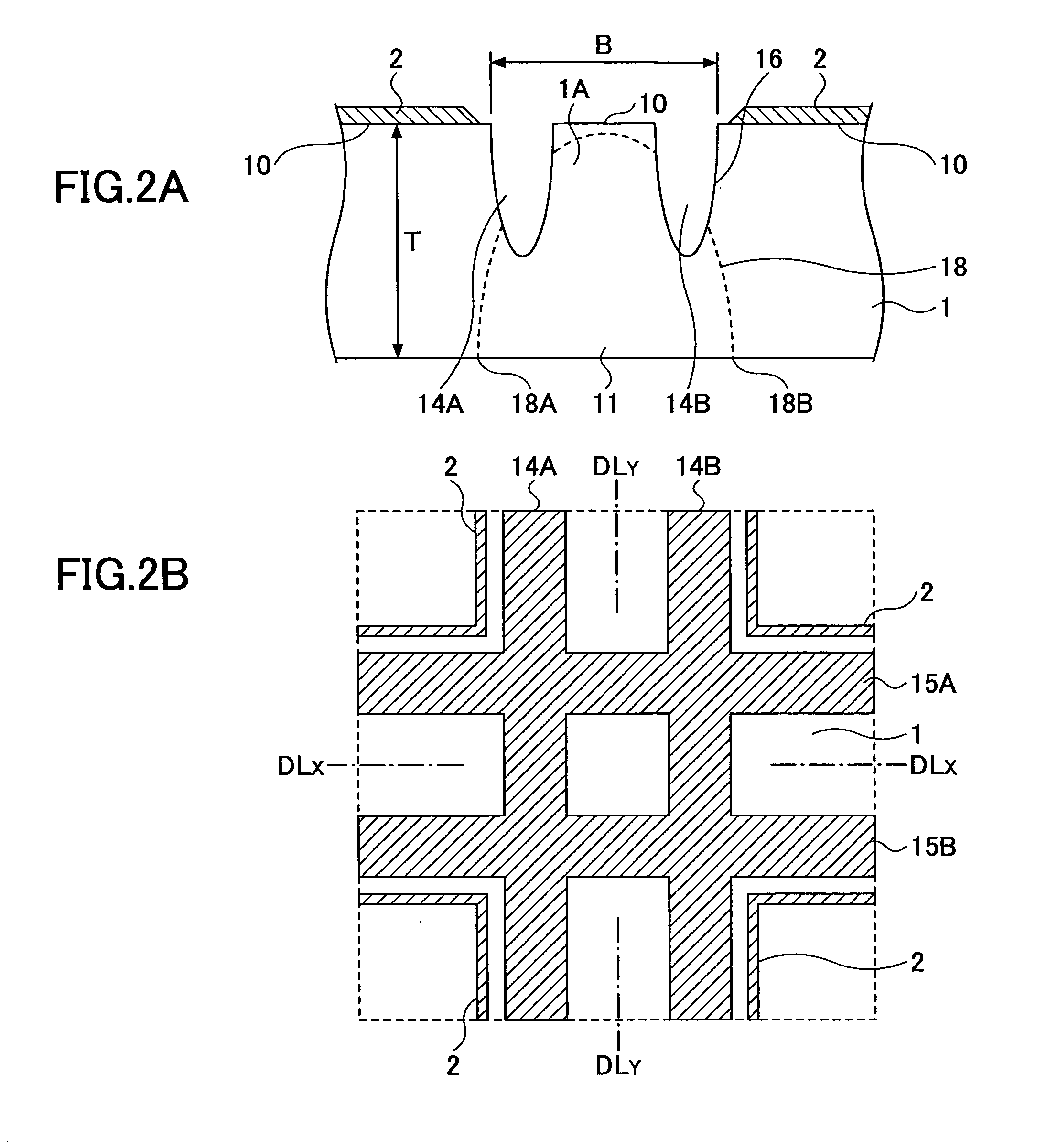

Manufacturing process and structure of through silicon via

InactiveUS20090014843A1Improve manufacturing yieldSemiconductor/solid-state device detailsSolid-state devicesSemiconductorThrough-silicon via

A through silicon via reaching a pad from a second surface of a semiconductor substrate is formed. A penetration space in the through silicon via is formed of a first hole and a second hole with a diameter smaller than that of the first hole. The first hole is formed from the second surface of the semiconductor substrate to the middle of the interlayer insulating film. Further, the second hole reaching the pad from the bottom of the first hole is formed. Then, the interlayer insulating film formed on the first surface of the semiconductor substrate has a step shape reflecting a step difference between the bottom surface of the first hole and the first surface of the semiconductor substrate. More specifically, the thickness of the interlayer insulating film between the bottom surface of the first hole and the pad is smaller than that in other portions.

Owner:RENESAS ELECTRONICS CORP

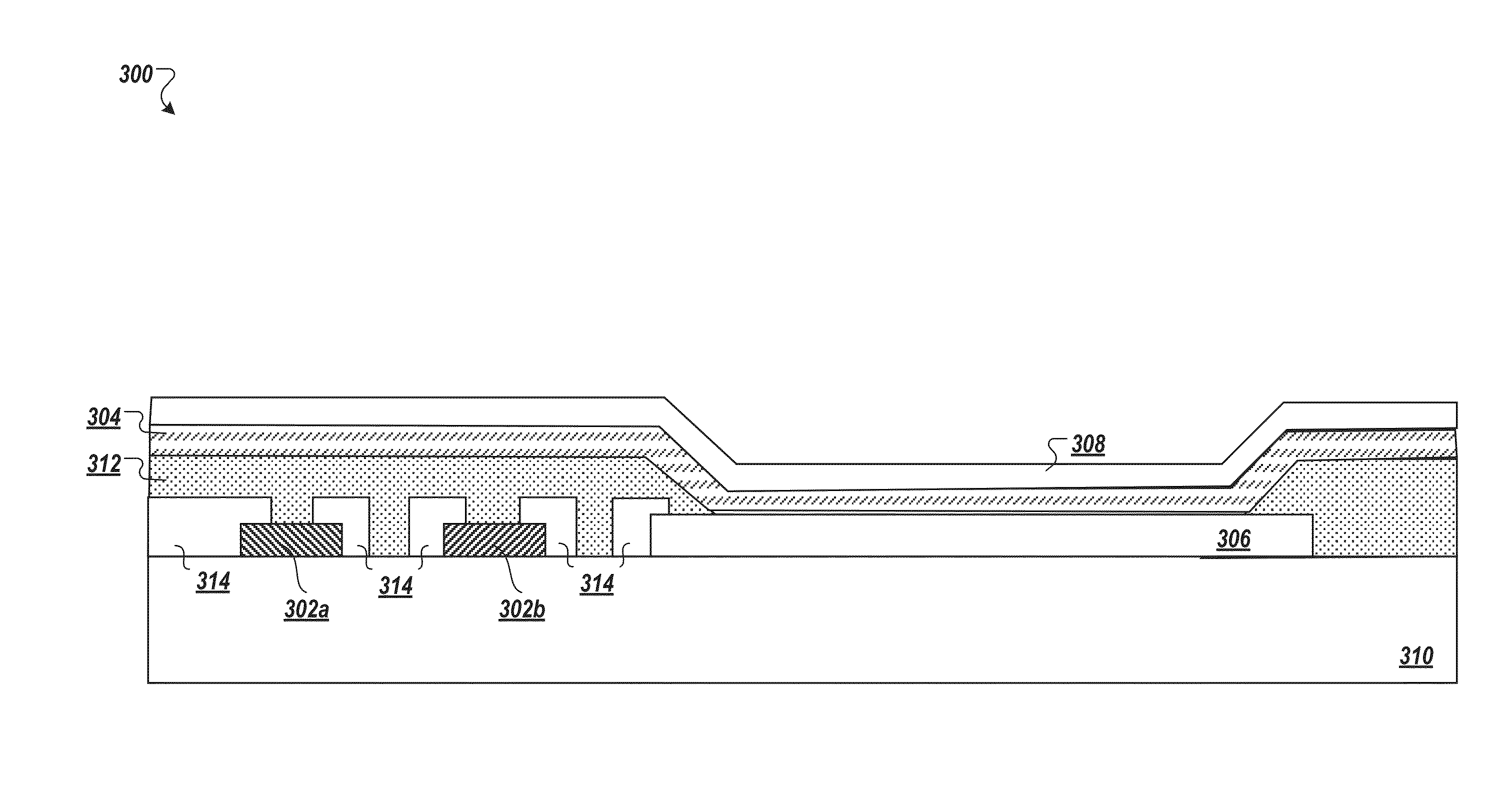

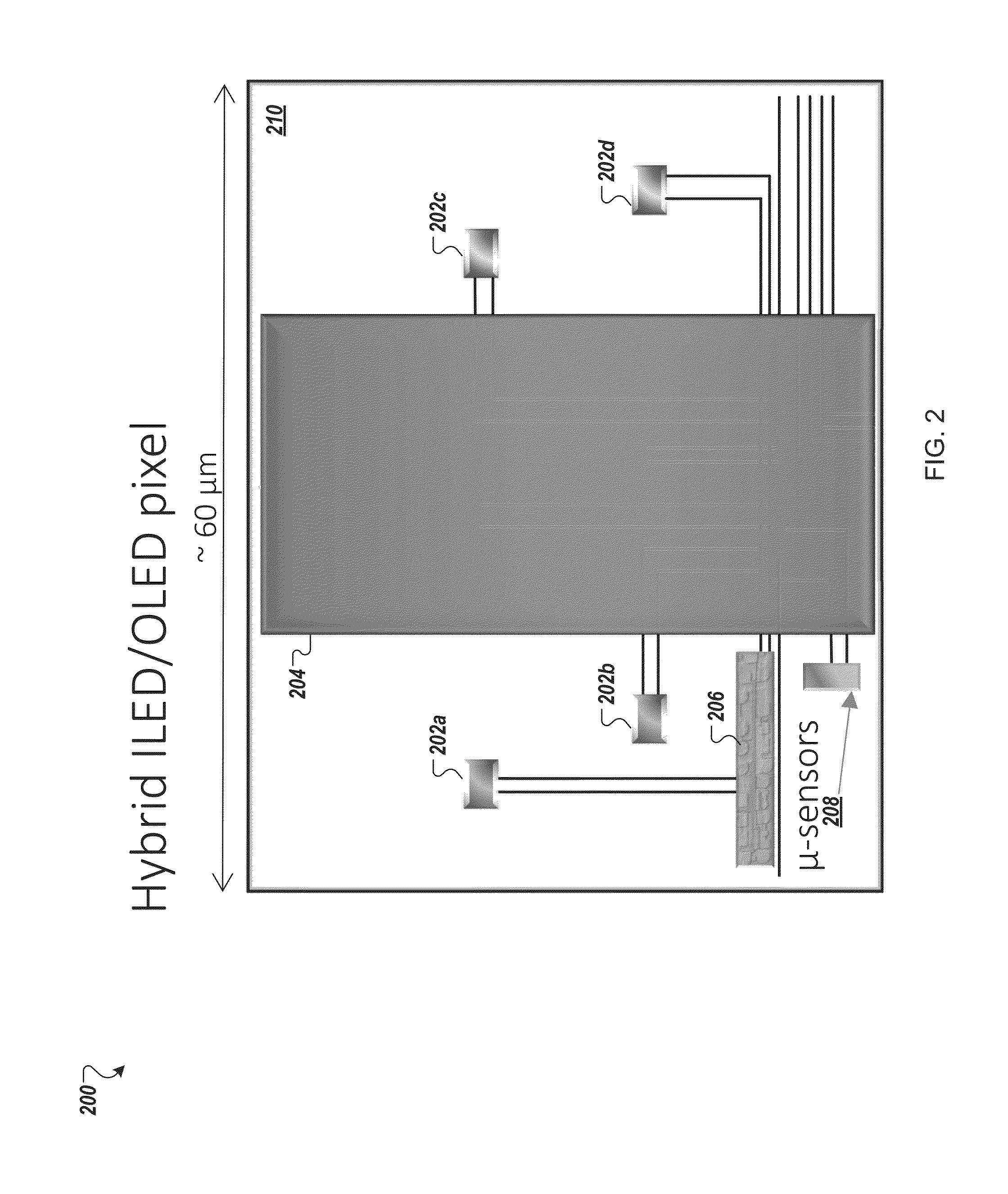

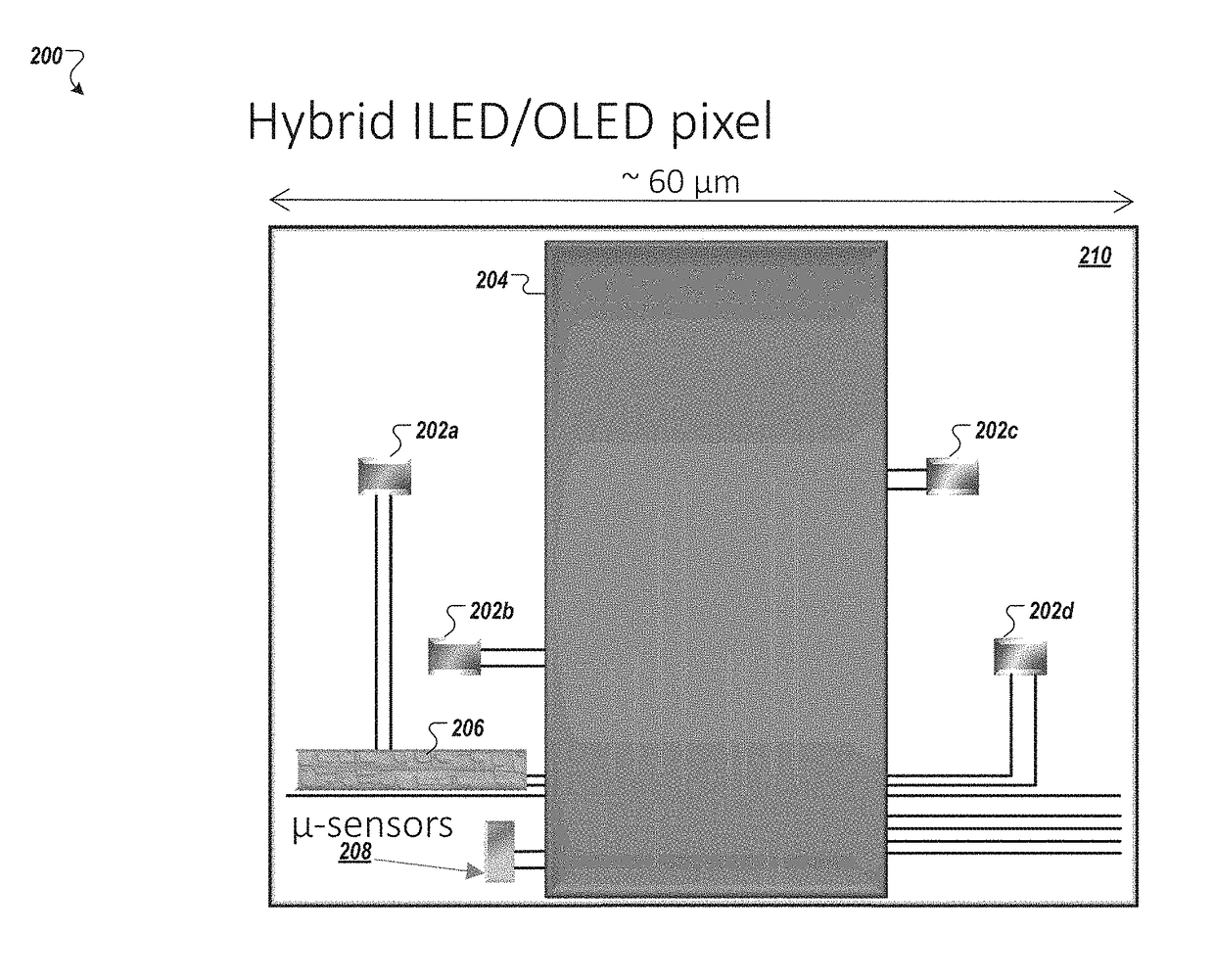

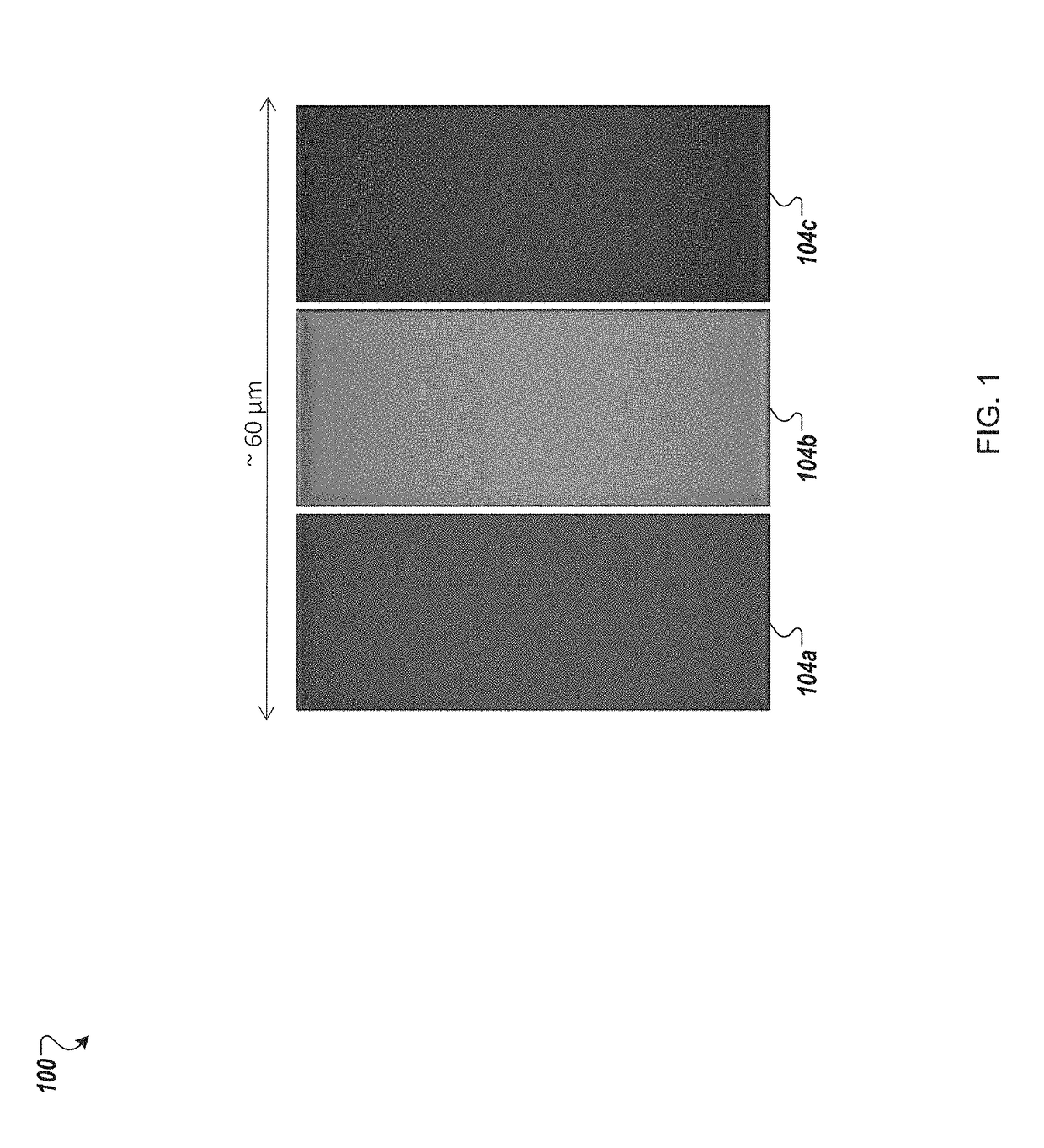

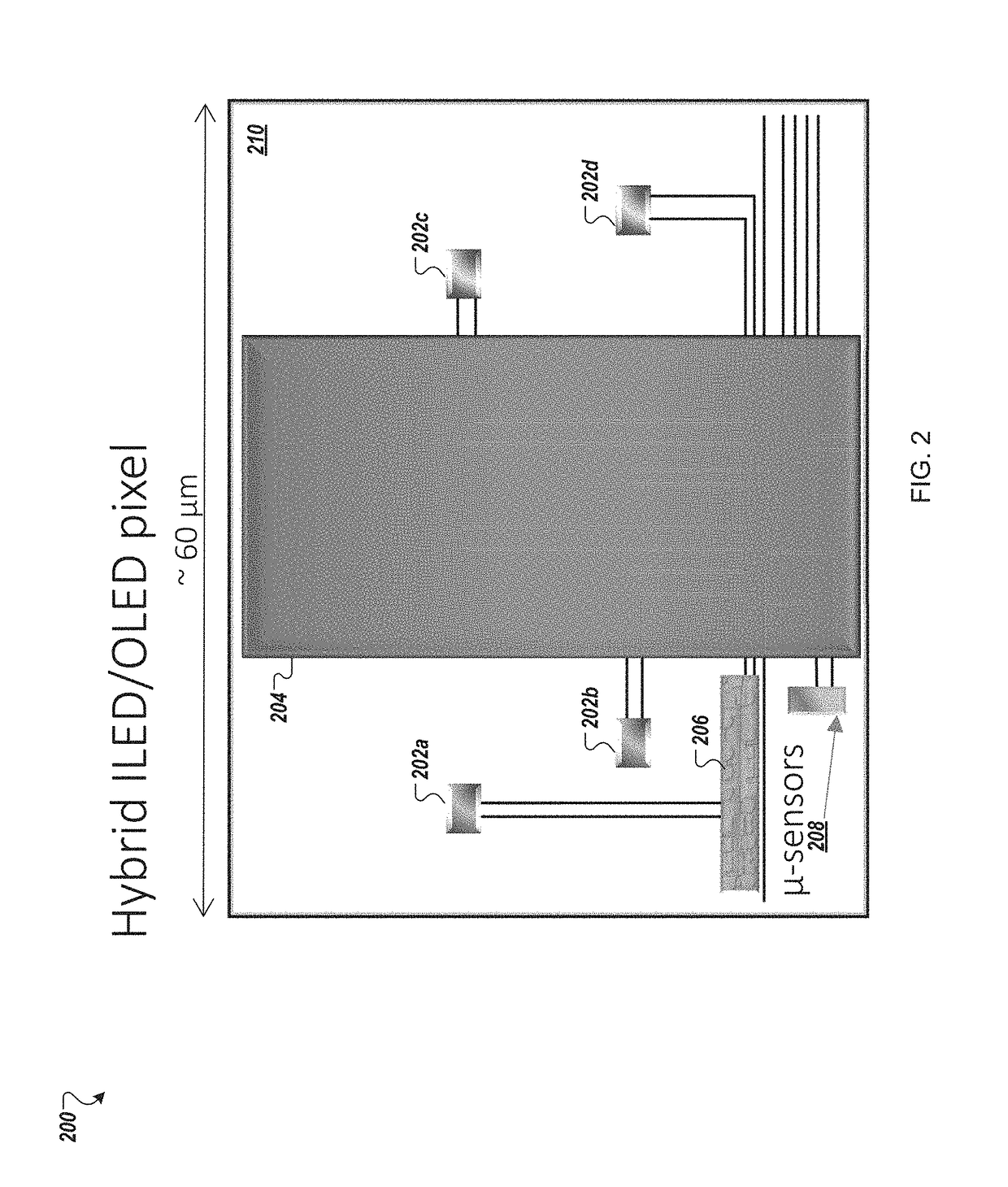

Micro assembled hybrid displays and lighting elements

ActiveUS20160064363A1Improve efficiencyImprove manufacturabilityFinal product manufactureElectroluminescent light sourcesLithographic artistDisplay device

The disclosed technology relates generally hybrid displays with pixels that include both inorganic light emitting diodes (ILEDs) and organic light emitting diodes (OLEDs). The disclosed technology provides a hybrid display that uses a mixture of ILEDs and OLEDs in each pixel. In certain embodiments, each pixel in the hybrid display includes a red ILED, a blue ILED, and a green OLED. In this instance, the OLED process would not require a high resolution shadow mask, thereby enhancing the manufacturability of OLEDs for larger format displays. Additionally, the OLED process in this example would not require any fine lithography. The OLED subpixel (e.g., green subpixel) can be larger and the ILEDs can be small (e.g., micro-red and micro-blue ILEDs). The use of small ILEDs allows for other functions to be added to the pixel, such as micro sensors and micro integrated circuits.

Owner:X DISPLAY CO TECH LTD

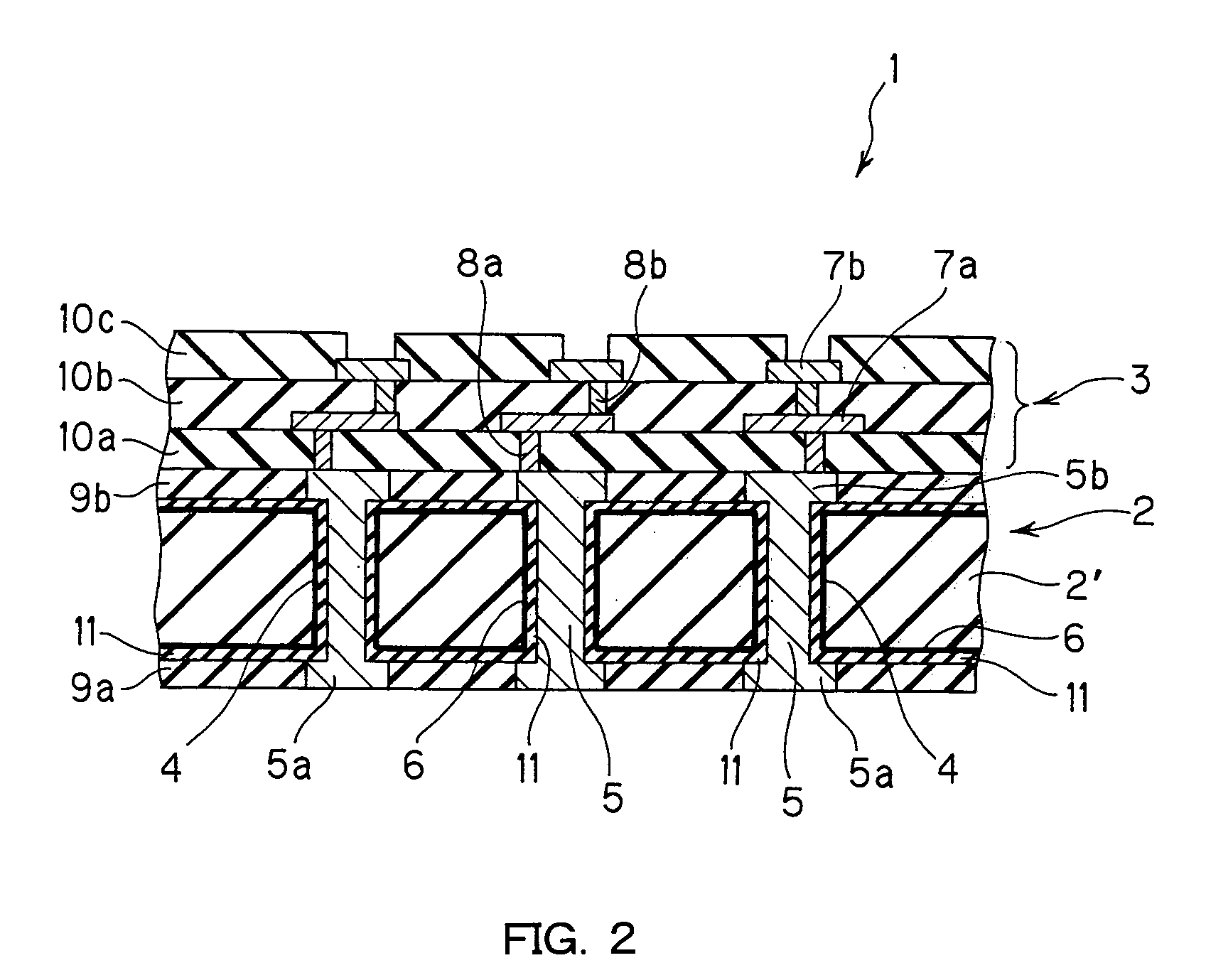

Multilayer wiring board and manufacture method thereof

ActiveUS20050012217A1Improve electrical performanceBroaden your optionsInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsEngineeringThermal expansion

In a multilayer wiring board comprising a core board, and a wiring layer and an electrically insulating layer that are stacked on one surface of said core board, a thermal expansion coefficient of said core board in XY directions falls within a range of 2 to 20 ppm, a core member for said core board is a core member selected from silicon, ceramics, glass, a glass-epoxy composite, and metal, said core board is provided with a plurality of through holes that are made conductive between the front and the back by a conductive material, and a capacitor is provided on one surface of said core board, wherein said capacitor comprises an upper electrode being the conductive material in said through hole, and a lower electrode disposed so as to confront said upper electrode via a dielectric layer.

Owner:DAI NIPPON PRINTING CO LTD

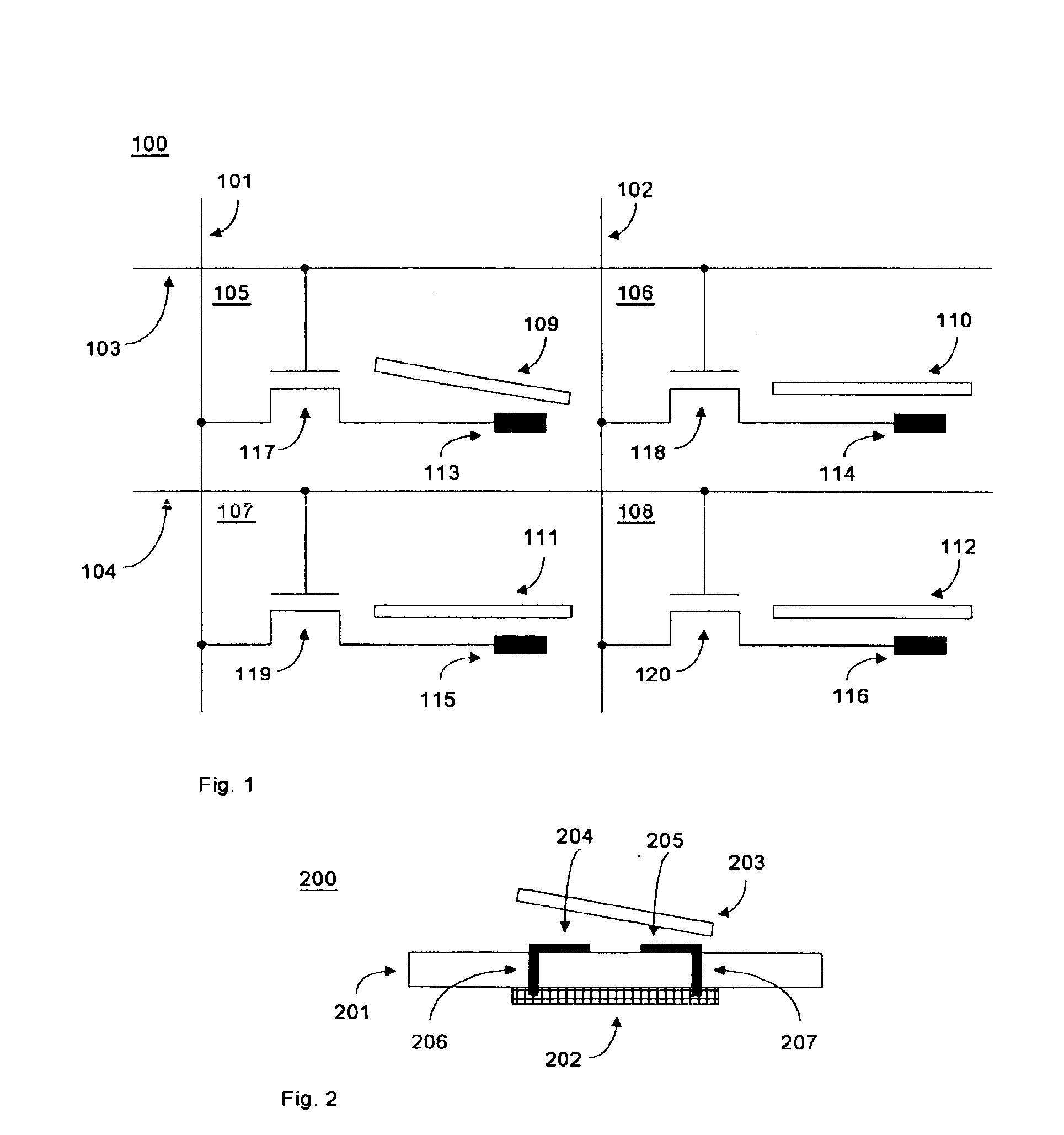

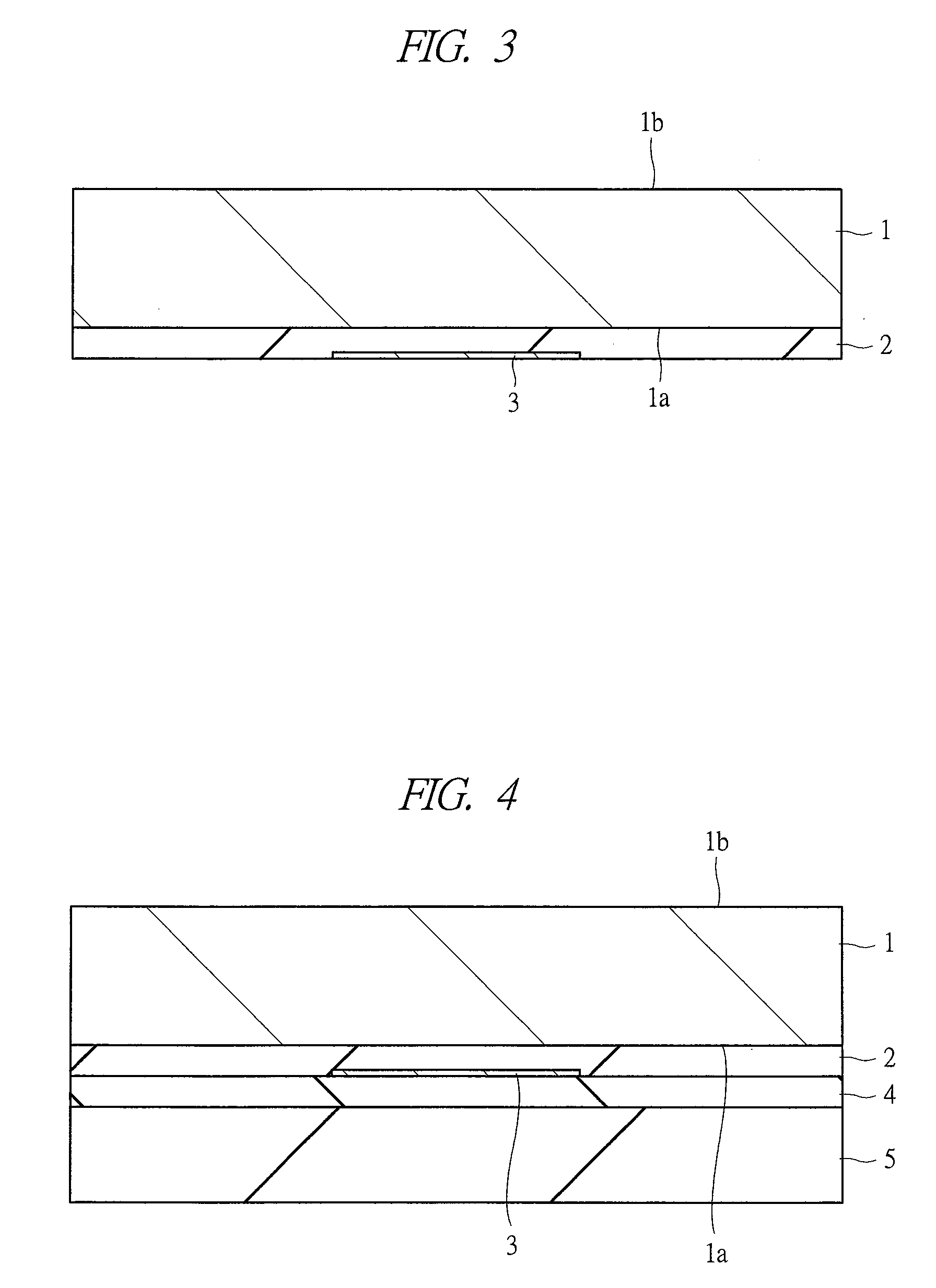

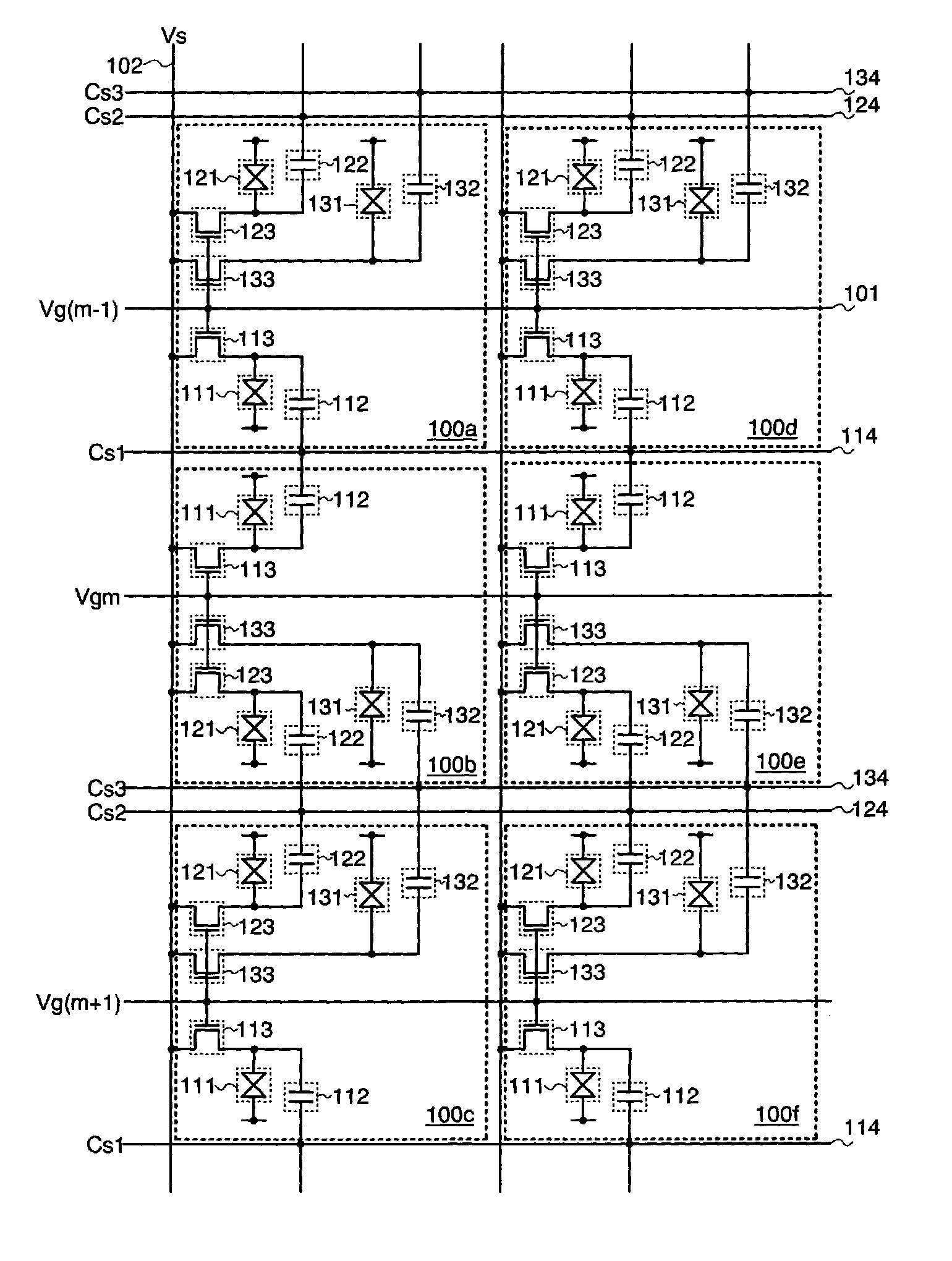

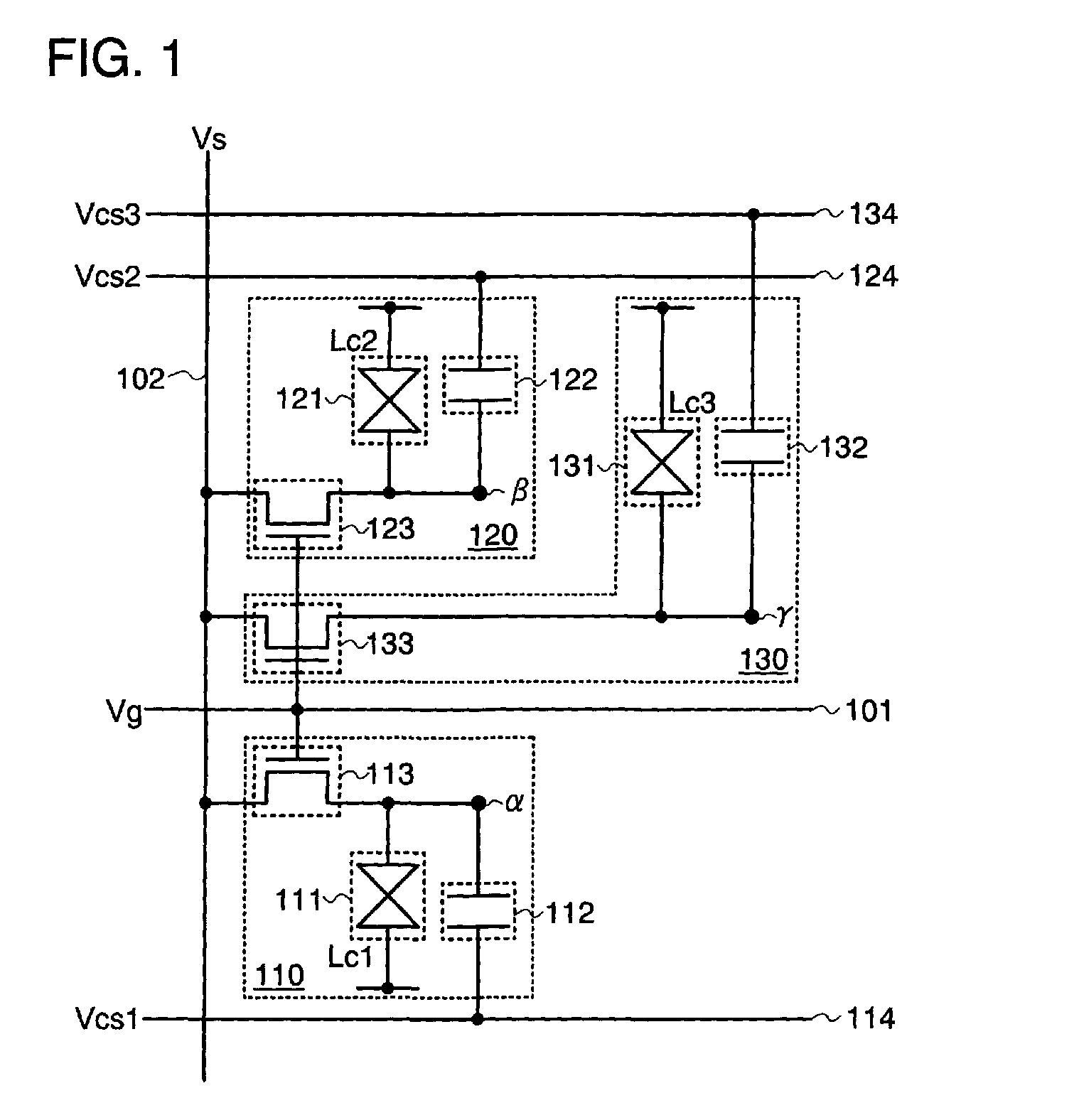

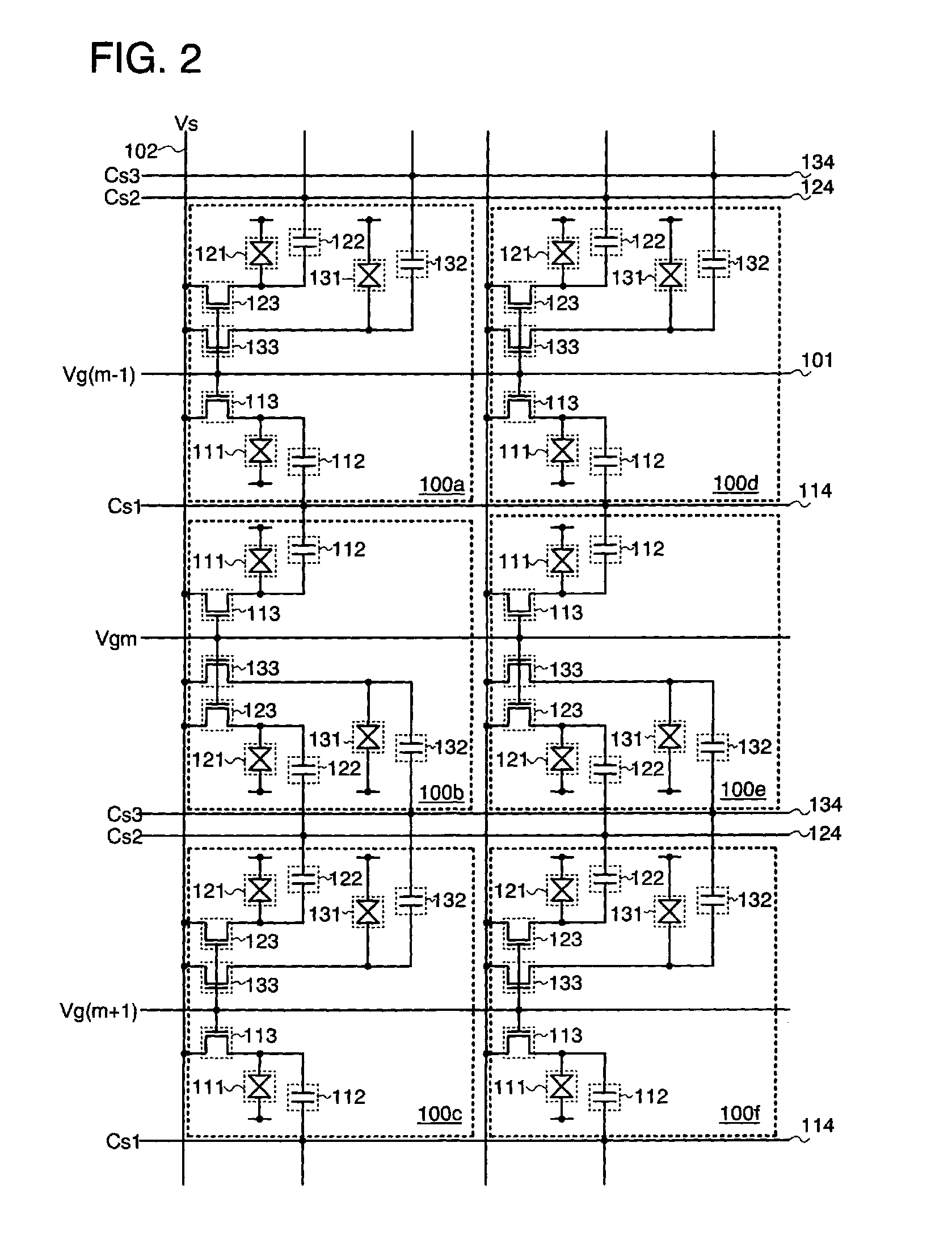

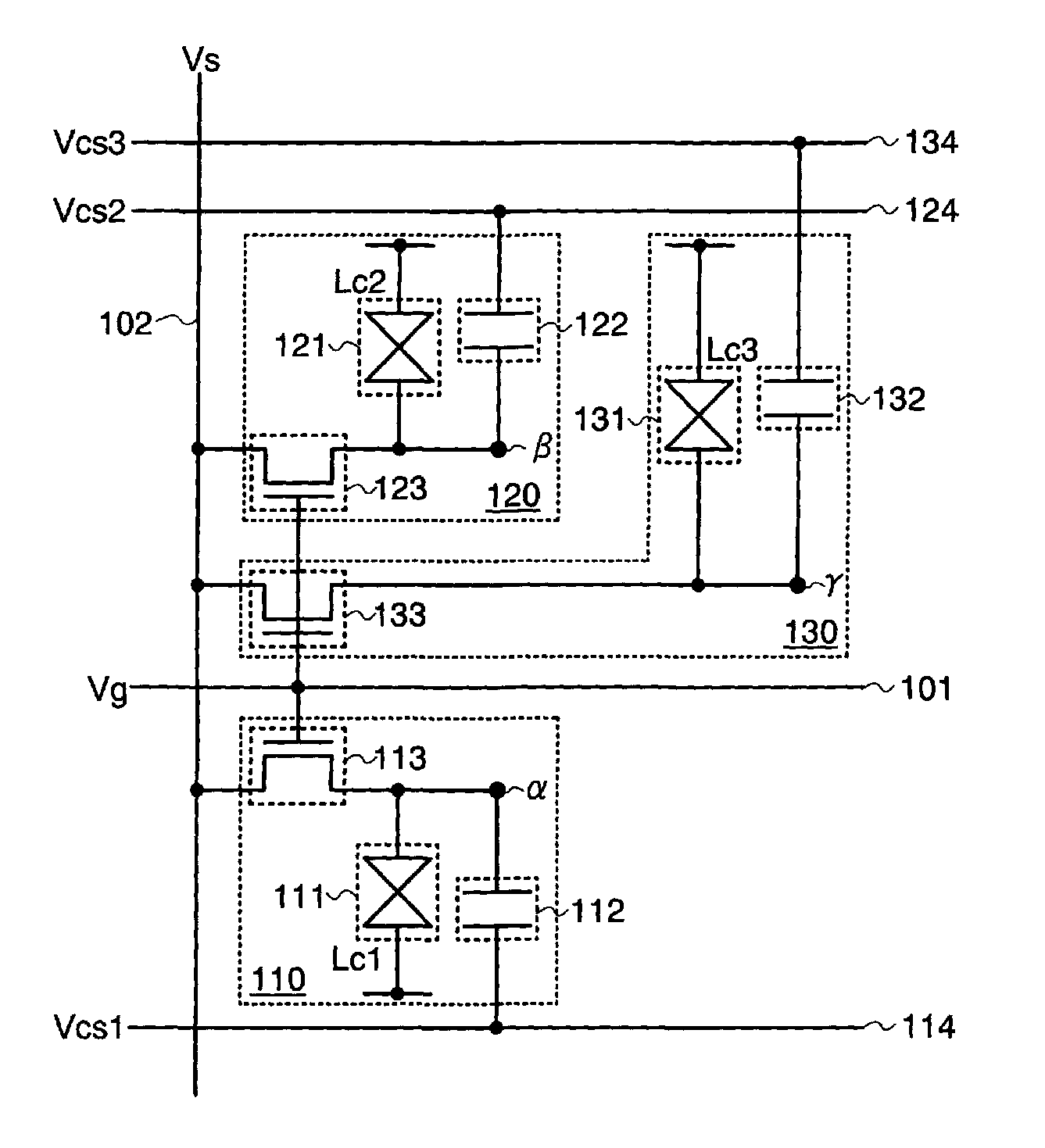

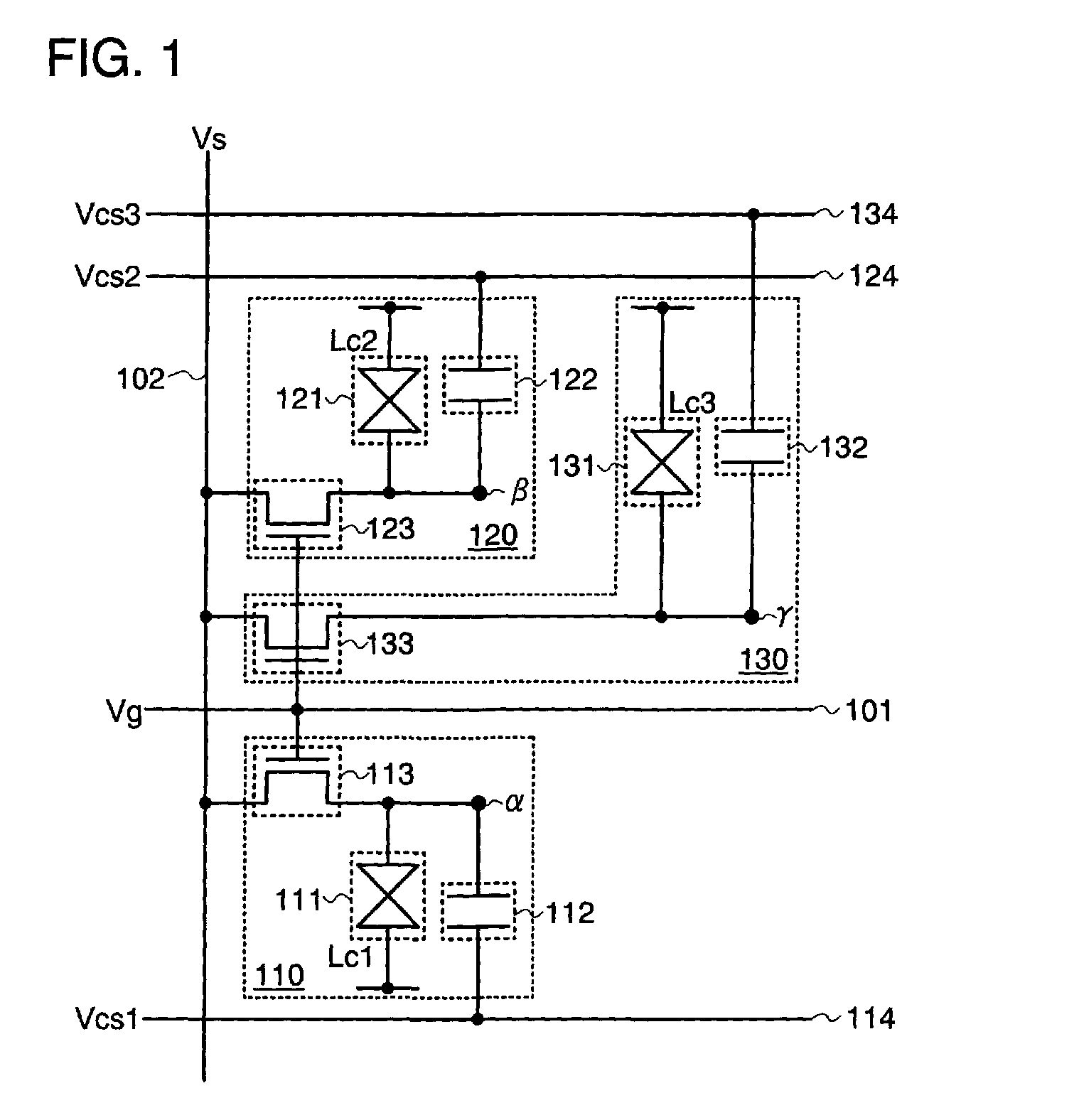

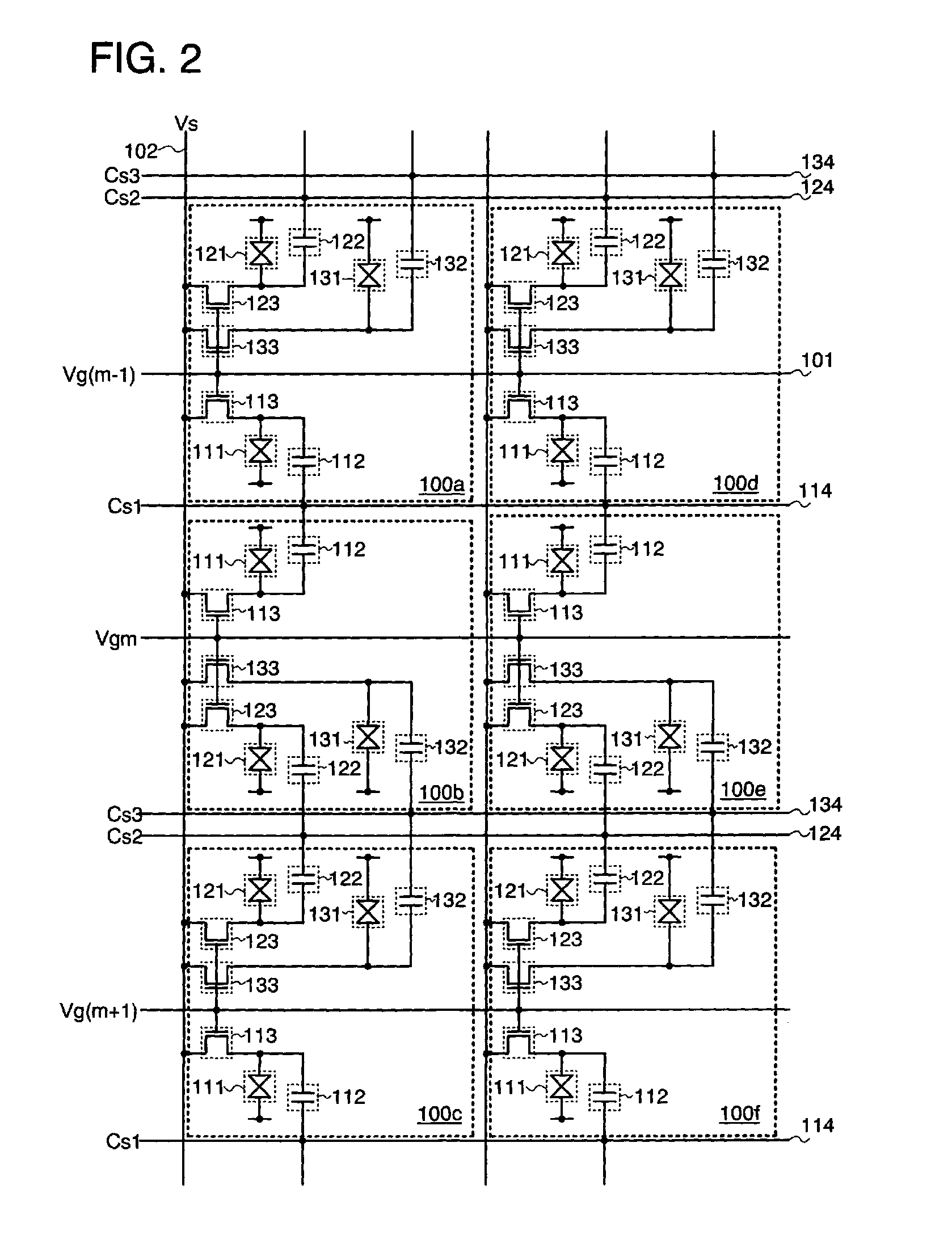

Liquid crystal display device

ActiveUS20080284931A1Widen perspectiveImprove image qualityStatic indicating devicesNon-linear opticsElectricityLiquid-crystal display

To provide a display device in which a viewing angle characteristic is improved by providing a plurality of sub-pixels to one pixel. Alternatively, to provide a display device in which an aperture ratio is suppressed even when a plurality of sub-pixels is provided. A pixel including first sub-pixel, a second sub-pixel, and a third sub-pixel, a scanning line, a signal line, a first capacitor wiring, a second capacitor wiring and a third capacitor wiring are provided. Pixel electrodes each electrically connected to one electrode of the first to third capacitor elements, and the first to third capacitor wirings, respectively, are provided to the first to third sub-pixels electrodes, respectively. Potentials of the first capacitor wiring and the second capacitor wiring are changed and a potential of the third capacitor wiring is kept almost constant.

Owner:SEMICON ENERGY LAB CO LTD

Micro assembled hybrid displays and lighting elements

ActiveUS9716082B2Improve efficiencyImprove manufacturabilityFinal product manufactureElectroluminescent light sourcesDisplay deviceLight-emitting diode

The disclosed technology relates generally hybrid displays with pixels that include both inorganic light emitting diodes (ILEDs) and organic light emitting diodes (OLEDs). The disclosed technology provides a hybrid display that uses a mixture of ILEDs and OLEDs in each pixel. In certain embodiments, each pixel in the hybrid display includes a red ILED, a blue ILED, and a green OLED. In this instance, the OLED process would not require a high resolution shadow mask, thereby enhancing the manufacturability of OLEDs for larger format displays. Additionally, the OLED process in this example would not require any fine lithography. The OLED subpixel (e.g., green subpixel) can be larger and the ILEDs can be small (e.g., micro-red and micro-blue ILEDs). The use of small ILEDs allows for other functions to be added to the pixel, such as micro sensors and micro integrated circuits.

Owner:X DISPLAY CO TECH LTD

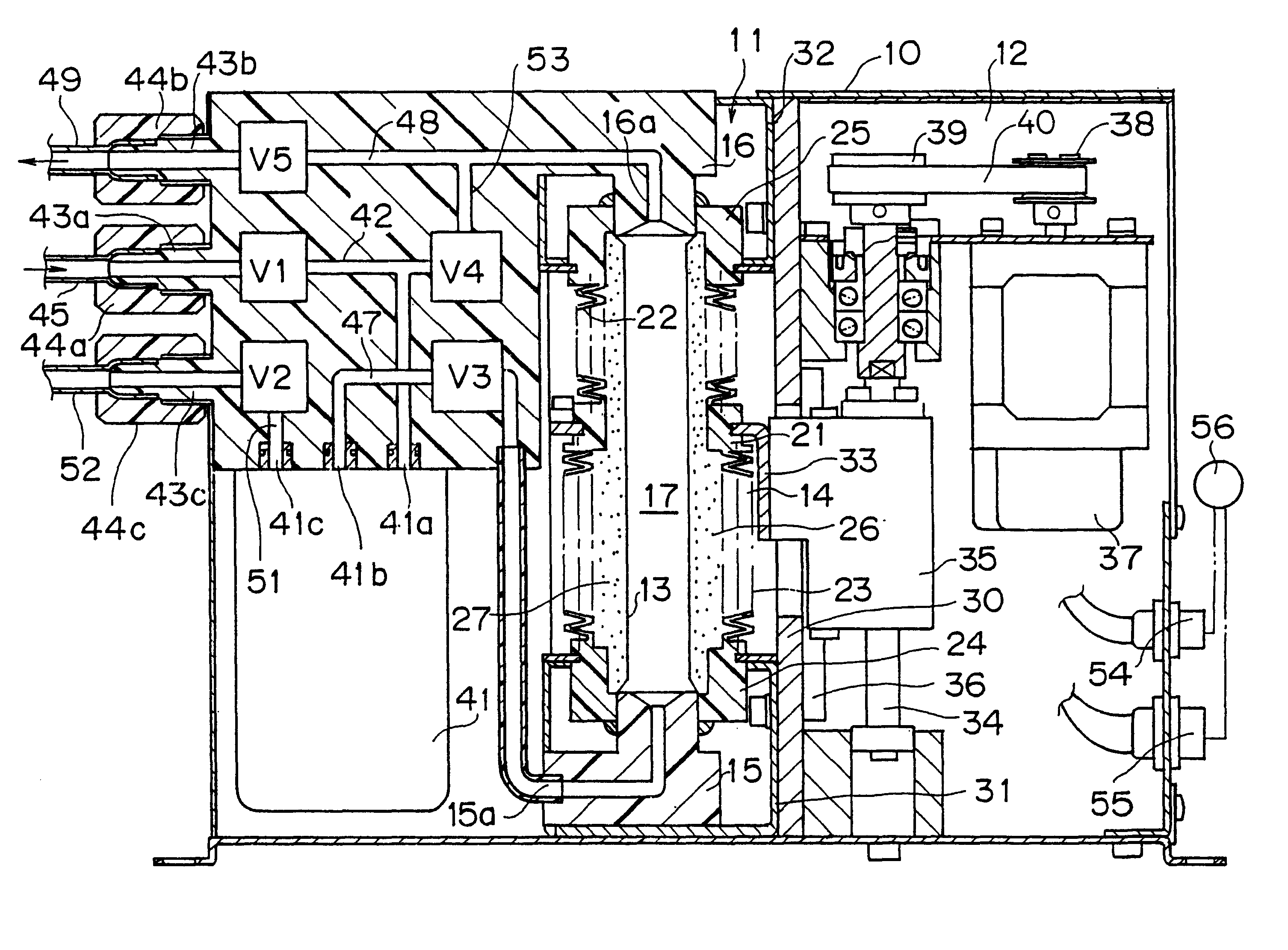

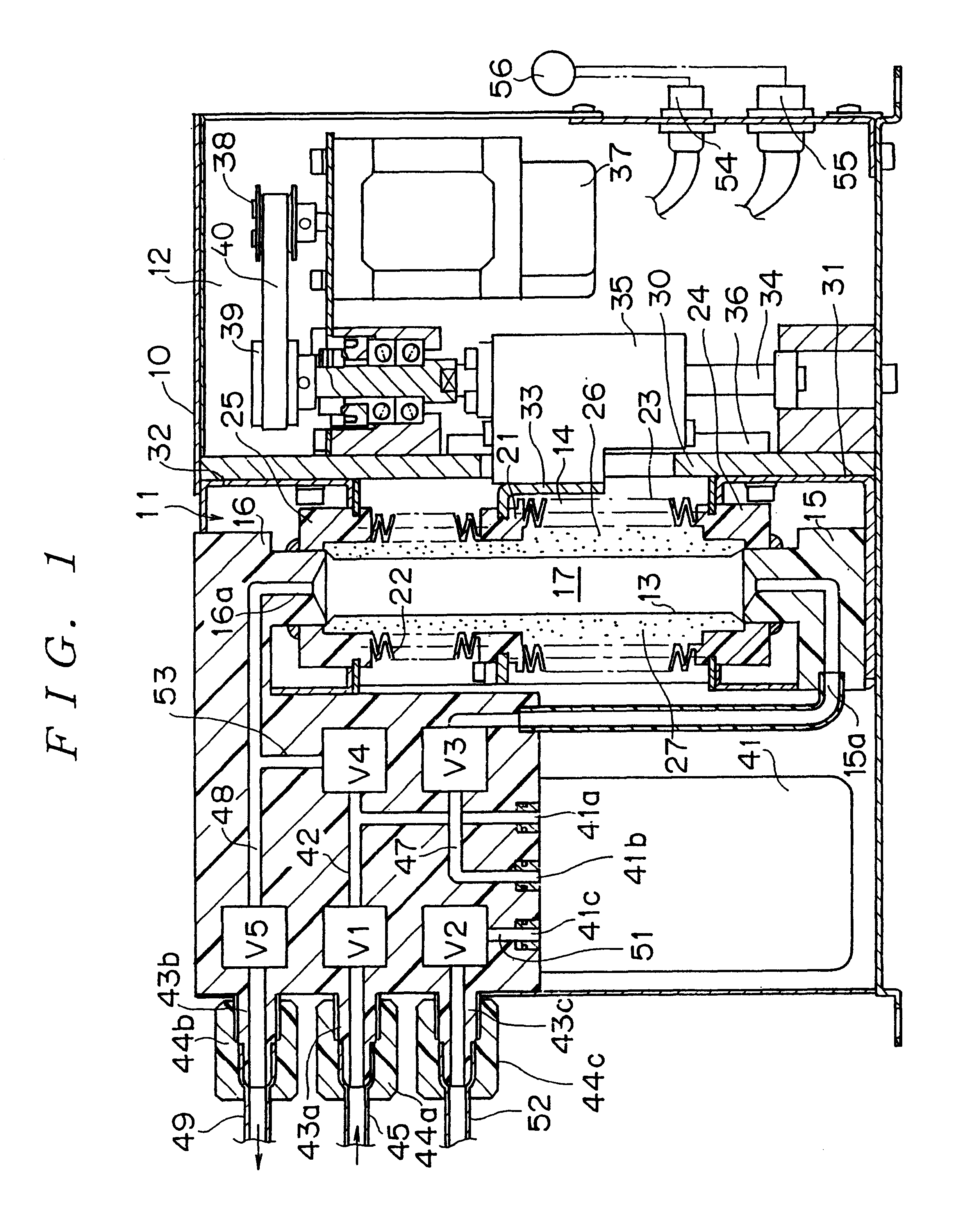

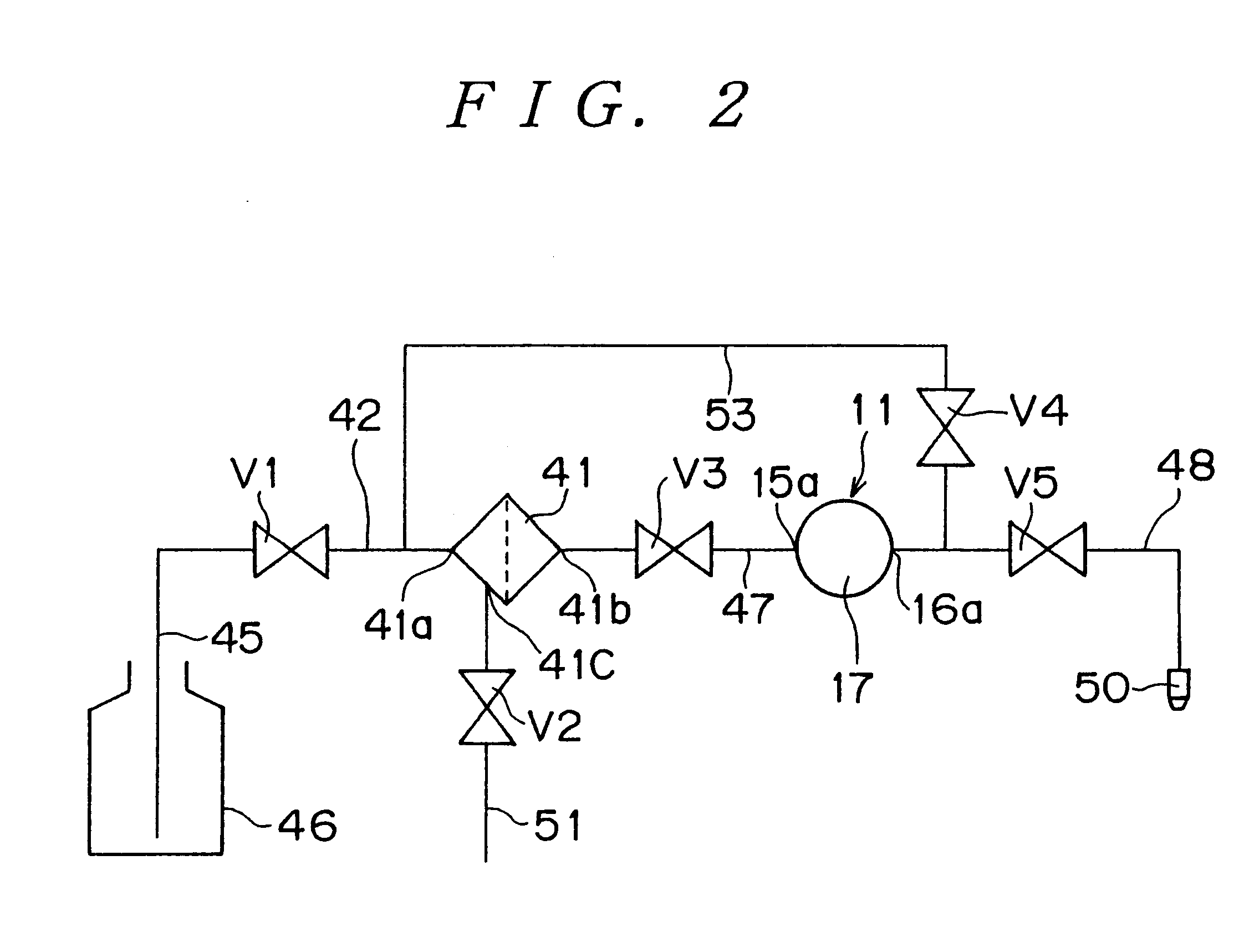

Chemical liquid supply method and apparatus thereof

InactiveUS6238576B1Improve cleanlinessPrevent penetrationLiquid separation auxillary apparatusFlexible member pumpsPump chamberInlet flow

Impure portions such as air bubbles and gelled portions in a liquid are removed so that the liquid can be discharged with improved cleanliness. Under condition that a return flow path and a liquid discharge flow path are closed, a pump chamber is expanded, thereby sucking the liquid in a liquid container portion into a pump chamber through a filter. Under condition that a vent port of the filter and the return flow path are opened and a liquid introducing flow path, the liquid discharge flow path, and a pump inlet flow path are closed, the pump chamber is contracted, thereby returning the liquid in the pump chamber toward the filter so that air in the filter is exhausted to the outside. Under condition that the return flow path and the pump inlet flow path are closed, the pump chamber is contracted, thereby discharging the liquid from the nozzle.

Owner:KOGANEI

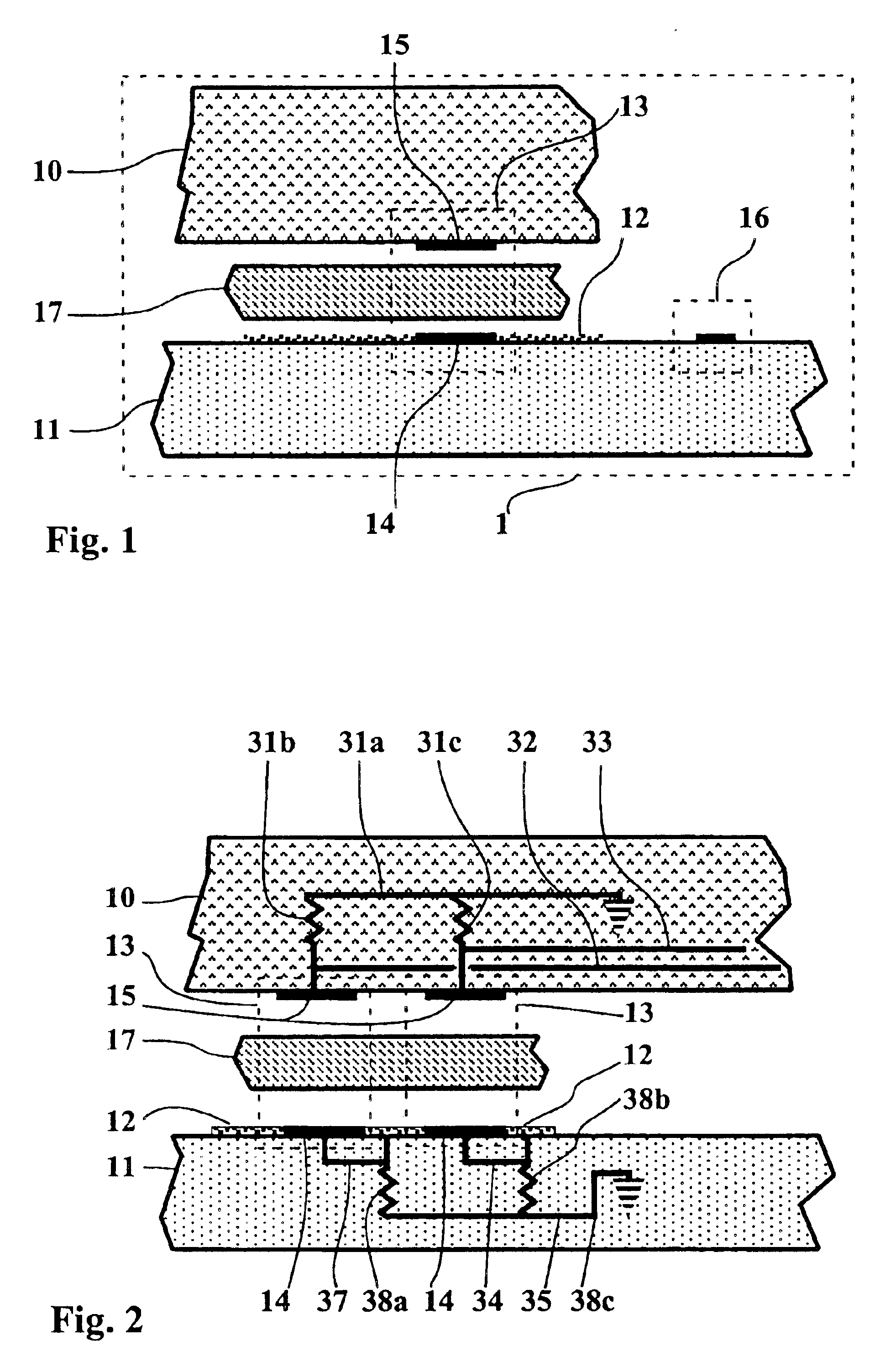

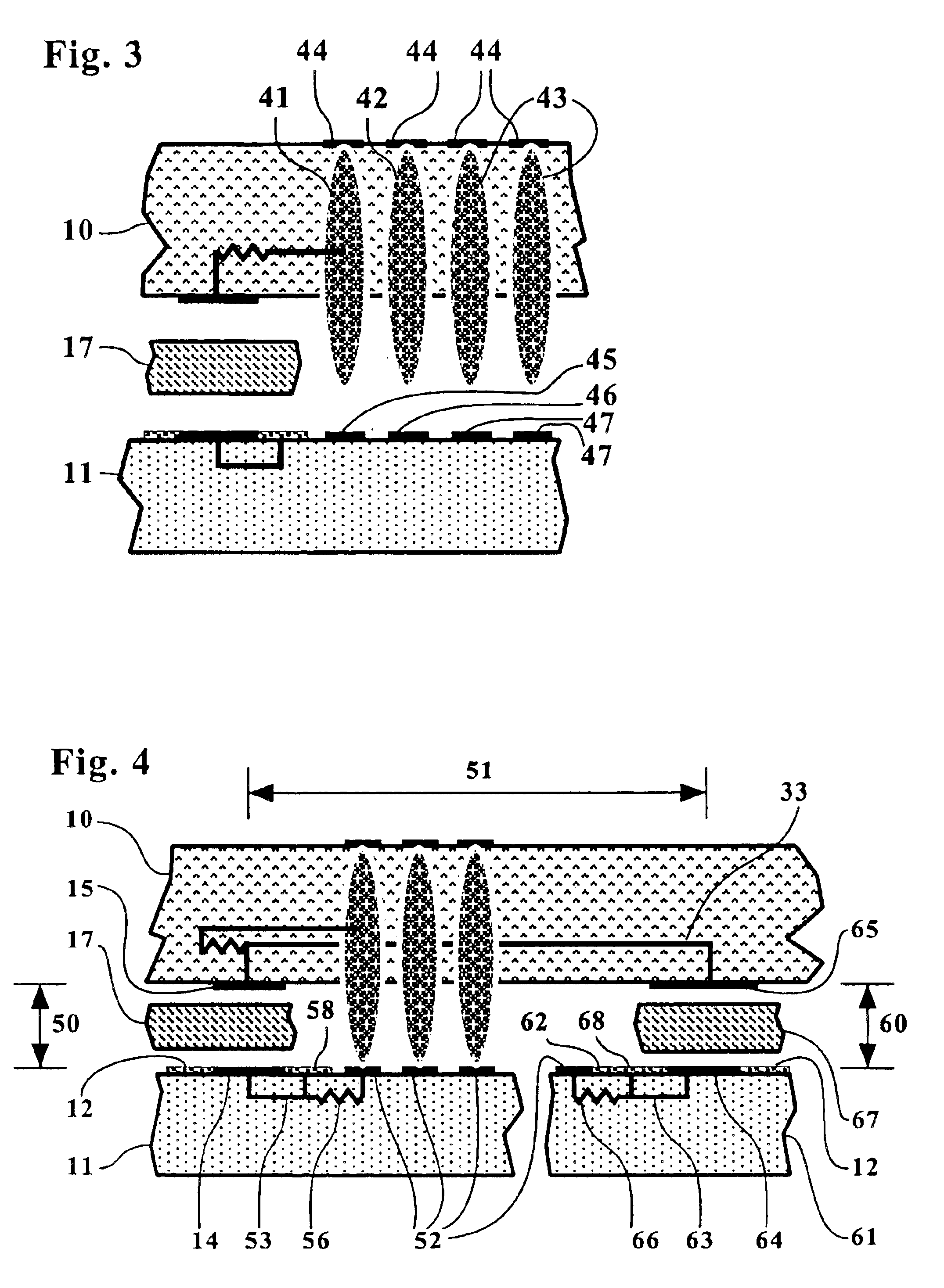

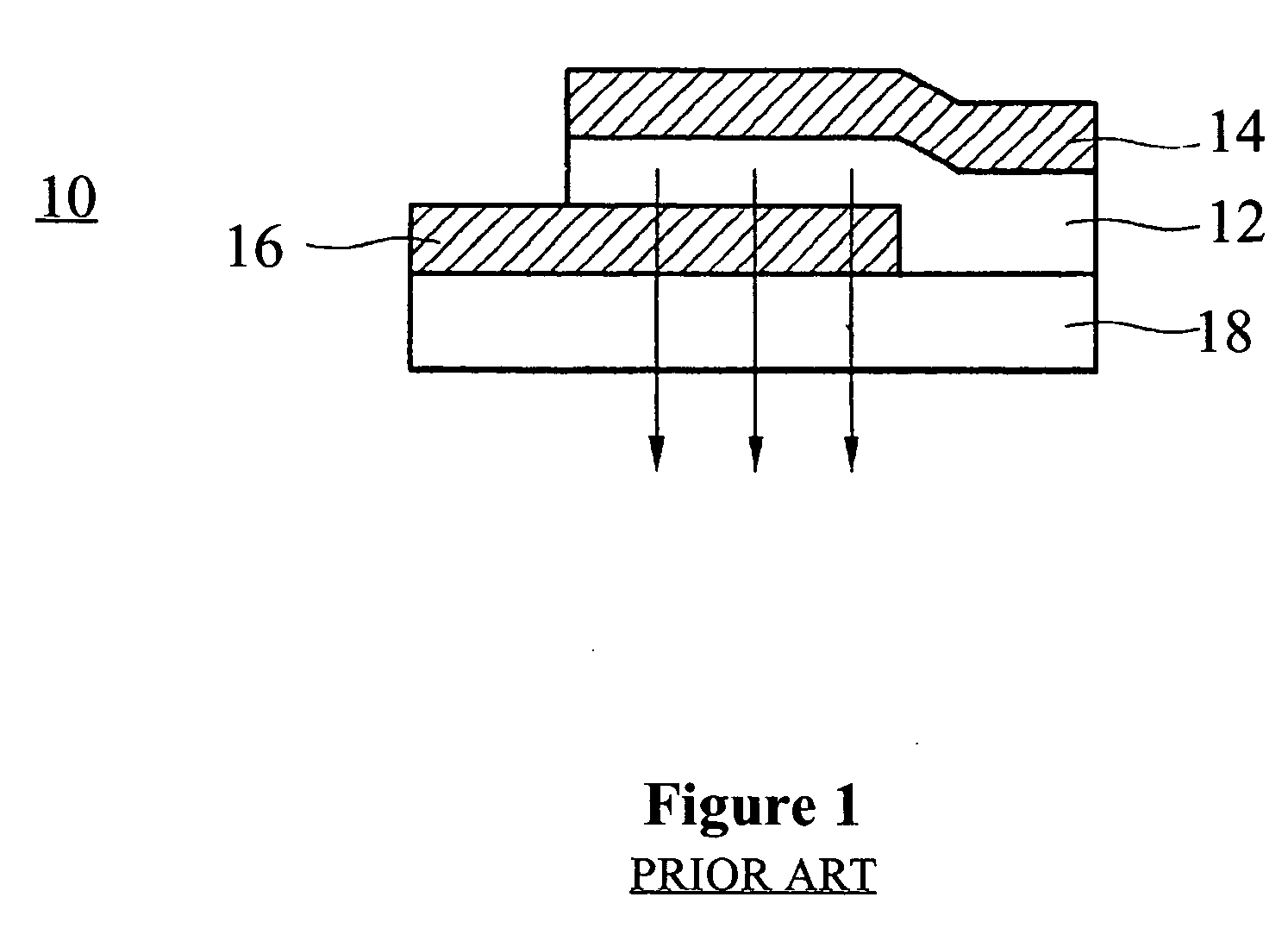

Method and apparatus for non-conductively interconnecting integrated circuits

InactiveUS6916719B1Increased signal noiseIncrease speedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsLead bondingComputer module

Methods and apparatus are described for capacitively signaling between different semiconductor chips and modules without the use of connectors, solder bumps, wire-bond interconnections or the like. Preferably, pairs of half-capacitor plates, one half located on each chip, module or substrate are used to capacitively couple signals from one chip, module or substrate to another. The use of plates relaxes the need for high precision alignment as well as reduces the area needed to effect signaling, and reduces or eliminates the requirements for exotic metallurgy.

Owner:SUN MICROSYSTEMS INC

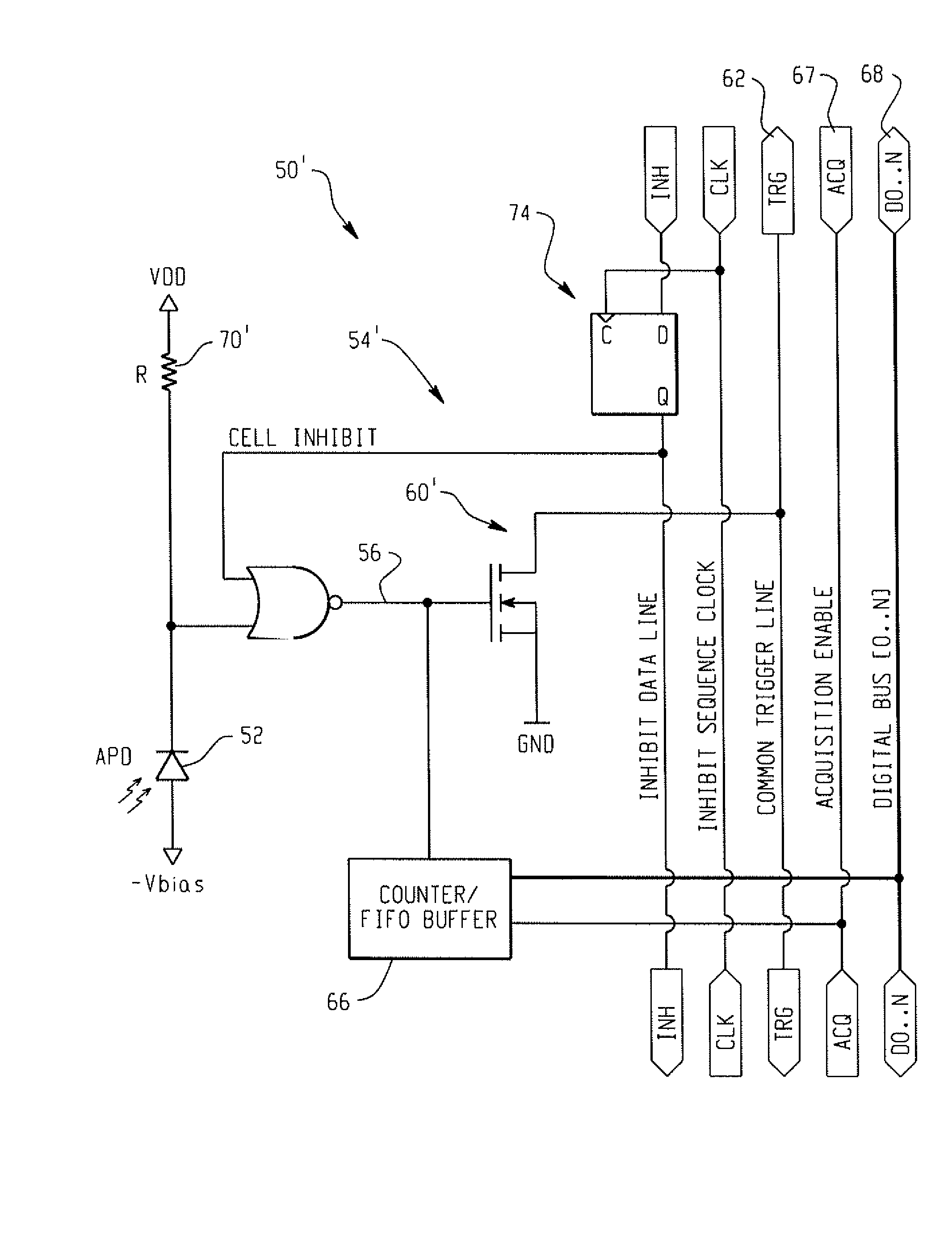

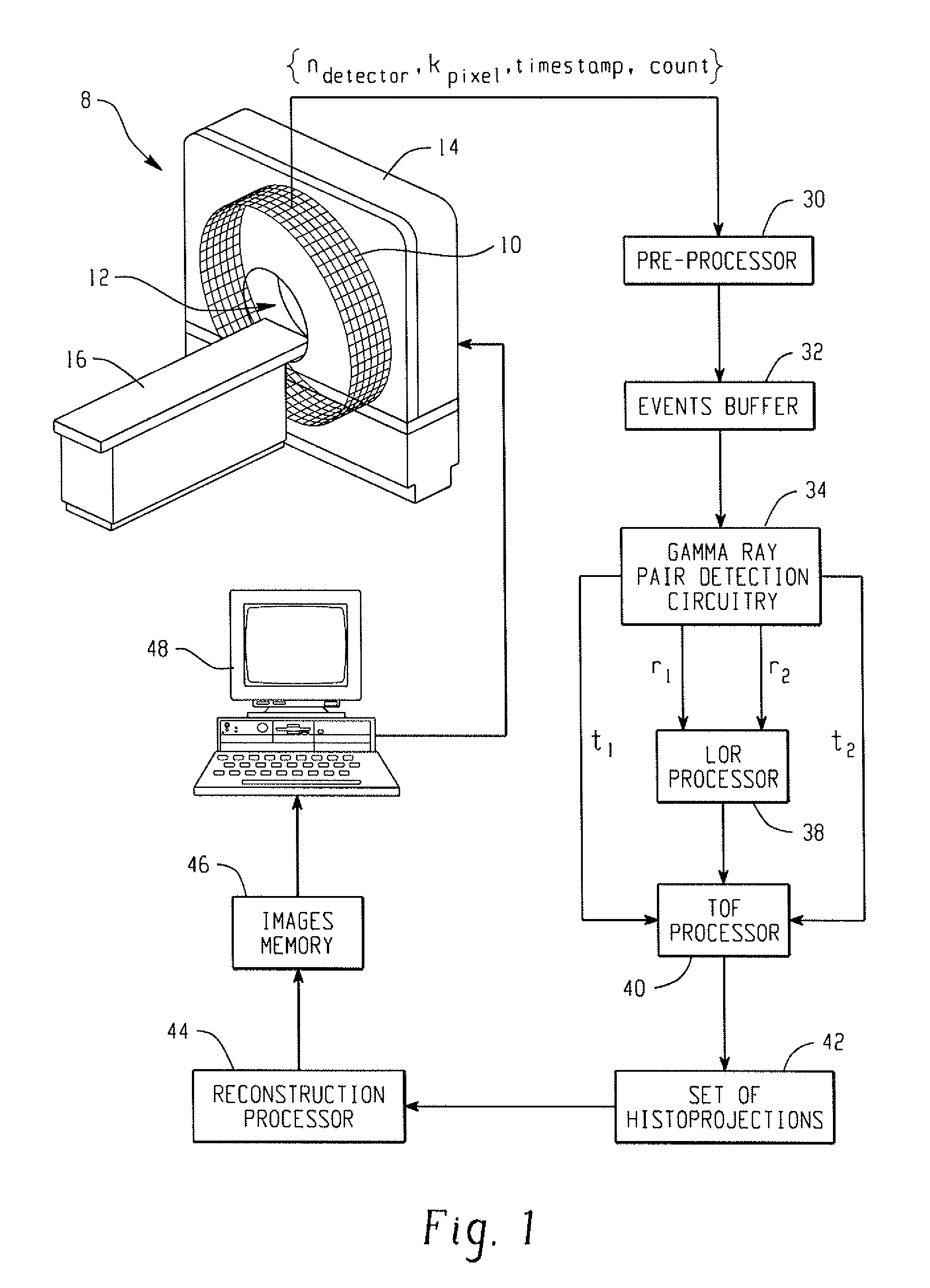

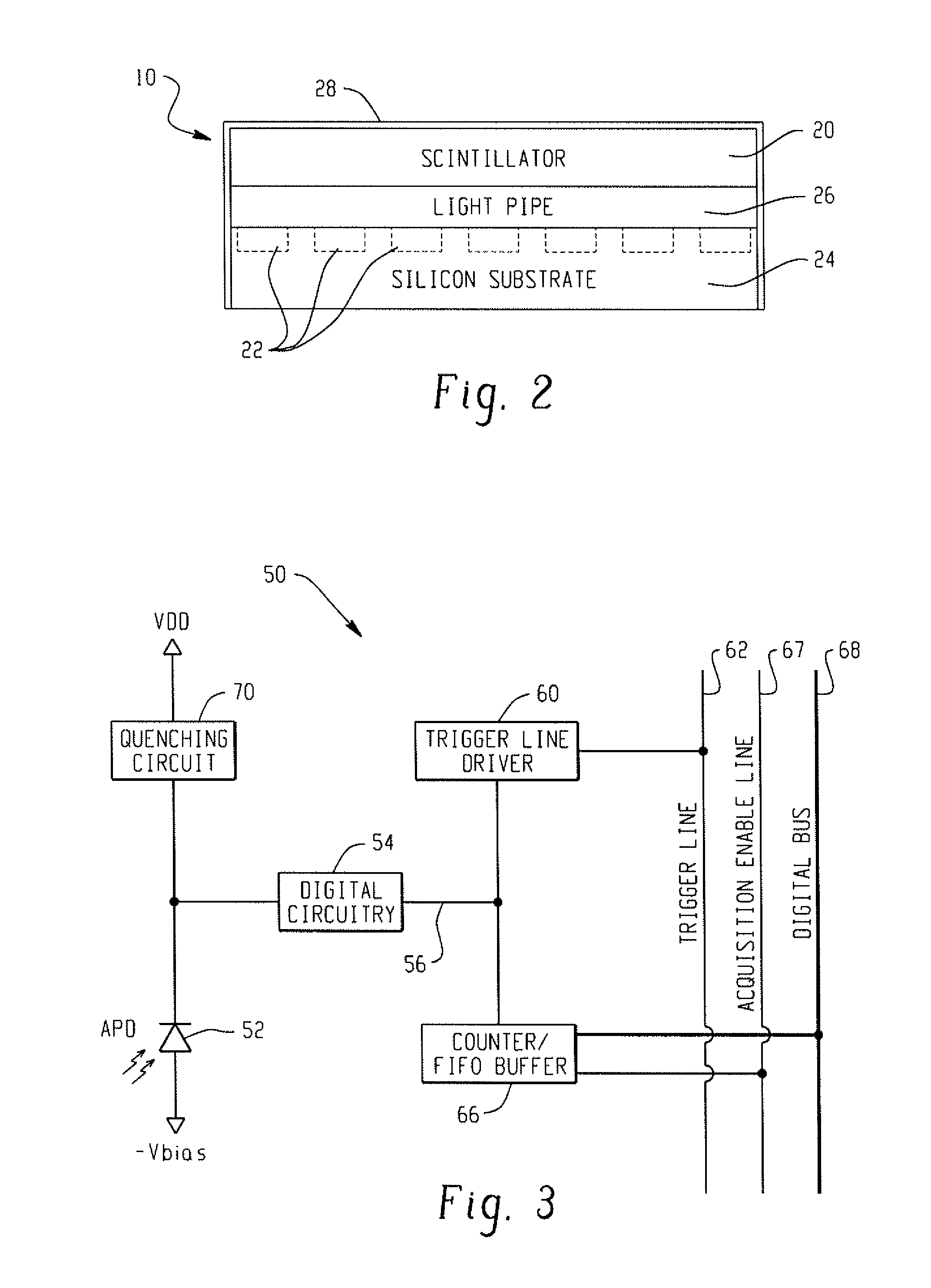

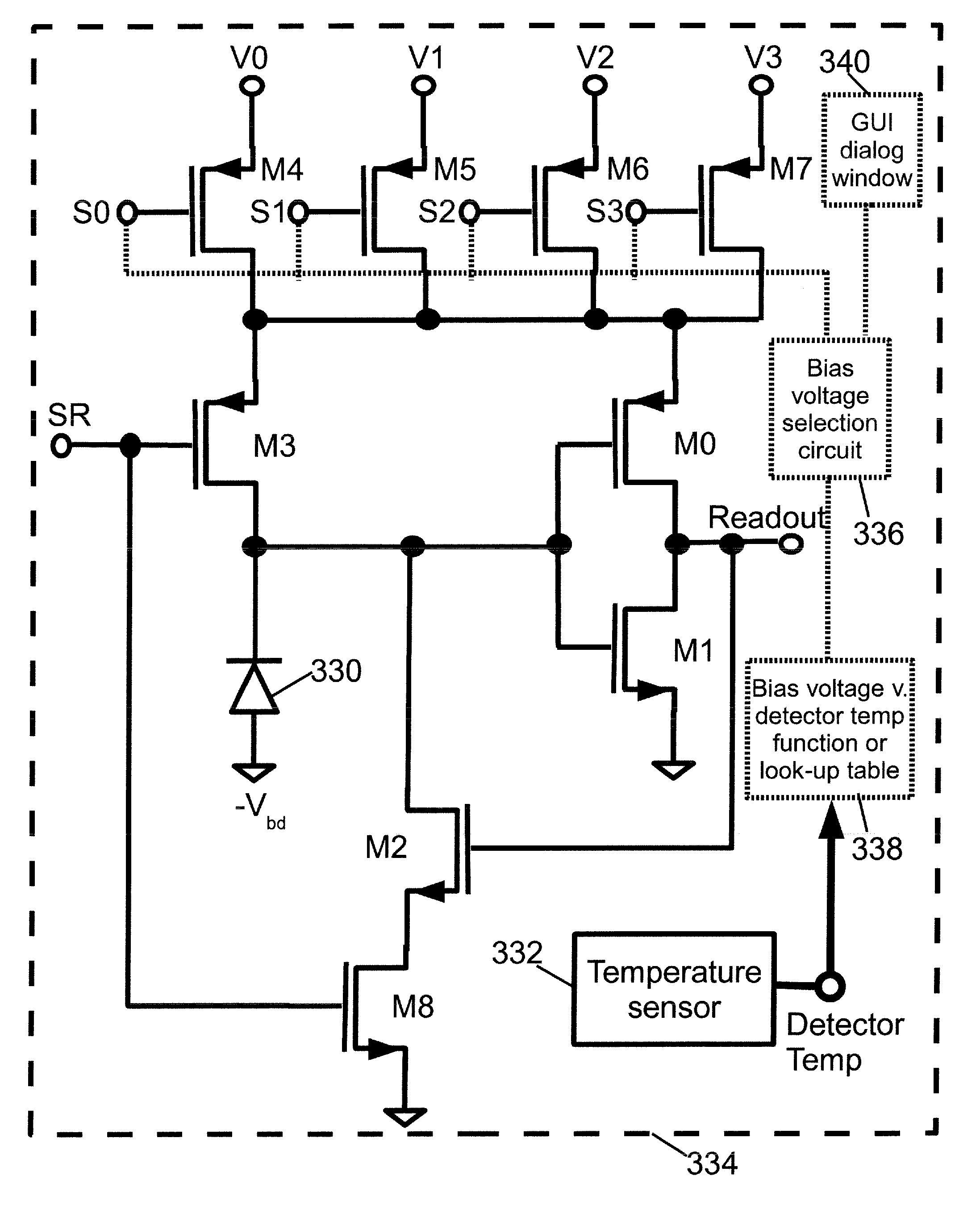

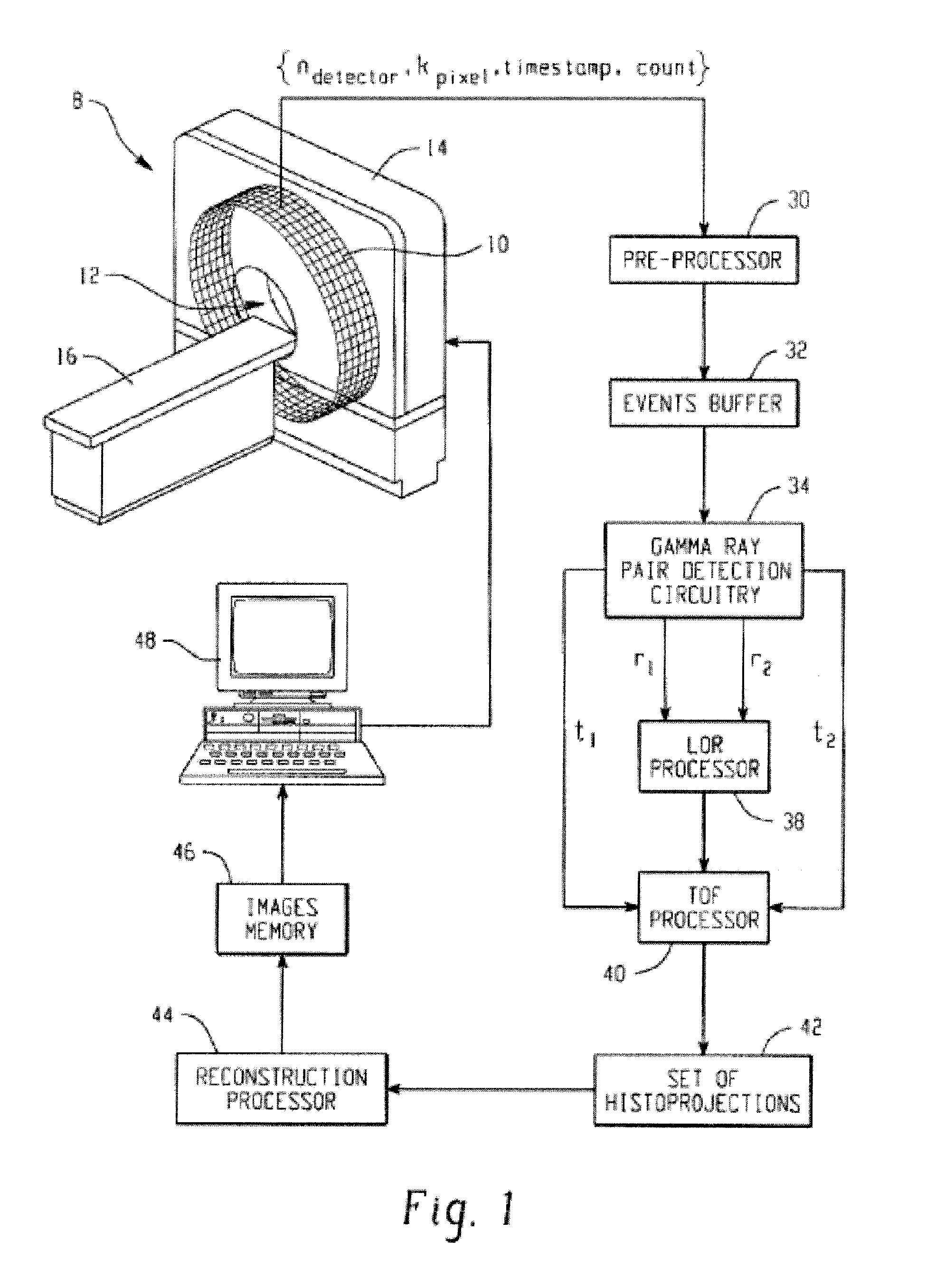

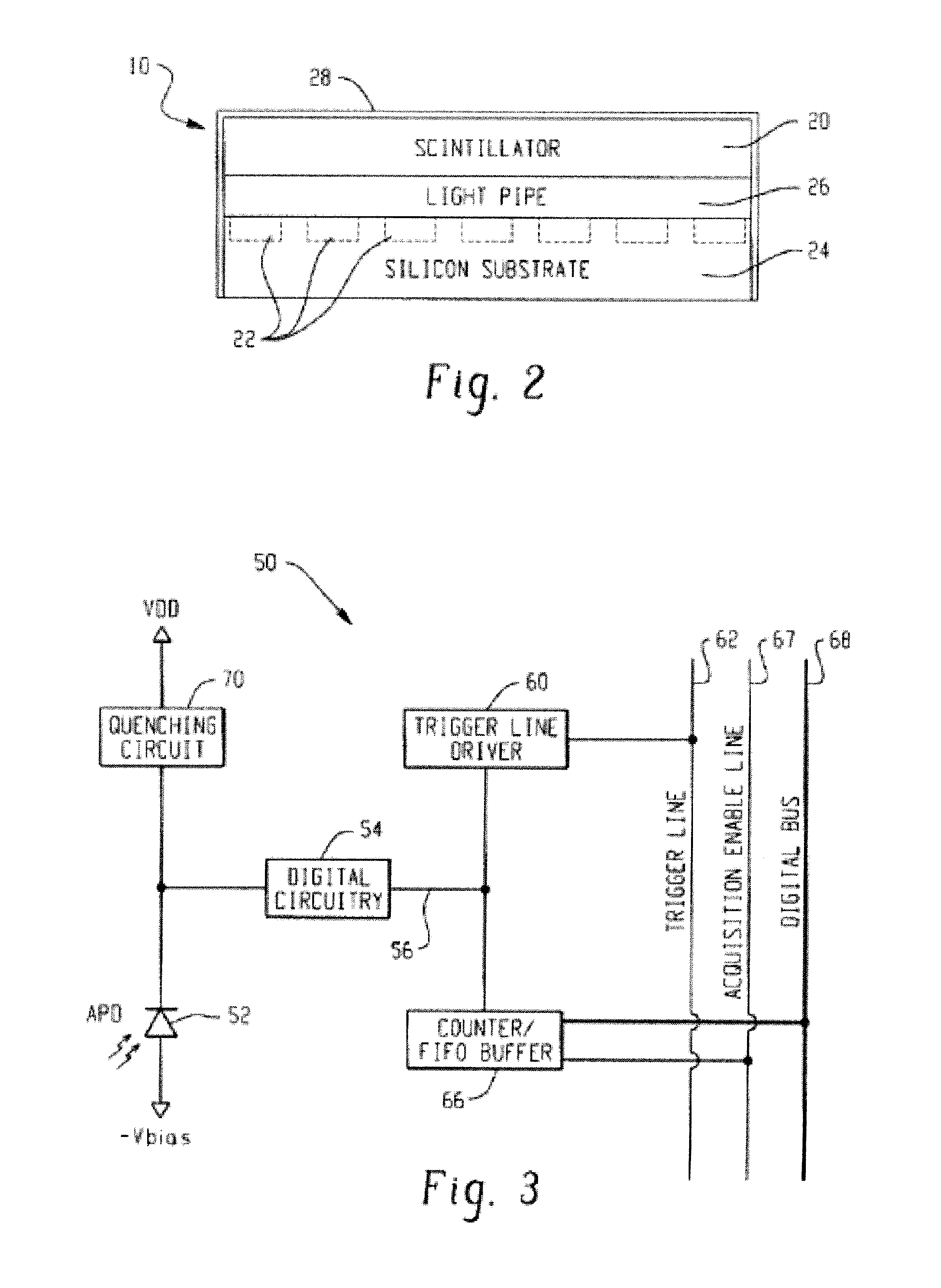

Digital silicon photomultiplier for TOF-PET

ActiveUS20080203309A1High data-rate radiation detectionImproved spatial detector resolutionMaterial analysis by optical meansTomographyQuiescent stateSilicon photomultiplier

A radiation detector includes an array of detector pixels each including an array of detector cells. Each detector cell includes a photodiode biased in a breakdown region and digital circuitry coupled with the photodiode and configured to output a first digital value in a quiescent state and a second digital value responsive to photon detection by the photodiode. Digital triggering circuitry is configured to output a trigger signal indicative of a start of an integration time period responsive to a selected number of one or more of the detector cells tranisitioning from the first digital value to the second digital value. Readout digital circuitry accumulates a count of a number of transitions of detector cells of the array of detector cells from the first digital state to the second digital state over the integration time period.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Semiconductor device and method for manufacturing the same

InactiveUS20070029676A1Improve reliabilityImprove manufacturing yieldSemiconductor/solid-state device detailsSolid-state devicesDevice materialElectrical connection

A resistor element formed of a peel-preventive film, a recording layer made of chalcogenide, and an upper electrode film is formed on a semiconductor substrate, first and second insulation films are formed so as to cover the resistor element, a via hole for exposing the upper electrode film is formed through the first and second insulation films, and a plug for electrical connection to the upper electrode film is formed in the via hole. To form the via hole, the first insulation film made of silicon nitride is used as an etching stopper to perform dry etching on the second insulation film. Then, dry etching is performed on the first insulation film to expose the upper electrode film from the via hole.

Owner:RENESAS TECH CORP

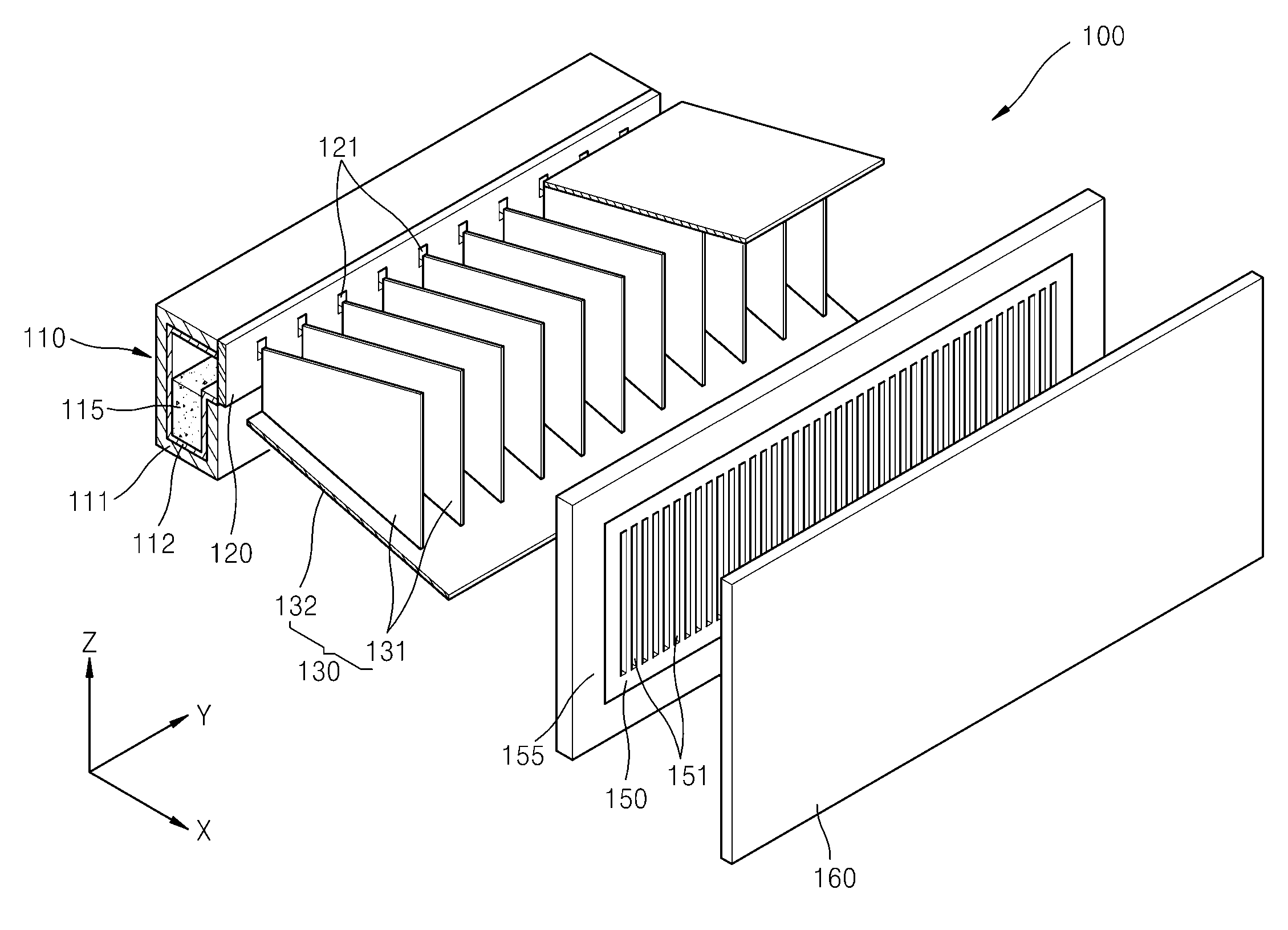

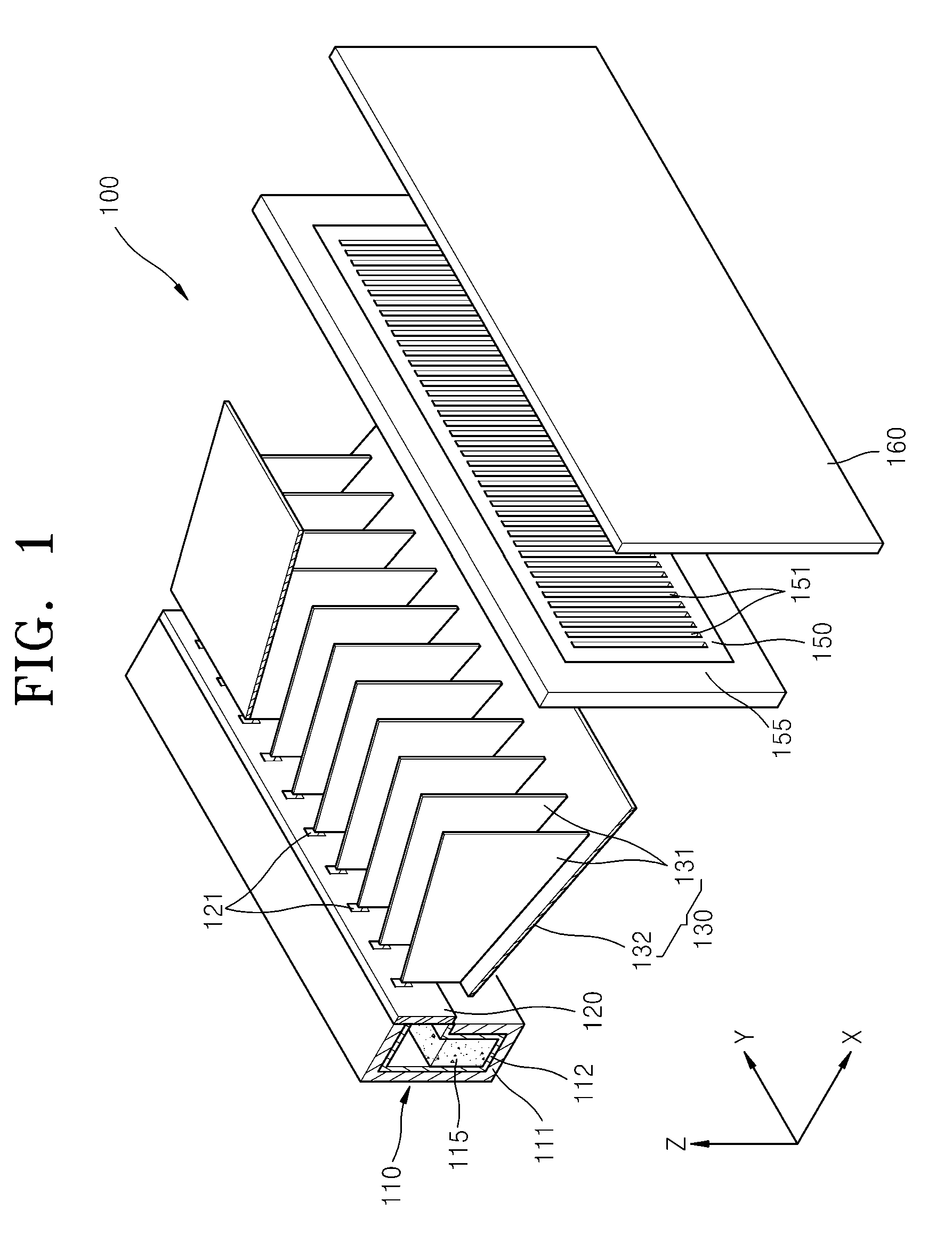

Thin film deposition apparatus

ActiveUS20100297349A1Easy to manufactureImprove manufacturing yieldVacuum evaporation coatingSputtering coatingEngineeringNozzle

A thin film deposition apparatus used to produce large substrates on a mass scale and improve manufacturing yield. The thin film deposition apparatus includes a deposition source; a first nozzle disposed at a side of the deposition source and including a plurality of first slits arranged in a first direction; a second nozzle disposed opposite to the first nozzle and including a plurality of second slits arranged in the first direction; and a barrier wall assembly including a plurality of barrier walls arranged in the first direction so as to partition a space between the first nozzle and the second nozzle.

Owner:SAMSUNG DISPLAY CO LTD

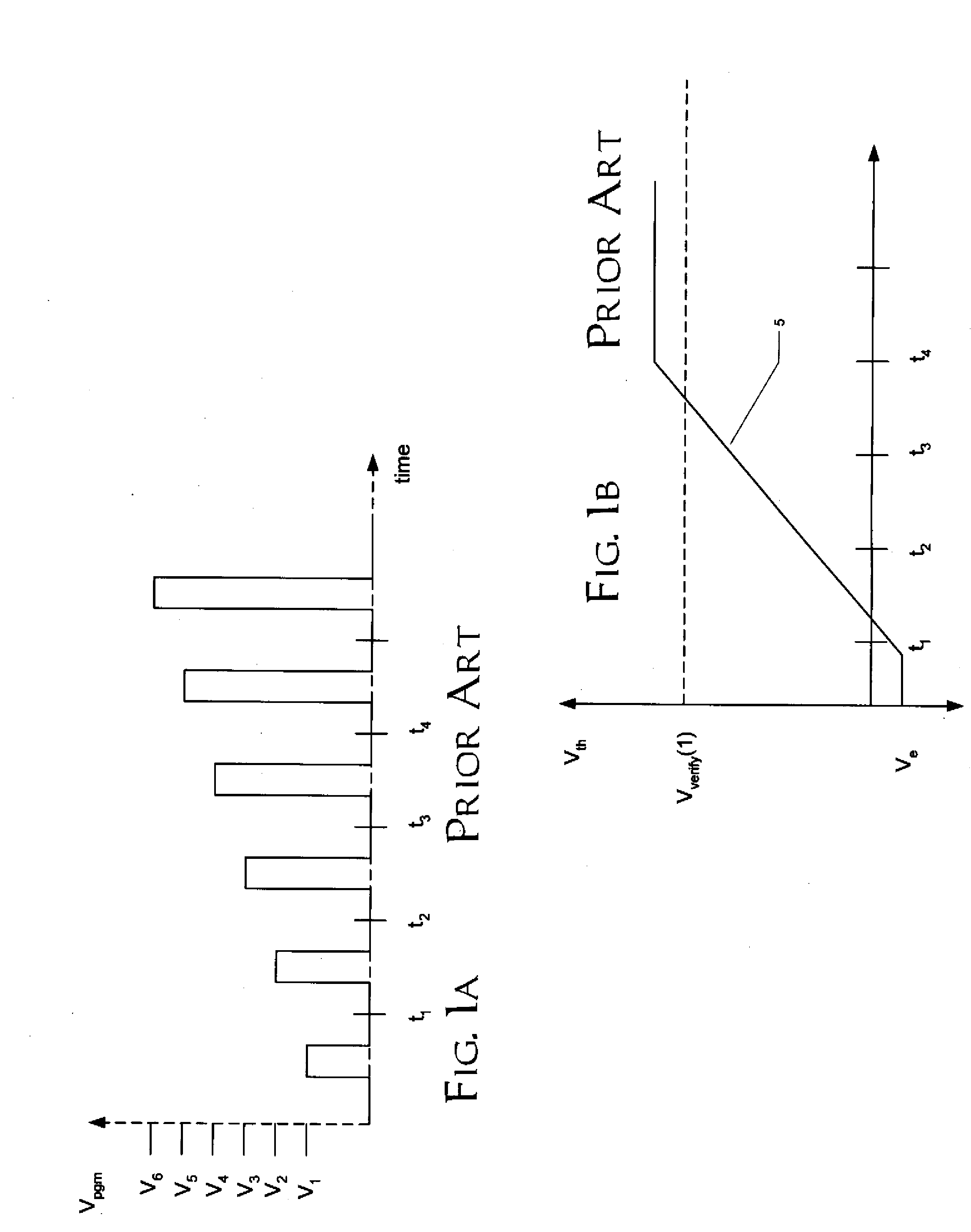

Partial Page Fail Bit Detection in Flash Memory Devices

ActiveUS20080002468A1Improve efficiencyEarly terminationError detection/correctionRead-only memoriesDetection thresholdError correction coding

A flash memory device, and a method of operating the same, is disclosed. The array of the flash memory device is arranged in pages of memory cells, each page having memory cells associated into groups of memory cells within the page for purposes of fail bit detection in program verification. For example, these groups may correspond to sectors within the page. In a programming operation, the verify process determines whether each group of memory cells within the page has fewer than a selected ignore bit limit for the sector. If not, additional programming is required for the insufficiently programmed cells in the page. By applying a fail bit detection threshold for each of multiple groups within the page, the efficiency of error correction coding in the flash memory is improved. A similar verify and fail bit detection approach may be used in erase and soft programming operations.

Owner:SANDISK TECH LLC

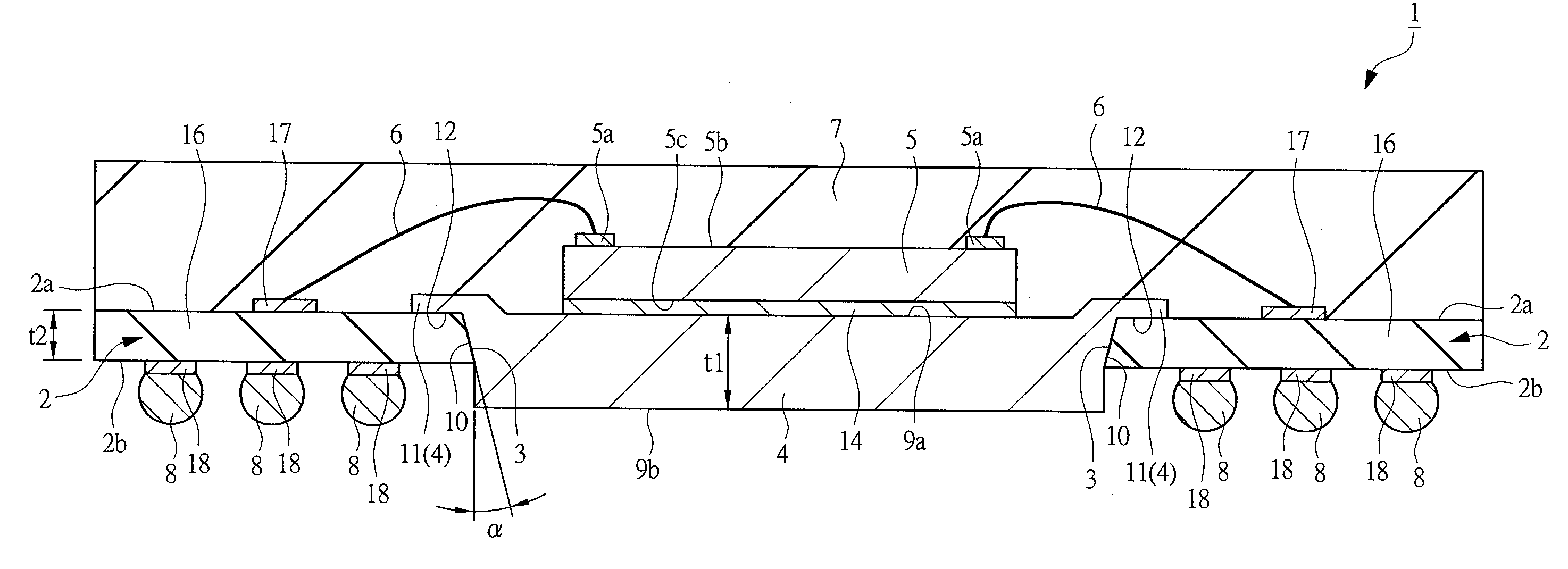

Semiconductor device and manufacturing method of the same

ActiveUS20090309213A1Improve cooling effectImprove manufacturing yieldSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSolder ball

A semiconductor chip is mounted on a heat sink disposed inside a through-hole of a wiring board, electrodes of the semiconductor chip and connecting terminals of the wiring board are connected by bonding wires, a sealing resin is formed to cover the semiconductor chip and the bonding wires, and solder balls are formed on the lower surface of the wiring board, thereby constituting the semiconductor device. The heat sink is thicker than the wiring board. The heat sink has a protruded portion protruding to outside from the side surface of the heat sink, the protruded portion is located on the upper surface of the wiring board outside the through-hole, and the lower surface of the protruded portion contacts to the upper surface of the wiring board. When the semiconductor device is manufactured, the heat sink is inserted from the upper surface side of the wiring board.

Owner:RENESAS ELECTRONICS CORP

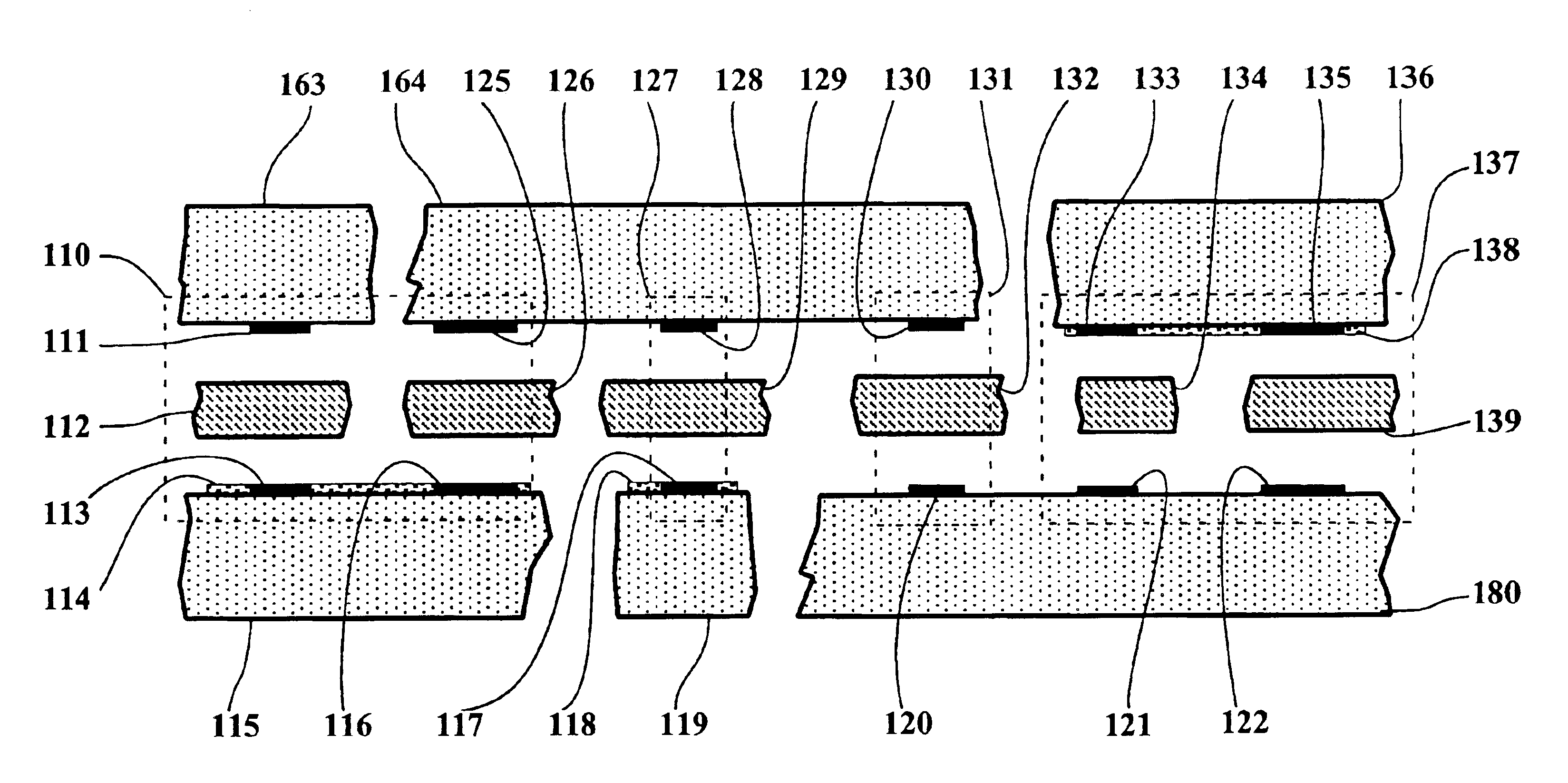

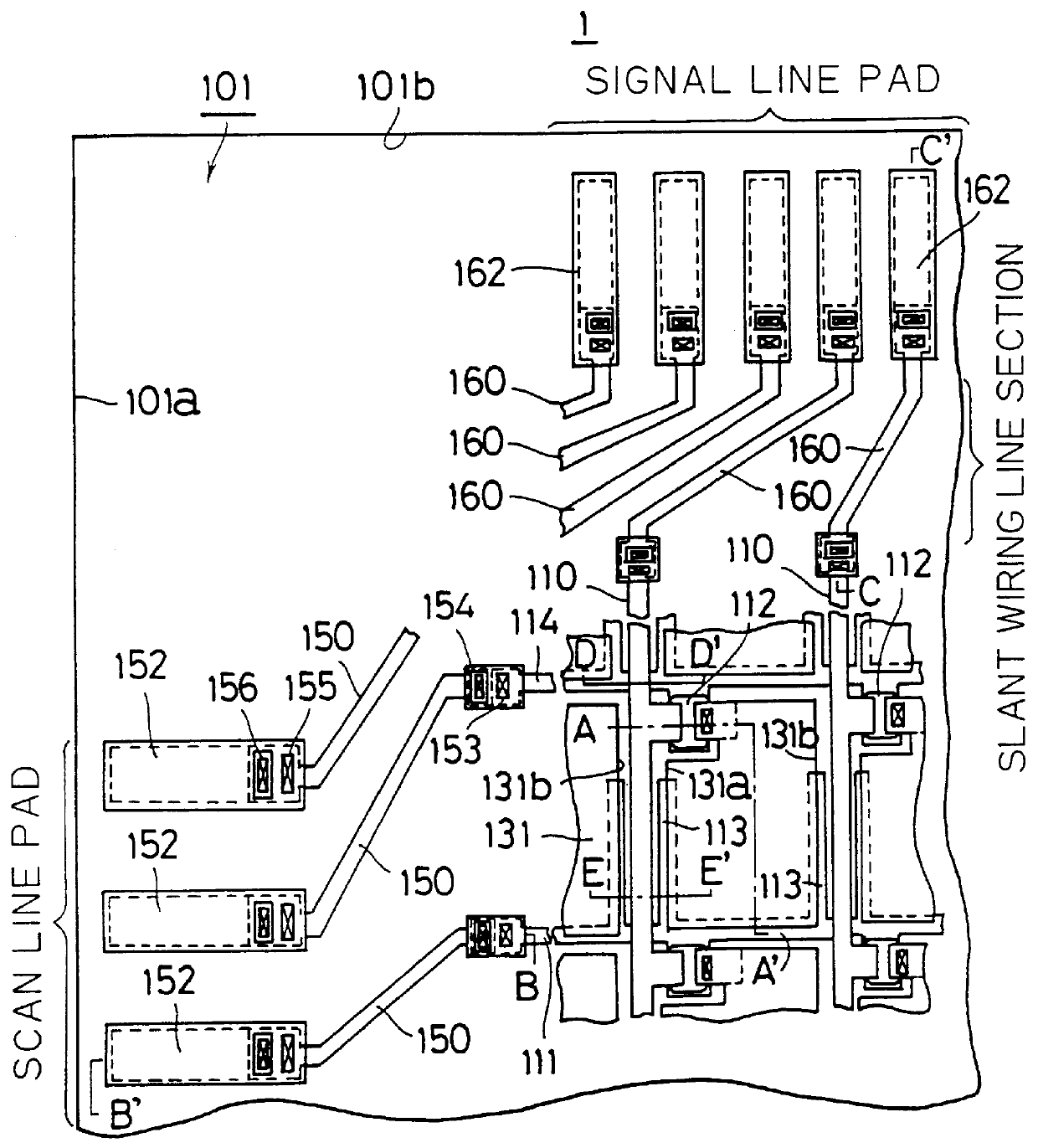

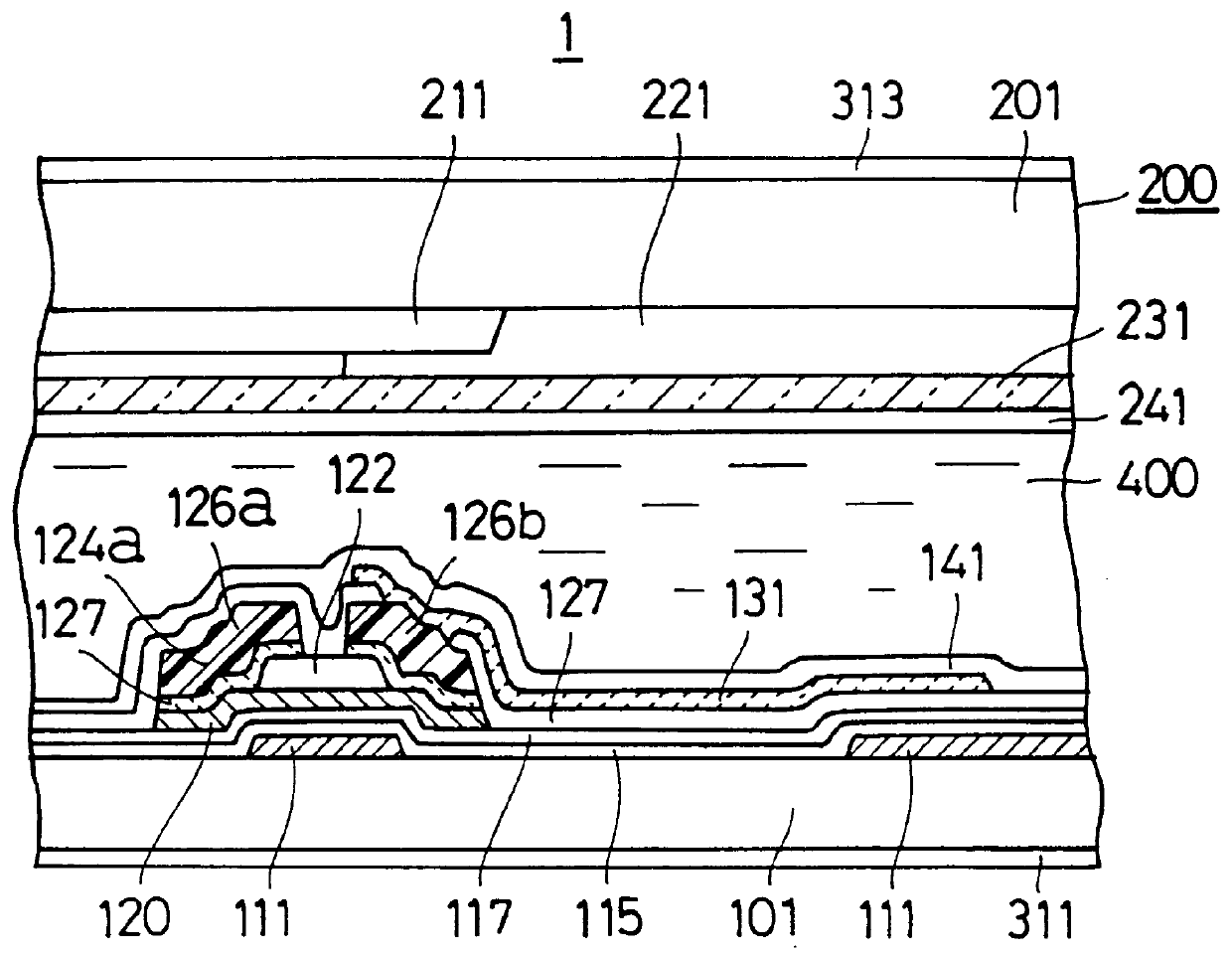

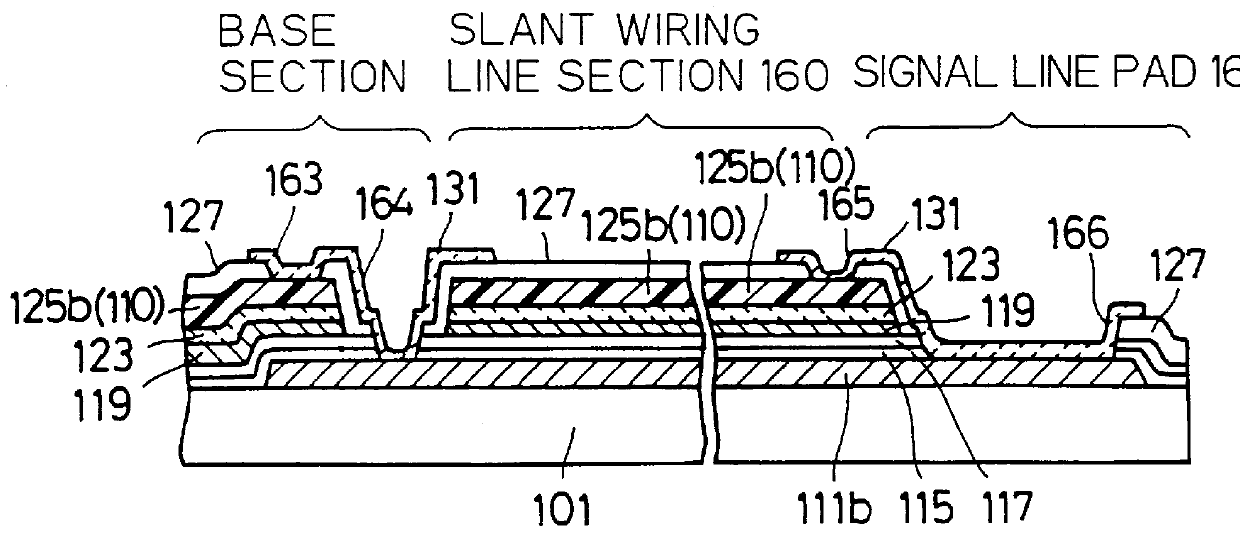

Array substrate comprising semiconductor contact layers having same outline as signal lines

InactiveUS6078366AImprove eliminationReduce the ratioSolid-state devicesSemiconductor/solid-state device manufacturingContact layerAperture ratio

An array substrate includes plural scanning lines (111); a thin film transistor (112) having a first dielectric film (115), (117), a semiconductor film (120) thereon, and a source electrode (126b) electrically coupled to the semiconductor film (120) and a drain electrode (126a); a signal line (110) as taken out of the drain electrode (126a) to extend at substantially right angles to the scanning lines (111); and a pixel electrode (131) electrically connected to the source electrode (126b), wherein the pixel electrode (131) is electrically connected to the source electrode (126b) through a second dielectric film (127) as disposed on at least the signal line (110) while the pixel electrode (131) overlaps an elongate region (113) from its neighboring scanning line (111) through the first and second dielectric films (115), (117), (127). With such an arrangement, an appropriate storage capacitor can be formed by causing the scanning lines and pixel electrode to overlap each other without having to decrease the manufacturing yield while enabling achievement of high aperture ratio.

Owner:JAPAN DISPLAY CENTRAL CO LTD

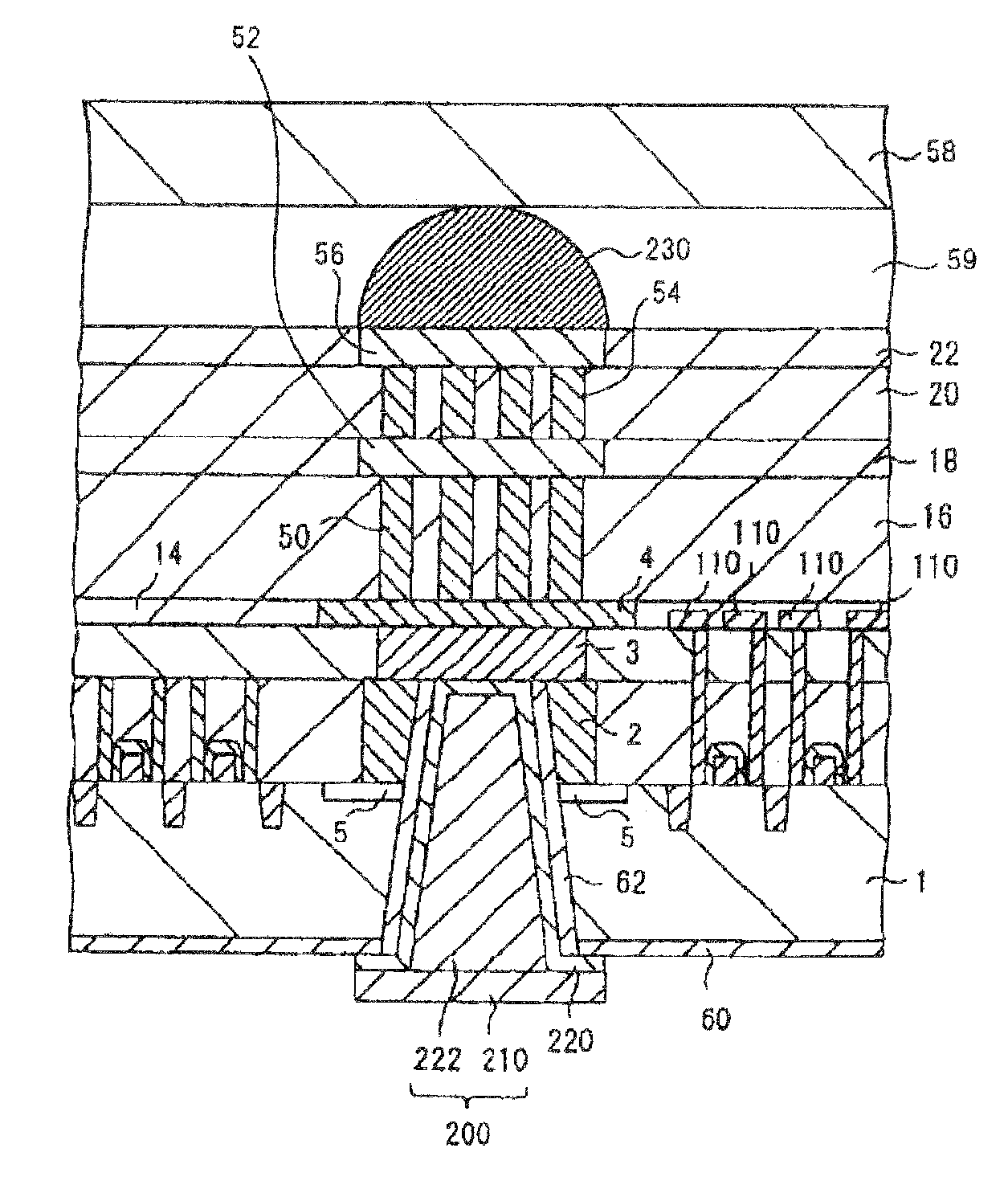

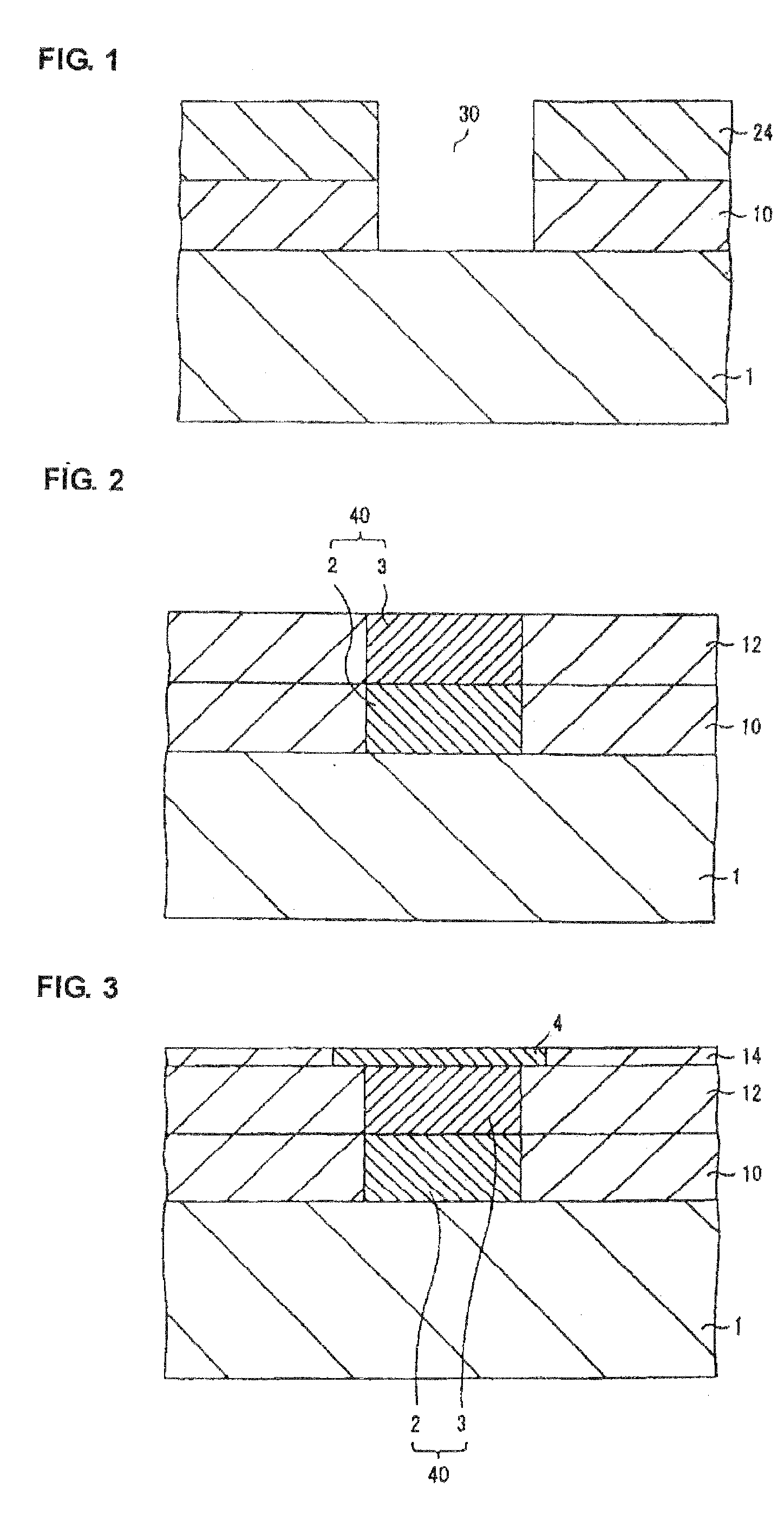

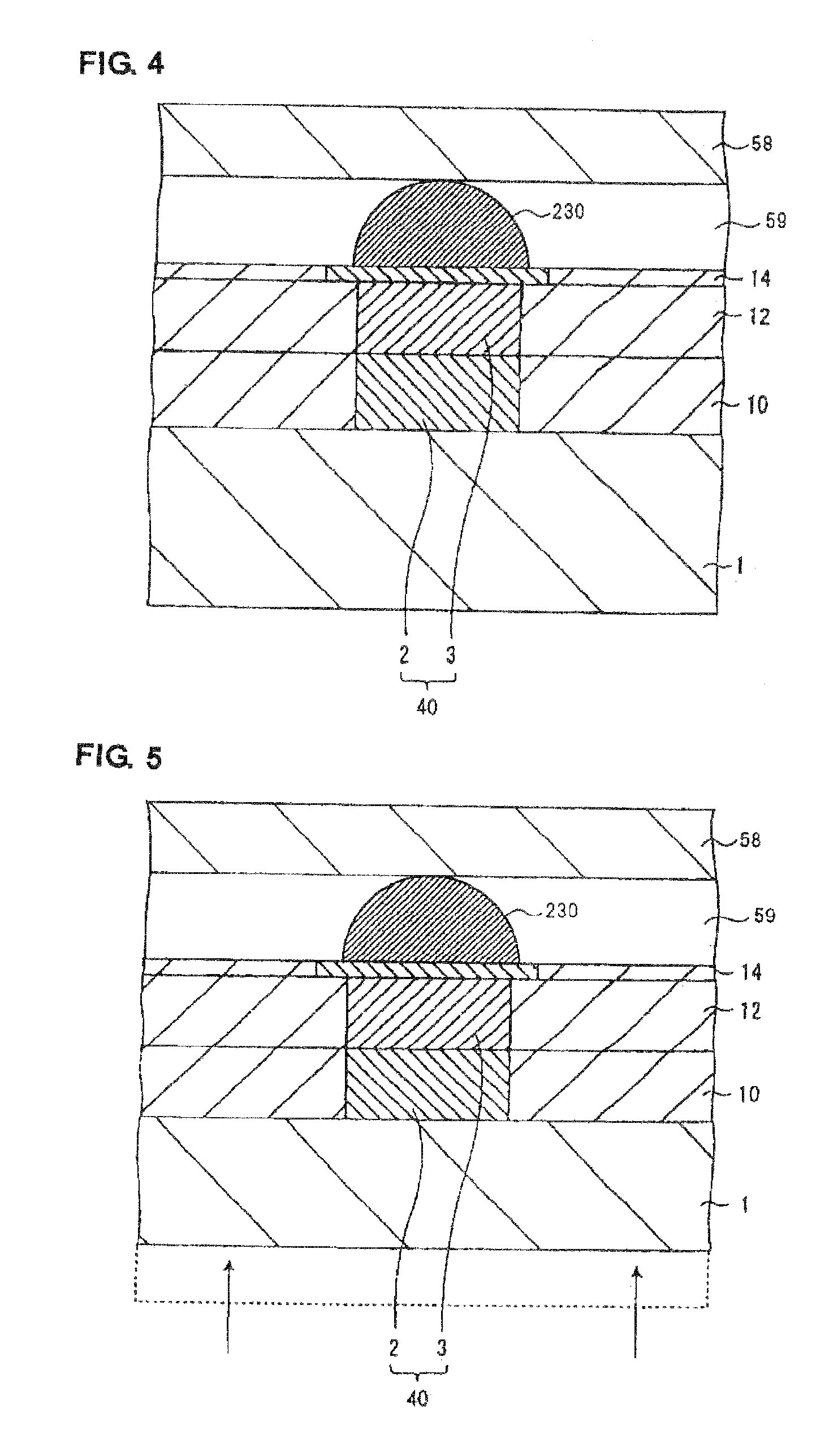

Semiconductor device and method for manufacturing the same

ActiveUS20090108464A1Well formedImprove manufacturing yieldSemiconductor/solid-state device detailsSolid-state devicesContact padSemiconductor

A first insulating layer including a first contact pad made of conductive polysilicon and a second insulating layer including a second contact pad are formed over a semiconductor silicon layer. After this, a via hole for a through-hole electrode is formed until the via hole penetrates through at least the semiconductor silicon layer and the first contact pad and reaches to the second contact pad.

Owner:LONGITUDE LICENSING LTD

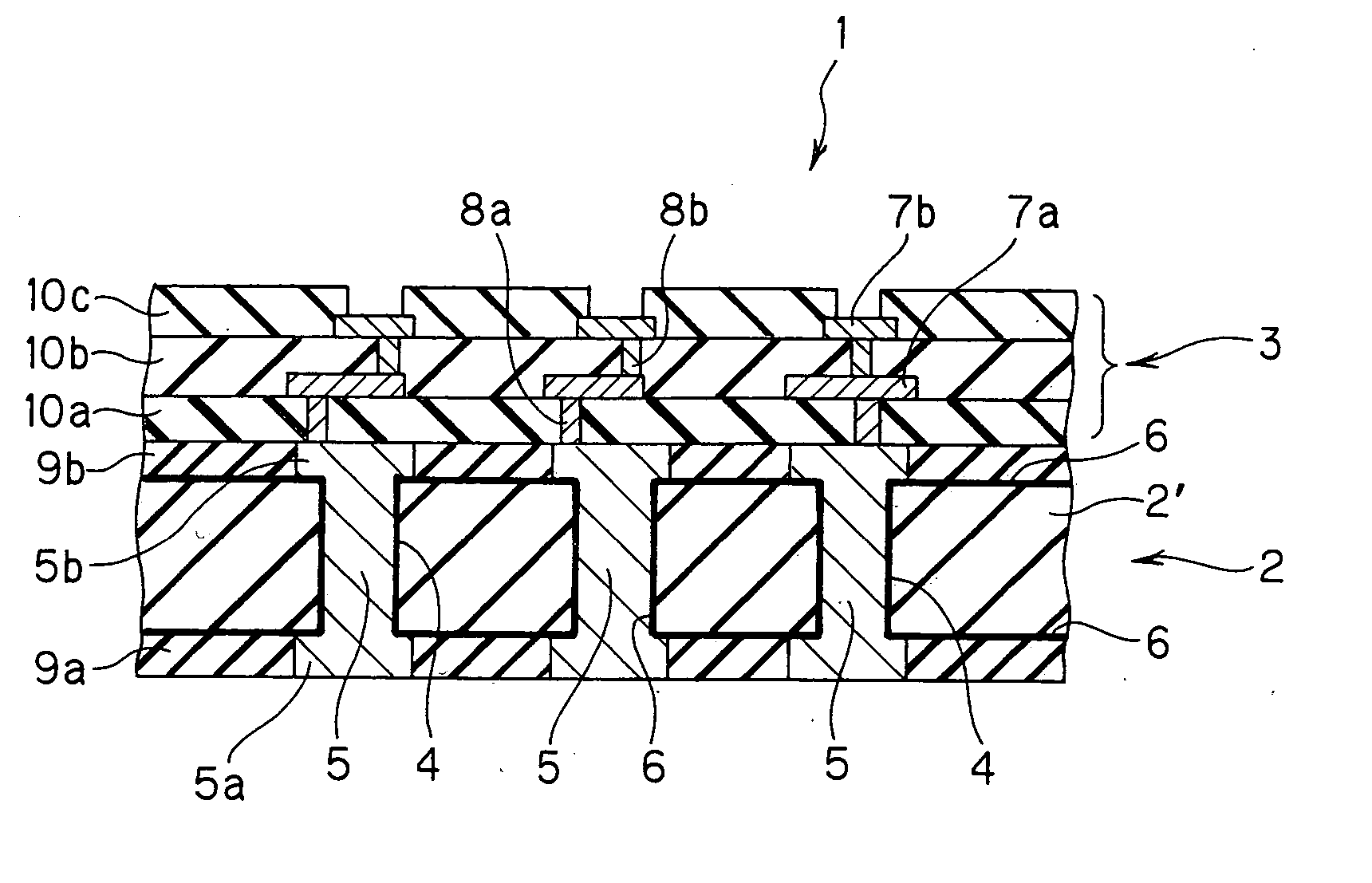

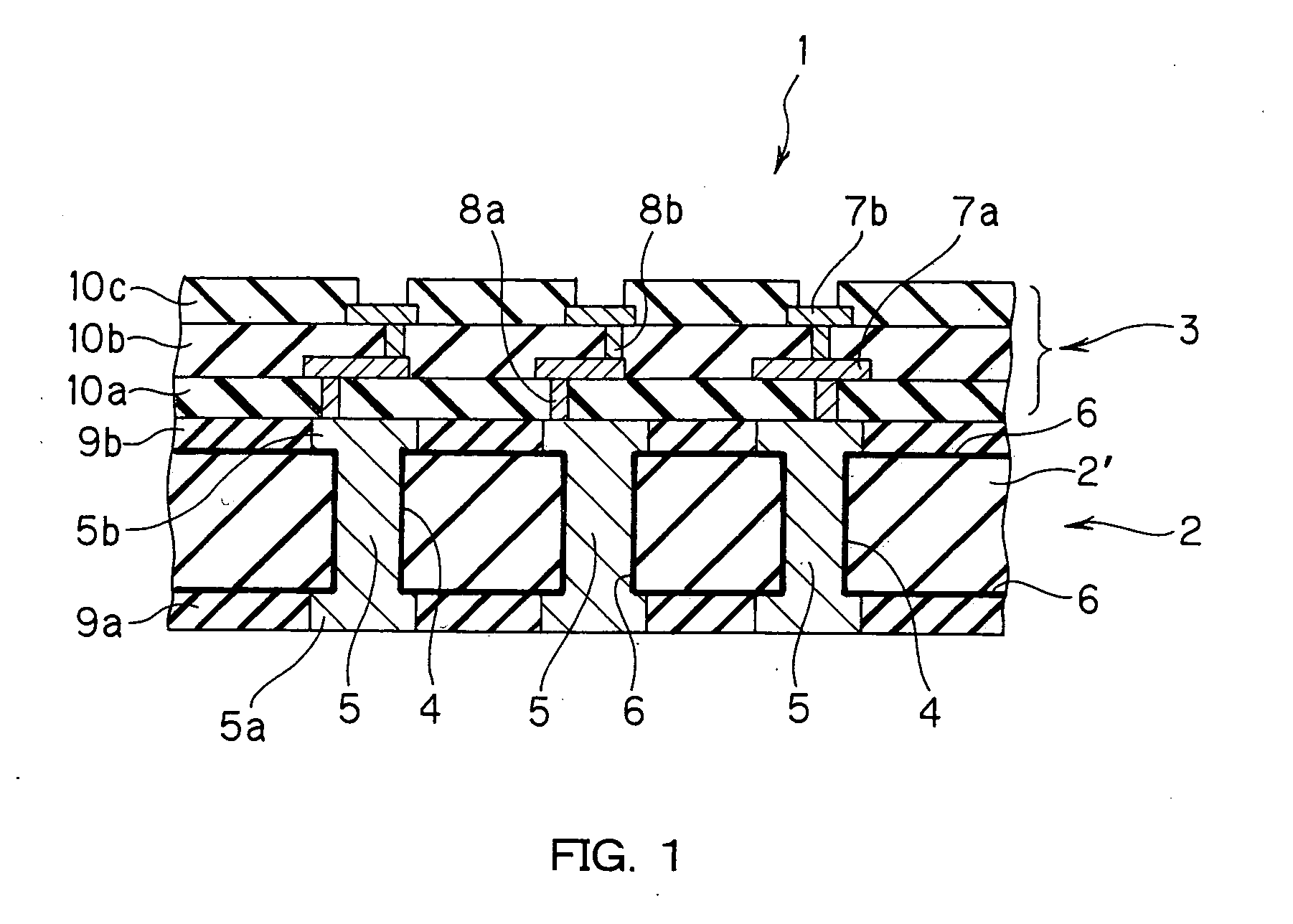

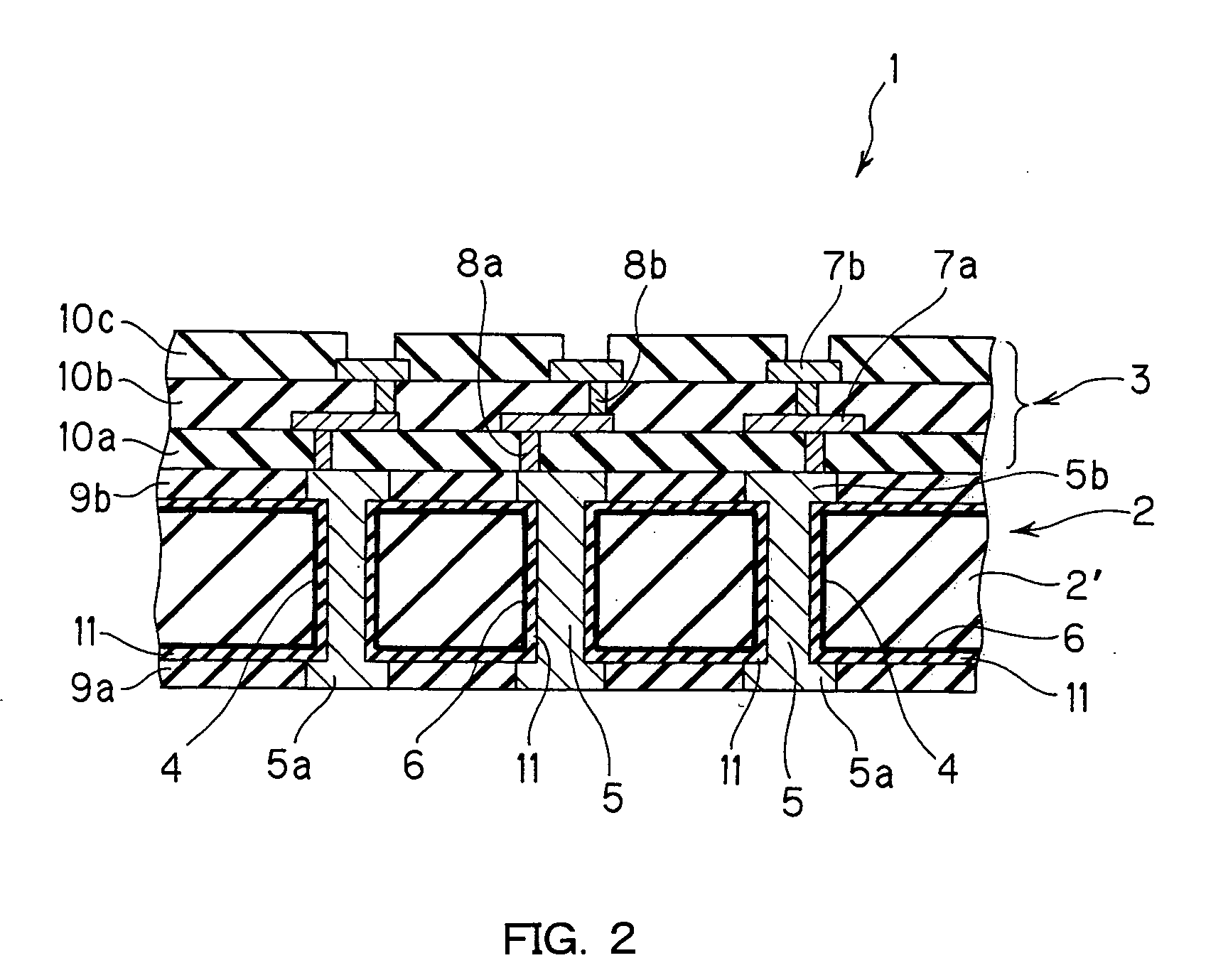

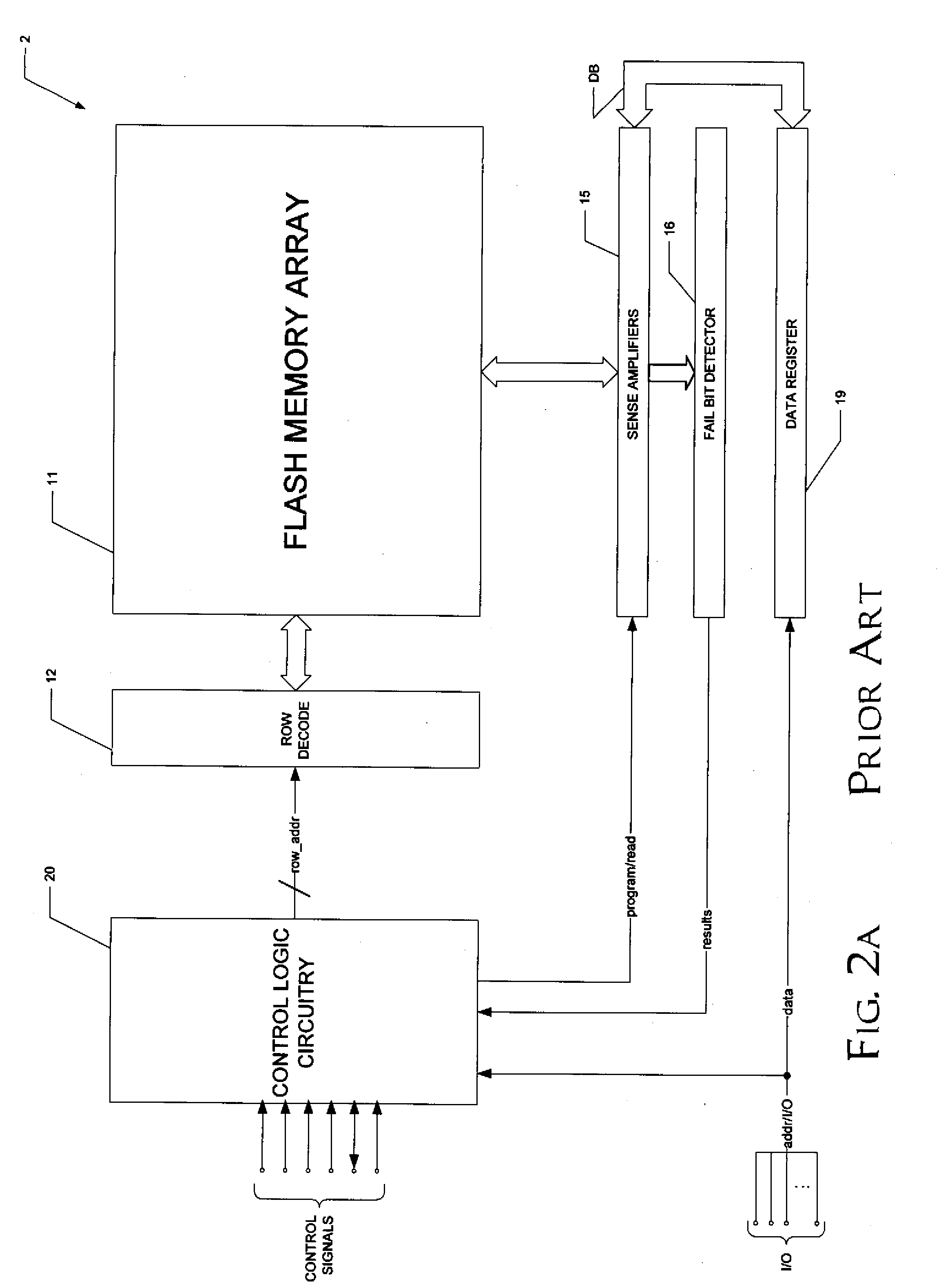

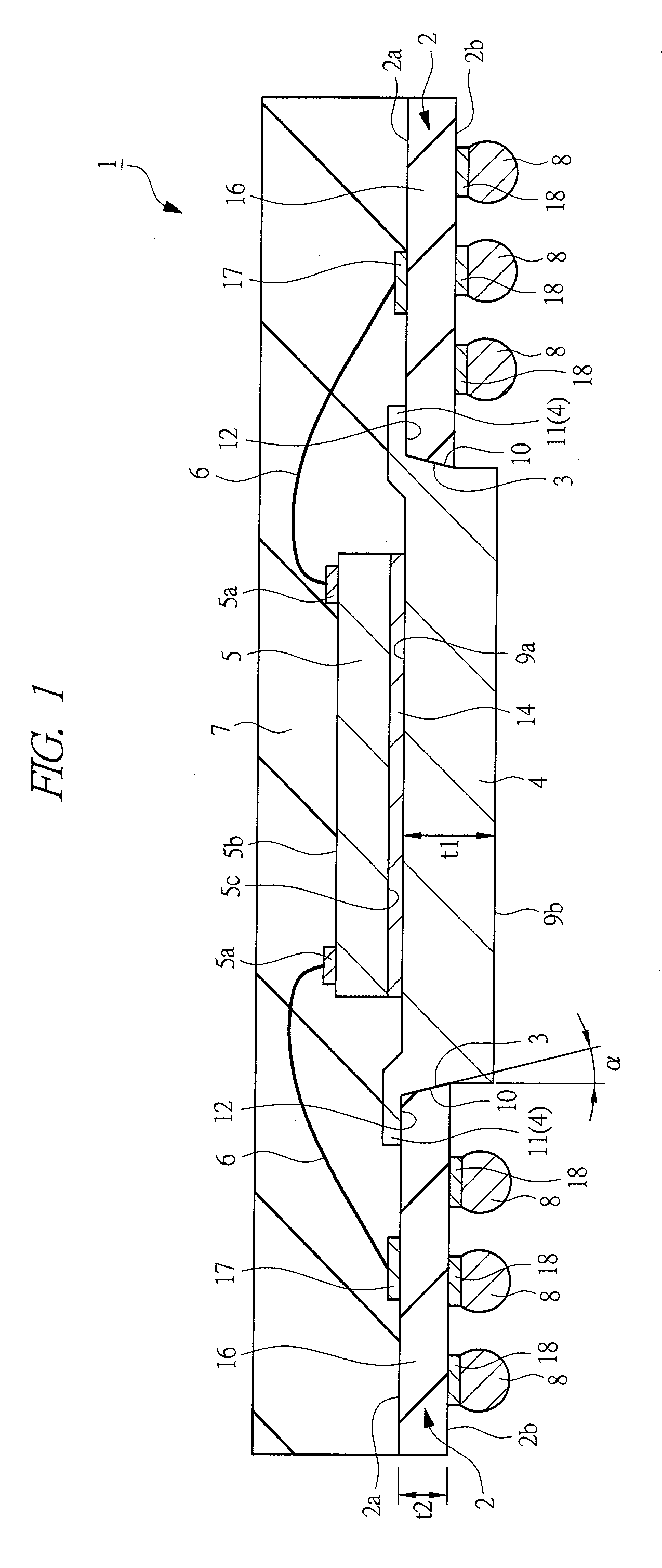

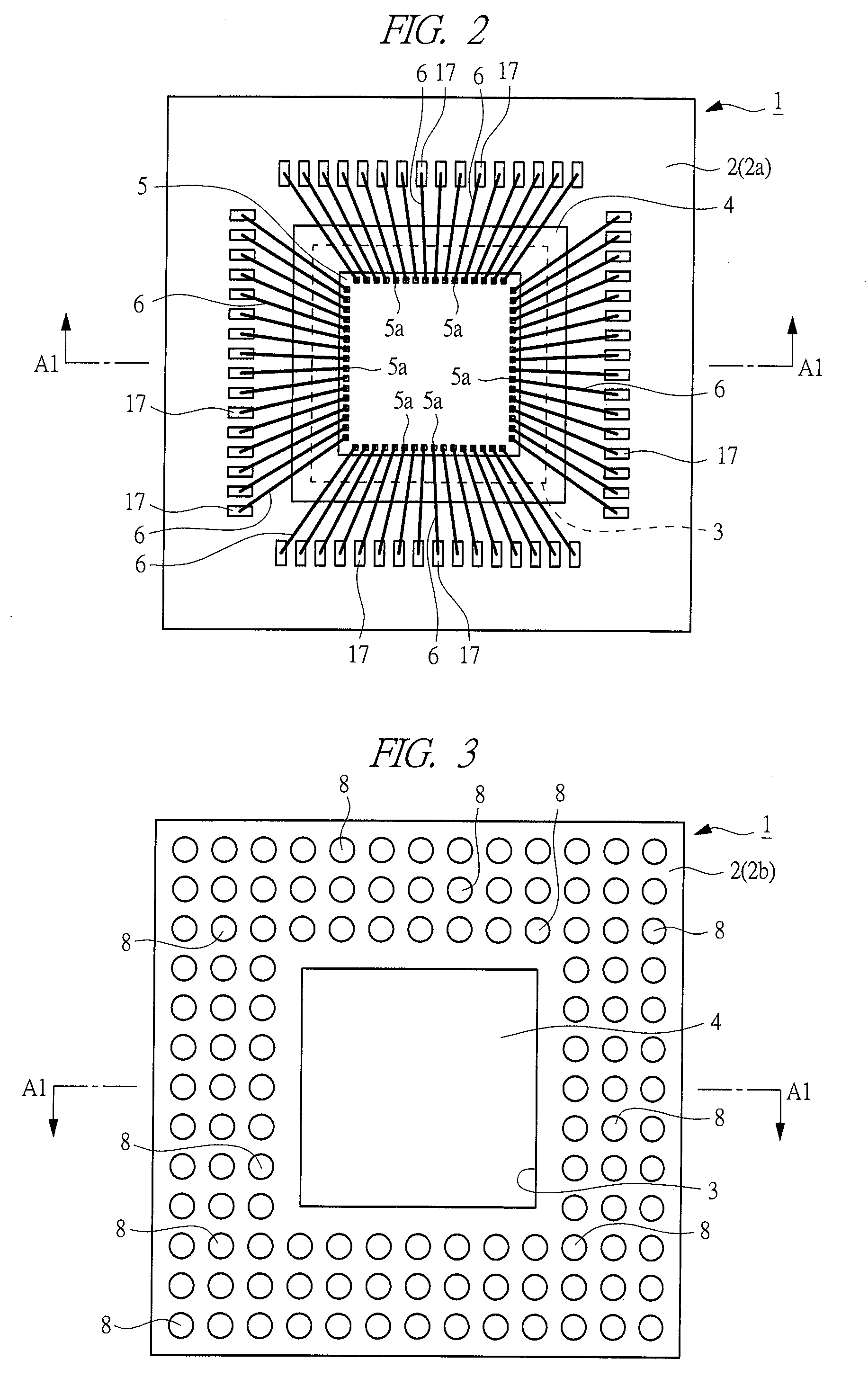

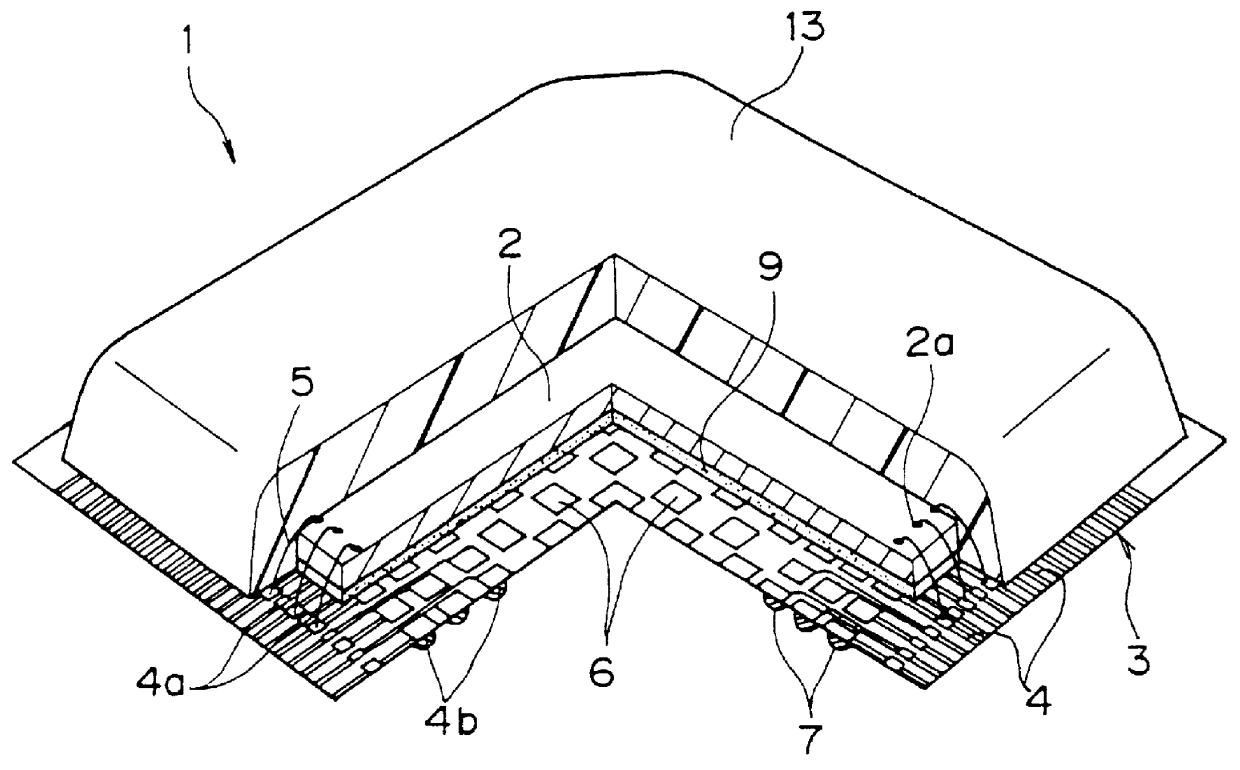

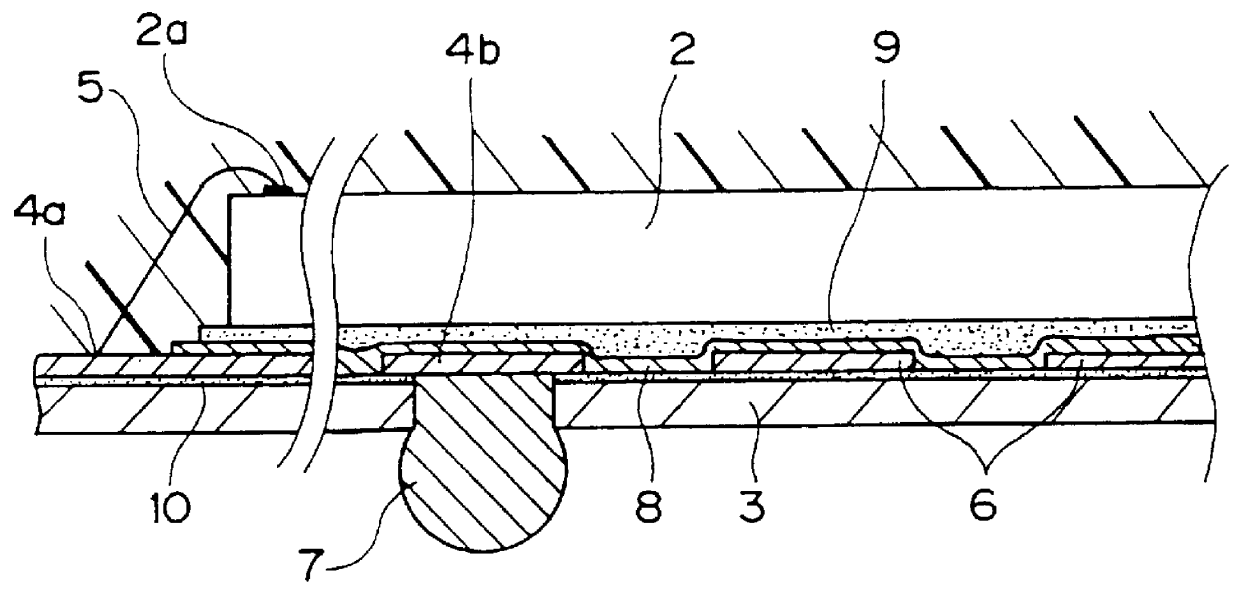

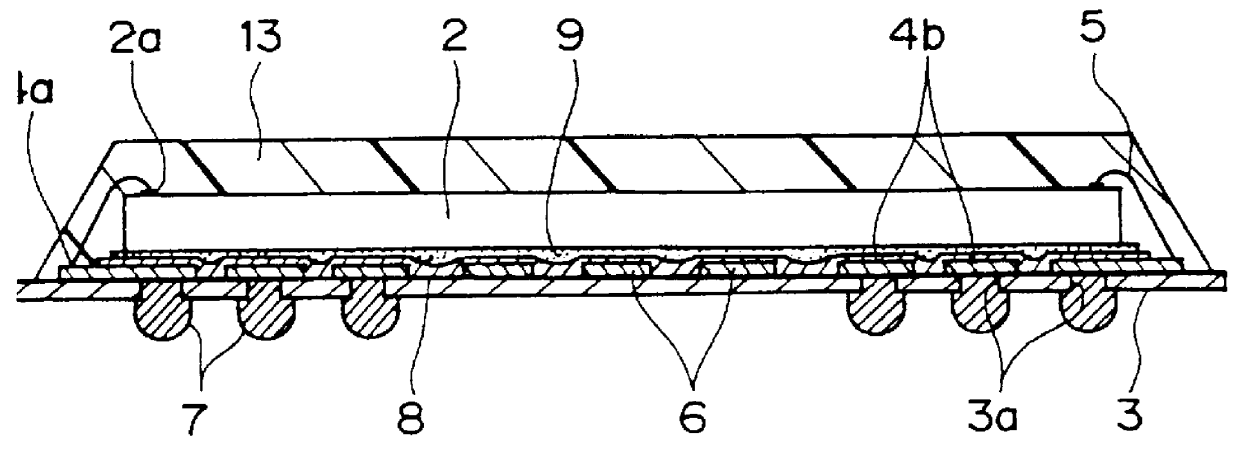

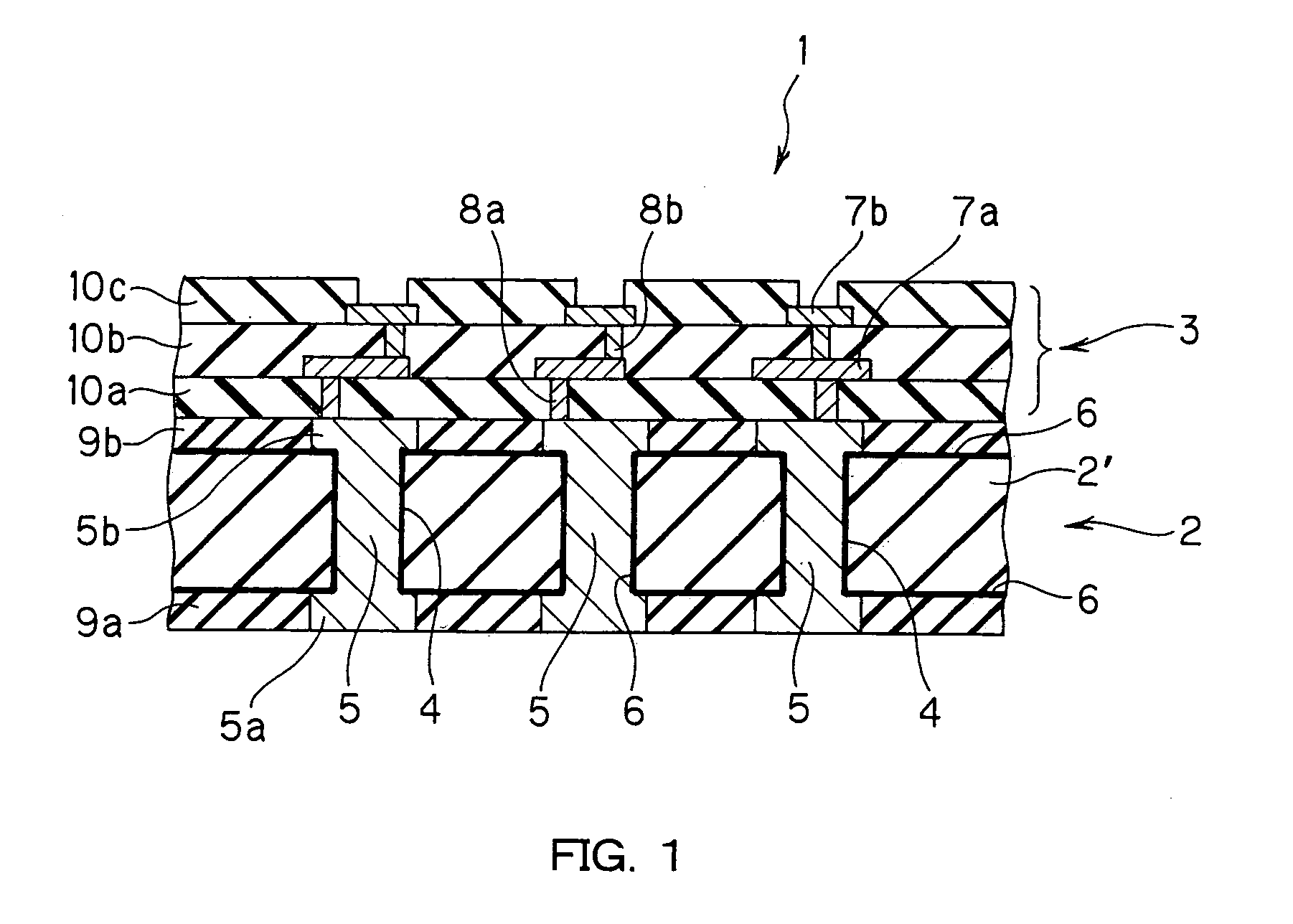

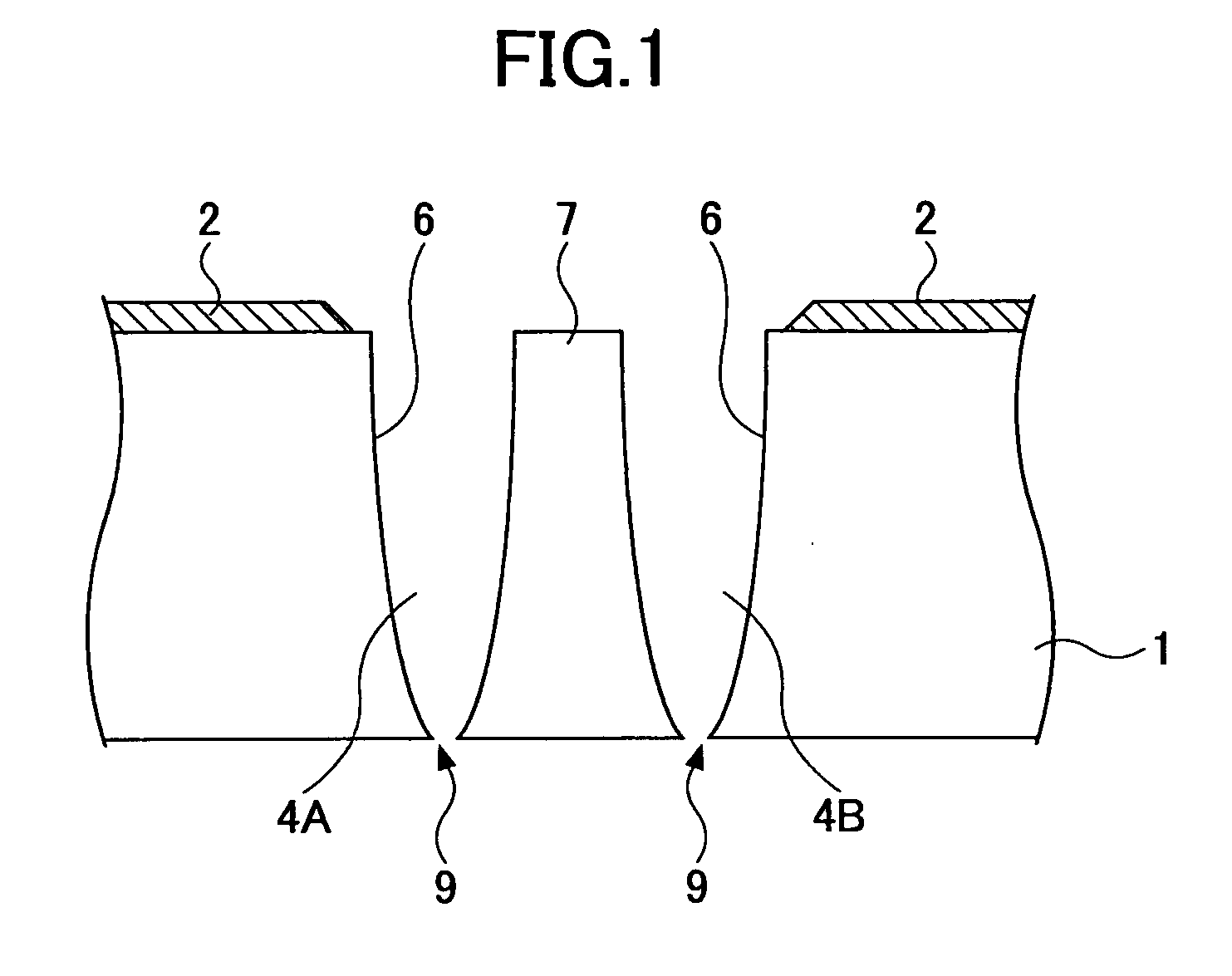

Semiconductor device and manufacturing method

InactiveUS6087717AAvoid separationAvoid crackingSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorElectrical connection

To completely suppress or minimize the voids formed between the insulating substrate and the IC chip in order to prevent the problems of separation and cracking of the chip caused by the aforementioned voids. The present invention is preferably adopted for the Chip Six Package type package or other package types equipped with solder bumps or other external connecting terminals directly beneath the IC chip. For insulating substrate (3), on its chip-carrying surface, there is pattern element (6) in the region beneath the IC chip and free of conductor pattern elements (4) in addition to conductor pattern element (4) for forming electrical connection between the electrode pads and the external connecting terminals of the chip. Said pattern element (6) divides said region into plural small regions A. IC chip (2) is bonded through die paste on insulating substrate (3) such that an end of conductor pattern element (4), pattern element (6) and divided small regions A are covered. Pattern element (6) acts to reduce the shifting of die paste (9) before curing due to the surface tension. As a result, the formation of voids beneath the chip can be completely prevented or minimized.

Owner:TEXAS INSTR INC

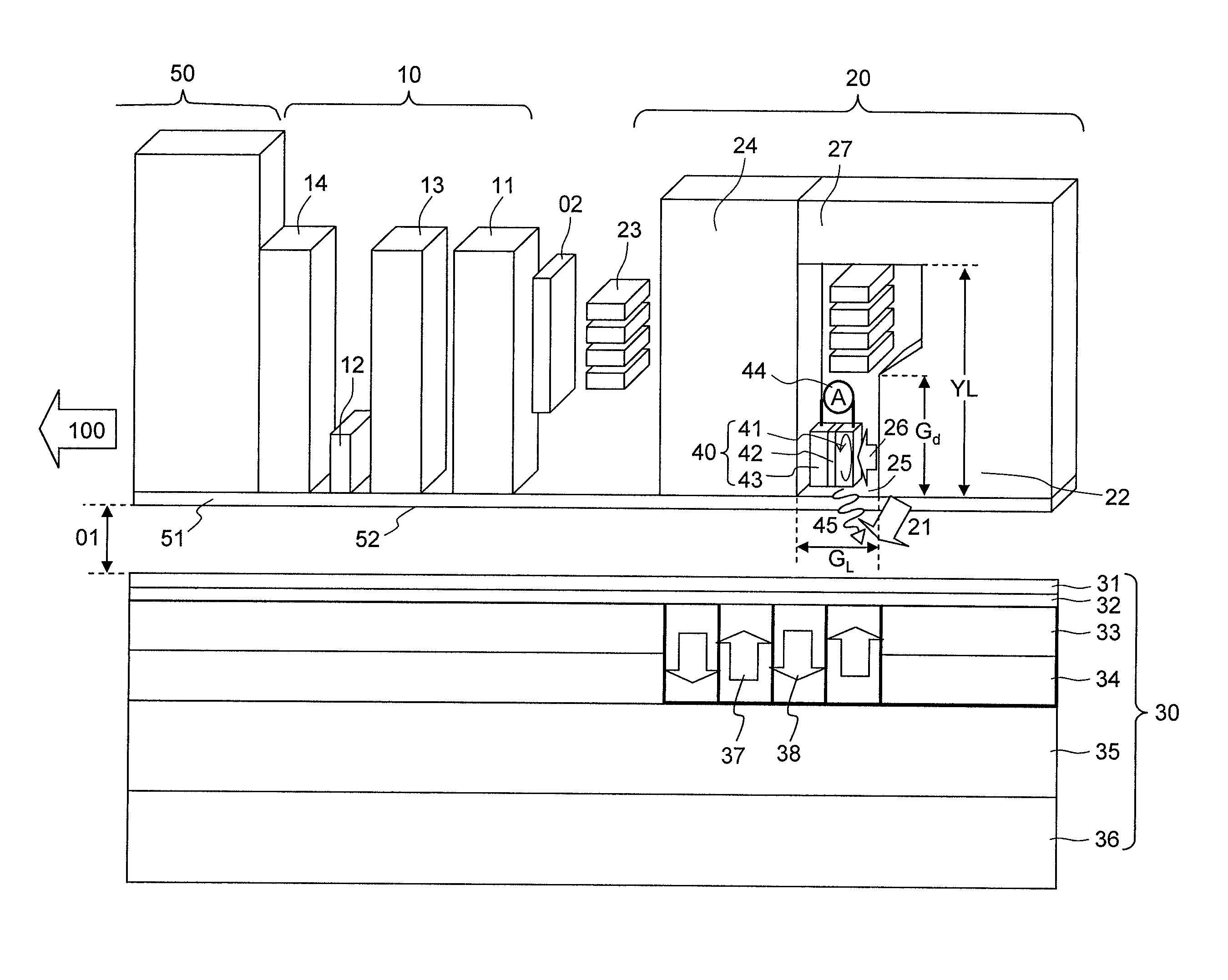

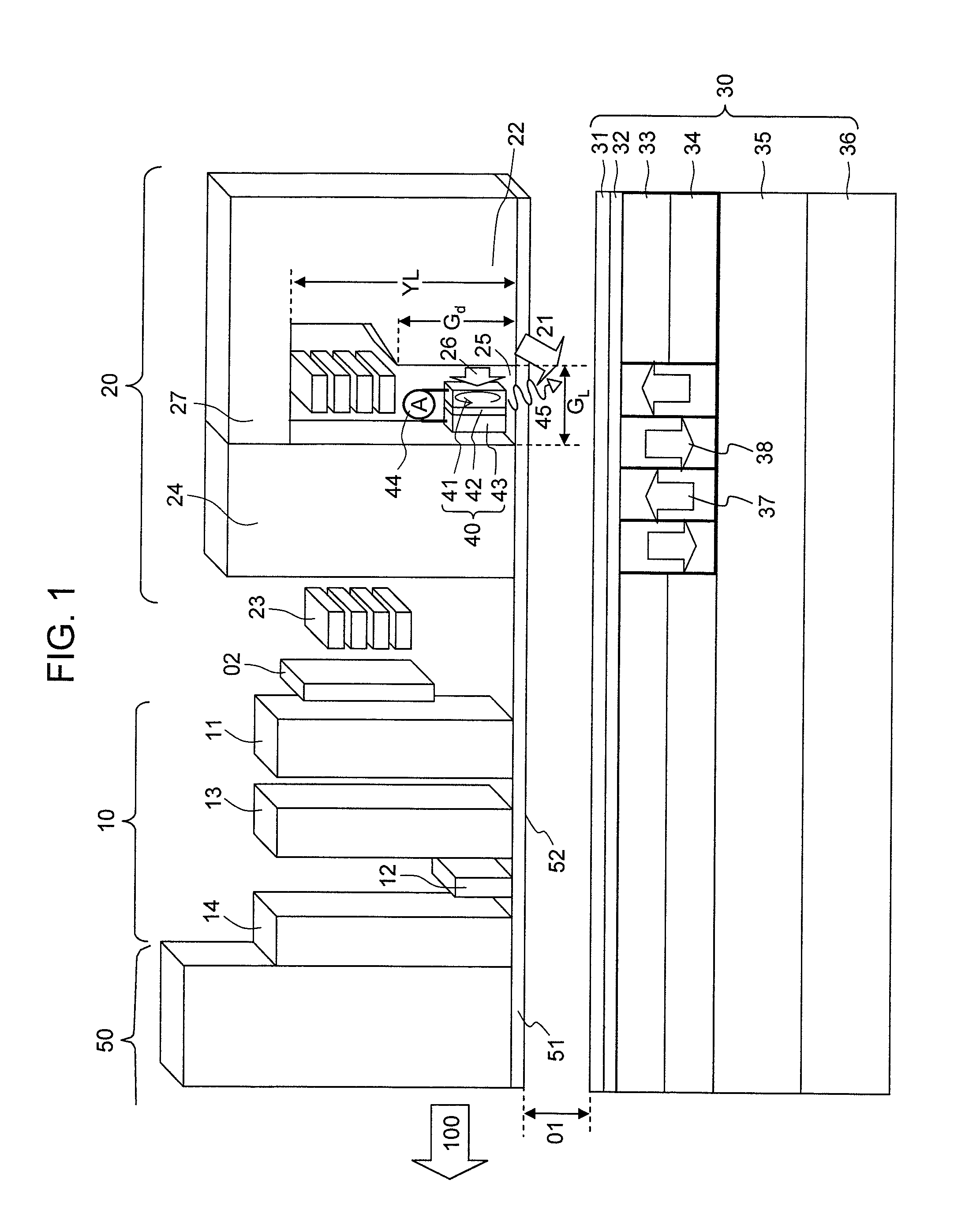

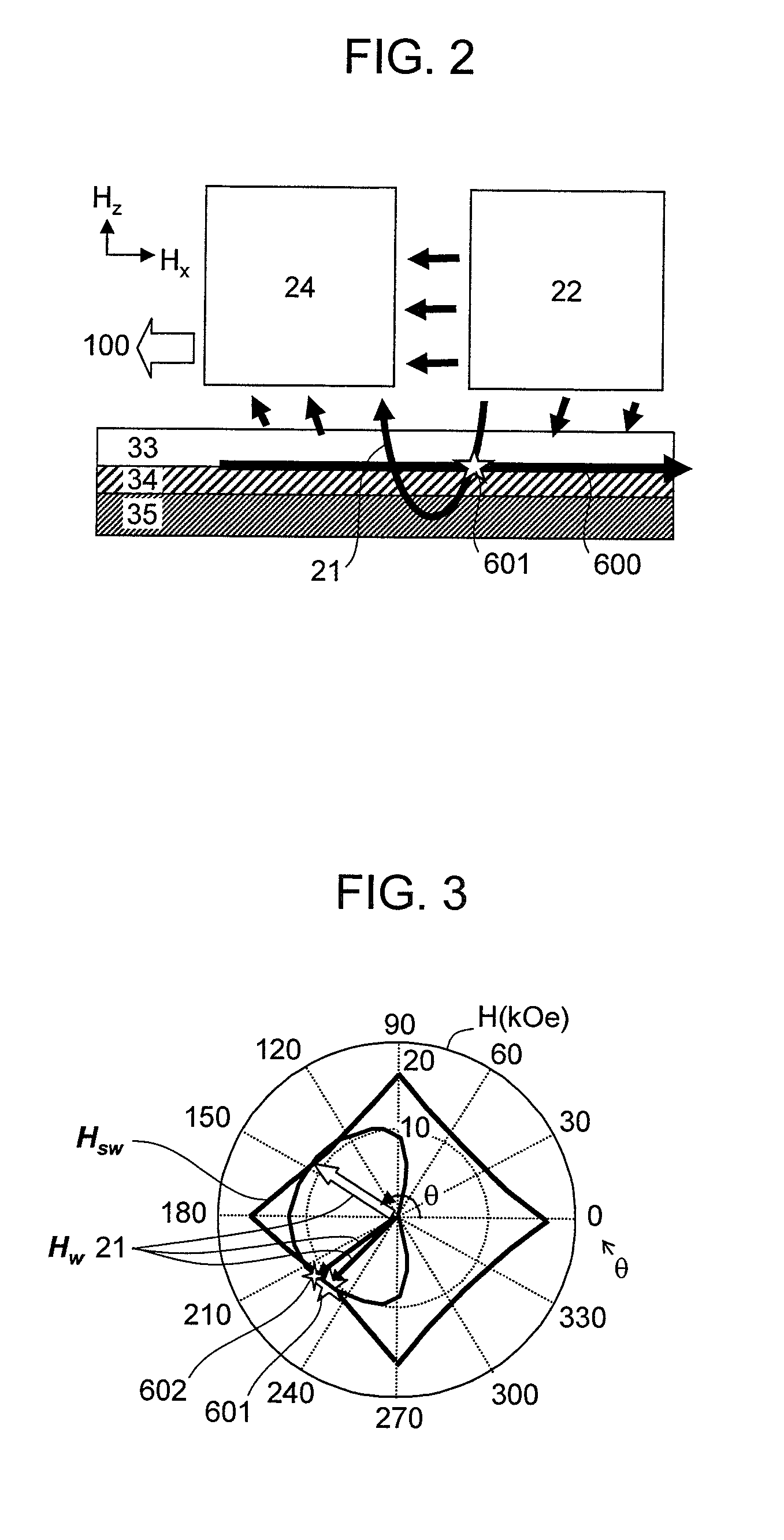

Magnetic head, magnetic recording method and apparatus for controlling magnetic head with spin torque oscillator in a disk drive

ActiveUS9275672B2Improve recording densityHigh densityManufacture head surfaceDriving/moving recording headsSpin torque oscillatorsMagnetic poles

A microwave assisted magnetic recording head includes a recording magnetic pole unit that produces a recording field for writing to a perpendicular magnetic recording medium, and a high-frequency magnetic field oscillator that produces a high-frequency magnetic field. The recording magnetic pole unit includes a magnetic core with a write gap portion at which a main recording field component is concentrated, and the high-frequency magnetic field oscillator is disposed in the write gap.

Owner:HITACHI LTD

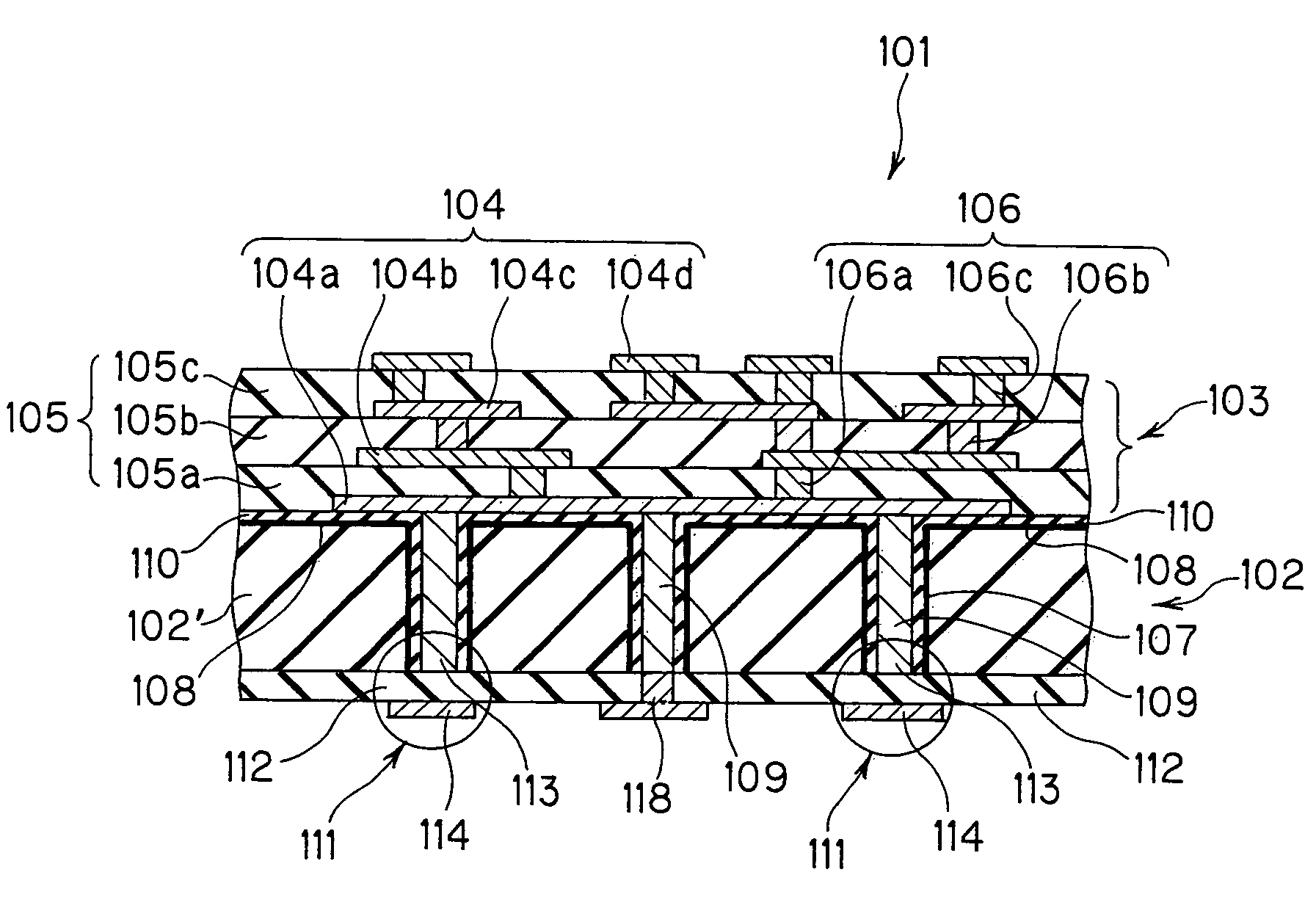

Multilayer wiring board and manufacture method thereof

InactiveUS7091589B2Improve electrical performanceBroaden your optionsInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsEngineeringConductive materials

In a multilayer wiring board comprising a core board, and a wiring layer and an electrically insulating layer that are stacked on one surface of said core board, a thermal expansion coefficient of said core board in XY directions falls within a range of 2 to 20 ppm, a core member for said core board is a core member selected from silicon, ceramics, glass, a glass-epoxy composite, and metal, said core board is provided with a plurality of through holes that are made conductive between the front and the back by a conductive material, and a capacitor is provided on one surface of said core board, wherein said capacitor comprises an upper electrode being the conductive material in said through hole, and a lower electrode disposed so as to confront said upper electrode via a dielectric layer.

Owner:DAI NIPPON PRINTING CO LTD

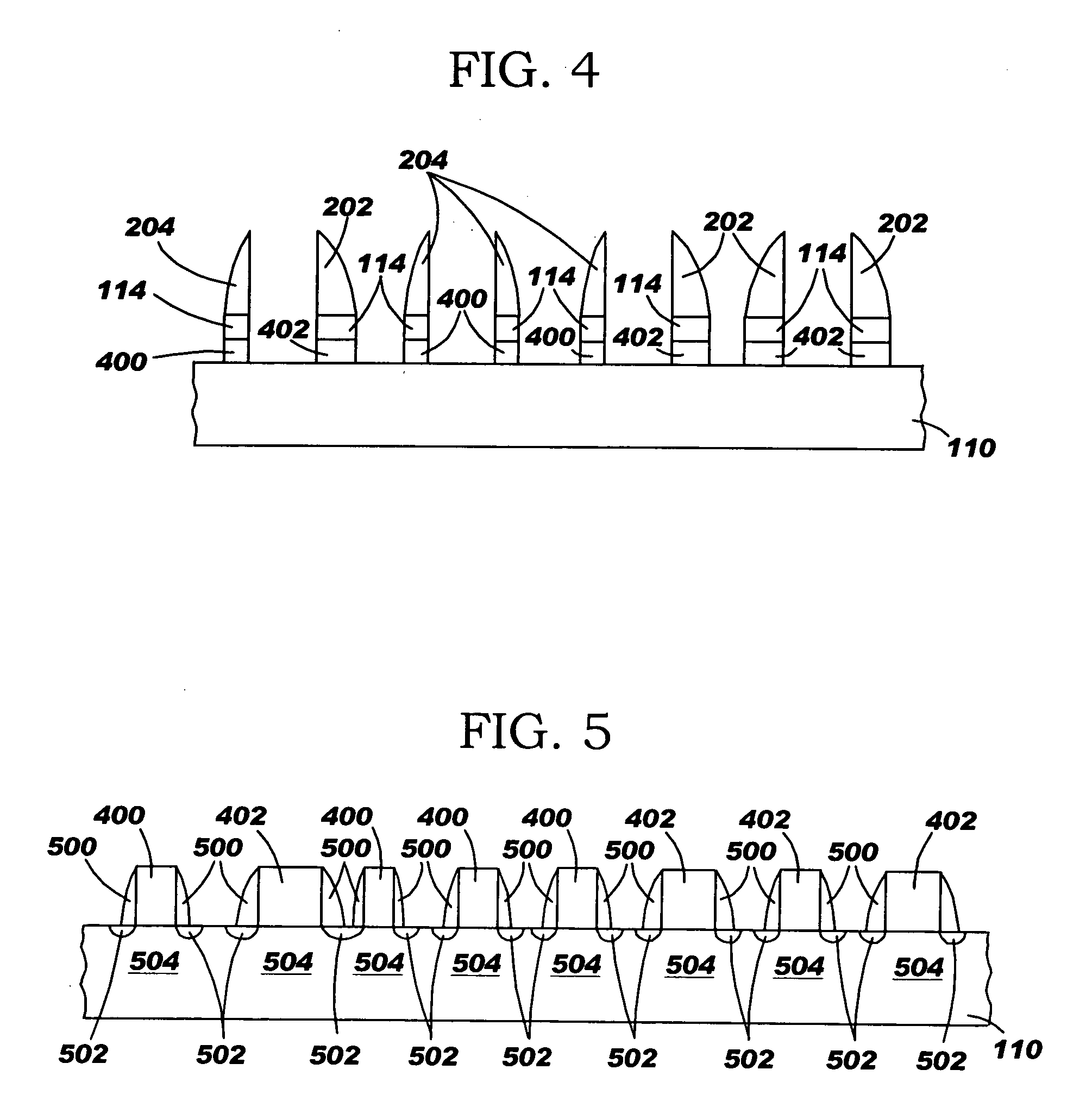

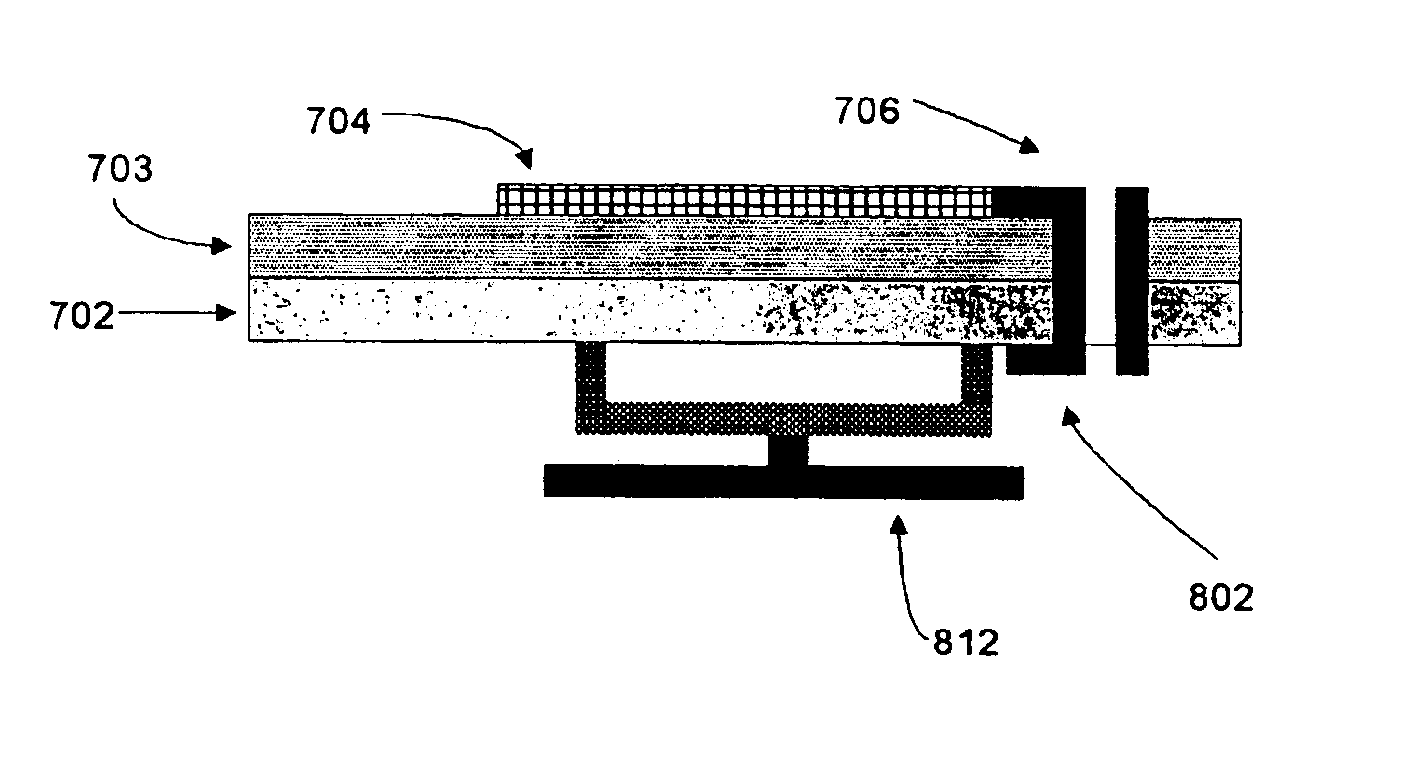

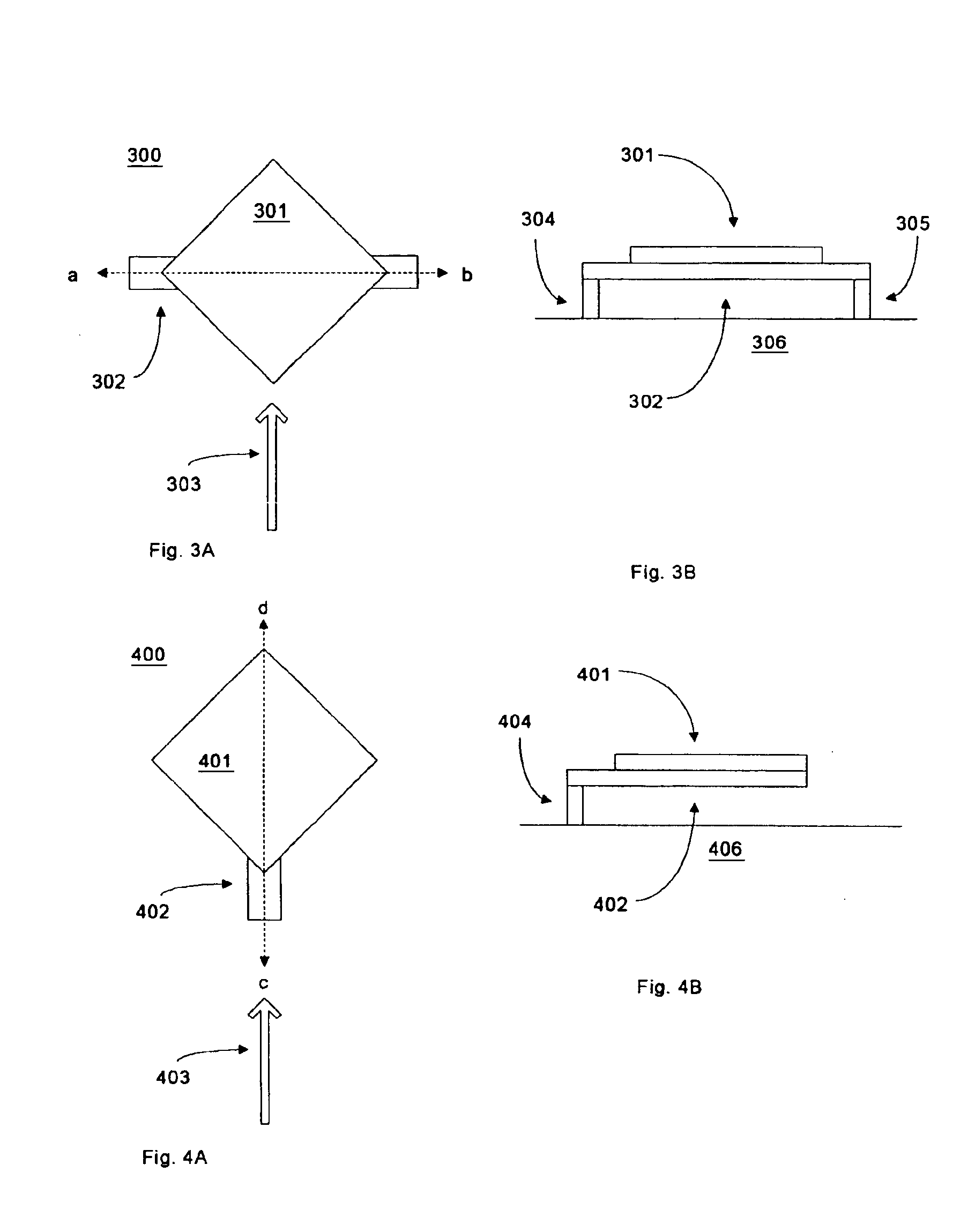

Vacuum packaged micromirror arrays and methods of manufacturing the same

ActiveUS6903860B2Improved dielectric isolationImprove isolationOptical elementsSpatial light modulatorFrit

A vacuum packaged electromechanical micromirror array comprises a 1st packaging substrate, a 2nd packaging substrate, a device substrate with a 1st surface and a 2nd surface, control circuitry on said 1st surface, and micromirrors on said 2nd surface. The device substrate resides on the 1st packaging substrate with electrical connections between them. The electromechanical micromirror array is sealed in a vacuum package formed by the packaging substrates. The vacuum packaged micromirror array may be used as a spatial light modulator (SLM). Methods of fabricating the vacuum packaged array are disclosed. Such methods generally involve providing a device substrate with a 1st surface and a 2nd surface, fabricating control circuitry on the 1st surface, fabricating micromirrors on the 2nd surface, providing a 1st packaging substrate, mounting the device substrate on the 1st packaging substrate by flip-chip assembly, providing a 2nd packaging substrate, and sealing the packaging substrates by glass frit sealing.

Owner:IGNITE INC

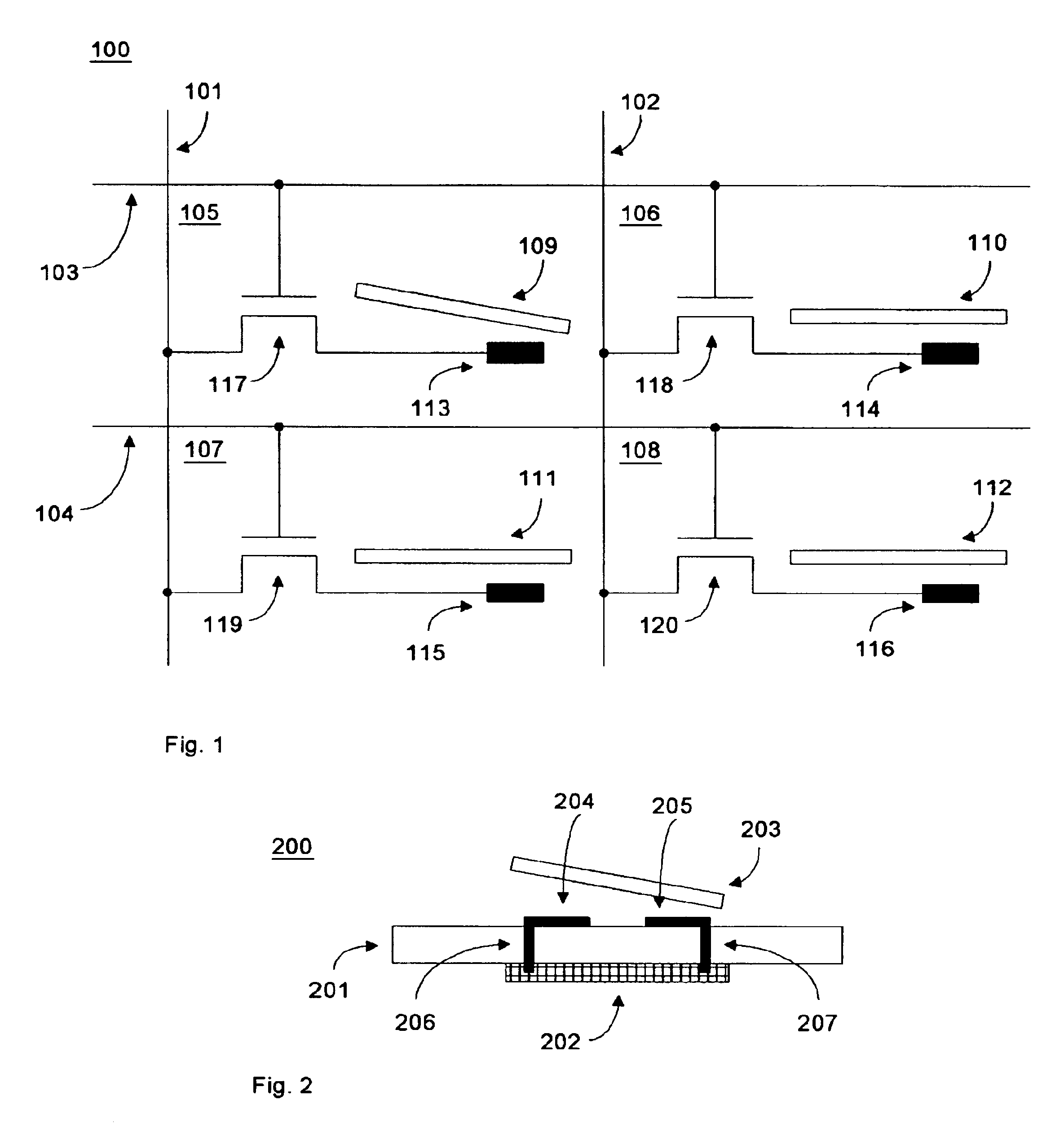

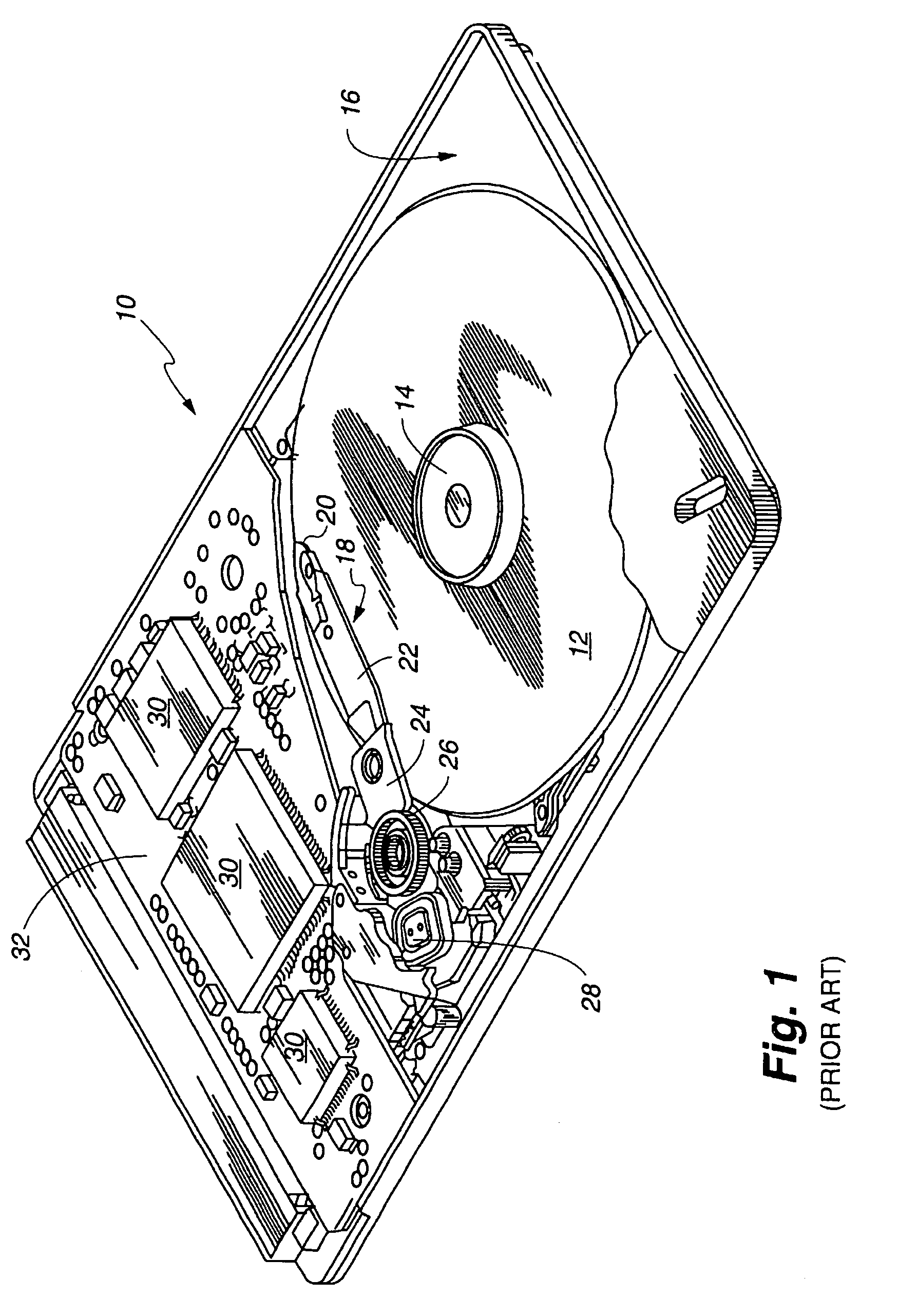

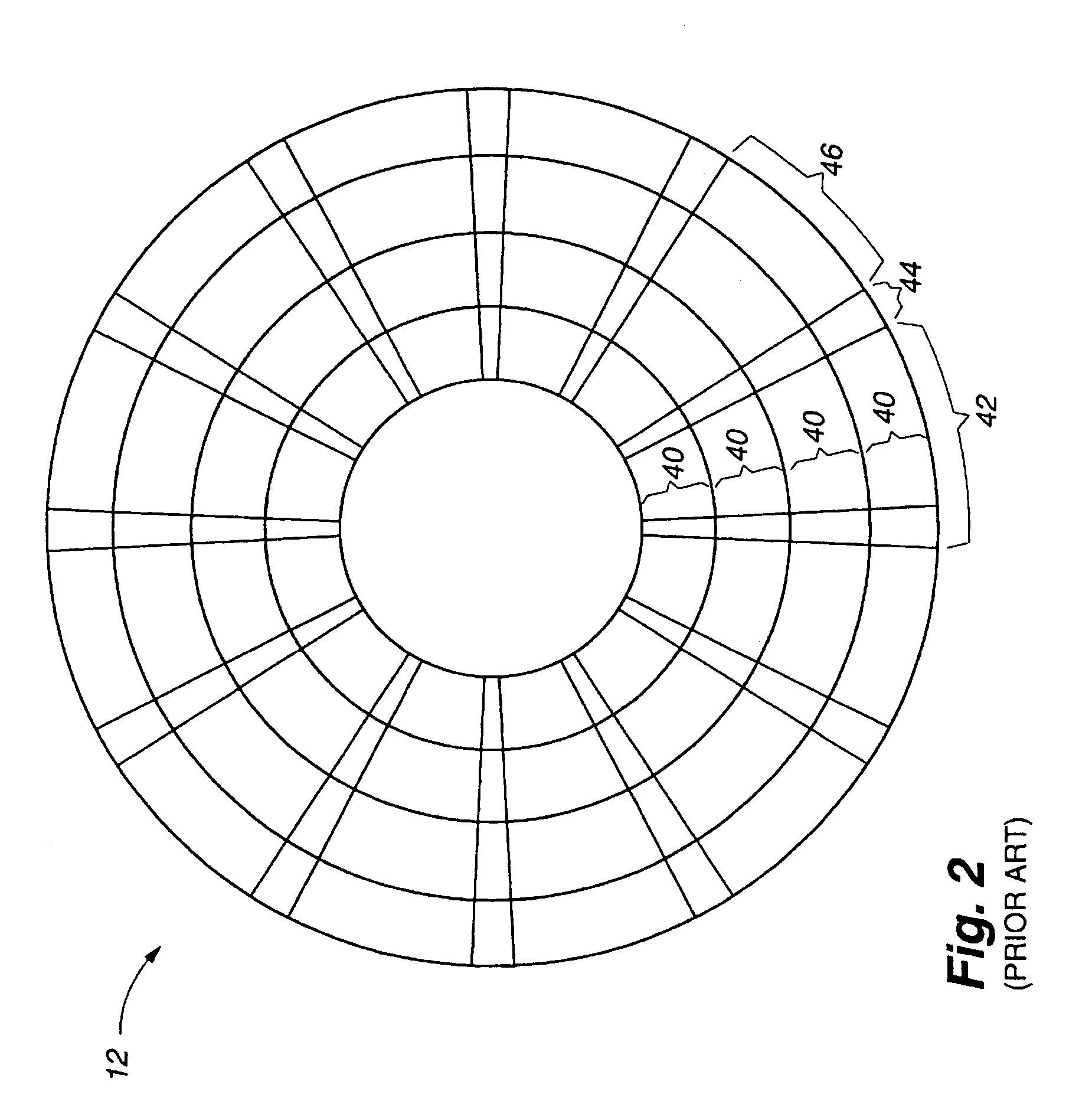

Apparatus for writing servo bursts on a disk with servo track pitch based on read element width and methods of manufacturing same

InactiveUS7154689B1VariabilityImprove manufacturing yieldDriving/moving recording headsRecord information storageTransducerEngineering

Methods for making a disk drive, apparatus for writing servo bursts on a disk, and disk drive apparatus are provided. The disk drive includes a disk and transducer adjacent to the disk. The transducer includes a read element and a write element. A width of the read element is determined. A servo track pitch is determined based on the read element width. Servo bursts are written in servo tracks on the disk with the write element based on the servo track pitch.

Owner:MAXTOR

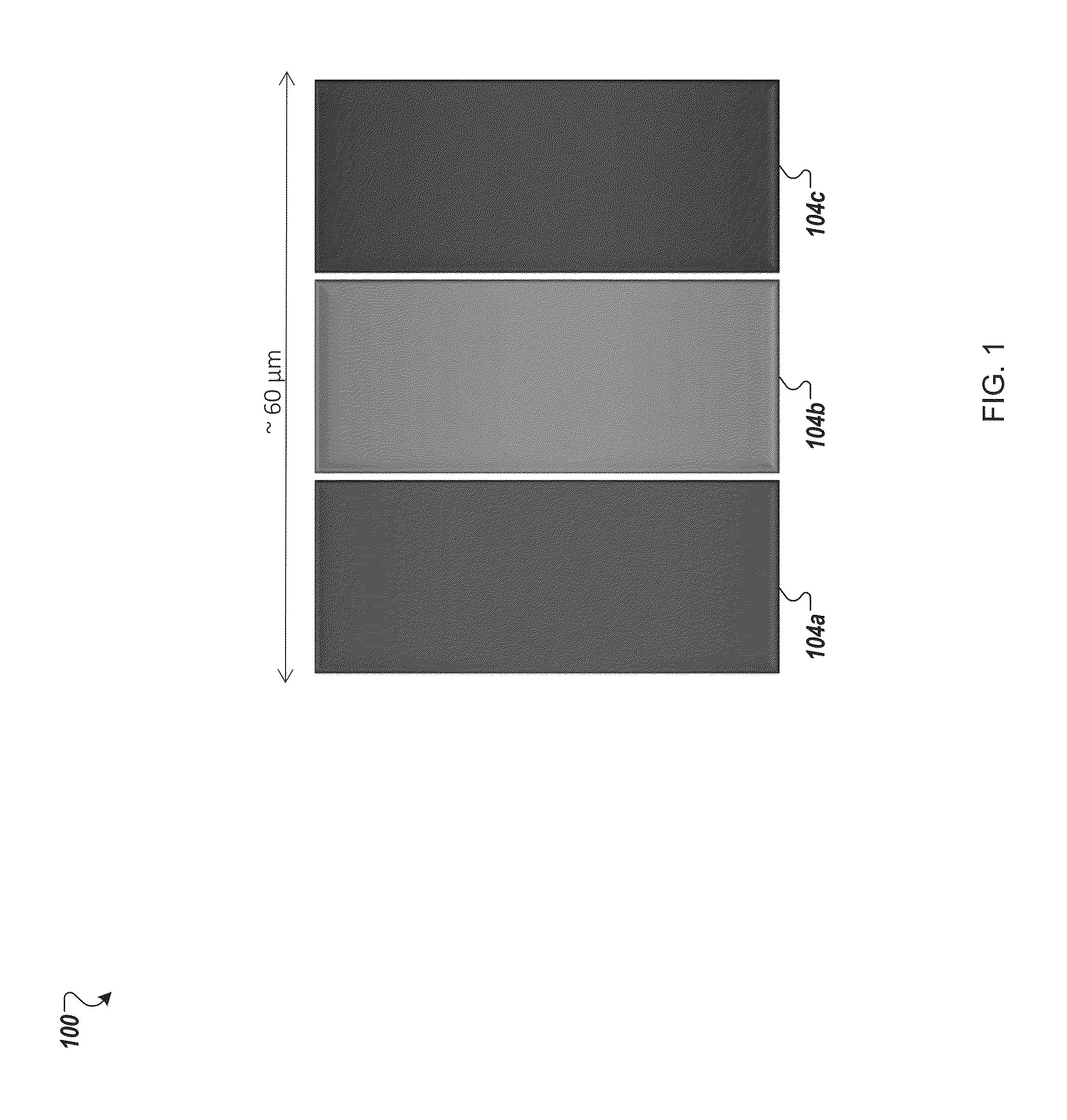

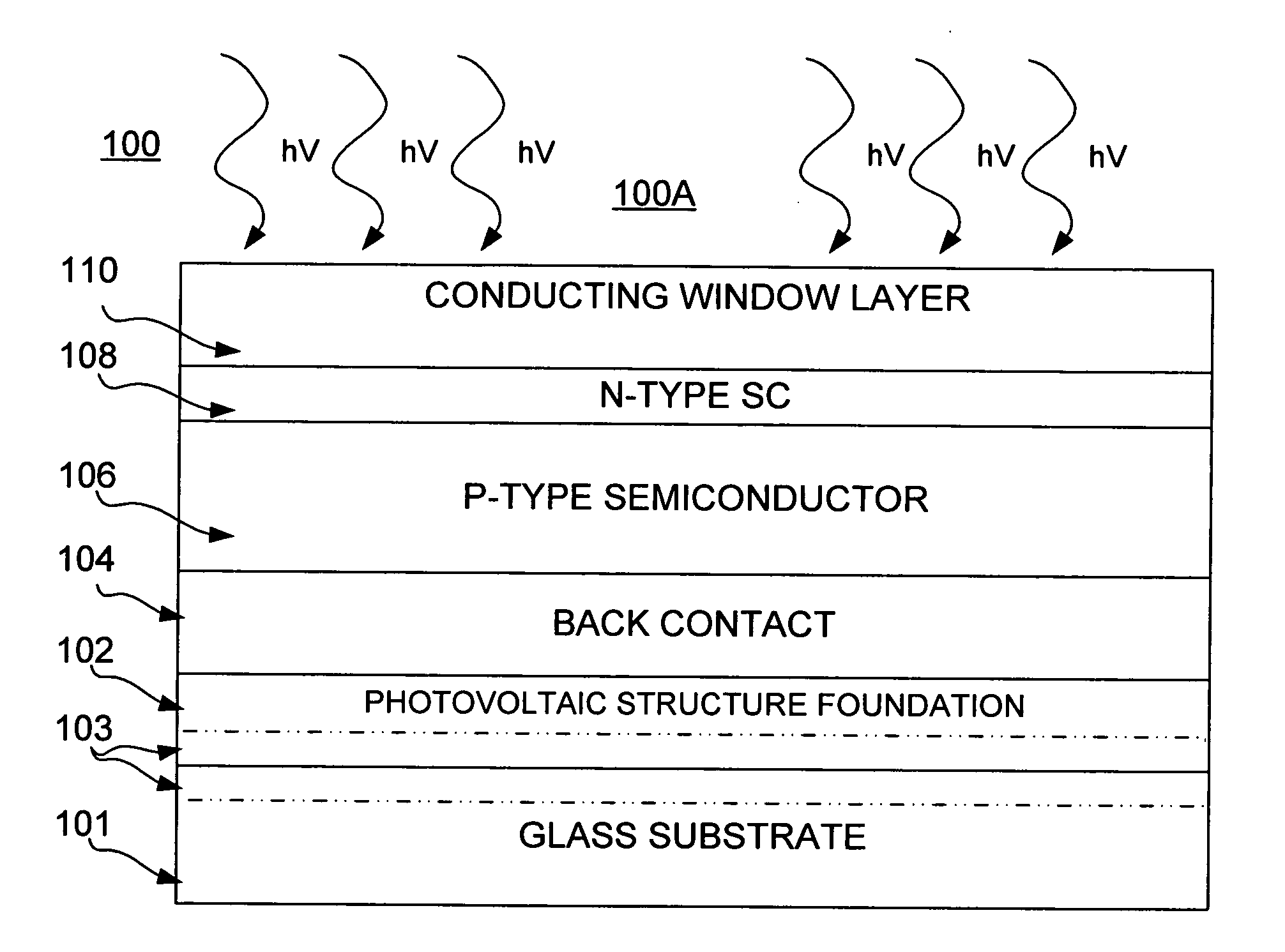

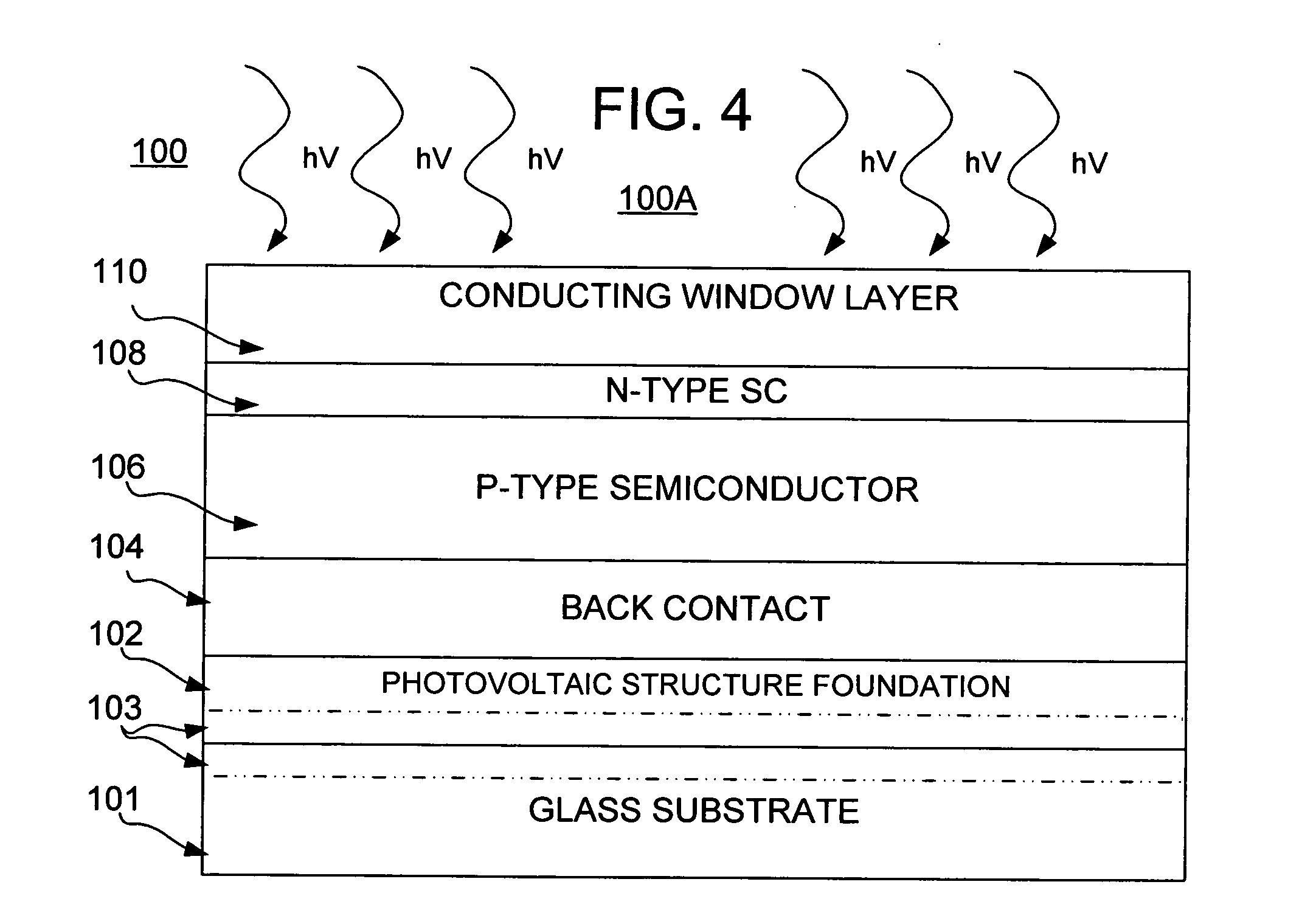

Thin film photovoltaic structure

InactiveUS20070277875A1Improve conversion efficiencyWide range of designsPhotovoltaic energy generationSemiconductor devicesSingle crystalEngineering

Photovoltaic devices include an insulator structure bonded to an exfoliation layer, preferably of a substantially single-crystal donor semiconductor wafer, and at least one photovoltaic device layer, such as a conductive layer. In a preferred embodiment, a device may include a conductive layer adjacent to the insulator substrate and integral to the exfoliation layer, near the side that faces the insulator substrate, such as between the insulator substrate and the exfoliation layer. In a further preferred embodiment, a device may include a plurality of photovoltaic device layers distal to the insulator substrate and in or on the exfoliation layer, preferably having been epitaxially grown on the exfoliation layer after the exfoliation layer has been anodically bonded to the insulator substrate by means of electrolysis.

Owner:CORNING INC

Digital silicon photomultiplier for TOF PET

ActiveUS8395127B1High data-rate radiation detectionImproved spatial detector resolutionSolid-state devicesMaterial analysis by optical meansQuiescent stateSilicon photomultiplier

A radiation detector includes an array of detector pixels each including an array of detector cells. Each detector cell includes a photodiode biased in a breakdown region and digital circuitry coupled with the photodiode and configured to output a first digital value in a quiescent state and a second digital value responsive to photon detection by the photodiode. Digital triggering circuitry is configured to output a trigger signal indicative of a start of an integration time period responsive to a selected number of one or more of the detector cells transitioning from the first digital value to the second digital value. Readout digital circuitry accumulates a count of a number of transitions of detector cells of the array of detector cells from the first digital state to the second digital state over the integration time period.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

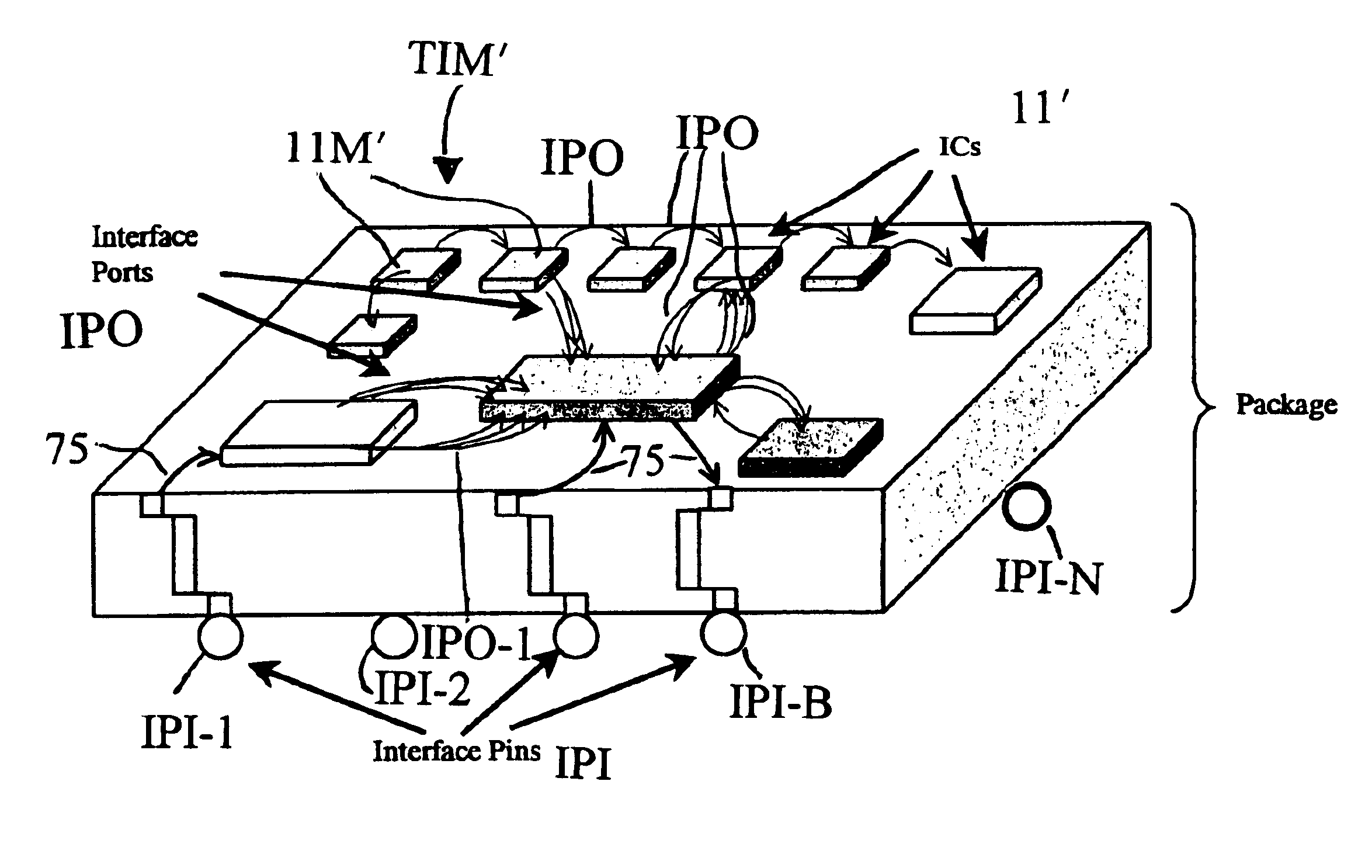

Tailored interconnect module

InactiveUS6908314B2Improve scalabilityMinimize the numberSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit interconnectComputer module

An integrated circuit interconnect module for reducing interconnections between integrated circuit chips MOUNTED ON a support substrate. At least one primary integrated circuit (IC) device chip and a plurality of interacting peripheral integrated chip devices. The interconnect module including a plurality of interface pins, each integrated circuit device having a plurality of interface ports. At least one interface port of which is connected to another one of said plurality of integrated circuit devices, at least one of said integrated circuit devices having an interface port connected to an interface pin whereby the majority of nodes on the interacting peripheral devices are adapted to interface with nodes of the primary IC devices in such a way as to condense the number of nets so that the total number of nodes connected to external pins is minimized.

Owner:ALCATEL LUCENT SAS

Passive matrix OLED display having increased size

InactiveUS20060091794A1Bright enoughImprove lighting efficiencyDischarge tube luminescnet screensElectroluminescent light sourcesCurrent limitingDisplay device

A passive matrix OLED display free of line dropout defects in the image region and providing full-frame brightness of at least 50 nits is disclosed. In one embodiment of the invention, the display may have a diagonal surface dimension in excess of 10 inches and may have more than 150 row lines. In a specific embodiment, a passive matrix OLED display is described comprising an array of individually addressable OLED pixels arranged in column and row lines in an imaging area of the display, wherein at least one pixel comprises at least one current-limiting component connected in series with an electroluminescent diode, and wherein the electroluminescent diode comprises a plurality of electroluminescent units connected in series between an anode and a cathode.

Owner:EASTMAN KODAK CO

Semiconductor-device manufacturing method

InactiveUS20060223234A1Easy to produceHigh dimensional accuracySemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

In a manufacturing method of a semiconductor device, a semiconductor substrate having a plurality of semiconductor chips formed on one of principal surfaces of the substrate is cut into the plurality of semiconductor chips through dicing. A first cutting process is formed on one of the principal surfaces of the substrate to produce two cutting grooves between two neighboring ones of the plurality of semiconductor chips, each cutting groove being adjacent to one of the neighboring ones of the plurality of semiconductor chips. A second cutting process is performed on the other of the principal surfaces of the substrate to produce a cutting groove overlapping the two cutting grooves produced by the first cutting process.

Owner:FUJITSU SEMICON LTD

Liquid crystal display device

ActiveUS8619011B2Widen perspectiveImprove image qualityStatic indicating devicesNon-linear opticsElectricityLiquid-crystal display

To provide a display device in which a viewing angle characteristic is improved by providing a plurality of sub-pixels to one pixel. Alternatively, to provide a display device in which an aperture ratio is suppressed even when a plurality of sub-pixels is provided. A pixel including first sub-pixel, a second sub-pixel, and a third sub-pixel, a scanning line, a signal line, a first capacitor wiring, a second capacitor wiring and a third capacitor wiring are provided. Pixel electrodes each electrically connected to one electrode of the first to third capacitor elements, and the first to third capacitor wirings, respectively, are provided to the first to third sub-pixels electrodes, respectively. Potentials of the first capacitor wiring and the second capacitor wiring are changed and a potential of the third capacitor wiring is kept almost constant.

Owner:SEMICON ENERGY LAB CO LTD

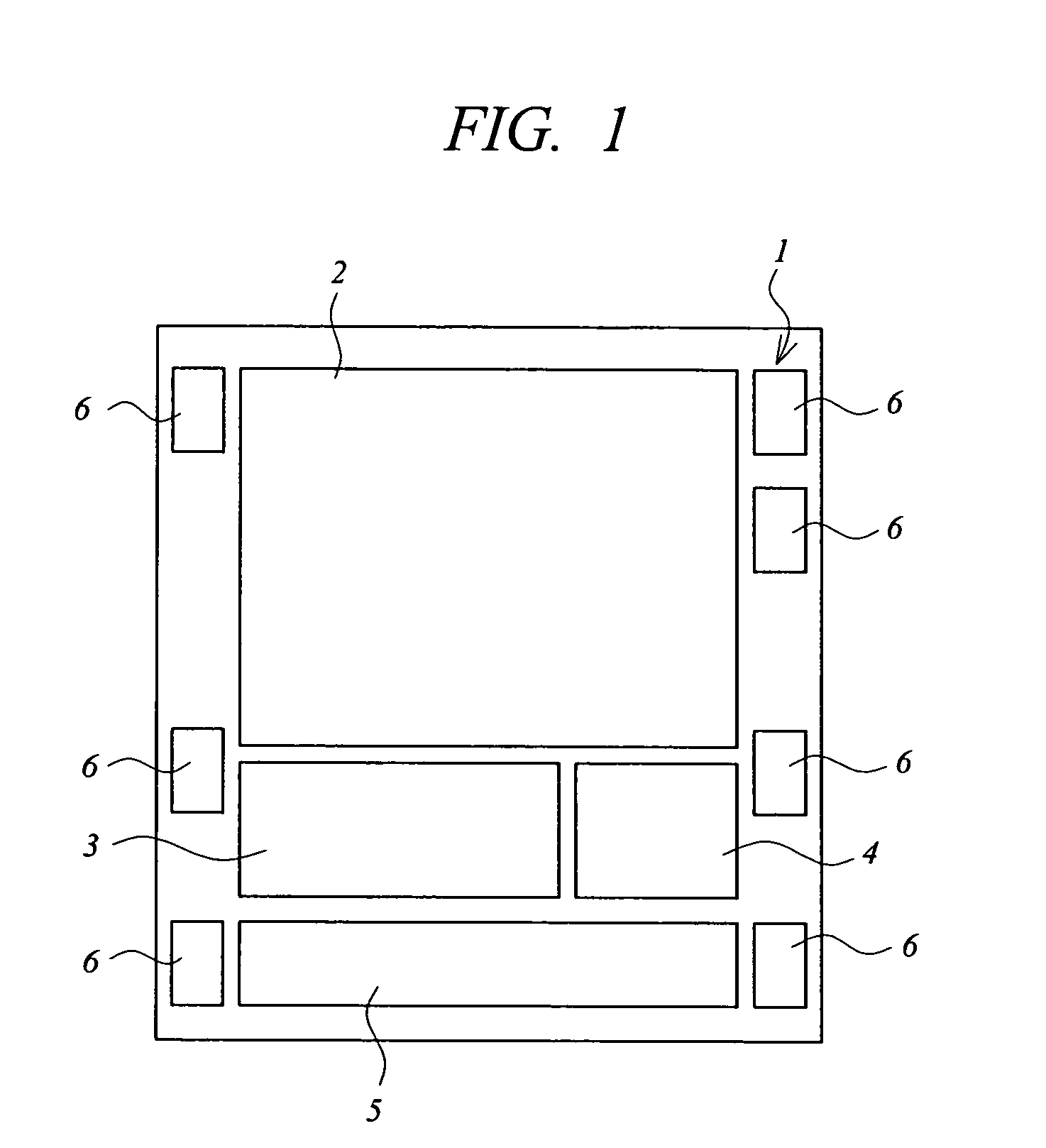

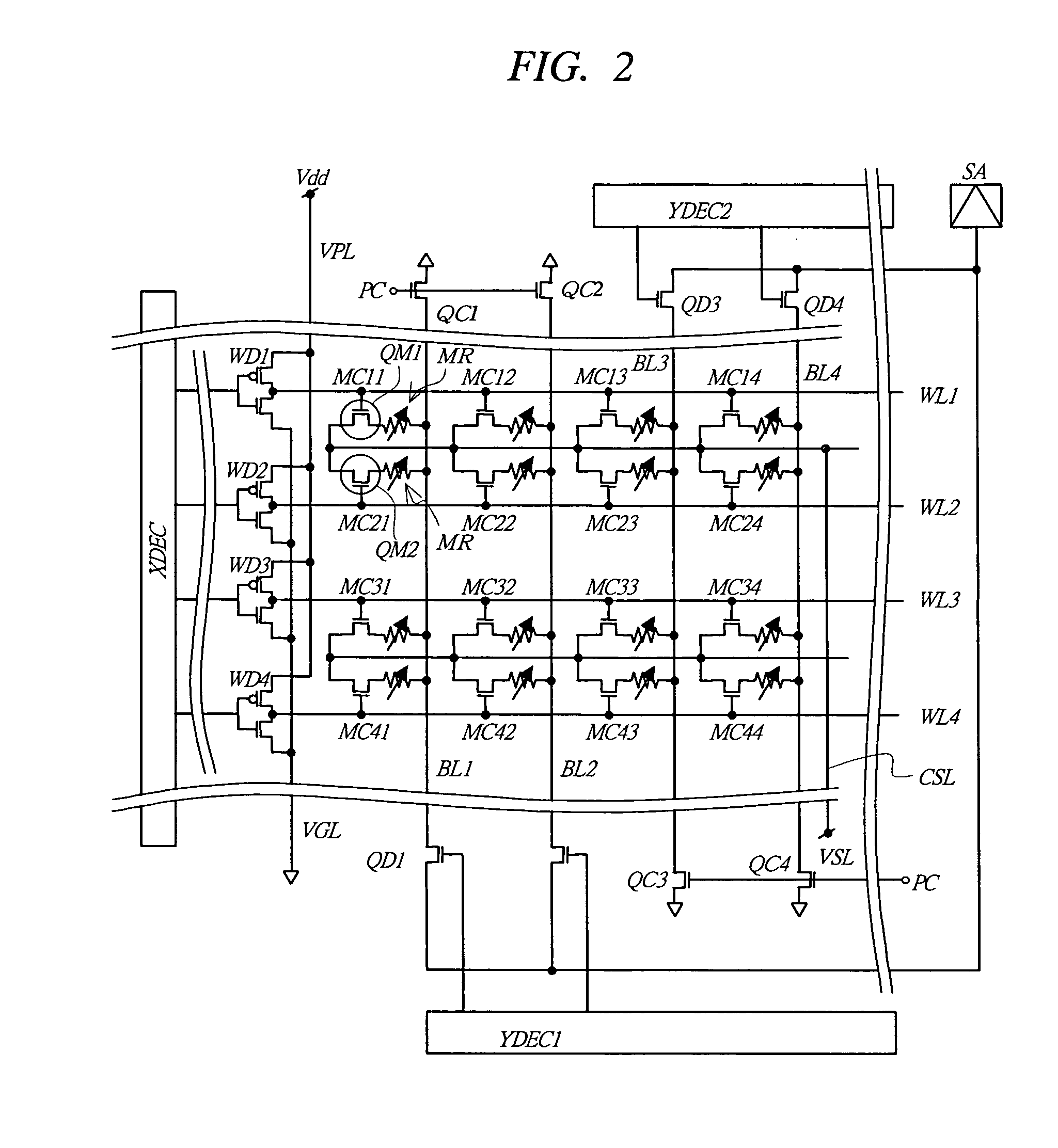

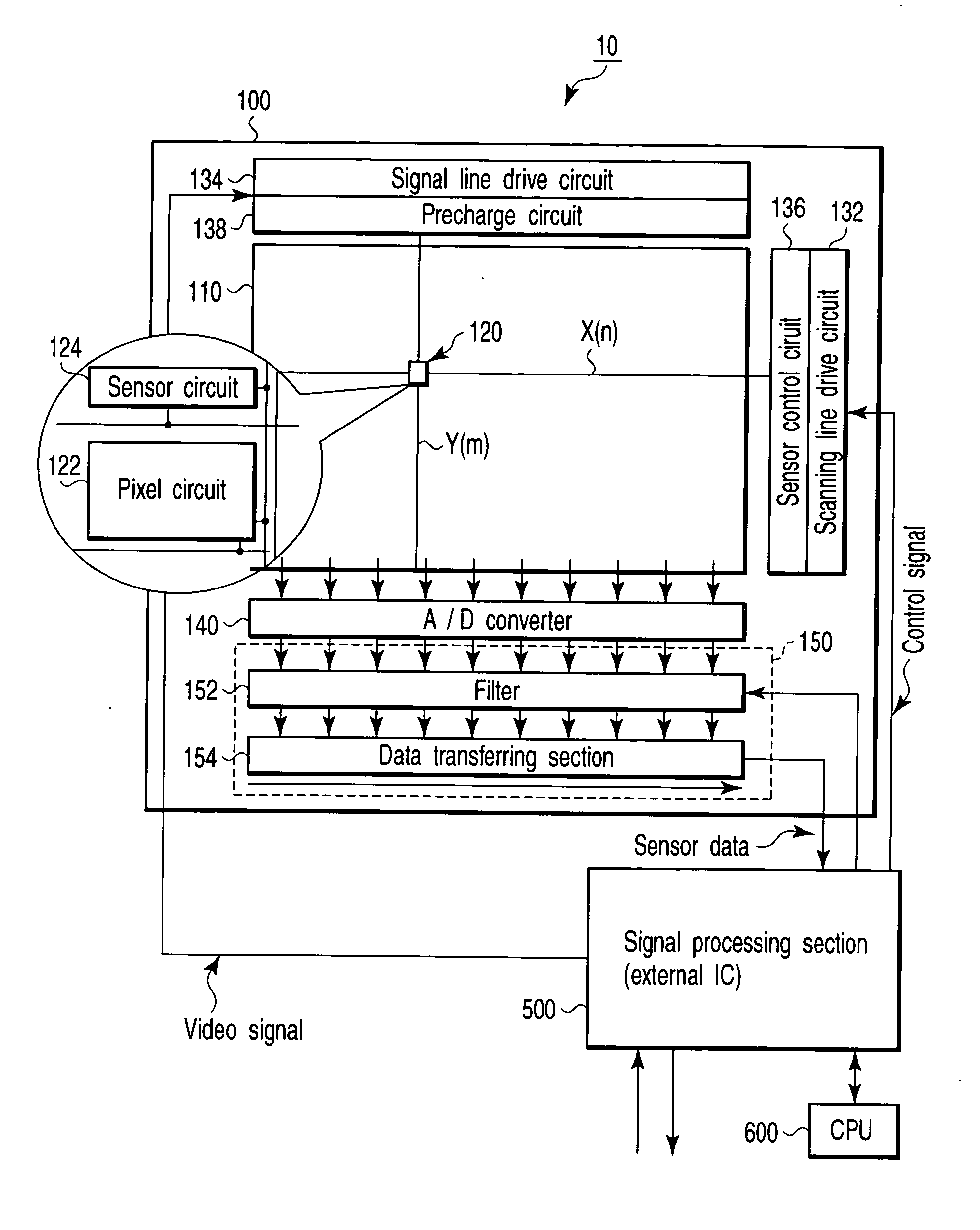

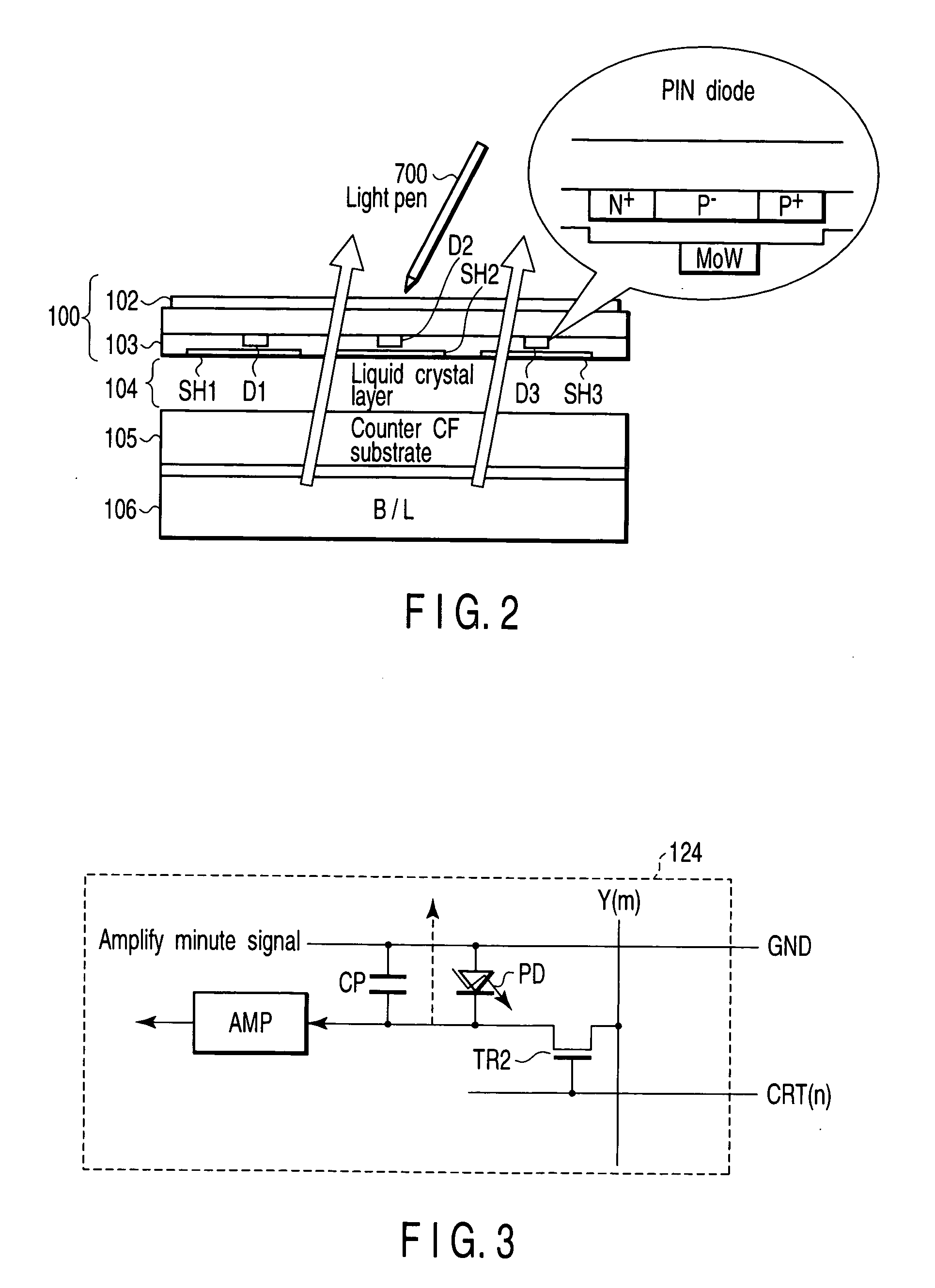

Display device with optical input function

InactiveUS20060033729A1Improve scaleImprove manufacturing yieldCathode-ray tube indicatorsFlushingDisplay deviceEngineering

A display device includes a plurality of scanning lines, a plurality of signal lines, a plurality of pixel circuits and sensor circuits, a signal line drive circuit and scanning line drive circuit which drive the plurality of pixel circuits, and a precharge circuit and sensor control circuit which drive the sensor circuits. A filter subjects image data to an interpolation process to compensate for a gradation value of an output. In a signal processing section, the area of a light receiving area is calculated and it is determined that a light source is set in contact with a display screen.

Owner:JAPAN DISPLAY CENTRAL CO LTD

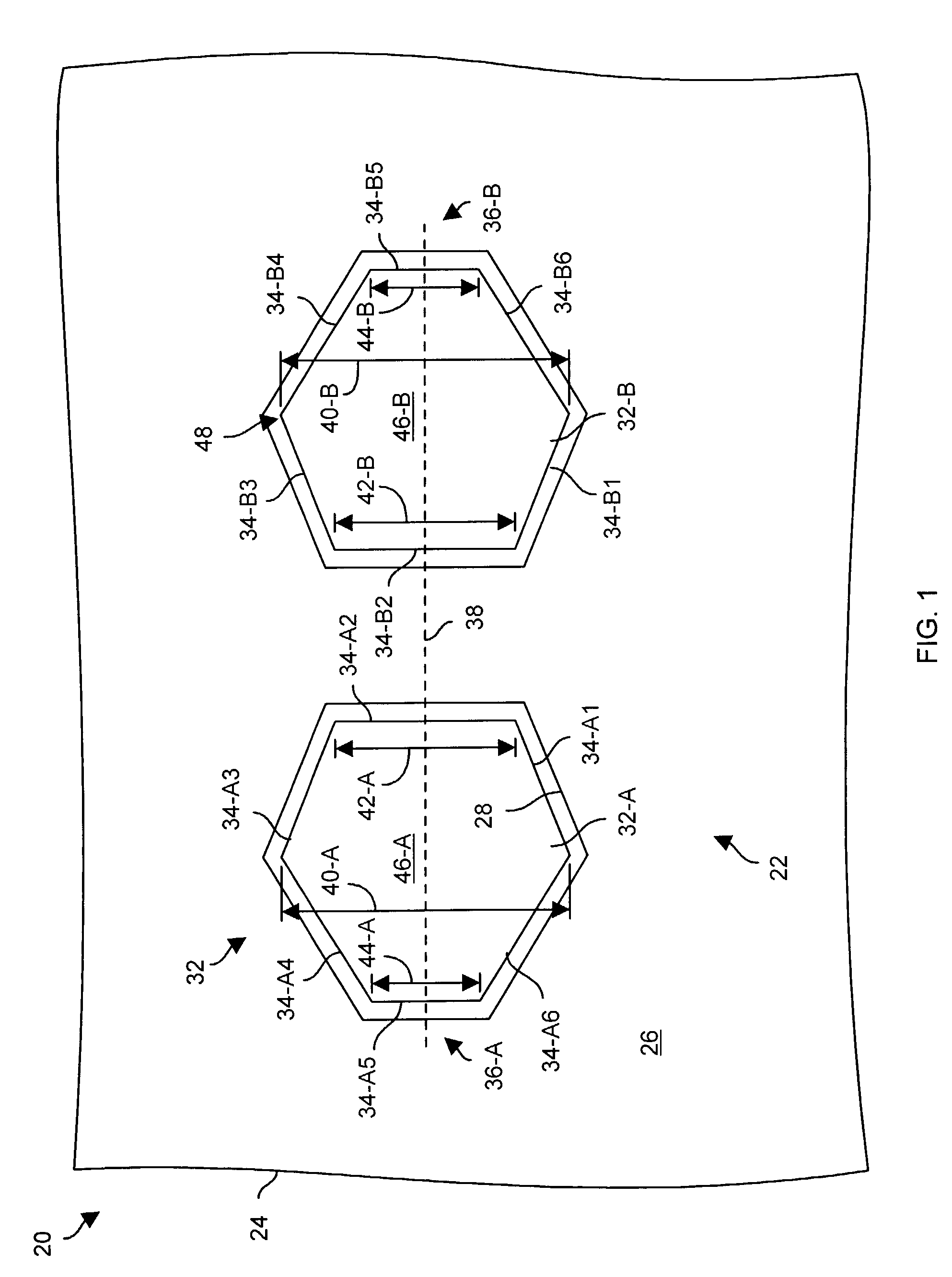

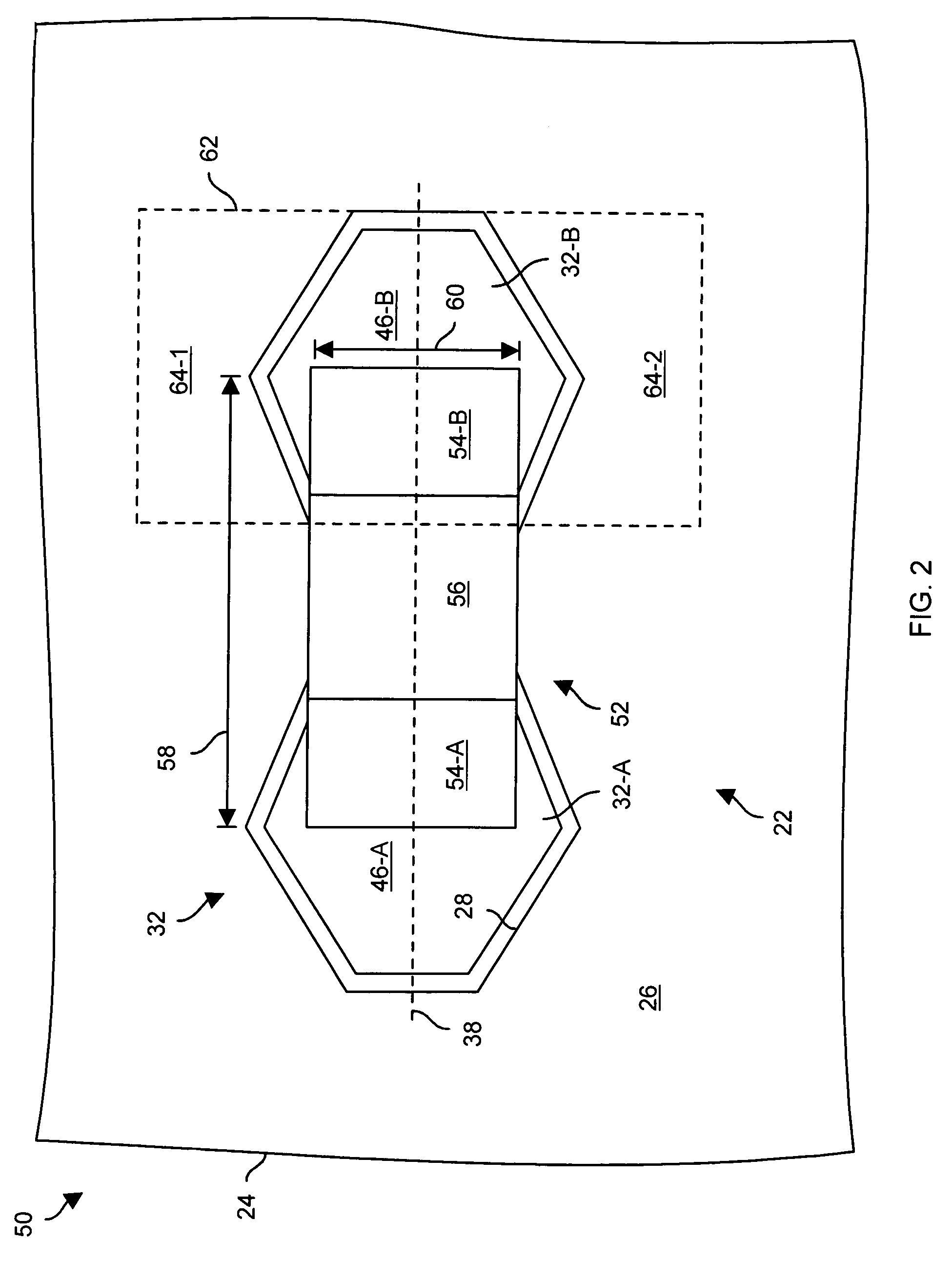

Techniques for mounting a circuit board component to a circuit board

ActiveUS7084353B1Easily distinguishDifficult to readFinal product manufacturePrinted circuit aspectsSolderingEngineering

A circuit board has a layer of non-conductive material, and a set of soldering pads disposed on the layer of non-conductive material. The set of soldering pads defines a common axis that extends substantially through a midline of each soldering pad. Each soldering pad has, as measured perpendicularly through the common axis, an inner width, a first edge width and a second edge width. The inner width is longer than each of the first and second edge widths. Additionally, the first edge width is longer than the second edge width. Accordingly, the pads have less corner spaces that could otherwise, with melted solder, draw a circuit board component into an incorrect orientation which would result in incorrect mounting of the component. As a result, the component terminals tend to be drawn toward central regions of each pad for robust and reliable solder joint formation.

Owner:EMC IP HLDG CO LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com