Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

980 results about "Chalcogenide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

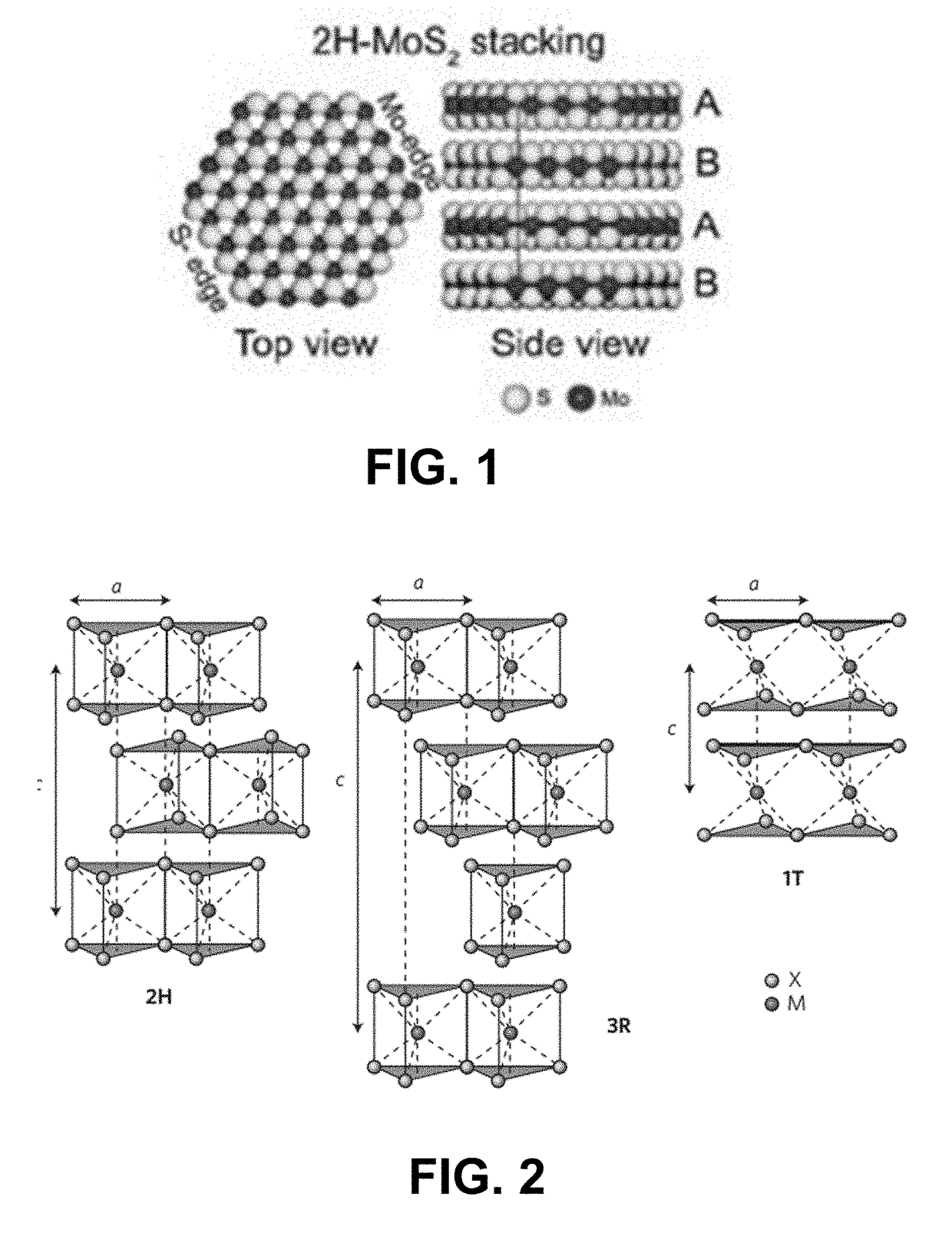

A chalcogenide is a chemical compound consisting of at least one chalcogen anion and at least one more electropositive element. Although all group 16 elements of the periodic table are defined as chalcogens, the term chalcogenide is more commonly reserved for sulfides, selenides, tellurides, and polonides, rather than oxides. Many metal ores exist as chalcogenides. Photoconductive chalcogenide glasses are used in xerography. Some pigments and catalysts are also based on chalcogenides. The metal dichalcogenide MoS₂ is a common solid lubricant.

Memory cell incorporating a chalcogenide element and method of making same

Owner:ROUND ROCK RES LLC

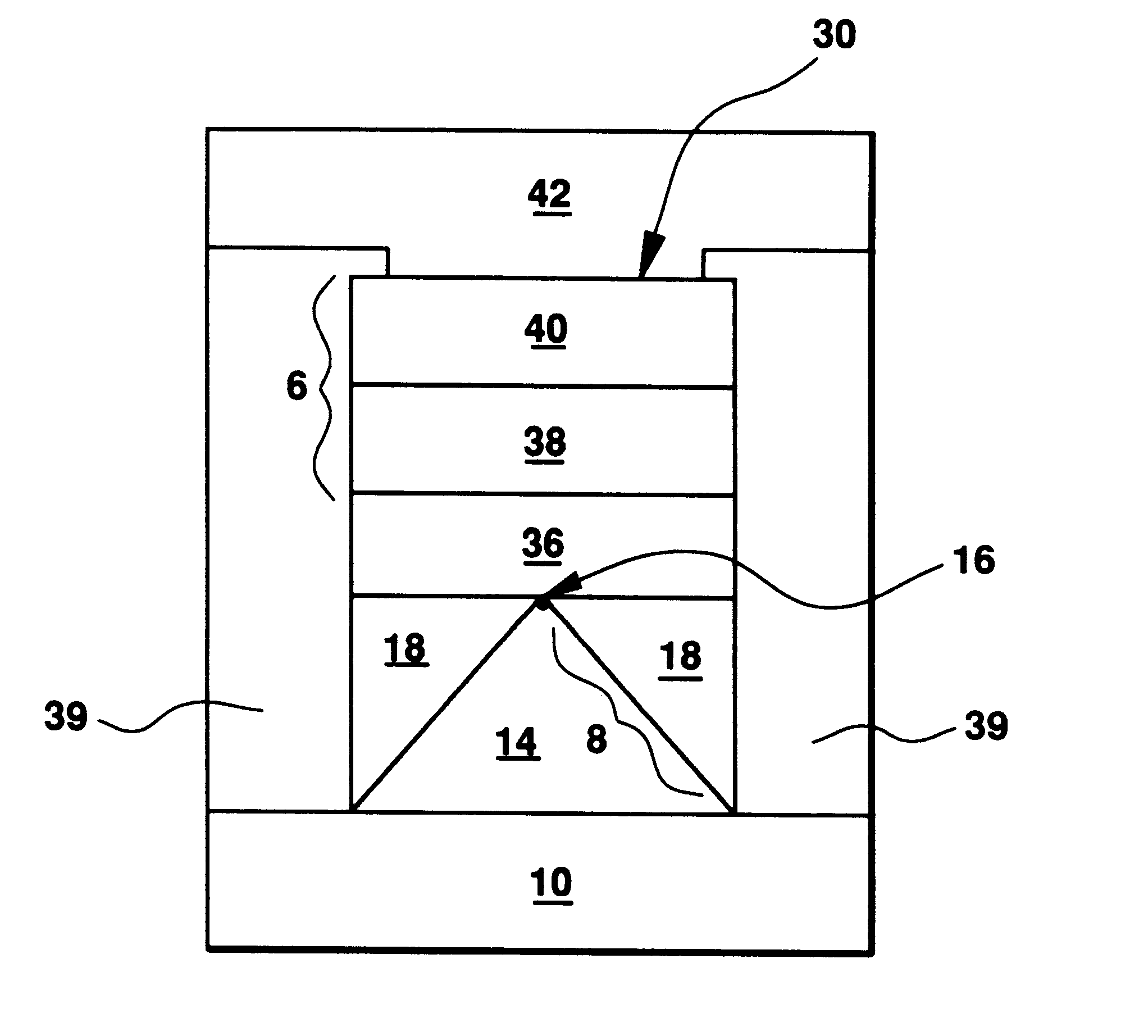

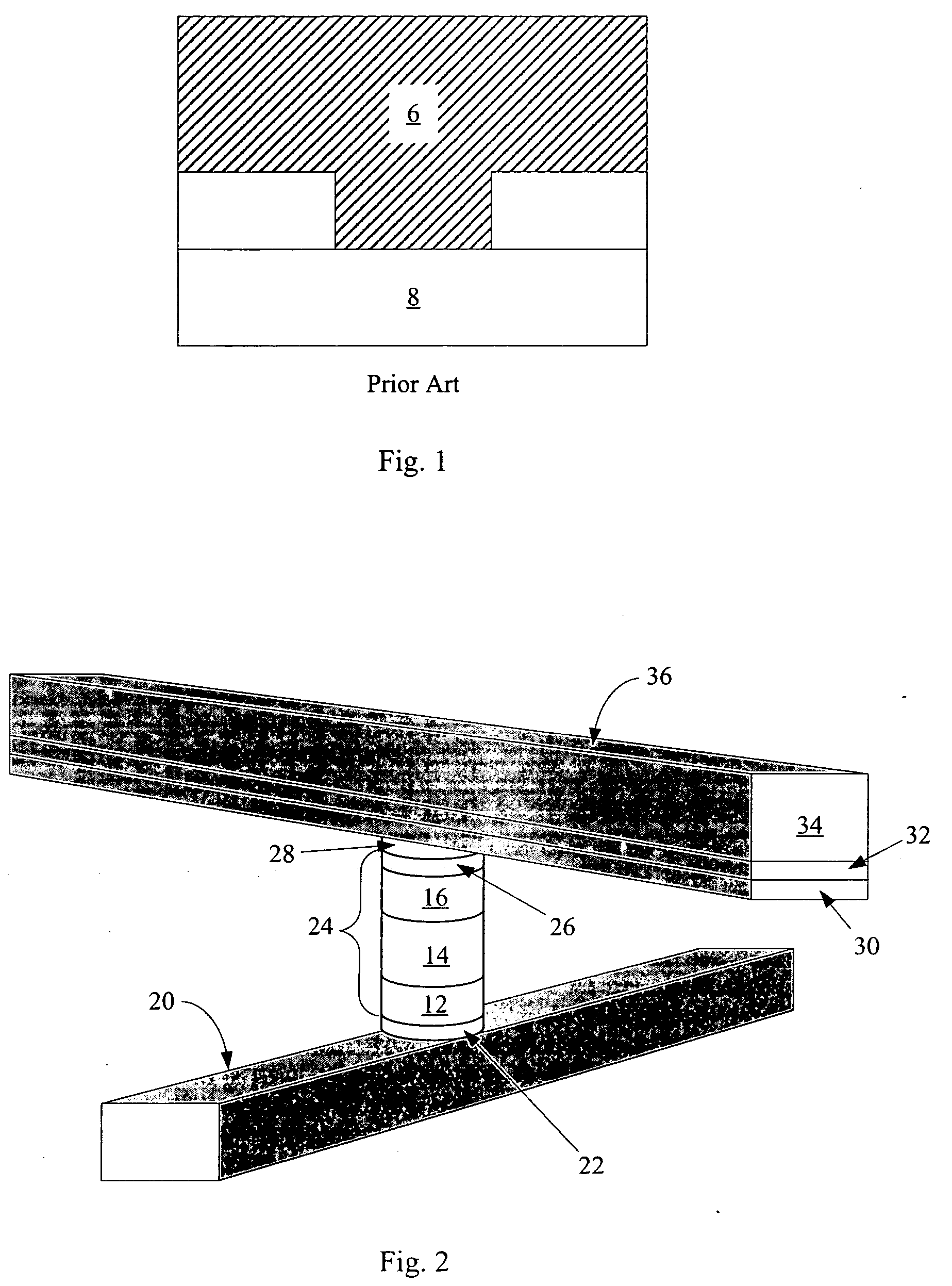

Multibit single cell memory element having tapered contact

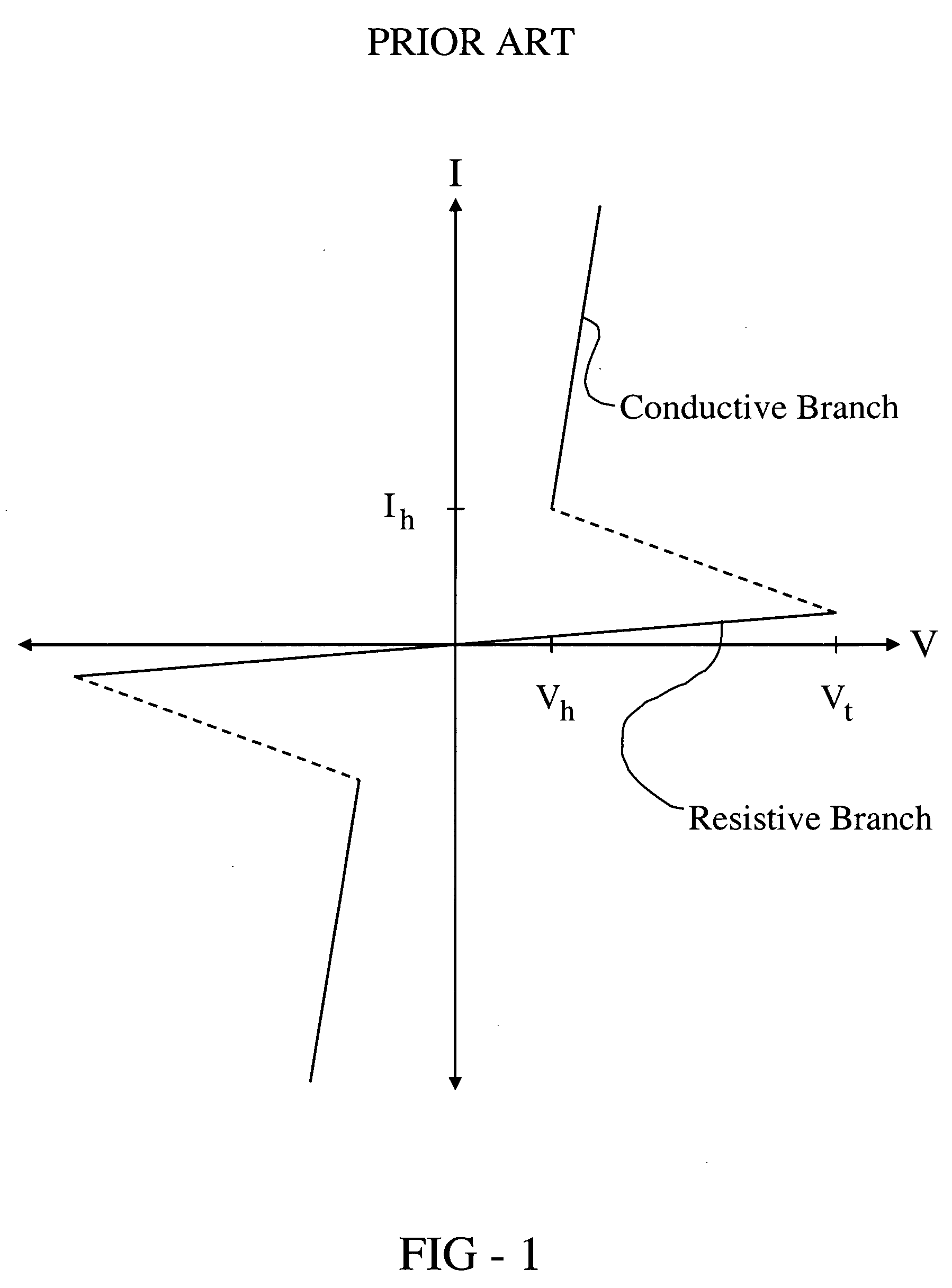

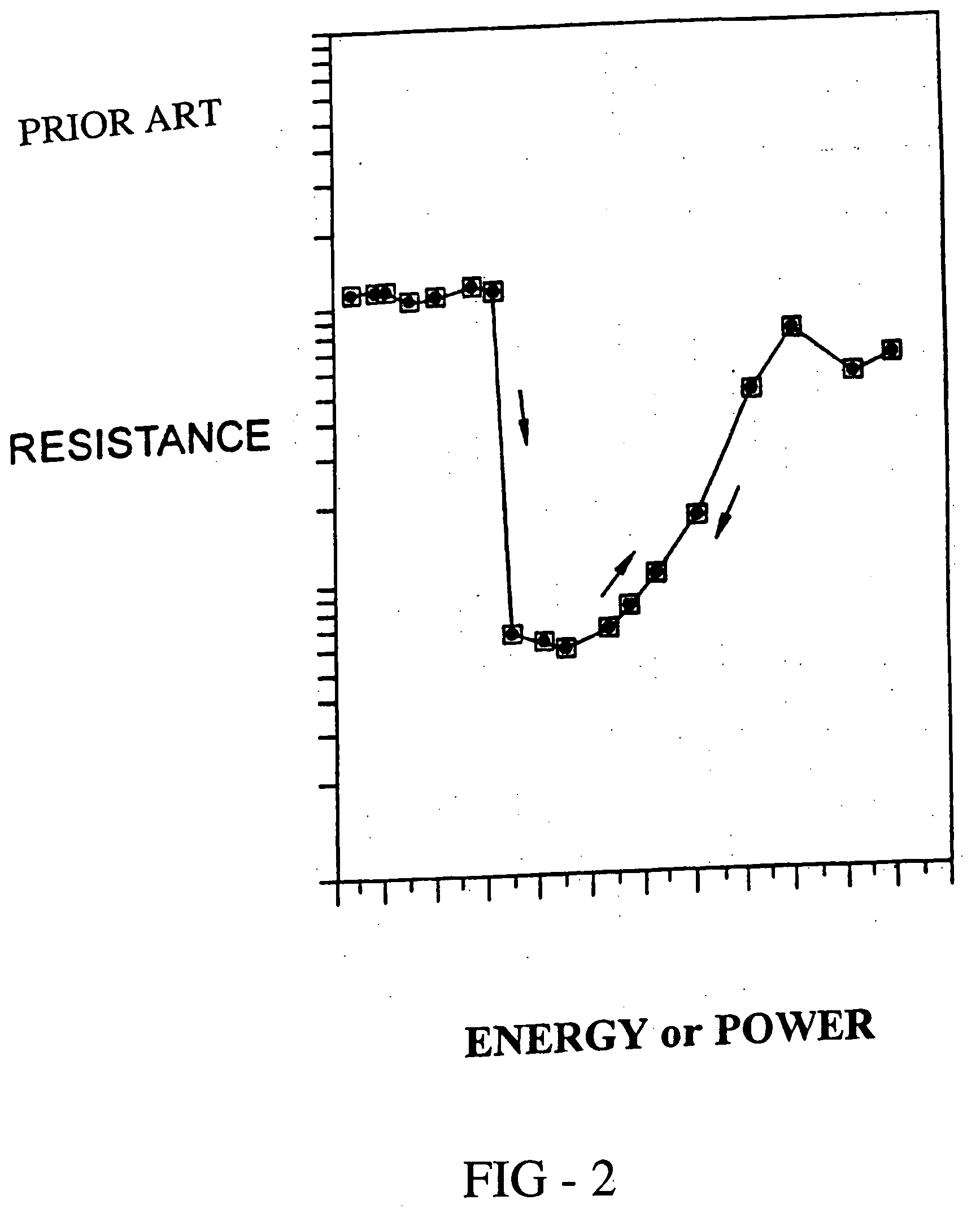

InactiveUSRE37259E1Large electric resistance valueSolid-state devicesRead-only memoriesPeak valueEngineering

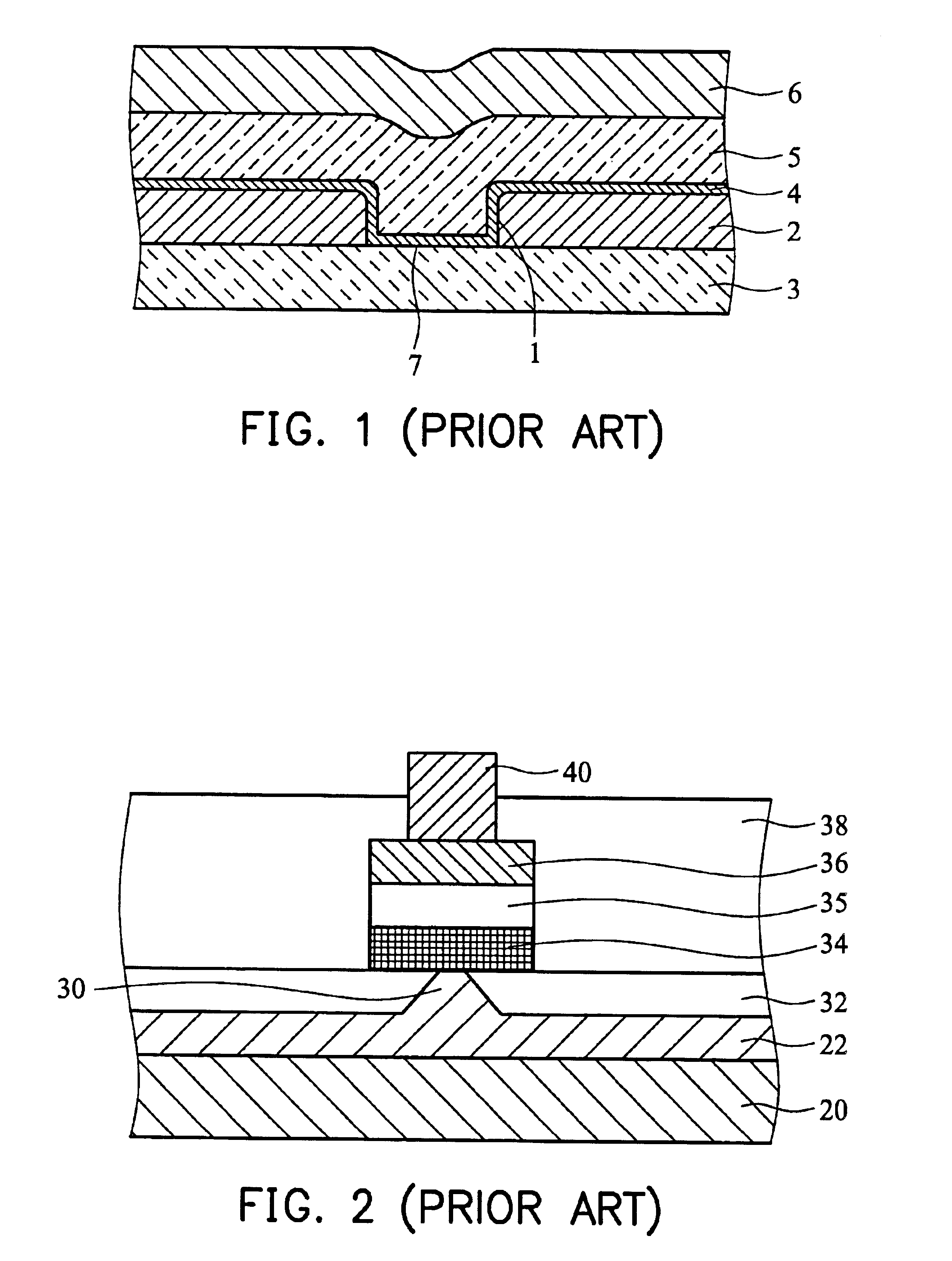

An electrically operated, directly overwritable, multibit, single-cell chalcogenide memory element with multibit storage capabilities and having at least one contact for supplying electrical input signals to set the memory element to a selected resistance value, the second contact tapering to a peak adjacent to the memory element. In this manner the tapered contact helps define the size and position of a conduction path through the memory element.

Owner:OVONYX MEMORY TECH LLC

Programmable metallization cell structure and method of making same

InactiveUS6084796ASolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceElectrical conductor

A programmable metallization cell ("PMC") comprises a fast ion conductor such as a chalcogenide-metal ion and a plurality of electrodes (e.g., an anode and a cathode) disposed at the surface of the fast ion conductor and spaced a set distance apart from each other. Preferably, the fast ion conductor comprises a chalcogenide with Group IB or Group IIB metals, the anode comprises silver, and the cathode comprises aluminum or other conductor. When a voltage is applied to the anode and the cathode, a non-volatile metal dendrite grows from the cathode along the surface of the fast ion conductor towards the anode. The growth rate of the dendrite is a function of the applied voltage and time. The growth of the dendrite may be stopped by removing the voltage and the dendrite may be retracted by reversing the voltage polarity at the anode and cathode. Changes in the length of the dendrite affect the resistance and capacitance of the PMC. The PMC may be incorporated into a variety of technologies such as memory devices, programmable resistor / capacitor devices, optical devices, sensors, and the like. Electrodes additional to the cathode and anode can be provided to serve as outputs or additional outputs of the devices in sensing electrical characteristics which are dependent upon the extent of the dendrite.

Owner:AXON TECH +1

Small electrode for a chalcogenide switching device and method for fabricating same

InactiveUS6189582B1Solid-state devicesSemiconductor/solid-state device manufacturingDielectric layerElectrode material

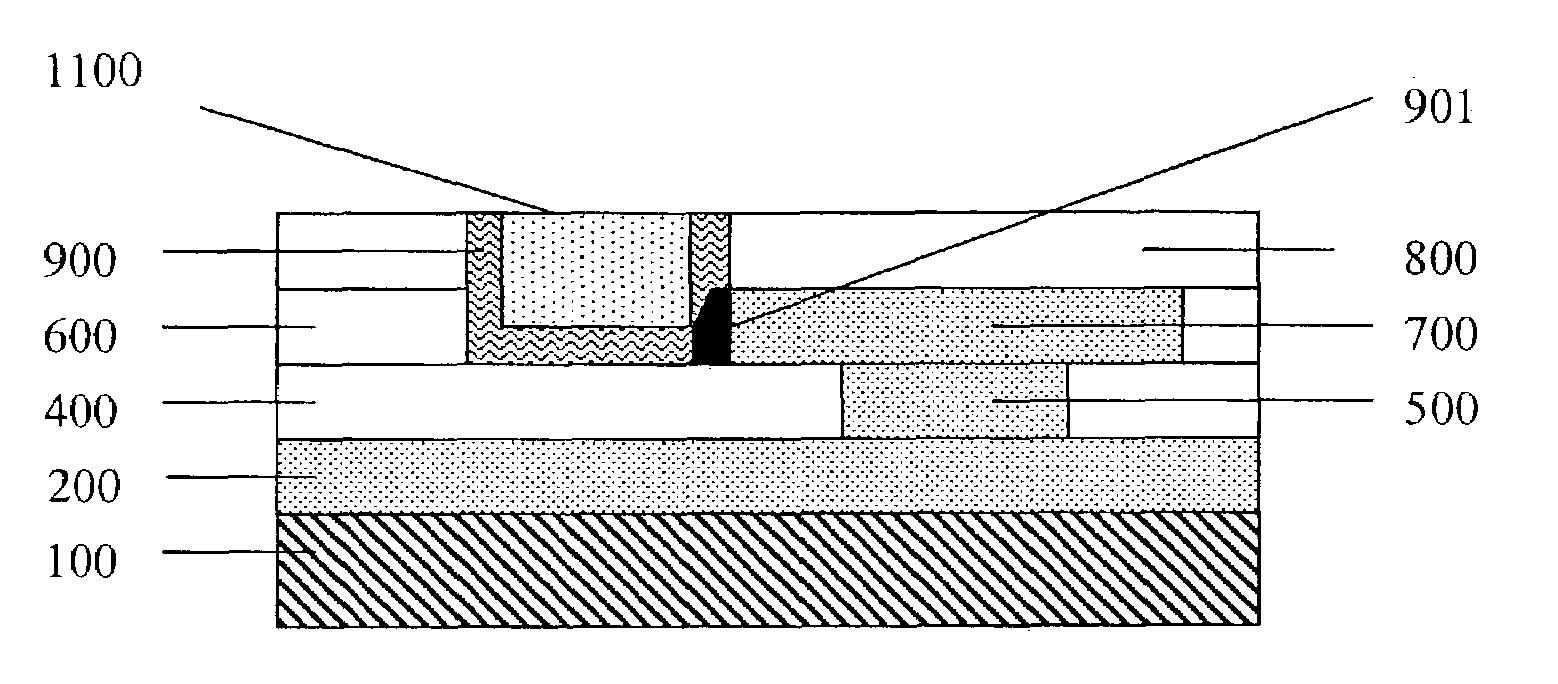

A memory cell and a method of fabricating the memory cell having a small active area. By forming a spacer in a window that is sized at the photolithographic limit, a pore may be formed in dielectric layer which is smaller than the photolithographic limit. Electrode material is deposited into the pore, and a layer of structure changing material, such as chalcogenide, is deposited onto the lower electrode, thus creating a memory element having an extremely small and reproducible active area.

Owner:ROUND ROCK RES LLC

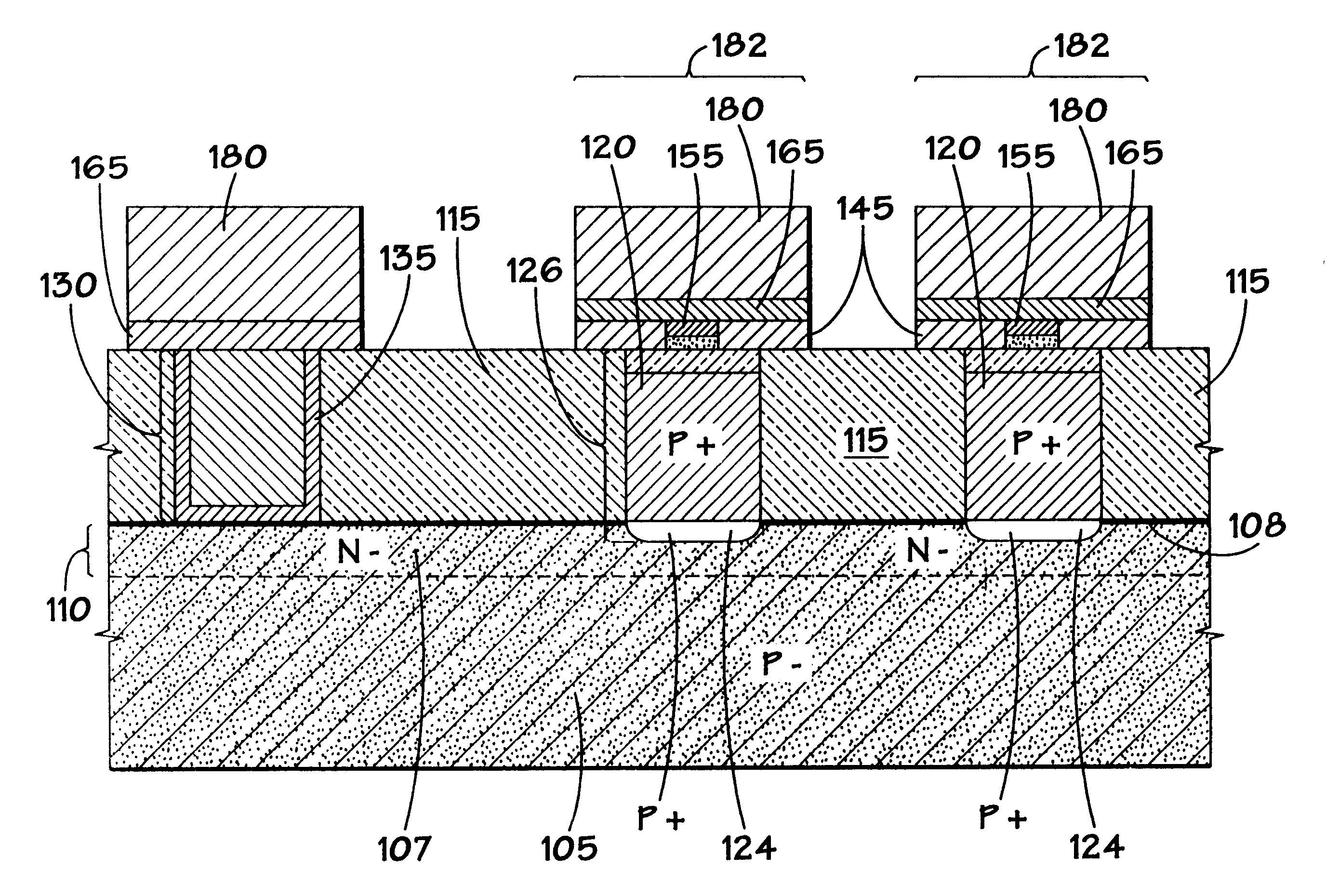

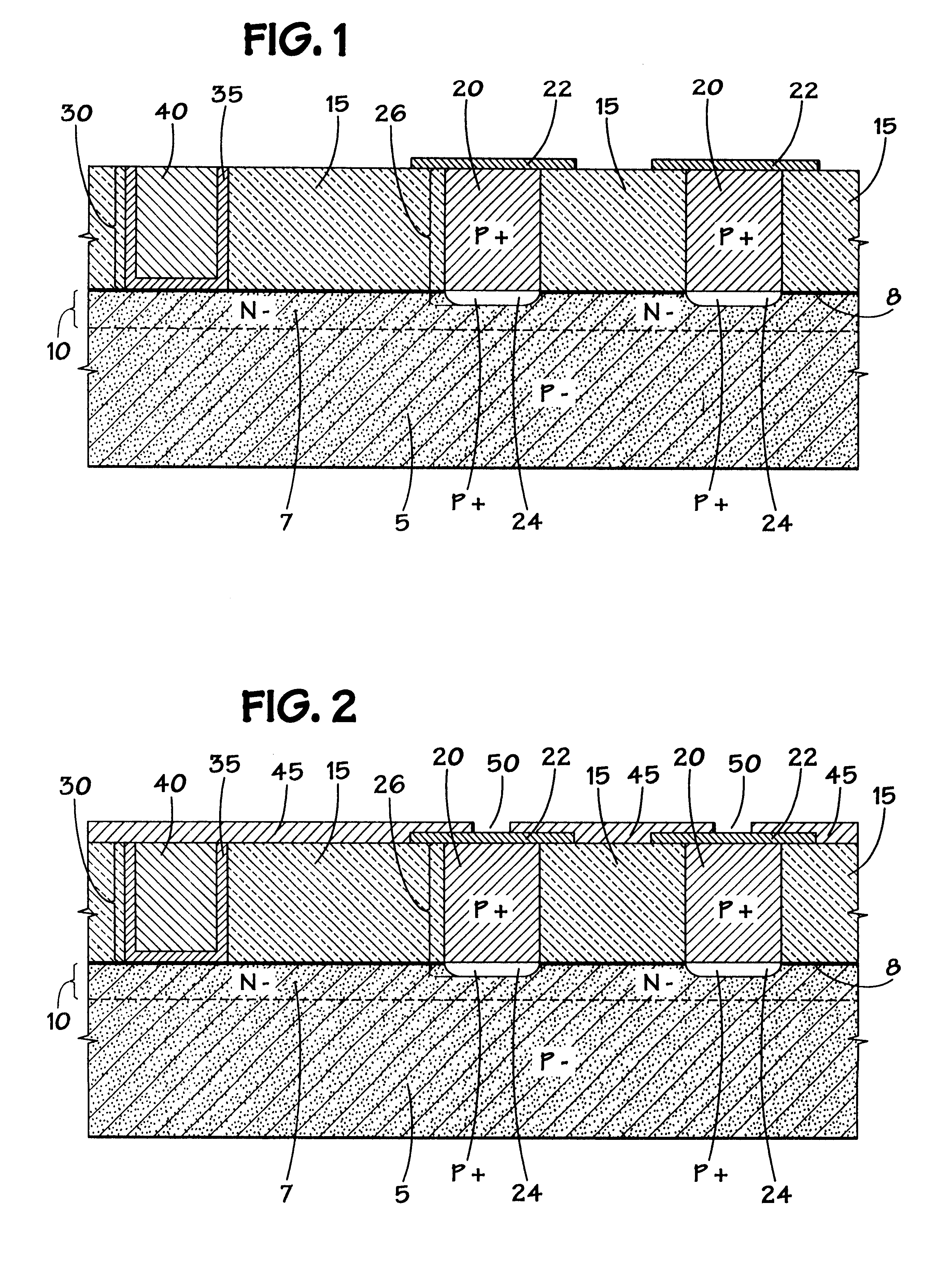

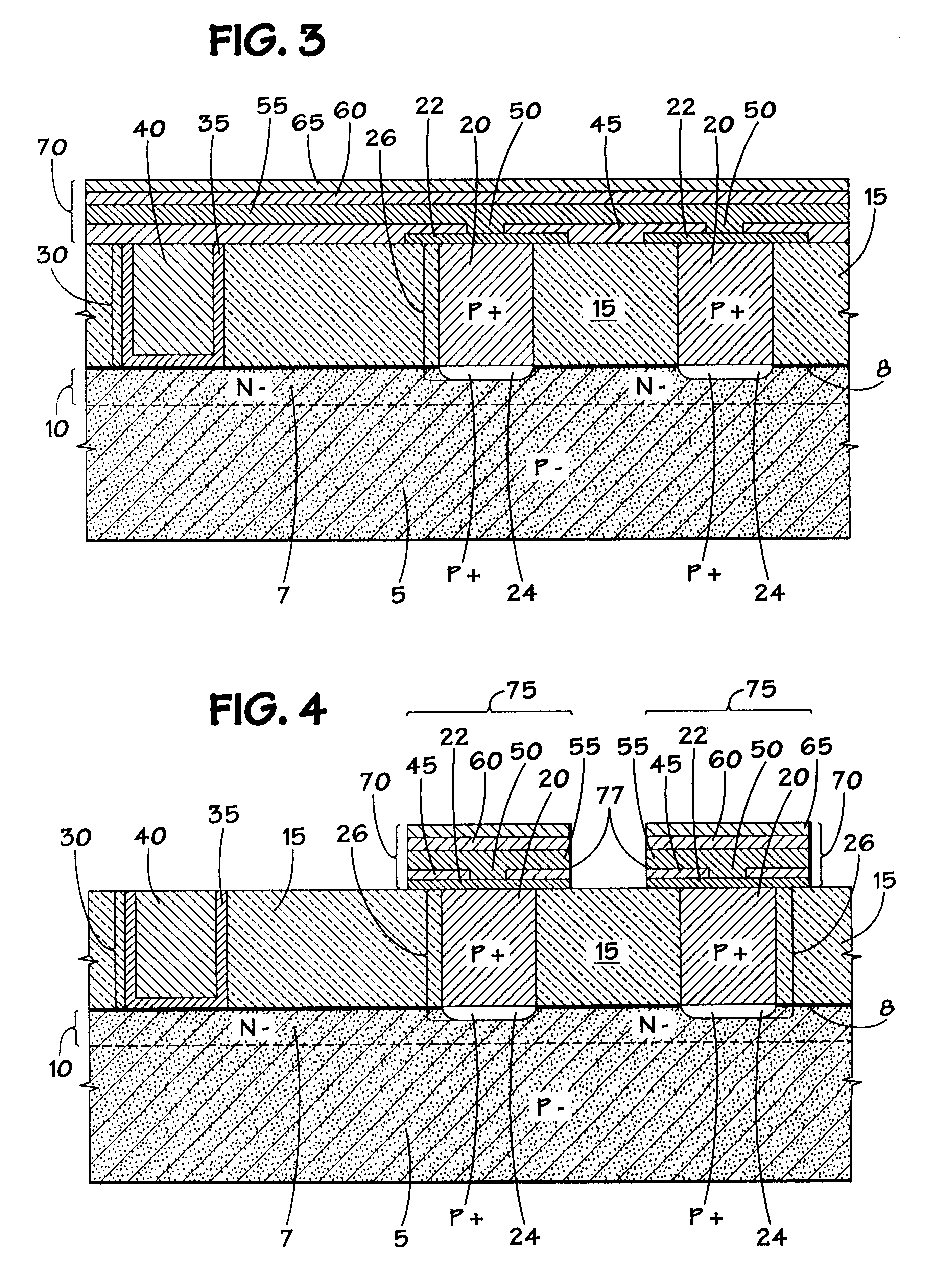

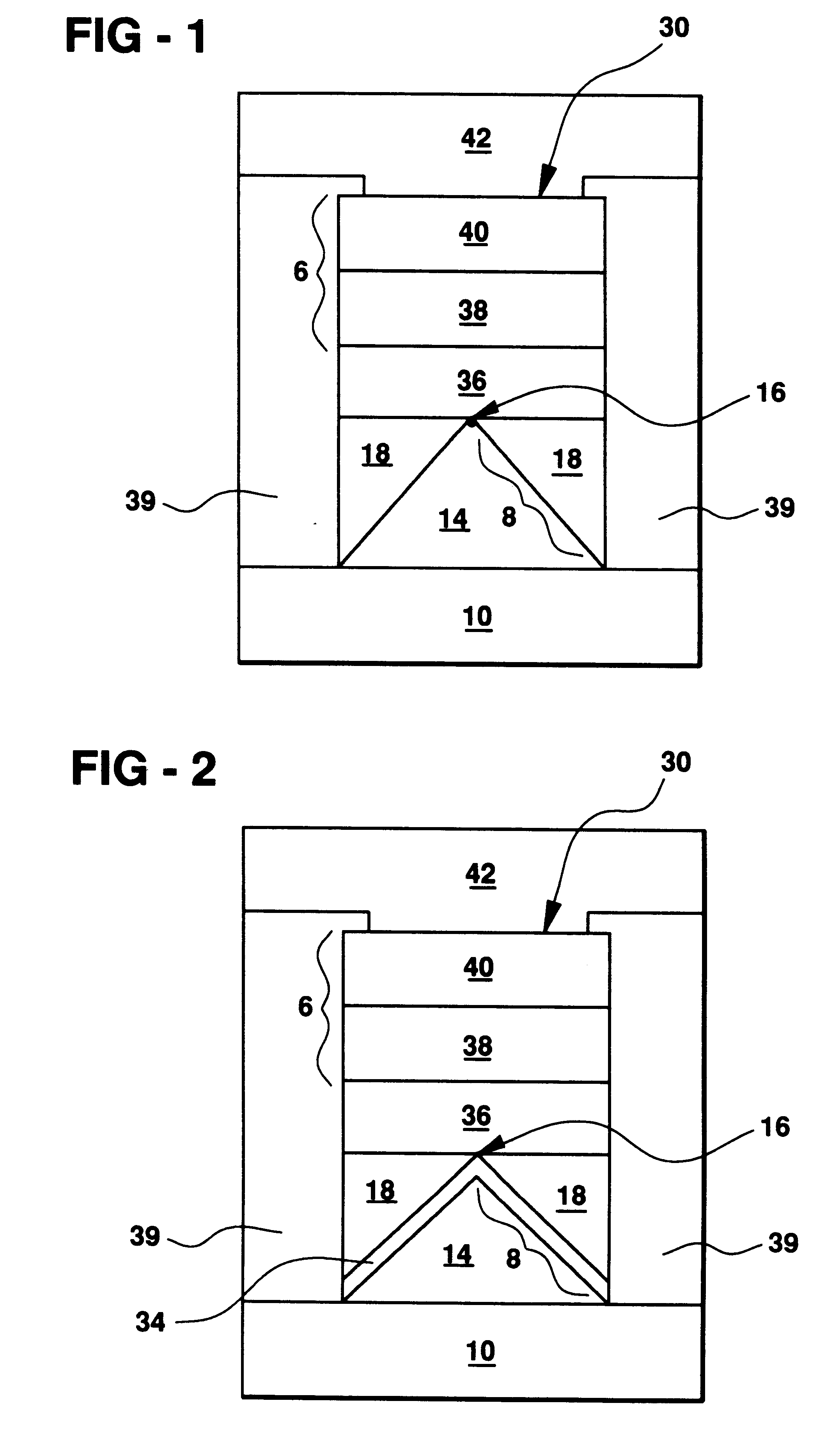

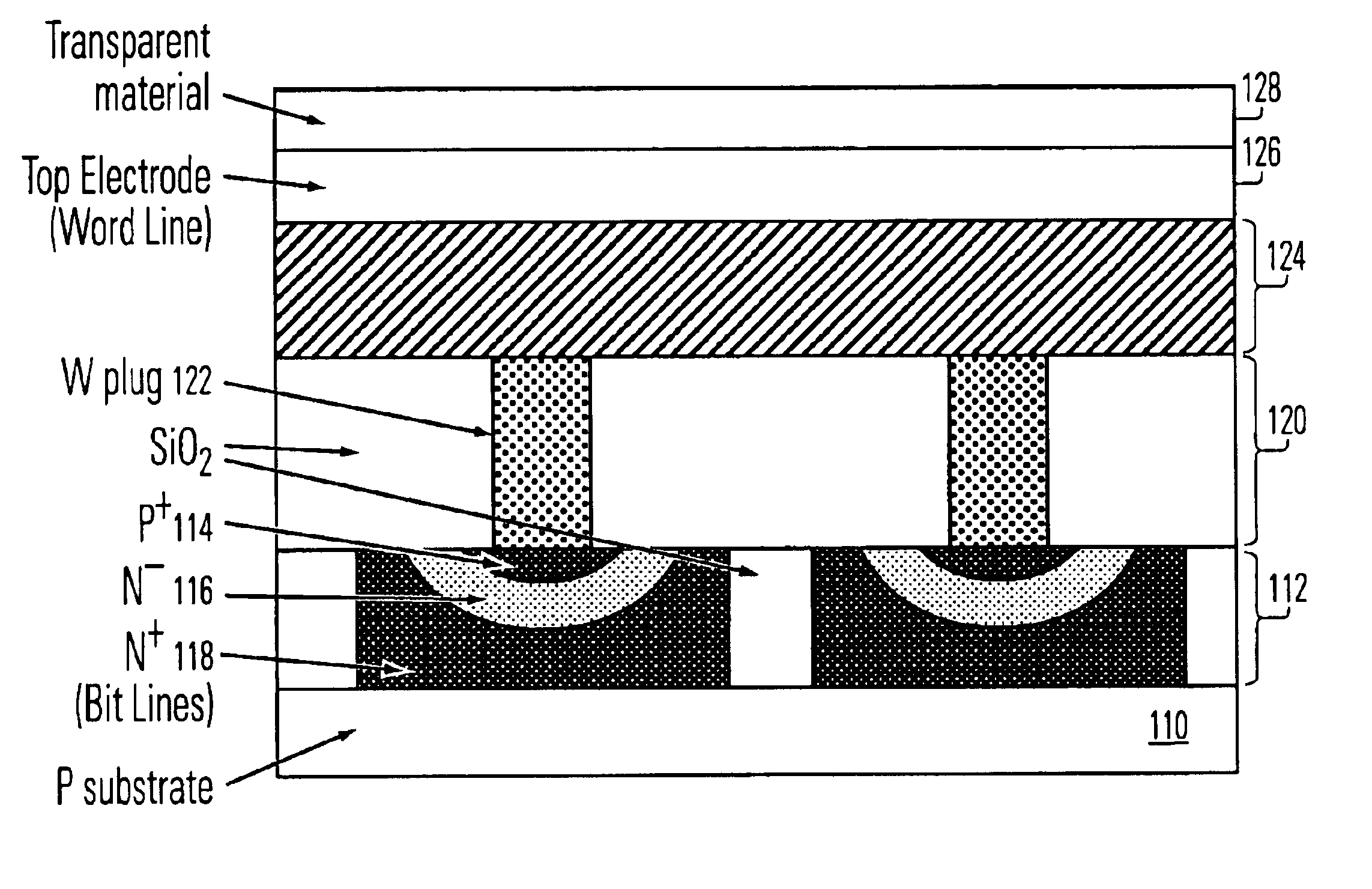

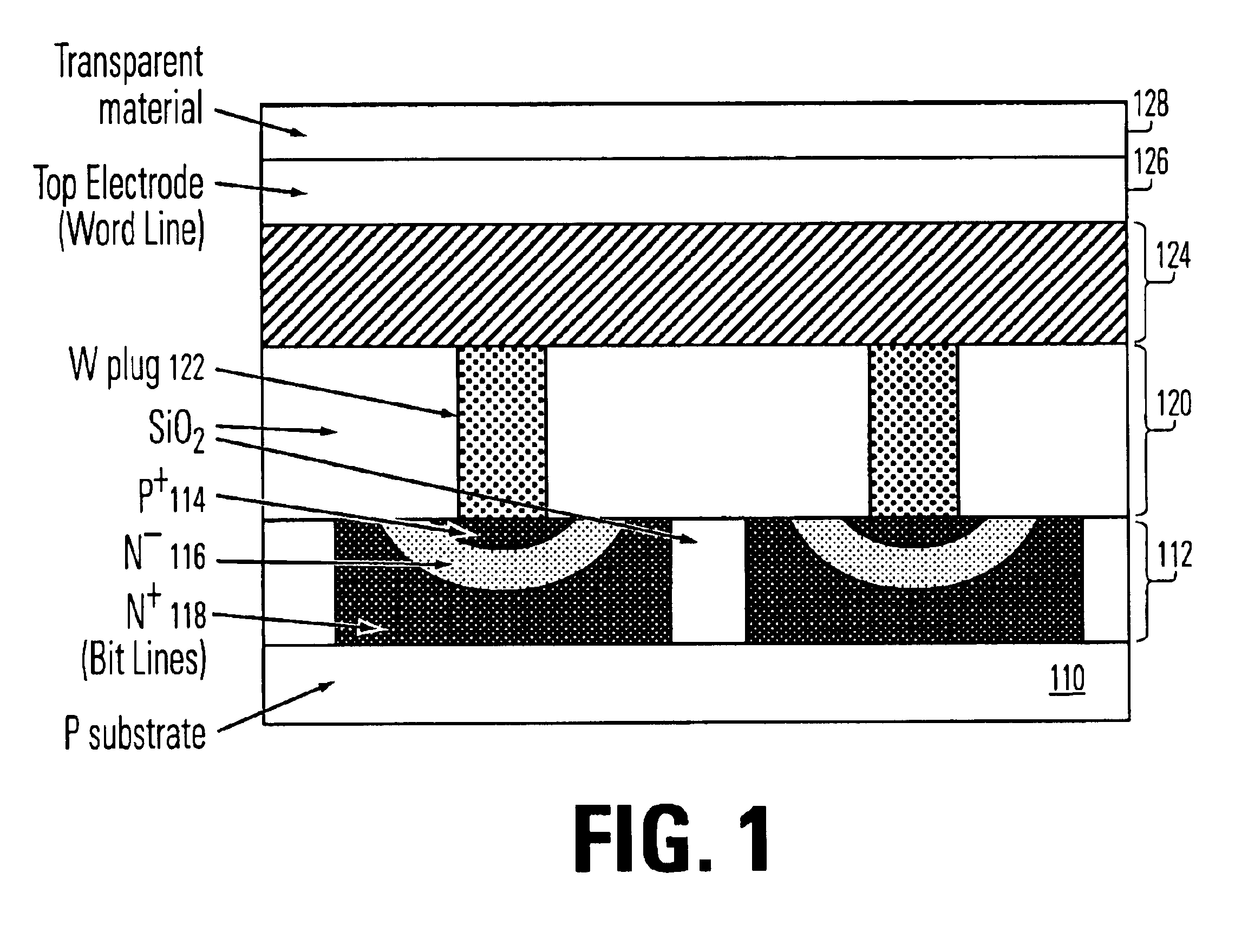

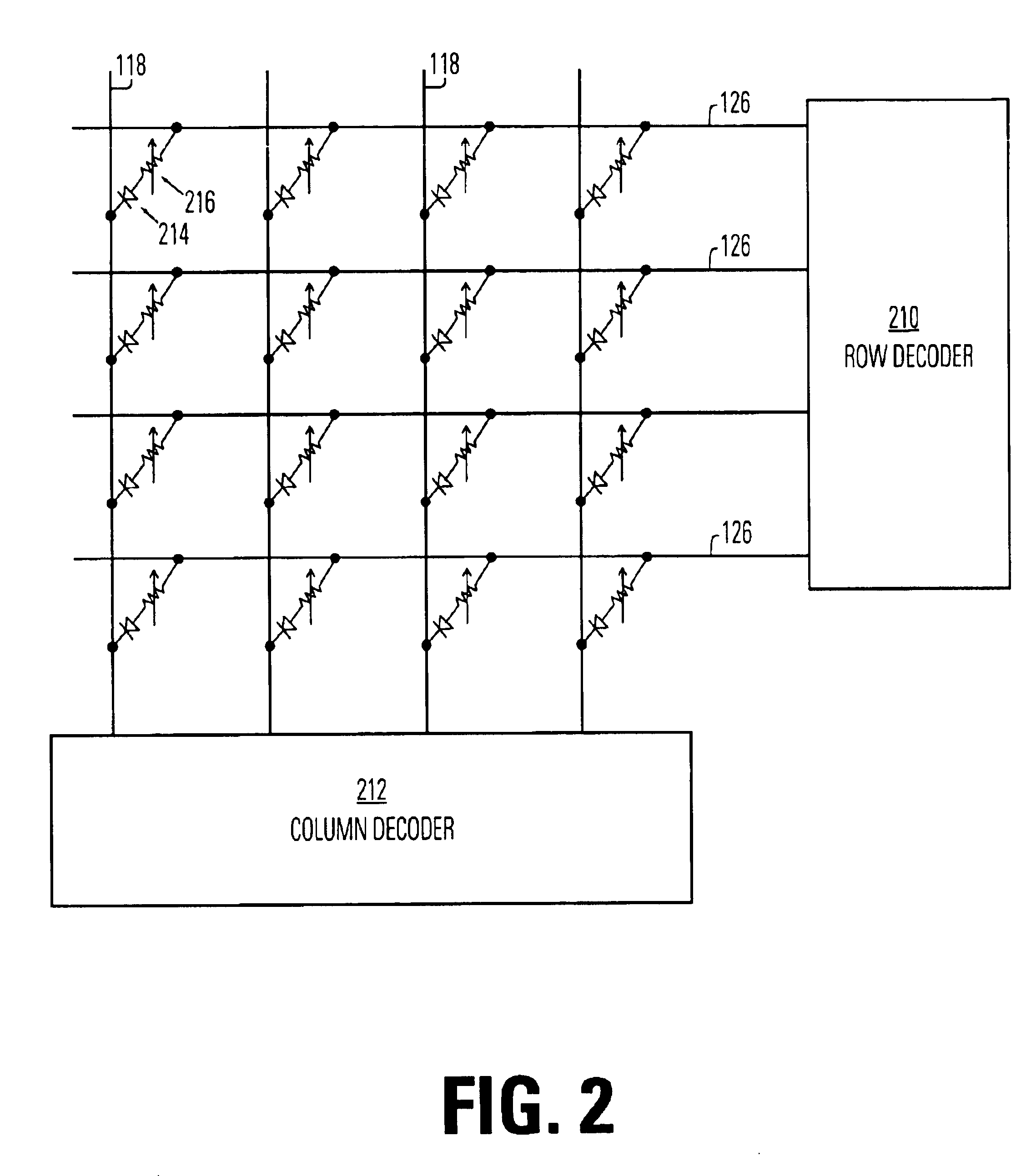

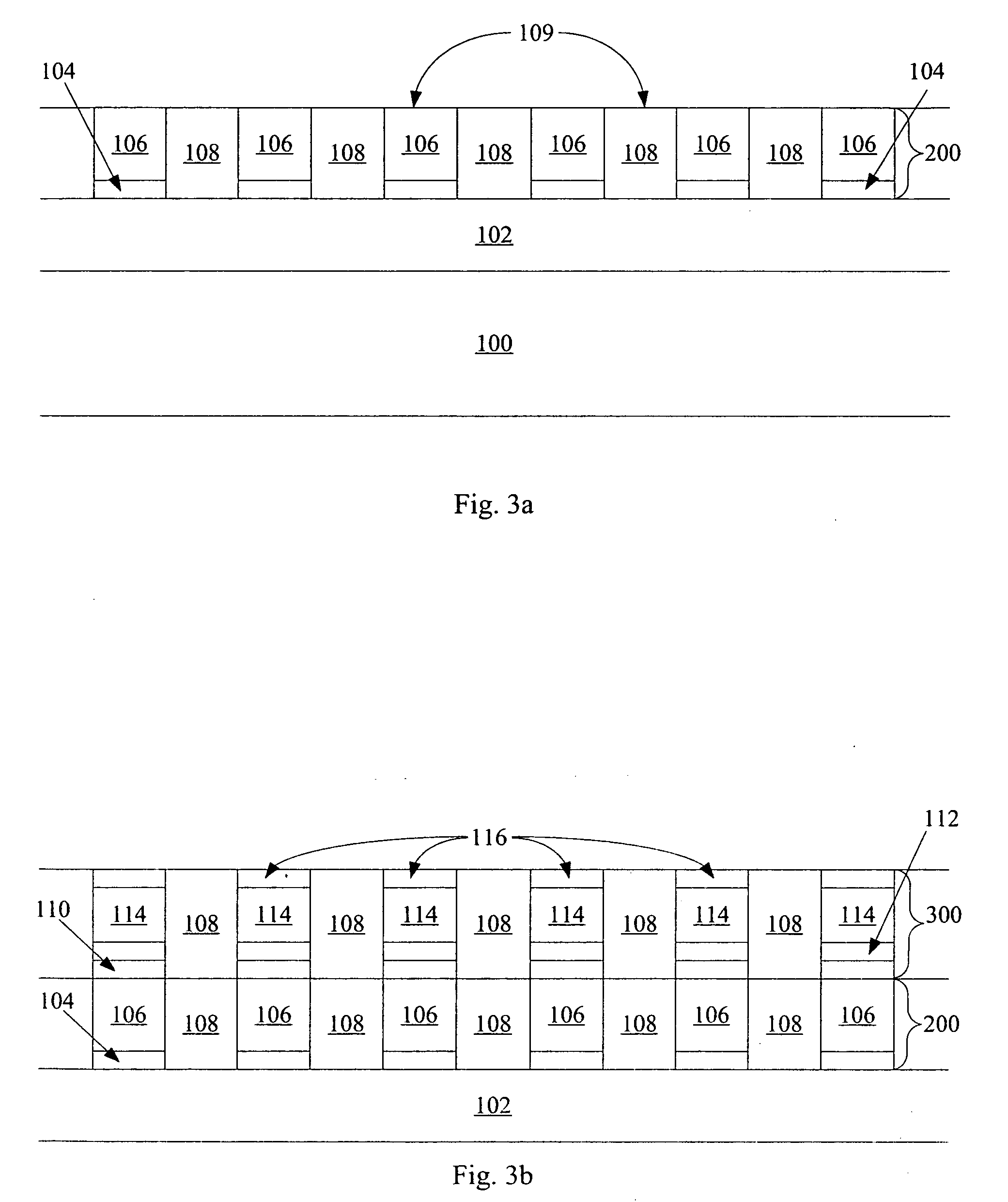

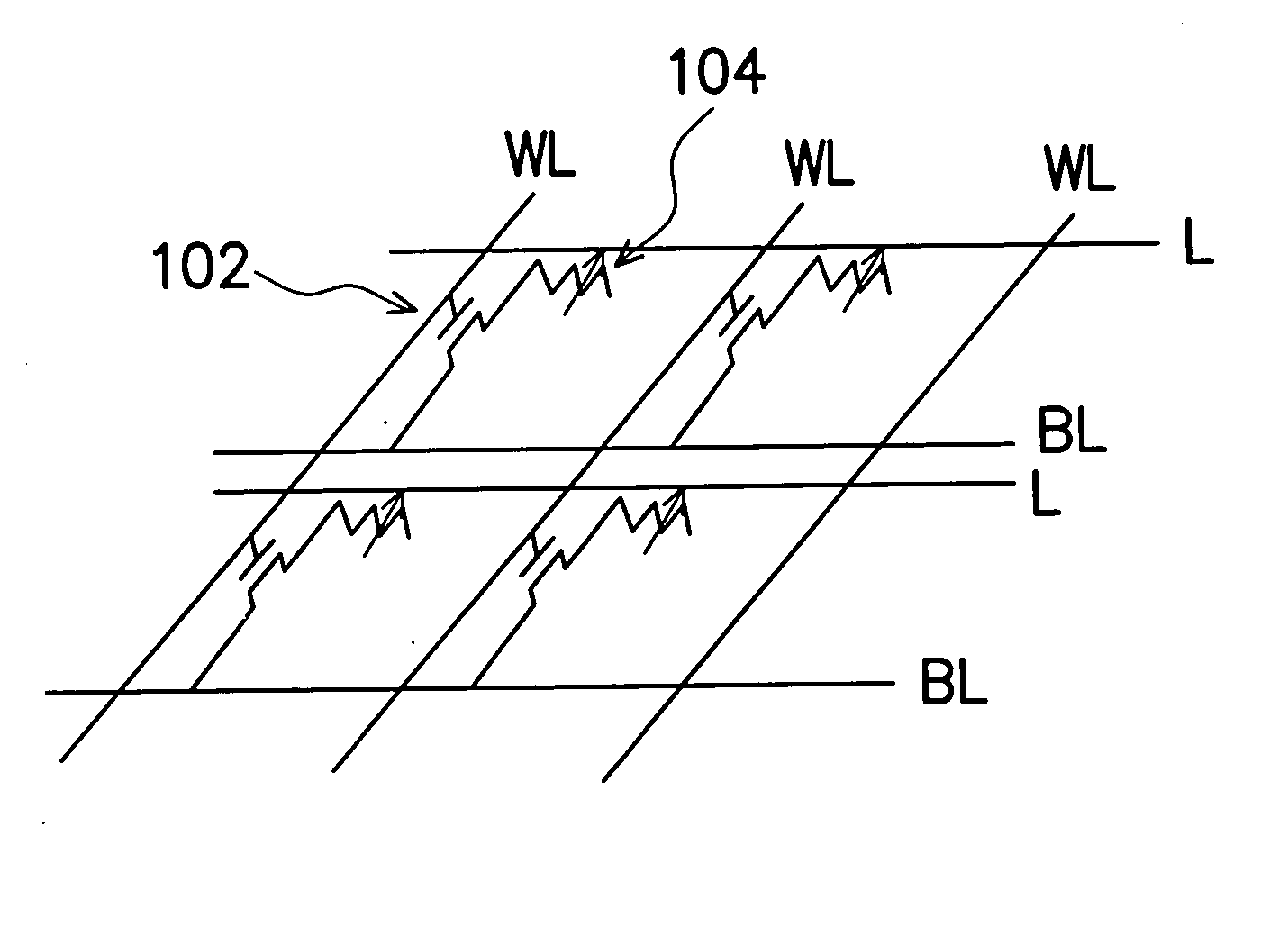

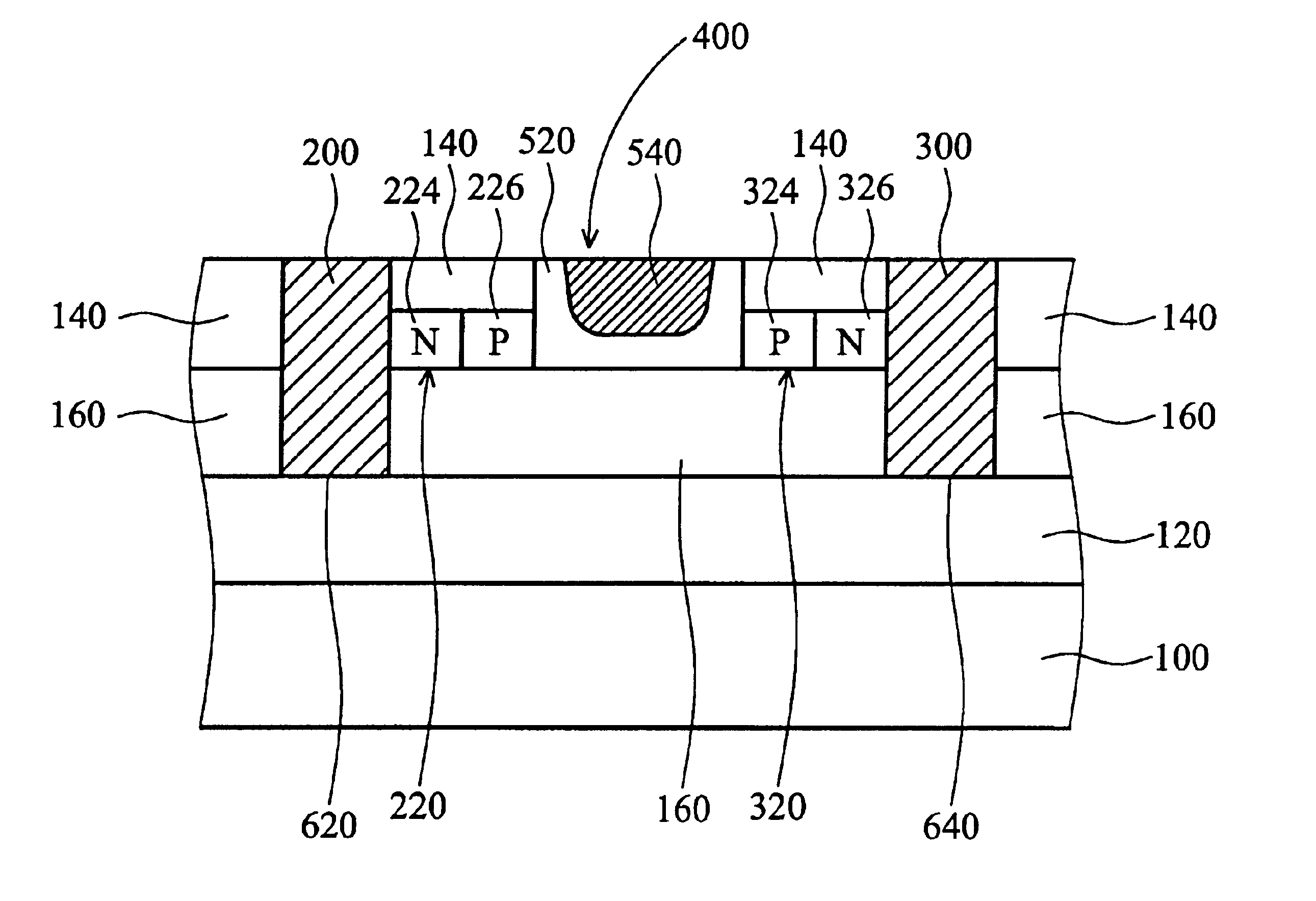

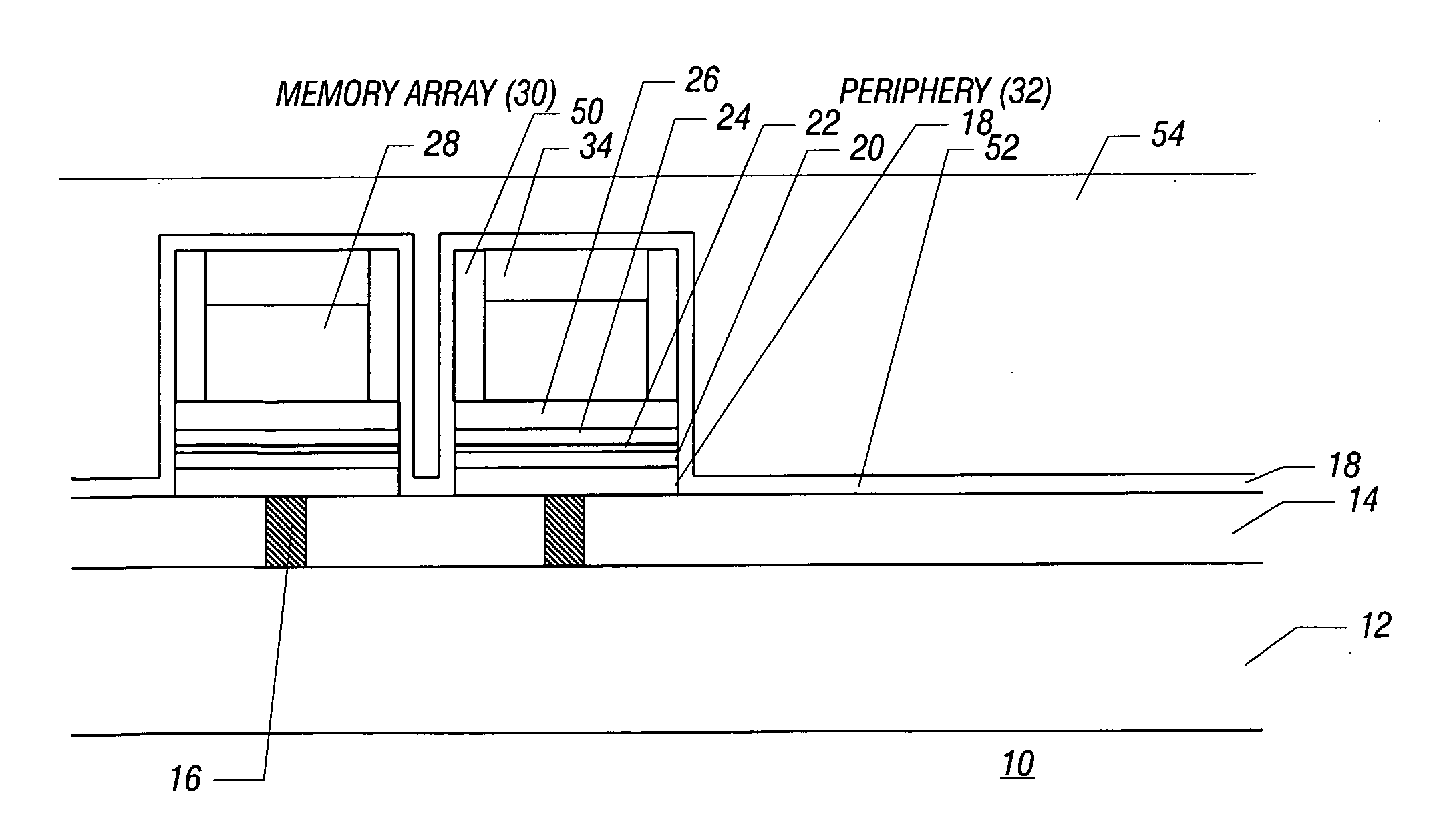

Memory cell incorporating a chalcogenide element

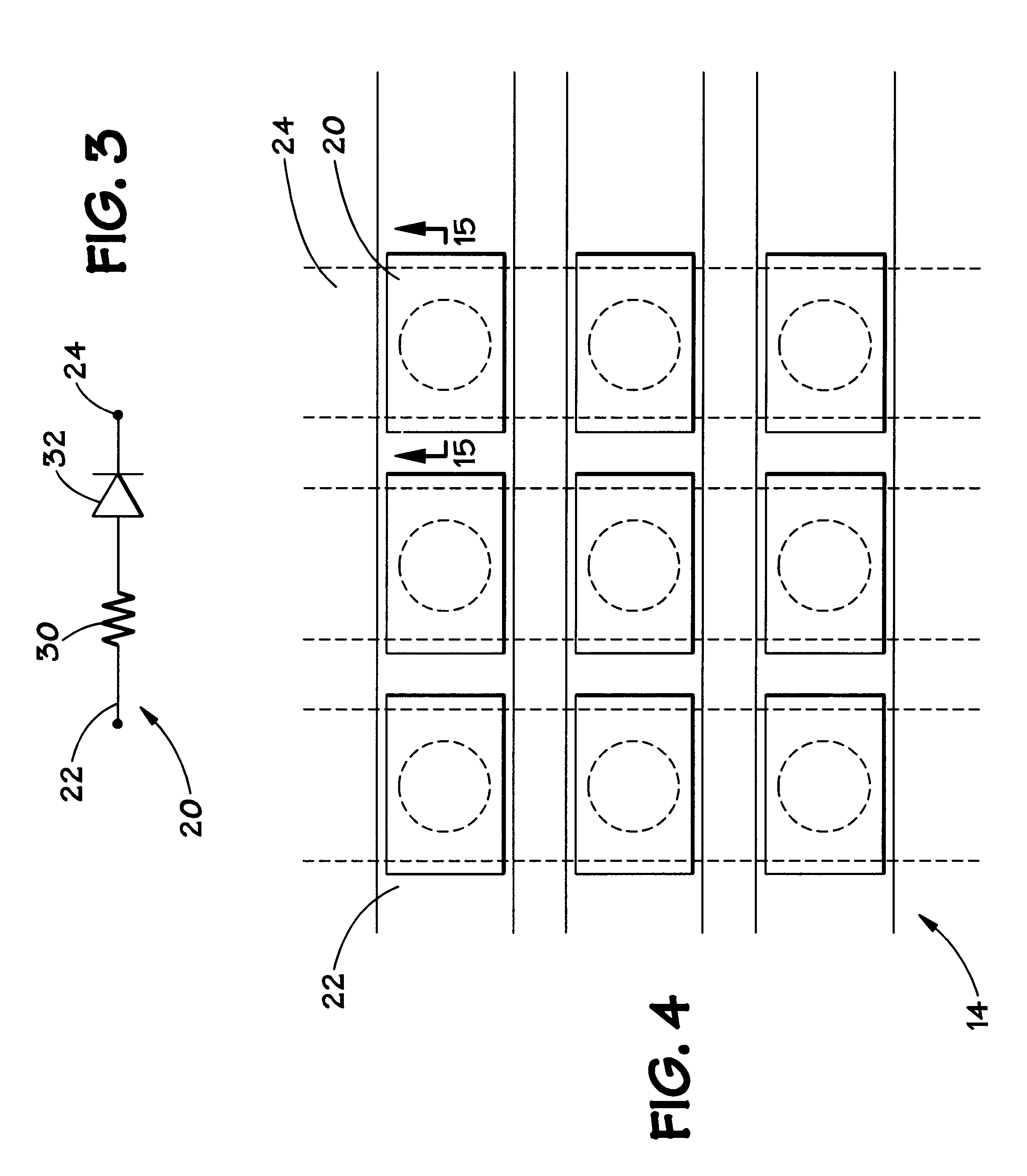

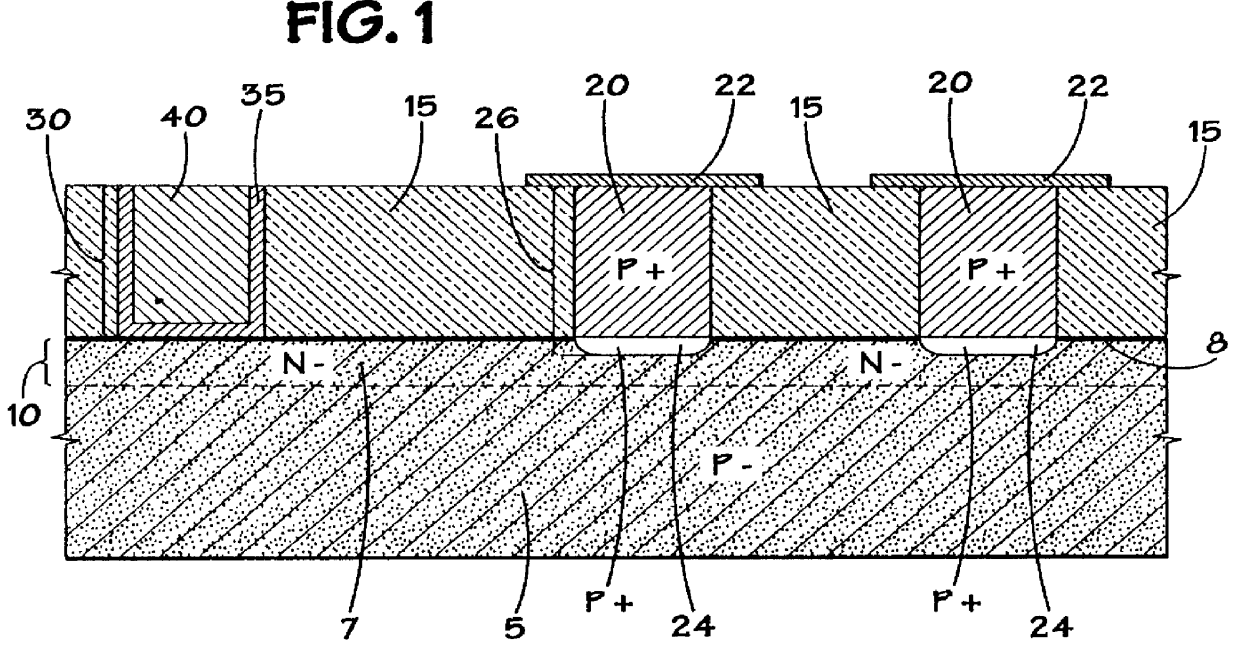

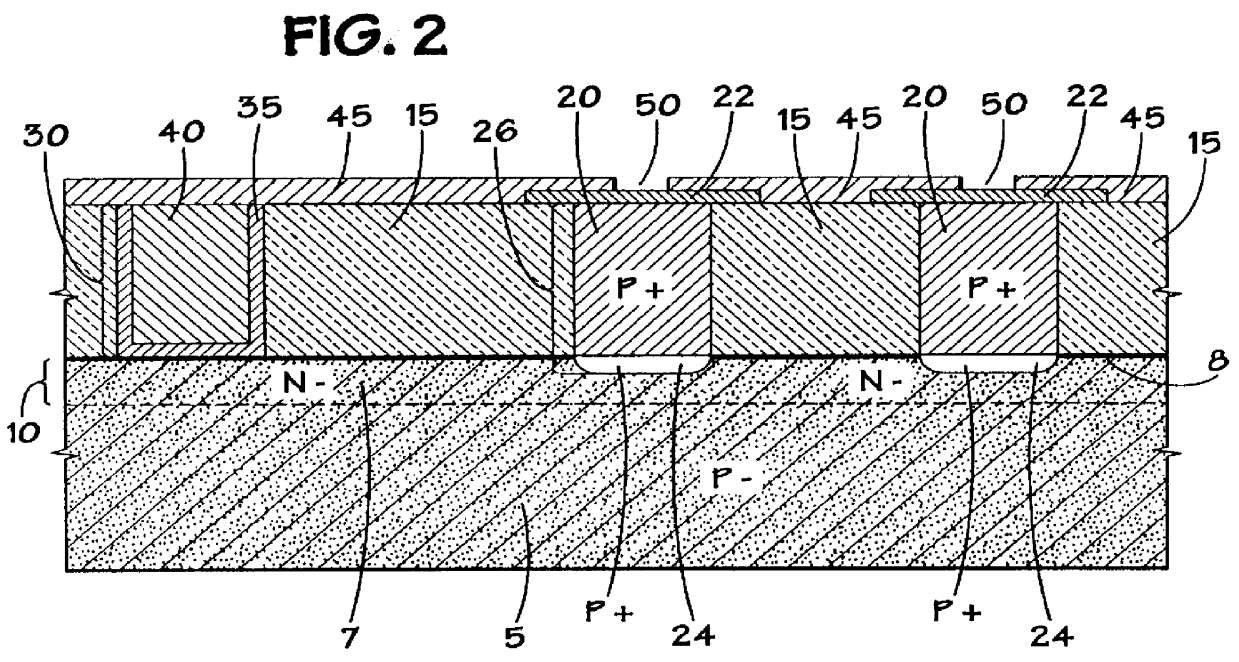

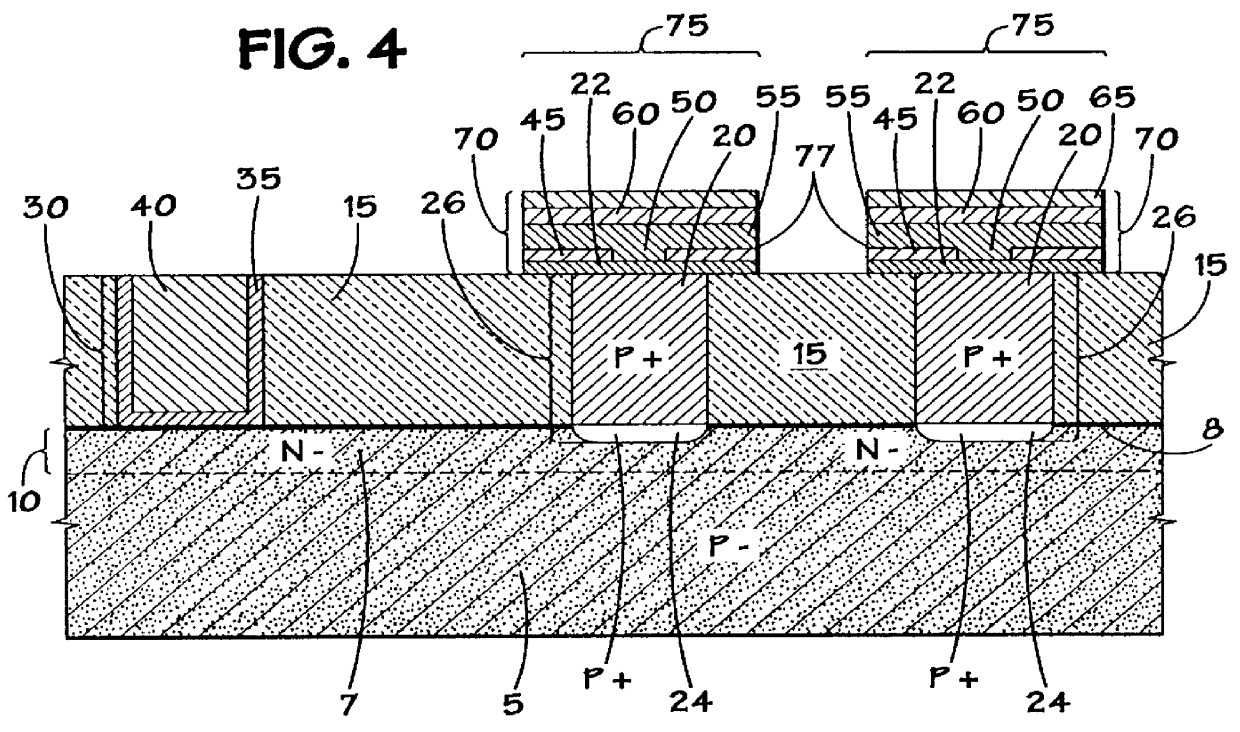

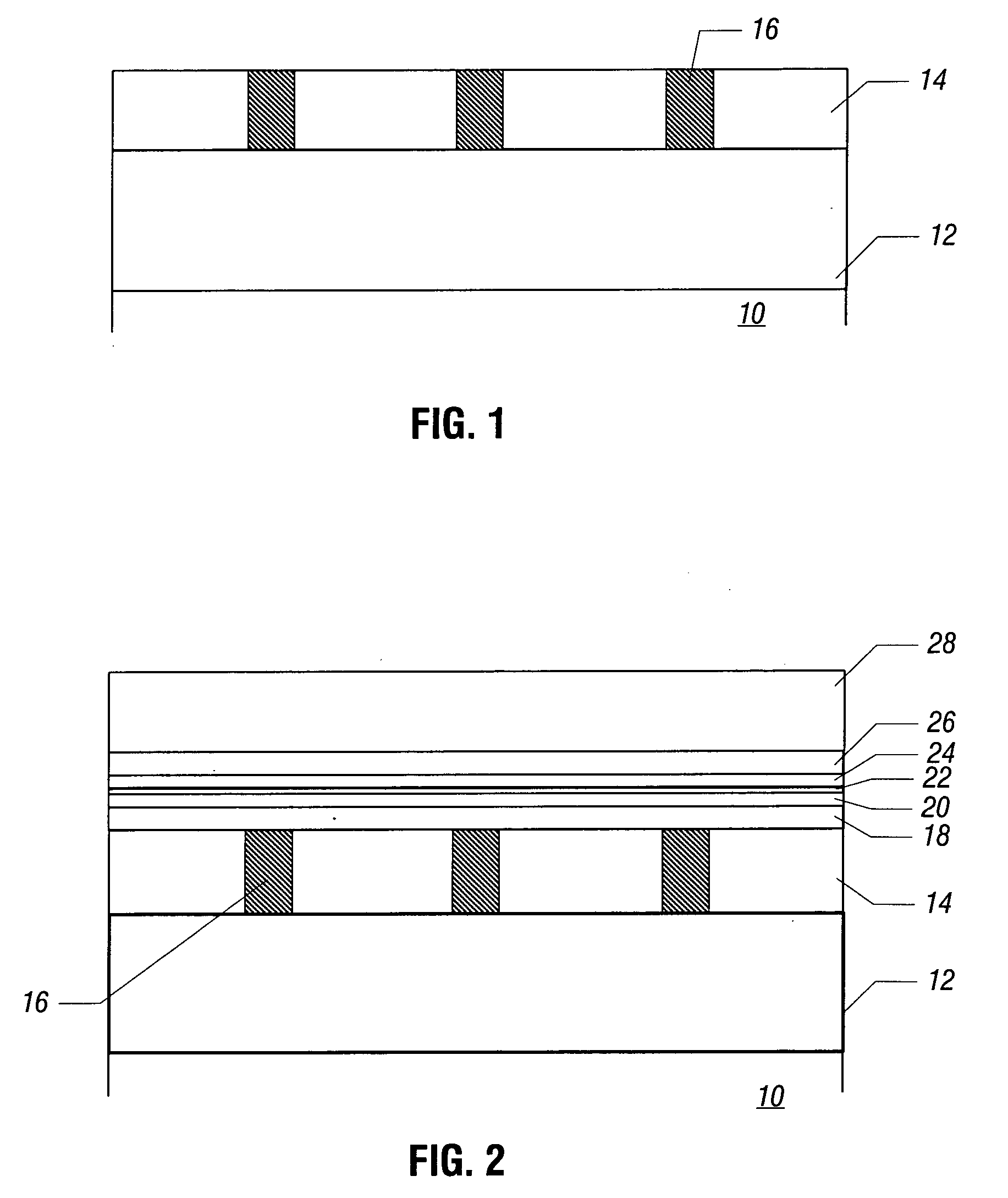

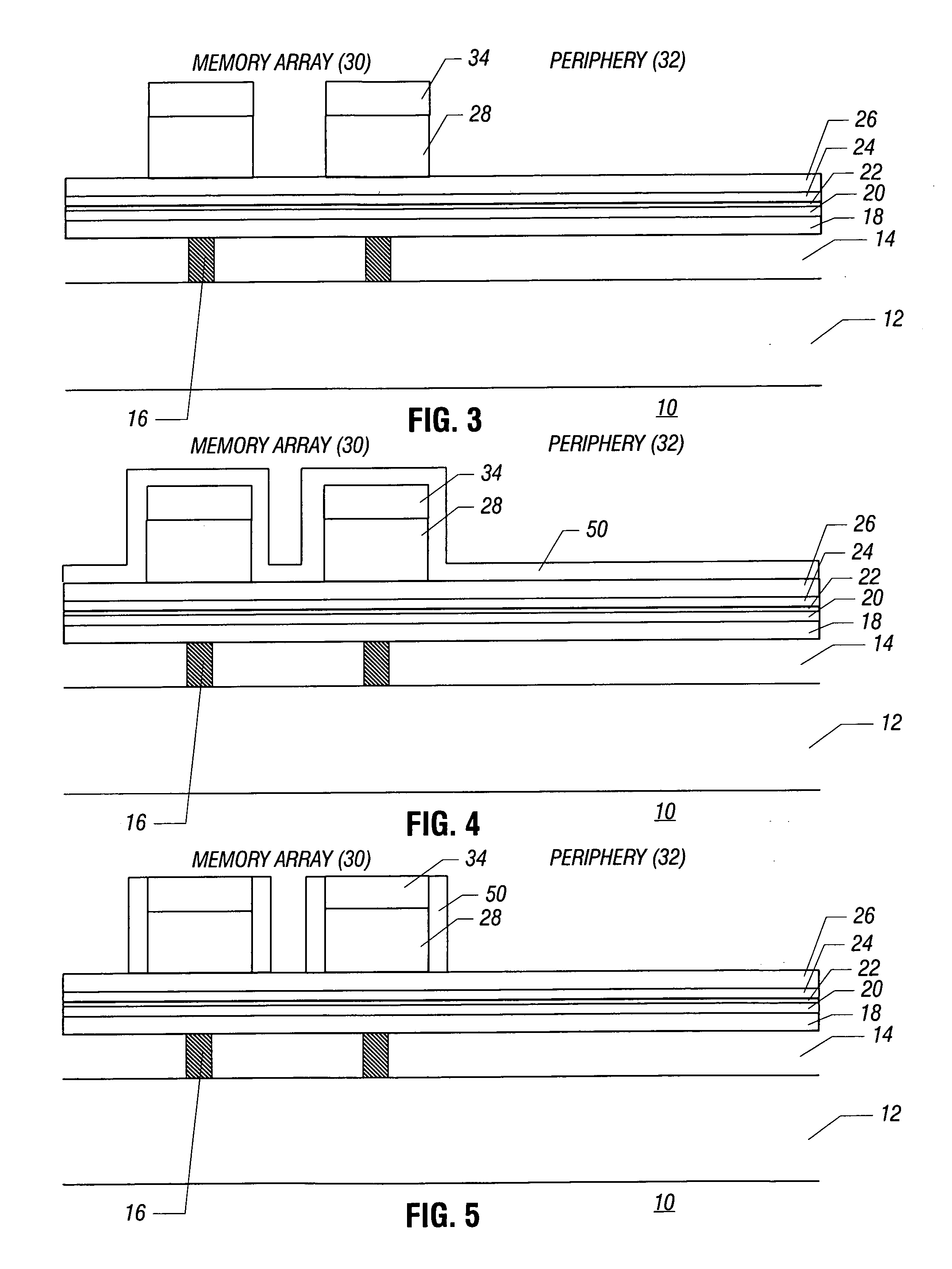

A memory cell incorporating a chalcogenide element and a method of making same is disclosed. In the method, a doped silicon substrate is provided with two or more polysilicon plugs to form an array of diode memory cells. A layer of silicon nitride is disposed over the plugs. Using a poly-spacer process, small pores are formed in the silicon nitride to expose a portion of the polysilicon plugs. A chalcogenide material is disposed in the pores by depositing a layer of chalcogenide material on the silicon nitride layer and planarizing the chalcogenide layer to the silicon nitride layer using CMP. A layer of TiN is next deposited over the plugs, followed by a metallization layer. The TiN and metallization layers are then masked and etched to define memory cell areas.

Owner:ROUND ROCK RES LLC

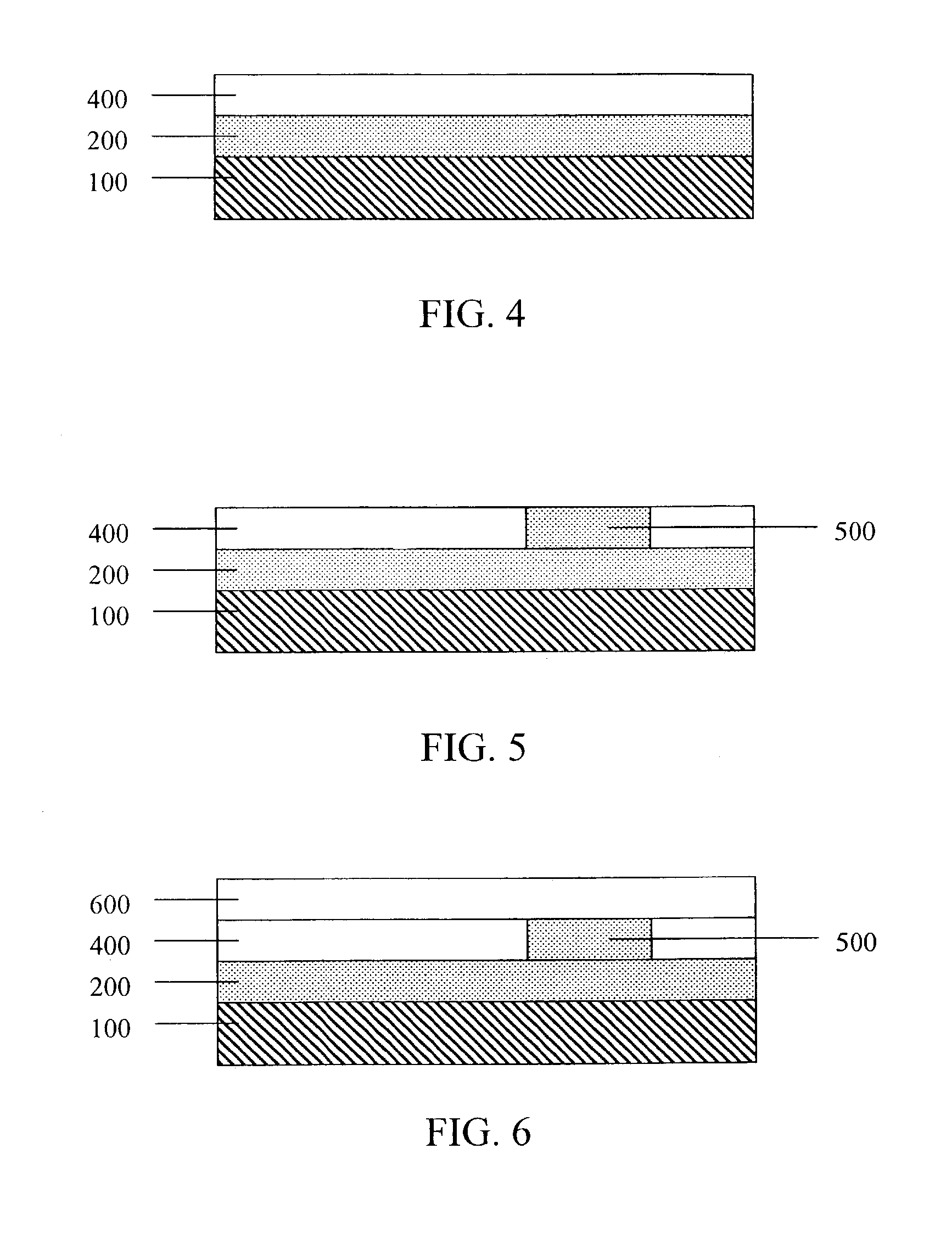

Method of Producing Transition Metal Dichalcogenide Layer

ActiveUS20170250075A1Advantageously producedSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDeposition temperatureChalcogen

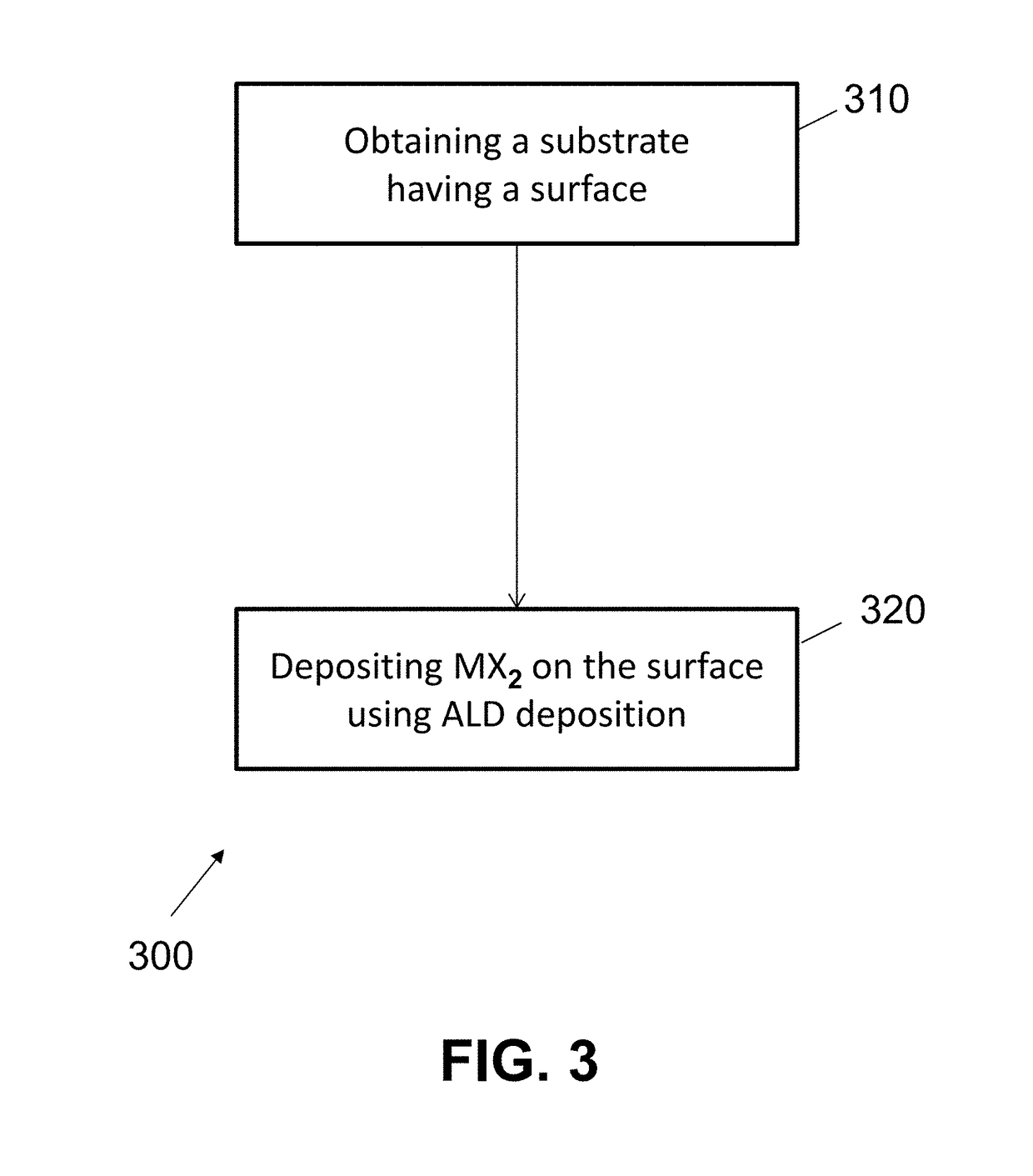

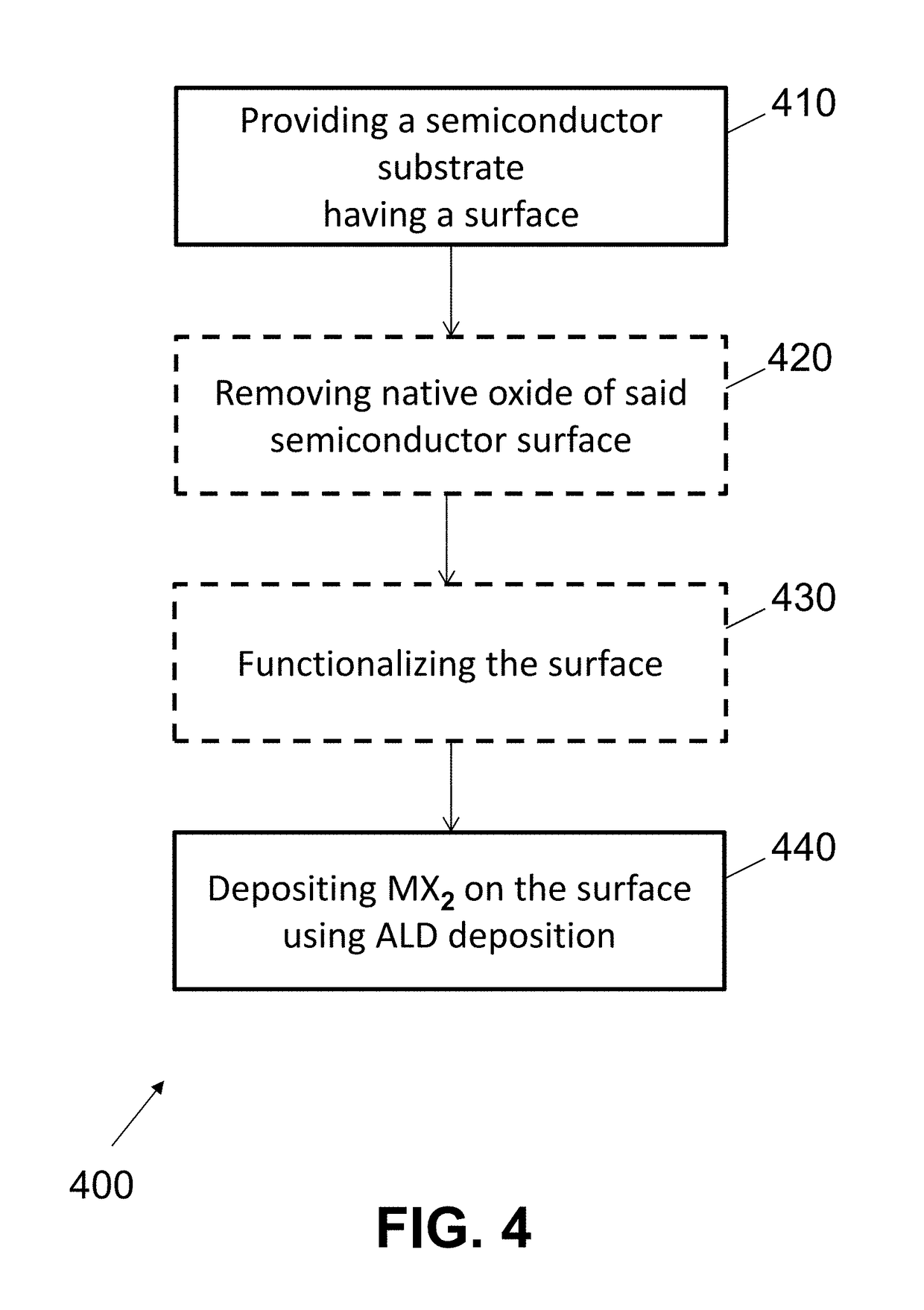

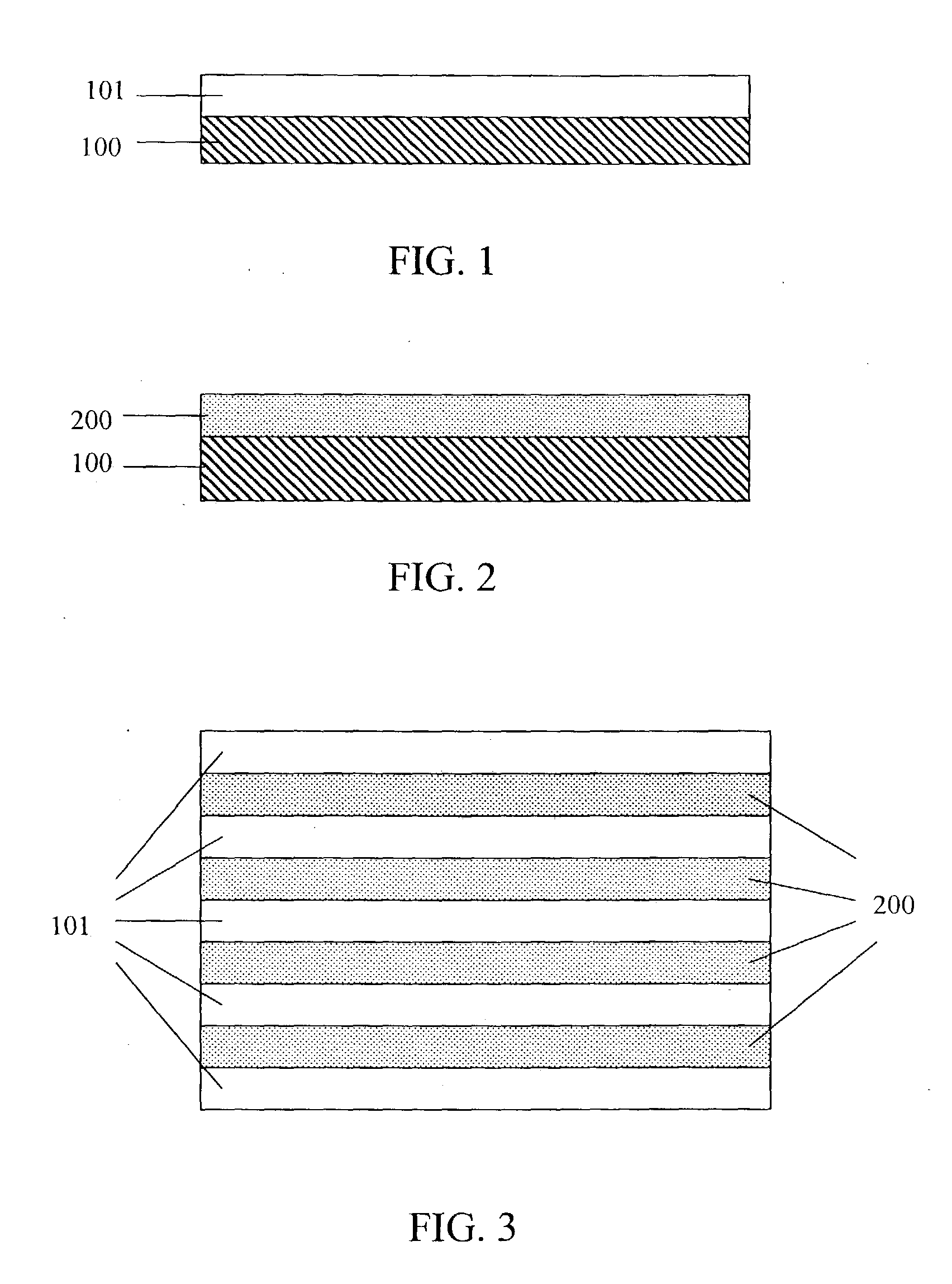

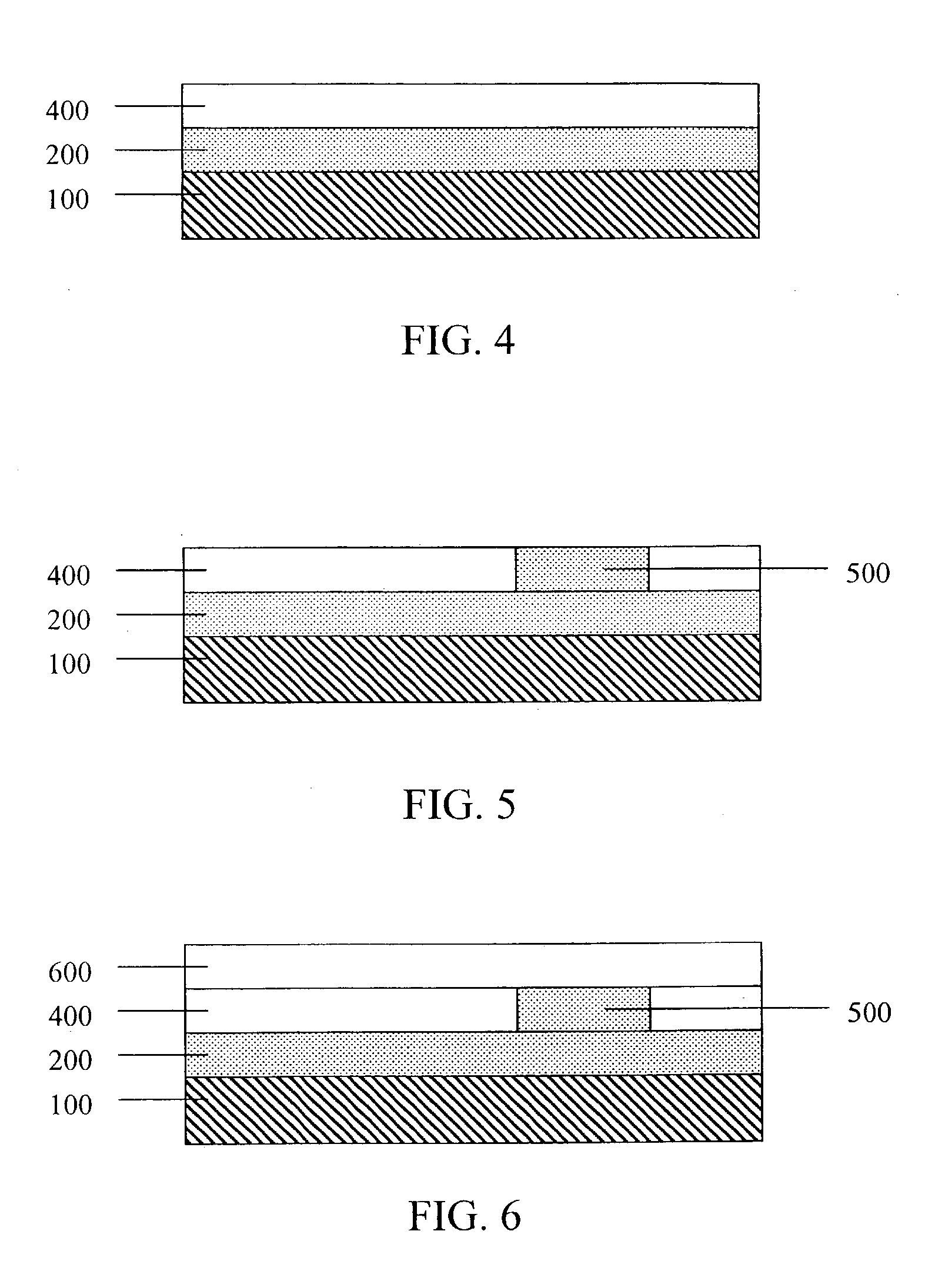

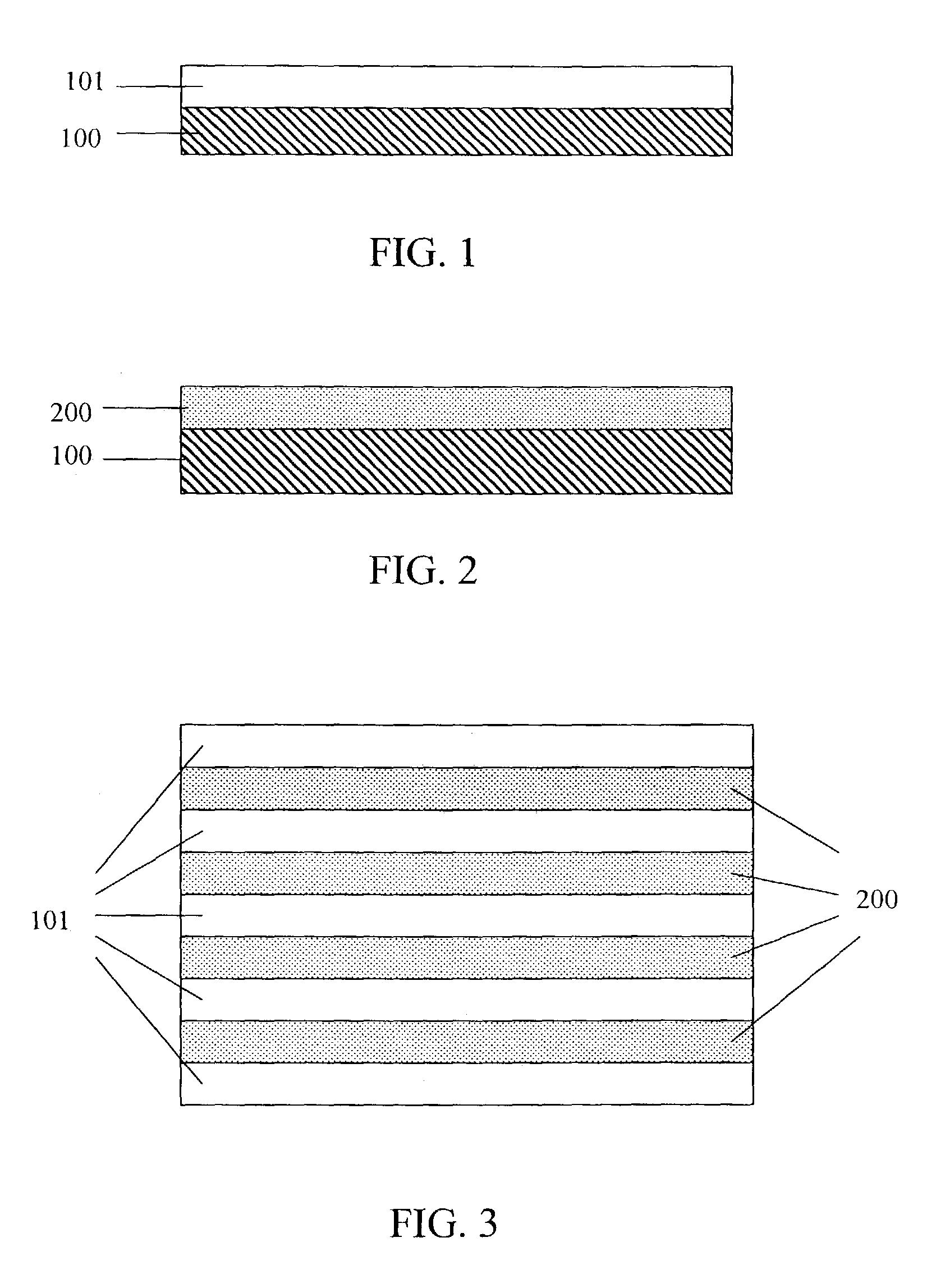

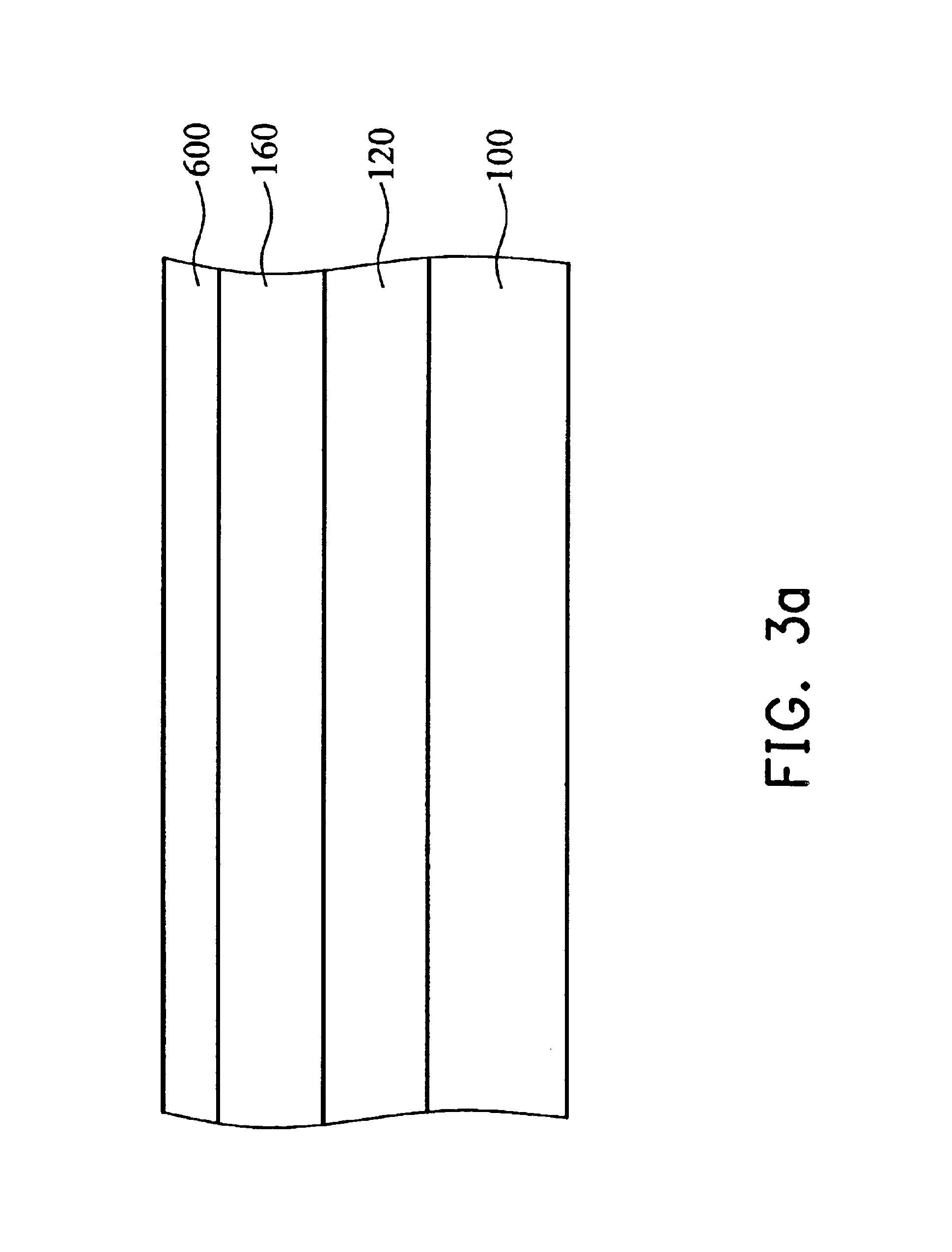

Method of producing one or more transition metal dichalcogenide (MX2) layers on a substrate, comprising the steps of: obtaining a substrate having a surface and depositing MX2 on the surface using ALD deposition, starting from a metal halide precursor and a chalcogen source (H2X), at a deposition temperature of about 300° C. Suitable metals are Mo and W, suitable chalcogenides are S, Se and Te. The substrate may be (111) oriented. Also mixtures of two or more MX2 layers of different compositions can be deposited on the substrate, by repeating at least some of the steps of the method.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

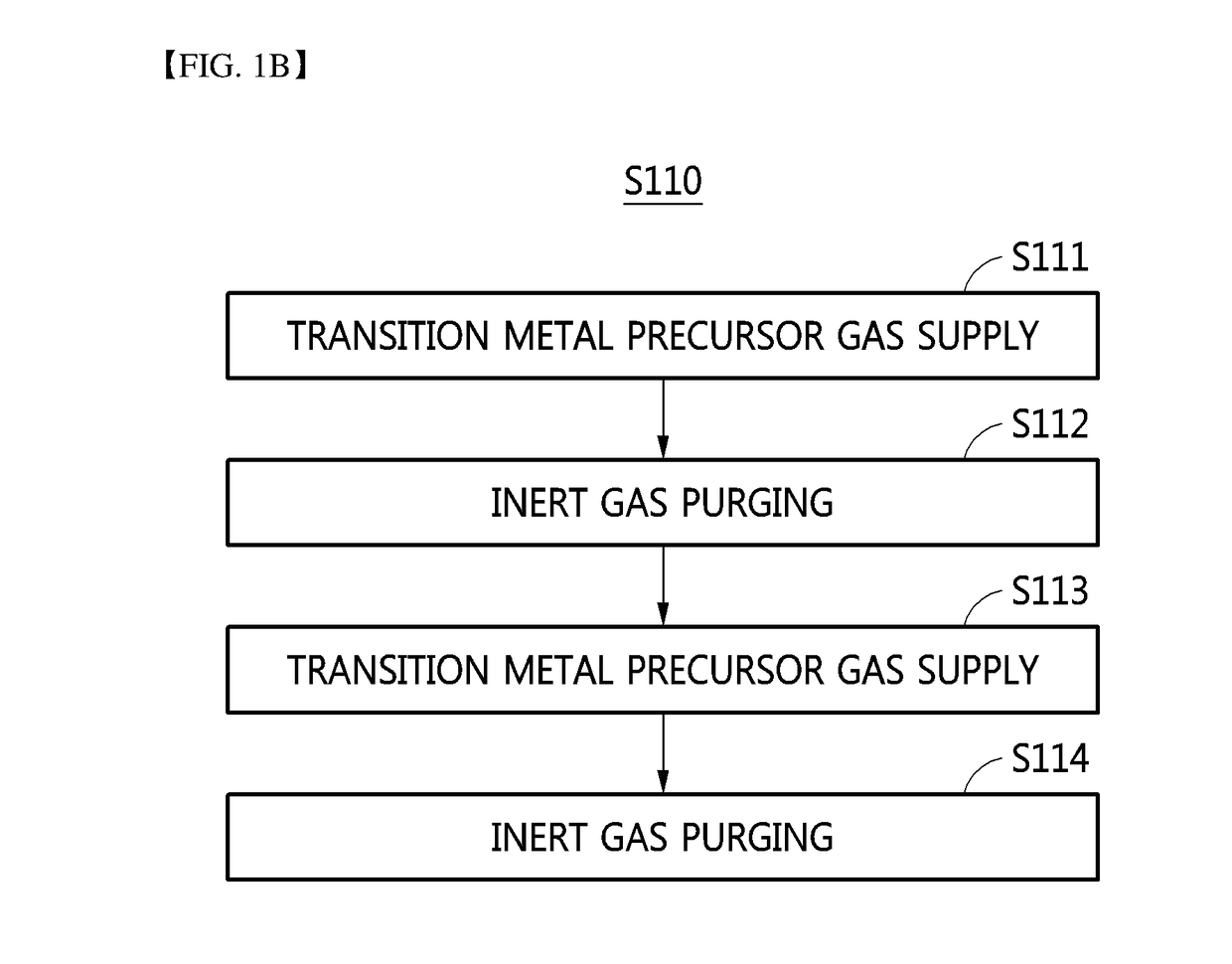

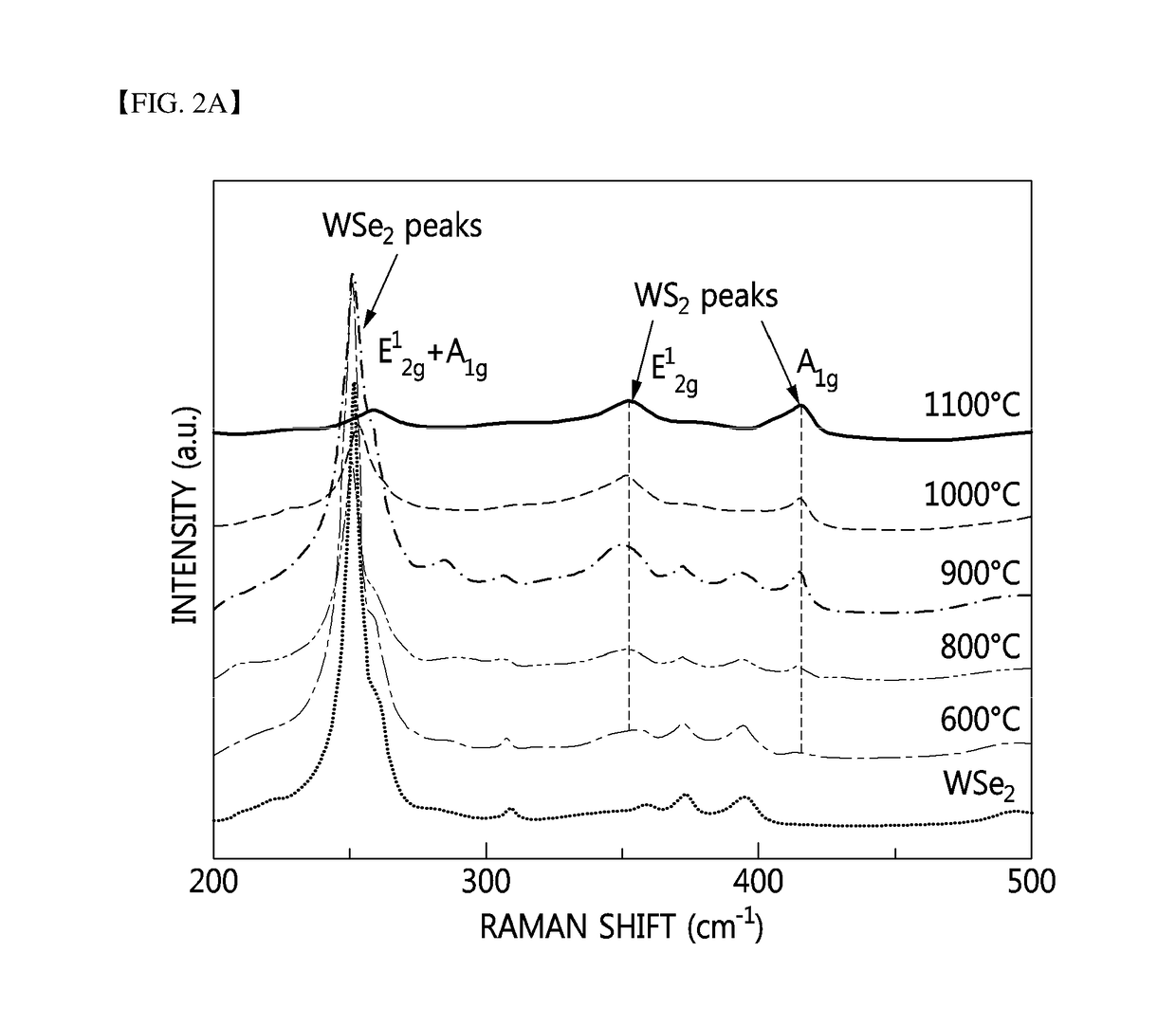

Transition metal dichalcogenide alloy and method of manufacturing the same

ActiveUS20170267527A1Semiconductor/solid-state device manufacturingSelenium/tellurium compounds with other elementsSulfurAlloy

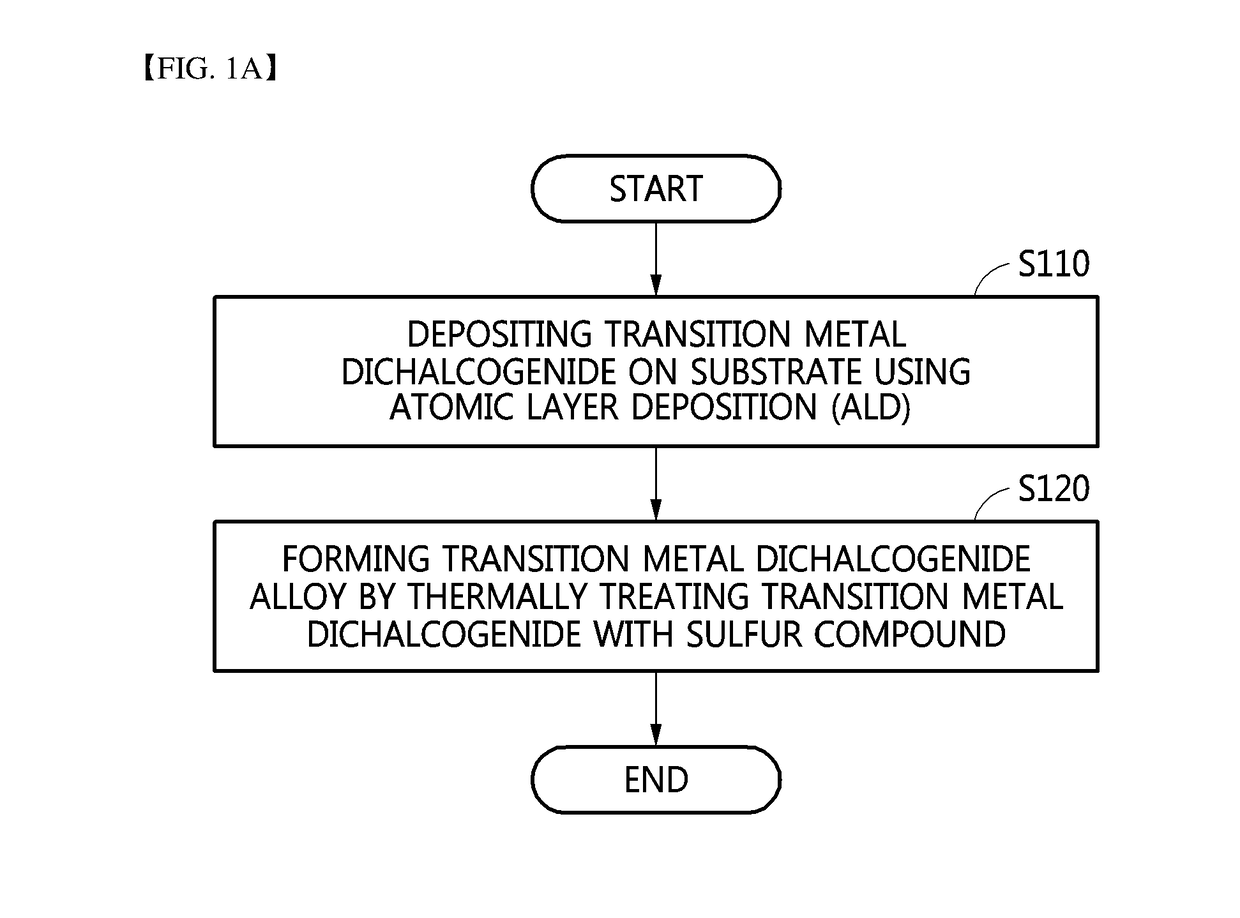

Disclosed are a transition metal dichalcogenide alloy and a method of manufacturing the same. A method of manufacturing a transition metal dichalcogenide alloy according to an embodiment of the present disclosure includes a step of depositing transition metal dichalcogenide on a substrate using atomic layer deposition (ALD); and a step of forming a transition metal dichalcogenide alloy by thermally treating the transition metal dichalcogenide with a sulfur compound.

Owner:IND ACADEMIC CORP FOUND YONSEI UNIV

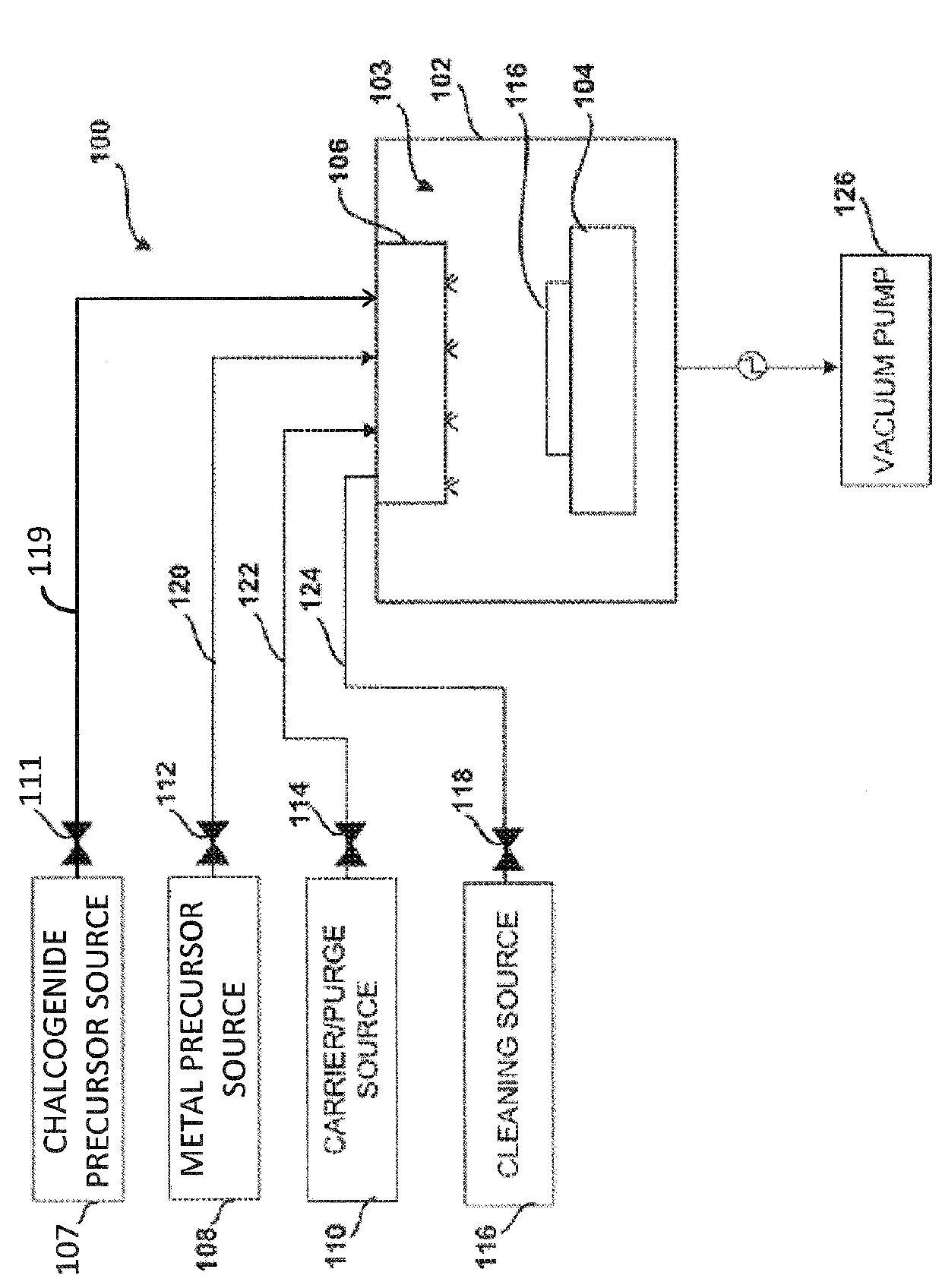

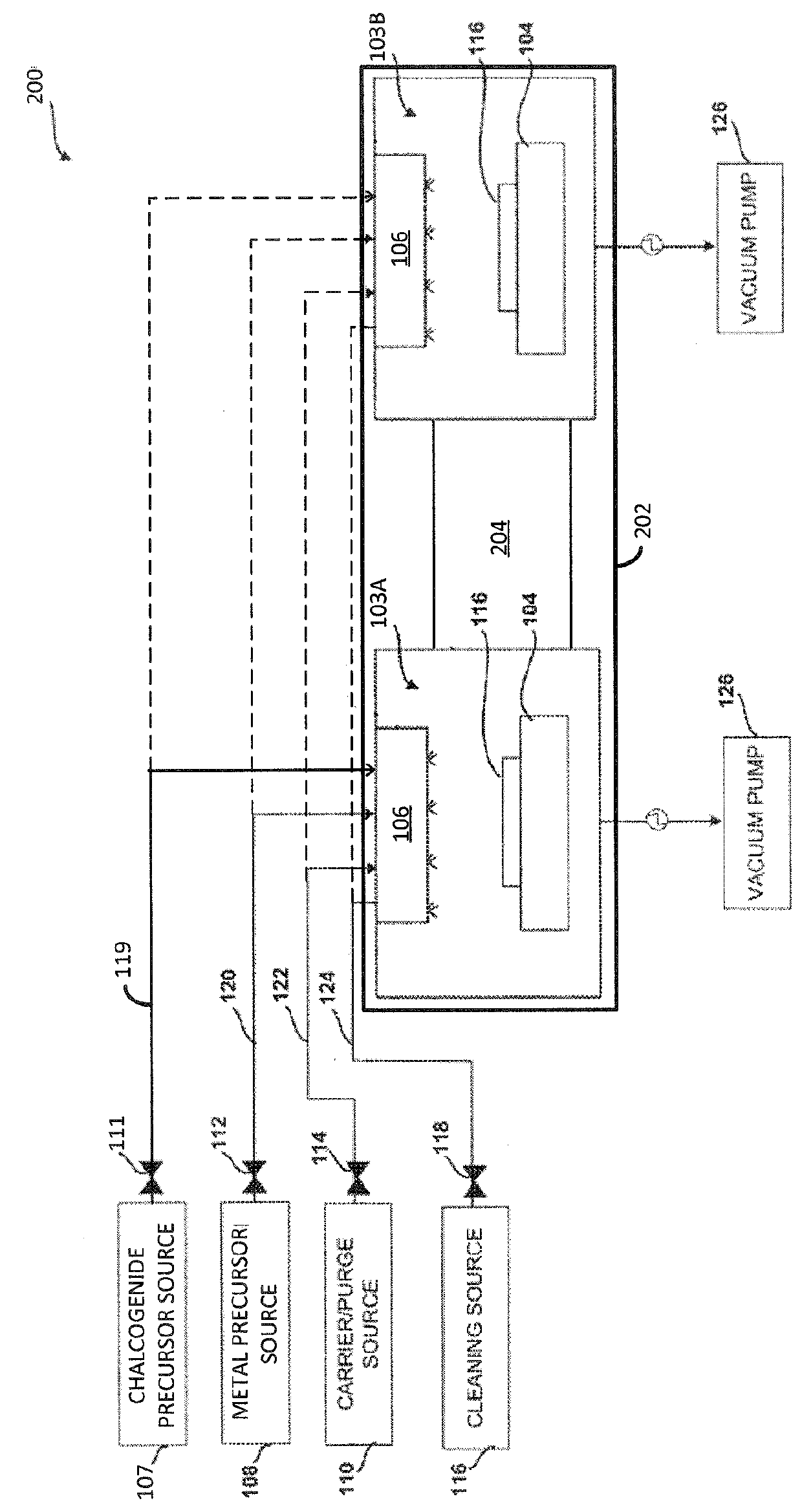

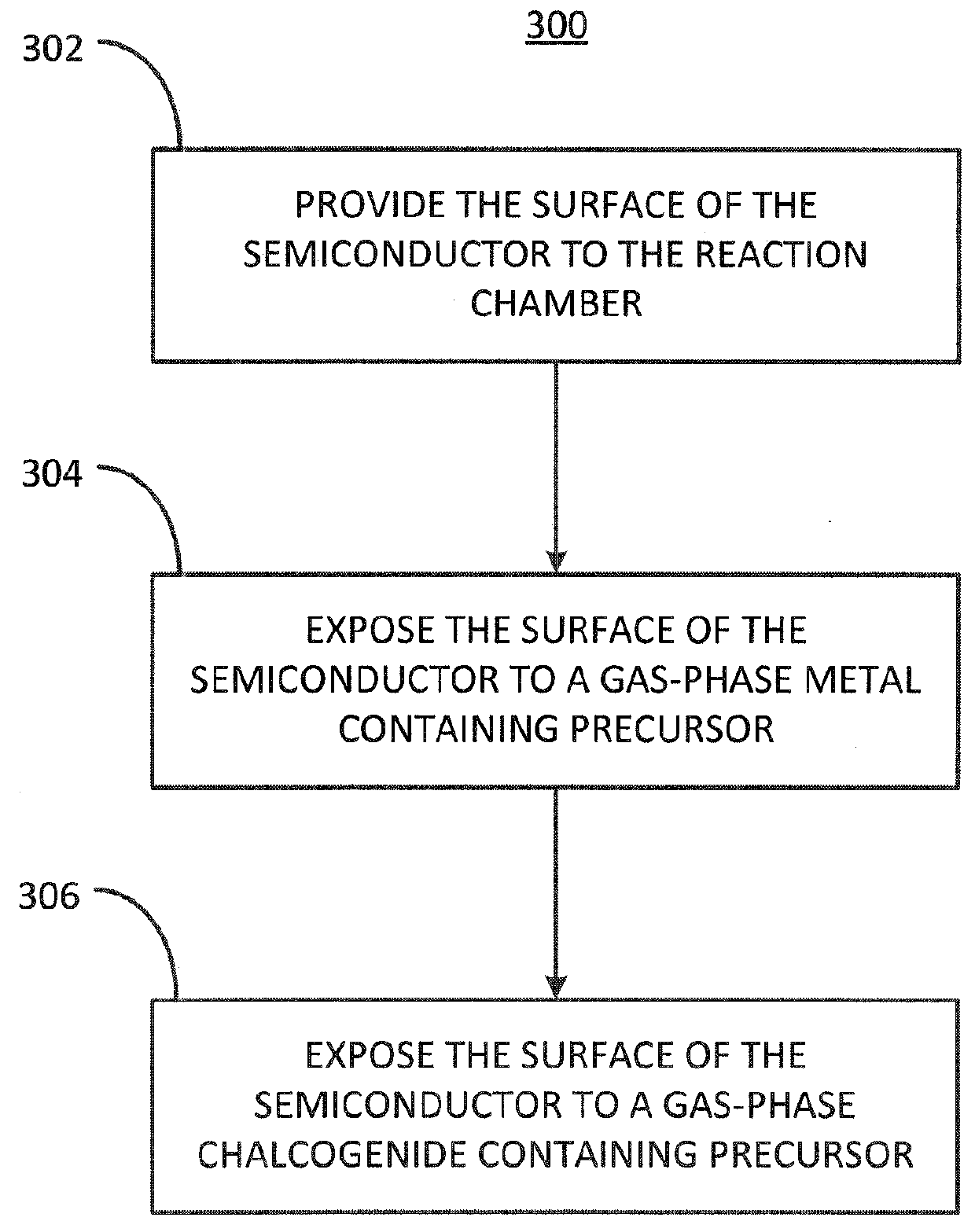

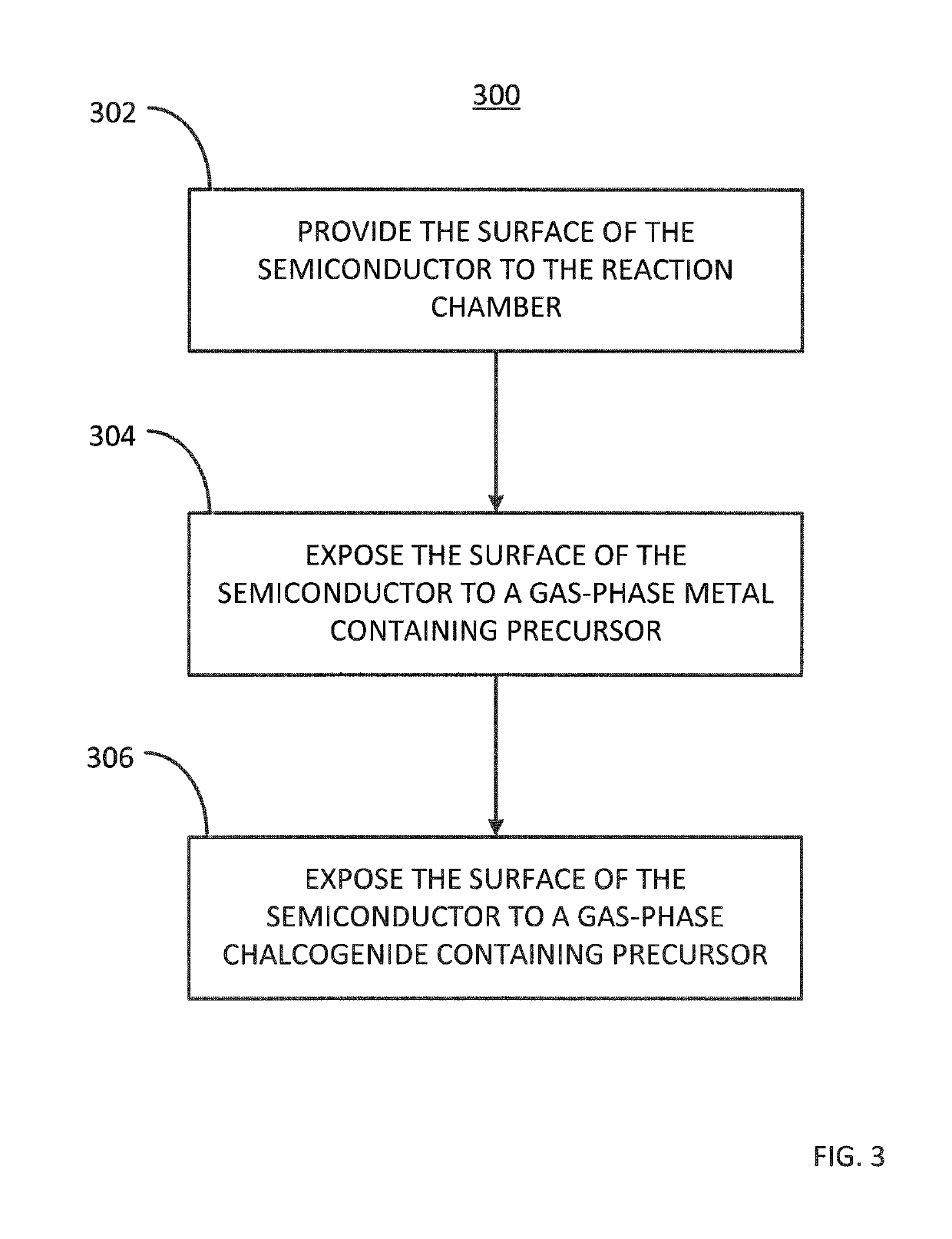

Method for passivating a surface of a semiconductor and related systems

ActiveUS20180108587A1Semiconductor/solid-state device detailsSolid-state devicesGas phaseSemiconductor

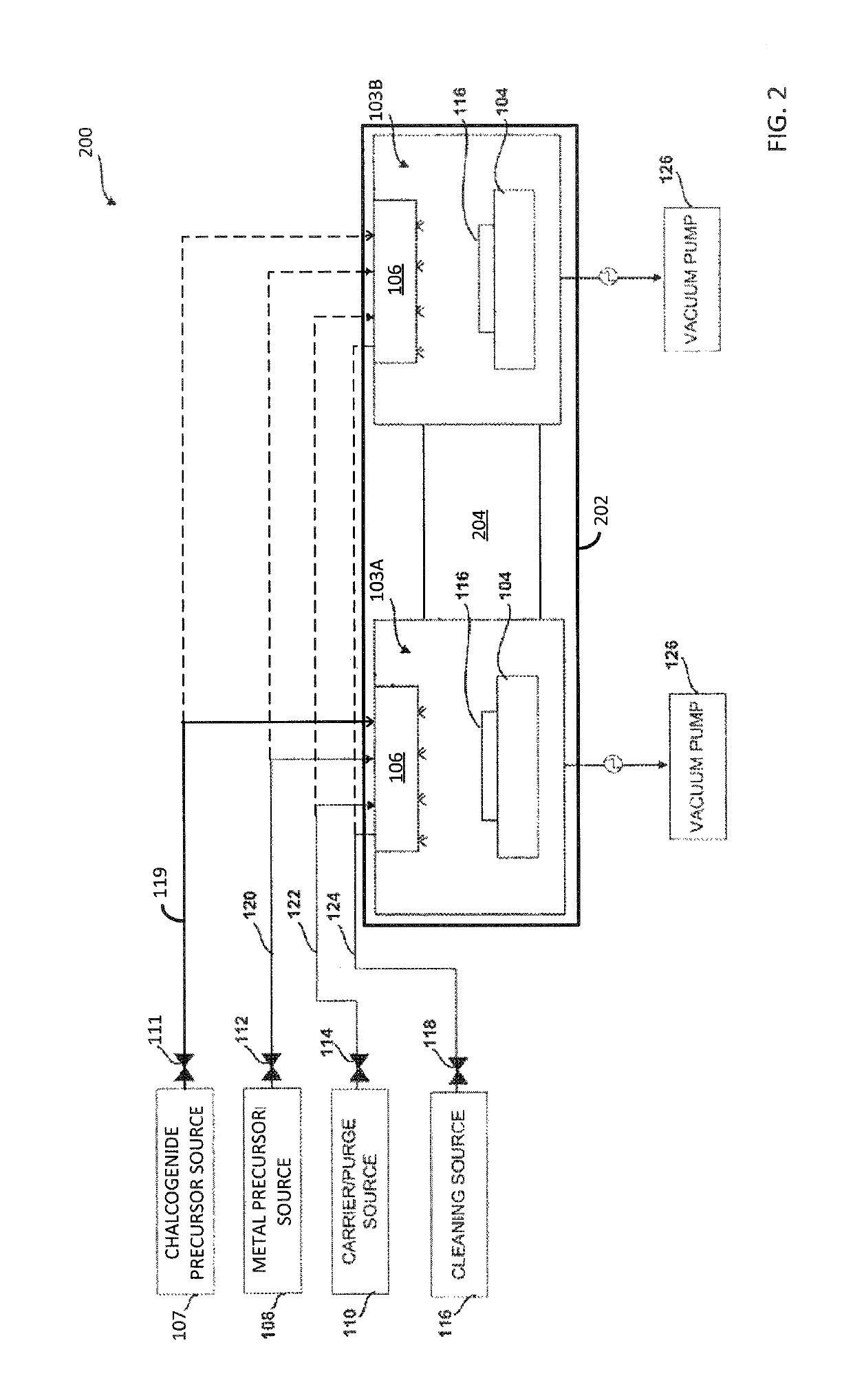

A system and a method for passivating a surface of a semiconductor. The method includes providing the surface of the semiconductor to a reaction chamber of a reactor, exposing the surface of the semiconductor to a gas-phase metal containing precursor in the reaction chamber and exposing the surface of the semiconductor to a gas-phase chalcogenide containing precursor. The methods also include passivating the surface of the semiconductor using the gas-phase metal containing precursor and the gas-phase chalcogenide containing precursor to form a passivated surface. The system for passivating a surface of a semiconductor may include a reactor, a metal containing precursor source fluidly coupled to the reactor, and a chalcogenide containing precursor source fluidly couple to the reactor, wherein the metal containing precursor source provides a gas-phase metal containing precursor to a reaction chamber of the reactor, and wherein the chalcogenide containing precursor source provides a gas-phase chalcogenide containing precursor to a reaction chamber of the reactor.

Owner:ASM IP HLDG BV

Electroless plating of metal caps for chalcogenide-based memory devices

InactiveUS20060094236A1Good electrical contactSemiconductor/solid-state device manufacturingPlatinumSulfur

A method of forming a metal cap over a conductive interconnect in a chalcogenide-based memory device is provided and includes, forming a layer of a first conductive material over a substrate, depositing an insulating layer over the first conductive material and the substrate, forming an opening in the insulating layer to expose at least a portion of the first conductive material, depositing a second conductive material over the insulating layer and within the opening, removing portions of the second conductive material to form a conductive area within the opening, recessing the conductive area within the opening to a level below an upper surface of the insulating layer, forming a cap of a third conductive material over the recessed conductive area within the opening, the third conductive material selected from the group consisting of cobalt, silver, gold, copper, nickel, palladium, platinum, and alloys thereof, depositing a stack of a chalcogenide based memory cell material over the cap, and depositing a conductive material over the chalcogenide stack.

Owner:MICRON TECH INC

Laser programmable electrically readable phase-change memory method and device

InactiveUS6850432B2Simple and low power-consumingSimple and low and electrical circuitRead-only memoriesDigital storagePhase-change memoryEngineering

Roughly described, a phase-change memory such as a chalcogenide-based memory is programmed optically and read electrically. No complex electrical circuits are required for programming the cells. On the other hand, this memory can be read by electrical circuitry directly. The read out speed is much faster than for optical disks, and integrated circuit chips made this way are more compatible with other electrical circuits than are optical disks. Thus memories according to the invention can have simple, low power-consuming, electrical circuits, and do not require slow and power-hungry disk drives for reading. The invention therefore provides a unique low power, fast read / write memory with simple electrical circuits.

Owner:MACRONIX INT CO LTD

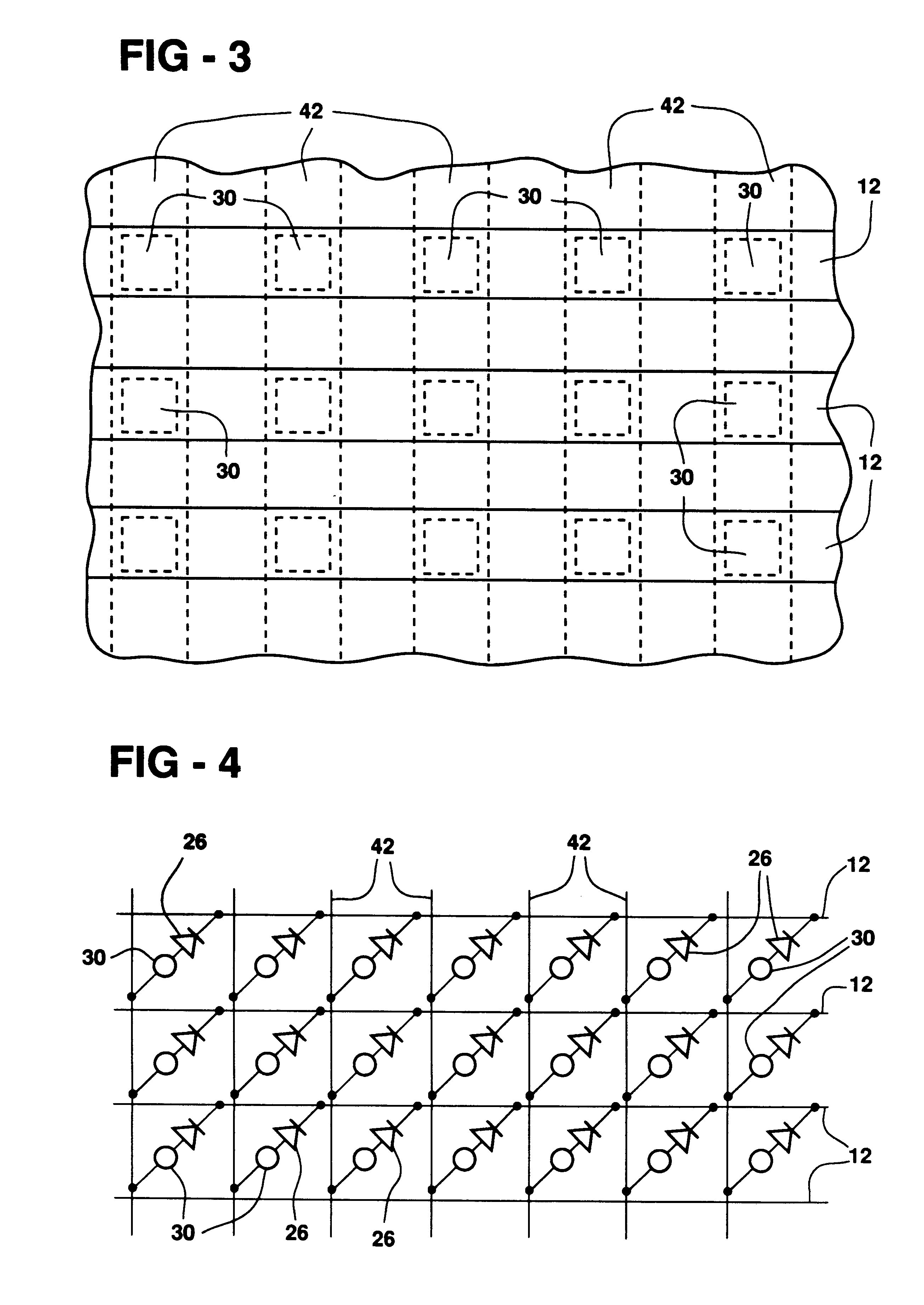

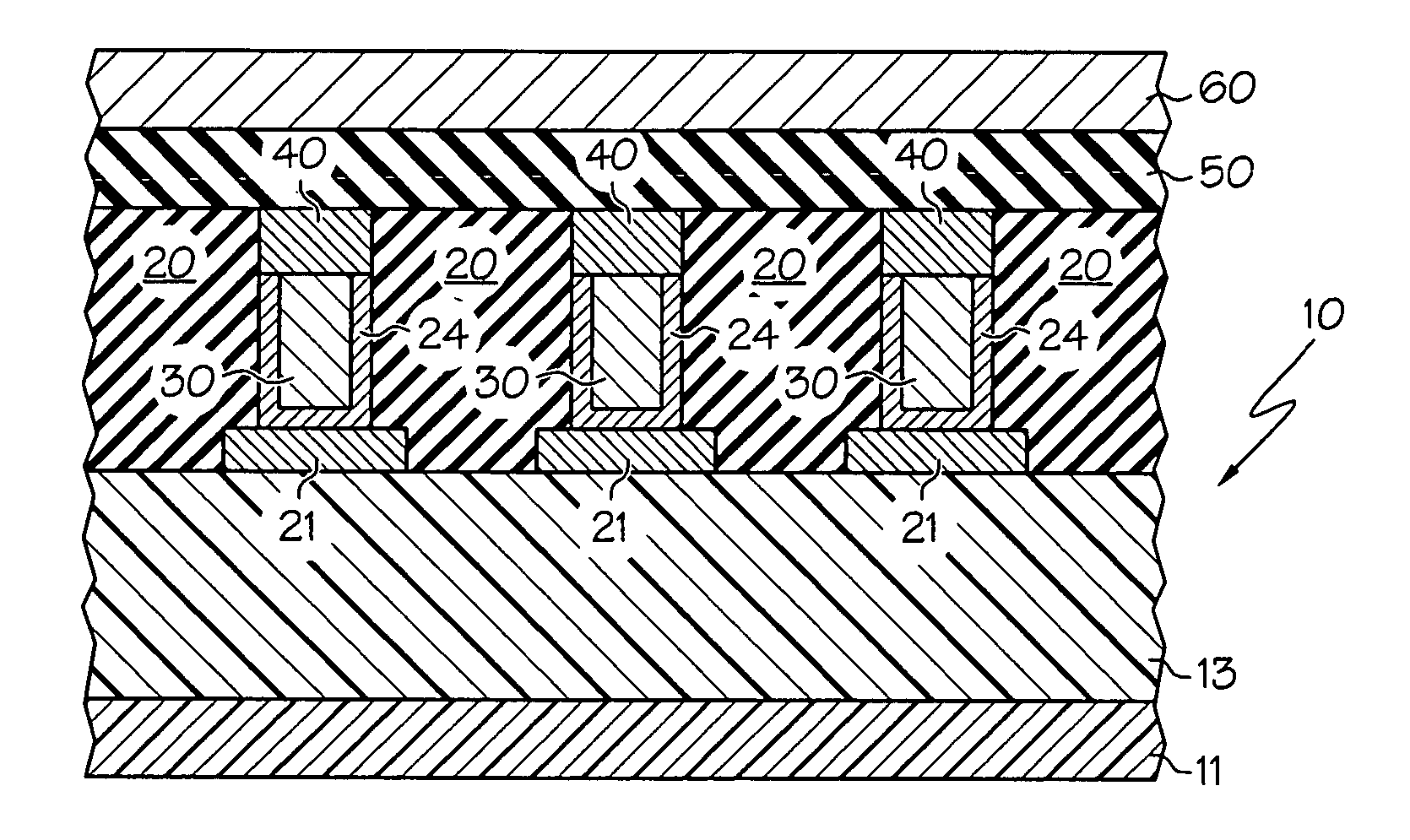

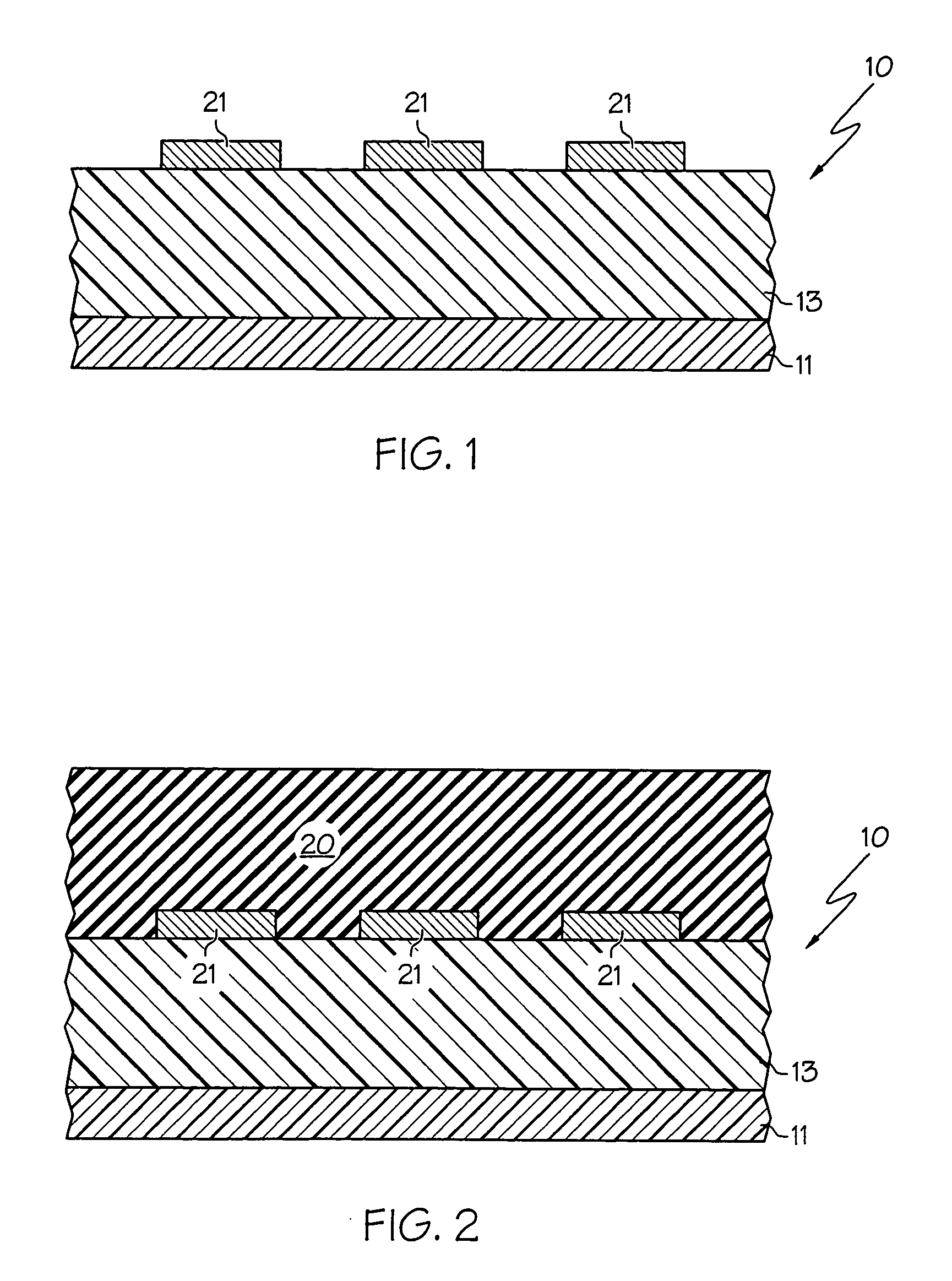

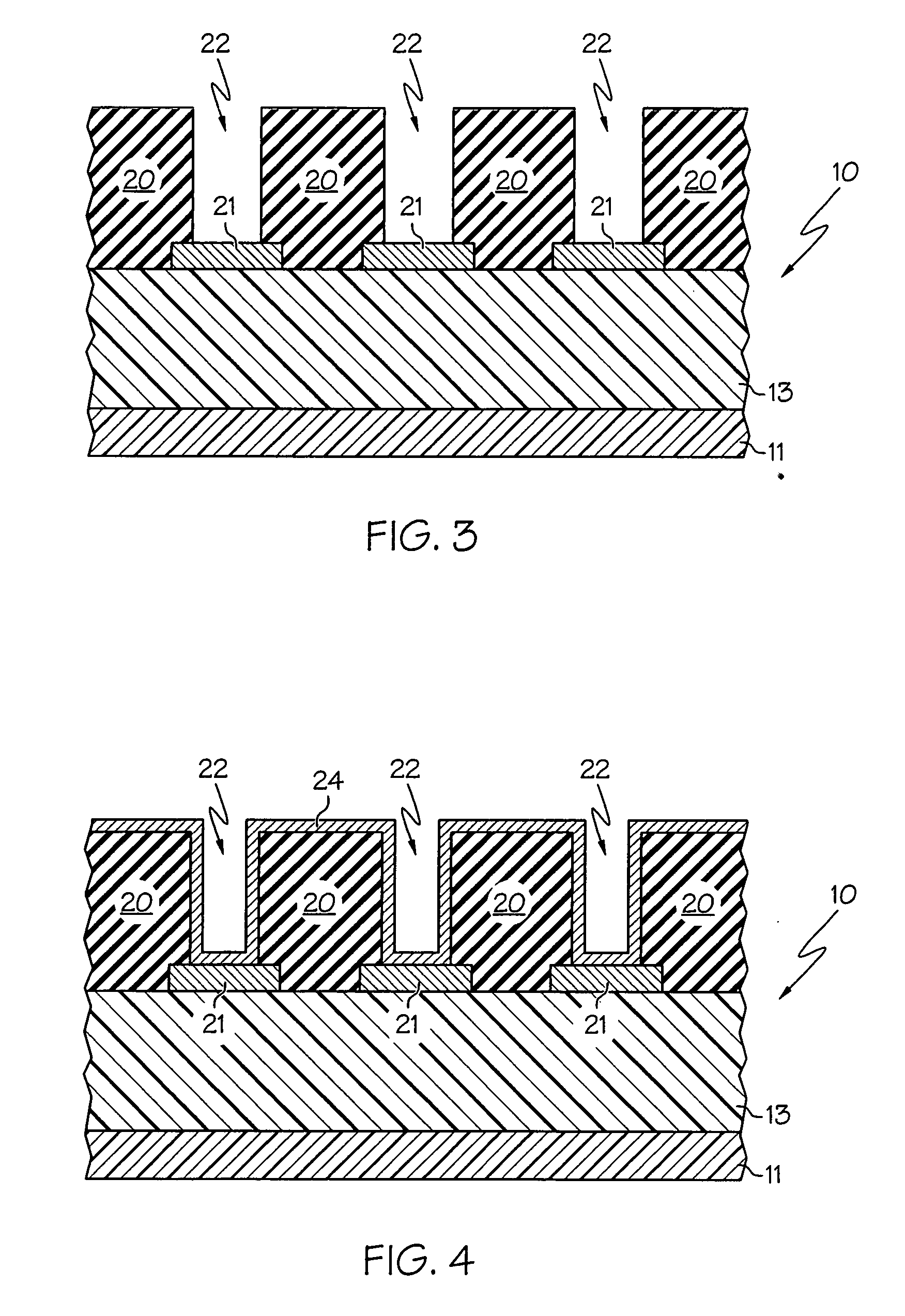

High density chalcogenide memory cells

ActiveUS20040248339A1Tight and repeatable controlImprove electrical isolationSolid-state devicesSemiconductor/solid-state device manufacturingHigh densityAlloy

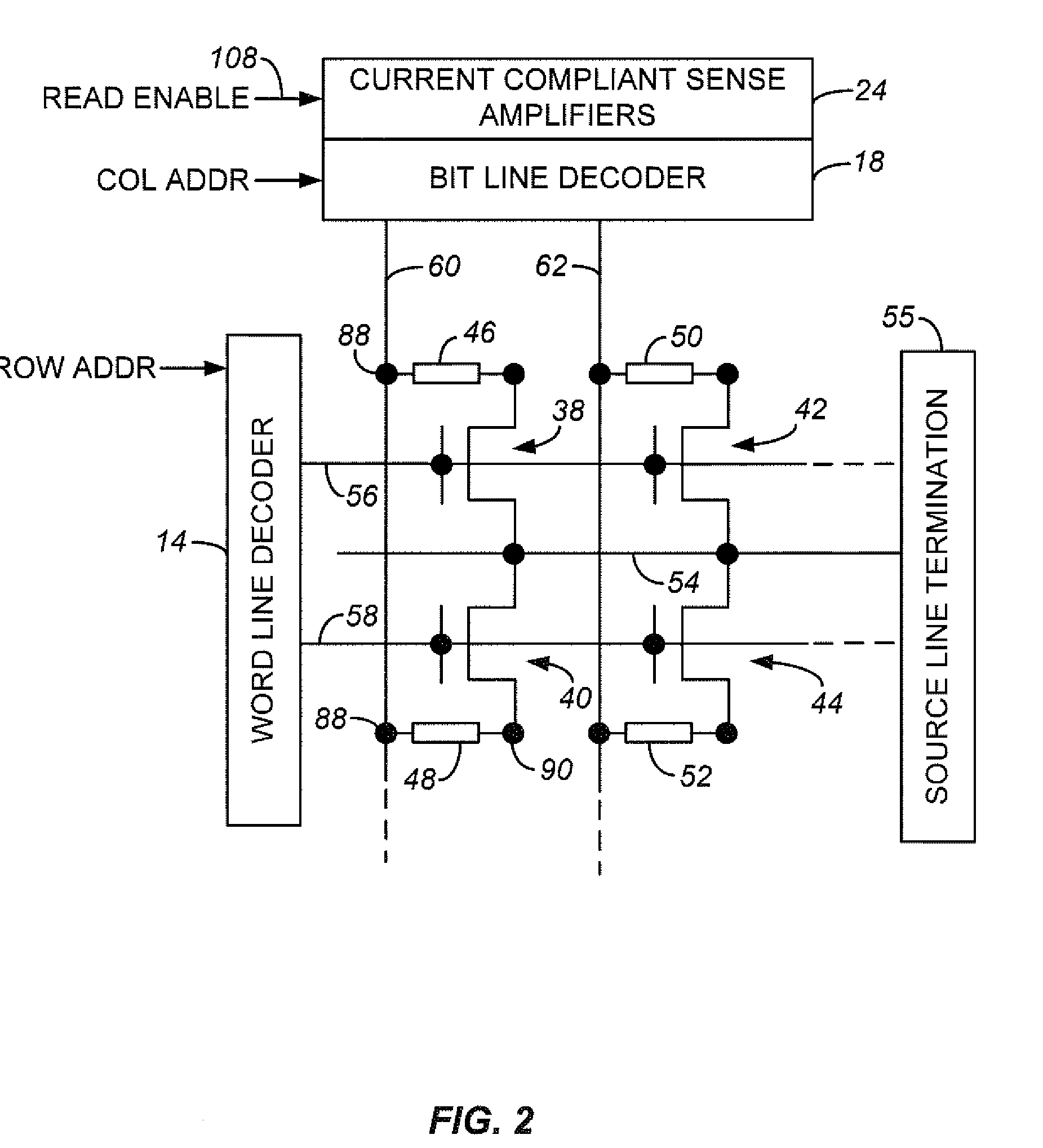

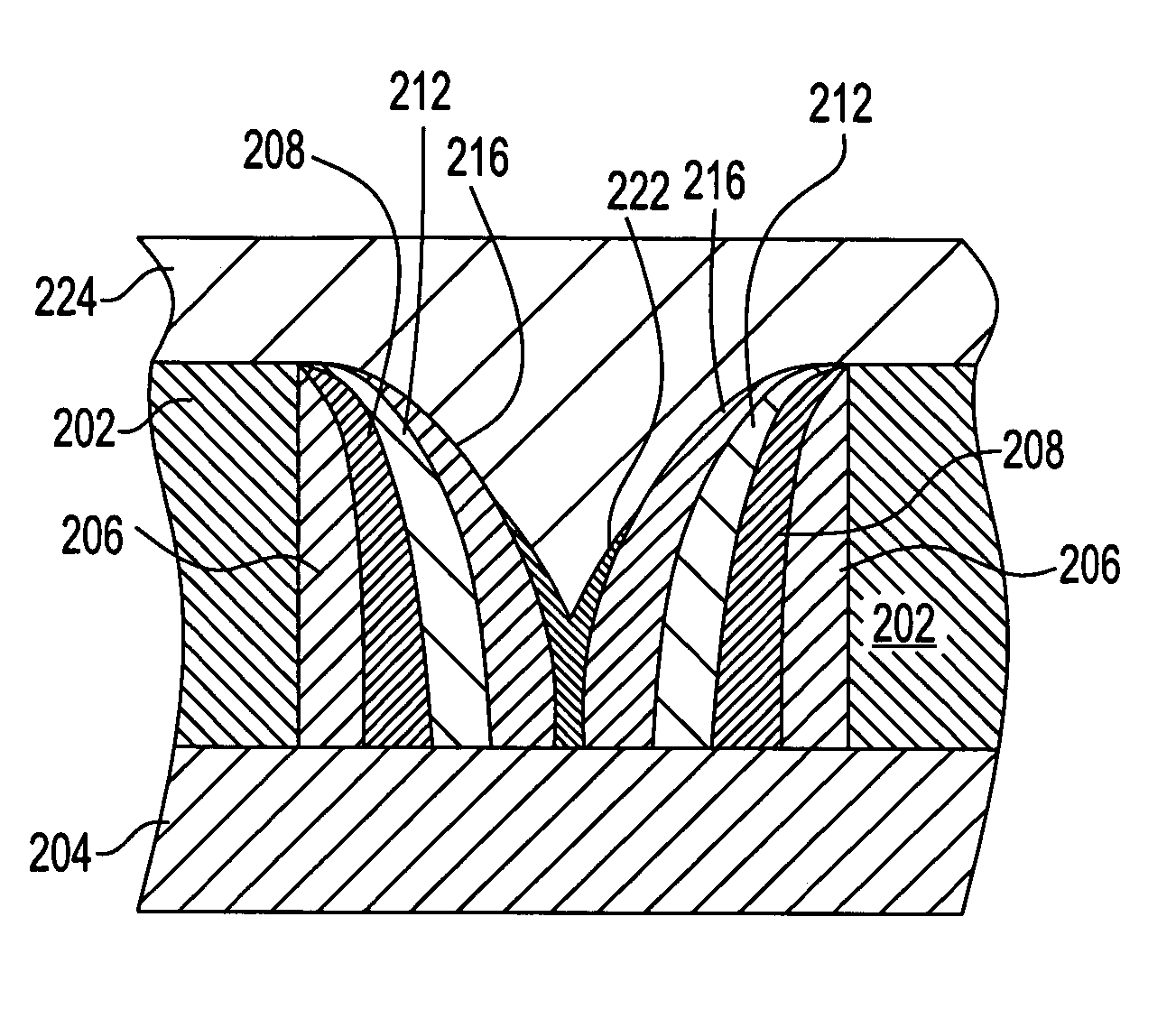

A non-volatile memory cell is constructed from a chalcogenide alloy structure and an associated electrode side wall. The electrode is manufactured with a predetermined thickness and juxtaposed against a side wall of the chalcogenide alloy structure, wherein at least one of the side walls is substantially perpendicular to a planar surface of the substrate. The thickness of the electrode is used to control the size of the active region created within the chalcogenide alloy structure. Additional memory cells can be created along rows and columns to form a memory matrix. The individual memory cells are accessed through address lines and address circuitry created during the formation of the memory cells. A computer can thus read and write data to particular non-volatile memory cells within the memory matrix.

Owner:MACRONIX INT CO LTD

High density chalcogenide memory cells

InactiveUS7067865B2Tight and repeatable controlImprove electrical isolationTransistorSolid-state devicesHigh densityAlloy

A non-volatile memory cell is constructed from a chalcogenide alloy structure and an associated electrode side wall. The electrode is manufactured with a predetermined thickness and juxtaposed against a side wall of the chalcogenide alloy structure, wherein at least one of the side walls is substantially perpendicular to a planar surface of the substrate. The thickness of the electrode is used to control the size of the active region created within the chalcogenide alloy structure. Additional memory cells can be created along rows and columns to form a memory matrix. The individual memory cells are accessed through address lines and address circuitry created during the formation of the memory cells. A computer can thus read and write data to particular non-volatile memory cells within the memory matrix.

Owner:MACRONIX INT CO LTD

Non-volatile memory cell comprising a dielectric layer and a phase change material in series

The invention provides for a nonvolatile memory cell comprising a dielectric material in series with a phase change material, such as a chalcogenide. Phase change is achieved in chalcogenide memories by thermal means. Concentrating thermal energy in a relatively small volume assists this phase change. By applying high voltage across a dielectric layer, dielectric breakdown occurs, forming a low-resistance rupture region traversing the dielectric layer. This rupture region can serve to concentrate thermal energy in a phase-change memory cell. In a preferred embodiment, such a cell can be used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

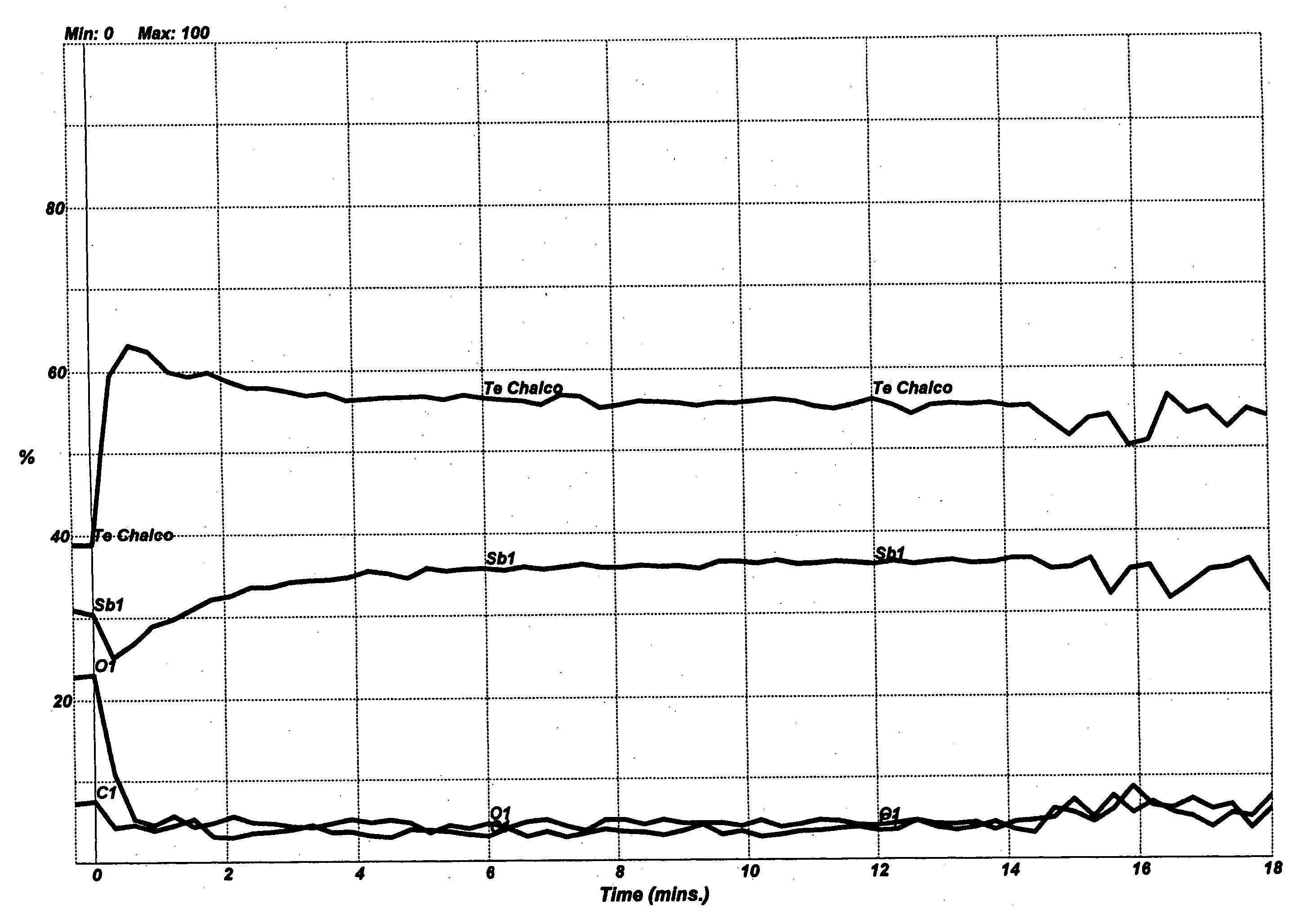

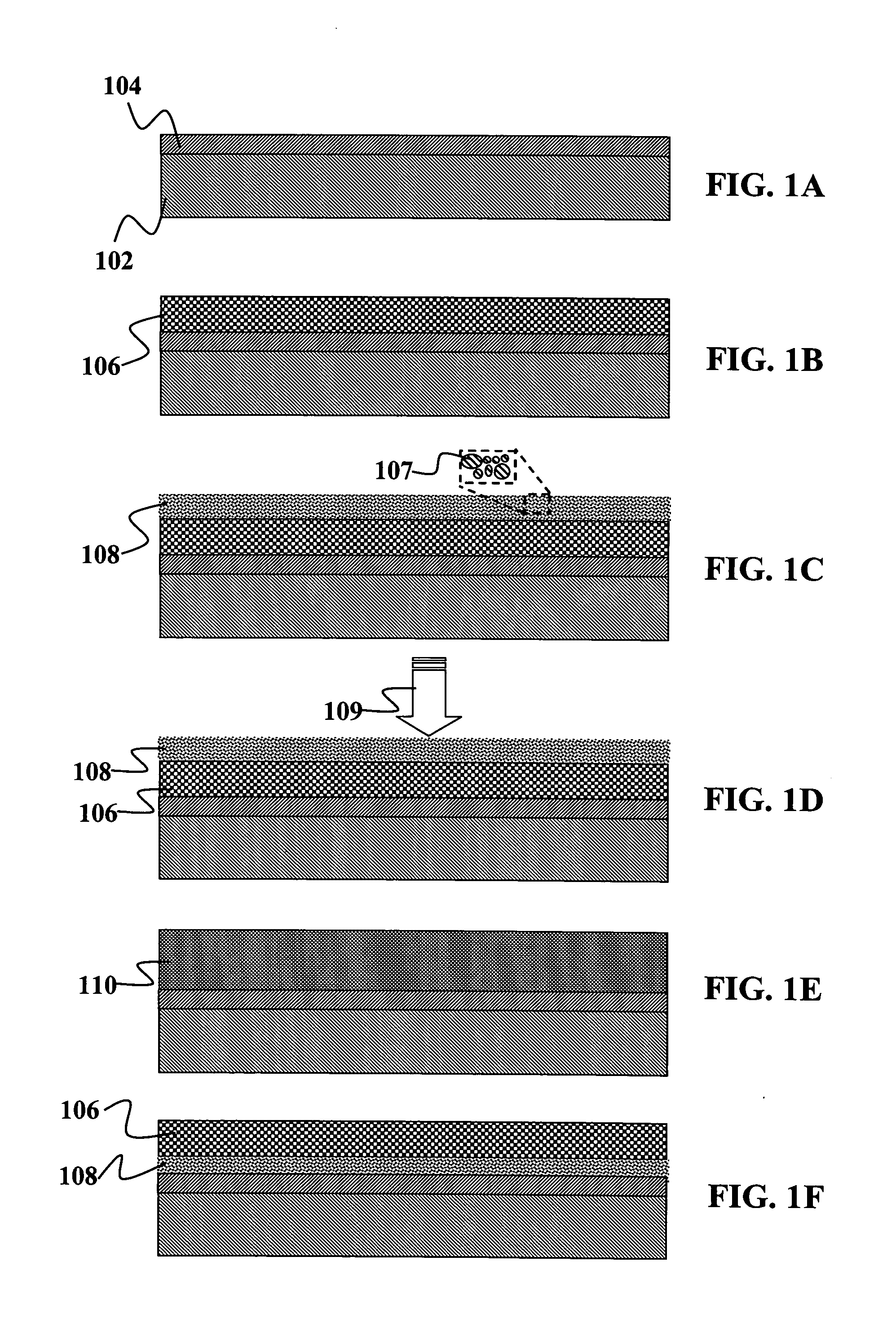

Chemical vapor deposition of chalcogenide materials

A chemical vapor deposition (CVD) process for preparing electrical and optical chalcogenide materials. In a preferred embodiment, the instant CVD-deposited materials exhibit one or more of the following properties: electrical switching, accumulation, setting, reversible multistate behavior, resetting, cognitive functionality, and reversible amorphous-crystalline transformations. In one embodiment, a multilayer structure, including at least one layer containing a chalcogen element, is deposited by CVD and subjected to post-deposition application of energy to produce a chalcogenide material having properties in accordance with the instant invention. In another embodiment, a single layer chalcogenide material having properties in accordance with the instant invention is formed from a CVD deposition process including three or more deposition precursors, at least one of which is a chalcogen element precursor. Preferred materials are those that include the chalcogen Te along with Ge and / or Sb.

Owner:OVONYX

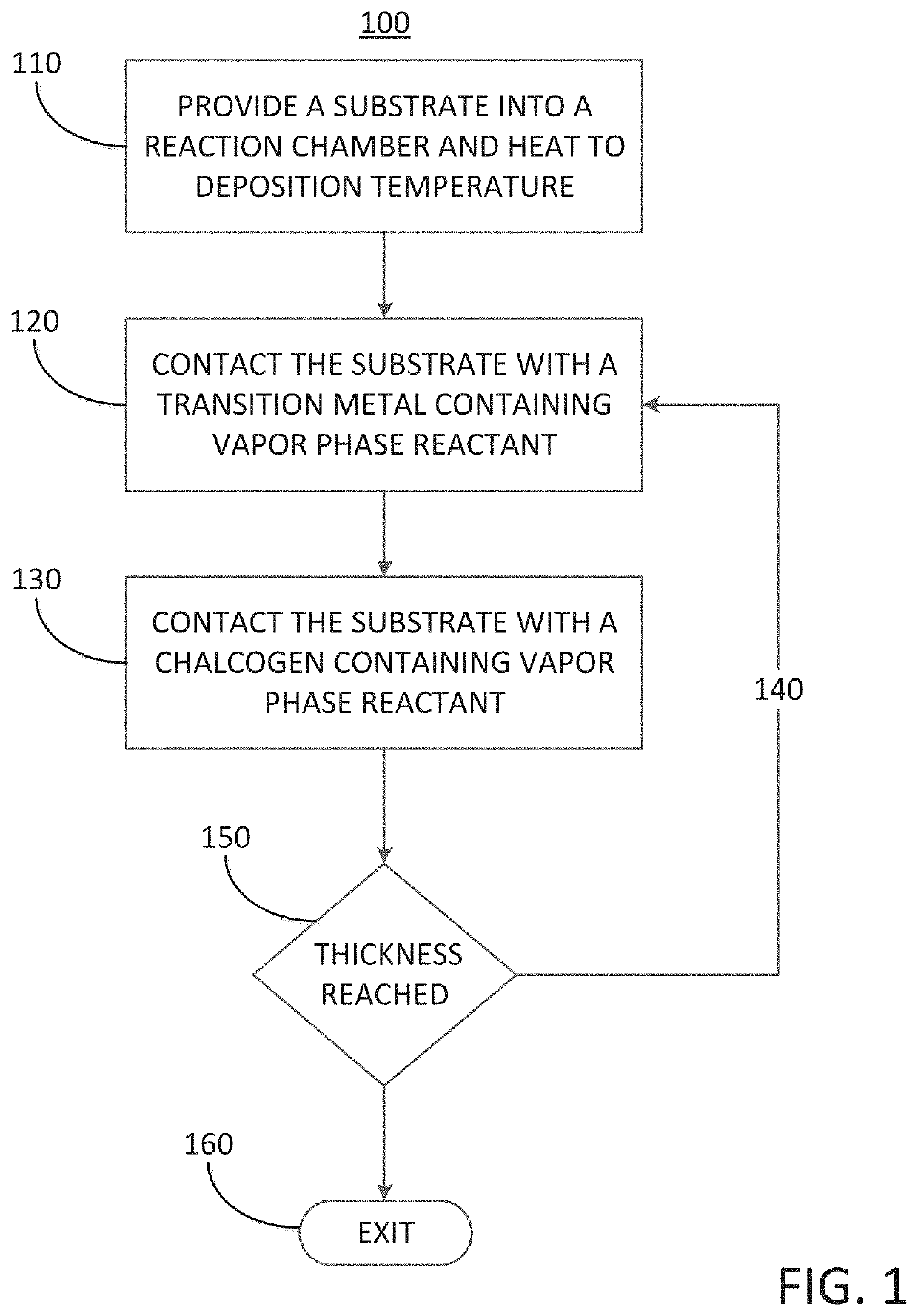

Methods for depositing a transition metal chalcogenide film on a substrate by a cyclical deposition process

ActiveUS20200161129A1TransistorSemiconductor/solid-state device manufacturingDevice materialPhysical chemistry

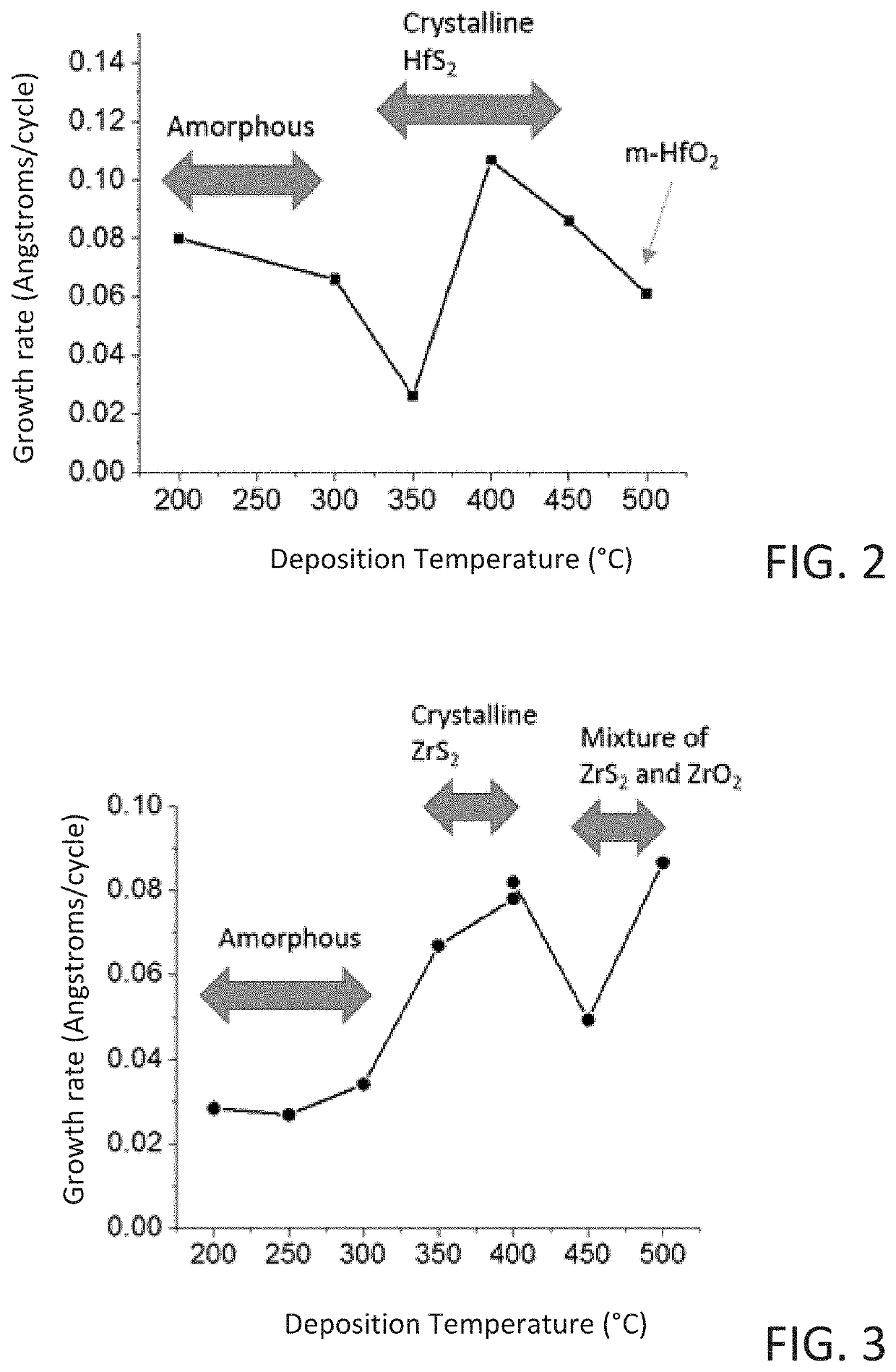

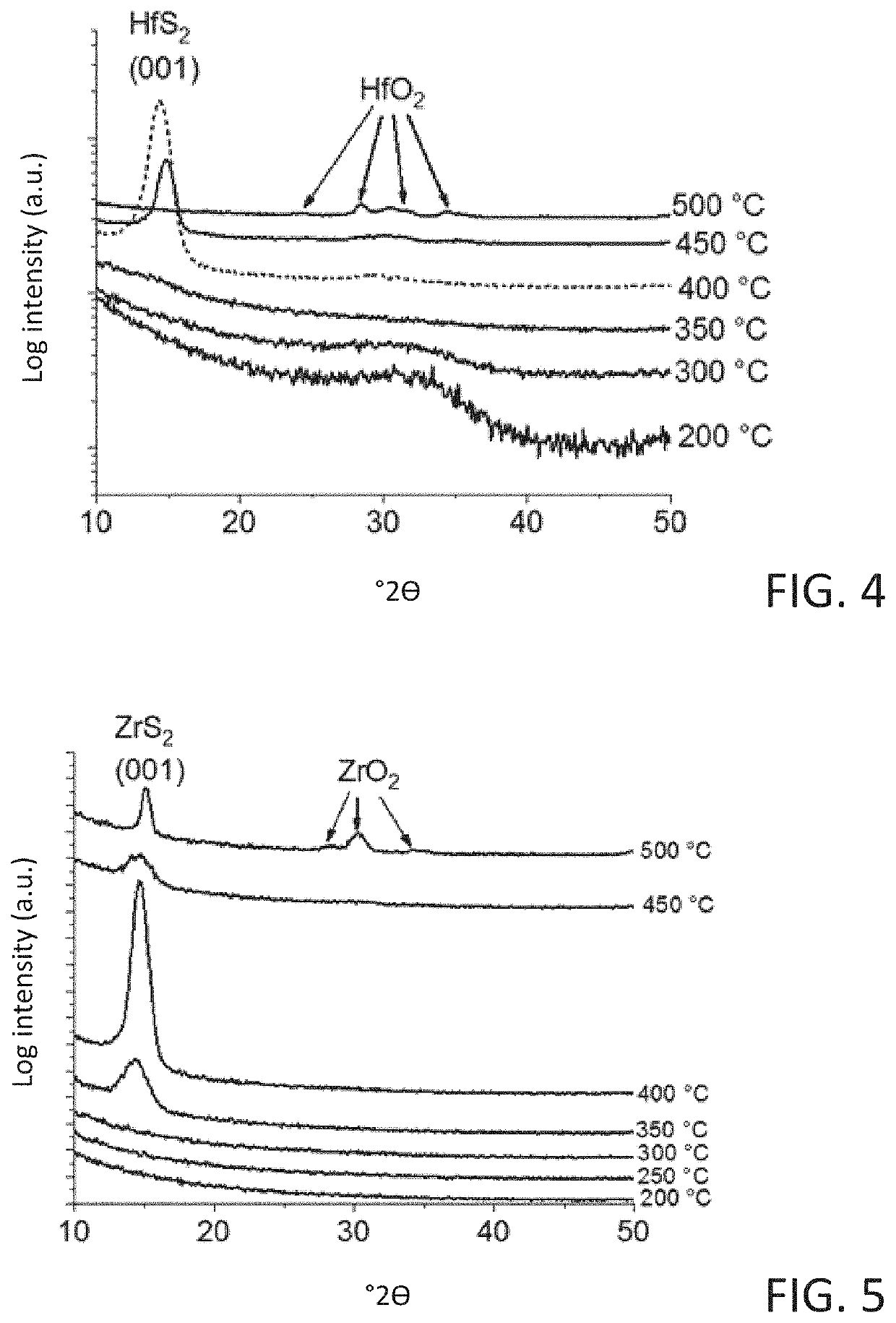

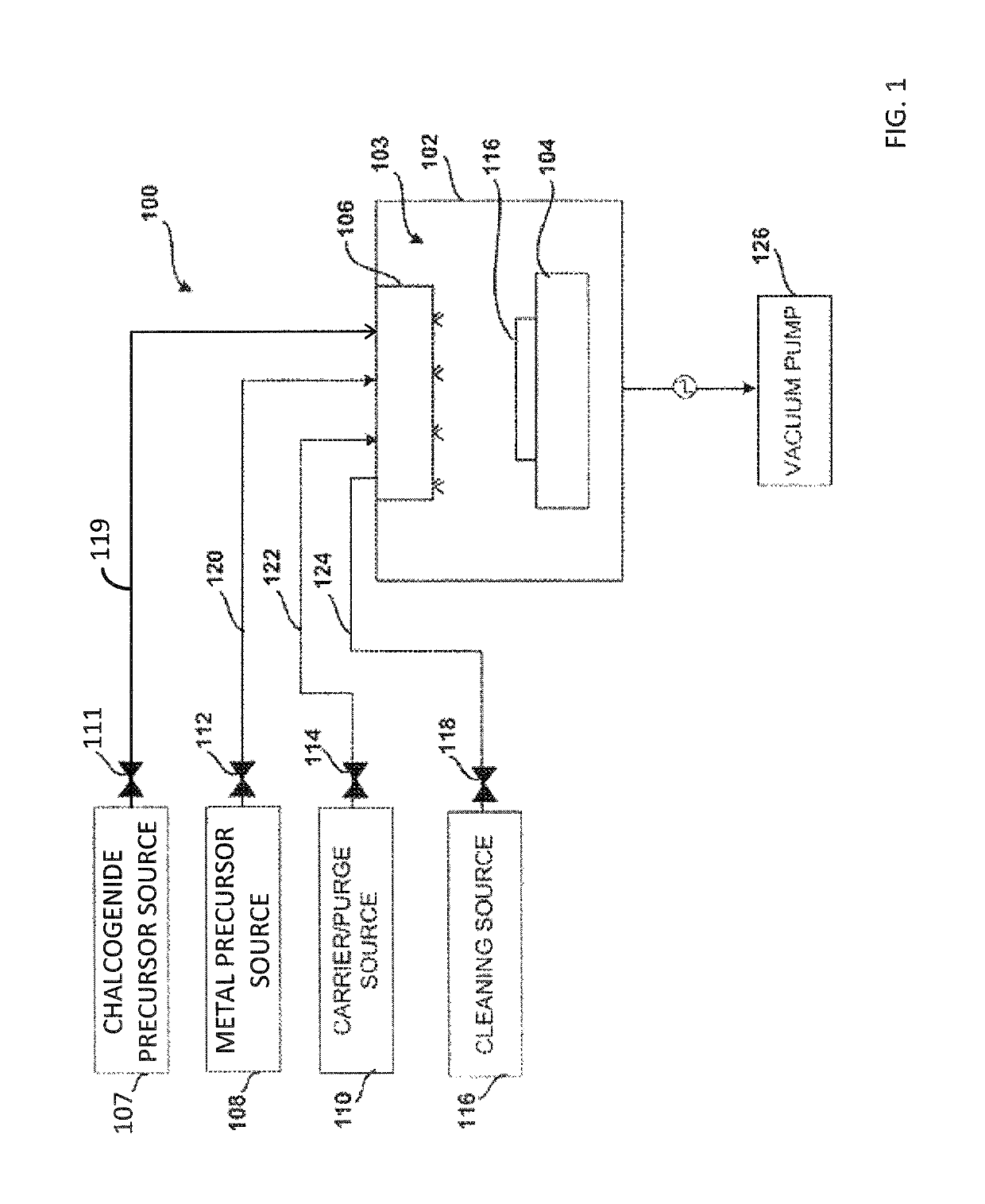

Methods for depositing a transition metal chalcogenide film on a substrate by cyclical deposition process are disclosed. The methods may include, contacting the substrate with at least one transition metal containing vapor phase reactant comprising at least one of a hafnium precursor, or a zirconium precursor, and contacting the substrate with at least one chalcogen containing vapor phase reactant. Semiconductor device structures including a transition metal chalcogenide film deposited by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

Method for passivating a surface of a semiconductor and related systems

A system and a method for passivating a surface of a semiconductor. The method includes providing the surface of the semiconductor to a reaction chamber of a reactor, exposing the surface of the semiconductor to a gas-phase metal containing precursor in the reaction chamber and exposing the surface of the semiconductor to a gas-phase chalcogenide containing precursor. The methods also include passivating the surface of the semiconductor using the gas-phase metal containing precursor and the gas-phase chalcogenide containing precursor to form a passivated surface. The system for passivating a surface of a semiconductor may include a reactor, a metal containing precursor source fluidly coupled to the reactor, and a chalcogenide containing precursor source fluidly couple to the reactor, wherein the metal containing precursor source provides a gas-phase metal containing precursor to a reaction chamber of the reactor, and wherein the chalcogenide containing precursor source provides a gas-phase chalcogenide containing precursor to a reaction chamber of the reactor.

Owner:ASM IP HLDG BV

Chalcogenide phase-change non-volatile memory, memory device and method for fabricating the same

InactiveUS20050062087A1High speedIncrease the rate of crystallizationSolid-state devicesRead-only memoriesPhase-change memoryAlloy

A memory device adapted to a chalcogenide phase-change memory is disclosed. The memory device comprises a top electrode, a bottom electrode, and a phase-change thin film between the top electrode and the bottom electrode. The phase-change thin film is a chalcogenide (Ge-Sb-Te) alloy doped with Tin (Sn) therein. Tin (Sn) doped in the chalcogenide (Ge-Sb-Te) alloy can enhance the crystallization rate of the phase-change thin film for improving the operation speed of the memory.

Owner:MACRONIX INT CO LTD

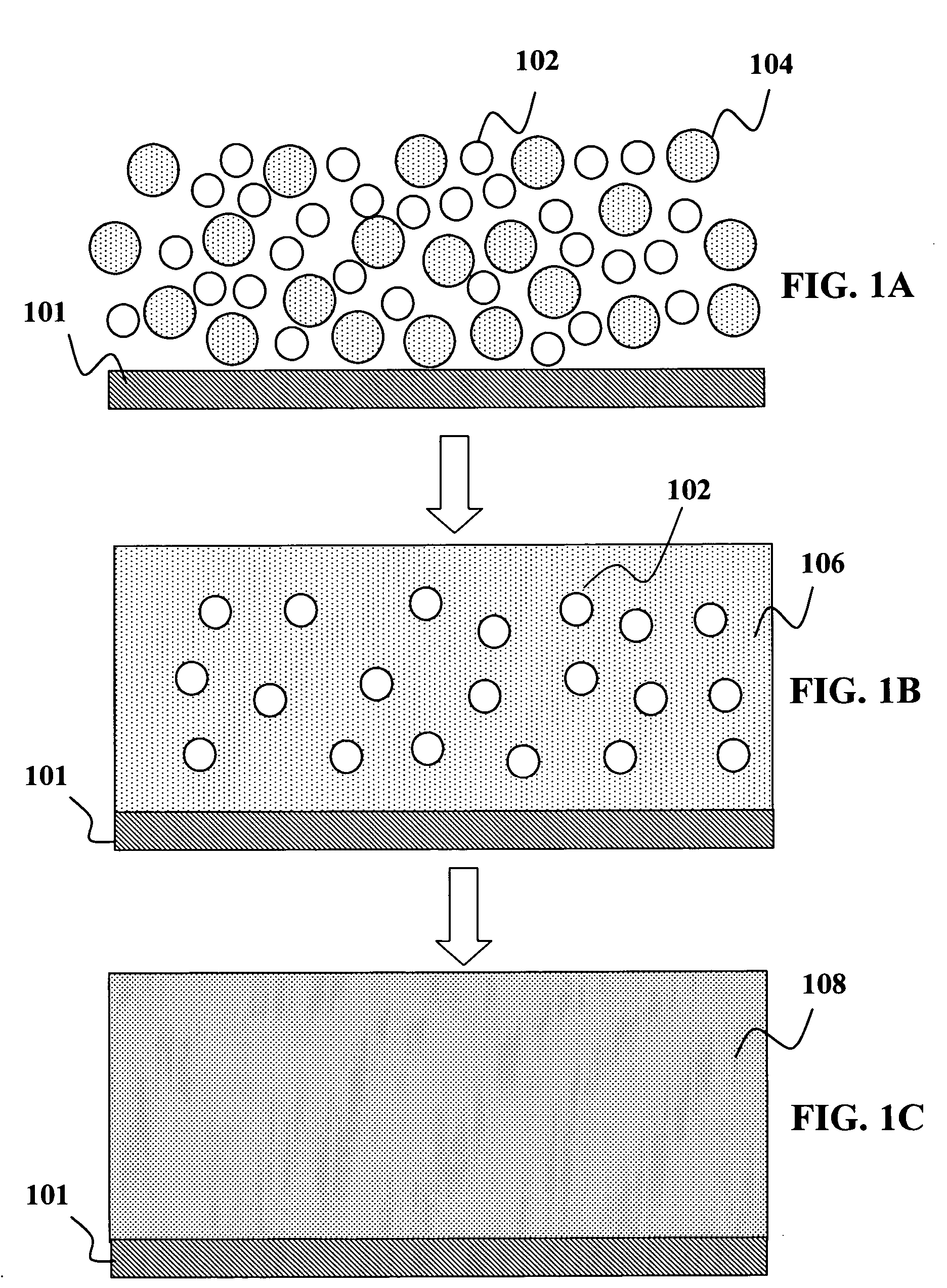

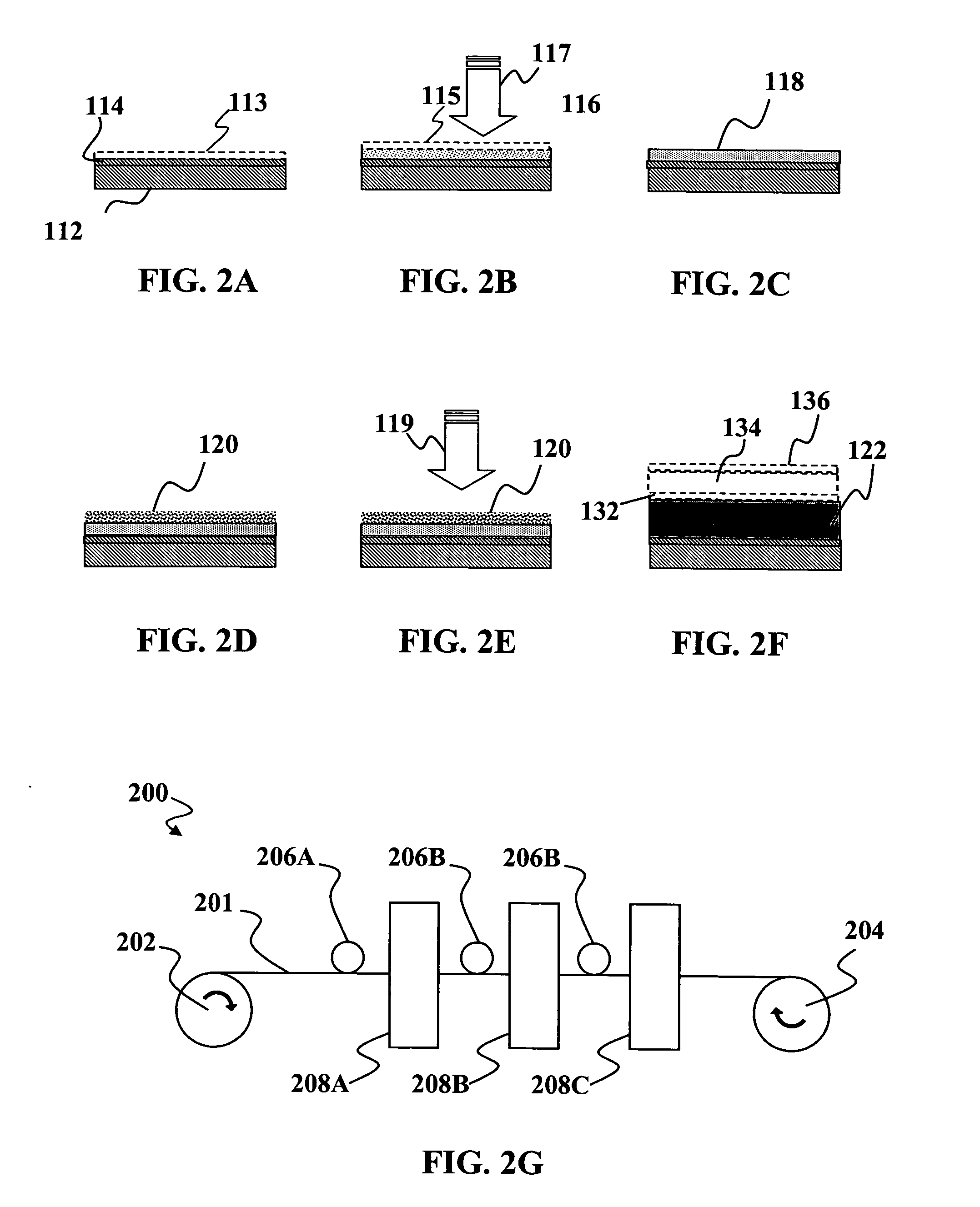

High-throughput printing of semiconductor precursor layer by use of chalcogen-containing vapor

InactiveUS20070169810A1Well mixedReduce lossesLiquid/solution decomposition chemical coatingPhotovoltaic energy generationSulfurChalcogen

A high-throughput method of forming a semiconductor precursor layer by use of a chalcogen-containing vapor is disclosed. In one embodiment, the method comprises forming a precursor material comprising group IB and / or group IIIA particles of any shape. The method may include forming a precursor layer of the precursor material over a surface of a substrate. The method may further include heating the particle precursor material in a substantially oxygen-free chalcogen atmosphere to a processing temperature sufficient to react the particles and to release chalcogen from the chalcogenide particles, wherein the chalcogen assumes a liquid form and acts as a flux to improve intermixing of elements to form a group IB-IIIA-chalcogenide film at a desired stoichiometric ratio. The chalcogen atmosphere may provide a partial pressure greater than or equal to the vapor pressure of liquid chalcogen in the precursor layer at the processing temperature.

Owner:NANOSOLAR

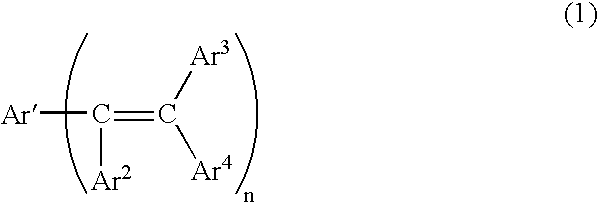

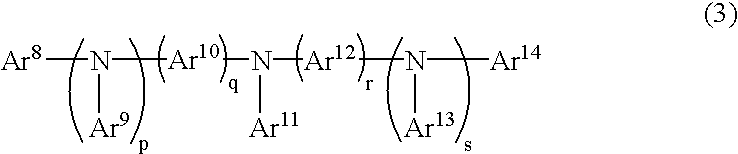

Organic electroluminescent device and method of manufacture thereof

InactiveUS6416888B1Increased durabilityReduce the driving voltageDischarge tube luminescnet screensElectroluminescent light sourcesInorganic compoundThin layer

An organic EL device having a low driving voltage and exhibiting high luminous brightness and superior durability, and a method of manufacturing the same. The organic EL device has an anode layer, an organic light-emitting layer, and a cathode layer. An inorganic thin layer, comprising an inorganic compound of Ge, Sn, Zn, Cd, etc. and an inorganic compound of an element of Group 5A to Group 8 in the periodic table in combination, is provided between the anode layer and the organic light-emitting layer and between the cathode layer and the organic light-emitting layer, or the anode layer or the cathode layer comprises a chalcogenide of Si, Ge, Sn, Pb, Ga, In, Zn, Cd, Mg, etc. and an inorganic compound of an element of Group 5A to Group 8 in the periodic table in combination.

Owner:IDEMITSU KOSAN CO LTD

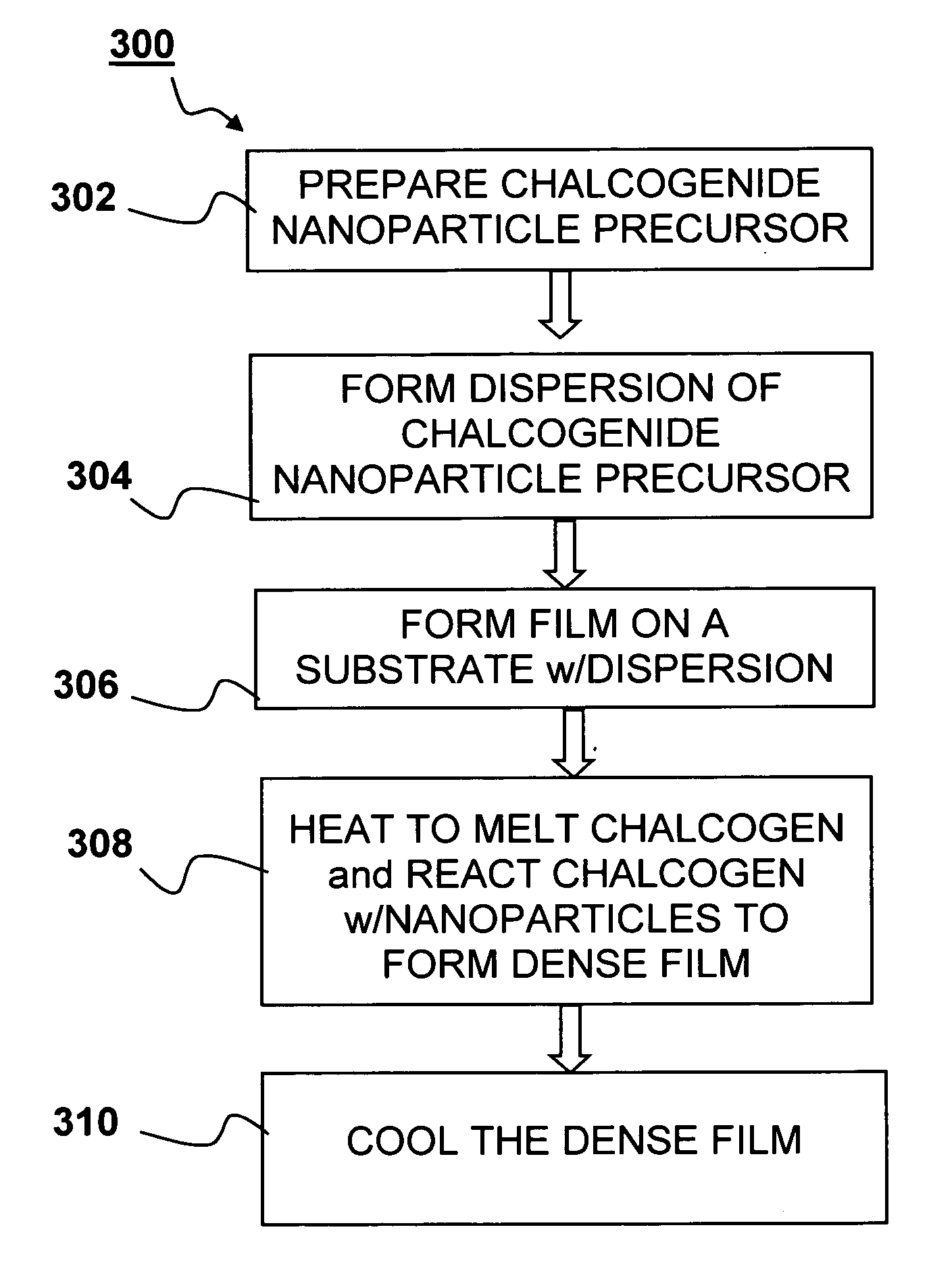

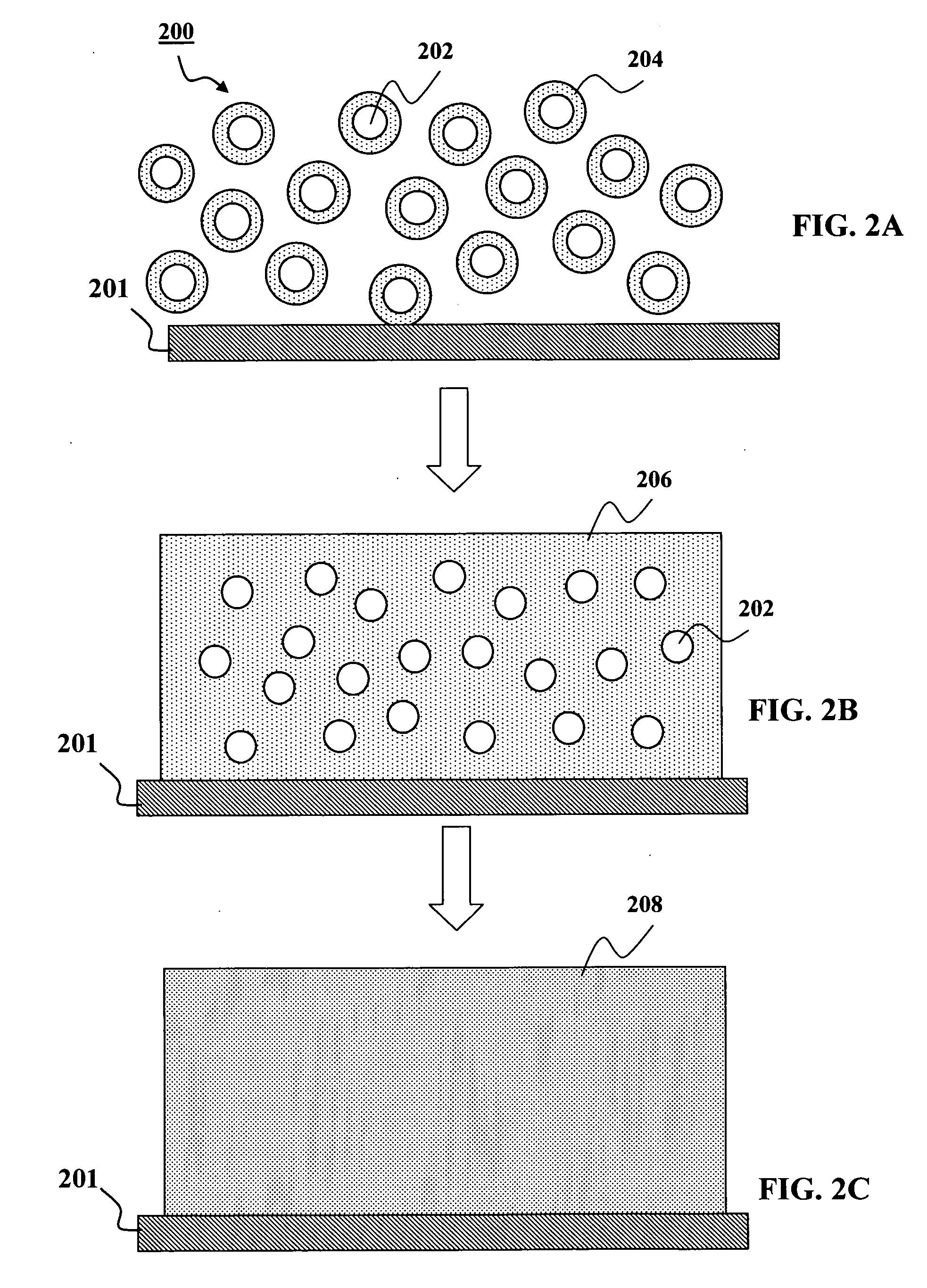

High-throughput printing of chalcogen layer and the use of an inter-metallic material

InactiveUS20070163643A1Reduce the temperaturePretreated surfacesLiquid/solution decomposition chemical coatingNanoparticleSulfur

Methods and devices for high-throughput printing of a precursor material for forming a film of a group IB-IIIA-chalcogenide compound are disclosed. In one embodiment, the method comprises forming a precursor layer on a substrate, wherein the precursor layer comprises one or more discrete layers. The layers may include at least a first layer containing one or more group IB elements and two or more different group IIIA elements and at least a second layer containing elemental chalcogen particles. The precursor layer may be heated to a temperature sufficient to melt the chalcogen particles and to react the chalcogen particles with the one or more group IB elements and group IIIA elements in the precursor layer to form a film of a group IB-IIIA-chalcogenide compound. At least one set of the particles in the precursor layer are inter-metallic particles containing at least one group IB-IIIA inter-metallic alloy phase. The method may also include making a film of group IB-IIIA-chalcogenide compound that includes mixing the nanoparticles and / or nanoglobules and / or nanodroplets to form an ink, depositing the ink on a substrate, heating to melt the extra chalcogen and to react the chalcogen with the group IB and group IIIA elements and / or chalcogenides to form a dense film.

Owner:NANOSOLAR

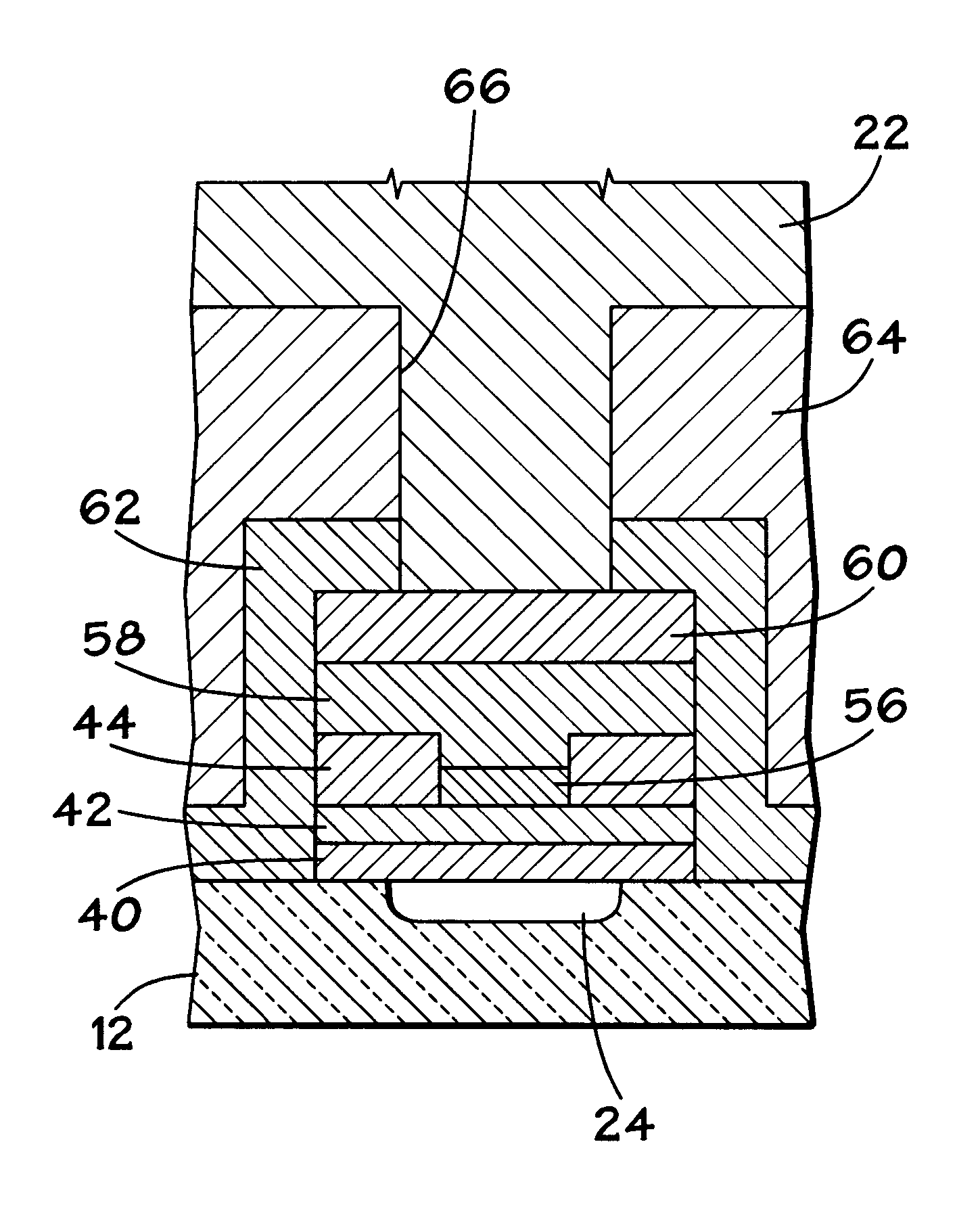

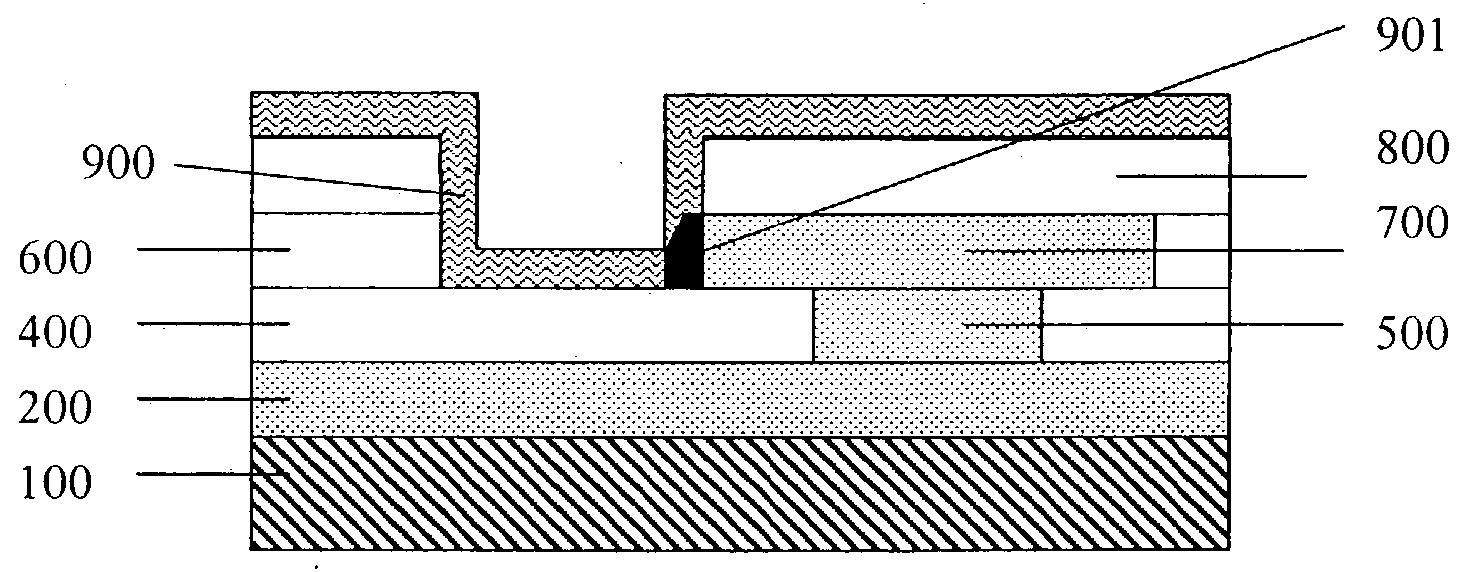

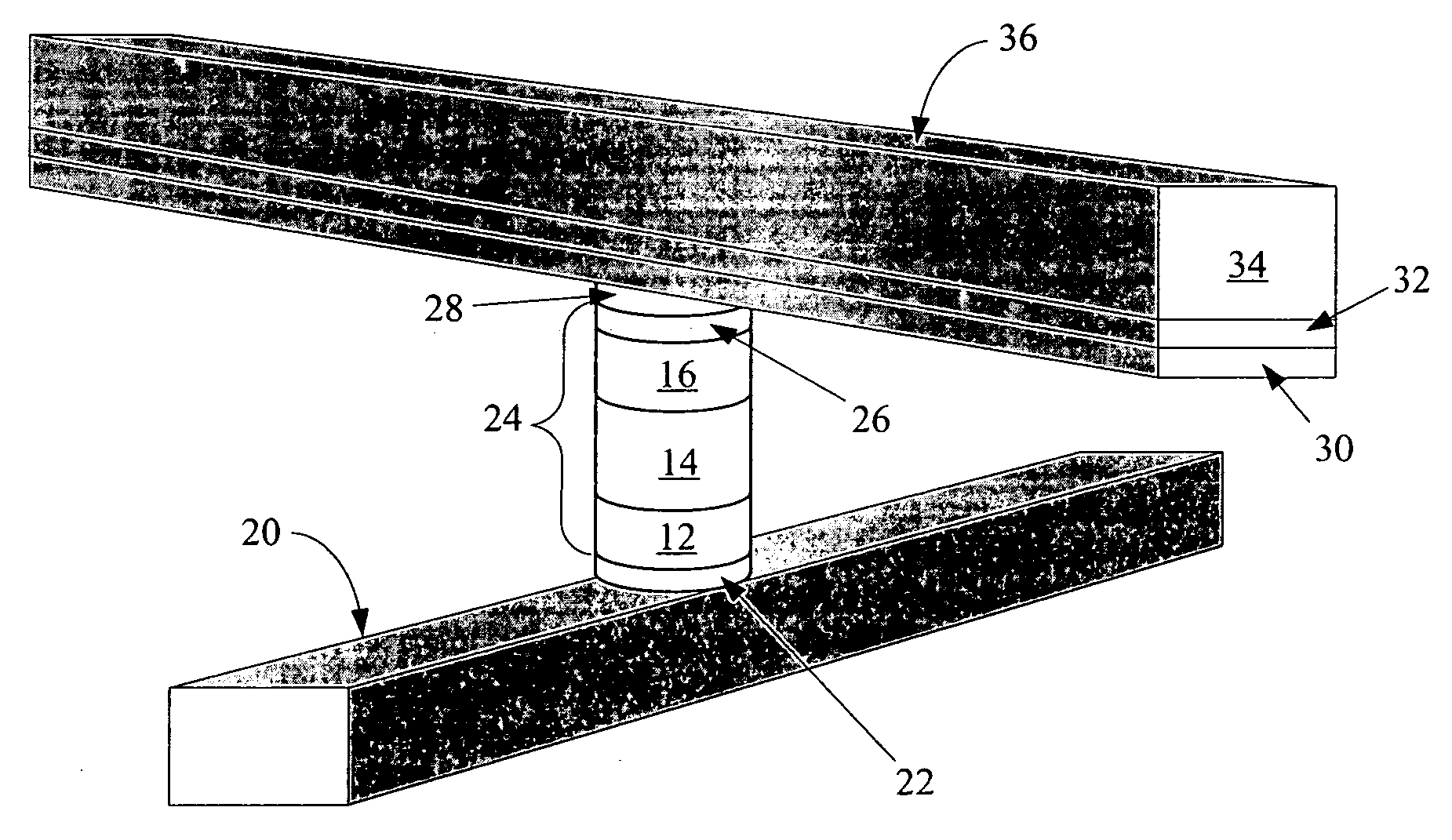

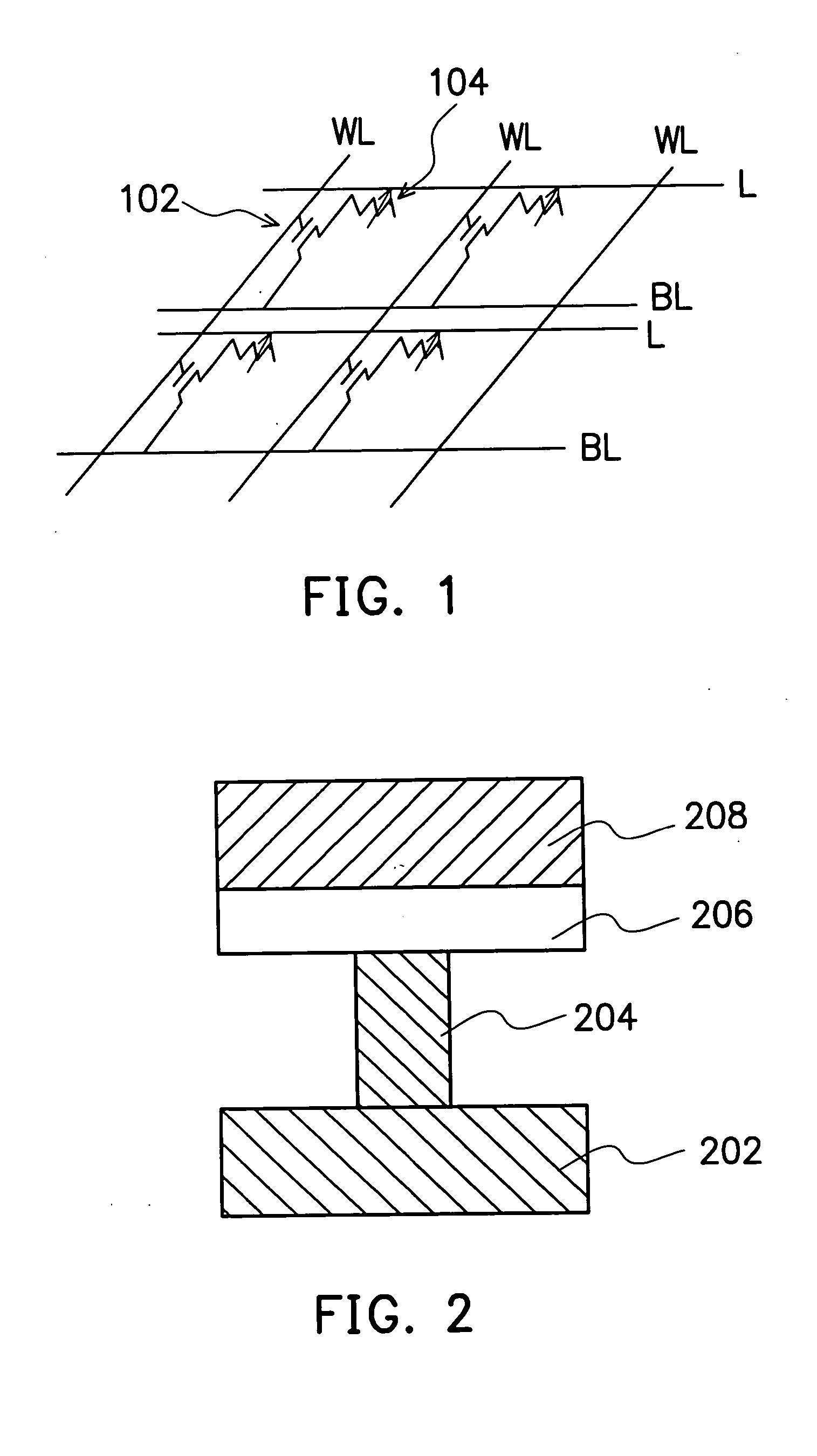

Chalcogenide memory device with multiple bits per cell

InactiveUS6838692B1Reduce energy inputSave energySolid-state devicesDigital storagePhase-change materialSemiconductor

A memory device with multiple bits per-cell. The memory device includes a side electrode; a doped semiconductor region disposed laterally in contact with a sidewall of the side electrode, such that the doped semiconductor region forms a diode, or the junction between the side electrode and the doped semiconductor region forms a diode; a layer of phase-changing material disposed laterally in contact with a sidewall of the doped semiconductor region, such that the doped semiconductor region is disposed between the layer of phase-changing material and the side electrode; and an upper electrode disposed on the layer of phase-changing material. Many storage regions can be stacked vertically, and multiple bits can be stored in one cell. Also, the contact area is reduced to a minimum dimension below the photolithographic limit.

Owner:MACRONIX INT CO LTD

Phase Change Memory Cell with Thermal Barrier and Method for Fabricating the Same

InactiveUS20080137400A1Semiconductor/solid-state device manufacturingDigital storageElectrically conductiveChalcogenide

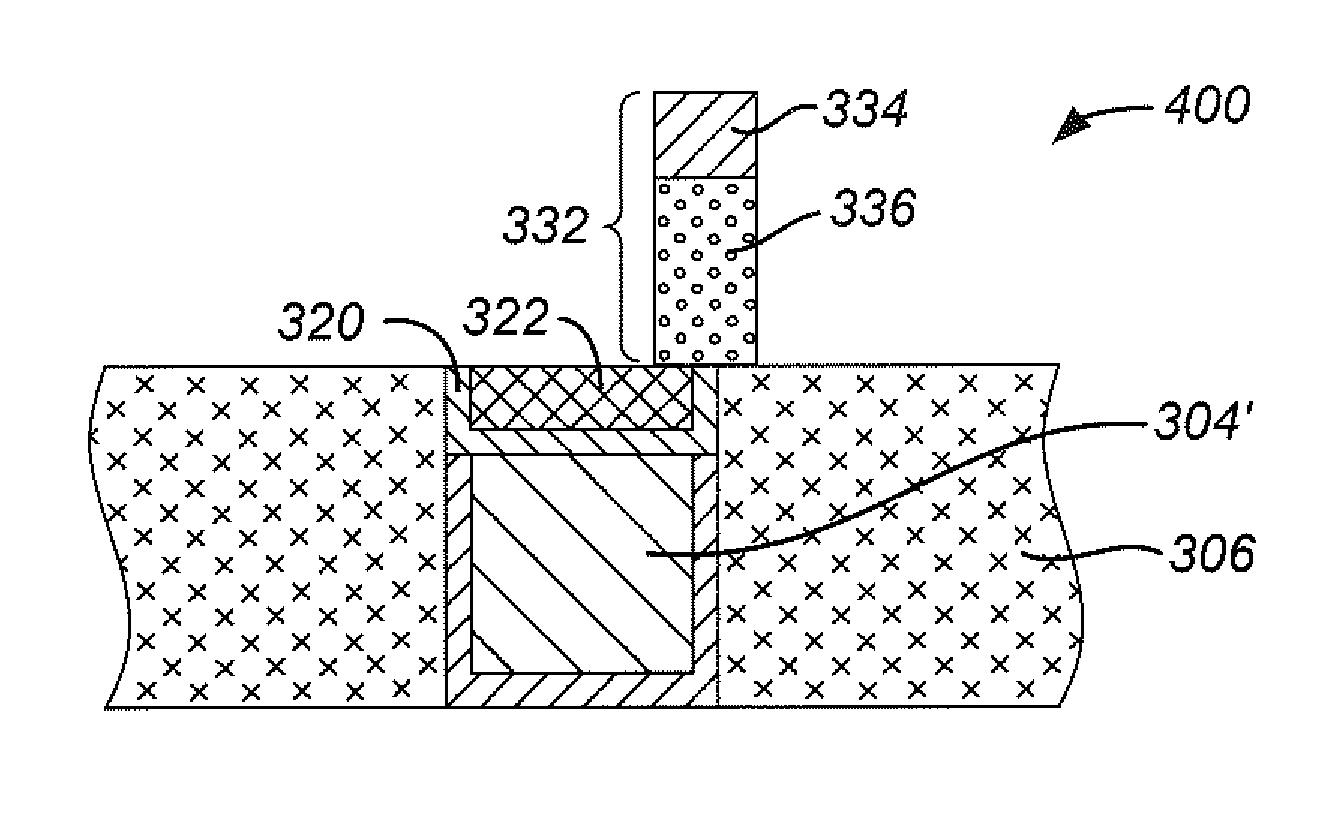

A memory cell has thermal isolation material between a bottom electrode and a plug contact to confine heat in a memory element during programming and reset operations. In a particular embodiment, the memory element is a chalcogenide, such as GST. An electrically conductive barrier layer deposited over the contact and on sidewalls of a recess formed over the contact electrically couples the bottom electrode to the contact.

Owner:MACRONIX INT CO LTD

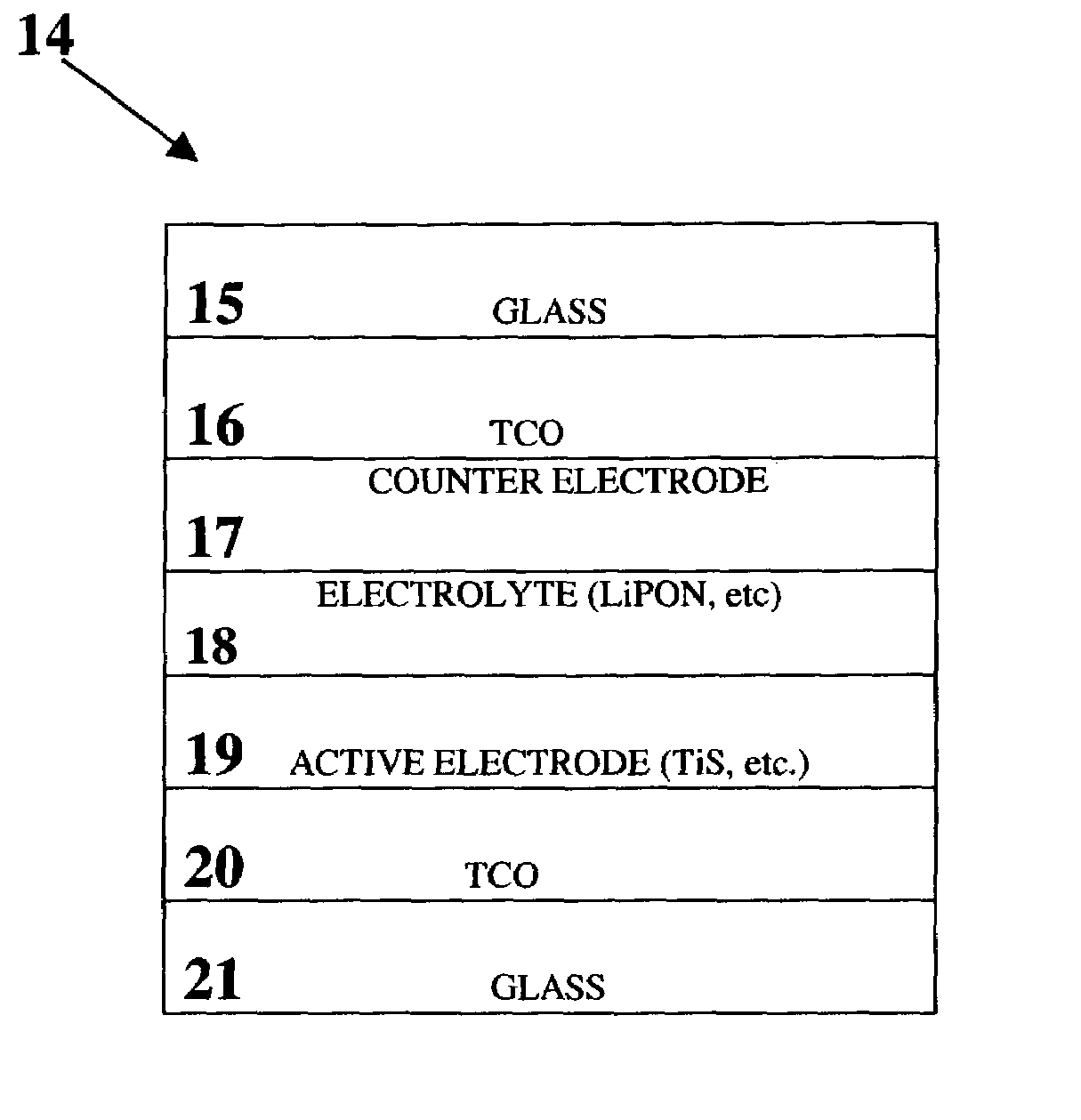

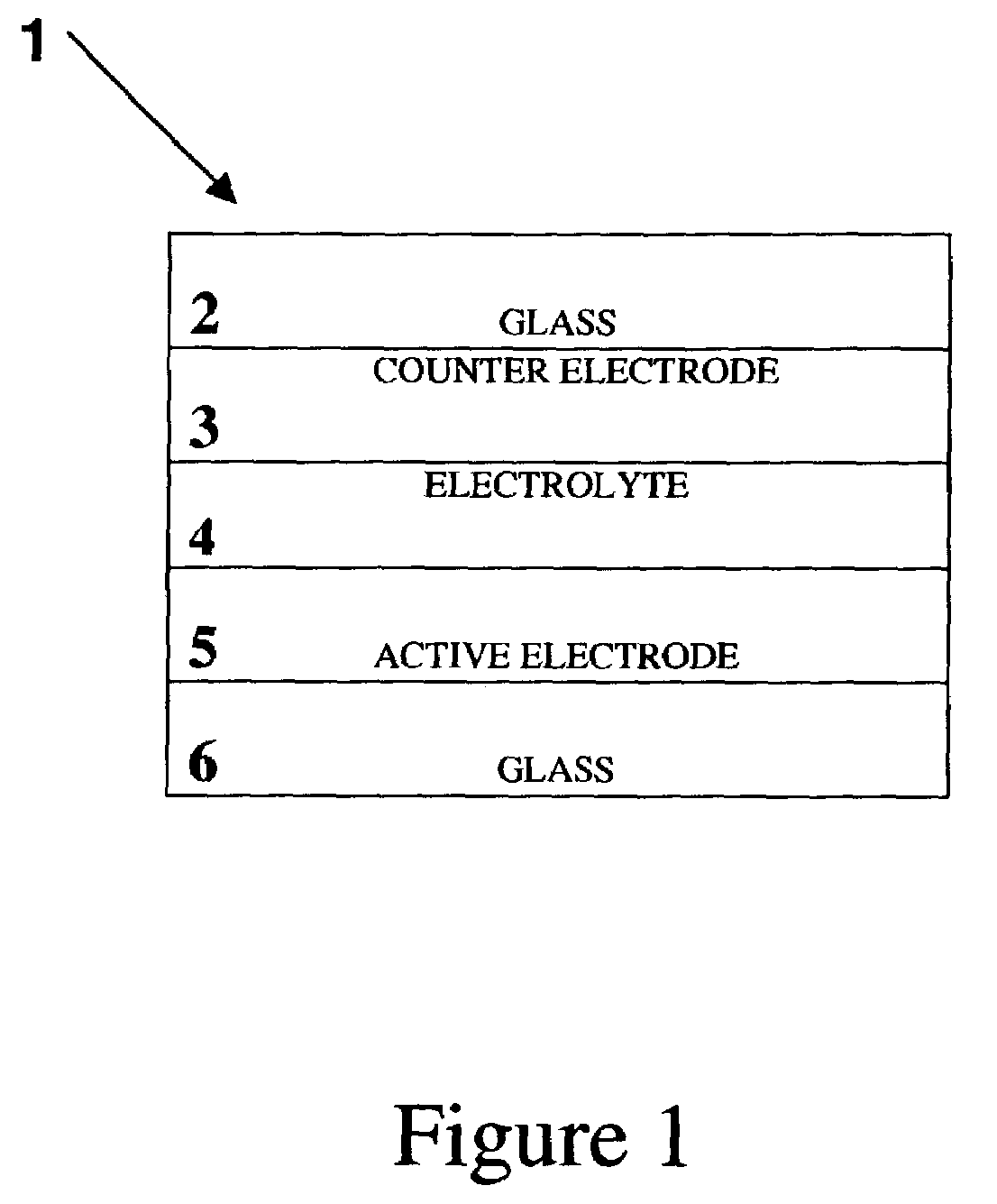

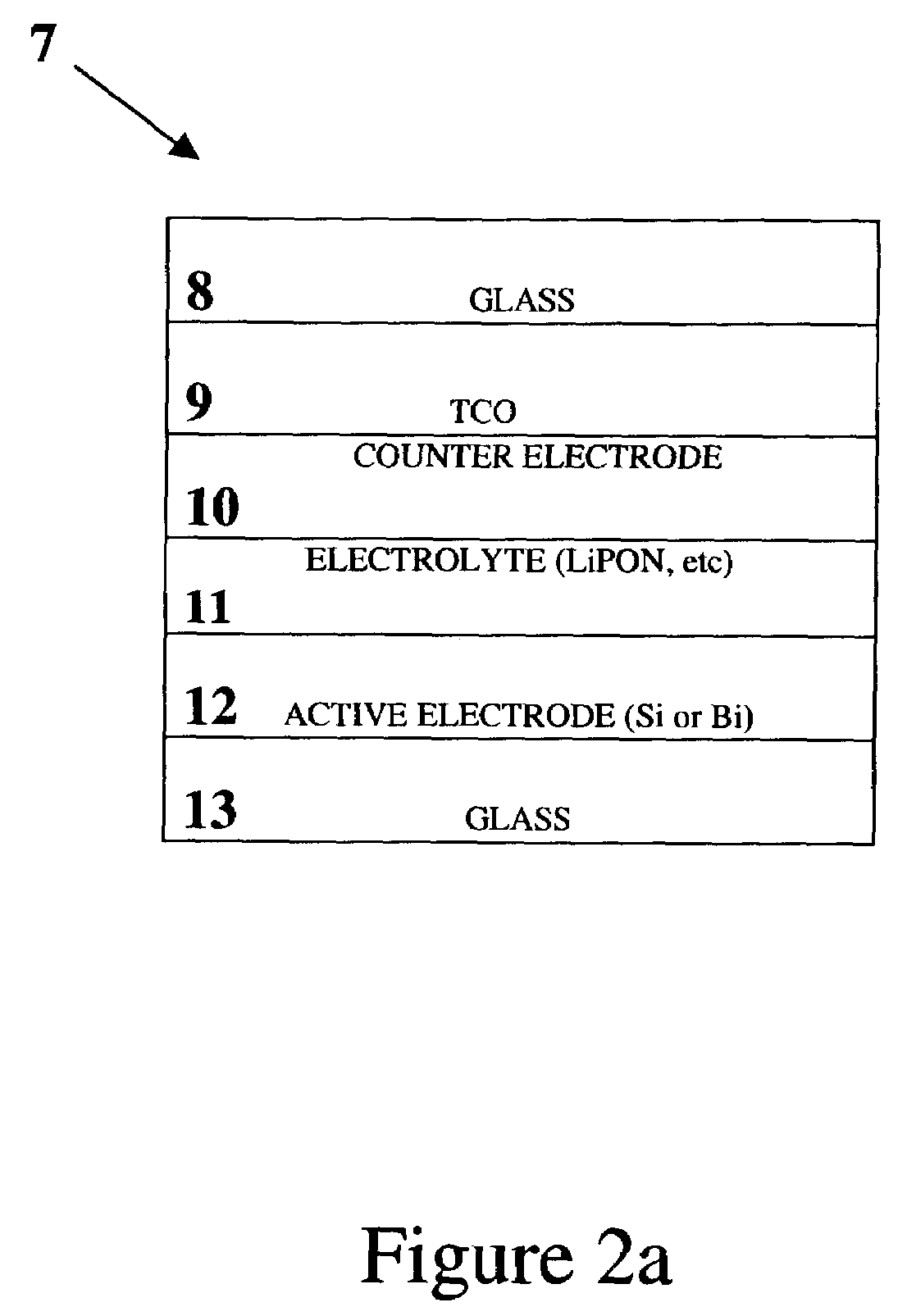

Electrochromic devices based on lithium insertion

Electrochromic devices having as an active electrode materials comprising Sb, Bi, Si, Ge, Sn, Te, N, P, As, Ga, In, Al, C, Pb, I and chalcogenides are disclosed. The addition of other metals, i.e. Ag and Cu to the active electrode further enhances performance.

Owner:RGT UNIV OF CALIFORNIA

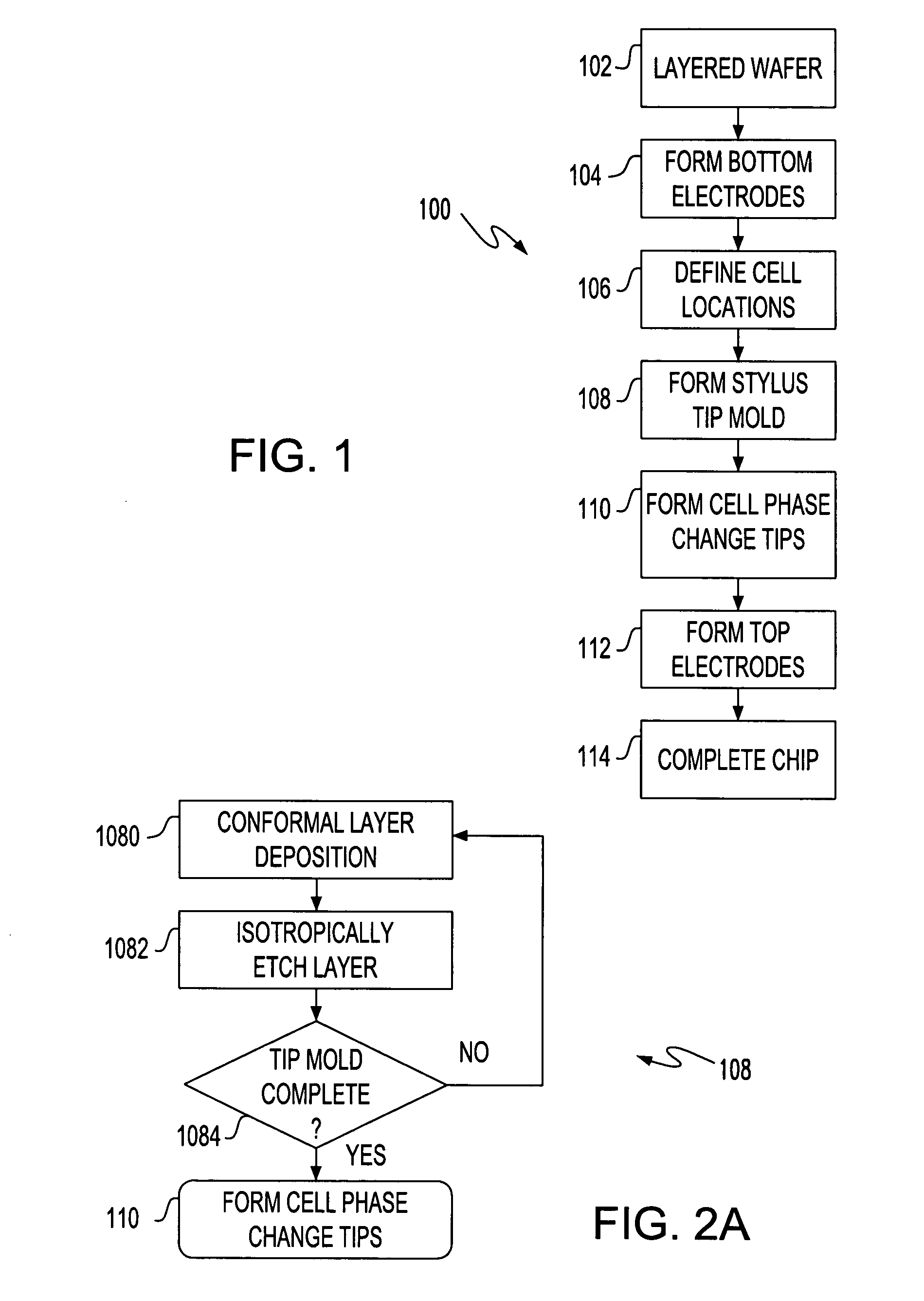

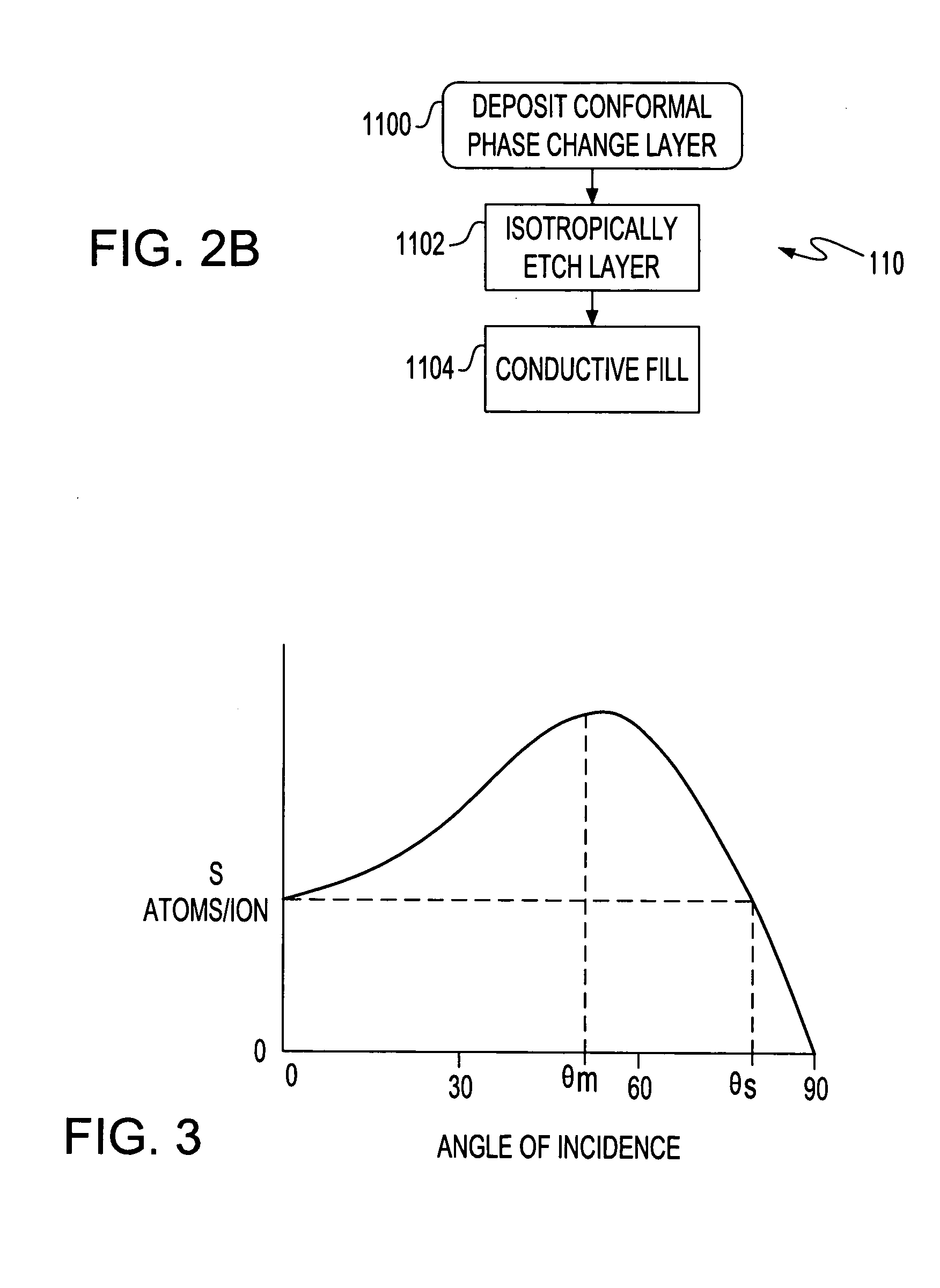

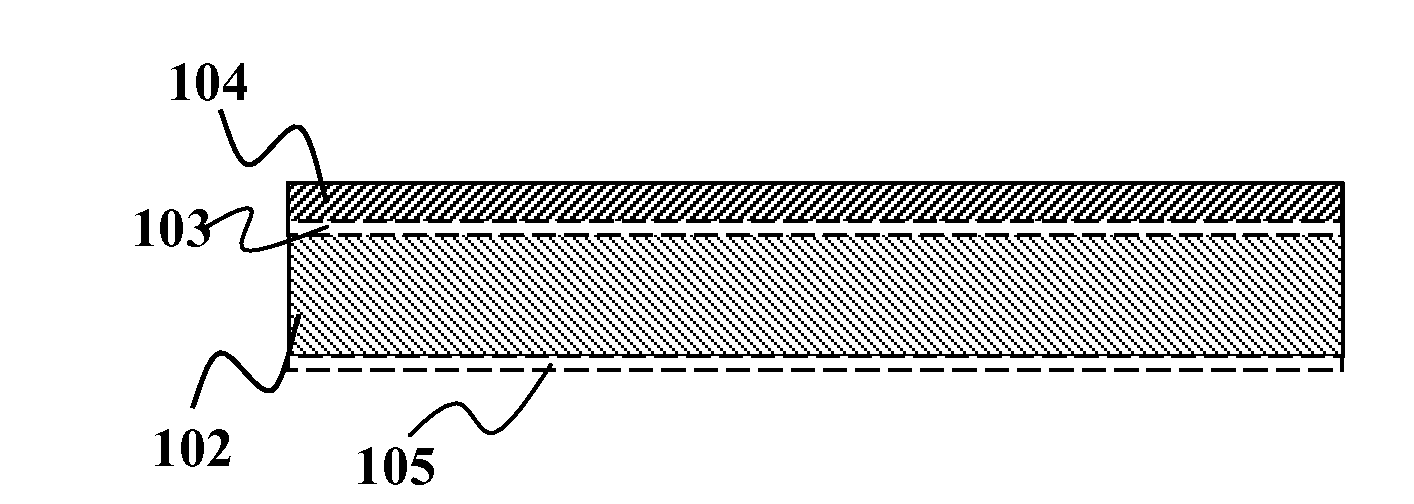

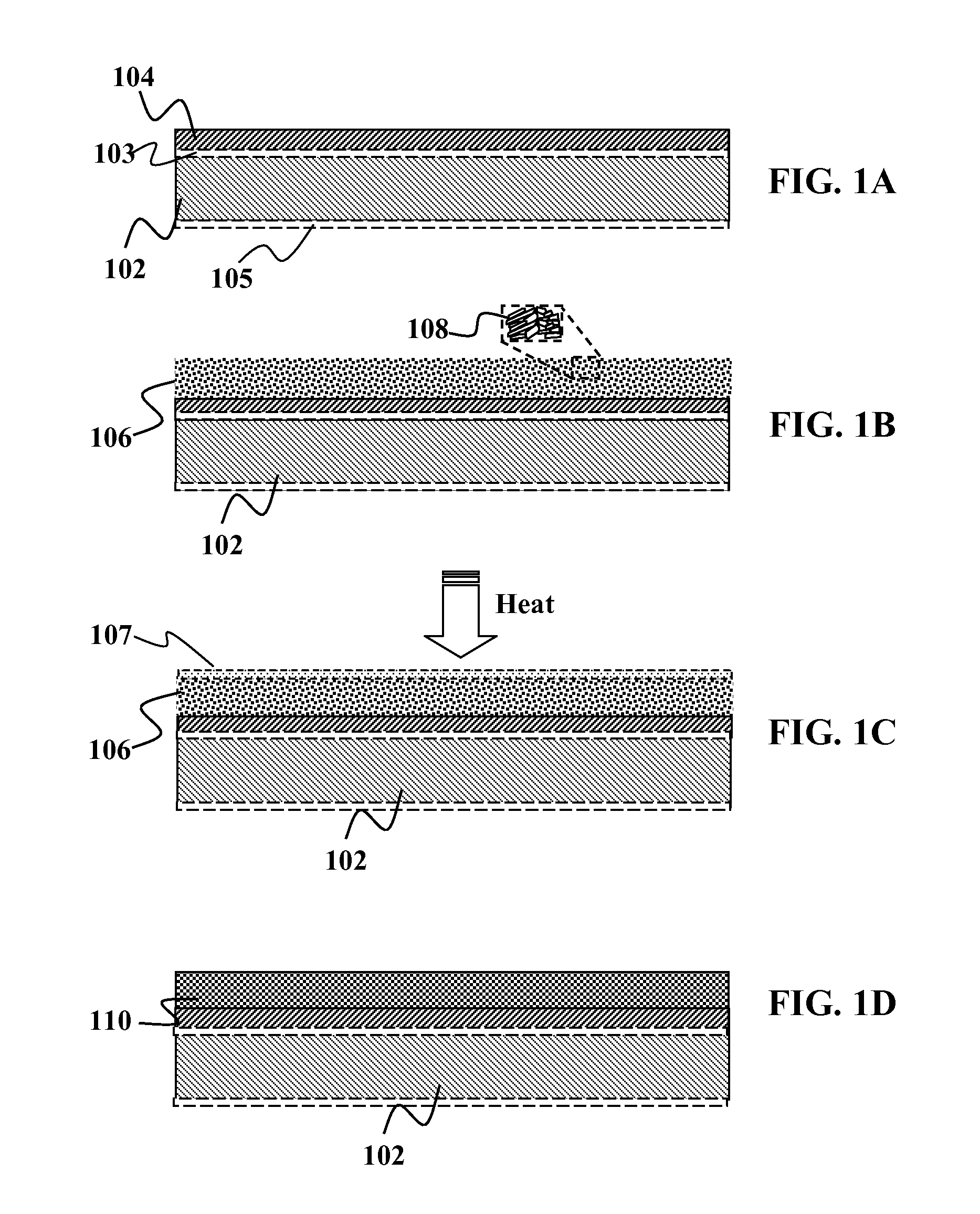

Phase change tip storage cell

ActiveUS20050127349A1Reduce the required powerSolid-state devicesDigital storageTitanium nitrideTe element

A storage cell, integrated circuit (IC) chip with one or more storage cells that may be in an array of the storage cells and a method of forming the storage cell and IC. Each storage cell includes a stylus, the tip of which is phase change material. The phase change tip may be sandwiched between an electrode and conductive material, e.g., titanium nitride (TiN), tantalum nitride (TaN) or n-type semiconductor. The phase change layer may be a chalcogenide and in particular a germanium (Ge), antimony (Sb), tellurium (Te) (GST) layer.

Owner:GLOBALFOUNDRIES US INC

High-throughput printing of semiconductor precursor layer from chalcogenide microflake particles

InactiveUS20080121277A1Efficient and simplified creationIncrease contactMolten spray coatingTransportation and packagingNanoparticleParticle method

Methods and devices are provided for high-throughput printing of semiconductor precursor layer from microflake particles. In one embodiment, the method comprises of transforming non-planar or planar precursor materials in an appropriate vehicle under the appropriate conditions to create dispersions of planar particles with stoichiometric ratios of elements equal to that of the feedstock or precursor materials, even after settling. In particular, planar particles disperse more easily, form much denser coatings (or form coatings with more interparticle contact area), and anneal into fused, dense films at a lower temperature and / or time than their counterparts made from spherical nanoparticles. These planar particles may be microflakes that have a high aspect ratio. The resulting dense film formed from microflakes is particularly useful in forming photovoltaic devices. In one embodiment, at least one set of the particles in the ink may be inter-metallic flake particles (microflake or nanoflake) containing at least one group IB-IIIA inter-metallic alloy phase.

Owner:AERIS CAPITAL SUSTAINABLE IP

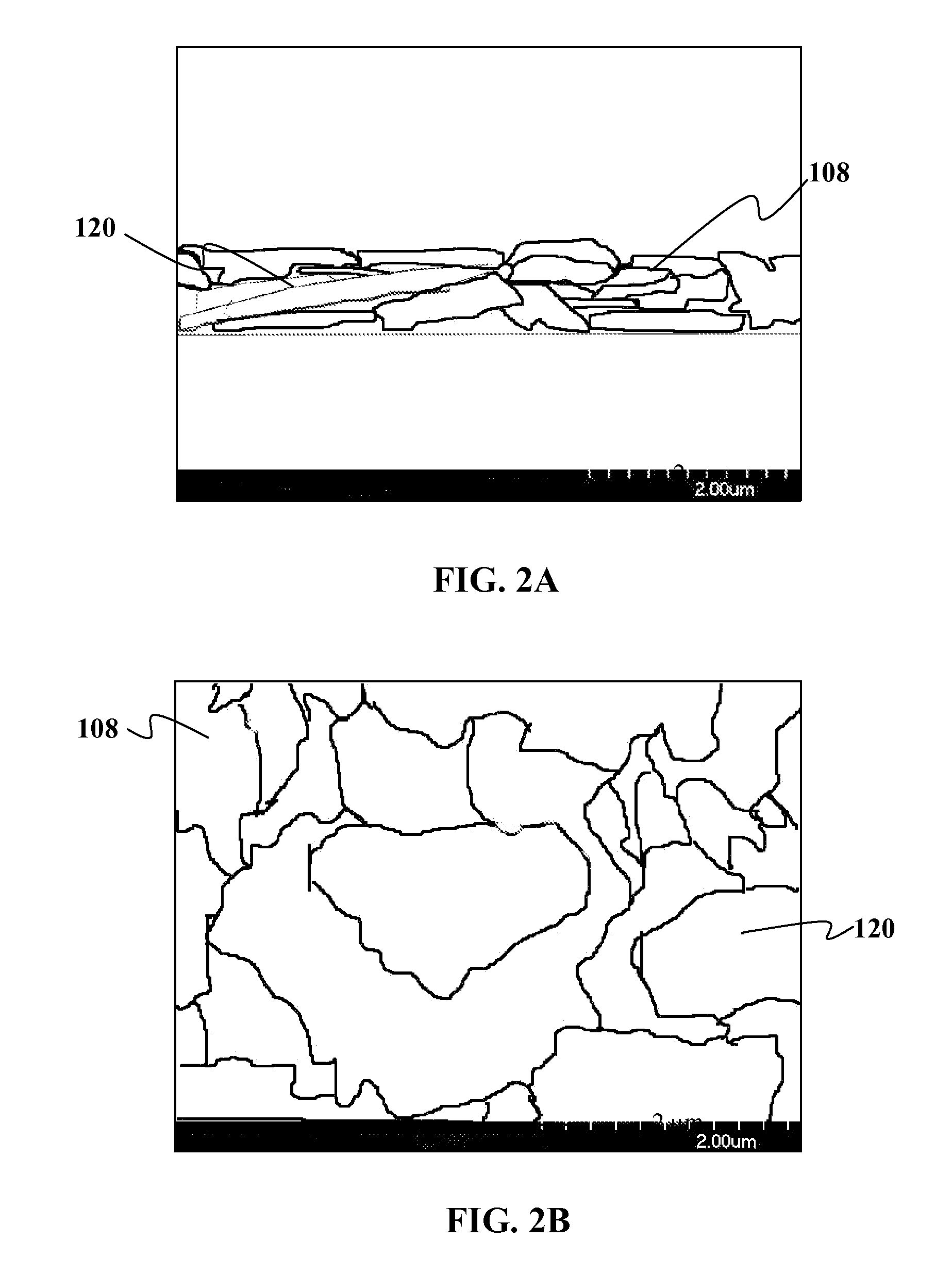

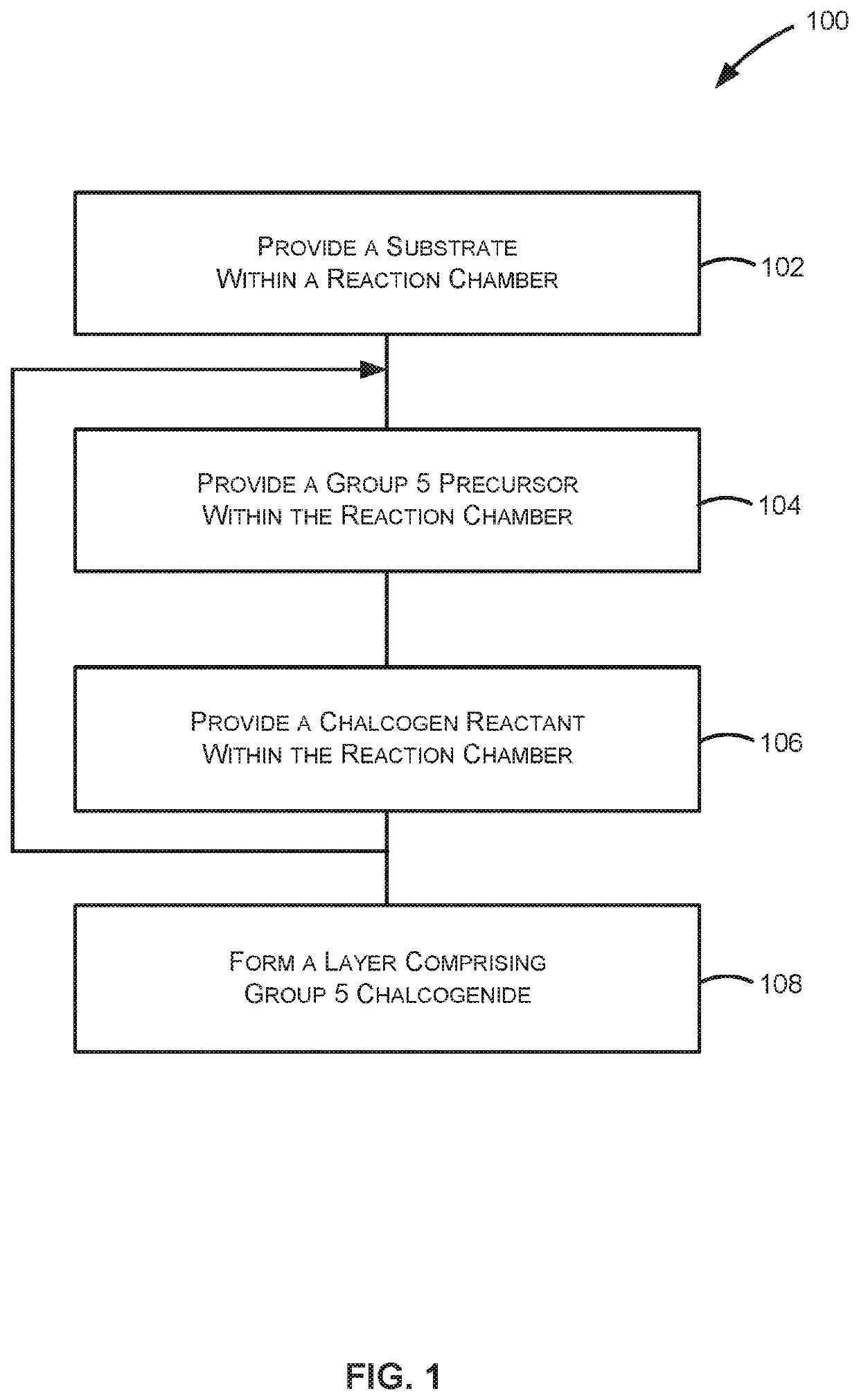

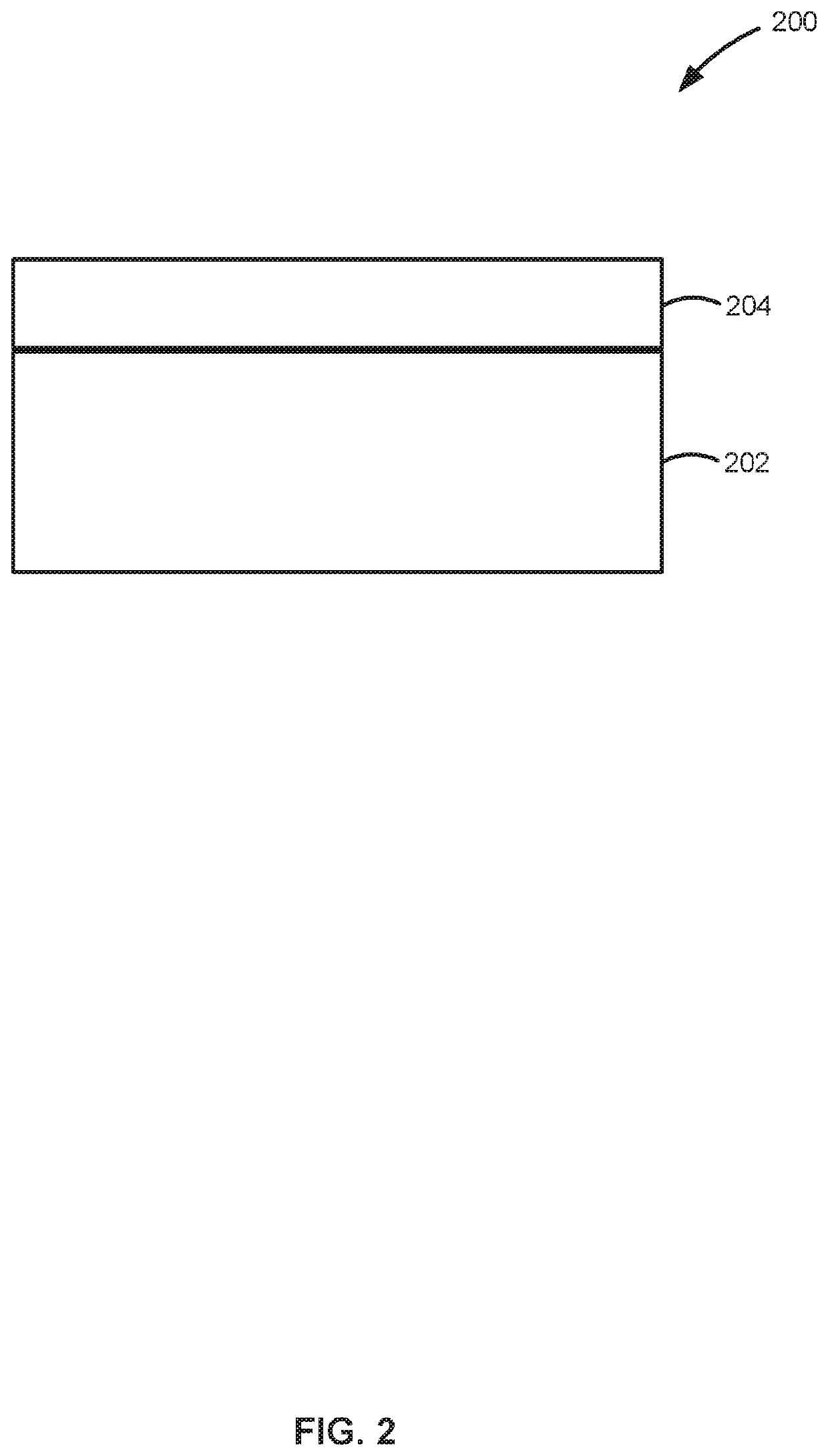

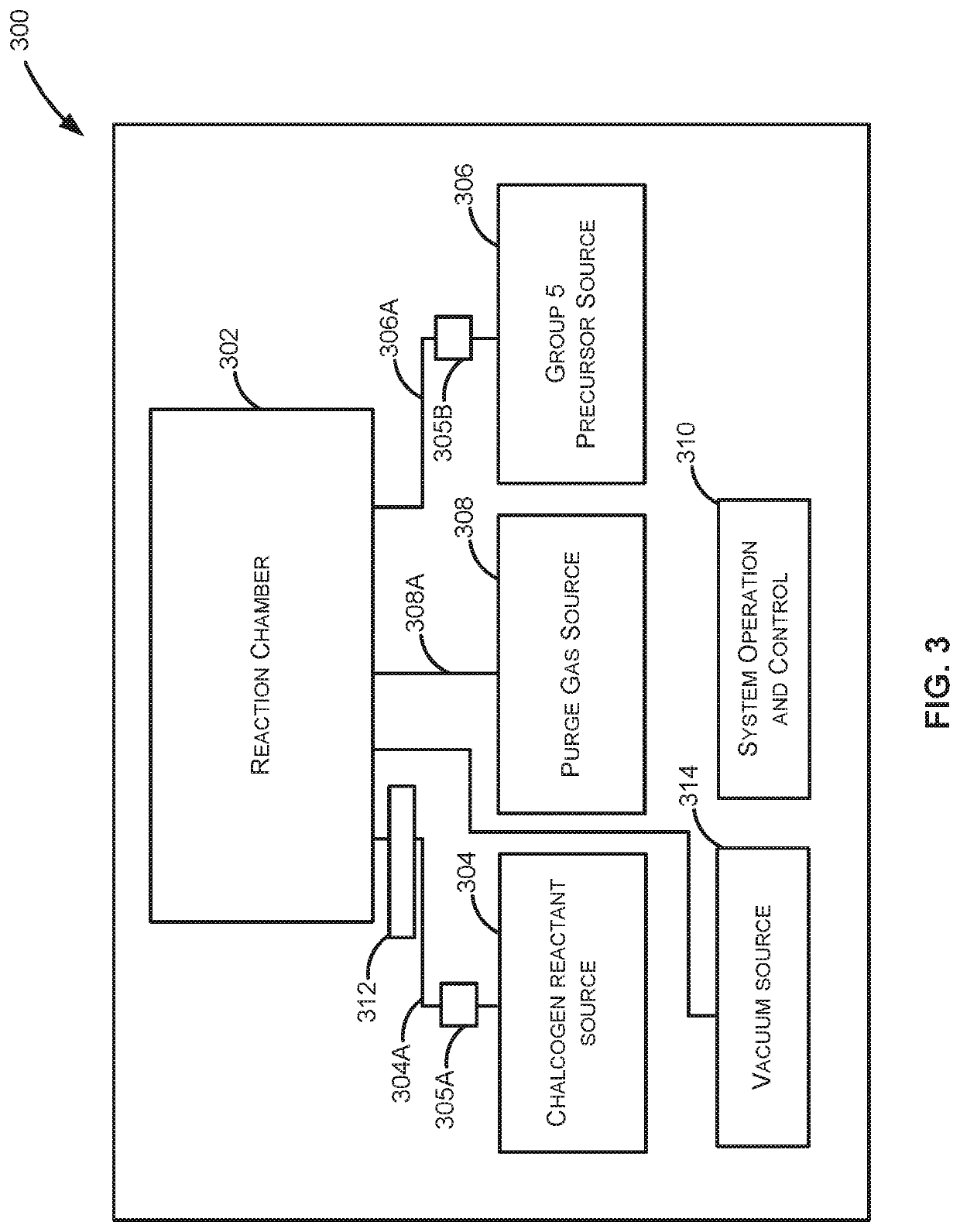

Methods and apparatus for depositing a chalcogenide film and structures including the film

PendingUS20210066080A1Readily apparentSemiconductor/solid-state device manufacturingChemical vapor deposition coatingChalcogenChalcoides

Methods for depositing group 5 chalcogenides on a substrate are disclosed. The methods include cyclical deposition techniques, such as atomic layer deposition. The group 5 chalcogenides can be two-dimensional films having desirable electrical properties.

Owner:ASM IP HLDG BV

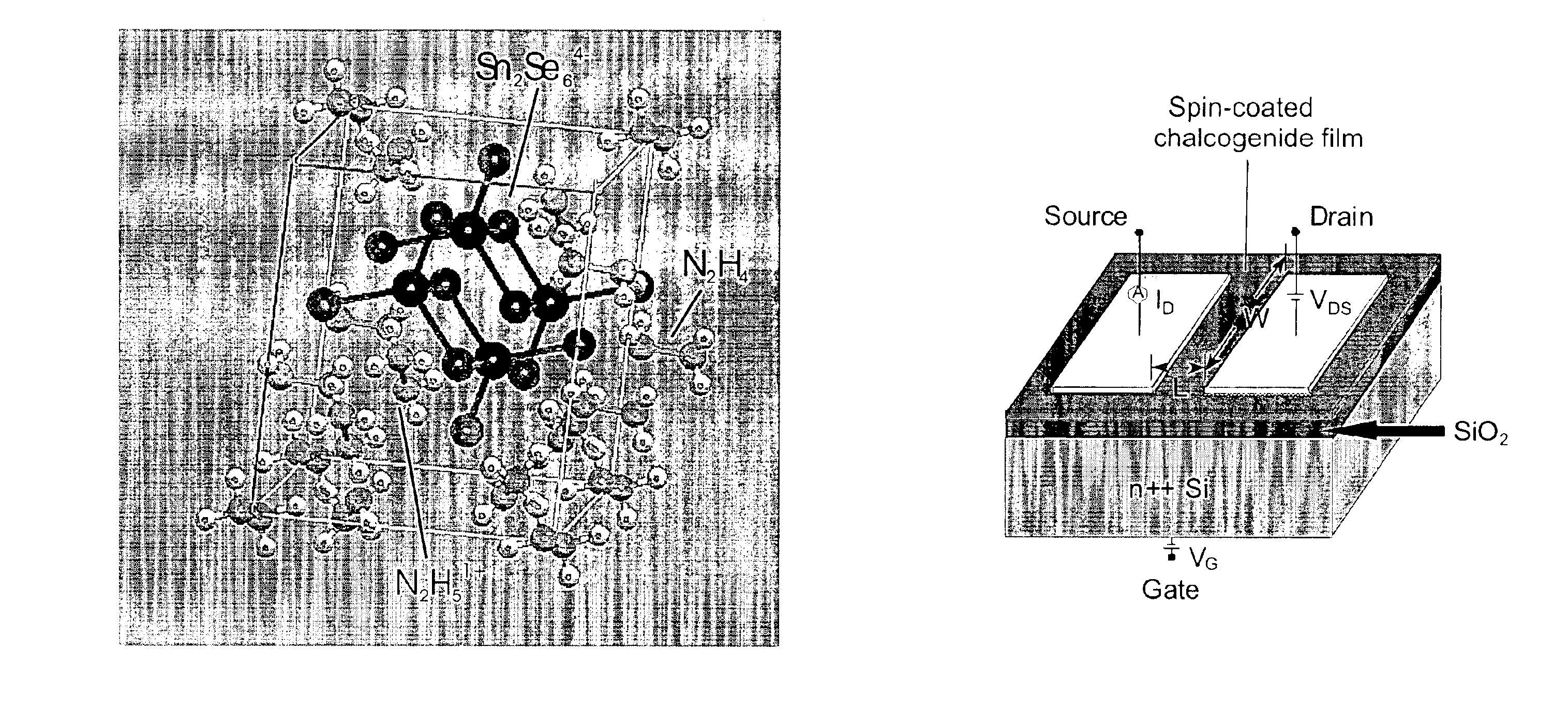

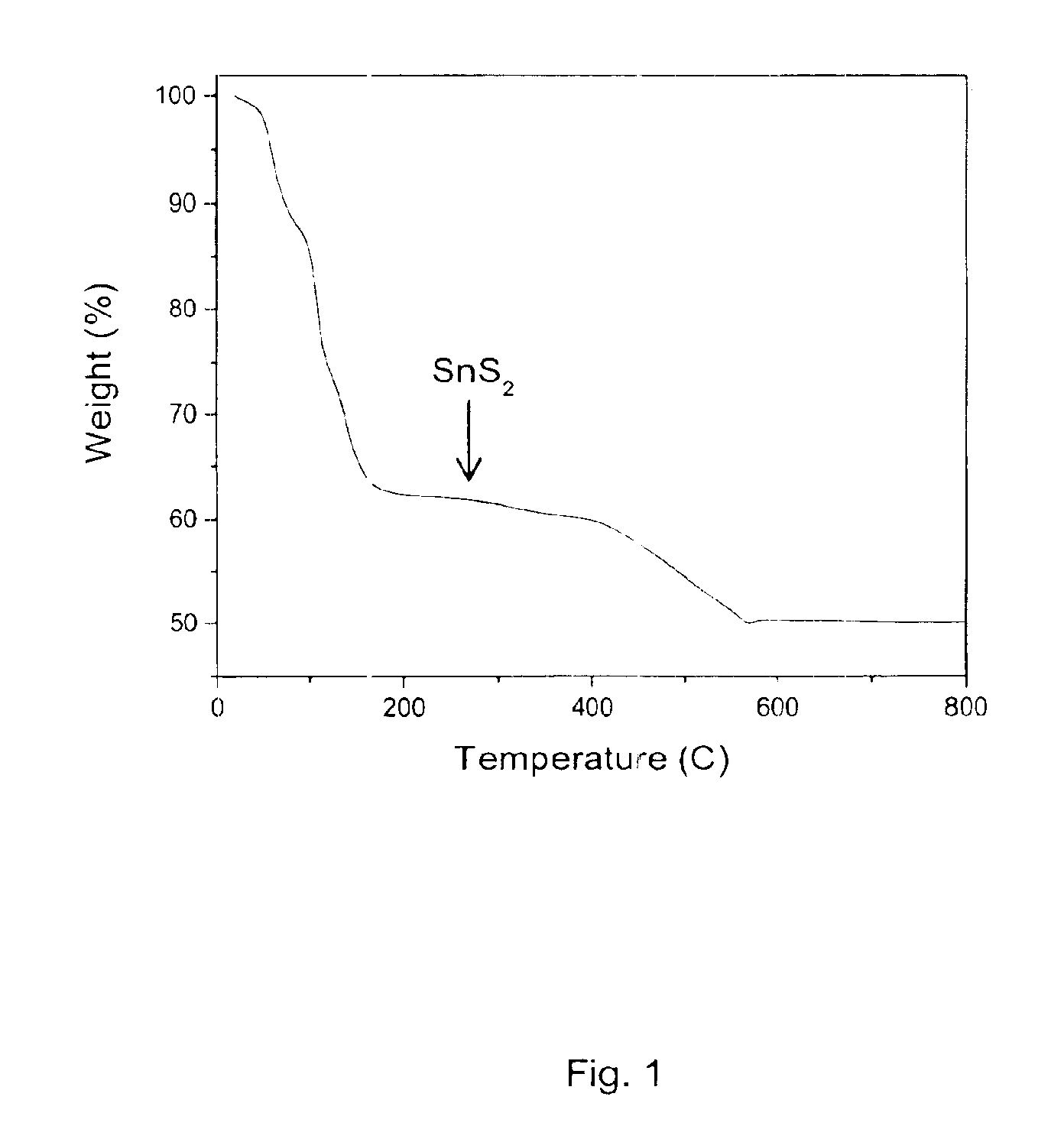

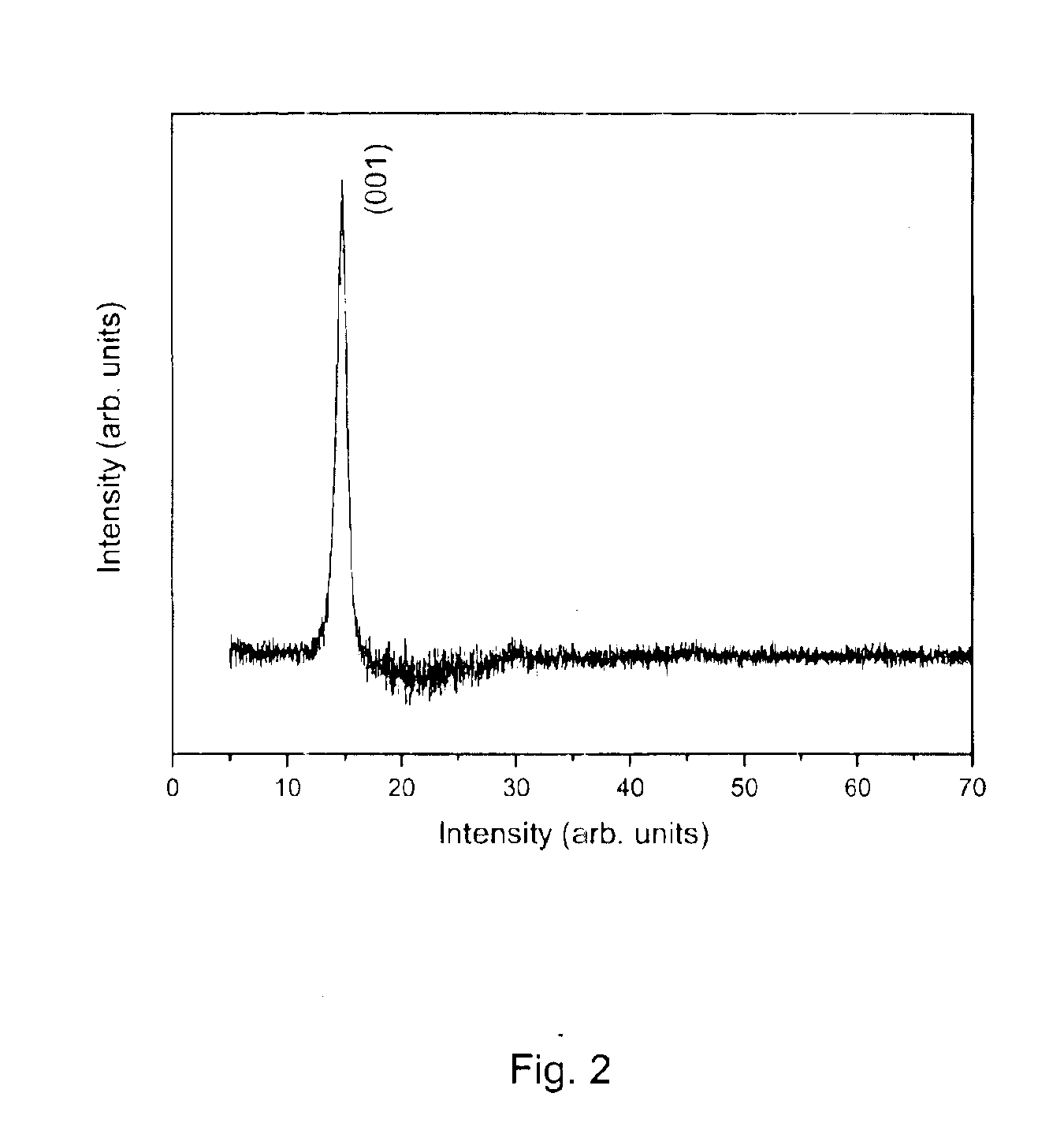

Solution deposition of chalcogenide films

A method of depositing a film of a metal chalcogenide. The first of these methods includes the steps of: contacting at least one metal chalcogenide, a hydrazine compound and optionally, an elemental chalcogen, to produce a solution of a hydrazinium-based precursor of the metal chalcogenide; applying the solution of the hydrazinium-based precursor of the metal chalcogenide onto a substrate to produce a film of the precursor; and thereafter annealing the film of the precursor to remove excess hydrazine and hydrazinium chalcogenide salts to produce a metal chalcogenide film on the substrate. The second of these methods includes the steps of: contacting: at least one metal chalcogenide and a salt of an amine compound to produce an ammonium-based precursor of the metal chalcogenide; contacting the ammonium-based precursor of the metal chalcogenide and a hydrazine compound, and optionally, an elemental chalcogen, to produce a solution of a hydrazinium-based precursor of the metal chalcogenide in the hydrazine compound; applying the solution of the hydrazinium-based precursor onto a substrate to produce a film; and thereafter, annealing to produce a metal chalcogenide film. Also provided is a thin-film field-effect transistor device using the metal chalcogenides as the channel layer.

Owner:GLOBALFOUNDRIES INC

Reducing oxidation of phase change memory electrodes

A phase change memory may be formed in a way which reduces oxygen infiltration through a chalcogenide layer overlying a lower electrode. Such infiltration may cause oxidation of the lower electrode which adversely affects performance. In one such embodiment, an etch through an overlying upper electrode layer may be stopped before reaching a layer which overlies said chalcogenide layer. Then, photoresist used for such etching may be utilized in a high temperature oxygen plasma. Only after such plasma treatment has been completed is that overlying layer removed, which ultimately exposes the chalcogenide.

Owner:INTEL CORP

Inorganic dopants, inks and related nanotechnology

InactiveUS6849109B2Facilitated DiffusionLower transition temperatureSelenium/tellurium compundsCell electrodesIndiumCerium

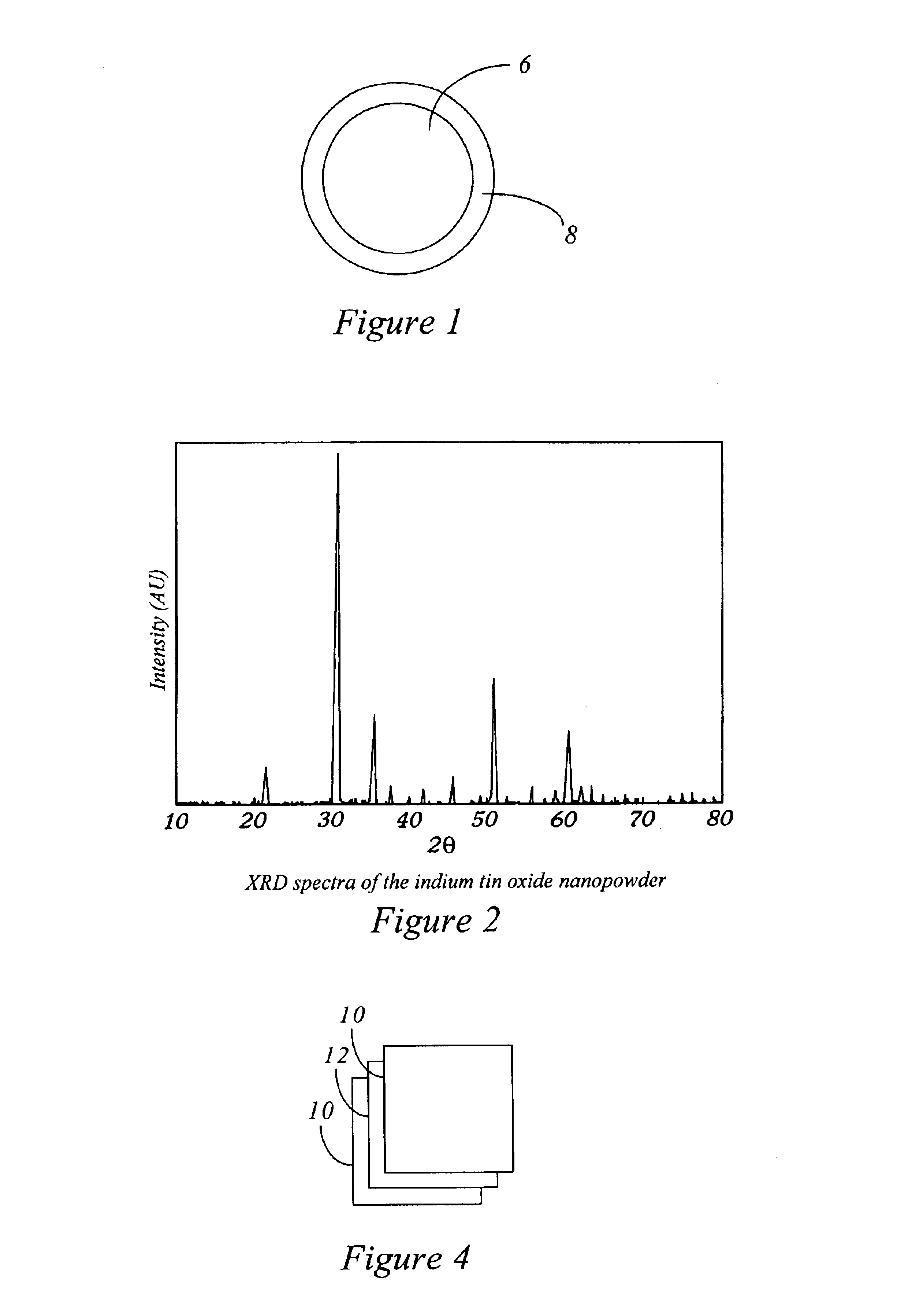

Ink compositions with modified properties result from using a powder size below 100 nanometers. Colored inks are illustrated. Nanoscale coated, uncoated, whisker inorganic fillers are included. The pigment nanopowders taught comprise one or more elements from the group actinium, aluminum, antimony, arsenic, barium, beryllium, bismuth, cadmuim, calcium, cerium, cesium, chalcogenide, cobalt, copper, dysprosium, erbium, europium, gadolinium, gallium, gold, hafnium, hydrogen, indium, iridium, iron, lanthanum, lithium, magnesium, manganese, mendelevium, mercury, molybdenum, neodymium, neptunium, nickel, niobium, nitrogen, oxygen, osmium, palladium, platinum, potassium, praseodymium, promethium, protactinium, rhenium, rubidium, scandium, silver, sodium, strontium, tantalum, terbium, thallium, thorium, tin, titanium, tungsten, vanadium, ytterbium, yttrium, zinc, and zirconium.

Owner:PPG IND OHIO INC

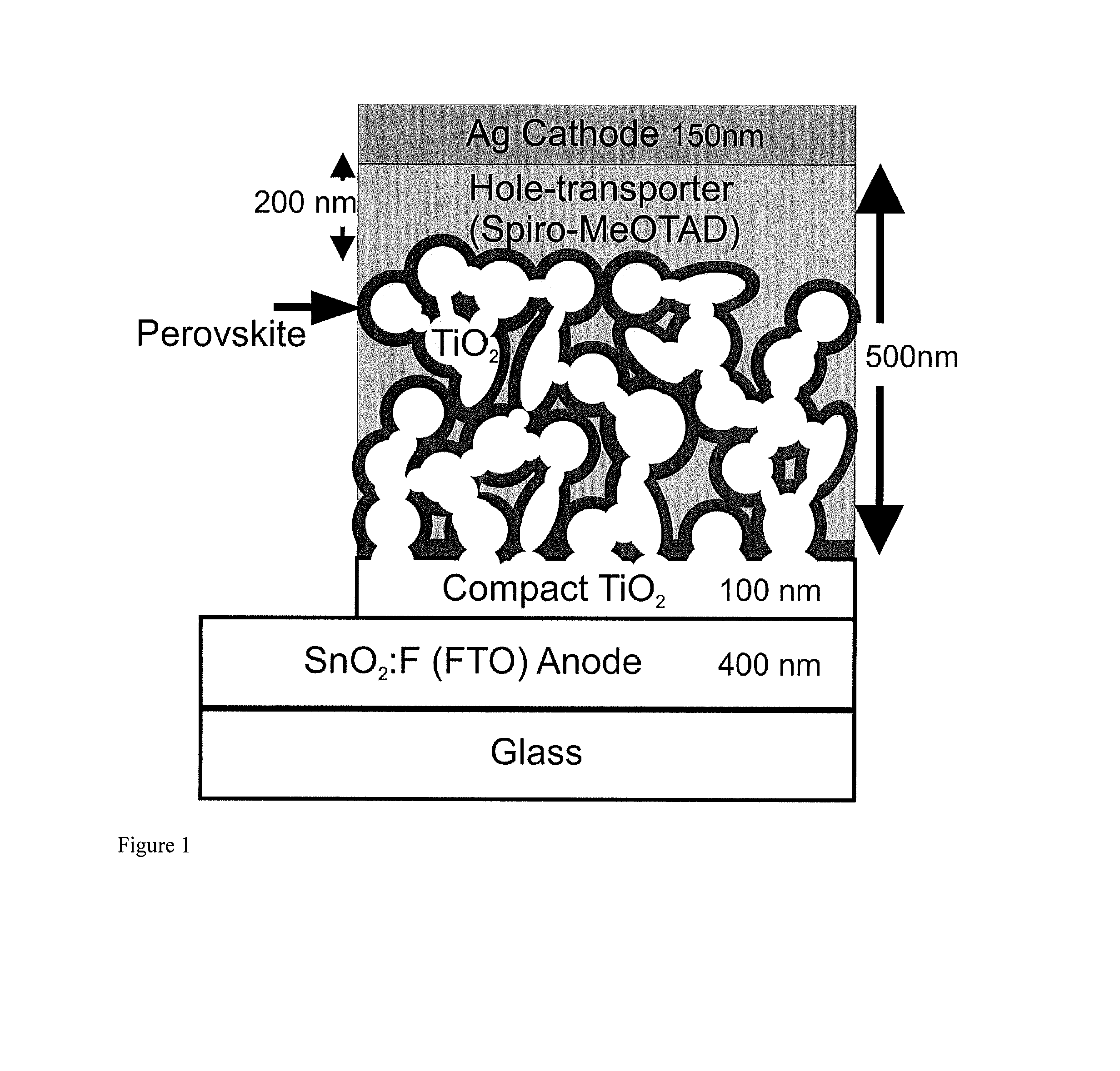

Optoelectronic devices with organometal perovskites with mixed anions

ActiveUS20150136232A1Cheap to makeImprove conversion efficiencyTin organic compoundsElectrolytic capacitorsSulfurDivalent metal

The invention provides an optoelectronic device comprising a mixed-anion perovskite, wherein the mixed-anion perovskite comprises two or more different anions selected from halide anions and chalcogenide anions. The invention further provides a mixed halide perovskite of the formula (I) [A][B][X]3 wherein: [A] is at least one organic cation; [B] is at least one divalent metal cation; and [X] is said two or more different halide anions. In another aspect, the invention provides the use of a mixed-anion perovskite as a sensitizer in an optoelectronic device, wherein the mixed-anion perovskite comprises two or more different anions selected from halide anions and chalcogenide anions. The invention also provides a photosensitizing material for an optoelectronic device comprising a mixed-anion perovskite wherein the mixed-anion perovskite comprises two or more different anions selected from halide anions and chalcogenide anions.

Owner:OXFORD UNIV INNOVATION LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com