Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

203 results about "Os element" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

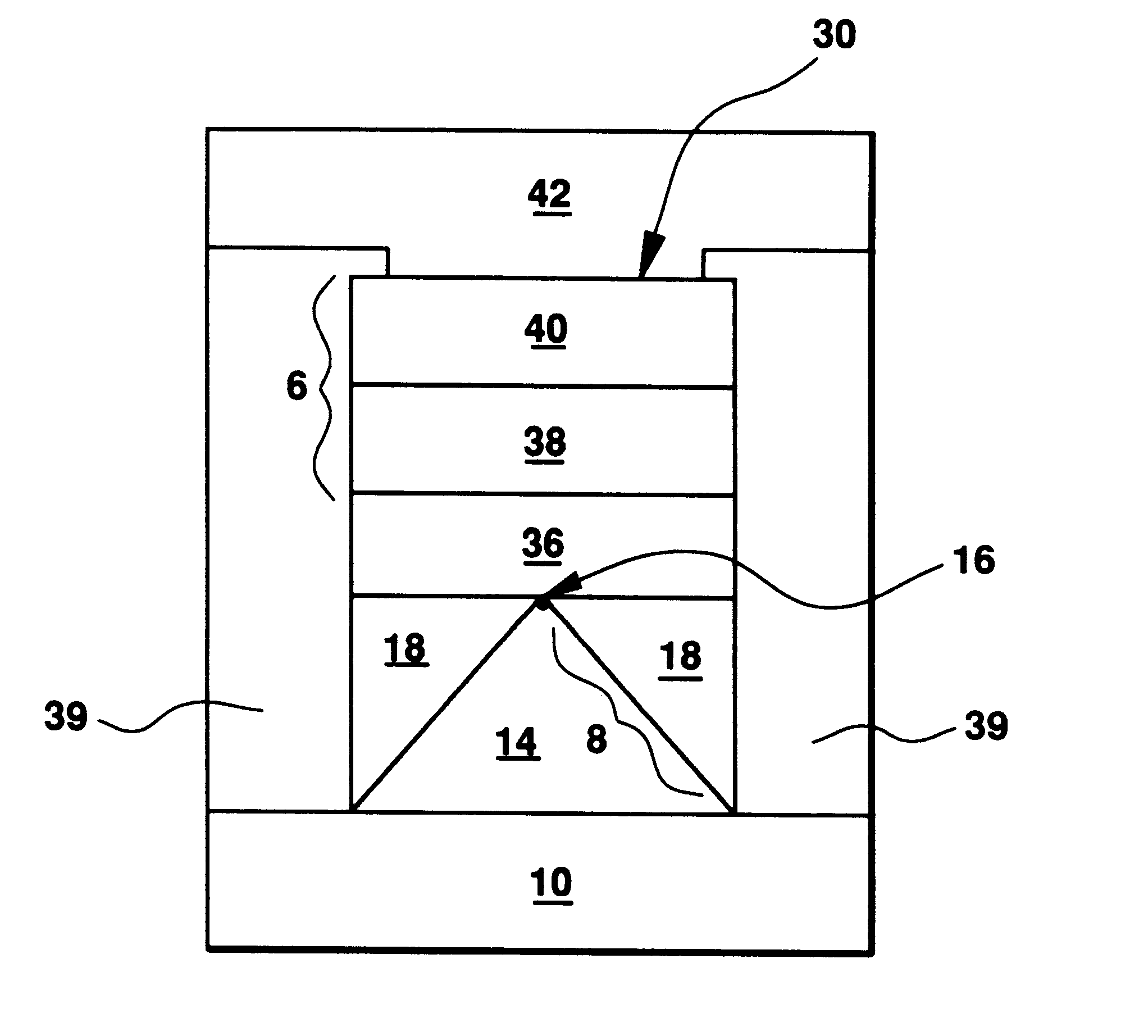

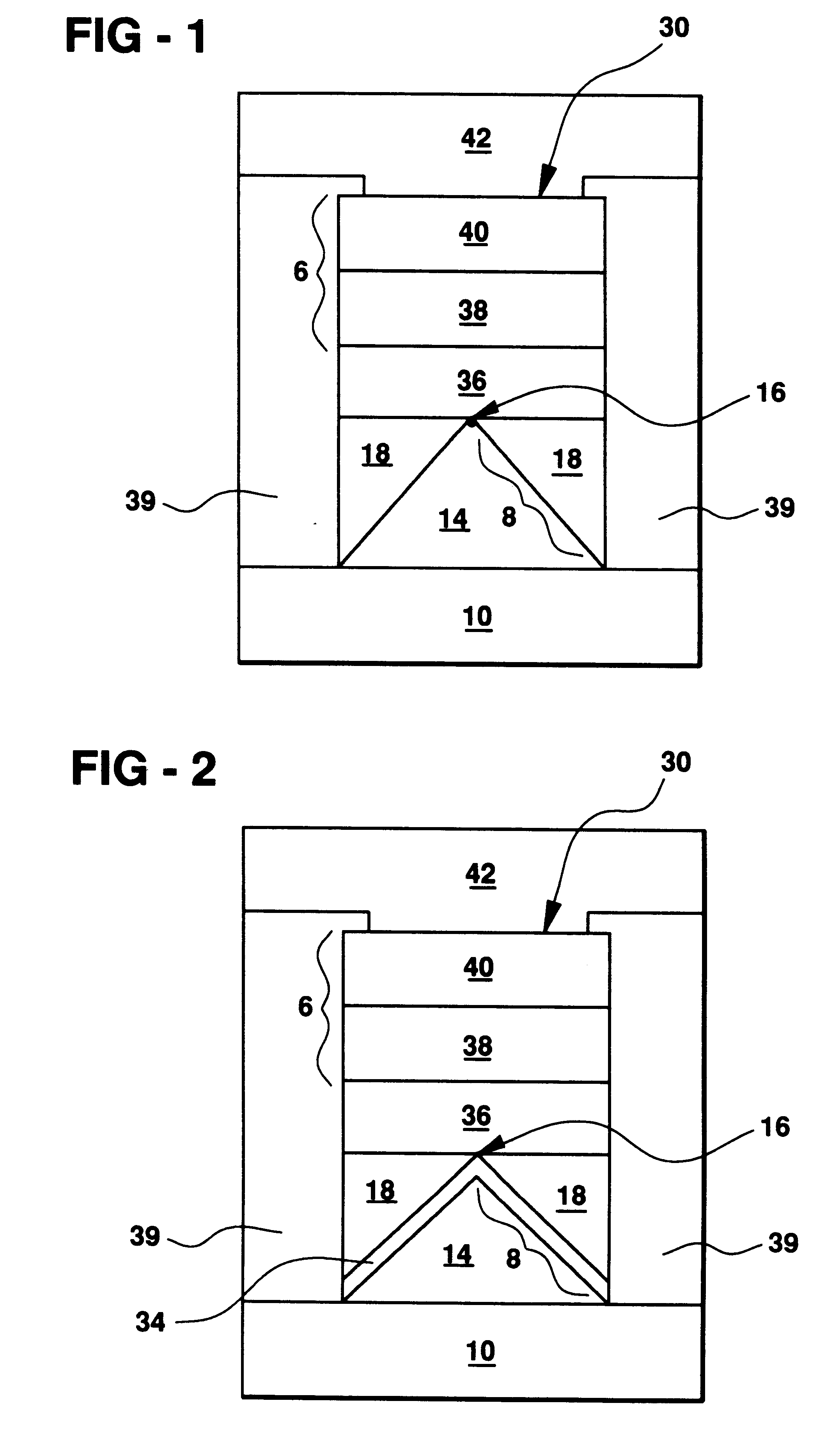

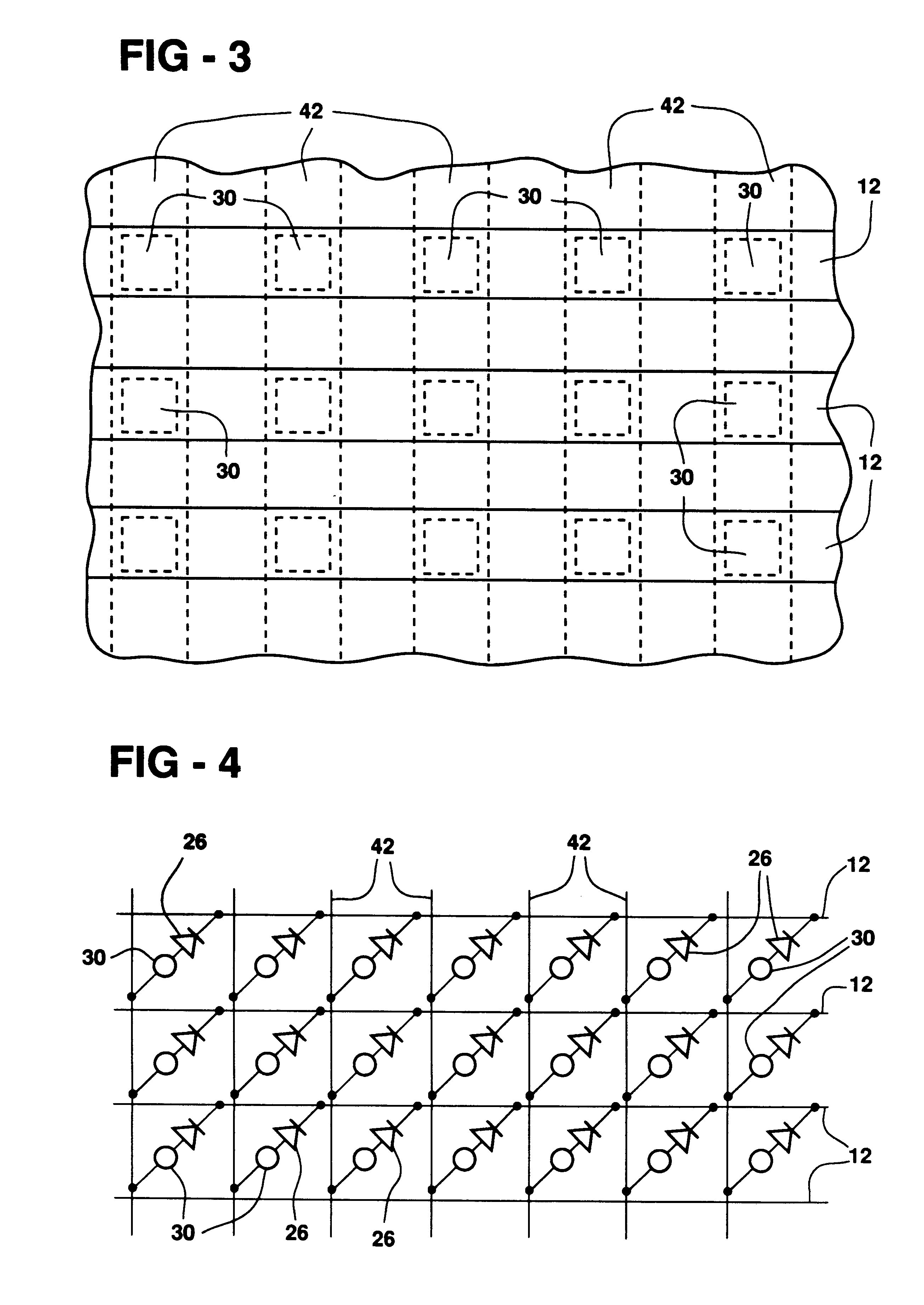

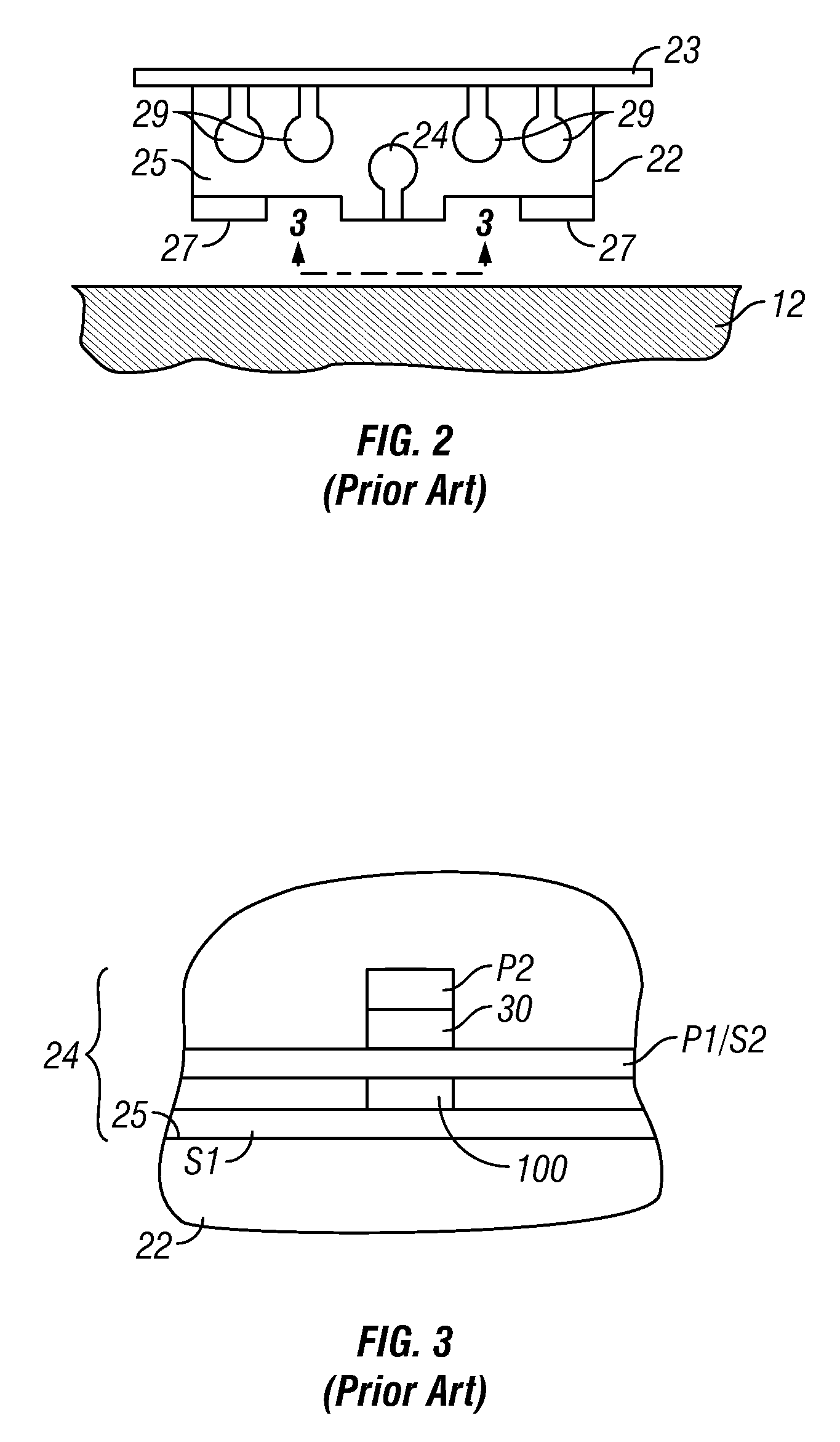

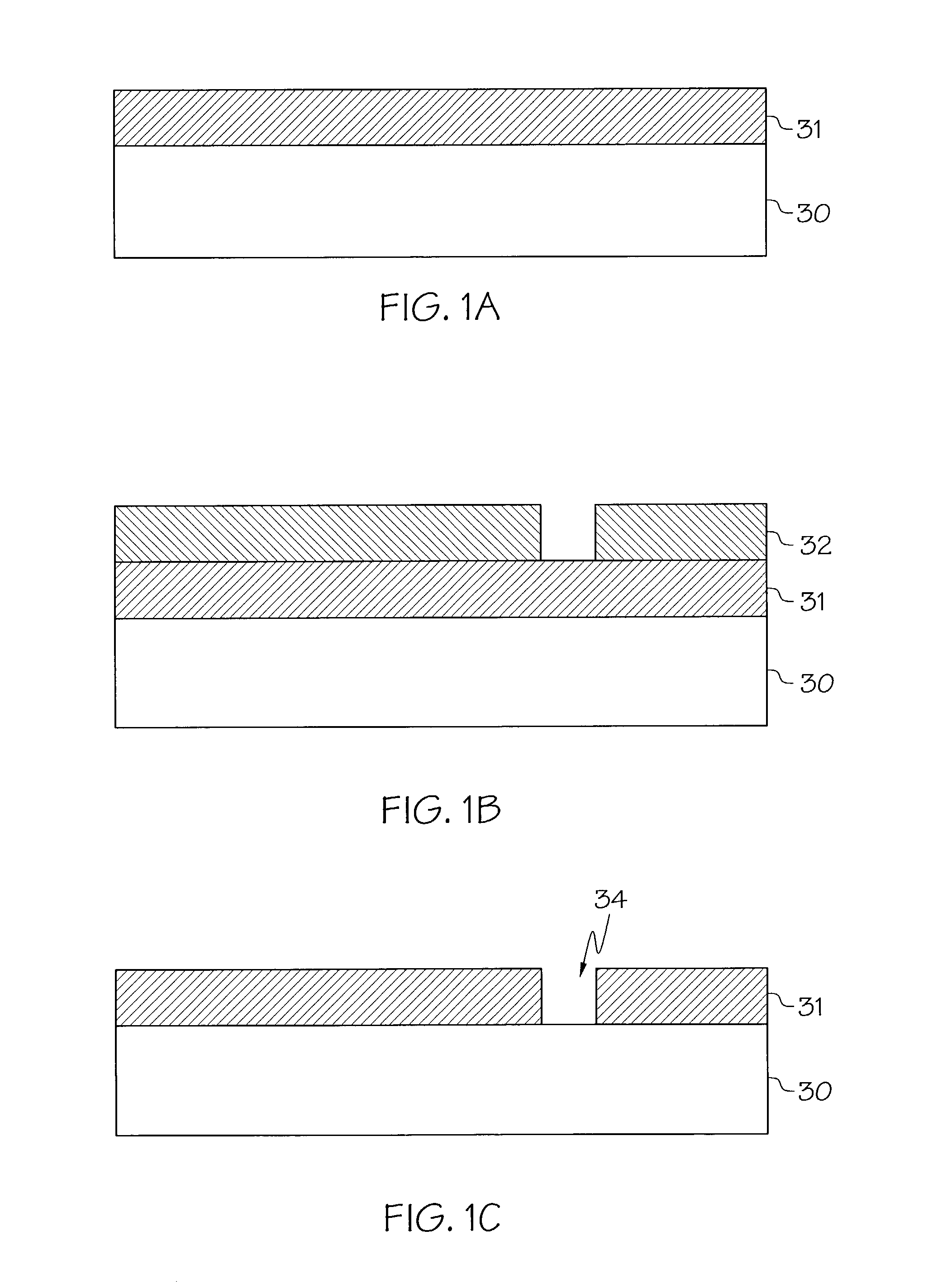

Multibit single cell memory element having tapered contact

InactiveUSRE37259E1Large electric resistance valueSolid-state devicesRead-only memoriesPeak valueEngineering

An electrically operated, directly overwritable, multibit, single-cell chalcogenide memory element with multibit storage capabilities and having at least one contact for supplying electrical input signals to set the memory element to a selected resistance value, the second contact tapering to a peak adjacent to the memory element. In this manner the tapered contact helps define the size and position of a conduction path through the memory element.

Owner:OVONYX MEMORY TECH LLC

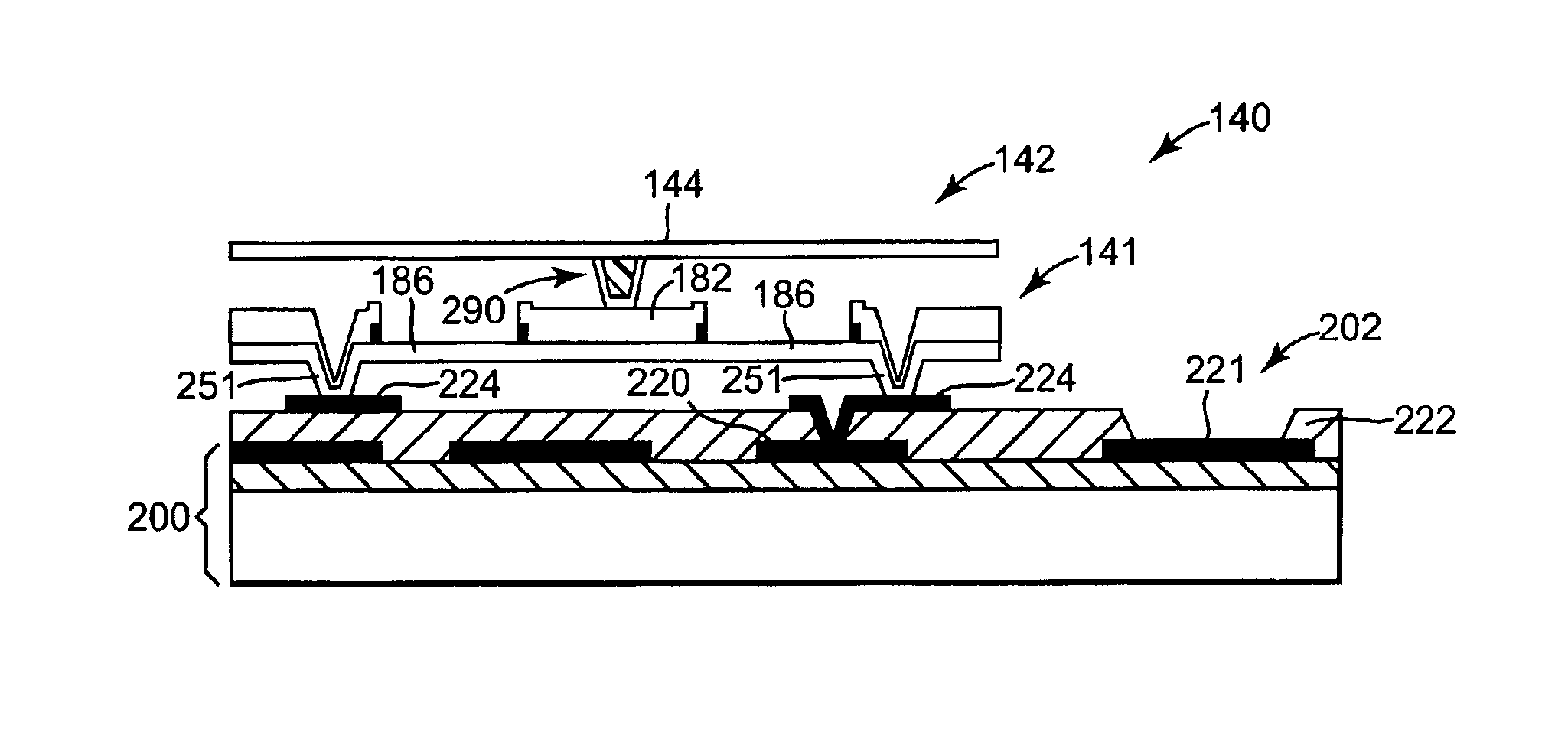

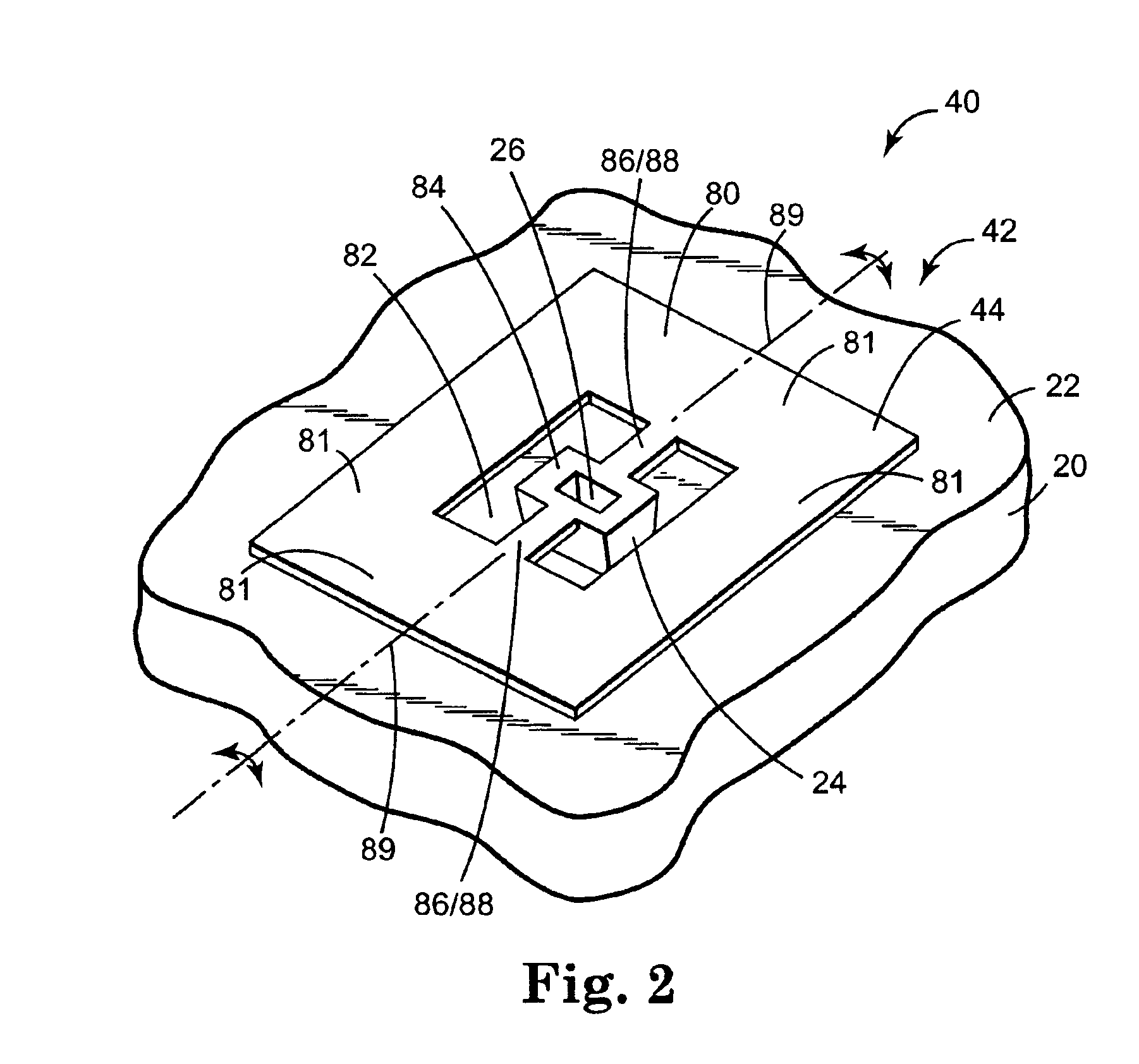

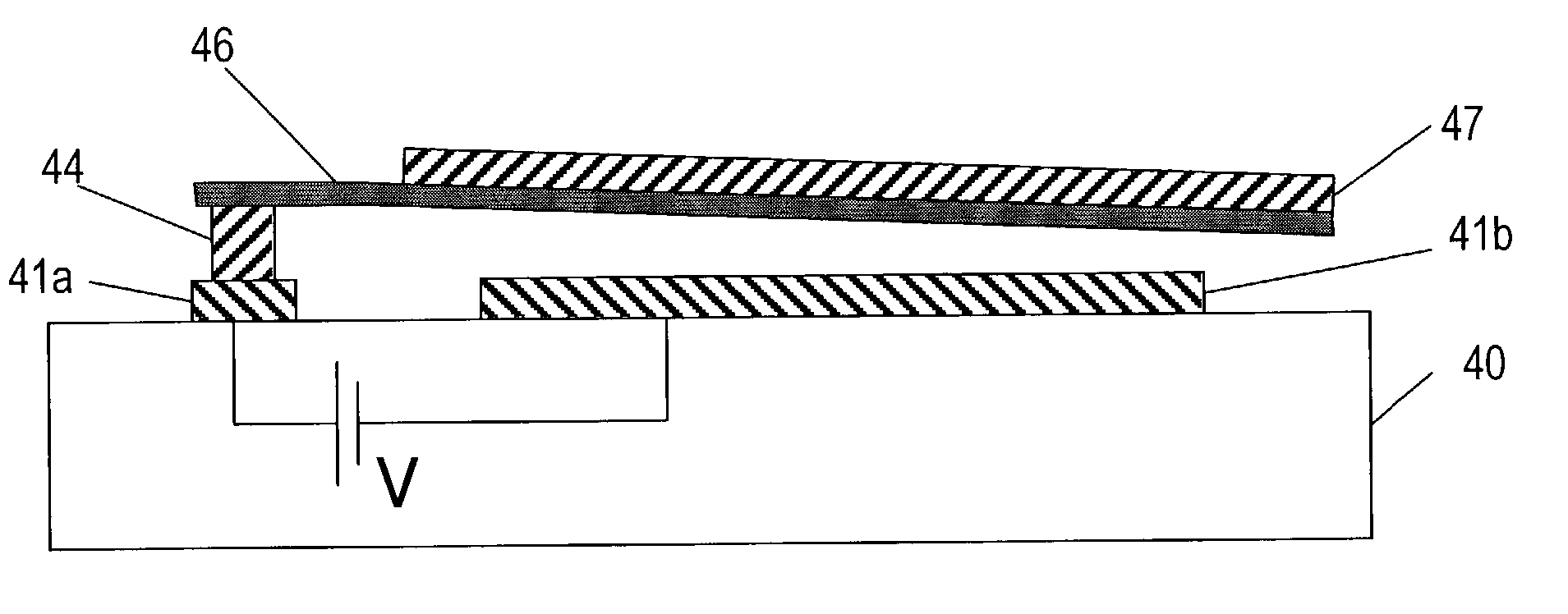

Method of forming MEMS device

InactiveUS6861277B1Decorative surface effectsSemiconductor/solid-state device manufacturingConductive materialsOptoelectronics

A method of forming a MEMS device includes depositing a conductive material on a substructure, forming a first sacrificial layer over the conductive material, including forming a substantially planar surface of the first sacrificial layer, and forming a first element over the substantially planar surface of the first sacrificial layer, including communicating the first element with the conductive material through the first sacrificial layer. In addition, the method includes forming a second sacrificial layer over the first element, including forming a substantially planar surface of the second sacrificial layer, forming a support through the second sacrificial layer to the first element after forming the second sacrificial layer, including filling the support, and forming a second element over the support and the substantially planar surface of the second sacrificial layer. As such, the method further includes substantially removing the first sacrificial layer and the second sacrificial layer, thereby supporting the second element relative to the first element with the support.

Owner:TAIWAN SEMICON MFG CO LTD

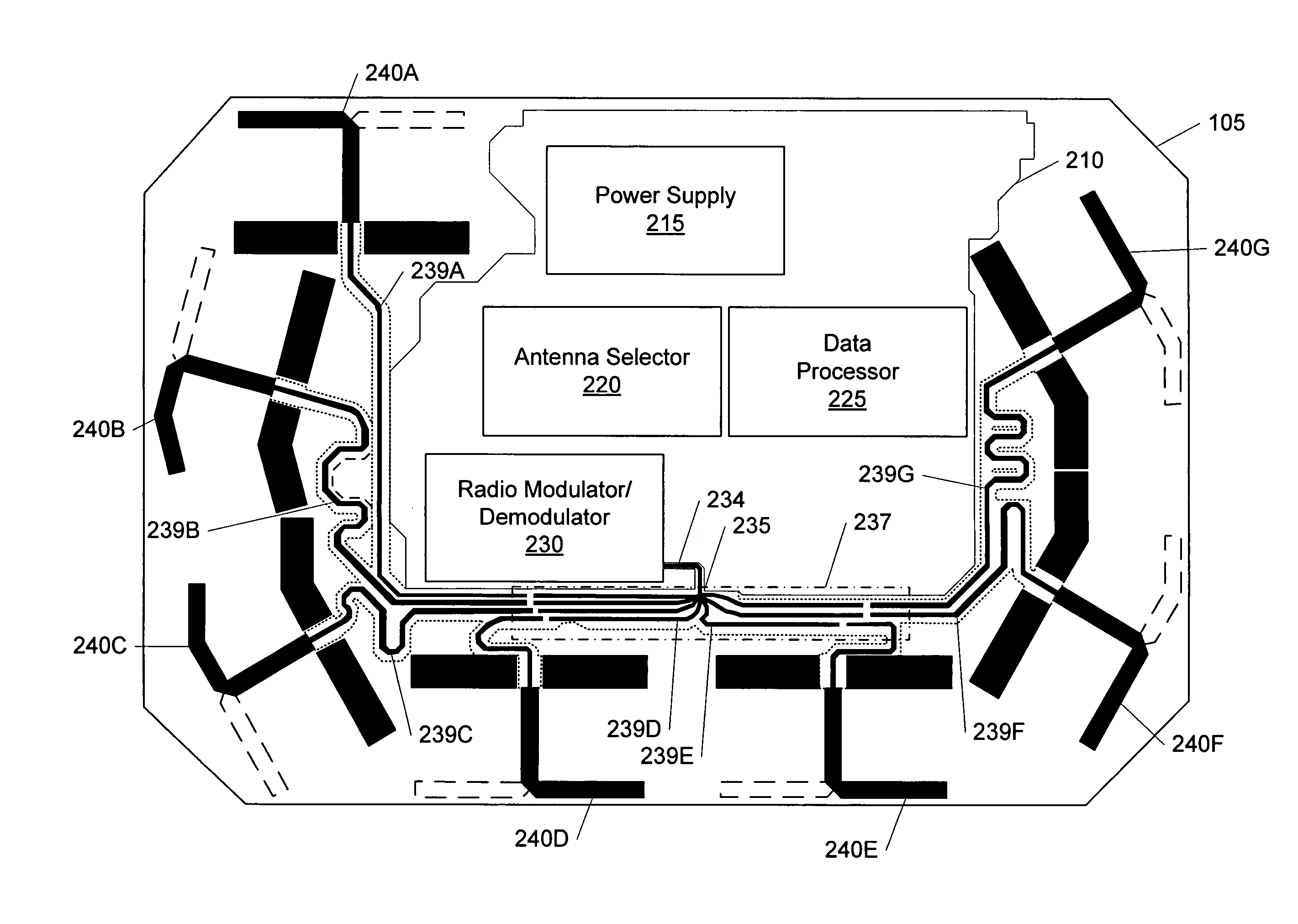

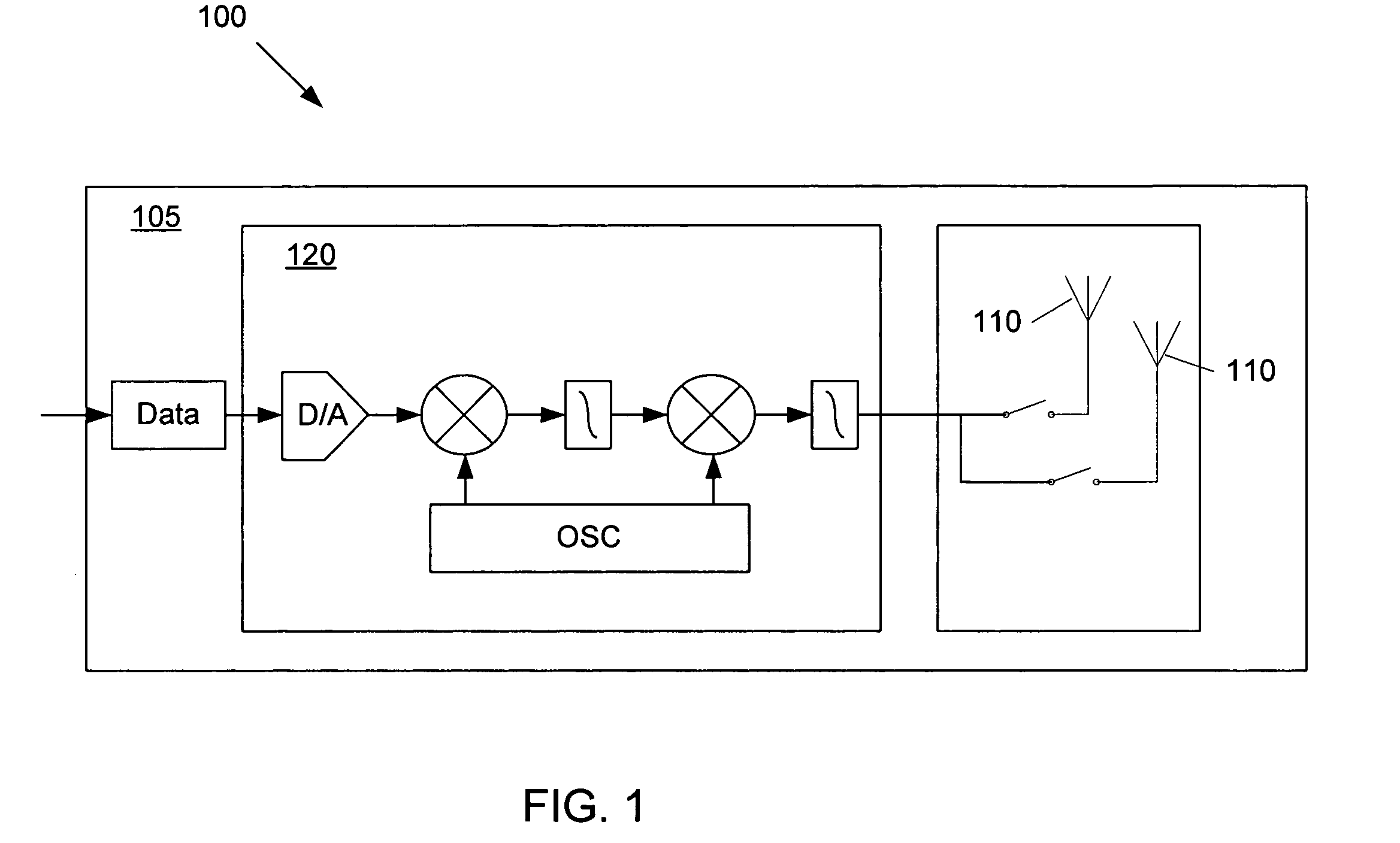

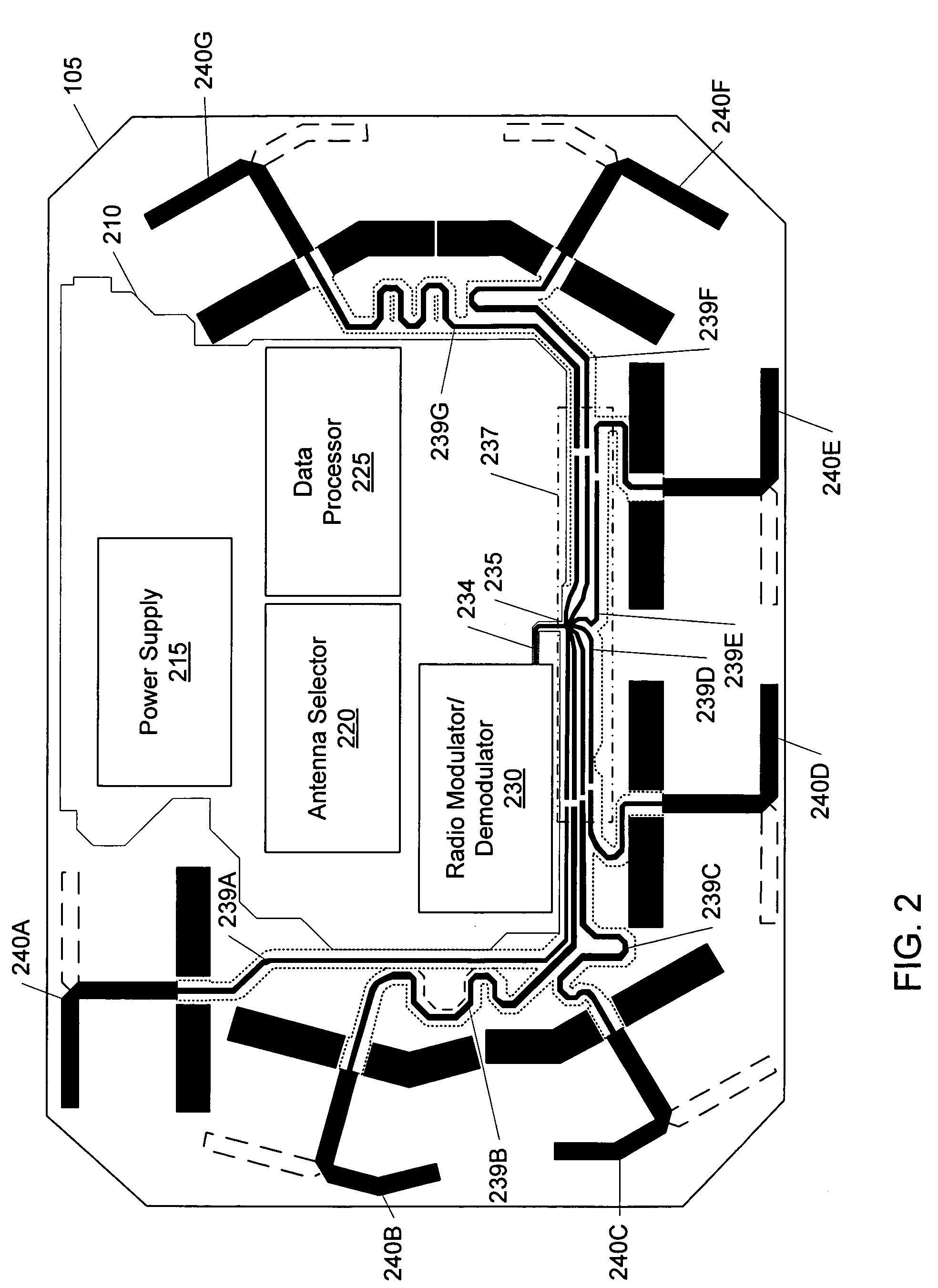

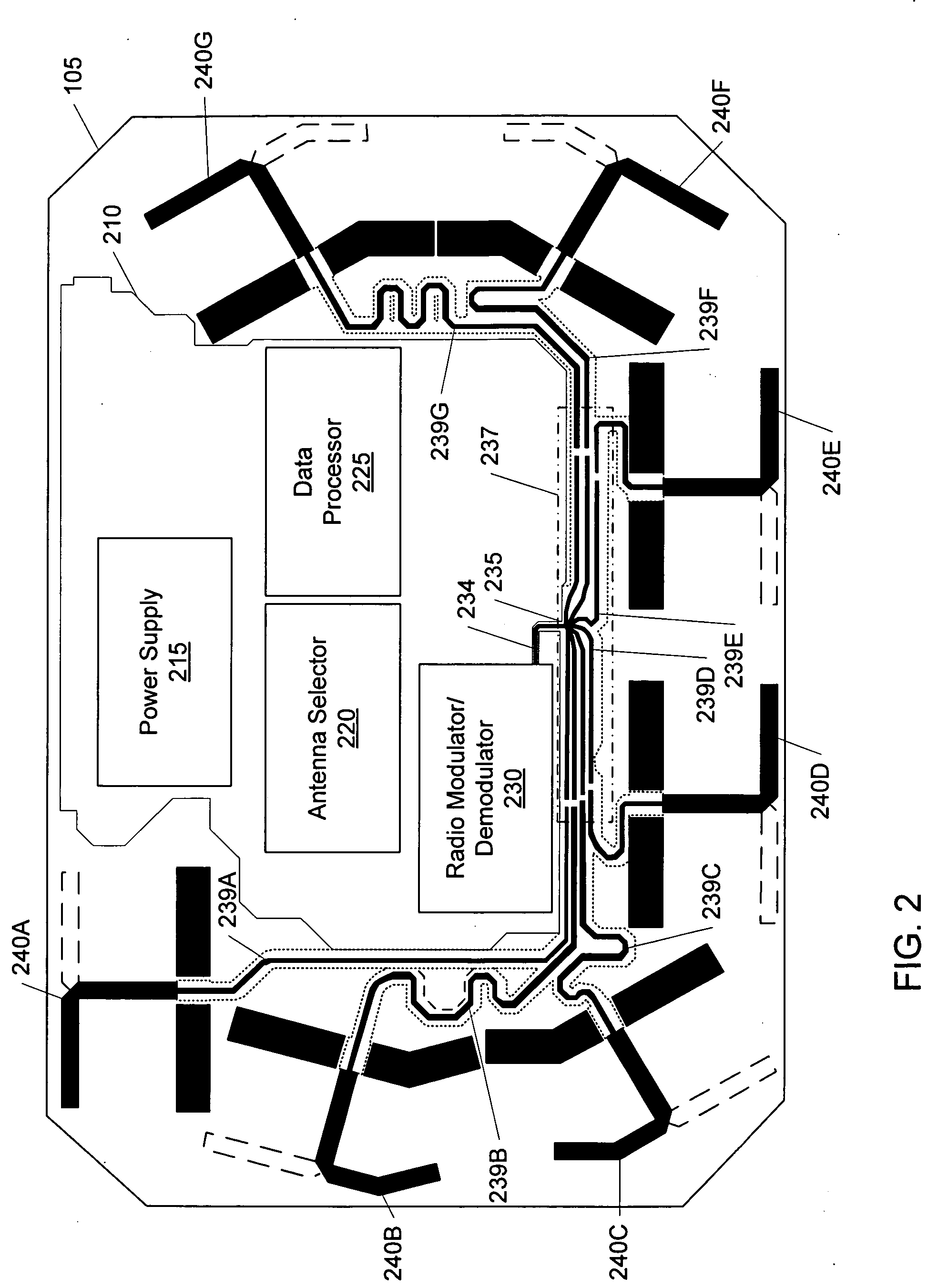

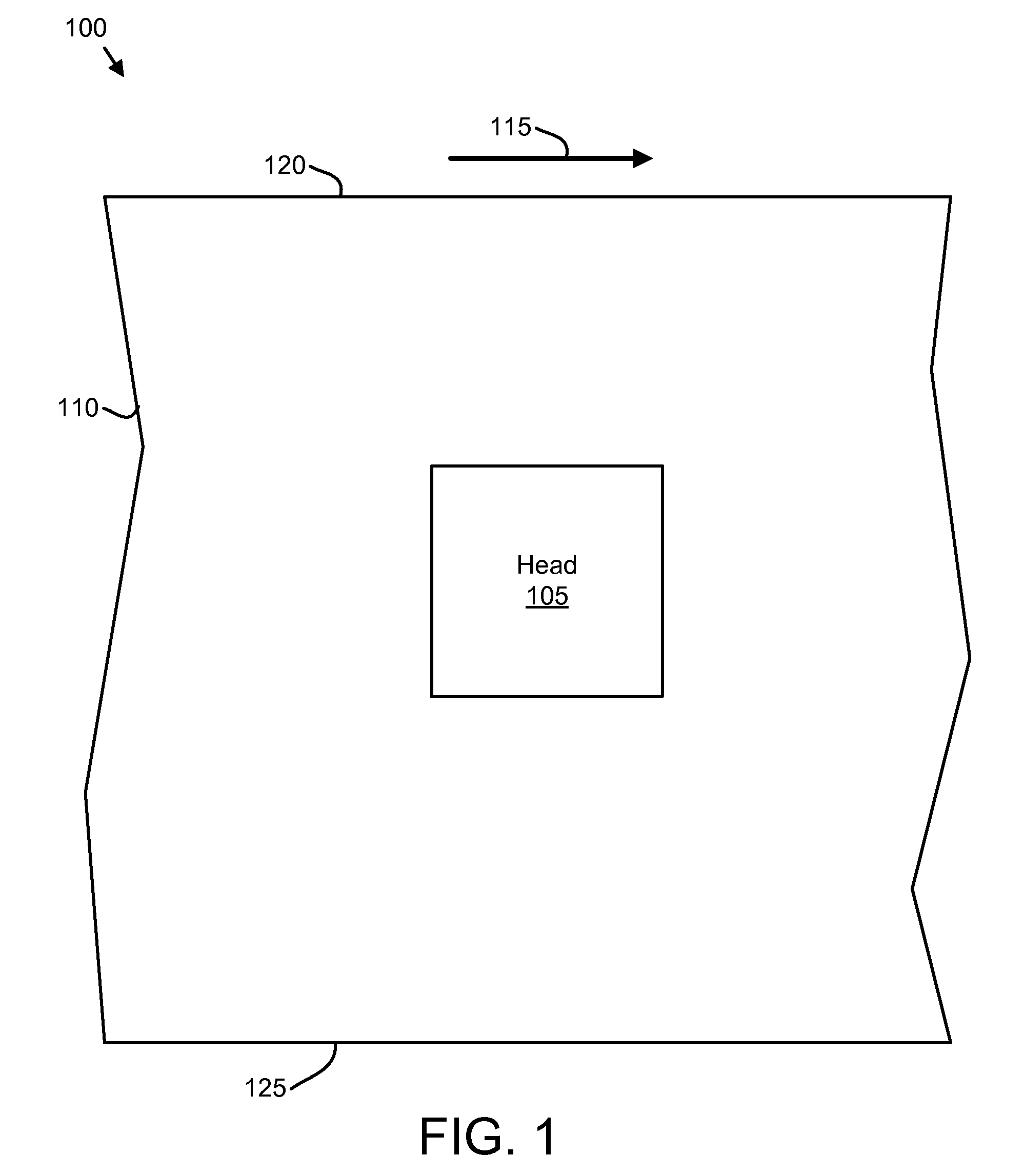

Circuit board having a peripheral antenna apparatus with selectable antenna elements

ActiveUS7193562B2Simultaneous aerial operationsPrinted electric component incorporationImpedance matchingRadio frequency

A circuit board for wireless communications includes communication circuitry for modulating and / or demodulating a radio frequency (RF) signal and an antenna apparatus for transmitting and receiving the RF signal, the antenna apparatus having selectable antenna elements located near one or more peripheries of the circuit board. A first antenna element produces a first directional radiation pattern; a second antenna element produces a second directional radiation pattern offset from the first radiation pattern. The antenna elements may include one or more reflectors configured to provide gain and broaden the frequency response of the antenna element. A switching network couples one or more of the selectable elements to the communication circuitry and provides impedance matching regardless of which or how many of the antenna elements are selected. Selecting different combinations of antenna elements results in a configurable radiation pattern; alternatively, selecting several elements may result in an omnidirectional radiation pattern.

Owner:ARRIS ENTERPRISES LLC

Antenna with active elements

Owner:KYOCERA AVX COMPONENTS (SAN DIEGO) INC

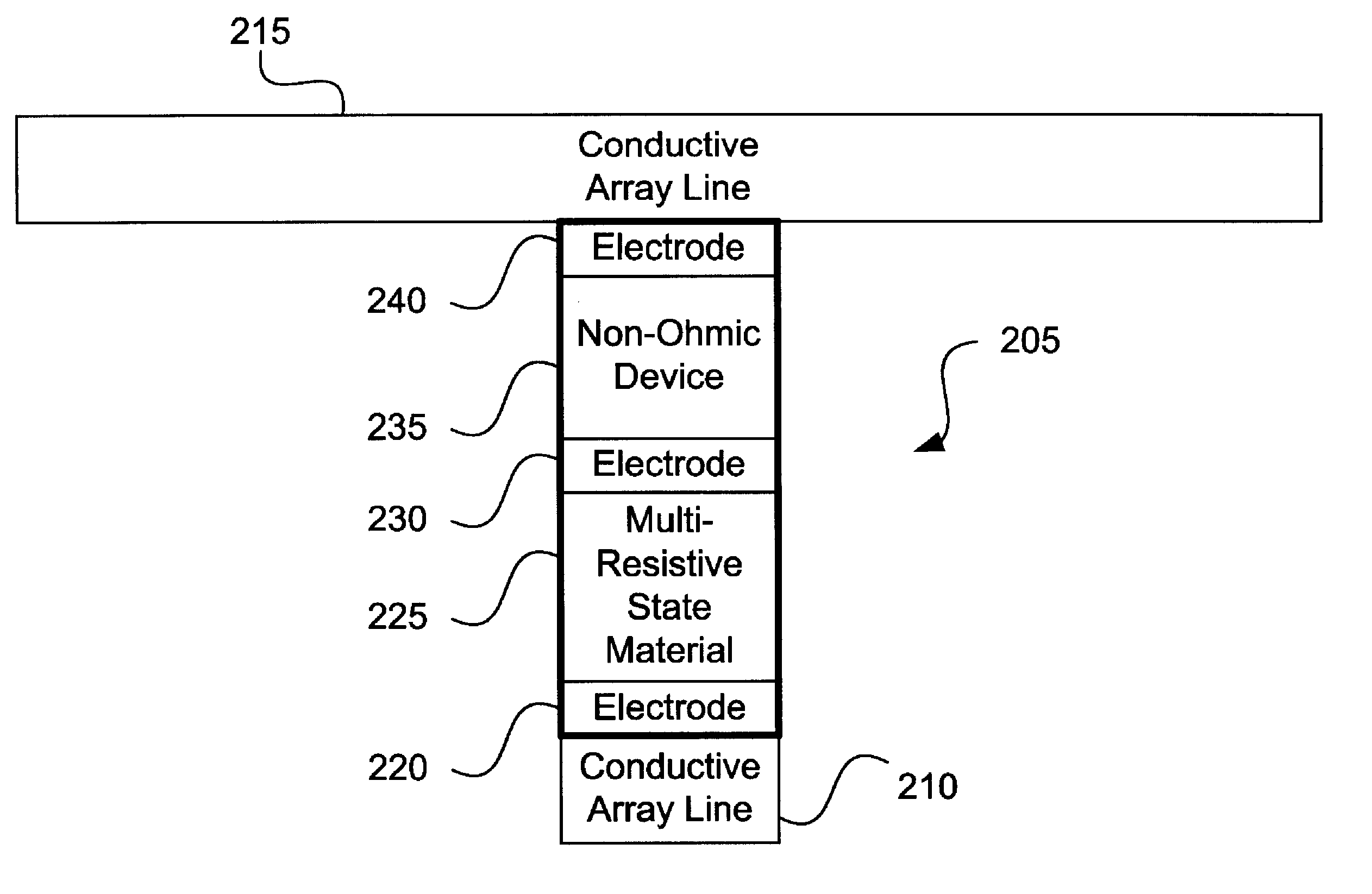

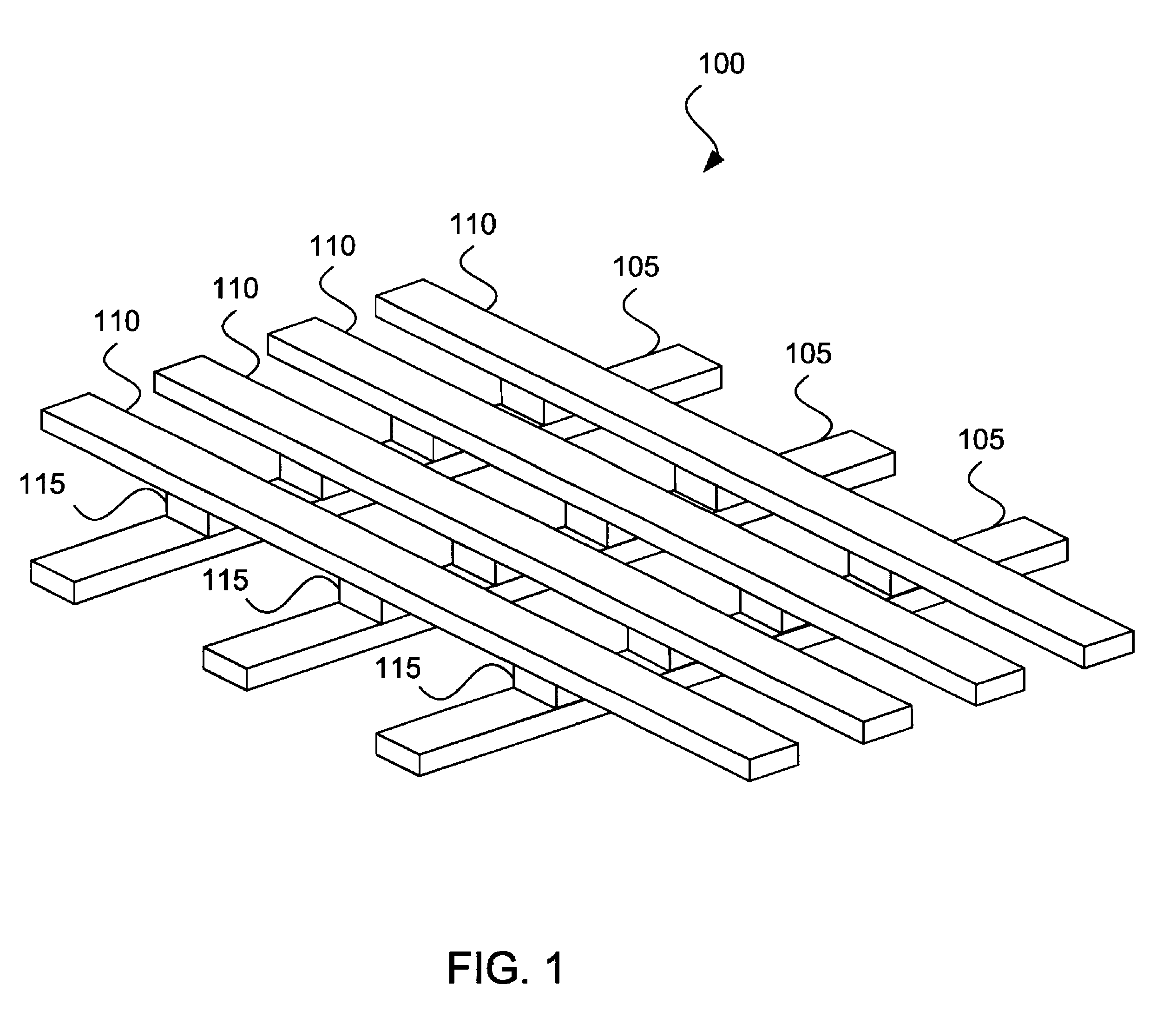

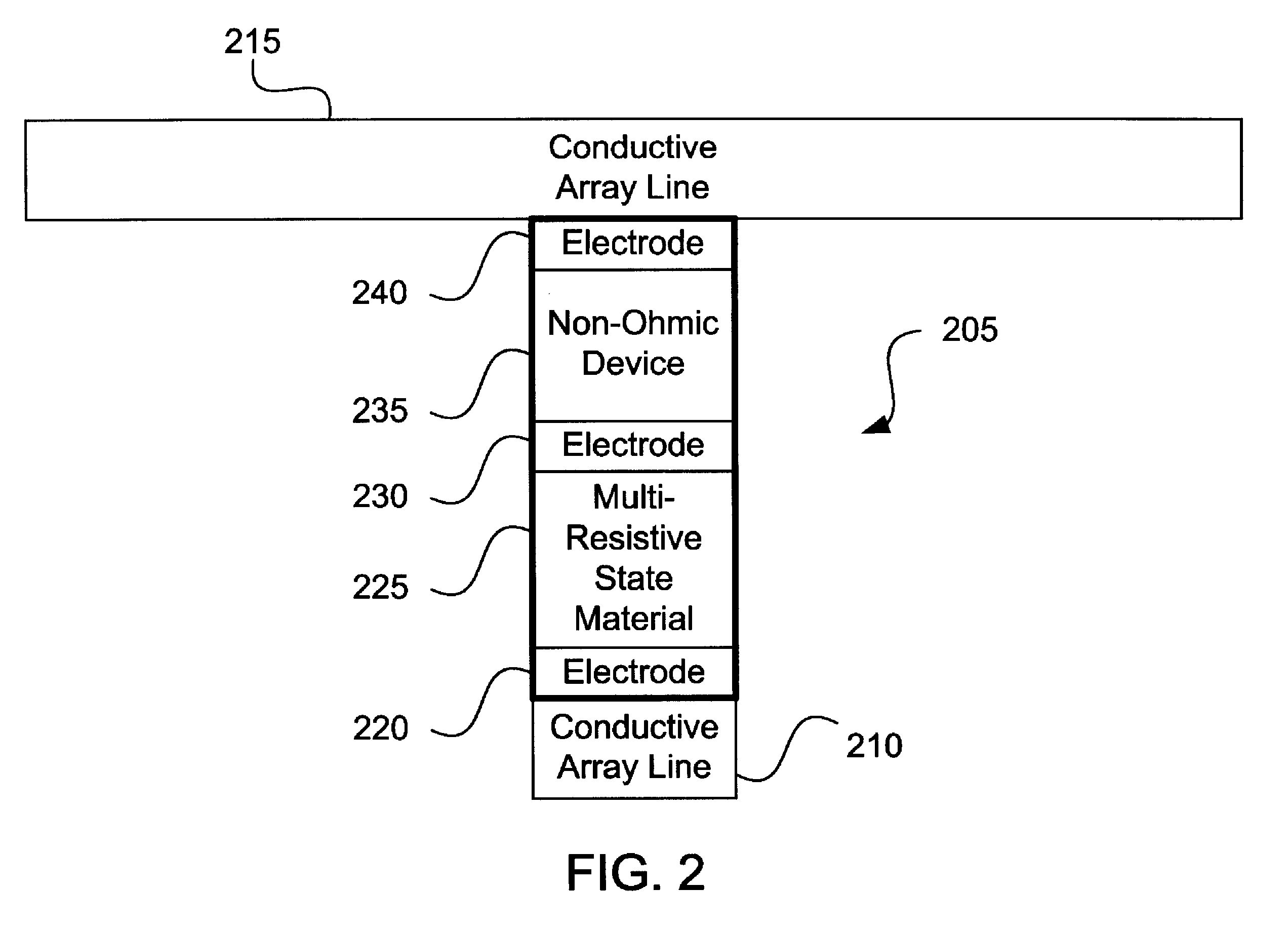

Re-writable memory with non-linear memory element

A re-writable memory that uses resistive memory cell elements with non-linear IV characteristics is disclosed. Non-linearity is important in certain memory arrays to prevent unselected cells from being disturbed and to reduce the required current. Non-linearity refers to the ability of the element to block the majority of current up to a certain level, but then, once that level is reached, the element allows the majority of the current over and above that level to flow.

Owner:UNITY SEMICON

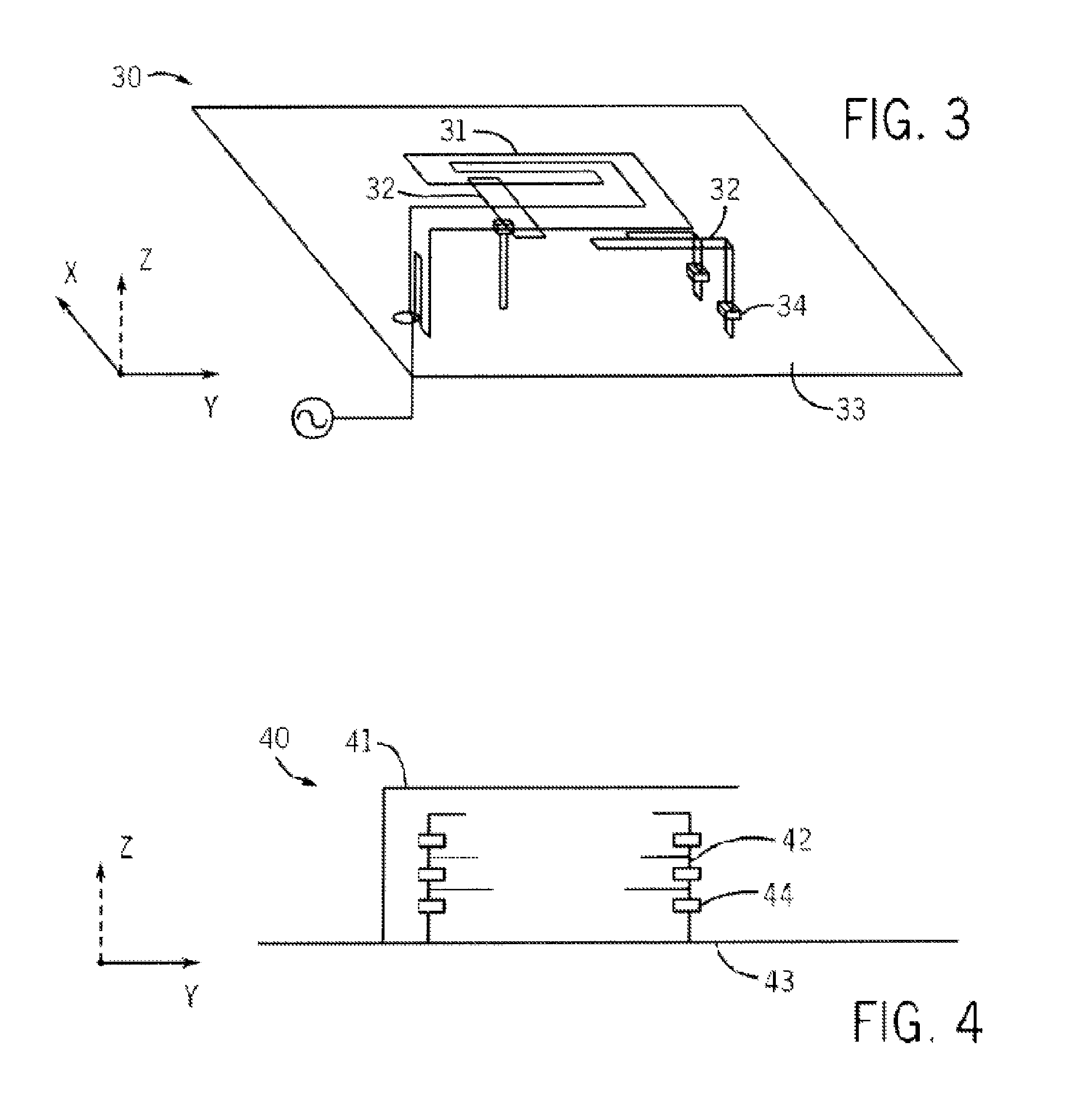

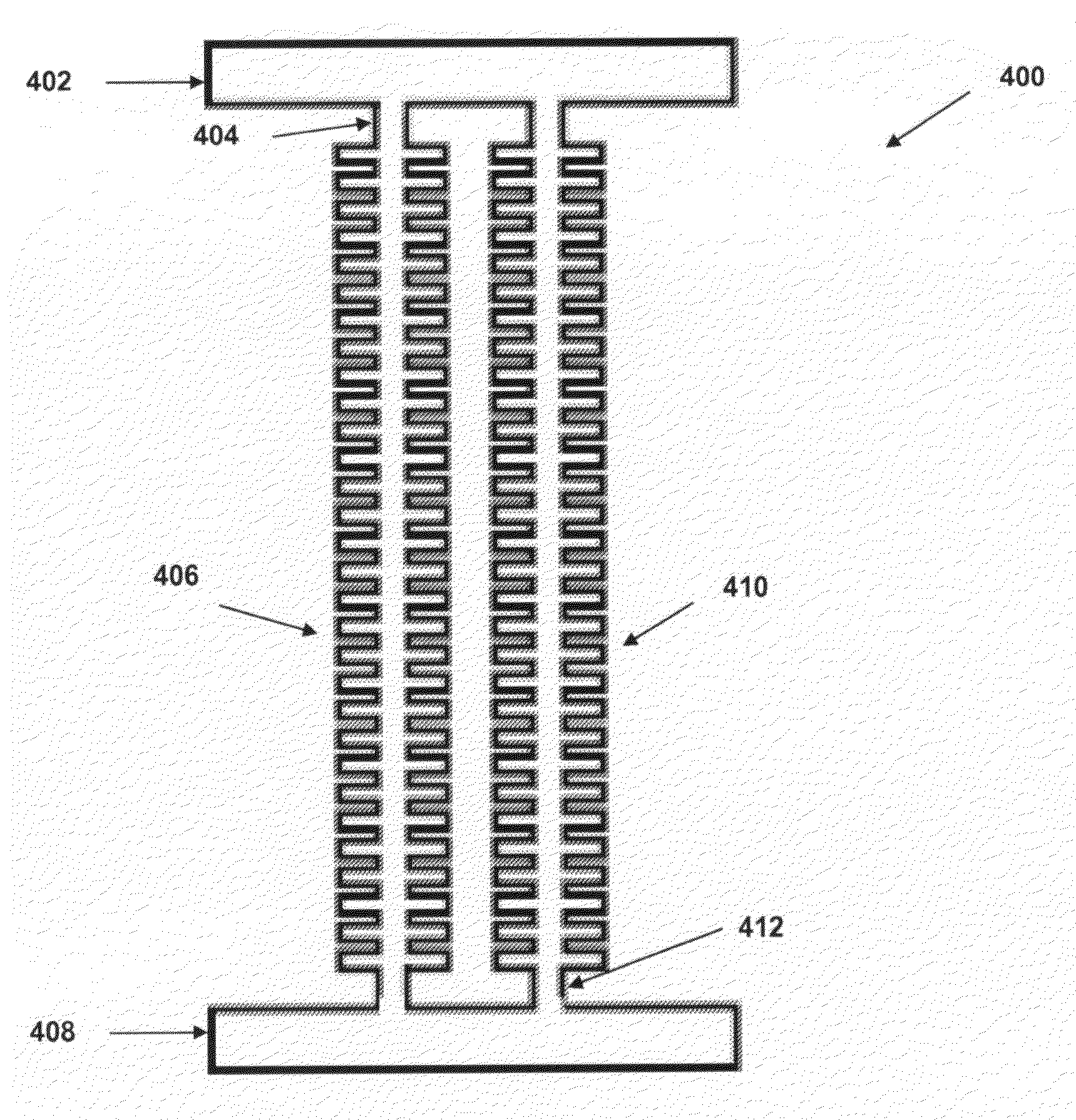

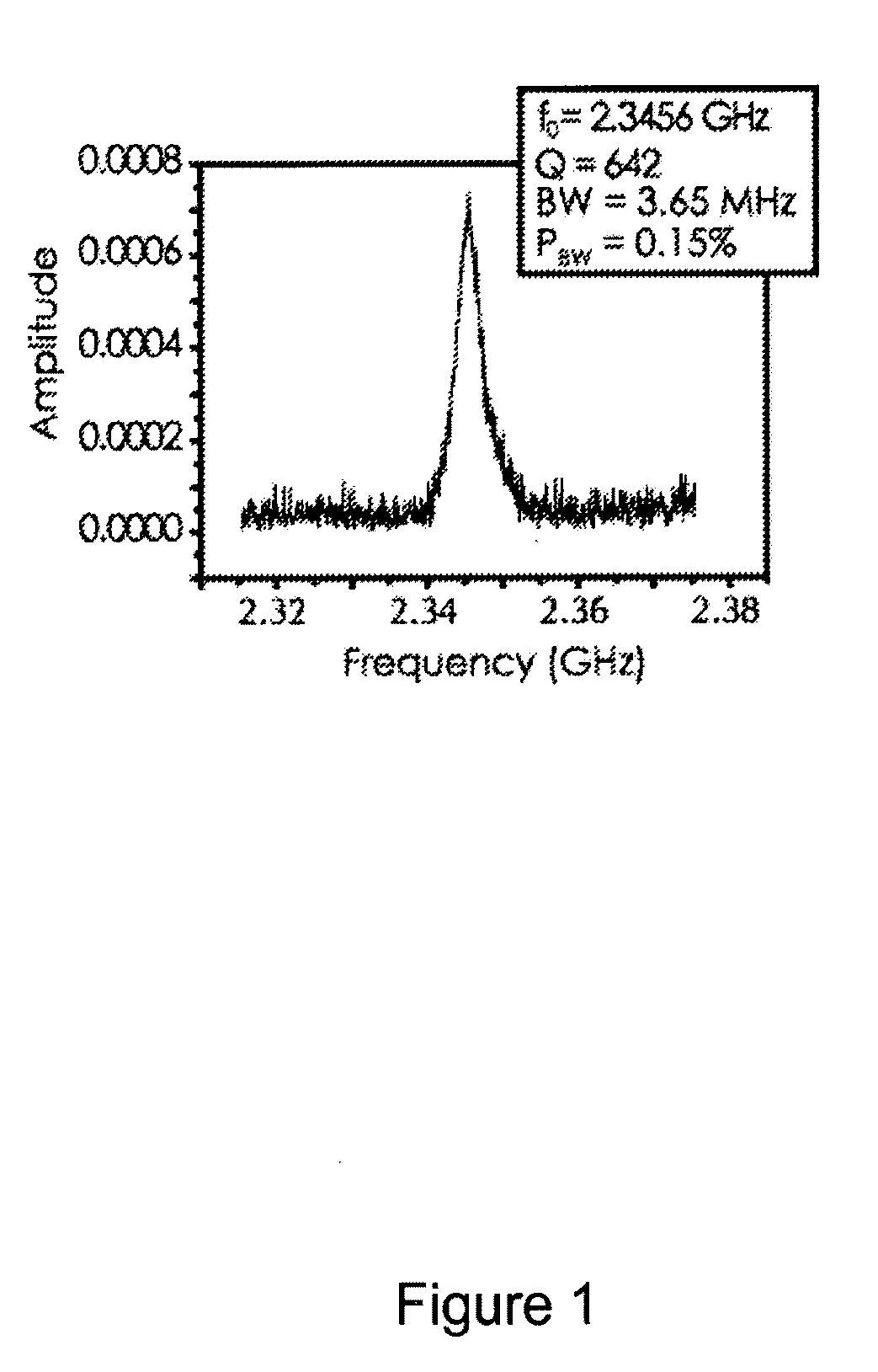

Nano electromechanical integrated-circuit filter

InactiveUS20100007443A1More powerIncrease spaceImpedence networksSemiconductor devicesFundamental frequencySilicon

A nano electromechanical integrated circuit filter and method of making. The filter comprises a silicon substrate; a sacrificial layer; a device layer including at least one resonator, wherein the resonator includes sub-micron excitable elements and wherein the at least one resonator possess a fundamental mode frequency as well as a collective mode frequency and wherein the collective mode frequency of the at least one resonator is determined by the fundamental frequency of the sub-micron elements.

Owner:CLARIANT INT LTD +1

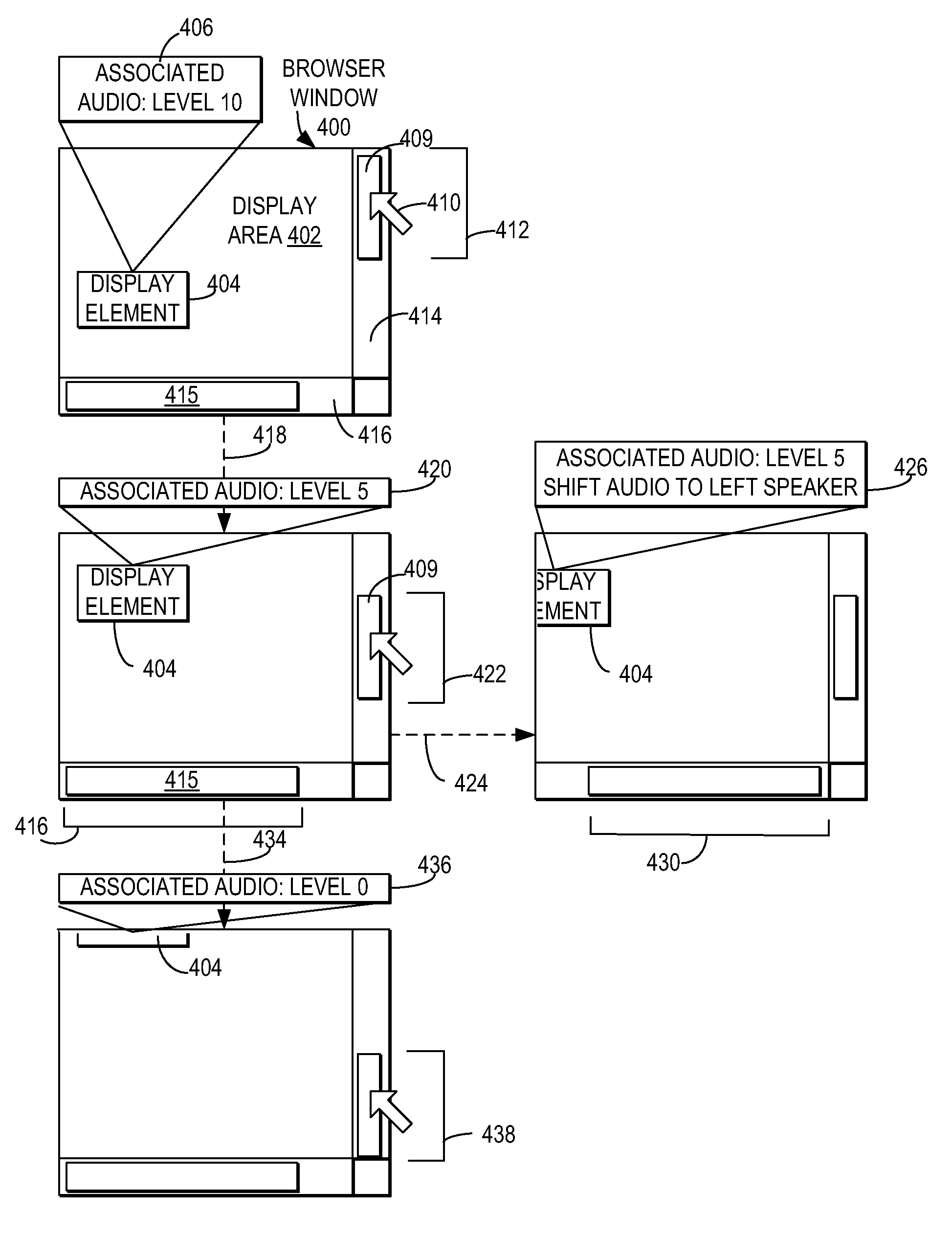

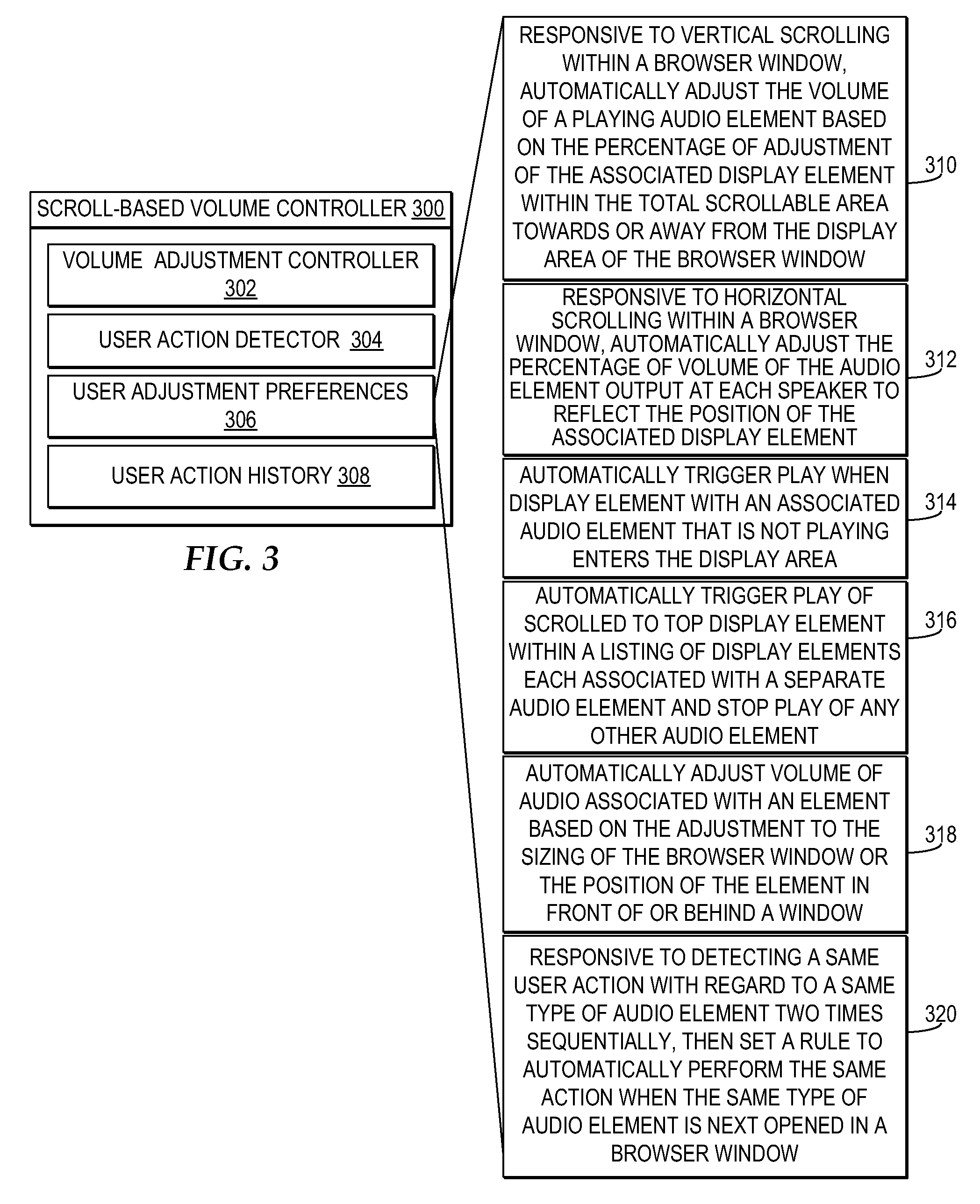

Adjusting the volume of an audio element responsive to a user scrolling through a browser window

InactiveUS20080025529A1Easy volume controlSmall sizeManually-operated gain controlSpecial data processing applicationsHuman–computer interactionOs element

A scroll-based volume controller detects a user selection to scroll through a browser window loaded with data comprising at least one display element, wherein an audio element is associated with the display element and wherein the size of the displayable data is larger than the display area of the browser window. The scroll-based volume controller, responsive to detecting the user selection to scroll through the browser window, calculates a change in position of the display element relative to the browser window. The audio element may include an audio file that is downloaded or streamed to the browser. Next, the scroll-based volume controller automatically adjusts a volume of the associated audio element based on the calculated change in position of the display element relative to the browser window, such that the volume of the audio element, associated with said display element, is automatically adjusted as the position of the display element changes relative to the particular browser window when the user scrolls through the data in the browser window, without the user having to separately select to adjust the volume of the audio element using a separate volume control input.

Owner:LINKEDIN

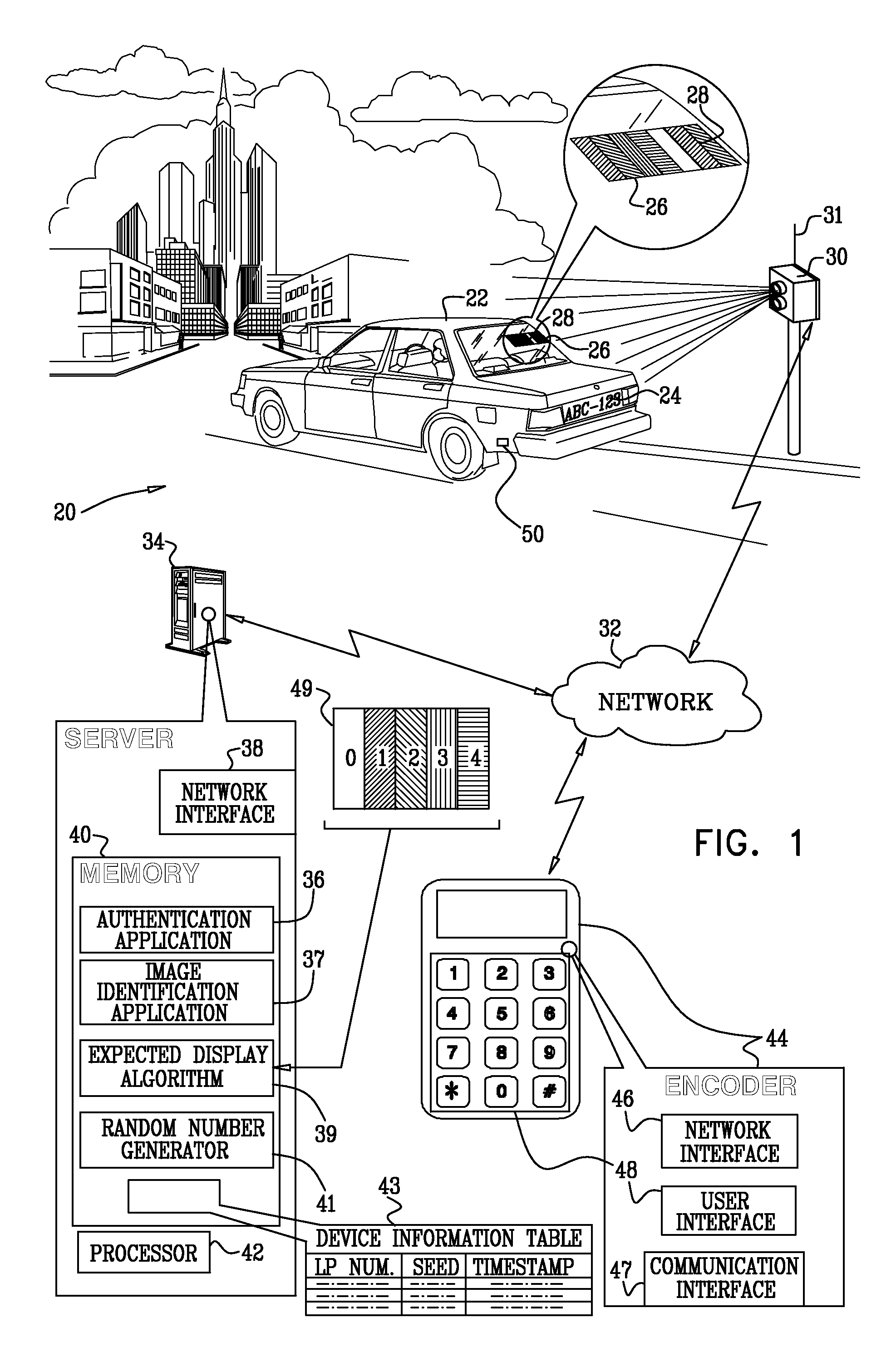

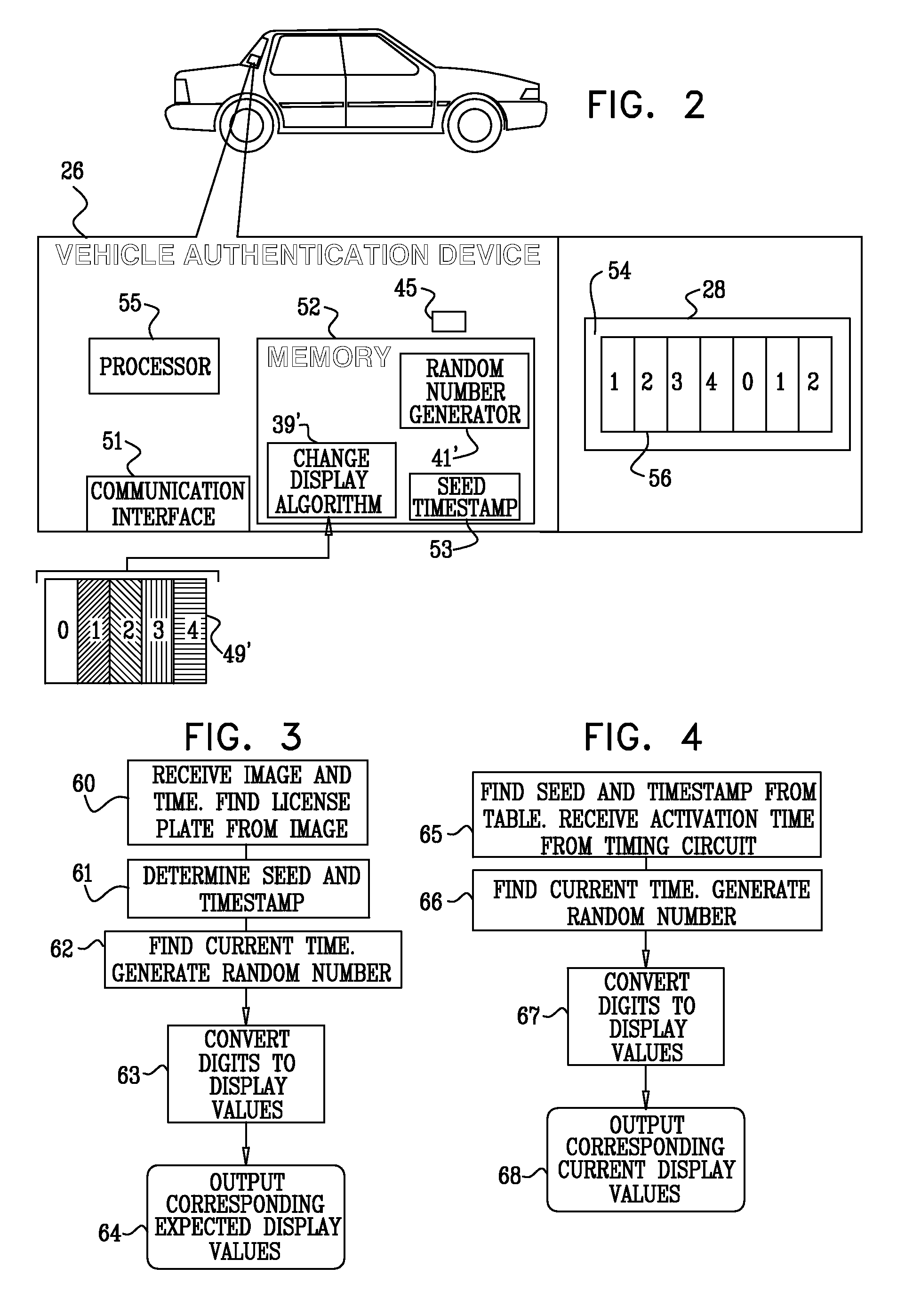

Verifying Vehicle Authenticity

A method for verifying authenticity of a vehicle, including programming a device to sequentially change a device element to an altered device element according to a change device element algorithm, and attaching the device to the vehicle. The method also includes generating the altered device element, and verifying that the altered device element matches an expected device element generated by the algorithm.

Owner:IBM CORP

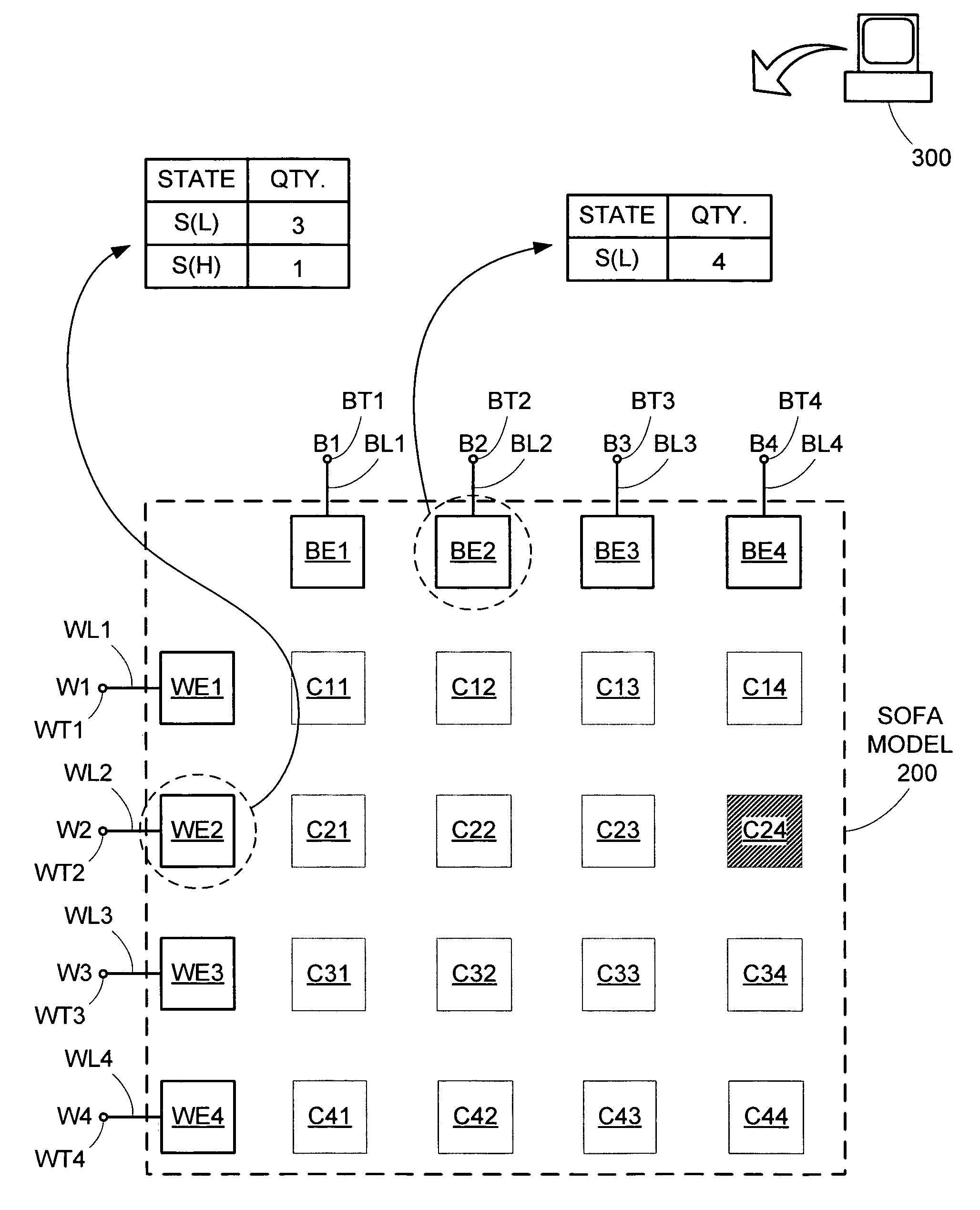

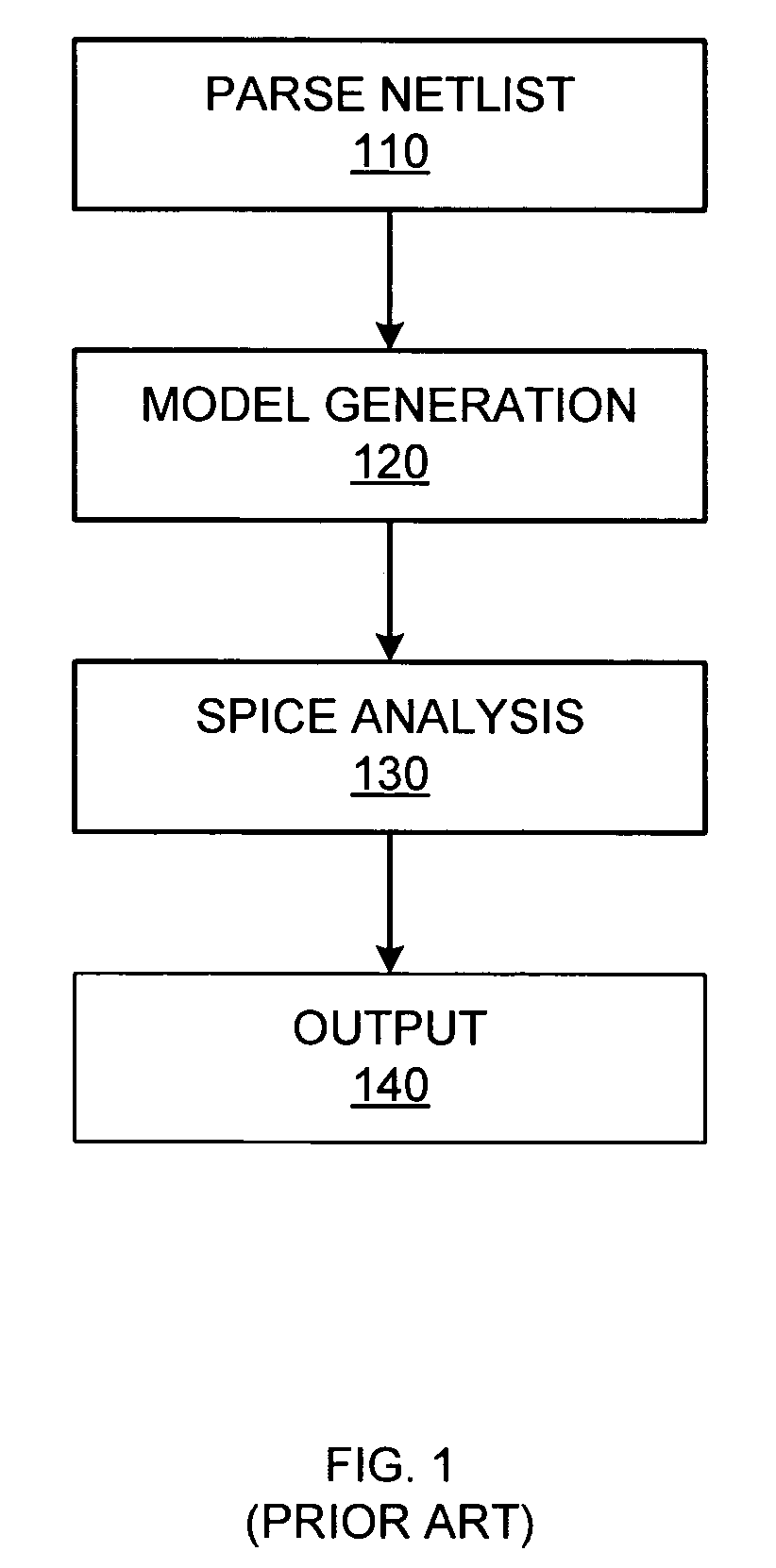

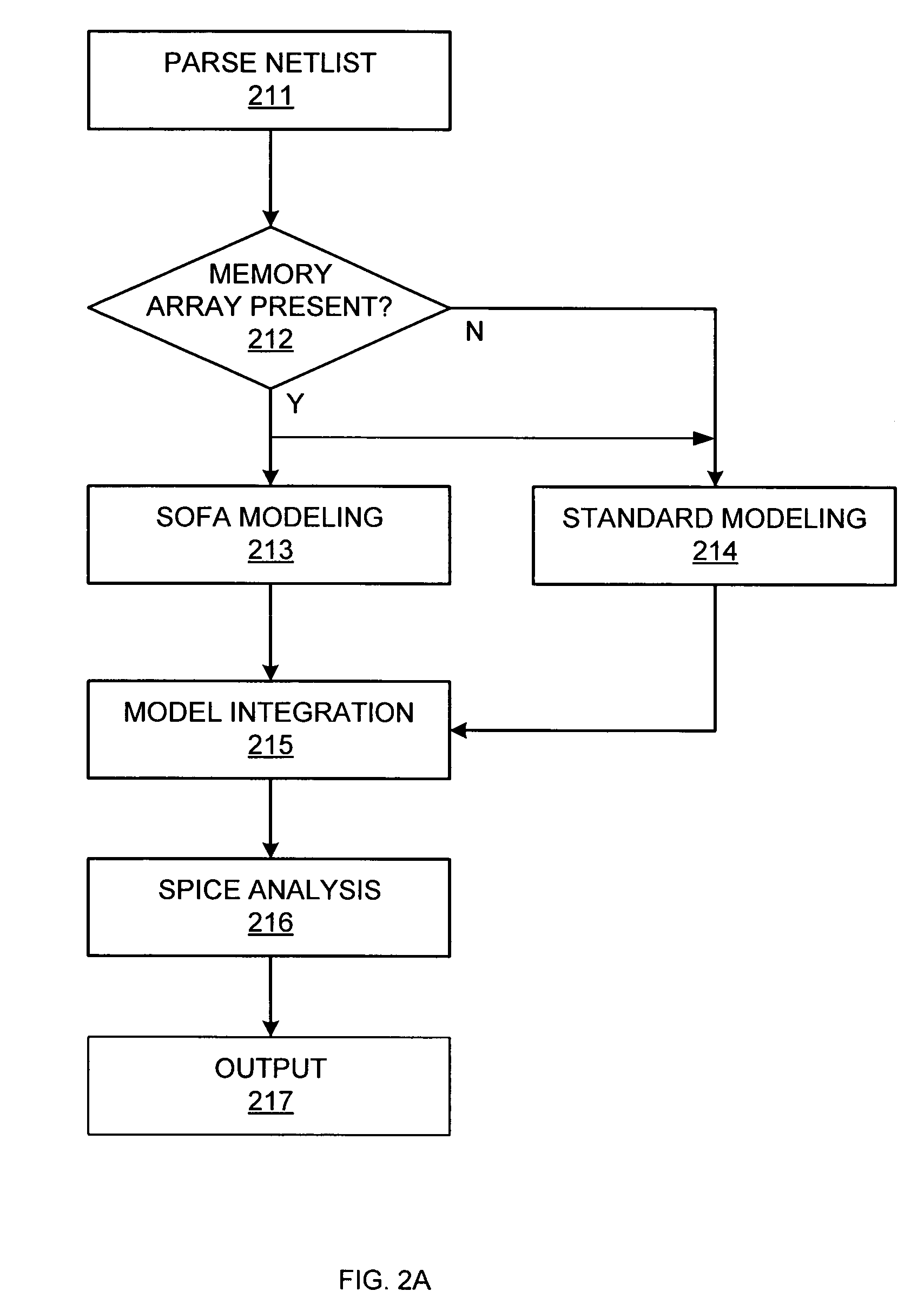

SPICE optimized for arrays

ActiveUS7324363B2Efficiently and accurately simulateMinimization requirementsDigital storageComputer aided designParallel computingCell state

A memory array can be optimized for SPICE simulation by modeling the memory array as a collection of boundary elements that track the cell states of memory cells connected to a particular array terminal. By maintaining a cell state distribution for each boundary element, the simulation behavior at the array terminal associated with that boundary element can be accurately determined by modeling each unique cell state, multiplying the results by the corresponding quantities from the cell state distribution, and then adding the results to obtain final values for the array terminal. This allows accurate simulation results to be achieved without needing to simulate each cell independently. Furthermore, by removing any references to unoccupied cell states (e.g., by removing such states from the cell state distribution and / or eliminating model equations for such states), the memory and cpu usage requirements during the simulation can be minimized.

Owner:SYNOPSYS INC

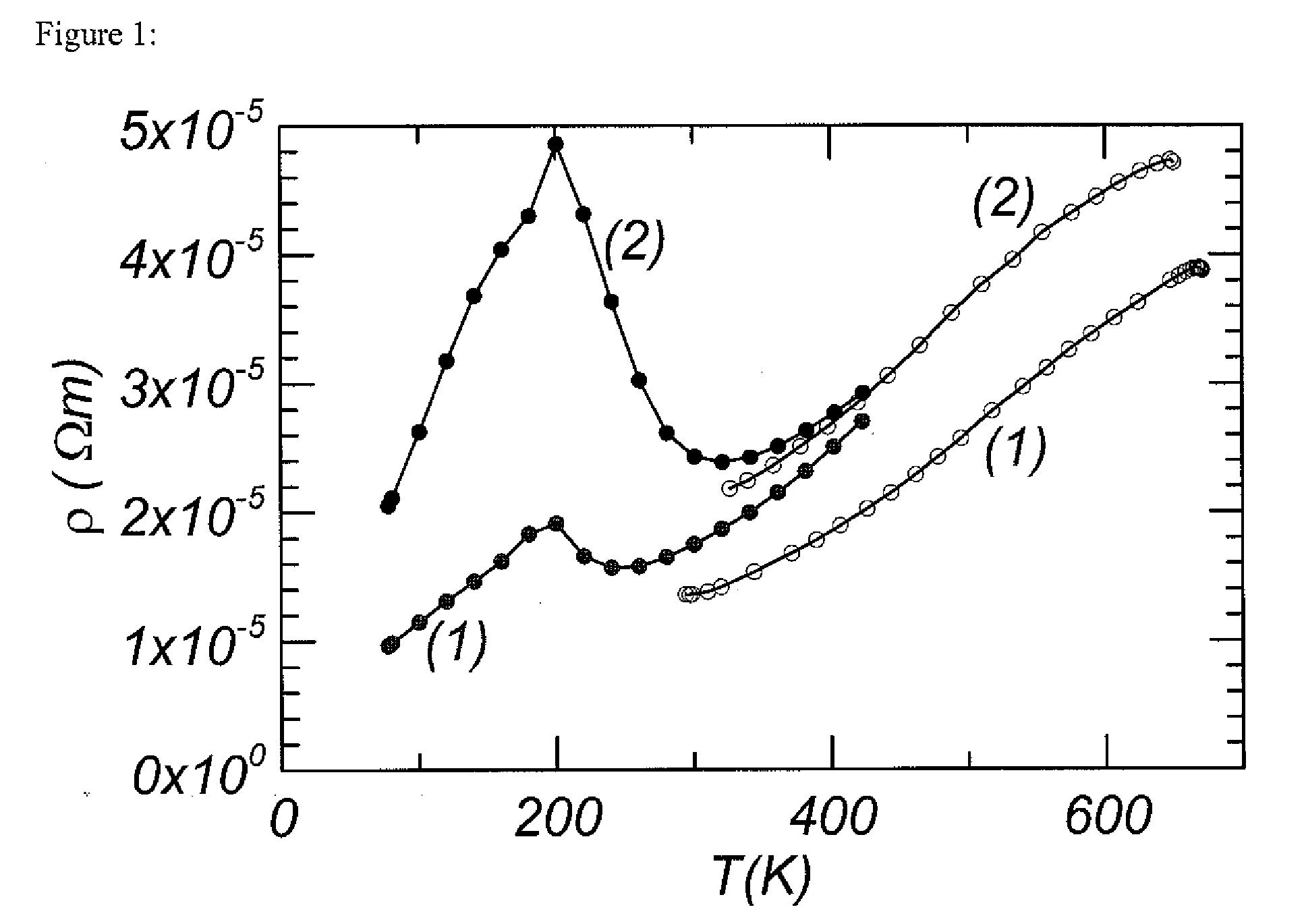

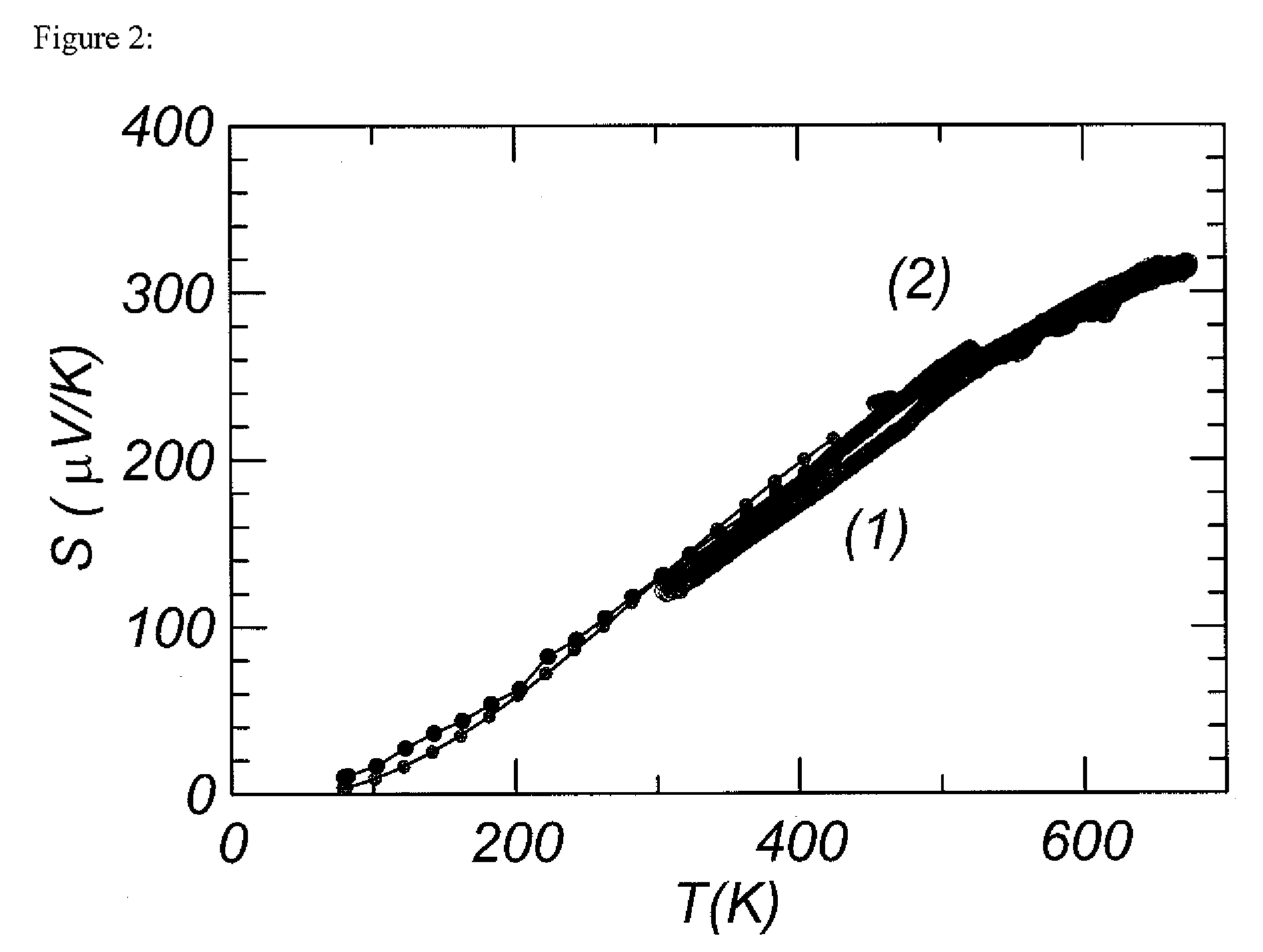

Thermoelectric figure of merit enhancement by modification of the electronic density of states

InactiveUS20090178700A1Material nanotechnologyThermoelectric device manufacture/treatmentOs elementChromium

A thermoelectric material and a method of fabricating a thermoelectric material are provided. The thermoelectric material includes a doped compound of at least one Group IV element and at least one Group VI element. The compound is doped with at least one dopant selected from the group consisting of: at least one Group Ia element, at least one Group IIb element, at least one Group IIIa element, at least one Group IIIb element, at least one lanthanide element, and chromium. The at least one Group IV element is on a first sublattice of sites and the at least one Group VI element is on a second sublattice of sites, and the at least one Group IV element includes at least 95% of the first sublattice sites. The compound has a peak thermoelectric figure of merit ZT value greater than 0.7 at temperatures greater than 500 K.

Owner:THE OHIO STATE UNIV RES FOUND

Circuit board having a peripheral antenna apparatus with selectable antenna elements

ActiveUS20060109191A1Printed electric component incorporationRadiating elements structural formsEngineeringImpedance matching

A circuit board for wireless communications includes communication circuitry for modulating and / or demodulating a radio frequency (RF) signal and an antenna apparatus for transmitting and receiving the RF signal, the antenna apparatus having selectable antenna elements located near one or more peripheries of the circuit board. A first antenna element produces a first directional radiation pattern; a second antenna element produces a second directional radiation pattern offset from the first radiation pattern. The antenna elements may include one or more reflectors configured to provide gain and broaden the frequency response of the antenna element. A switching network couples one or more of the selectable elements to the communication circuitry and provides impedance matching regardless of which or how many of the antenna elements are selected. Selecting different combinations of antenna elements results in a configurable radiation pattern; alternatively, selecting several elements may result in an omnidirectional radiation pattern.

Owner:ARRIS ENTERPRISES LLC

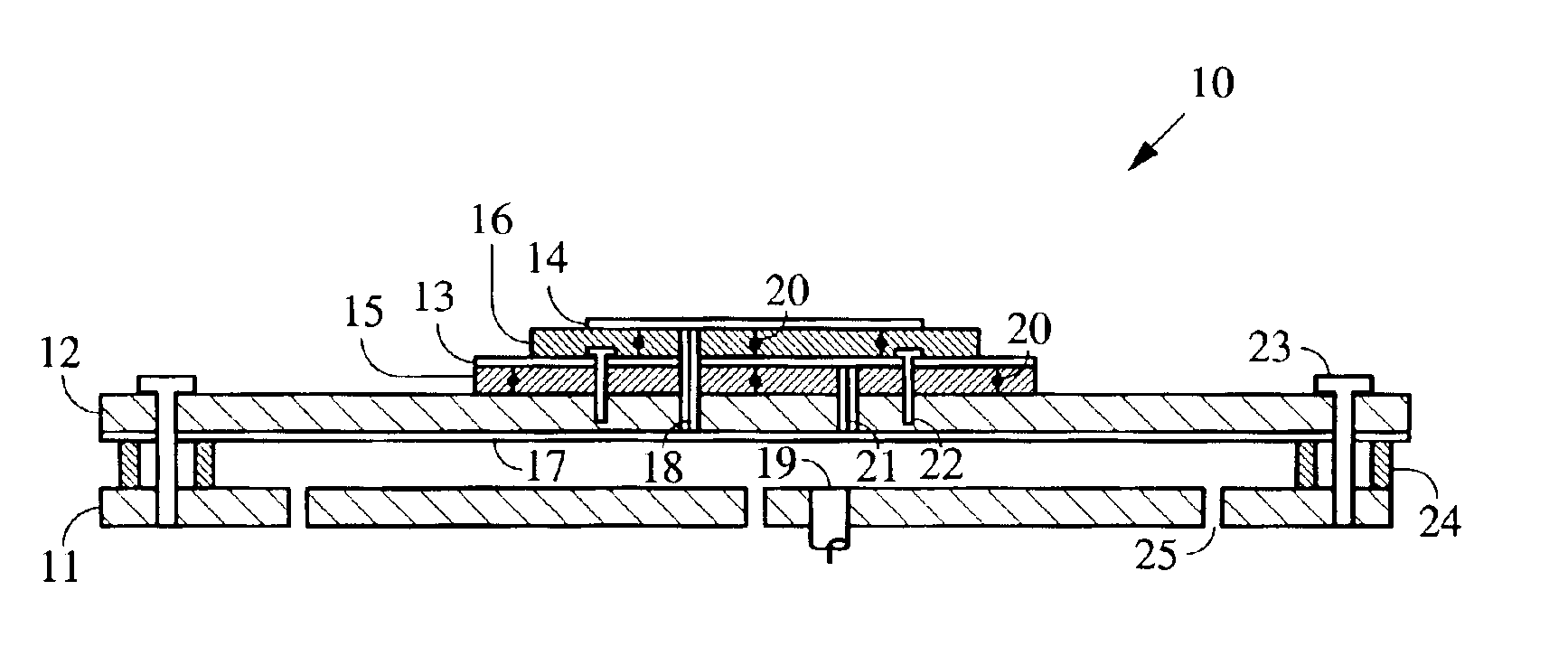

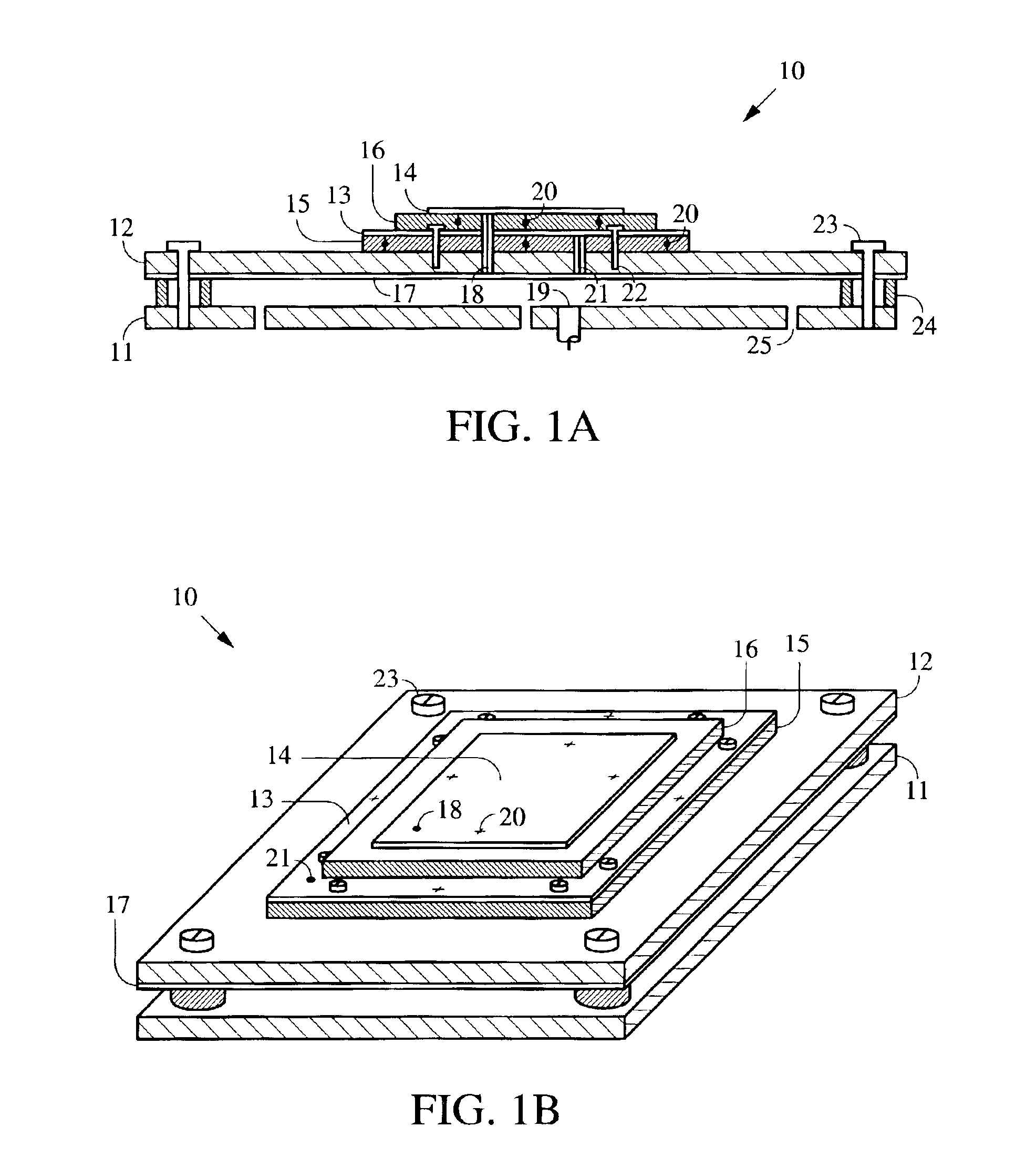

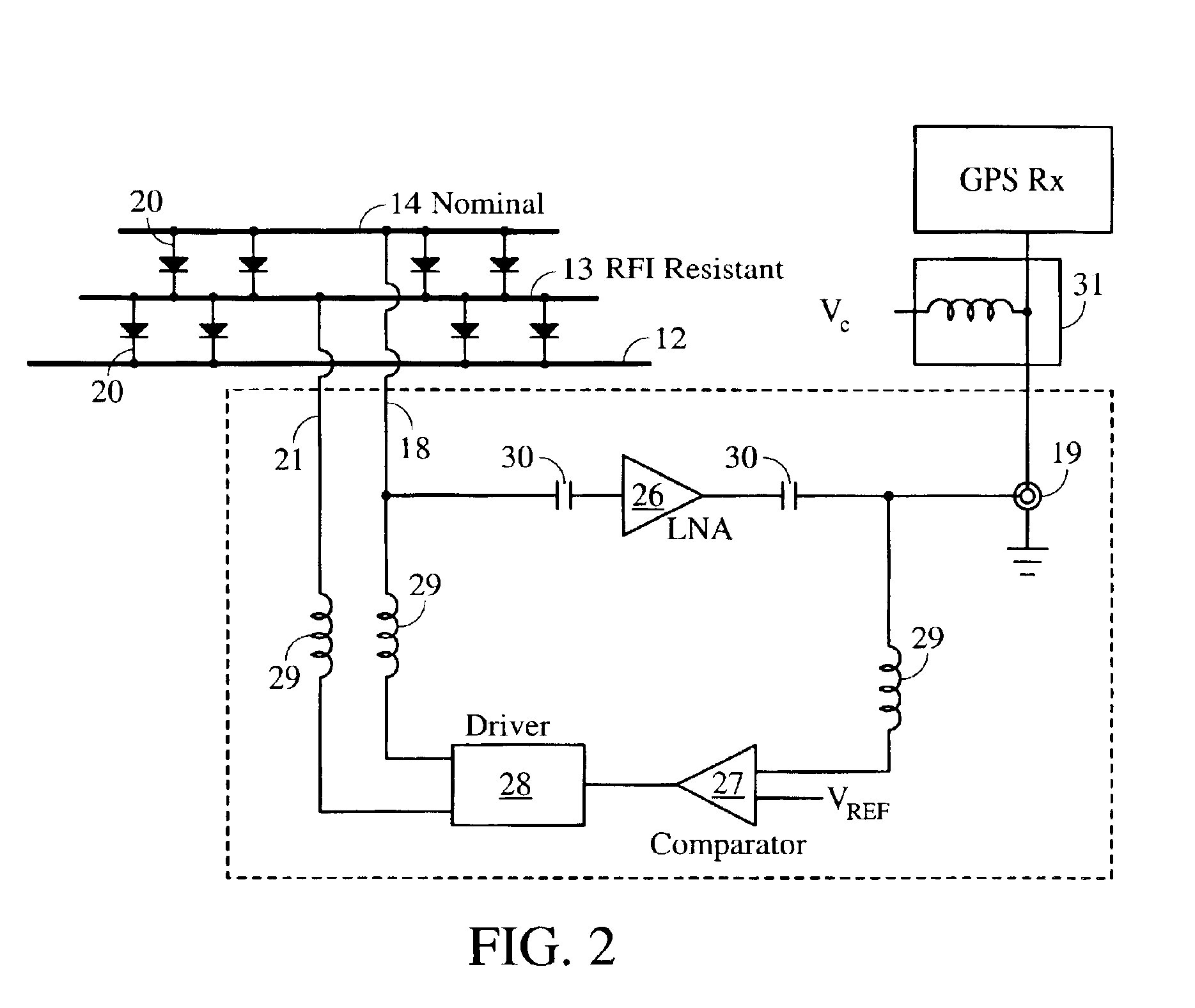

Dual-element microstrip patch antenna for mitigating radio frequency interference

InactiveUS6930639B2High sensitivityLess sensitivitySimultaneous aerial operationsRadiating elements structural formsMicrostrip patch antennaHorizon

Method and apparatus for reducing radio frequency interference (RFI) using a dual-element patch antenna [10]. The antenna possesses two antenna elements [13, 14] having distinct radiation patterns. Either element may be independently selected using a DC bias voltage. Diodes [20] connected to the elements serve to disable one element when the other is selected. In one selected mode, a nominal radiation pattern provides a broad, hemispherical shaped sensitivity that is designed for acquiring and tracking all navigation satellites above the horizon. This nominal radiation pattern, however, is susceptible to interference that is present near or below the horizon. The second selectable radiation pattern of the dual-element antenna has comparatively higher gain toward zenith, and lower gain at and below the horizon to mitigate interference. This combination of features is packaged in a single antenna unit that can be a direct replacement for existing antennas. The dual-element antenna unit has a low vertical profile and is suitable for mounting on high-speed moving vehicles.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

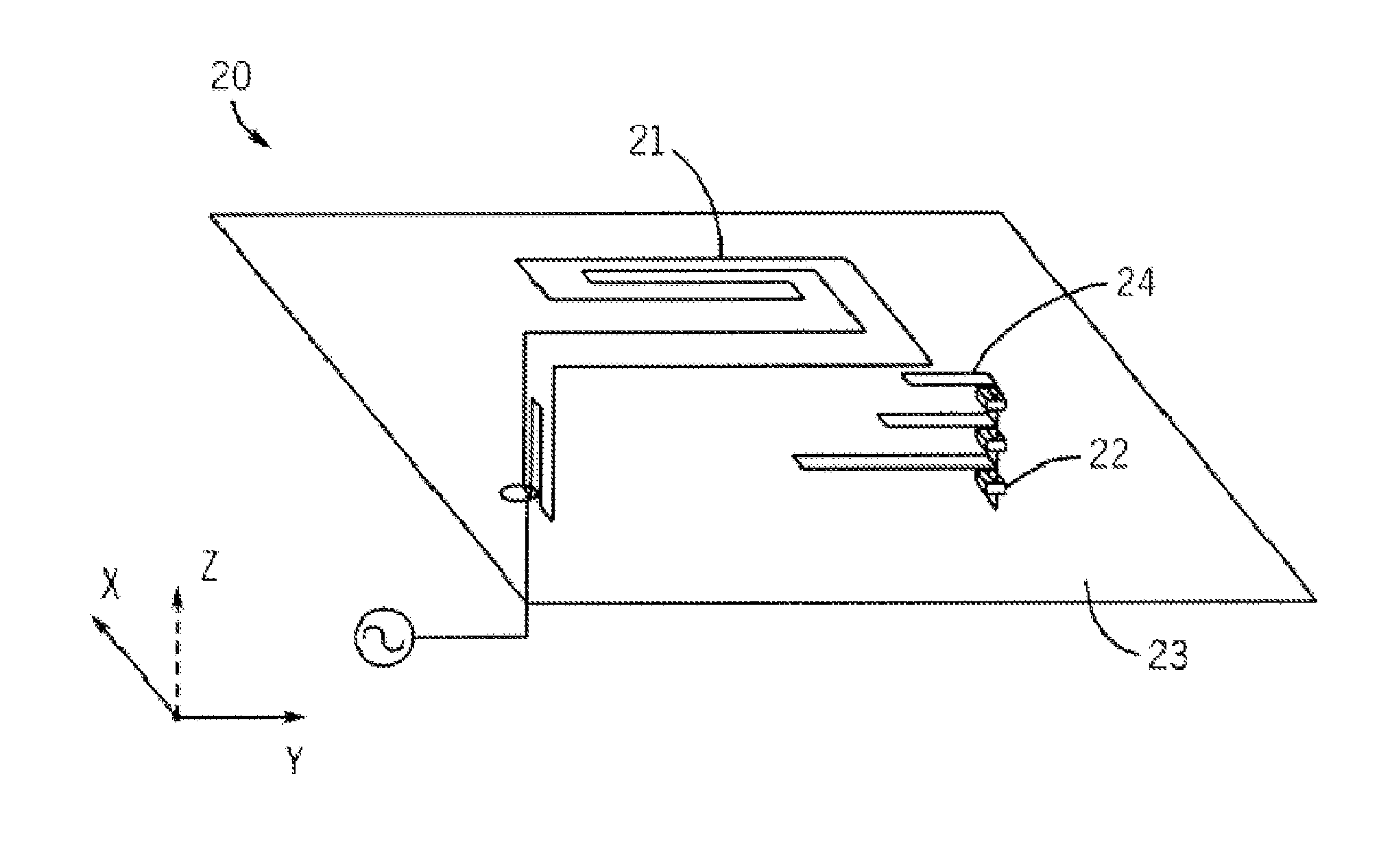

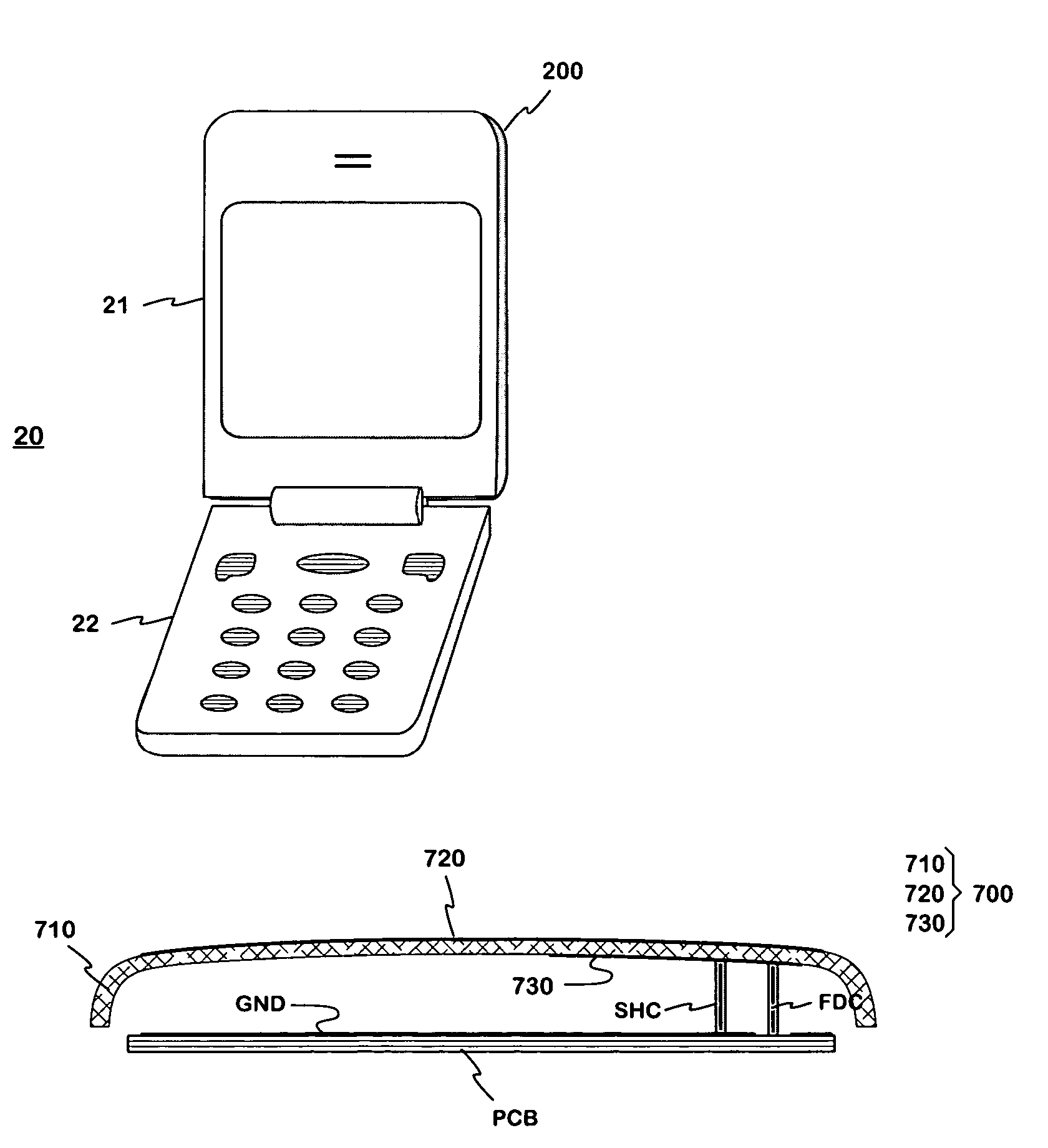

Antenna element for a radio device

ActiveUS7391378B2Low production costEnhanced radiationSimultaneous aerial operationsAntenna supports/mountingsRadio equipmentAntenna element

A radiating antenna element intended to be used in small-sized radio devices, and a radio device having an antenna element according to the invention. The antenna element is part of the covers of a radio device. The antenna element may be conductive throughout, or it may comprise a dielectric portion and a conductive portion, which constitute a single integral component. The radiating portion of the antenna element is relatively large, e.g. in a foldable phone (20) the antenna element (200) may comprise the whole cover of a foldable part (21) except for the front side. The radiating element is advantageously fed electromagnetically through a feed element. As the radiating element is relatively large and is located on the outer surface of the device, the radiation characteristics of the antenna are good, and the space required by the antenna inside the device is relatively small.

Owner:PULSE FINLAND

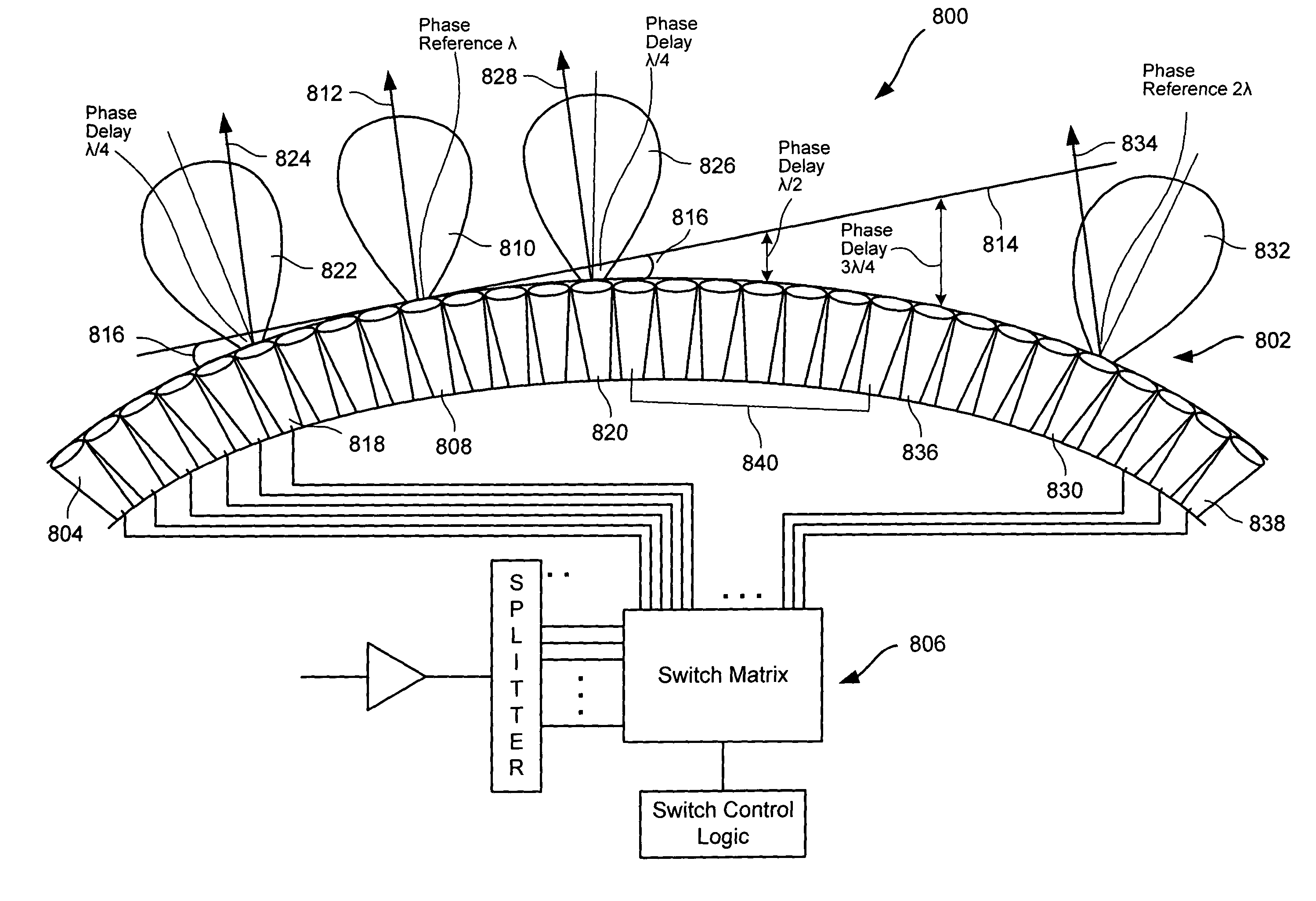

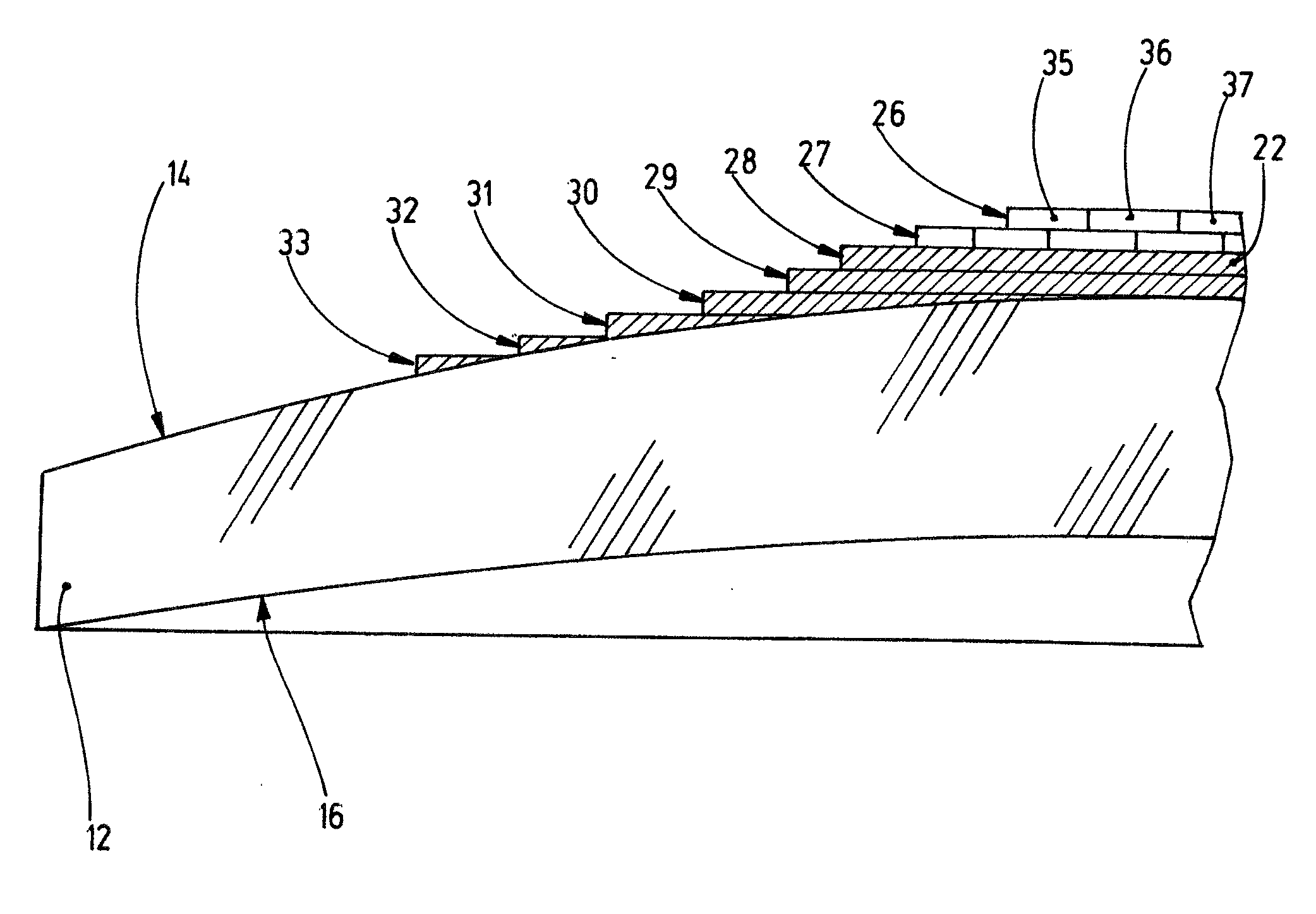

High-gain conformal array antenna

ActiveUS6961025B1Antenna adaptation in movable bodiesIndividually energised antenna arraysControl signalBeam direction

An antenna array system comprising a plurality of antenna elements organized in an array and configured to form a non-planar shaped antenna array surface. The antenna array system further comprises switching circuitry configured to switch each of the plurality of antenna elements on or off based on control signals. In one embodiment, the antenna array system is configured such that the antenna beam direction can be steered in a first direction by switching on a first set of antenna elements, and the antenna beam direction can be steered in a second direction by switching on a second set of antenna elements. In one embodiment, the second set of antenna elements can include one or more antenna elements from the first set of antenna elements, or the second set of antenna elements may not include any antenna elements from the first set.

Owner:LOCKHEED MARTIN CORP

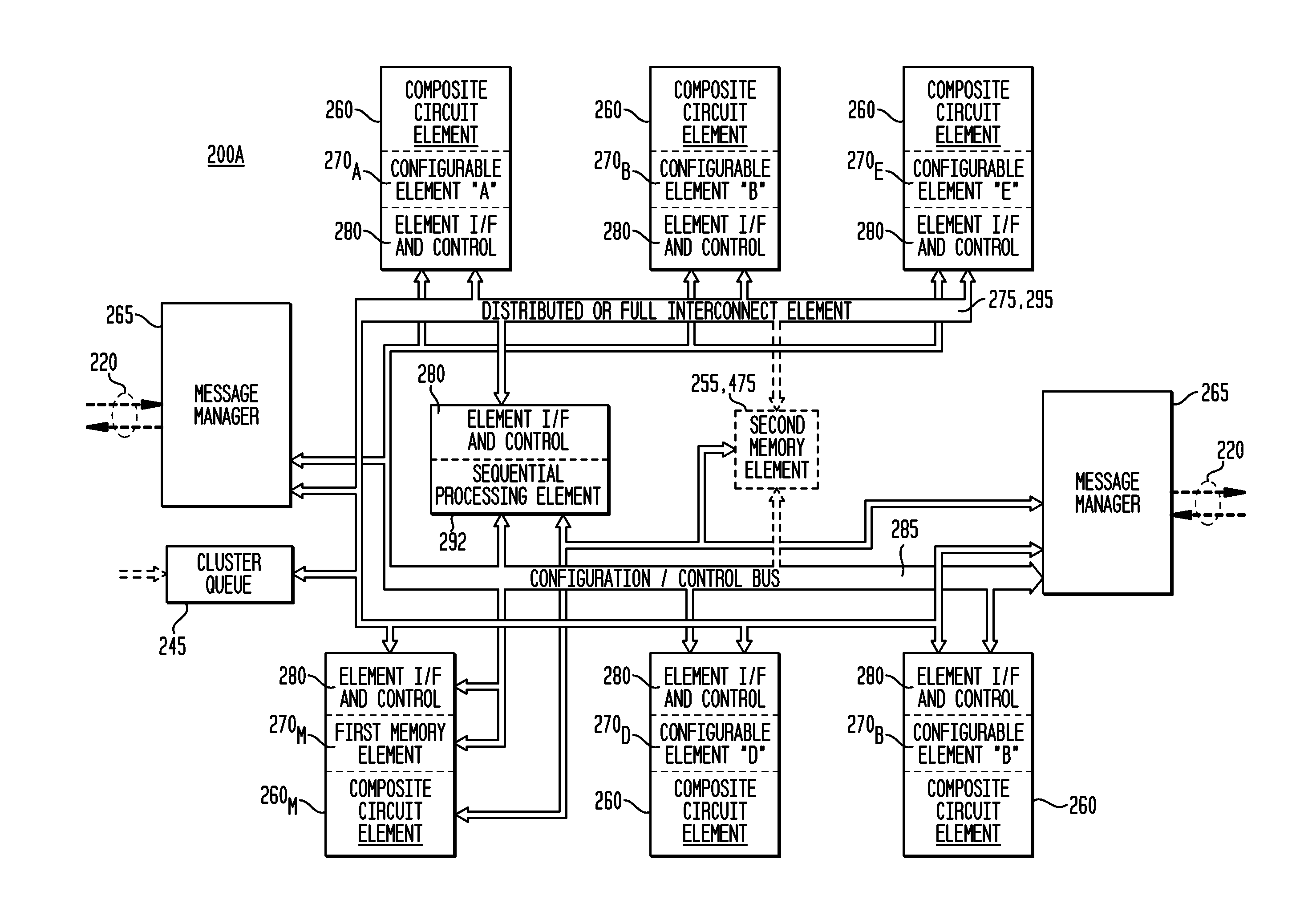

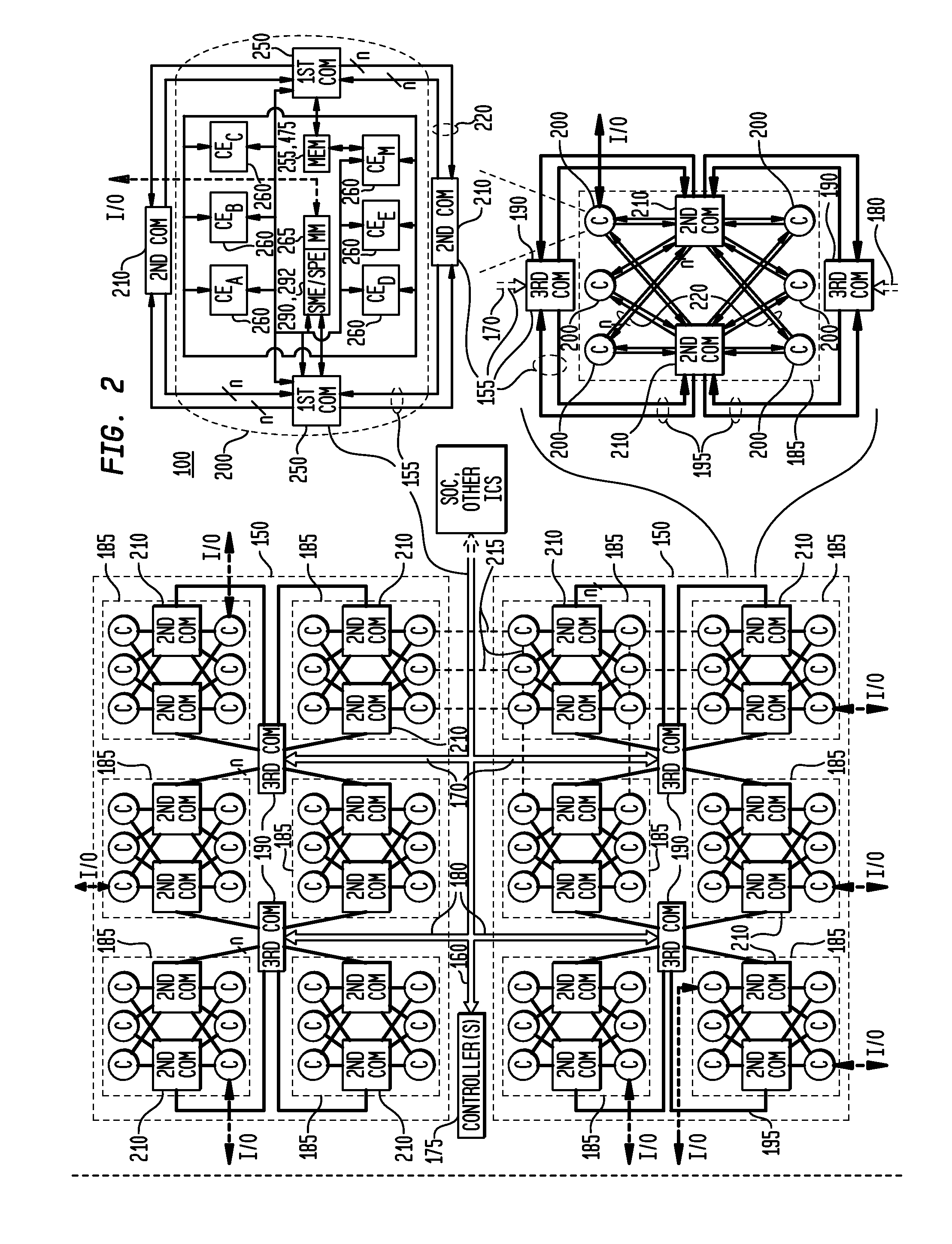

Hierarchically-Scalable Reconfigurable Integrated Circuit Architecture With Unit Delay Modules

InactiveUS20120126850A1Significant resiliencyError detection/correctionFail-safe circuitsData operationsTime delays

The exemplary embodiments provide a reconfigurable integrated circuit architecture having a predetermined, unit timing increment (or delay) for both data operations and data word transfers within every zone and between zones, which are independent of application placement and routing. An exemplary IC comprises a plurality of circuit zones, with each zone comprising: a plurality of composite circuit elements, a plurality of cluster queues, and a full interconnect bus. Each composite circuit element comprises: a configurable circuit element circuit and an element interface and control circuit, with the element interface and control circuit comprising an input queue and an output queue. Each cluster queue comprises an element interface and control having an input queue and an output queue. The full interconnect bus couples every output queue within the zone to every input queue within the zone. Any data operation performed by a composite circuit element, any data word transfer through a cluster queue, and any data word transfer over the first full interconnect bus, is completed within a predetermined unit time delay which is independent of application placement and application data routing on the reconfigurable IC.

Owner:ELEMENT CXI

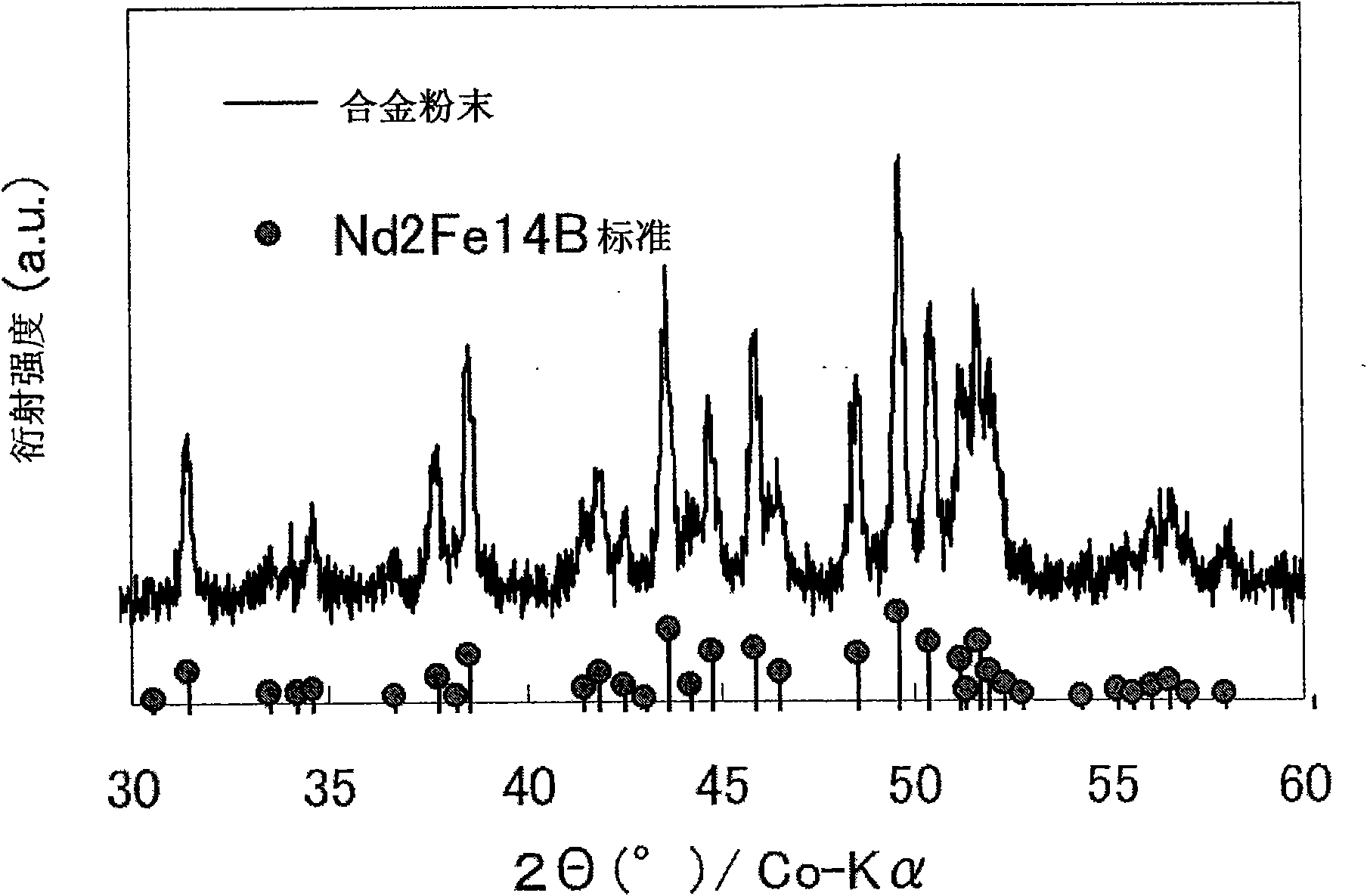

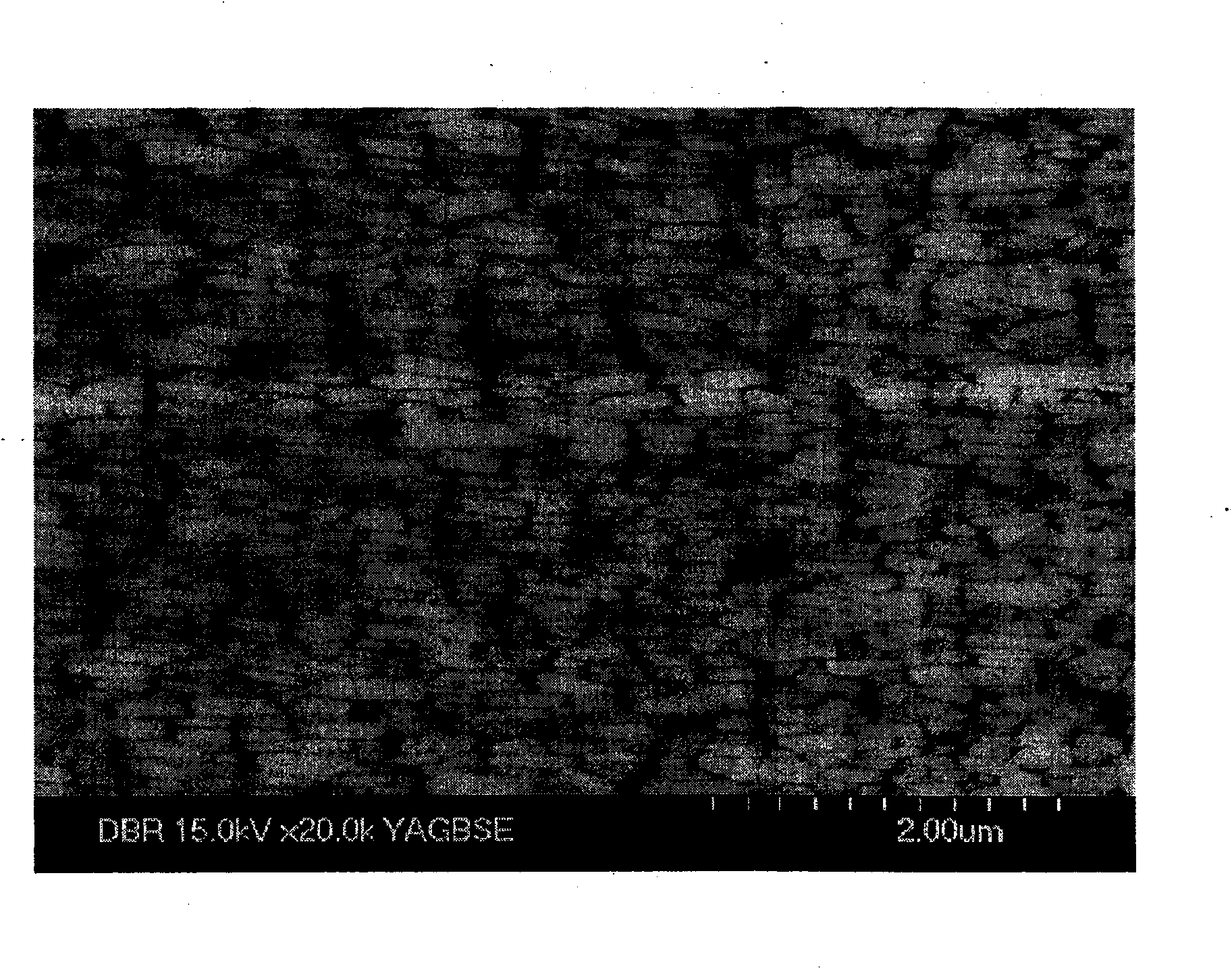

Rare earth magnet and production process thereof

InactiveCN101640087ATransportation and packagingMetal-working apparatusRare-earth magnetGrain boundary

The present invention provides a rare earth magnet, which is formed through at least hot molding, the rare earth magnet containing grains including an R 2 X 14 B phase as a main phase, and a grain boundary phase surrounding peripheries of the grains, in which R is at least one element selected from the group consisting of Nd, Pr, Dy, Tb and Ho, and X is Fe or Fe with a part being substituted by Co; in which an element RH is more concentrated in the grain boundary phase than in the grains, in which the element RH is at least one element selected from the group consisting of Dy, Tb and Ho; and the element RH is present with a substantially constant concentration distribution from the surface part of the magnet to the central part of the magnet.

Owner:DAIDO STEEL CO LTD

Scissoring-type current-perpendicular-to-the-plane giant magnetoresistance (cpp-gmr) sensors with damped free layer structures

A “scissoring-type” current-perpendicular-to-the-plane giant magnetoresistive (CPP-GMR) sensor has magnetically damped free layers. In one embodiment each of the two free layers is in contact with a damping layer that comprises Pt or Pd, or a lanthanoid (an element selected from the group consisting of La, Ce, Pr, Nd, Pm, Sm, Eu, Gd, Tb, Dy, Ho, Er, Th, Yb, and Lu). Each of the two free layers has one of its surfaces in contact with the sensor's electrically conducting nonmagnetic spacer layer and its other surface in contact with its associated damping layer. A nonmagnetic film may be located between each free layer and its associated damping layer. In another embodiment the damping element is present as a dopant or impurity in each of the two free layers. In another embodiment a nanolayer of the damping element is located within each of the two free layers.

Owner:WESTERN DIGITAL TECH INC

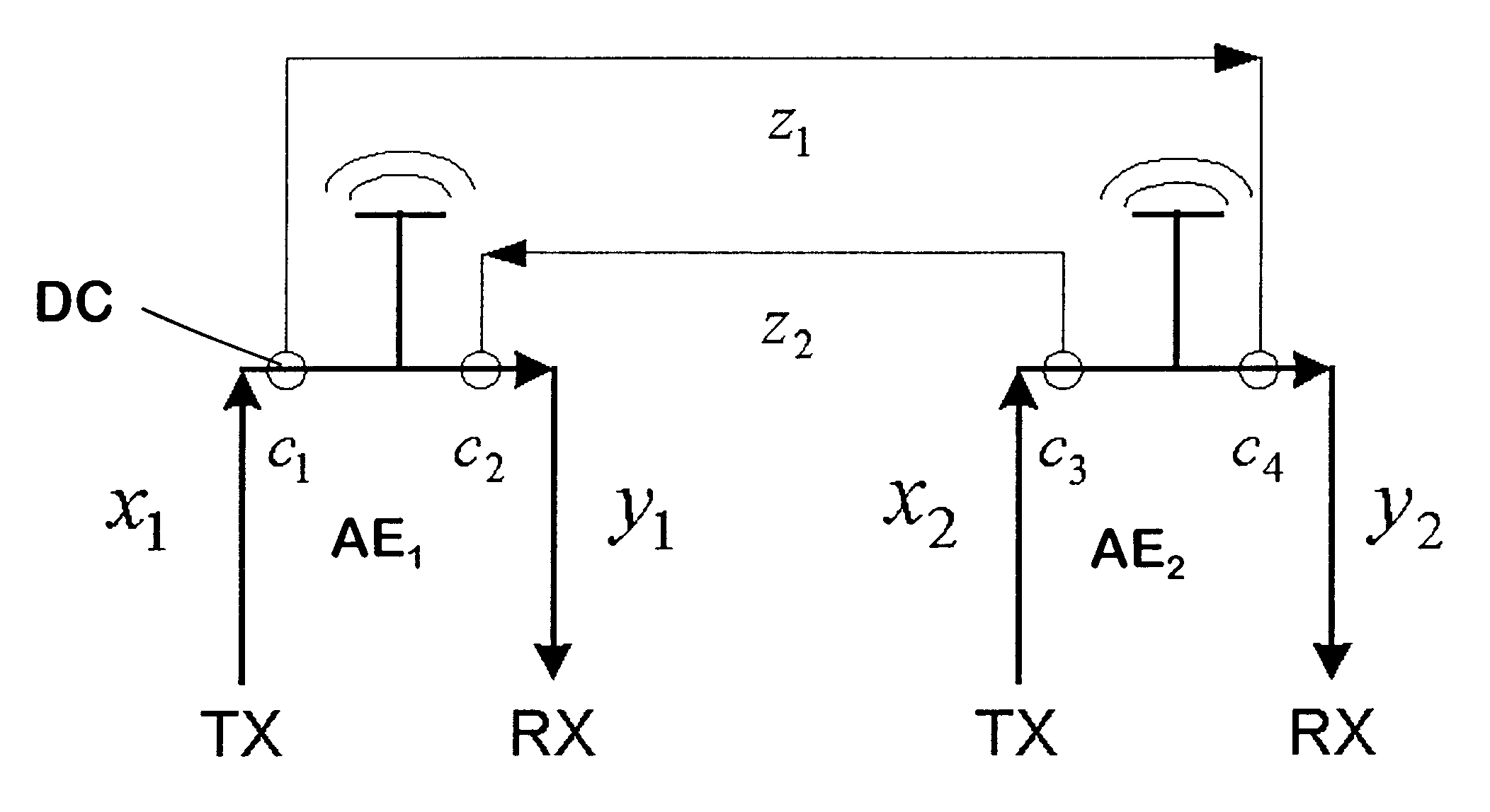

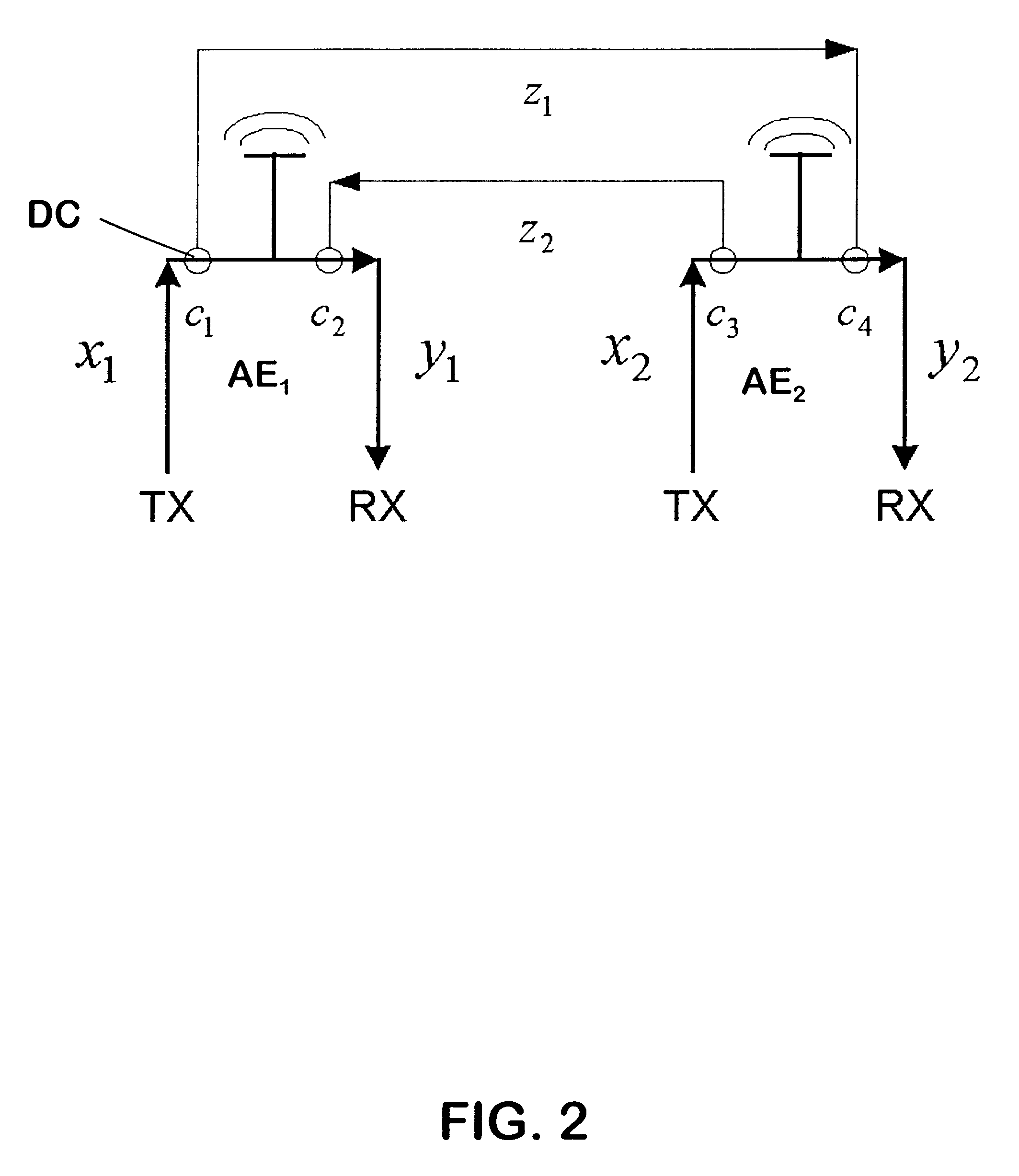

Method for calibrating a smart-antenna array radio transceiver unit and calibrating system

InactiveUS6496140B1Radio wave direction/deviation determination systemsAntennasTransceiverSmart antenna

The invention relates to a method for calibrating a smart-antenna array of a wireless access system using TDD, which antenna array comprises antenna elements with a transmit and a receive branch each. In order to enable a time stable calibration, it is proposed that at least some of the antenna elements are selected in turns to be employed for transmitting broadcast messages. This provides time periods in which only one of said elements is transmitting. Each transmit branch is connected to at least one of the receive branches of another element, signals transmitted via these connections being evaluated for calibration. If receive branches are connected to transmit branches of several elements, it is ensured with the proposed selection that during the broadcast periods these receive branches receive at the most a signal from one element, thus avoiding the need for switches. The invention equally relates to a corresponding radio transceiver unit and a corresponding calibration system.

Owner:NOKIA TECHNOLOGLES OY

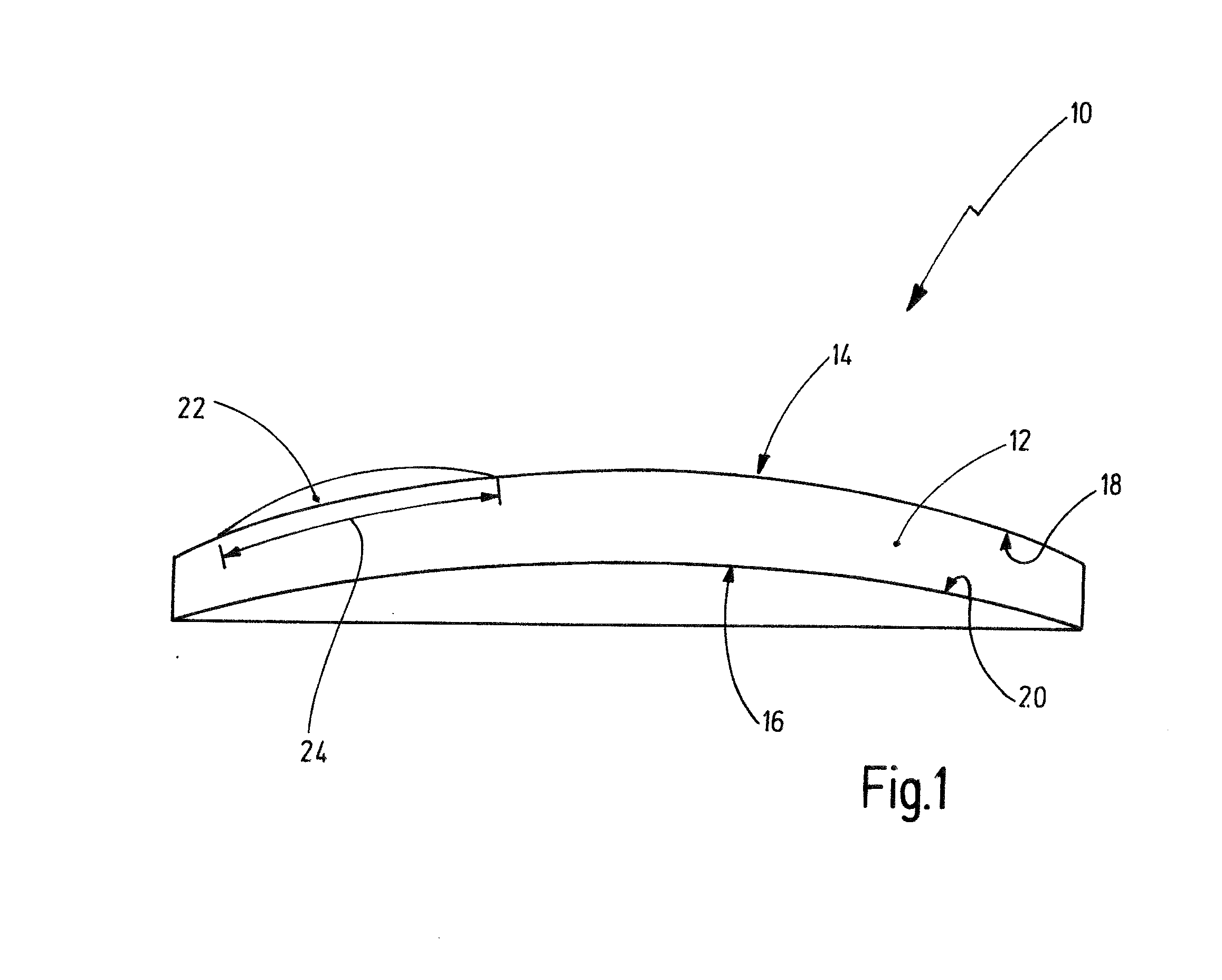

Spectacle lens and method for making the same

ActiveUS20150153589A1Simple preparation processCost-effectiveOptical articlesCellulose adhesivesSpherical powerEyewear

A method for manufacturing a spectacle lens includes the steps of providing an integral main lens. The integral main lens has a front surface and a back surface and is at least one selected from a group consisting of a spherical power lens, an astigmatic power lens, and a lens having a main curvature of the front surface in a first meridian and a main curvature of the back surface in the first meridian which are different so as to provide for a spherical power different from zero; and applying at least one additional lens element to at least a part of the front surface and / or at least a part of the back surface, wherein the at least one additional lens element includes at least one layer having a multitude of layer elements, in particular printed layer elements. Further, the invention is directed to a corresponding spectacle lens.

Owner:CARL ZEISS VISION INT GMBH +1

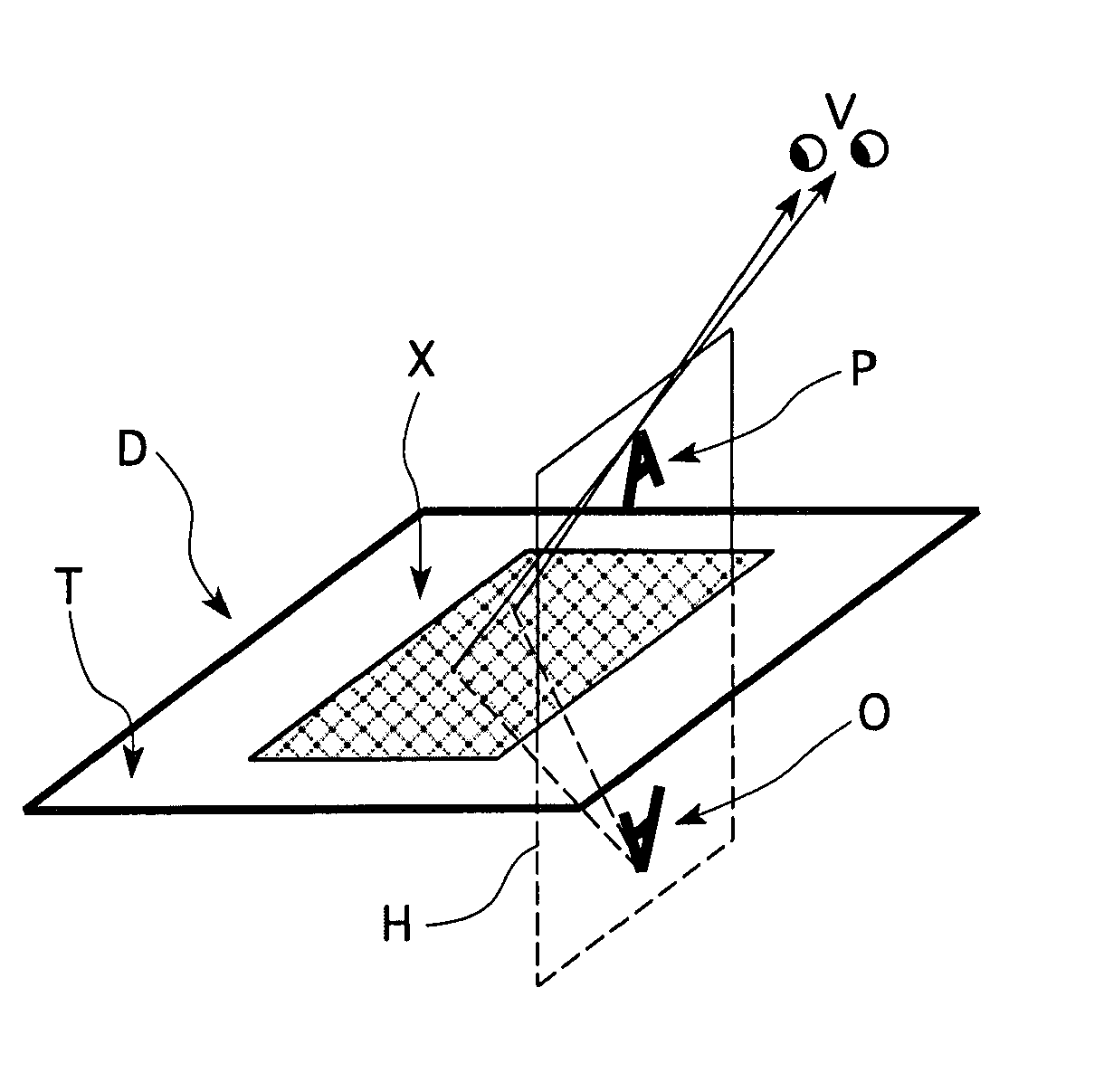

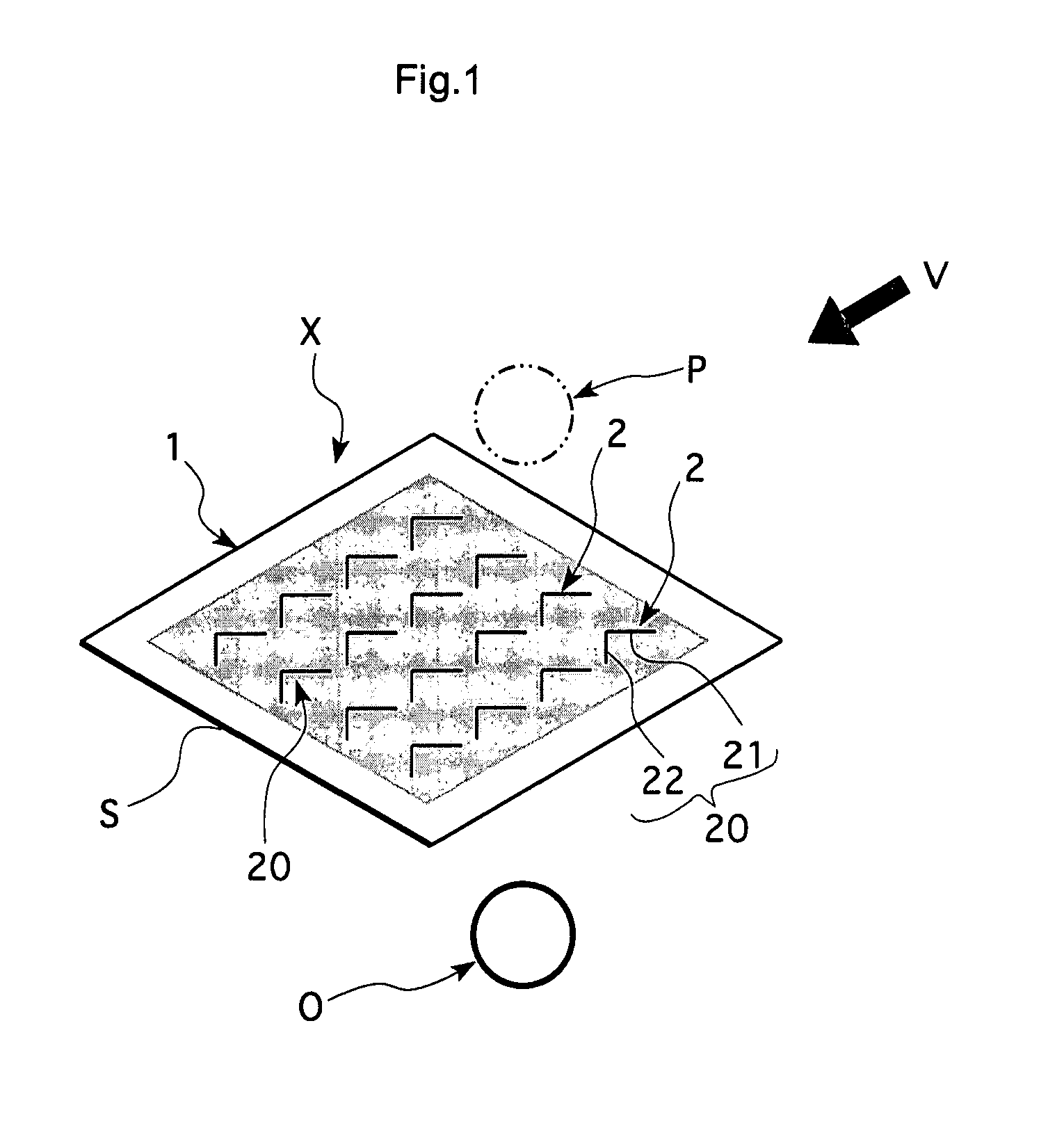

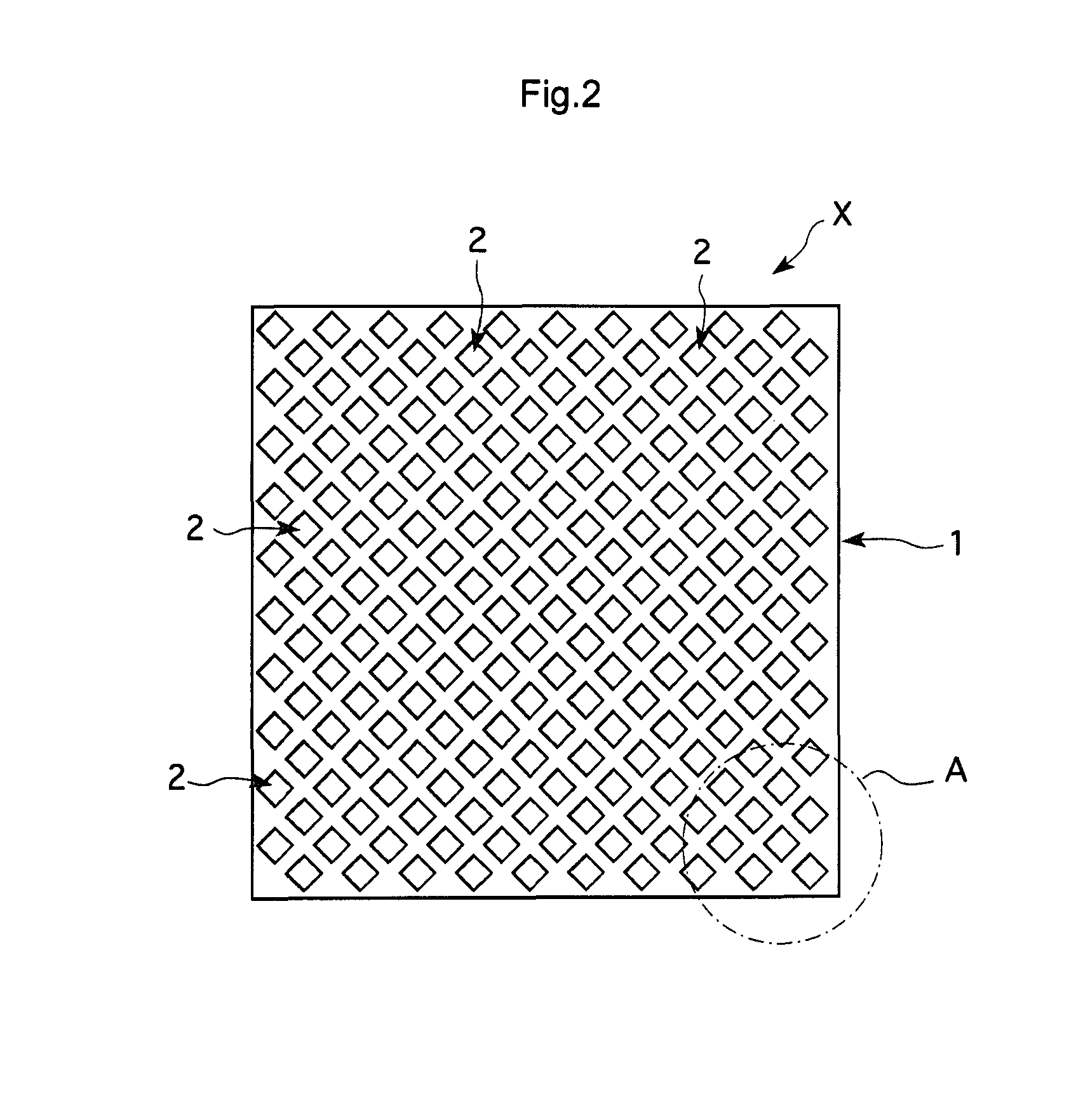

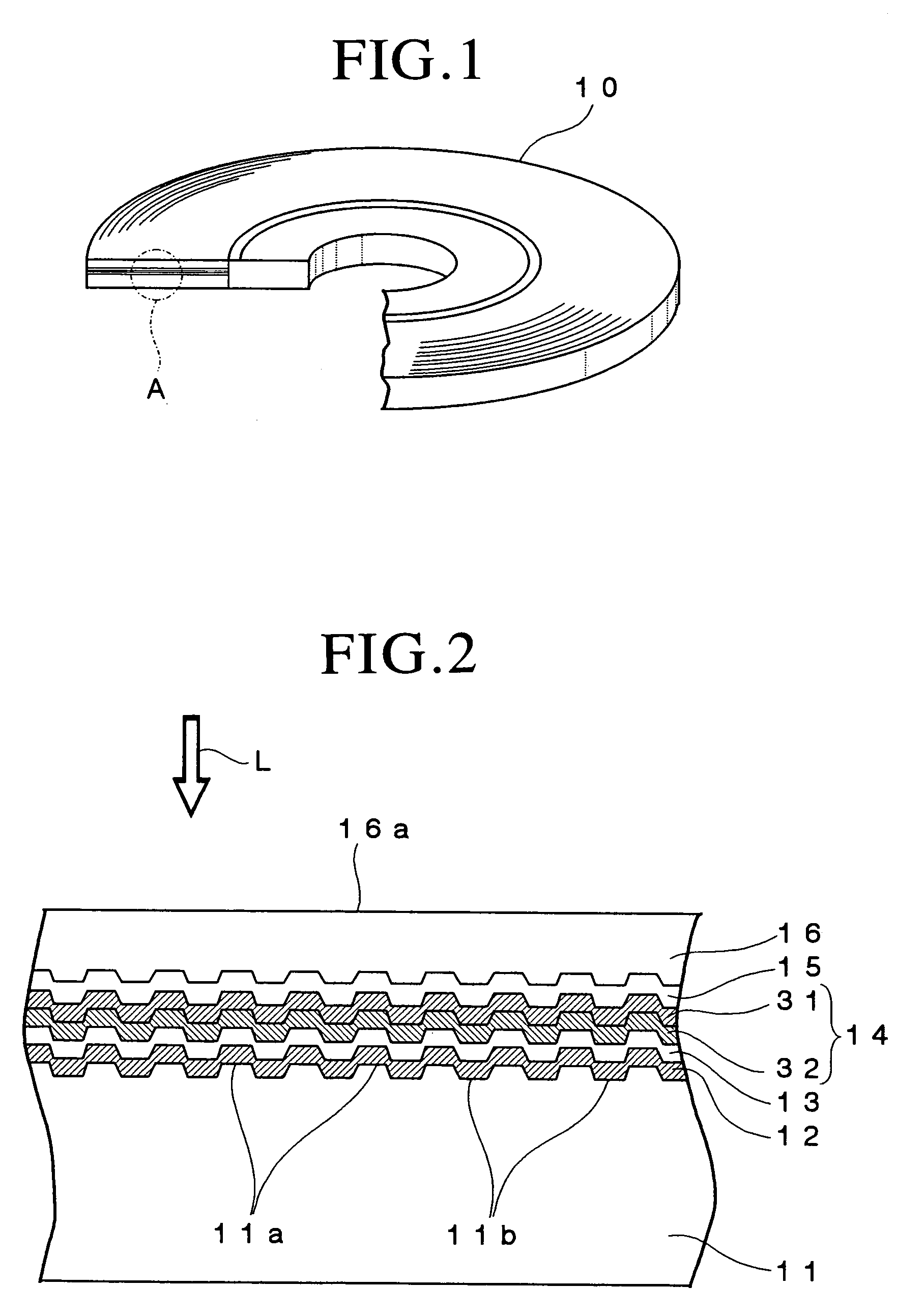

Imageing element and display

As optical elements for bending a light beam when it passes through an element face constituting one plane, a plurality of unit optical elements for reflecting light on one or more mirror surfaces arranged perpendicularly or at an angle nearly perpendicular to the element face are disposed to constitute an optical imaging element. Light emitted from projection object disposed on one side of the element face is reflected on the mirror surface when it passes through the element face so that a real image is formed in a space on the other side of the element face where a physical entity does not exist, thus constituting a display equipped with the optical imaging element. An aerial picture projection system not existing heretofore is also provided.

Owner:NAT INST OF INFORMATION & COMM TECH

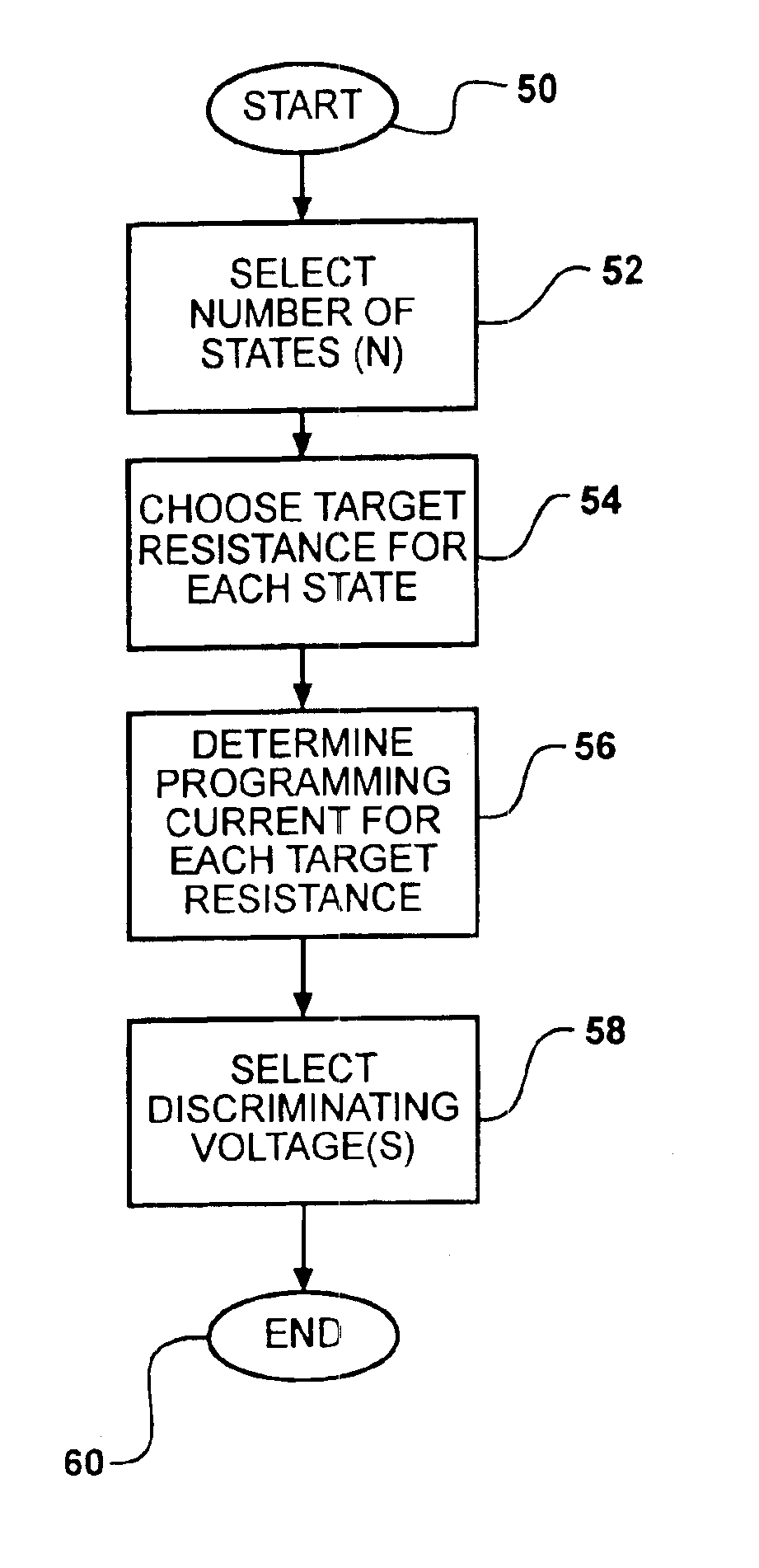

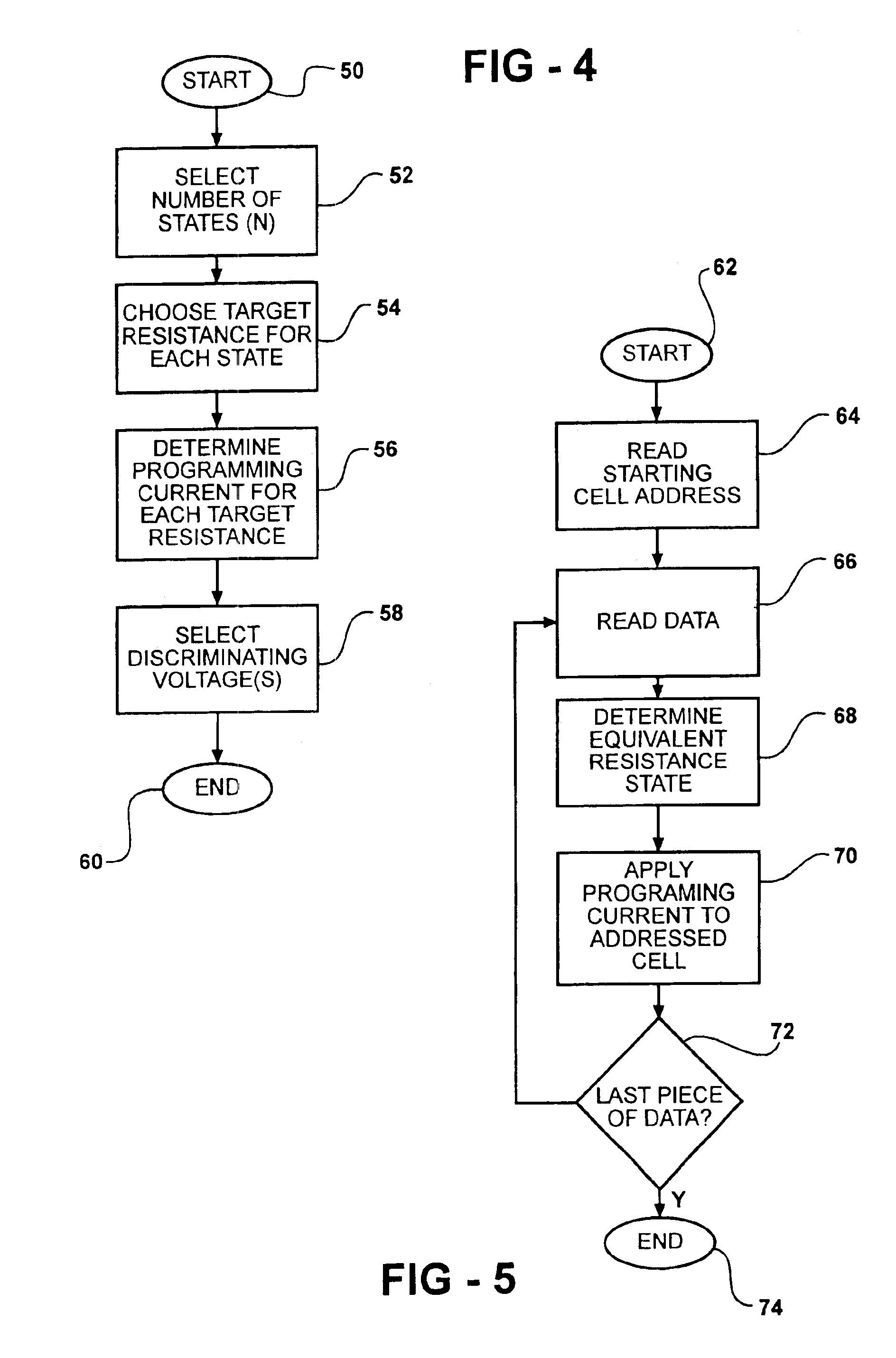

Phase-change memory element and method of storing data therein

InactiveUS6859390B2Lower average energyStructural failureRead-only memoriesDigital storagePhase-change memoryEngineering

A phase-change memory element including a phase-change material. The phase-change memory element has a plurality of memory state wherein each of the memory states has a corresponding threshold voltage. The threshold voltages may be used to determine the current memory state of the memory element. The phase-change material may include a chalcogen element.

Owner:OVONYX MEMORY TECH LLC

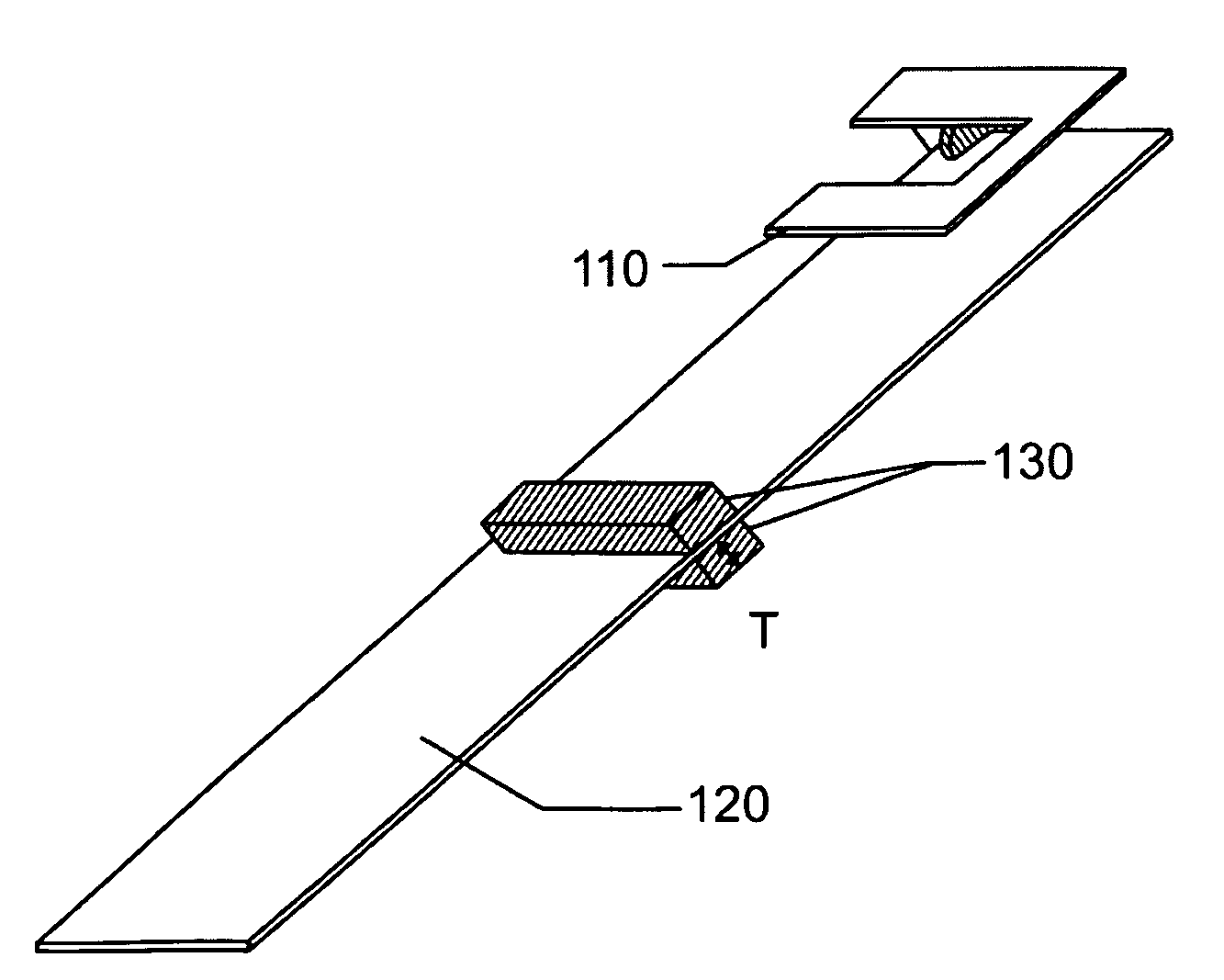

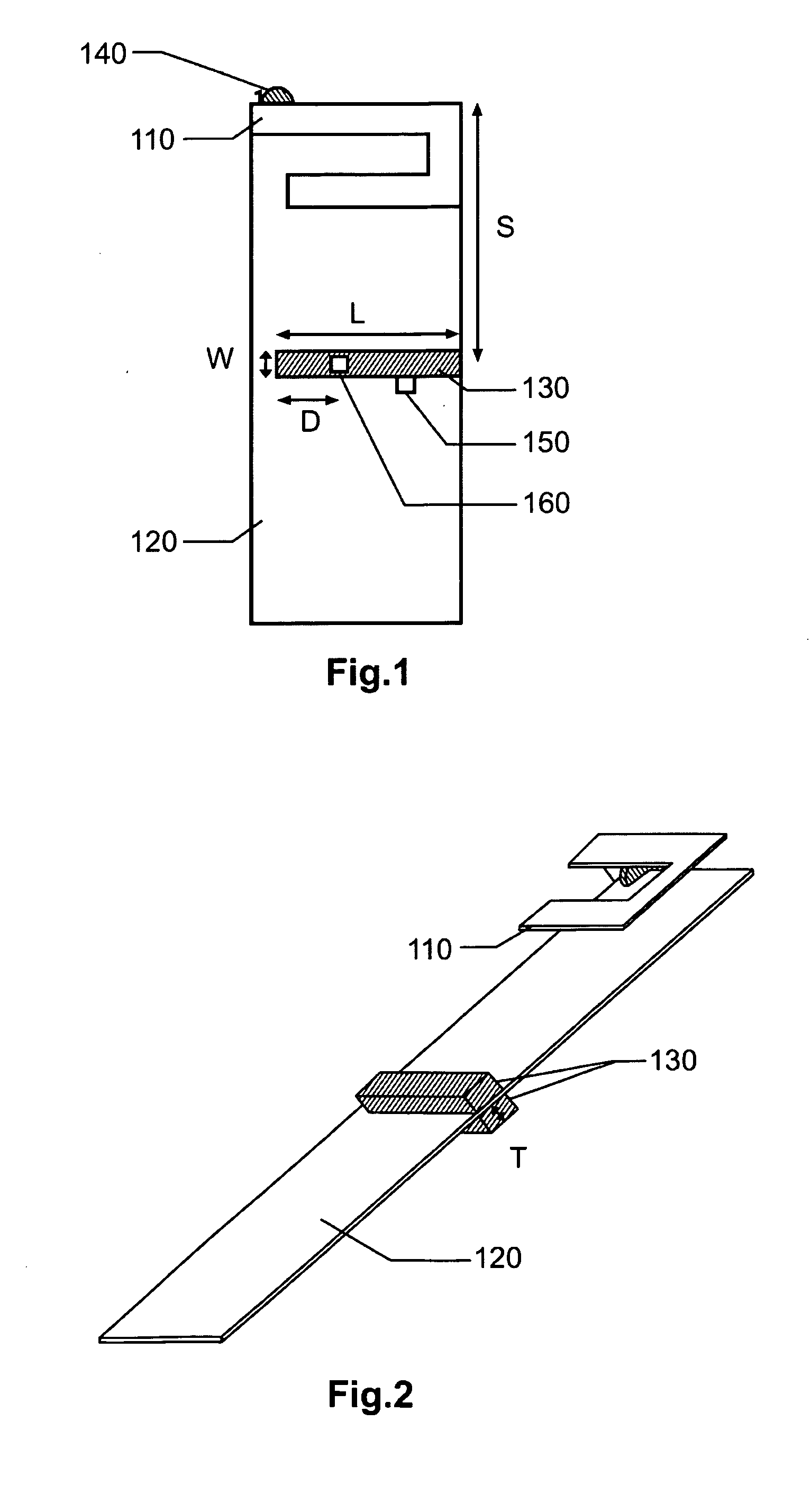

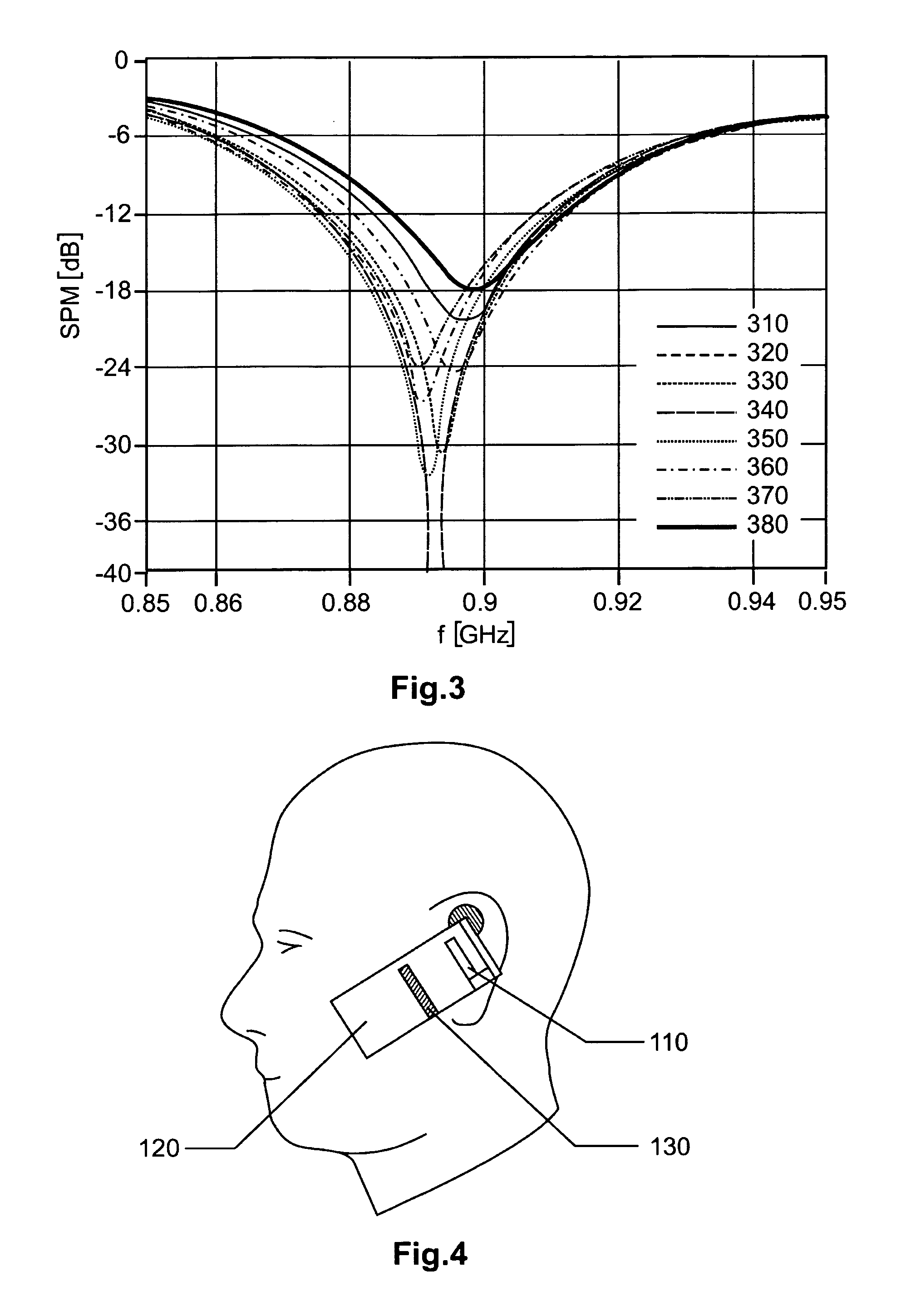

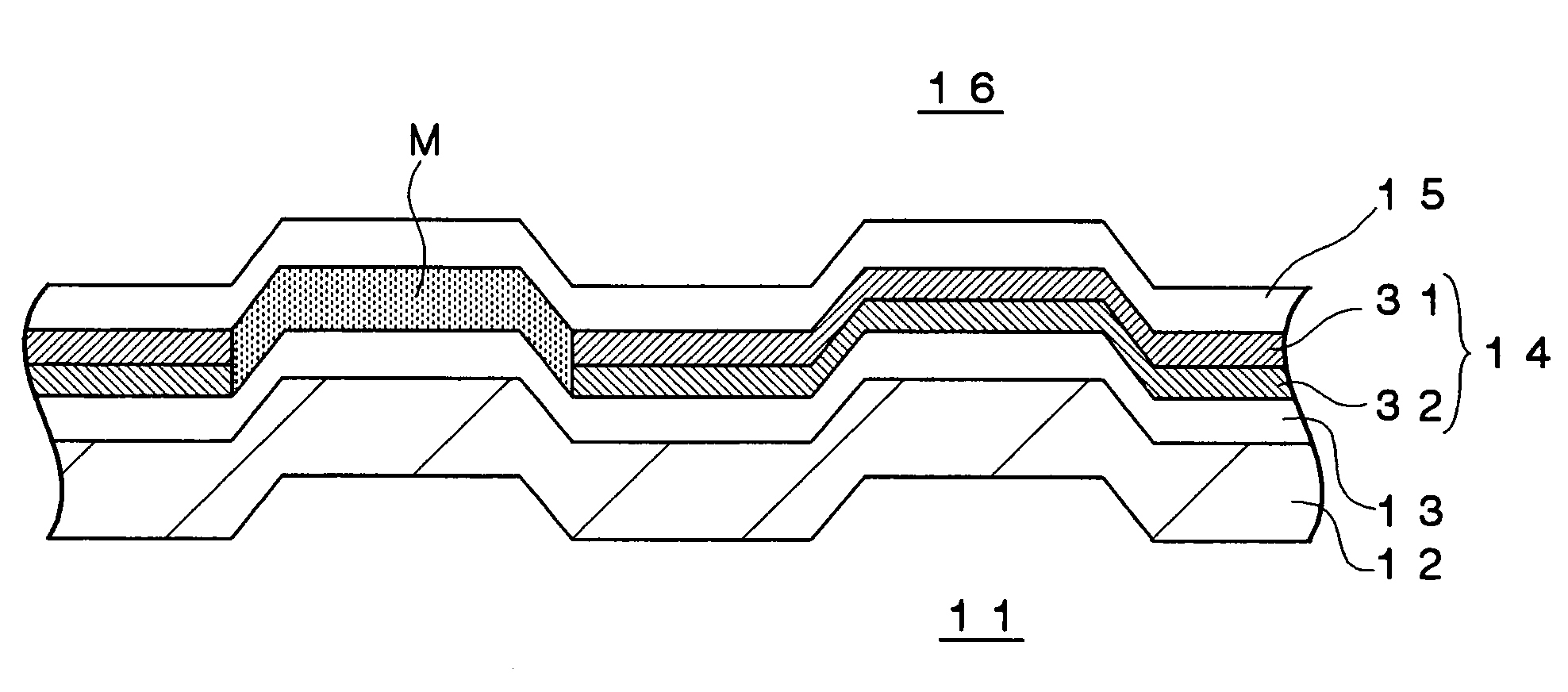

Performance improvement of antennas

InactiveUS20090322619A1Increase electrical lengthImprove performanceAntenna supports/mountingsAntenna earthingsGround planeEngineering

The present invention relates to an antenna arrangement, an adaptive system comprising such arrangement, a portable electronic device comprising such arrangement or adaptive system, a method of manufacturing such an arrangement, and a computer-readable storage medium encoded with instructions for performing such method. The antenna arrangement can comprise at least one antenna element (110) configured to supply a current, at least one ground plane element (120) configured to conduct the current, and at least one magnetic element (130) configured to influence at least a part of the current in order to modify an electrical length of the at least one ground plane element (120). It enables to increase the electrical length of a terminal chassis, which may increase the operation bandwidth of the antenna-chassis combination. This effect can be further increased when combining at least one slot and at least one magnetic element covering the same at least partially.

Owner:NOKIA CORP

Optical recording medium

ActiveUS7018695B2Excellent initial recording characteristicOptimizationLayered productsPhotomechanical apparatusRecording layerOptical recording

An optical recording medium includes a substrate and a recording layer in which data can be recorded by projecting a laser beam thereonto, the recording layer including a first recording film containing an element selected from the group consisting of Si, Ge, C, Sn, Au, Zn and Cu as a primary component and a second recording film containing Cu as a primary component.The thus constituted optical recording medium has an excellent initial recording characteristic and can store recorded data in a good condition over the long term.

Owner:TDK CORPARATION

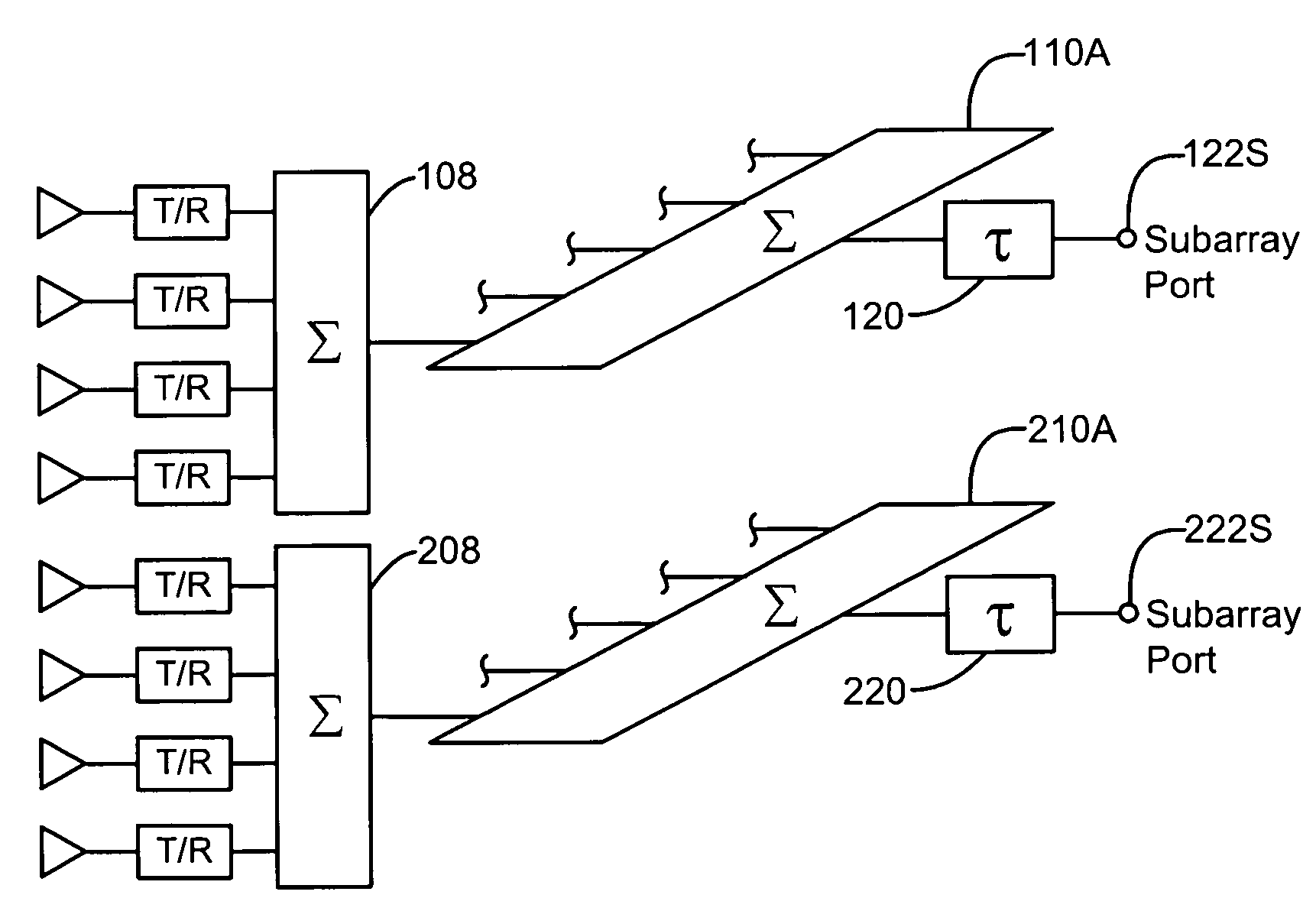

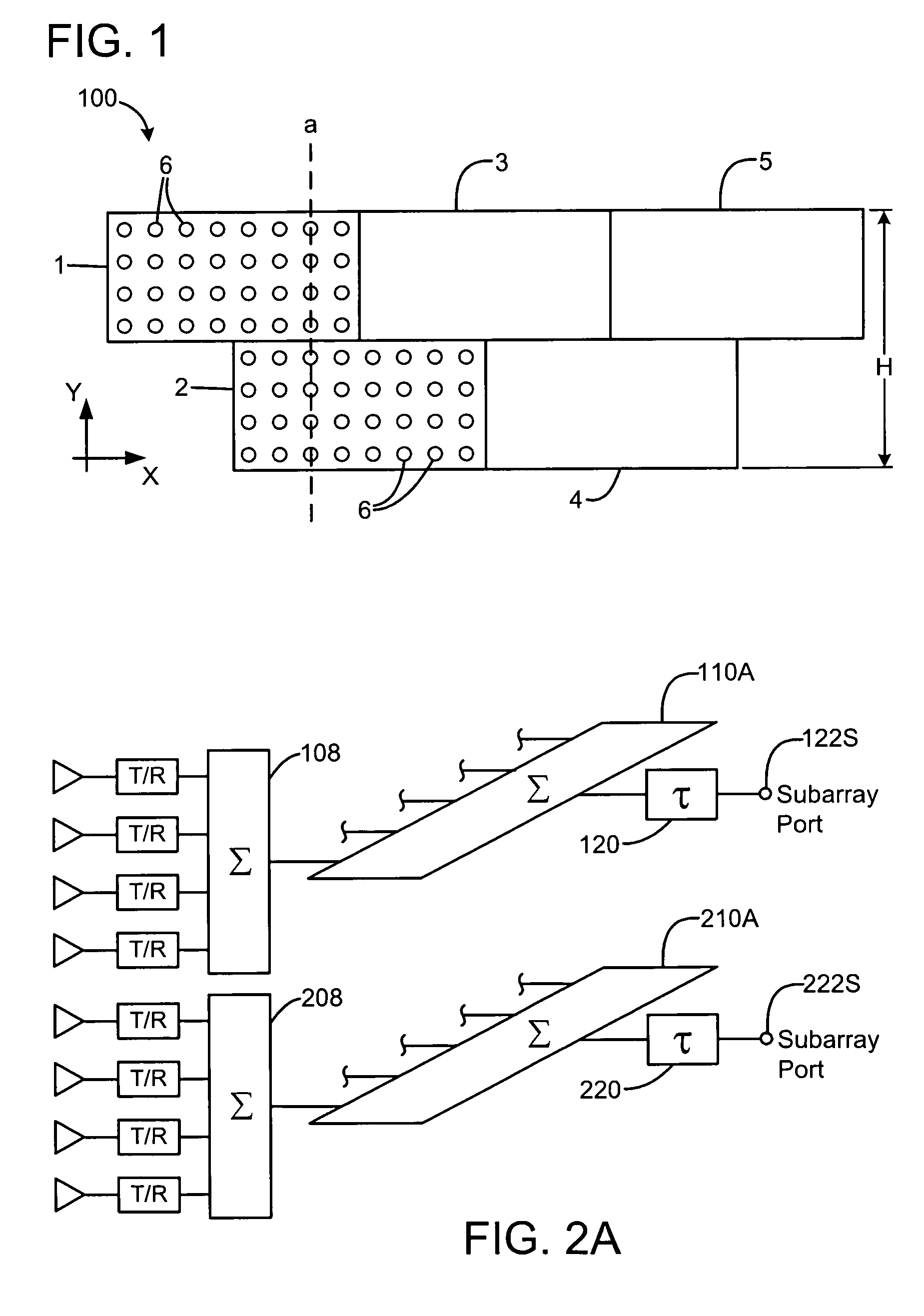

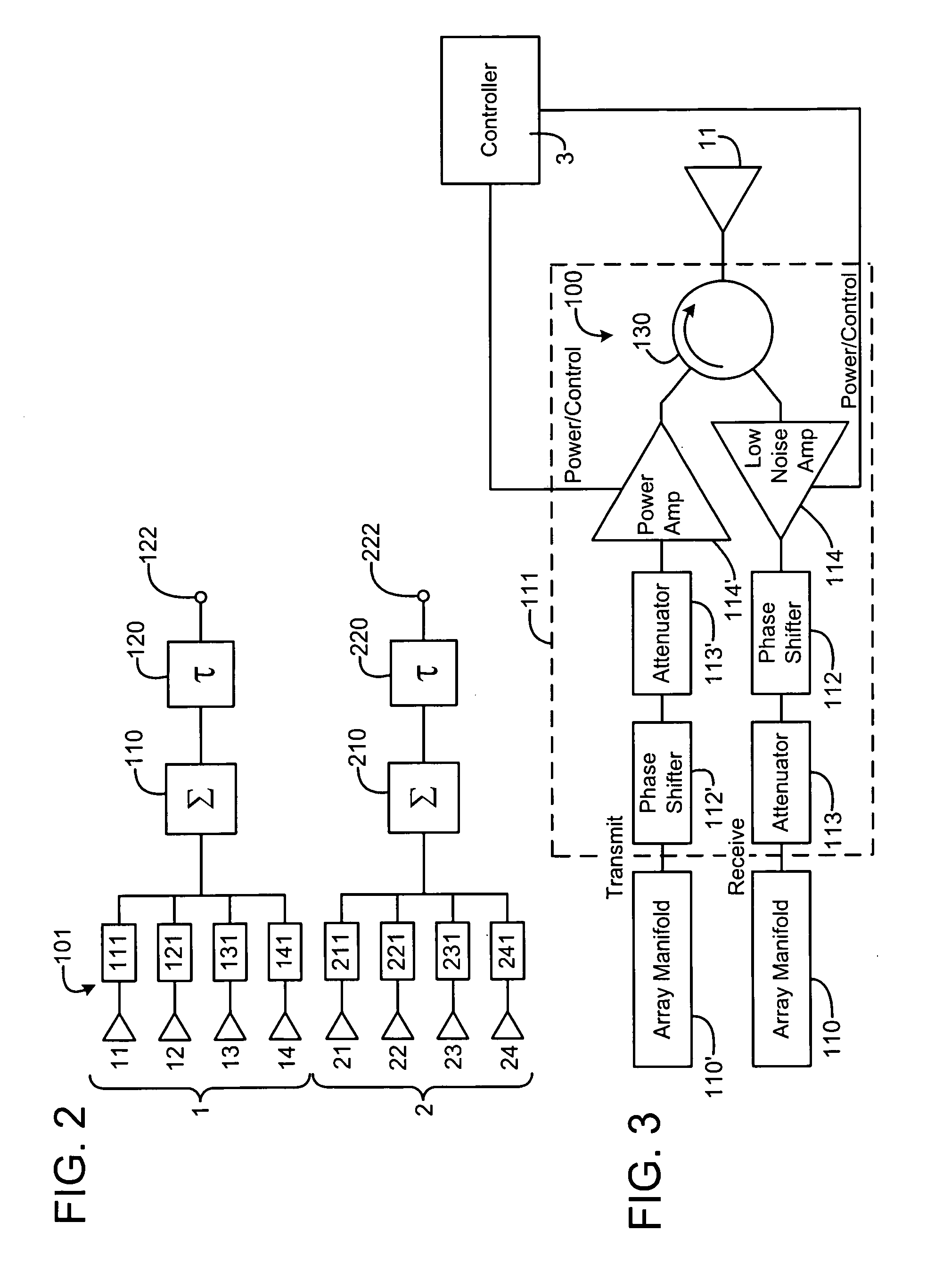

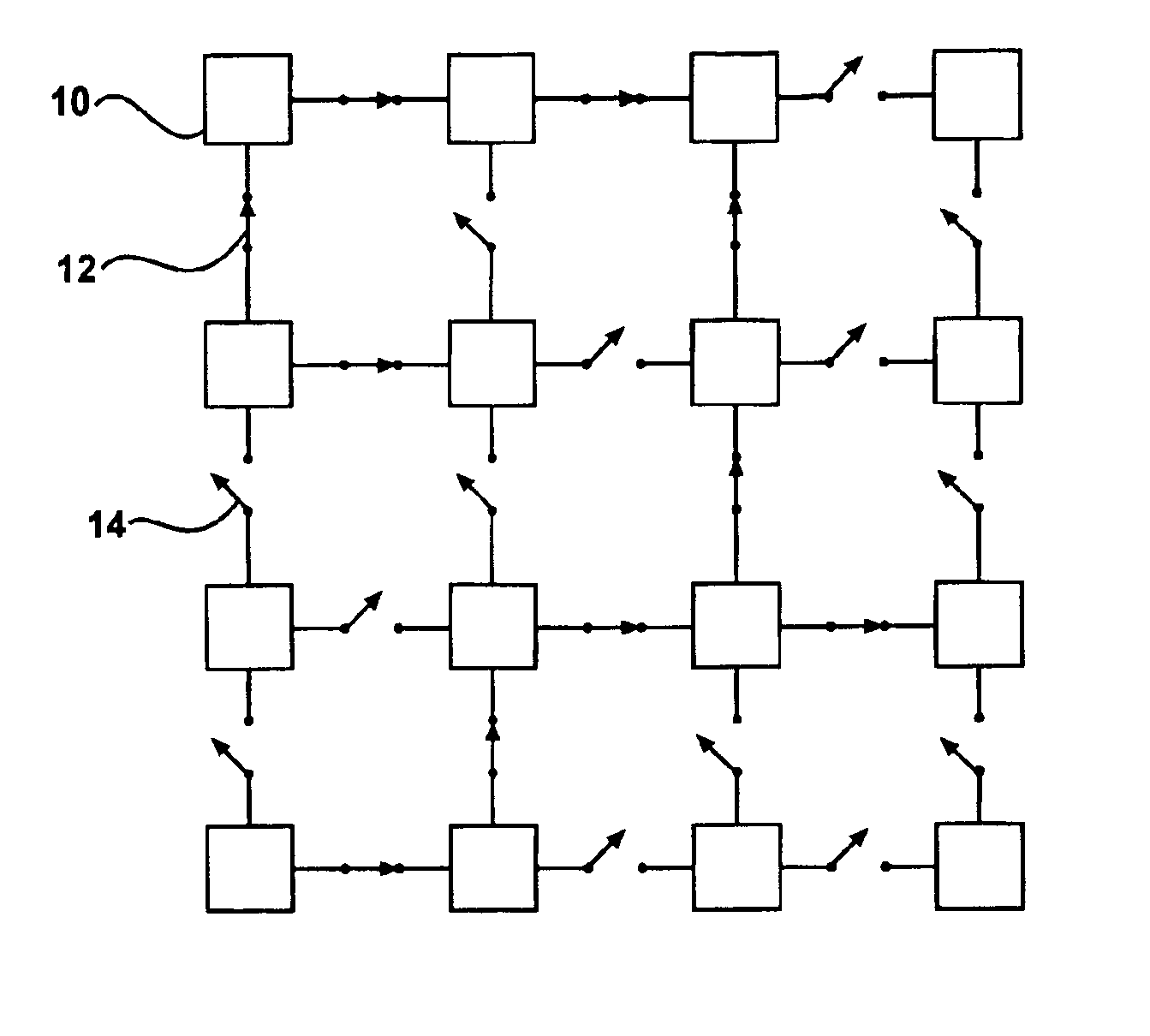

Overlapping subarray architecture

An embodiment of an electronically scanned array antenna includes an array of radiative elements having an array height. A plurality of separate subarrays of the radiative elements include a first row comprising a first plurality of subarrays, wherein subarrays of the first plurality of subarrays are horizontally non-overlapping with one another, and a second row comprising a second plurality of subarrays. The subarrays of the second row are arranged vertically adjacent to the subarrays of the first row, wherein subarrays of the second plurality of subarrays are horizontally non-overlapping with one another. The radiative elements of the separate subarrays are not shared with any other subarray. The subarrays of the radiative elements have subarray heights which are smaller than the array height. In another embodiment, a method for suppressing grating lobe formation in a steered subarray antenna includes applying a first illumination function to a first subarray; applying a second illumination function to a second subarray; wherein the first illumination function is different from the second illumination function.

Owner:RAYTHEON CO

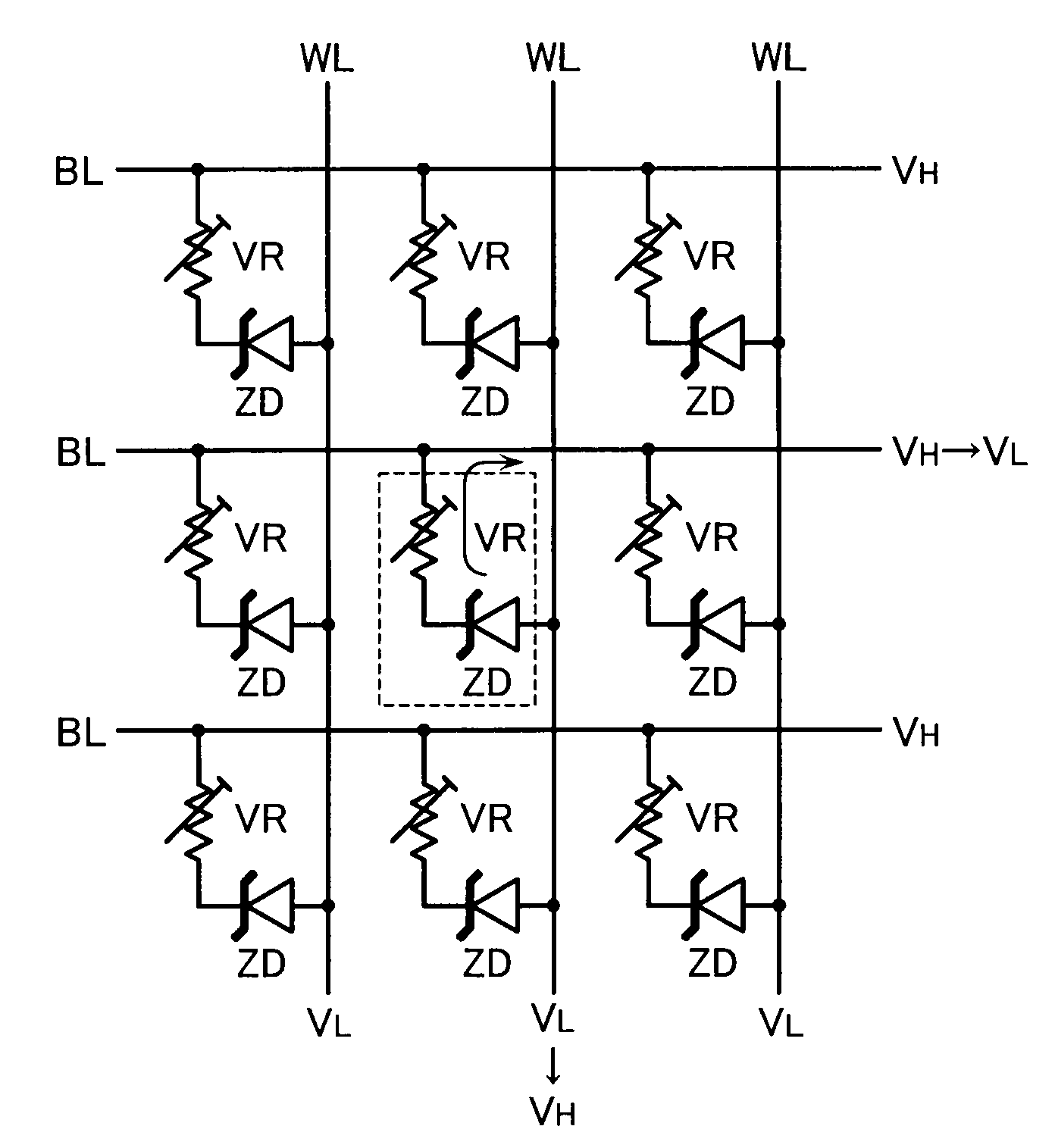

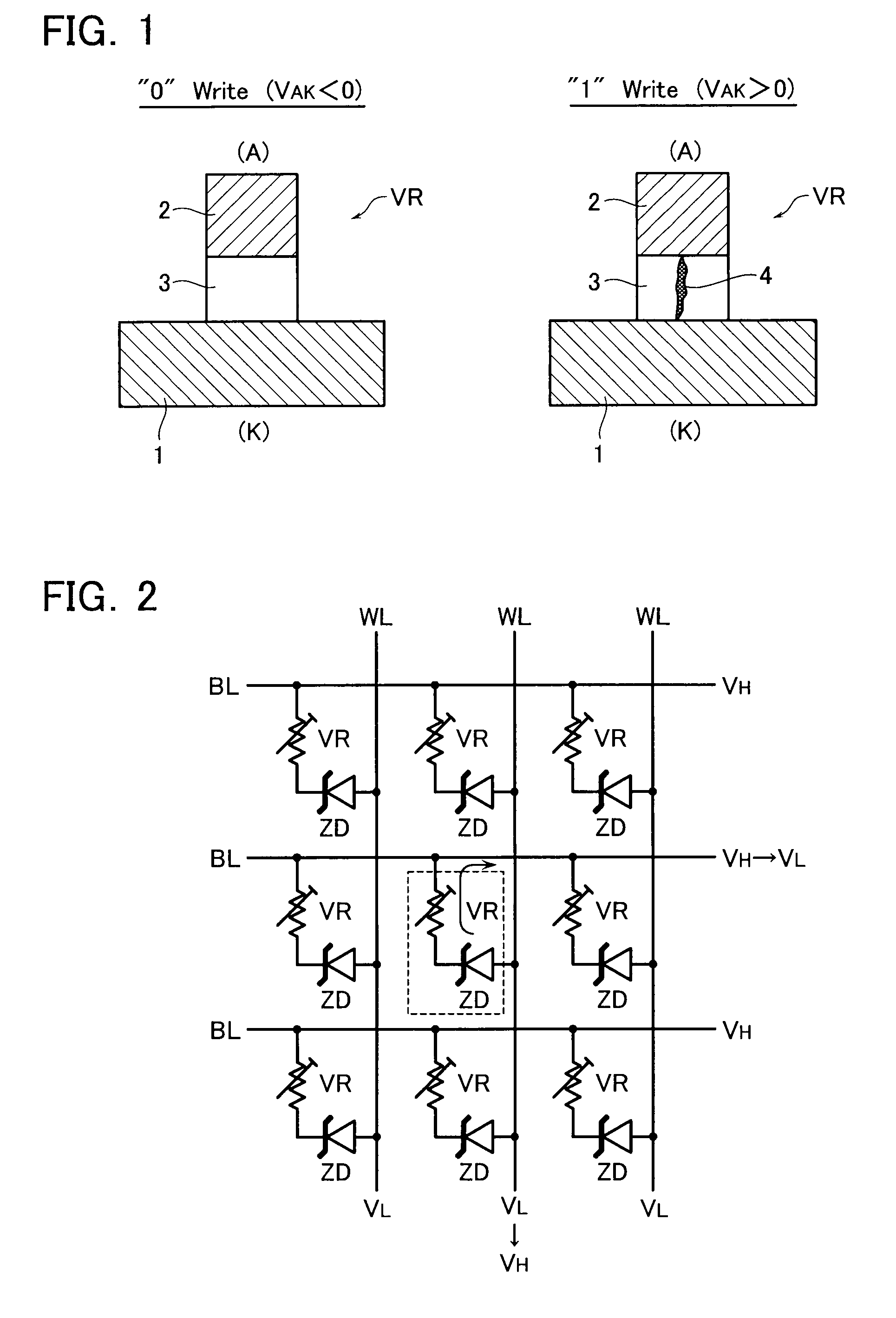

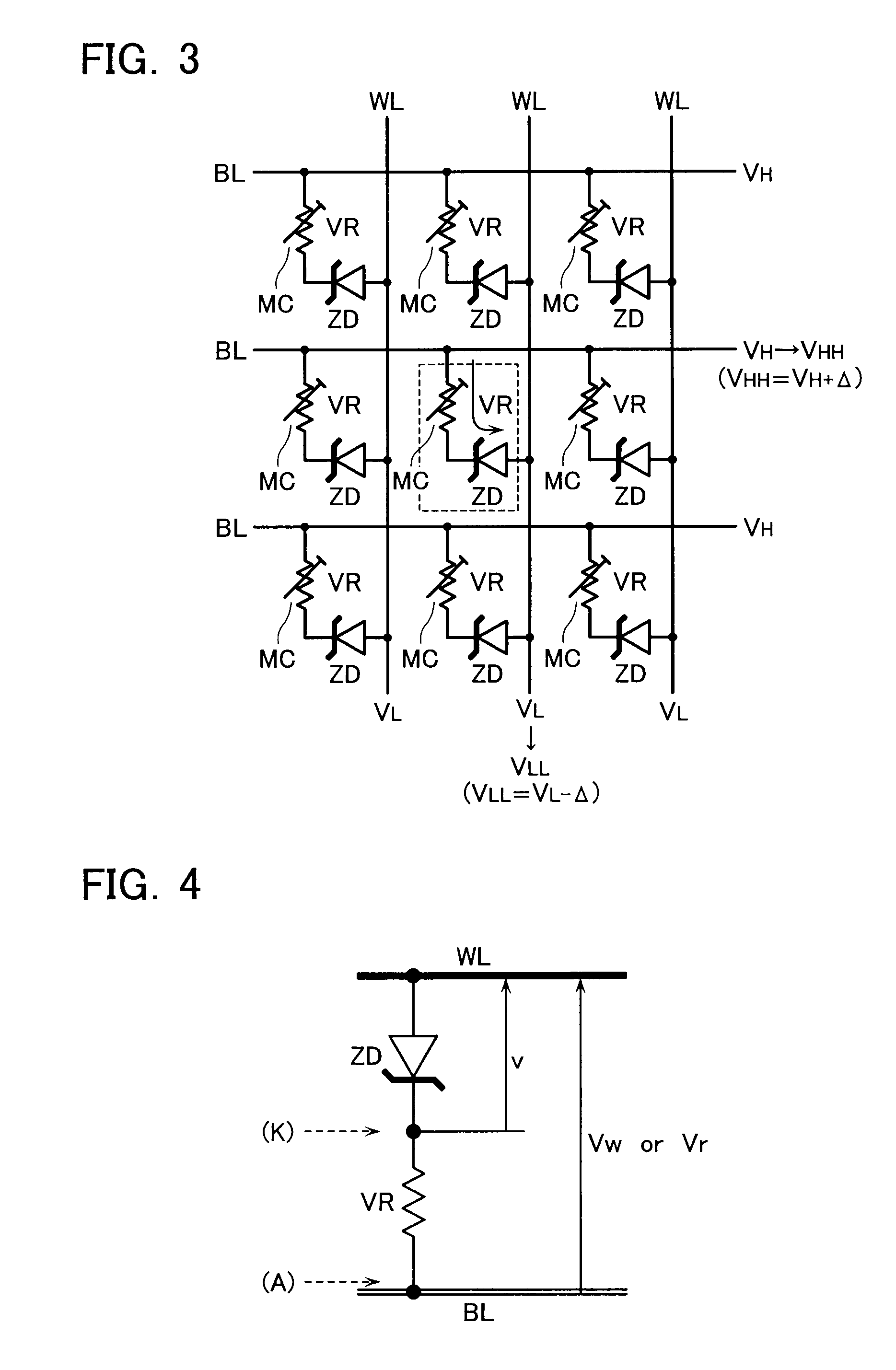

Resistance change memory device

A resistance change memory device including: a semiconductor substrate; at least one cell array formed above the semiconductor substrate, each memory cell having a stack structure of a variable resistance element and an access element, the access element having such an off-state resistance value in a certain voltage range that is ten times or more as high as that in a select state; and a read / write circuit formed on the semiconductor substrate as underlying the cell array, wherein the variable resistance element comprises a recording layer formed of a first composite compound expressed by AxMyOz (where “A” and “M” are cation elements different from each other; “O” oxygen; and 0.5≦x≦1.5, 0.5≦y≦2.5 and 1.5≦z≦4.5) and a second composite compound containing at least one transition element and a cavity site for housing a cation ion.

Owner:TOSHIBA MEMORY CORP

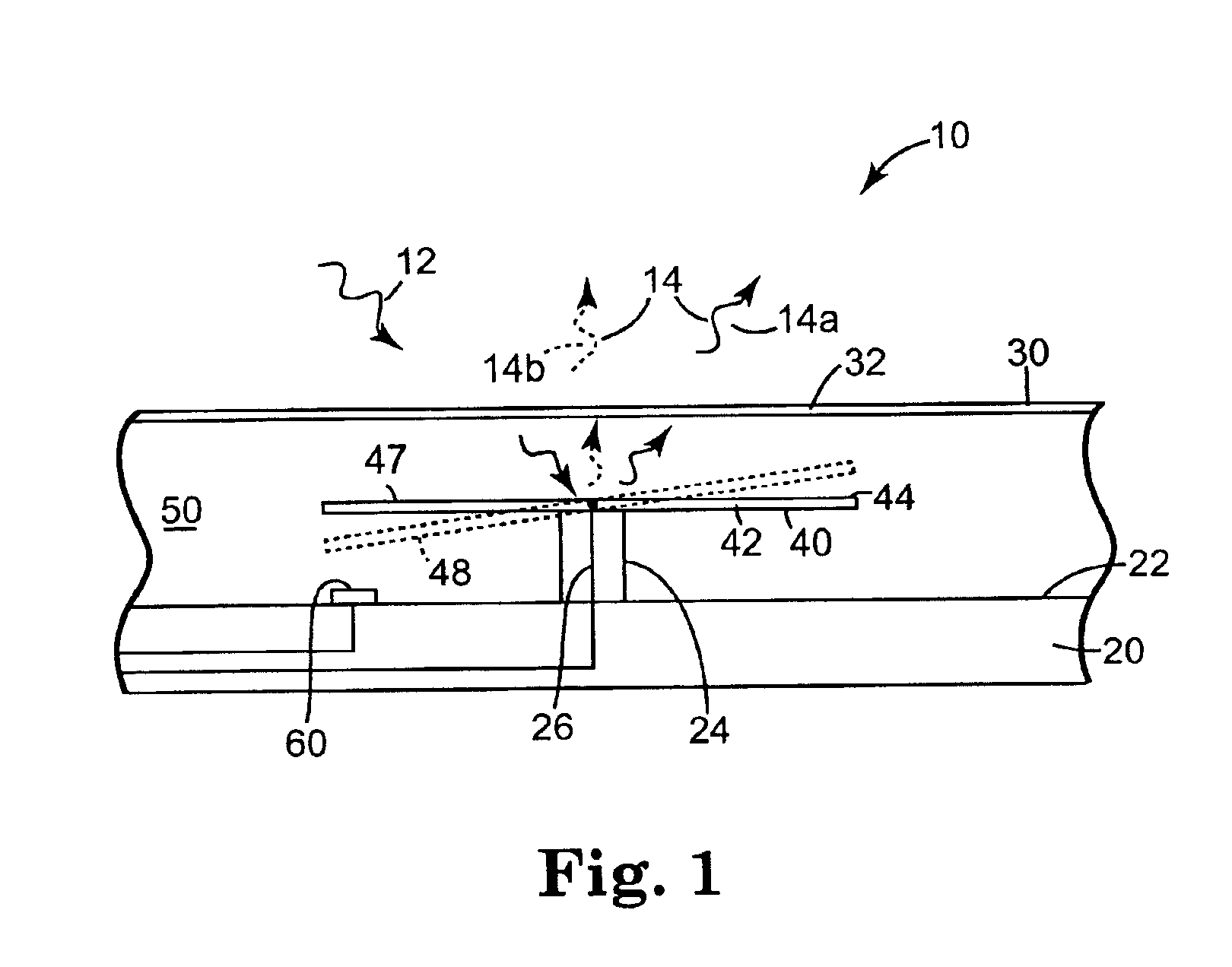

Apparatus, system, and method for tape drive head

InactiveUS20090213493A1Improve reliabilityAlignment for track following on tapesRecord information storageEngineeringTape drive

An apparatus, system, and method are disclosed for a tape drive head. An upper servo element reads an upper servo track conforming to a specified format. A lower servo element reads a lower servo track conforming to the specified format. A mid servo element reads a mid servo track. The mid servo element is disposed between the upper servo element and the lower servo element. Sixteen legacy read elements are disposed between the upper server element and the lower servo element. The legacy read elements read legacy data tracks conforming to the specified format. At least eight incremental read elements are interleaved between the legacy read elements. One incremental read element is adjacent to each legacy read element on a side of the legacy read element away from the mid servo element.

Owner:IBM CORP

MEMS device made of transition metal-dielectric oxide materials

InactiveUS7057251B2Resistant to oxidationSuitable elasticitySolid-state devicesSemiconductor/solid-state device manufacturingDielectricAccelerometer

Micromechanical devices are provided that are capable of movement due to a flexible portion. The micromechanical device can have a flexible portion formed of an oxide of preferably an element from groups 3A to 6A of the periodic table (preferably from the first two rows of these groups) and a late transition metal (preferably from groups 8B or 1B of the periodic table). The micromechanical devices can be any device, particularly MEMS sensors or actuators preferably having a flexible portion such as an accelerometer, DC relay or RF switch, optical cross connect or optical switch, or a micromirror part of an array for direct view and projection displays. The flexible portion is preferably formed by sputtering a target having a group 8B or 1B element and a selected group 3A to 6A element, namely B, Al, In, Si, Ge, Sn, or Pb. The target can have other major constituents or impurities (e.g. additional group 3A to 6A element(s)). The target is reactively sputtered in a oxygen ambient so as to result in a sputtered hinge. It is possible to form both stiff and / or flexible portions of the micromechanical device in this way.

Owner:TEXAS INSTR INC +1

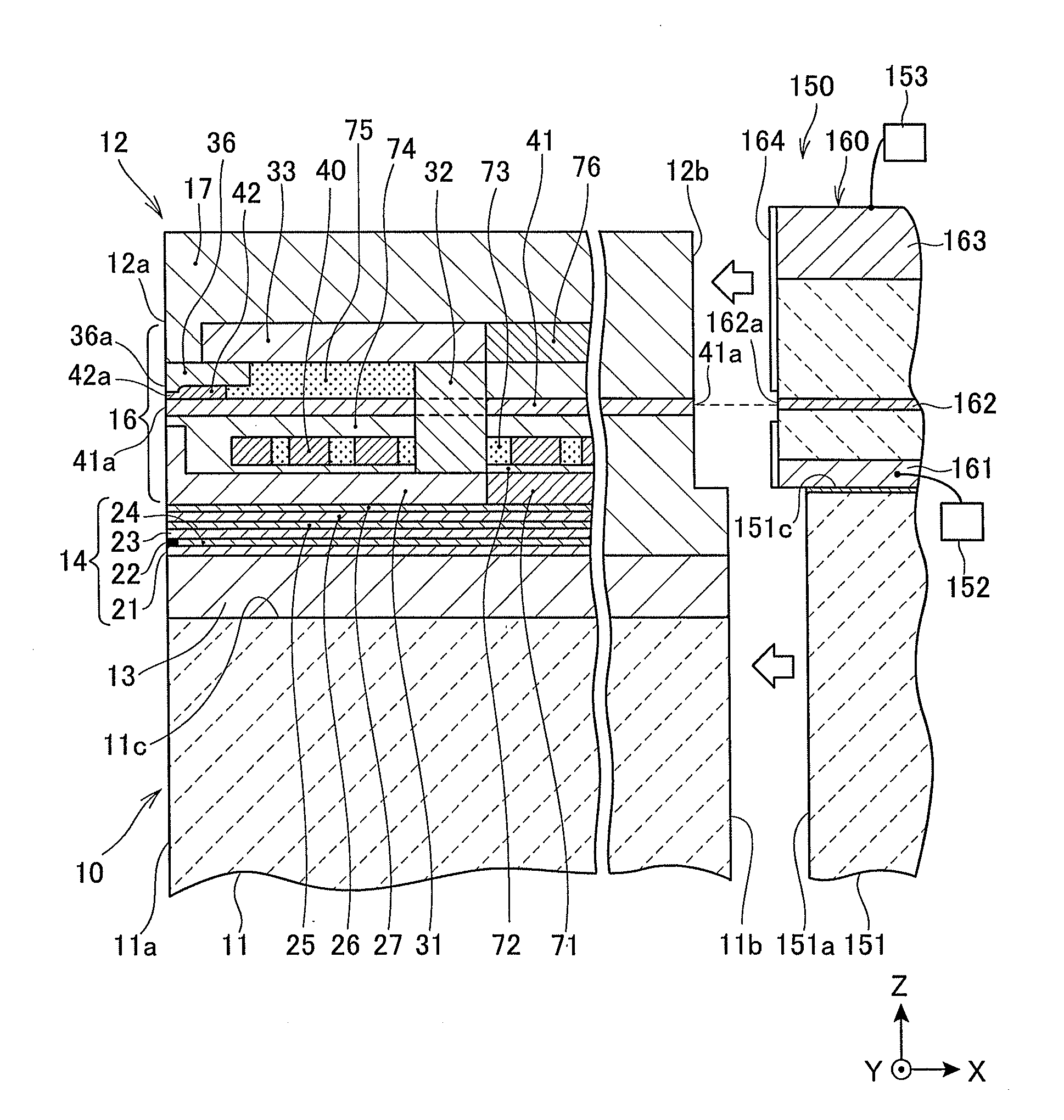

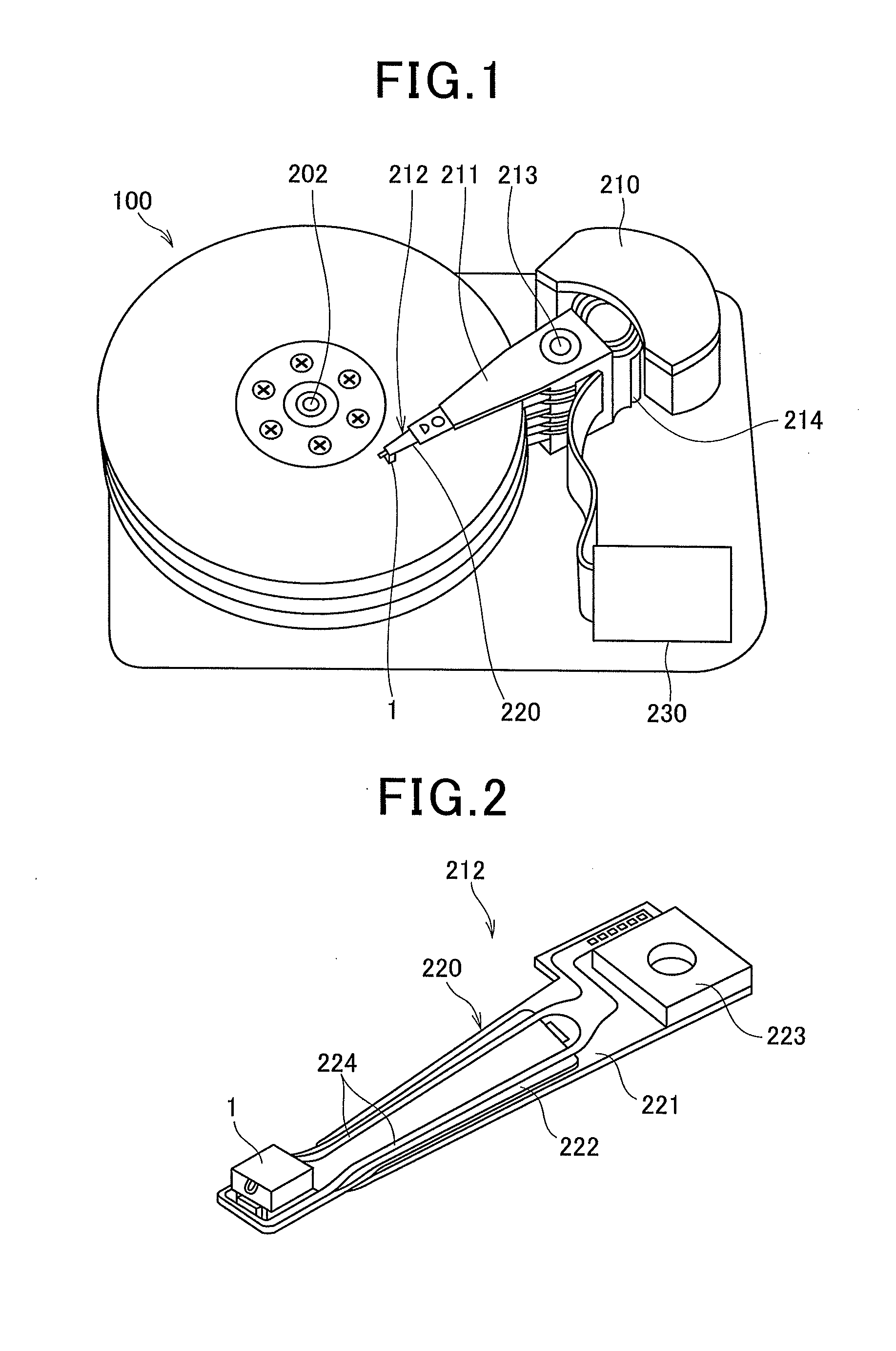

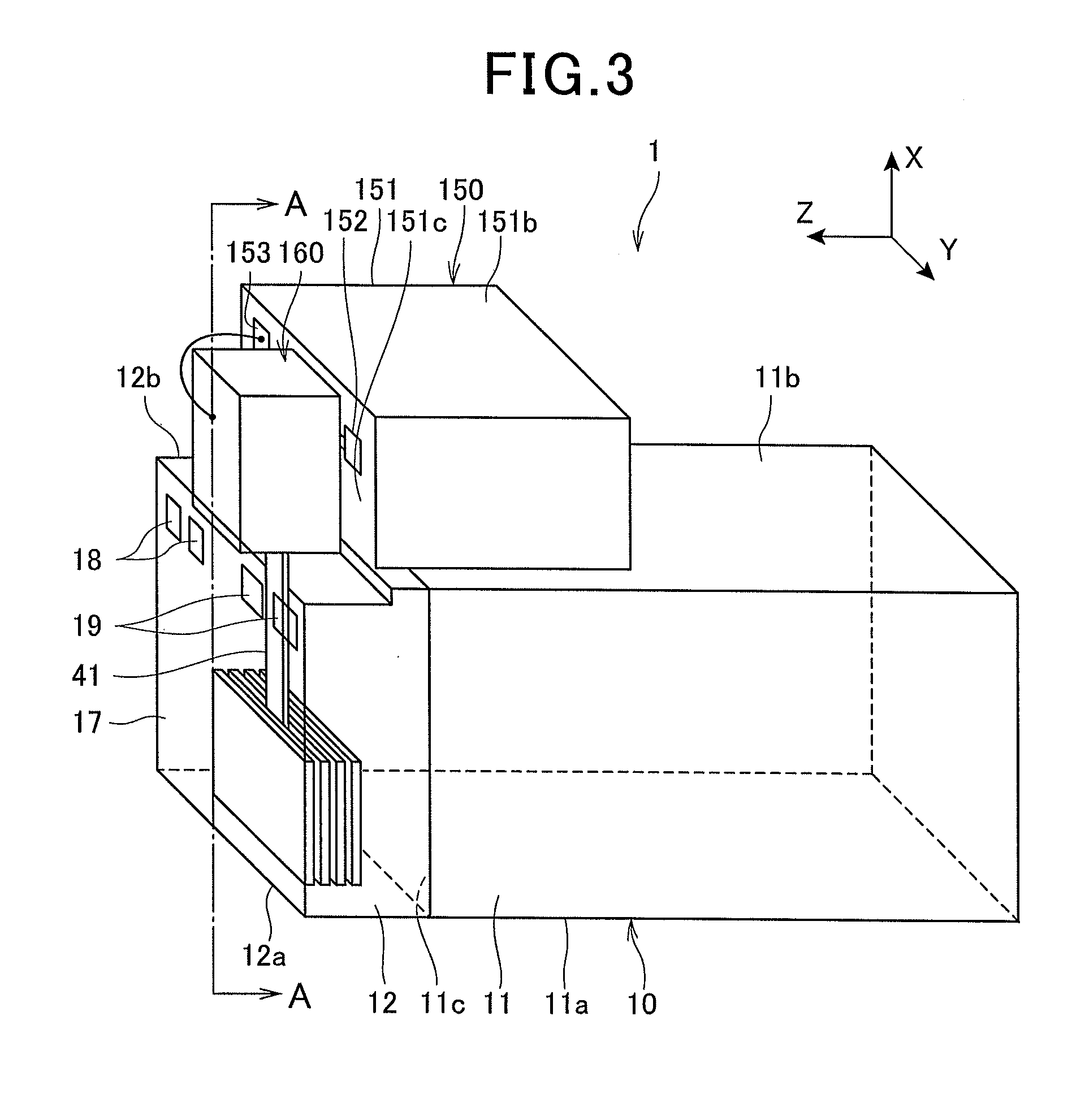

Plasmon generator and thermally-assisted magnetic recording head having the same

ActiveUS20140043948A1Laser detailsRecord information storageHeat-assisted magnetic recordingPlasma generator

A plasmon-generator of the invention is configured to include a first configuration member including a near-field light generating end surface; and a second configuration member joined and integrated with the first configuration member and not including the near-field light generating end surface. The first configuration member is configured to contain Au as a primary component and to contain any one or more elements selected from a group of Co, Fe, Sb, Nb, Zr, Ti, Hf, and Ta, and is configured so that a content percentage X1 of the contained element is within a range between 0.2 at % or more and 2.0 at % or less. Thereby, thermostability, optical characteristic, and the process stability are satisfied. Also, heat dissipation and heat generation suppression effect are extremely superior.

Owner:TDK CORPARATION

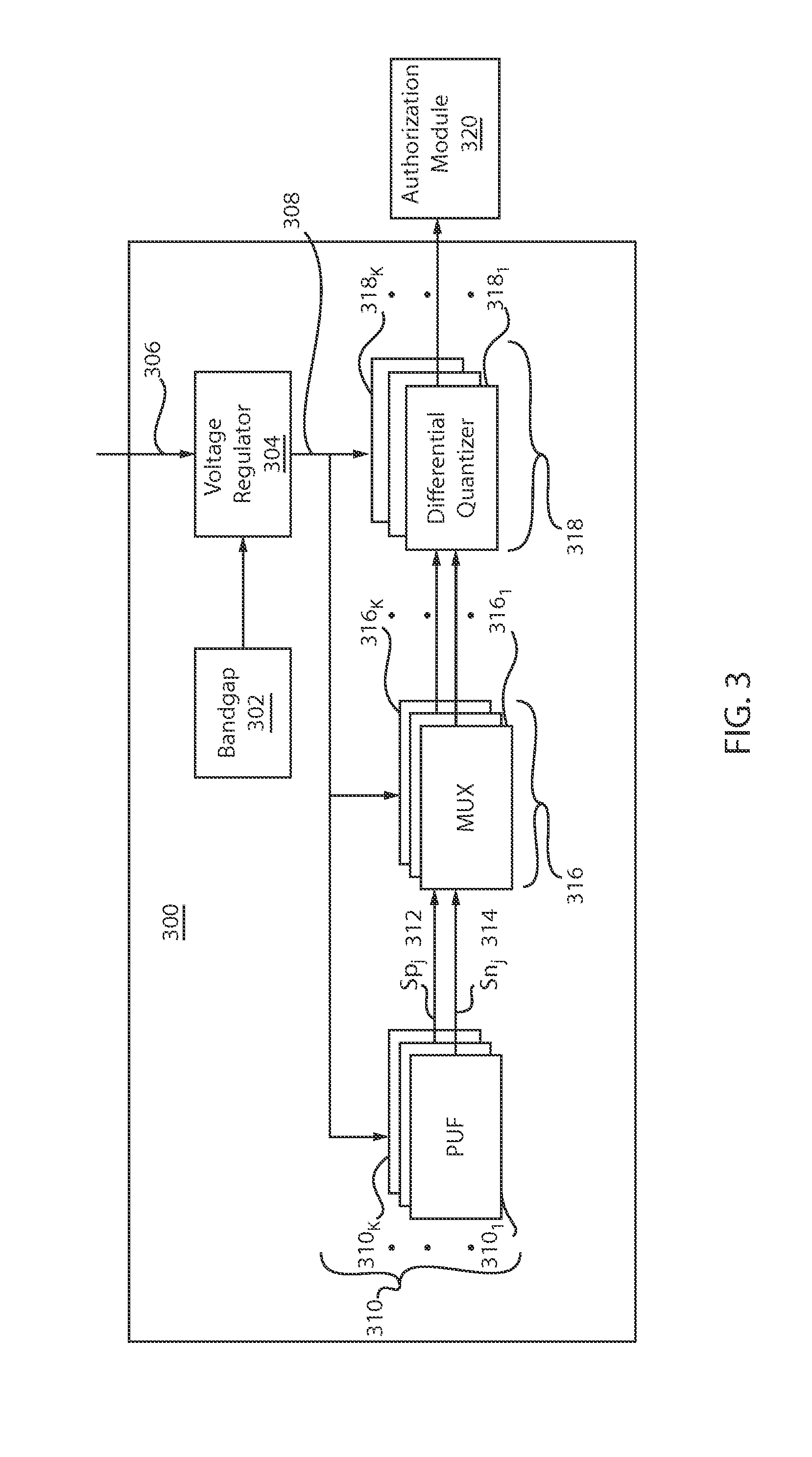

Physical unclonable function generation and management

ActiveUS20140327469A1Reliability increasing modificationsComputer hardwarePhysical unclonable function

Methods, systems and devices related to authentication of chips using physical physical unclonable functions (PUFs) are disclosed. In accordance one such method, a test voltage is applied to a PUF system including a first subset of PUF elements that are arranged in series and a second subset of PUF elements that are arranged in series, where the first subset of PUF elements is arranged in parallel with respect to the second subset of PUF elements. In addition, the PUF system is measured to obtain at least one differential of states between the first subset of PUF elements and the second subset of PUF elements. Further, the method includes outputting an authentication sequence for the circuit that is based on the one or more differentials of states.

Owner:GLOBALFOUNDRIES US INC

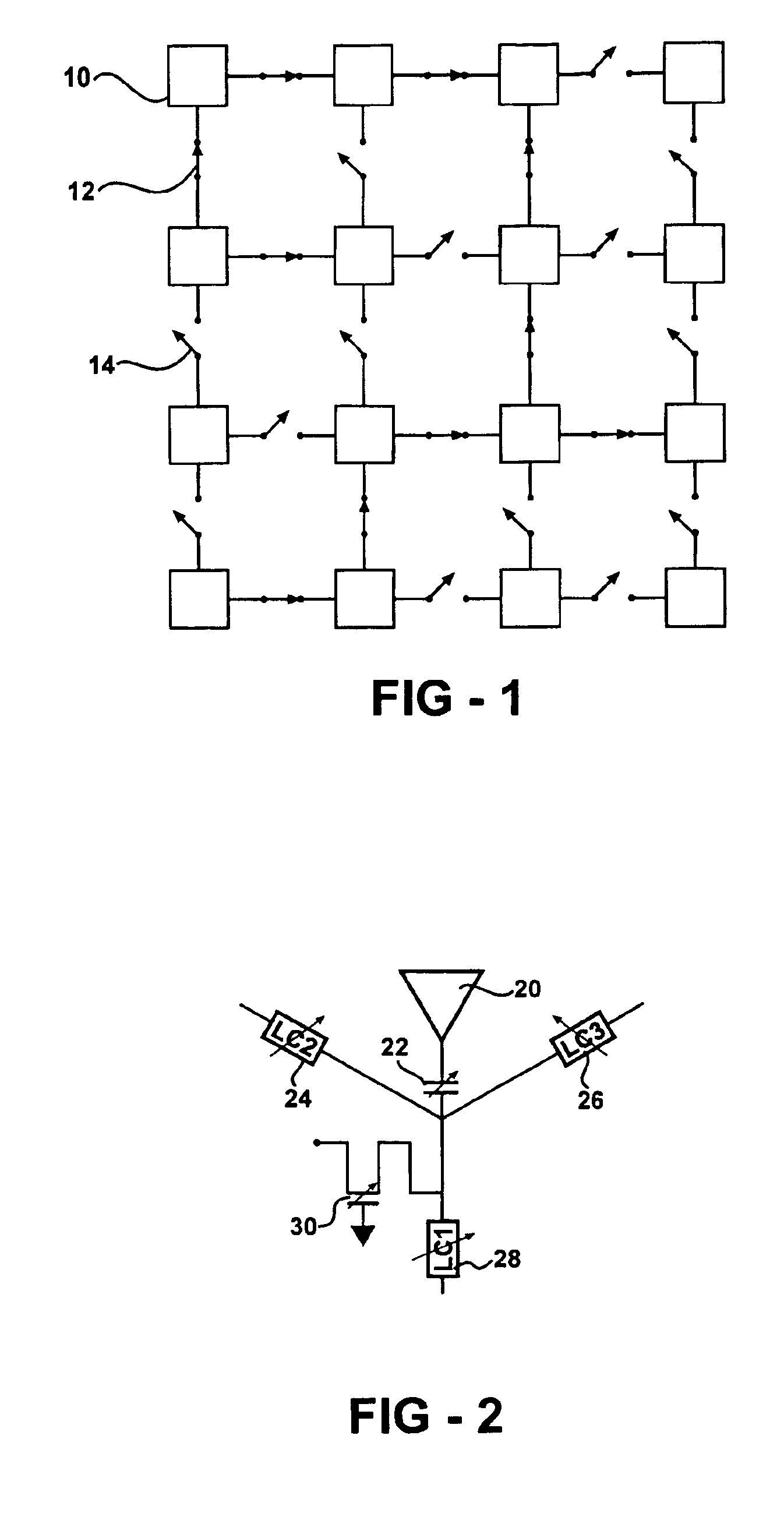

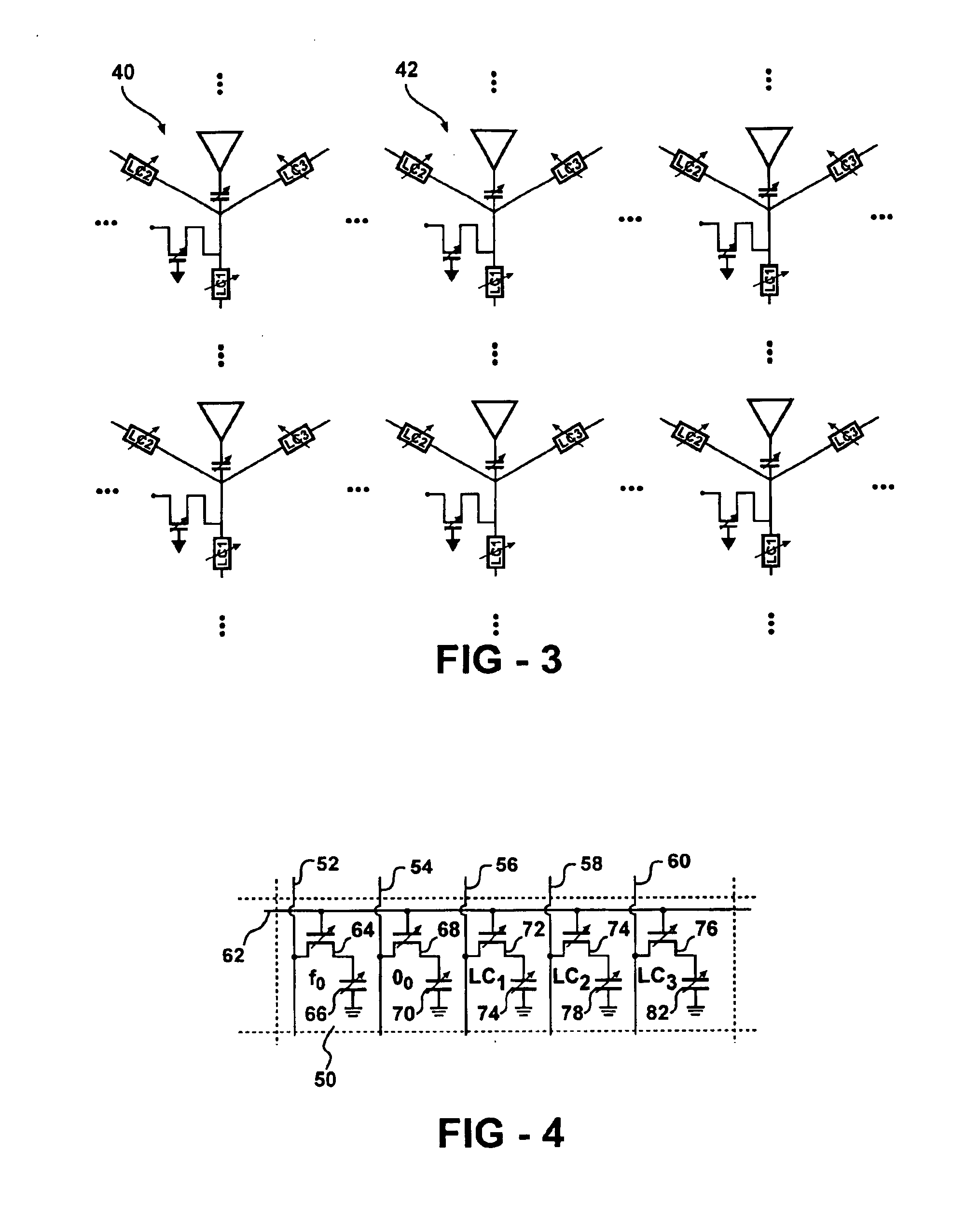

Actively reconfigurable pixelized antenna systems

InactiveUS6885345B2Efficient and flexible and low-cost controlSimultaneous aerial operationsRadiating elements structural formsCost ControlsEngineering

Passive or active pixelized antenna structures are described in which the radio-frequency (RF) tuning of individual antenna pixel elements, the connections of individual antenna pixel elements to other antenna elements, and optionally the local phase of individual elements or groups of elements, is varied and controlled using tunable elements. Efficient and low-cost control of a large number of tunable elements is provided by matrix addressing techniques.

Owner:PENN STATE RES FOUND

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com