Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

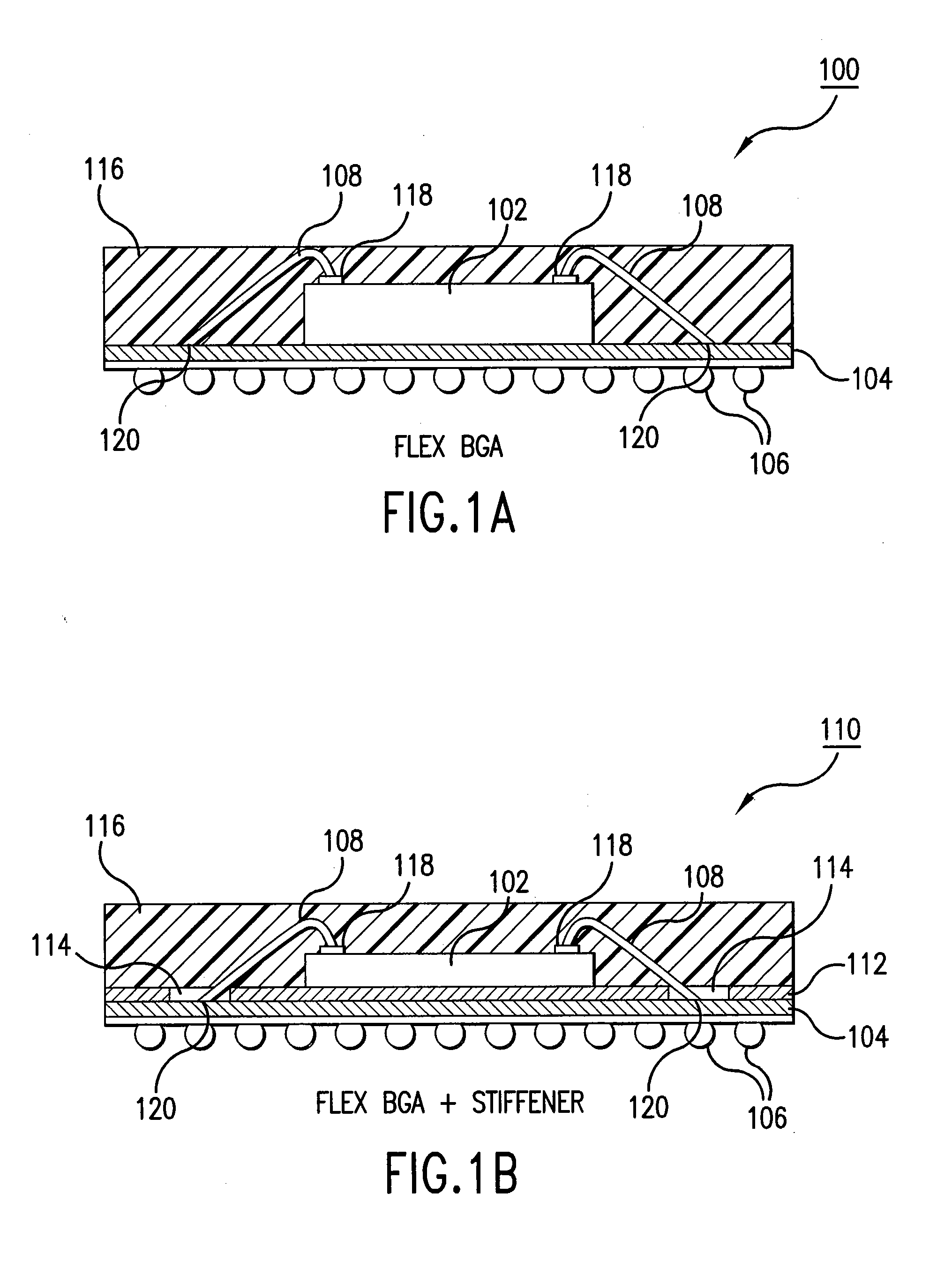

768results about How to "Enhanced radiation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

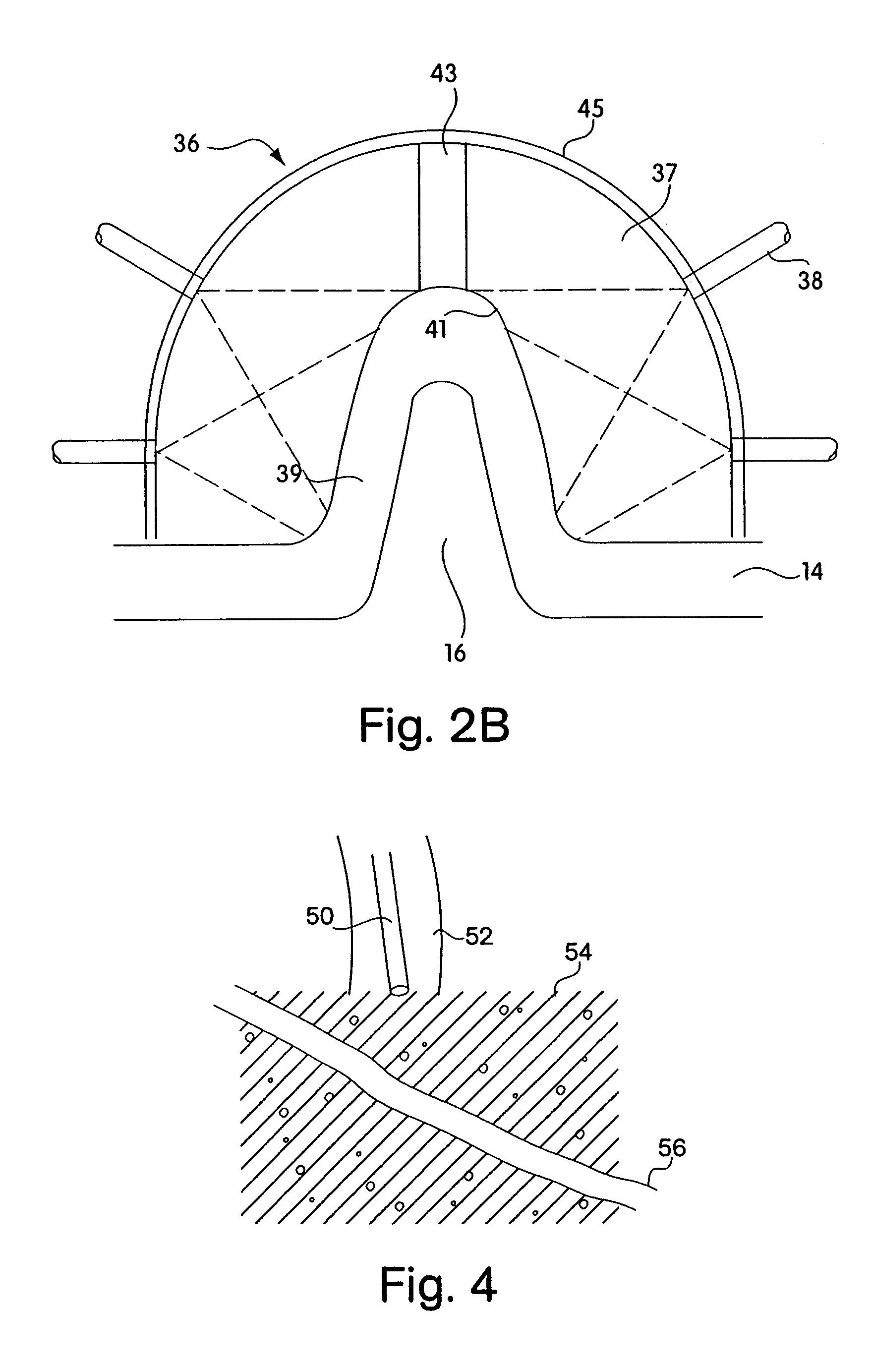

Electromagnetic susceptors with coatings for artificial dielectric systems and devices

InactiveUS20030226840A1Enhanced radiationLow dielectric constantGas treatmentMethane captureChemical treatmentSusceptor

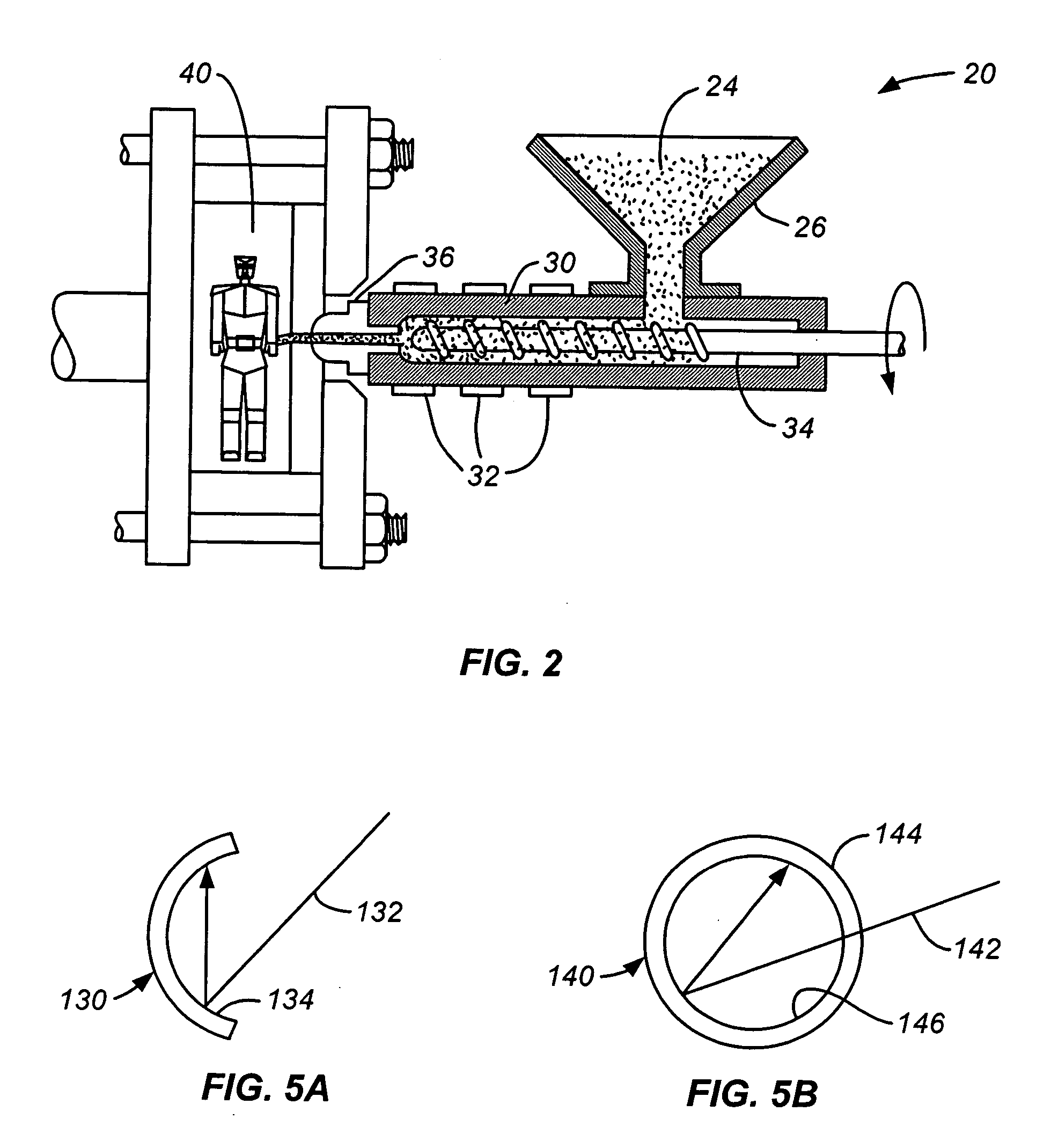

A coated susceptor of electromagnetic energy for chemical processing made of a matrix material that surrounds a non-matrix material that is made from a material that is different from the matrix material, in which the matrix material is constructed of material having lower dielectric losses compared to the non-matrix material, the non-matrix material initially absorbs electromagnetic energy applied to the electromagnetic susceptor to a greater extent than the matrix material, the non-matrix material produces subsequent heat in the matrix material, and the surface of the susceptor is coated with a material that interacts with applied electromagnetic energy of at least one frequency and initially absorbs electromagnetic energy and produces heat.

Owner:DALTON ROBERT C

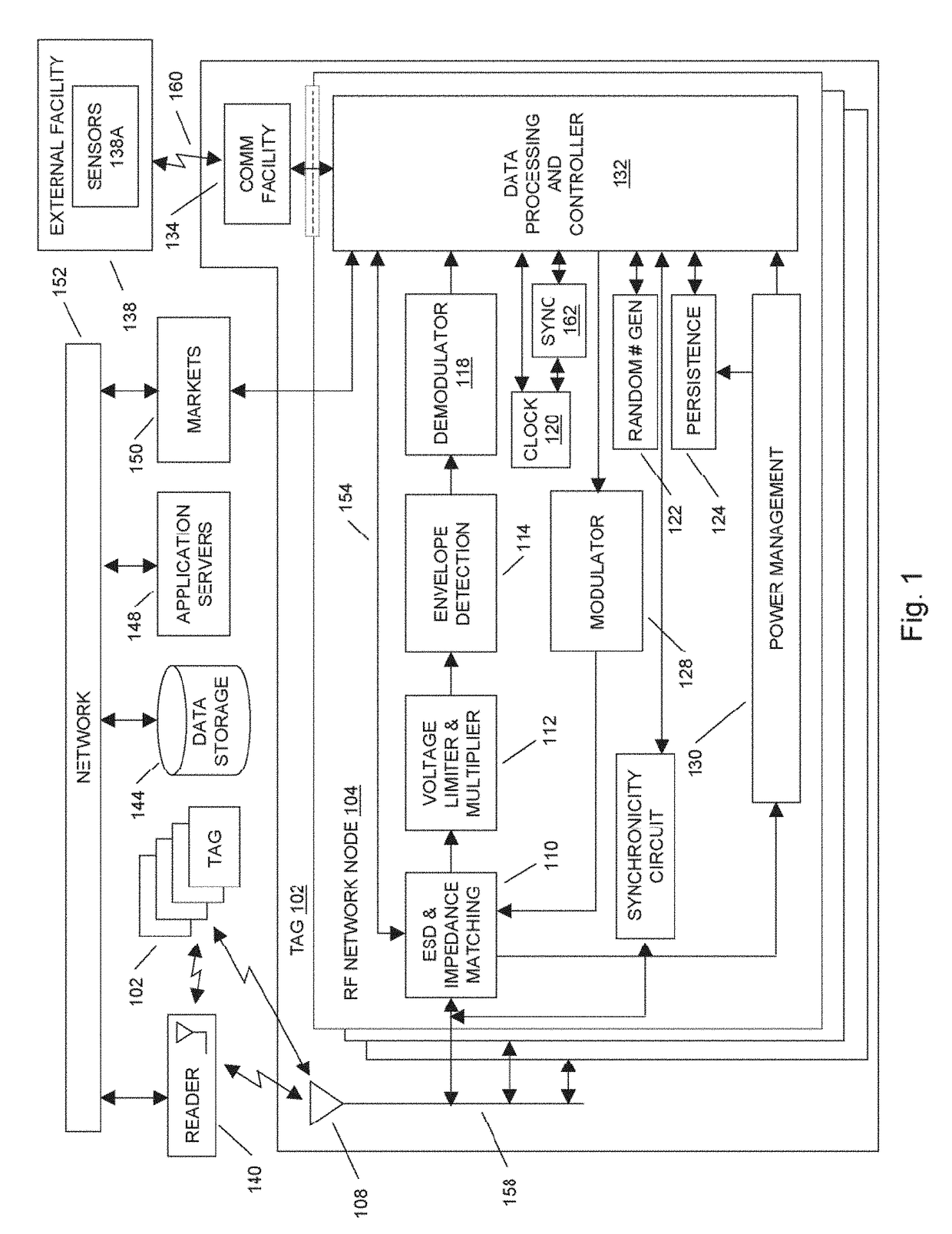

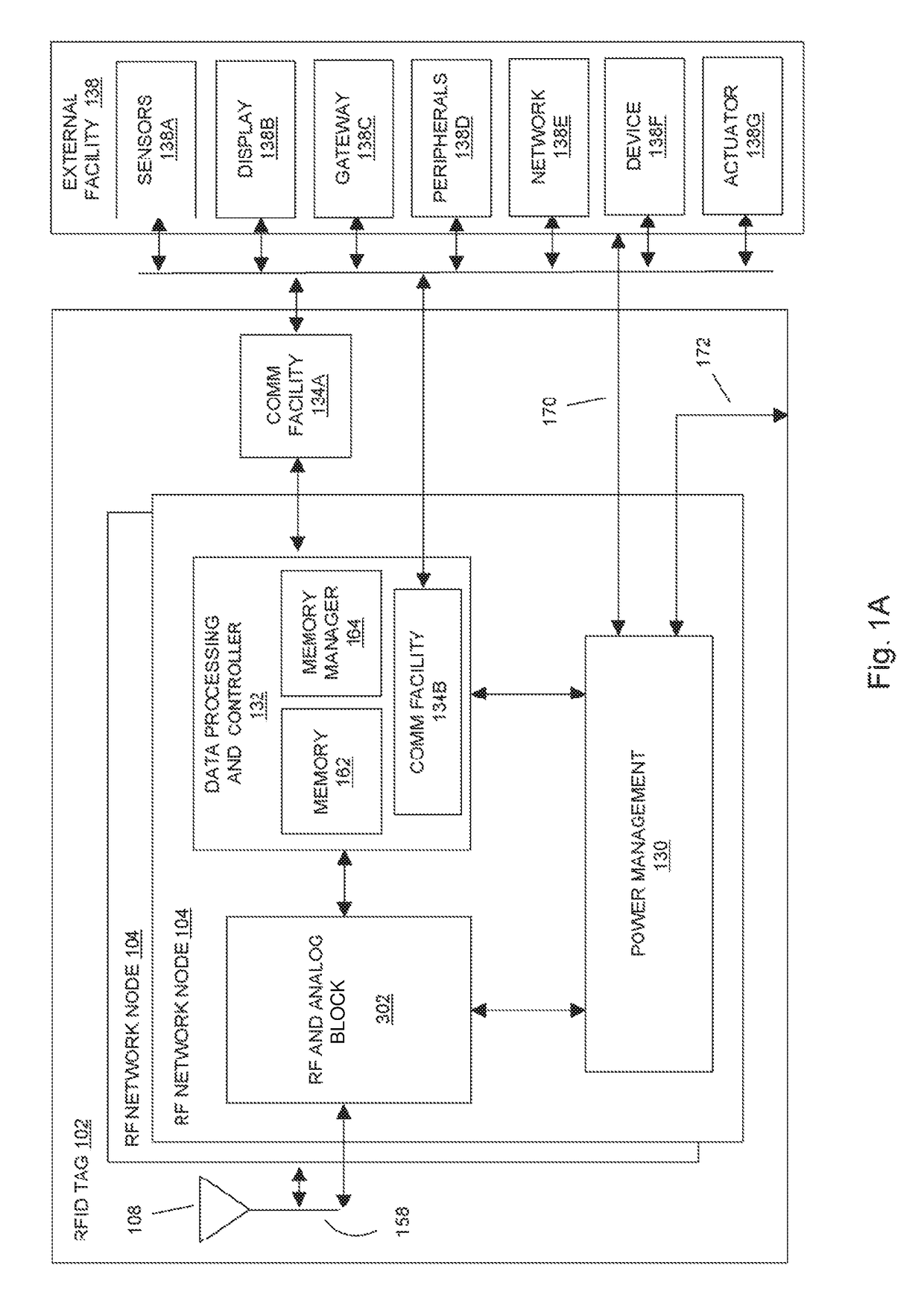

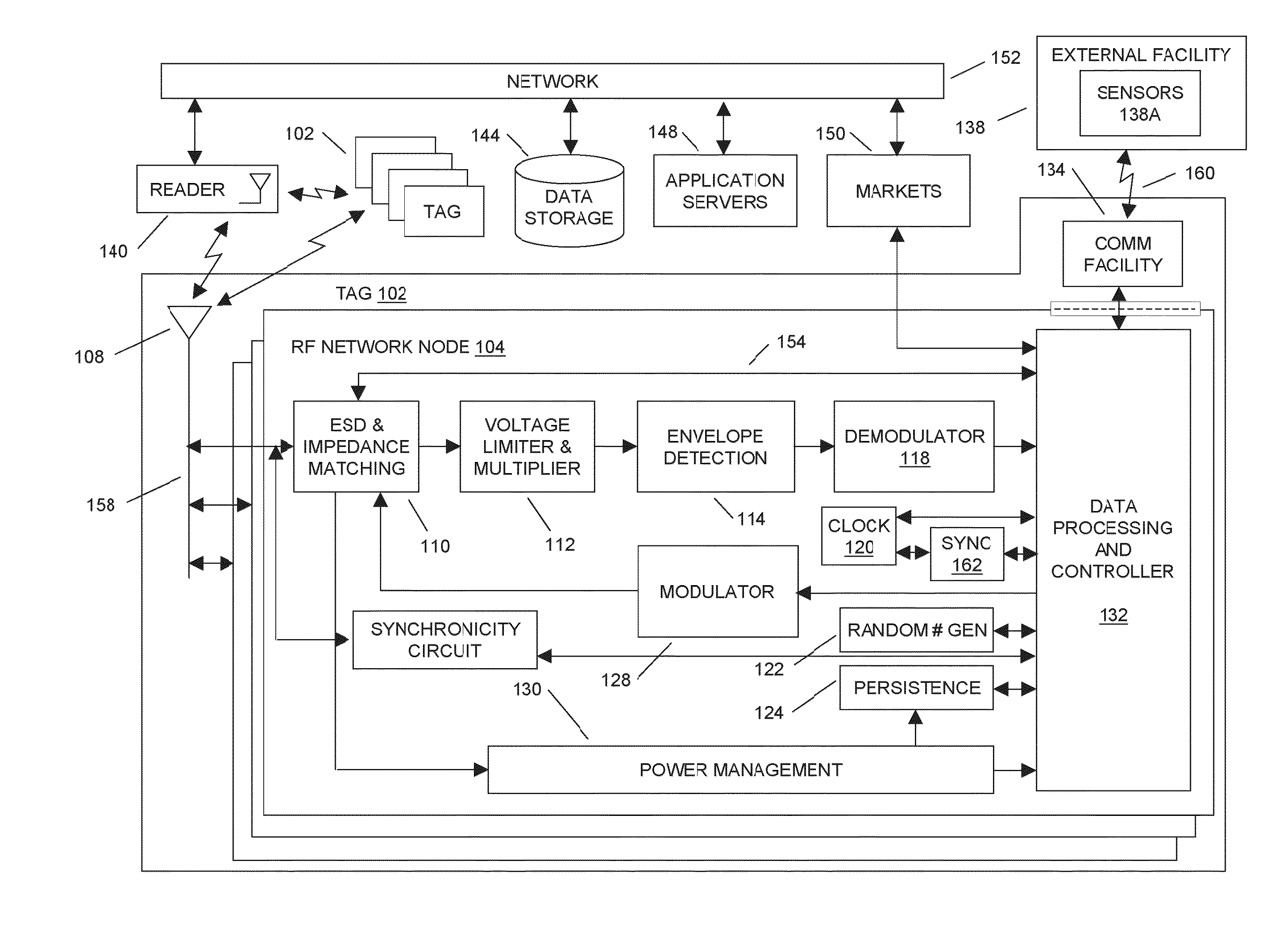

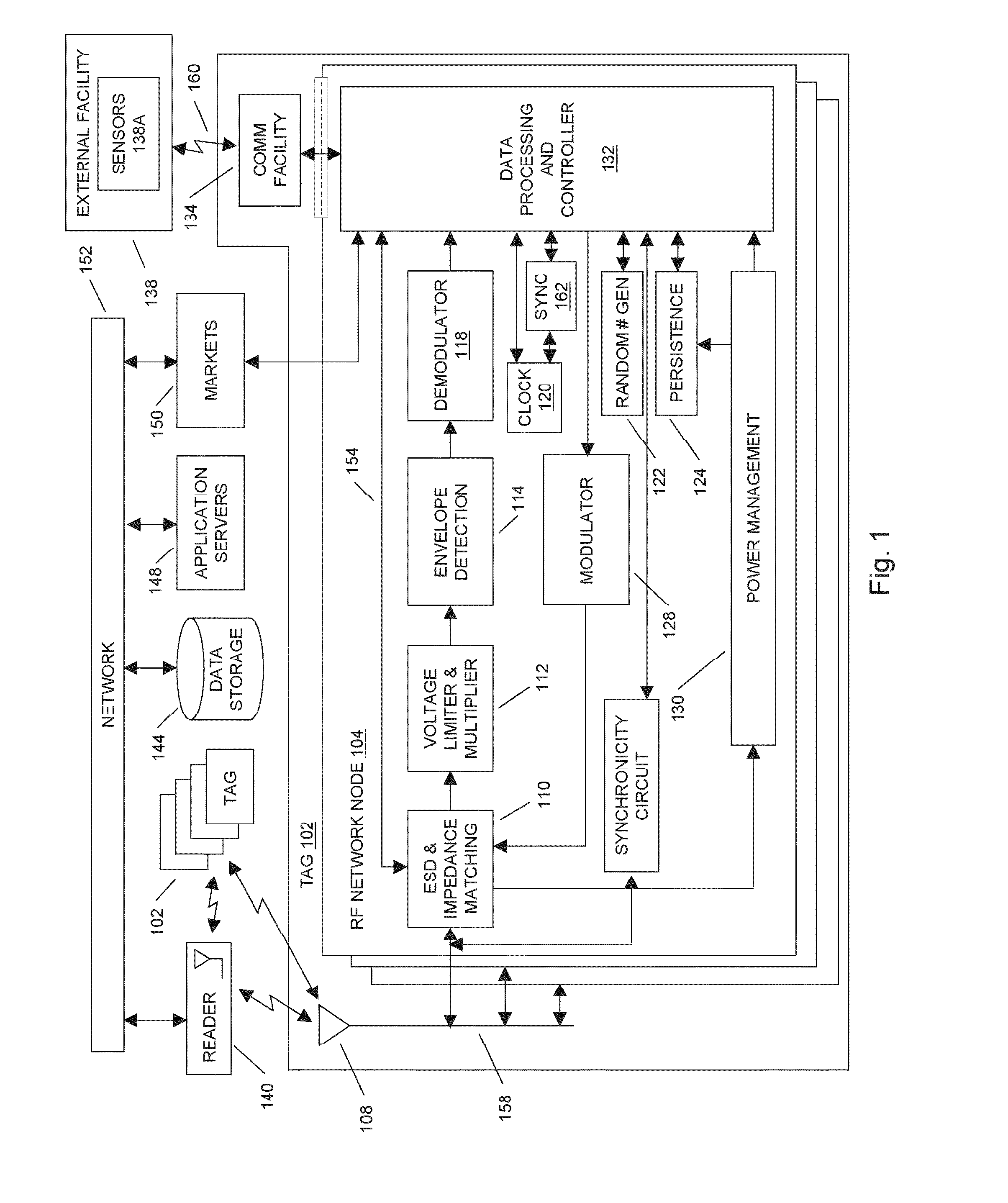

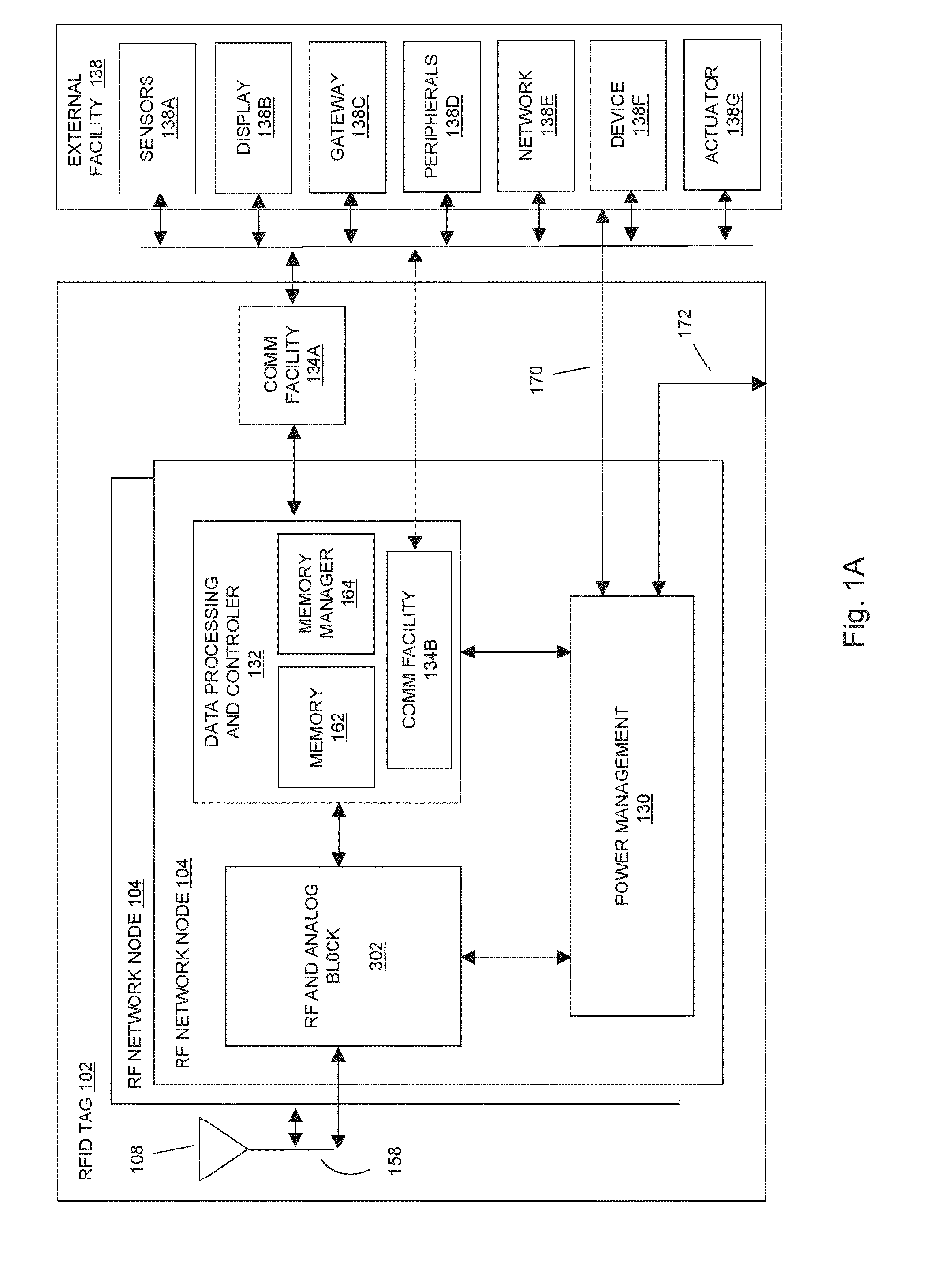

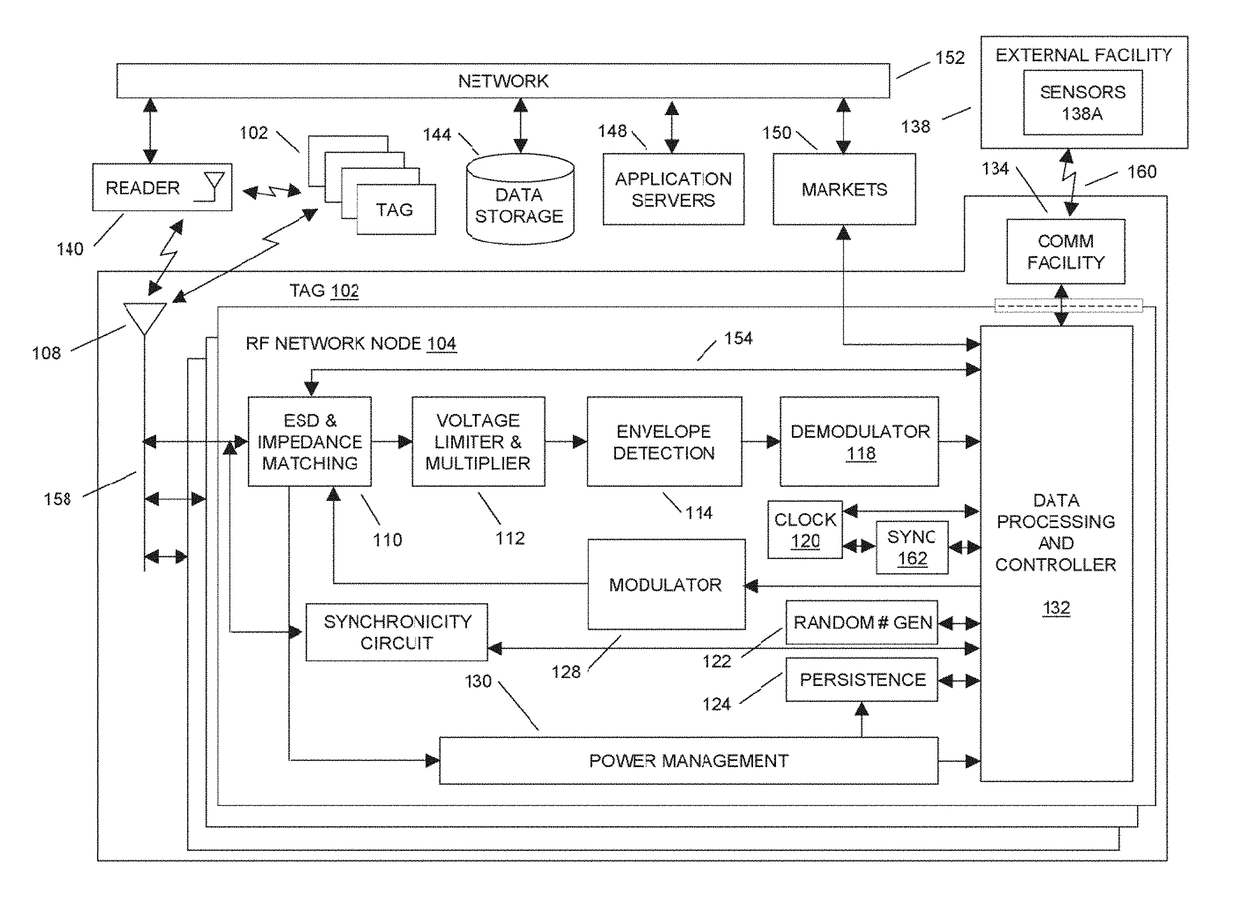

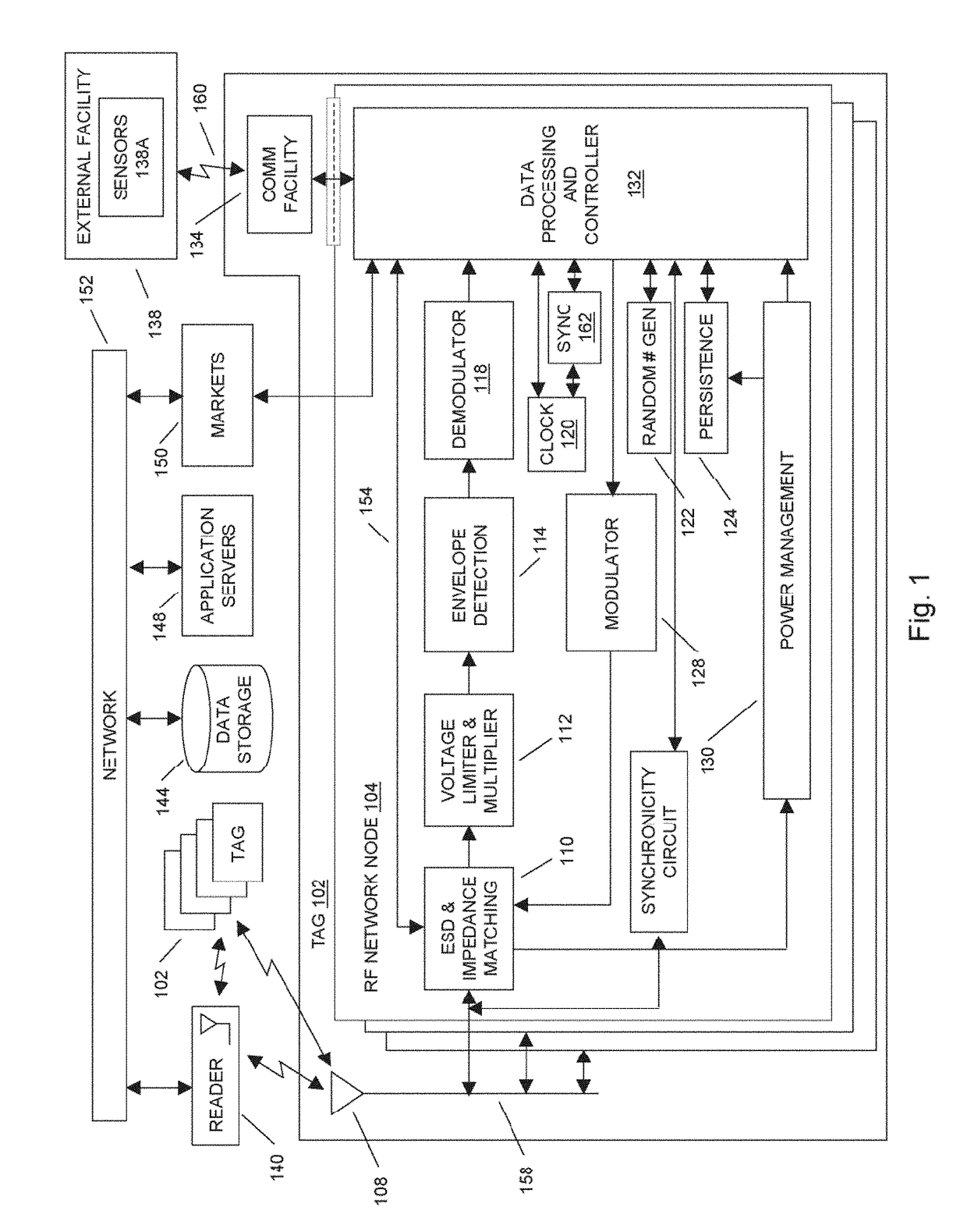

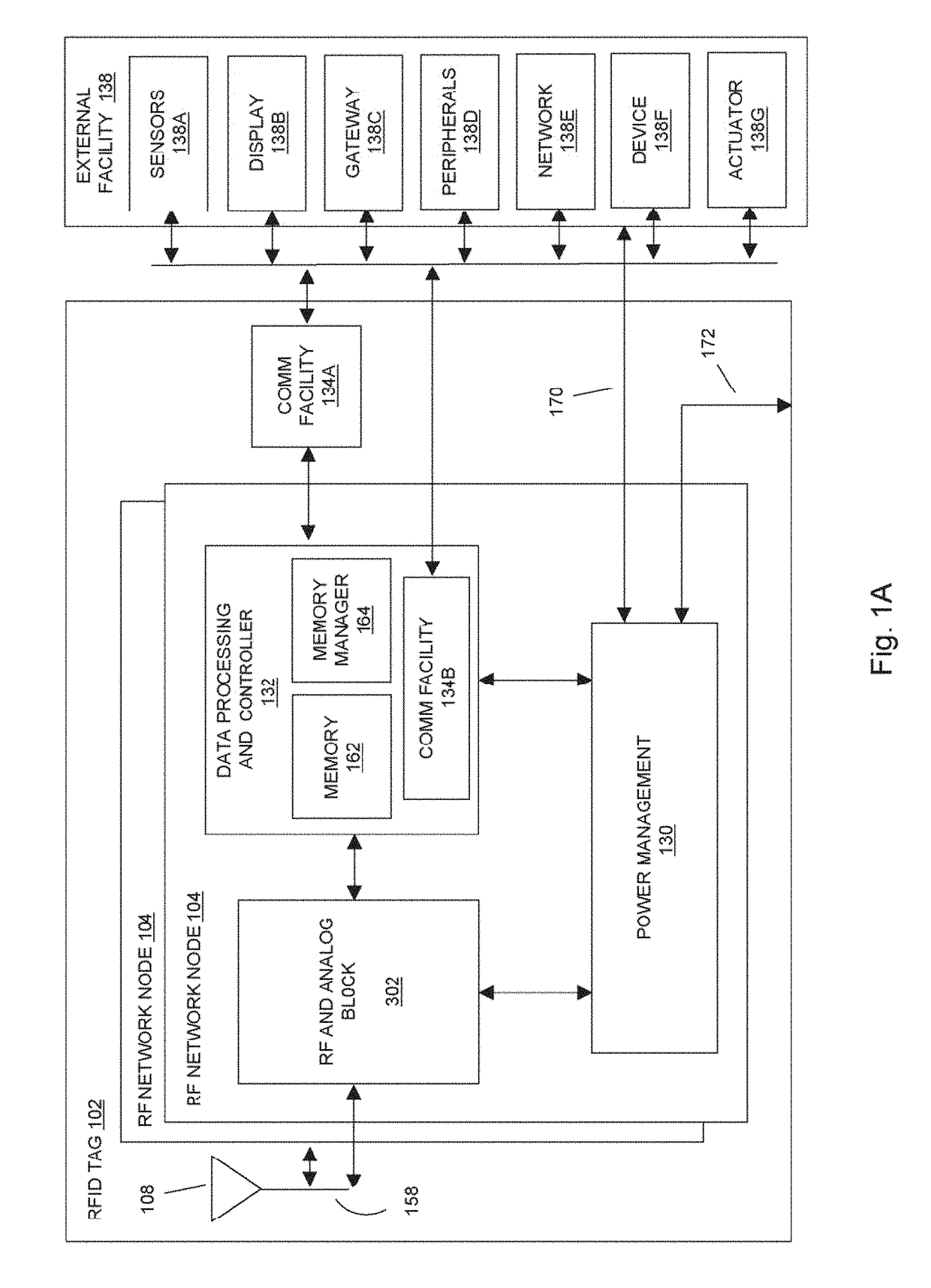

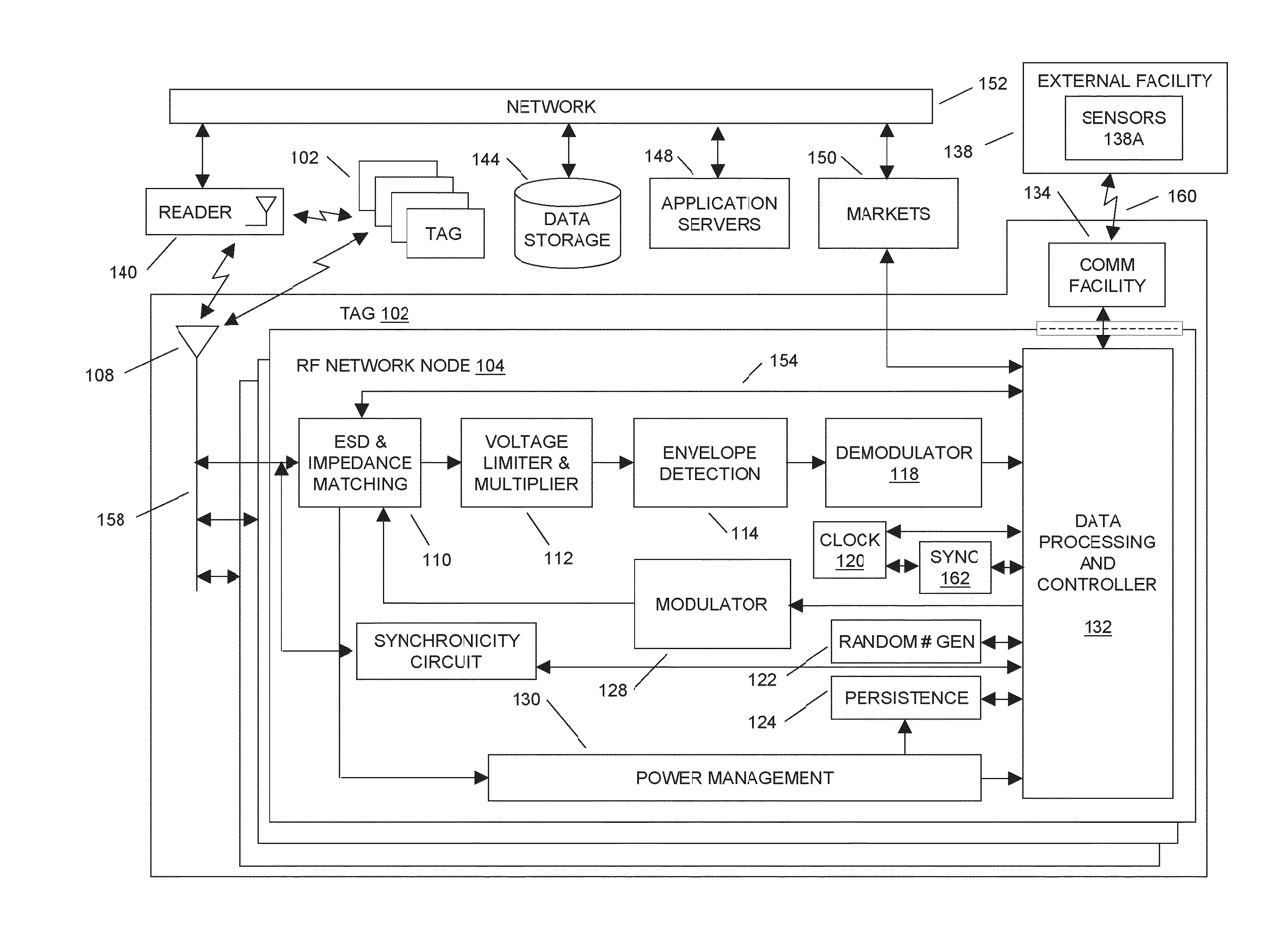

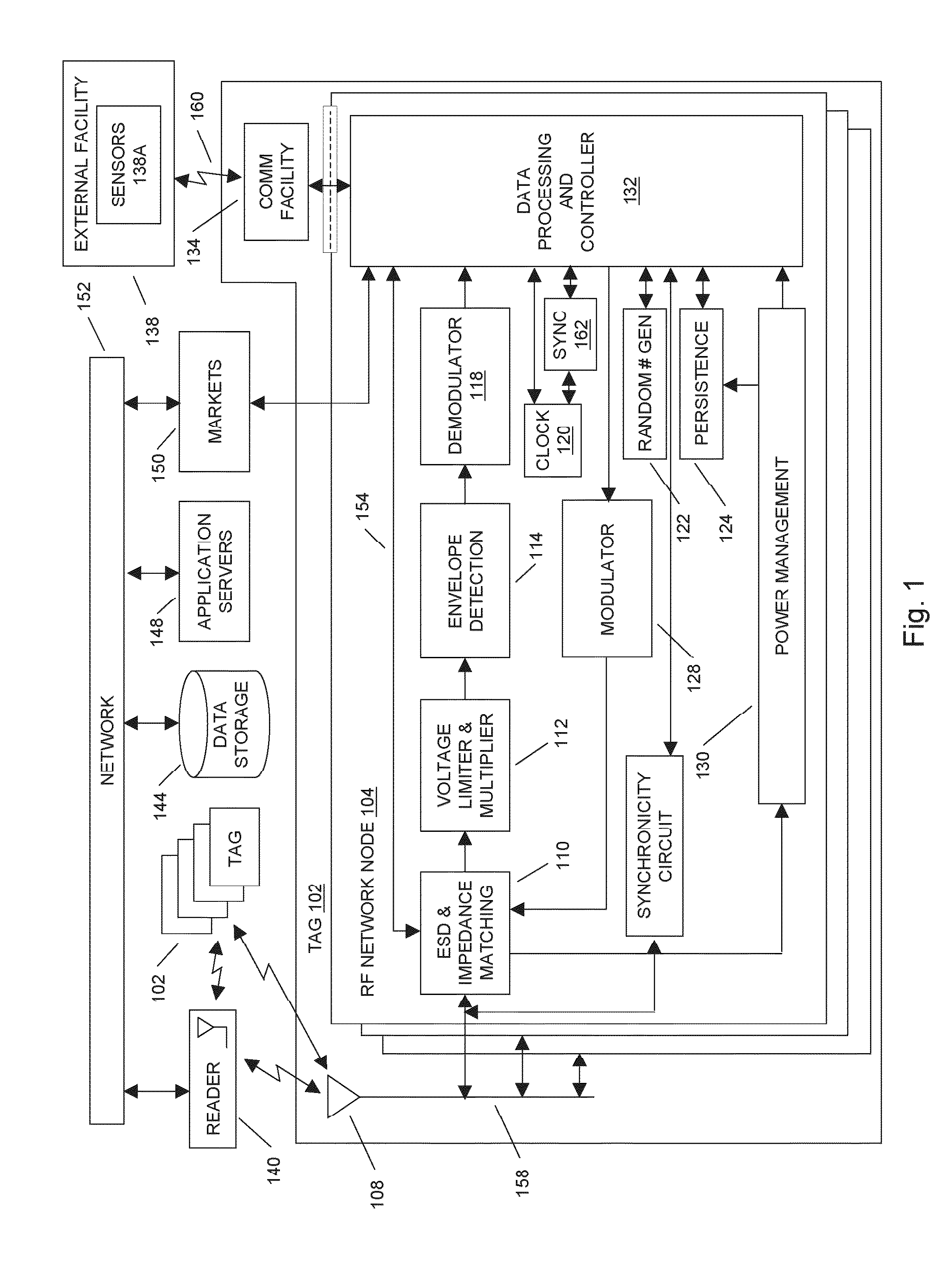

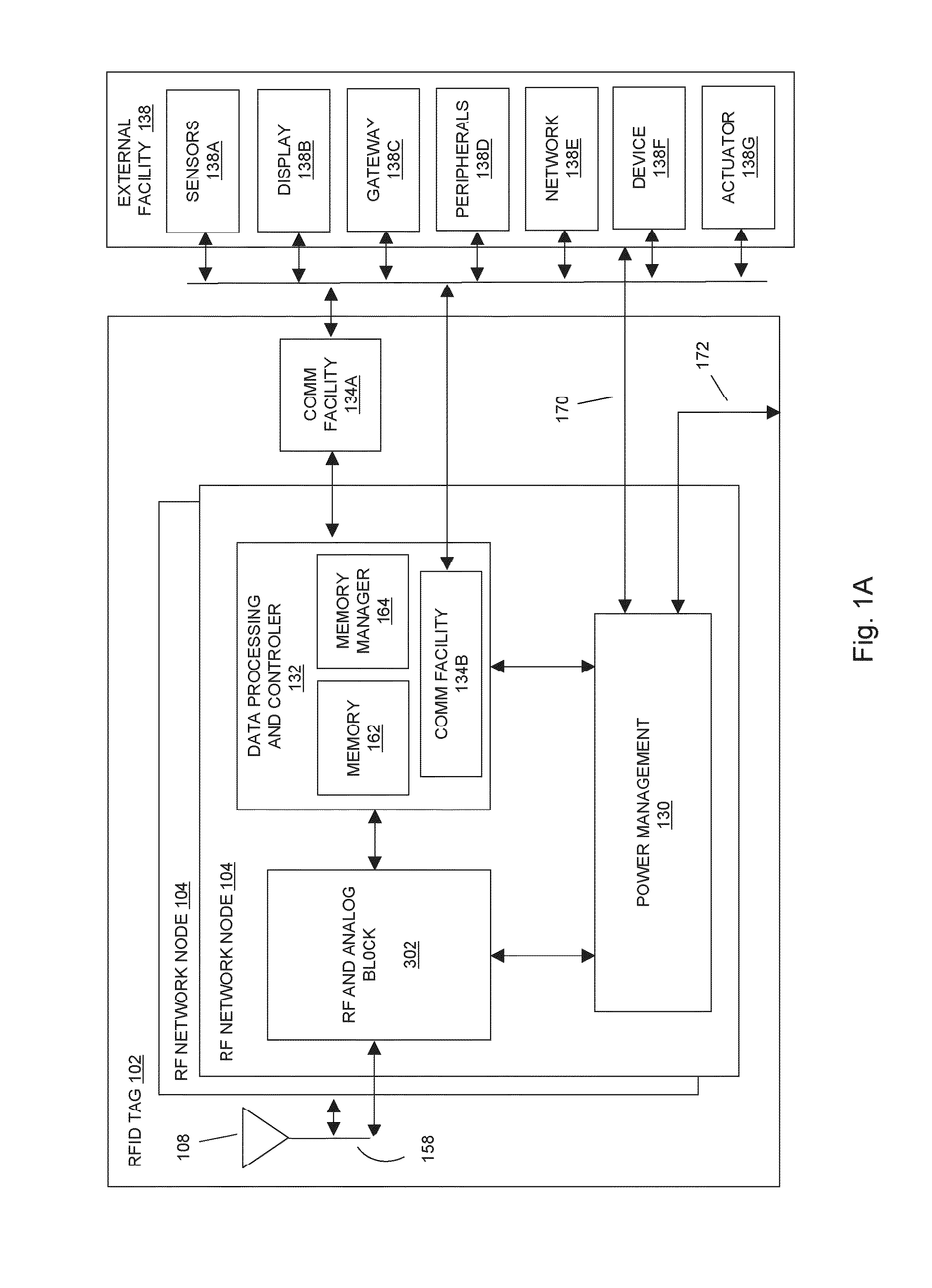

Operating systems for an RFID tag

ActiveUS9953193B2Enhanced radiationMemory record carrier reading problemsCo-operative working arrangementsComputer hardwareOperational system

Owner:TEGO INC

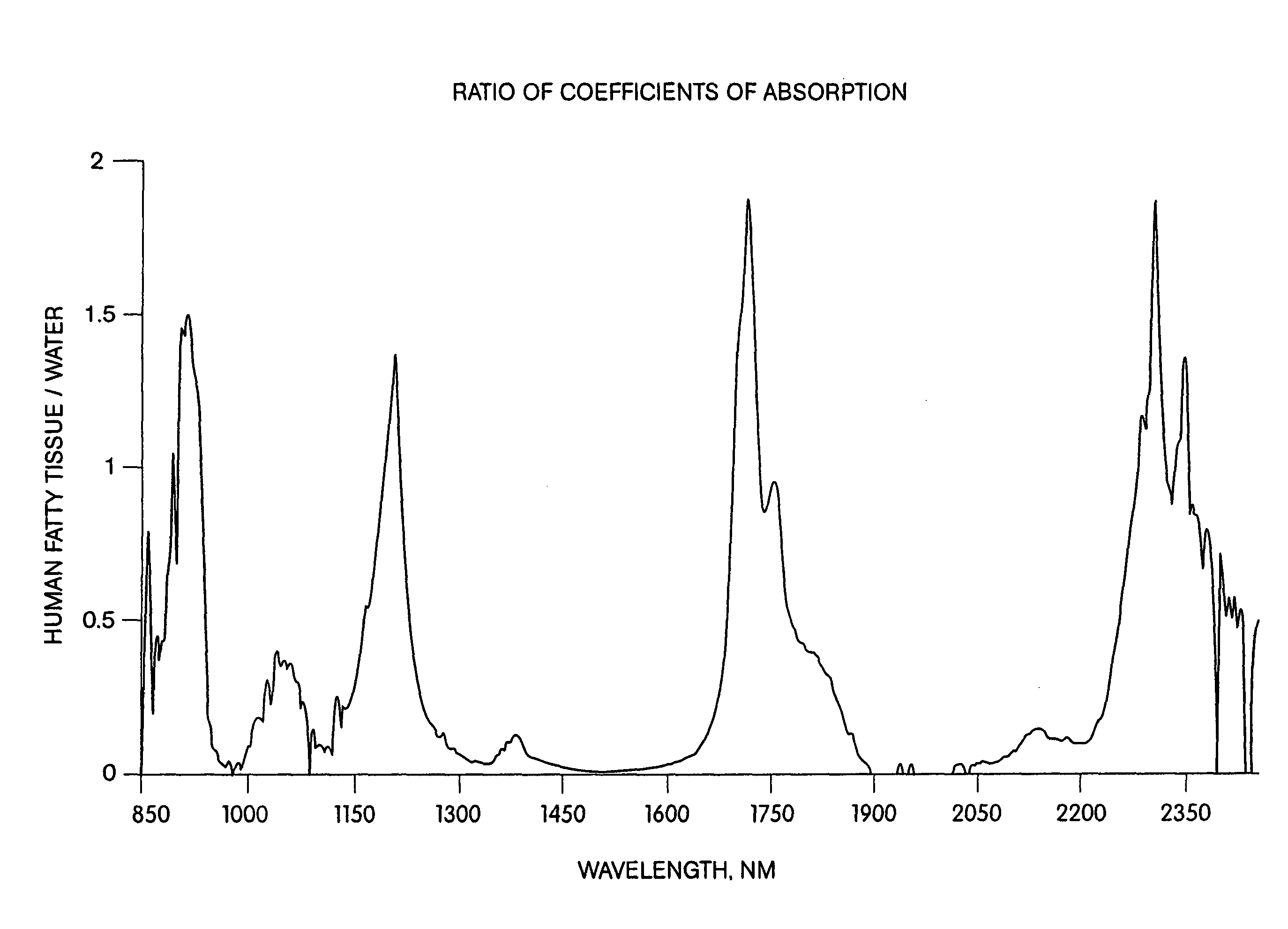

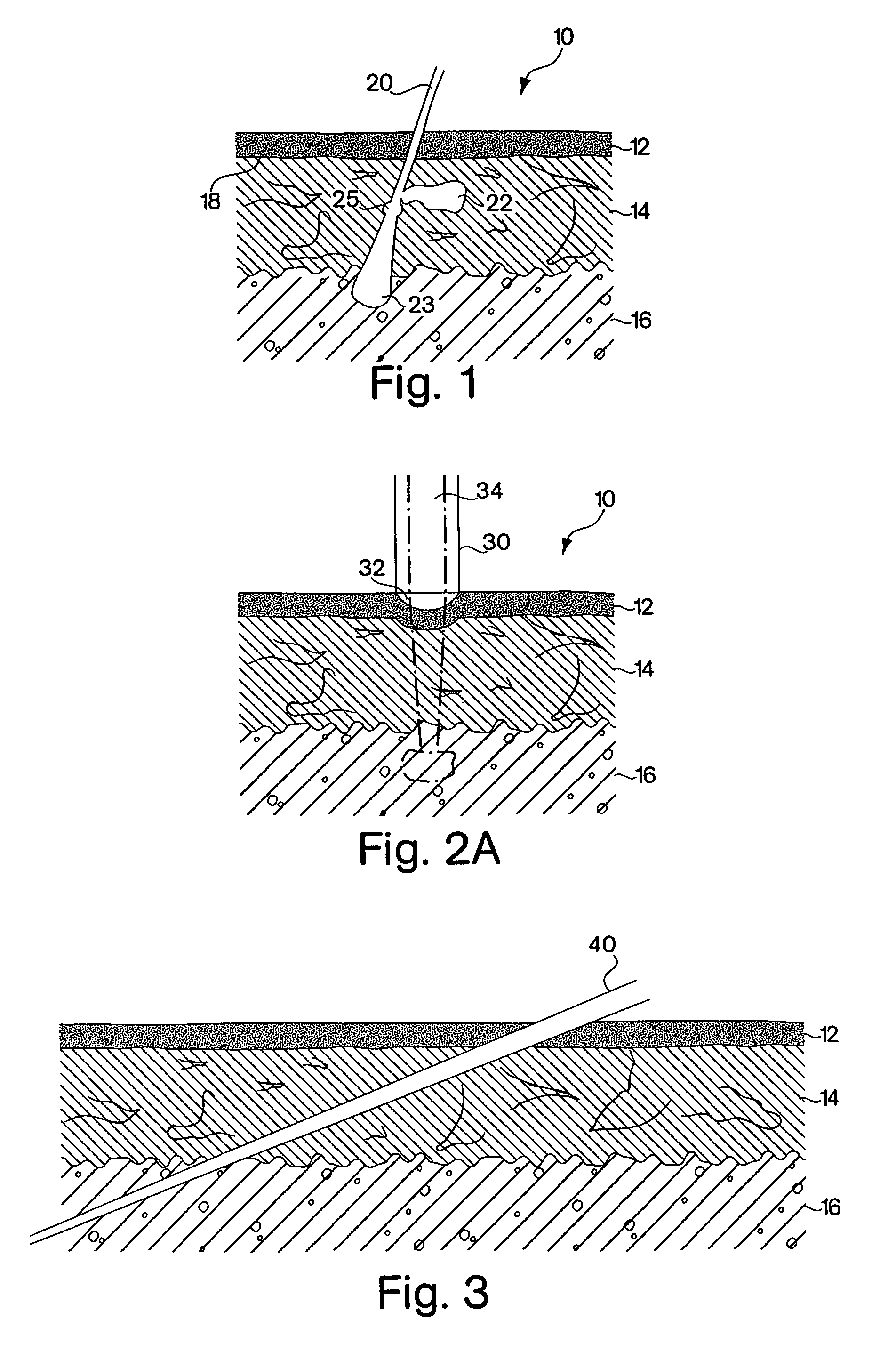

Method and apparatus for the selective targeting of lipid-rich tissues

InactiveUS7060061B2Desired treatmentSufficient durationSurgical instrument detailsSurgical pincettesHair removalLipid formation

A method and apparatus are provided for targeting lipid-rich tissue to effect a desired, the method / apparatus involving irradiating the lipid-rich tissue with energy at a wavelength preferentially absorbed by lipid cells, such wavelength being preferably in a band between 880 nm and 935 nm, 1150 nm and 1230 nm, 1690 nm to 1780 nm, or 2250 nm to 2450 nm with a fluence and duration sufficient to achieve a desired treatment. For preferred embodiments, the irradiation wavelength is between 900–930 nm, 1190–1220 nm, 1700–1730 nm, or 2280–2350 nm. The method and apparatus may for example be used to target one or more sebaceous glands for the treatment of acne or hair removal, to target subcutaneous fat for removal thereof or for targeting fat on anatomical elements for various purposes.

Owner:PALOMAR MEDICAL TECH

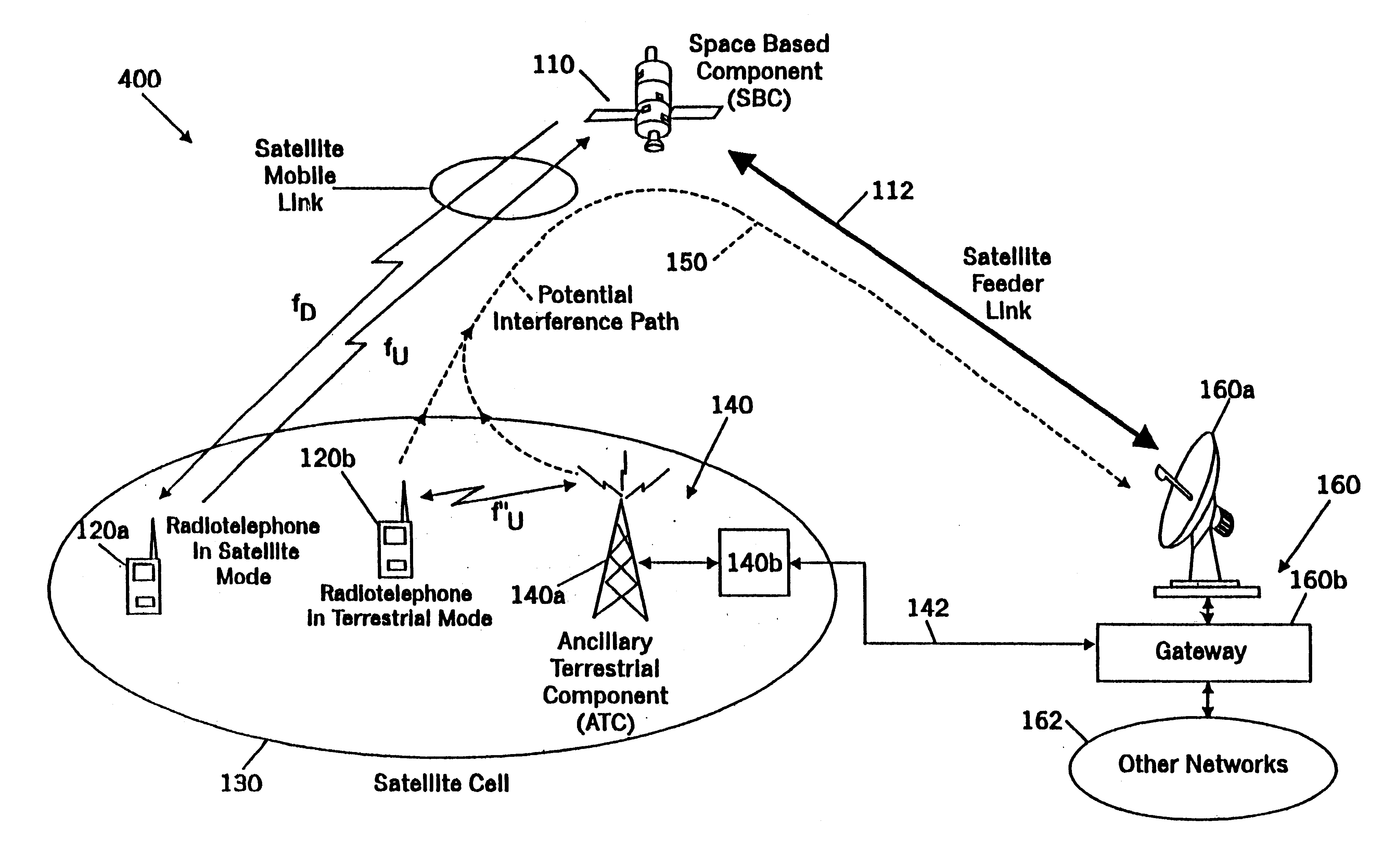

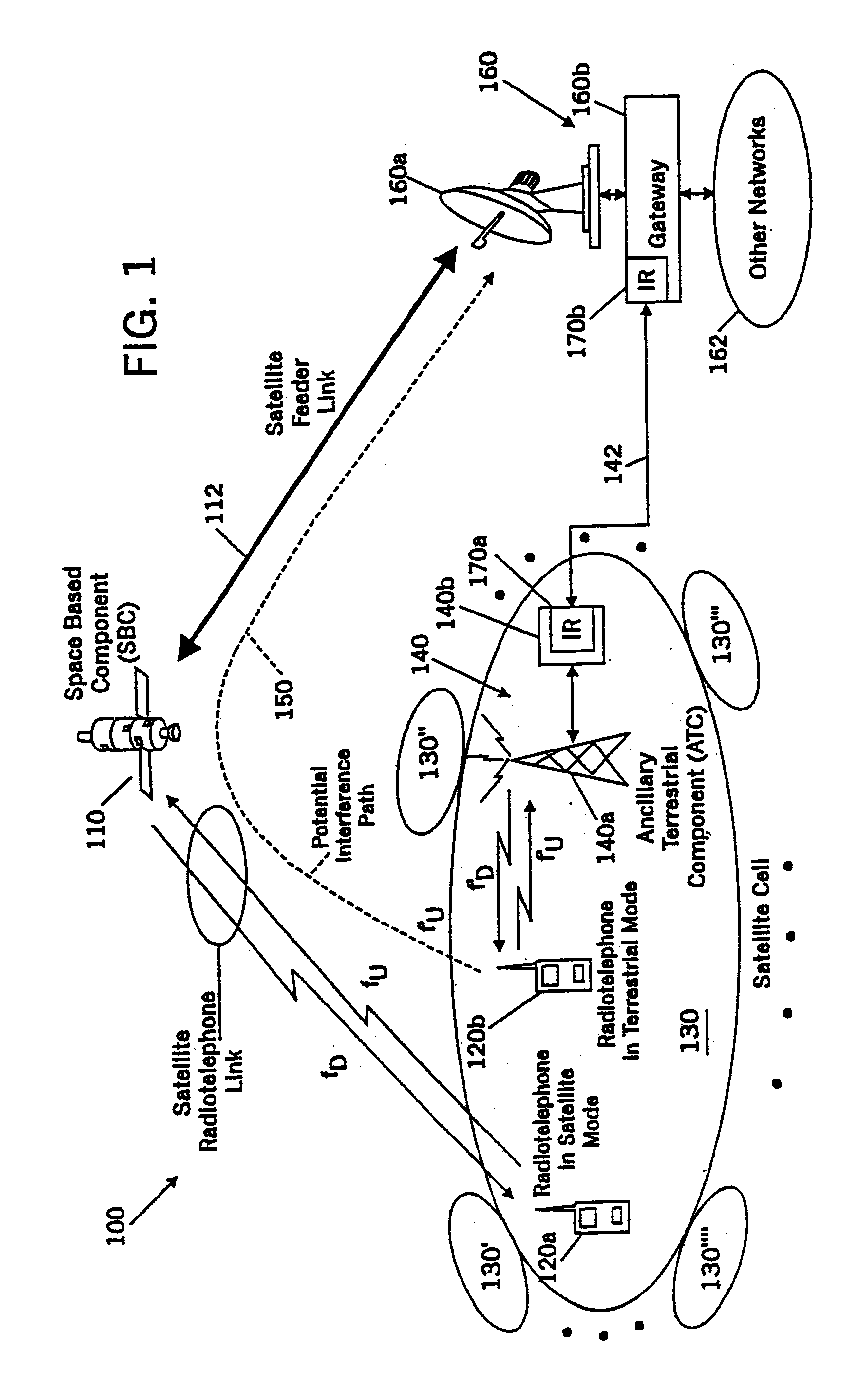

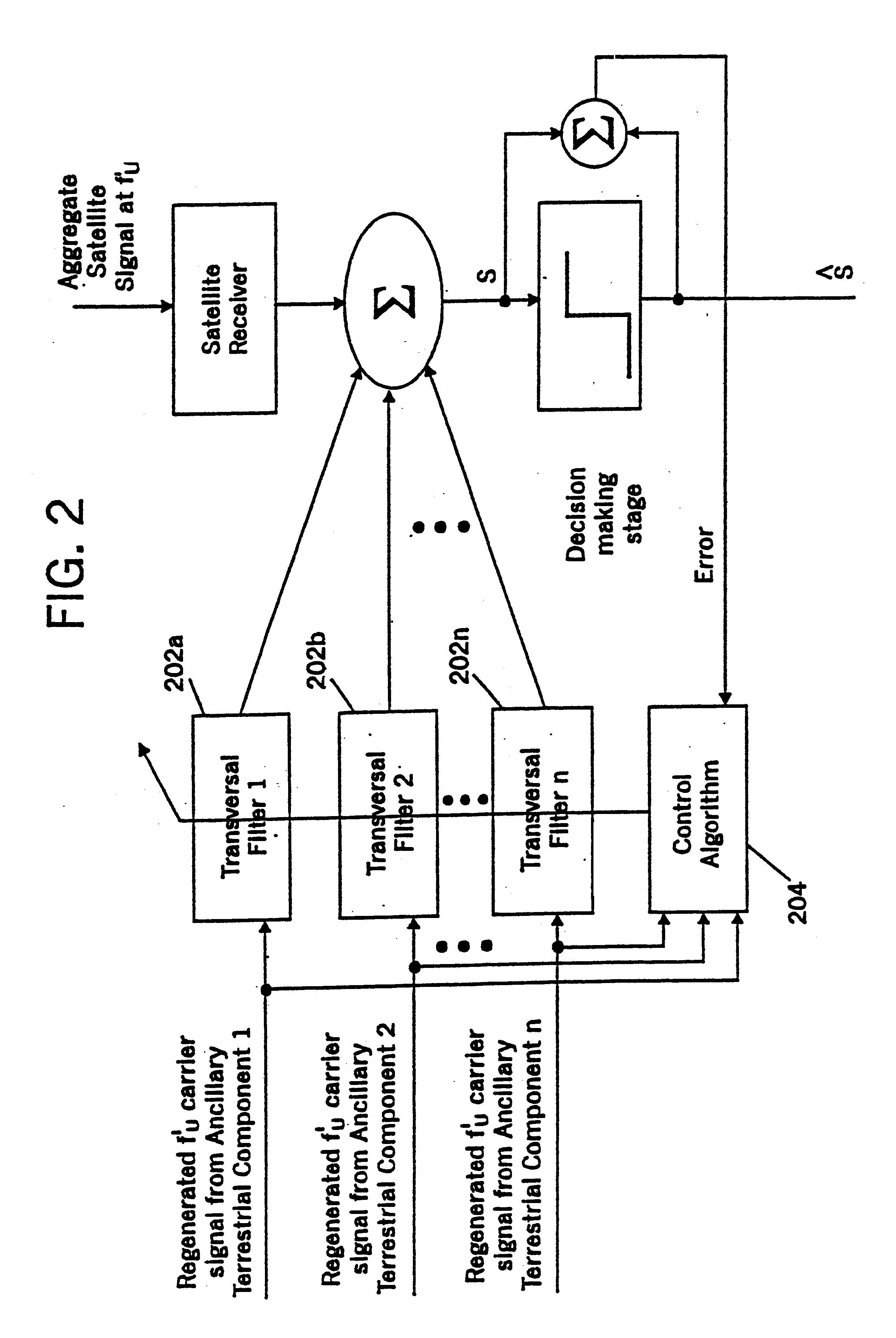

Filters for combined radiotelephone/GPS terminals

A satellite radiotelephone system includes a space-based component, a plurality of ancillary terrestrial components, and a plurality of radiotelephones. The space-based component is configured to provide wireless radiotelephone communications using satellite radiotelephone frequencies. The plurality of ancillary terrestrial components include a plurality of ancillary terrestrial component antennas configured to provide wireless radiotelephone communications using at least one of the satellite radiotelephone frequencies in a radiation pattern that increases radiation below the horizon compared to above the horizon. The plurality of radiotelephones are configured to communicate with the space-based component and with the plurality of ancillary terrestrial components. Each radiotelephone also includes a GPS signal processor and a GPS mode filter that is configured to suppress energy at (1575.42-.DELTA.) MHz, where 0<.DELTA..ltoreq.16.42 MHz. Related radiotelephones and methods are also discussed.

Owner:ATC TECH LLC

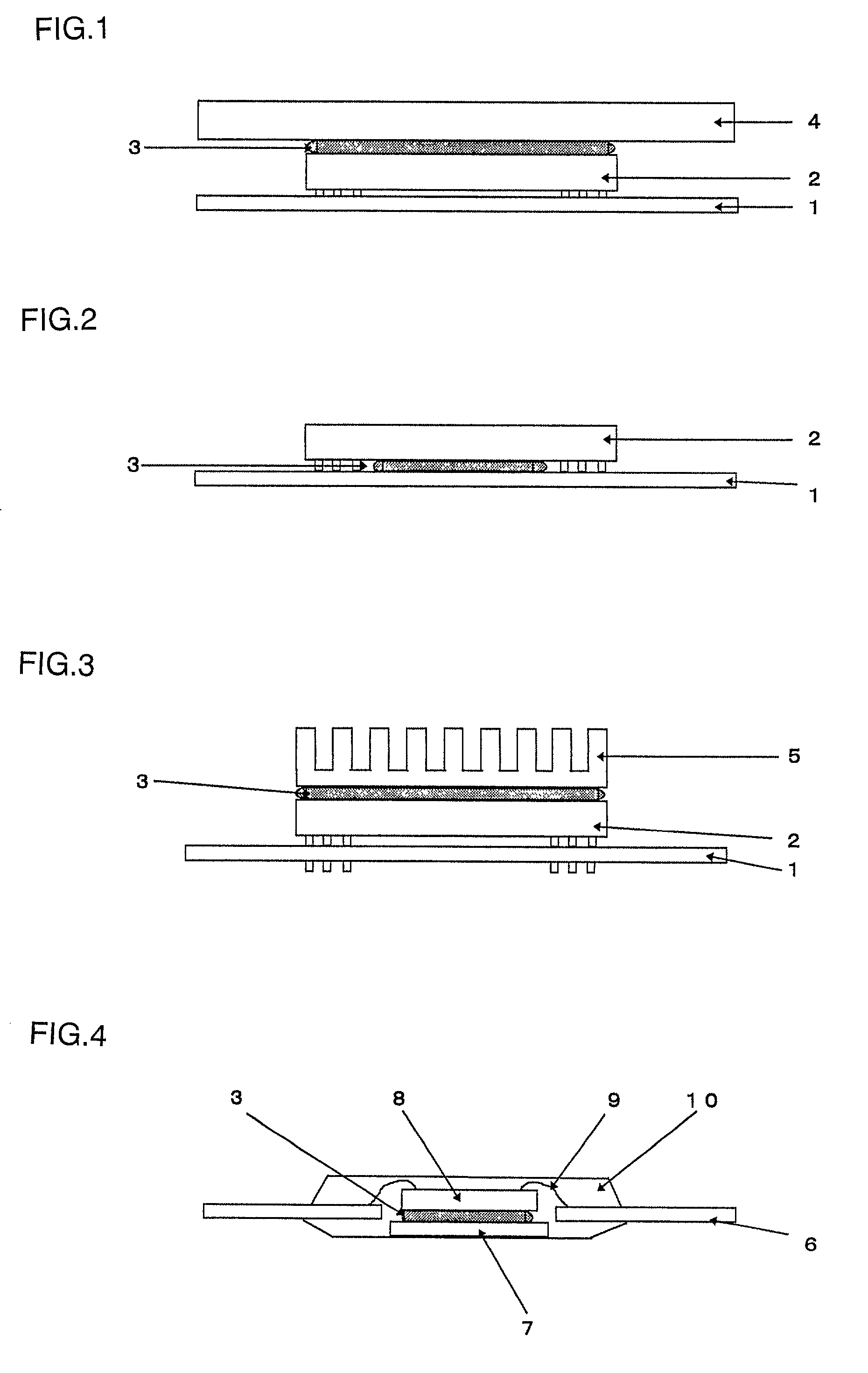

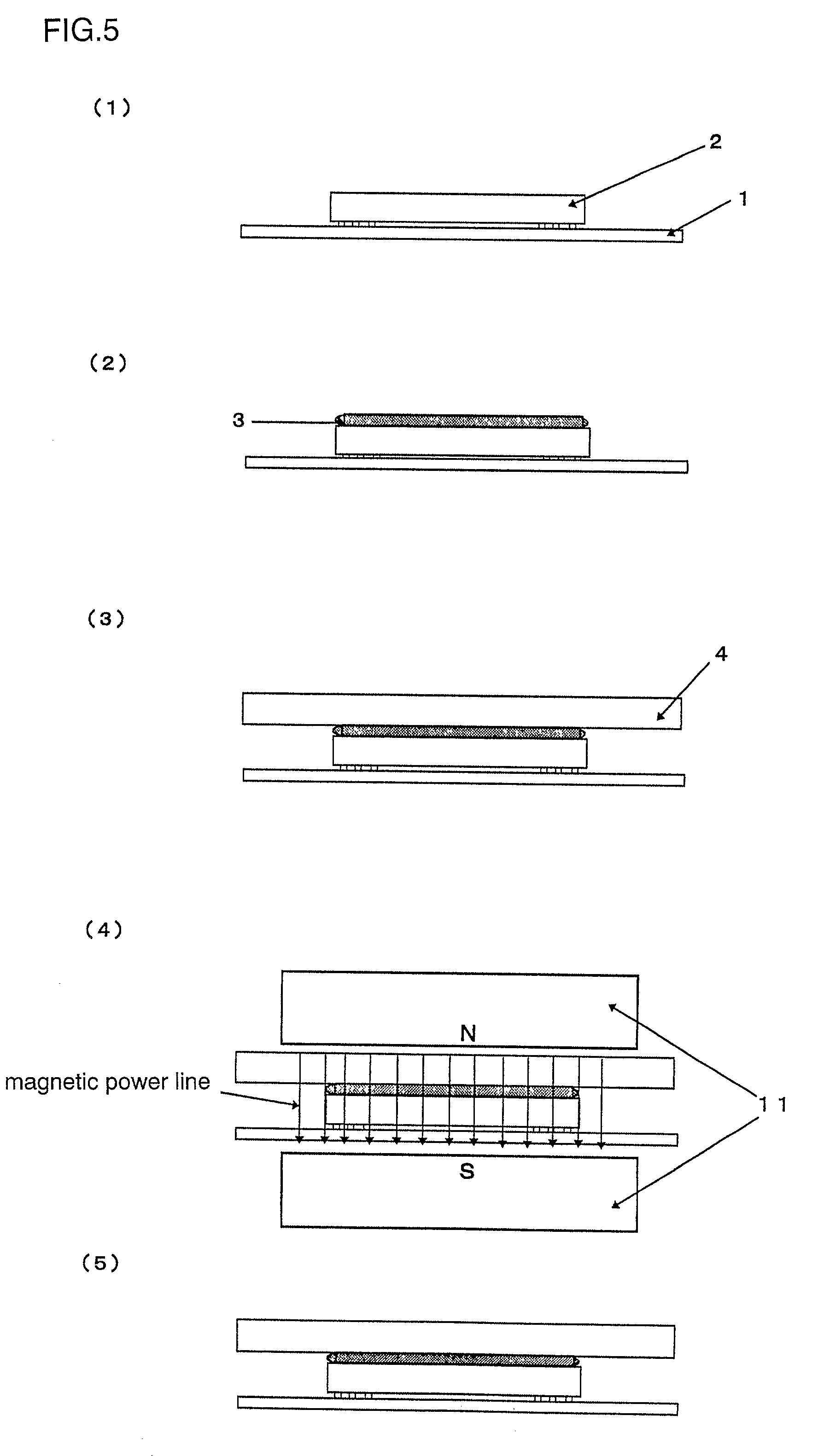

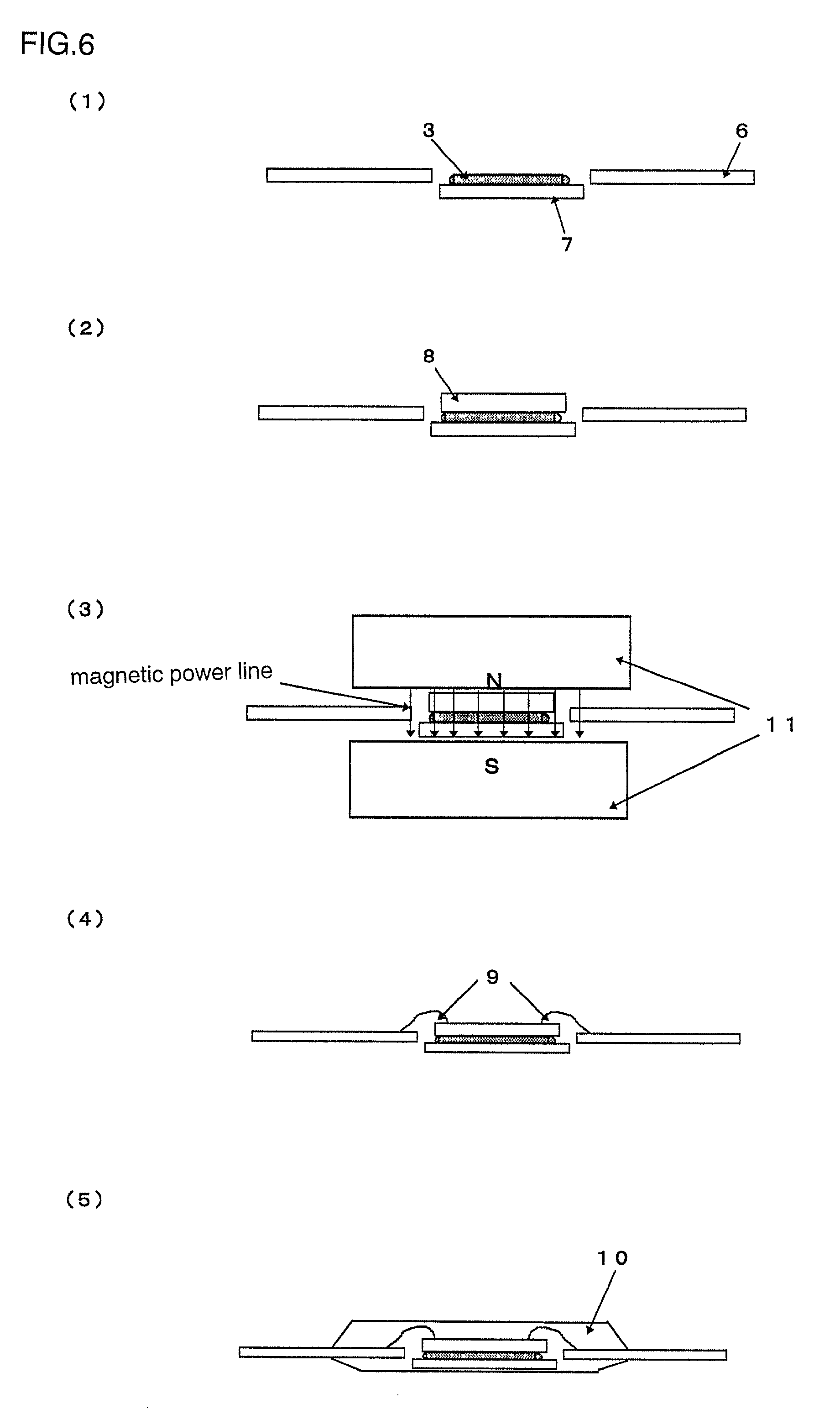

Adhesion method and electronic component

InactiveUS20010004131A1Efficiently dissipatedEnhanced radiationAdhesive processesLamination ancillary operationsAdhesiveBoron nitride

The present invention provides an adhesion method of improving the heat conduction in a fixed direction by using a heat conductive adhesive made by blending boron nitride powder and adhesive polymer and adhering by orienting boron nitride powder in the heat conductive adhesive to the fixed direction under the magnetic atmosphere and an electronic component for effectively dissipating heat generated from semiconductor device 2, power source 4, light source or other components used for the electric products, and an electronic component excellent in radiation.

Owner:POLYMATECH CO LTD

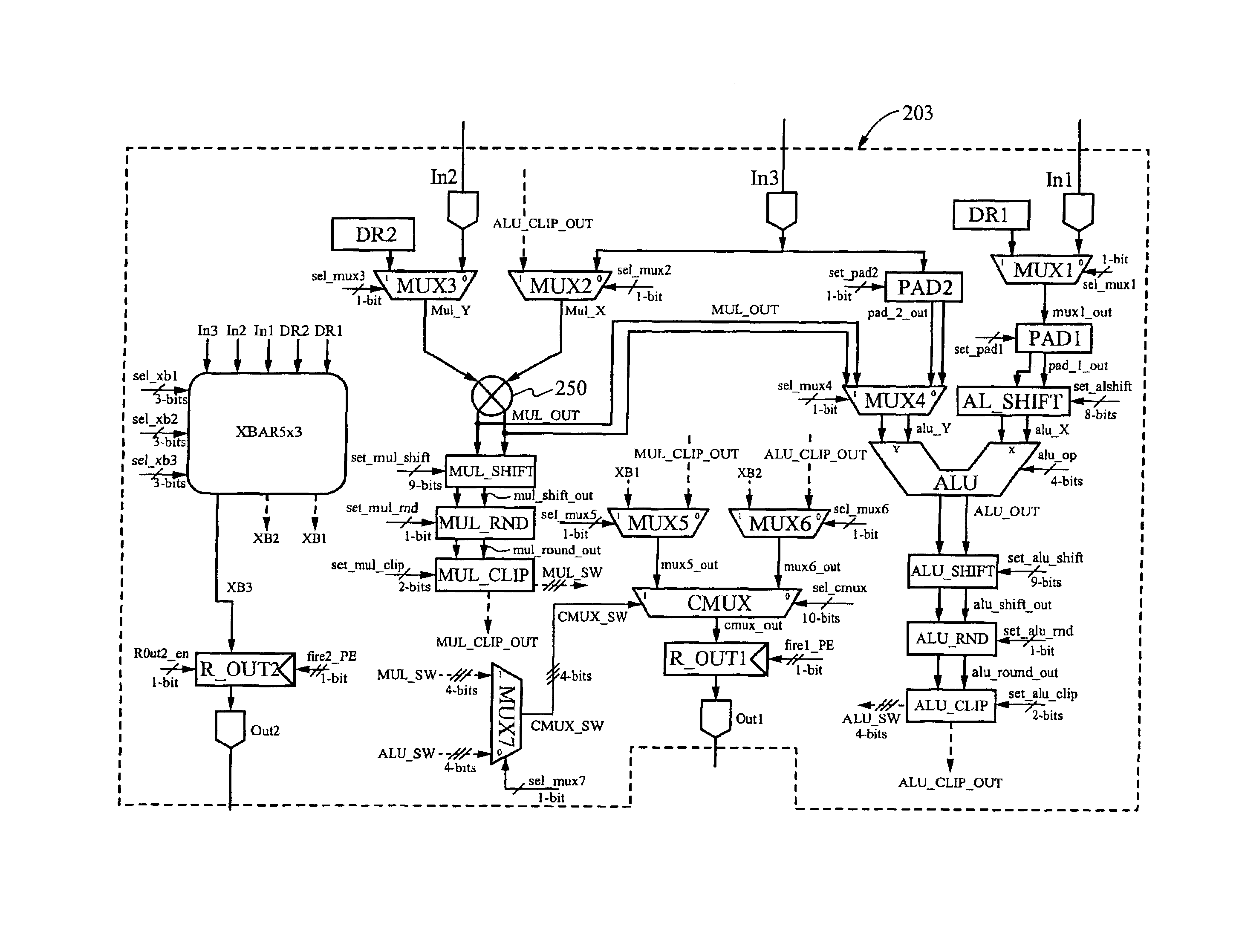

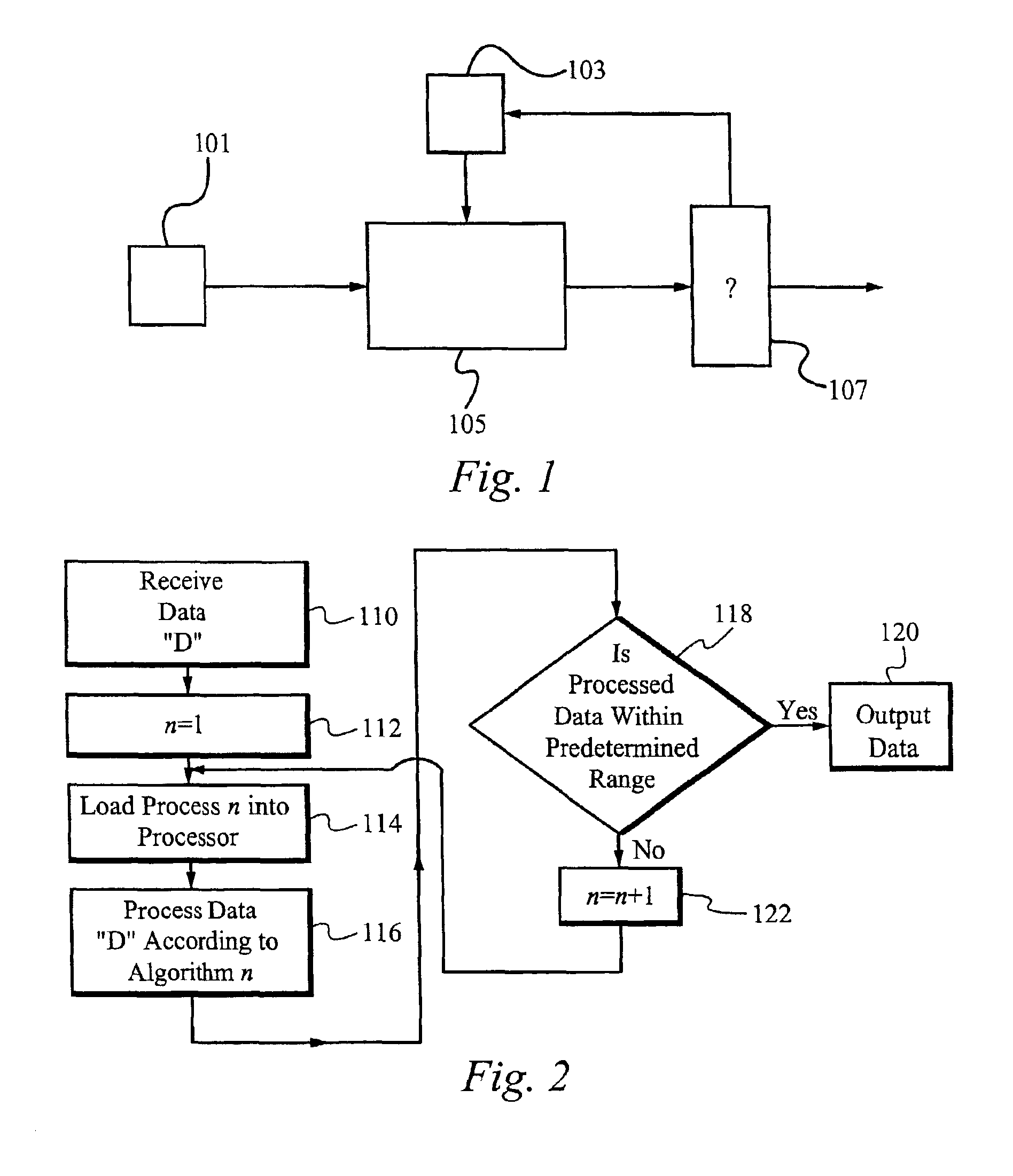

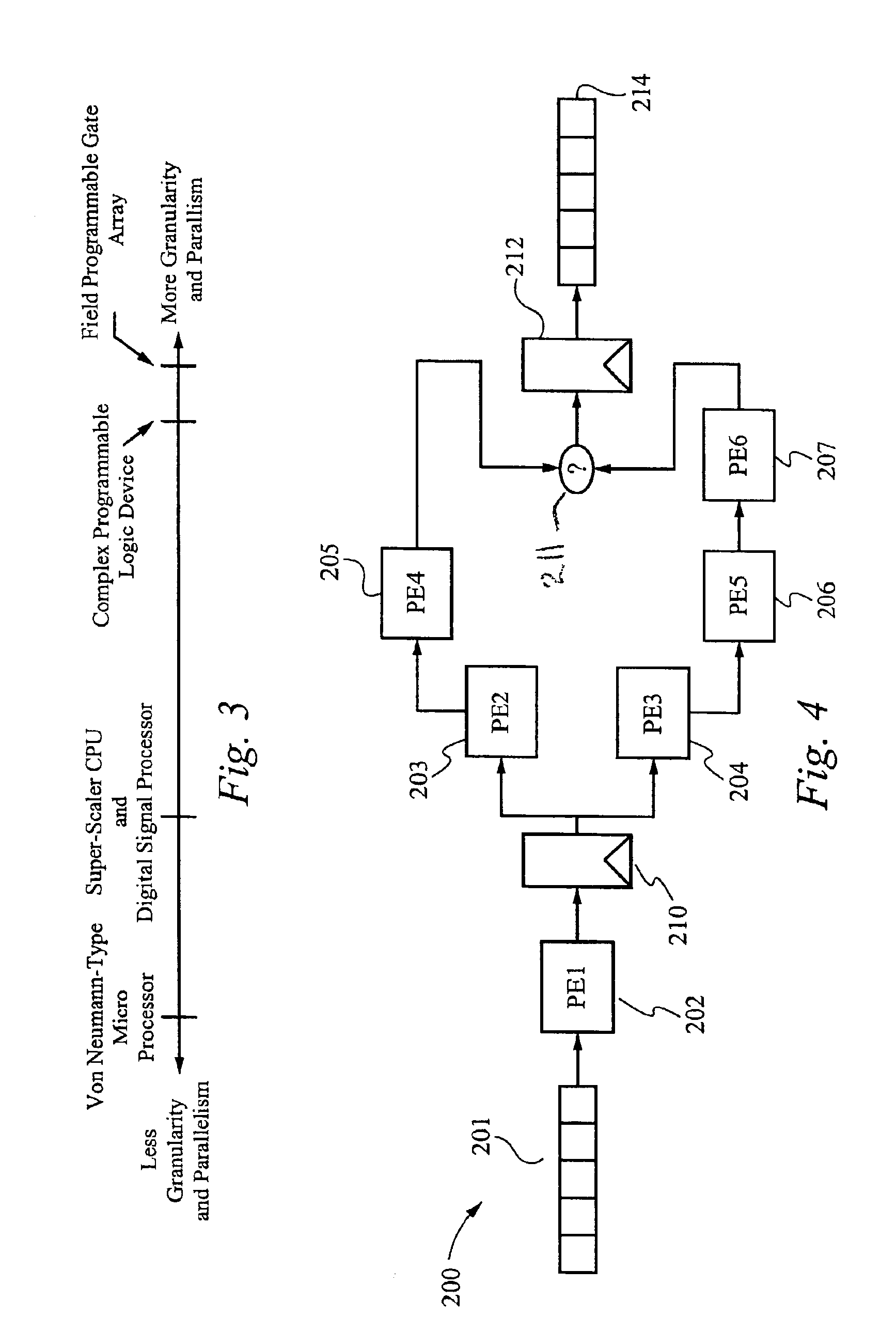

Reconfigurable data path processor

InactiveUS6883084B1Eliminates branchingCycle simpleEnergy efficient ICTConditional code generationMultiplexerProcessing element

A reconfigurable data path processor comprises a plurality of independent processing elements. Each of the processing elements advantageously comprising an identical architecture. Each processing element comprises a plurality of data processing means for generating a potential output. Each processor is also capable of through-putting an input as a potential output with little or no processing. Each processing element comprises a conditional multiplexer having a first conditional multiplexer input, a second conditional multiplexer input and a conditional multiplexer output. A first potential output value is transmitted to the first conditional multiplexer input, and a second potential output value is transmitted to the second conditional multiplexer output. The conditional multiplexer couples either the first conditional multiplexer input or the second conditional multiplexer input to the conditional multiplexer output, according to an output control command. The output control command is generated by processing a set of arithmetic status-bits through a logical mask. The conditional multiplexer output is coupled to a first processing element output. A first set of arithmetic bits are generated according to the processing of the first processable value. A second set of arithmetic bits may be generated from a second processing operation. The selection of the arithmetic status-bits is performed by an arithmetic-status bit multiplexer selects the desired set of arithmetic status bits from among the first and second set of arithmetic status bits. The conditional multiplexer evaluates the select arithmetic status bits according to logical mask defining an algorithm for evaluating the arithmetic status bits.

Owner:STC UNM +1

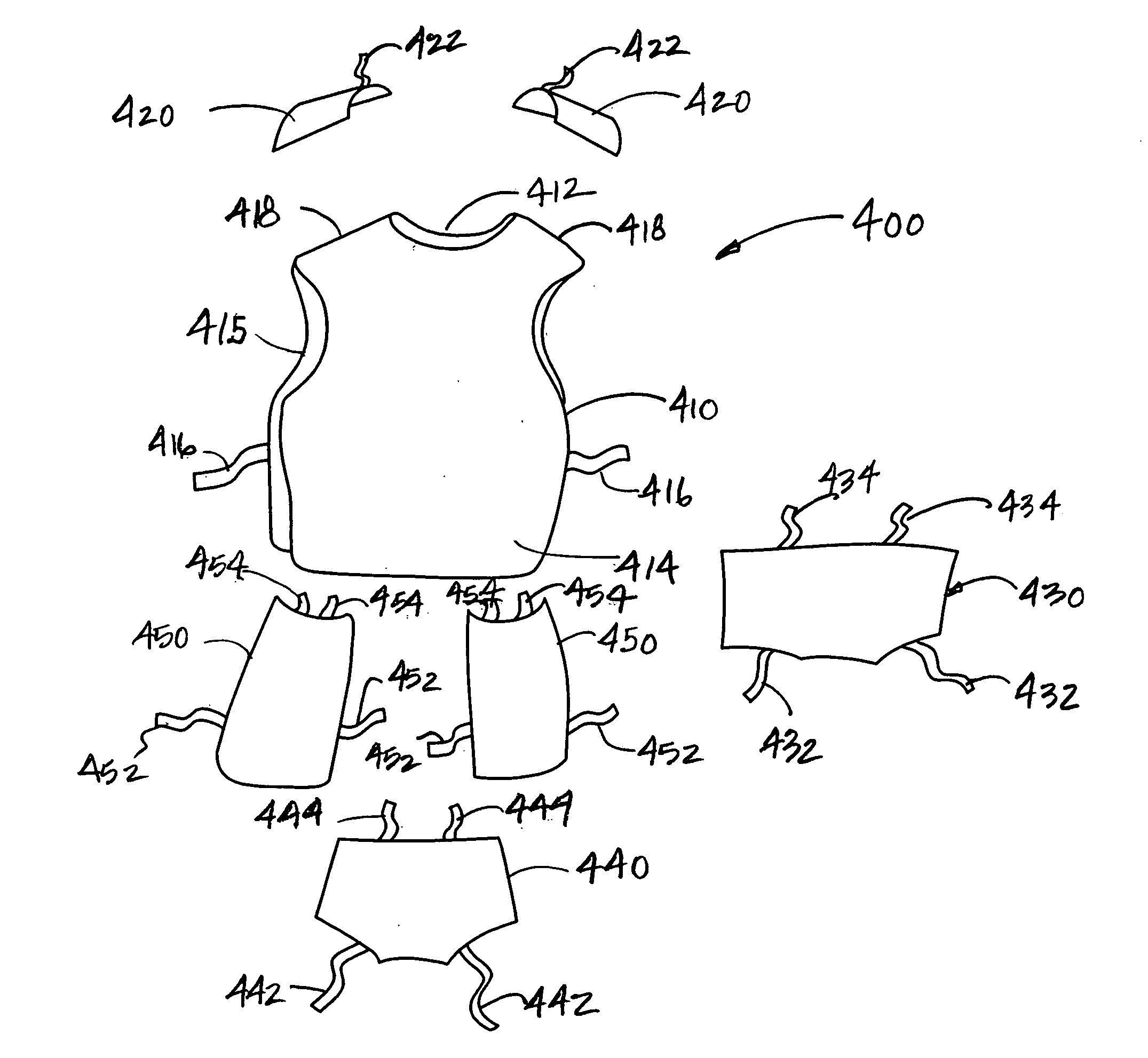

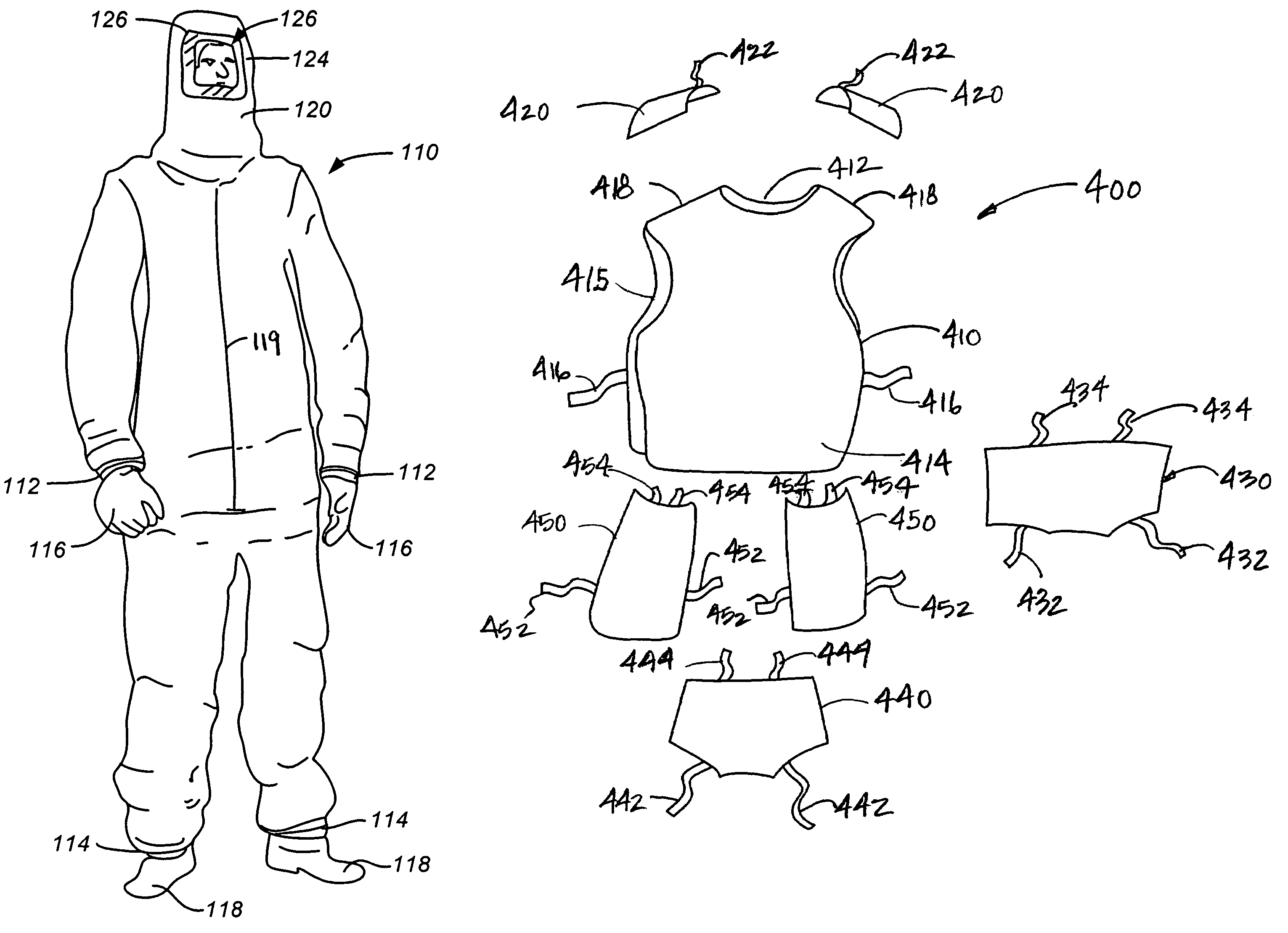

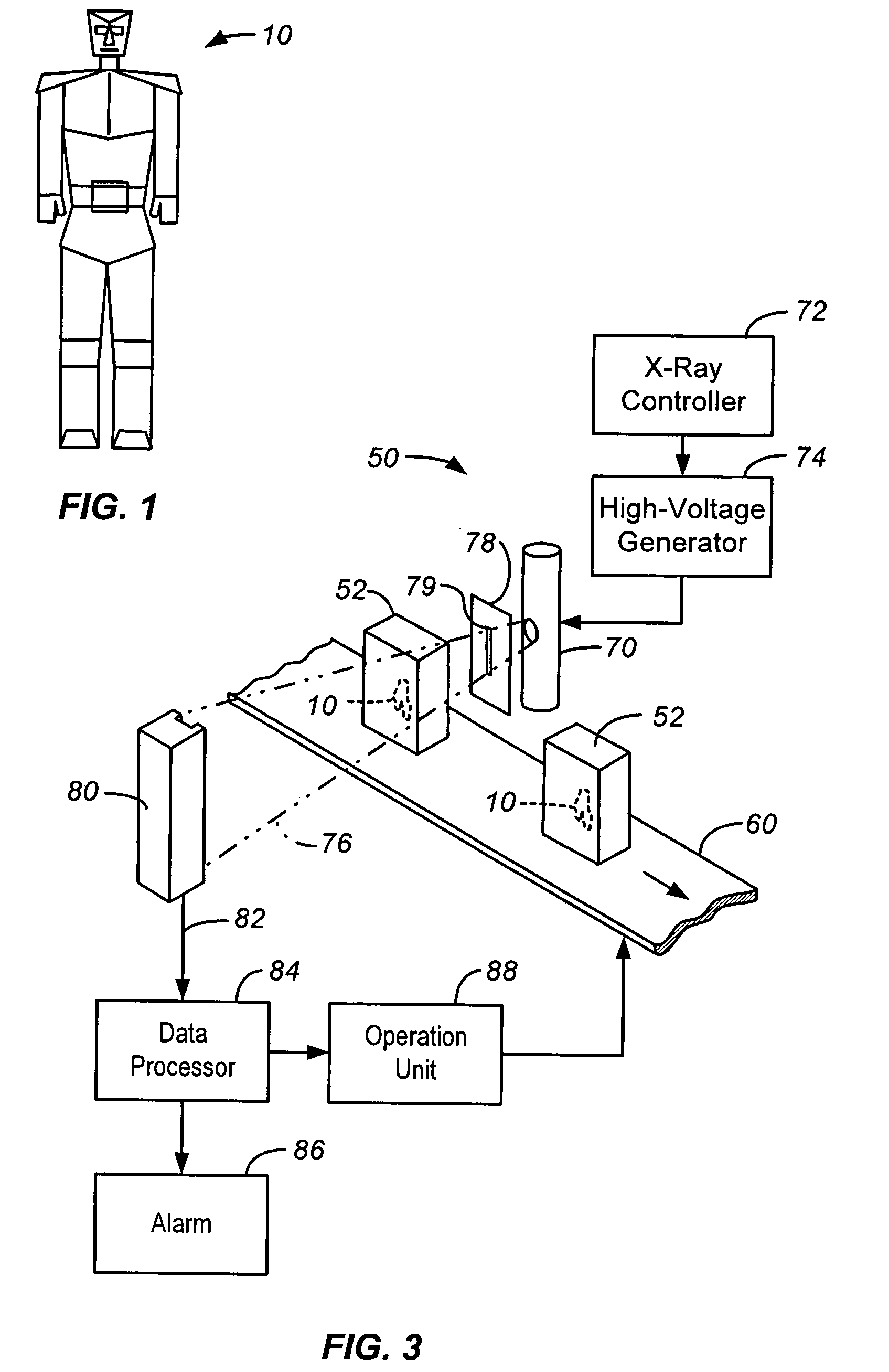

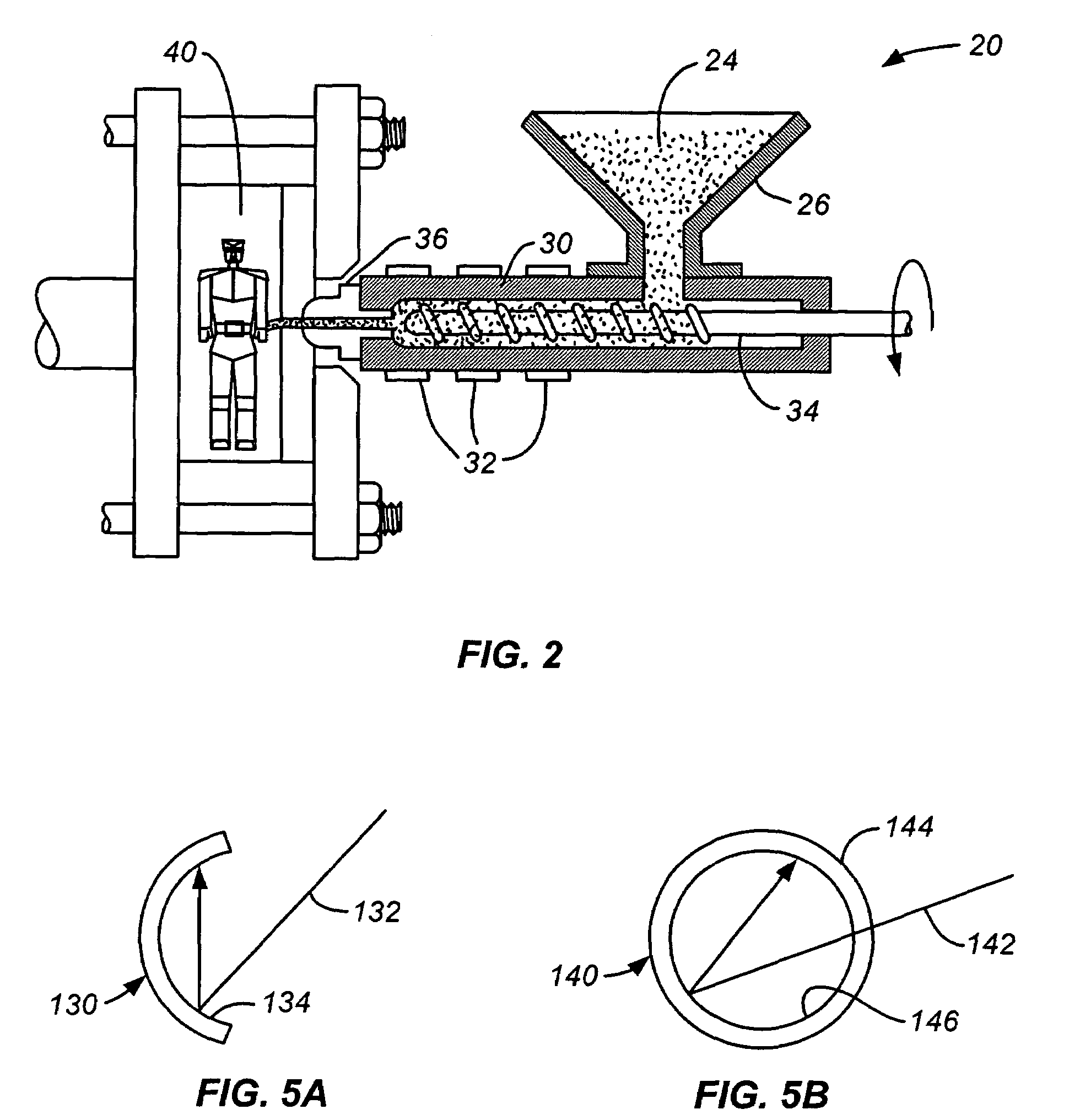

Radiation detectable and protective articles

InactiveUS20050211930A1Attribute be easilyPresence be easilyNuclear engineering problemsNuclear engineering solutionsEmulsionCompound (substance)

Compositions and processes for forming radiopaque polymeric articles are disclosed. In one embodiment, radiation inspection apparatuses and methods are then used to determine the presence and attributes of such radiopaque polymeric articles. A radiopaque polymeric article of the present invention can be created by mixing a radiopaque material, such as barium, bismuth, tungsten or their compounds, with a powdered polymer, pelletized polymer or liquid solution, emulsion or suspension of a polymer in solvent or water. In addition to creating radiation detectable objects, the radiopaque polymeric materials of the present invention can be used to create radiation protective articles, such as radiation protective garments and bomb containment vessels. Enhanced radiation protection can also be achieved through the use of nano-materials. The principals of the present invention can be used to provide protection against other types of hazards, including fire, chemical, biological and projectile hazards.

Owner:MERIDIAN RES & DEV

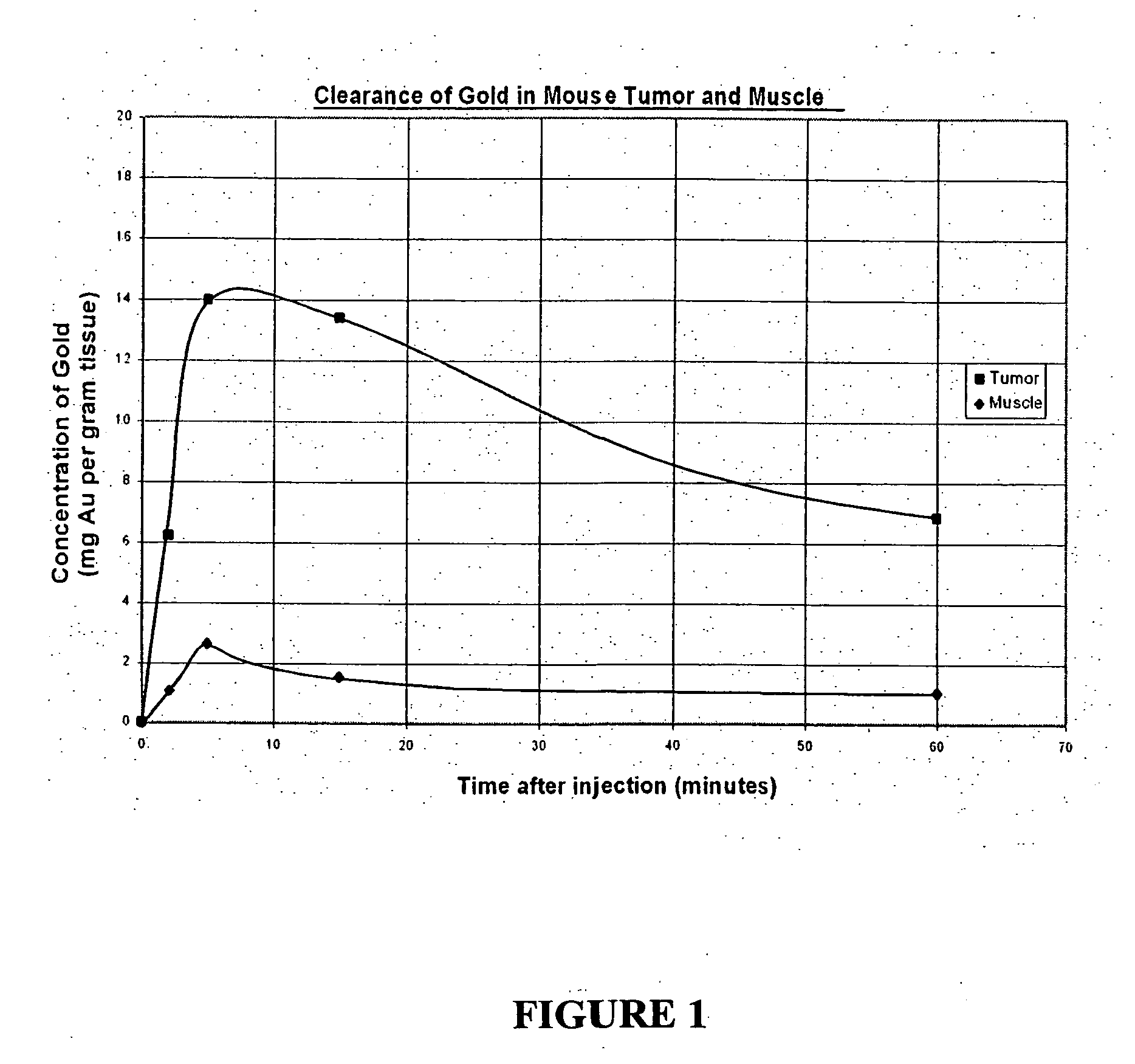

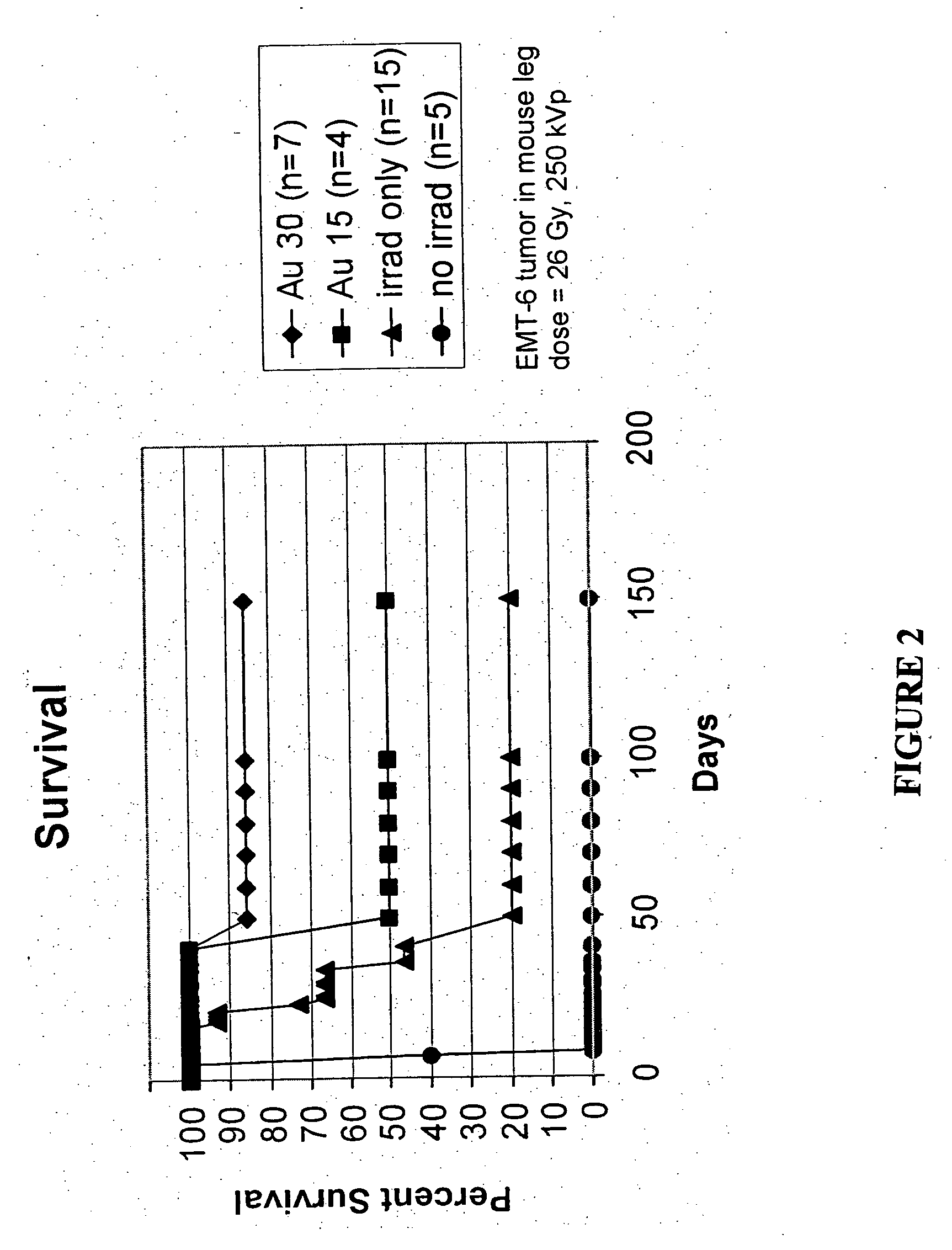

Methods of enhancing radiation effects with metal nanoparticles

Owner:NANOPROBES

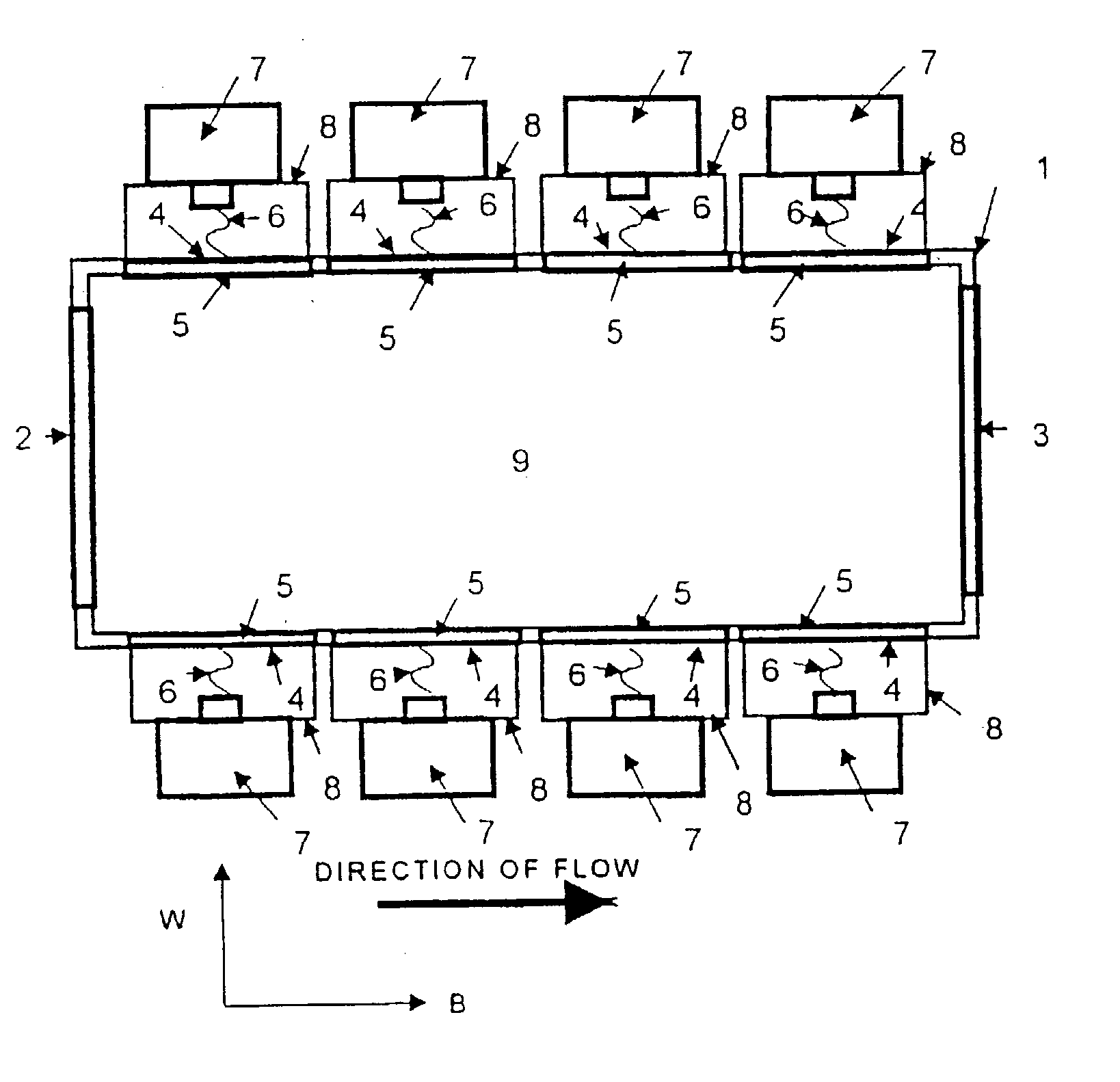

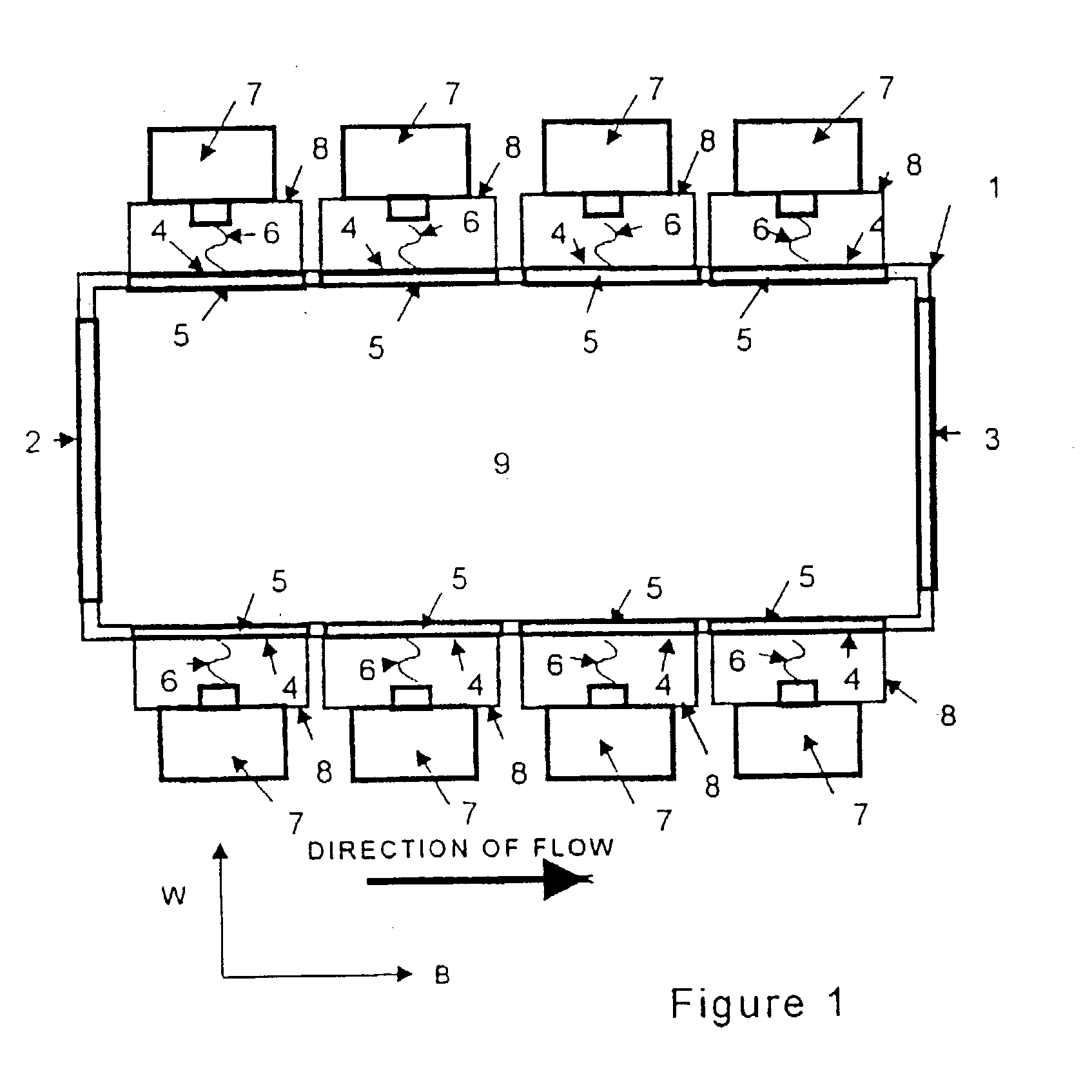

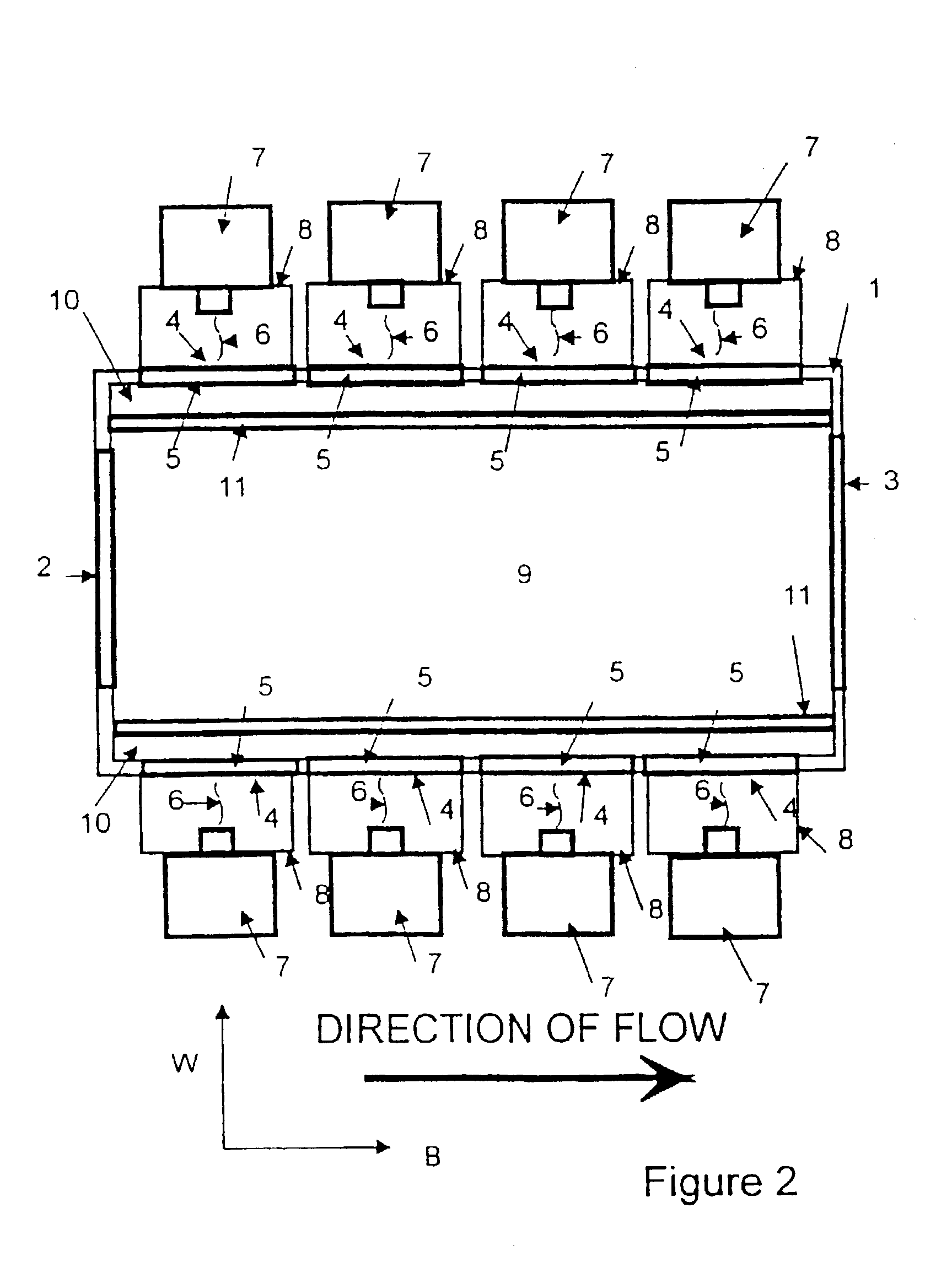

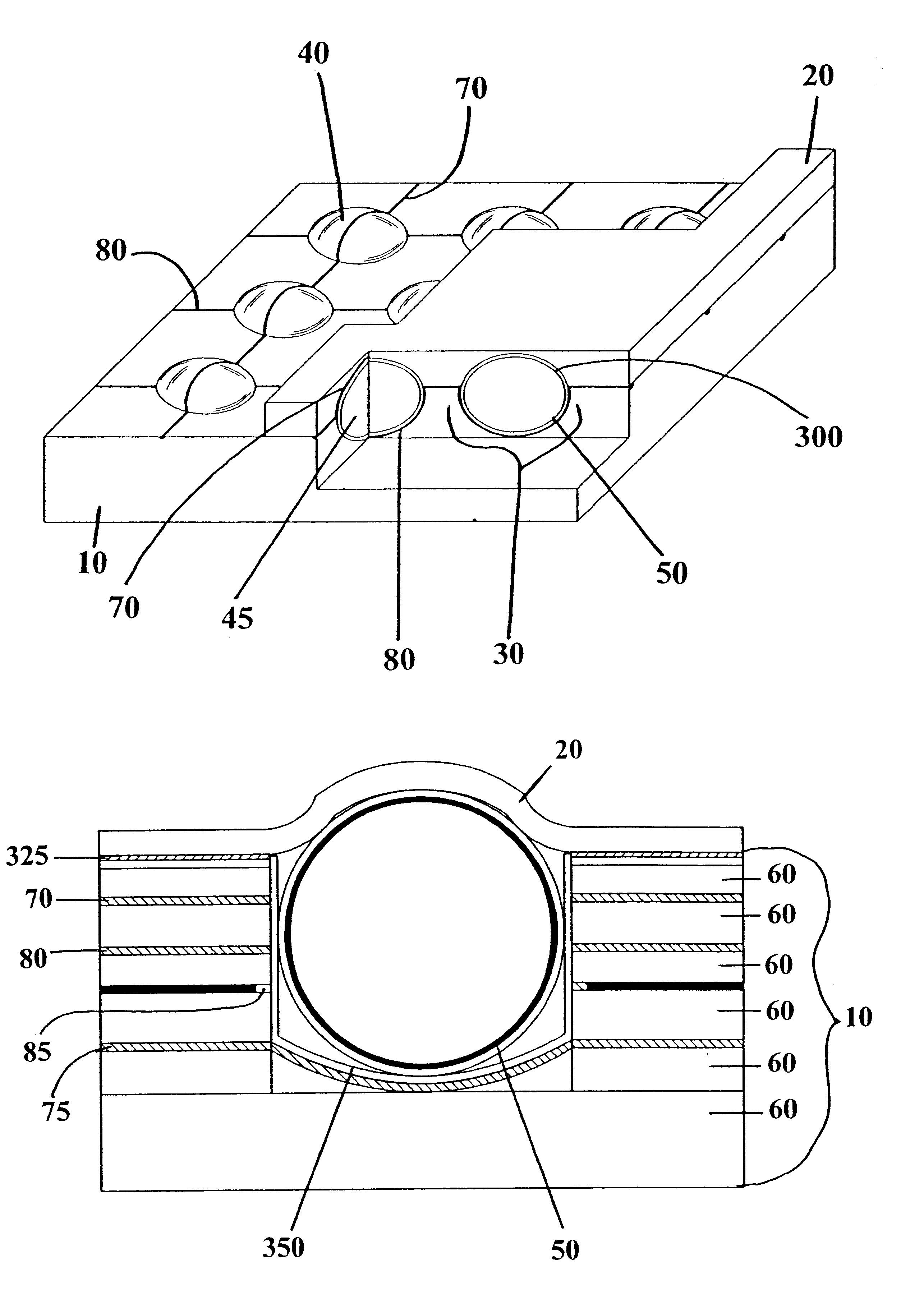

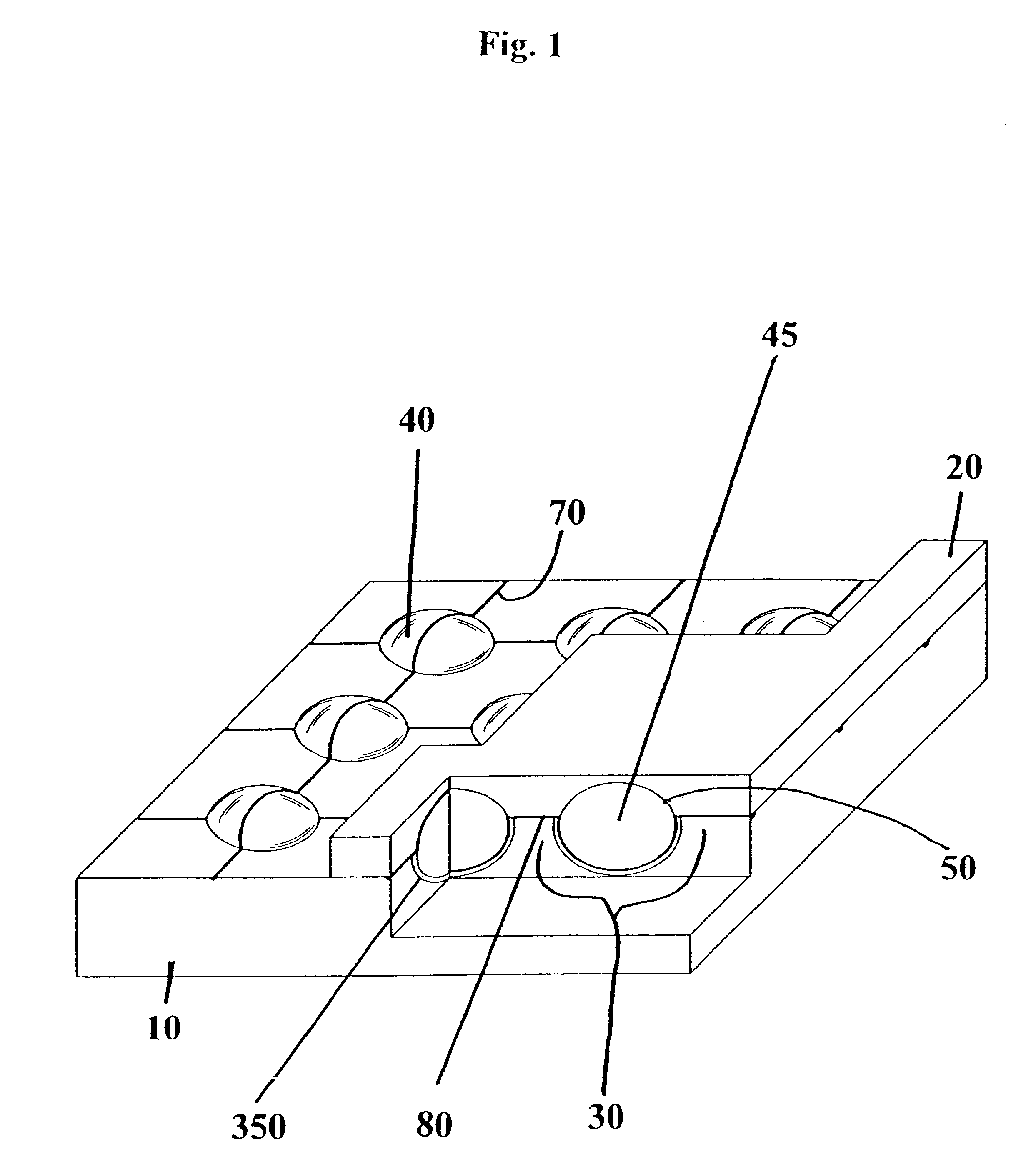

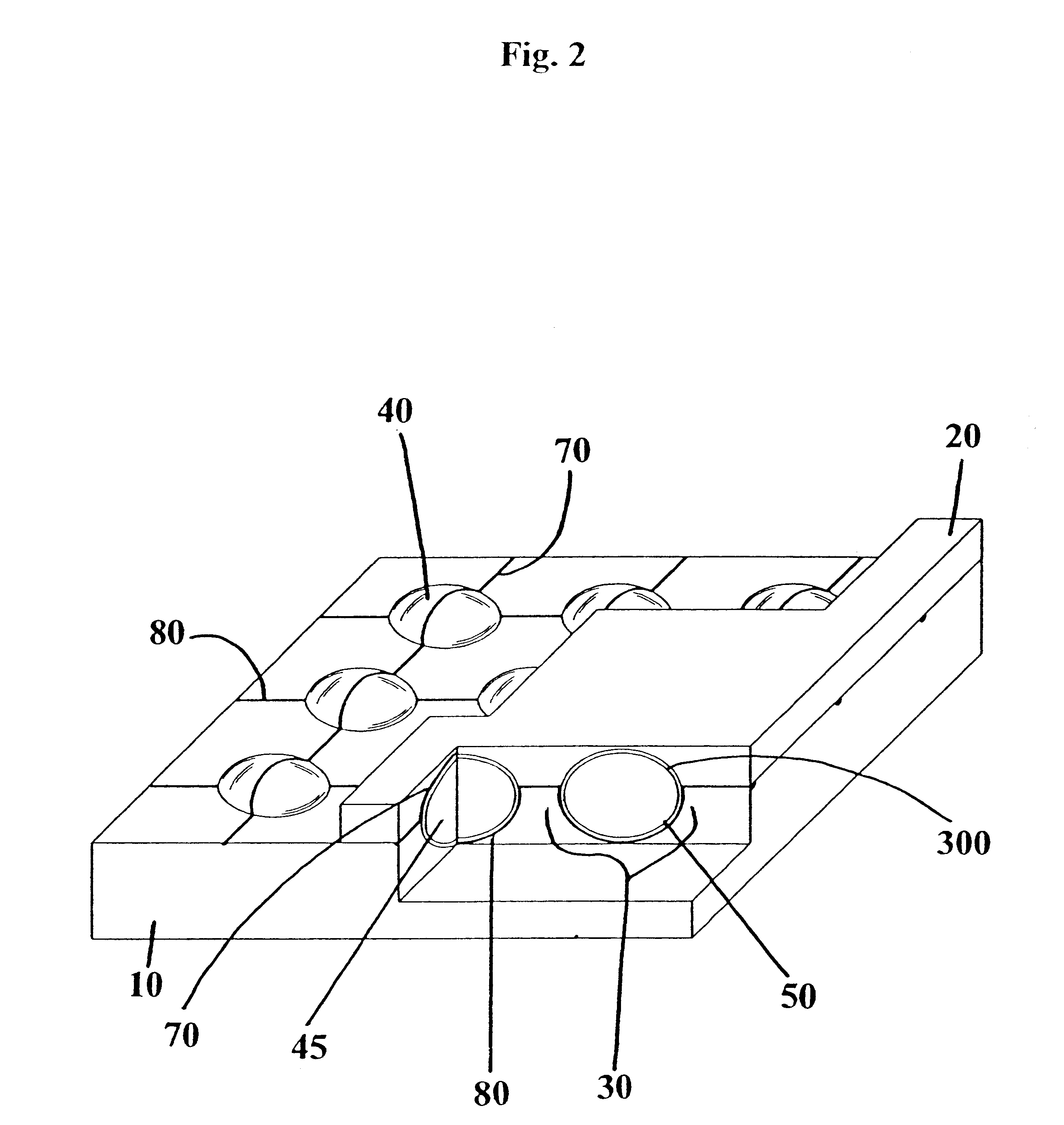

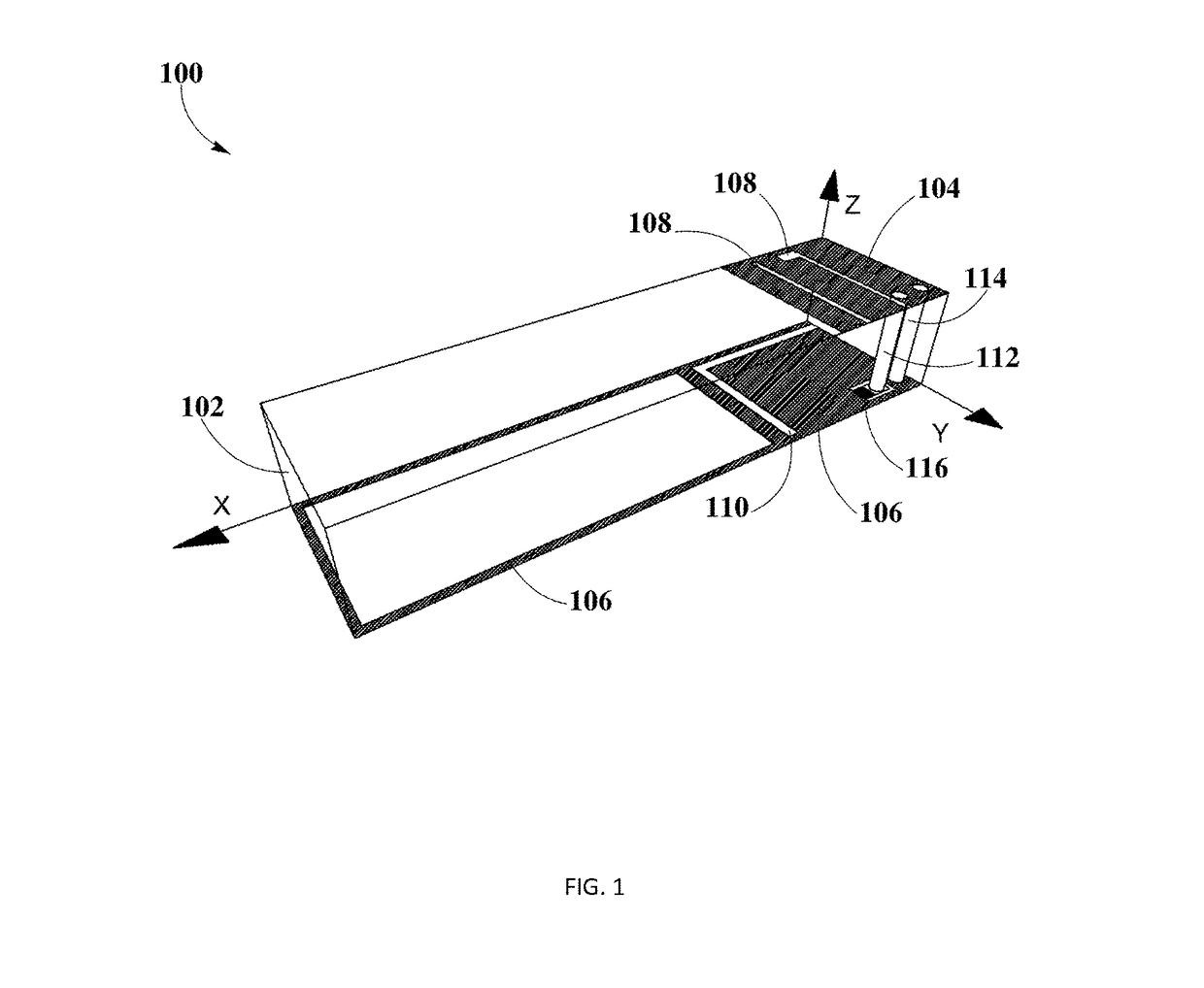

Socket for use with a micro-component in a light-emitting panel

InactiveUS6545422B1Sufficient resolutionManufactured very thinEmission spectroscopyStatic indicating devicesIonizationVoltage

An improved light-emitting panel having a plurality of micro-components at least partially disposed in a socket and sandwiched between two substrates is disclosed. Each micro-component contains a gas or gas-mixture capable of ionization when a sufficiently large voltage is supplied across the micro-component via at least two electrodes.

Owner:LEIDOS

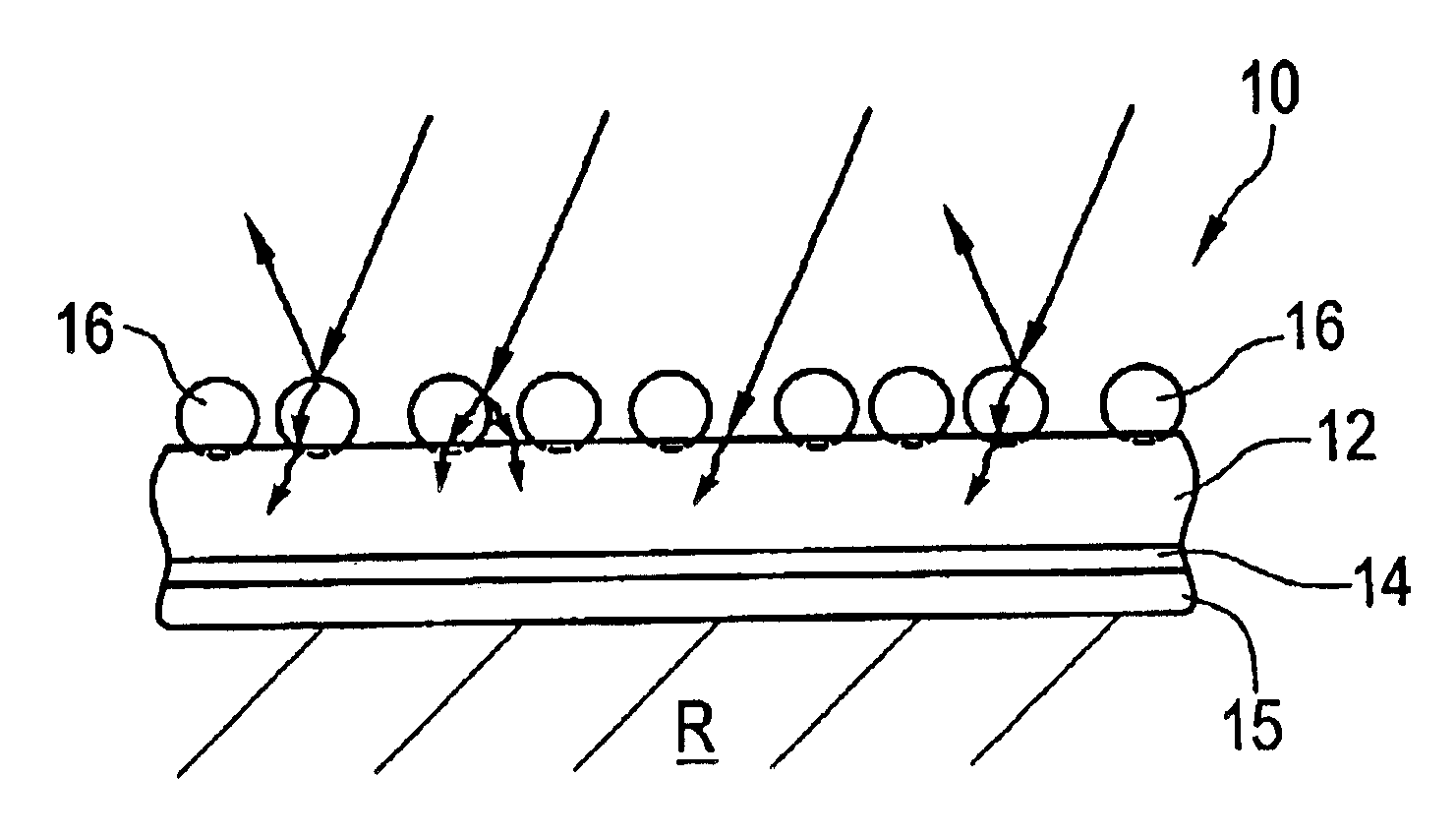

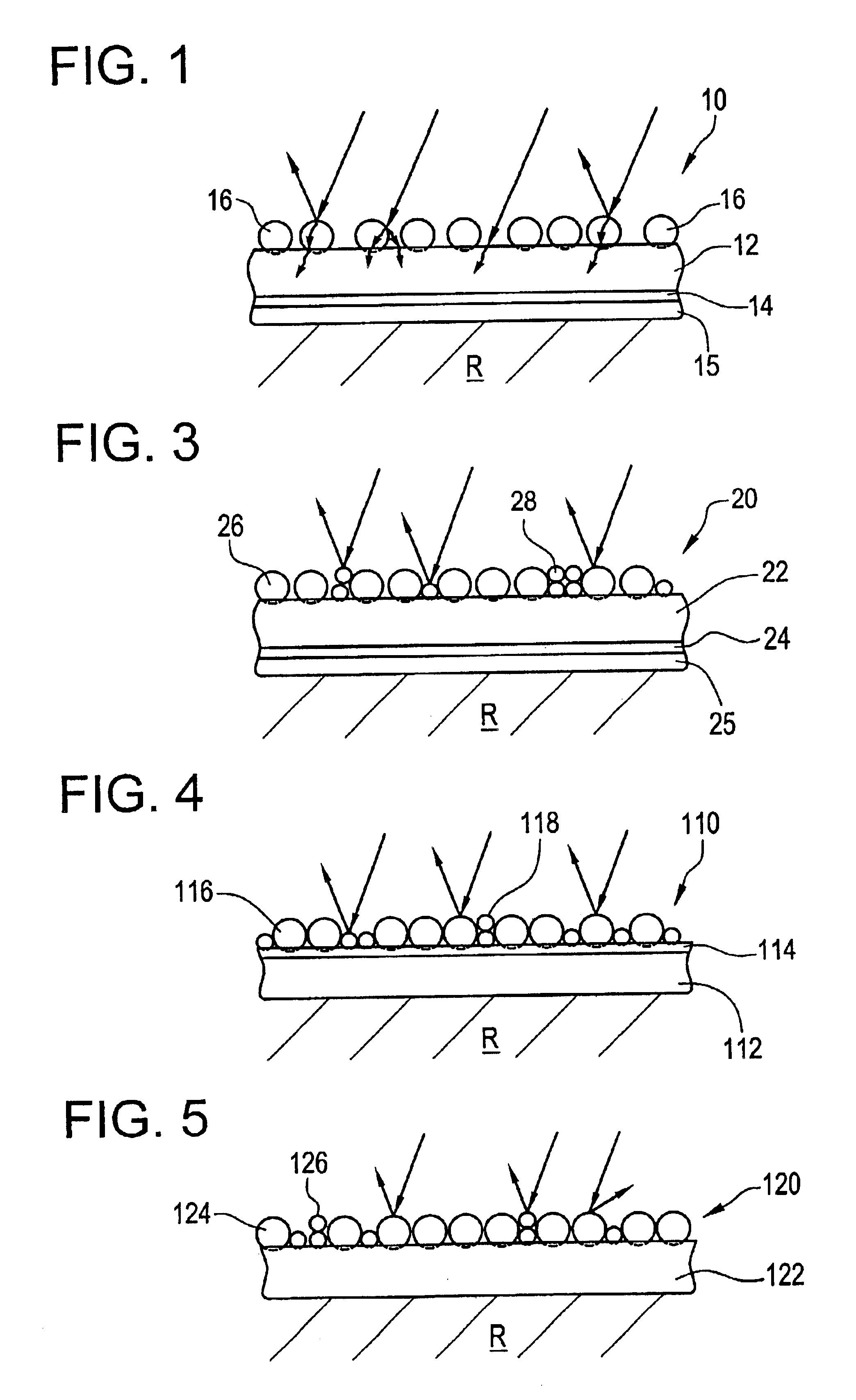

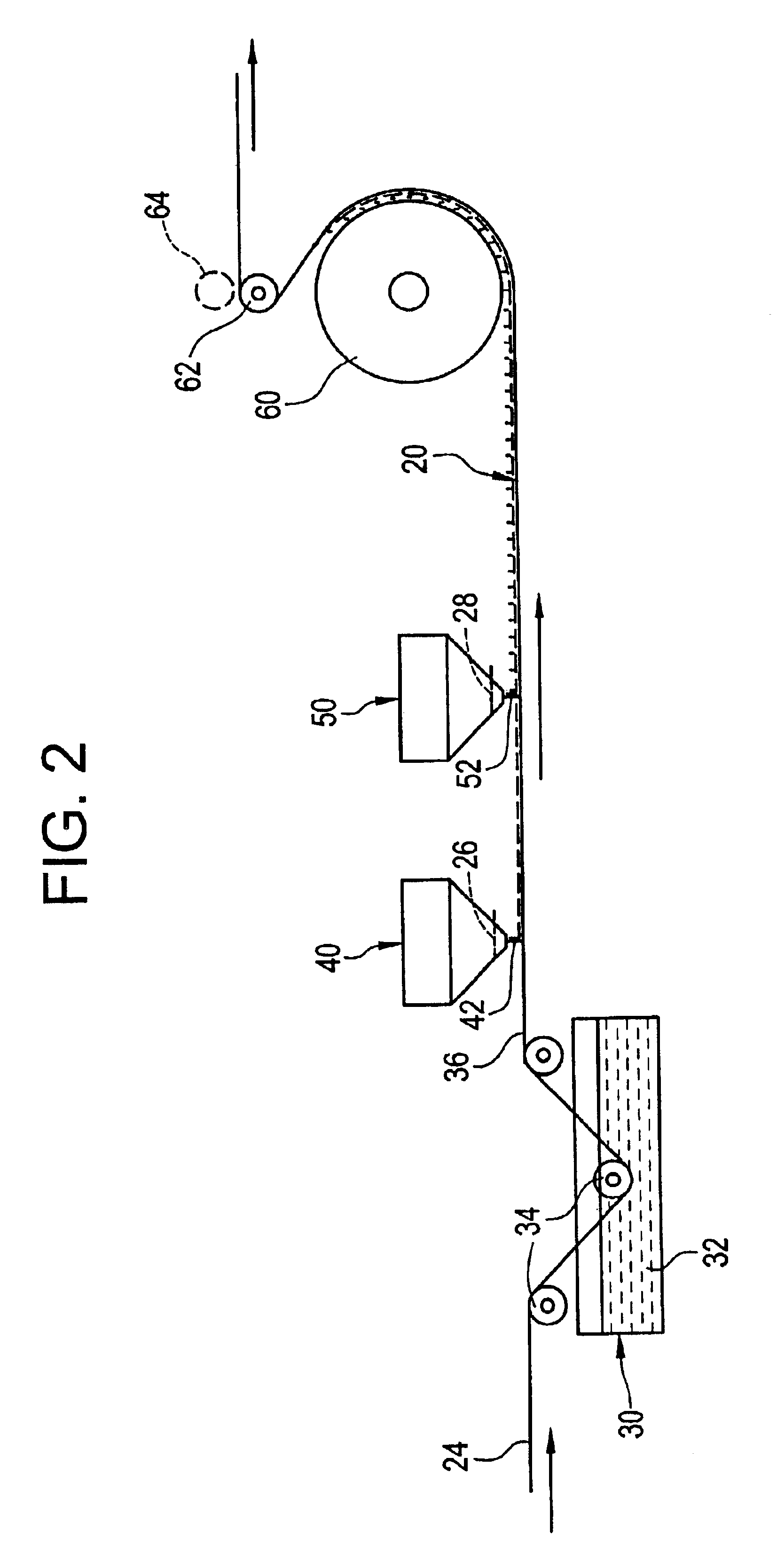

Method of forming an improved roofing material

InactiveUS6933007B2Improve reflectivityIncrease temperatureRoof covering using tiles/slatesCovering/liningsMaterials scienceReflectivity

A method of coating highly reflective granules on an adhering material of a roofing or siding material to form a roofing or siding material having an average resulting reflectivity on an upper surface of at least about 45%. The method includes the selecting of highly reflective granules and applying the highly reflective granules on an adhering material until over about 95% of a top surface of the adhering material is covered by the granules.

Owner:GARLAND INDS

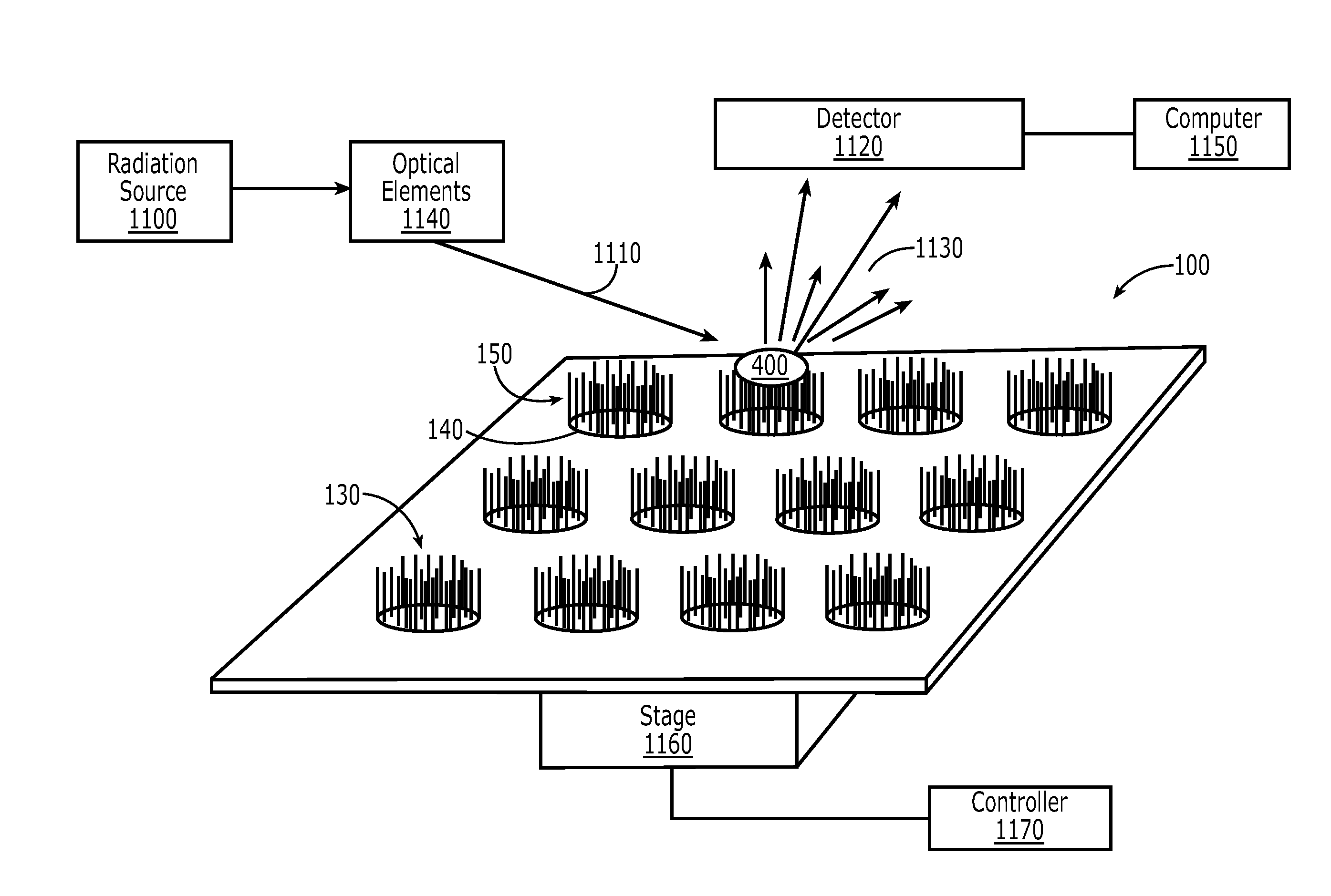

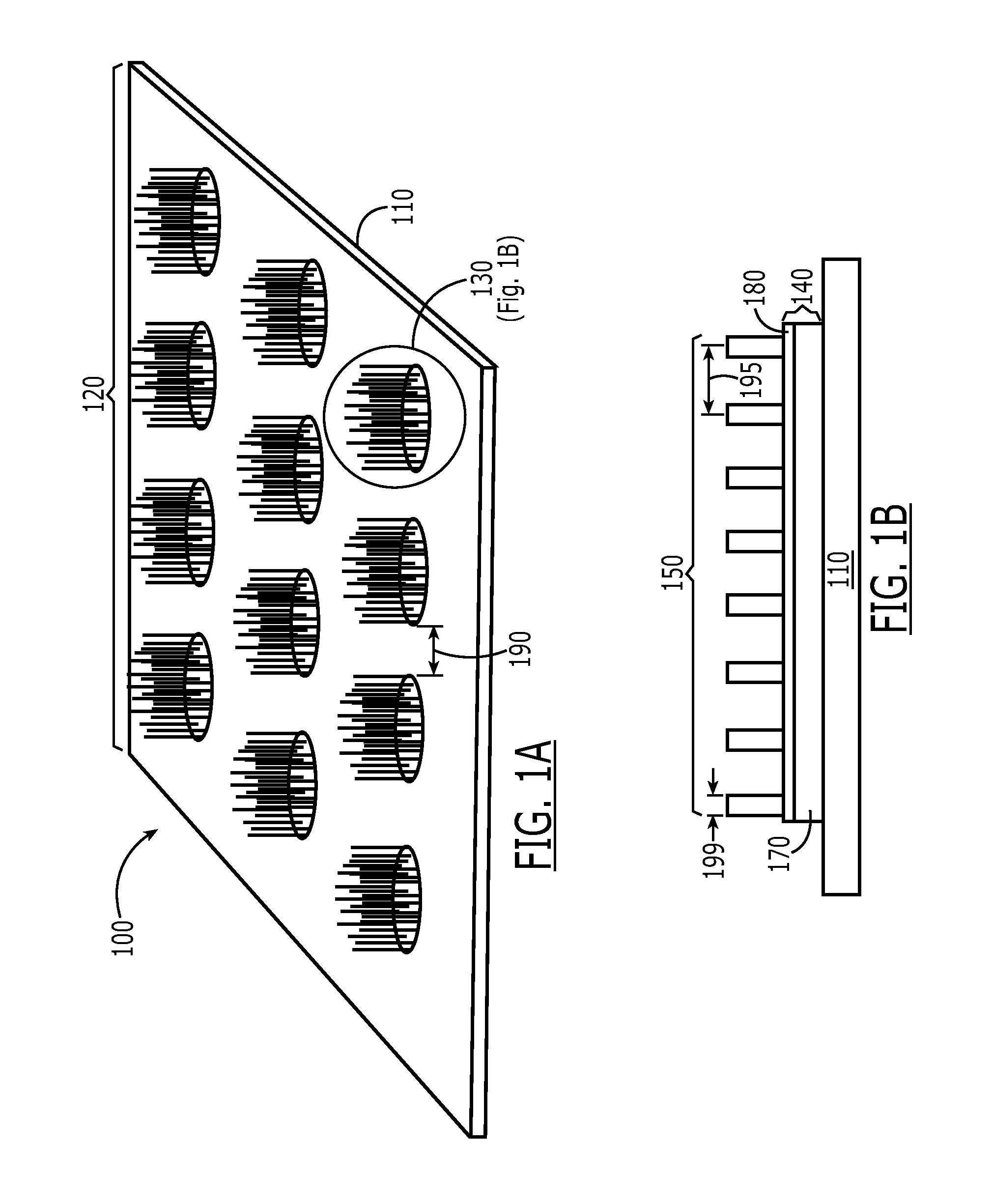

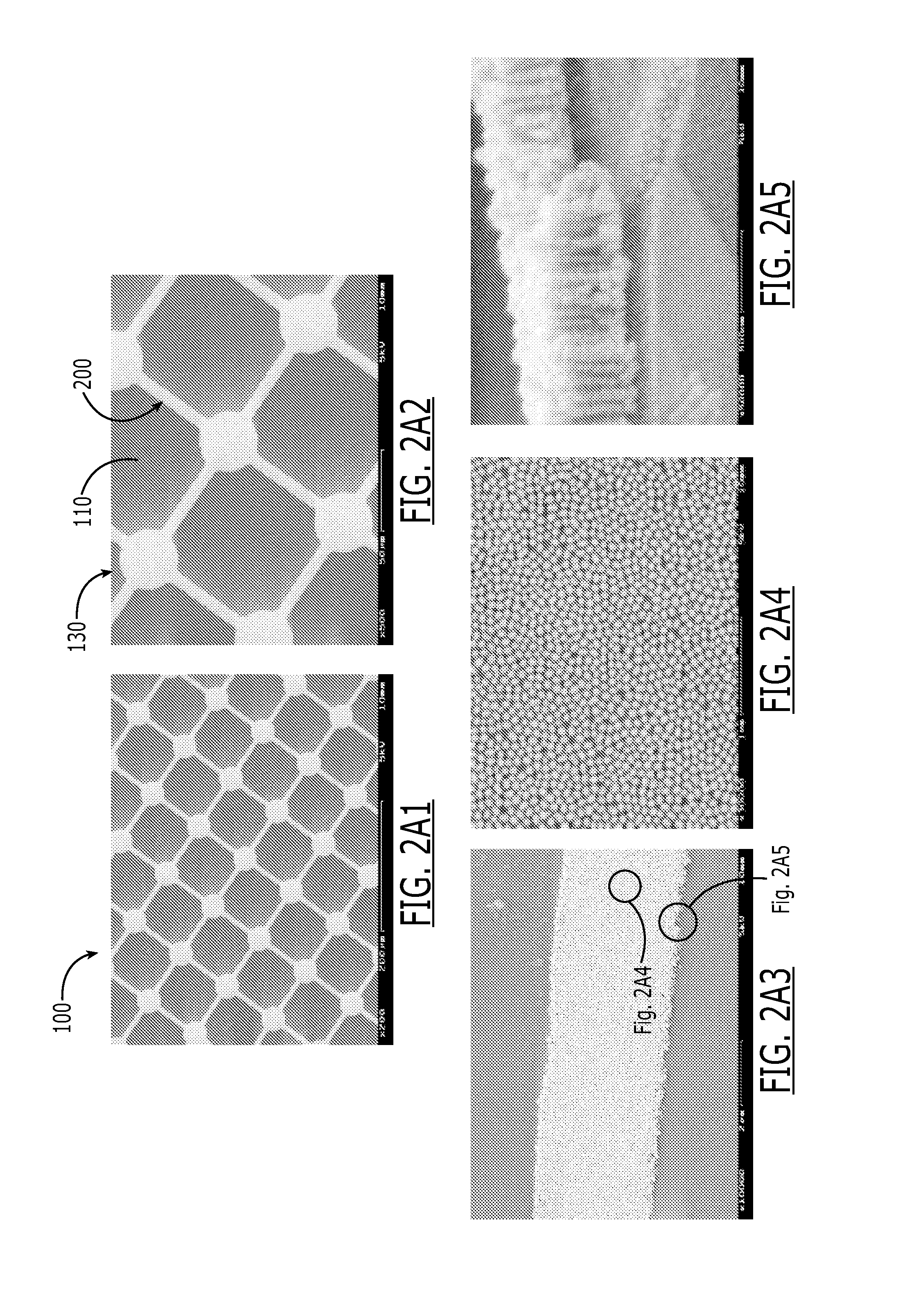

Nanostructured substrates for surface enhanced raman spectroscopy (SERS) and detection of biological and chemical analytes by electrical double layer (EDL) capacitance

InactiveUS20110053794A1Enhanced radiationMaterial nanotechnologySequential/parallel process reactionsCapacitanceNanopillar

Provided according to embodiments of the invention are nanostructured surfaces that include a substrate; and an array of metallic nanopillar islands on the substrate, wherein each metallic nanopillar island includes a metal base layer on the substrate and a plurality of metallic nanopillars on the metal base layer, and wherein portions of the substrate between adjacent metallic nanopillar islands are free of the metal base layer. Also provided according to some embodiments of the invention are nanostructured surfaces that include a non-conductive substrate; and at least one nanoelectrode defined within the non-conductive substrate, wherein the at least one nanoelectrode is sized and / or shaped to immobilize an analyte or a probe molecule. Also provided are apparatuses and methods for SERS and detection of analytes or biological binding by EDL capacitance.

Owner:CLEMSON UNIV RES FOUND

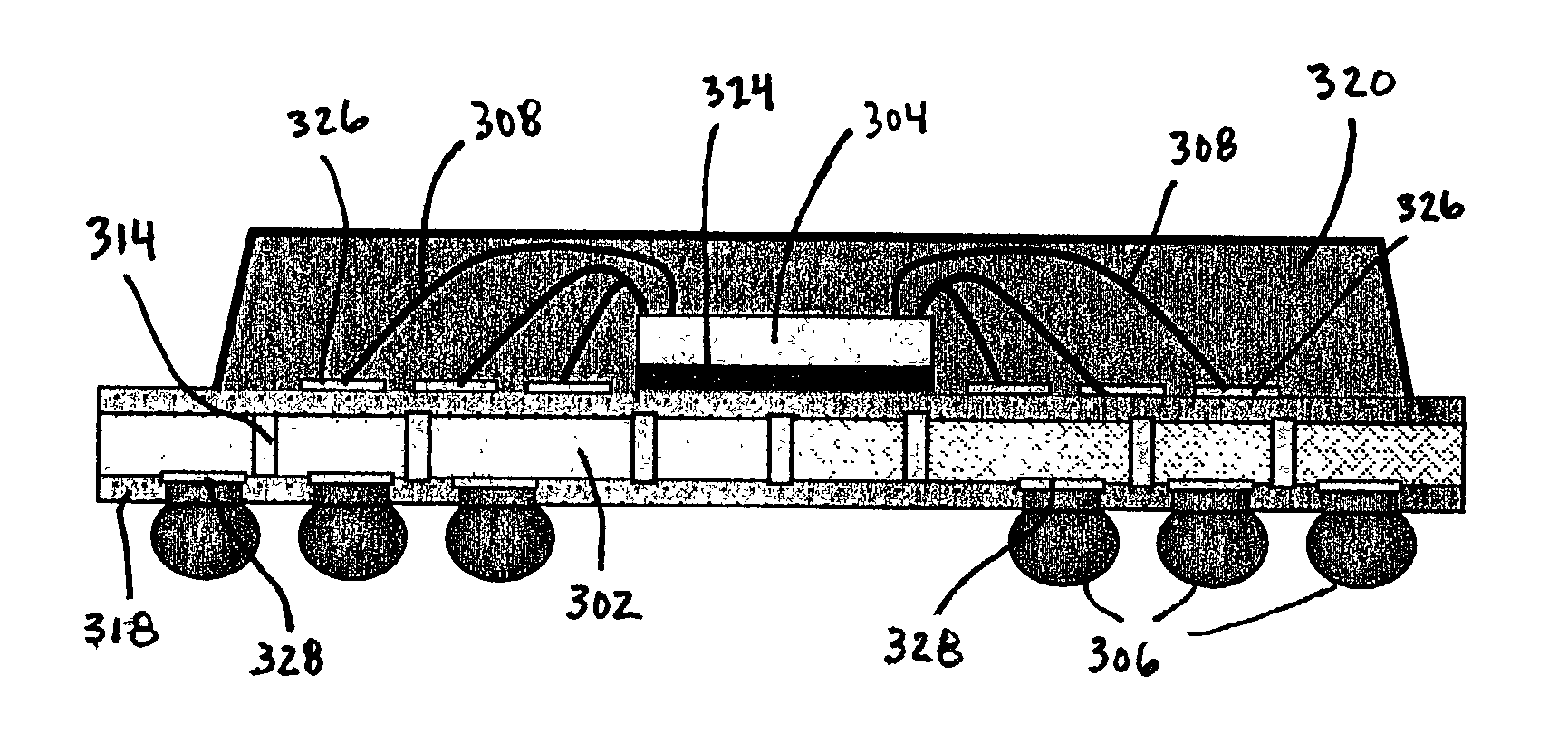

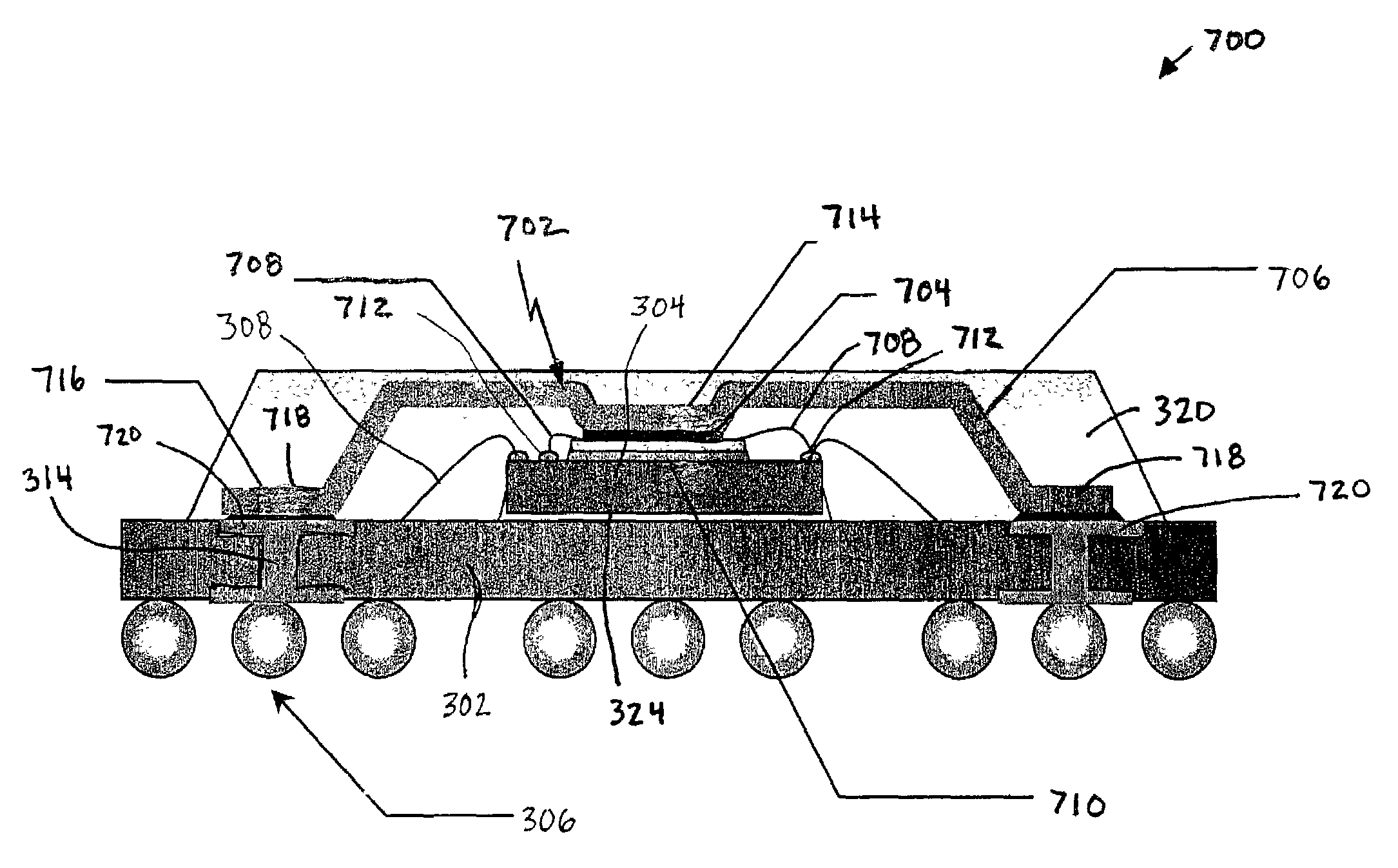

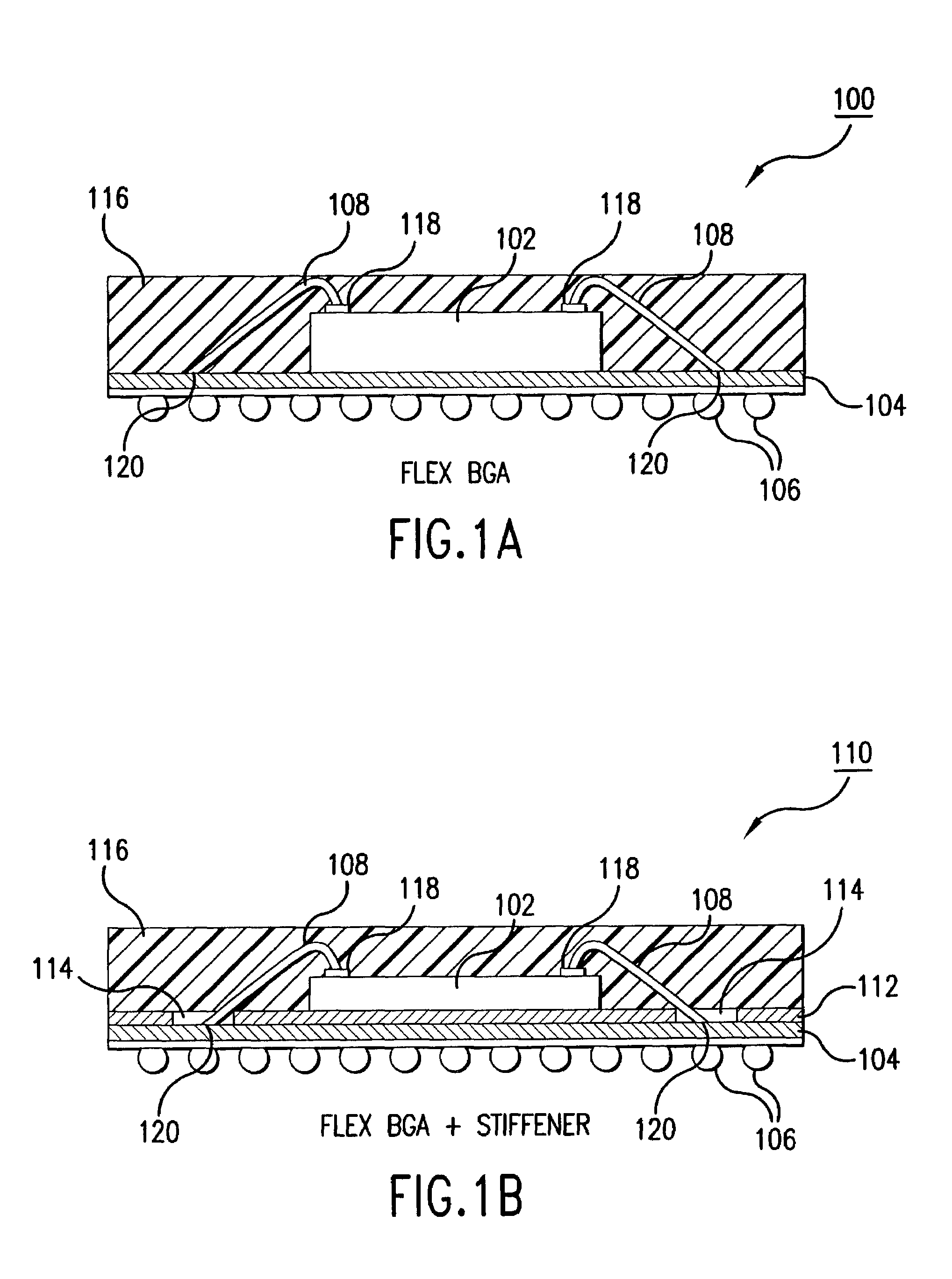

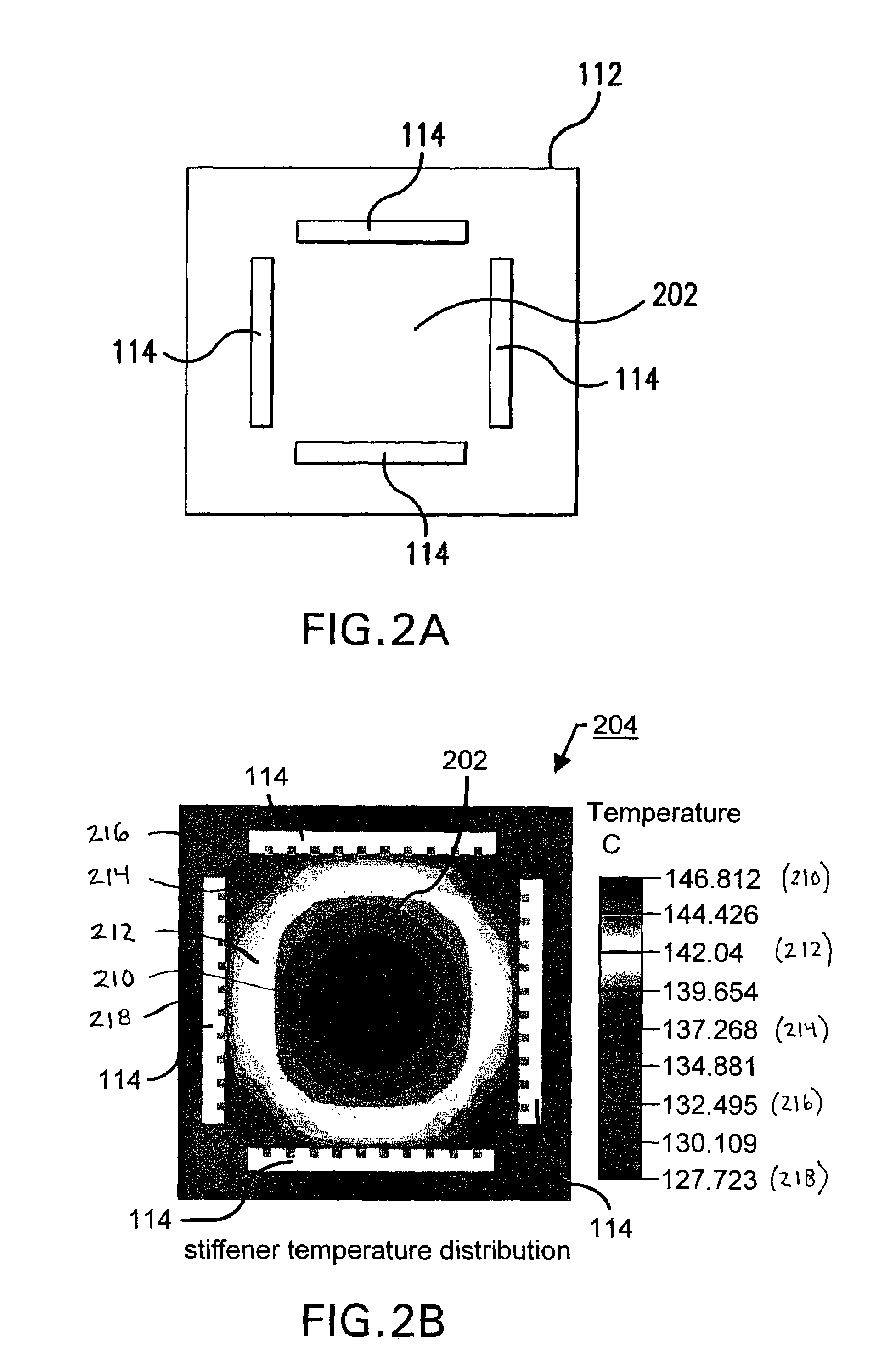

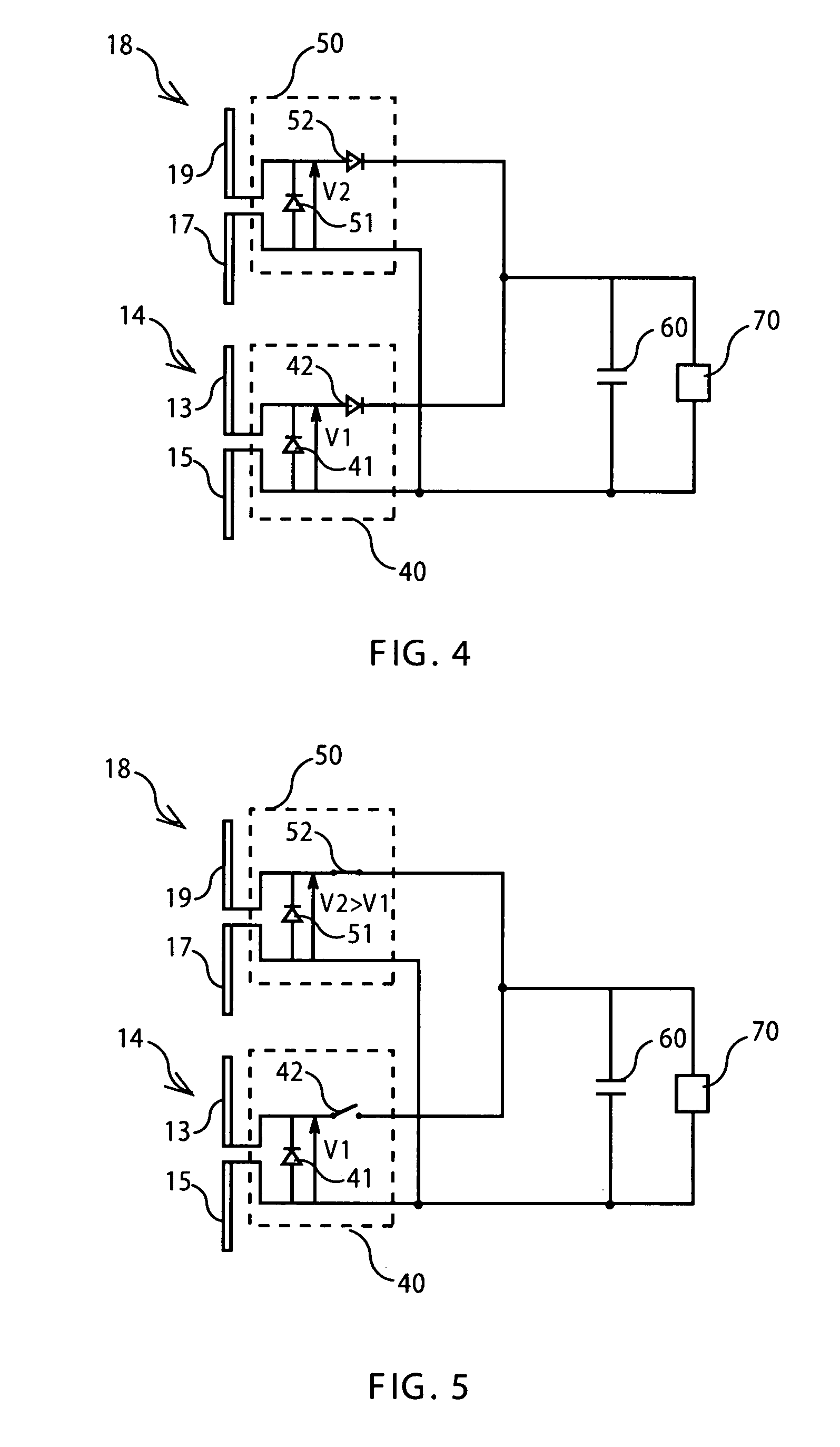

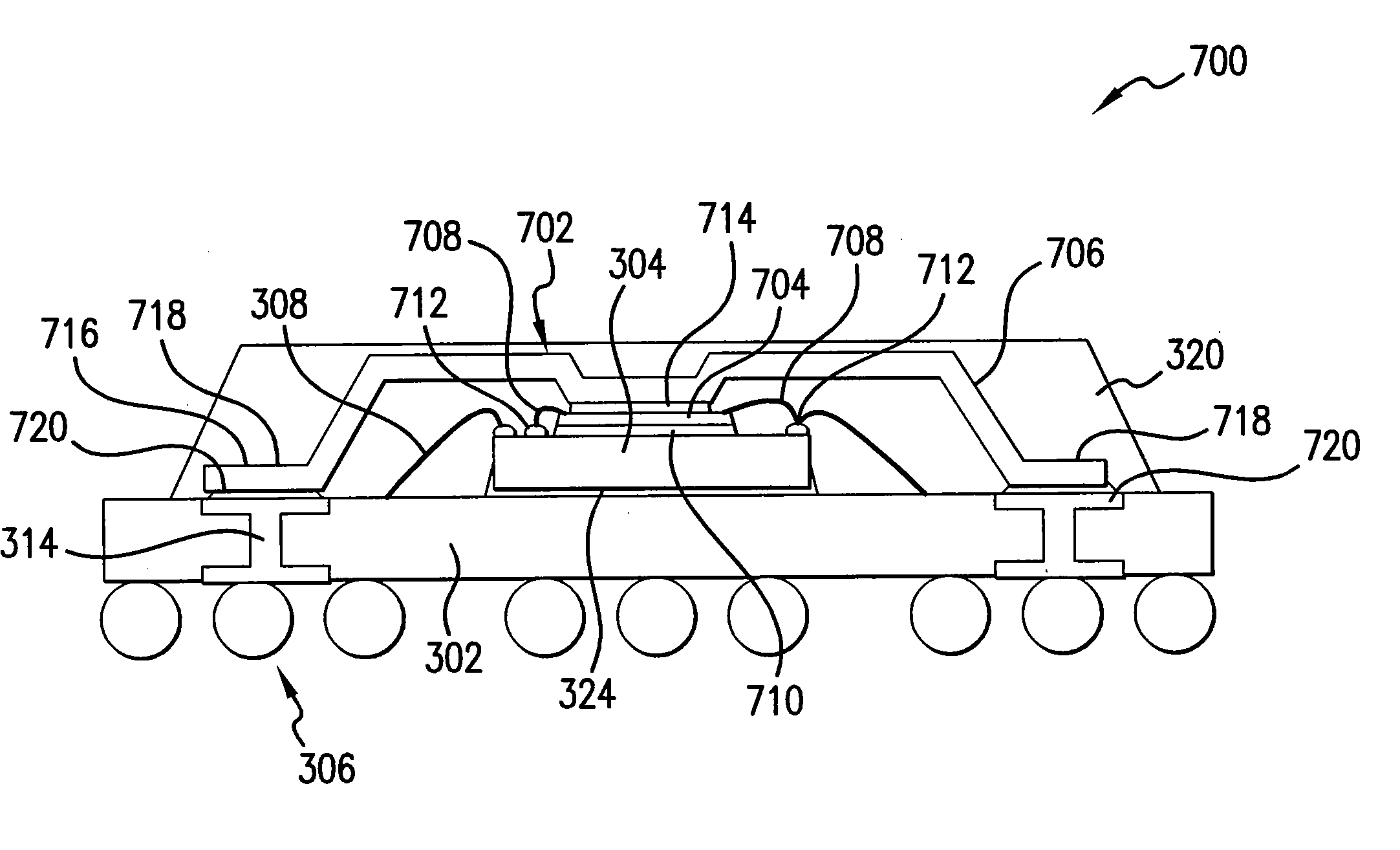

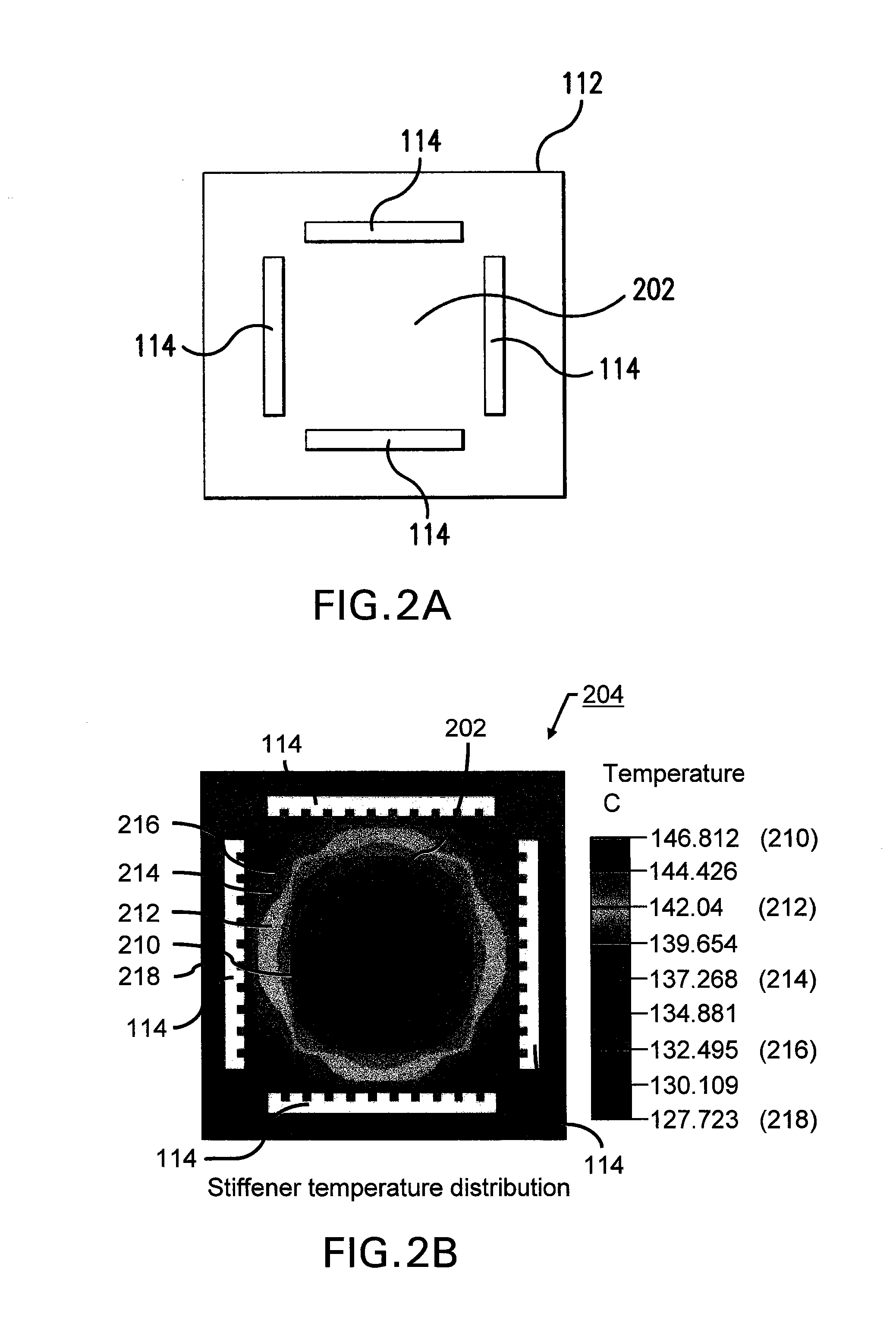

Low voltage drop and high thermal perfor mance ball grid array package

InactiveUS20030179549A1Optimized heat conduction pathImprove the environmentSemiconductor/solid-state device detailsSolid-state devicesContact padIntegrated circuit

An apparatus and method for a low voltage drop and thermally enhanced integrated circuit (IC) package are described. A substantially planar substrate having a plurality of contact pads on a first surface is electrically connected through the substrate to a plurality of solder ball pads on a second surface of the substrate. An IC die having a first surface is mounted to the first surface of the substrate. The IC die has a plurality of I / O pads electrically connected to the plurality of contact pads on the first surface of the substrate. A heat sink assembly is coupled to a second surface of the IC die and to a first contact pad on the first surface of the substrate to provide a thermal path from the IC die to the first surface of the substrate. The heat sink assembly can also provide an electrical path from the IC die to the first surface of the substrate. The heat sink assembly may have one or two heat sink elements to provide thermal and / or electrical connectivity between the IC die and the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

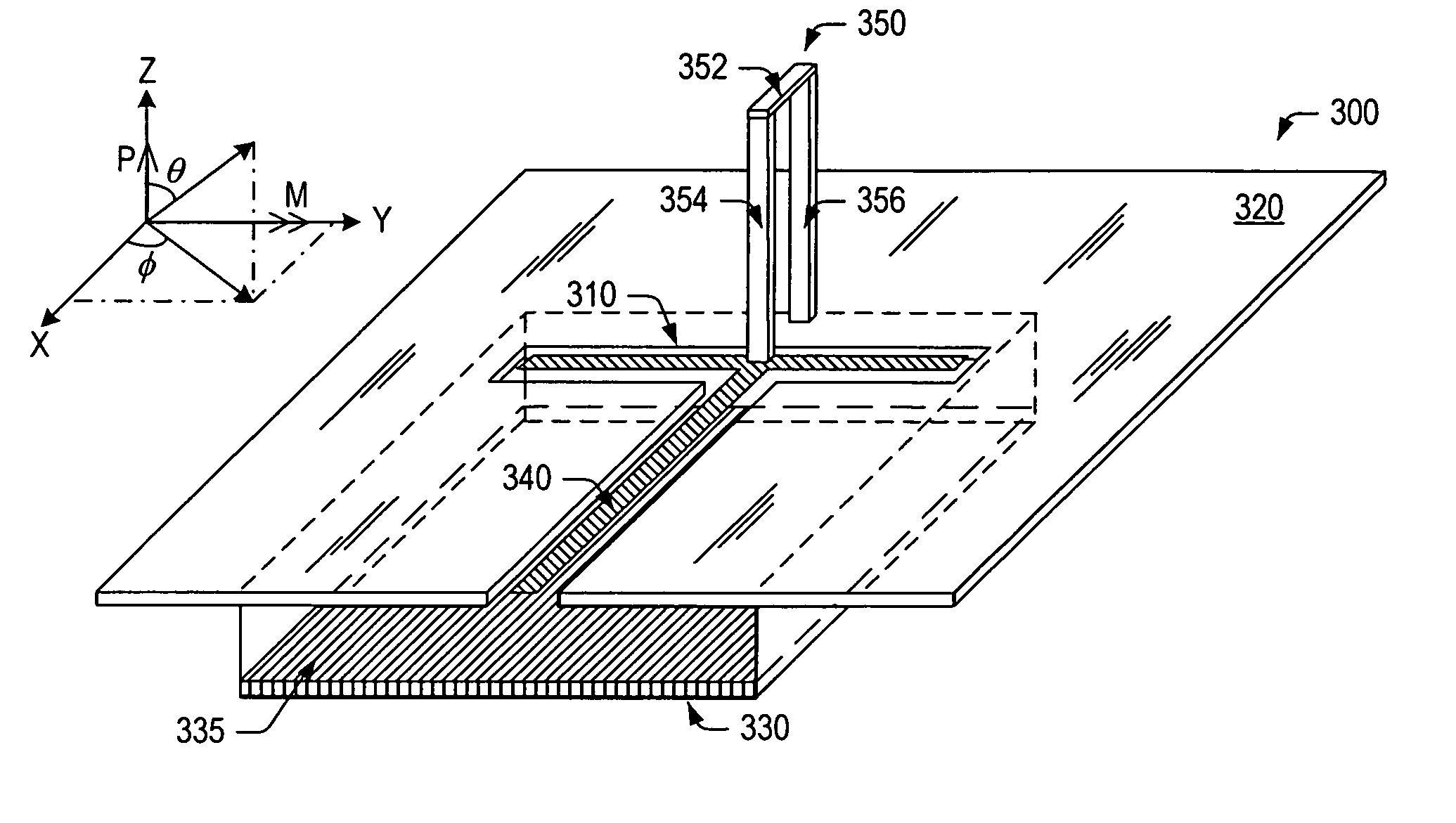

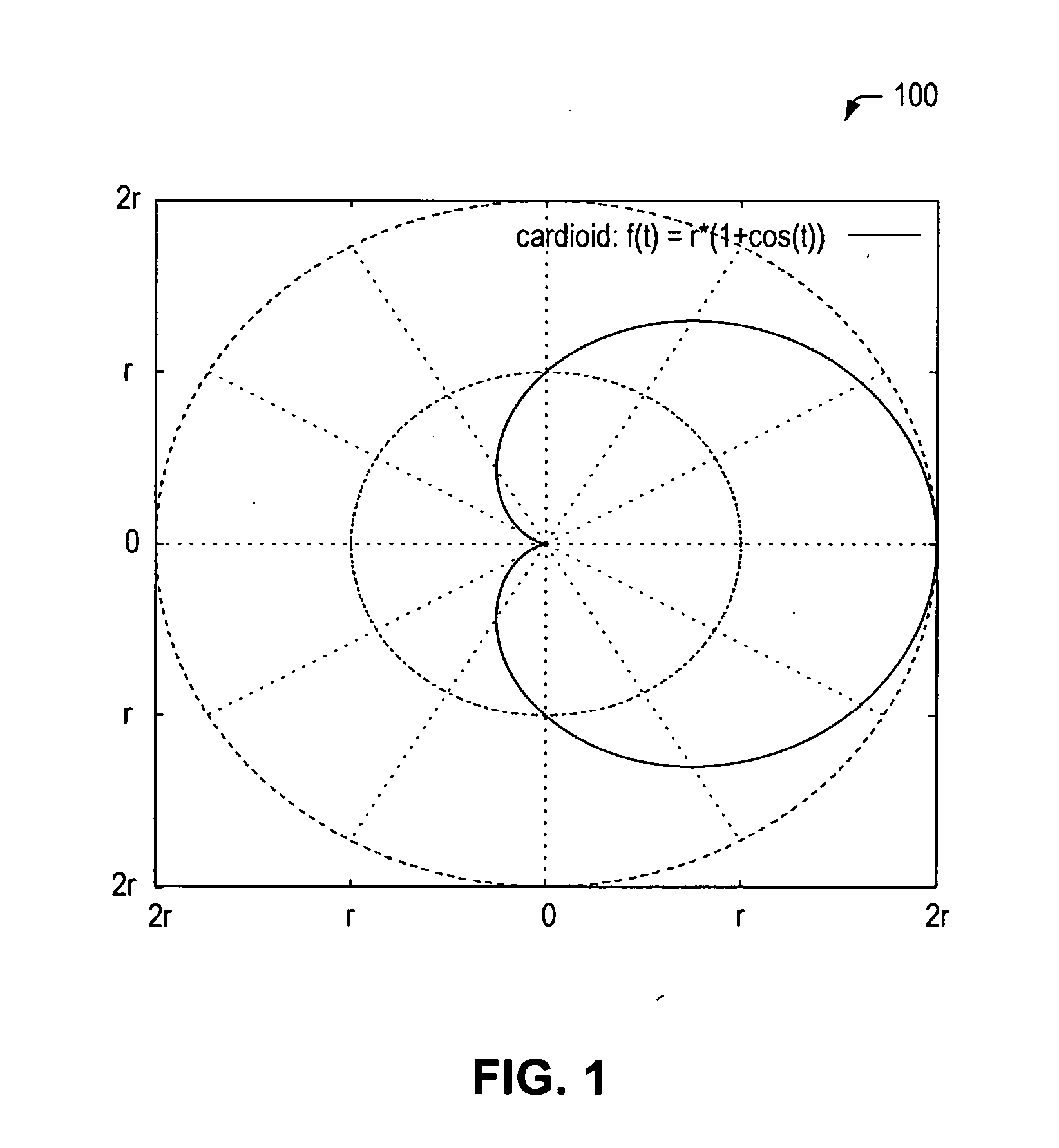

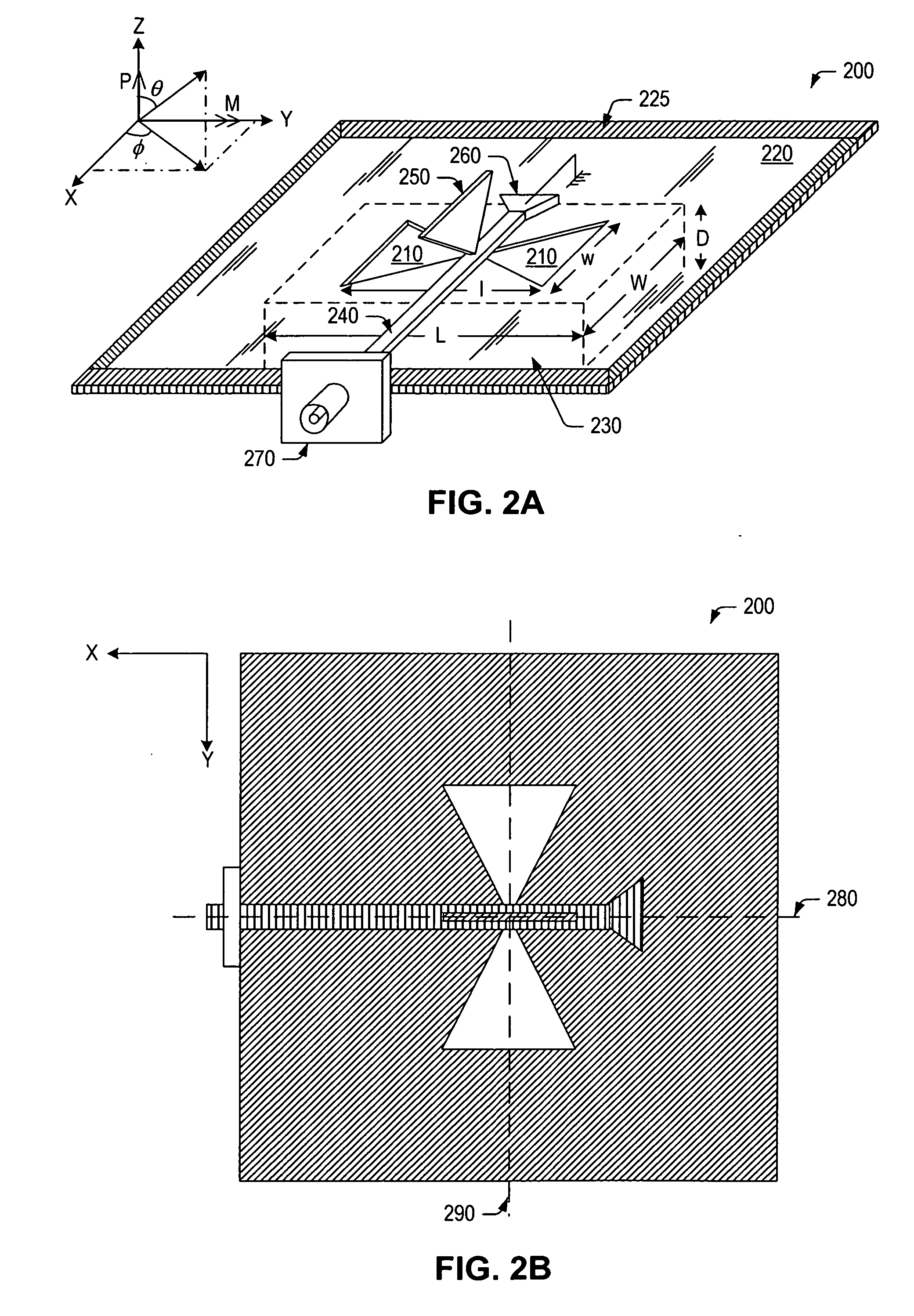

PxM antenna with improved radiation characteristics over a broad frequency range

InactiveUS20070080878A1Reduce lossImprove efficiencyAntenna arraysSimultaneous aerial operationsElectrical resistance and conductanceBroadband

A low-loss, high-efficiency, broadband antenna including both electric and magnetic dipole radiators is provided herein. The broadband antenna may be referred to as a “P×M antenna” and may generally include a ground plane; a magnetic radiator formed within the ground plane; a conductive feed arranged within a first plane, which is parallel to the ground plane; and an electric radiator arranged within a second plane, which is perpendicular to the ground plane and coupled at one end to the conductive feed. According to a particular aspect of the invention, the electric and magnetic radiators are substantially complementary to one another and are coupled for producing a P×M radiation pattern over a broad range of operating frequencies. One advantage of the P×M antenna described herein is that the complementary antenna elements are combined without the use of a lossy, resistive matching network, thereby increasing the efficiency with which the P×M radiation pattern is produced.

Owner:TDK CORPARATION

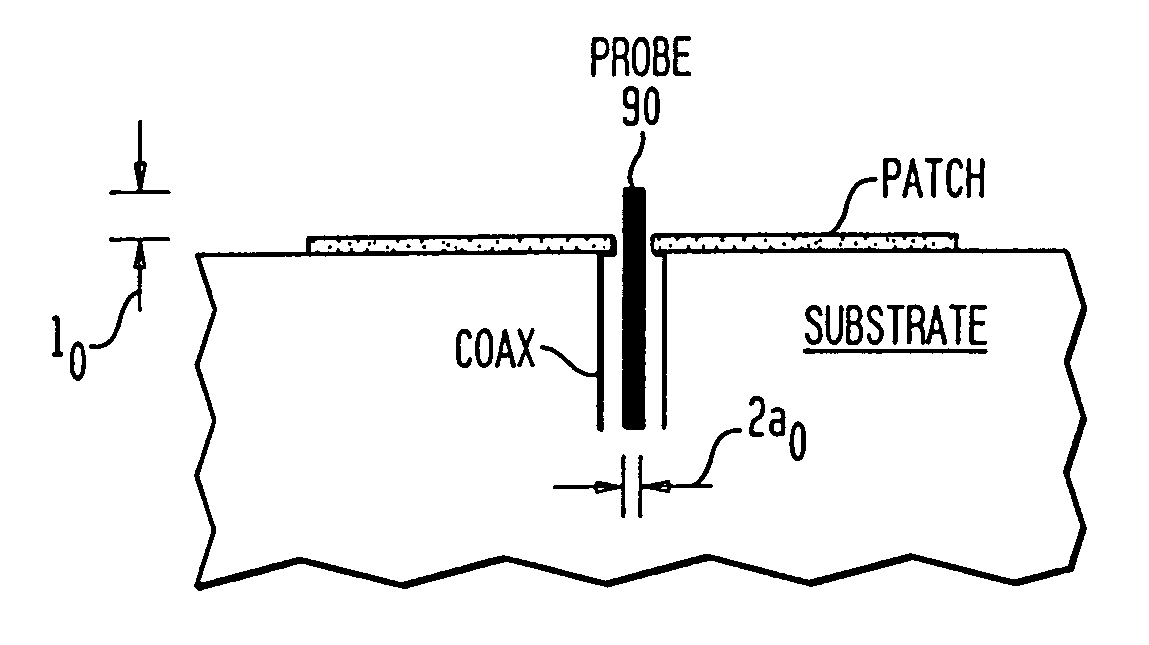

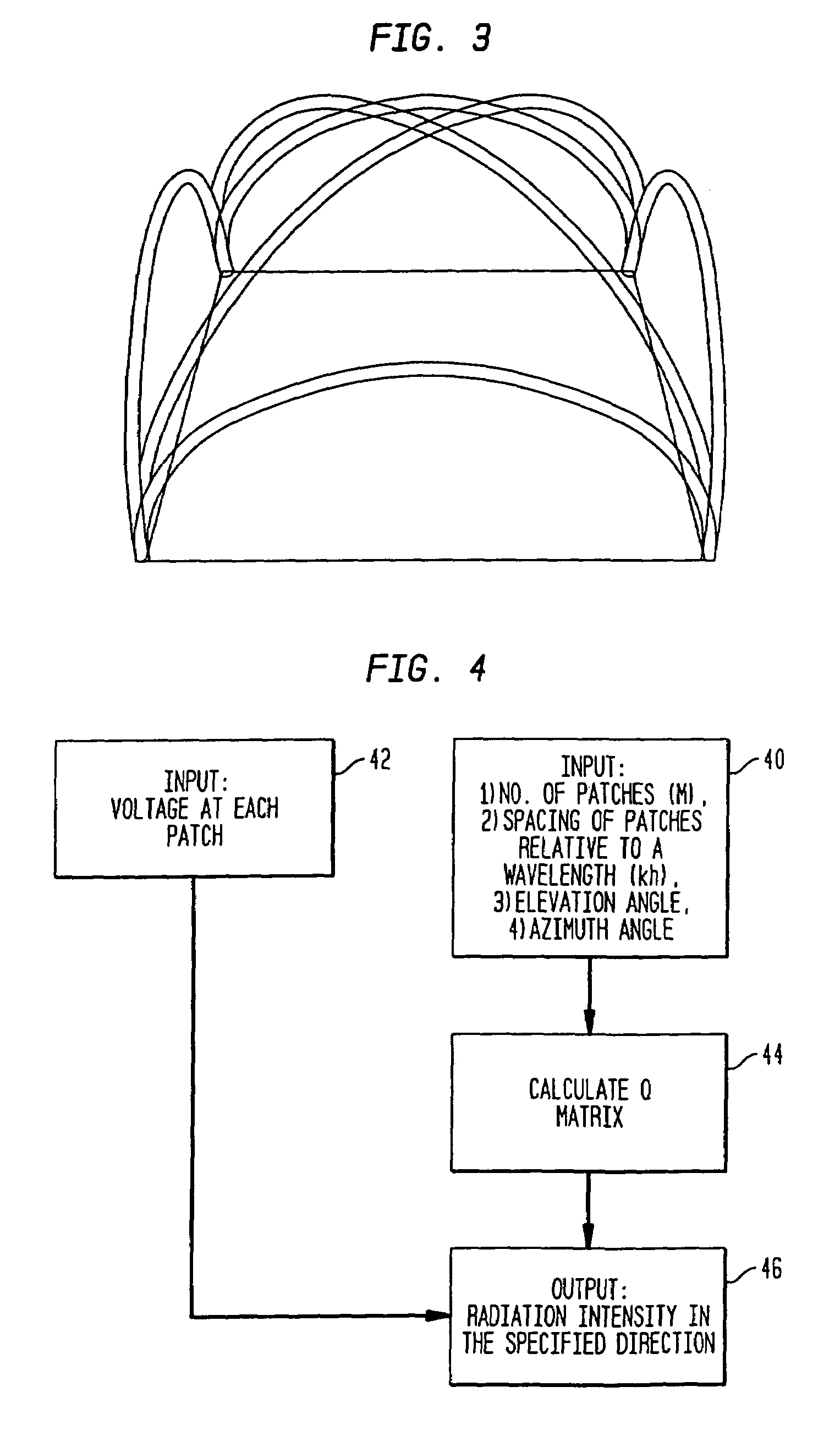

Systems and methods for providing optimized patch antenna excitation for mutually coupled patches

InactiveUS7298329B2Enhanced radiationImprove efficiencyParticular array feeding systemsSimultaneous aerial operationsMicrostrip patch antennaLight beam

An antenna array (e.g., microstrip patch antenna) operates in a manner that exploits the particular susceptibility of the mutual coupling effects between radiating elements in the array. Various differential-mode excitation schemes are provided for determining optimal differential-mode voltages or optimal differential-mode currents that are applied to the radiating elements (e.g., microstrip patches) to thereby achieve certain desirable radiation characteristics including, for example, aiming a radiated beam in a prescribed direction, steering the beam, shaping the radiated beam, and / or optimizing the gain of the antenna in a specified direction.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

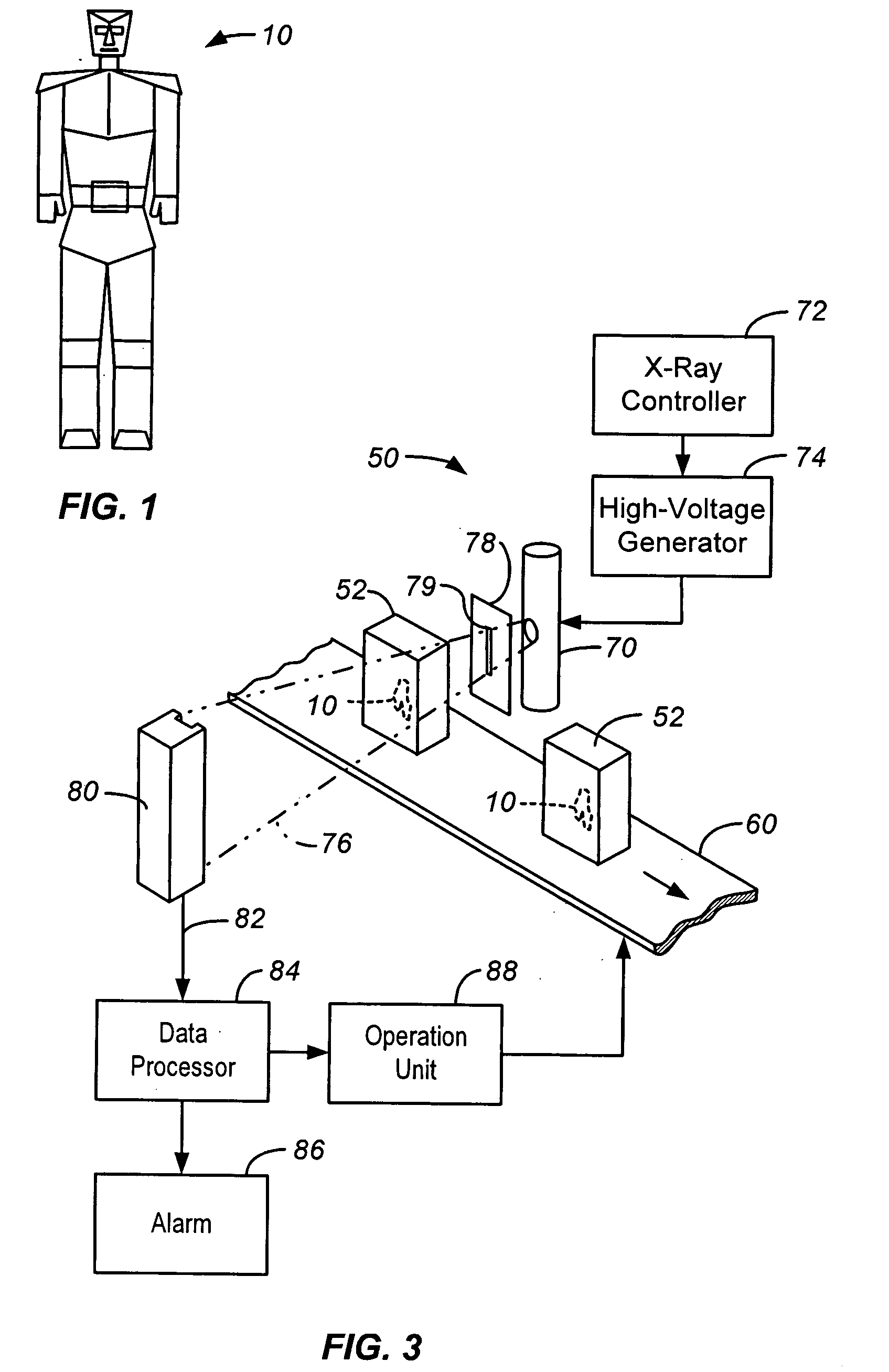

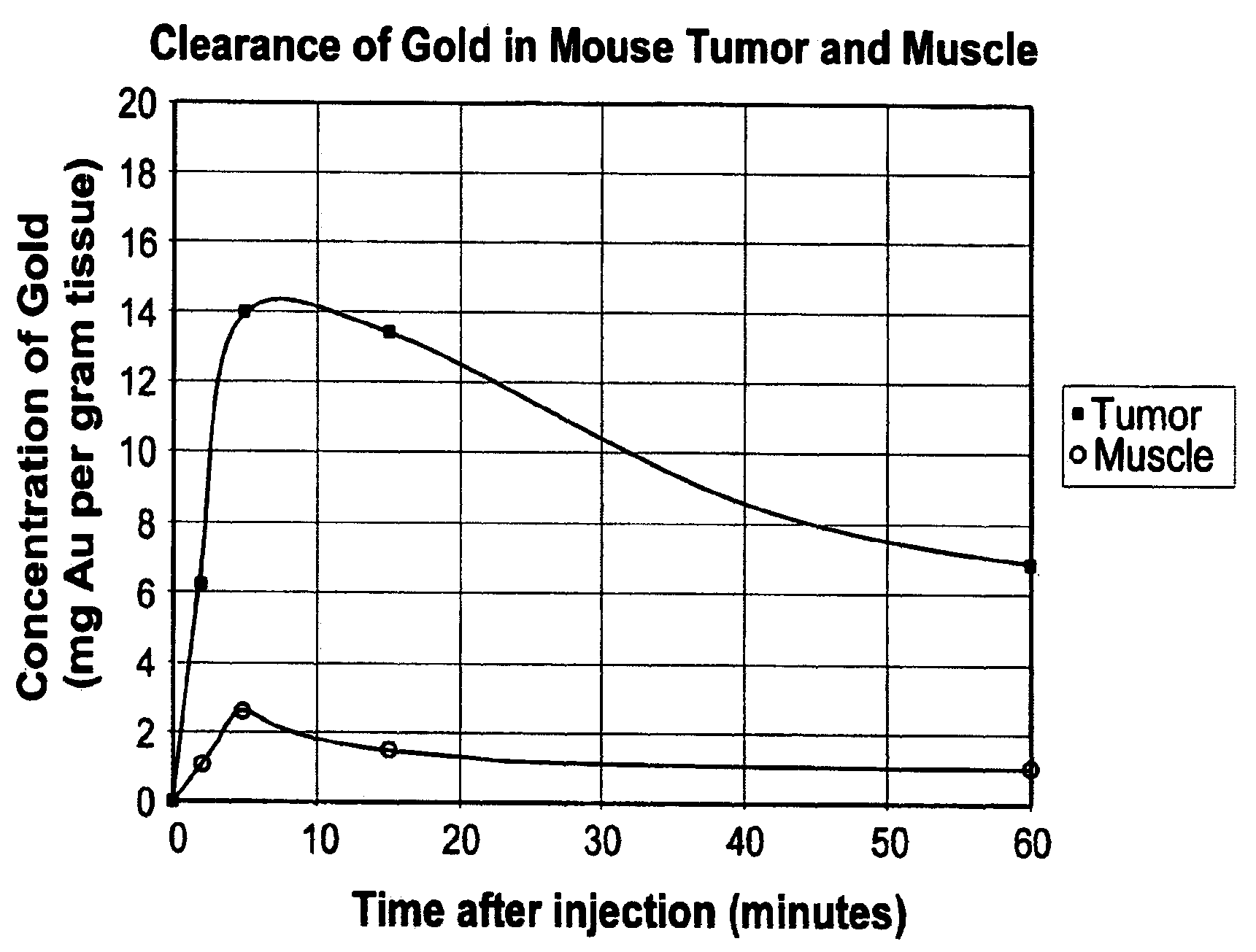

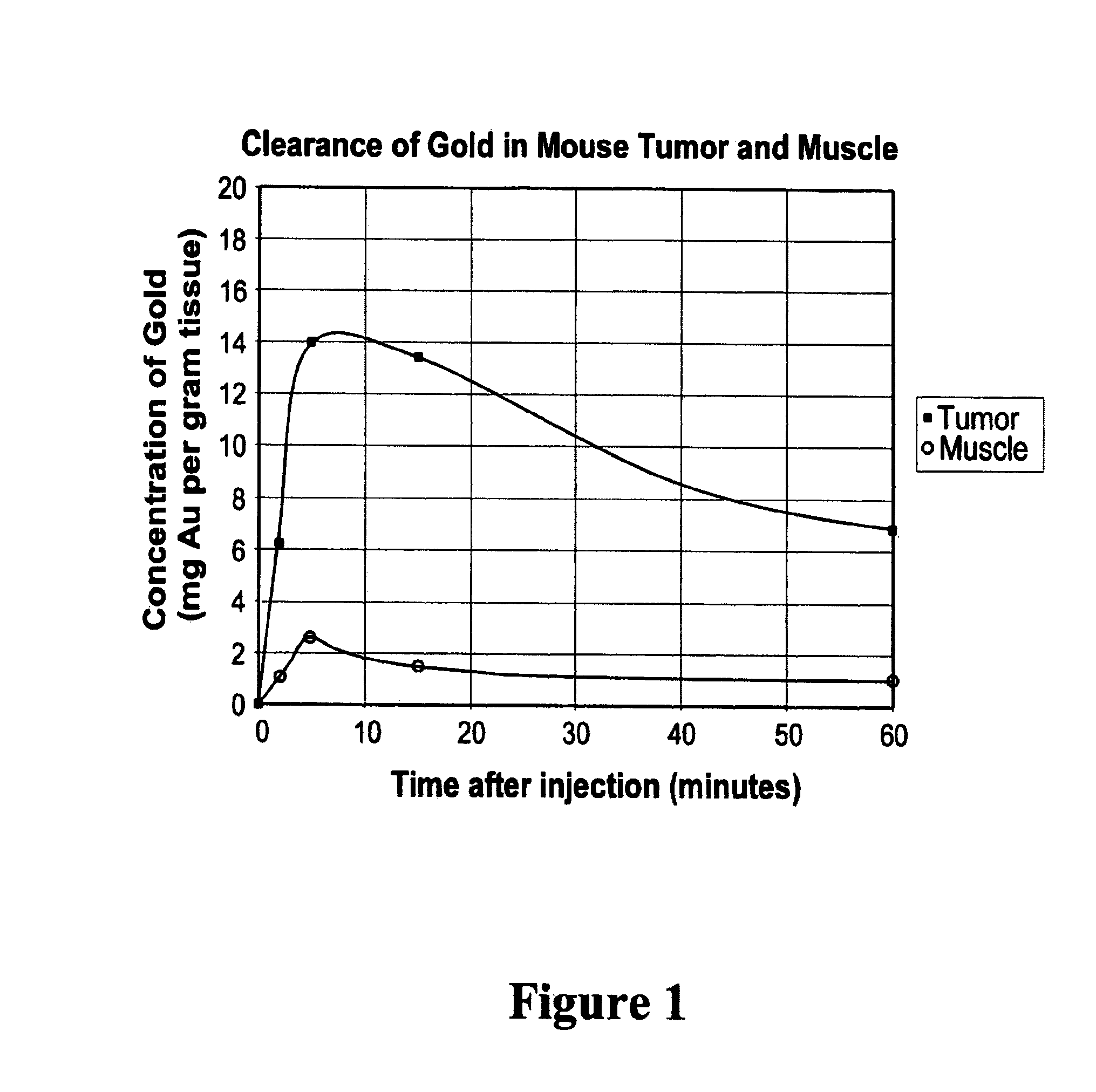

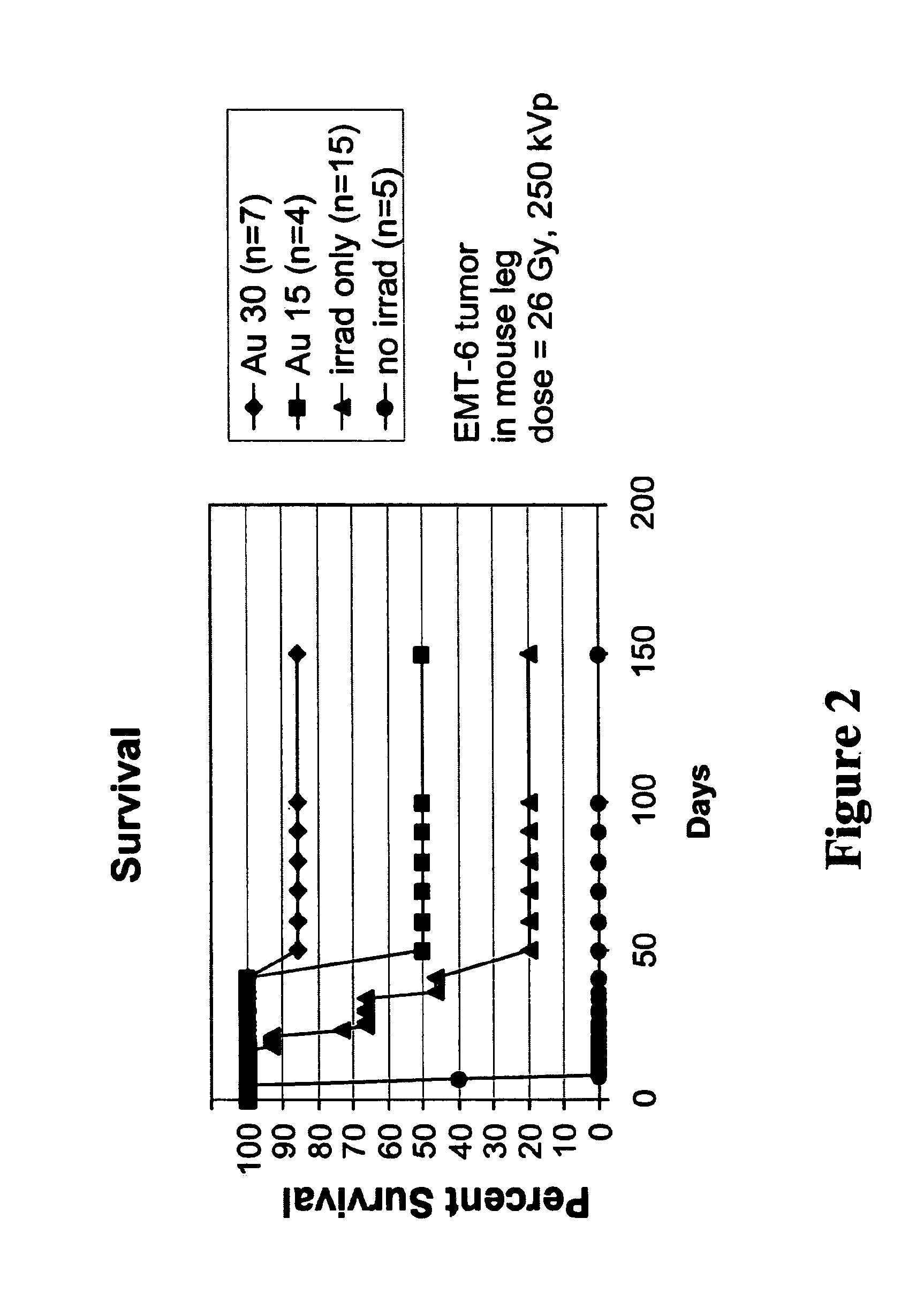

Methods of enhancing radiation effects with metal nanoparticles

InactiveUS20050020869A1Good effectSignificant toxicityPowder deliveryElectrotherapyAbnormal tissue growthCompound (substance)

The present invention provides methods of using metal nanoparticles 0.5 to 400 nm in diameter to enhance the dose and effectiveness of x-rays or of other kinds of radiation in therapeutic regimes of ablating a target tissue, such as tumor. The metal nanoparticles can be administered intravenously, intra-arterially, or locally to achieve specific loading in and around the target tissue. The metal nanoparticles can also be linked to chemical and / or biochemical moieties which bind specifically to the target tissue. The enhanced radiation methods can also be applied to ablate unwanted tissues or cells ex vivo.

Owner:NANOPROBES

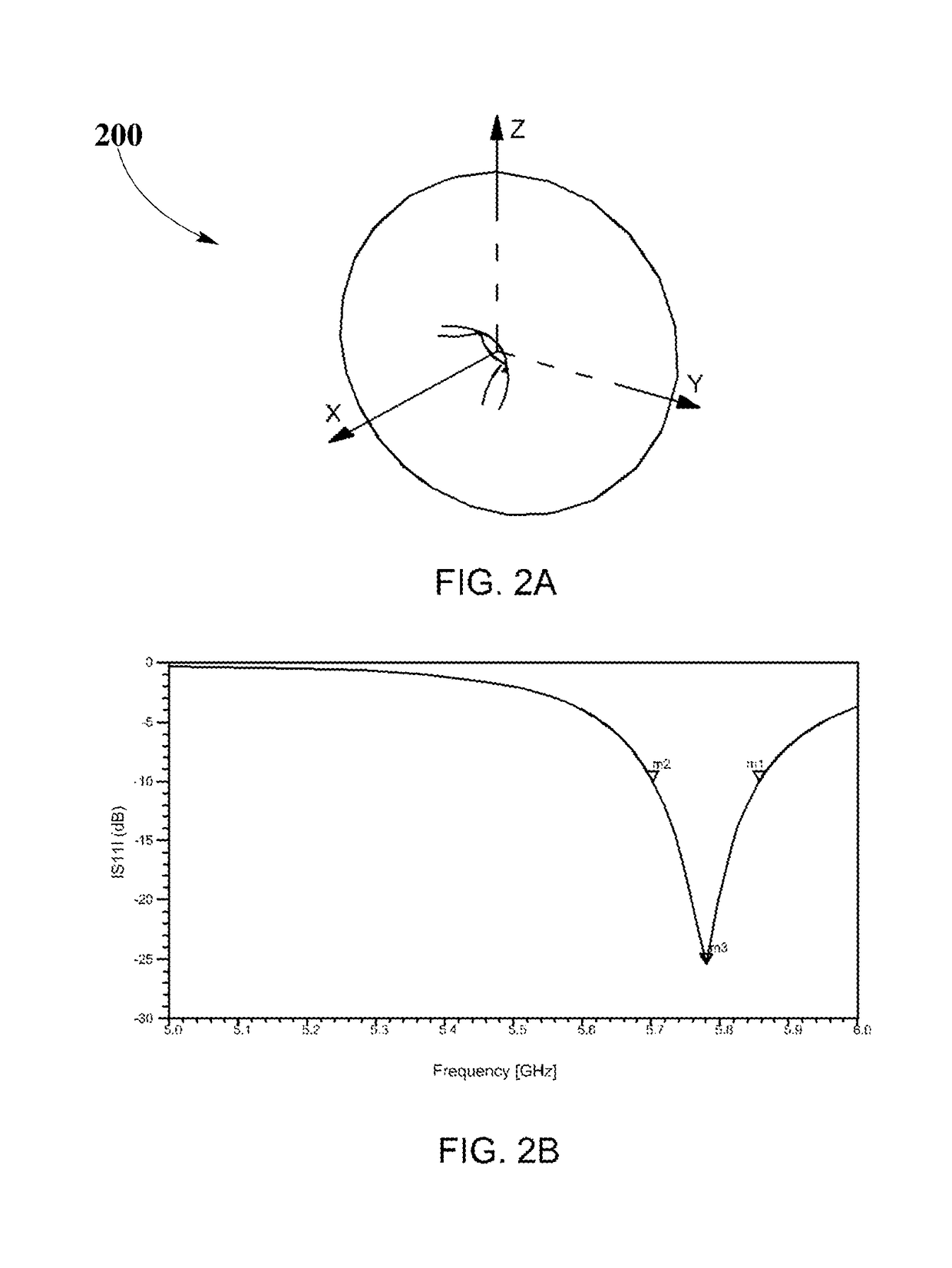

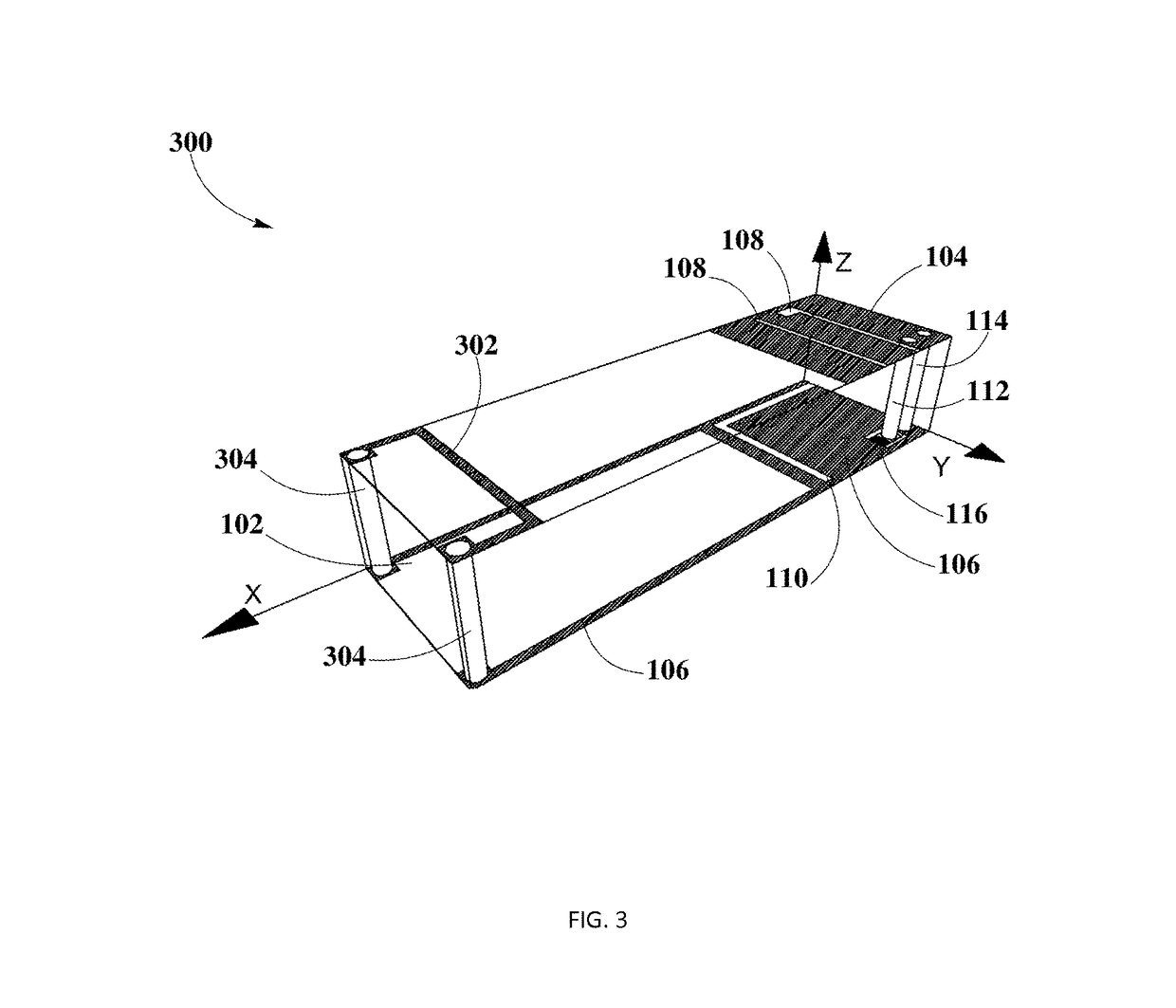

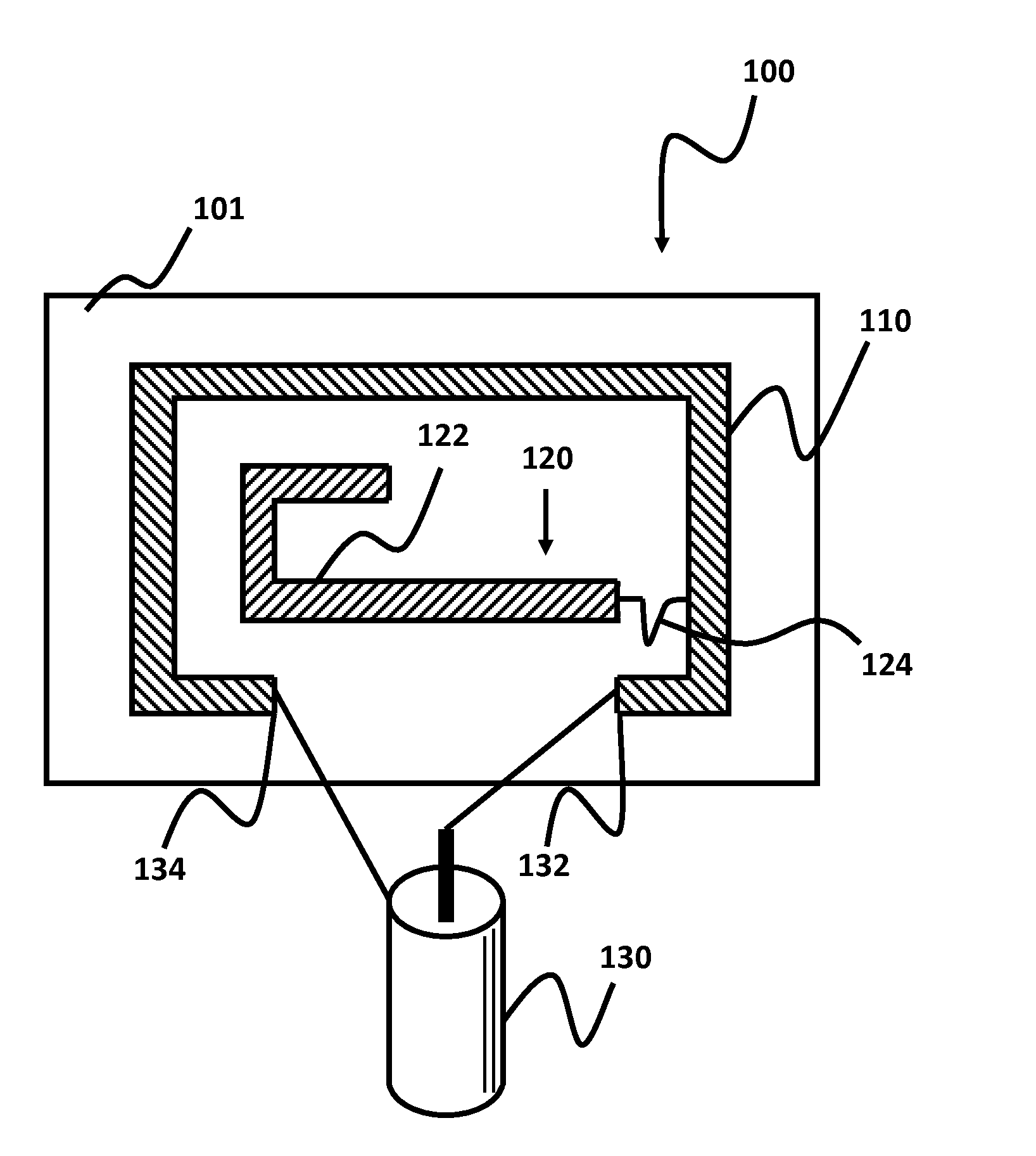

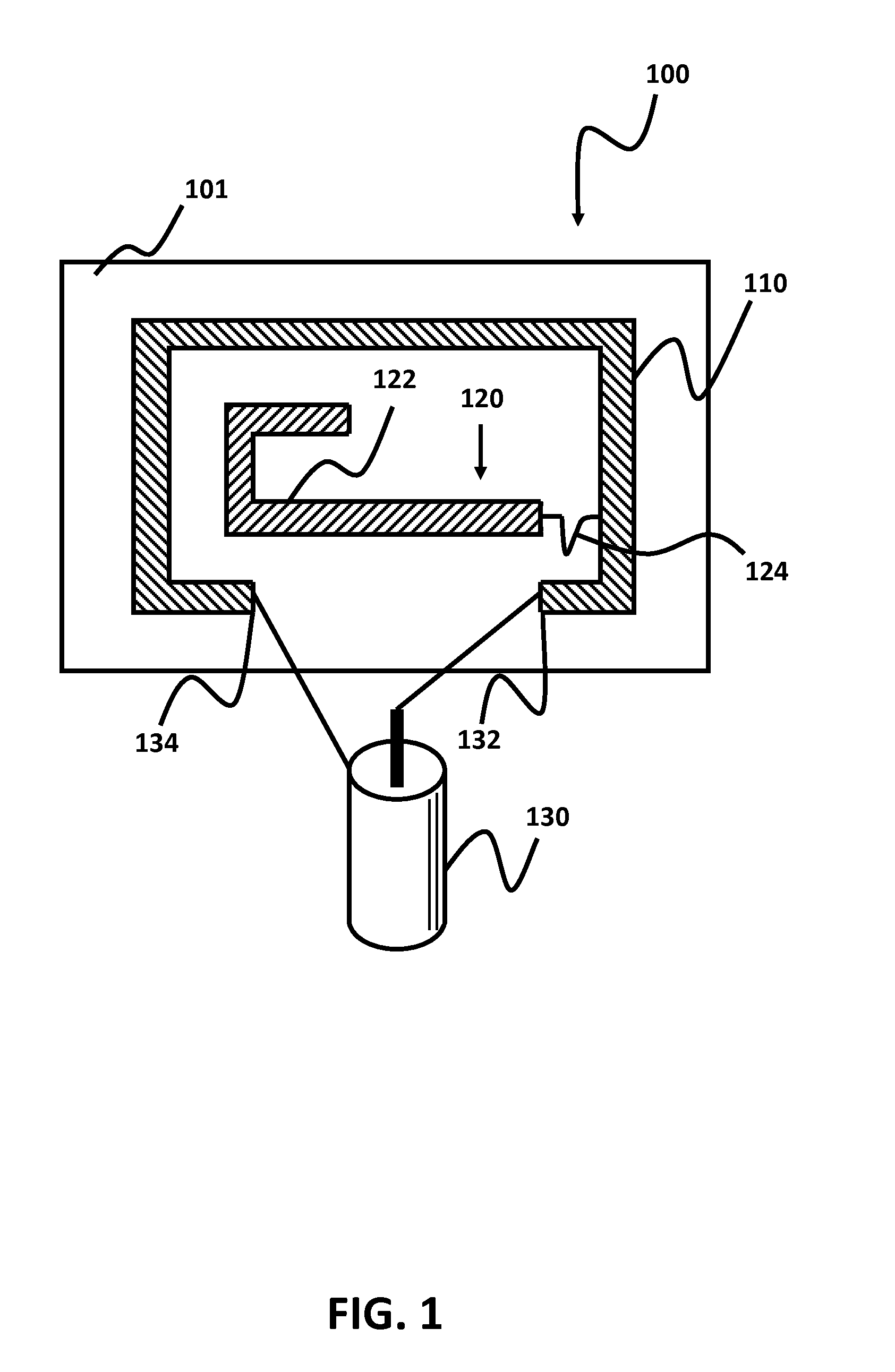

Compact PIFA antenna

ActiveUS10205239B1Antenna area can be reducedSuitable impedance bandwidthElectromagnetic wave systemSimultaneous aerial operationsPlanar inverted f antennaEngineering

Various planar inverted-F antenna configurations may include an antenna element formed on the top of a PCB and a ground element formed on the bottom of the PCB. Two or more slots may be included in the antenna element for reducing the antenna area while maintaining a suitable impedance bandwidth. A slot may be included in the ground element for reducing the ground area while increasing radiation efficiency. A folded ground may be formed on the top of the PCB for reducing system area while maintaining suitable performance. By moving the folded ground closer to the antenna element and increasing the PCB thickness, significant reductions in system area may be achieved, while maintaining or improving performance in terms of radiation pattern, radiation efficiency and impedance bandwidth.

Owner:ENERGOUS CORPORATION

Self-contained counterpoise compound loop antenna

ActiveUS20110018777A1High bandwidthLow QLoop antennas with ferromagnetic coreResonant long antennasHigh bandwidthUltimate tensile strength

The present invention relates to a self-contained counterpoise compound field antenna. Improvements relate particularly, but not exclusively, to compound loop antennas having coplanar electric field radiators and magnetic loops with electric fields orthogonal to magnetic fields that achieve performance benefits in higher bandwidth (lower Q), greater radiation intensity / power / gain, and greater efficiency. Embodiments of the self-contained antenna include a transition formed on the magnetic loop and having a transition width greater than the width of the magnetic loop. The transition substantially isolates a counterpoise formed on the magnetic loop opposite or adjacent the electric field radiator.

Owner:DOCKON

Low voltage drop and high thermal performance ball grid array package

InactiveUS7196415B2Fast heat conductionEnhanced thermal and electrical connectionSemiconductor/solid-state device detailsSolid-state devicesContact padLow voltage

Owner:AVAGO TECH INT SALES PTE LTD

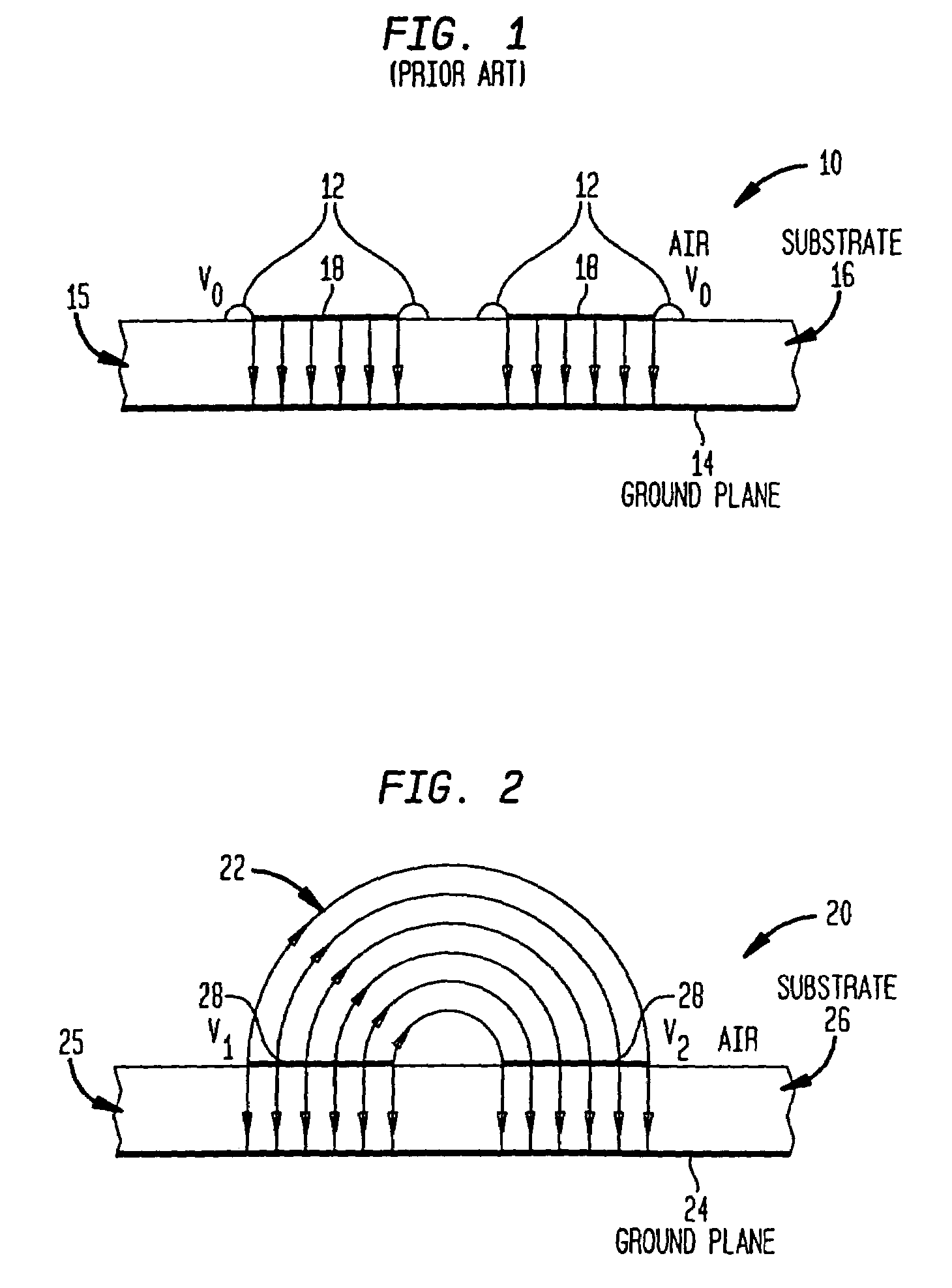

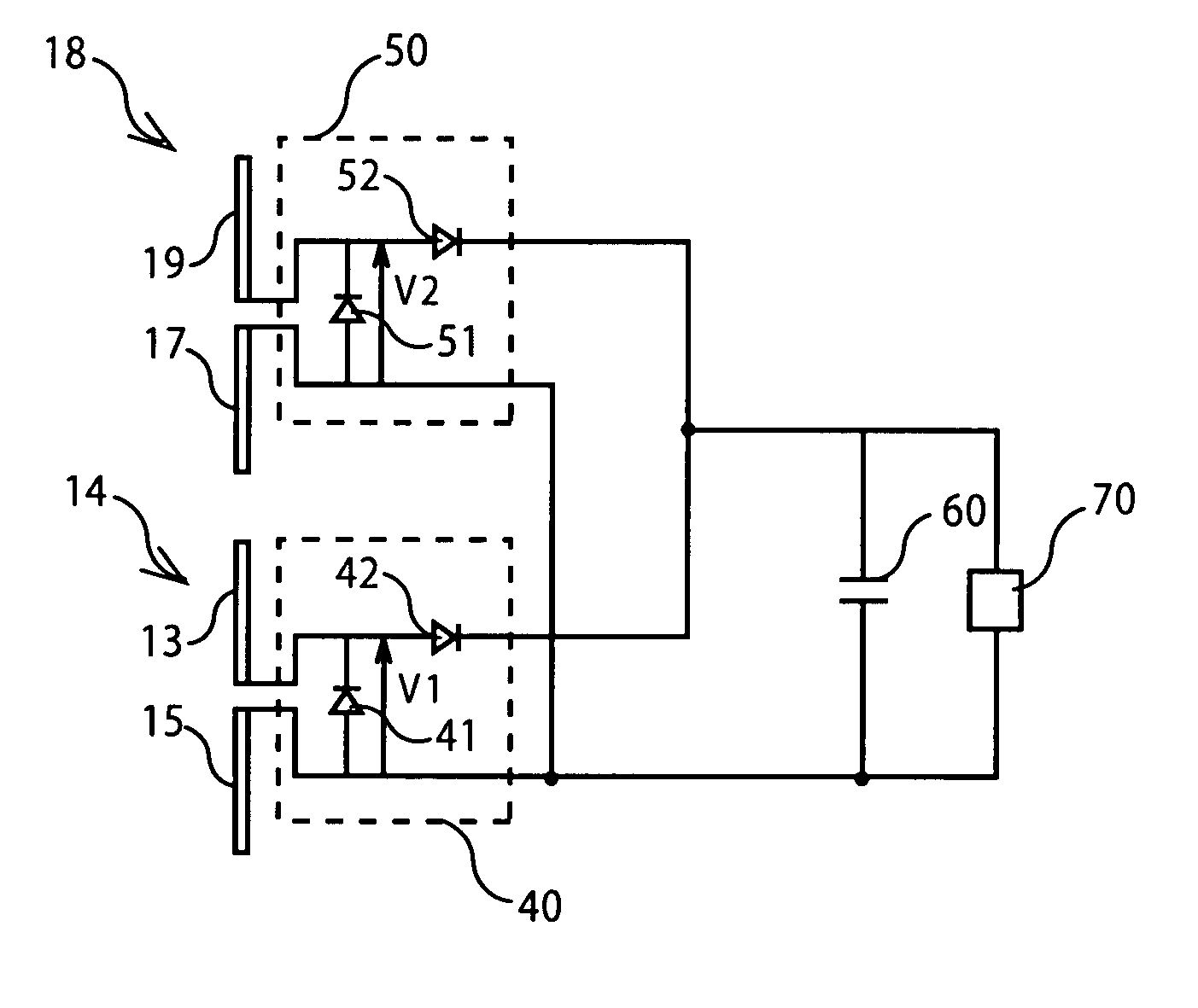

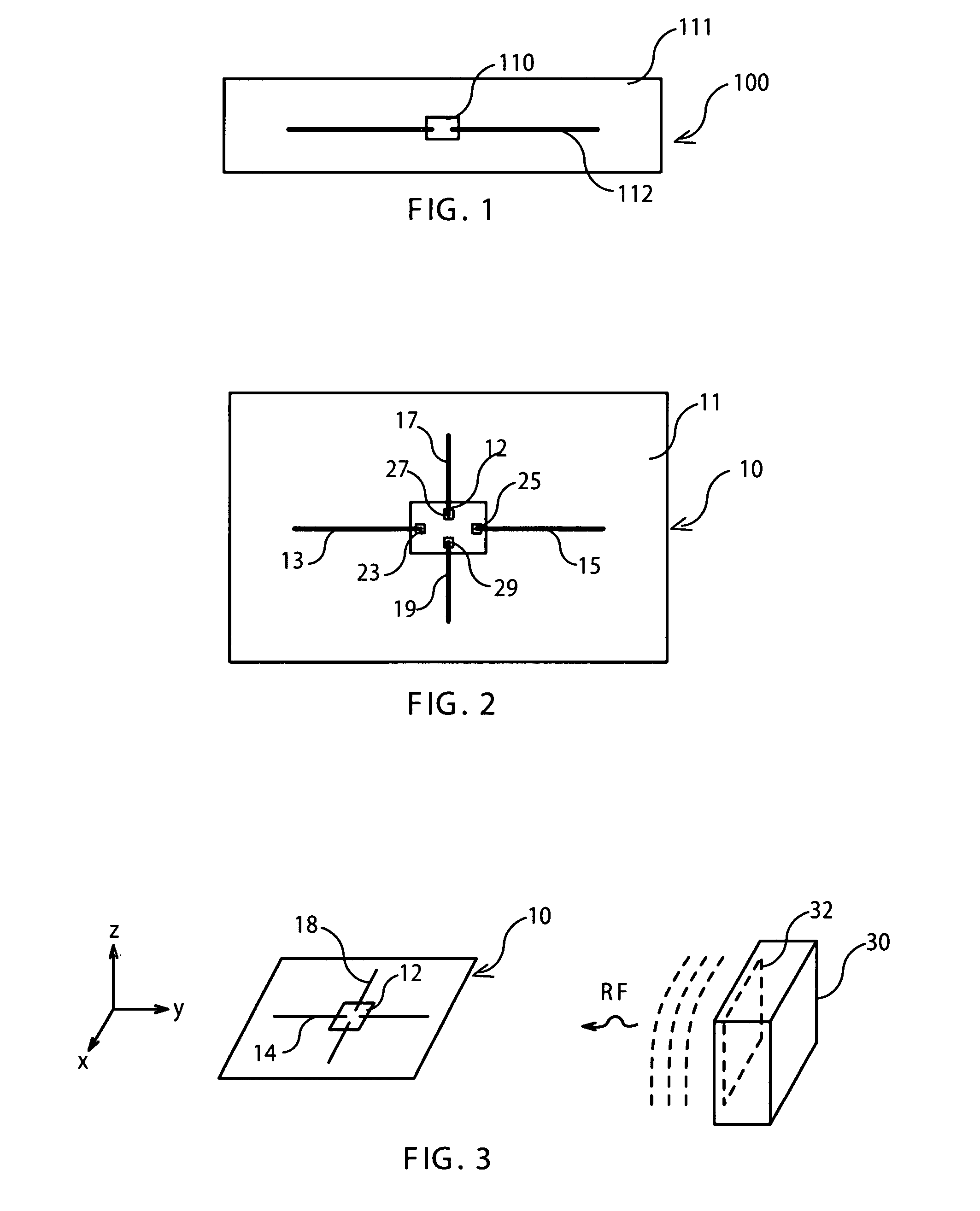

Contactless radiofrequency device featuring several antennas and related antenna selection circuit

InactiveUS20080068132A1Enhanced radiationSpatial transmit diversityNear-field in RFIDAntenna designEngineering

The invention relates to an integrated circuit for contactless radiofrequency device connected to a first antenna and to a second antenna designed to receive a radiofrequency signal coming from a reader. According to a main characteristic, the integrated circuit includes a first rectifier circuit and a second rectifier circuit to rectify each radiofrequency signal received from the first antenna and the second antenna, respectively, so as to produce two positive output voltages V1 and V2, the rectifier circuits being mounted in parallel in order to select an output voltage value that corresponds to the maximum voltage value between V1 and V2.

Owner:ASK SA (FR)

Low Voltage Drop and High Thermal Performance Ball Grid Array Package

InactiveUS20070108598A1Fast heat conductionEnhanced thermal and electrical connectionSemiconductor/solid-state device detailsSolid-state devicesContact padLow voltage

An apparatus and method for a low voltage drop and thermally enhanced integrated circuit (IC) package are described. A substantially planar substrate having a plurality of contact pads on a first surface is electrically connected through the substrate to a plurality of solder ball pads on a second surface of the substrate. An IC die having a first surface is mounted to the first surface of the substrate. The IC die has a plurality of I / O pads electrically connected to the plurality of contact pads on the first surface of the substrate. A heat sink assembly is coupled to a second surface of the IC die and to a first contact pad on the first surface of the substrate to provide a thermal path from the IC die to the first surface of the substrate. The heat sink assembly can also provide an electrical path from the IC die to the first surface of the substrate. The heat sink assembly may have one or two heat sink elements to provide thermal and / or electrical connectivity between the IC die and the substrate.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

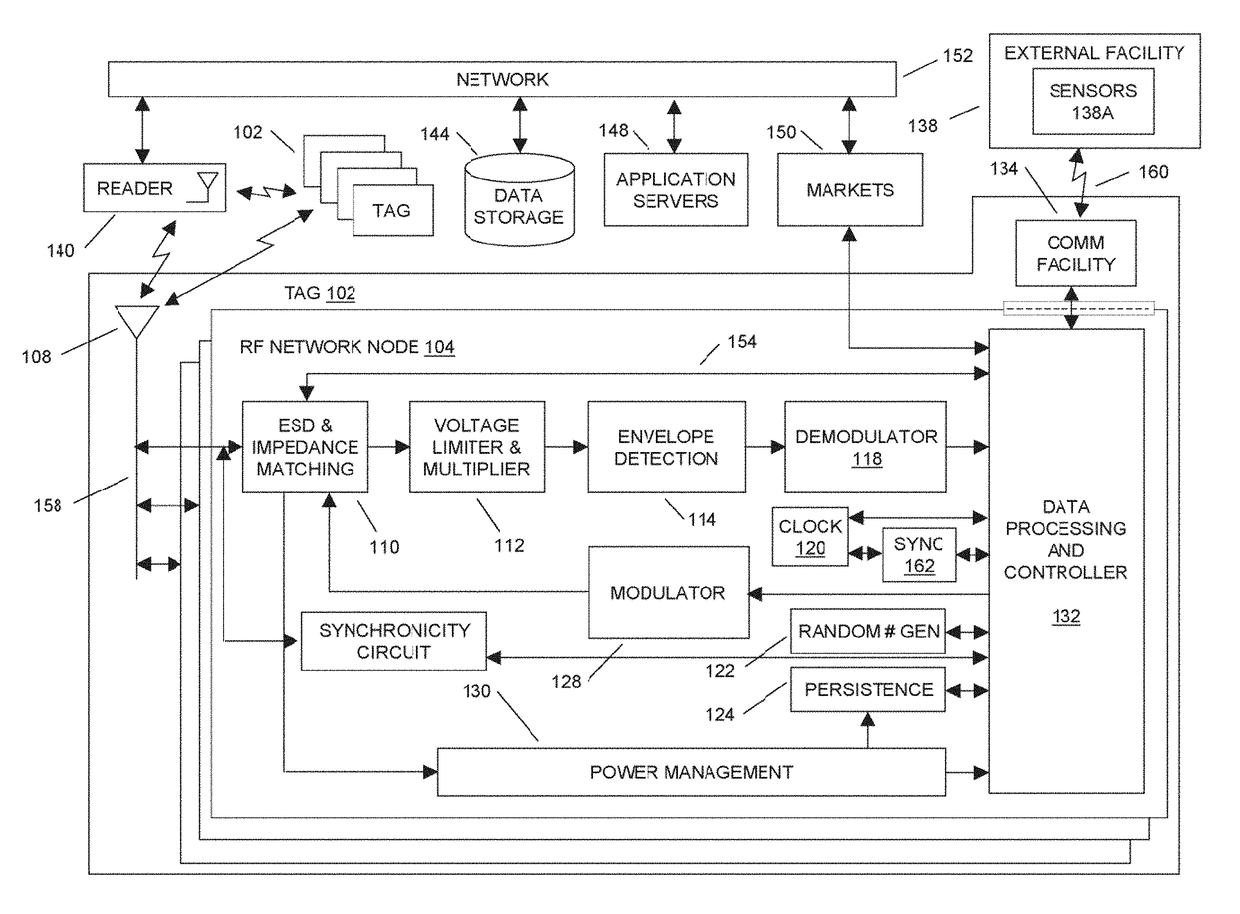

Operating systems for an RFID tag

ActiveUS20160048712A1Enhanced radiationMemory record carrier reading problemsRadiating elements structural formsOperational systemData memory

In embodiments of the present invention improved capabilities are described for a radio frequency (RF) computing tag comprising mounting an antenna and an RF computing device that is enabled for RF communication and for computing on a single substrate, the RF computing device comprising: (i) an RF and analog block for receiving and transmitting an RF signal through the antenna, wherein the energy from a received RF signal provides power to the RF computing device, (ii) a power management block for managing power requirements of the RF computing device, and (iii) a processor-based data processing and controller block for digital information management, comprising an operating system, a programmable memory, a programmable memory, and a data store, wherein the programmable memory stores an operating system for operation of the RF computing device.

Owner:TEGO INC

Operating systems for an RFID tag

ActiveUS20170270323A1Increase in ionize radiationEnhanced radiationMemory record carrier reading problemsCo-operative working arrangementsData processingComputer hardware

In embodiments of the present invention improved capabilities are described for a wireless computing device, comprising an antenna; an analog block for receiving and transmitting an RF signal through the antenna, wherein the energy from the received RF signal provides power to the wireless computing device; and a data processing and controller block for data management, wherein the data processing and controller block comprises: (i) a first program memory adapted to store a first set of instructions comprising a system call adapted to perform at least one function, and (ii) a second program memory adapted to store a second set of instructions comprising an instruction to call the system call, wherein the data processing and controller block is adapted to execute the first set of instructions and the second set of instructions,wherein the antenna, analog block, and data processing and controller block are mounted on a single substrate.

Owner:TEGO INC

Information RFID tagging facilities

ActiveUS20160048709A1Enhanced radiationMemory record carrier reading problemsRadiating elements structural formsEngineeringRadio frequency

In embodiments of the present invention improved capabilities are described for a system of information RFID tagging facilities comprising a first radio frequency (RF) tag and a second RF tag, wherein the first RF tag and the second RF tag are adapted to operate using energy received from an RF signal, wherein: (i) at least one of the first RF tag and the second RF tag receives an RF signal from an RF device, (ii) the first RF tag transmits data to the second RF tag, and (iii) the second RF tag stores the transmitted data from the first RF tag in a memory on the second RF tag.

Owner:TEGO INC

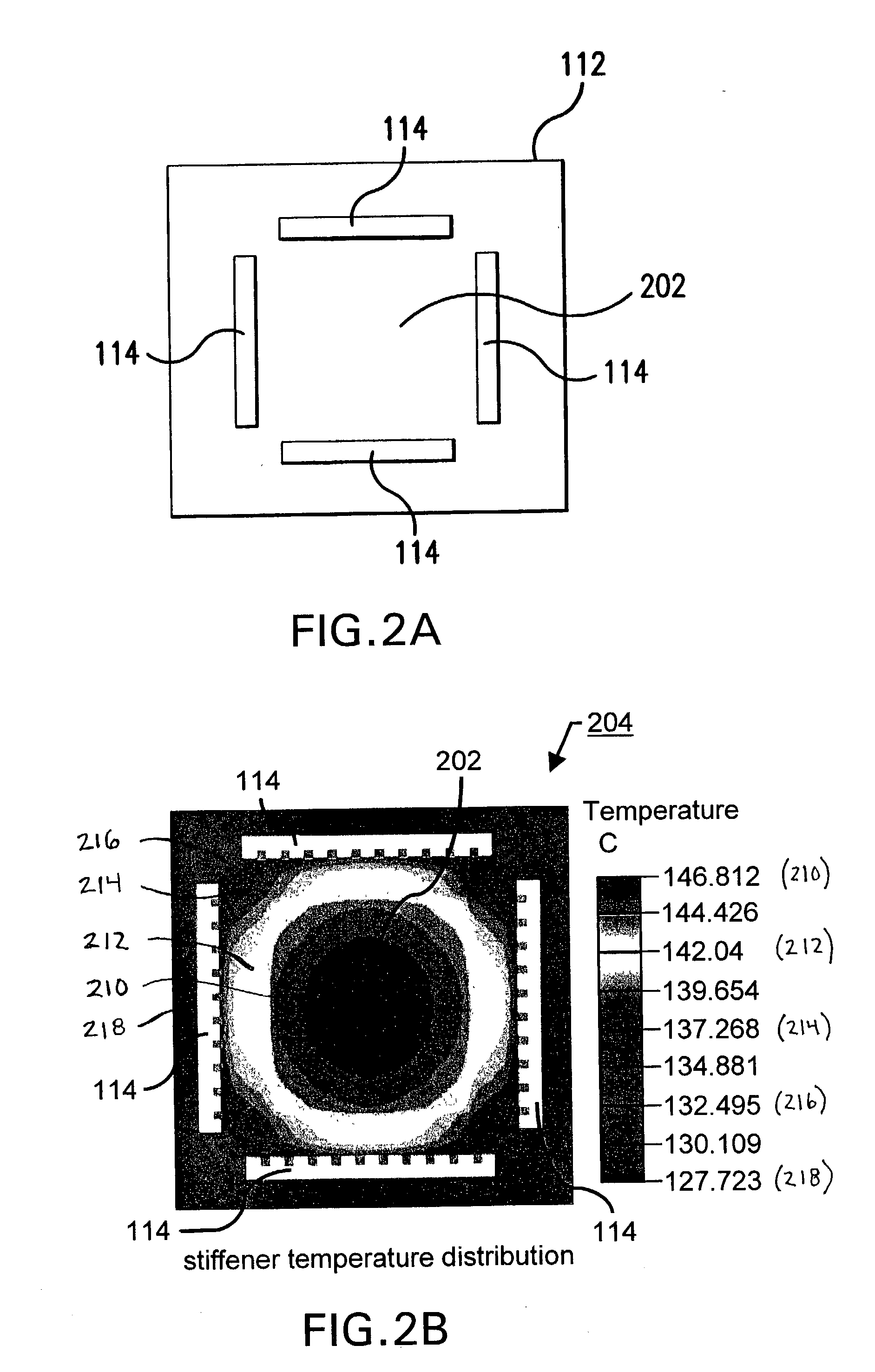

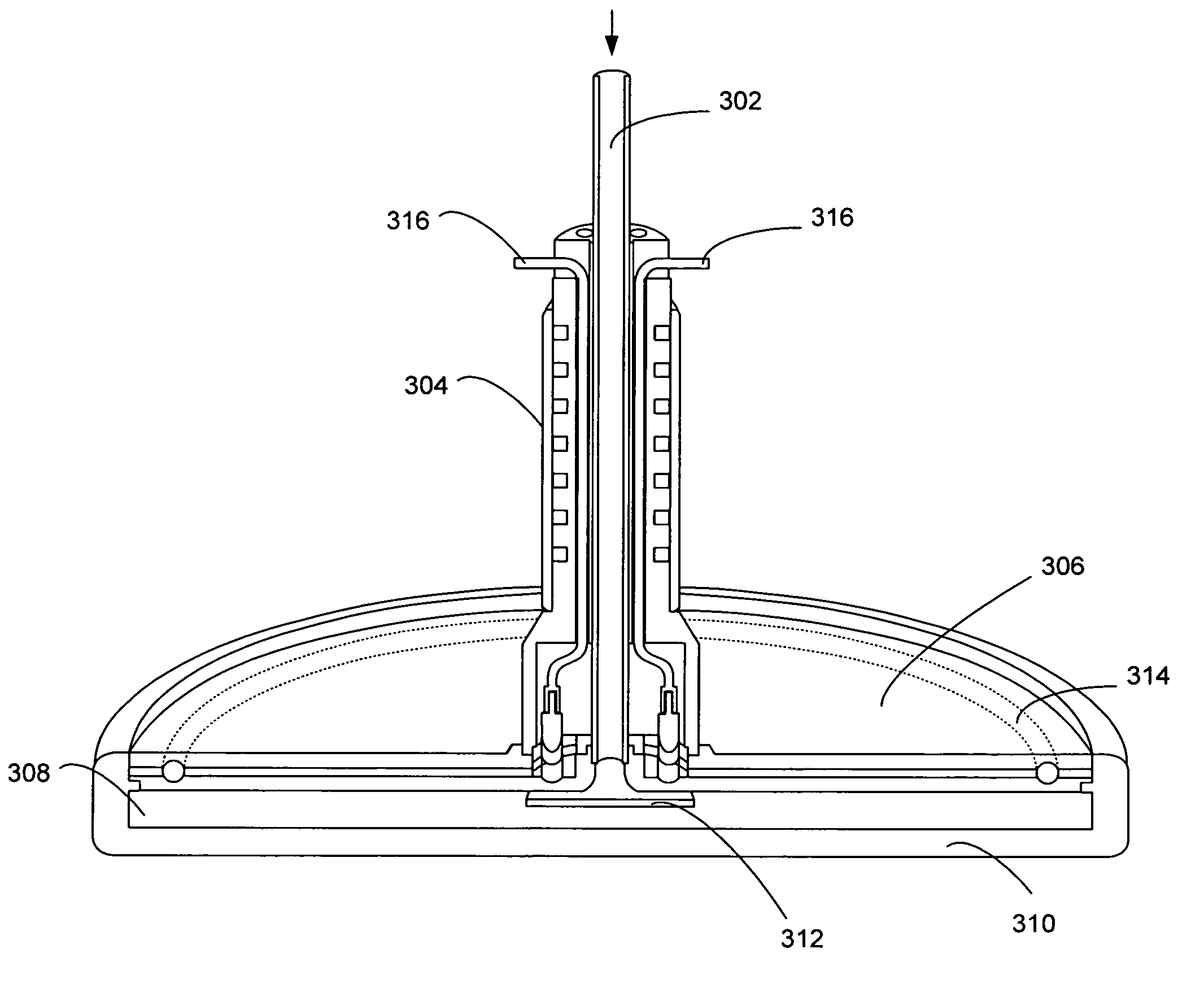

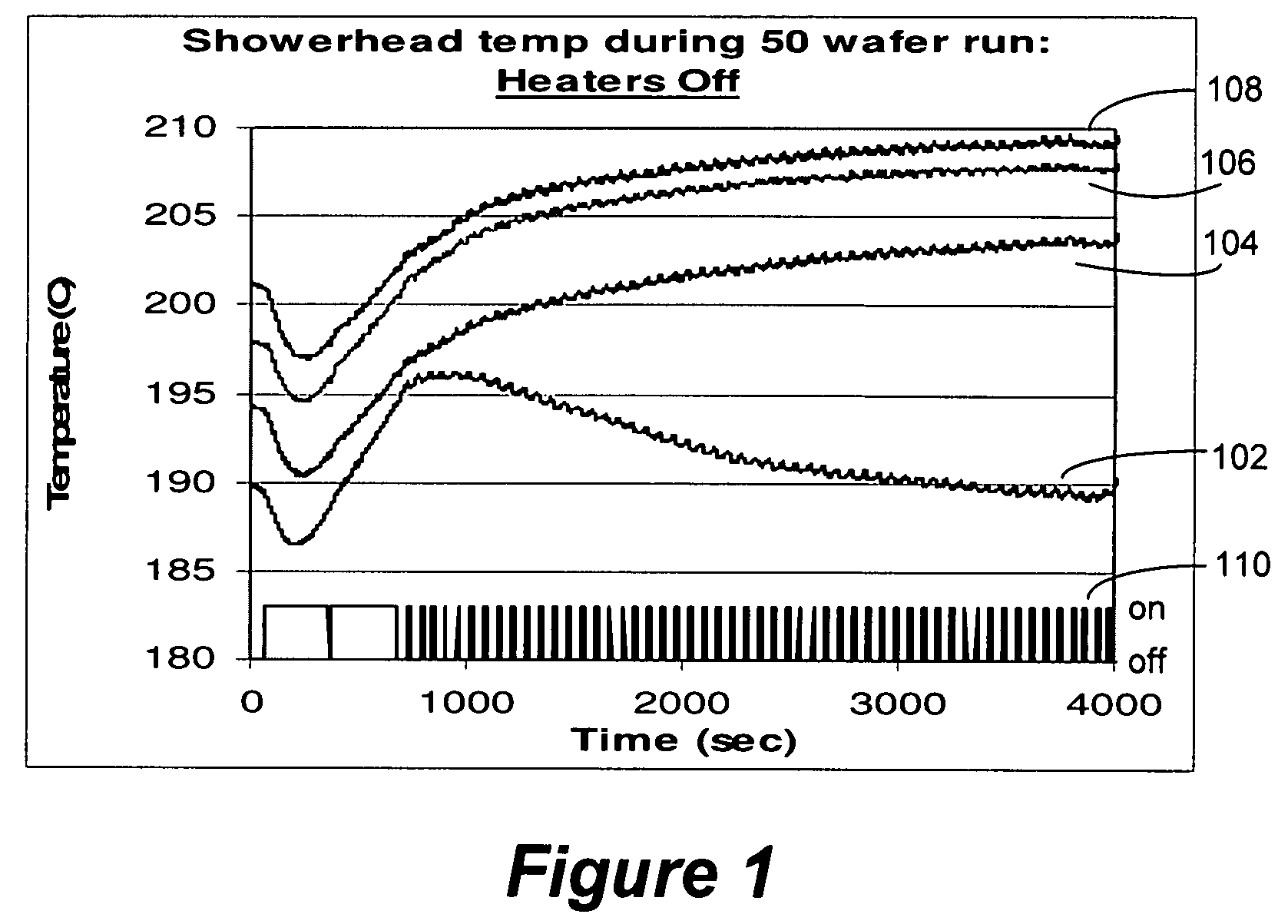

Temperature controlled showerhead

ActiveUS8137467B2Improve cooling effectPrecise and stable temperature controlLiquid surface applicatorsSemiconductor/solid-state device manufacturingTemperature controlControl system

A temperature controlled showerhead for chemical vapor deposition (CVD) chambers enhances heat dissipation to enable accurate temperature control with an electric heater. Heat dissipates by conduction through a showerhead stem and fluid passageway and radiation from a back plate. A temperature control system includes one or more temperature controlled showerheads in a CVD chamber with fluid passageways serially connected to a heat exchanger.

Owner:NOVELLUS SYSTEMS

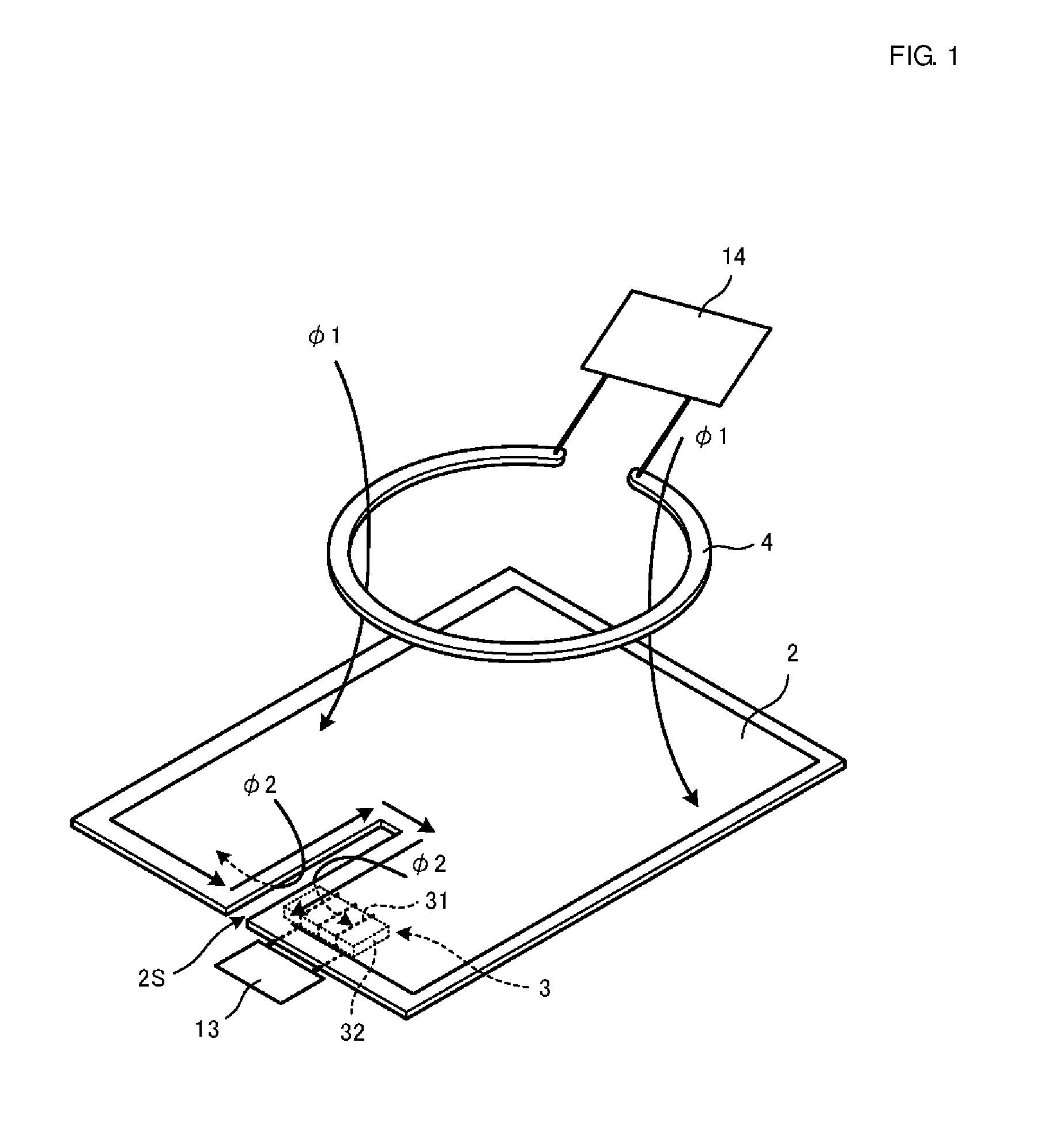

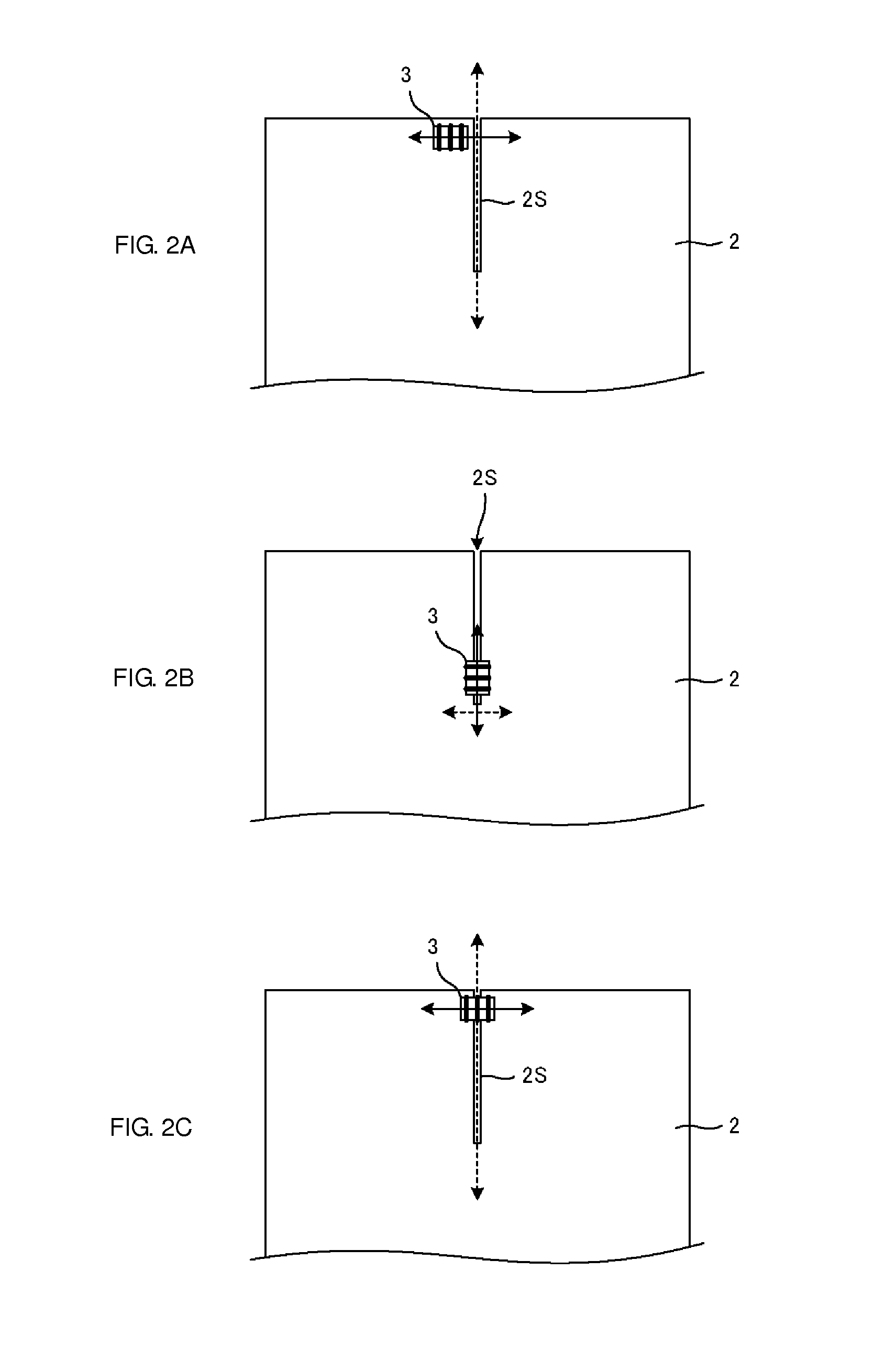

Antenna device and wireless communication device

ActiveUS20130307746A1Enhanced radiationImprove radiation efficiencyLoop antennas with ferromagnetic coreRadiating elements structural formsMagnetic coreRFIC

An antenna device includes a feed coil and a sheet conductor. The feed coil includes a magnetic core and a coil-shaped conductor, which is provided around the magnetic core. An RFIC is connected to the feed coil. The sheet conductor has a larger area than the feed coil. A slit that extends from a portion of the edge of the sheet conductor toward the inner side of the sheet conductor is provided in the sheet conductor. The feed coil is arranged such that the direction of the axis around which the feed coil is disposed is parallel or substantially parallel to the directions in which the sheet conductor extends. The feed coil is arranged such that the feed coil is close to the slit and one of coil openings at the ends of the feed coil faces the slit.

Owner:MURATA MFG CO LTD

Radiation detectable and protective articles

InactiveUS7476889B2Small sizeLarge specific surface areaNuclear engineering problemsNuclear engineering solutionsEmulsionCompound (substance)

Compositions and processes for forming radiopaque polymeric articles are disclosed. In one embodiment, radiation inspection apparatuses and methods are then used to determine the presence and attributes of such radiopaque polymeric articles. A radiopaque polymeric article of the present invention can be created by mixing a radiopaque material, such as barium, bismuth, tungsten or their compounds, with a powdered polymer, pelletized polymer or liquid solution, emulsion or suspension of a polymer in solvent or water. In addition to creating radiation detectable objects, the radiopaque polymeric materials of the present invention can be used to create radiation protective articles, such as radiation protective garments and bomb containment vessels. Enhanced radiation protection can also be achieved through the use of nano-materials. The principals of the present invention can be used to provide protection against other types of hazards, including fire, chemical, biological and projectile hazards.

Owner:MERIDIAN RES & DEV

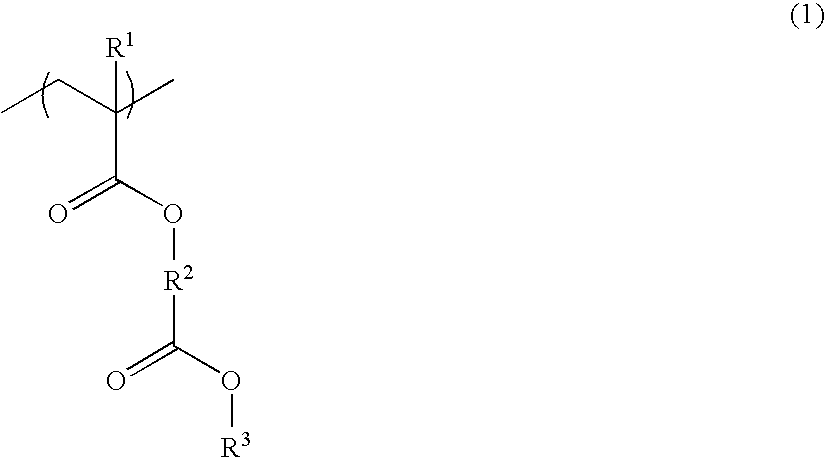

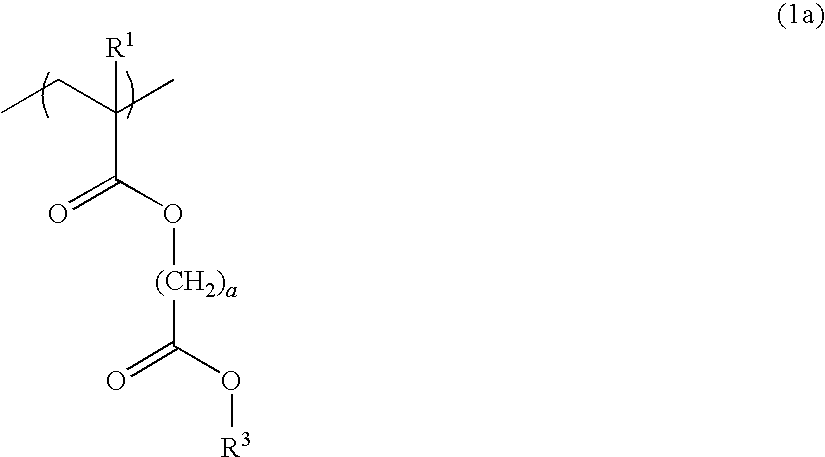

Resist composition and patterning process

ActiveUS20100266957A1Readily availableEasy to handlePhotosensitive materialsElectric discharge tubesResistOrganic solvent

An additive polymer comprising recurring units of formula (1) is added to a resist composition comprising a base resin, a photoacid generator, and an organic solvent. R1 is hydrogen or methyl, R2 is alkylene or fluoroalkylene, and R3 is fluoroalkyl. The additive polymer is highly transparent to radiation with wavelength of up to 200 nm. Water repellency, water slip, acid lability, hydrolysis and other properties of the polymer may be adjusted by a choice of polymer structure.

Owner:SHIN ETSU CHEM IND CO LTD

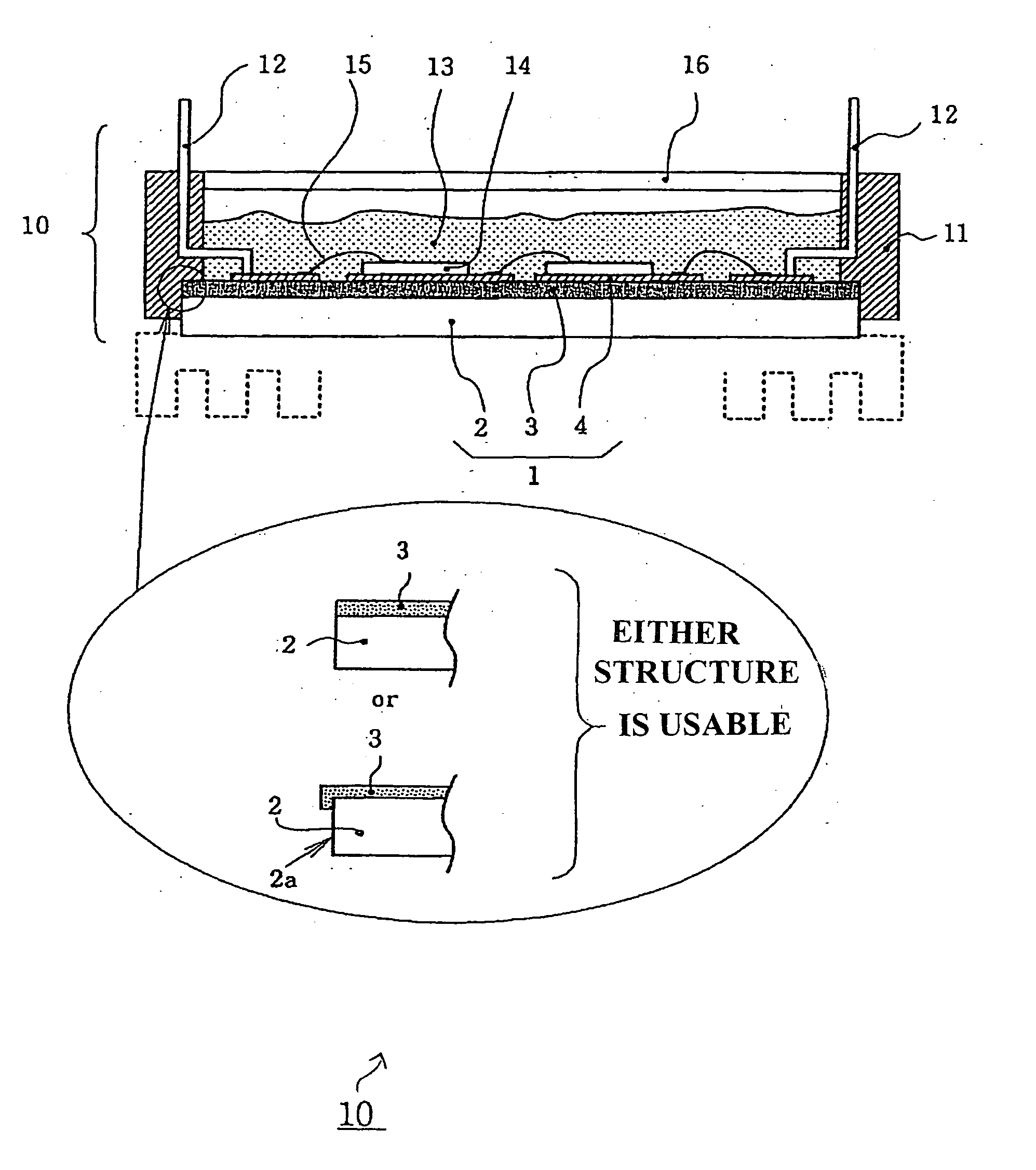

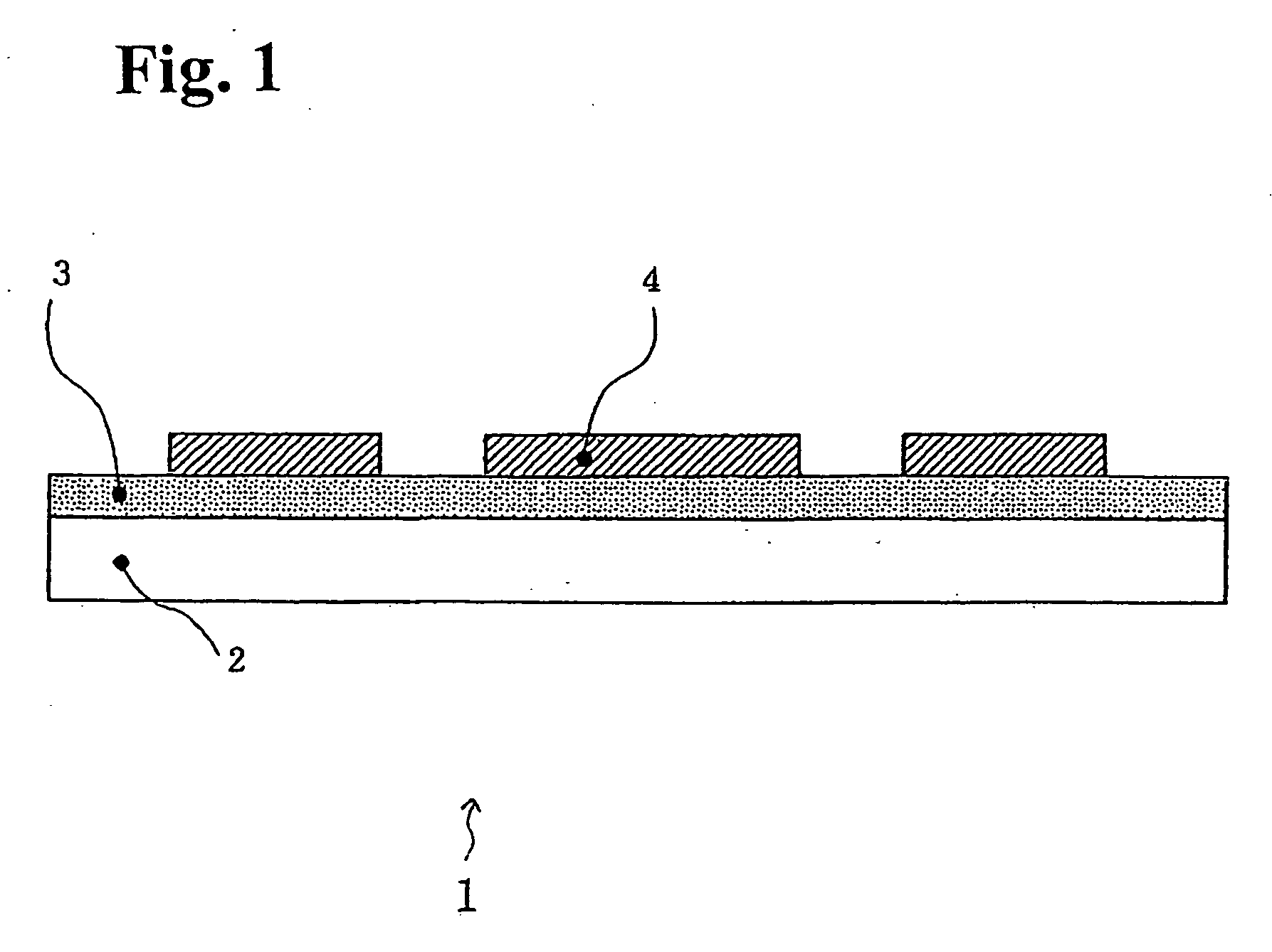

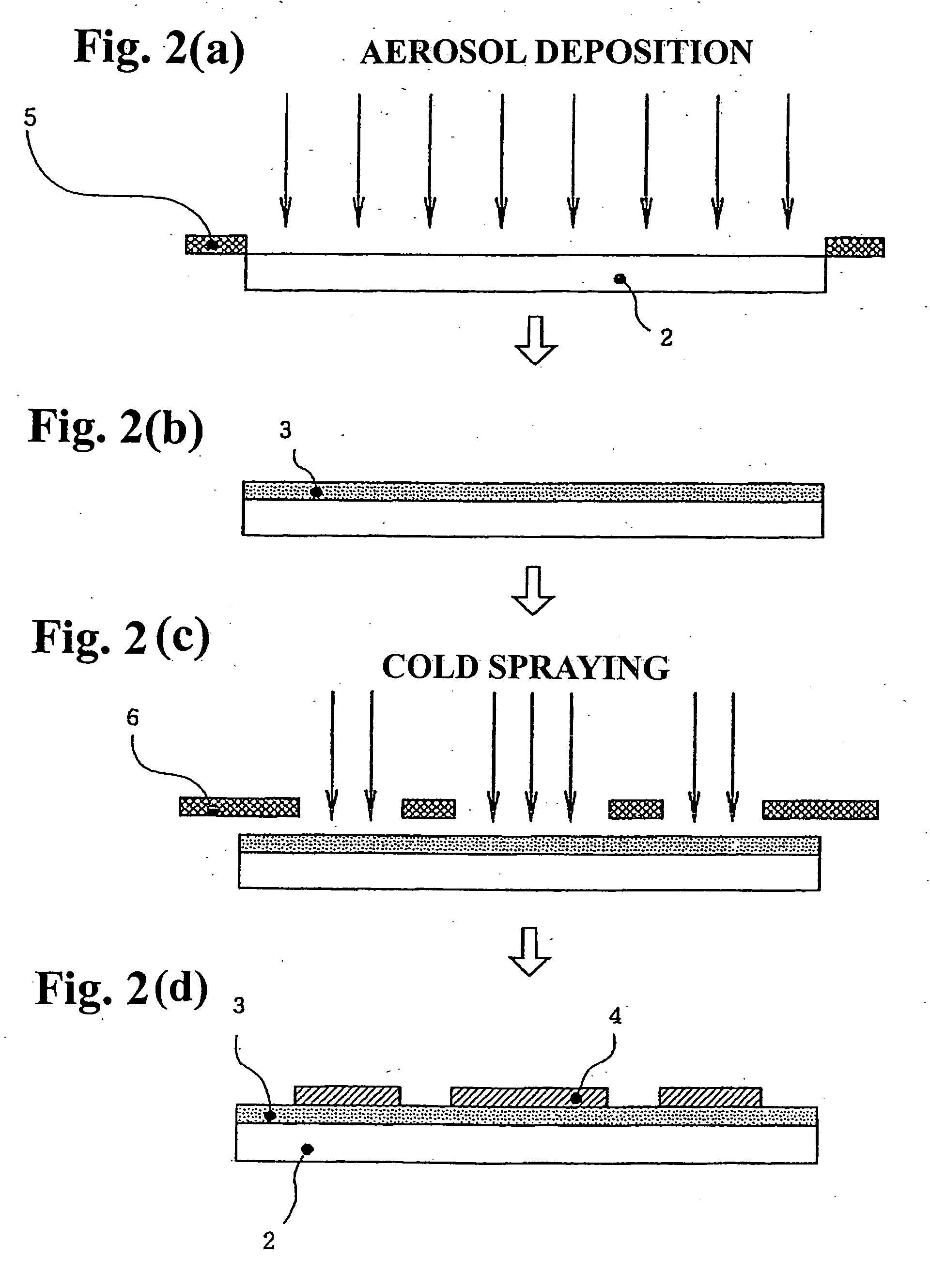

Insulating substrate and semiconductor device

ActiveUS20060108601A1Reduce manufacturing stepsImprove heat radiation performanceMolten spray coatingSemiconductor/solid-state device detailsDevice materialRoom temperature

An insulating substrate includes a metal base as a base member, an insulating layer which is a room temperature, aerosol deposited shock solidification film formed on the metal base, and a circuit pattern which is a cold sprayed thermal spray coating formed on the insulating layer. A semiconductor device incorporates the insulating substrate, and thereby has improved heat radiation characteristics.

Owner:FUJI ELECTRIC HLDG CO LTD

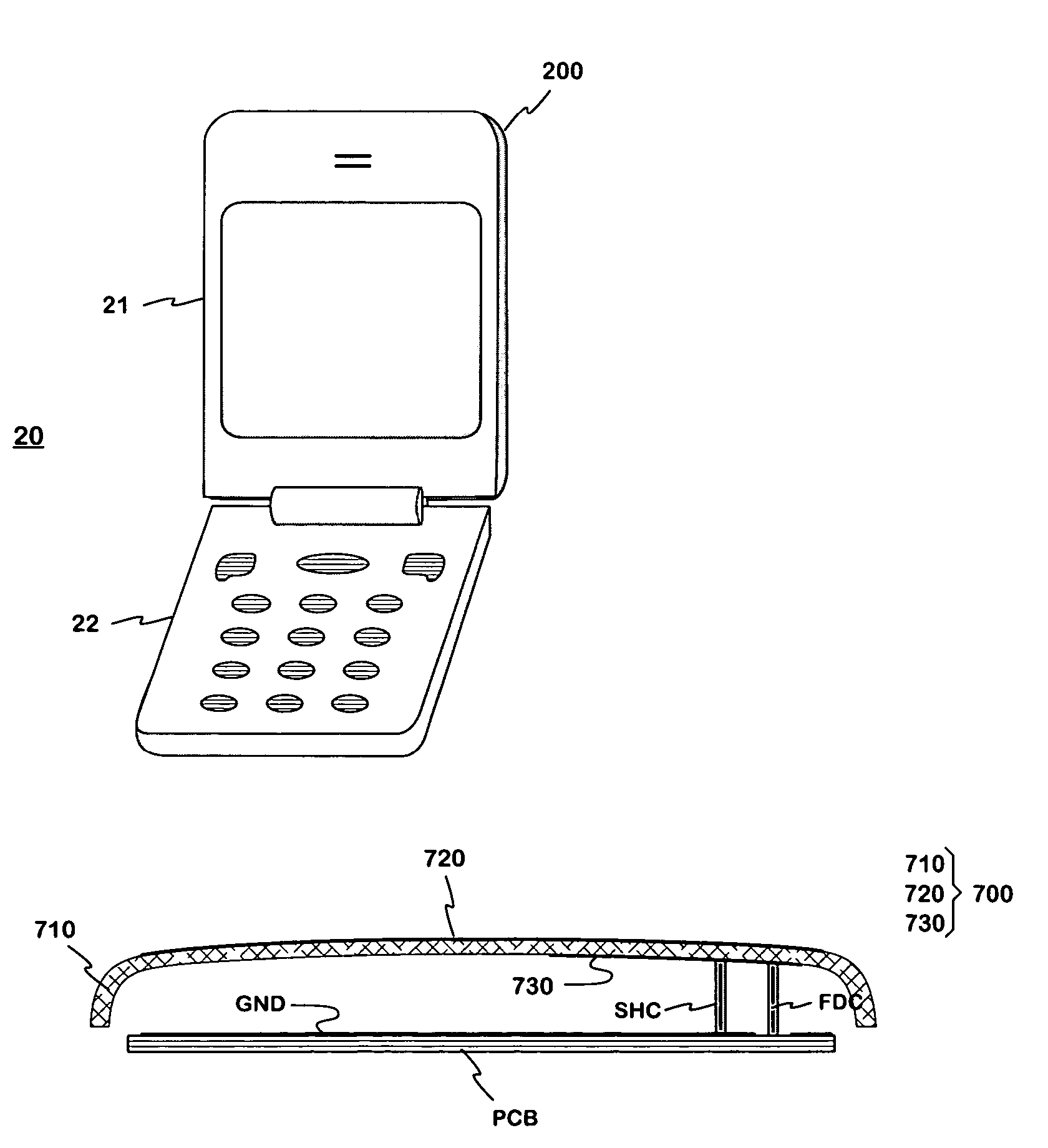

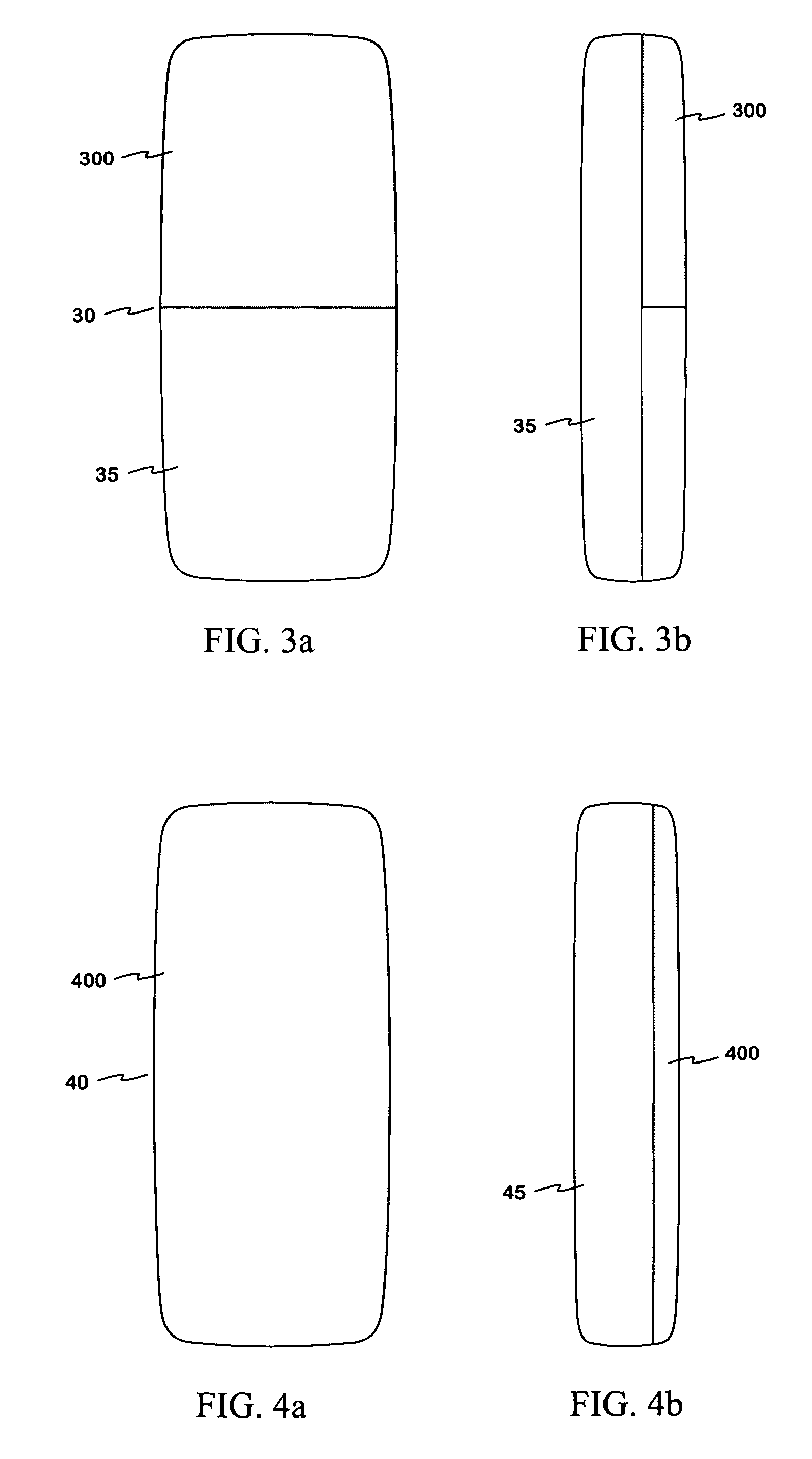

Antenna element for a radio device

ActiveUS7391378B2Low production costEnhanced radiationSimultaneous aerial operationsAntenna supports/mountingsRadio equipmentAntenna element

A radiating antenna element intended to be used in small-sized radio devices, and a radio device having an antenna element according to the invention. The antenna element is part of the covers of a radio device. The antenna element may be conductive throughout, or it may comprise a dielectric portion and a conductive portion, which constitute a single integral component. The radiating portion of the antenna element is relatively large, e.g. in a foldable phone (20) the antenna element (200) may comprise the whole cover of a foldable part (21) except for the front side. The radiating element is advantageously fed electromagnetically through a feed element. As the radiating element is relatively large and is located on the outer surface of the device, the radiation characteristics of the antenna are good, and the space required by the antenna inside the device is relatively small.

Owner:PULSE FINLAND

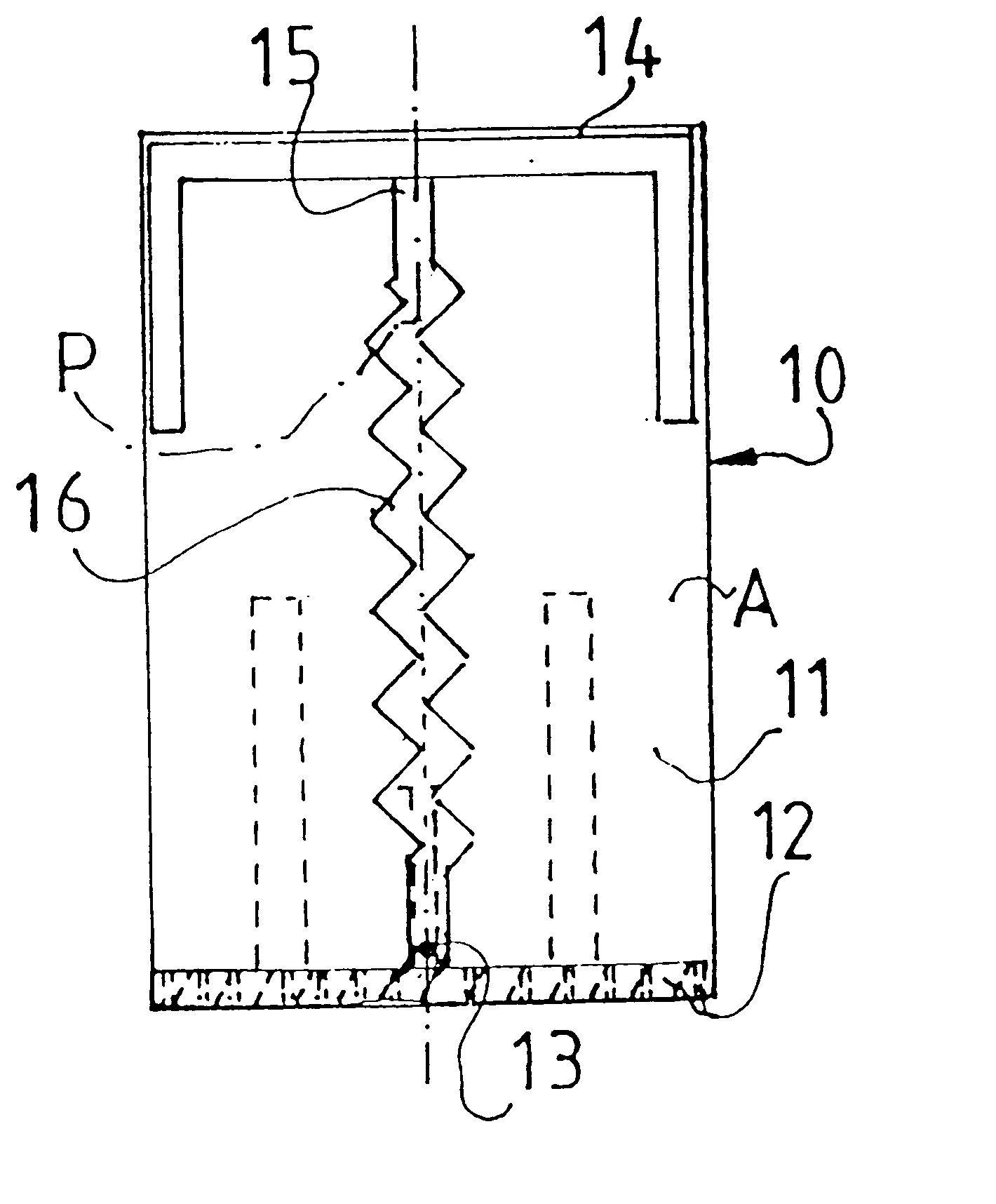

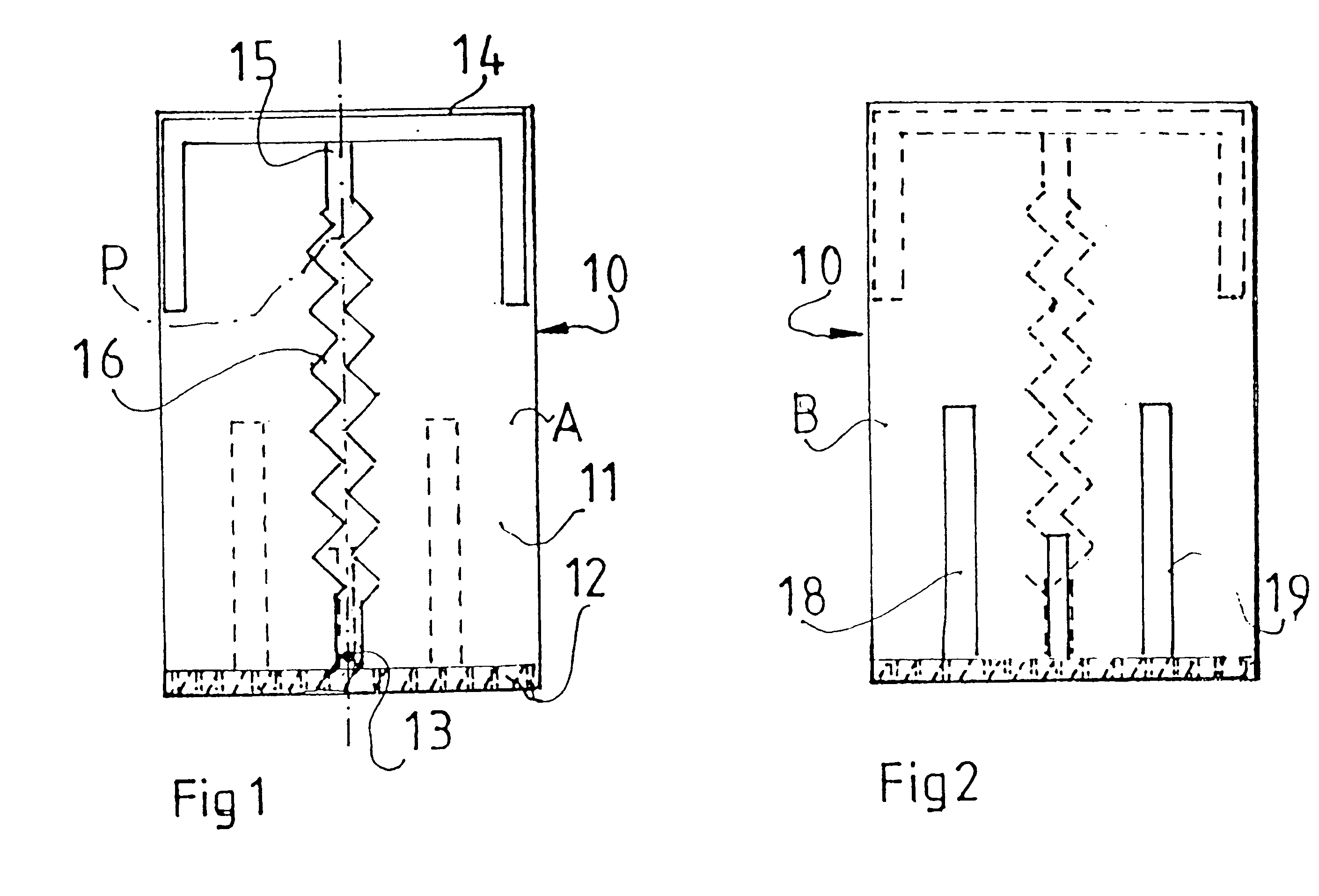

Communication antenna and equipment

InactiveUS6392599B1Reduce antenna sizeHigh bandwidthSimultaneous aerial operationsAntenna supports/mountingsShortest distanceImpedance matching

A communication antenna (10) having a driven element (16) extending between a feed point (13) and an attachment point (15) to a top loaded element in which the driven element (16) is longer than the shortest distance (P) between the feed point (13) and the attachment point (15), the driven element (16) being configured to follow a meandering path between the feed point (13) and the attachment point (15). The driven element (16) is at least in part in the form of straight sections joined to give a zigzag configuration (16). Alternatively the driven element (16) is at least in part in the form of curved sections. At least a pair of parasitic elements (18, 19) can be provided with the members of the pair (18, 19) being disposed on opposite sides of, and off-set from, the driven element (16) and parallel to a straight ling (P) linking the feed point (13) to the attachment point (15); the parasitic elements (18, 19) serving to provide impedance matching and increased bandwidth and providing shielding against radiation from the antenna in a predetermined direction. Typically passive elements can be incorporated with the parasitic elements (18, 19) to provide for the overall reduction in the size of the antenna (10.

Owner:GANESHMOORTHY DAVID +2

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com