Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

146 results about "Quiescent state" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Quiescence (/kwiˈɛsəns/) is a state of quietness or inactivity. It may refer to: Quiescence search, in game tree searching (adversarial search) in artificial intelligence, a quiescent state is one in which a game is considered stable and unlikely to change drastically the next few plays. Seed dormancy, a form of delayed seed germination.

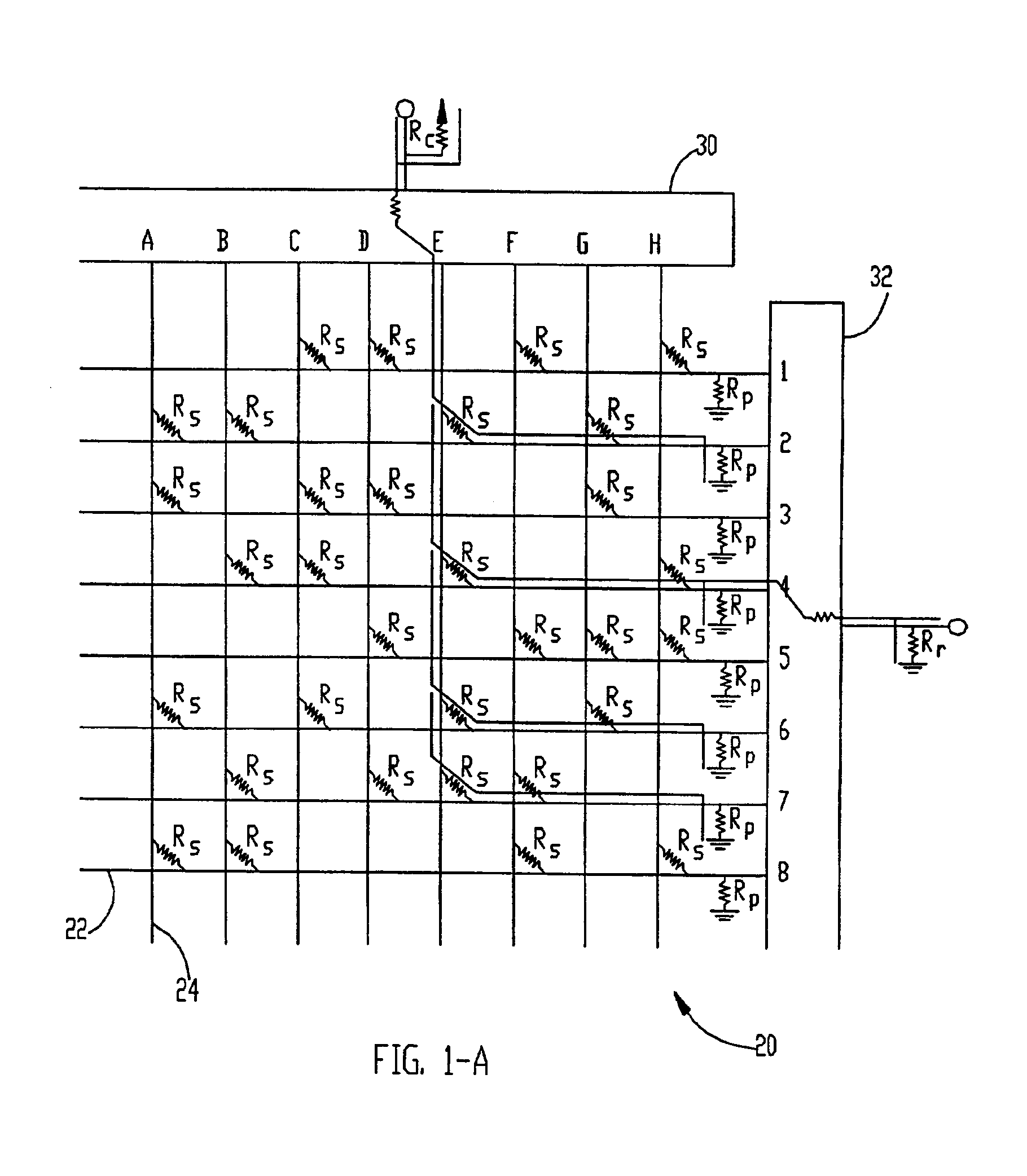

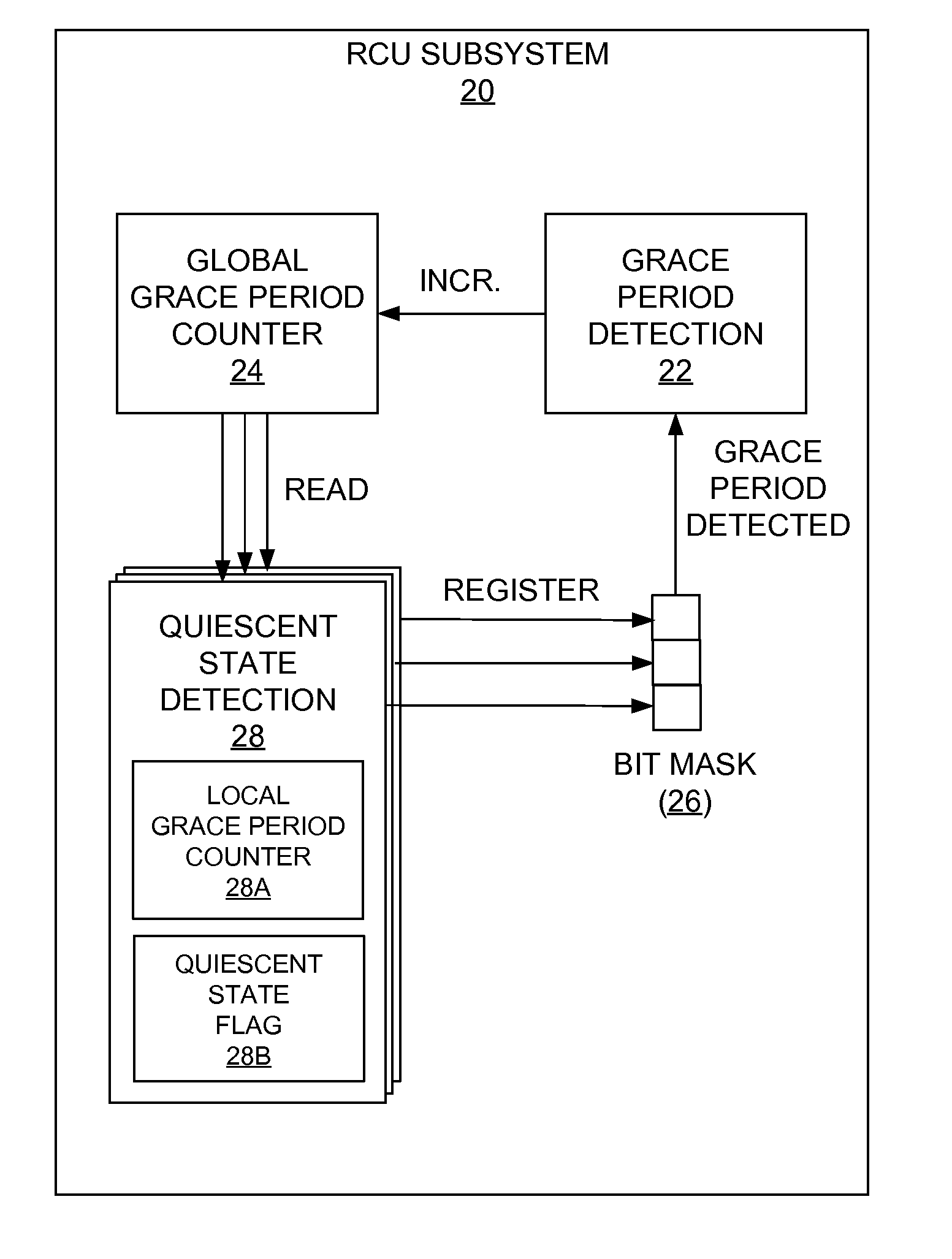

High speed methods for maintaining a summary of thread activity for multiprocessor computer systems

InactiveUS6886162B1Reduce in quantityMultiprogramming arrangementsMemory systemsQuiescent stateProcessor node

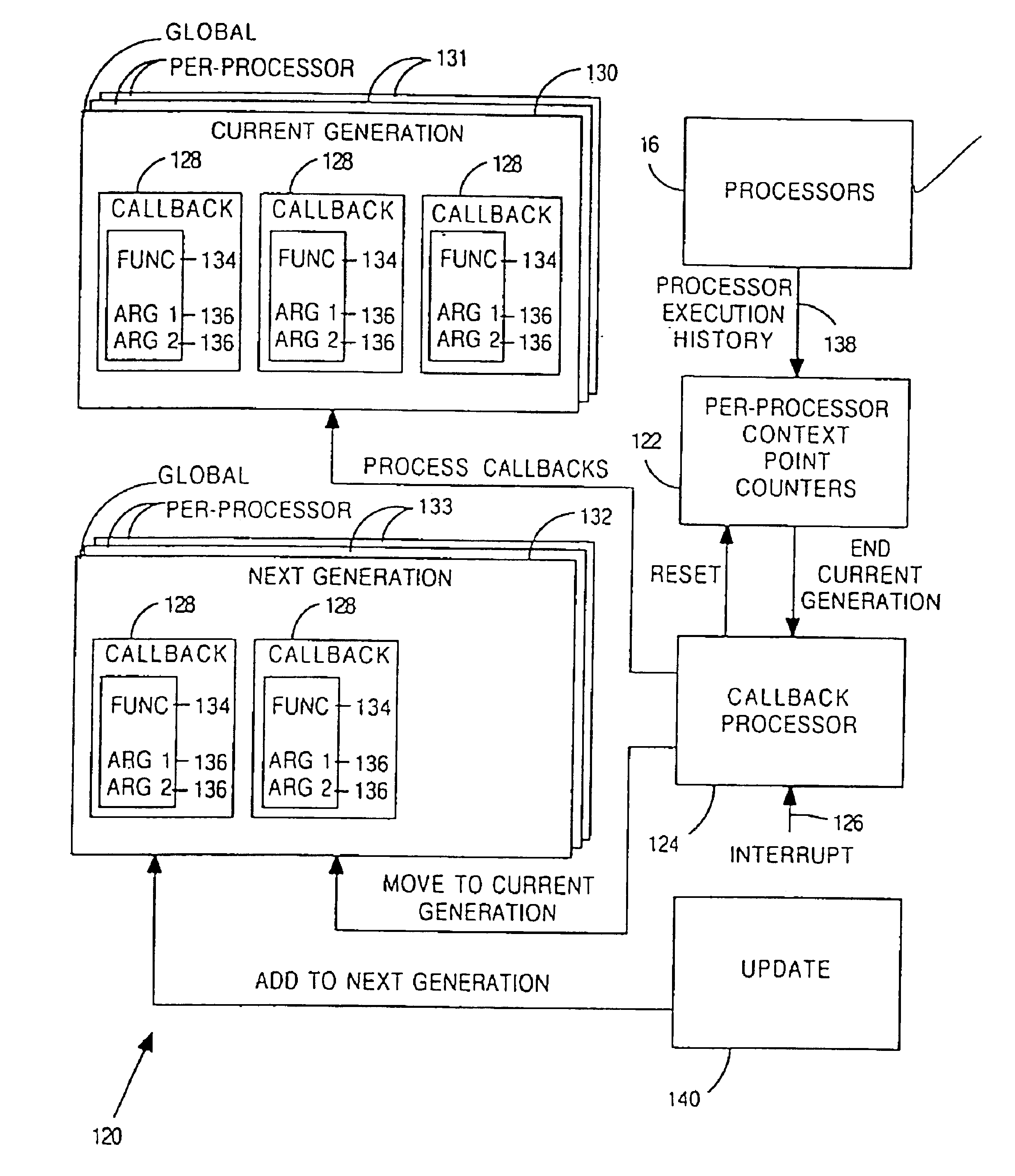

A high-speed method for maintaining a summary of thread activity reduces the number of remote-memory operations for an n processor, multiple node computer system from n2 to (2n−1) operations. The method uses a hierarchical summary of-thread-activity data structure that includes structures such as first and second level bit masks. The first level bit mask is accessible to all nodes and contains a bit per node, the bit indicating whether the corresponding node contains a processor that has not yet passed through a quiescent state. The second level bit mask is local to each node and contains a bit per processor per node, the bit indicating whether the corresponding processor has not yet passed through a quiescent state. The method includes determining from a data structure on the processor's node (such as a second level bitmask) if the processor has passed through a quiescent state. If so, it is then determined from the data structure if all other processors on its node have passed through a quiescent state. If so, it is then indicated in a data structure accessible to all nodes (such as the first level bitmask) that all processors on the processor's node have passed through a quiescent state. The local generation number can also be stored in the data structure accessible to all nodes. If a processor determines from this data structure that the processor is the last processor to pass through a quiescent state, the processor updates the data structure for storing a number of the current generation stored in the memory of each node.

Owner:SEQUENT COMPUTER SYSTEMS

Reconfiguring a network by utilizing a predetermined length quiescent state

InactiveUS7069320B1Substation remote connection/disconnectionMultiple digital computer combinationsQuiescent stateDistributed computing

A network having a plurality of nodes is reconfigured to reflect a change in topology of the network. In particular, upon receiving a reconfiguration request, each node enters a quiescent state for a predetermined period of time sufficient to allow at least one other node to also enter a quiescent state. Then, upon termination of the quiescent state, the node is reconfigured to reflect the change in the topology of the network without having to check with any other nodes of the network. In other embodiments, the predetermined period of time is sufficient to allow currently executing protocols to complete execution as well as to allow the transmission of reconfiguration requests for propagating reconfiguration in the network.

Owner:TWITTER INC

Method and system for executing a program under one of a plurality of mutually exclusive operating environments

InactiveUS6678712B1Program initiation/switchingSoftware simulation/interpretation/emulationMass storageData processing system

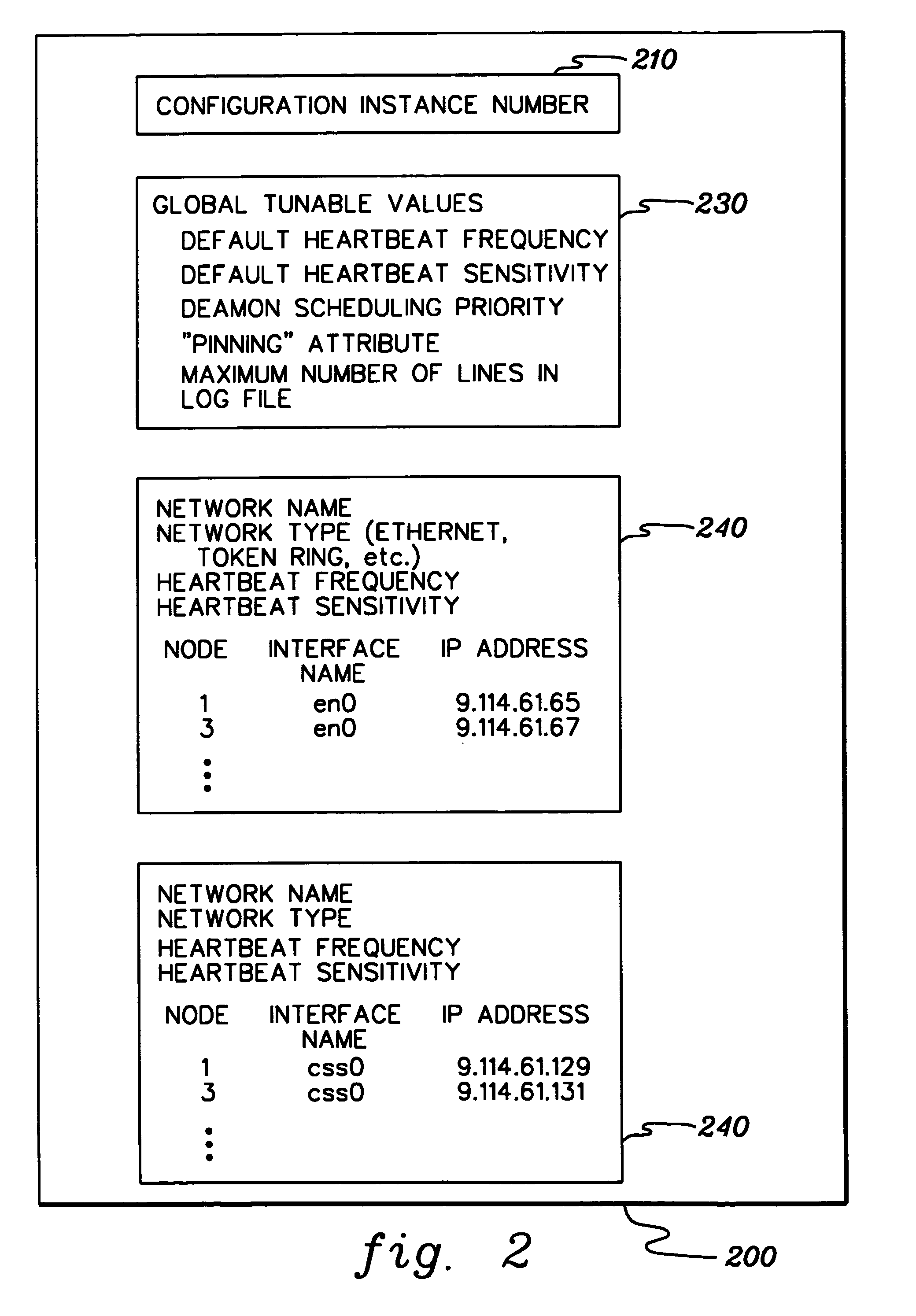

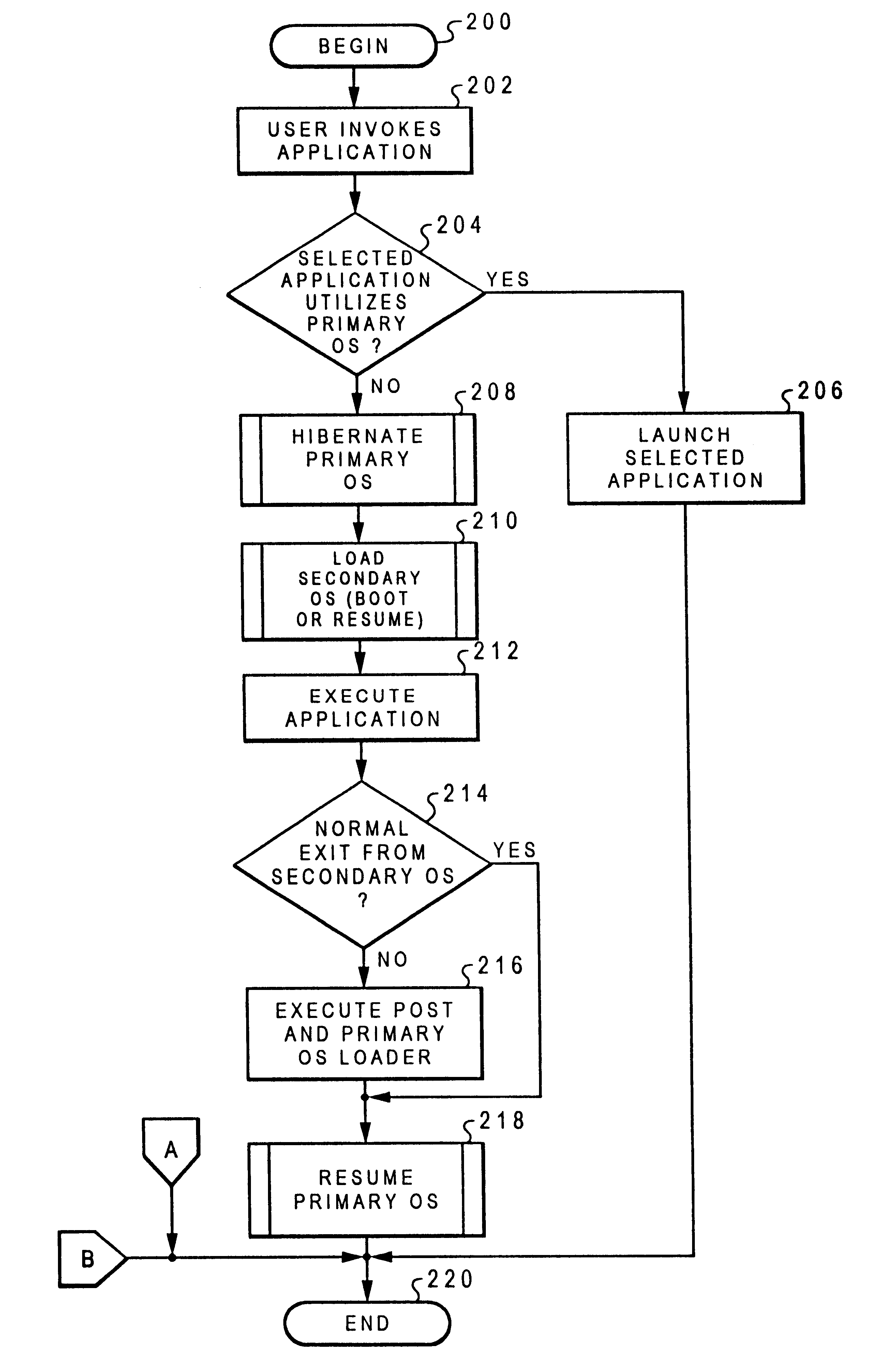

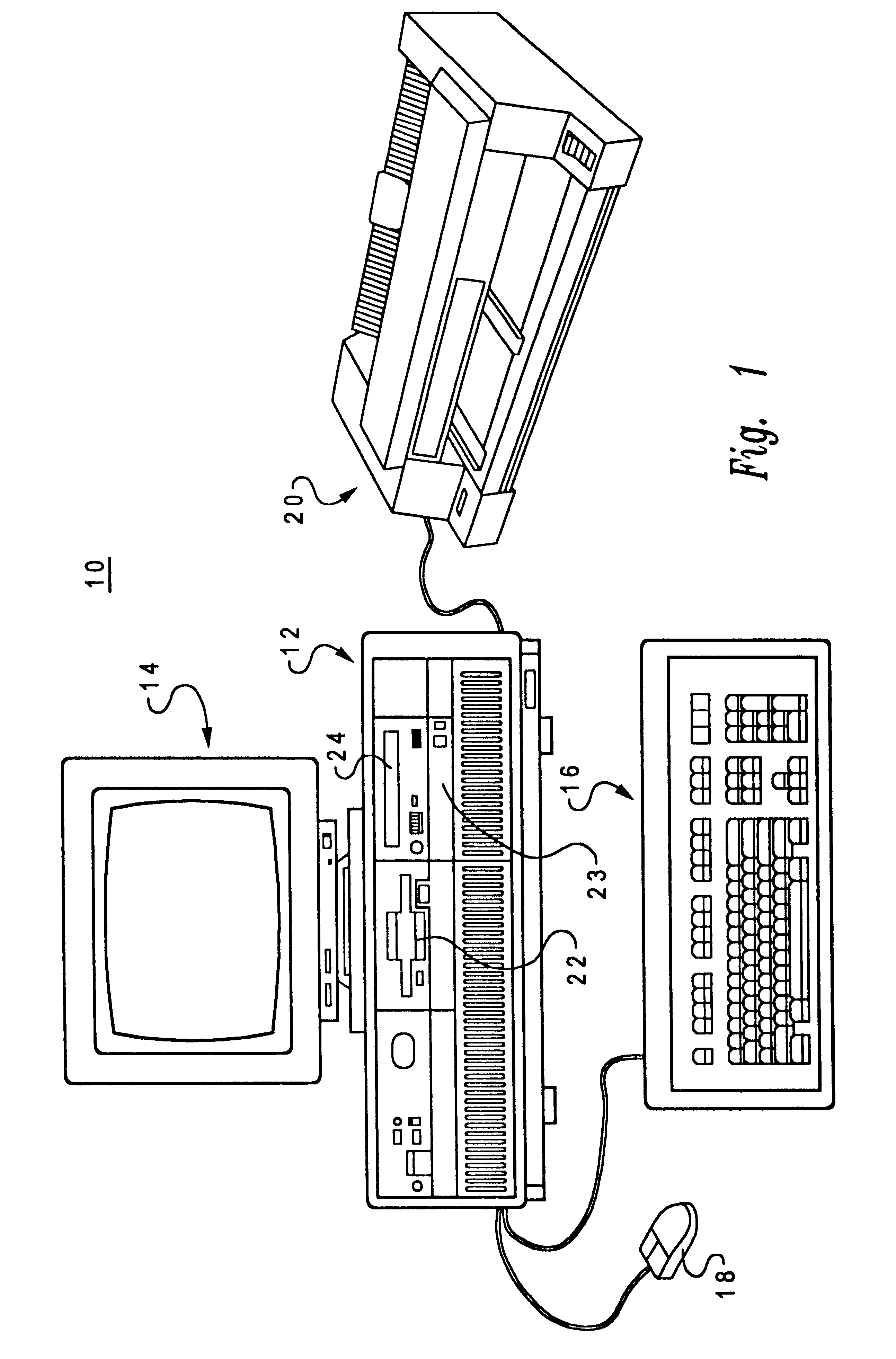

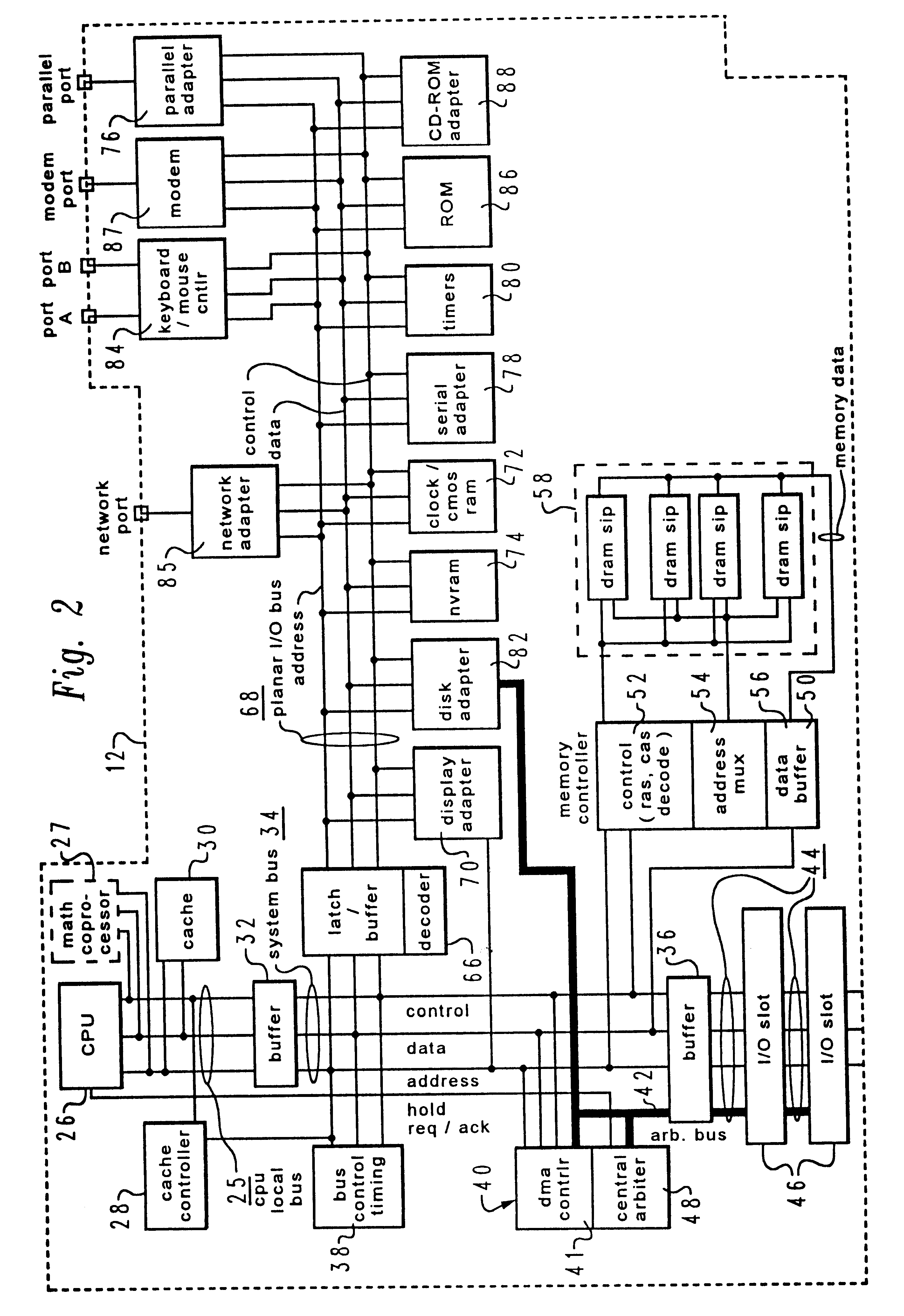

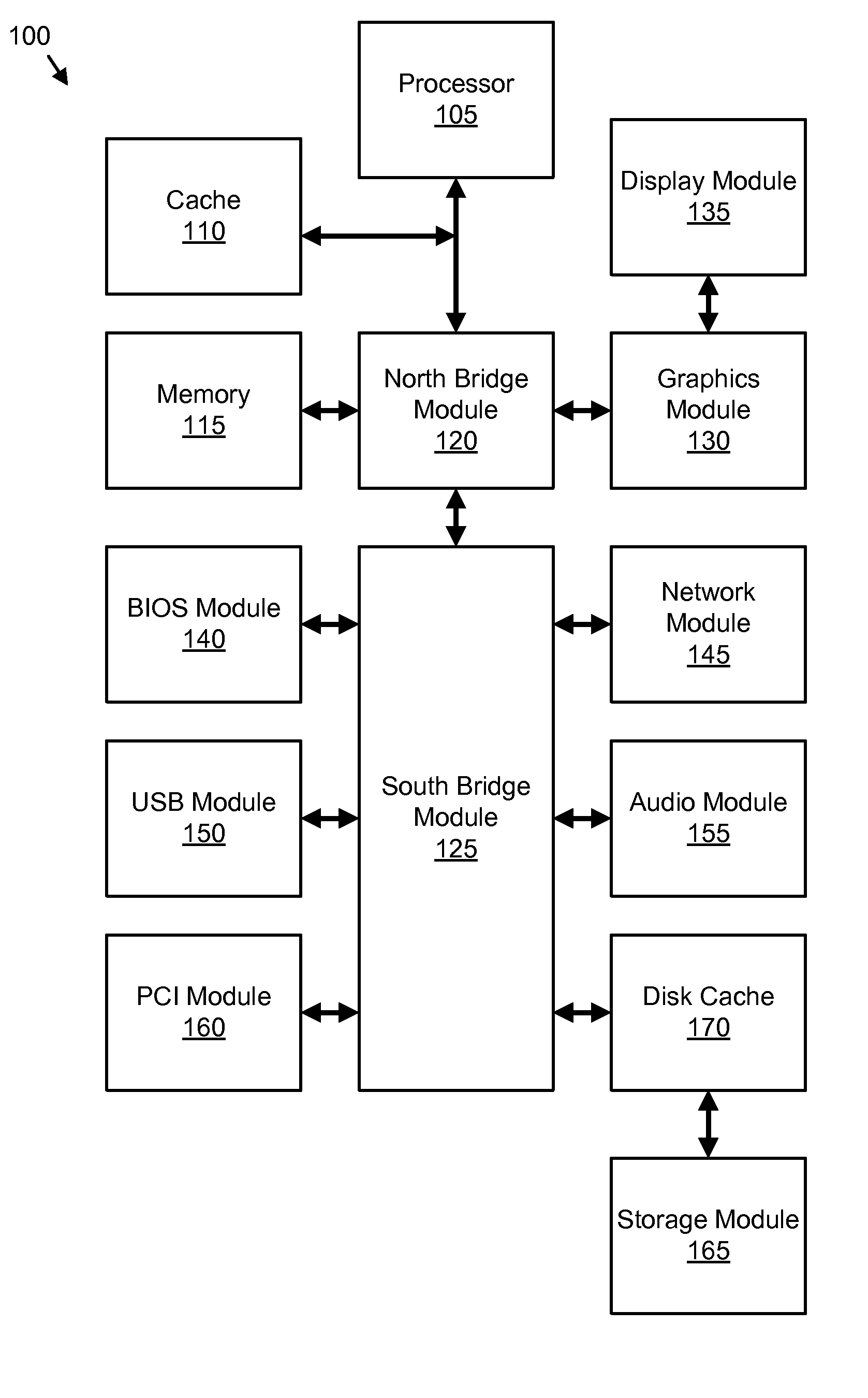

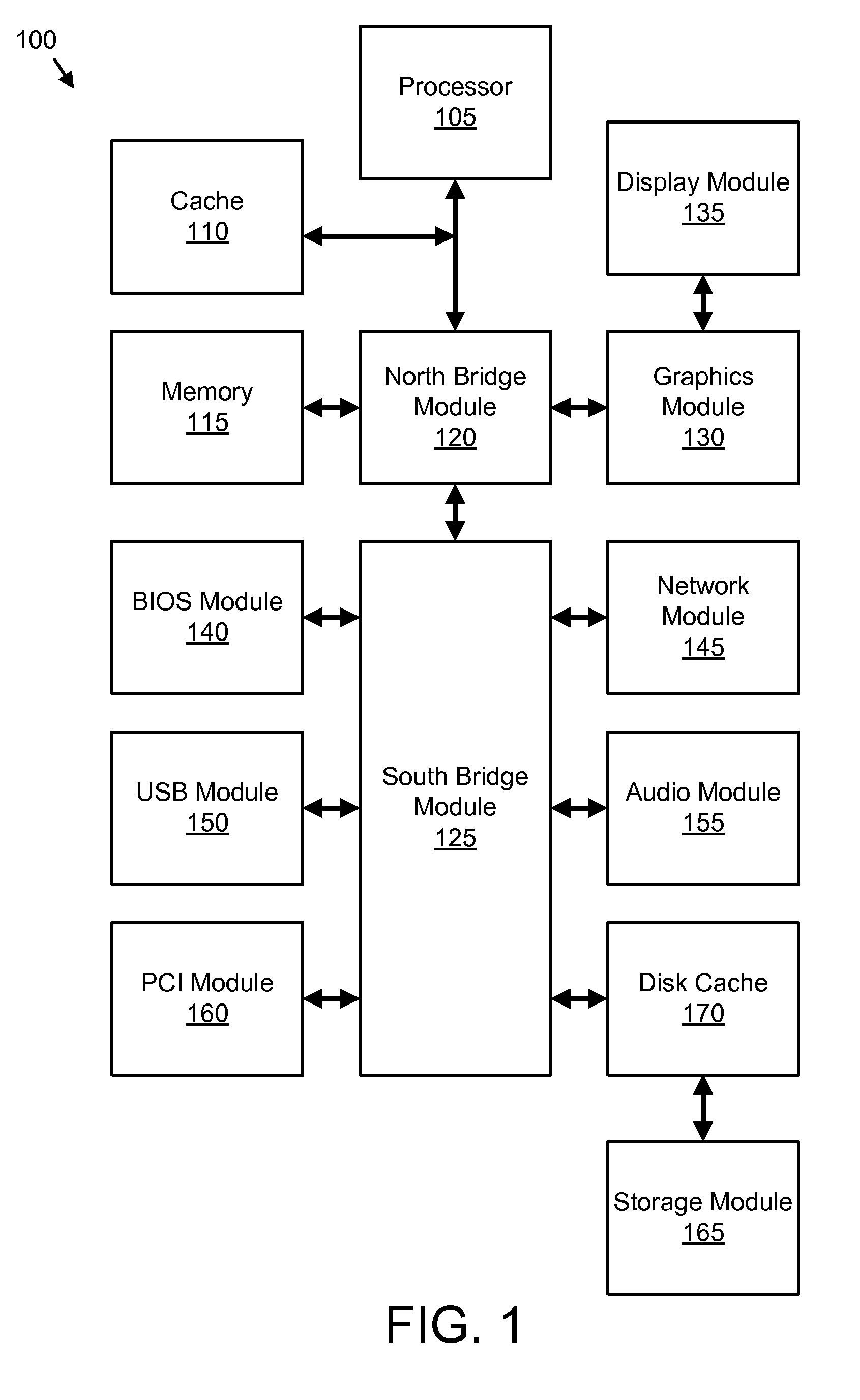

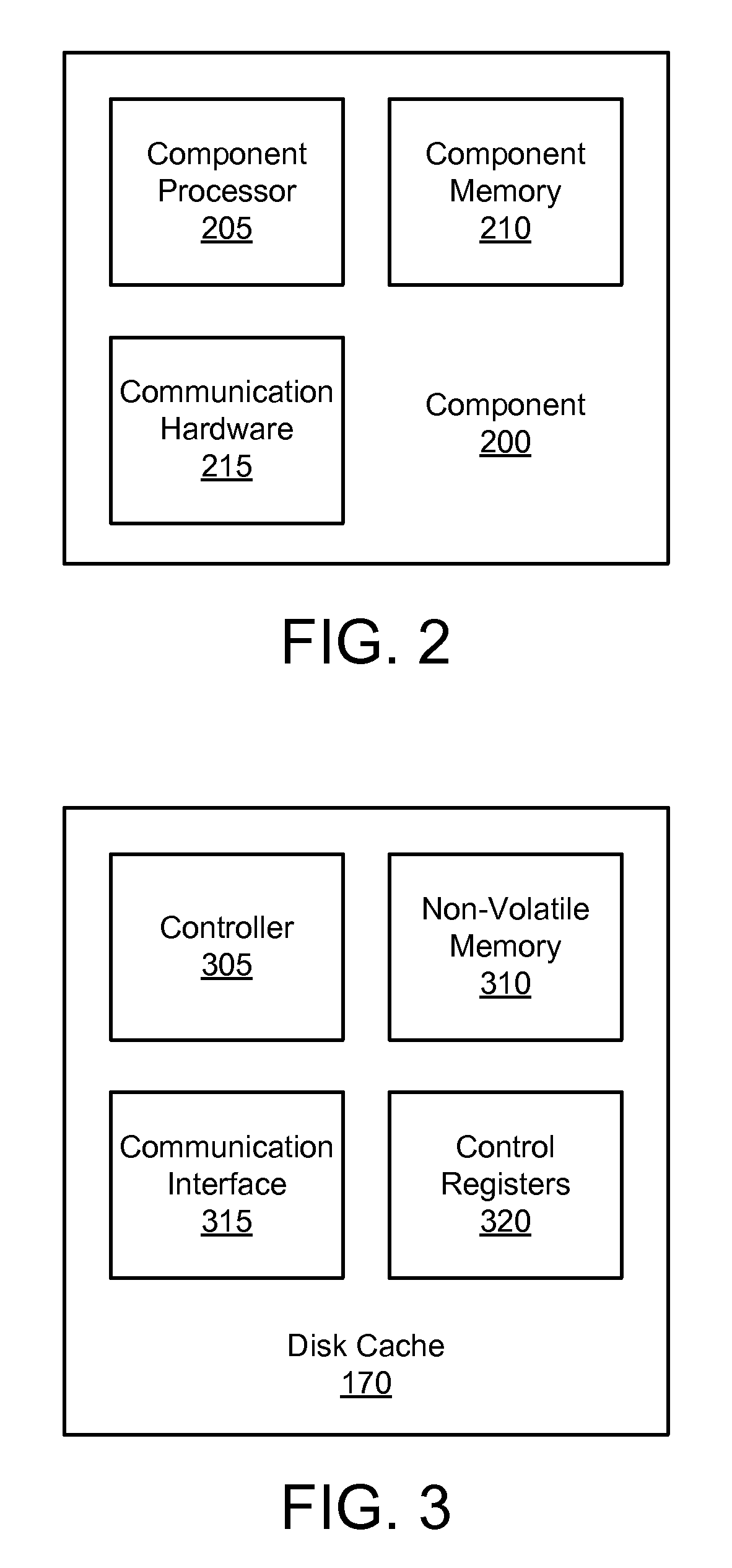

A method and system within a data processing system for executing a program under one of a number of mutually exclusive operating systems are disclosed. The data processing system includes a nonvolatile mass storage device, a volatile memory, and a processor. According to the present invention, a program which executes under a second operating system is invoked while the processor is executing a first operating system. In response to invocation of the program, the data processing system is forced to a quiescent state. A state of the first operating system is then determined from contents of the volatile memory and stored within either the volatile memory or the nonvolatile mass storage device. In response to storage of the state of the first operating system, at least a portion of the second operating system is automatically loaded into the volatile memory. Thereafter, the program is executed under the second operating system, wherein interchange between mutually incompatible operating systems within a single data processing system is efficiently accomplished. In a preferred embodiment of the present invention, the method of the present invention is embodied within a computer program product for causing a data processing system to perform the foregoing steps.

Owner:IBM CORP

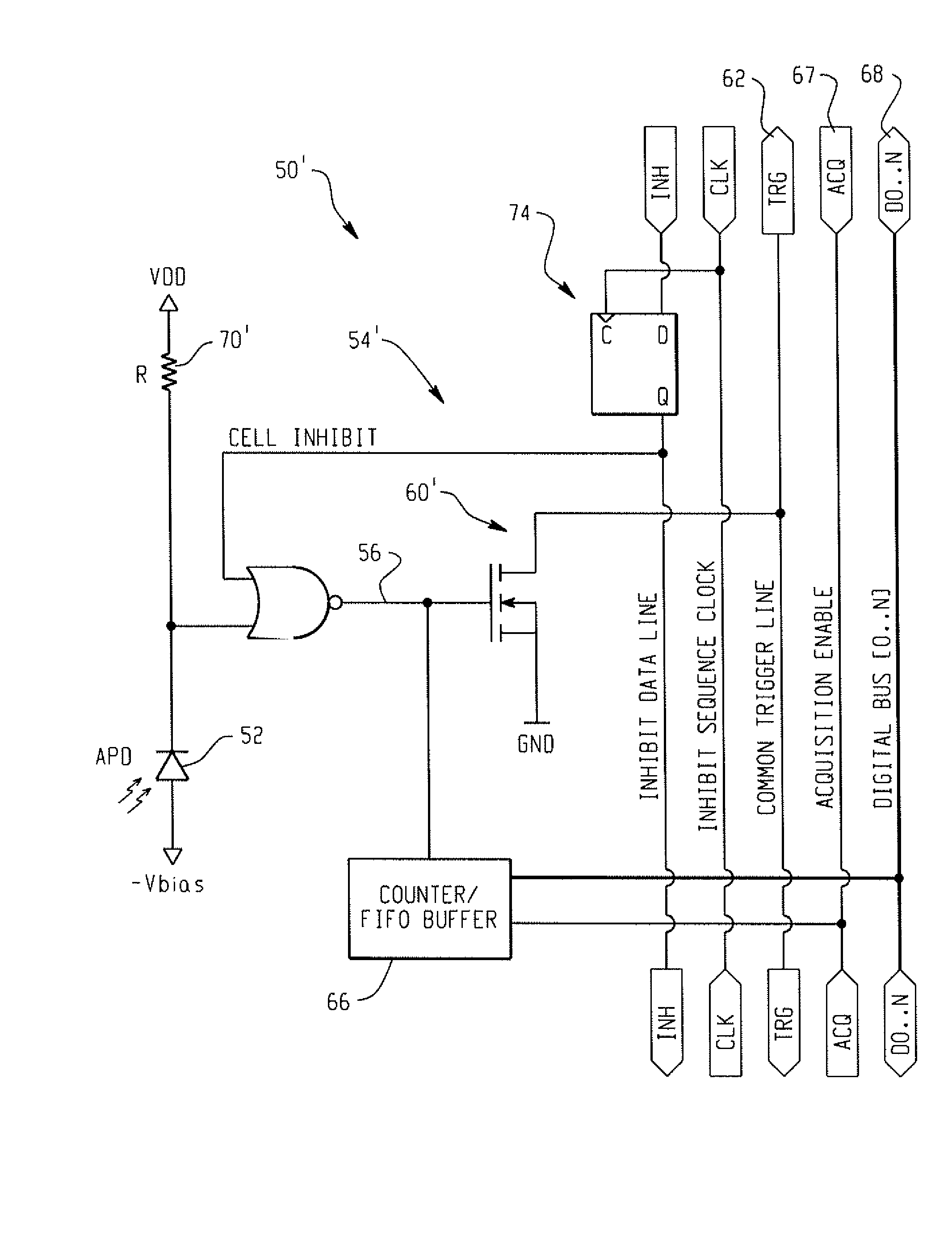

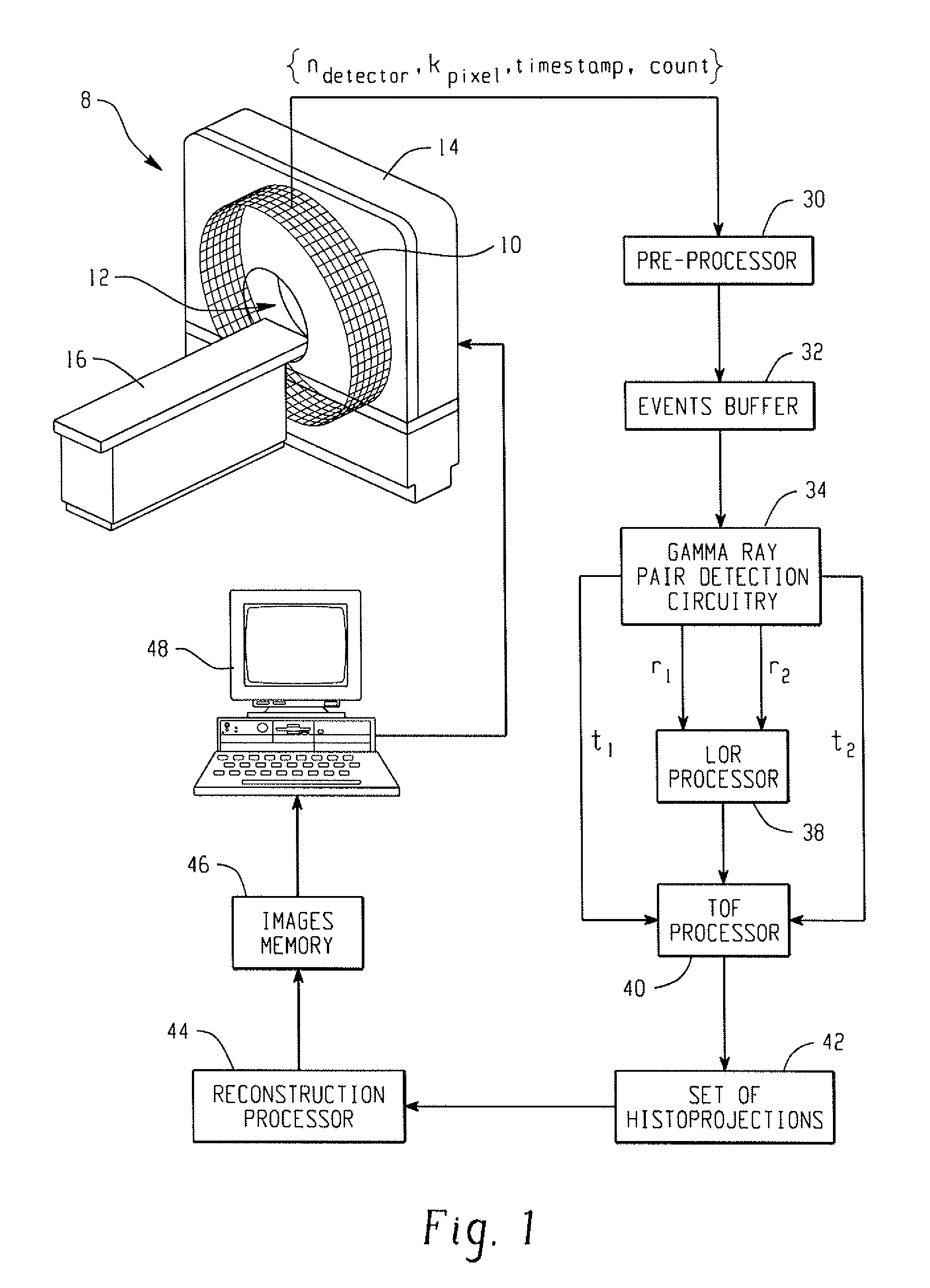

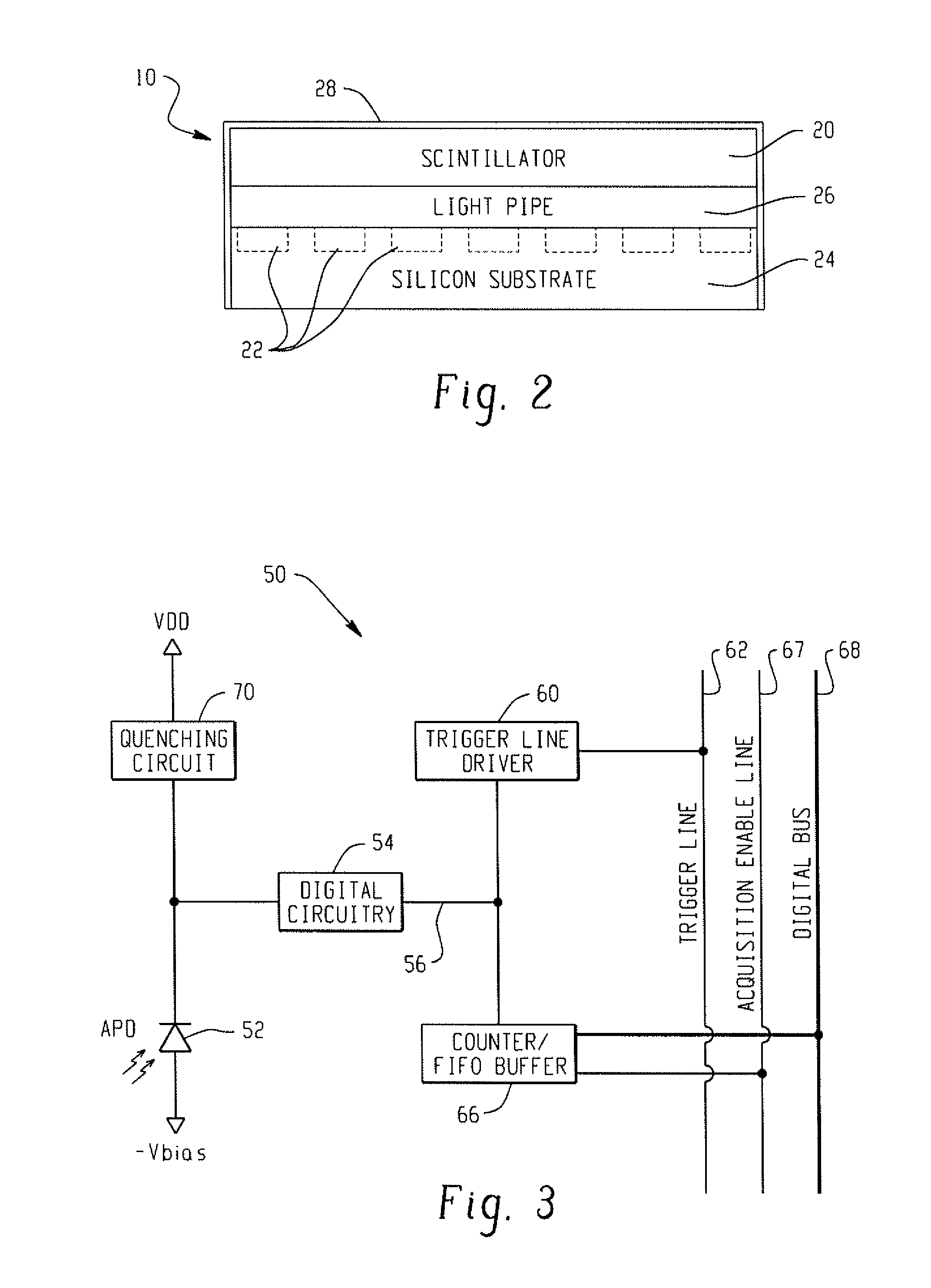

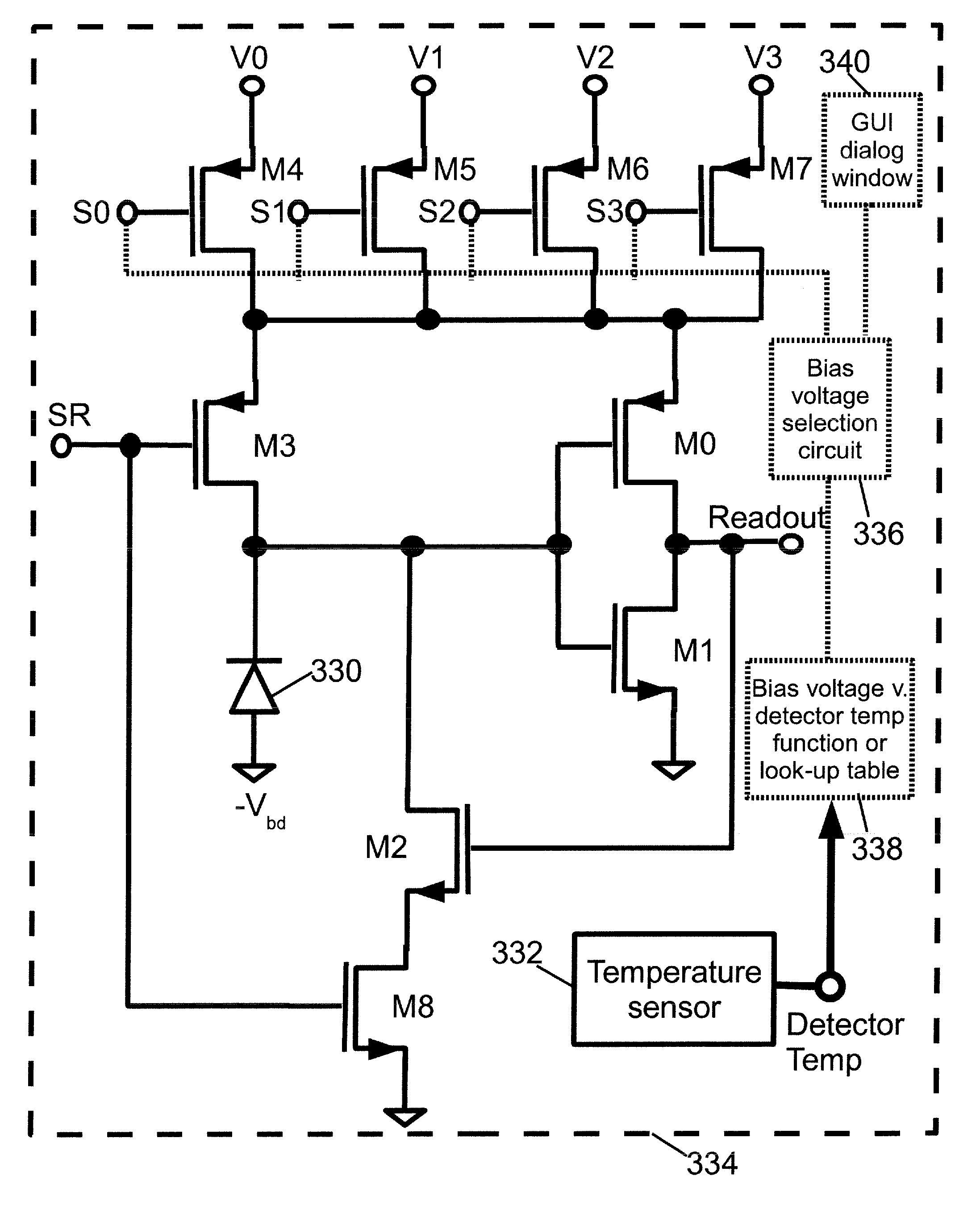

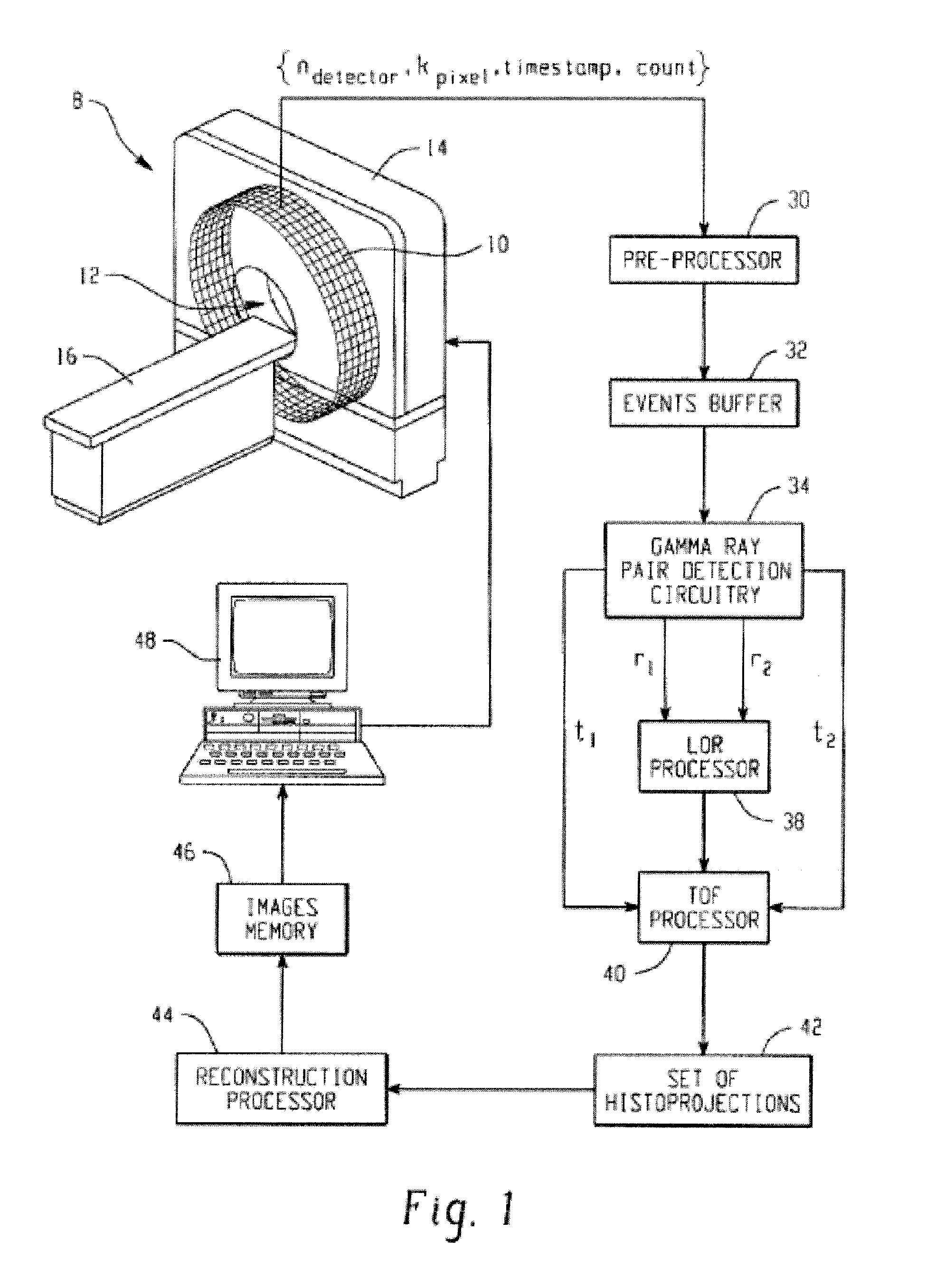

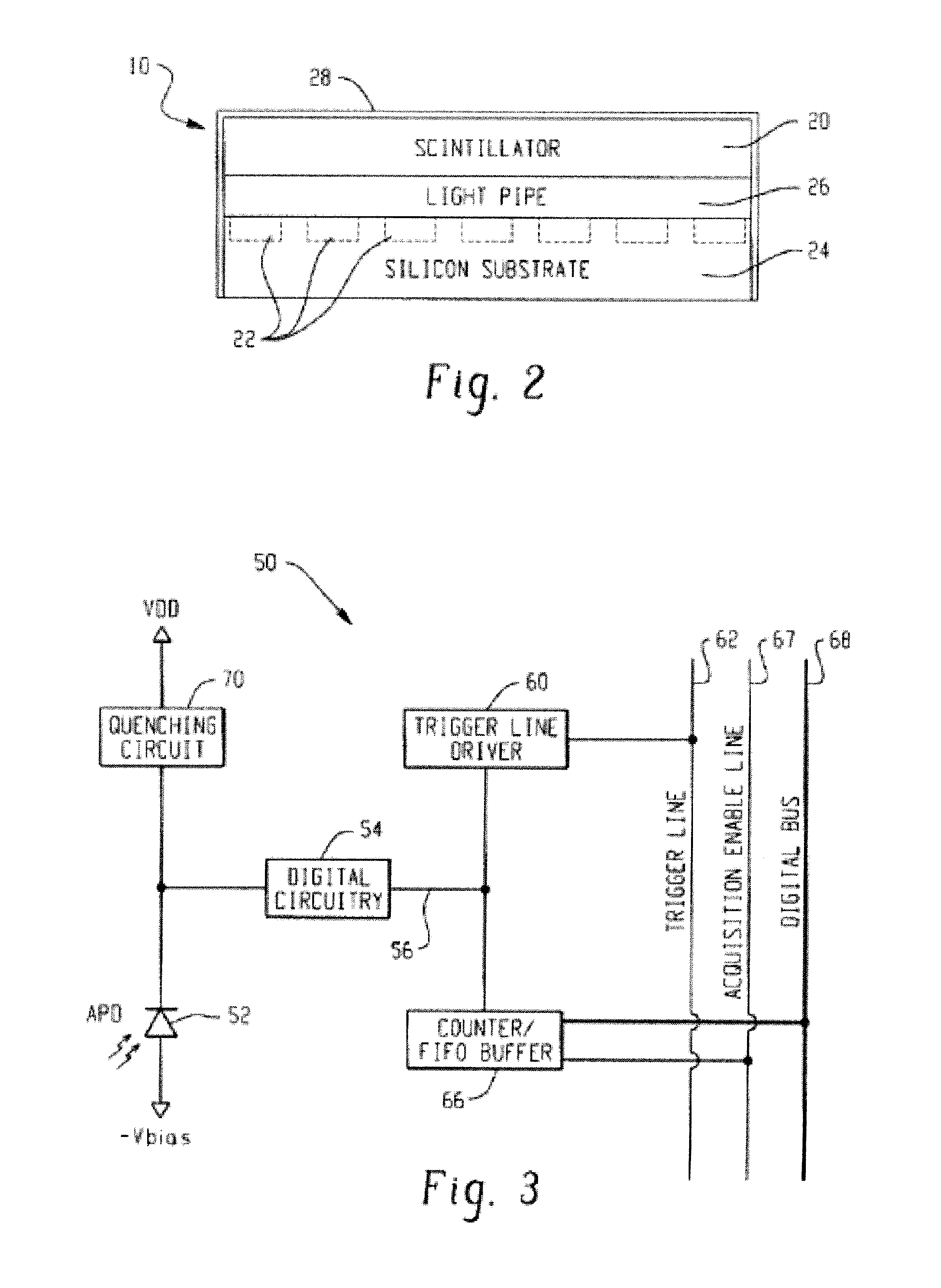

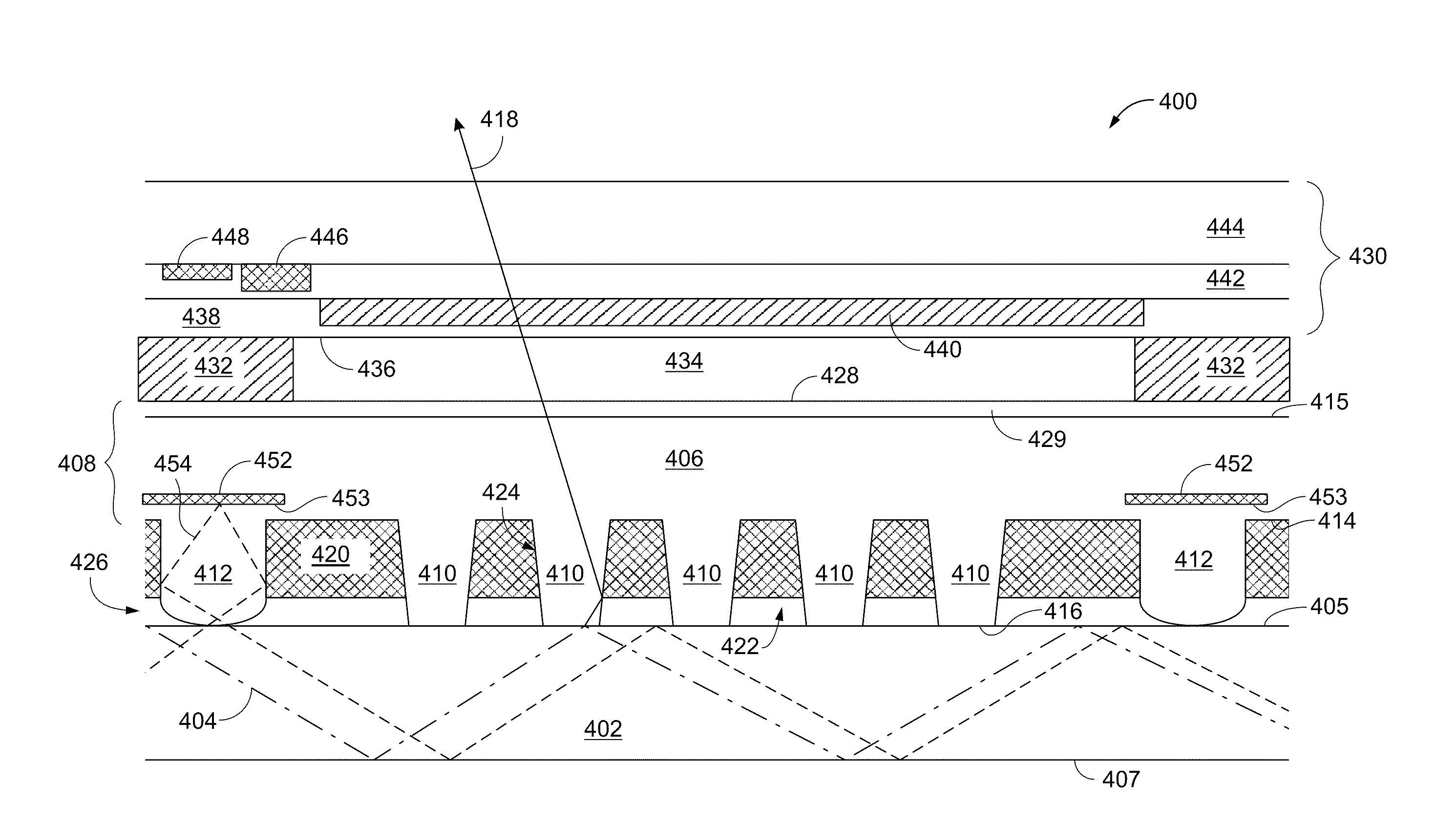

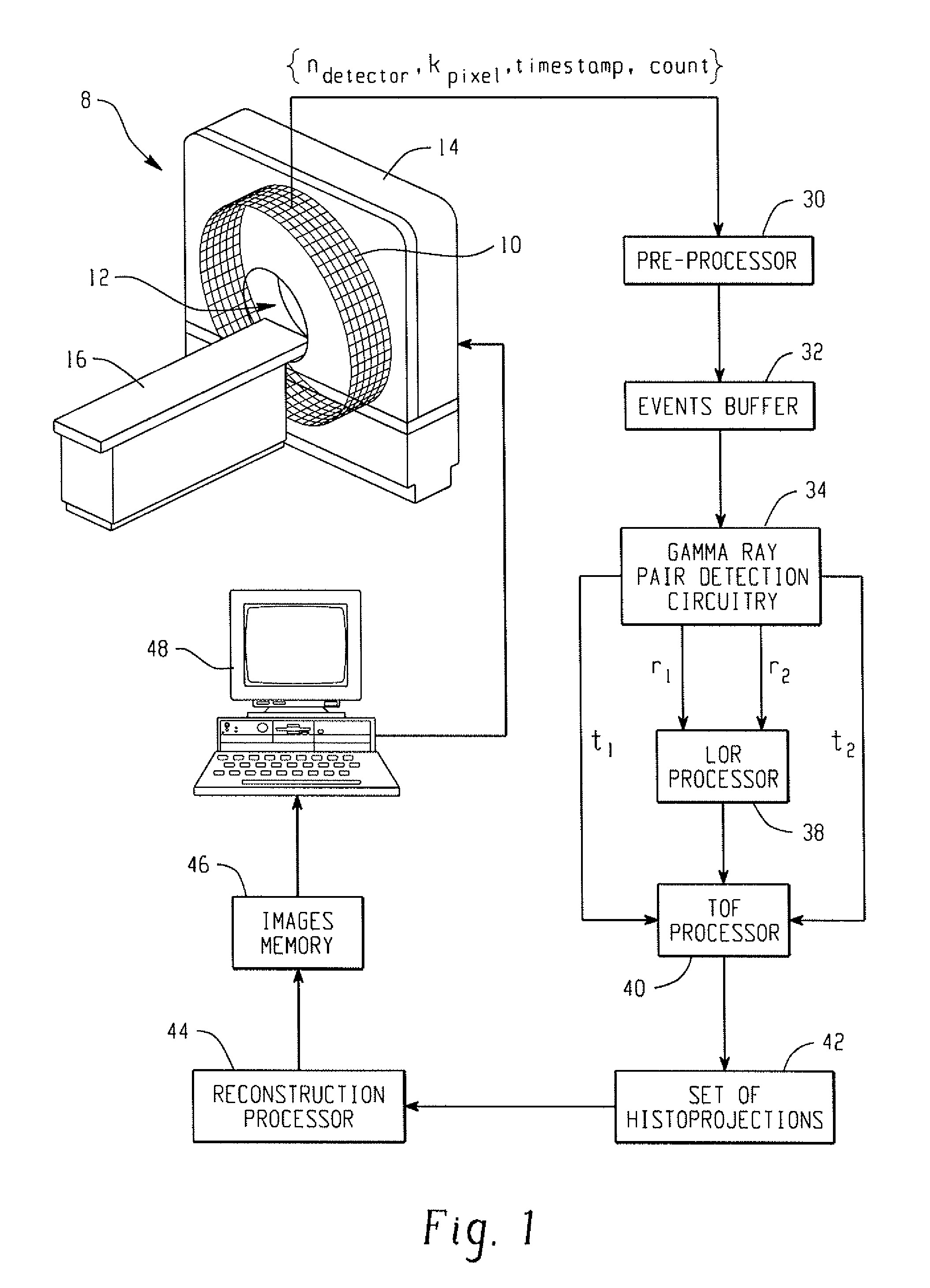

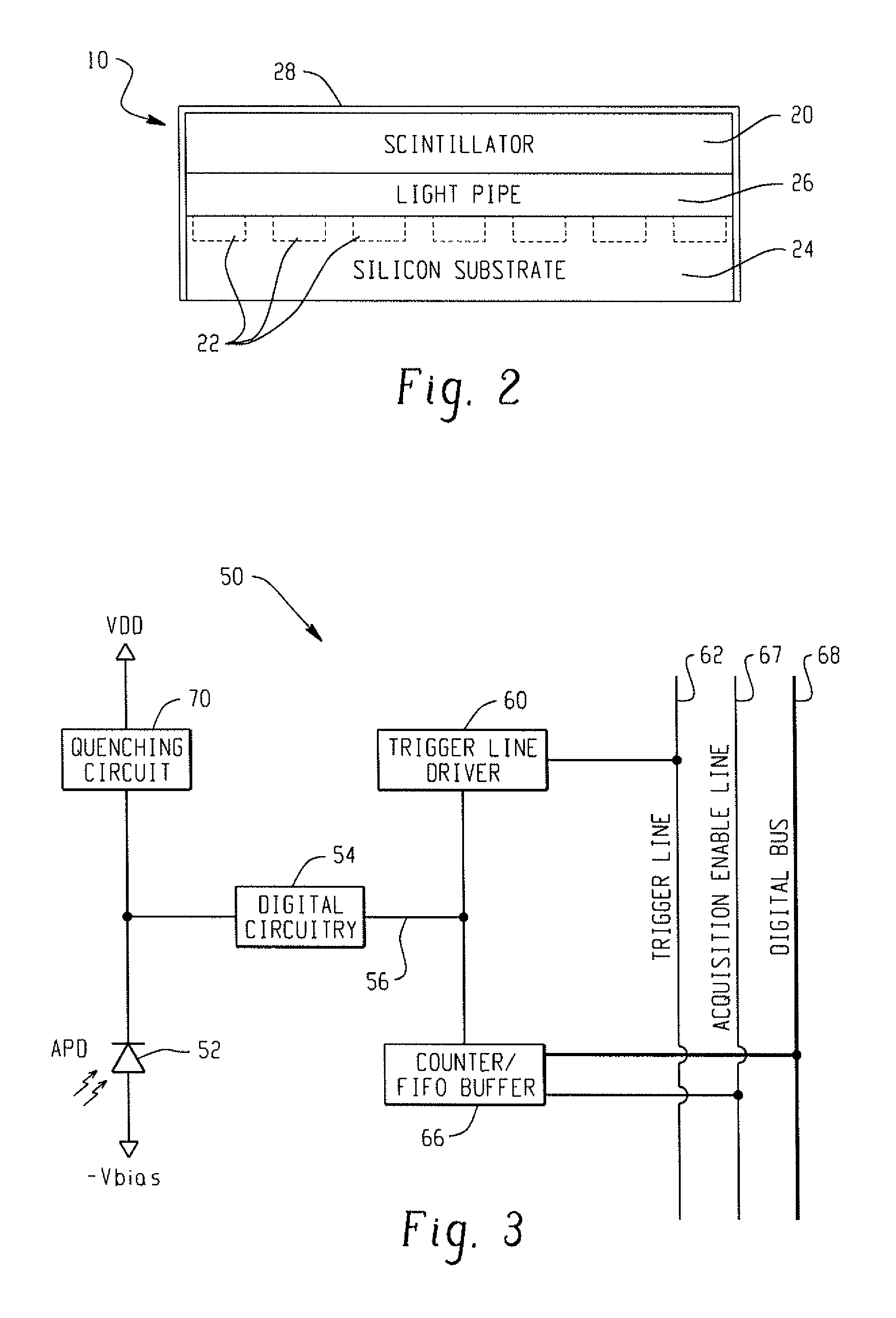

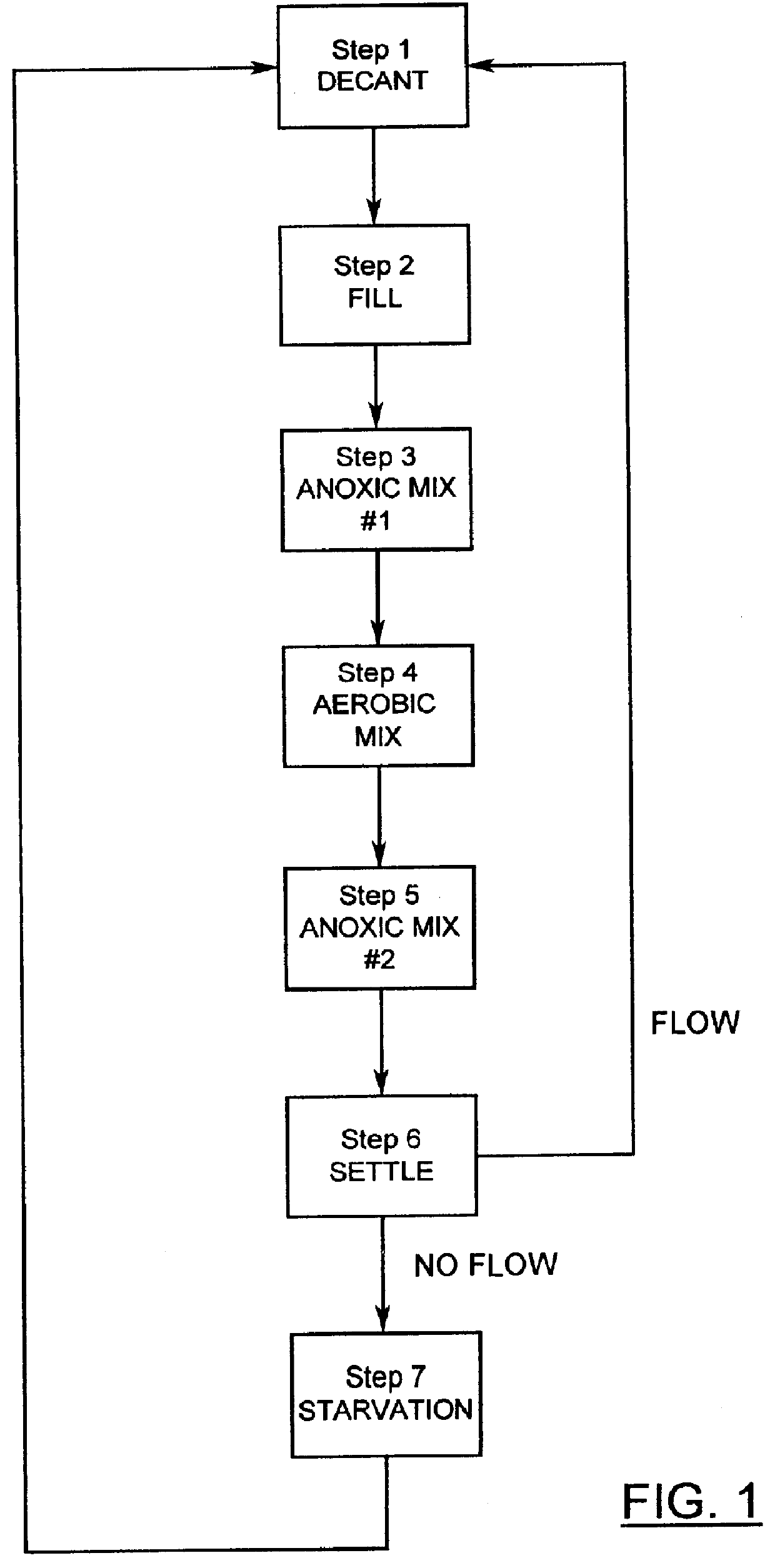

Digital silicon photomultiplier for TOF-PET

ActiveUS20080203309A1High data-rate radiation detectionImproved spatial detector resolutionMaterial analysis by optical meansTomographyQuiescent stateSilicon photomultiplier

A radiation detector includes an array of detector pixels each including an array of detector cells. Each detector cell includes a photodiode biased in a breakdown region and digital circuitry coupled with the photodiode and configured to output a first digital value in a quiescent state and a second digital value responsive to photon detection by the photodiode. Digital triggering circuitry is configured to output a trigger signal indicative of a start of an integration time period responsive to a selected number of one or more of the detector cells tranisitioning from the first digital value to the second digital value. Readout digital circuitry accumulates a count of a number of transitions of detector cells of the array of detector cells from the first digital state to the second digital state over the integration time period.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

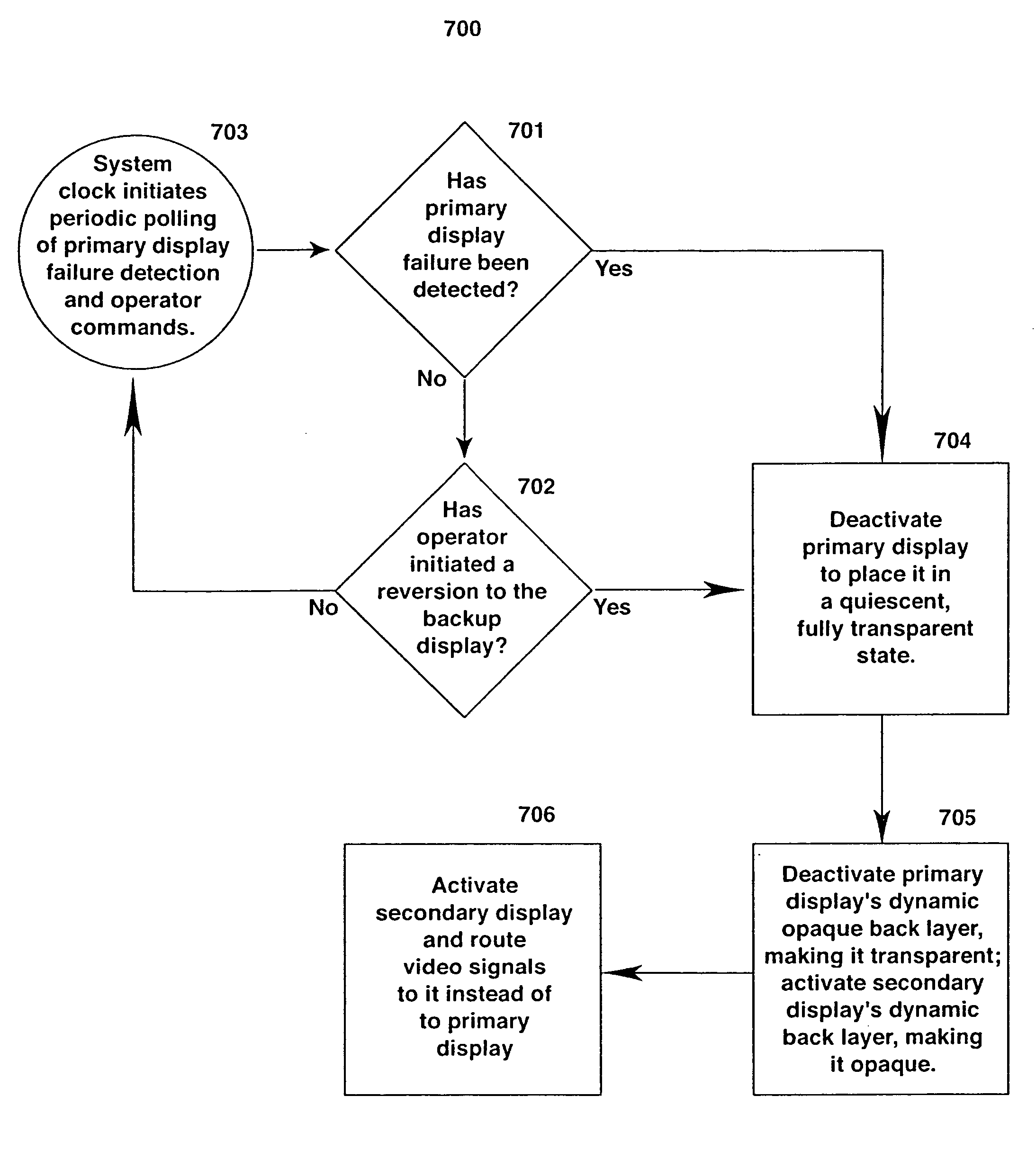

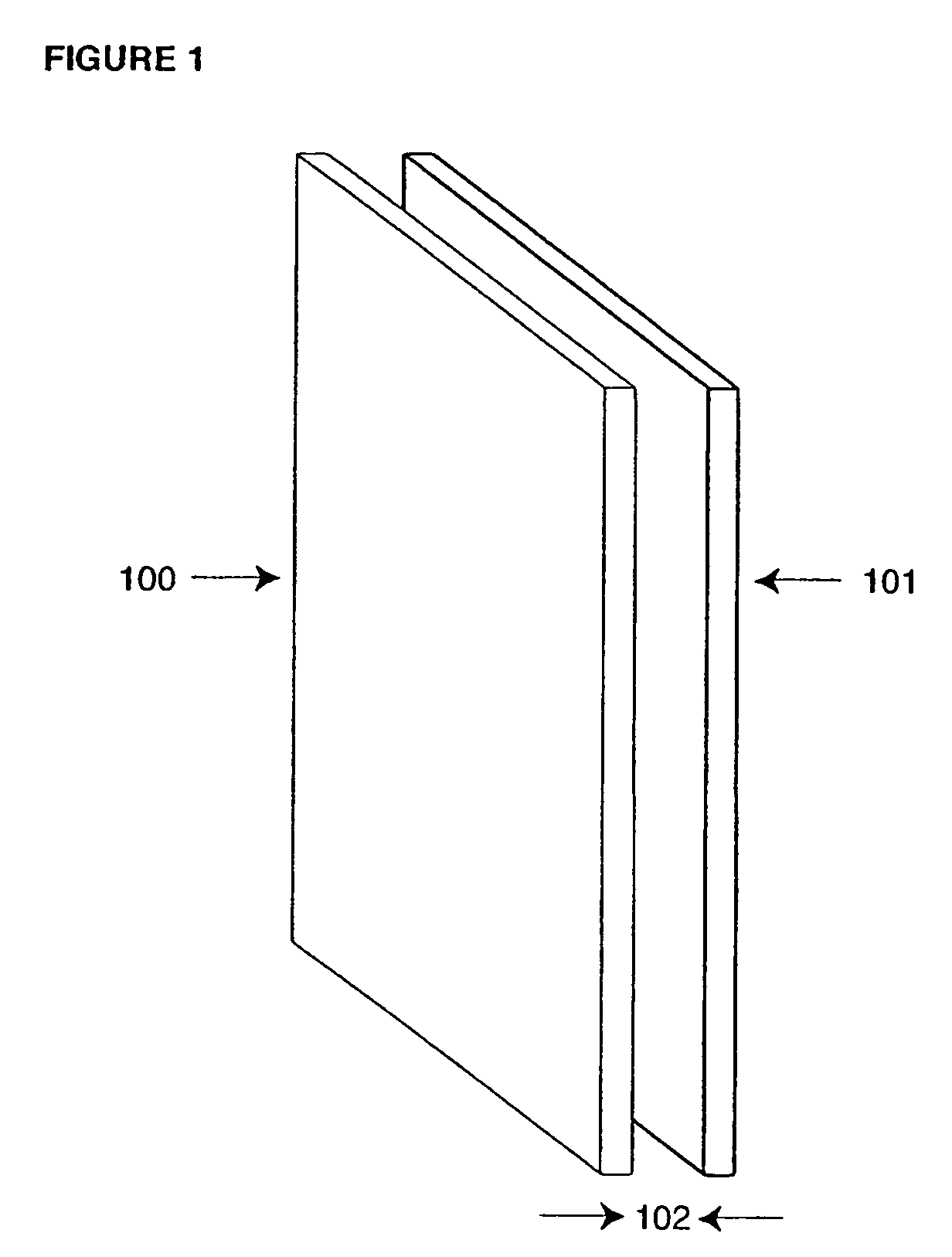

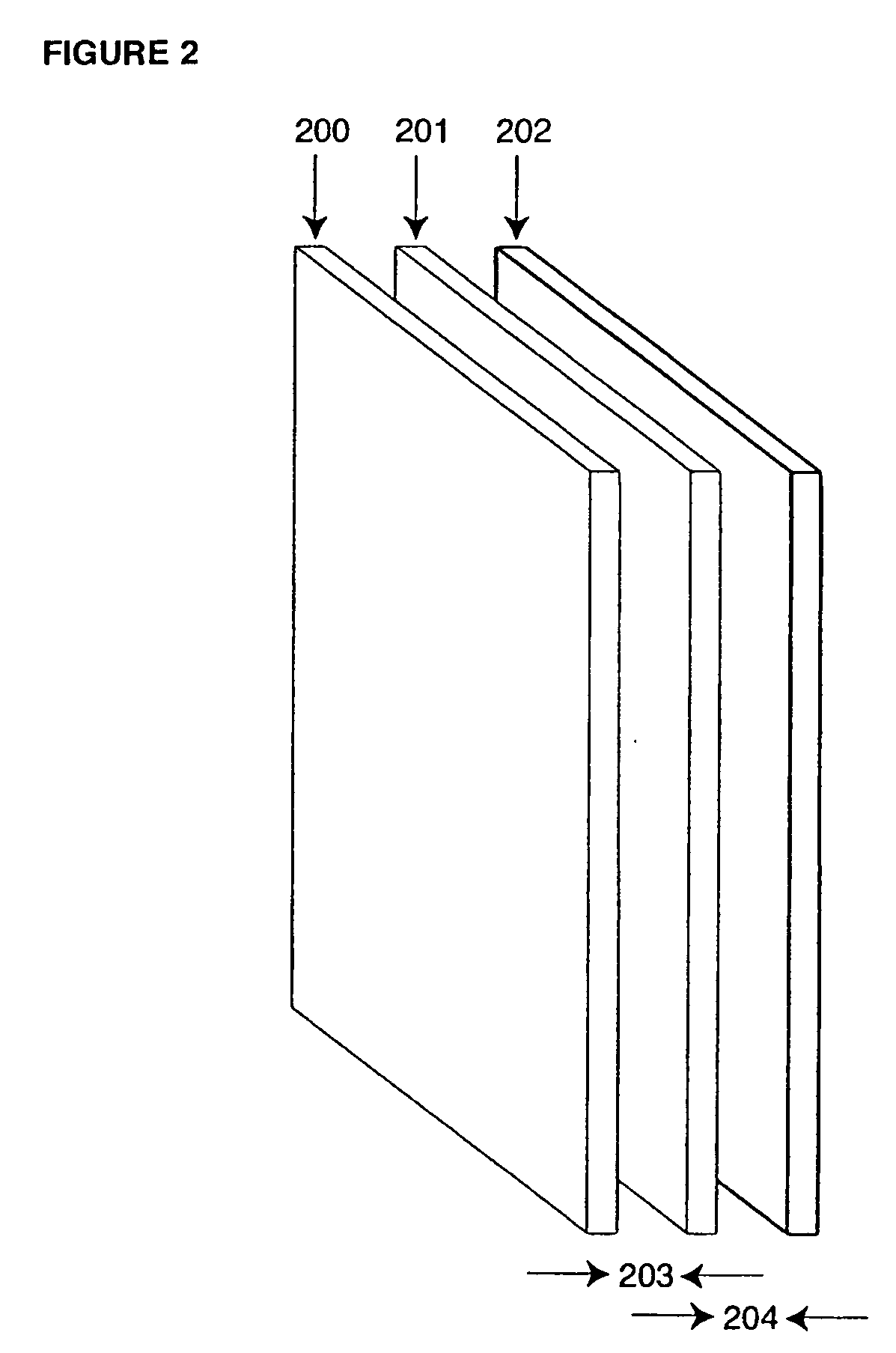

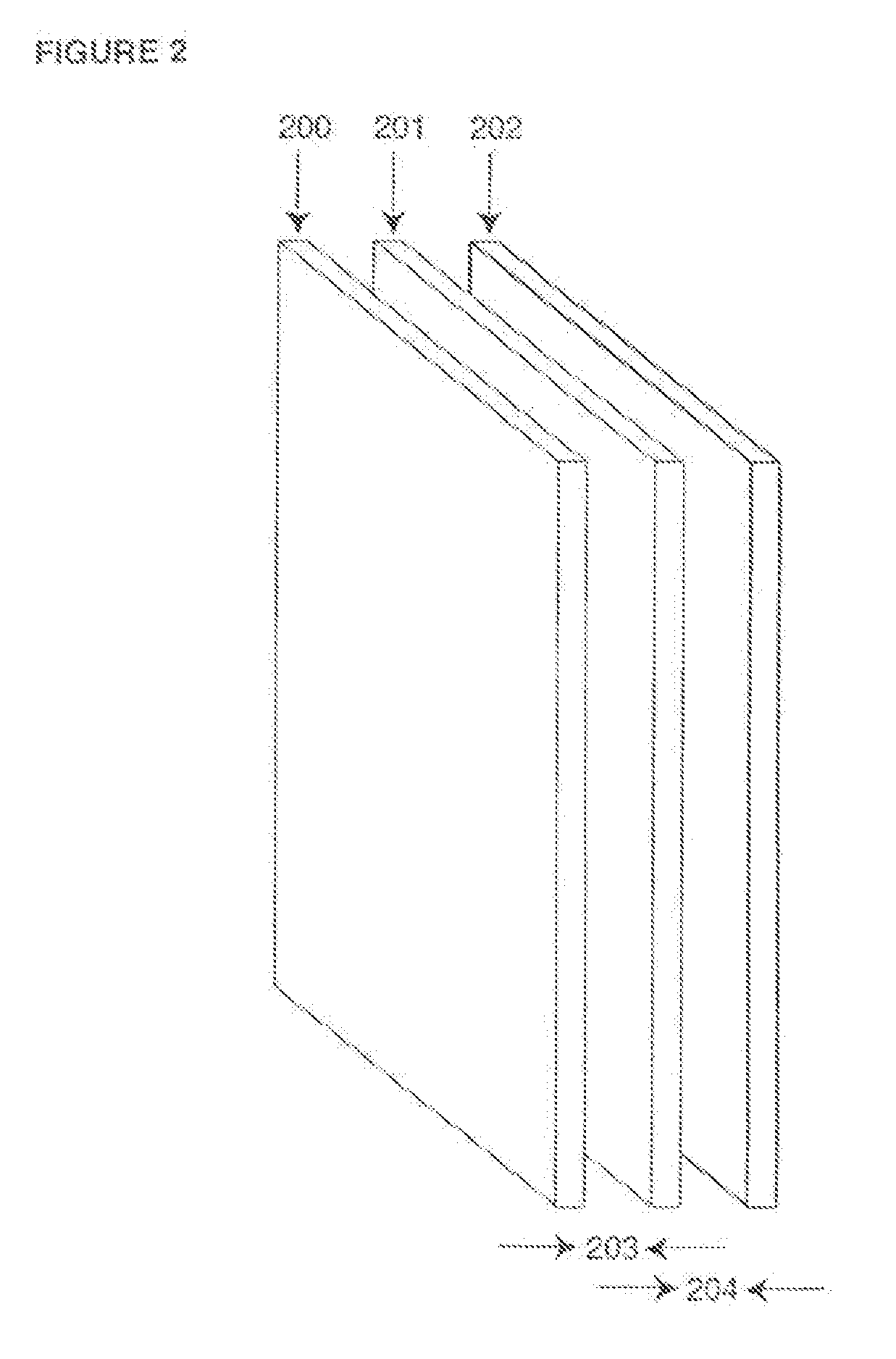

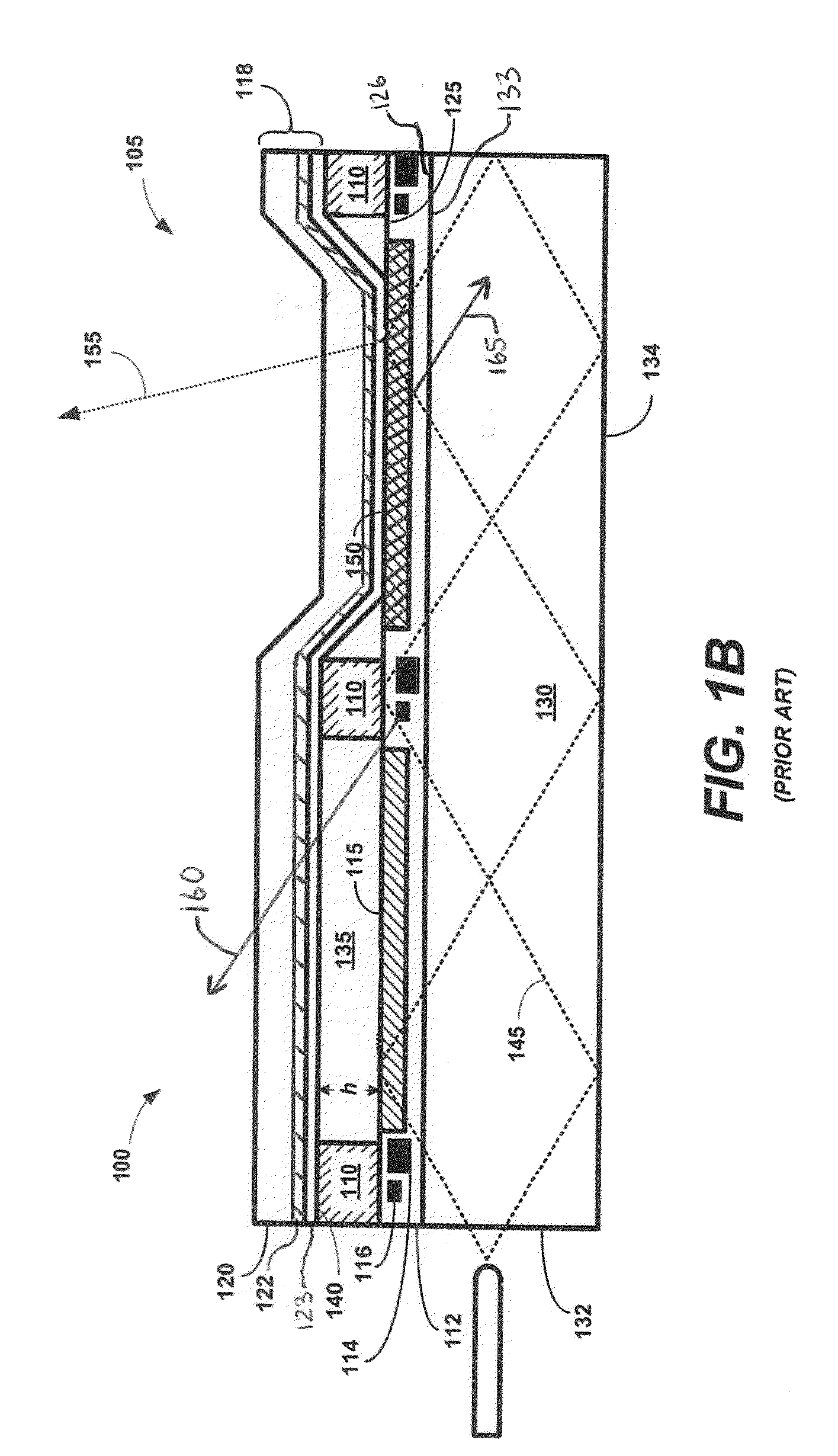

Z-axis redundant display/multilayer display

InactiveUS20050073471A1Free up surface areaConvenient spacingInstrument arrangements/adaptationsCathode-ray tube indicatorsQuiescent stateComputer graphics (images)

A display system for presenting one or more planes of display information. The display system may include two or more display modules positioned in a spaced relationship in a stacked formation substantially along a Z-axis perpendicular to a display face of a display module. Each display module may be selectively activated to display a visual image or deactivated to a quiescent state. Further, when a display module is activated to display the viewed image, the viewed image can be viewed through a prior display module which is deactivated to a quiescent state.

Owner:RAMBUS INC

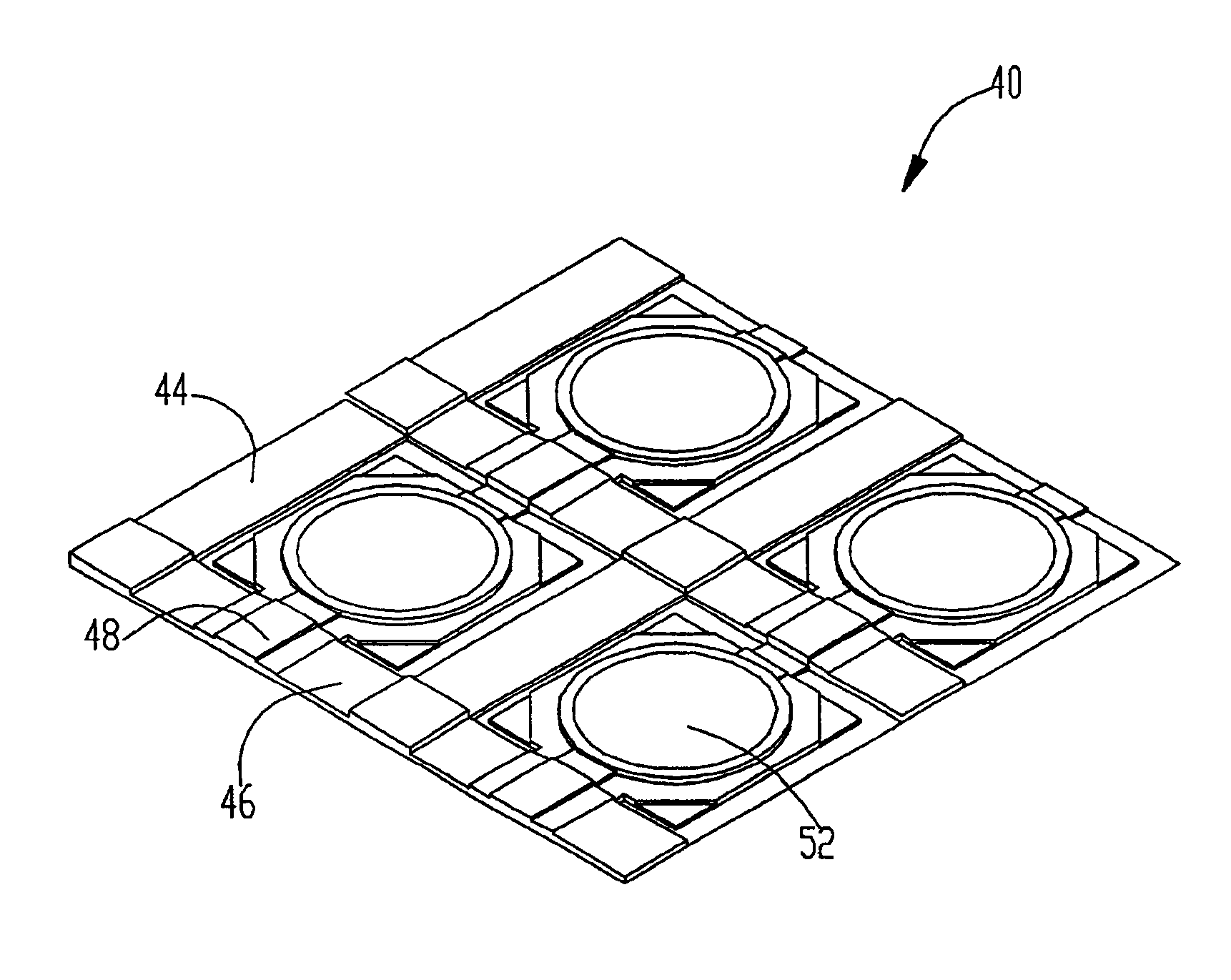

Fingerprint sensors using membrane switch arrays

InactiveUS6889565B2Electrostatic/electro-adhesion relaysResistance/reactance/impedenceMembrane switchEngineering

A sensor for identifying fingerprints or other skin textures includes an array of cells each including a membrane switch. Each switch includes a fixed lower electrode disposed on a chip substrate, and a flexible membrane disposed over the lower electrode and capable of flexing downward to establish electrical contact between the lower electrode and an upper electrode. The upper electrode can form the membrane itself or a layer of the membrane, or can be attached to other membrane layers. Switches situated underneath skin ridges change state (e.g. are closed) by the applied pressure, while switches underneath skin valleys remain in their quiescent state (e.g. open). Adjacent switch chambers are connected by fluid tunnels which allow the passage of air between the chambers. Each chamber is substantially closed to the exterior of the sensor, such that particles from the environment cannot contaminate the switch contact surface defined between the switch electrodes. The cells are preferably not hermetically sealed, such that the pressure within the chamber interiors can stay equal to the external (atmospheric) pressure in varying environmental conditions. The membrane design of the cells according to the preferred embodiment allows improved sensor robustness, enhanced resistance to impact forces, decreased vulnerability to particle contamination, and reduced inter-cell crosstalk.

Owner:LENOVO PC INT

Z-Axis Redundant Display / Multilayer Display

InactiveUS20070091011A1Free up surface areaConvenient spacingInstrument arrangements/adaptationsCathode-ray tube indicatorsQuiescent stateComputer graphics (images)

A display system for presenting one or more planes of display information. The display system may include two or more display modules positioned in a spaced relationship in a stacked formation substantially along a Z-axis perpendicular to a display face of a display module. Each display module may be selectively activated to display a visual image or deactivated to a quiescent state. Further, when a display module is activated to display the viewed image, the viewed image can be viewed through a prior display module which is deactivated to a quiescent state.

Owner:RAMBUS DELAWARE

Digital silicon photomultiplier for TOF PET

ActiveUS8395127B1High data-rate radiation detectionImproved spatial detector resolutionSolid-state devicesMaterial analysis by optical meansQuiescent stateSilicon photomultiplier

A radiation detector includes an array of detector pixels each including an array of detector cells. Each detector cell includes a photodiode biased in a breakdown region and digital circuitry coupled with the photodiode and configured to output a first digital value in a quiescent state and a second digital value responsive to photon detection by the photodiode. Digital triggering circuitry is configured to output a trigger signal indicative of a start of an integration time period responsive to a selected number of one or more of the detector cells transitioning from the first digital value to the second digital value. Readout digital circuitry accumulates a count of a number of transitions of detector cells of the array of detector cells from the first digital state to the second digital state over the integration time period.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

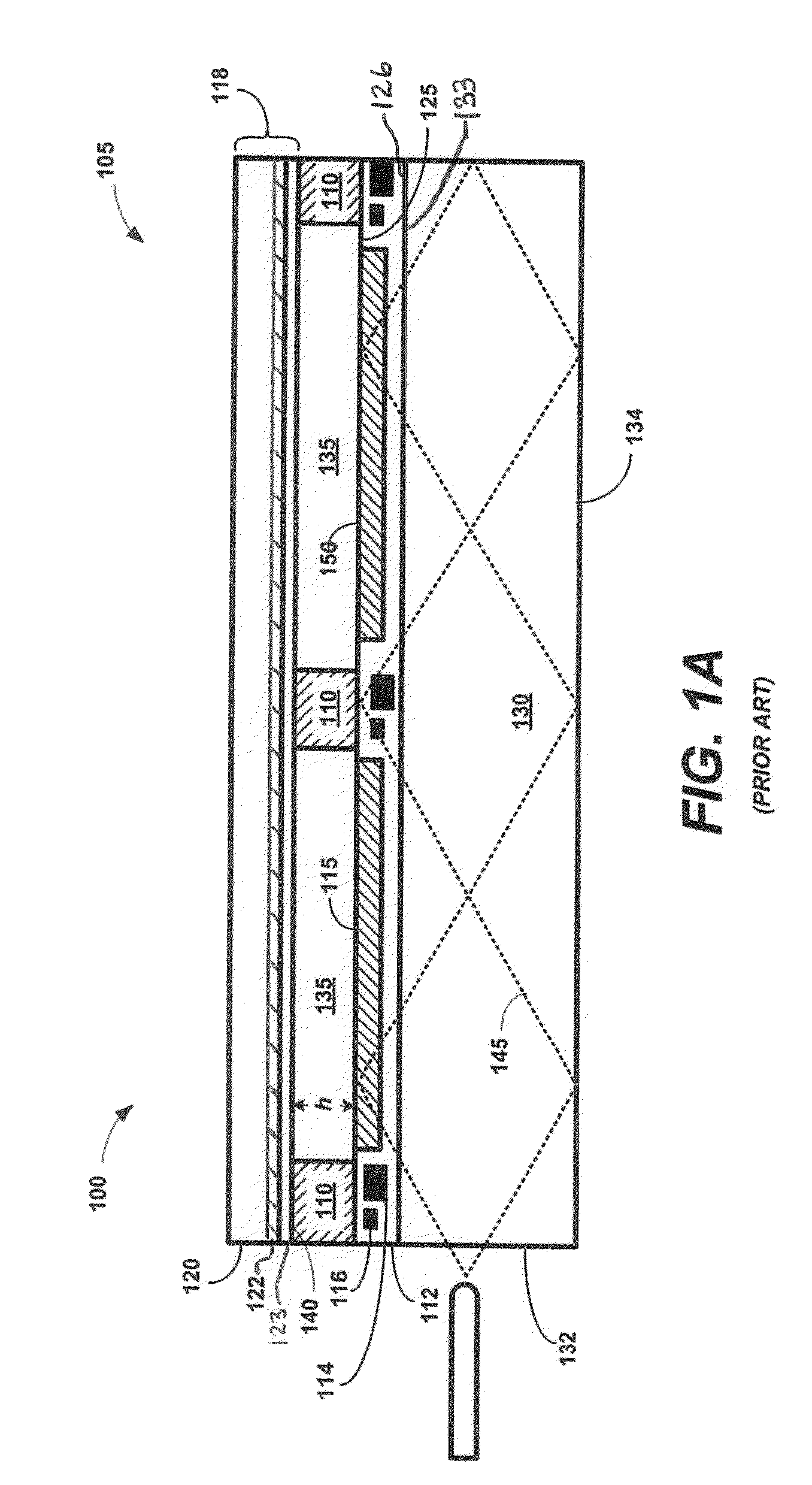

Normally emitting pixel architecture for frustrated total internal reflection displays

InactiveUS20100079843A1Discharge tube luminescnet screensStatic indicating devicesQuiescent stateTotal internal reflection

The present invention provides an apparatus that includes a waveguide and one or more pixels deployed adjacent the top surface of the waveguide which contains TIR light therein. Each pixel includes a deformable active layer having a first conductor and a driver electronics layer having a second conductor. The driver electronics layer is deployed in spaced-apart relation to the active layer and opposite the waveguide. In a quiescent state of a pixel, the active layer is in contact or near contact with the top surface of the waveguide so as to optically couple light out via FTIR (i.e., pixel's ON state). To actuate the pixel, the electronics layer is configured to selectively apply an electrical potential difference to the second conductor thereby causing the active layer to move away from the top surface so as to prevent the optical coupling of light out of the waveguide (i.e., pixel's OFF state).

Owner:RAMBUS DELAWARE

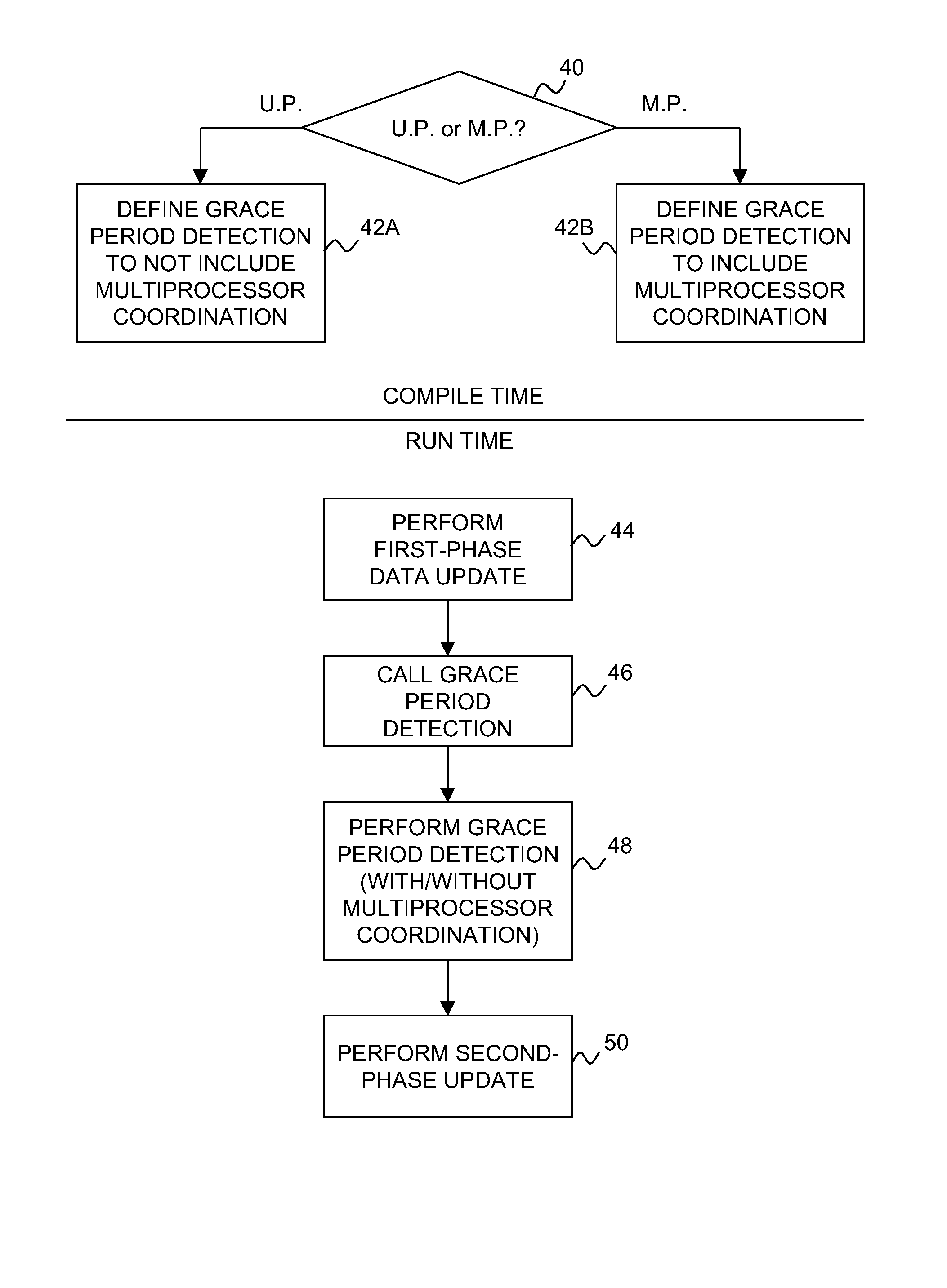

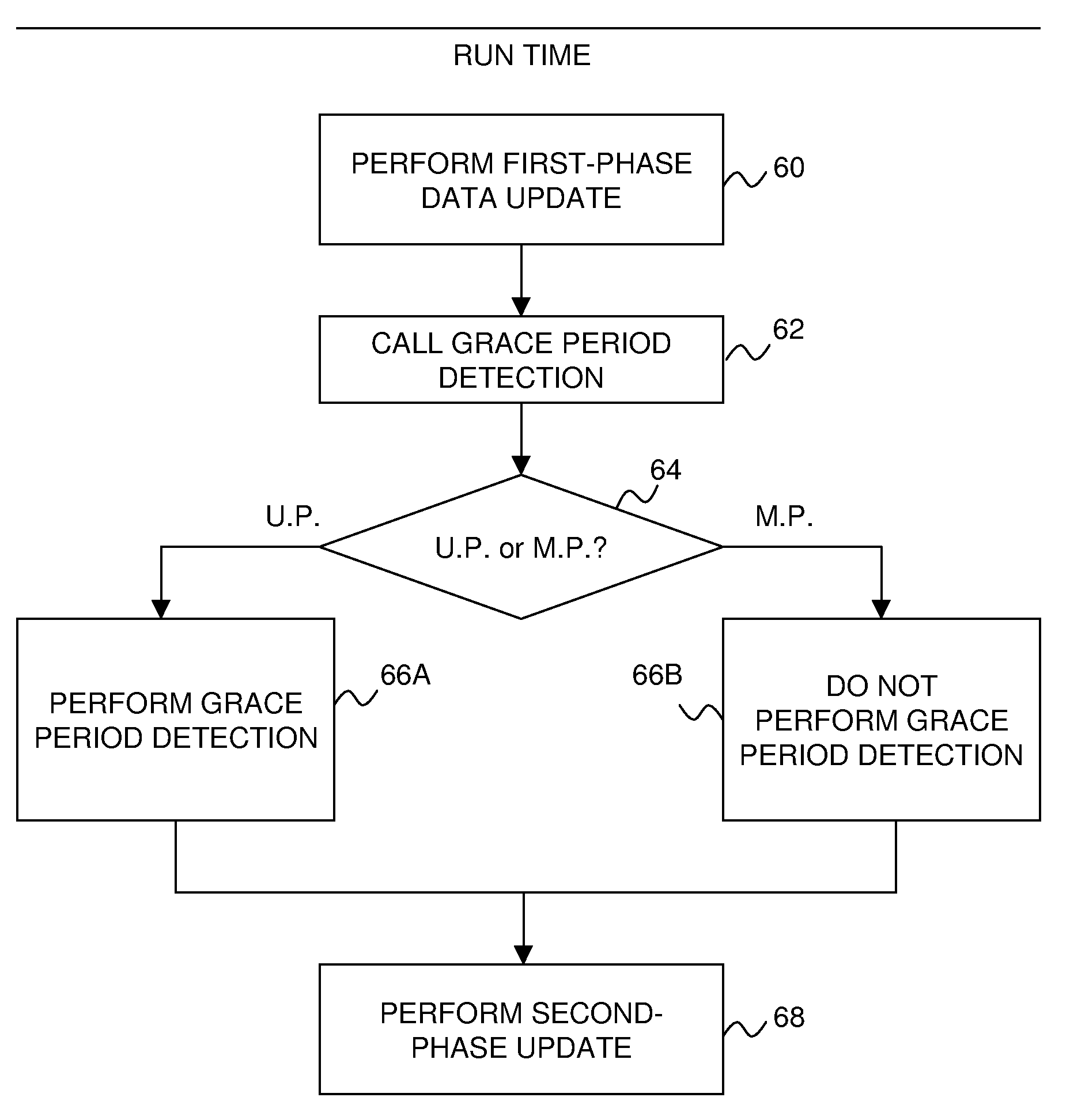

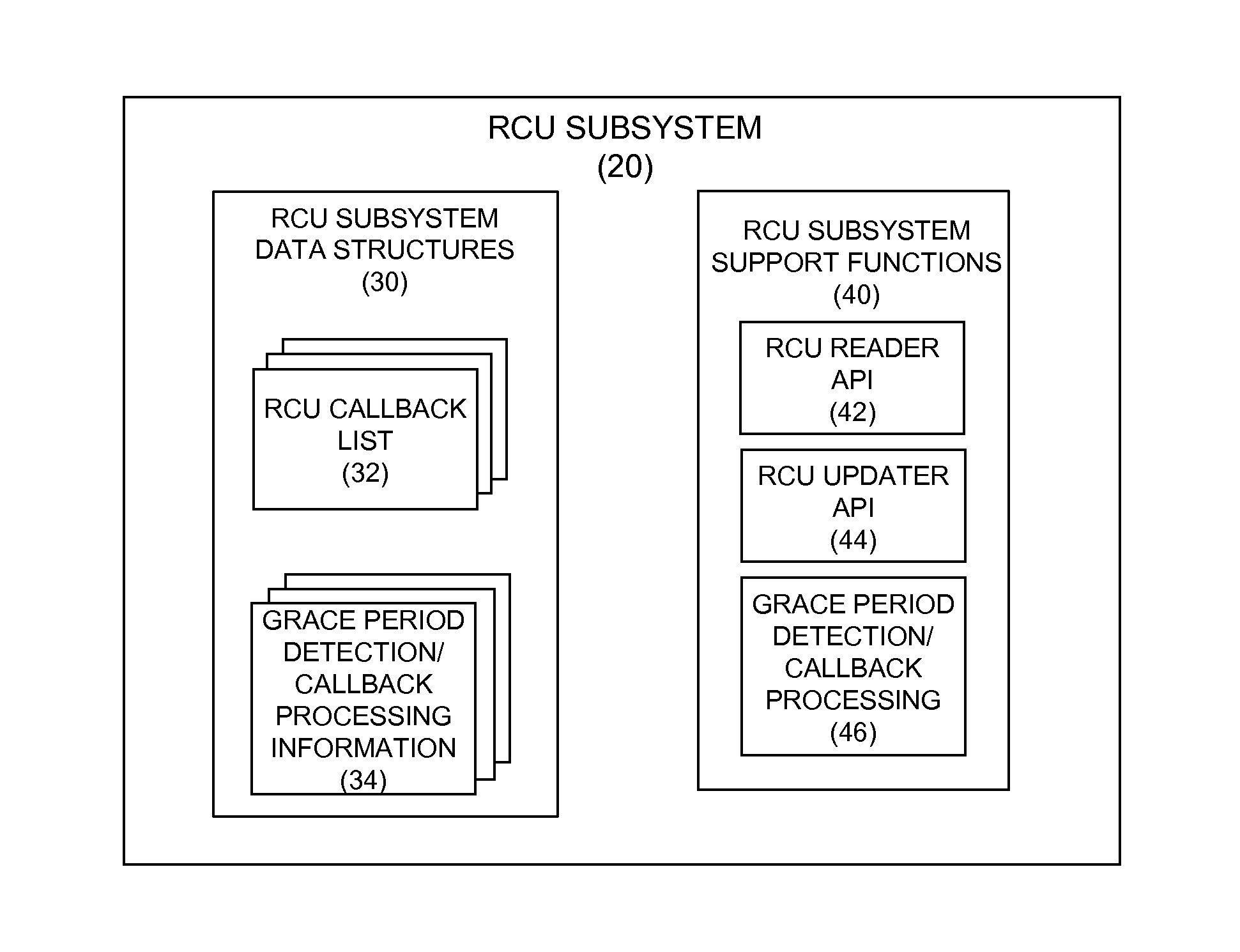

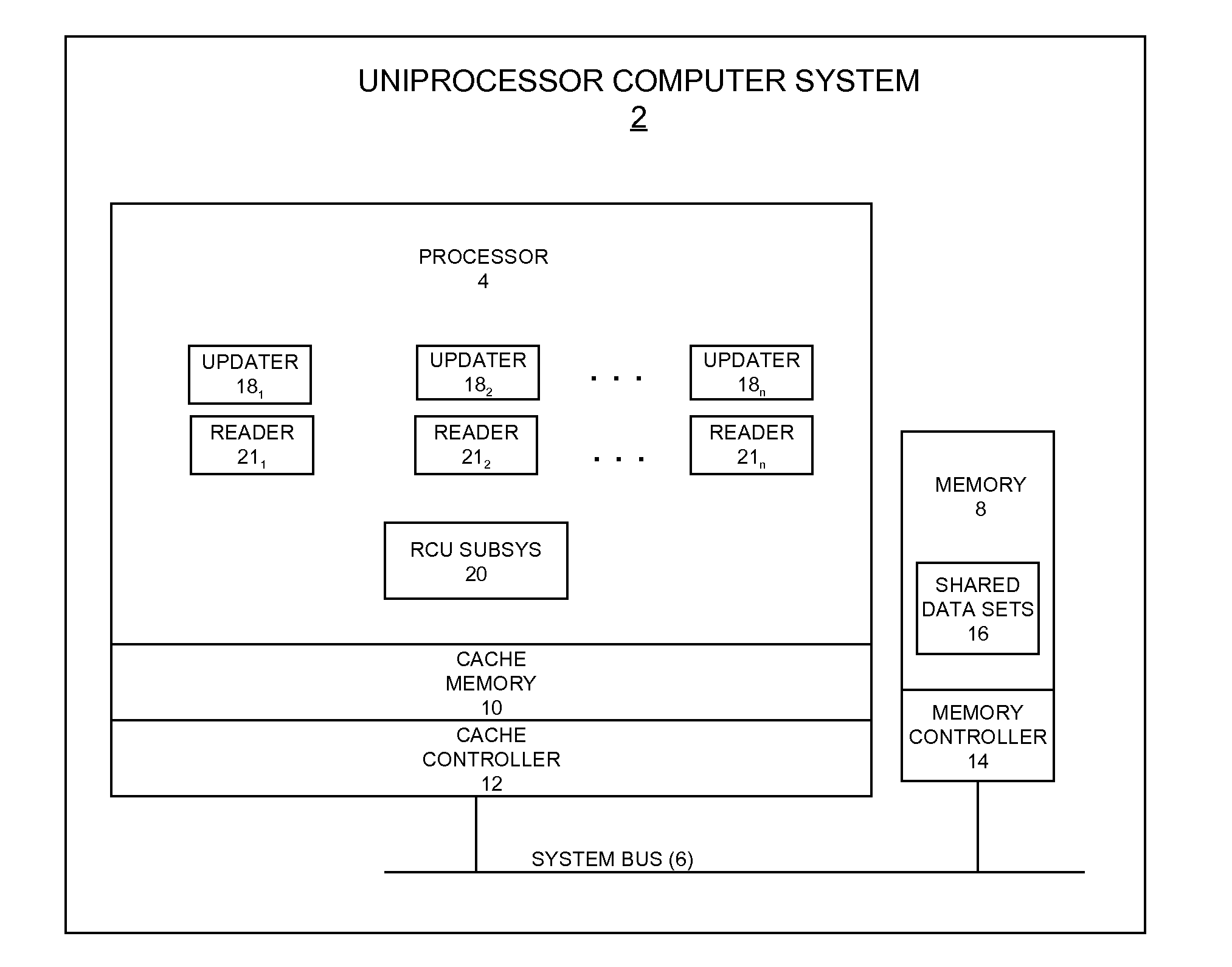

Optimizing grace period detection for preemptible read-copy update on uniprocessor systems

InactiveUS7953708B2Program synchronisationDigital data processing detailsUniprocessor systemData processing system

Owner:INT BUSINESS MASCH CORP

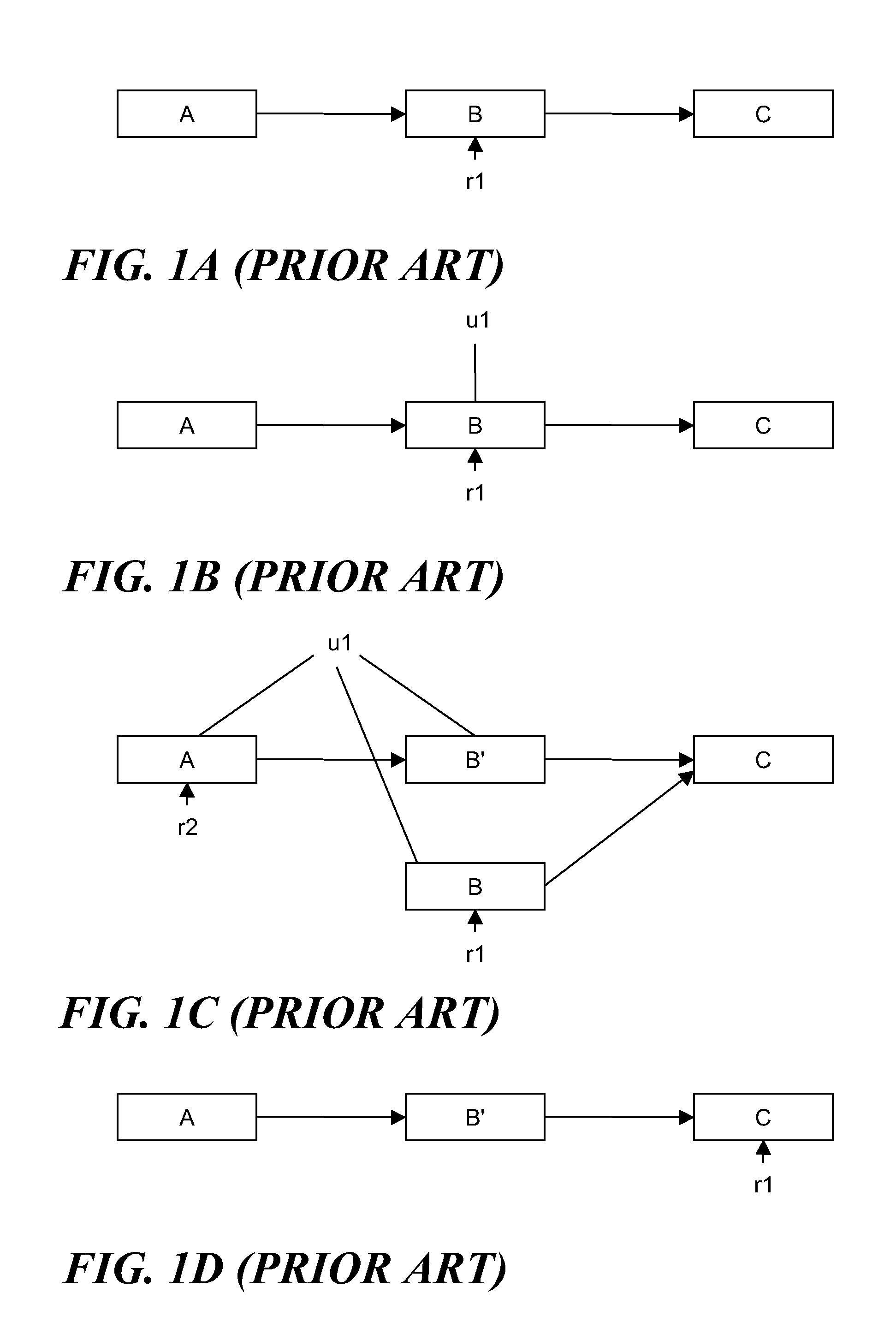

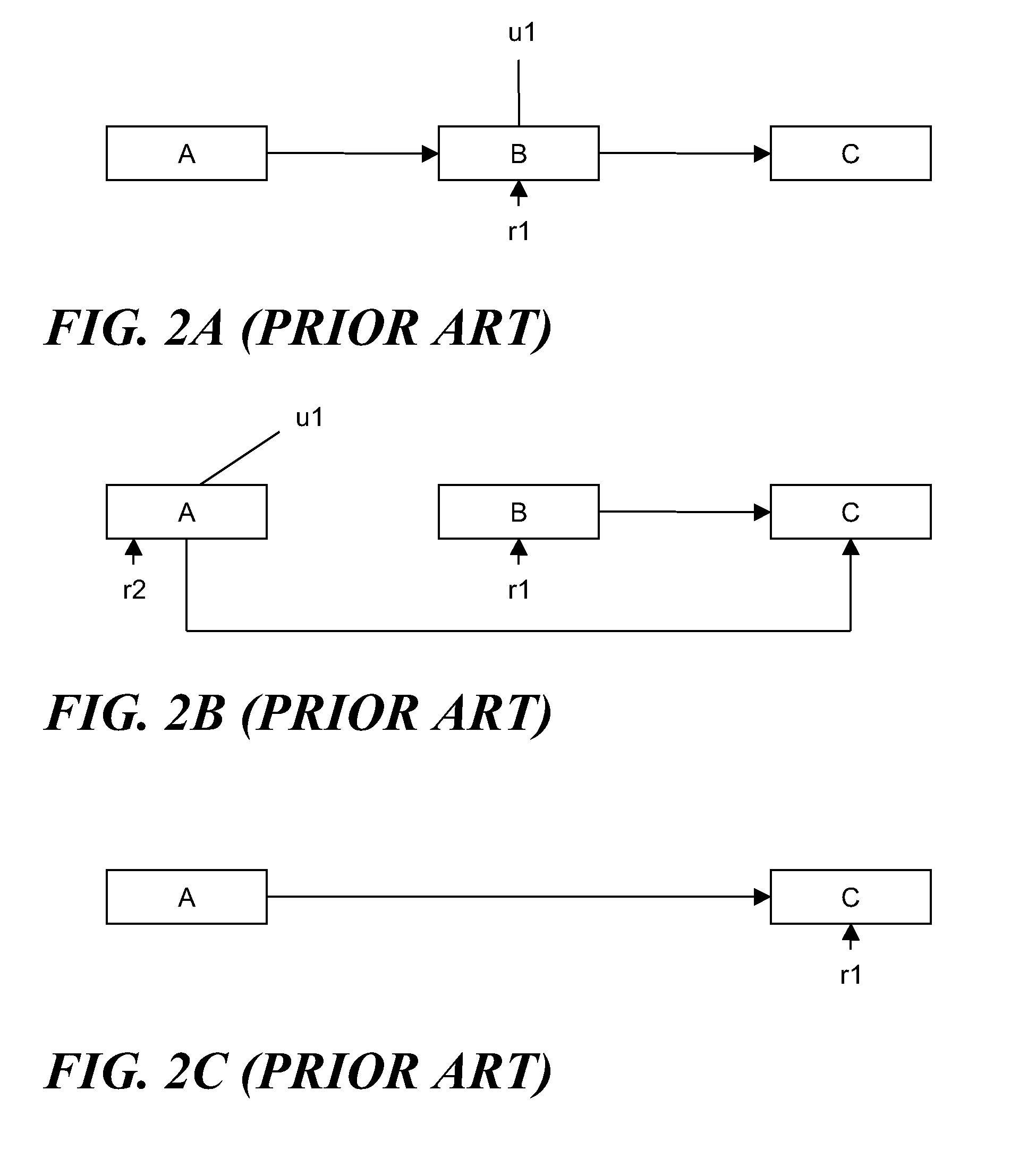

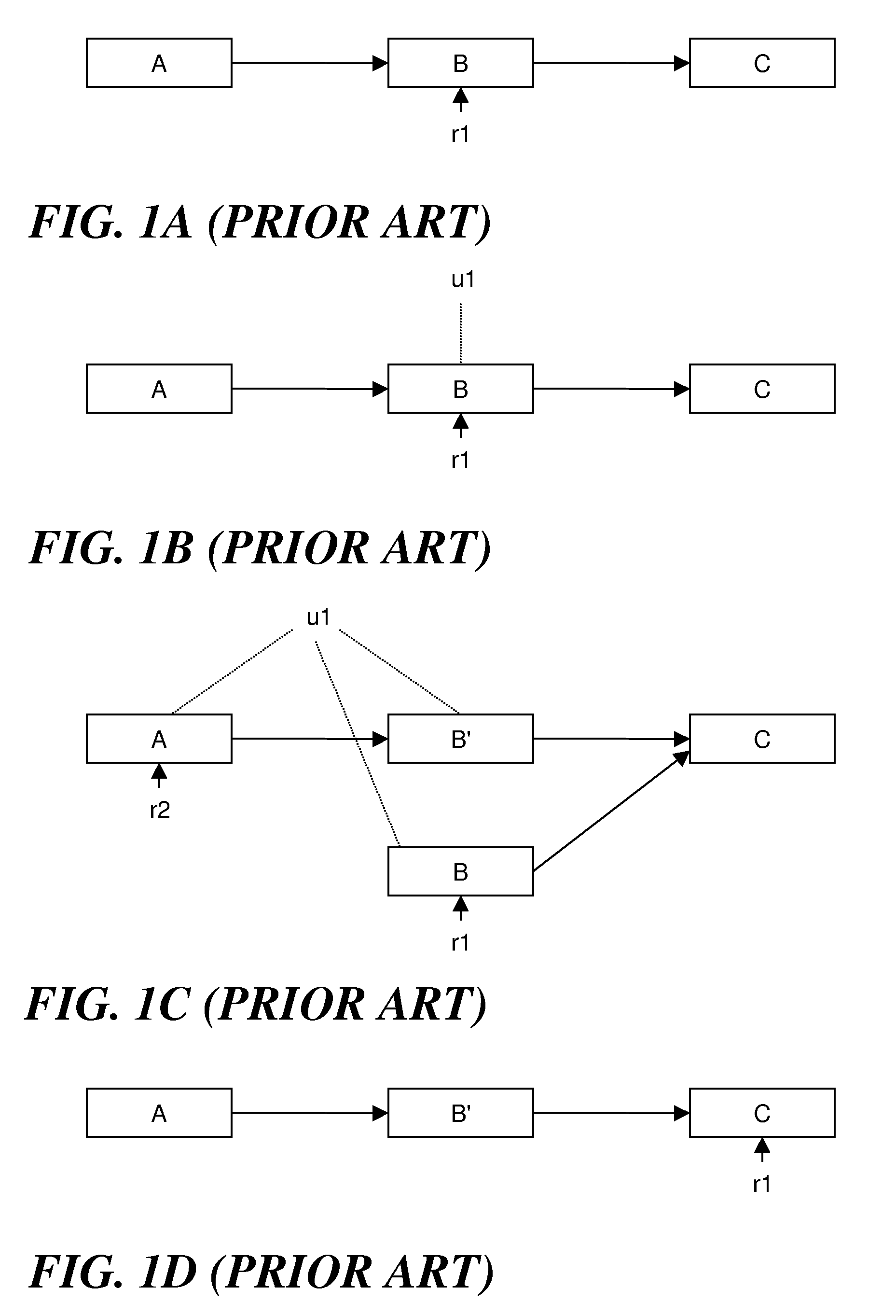

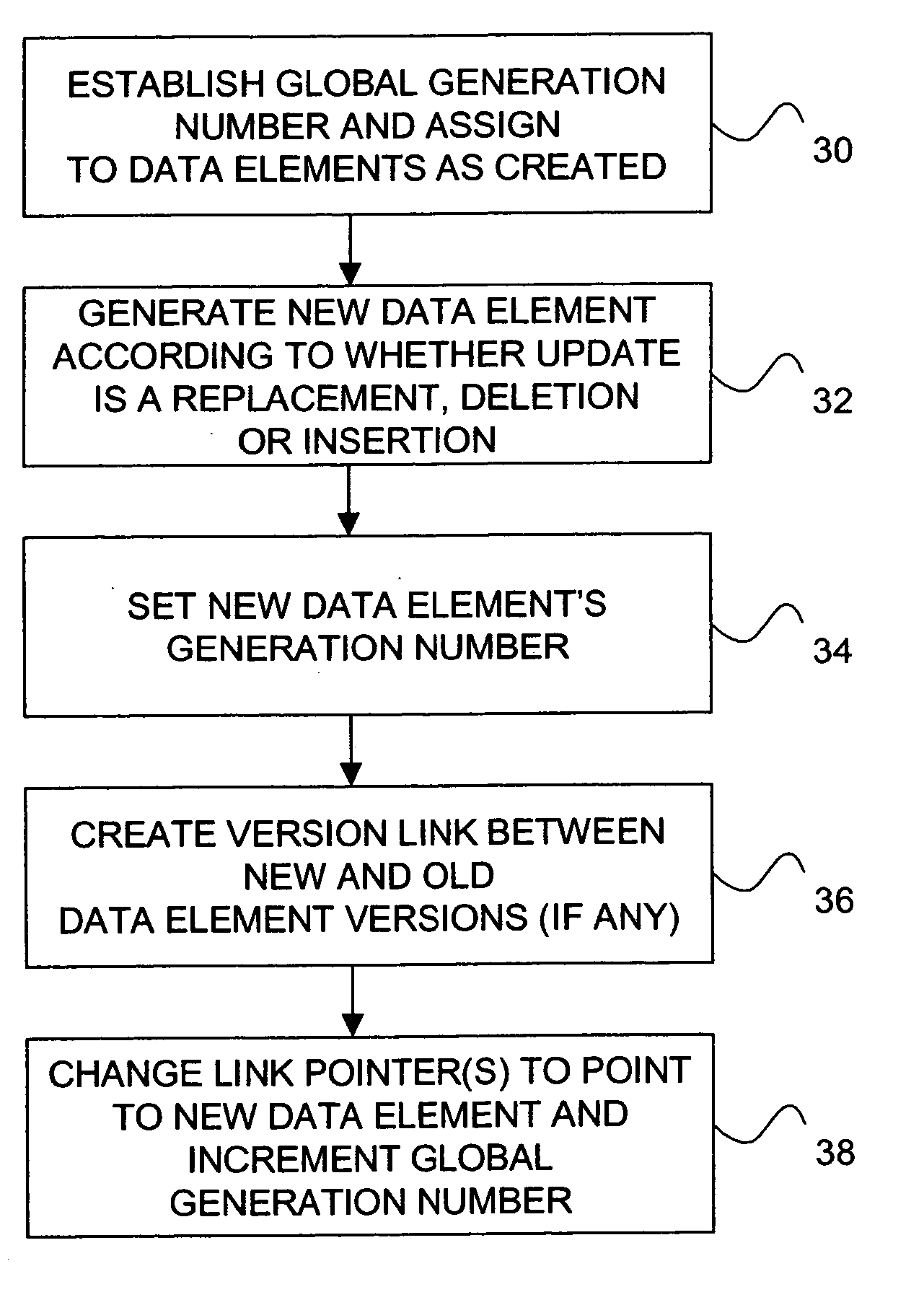

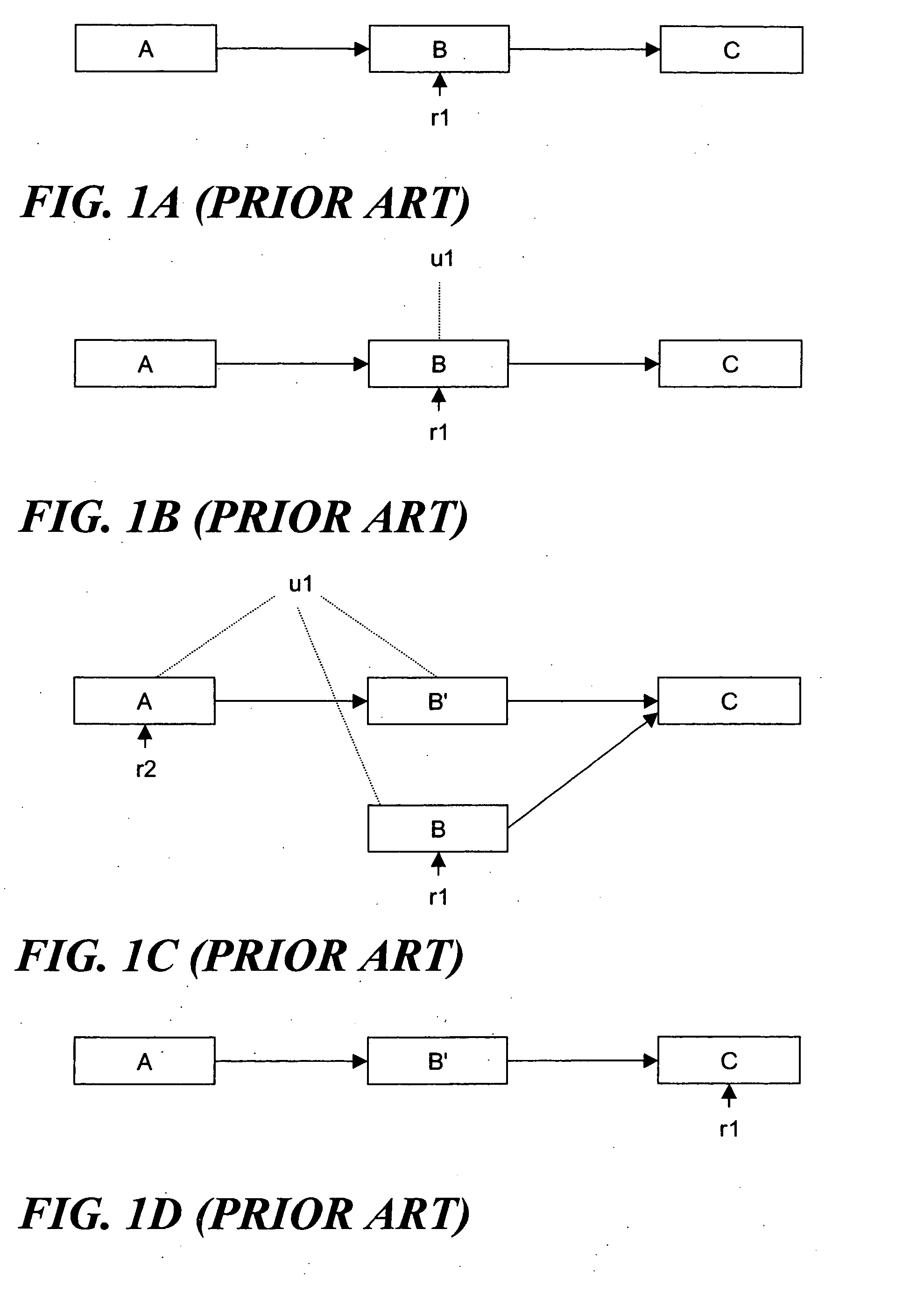

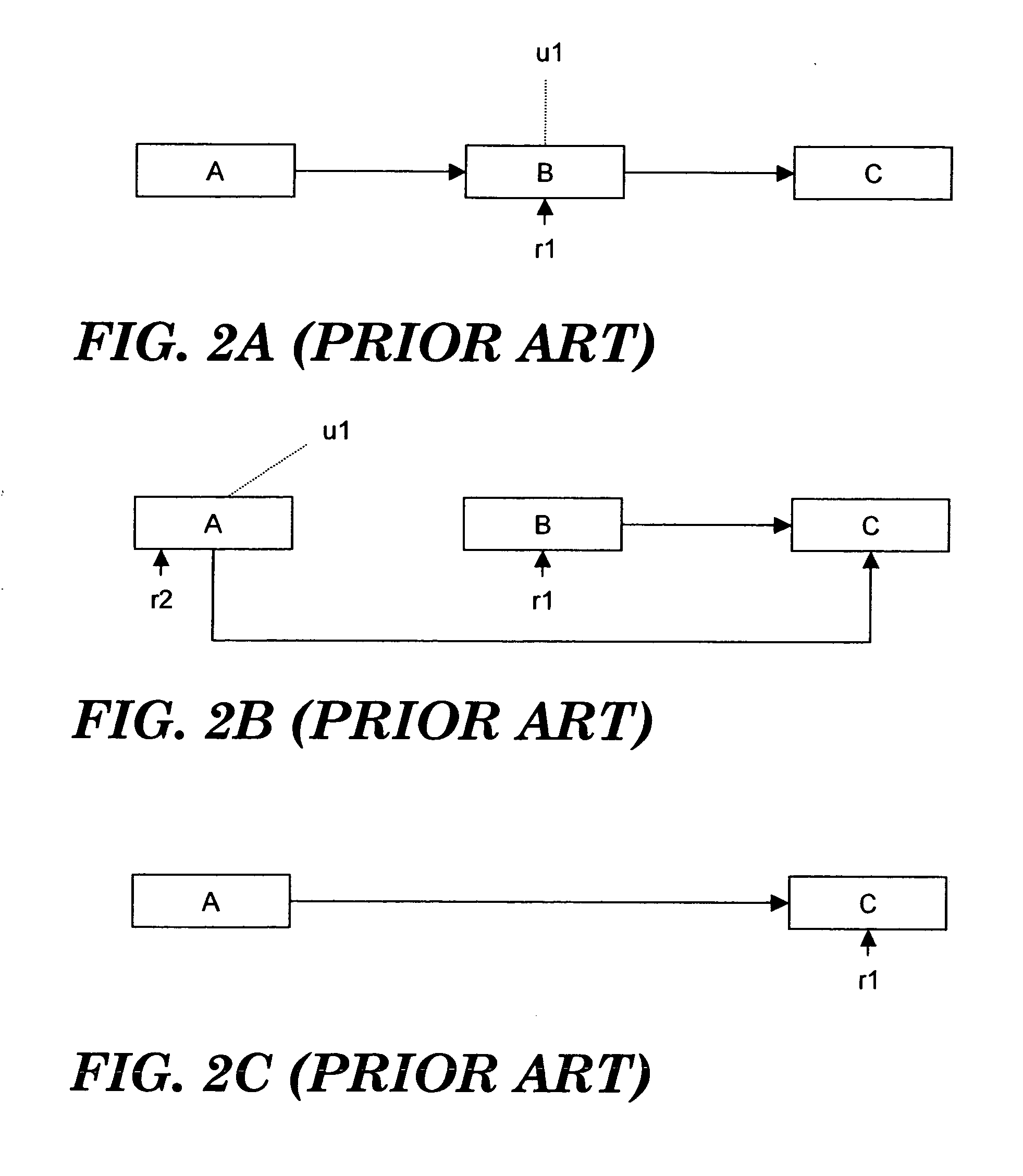

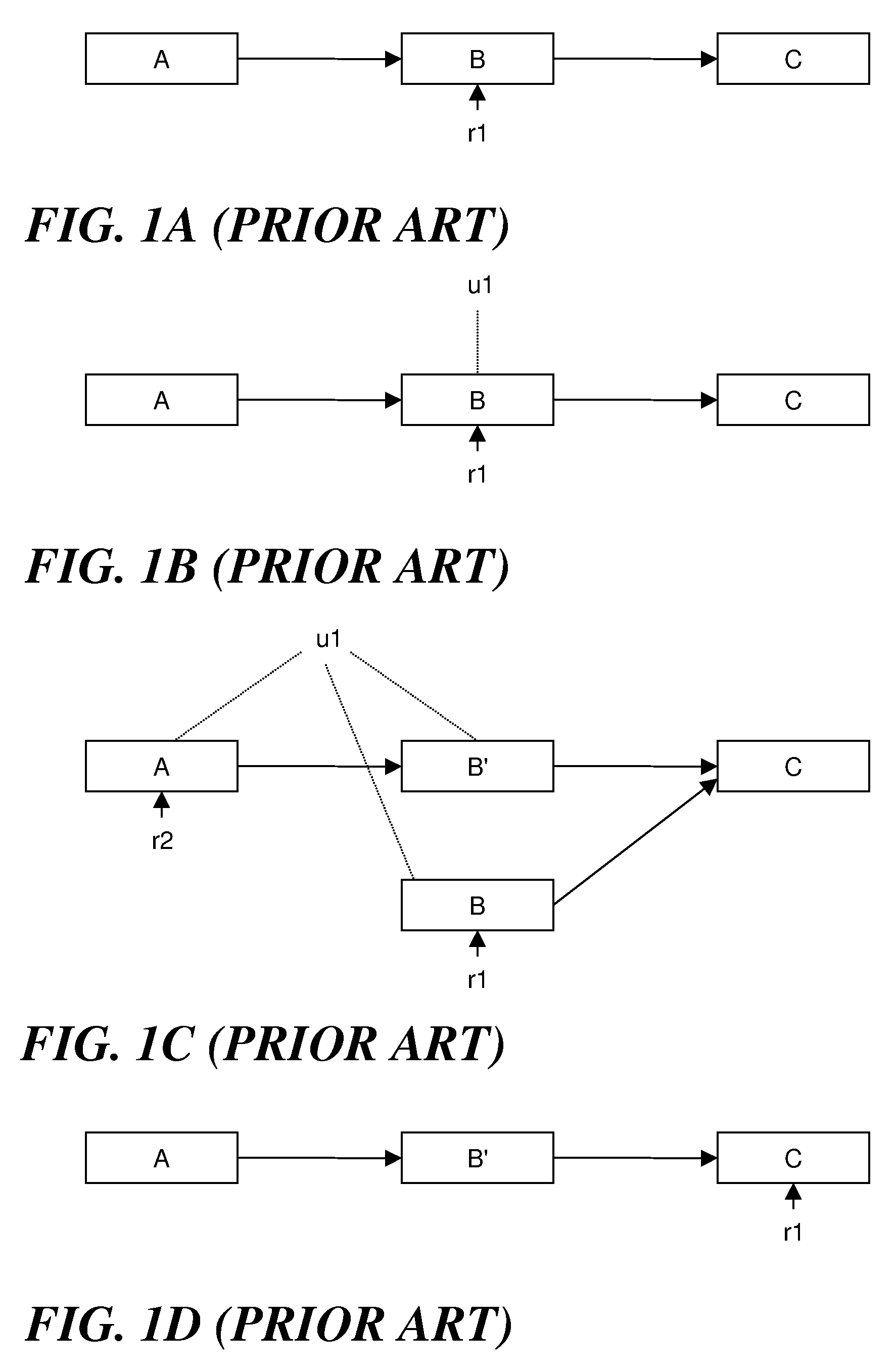

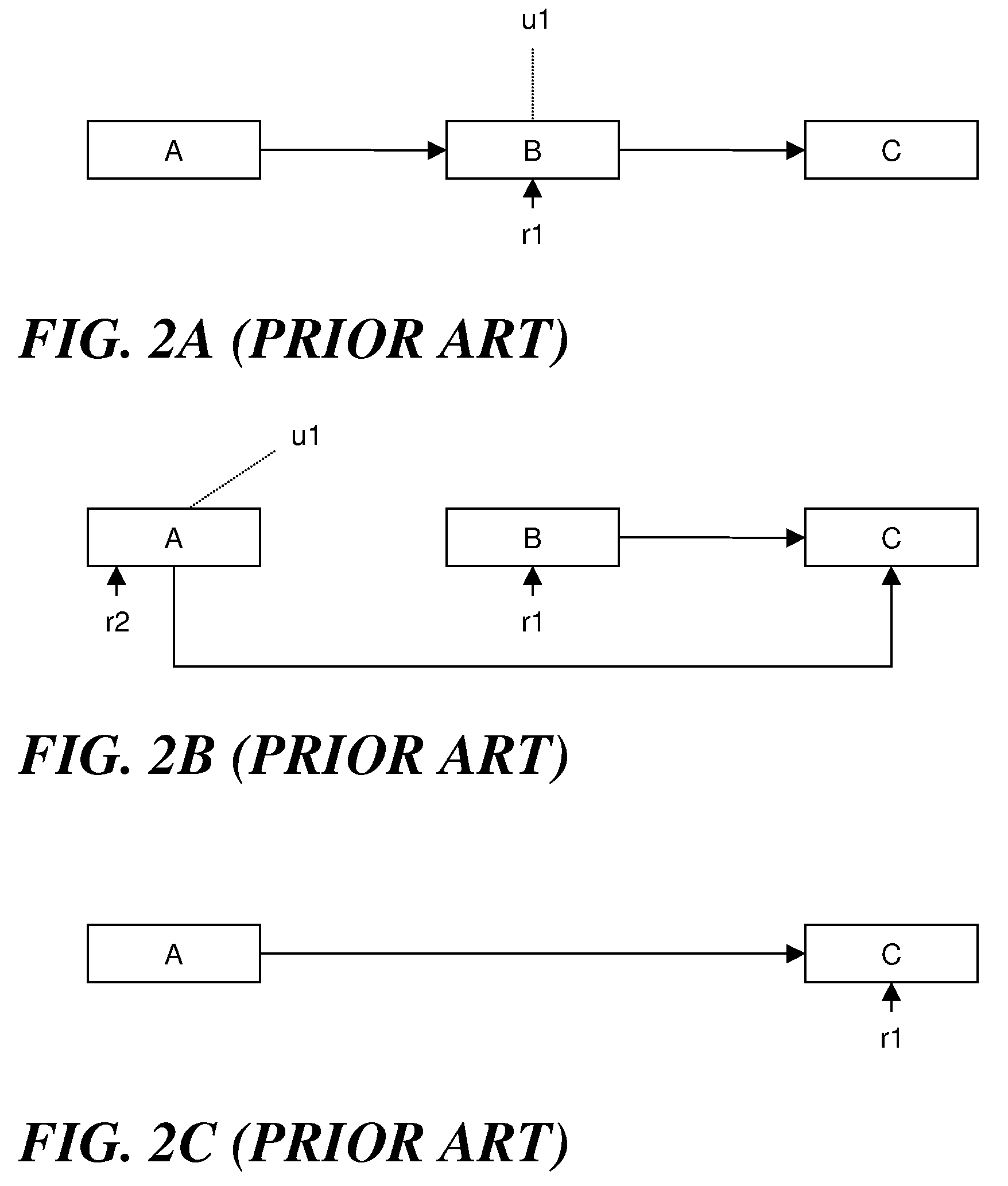

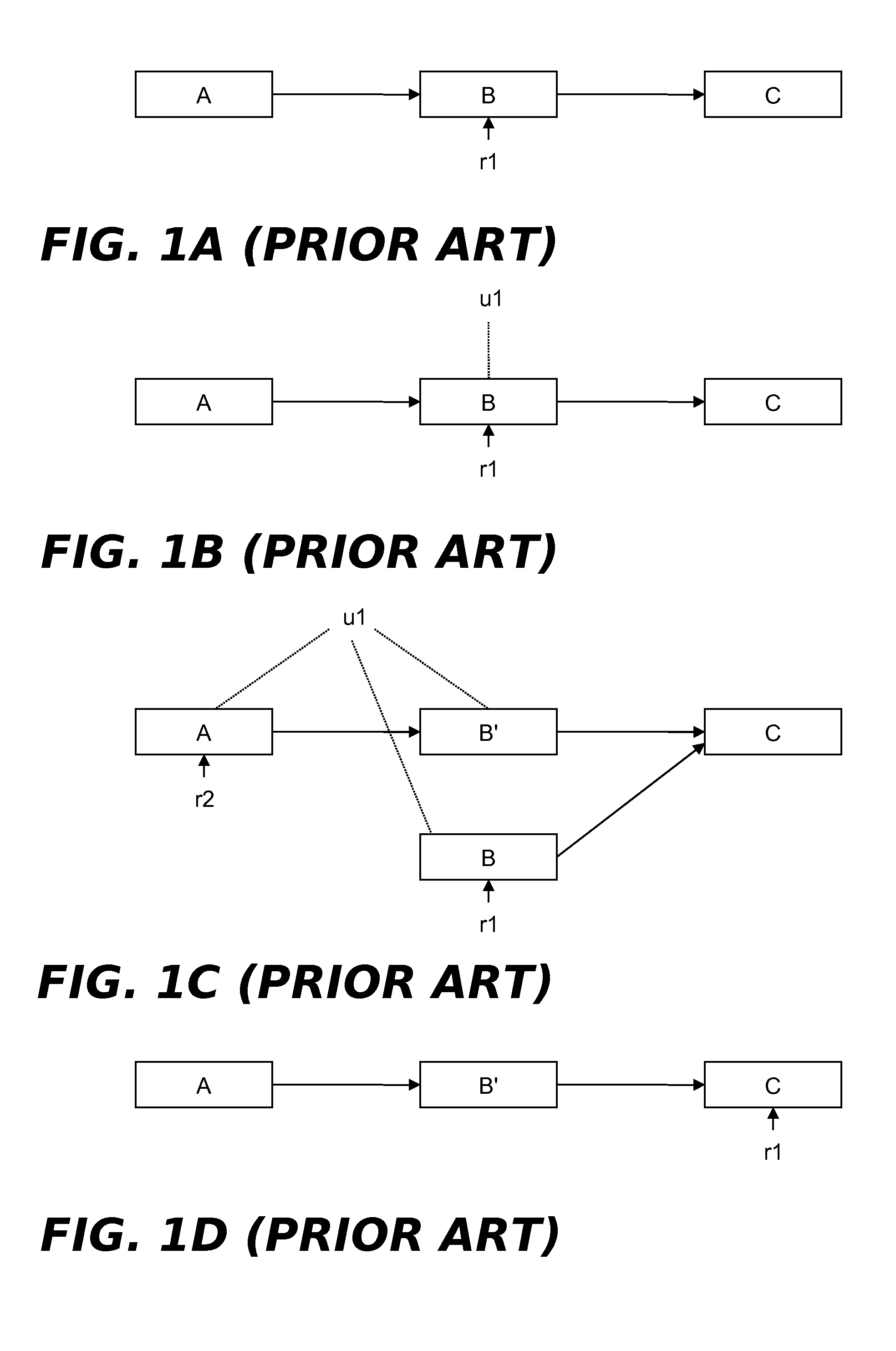

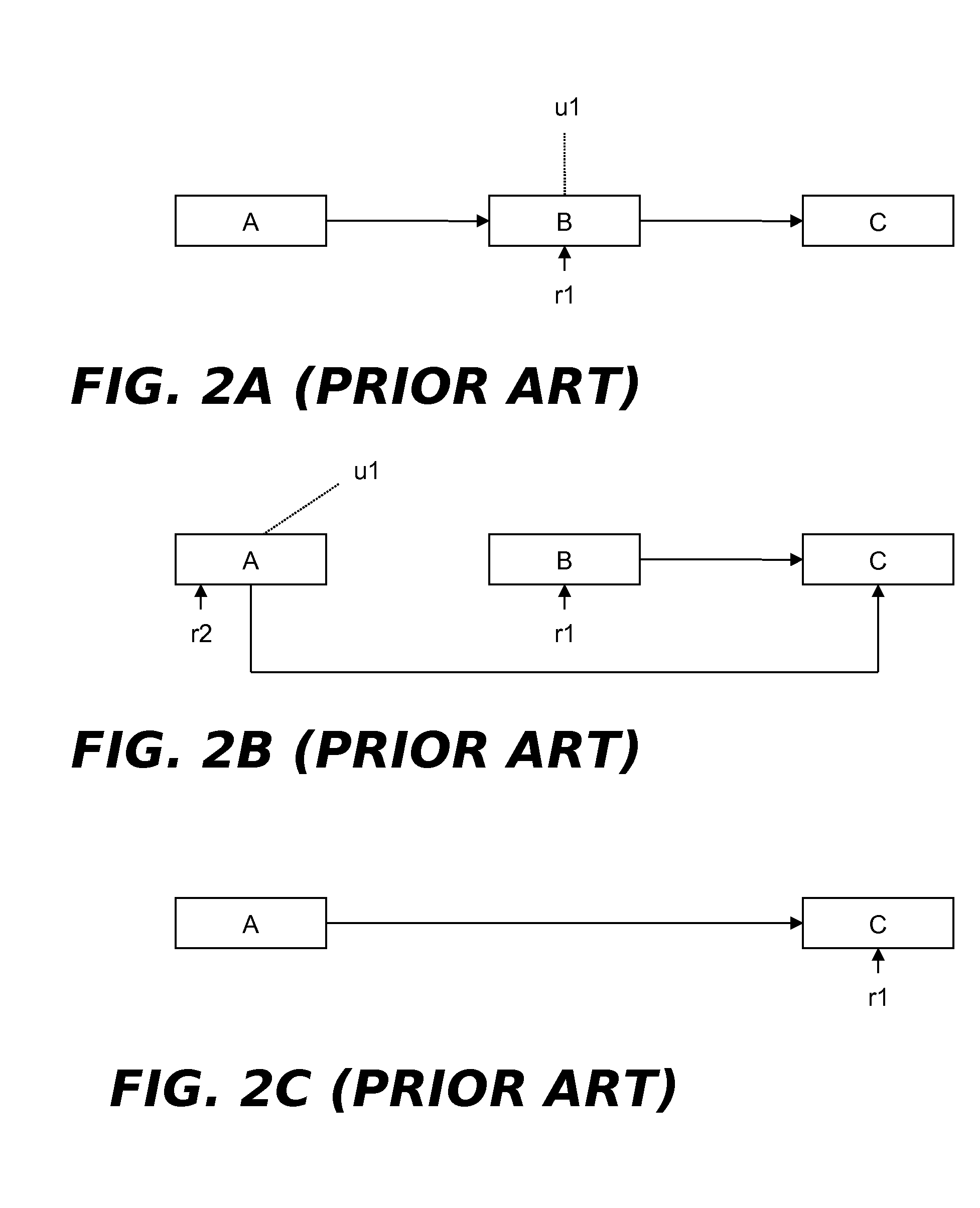

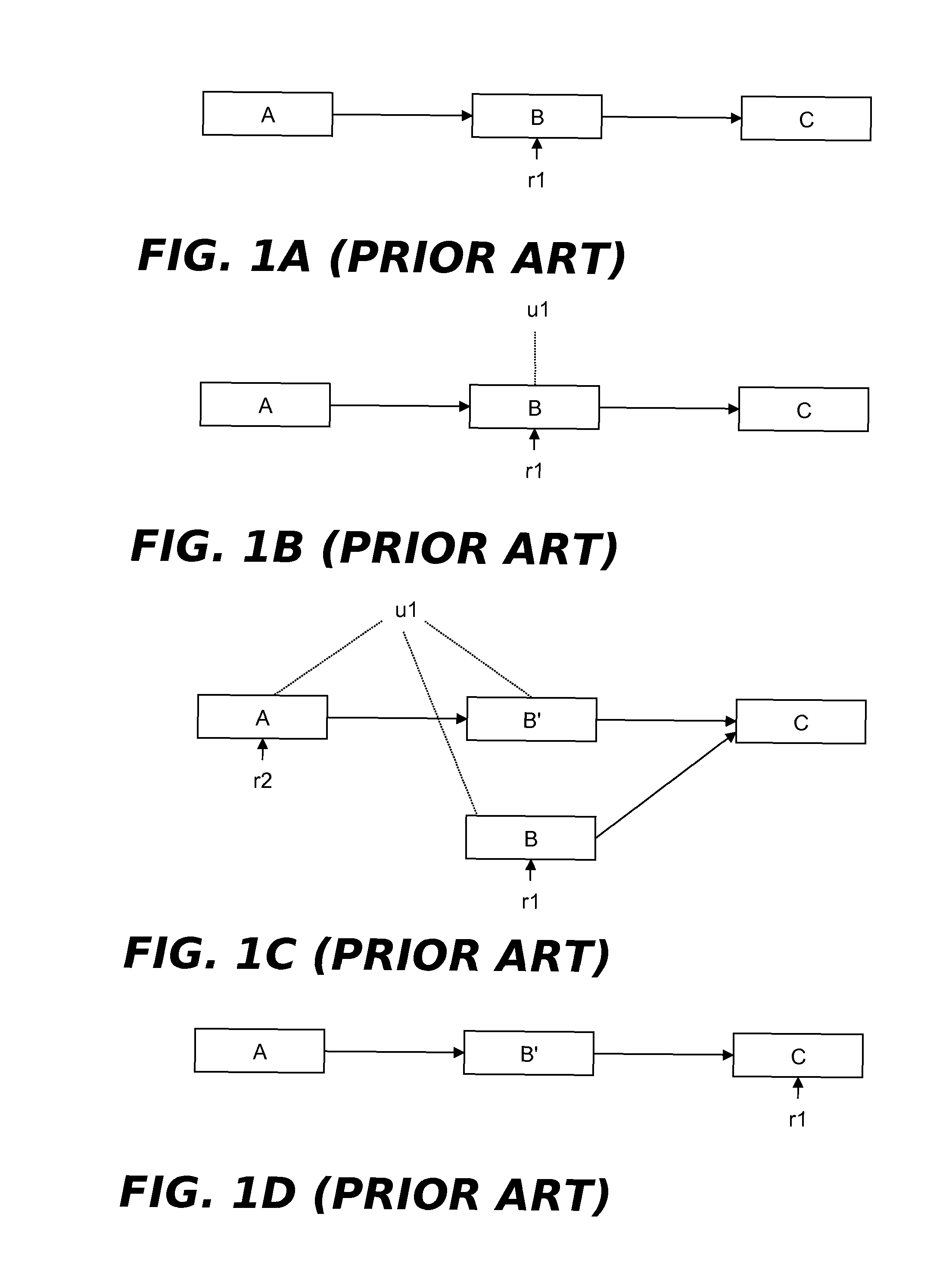

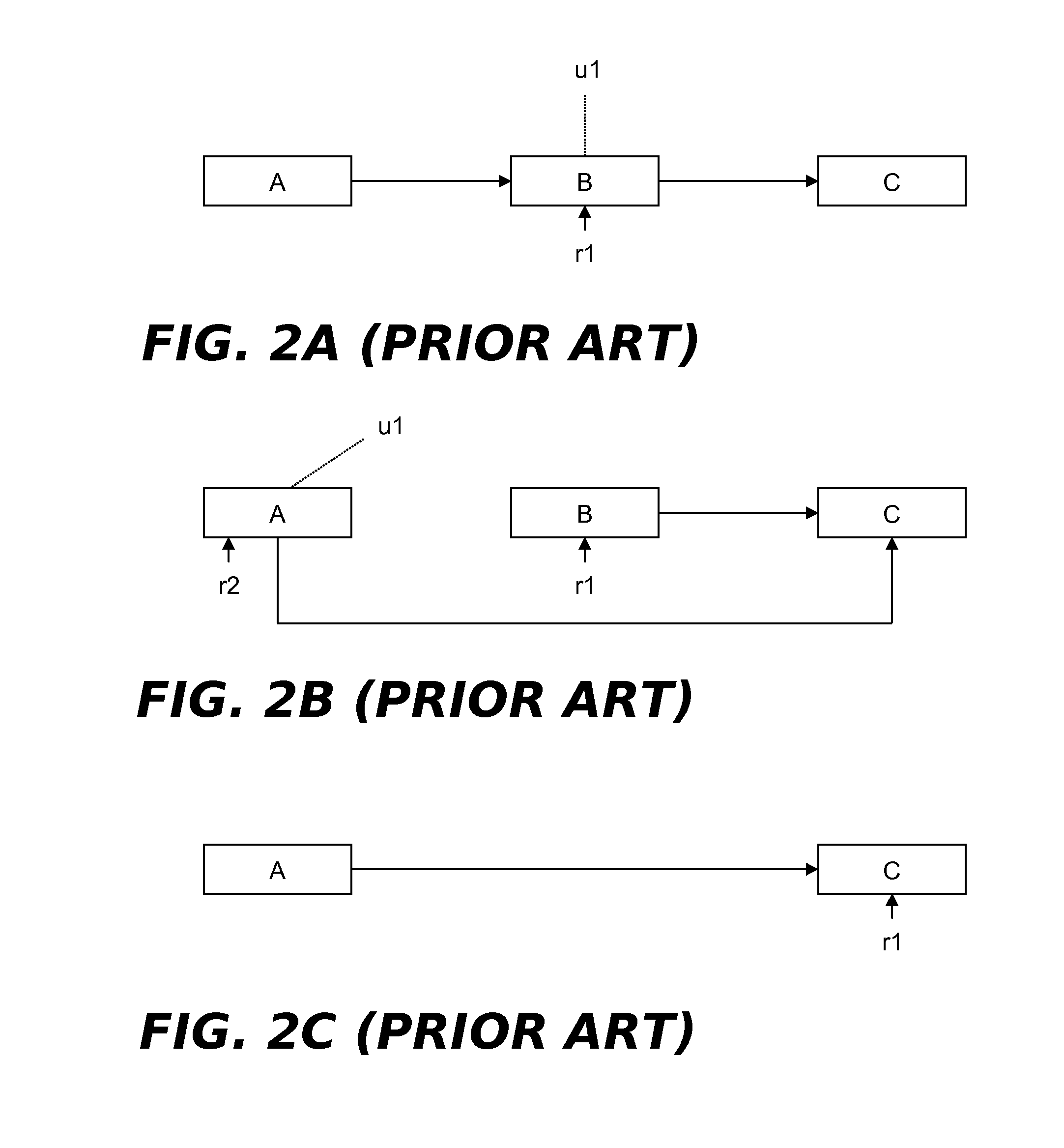

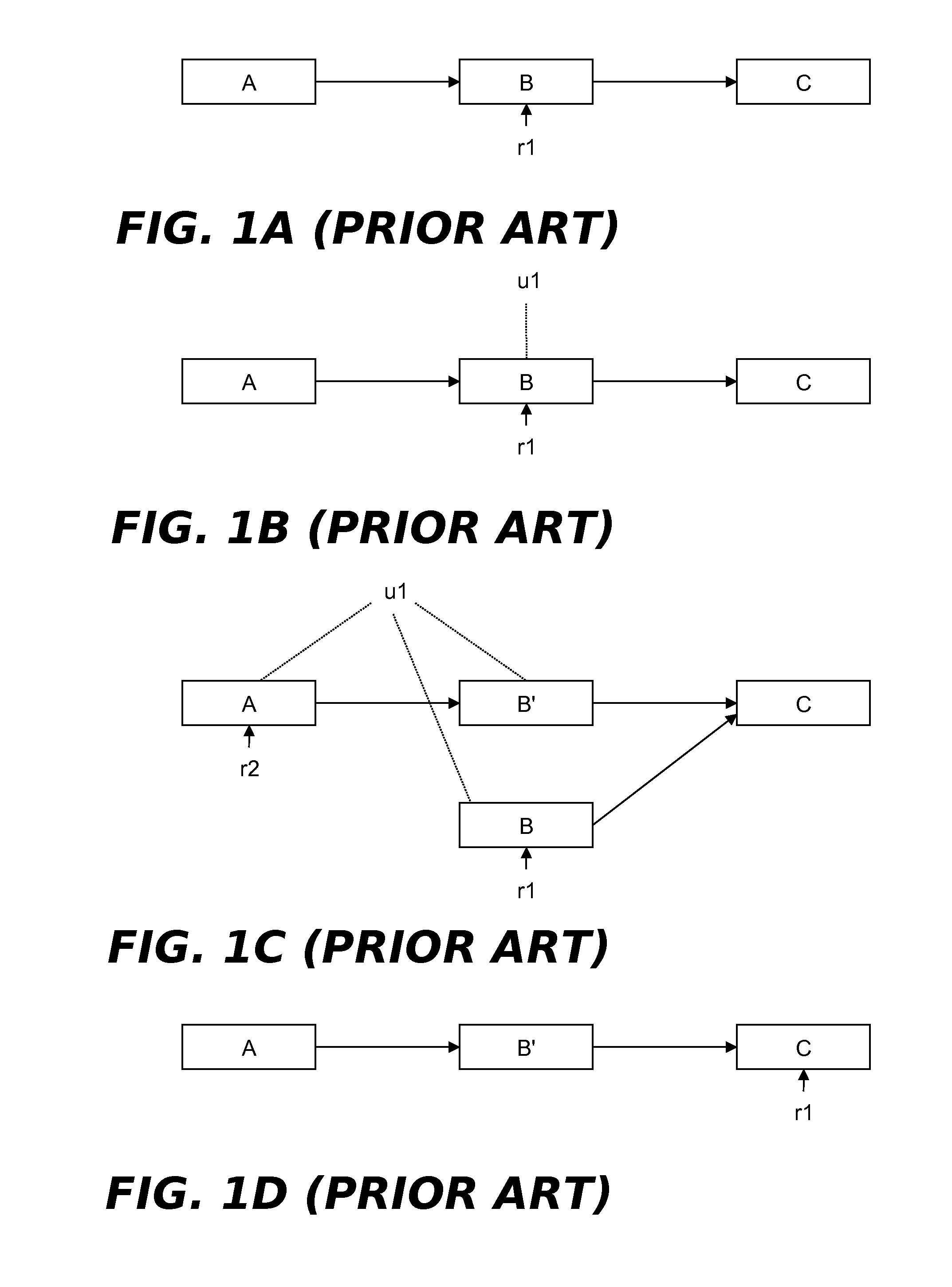

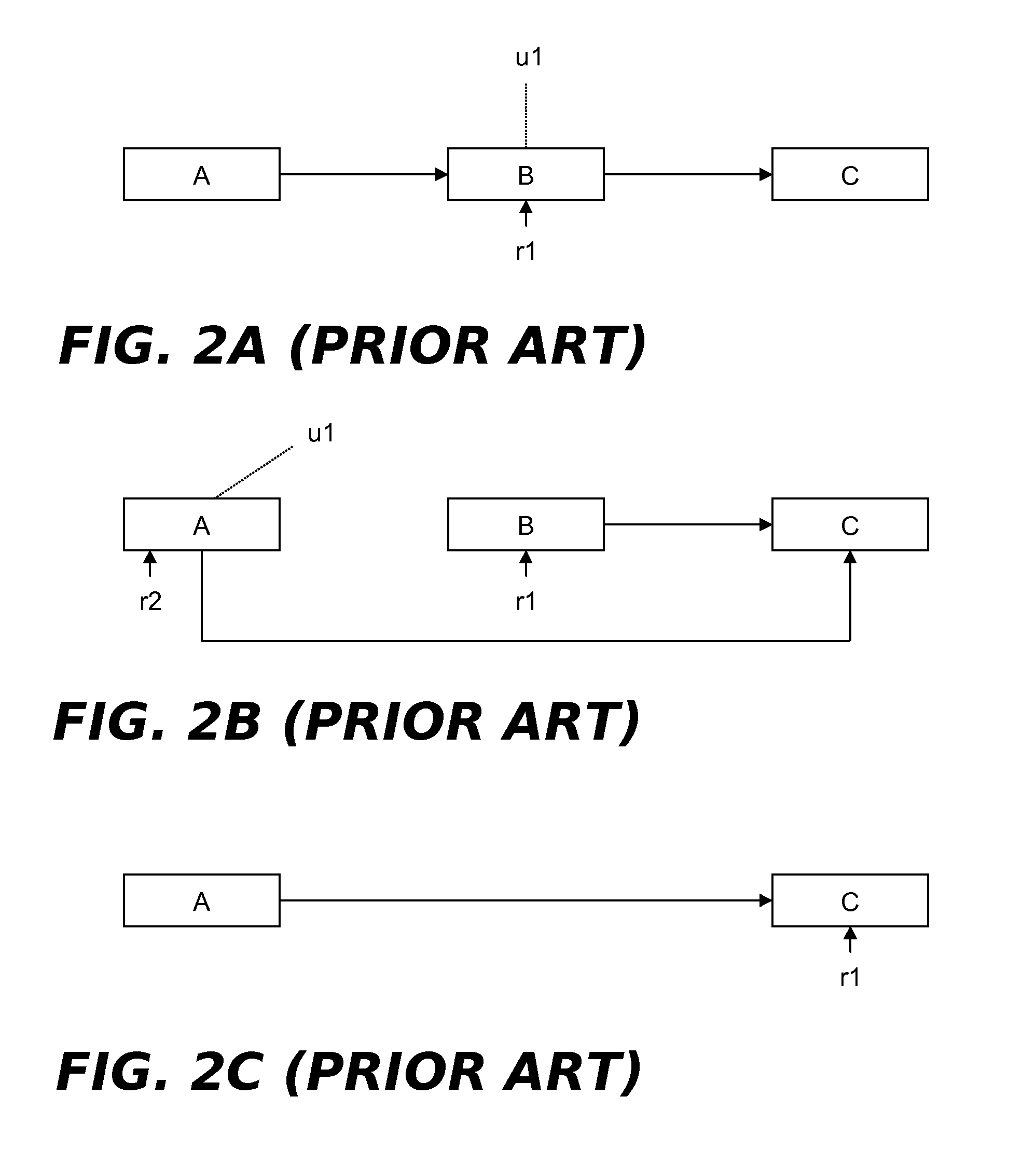

Efficient support of consistent cyclic search with read-copy-update

InactiveUS7426511B2Data processing applicationsDigital data information retrievalQuiescent stateRead-copy-update

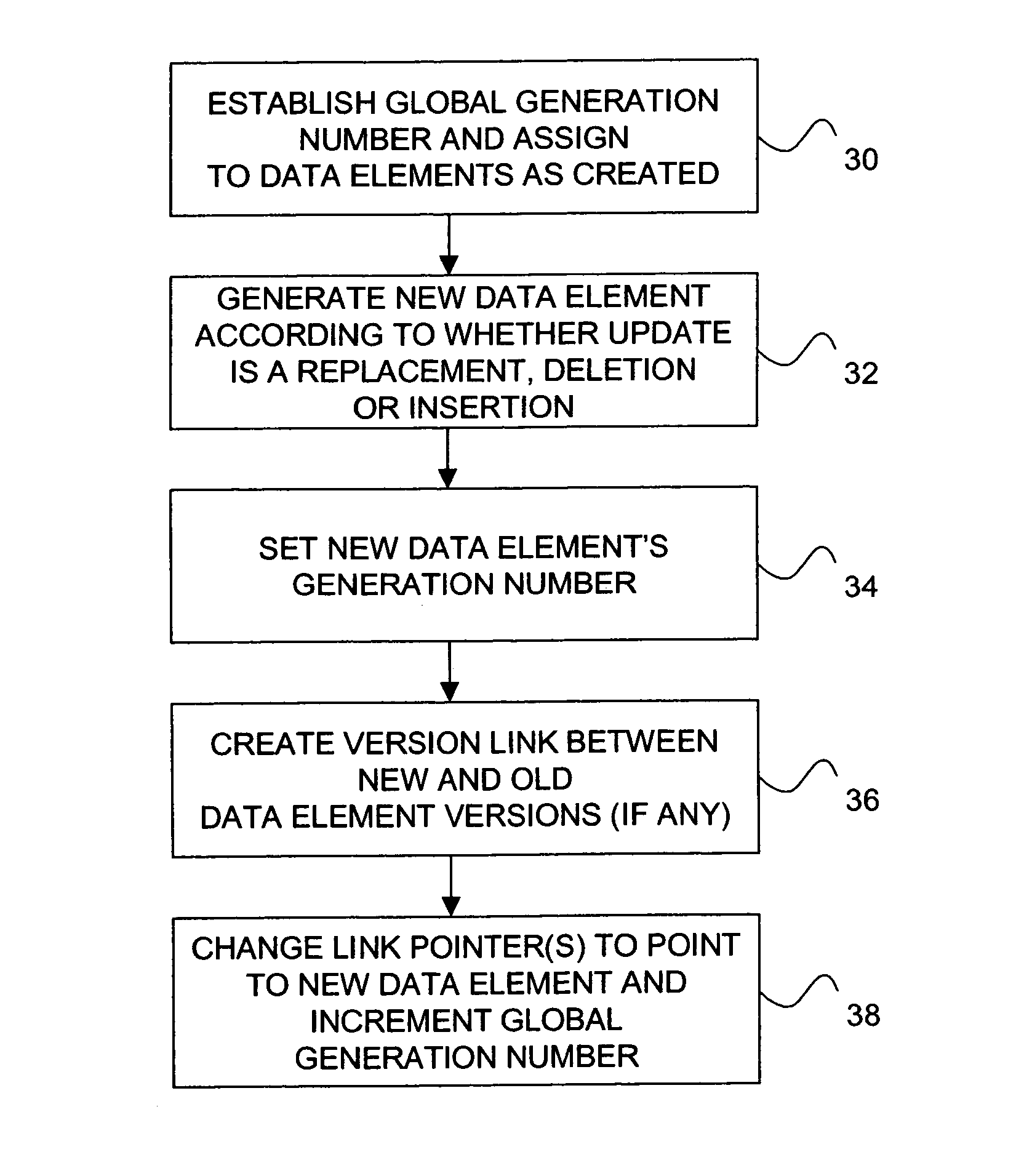

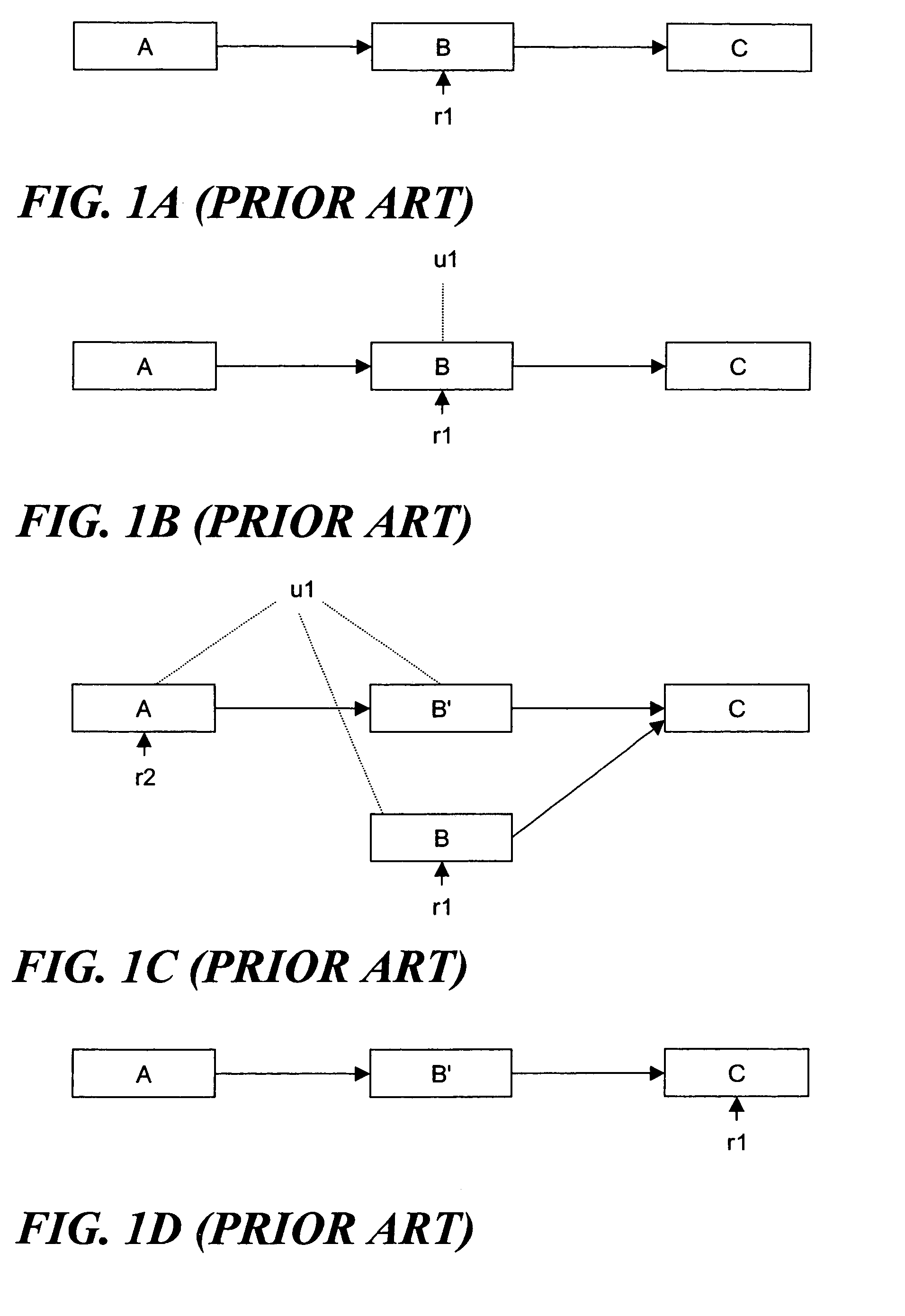

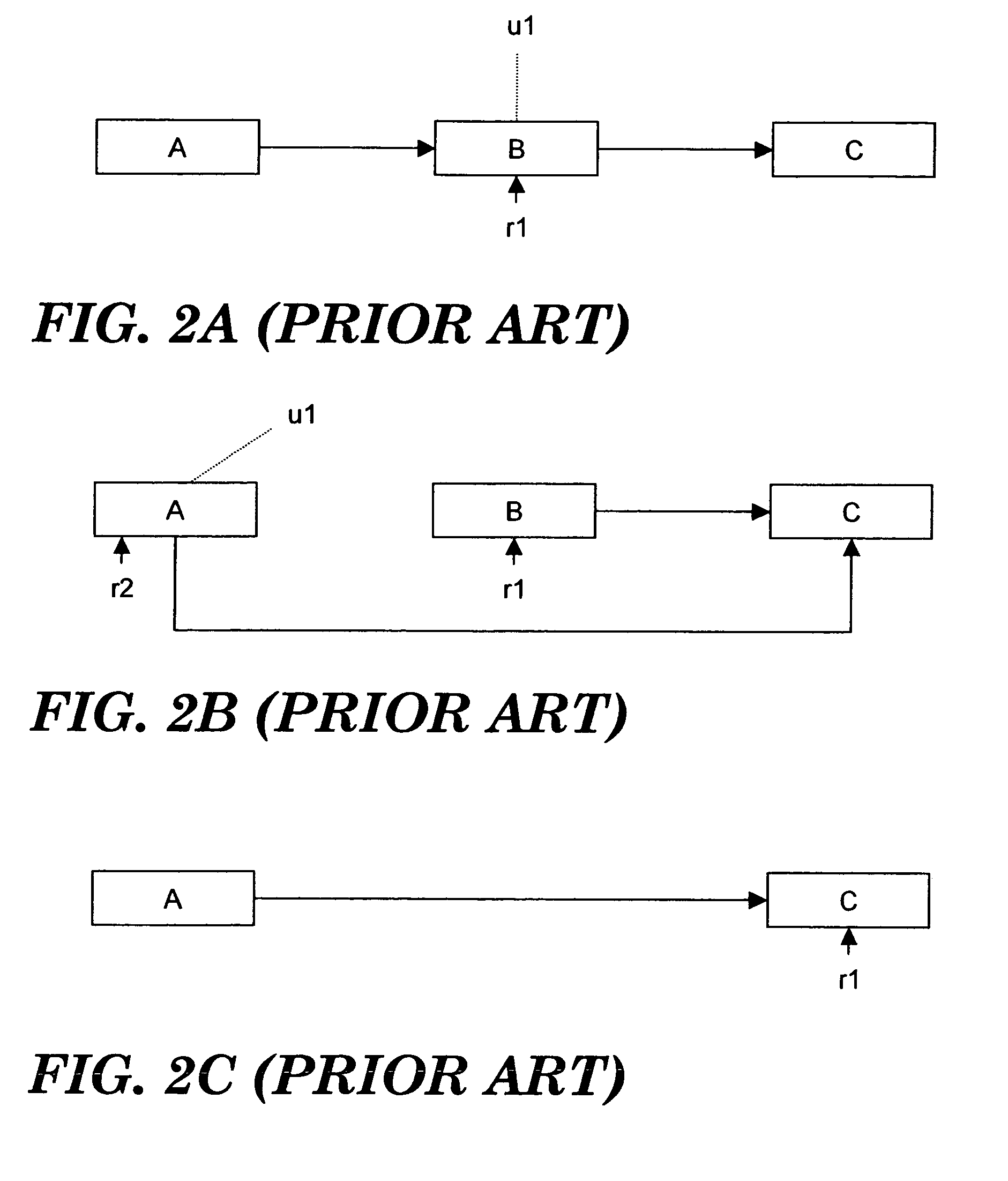

A method, system and computer program product for modifying data elements in a shared data element group that must be updated atomically for the benefit of readers requiring group integrity. A global generation number is associated with the data element group and each member receives a copy of this number when it is created. Each time an update is performed, the global generation number is incremented and the updated element's copy of this number is set to the same value. For each updated data element, a link is maintained from the new version to the pre-update version thereof, either directly or using pointer-forwarding entities. When a search is initiated, the current global generation number is referenced at the commencement of the search. As data elements in the group are traversed, the reader traverses the links between new and old data element versions to find a version having a matching generation number, if any. Following the occurrence of a grace period in which all readers have passed through quiescent states, all old data element versions are freed.

Owner:INT BUSINESS MASCH CORP

Digital silicon photomultiplier for TOF-PET

ActiveUS7723694B2Improve manufacturing yieldReduce sensitivityMaterial analysis by optical meansTomographyQuiescent stateSilicon photomultiplier

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

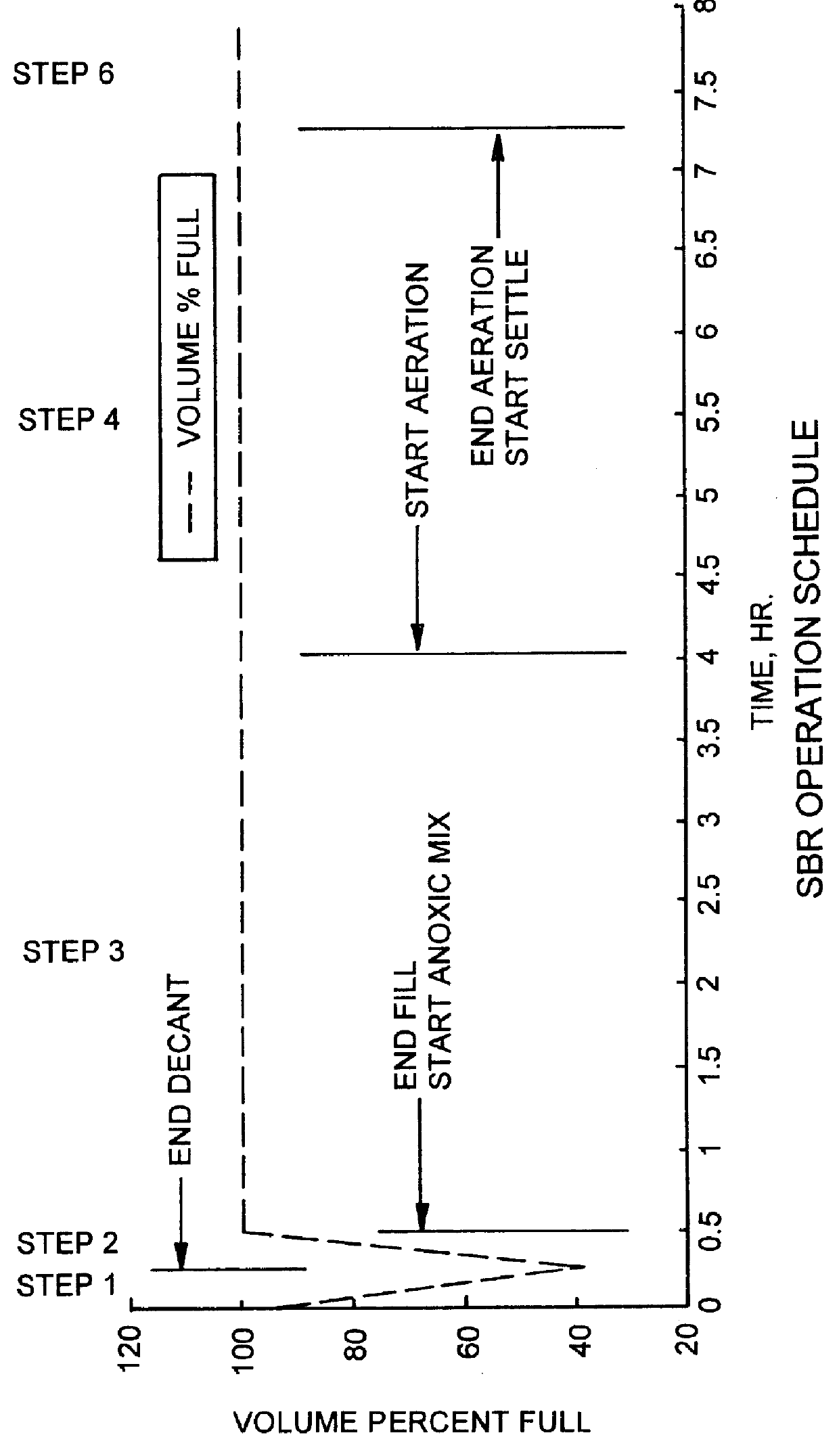

Process for the biological treatment of wastewater with periods of biomass starvation

A biological treatment of wastewater from intermittent and / or sporadic sources is described. The process includes the step of: maintaining treated wastewater effluent and biomass in a quiescent state without stirring, aeration or agitation during biomass starvation wherein said biomass retains the capacity for biological wastewater treatment following the period of prolonged biomass starvation.

Owner:HAGGERTY KEN

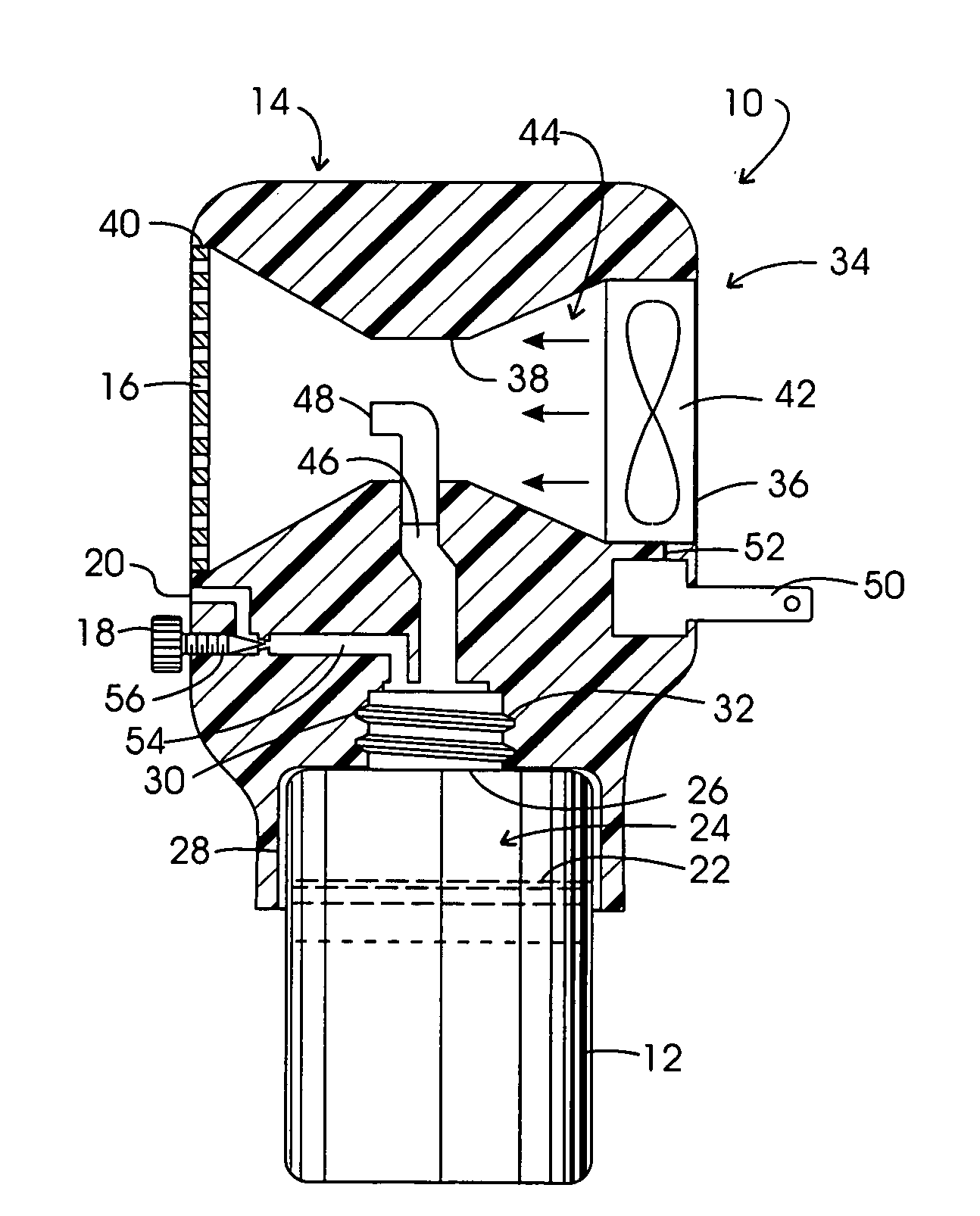

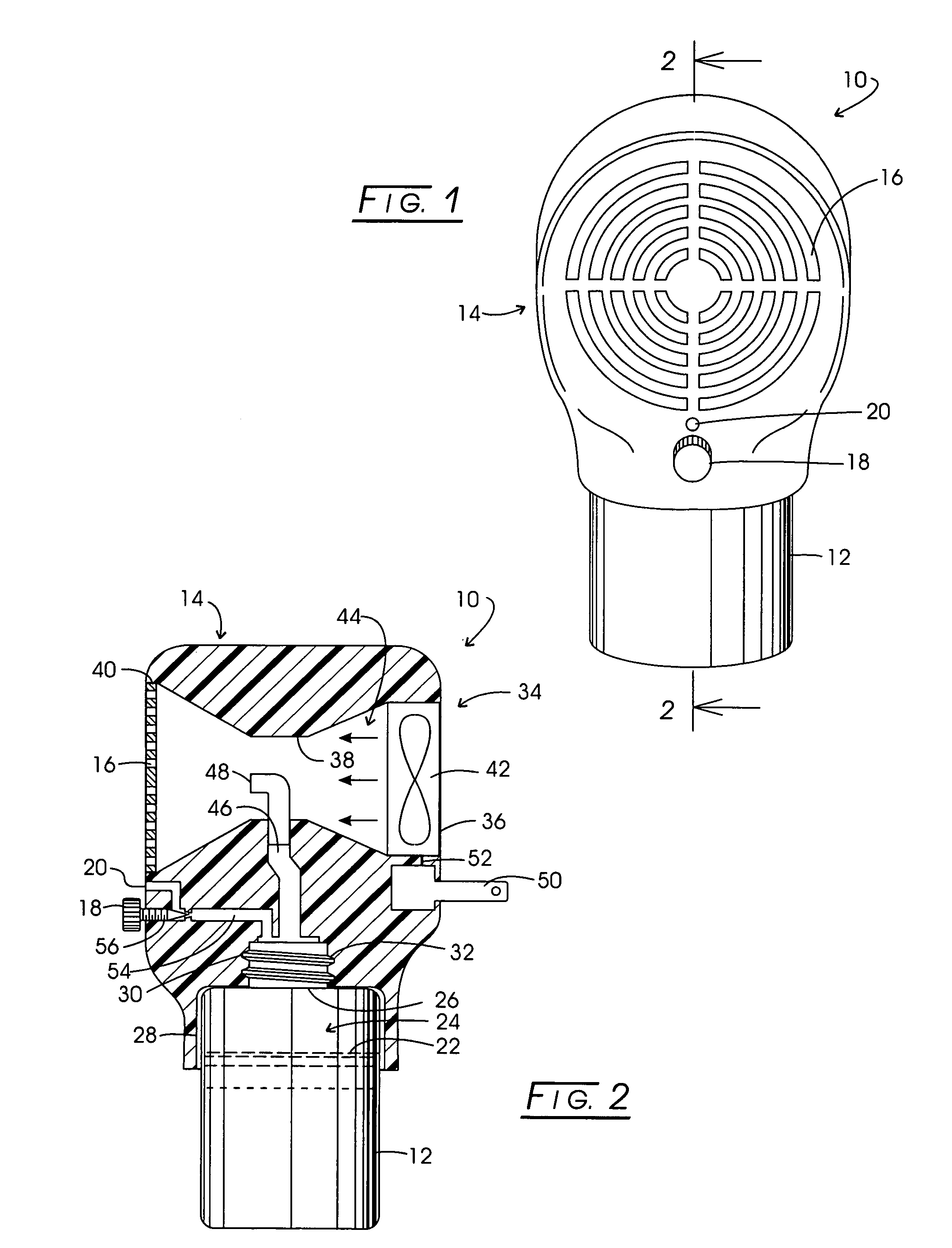

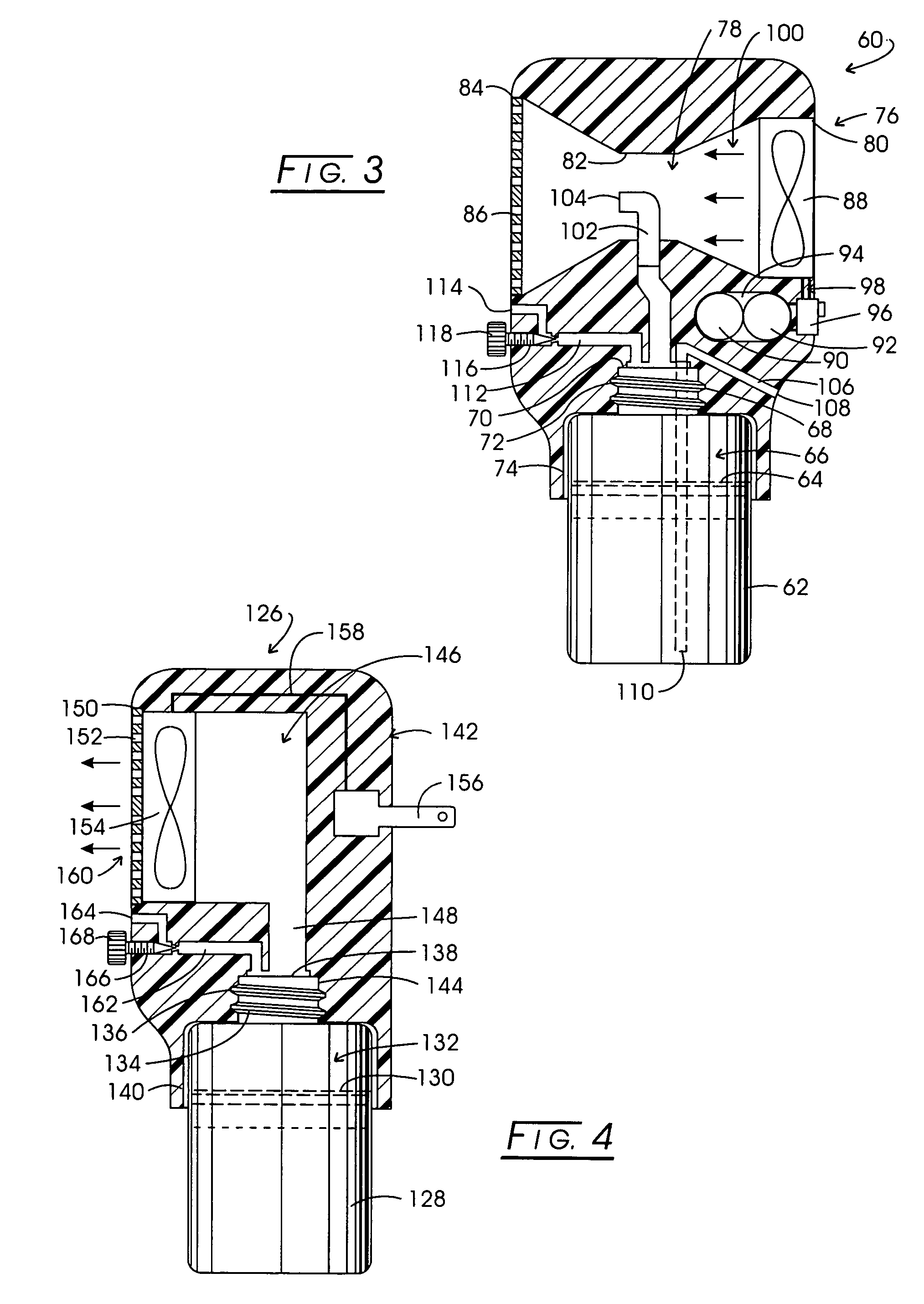

Fragrancing system and method

InactiveUS7377493B2Reduce pressureSpeed up evaporationCarburetting airFlow mixersQuiescent stateEngineering

System and method for emanating fragrance vapor into a region. Fragrance liquid within a receptacle exhibits a liquid phase-vapor phase interface surface when in a quiescent state. Utilizing sub-pressure generators such as fan driven systems, the pressure above the interface is lowered to promote the escape of vapor molecules for dissemination into the atmosphere. The surface area of the fragrance fluid may be increased through the use of a bubbling technique to derive an effective area permitting a larger vapor molecule escape.

Owner:INNOVATIVE PROD MANAGEMENT

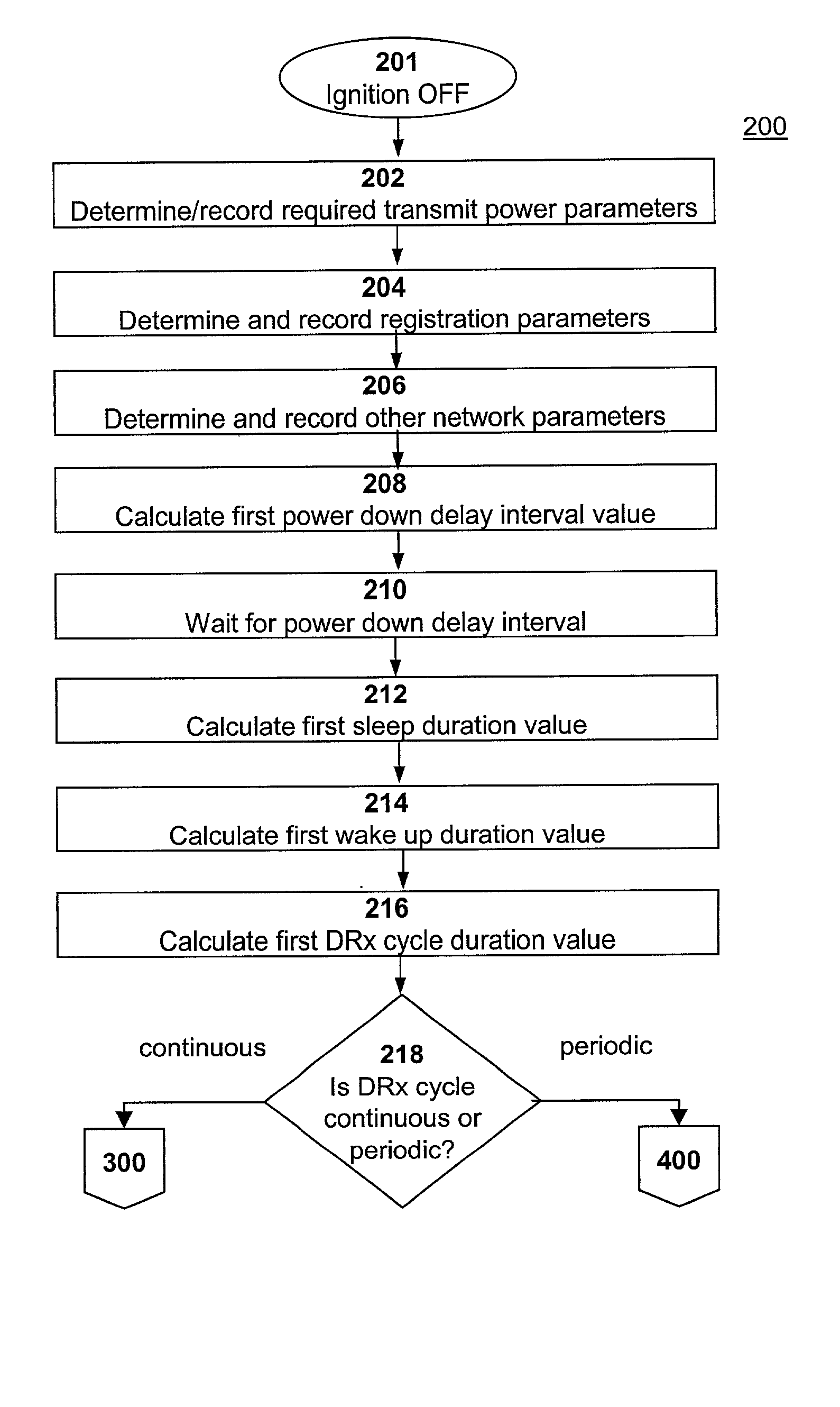

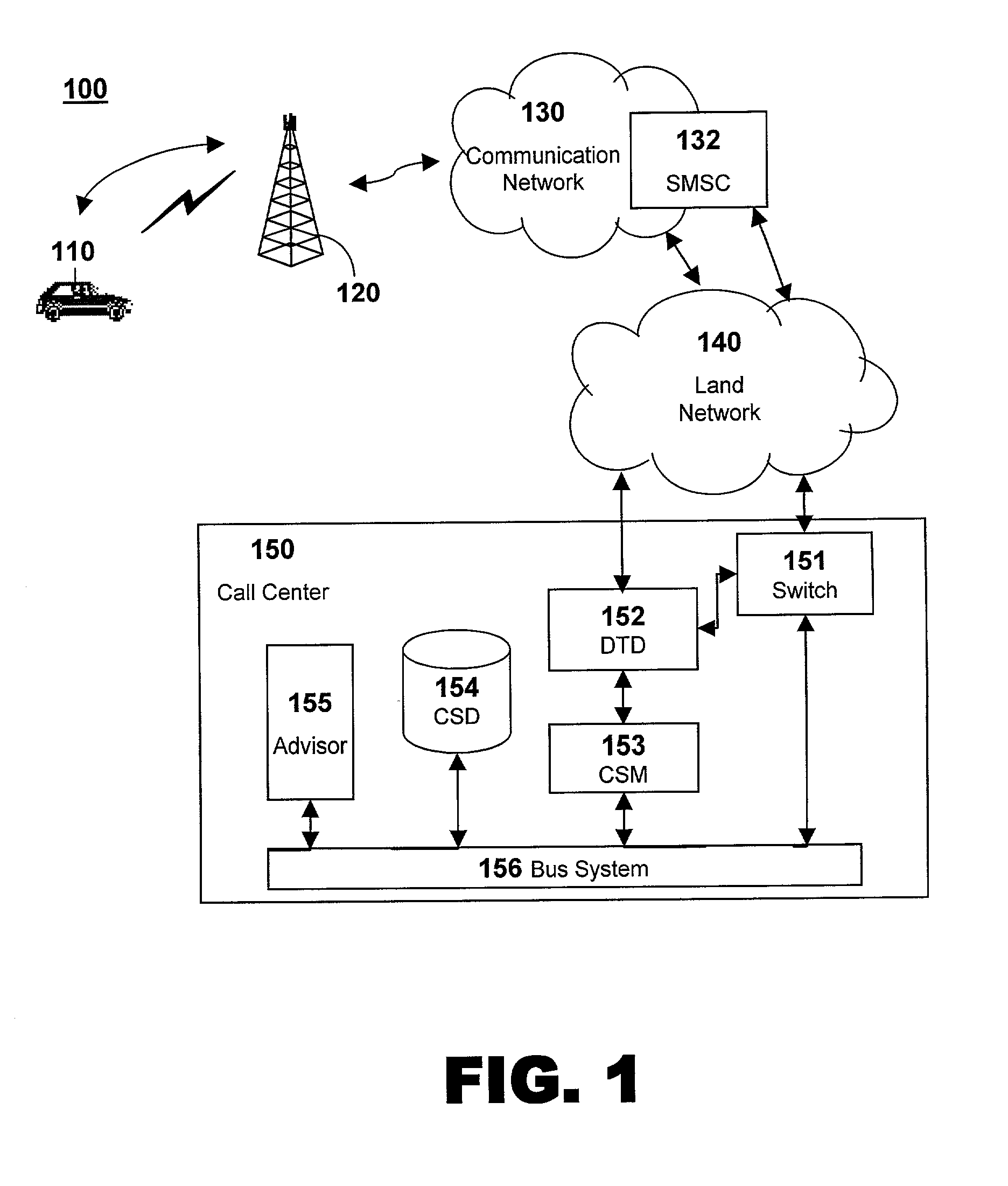

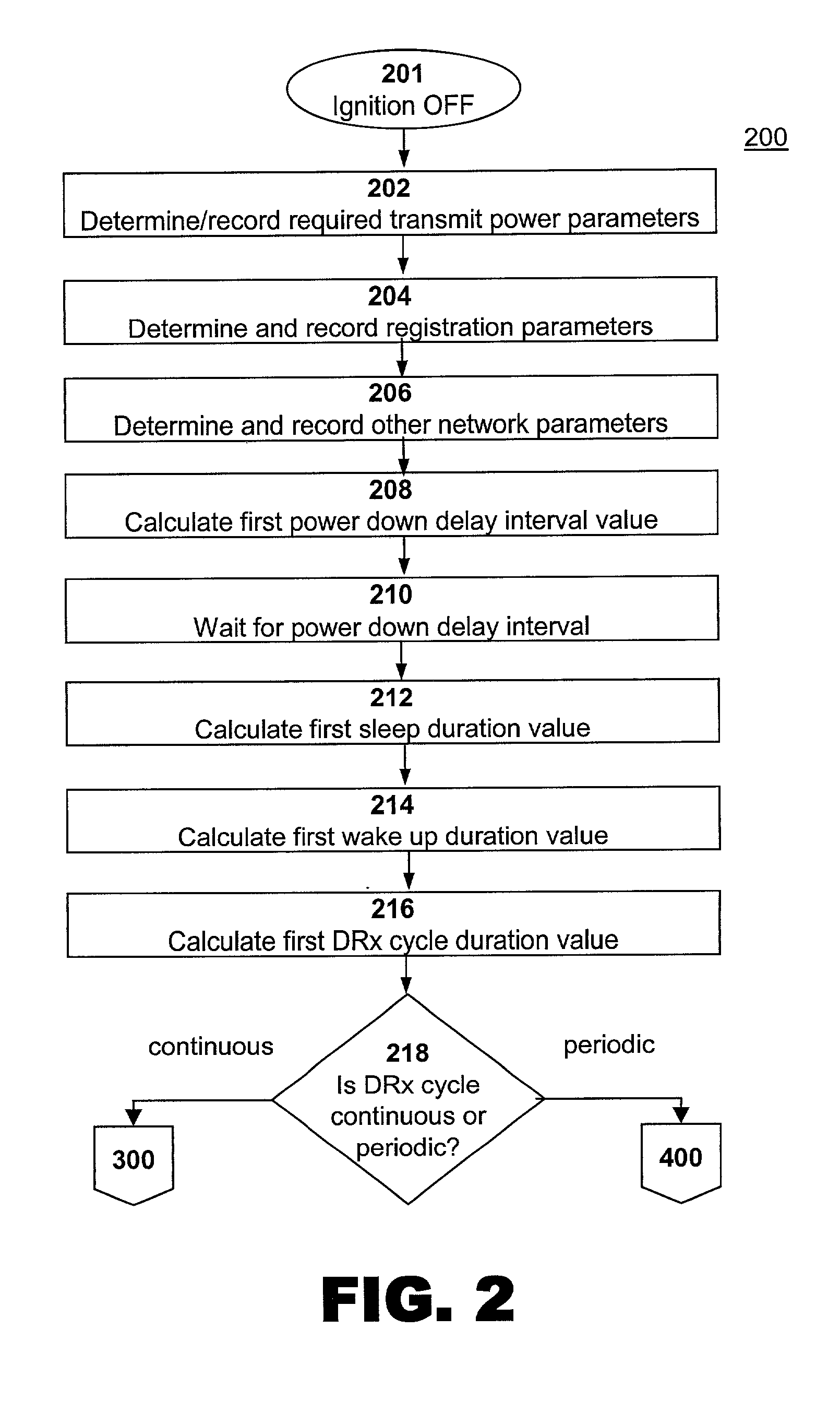

Mobile vehicle quiescent cycle control method

The present invention provides a method of accessing a quiescent mobile vehicle using a wireless communication system. At least one transmit power parameter of a vehicle communication device is determined. At least one sleep duration value is calculated based on the transmit power parameter. The vehicle communication device is placed into a quiescent state based on the sleep duration value. Programs and systems of using the method are also provided.

Owner:GENERA MOTORS LLC

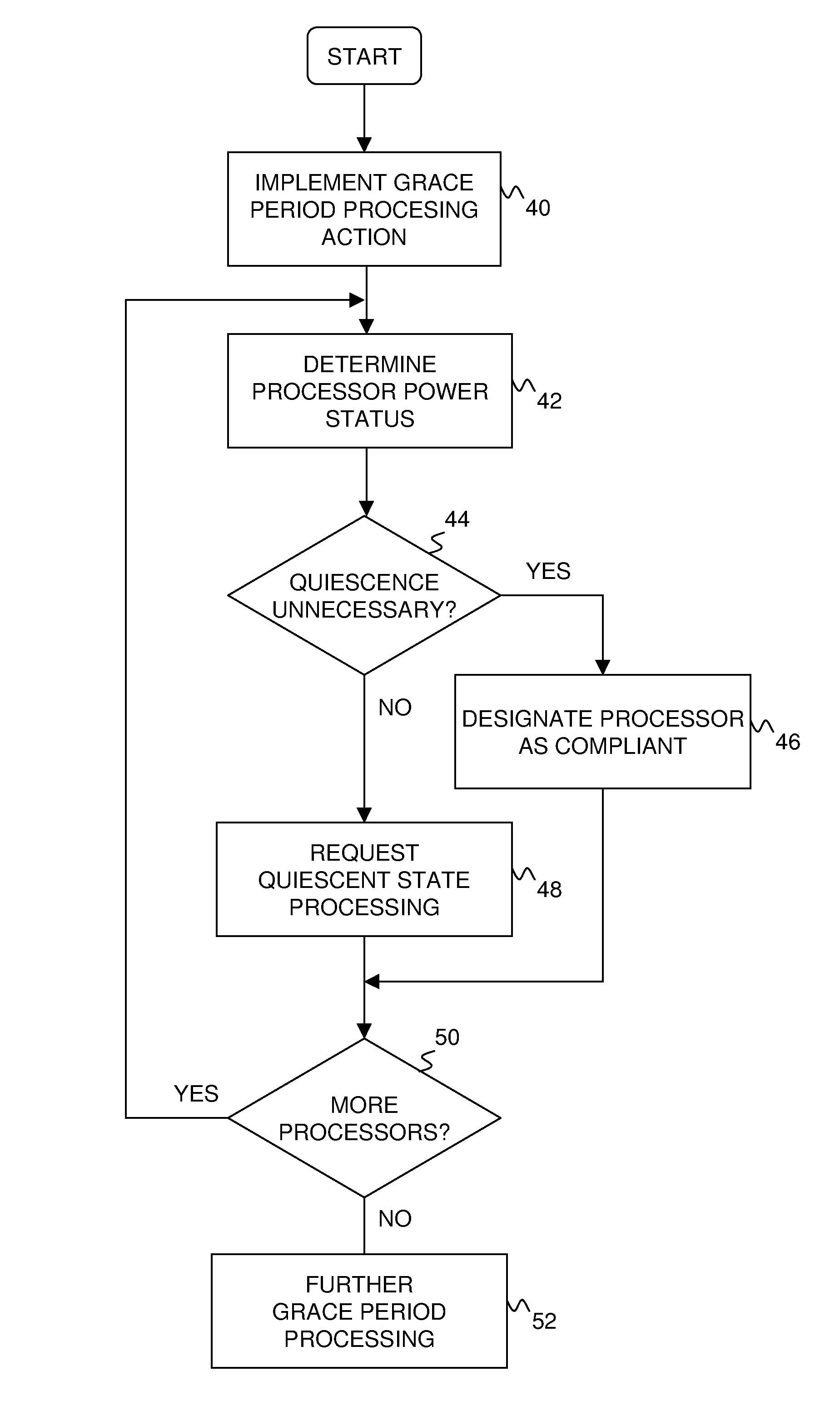

Optimizing non-preemptible read-copy update for low-power usage by avoiding unnecessary wakeups

A technique for low-power detection of a grace period following a shared data element update operation that affects non-preemptible data readers. A grace period processing action is implemented that requires a processor that may be running a non-preemptible reader of the shared data element to pass through a quiescent state before further grace period processing can proceed. A power status of the processor is also determined. Further grace period processing may proceed without requiring the processor to pass through a quiescent state if the power status indicates that quiescent state processing by the processor is unnecessary.

Owner:INT BUSINESS MASCH CORP

Method and system for accelerated data quality enhancement

ActiveUS20110138312A1Digital data information retrievalDigital data processing detailsQuiescent stateData set

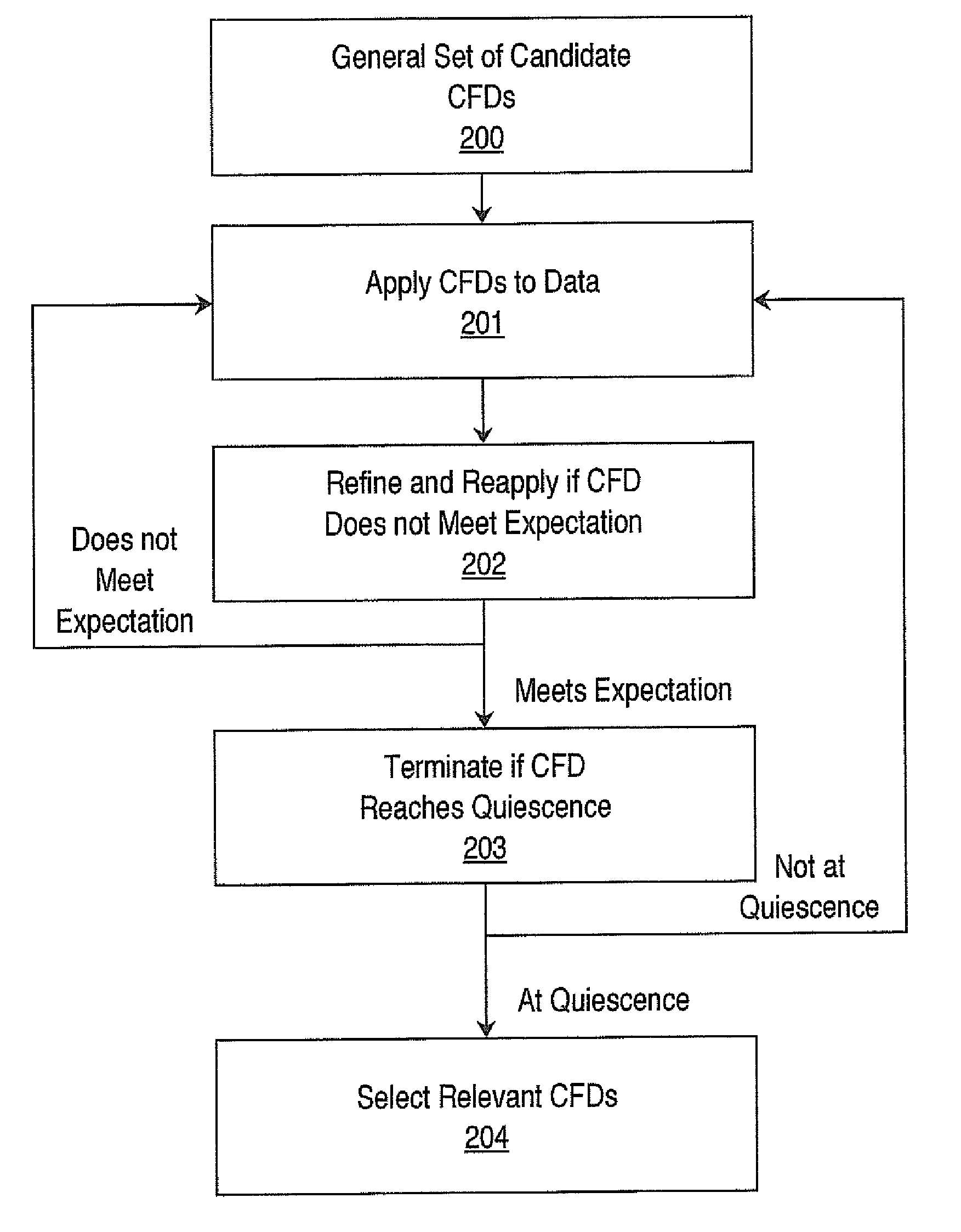

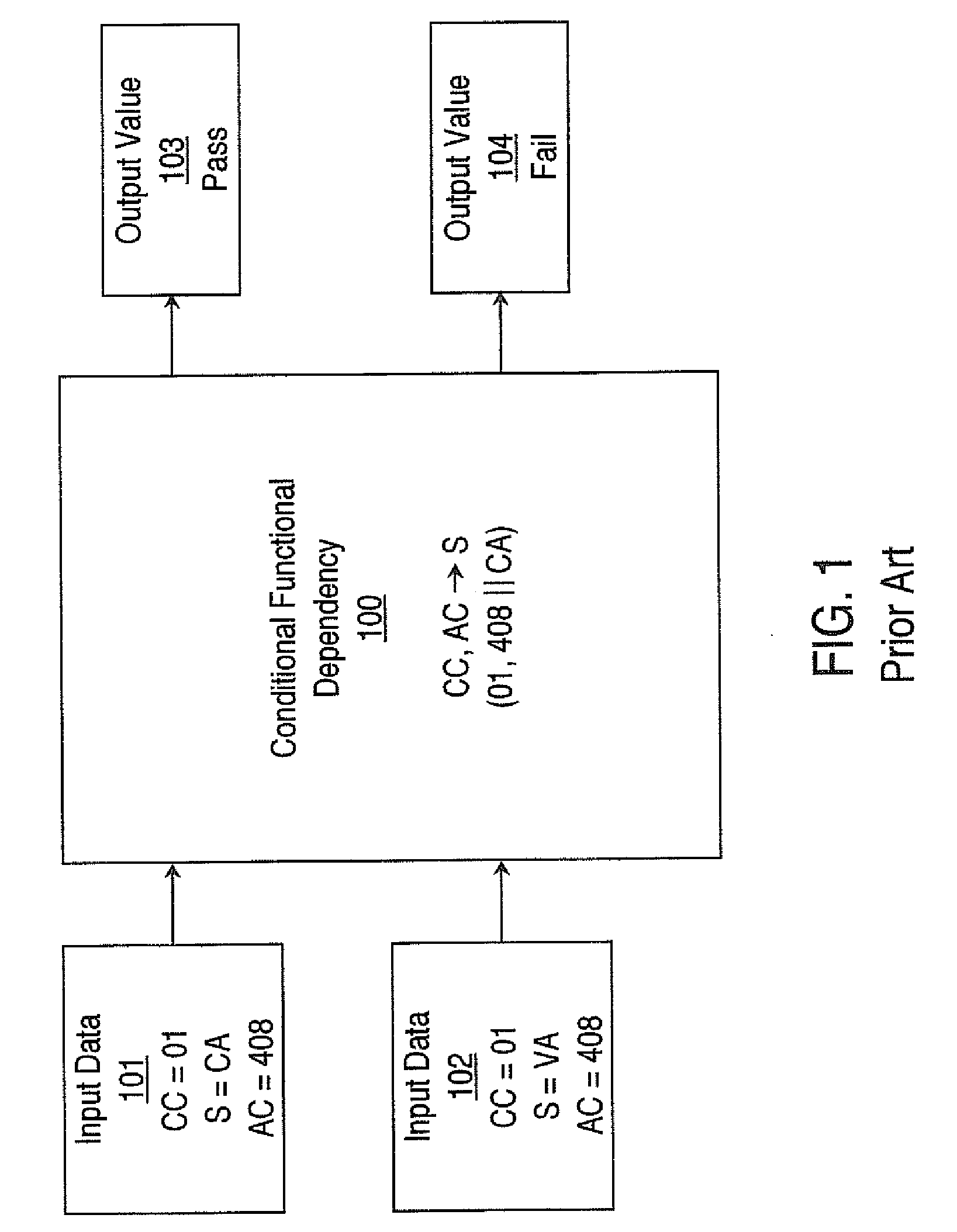

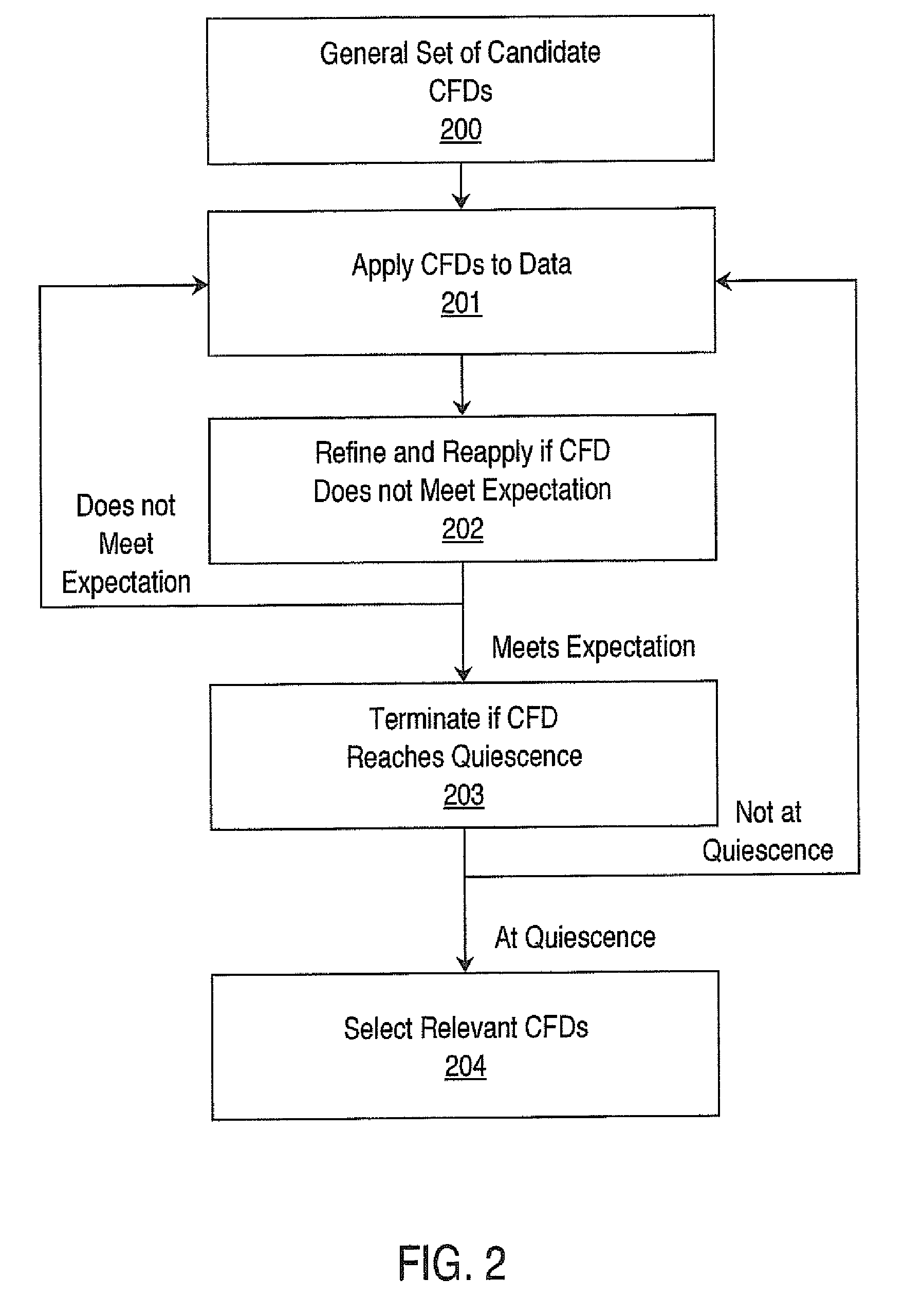

Embodiments of the present invention solve the technical problem of identifying, collecting, and managing rules that improve poor quality data on enterprise initiatives ranging from data governance to business intelligence. In a specific embodiment of the present invention, a method is provided for producing data quality rules for a data set. A set of candidate conditional functional dependencies are generated comprised of candidate seeds of attributes that are within a certain degree of relatedness in the ontology of the data set. The candidate conditional functional dependencies are then applied to the data refined until they reach a quiescent state where they have not been refined even though the data they have been applied to has been stable. The resulting refined candidate conditional functional dependencies are the data enhancement rules for the data set and other related data sets. In another specific embodiment of the present invention, a computer system for the development of data quality rules is provided having a rule repository, a data quality rules discovery engine, and a user interface.

Owner:ACCENTURE GLOBAL SERVICES LTD

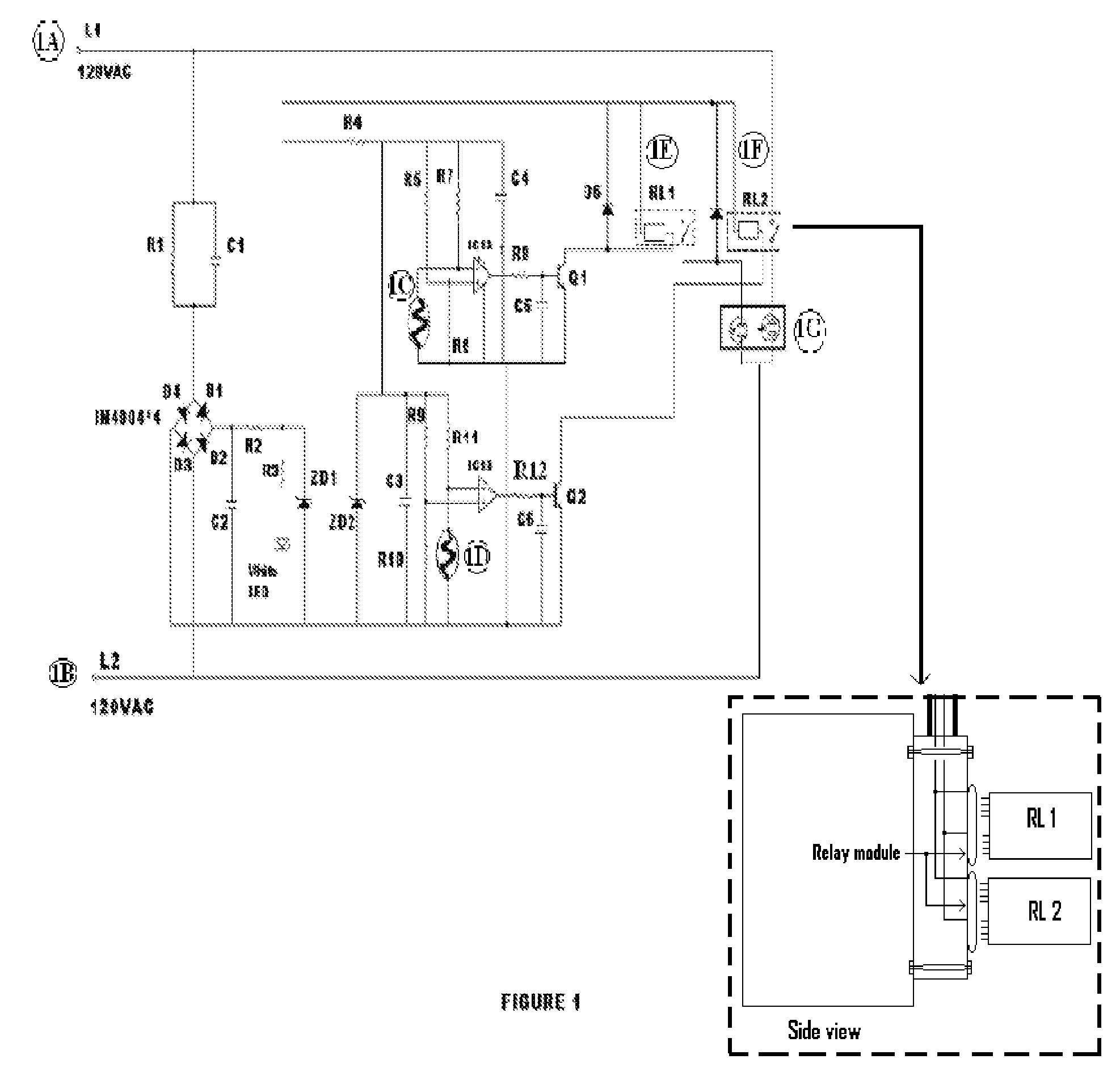

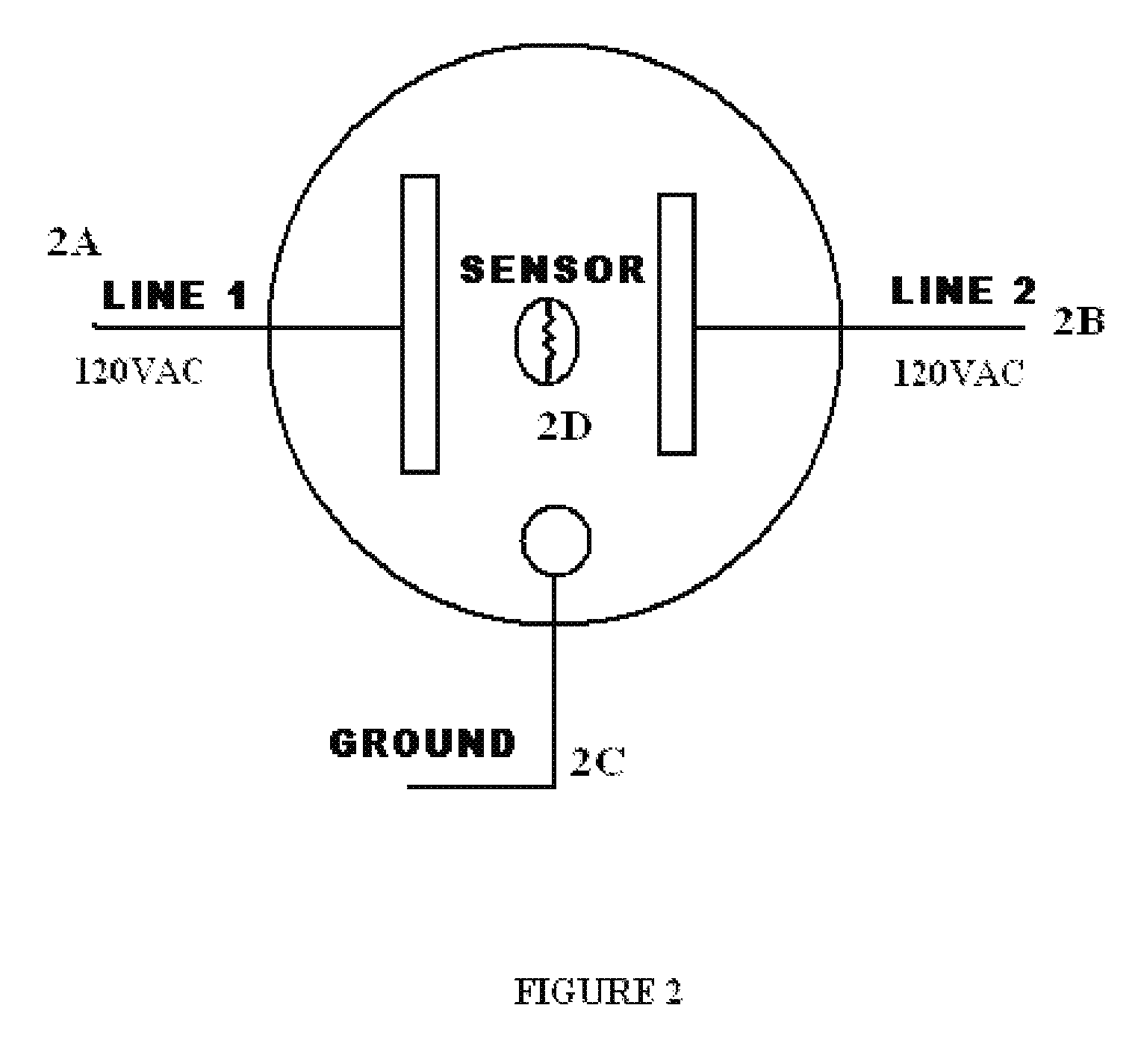

Electrically safe receptacle

InactiveUS7575467B2Shorten the timeEasy to replaceElectrically conductive connectionsTwo pole connectionsElectricityQuiescent state

An electrically safe receptacle that in it's normal quiescent state will not have electrical current flow. Said electrically safe receptacle will be equipped with normally-open switches on one or both female conductors that are controlled by a strategically placed sensor to detect the insertion of a male plug. Detection of the male plug insertion will signal the normally open switches to close the circuit pathway and allow for the flow of electrical current to the device permitting normal operation. Insertion of a foreign conductive device such as a hair pin, knife blade, or metallic tool in one or both female conductors will fail to activate the sensor and thereby reduce or eliminate the possibility of accidental electrocution by preventing the flow of electrical current.

Owner:FERGUSON THOMAS WILMER +1

Efficient support of consistent cyclic search with read-copy-update

InactiveUS20050198030A1Data processing applicationsDigital data information retrievalQuiescent stateRead-copy-update

A method, system and computer program product for modifying data elements in a shared data element group that must be updated atomically for the benefit of readers requiring group integrity. A global generation number is associated with the data element group and each member receives a copy of this number when it is created. Each time an update is performed, the global generation number is incremented and the updated element's copy of this number is set to the same value. For each updated data element, a link is maintained from the new version to the pre-update version thereof, either directly or using pointer-forwarding entities. When a search is initiated, the current global generation number is referenced at the commencement of the search. As data elements in the group are traversed, the reader traverses the links between new and old data element versions to find a version having a matching generation number, if any. Following the occurrence of a grace period in which all readers have passed through quiescent states, all old data element versions are freed.

Owner:IBM CORP

Eliminating synchronous grace period detection for non-preemptible read-copy update on uniprocessor systems

ActiveUS8195893B2Program synchronisationDigital data processing detailsData processing systemQuiescent state

A technique for optimizing grace period detection in a uniprocessor environment. An update operation is performed on a data element that is shared with non-preemptible readers of the data element. A call is issued to a synchronous grace period detection method. The synchronous grace period detection method performs synchronous grace period detection and returns from the call if the data processing system implements a multi-processor environment at the time of the call. The synchronous grace period detection determines the end of a grace period in which the readers have passed through a quiescent state and cannot be maintaining references to the pre-update view of the shared data. The synchronous grace period detection method returns from the call without performing grace period detection if the data processing system implements a uniprocessor environment at the time of the call.

Owner:INT BUSINESS MASCH CORP

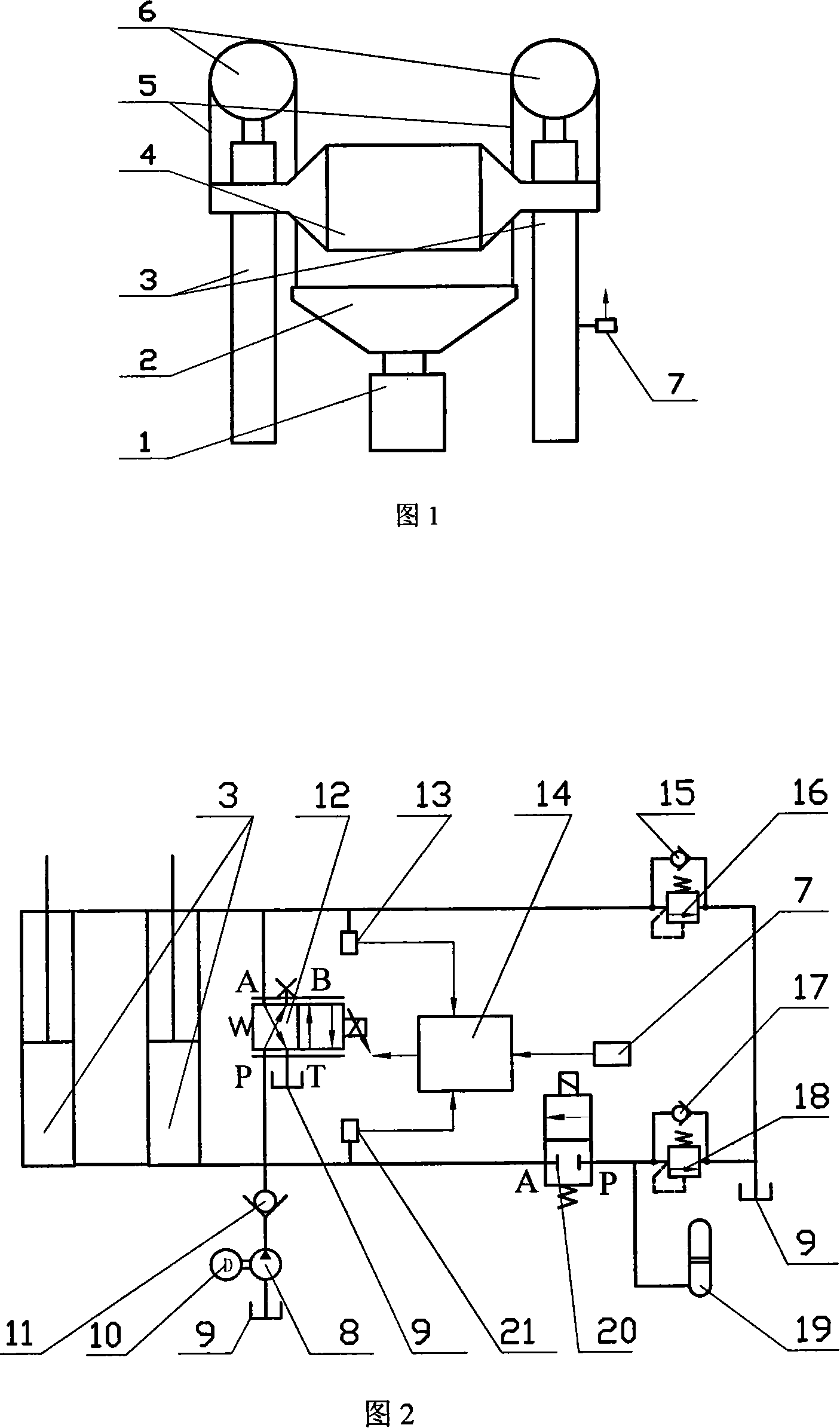

Drilling column heave compensator for floating drill platform in the sea

InactiveCN101130949ALimit consumptionImprove the compensation effectArtificial islandsUnderwater structuresCompensation effectEngineering

The present invention discloses one kind of heave compensation system for drill stem of marine floating drilling platform. High pressure hydraulic oil is led from the energy accumulator through a compensation control valve to the compensating hydraulic cylinder, so as to provide one additional force controlled based on the heave motion of the platform for raised compensation effect. The control unit detects the vertical motion of the platform to control the hydraulic system for compensating the heave motion of the platform by means of the steel cable or chain to make the crossbeam and rotary hook in vertically quiescent state relative to the well bottom. The present invention is superior to traditional passive heave compensation system, and has high reaction speed, high compensation precision, low power consumption and low operation cost.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

Making read-copy update free-running grace period counters safe against lengthy low power state sojourns

InactiveUS8407503B2Avoid disruptionVolume/mass flow measurementPower supply for data processingQuiescent stateRead-copy-update

A technique for making a free-running grace period counter safe against lengthy low power state processor sojourns. The grace period counter tracks grace periods that determine when processors that are capable executing read operations have passed through a quiescent state that guarantees the readers will no longer maintain references to shared data. Periodically, one or more processors may be placed in a low power state in which the processors discontinue performing grace period detection operations. Such processors may remain in the low power state for a complete cycle of the grace period counter. This scenario can potentially disrupt grace period detection operations if the processors awaken to see the same grace period counter value. To rectify this situation, processors in a low power state may be periodically awakened at a predetermined point selected prevent the low power state from extending for an entire roll over of the grace period counter.

Owner:INT BUSINESS MASCH CORP

Naturally differentiated sensor

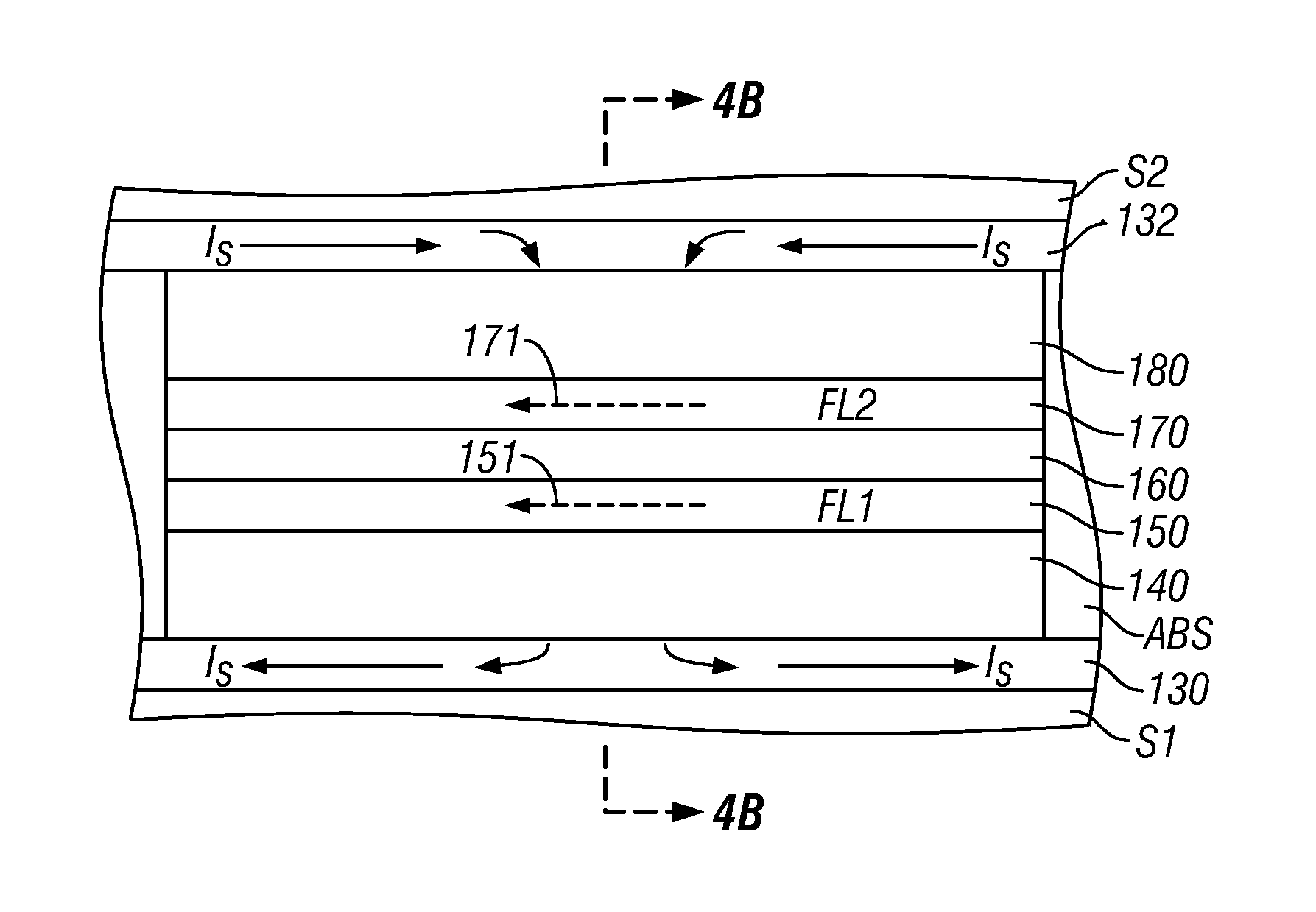

A differentiated sensor includes a pair of magnetic layers having magnetization directions that are substantially antiparallel in a quiescent state. At least one of the magnetic layers is a free layer. A spacer layer is disposed between the pair of magnetic layers.

Owner:SEAGATE TECH LLC

Method, apparatus, and system for quiescing a boot environment

ActiveUS20100115256A1Reliable updateDigital computer detailsSpecific program execution arrangementsQuiescent stateEmbedded system

An apparatus, system, and method are disclosed for quiescing a boot environment. A reservation module reserves a portion of a first storage device. A store module stores an update boot image to the reserved portion. A detection module detects the update boot image stored on the first storage device when the computer boots and executes the update boot image in place of a standard boot image in response to detecting the update boot image. The update boot image places a computer in a known quiescent state.

Owner:LENOVO PC INT

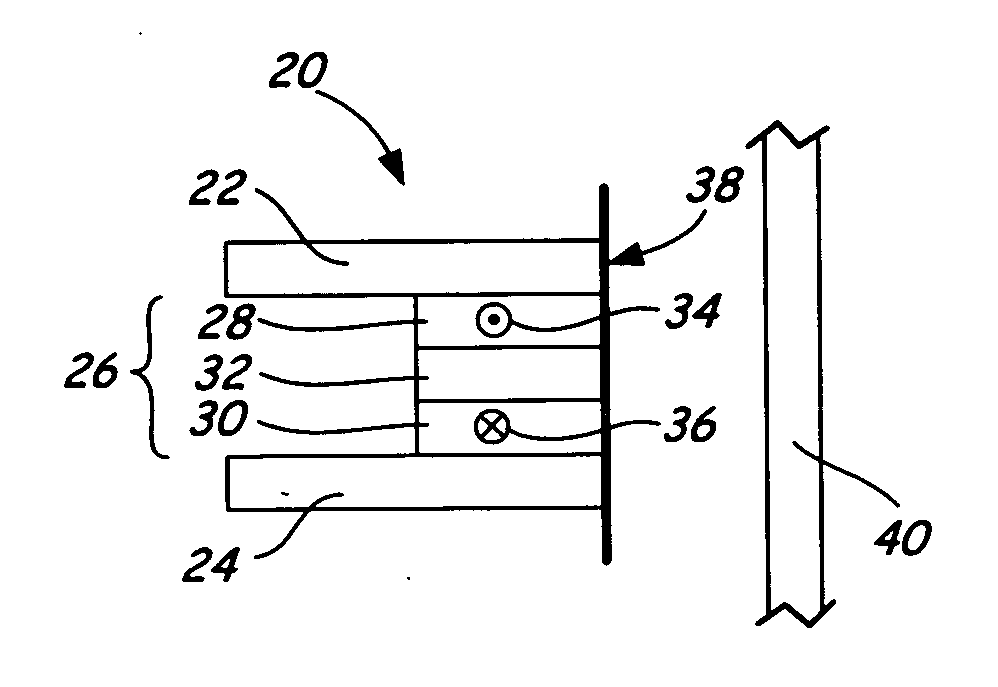

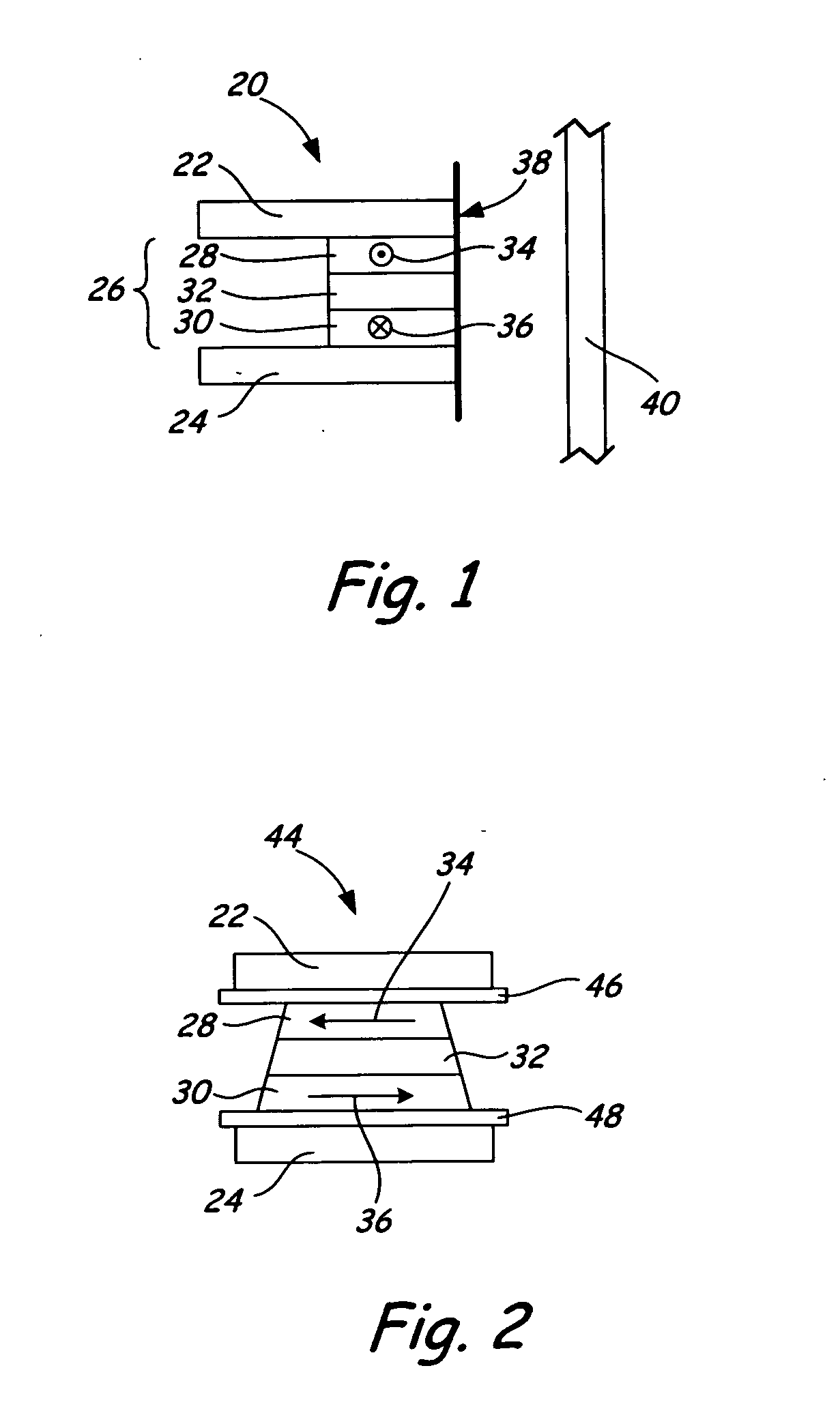

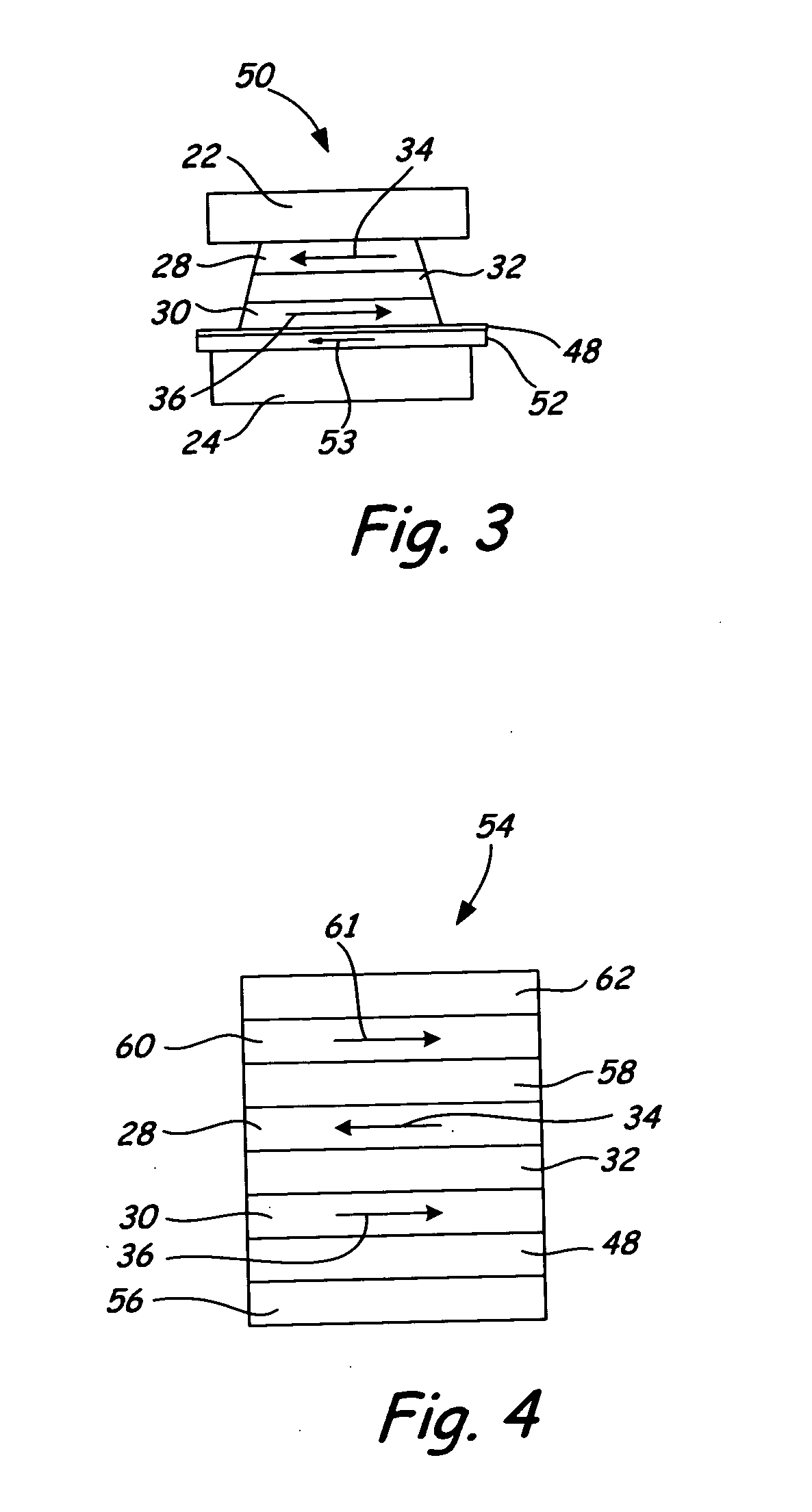

Method for making a scissoring-type current-perpendicular-to-the-plane (CPP) magnetoresistive sensor

A “scissoring-type” current-perpendicular-to-the-plane (CPP) magnetoresistive sensor with dual ferromagnetic sensing or free layers separated by a nonmagnetic spacer layer has improved stability as a result of etch-induced uniaxial magnetic anisotropy in each of the free layers. Each of the two ferromagnetic free layers has an etch-induced uniaxial magnetic anisotropy and an in-plane magnetic moment substantially parallel to its uniaxial anisotropy in the quiescent state, i.e., the absence of an applied magnetic field. The etch-induced uniaxial anisotropy of each of the free layers is achieved either by direct ion etching of each of the free layers, and / or by ion etching of the layer on which each of the free layers is deposited. A strong magnetic anisotropy is induced in the free layers by the etching, which favors generally orthogonal orientation of the two free layers in the quiescent state.

Owner:WESTERN DIGITAL TECH INC

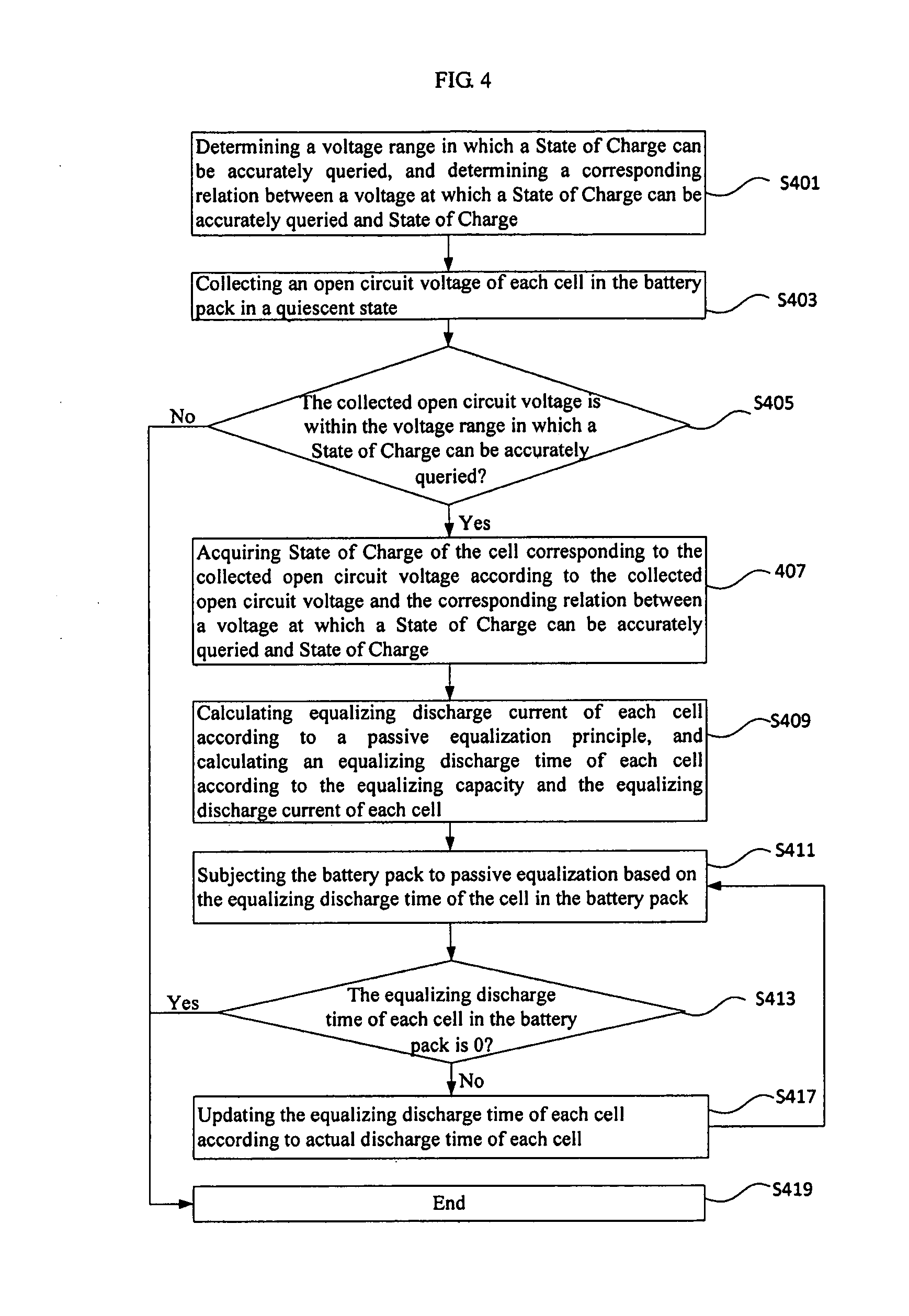

Passive equalization method and system for lithium iron phosphate battery pack

ActiveUS20160190829A1Improve reliabilityCorrect differenceCircuit monitoring/indicationCharge equalisation circuitQuiescent stateLithium iron phosphate

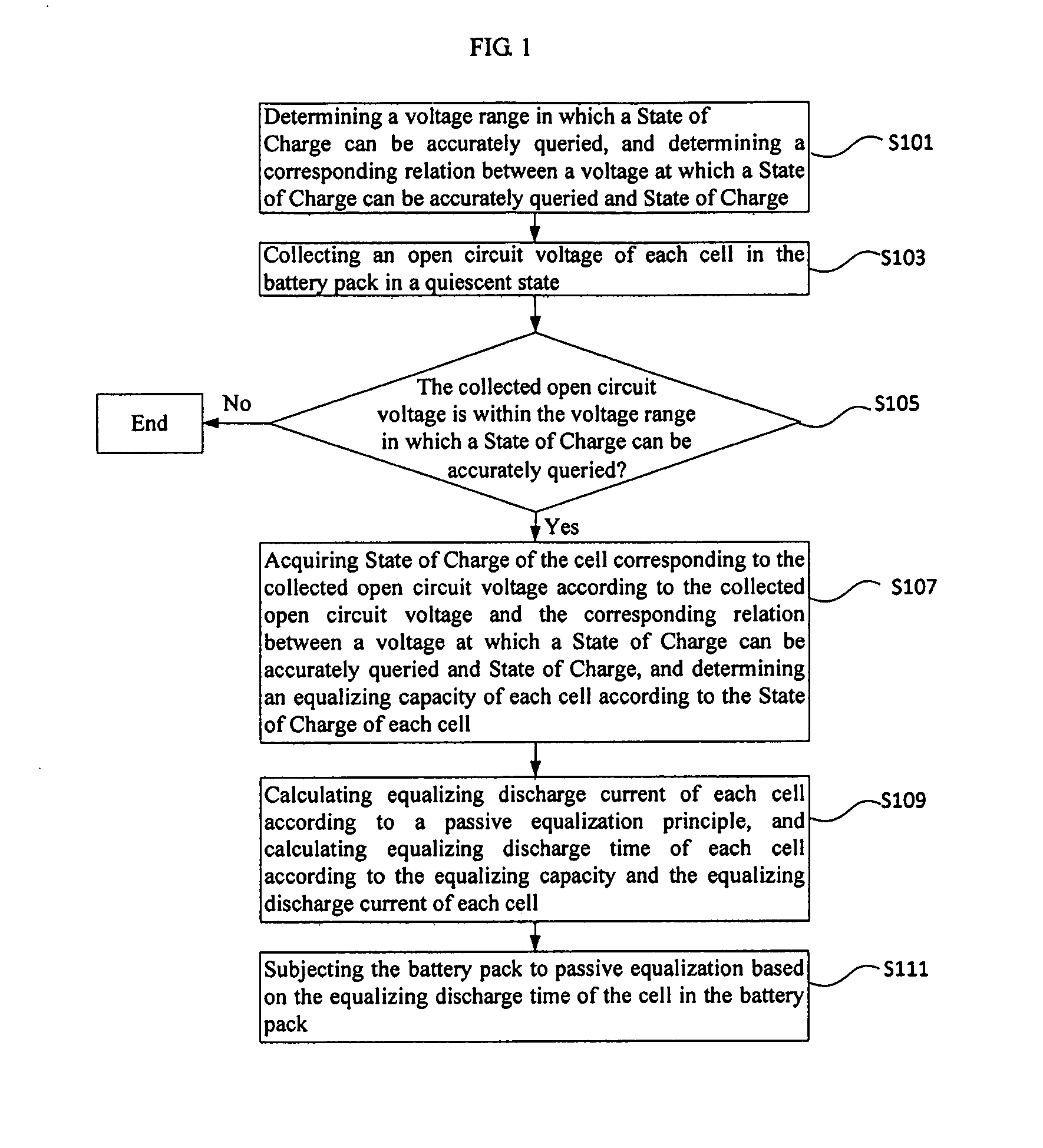

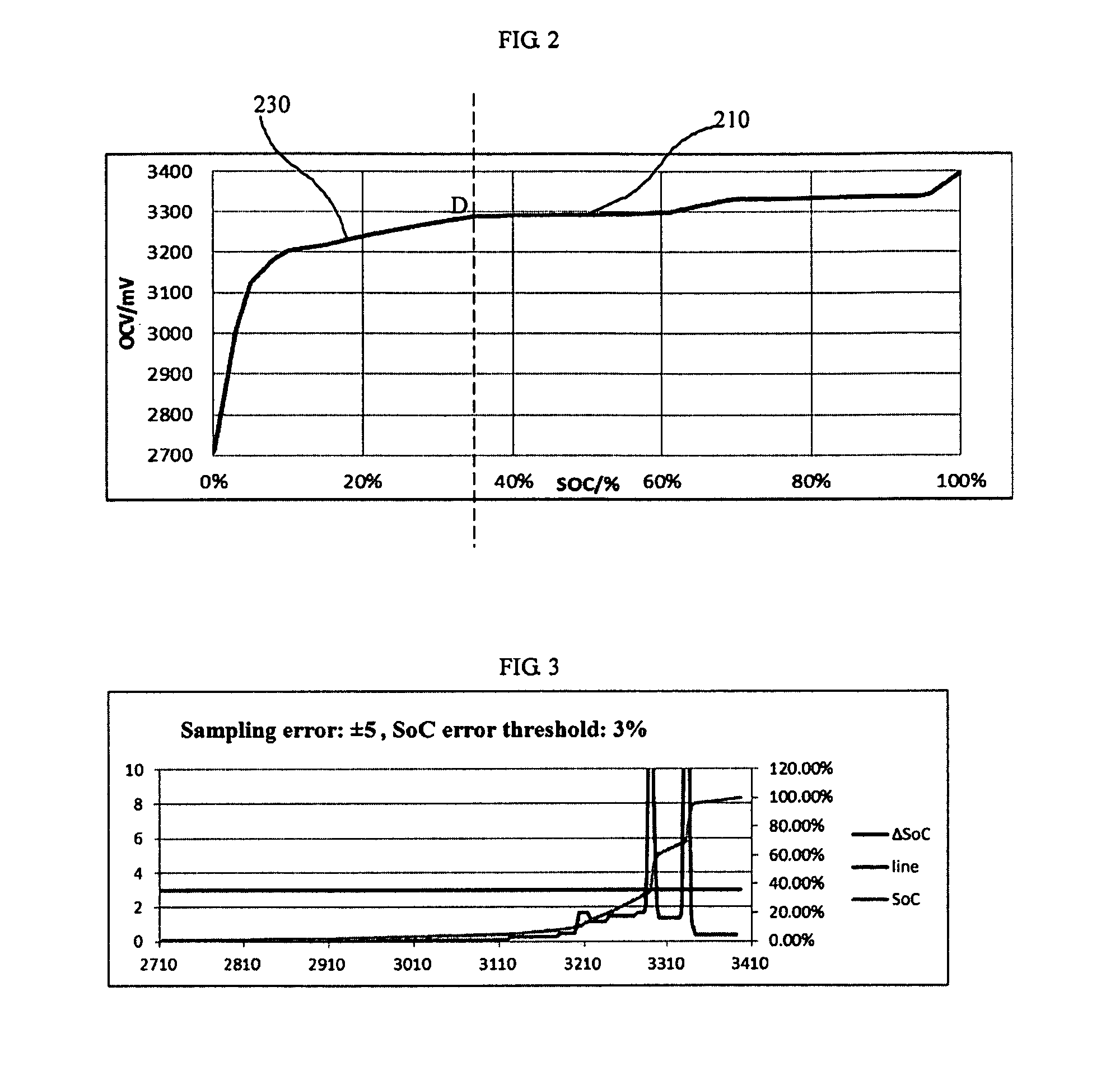

The invention discloses a passive equalization method for a lithium iron phosphate battery pack, comprising: determining a voltage range in which a State of Charge can be accurately queried for a cell in the battery pack, and determining a corresponding relation between a voltage at which a State of Charge can be accurately queried and the State of Charge; collecting an open circuit voltage of each cell in a quiescent state; judging whether the open circuit voltage is within the voltage range in which a State of Charge can be accurately queried; if the open circuit voltage is within the voltage range in which a State of Charge can be accurately queried, acquiring the State of Charge of the cell corresponding to the open circuit voltage according to the open circuit voltage and the corresponding relation between a voltage at which a State of Charge can be accurately queried and the State of Charge, and determining equalizing capacity of each cell according to the State of Charge of each cell; calculating equalizing discharge current of each cell according to a passive equalization principle, and calculating equalizing discharge time of each cell according to the equalizing capacity and the equalizing discharge current of each cell; and subjecting the battery pack to passive equalization based on the equalizing discharge time of each cell.

Owner:CONTEMPORARY AMPEREX RUNZHI SOFTWARE TECH LTD

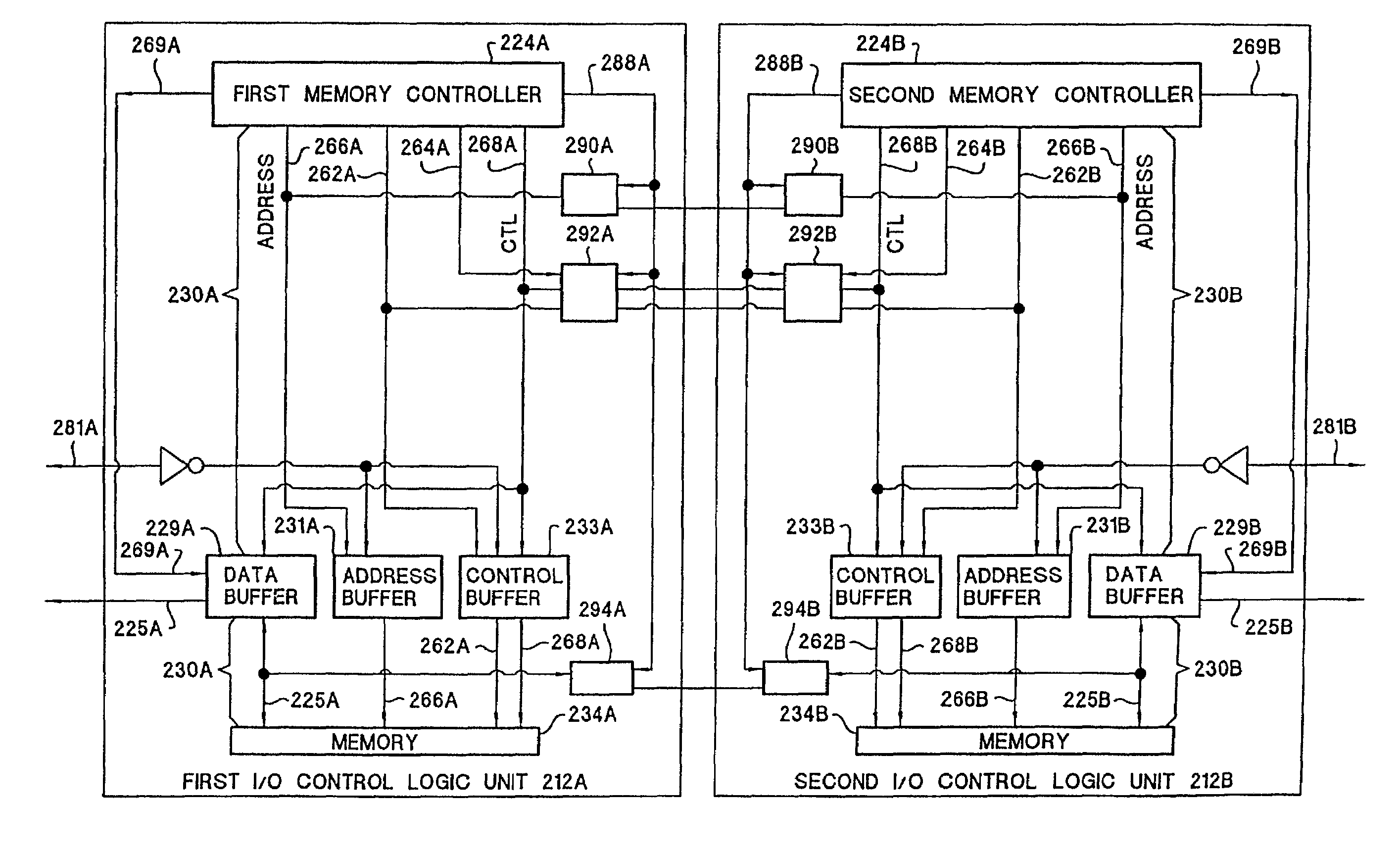

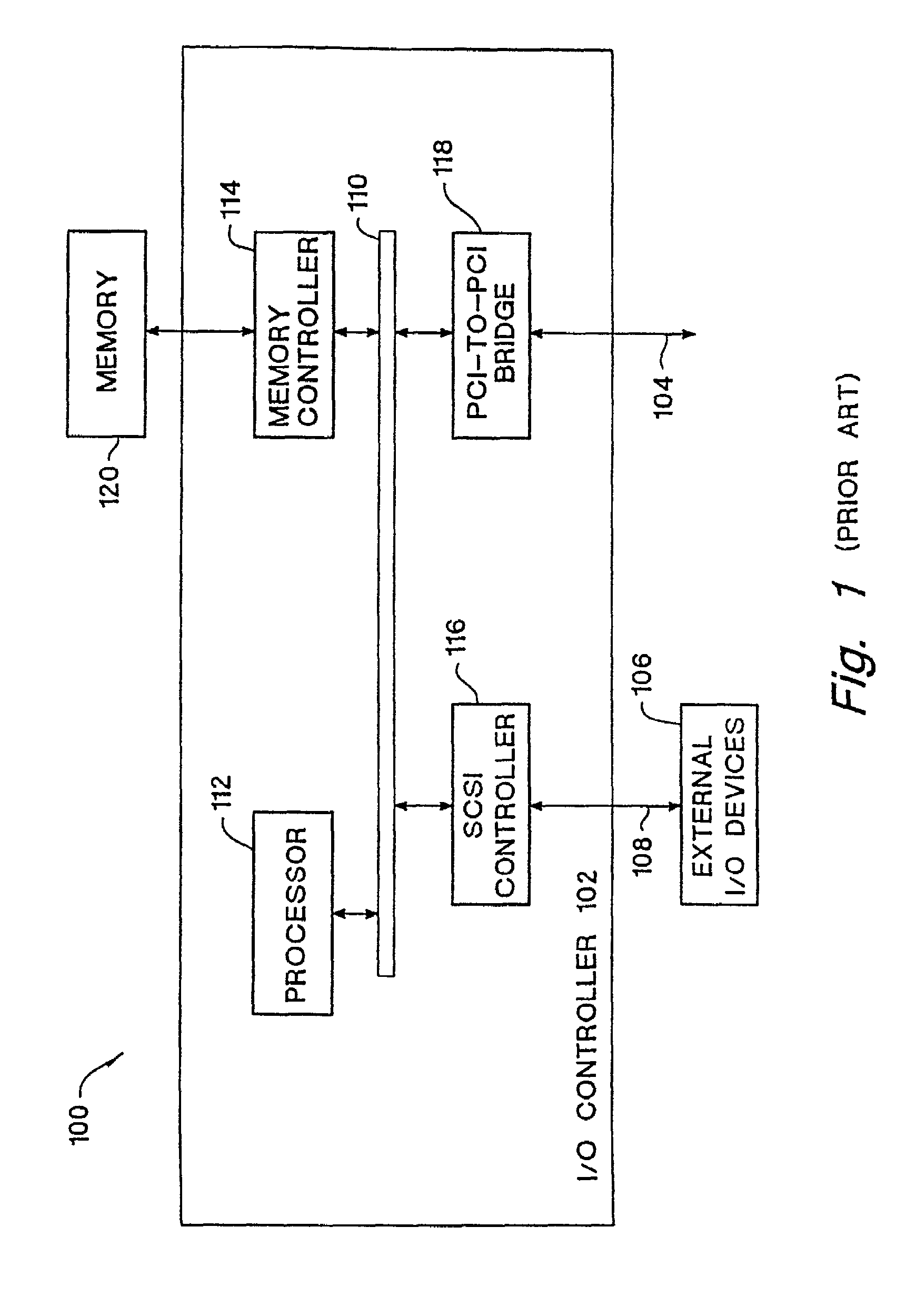

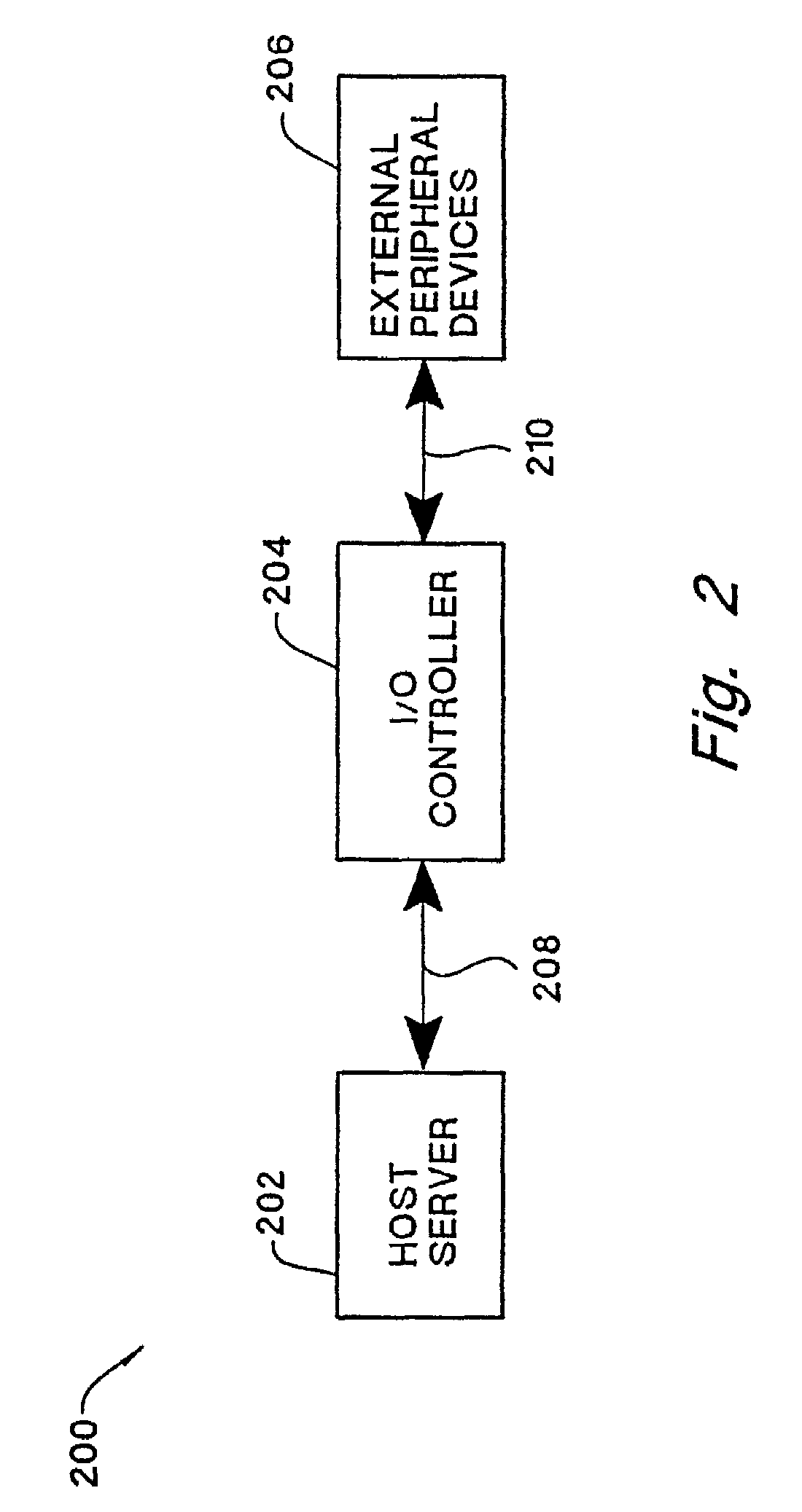

Memory controller supporting redundant synchronous memories

A reliable fault-tolerant I / O controller supporting redundant synchronous memories is described. The I / O controller includes multiple I / O control logic units where each I / O control logic unit is in communication with a host server and external peripheral devices. Each I / O control logic unit includes a processor, a memory, and a memory controller. A master I / O control logic unit services I / O transactions from the host server and the external peripheral devices. A slave I / O control logic unit operates in a quiescent state until the master I / O control logic unit experiences a memory failure. At such time, the slave I / O control logic unit resumes operation of the I / O controller. In order to facilitate the switchover from the master I / O control logic unit to the slave I / O control logic unit, the master memory controller performs concurrent memory write operations in both the master and slave memories. The concurrent memory write operations ensure that the memories in both I / O control logic units are in a consistent state in order for the switchover to occur without loss of data.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Expedited module unloading for kernel modules that execute read-copy update callback processing code

InactiveUS9256476B2Program synchronisationDigital data processing detailsQuiescent stateOperational system

A technique for expediting the unloading of an operating system kernel module that executes read-copy update (RCU) callback processing code in a computing system having one or more processors. According to embodiments of the disclosed technique, an RCU callback is enqueued so that it can be processed by the kernel module's callback processing code following completion of a grace period in which each of the one or more processors has passed through a quiescent state. An expediting operation is performed to expedite processing of the RCU callback. The RCU callback is then processed and the kernel module is unloaded.

Owner:IBM CORP

Expedited Module Unloading For Kernel Modules That Execute Read-Copy Update Callback Processing Code

InactiveUS20130152095A1Block completeMultiprogramming arrangementsMemory systemsHandling CodeQuiescent state

A technique for expediting the unloading of an operating system kernel module that executes read-copy update (RCU) callback processing code in a computing system having one or more processors. According to embodiments of the disclosed technique, an RCU callback is enqueued so that it can be processed by the kernel module's callback processing code following completion of a grace period in which each of the one or more processors has passed through a quiescent state. An expediting operation is performed to expedite processing of the RCU callback. The RCU callback is then processed and the kernel module is unloaded.

Owner:IBM CORP

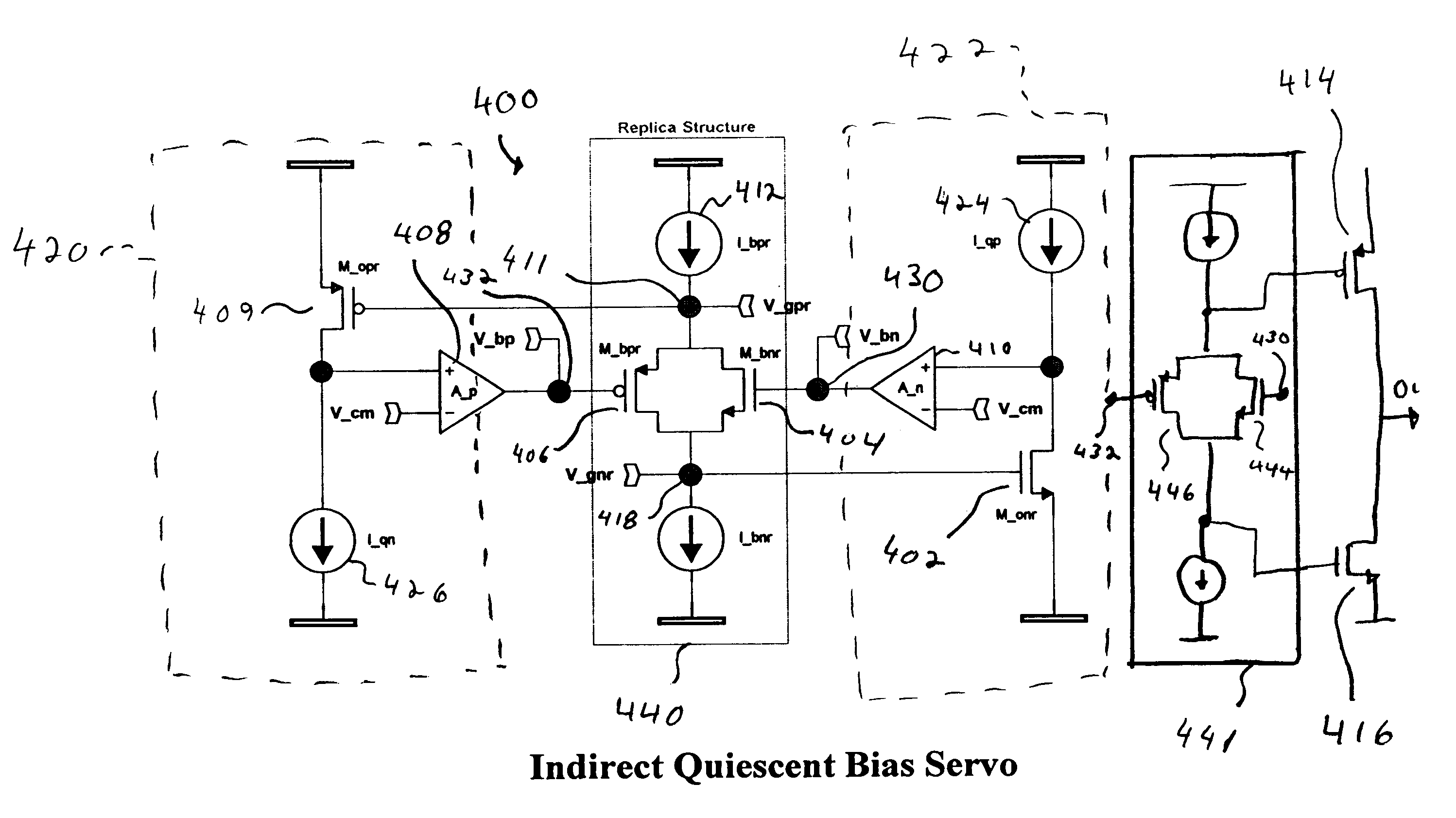

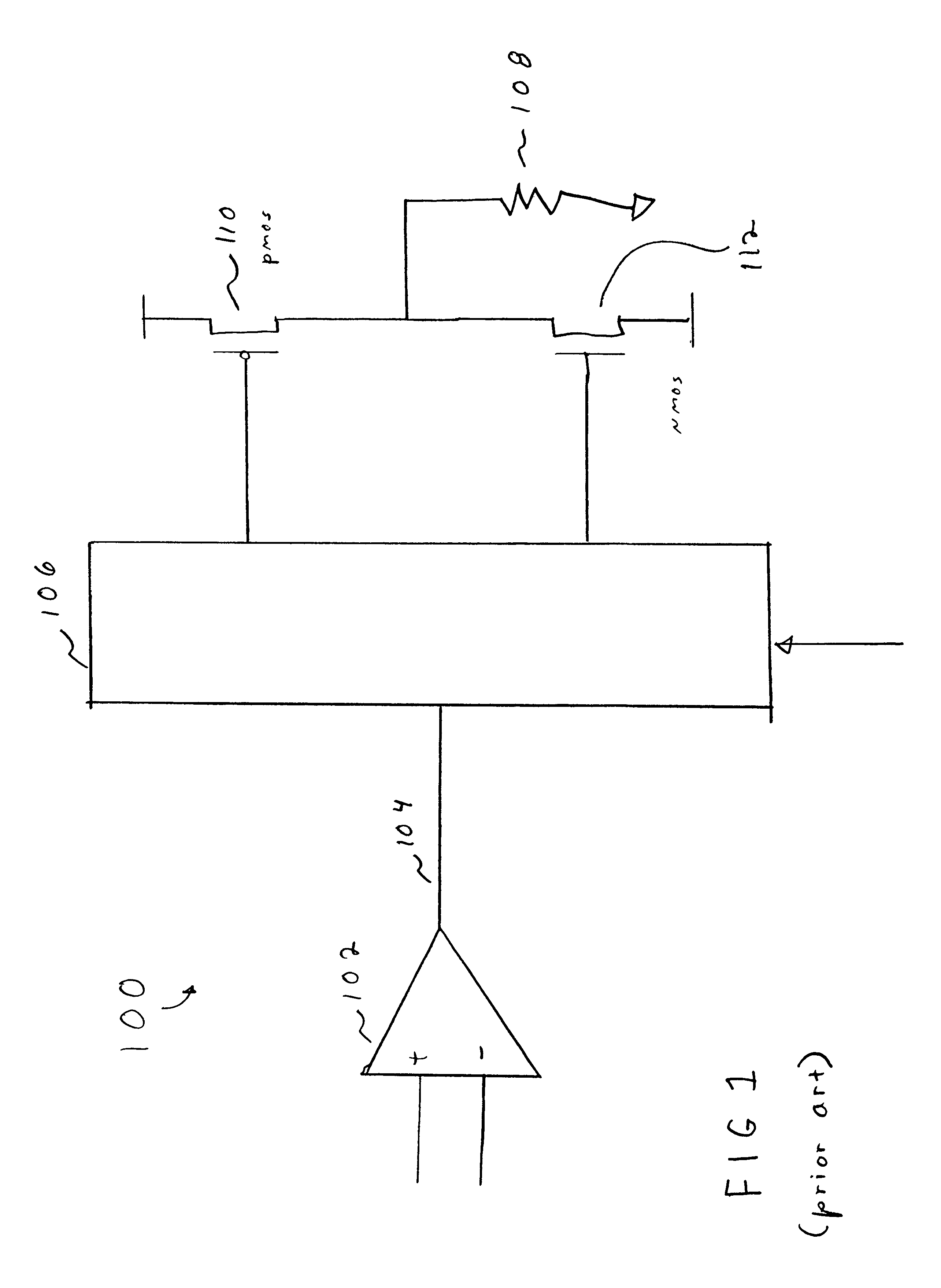

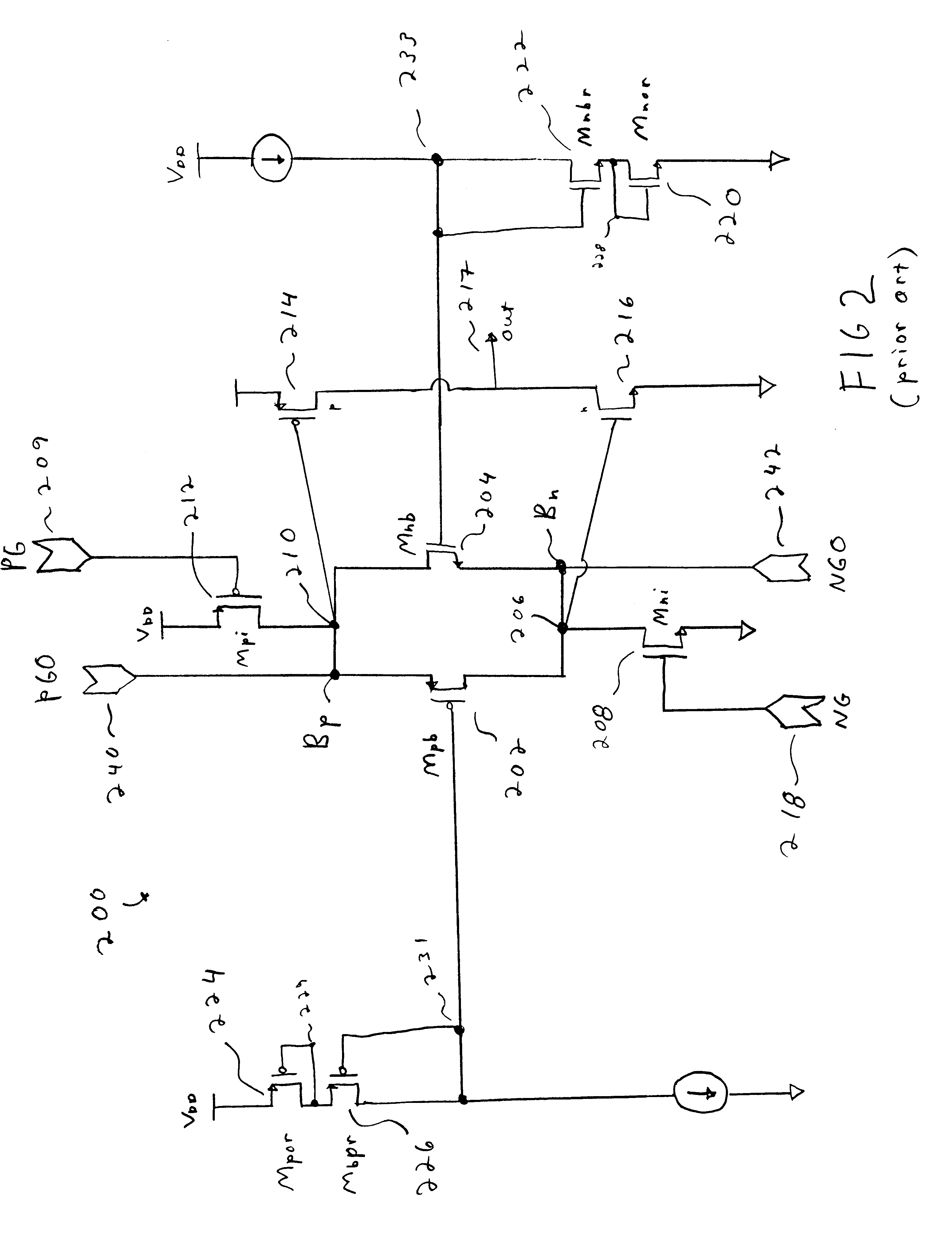

Apparatus and methods for improved control of quiescent state of output transistors in a class AB amplifier

InactiveUS6369653B1Easy to operatePush-pull amplifiersPhase-splittersQuiescent stateAudio power amplifier

A class AB amplifier biasing circuit is provided for controlling the quiescent state of a pull-up output device and a complimentary pull-down output device. The biasing circuit includes first and second current sources, each having a floating resistor configured to supply current to the pull-up and pull-down devices, respectively. The biasing circuit also includes gate control circuits for controlling the gate voltages of the first and second floating resistors. A device replica transistor is connected to a voltage node associated with the gate of the either the pull-up device or the pull-down device.

Owner:MACOM TECH SOLUTIONS HLDG INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com