Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

19482results about "Program initiation/switching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Techniques for managing multiple threads in a browser environment

Techniques for managing multiple threads in an asynchronous environment, such as a browser, are described. As a method, instantiating an event thread in response to a user event by a shell event handler block that provides shell functions for a user event. Once the event thread as been instantiated, managing the event thread by a generic thread manager block that provides a plurality of multithread management functions for the shell event handler. When required, blocking and unblocking the event thread by a blocking system that is arranged to block and unblock threads.

Owner:ORACLE INT CORP

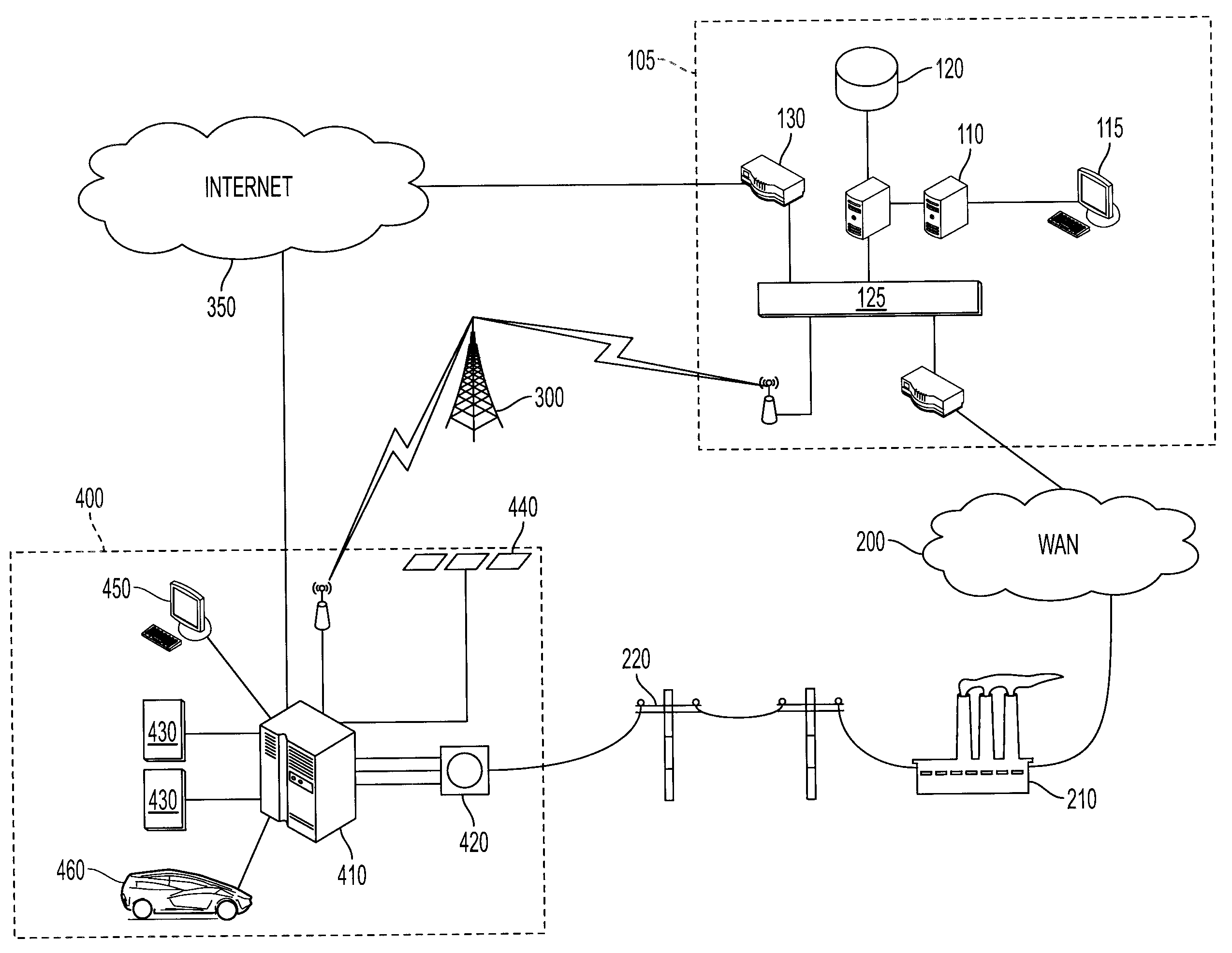

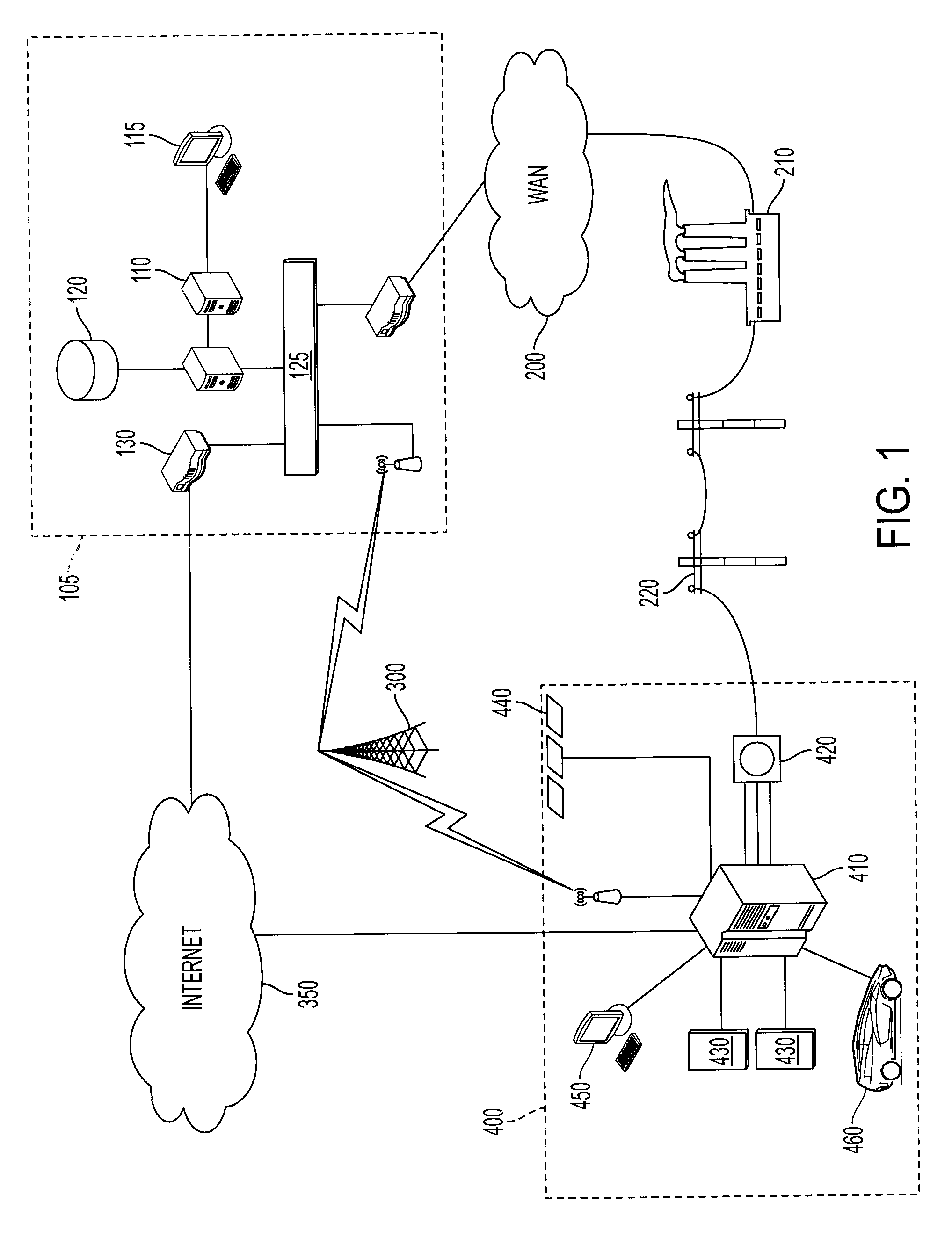

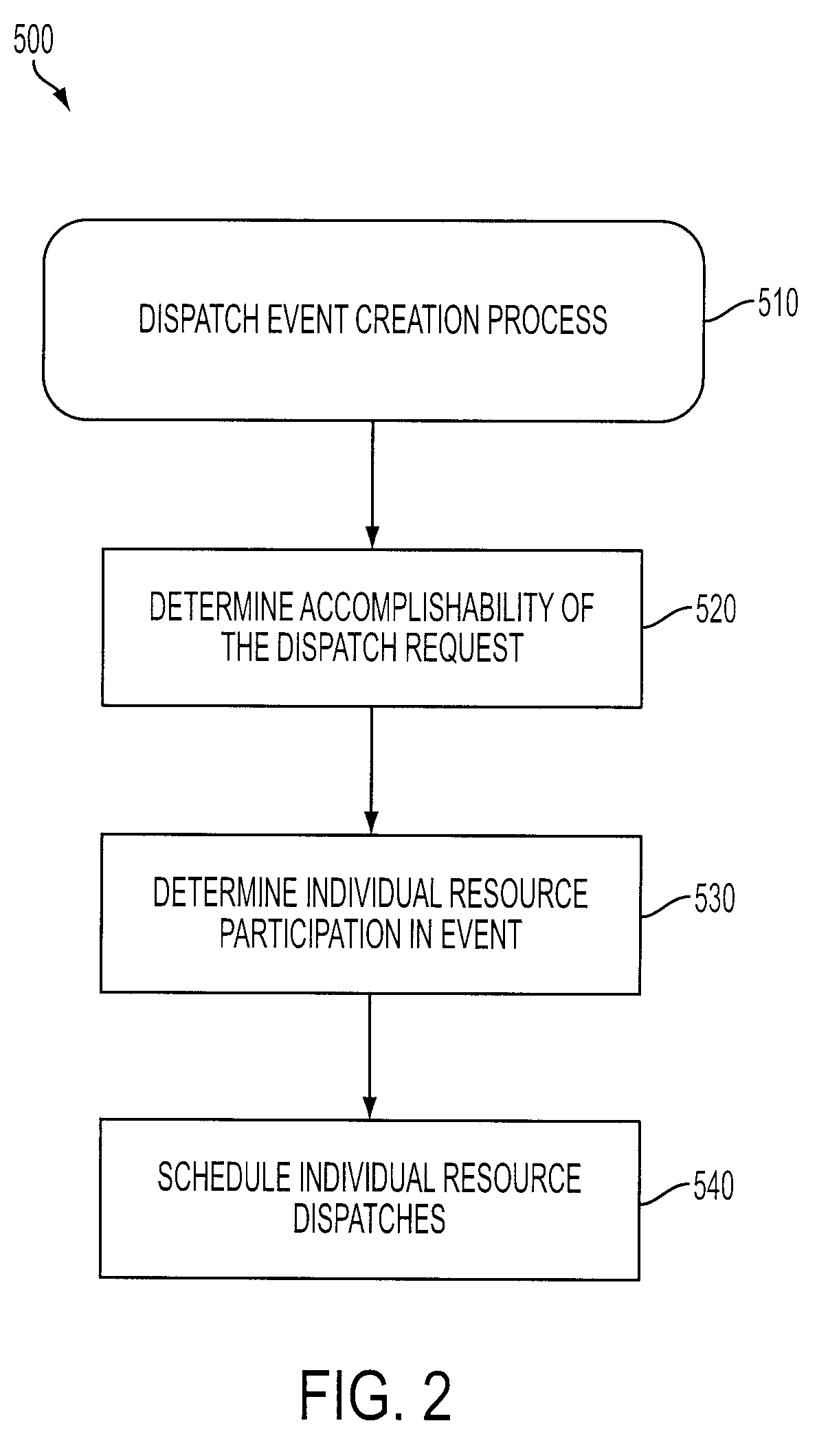

Method and system for scheduling the discharge of distributed power storage devices and for levelizing dispatch participation

Disclosed is a computerized method for dispatching energy from distributed resources in a discharge event so that the energy stored in individual devices is levelized, or so that an operator request is met. Evaluation of event parameters may be deferred. The method may be utilized to dispatch energy from plug-in electric vehicles. Systems and methods to account for electricity dispatched to or from electric vehicles are disclosed. Systems and methods for incentivizing consumers to participate in a dispatch event or curtail energy use are disclosed.

Owner:GRIDPOINT

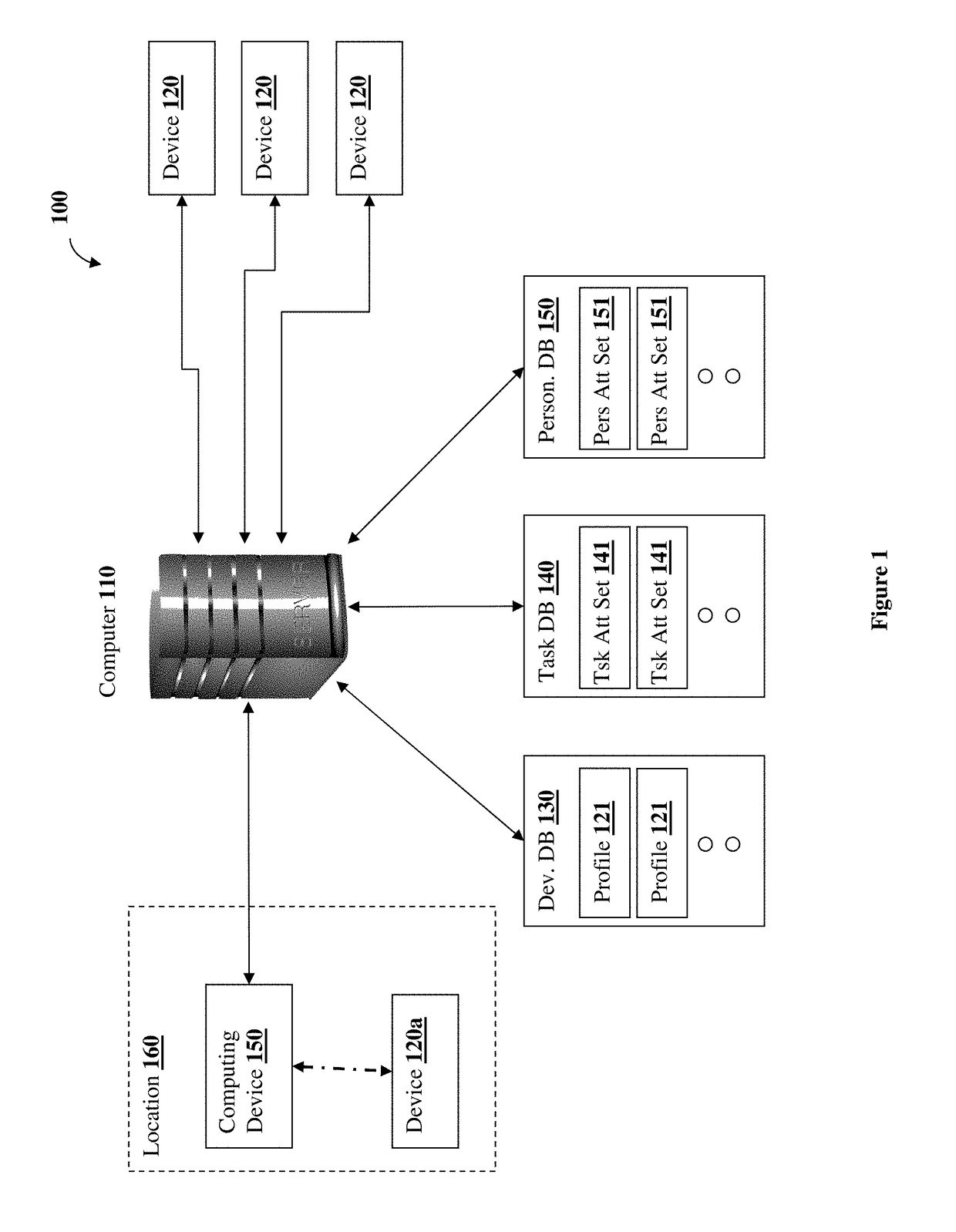

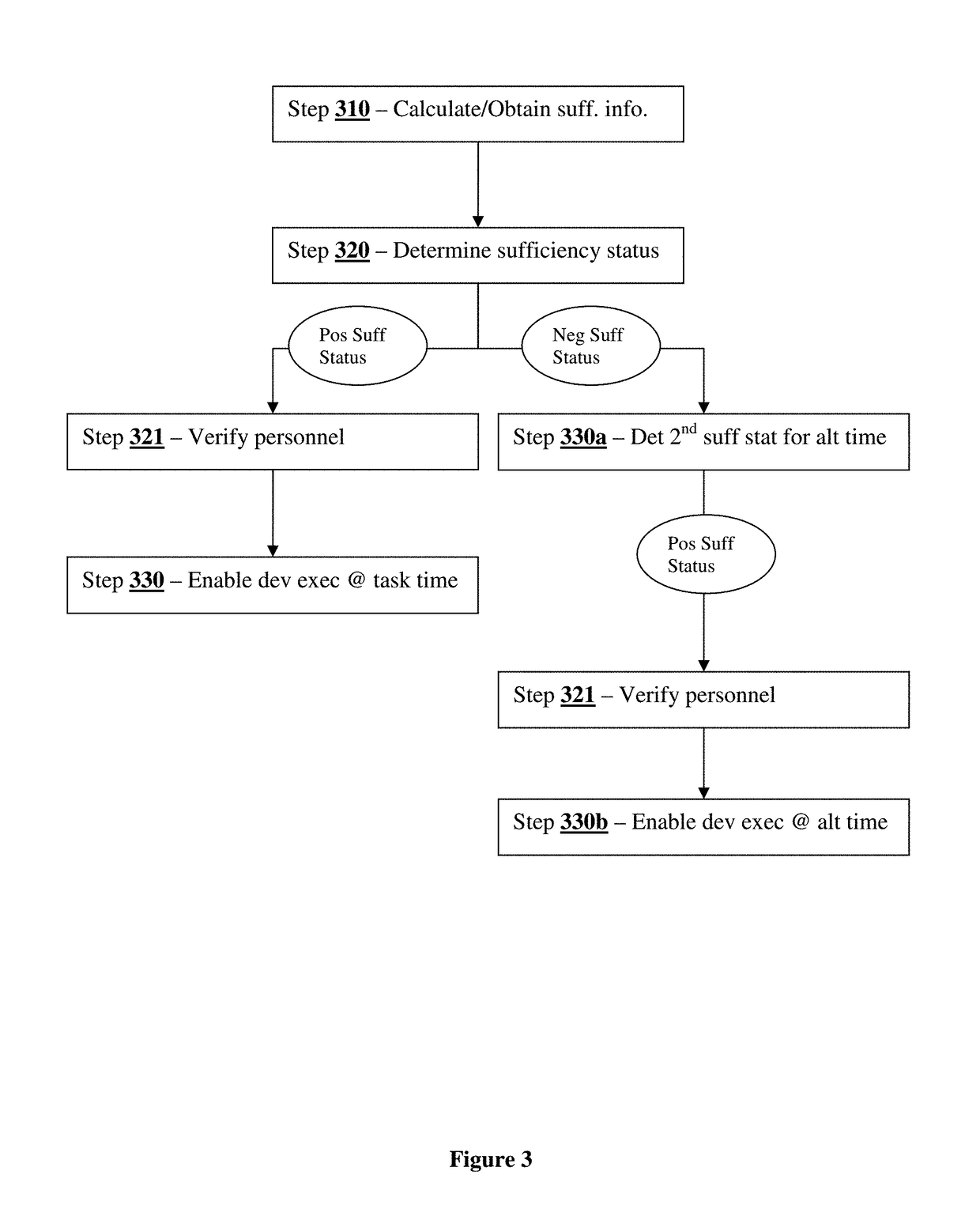

Systems and methods of ensuring and maintaining equipment viability for a task

ActiveUS10163065B1Adjust in timeExtension of timeProgram initiation/switchingOffice automationMonitor equipmentSTAFFING SCHEDULING

A device management system that is capable of scheduling connected devices and personnel for tasks, monitoring the ability of the devices to perform the scheduled task by checking in with the devices based on their uses and locations, and to modify the functioning of the devices according to the tasks scheduled for the devices and their uses. Additionally, the system can incorporate uncommunicated “dumb” devices into the scheduling of tasks and track and manage those devices.

Owner:NMETRIC

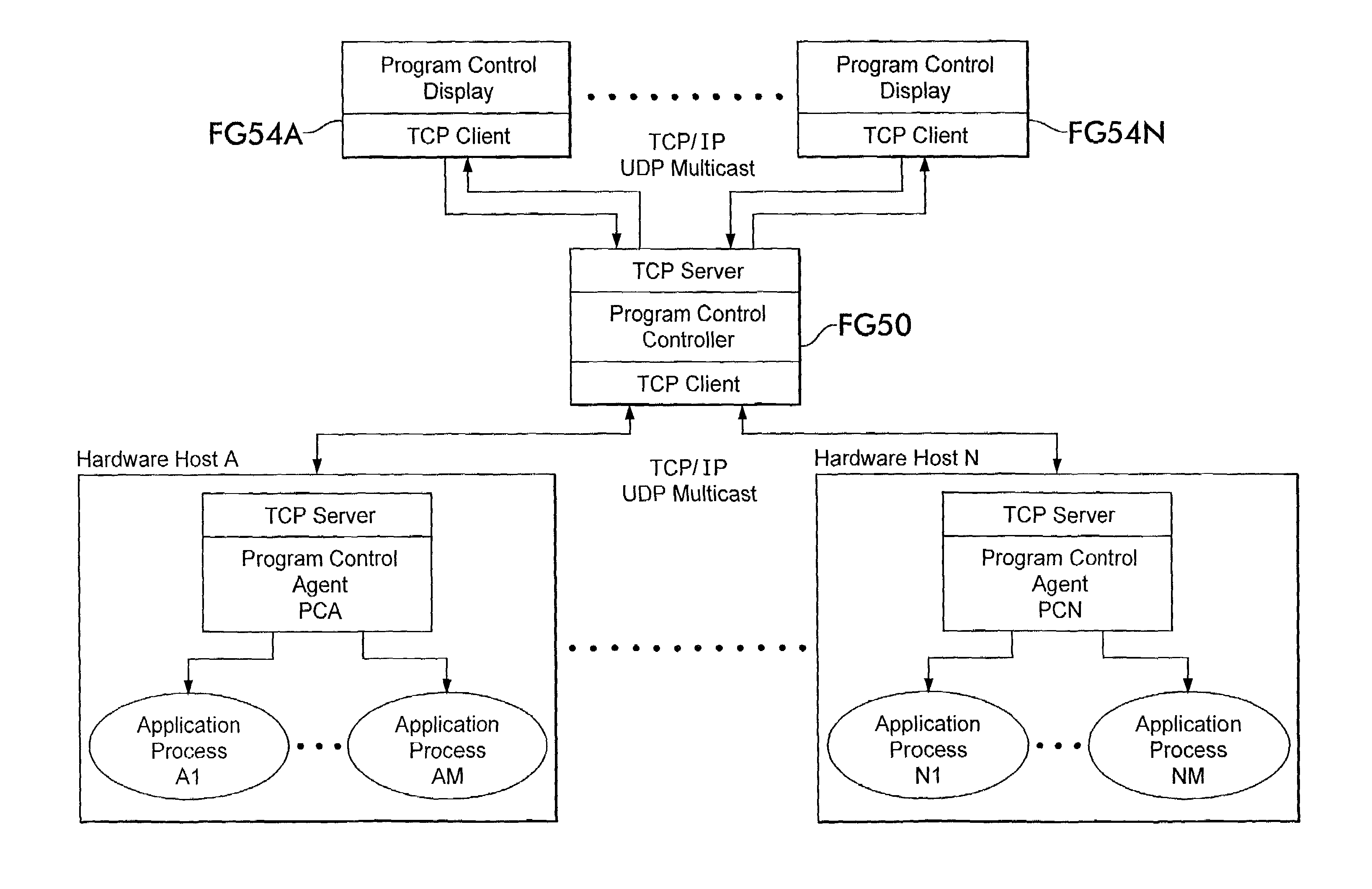

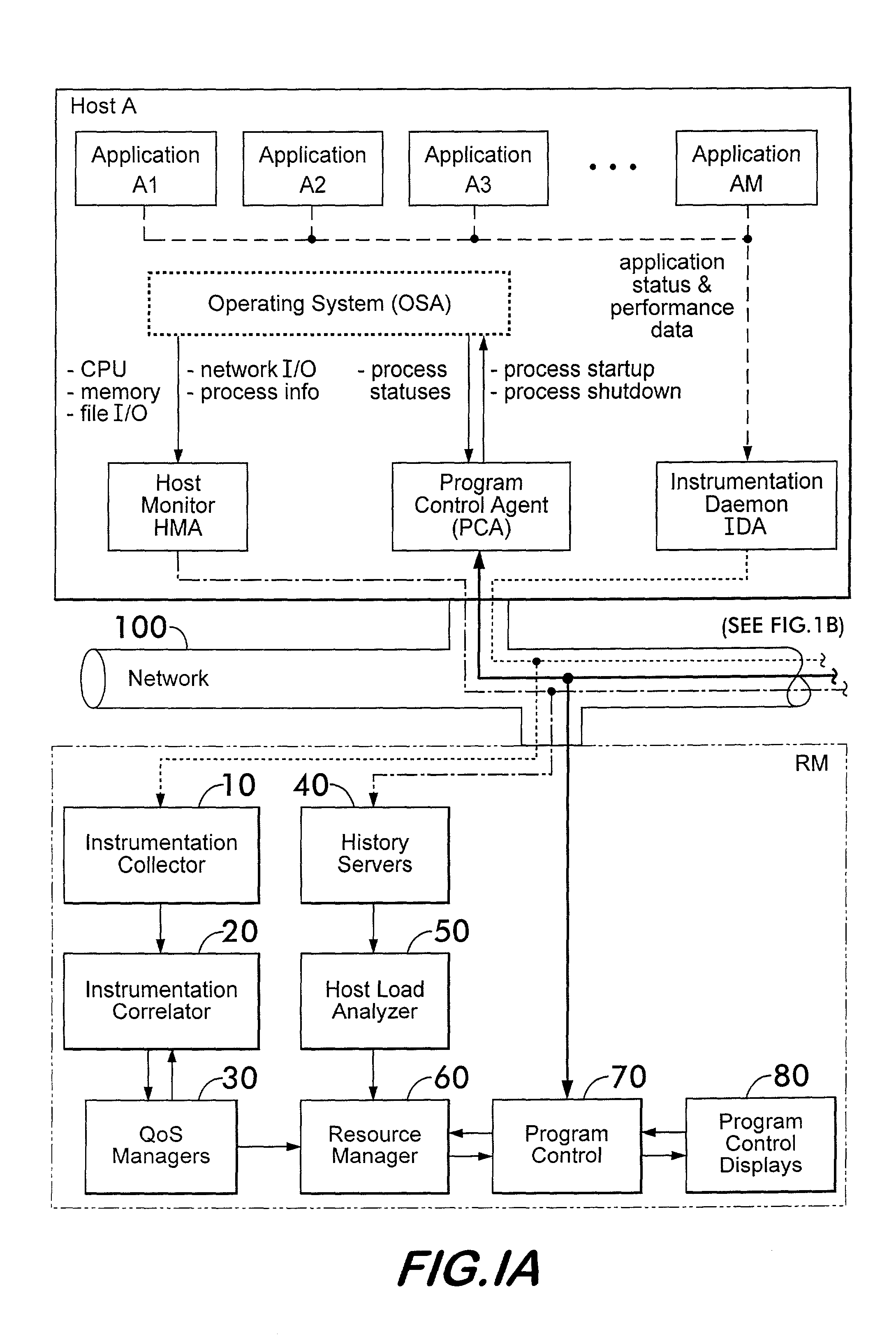

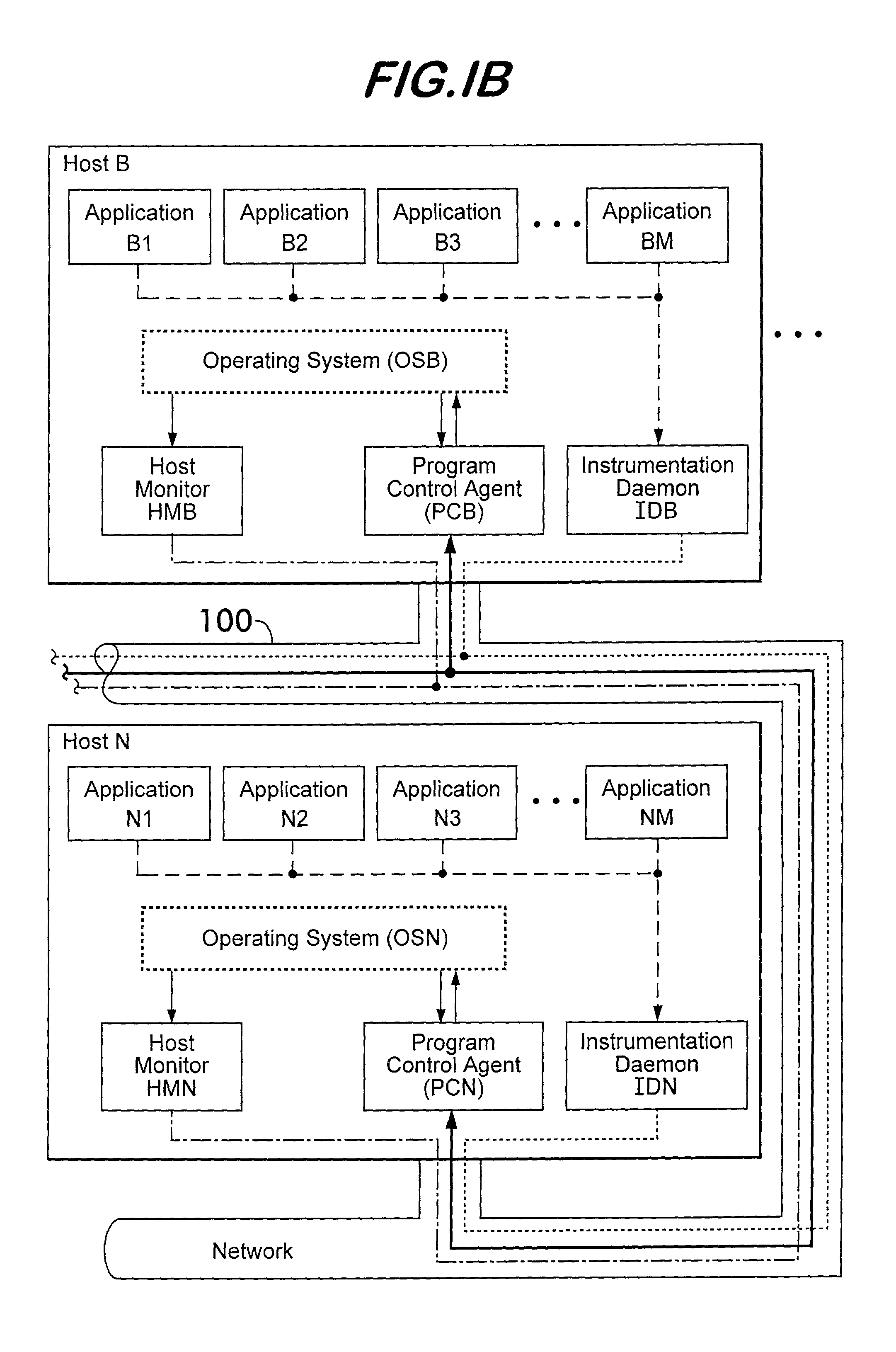

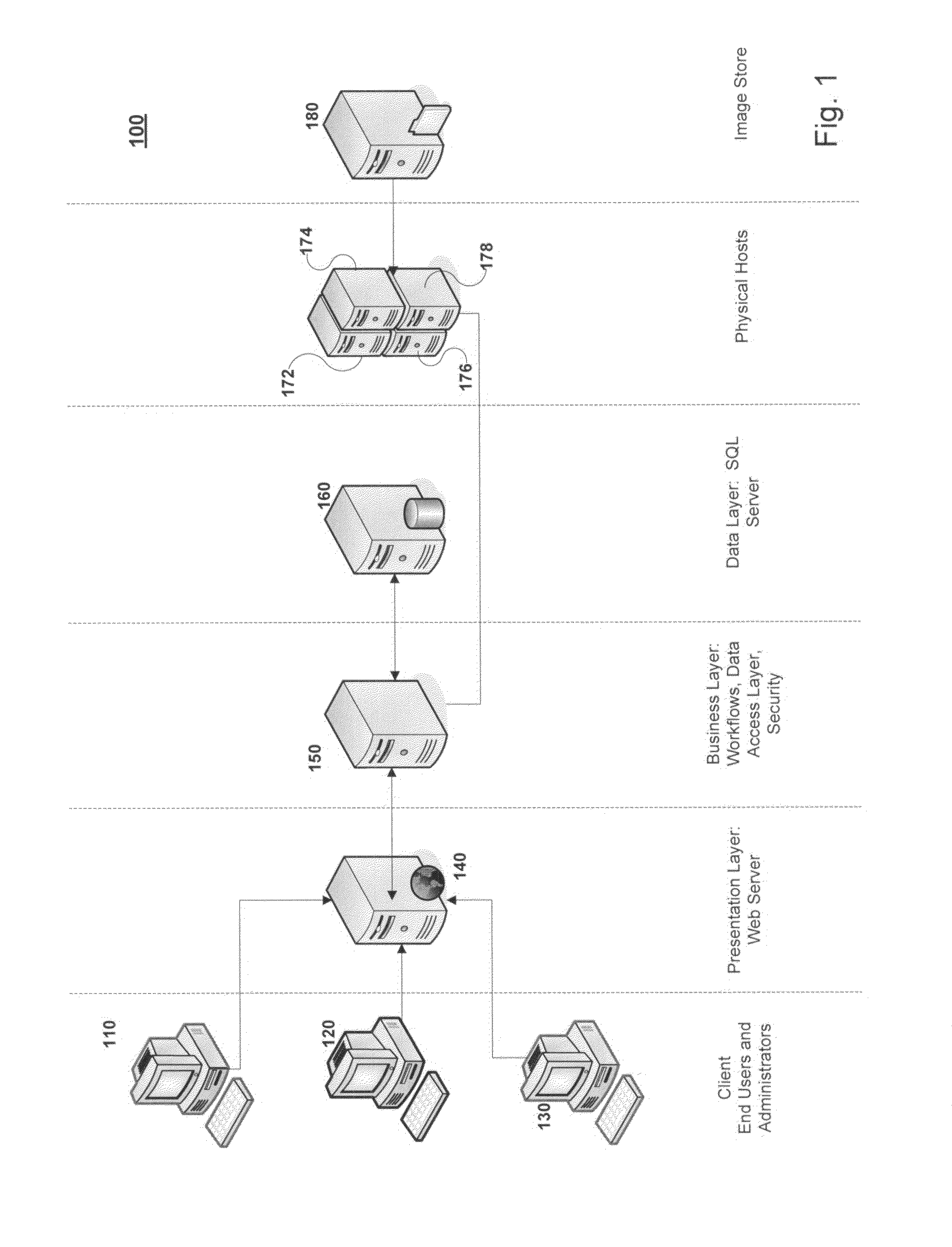

System for monitoring and reporting performance of hosts and applications and selectively configuring applications in a resource managed system

ActiveUS7051098B2Program initiation/switchingResource allocationResource Management SystemMonitoring system

A monitoring system for a distributed environment including a plurality of hosts capable of executing multiple copies of a scalable application includes a first device for generating first data corresponding to performance of all copies of the scalable application; a second device for generating second data corresponding to performance of all host in the distributed environment; and a third device for generating performance metrics based on the first and second data.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

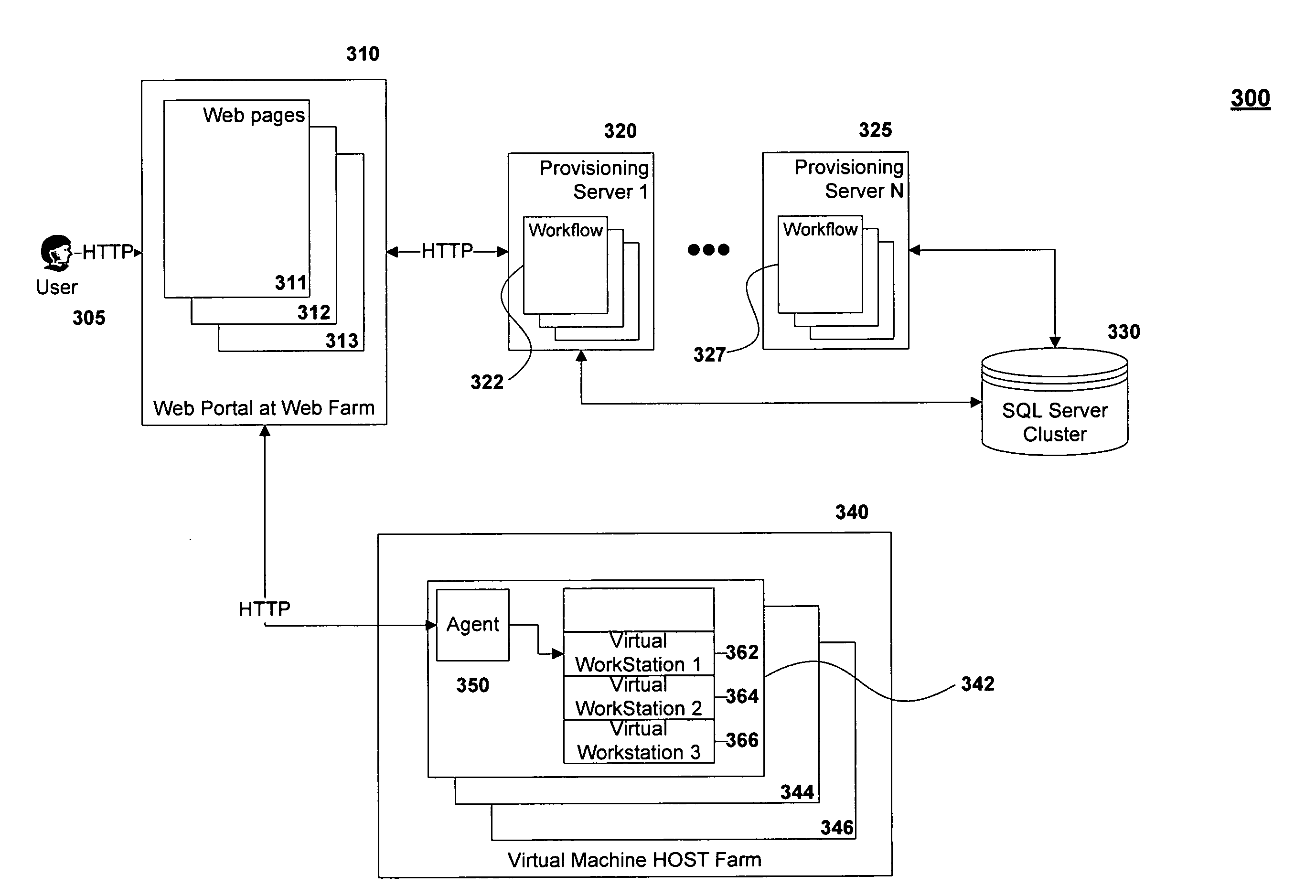

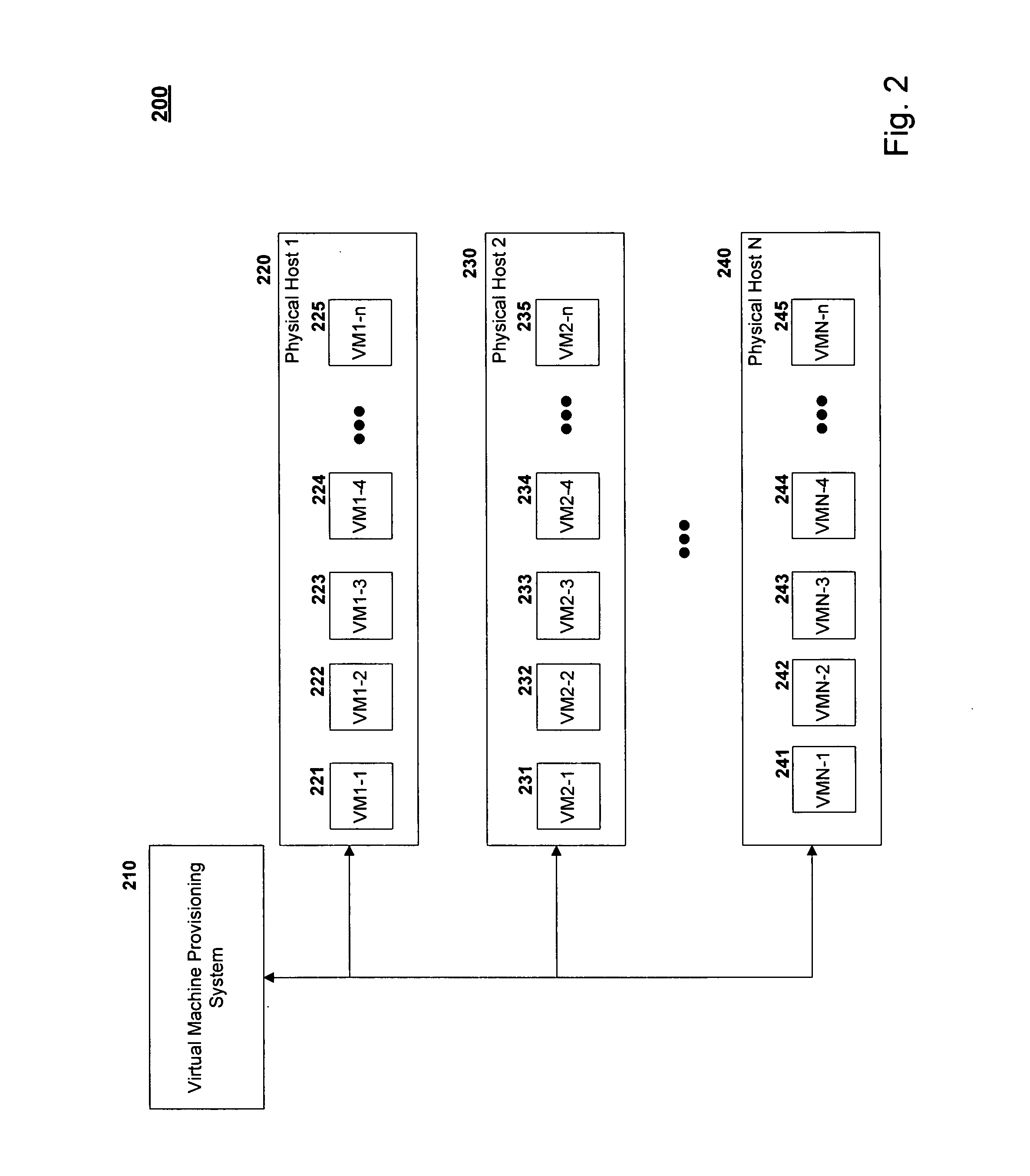

Method and system for managing virtual and real machines

ActiveUS20080244579A1Program initiation/switchingResource allocationVirtual machineConfiguration system

Managing virtual and real machines through a provisioning system. The provisioning system allows a user to create and manage machines through a “self-service” approach. The provisioning system interacts with one or more agents that manage the lifecycle of a machine. The system may provide templates that enable a user to readily create a virtual machine. The system may also include interfaces for administrators to manage virtual and real machine resources.

Owner:VMWARE INC

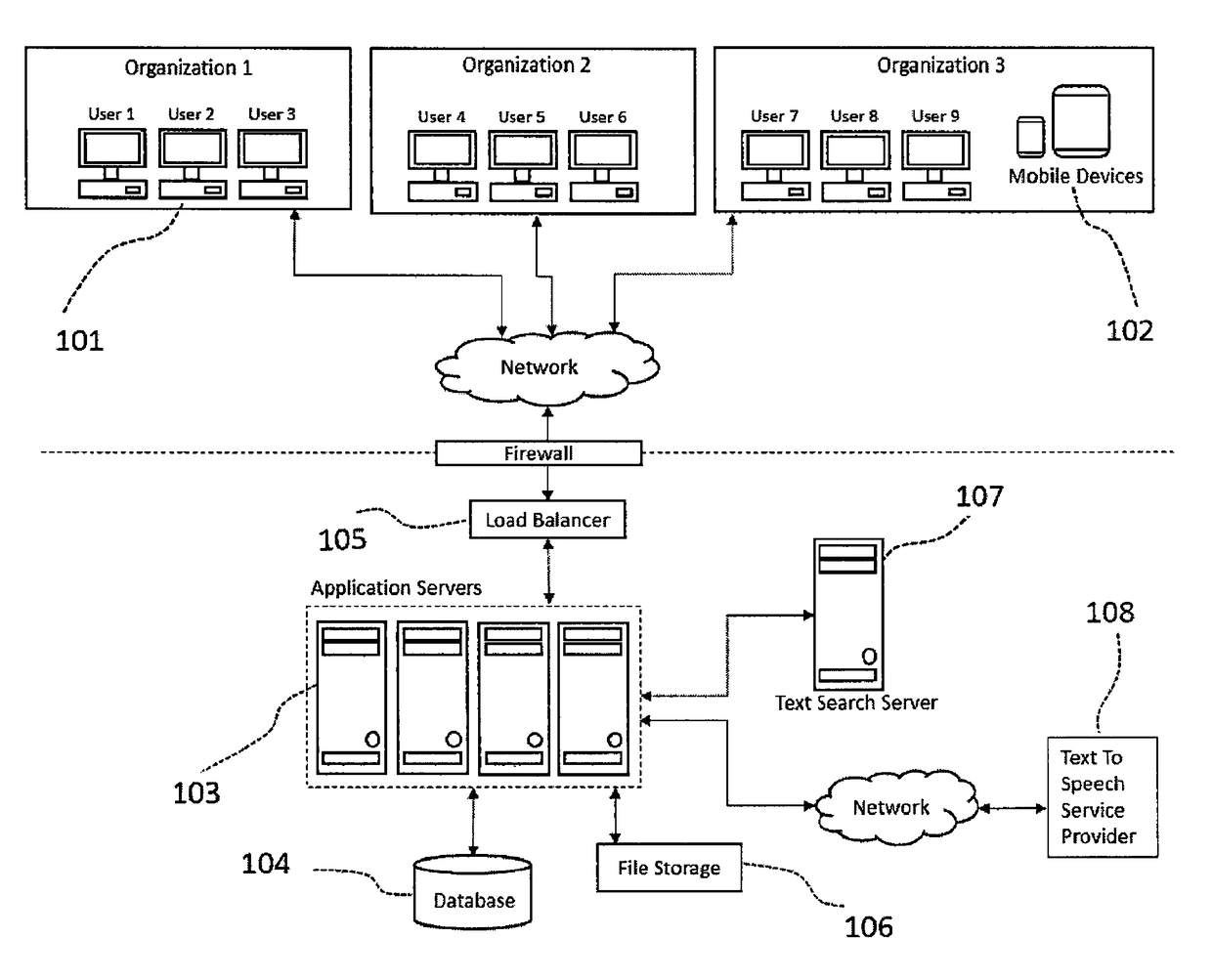

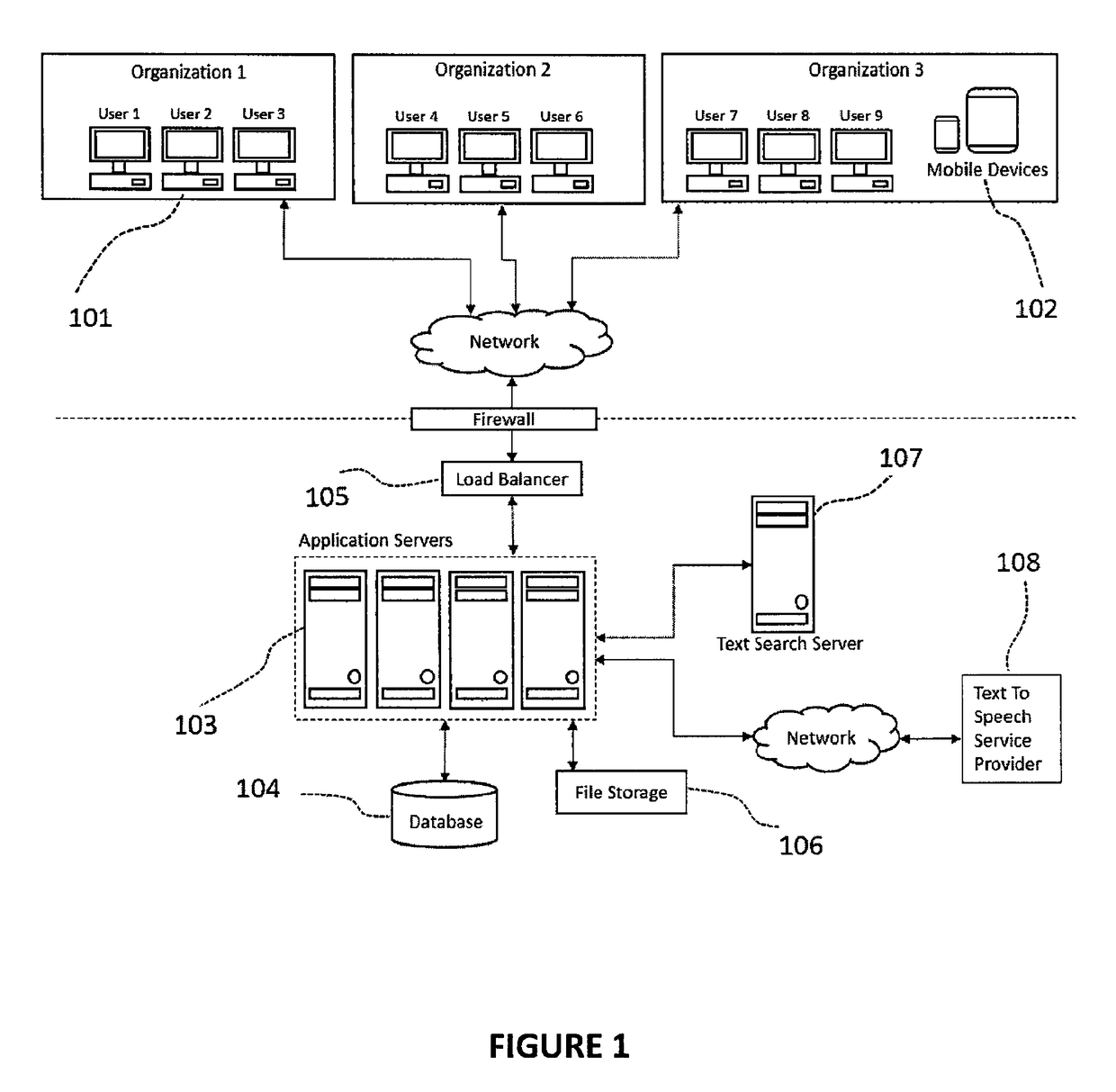

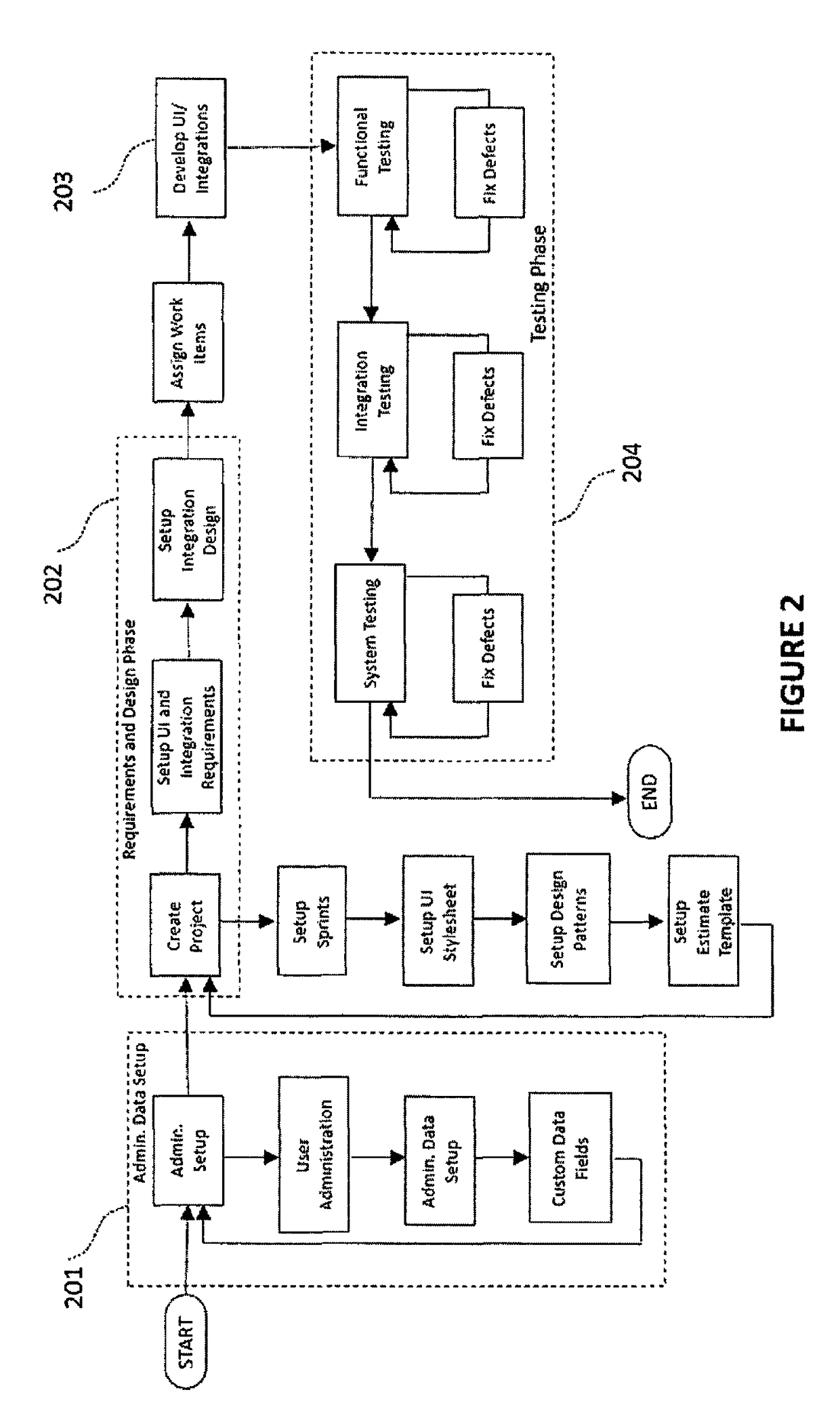

Integrated system for software application development

InactiveUS10001975B2Equally distributedProgram initiation/switchingVersion controlIntegrated softwareProject management

Methods and systems are disclosed for developing a software application through requirements specification, design, effort estimation, assigning and tracking work items, development, testing, collaboration and project management. The system is structured as an integrated software development system allowing for structured, systematic and user friendly set up of requirements specification (including workflow, user interface, business rules and integrations), technical design for UI features and integrations using design patterns, automated effort estimation, automated story card and task creation. The system also provides a novel, audio-video playback capability for workflow visualization. Further, the system provides visual depiction of defects and changed items side-by-side with requirements, as well as predictive modeling of defects that allows for forecasting of defect completion rate. In the preferred embodiment, the system is delivered as a multi-tenant Software as a Service.

Owner:BHARTHULWAR SHRIDHAR V

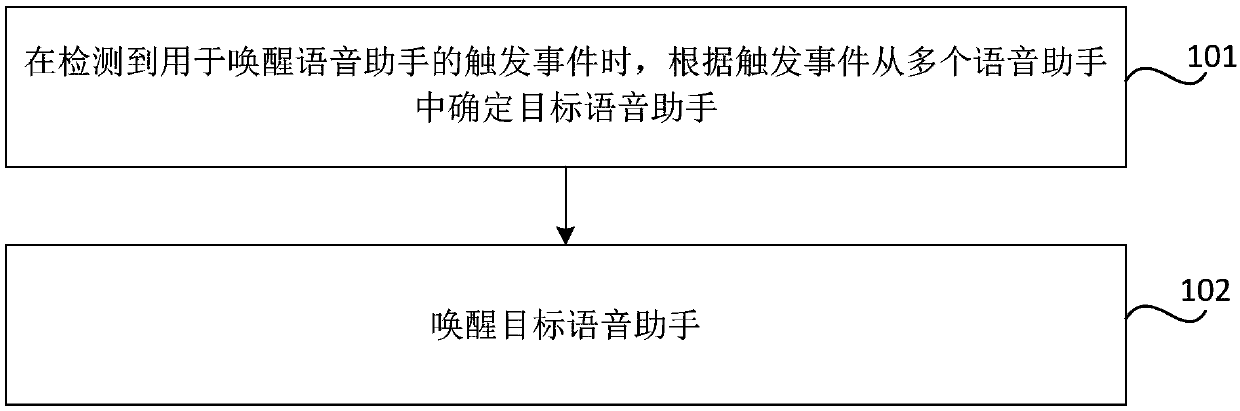

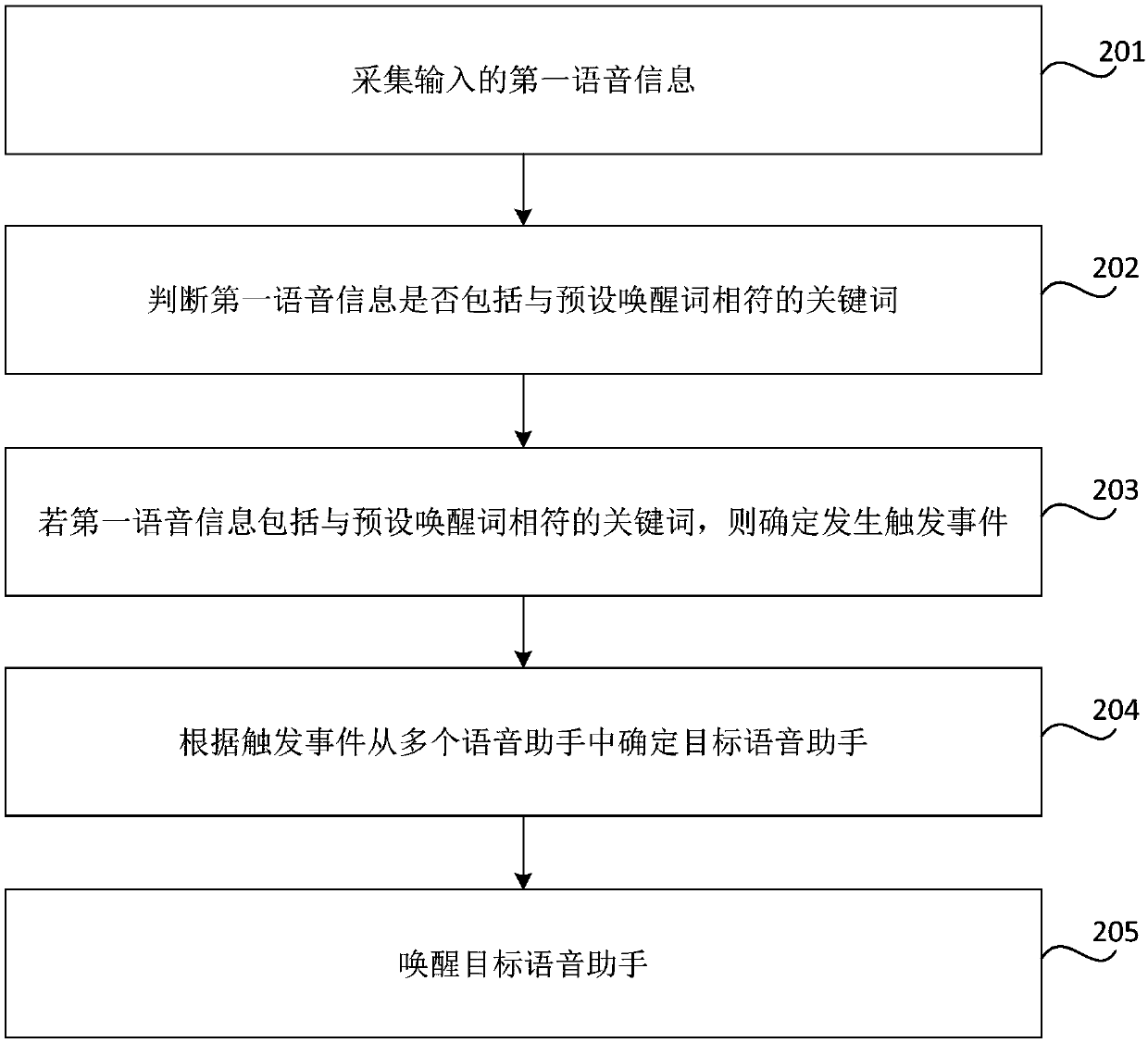

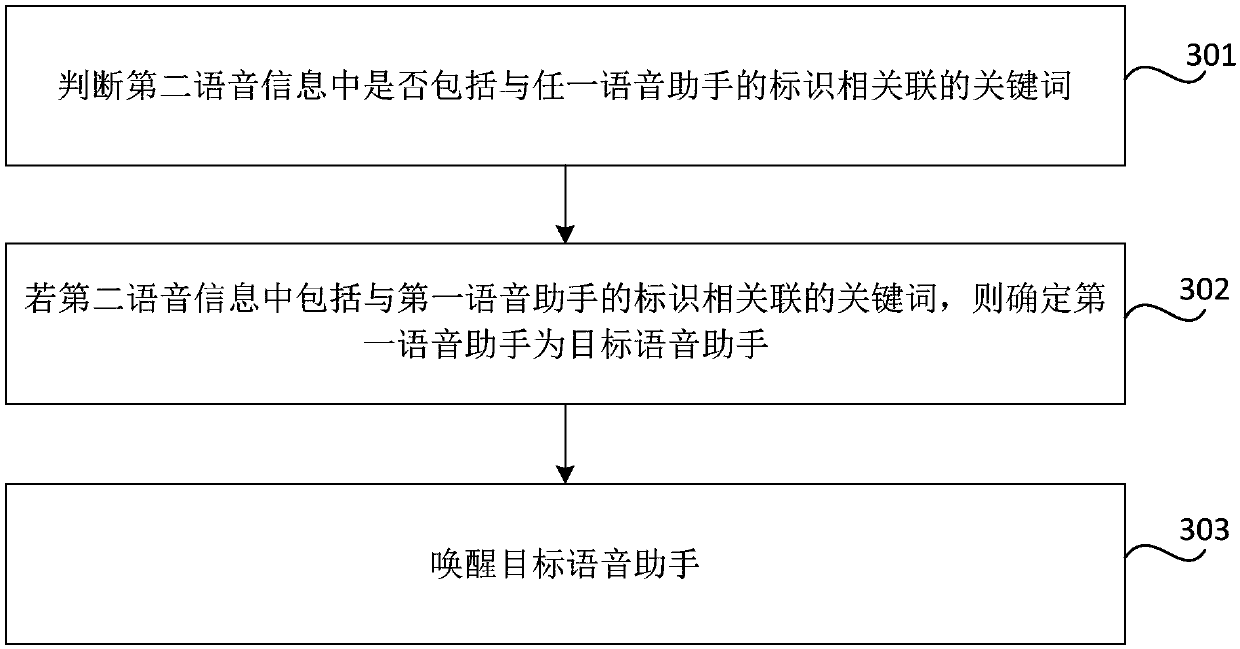

Control method and apparatus of multiple voice assistants, and computer readable storage medium

The invention discloses a control method and apparatus of multiple voice assistants, and a computer readable storage medium, aiming at solving the technical problem that when current electronic equipment switches voice assistants, the current electronic equipment needs to enable the voice assistants manually and the switching mode is not flexible. The control method of multiple voice assistants isapplied to electronic equipment integrated with multiple voice assistants, and includes the steps: when detecting a trigger event for wakening the voice assistants, according to the trigger event, determining the target voice assistant from the multiple voice assistants, wherein the wakening functions of the multiple voice assistants are in the enabled state; and wakening the target voice assistant.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

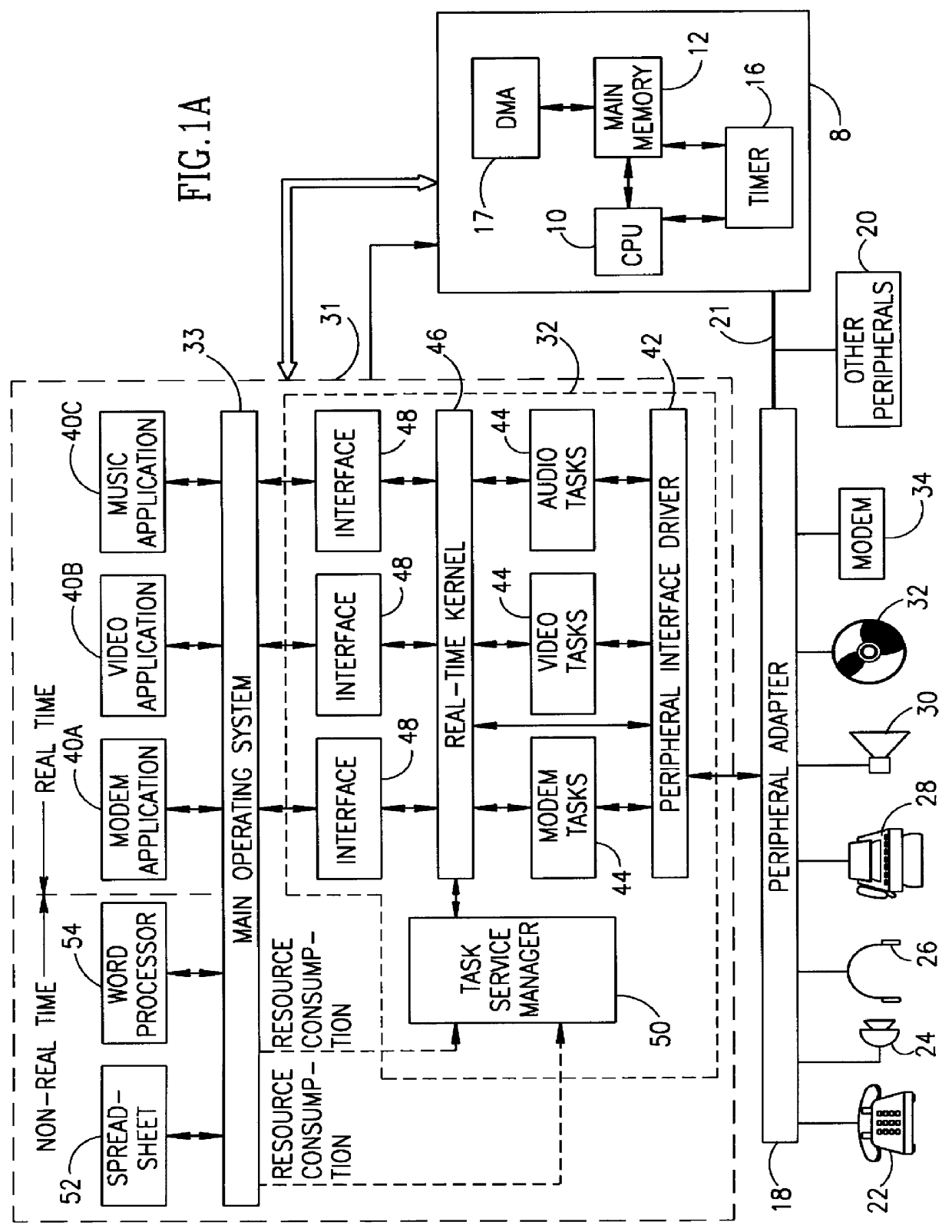

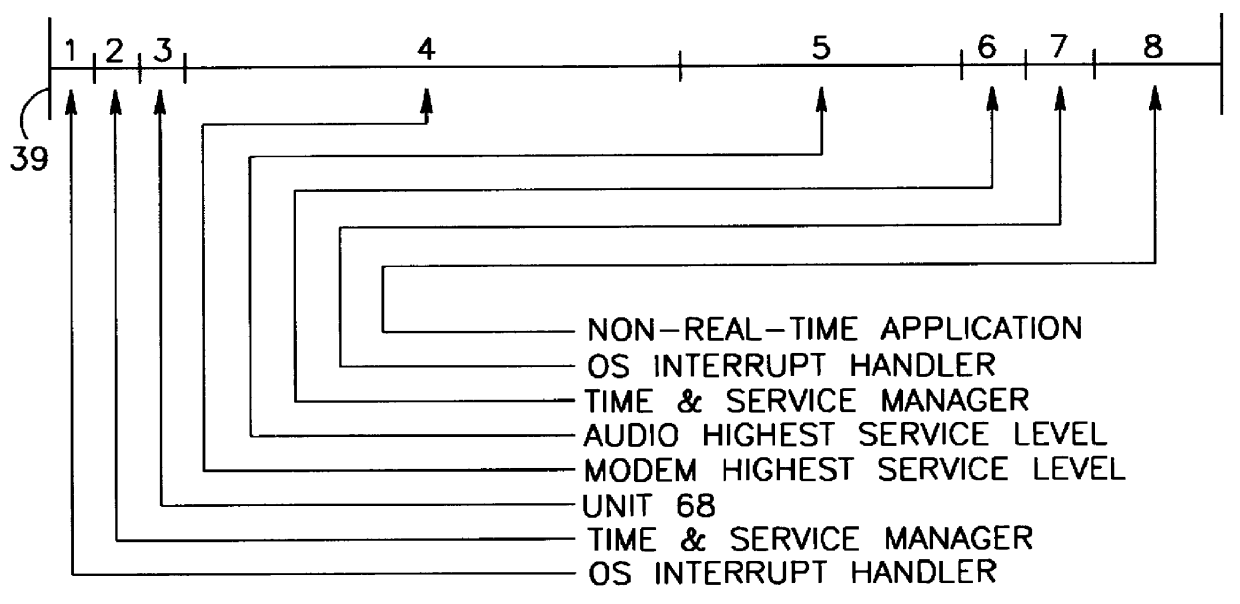

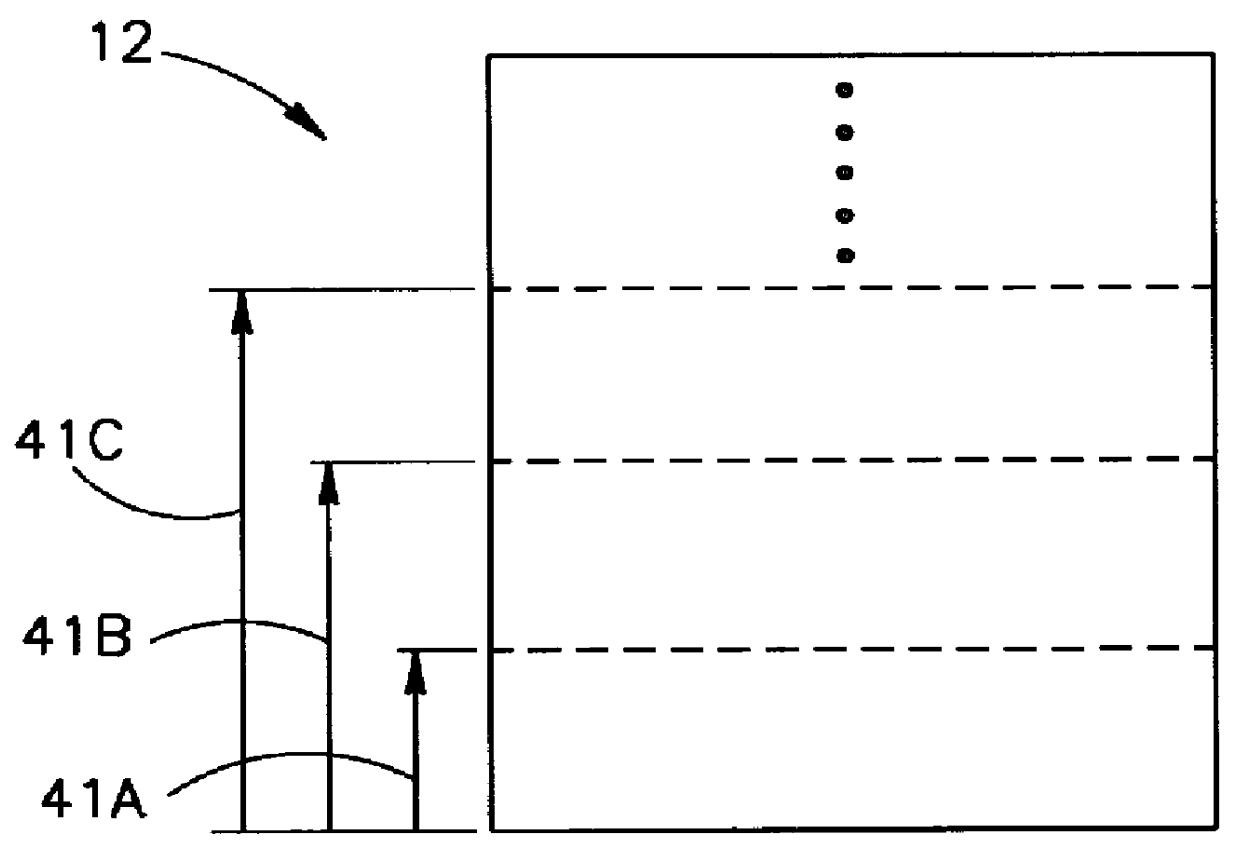

Real-time task manager for a personal computer

InactiveUS6092095ALoadChange levelProgram initiation/switchingMemory systemsPersonal computerReal time management

A real-time manager for a personal computer manages the operation of real-time tasks while the personal computer also performs other tasks. The real-time manager includes at least one real-time kernel and a task service manager. The real-time kernel activates and controls the real-time tasks. The task service manager allocates time between the real-time tasks and the other tasks, selects the service levels of the real-time tasks in response to the activity levels of the other tasks, and invokes the real-time kernel to activate and control the real-time tasks at the selected service levels.

Owner:SMART LINK

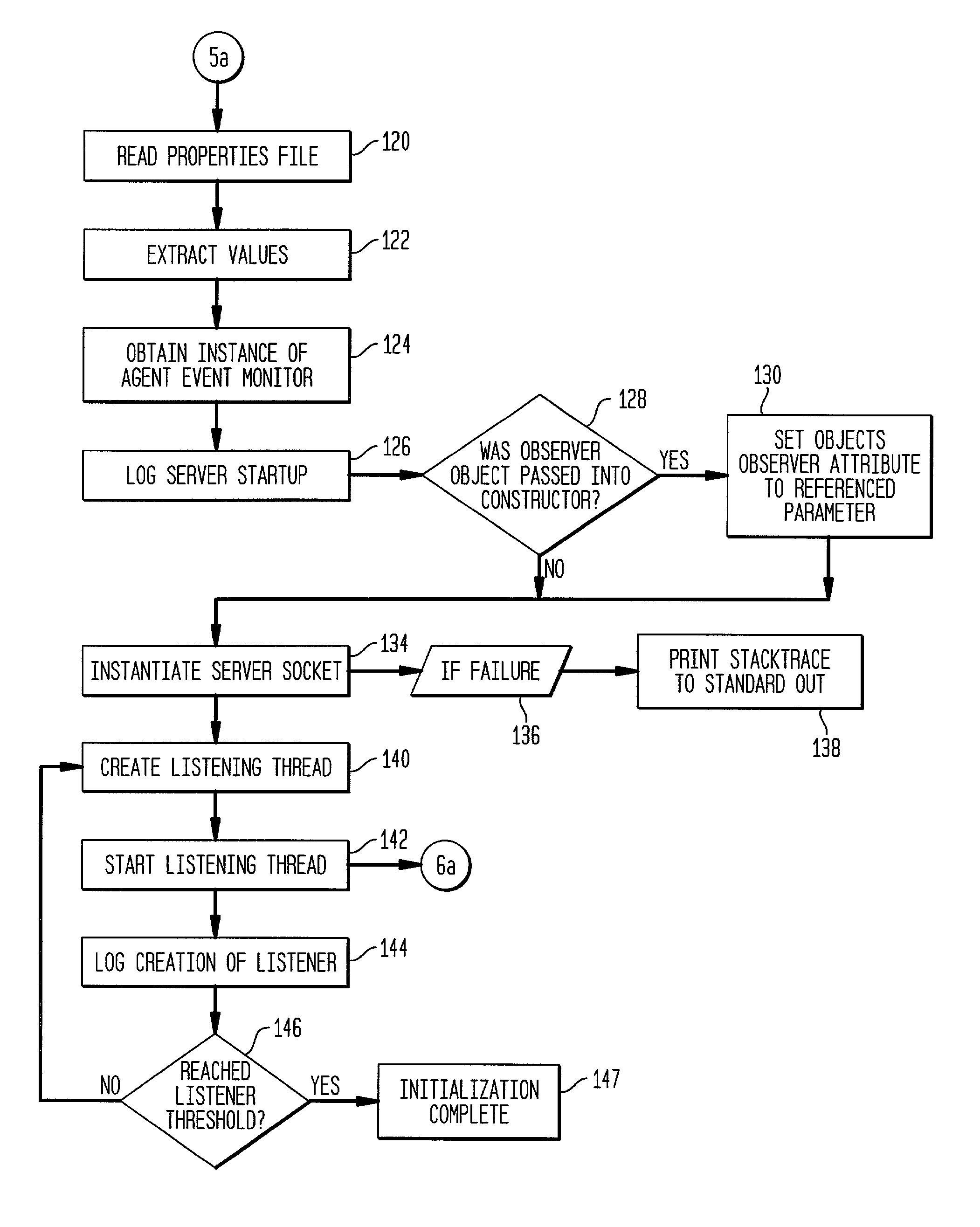

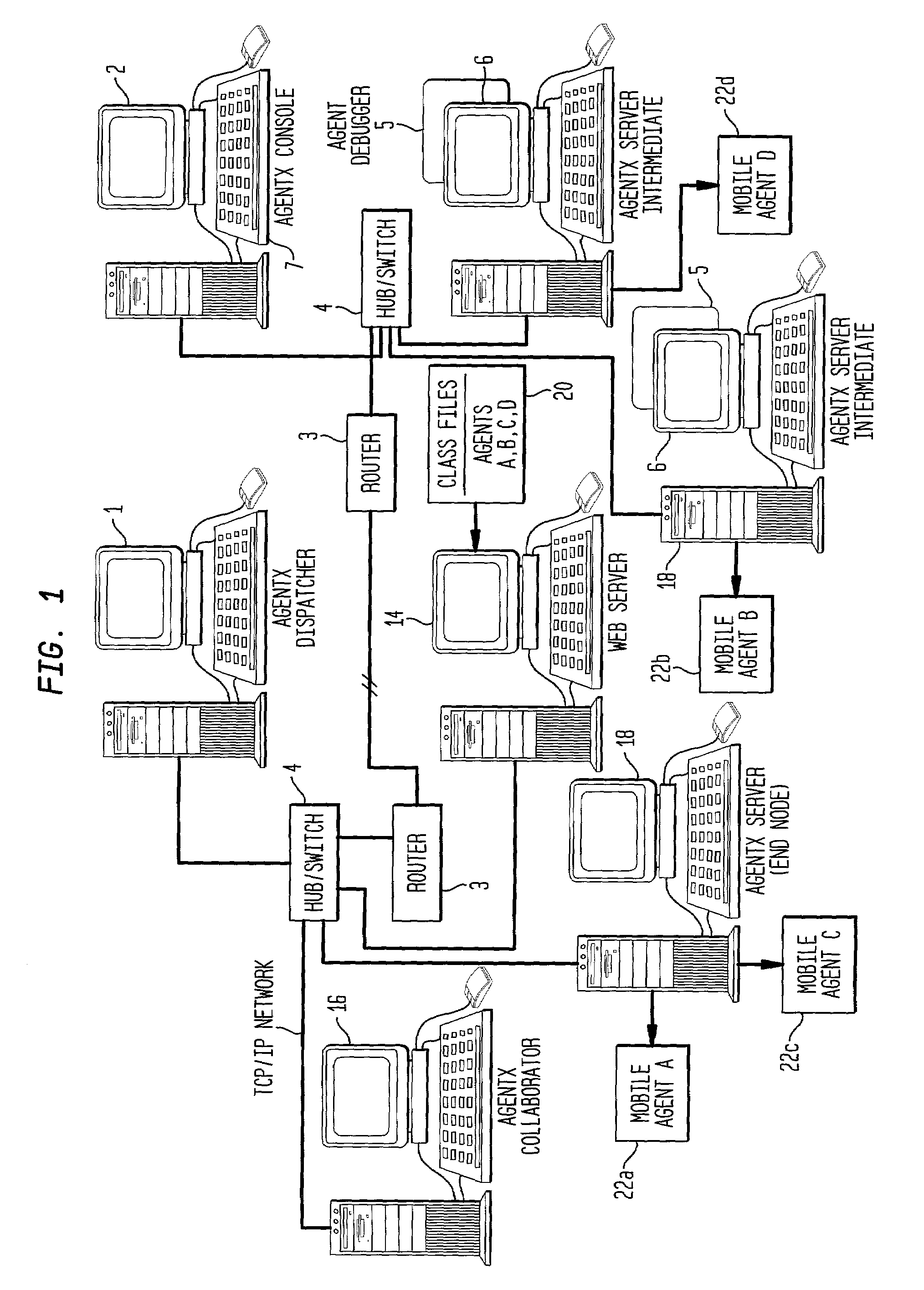

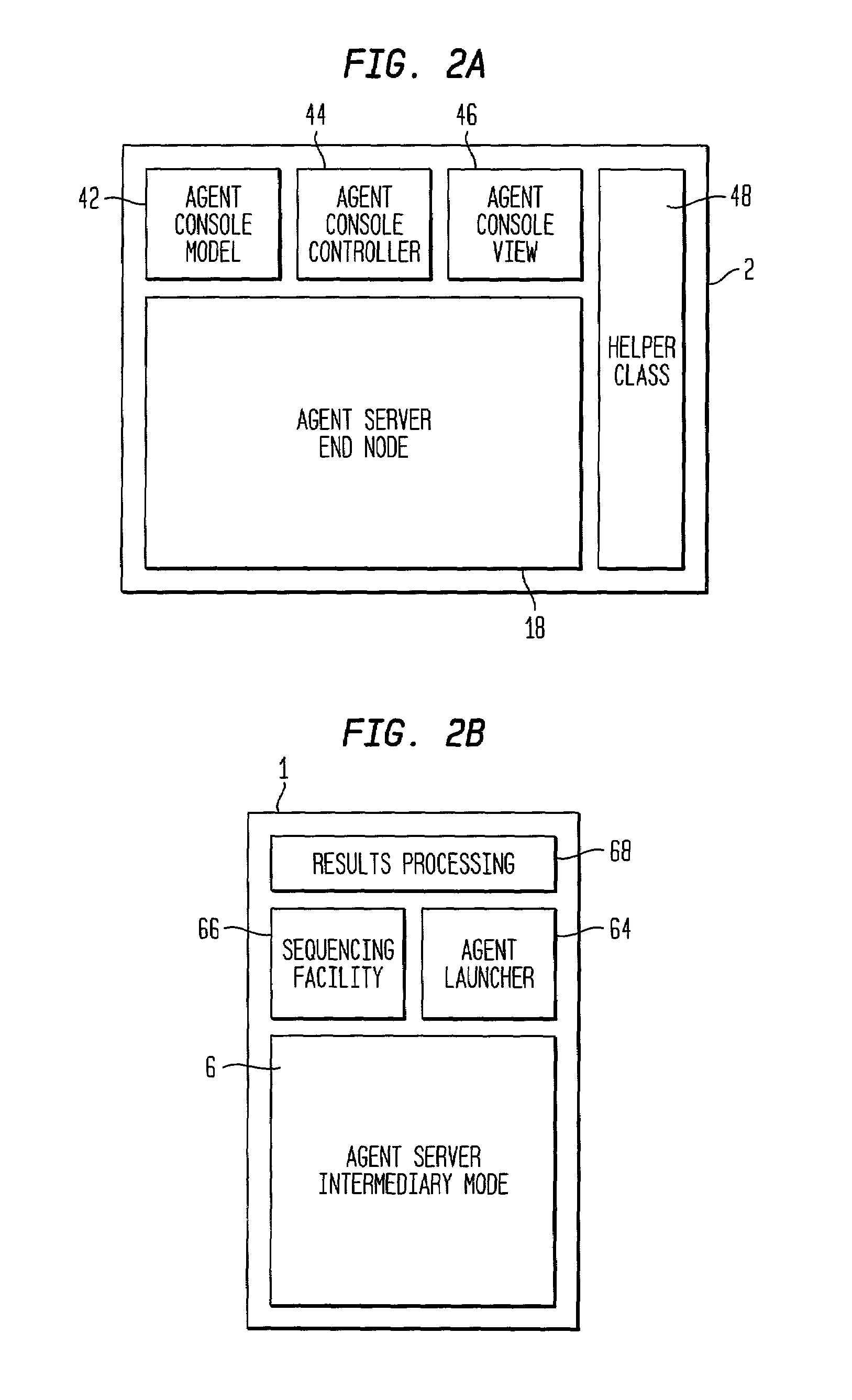

Method and apparatus for breaking down computing tasks across a network of heterogeneous computer for parallel execution by utilizing autonomous mobile agents

InactiveUS7082604B2Ease of parallel processingProgram initiation/switchingResource allocationApplication softwareLarge applications

A method and apparatus is provided for breaking down computing tasks within a larger application and distributing such tasks across a network of heterogeneous computers for simultaneous execution. The heterogeneous computers may be connected across a wide or local area network. The invention supports mobile agents that are self-migrating and can transport state information and stack trace information as they move from one host to another, continuing execution where the mobile agents may have left off. The invention includes a server component for providing an execution environment for the agents, in addition to sub-components which handle real-time collaboration between the mobile agents as well as facilities monitoring during execution. Additional components provide realistic thread migration for the mobile agents. Real-time stack trace information is stored as the computing tasks are executed, and if over-utilization of the computing host occurs, execution of the computing task can be halted and the computing task can be transferred to another computing hosts where execution can be seamlessly resumed using the stored, real-time state information and stack trace information.

Owner:MOBILE AGENT TECH

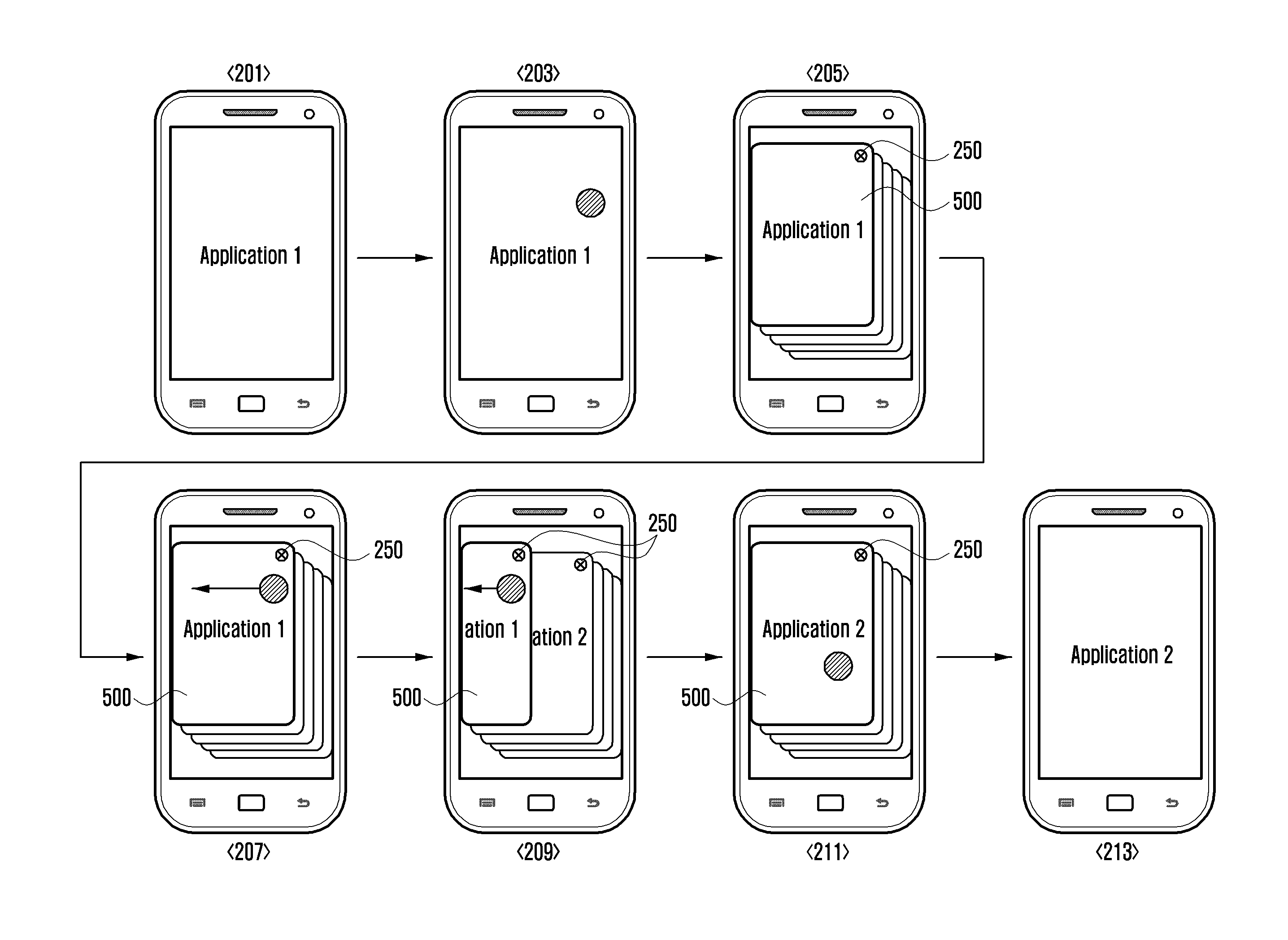

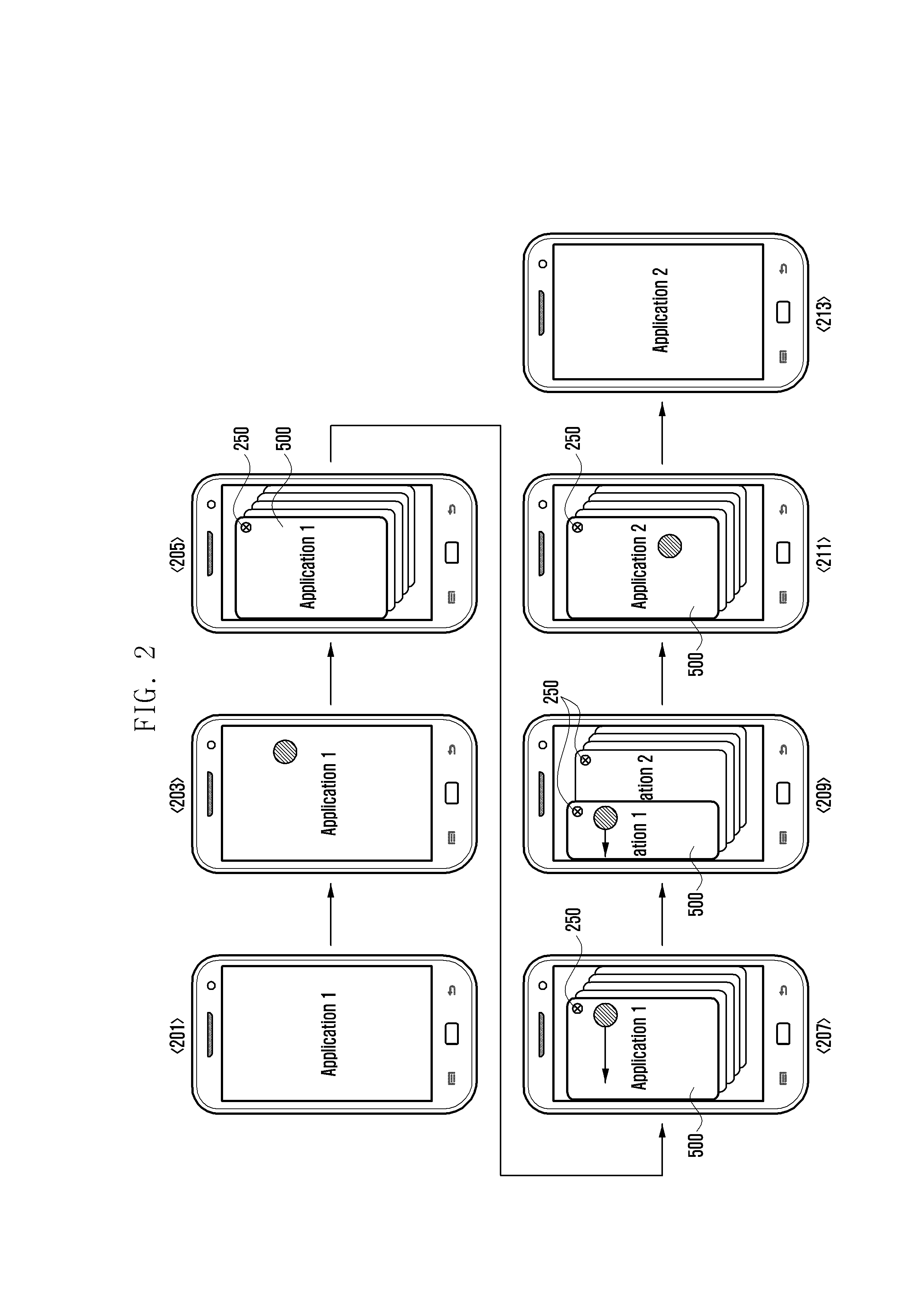

Multitasking method and apparatus of user device

ActiveUS20130174179A1Facilitate functioningQuickly switching among the tasksProgram initiation/switchingExecution for user interfacesUser deviceApplication software

A multitasking method and apparatus of a user device is provided for intuitively and swiftly switching between background and foreground tasks running on the user device. The multitasking method includes receiving an interaction to request for task-switching in a state where an execution screen of a certain application is displayed, displaying a stack of tasks that are currently running, switching a task selected from the stack to a foreground task, and presenting an execution window of the foreground task.

Owner:SAMSUNG ELECTRONICS CO LTD

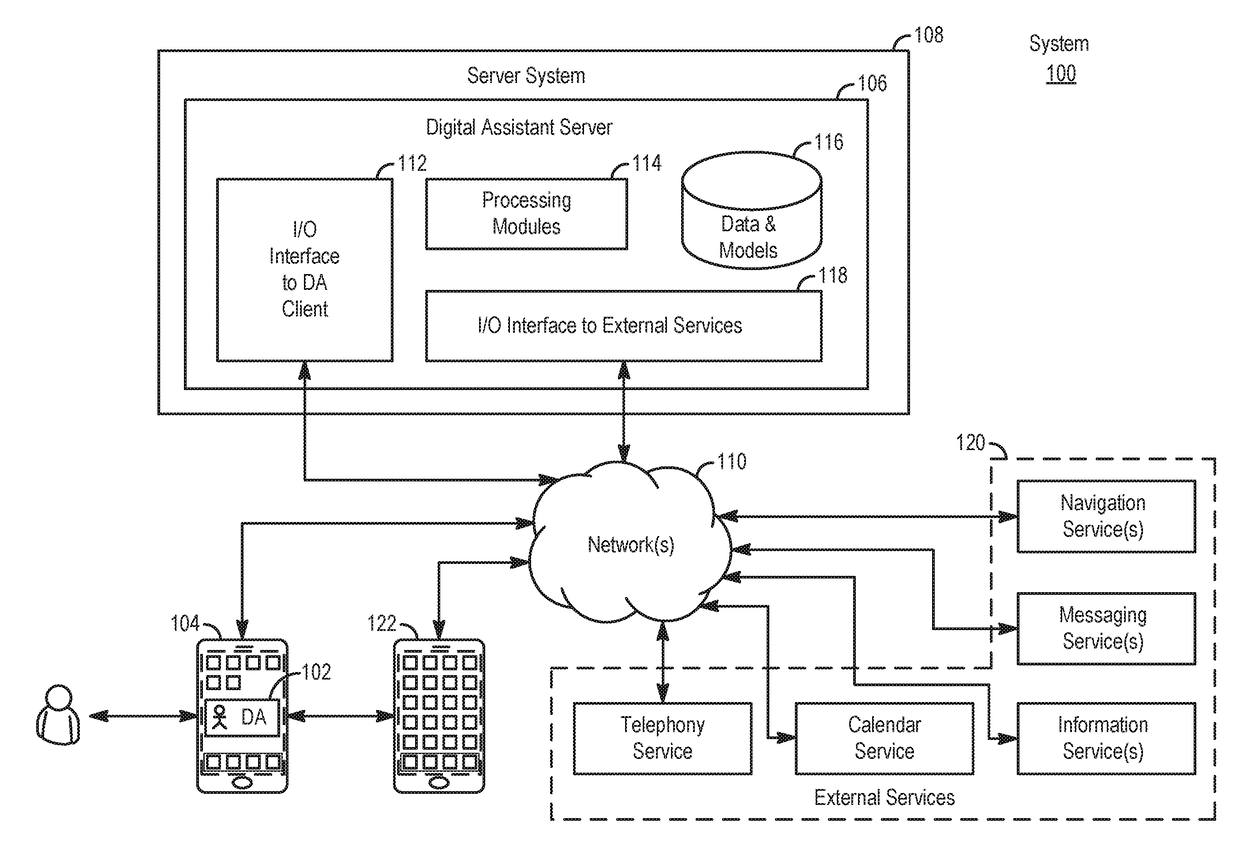

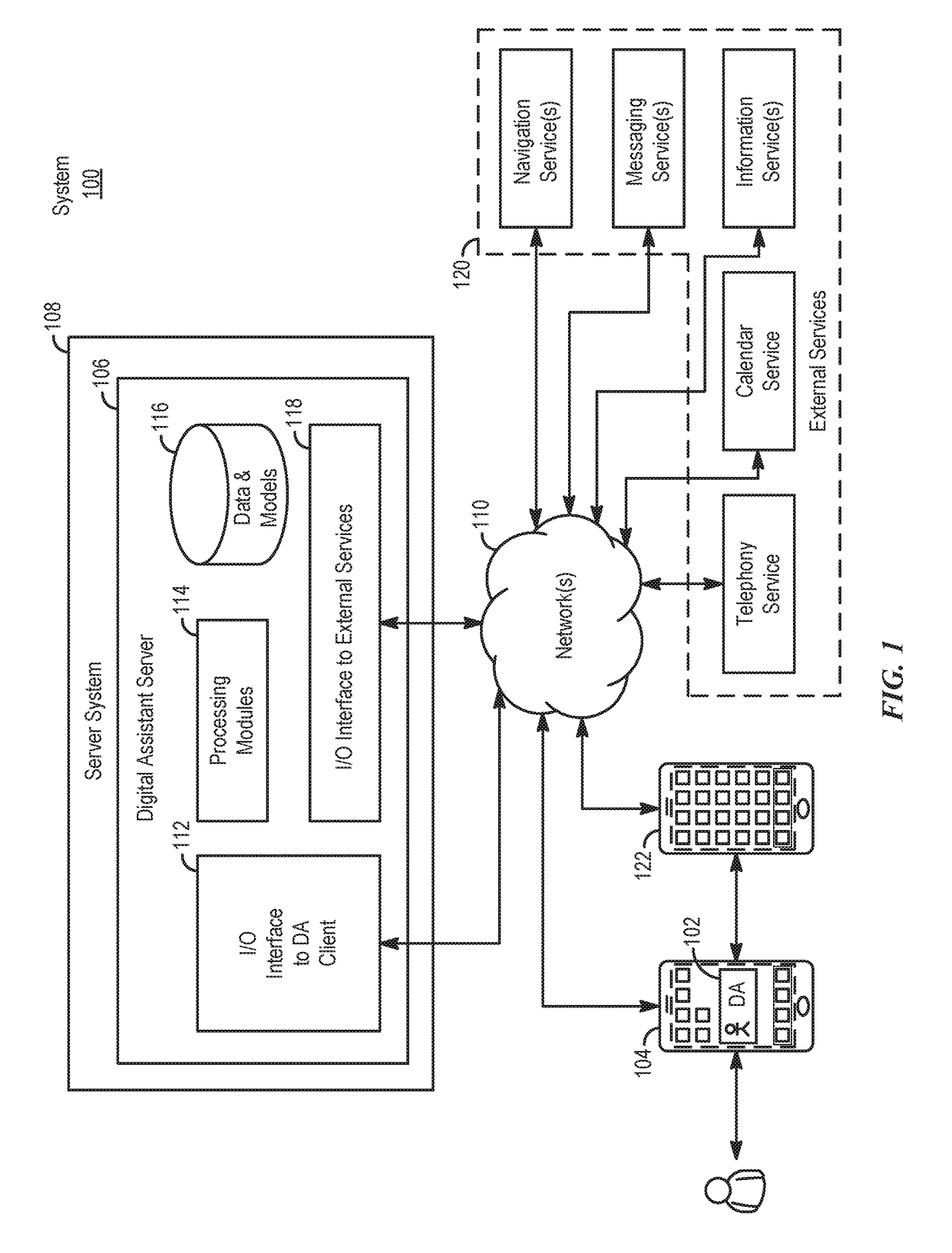

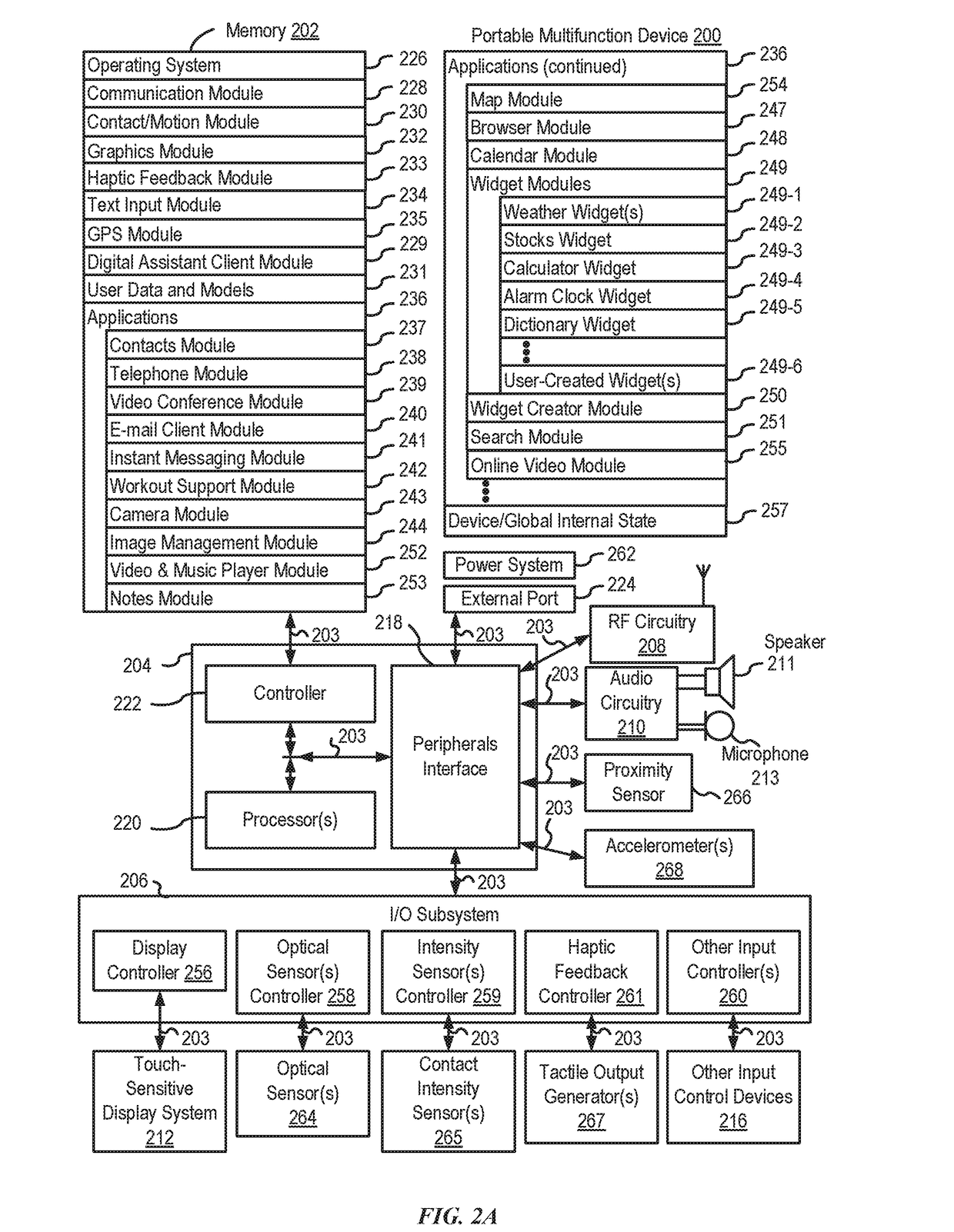

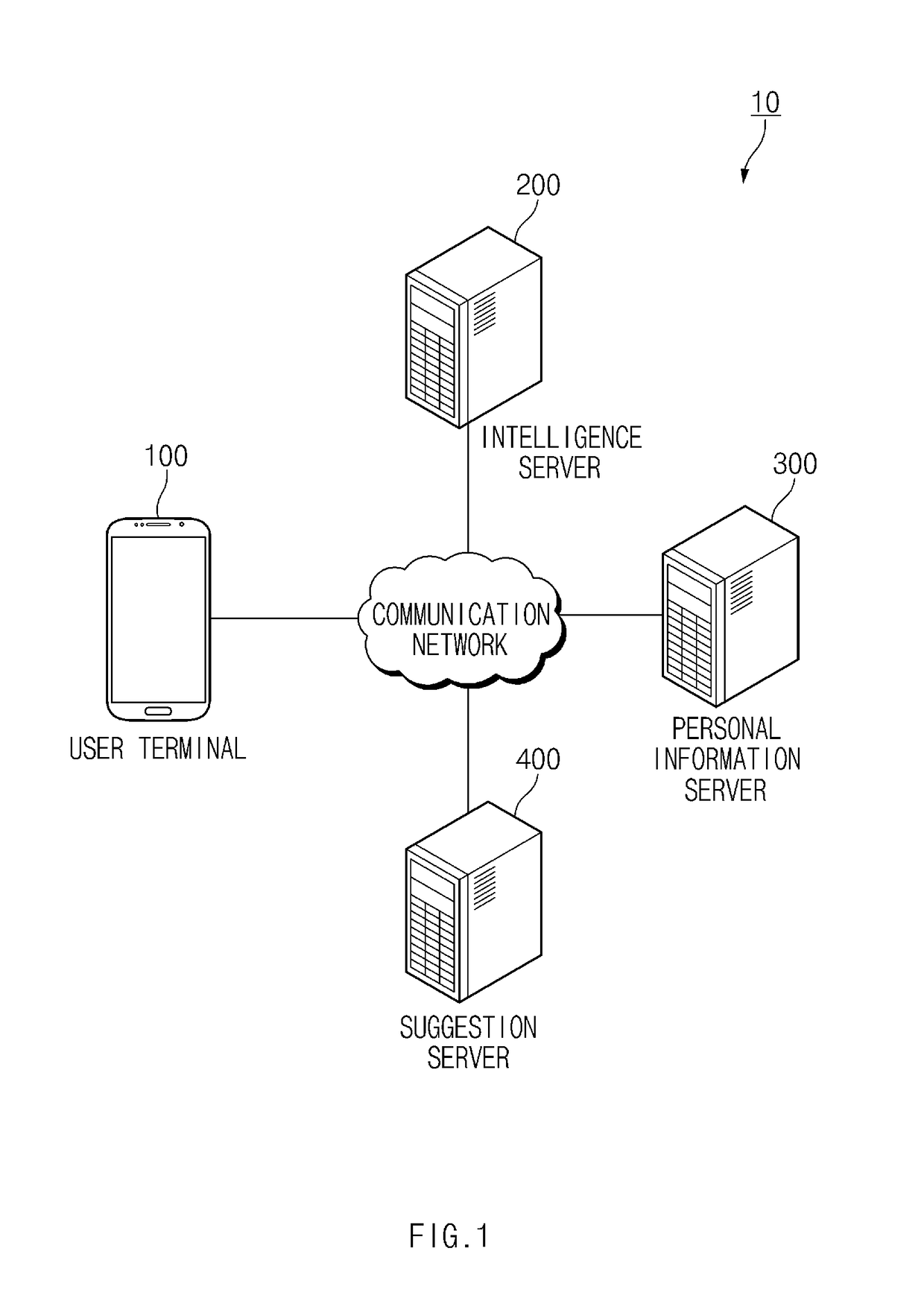

Distributed personal assistant

ActiveUS20170068550A1Faster and efficient methodReduce cognitive loadProgram initiation/switchingArtificial lifeReal-time computing

An exemplary method for using a virtual assistant may include, at an electronic device configured to transmit and receive data, receiving a user request for a service from a virtual assistant; determining at least one task to perform in response to the user request; estimating at least one performance characteristic for completion of the at least one task with the electronic device, based on at least one heuristic; based on the estimating, determining whether to execute the at least one task at the electronic device; in accordance with a determination to execute the at least one task at the electronic device, causing the execution of the at least one task at the electronic device; in accordance with a determination to execute the at least one task outside the electronic device: generating executable code for carrying out the least one task; and transmitting the executable code from the electronic device.

Owner:APPLE INC

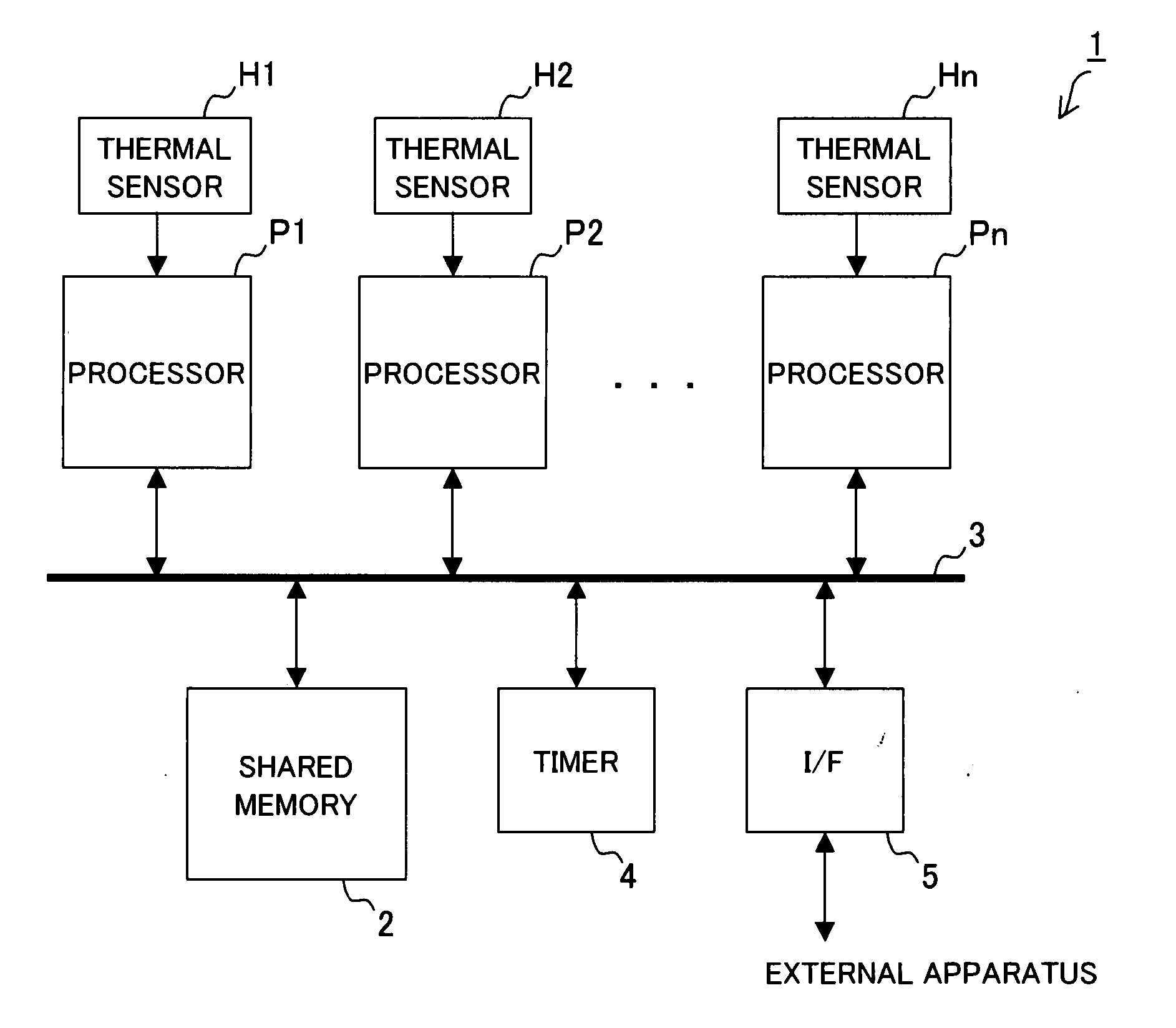

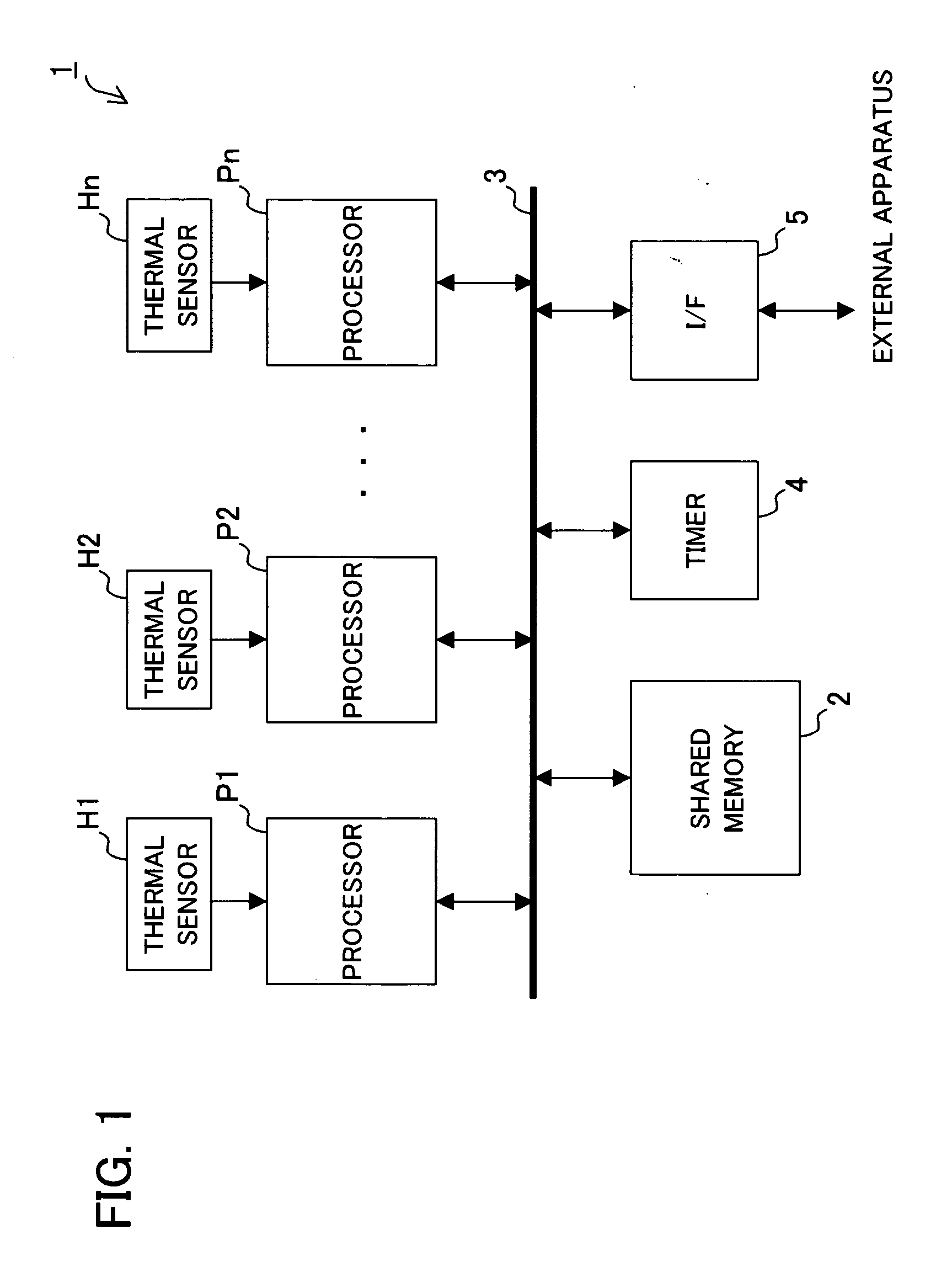

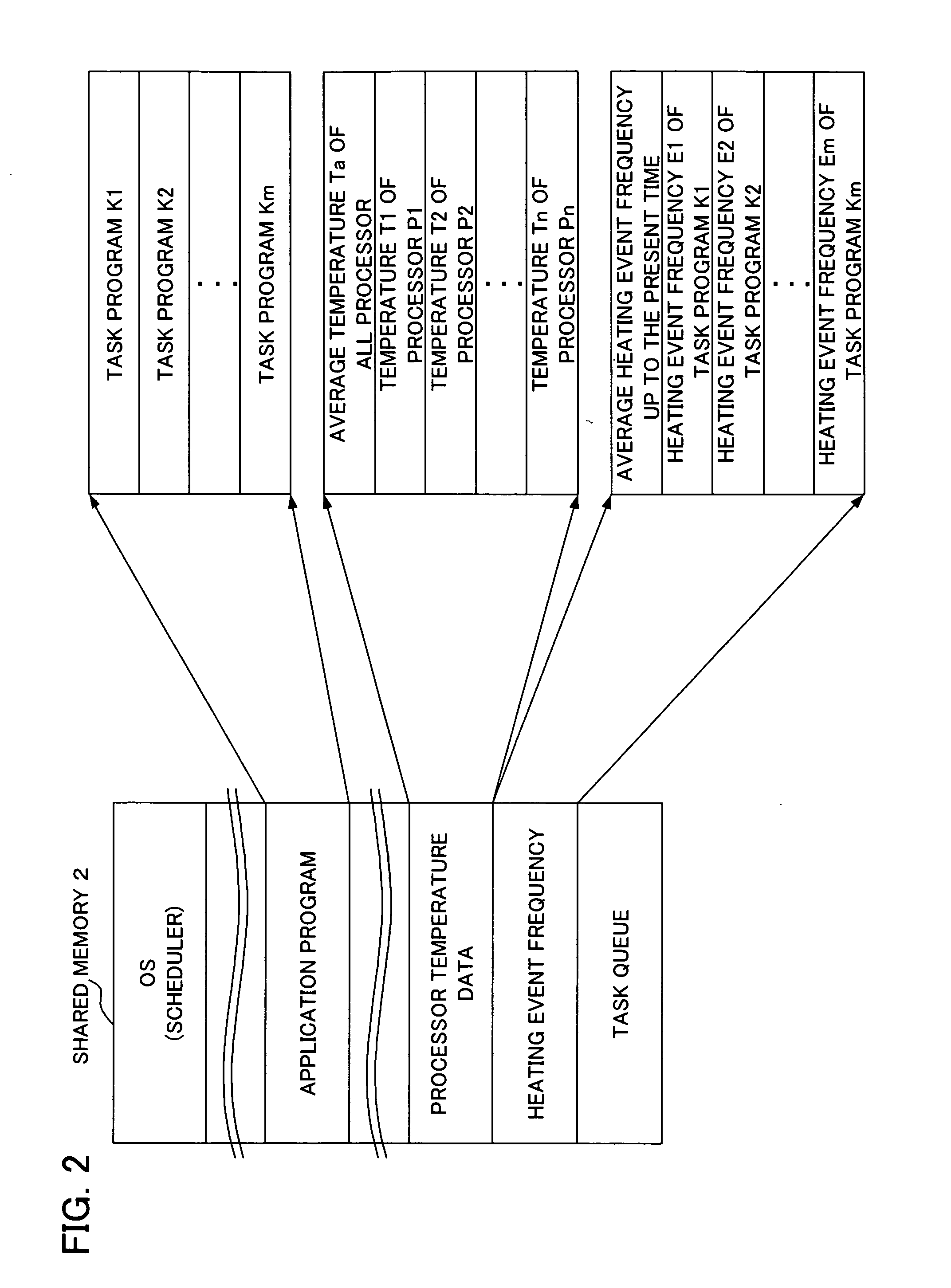

Task scheduling apparatus in distributed processing system

InactiveUS20050278520A1Raise the processing temperatureReduce heatEnergy efficient ICTProgram initiation/switchingProcessing elementHandling system

A task scheduling apparatus of a distributed processing system having a plurality of processing units for processing a plurality of distributed tasks is provided. As a first task scheduling method, the task scheduling apparatus allocates a task to a processing unit having the lowest temperature. As a second task scheduling method, the task scheduling apparatus selects a task based on both temperature of each processing unit and characteristic values of tasks related to degree of temperature rise or consumption power increase caused by execution, and allocates the selected task to the object processing unit. For example, as the second task scheduling method, a task producing a large degree of temperature rise (for example, a task having a number of instructions to be processed per unit time) is allocated to a processing unit having a low temperature. With such a scheduling method, uniform temperature of each processing unit can be obtained.

Owner:FUJITSU LTD

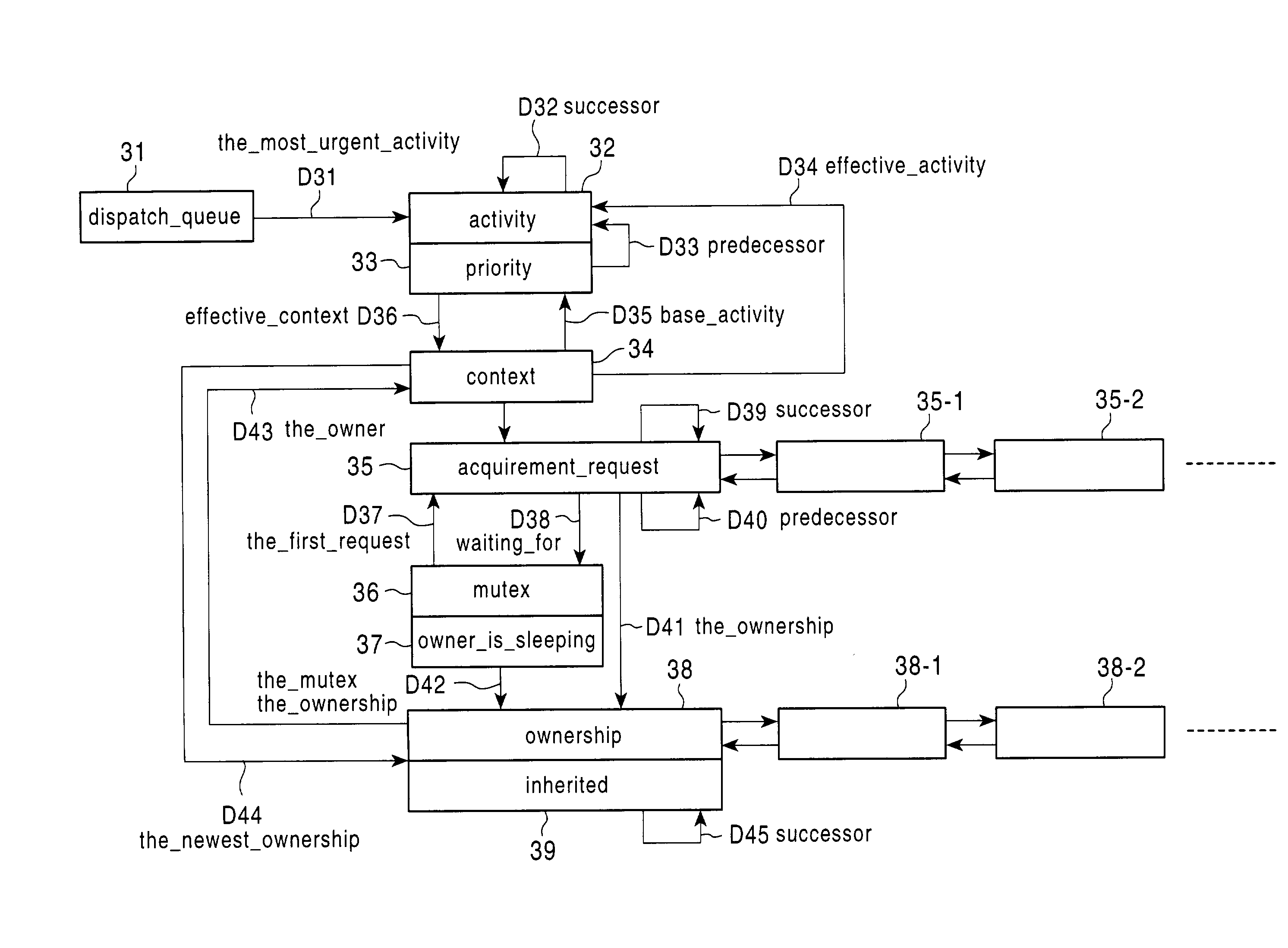

Task management system

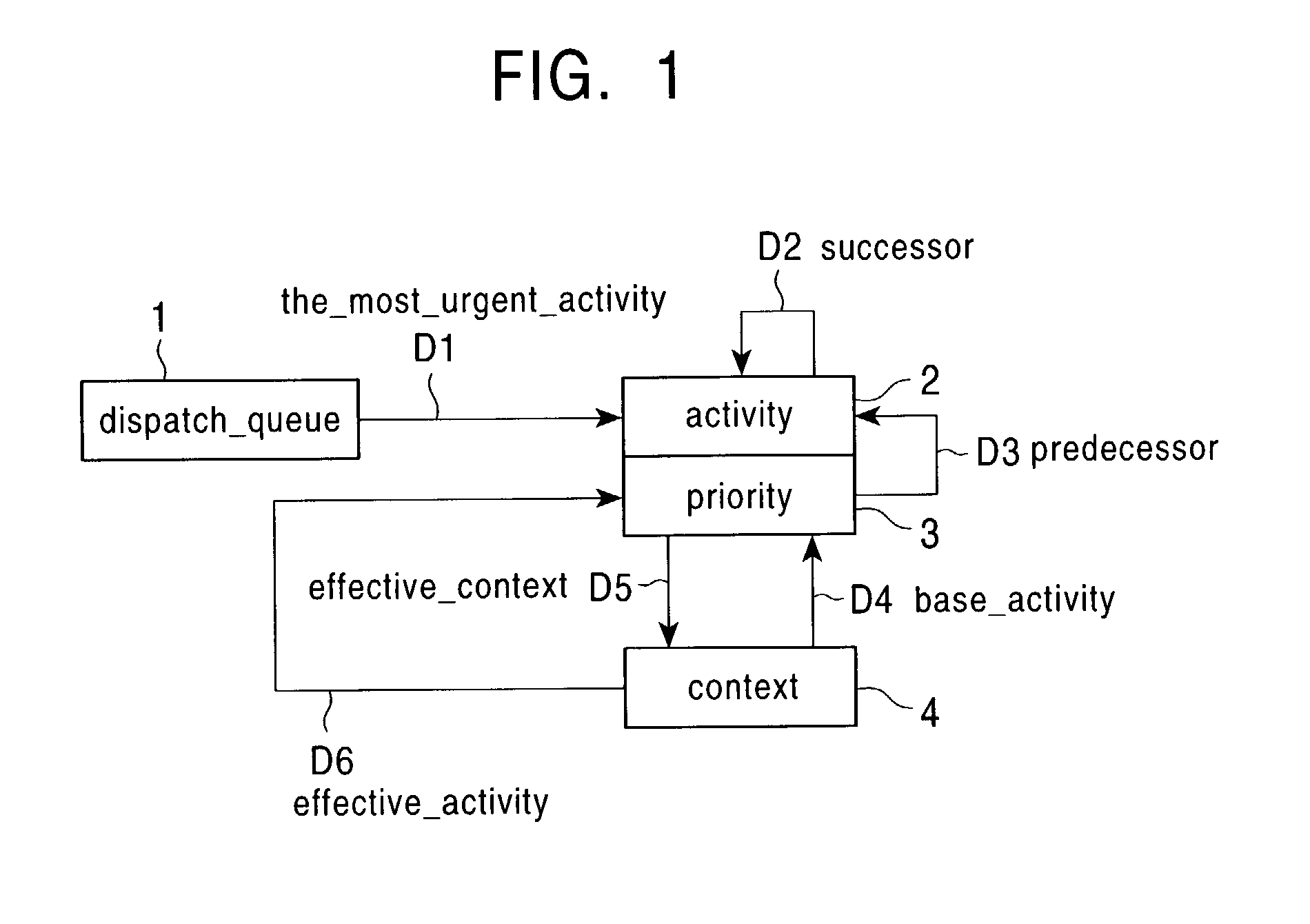

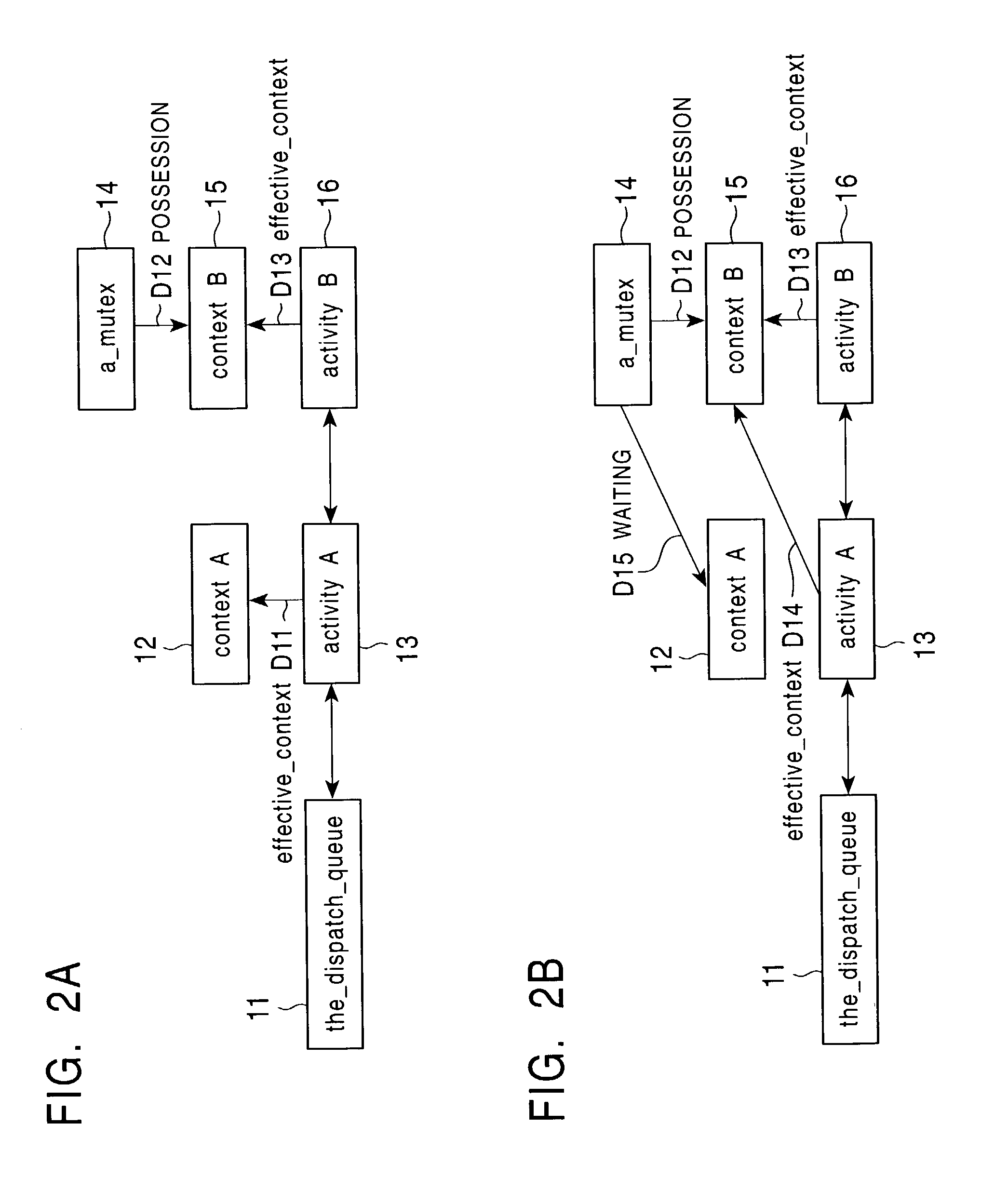

InactiveUS7302686B2Shorten the timeReduce overheadProgram initiation/switchingMultiple digital computer combinationsTask managementMutual exclusion

A task management system that inherit priority and that can reduce the queue operation required for transition to / return from a mutual exclusion awaiting state The task management system can execute a task without considering its priority, start or stop a server task and inherit priority without operating the dispatch queue. The task management system includes activity retaining information, context retaining information, and a dispatch queue used to select the highest priority task. Information on a task is divided and managed by the activity and the context, where each activity is inserted into / deleted from the dispatch queue. When the priority of a task is inherited by another task, only the correspondence between activity and context is changed.

Owner:SONY CORP

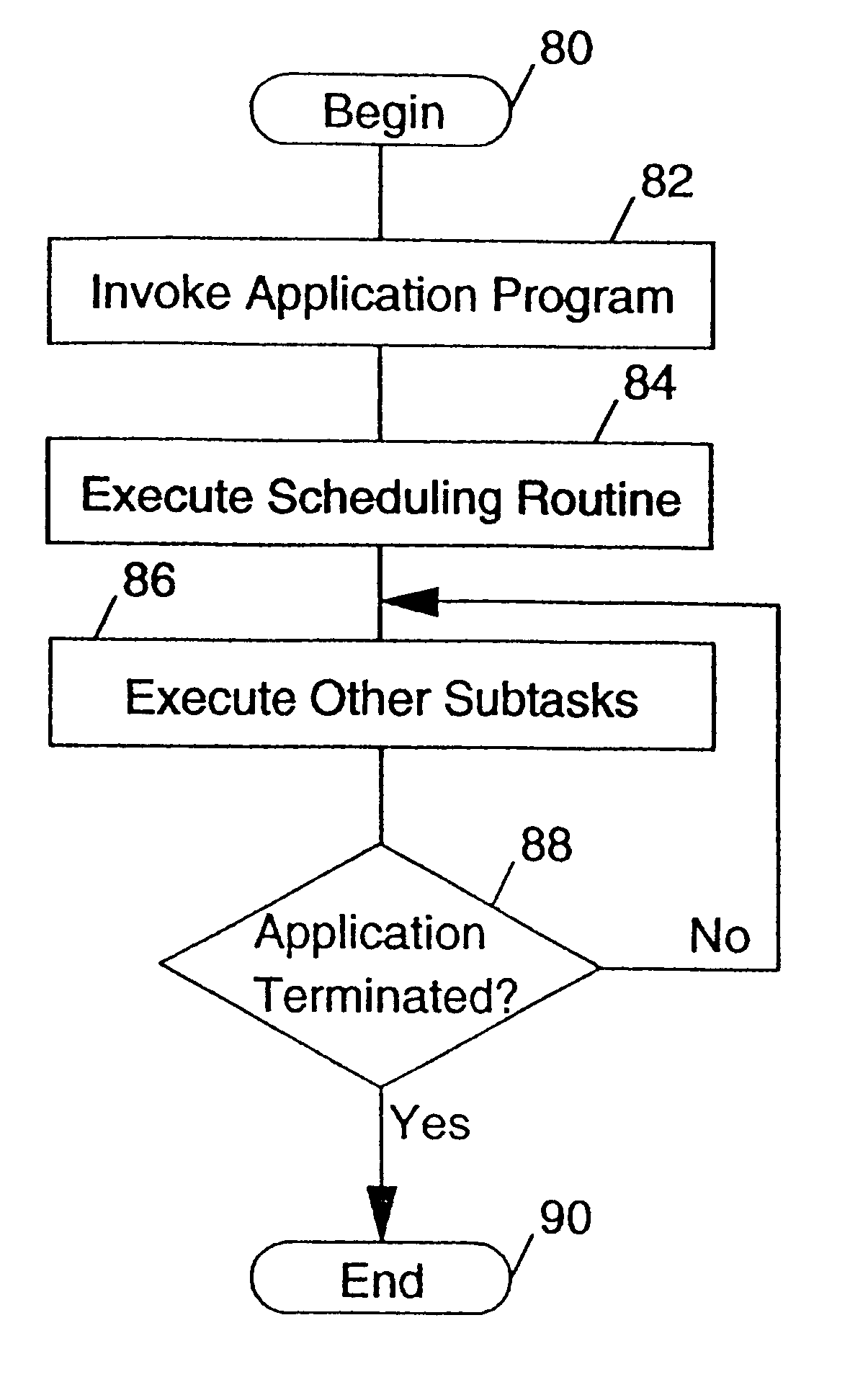

Data processing system and method of task management within a self-managing application

InactiveUS6223201B1Program initiation/switchingMemory systemsData processing systemApplication software

A data processing system and method of task management within a self-managing application program including a number of tasks and a processing time monitor are disclosed. In accordance with the present invention, a selected portion of processing time is allocated to each of the tasks in the self-managing application and the tasks are executed by the data processing system. Utilizing the processing time monitor, a determination is periodically made whether an actual portion of processing time utilized by each of the tasks exceeds the selected portion of processing time allocated to that task. In response to a determination that an actual portion of processing time utilized by a particular task exceeds the selected portion of processing time allocated that task, execution of the particular task is suspended for a selected penalty time. In one embodiment, the penalty time is selected such that following the expiration of the penalty time, the actual portion of processing time utilized by the particular task will be no greater than the selected portion of processing time allocated to the particular task.

Owner:IBM CORP

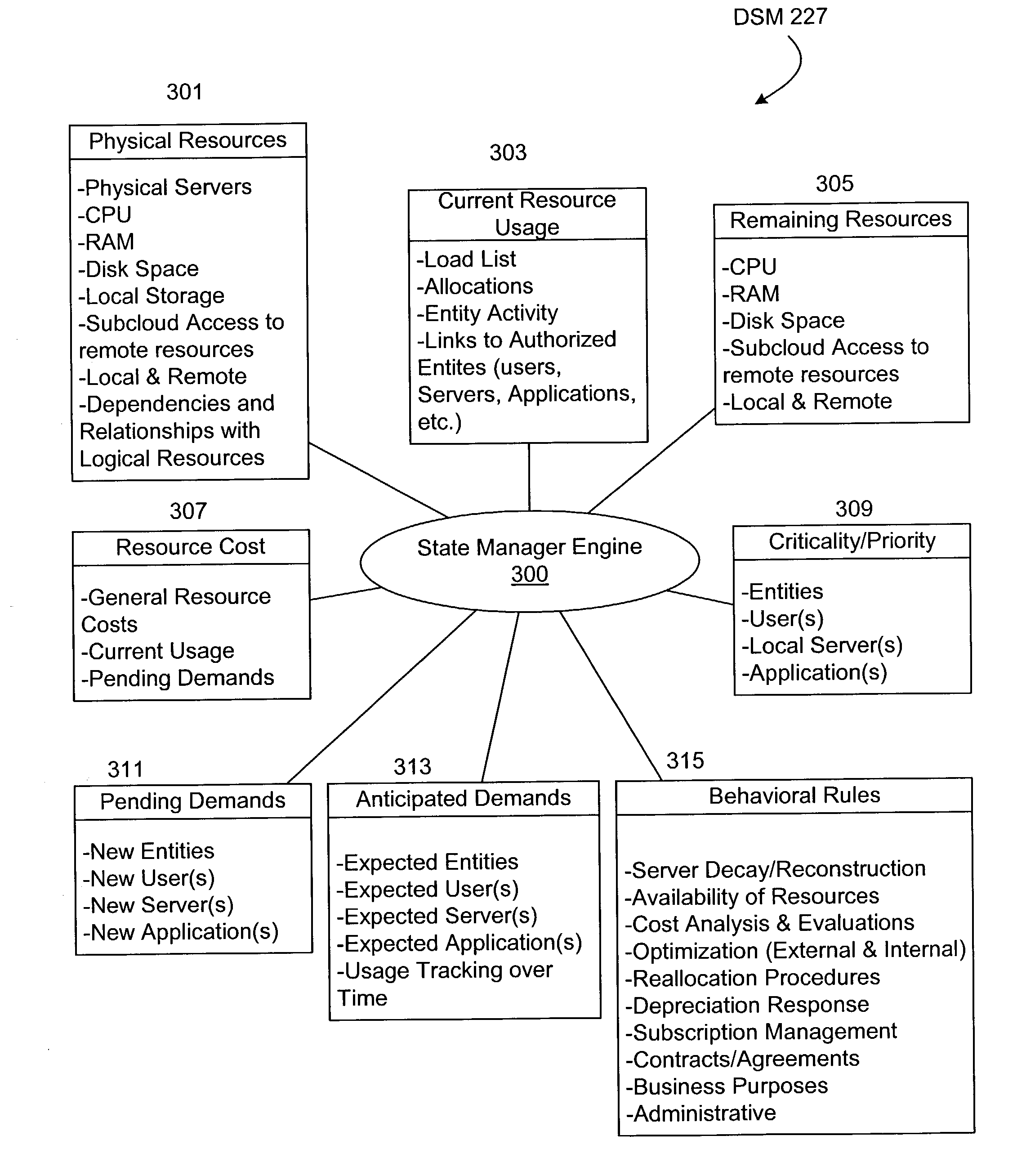

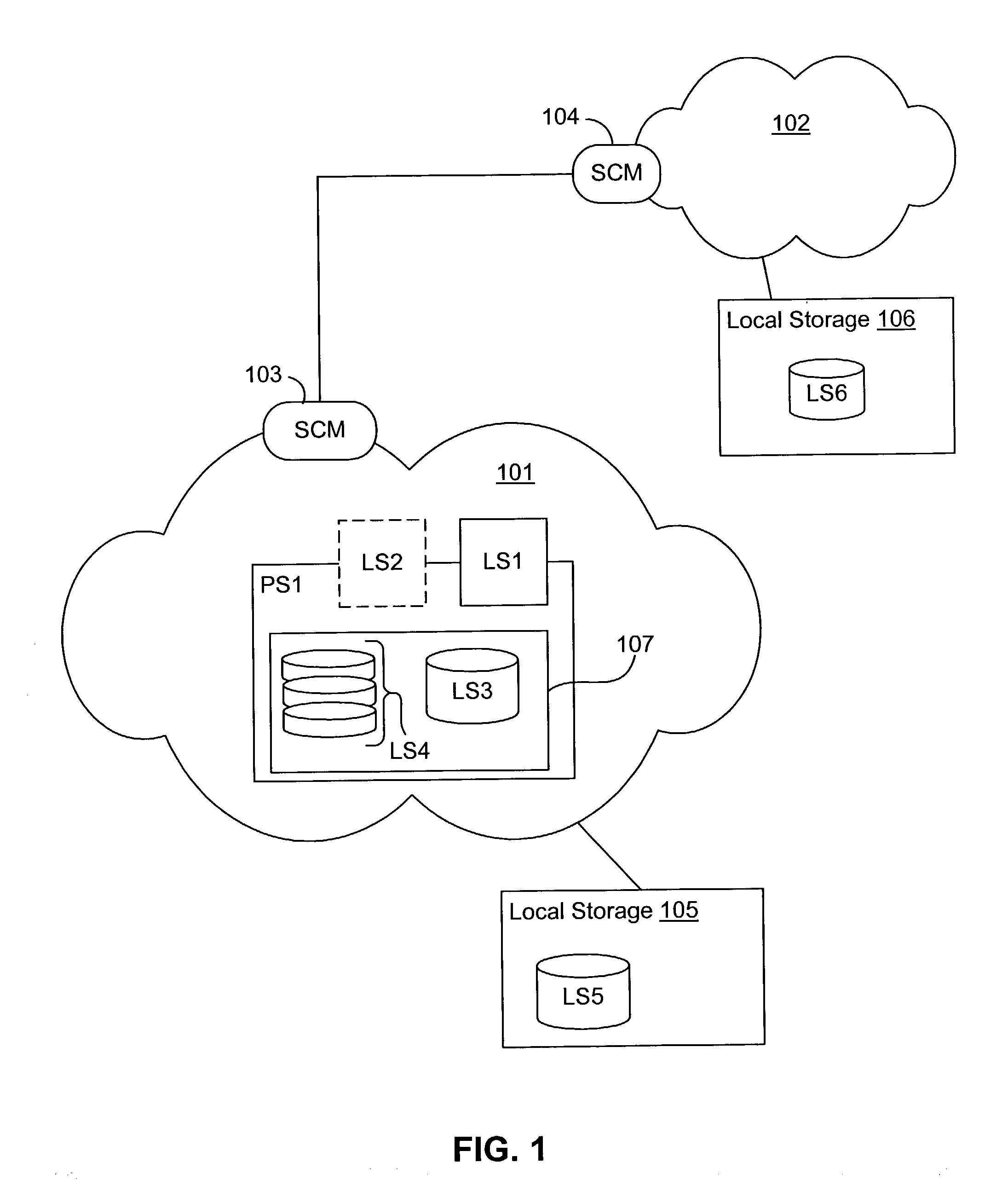

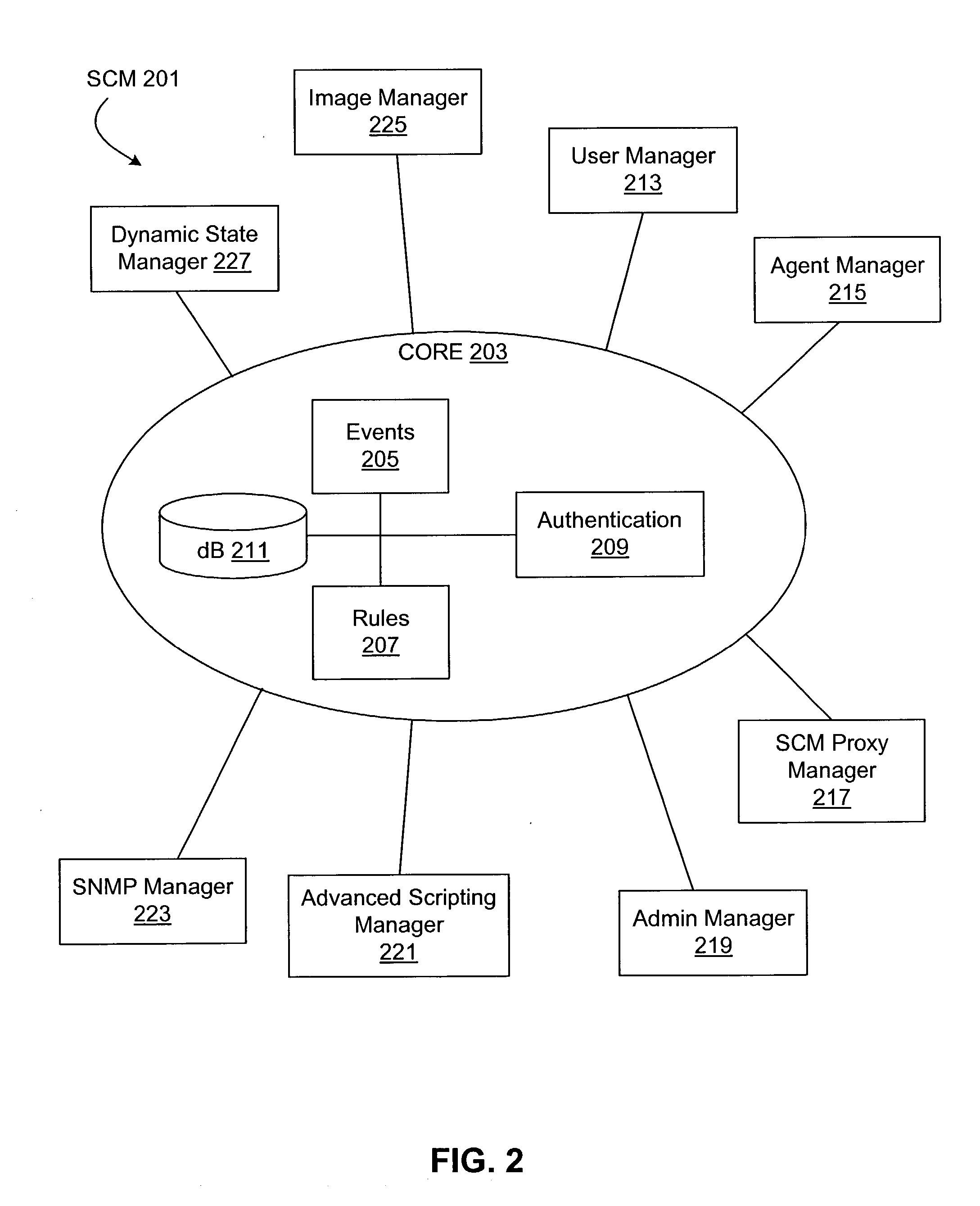

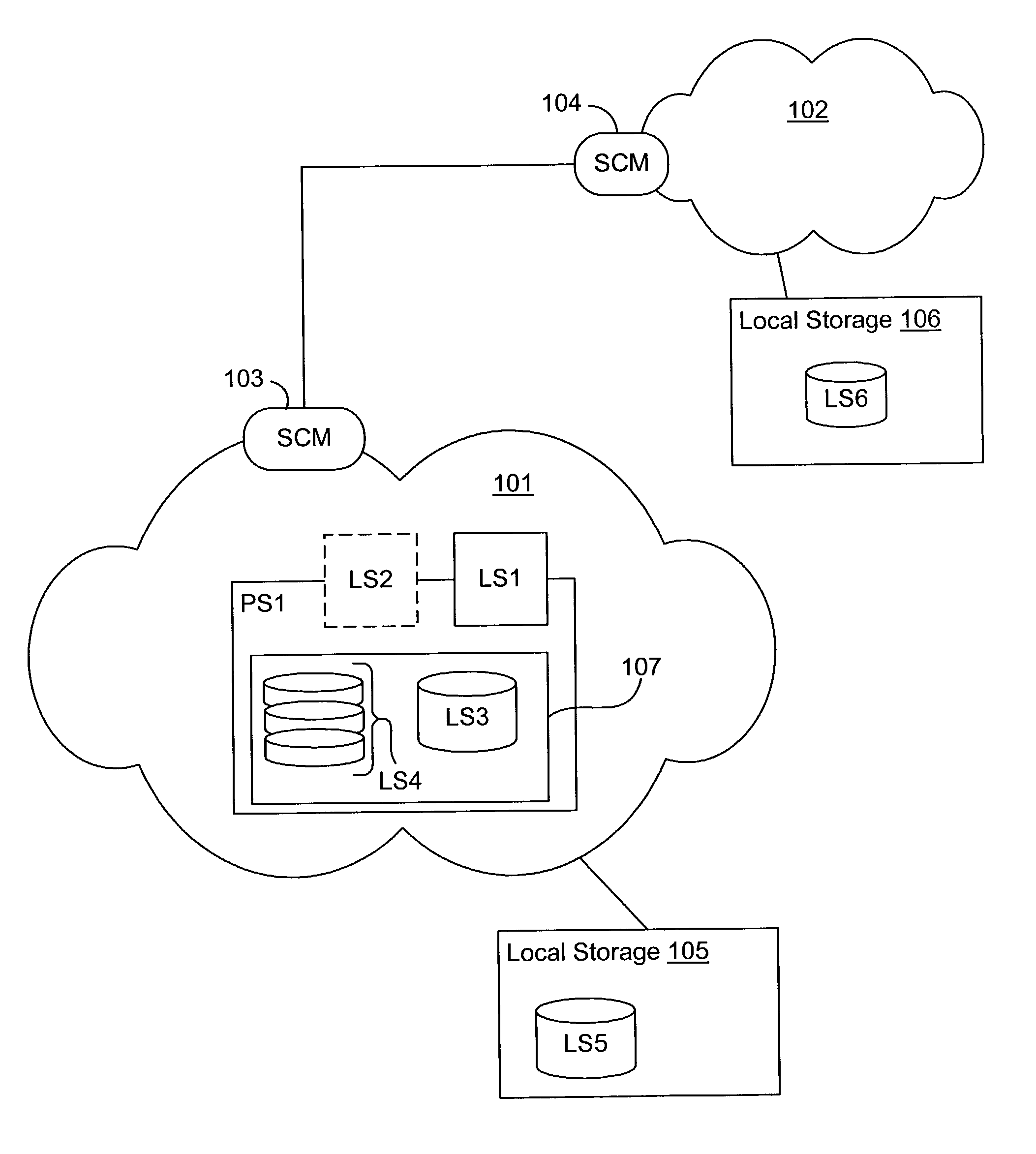

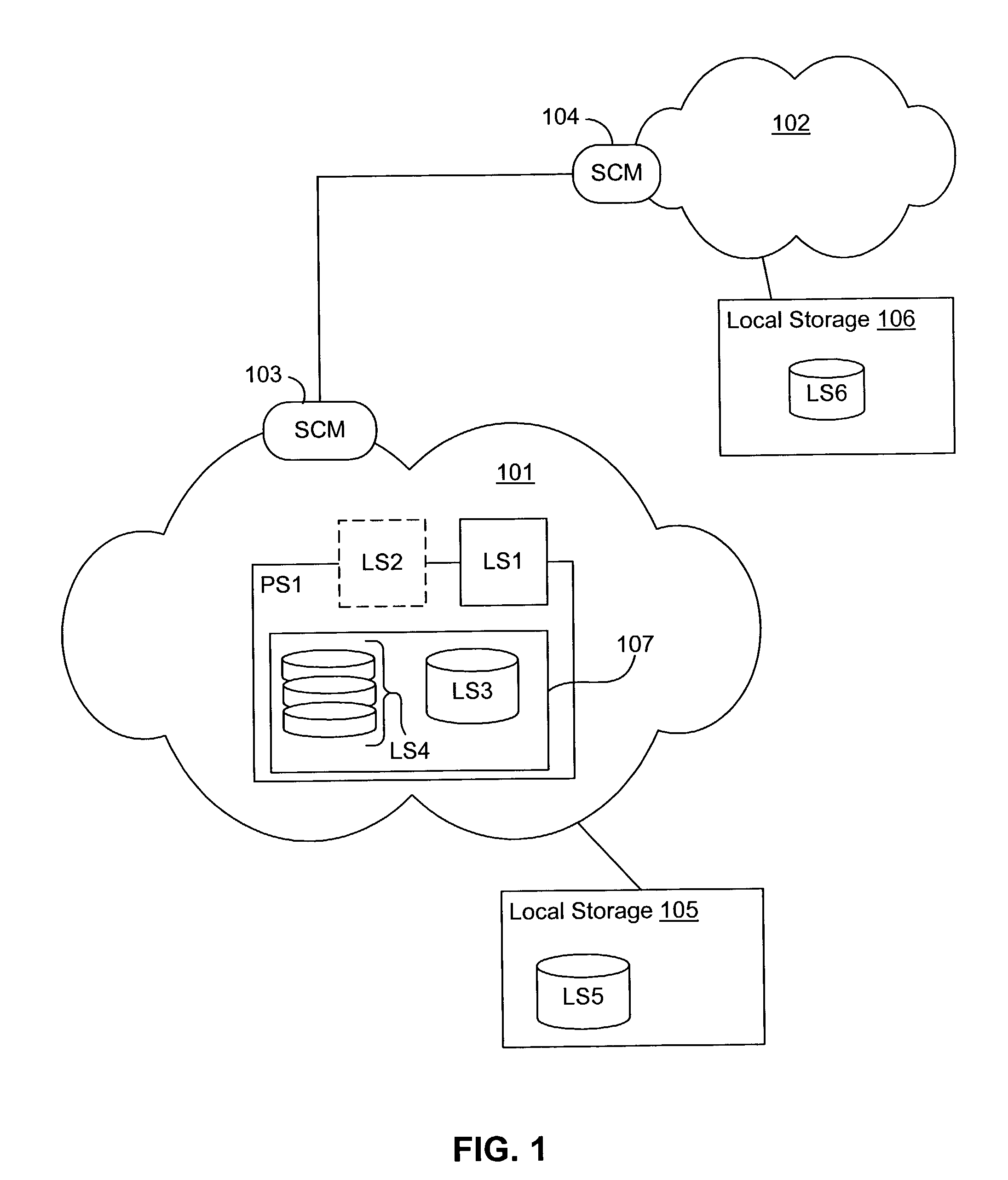

Near on-line servers

InactiveUS20030177176A1Maximize resource utilizationEnsure availabilityProgram initiation/switchingResource allocationVirtualizationResource utilization

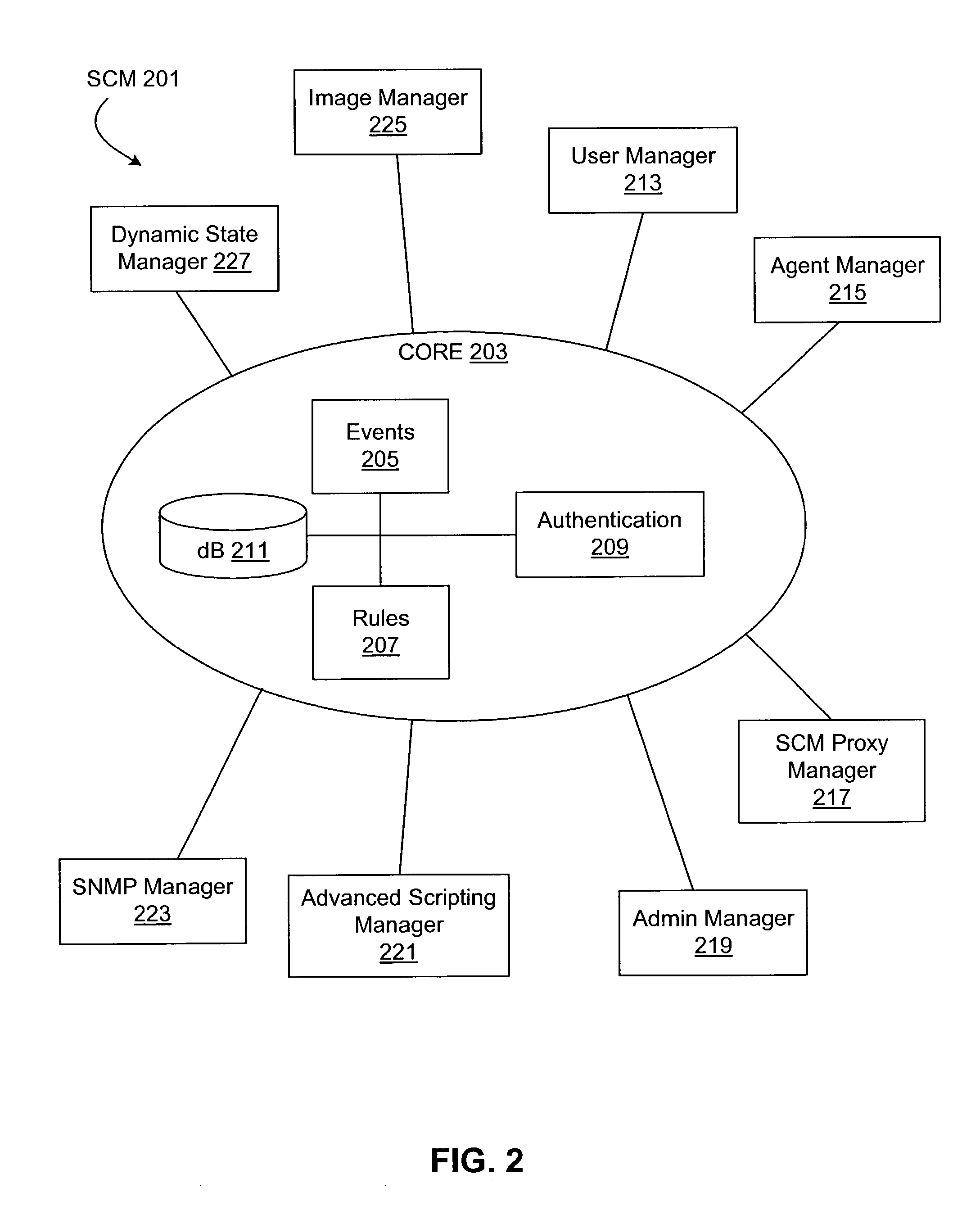

A dynamic state manager (DSM) for a server cloud manager (SCM) of a virtualized logical server cloud including a resource definition, a rules module and a state manager engine. The resource definition incorporates information of the available physical and logical resources of the server cloud, including cost, priority, usage and demand information of the resources. The resource definition further incorporates dependencies and relationships between physical and logical resources. The rules module includes predetermined behavioral rules based on demand, usage, priority and cost information. The behavioral rules define optimized resource utilization of the resources of the server cloud. The state manager engine is linked to the resource definition and the rules module and cooperates with the SCM to apply the behavioral rules to achieve optimized resource utilization.

Owner:DELL PROD LP

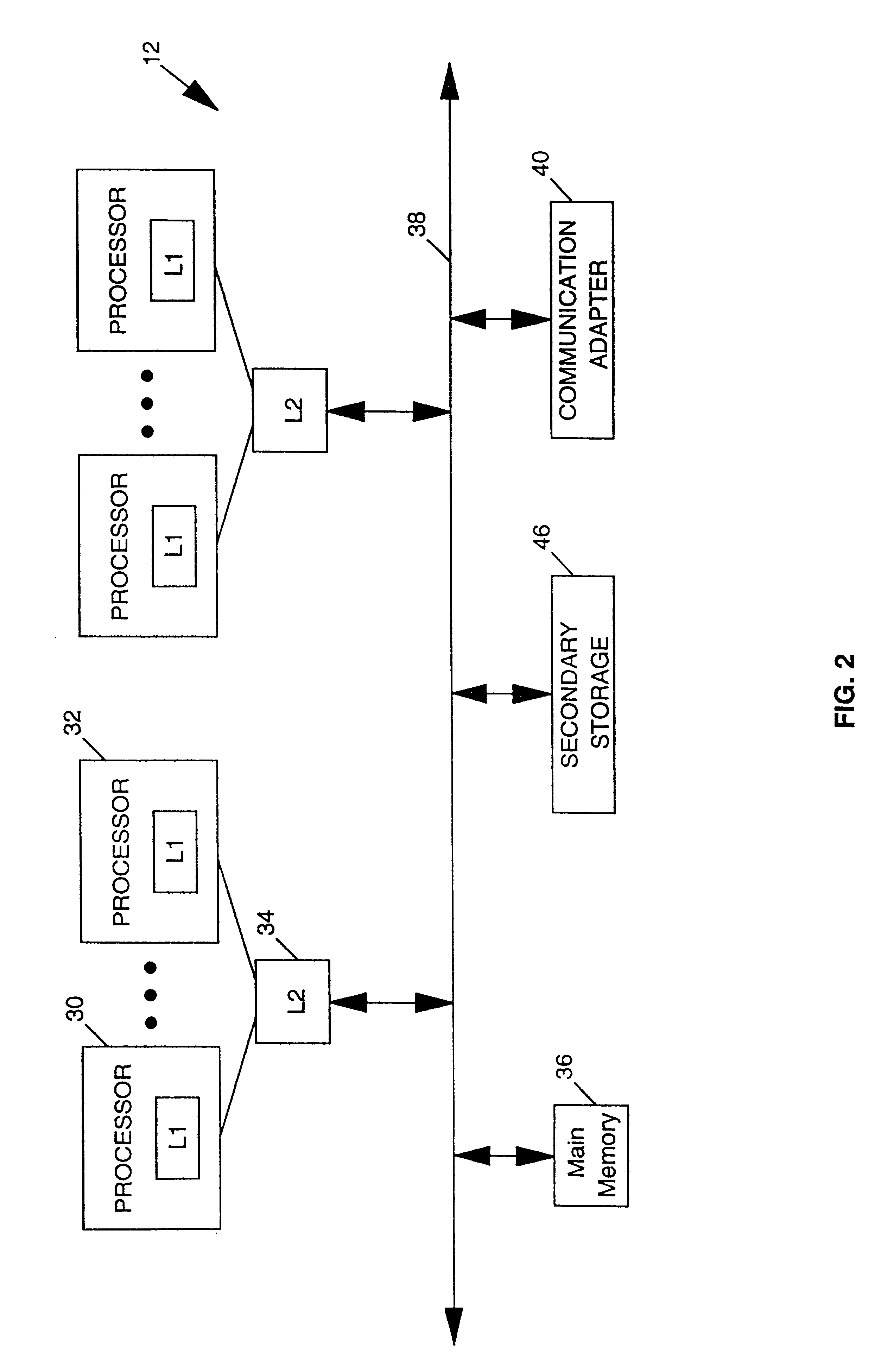

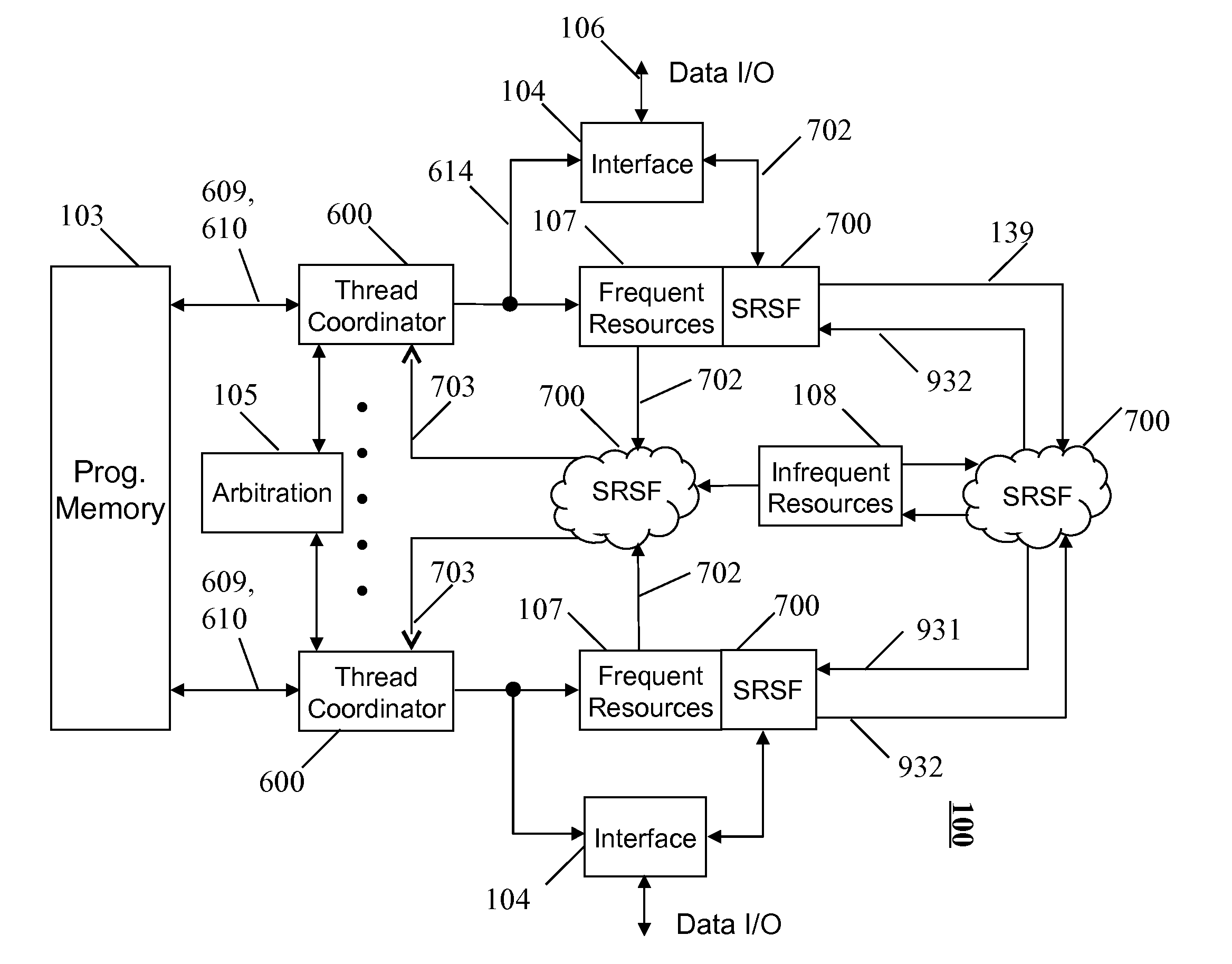

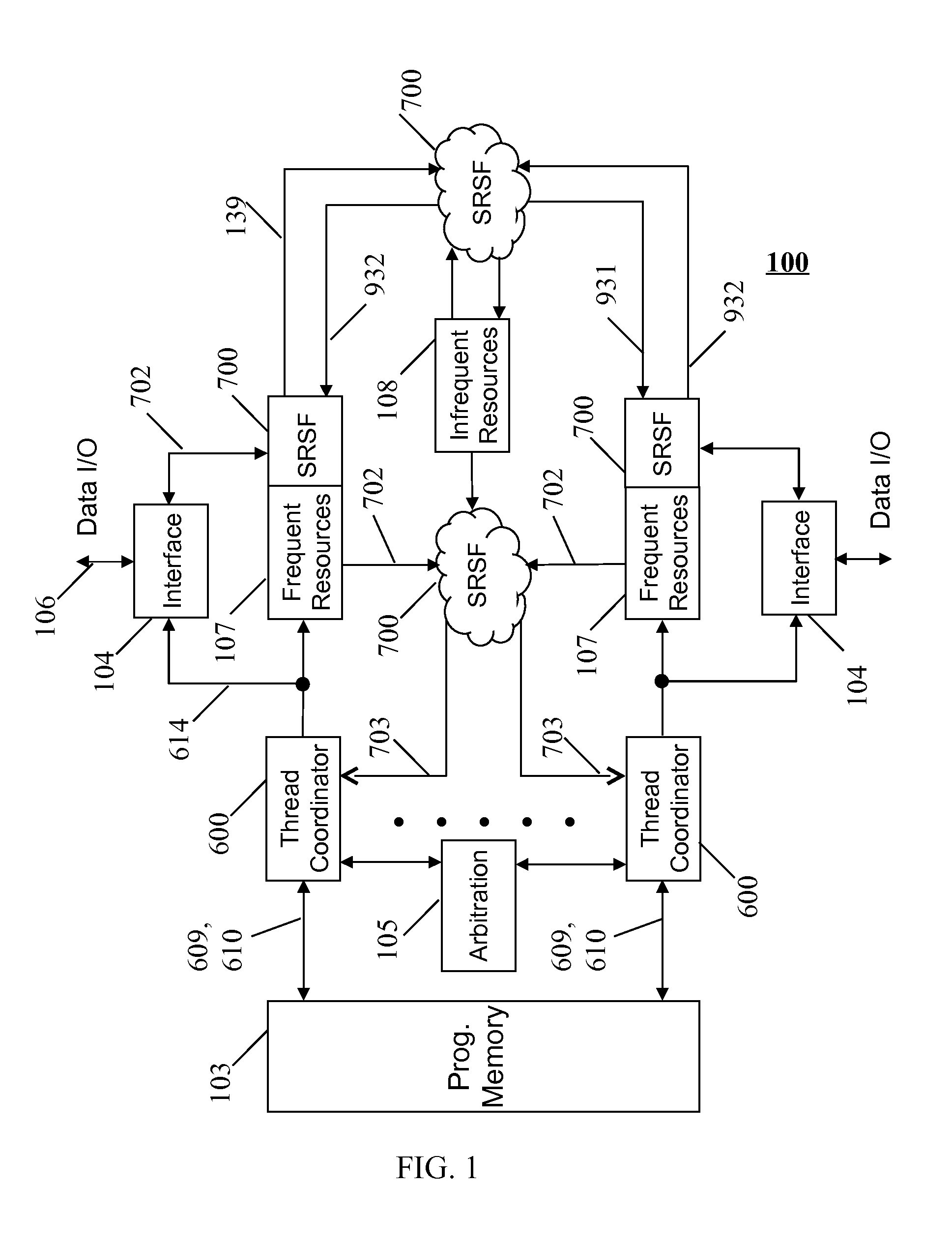

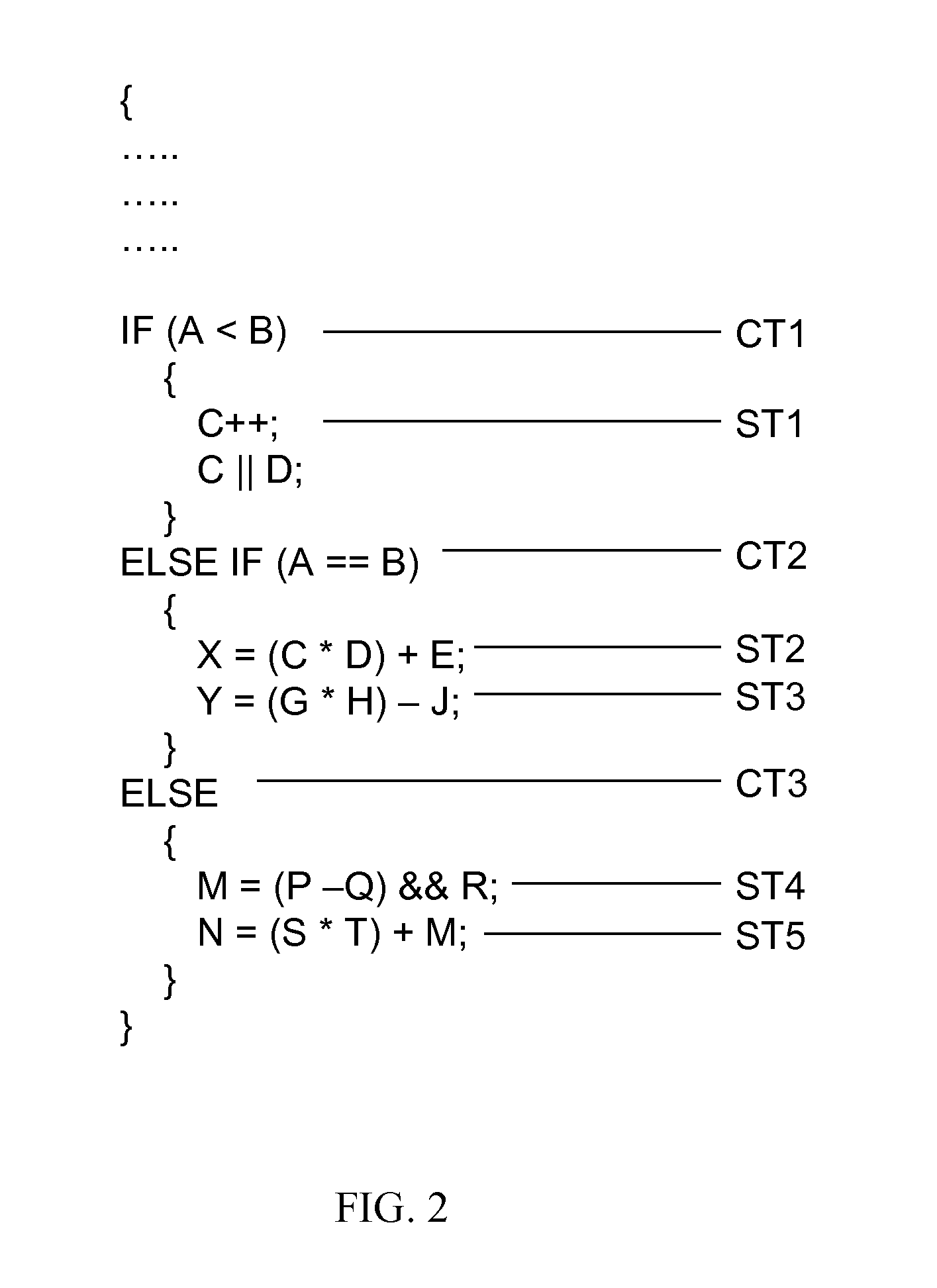

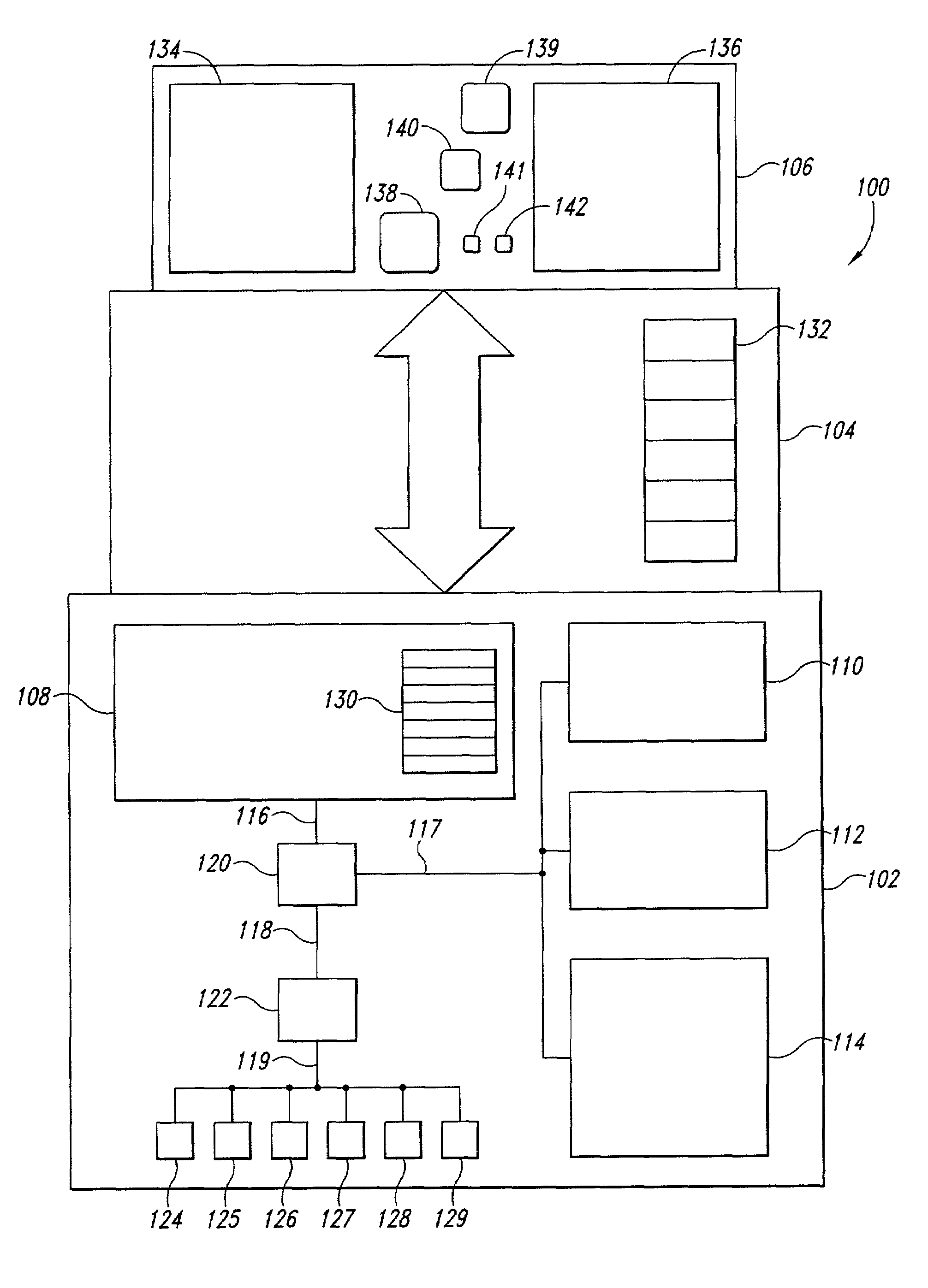

Shared resource multi-thread processor array

ActiveUS20120089812A1Dataflow computersProgram initiation/switchingProgrammable circuitsSwitched fabric

A shared resource multi-thread processor array wherein an array of heterogeneous function blocks are interconnected via a self-routing switch fabric, in which the individual function blocks have an associated switch port address. Each switch output port comprises a FIFO style memory that implements a plurality of separate queues. Thread queue empty flags are grouped using programmable circuit means to form self-synchronised threads. Data from different threads are passed to the various addressable function blocks in a predefined sequence in order to implement the desired function. The separate port queues allows data from different threads to share the same hardware resources and the reconfiguration of switch fabric addresses further enables the formation of different data-paths allowing the array to be configured for use in various applications.

Owner:SMITH GRAEME ROY

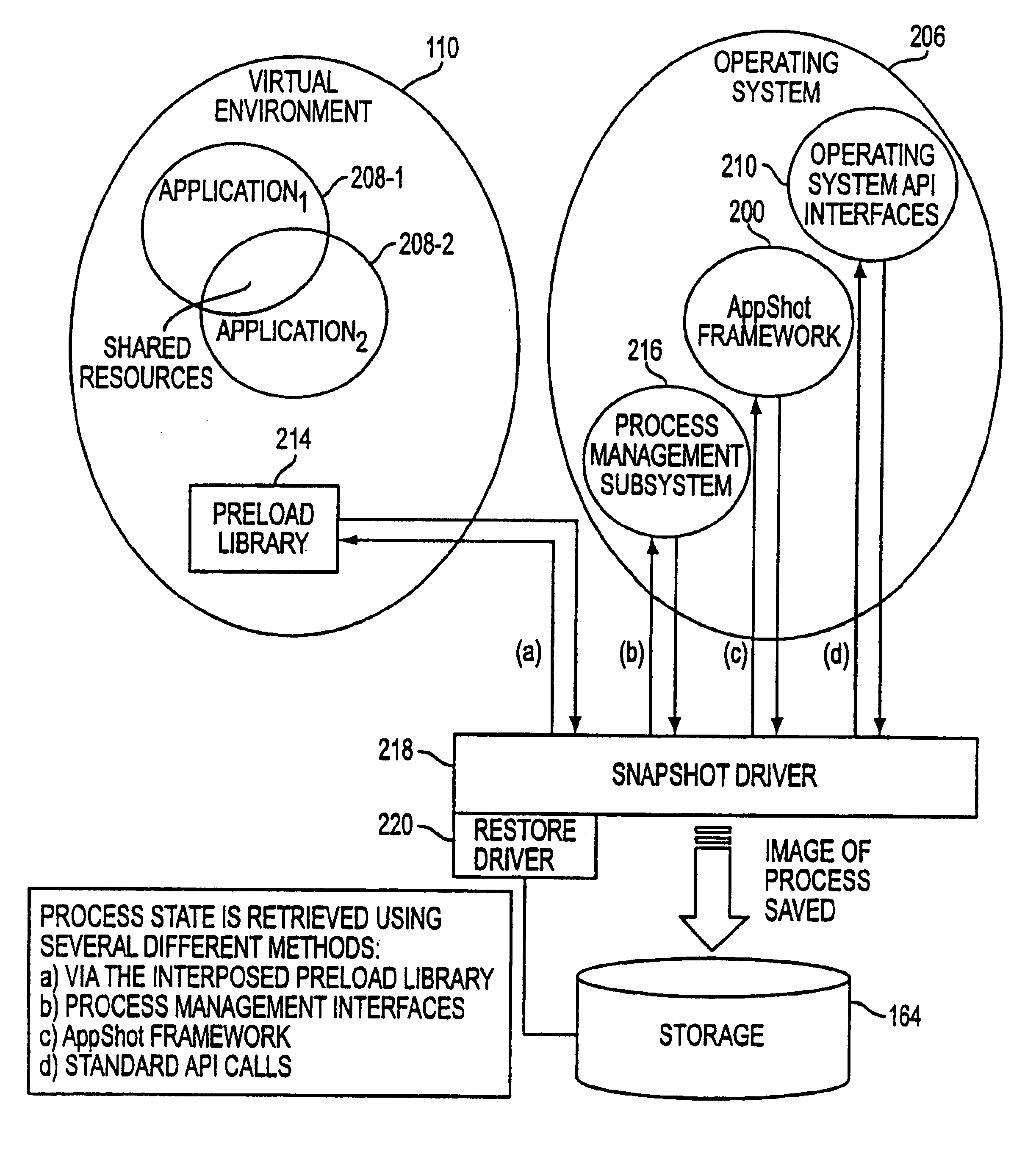

Snapshot restore of application chains and applications

InactiveUS6848106B1Data processing applicationsProgram initiation/switchingOperational systemSystem call

The present invention saves all process state, memory, and dependencies related to a software application to a snapshot image. Interprocess communication (IPC) mechanisms such as shared memory and semaphores must be preserved in the snapshot image as well. IPC mechanisms include any resource that is shared between two process or any communication mechanism or channel that allow two processes to communicate or interoperate is a form of IPC. Between snapshots, memory deltas are flushed to the snapshot image, so that only the modified-pages need be updated. Software modules are included to track usage of resources and their corresponding handles. At snapshot time, state is saved by querying the operating system kernel, the application snapshot / restore framework components, and the process management subsystem that allows applications to retrieve internal process-specific information not available through existing system calls. At restore time, the reverse sequence of steps for the snapshot procedure is followed and state is restored by making requests to the kernel, the application snapshot / restore framework, and the process management subsystem.

Owner:SYMANTEC OPERATING CORP

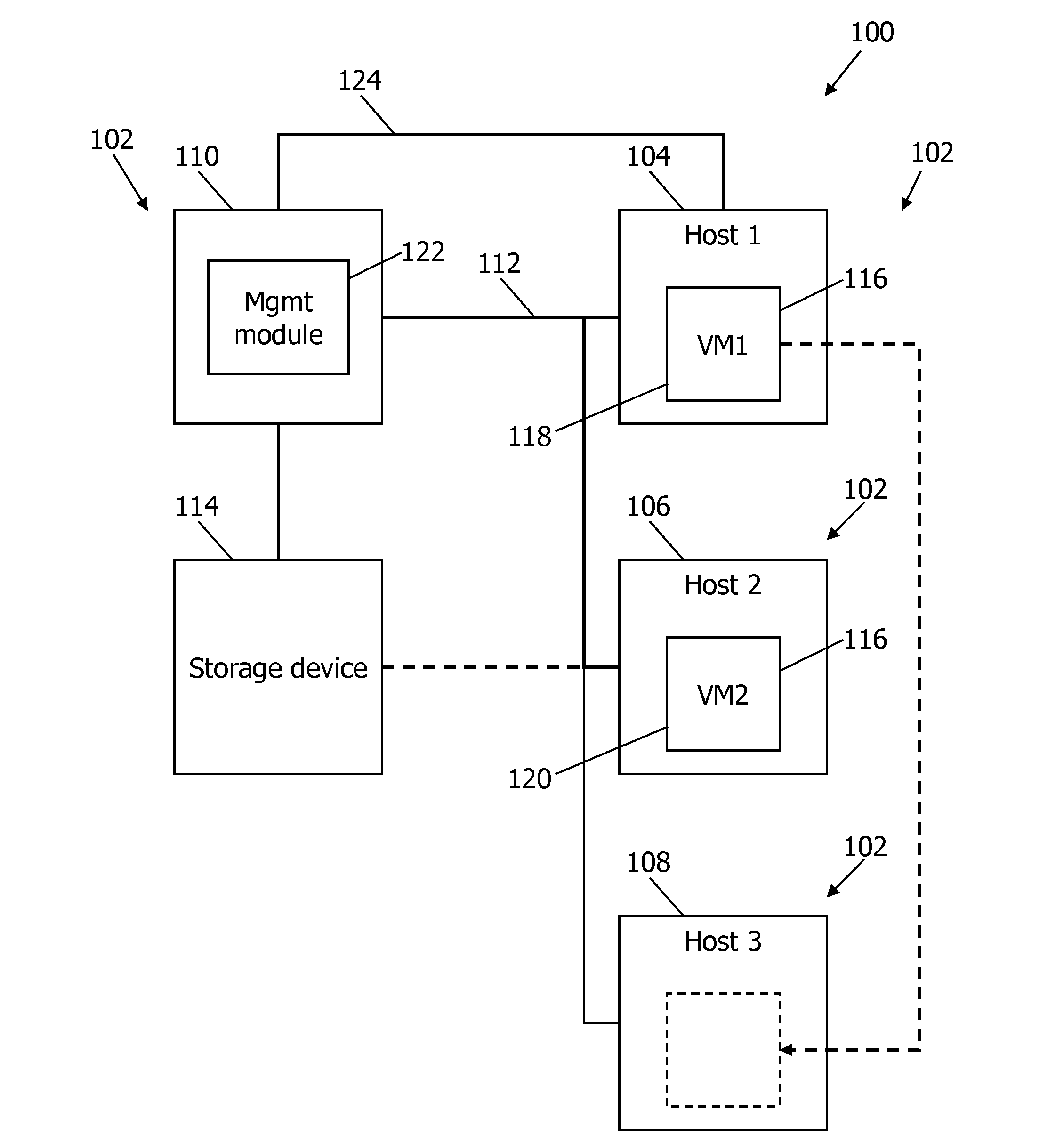

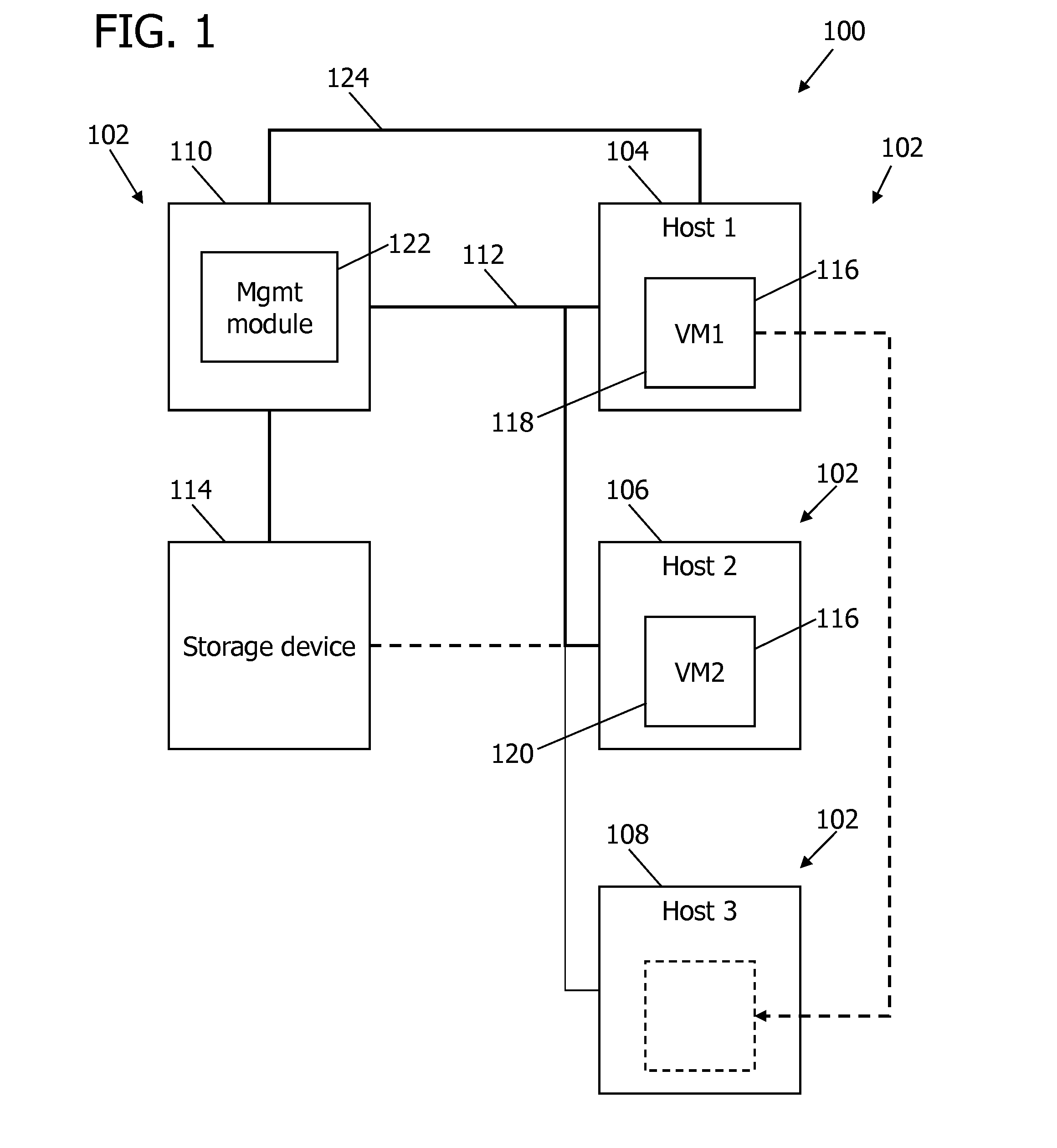

Systems and methods for migrating virtual machines

A system includes a first computing device including a virtual machine (VM), a second computing device, and a third computing device coupled to the first computing device and to the second computing device. The third computing device includes a management module configured to create a backup image of the VM while the VM is executing on the first computing device, create at least one delta file for use in storing changes to the VM that occur after the backup image is created, and copy the backup image to the second computing device while the VM is executing. The management module is also configured to suspend the VM on the first computing device after the backup image has been copied to the second computing device, and execute the VM on the second computing device using the backup image and the at least one delta file.

Owner:THE BOEING CO

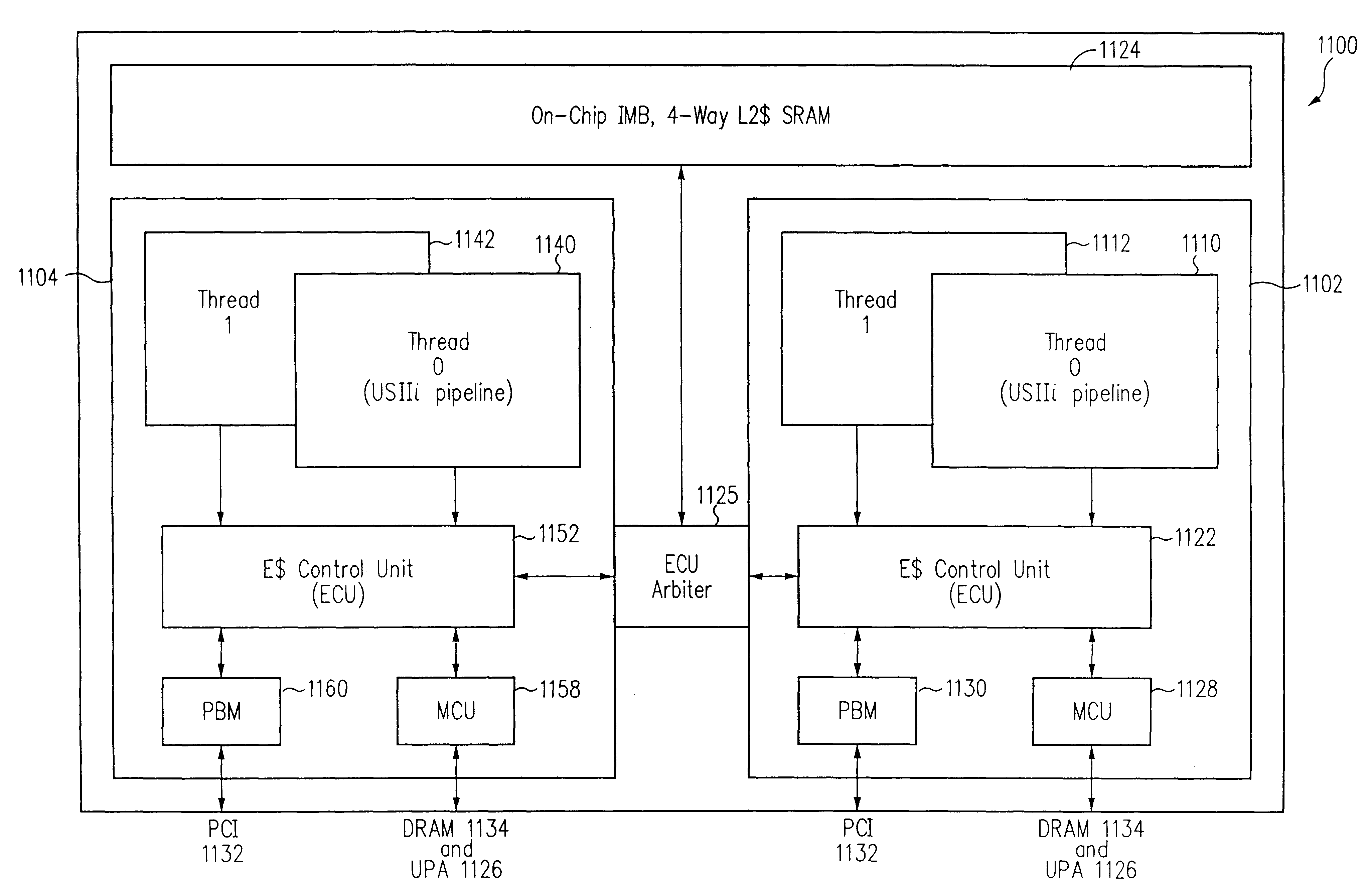

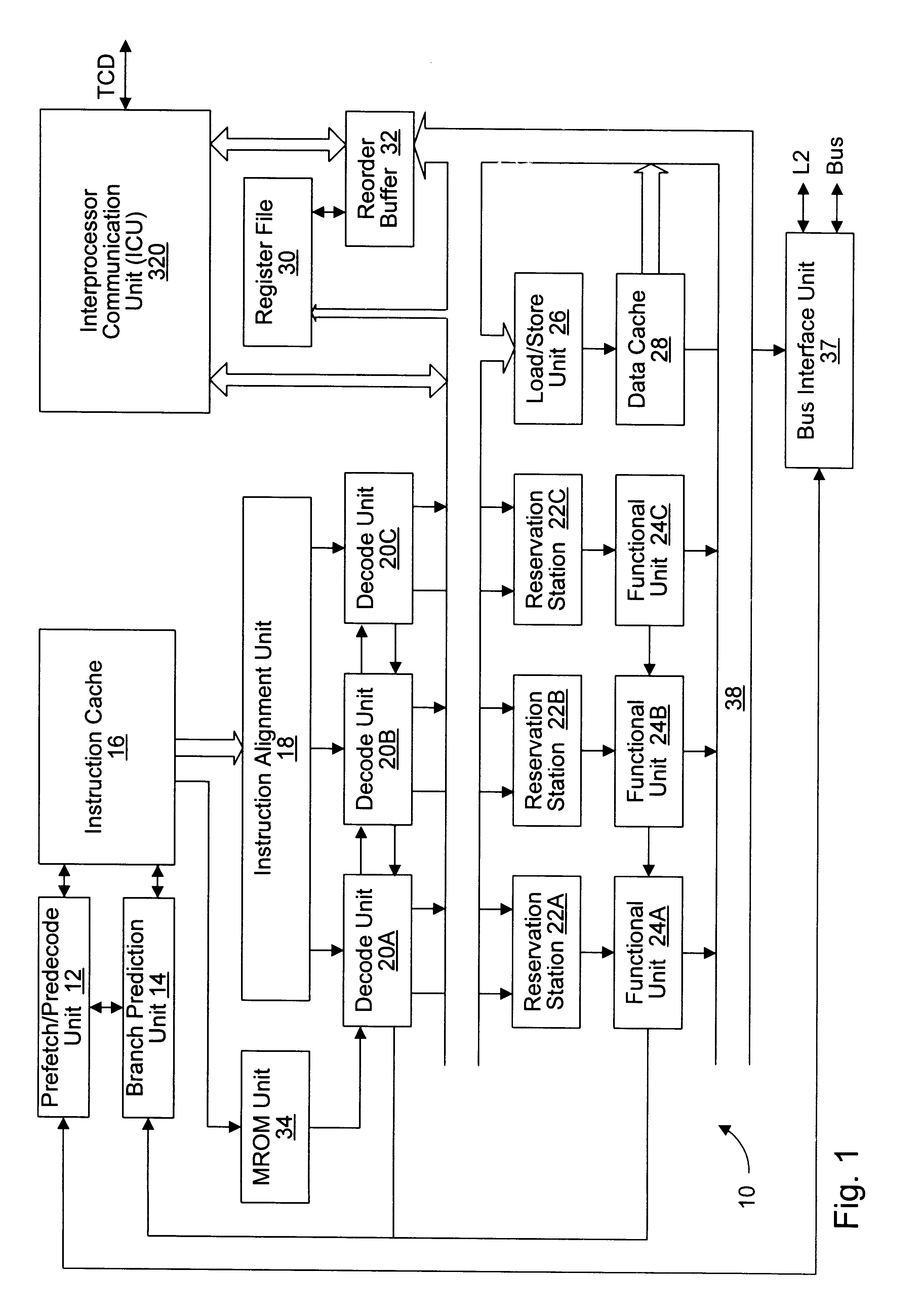

Switching method in a multi-threaded processor

InactiveUS6507862B1Program initiation/switchingDigital computer detailsOperational systemEmbedded system

A processor includes logic for attaining a very fast exception handling functionality while executing non-threaded programs by invoking a multithreaded-type functionality in response to an exception condition. The processor, while operating in multithreaded conditions or while executing non-threaded programs, progresses through multiple machine states during execution. The very fast exception handling logic includes connection of an exception signal line to thread select logic, causing an exception signal to evoke a switch in thread and machine state. The switch in thread and machine state causes the processor to enter and to exit the exception handler immediately, without waiting to drain the pipeline or queues and without the inherent timing penalty of the operating system's software saving and restoring of registers.

Owner:ORACLE INT CORP

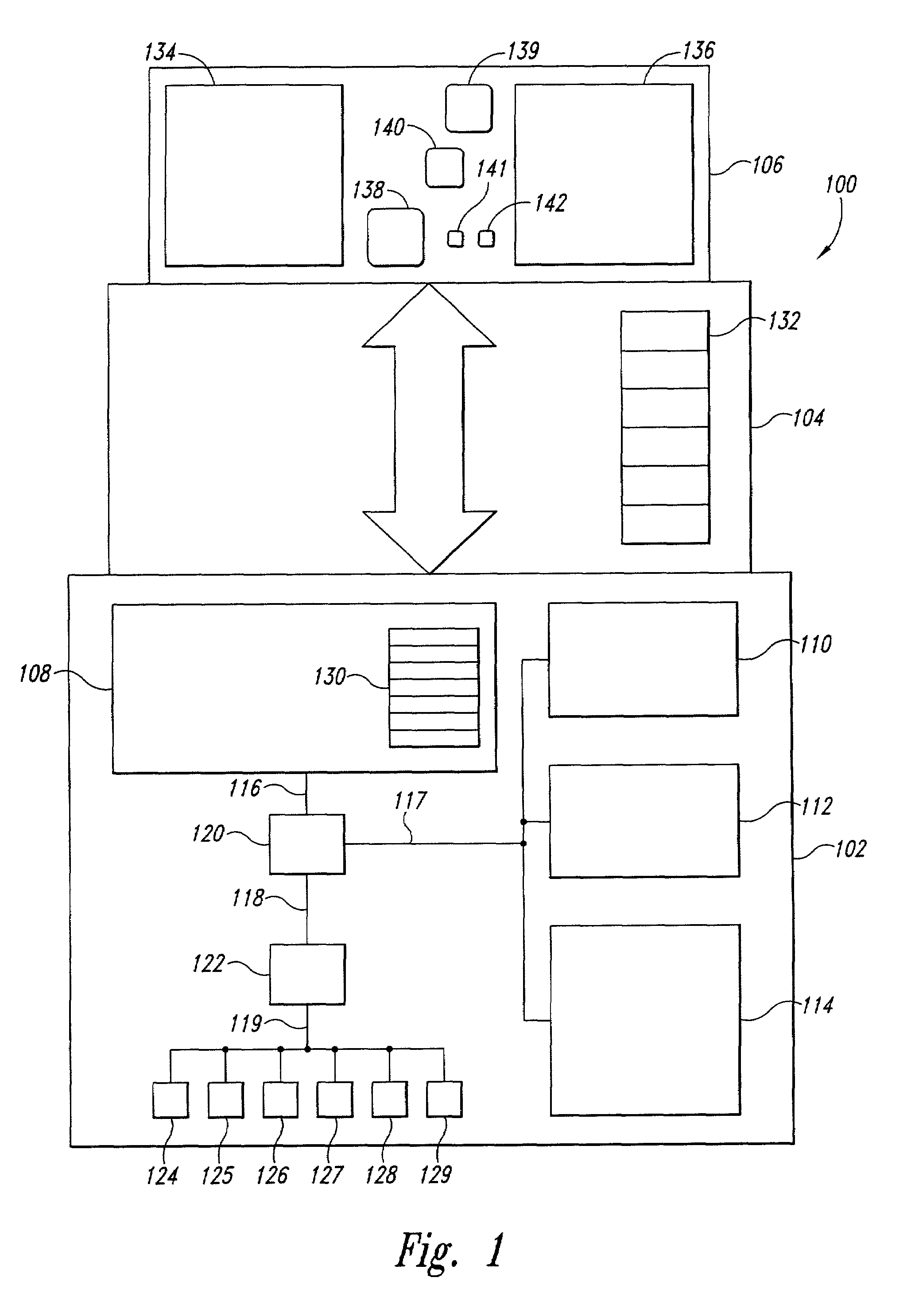

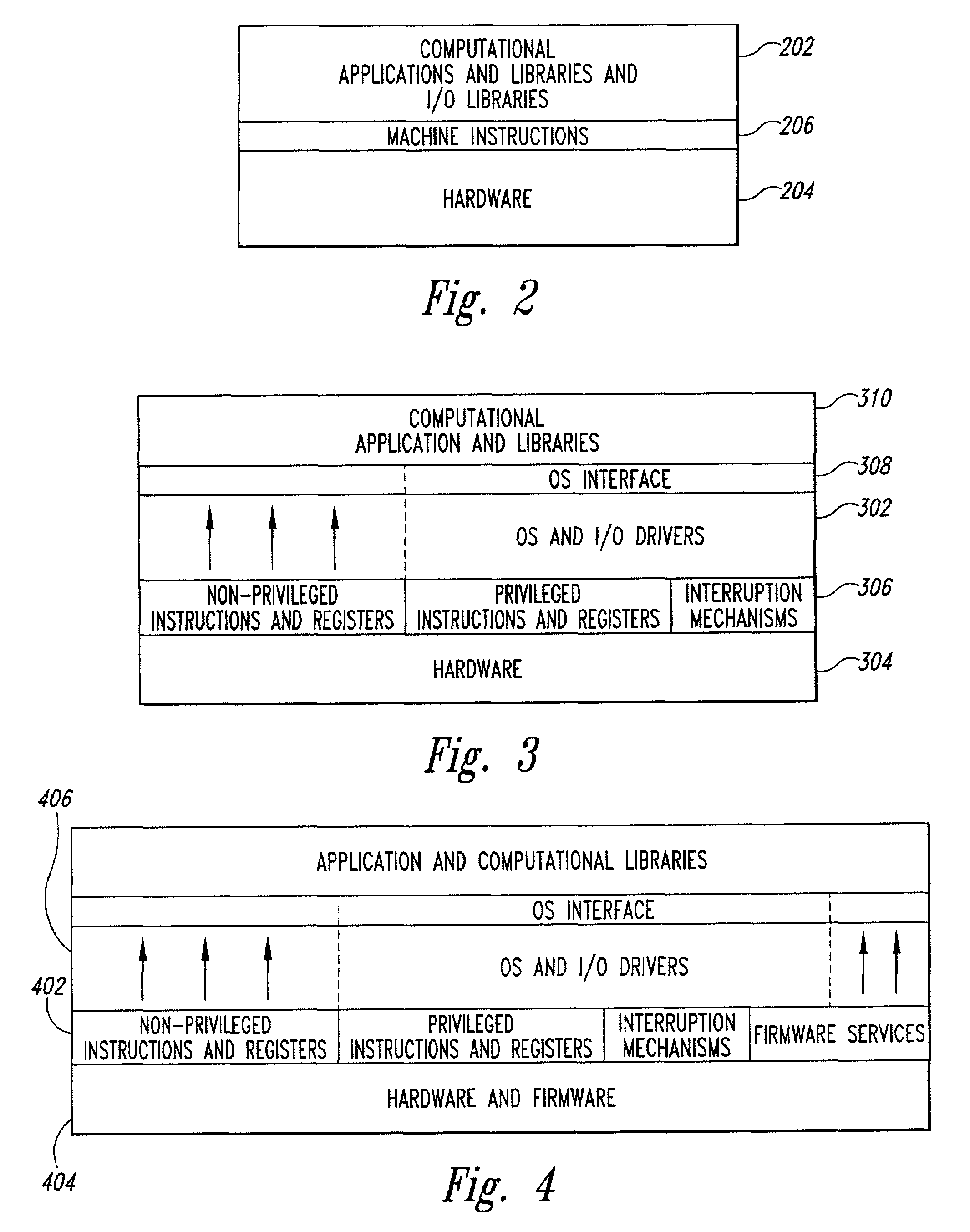

Secure machine platform that interfaces to operating systems and customized control programs

ActiveUS7073059B2Program initiation/switchingError detection/correctionOperational systemService provision

A combined-hardware-and-software secure-platform interface to which operating systems and customized control programs interface within a computer system. The combined-hardware-and-software secure-platform interface employs a hardware platform that provides at least four privilege levels, non-privileged instructions, non-privileged registers, privileged instructions, privileged registers, and firmware interfaces. The combined-hardware-and-software secure-platform interface conceals all privileged instructions, privileged registers, and firmware interfaces and privileged registers from direct access by operating systems and custom control programs, providing to the operating systems and custom control programs the non-privileged instructions and non-privileged registers provided by the hardware platform as well as a set of callable software services. The callable services provide a set of secure-platform management services for operational control of hardware resources that neither exposes privileged instructions, privileged registers, nor firmware interfaces of the hardware nor simulates privileged instructions and privileged registers. The callable services also provide a set of security-management services that employ internally generated secret data, each compartmentalized security-management service managing internal secret data without exposing the internal secret data to computational entities other than the security-management service itself.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

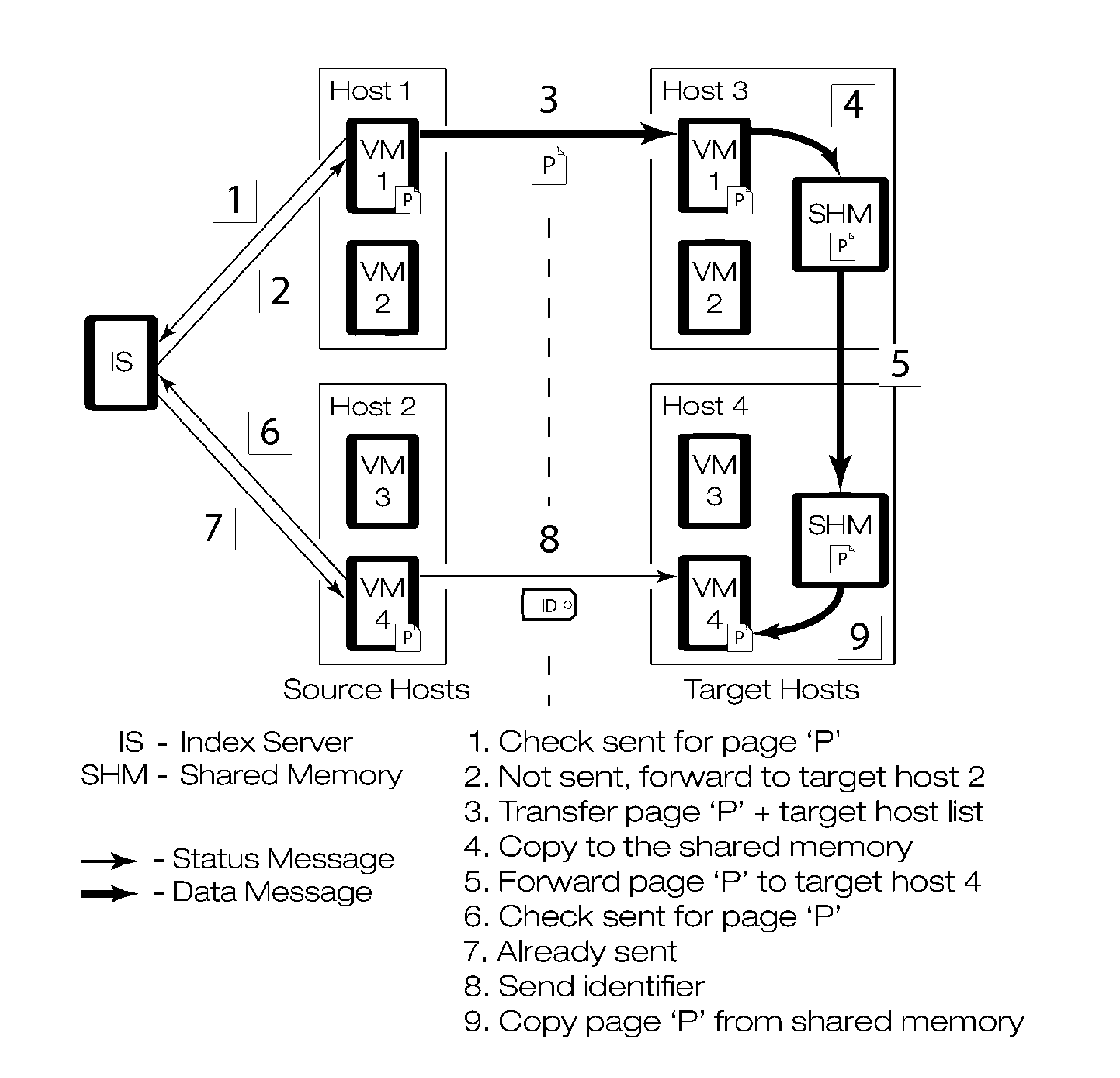

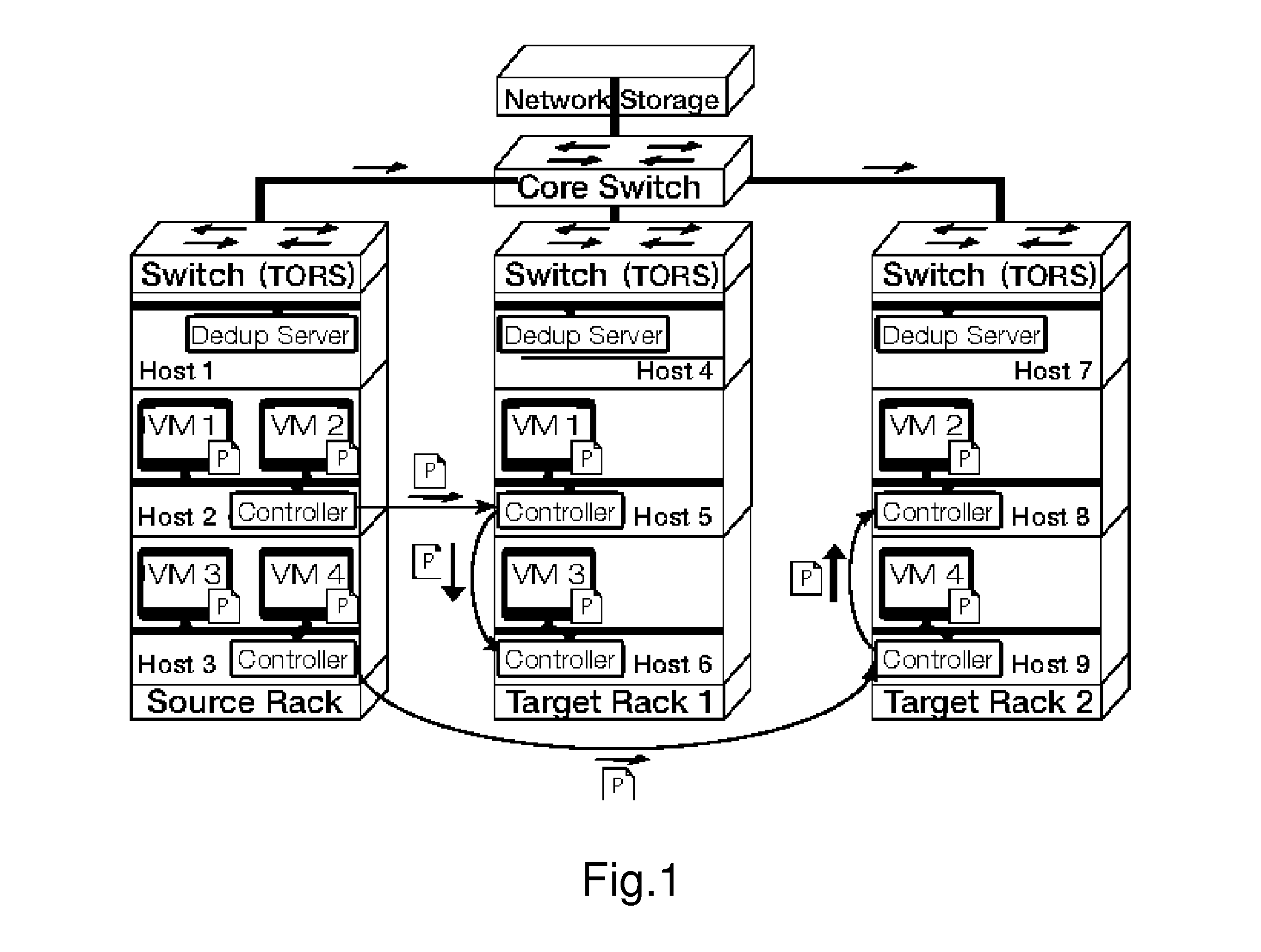

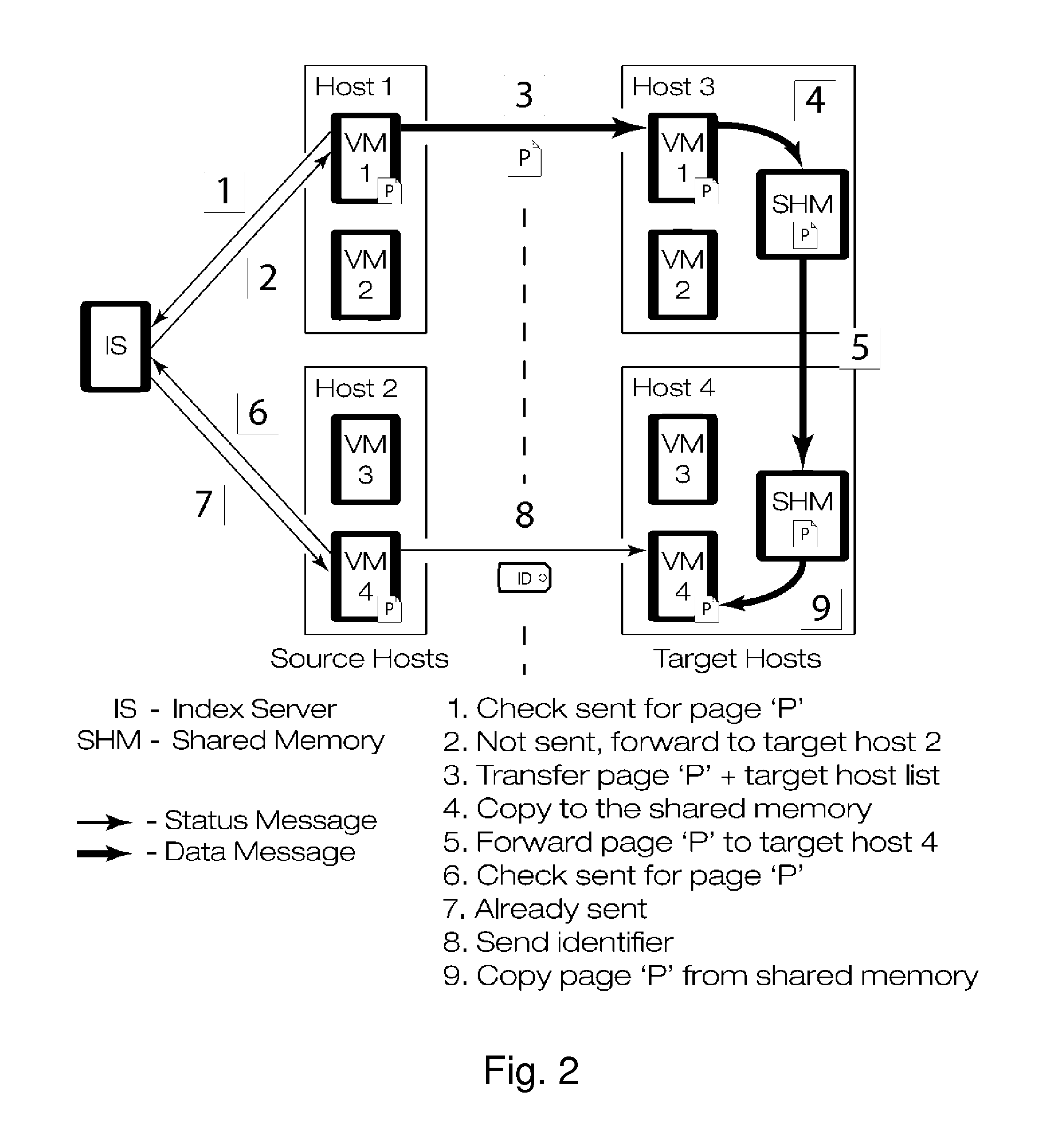

Gang migration of virtual machines using cluster-wide deduplication

ActiveUS20140196037A1Reduce throughputIncrease delayMemory architecture accessing/allocationProgram initiation/switchingTraffic capacityData center

Datacenter clusters often employ live virtual machine (VM) migration to efficiently utilize cluster-wide resources. Gang migration refers to the simultaneous live migration of multiple VMs from one set of physical machines to another in response to events such as load spikes and imminent failures. Gang migration generates a large volume of network traffic and can overload the core network links and switches in a data center. The present technology reduces the network overhead of gang migration using global deduplication (GMGD). GMGD identifies and eliminates the retransmission of duplicate memory pages among VMs running on multiple physical machines in the cluster. A prototype GMGD reduces the network traffic on core links by up to 51% and the total migration time of VMs by up to 39% when compared to the default migration technique in QEMU / KVM, with reduced adverse performance impact on network-bound applications.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

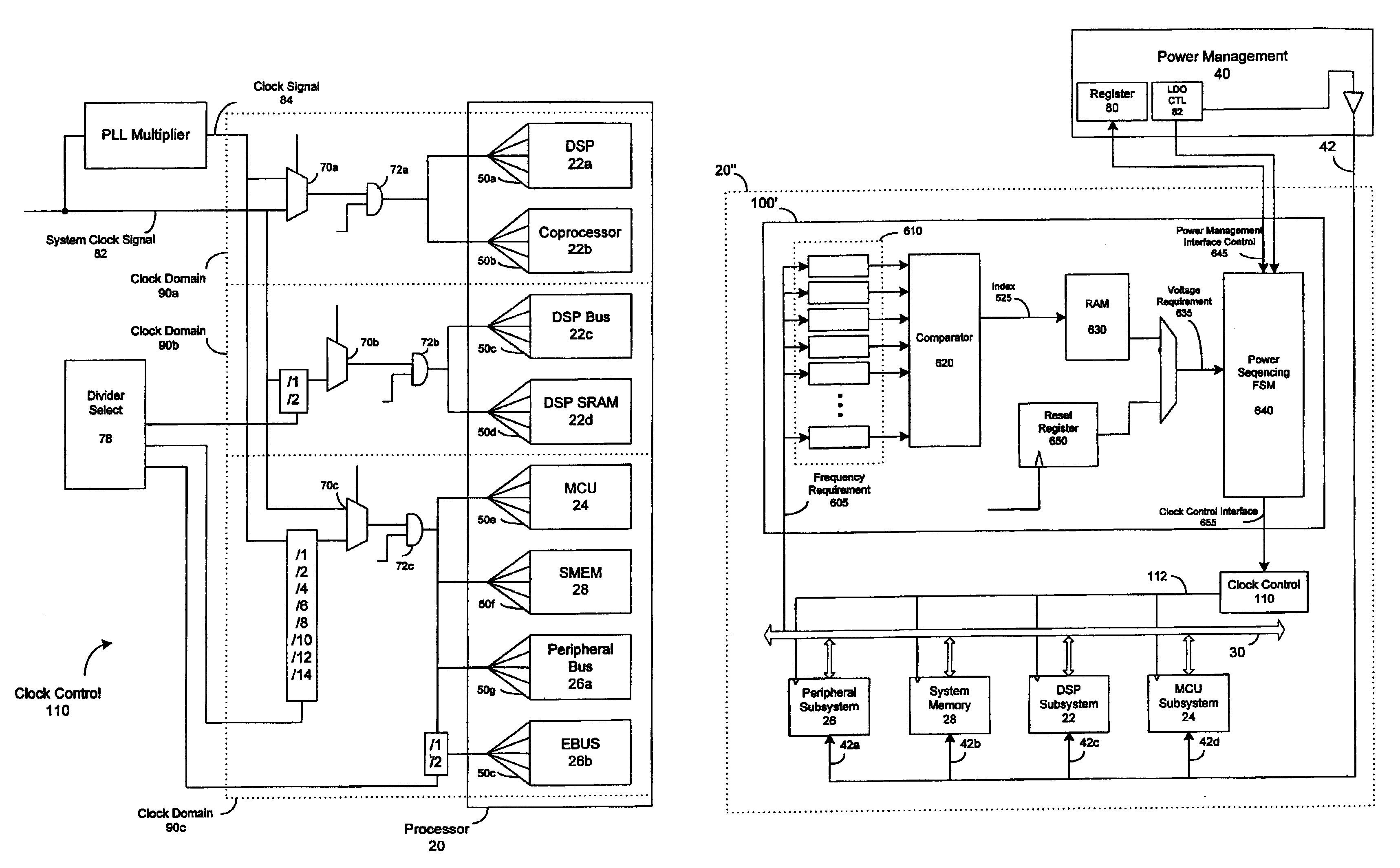

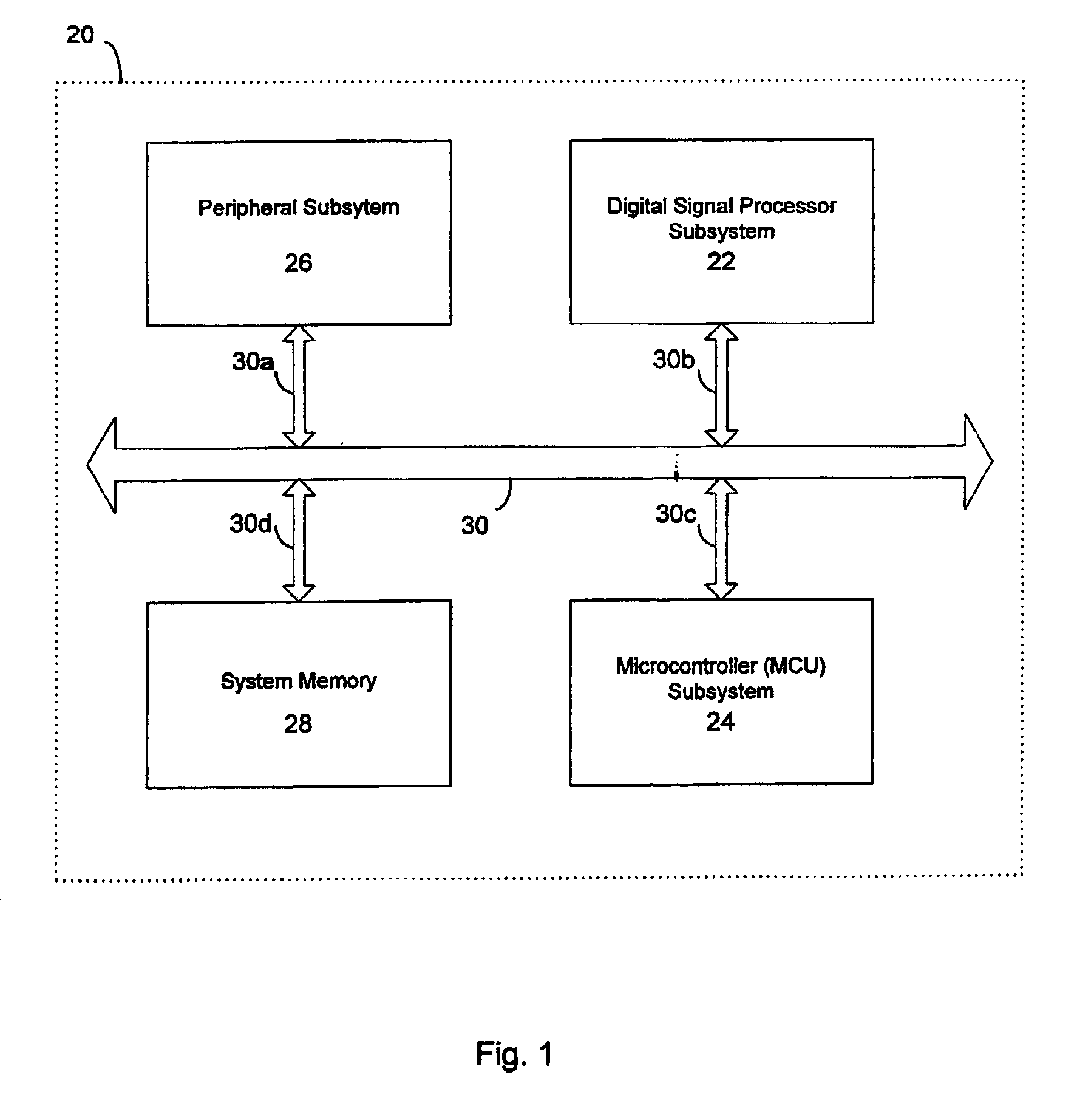

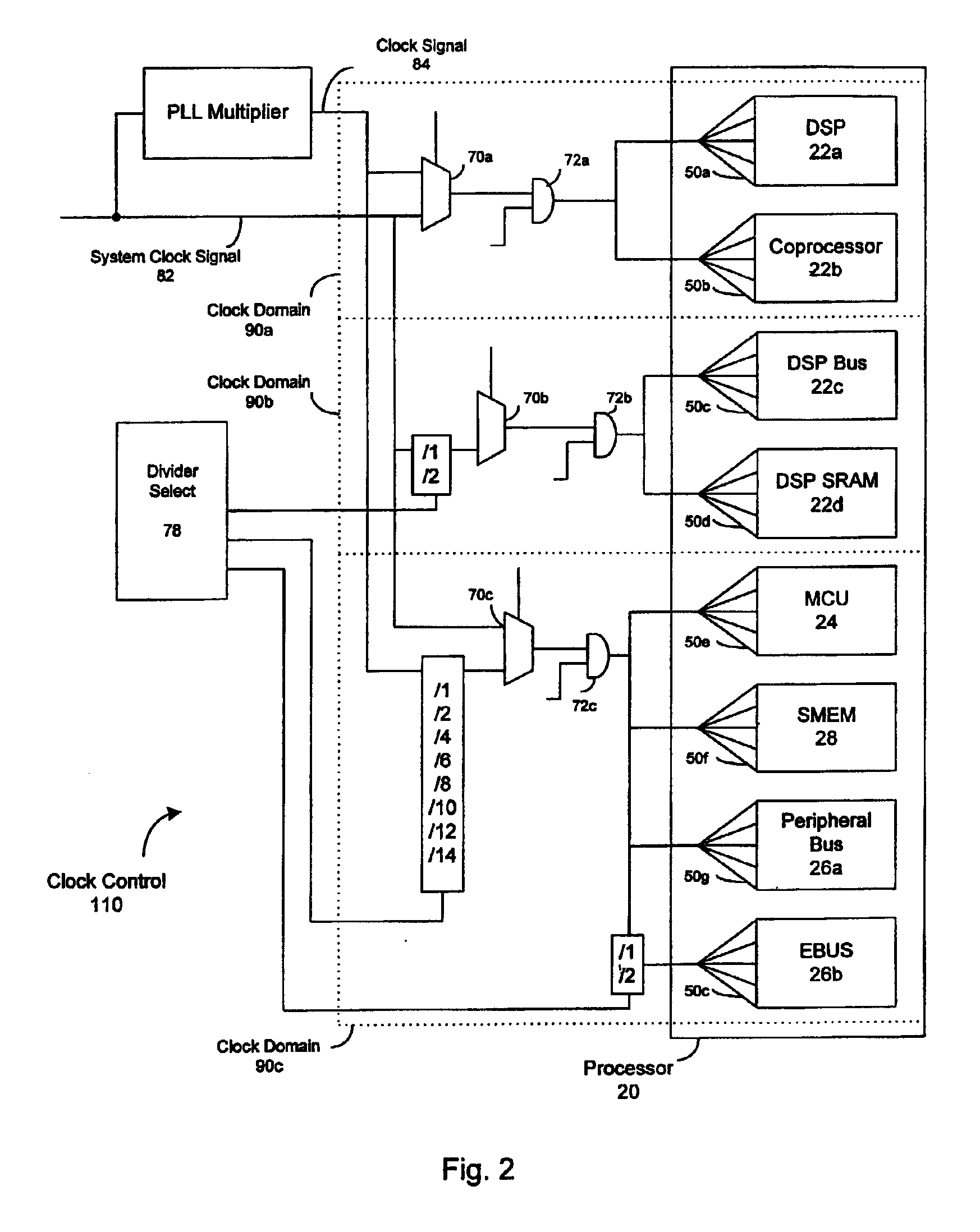

Dynamic voltage control method and apparatus

Owner:MEDIATEK INC

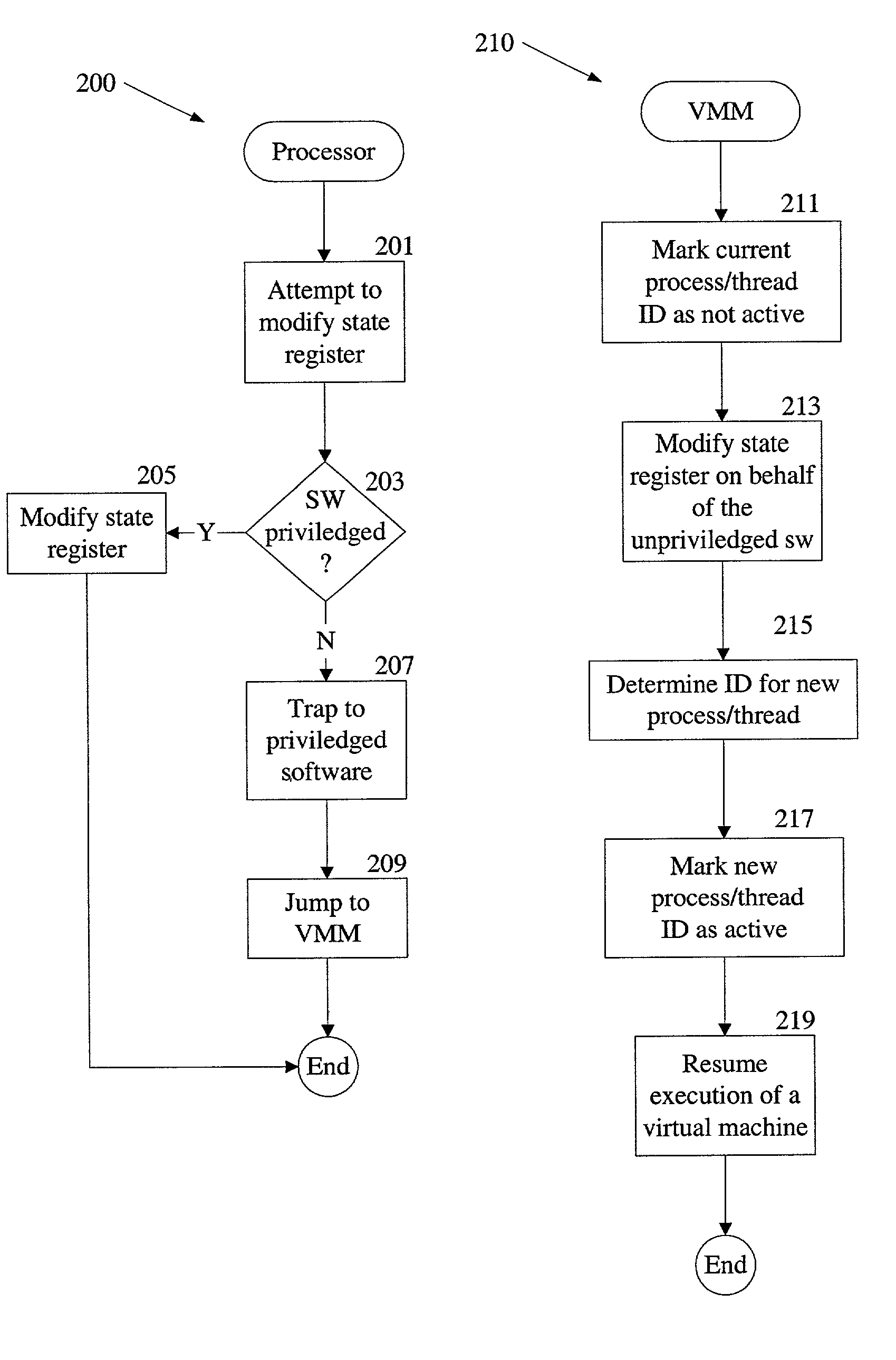

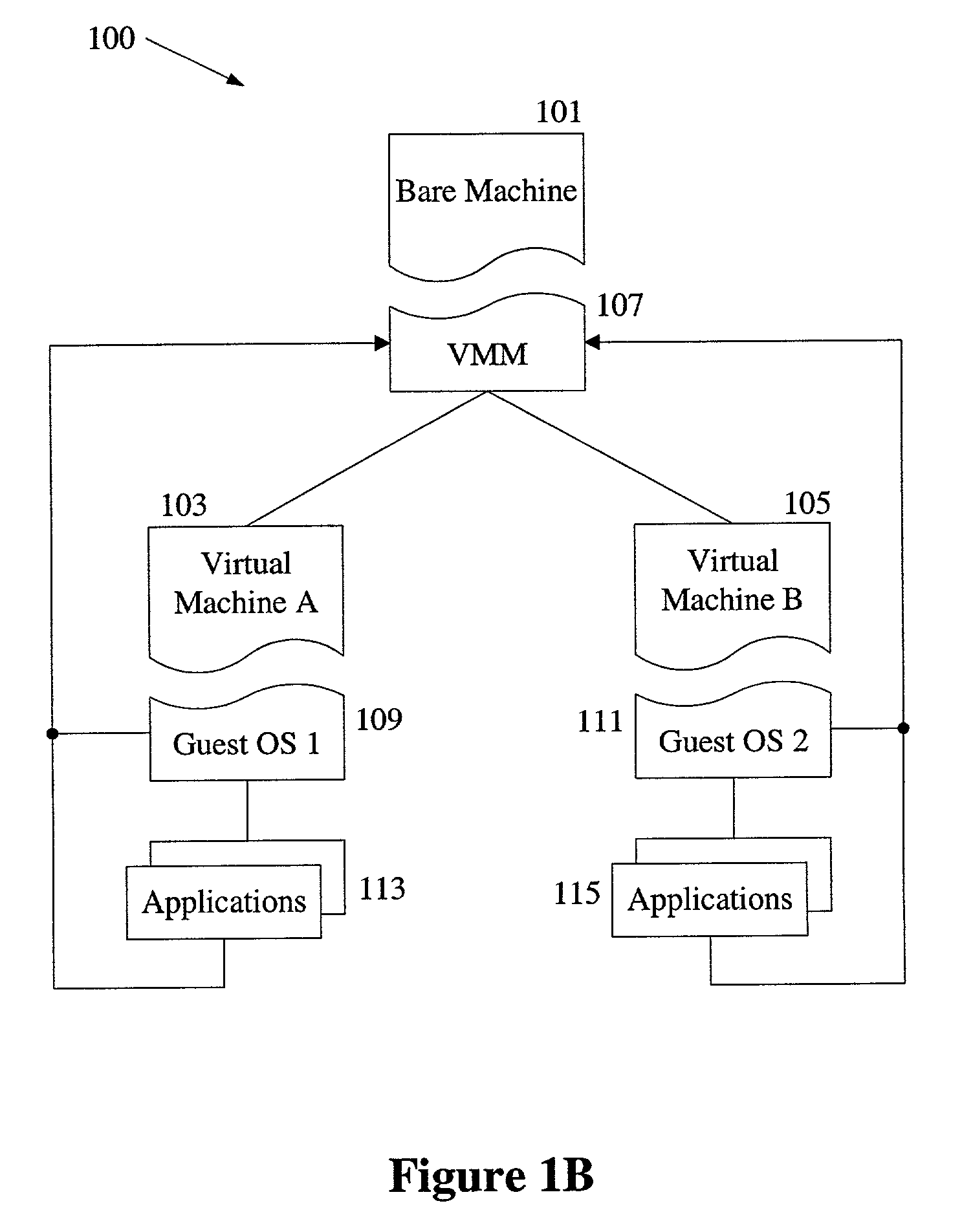

Tracking operating system process and thread execution and virtual machine execution in hardware or in a virtual machine monitor

Transitions among schedulable entities executing in a computer system are tracked in computer hardware or in a virtual machine monitor. In one aspect, the schedulable entities are operating system processes and threads, virtual machines, and instruction streams executing on the hardware. In another aspect, the schedulable entities are processes or threads executing within the virtual machines under the control of the virtual machine monitor. The virtual machine monitor derives scheduling information from the transitions to enable a virtual machine system to guarantee adequate scheduling quality of service to real-time applications executing in virtual machines that contain both real-time and non-real-time applications. In still another aspect, a parent virtual machine monitor in a recursive virtualization system can use the scheduling information to schedule a child virtual machine monitor that controls multiple virtual machines.

Owner:INTEL CORP

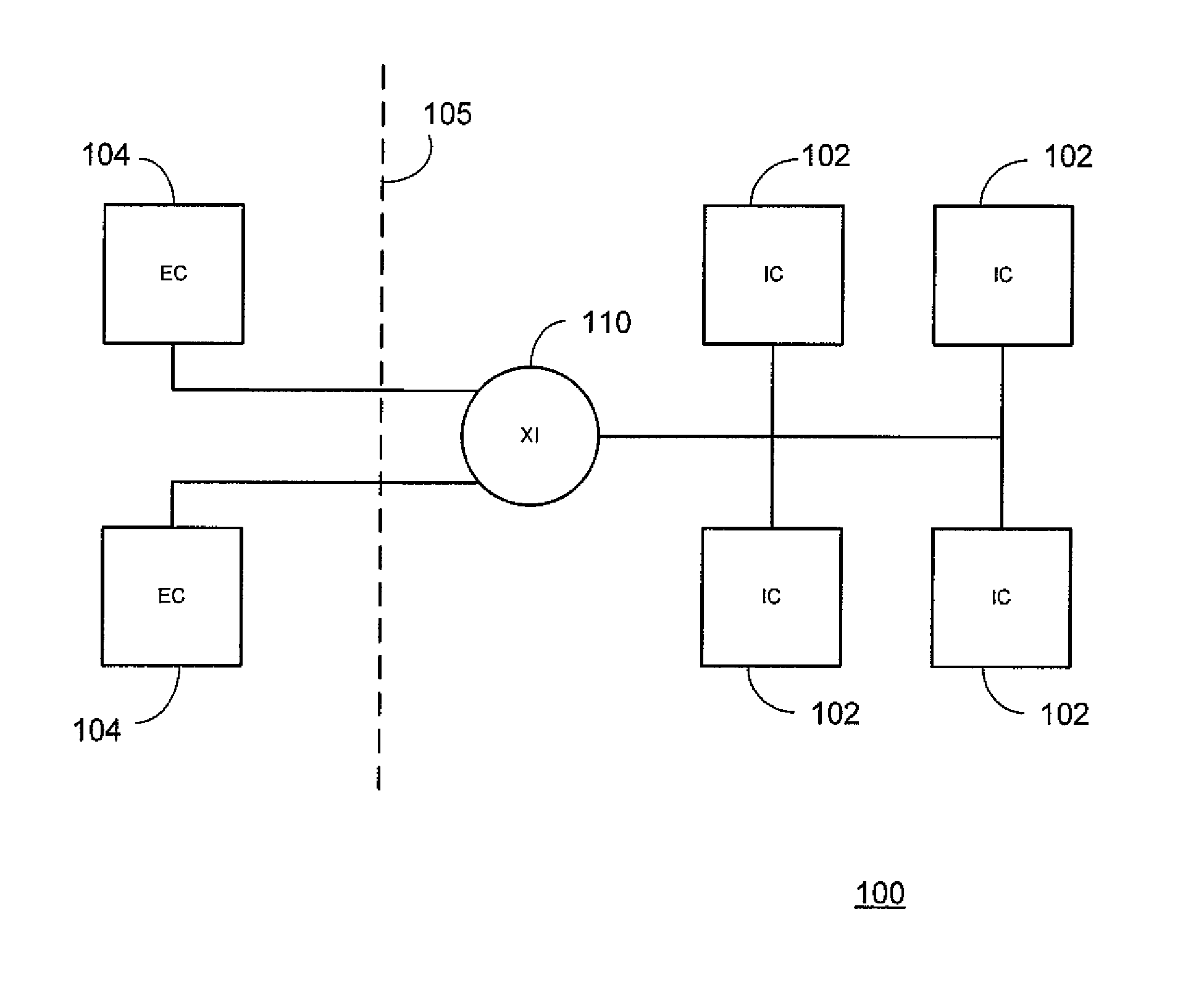

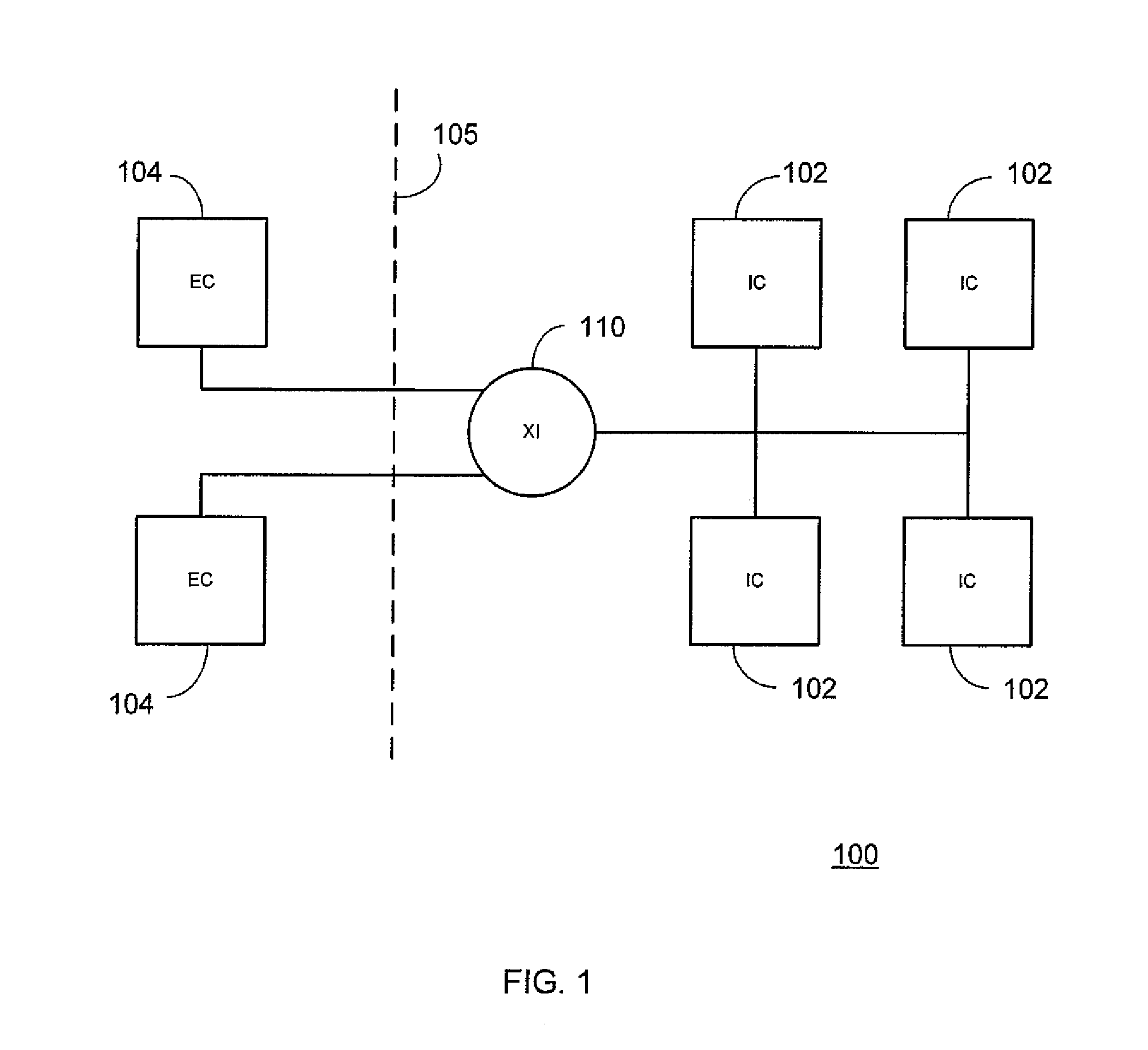

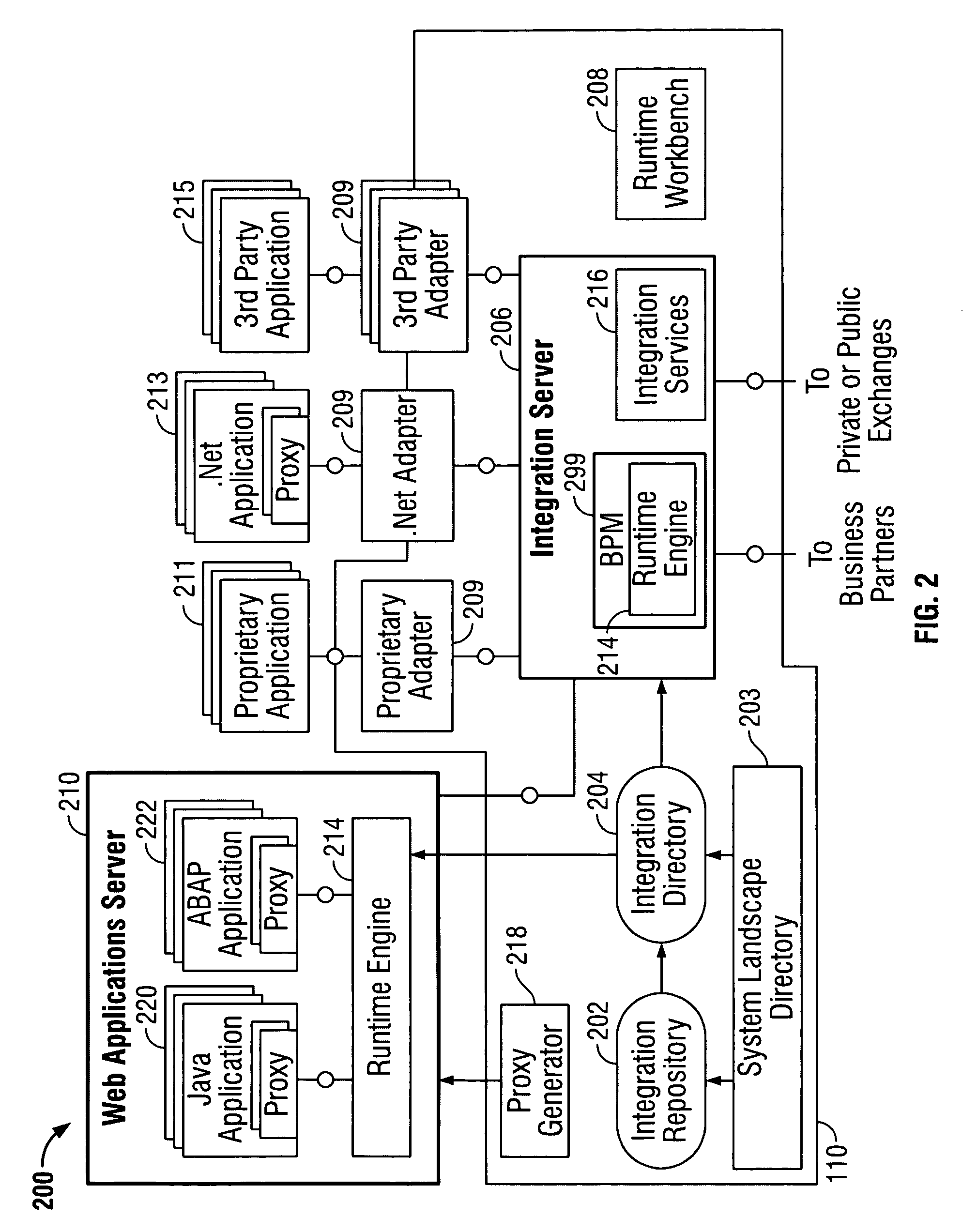

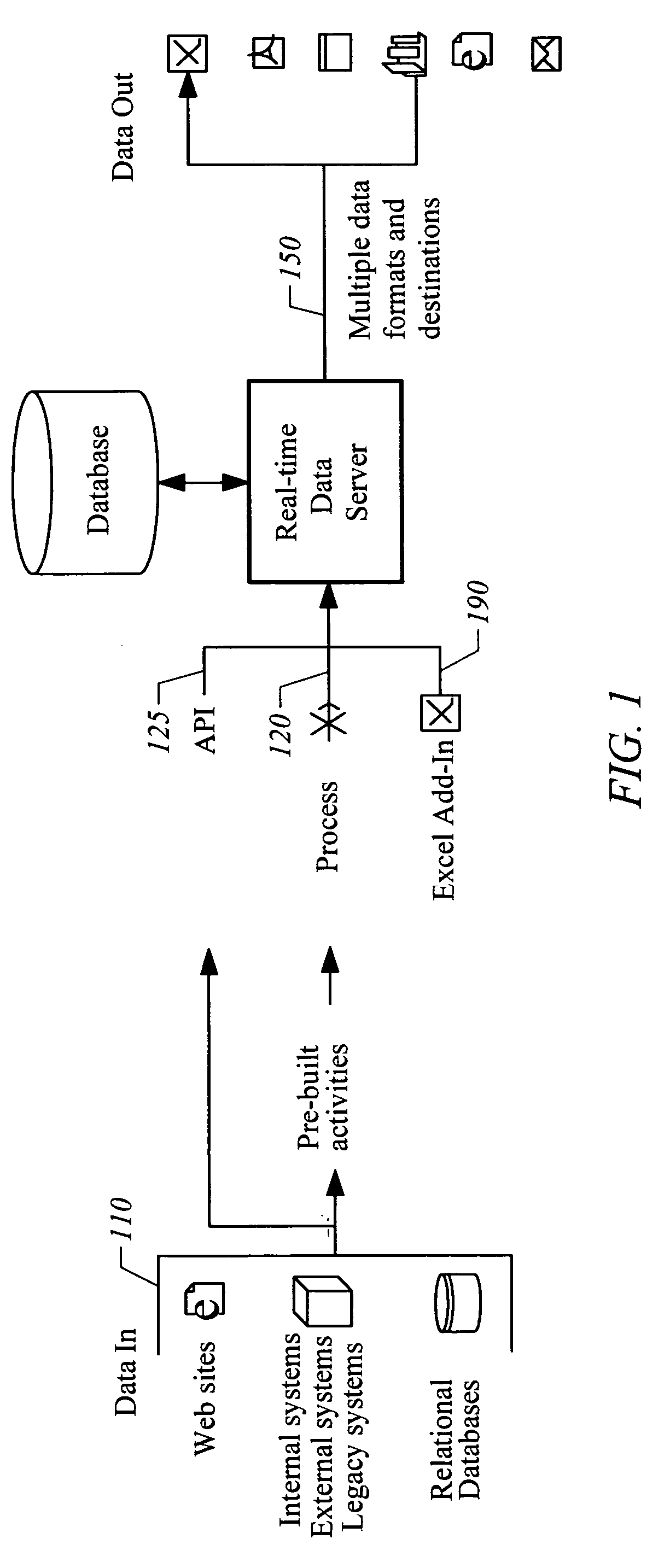

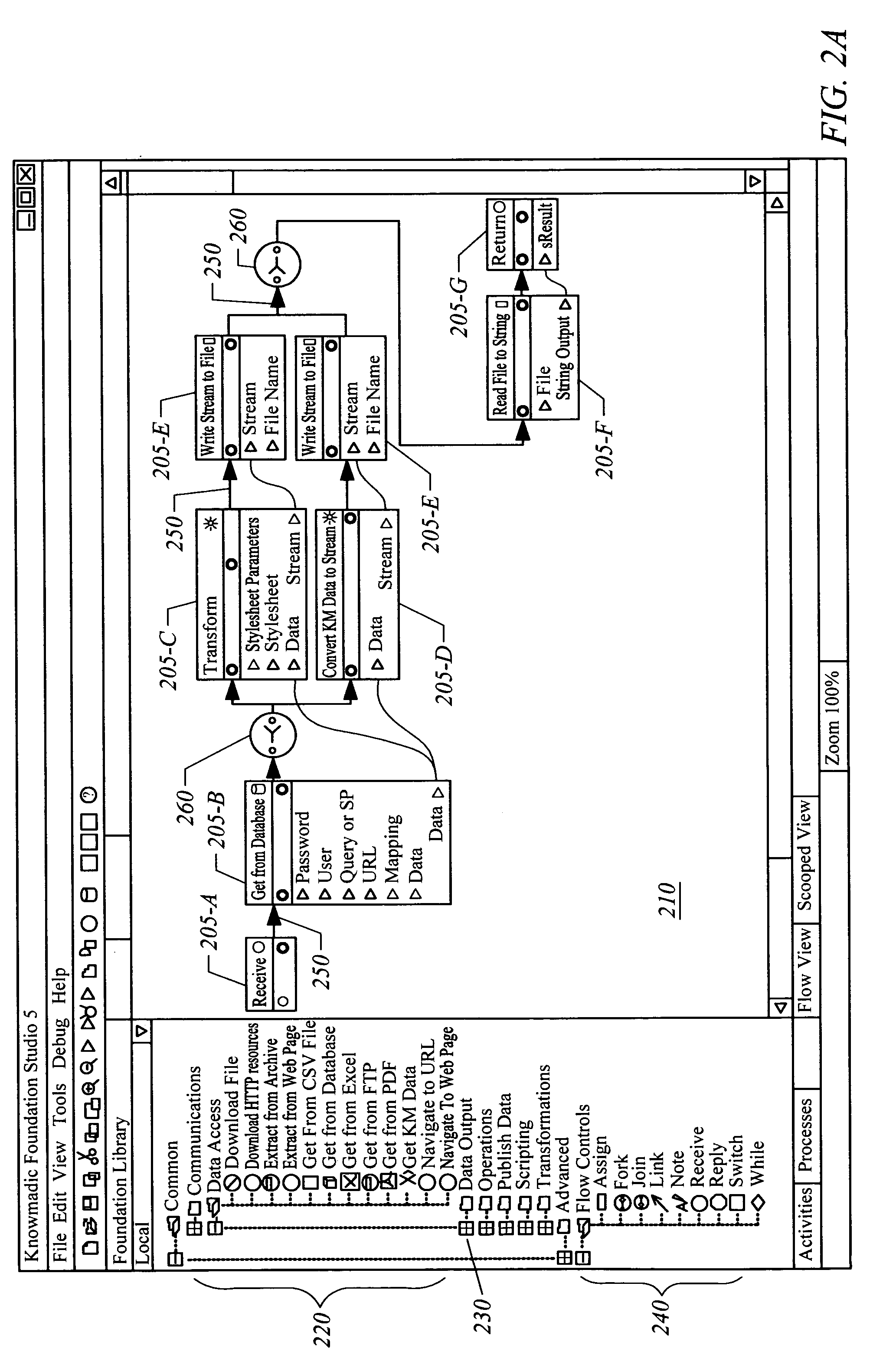

Business process management for a message-based exchange infrastructure

Methods and systems for managing integration of a heterogeneous application landscape are disclosed. The landscape is defined by one or more business process. A business process management system includes an integration server connected between two or more applications in the landscape. The integration server includes a business process engine configured to execute one or more business processes that define message-based interactions between the two or more applications. The business process management system further includes a runtime engine, under direction of the business process engine, for executing one or more messaging services on the message-based interactions between the two or more applications.

Owner:SAP AG

Near on-line server

InactiveUS6990666B2Program initiation/switchingResource allocationVirtualizationResource utilization

Owner:DELL PROD LP

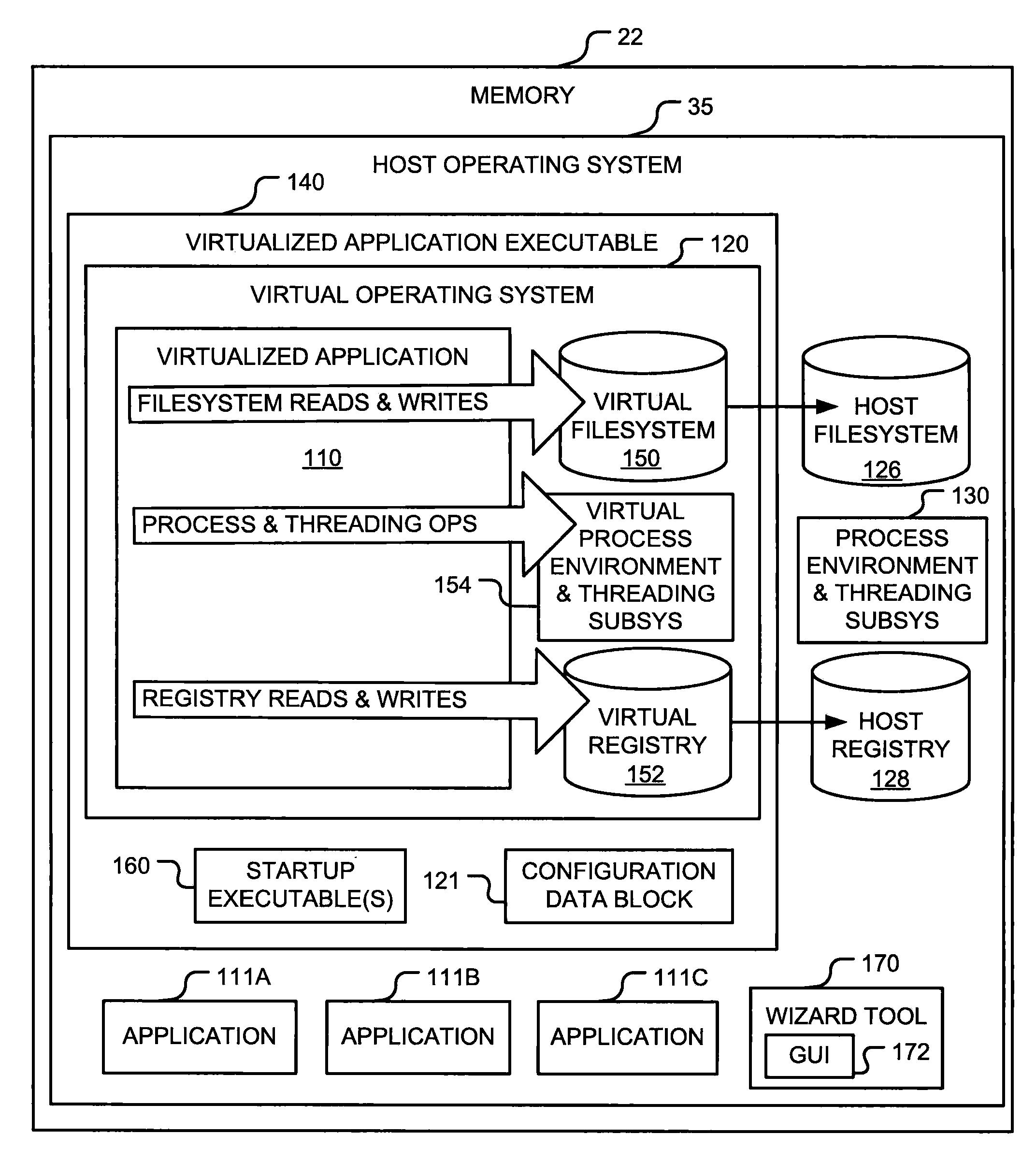

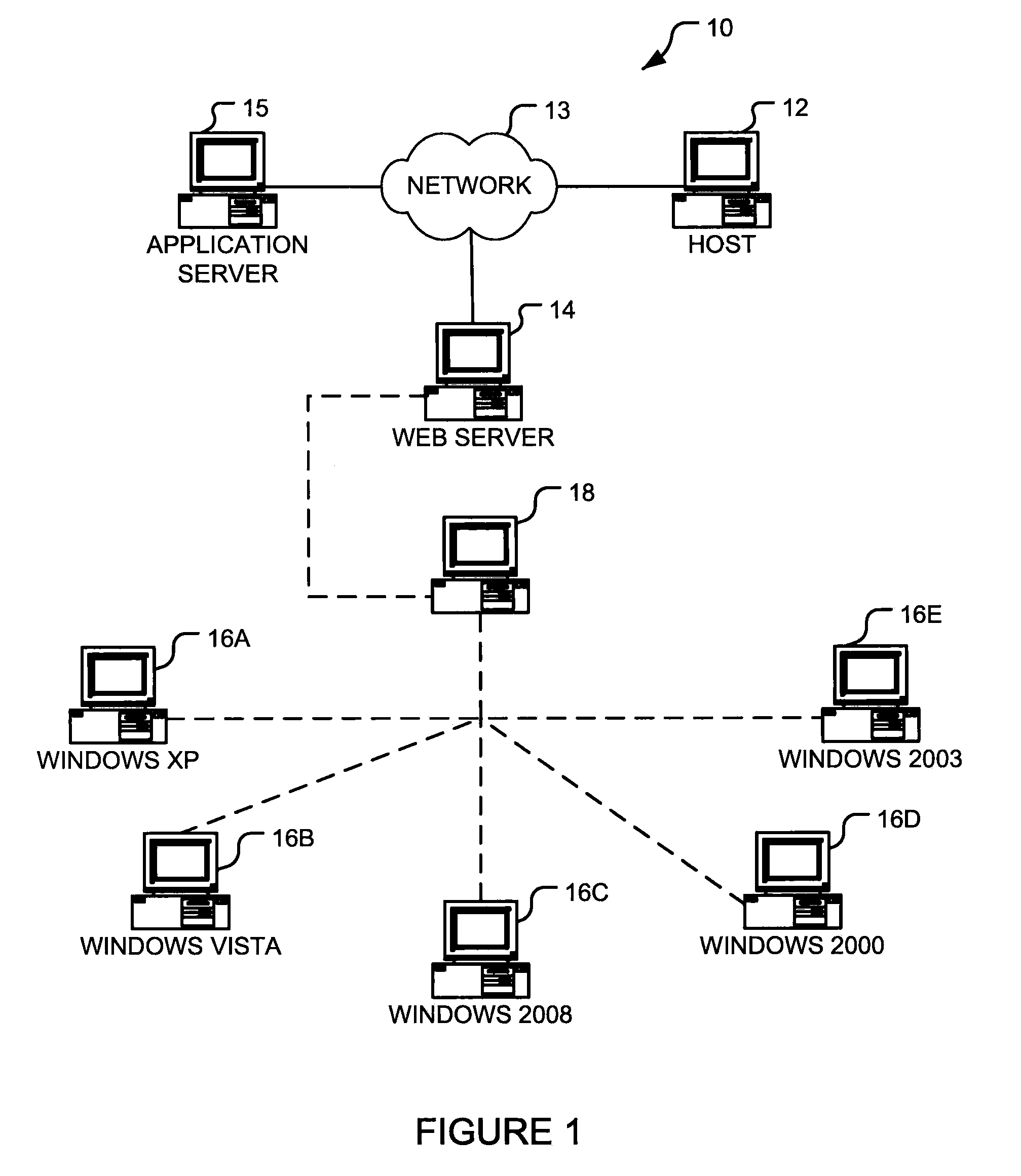

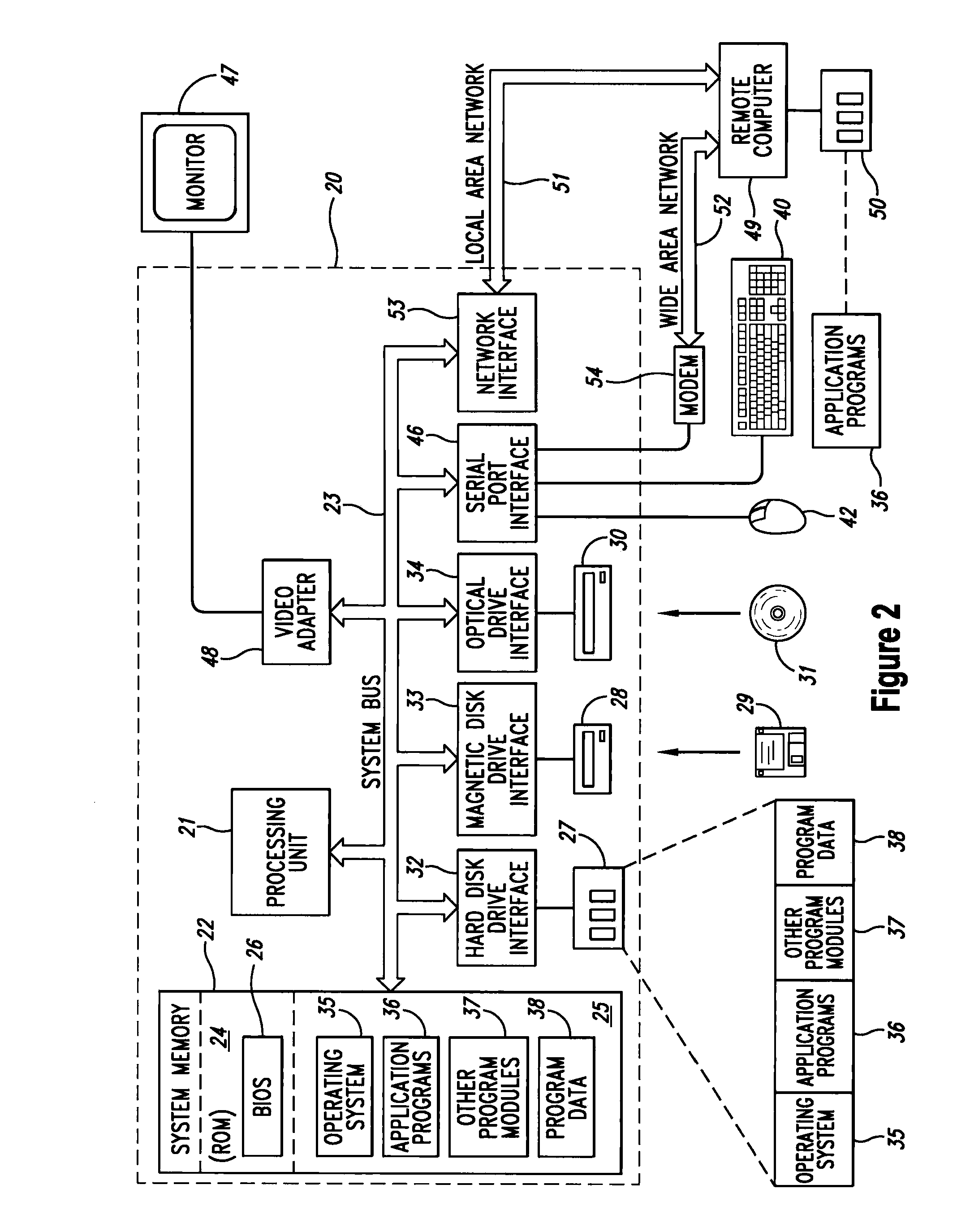

Method and system for virtualization of software applications

A method of virtualizing an application to execute on a plurality of operating systems without installation. The method includes creating an input configuration file for each operating system. The templates each include a collection of configurations that were made by the application during installation on a computing device executing the operating system. The templates are combined into a single application template having a layer including the collection of configurations for each operating system. The collection of configurations includes files and registry entries. The collections also identifies and configures environmental variables, systems, and the like. Files in the collection of configurations and references to those files may be replaced with references to files stored on installation media. The application template is used to build an executable of the virtualized application. The application template may be incorporated into a manifest listing other application templates and made available to users from a website.

Owner:CODE SYST CORPOATION

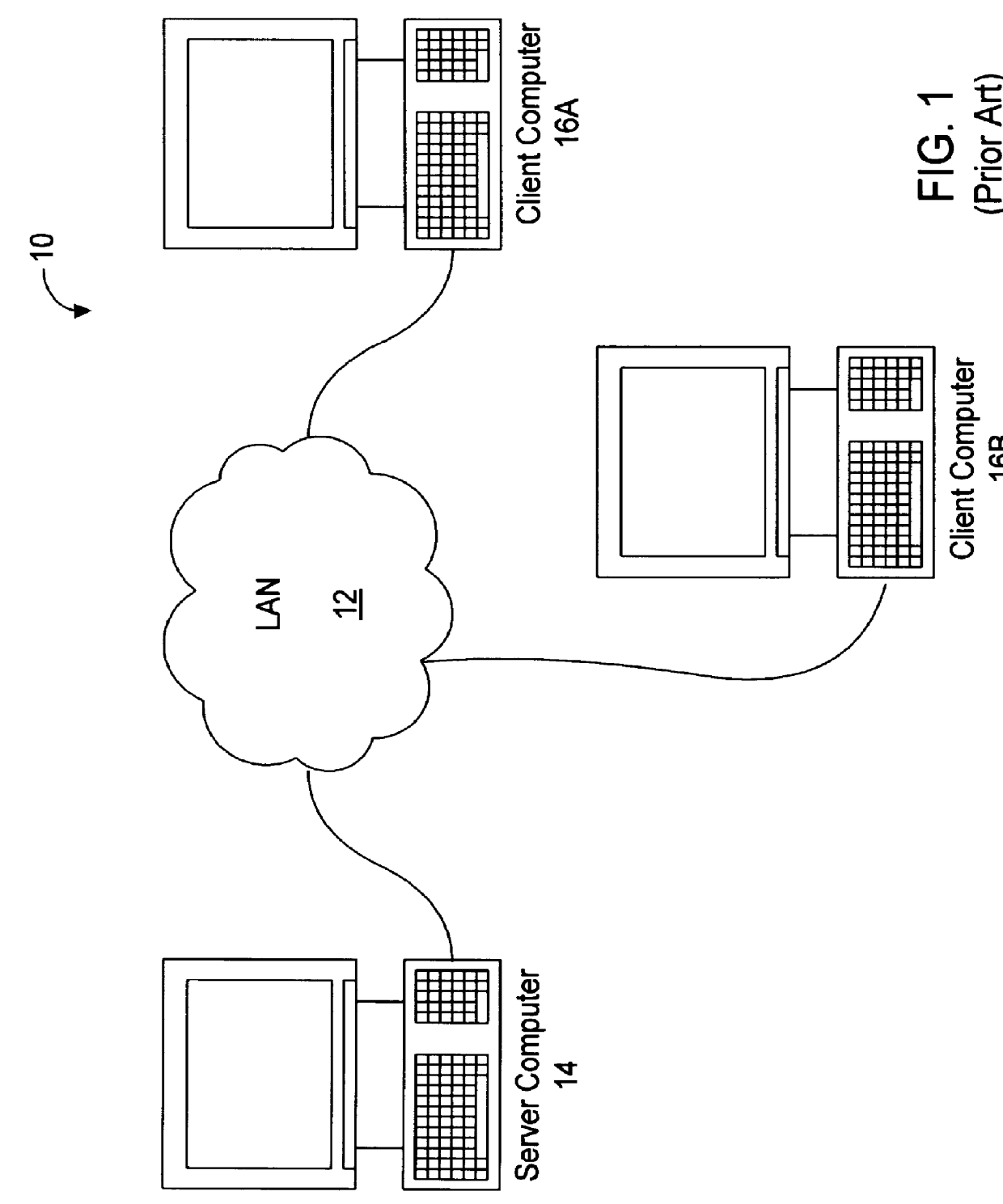

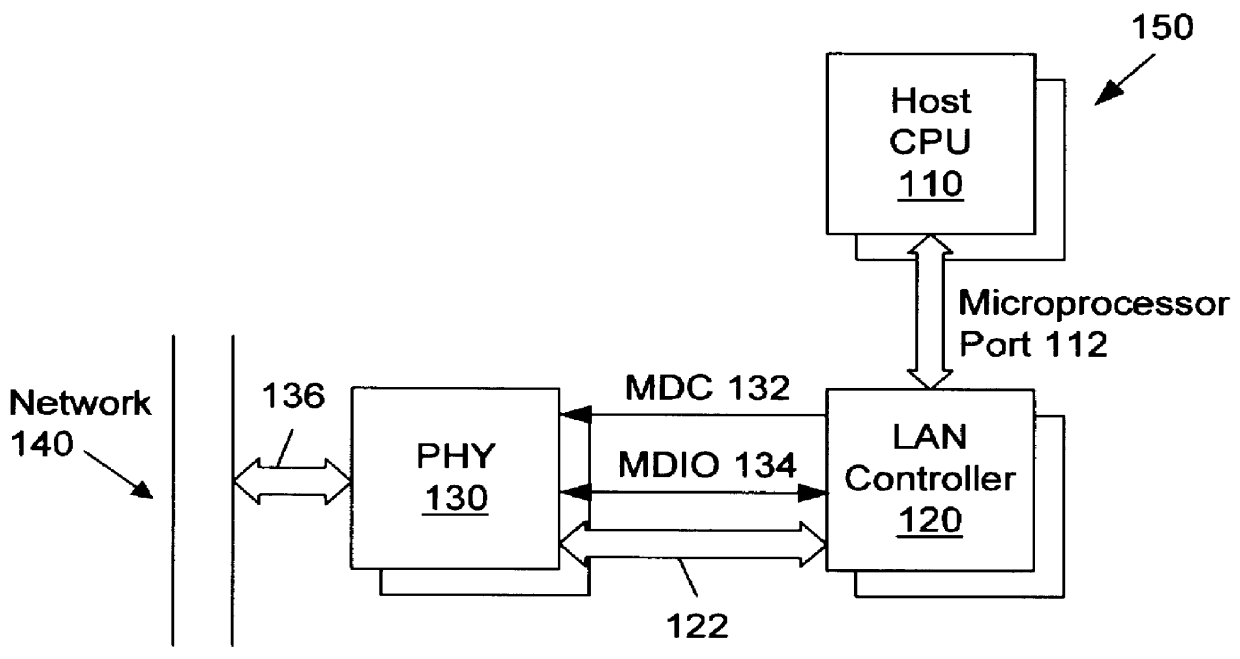

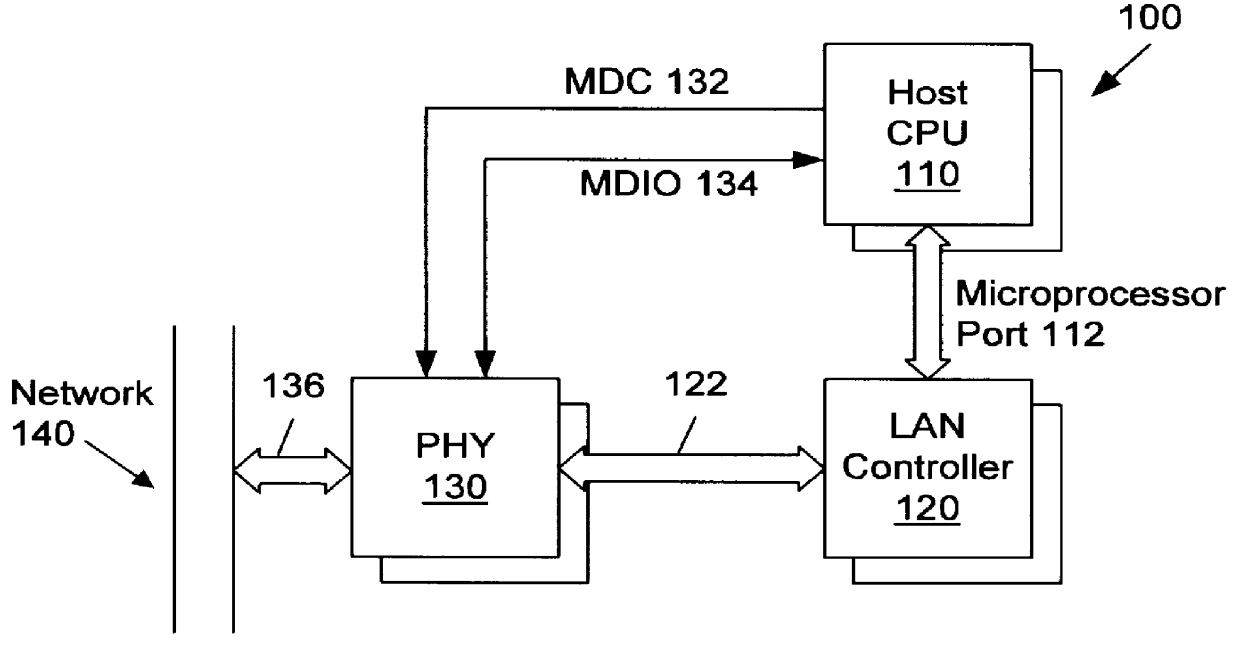

Auto-polling unit for interrupt generation in a network interface device

A system and method for auto-polling a status register within a physical layer (PHY) interface to a local area network (LAN). The system includes a host CPU which needs to detect and service interrupts generated by a PHY device on the LAN which is coupled between a first transmission medium (such as copper or fiber cable) and a management interface to the system. The system further includes an auto-polling unit which monitors activity on the management interface of the PHY device. When the auto-polling unit detects a lack of activity on the management interface of the PHY for a predetermined interval, the auto-polling unit reads a first value from the PHY status register. This first status value is then compared to a previously stored value which corresponds to the last PHY status value read by the host CPU. If a mismatch is detected between these two values, an interrupt is generated to the CPU. In response to receiving the interrupt, auto-polling is suspended (to avoid changing the status data that caused the interrupt) and the CPU requests a read of the status value in the first register. In this manner, the CPU is able to access the status value which caused the interrupt and determine the appropriate course of action. This status read by the CPU also has the effect of clearing the interrupt. This system frees the CPU from having to continually poll the PHY status register to determine if a change in status has occurred.

Owner:JATO TECH

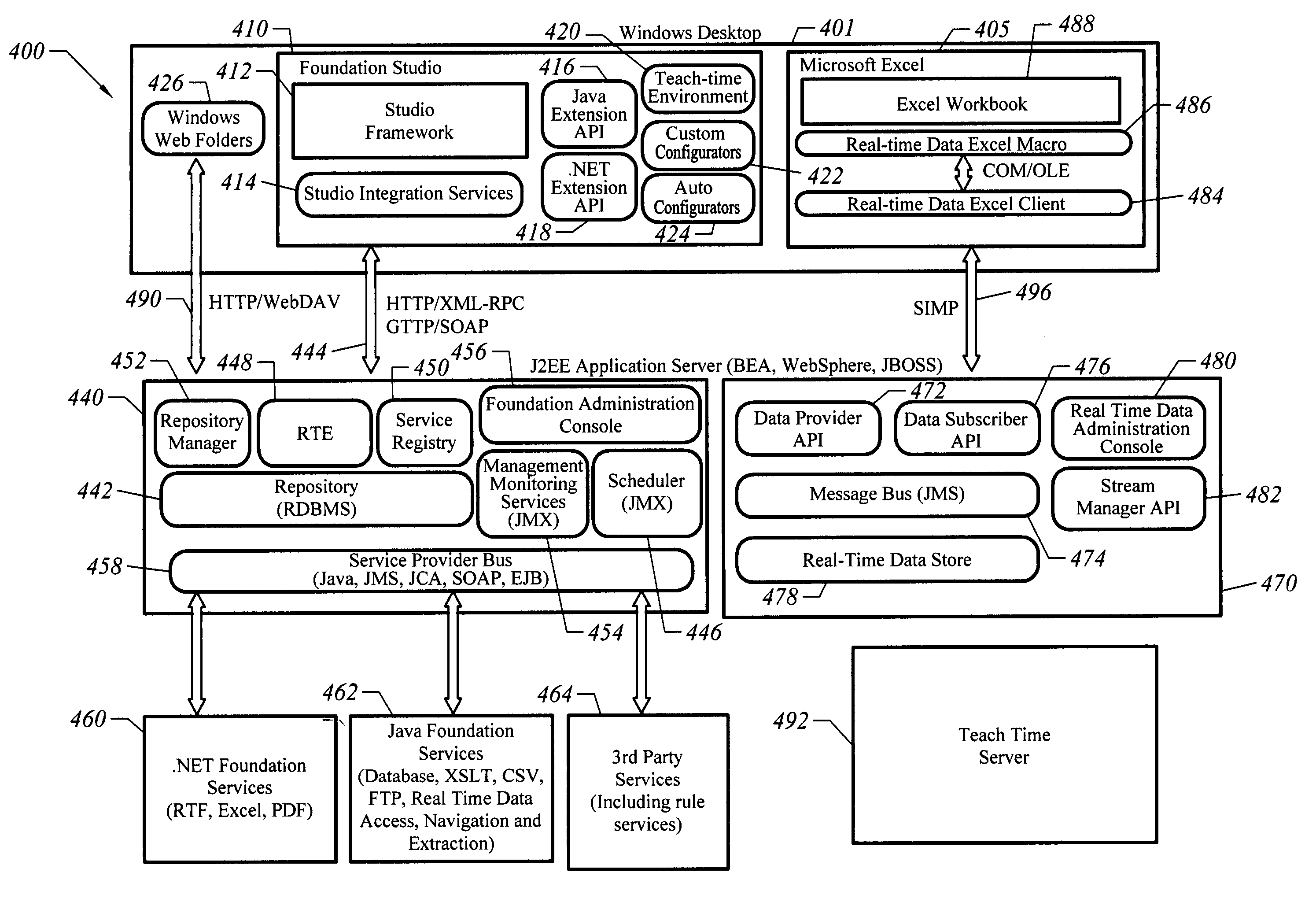

Apparatus and method for providing streaming data

InactiveUS20060004802A1Special service provision for substationProgram initiation/switchingStreaming dataBusiness process

A Java based server is disclosed for providing streaming data. Streaming data is received in a publisher interface and processed to generate Java messages describing real time updated. One application of the Java based server is to provide streaming data for business process.

Owner:STRIPE INC

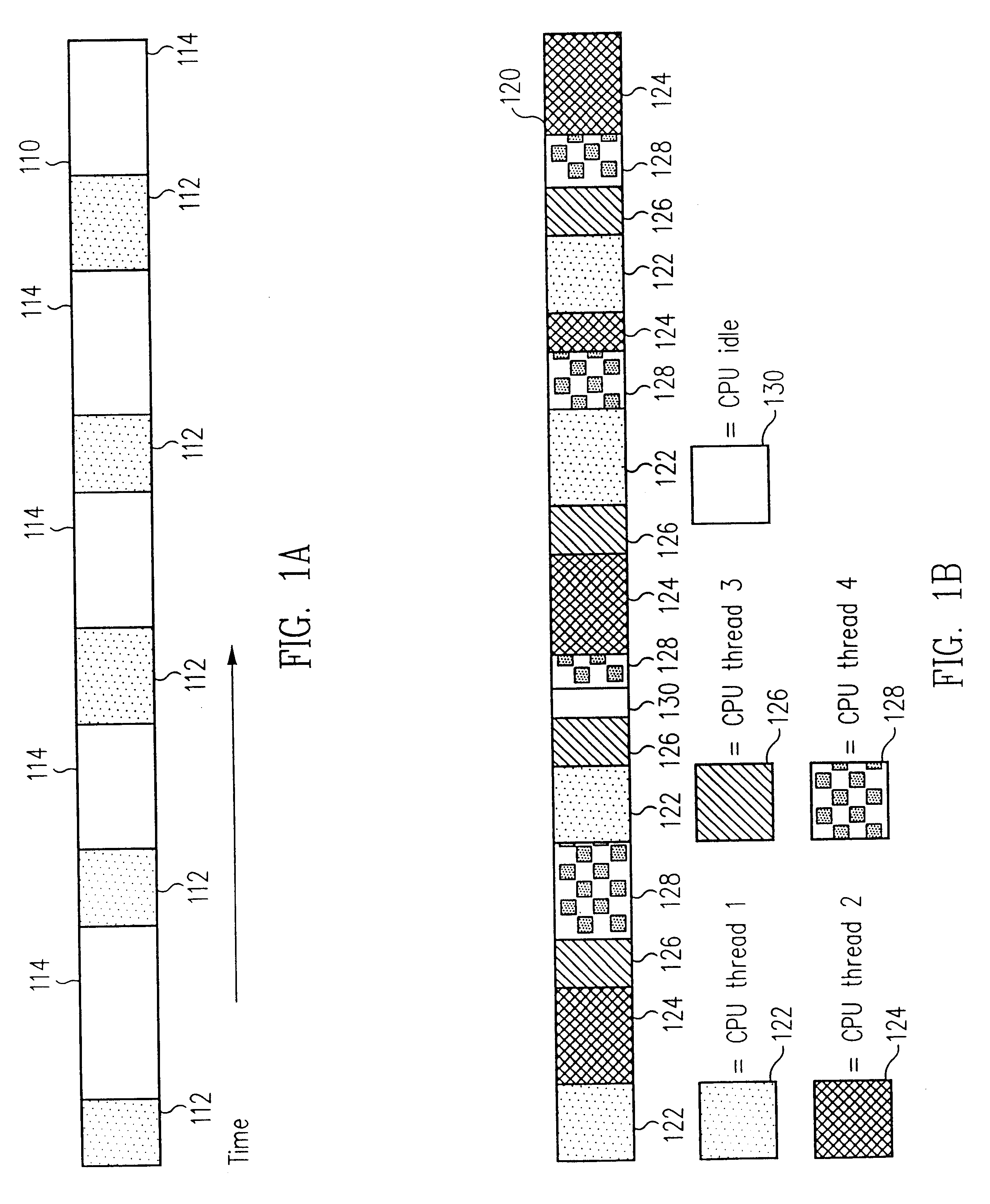

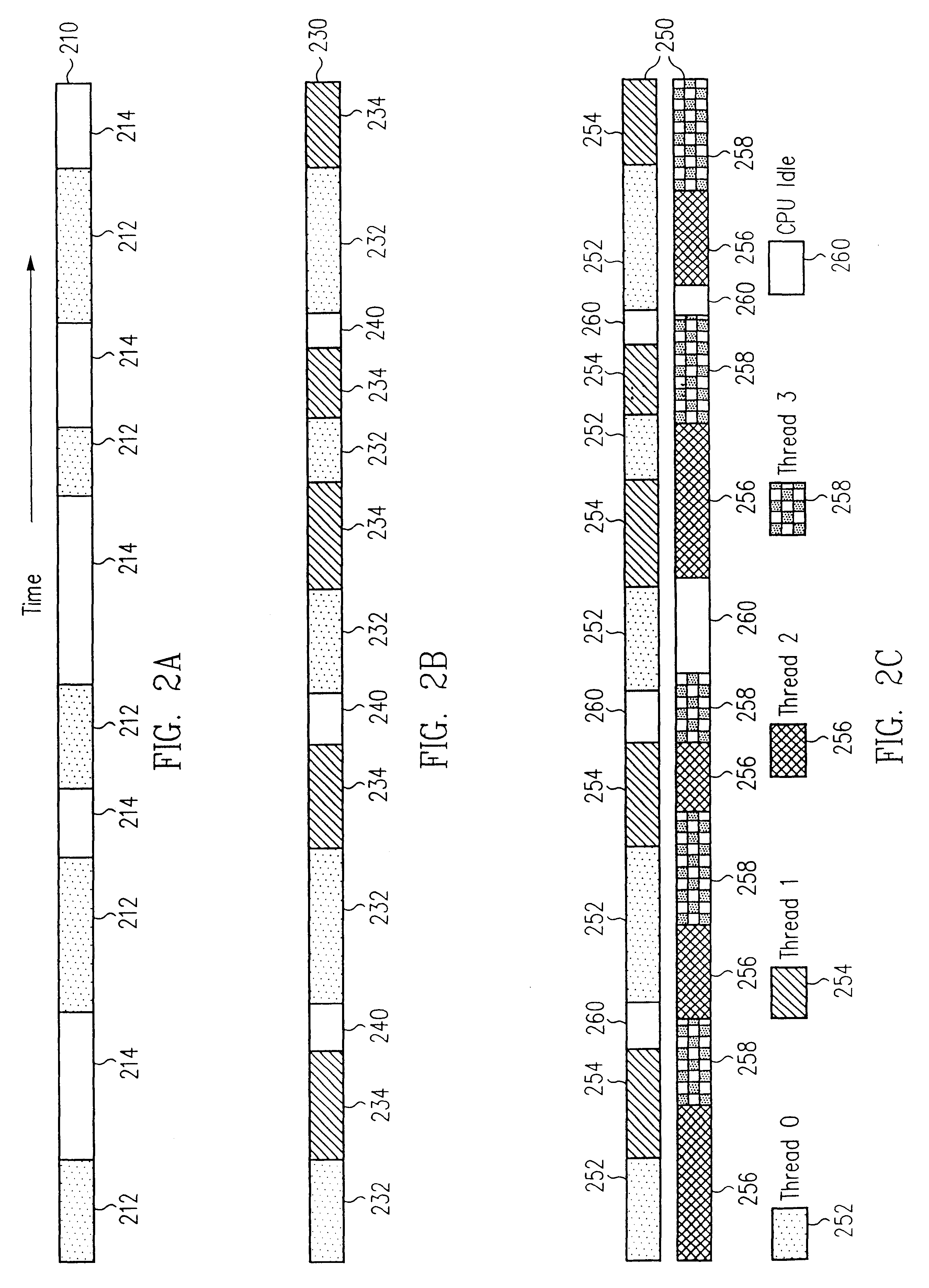

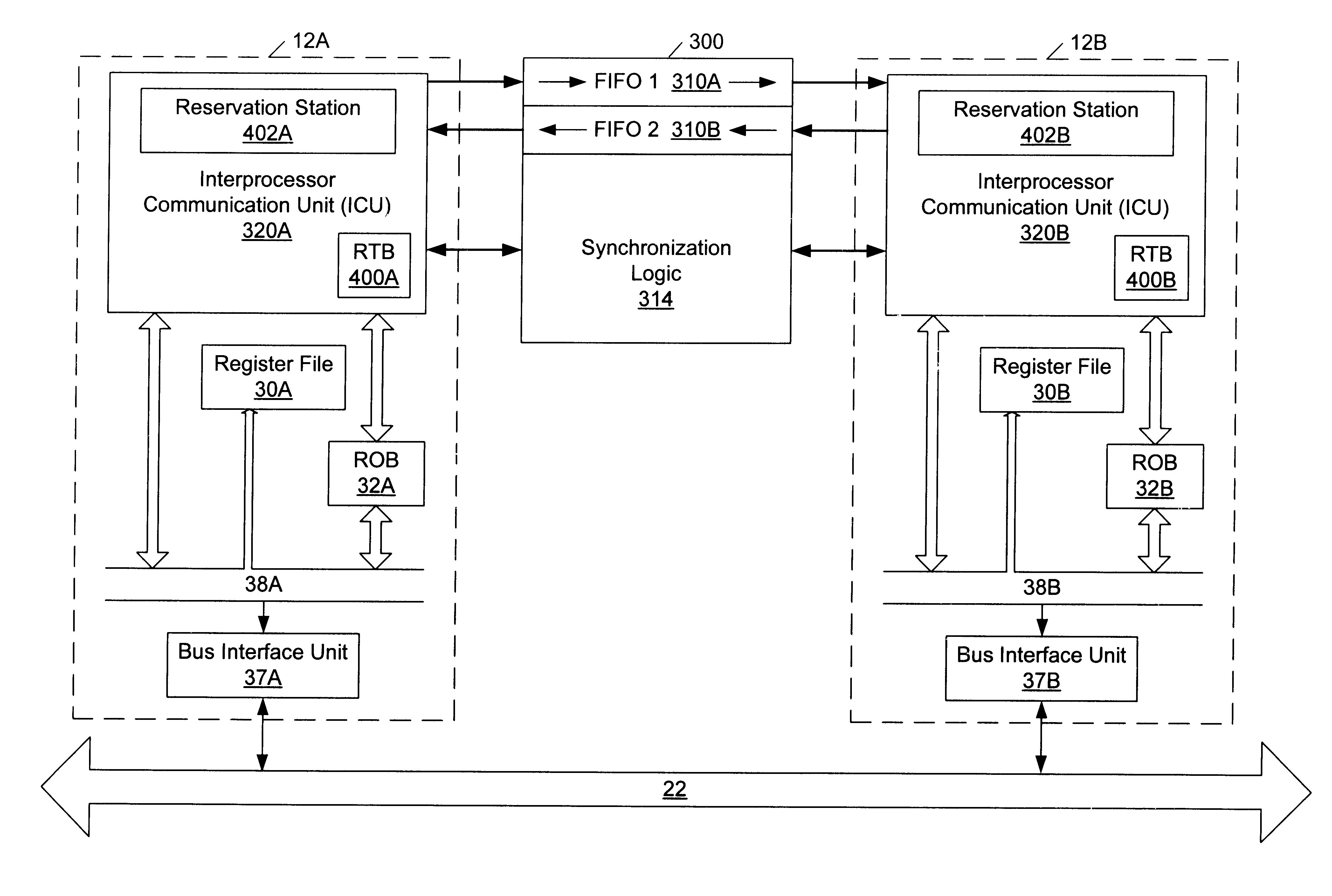

Method and mechanism for speculatively executing threads of instructions

InactiveUS6574725B1Program initiation/switchingGeneral purpose stored program computerSpeculative executionOperational system

A processor architecture containing multiple closely coupled processors in a form of symmetric multiprocessing system is provided. The special coupling mechanism allows it to speculatively execute multiple threads in parallel very efficiently. Generally, the operating system is responsible for scheduling various threads of execution among the available processors in a multiprocessor system. One problem with parallel multithreading is that the overhead involved in scheduling the threads for execution by the operating system is such that shorter segments of code cannot efficiently take advantage of parallel multithreading. Consequently, potential performance gains from parallel multithreading are not attainable. Additional circuitry is included in a form of symmetrical multiprocessing system which enables the scheduling and speculative execution of multiple threads on multiple processors without the involvement and inherent overhead of the operating system. Advantageously, parallel multithreaded execution is more efficient and performance may be improved.

Owner:GLOBALFOUNDRIES INC

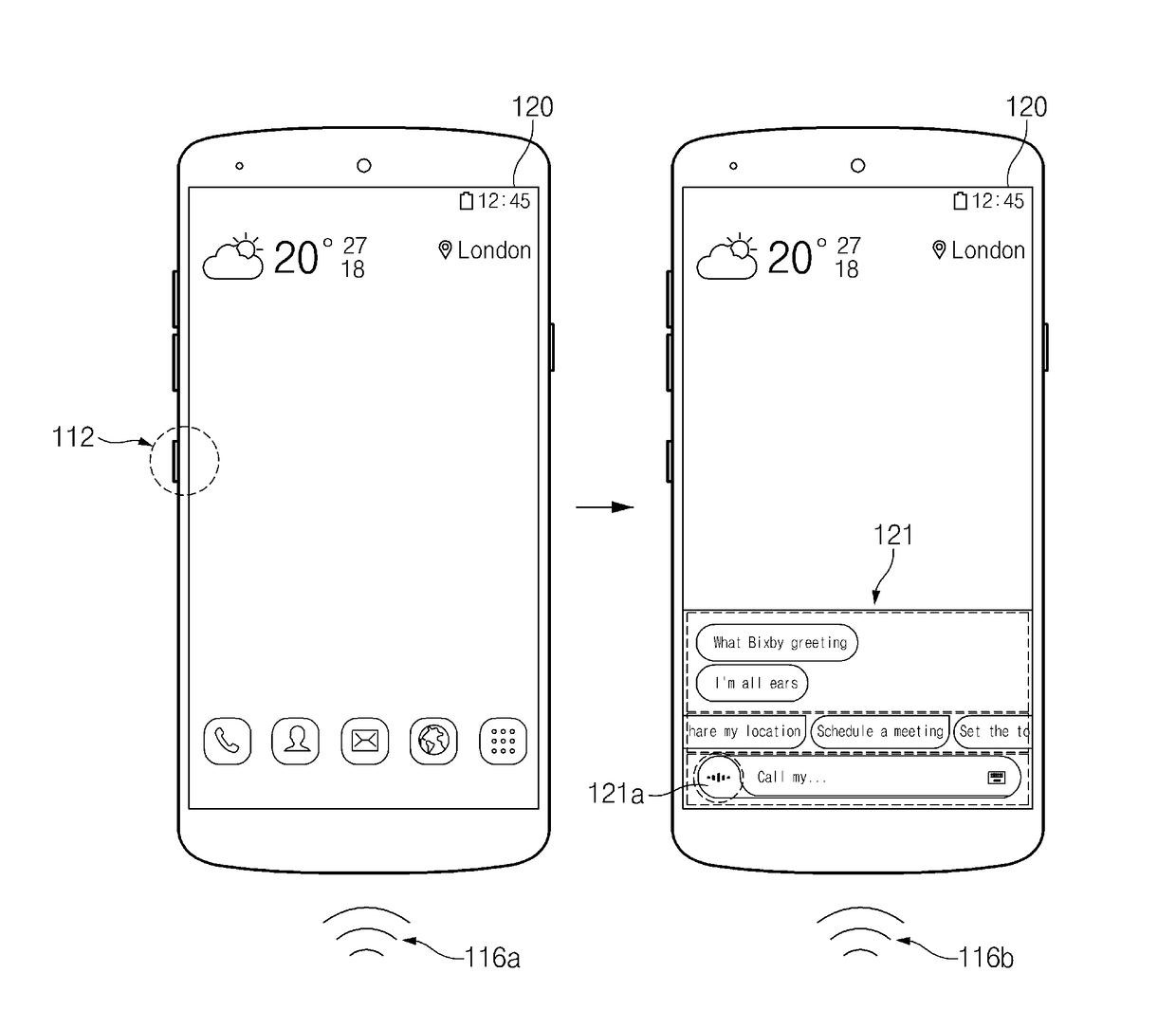

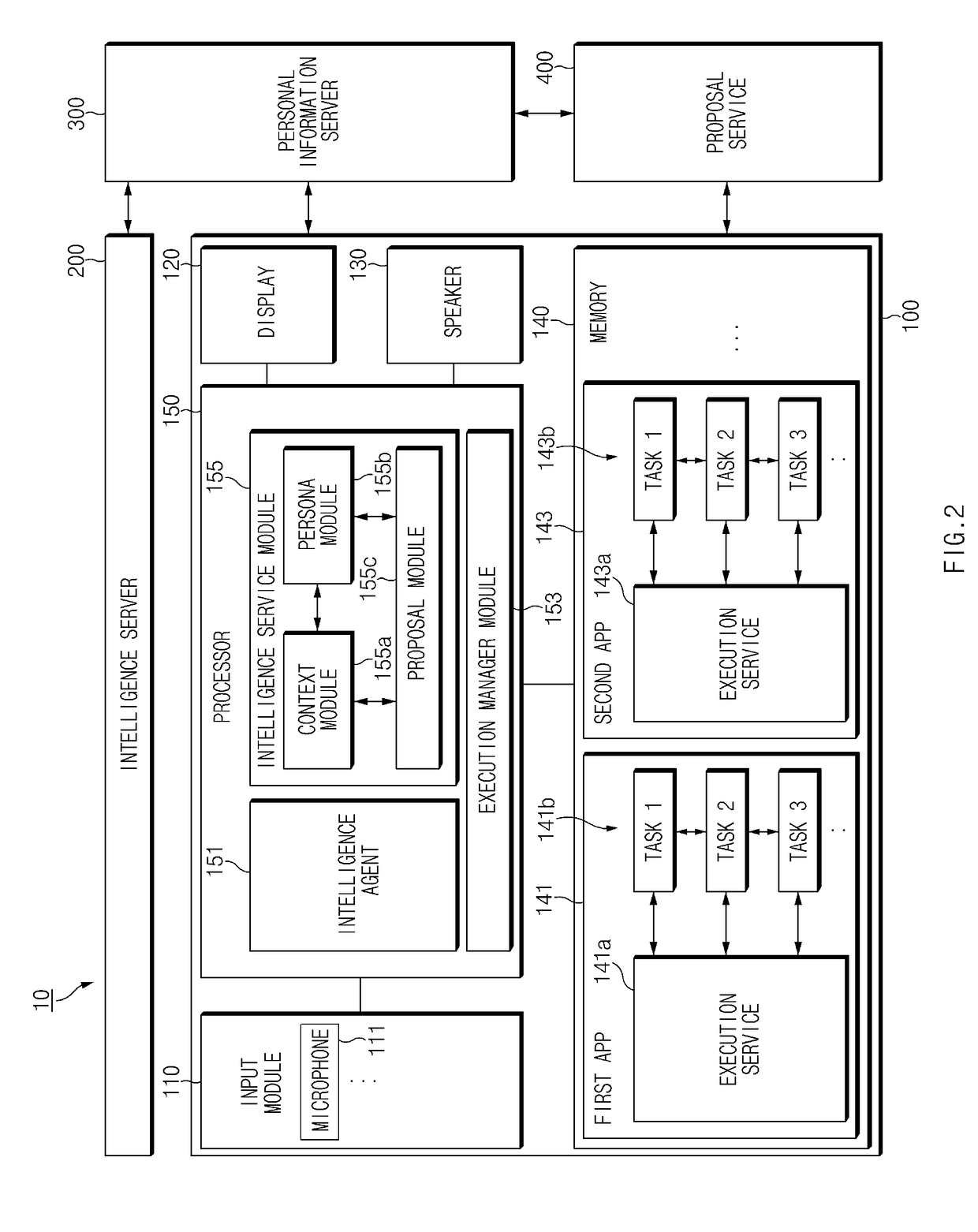

Voice data processing method and electronic device supporting the same

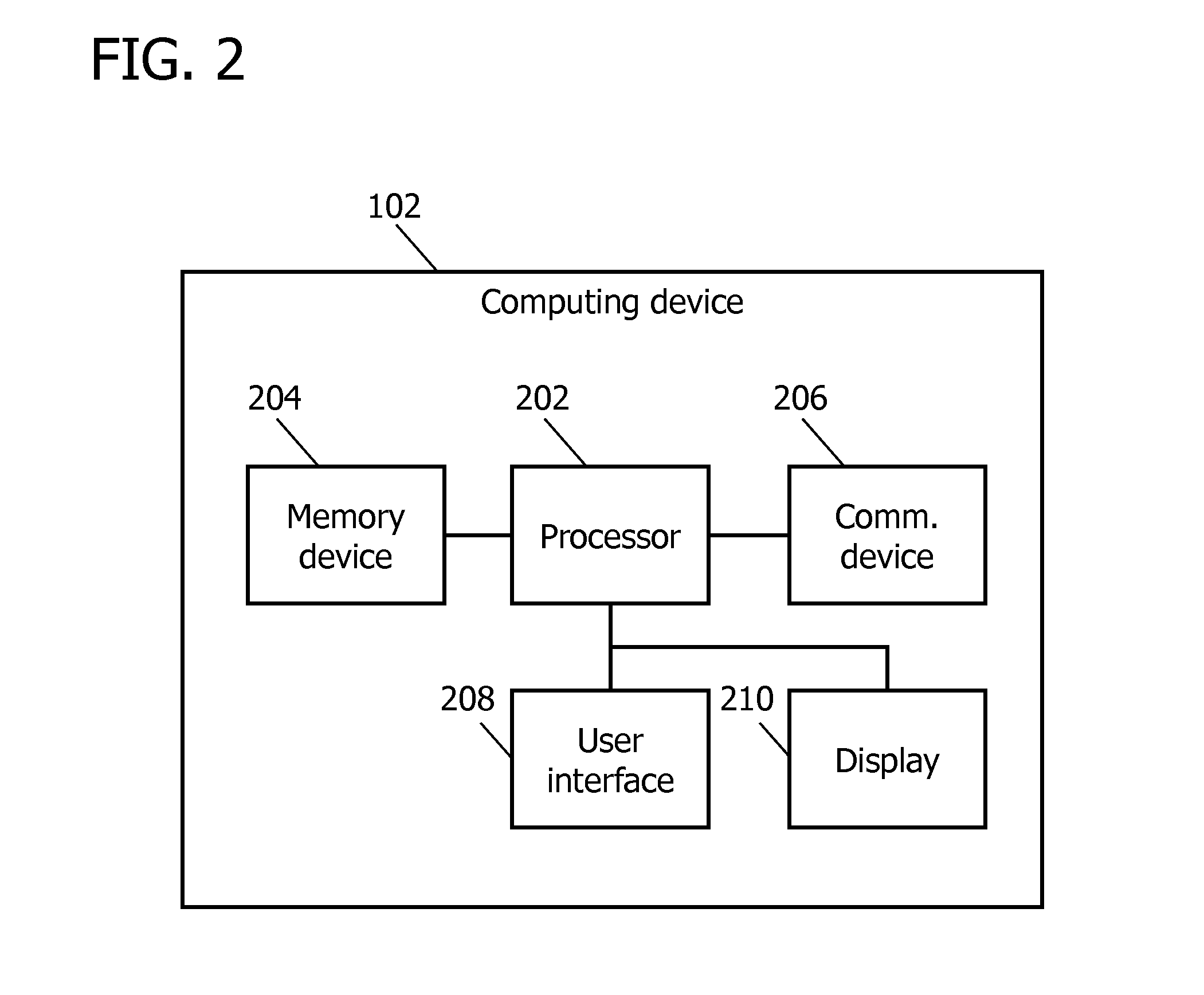

ActiveUS20180314552A1Improve recognition rateIncreases time-out timeInput/output for user-computer interactionProgram initiation/switchingComputer hardwareDisplay device

An electronic device includes a display, a microphone, a communication circuit, a memory configured to store at least one application, and one or more processor(s), wherein the processor is configured to obtain voice data corresponding to the user's voice received through the microphone, transmit the voice data to an external electronic device through the communication circuit, receive a sequence of tasks for performing a first function of the at least one application, which is determined based on the voice data, from the external electronic device through the communication circuit; and while performing the tasks based on the sequence of tasks, when it is determined that execution of a first task in the sequence of tasks is not completed within a specified time, extending a time-out time of the first task and switching the execution of the first task to the execution in background.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com