Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1479 results about "Total current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Finding Total Current of a Series Circuit Connection Find the total resistance of the circuit. Identify the total voltage of the resistor. Calculate the total current of the system. Remember Ohm's law. Try working with an example. Use Ohm’s Law for computing the total current: V(total) = I(total) x R(total).

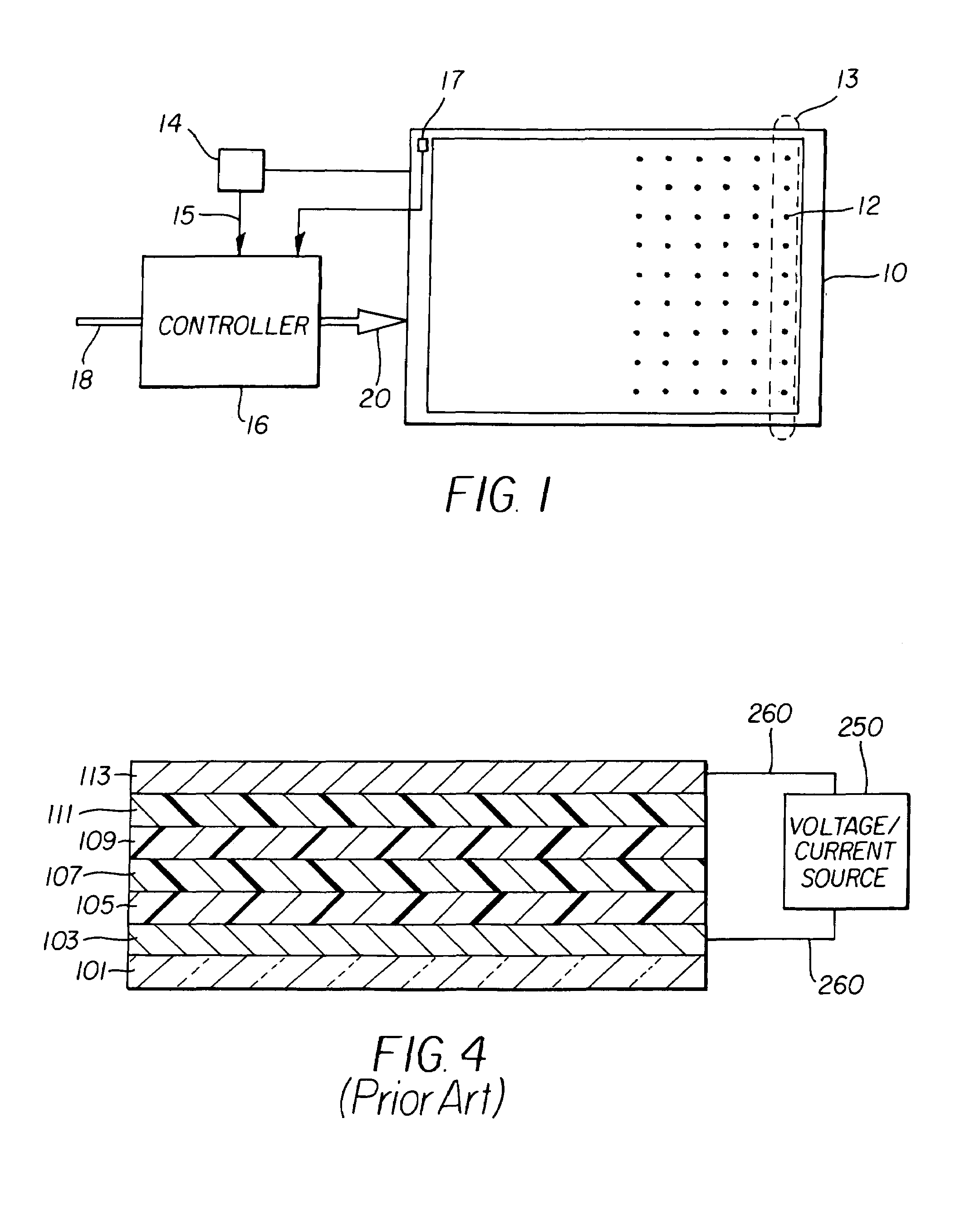

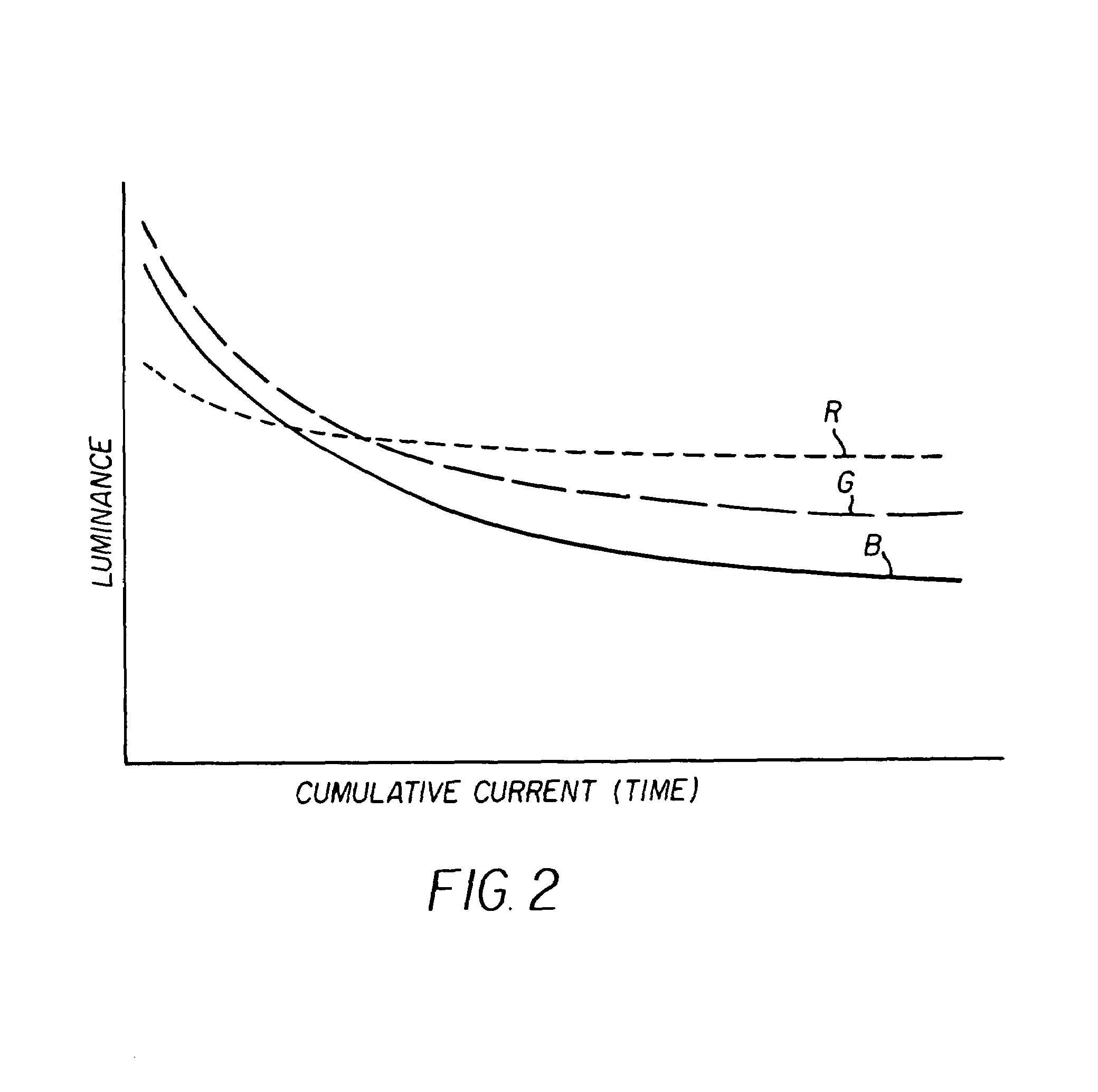

OLED display with aging compensation

An OLED display includes a plurality of light emitting elements divided into two or more groups, the light emitting elements having an output that changes with time or use; a current measuring device for sensing the total current used by the display to produce a current signal; and a controller for simultaneously activating all of the light emitting elements in a group and responsive to the current signal for calculating a correction signal for the light emitting elements in the group and applying the correction signal to input image signals to produce corrected input image signals that compensate for the changes in the output of the light emitting elements of the group.

Owner:GLOBAL OLED TECH

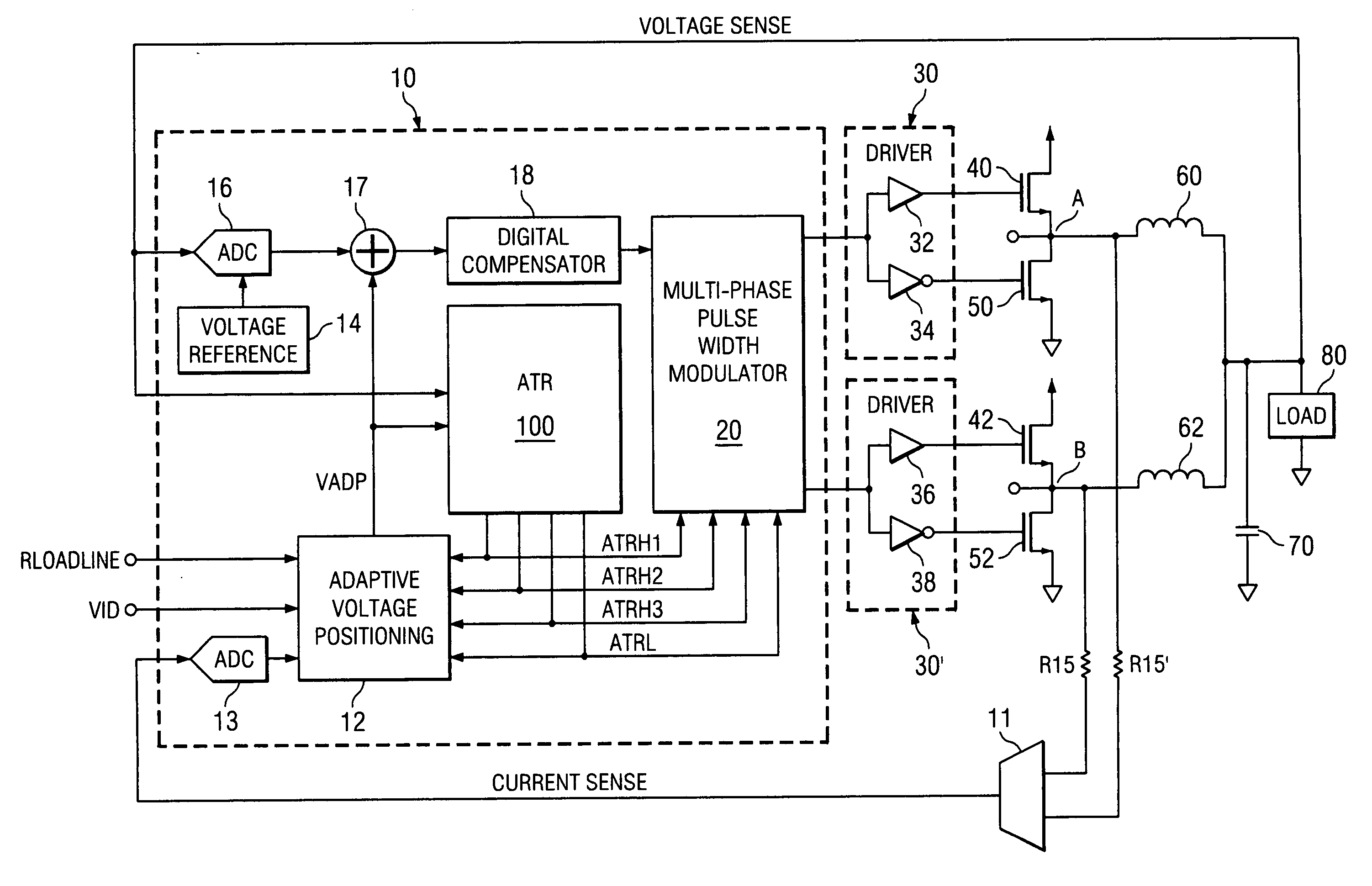

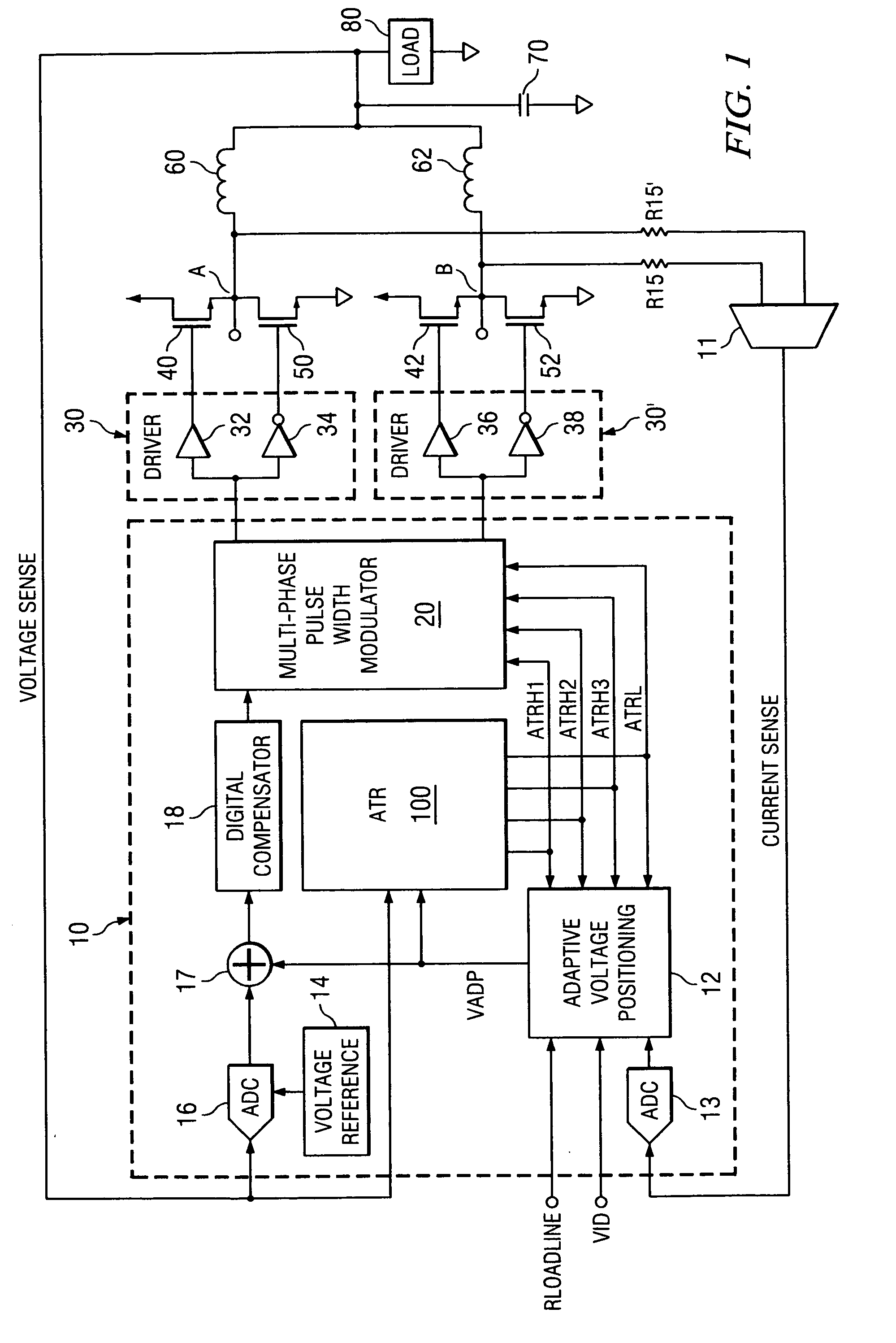

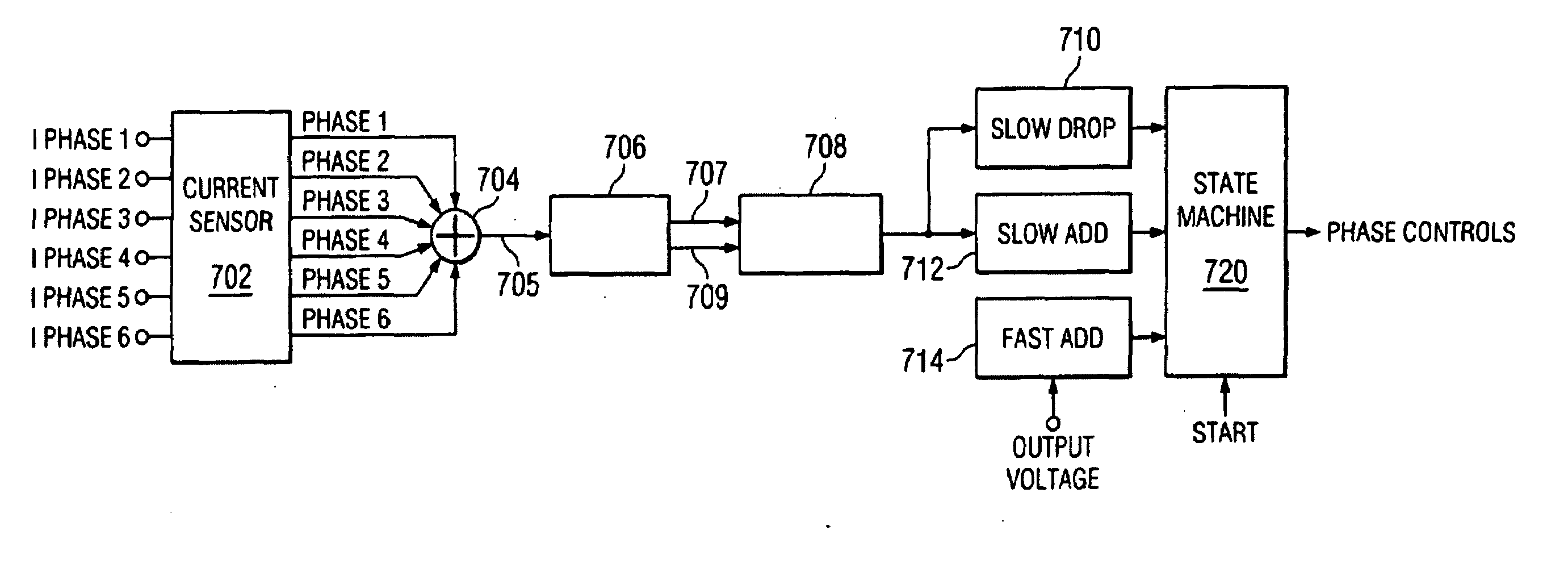

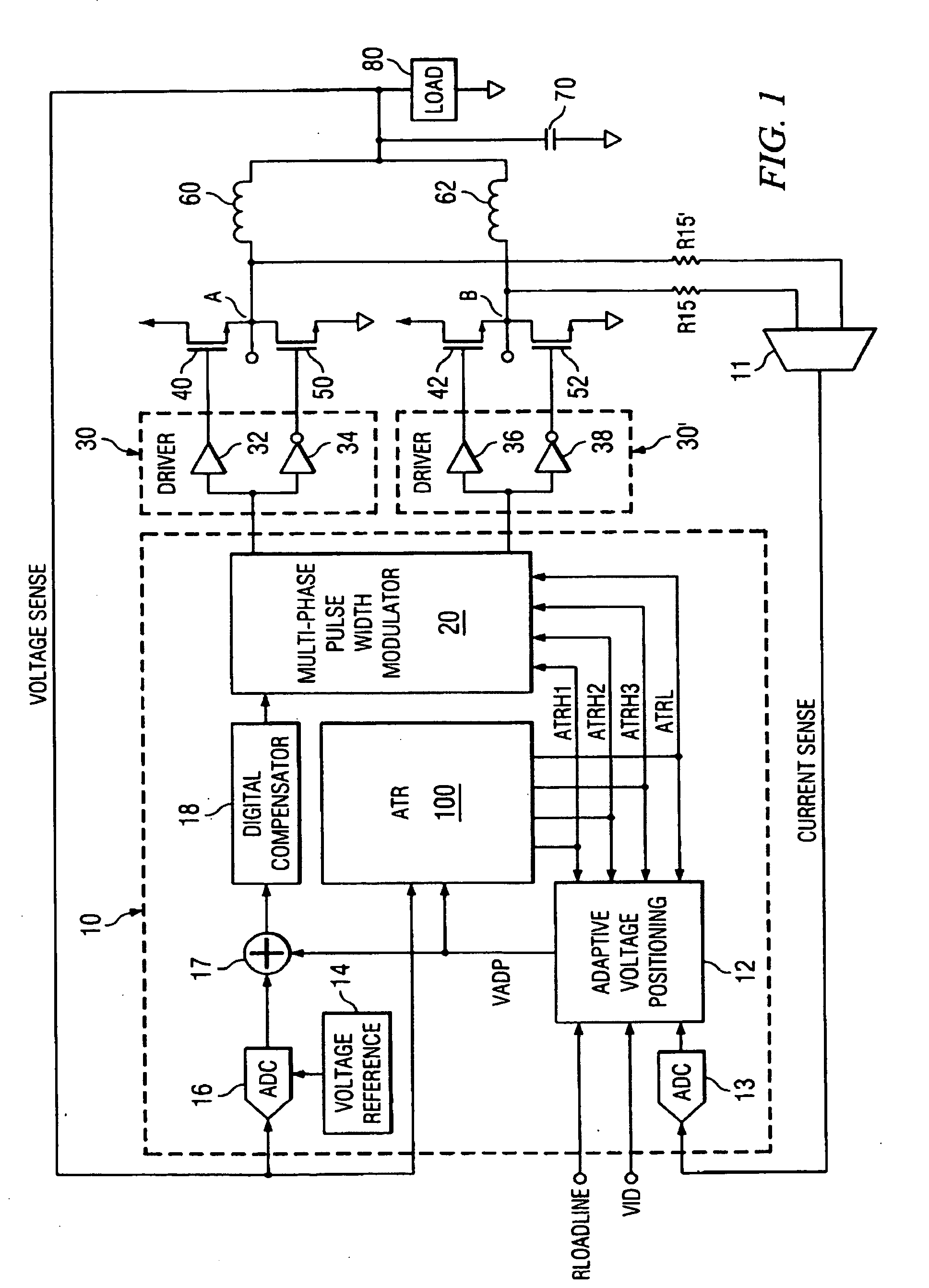

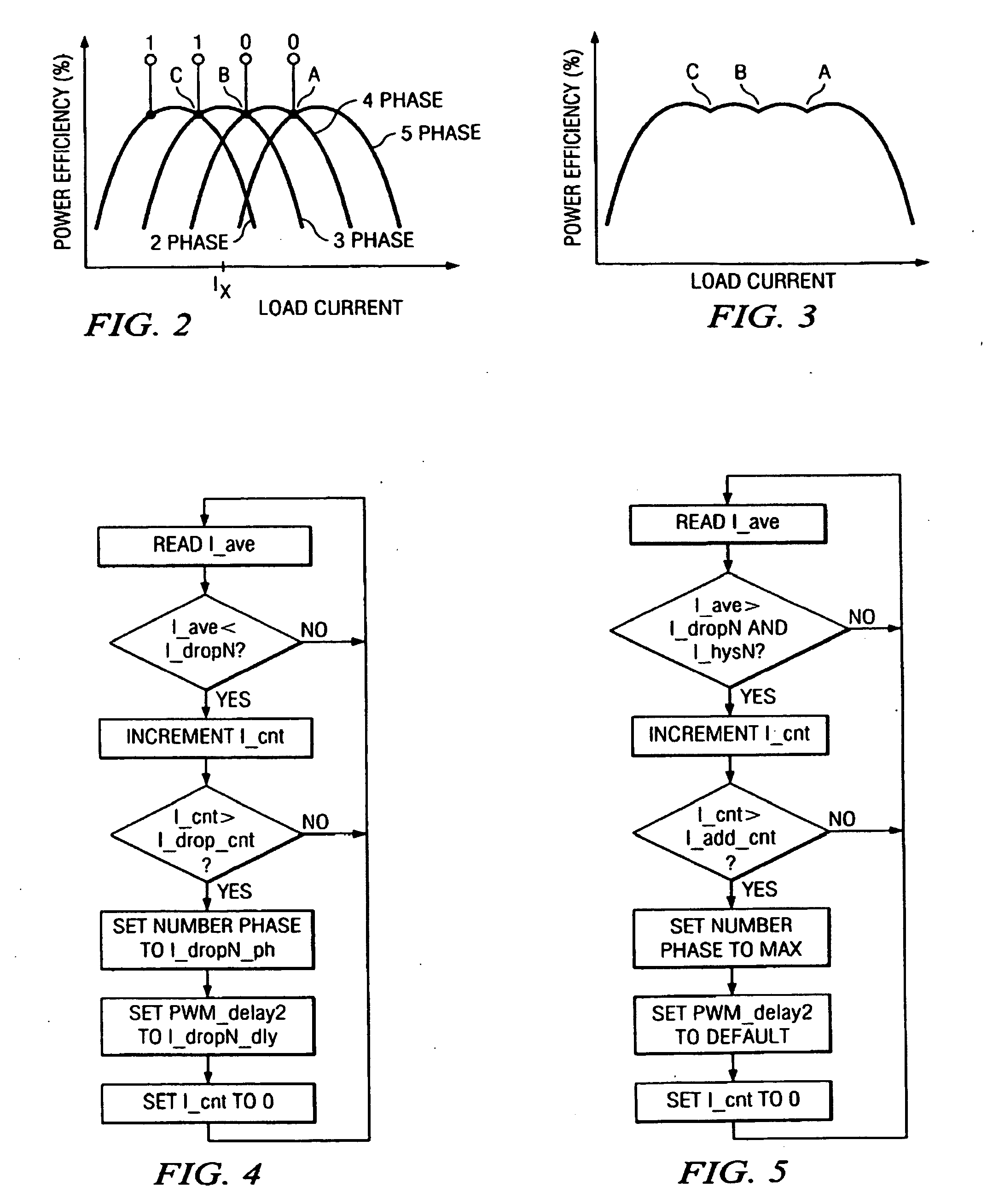

Multiphase power regulator with load adaptive phase control

ActiveUS20070013350A1Maximize efficiencyImprove efficiencyDc-dc conversionAc network voltage adjustmentEngineeringActive phase

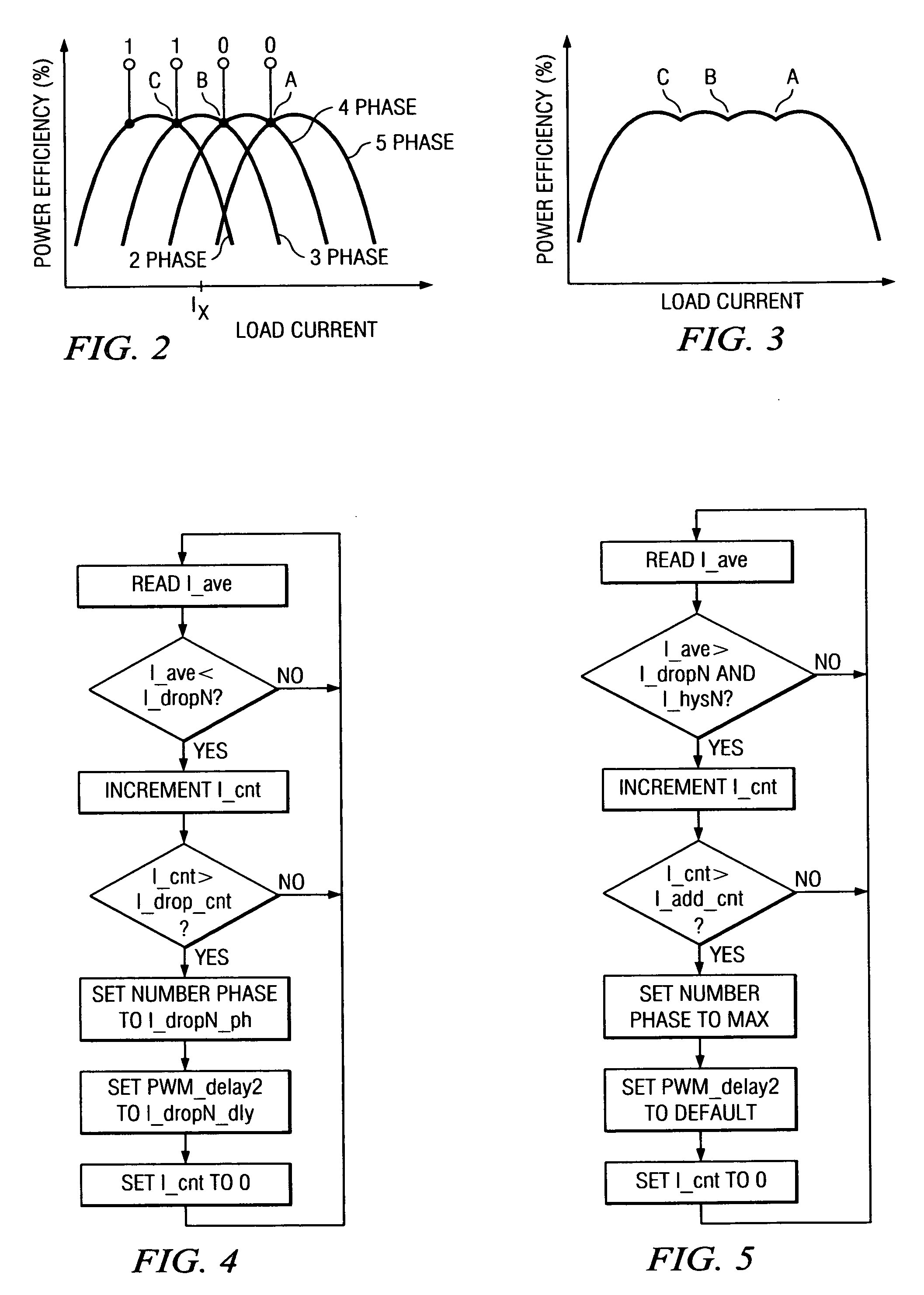

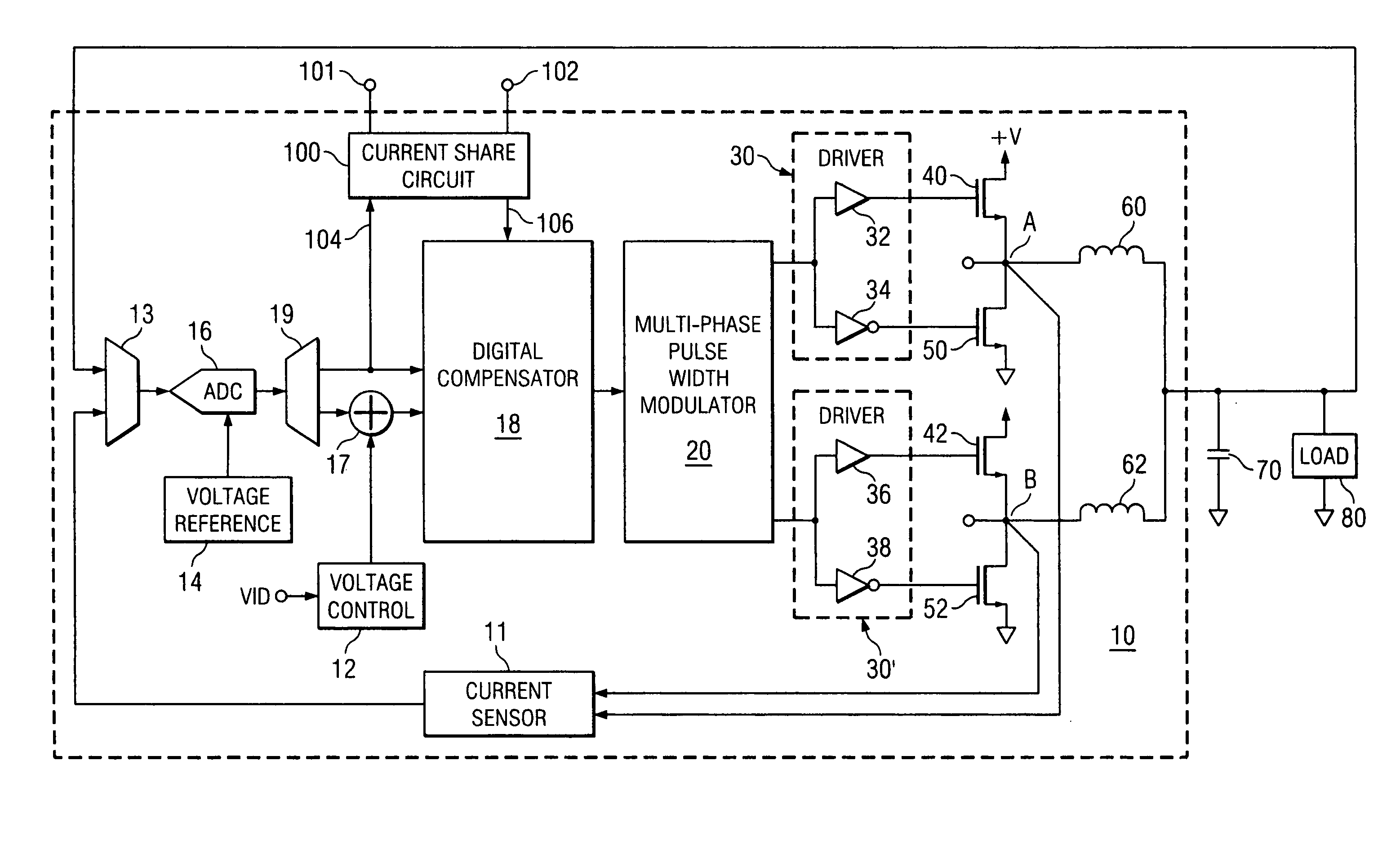

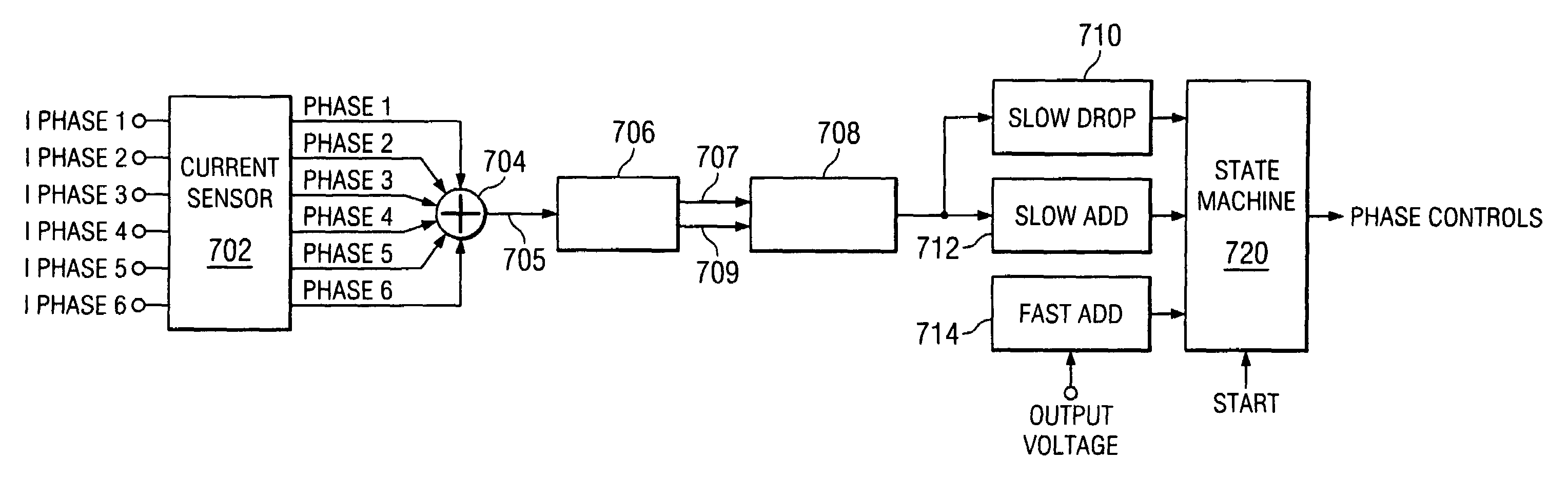

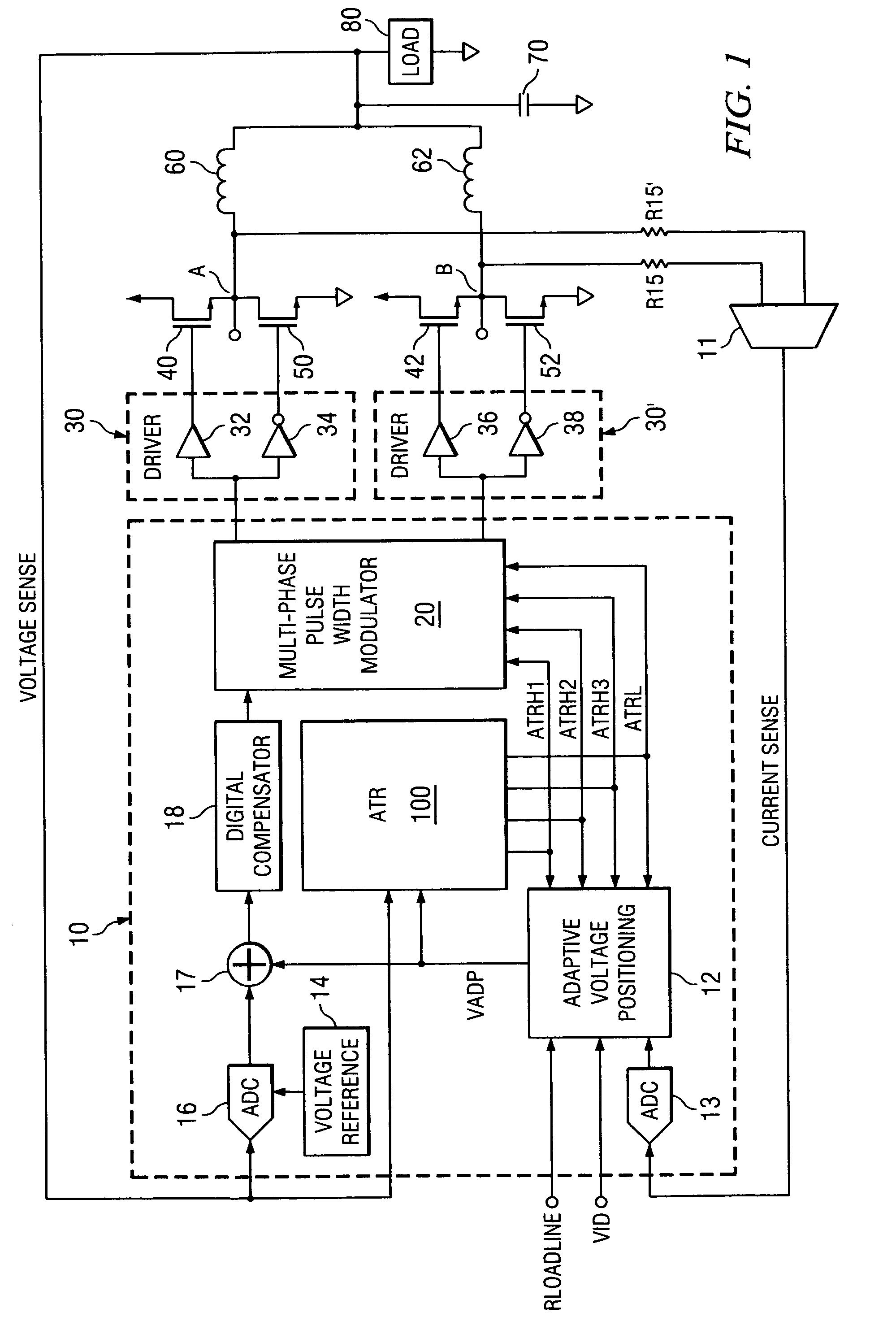

Disclosed is a power regulator for providing precisely regulated power to a microelectronic device such as a microprocessor. Improved power regulation is accomplished by optimizing the power efficiency of the power regulator. In particular, in a multiphase system, the number of active phases is increased or decreased to achieve optimum power efficiency. The multiphase voltage regulator adapts the operating mode to maximize efficiency as the load current demand of the load device changes by adjusting the number of active phases to maximize efficiency. The total value of current provided by the regulator and the total number of active phases is determined, the total number of active phases is compared with the number of active phases required to provide the total value of current at maximum efficiency; and the number of active phases is adjusted to provide the total value of current at maximum efficiency. A current sense circuit senses the current at each phase, a summing circuit coupled to the output of the current sense circuit provides the total current value of all the measured phases, a circuit coupled to the output of the summing circuit provides the time averaged total current value to a threshold detecting circuit that determines the number of phases at which the voltage regulator should be operating for maximum efficiency, and a circuit for comparing the number of phases that are operating to the number of phases at which the voltage regulator should be operating adjusts the number of active phases to the number of phases at which the voltage regulator should be operating for maximum efficiency.

Owner:INFINEON TECH AUSTRIA AG

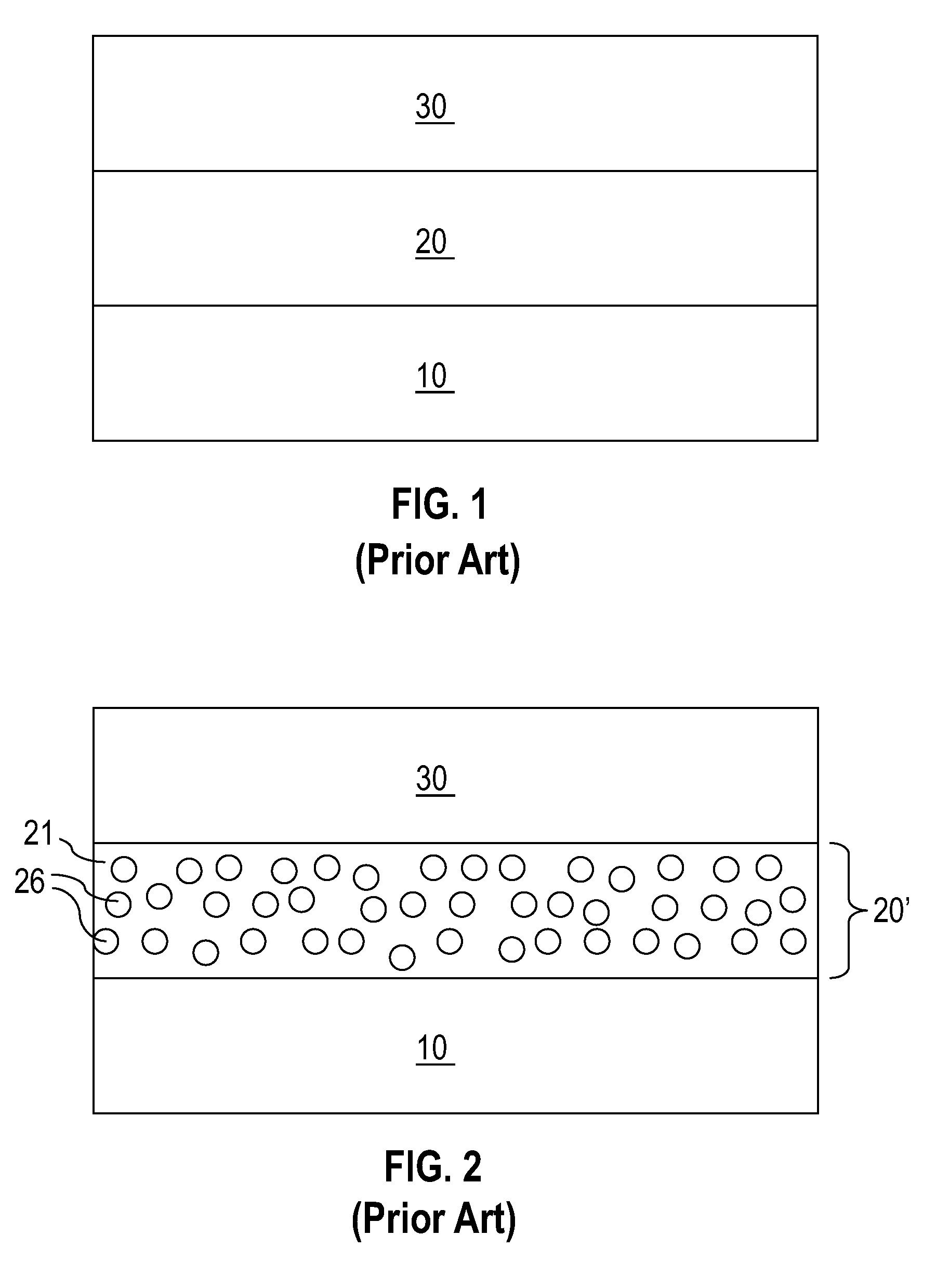

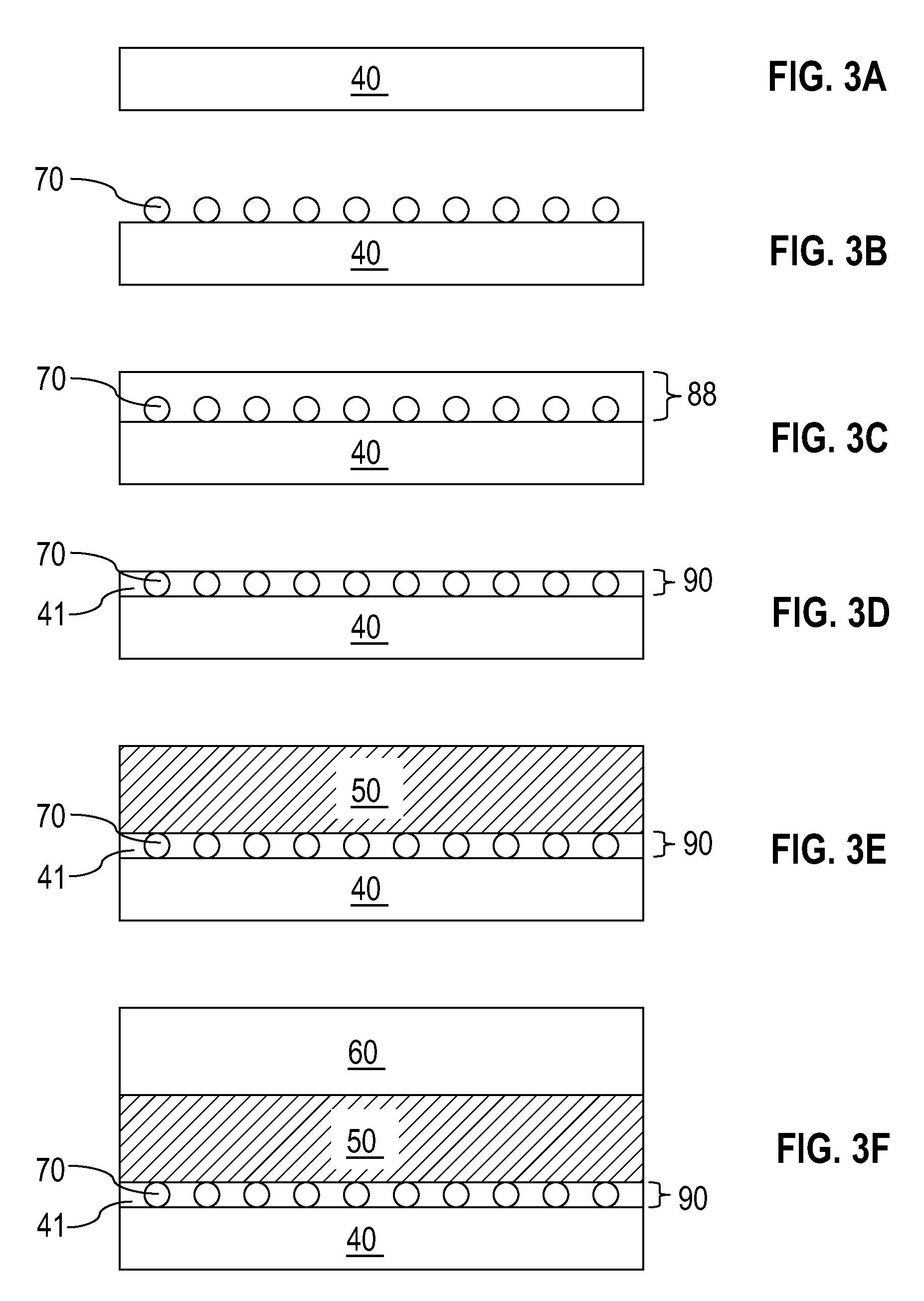

Current constricting phase change memory element structure

InactiveUS20090014704A1Small sizeHigh local temperatureNanoinformaticsBulk negative resistance effect devicesPhase-change memoryCurrent limiting

A layer of nanopaiticles having a dimension on the order of 10 nm is employed to form a current constricting layer or as a hardmask for forming a current constricting layer from an underlying insulator layer. The nanoparticles are preferably self-aligning and / or self-planarizing on the underlying surface. The current constricting layer may be formed within a bottom conductive plate, within a phase change material layer, within a top conductive plate, or within a tapered liner between a tapered via sidewall and a via plug contains either a phase change material or a top conductive material. The current density of the local structure around the current constricting layer is higher than the surrounding area, thus allowing local temperature to rise higher than surrounding material. The total current required to program the phase change memory device, and consequently the size of a programming transistor, is reduced due to the current constricting layer.

Owner:MACRONIX INT CO LTD +2

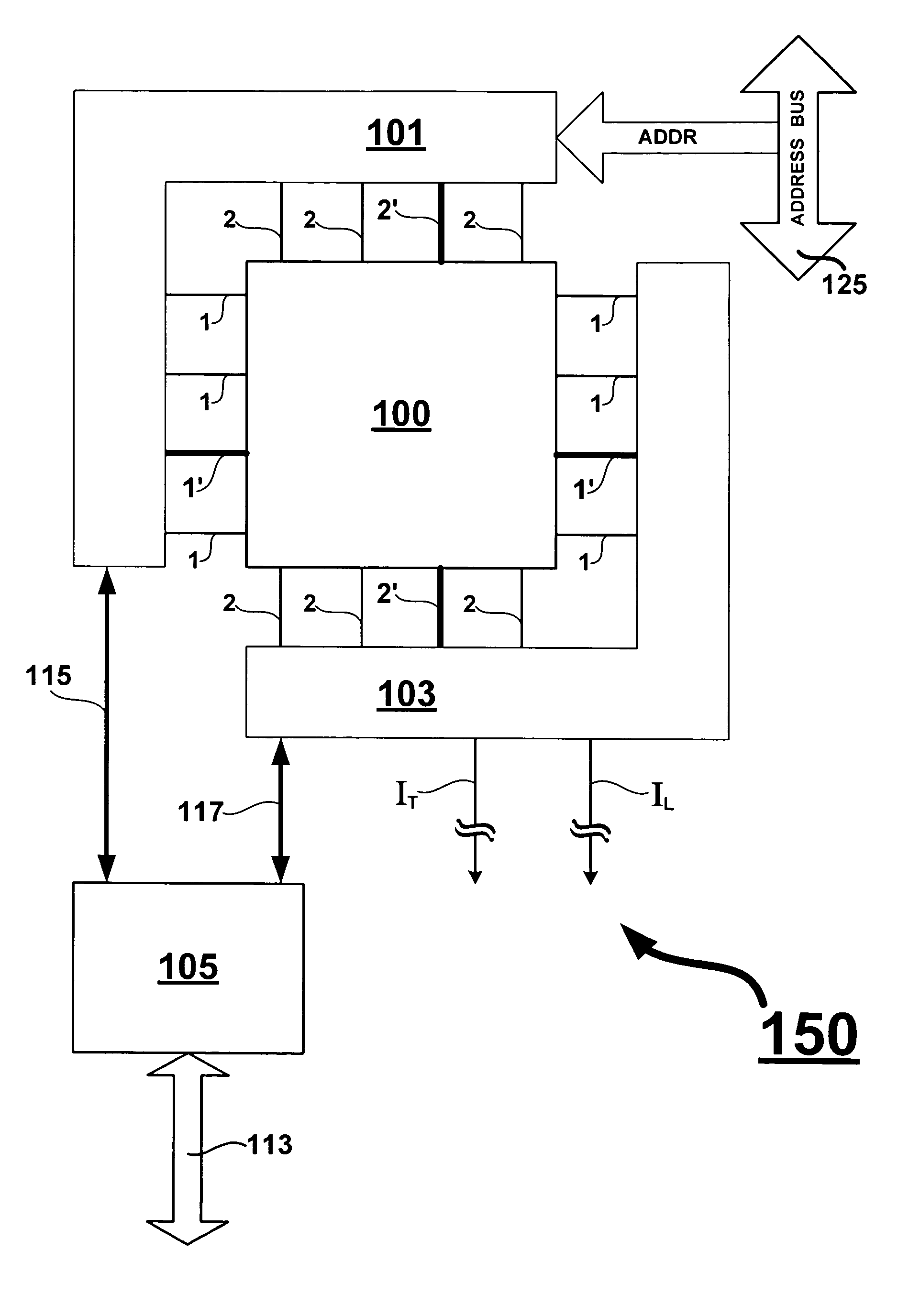

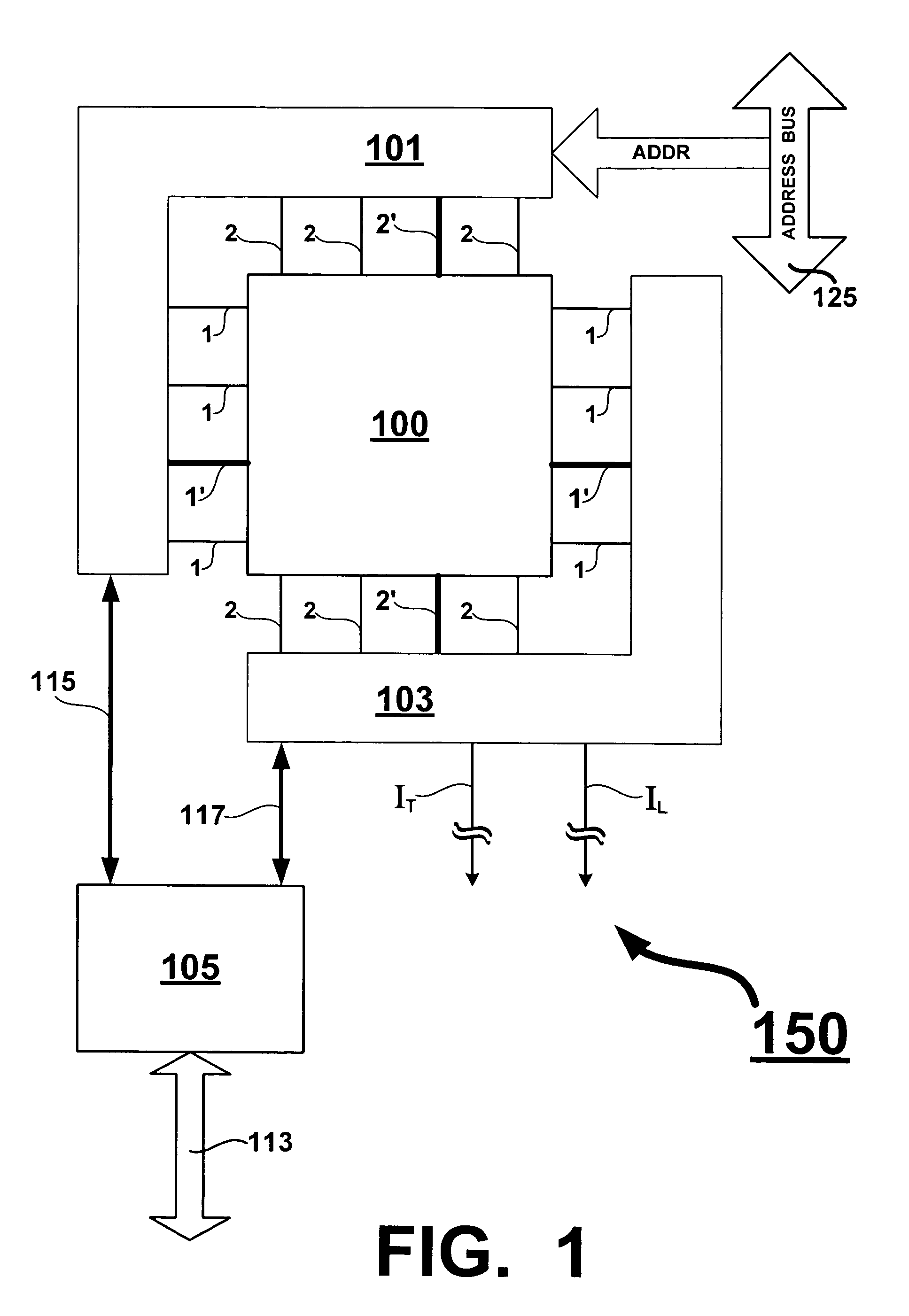

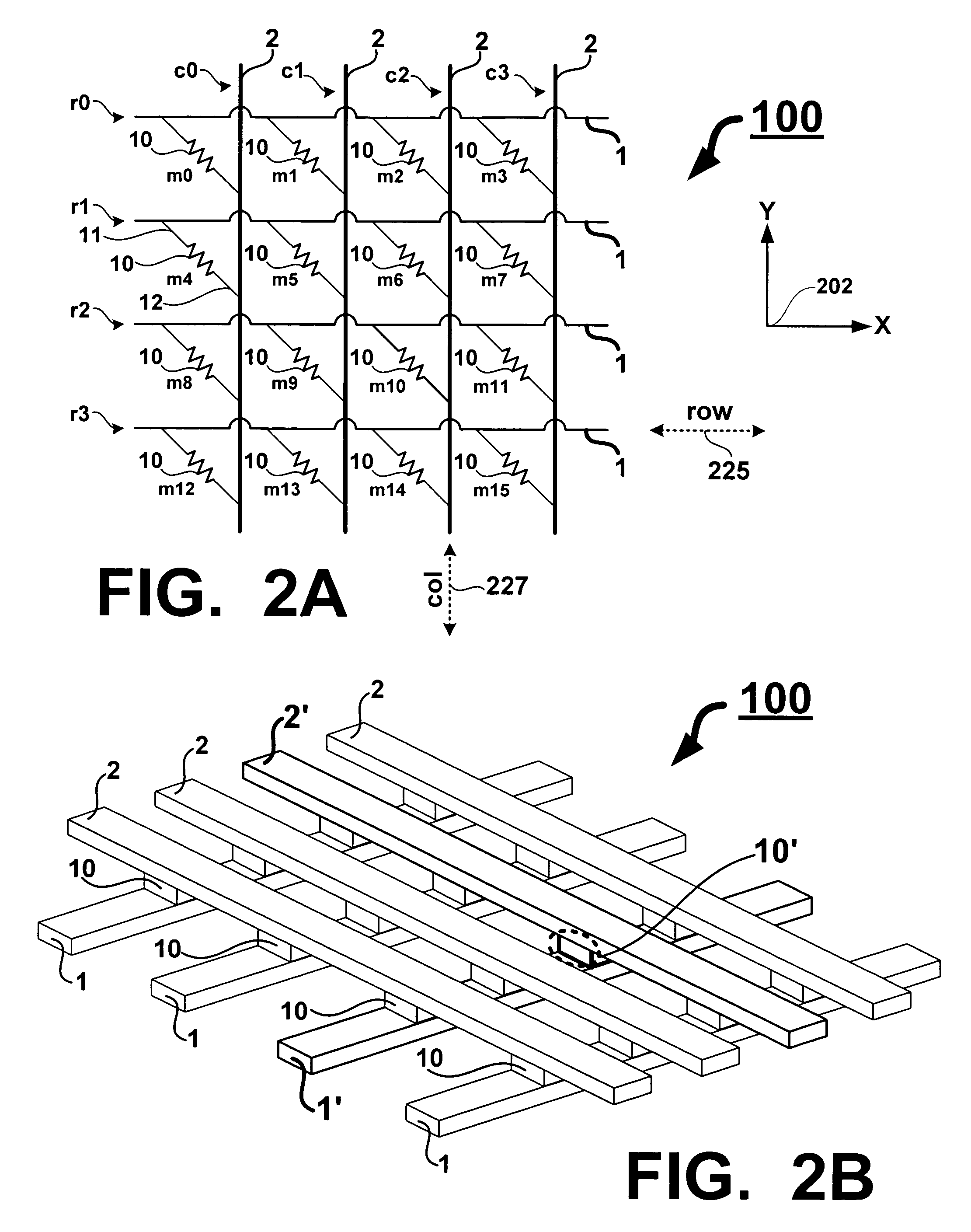

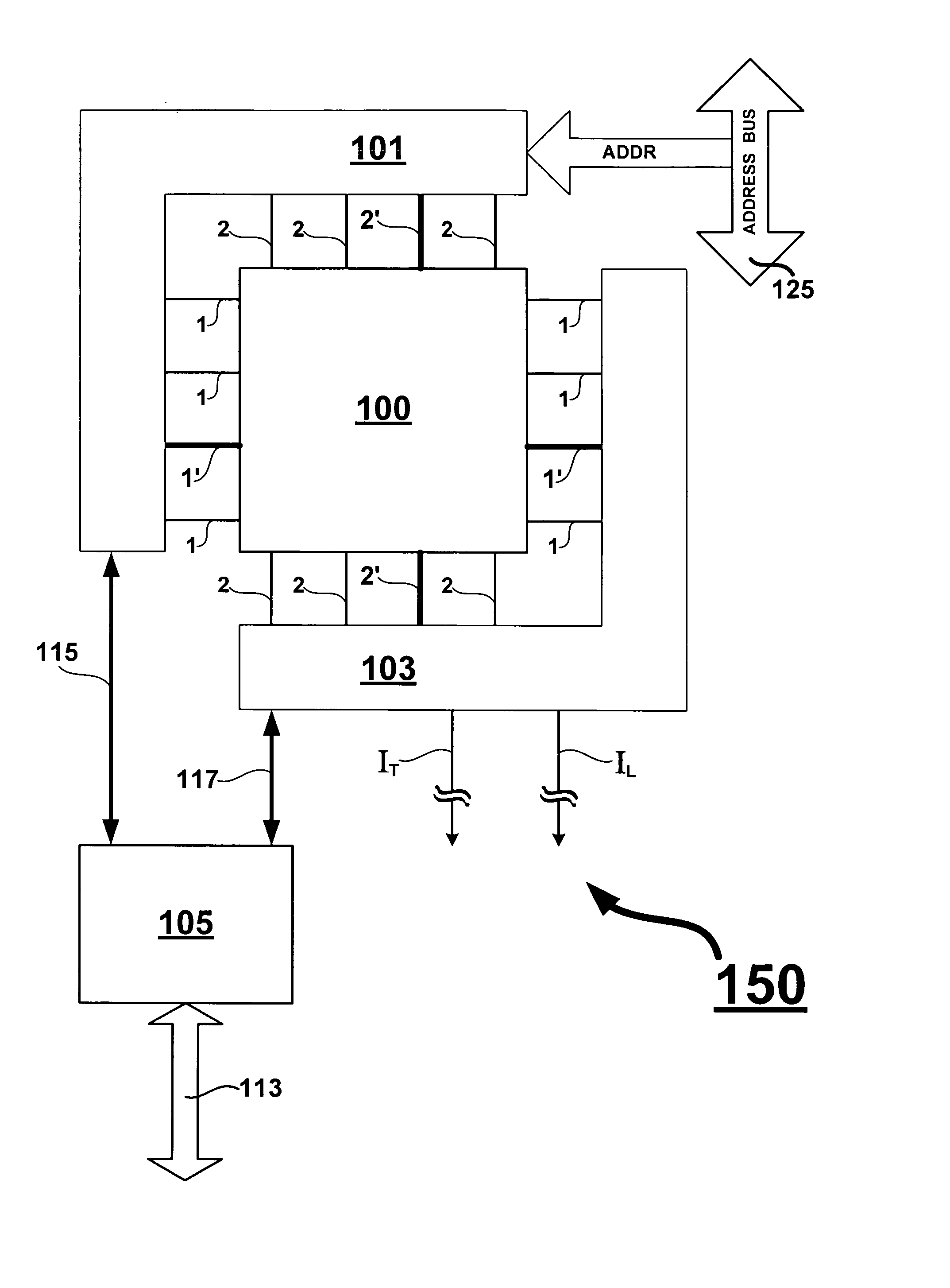

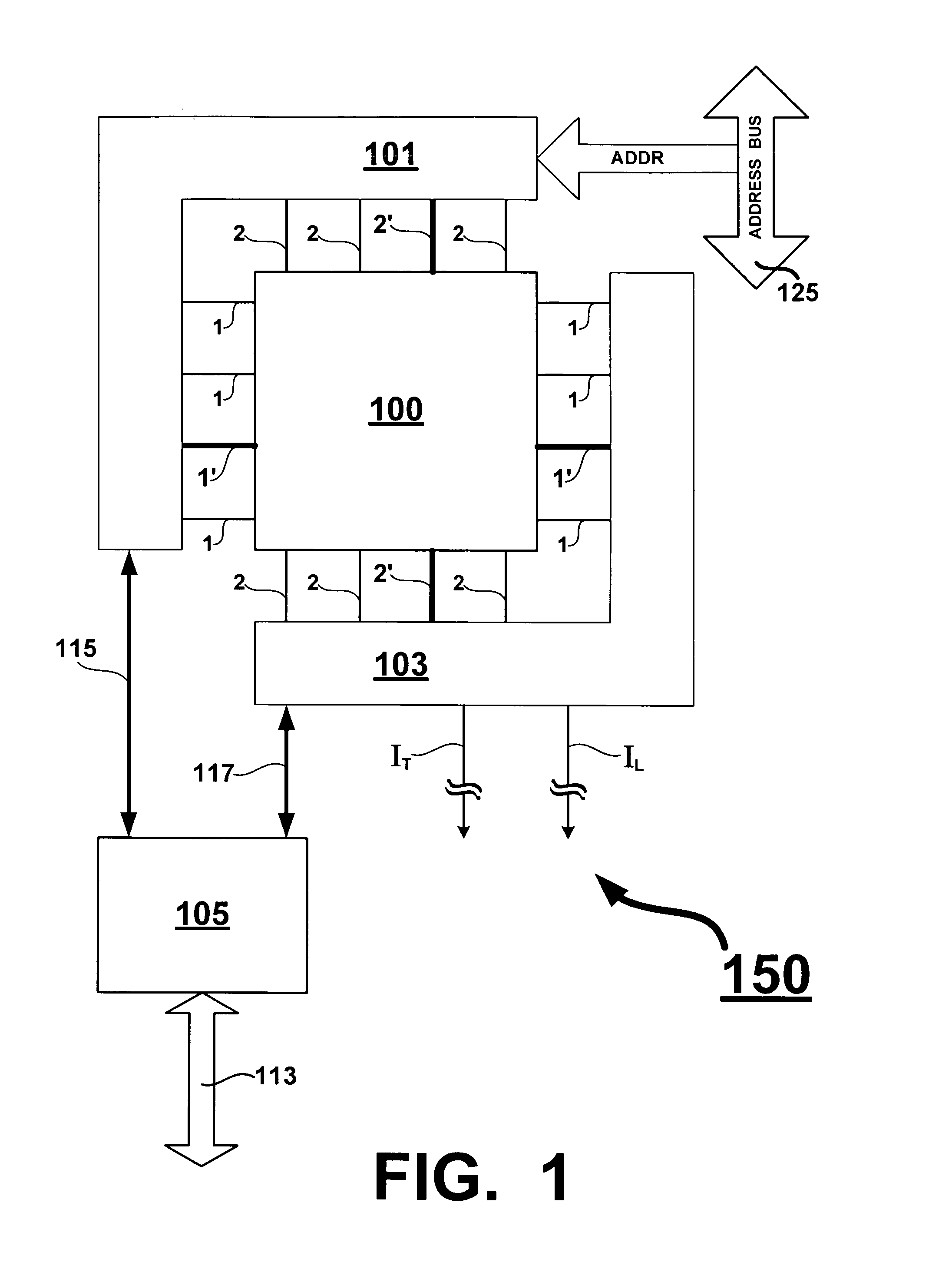

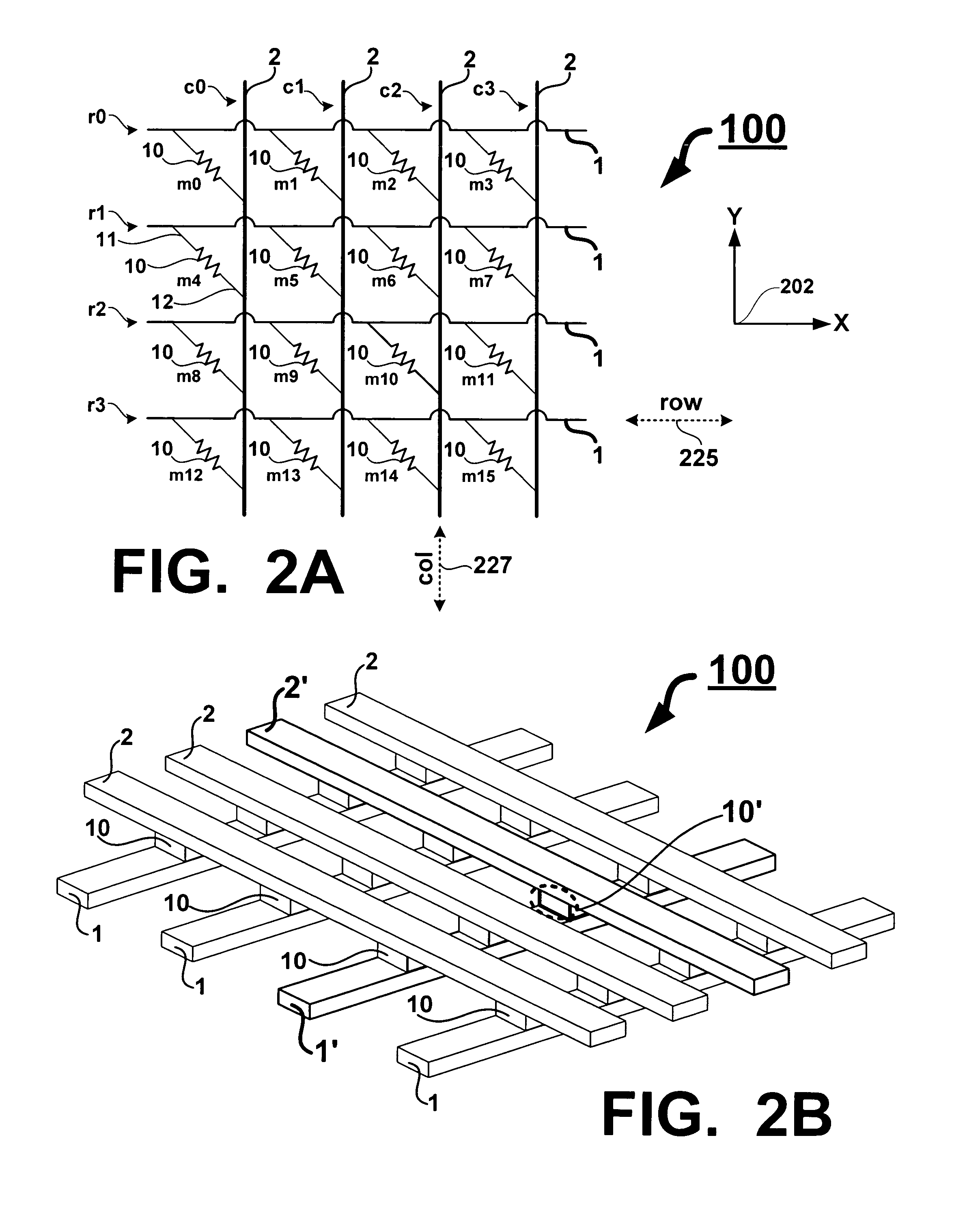

Two-cycle sensing in a two-terminal memory array having leakage current

A two-terminal memory array includes a plurality of first and second conductive traces. An address unit operatively applies a select voltage across a selected pair of the first and second conductive traces and applies a non-select voltage potential to unselected traces. A total current flowing in the selected first conductive trace and a leakage current flowing through unselected second conductive traces are sensed by a sense unit in a one cycle or a two cycle pre-read operation. The total and leakage currents can be combined with a reference signal to derive a data signal indicative of one of a plurality of conductivity profiles that represent stored data. The conductivity profiles can be stored in a resistive state memory element that is electrically in series with the selected first and second conductive traces.

Owner:III HLDG 1

Sensing a signal in a two-terminal memory array having leakage current

A two-terminal memory array includes a plurality of first and second conductive traces. An address unit operatively applies a select voltage across a selected pair of the first and second conductive traces and applies a non-select voltage potential to unselected traces. A total current flowing in the selected first conductive trace and a leakage current flowing through unselected second conductive traces are sensed by a sense unit in a one cycle or a two cycle pre-read operation. The total and leakage currents can be combined with a reference signal to derive a data signal indicative of one of a plurality of conductivity profiles that represent stored data. The conductivity profiles can be stored in a resistive state memory element that is electrically in series with the selected first and second conductive traces.

Owner:UNITY SEMICON

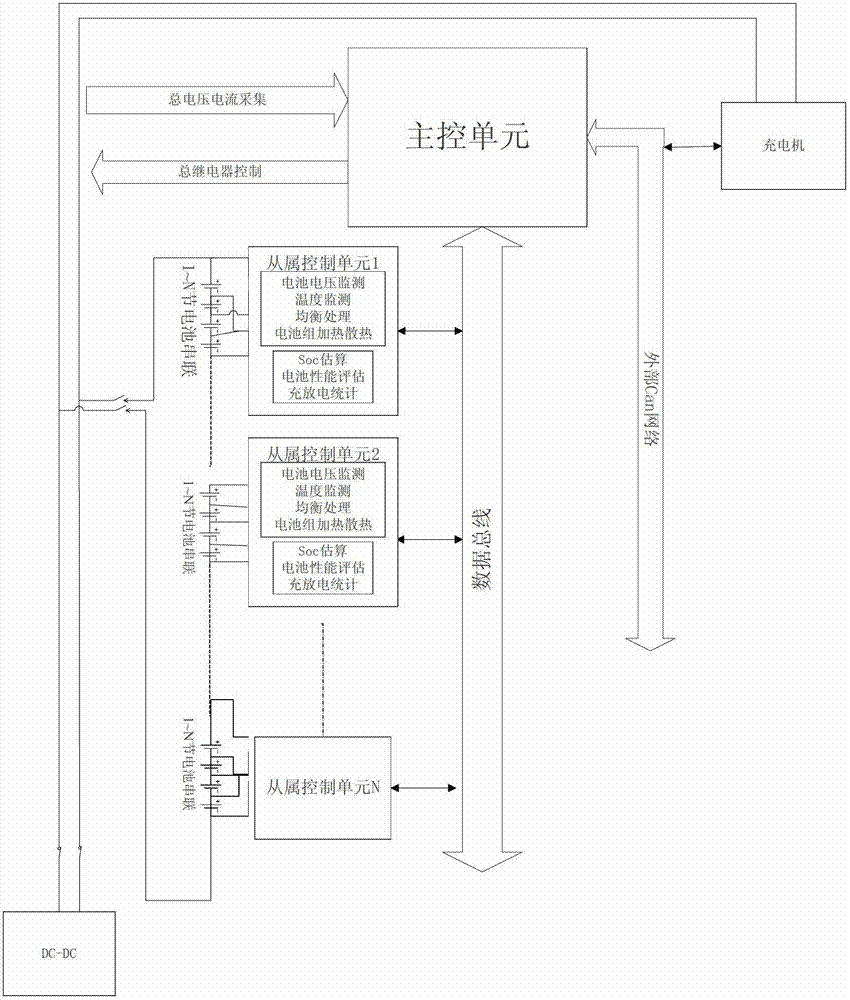

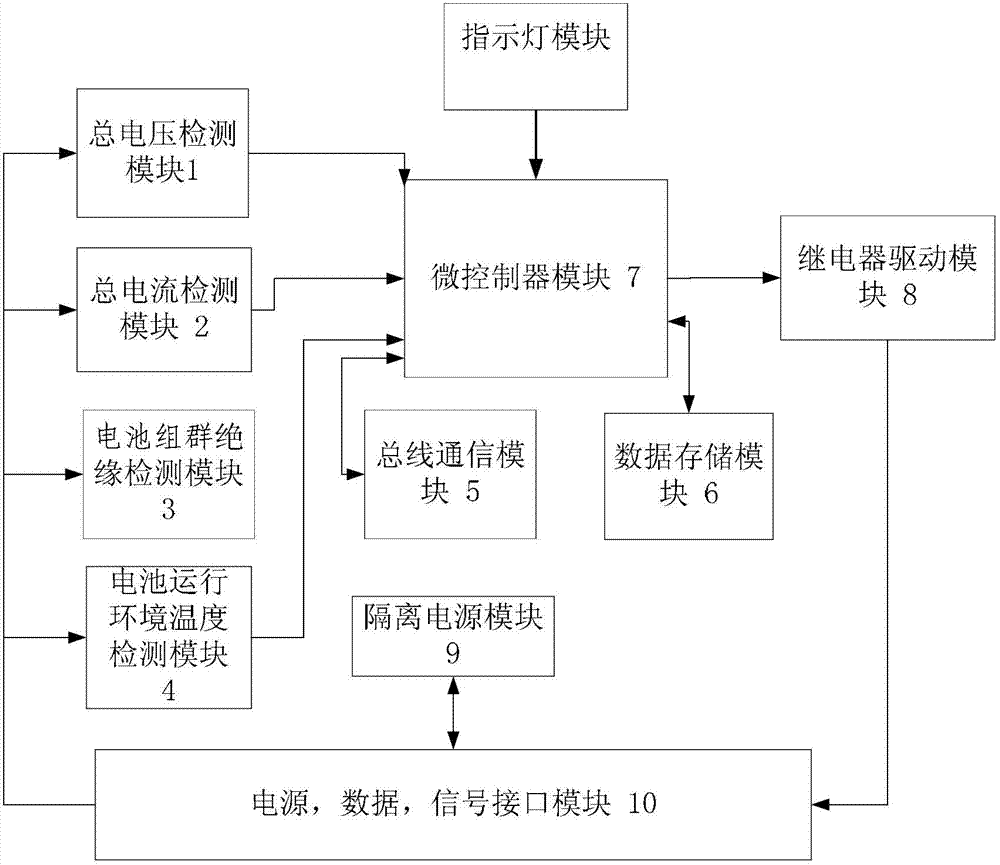

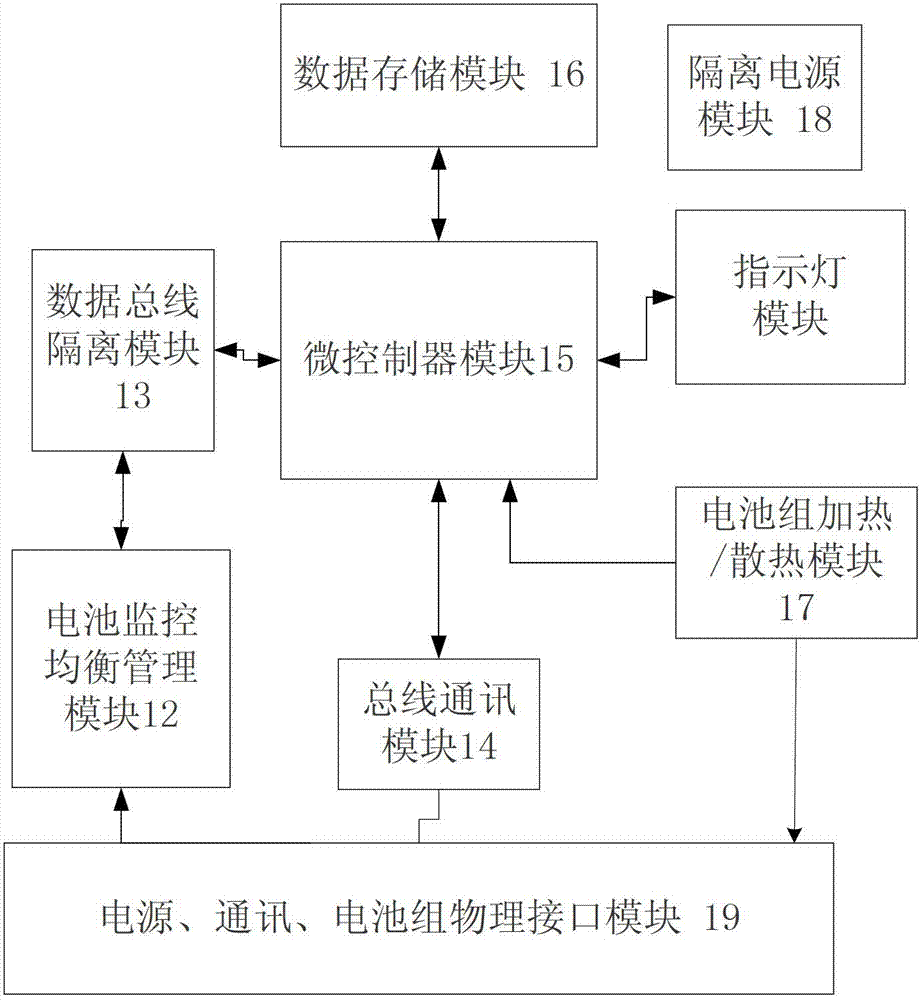

Battery management system of vehicle-mounted lithium power battery

InactiveCN102738525ASimple structureImprove scalabilitySecondary cells servicing/maintenanceMicrocontrollerElectrical battery

The invention discloses a battery management system of a vehicle-mounted lithium power battery. The system includes a master control unit and slave control units. The master control unit is in communication connection with the multiple slave control units through a data bus. The master control unit is in connection with battery groups, the total voltage and total current of which are acquired. The master control unit is also connected to a DC power supply, and is in connection with a charger through an external CAN bus. The master control unit mainly includes: a master microcontroller module, a total voltage detection module, a total current detection module, a battery system insulation detection module, a battery operating environment temperature detection module, a relay driving module, a data storage module, a bus communication module, an isolated power supply module, and a physical interface module of power supplies, data, signals, etc. The system provided in the invention has the advantages of simple structure, strong expansibility, and adaptability to different numbers of batteries. Being fully functional, the system has the functions of temperature control, equalization processing, battery performance evaluation, and battery self-protection, etc.

Owner:沈阳中科正方新能源技术有限公司

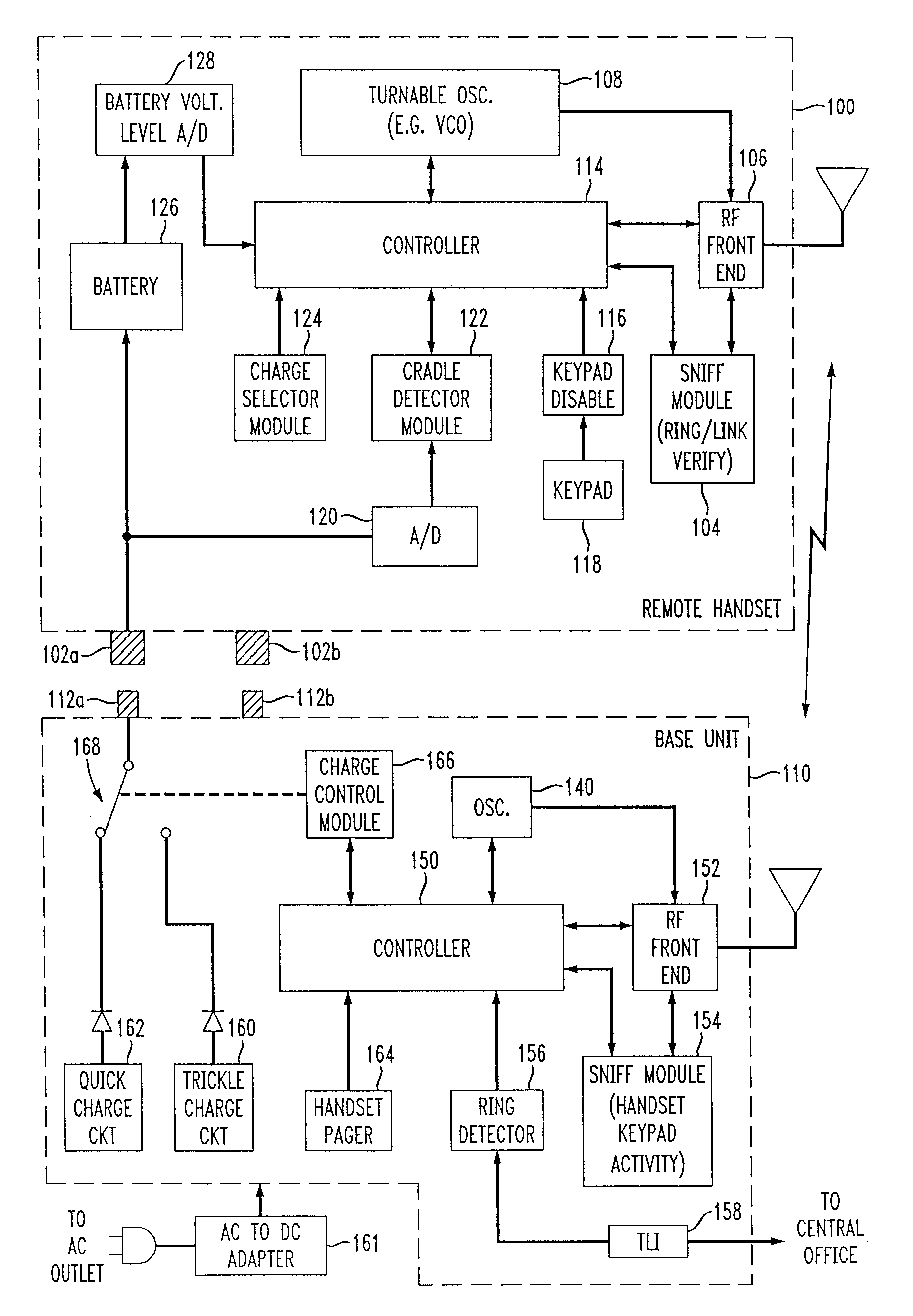

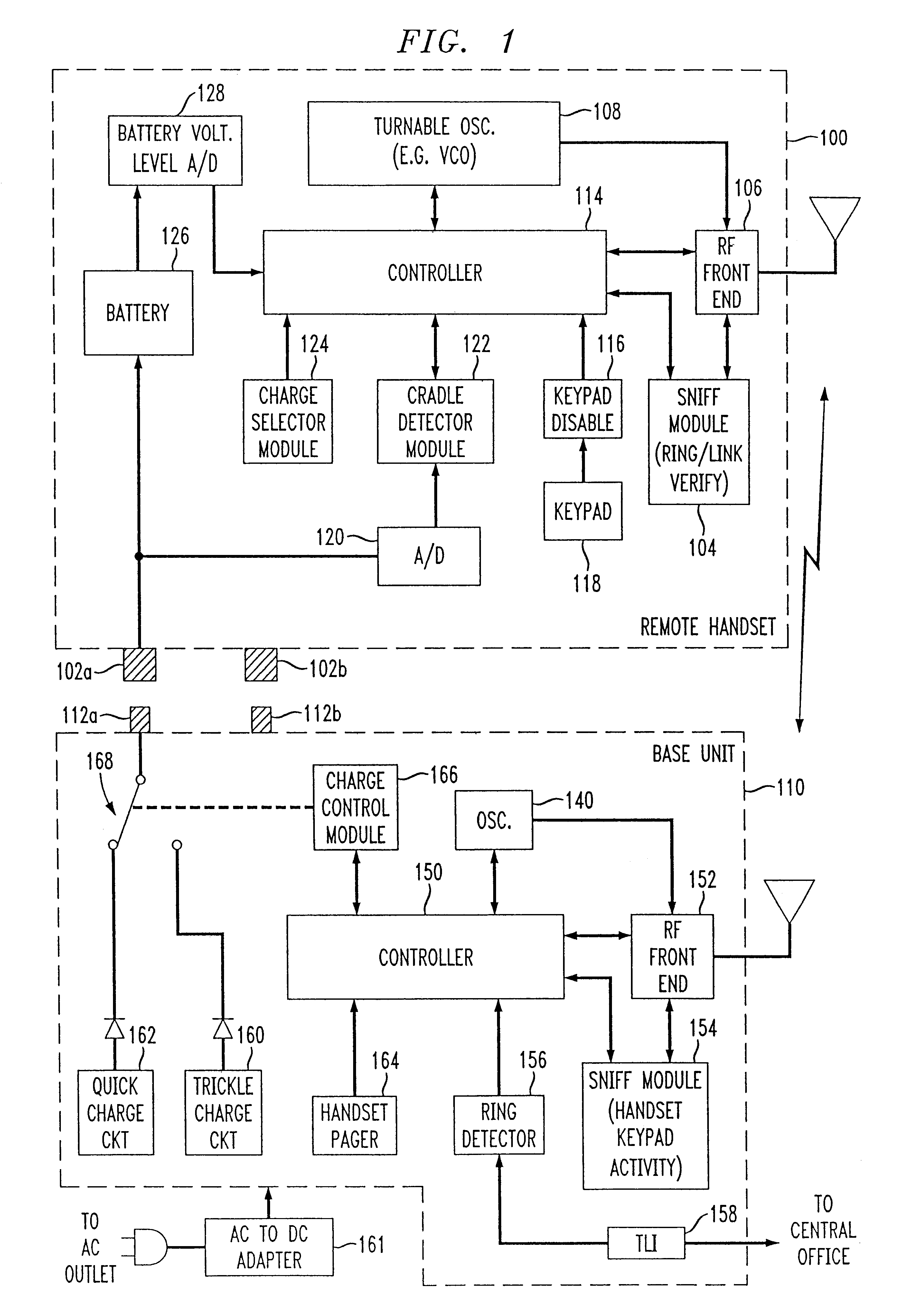

Low power consumption quick charge for wireless device

The current draw of a wireless device, e.g., a cordless telephone, is minimized for a cradled remote handset drawing power from an AC outlet. This allows a greater portion of the total current amperage provided by the AC to DC converter to be allowed to charge the battery in the remote unit, and reduces the overall maximum or peak value of the current draw of the wireless device. With an improved peak power budget, a smaller (and presumably less expensive) AC to DC adapter than otherwise necessary may be used to power the wireless device. In one aspect, sniff operations of the remote handset are disabled or otherwise suppressed while the remote handset is in the cradle of the base unit, e.g., receiving a quick charge or trickle charge to its battery. In a second aspect, sniff operations of the base unit are disabled or otherwise suppressed while the remote handset is in the cradle of the base unit. In a last aspect, the charging mode of the battery in the remote handset of a wireless device changes based on activity in the remote handset.

Owner:LUCENT TECH INC

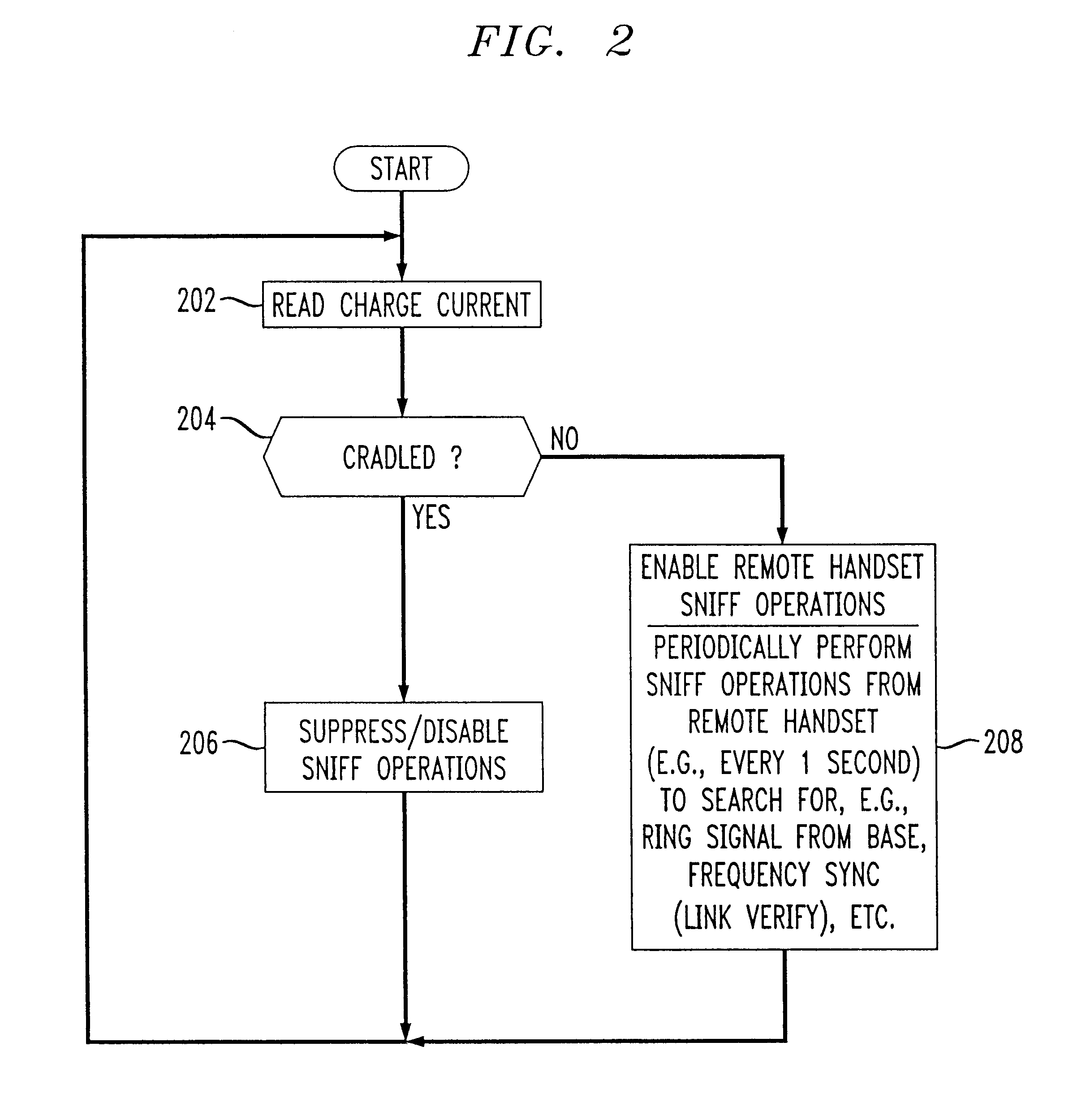

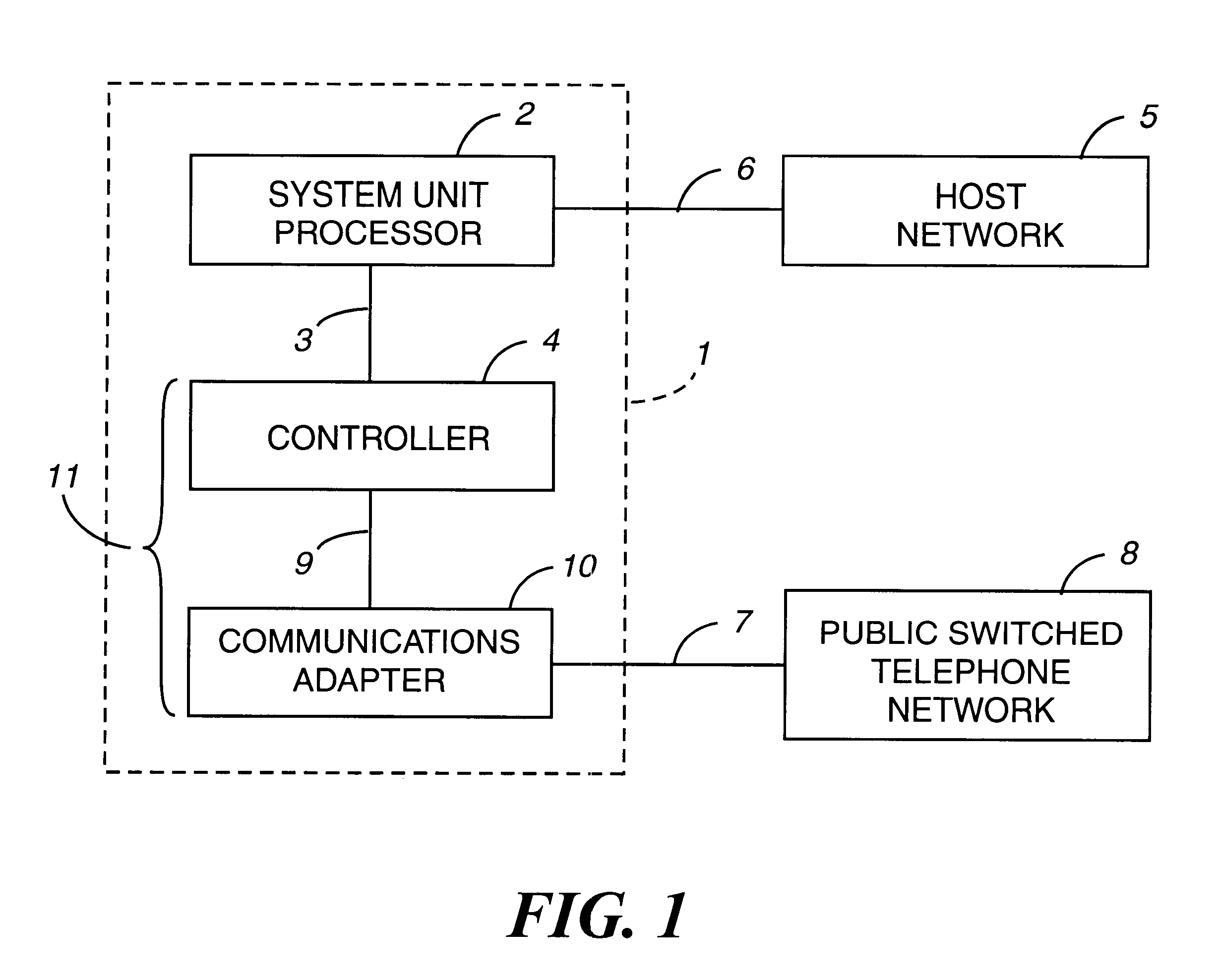

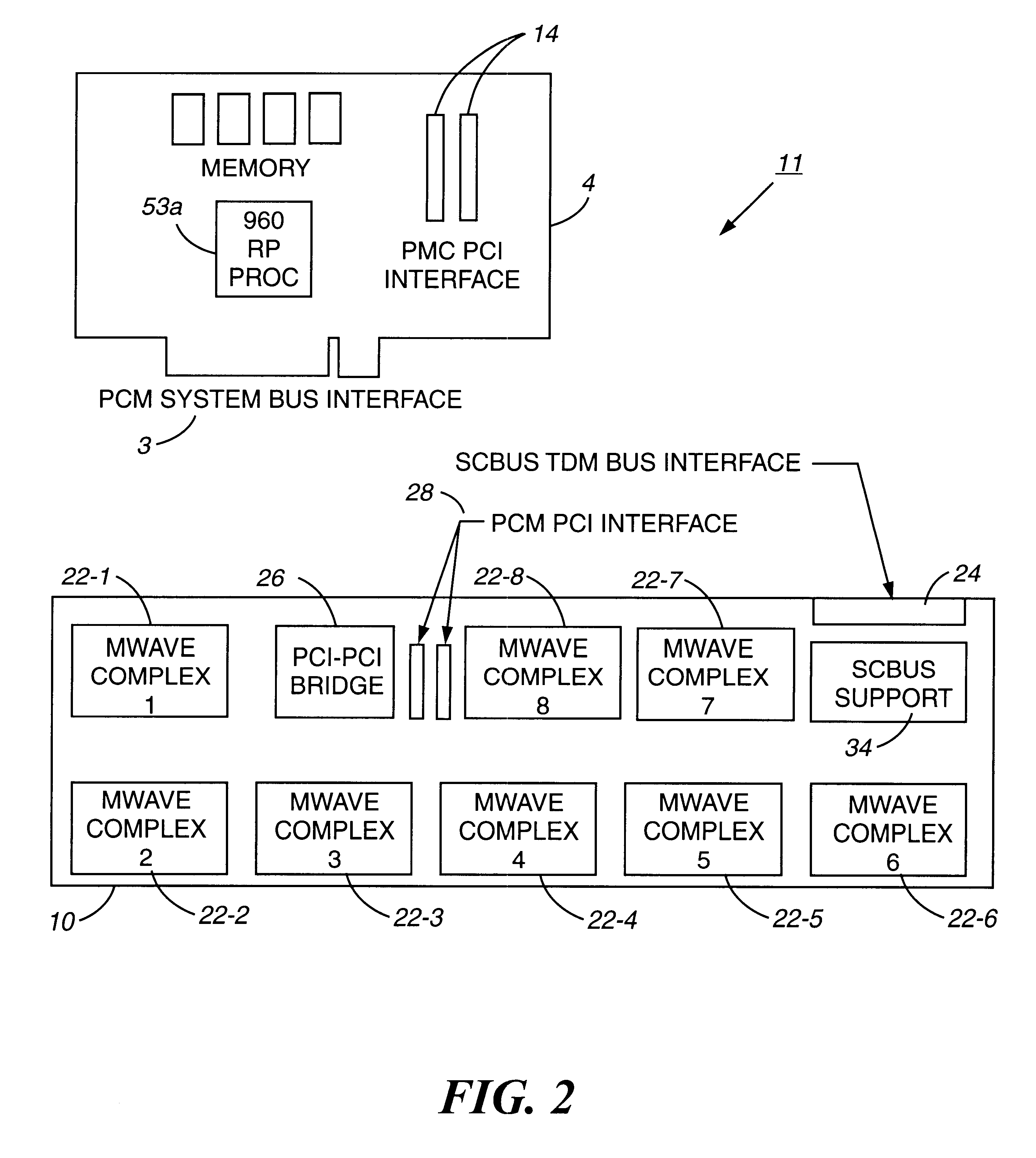

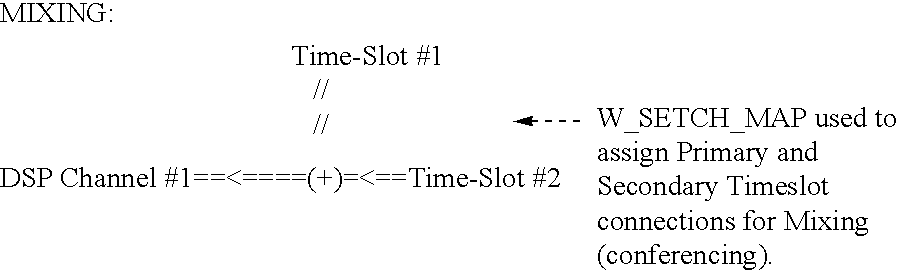

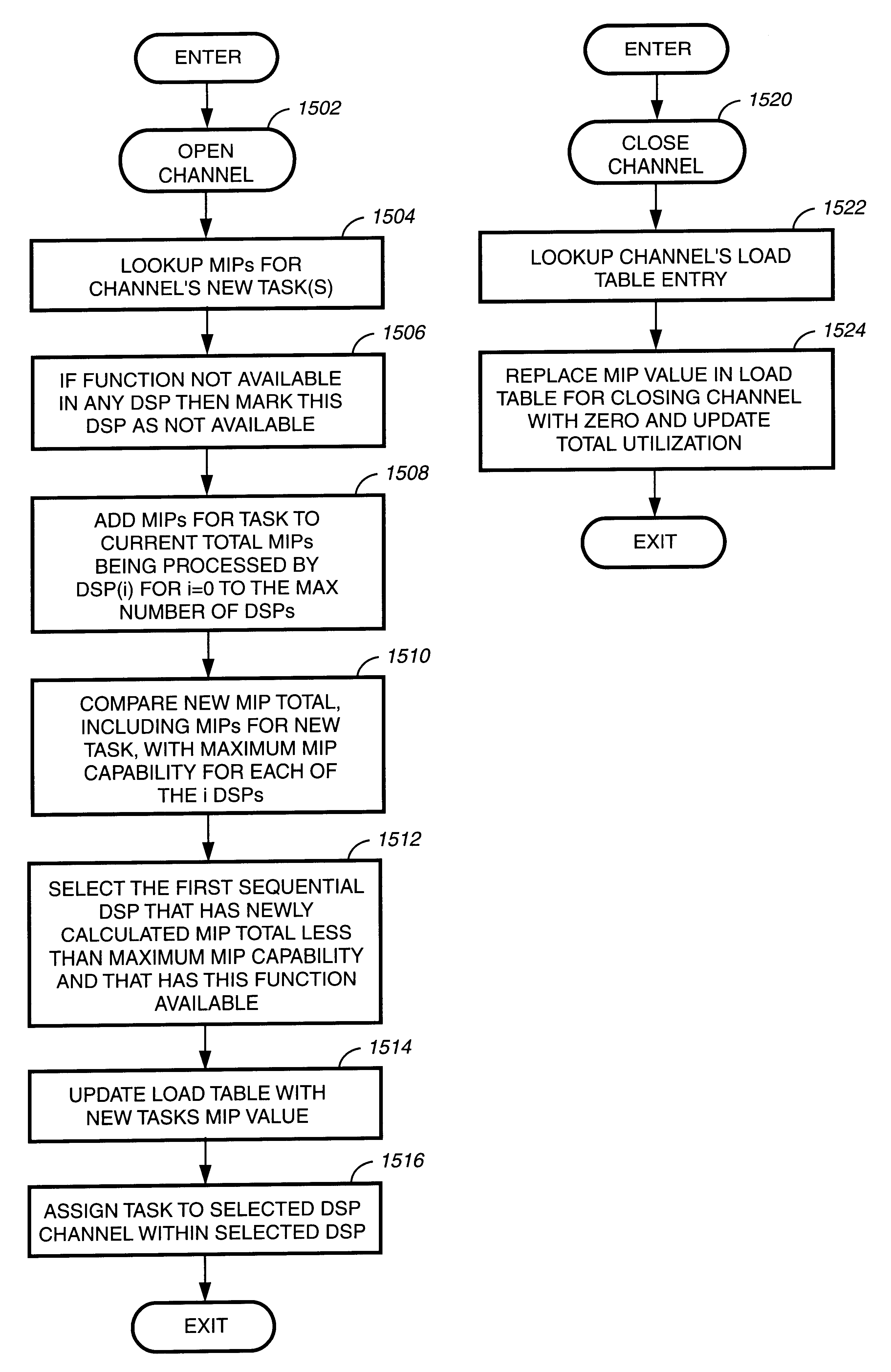

Adaptive method and apparatus for allocation of DSP resources in a communication system

InactiveUS6338130B1Resource allocationGeneral purpose stored program computerComputer architectureCommunications system

A communication system (100) includes at least one digital signal processor (DSP) and a WAN driver (80) operating on a processor that is electrically coupled to a memory. The WAN driver (80) receives task allocation requests from a host to open / close communication channels that are handled by the at least one DSP. Each task is allocated to one of the at least one DSP according to a total current task processing load for each of the at least one DSP, a maximum processing capability for each of the at least one DSP, and a processing requirement for each task being allocated to the one of the at least one DSP that can handle the additional processing load of the task being allocated. A configuration controller (92) keeps track of the MIPs processing requirement of each task available for allocation across the plurality of DSPs and the maximum processing capability of each DSP of the plurality of DSPs in response to changes in configuration of the communication system (100).

Owner:IBM CORP

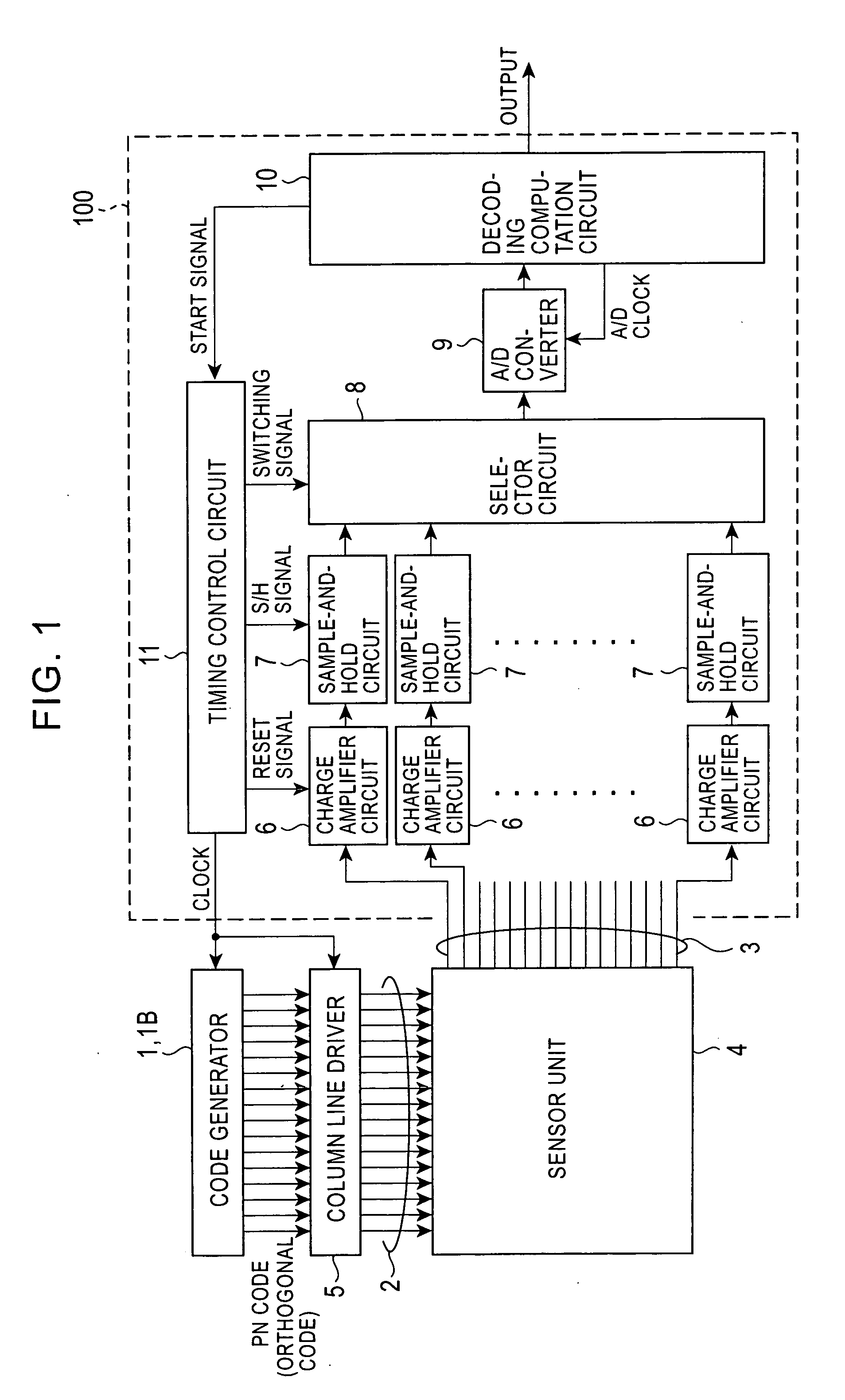

Capacitance detecting circuit and method, and fingerprint sensor using the same

ActiveUS20060158202A1Improve signal-to-noise ratioSmall capacitanceResistance/reactance/impedencePerson identificationCode generationHemt circuits

In a capacitance detecting circuit, changes in capacitances at intersections between a plurality of column lines and a row line are detected as voltages. The capacitance detecting circuit includes a code generator for generating code having orthogonality in chronological order. A column-line driver drives the plurality of column lines based on the code by dividing the column lines into a first column line group and a second column line group. A capacitance detector, which is connected to the row line, converts the total of currents generated in capacitances at the intersections with the driven column lines into a voltage signal and outputs the converted voltage signal. A decoding computation unit determines the voltages corresponding to the capacitances at the intersections for each of the column line groups by performing product sum computation between the measured voltages and the code. In a period for detecting the capacitances, the column-line driver drives the first column line group and the second column line group by complementary voltages according to the code or information indicating the inversion of the code.

Owner:SYNAPTICS INC

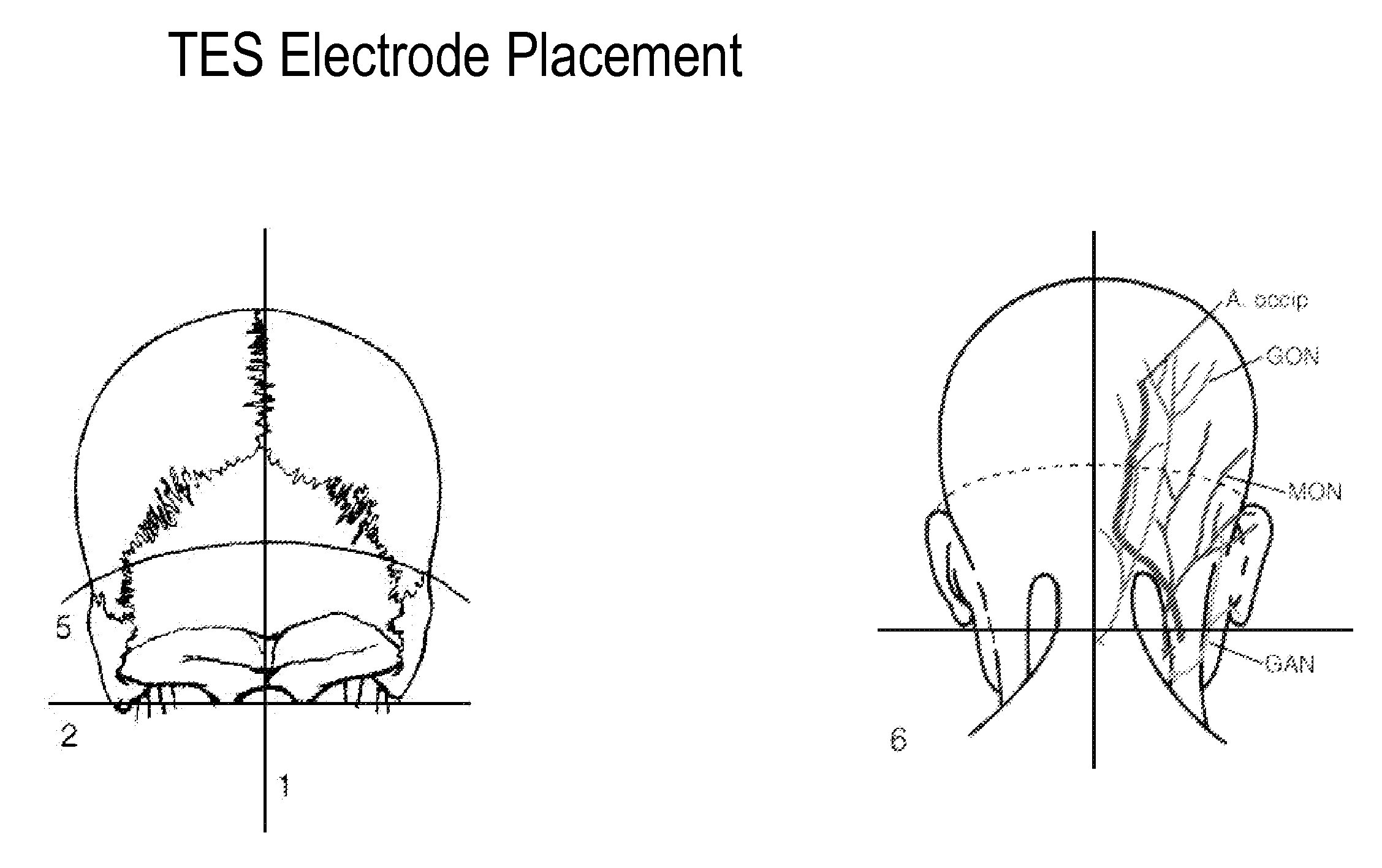

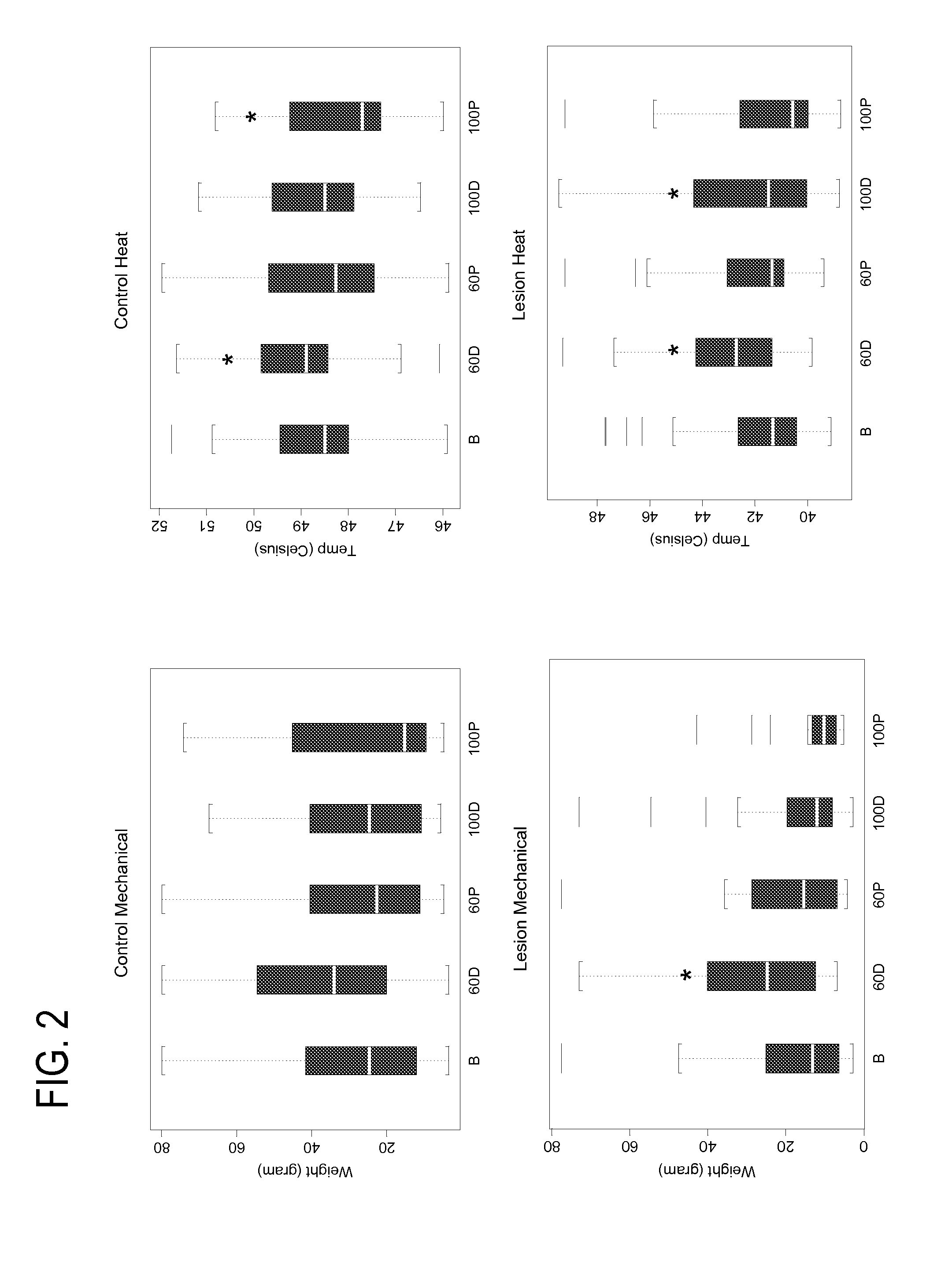

Eliciting analgesia by transcranial electrical stimulation

ActiveUS20110093033A1Promote healingFunction increaseInternal electrodesExternal electrodesTranscranial Electrical StimulationsAbsolute deviation

A method of eliciting analgesia in a human subject by Transcranial Electrical Stimulation (TCES, herein “TES”) is provided. Electrodes secured to the skin of the subject's head at particular sites provide an electrical current that includes a direct current combined with rectangular AC current pulses delivered at a particular frequency of between 10 and 100 Hz. In an embodiment the total current transmitted, a sum of the DC component and a Mean Absolute Deviation (MAD) of the current pulses, has a value between 0.2 and 20 mA. The method is used to produce analgesia during perioperative period, surgery and the post-operative procedure. It can also be used for treating acute chronic pain and a wide variety of other conditions.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

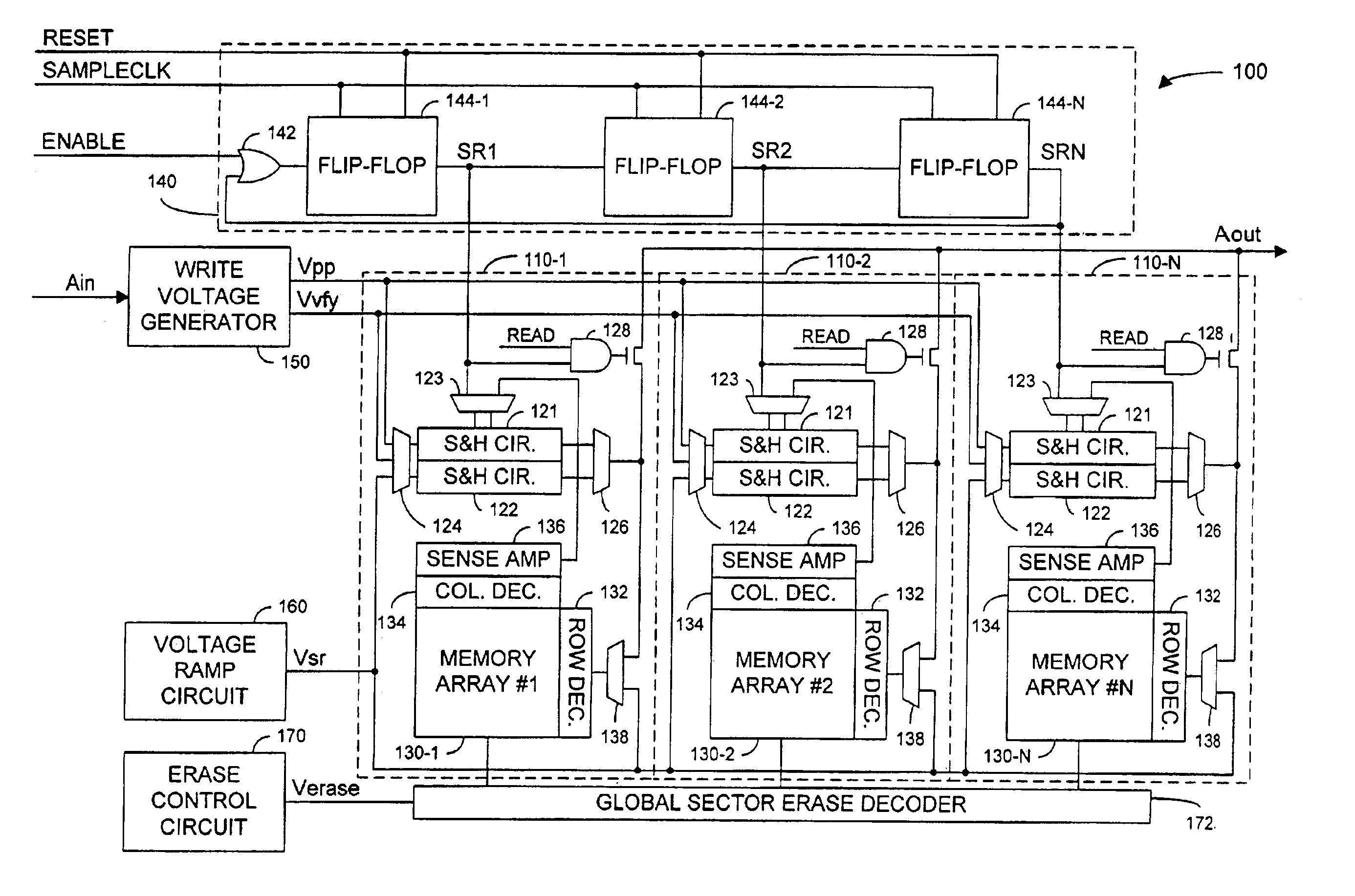

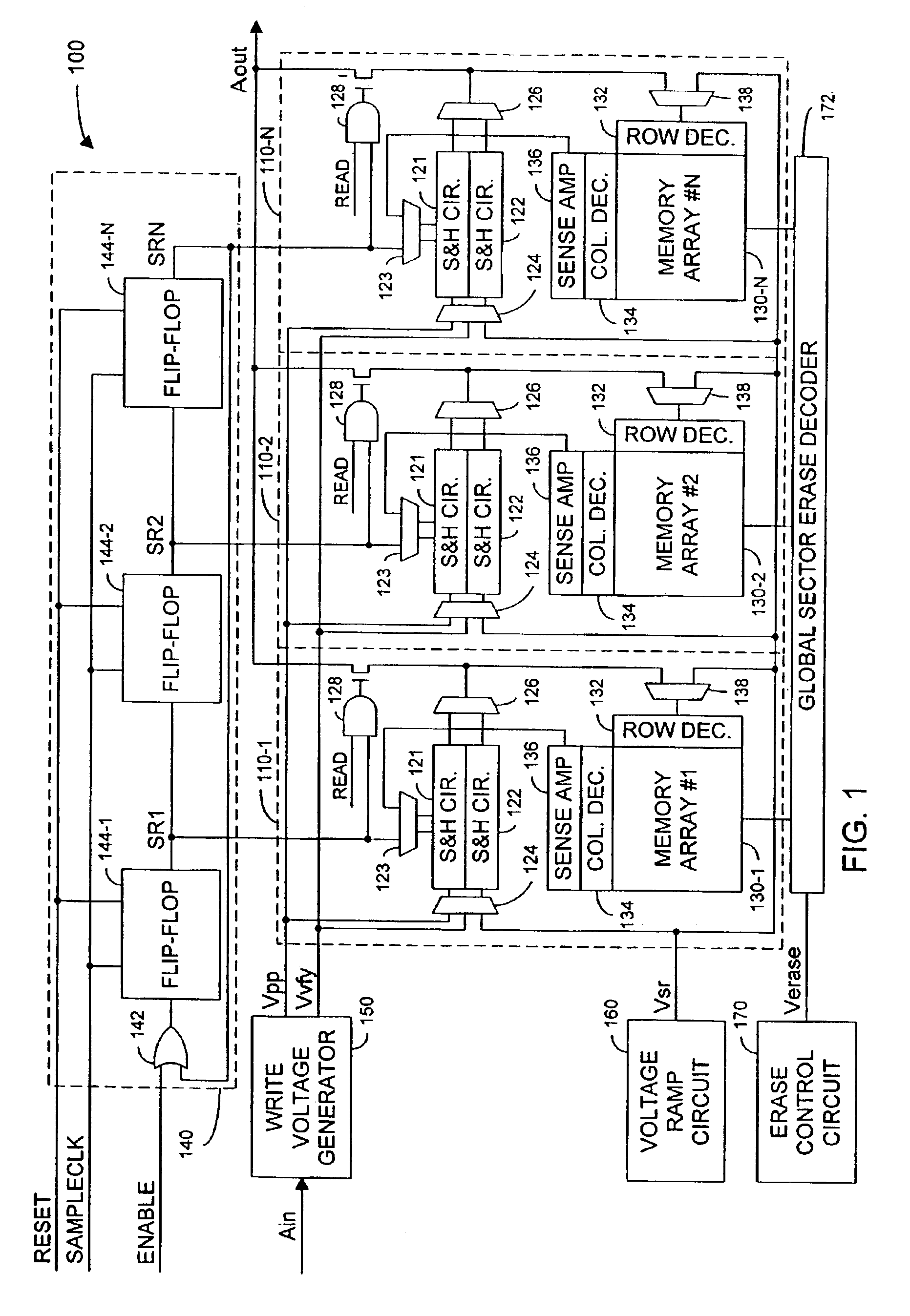

High data rate write process for non-volatile flash memories

InactiveUS6944058B2Reduce noiseIncrease data rateElectric analogue storesRead-only memoriesVoltage regulationTotal current

A non-volatile semiconductor memory includes: multiple write pipelines, each including a memory array; a timing circuit which sequentially starts programming operations in the pipelines; and a shared charge pump and voltage regulation circuit that drives a current through the memory cells being programmed. Staggering the starts of programming operations reduces the current demand on the charge pump because spikes that occur at the starts of programming operations, for example, when using channel hot electron injection, are distributed over time rather than occurring all at once. Noise, which can reduce the accuracy of write operations, is also reduced because the total current required from the charge pump is more nearly constant. As further aspect of the invention, each write pipeline can perform a write operation as alternating programming cycles and verify cycles. During a programming cycle, the shared charge pump drives a current through a selected memory cell to change the threshold voltage of the selected memory cell. During a verify cycle, the write circuit determines whether the selected memory cell has reached its target threshold voltage level. The write pipelines can be partitioned into two banks where pipelines in one bank perform programming cycles while pipelines in the other bank perform verify cycles. More generally the write pipelines are partitioned into multiple banks where each bank starts programming cycles at times that differ from the starts of programming cycles in the other banks.

Owner:INNOVATIVE MEMORY SYST INC

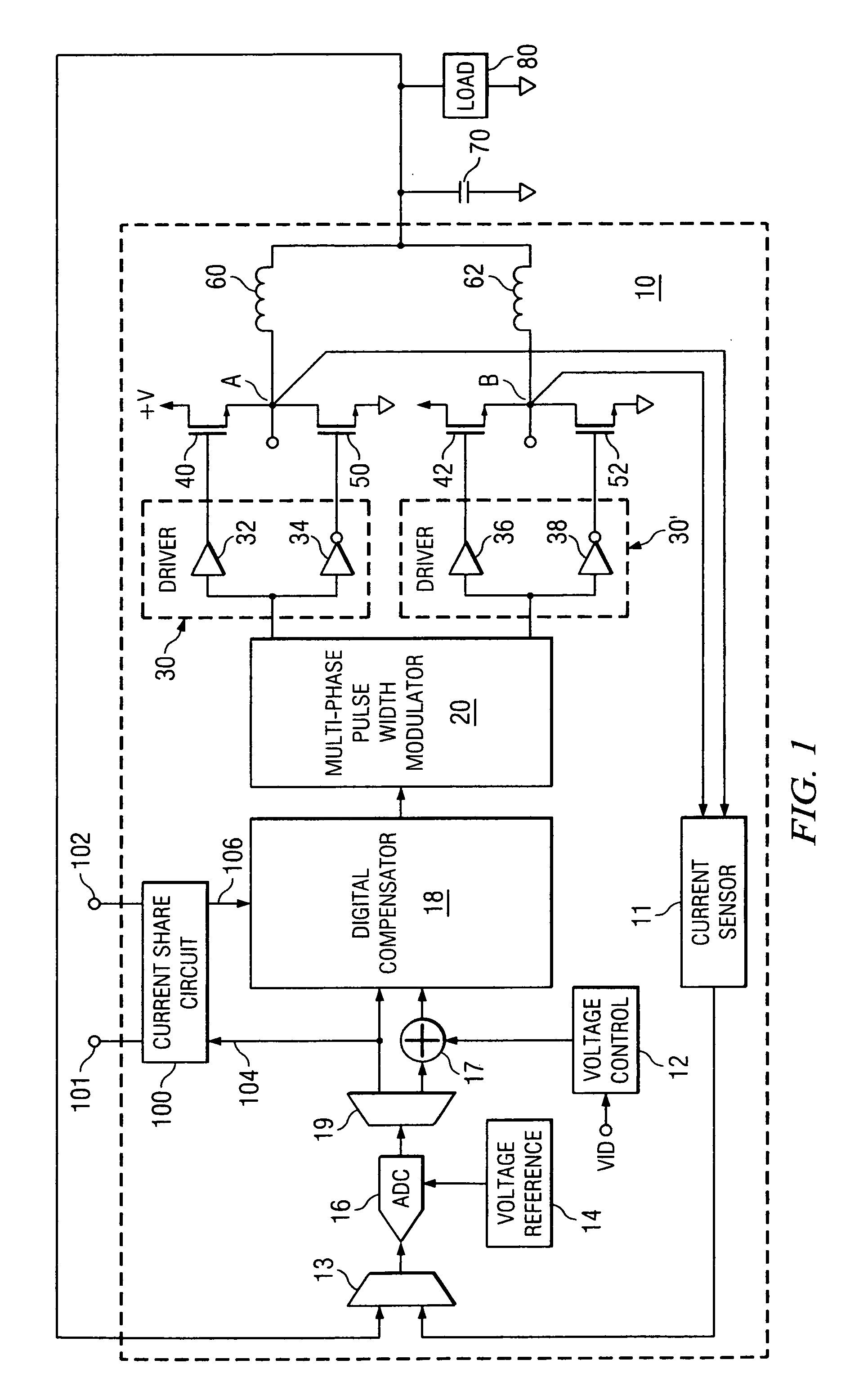

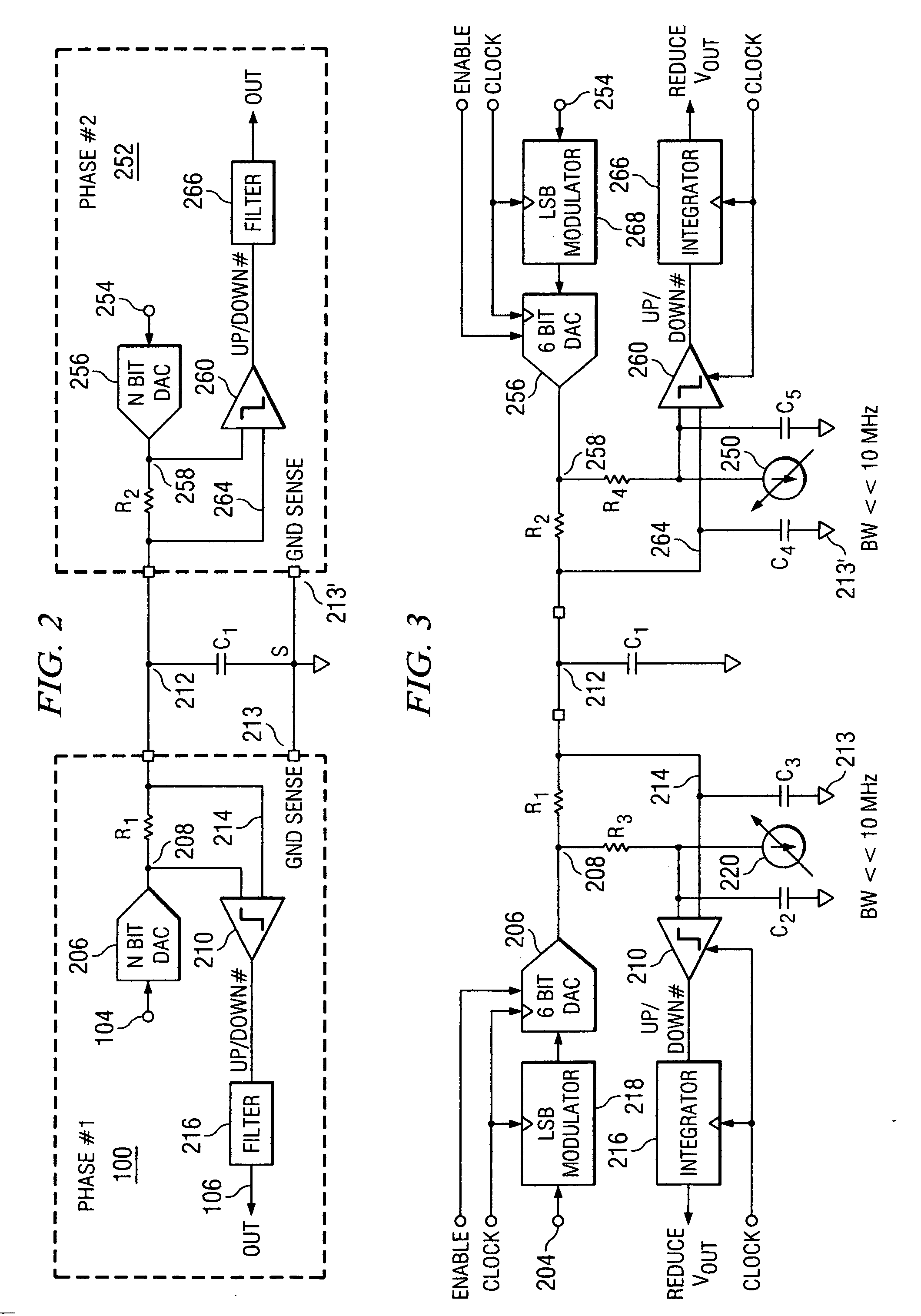

Regulated power supply with multiple regulators sharing the total current supplied to a load

Disclosed is a digital current sharing structure and method in which a plurality of regulators are configured to share the load current. Current share circuits in each of the regulators are configured to measure and compare the average current provided by that particular regulator with the overall average current provided by all the regulators. Each of the current share circuits then provides an output so that the output of each regulator is adjusted to provide the same amount of current to the load. Digital processing with both analog and digital averaging are disclosed. Also disclosed is a programmable hysteresis technique to eliminate relatively trivial adjustments.

Owner:INFINEON TECH AUSTRIA AG

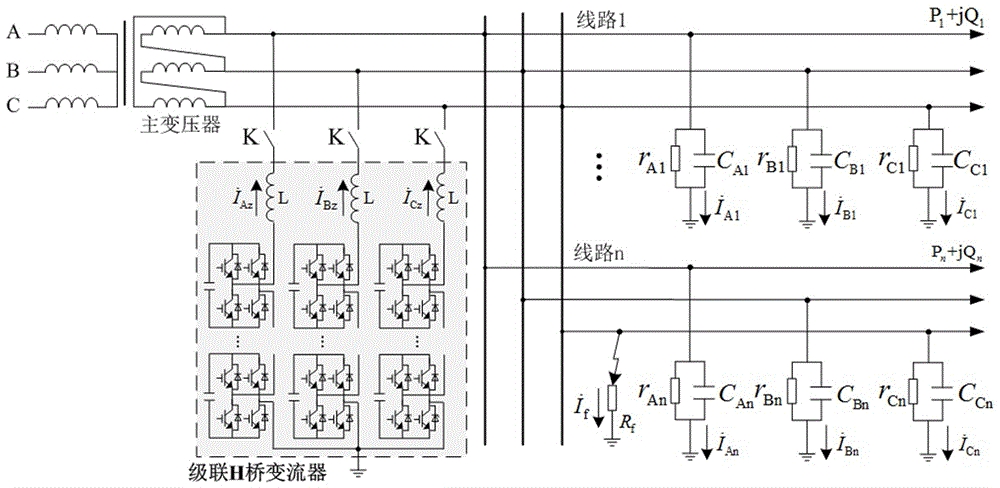

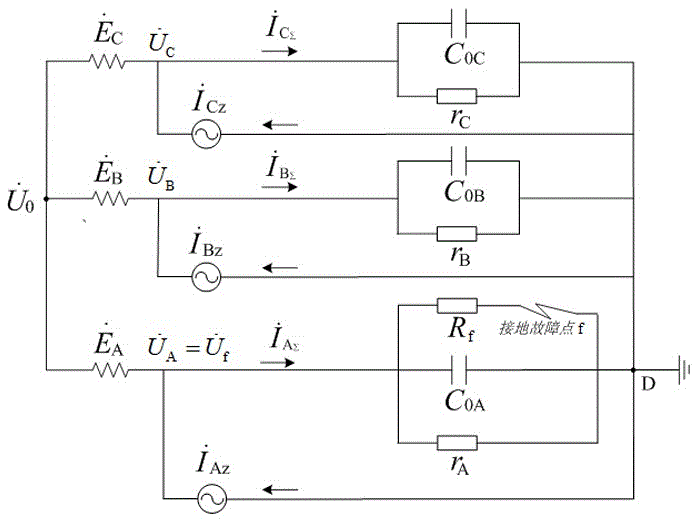

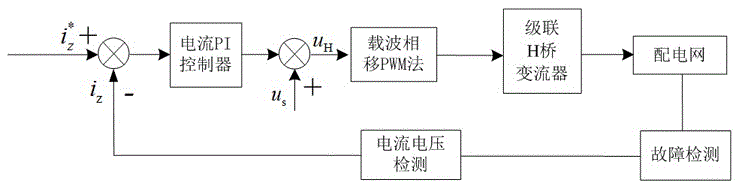

Power distribution network fault arc extinction method by connecting neutral point to the ground through multi-level converter

ActiveCN104218563AReduce switching frequencyLarge power capacityEmergency protective arrangements for limiting excess voltage/currentHarmonic reduction arrangementEngineeringTotal current

The invention relates to a power distribution network fault arc extinction method by connecting a neutral point to the ground through multi-level converter. The power distribution network fault arc extinction method is characterized in that the cascade H-bridge multi-level converter is adopted and directly connected at the position of the neutral point of a power distribution network through a reactor; at the initial moment when the power distribution network has a single-phase earth fault, synthetic operation is conducted to generate offset currents needed to be injected (img file='69356dest_path_image001. TIF'wi'19' he'=25' / ), then the offset currents are quickly put into the multi-level converter, the multi-level converter is controlled by aid of the current tracking control algorithm and the PWM (Pulse-Width Modulation) modulation strategy to generate offset currents (img file='652784dest_path_image001. TIF'wi'19' he'=25' / ), and the offset currents are put into the neutral point of the power distribution network so as to compensate grounding total currents of the fault point. In addition, the fault phase voltage is forced to be 0 constantly so the instantaneous grounding fault can be cleared automatically, and further the technical problem of the existing fault arc extinction technology of poor arc extinction effect can be solved.

Owner:SHANGHAI HOLYSTAR INFORMATION TECH

Multiphase power regulator with load adaptive phase control

ActiveUS7492134B2Maximize efficiencyImprove efficiencyDc-dc conversionAc network voltage adjustmentEngineeringActive phase

Disclosed is a power regulator for providing precisely regulated power to a microelectronic device such as a microprocessor. Improved power regulation is accomplished by optimizing the power efficiency of the power regulator. In particular, in a multiphase system, the number of active phases is increased or decreased to achieve optimum power efficiency. The multiphase voltage regulator adapts the operating mode to maximize efficiency as the load current demand of the load device changes by adjusting the number of active phases to maximize efficiency. The total value of current provided by the regulator and the total number of active phases is determined, the total number of active phases is compared with the number of active phases required to provide the total value of current at maximum efficiency; and the number of active phases is adjusted to provide the total value of current at maximum efficiency.A current sense circuit senses the current at each phase, a summing circuit coupled to the output of the current sense circuit provides the total current value of all the measured phases, a circuit coupled to the output of the summing circuit provides the time averaged total current value to a threshold detecting circuit that determines the number of phases at which the voltage regulator should be operating for maximum efficiency, and a circuit for comparing the number of phases that are operating to the number of phases at which the voltage regulator should be operating adjusts the number of active phases to the number of phases at which the voltage regulator should be operating for maximum efficiency.

Owner:INFINEON TECH AUSTRIA AG

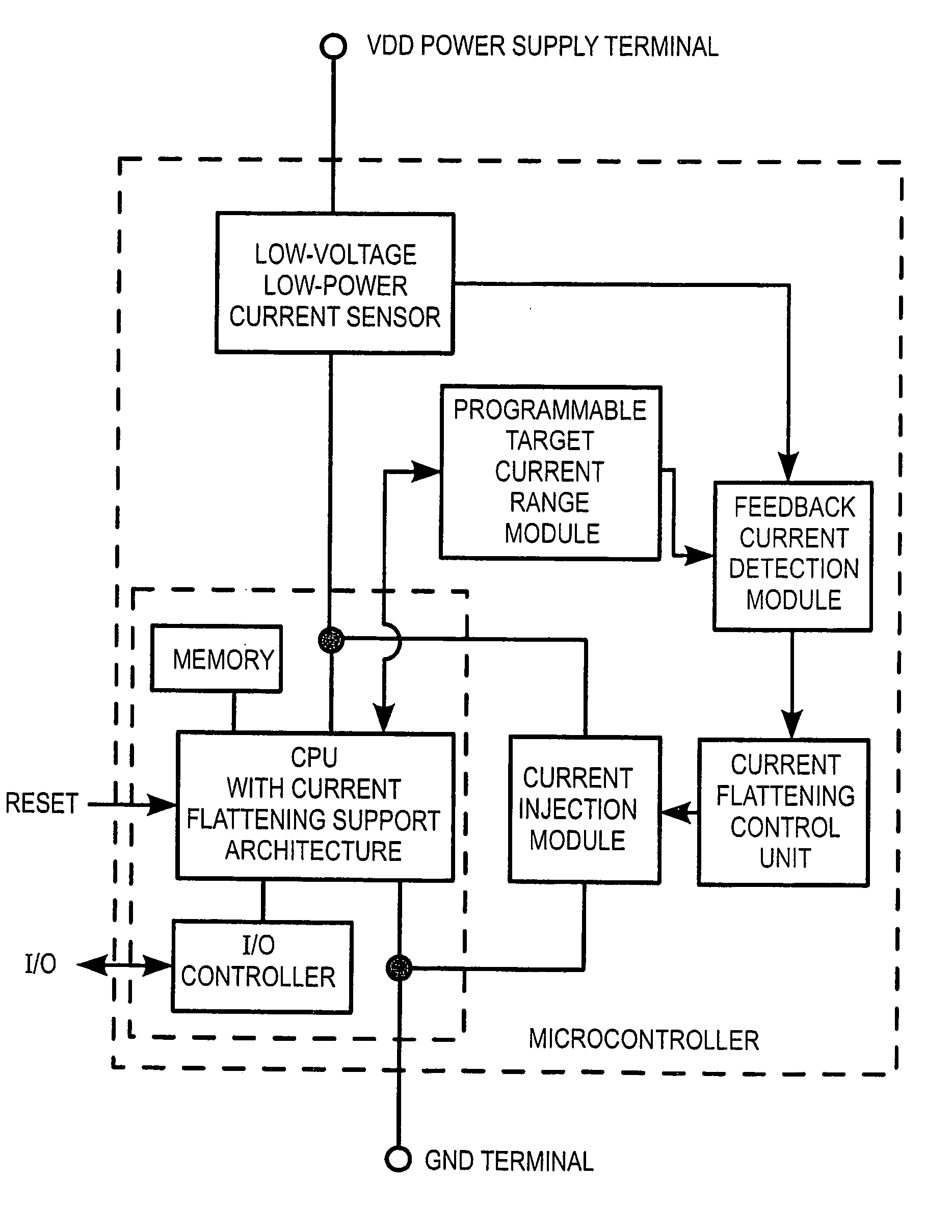

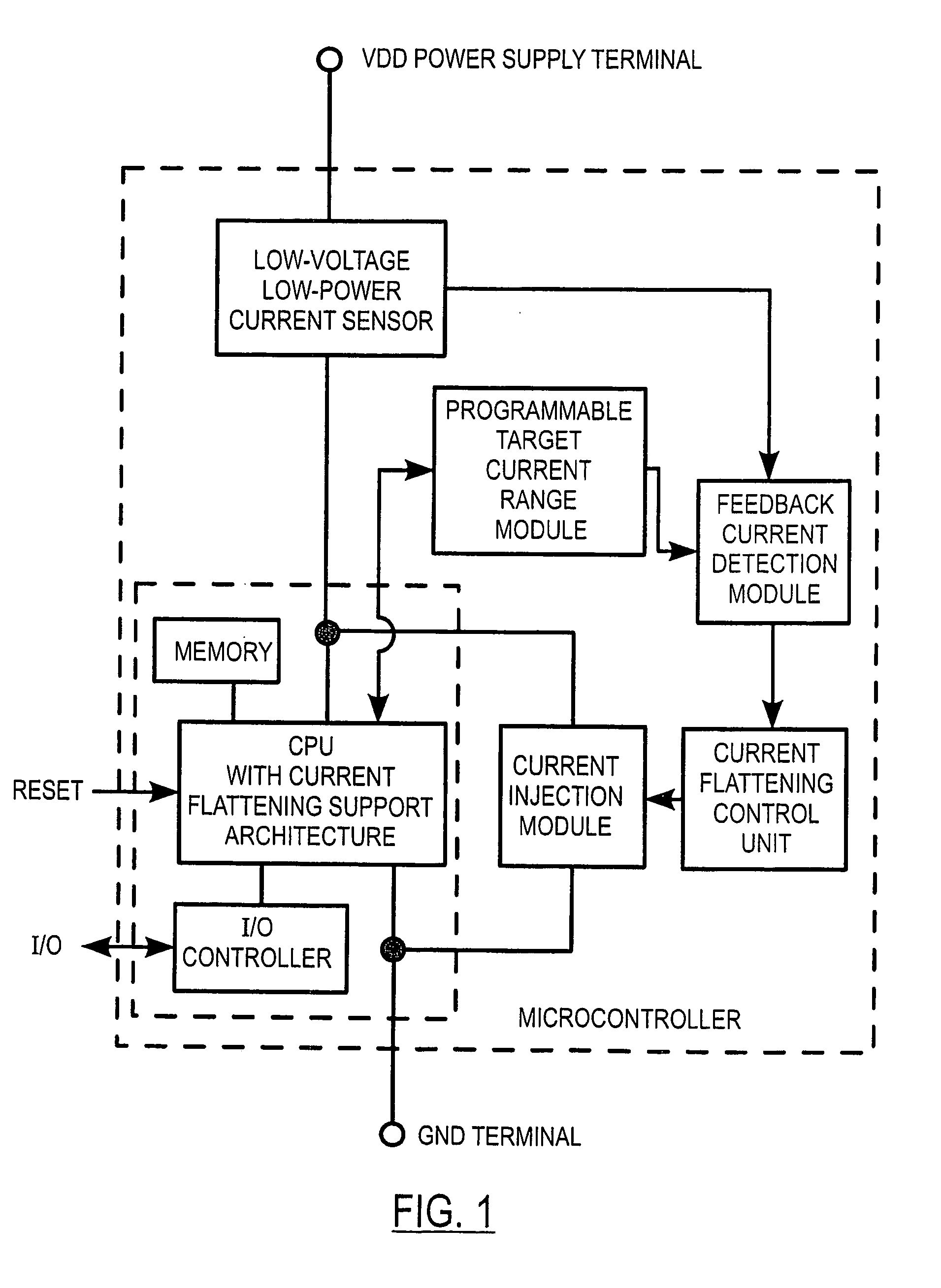

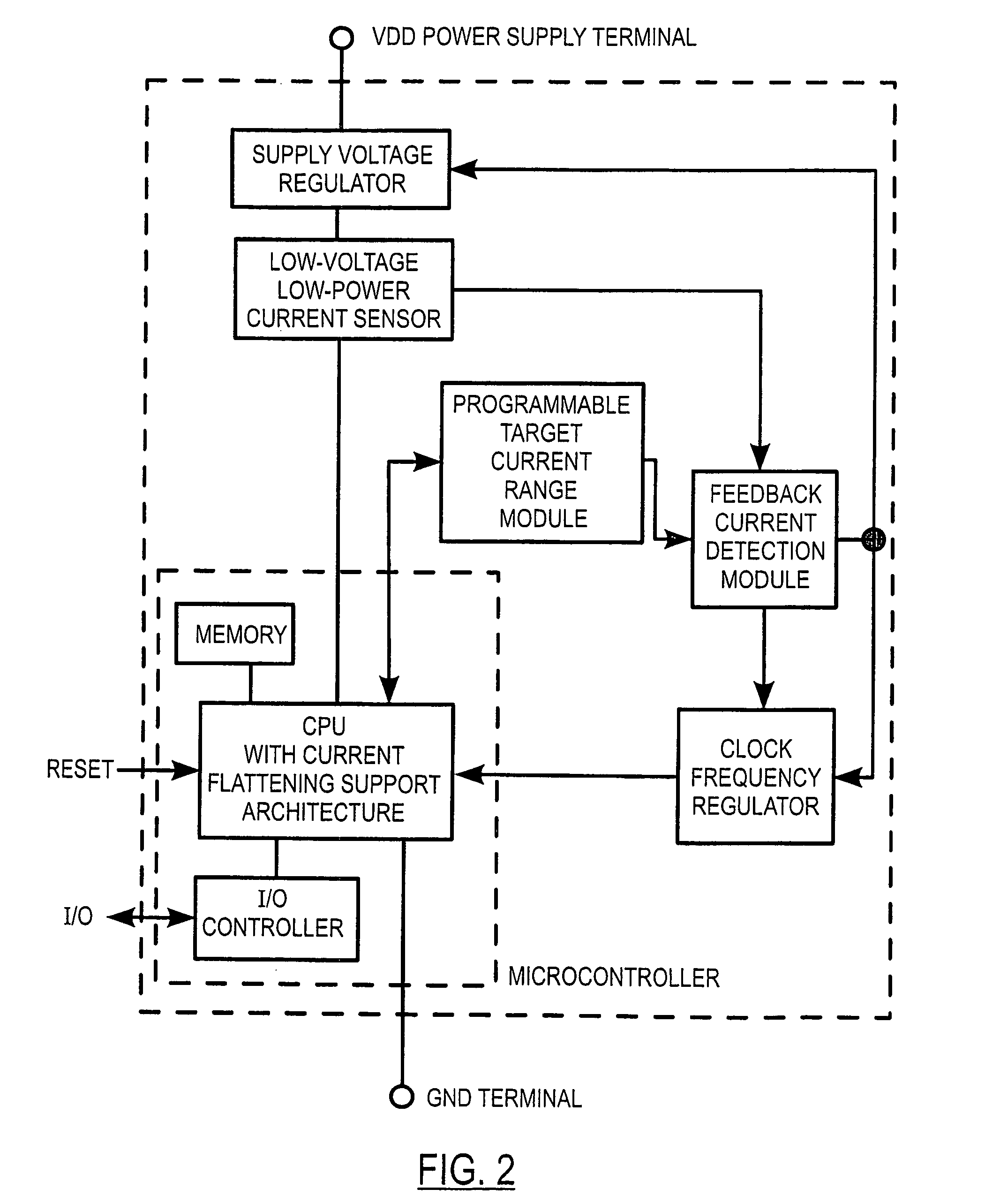

Current flattening and current sensing methods and devices

InactiveUS20070076890A1Flattening total current consumptionCurrent consumptionDigital data processing detailsHardware monitoringReference currentCurrent sensor

Flattening total current consumption of system having processing core and power supply input by current sensing within system at power supply input and controlling system current consumption such that system current is reduced if over reference current threshold, and increased if below reference current threshold. Inject additional current through digital injections cells working higher frequencies, by increasing switching activity, by increasing voltage supply to core, and by increasing operating frequency of processor core. Feedback signal indicates current consumption of system. Current consumption similarly decreased. Current sensed by mirroring input current inline with power supply input and compensating for voltage drop introduced by mirroring using opposing field effect transistors and maintaining outputs at same voltage through feedback control loop. Processor core may be general purpose processor core or cryptographic processor core. System may be system-on-chip or system-on-package. System includes processor core and current flattening device based on method. Also, current flattening device and current sensor. On chip current sensor sensing current draw of processor core.

Owner:GREGORI STEFANO +1

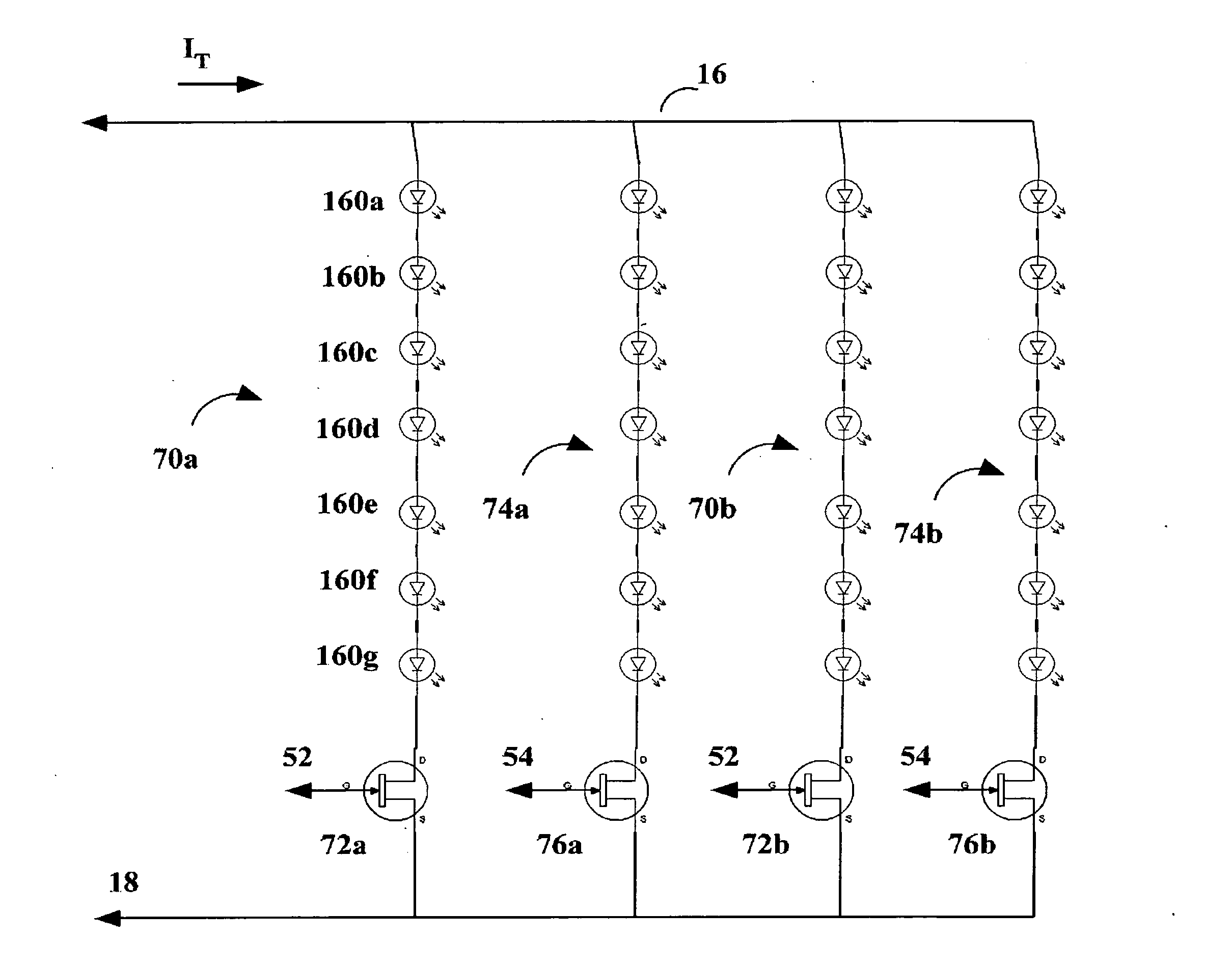

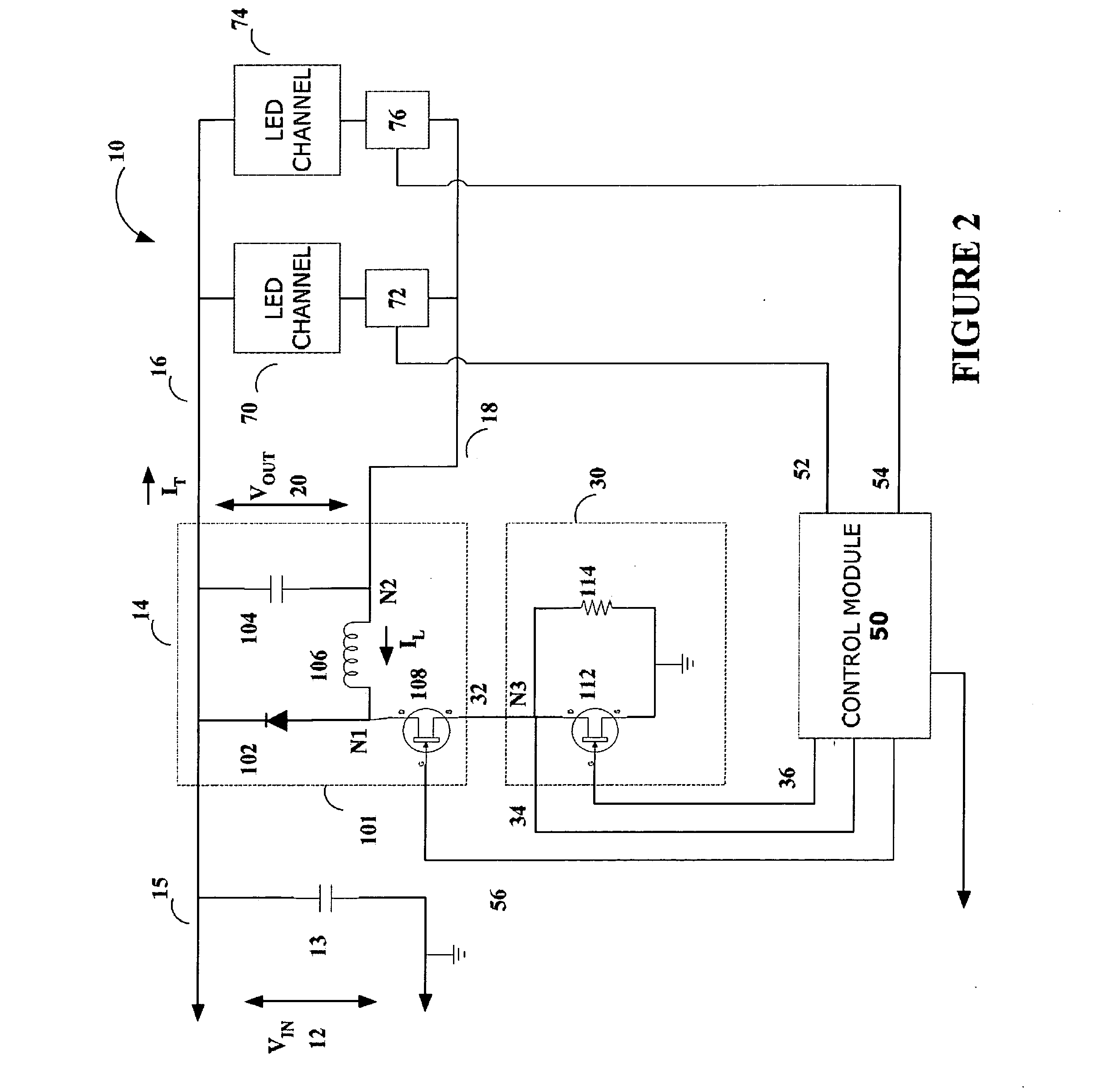

Control apparatus incorporating a voltage converter for controlling lighting apparatus

ActiveUS20130015774A1High resolutionElectrical apparatusElectroluminescent light sourcesVoltage converterLight equipment

A lighting apparatus may comprise a voltage converter operable to supply a current to at least two LED channels coupled between a high voltage rail and a low voltage rail coupled to the voltage converter output. The LED channels may be operated to selectively allow a current to flow through them. The lighting apparatus may have a control module operable to control the total current from the voltage converter and the current through each of the LED channels. The control module may also be operable to set the respective control signals to maintain a constant total current from the voltage converter while permitting aspects of the light output including, the intensity, color, and color temperature to be set and varied. Additionally, the control module may be operable to synchronize the various control signals, obtain a representative sample of the current through the voltage converter, and operate in different modes.

Owner:ARKALUMEN

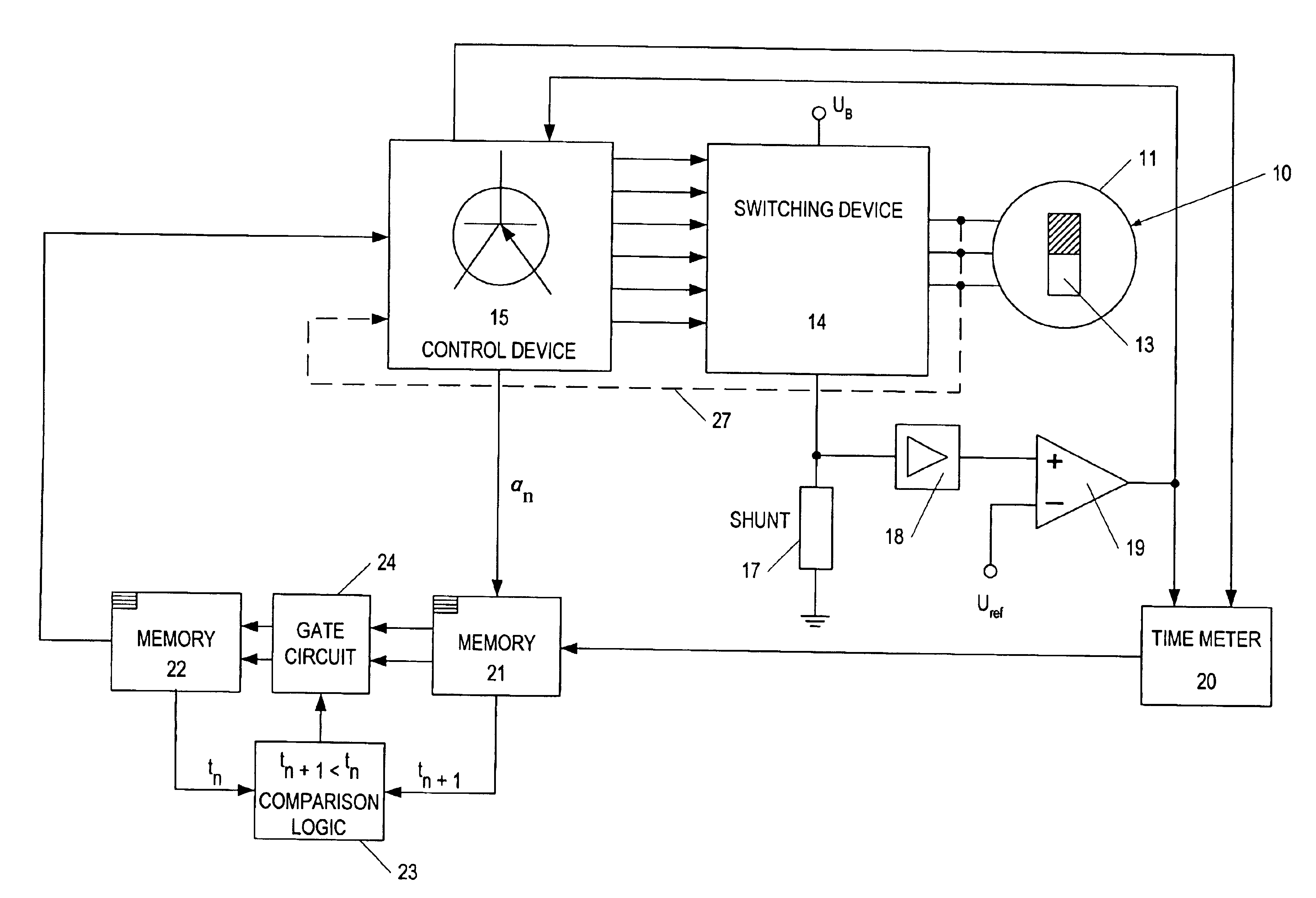

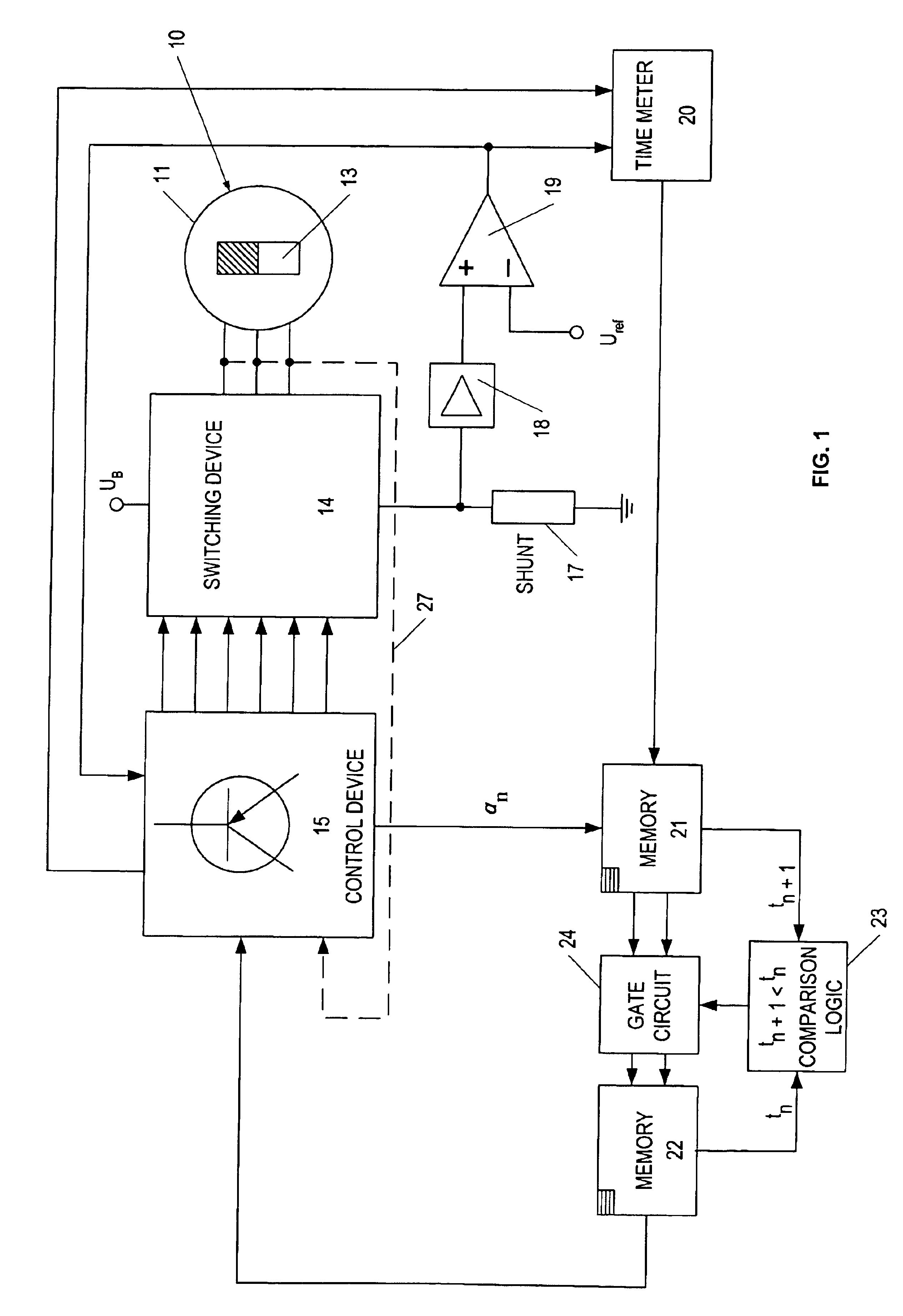

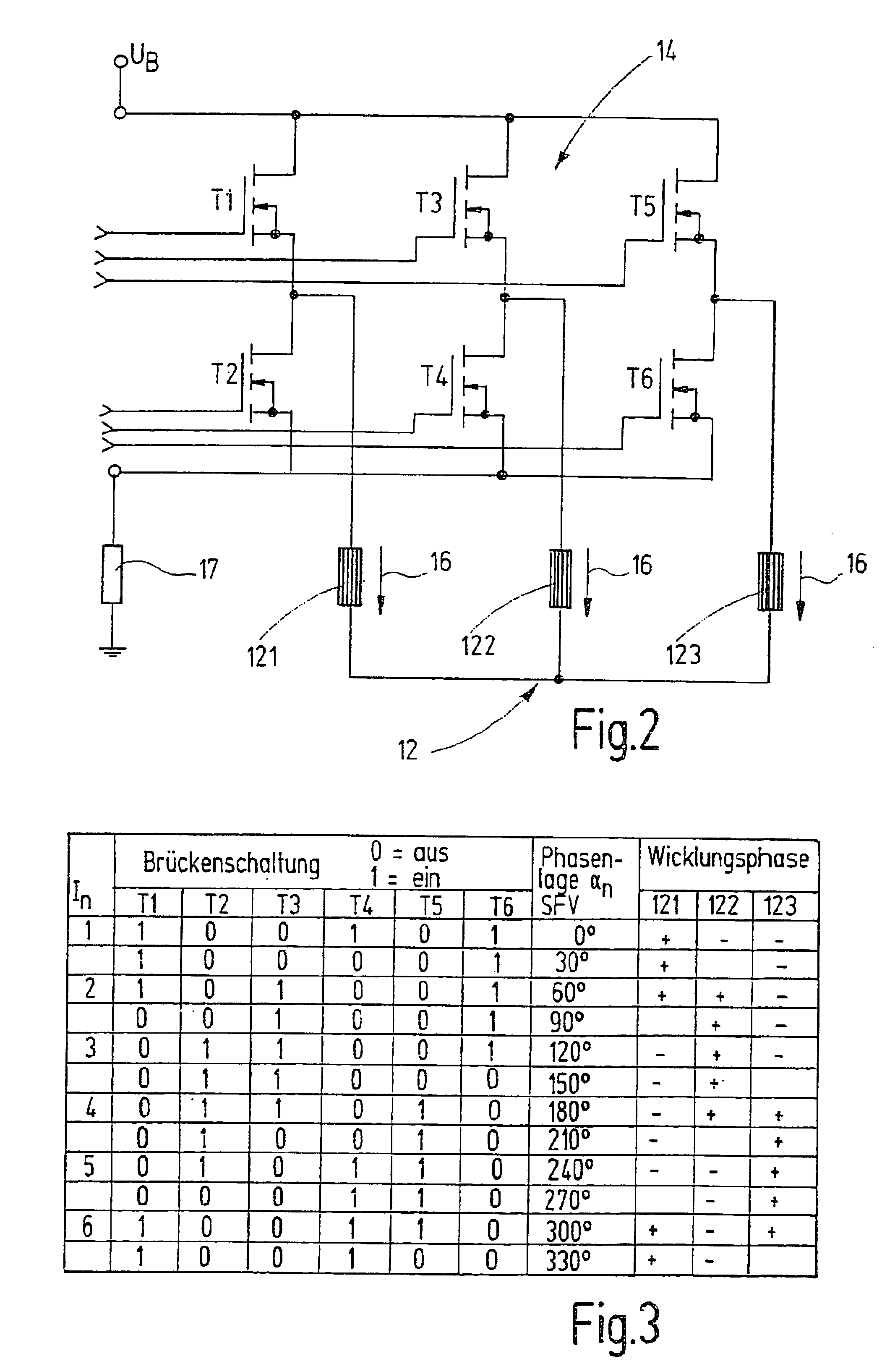

Method for starting a brushless d.c. motor

Owner:ROBERT BOSCH GMBH

Distribution network ground fault arc suppression method based on three-phase cascade H bridge converters

ActiveCN105610147AEmergency protective arrangements for limiting excess voltage/currentCapacitanceTransformer

The invention relates to a distribution network ground fault arc suppression method based on three-phase cascade H bridge converters. The three-phase cascade H bridge converters are adopted to replace arc suppression coils and mounted between phase lines and the ground, and power is supplied to capacitors on the direct current side of the converters by using phase voltages, so that boosting transformers and grounding transformers are saved, and the problem of source taking difficulty on the direct current side of the converters is solved. The converters inject current to a distribution network in a phase splitting mode to compensate the total current of a ground fault to be zero or to inhibit the phase voltage of the fault to be zero, so that the arc is automatically extinguished; and the reference compensation current is calculated by using real-time measured zero sequence voltage, so that the fault phase identification link is saved. The operation is simplified by using the voltage arc suppression method of controlling the zero sequence voltage to adjust the injected compensation current. In view of the influence of circuit parameters and load current on the arc suppression effect and the deduced relation between the ground fault residual current after the voltage arc suppression method is applied and the zero sequence voltage after the fault, an adaptive arc suppression method is put forward by using the zero sequence voltage as a voltage and current arc suppression method.

Owner:SHANGHAI HOLYSTAR INFORMATION TECH

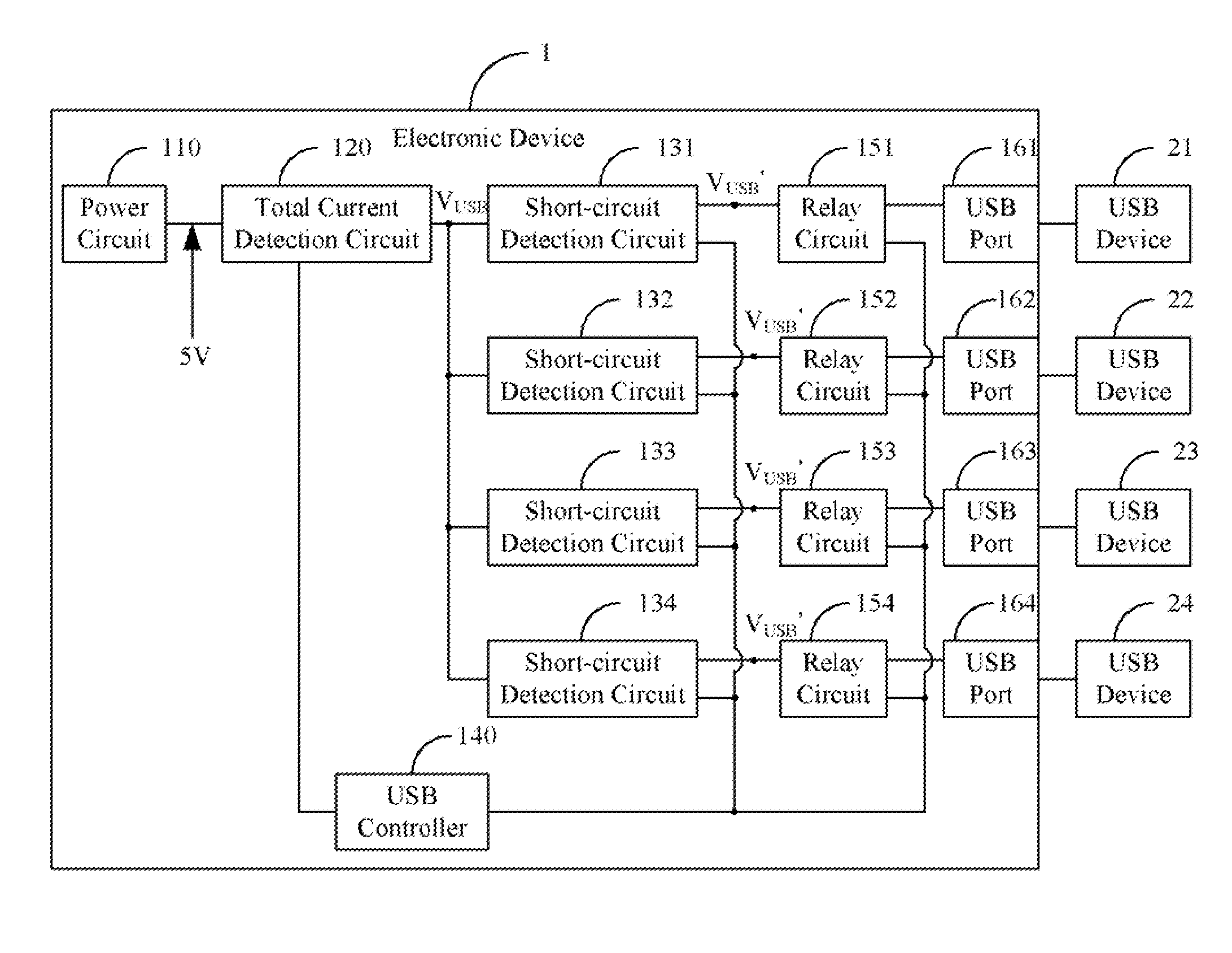

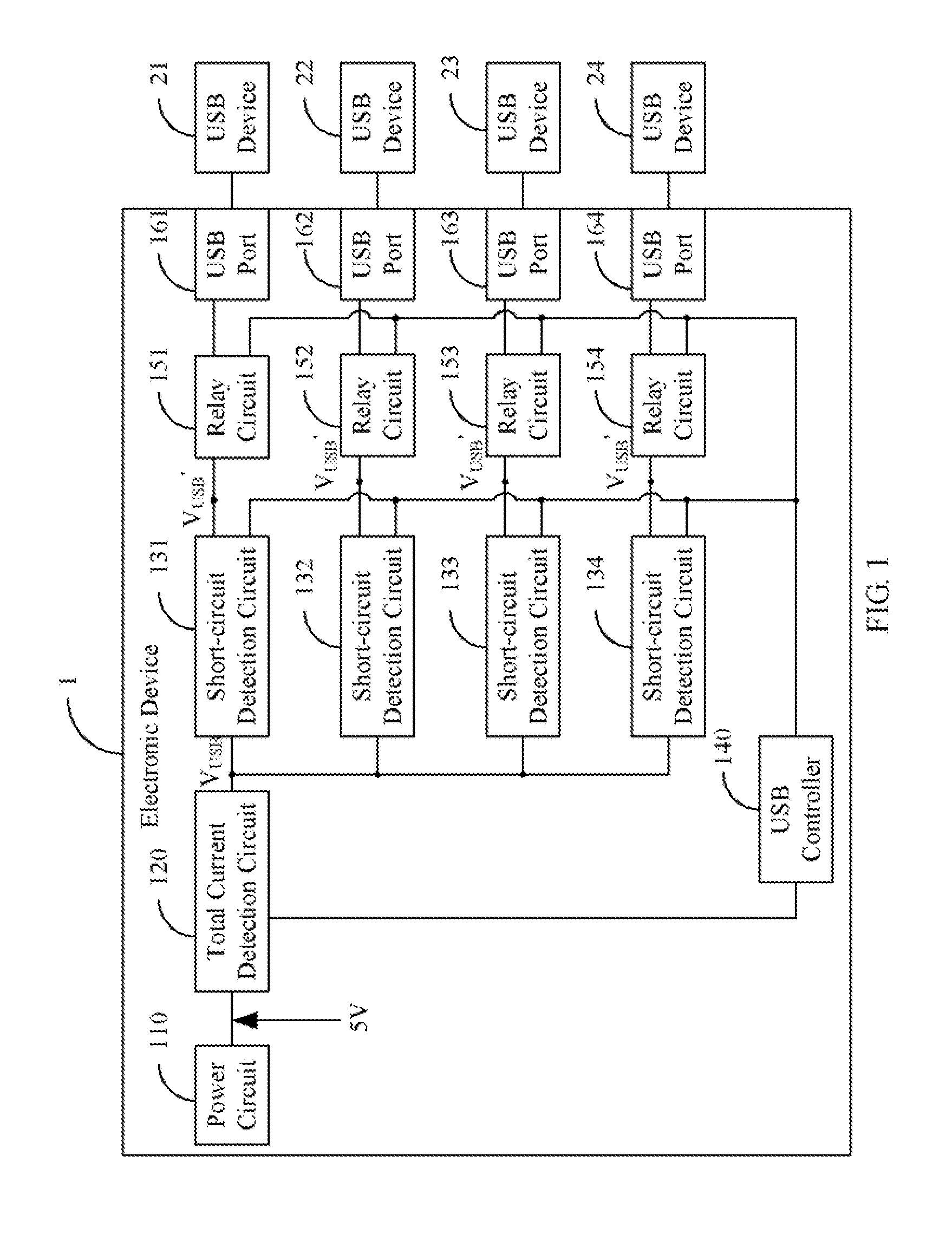

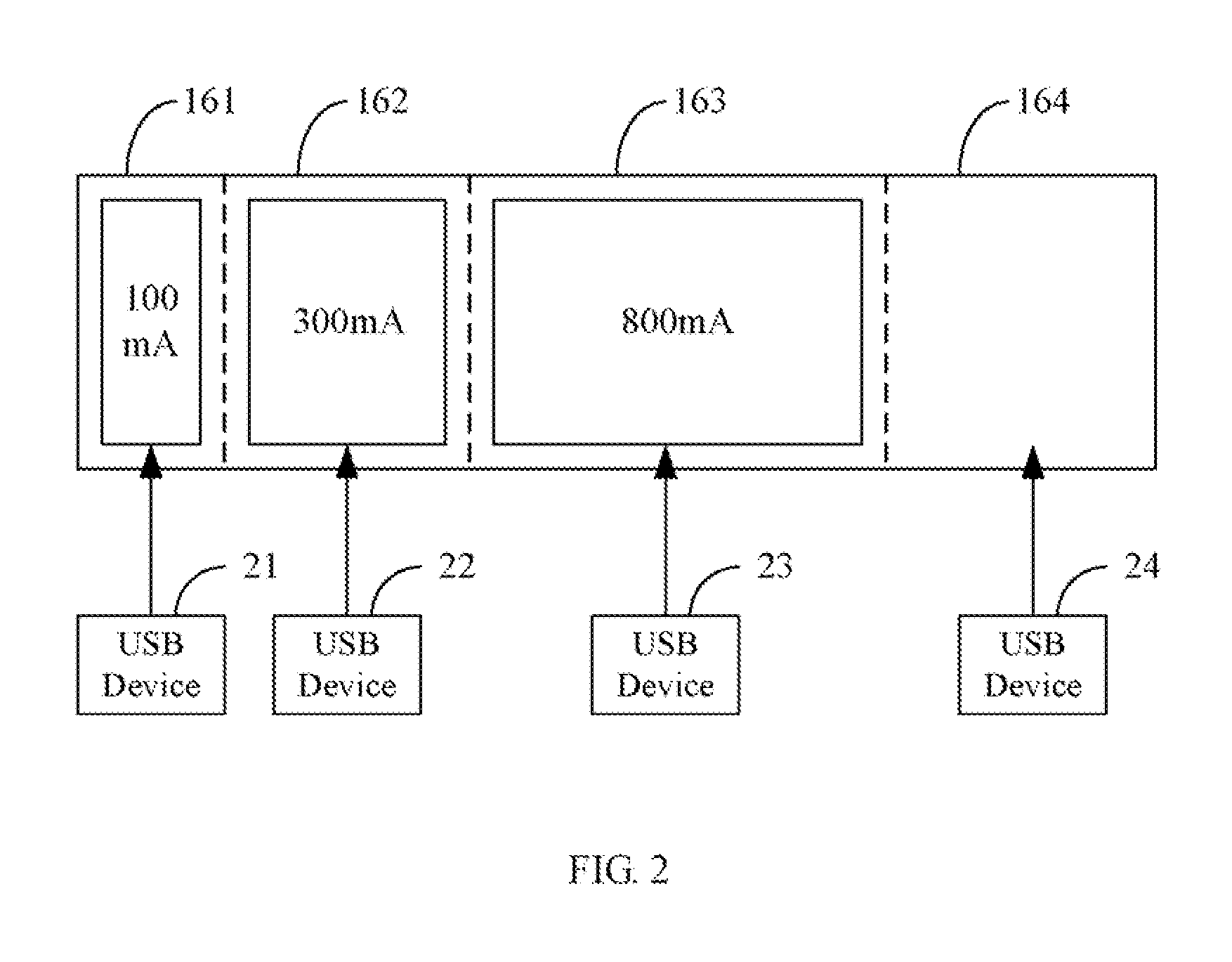

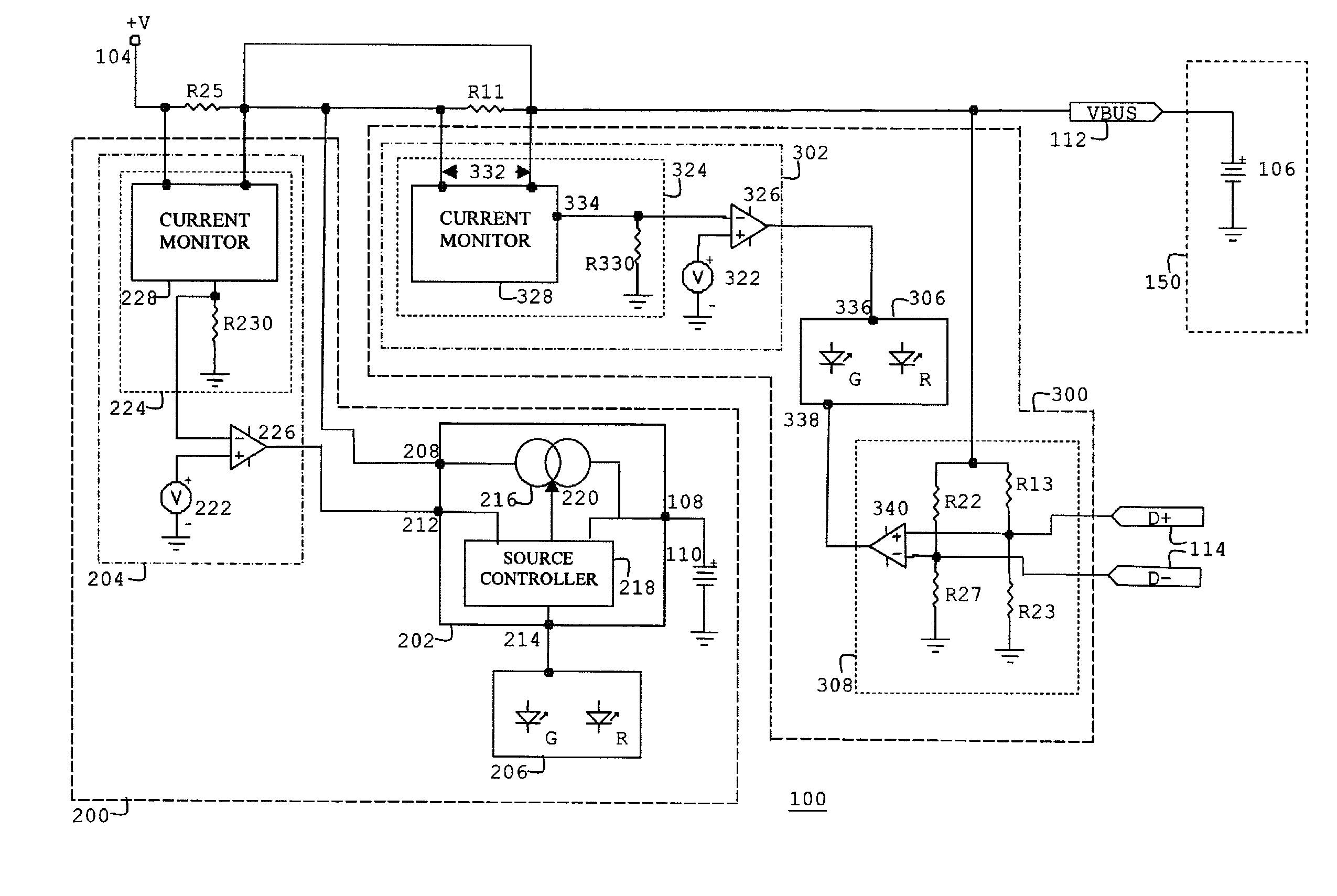

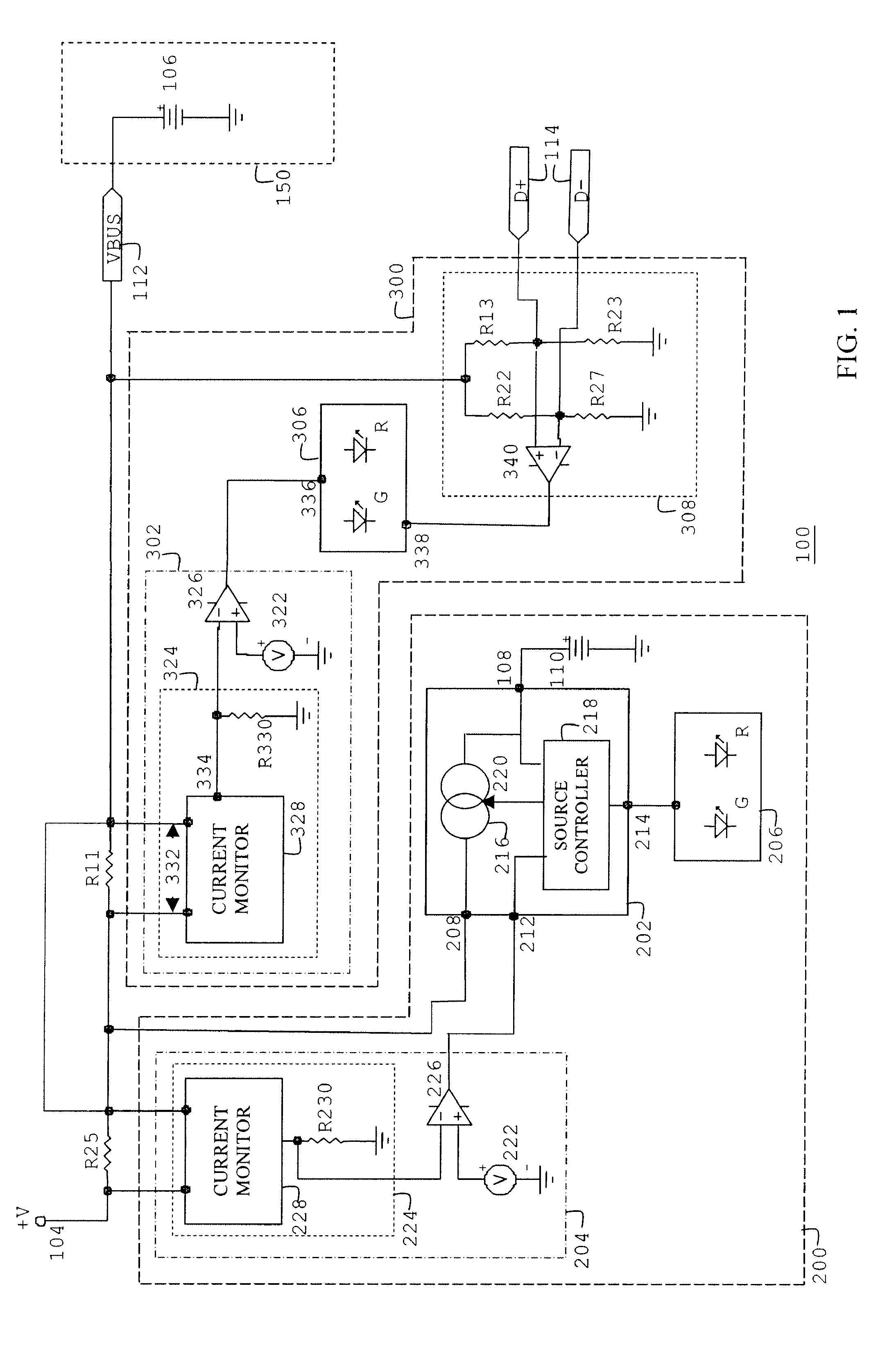

Electronic device and method for dynamic USB power assignment

ActiveUS20110018344A1Current exceedingDc network circuit arrangementsPower supply for data processingControl signalTotal current

An electronic device assigns power to USB ports dynamically. A total current detection circuit transmits driving voltage signals to the USB ports, and detects whether a total current provided to the USB ports exceeds a rated total current and output a total current detection signal. A plurality of short-circuit detection circuits detects whether USB devices connected to the corresponding USB ports are shorted and to output a short-circuit detection signal. A plurality of relay circuits switch connection between the USB ports and the power circuit. A USB controller outputs a control signal according to the total current detection signal and the short-circuit detection signal and directs the relay circuits to switch connection between the corresponding USB ports and the power circuit on and off.

Owner:HON HAI PRECISION IND CO LTD

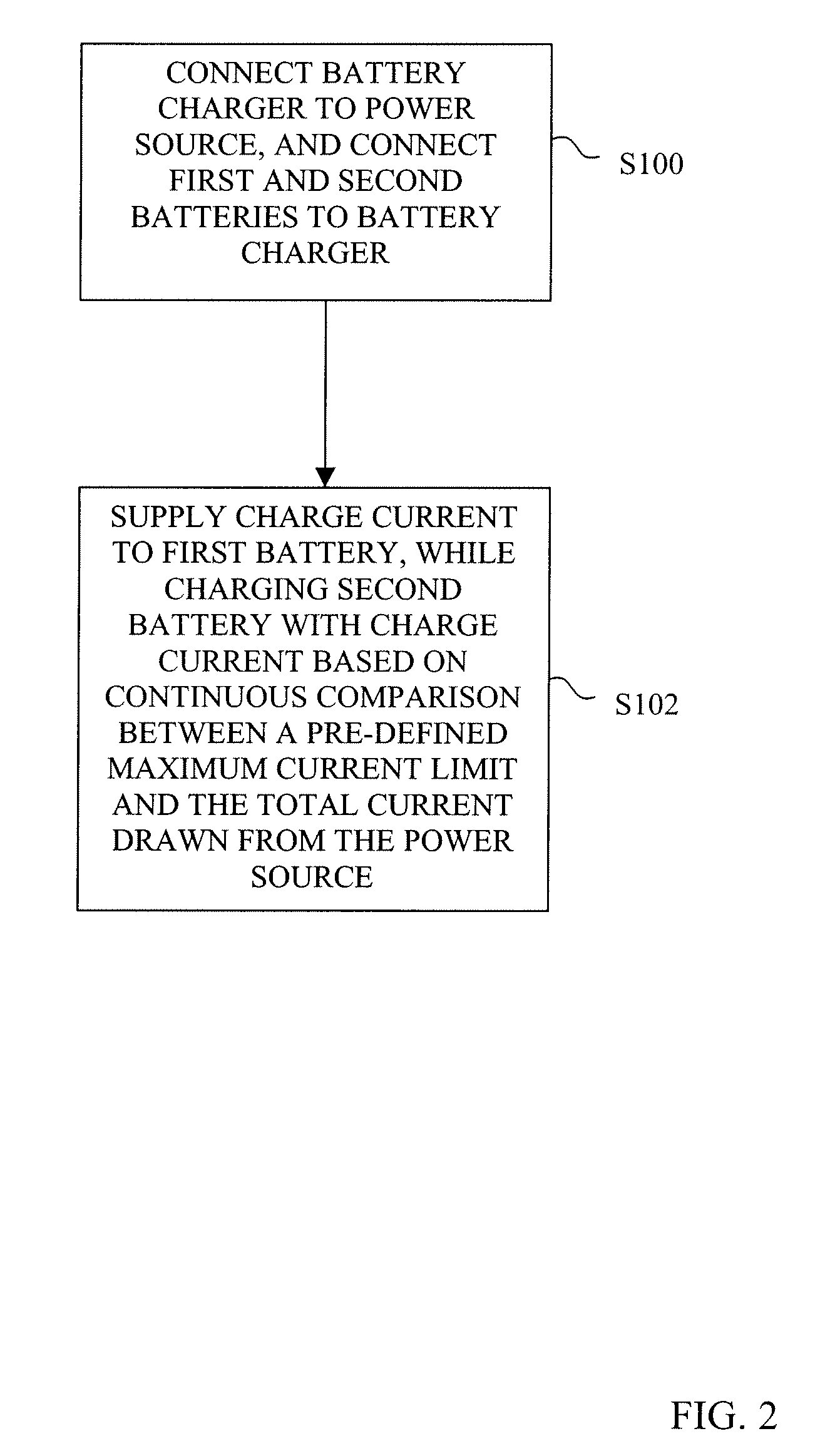

Battery charger for a handheld computing device and an external battery

Owner:MALIKIE INNOVATIONS LTD

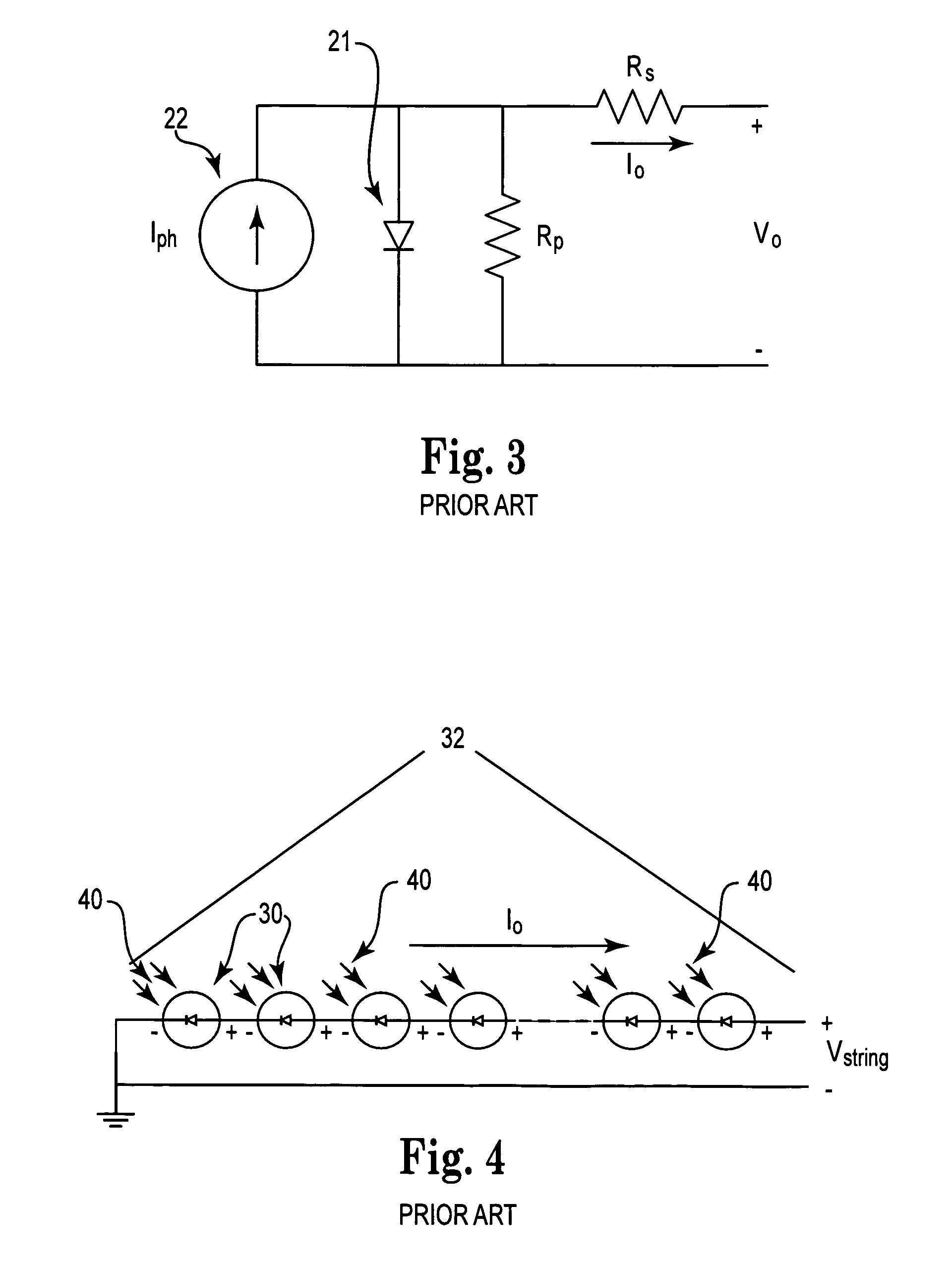

Solar systems that include one or more shade-tolerant wiring schemes

InactiveUS20100032004A1Improved shadow toleranceInhibition of activationSolar heating energySolar heat collector controllersComputer moduleEngineering

The present invention provides shade tolerant wiring solutions for solar systems. Elements are grouped and wired in parallel within a group such that the total current of a group is substantially the same among multiple groups. Such a wiring scheme can be applied to solar targets (e.g., solar cells), solar , and solar modules.

Owner:EMCORE INC

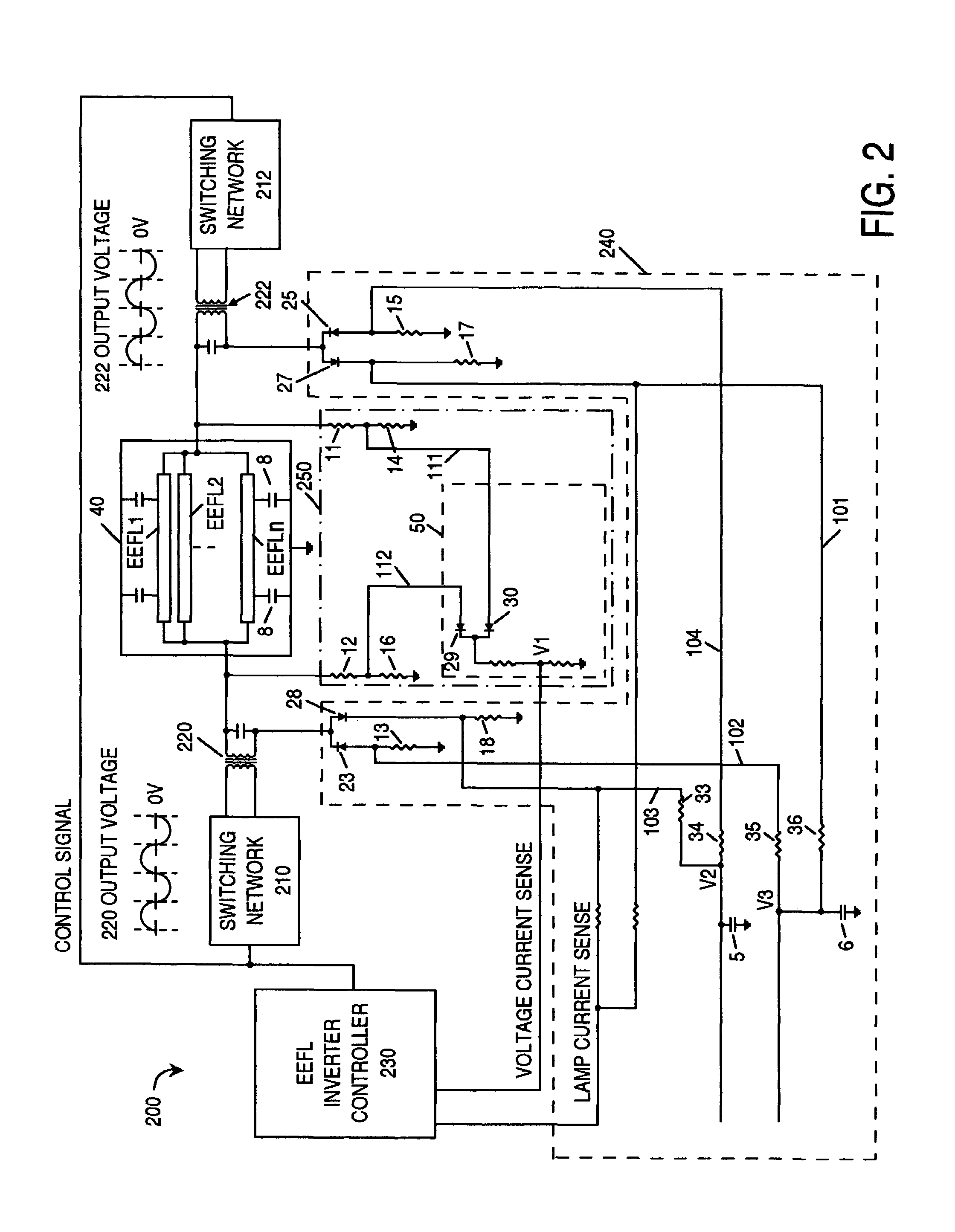

Protection for external electrode fluorescent lamp system

InactiveUS7126289B2Total current dropElectrical apparatusElectric light circuit arrangementDriver circuitTransformer

The present invention provides a driving circuit with protection function for driving a set of external electrode fluorescent lamps (EEFL). The drive circuit includes a transformer connected to the set of EEFLs, a switching network connected to the transformer which delivers power to the transformer, a sensing circuit connected to the set of EEFLs which detects disconnection if one light source is disconnected, and a controller connected to the switching network which controls the switching network to reduce the total current supplied to the EEFLs which remain connected, if the sensing circuit detects that one EEFL is disconnected. Appropriate protection can therefore be implemented when the EEFL is disconnected on one end or both ends.

Owner:O2 MICRO INT LTD

Multi-purpose WAN driver for DSP resource adapter

InactiveUS6549945B1Resource allocationMultiple digital computer combinationsCommunications systemTotal current

A communication system (100) includes at least one digital signal processor (DSP) and a WAN driver (80) operating on a processor that is electrically coupled to a memory. The WAN driver (80) receives task allocation requests from a host to open / close communication channels that are handled by the at least one DSP. Each task is allocated to one of the at least one DSP according to a total current task processing load for each of the at least one DSP, a maximum processing capability for each of the at least one DSP, and a processing requirement for each task being allocated to the one of the at least one DSP that can handle the additional processing load of the task being allocated.

Owner:IBM CORP

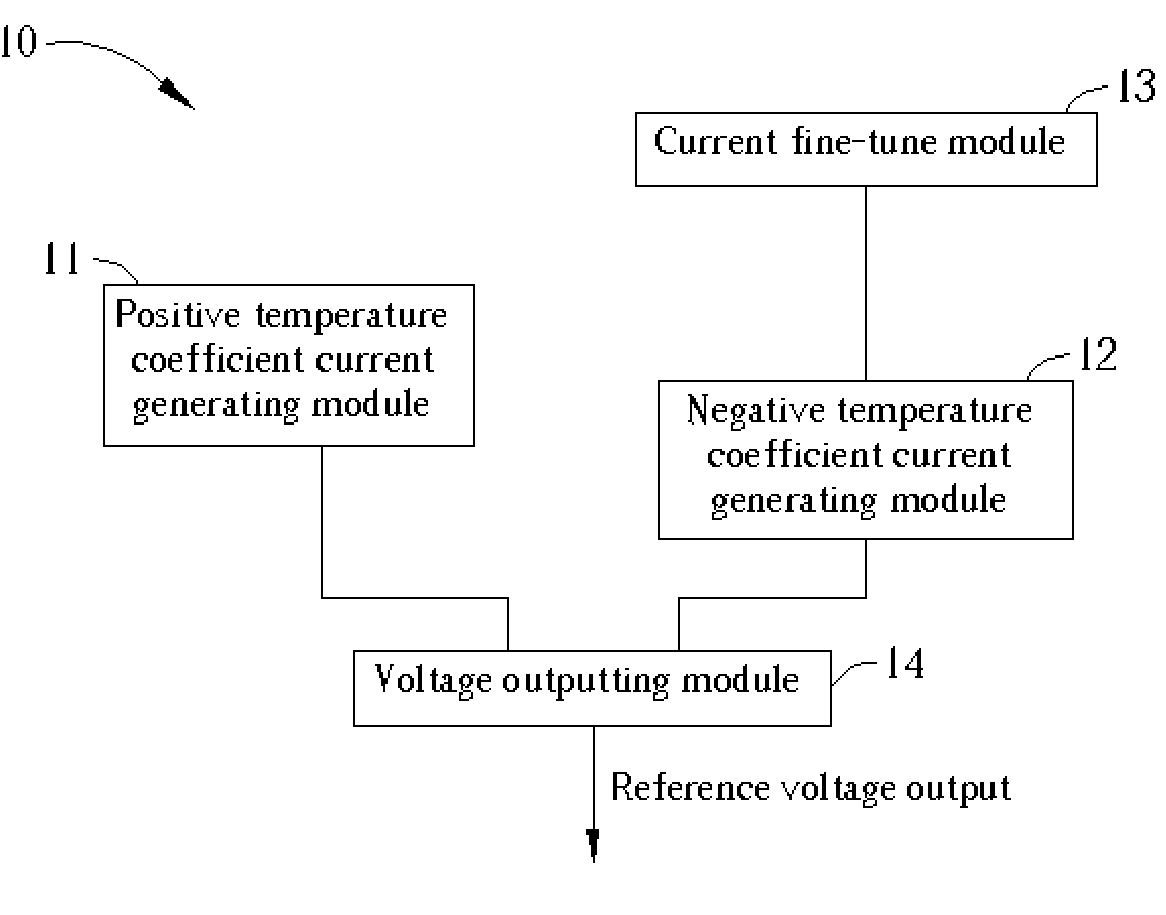

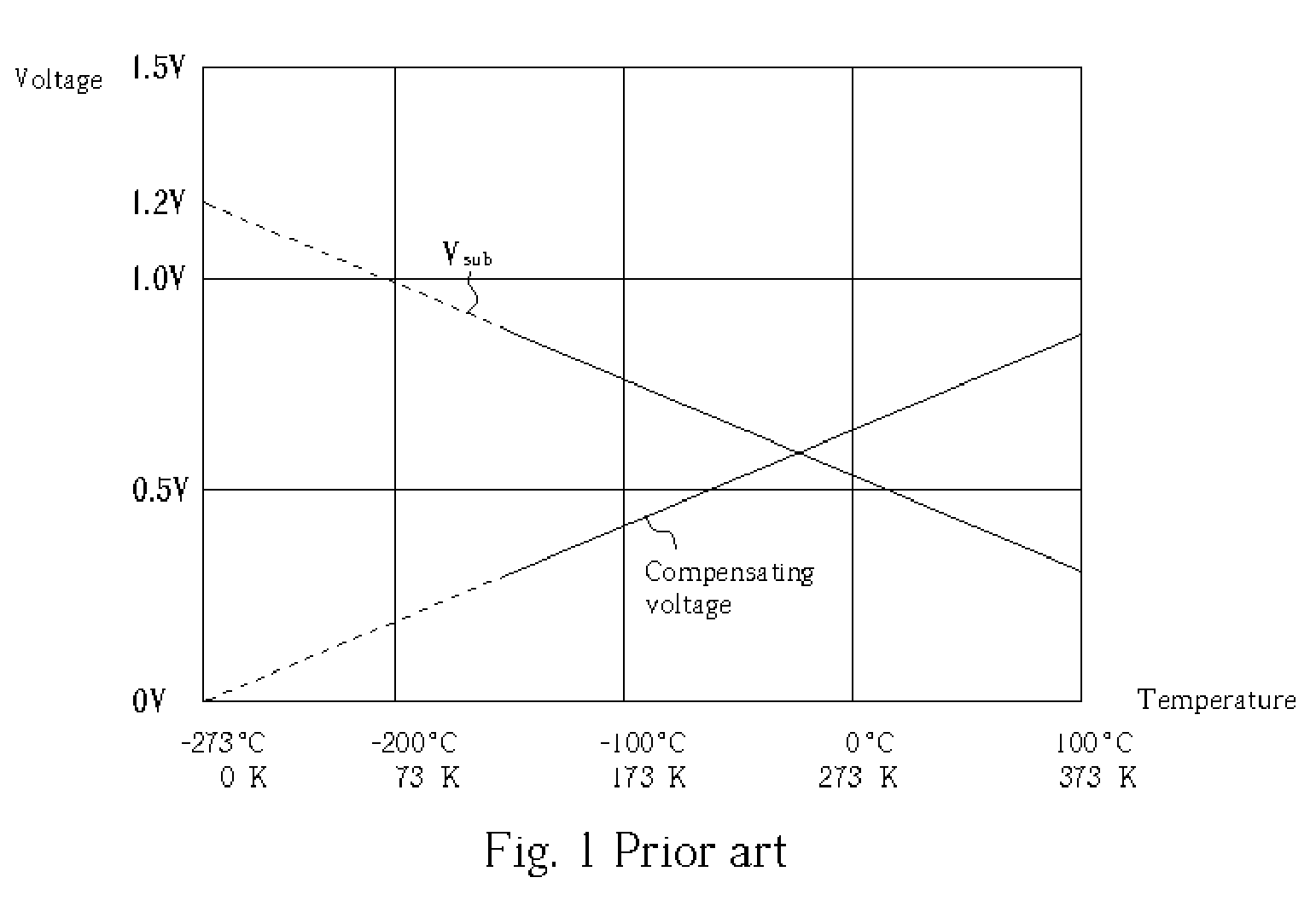

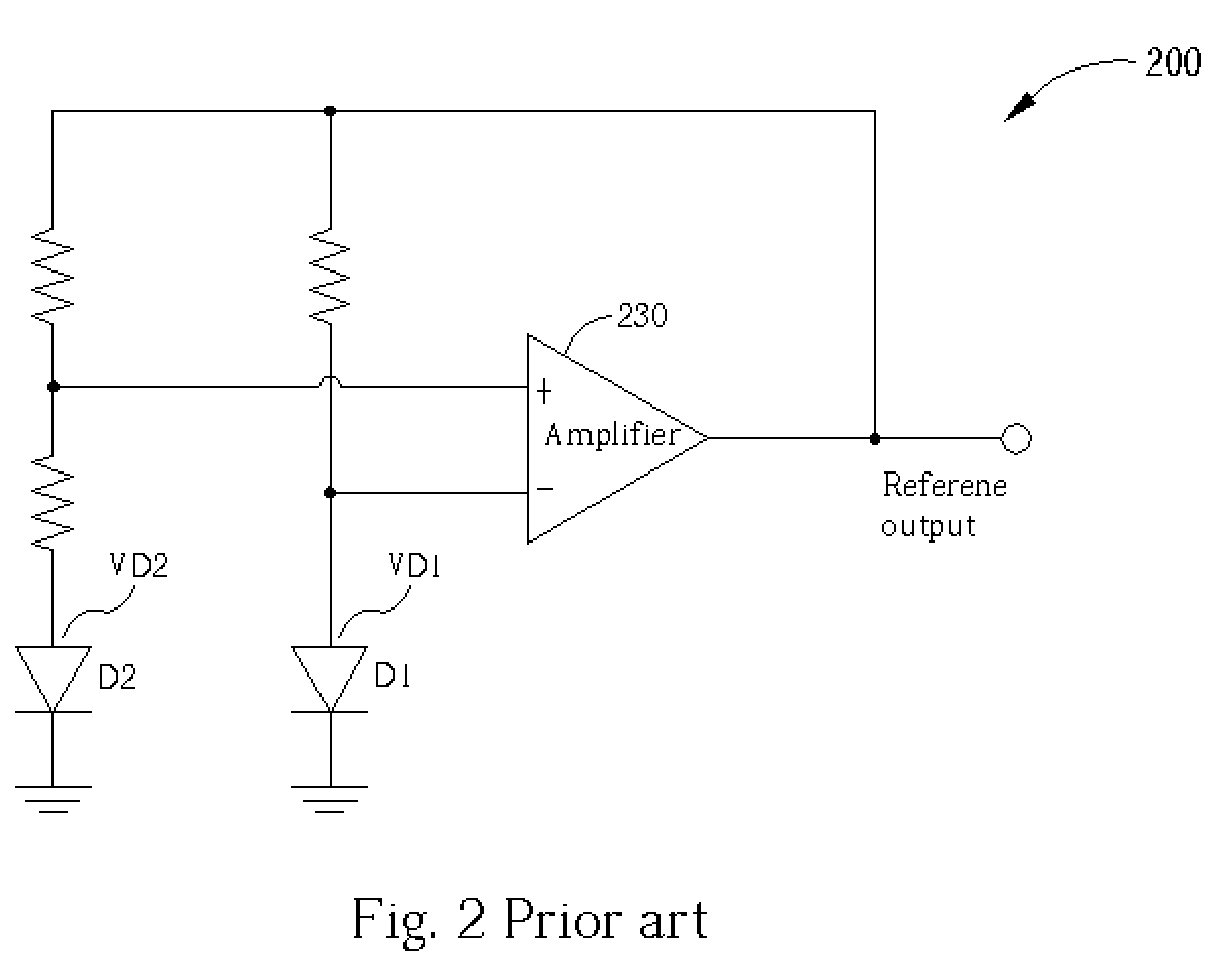

Voltage generating apparatus with a fine-tune current module

ActiveUS6958597B1Increase currentTotal current dropPower supply linesElectric variable regulationSub thresholdNegative temperature

Voltage generating apparatus includes a positive temperature coefficient current generating module, a negative temperature coefficient current generating module, a fine-tune current module and a voltage output module. The function of the positive temperature coefficient current generating module and the negative temperature coefficient current generating module, which take advantage of characteristics of MOS devices operated in the sub-threshold region, is to generate a stable current of positive temperature coefficient and a stable current of negative temperature coefficient, respectively. The current fine-tune module increases or decreases output current of the negative temperature coefficient current generating module. The voltage output module sums two output currents of the positive temperature coefficient current generating module and the negative temperature coefficient current generating module and transforms the total current into output voltage that is stable under temperature and process variation.

Owner:EMEMORY TECH INC

Multiphase power regulator with load adaptive phase control

ActiveUS20090224731A1Maximize efficiencyImprove efficiencyDc-dc conversionAc network voltage adjustmentActive phaseEngineering

Disclosed is a power regulator for providing precisely regulated power to a microelectronic device such as a microprocessor. Improved power regulation is accomplished by optimizing the power efficiency of the power regulator. In particular, in a multiphase system, the number of active phases is increased or decreased to achieve optimum power efficiency. The multiphase voltage regulator adapts the operating mode to maximize efficiency as the load current demand of the load device changes by adjusting the number of active phases to maximize efficiency. The total value of current provided by the regulator and the total number of active phases is determined, the total number of active phases is compared with the number of active phases required to provide the total value of current at maximum efficiency; and the number of active phases is adjusted to provide the total value of current at maximum efficiency.A current sense circuit senses the current at each phase, a summing circuit coupled to the output of the current sense circuit provides the total current value of all the measured phases, a circuit coupled to the output of the summing circuit provides the time averaged total current value to a threshold detecting circuit that determines the number of phases at which the voltage regulator should be operating for maximum efficiency, and a circuit for comparing the number of phases that are operating to the number of phases at which the voltage regulator should be operating adjusts the number of active phases to the number of phases at which the voltage regulator should be operating for maximum efficiency.

Owner:INFINEON TECH AUSTRIA AG

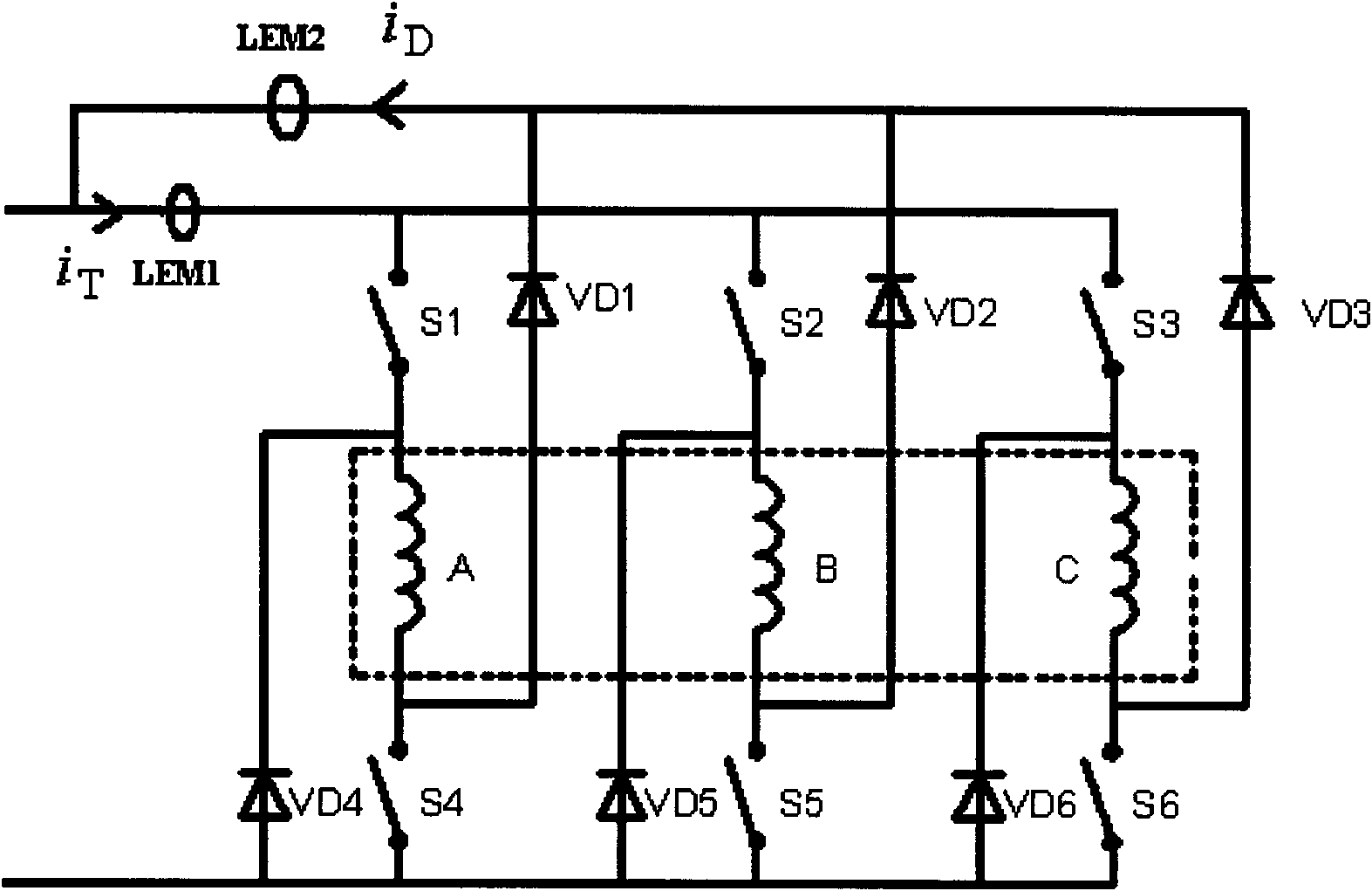

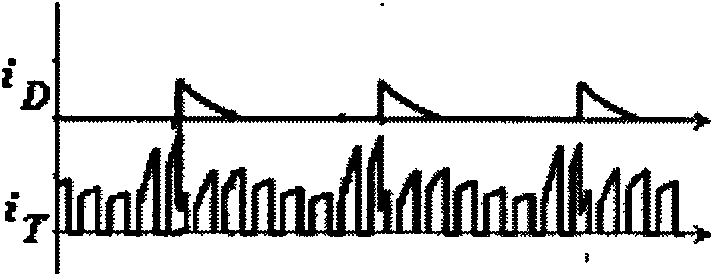

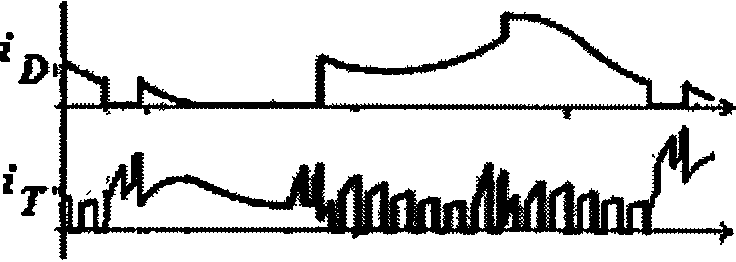

Switch reluctance motor double master switch power converter master switch fault diagnosis method

ActiveCN101666858ARapid identificationRapid diagnosisCurrent/voltage measurementCircuit interrupters testingSwitched currentDiagnosis methods

The invention provides a switch reluctance motor double master switch power converter master switch fault diagnosis method. A current sensor LEM1 is arranged on the master switch current circuit (DC)busand and is used for testing the total current of the main switch on the DC bus, a current sensor LEM2 is arranged on the free-wheeling diode DC bus and is used for testing the total current feedback by the free-wheeling diode on the DC bus, the wires of the two current sensors are connected with a receiver to obtain the total current signal of the master switch and the total current signal fedback by the free-wheeling diode. The invention can be used for judging that short trouble occurs to both the upper master switch tube and the lower master switch tube and open fault occurs to both theupper main switch tube and the lower main switch tube, and can be used for carrying out fault location, thus having convenient fault-tolerant control, and wide application prospects.

Owner:CHINA UNIV OF MINING & TECH

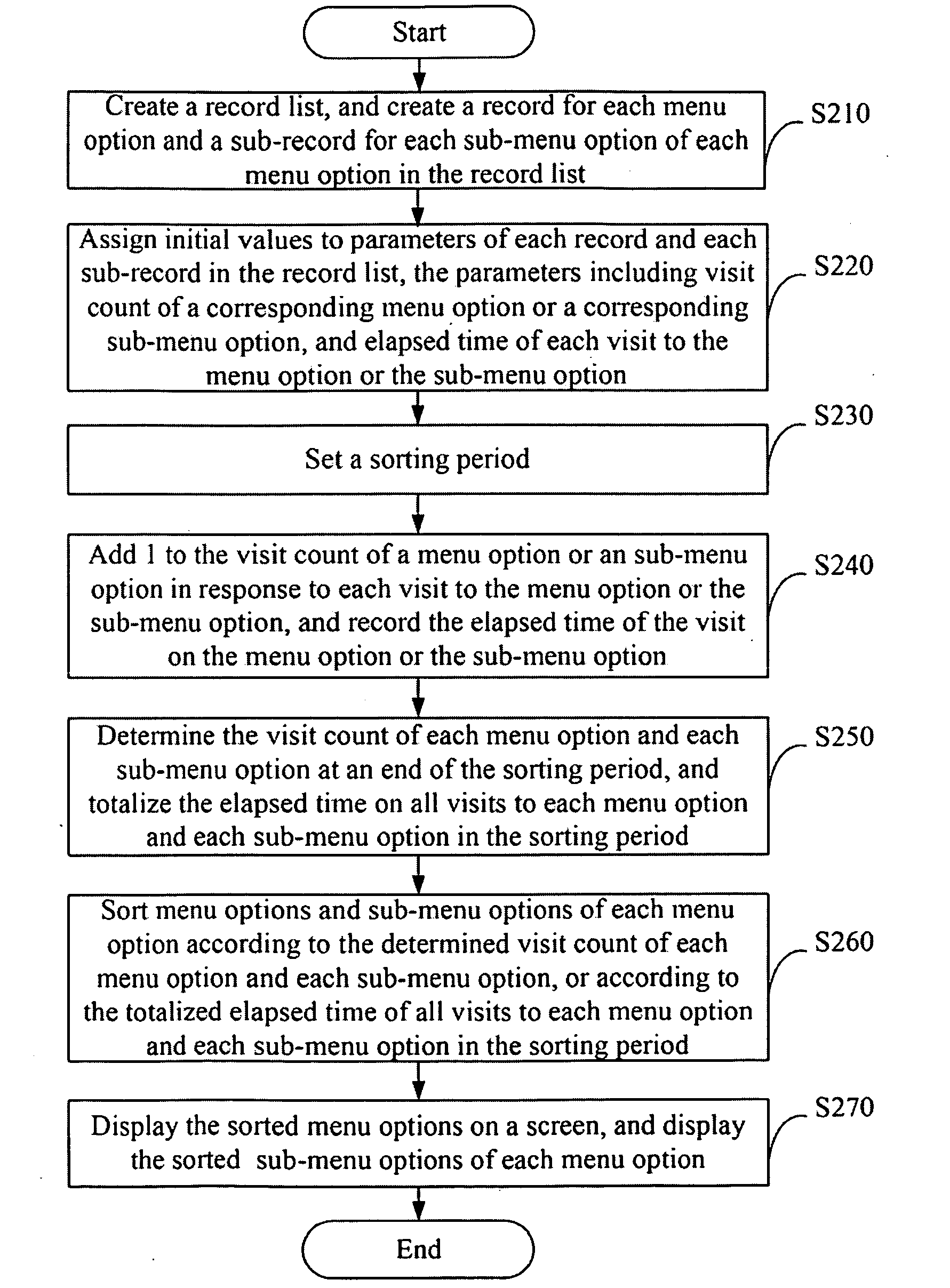

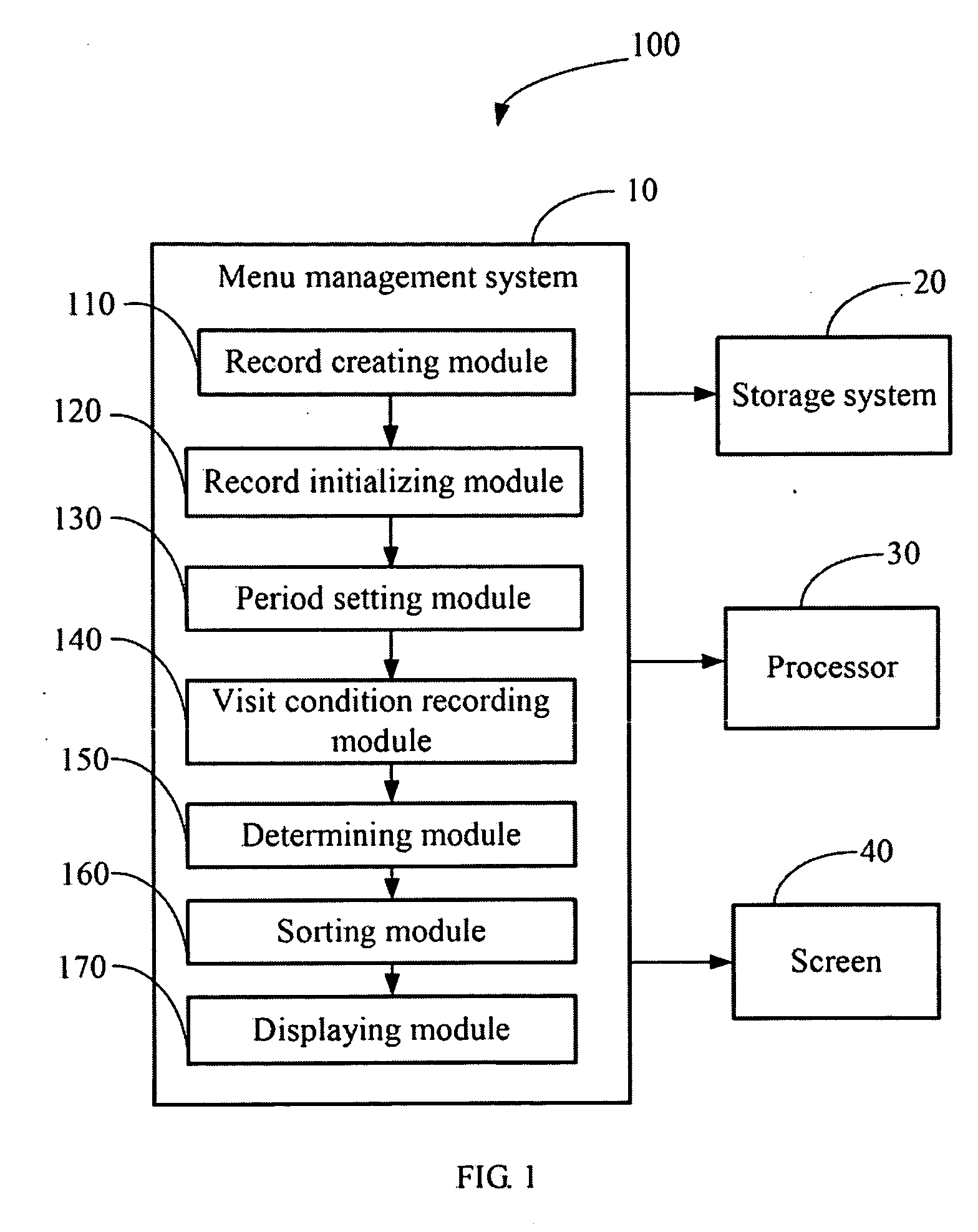

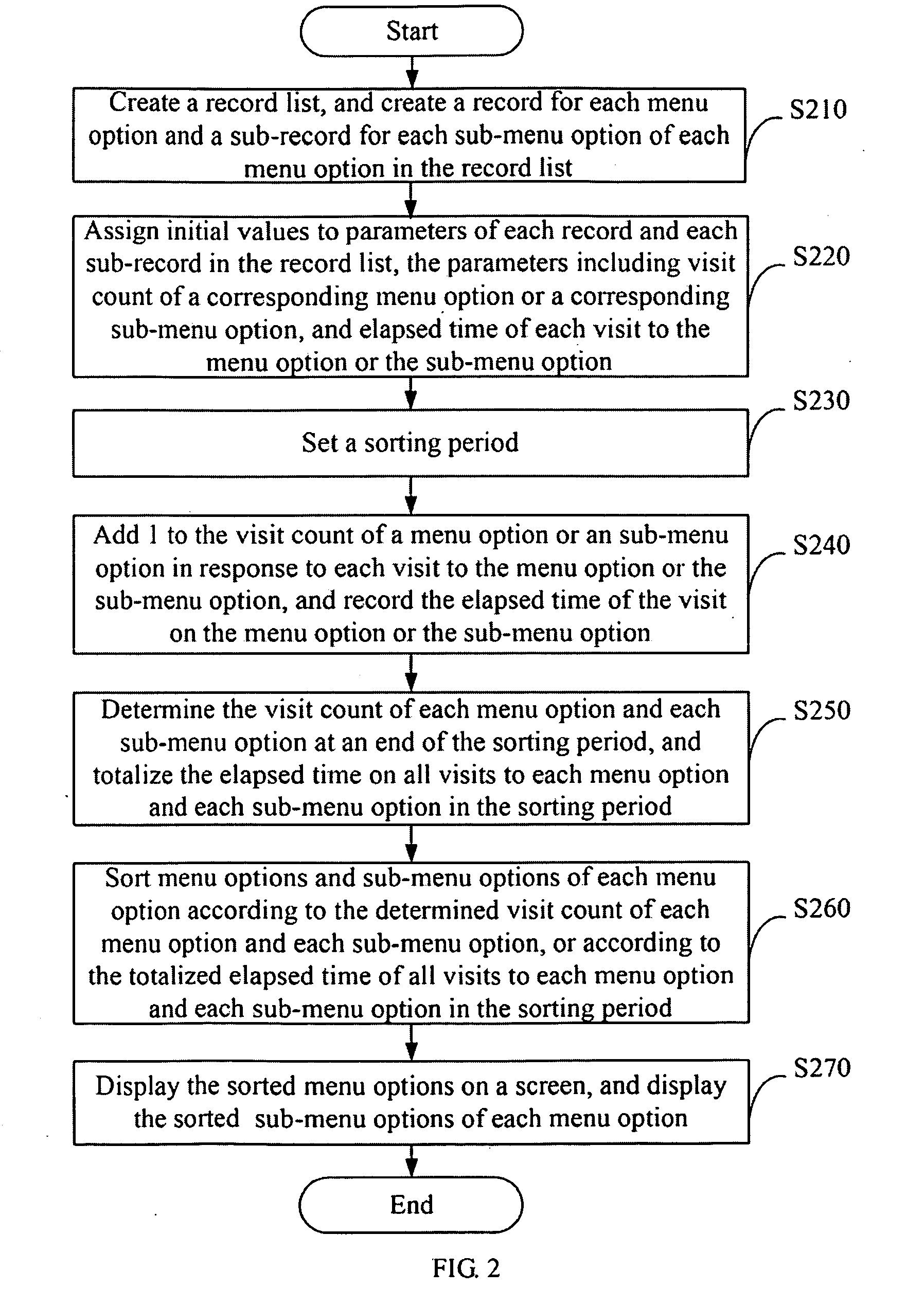

Menu management system and method

InactiveUS20100042949A1Substation equipmentInput/output processes for data processingTotal currentComputer science

A computer-based menu management system and method creates a record for each of the menu options in a main menu of an electronic device, creates a sub-record for each of sub-menu options in a low hierarchy of each of the menu options, and assigns initial values to parameters of each record and each sub-record. The system and method further adds a predetermined value to each of the parameters of each record or each sub-record, in response to each visit to a corresponding menu option or a corresponding sub-menu option. In addition, the system and method totals current values of the parameters, and sorts the menu options and sub-menu options of each of the menu options according to the current values of the parameters of each record and each sub-record in a predetermined sorting period.

Owner:CHI MEI COMM SYST INC

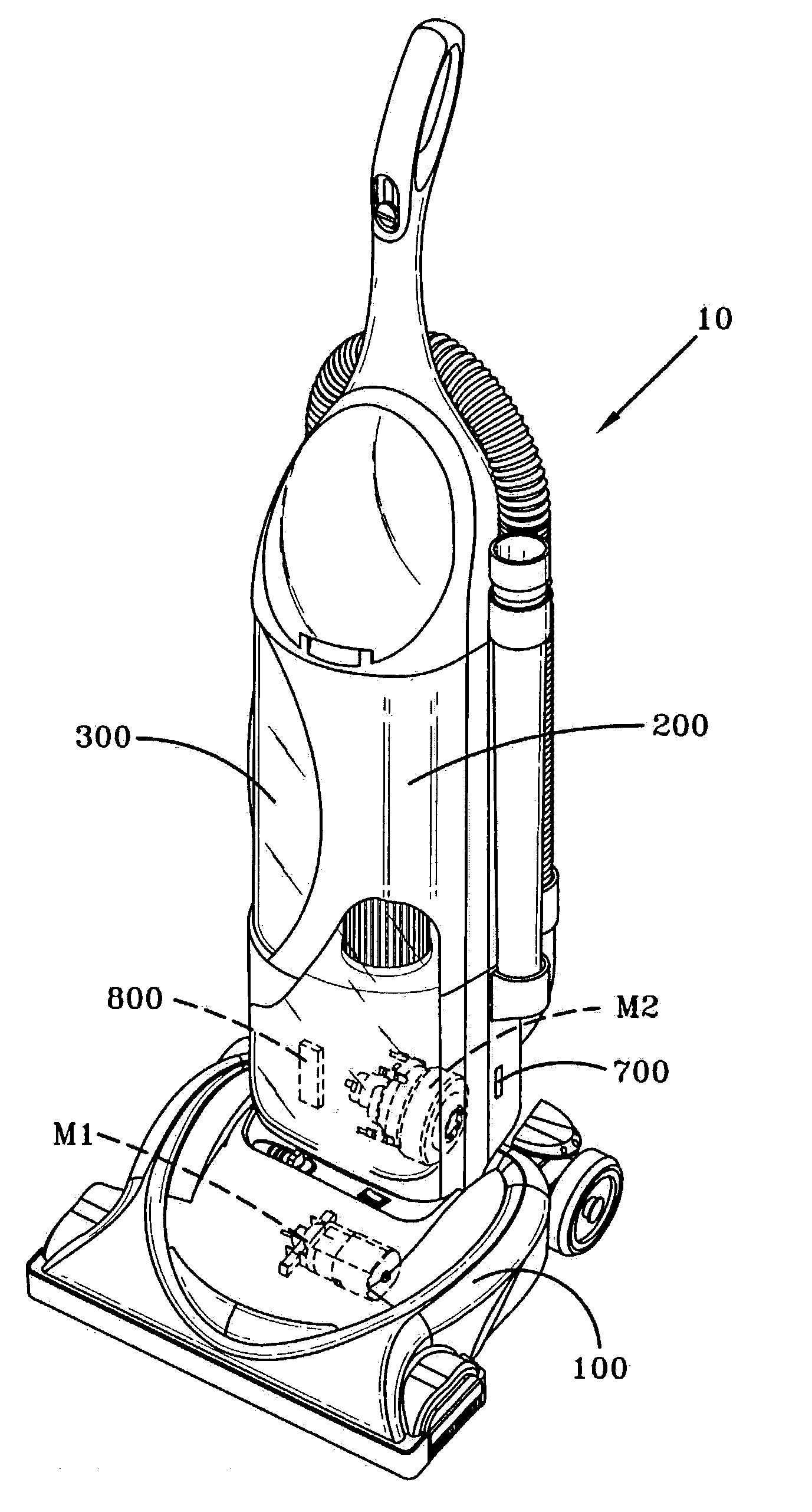

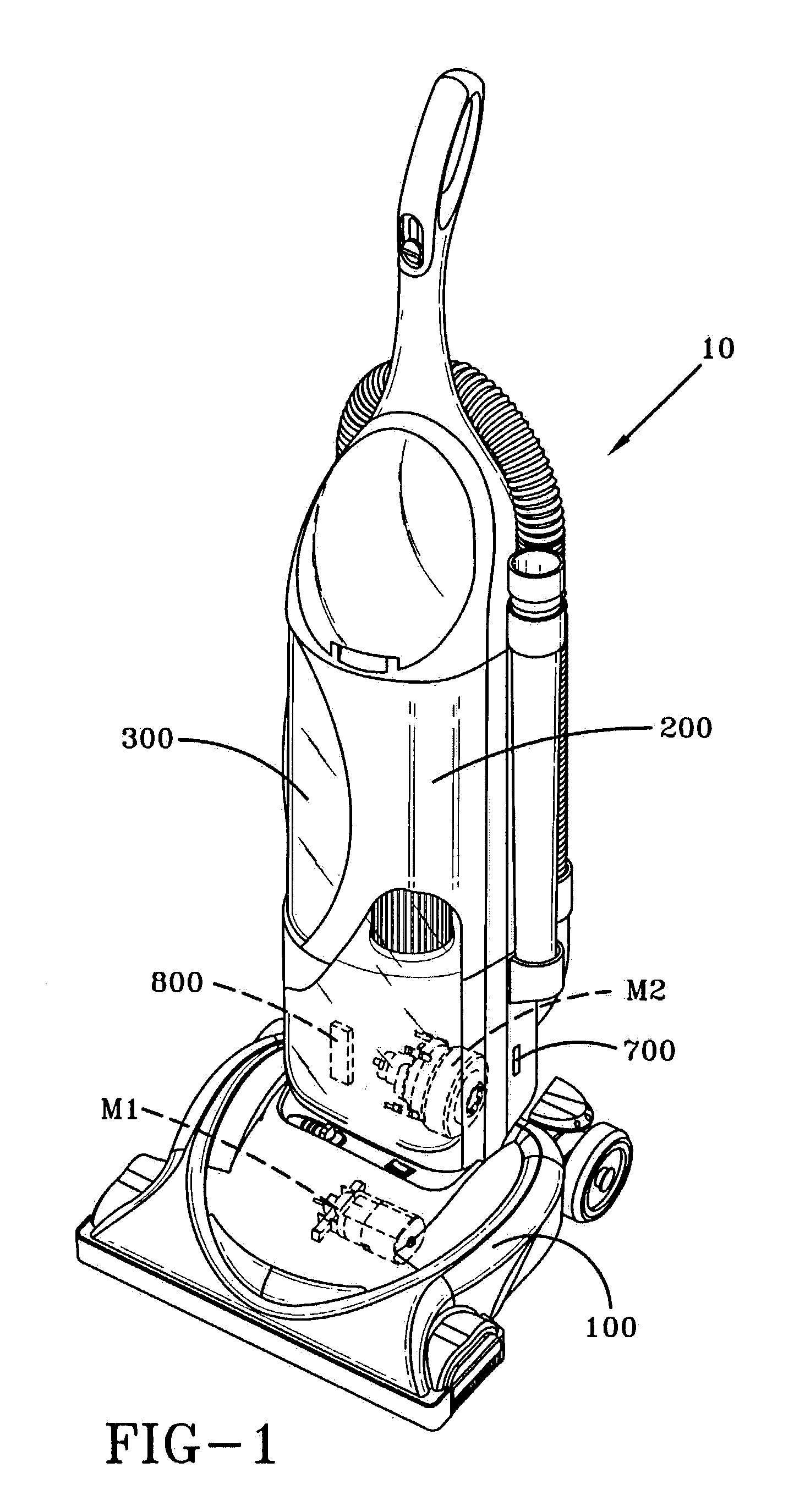

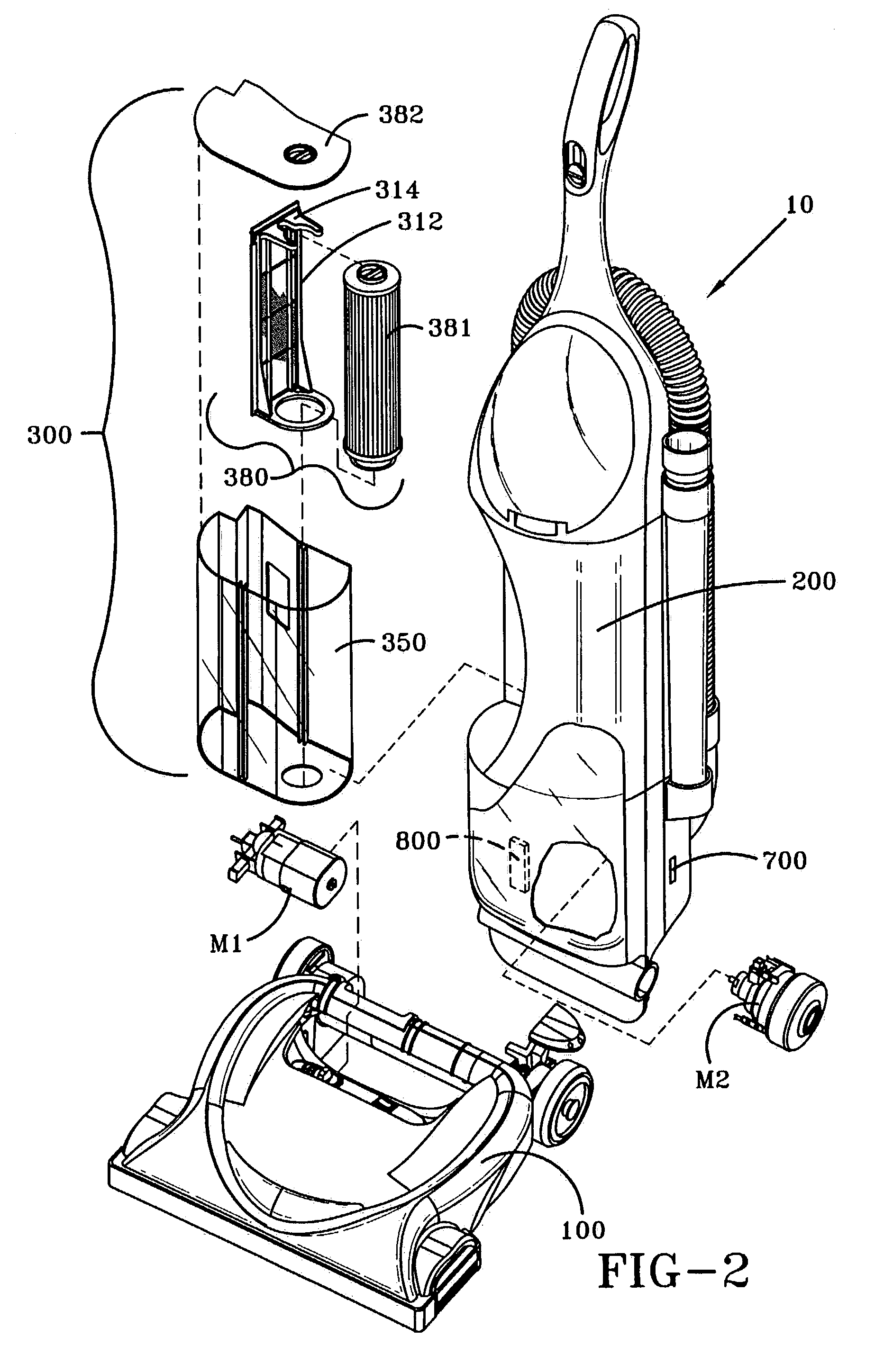

Power management system for a floor care appliance

A floor care appliance is provided with an improved power management system for controlling the total amount of current provided to at least a first and a second load device of an appliance. The power management system is comprised of a microprocessor, an alternating current voltage source, a voltage regulating circuit, a clamping circuit, at least two load devices, and a MOC and a triac for each of the at least two load devices. The clamping circuit outputs a fixed voltage of 5.7 volts during the positive portion of the ac cycle and a fixed voltage of −0.7 volts during the negative portion of the ac cycle. The fixed voltages are input to a microprocessor which utilizes these inputs to control the average voltage and the amount of time the current is turned on to each of the at least first and second load devices. A current sensing circuit is used to monitor the current to one of the at least two load devices to provide feedback to the microprocessor so that the microprocessor can adjust the average voltage and current to the at least two load devices so that the total current consumed does not exceed a pre-determined level.

Owner:HOOVER LIMITED

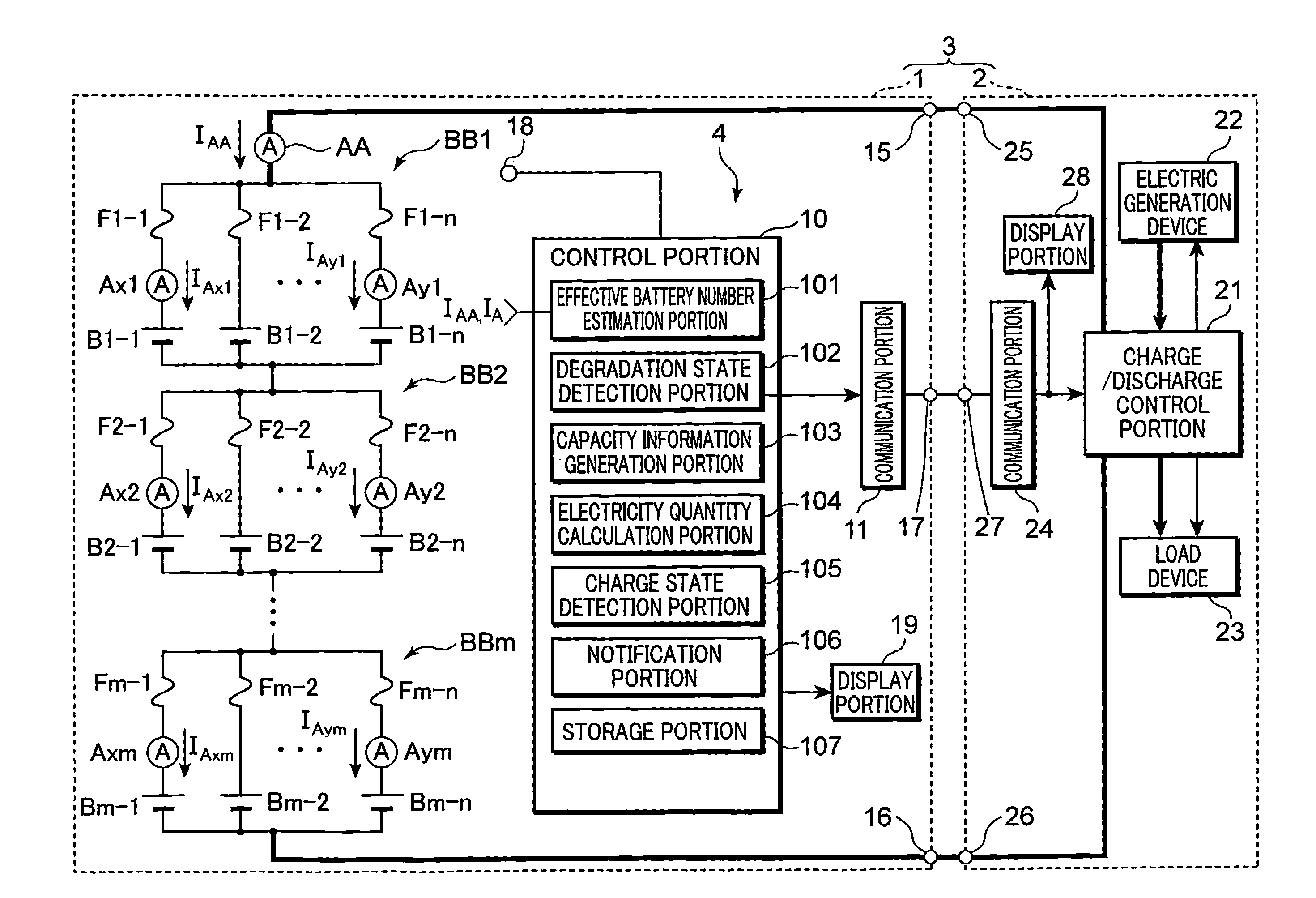

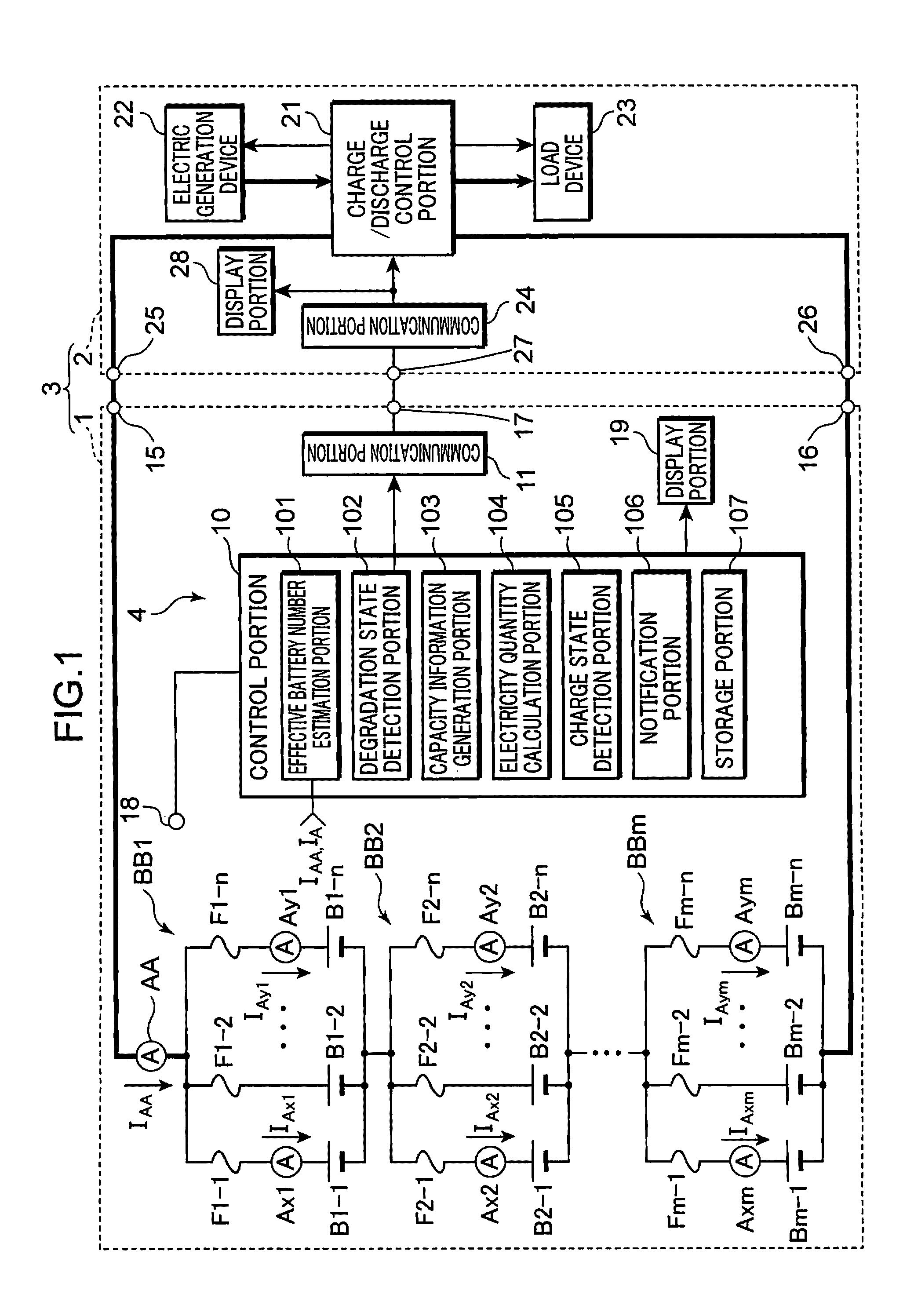

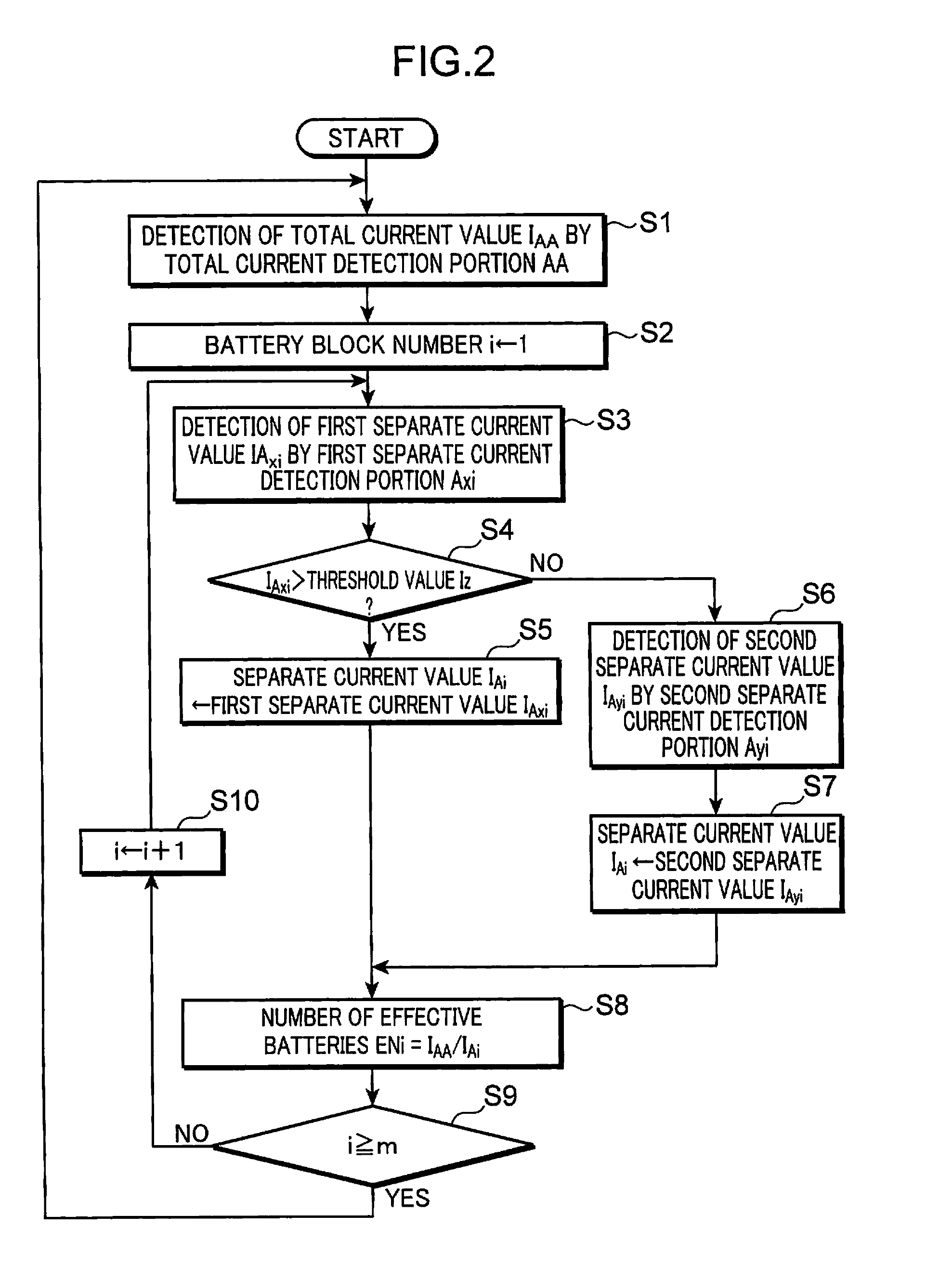

Charge state detection circuit, battery power supply device, and battery information monitoring device

InactiveUS20120119749A1Charge equalisation circuitCircuit monitoring/indicationElectricityElectrical battery

A charge state detection circuit, which detects a state of charge of a battery block in which are parallel-connected a plurality of series circuits of a secondary battery and a cutoff element which assumes a cutoff state of cutting off the charge / discharge path of the secondary battery and a conducting state different from the cutoff state, the charge state detection circuit comprising: an effective battery number detection portion which detects, as the number of effective batteries, the number of cutoff elements in the conducting state from among the plurality of cutoff elements included in the battery block; a capacity information generation portion which, based on the number of effective batteries, generates capacity information related to actual full charge capacity, which is the actual full charge capacity of the battery block; a total current detection portion, which detects as a total current value a current flowing in the entire battery block; an electricity quantity calculation portion, which calculates, as a stored electricity quantity, an electricity quantity stored in the battery block, by integrating the total current value; and a charge state detection portion, which, based on the capacity information and the stored electricity quantity, detects a state of charge, which is a ratio of the stored electricity quantity to the actual full charge capacity.

Owner:PANASONIC CORP

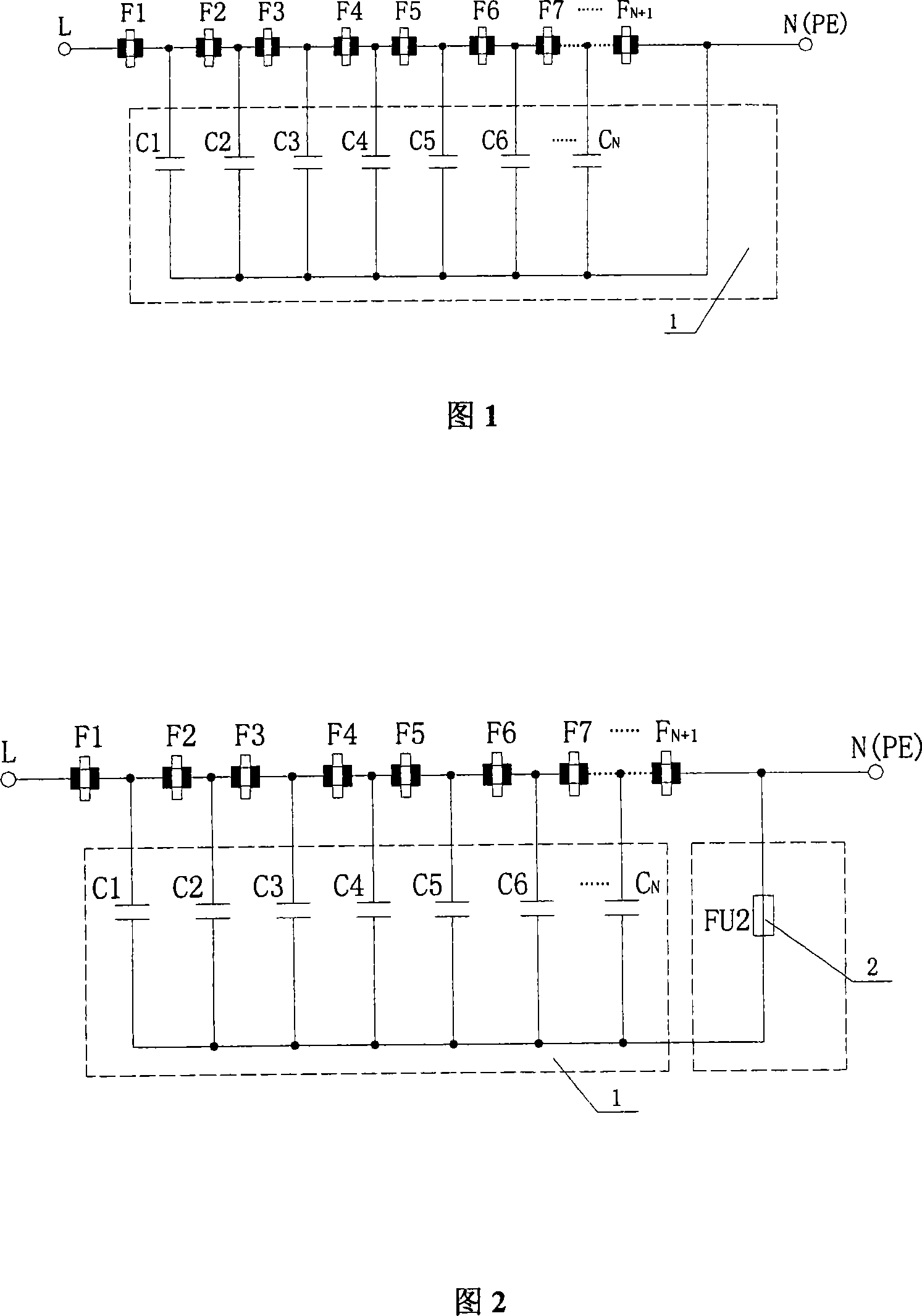

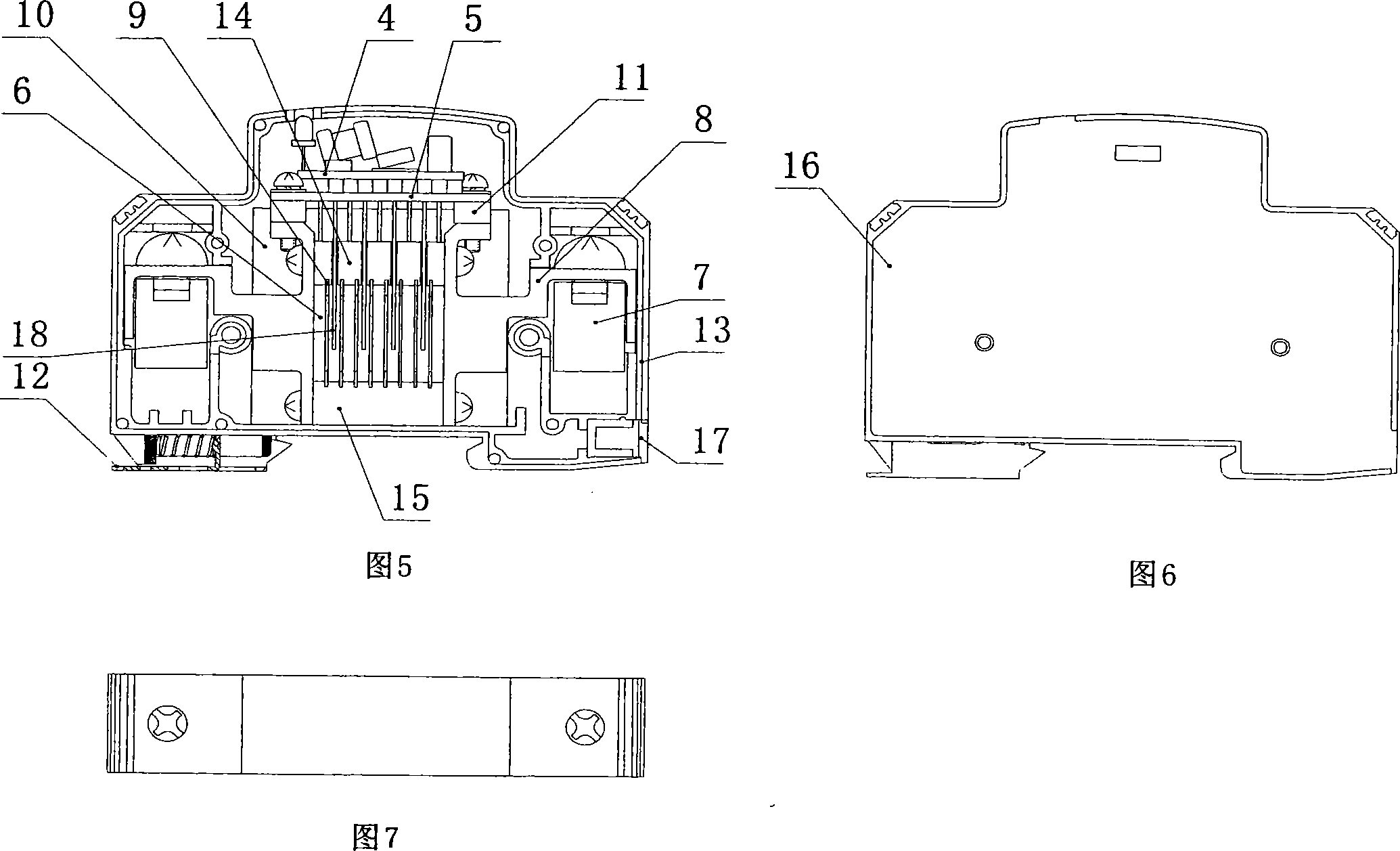

High efficient laminated graphic discharge gap device

ActiveCN101090197AImprove conductivityHigh melting pointOvervoltage arrestors using spark gapsCapacitanceGraphite electrode

This invention relates to an efficient laminated graphite discharge arc gap device including: N+1 arc gaps and a pi-shaped connection capacitor set with N capacitors in the same capacitance value, in which, the gaps are serial to each other, the first one is connected with the live wire, the last one is connected to the earth, one end of each capacitor in the set is connected with the conduction piece between the two arc gaps and the other end is connected to the earth, the arc gap is made of graphite, insulation ring pad is set between the graphite electrodes, the arc gaps are assembled in lamination, parameter of each capacitor in the set is selected according to C=In / 2pifVK, in which, In is the induced discharge current on the capacitors, In=I / N, I is the total current of the set, N is the number of capacitors, f is a lightning wave frequency, V is a rating voltage and K is a safety factor greater than or equal to 1.

Owner:SICHUAN ZHONGGUANG LIGHTNING PROTECTION TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com