Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1440 results about "Switched current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

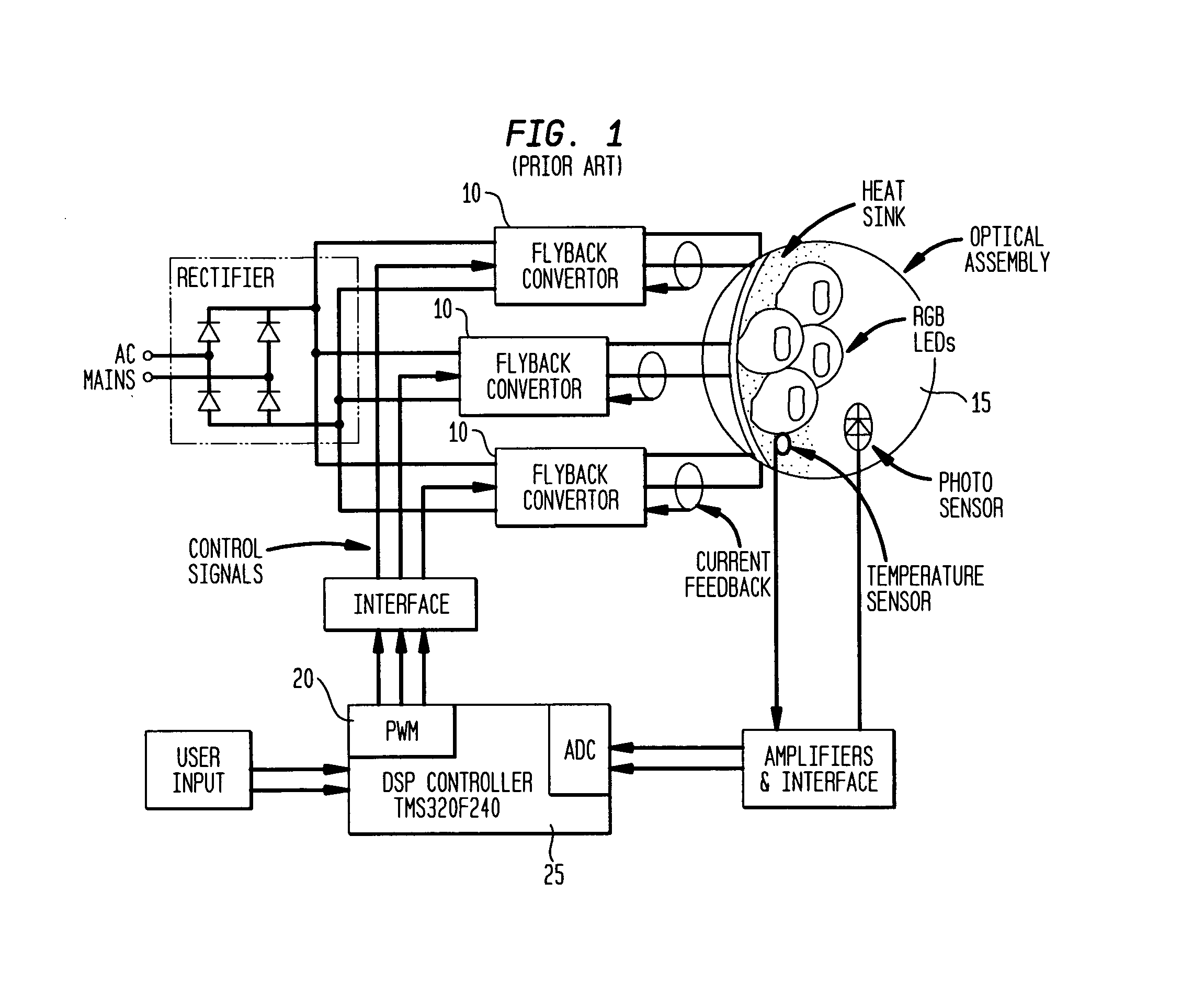

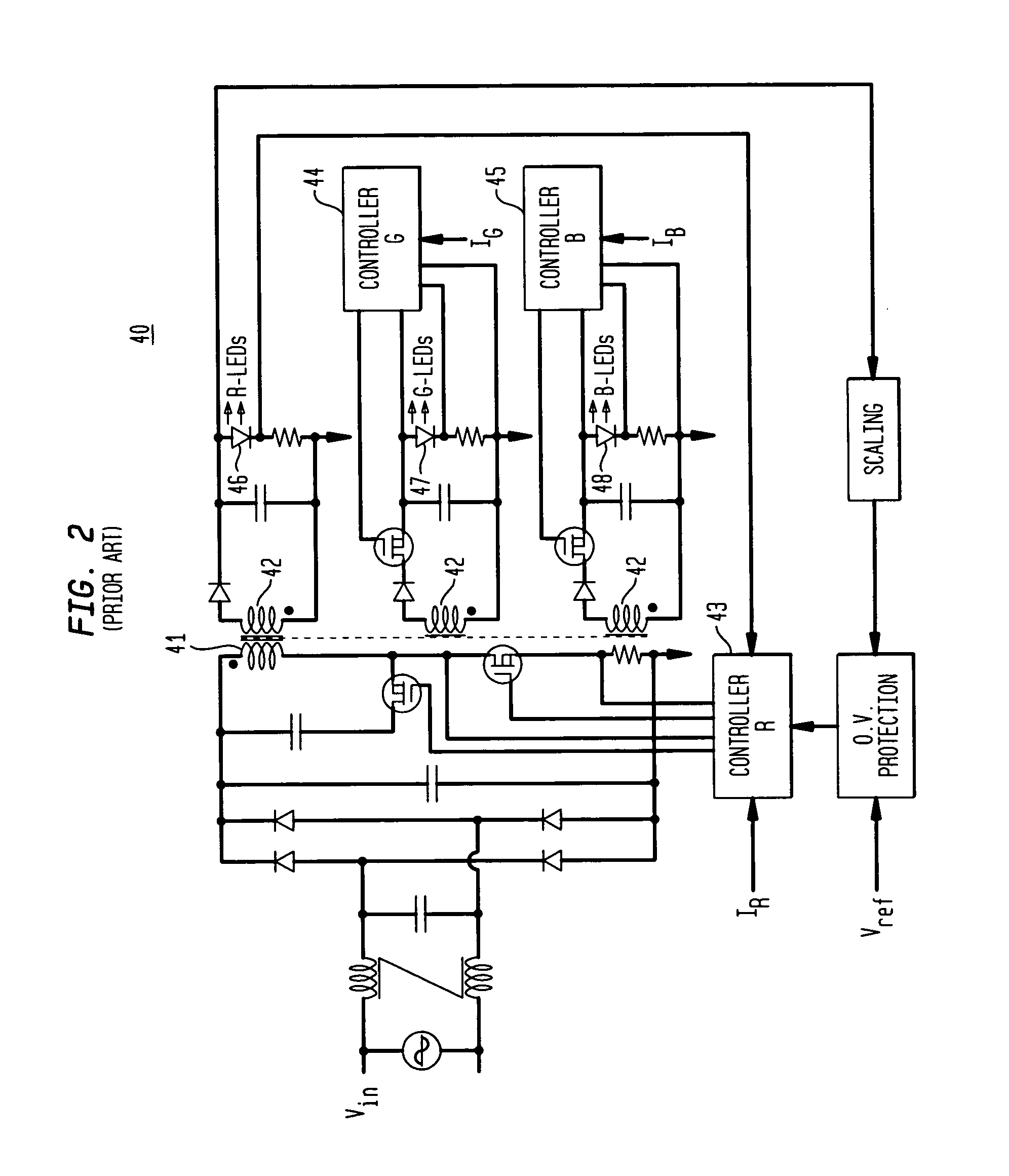

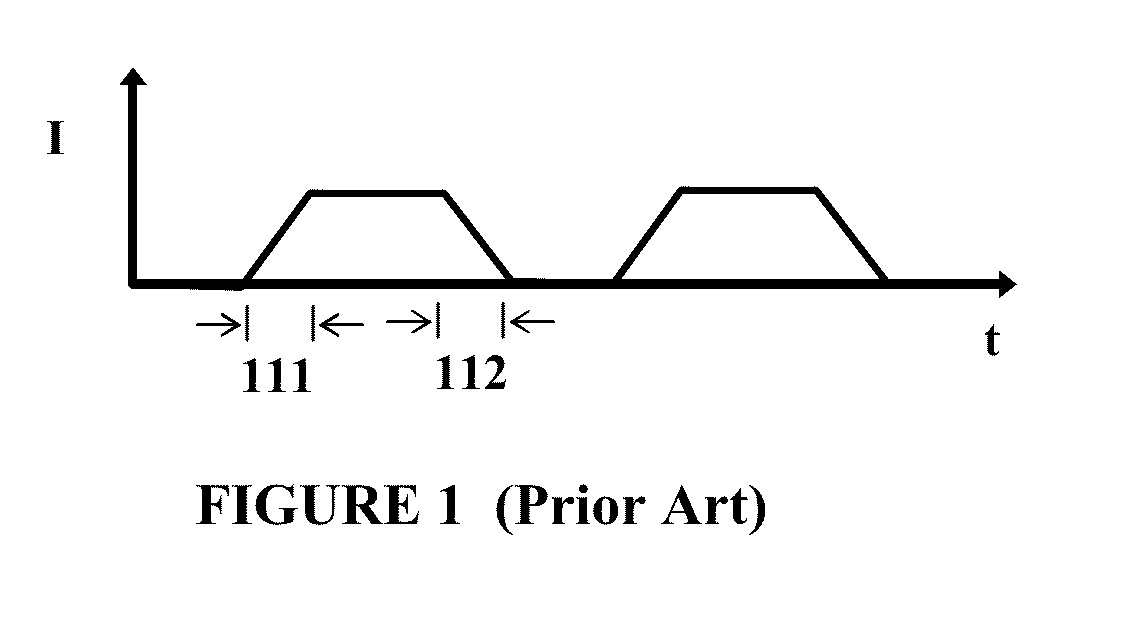

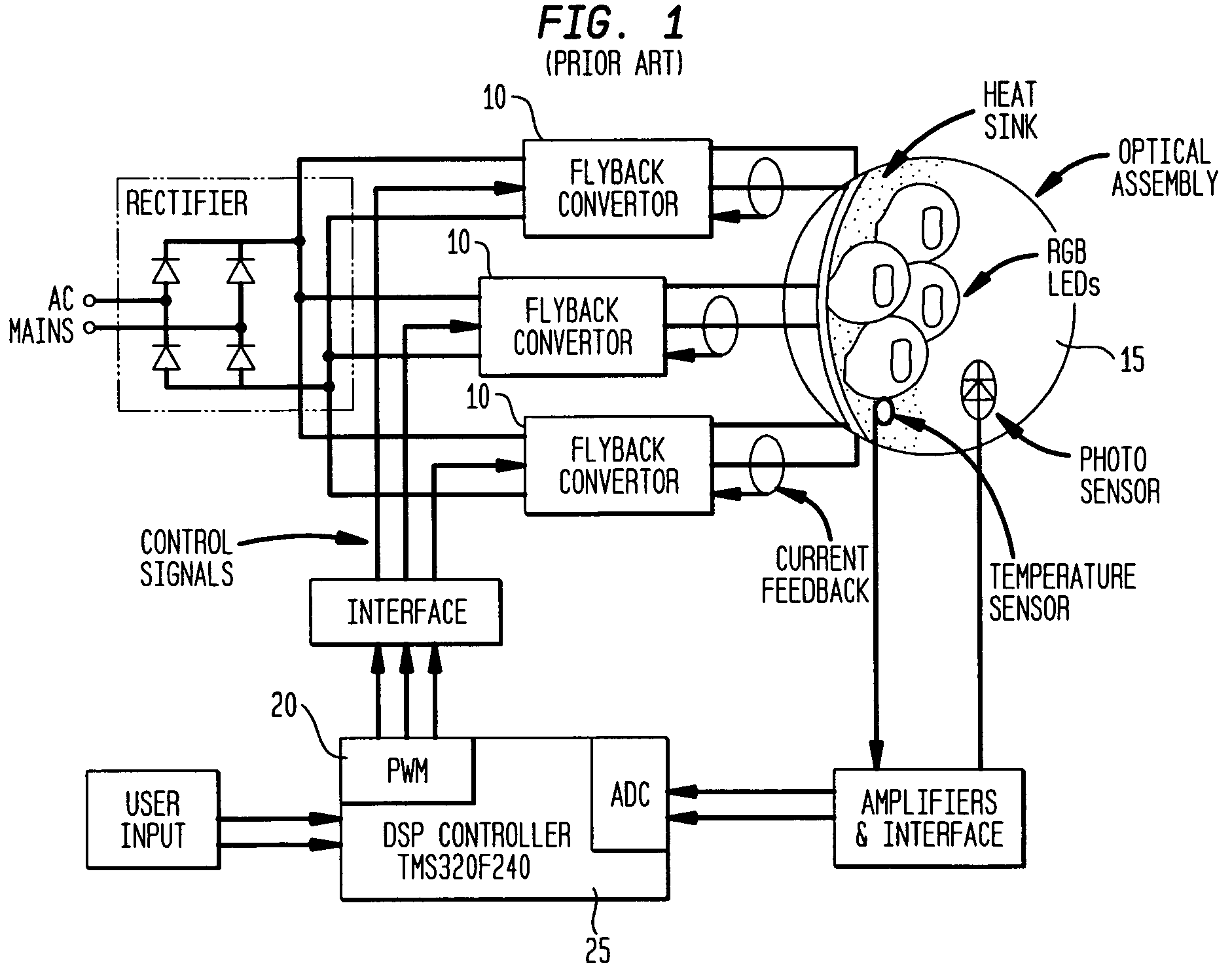

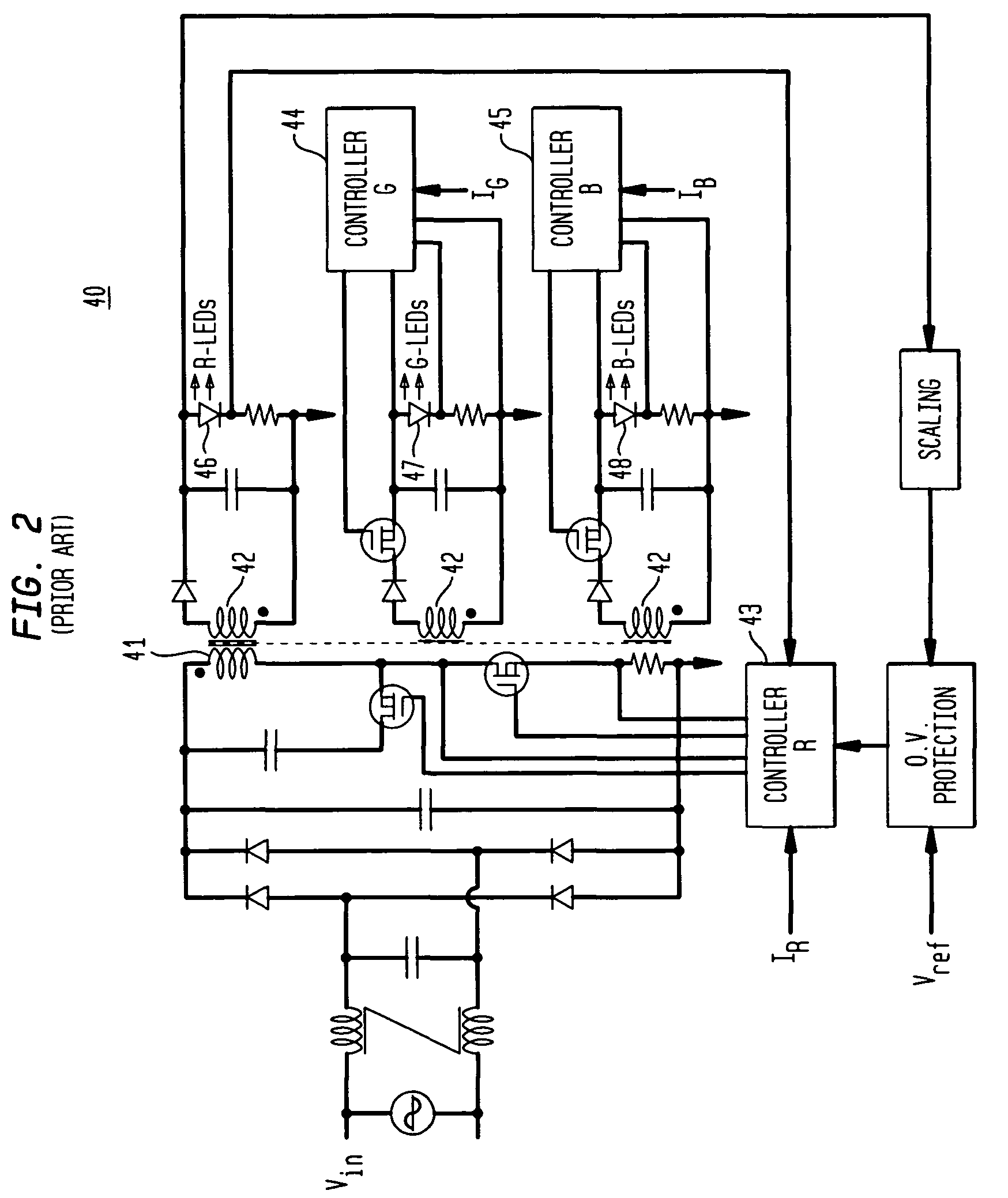

Time division modulation with average current regulation for independent control of arrays of light emitting diodes

ActiveUS20080116818A1Low costFast response timeElectrical apparatusElectroluminescent light sourcesSwitched currentAverage current

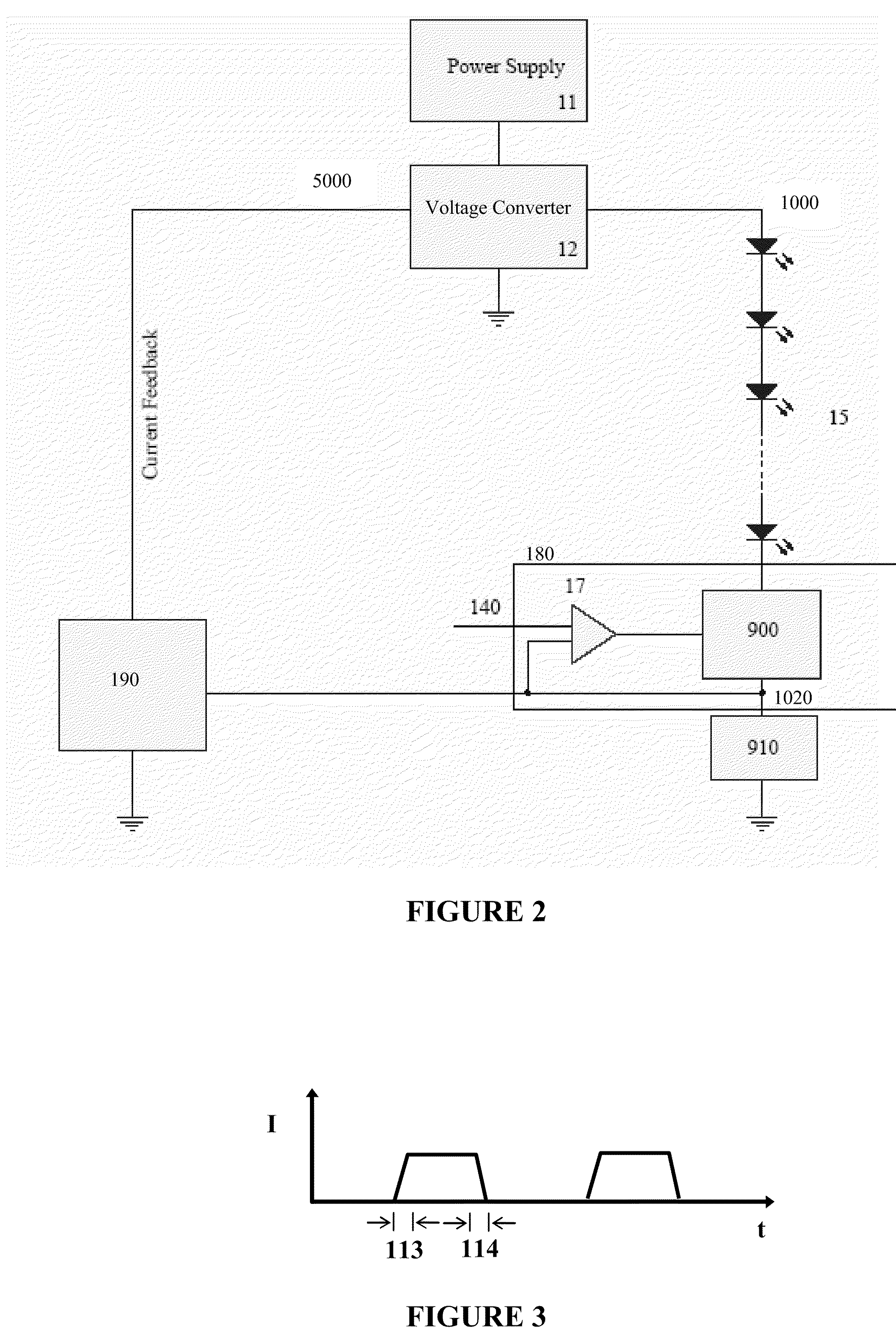

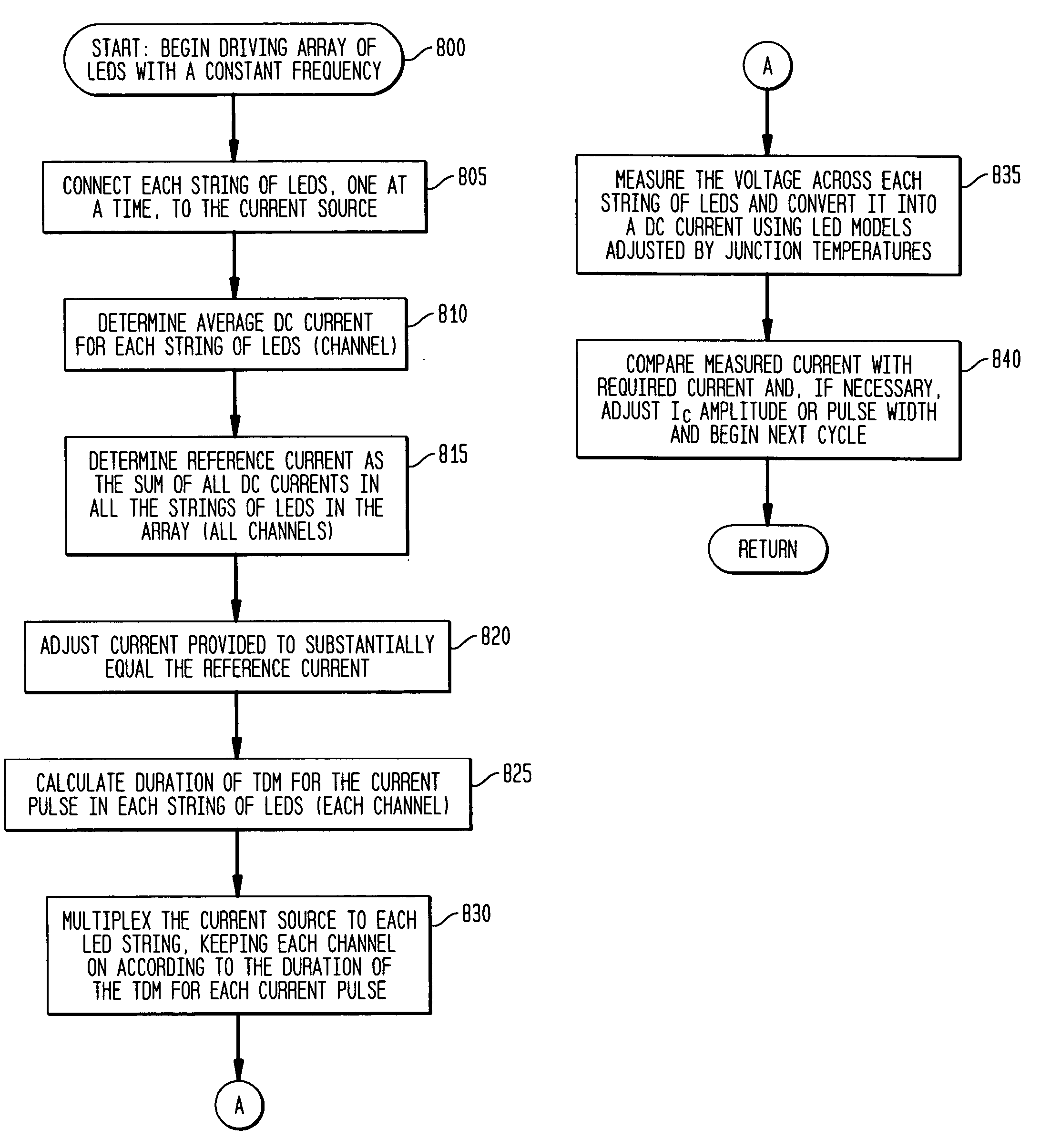

Exemplary apparatus, method and system embodiments provide for separately and independently sourcing current to a series of light emitting diodes of a plurality of series of light-emitting diodes. An exemplary apparatus comprises a power converter which generates a current, a first multiplexer, and a controller. The controller provides for sequential and separate switching of the current through the first multiplexer to each of the series of light-emitting diodes for a corresponding period of time. An average current provided by the power converter is determined as substantially equal to a sum of the corresponding currents through the plurality of series of light-emitting diodes. A total period for switching current to all of the series of light-emitting diodes is also determined. A corresponding time period for switching current to a selected corresponding series of light-emitting diodes is substantially equal to a proportion of the total period determined as a ratio of the corresponding current for the selected corresponding series of light-emitting diodes to the average current provided by the power converter.

Owner:CHEMTRON RES

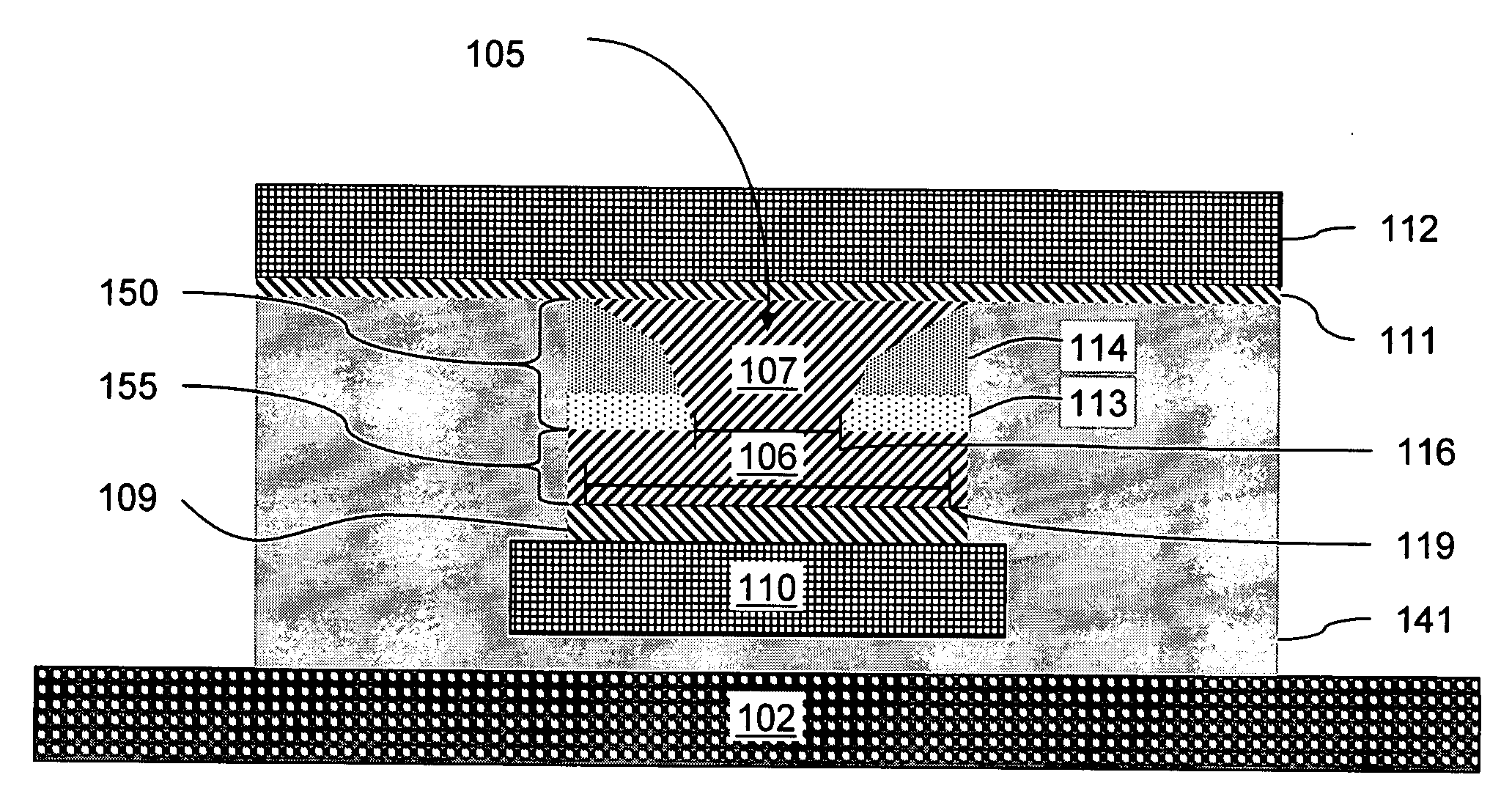

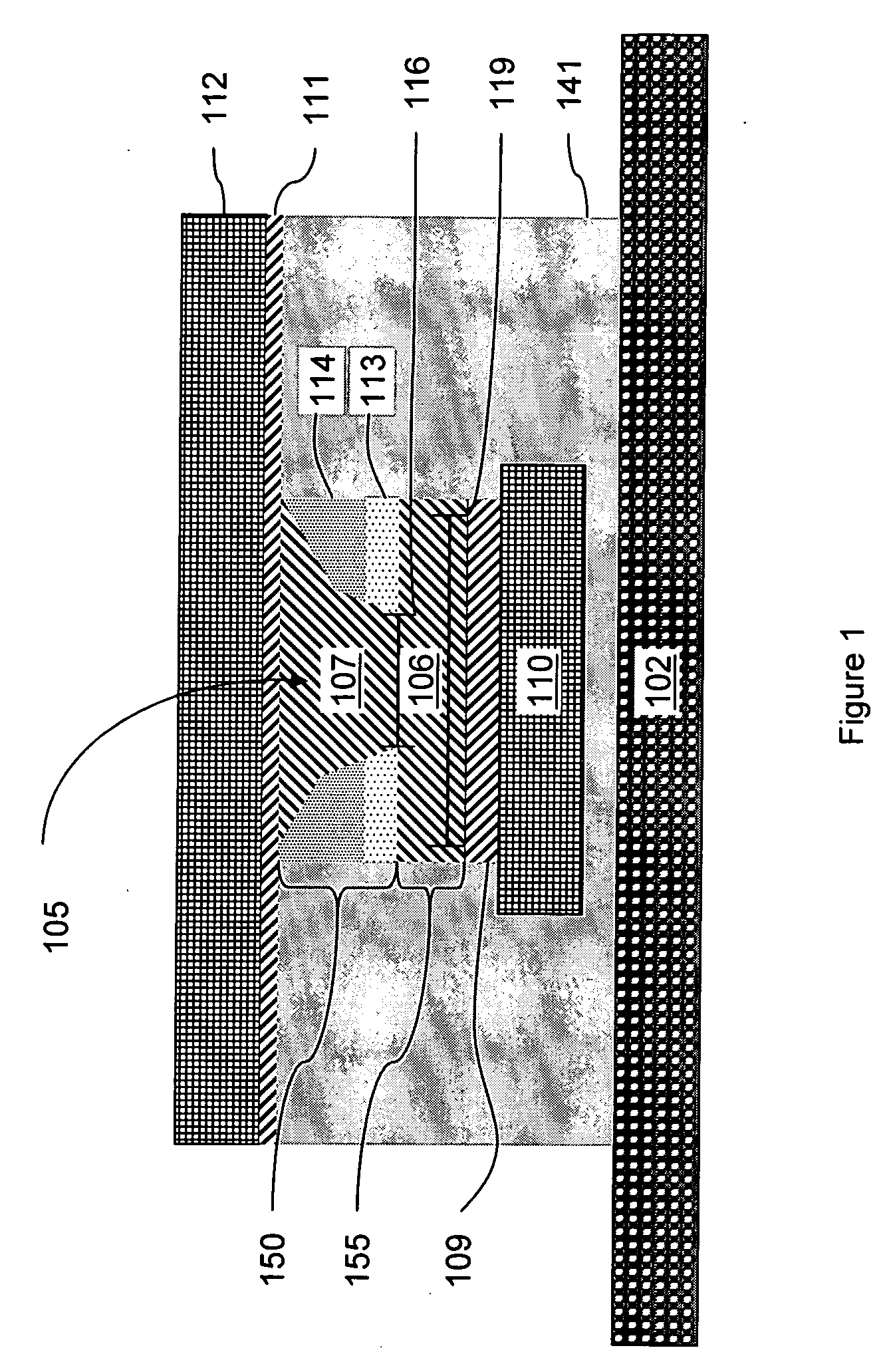

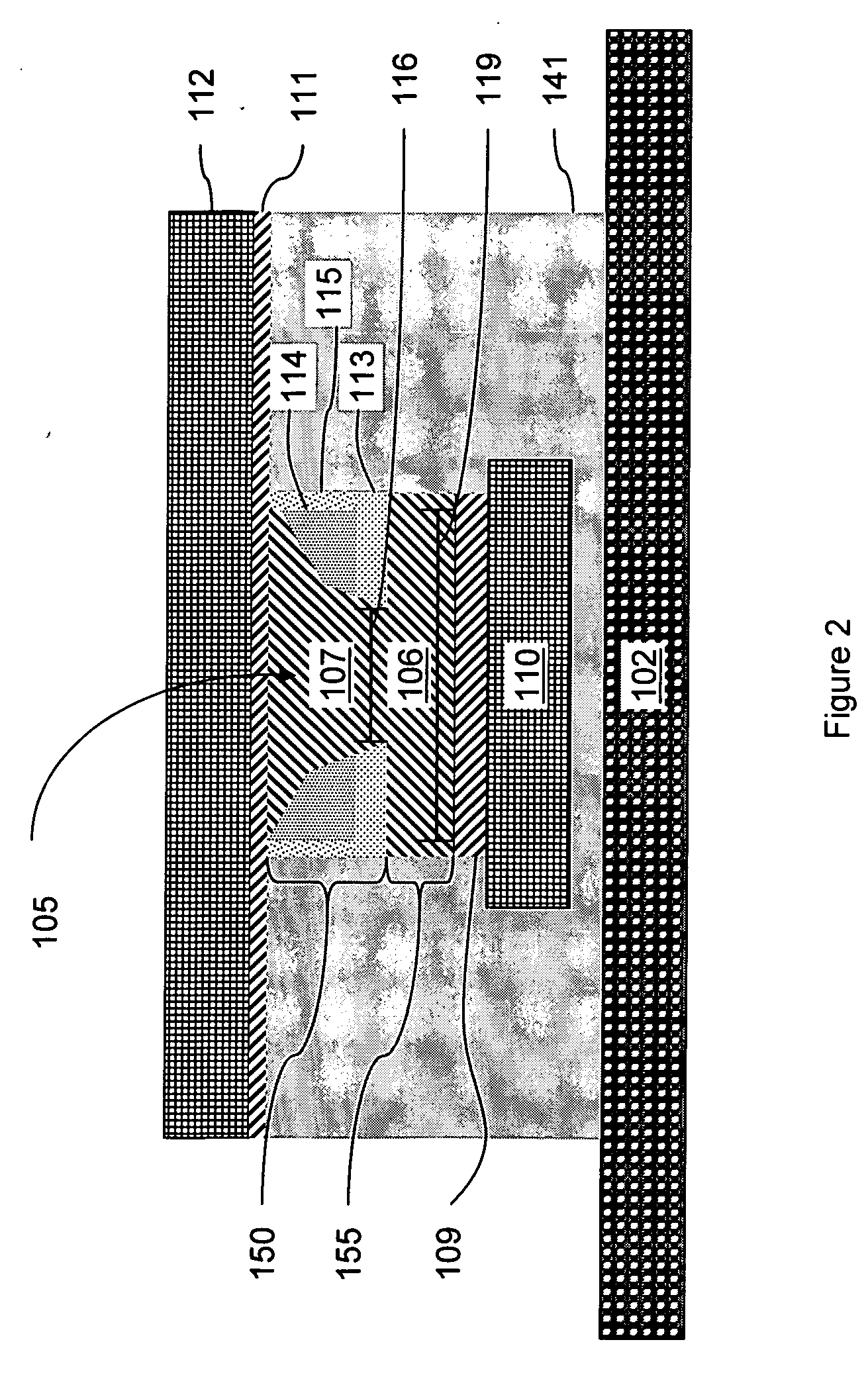

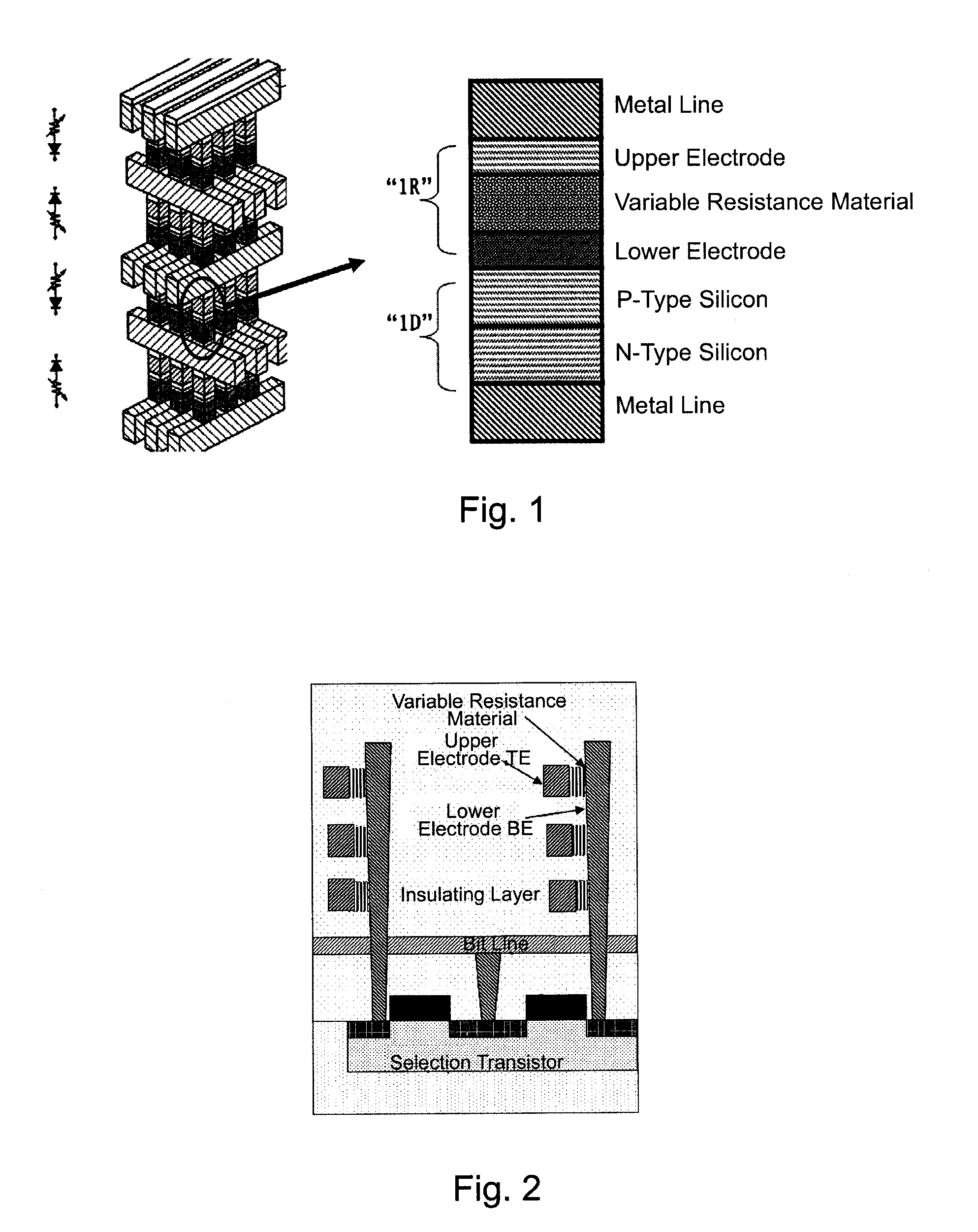

Structure for confining the switching current in phase memory (PCM) cells

InactiveUS20060226409A1Heat dissipation is limitedHigh densityBulk negative resistance effect devicesSemiconductor devicesPhase-change memorySwitched current

Disclosed are a phase change memory cell and a method of forming the memory cell. The memory cell comprises a main body of phase change material connected directly to a bottom contact and via a narrow channel of phase change material to a top contact. The channel is tapered from the top contact towards the main body. A minimum width of the channel has a less than minimum lithographic dimension and is narrower than a width of the main body. Therefore, the channel provides a confined region for the switching current path and restricts phase changing to within the channel. In addition an embodiment of the memory cell isolates the main body of phase change material by providing a space between the phase change material and the cell walls. The space allows the phase change material to expand and contract and also limits heat dissipation.

Owner:IBM CORP

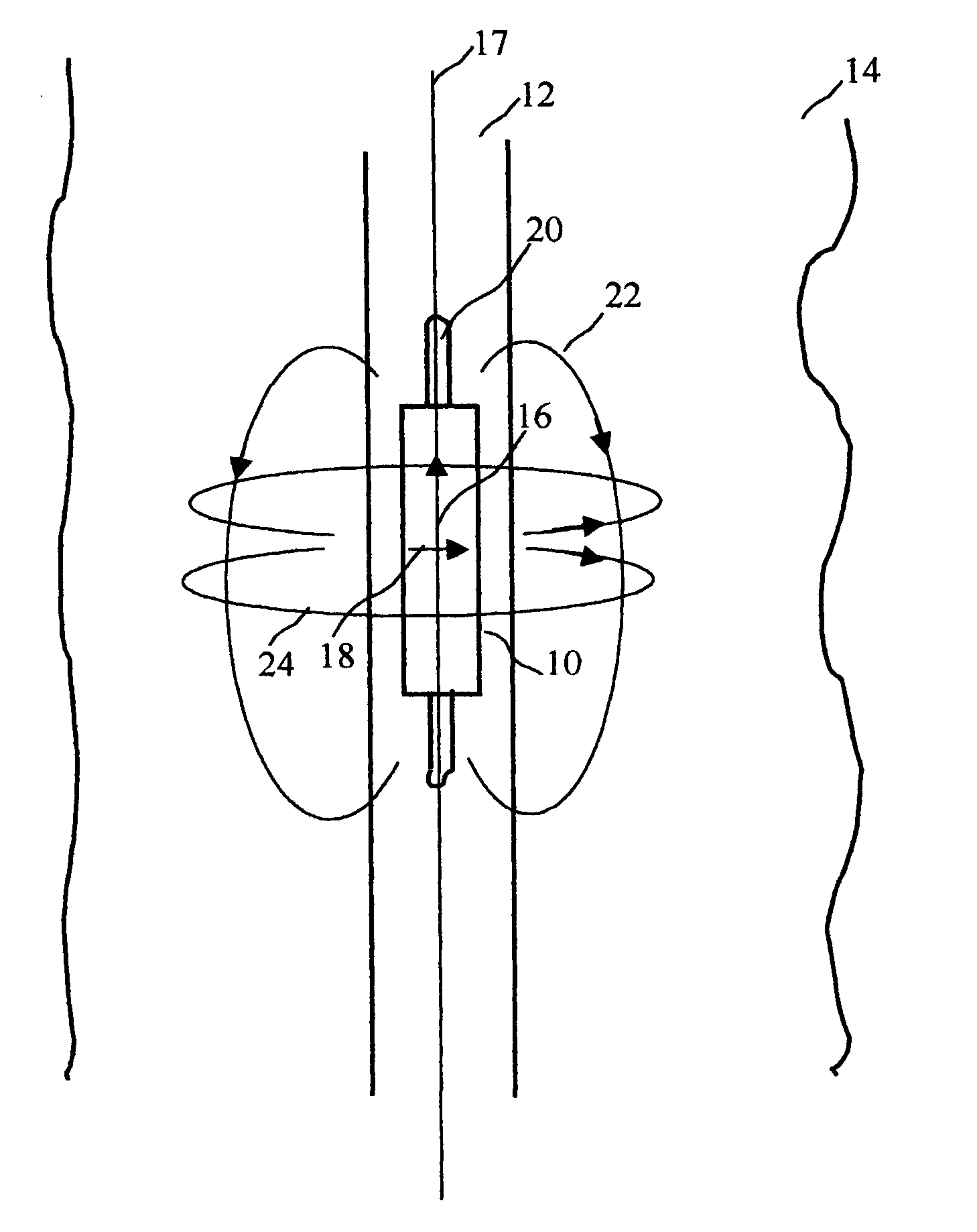

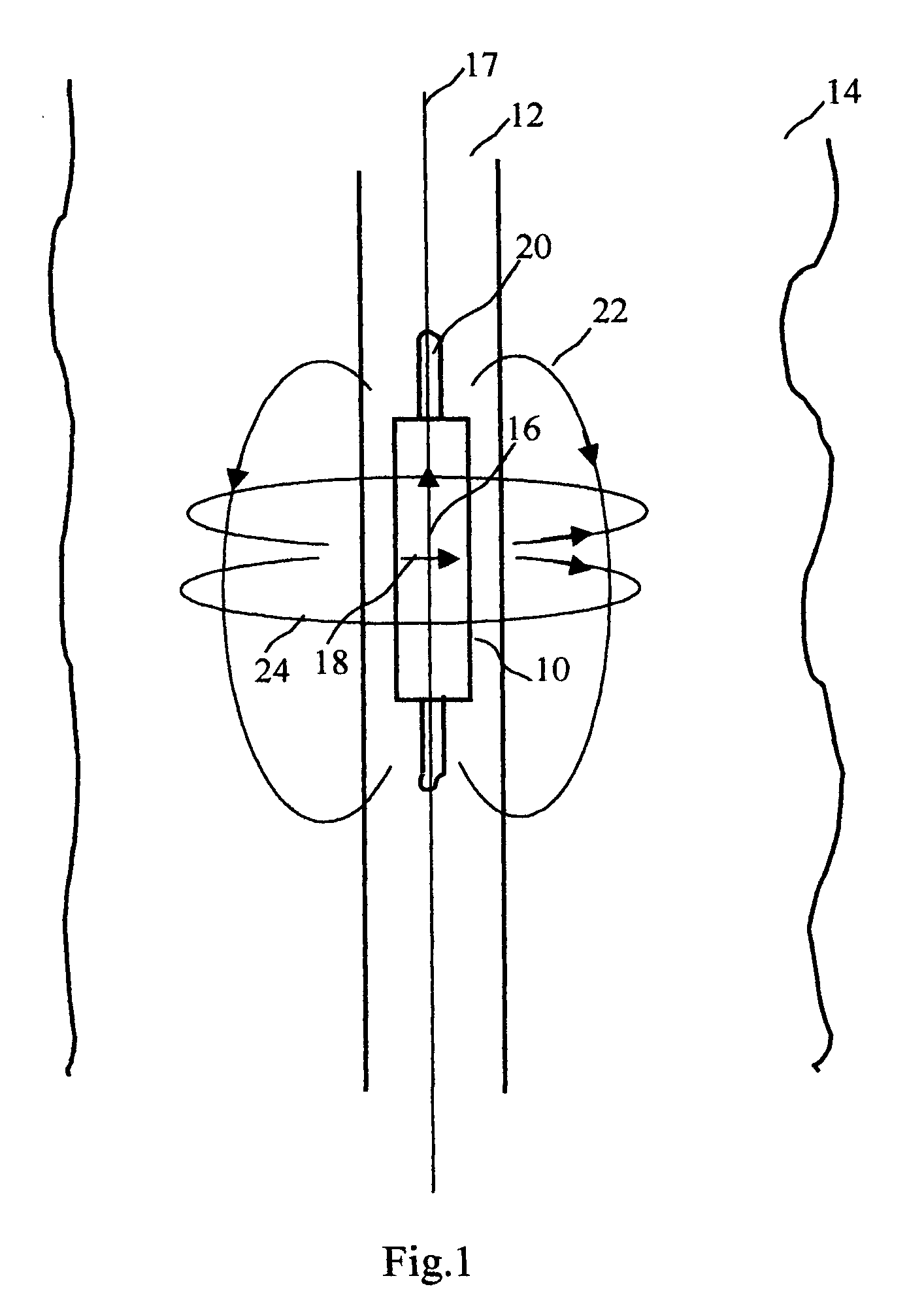

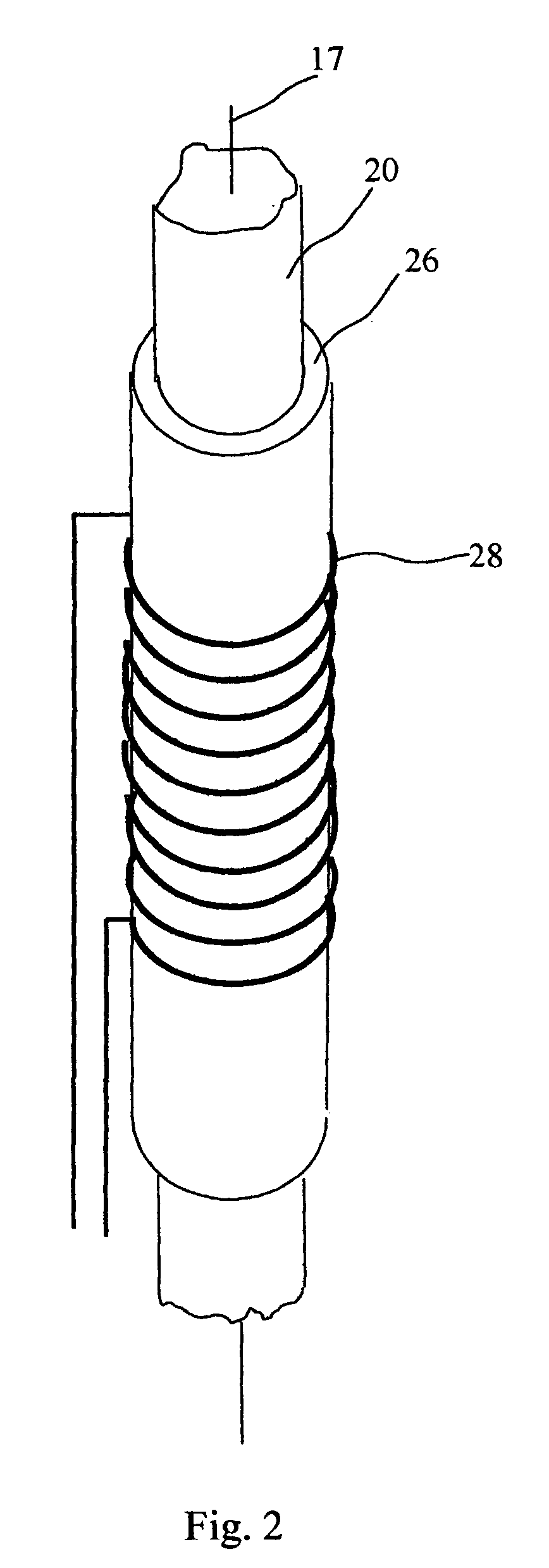

Method and apparatus of using magnetic material with residual magnetization in transient electromagnetic measurement

ActiveUS20050189945A1Facilitates highly effective generationQuick switchElectric/magnetic detection for well-loggingAcoustic wave reradiationWell loggingTransmitter antenna

Owner:BAKER HUGHES INC

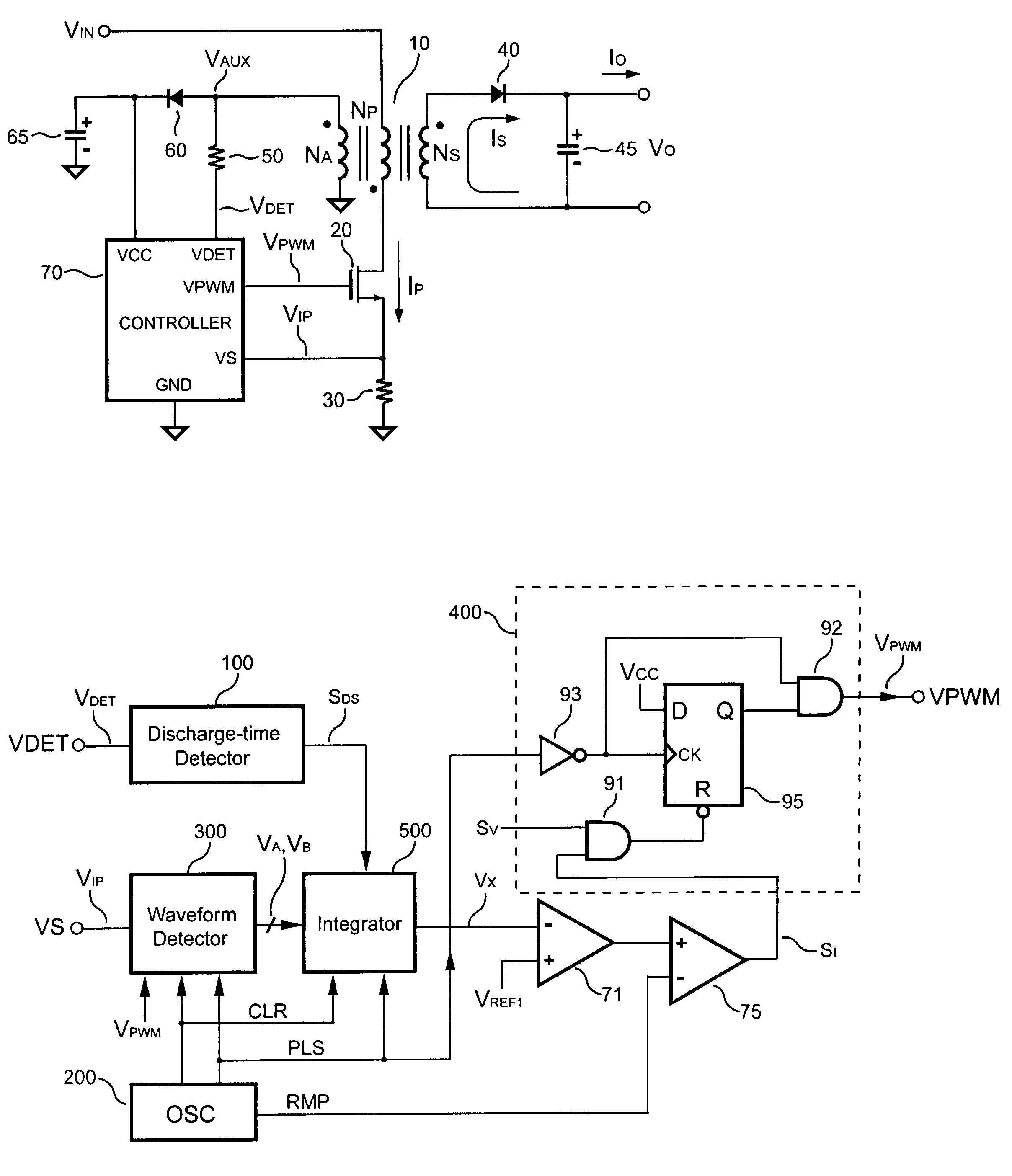

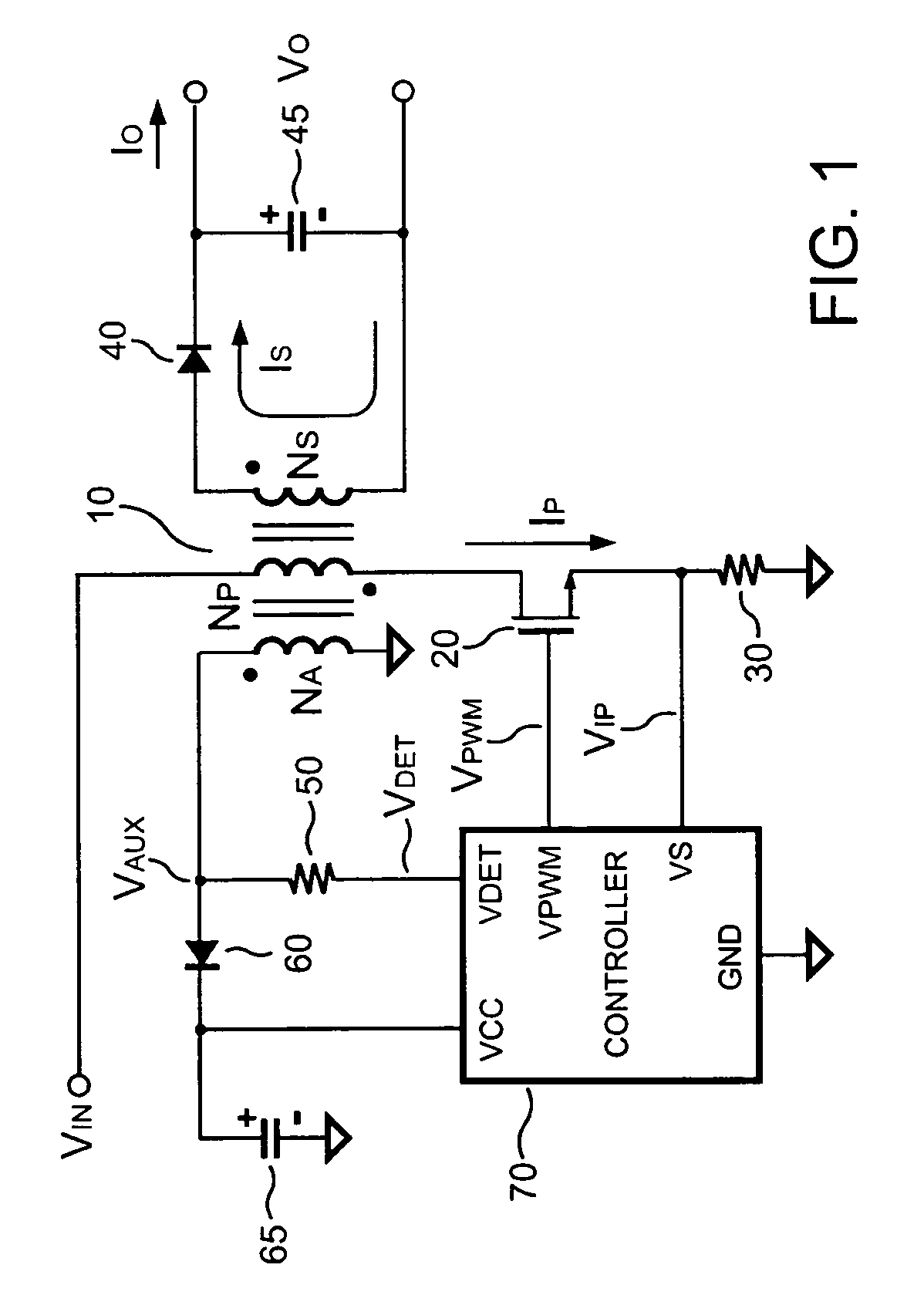

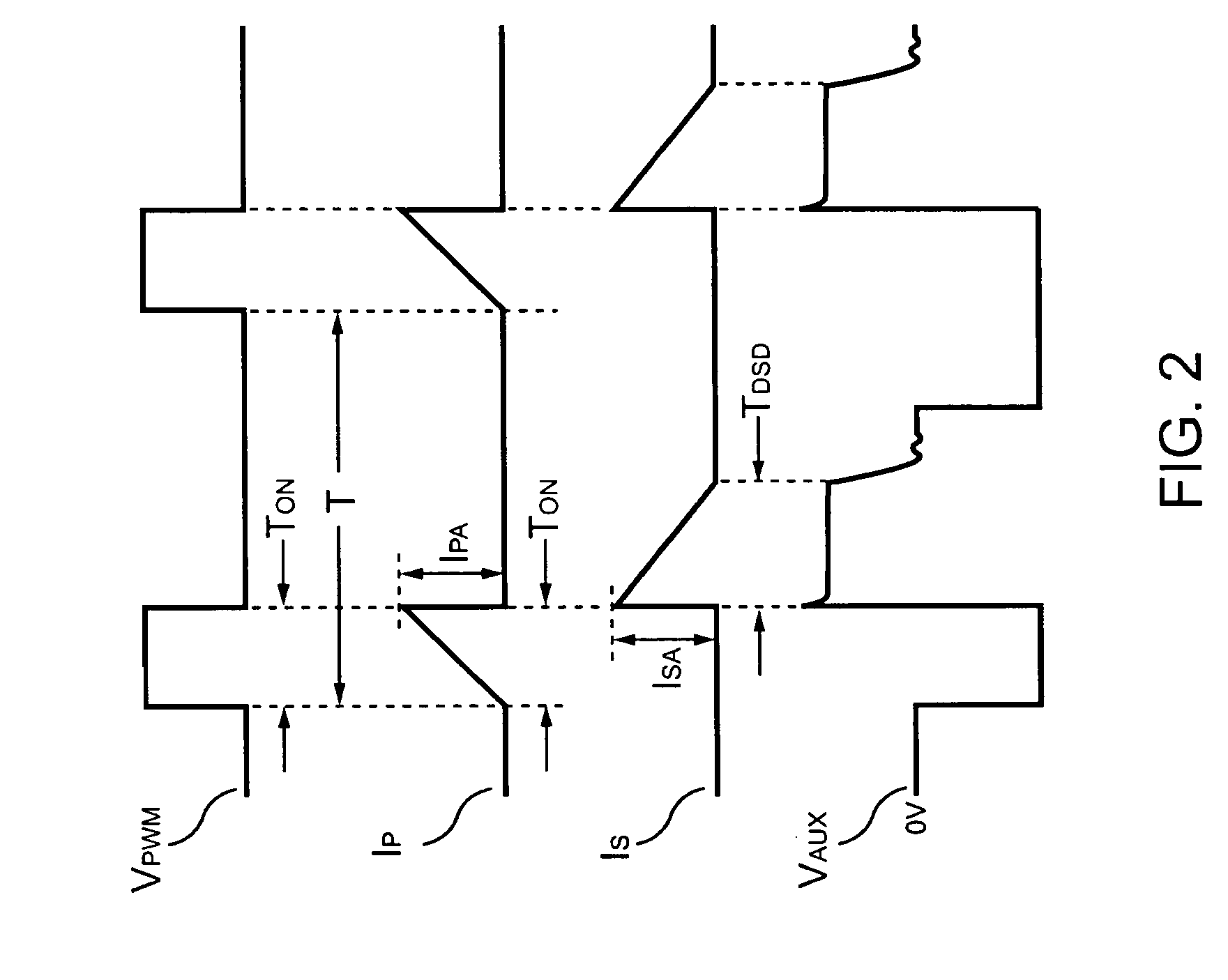

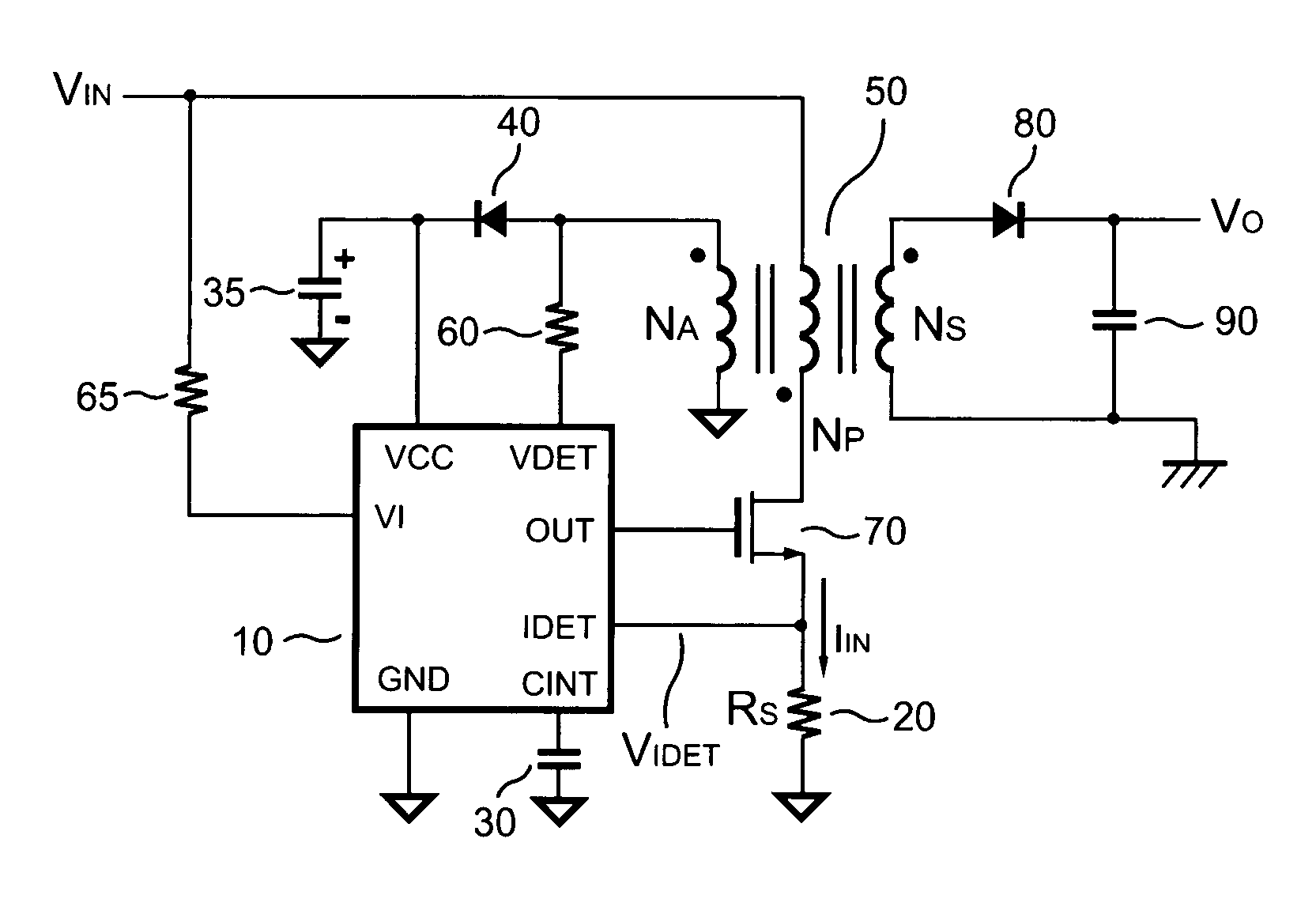

Control circuit for controlling output current at the primary side of a power converter

A control circuit controlling output current at the primary side of a power converter is provided. A waveform detector generates a current-waveform signal. A discharge-time detector detects a discharge-time of a secondary side switching current. An oscillator generates an oscillation signal for determining the switching frequency of the switching signal. An integrator generates an integrated signal by integrating an average current signal with the discharge-time. The average current signal is generated in response to the current-waveform signal. The time constant of the integrator is correlated with the switching period of the switching signal, therefore the integrated signal is proportional to the output current. An error amplifier amplifies the integrated signal and provides a loop gain for output current control. A comparator controls the pulse width of the switching signal in reference to the output of the error amplifier. Therefore, the output current of the power converter can be regulated.

Owner:SEMICON COMPONENTS IND LLC

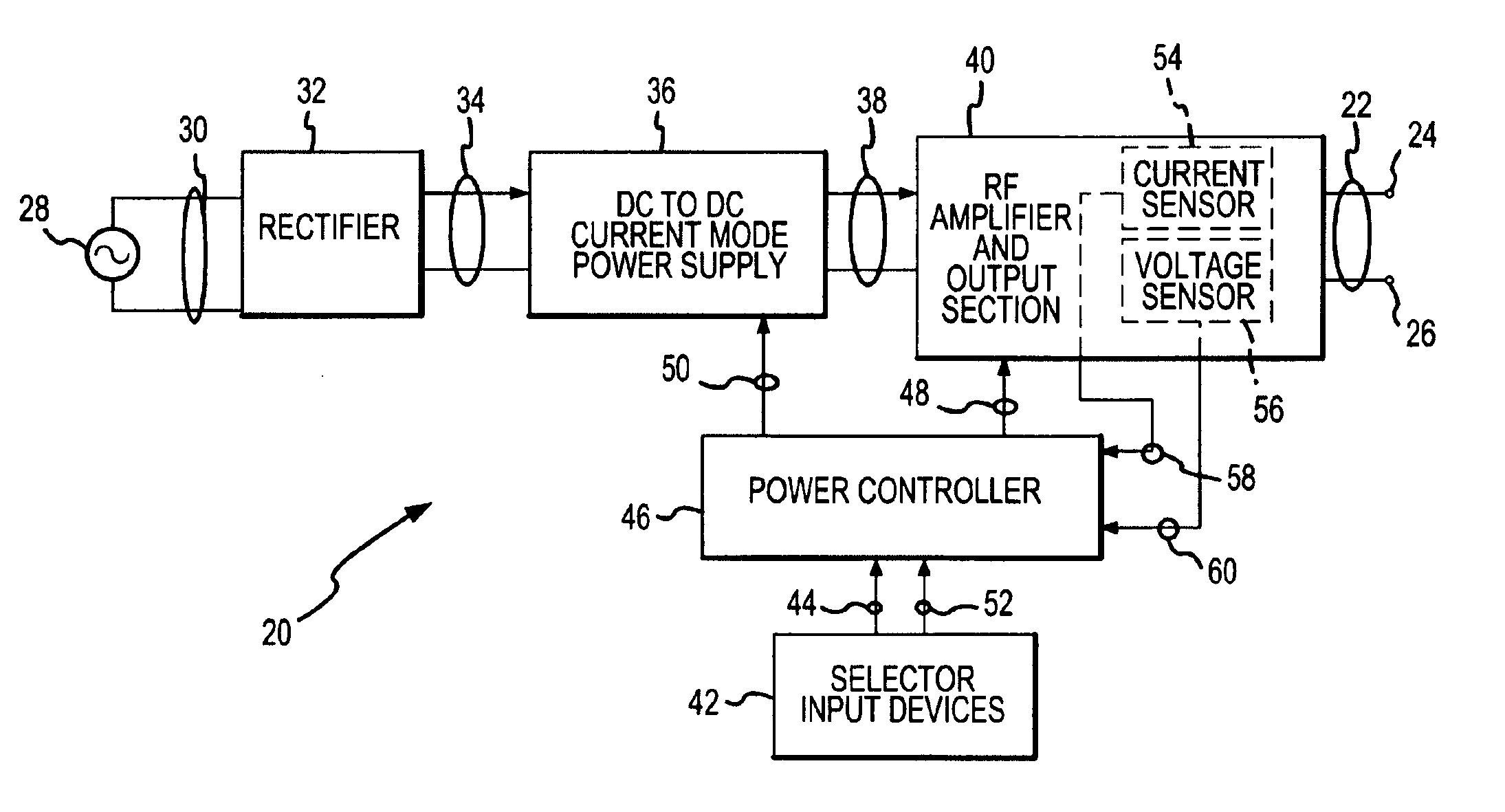

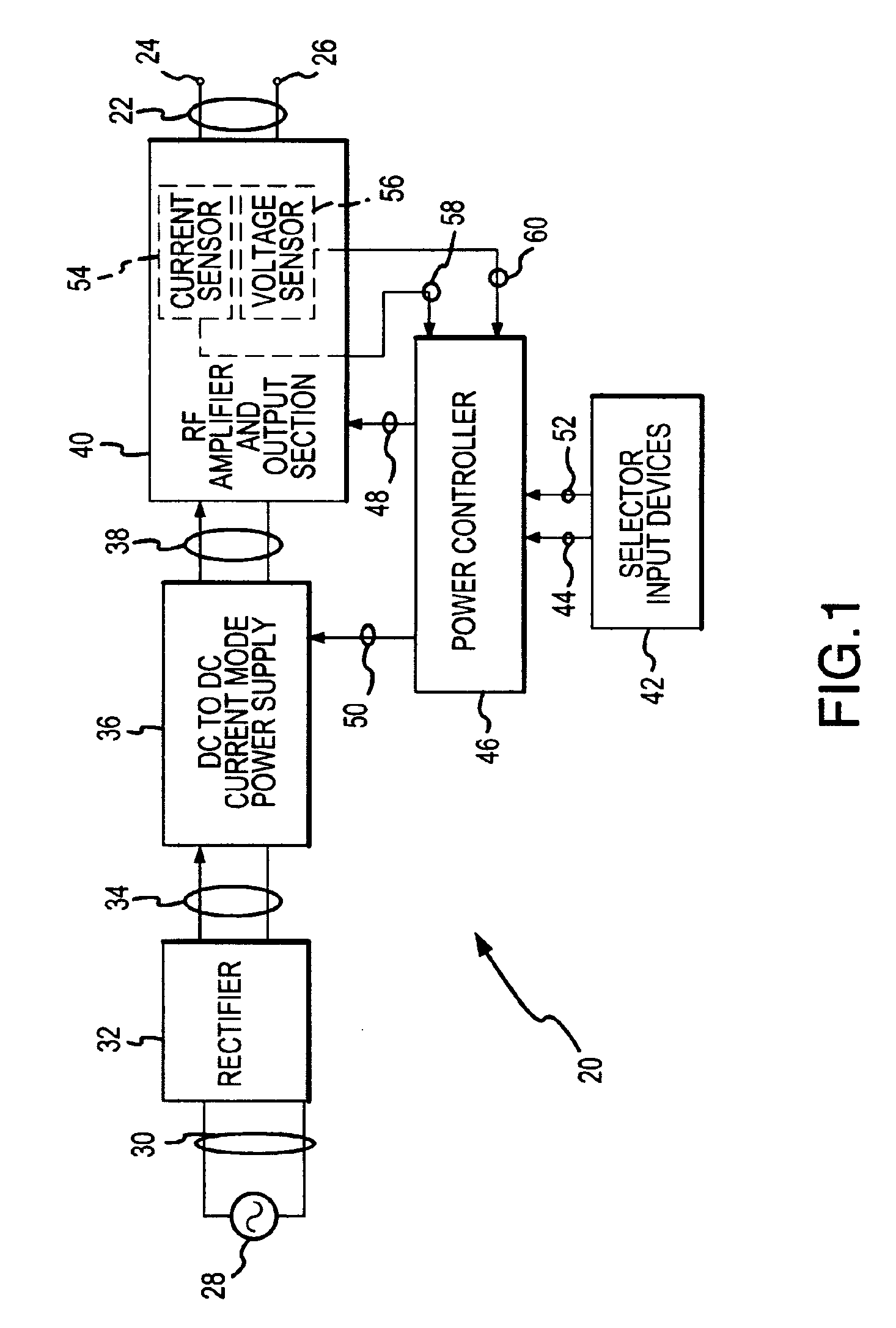

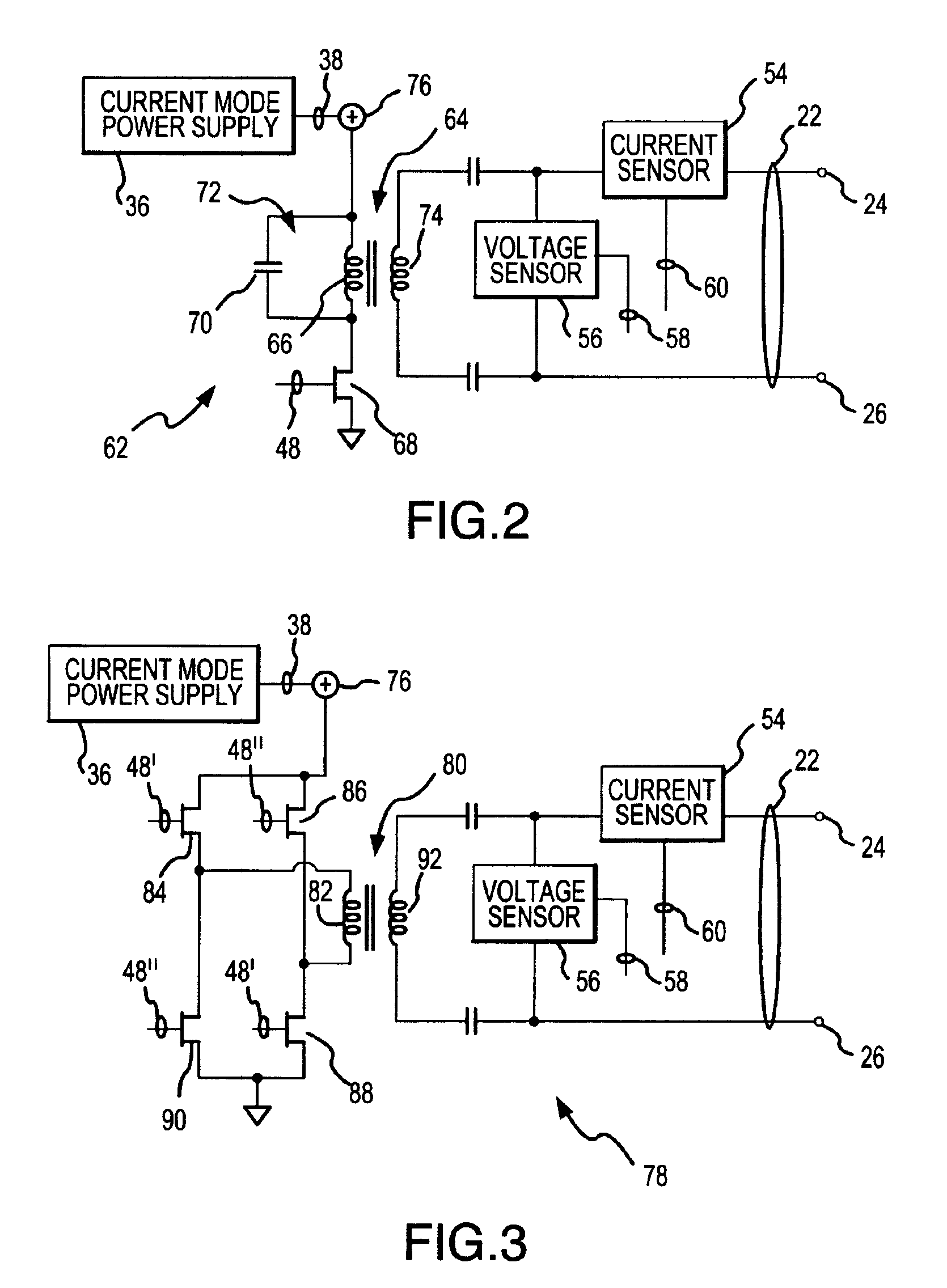

Electrosurgical generator and method with voltage and frequency regulated high-voltage current mode power supply

ActiveUS6939347B2Efficient implementationEfficient and effective power controlDiagnosticsEmergency protective circuit arrangementsSwitched currentTransformer

DC input energy is converted into DC output voltage by the use of a switched current mode high-voltage power supply. Pulses of input current are switched through a conversion transformer and the energy content of each pulse is converted into the DC output voltage. The time widths of the input current pulses are regulated relative to the DC input and output voltages, the magnitude of the current within each input current pulse, and in relation to maintaining a plurality of different selected operational conditions. The rate at which the input current pulses are converted is changed relative to the level of the DC output voltage.

Owner:CONMED CORP

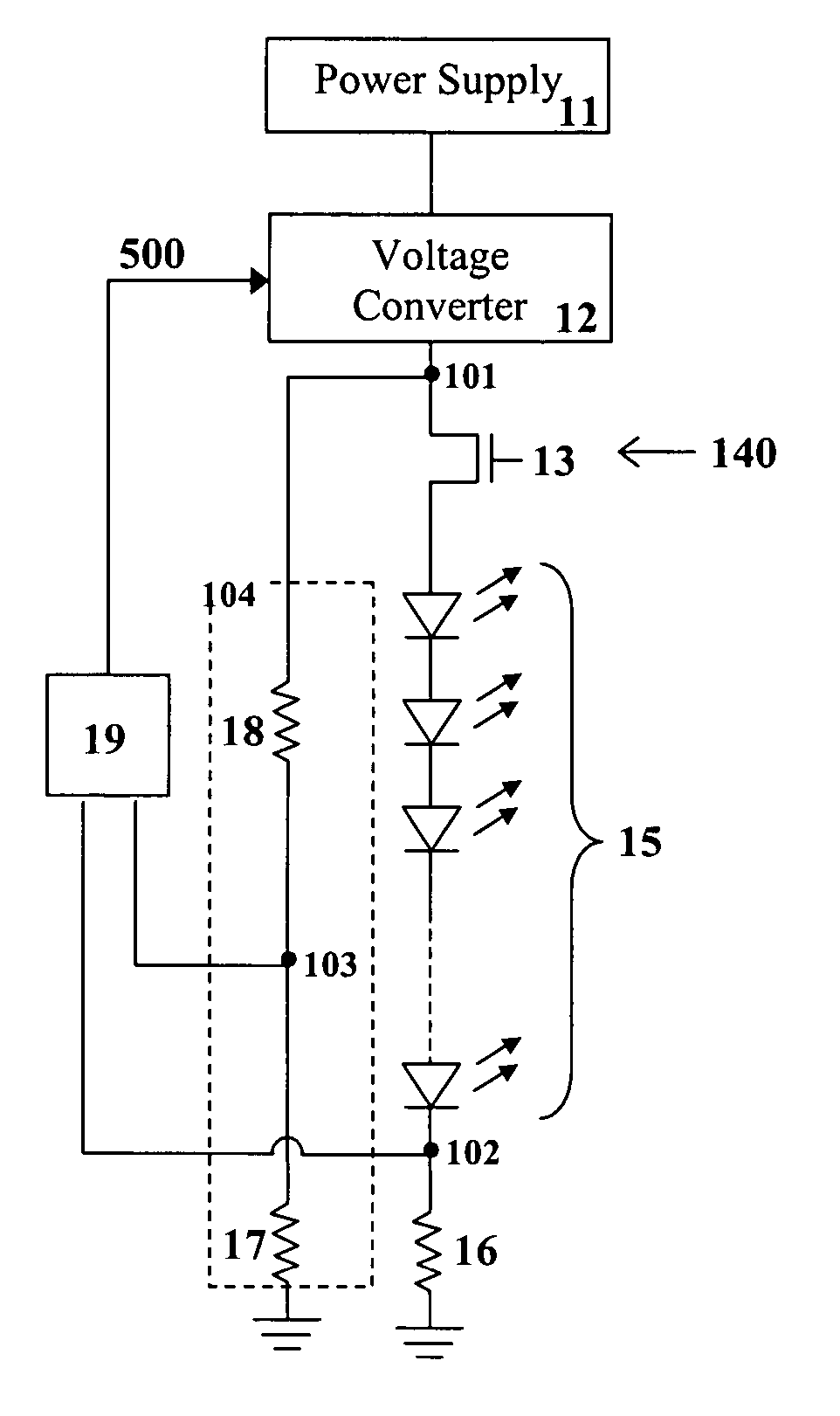

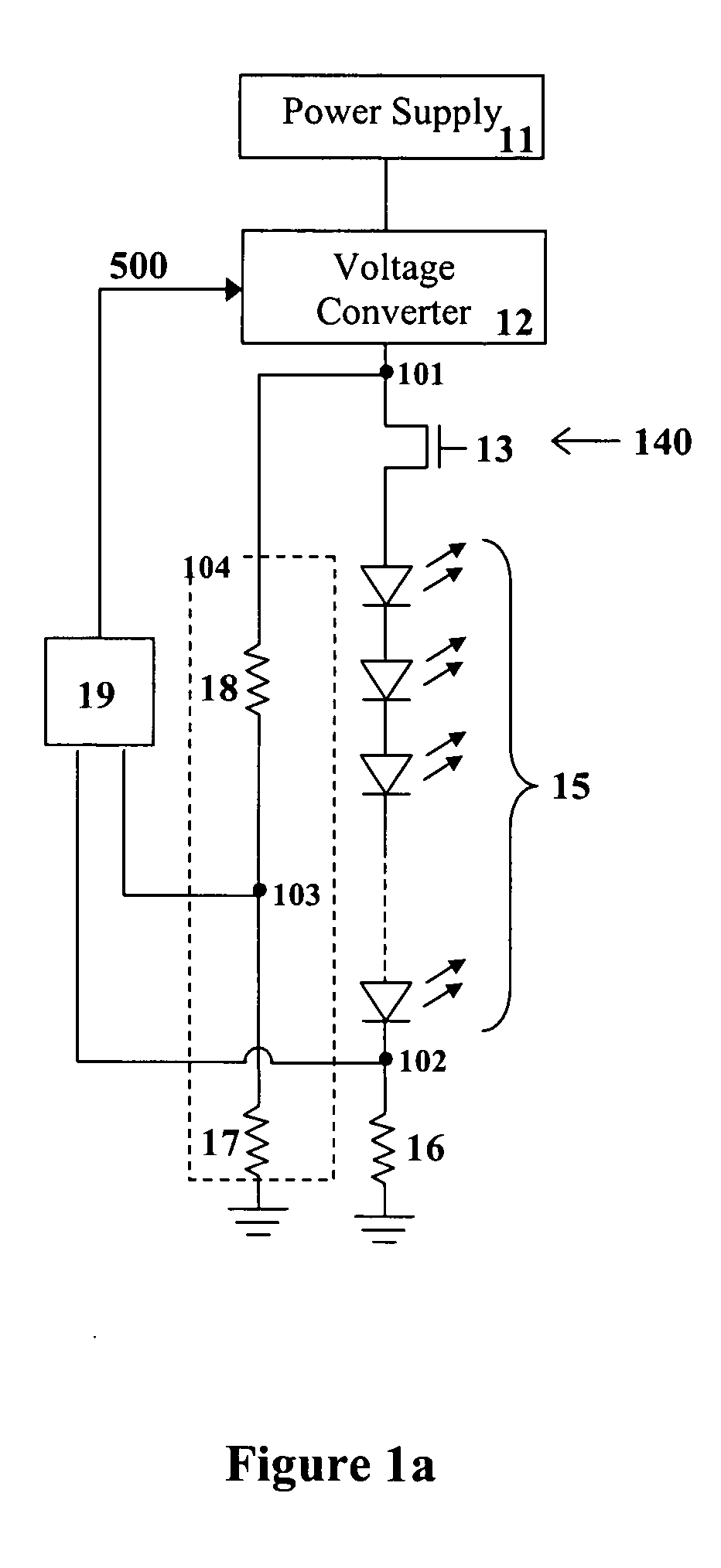

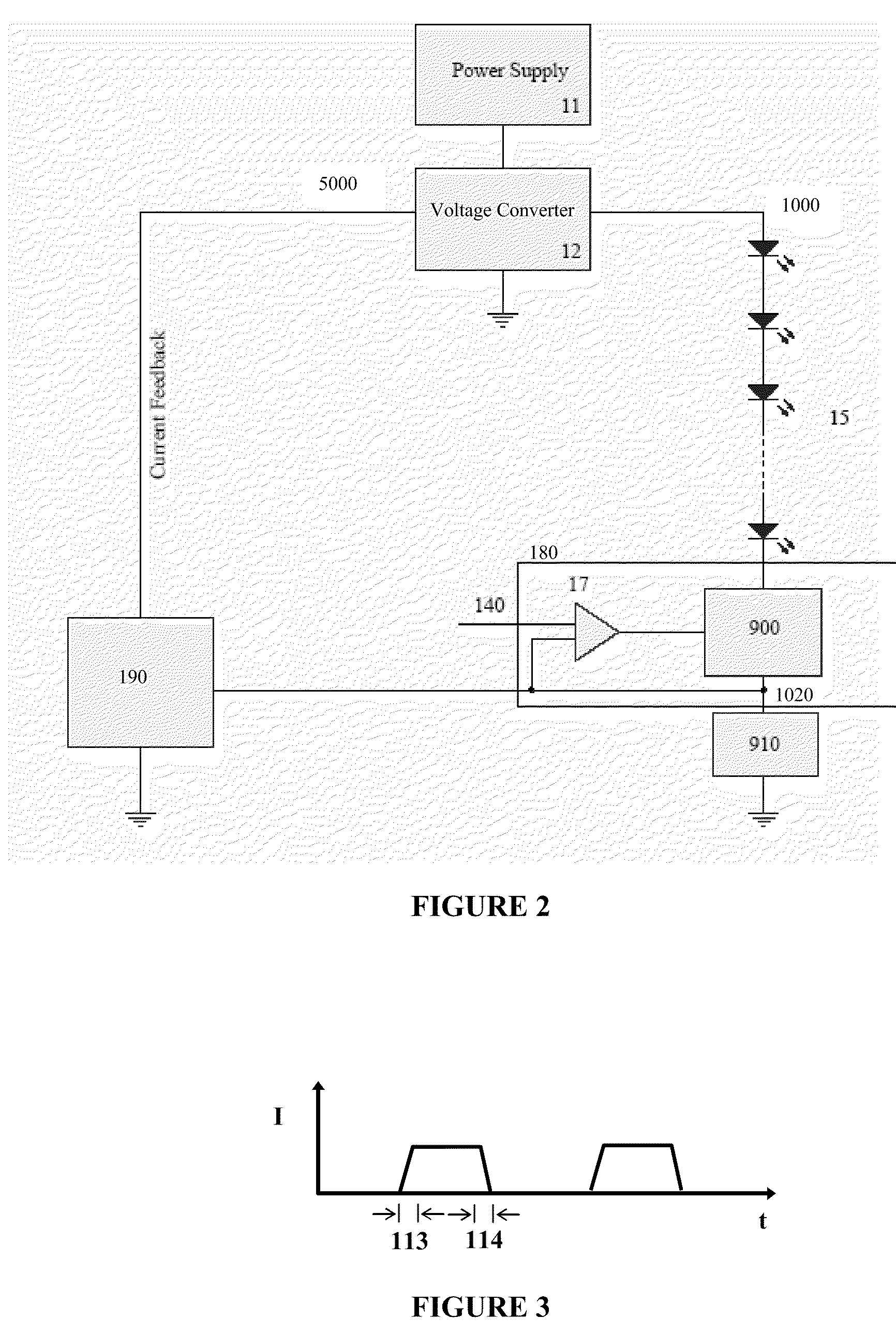

Switched constant current driving and control circuit

ActiveUS20060001381A1Full dimming without large power lossesConstant currentElectrical apparatusElectroluminescent light sourcesControl signalInput control

The driving and control device according to the present invention provides a desired switched current to a load including a string of one or more electronic devices, and comprises one or more voltage conversion means, one or more dimming control means, one or more feedback means and one or more sensing means. The voltage conversion means may be a DC-to-DC converter for example and based on an input control signal converts the magnitude of the voltage from the power supply to another magnitude that is desired at the high side of the load. The dimming control means may comprise a switch such as a FET, BJT, relay, or any other type of switching device, for example, and provides control for activation and deactivation of the load. The feedback means is coupled to the voltage conversion means and a current sensing means and provides a feedback signal to the voltage conversion means that is indicative of the voltage drop across the current sensing means which thus represents the current flowing through the load. The current sensing means may comprise a fixed resistor, variable resistor, inductor, or some other element which has a predictable voltage-current relationship and thus will provide a measurement of the current flowing through the load based on a collected voltage signal. Based on the feedback signal received, the voltage conversion means can subsequently adjust its output voltage such that a constant switched current is provided to the load.

Owner:SIGNIFY HLDG BV

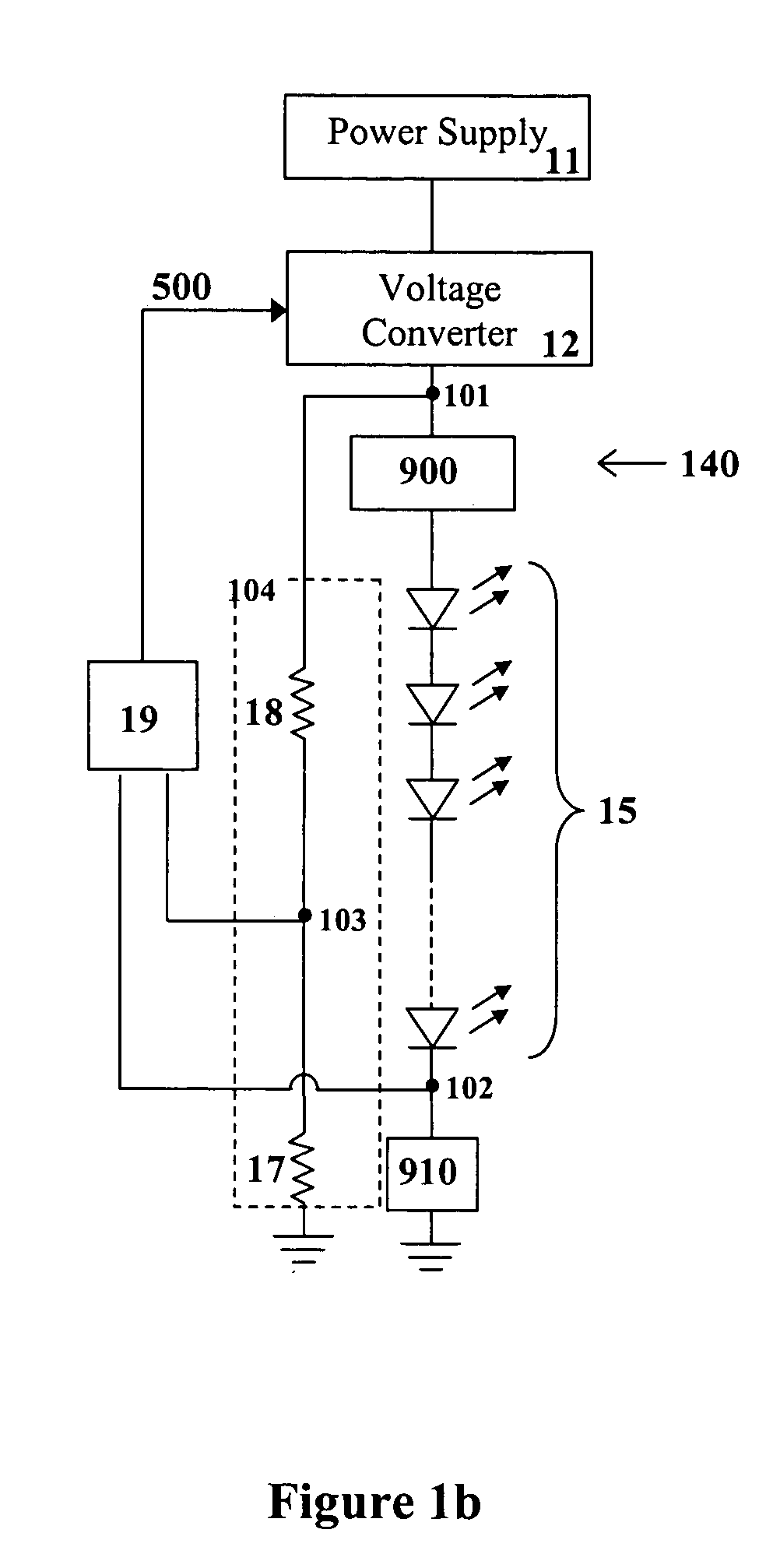

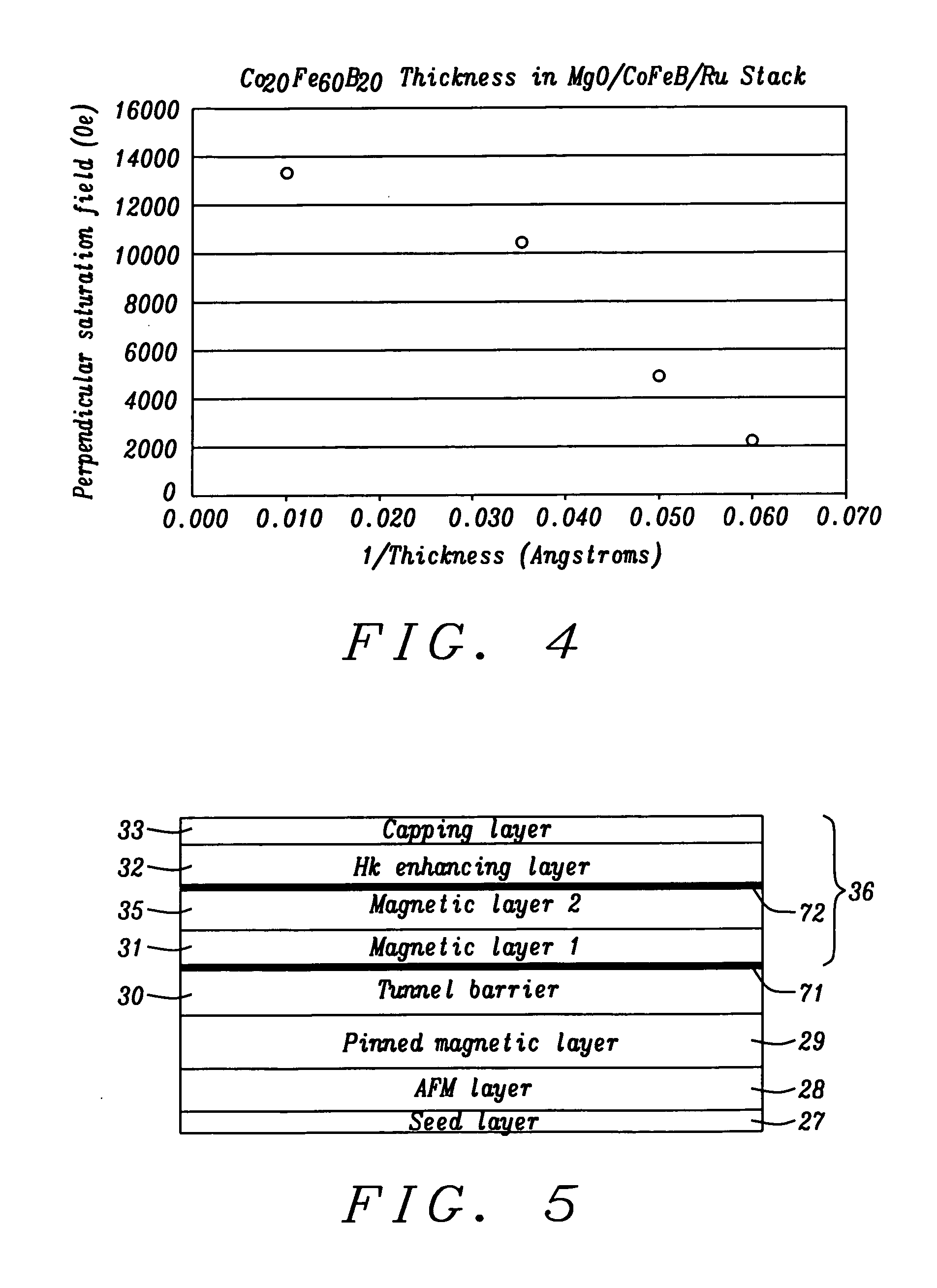

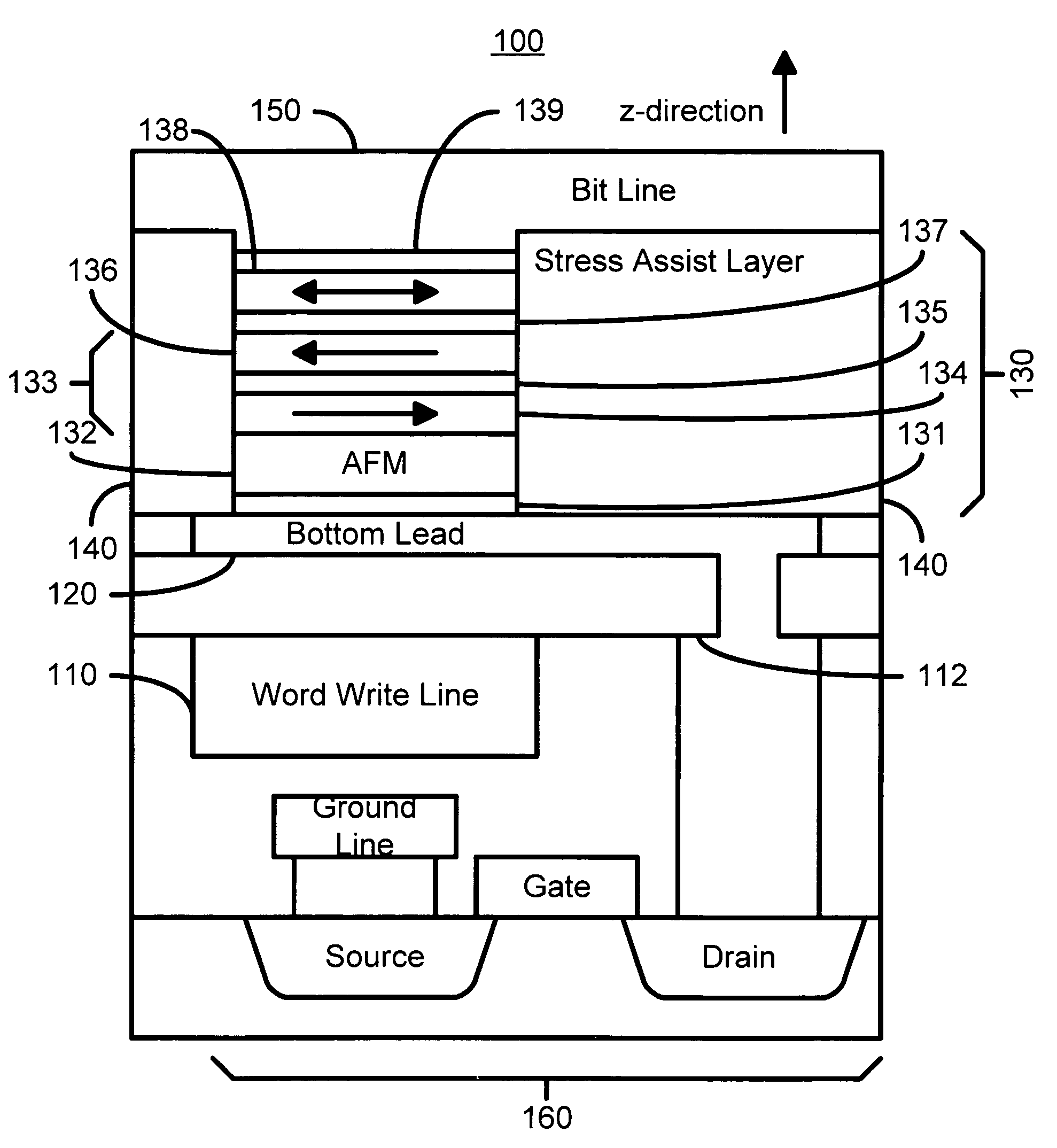

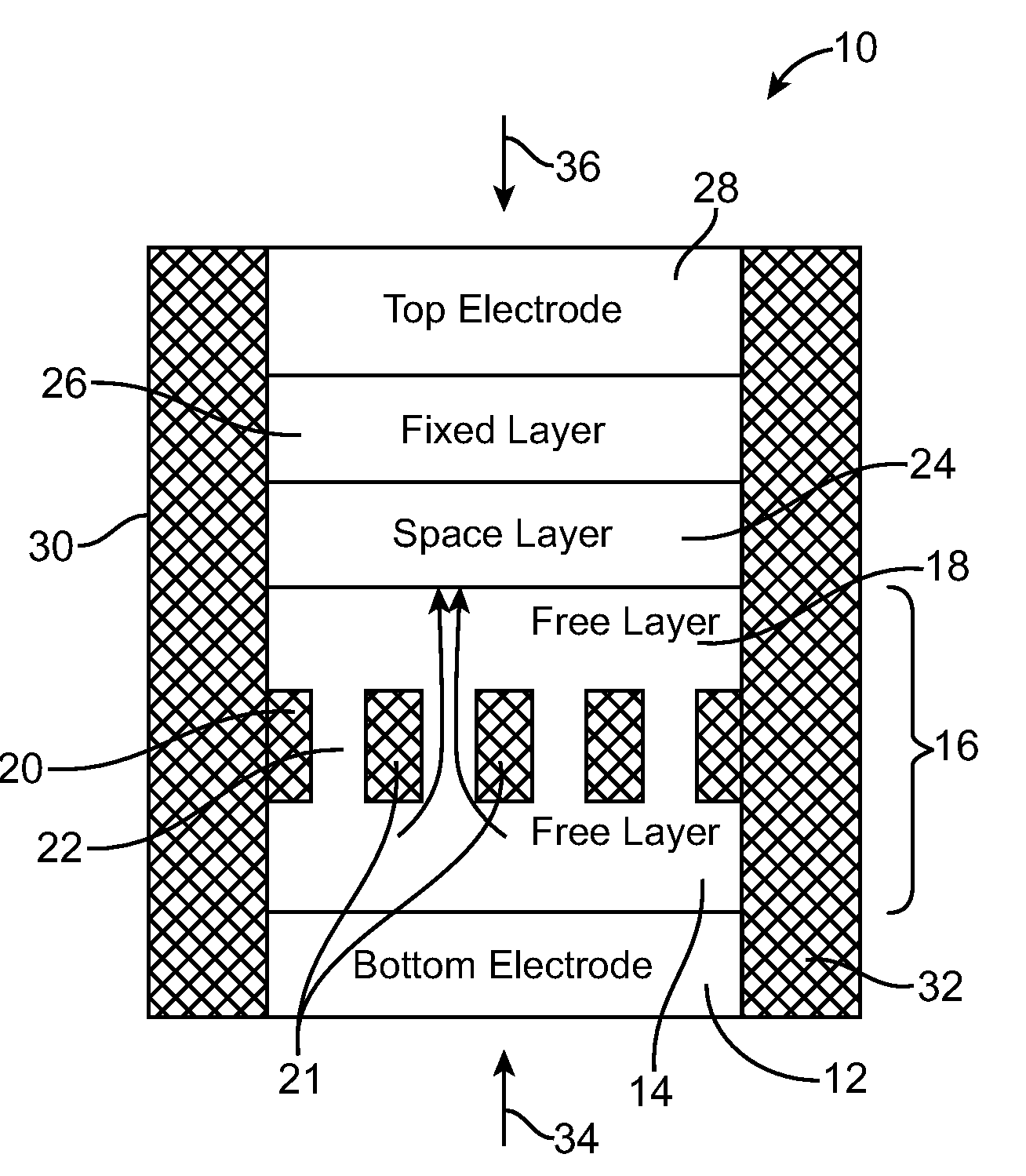

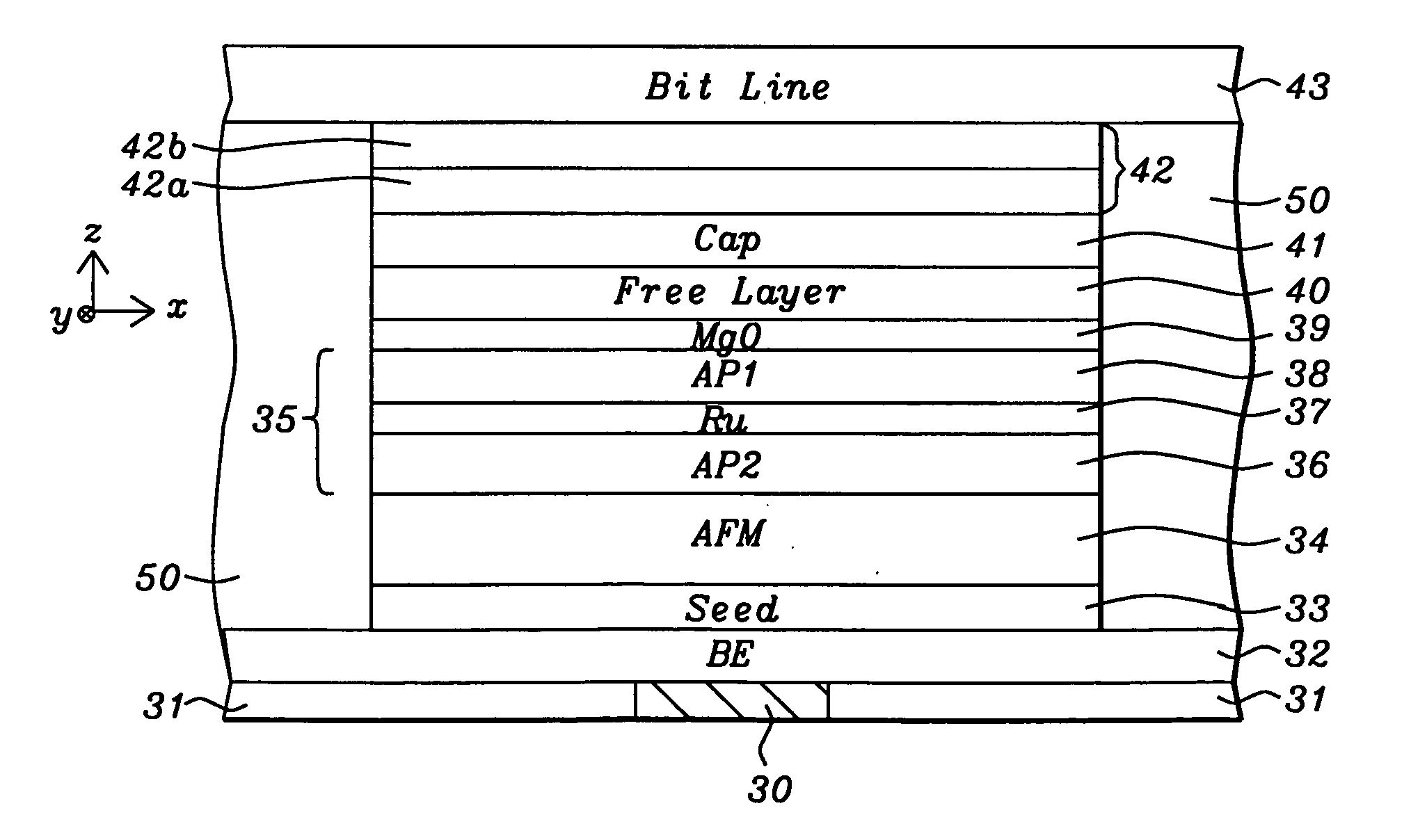

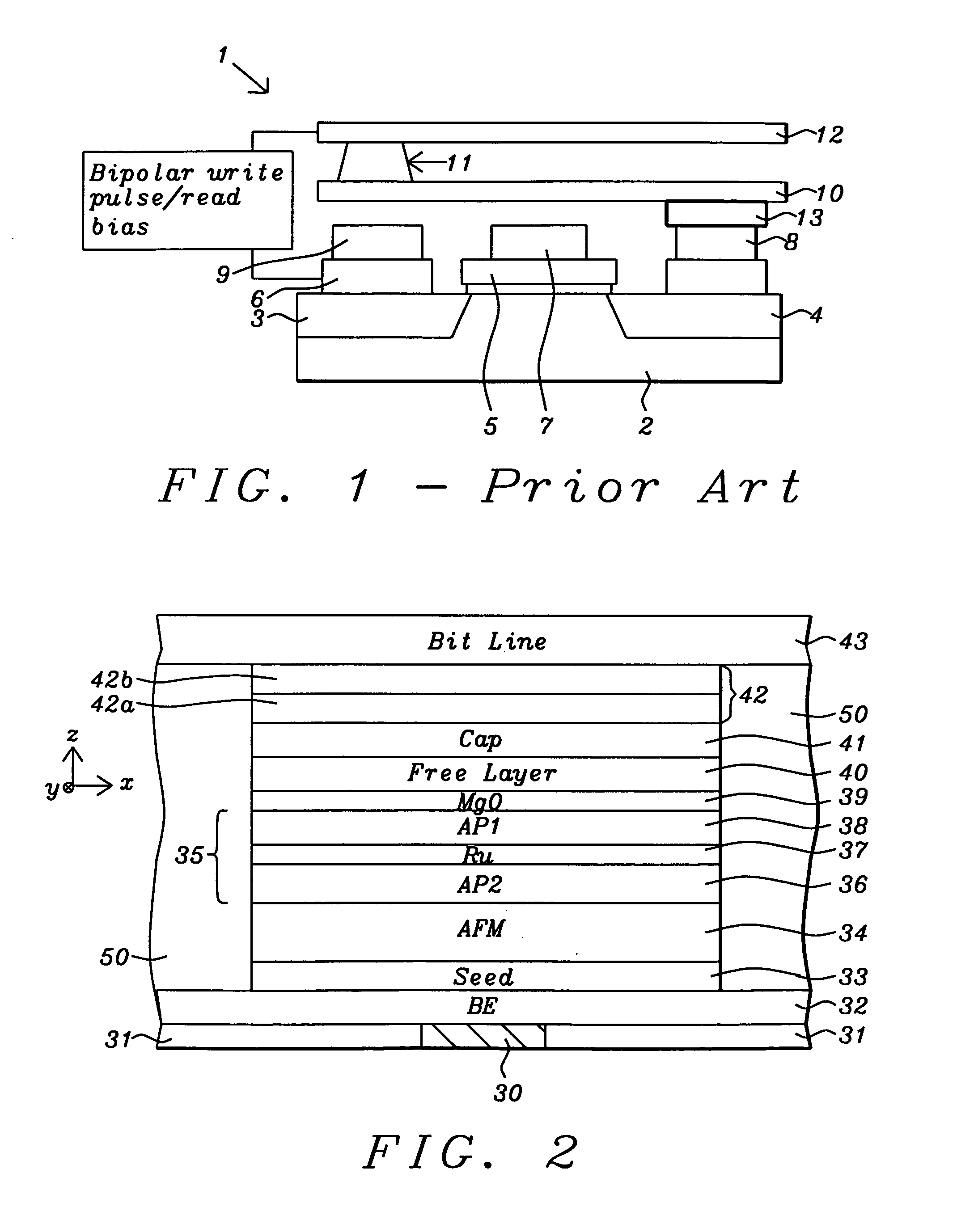

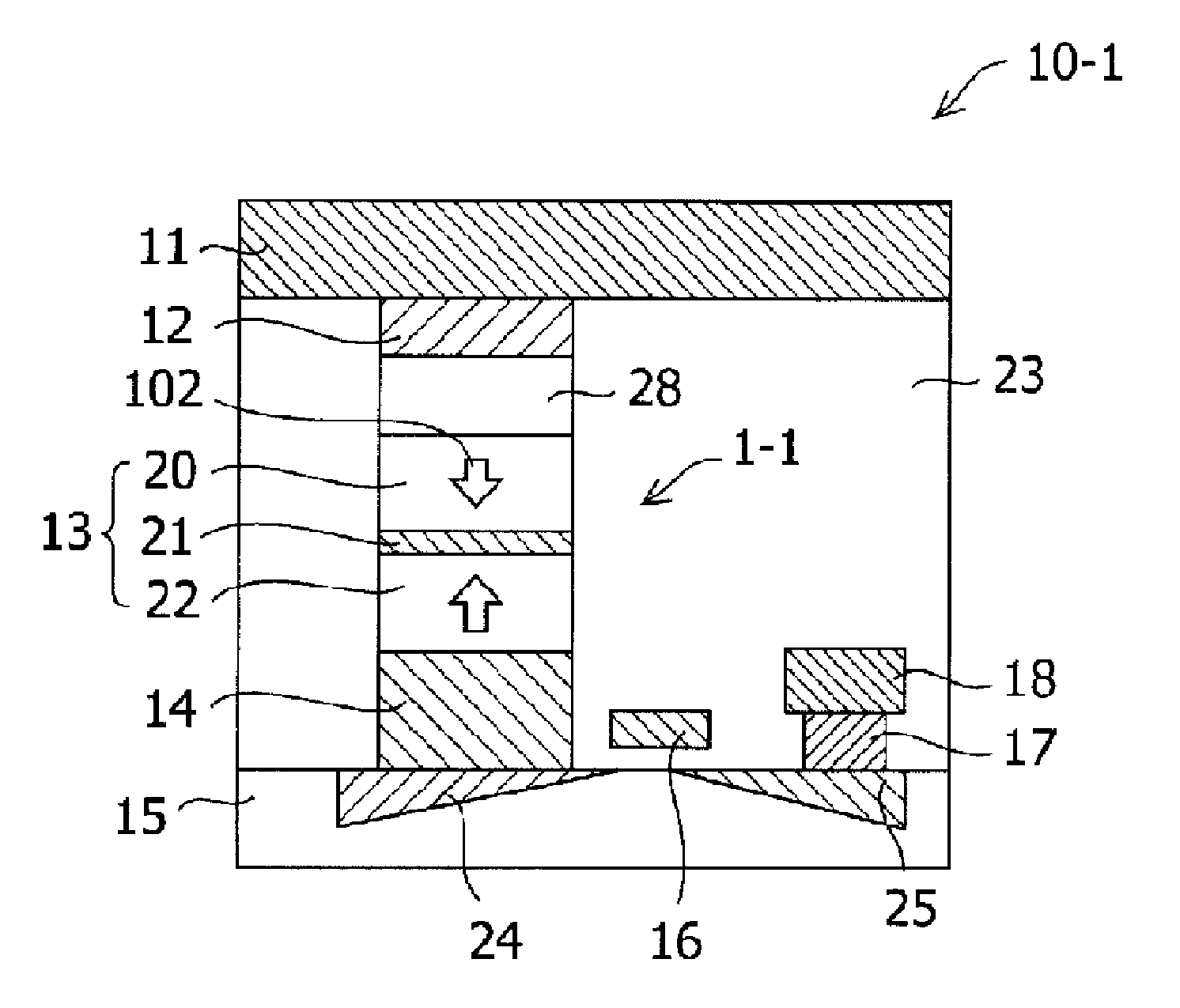

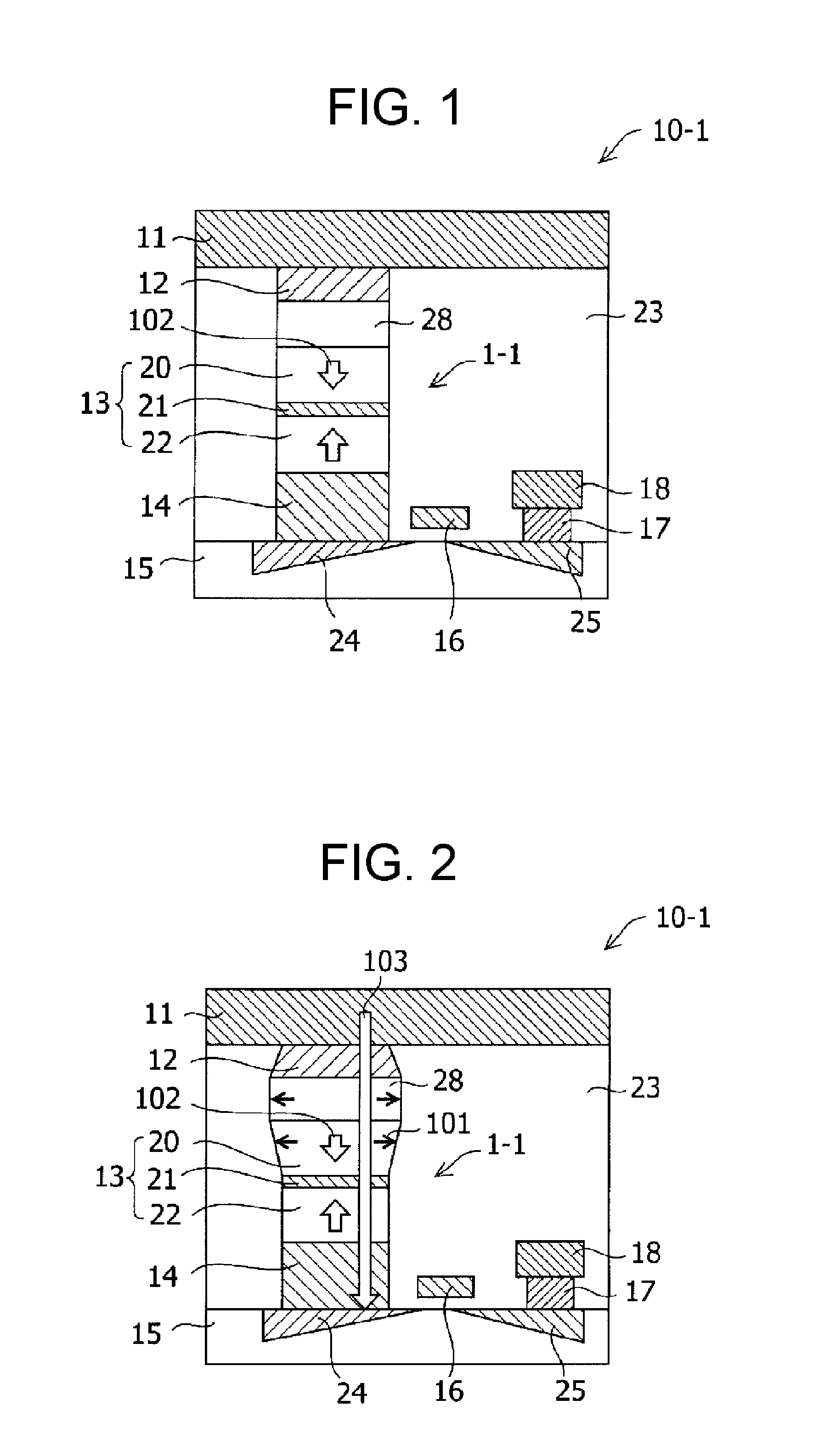

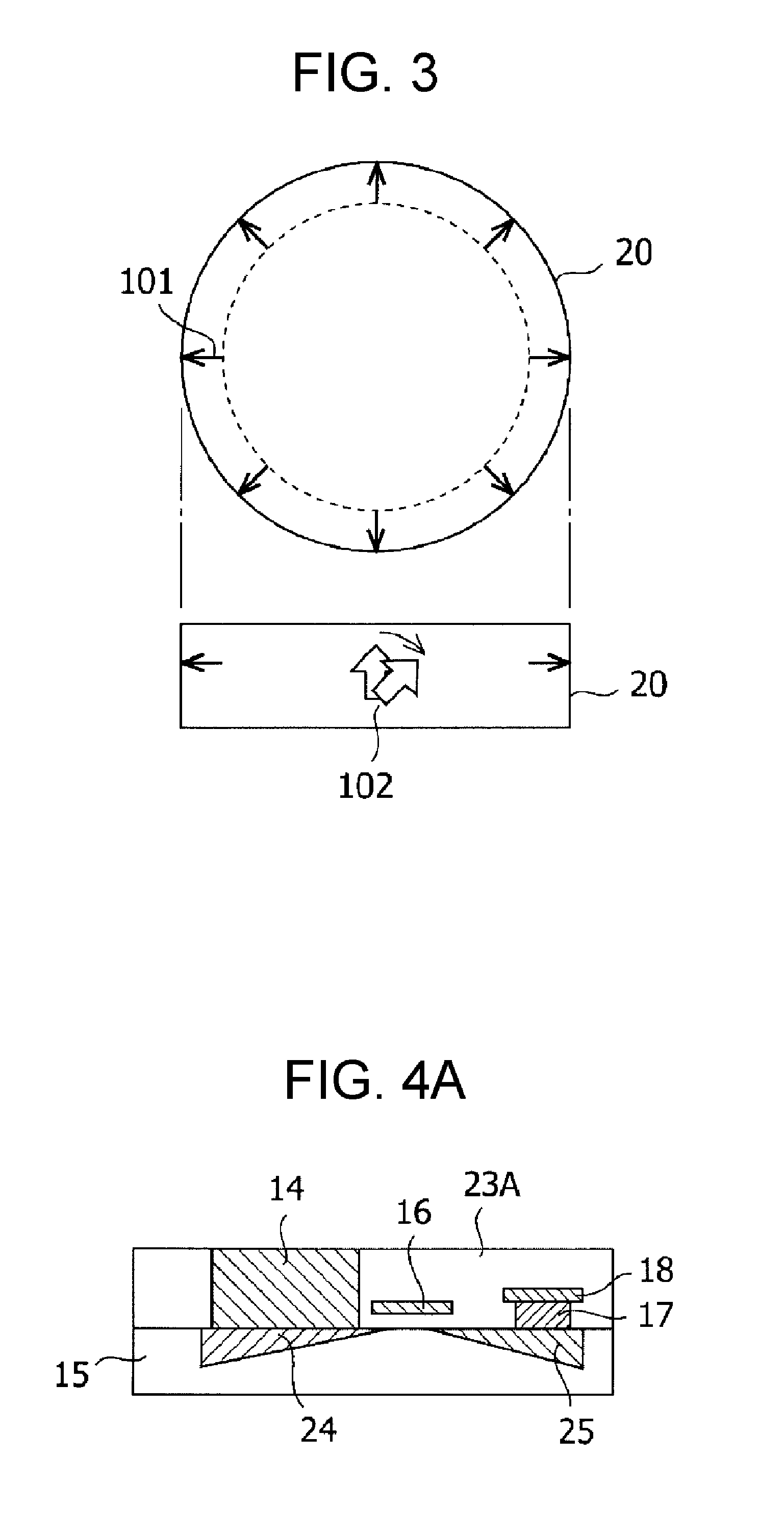

Magnetic element with improved out-of-plane anisotropy for spintronic applications

ActiveUS20120205758A1Without degrading thermal stability and MR ratioEnhanced interfacial perpendicular anisotropyMagnetic-field-controlled resistorsGalvano-magnetic material selectionPerpendicular anisotropyAlloy

A magnetic element is disclosed wherein first and second interfaces of a free layer with a Hk enhancing layer and tunnel barrier, respectively, produce enhanced surface perpendicular anisotropy to lower switching current or increase thermal stability in a magnetic tunnel junction (MTJ). In a MTJ with a bottom spin valve configuration where the Hk enhancing layer is an oxide, the capping layer contacting the Hk enhancing layer is selected to have a free energy of oxide formation substantially greater than that of the oxide. The free layer may be a single layer or composite comprised of an Fe rich alloy such as Co20Fe60B20. With a thin free layer, the interfacial perpendicular anisotropy may dominate the shape anisotropy to generate a magnetization perpendicular to the planes of the layers. The magnetic element may be part of a spintronic device or serve as a propagation medium in a domain wall motion device.

Owner:TAIWAN SEMICON MFG CO LTD

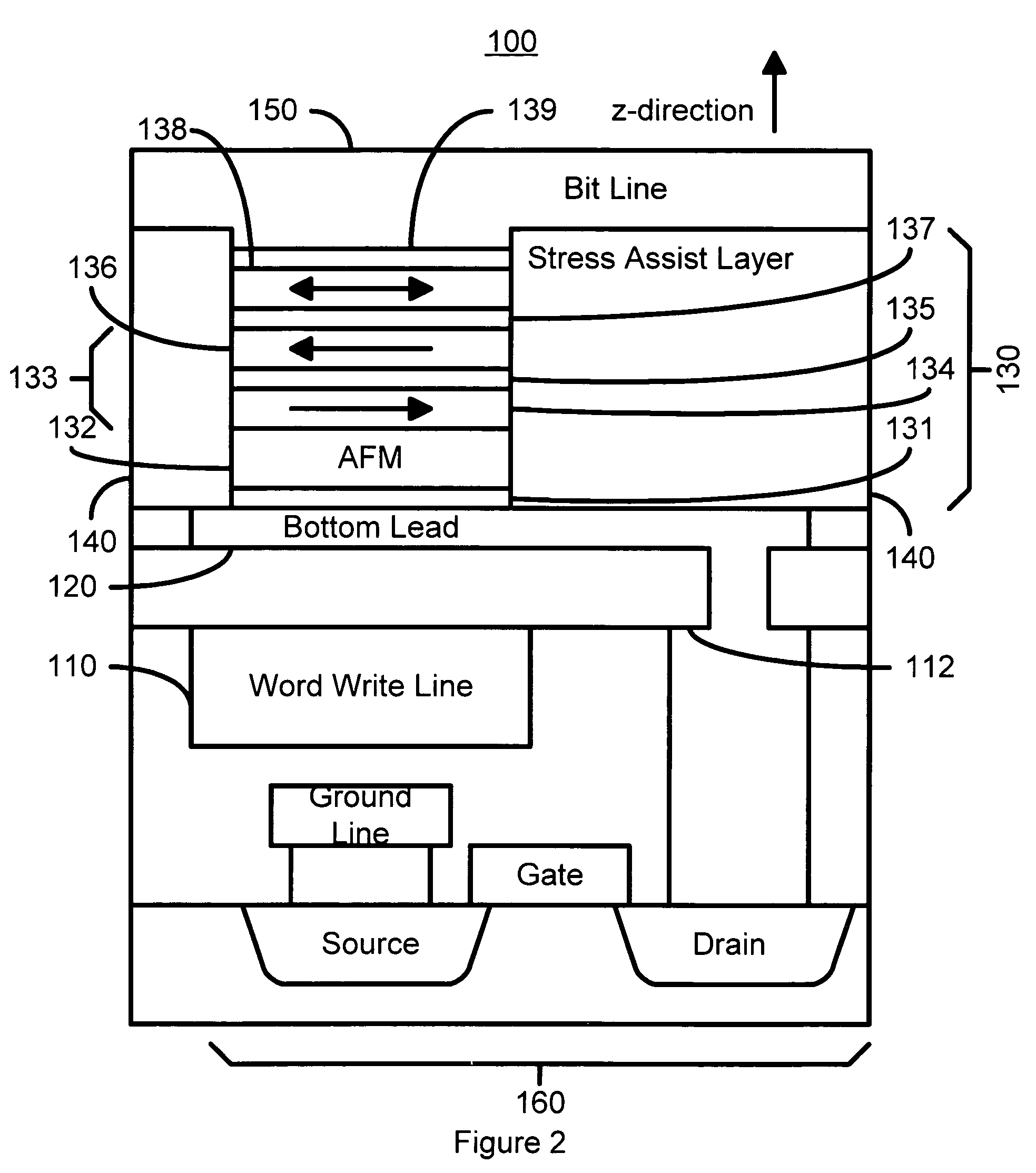

Stress assisted current driven switching for magnetic memory applications

A method and system for providing a magnetic memory is disclosed. The method and system include providing a plurality of magnetic elements and providing at least one stress-assist layer. Each of the plurality of magnetic elements is configured to be written using spin transfer. The at least one stress-assist layer is configured to exert at least one stress on at least one magnetic element of the plurality of magnetic elements during writing. The reduction of spin-transfer switching current is due to stress exerted by the stress-assist layer on the magnetic elements during writing. Stability of the magnetic memory with respect to thermal fluctuations is not compromised because the energy barrier between the two magnetization states is unchanged once the switching current is turned off.

Owner:SAMSUNG SEMICON

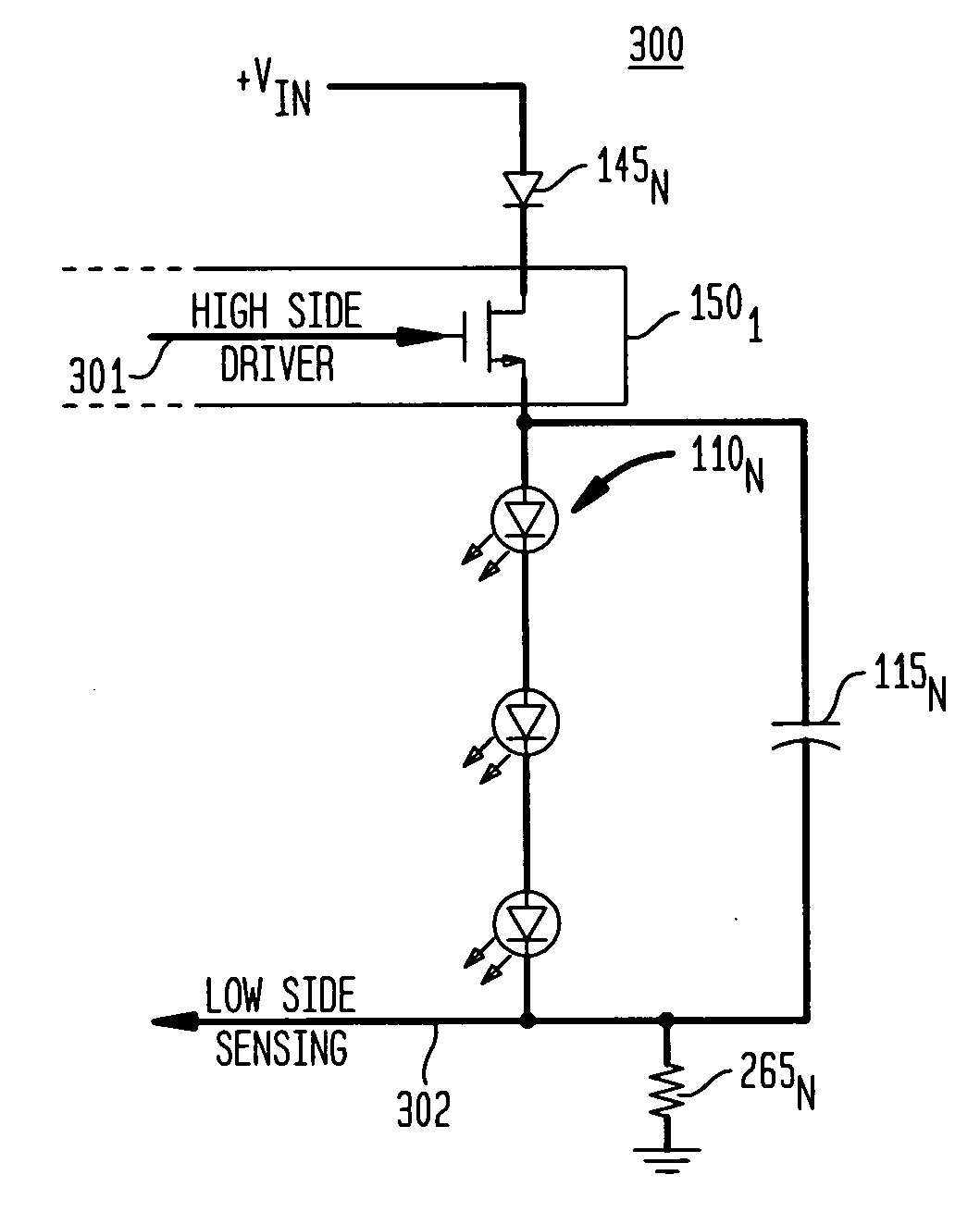

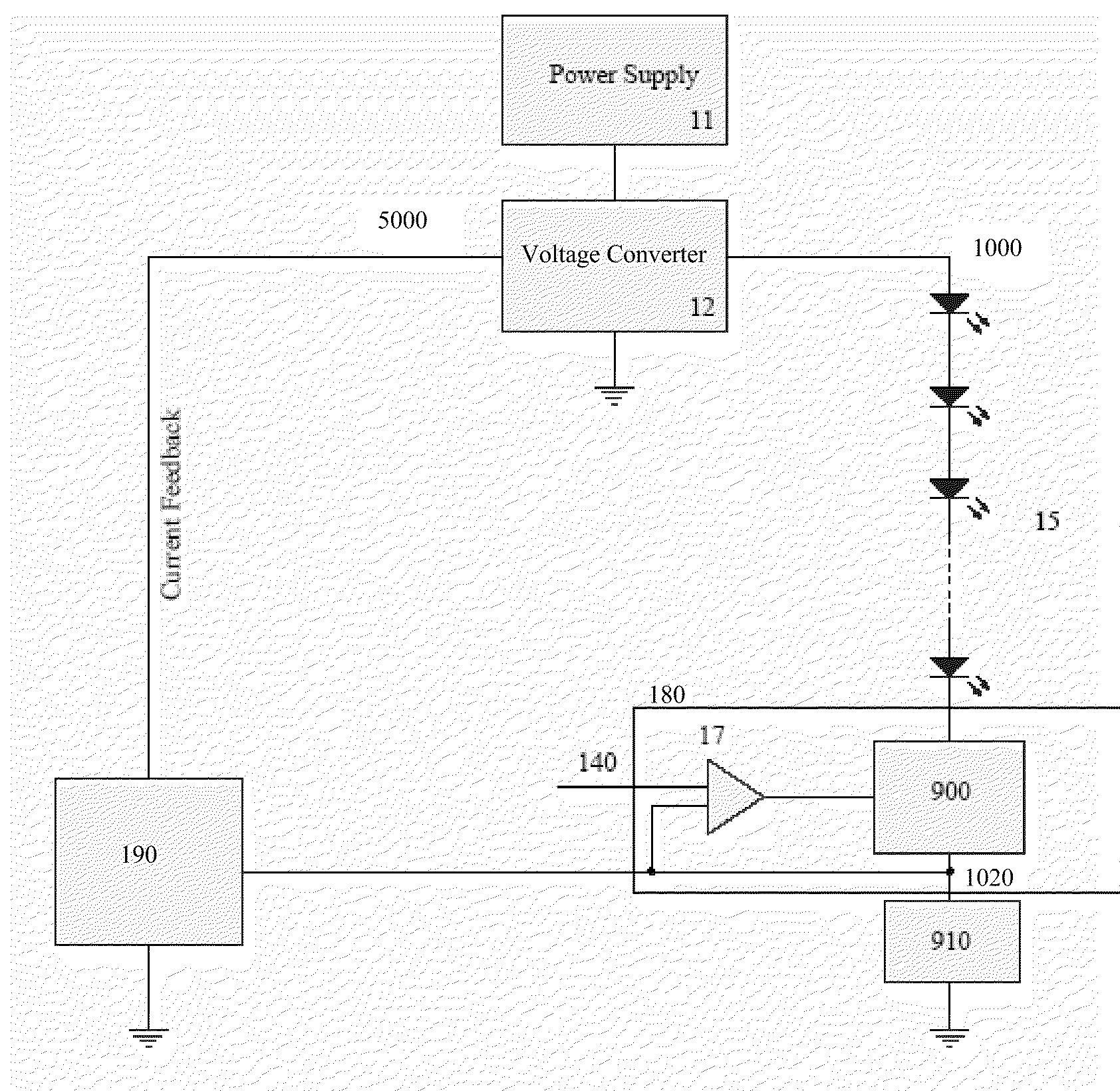

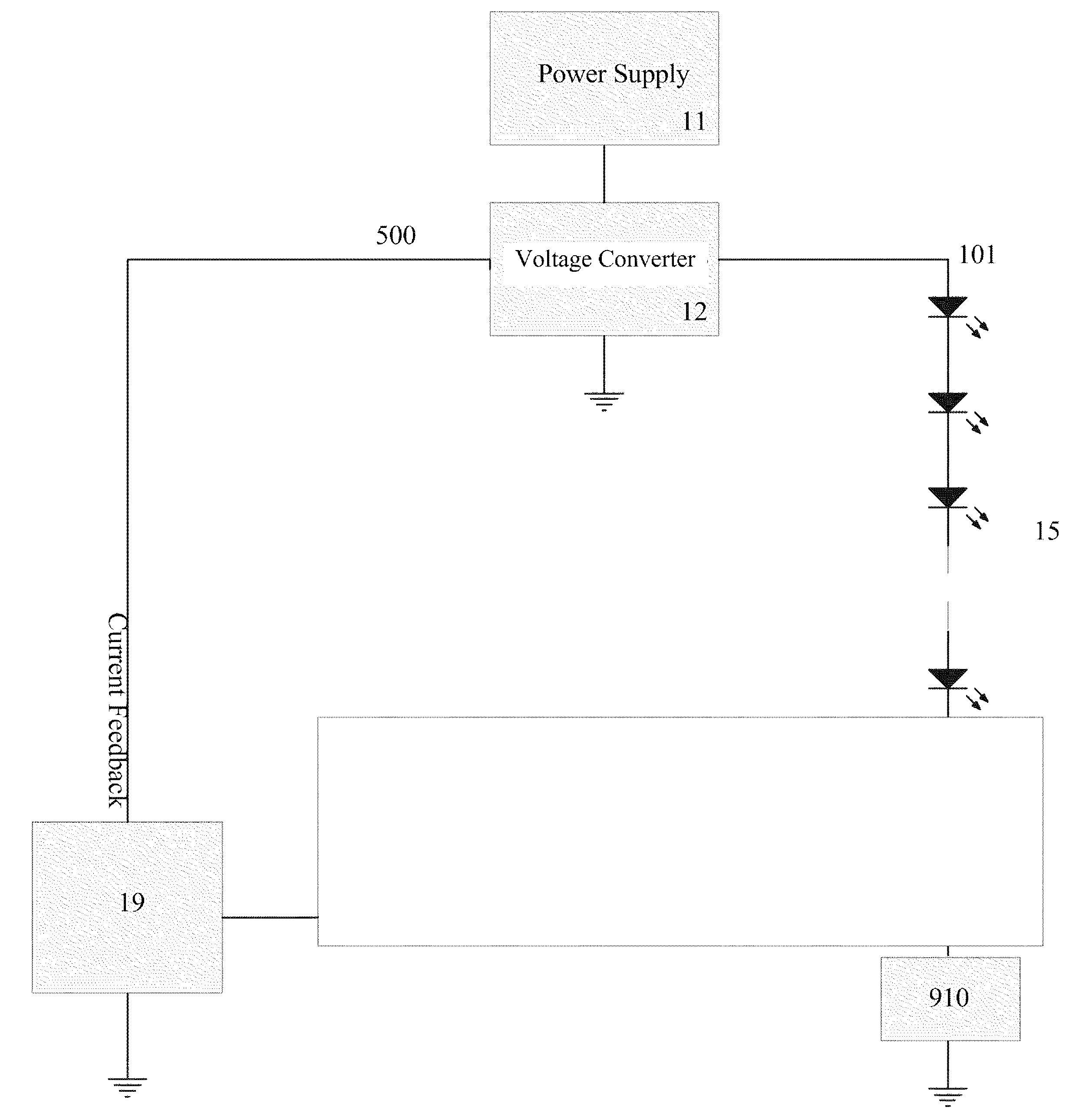

Method and Apparatus for Controlling Current Supplied to Electronic Devices

InactiveUS20090134817A1Electrical apparatusElectroluminescent light sourcesSwitched currentCurrent limiting

The present invention provides a drive and control apparatus provides a desired switched current to a load including a string of one or more electronic devices. A voltage conversion means, based on an input control signal converts the magnitude of the voltage from the power supply to another magnitude that is desired at the high side of the load. A dimming control means provides control for activation and deactivation of the load and may further provide a means for current limiting. A feedback means is coupled to the voltage conversion means and a current sensing means and provides a control signal to the voltage conversion means that is indicative of voltage drop across the current sensing means which represents the current flowing through the load. Based on the control signal received, the voltage conversion means can subsequently adjust its output voltage such that a constant switched current is provided to the load.

Owner:SIGNIFY HLDG BV

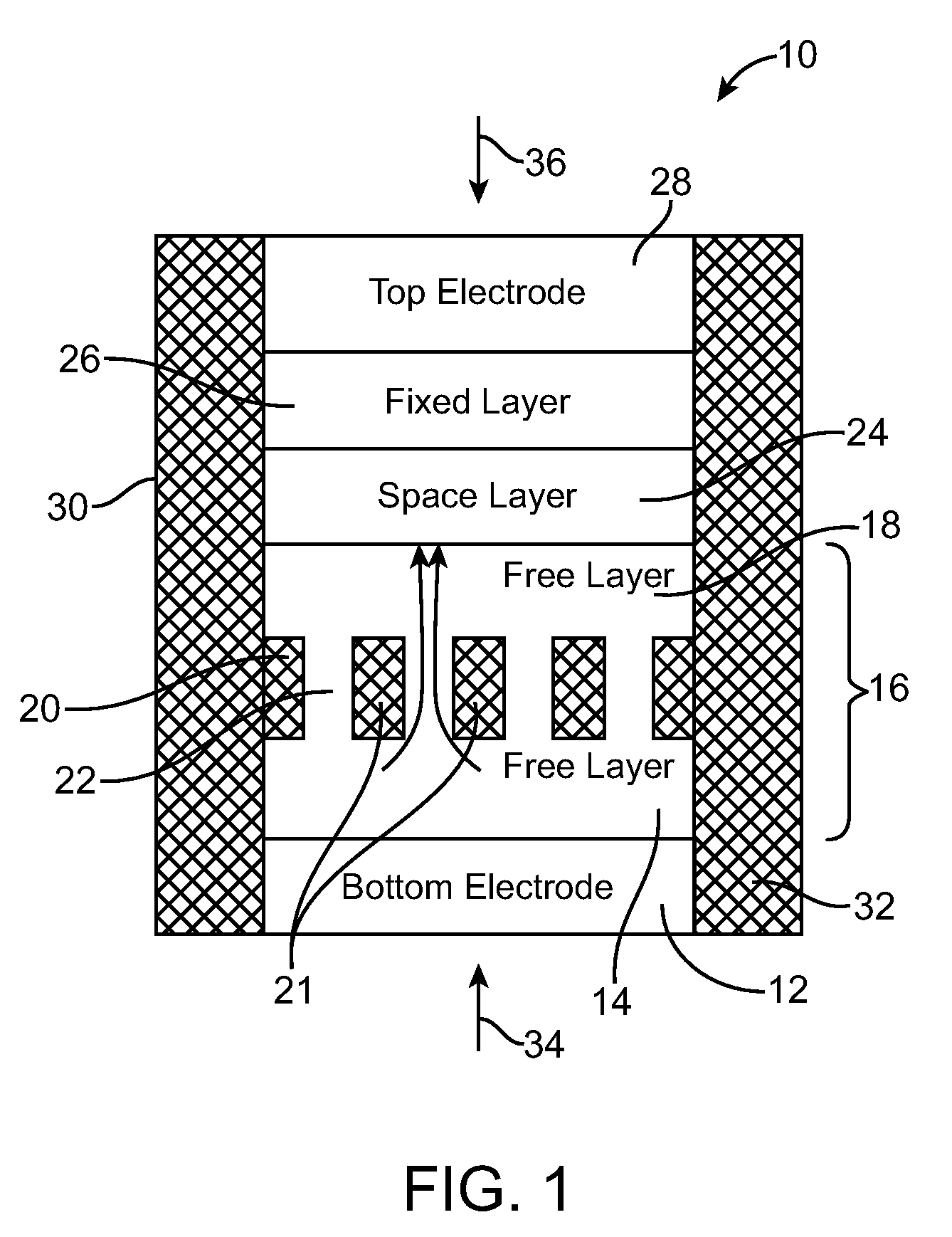

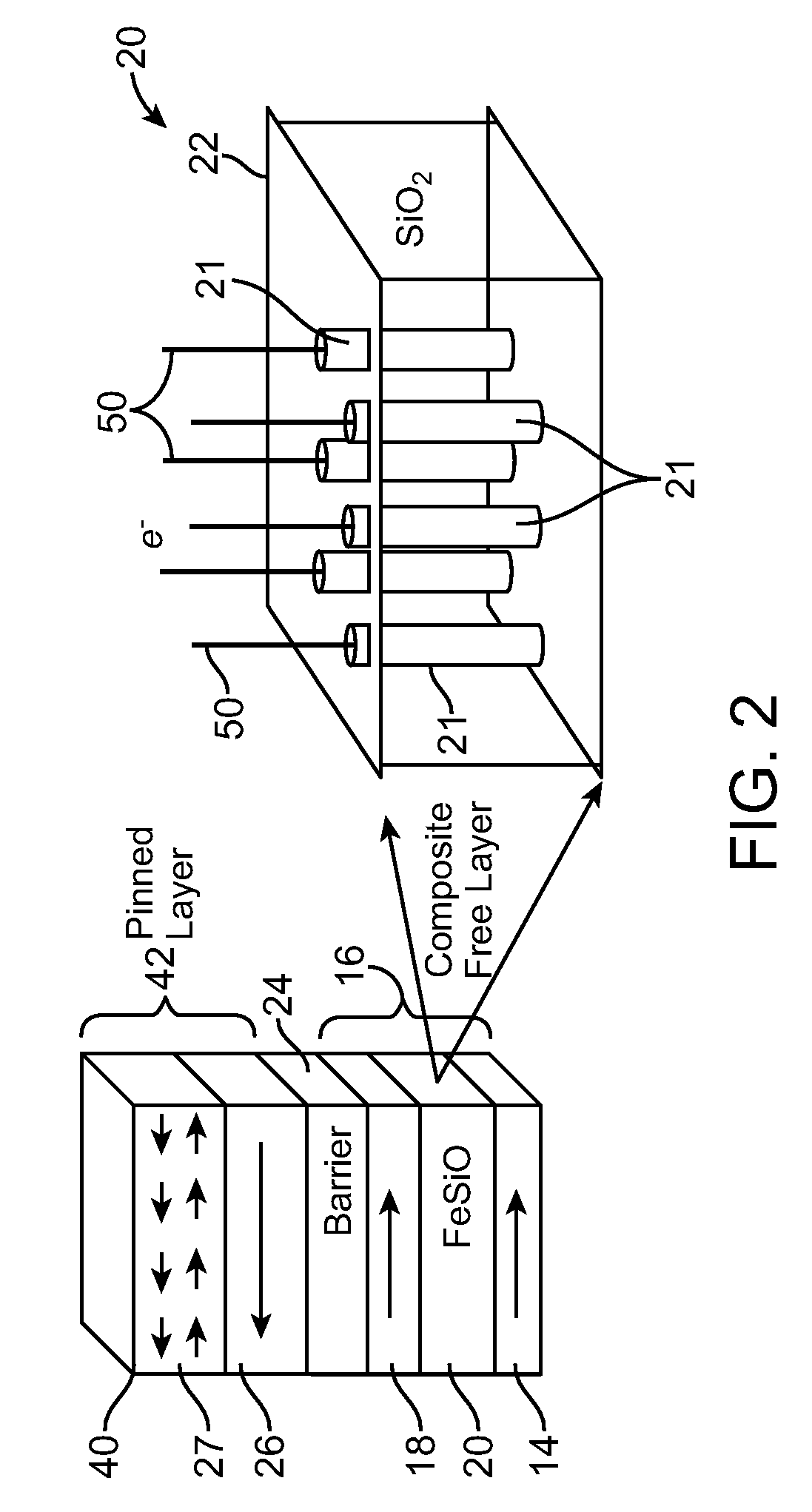

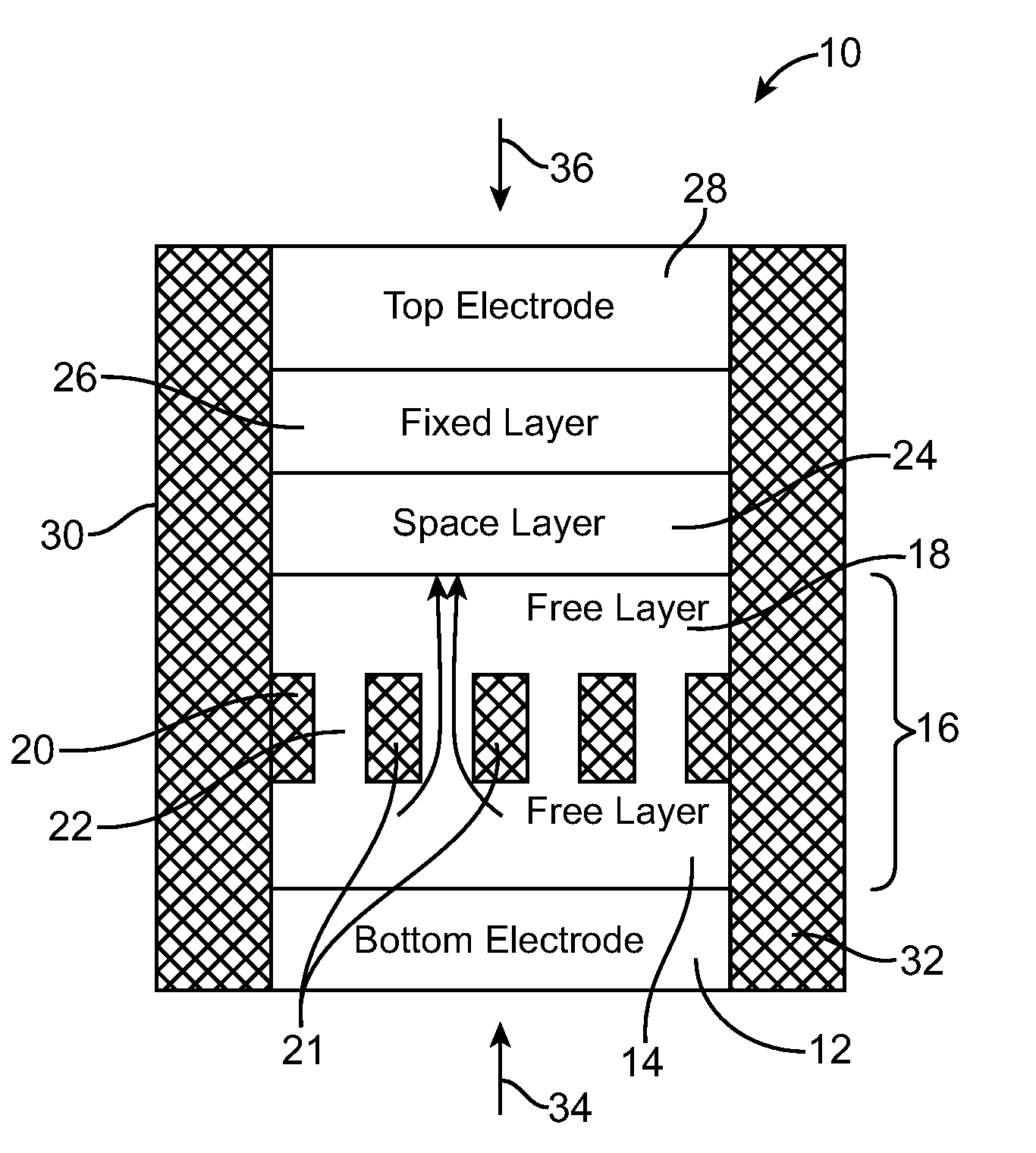

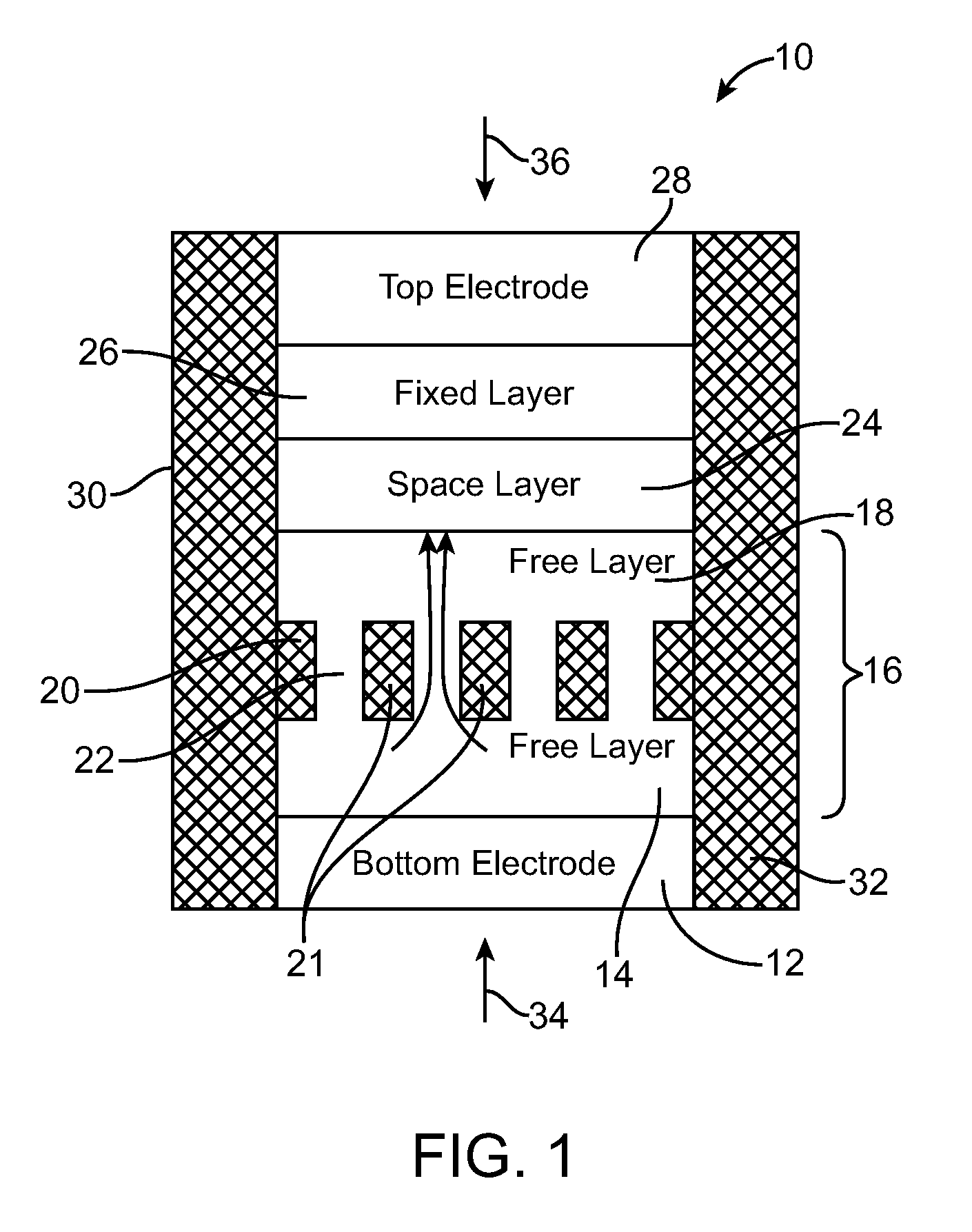

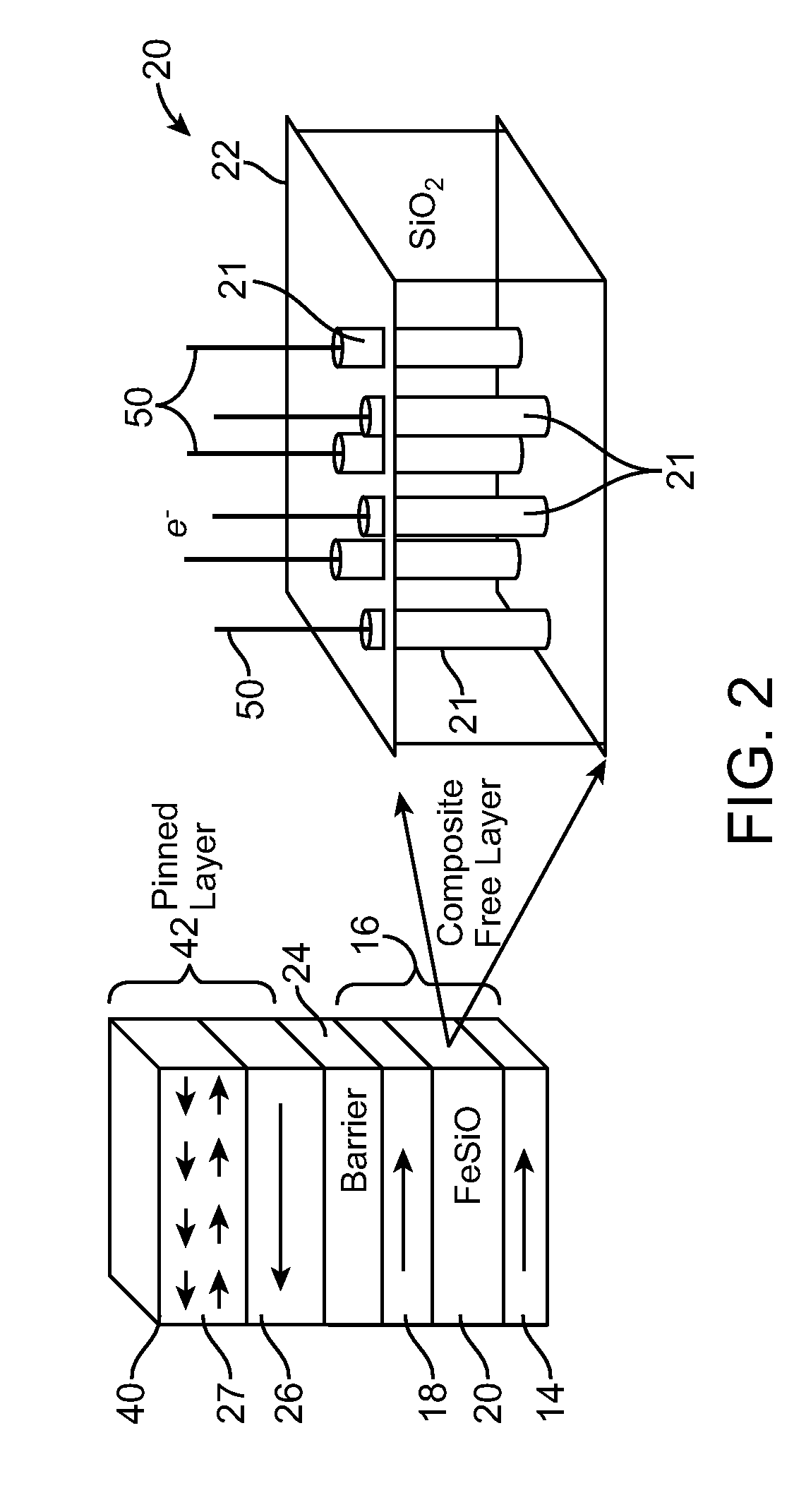

Current-confined effect of magnetic nano-current-channel (NCC) for magnetic random access memory (MRAM)

ActiveUS7732881B2Magnetic-field-controlled resistorsSemiconductor/solid-state device manufacturingCurrent limitingCurrent channel

One embodiment of the present invention includes a memory element having a composite free layer including a first free sub-layer formed on top of the bottom electrode, a nano-current-channel (NCC) layer formed on top of the first free sub-layer, and a second free sub-layer formed on top of the NCC layer, wherein when switching current is applied to the memory element, in a direction that is substantially perpendicular to the layers of the memory element, local magnetic moments of the NCC layer switch the state of the memory element.

Owner:AVALANCHE TECH

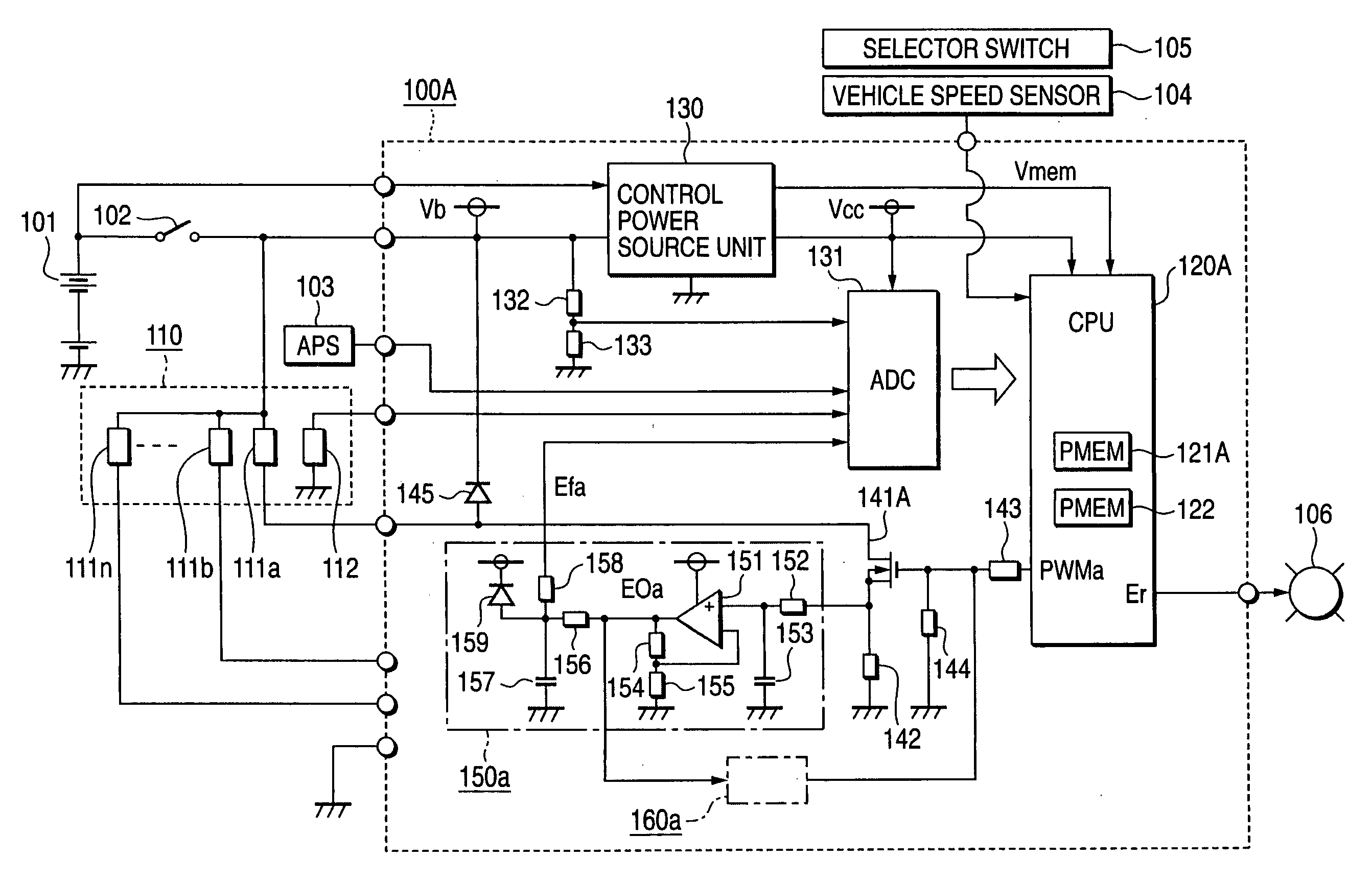

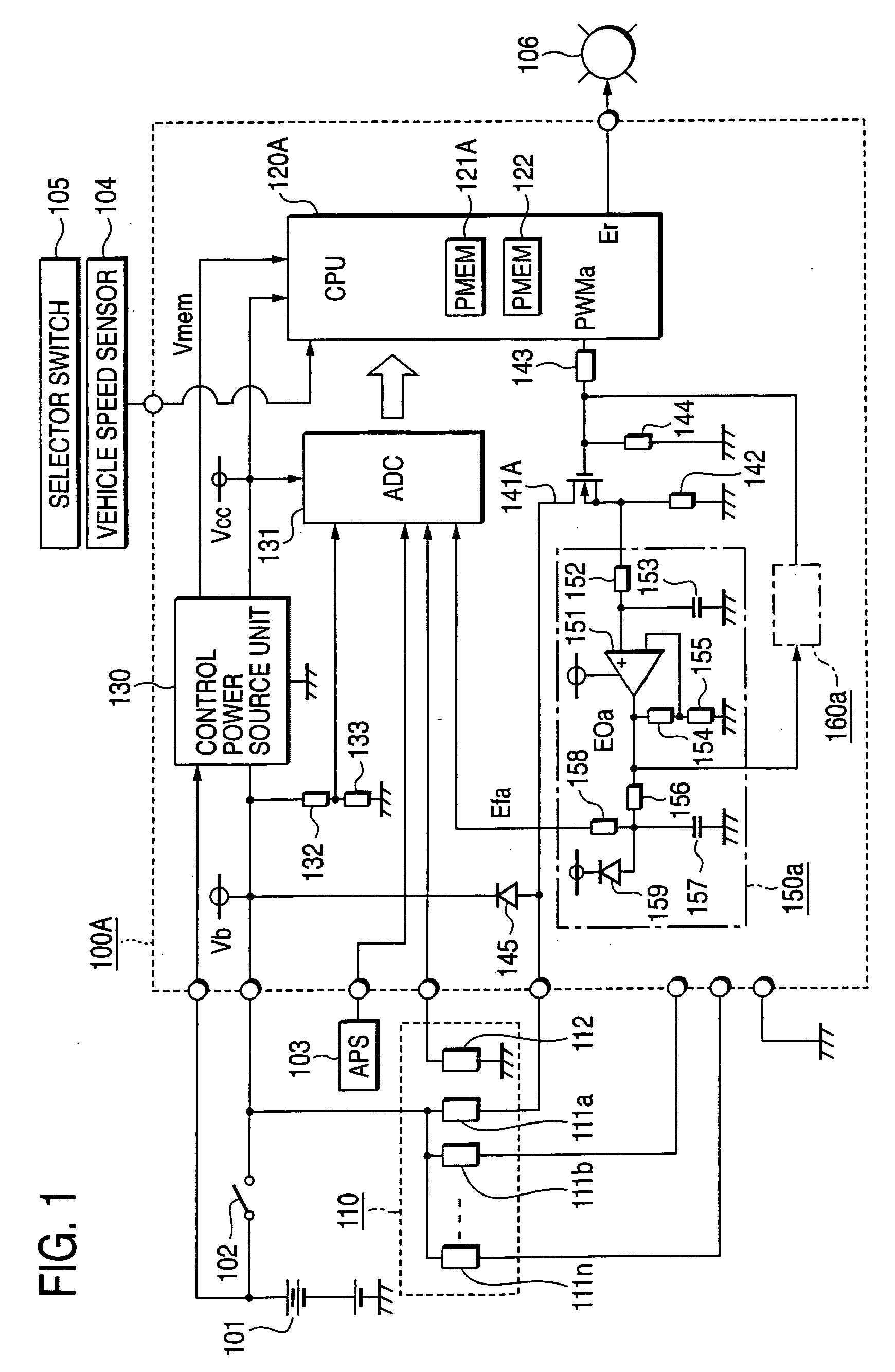

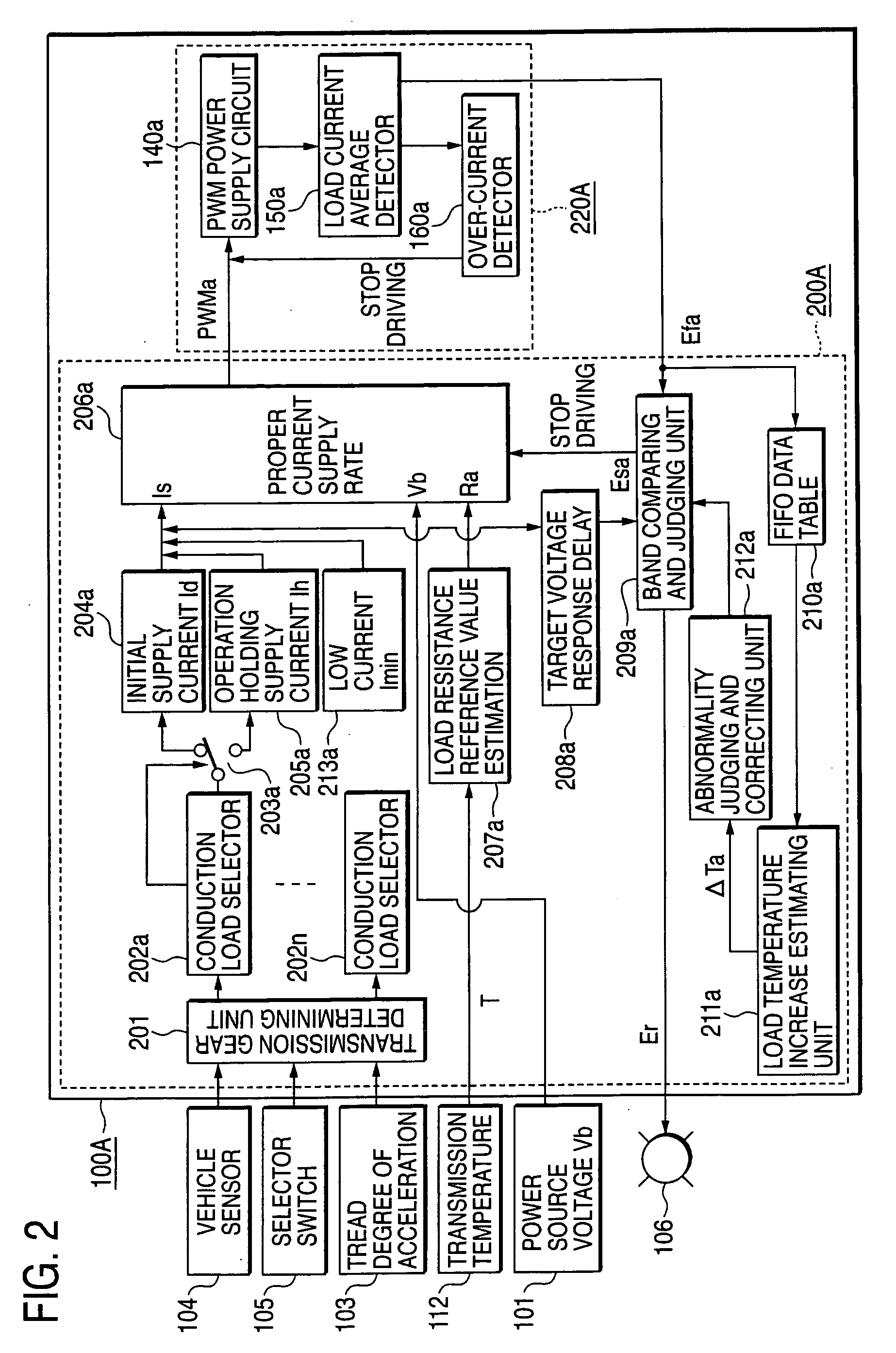

Non-feedback type load current controller

InactiveUS20070030068A1Improve securityThermometer detailsDigital computer detailsLoop controlSwitched current

An electrical load is supplied with power from a driving power source, and a microprocessor (CPU) controls the opening / closing current supply rate (duty factor) of an opening / closing element in accordance with target current and driving power source voltage so that open loop control is carried out to achieve predetermined target current. The voltage between both the ends of a current detecting resistor connected to the ground side of the opening / closing element is input as a monitoring voltage from a current detecting amplifying circuit portion through a multichannel AD converter to CPU. When the error between the comparison target voltage corresponding to the target current and the monitoring voltage is above a first permissible error, CPU judges that there is an abnormality sign, and if the error is above a larger second permissible error, CPU judges that there is appearing abnormality. Accordingly, an abnormality sign of a semi-wire-breaking / semi-short-circuit state of the electrical load can be sensed, and abnormality notification can be carried out.

Owner:MITSUBISHI ELECTRIC CORP

Current-Confined Effect of Magnetic Nano-Current-Channel (NCC) for Magnetic Random Access Memory (MRAM)

ActiveUS20080180991A1Magnetic-field-controlled resistorsDigital storageCurrent channelSwitched current

One embodiment of the present invention includes a memory element having a composite free layer including a first free sub-layer formed on top of the bottom electrode, a nano-current-channel (NCC) layer formed on top of the first free sub-layer, and a second free sub-layer formed on top of the NCC layer, wherein when switching current is applied to the memory element, in a direction that is substantially perpendicular to the layers of the memory element, local magnetic moments of the NCC layer switch the state of the memory element.

Owner:AVALANCHE TECH

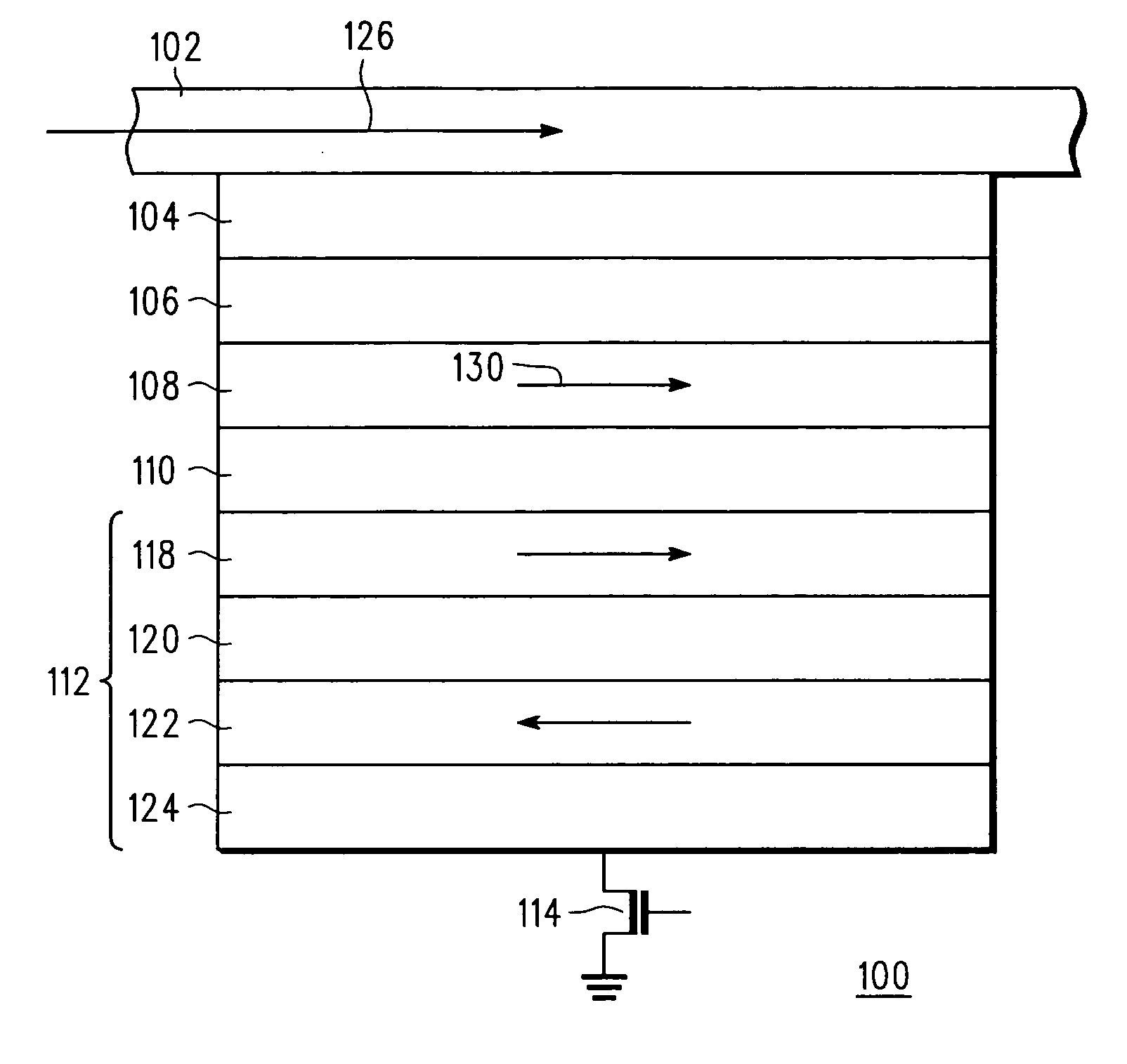

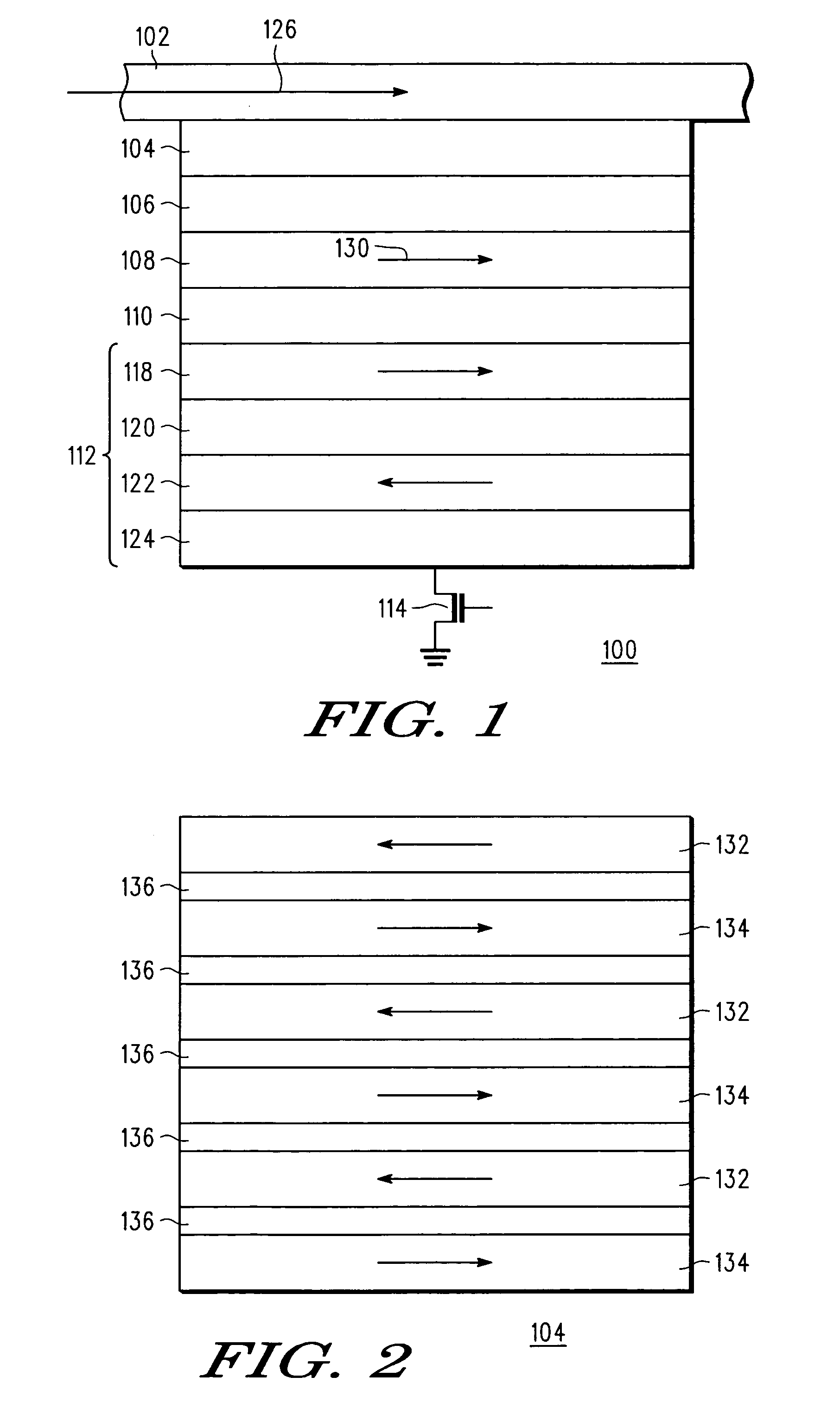

Spin-transfer based MRAM with reduced critical current density

A magnetic random access memory device comprises a spin torque MRAM cell (100) having a reduced switching current (Ic) wherein standard materials may be used for a free layer (108). A fixed magnetic element (112) polarizes electrons passing therethrough, and the free magnetic element (108) having a first plane anisotropy comprises a first magnetization (130) whose direction is varied by the spin torque of the polarized electrons. An insulator (110) is positioned between the fixed magnetic element (112) and the free magnetic element (108), and a keeper layer (104) positioned contiguous to the free magnetic element (108) and having a second plane anisotropy orthogonal to the first plane anisotropy, reduces the first plane anisotropy and hence reduces the spin torque switching current (Ic). The keeper layer (104) may comprise alternating synthetic antiferromagnetic layers (132, 134) of magnetization approximately equal in magnitude and opposite in direction.

Owner:EVERSPIN TECHNOLOGIES

Method and apparatus for controlling current supplied to electronic devices

InactiveUS7999484B2Electrical apparatusElectroluminescent light sourcesCurrent limitingSwitched current

The present invention provides a drive and control apparatus provides a desired switched current to a load including a string of one or more electronic devices. A voltage conversion means, based on an input control signal converts the magnitude of the voltage from the power supply to another magnitude that is desired at the high side of the load. A dimming control means provides control for activation and deactivation of the load and may further provide a means for current limiting. A feedback means is coupled to the voltage conversion means and a current sensing means and provides a control signal to the voltage conversion means that is indicative of voltage drop across the current sensing means which represents the current flowing through the load. Based on the control signal received, the voltage conversion means can subsequently adjust its output voltage such that a constant switched current is provided to the load.

Owner:SIGNIFY HLDG BV

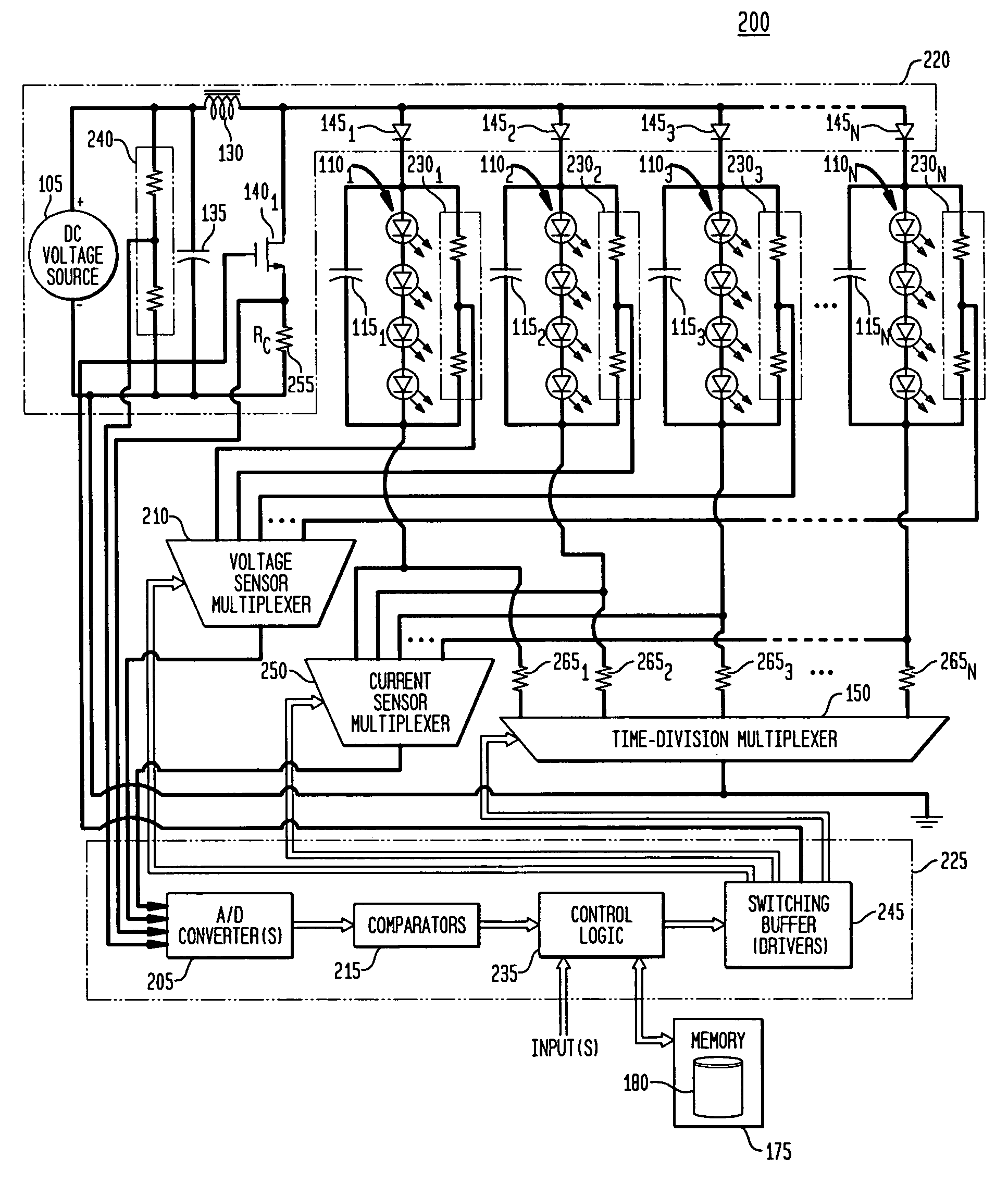

Pulsed current averaging controller with amplitude modulation and time division multiplexing for arrays of independent pluralities of light emitting diodes

ActiveUS7888881B2Improve efficiencySmall sizeElectrical apparatusElectroluminescent light sourcesSwitched currentAverage current

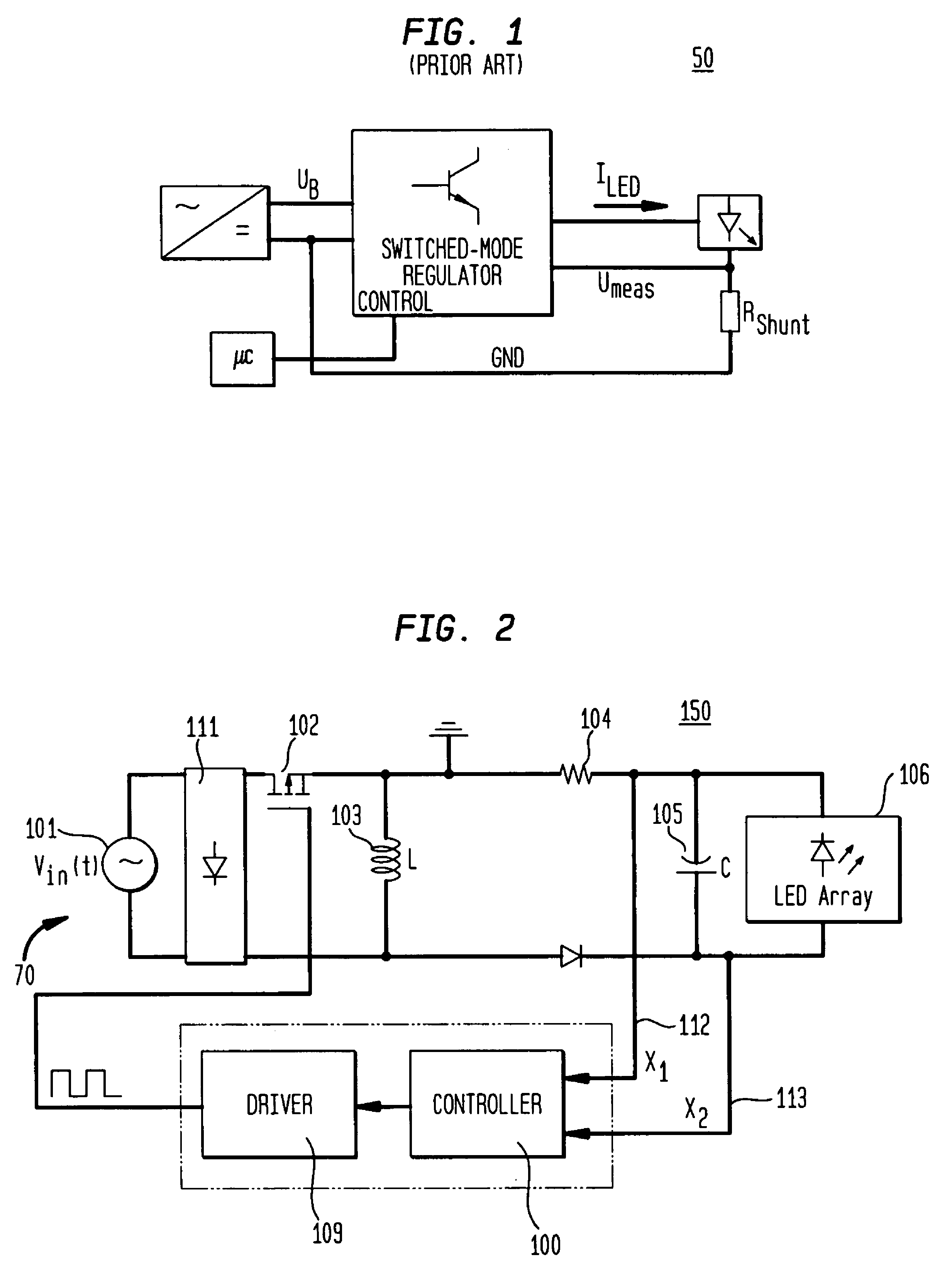

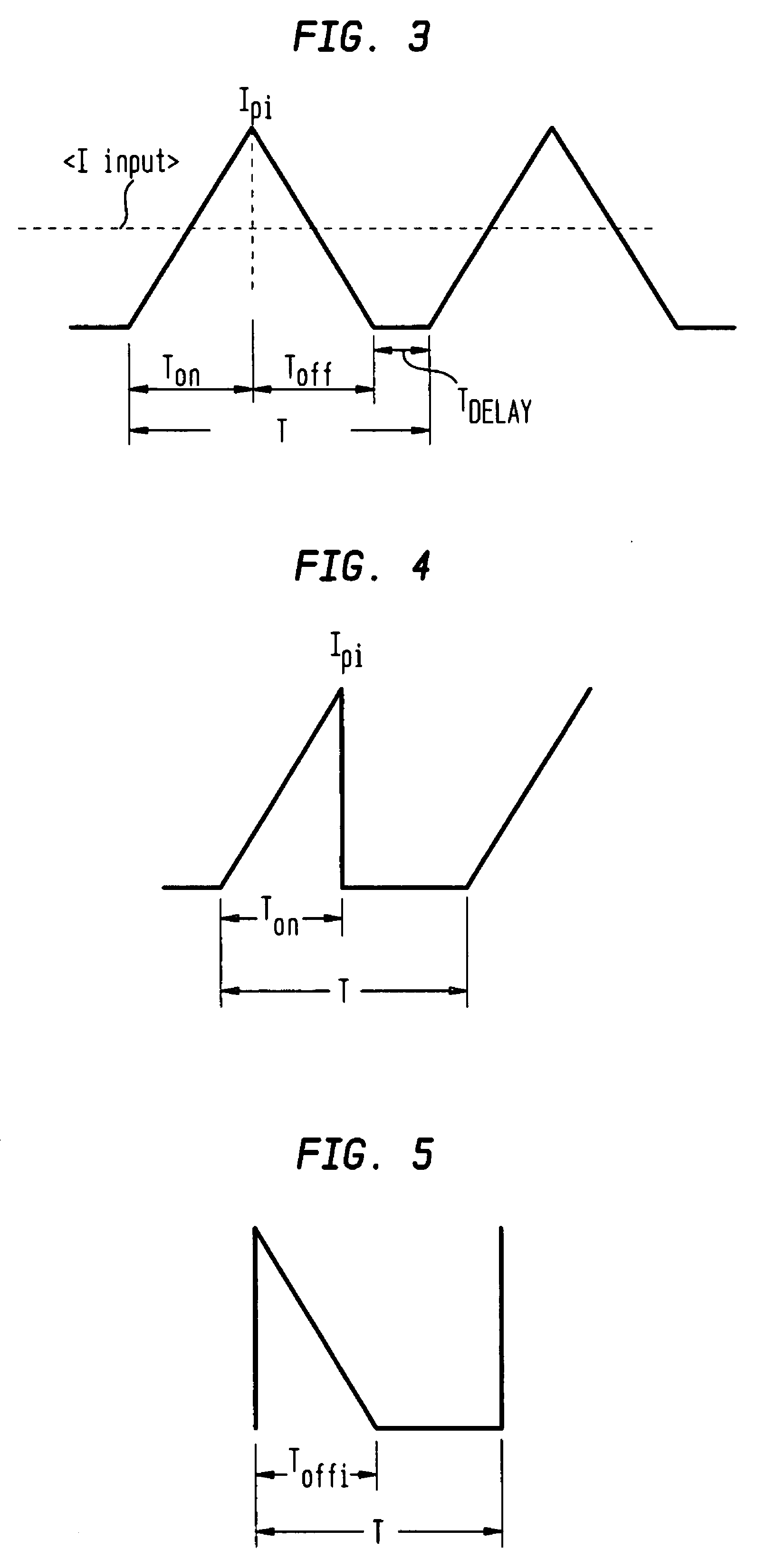

Exemplary embodiments provide a system, method and apparatus for regulating current in loads, such as in an array of independent pluralities of light emitting diodes (“LEDs”). An exemplary system comprises a multiplexer adapted to switch current to each independent string of LEDs; a first controller to maintain a substantially constant average current level to the plurality of LEDs; and a second controller to modulate a current amplitude and duration of time division multiplexing for each independent string of LEDs. Another aspect of the system provides for modulating the on time for switching current to maintain a substantially constant average current level and to respond and converge quickly to changing current reference levels.

Owner:CHEMTRON RES

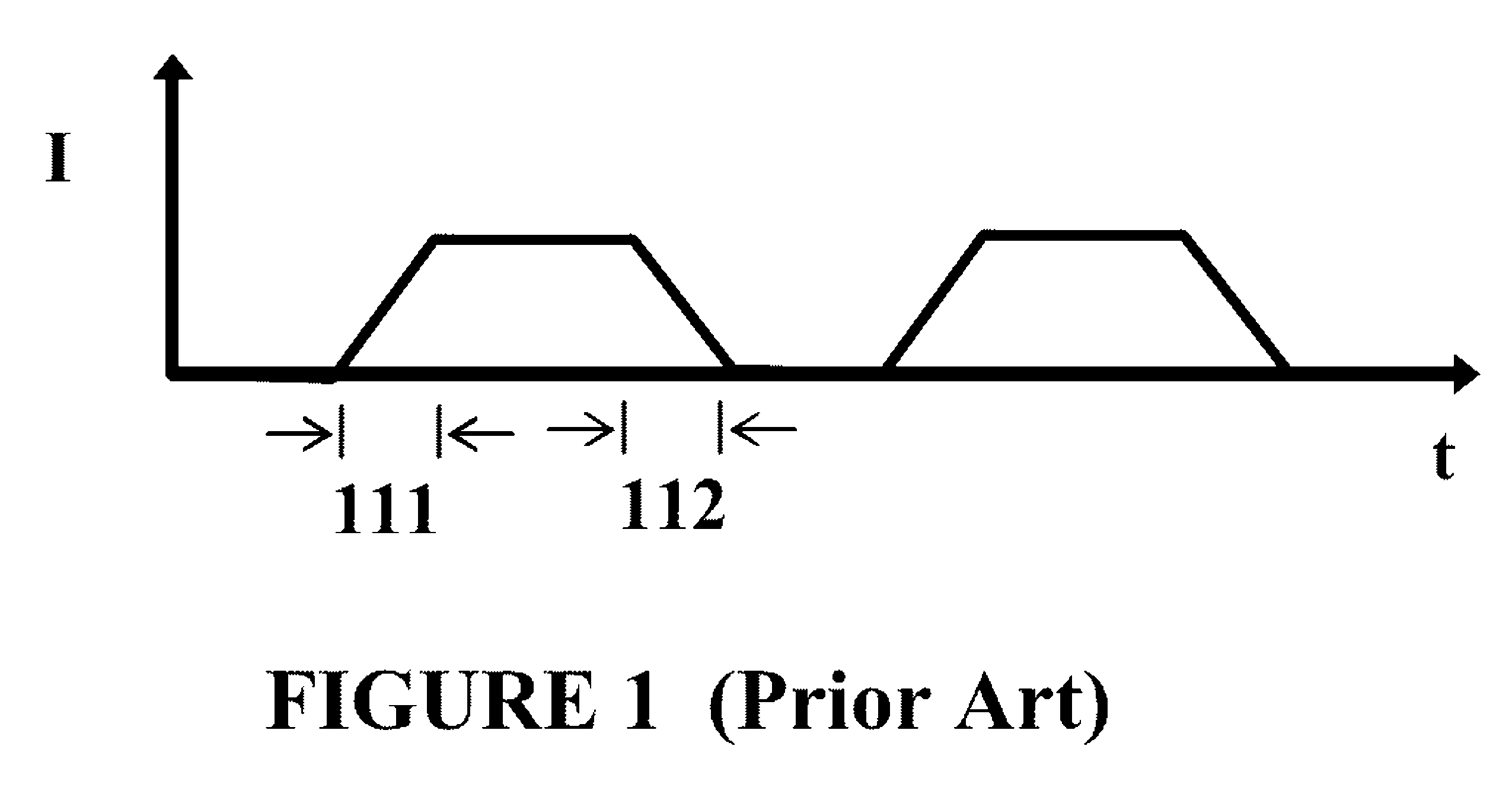

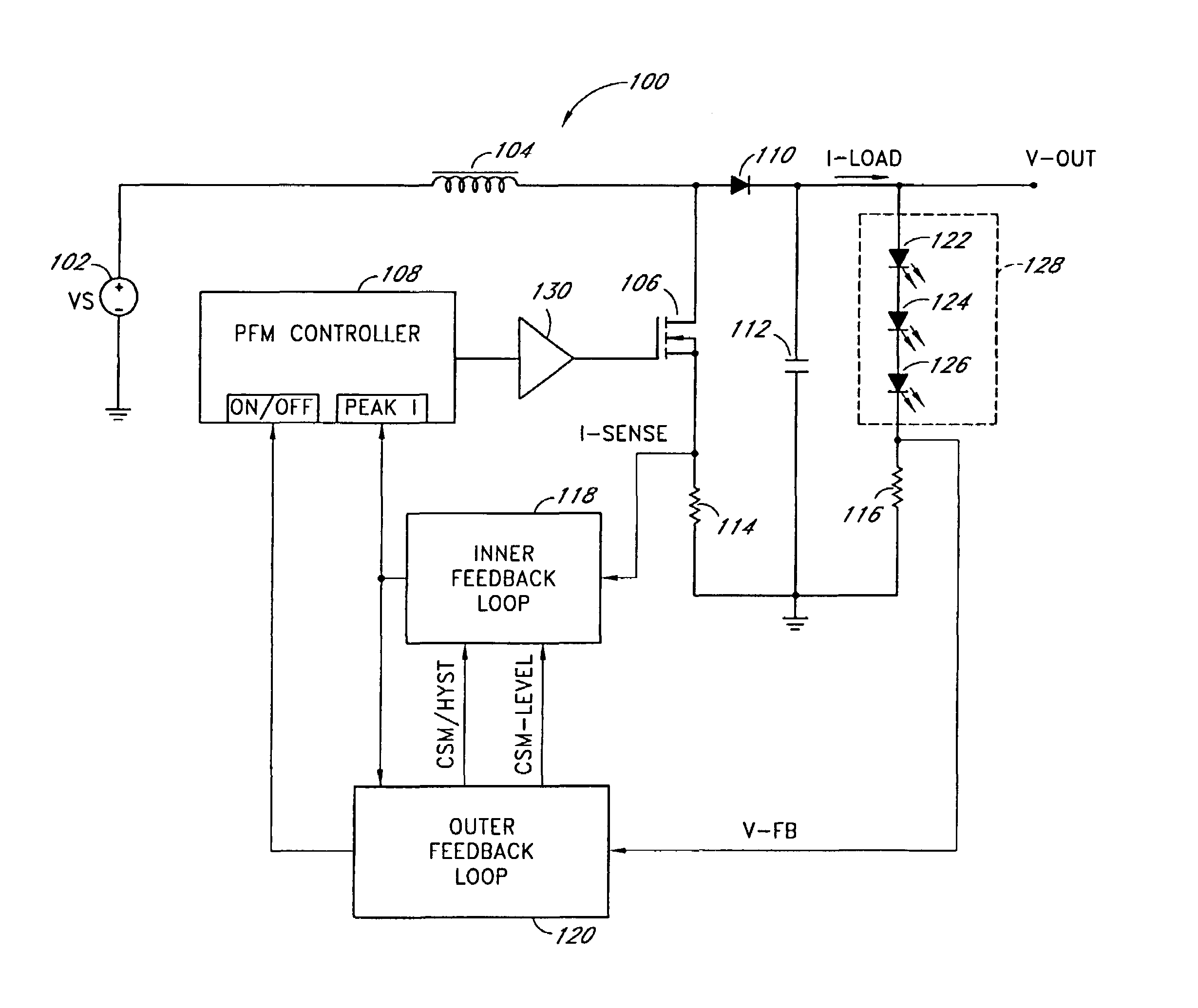

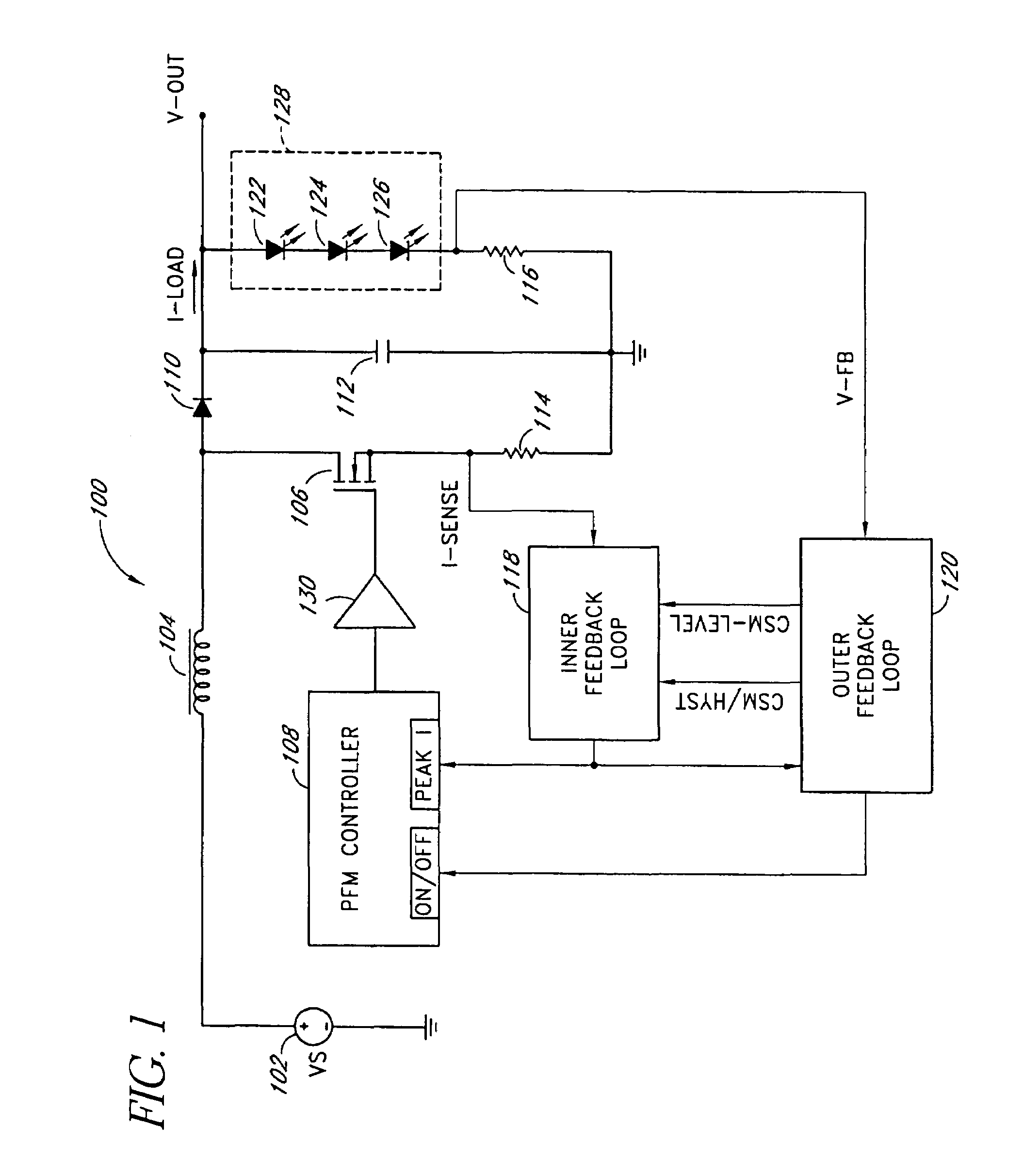

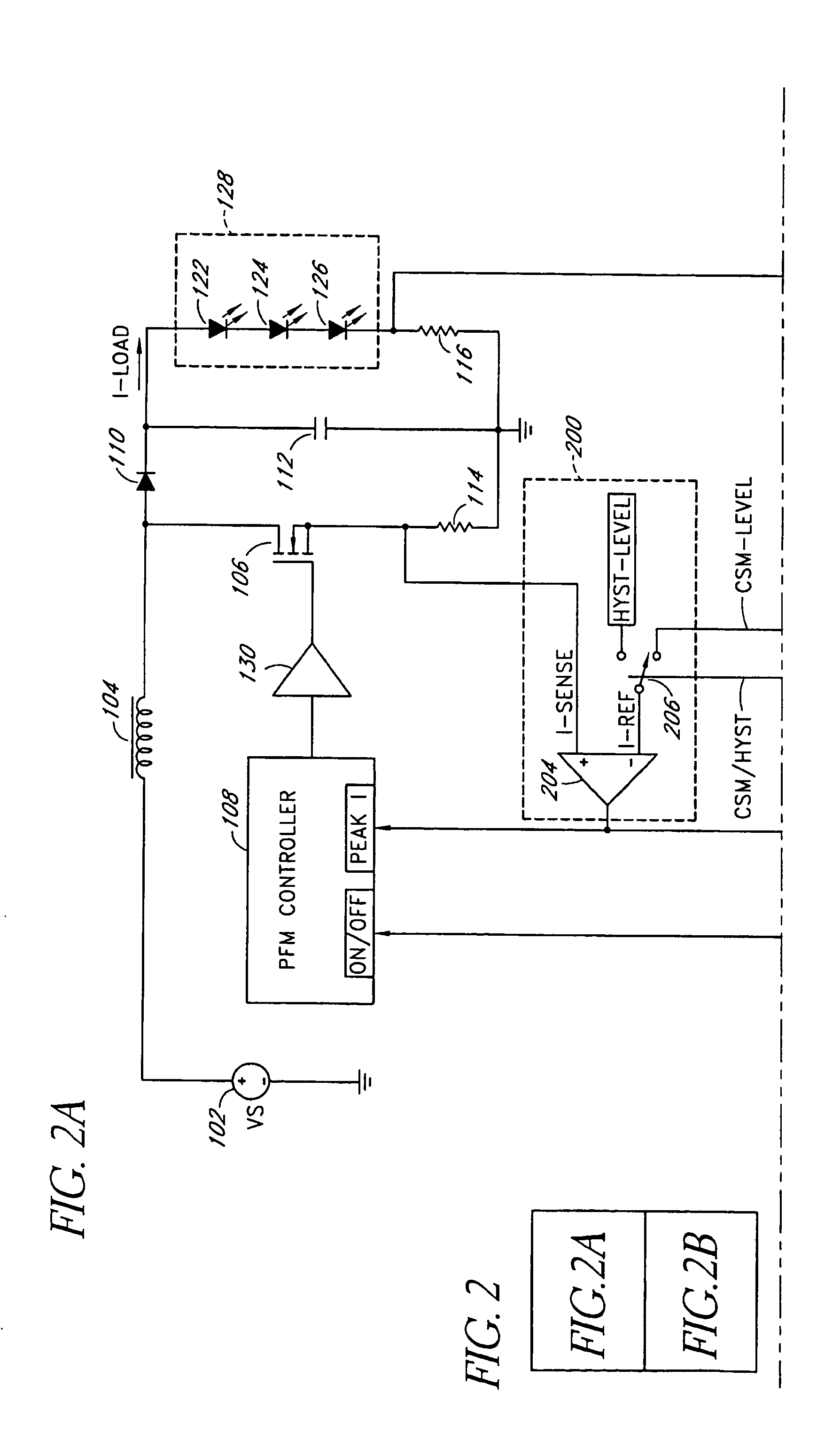

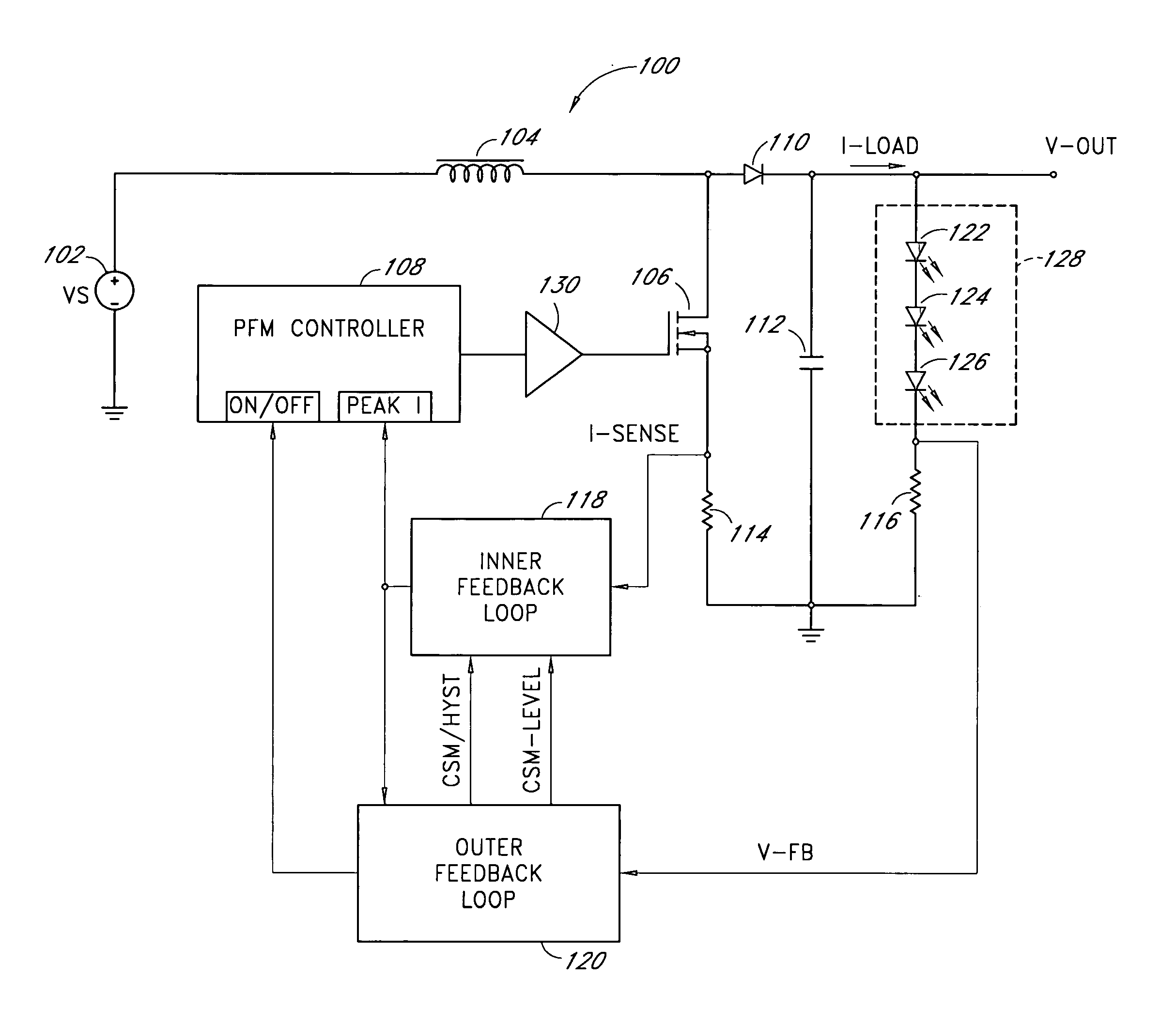

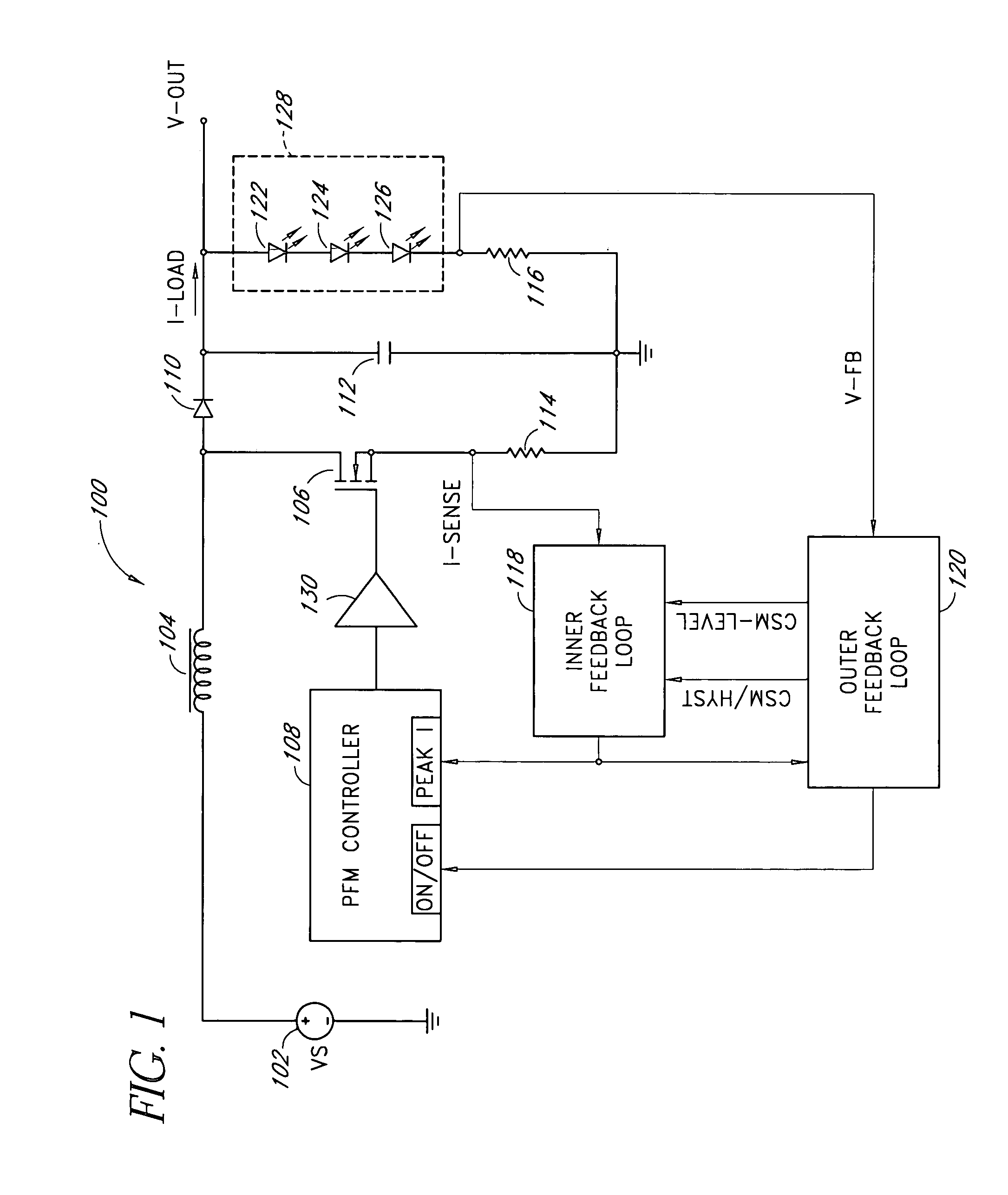

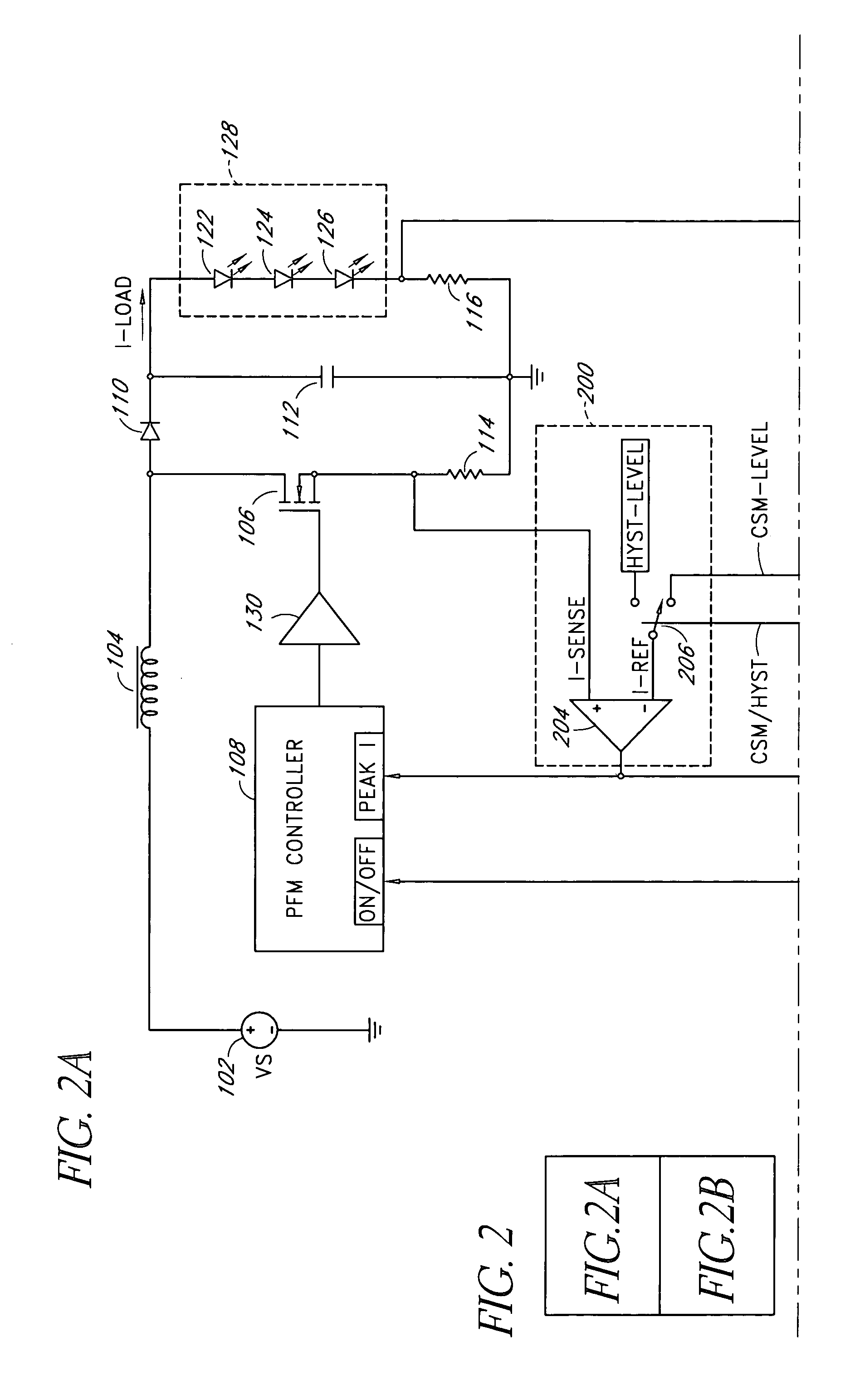

Dual-mode PFM boost converter

InactiveUS7102340B1Conduction loss downReduce switching lossesElectric lighting sourcesDc-dc conversionSwitched currentDual mode

A dual-mode pulse frequency modulation boost converter operates in a hysteretic mode during light load currents to regulate an output voltage using a substantially fixed peak switching current and operates in a continuous mode during heavy load currents to regulate the output voltage using a variable peak switching current. The boost converter senses load power to automatically switch between the hysteretic mode and the continuous mode.

Owner:MICROSEMI

Time division modulation with average current regulation for independent control of arrays of light emitting diodes

ActiveUS7902771B2Low costFast response timeElectrical apparatusElectroluminescent light sourcesSwitched currentAverage current

Exemplary apparatus, method and system embodiments provide for separately and independently sourcing current to a series of light emitting diodes of a plurality of series of light-emitting diodes. An exemplary apparatus comprises a power converter which generates a current, a first multiplexer, and a controller. The controller provides for sequential and separate switching of the current through the first multiplexer to each of the series of light-emitting diodes for a corresponding period of time. An average current provided by the power converter is determined as substantially equal to a sum of the corresponding currents through the plurality of series of light-emitting diodes. A total period for switching current to all of the series of light-emitting diodes is also determined. A corresponding time period for switching current to a selected corresponding series of light-emitting diodes is substantially equal to a proportion of the total period determined as a ratio of the corresponding current for the selected corresponding series of light-emitting diodes to the average current provided by the power converter.

Owner:CHEMTRON RES

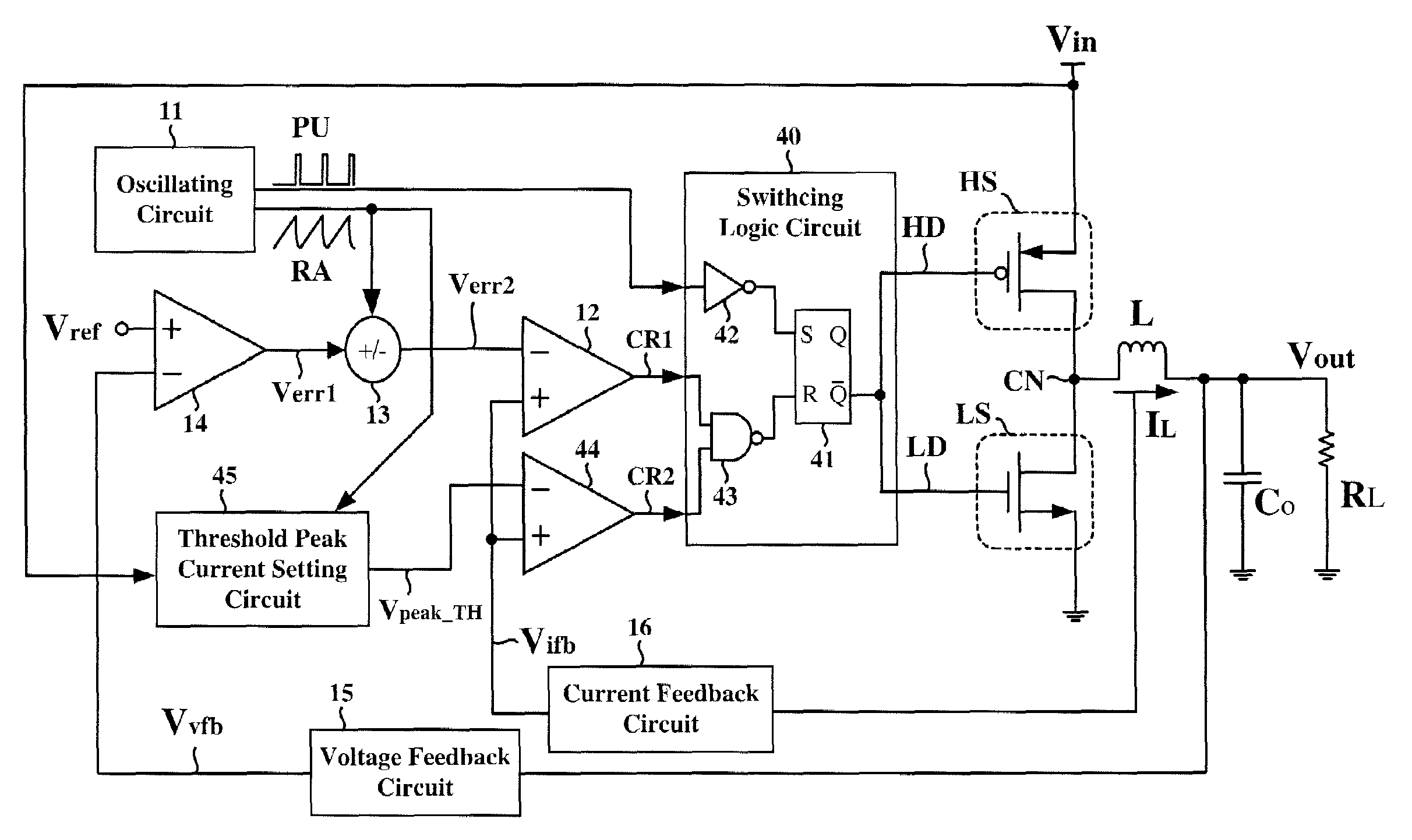

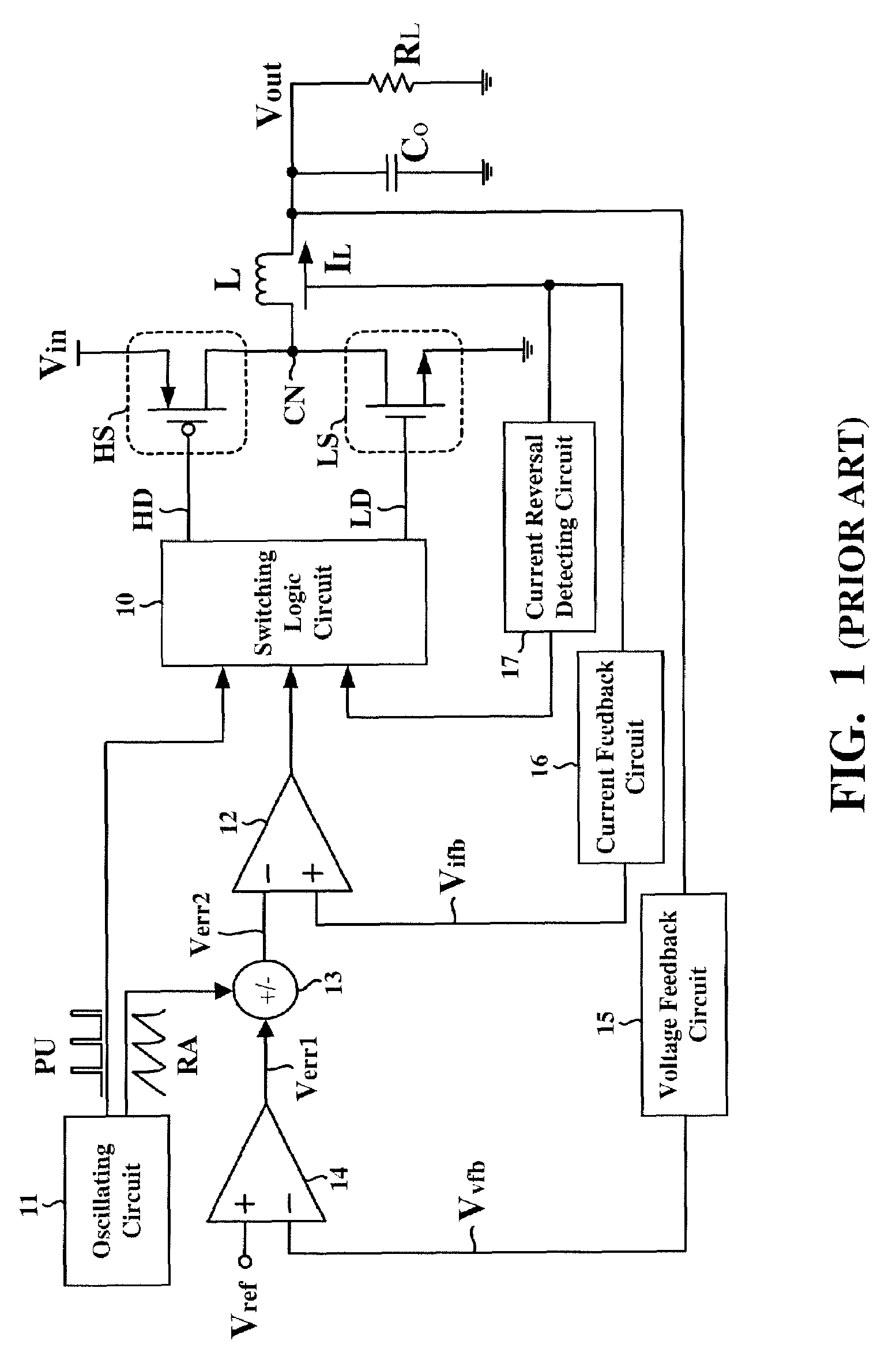

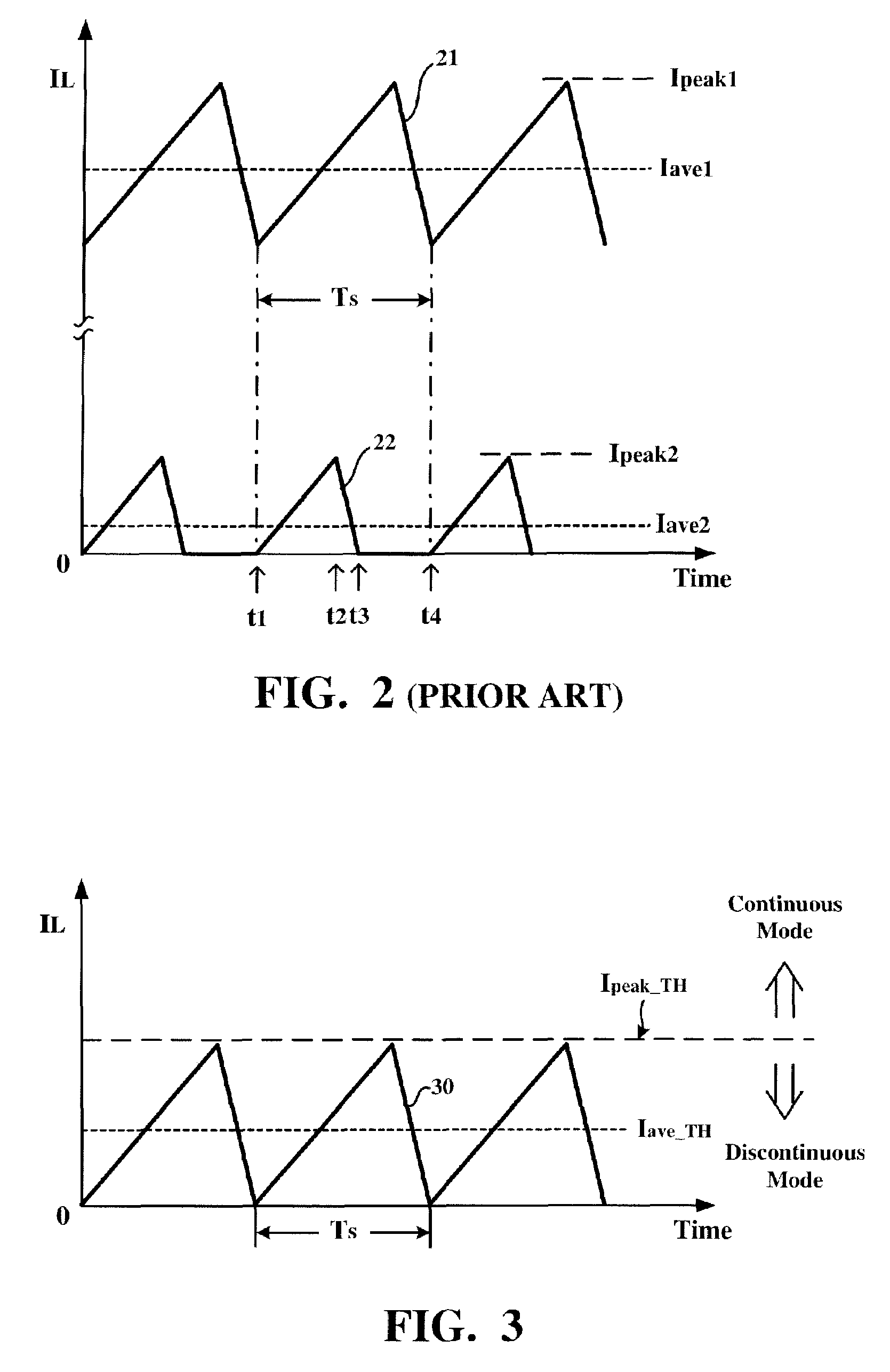

Switching voltage regulator operating without a discontinuous mode

InactiveUS7180274B2Avoid disadvantagesReduce switchingEfficient power electronics conversionDc-dc conversionValue setSwitched current

A switching circuit operates with a first operating state and a second operating state. During the first operating state, the switching circuit allows a switching current to linearly increase. During the second operating state, the switching circuit allows the switching current to linearly decrease. A control circuit is coupled to the switching circuit for controlling the switching circuit to operate with the first operating state or the second operating state. A setting circuit generates a threshold signal for the control circuit to ensure that during the first operating state the switching current linearly increases to become higher than or equal to a current value set by the threshold signal. Thereby, the switching current is prevented from linearly decreasing to reverse polarity during the second operating state.

Owner:GLOBAL MIXED MODE TECH

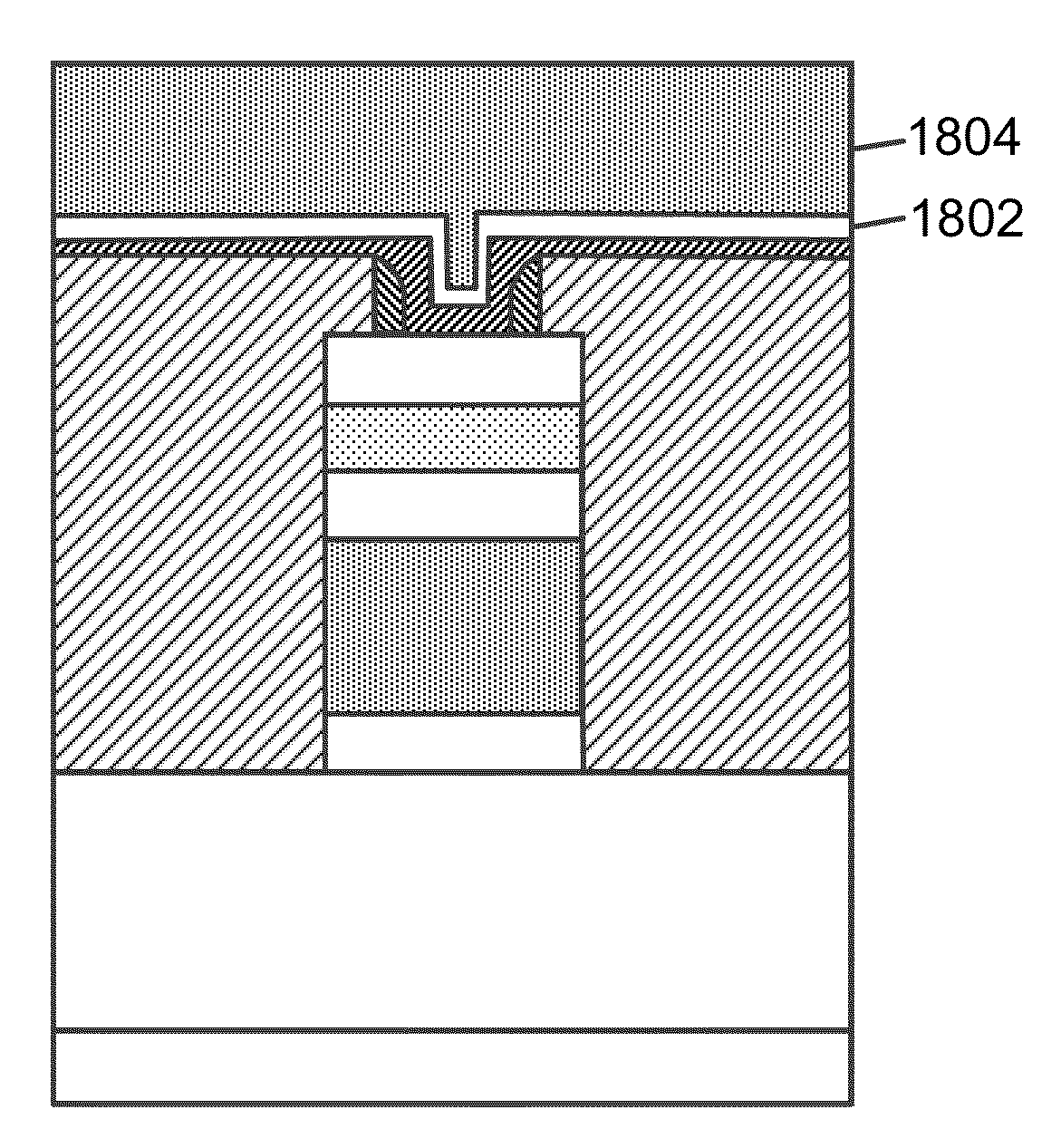

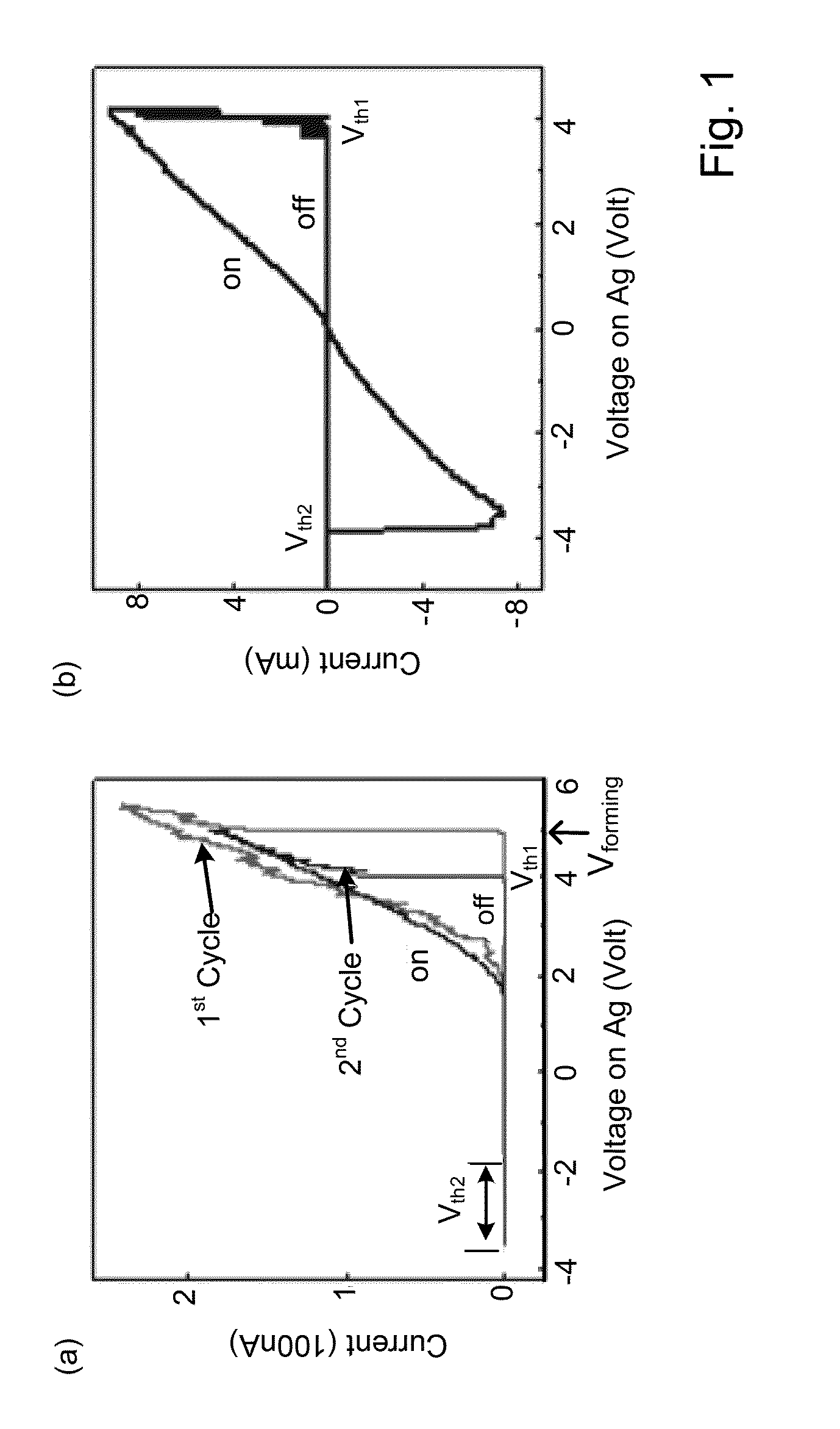

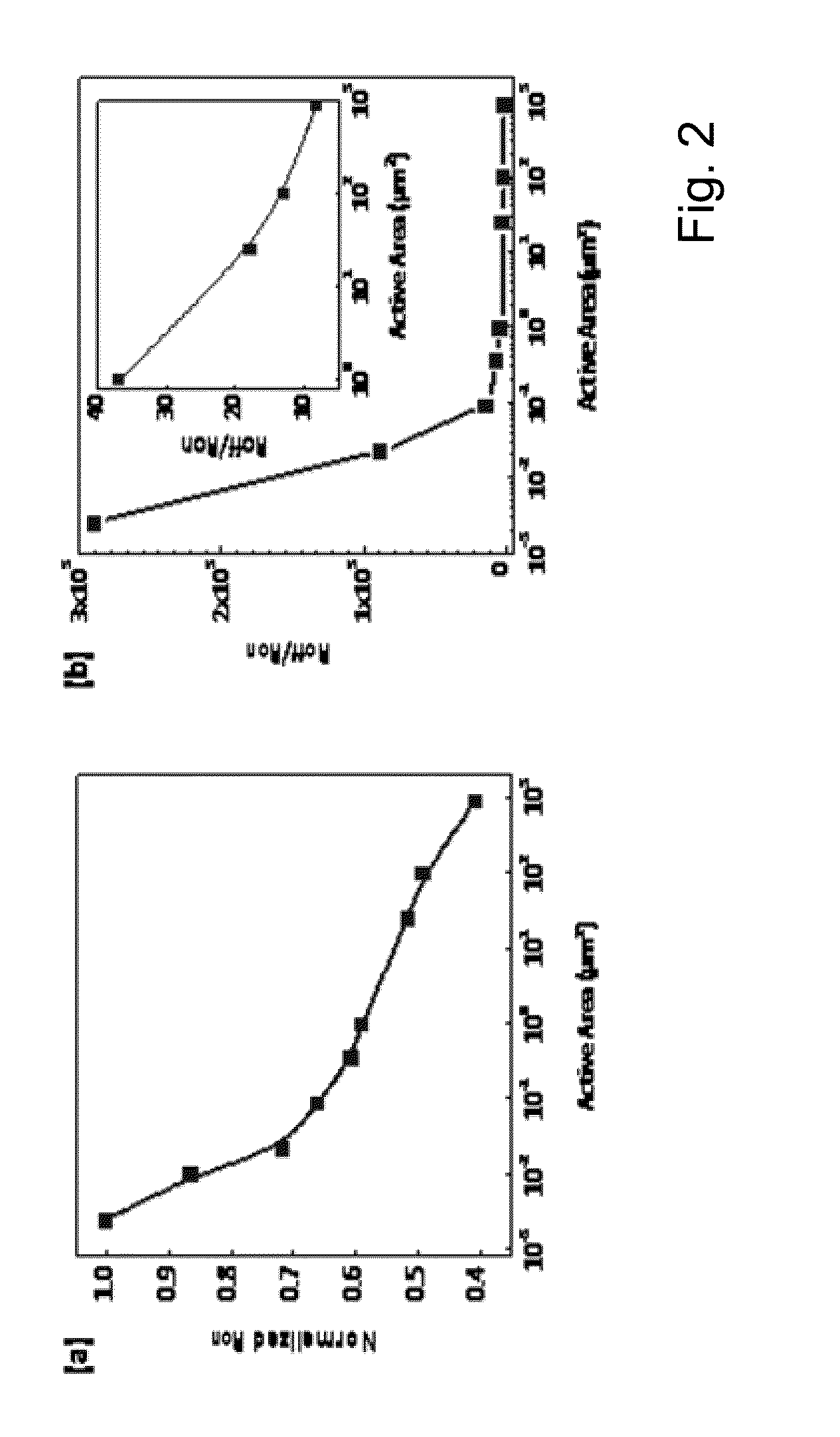

Improved on/off ratio for non-volatile memory device and method

ActiveUS20120012806A1Quick switchWide rangeSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesSwitched currentEngineering

This application describes a method of forming a switching device. The method includes forming a first dielectric material overlying a surface region of a substrate. A bottom wiring material is formed overlying the first dielectric material and a switching material is deposited overlying the bottom wiring material. The bottom wiring material and the switching material is subjected to a first patterning and etching process to form a first structure having a top surface region and a side region. The first structure includes at least a bottom wiring structure and a switching element having a top surface region including an exposed region of the switching element. A second dielectric material is formed overlying at least the first structure including the exposed region of the switching element. The method forms a first opening region in a portion of the second dielectric layer to expose a portion of the top surface region of the switching element. A dielectric side wall structure is formed overlying a side region of the first opening region. A top wiring material including a conductive material is formed overlying at lease the top surface region of the switching element such that the conductive material is in direct contact with the switching element. The side wall spacer reduces a contact area for the switching element and the conductive material and thus a reduced active device area for the switching device. In a specific embodiment, the reduced area provides for an increase in device ON / OFF current ratio.

Owner:CROSSBAR INC

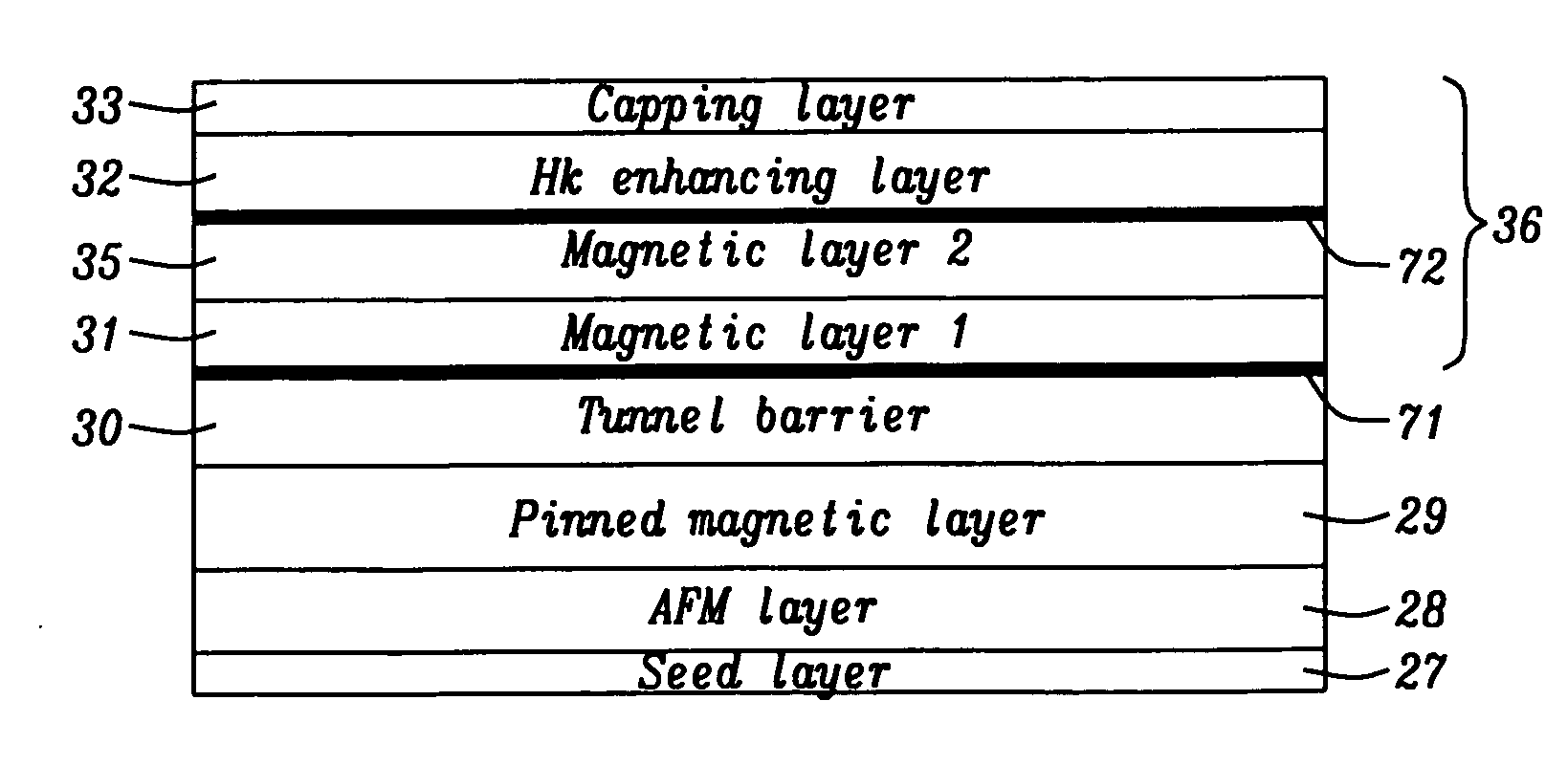

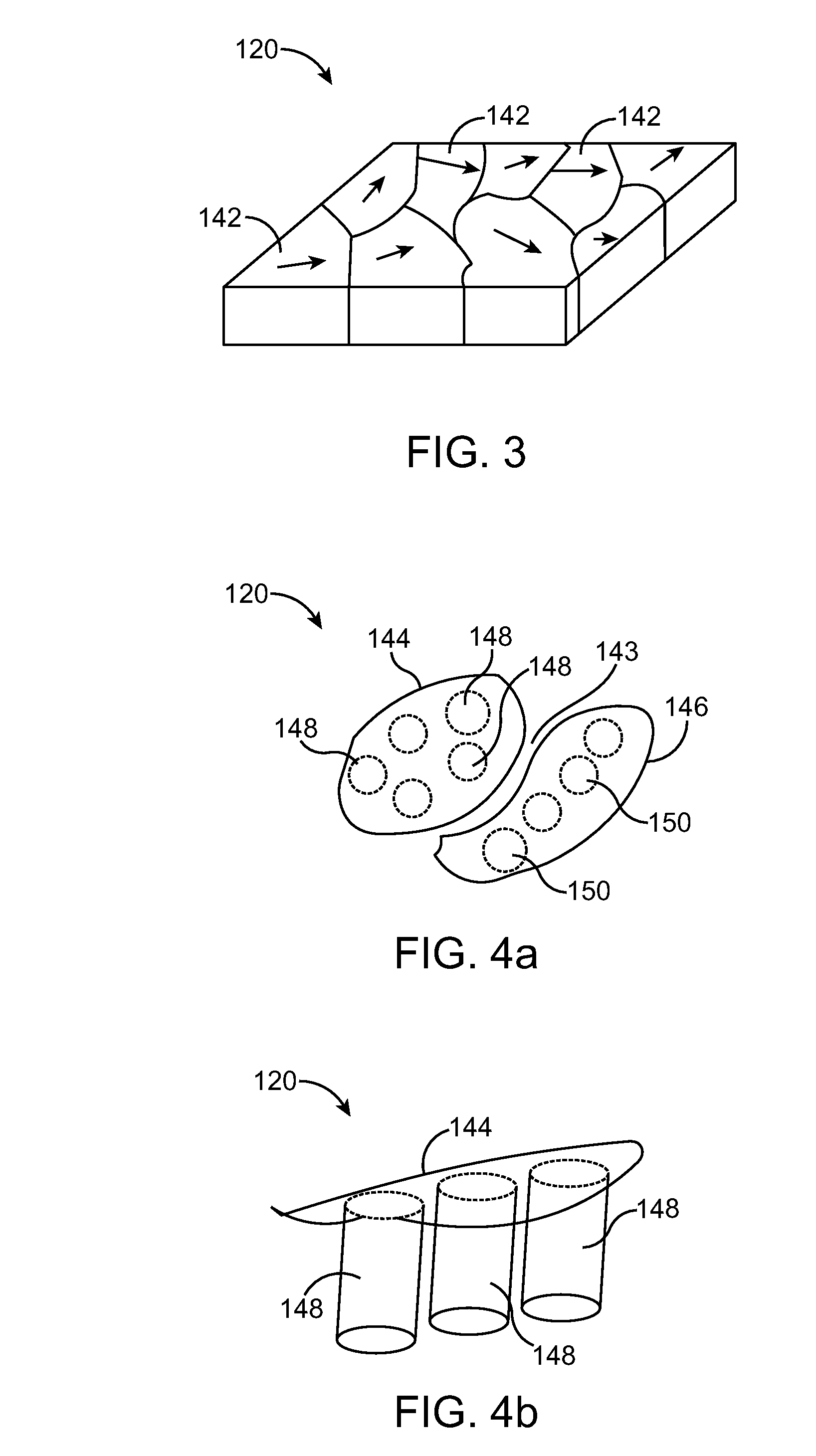

Structure and method for enhancing interfacial perpendicular anisotropy in CoFe(B)/MgO/CoFe(B) Magnetic Tunnel Junctions

ActiveUS20120135273A1Magnetic materials for record carriersVacuum evaporation coatingSwitched currentPerpendicular anisotropy

A STT-RAM MTJ is disclosed with a MgO tunnel barrier formed by natural oxidation process. A Co10Fe70B20 / NCC / Co10Fe70B20, Co10Fe70B20 / NCC / Co10Fe70B20 / NCC, or Co10Fe70B20 / NCC / Co10Fe70B20 / NCC / Co10Fe70B20 free layer configuration where NCC is a nanocurrent channel layer made of Fe(20%)-SiO2 is used to minimize Jc0 while enabling higher thermal stability, write voltage, read voltage, Ho, and Hc values that satisfy 64 Mb design requirements. The NCC layer is about 10 Angstroms thick to match the minimum Fe(Si) grain diameter size. The MTJ is annealed with a temperature of about 330° C. to maintain a high magnetoresistive ratio while maximizing Hk⊥(interfacial) for the free layer thereby reducing Heff and lowering the switching current. The Co10Fe70B20 layers are sputter deposited with a low pressure process with a power of about 15 Watts and an Ar flow rate of 40 standard cubic centimeters per minute to lower Heff for the free layer.

Owner:TAIWAN SEMICON MFG CO LTD

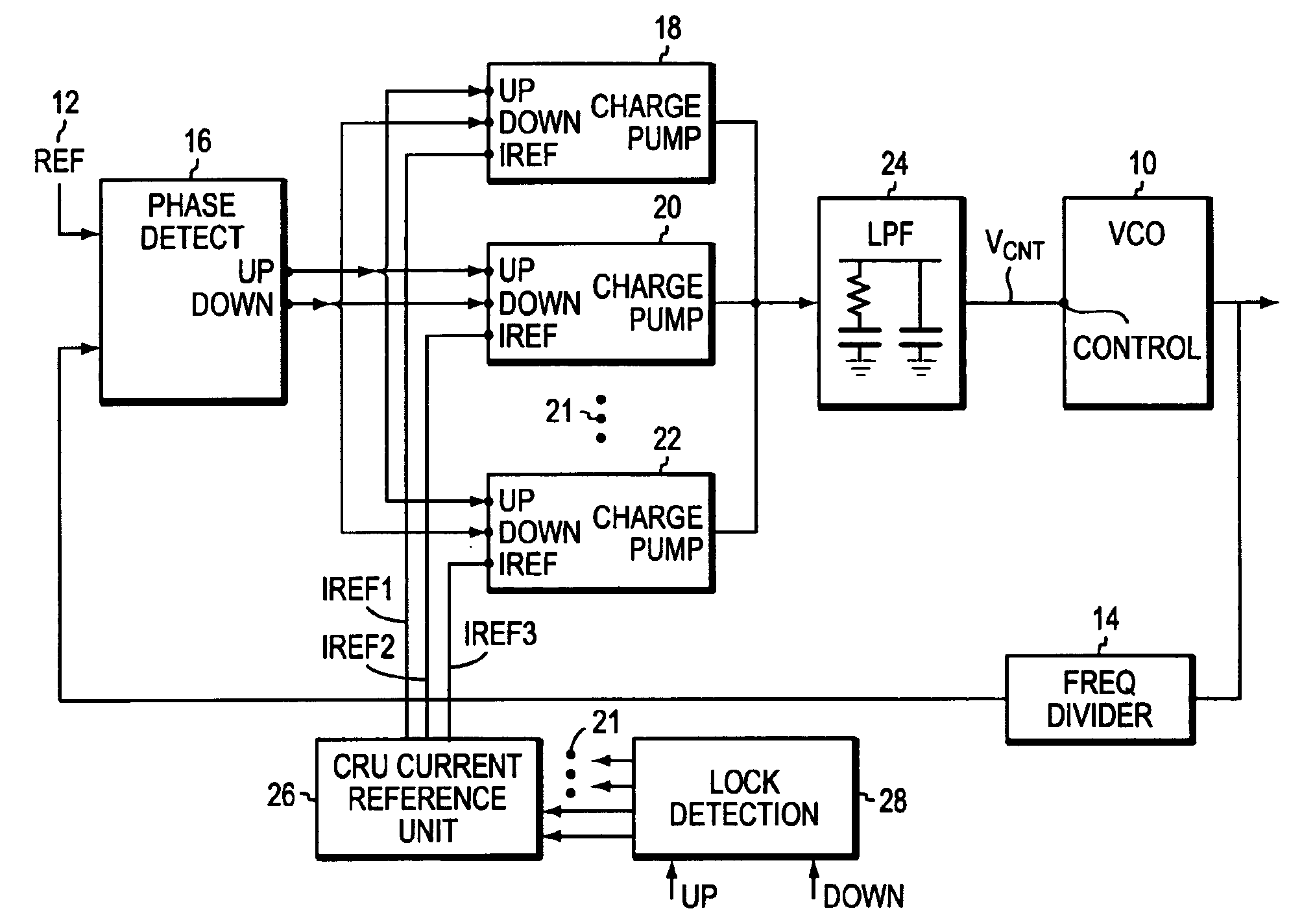

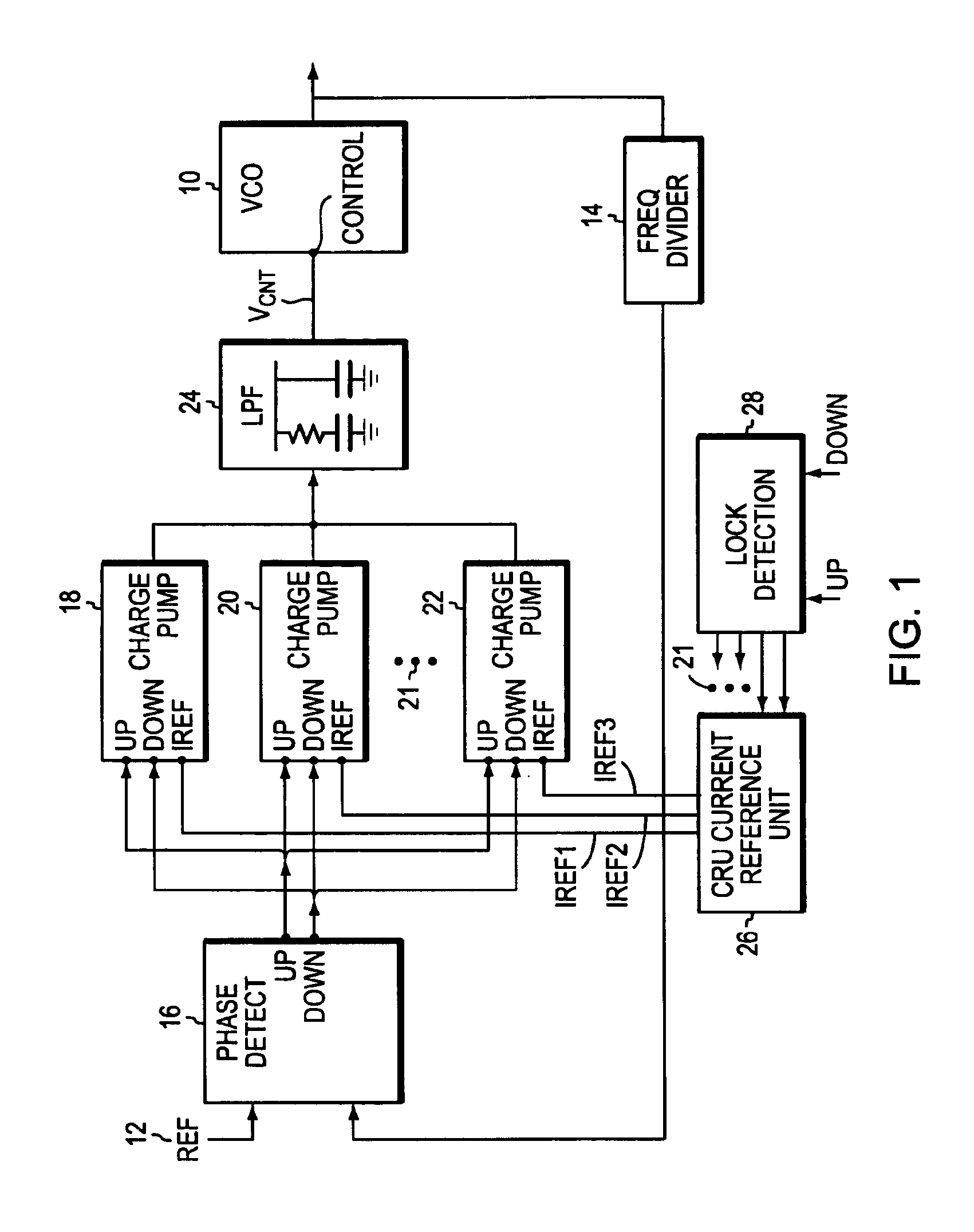

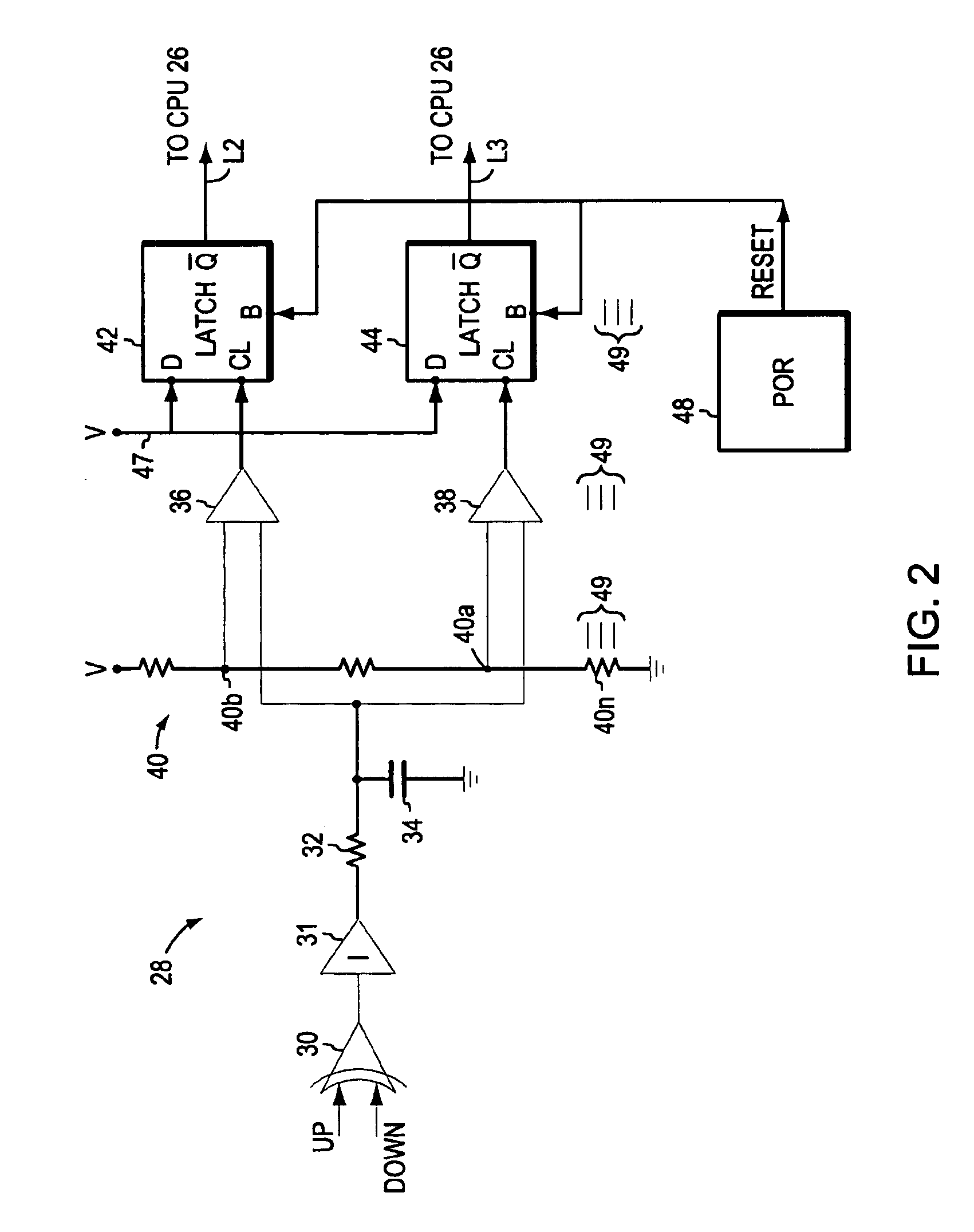

Circuitry to reduce PLL lock acquisition time

ActiveUS6940356B2Decrease frequency/phase errorFast frequencyPulse automatic controlOscillator tubesPhase detectorSwitched current

A phase locked loop, PLL, is described with multiple parallel charge pumps that are selectively disabled as phase lock is approached. A lock detection circuit is described that enabled reference currents to be fed to the parallel charge pumps. The error signal from a phase detector is arranged as UP and a DOWN signals that are averaged in the lock detector. When the average error is large, all the reference currents feed the charge pumps that provide a high loop gain to reduce the lock time. As the lock becomes closer selective reference currents are disabled to reduce loop gain so that a smooth transition to lock is made. Selectively switching currents into a low pass filter that usually follows a charge pump in a PLL circuit automatically reduces switching noise by the operation of the low pass filter.

Owner:SEMICON COMPONENTS IND LLC

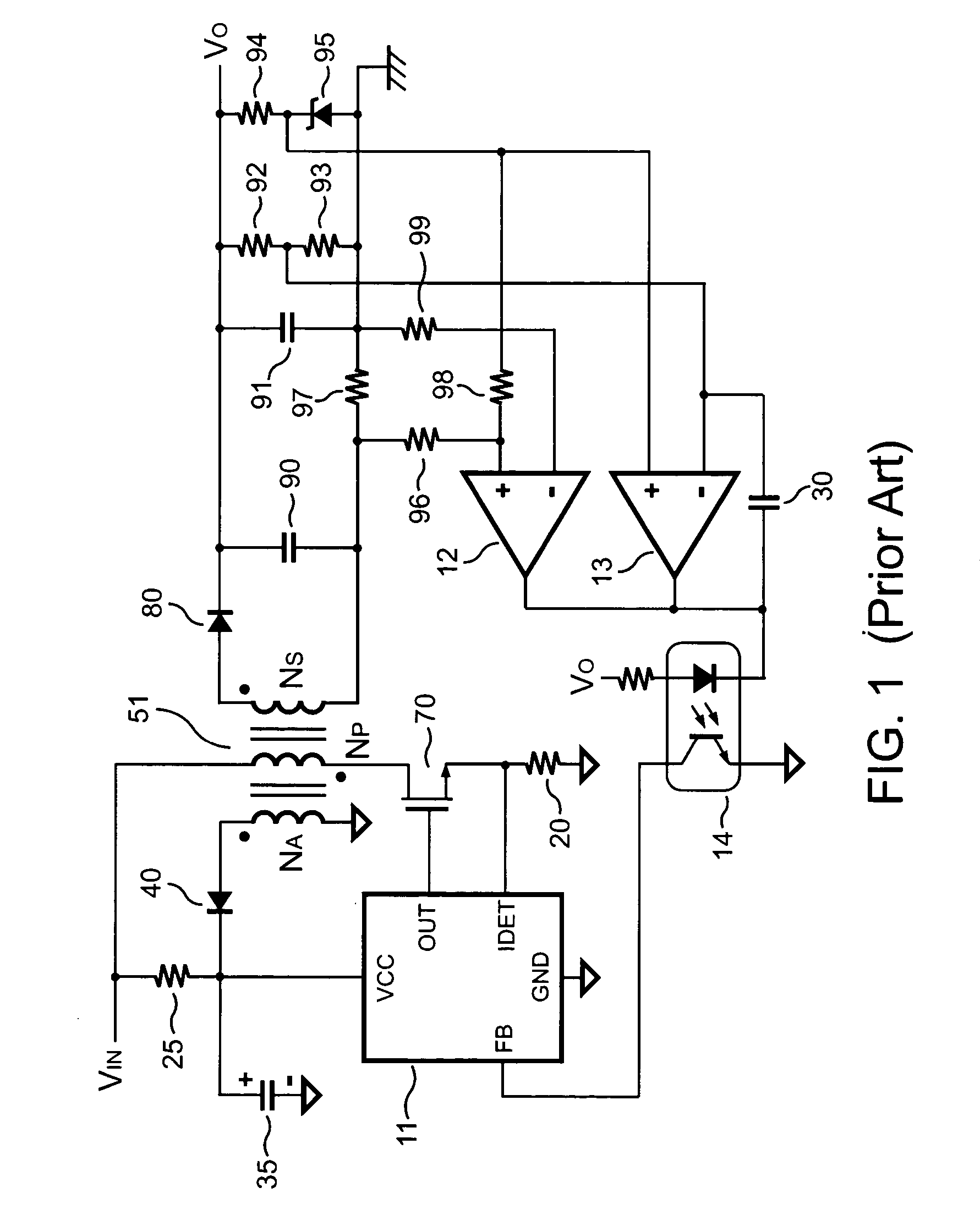

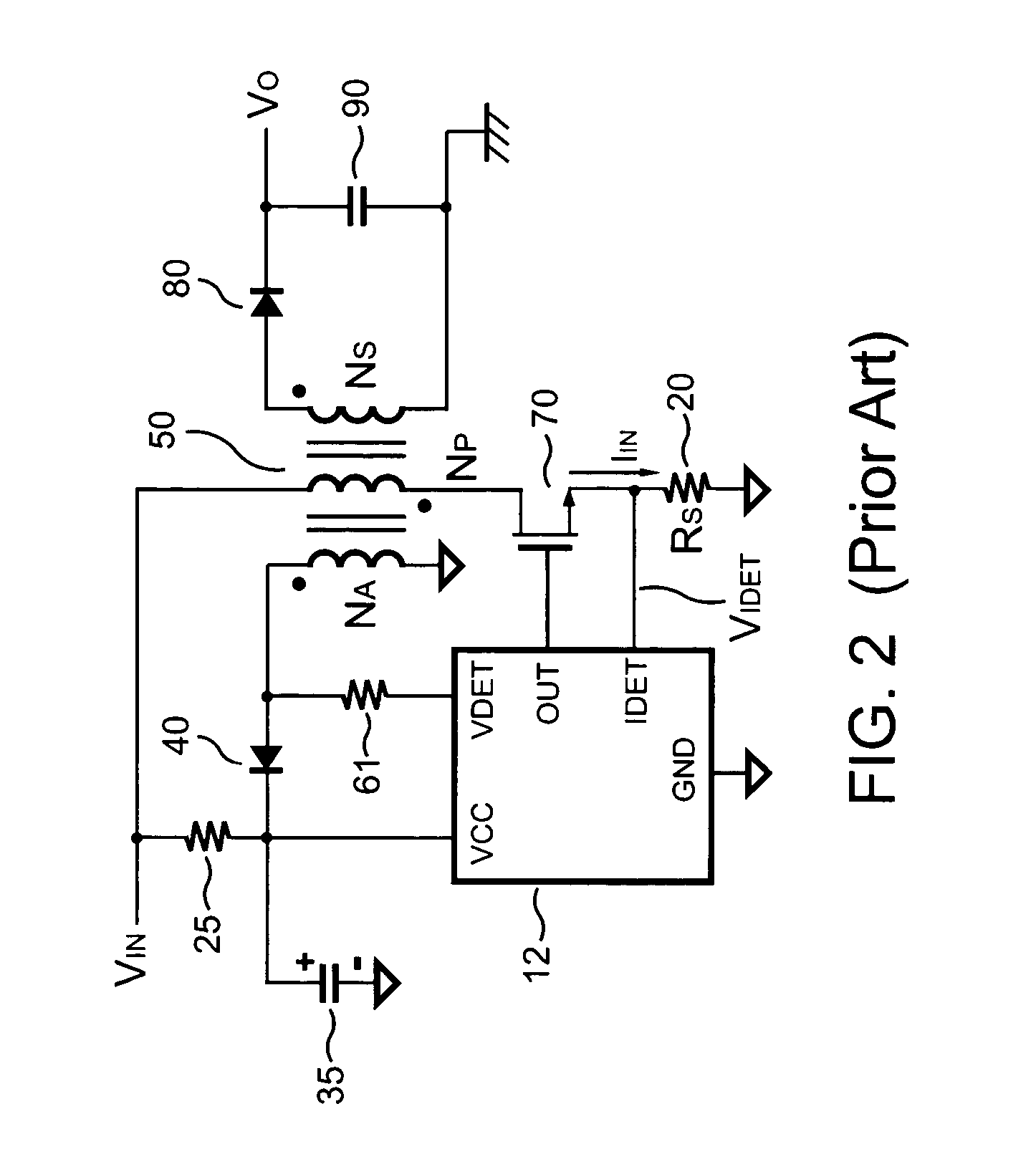

Power-mode controlled power converter

A power-mode controlled power converter is capable of supplying a constant output voltage and output current. A PWM controller generates a PWM signal in response to a voltage sampled from a transformer auxiliary winding. A programmable current-sink and a detection resistor compensate for a voltage drop of an output rectifier. A low-pass filter integrates a switching-current voltage to an average-current signal. An attenuator produces an input-voltage signal from a line-voltage input signal. The PWM controller multiplies the average-current signal with the input-voltage signal to generate a power-control signal. An error-amplifier compares the power-control signal with a power-reference voltage to generate a limit voltage. The limit voltage controls the power delivered from a primary-side circuit to a secondary-side circuit of the power-mode controlled power converter. Since the power-reference voltage varies in proportional to output voltage variations, a constant output current is therefore achieved.

Owner:SEMICON COMPONENTS IND LLC

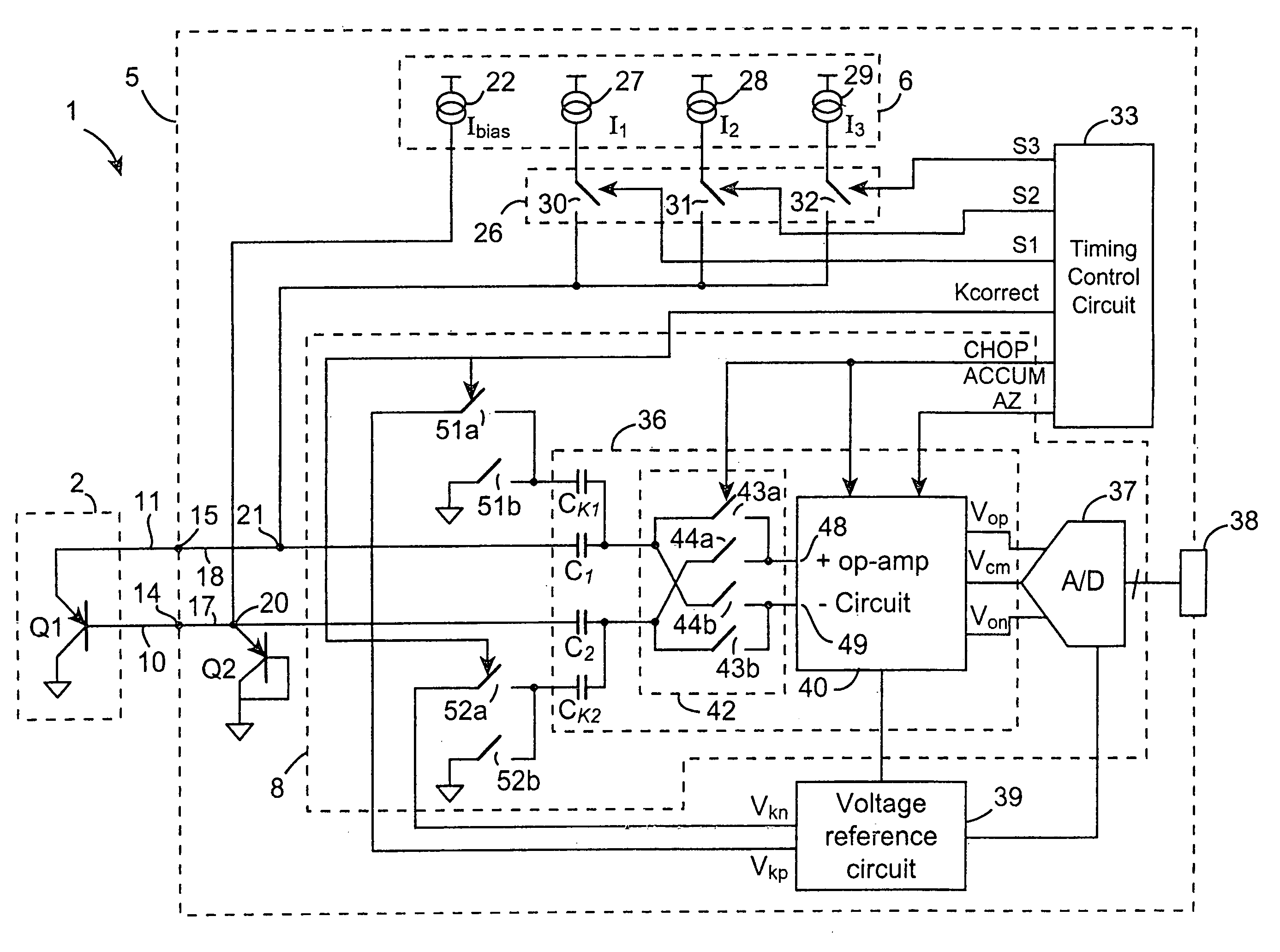

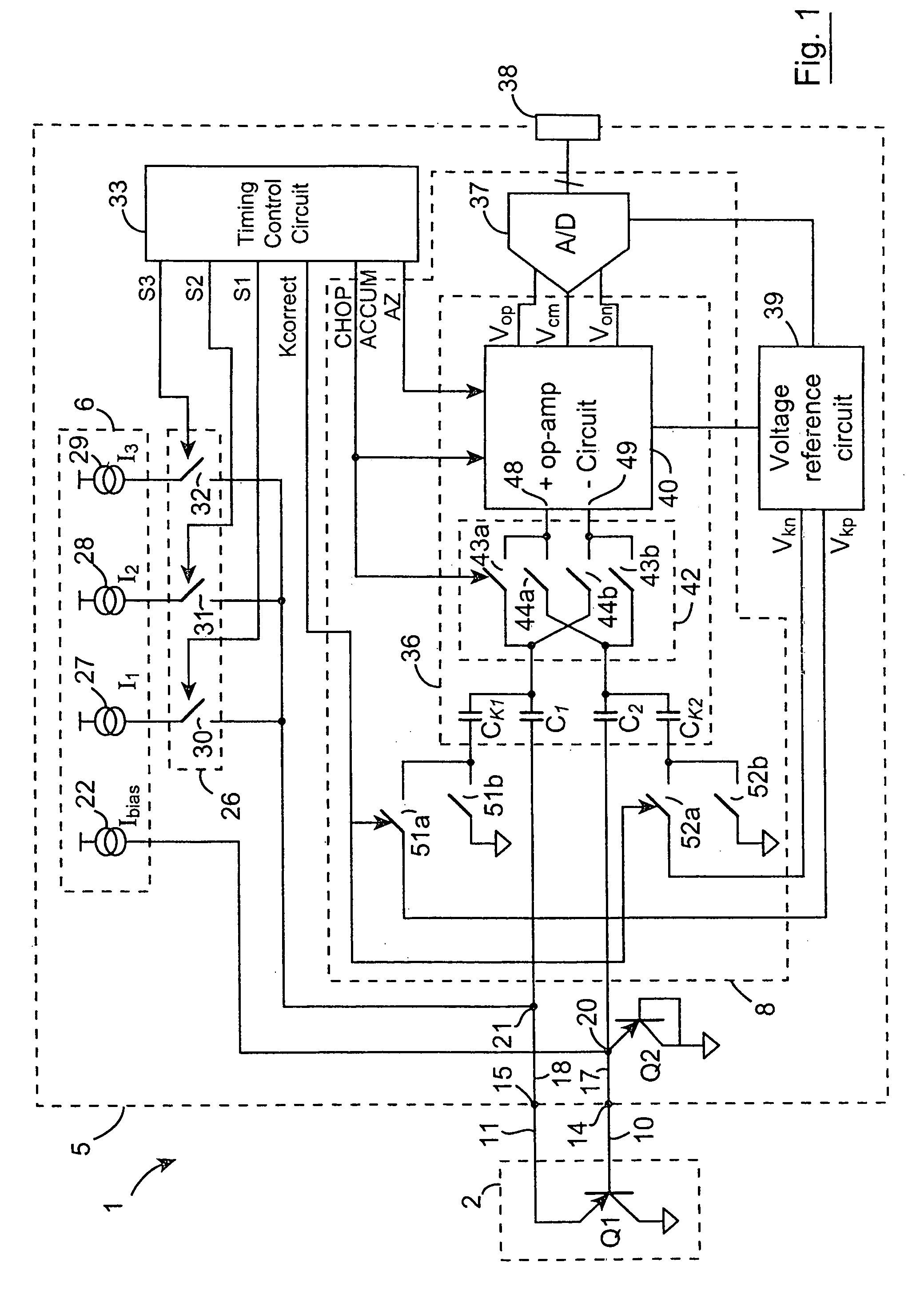

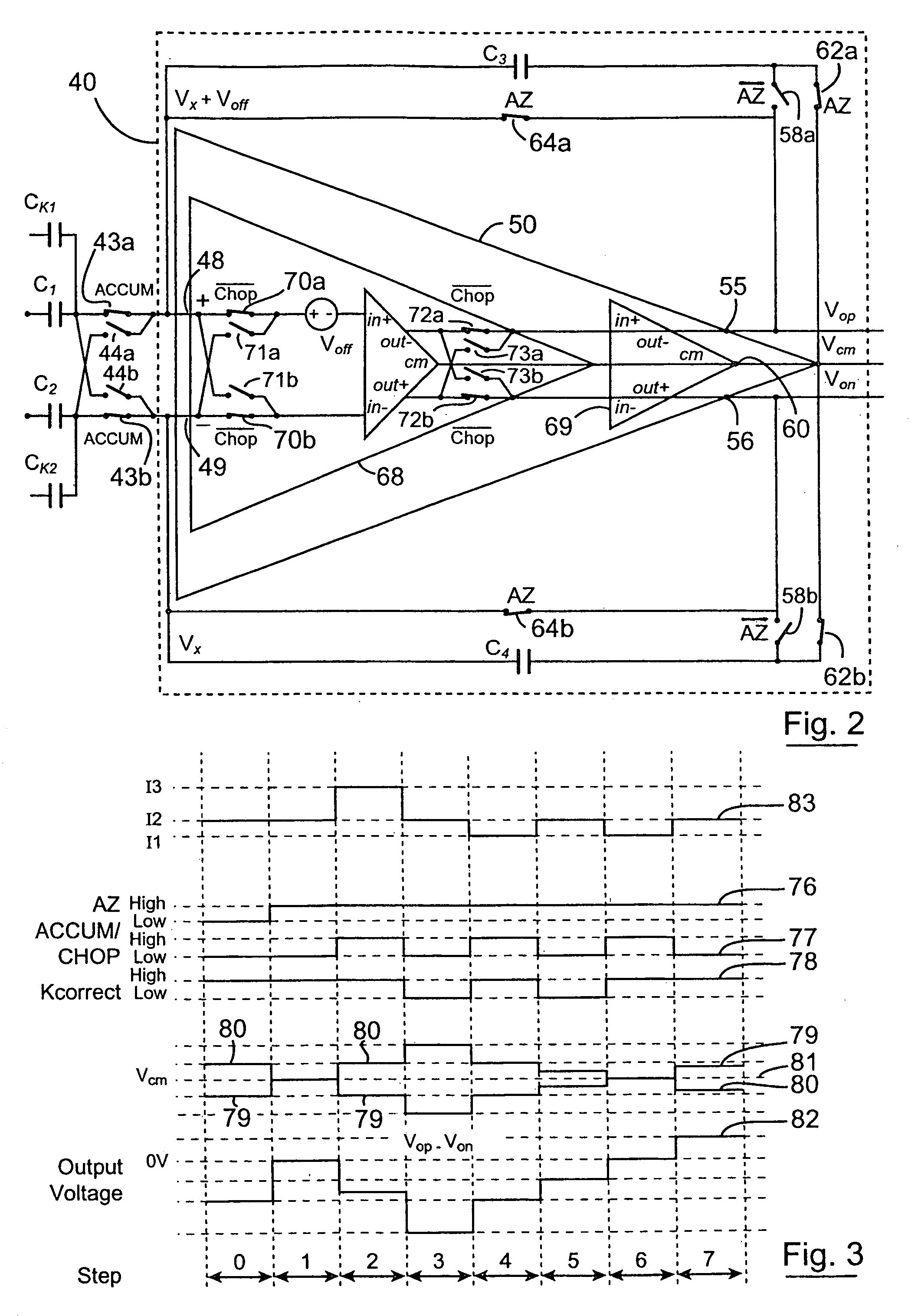

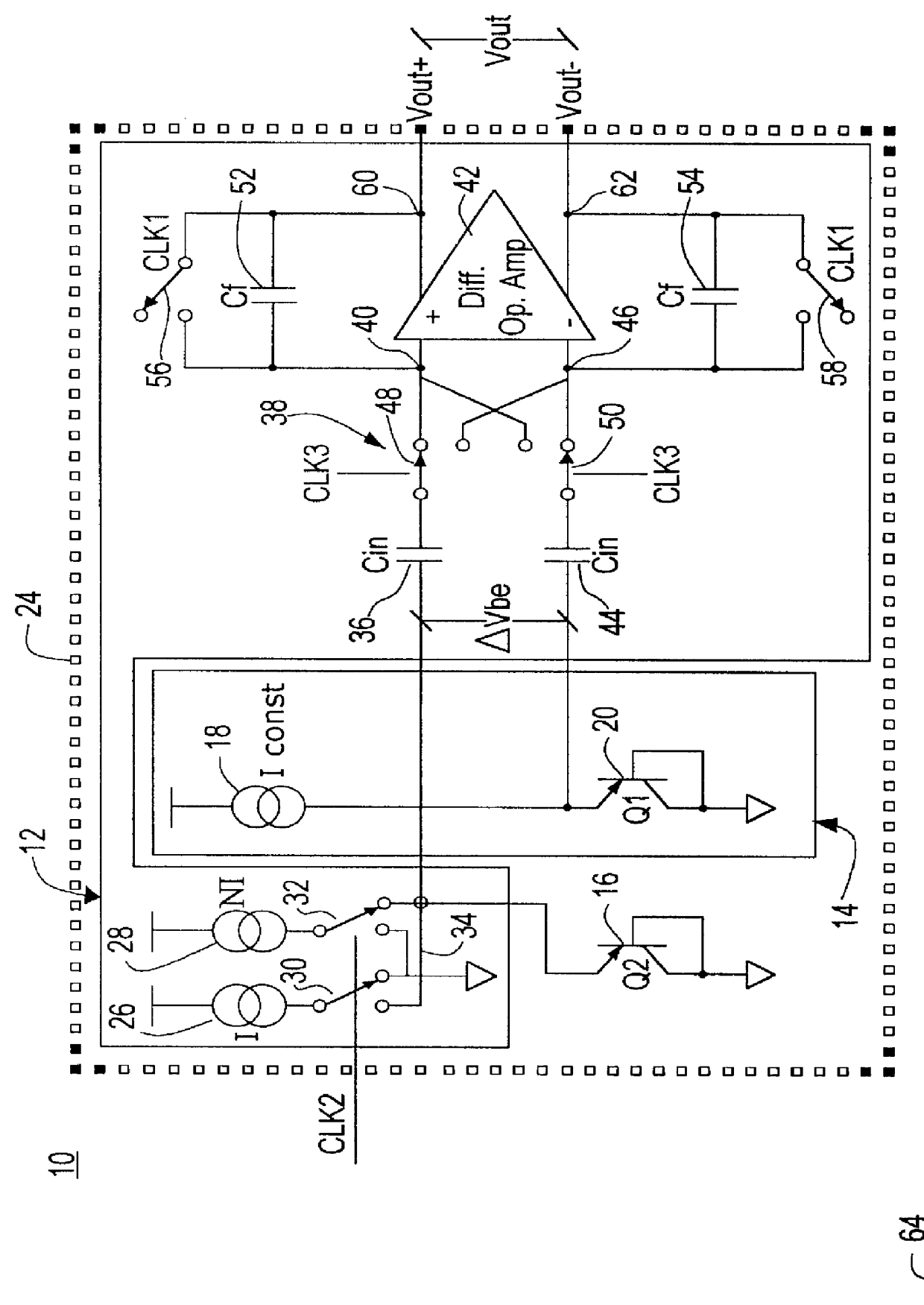

Method and a measuring circuit for determining temperature from a PN junction temperature sensor, and a temperature sensing circuit comprising the measuring circuit and a PN junction

ActiveUS7010440B1Accurate representationEliminate the effects ofThermometer detailsThermometers using material expansion/contactionSwitched currentExcitation current

A switched current temperature sensing circuit (1) comprises a measuring transistor (Q1) which is located remotely of a measuring circuit (5) which applies three excitation currents (I1,I2,I3) of different values to the measuring transistor (Q1) in a predetermined current sequence along lines (10,11). Resulting base / emitter voltages from the measuring transistor (Q1) are applied to the measuring circuit (5) along the same two lines (10,11) as the excitation currents are applied to the measuring transistor (Q1). Voltage differences ΔVbe of successive base / emitter voltages resulting from the excitation currents are integrated in an integrating circuit (36) of the measuring circuit (5) to provide an output voltage indicative of the temperature of the measuring transistor (Q1). By virtue of the fact that the measuring transistor (Q1) is excited by excitation currents of three different values, the effect of current path series resistance in the lines (10,11) on the output voltage indicative of temperature is eliminated. The predetermined current sequence in which the excitation currents are applied to the measuring transistor (Q1) is selected to minimize the voltages in the integrating circuit (36) during integration of the voltage differences ΔVbe.

Owner:ANALOG DEVICES INC

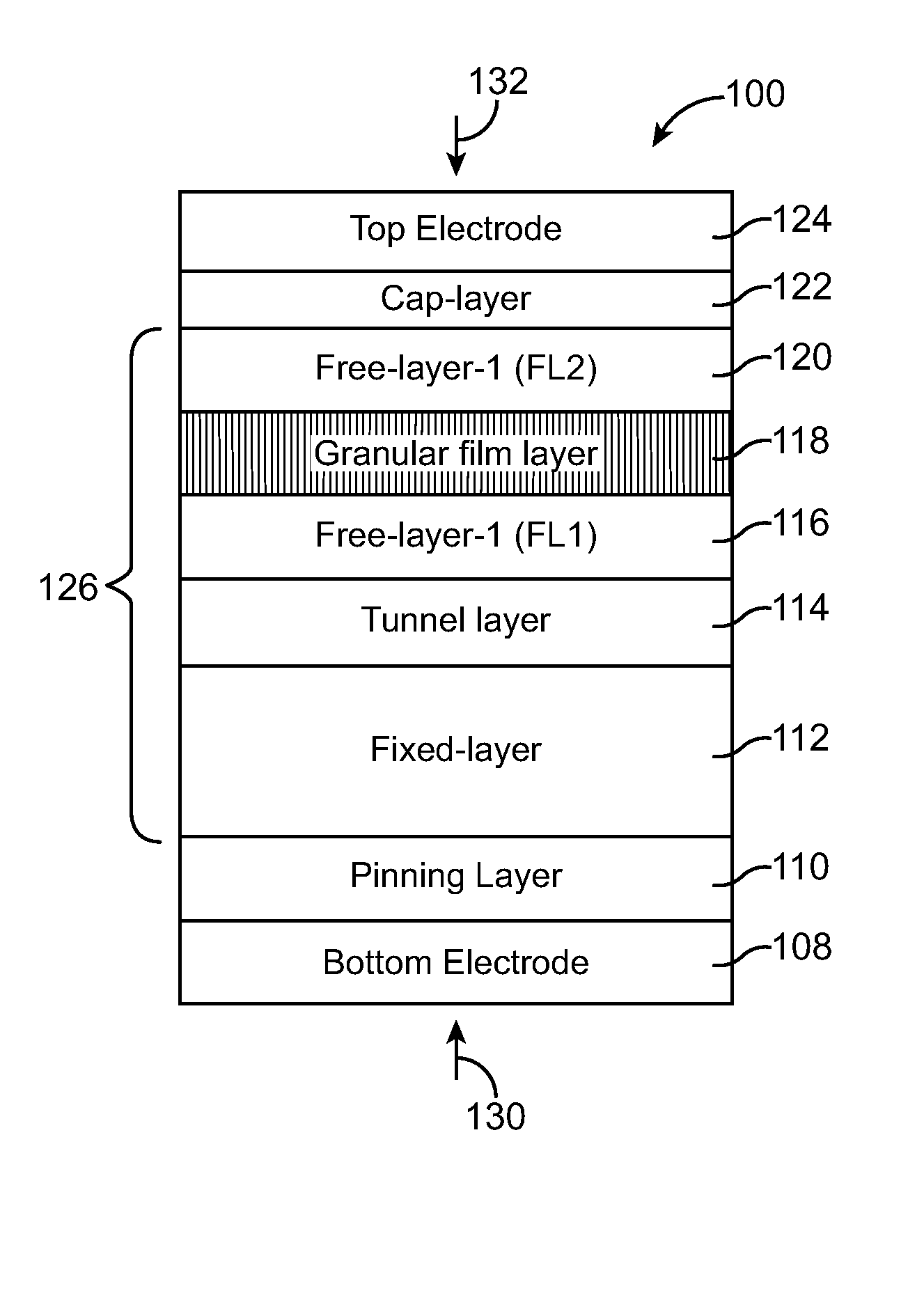

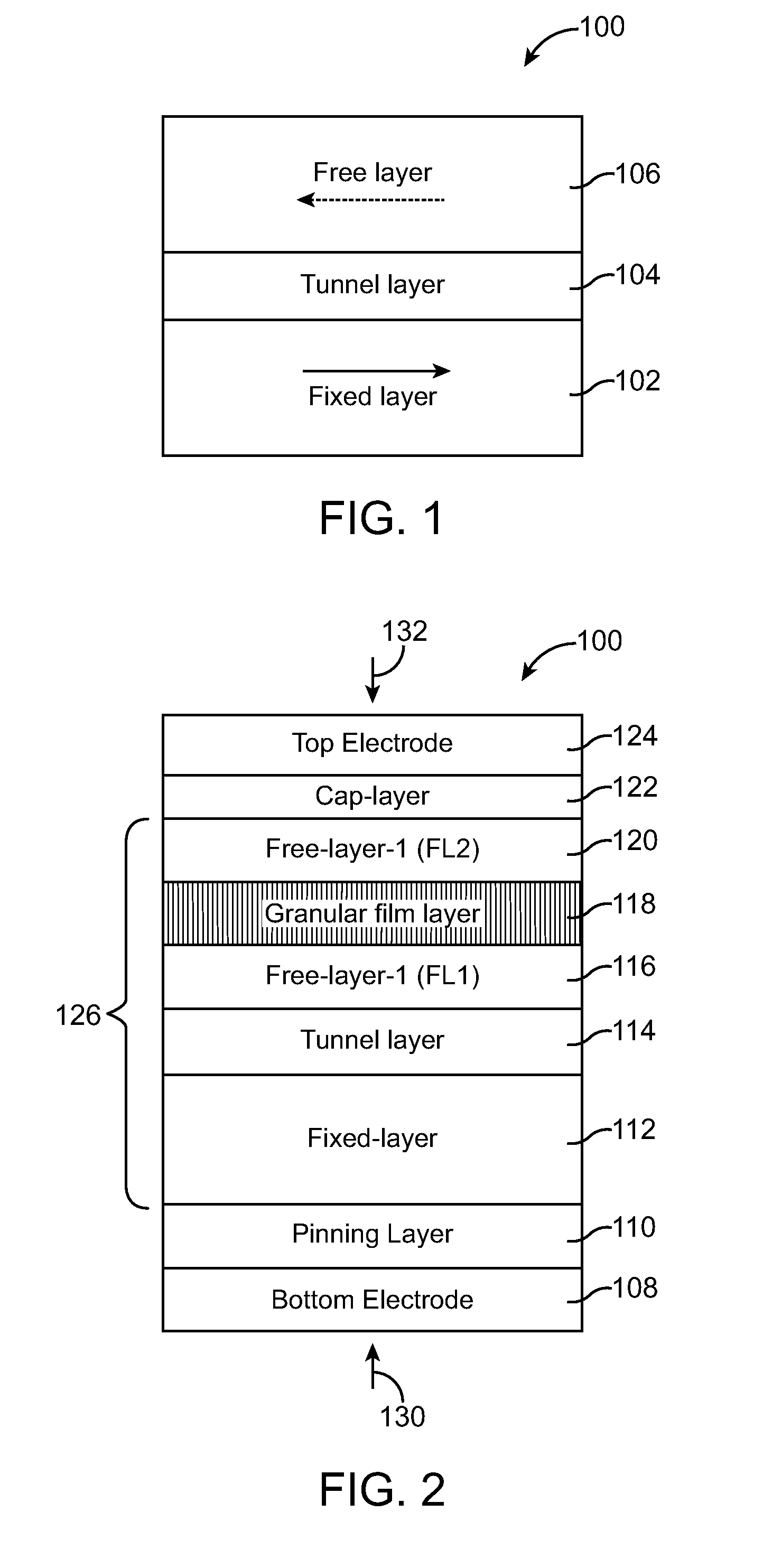

Non-Volatile Magnetic Memory with Low Switching Current and High Thermal Stability

One embodiment of the present invention includes a an embodiment of the present invention includes a non-volatile current-switching magnetic memory element including a bottom electrode; a pinning layer formed on top of the bottom electrode; a fixed layer formed on top of the pinning layer; a tunnel layer formed on top of the pinning layer; a first free layer formed on top of the tunnel layer; a granular film layer formed on top of the free layer; a second free layer formed on top of the granular film layer; a cap layer formed on top of the second layer; and a top electrode formed on top of the cap layer.

Owner:AVALANCHE TECH

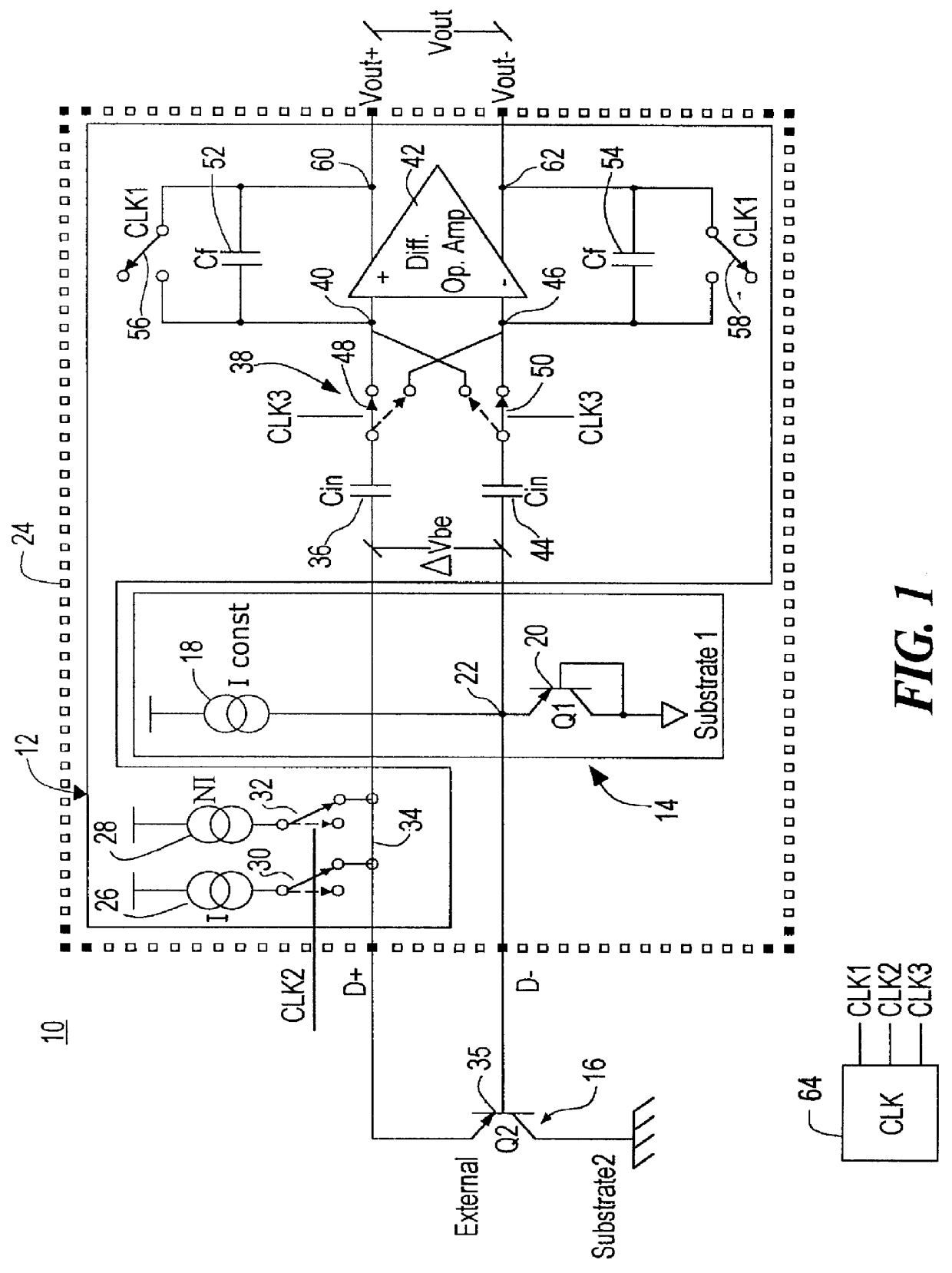

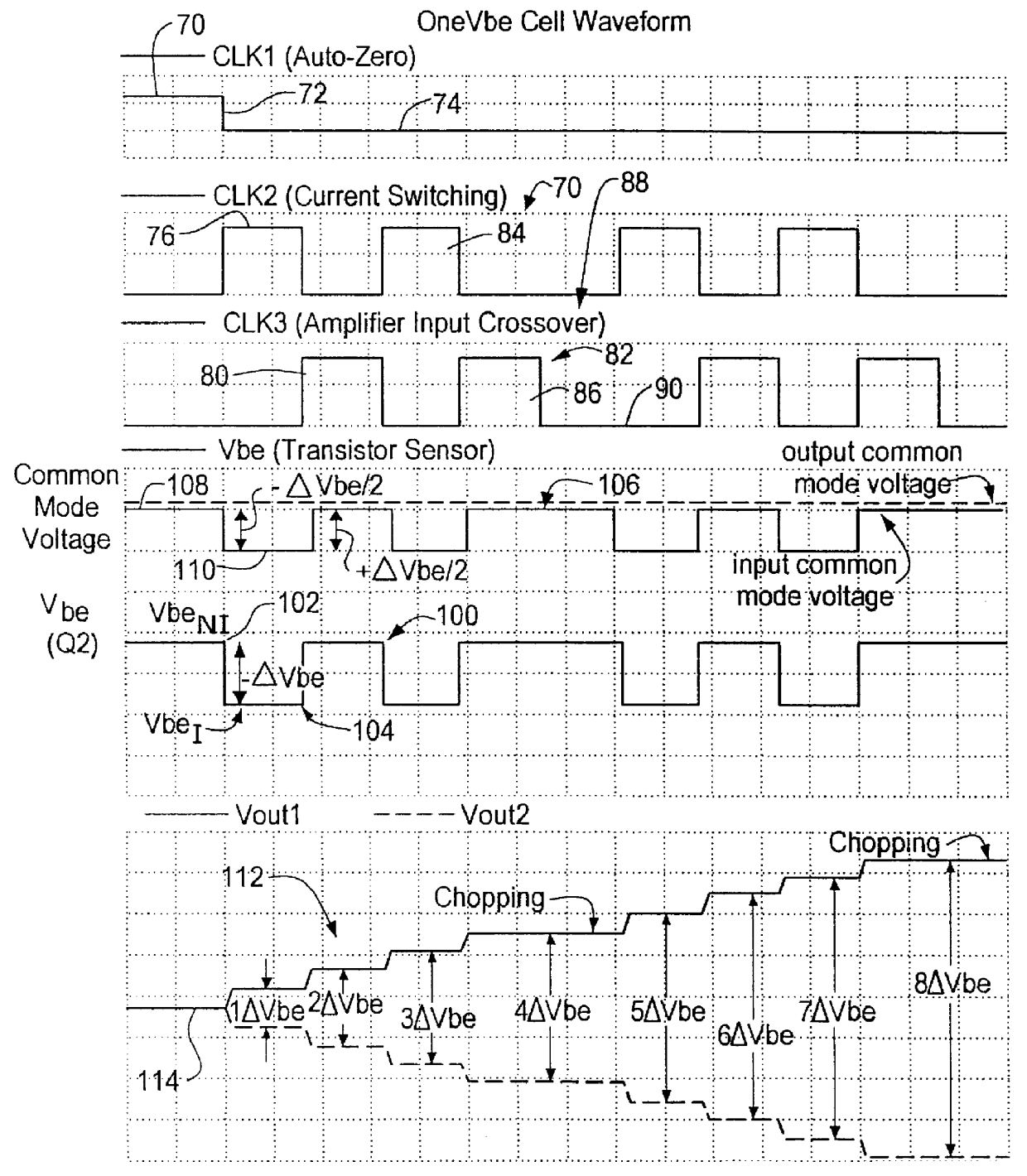

Decoupled switched current temperature circuit with compounded DELTA V be

InactiveUS6097239AThermometers using electric/magnetic elementsElectronic switchingDelta-vAudio power amplifier

A decoupled switched current temperature circuit with compounded DELTA Vbe includes an amplifier having an inverting input with corresponding non-inverting output and a non-inverting input with a corresponding inverting output; a PN junction connected to the non-inverting input through a first input capacitor and a voltage reference circuit is connected to the inverting input through a second input capacitor; a current supply includes a low current source and a high current source; a switching device applies the high current source to the PN junction and applies the low current source to the PN junction for providing the DELTA Vbe of the PN junction to the first capacitor; a first feedback capacitor is interconnected between the inverting output and the non-inverting input and a second feedback capacitor is interconnected between the non-inverting output and inverting input of the amplifier to define the gain on each of the inputs to produce a differential voltage across the outputs representative of the temperature of the PN junction; first and second reset switching devices discharge the first and second feedback capacitors, respectively, and a multi-phase switched device alternately interchanges the connection of the first and second input capacitors with the amplifier inputs for compounding the single DELTA Vbe .

Owner:ANALOG DEVICES INC

Method and apparatus to switch operating modes in a PFM converter

InactiveUS7102339B1Conduction loss downReduce switching lossesDc-dc conversionElectric variable regulationSwitched currentDual mode

A dual-mode pulse frequency modulation boost converter operates in a hysteretic mode during light load currents to regulate an output voltage using a substantially fixed peak switching current and operates in a continuous mode during heavy load currents to regulate the output voltage using a variable peak switching current. The boost converter senses load power to automatically switch between the hysteretic mode and the continuous mode.

Owner:MICROSEMI

Battery charger

InactiveUS6191560B1Short timeIncrease the allowable valueSecondary cells charging/dischargingElectric powerSwitched currentBattery charge

A map is retrieved based on a battery temperature and a temperature rise value (in a step S40) and an allowable current value, with which a battery can be charged while battery temperature rise is being suppressed, is obtained and the battery is charged with the allowable current value (in a step S42). By doing so, it is possible to charge a nickel metal hydride battery in a short time without causing deterioration due to temperature rise. If it is determined that a battery state is not in a final charging period from the change of battery voltage ("Yes' in a step S30), a change in temperature is corrected (in a step S34) and a relatively high allowable current value is thereby obtained from the map (in a step S40). That is, before the final charging period, battery charge can be completed in a short time by applying high current without switching current values for adjustment purposes.

Owner:MAKITA CORP

Magnetic memory element and storage device using the same

ActiveUS20120075922A1Magnetic anisotropic energy decreaseImprove thermal stabilityNanomagnetismMagnetic-field-controlled resistorsPerpendicular magnetizationSwitched current

A magnetic memory element capable of maintaining high thermal stability (retention characteristics) while reducing a writing current. The magnetic memory element includes a magnetic tunnel junction having a first magnetic body including a perpendicular magnetization film, an insulating layer, and a second magnetic body serving as a storage layer including a perpendicular magnetization film, which are sequentially stacked. A thermal expansion layer is disposed in contact with the magnetic tunnel junction portion. The second magnetic body is deformed in a direction in which the cross section thereof increases or decreases by the thermal expansion or contraction of the thermal expansion layer due to the flow of a current, thereby reducing a switching current threshold value required to change the magnetization direction.

Owner:III HLDG 3

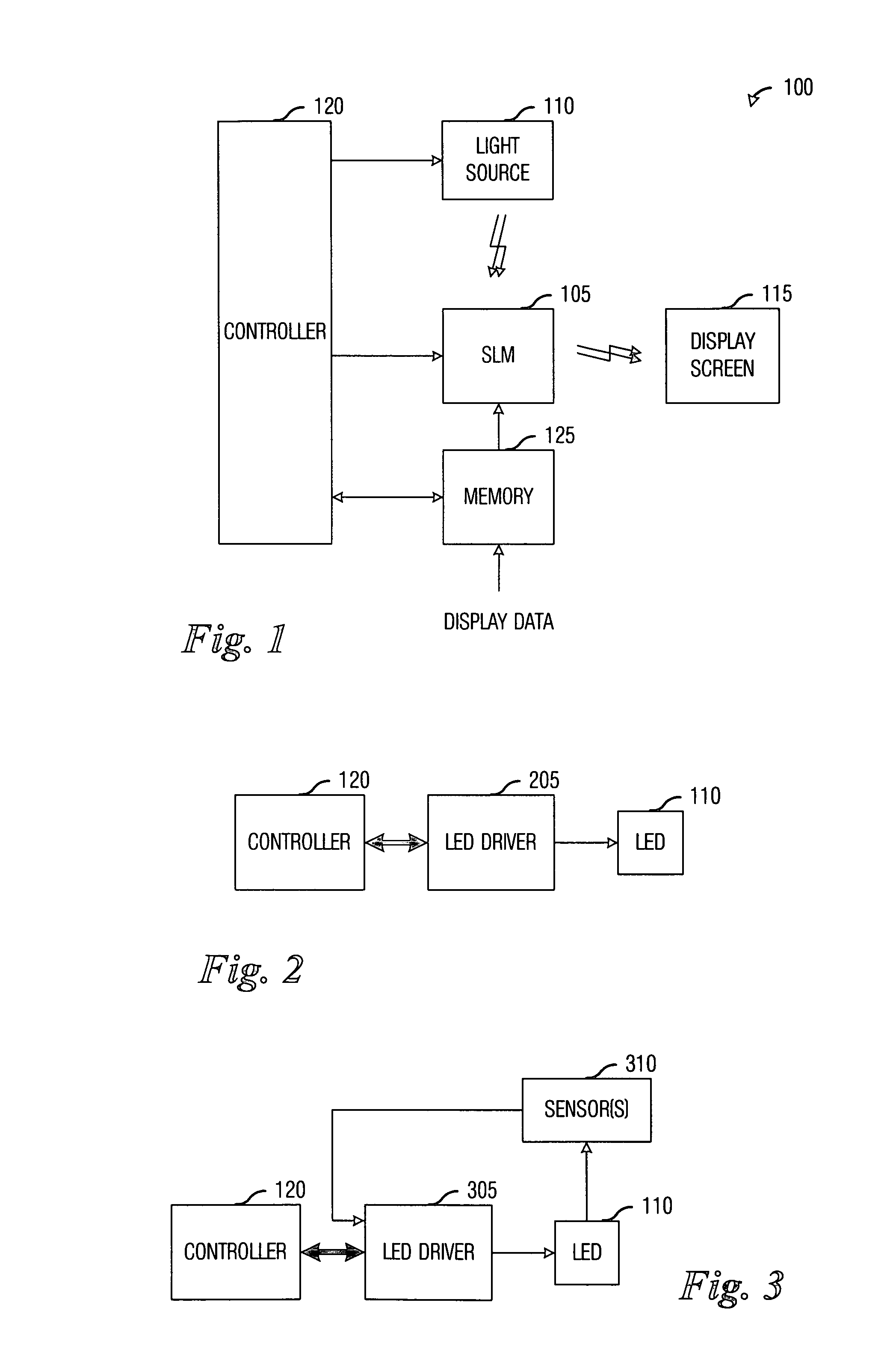

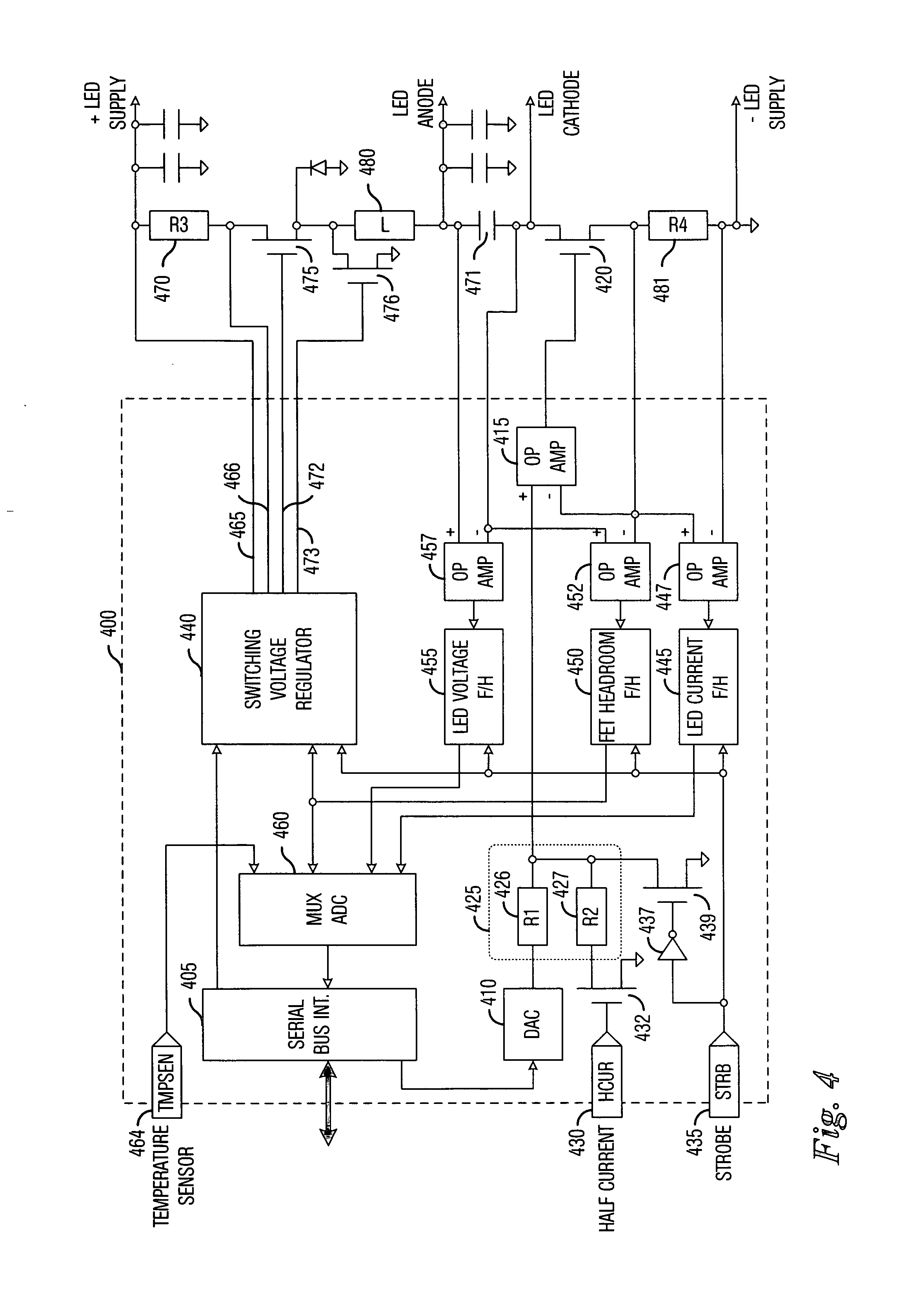

System and method for driving light-emitting diodes (LEDs)

ActiveUS20070035538A1Minimum heat dissipationEfficient power supplyElectrical apparatusElectroluminescent light sourcesSwitched currentControl signal

System and method for improving efficiency in driving LEDs. A preferred embodiment comprises a switch current regulator coupled to a current control signal input, the switch current regulator to control an amount of current provided to the LED based upon a magnitude of a voltage on the current control signal input, a switching voltage regulator coupled to the switch current regulator and the LED, the switching voltage regulator to provide current to the LED, and a sensor coupled to the switch current regulator, the LED, and a signal feedback circuit, the sensor to measure status information regarding the switch current regulator and the LED and provides the information to a controller, wherein the status information can be used to adjust the current on the current control signal input.

Owner:TEXAS INSTR INC

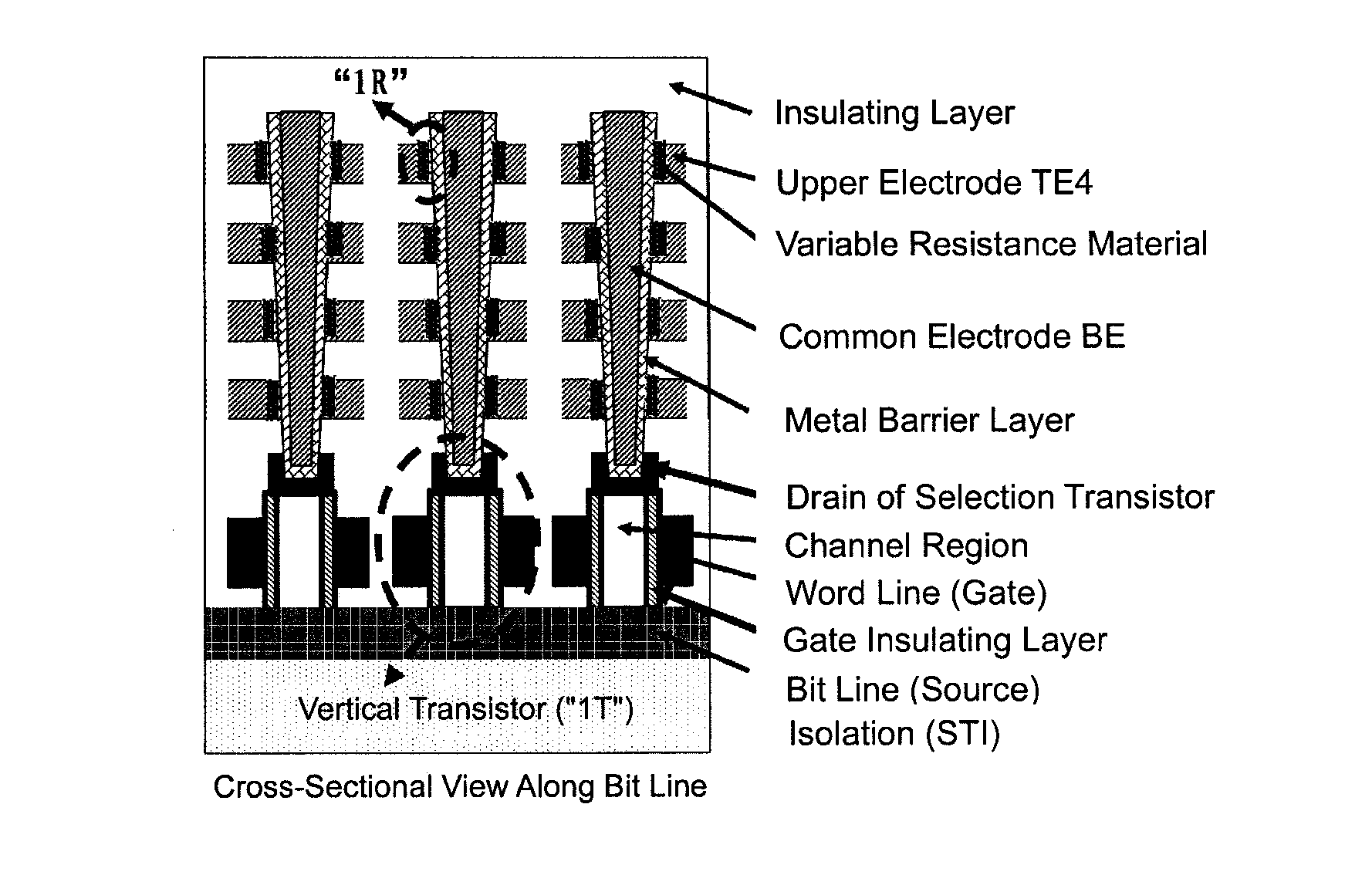

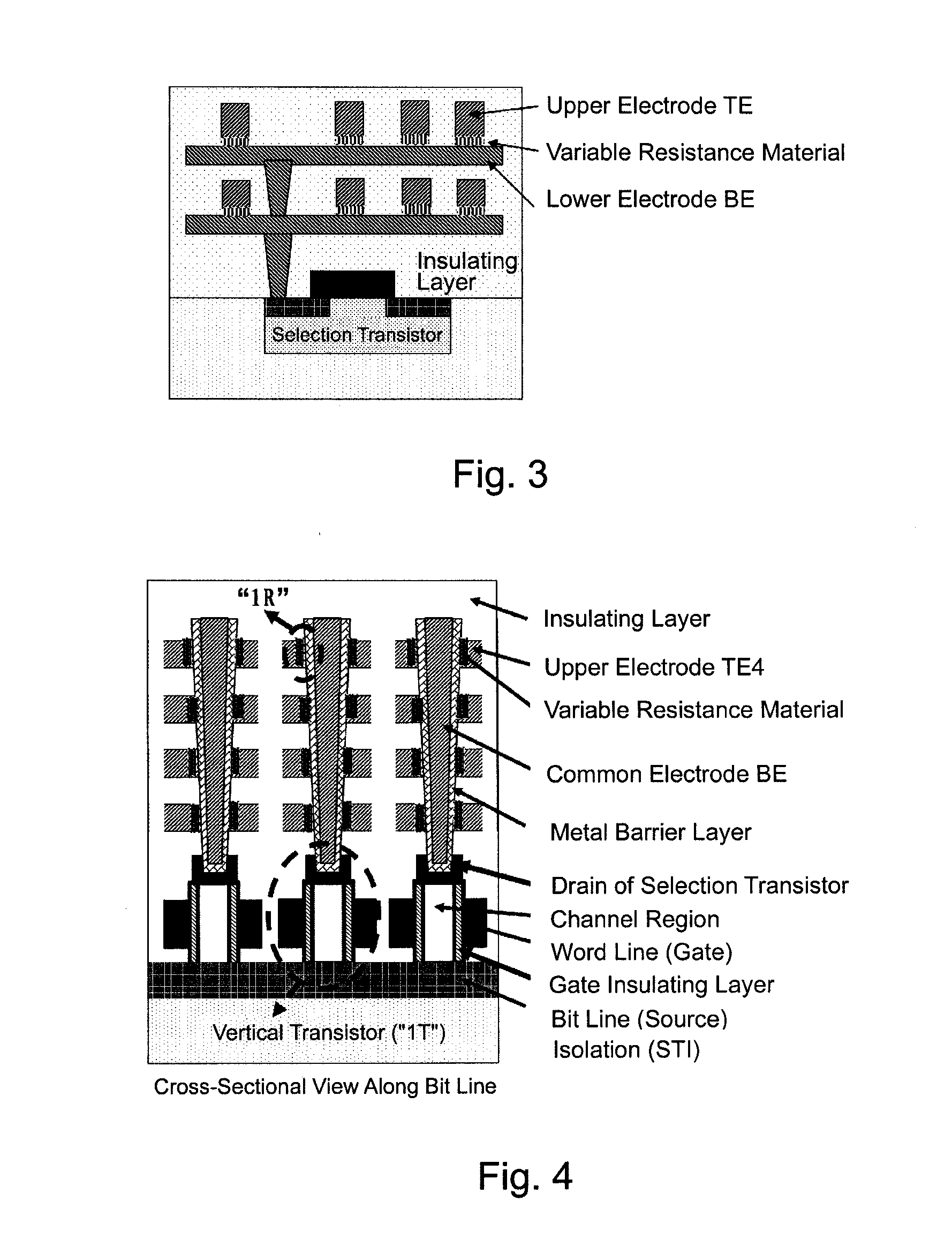

3D semiconductor memory device and manufacturing method thereof

ActiveUS20120161094A1Small sizeBig ratioSolid-state devicesSemiconductor/solid-state device manufacturingMemory cellHigh density

The present application discloses a 3D semiconductor memory device having 1T1R memory configuration based on a vertical-type gate-around transistor, and a manufacturing method thereof. A on / off current ratio can be well controlled by changing a width and a length of a channel of the gate-around transistor, so as to facilitate multi-state operation of the 1T1R memory cell. Moreover, the vertical transistor has a smaller layout size than a horizontal transistor, so as to reduce the layout size effectively. Thus, the 3D semiconductor memory device can be integrated into an array with a high density.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com