Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

50results about How to "Improved reverse recovery characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

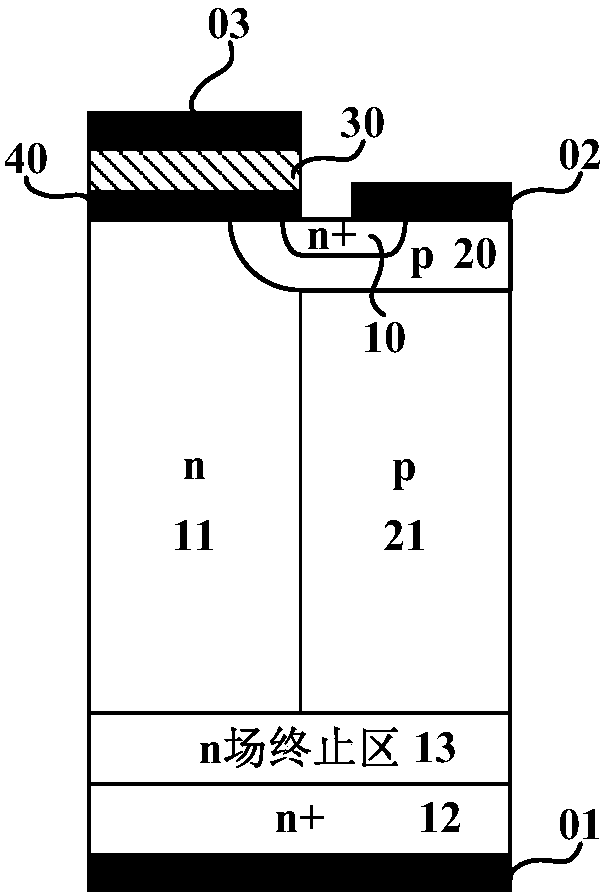

Method for manufacturing planar high-voltage ultrafast soft recovery diode

ActiveCN102569067ALow costMeet the requirements of mass productionSemiconductor/solid-state device manufacturingPlatinumLow leakage

The invention discloses a method for manufacturing a planar high-voltage ultrafast soft recovery diode. The method comprises the following steps of: oxidizing, and photoetching to form an active region and a field limiting ring; doping and pushing; manufacturing a polycrystalline silicon field plate; performing platinum diffusion; thinning; forming an N-type buffer layer; performing contact doping and annealing; and metalizing. The method can be used for manufacturing an ultrafast soft recovery diode chip which is low in cost and short in recovery time and has high-voltage resistance, low leakage current, low forward voltage drop and soft recovery characteristics.

Owner:BEIJING MXTRONICS CORP +1

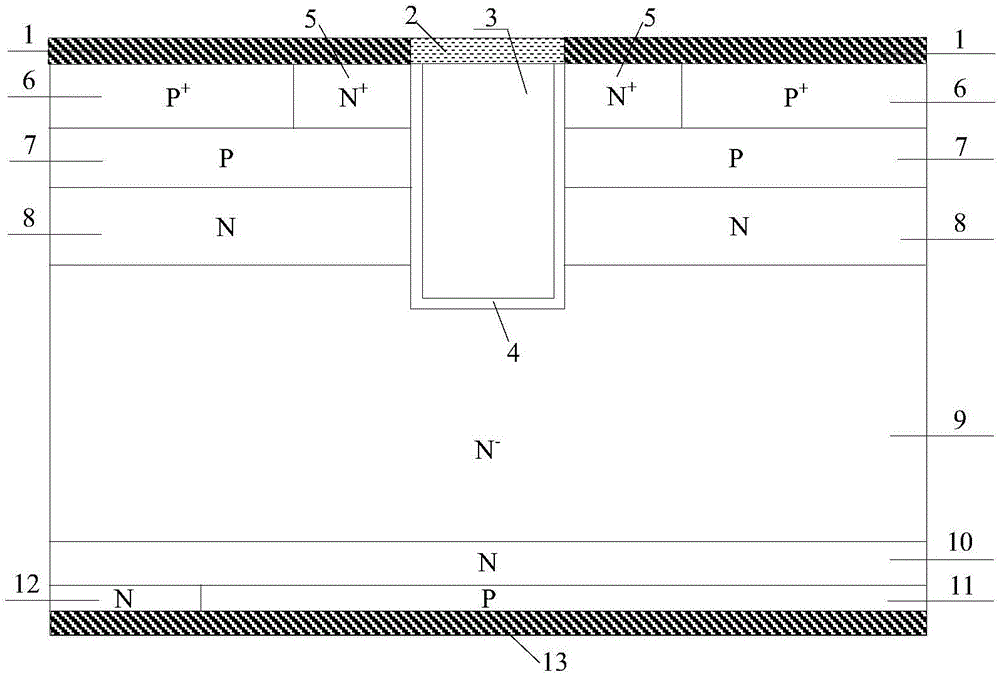

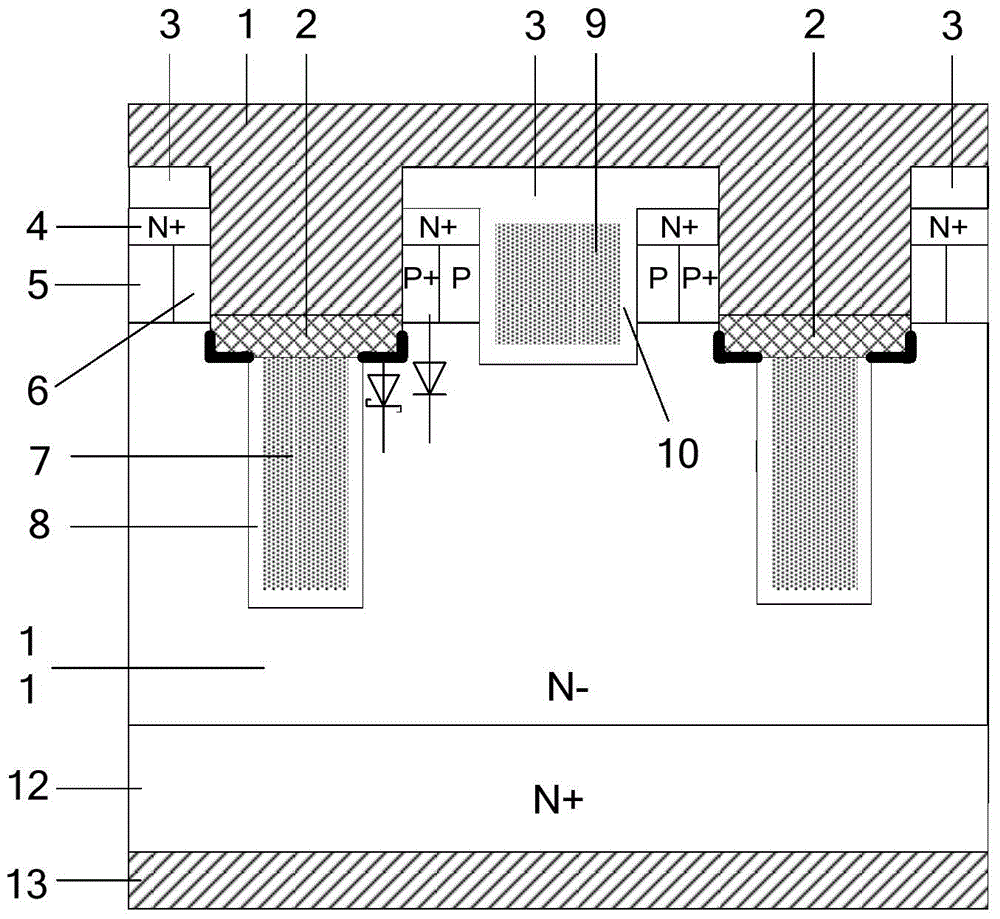

Groove gate VDMOS device integrated with Schottky diode

The invention discloses a groove gate VDMOS device integrated with a Schottky diode and belongs to the technical field of semiconductor devices. According to the groove gate VDMOS device integrated with the Schottky diode, an additional structure composed of a piece of Schottky junction metal and a body electrode conductive material is additionally arranged on each of drift regions on the two sides of a groove gate structure of a conventional groove gate VDMOS device, the upper portion of each piece of Schottky junction metal is in contact with source electrode metal, the lower portion of each piece of Schottky junction metal is in contact with a corresponding body electrode conductive material, and the lower surface and the lateral sides of the each piece Schottky junction metal are in contact with a corresponding drift region to form a Schottky junction; dielectric layers are arranged between the lateral sides of each body electrode conductive material and a corresponding drift region and between the bottom surface of each body electrode conductive material and the corresponding drift region. Compared with a traditional groove gate VDMOS device with the same size, the groove gate VDMOS device integrated with the Schottky diode has the advantages that due to the fact that higher drift region dosage concentration is adopted under the condition of same puncture voltage, turn-on resistance is reduced obviously, and the reverse recovery property of the diode is improved obviously.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

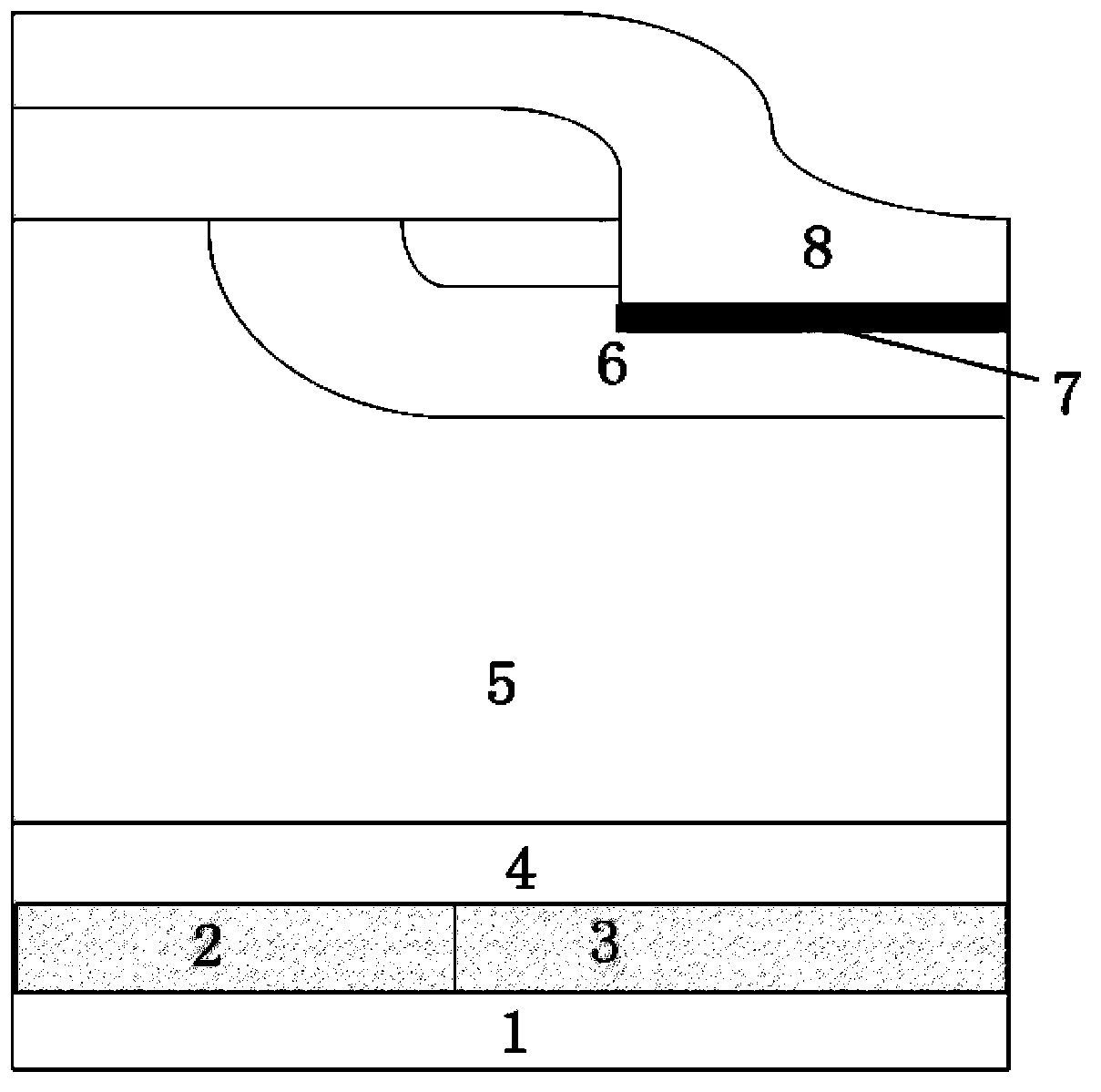

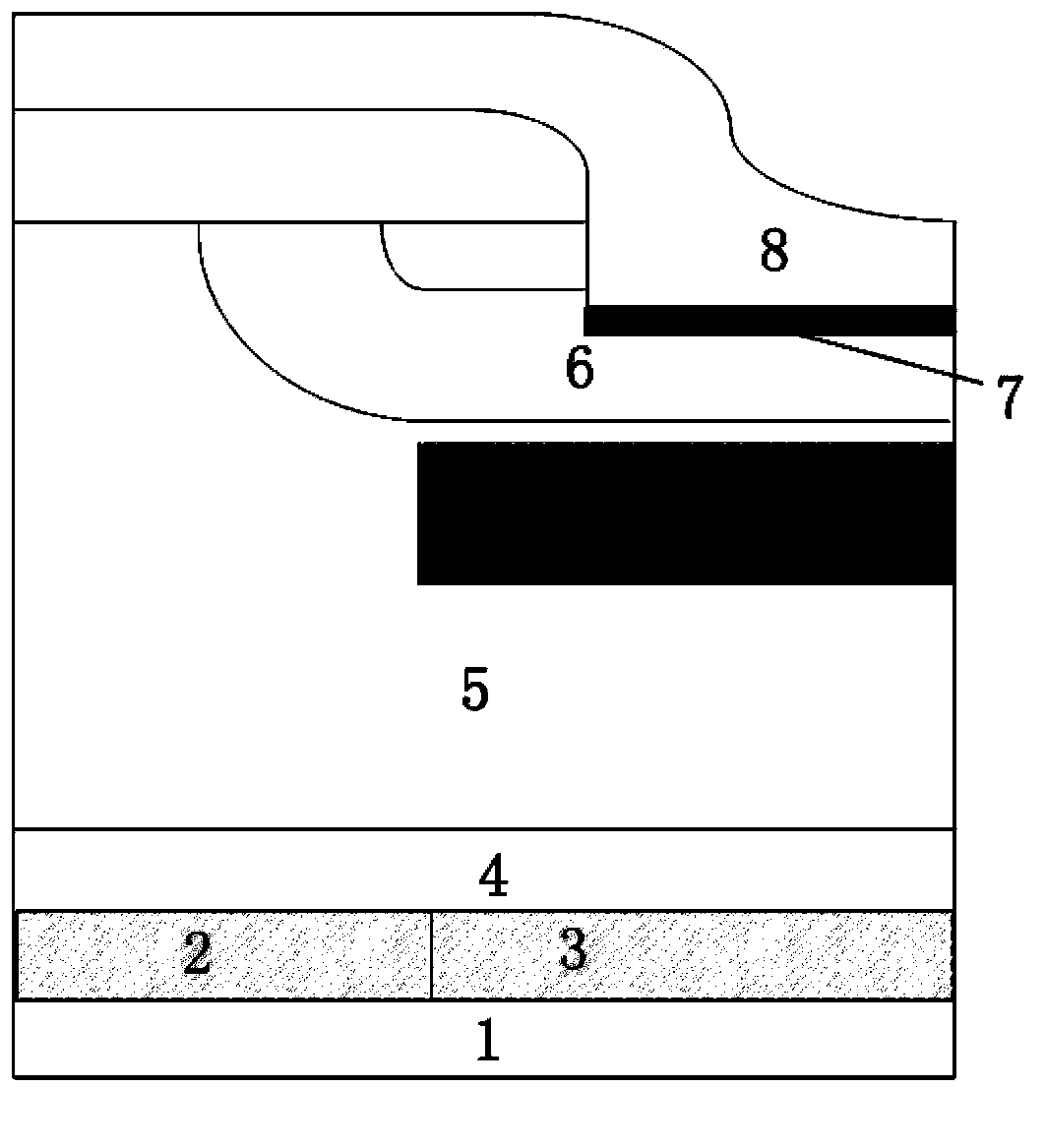

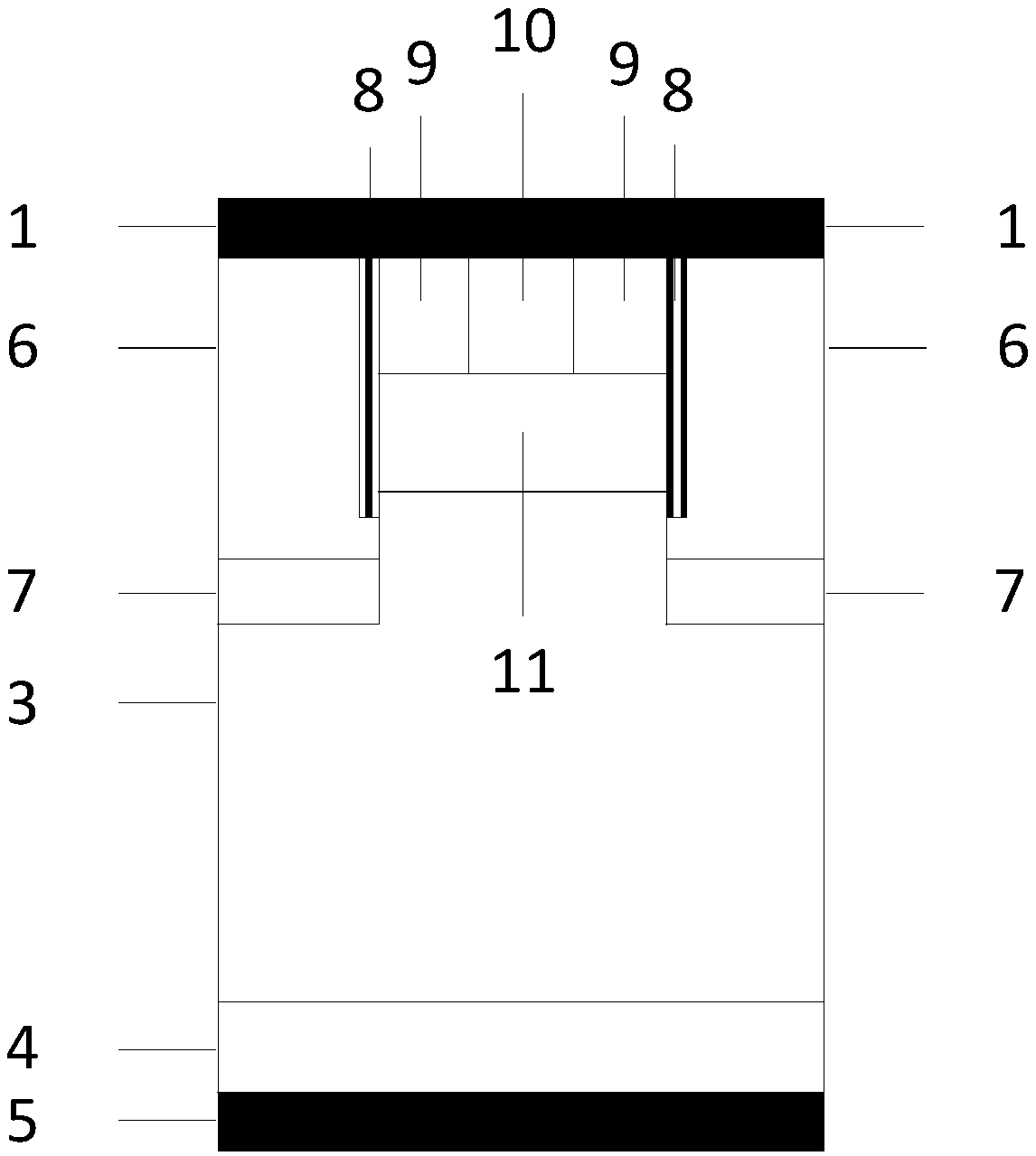

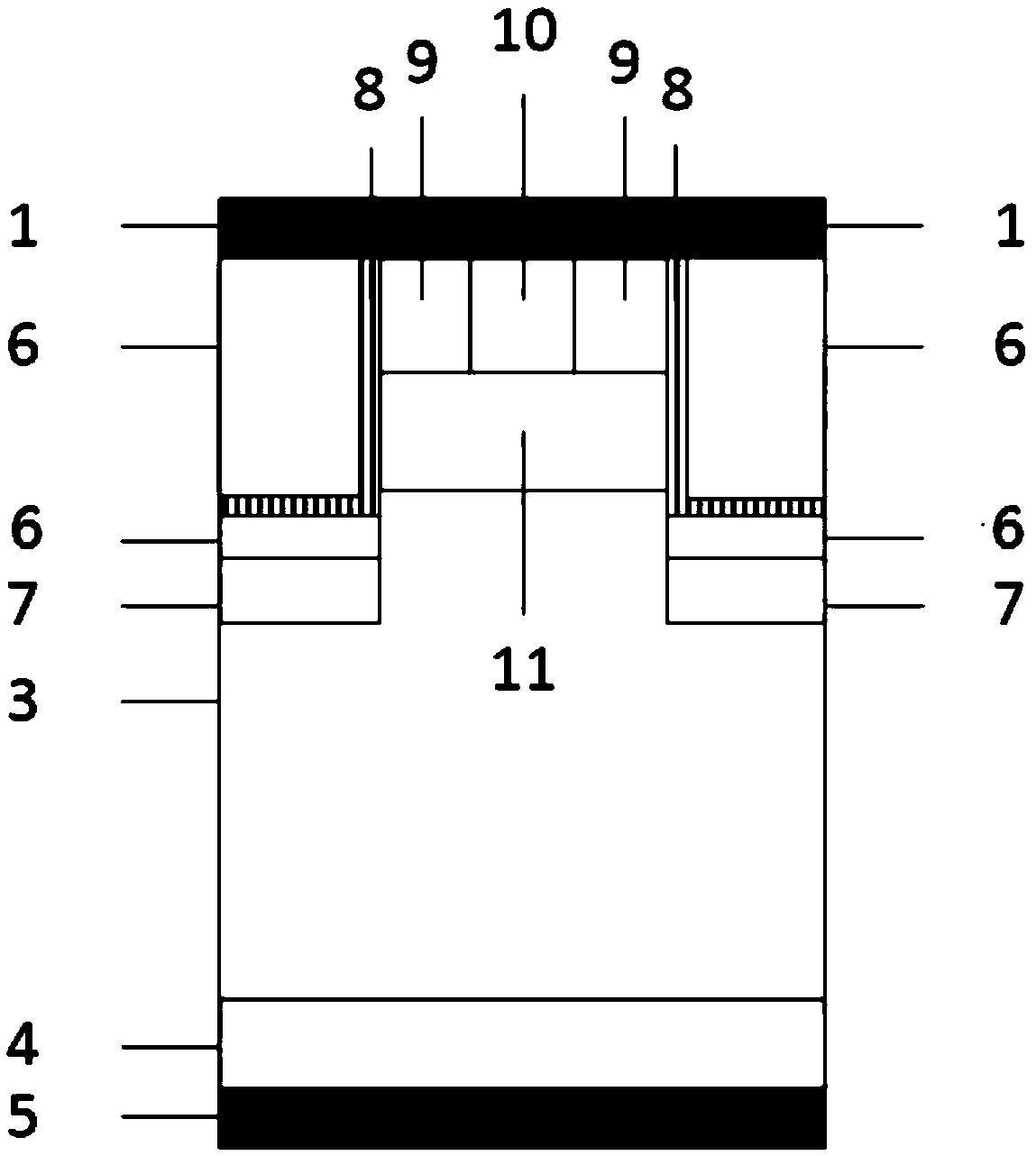

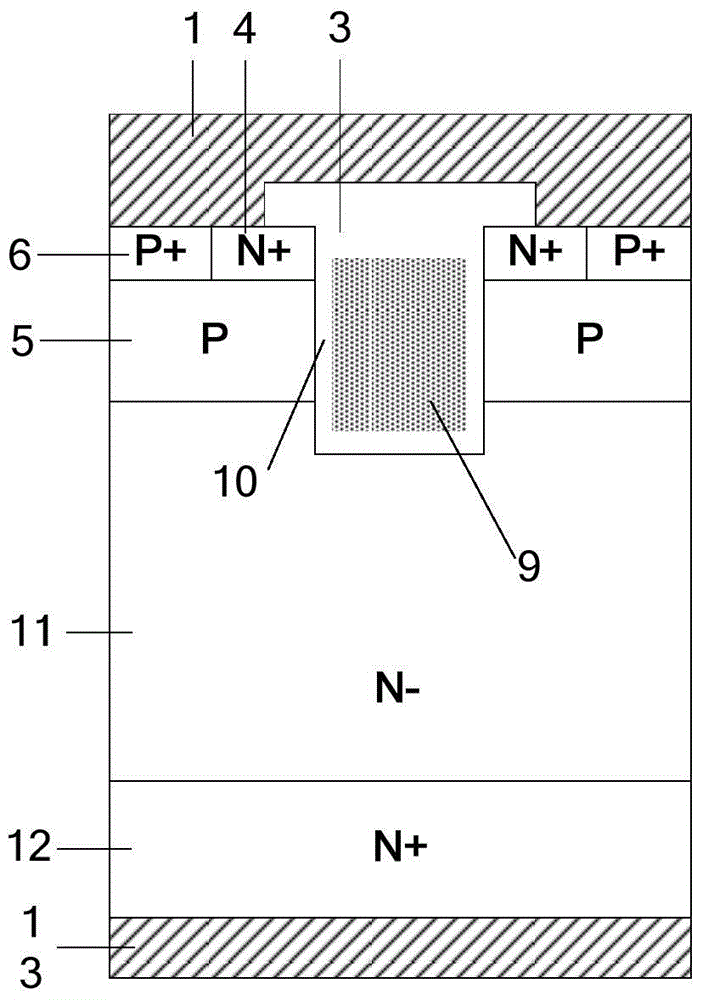

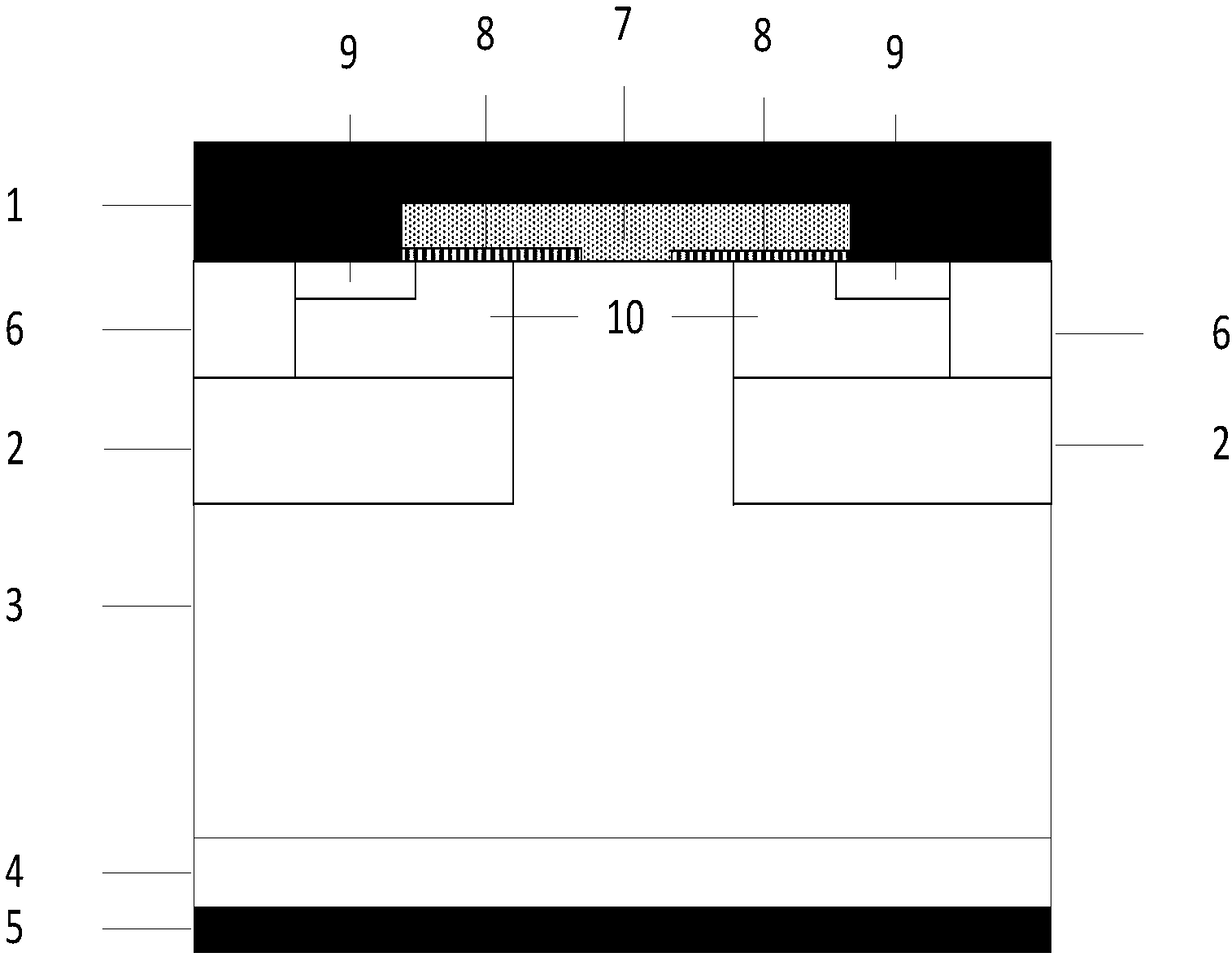

Fast recovery metal oxide semiconductor diode with low power consumption

ActiveCN101976687AImproved reverse recovery characteristicsImprove breakdown voltageSemiconductor devicesSemiconductor structureJFET

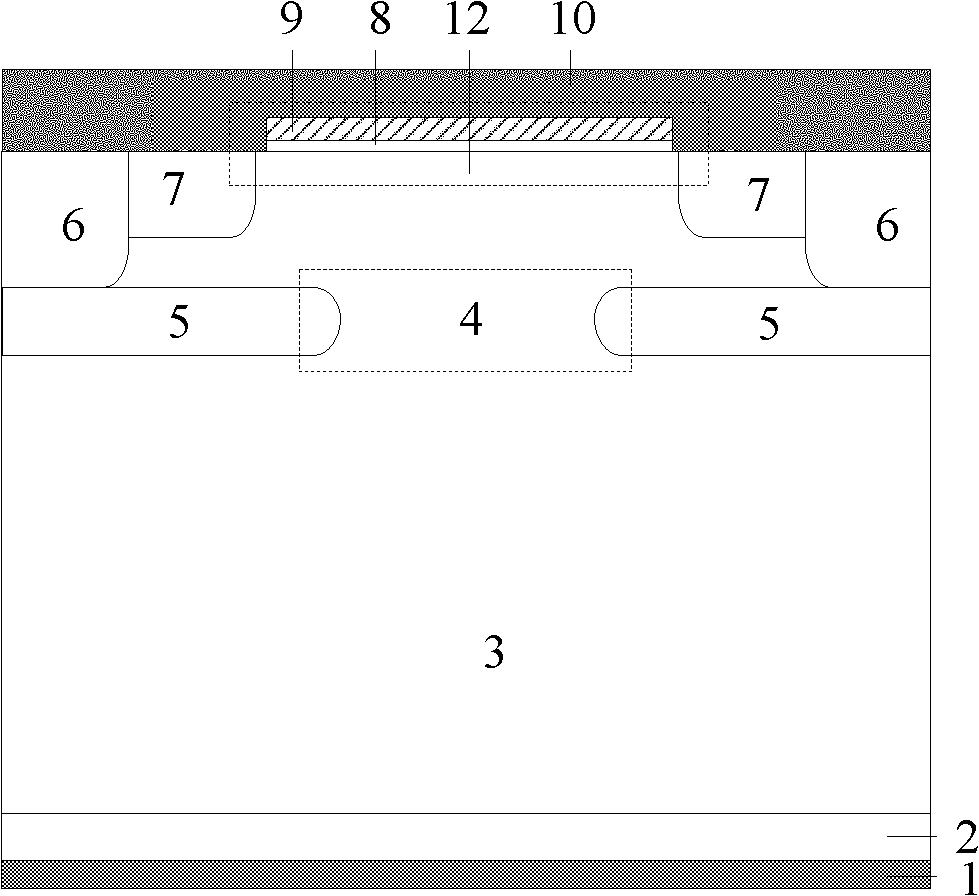

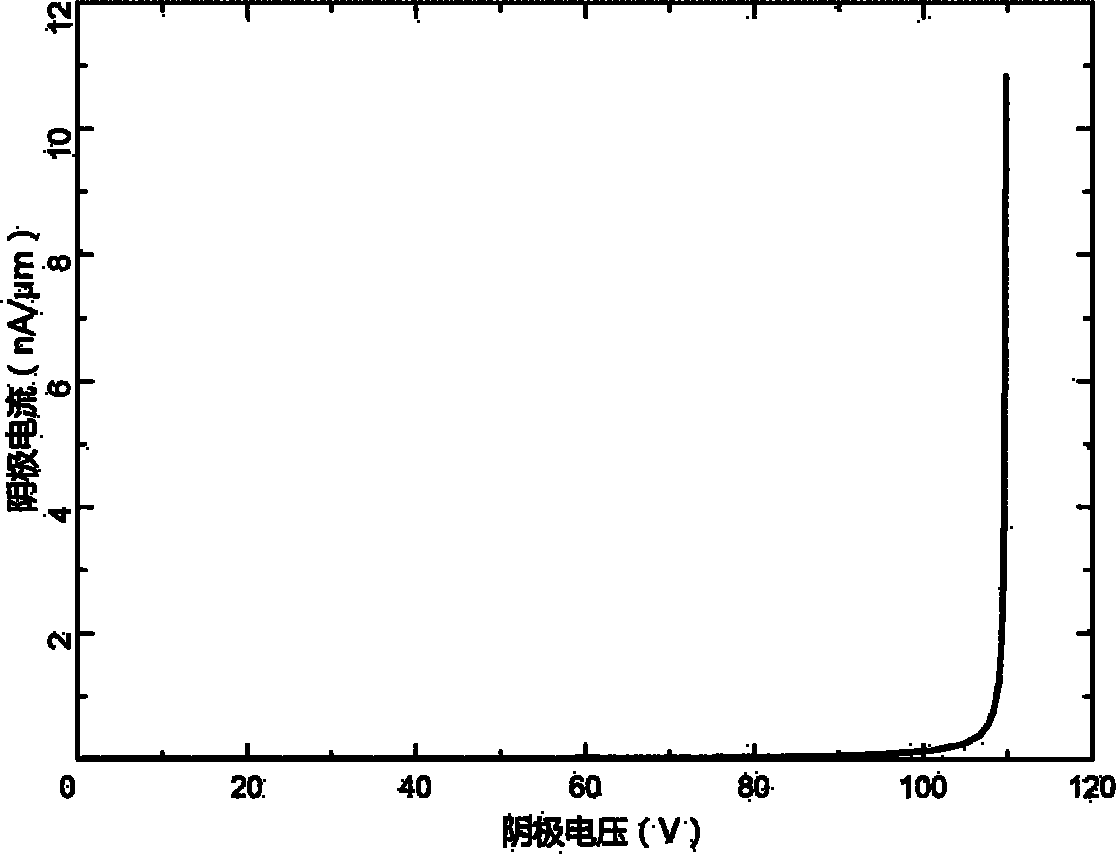

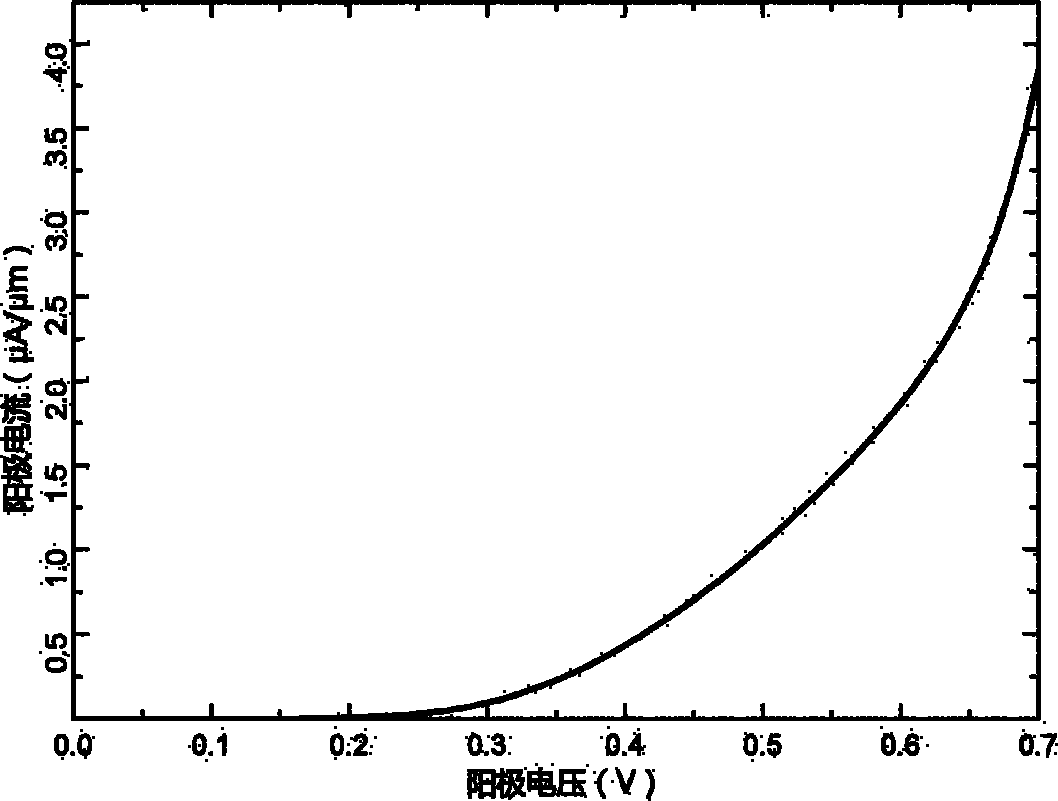

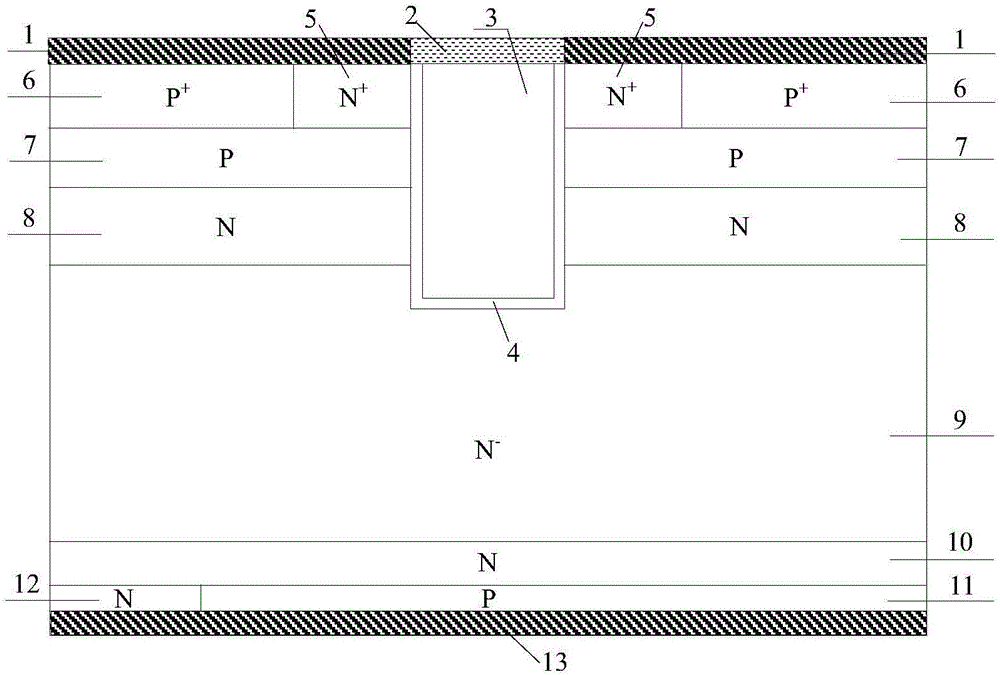

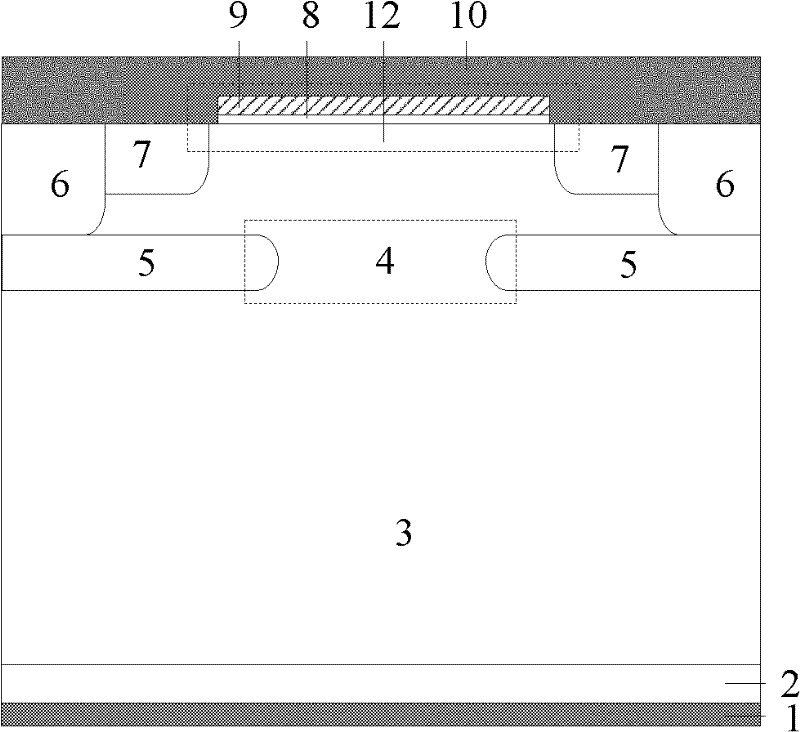

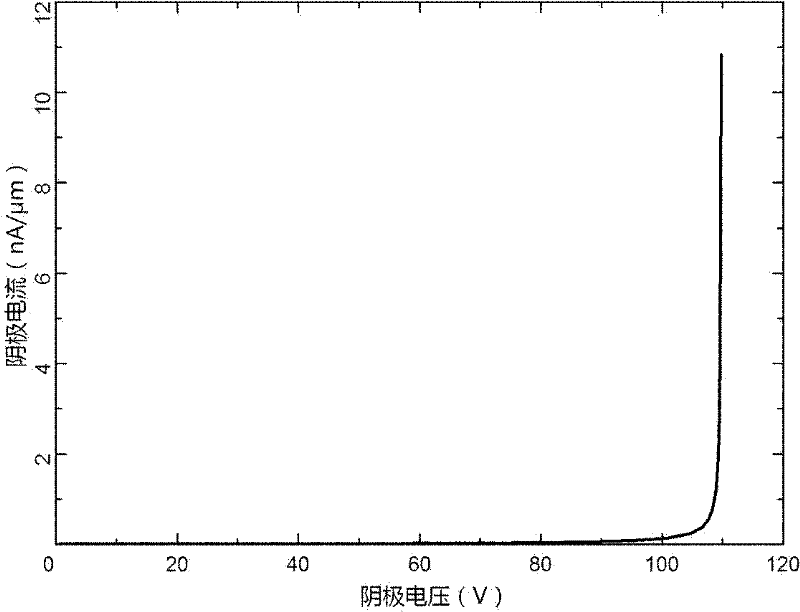

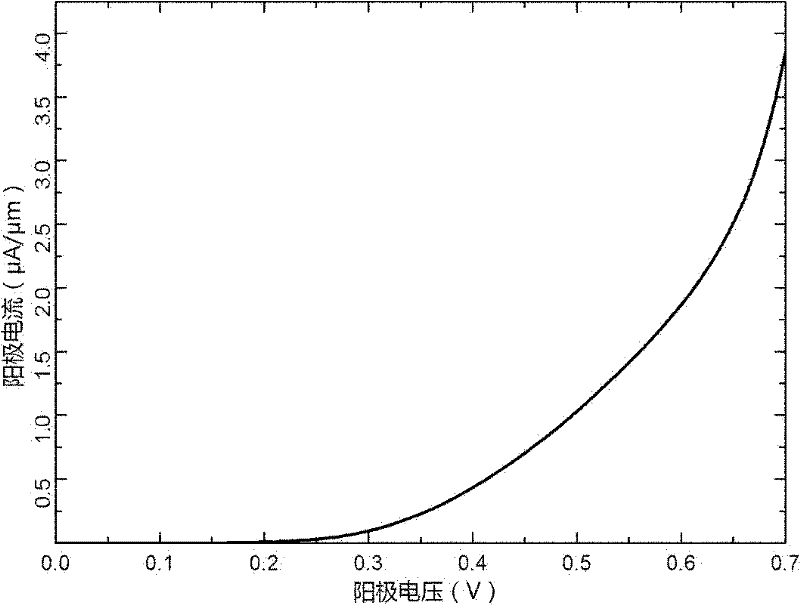

A fast recovery metal oxide semiconductor diode with low power consumption belongs to the technical field of semiconductor devices. The diode is provided with a junction field effect transistor region (4) and an electron accumulation layer structure (12), wherein the junction field effect transistor region (4) comprises two deep P regions (5) and an N-epitaxial layer (3) between the two deep P regions; and the electron accumulation layer structure (12) comprises two N heavily doped regions (7), the N-epitaxial layer (3), a gate oxide layer (8) on the surface of the N-epitaxial layer (3) and a gate electrode (9). By utilizing the following surface electric field effect of the metal oxide semiconductor structure: a plurality of sub-accumulation layers are formed in case of forward voltage while a plurality of sub-depletion layers are formed in case of backward voltage, the diode can obtain quite low turn-on voltage drop and can simultaneously bear high reverse breakdown voltage and leak less current, thus better realizing compromise between the forward turn-on voltage drop and the backward recovery time.

Owner:GUIZHOU YAGUANG ELECTRONICS TECH

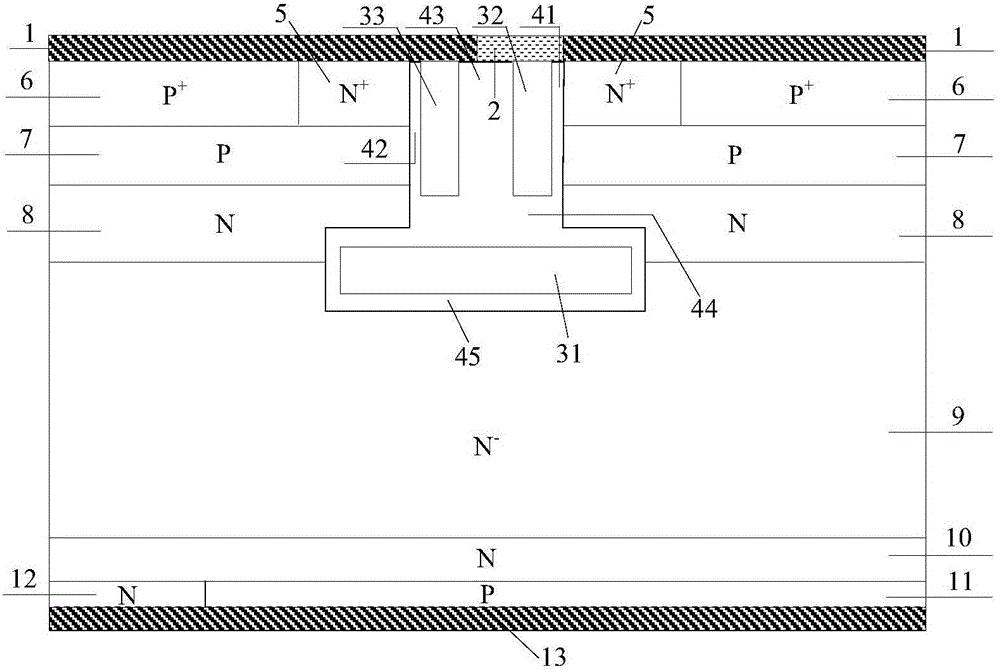

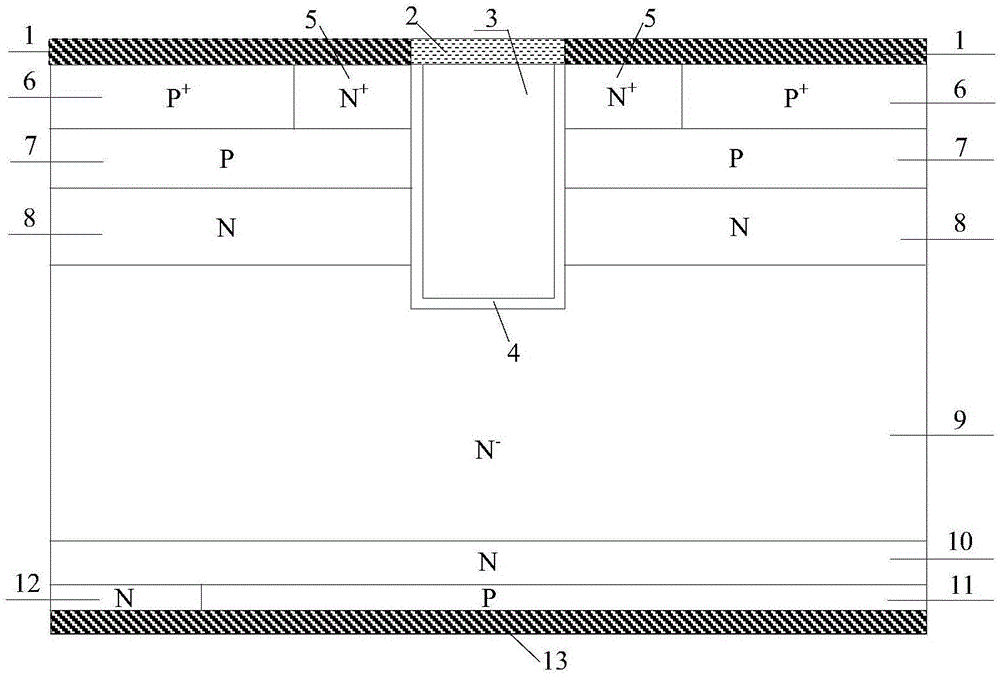

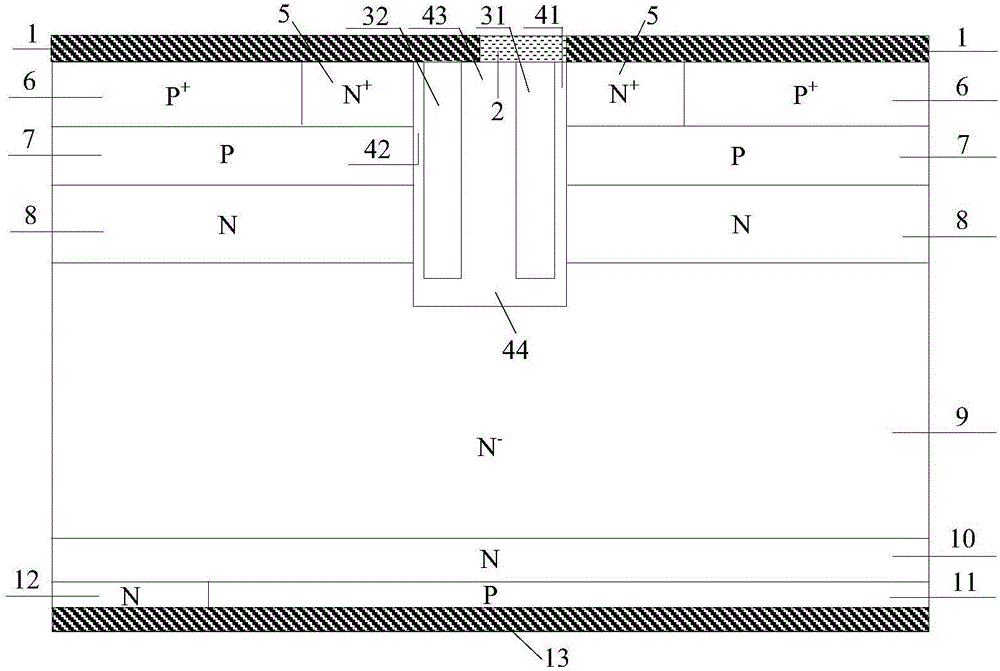

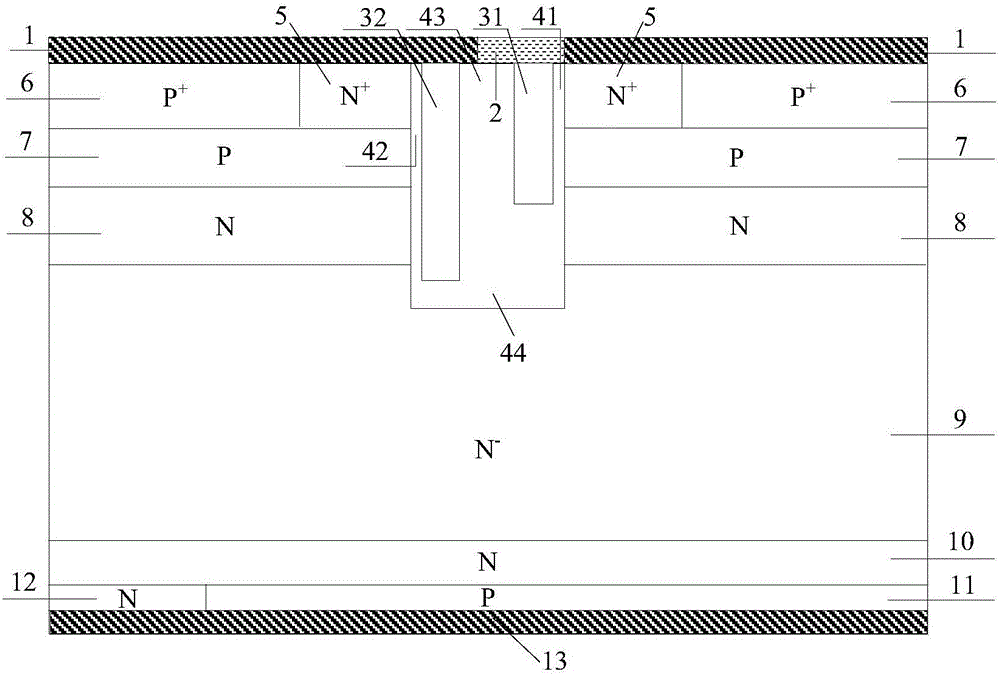

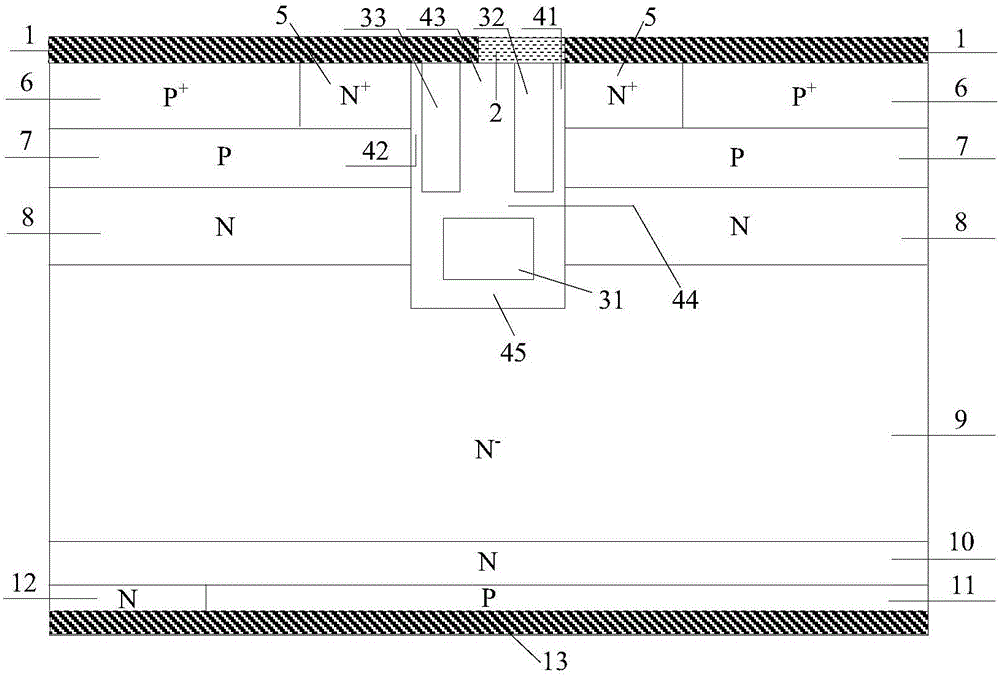

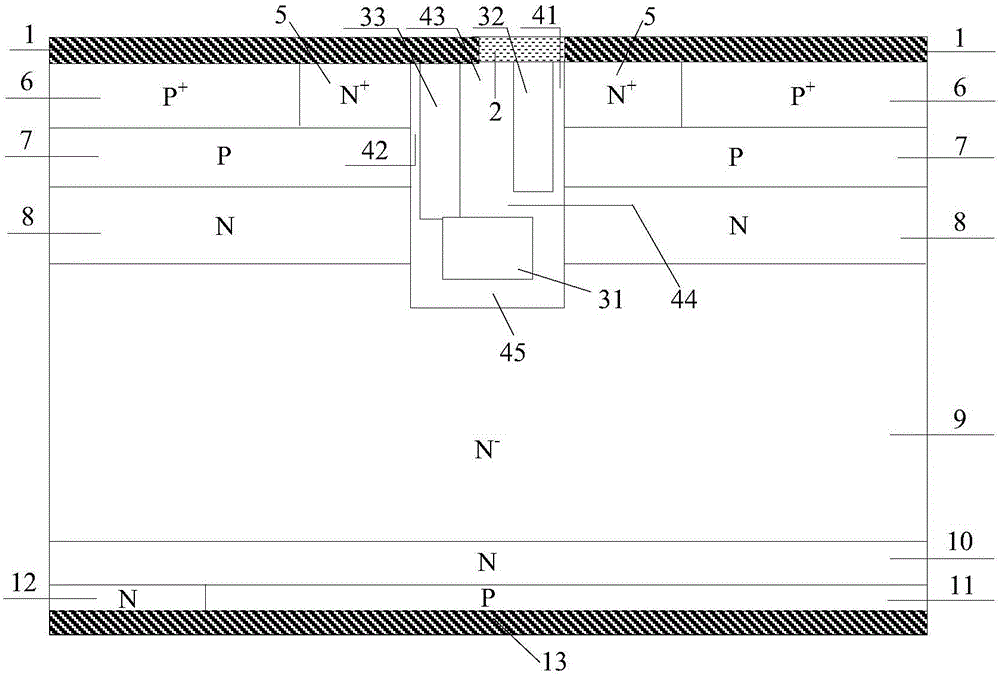

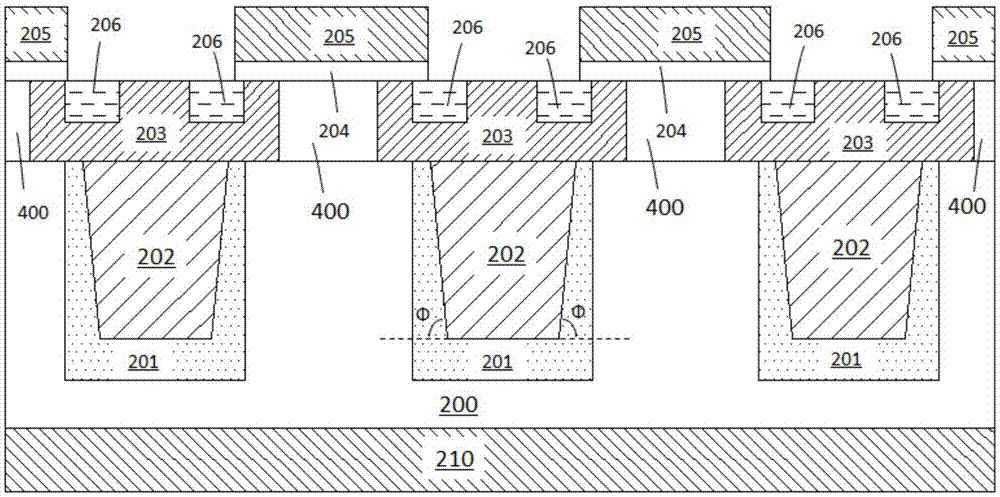

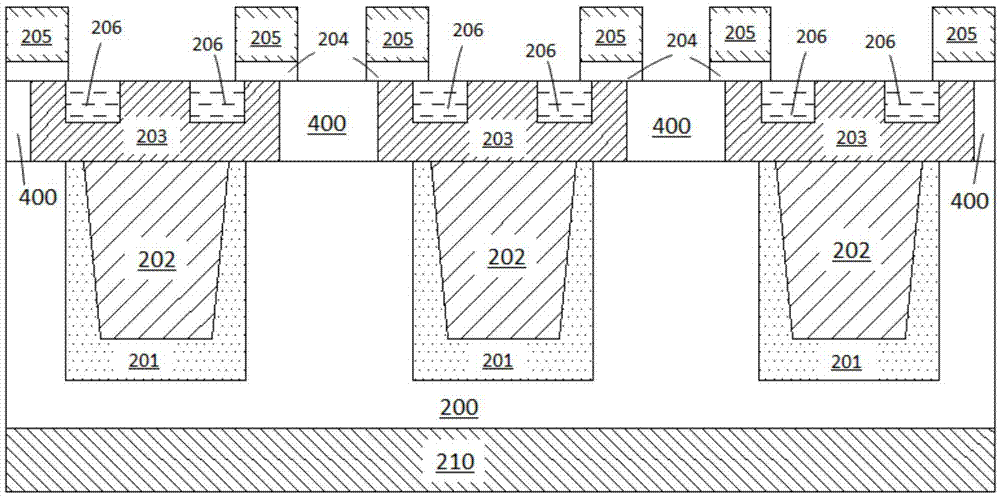

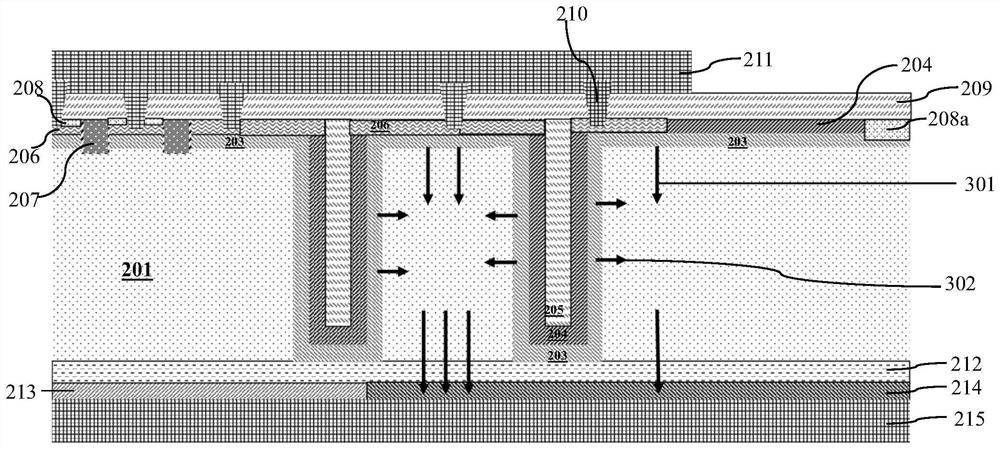

Double split trench gate charge storage-type RC-IGBT and manufacturing method thereof

ActiveCN105742346AReduced carrier concentration distributionReduced short-circuit safe operating areaSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringFlyback diode

The invention belongs to the technical field of power semiconductor devices, and particularly relates to a reverse trench gate charge storage-type insulated gate bipolar transistor. Double split electrodes which are equal to an emitter in potential and dielectric layers between the double split electrodes and a gate electrode are introduced into the bottom part and the side surface of the gate electrode in a trench of an RC-IGBT device, so that the switching speed of the device in the IGBT working mode is improved; the carrier concentration distribution of the whole N-type drift region is improved; the switching loss of the device is reduced; the saturated current density of the device is reduced; the short-circuit safe operation area of the device is improved; the reliability is improved; a reverse free-wheeling diode has a low diode conduction voltage drop in a reverse free-wheeling diode working mode; the reverse recovery characteristics of the free-wheeling diode are improved; and meanwhile, the manufacturing method of the double split trench gate charge storage-type IGBT does not need to increase an extra processing step and is compatible with a traditional RC-IGBT manufacturing method.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

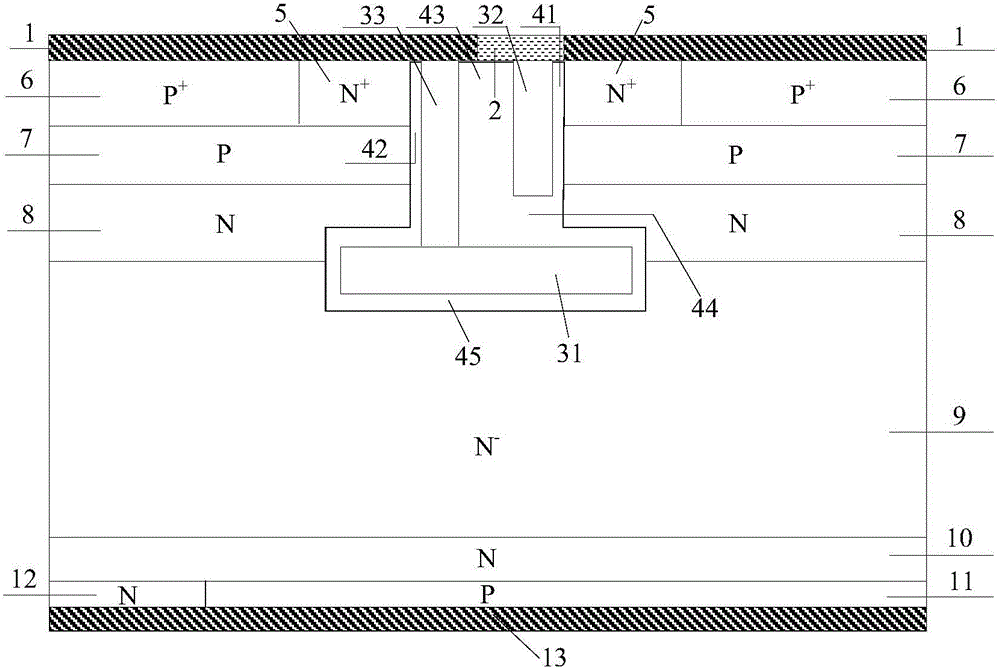

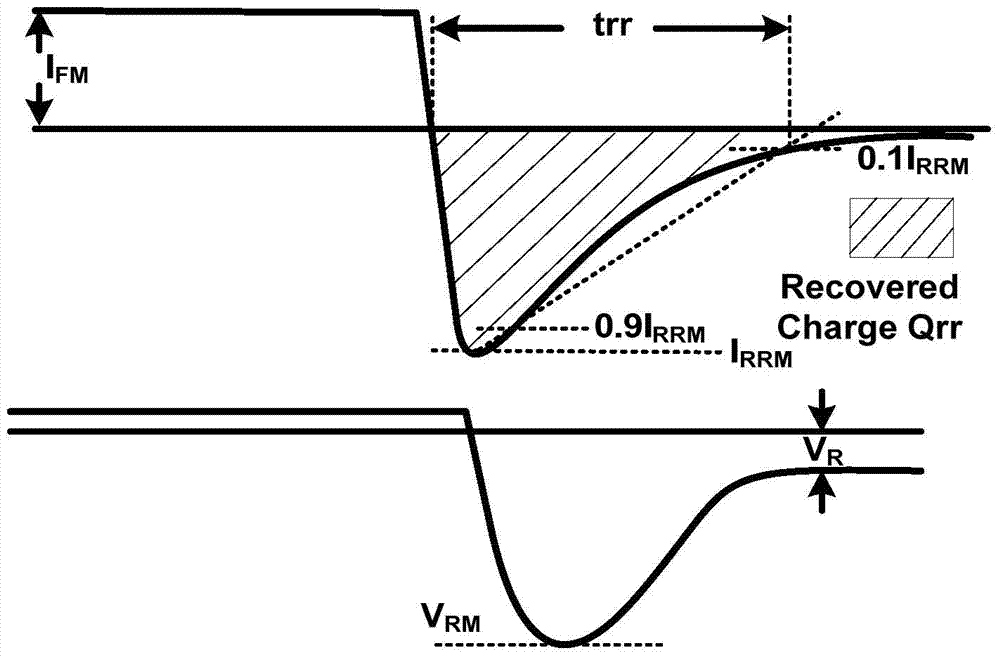

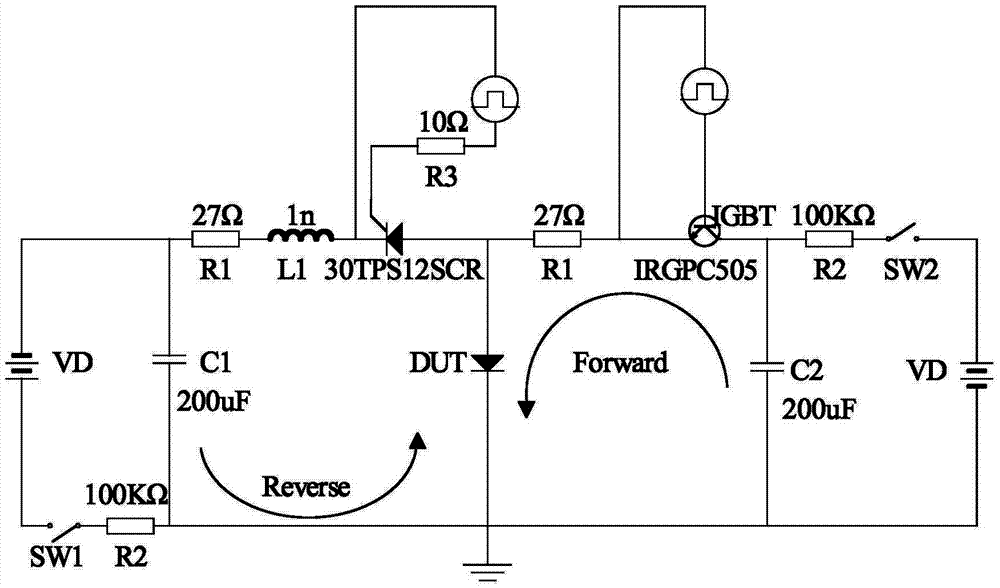

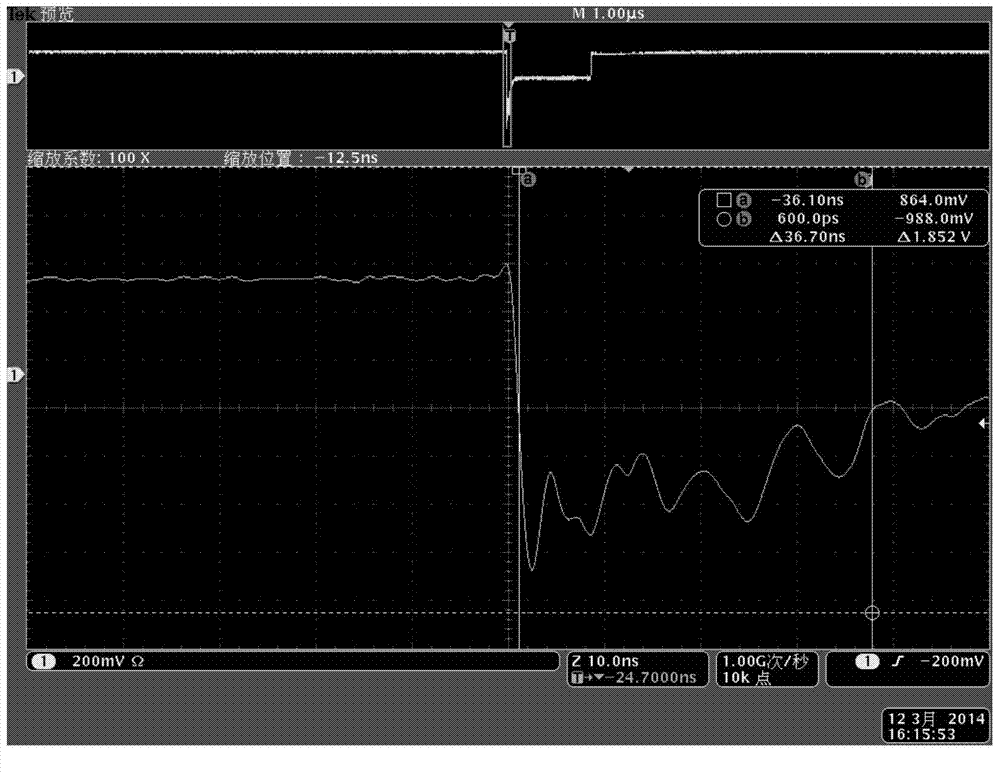

System for preventing reverse recovered charges in DUT

ActiveCN103929156AImproved reverse recovery characteristicsReduce switching lossesPulse shapingReverse recoveryElectromagnetic interference

The invention discloses a system for preventing reverse recovered charges in a DUT. The system is a current injection circuit connected to the two ends of the DUT in a forward bias mode. The injected current circuit comprises a pulse nS-level pulse signal generator formed by an SRD and a pulse edge acceleration circuit formed by a BG2 and a BG1, wherein the pulse edge acceleration circuit is tightly connected with the back of the pulse nS-level pulse signal generator and used for shortening the rising edge time and the falling edge time of pulses. The system has the advantages that the reverse recovered features of the DUT can be improved, the reverse recovered charges can be reduced, and the reverse recovered time can be shortened; meanwhile, switching losses and conduction losses of the DUT can be reduced, electromagnetic interference and surges can be restrained, and efficiency is improved.

Owner:HAIMEN THE YELLOW SEA ENTREPRENEURSHIP PARK SERVICE CO LTD

Trench gate charge storage reverse-conducting insulated-gate bipolar transistor (RC-IGBT) and fabrication method thereof

ActiveCN105870179AReduce gate capacitanceLow densitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePower semiconductor device

The invention belongs to the technical field of a power semiconductor device, in particular relates to a reverse-conducting trench gate charge storage insulated-gate bipolar transistor (IGBT). By introducing a side-surfaces split electrode connected with an emitter into a trench on the condition of a certain device trench depth and a certain trench metal oxide semiconductor (MOS) structure density, the gate capacitance of the device is reduced, the switching speed of the device is increased, the switching loss is reduced, and the positive conduction voltage drop and the average switching loss are improved; meanwhile, the density of an MOS channel is reduced, the short-circuit safety working region of the IGBT is improved, and the performance and the reliability of the device are improved; and a reverse freewheeling diode works in multiple submodes in a working mode of the reverse freewheeling diode, the IGBG has low diode conduction voltage drop, and the reverse recovery characteristic of the freewheeling diode is improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Manufacturing method of high-voltage quick-recovery diode

ActiveCN102842501ALow costReduce processing stepsSemiconductor/solid-state device manufacturingDiffusion methodsImpurity doping

The invention provides a manufacturing method of a high-voltage quick-recovery diode, and the method comprises following steps of simultaneously implementing P-type impurity doping of an anode area and a terminal field limiting ring on the front surface of an N-type monocrystalline silicon sheet which is uniformly doped through field oxidation and ion injection; adopting a diffusion method to simultaneously implement the N-type impurity doping of a silicon sheet front surface groove interception ring and a silicon-sheet back surface cathode area after the anode area and the terminal field limiting ring area are protected by an oxidation film; implementing the heat diffusion propulsion simultaneously for the P-type impurities and N-type impurities in a high-temperature diffusion furnace; and implementing the back surface metallization after completing the front surface metallization, electron radiation minority carrier lifetime control and removal of a back surface damaged layer. According to the method, the machining steps are simple, and a deep N-type doped layer on the back surface of the silicon sheet is favorable for improving the reverse recovery characteristic of the diode and improving the blocking voltage.

Owner:CHINA ELECTRIC POWER RES INST +1

Double split trench gate charge storage-type RC-IGBT and manufacturing method thereof

ActiveCN105870180ALower saturation current densityFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesFlyback diodeTransistor

The invention belongs to the technical field of power semiconductor devices, and particularly relates to a reverse conducting trench gate charge storage-type insulated-gate bipolar transistor. Double split electrodes which are equipotential to an emitter and dielectric layers between the double split electrodes and a gate electrode are introduced into the bottom part and the side surfaces of the gate electrode in a trench of an RC-IGBT device, so that the switching speed of the device is improved in the working mode of the IGBT; the switching loss of the device is reduced; the saturation current density of the device is reduced; a short-circuit safe operation area of the device is improved; and the reliability is improved. A reverse free-wheeling diode has a low diode turn-on voltage drop in the working mode of the reverse free-wheeling diode; and the reverse recovery characteristics of the free-wheeling diode are improved. Meanwhile, by the manufacturing method of the double split trench gate charge storage-type RC-IGBT provided by the invention, an additional process step does not need to be added; and the manufacturing method is compatible with a traditional manufacturing method of the RC-IGBT.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

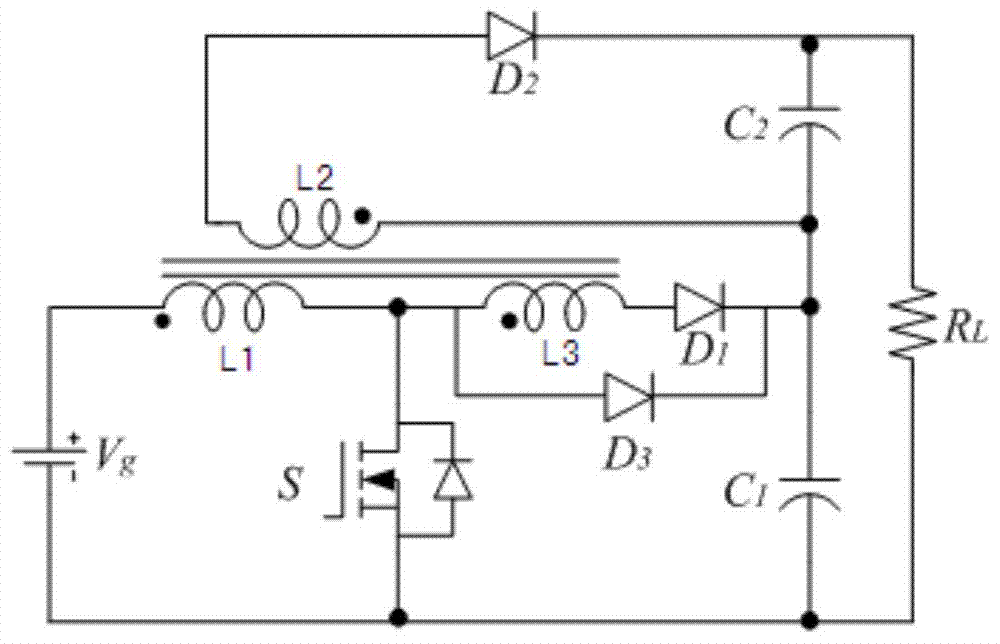

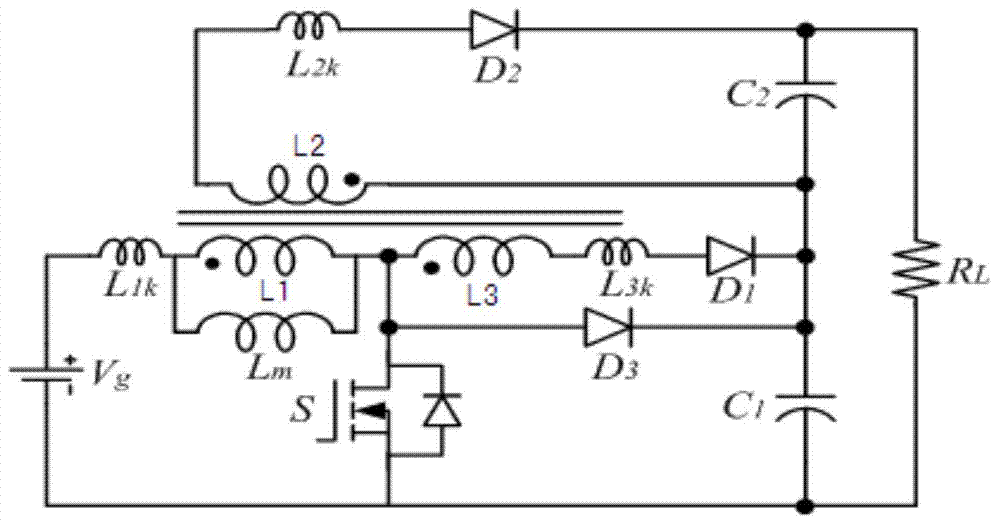

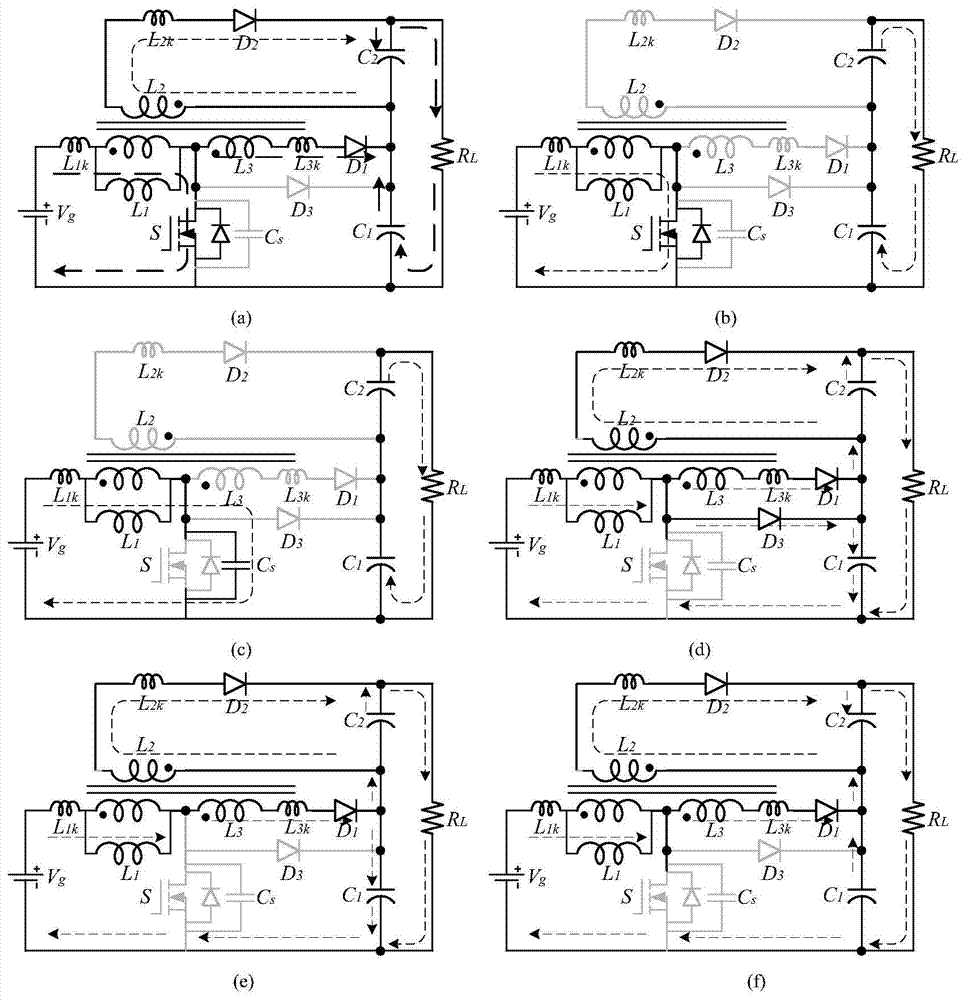

Booster-flyback convertor of built-in switch coupling inductance

InactiveCN104242626AAvoid Extreme Duty Cycle SituationsReasonable structural designPower conversion systemsCapacitanceEngineering

The invention belongs to the technique field of power electron and relates to a booster-flyback convertor of built-in switch coupling inductance, and the booster-flyback convertor of built-in switch coupling inductance comprises a boosting module and a flyback module; the direct current power positive pole end of the boosting module is connected to the first winding dotted terminal, and the negative pole end is connected to the source of the power switch tube, the negative pole end of the output capacitor and one end of the load, the first winding synonym terminal is connected to the drain of the power switch tube, anode of catching diode and one end of the third winding, the other end of the third winding is connected to the anode of fly-wheel diode, the cathode of the fly-wheel diode is connected to the cathode of the catching diode, the positive pole of the output capacitor and flyback module; the second winding dotted terminal of flyback module is connected to the negative pole of the output capacitor and the boosting module, the synonym terminal is connected to the anode of the fly-wheel diode, the cathode of the fly-wheel diode is connected to the positive pole of the output capacitor and the other end of the load; the circuit structure is reasonable in design, safe and reliable in use, low in cost and friendly in environment with great utilization potentiality.

Owner:QINGDAO TECHNOLOGICAL UNIVERSITY

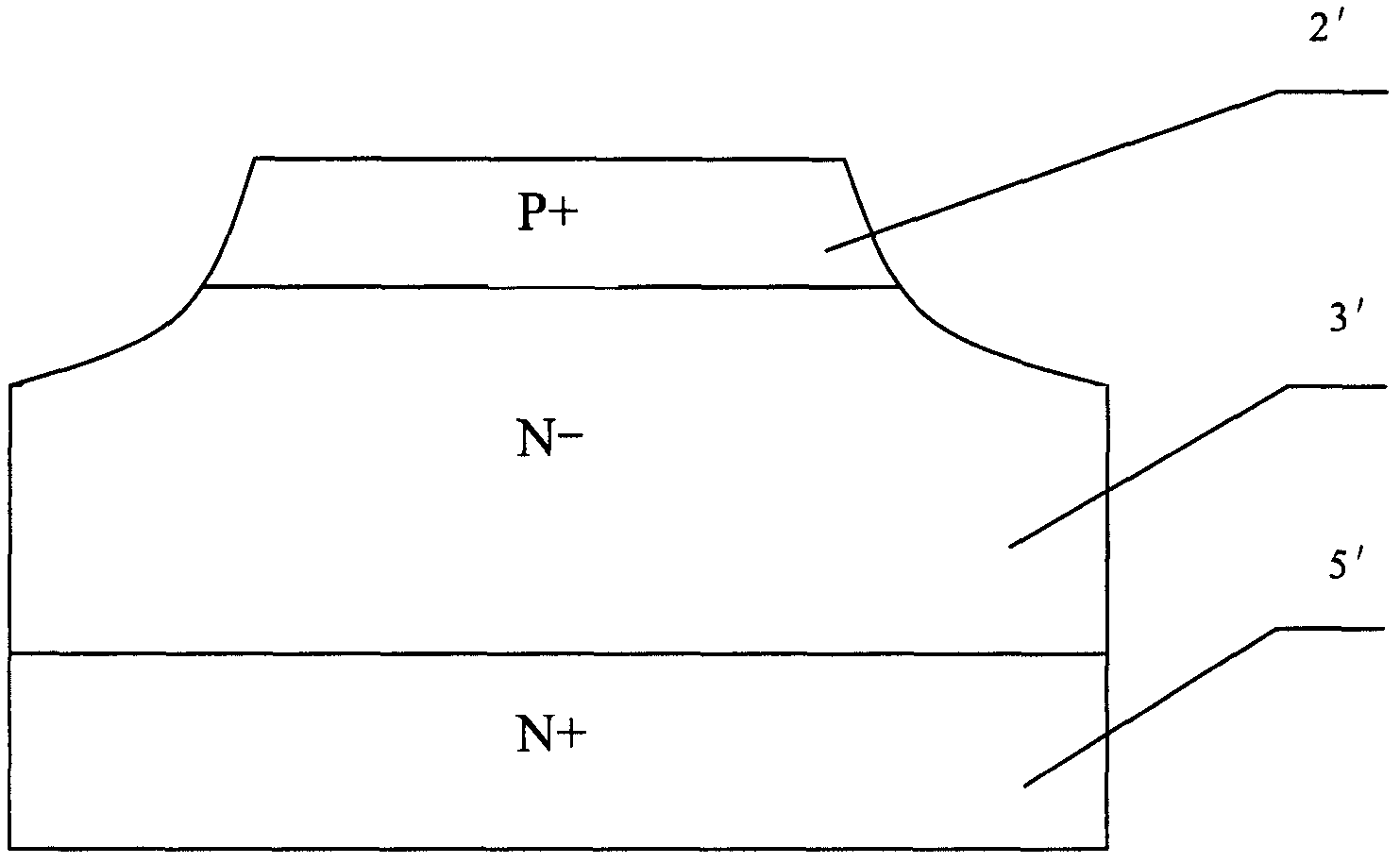

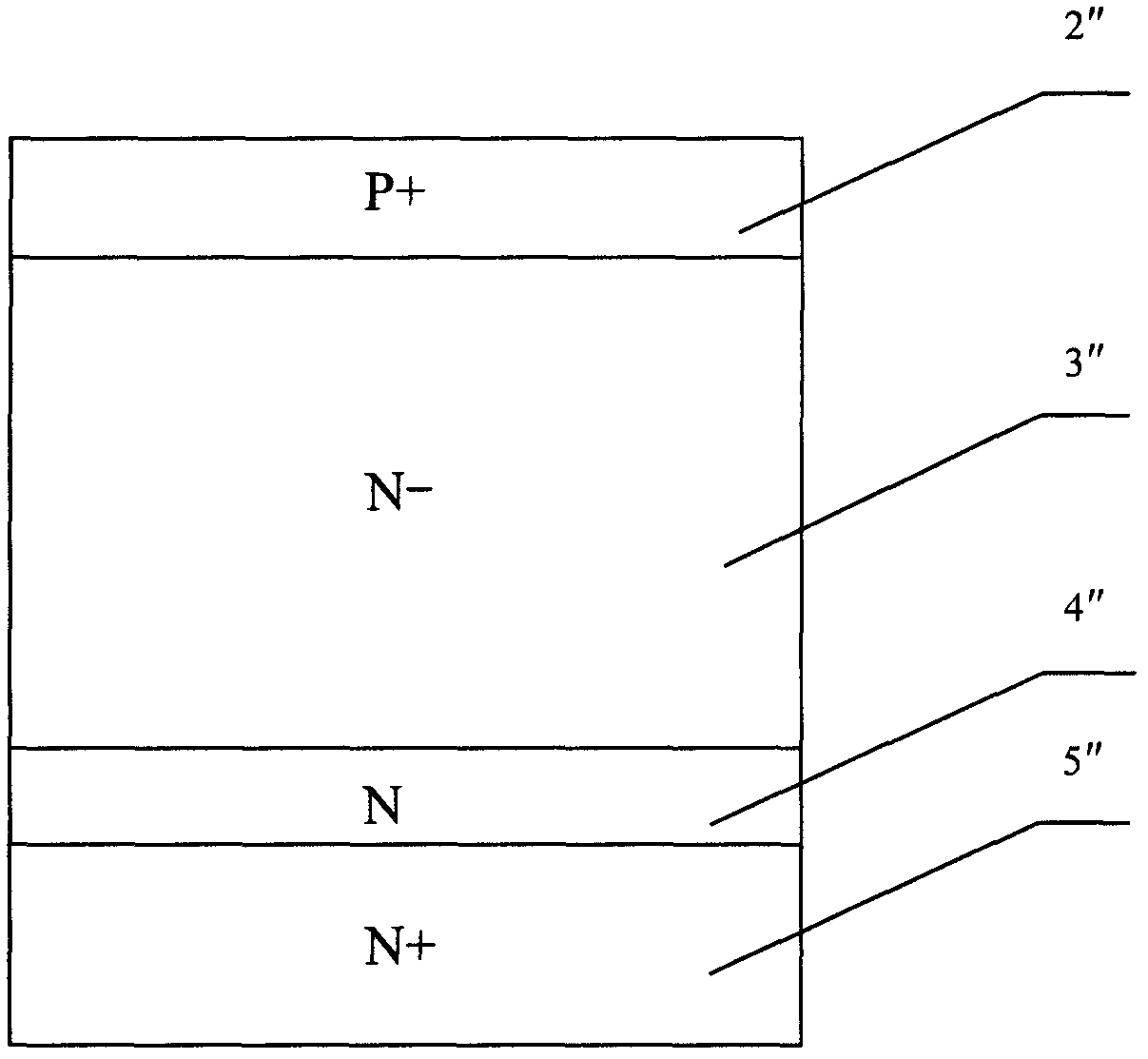

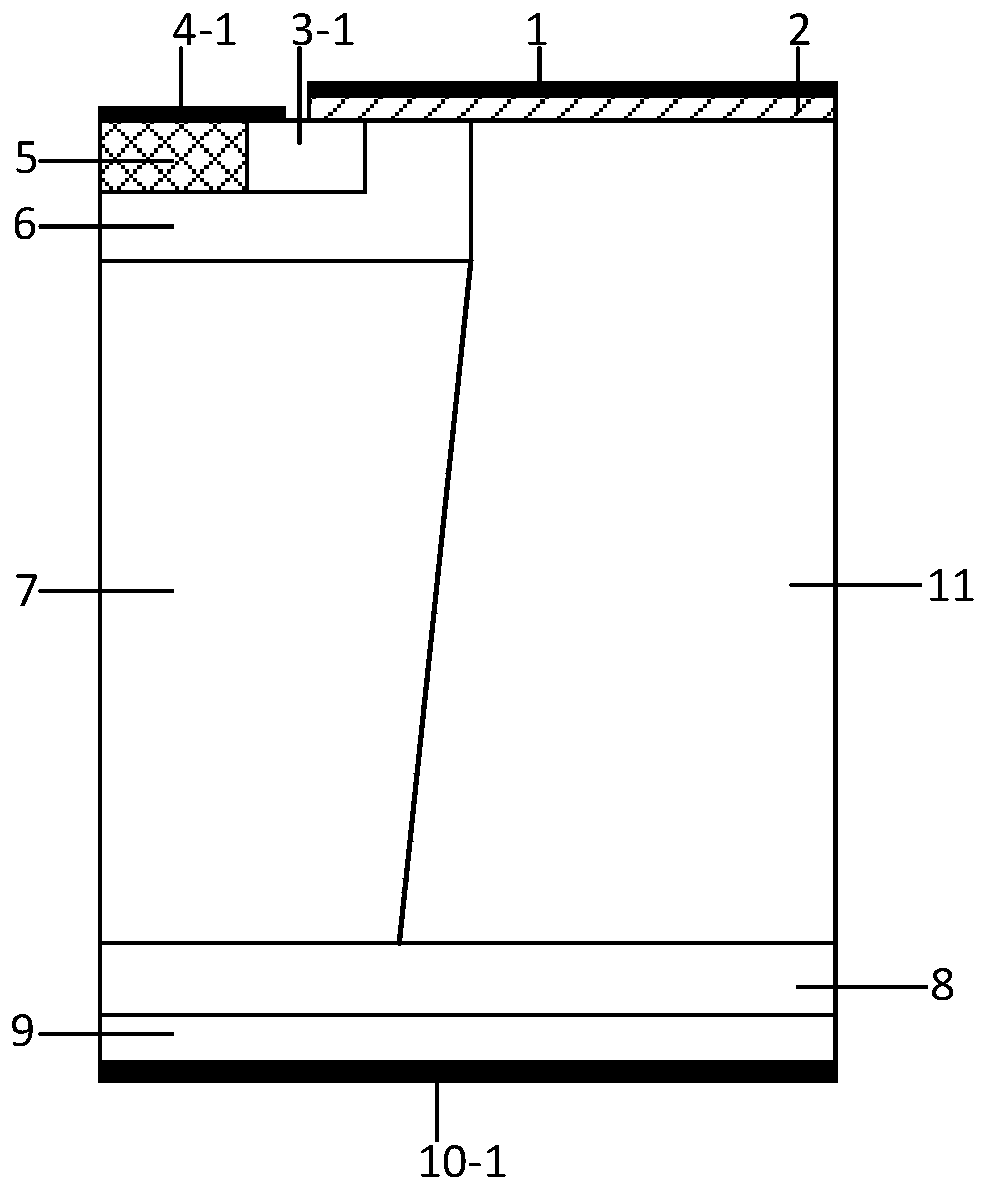

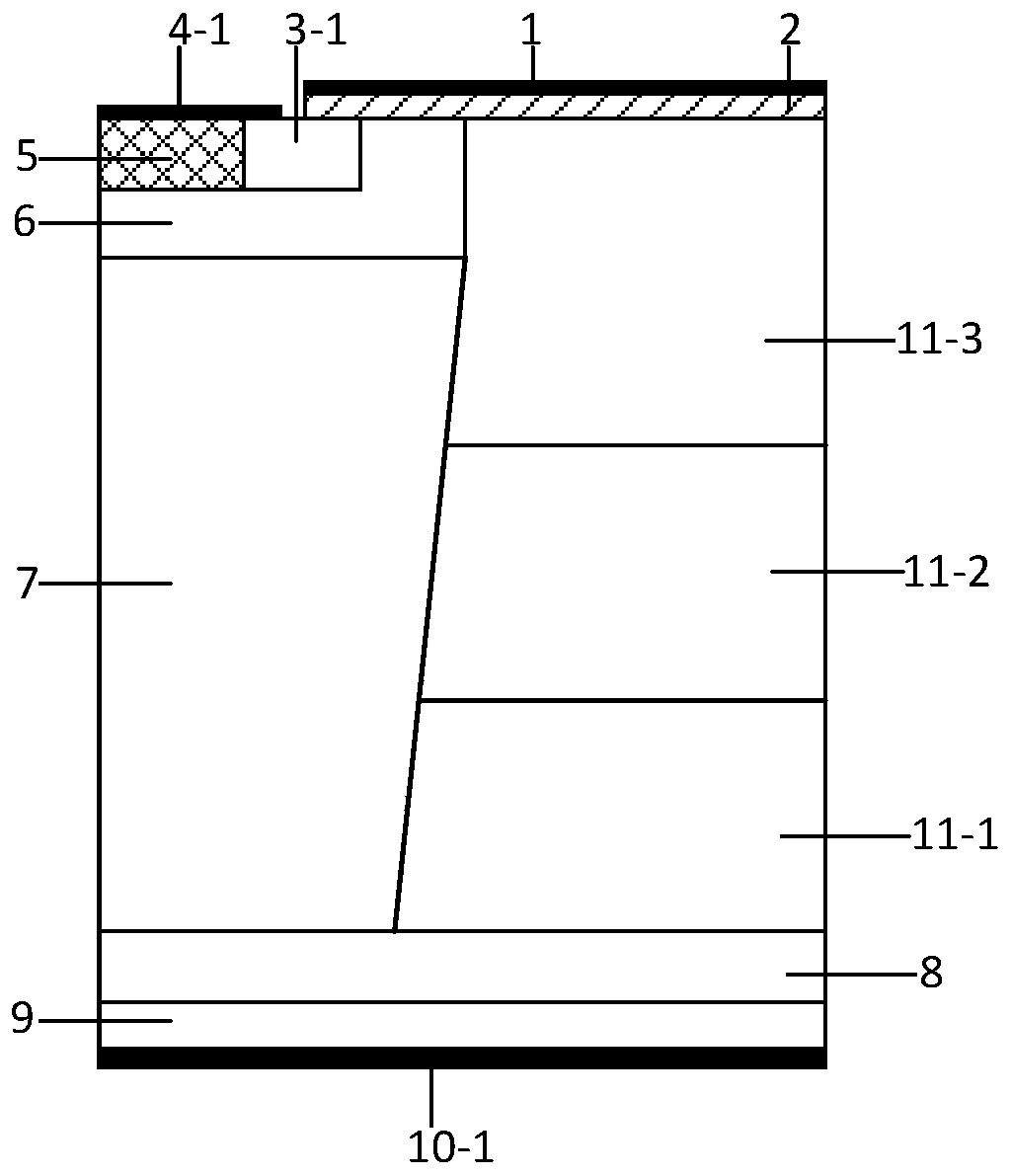

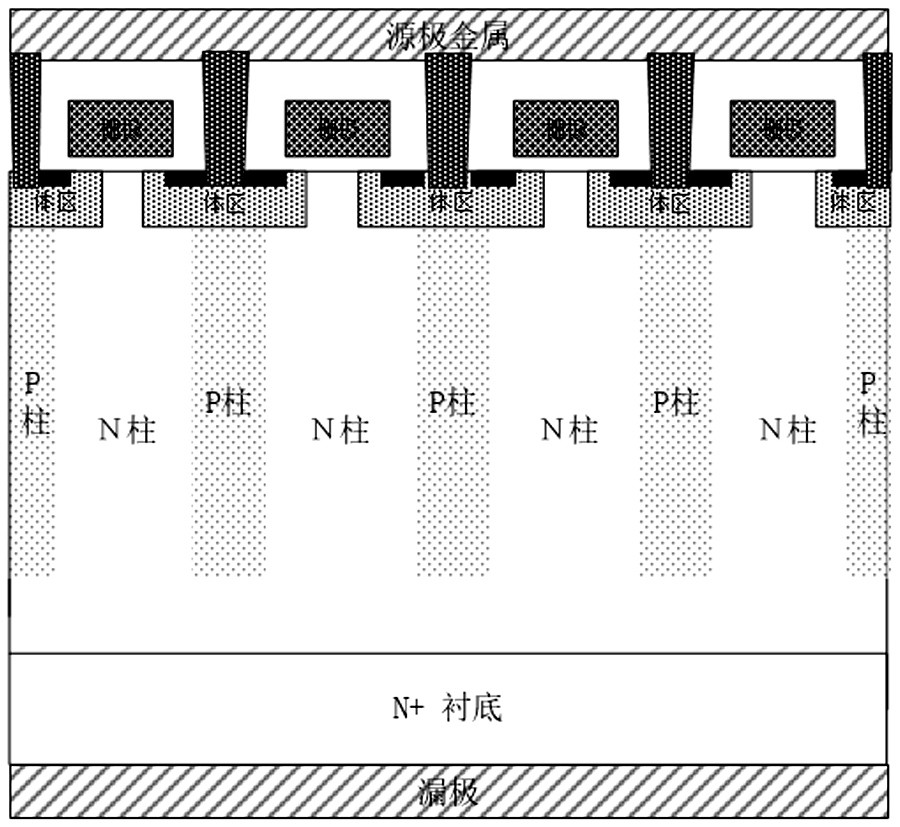

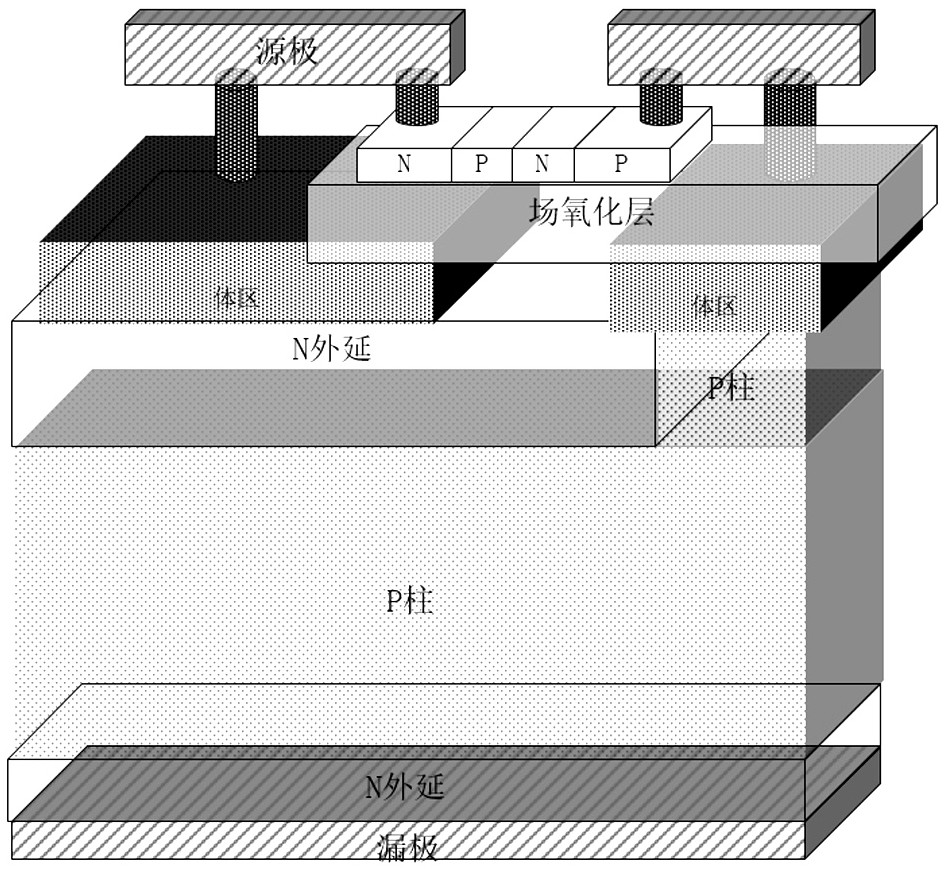

Super junction power MOSFET with soft recovery diode

ActiveCN108231903AIncrease softnessNo increase in specific on-resistanceDiodePower flowReverse recovery

The invention relates to super junction power MOSFET with a soft recovery diode, and belongs to the technical field of semiconductor power devices. A new pressure resisting layer is built in existingsuper junction power MOSFET, the structure of a substrate area is changed, or a buffer area and a supplementary area are added, the softness of the reverse recovery current of a parasitic diode is effectively enhanced, the reverse recovery characteristic is improved, and the specific on-resistance of a device is not increased. The enhancement of the softness of the reverse recovery current makes that the oscillation can not easily appear on the device during a switching process, electromagnetic interference signals are inhibited, and the device work is safer and more reliable. Therefore, the device with the super junction power MOSFET is more applicable to the inverter hard switching circuit.

Owner:杰平方半导体(上海)有限公司

Super junction MOS (Metal Oxide Semiconductor) type power semiconductor device and preparation method thereof

InactiveCN110459598AImprove balanceImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionPower semiconductor device

The invention relates to a super junction MOS (Metal Oxide Semiconductor) type power semiconductor device and a preparation method thereof, and belongs to the technical field of power semiconductors.The invention provides a power semiconductor device which comprises a multi-layer first conduction type semiconductor column region and uses a heterojunction as an unbalanced carrier barrier, realizesa charge balance effect, reduces the high injection efficiency at one side of a source electrode, solves the problems of reduced breakdown voltage and deteriorated reverse recovery characteristic ofa body diode caused by charge imbalance brought about by the actual process, improves the breakdown voltage of the device and improves the reverse recovery characteristic of the body diode. In addition, the invention further provides a preparation method of the super junction MOS type power semiconductor device, which is simple and controllable in manufacturing process and has strong compatibilitywith the existing process.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

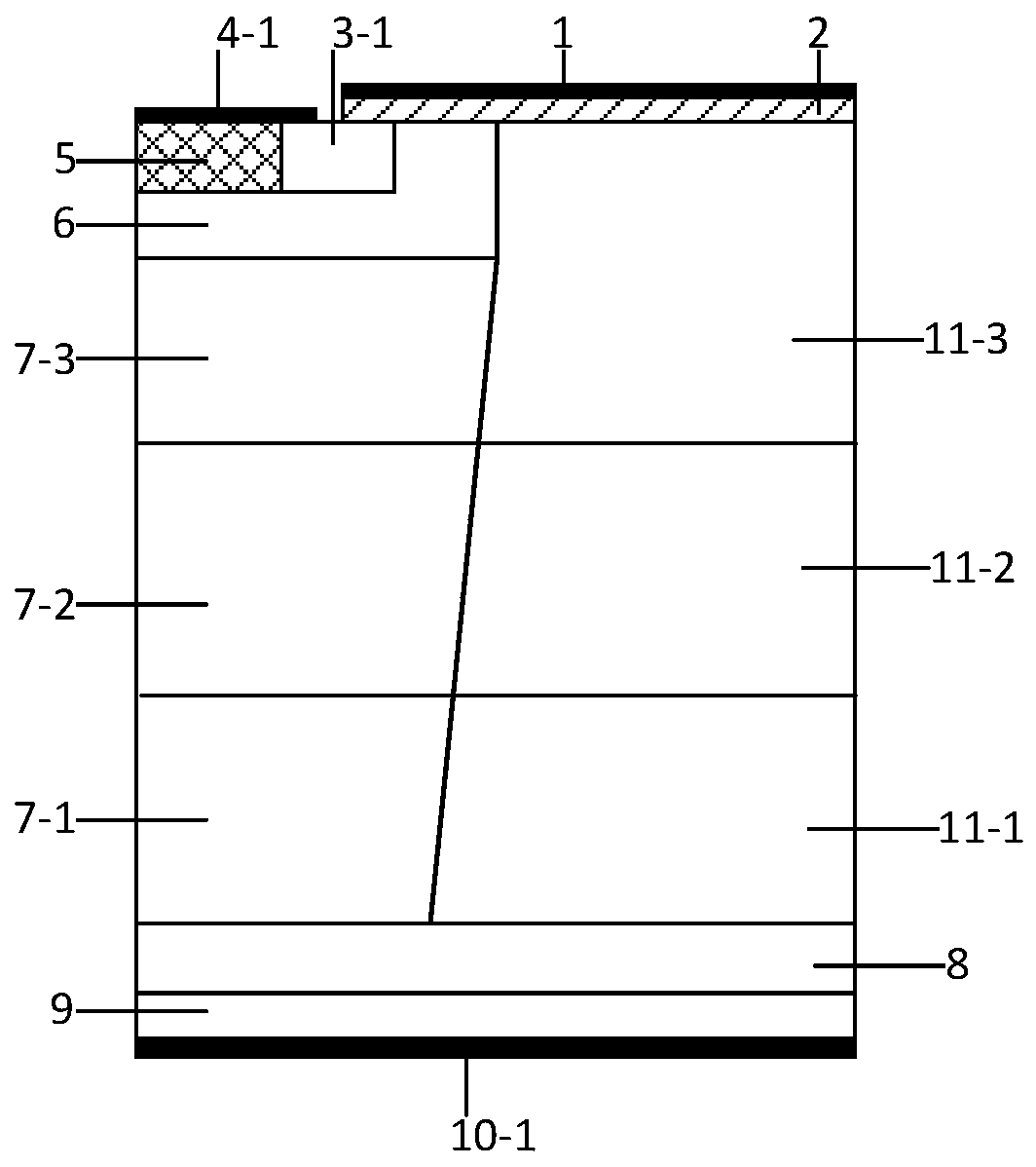

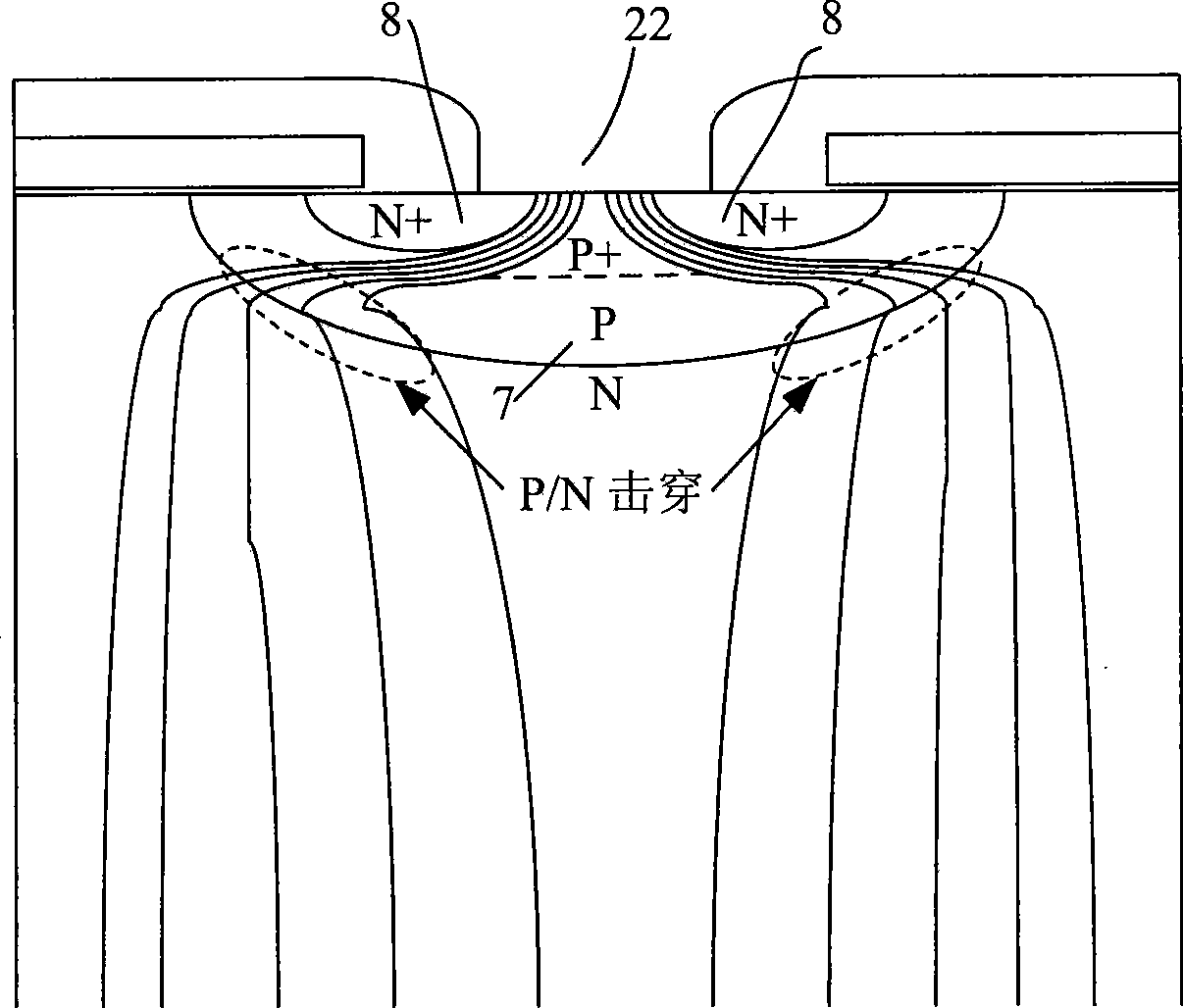

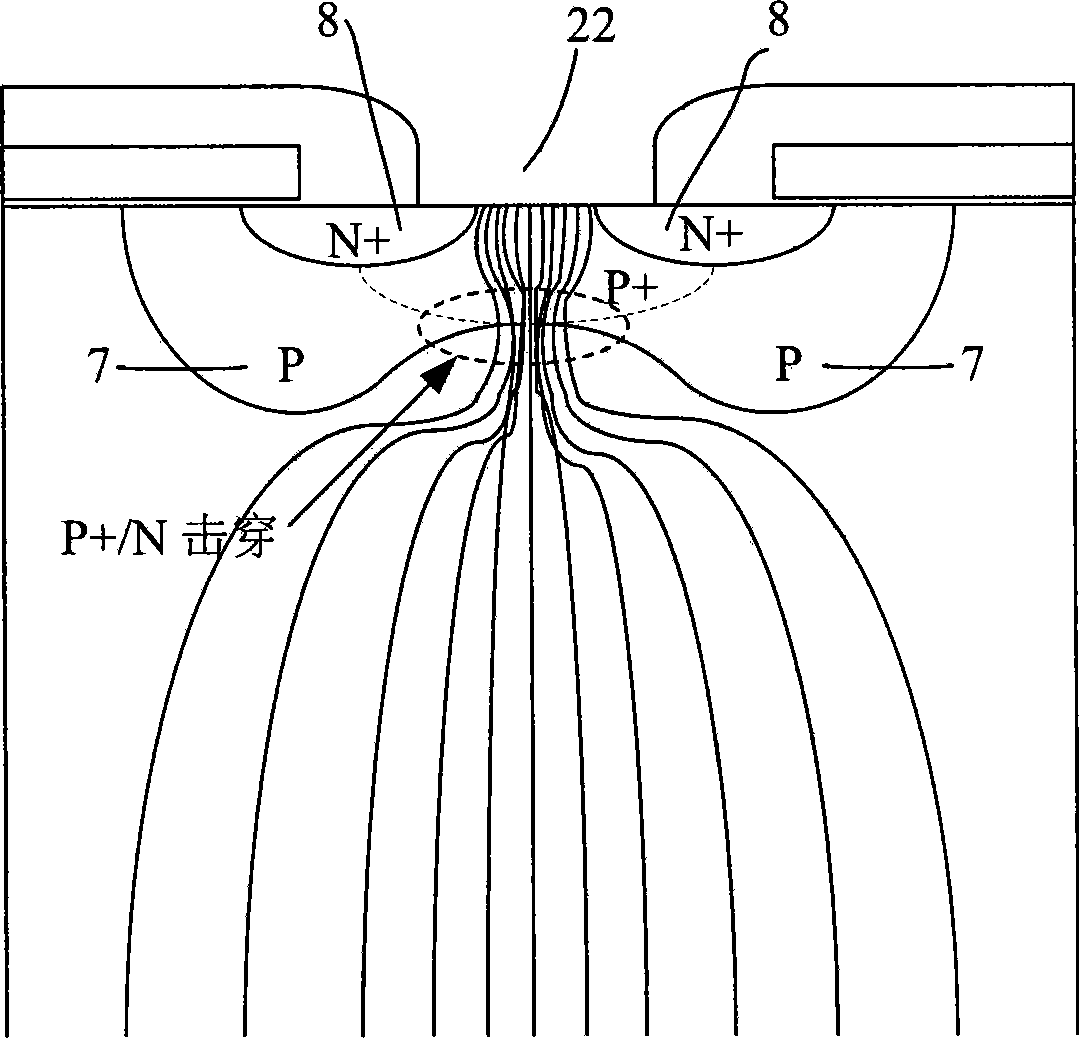

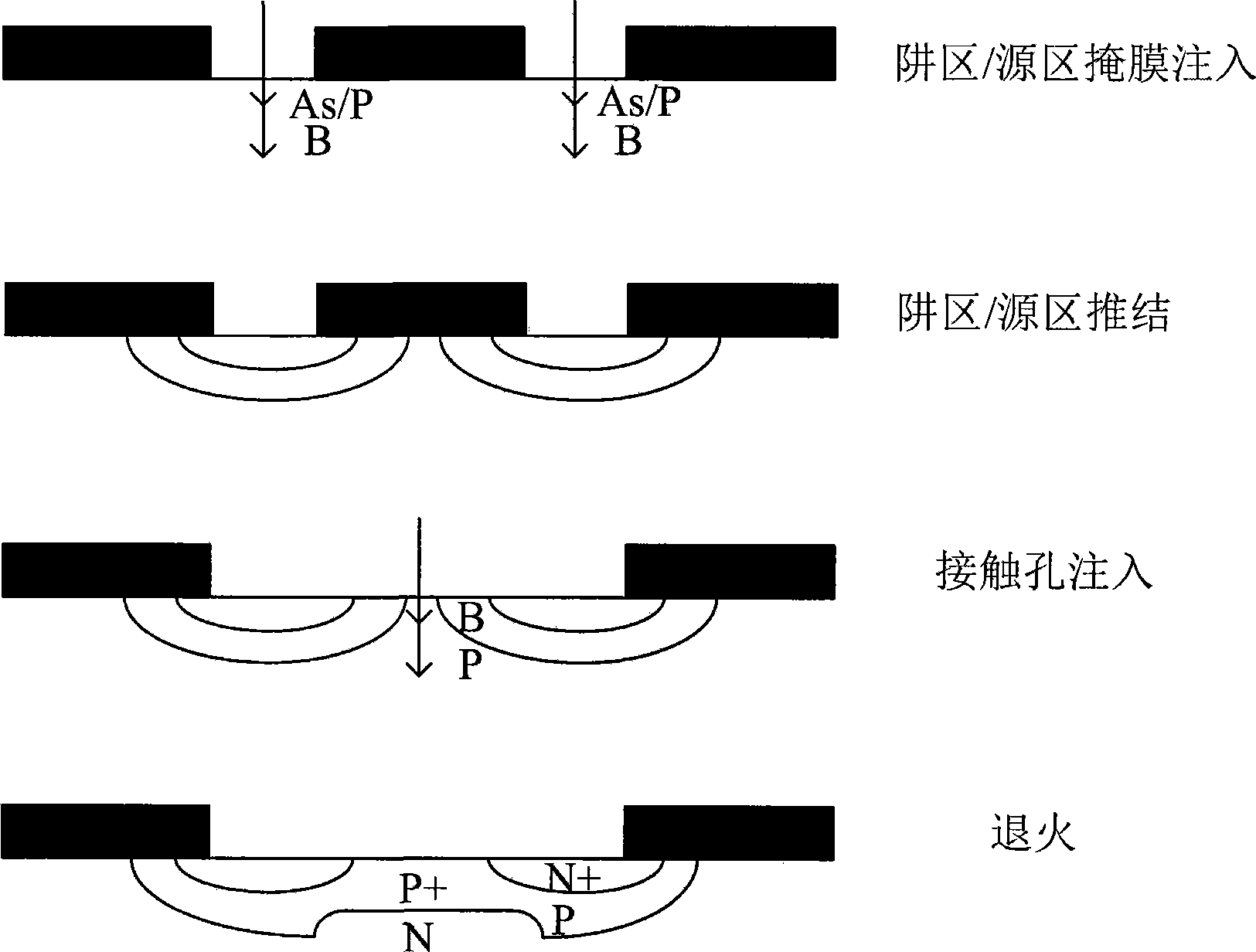

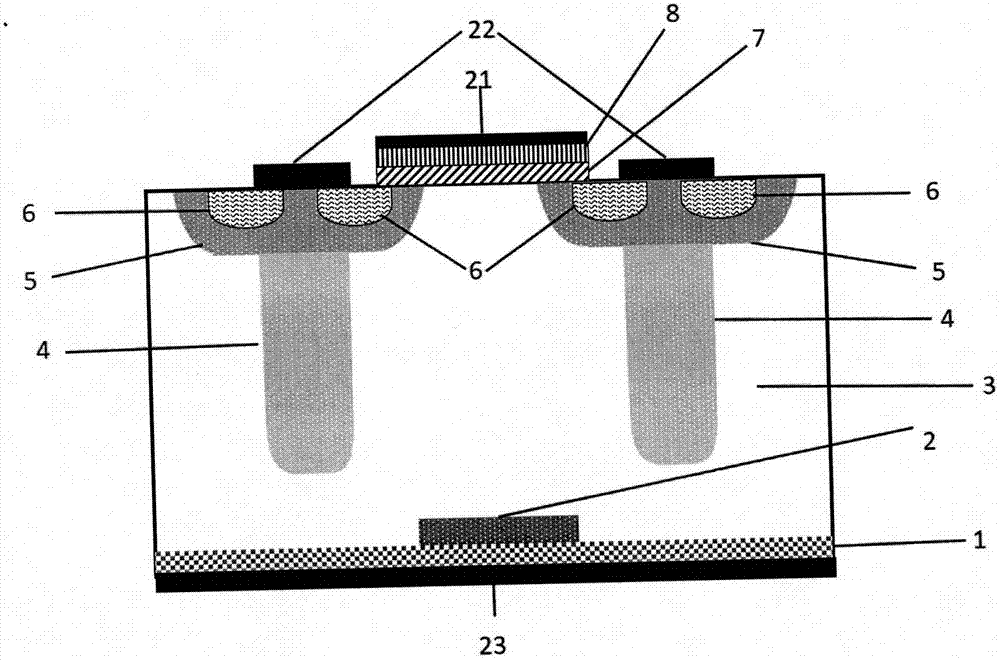

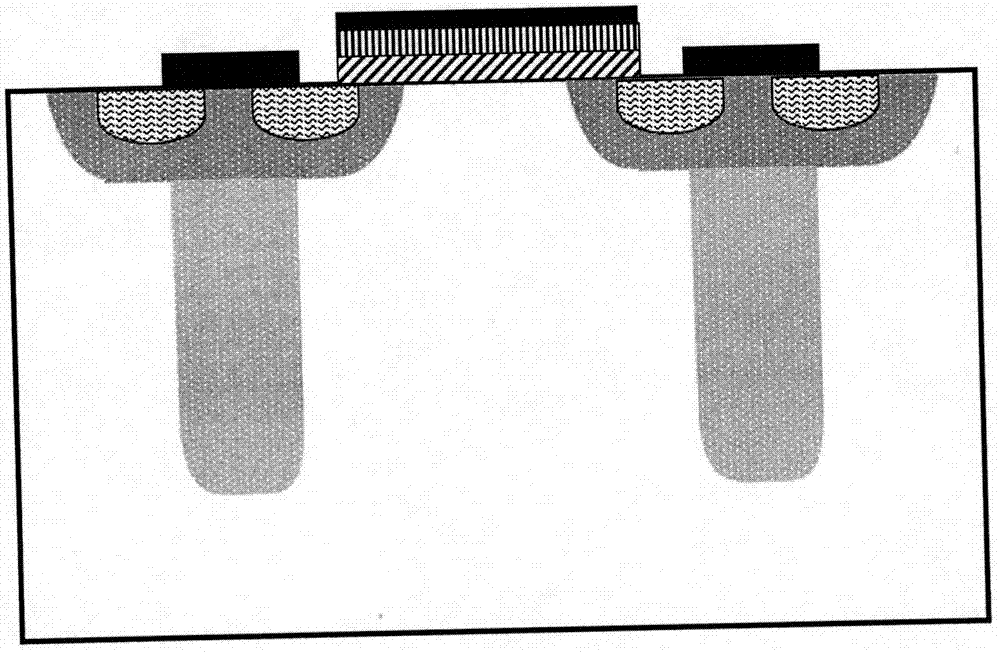

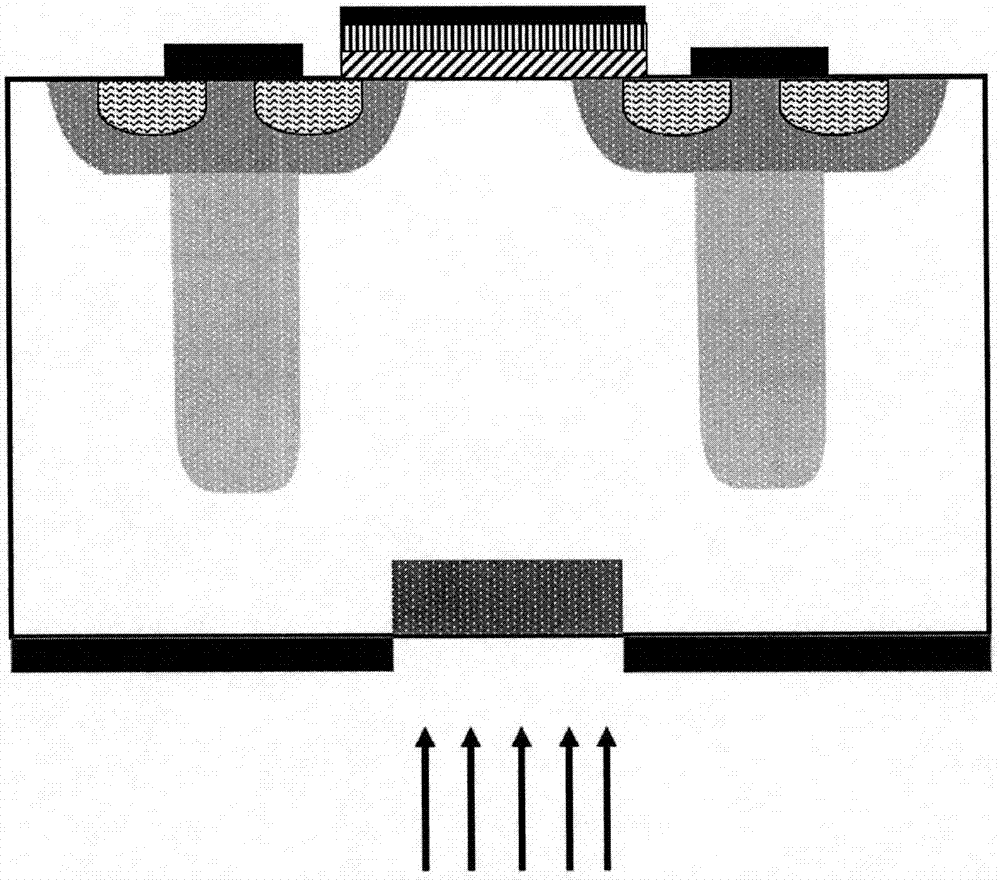

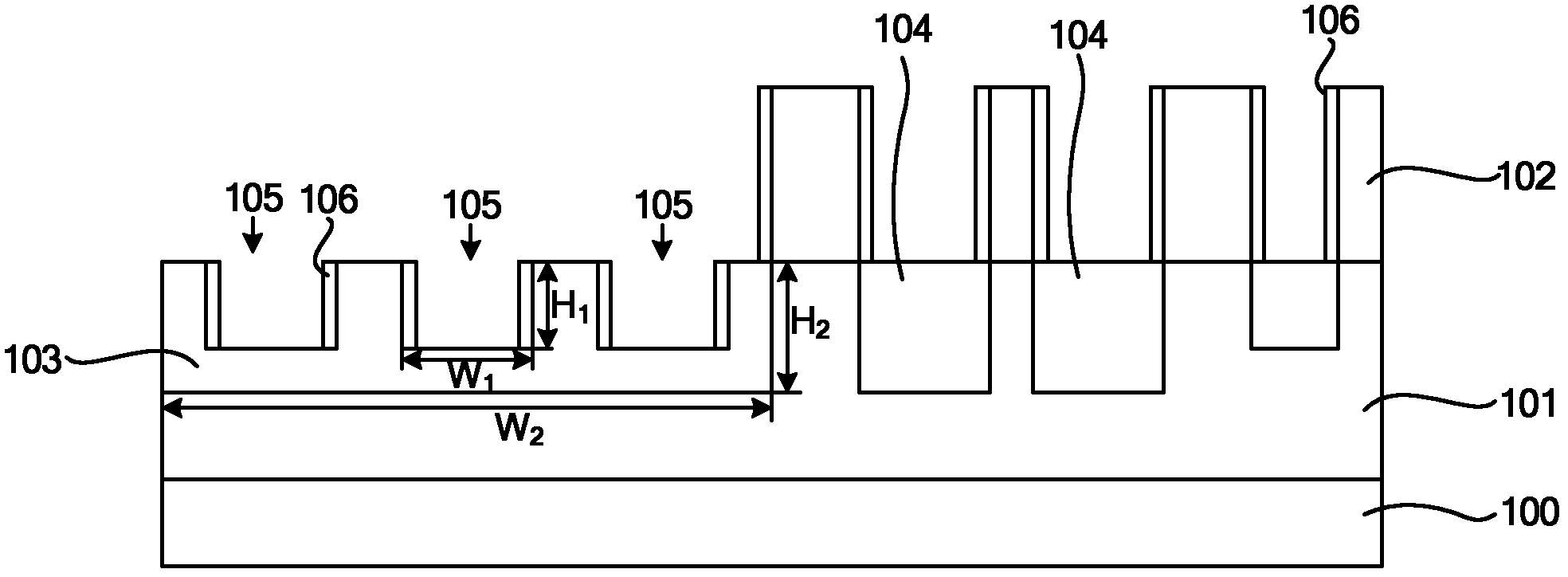

Method for implementing well division construction in super-high density slot type power device design

InactiveCN101393857AShorten the development cycleReduce R&D costsSemiconductor/solid-state device manufacturingHigh densityHigh energy

The invention relates to a novel method for achieving a Split Well structure in the design of an ultrahigh-density groove-type power device, and is effective in solving the problem that the Split Well structure (21) is incompatible with the ultrahigh-density design. Based on the impurity compensation theory, the method is characterized in that the high-energy N-type ion injection (18) and the quick annealing are carried out through a contact hole (22) so as to ensure that the Split Well structure (21) is formed at the bottom part in the middle of a well area (7). With the contact hole (22) over-etched below a silicon surface (23), the process ensures that the energy demand for sequential N-type ion injections is effectively reduced, thereby reducing the probability of injection damage to the well area (7) with less leakage sources that cause current to leak out from the device. Moreover, a higher integrated level can be attained with the Split Well structure 21 achieved in Z direction. The novel Split Well technology leads to a substantial improvement on the design of the device which ensures the long-standing reliability of the device as well as the workability of the on-resistance of the device, the firmness of the device and the reverse recovery characteristic of the body diode of the device.

Owner:成都方舟微电子有限公司

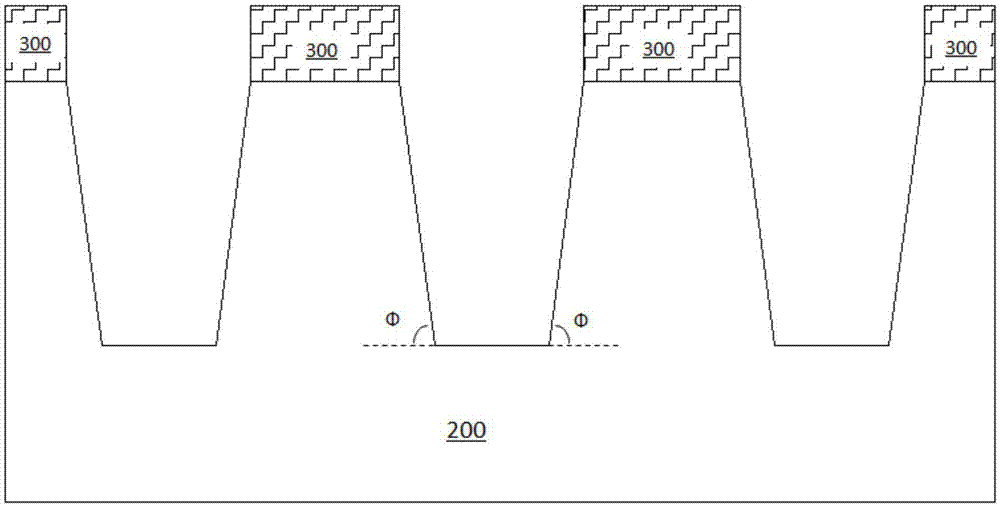

Fin type fast recovery super-junction power semiconductor transistor and preparation method thereof

ActiveCN106024910AInhibit onPrevent inflowFinal product manufactureSemiconductor/solid-state device manufacturingPolysilicon gateBody region

The invention discloses a fin type fast recovery super-junction power semiconductor transistor and a preparation method thereof. The fin type fast recovery super-junction power semiconductor transistor comprises an N-type substrate, wherein an N-type epitaxial layer is arranged on the N-type substrate; second columnar P-type body regions are arranged in the N-type epitaxial layer; a first P-type body region is arranged on the top of the N-type epitaxial layer, and the first P-type body region is positioned between the two second columnar P-type body regions; the surface of the N-type epitaxial layer is provided with an N-type heavily-doped source region and a P-type heavily-doped semiconductor contact region; the N-type heavily-doped source region, the P-type heavily-doped semiconductor contact region and the second P-type body region are connected with source electrode metals; polysilicon gates are arranged on two sides of the first P-type body region respectively; the second columnar P-type body regions are terminated at the lower surfaces of the polysilicon gates, and the second columnar P-type body regions are lower than the first P-type body region; gate oxide layers are arranged between the polysilicon gates and the first P-type body region, the N-type epitaxial layer and the second P-type body regions; insulated layers are arranged between the polysilicon gates and the source electrode metals; and the gate oxide layers enable the first P-type body region and the second P-type body regions to be separated from each other.

Owner:SOUTHEAST UNIV

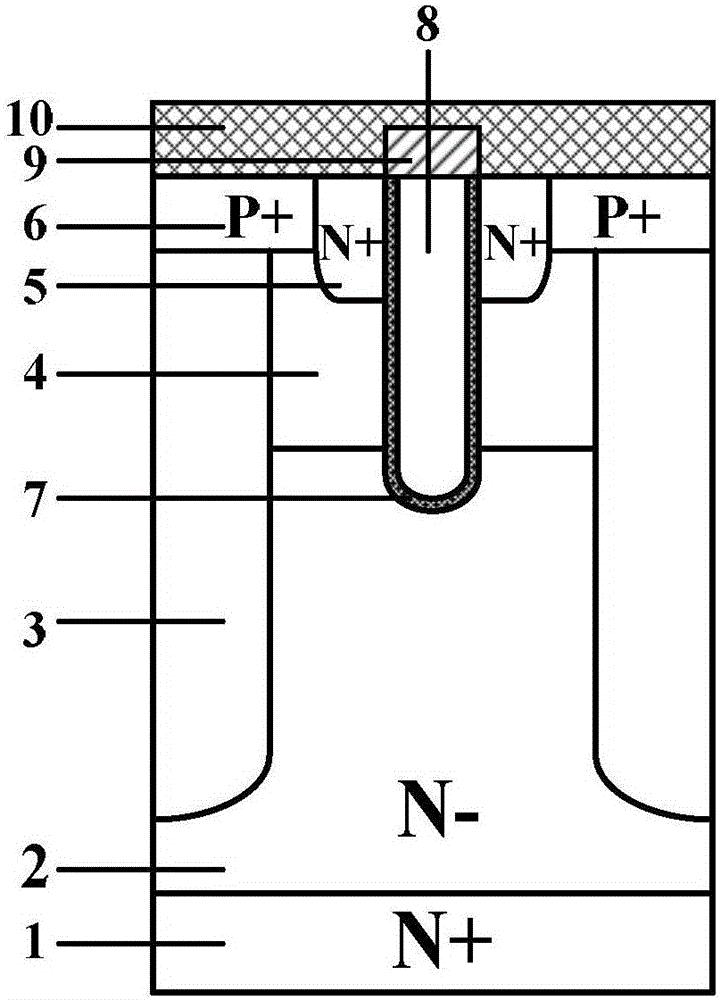

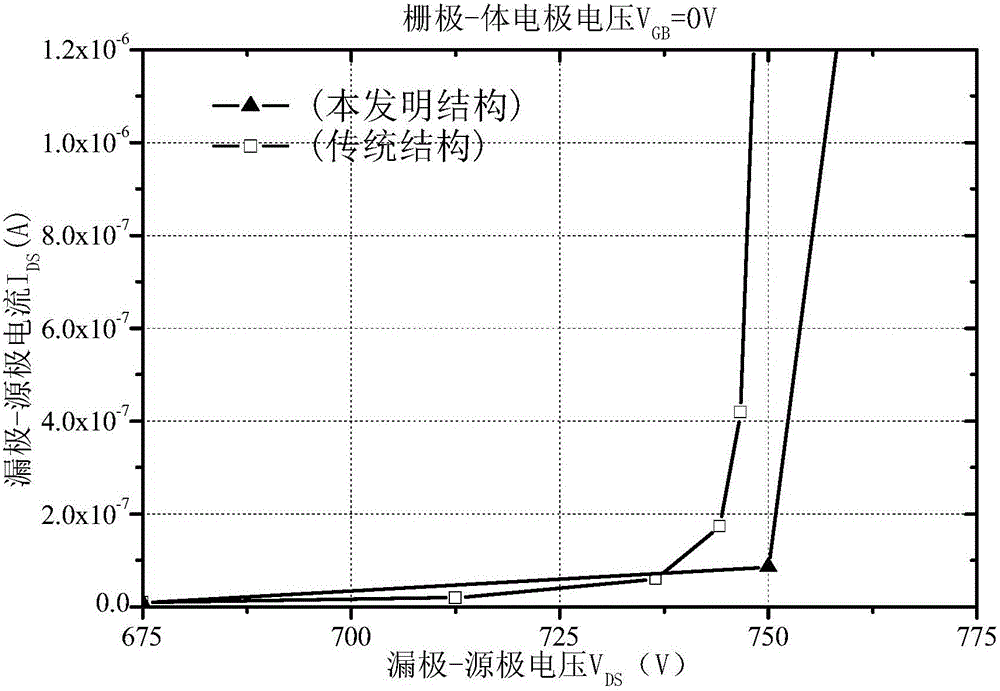

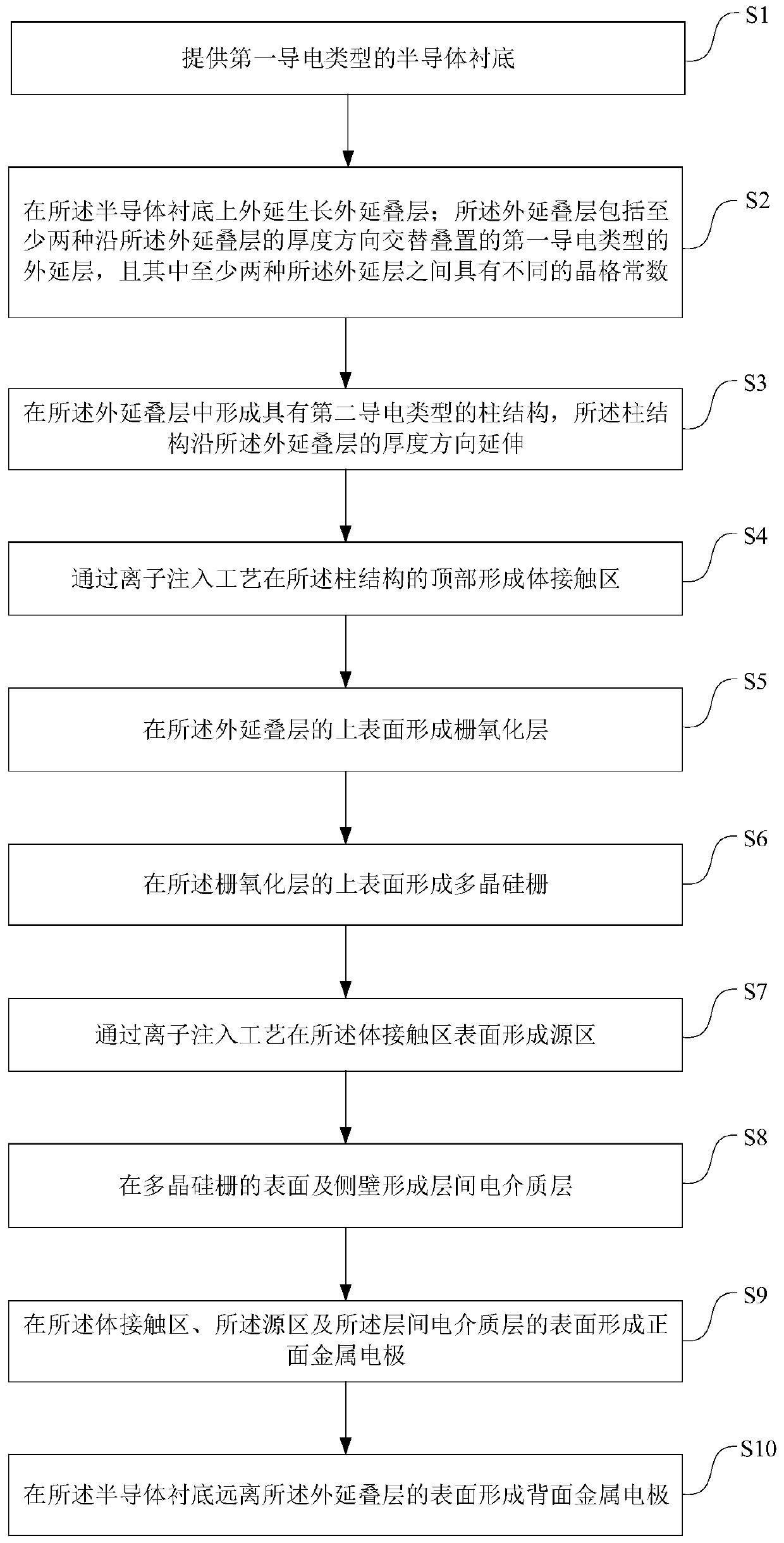

Super junction device structure and preparation method thereof

ActiveCN110137245AIncrease chance of compoundingImproved reverse recovery characteristicsFinal product manufactureSemiconductor/solid-state device manufacturingLattice defectsHigh volume manufacturing

The present invention provides a super junction device structure and a preparation method thereof. The super junction device structure includes a semiconductor substrate of a first conductivity type,an epitaxial stack layer formed on the semiconductor substrate, and a column structure of a second conductivity type, wherein the epitaxial stack layer includes at least two epitaxial layers of a first conductivity type alternately stacked along the thickness direction of the epitaxial stack layer, at least one epitaxial layer has a lattice constant different from that of the semiconductor substrate, the column structure is formed in the epitaxial stack layer and extends in the thickness of the epitaxial stack layer. According to the invention, a lattice defect is introduced by growing epitaxial layers of different lattice constants, the carrier recombination probability is increased, and the reverse recovery characteristics of a super junction power device is optimized. Uniformly controllable defect distribution is obtained by introducing the epitaxial stack layer with at least two alternately stacked epitaxial layers. The preparation method provided by the invention has the advantages of simple process and low cost and is suitable for mass production.

Owner:上海功成半导体科技有限公司

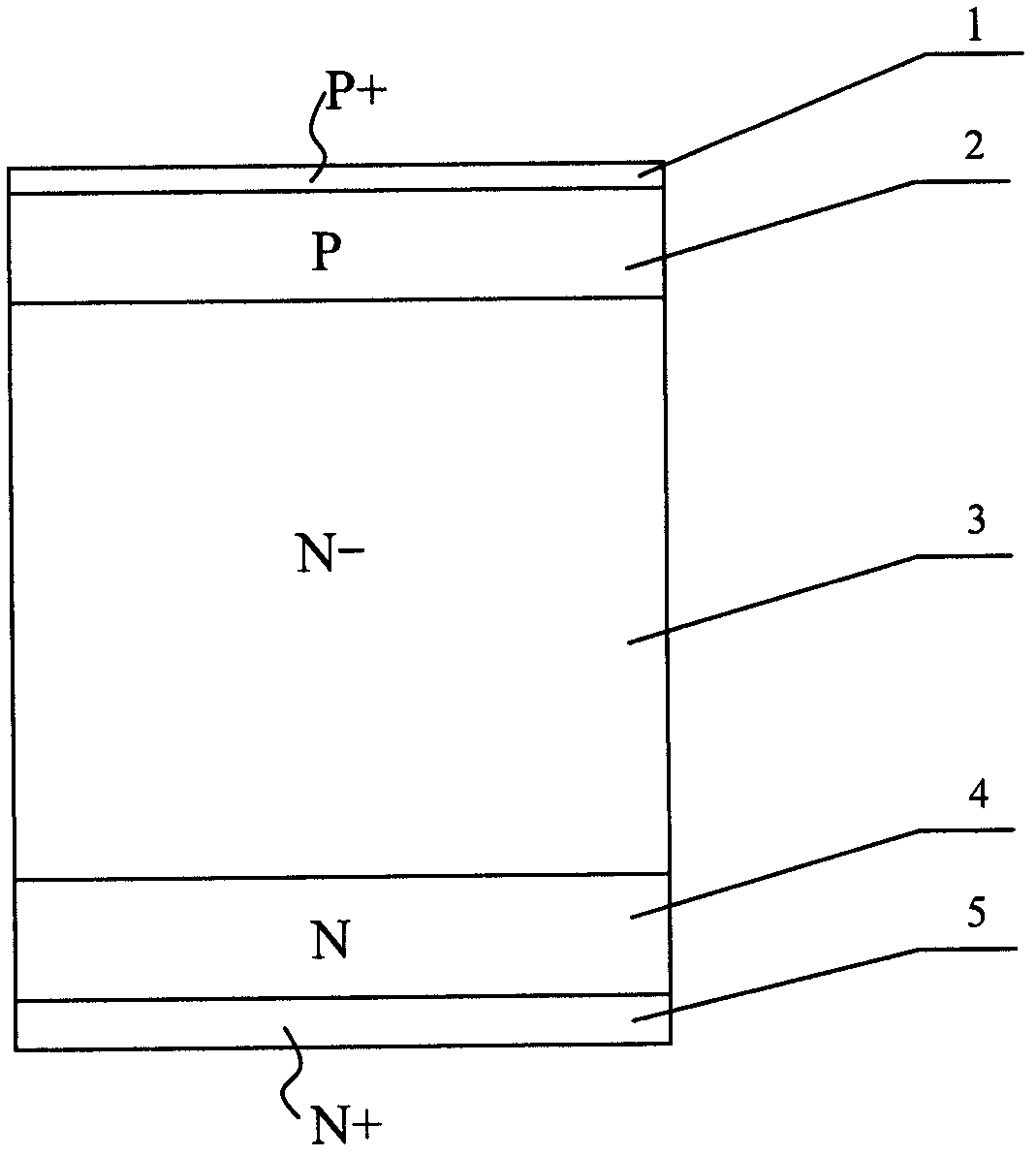

Method and apparatus for optimizing reverse recovery characteristic of body diode

InactiveCN107359125AIncrease softnessImproved reverse recovery characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryPhysics

The invention discloses a method and an apparatus for optimizing reverse recovery characteristic of a body diode. Processing is preformed for a COOLMOS device, wherein a drain region is formed at the bottom of the COOLMOS device; and the doping concentration of an n heavily doped region is higher than that of an n doped substrate region. By forming the n type heavy doping to partial regions on the back surface of the device after the device is thinned, a partial buffer layer structure can be formed, so that the reverse recovery softness of the body diode is improved and reverse voltage conversion rate (dv / dt) is lowered, thereby optimizing the reverse recovery characteristic of the body diode.

Owner:苏州达晶微电子有限公司

Super junction power device and manufacturing method thereof

ActiveCN107134492AImprove breakdown voltageImproved reverse recovery characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsBody region

A super junction power device disclosed by the invention comprises a substrate epitaxial layer of a first doping type, body regions of a second doping type, and JFET regions. The substrate epitaxial layer is internally provided with a drain region of the first doping type and a plurality of sidewall-sloped columnar epitaxial doped regions of the second doping type. The body regions are respectively arranged on the top ends of the columnar epitaxial doped regions, and each body region is internally provided with source regions of the first doping type. Each JFET region is disposed between every two adjacent body regions. A gate oxide layer is arranged on the body regions and the JFET regions. Gates are arranged on the gate oxide layer. Compensation injection regions are arranged in the substrate epitaxial layer at the two sides of the sidewalls and at the bottom of the columnar epitaxial doped regions. The breakdown voltage is increased and the reverse recovery characteristic is improved under the condition that the on resistance of the super junction power device is basically unchanged. The manufacturing process is simple and easy to implement.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

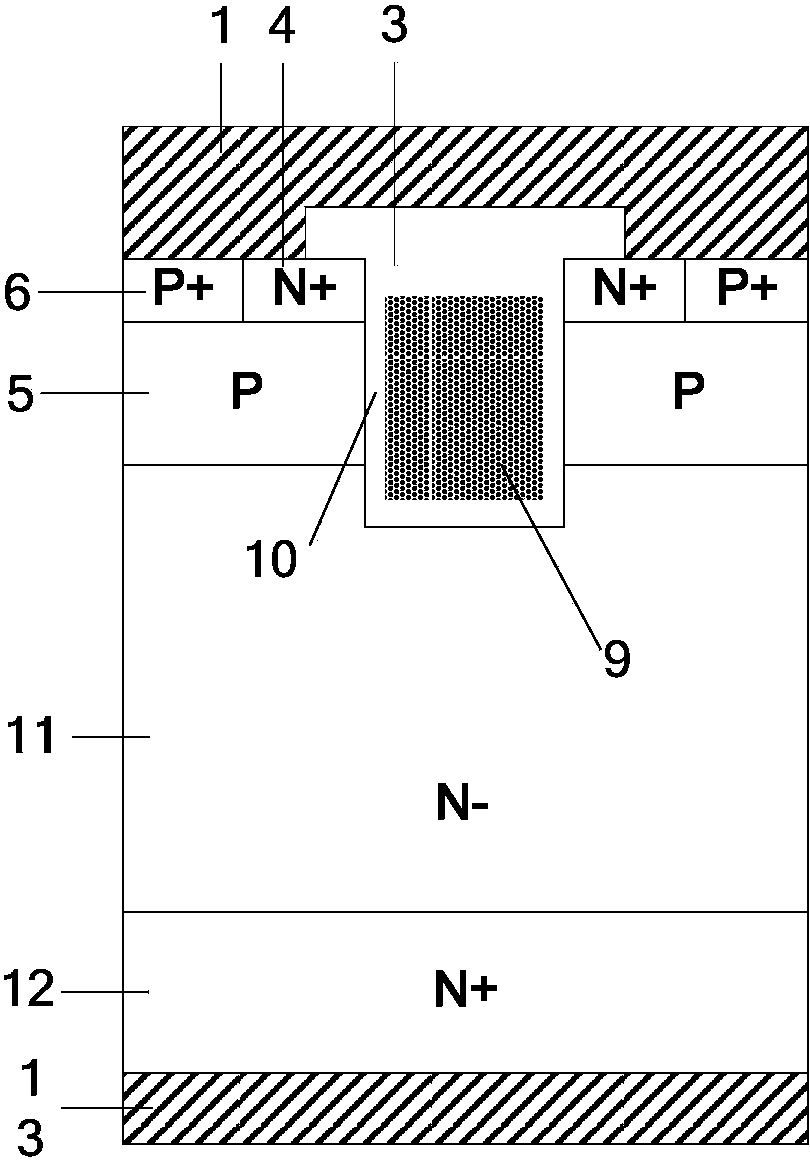

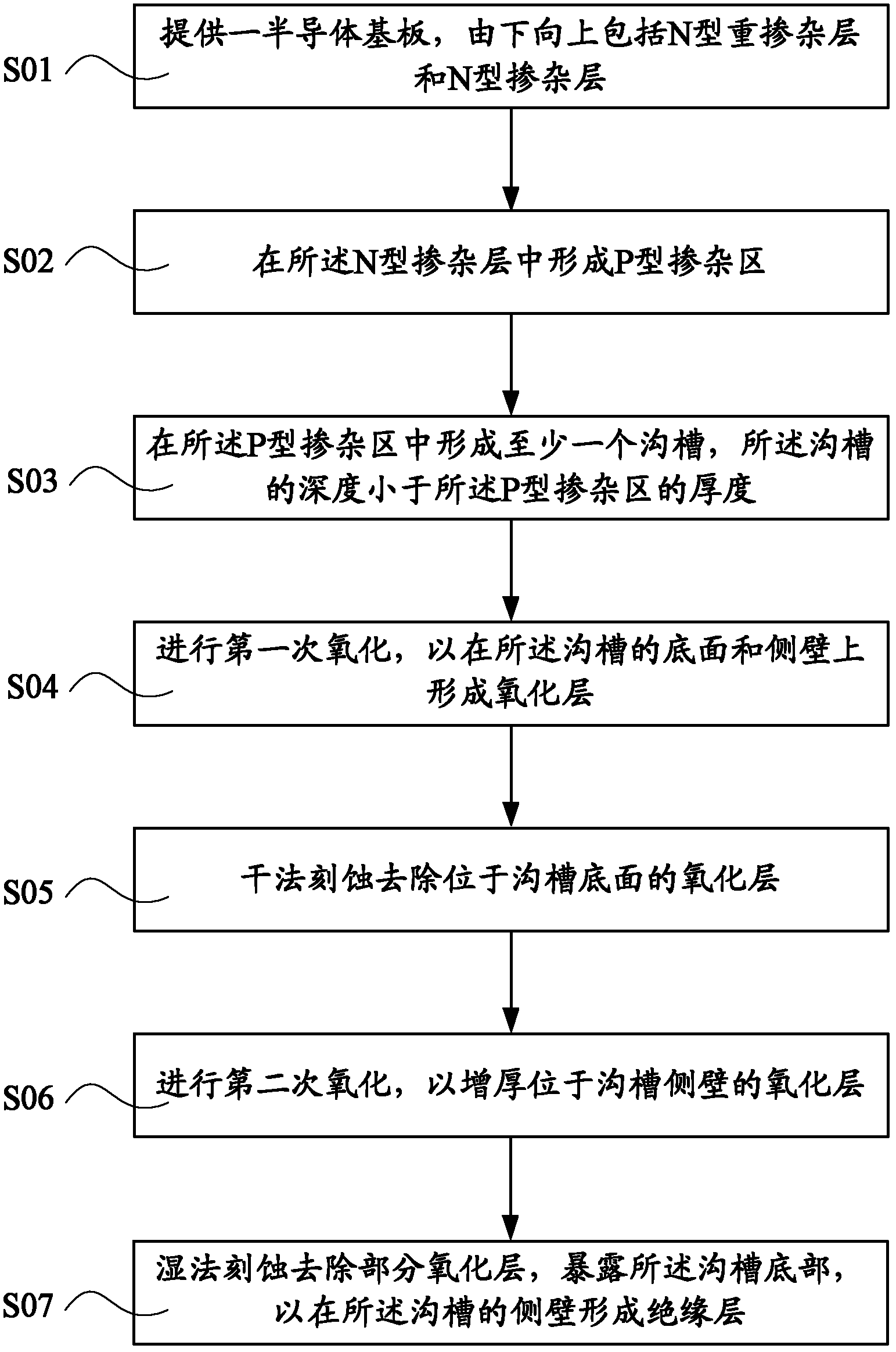

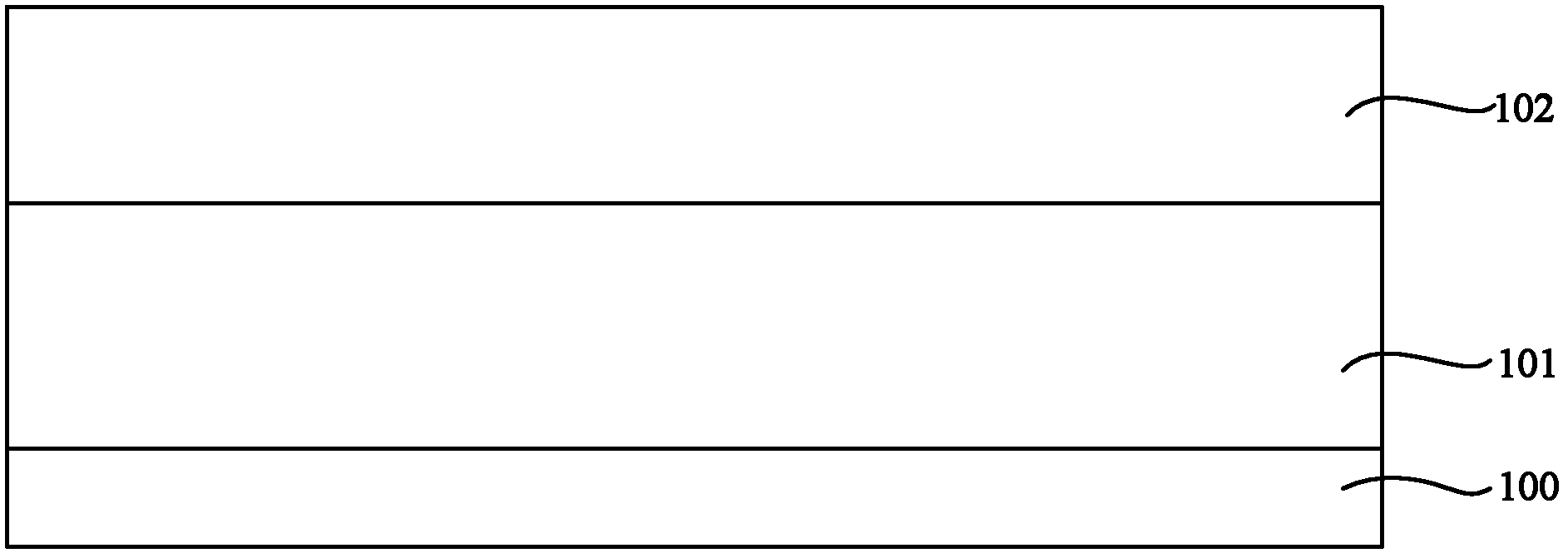

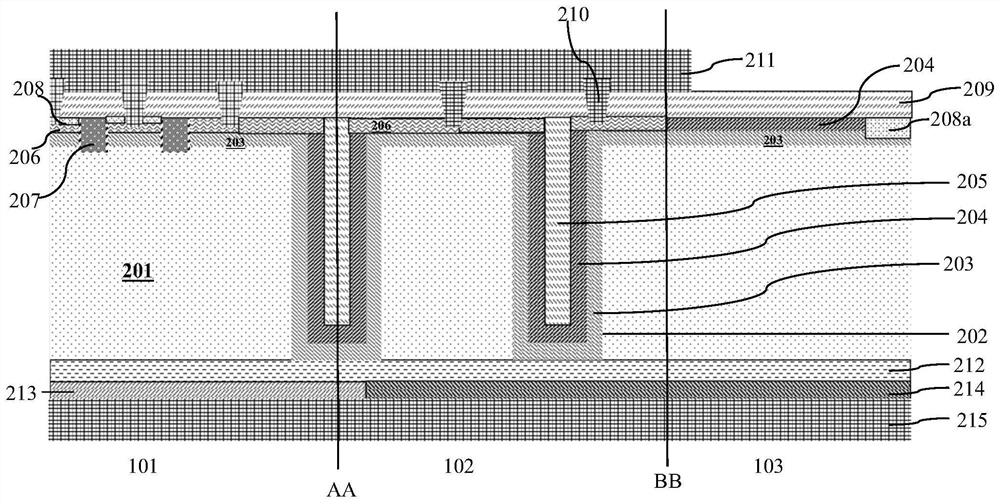

Fast recovery diode (FRD) device structure and manufacturing method thereof

ActiveCN102437200AImproved reverse recovery characteristicsImprove on-state pressure dropSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerCharge carrier

The invention provides a fast recovery diode (FRD) device structure and a manufacturing method thereof. An insulation layer is formed on the side wall of a trench of the FRD device structure, and the insulation layer is combined with the surface of a P-type doped region to form a combining center, so that a combining route from the P-type doped region to the insulation layer is formed, and the reverse recovery characteristic of the device is improved effectively; furthermore, due to the presence of the insulation layer on the side wall of the trench, partial combined current carriers which reach the upper surface of the P-type doped region from the P-type doped region through the combining route are shielded by the insulation layer and combined on the surface of the insulation layer, so that the emission efficiency is improved and the state voltage drop is reduced; moreover, the doping concentration at the bottom of the trench in the P-type doped region is controlled, so that the diffusion length of the current carriers is prevented from being dramatically reduced, the scattering of the current carriers and an auger combining effect are avoided, the emission efficiency of the bottom region of the trench in the P-type doped region is improved, the rising of the state voltage drop of the trench caused by doping reduction is compensated, and the forward voltage drop is improved.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

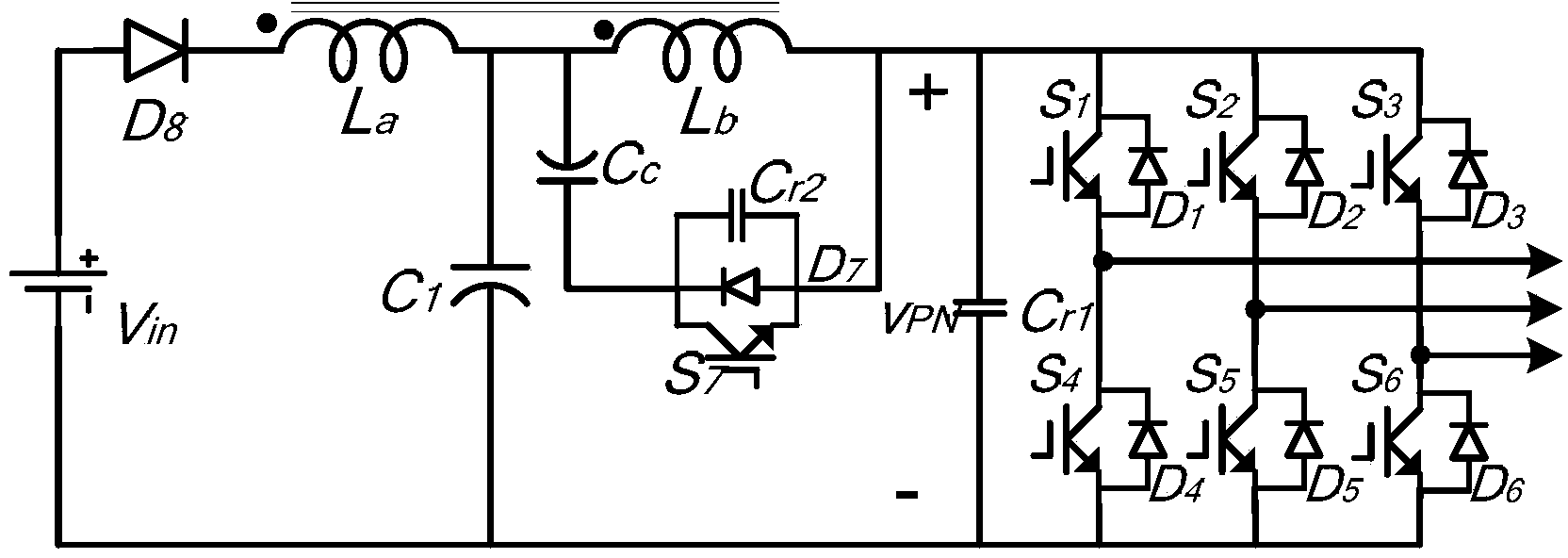

Active clamping high-gain single-stage inverter with pressure capable of being boosted

InactiveCN103840697AAchieving Zero Voltage SwitchingAchieve lossless absorptionEfficient power electronics conversionAc-dc conversionCapacitanceEngineering

The invention belongs to the technical field of direct current-alternating current inversion equipment, and relates to an active clamping high-gain single-stage inverter with pressure capable of being boosted. A first winding and a second winding of a coupling inductor are dotted terminals of each other, an anode of a rectifier diode is connected with the positive pole of a direct current power supply, and the cathode of the rectifier diode is connected with the first winding of the coupling inductor. The positive pole of a capacitor is connected with the public end of the first winding and the second winding, the negative pole of the capacitor is connected with the negative pole of the direct current power supply and one end of a first resonance capacitor, and the other end of the first resonance capacitor is connected with the second winding, and the first resonance capacitor and a three-phase voltage type bridge inverter circuit are connected in parallel. An auxiliary power switching tube is respectively connected with an antiparallel diode of the auxiliary power switching tube and a second resonance capacitor in parallel and is connected with a clamping capacitor in series to form an active clamping circuit, and the active clamping circuit is connected with the second winding of the coupling inductor in parallel. The active clamping high-gain single-stage inverter is simple in structure, small in electromagnetic interference influence, few in loss, low in cost, high in energy conversion efficiency and environmentally friendly.

Owner:QINGDAO TECHNOLOGICAL UNIVERSITY

Reverse conducting IGBT

PendingCN114464676AAdjust the average emission efficiencyImprove emission efficiencyTransistorSolid-state devicesEngineering physicsMaterials science

The invention discloses a reverse conducting IGBT. A forming area of the IGBT and a forming area of an FRD are adjacent to each other and are isolated from each other in the transverse direction. A drift region and a field stop layer are formed in the forming region of the IGBT and the FRD; in the formation region of the IGBT, a collector region is formed on the back surface of the field stop layer. In the formation region of the FRD, a first electrode region is formed on the back surface of the field stop layer. A deep trench through the drift region is formed in the formation region of the FRD. A first epitaxial layer and a second epitaxial layer which are opposite in doping type are formed on the surfaces of the deep groove and the drift region, and the deep groove is further filled with a third insulating medium layer. And second conductive type doped well regions are formed on the surfaces of the first epitaxial layer and the second epitaxial layer on the drift region. The IGBT and the FRD can be well isolated, flyback of the IGBT can be restrained, the performance of the FRD can be locally optimized at the same time, the injection efficiency of the FRD can be improved, the minority carrier lifetime of the FRD can be controlled, the structure of a terminal area can be optimized, and the area can be saved.

Owner:上海擎茂微电子科技有限公司

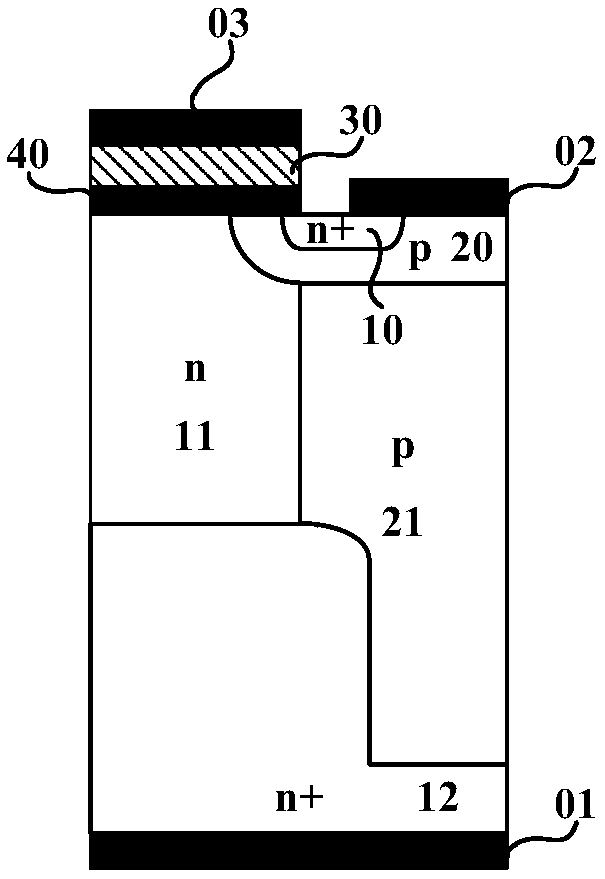

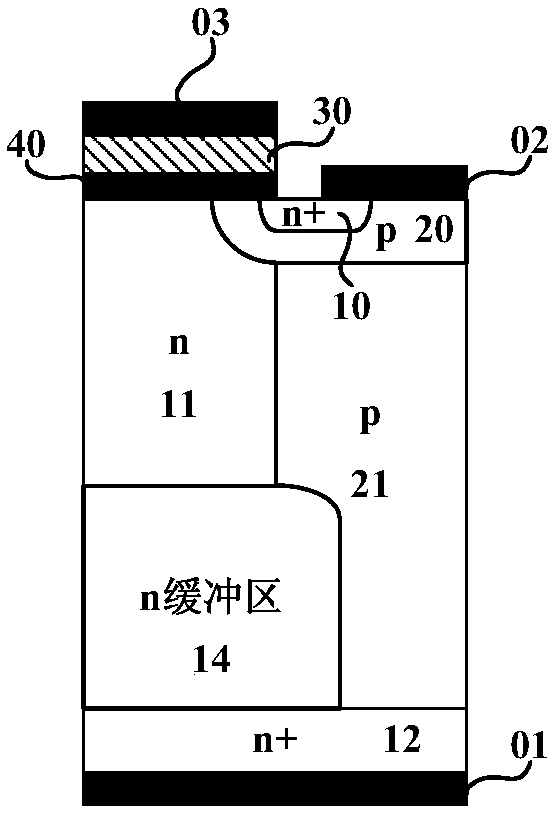

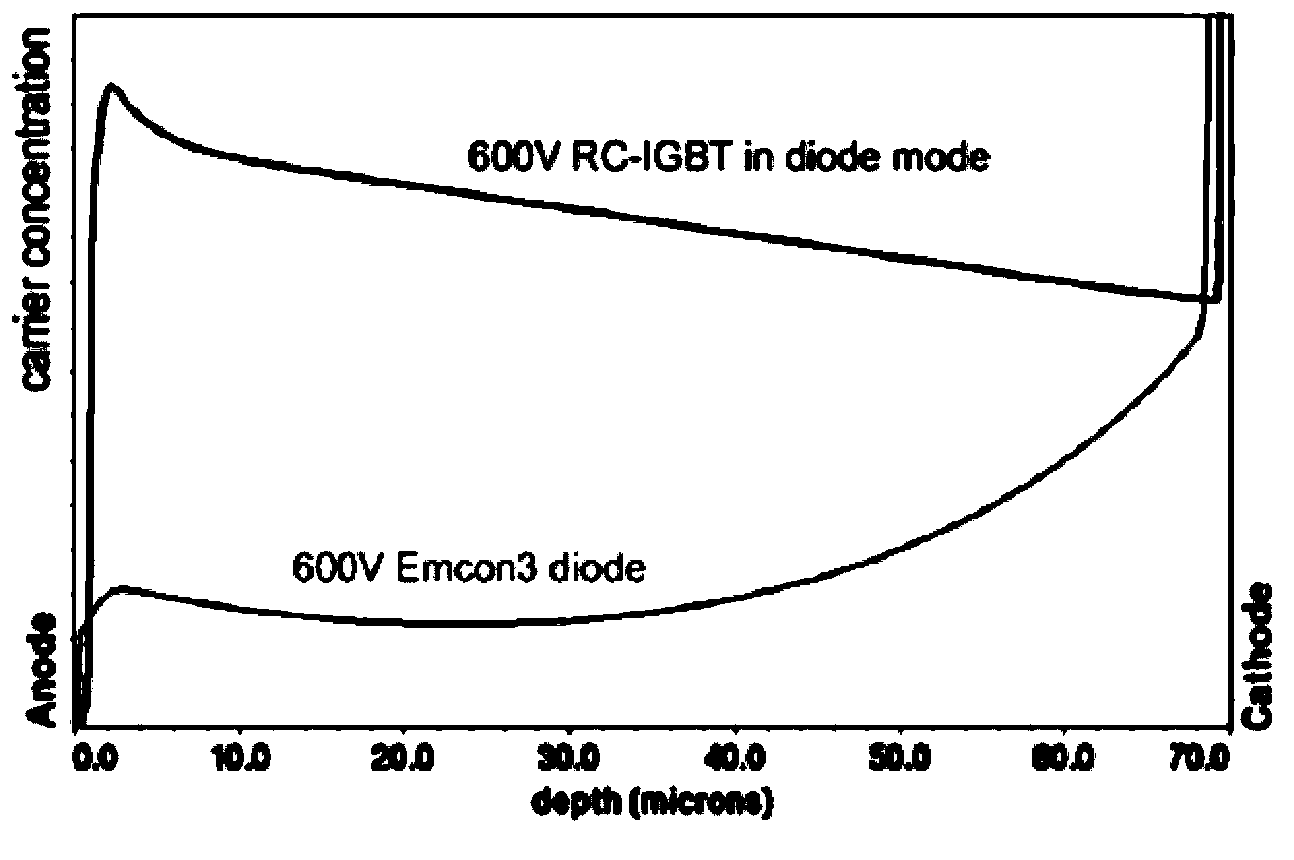

Reverse-conducting type insulated gate bipolar transistor structure and manufacturing method thereof

ActiveCN103855203AIncrease the doping concentrationNo significant increase in preparation costsSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoverySemiconductor

The invention discloses a reverse-conducting type insulated gate bipolar transistor structure and a manufacturing method of the reverse-conducting type insulated gate bipolar transistor structure, and belongs to the technical field of semiconductor power devices. The reverse-conducting type insulated gate bipolar transistor structure comprises a collector, a second P+ doped layer, an N+ doped layer, an N+ buffer layer, an N- base region, a P- substrate, a first P+ doped layer and an emitting electrode, wherein the P- substrate is arranged on the top of the N- base region, the N+ buffer layer is arranged at the bottom of the N- base region, the first P+ doped layer is arranged on the top of the P- substrate, the emitting electrode is formed on the top of the first P+ doped layer, the second P+ doped layer and the N+ doped layer are arranged on the reverse side of a reverse-conducting type insulated gate bipolar transistor, the collector is formed at the bottom of the second P+ doped layer and the bottom of the N+ doped layer, and a local area service life control area is arranged on the portion, close to the P- substrate, of the N- base region. According to the reverse-conducting type insulated gate bipolar transistor structure and the manufacturing method of the reverse-conducting type insulated gate bipolar transistor structure, the reverse recovery characteristic of the reverse-conducting type IGBT in the diode mode can be remarkably improved on the basis that the manufacturing cost of the IGBT is not remarkably increased.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +2

Diode and manufacturing method thereof

ActiveCN108735823AImproved reverse recovery characteristicsImprove compromise propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryBody region

The invention discloses a diode device and a manufacturing method thereof, and belongs to the technical field of power semiconductor devices. A cellular structure of the device comprises a metal negative electrode, an N+ substrate and an N- epitaxial layer; a trench structure is arranged on the two sides of the top layer of the epitaxial layer; the trench structure comprises a P-type semiconductorregion and a heterogeneous semiconductor from the bottom up; the top layer of the N-epitaxial layer is also provided with a P-type body region, an N+ source region and a P+ contact region; the N+ source region, the P-type body region, a part of the N- epitaxial layer and the heterogeneous semiconductor are in contact through a dielectric layer of the side wall of the trench; the surface of the device is covered with a metal positive electrode; and the heterogeneous semiconductor, the dielectric layer, the source region, the body region and the epitaxial layer form an ultra-potential barrier structure. By virtue of the diode device and the manufacturing method thereof, the problems of high forward opening voltage, poor reverse recovery capability and the like existing in the existing PIN diode device can be solved; and in addition, lower electric leakage and a larger safe working region are achieved on the premise that the withstand voltage is not affected, and the reliability of the device is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

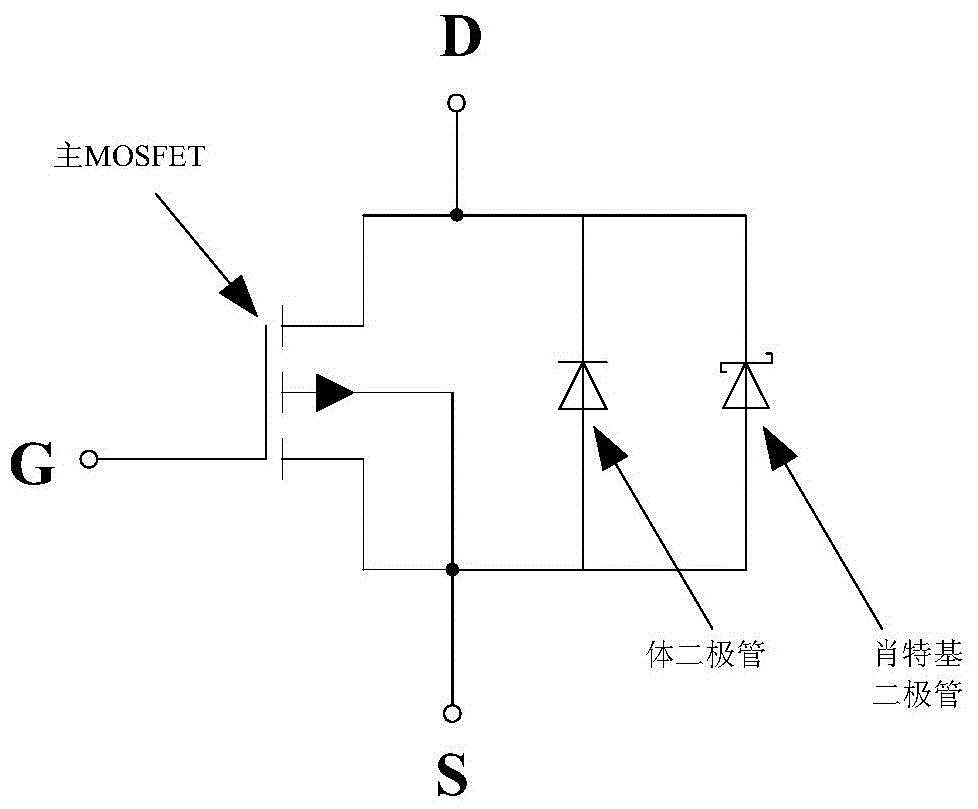

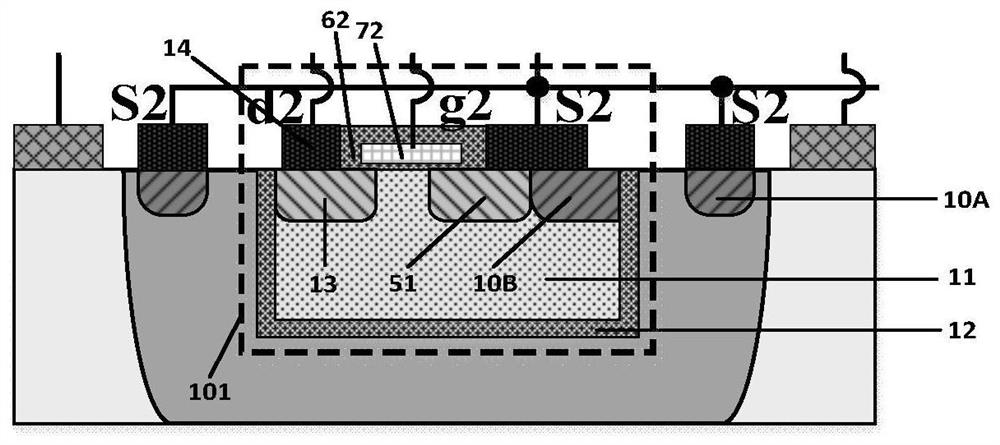

A trench-gate vdmos device with integrated schottky diode

InactiveCN103441148BReduced injection efficiencyShort storage timeDiodeContact formationReverse recovery

A trench gate VDMOS device integrating Schottky diodes belongs to the technical field of semiconductor devices. In the present invention, an additional structure composed of Schottky junction metal and body electrode conductive material is respectively added to the drift region on both sides of the groove gate structure of the conventional groove gate VDMOS device; It is in contact with the conductive material of the body electrode, and the rest of the lower surface and side parts are in contact with the drift region to form a Schottky junction; the side and bottom surfaces of the conductive material of the body electrode and the drift region are separated by a layer of dielectric layer. Compared with the traditional trench-gate VDMOS device with the same size, the present invention can adopt a higher doping concentration in the drift region under the same breakdown voltage, so the on-resistance is significantly reduced, and the reverse recovery characteristic of the diode is significantly improved. improvement.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Diode and manufacturing method thereof

ActiveCN108550630ASolve lossSolve the characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceReverse recovery

The invention discloses a diode and a manufacturing method thereof, and belongs to the technical field of power semiconductor devices. The cellular structure of the device comprises a metal cathode, an N+ substrate, an N- epitaxial layer and a metal anode, wherein groove structures are arranged on two sides of the top layer of the N- epitaxial layer, each groove structure comprises a P+ semiconductor area and a P-type semiconductor Well area from the bottom up, each P-type semiconductor Well area contacts the metal anode thereon, dielectric layers are arranged on the upper surfaces of the partof the P-type semiconductor Well area and the part of the N- semiconductor epitaxial layer; heterogeneous semiconductors are arranged on the upper surfaces of the dielectric layers and the N-semiconductor epitaxial layer; the heterogeneous semiconductors, the dielectric layers, the P-type semiconductor Well area and the N- semiconductor epitaxial layer form a super barrier structure. According tothe diode and the manufacturing method thereof provided by the invention, the traditional PIN device forward opening voltage is significantly reduced without influencing the device performance, the reverse recovery property of the device is optimized, and the good property of compromise between the forward breakover voltage drop and turn-off losses is acquired. In addition, the device provided bythe invention also provides a plurality of working modes for selection, so as to be greatly conveniently used in actual applications.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

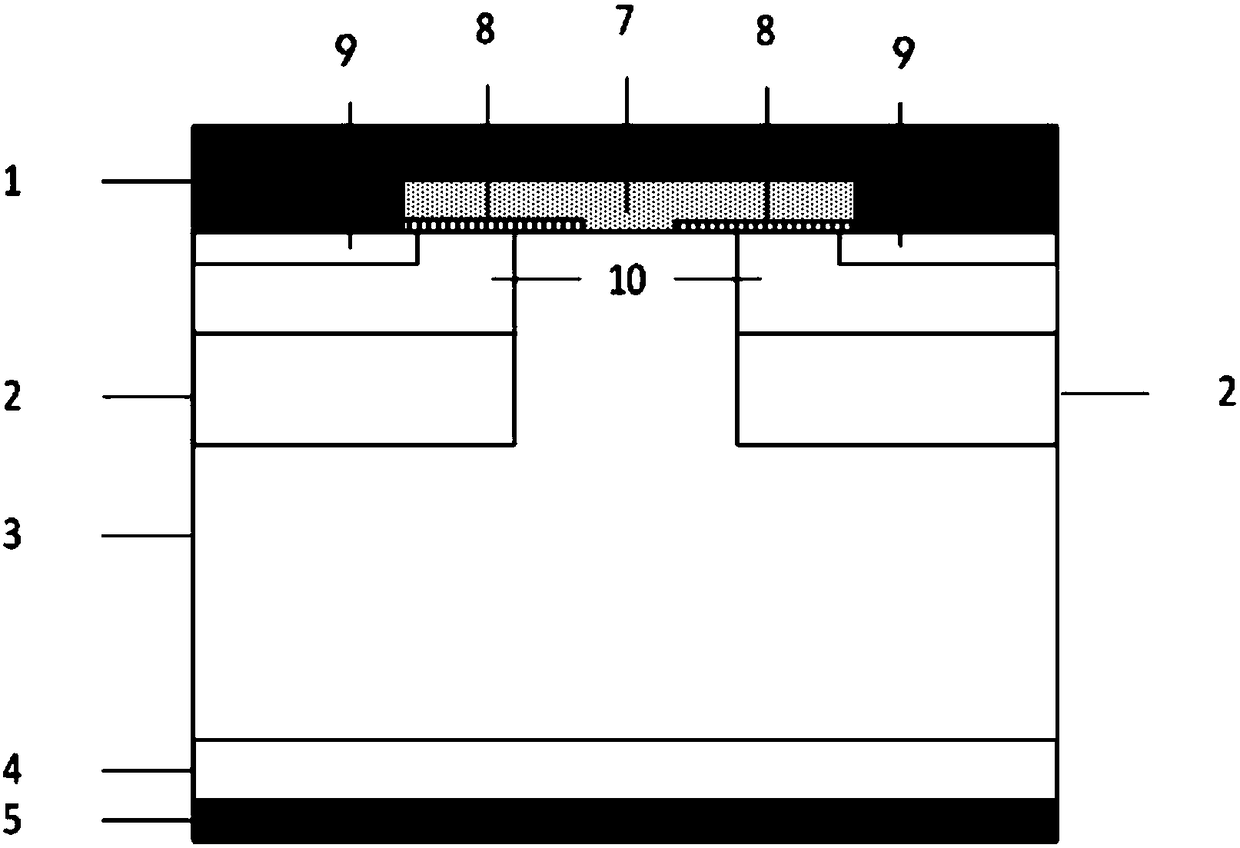

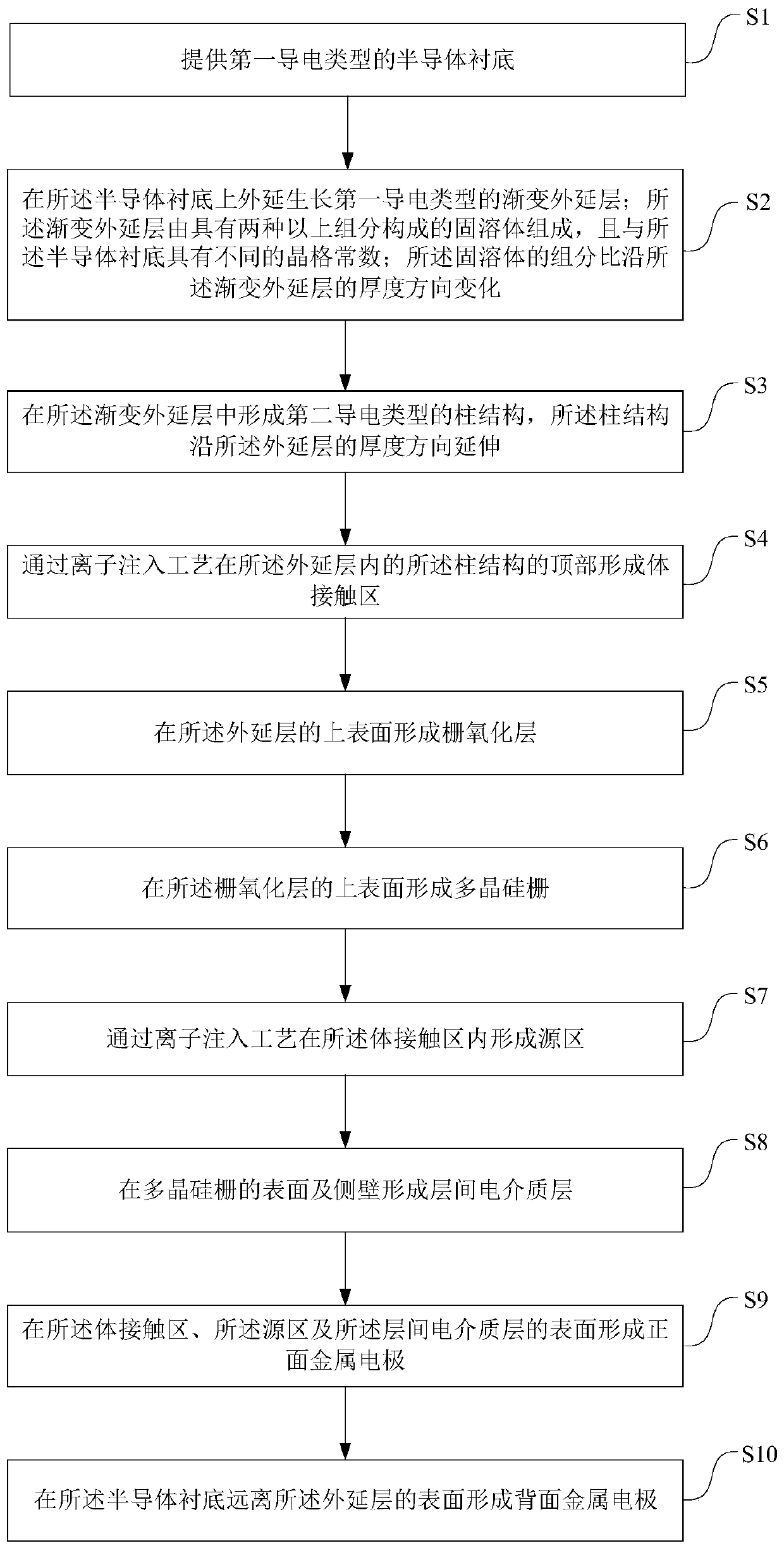

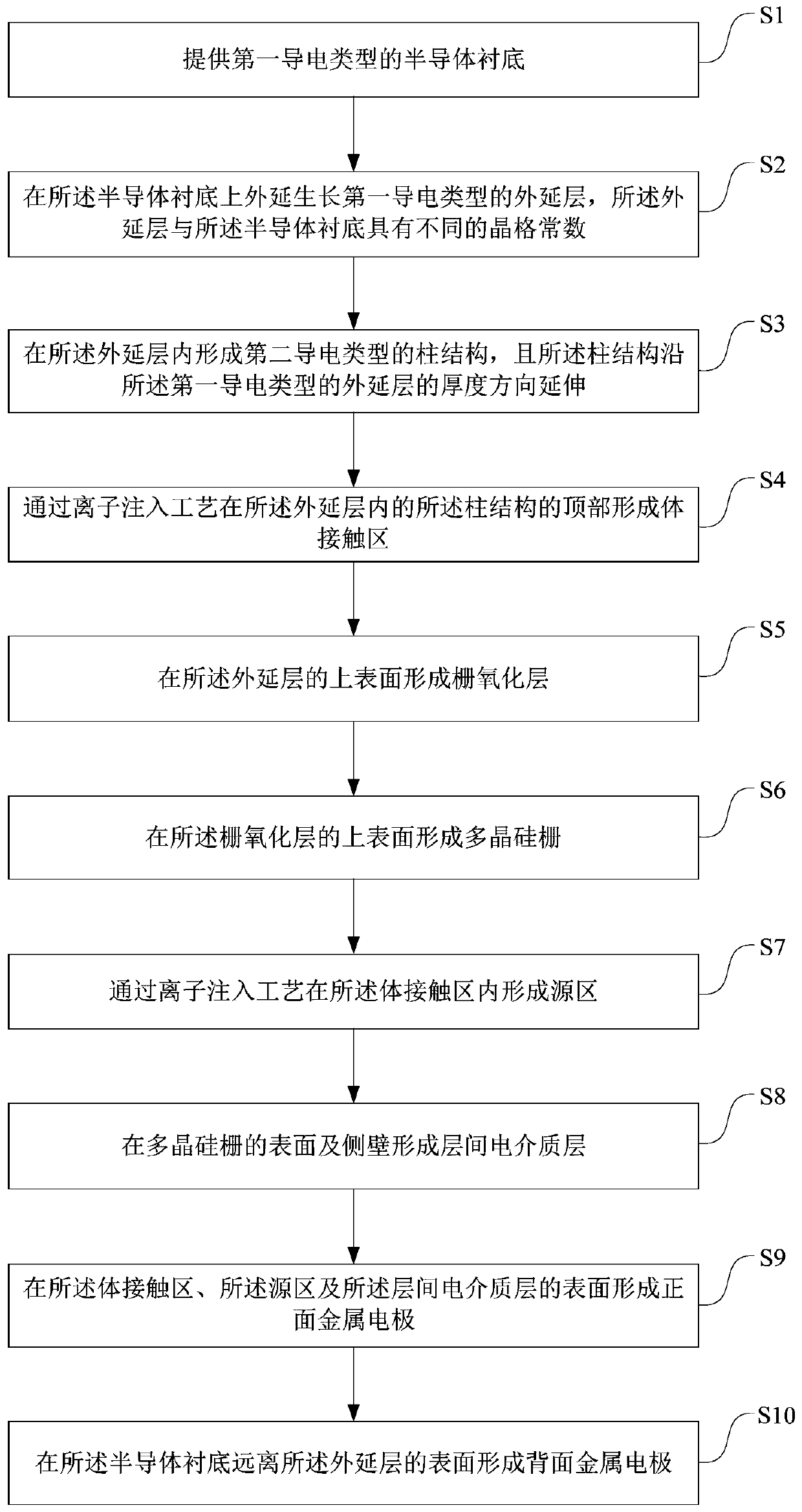

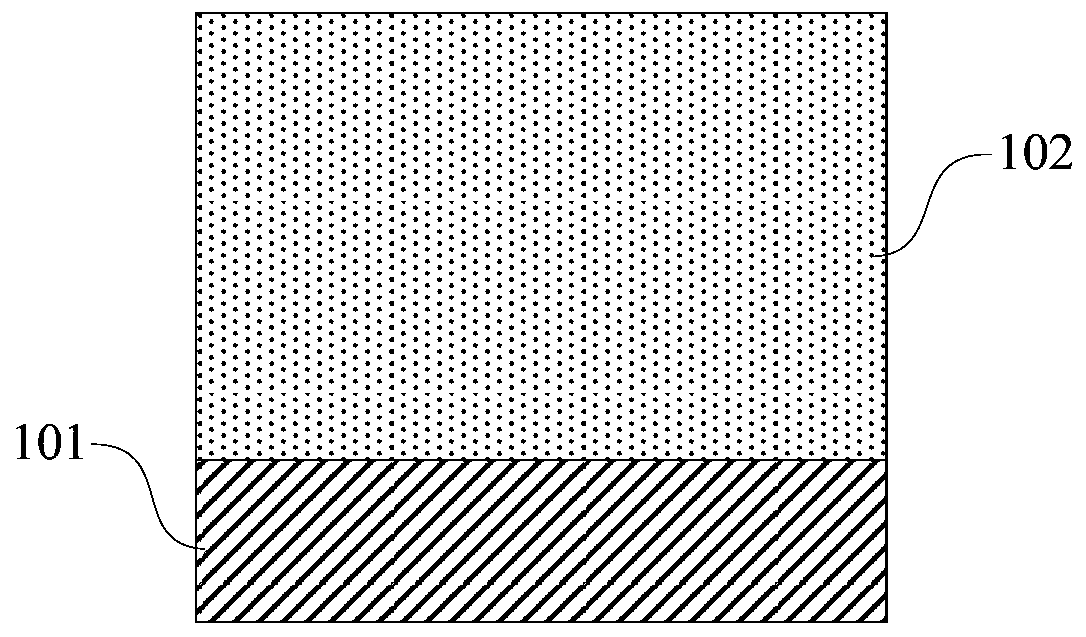

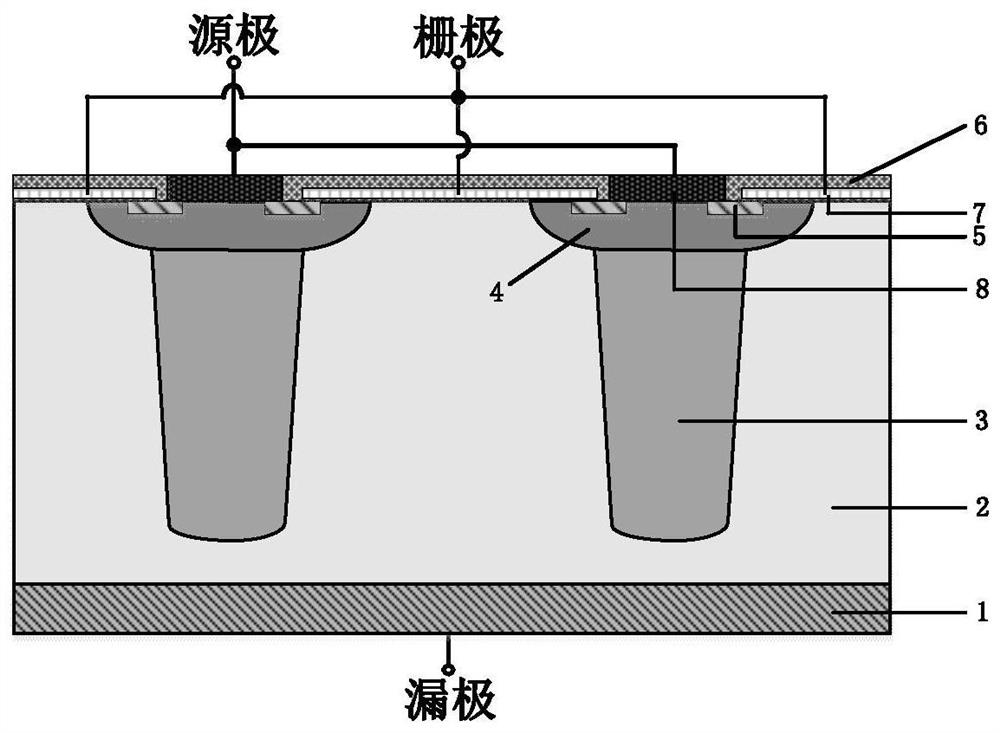

Superjunction device structure and method for fabricating same

InactiveCN110246888AImproved reverse recovery characteristicsCarrier reductionSemiconductor/solid-state device manufacturingSemiconductor devicesLattice defectsReverse recovery

The invention provides a superjunction device structure and a method for fabricating the same. The superjunction device structure comprises a first conductivity type of semiconductor substrate; a first conductivity type of graded epitaxial layer formed on the semiconductor substrate, composed of a solid solution having more than two components, and having a different lattice constant from the semiconductor substrate, wherein the component ratio of the solid solution varies in the thickness direction of the graded epitaxial layer; and a second conductivity type of pillar structure formed in the graded epitaxial layer and extending in the thickness direction of the epitaxial layer. The lattice defect is uniformly controllable in the thickness direction of the epitaxial layer by growing the graded epitaxial layer in which the solid solution components vary in the thickness direction and which has a different lattice constant from the semiconductor substrate. The reverse recovery characteristic of a device is optimized to realize a purpose of rapidly reducing carriers during the turn-off phase of the device. The superjunction device structure is simple in process, low in cost, and suitable for mass production.

Owner:上海功成半导体科技有限公司

Superjunction device structure and preparation method thereof

InactiveCN110212030AIncrease chance of compoundingShort lifeSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryCharge carrier

The invention provides a superjunction device structure and a preparation method thereof. The superjunction device structure comprises a first conducting type semiconductor substrate; a first conducting type epitaxial layer arranged on the upper surface of the semiconductor substrate, wherein the epitaxial layer and the semiconductor substrate have different lattice constants; and a second conducting type column structure, which is arranged in the epitaxial layer and extends in the thickness direction of the epitaxial layer. By growing the epitaxial layer with different lattice constants fromthe semiconductor substrates, and introducing uniform controllable defects, probability of carrier recombination is increased and carrier life is reduced to optimize the reverse recovery characteristic of the superjunction power device and realize the purpose of rapid reduction of carriers at the turn-off stage of the device; and the preparation method is simple in preparation process, low in costand suitable for large-scale manufacture.

Owner:上海功成半导体科技有限公司

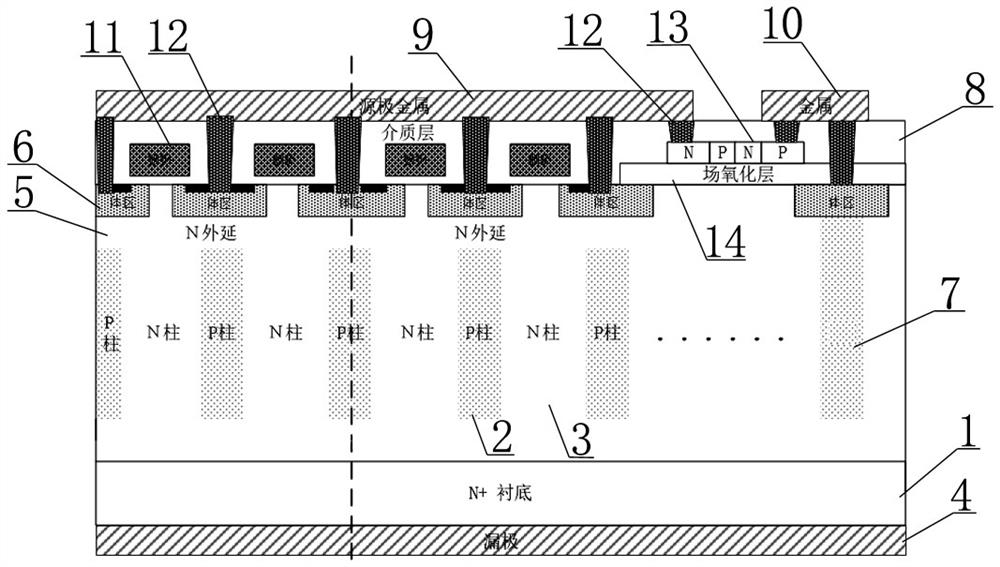

An extremely low reverse recovery charge superjunction power vdmos

ActiveCN109830524BImprove reverse recovery characteristicsReduce the total hole chargeSolid-state devicesSemiconductor devicesReverse recoverySchottky diode

The present invention relates to a super-junction power VDMOS having an extremely low reverse recovery charge, comprising an N-type substrate also serving as a drain and an N-type drift region. A first P column is provided in the N-type drift region; a first P-type body region is provided in the top of the first P column; an NMOS is provided in the first P-type body region; a SiO2 isolation layer is provided between the NMOS and the first P-type body region; and a first P-type heavily doped region is provided in the first P-type body region. Source metal of a super-junction VDMOS, source metal of the NMOS, and the first P-type heavily doped region are connected; the drain of the super-junction VDMOS serves as the drain of the super-junction power VDMOS; the gate of the super-junction VDMOS and the gate of the NMOS are connected and serve as the gate of the super-junction power VDMOS; the drain of the NMOS serves as the source of the super-junction power VDMOS; and an N-type drift region of the super-junction VDMOS is provided with a Schottky contact which is connected to the drain of the NMOS, so as to form a Schottky diode of which the cathode and anode are respectively connected to the drain and source in the structure provided by the present invention.

Owner:SOUTHEAST UNIV

Superjunction device and method of manufacturing the same

ActiveCN108110039BImprove softness factorImproved output capacitor characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceReverse recovery

The invention discloses a super-junction device. At least one of an N type column and a P type column in each super-junction unit is of a vertical three-section structure having doping concentrations;the vertical three-section structure includes a bottom section, a middle section, and a top section along a vertical direction; the doping concentration of the middle section is lower than the dopingconcentration of the bottom section; the doping concentration of the middle section is lower than the doping concentration of the top section; after the column of the vertical three-section structureis depleted, impurity ions of the middle section, the bottom section, and the top section form an electric field trap in the middle section; and the electric field trap enhances the difficulty of being extracted of residual minority carries, and therefore, the softness factor of the reverse recovery of the device can be increased. The invention also discloses a manufacturing method of the super-junction device. With the manufacturing method of the invention adopted, the reverse recovery characteristic of the body diode of the device and the output capacitance characteristic of the device canbe significantly improved, the breakdown voltage of the device can be increased, and the output capacitance characteristic of the device can be adjusted.

Owner:SHENZHEN SANRISE TECH CO LTD

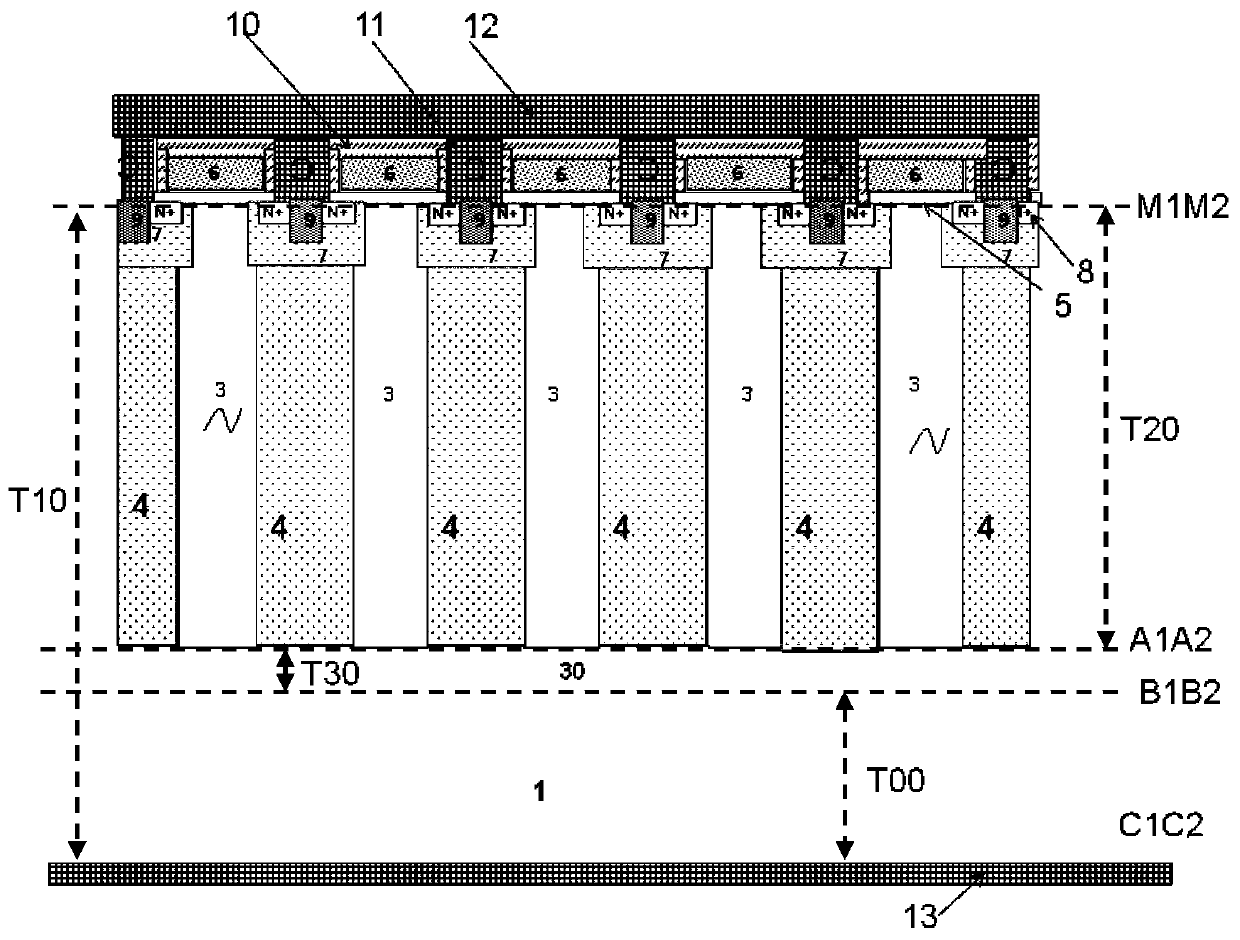

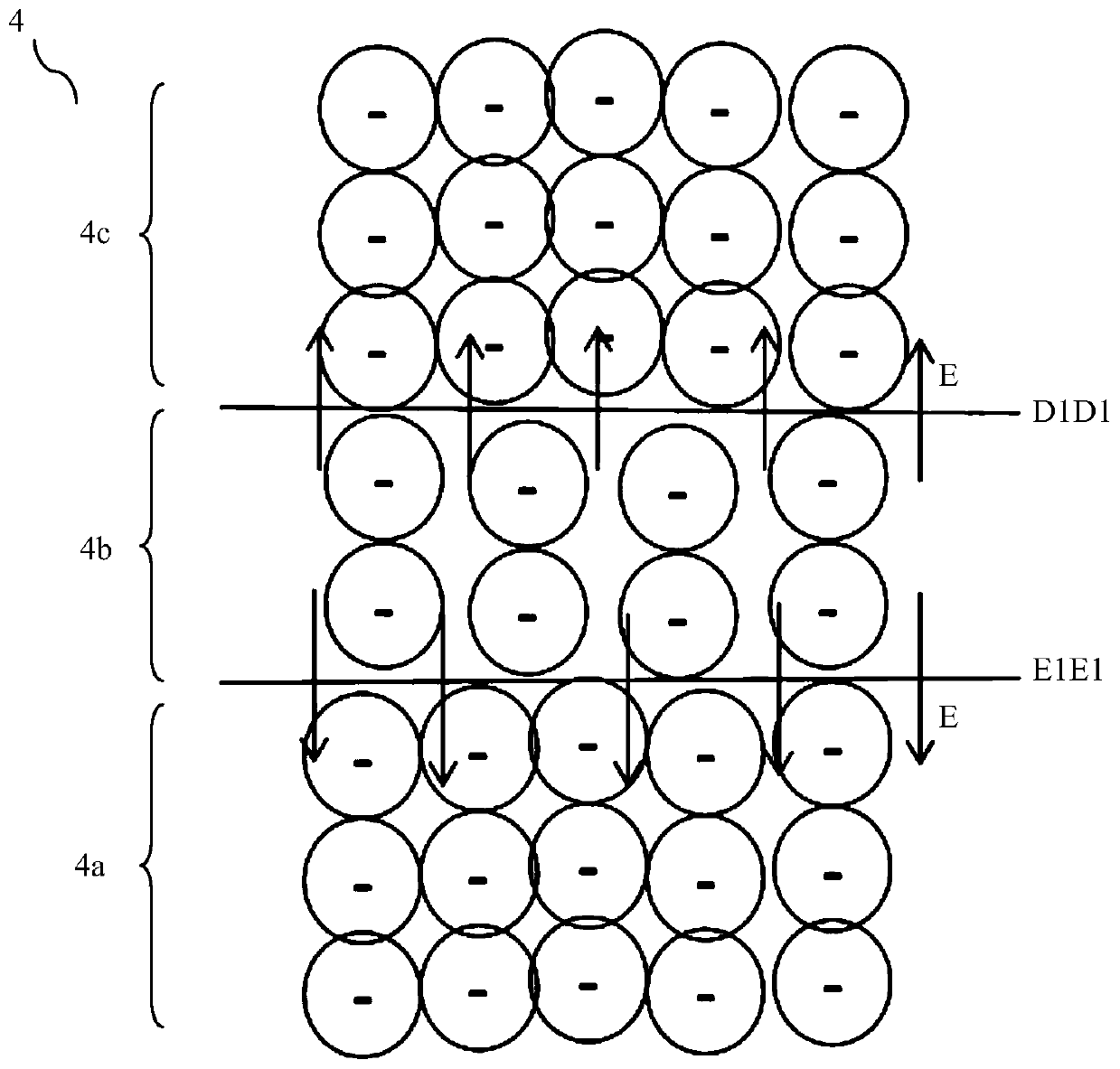

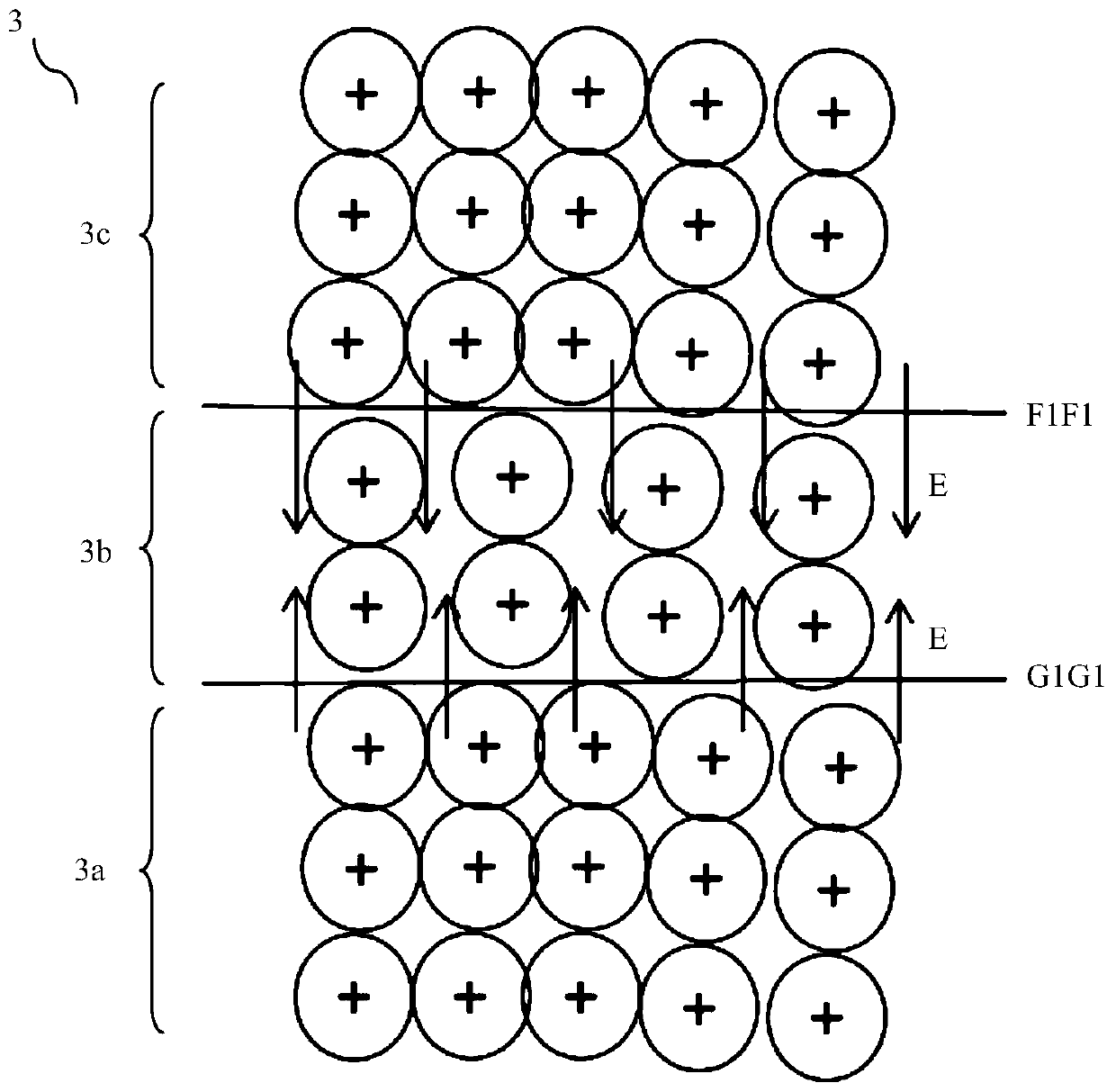

Fast recovery metal oxide semiconductor diode with low power consumption

ActiveCN101976687BImproved reverse recovery characteristicsImprove breakdown voltageSemiconductor devicesSemiconductor structureJFET

A fast recovery metal oxide semiconductor diode with low power consumption belongs to the technical field of semiconductor devices. The diode is provided with a junction field effect transistor region (4) and an electron accumulation layer structure (12), wherein the junction field effect transistor region (4) comprises two deep P regions (5) and an N-epitaxial layer (3) between the two deep P regions; and the electron accumulation layer structure (12) comprises two N heavily doped regions (7), the N-epitaxial layer (3), a gate oxide layer (8) on the surface of the N-epitaxial layer (3) and agate electrode (9). By utilizing the following surface electric field effect of the metal oxide semiconductor structure: a plurality of sub-accumulation layers are formed in case of forward voltage while a plurality of sub-depletion layers are formed in case of backward voltage, the diode can obtain quite low turn-on voltage drop and can simultaneously bear high reverse breakdown voltage and leakless current, thus better realizing compromise between the forward turn-on voltage drop and the backward recovery time.

Owner:GUIZHOU YAGUANG ELECTRONICS TECH

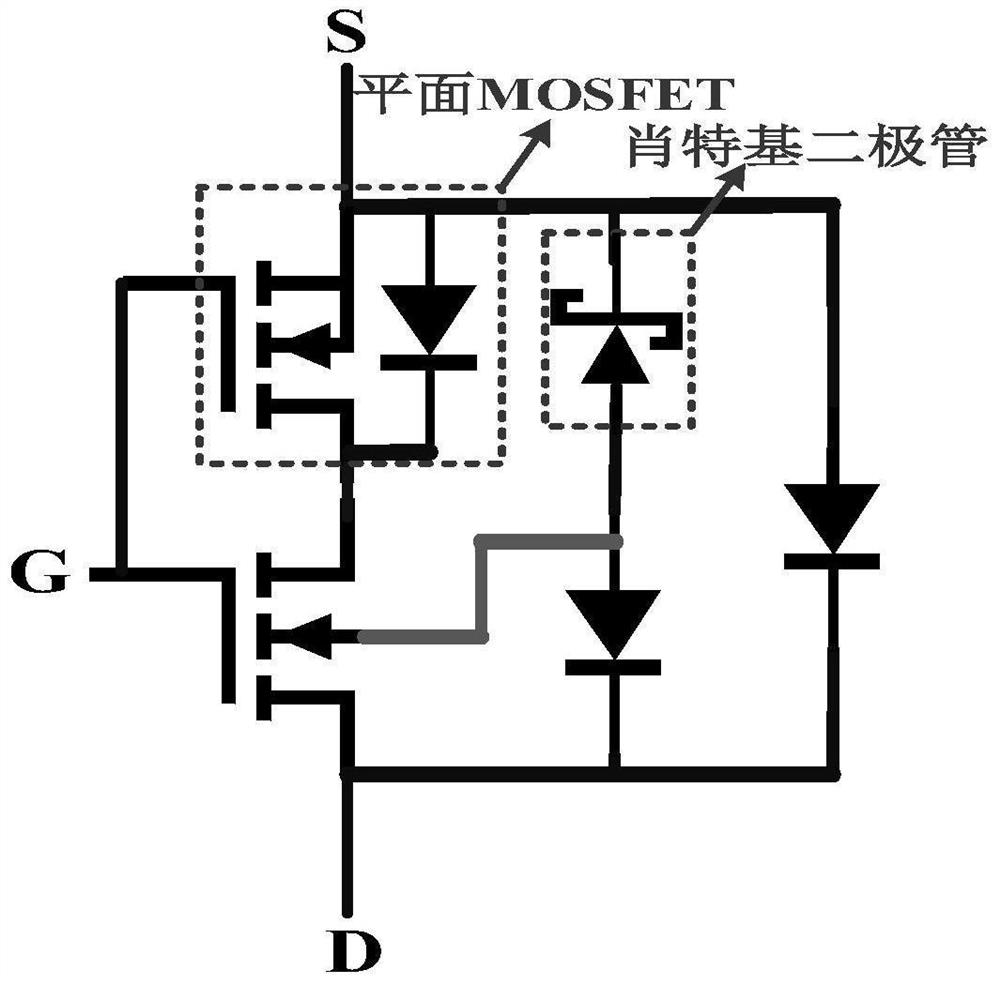

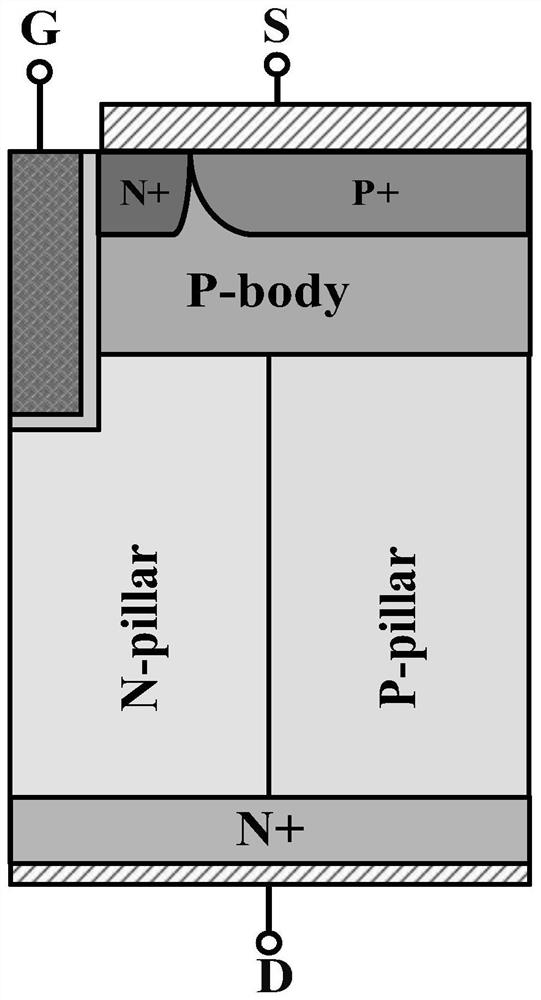

A Superjunction MOSFET with Improved Reverse Recovery Characteristics

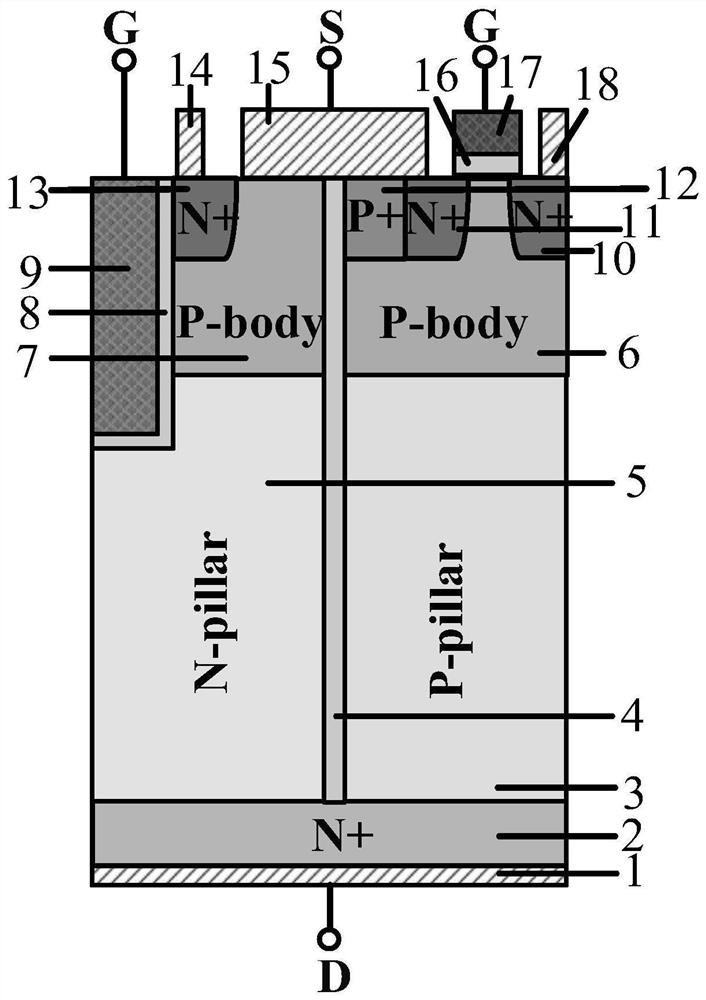

The invention relates to power semiconductor technology, and relates to a super junction MOSFET with improved reverse recovery characteristics. Compared with the traditional MOSFET, the present invention introduces an insulating medium between the P-type drift region and the N-type drift region, and at the same time separates the P-type well region into the first P-type well region located on the N-type drift region and the first P-type well region located on the P-type drift region. Two parts on the second P-type well region. The first P-type well region forms a Schottky contact with the source metal. A planar N-type MOSFET is introduced in the second P-type well region, and the N+ source region of the device is connected to the drain of the planar N-type MOSFET through a floating metal. The source of the N-type MOSFET is used as the source of the device of the present invention, and its gate is connected with the gate of the device of the present invention. When the device conducts in reverse, since the Schottky diode is in a reverse bias state, the body diode on the side of the N-type drift region connected to it does not conduct, and only the body diode on the side of the P-type drift region conducts, so when the reverse conduction The charge stored in the drift region is reduced. The invention improves the reverse recovery characteristic of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Super-junction MOSFET device with improved reverse recovery characteristic

PendingCN113611749ABreakdown voltage is not affectedReduce emission efficiencyDiodeMOSFETReverse recovery

The invention discloses a super-junction MOSFET device with an improved reverse recovery characteristic, which comprises an N + substrate layer and a plurality of P columns and N columns which are alternately arranged on the N + substrate layer. A drain electrode is arranged at the bottom of the N + substrate layer; the top of the P column and the top of the N column are provided with an N epitaxial layer, the N epitaxial layer is provided with P-type body regions corresponding to the P columns in position and number, the P columns in a partial region in the super-junction MOSFET device body extend upwards to form epitaxial P columns, and the epitaxial P columns penetrate through the N epitaxial layer and are connected with the P-type body regions at the corresponding positions so as to maintain the same potential; and a dielectric layer is arranged at the tops of the P-type body regions, a source metal layer and a first metal layer which respectively correspond to the positions of the P columns and the epitaxial P columns are arranged at the top of the dielectric layer, a plurality of connecting holes are formed in the dielectric layer, and at least one diode is connected in series between the epitaxial P column and the source metal layer of the primitive cell in a forward direction or a reverse direction.

Owner:SHANGHAI DAOZHI TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com