Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

7795results about "Pulse shaping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

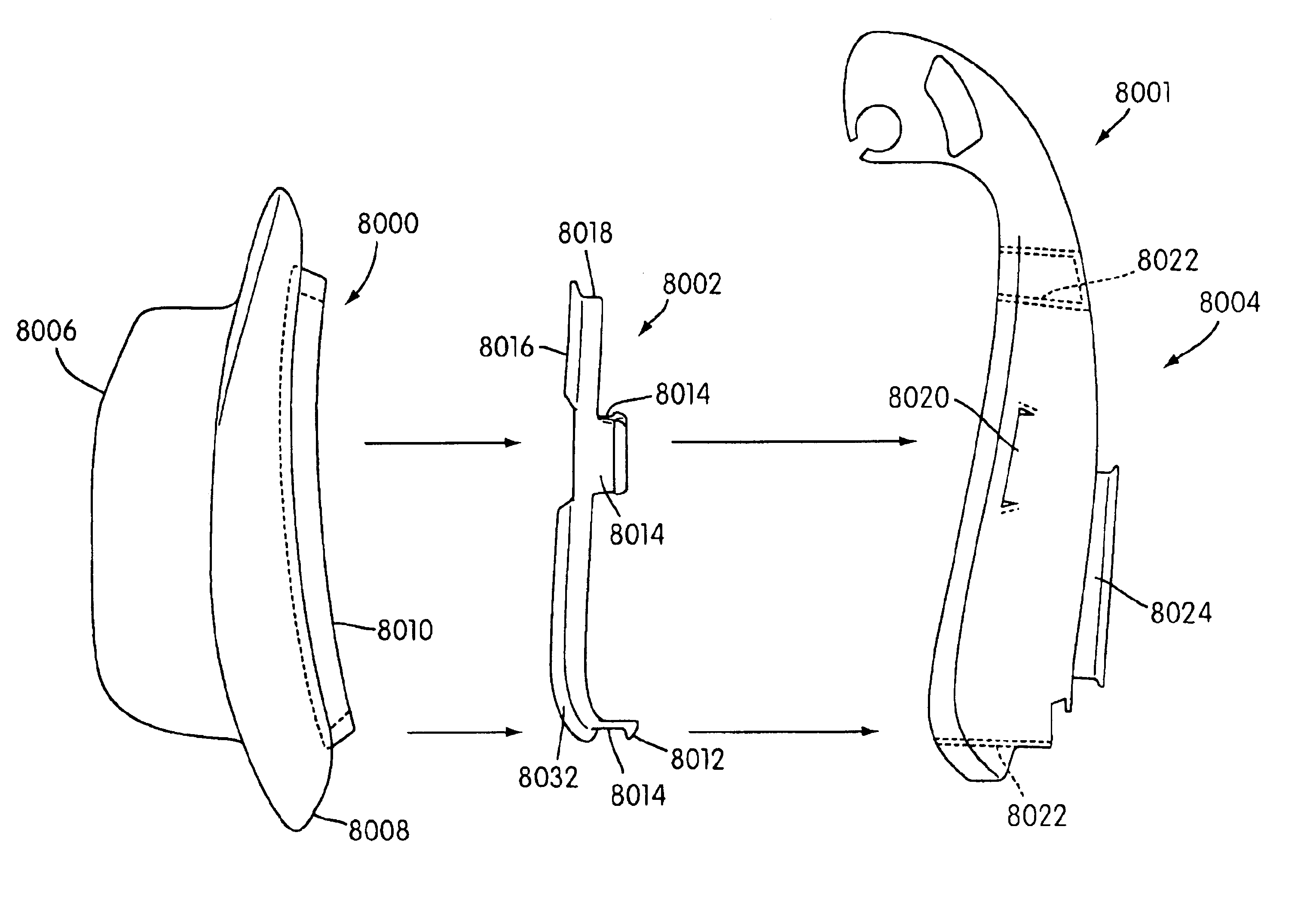

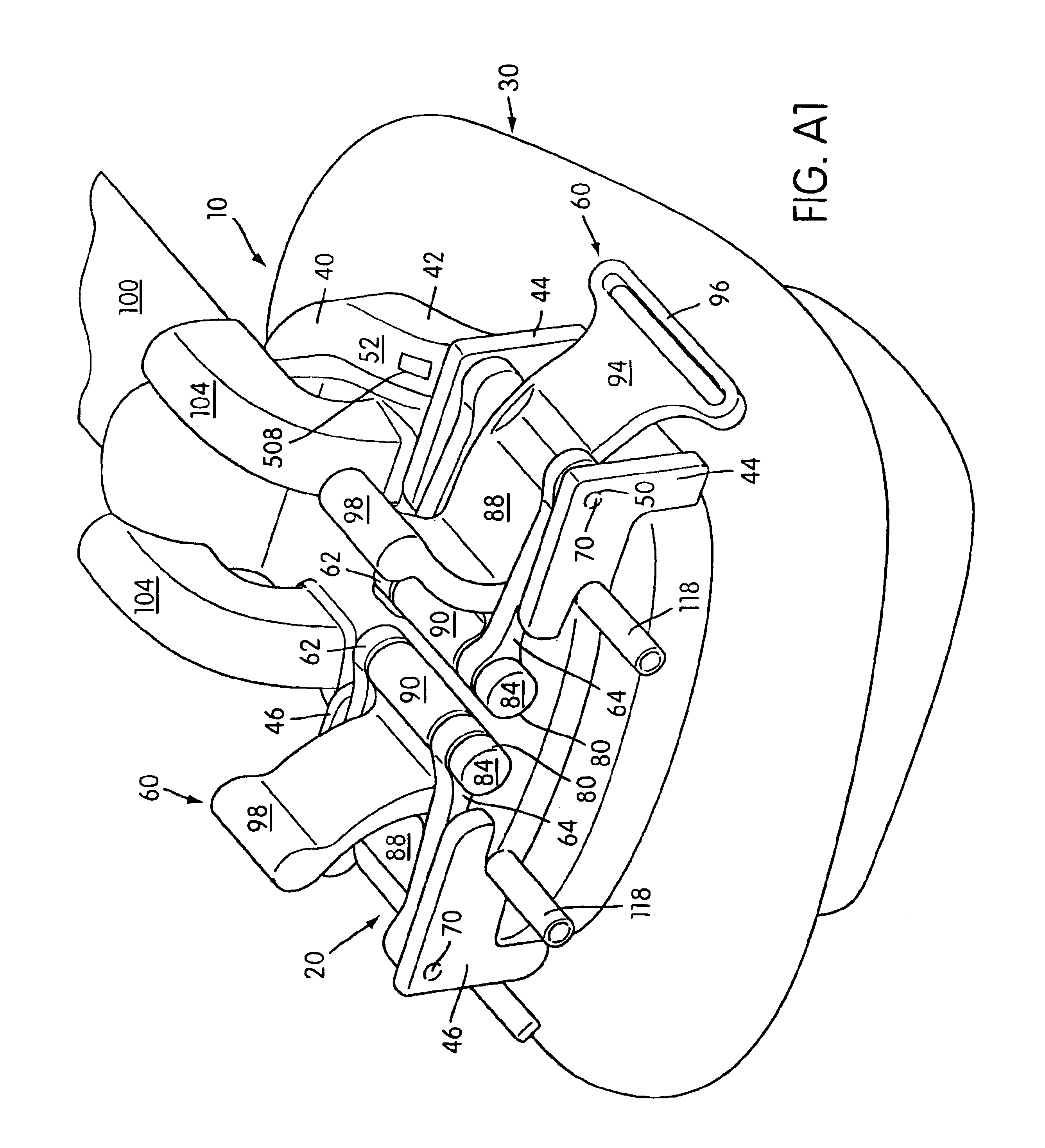

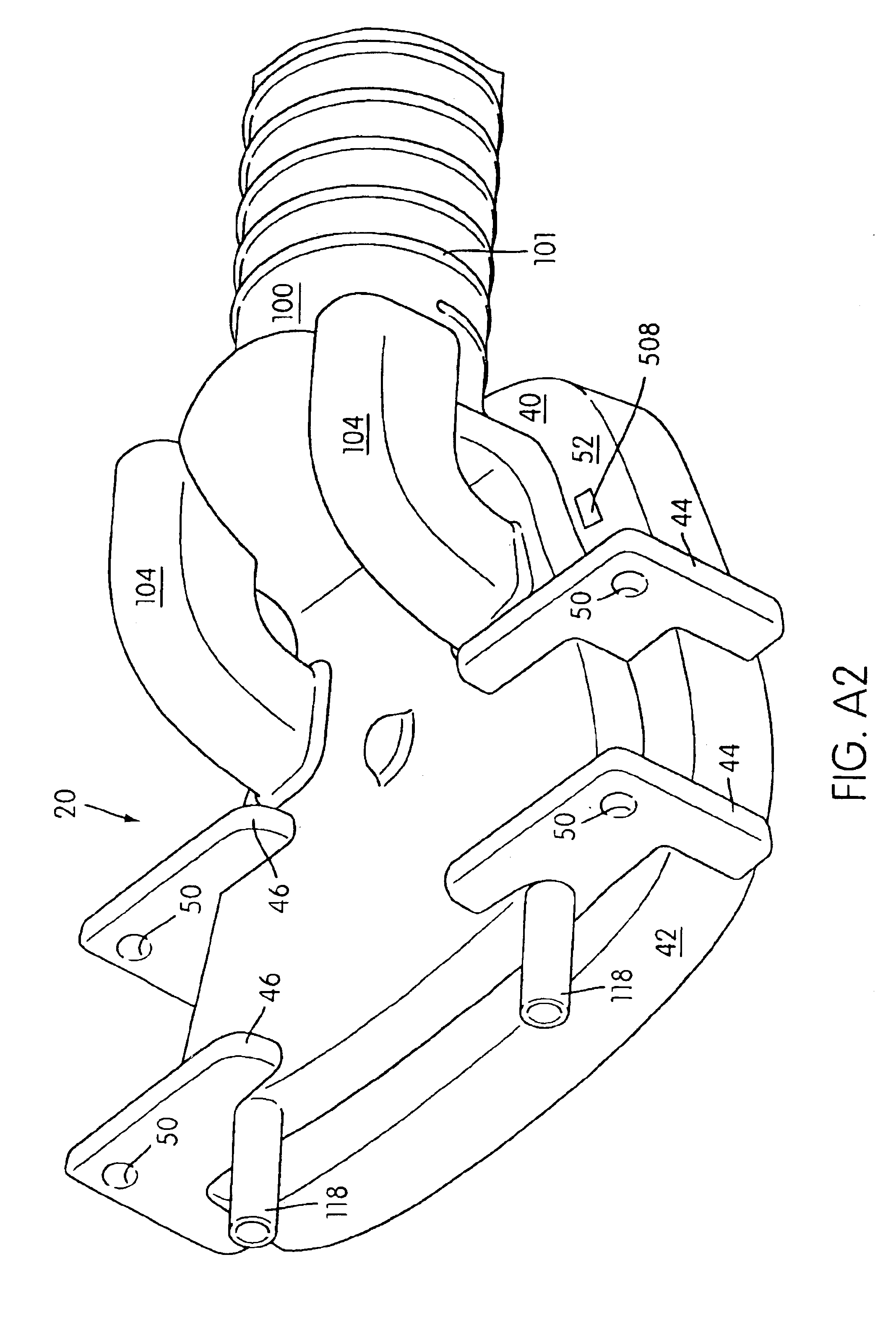

Mask assembly

A respiratory mask assembly for use in the delivery of non-invasive positive airway pressure to a user. The assembly includes a rigid shell having a channel portion defined by an inner wall, an outer wall and a channel floor, a face-contacting cushion acting to space the shell away from the user's face and a sealing tab extending from the cushion to engage a portion of the shell to provide a continuous airtight seal between the cushion and the shell. A retaining ring within the mask assembly is configured to secure the cushion to the shell. The retaining ring has a first portion including at least one clip configured to pass through at least one slot portion such that an underside surface of the at least one clip engages a section of the shell when the retaining ring is positioned within the channel.

Owner:RESMED LTD

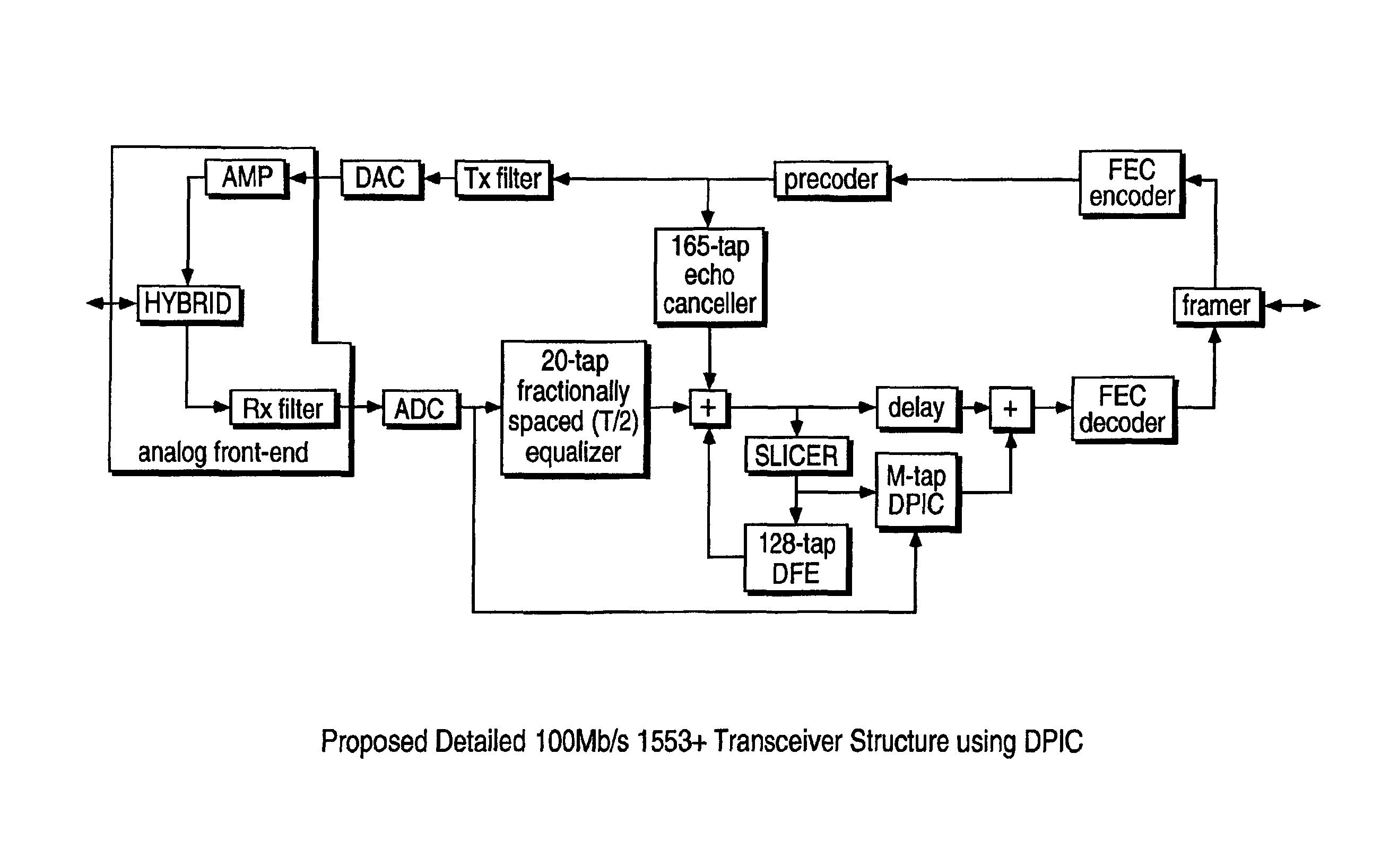

Channel equalization system and method

InactiveUS6904110B2Increase high performance and data rate capacityLow costMultiple-port networksChannel dividing arrangementsFiberEngineering

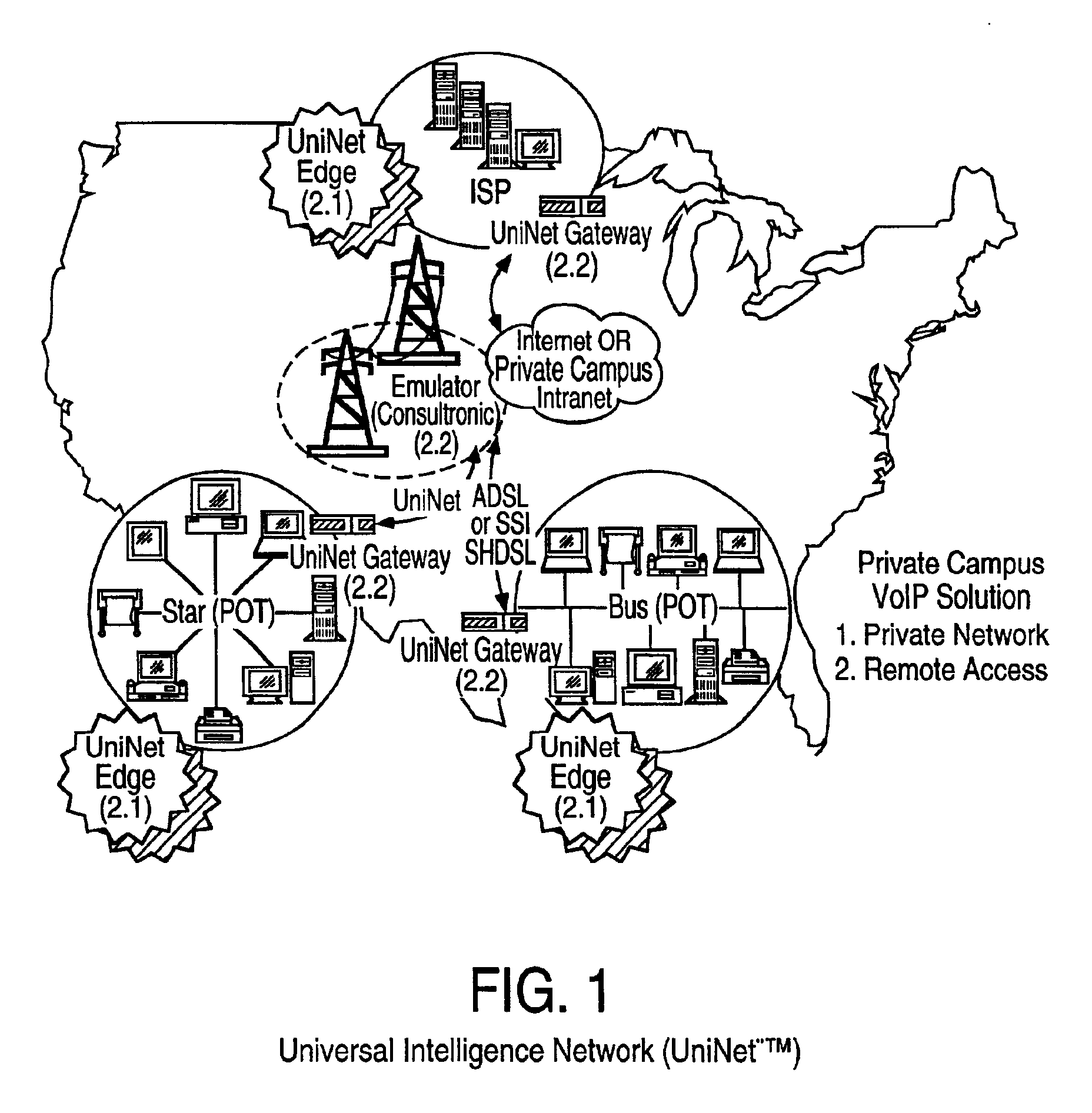

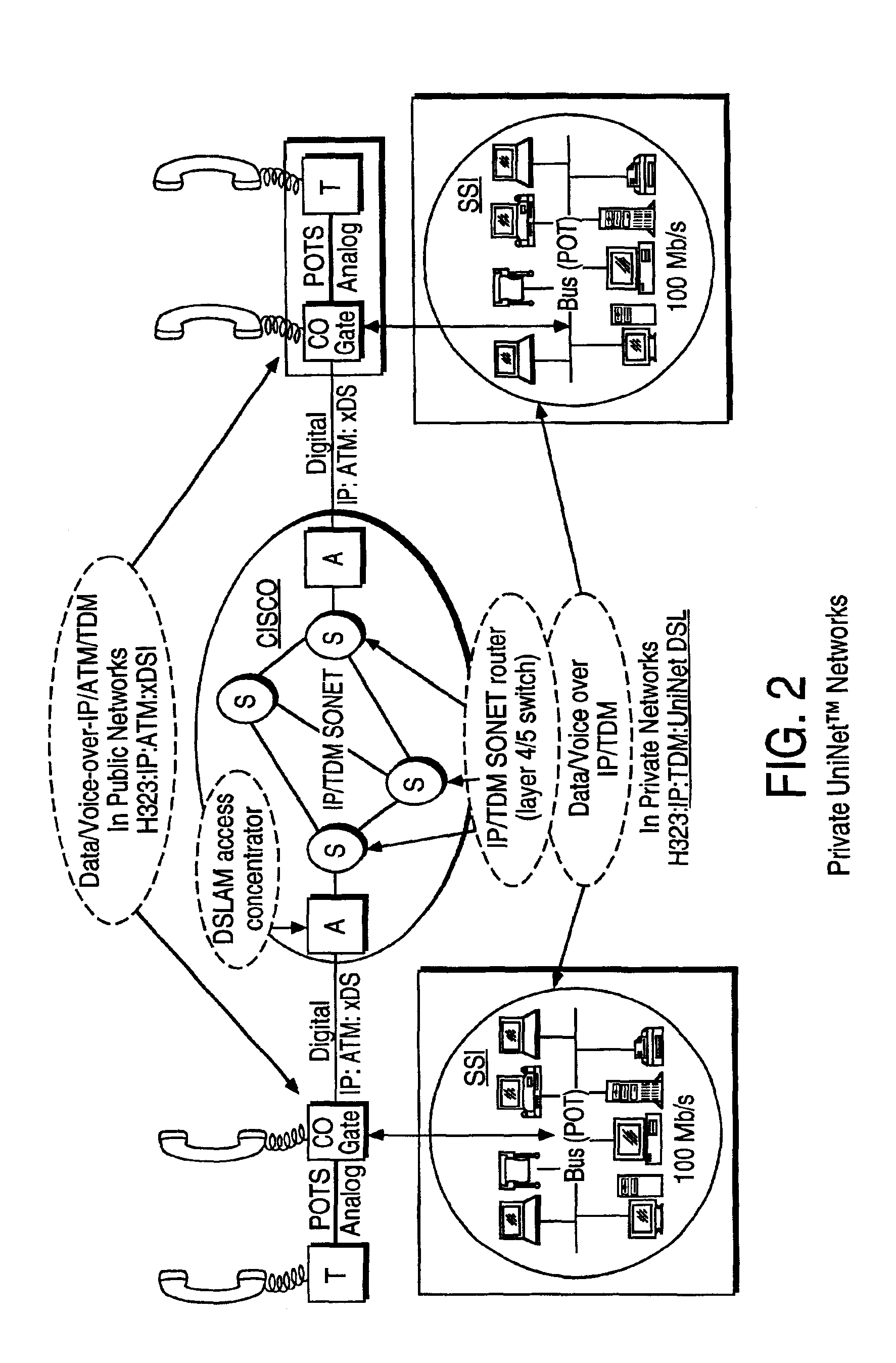

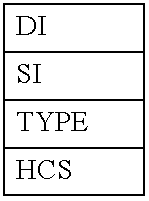

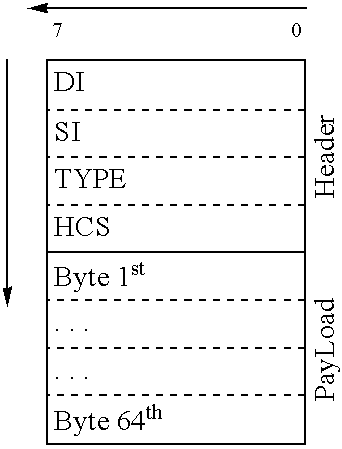

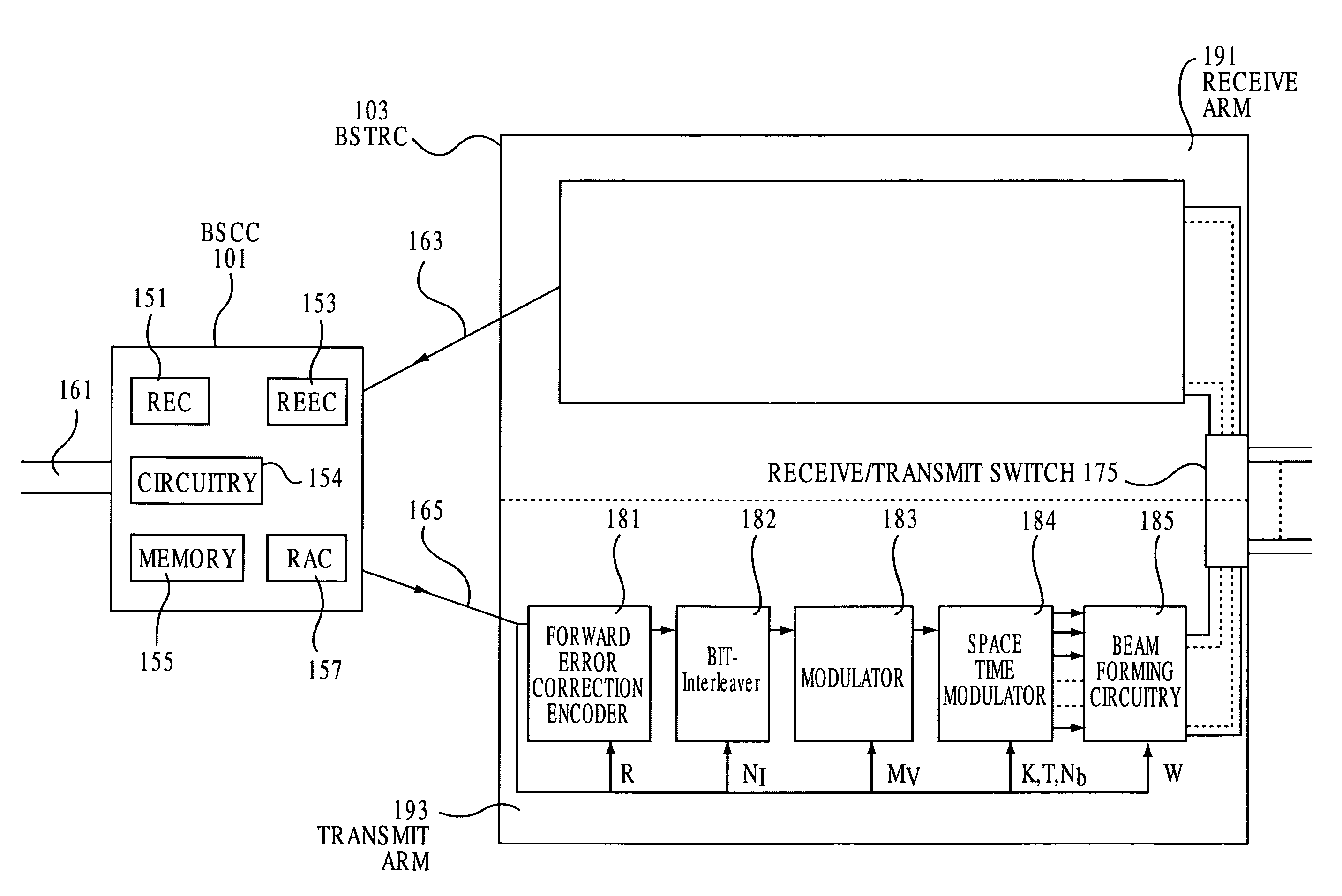

A system and method for delivering increases speed, security, and intelligence to wireline and wireless systems. The present invention increases channel capacity by using a parallel or multi-channel structure in such wireless and wireline at the edge or the core of. This new architecture of the present invention uses parallel bitstreams in a flexible way and distributed switching / routing technique, is not only to avoid the potential bottlenet of centralized switches, but also to increase speed with intelligence that is seamlessly integrating into the Fiber Optic Backbone such as WDM and SONET of the MAN / WAN network with a Real-time guarantees, different types of traffic (such as Stringent synchronous, isochronous, and asynchronous data messages) with different demands, and privacy & security of multi access and integrated services environment.

Owner:B C LEOW

Channel adaptive equalization precoding system and method

InactiveUS20030086515A1Increase high performance and data rate capacityLow costChannel dividing arrangementsError detection/prevention using signal quality detectorPrecodingOperational system

A system and method for delivering increased speed, security, and intelligence to wireline and wireless systems. The present invention includes a new generation Fast Circuit Switch (packet / circuit) Communication processors and platform which enables a new Internet Exchange Networking Processor Architecture at the edge and core of every communication system, for next generation Web Operating System or Environment (WOE) to operate on with emphasis of a non-local processor or networking processor with remote web computing capabilities.

Owner:TRANS FRANCOIS +1

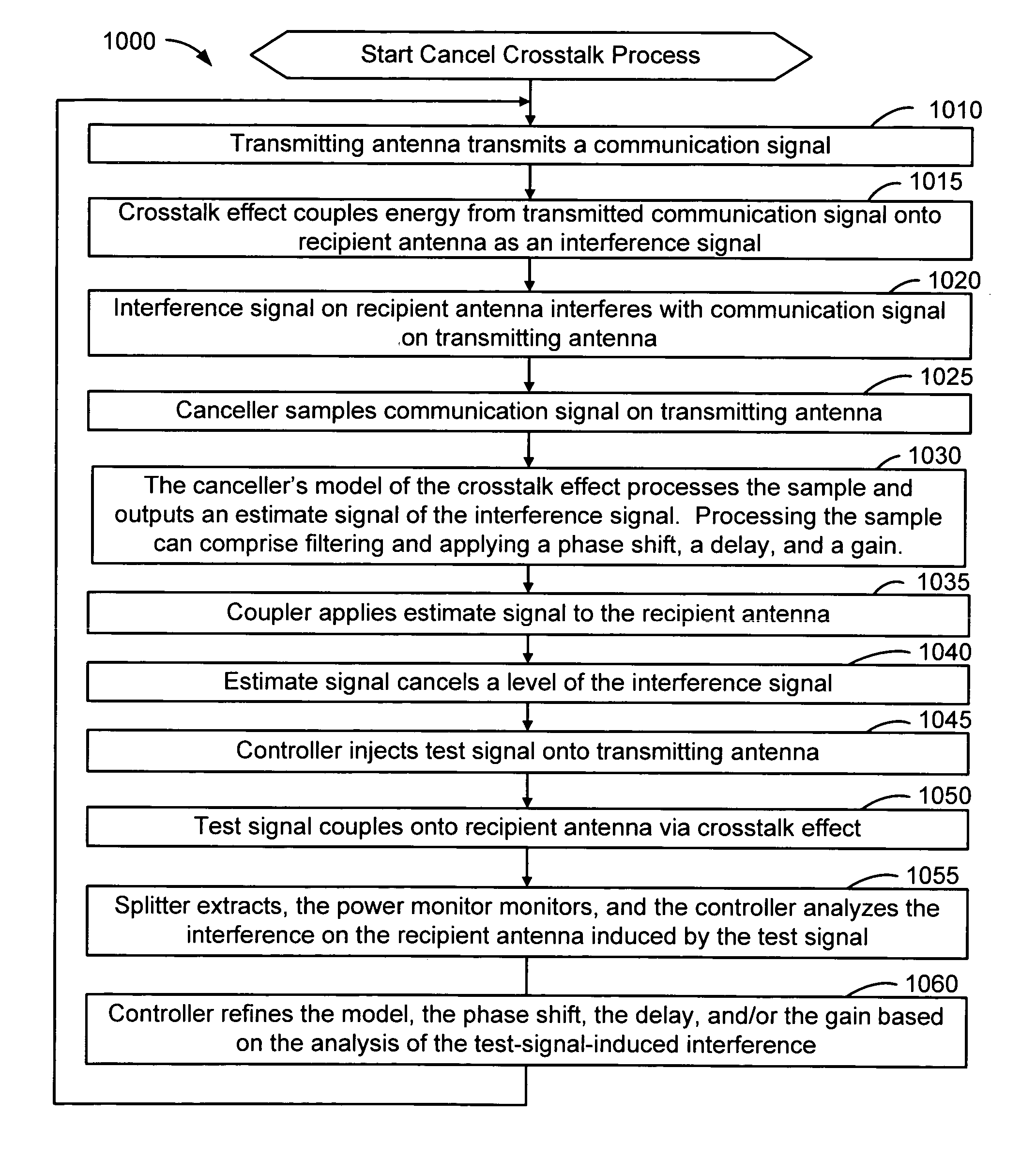

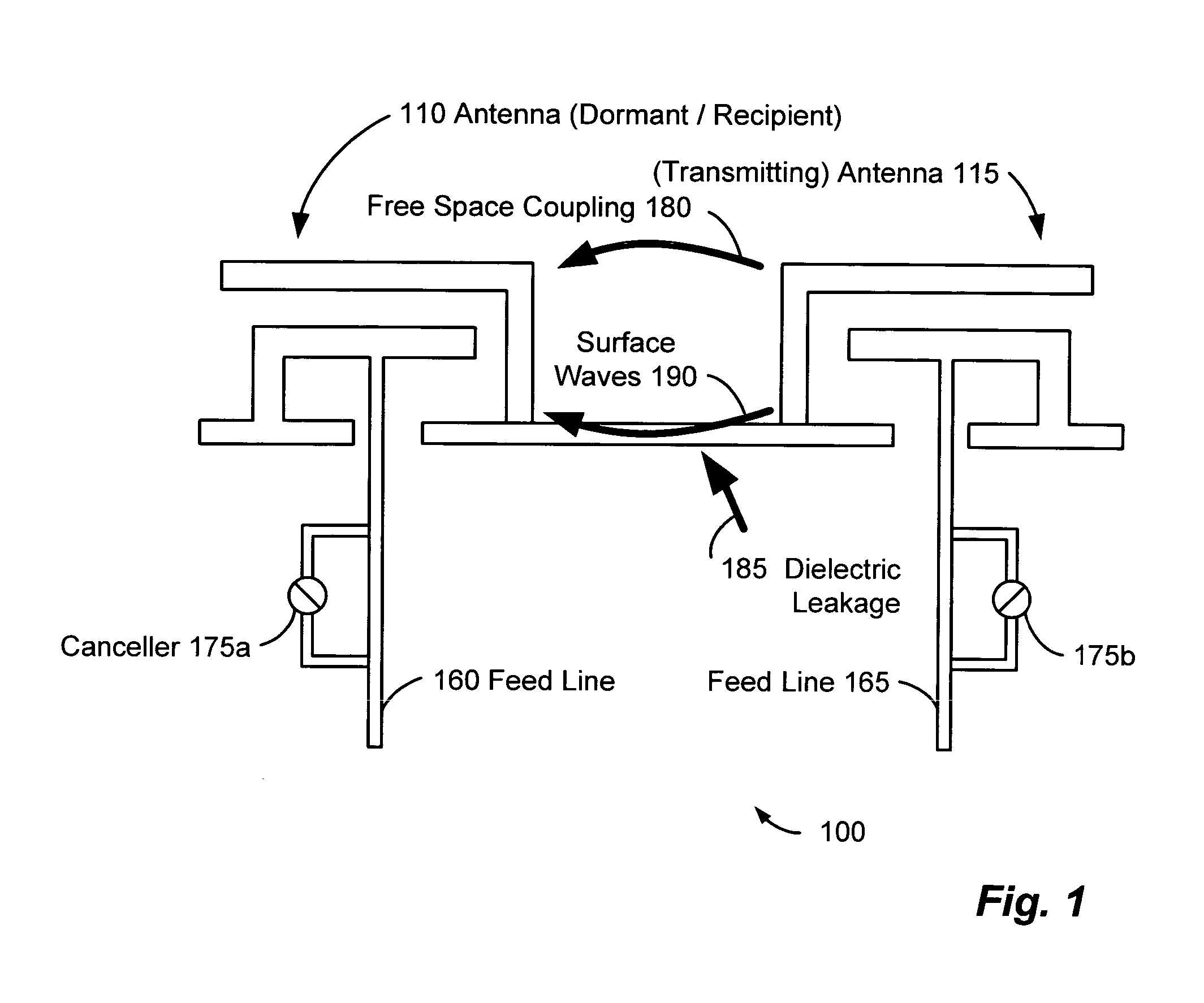

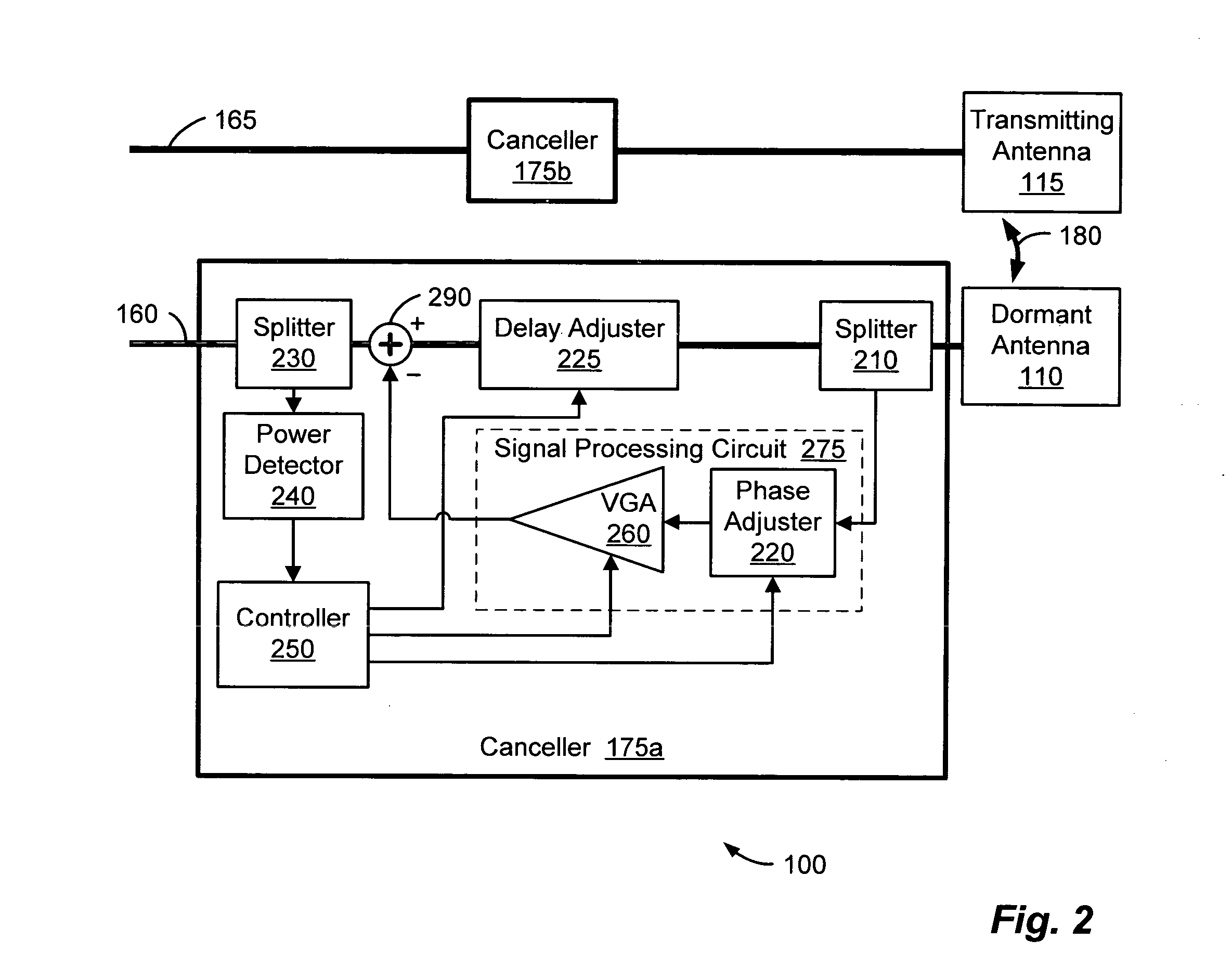

Method and system for antenna interference cancellation

InactiveUS20050226353A1Improve signal qualityHigh bandwidthCorrect operation testingLine-faulsts/interference reductionCommunications systemSignal on

A wireless communication system can comprise two or more antennas that interfere with one another via free space coupling, surface wave crosstalk, dielectric leakage, or other interference effect. The interference effect can produce an interference signal on one of the antennas. A cancellation device can suppress antenna interference by generating an estimate of the interference signal and subtracting the estimate from the interference signal. The cancellation device can generate the estimate based on sampling signals on an antenna that generates the interference or on an antenna that receives the interference. The cancellation device can comprise a model of the crosstalk effect. Transmitting test signals on the communication system can define or refine the model.

Owner:INTERSIL INC

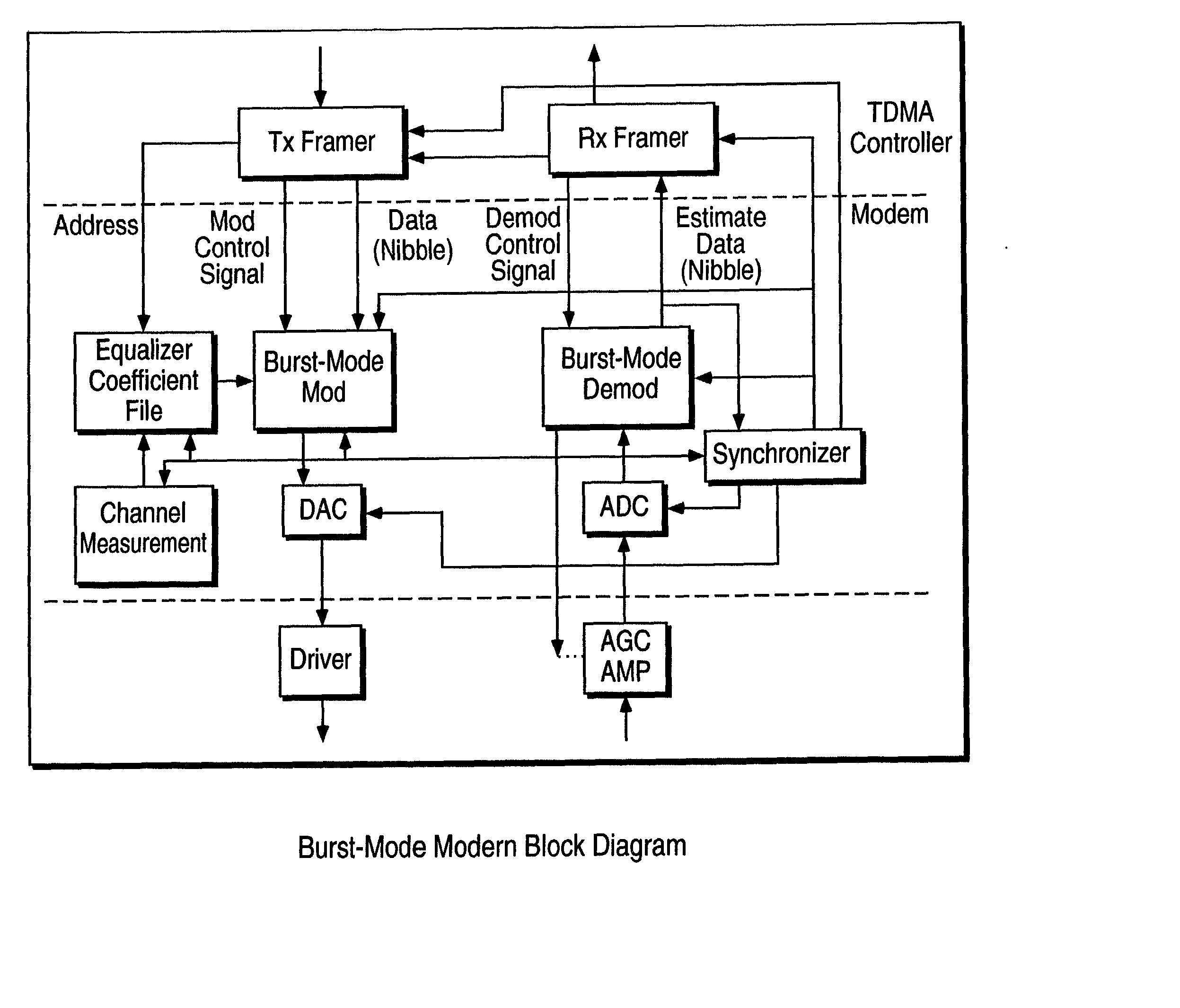

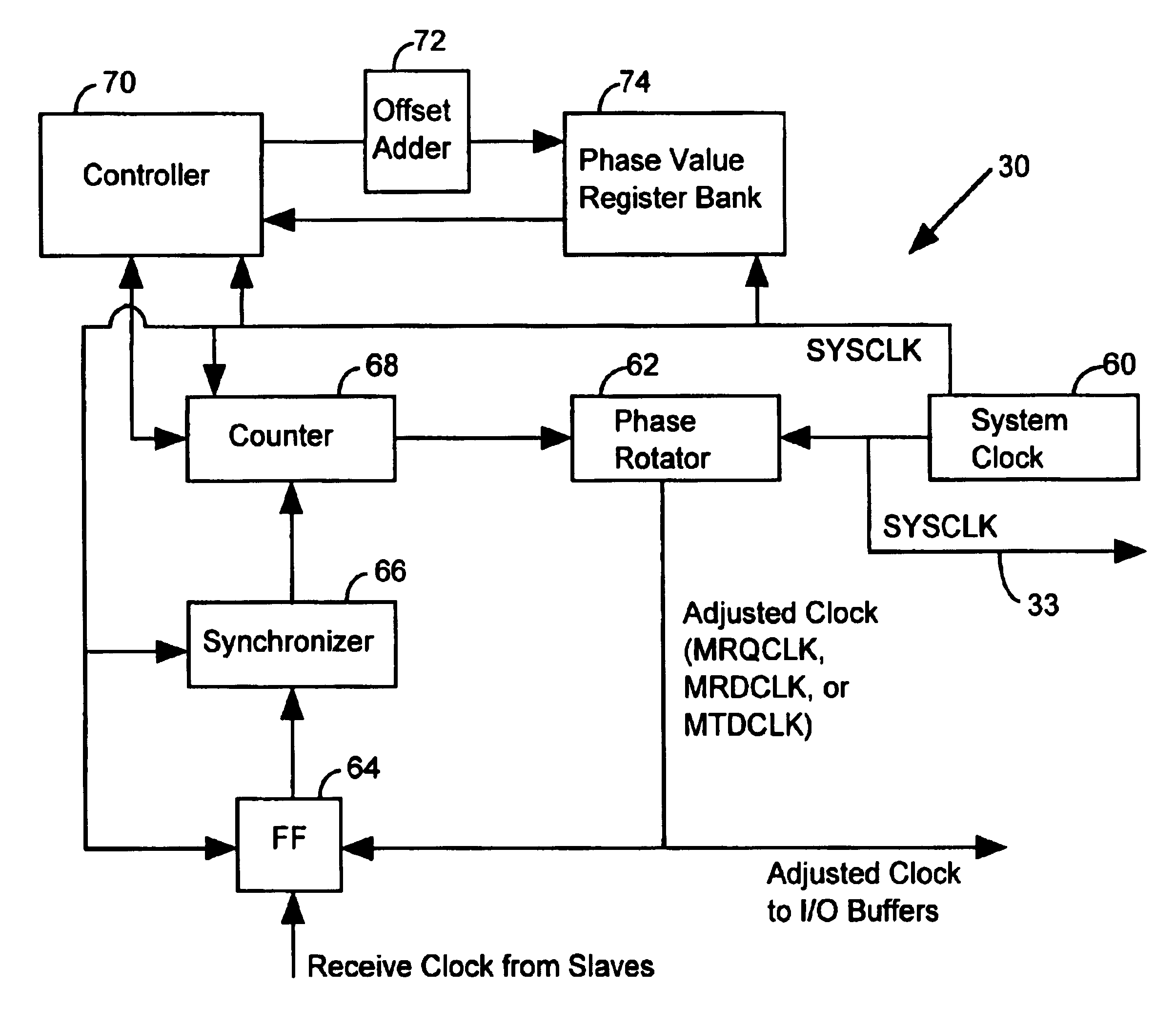

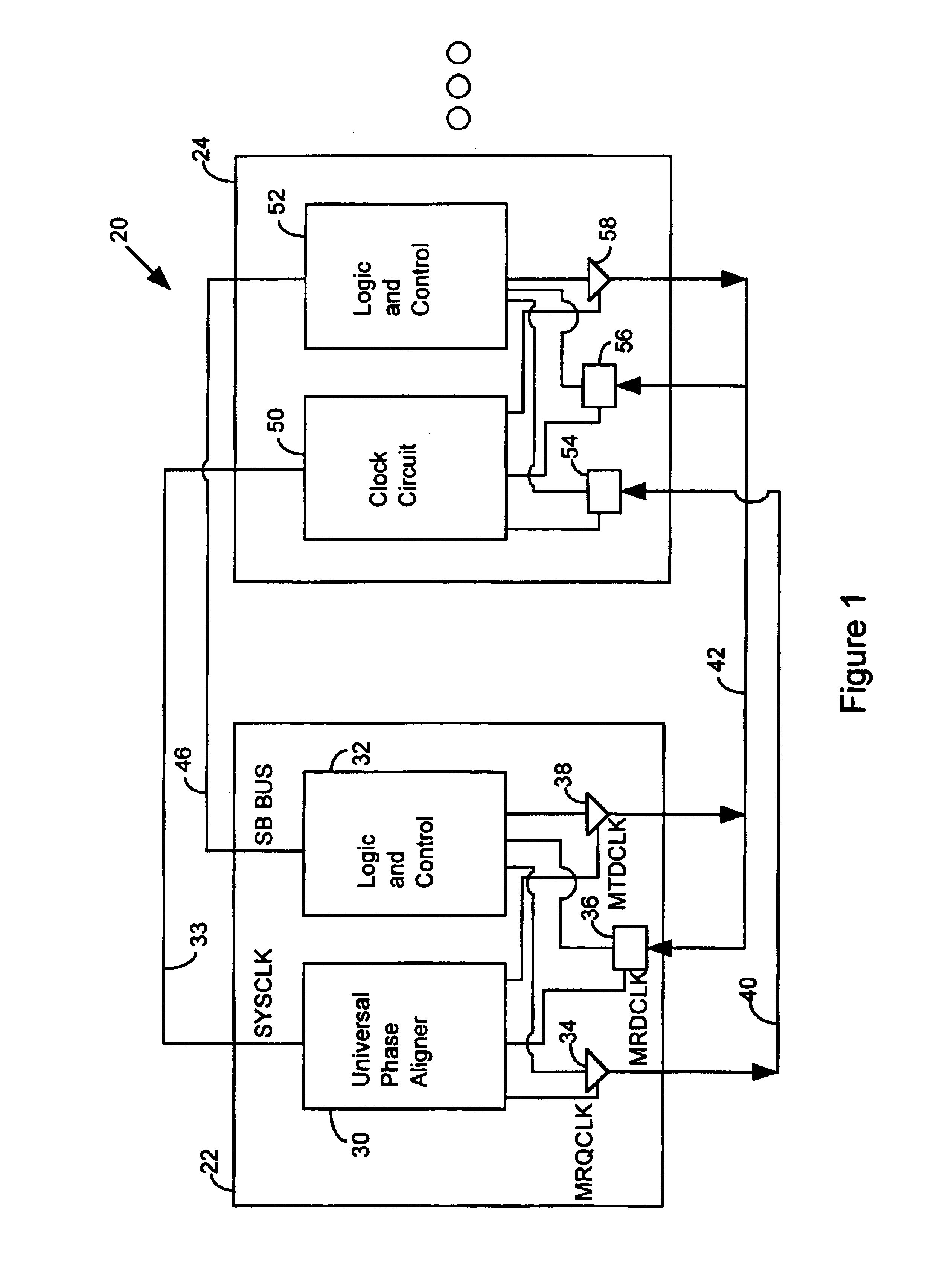

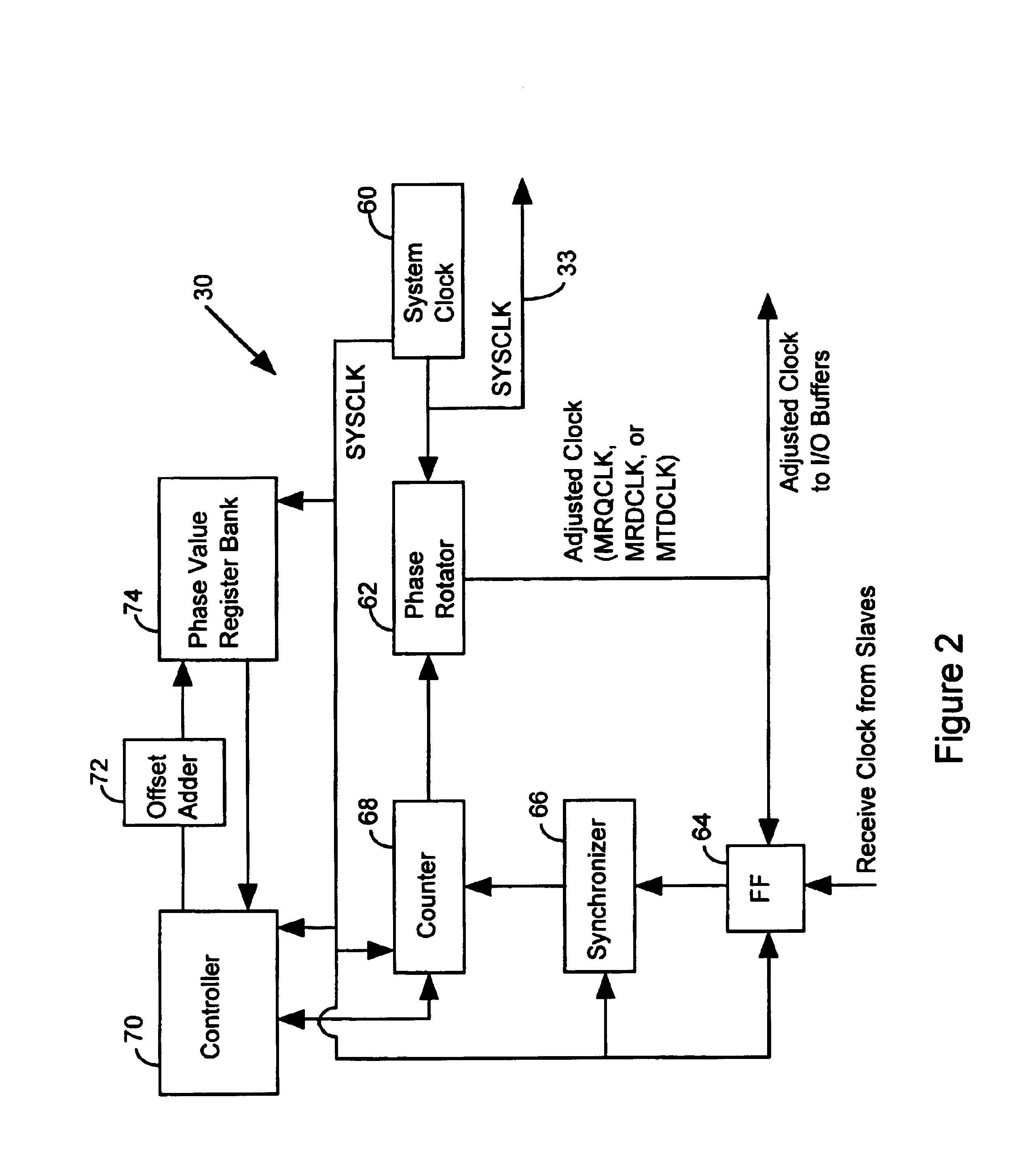

Apparatus and method for controlling a master/slave system via master device synchronization

InactiveUS6839393B1Reduce power consumptionImprove throughputEnergy efficient ICTPulse automatic controlComputer hardwareData shipping

A method of operating a master / slave system includes the step of identifying a master receive data phase value to coordinate the transfer of data from a slave device without phase alignment circuitry to a master device with a universal phase aligner. Data is transferred from the slave device to the master device in accordance with the master receive data phase value. The master device characterizes a master transmit data phase value to coordinate the transfer of data from the master device to the slave device. Subsequently, the master device routes data to the slave device in accordance with the master transmit data phase value.

Owner:RAMBUS INC

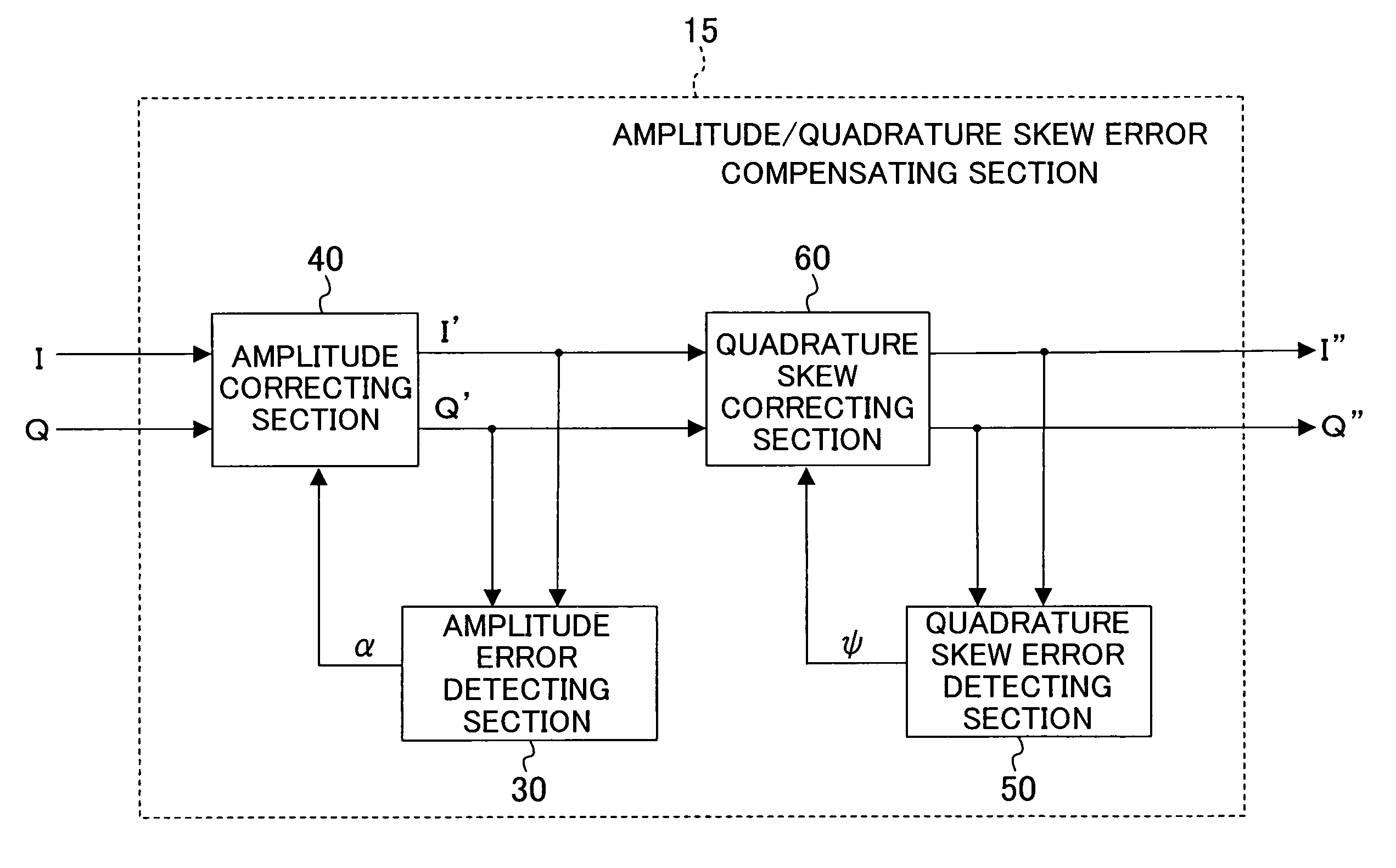

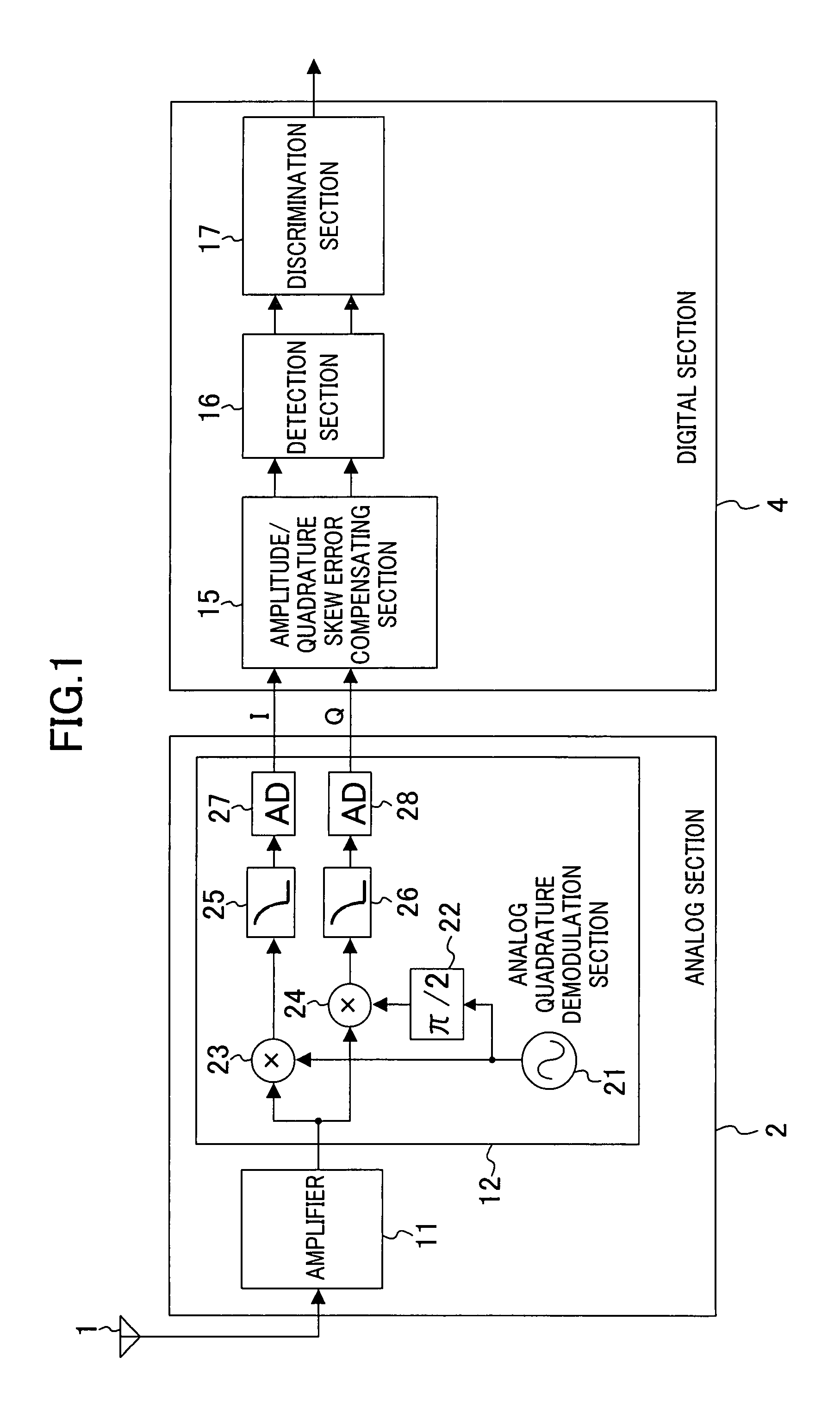

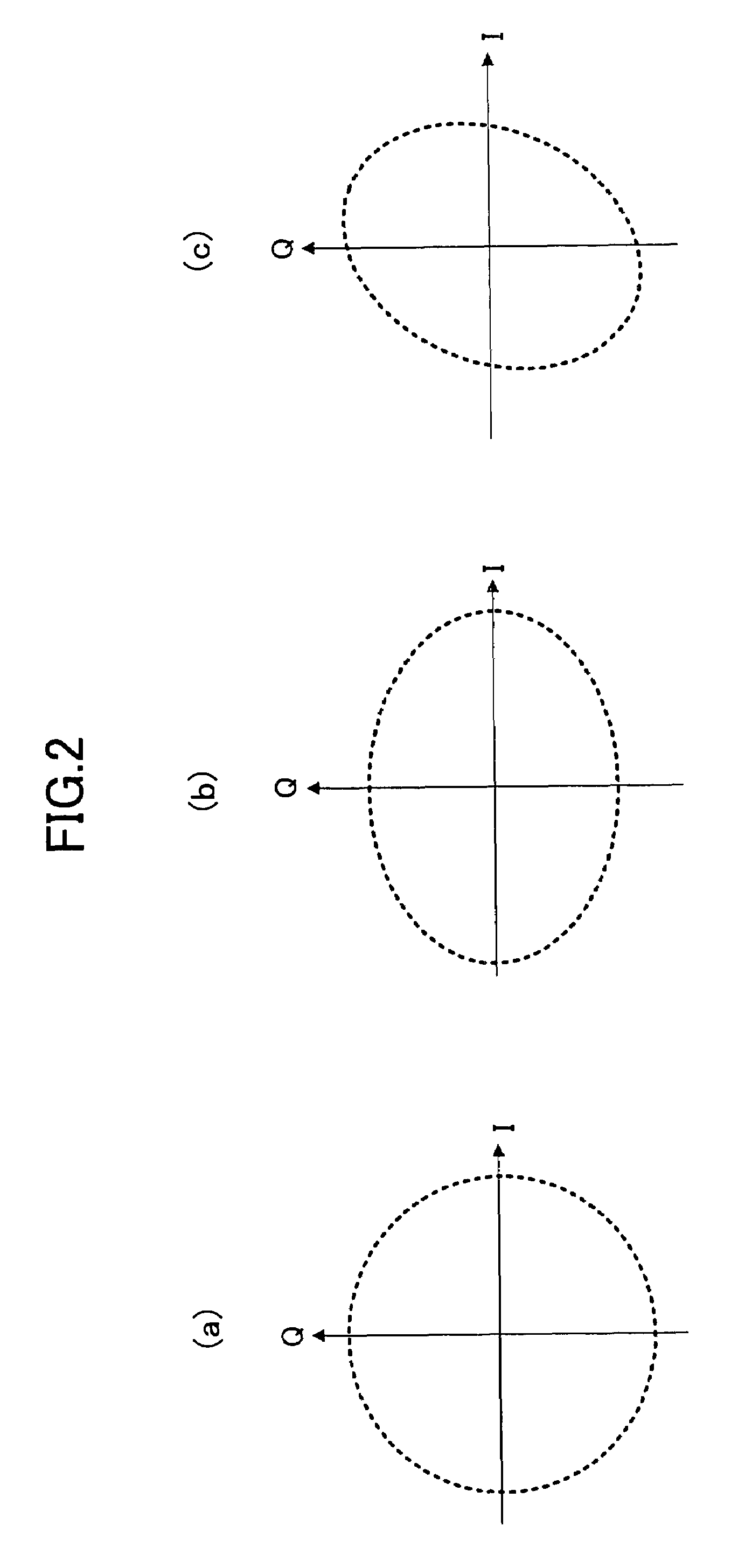

Amplitude error compensating device and quadrature skew error compensating device

InactiveUS7456683B2Error preventionLine-faulsts/interference reductionInformation controlQuadrature demodulation

An amplitude error compensating device comprises an amplitude correcting section for performing amplitude correction with respect to an in-phase component and a quadrature component of a complex signal obtained by quadrature demodulation, based on amplitude error information, and outputting a resultant amplitude-corrected complex signal, and an amplitude error detecting section for obtaining the amplitude error information, depending on amplitudes of an in-phase component and a quadrature component of the amplitude-corrected complex signal. The amplitude error detecting section comprises a power difference calculating section for obtaining as a power error a difference in power between the in-phase component and the quadrature component of the amplitude-corrected complex signal, a rotation detecting section for detecting a rotation of a signal point of the amplitude-corrected complex signal, an error information control section for outputting the power error when a rotation of the signal point has been detected, and 0 when a rotation of the signal point has not been detected, and a smoothing section for smoothing an output of the error information control section, and outputting the result as the amplitude error information.

Owner:SOCIONEXT INC

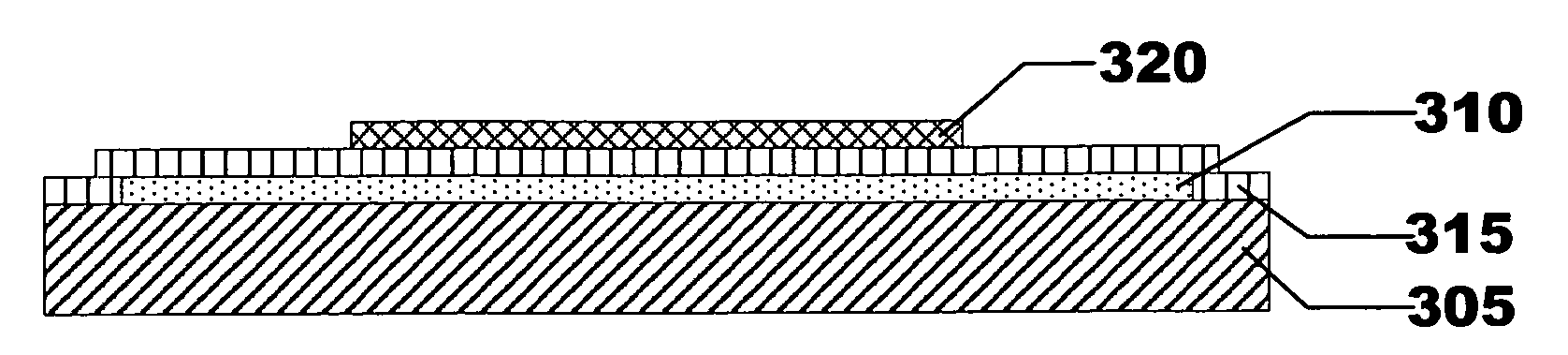

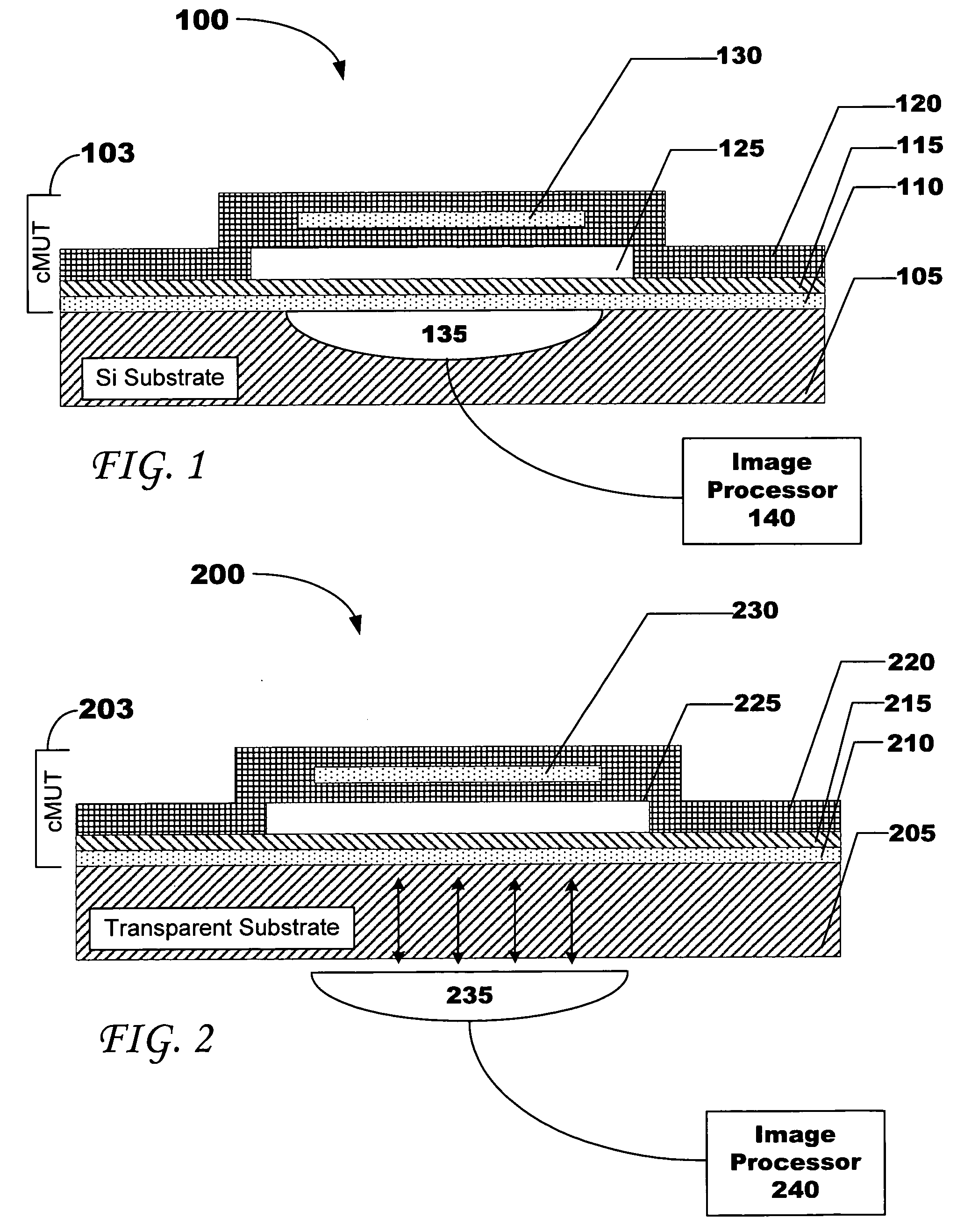

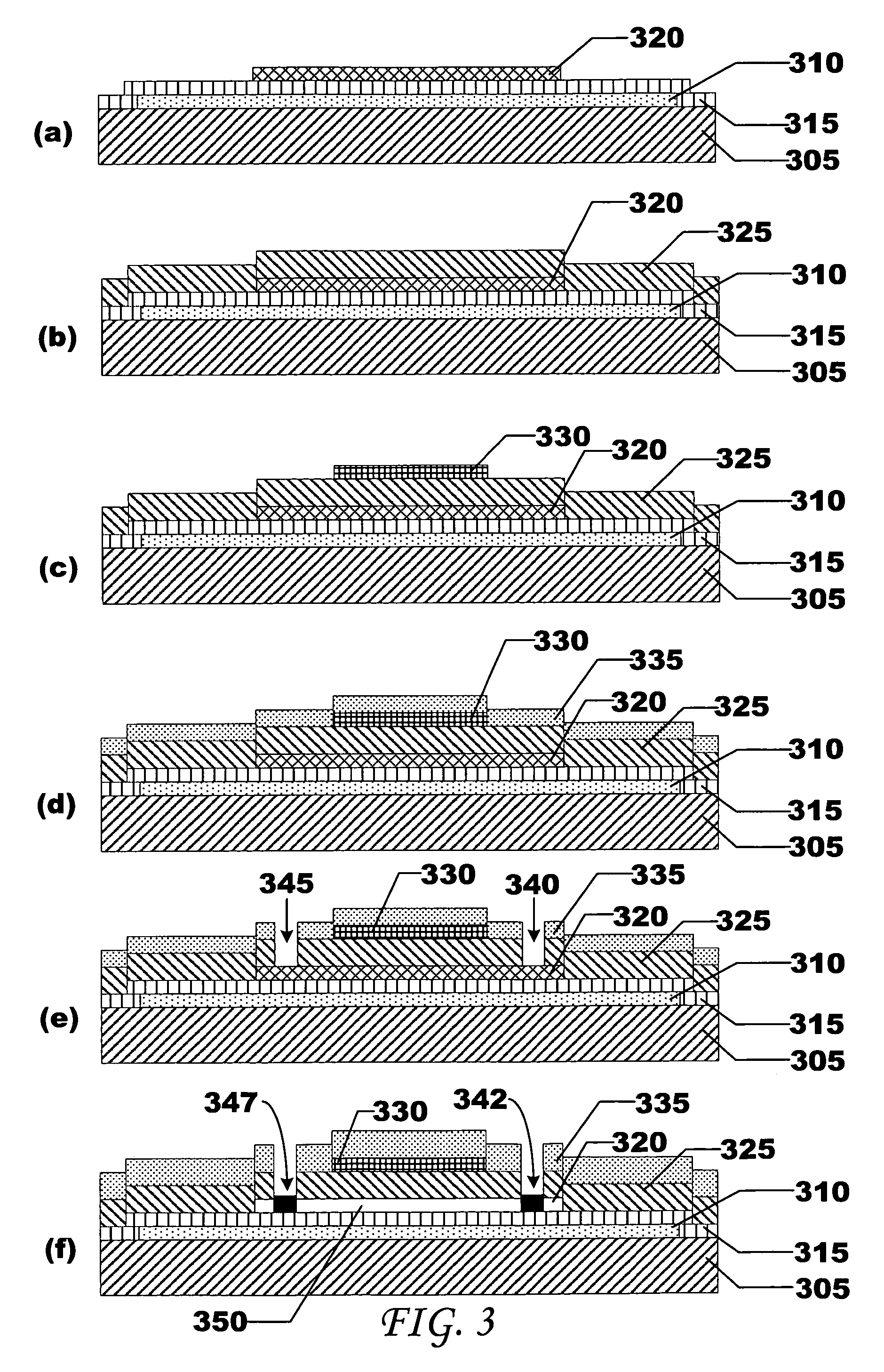

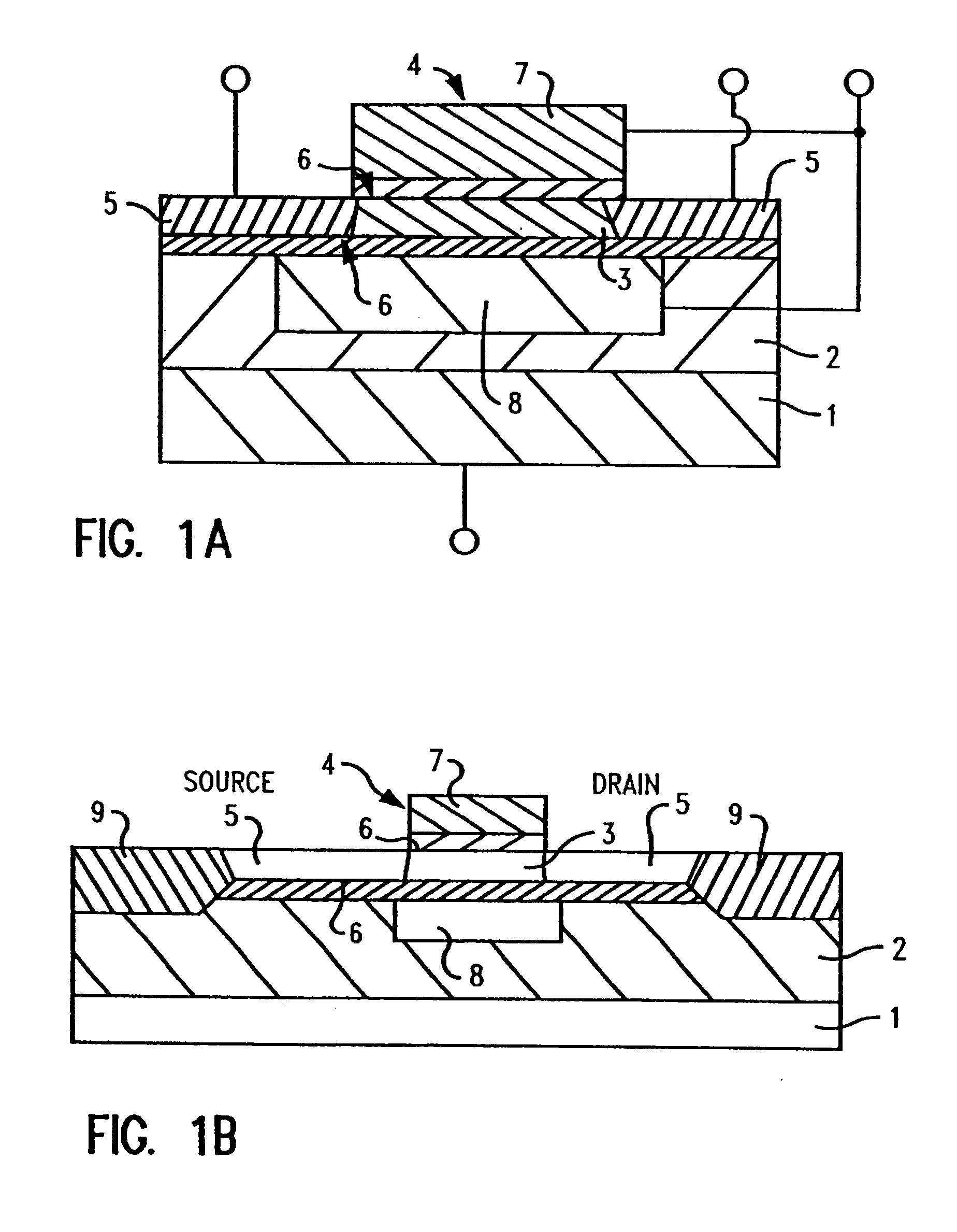

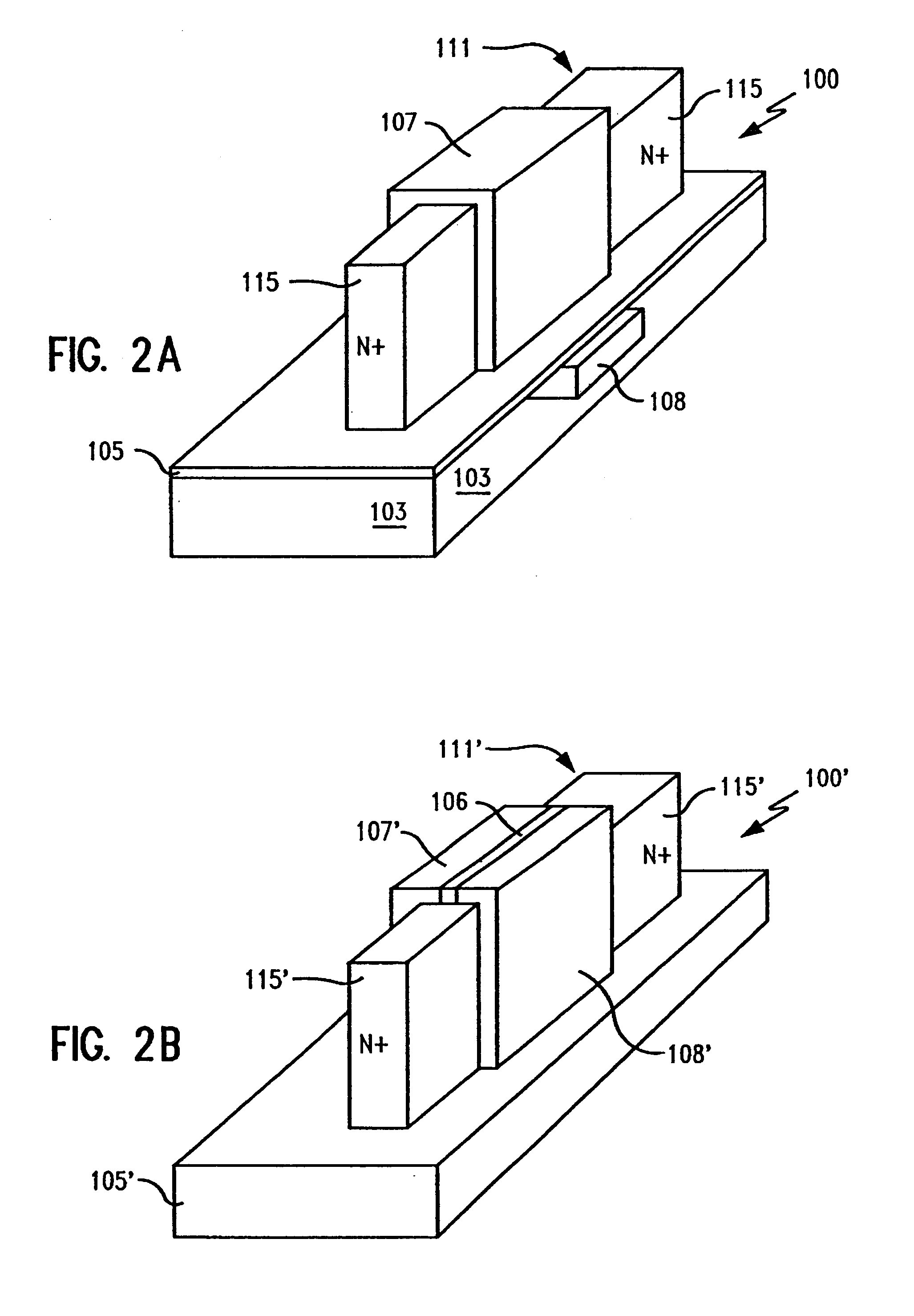

cMUT devices and fabrication methods

InactiveUS20050177045A1Reduce device parasitic capacitanceImprove electrical performanceMaterial analysis using sonic/ultrasonic/infrasonic wavesSurgeryCapacitanceCelsius Degree

Fabrication methods for capacitive-micromachined ultrasound transducers (“cMUT”) and cMUT imaging array systems are provided. cMUT devices fabricated from low process temperatures are also provided. In an exemplary embodiment, a process temperature can be less than approximately 300 degrees Celsius. A cMUT fabrication method generally comprises depositing and patterning materials on a substrate (400). The substrate (400) can be silicon, transparent, other materials. In an exemplary embodiment, multiple metal layers (405, 410, 415) can be deposited and patterned onto the substrate (400); several membrane layers (420, 435, 445) can be deposited over the multiple metal layers (405, 410, 415); and additional metal layers (425, 430) can be disposed within the several membrane layers (420, 435, 445). The second metal layer (410) is preferably resistant to etchants used to etch the third metal layer (415) when forming a cavity (447). Other embodiments are also claimed and described.

Owner:GEORGIA TECH RES CORP

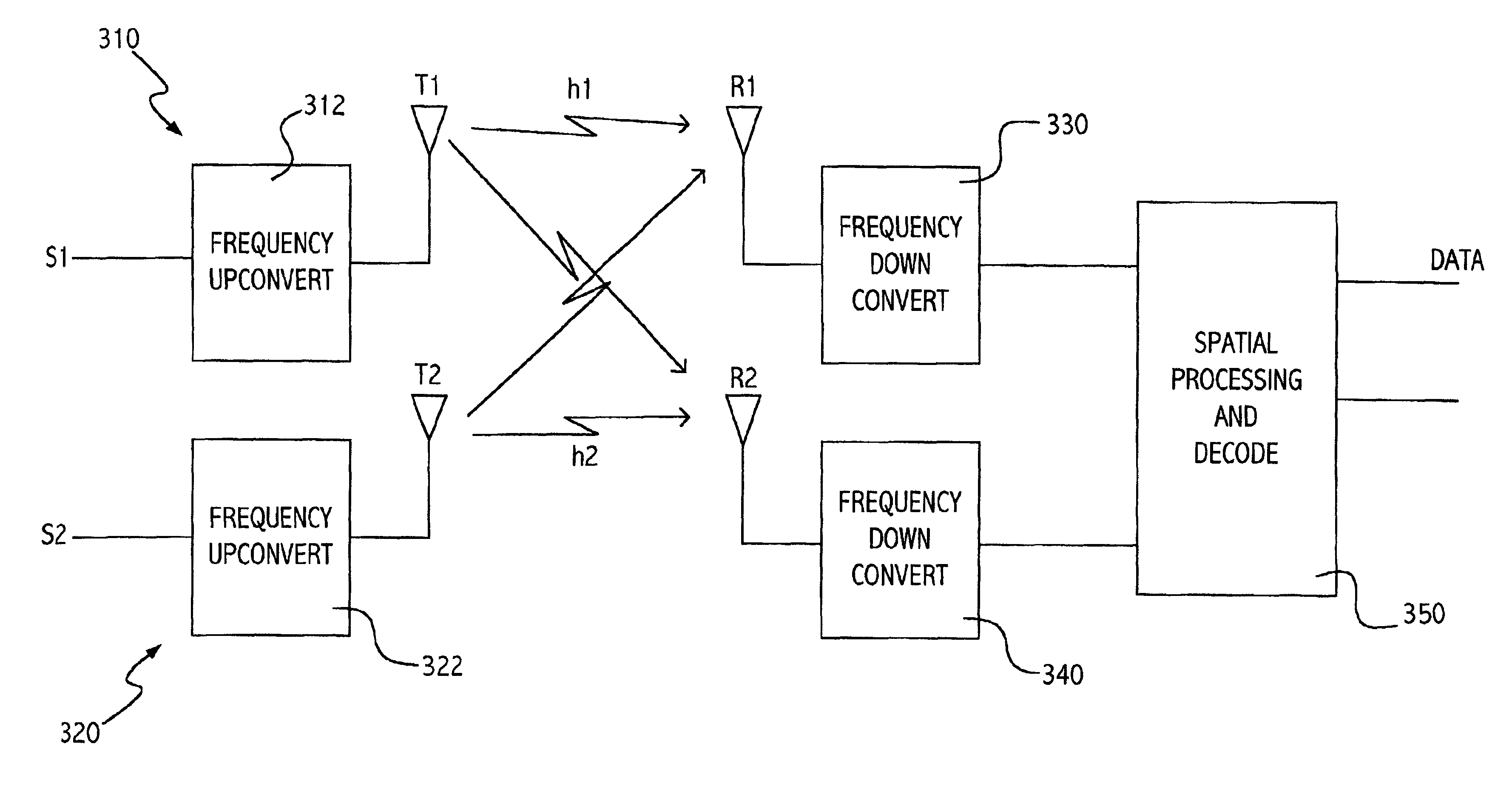

Method and system for multiple channel wireless transmitter and receiver phase and amplitude calibration

InactiveUS6862440B2Low costTransmitters monitoringReceivers monitoringTransmission channelEngineering

The present invention provides a method and system for estimating common amplitude and phase errors of a multiple channel wireless system. The multiple channel wireless system includes a plurality of transmission channels formed between a plurality of transmission antennas and a plurality of receiver antennas. The method includes estimating transmission channel elements between each transmission antenna and receiver antenna pair of the multiple channel wireless system. Calibration symbols are transmitted from each transmit antenna. Signals are received that correspond to the calibration symbols having traveled through the transmission channels. Received calibration symbols are estimated based upon spatial processing of the received signals and the estimated transmission channel elements. Common amplitude and phase errors are estimated for each transmit and receive antenna pair by comparing the transmitted calibration symbols with the received calibration symbols.

Owner:TAHOE RES LTD

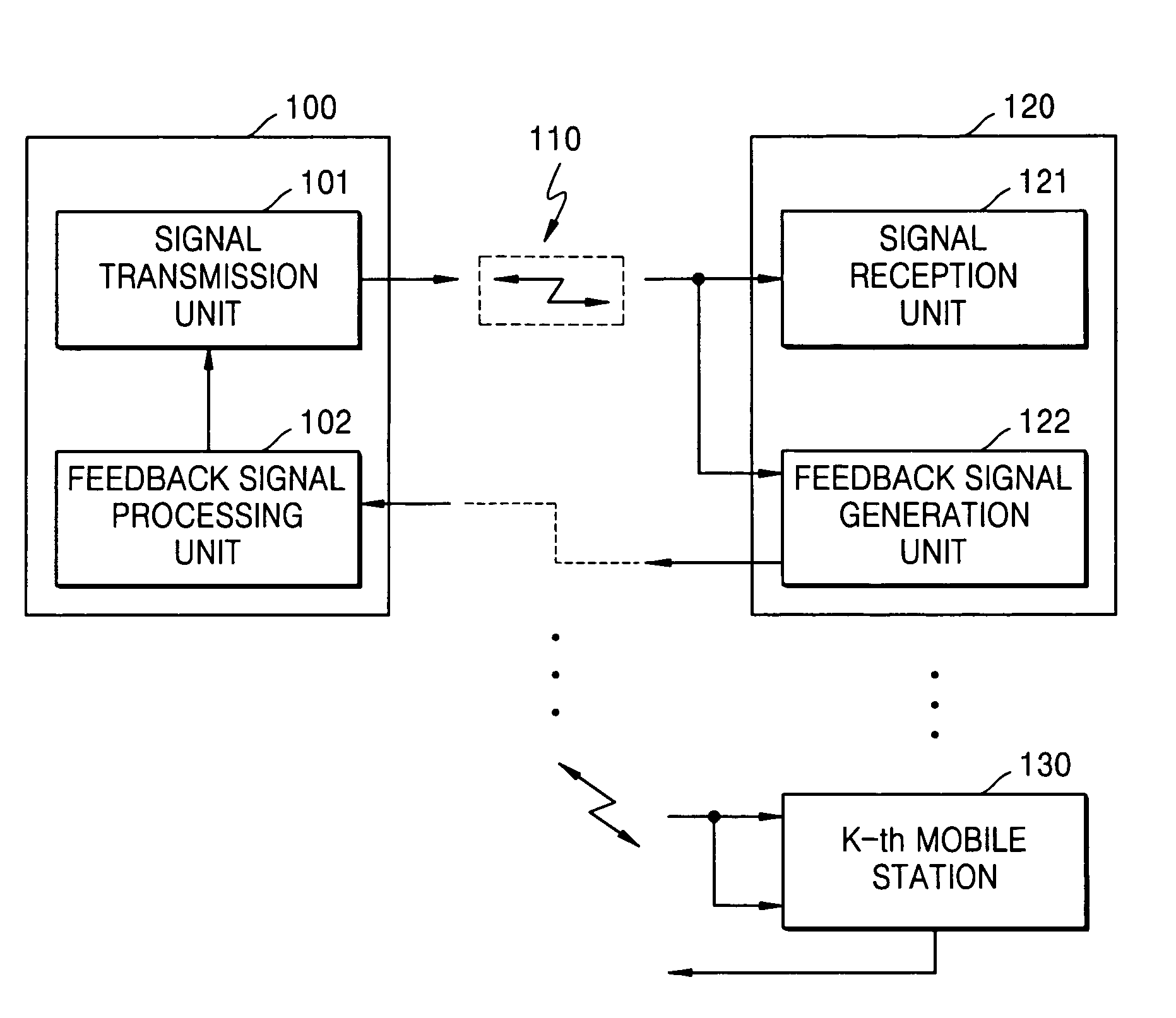

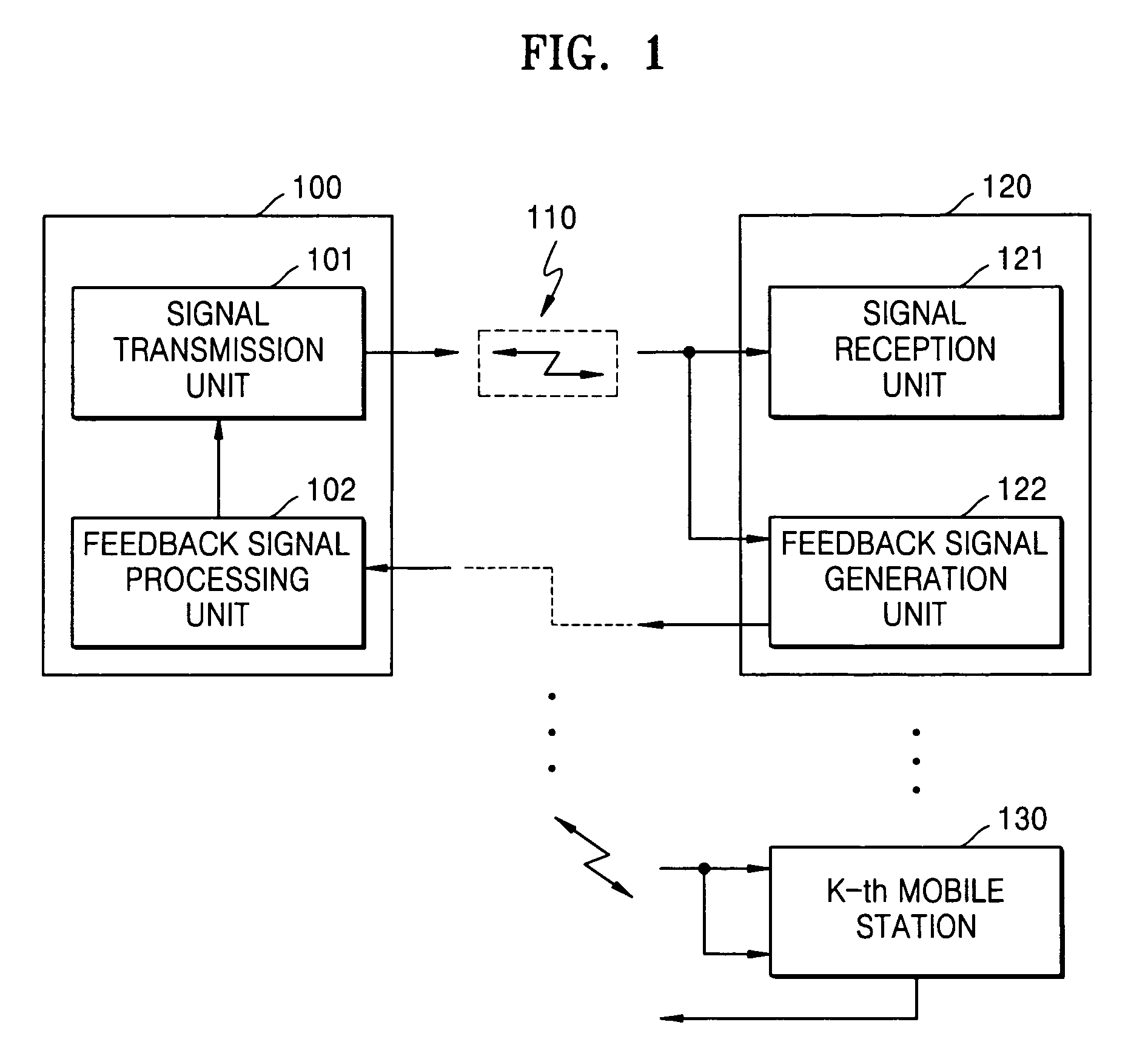

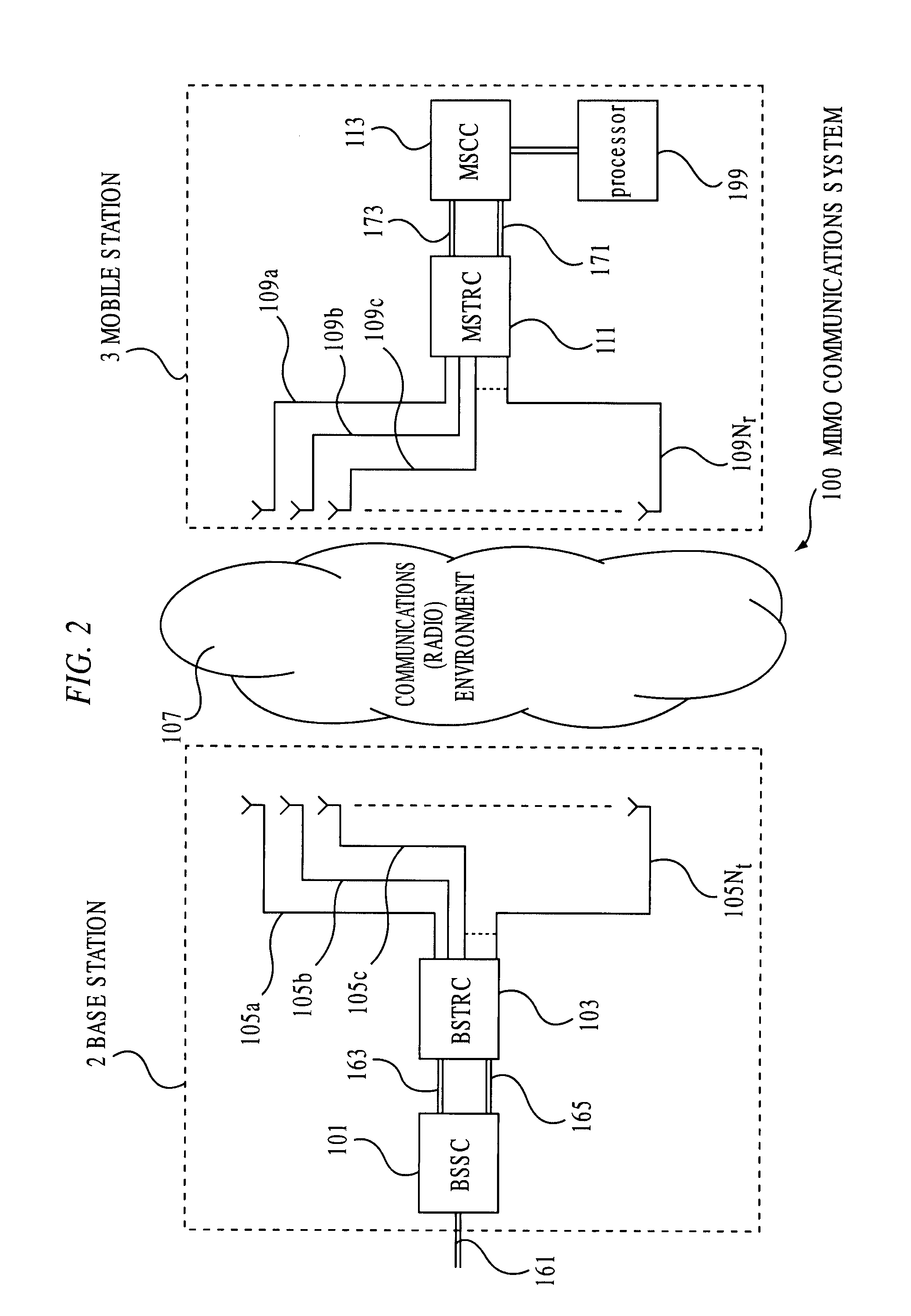

Wireless communication system and method using multiple antennas

ActiveUS7406337B2Guaranteed throughputError preventionFrequency-division multiplex detailsCommunications systemMobile station

A wireless communication system, and method using multiple antennas, includes a base station that applies predetermined weight vectors to multi-user signals and transmits the multi-user signals through a plurality of transmission antennas, and a plurality of mobile stations that receive and process the multi-user signals, wherein each mobile station includes a signal reception unit that processes the multi-user signals, and a feedback signal generation unit that estimates channel characteristics, over which the multi-user signals have been transmitted, from the multi-user signals, classifies a plurality of weight vectors to be applied to the estimated channel characteristics into a plurality of sets such that vectors orthogonal to one another are classified into a single set, selects a set maximizing a transmission capacity from among the classified sets, and feeds back weight indexes of weight vectors included in the selected set and weighted channel information to the base station.

Owner:NOKIA SOLUTIONS & NETWORKS OY

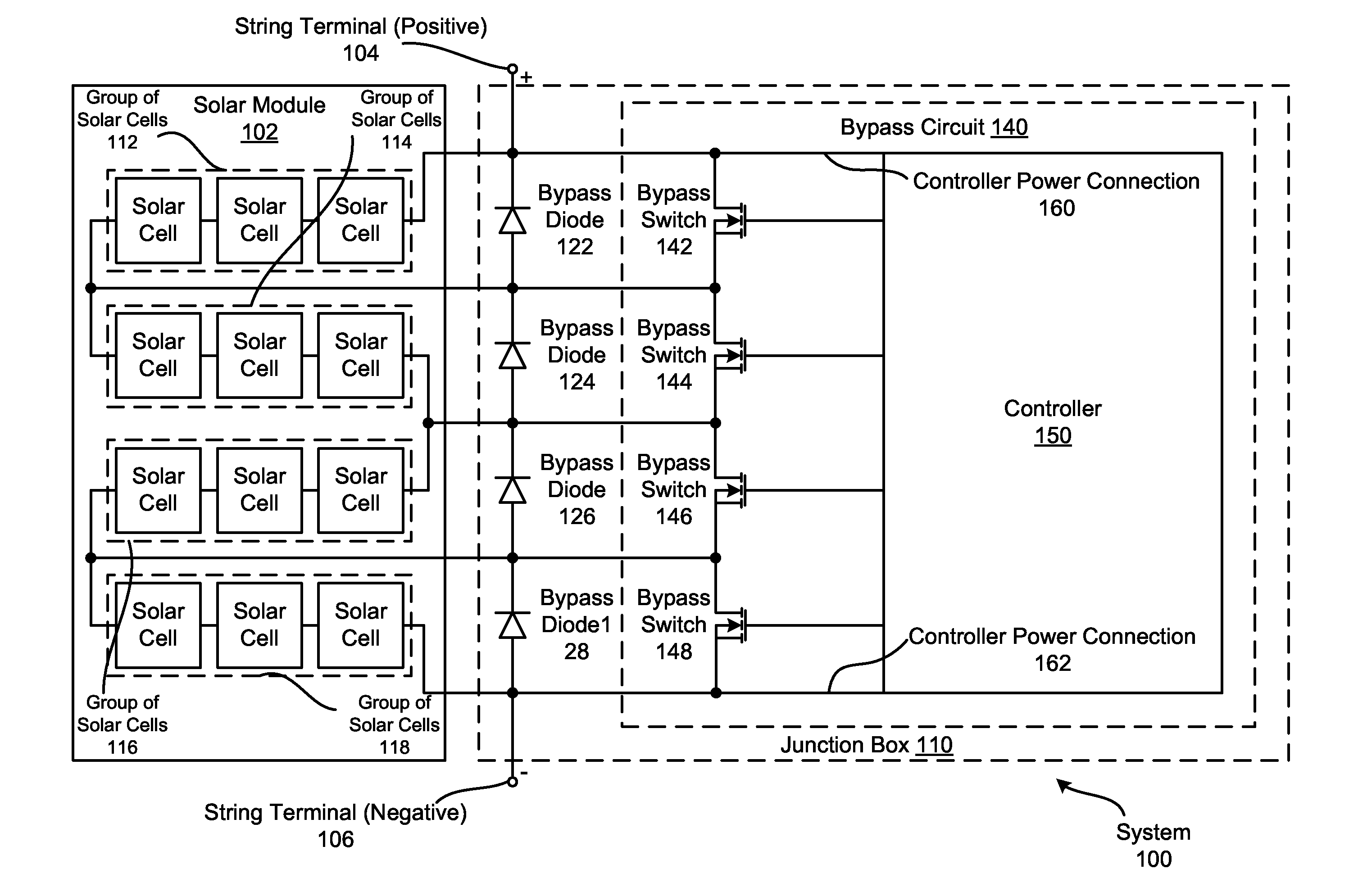

Systems and Methods to Provide Enhanced Diode Bypass Paths

Systems and methods are herein disclosed for efficiently allowing current to bypass a group of solar cells having one or more malfunctioning or shaded solar cells without overwhelming a bypass diode. This can be done using a switch (e.g., a MOSFET) connected in parallel with the bypass diode. By turning the switch on and off, a majority of the bypass current can be routed through the switch, which is configured to handle larger currents than the bypass diode is designed for, leaving only a minority of the current to pass through the bypass diode.

Owner:NEWLIGHT CAPITAL LLC

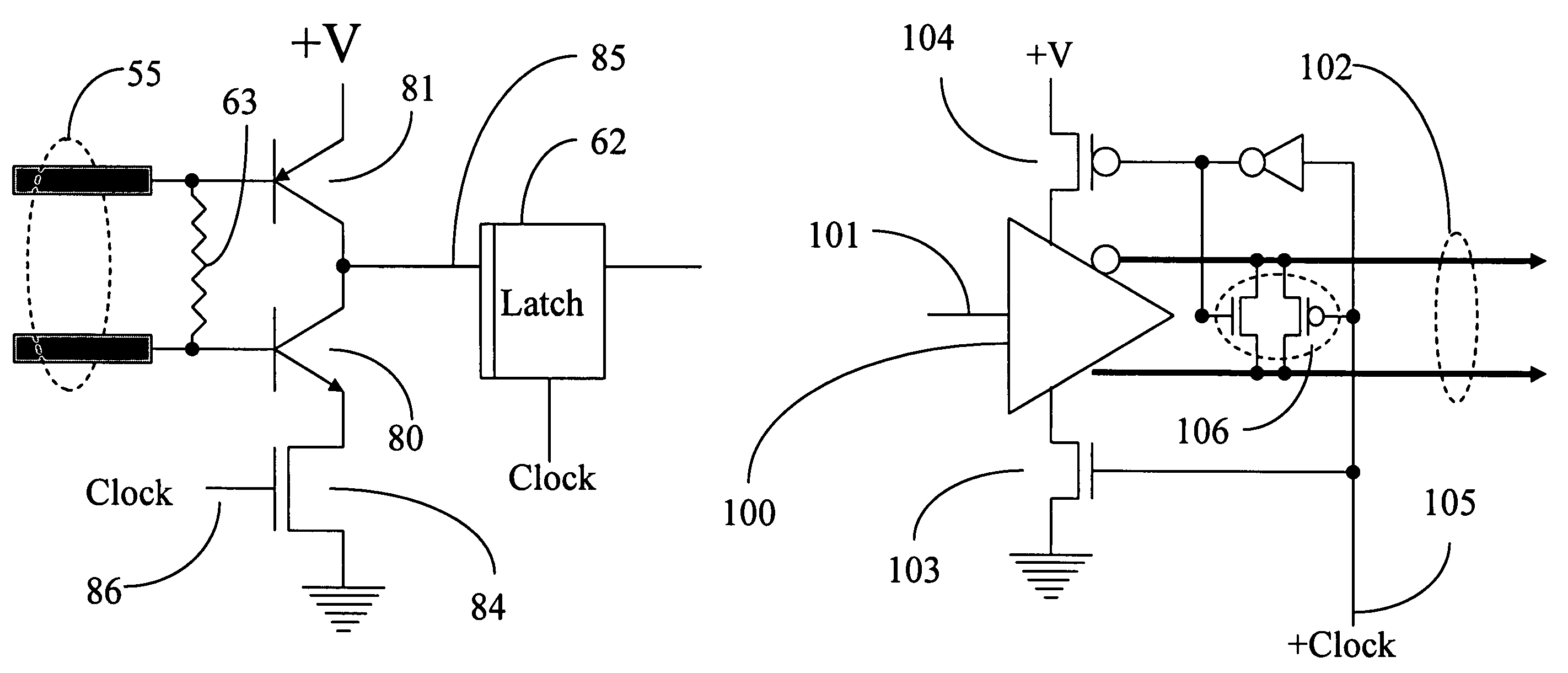

Integrated circuit communication techniques

ActiveUS7439773B2Reduce the required powerReduce power consumptionReliability increasing modificationsPower reduction by control/clock signalEngineeringSemiconductor

Owner:TAHOE RES LTD

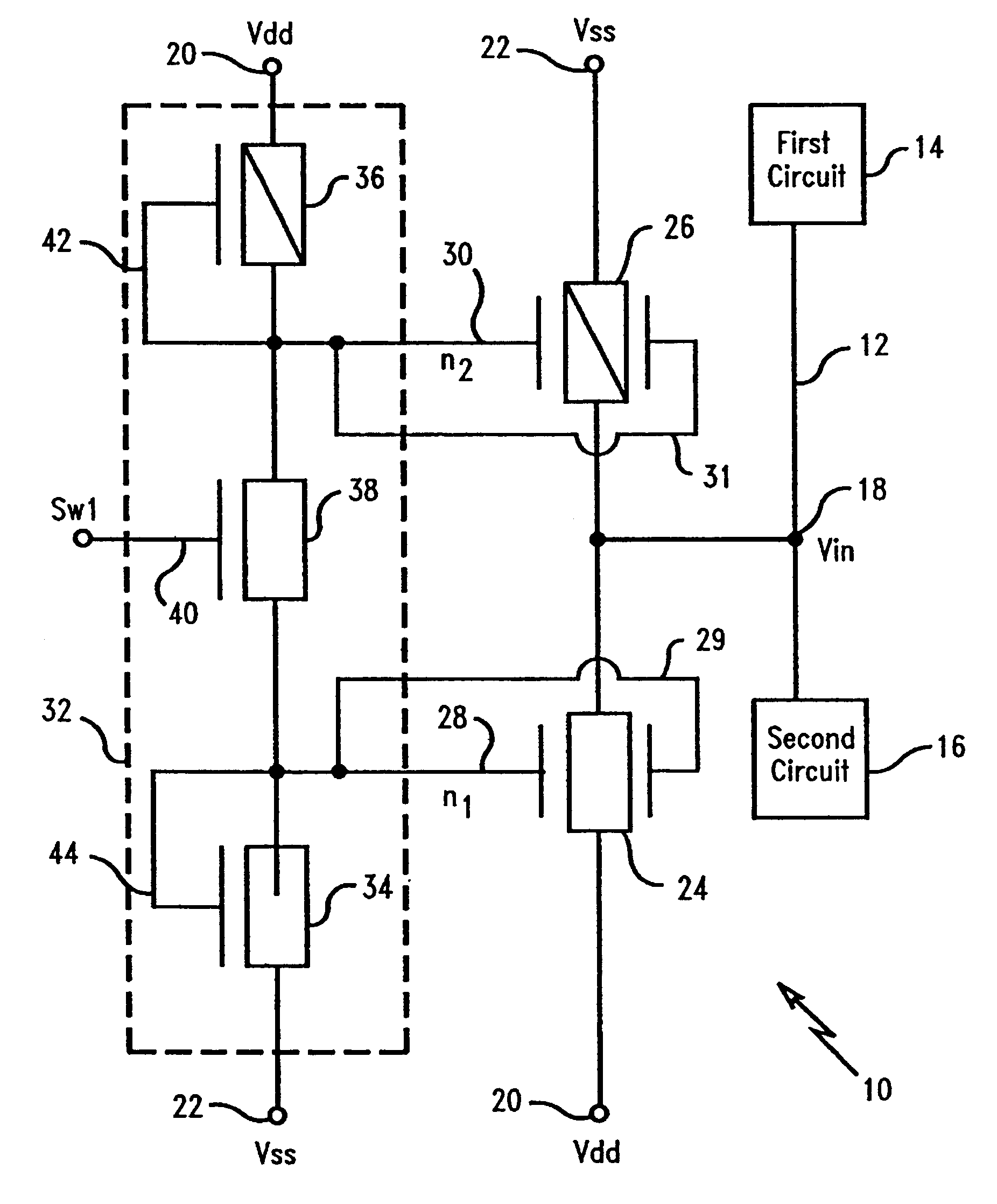

Double-gate low power SOI active clamp network for single power supply and multiple power supply applications

InactiveUS6433609B1Improve performanceReduce power consumptionTransistorPulse automatic controlActive clampLow voltage

A double-gated low power active clamp circuit for digital circuits includes a first double-gated MOSFET serially connected between an upper power supply voltage and an input terminal to be clamped, and a second double-gated MOSFET serially connected between a lower voltage power supply and the input terminal. The voltages at the gates of the first and second double-gated MOSFETs are held at constant reference voltages by a single or double reference circuits. The clamping action can be switched on or off. The double-gated active clamping network can be implemented with a single power supply voltage, or with multiple power supply voltages. The use of the back gates of the double-gated active clamping network enables additional clamping and ESD protection for smaller generations of transistors, such as, those having dimensions below 0.1 micron. The device is particularly suited for use with dynamic threshold double-gated silicon-on-insulator, FINFET, and bulk triple well technologies.

Owner:GLOBALFOUNDRIES US INC

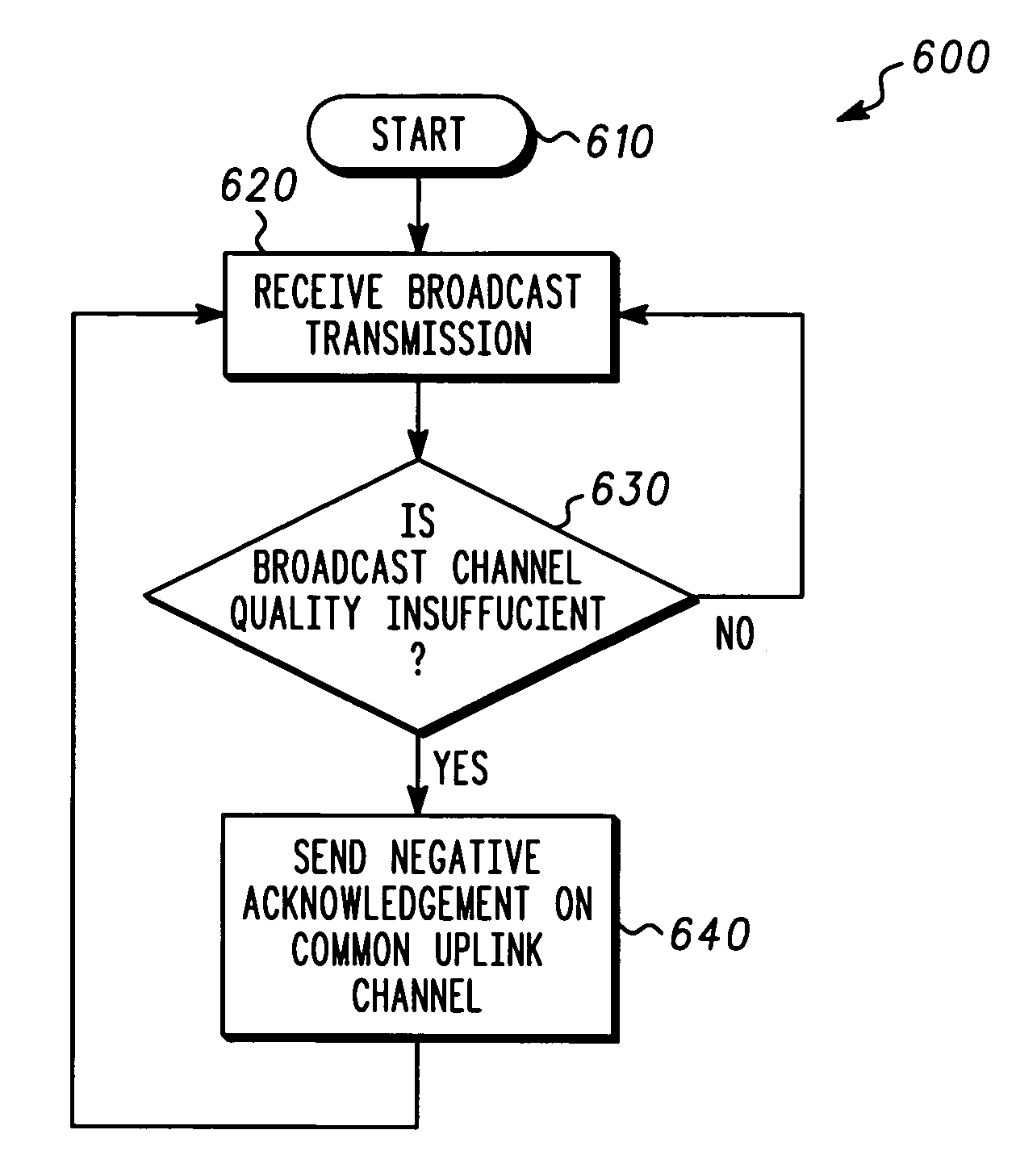

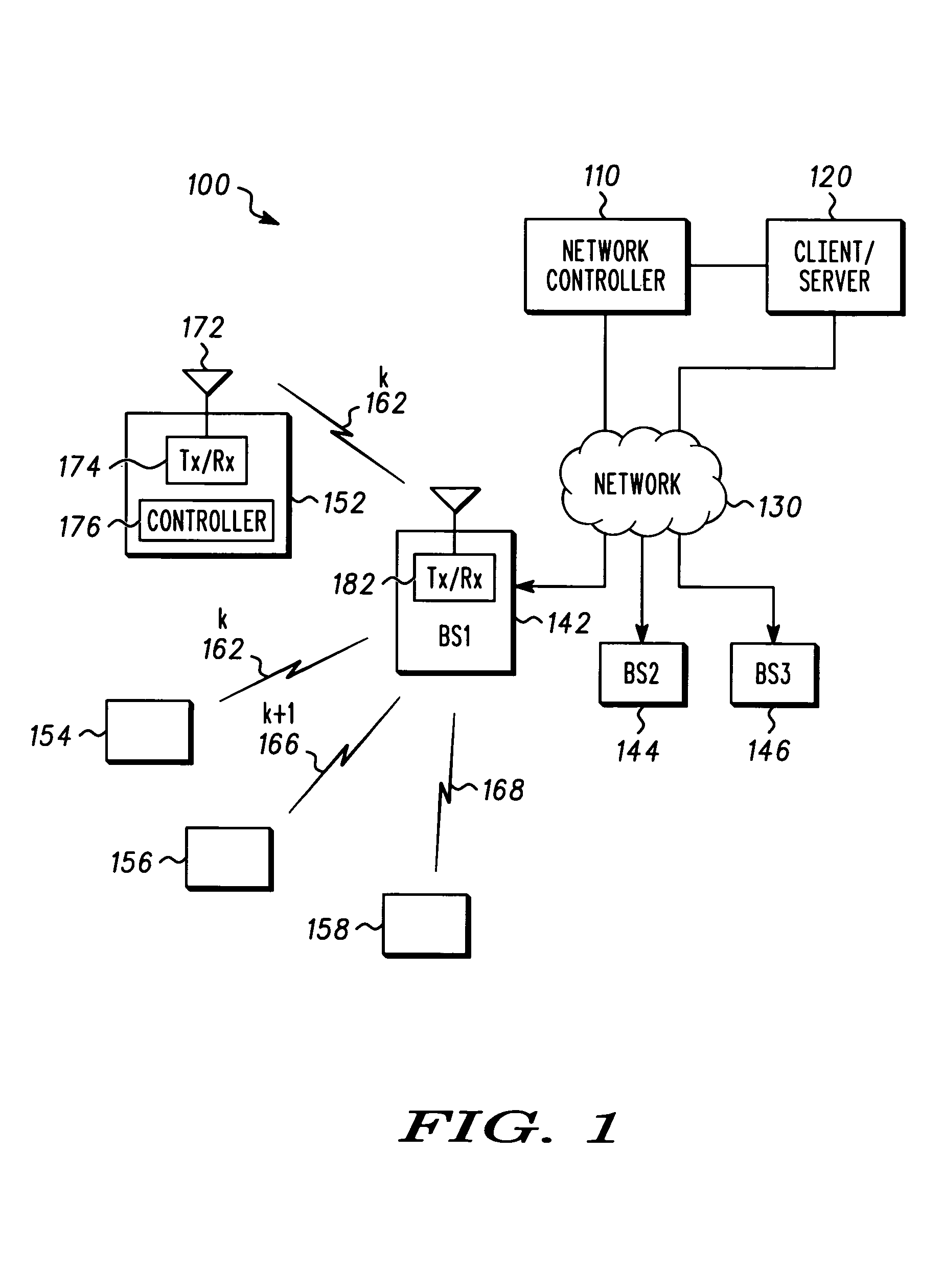

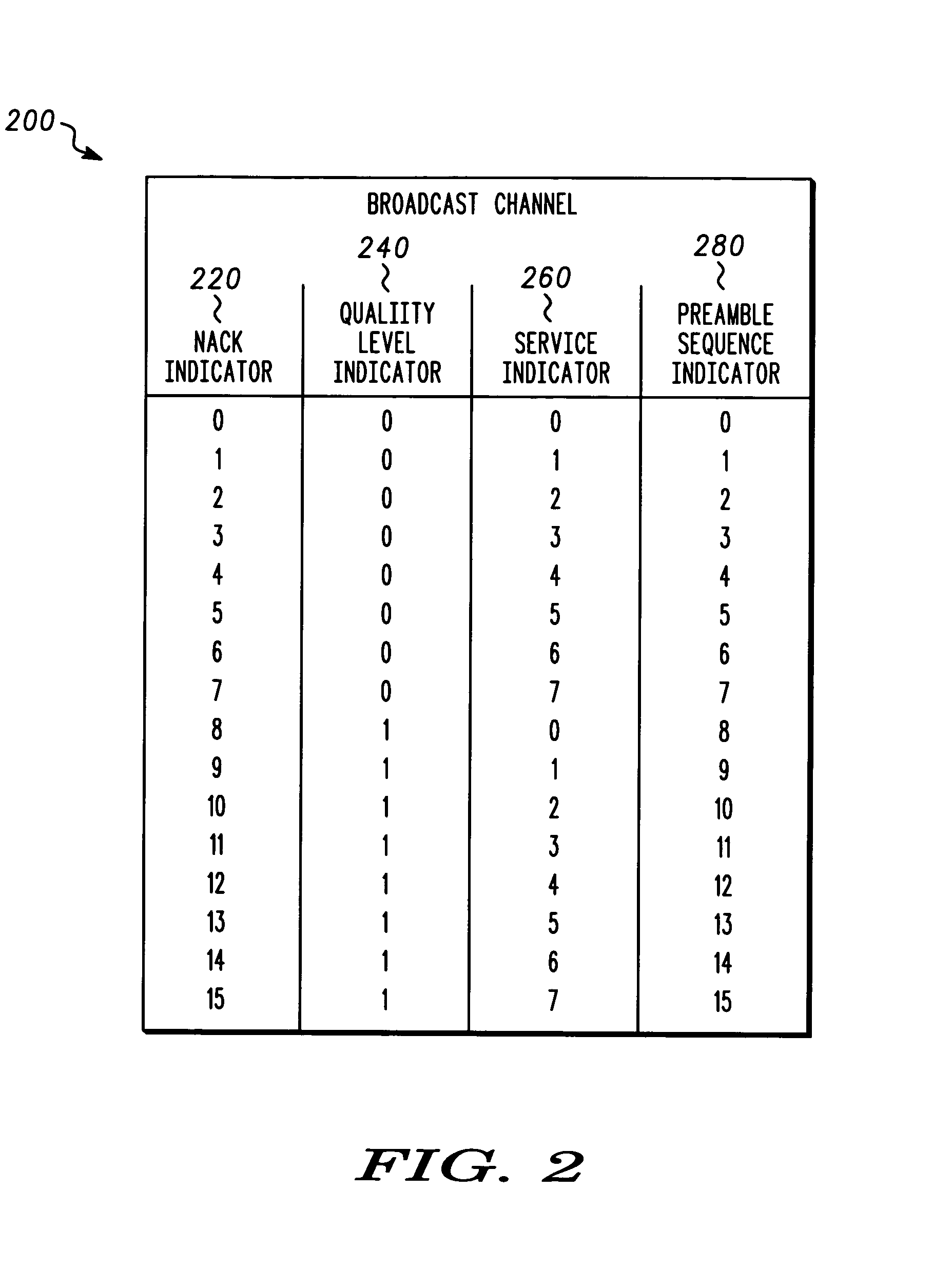

Apparatus and method for adaptive broadcast transmission

An apparatus and method for adaptive broadcast transmission. A broadcast transmission can be received. Insufficiency of a broadcast channel quality can be determined. A negative acknowledgement signal can be sent on a common uplink channel in response to determining the broadcast channel quality is insufficient. The negative acknowledgement signal can be received on the common uplink channel at another location, the negative acknowledgement signal indicating broadcast channel quality is insufficient. The broadcast channel quality can be adjusted in response to receiving the negative acknowledgement signal.

Owner:GOOGLE TECH HLDG LLC

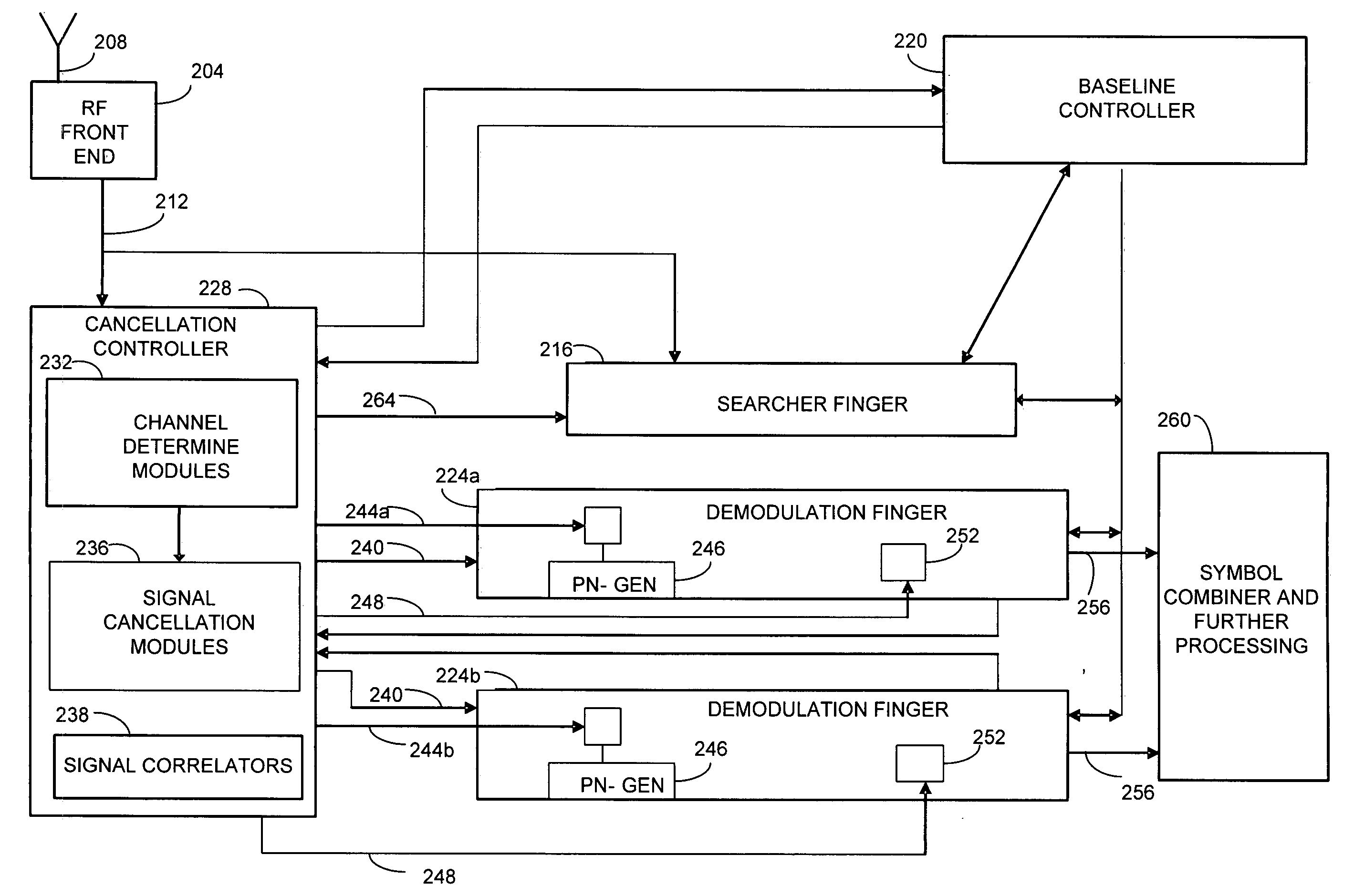

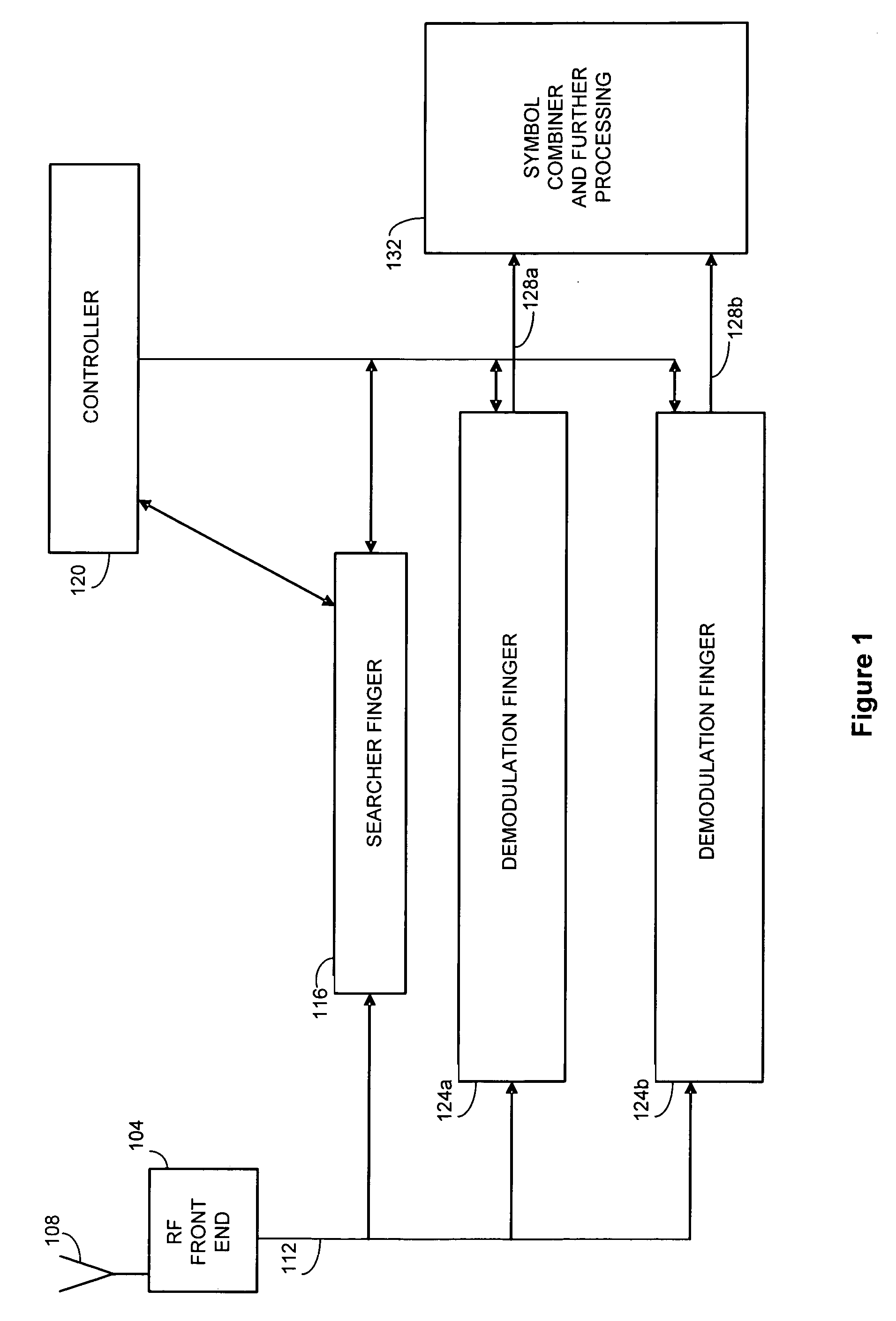

Method and apparatus for selectively applying interference cancellation in spread spectrum systems

ActiveUS20070183483A1High strengthIncrease signal strengthError preventionLine-faulsts/interference reductionSignal cancellationEngineering

The present invention is directed to the selective provision of interference canceled signal streams to demodulating fingers in a communication receiver. According to the present invention, potential interferer signal paths are identified. Signal streams having one or more potential interferer signals removed or canceled are created, and a correlation is performed to determine whether the strength of a desired signal path increased as a result. If the correlation indicates that the strength of a desired signal path was increased by the signal cancellation, the interference canceled signal stream is provided to the demodulation finger assigned to track the desired signal path. If the correlation determines that the strength of the desired signal path did not increase as a result of performing interference cancellation, the raw or a different interference canceled signal stream is provided to the demodulation finger.

Owner:III HLDG 1

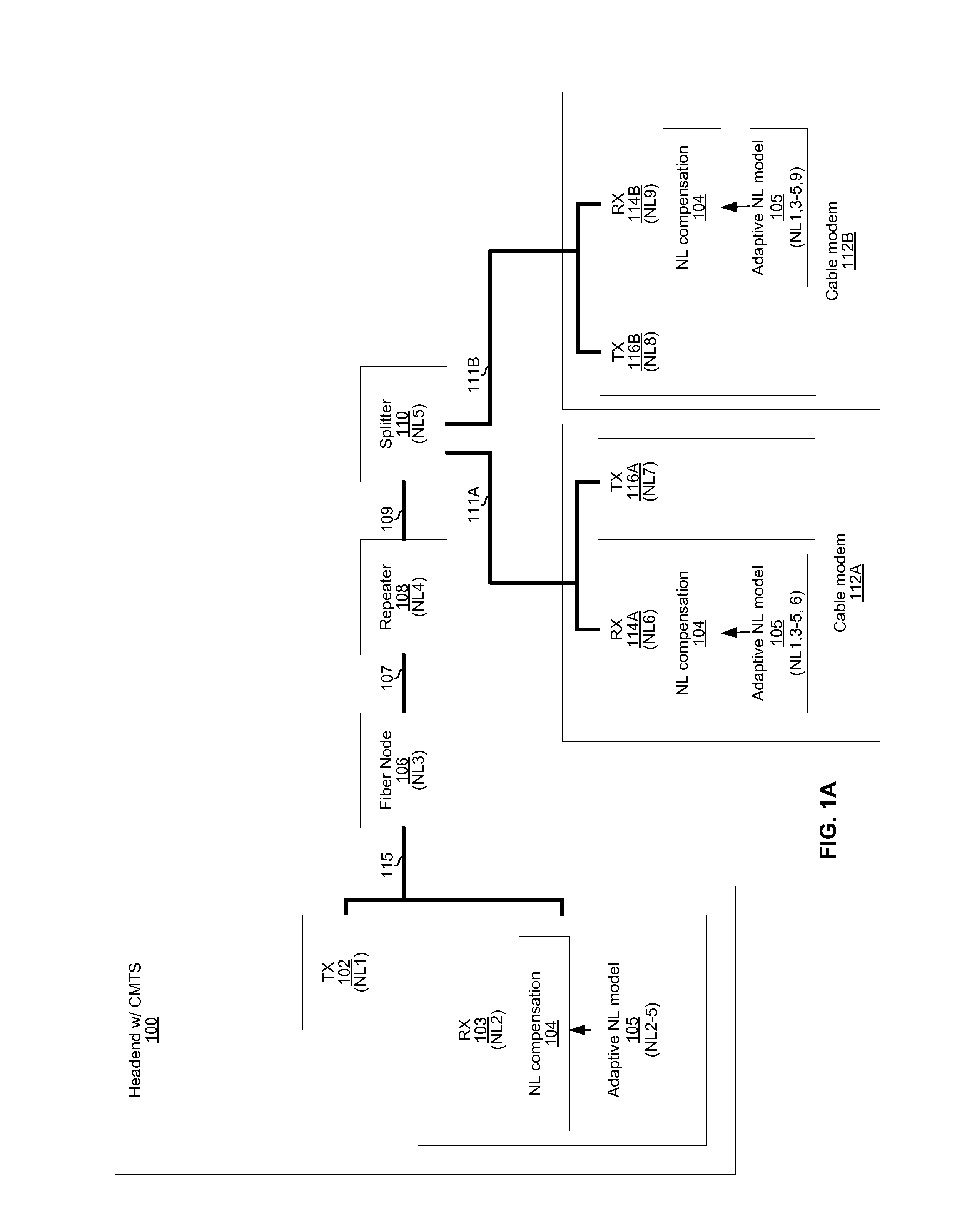

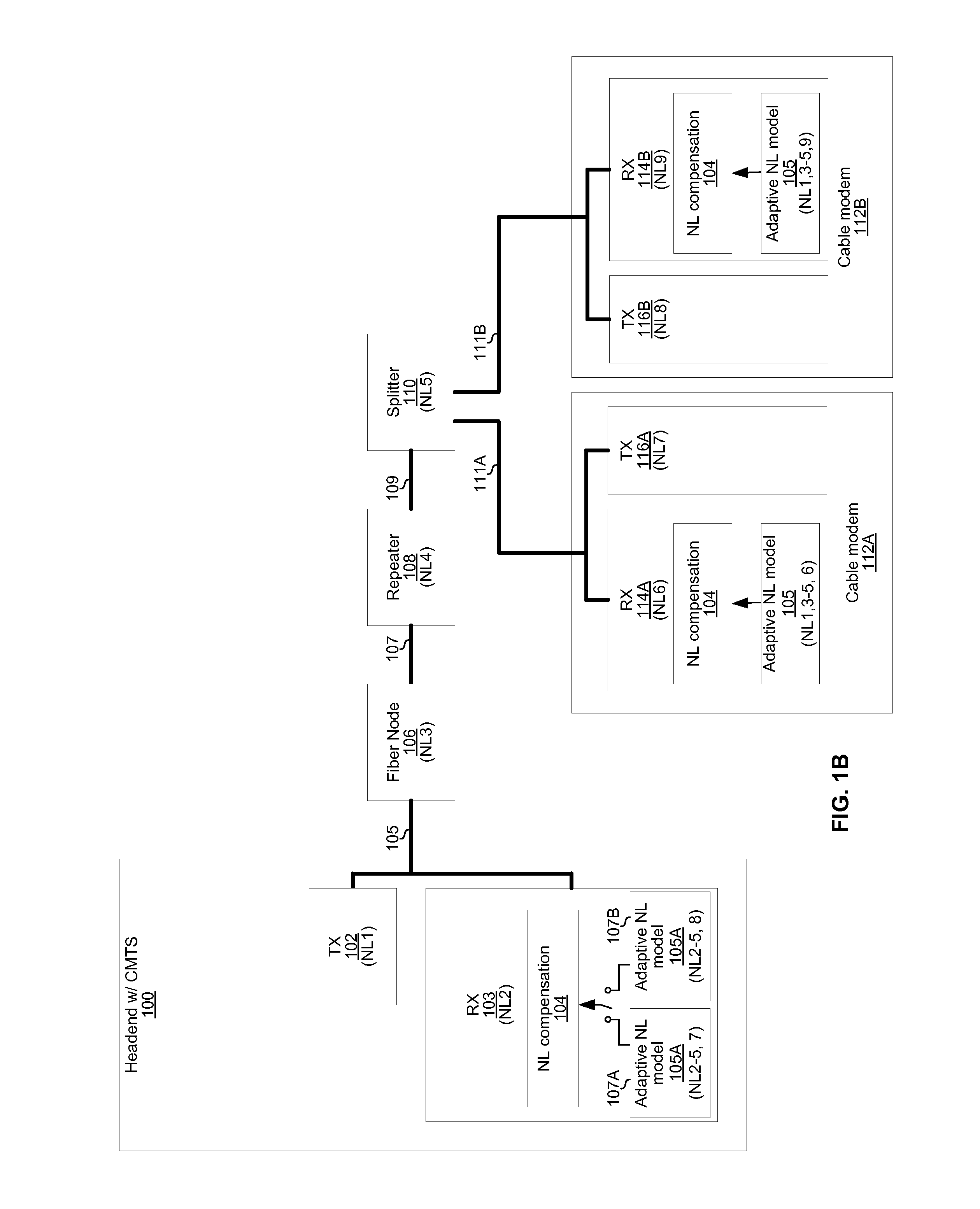

Communication methods and systems for nonlinear multi-user environments

InactiveUS20150207527A1Error preventionModulated-carrier systemsNonlinear distortionMulti user environment

An electronic receiver comprises a nonlinear distortion modeling circuit and a nonlinear distortion compensation circuit. The nonlinear distortion modeling circuit is operable to determine a plurality of sets of nonlinear distortion model parameter values, where each of the sets of nonlinear distortion model parameter values representing nonlinear distortion experienced by signals received by the electronic receiver from a respective one a plurality of communication partners. The nonlinear distortion compensation circuit is operable to use the sets of nonlinear distortion model parameter values for processing of signals from the plurality of communication partners. Each of the sets of nonlinear distortion model parameter values may comprises a plurality of values corresponding to a plurality of signal powers. The sets of nonlinear distortion model parameters may be stored in a lookup table indexed by a signal strength parameter.

Owner:AVAGO TECH INT SALES PTE LTD

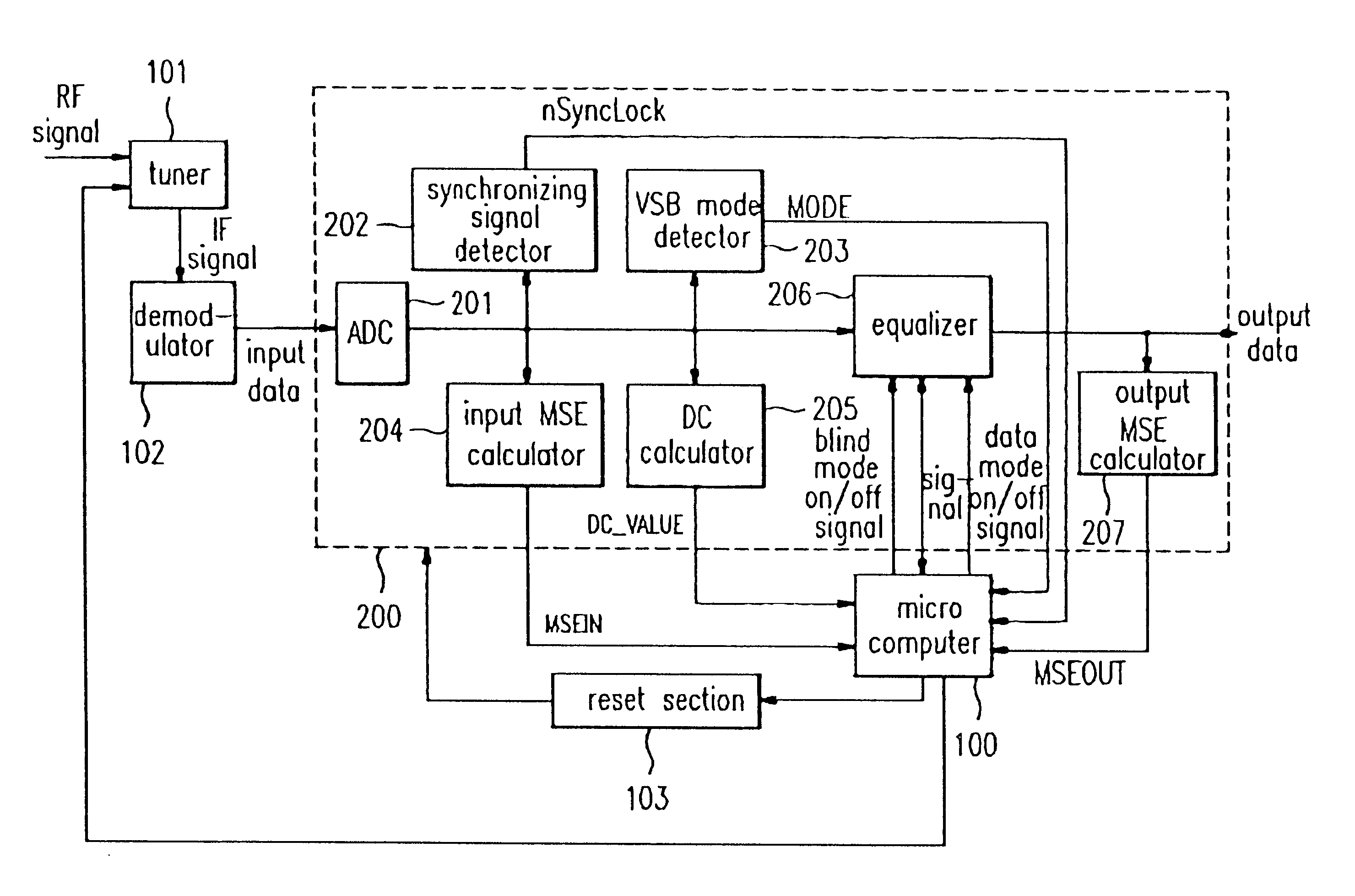

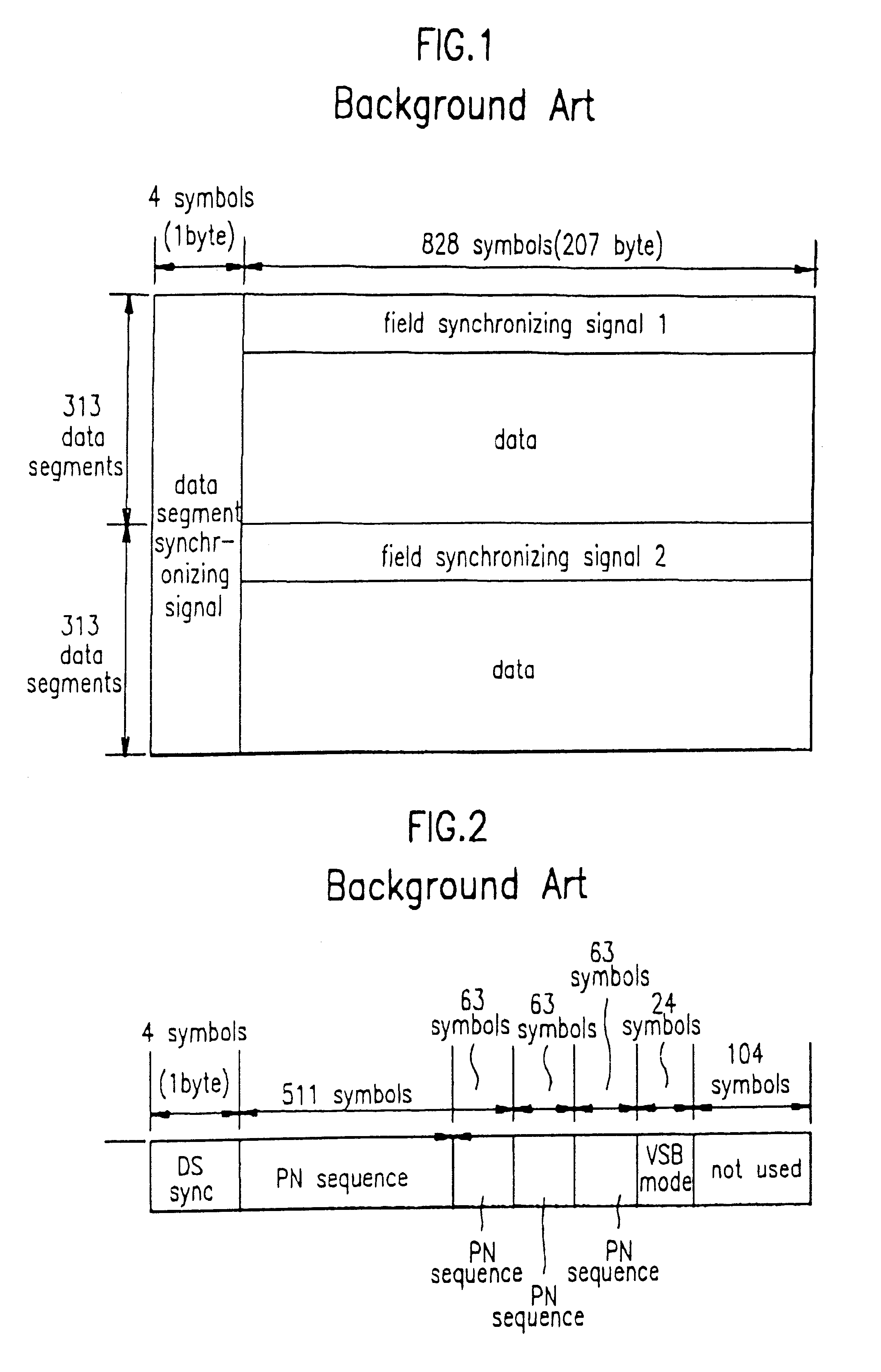

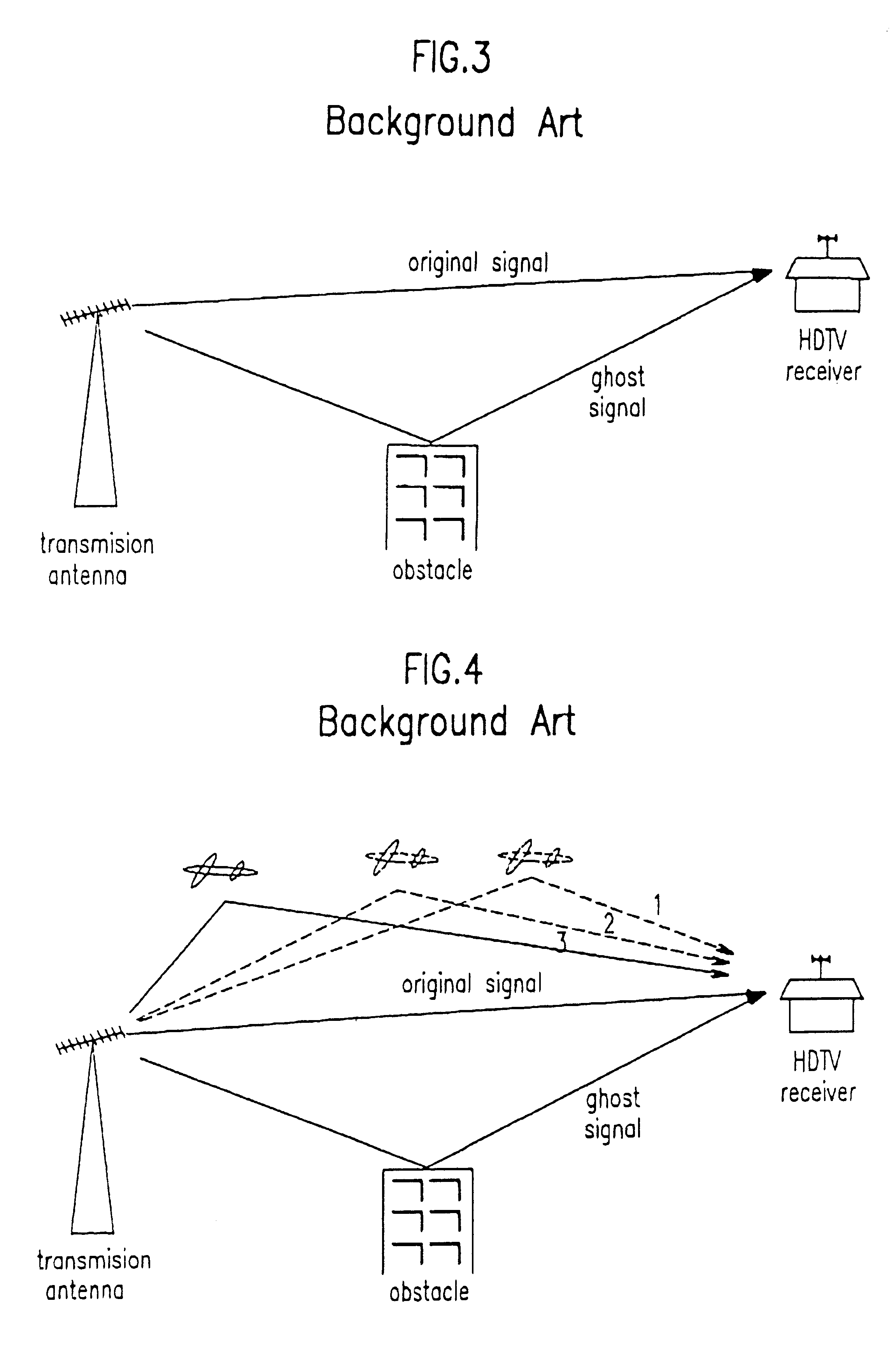

Method and apparatus which compensates for channel distortion

A method and apparatus for compensating for channel distortion is disclosed. In the present invention, equalization is performed in the treating sequence mode when the moving ghost does not exist in the channel and there is no possibility that the equalizer diverges, the data mode is cancelled and the equalization is carried out in the blind mode when the moving ghost does not exist in the channel but there is a possibility that the equalizer diverges, the equalizer is executed in the data mode when there is no possibility that the equalizer diverges but there exists the moving ghost including slowly moving ghosts in the channel, and the equalization is performed in the data mode and blind mode when the moving ghost exists and there is a possibility that the equalizer diverges.

Owner:LG ELECTRONICS INC

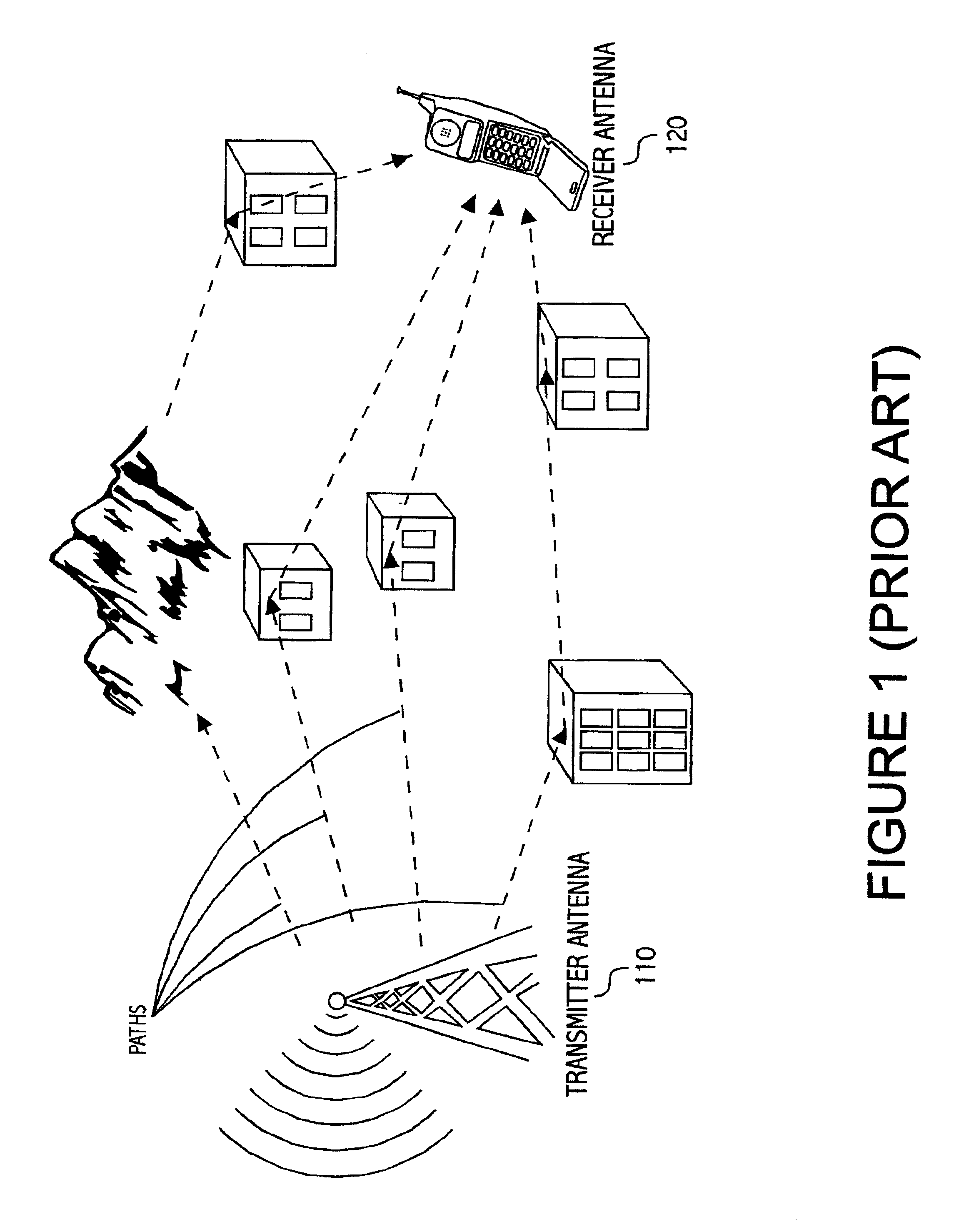

Transmitting and receiving methods

This invention describes a wireless system comprising a plurality of transmitters and receivers, wherein each transmitter has between 1 and n antennas and each receiver has between 1 and m antennas wherein one of said transmitter is arranged to transmit to one of the receivers, said one transmitter is controlled in dependence on at least one of at least one parameter of said transmitters, at least one parameter of said receiver, and at least one parameter of a wireless environment between said transmitter and said receiver.

Owner:NOKIA TECHNOLOGLES OY

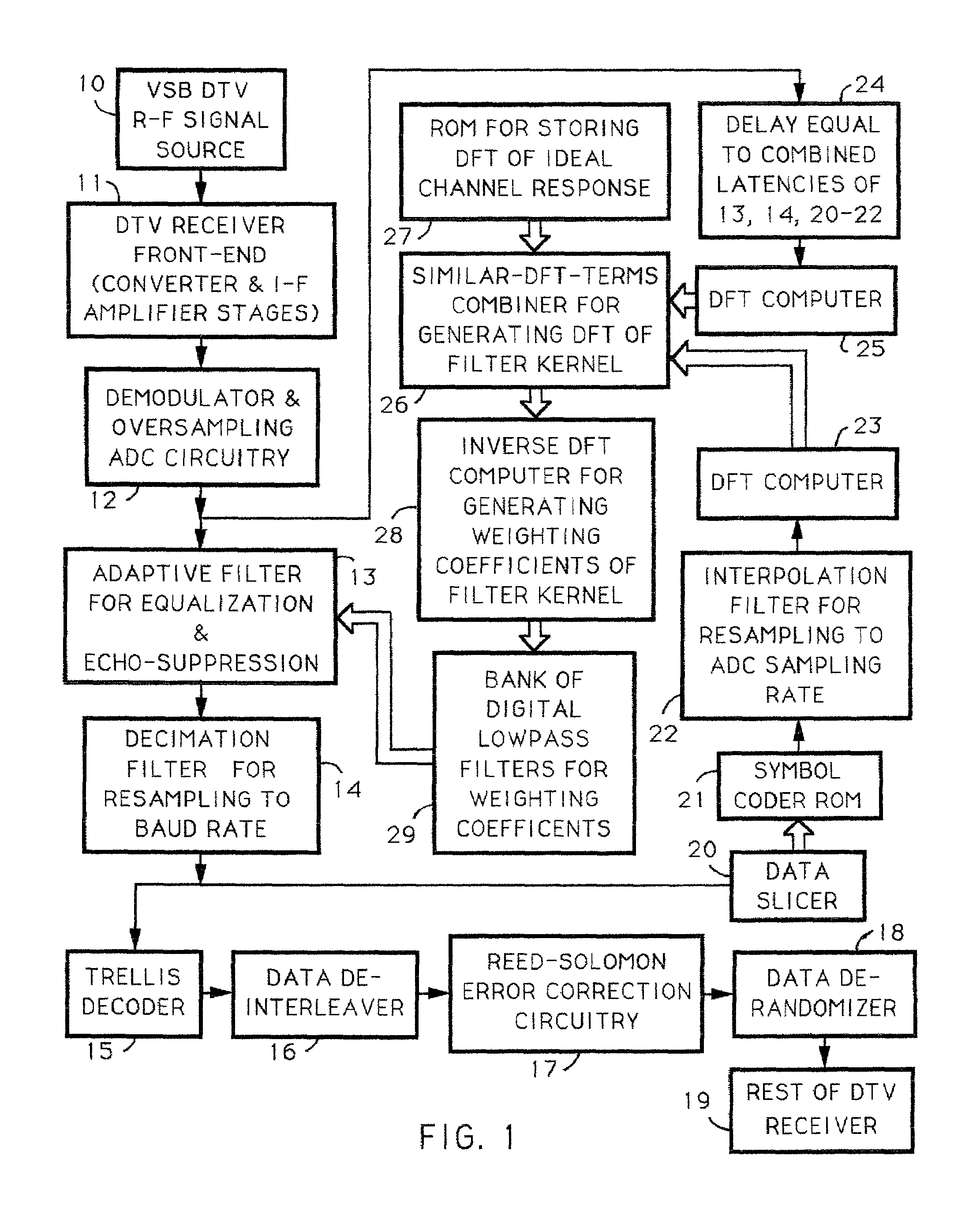

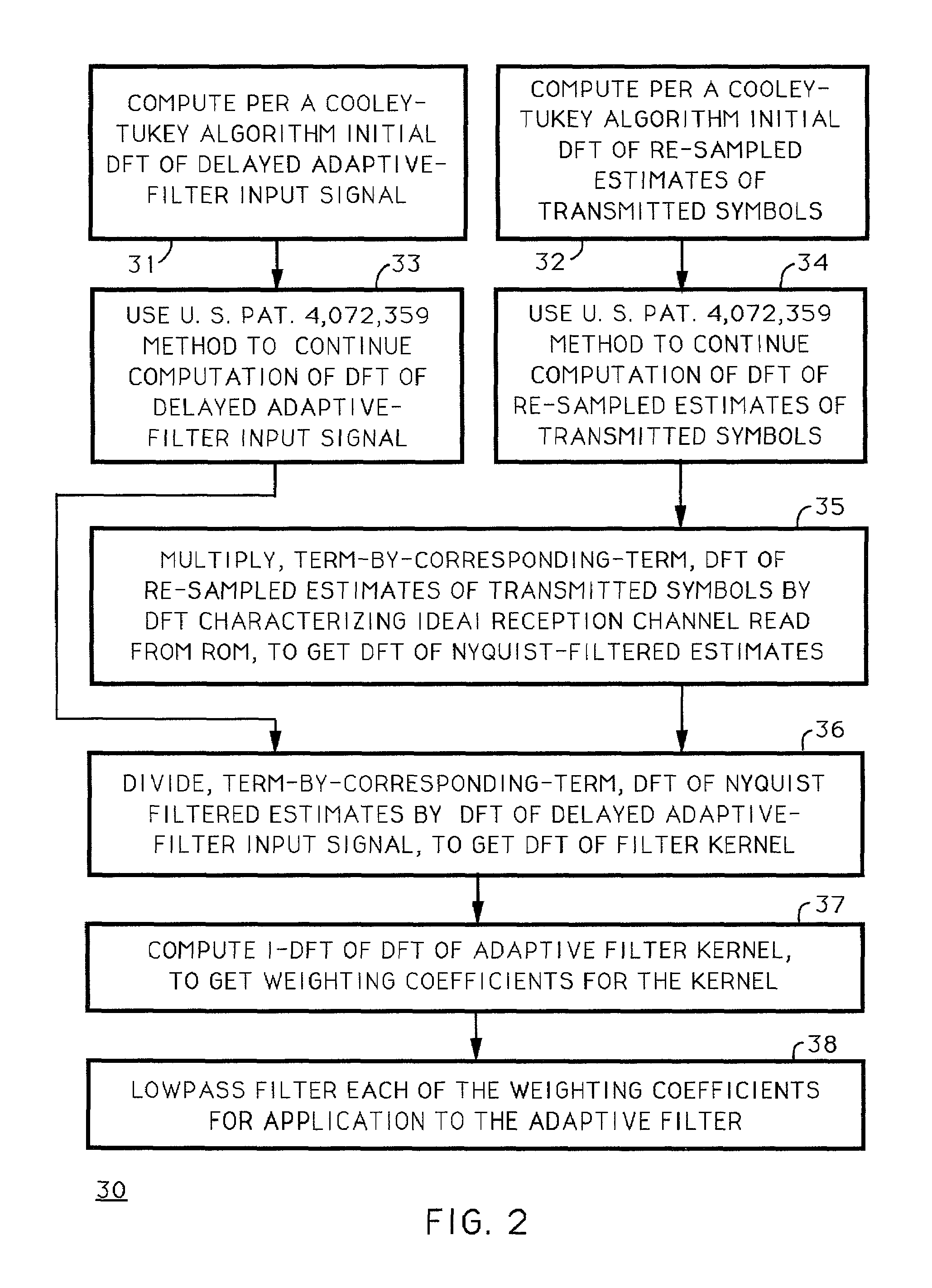

Digital modulation signal receiver with adaptive channel equalization employing discrete fourier transforms

InactiveUS6975689B1Extended durationTelevision system detailsError preventionInverse discrete fourier transformFourier transform on finite groups

Techniques for calculating the system characteristic of the adaptive filtering used for equalization and echo-suppression in a digital communications receiver, such as one used for receiving over-the-air broadcast digital television signal, are described. In these techniques, the system characteristic of the adaptive filtering is calculated from the discrete Fourier transform of successive portions of the input signal supplied to the adaptive filtering and from the discrete Fourier transform of corresponding portions of the transmitted signal, as estimated in the receiver. Receivers for implementing these techniques in various ways are also disclosed.

Owner:MCDONALD JAMES DOUGLAS +1

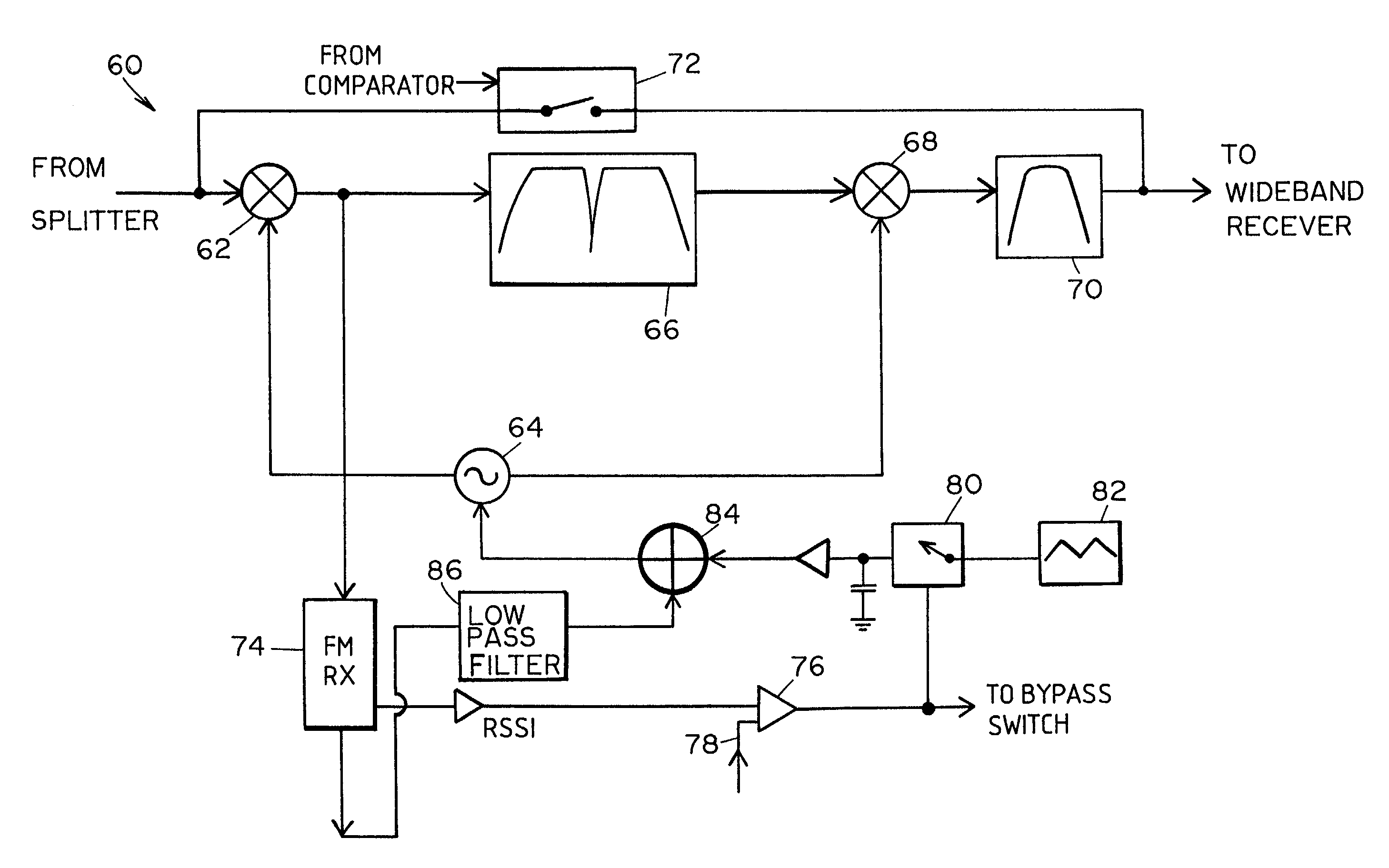

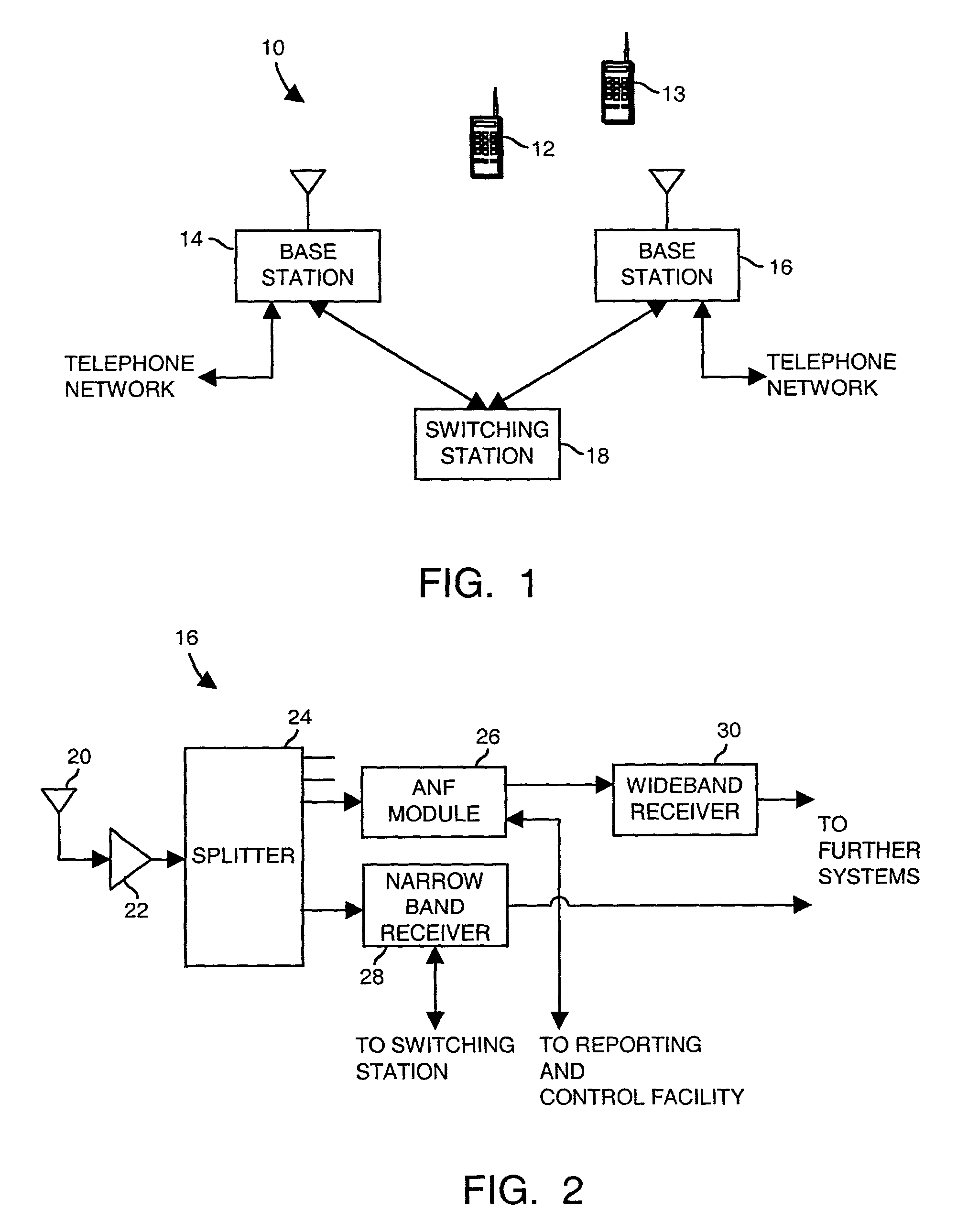

Interference detection, identification, extraction and reporting

An adaptive notch filter (ANF) module selectively filters a received wideband communication signal to eliminate narrowband interference that lies within the frequency spectrum of the wideband communication signal. To determine the presence of narrowband interference, the ANF module scans various known narrowband channels that lie within the frequency spectrum of the wideband communication signal and determines signal strengths for each of the narrowband channels. The signal strengths from the narrowband channels are compared to a threshold that is derived from the narrowband signal strengths. Narrowband channels having signal strengths that are greater than the threshold are determined to have interference.

Owner:ILLINOIS SUPERCONDUCTOR CORP

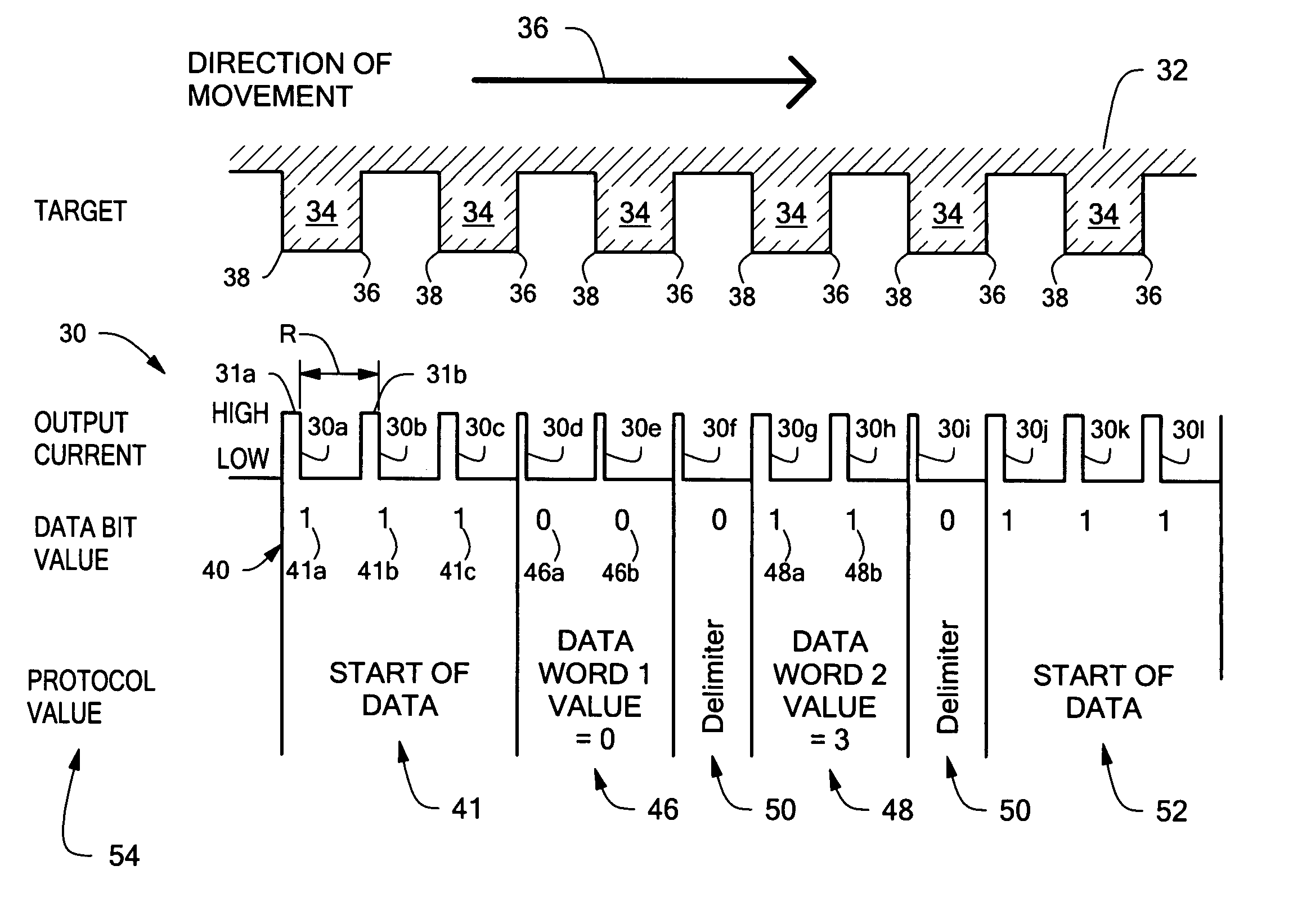

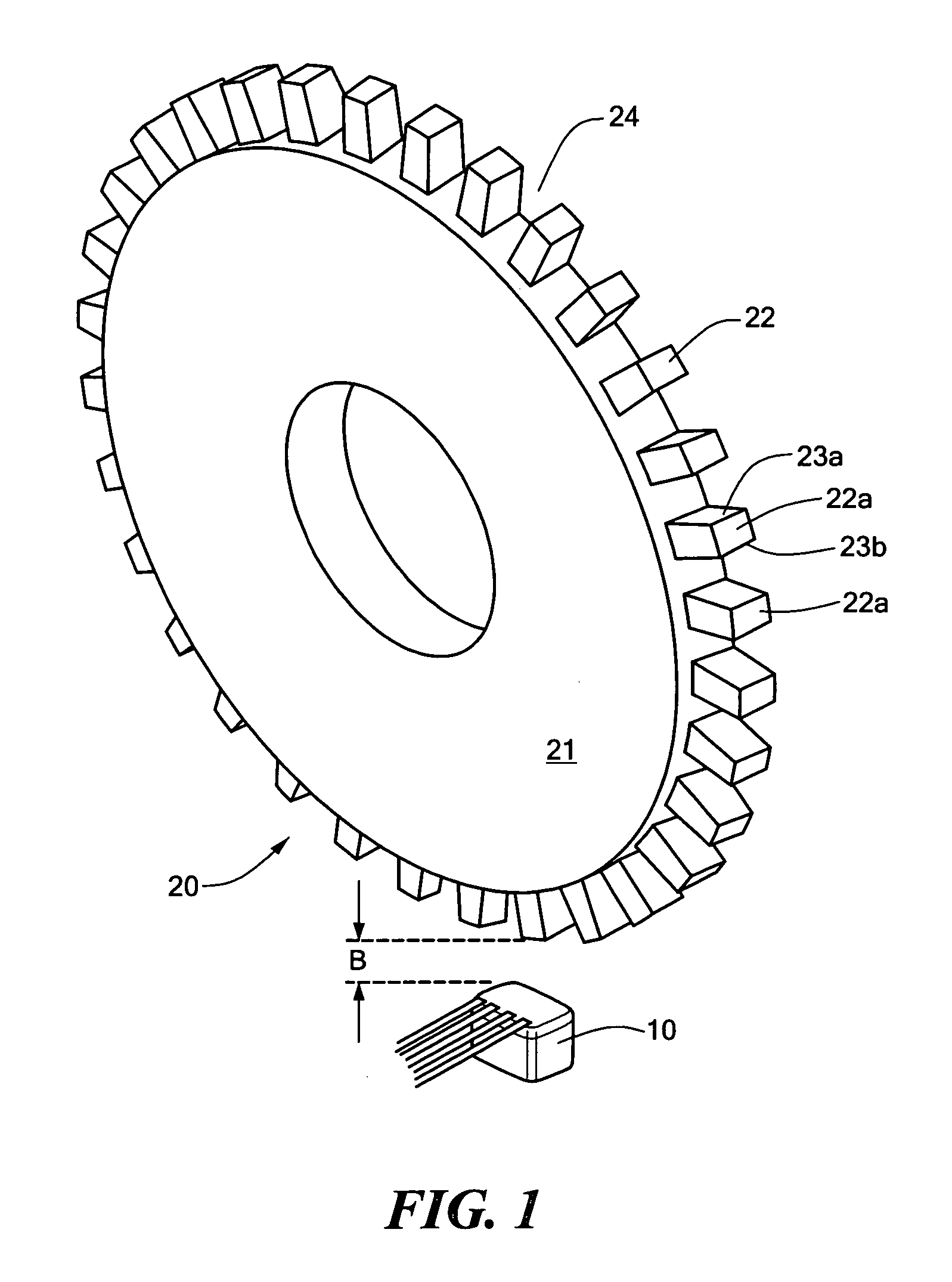

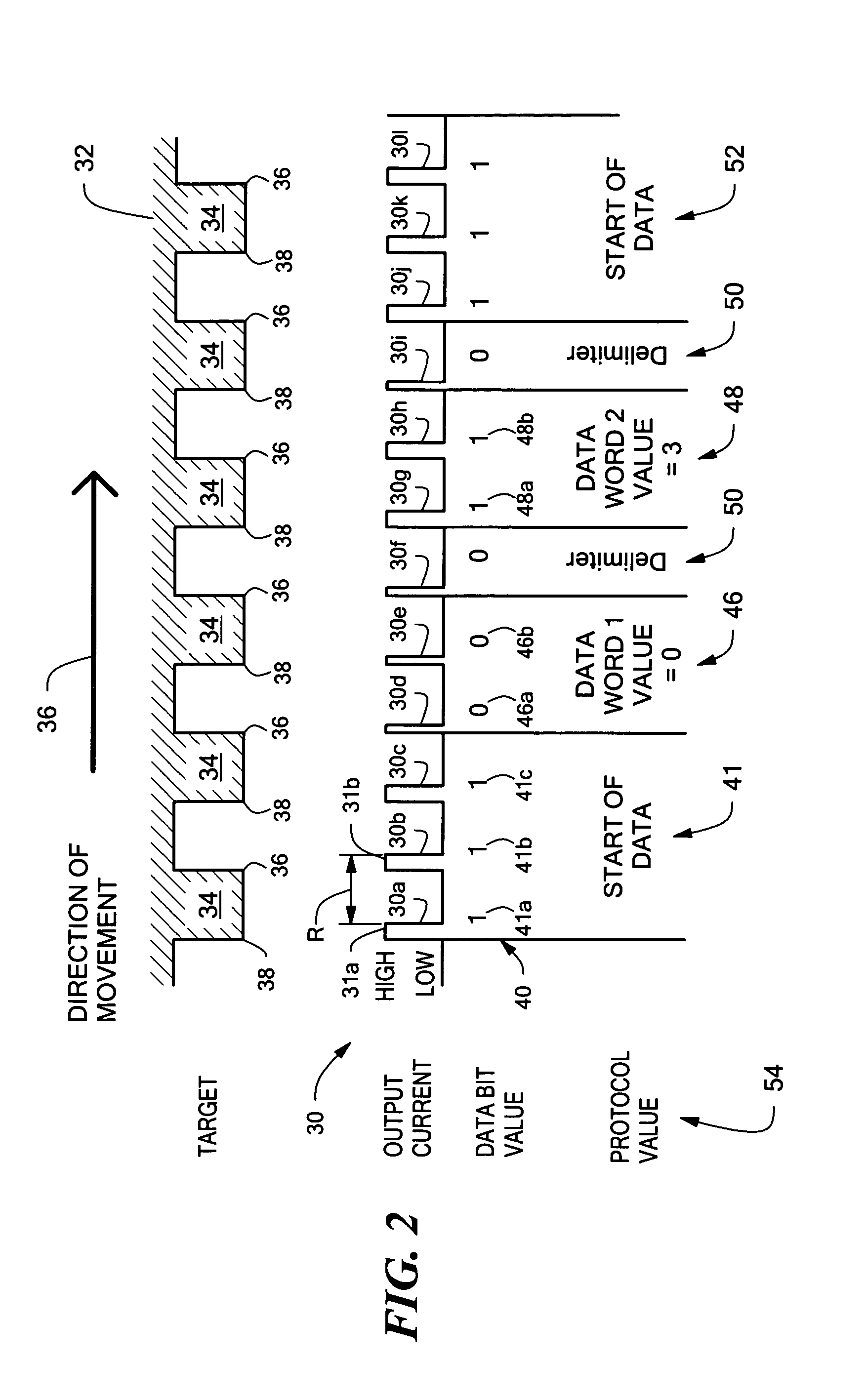

Method and apparatus for providing information from a speed and direction sensor

InactiveUS7026808B2Resistance/reactance/impedenceUsing electrical meansEngineeringDirection information

A method and apparatus for providing information from a speed and direction sensor is disclosed. The method and apparatus detect the presence of a ferromagnetic object as it moves past a sensor. The sensor determines speed and direction information regarding the ferromagnetic object, and further provides information relating to the environment surrounding the sensor or object, such as the status of an air gap between the sensor and the moving object, and the temperature of the environment in which the sensor or object is disposed.

Owner:ALLEGRO MICROSYSTEMS INC

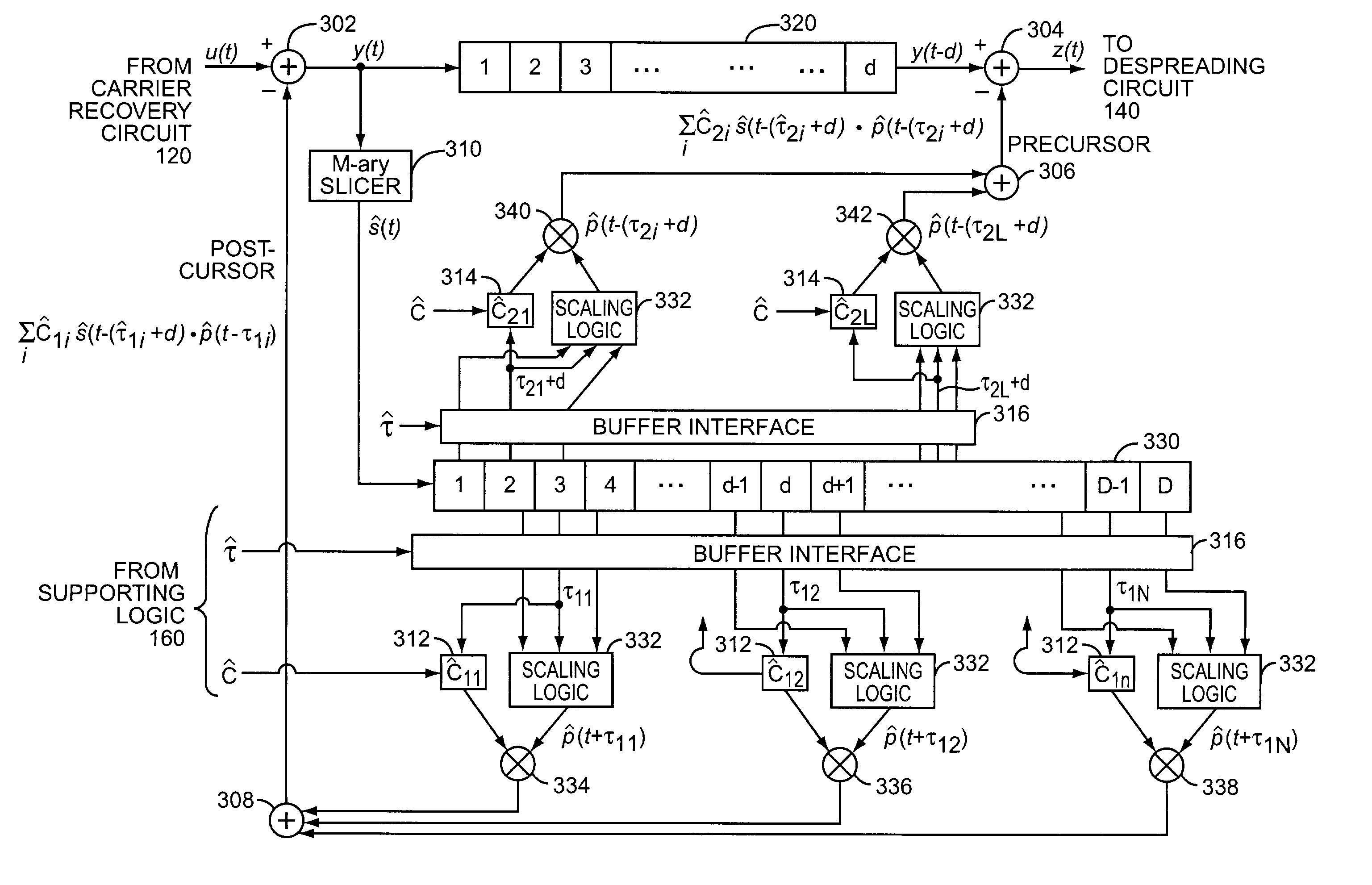

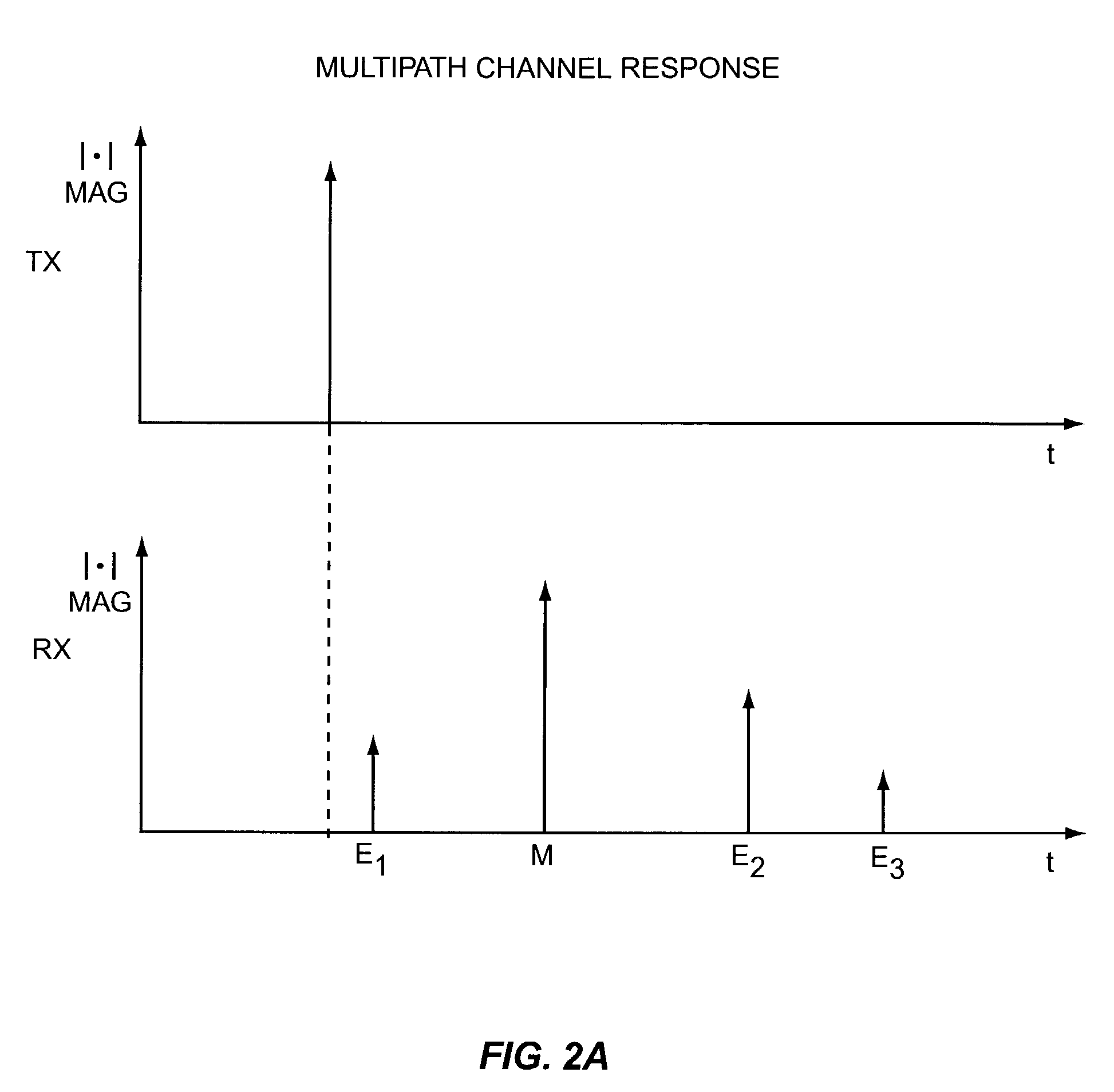

Method and apparatus for multipath signal compensation in spread-spectrum communications systems

ActiveUS7054396B2Effective multipath signal compensationChange effective lengthMultiple-port networksError preventionCommunications systemImage resolution

The equalizer of the present invention operates on input multipath signal samples, preferably at chip or sub-chip resolution, to remove or substantially cancel the effects of one or more secondary signals from the main path signal. Using predetermined path information for one or more of the secondary path signals, including magnitude, phase, and time offset relative to the main path signal, the equalizer compensates input multipath signal samples by subtracting estimated secondary signal values from the input samples. For each input sample, the equalizer forms a sliced sample, where the sliced sample represents a nominal phase value defined by the modulation scheme used in the original chip or symbol transmission that is closest in value to the actual phase of the input sample. These sliced samples are held in a running buffer and used, in combination with the predetermined path information and scaling logic, to form the estimated secondary signal values for compensating the input samples.

Owner:QORVO US INC

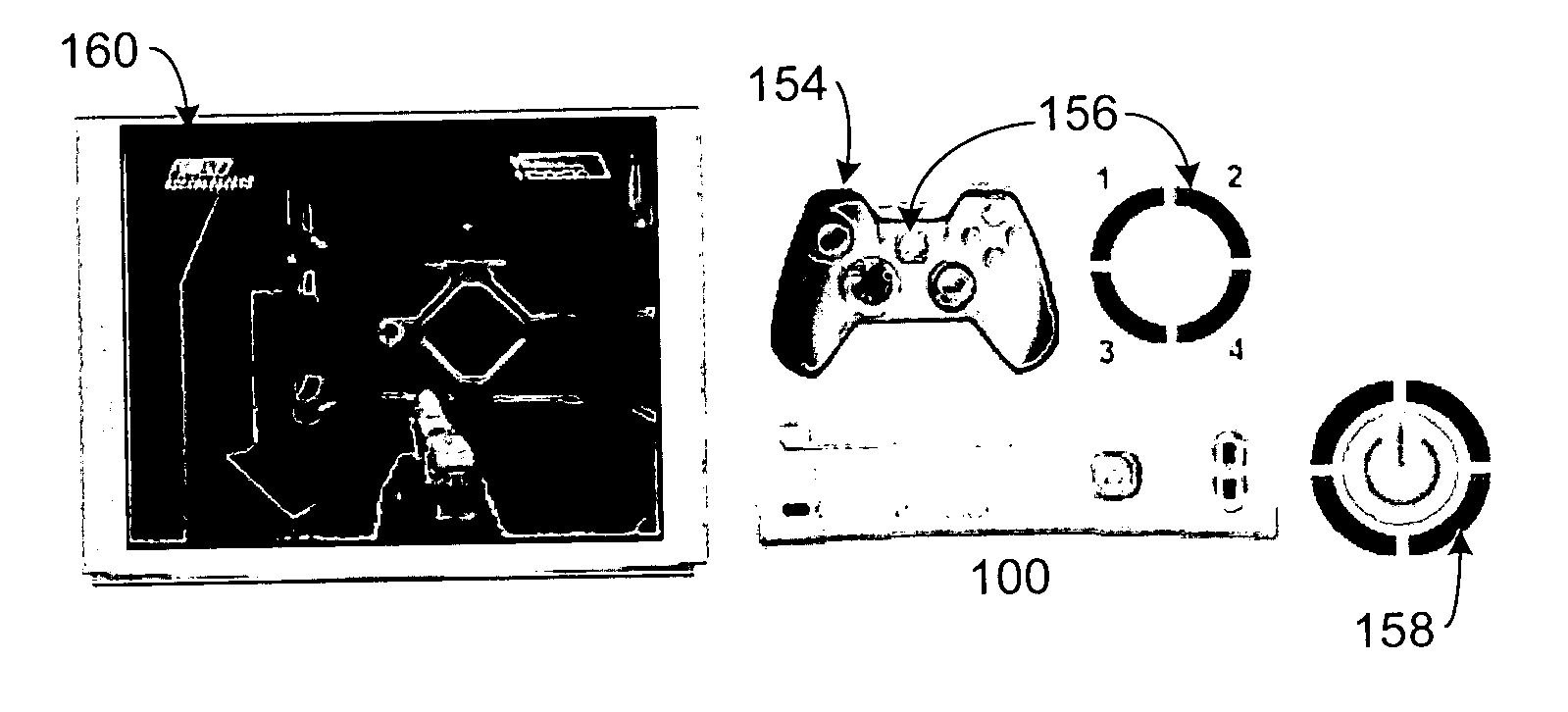

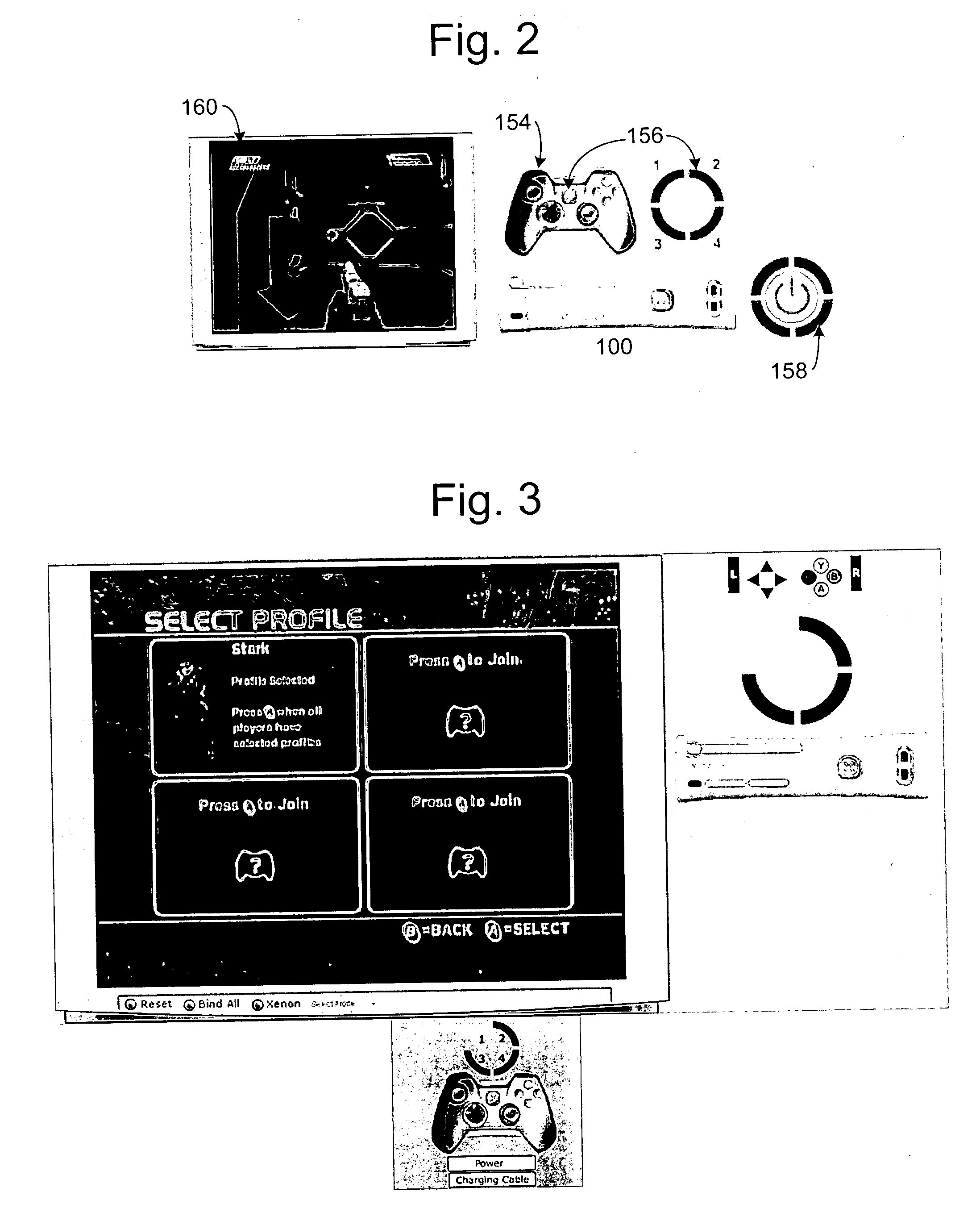

Game console notification system

Systems and methods for providing notifications to players of a gaming console of messages and system notifications. A controller and the gaming console include a four quadrant LED indicator. Each quadrant of the ring may be illuminated individually or together using an LED to indicate the messages and notifications. The quadrants may be illuminated in one of three colors and / or in patterns to indicate different types of notifications. Onscreen displays may be used to supplement the LED indicators to convey information to users. A method of binding and discovering a controller is also provided where the controller may be bound to a gaming console. After a controller is bound to a console, the controller may be discovered by the gaming console where it is assigned a virtual port and enabled for game play.

Owner:MICROSOFT TECH LICENSING LLC

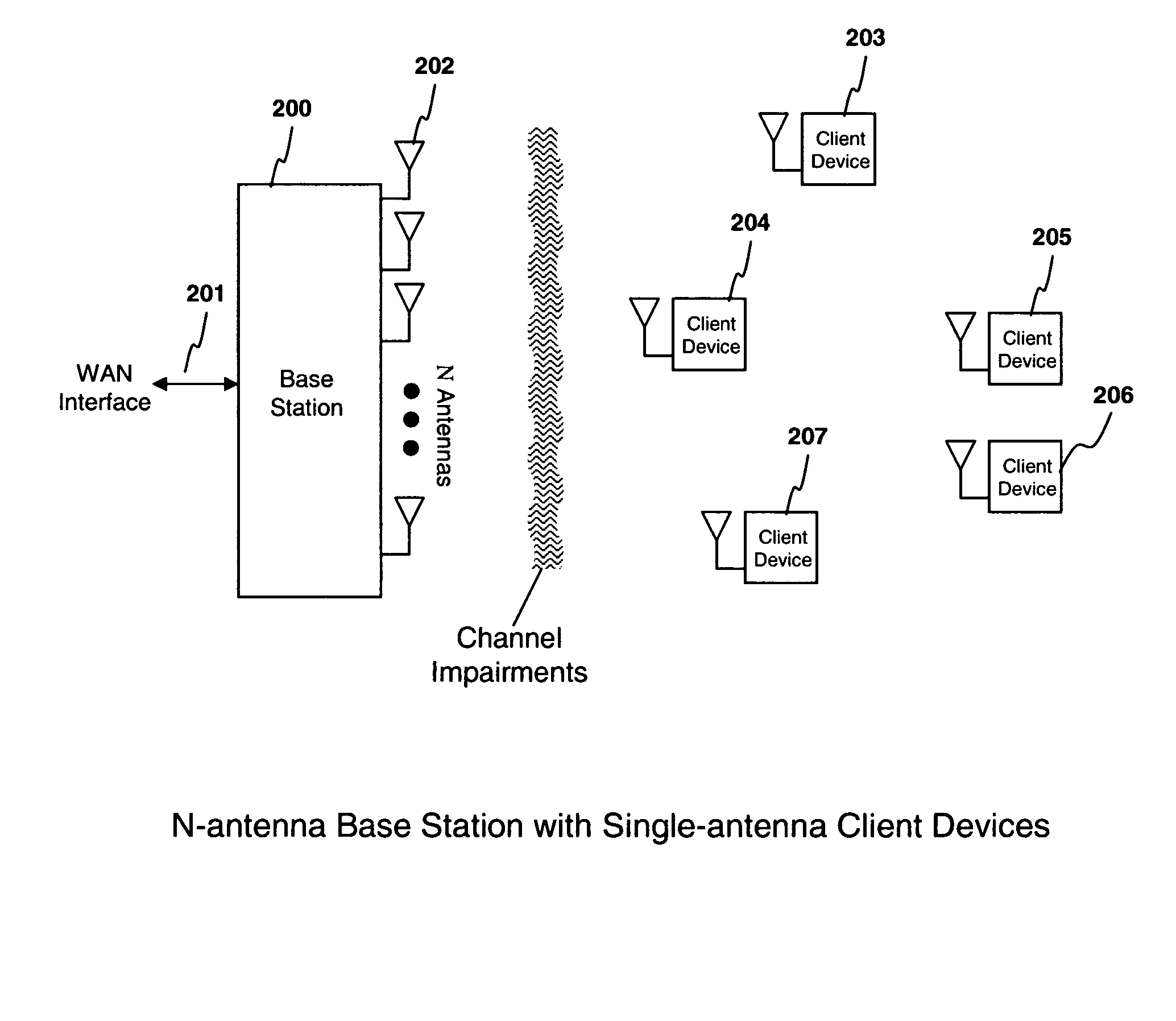

System and method for distributed input distributed output wireless communications

A system and method are described for compensating for frequency and phase offsets in a multiple antenna system (MAS) with multi-user (MU) transmissions (“MU-MAS”). For example, a method according to one embodiment of the invention comprises: transmitting a training signal from each antenna of a base station to one or each of a plurality of wireless client devices, one or each of the client devices analyzing each training signal to generate frequency offset compensation data, and receiving the frequency offset compensation data at the base station; computing MU-MAS precoder weights based on the frequency offset compensation data to pre-cancel the frequency offset at the transmitter; precoding training signal using the MU-MAS precoder weights to generate precoded training signals for each antenna of the base station; transmitting the precoded training signal from each antenna of a base station to each of a plurality of wireless client devices, each of the client devices analyzing each training signal to generate channel characterization data, and receiving the channel characterization data at the base station; computing a plurality of MU-MAS precoder weights based on the channel characterization data, the MU-MAS precoder weights calculated to pre-cancel frequency and phase offset and / or inter-user interference; precoding data using the MU-MAS precoder weights to generate precoded data signals for each antenna of the base station; and transmitting the precoded data signals through each antenna of the base station to each respective client device.

Owner:REARDEN

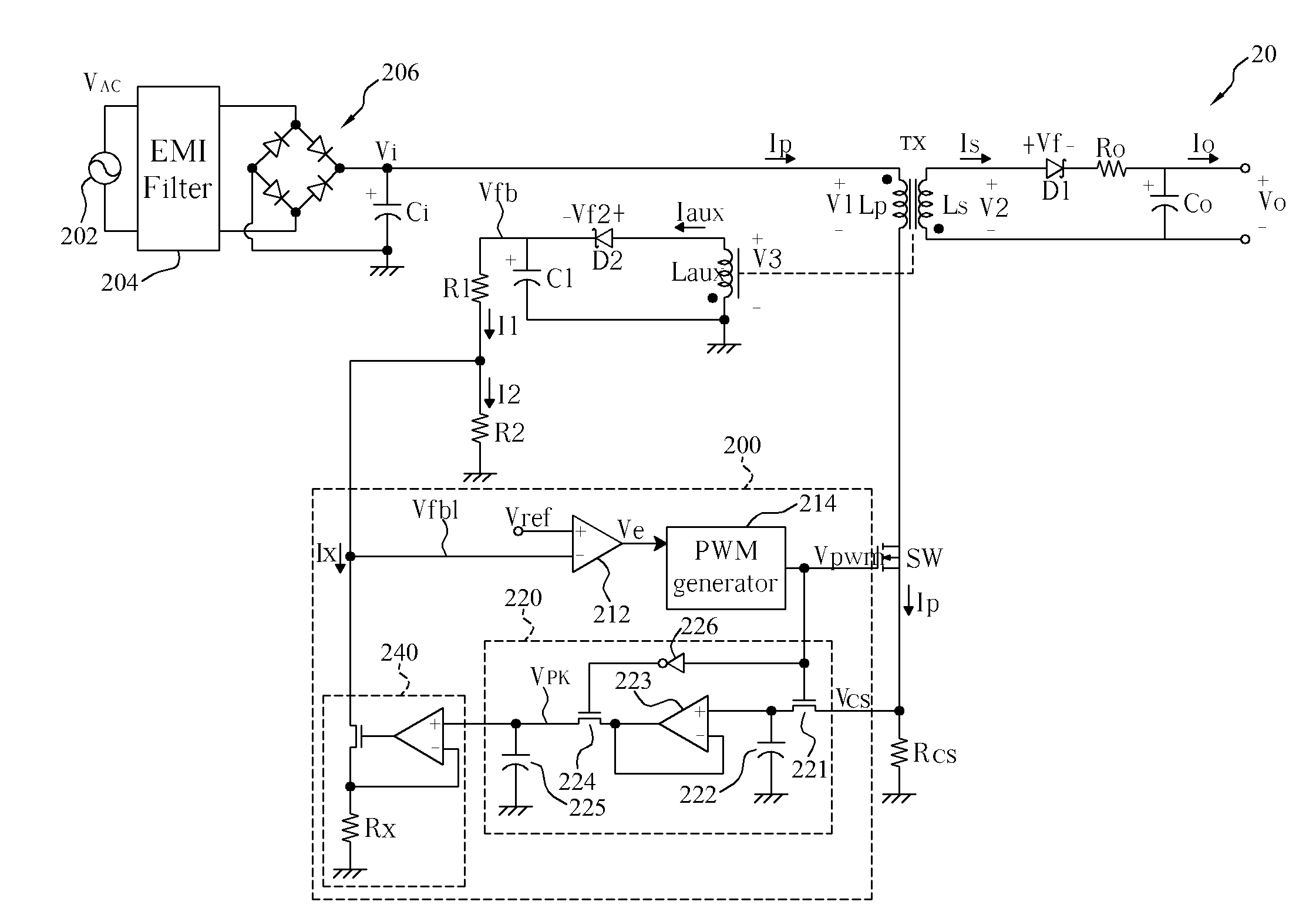

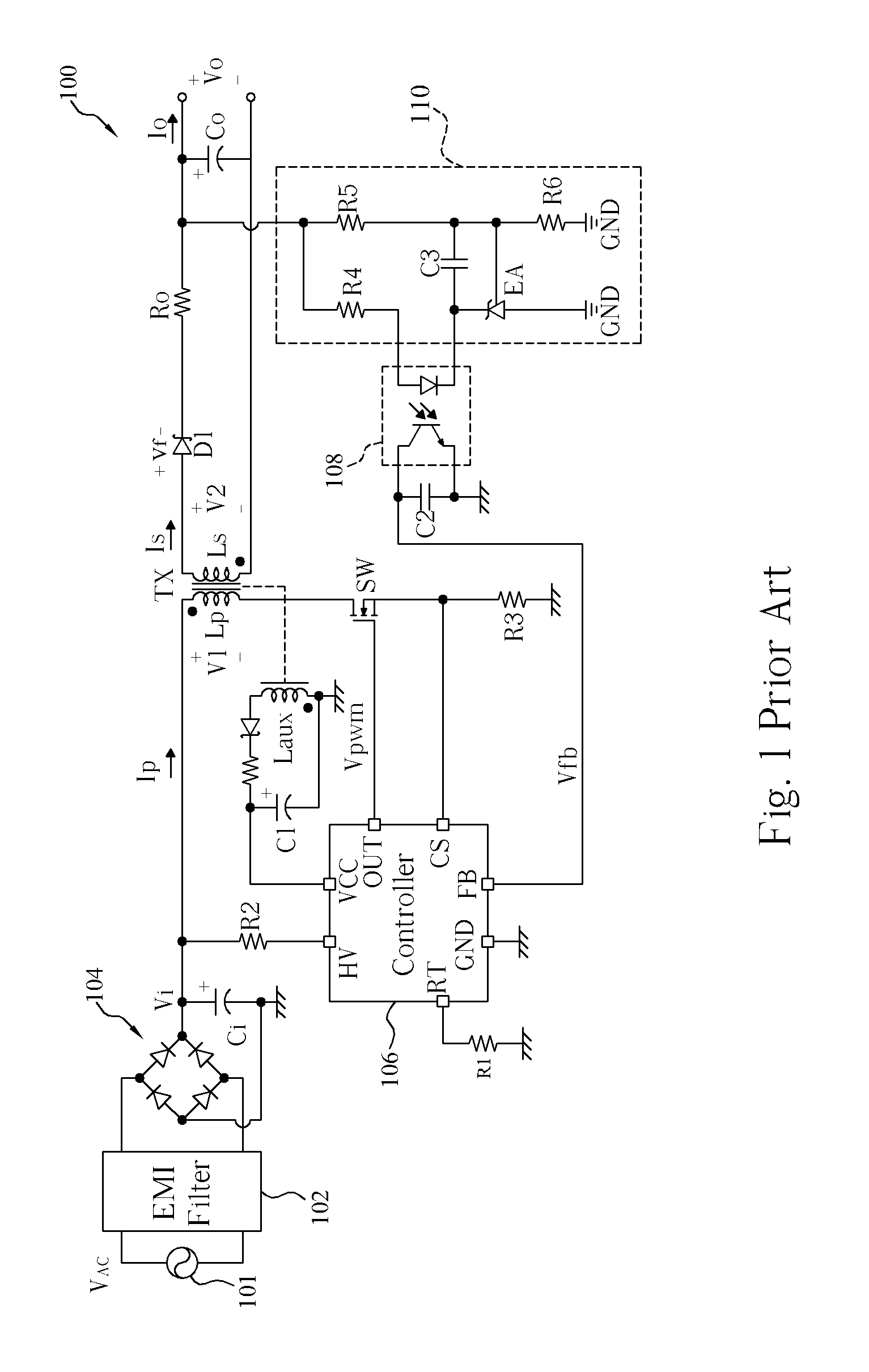

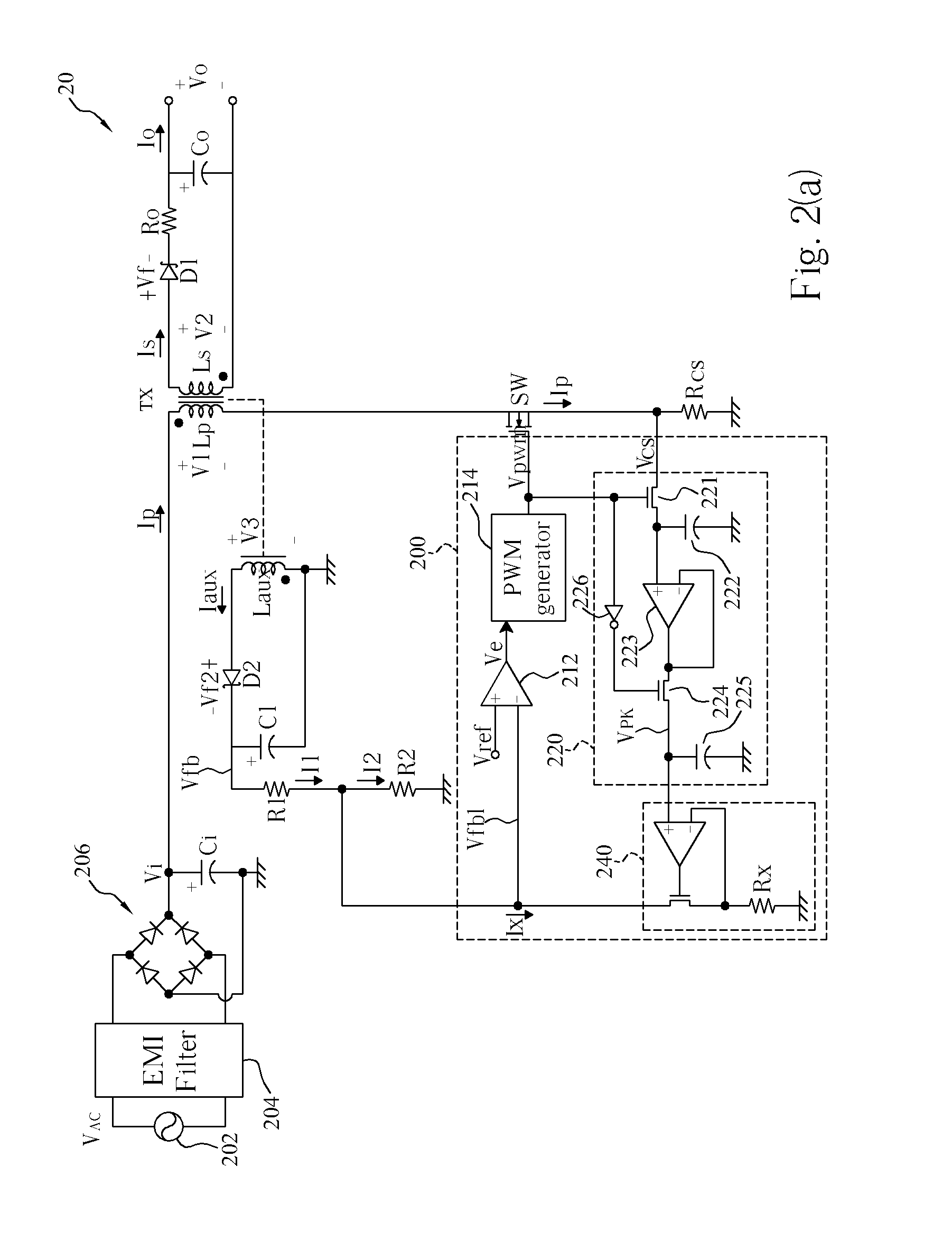

Switching-mode power converter and pulse-width-modulation control circuit with primary-side feedback control

A pulse-width-modulation control circuit of a switching-mode power converter with a primary-side feedback control is disclosed. The switching-mode power converter includes a transformer, a power switch, a current sensing resistor and the pulse-width-modulation control circuit. The transformer includes a primary-side winding, a secondary-side winding and an auxiliary winding. The pulse-width-modulation control circuit includes a sample and hold circuit, a transconductor circuit, an error amplifier and a pulse-width-modulation generator.

Owner:LEADTREND TECH

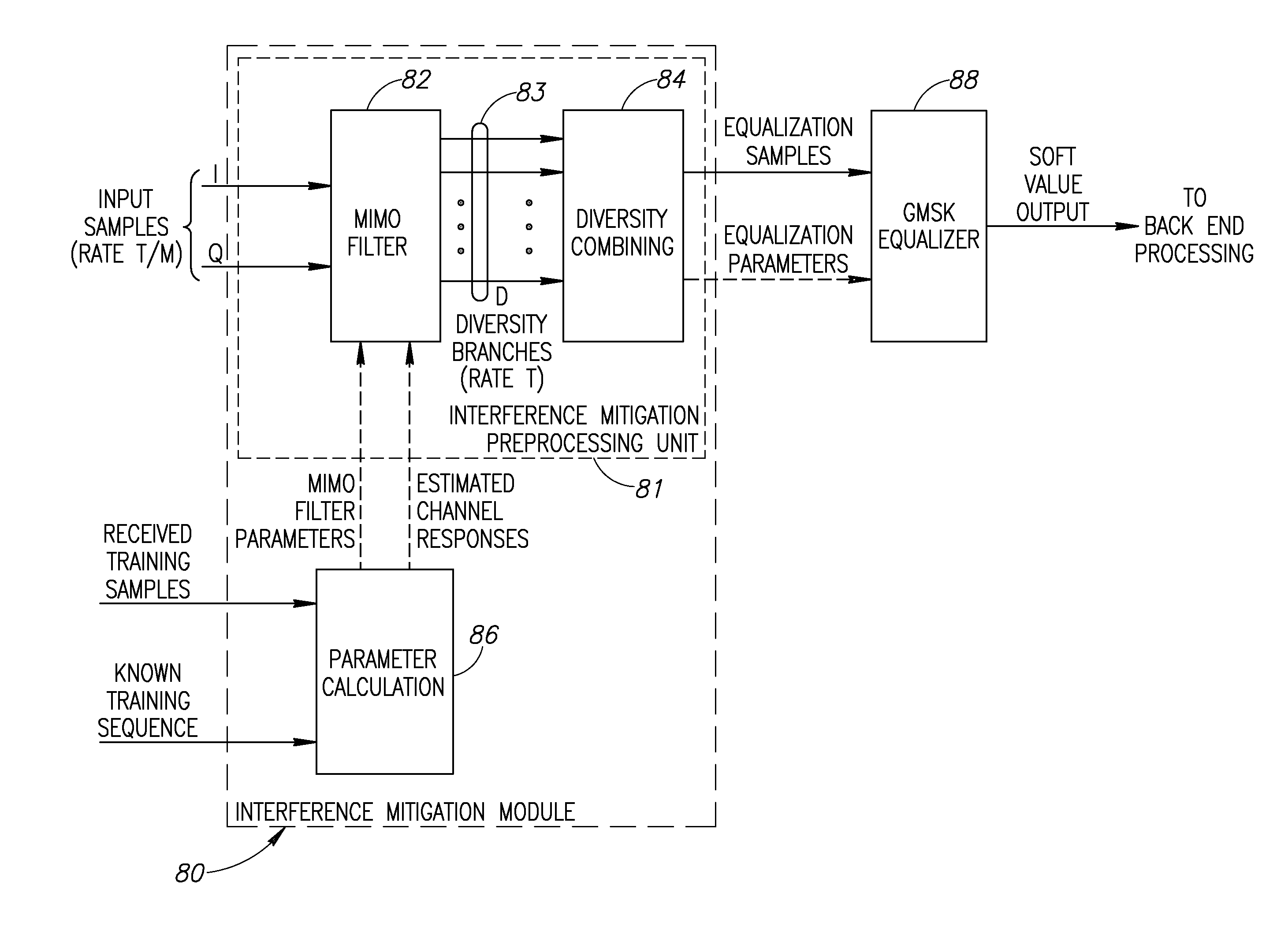

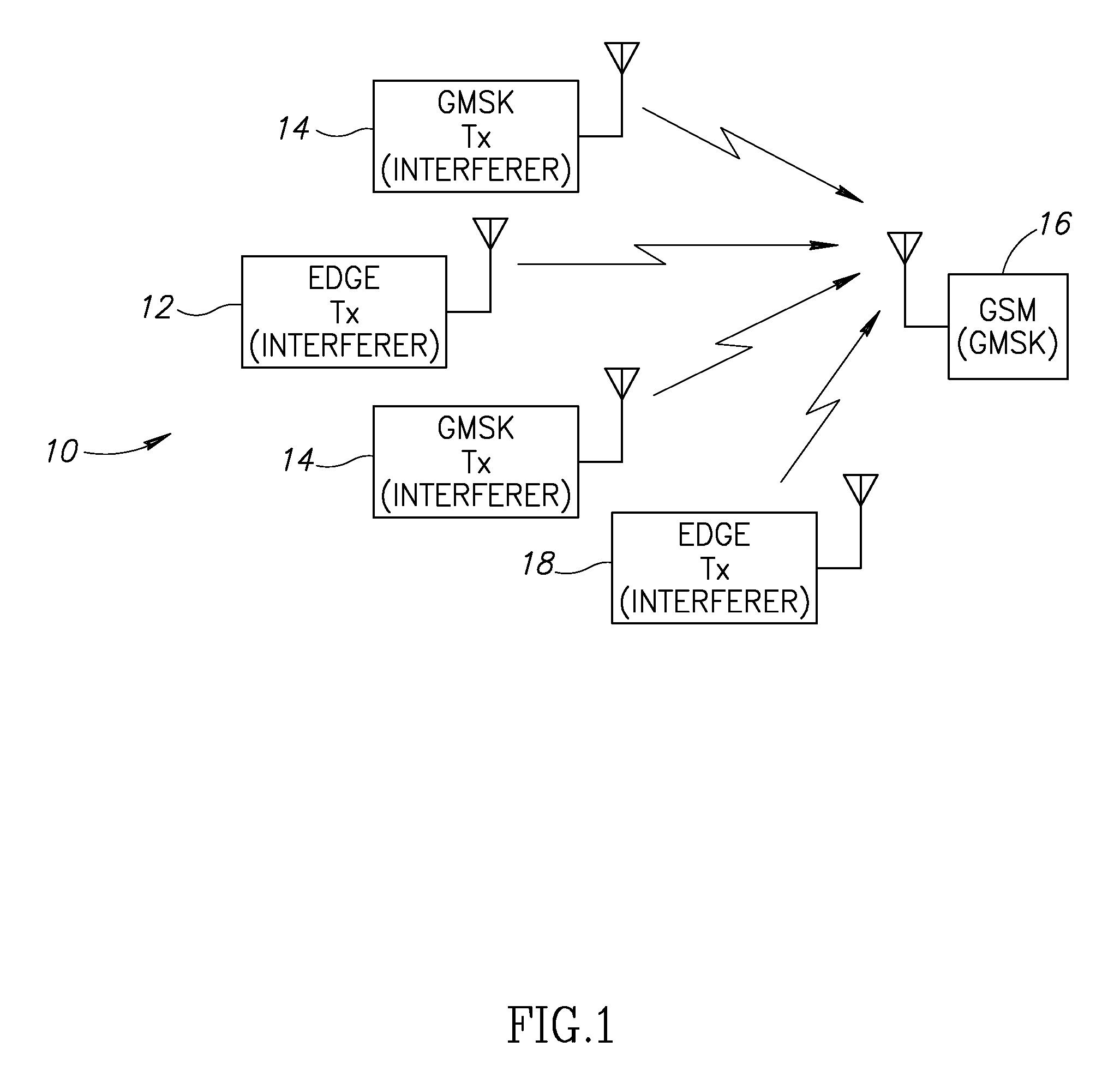

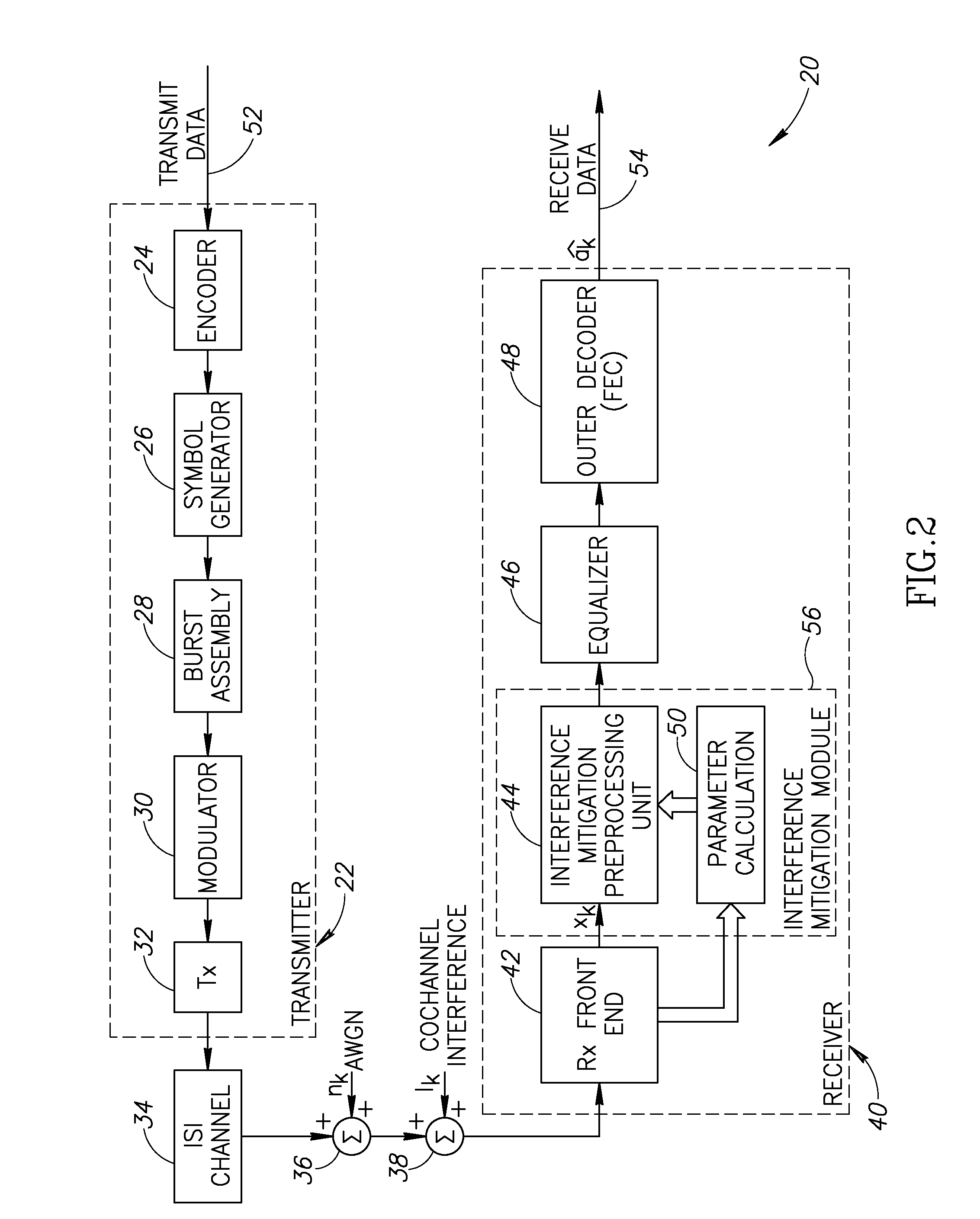

Blind interference mitigation in a digital receiver

InactiveUS20070127608A1Improve acceleration performanceReduce computational complexityError preventionLine-faulsts/interference reductionEngineeringCo-channel interference

A novel and useful apparatus for and method of Gaussian Minimum Shift Keying (GMSK) single antenna interference cancellation (SAIC) for use in a digital receiver. The invention comprises an interference mitigation module that treats the problem of GMSK SAIC in a blind manner. The interference mitigation mechanism is operative to compensate for the co-channel interference added in the communications channel which is subject to multipath propagation and fading, receiver filter and any pre-channel estimation filtering. The interference mitigation module takes advantage of the spatial diversity making up multiple branches of the received signal. The branches comprise the in-phase and quadrature elements of the received signal, the sampling phases if over sampling is applied (i.e. T / m sampling) and / or multiple antennas. The invention utilizes the spatial diversity of these multiple representations of the received signal and combines (i.e. collapses) the information in the plurality of branches into a single branch that is input to the equalizer.

Owner:COMSYS COMM & SIGNAL PROC

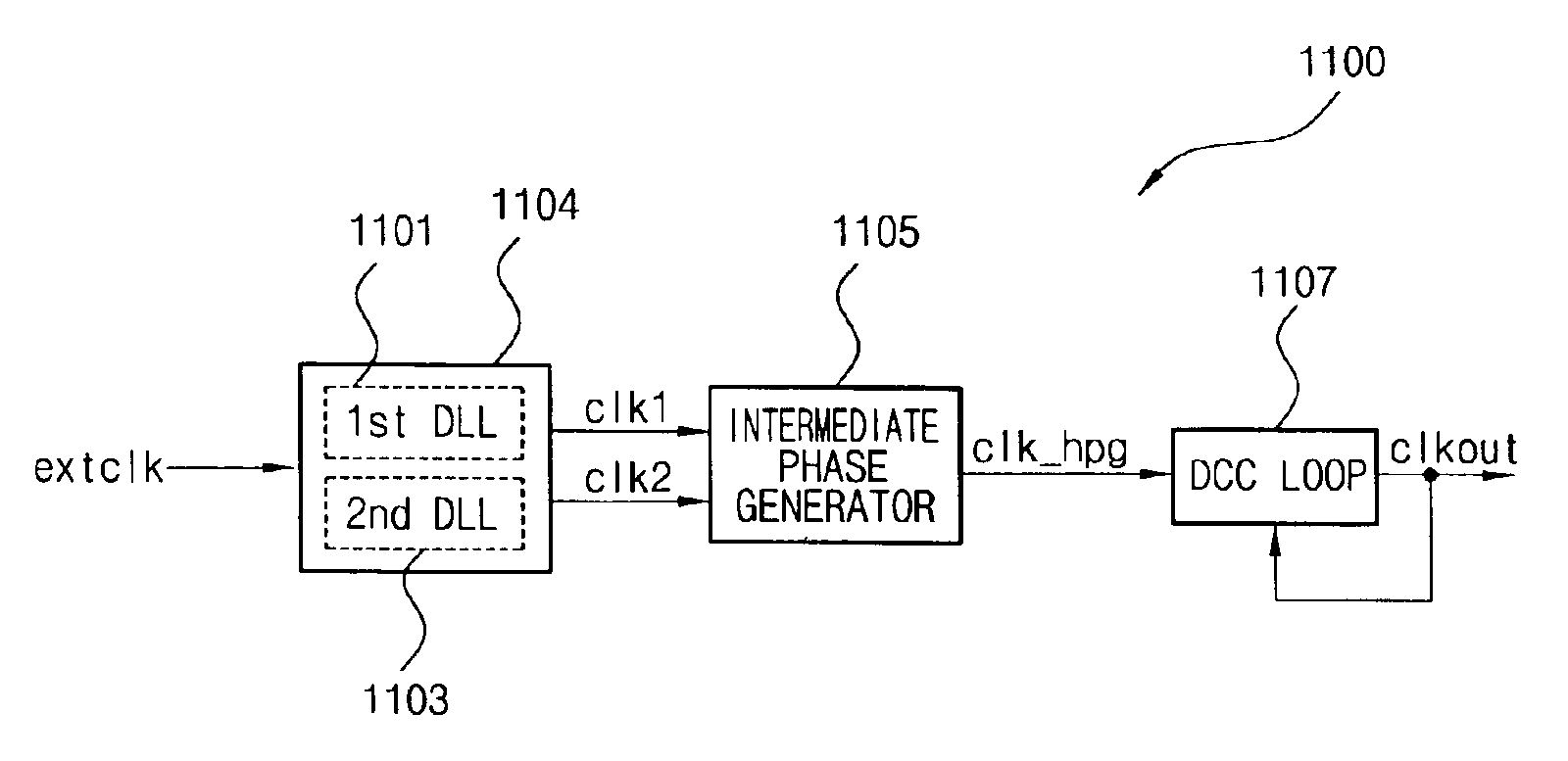

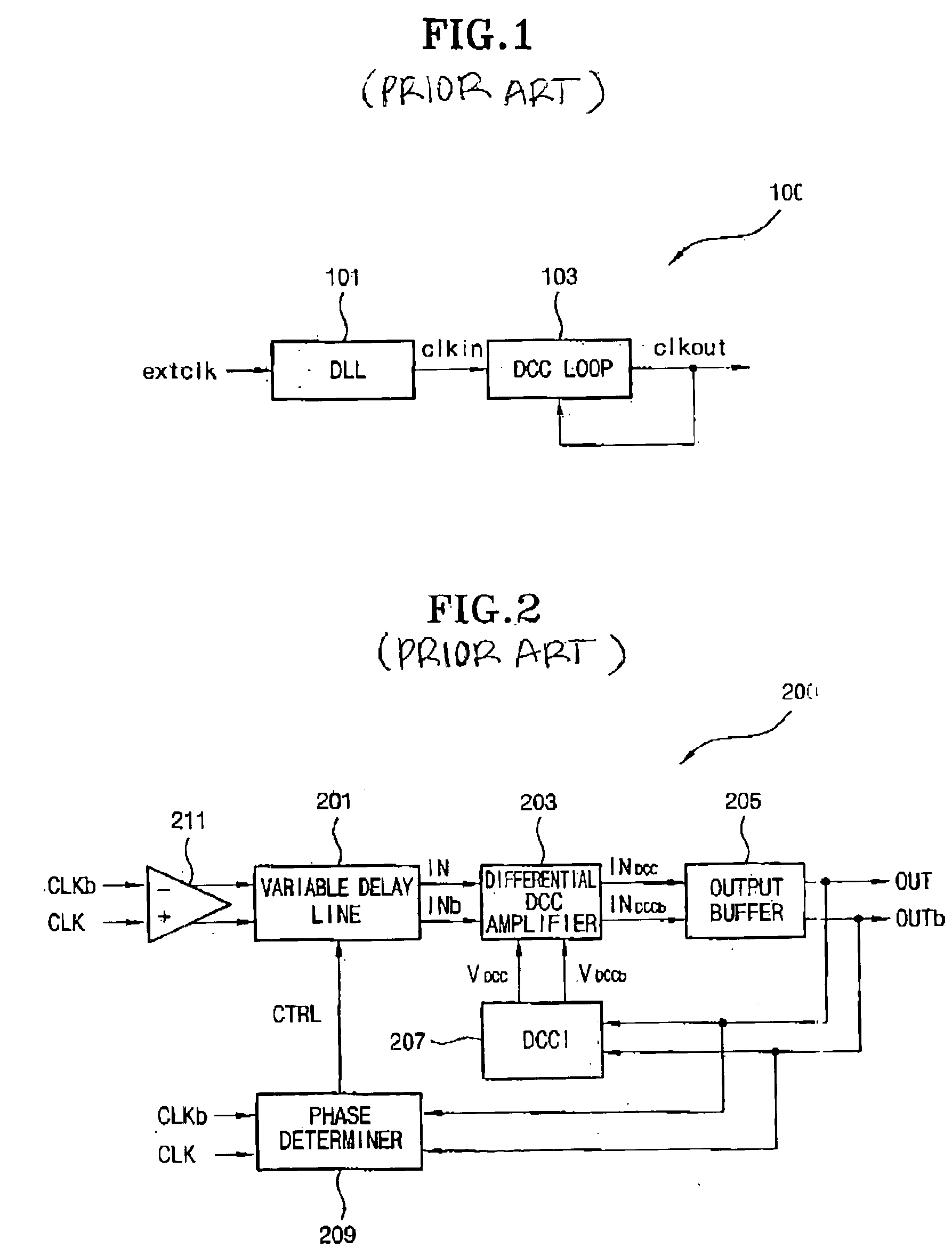

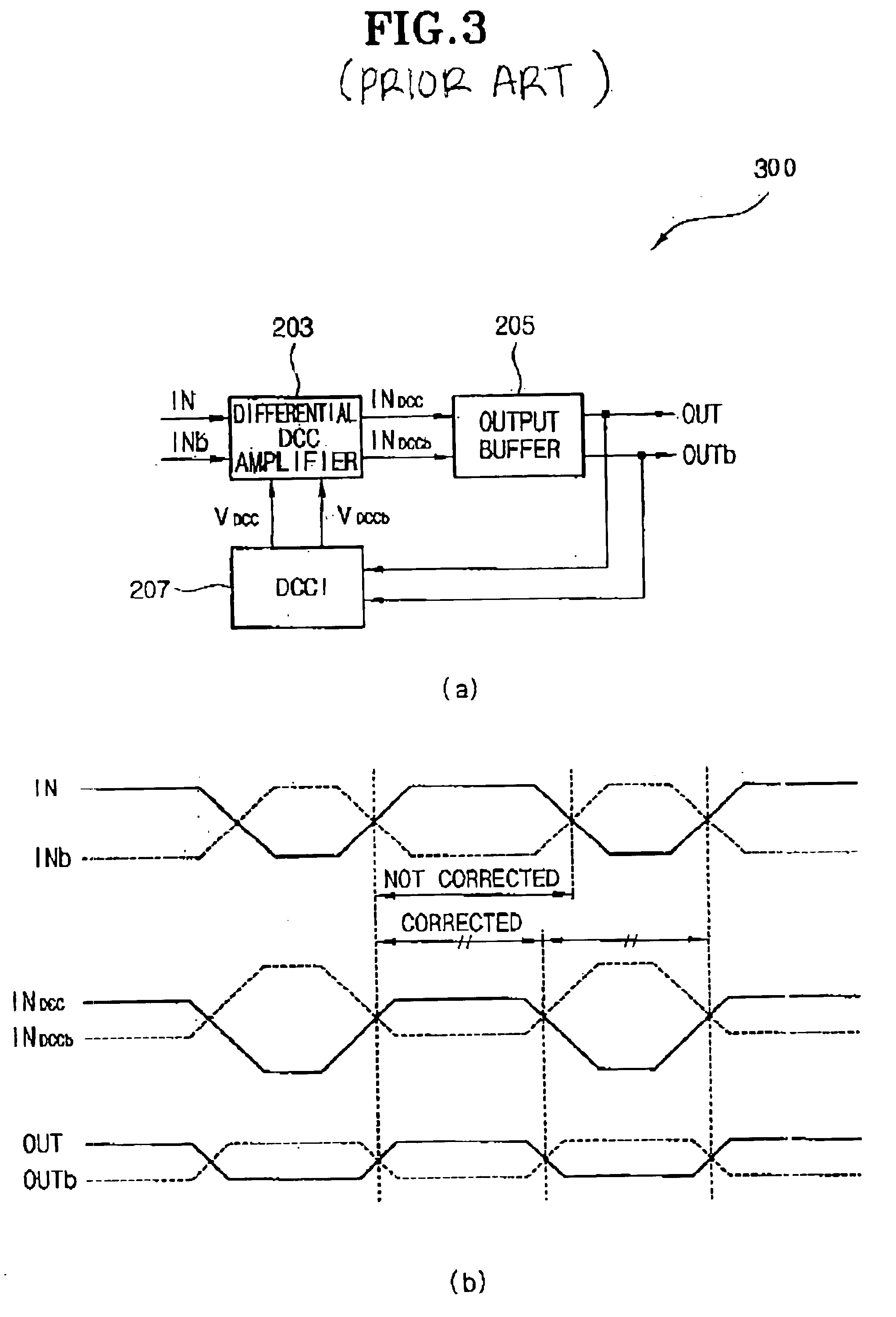

Delay locked loop circuit with duty cycle correction function

InactiveUS6853225B2Improve accuracyShort lock timePulse automatic controlContinuous to patterned pulse manipulationNegative feedbackDelay-locked loop

A delay locked loop (DLL) circuit having a structure in which a method of performing duty cycle correction (DCC) using two DLLs and an intermediate phase composer and a method of performing DCC by forming a closed loop using a negative feedback are combined with each other is provided. The DLL circuit includes a first DLL for receiving an external clock signal and generating a first clock signal and a second DLL for receiving an external clock signal and generating a second clock signal. The first clock signal and the second clock signal are synchronized with an external clock signal. The DLL circuit further includes an intermediate phase generation circuit for receiving the first and second clock signals and generating an intermediate phase clock signal and a DCC loop for receiving the intermediate phase clock signal and generating an output clock signal. The intermediate phase clock signal has an intermediate phase between the phases of the first and second clock signals. The output clock signal is generated through correction of the duty cycle of the intermediate phase clock signal using a value obtained by integrating the output clock signal.

Owner:SK HYNIX INC

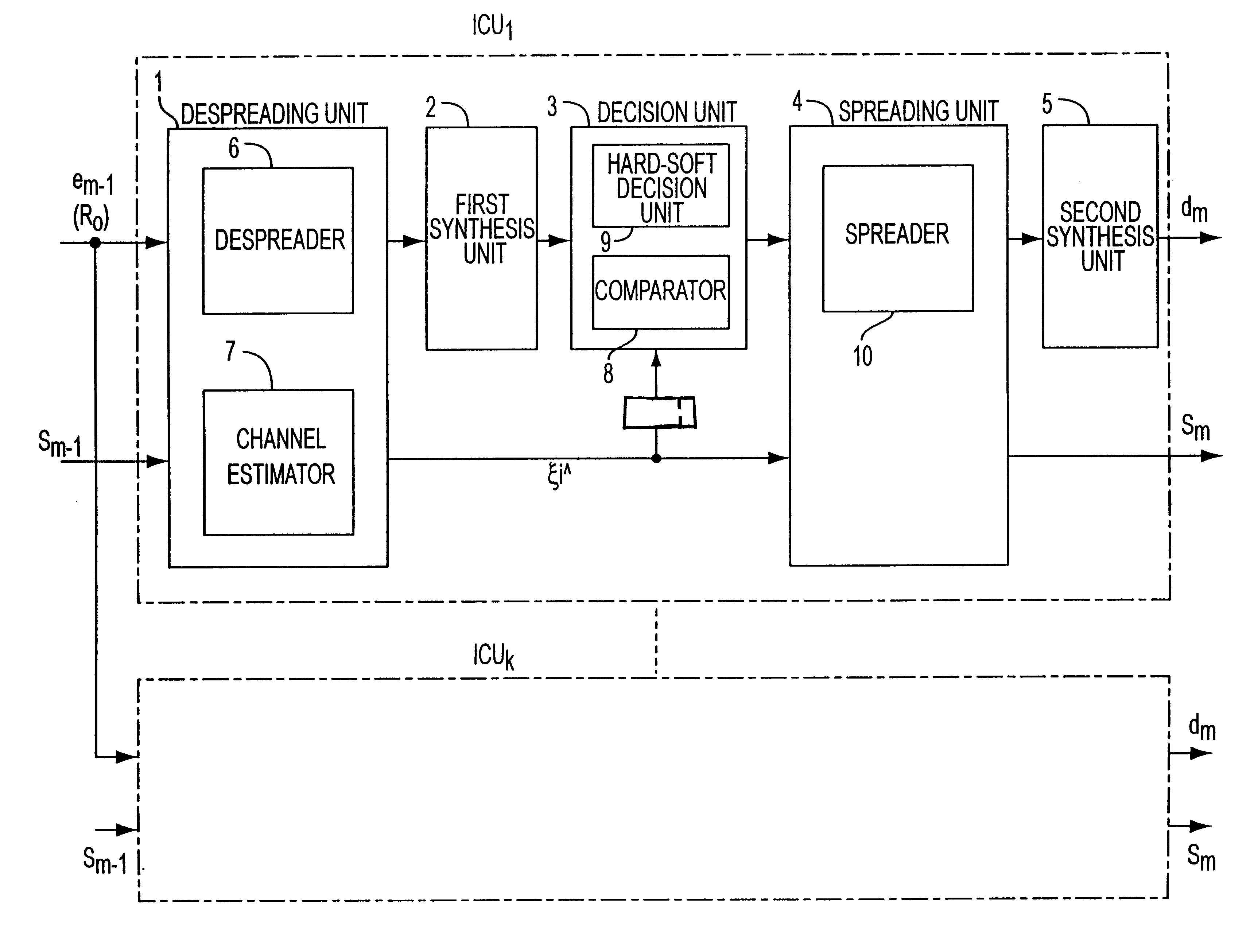

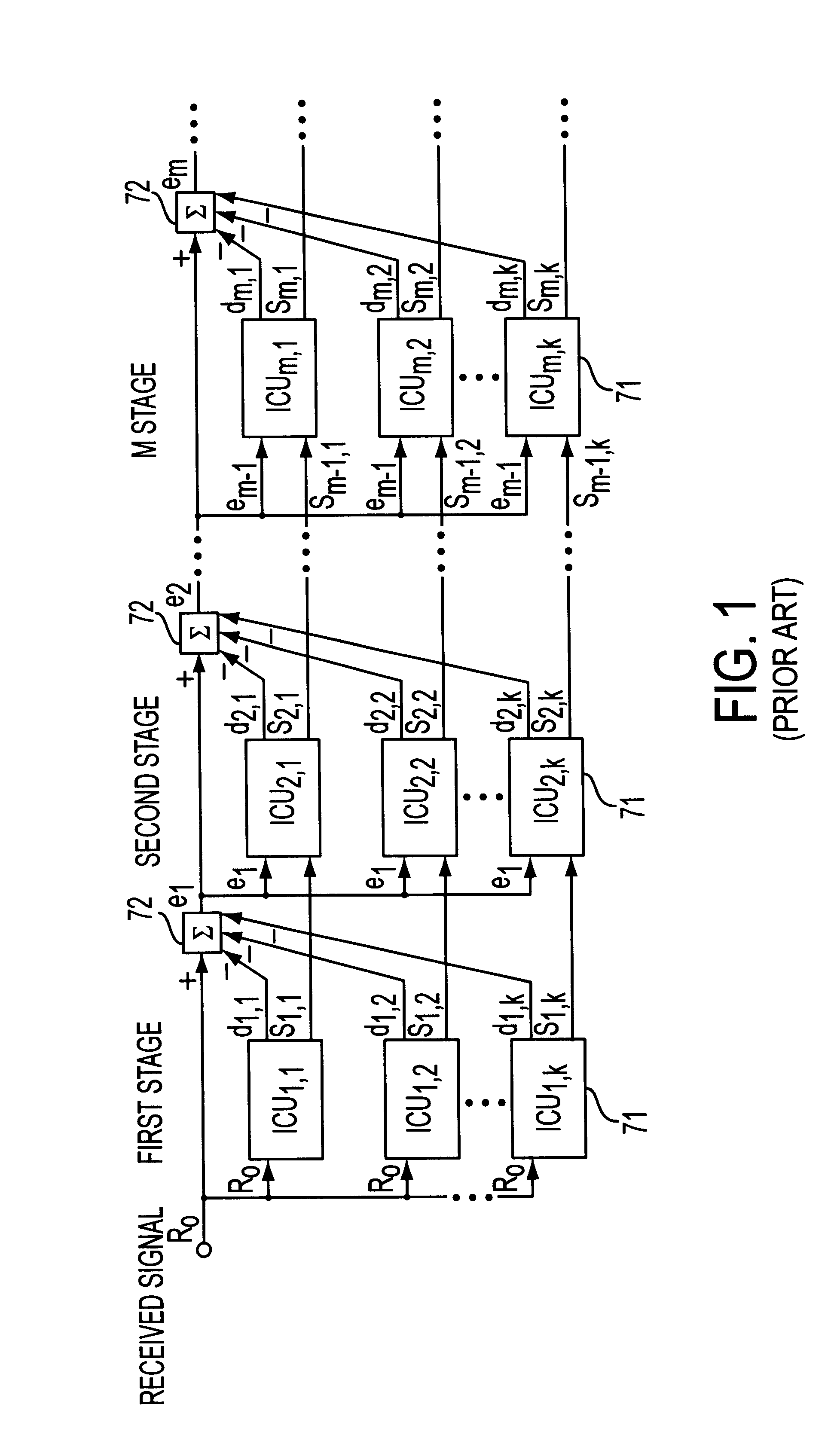

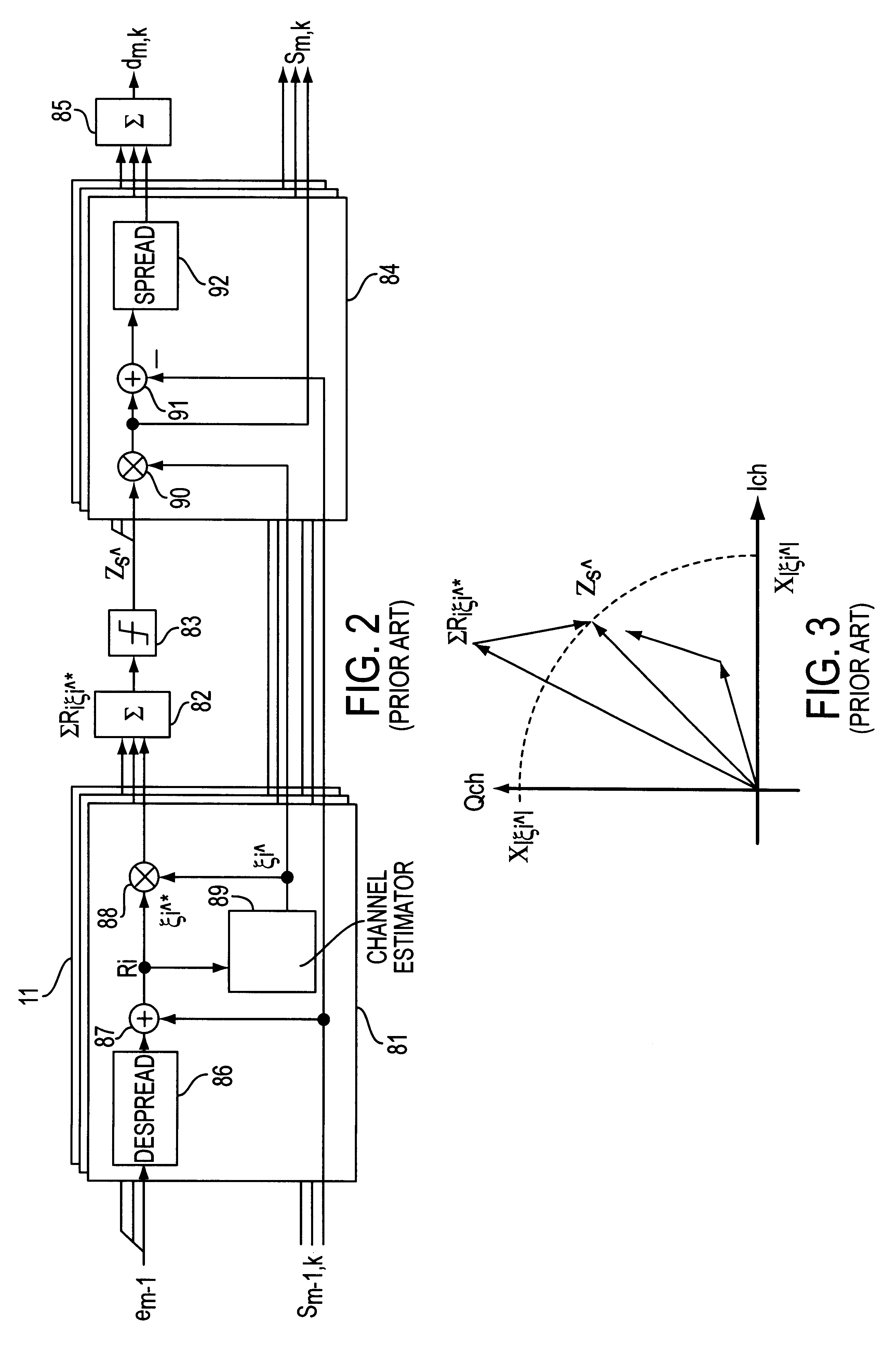

Multistage interference canceller

InactiveUS6192067B1Spatial transmit diversityError preventionInterference cancellerMultipath interference

A multistage interference canceller and method for removing interference between users and multipath interference from received signals in multiple stages includes a plurality of despreading units which produce a received symbol vector and an estimated channel value, a synthesis unit which synthesizes the received symbol vector, an amplitude of the received symbol vector and the amplitude of the estimated value from each reverse spreading unit, and a decision unit which executes a hard decision and a soft decision according to a result of comparing the total amplitude of the received symbol vector and the total amplitude of the estimated channel value.

Owner:FUJITSU LTD

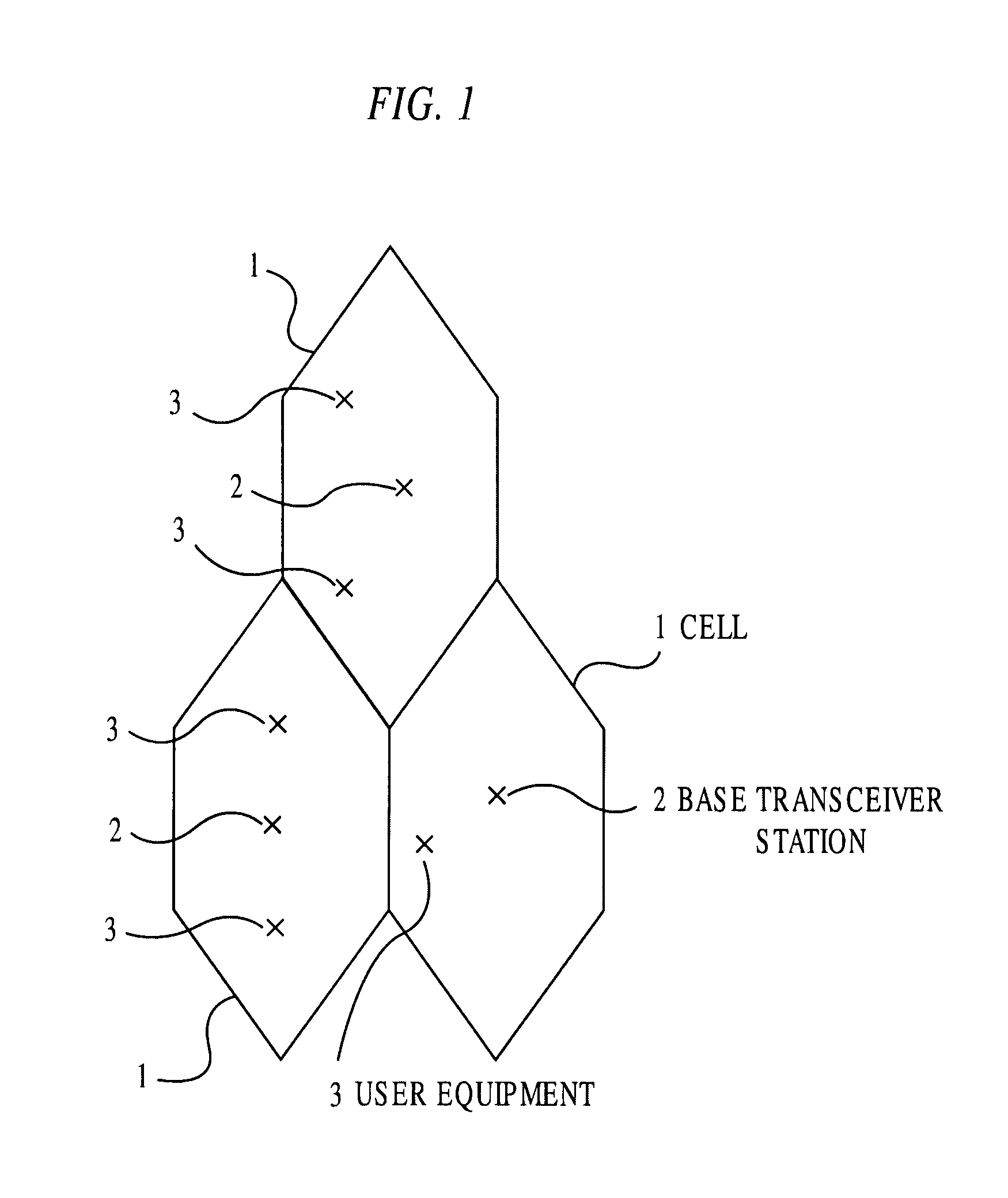

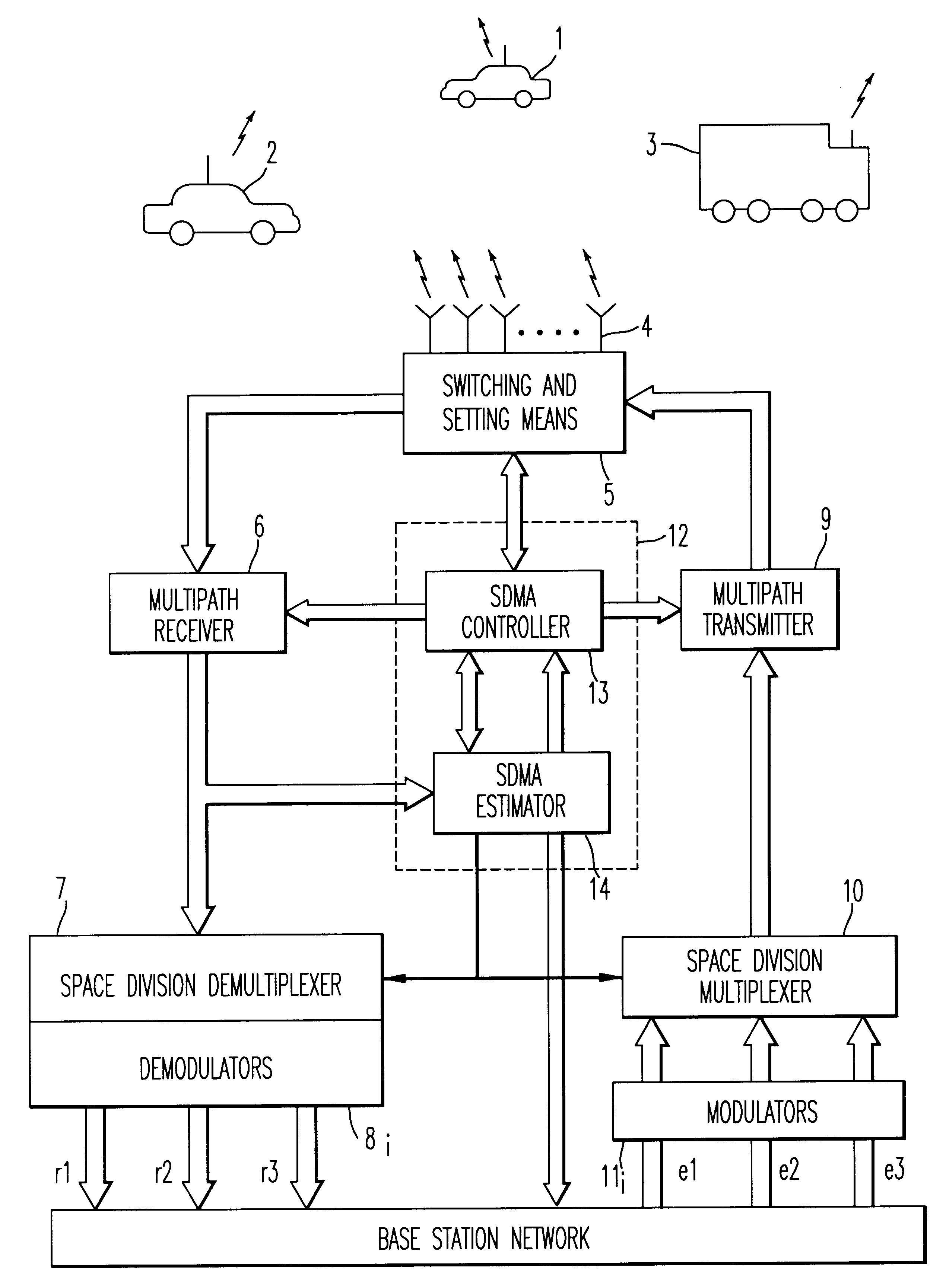

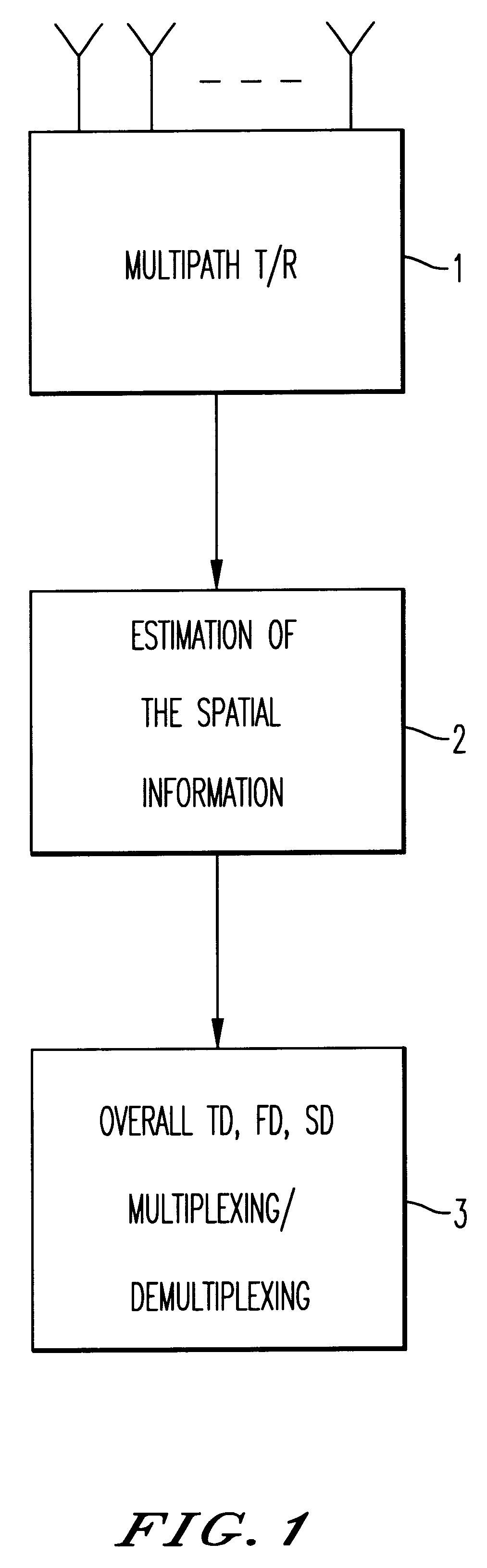

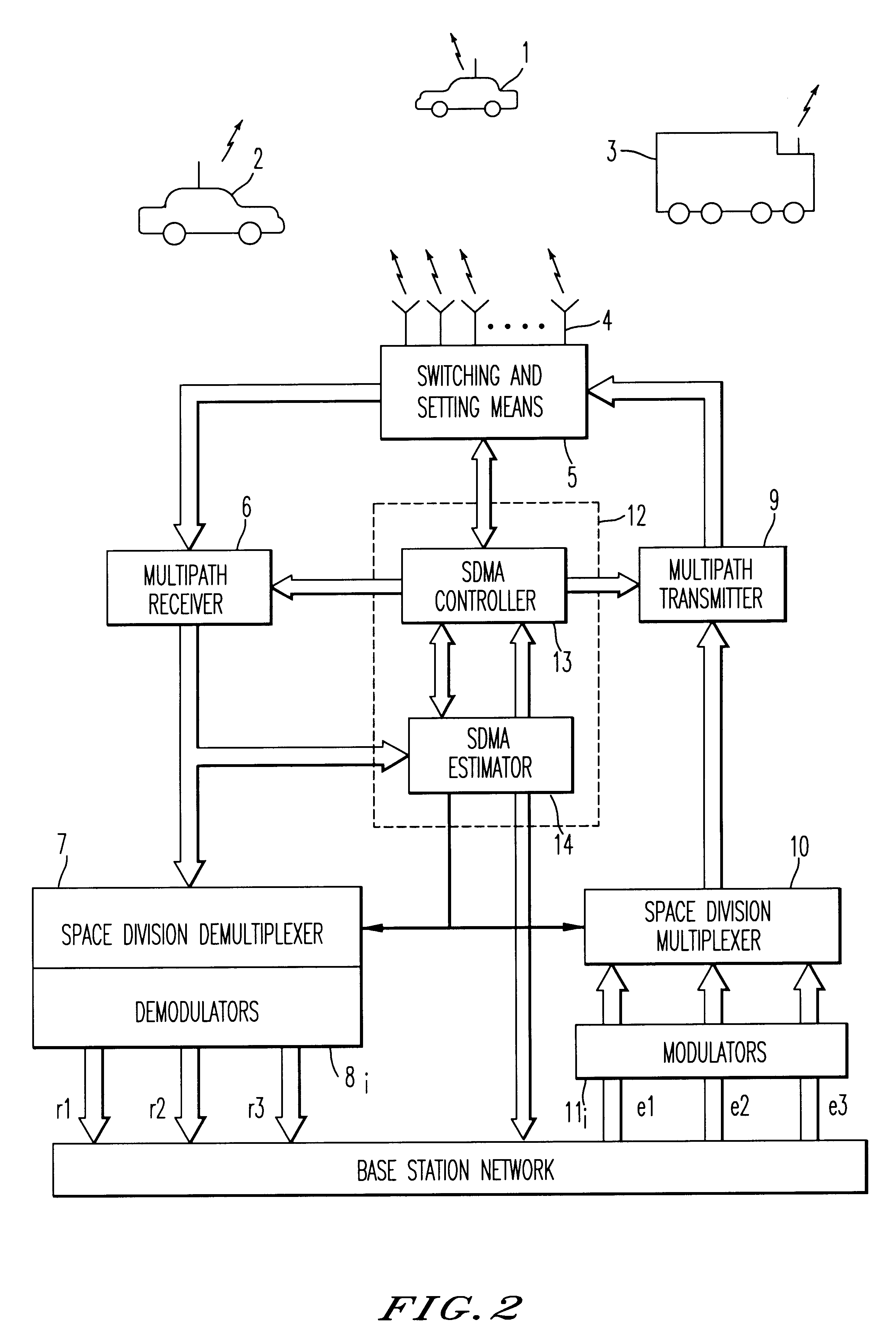

Method and device for space division multiplexing of radio signals transmitted in cellular radio communications

InactiveUS6240098B1Space can be allowedImprove performanceRadio wave direction/deviation determination systemsSpatial transmit diversityEngineeringTime-division multiplexing

A method and apparatus for spatial multiplexing and demultiplexing of radio signals. A multichannel transmitter and receiver is integrated in a base station and coupled to an antenna array. Using digital radio signals containing previously known or non-Gaussian sequences and arranged in frames, the spatial information about each mobile unit is estimated on the basis of the signal received by the receiver for the reception and transmission frequencies. This is done by known sequences or by blind source separation methods. The respective paths of each mobile unit with the power above a predetermined threshold is isolated by spatial filtering in the presence of multiple channel paths in order to provide spatial demultiplexing. Simultaneously, the intended signal is transmitted in the direction of the main path of each mobile unit while protecting each mobile unit from signals transmitted in the direction of other mobile units by spatial filtering with cancelling constraints in order to provide spatial multiplexing.

Owner:THOMSON CSF SA

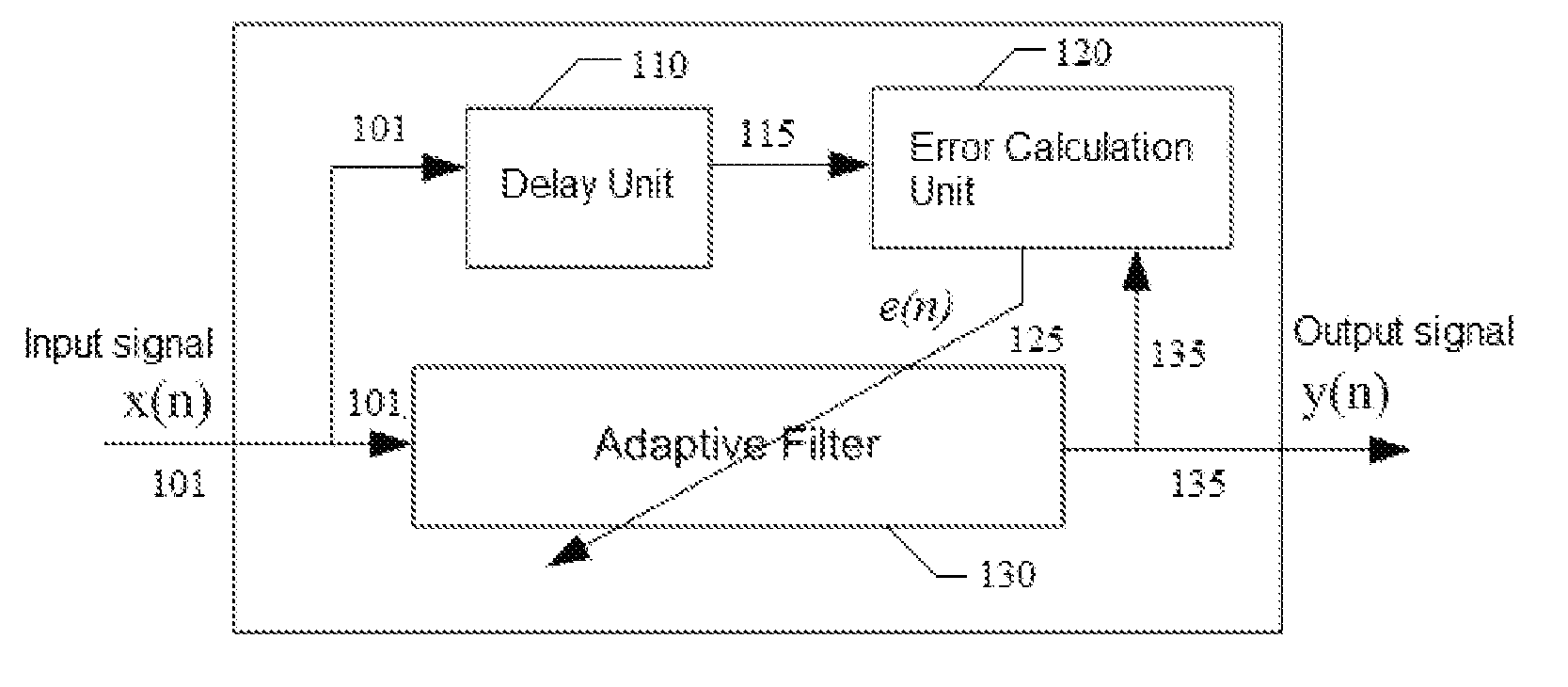

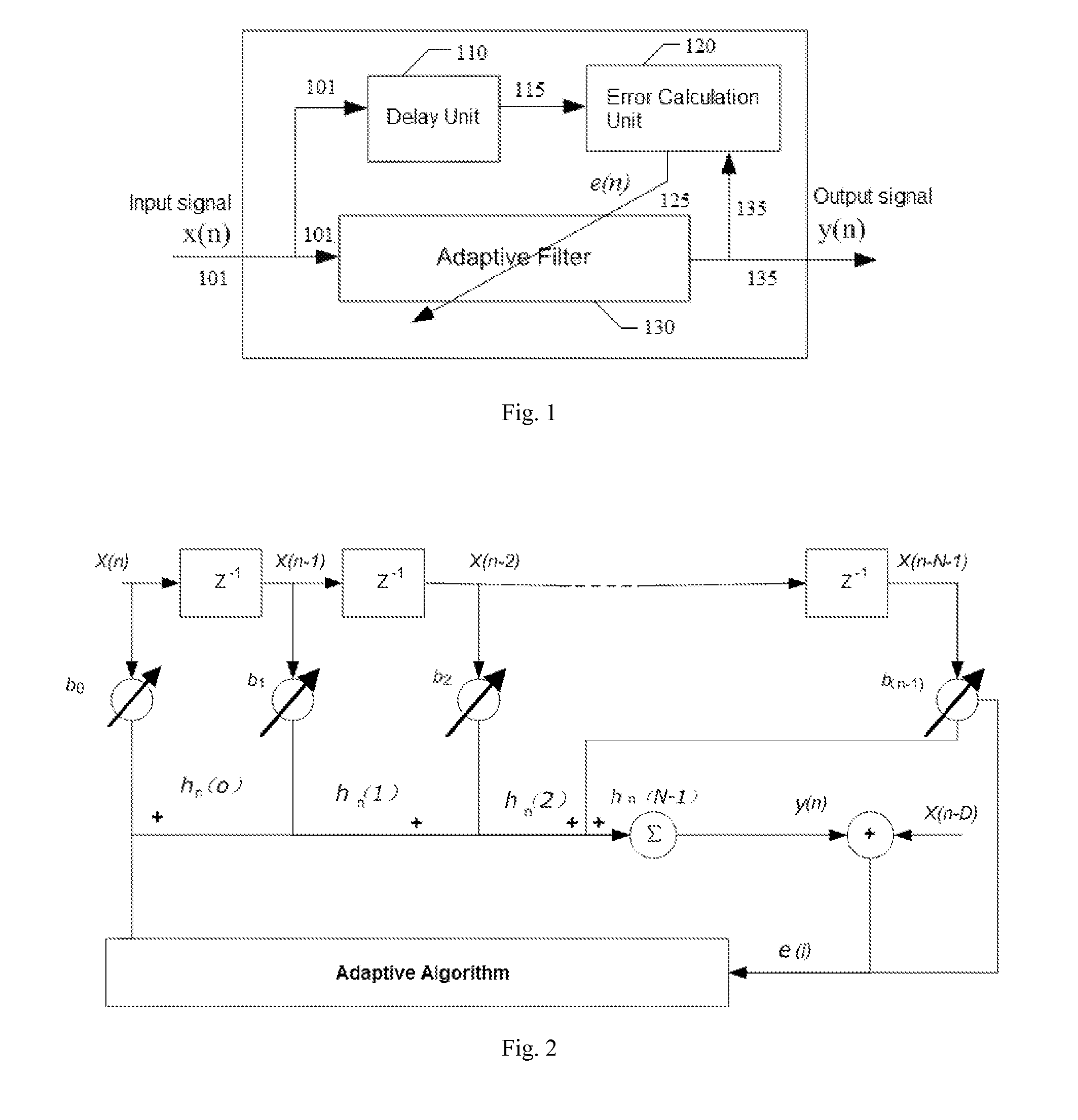

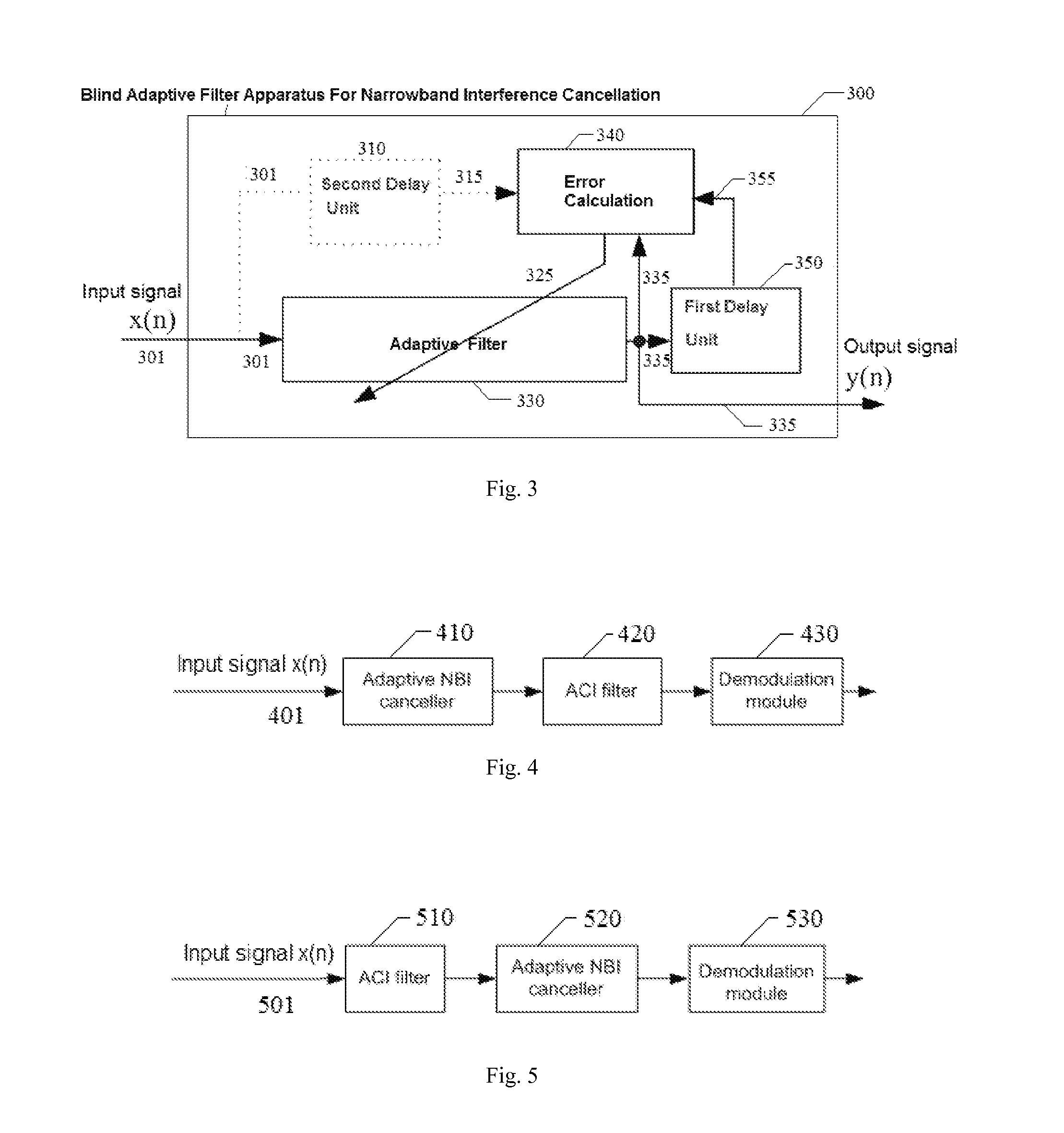

Blind adaptive filter for narrowband interference cancellation

ActiveUS20110305306A1Wide applicationError preventionDigital adaptive filtersSelf adaptiveSweep rate

The present invention relates to a blind adaptive filter for narrowband interference cancellation, which includes an adaptive filter, a delay unit coupled to the adaptive filter for generating a delayed signal with a predetermined delay length from the output signal of the adaptive filter, and an error calculation unit coupled to the adaptive filter and the delay unit. The error calculation unit compares the output signal from the adaptive filter and the delayed signal from the delay unit to extract error information, and feedback the first error information to the adaptive filter. The first error information is formed of a transfer function including a number of coefficients, and used to adjust the adaptive filter and remove interference in the next input signal. The disclosed technique is also applicable in wideband receivers, as well as resisting multiple strong narrowband interferences having a frequency sweep rate of tens of milliseconds.

Owner:MONTAGE TECHNOLOGY CO LTD

Dynamic digital communication system control

InactiveUS7158563B2Improve performanceMinimize impactError preventionFrequency-division multiplex detailsCommunications systemControl system

Methods, apparatus and systems for dynamically controlling a digital communication system, such as a DSL system, collect information about digital communication lines in the system and adaptively and / or dynamically determine line and signal characteristics of the digital communication lines, including interference effects. Based on the determined characteristics and the desired performance parameters, operation of the digital communication lines is adjusted to improve or otherwise control the performance of the system. The collection and processing of information may be performed by a party that is not a user in the system. This independent party also may control operational characteristics and parameters of the system. The invention can be used to eliminate or reduce signal interference such as crosstalk that can be induced on communication lines in systems such as DSL systems. Specific iterative power allocation and vectored transmission techniques and apparatus are disclosed.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com