Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

65results about How to "Short lock time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

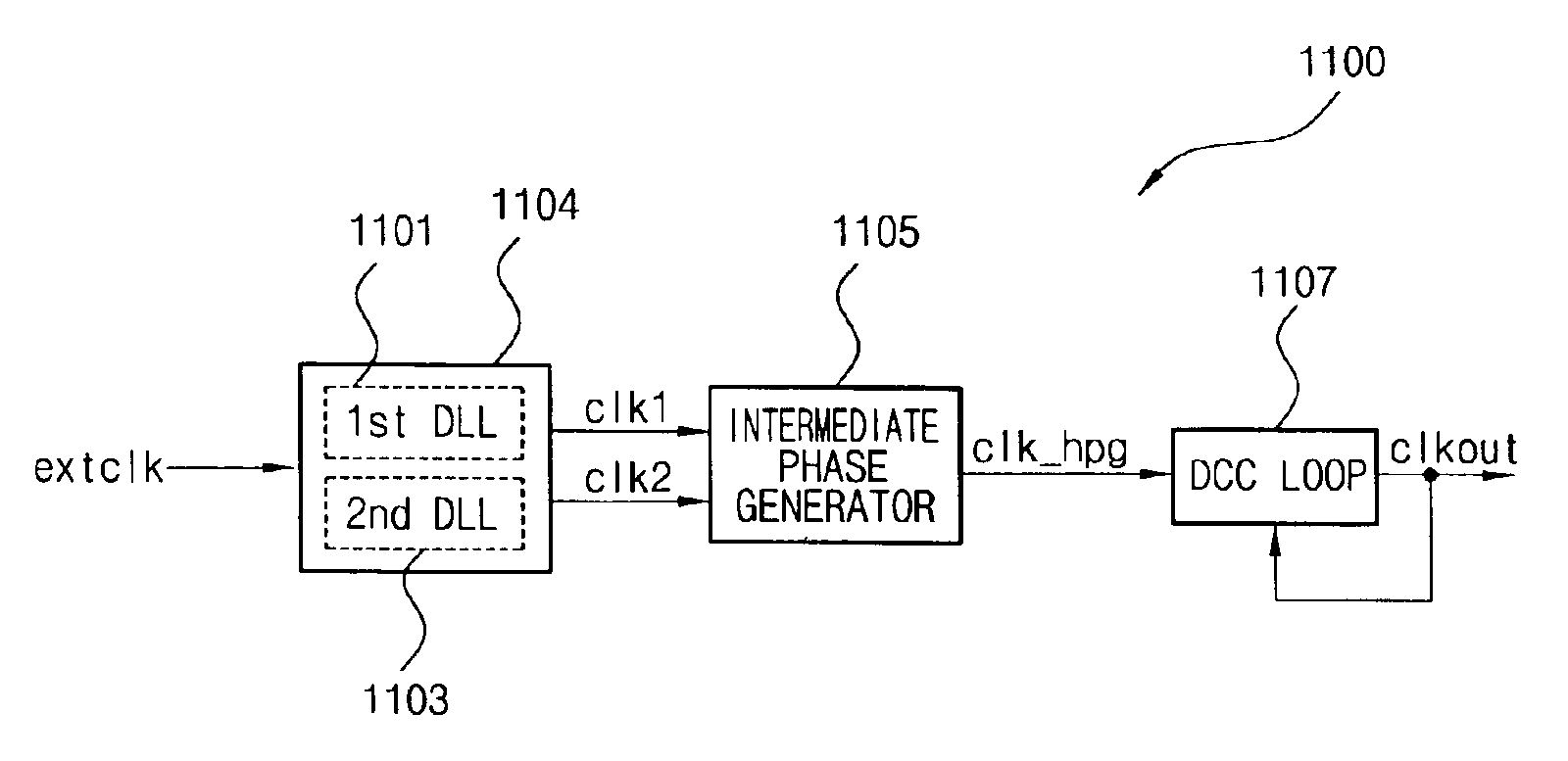

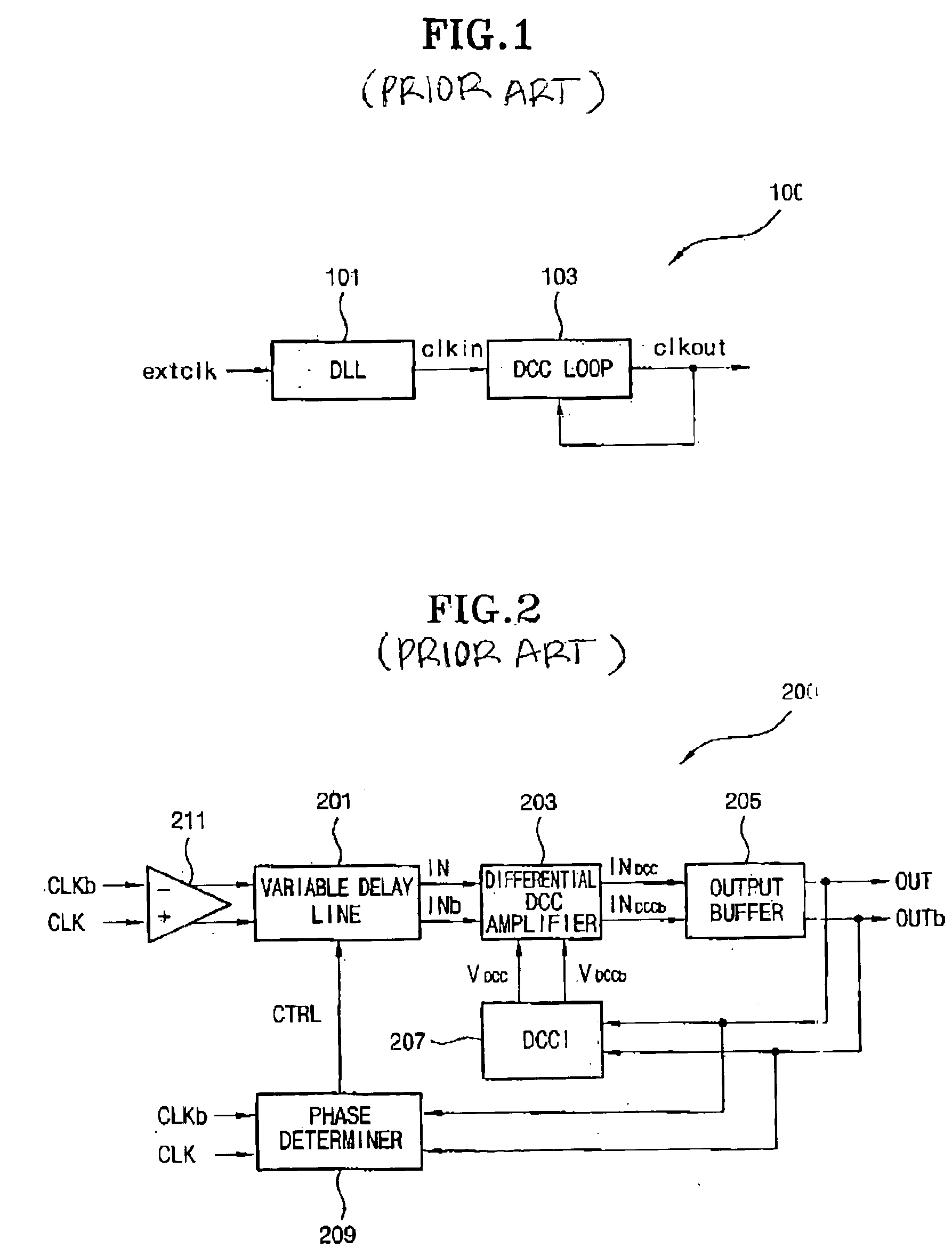

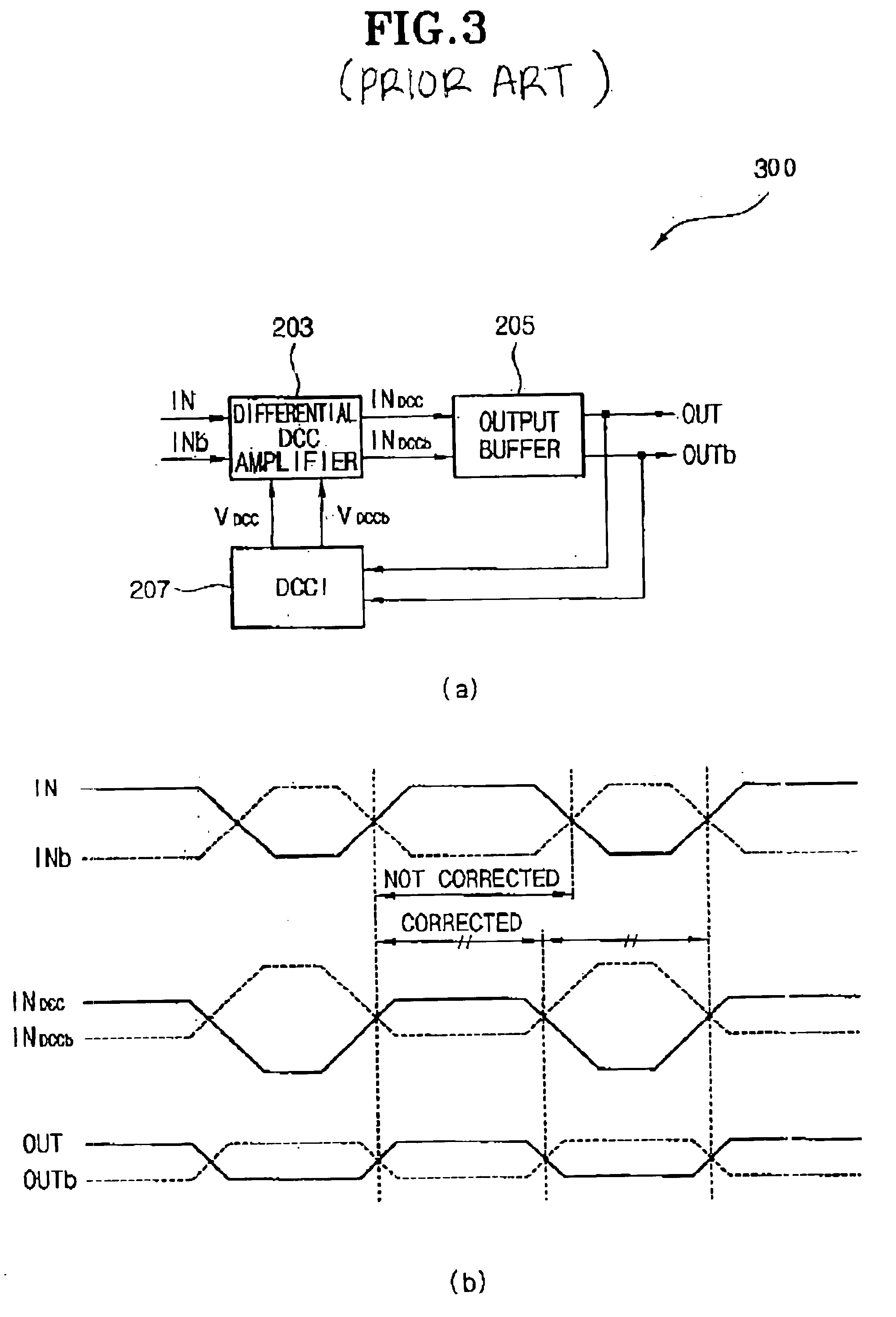

Delay locked loop circuit with duty cycle correction function

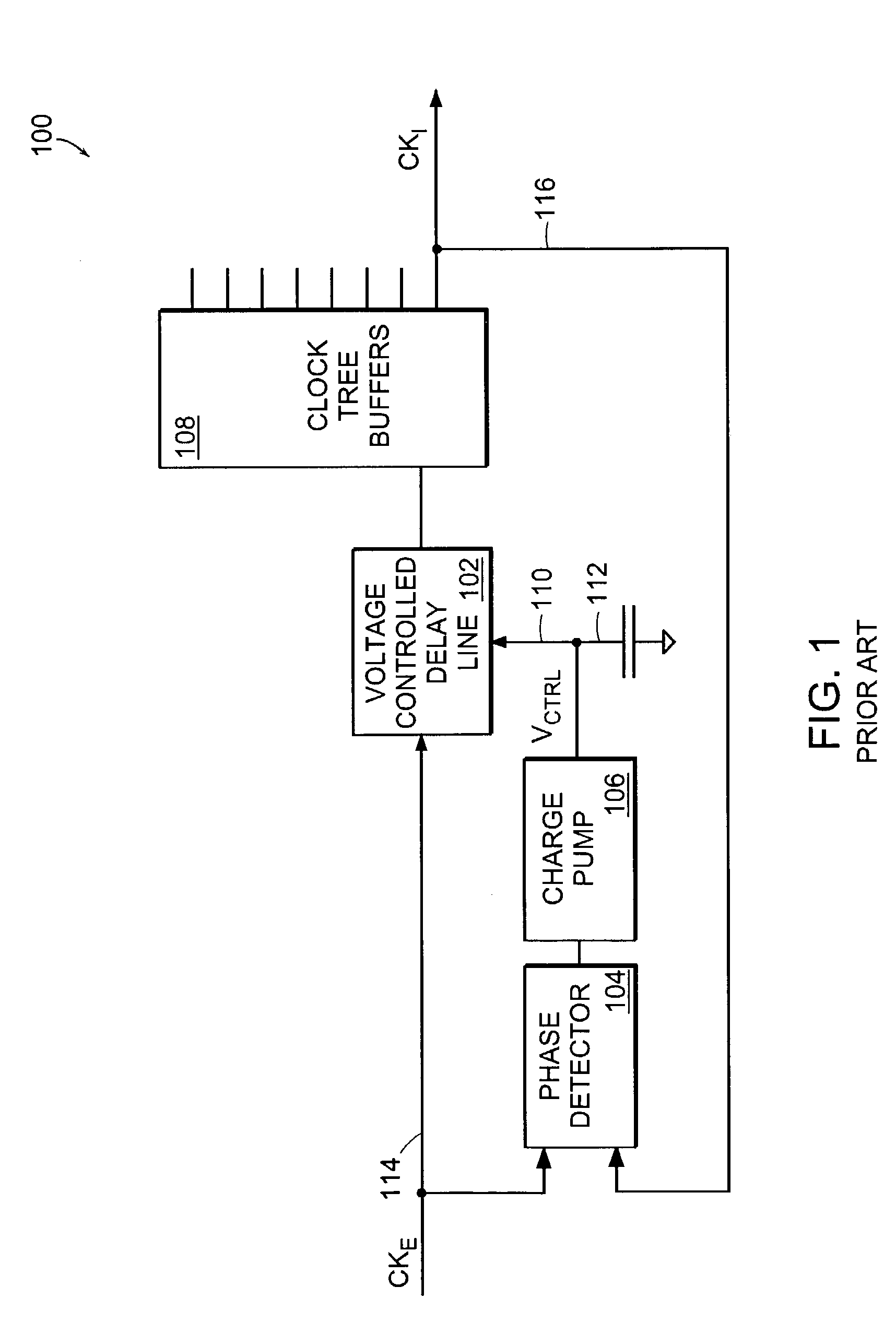

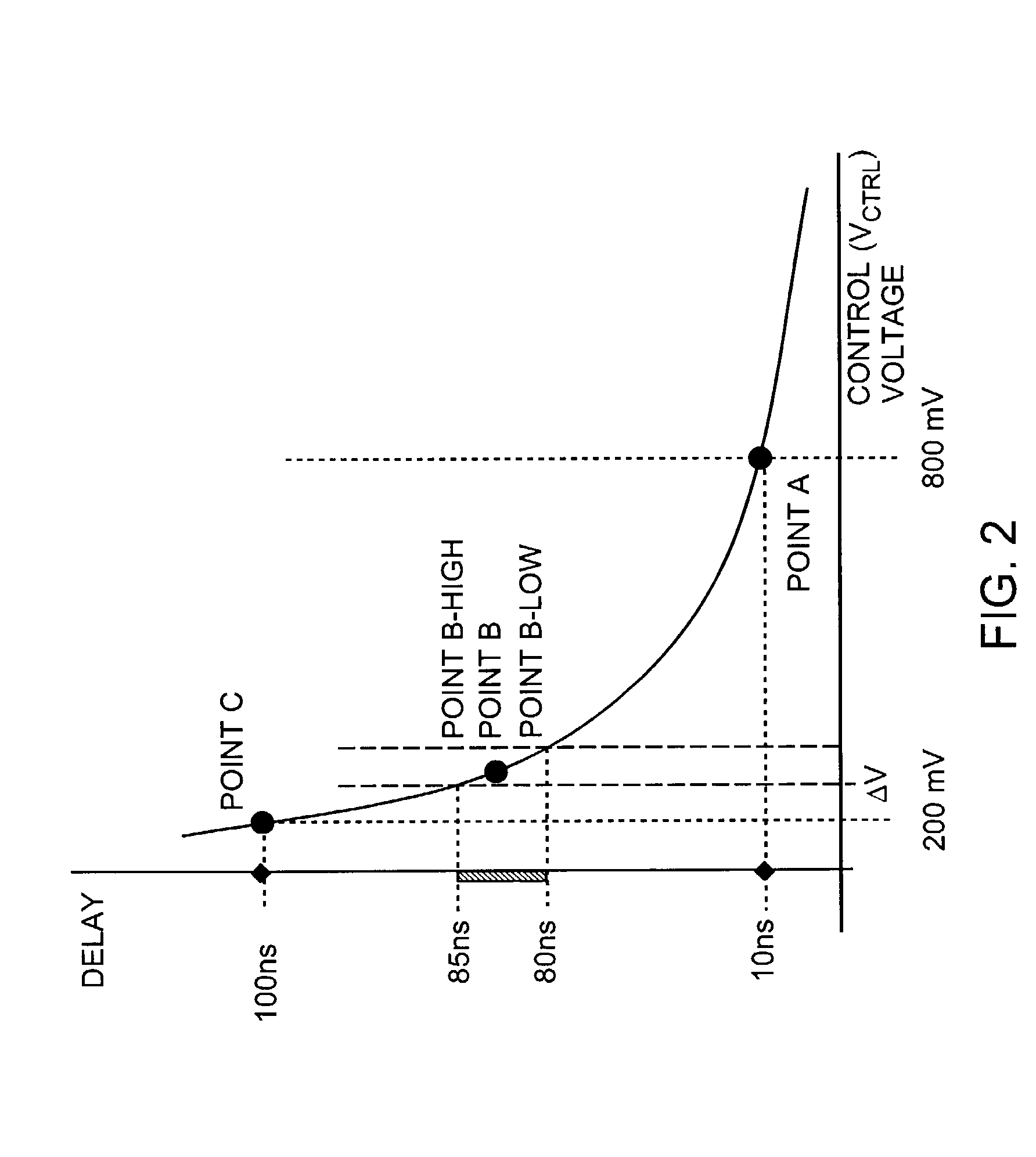

InactiveUS6853225B2Improve accuracyShort lock timePulse automatic controlContinuous to patterned pulse manipulationNegative feedbackDelay-locked loop

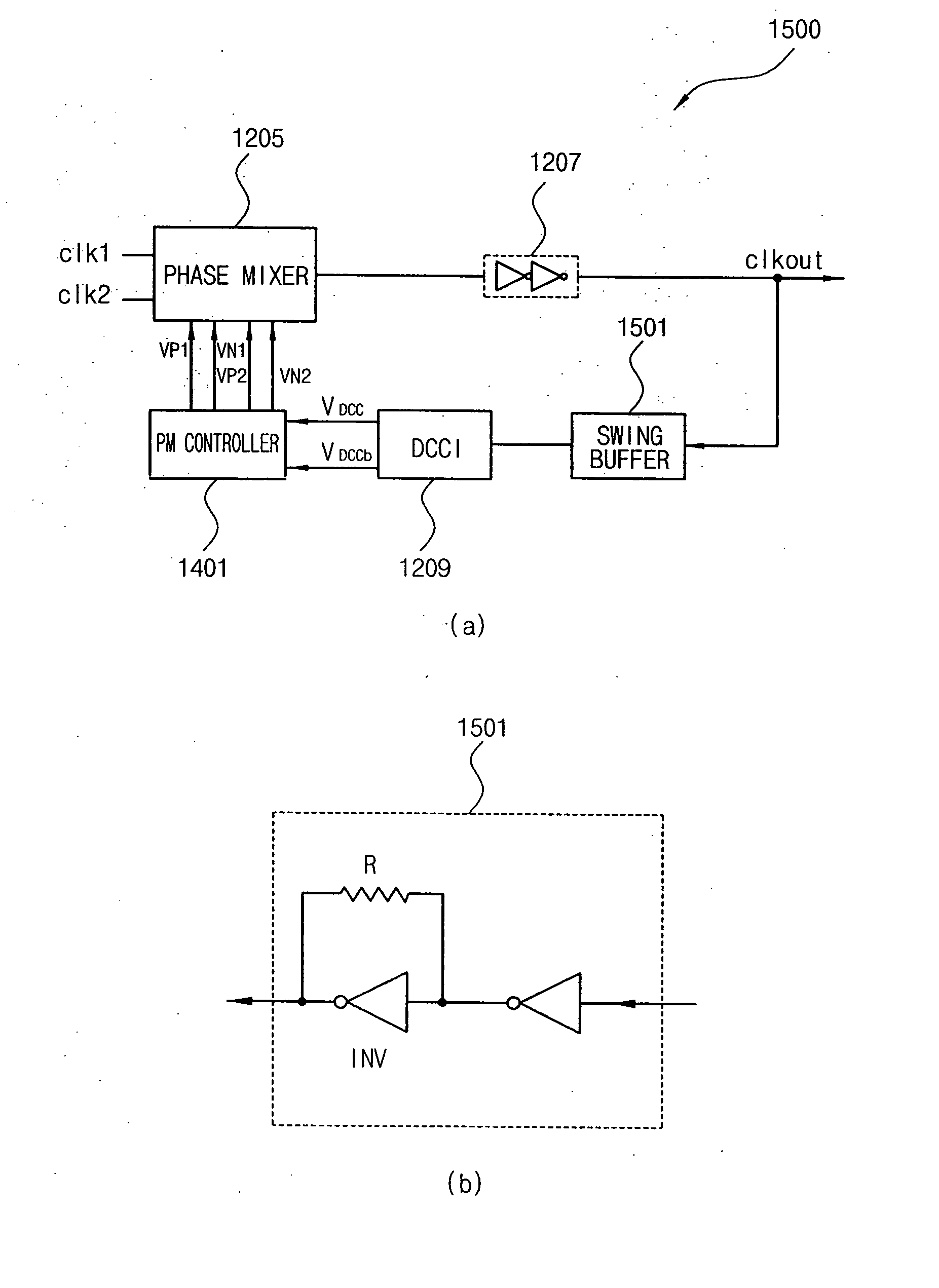

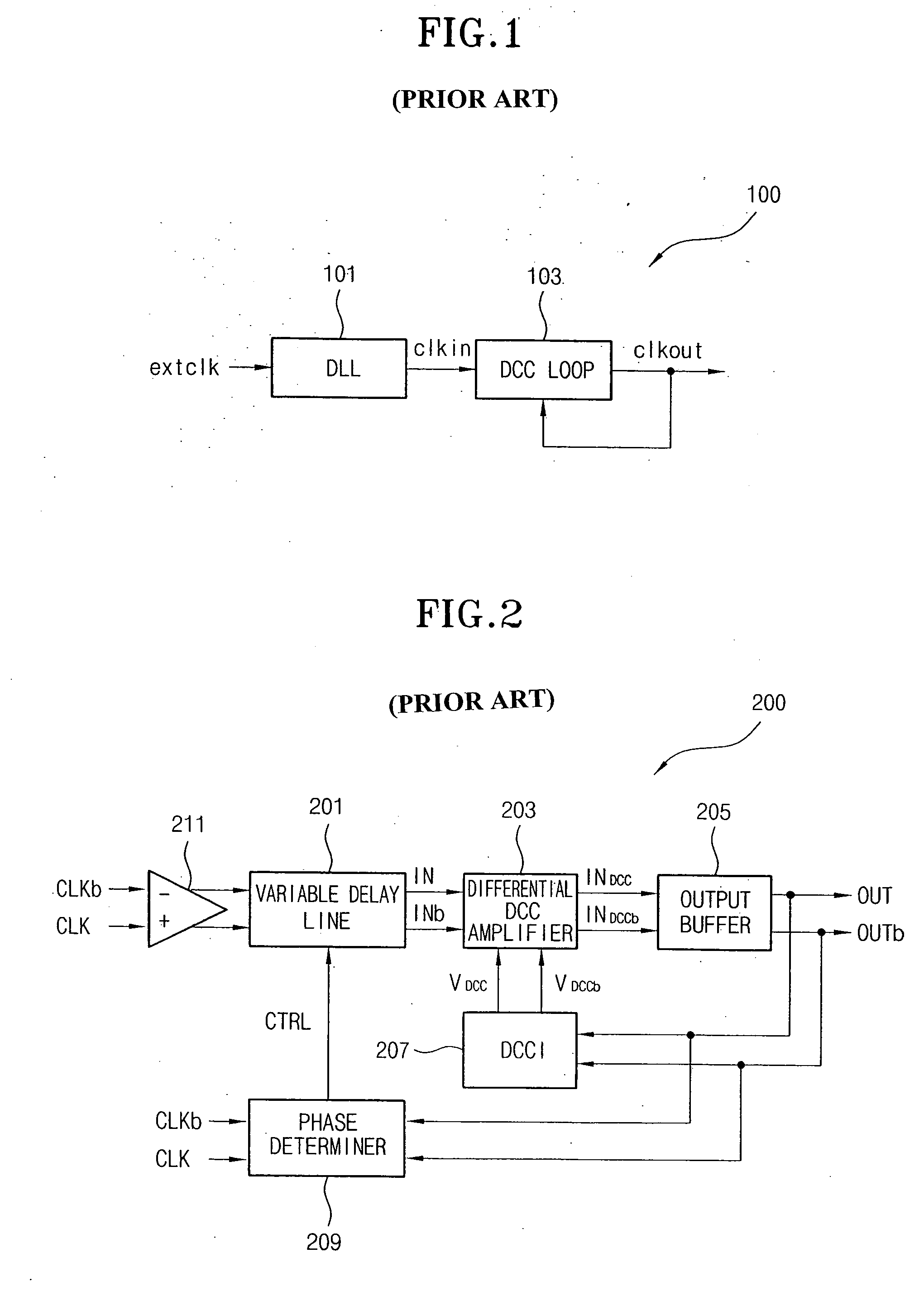

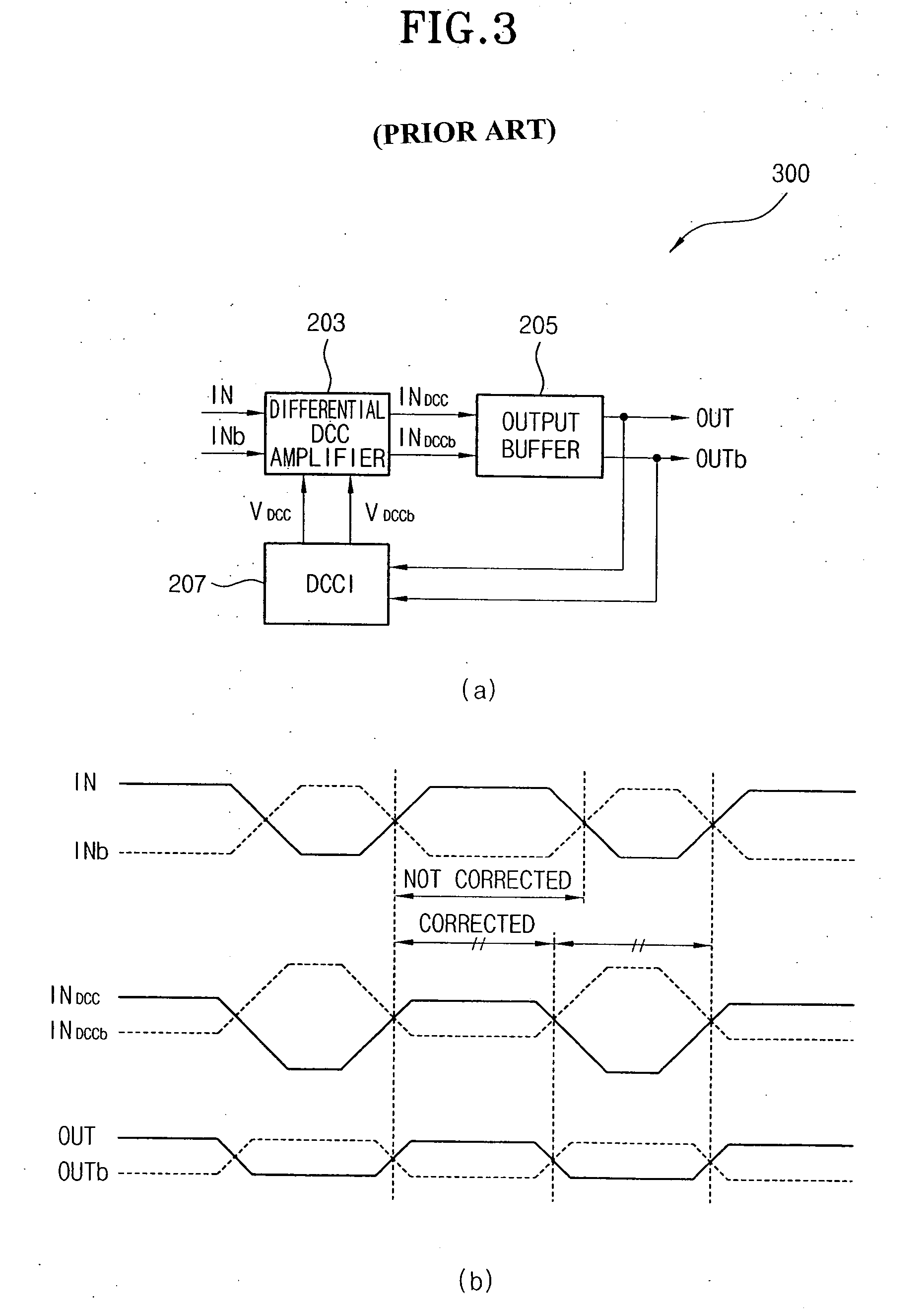

A delay locked loop (DLL) circuit having a structure in which a method of performing duty cycle correction (DCC) using two DLLs and an intermediate phase composer and a method of performing DCC by forming a closed loop using a negative feedback are combined with each other is provided. The DLL circuit includes a first DLL for receiving an external clock signal and generating a first clock signal and a second DLL for receiving an external clock signal and generating a second clock signal. The first clock signal and the second clock signal are synchronized with an external clock signal. The DLL circuit further includes an intermediate phase generation circuit for receiving the first and second clock signals and generating an intermediate phase clock signal and a DCC loop for receiving the intermediate phase clock signal and generating an output clock signal. The intermediate phase clock signal has an intermediate phase between the phases of the first and second clock signals. The output clock signal is generated through correction of the duty cycle of the intermediate phase clock signal using a value obtained by integrating the output clock signal.

Owner:SK HYNIX INC

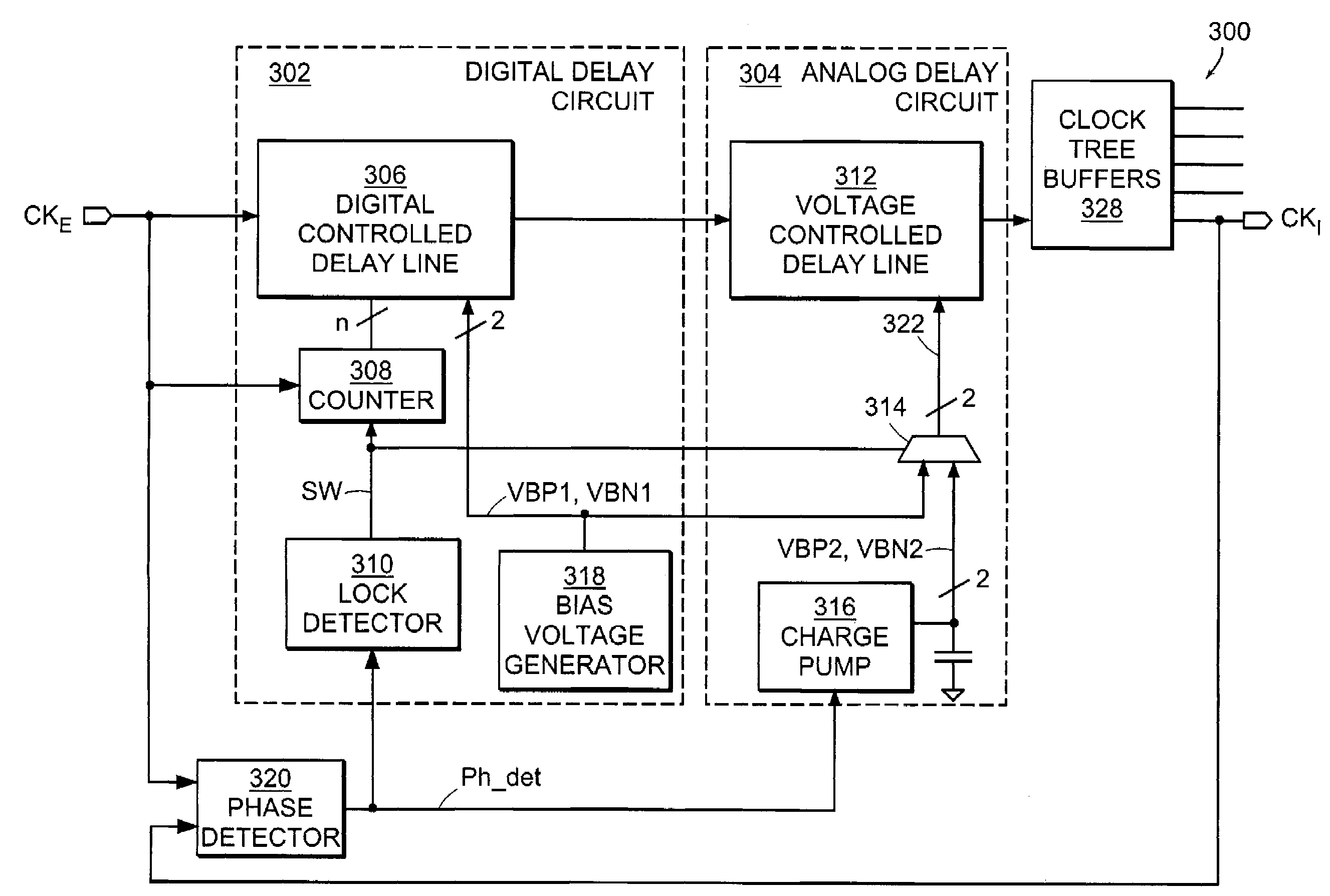

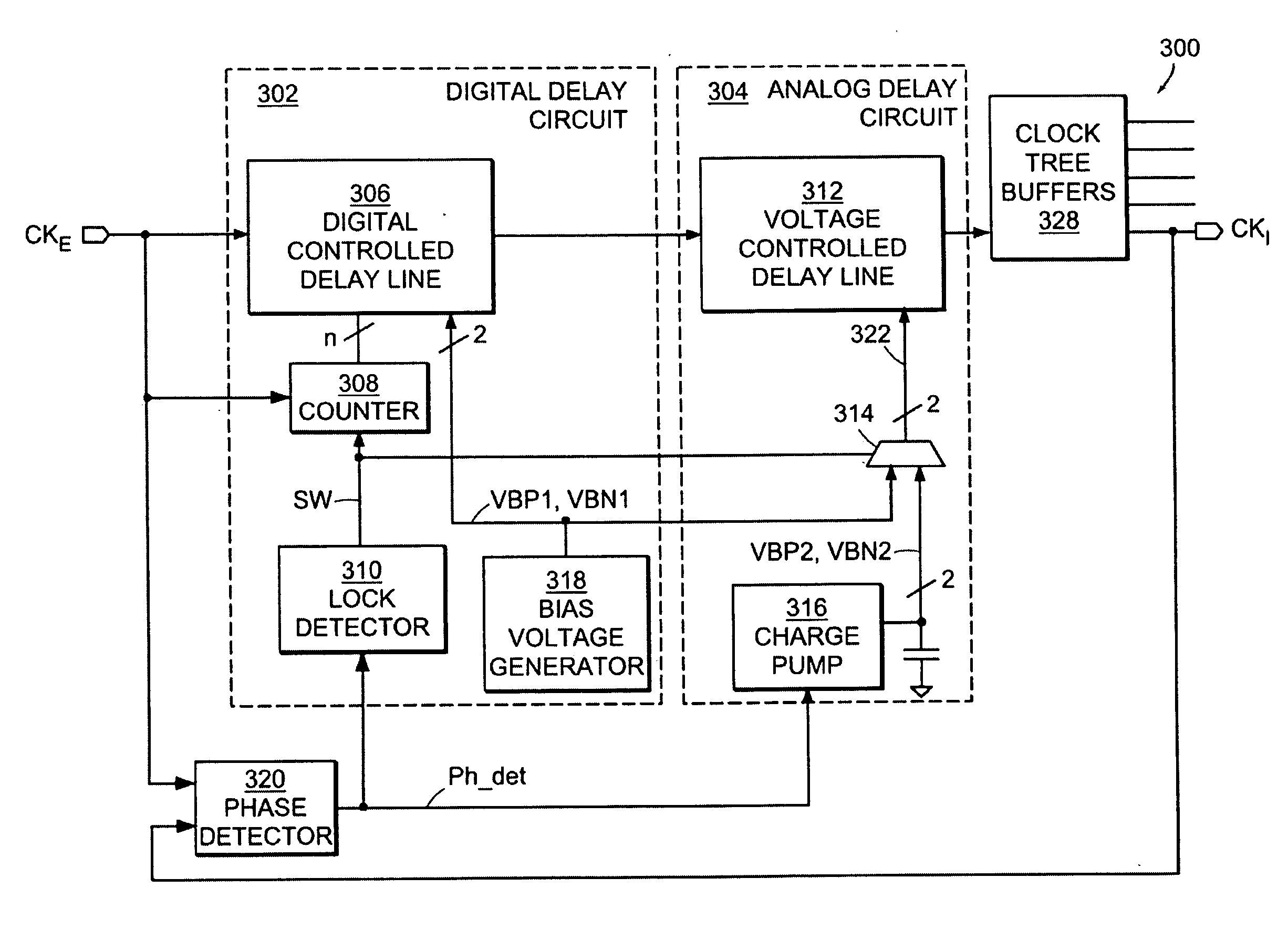

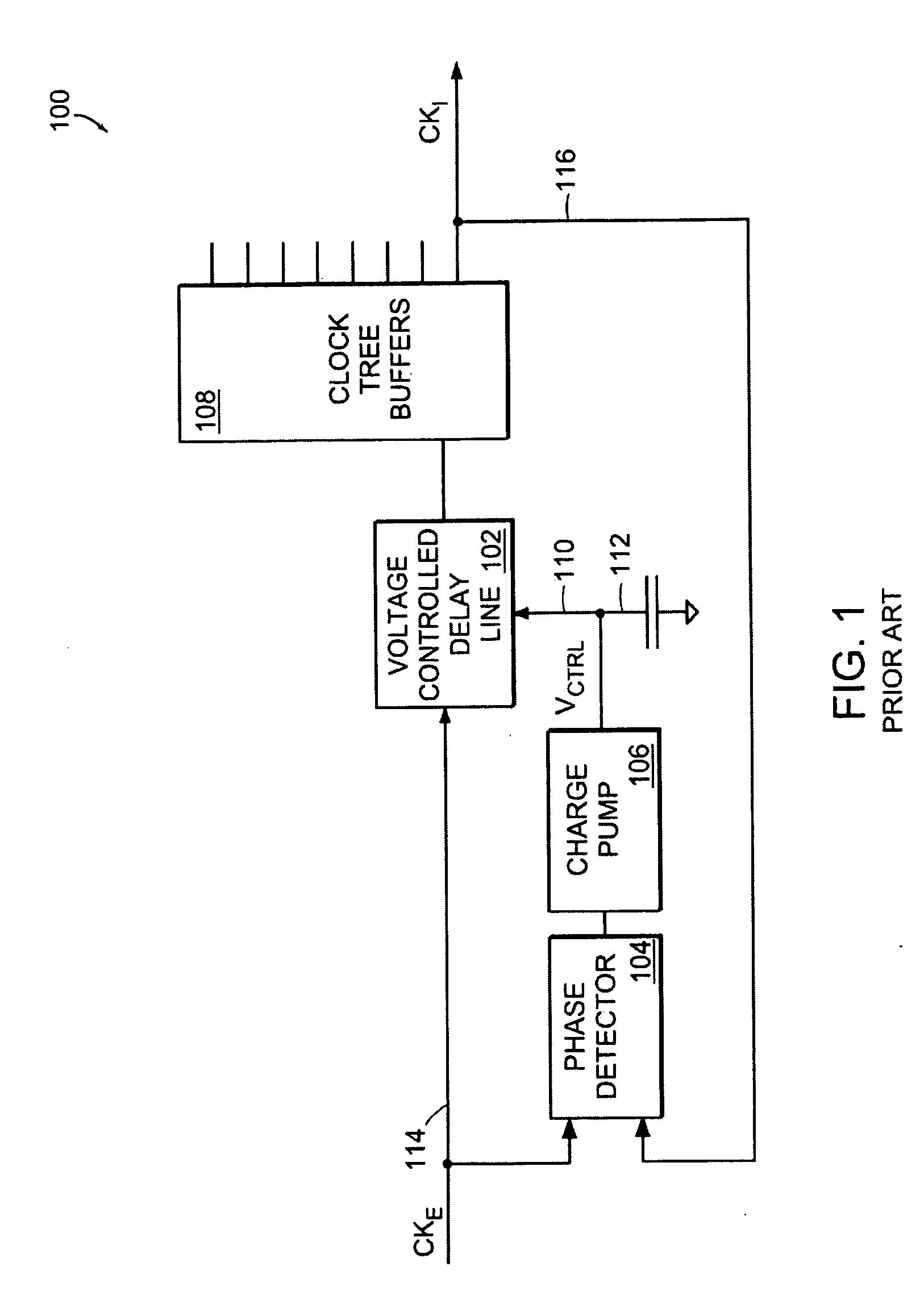

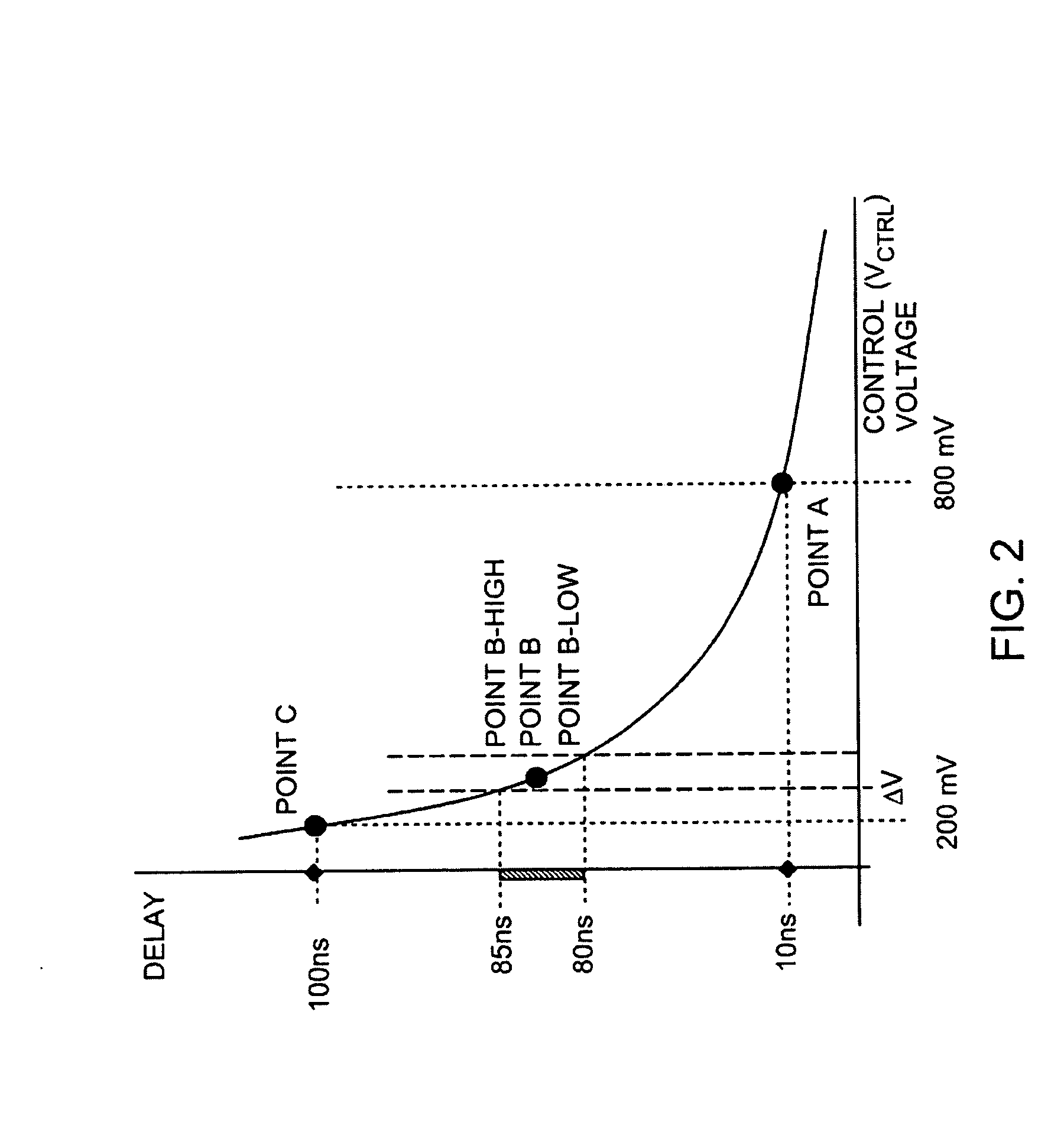

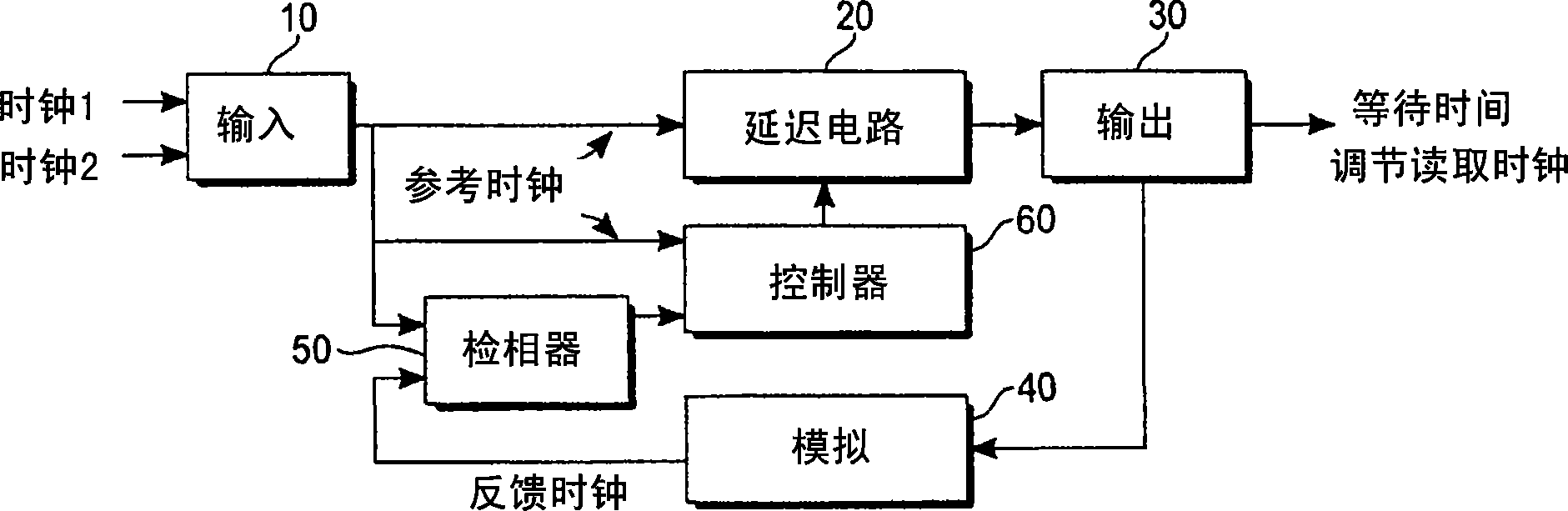

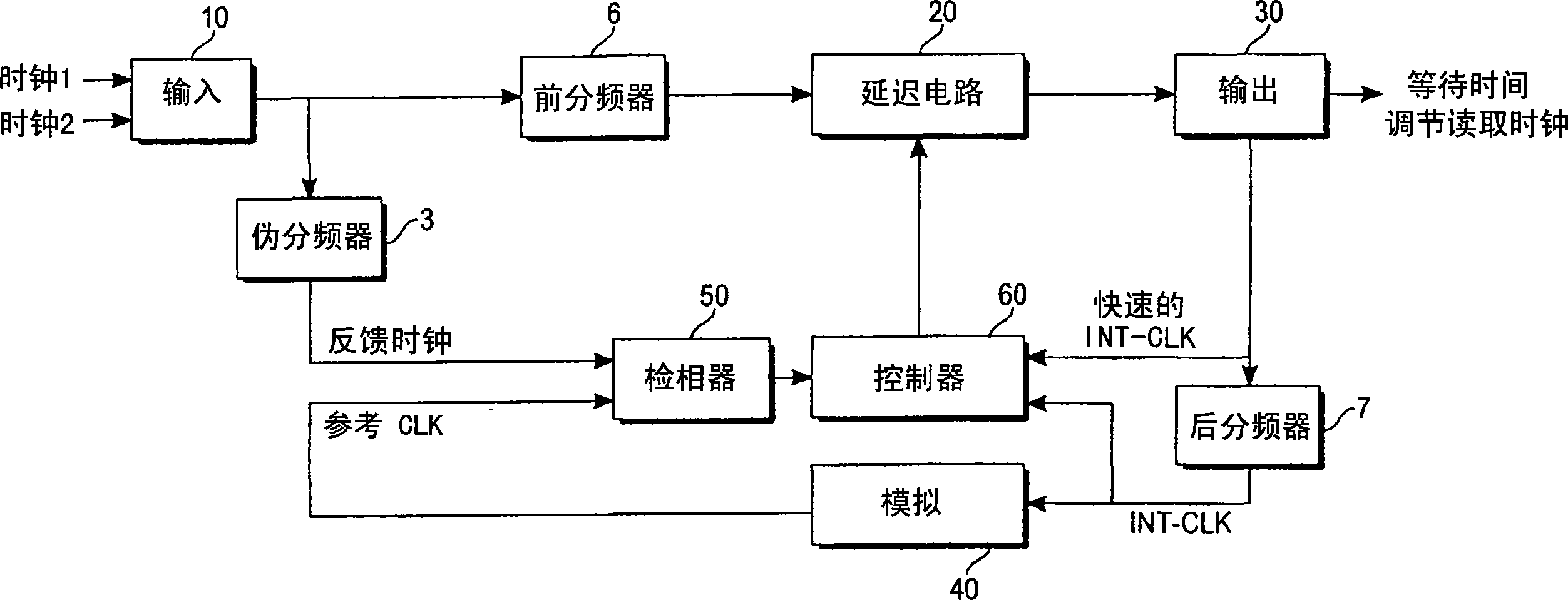

Wide frequency range delay locked loop

ActiveUS7336752B2Improve accuracyImprove stabilityPulse automatic controlAngle demodulation by phase difference detectionDelay-locked loopSilicon

A delay locked loop operates over a wide range of frequencies and has high accuracy, small silicon area usage, low power consumption and a short lock time. The DLL combines an analog domain and a digital domain. The digital domain is responsible for initial lock and operational point stability and is frozen after the lock is reached. The analog domain is responsible for normal operation after lock is reached and provides high accuracy using smaller silicon area and low power.

Owner:MOSAID TECH

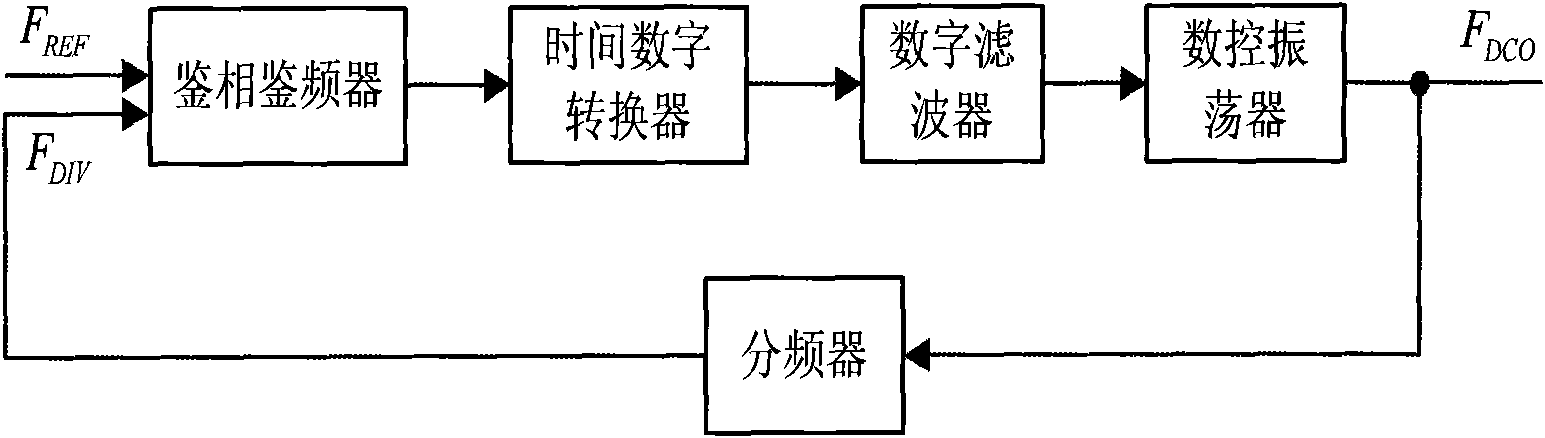

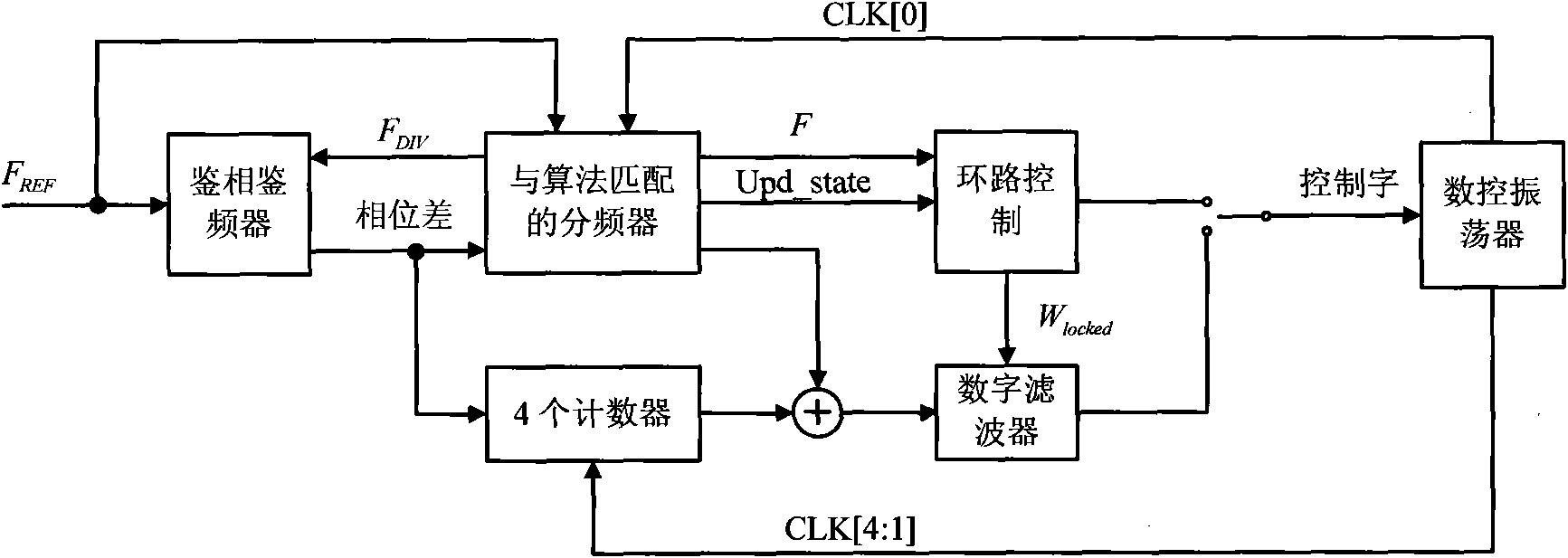

Rapid locking method for full digital phase-locked loop

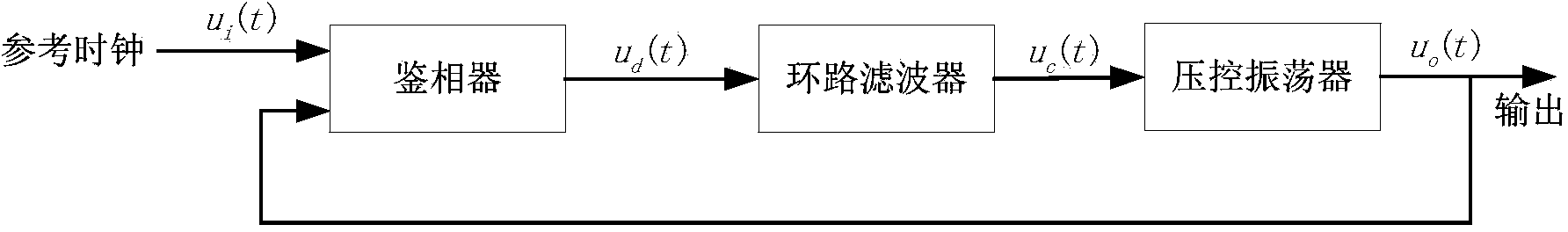

ActiveCN101640533AShort lock timeReduce forecast errorPulse automatic controlDiscriminatorPhase difference

The invention relates to a rapid locking method for a full digital phase-locked loop, which is used for locking the frequency of the full digital phase-locked loop comprising a phase detection discriminator, a time-to-digit converter, a digital filter, a digital controlled oscillator and a frequency divider in a short time. The method is characterized by comprising the following steps: finding a control word controlling the frequency of the digital controlled oscillator by a designed algorithm; dividing the frequency of a clock output by the digital controlled oscillator which is controlled bythe control word to obtain a divided-frequency clock with the frequency approximate to a reference clock frequency; and then, controlling the digital controlled oscillator to lock based on a phase difference between the reference clock and the divided-frequency clock which are distinguished by the phase detection discriminator. The full digital phase-locked loop is provided with a rapid frequencycapture loop and a phase-locked loop which alternately work, i.e. firstly, the rapid frequency capture loop finishes frequency capture, and then, the phase-locked loop finishes accurate locking.

Owner:SOUTHEAST UNIV

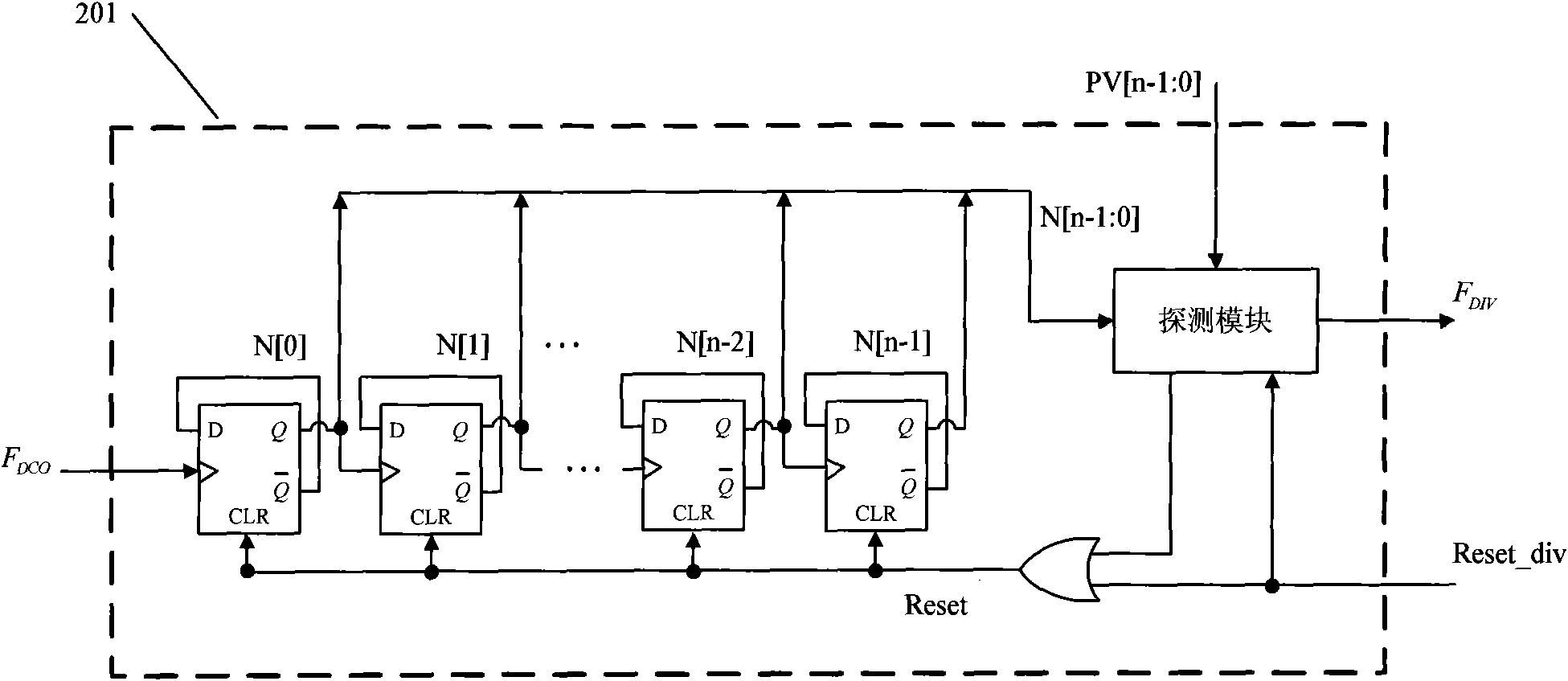

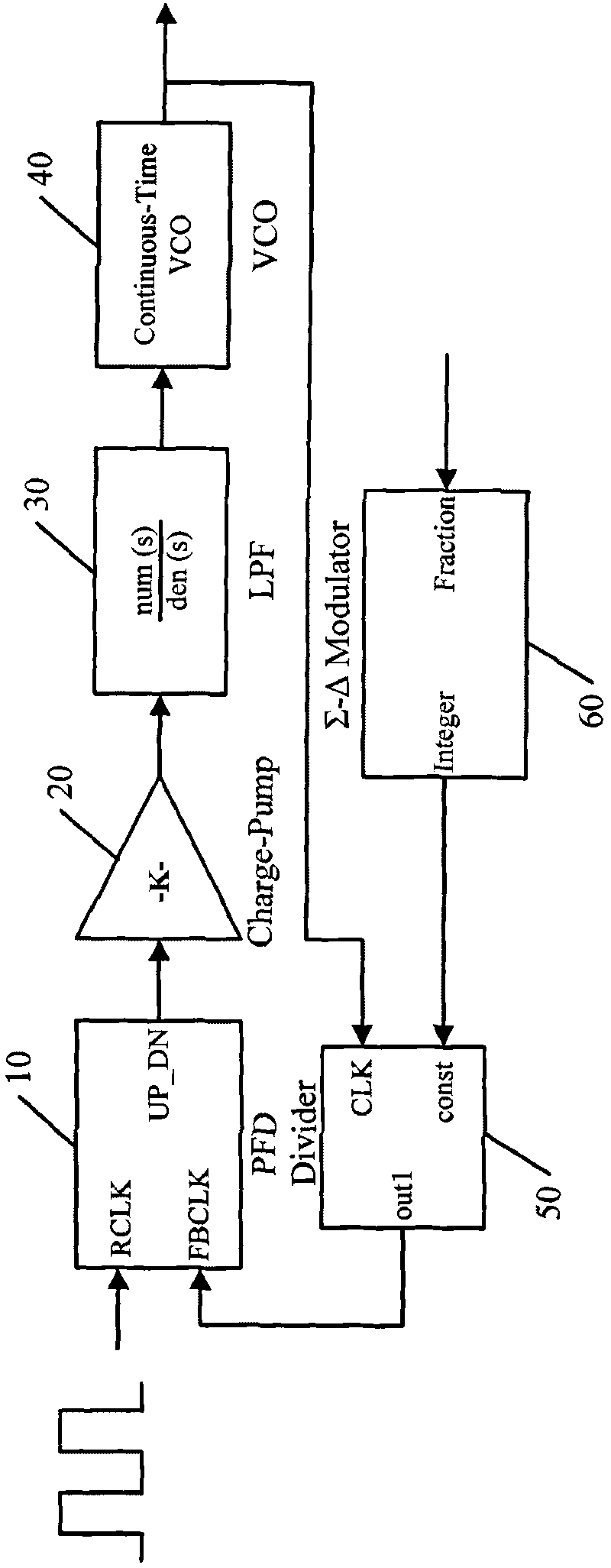

Full digital phase-locked loop applying rapid frequency capture method

ActiveCN101640534AShort lock timeReduce forecast errorPulse automatic controlDiscriminatorClock rate

The invention relates to a full digital phase-locked loop applying a rapid frequency capture method for locking the frequency of the full digital phase-locked loop comprising a phase detection discriminator, a time-to-digit converter, a digital filter, a digital controlled oscillator and a frequency divider in a short time. The full digital phase-locked loop is characterized by comprising the following steps: finding a control word controlling the frequency of the digital controlled oscillator by a designed algorithm; and dividing a frequency output by the digital controlled oscillator which is controlled by the control word to obtain a divided-frequency clock with the frequency approximate to a reference clock frequency. The full digital phase-locked loop is provided with a rapid frequency capture loop and a phase-locked loop which alternately work, i.e. firstly, the rapid frequency capture loop finishes frequency capture, and then, the phase-locked loop finishes accurate locking.

Owner:SOUTHEAST UNIV

Wide frequency range delay locked loop

InactiveUS20080089459A1Improve accuracyImprove stabilityPulse automatic controlAngle demodulation by phase difference detectionDelay-locked loopSilicon

A delay locked loop operates over a wide range of frequencies and has high accuracy, small silicon area usage, low power consumption and a short lock time. The DLL combines an analog domain and a digital domain. The digital domain is responsible for initial lock and operational point stability and is frozen after the lock is reached. The analog domain is responsible for normal operation after lock is reached and provides high accuracy using smaller silicon area and low power.

Owner:MOSAID TECH

Rapidly-locked frequency generator

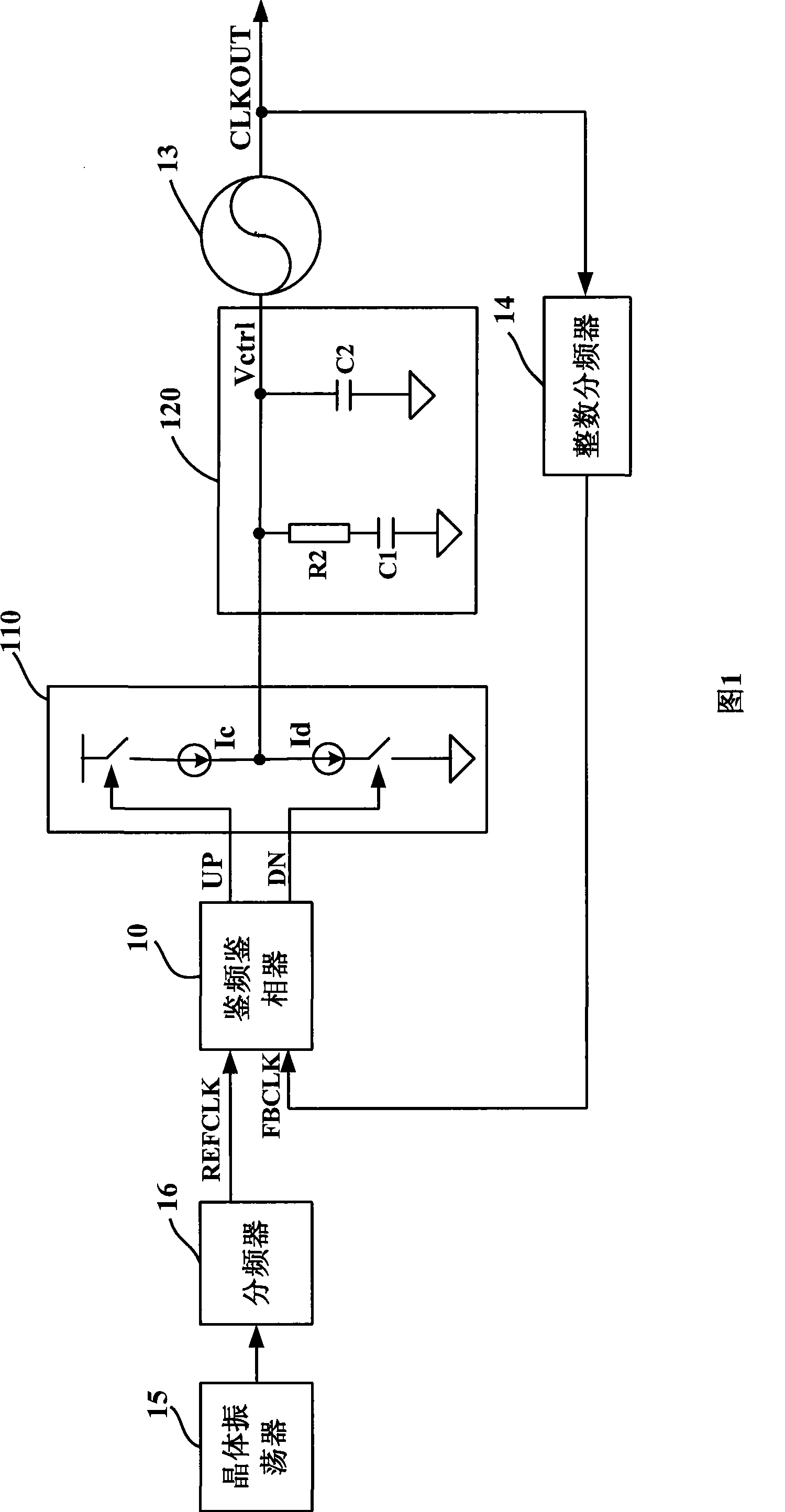

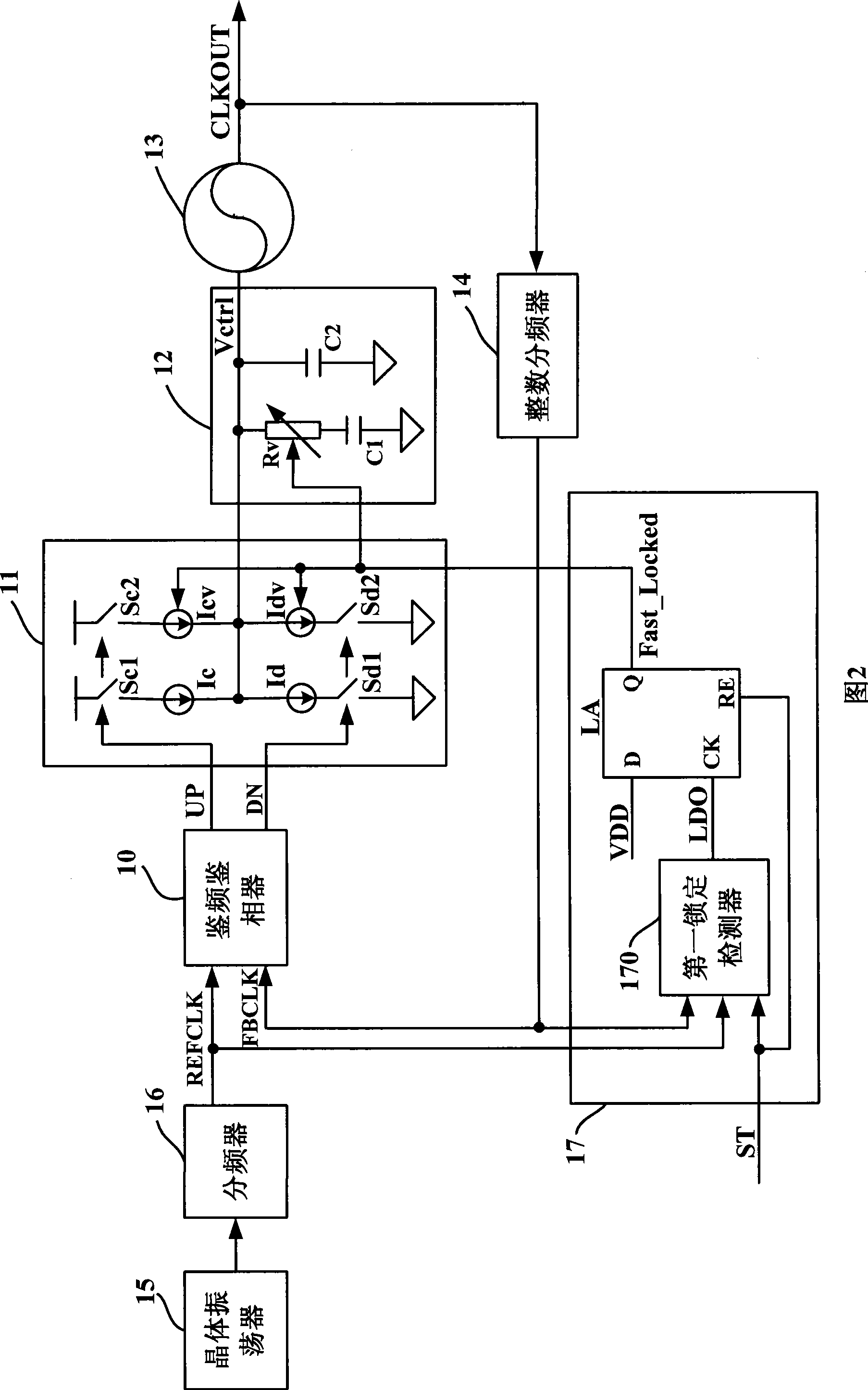

InactiveCN101436859AAccurate and stable outputShort lock timePulse automatic controlPhase differencePhase frequency detector

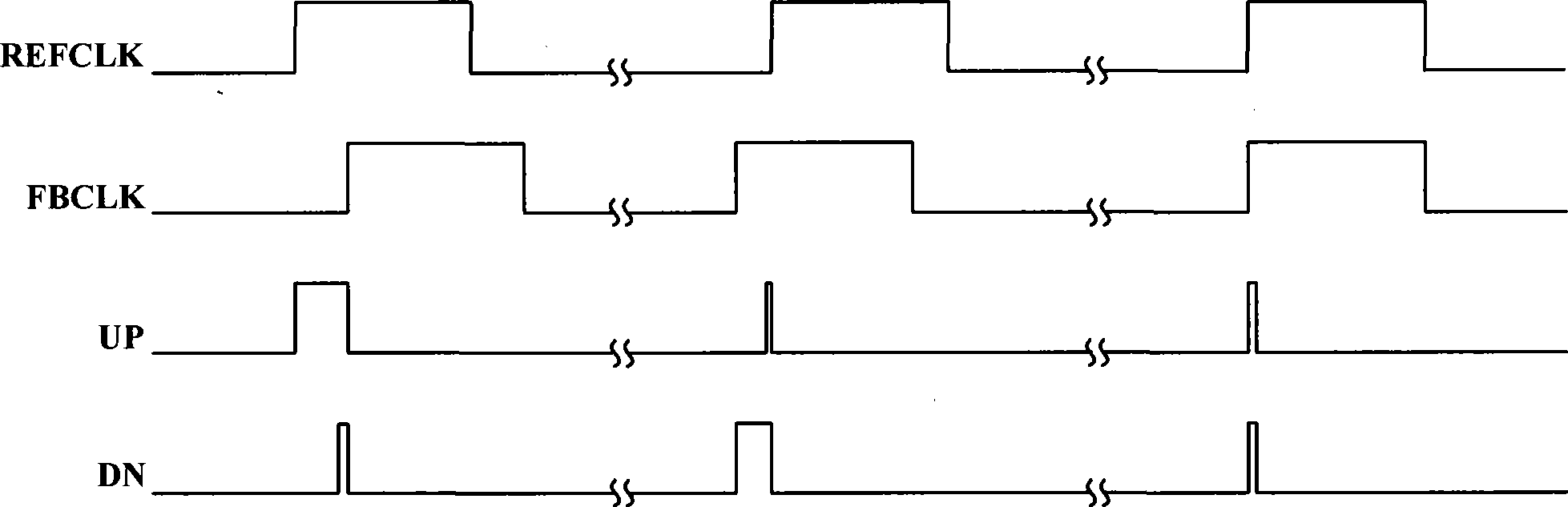

The invention provides a frequency generator for quick locking, which comprises a phase frequency detector, a charge pump, a filter, a voltage controlled oscillator and a first locking unit connected with the charge pump and the filter. When no phase difference is existed between reference clock signal and feedback clock signal, the first locking unit outputs a quick locking signal of decreasing charge-discharge current of the charge pump and increasing resistance of the filter. The frequency generator can shorten locking time of frequency and phase.

Owner:安凡微电子(上海)有限公司

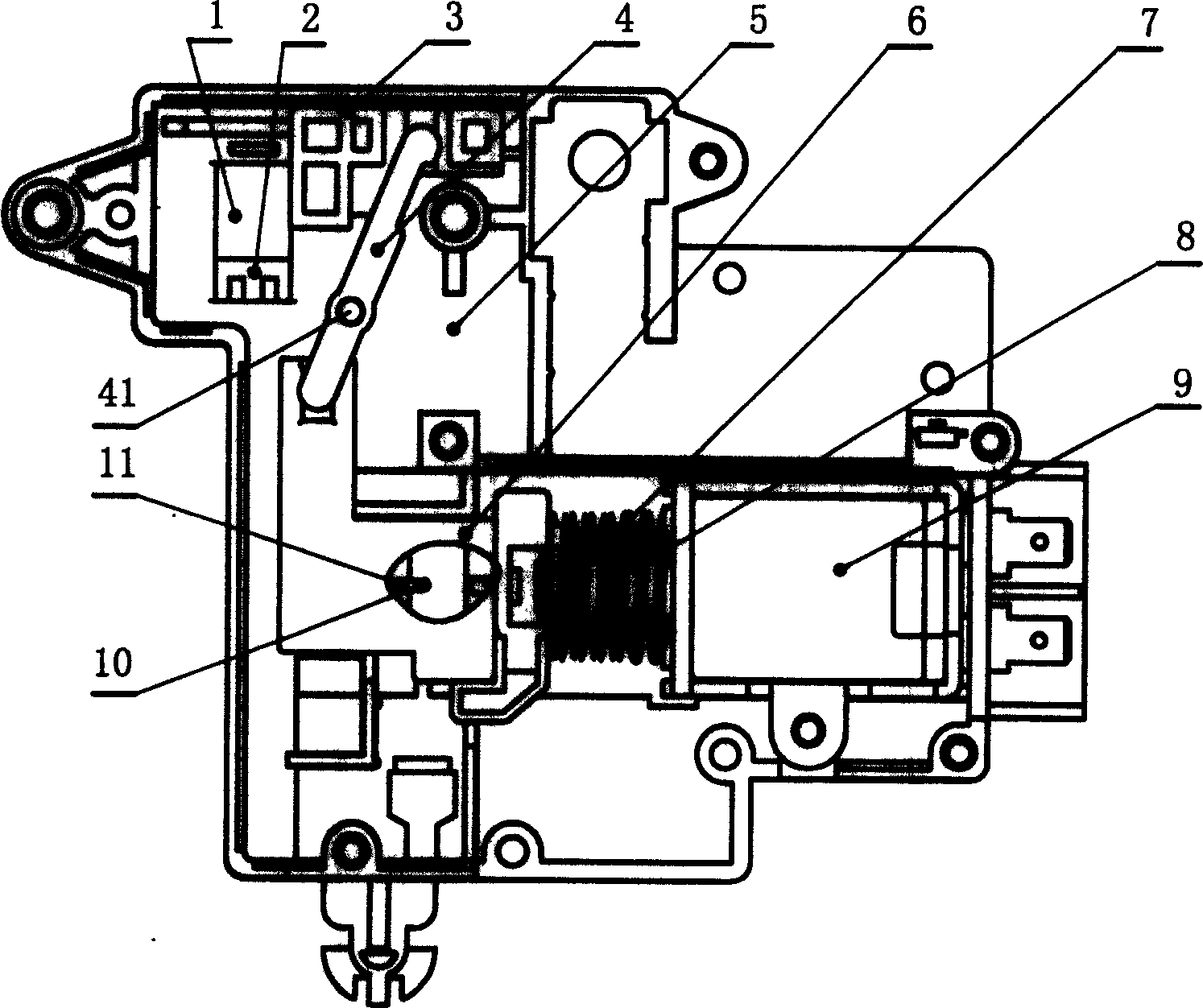

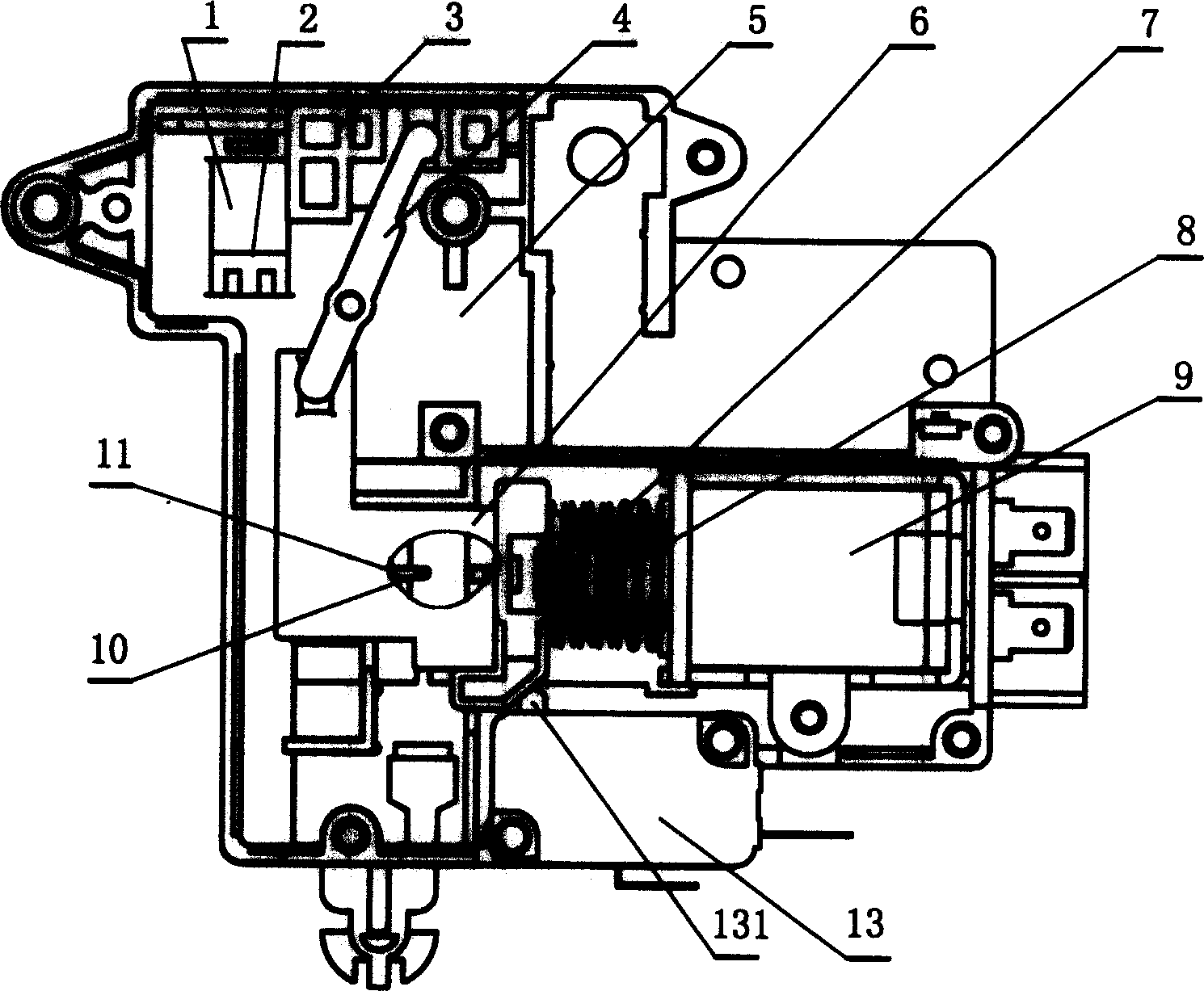

Door lock switch

Locking reliable also can fixed reconciliation locks or fast door interlock switch, has opens dog hole (1) substrate (5) and lap (12), the substrate (5) in is equipped with the magnet coil (9) and the operation slide (6), operates the slide (6) on the company to have the ferrite core (8) besides the jacket to have the spring (7) to be located the magnet coil between the operation slide, operates the slide (6) in to be equipped with 'the localization / replacement' guide way (11), is equipped with the guide pin (10) its end to fix to the substrate (5), another end is located guide way (11), The substrate (5) in is equipped with the slide (3) to be located dog hole (1) upside within the side direction region, is equipped with the release lever (4) its middle to be possible the pivot shaft change of scene set to the fulcrum pin (41), the release lever (4) an end AND-OPERATION slide (6) is connected, another end and the slide (3) unite. This invention mainly is suitable for rotary drum washer door lock locking and the solution lock.

Owner:HANGZHOU KAMBAYASHI ELECTRONICS

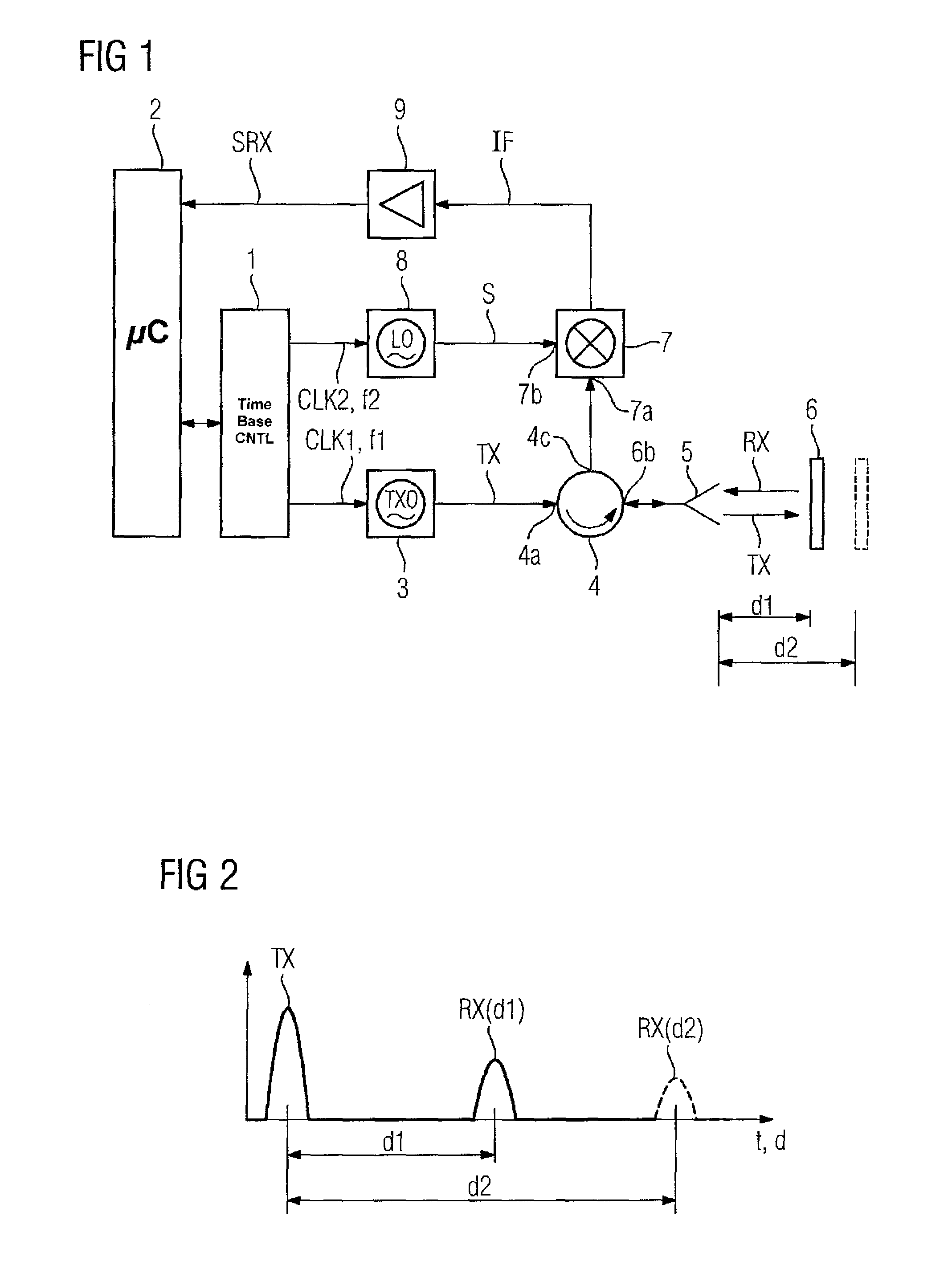

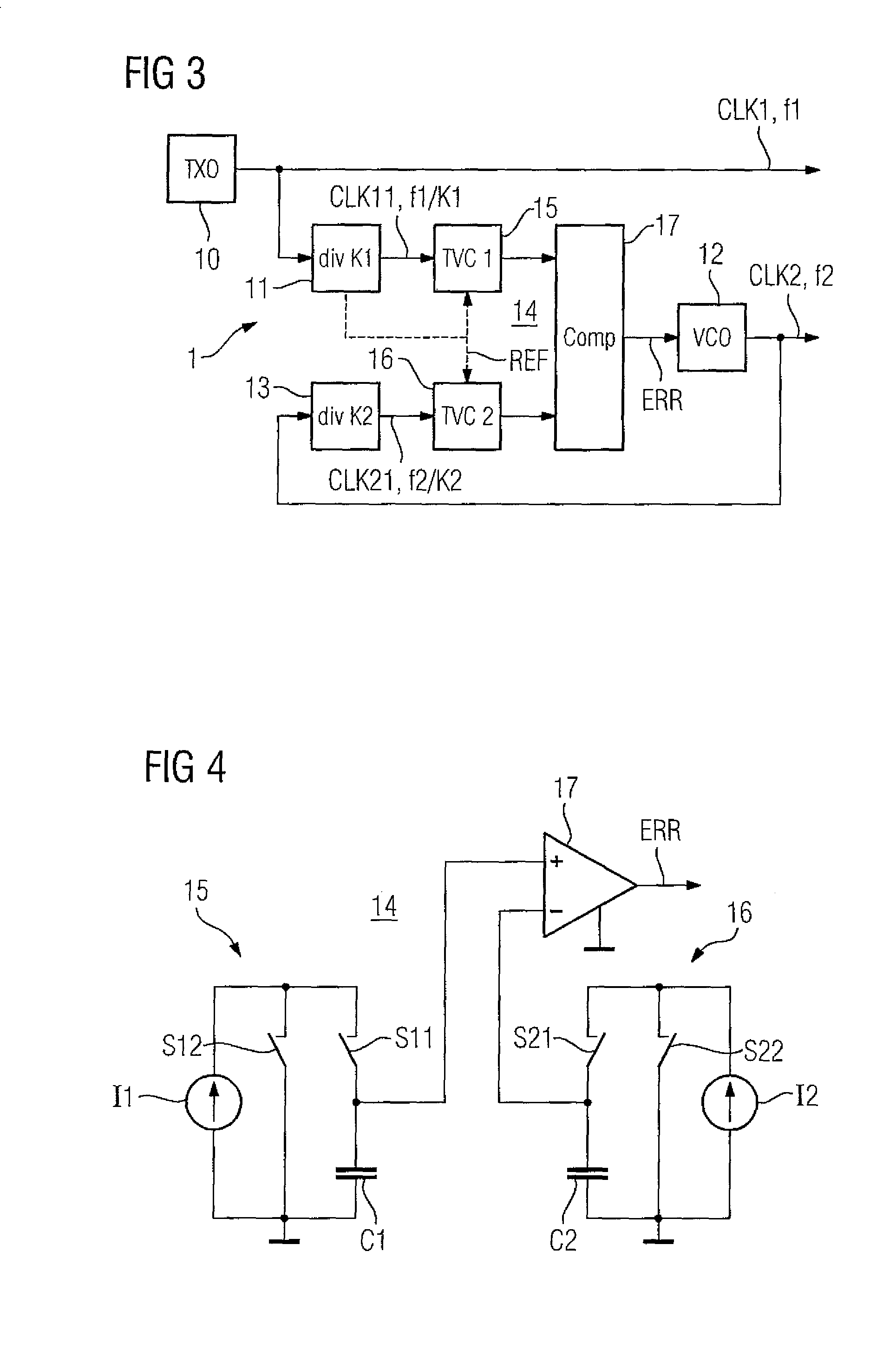

Time base generator and method for providing a first clock signal and a second clock signal

ActiveUS8390348B2Short lock timeMultiple input and output pulse circuitsWave based measurement systemsClock rateEngineering

A time base generator and method for providing a first clock signal and a second clock signal comprising generating the first clock signal at a first clock frequency, dividing the first clock frequency by a first integer to produce a first auxiliary signal, dividing the second clock signal by a second integer to produce a second auxiliary signal, generating an error signal by individually weighting and comparing cycle durations or phasing of the first and second auxiliary signals, and generating the second clock signal by a voltage-controlled oscillator controlled by the error signal such that two clock signals of slightly different frequencies with defined time or phase delay are provided.

Owner:SIEMENS AG

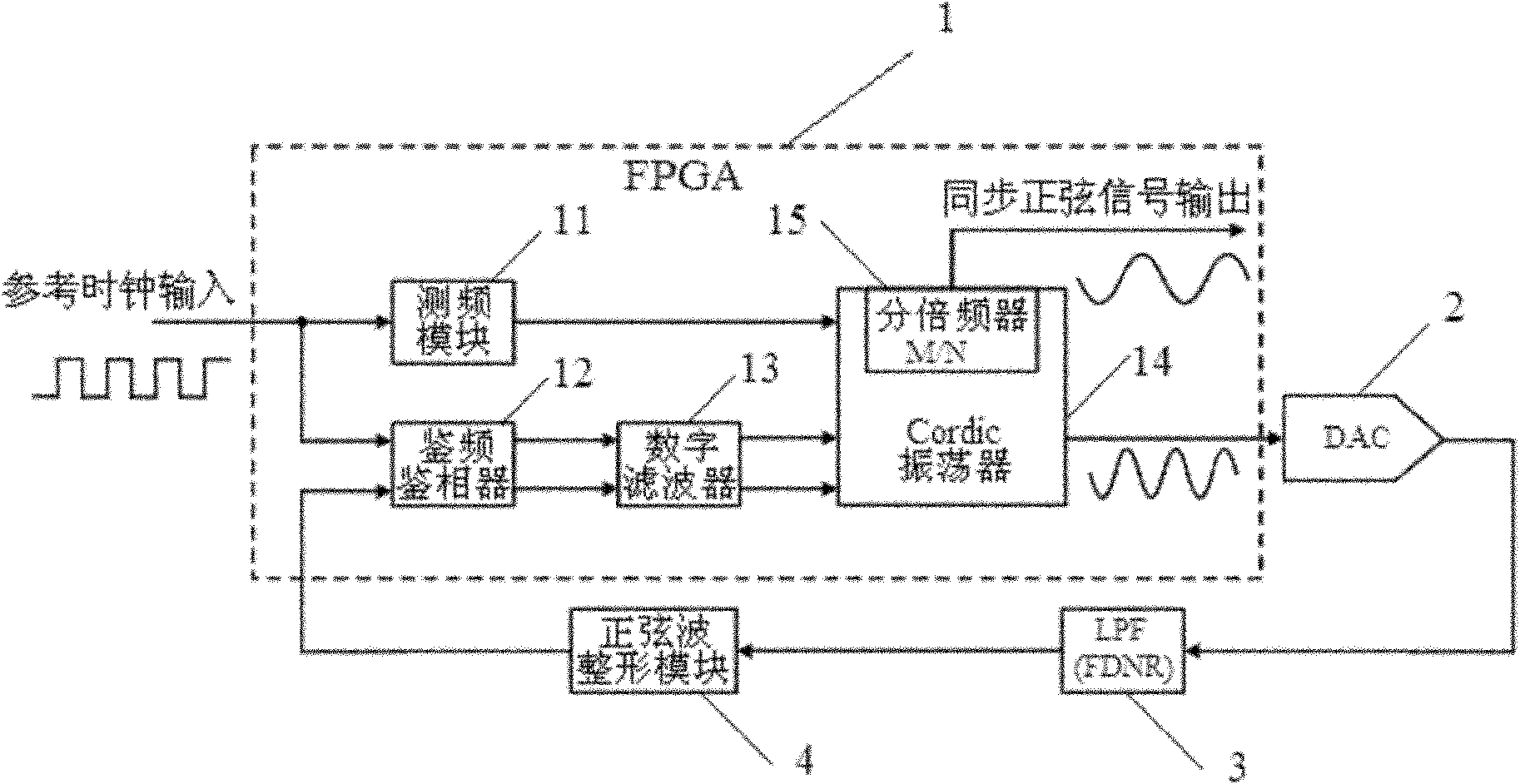

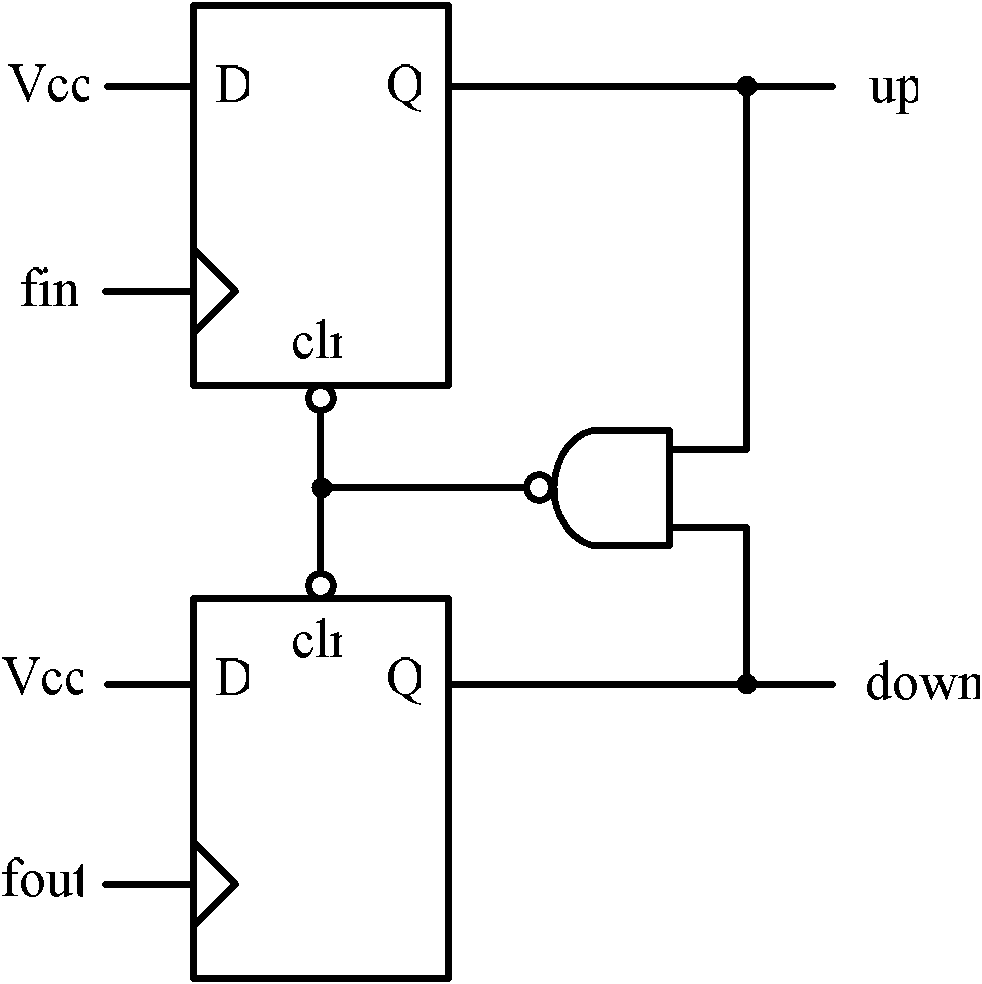

Digital phase-locked loop based on Cordic algorithm

InactiveCN102045062AShort lock timeImplement a feedback loopPulse automatic controlSignal averagingVIT signals

The invention discloses a digital phase-locked loop based on a Cordic algorithm, comprising: a controller for implementing a phase-locked loop algorithm for outputting a sinusoidal signal; the controller comprises: a frequency measuring module for performing segmental frequency measurement on a reference clock input signal; a phase and frequency discriminator for comparing the reference clock input signal with a feedback signal; a digital filter for equalizing an output signal of the phase and frequency discriminator; and an oscillator for receiving frequency measurement result from the frequency measuring module, generating an output signal having same frequency as the reference clock input signal, and receiving and adjusting phase of the output signal of the digital filter to be synchronous to the reference clock input signal; and a sine wave shaping module which is located at a feedback loop and used for converting the sinusoidal signal into a square signal. Compared with the priorart, the digital phase-locked loop based on the Cordic algorithm outputs a digital sinusoidal signal synchronous to a reference clock signal, and the digital sinusoidal signal is convenient for use in digital signal processing.

Owner:SUN YAT SEN UNIV

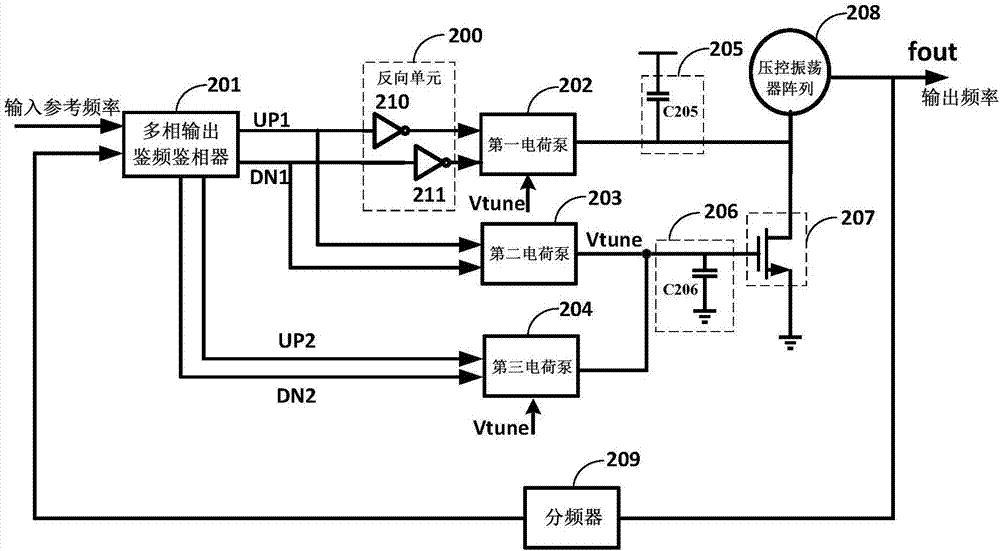

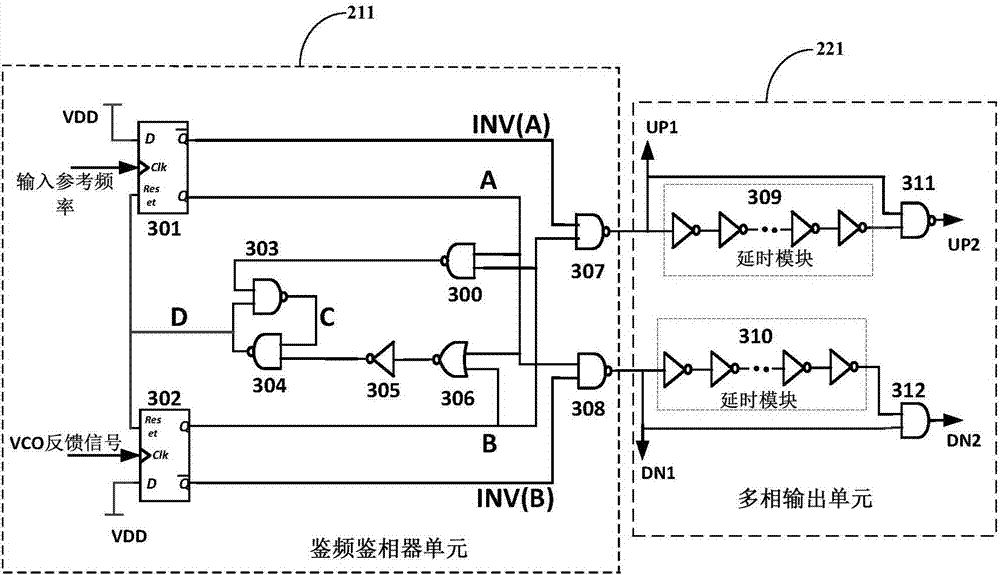

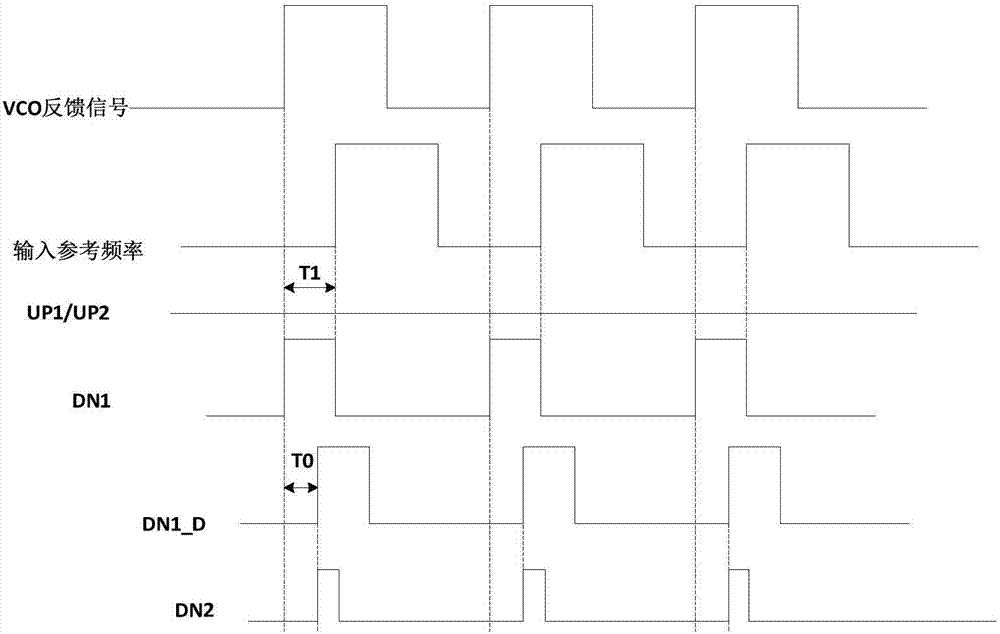

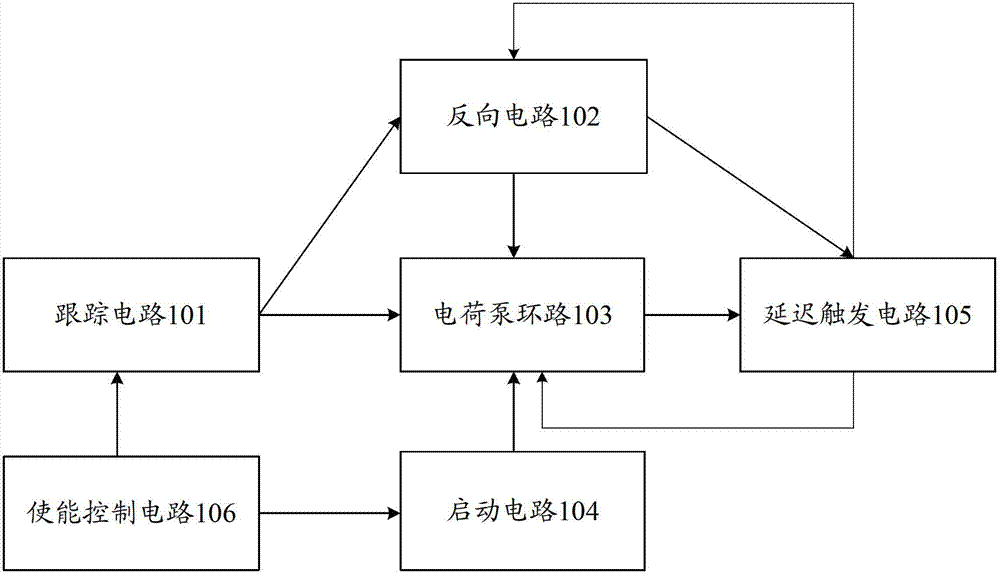

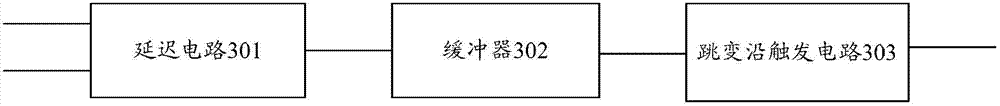

Multi-loop self-biasing phase-locked loop circuit and clock generator

ActiveCN106972857AReduce jitterShort lock timePulse automatic controlHigh level techniquesPhase locked loop circuitHemt circuits

The invention is applicable to the field of integrated circuits, and provides a multi-loop self-biasing phase-locked loop circuit and a clock generator. The circuit comprises a multi-phase output phase frequency detector, a reverse unit, a first charge pump, a second charge pump, a third charge pump, a switch unit, a voltage-controlled oscillator array and a frequency divider, wherein when a frequency difference between a signal output by the frequency divider and input reference frequency is less than a first threshold, the first and second charge pumps work simultaneously, the output current of the first charge pump is used for controlling a voltage-controlled oscillator to work so as to achieve output with a wide frequency range; the second charge pump and the third charge pump forms a control voltage on a second energy storage unit to control the current of the switch unit, so as to achieve dynamic adjustment of a ratio between the current of the chare pump and the current of the voltage-controlled oscillator. The multi-loop self-biasing phase-locked loop circuit provided by the invention has the advantages of being wide in application range, good in transportability, wide in input and output range and free from being affect by PVT, and having extremely strong capacity of resistant to technology, supply voltage and ambient temperature.

Owner:SHENZHEN STATE MICROELECTRONICS CO LTD

All digital phase-locked loop with widely locked frequency

ActiveUS8050376B2Efficient transferReduce time consumptionPulse automatic controlAngle demodulation by phase difference detectionDigital control oscillatorPhase difference

An all-digital phase-locked loop (ADPLL) composed of digital circuits is provided. The ADPLL includes a phase-frequency detector (PFD), a control unit, a digital controlled oscillator (DCO), and a plurality of frequency dividers. A first frequency divider divides a frequency of a feedback signal CKOUT by a natural number M to generate a first output signal CKOUT / M. The PFD generates a decrement signal dn and an increment signal up, based on a phase difference and a frequency between a first reference clock signal CKIN and the first output signal CKOUT / M. The DCO generates a clock signal CKDCO based on the digital control signals. A second frequency divider receives the digital control signals from the control unit and the CKDCO from the DCO and divides the frequency of the CKDCO by a bit number of the digital control signals to generate a feedback signal CKOUT to the first frequency divider.

Owner:NAT TAIWAN UNIV

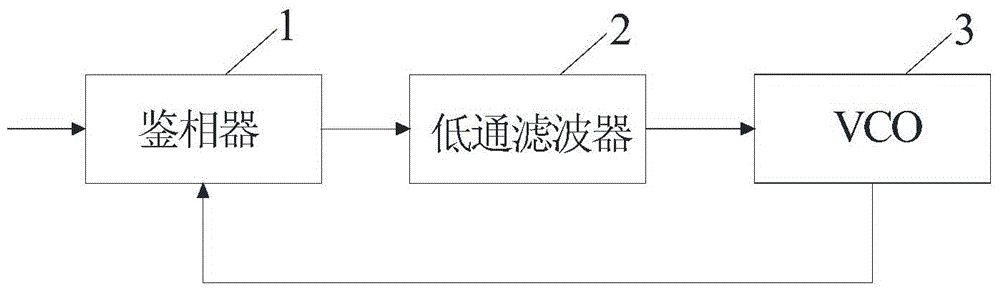

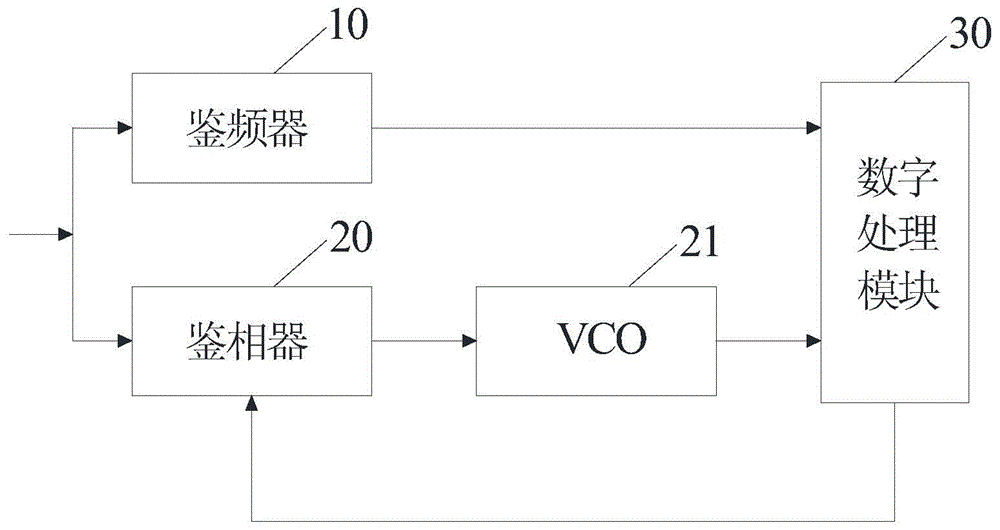

High-precision phase-locked loop and phase locking method

InactiveCN104104385APrevent discreteAvoid Phase Transient SituationsPulse automatic controlPhase detectorDiscriminator

The invention discloses a high-precision phase-locked loop comprising a frequency discriminator, a phase discriminator, a voltage-controlled oscillation module and a digital processing module. An input signal is inputted from the input ends of the phase discriminator and the frequency discriminator respectively. The output end of the frequency discriminator is connected with the digital processing module. The output end of the phase discriminator is connected with the input end of the voltage-controlled oscillation module. The input end of the voltage-controlled oscillation module is connected with the input end of the digital processing module. The output end of the digital processing module is connected with the feedback end of the phase discriminator. Frequency of an output signal is configured according to frequency of the input signal. Besides, phase difference between the input signals is adjusted via changing frequency change direction of the output signal so that the output signal is enabled to be matched with the input signal and an objective of phase locking is achieved.

Owner:SUN YAT SEN UNIV

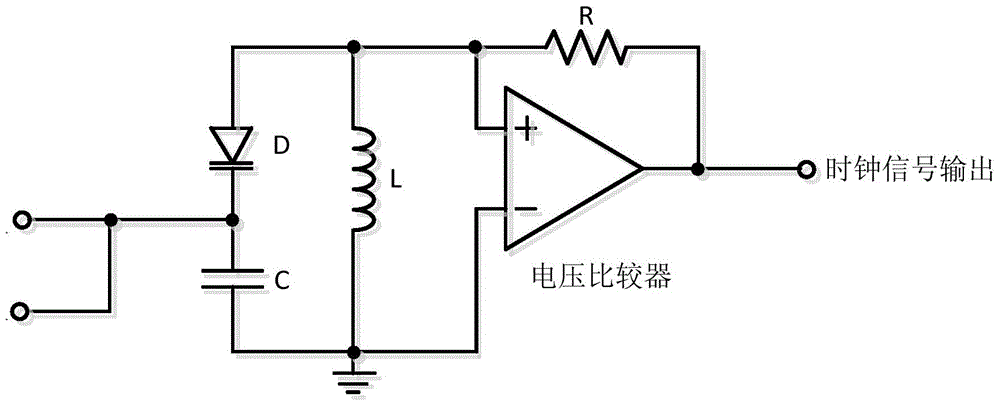

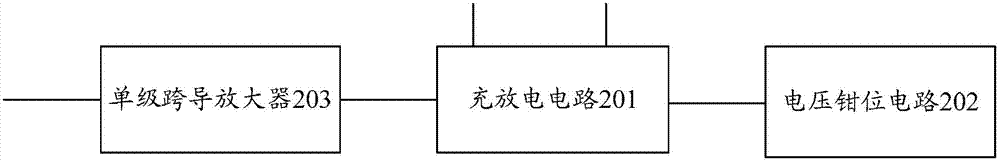

Clock pulse width modulation circuit and clock pulse width modulation method

ActiveCN102739209AReduce areaIncrease profitPulse duration/width modulationLock timeDigital conversion

The invention provides a clock pulse width modulation circuit and a clock pulse width modulation method. In the invention, an edge in one clock period of an output clock signal is generated by tracking one edge in one clock period of a to-be-modulated clock period, and another edge in one clock signal of the output clock signal is modulated directly by an initialized modulation circuit so as to obtain the output clock signal. The technical scheme provided by the invention can provide the output clock signal with high accuracy, low jitter and short locking time for a high-speed analog / digital conversion system on the premise of ensuring small chip area occupied by the modulation circuit.

Owner:成都启臣微电子股份有限公司

Phase locked loop circuit with selectable variable frequency dividers

InactiveUS6894571B2Short lock up timeLess electric powerPulse automatic controlPhysicsGenerating unit

A PLL circuit comprises a reference signal generating unit for generating reference signals of different phases, variable frequency dividers for dividing the frequency of the output signal of a voltage-controlled oscillator (VCO) and thereby outputting feedback signals, and a phase comparator for comparing the phase of each feedback signal with that of the corresponding reference signal and thereby outputting phase comparison signals. When the output signal is synchronized with a preset frequency signal, at least one variable frequency divider of the variable frequency dividers is operated, and the operation of the other is stopped.

Owner:SANYO ELECTRIC CO LTD +1

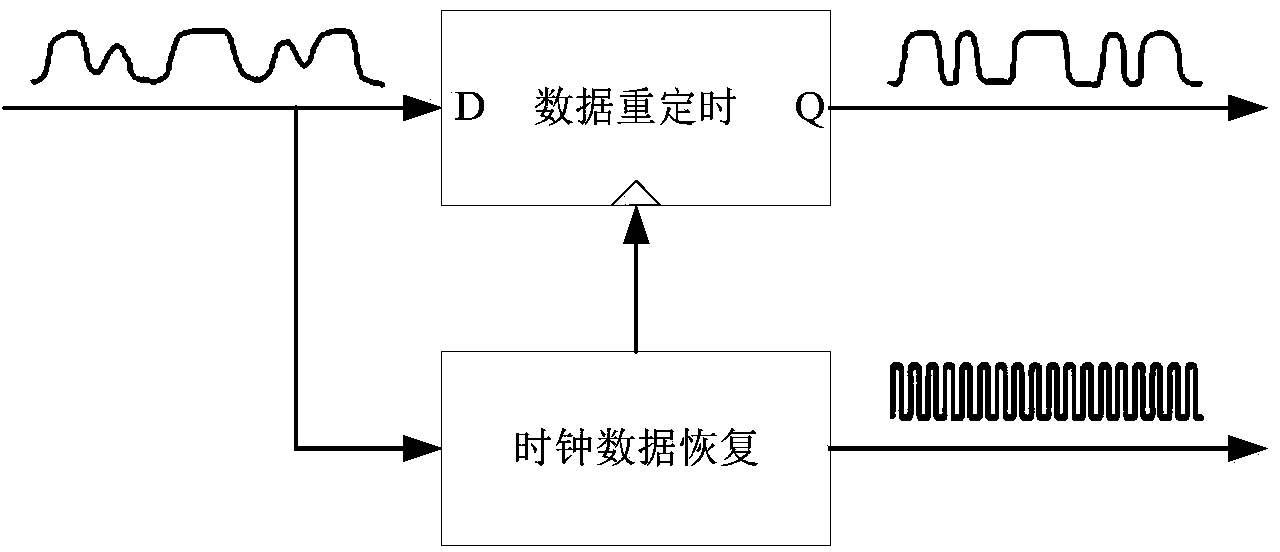

Clock and data recovery circuit and clock and data recovery method

ActiveCN104363016ASimple structureShort lock timePulse automatic controlDiscriminatorData recovery circuit

The invention discloses a clock and data recovery circuit and a clock and data recovery method. The clock and data recovery circuit comprises a clock generation module, a clock selection module, a phase discriminator and a digital correlation processing module, wherein the clock generation module is used for receiving input clock signals, generating multi-channel clock signals identical in frequency and different in phase and sending the multi-channel clock signals to the clock selection module; the clock selection module is used for selecting continuous multi-channel clock signals from the multi-channel clock signals identical in frequency and different in phase to the phase discriminator and selecting one-channel clock signal serving as a data lock to the digital correlation processing module; the phase discriminator is used for receiving input data, oversampling the input data according to multi-channel oversampling clocks and sending the oversampled data to the digital correlation processing module; the digital correlation processing module is used for processing the oversampled data, recovering the data and feeding back one clock selection signal to the clock selection module; according to the feedback clock selection signal, the clock selection module selects and outputs the clock signals as same as the recovered data in phase. The clock and data recovery circuit has he advantages of simple structure, short locking time, small recovered clock jitter and the like.

Owner:QINGDAO GOERTEK

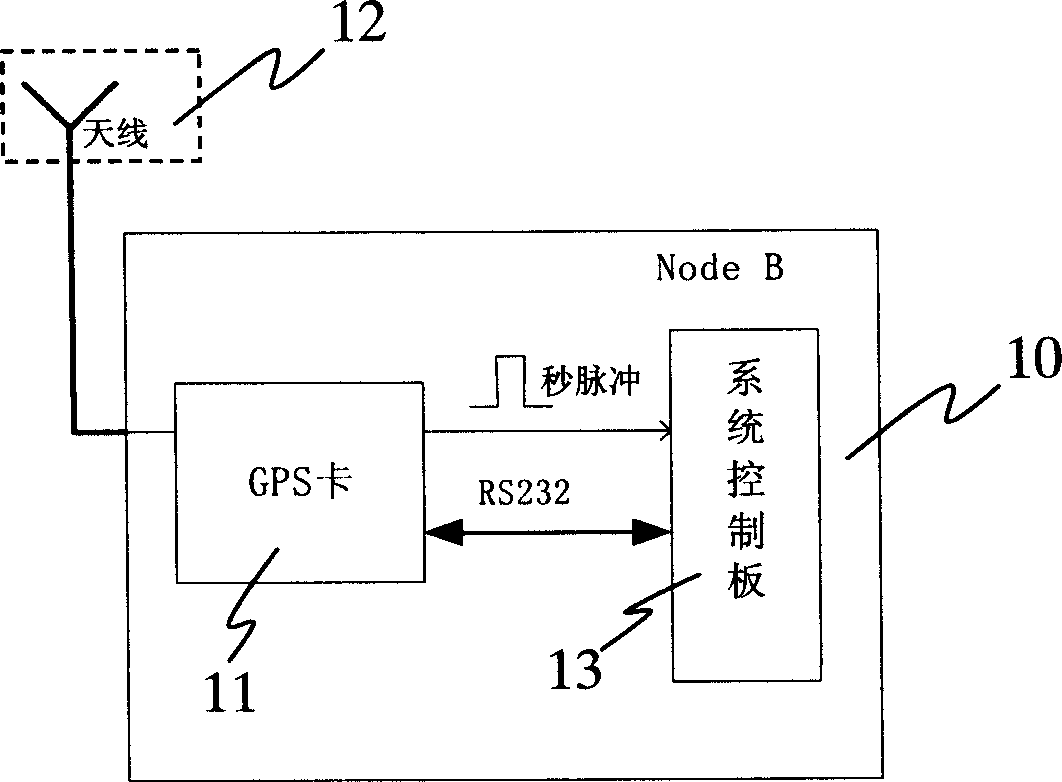

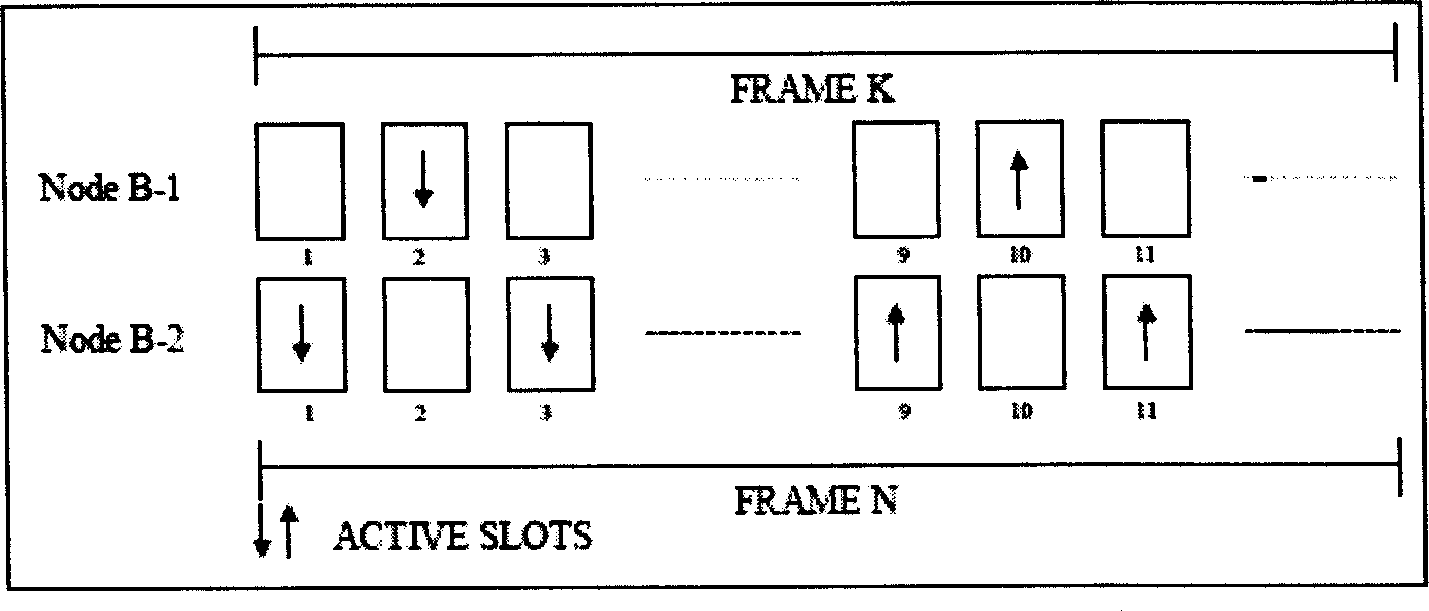

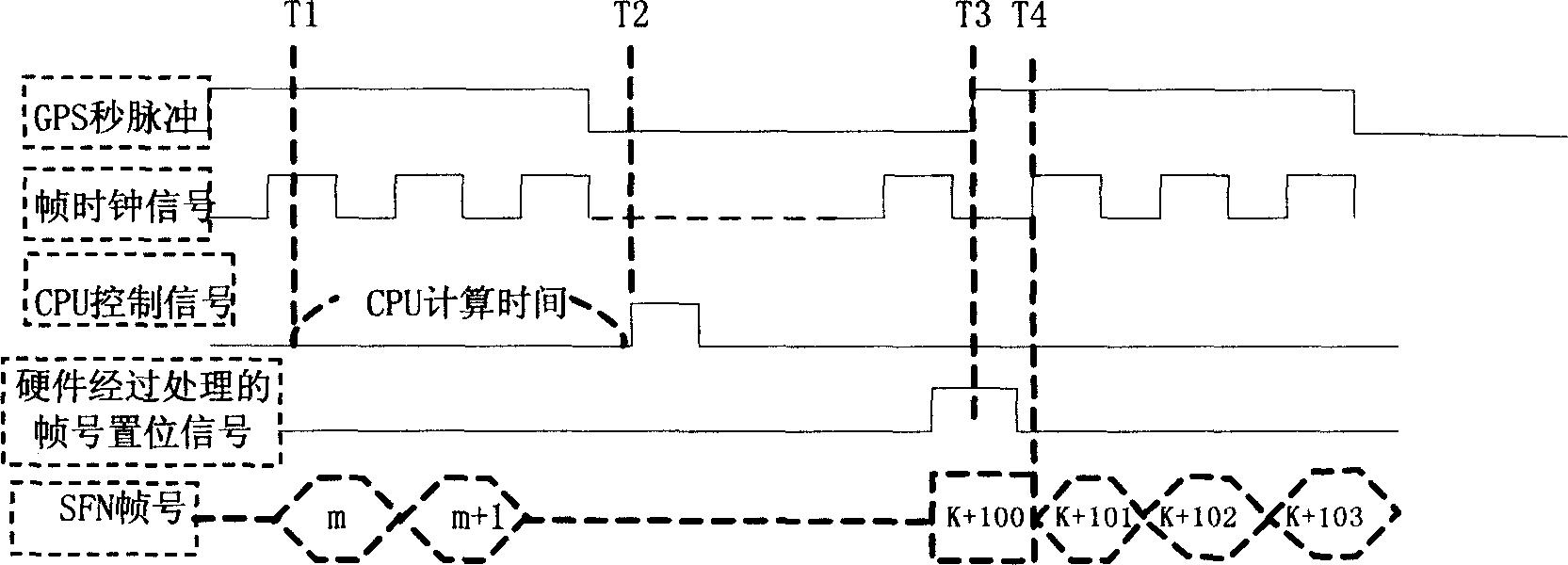

Method and device for air frame synchronization between TDD-SCDMA base stations

ActiveCN1731704ADifficult to solveSolve slow synchronizationRadio transmission for post communicationTime informationCode division multiple access

The invention discloses an apparatus and method for realizing frame synchronization between time-division duplex synchronizing code division multiple access base stations. The invention takes global positioning system (GPS) as reference; each base station gets frame number consistent to other base stations' according to the time information provided by GPS; the control clocks of each base station keep frequency and phase synchronizations with the pulse timing signal of GPS by loosely-coupled phase-locking mode. Without the participation of wireless network controller, the base stations can get same phase, same frequency and same frame time. It has the advantages of short locking time and zero frequency and phase cumulative error.

Owner:ZTE CORP

Delay locked loop circuit with duty cycle correction function

InactiveUS20050127966A1Short lock timeHigh correctnessPulse automatic controlContinuous to patterned pulse manipulationNegative feedbackClosed loop

Owner:SK HYNIX INC

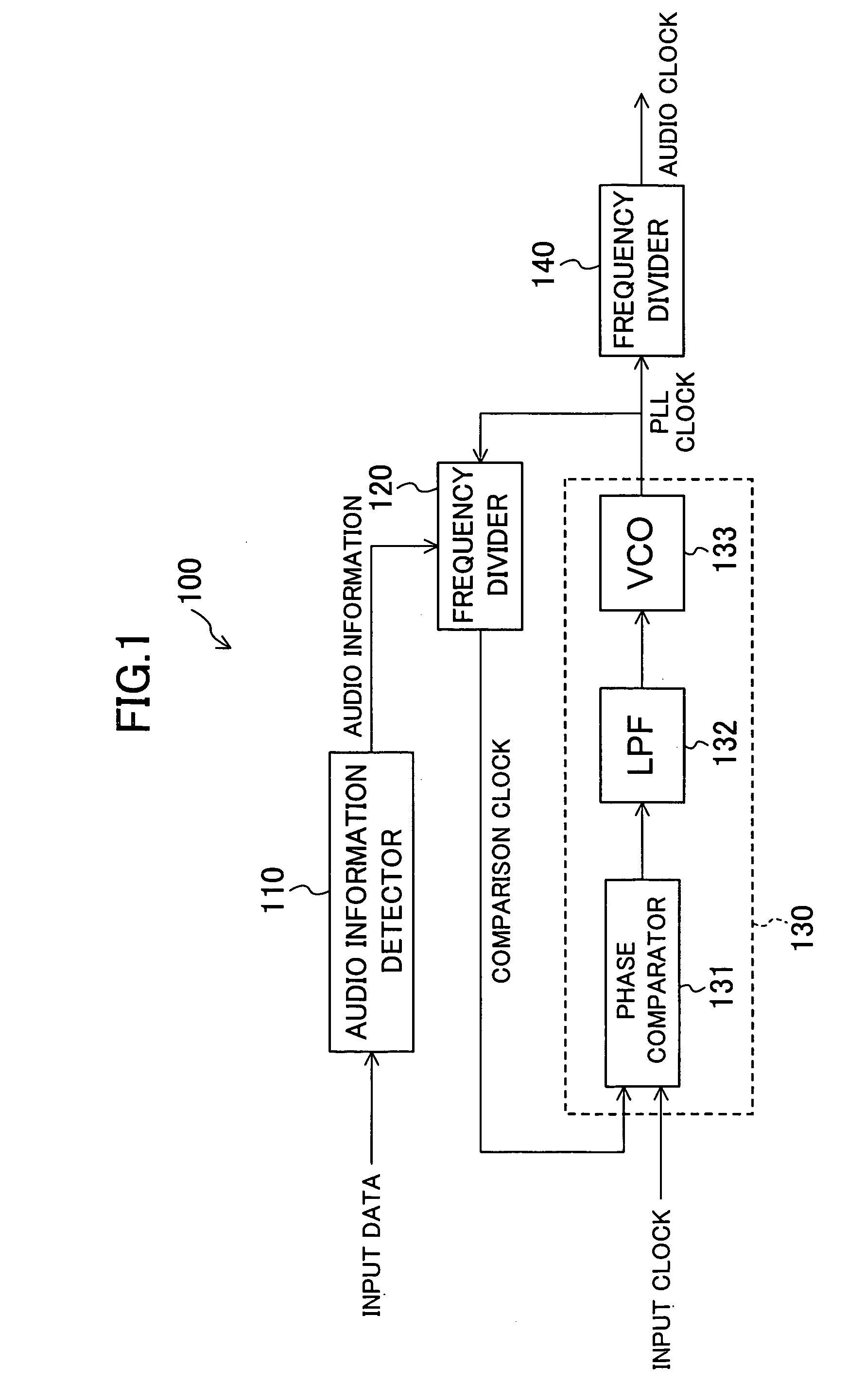

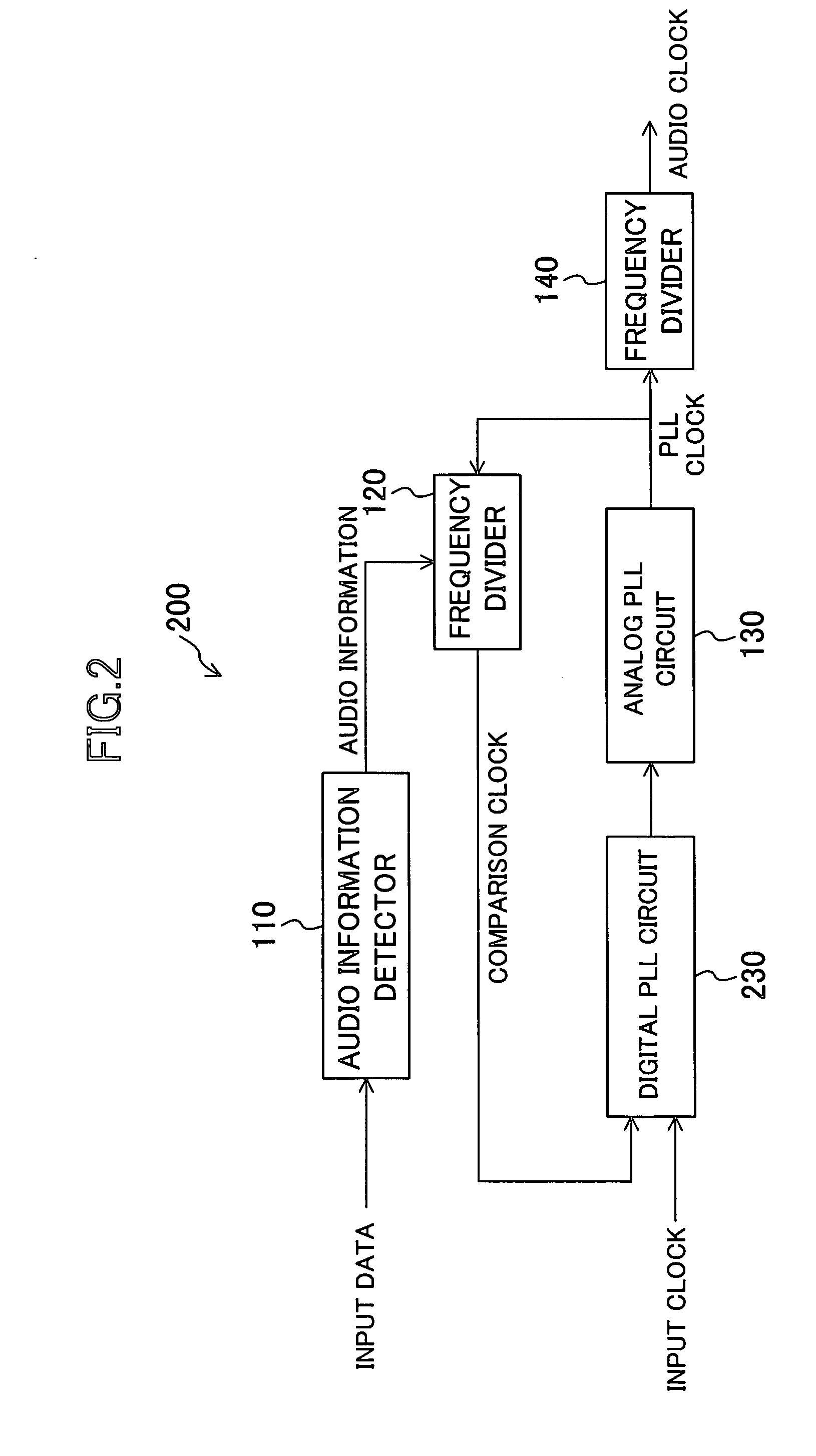

Audio processor

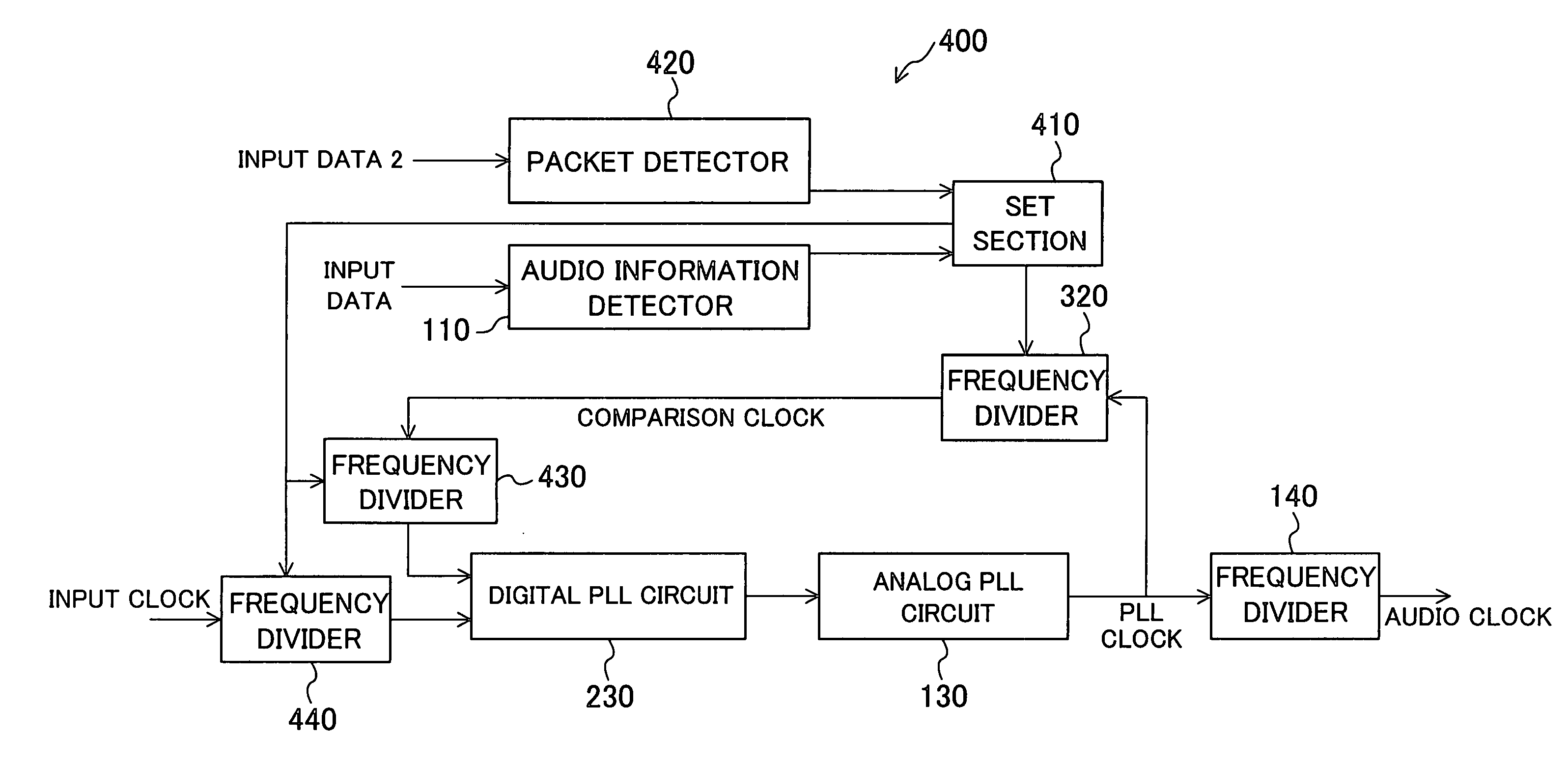

ActiveUS20070005163A1Reduce circuit sizeImprove scaleTime-division multiplexStereophonic systemsFeedback controlComputer science

An audio information detector extracts frequency information on audio data from a packet called an ASP in the HDMI standard and outputs the extracted frequency information to a frequency divider as audio information. The frequency divider determines a frequency division ratio based on the audio information, divides the frequency of a PLL clock signal output from an analog PLL circuit by the frequency division ratio and outputs the resultant signal as a comparison clock signal. The analog PLL circuit performs feedback control such that the comparison clock signal and a reference clock signal are synchronized with each other, and generates an audio clock signal obtained by performing frequency multiplication or division on the reference clock signal.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

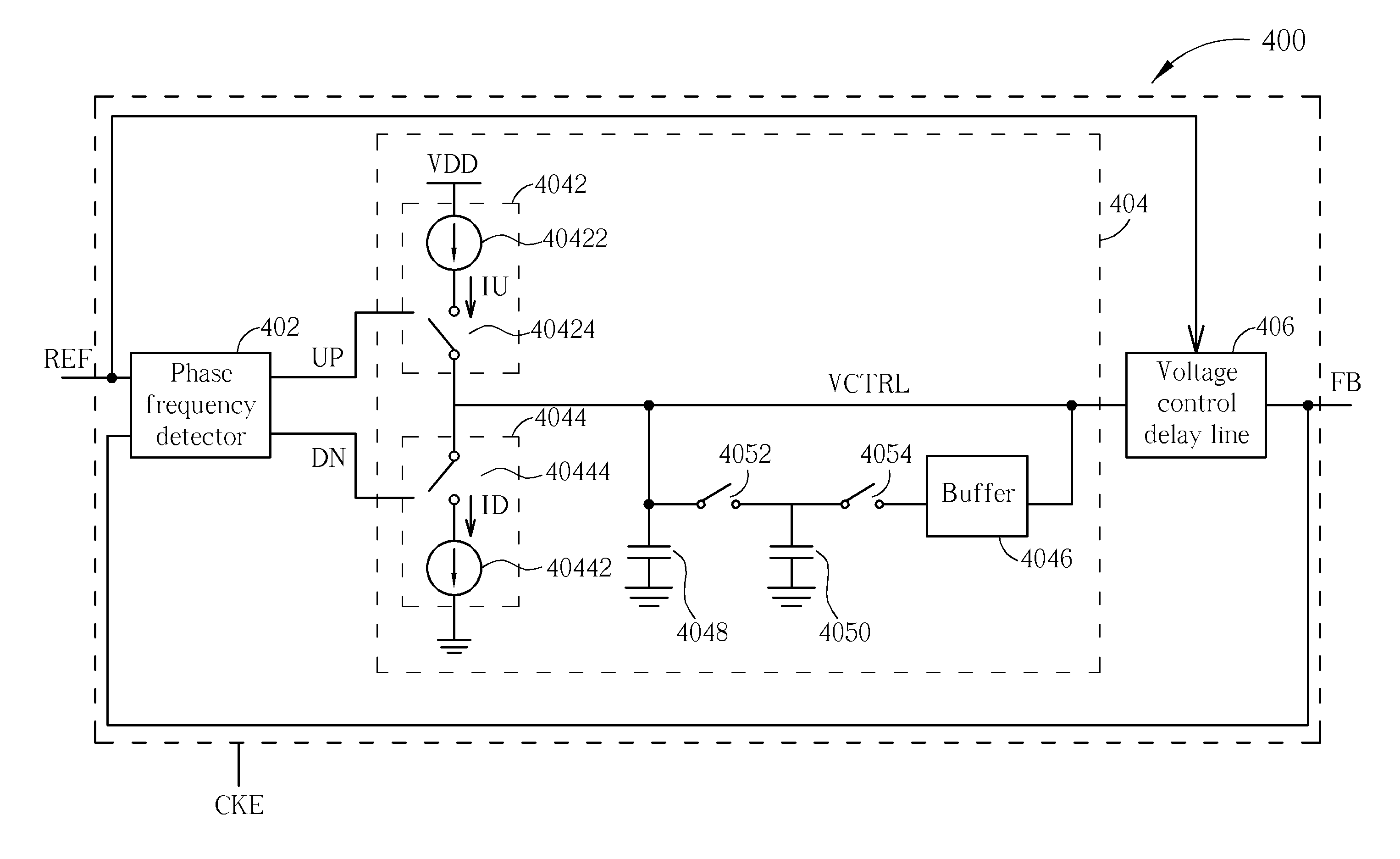

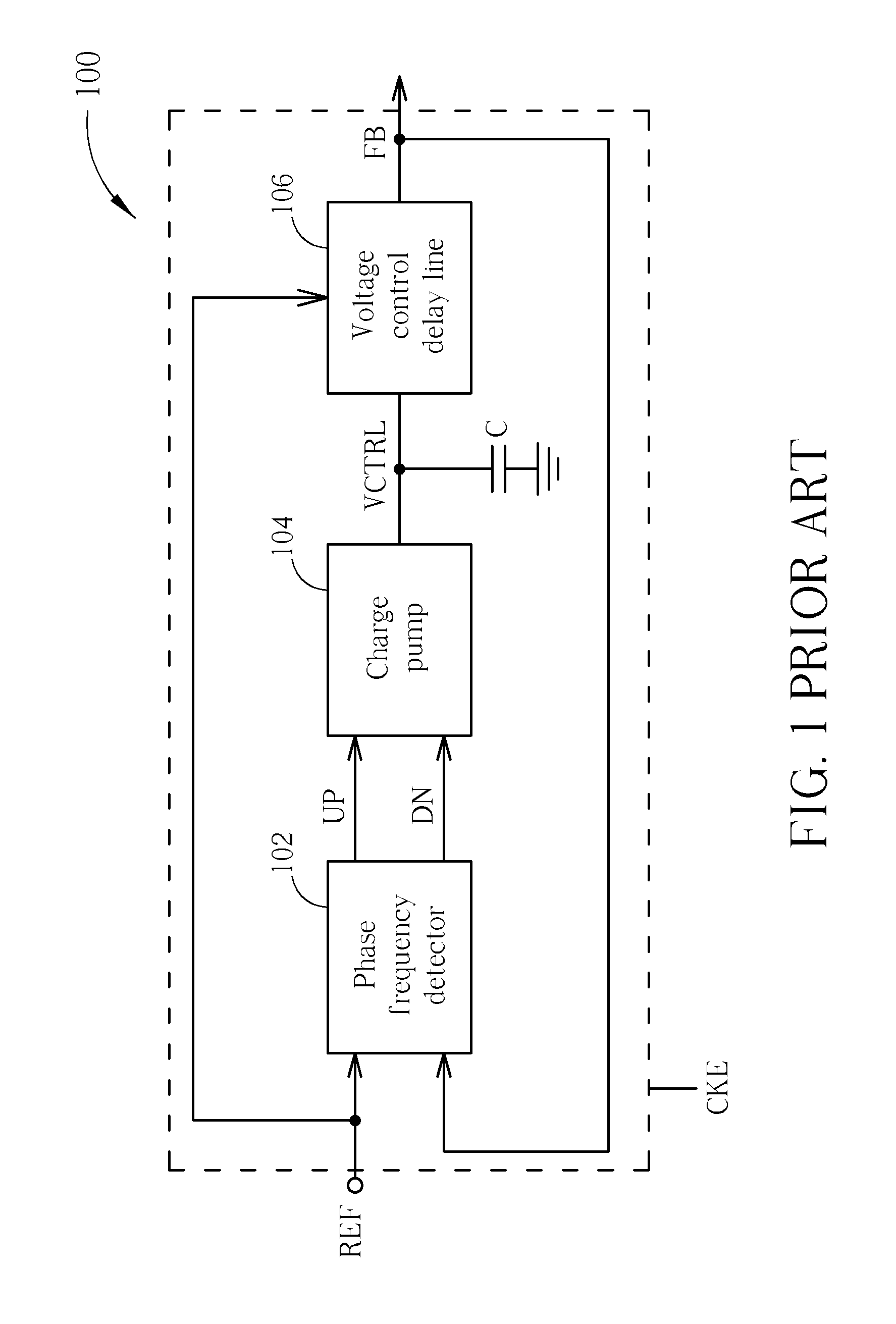

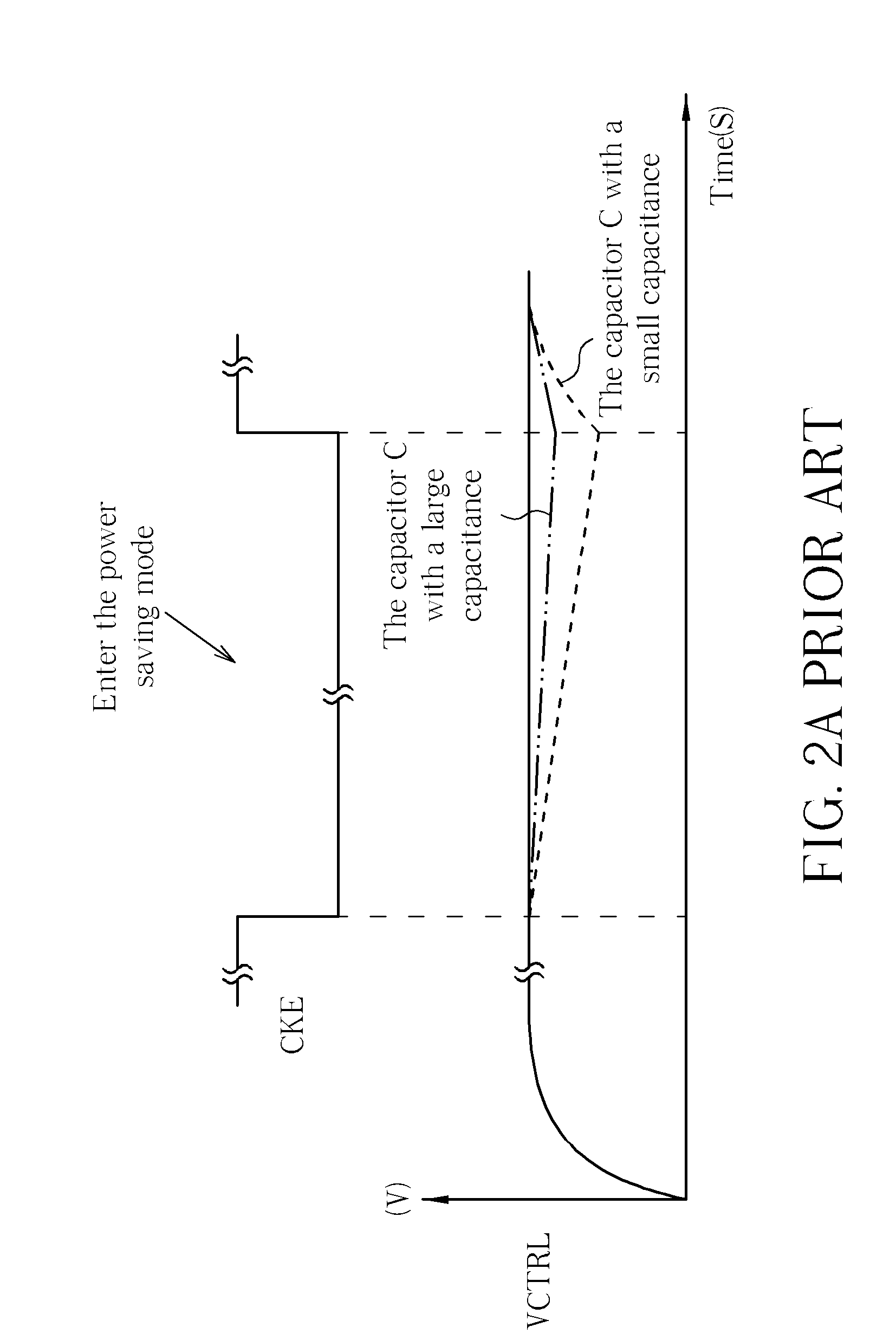

Delay lock loop with a charge pump, loop filter, and method of phase locking of a delay lock loop

ActiveUS20120256665A1Short lock timeReduce power consumptionPulse automatic controlLoop filterDelay-locked loop

A delay lock loop includes a phase frequency detector, a loop filter, and a voltage controlled delay circuit. The phase frequency detector is used for outputting an upper switch signal or a lower switch signal according to a reference clock and a feedback clock. The loop filter includes a first capacitor, a second capacitor, and a first switch. The first capacitor is charged or discharged and the first switch is turned off during a phase tracking period. The first capacitor and the second capacitor are charged or discharged and the first switch is turned on during a phase locking period. The voltage controlled delay circuit is used for outputting the feedback clock according to the reference clock and a control voltage outputted by the loop filter.

Owner:ETRON TECH INC

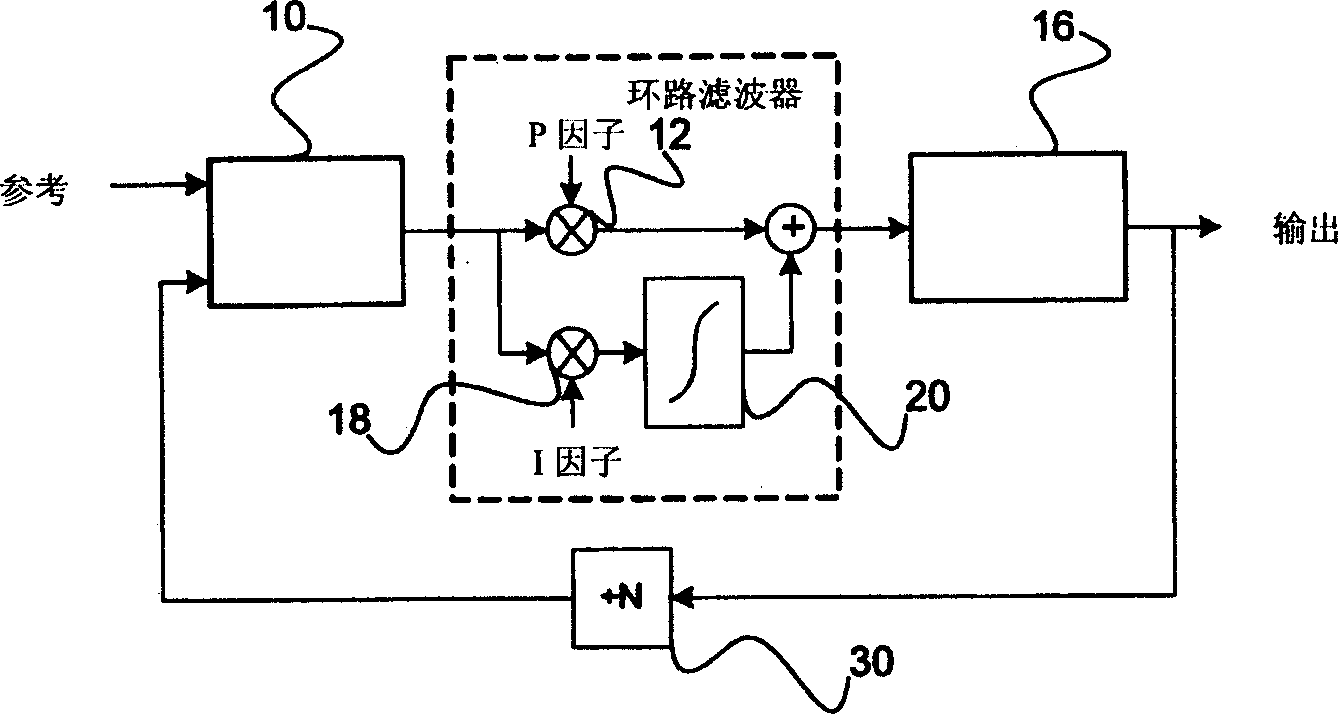

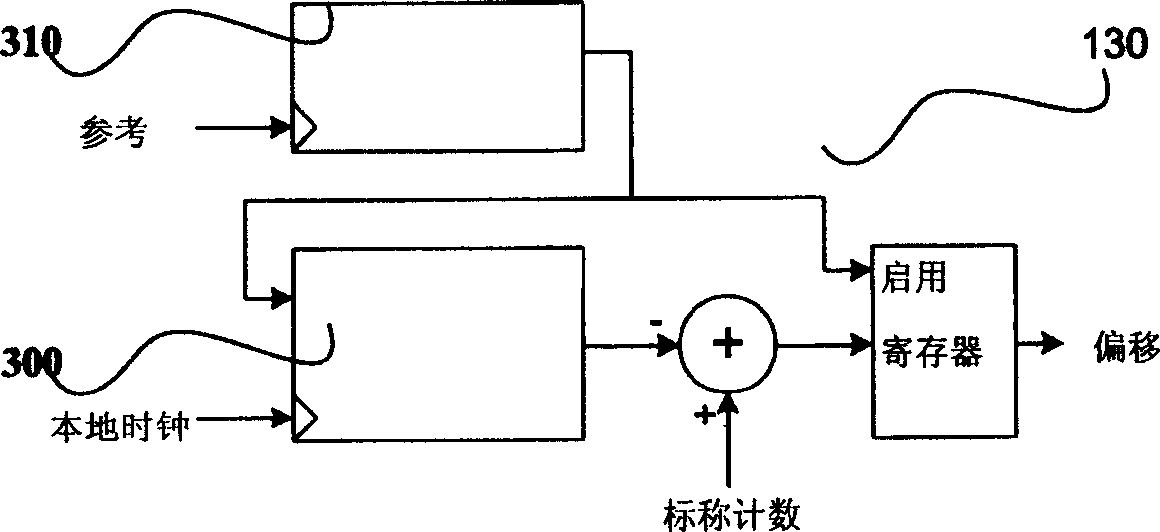

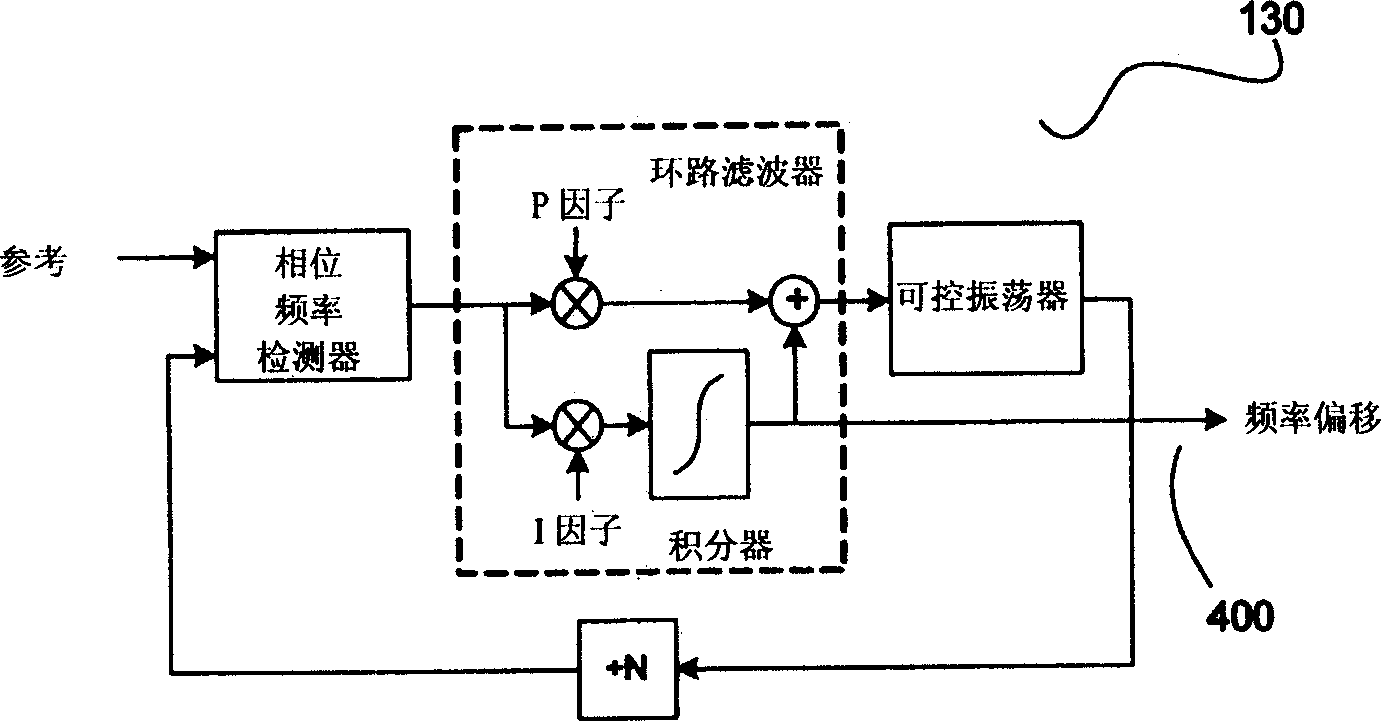

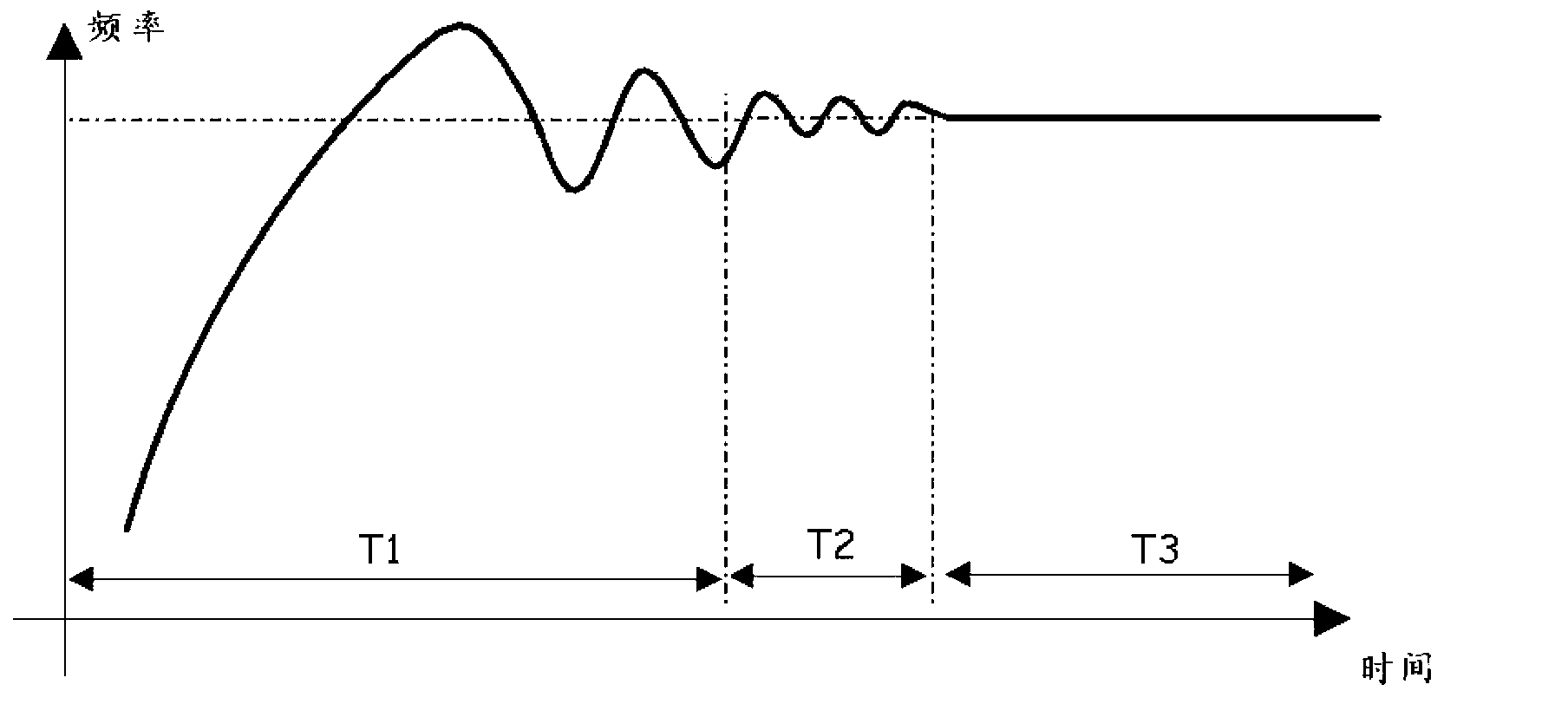

Phase locked loop fast lock method

The present invention is a method for quickly locking a Type II phase-locked loop (PLL) without degrading the output signal in large quantities after a frequency jump. The method disclosed herein to reduce settling time and improve output clock quality during settling includes the steps of estimating the new frequency offset with a separate circuit outside the PLL loop to accurately measure the frequency of the input signal. Ramp up the integrator to the new frequency offset. Perform phase compensation or phase pulling. When edge-to-edge alignment is required, the remaining phase offset is compensated. Conversely, the residual phase offset is pulled while disabling the integrator in the PLL loop filter. Reduce bandwidth and / or reduce damping to allow PLL tuning. Switch the PLL to the final bandwidth and damping required by the application.

Owner:ZARLINK SEMICON LTD

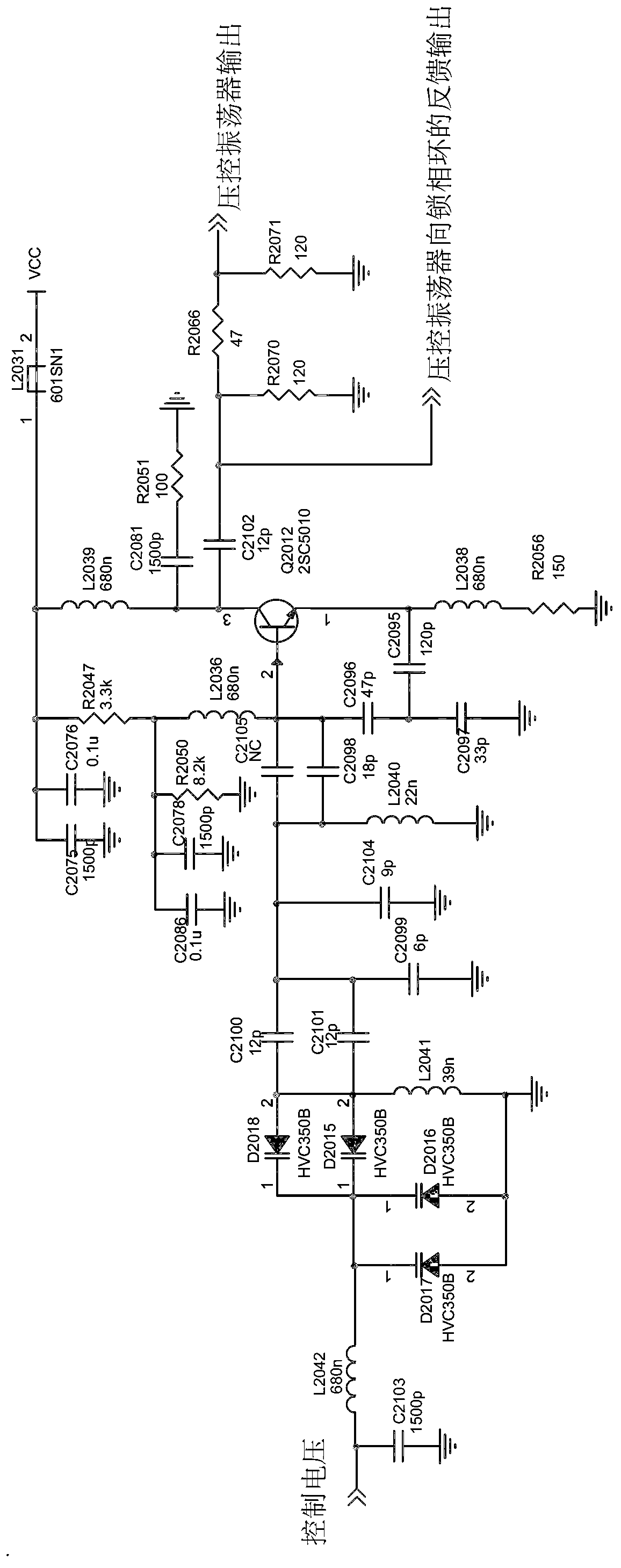

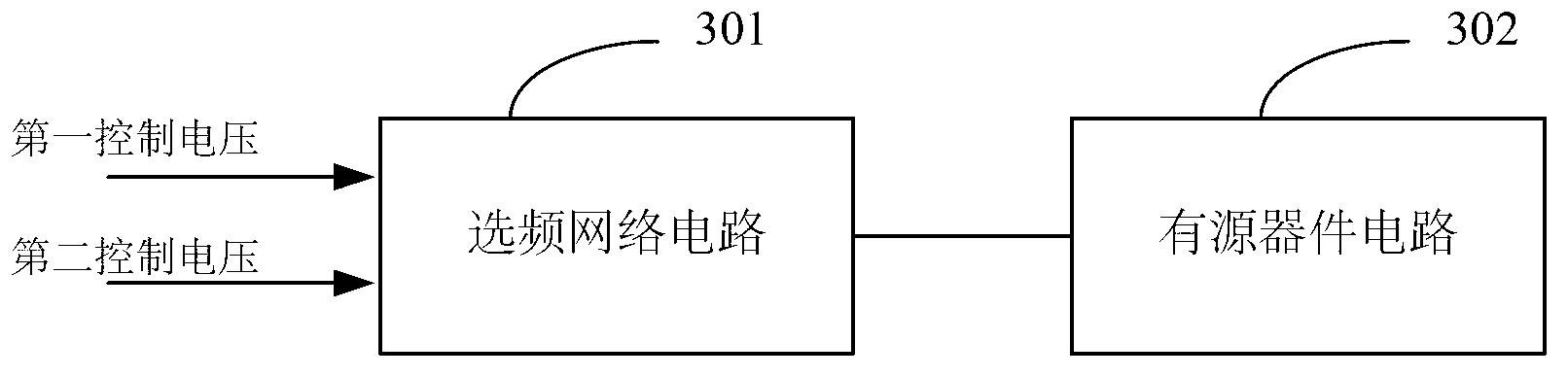

Frequency locking method, voltage-controlled oscillator and frequency generating unit

The invention process a frequency loading method, which comprises the following steps: a control unit generates auxiliary control voltage corresponding to target oscillation frequency and inputs the auxiliary control voltage to a voltage-controlled oscillator provided by the invention; a loop filter inputs the control voltage to the voltage-controlled oscillator; and the auxiliary control voltage enables an equivalent capacitance value of a frequency selective network circuit to change C1, and the control voltage enables an equivalent capacitance value of the frequency selective network circuit network circuit to change C2, wherein the sum of the C2 and the C2 is C3, the C3 is a capacitance value of the equivalent capacitance value change of the frequency selective network circuit when the frequency of a signal generated by the frequency selective network is changed into the target oscillation frequency from the current frequency, and the absolute value of the C3 is larger than of the C2. When the auxiliary control voltage is reasonable in design, the output frequency is changed to a certain degree, the difference value of the control voltage change is little, and therefore the frequency can be locked more rapidly. The invention also provides the voltage-controlled oscillator and a frequency generating unit.

Owner:HYTERA COMM CORP

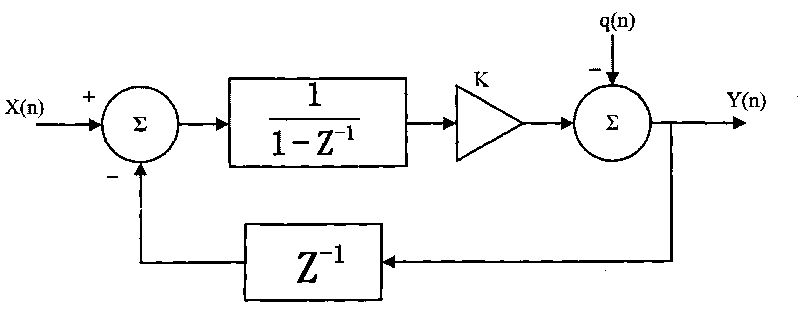

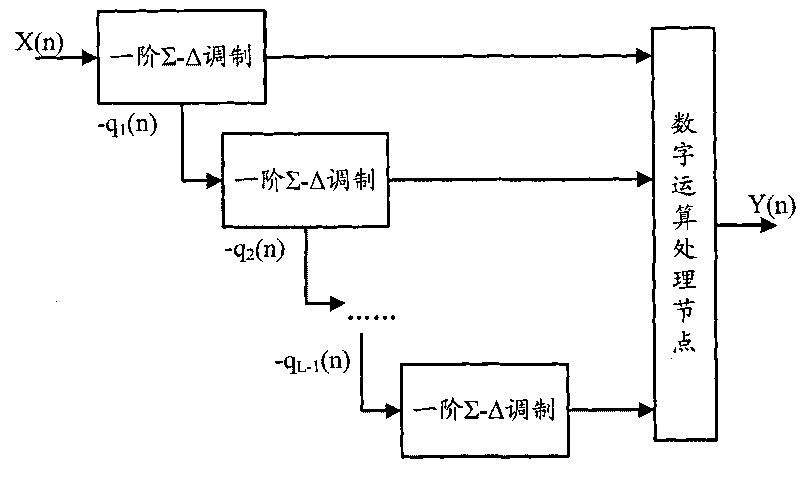

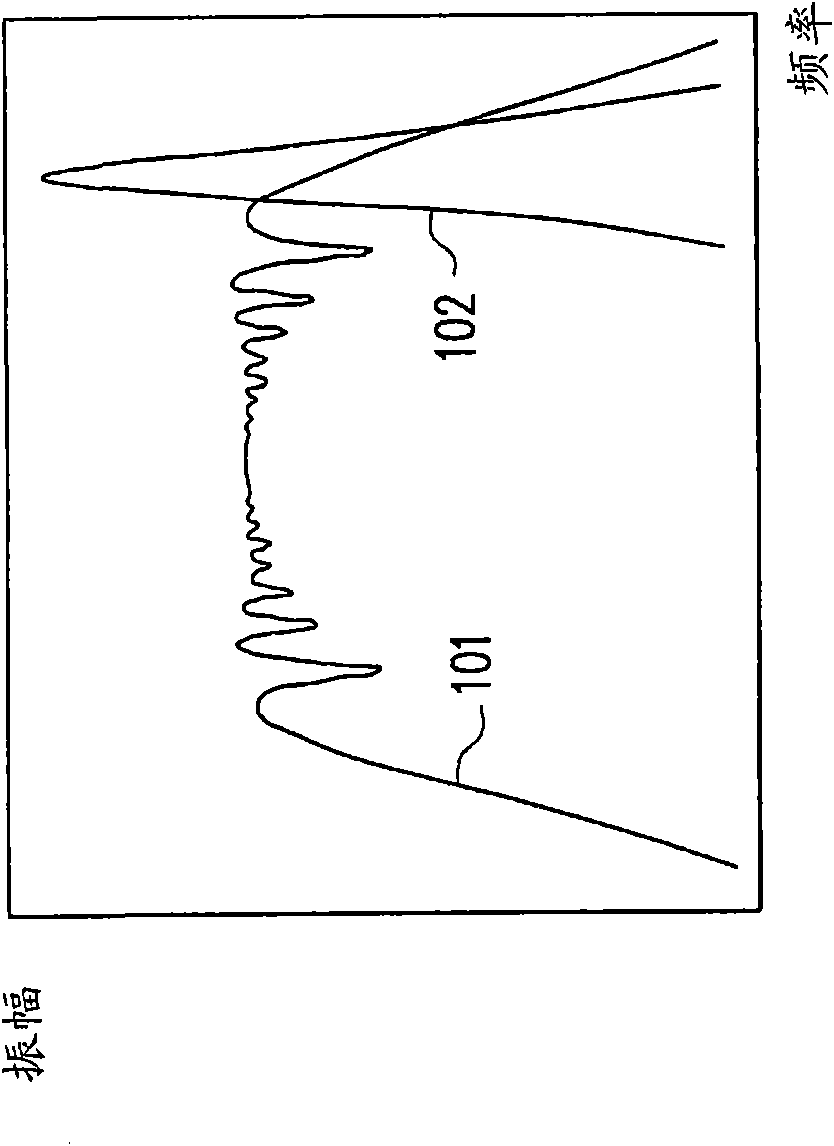

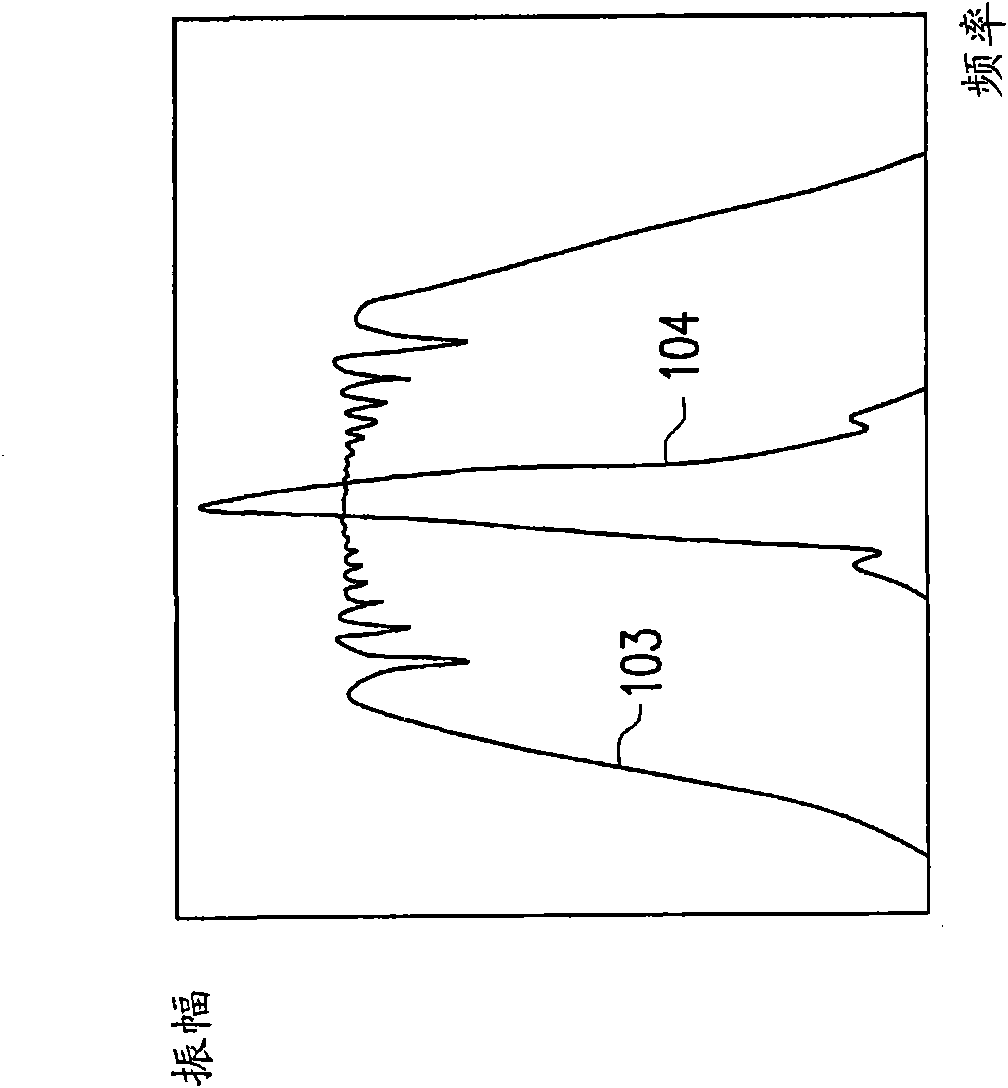

Sigma-Delta modulation circuit and method as well as corresponding phase-locked loop

InactiveCN101729066AFlexibleImprove stabilityPulse automatic controlEngineeringSigma delta modulation

The invention discloses Sigma-Delta modulation circuit and method as well as a corresponding phase-locked loop. The Sigma-Delta modulation is realized by utilizing the feedback of quantization noise so as to flexibly select output bits when selecting quantization output. The Sigma-Delta modulation circuit comprises a first summator, a quantizer, a subtracter, a plurality of quantization noise delay circuits and a second summator, wherein the first summator receives a score input signal and a feedback signal, generates and outputs a sum signal; the quantizer receives a unit delay signal of the sum signal generated by the first summator and generates an integer output signal after the unit delay unit is quantized; the subtracter receives the unit delay signal of the sum signal generated by the first summator and the integer output signal generated by the quantizer, subtracts the integer output signal from the unit delay signal of the sum signal, then generates and outputs the quantization noise; the plurality of quantization noise delay circuits respectively output the quantization noise after being delayed; and the second summator receives outputs of the plurality of quantization noise delay circuits, generates a feedback signal after the outputs are summed and provides the feedback signal for the first summator.

Owner:SEMICON MFG INT (SHANGHAI) CORP

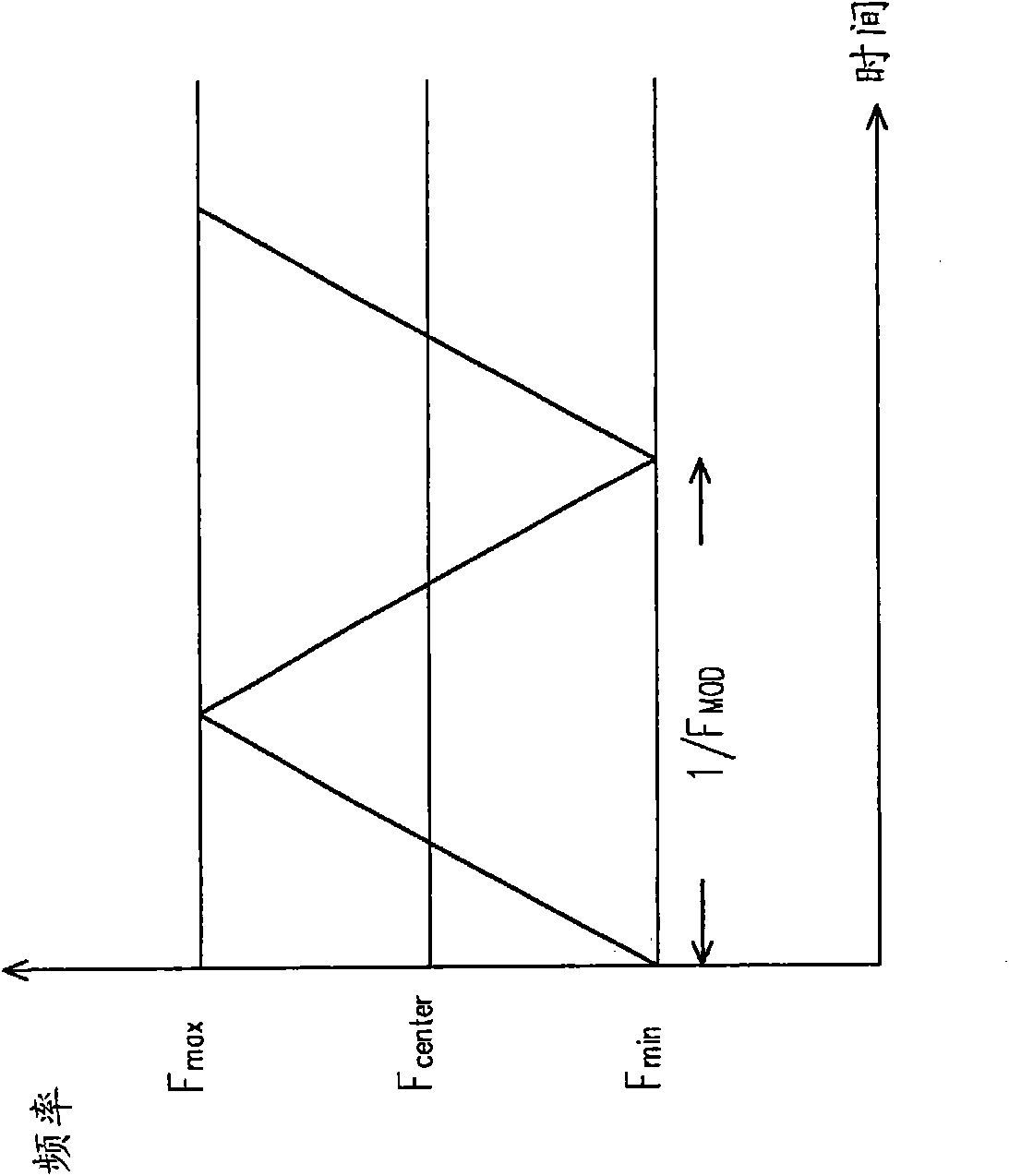

Spread spectrum clock generator

InactiveCN101667828AShort lock timeSolving Duty Cycle ProblemsPulse automatic controlSinusoidal oscillation interference reductionModulation functionSpread spectrum clock generator

The invention discloses a spread spectrum clock generator, which comprises a modulation module and a voltage control delayer, wherein the modulation module provides a control voltage; and the voltagecontrol delayer is coupled to the modulation module and performs frequency modulation on an input clock signal according to the control voltage so as to provide an output clock signal, wherein a modulation function of the output clock signal is a periodic function of time.

Owner:FARADAY TECH CORP

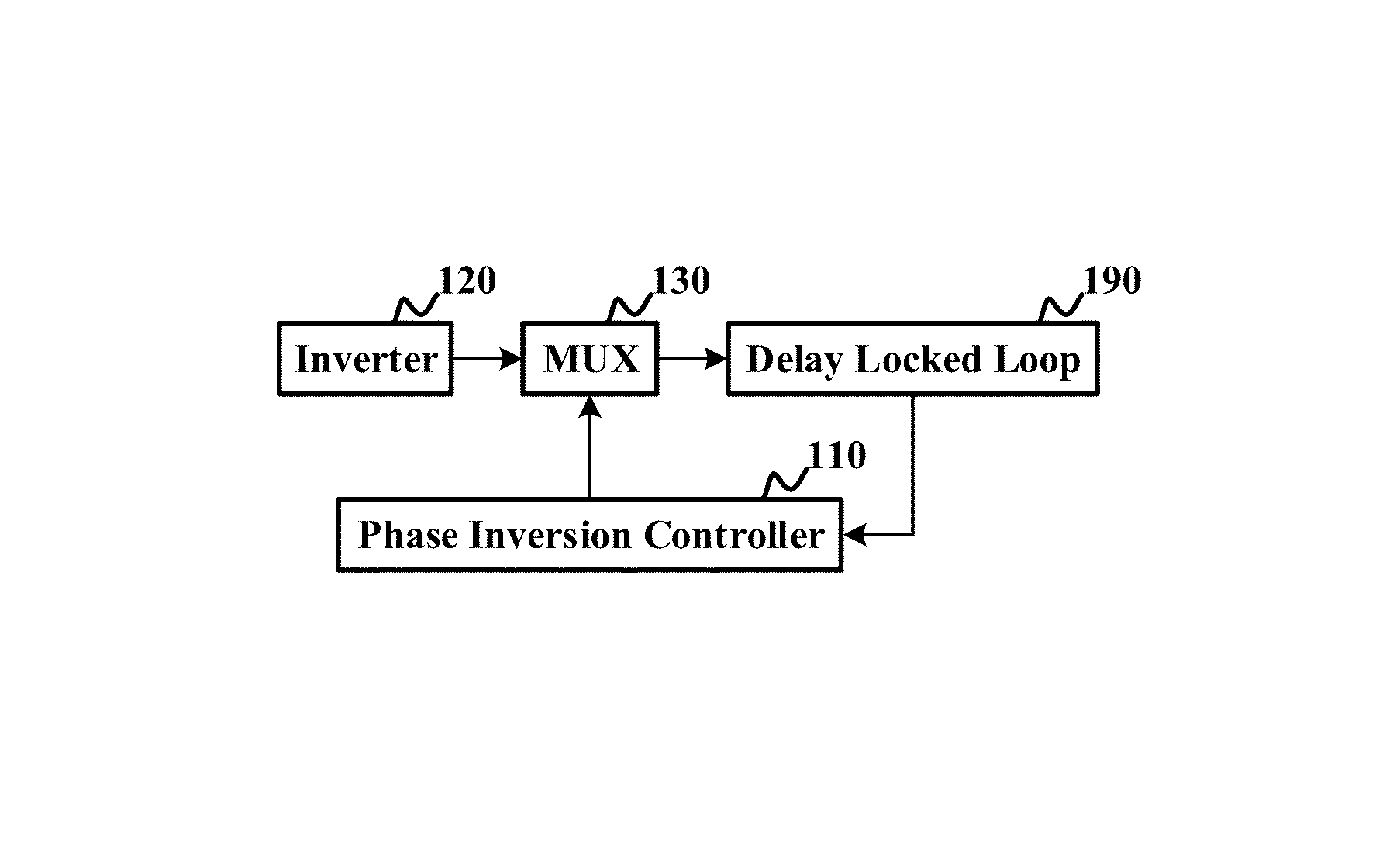

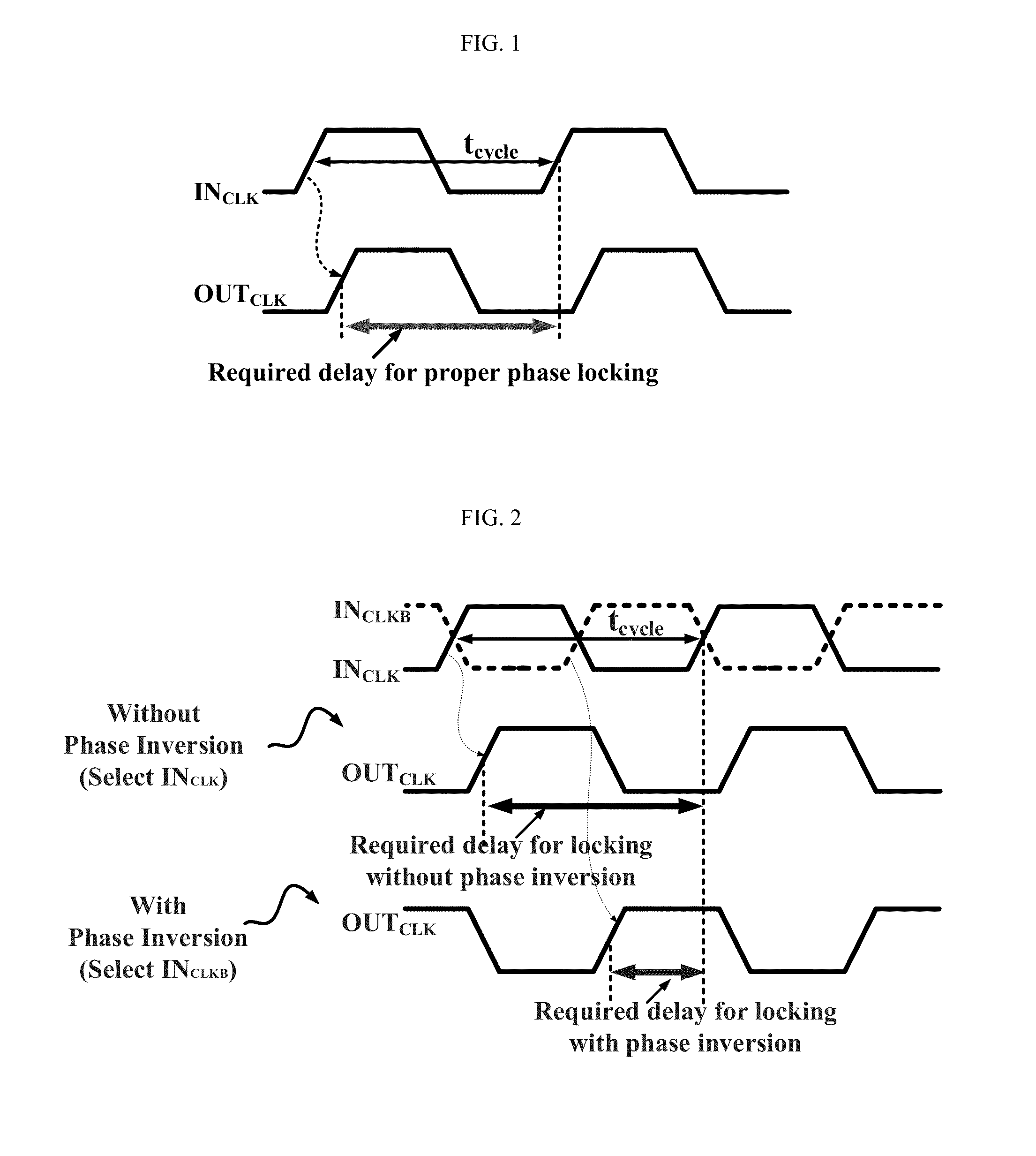

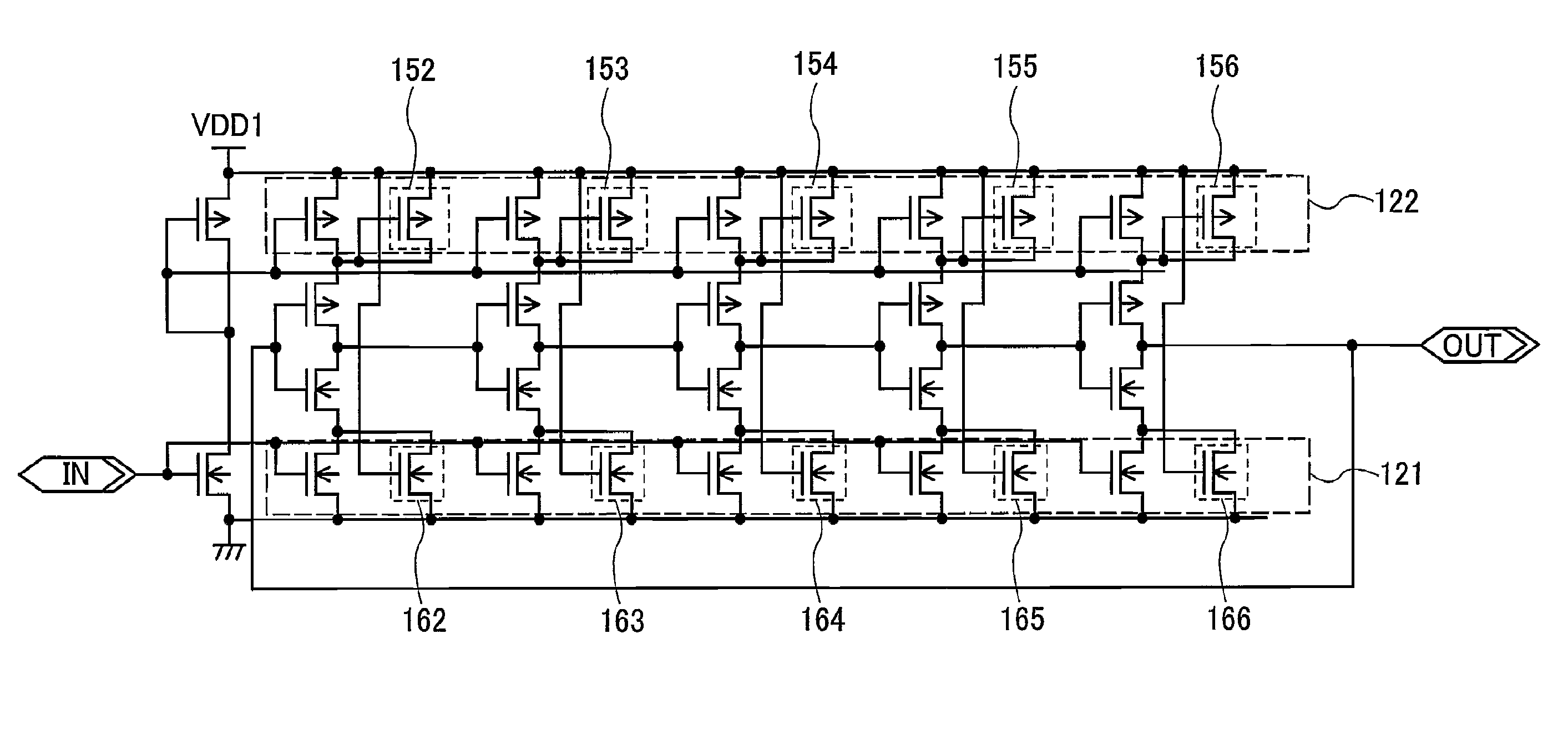

Digital delay-locked loop circuit using phase-inversion algorithm and method for controlling the same

InactiveUS8866522B1Wide operating frequency rangeShort lock timePulse automatic controlControl signalMultiplexer

Disclosed herein are a delay-locked loop circuit using a phase inversion locking algorithm and a method of controlling the same. There is provided a delay-locked loop circuit using a phase inversion locking algorithm, including a phase inversion controller configured to control whether or not to use the phase inversion locking algorithm by determining a phase error between an input clock signal and an output clock signal, an inverter configured to invert the input clock signal and output the inverted input clock signal, a multiplexer configured to receive the input clock signal and the inverted input clock signal of the inverter and output the input clock signal in response to the control signal of the phase inversion controller or the inverted input clock signal, and a delay-locked loop connected to the output terminal of the multiplexer and configured to perform phase synchronization in response to the output signal of the multiplexer.

Owner:HONGIK UNIV IND ACAD COOP FOUND

PLL circuit and semiconductor device having the same

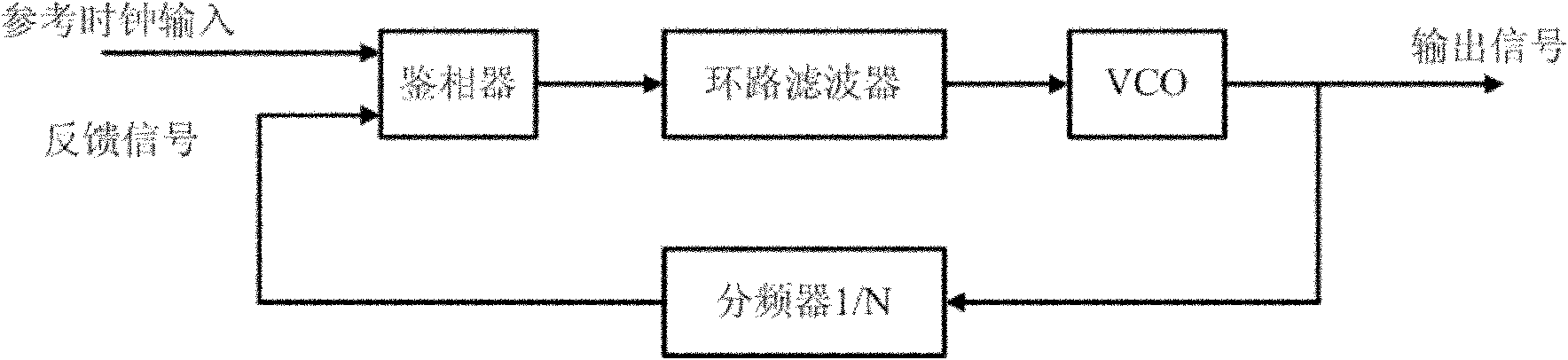

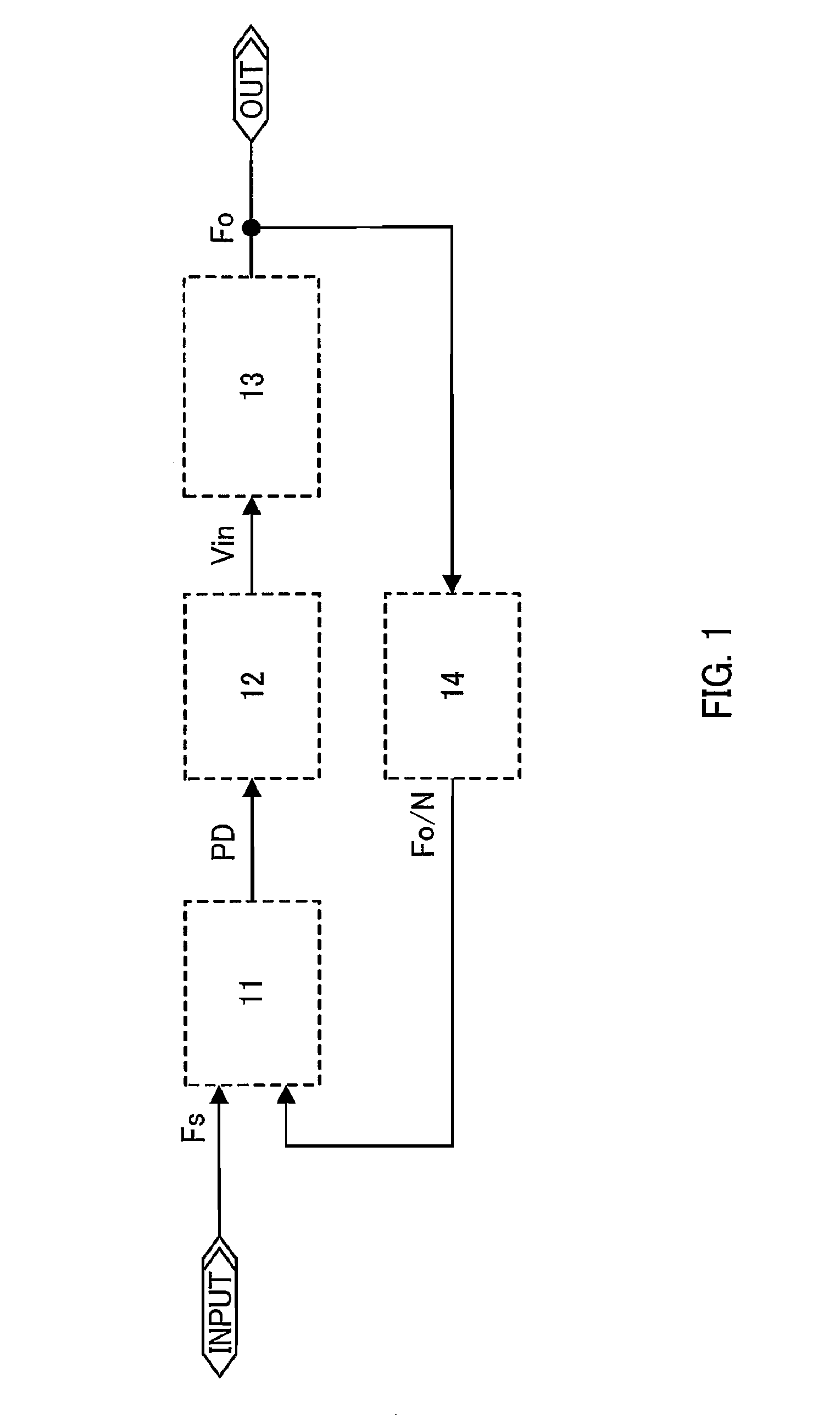

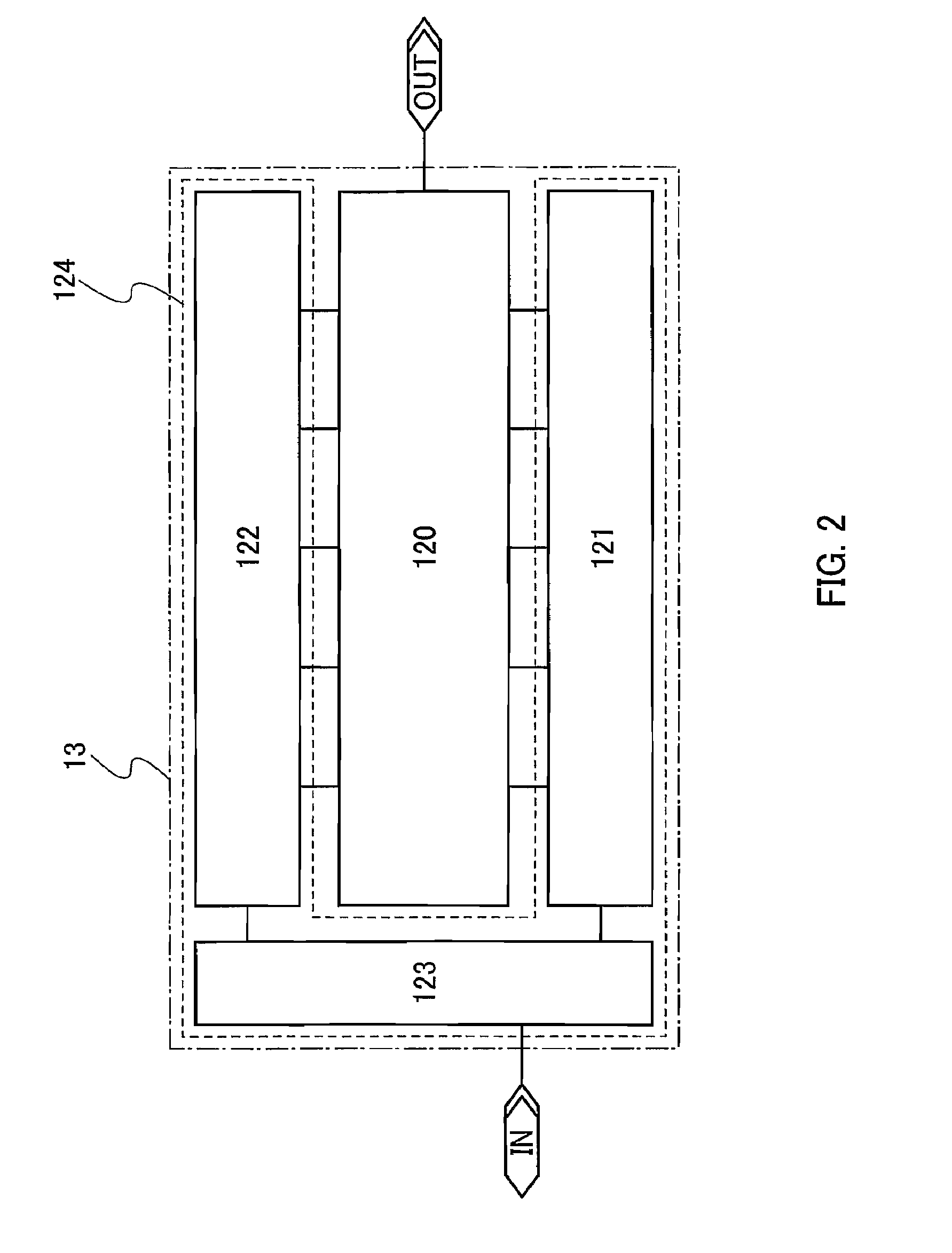

InactiveUS7800455B2Keep for a long timeShort lock timePulse automatic controlGenerator stabilizationLoop filterPhase detector

A PLL circuit includes a phase detector, a loop filter (LF), a voltage-controlled oscillator (VCO), and a frequency divider. The phase detector compares a phase of a signal Fs which is input from outside with a phase of a signal Fo / N which is input from the frequency divider. The loop filter generates a signal Vin by removing alternating current components from a signal input from the phase detector. The voltage-controlled oscillator outputs a signal Fo based on the signal Vin input from the loop filter. The frequency divider converts the signal Fo output from the voltage-controlled oscillator into Fo / N (frequency division by N), and outputs it to the phase detector.

Owner:SEMICON ENERGY LAB CO LTD

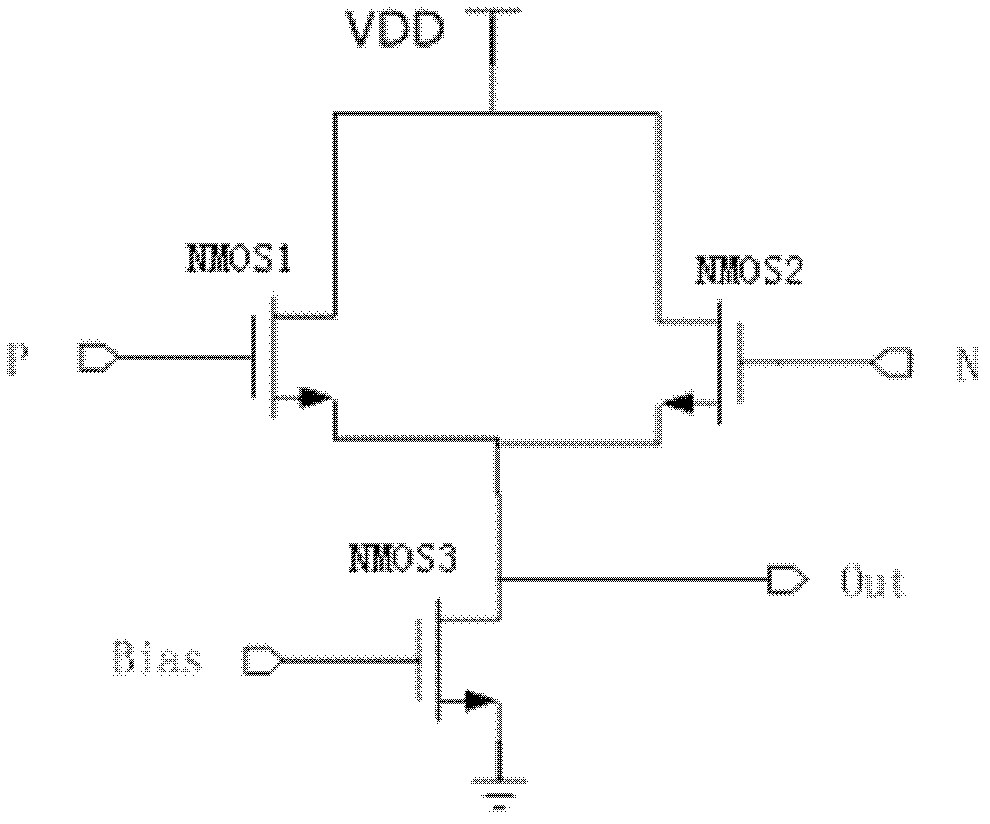

Voltage type automatic gain control circuit

The invention discloses a voltage type automatic gain control circuit. The voltage type automatic gain control circuit comprises an amplitude sampler used for sampling a controlled signal and a reference voltage signal respectively, voltage followers which are connected with the amplitude sampler and are used for isolating the sampled controlled signal and the reference voltage signal respectively so as to obtain a stable voltage signal, alternating current resistors which are connected with the voltage followers and are used for calculating an average value of the stable controlled signal and the reference voltage signal respectively by utilizing the resistors, and a bias current source, wherein a bias terminal of the bias current source is connected with the alternating current resistors, and an output terminal of the bias current source is taken as an output terminal of the voltage type AGC (automatic gain control) circuit and is used for outputting control current by utilizing the average value of the stable controlled signal and the average value of the reference voltage signal as bias voltage. According to the voltage type AGC (automatic gain control) circuit of the invention, output current can be stabilized in a short time, and proper locking precision is maintained.

Owner:北京中科微投资管理有限责任公司

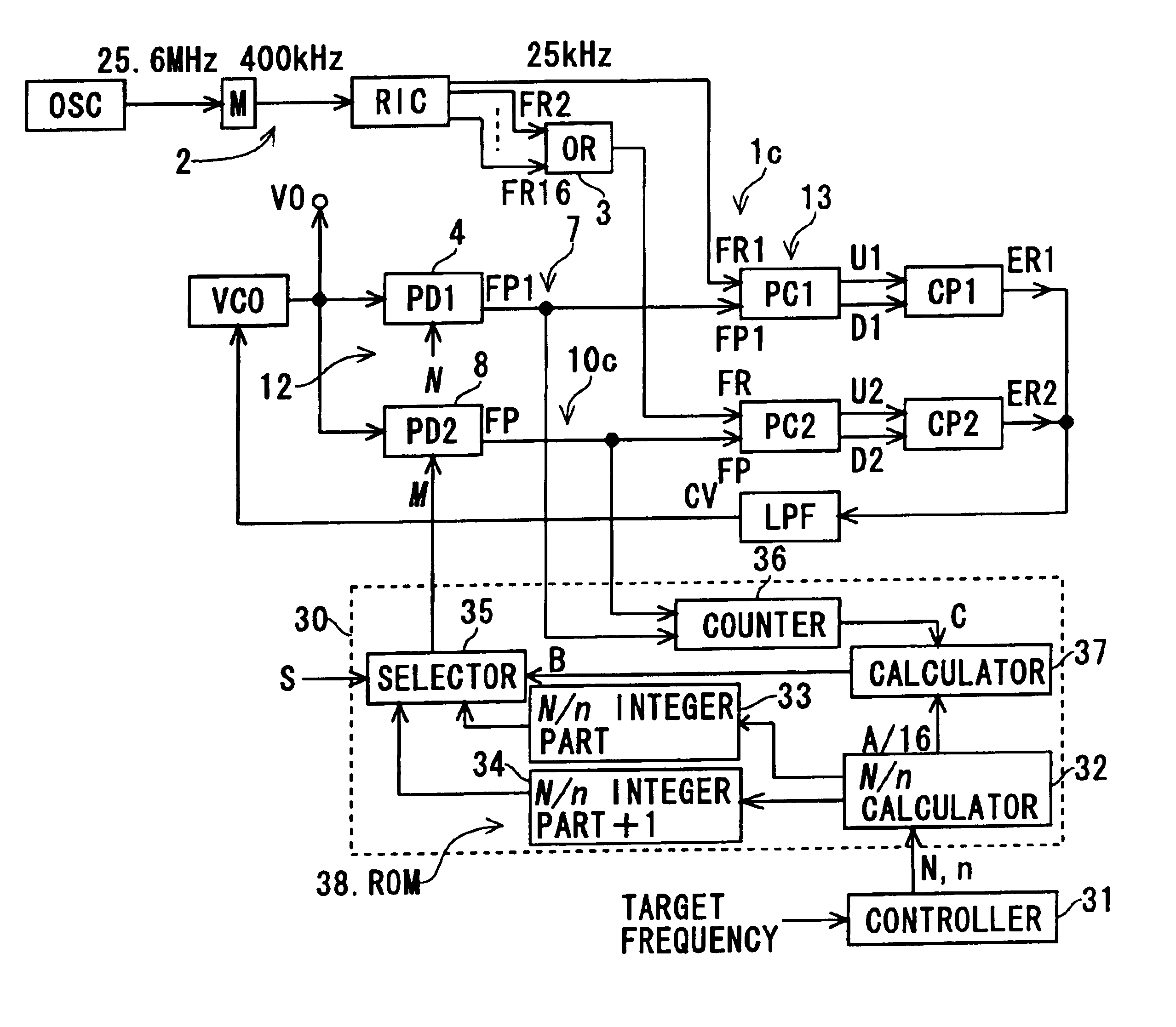

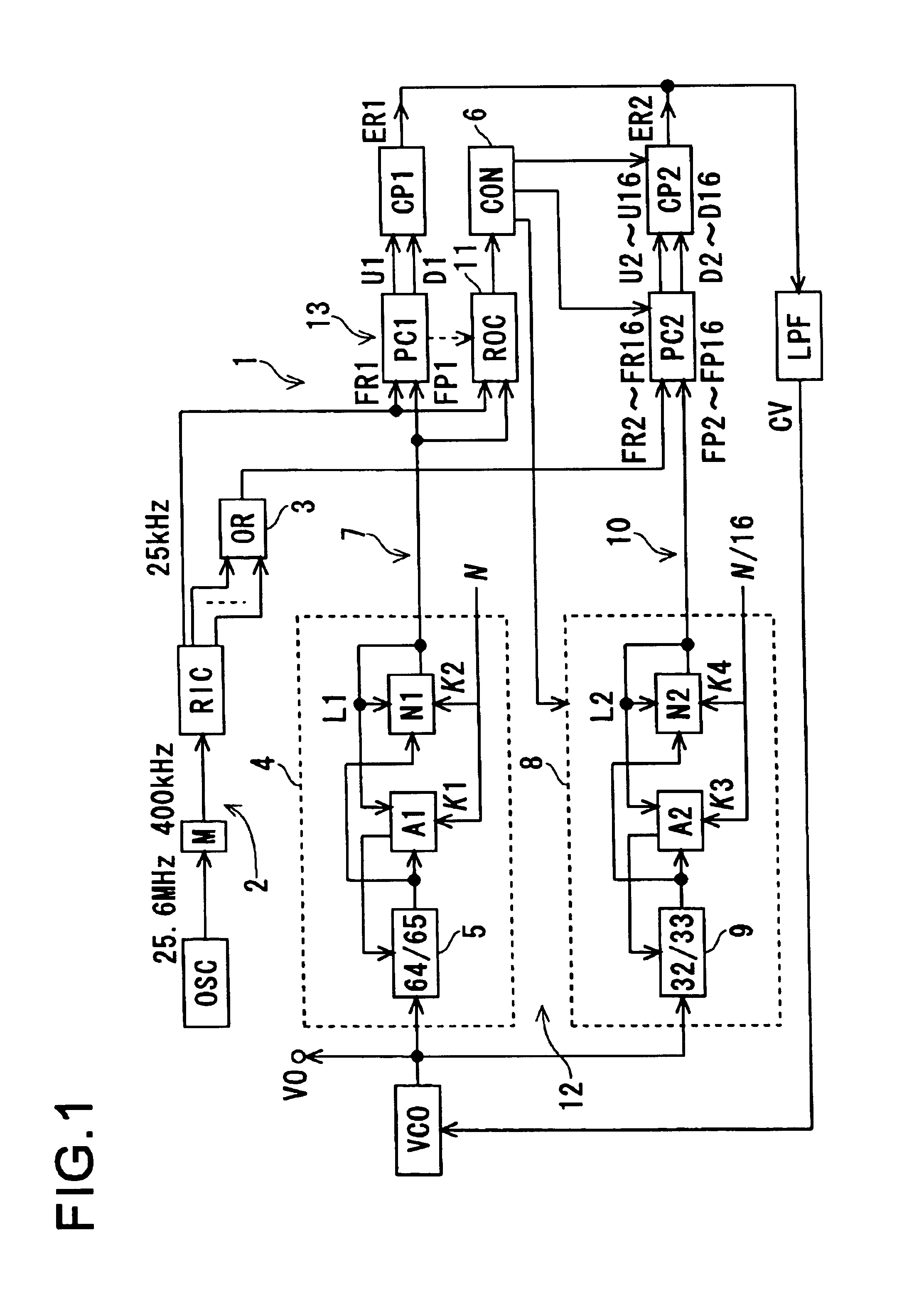

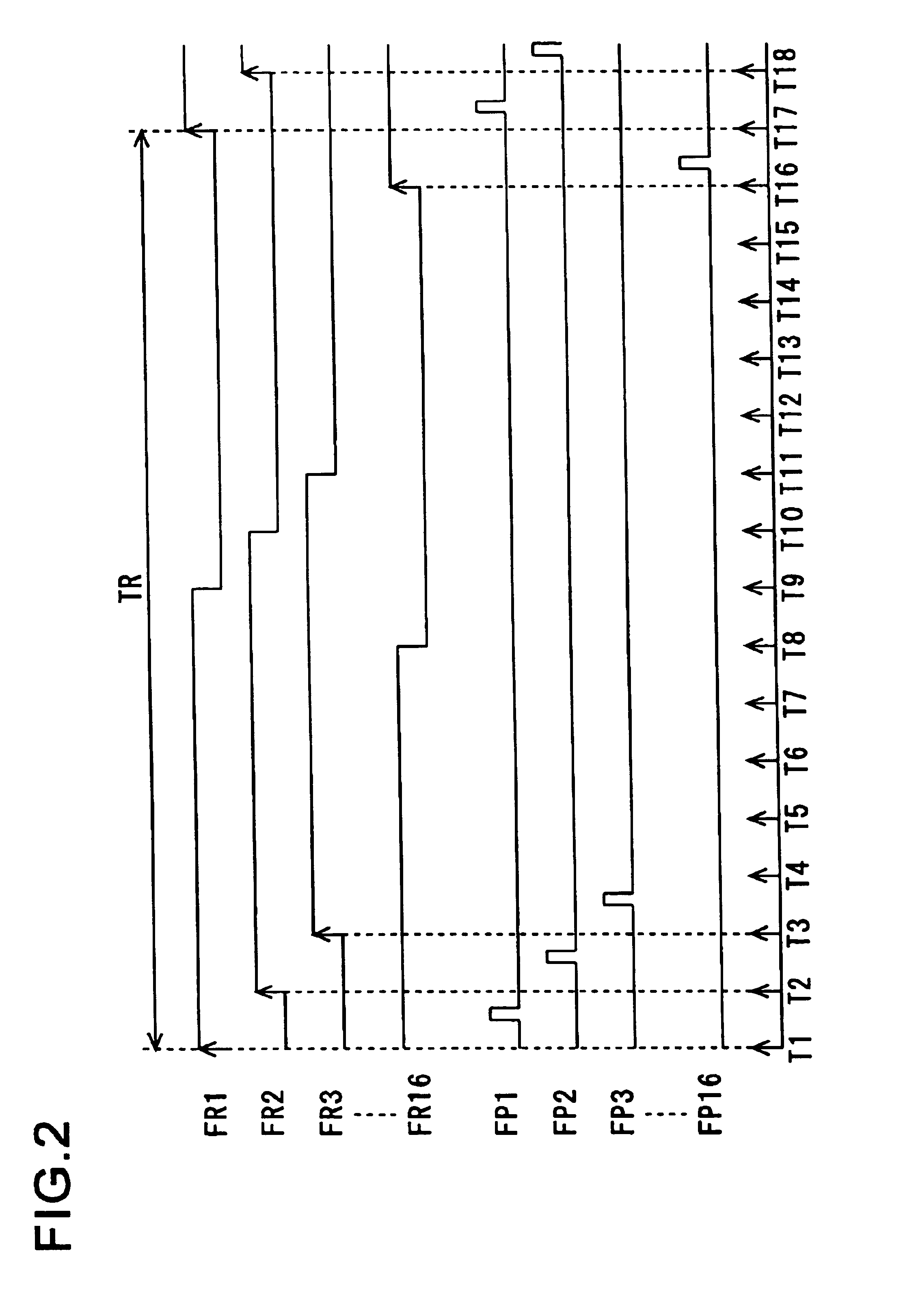

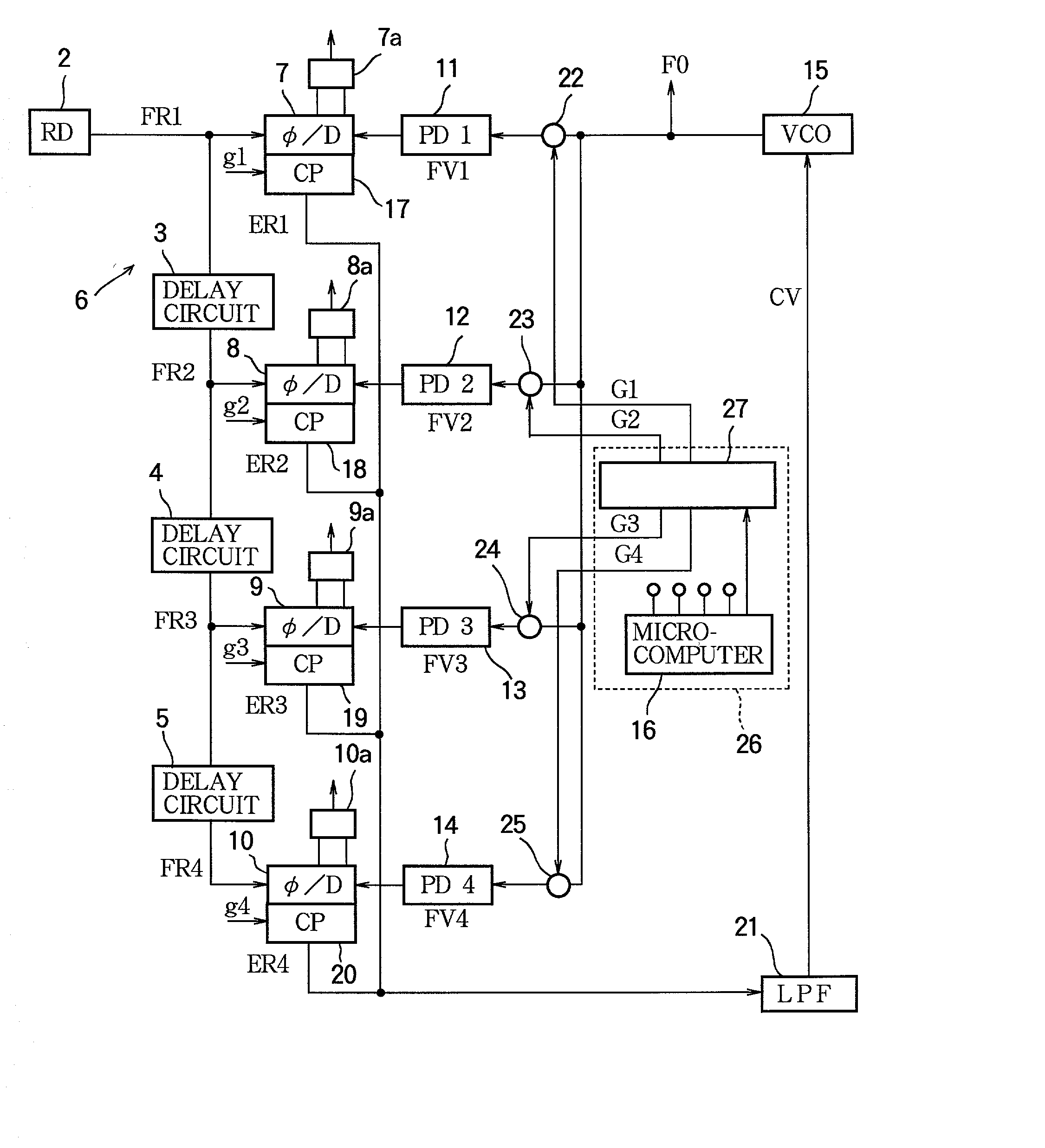

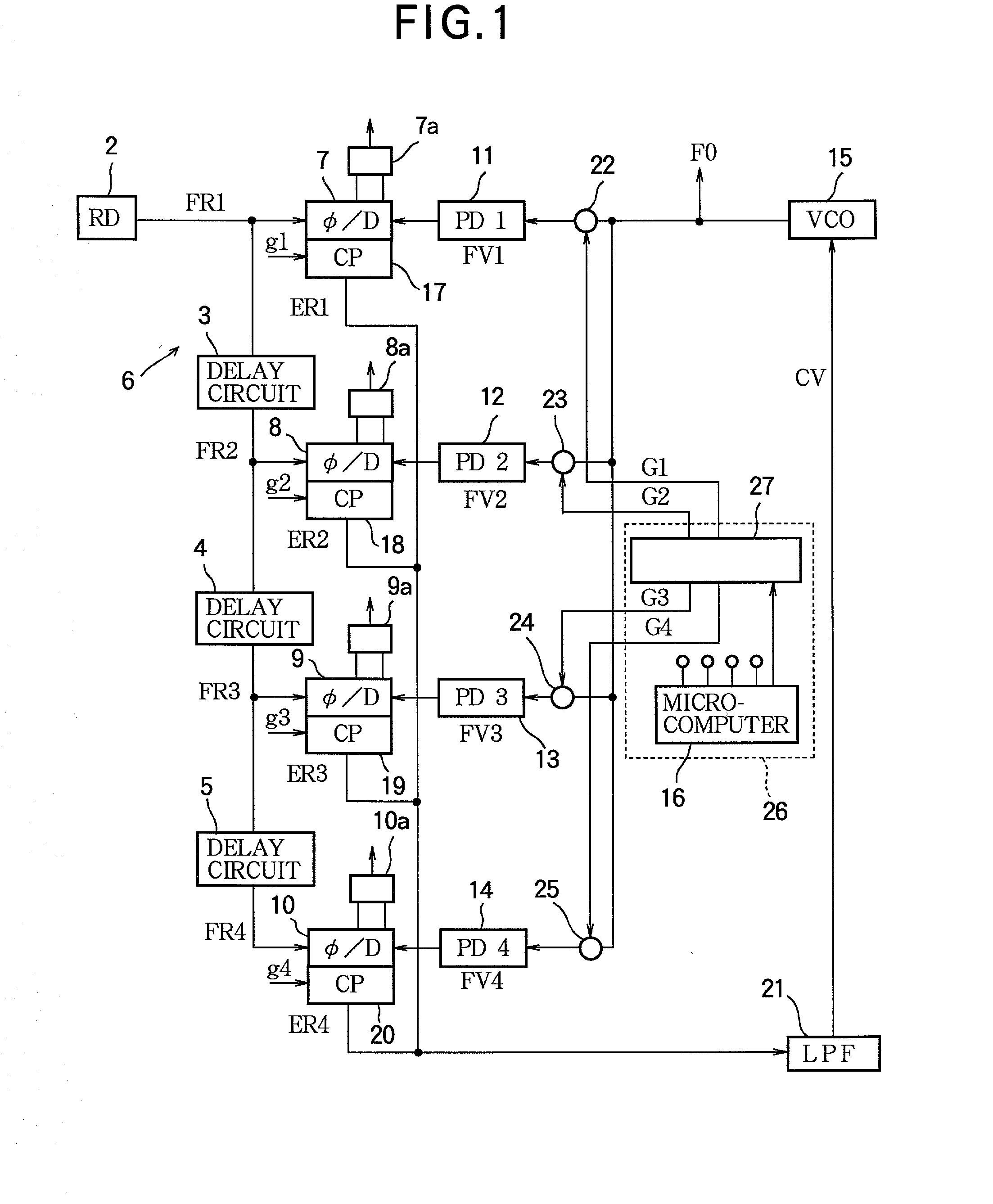

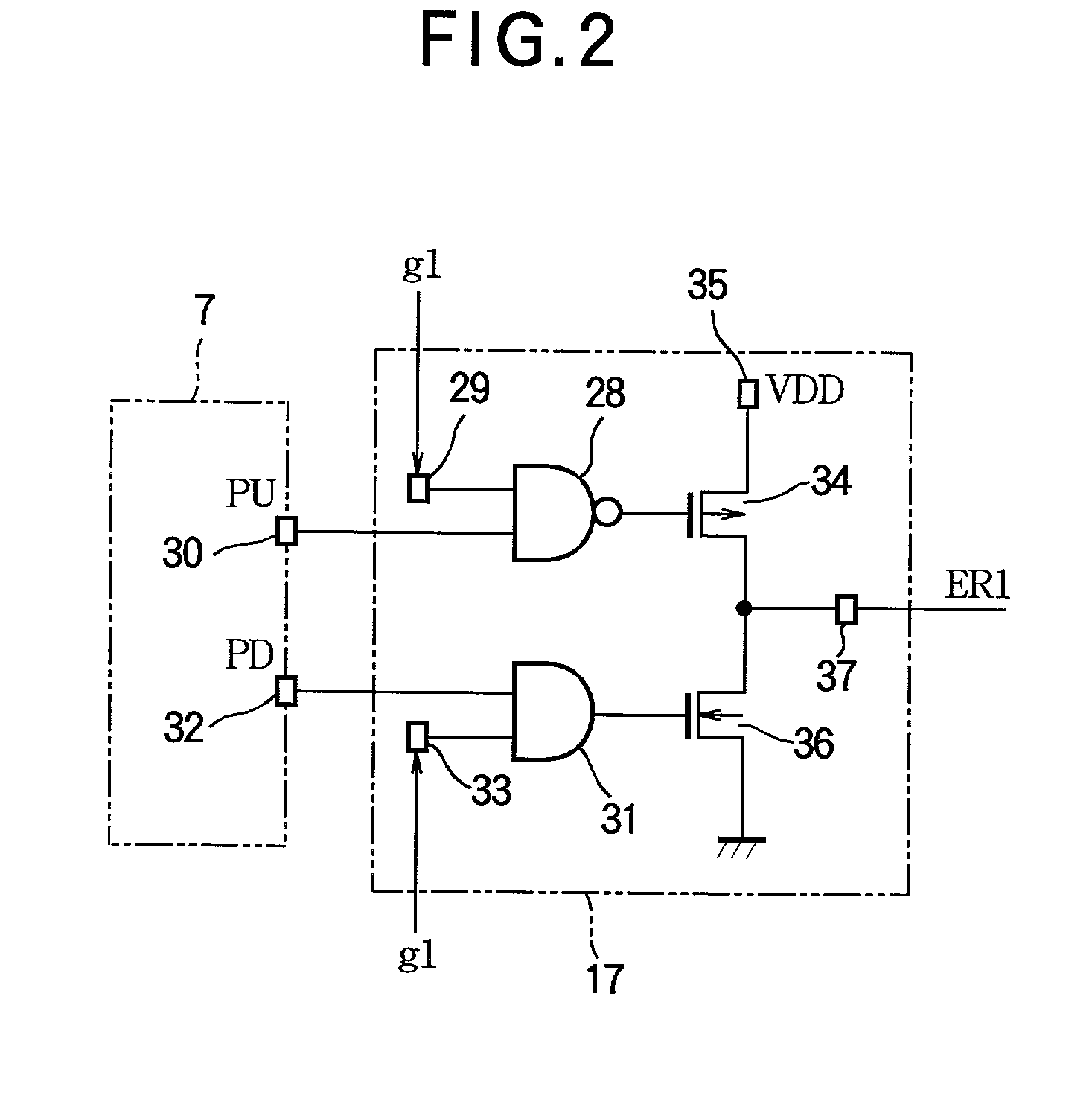

PLL device

InactiveUS20020118053A1Short lock timeGuaranteed multiple usePulse automatic controlLow-pass filterPhase difference

The PLL device includes means (6) for generating a, plurality of reference signals (FR1, FR2, FR3, FR4) having mutually differing phases, a variable frequency divider (11, 12, 13, 14) for dividing, in synchronization with the phases of a plurality of the reference signals, a frequency of an output signal (FO) of a voltage-controlled oscillator (15) that produces a signal having a frequency responsive to a control voltage (CV) supplied to generate a plurality of feedback signals (FV1, FV2, FV3, FV4) having mutually differing phases, phase comparators (7, 17, 8, 18, 9, 19, 10, 20) for comparing phases between the reference signals and the feedback signals corresponding to the reference signals respectively to produce a plurality of error signals (ER1, ER2, ER3, ER4), a low-pass filter (21) for filtering the error signals output from the phase comparators to produce the control voltage, and a control means (16, 26, 27) for controlling the number of the phase comparators that output the error signals to the low-pass filter in accordance with a phase difference between at least one of a plurality of the feedback signals and the reference signal corresponding to the one of a plurality of the feedback signals.

Owner:SANYO ELECTRIC CO LTD +1

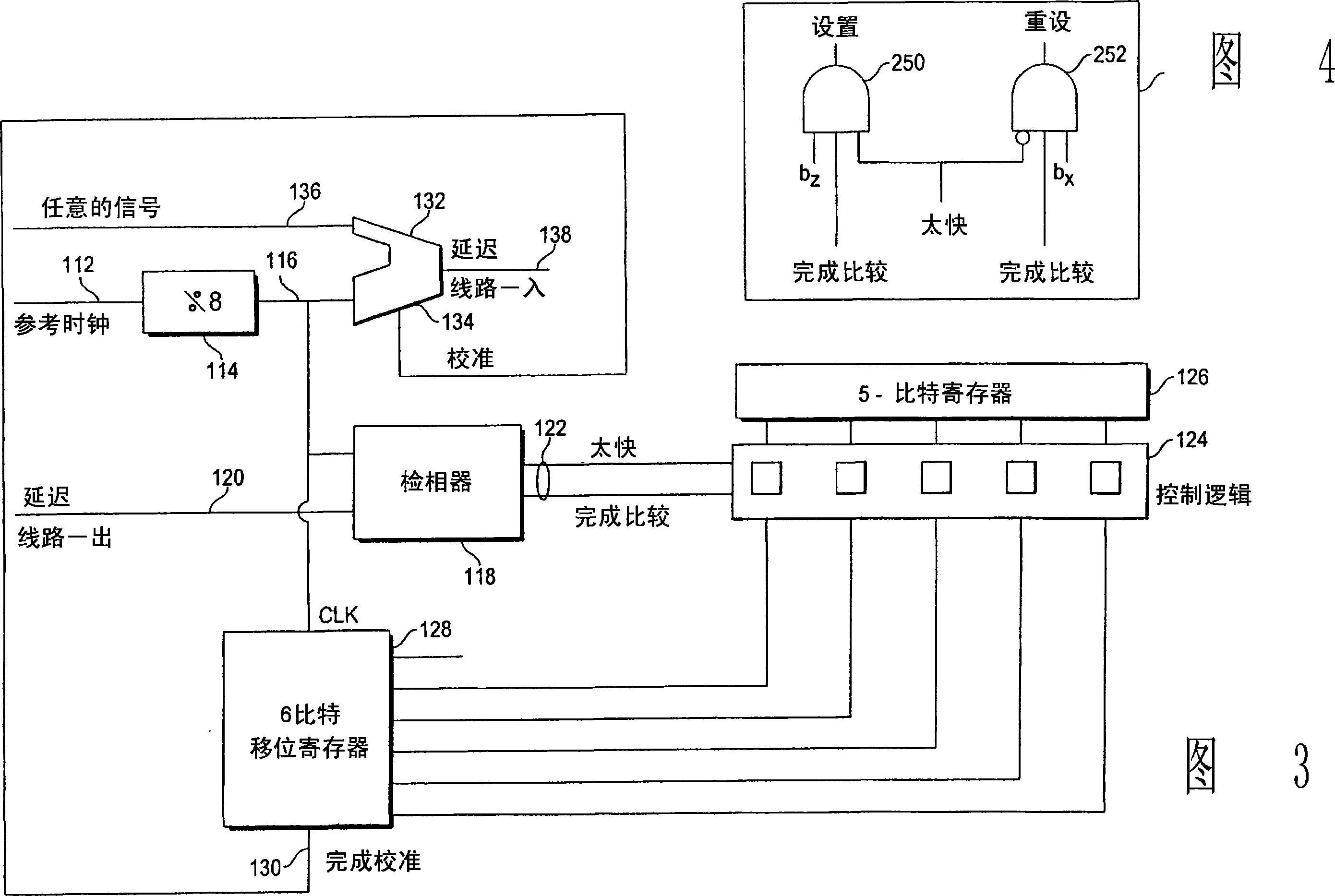

Current starved DAC-controlled delay locked loop

InactiveCN1883118AReduced Power RequirementsShort lock timePulse automatic controlElectric pulse generatorPhase detectorDriver circuit

A delay locked loop circuit with improved restart features. The circuit includes a clock input (1120, a clock output (116), a divider circuit (114), phase detector (118) and control logic (124). The circuit includes a means (126) for implementing a binary search of outputs from the control logic (124) for generating a calibration bit, which is applied to the transmission on an output line (120).

Owner:ATMEL CORP

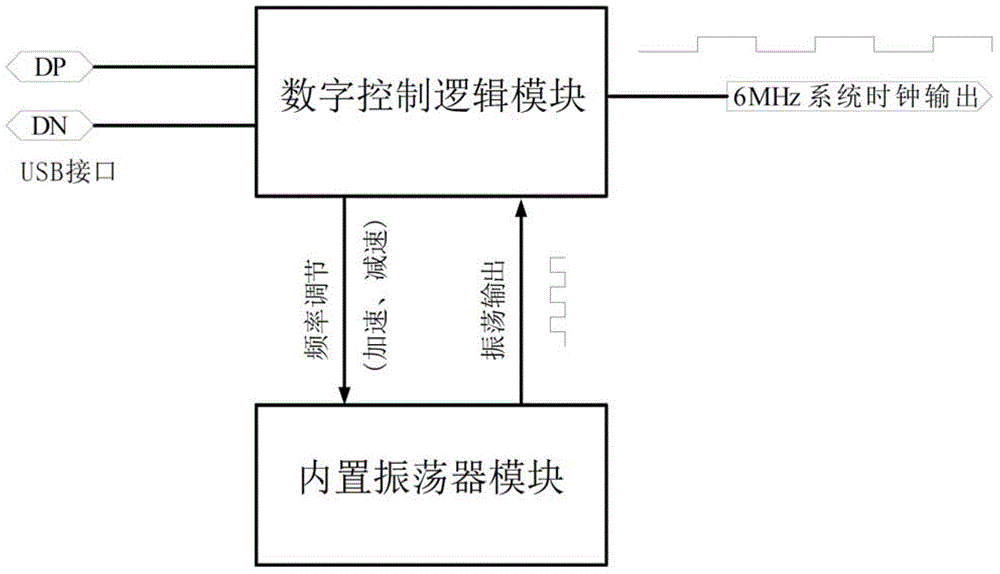

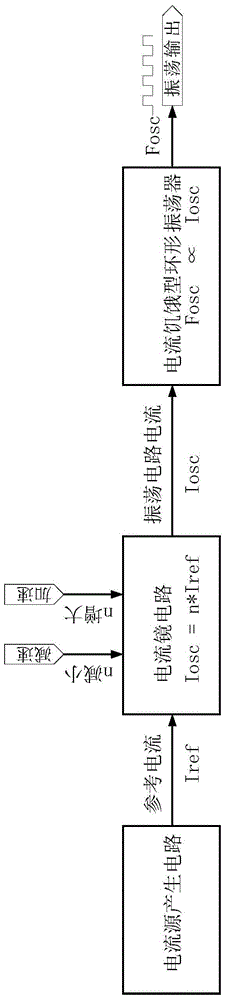

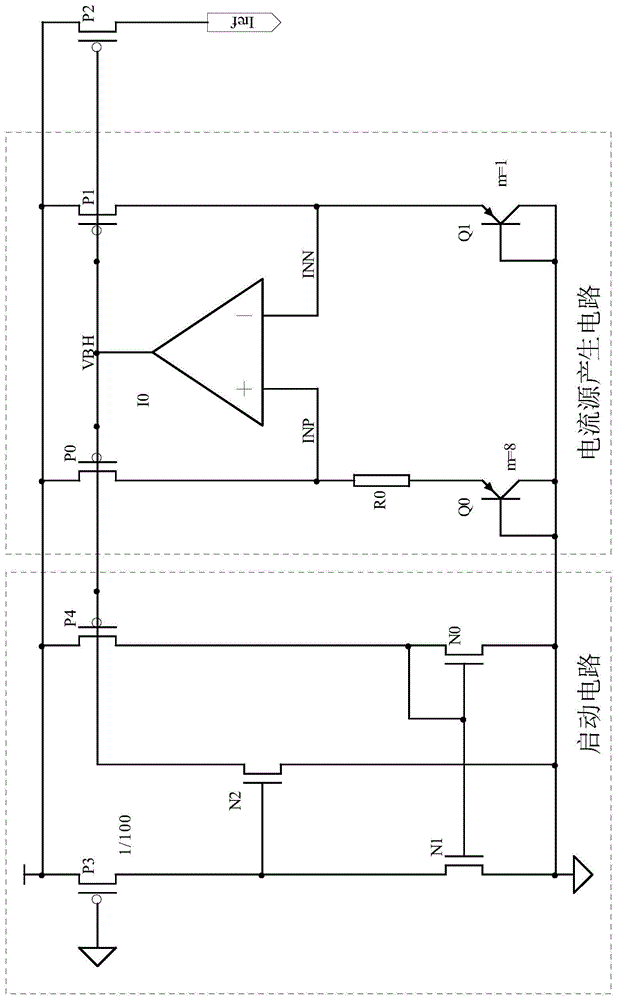

Circuit structure and method for realizing clock recovery on the basis of USB device

ActiveCN105337591AImprove reliabilityLow reliabilitySingle output arrangementsLow speedClock recovery

The invention relates to a circuit structure and method for realizing clock recovery on the basis of a USB device. The circuit structure comprises a built-in oscillator module for generating oscillation signals; and a digital control logic module which includes a USB clock recovery unit for sampling the oscillation signals of the built-in oscillator and performing the clock recovery and a frequency adjustment unit for adjusting the oscillation frequency of the built-in oscillator according to a comparison result between USB signals and the oscillation signals of the built-in oscillator. By using the circuit structure and method for realizing the clock recovery on the basis of the USB device through such a structure, an accurate system clock can be generated, a frequency tracking feature is exhibited, a USB data transmission frequency is compared with the frequency of the built-in oscillator through adoption of the digital control logic module, the frequency of the built-in oscillator is automatically switched among a low-speed state, a medium-speed state and a high-speed state, the system precision and the stability are guaranteed, the production cost is decreased, and the application scope is wider.

Owner:CRM ICBG (WUXI) CO LTD

Capacity expansion method and device for distributed database and electronic equipment

ActiveCN111459913AImprove usabilityEnsure consistencyDatabase updatingDatabase distribution/replicationHigh availabilityEngineering

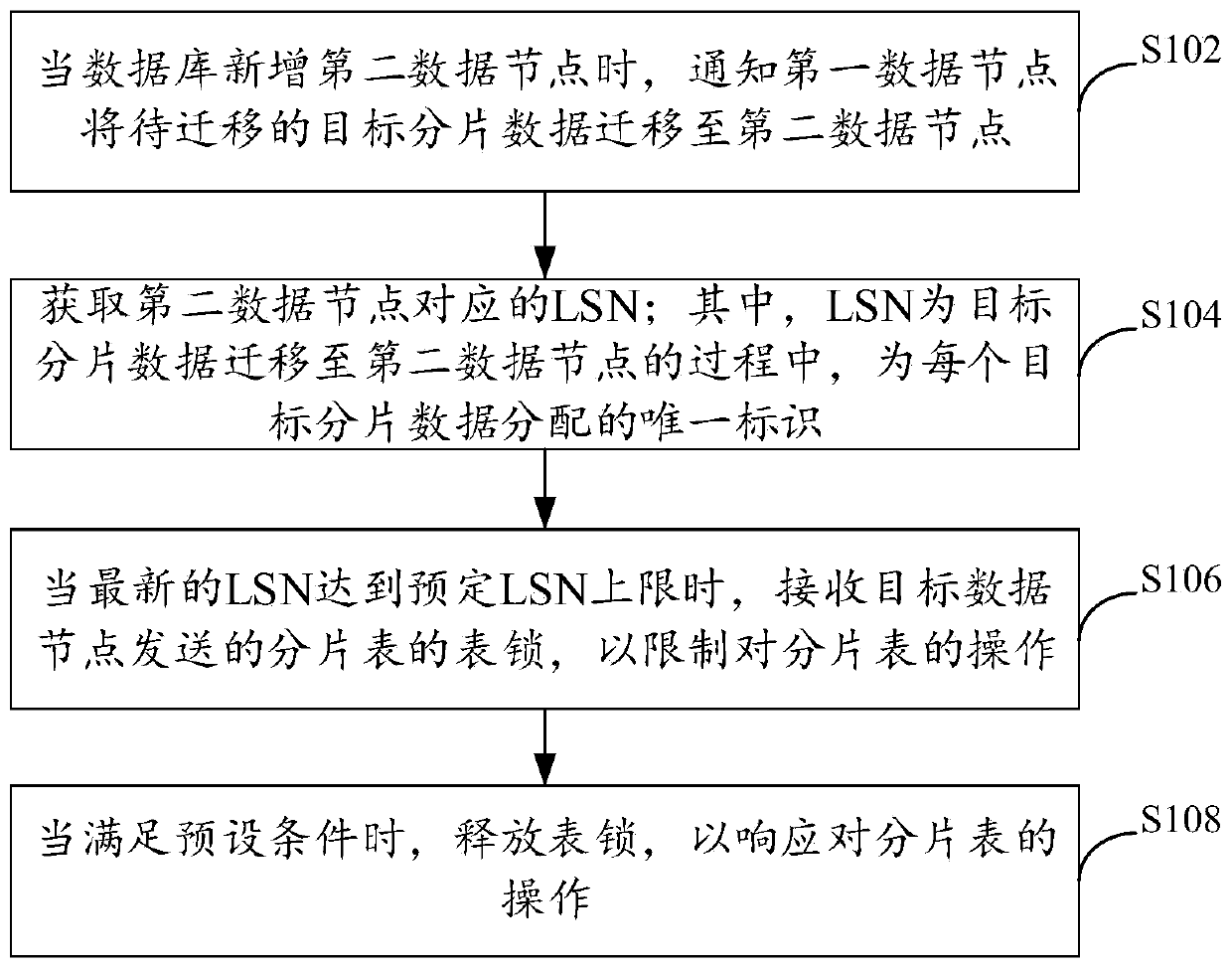

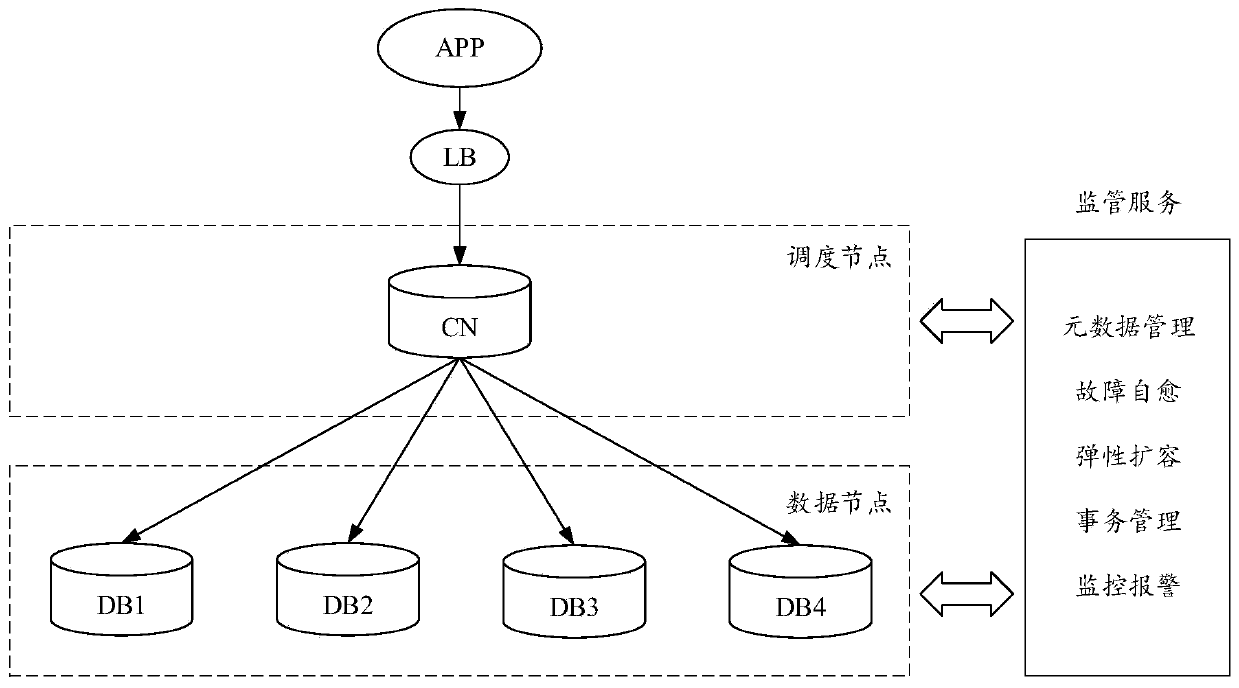

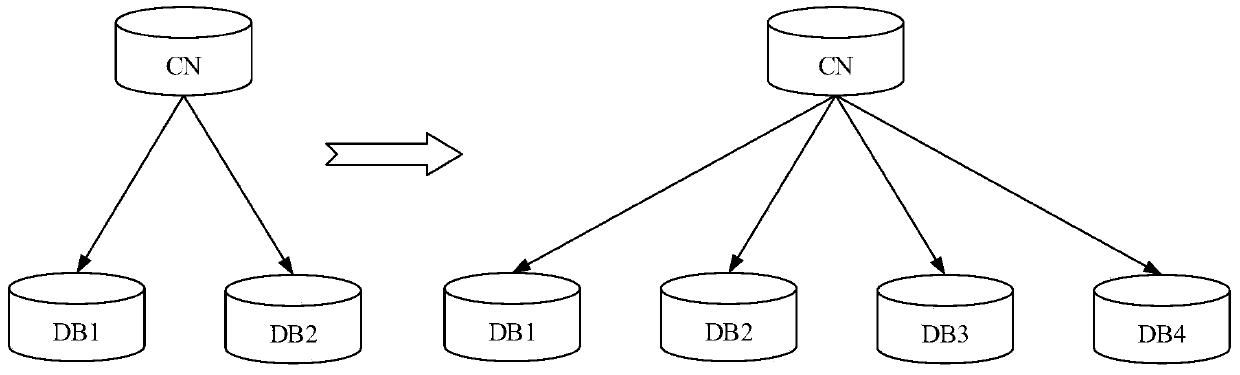

The invention provides a capacity expansion method and device for a distributed database and electronic equipment. The method relates to the field of cloud computing, a database comprises a schedulingnode and a plurality of existing first data nodes, and the method takes the scheduling node as an execution main body and comprises the following steps: when a second data node is newly added to thedatabase, notifying the first data nodes to migrate target fragmented data to be migrated to the second data node; obtaining an LSN corresponding to the second data node; when the latest LSN reaches apredetermined LSN upper limit, receiving a table lock of the fragmentation table sent by the target data node to limit the operation on the fragmentation table; wherein the target data node is a second data node corresponding to target fragmented data reaching a predetermined LSN upper limit; and when the preset condition is met, releasing the table lock to respond to the operation on the fragmentation table. According to the method, in the database expansion process, it can be well guaranteed that the database is not shut down and is continuous in service, and the high availability of the distributed database is effectively improved.

Owner:BEIJING KINGSOFT CLOUD NETWORK TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com