Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

359 results about "Low jitter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

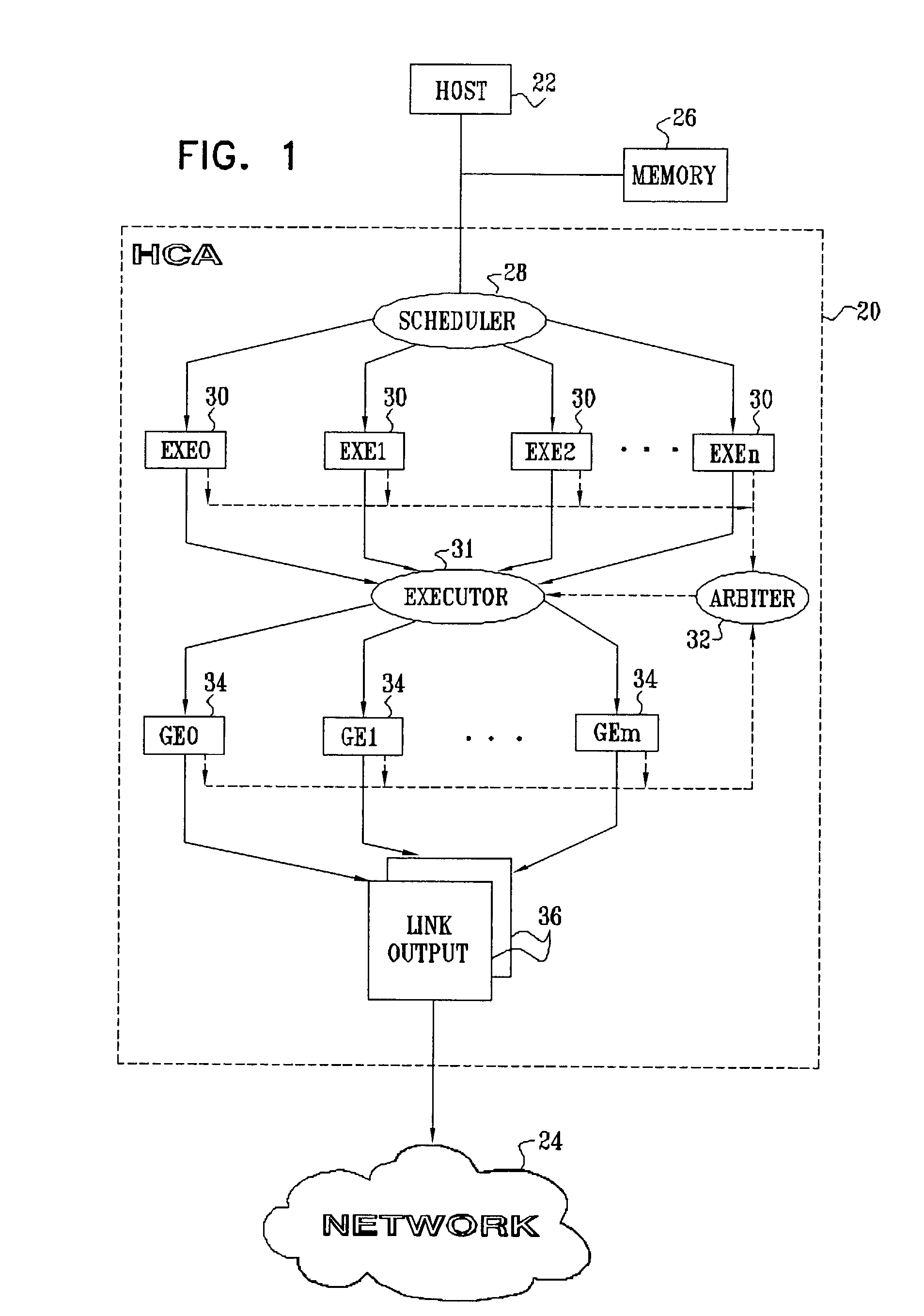

Round-robin arbiter with low jitter

InactiveUS7149227B2Reduce congestionReduced likelihoodTime-division multiplexRadio transmissionMultiplexingComputer network

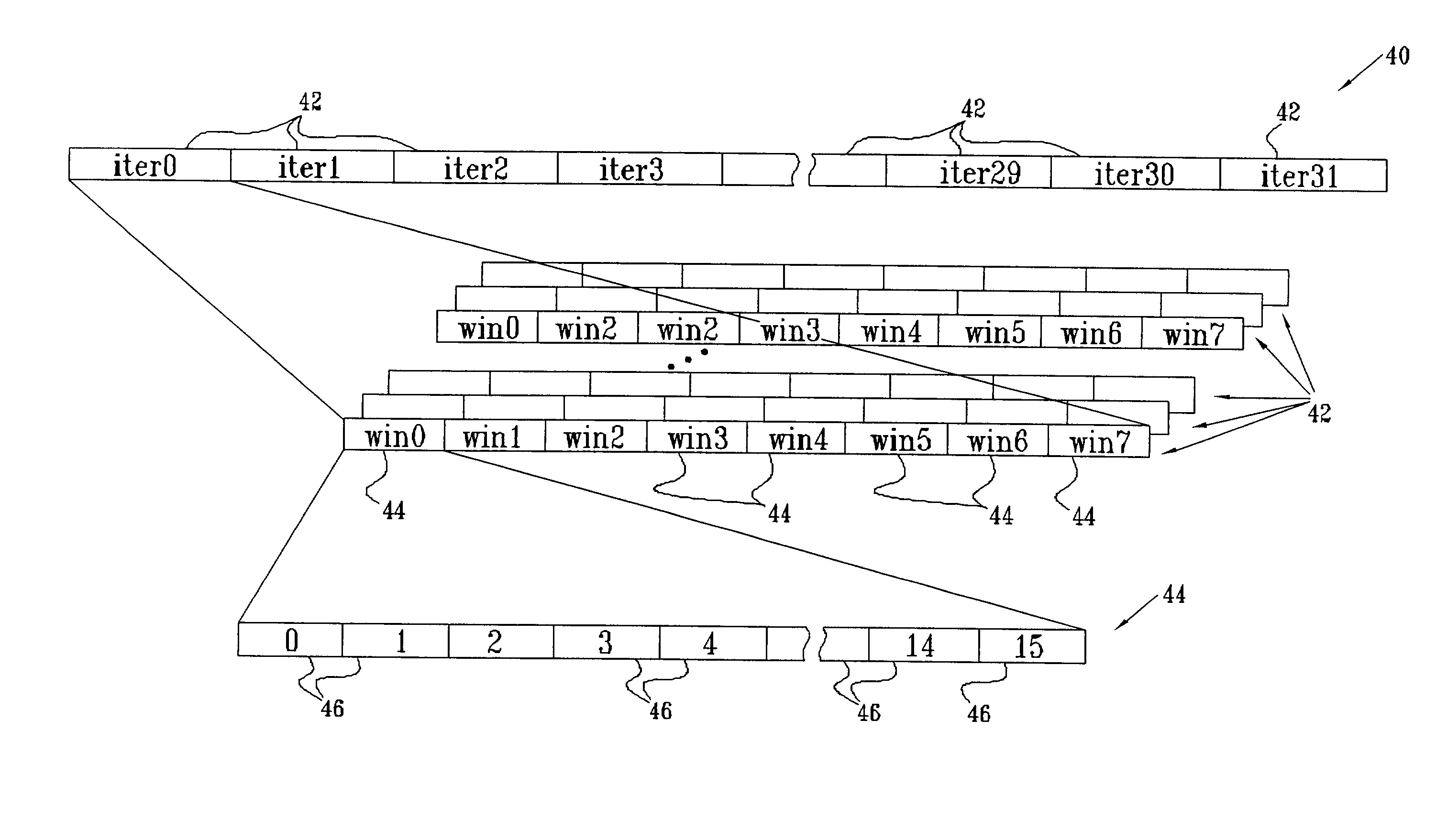

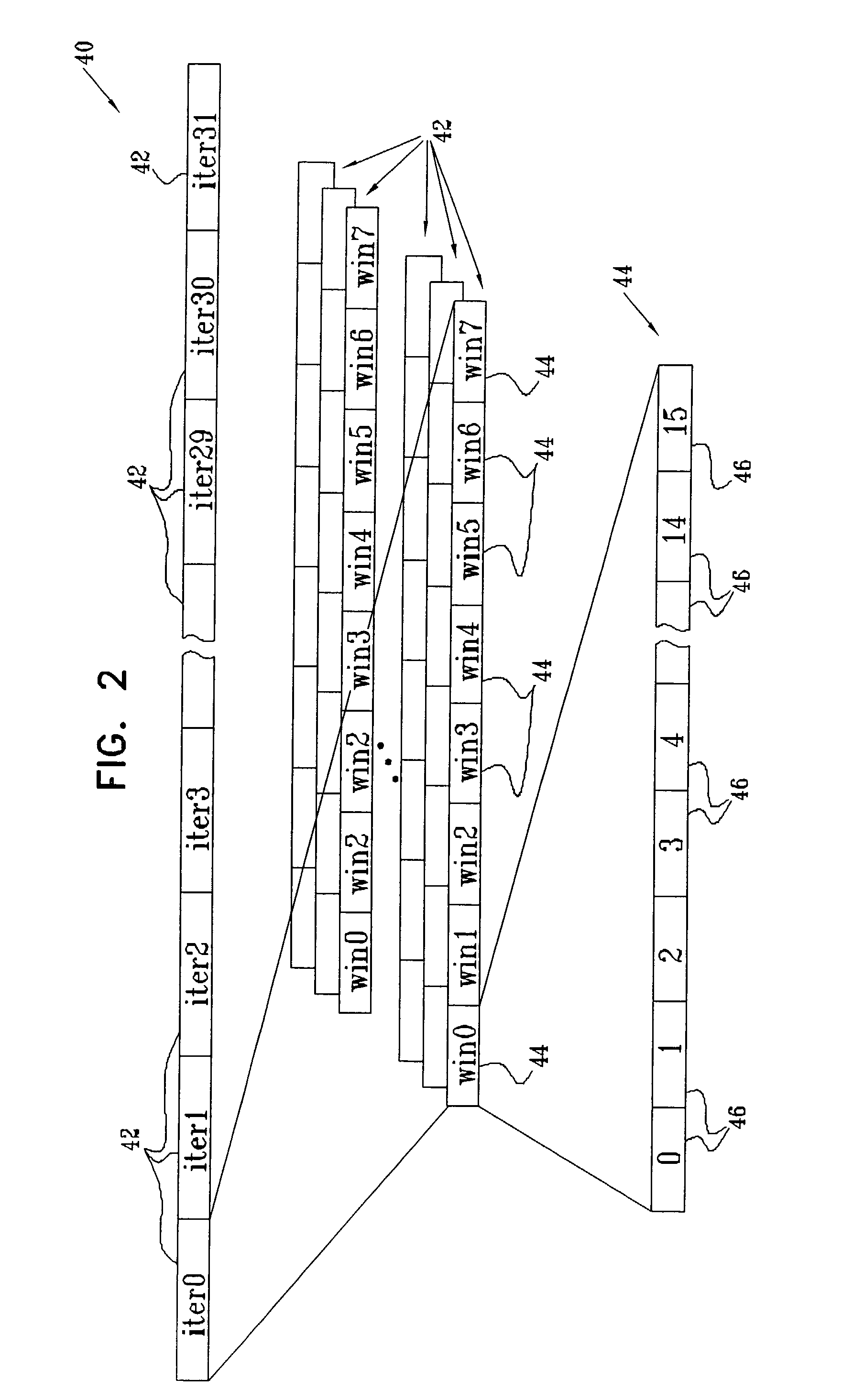

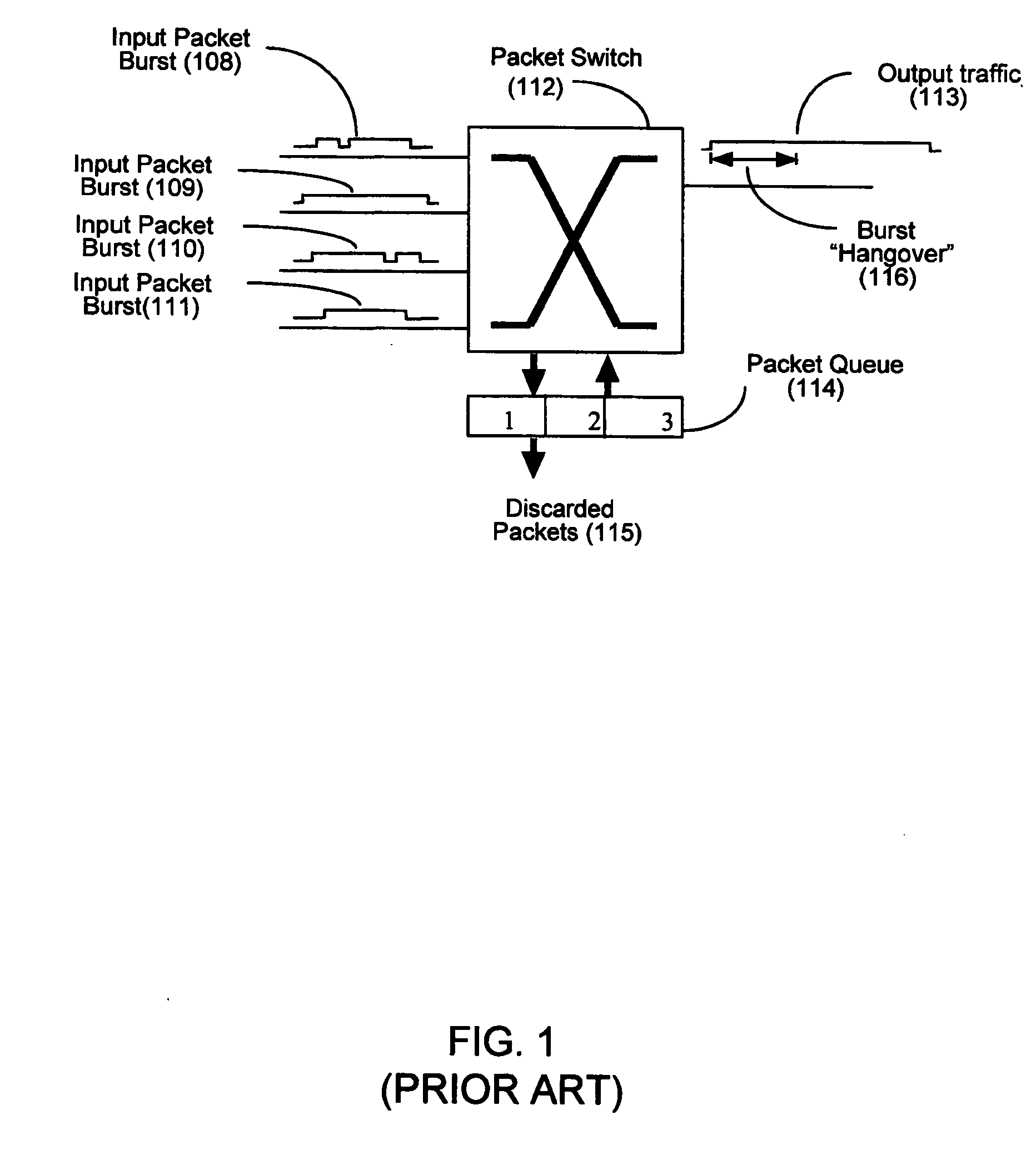

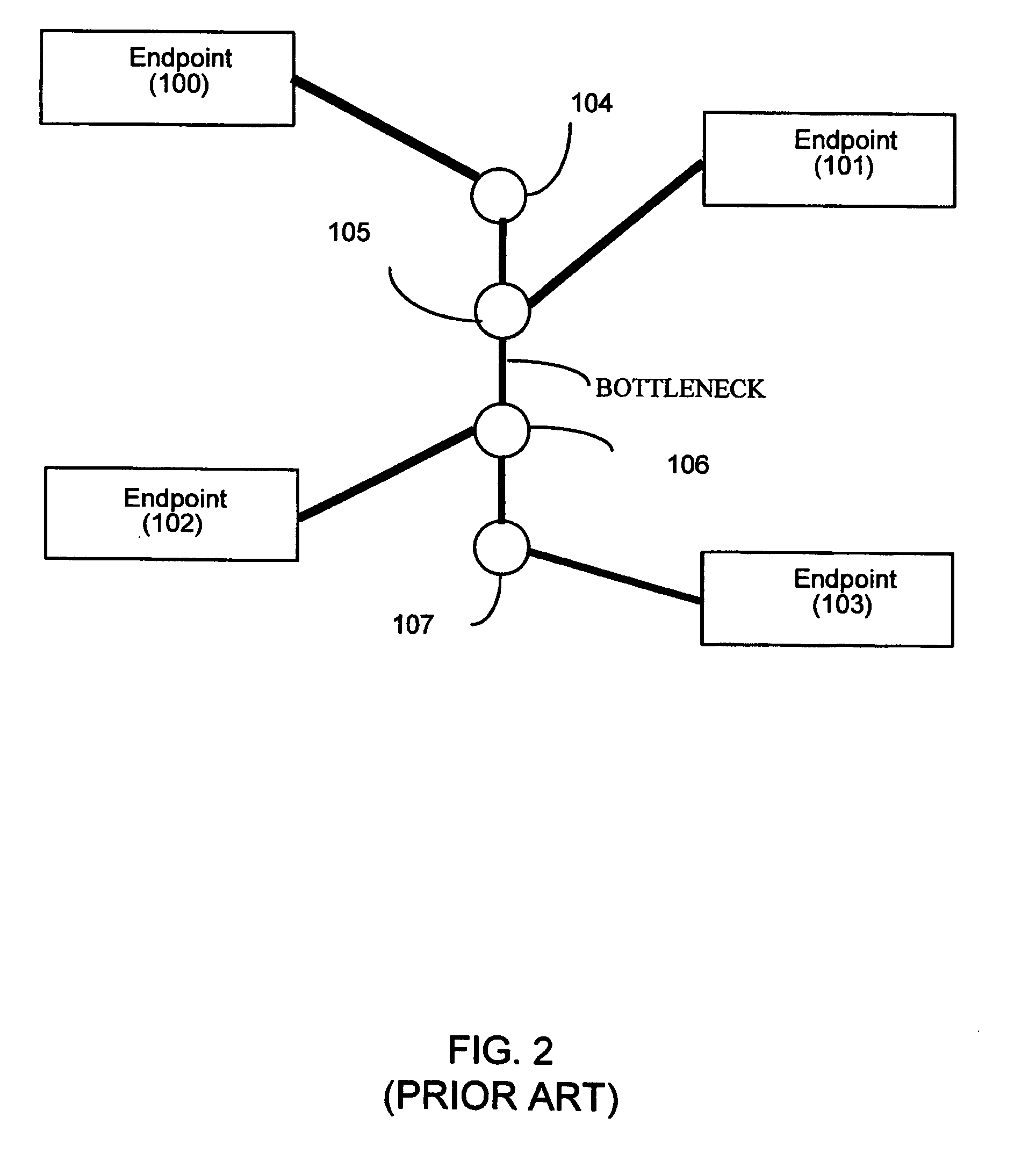

A method for allocating a processing resource among multiple inputs includes defining a sequence of multiplexing iterations, each such iteration including a first plurality of windows, each such window containing a second plurality of time slots. A respective weight is assigned to each of the inputs, and each of the inputs is allotted one of the time slots in each of a respective number of the windows in each of the iterations, the respective number being determined by the respective weight. Each of the inputs is then provided with access to the processing resource during the time slots allotted thereto.

Owner:MELLANOX TECHNOLOGIES LTD

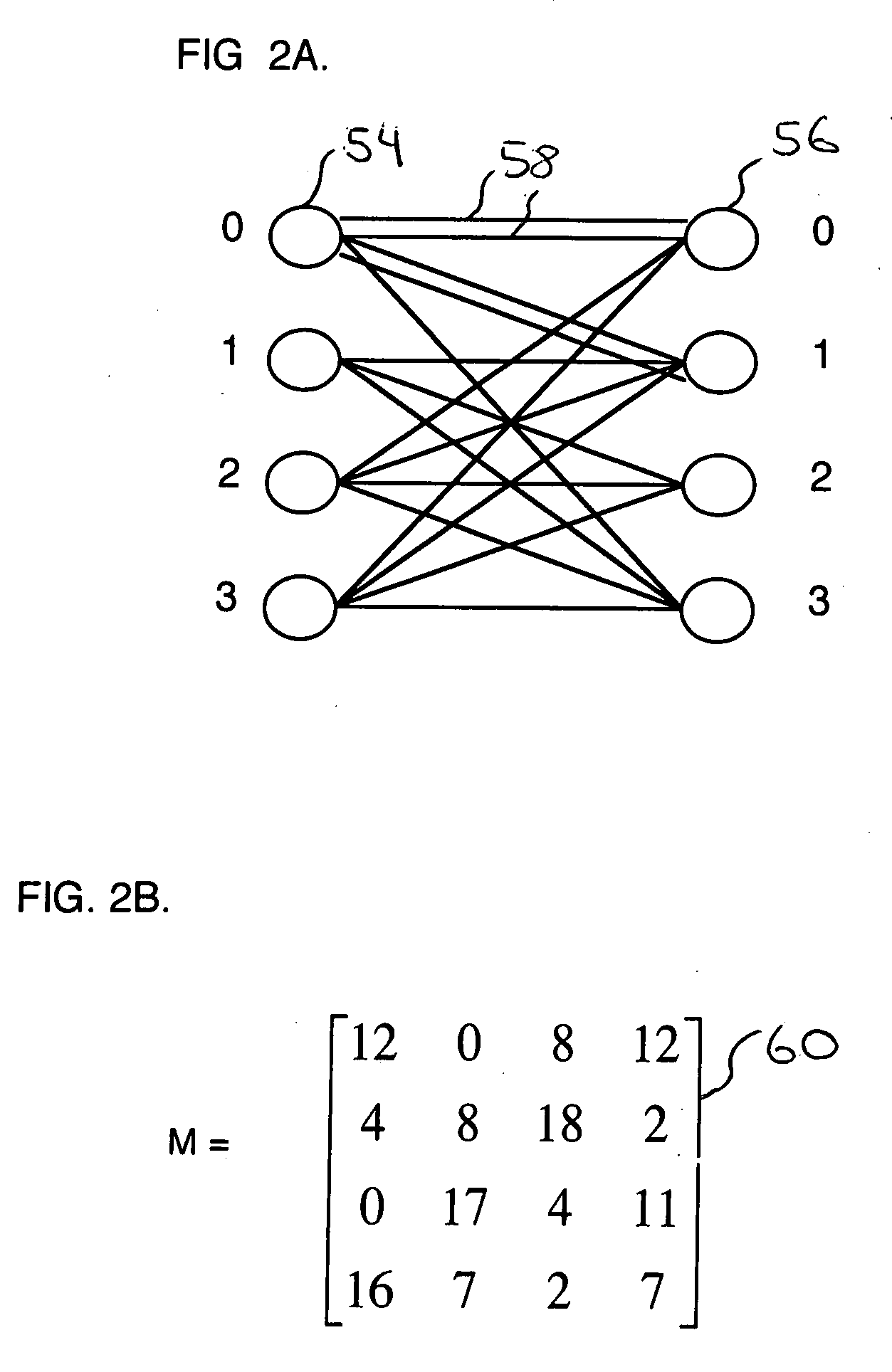

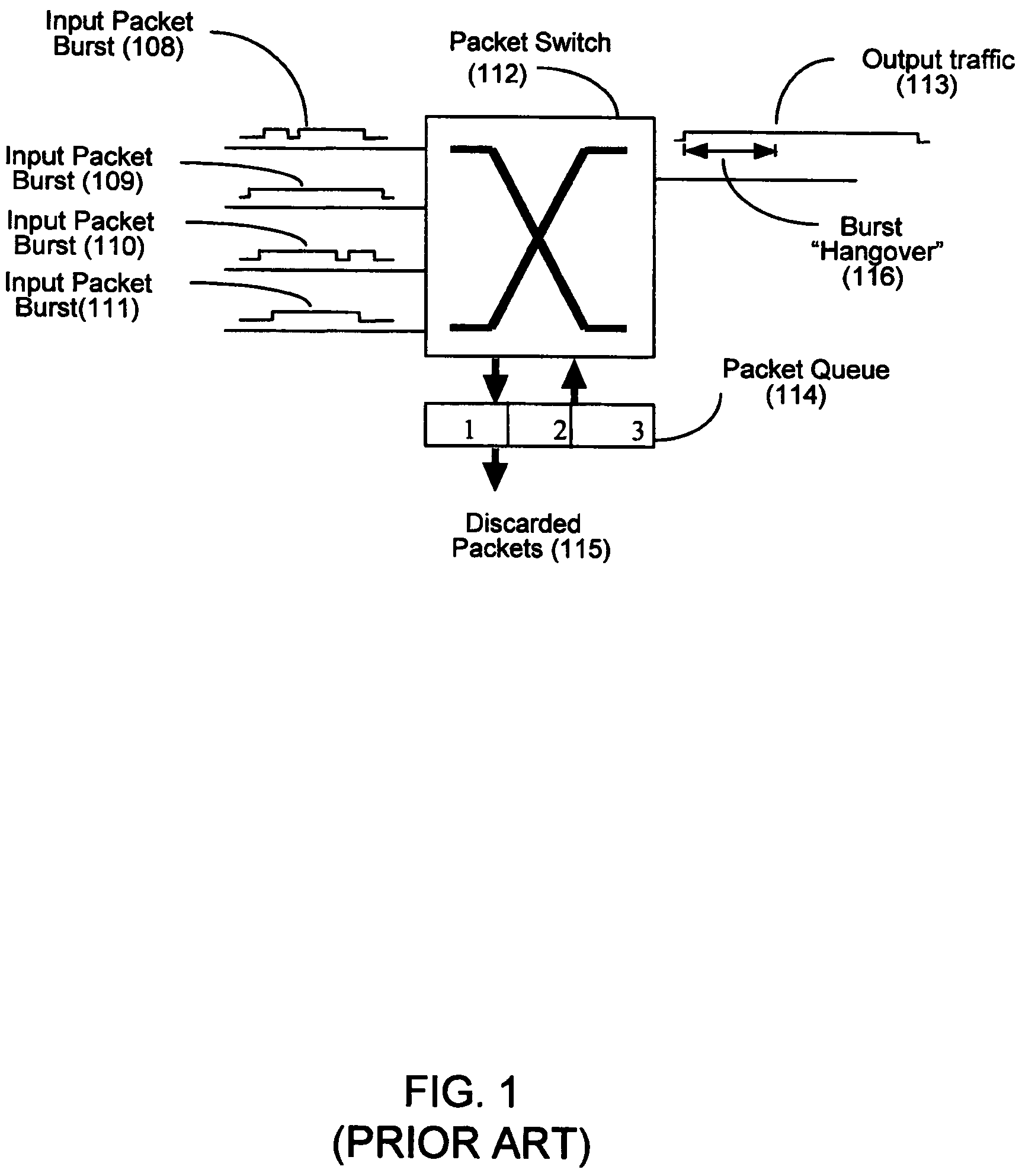

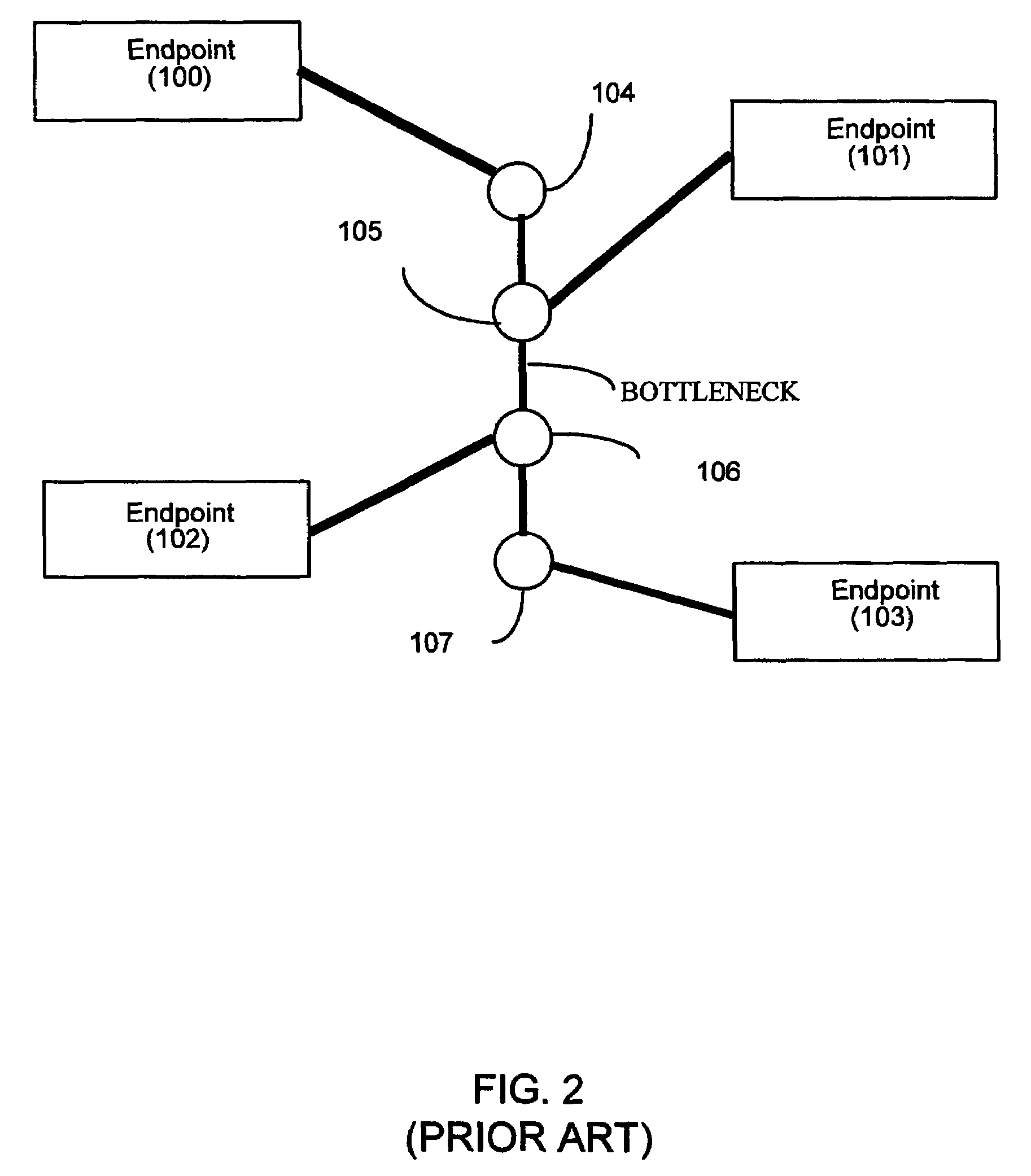

Method and apparatus to schedule packets through a crossbar switch with delay guarantees

ActiveUS20070280261A1Minimize delay jitterMeet bandwidth requirementsMultiplex system selection arrangementsData switching by path configurationCrossbar switchDifferentiated services

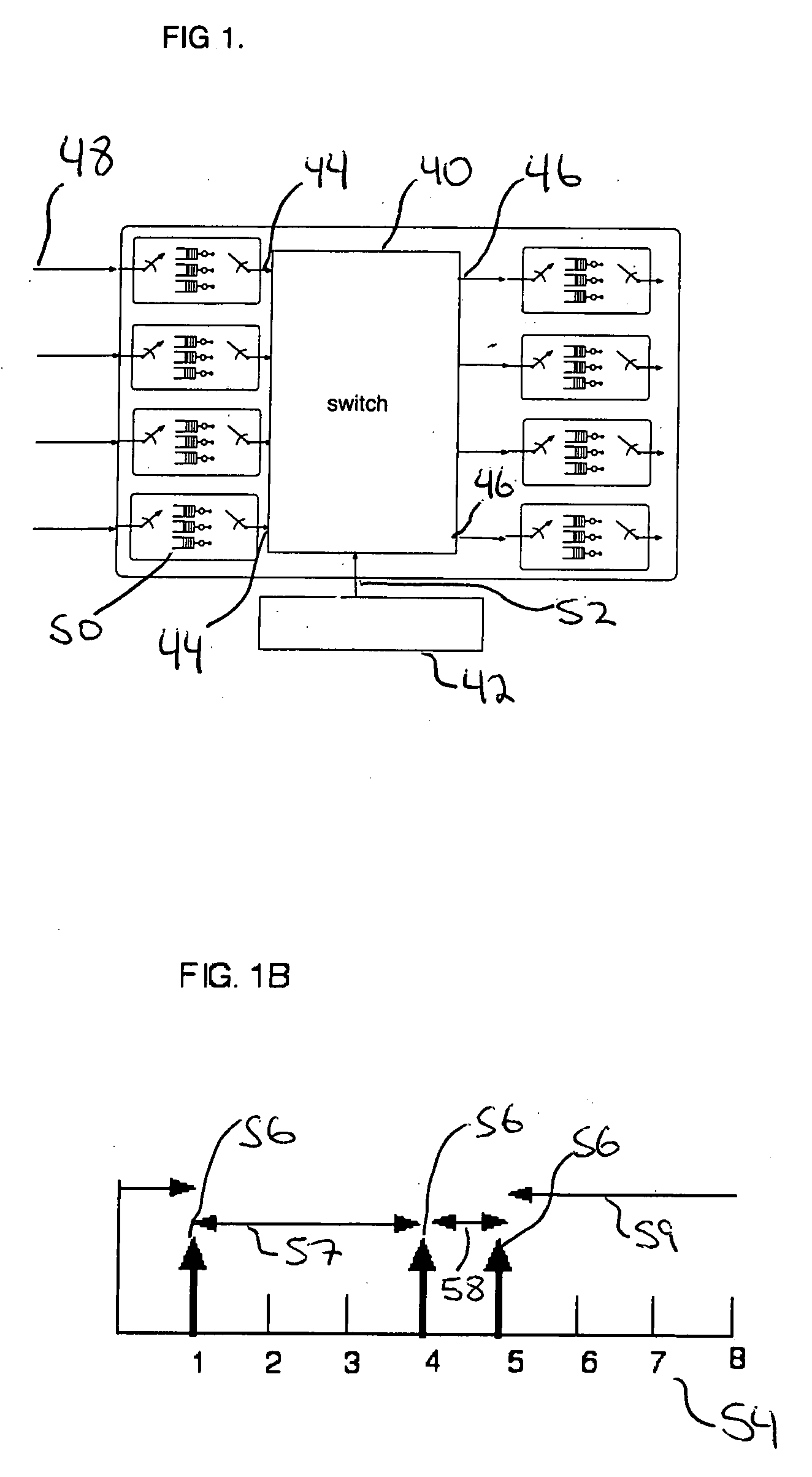

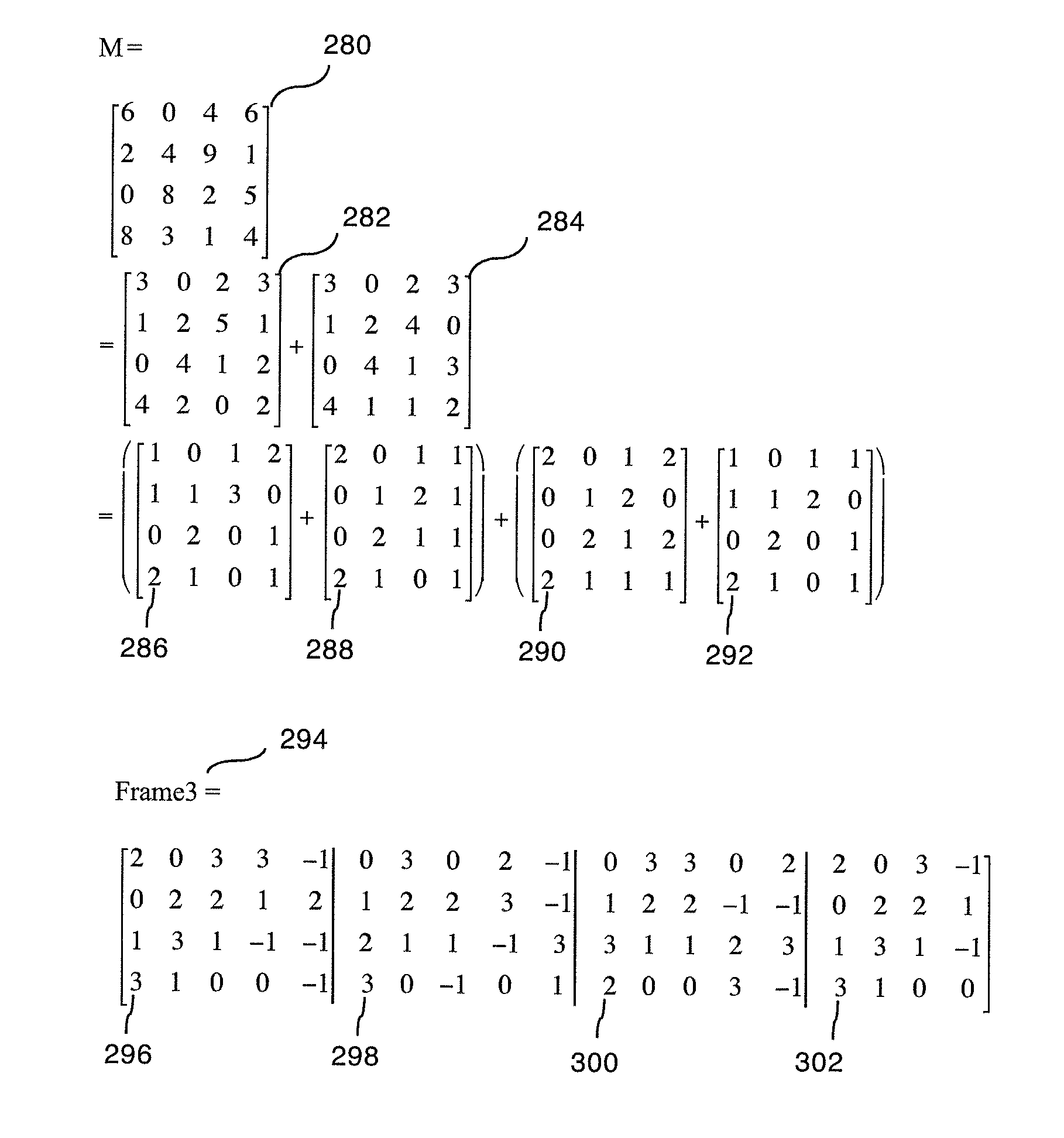

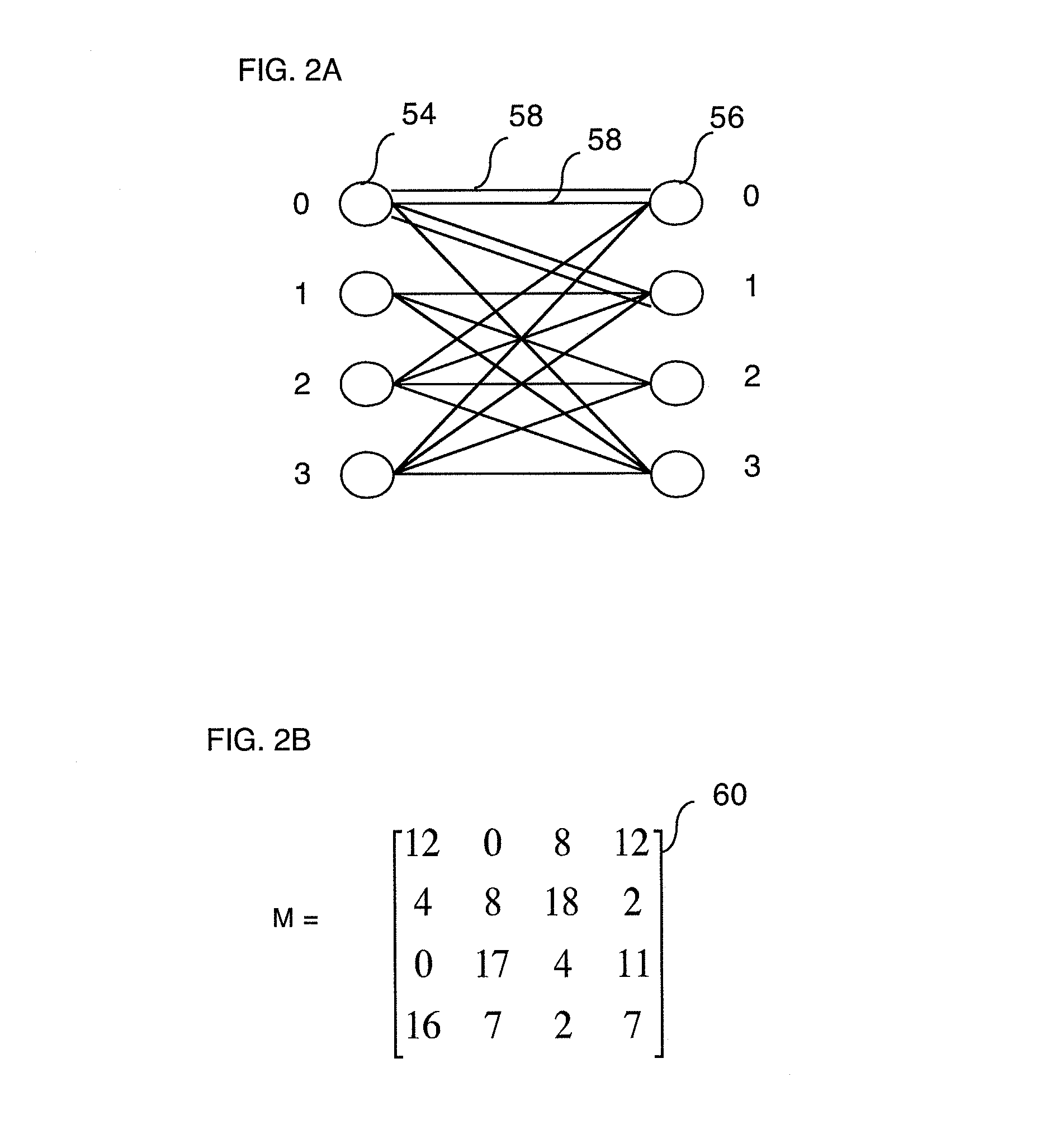

A method for scheduling cell transmissions through a switch with rate and delay guarantees and with low jitter is proposed. The method applies to a classic input-buffered N×N crossbar switch without speedup. The time axis is divided into frames each containing F time-slots. An N×N traffic rate matrix specifies a quantized guaranteed traffic rate from each input port to each output port. The traffic rate matrix is transformed into a permutation with NF elements which is decomposed into F permutations of N elements using a recursive and fair decomposition method. Each permutation is used to configure the crossbar switch for one time-slot within a frame of size F time-slots, and all F permutations result in a Frame Schedule. In the frame schedule, the expected Inter-Departure Time (IDT) between cells in a flow equals the Ideal IDT and the delay jitter is bounded and small. For fixed frame size F, an individual flow can often be scheduled in O(logN) steps, while a complete reconfiguration requires O(NlogN) steps when implemented in a serial processor. An RSVP or Differentiated Services-like algorithm can be used to reserve bandwidth and buffer space in an IP-router, an ATM switch or MPLS switch during a connection setup phase, and the proposed method can be used to schedule traffic in each router or switch. Best-effort traffic can be scheduled using any existing dynamic scheduling algorithm to fill the remaining unused switch capacity within each Frame. The scheduling algorithm also supports multicast traffic.

Owner:SZYMANSKI TED HENRYK

Clock generator for generating accurate and low-jitter clock

ActiveUS6900676B1Accurate and low jitterPulse automatic controlGenerating/distributing signalsControl signalPhase difference

A clock generator has a clock generating circuit, a phase difference detection circuit, and a control signal generating circuit. The clock generating circuit has a function for varying a clock phase in accordance with a control signal, the phase difference detection circuit compars the clock phase output from the clock generating circuit with a phase of a reference waveform, and detecting a phase difference therebetween, and the control signal generating circuit generates a control signal for controlling the clock phase of the clock generating circuit, based on phase difference information obtained from the phase difference detection circuit. The phase difference detection circuit has a plurality of phase detection units, at least one of the plurality of phase detection units carries out a direct phase detection in which a phase of the clock is directly compared with the phase of the reference waveform, and at least the other one of the plurality of phase detection units carries out an indirect phase detection using a phase-synchronized waveform generating circuit generating a waveform synchronized in phase with the reference waveform or an output of the clock generating circuit and a phase information extracting circuit extracting phase information from the phase-synchronized waveform.

Owner:FUJITSU LTD

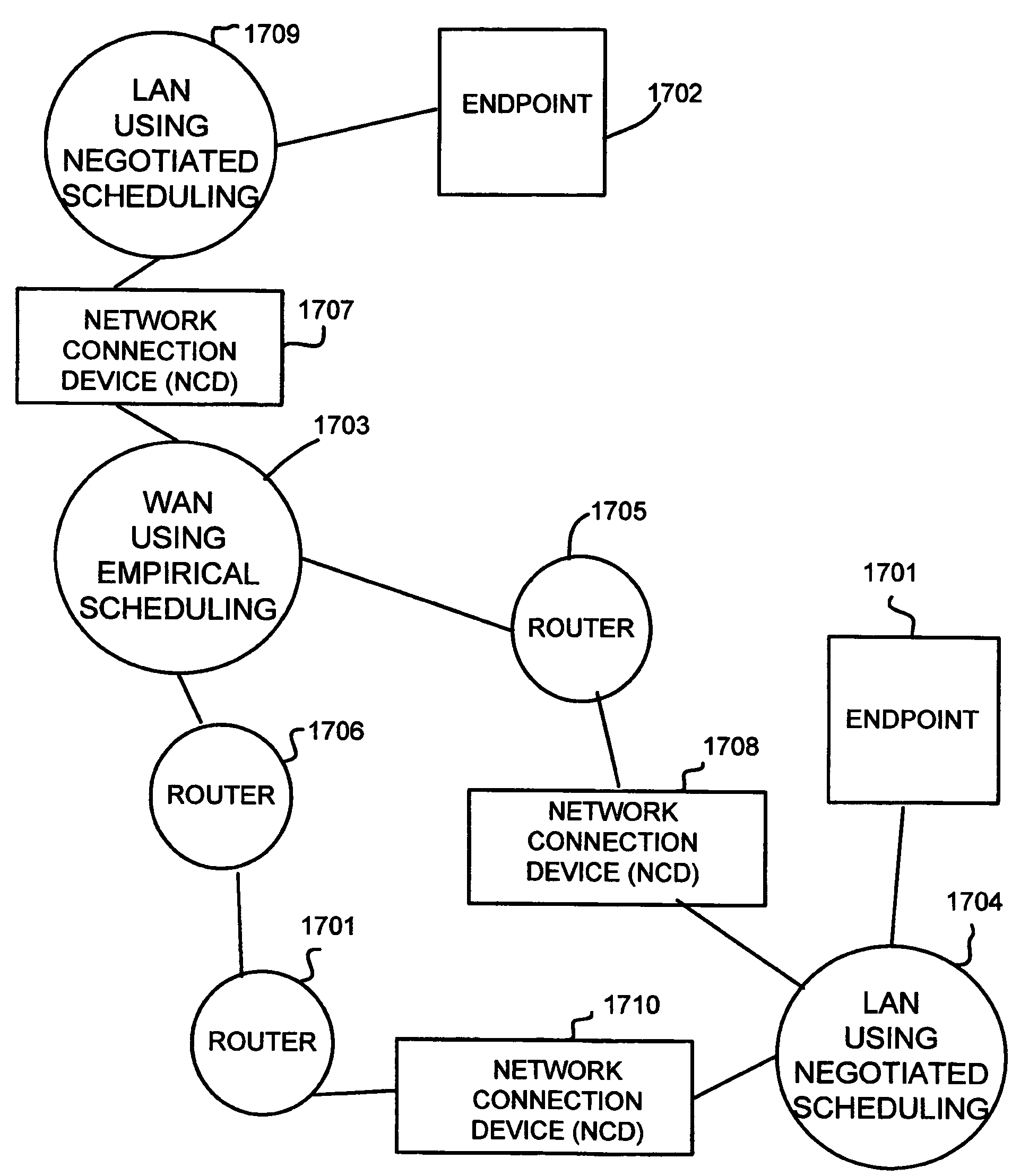

Network connection device

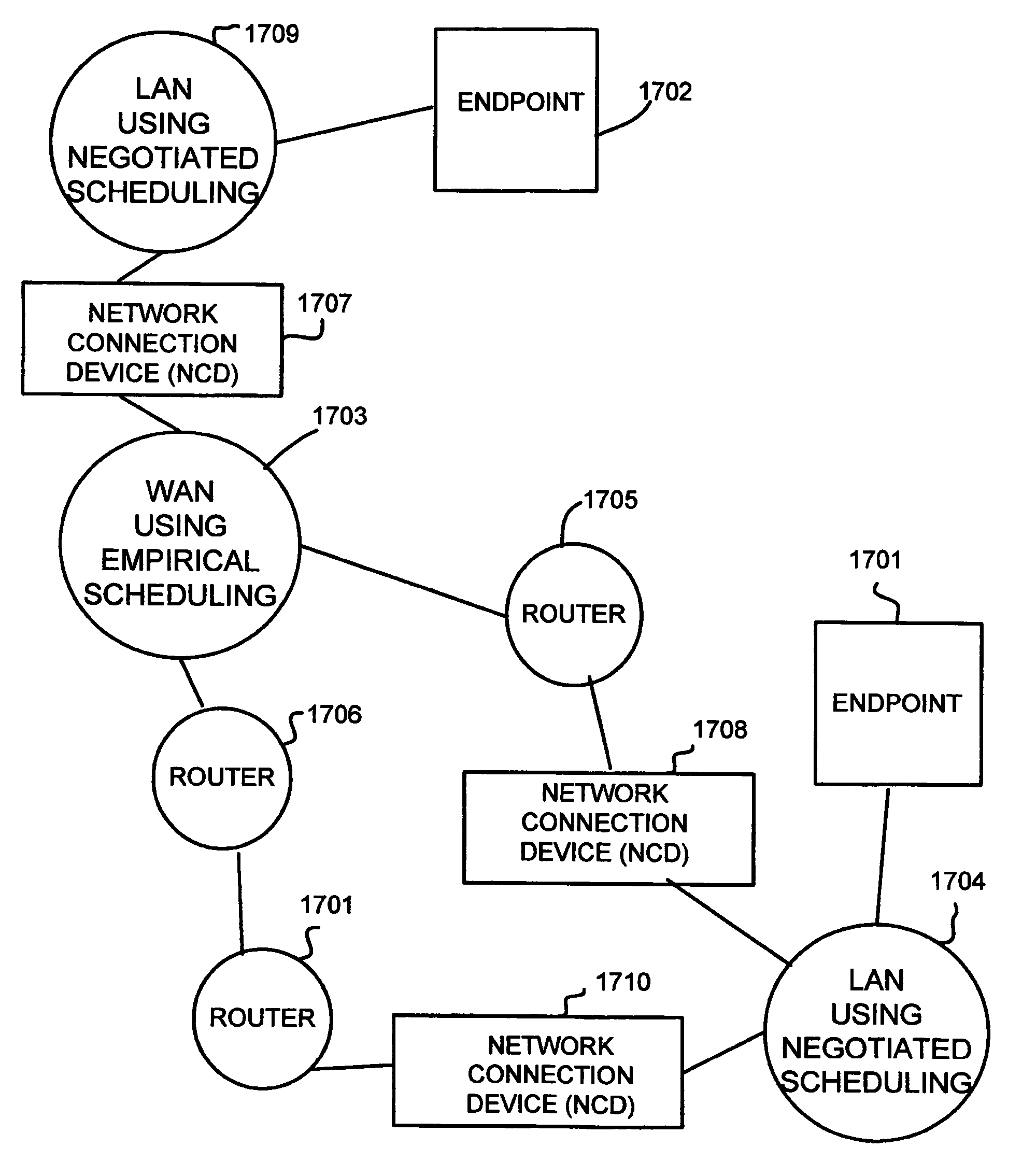

A network connection device bridges a first network that uses a negotiated packet delivery scheduling scheme and a second network that uses an empirically determined packet delivery scheduling scheme. The network connection device translates a request to communicate over the first network into a request to communicate over the second network, thus bridging the two networks. The negotiated packet delivery scheduling scheme permits endpoints to negotiate scheduled delivery times for packets, while the empirically determined packet delivery scheme tests various time interval locations in a network to determine favorable time locations for transmission. The two protocols are bridged by finding compatible overlaps between time interval locations in the two networks. This can provide error-free delivery with low jitter among packets.

Owner:RIVULET COMM INC

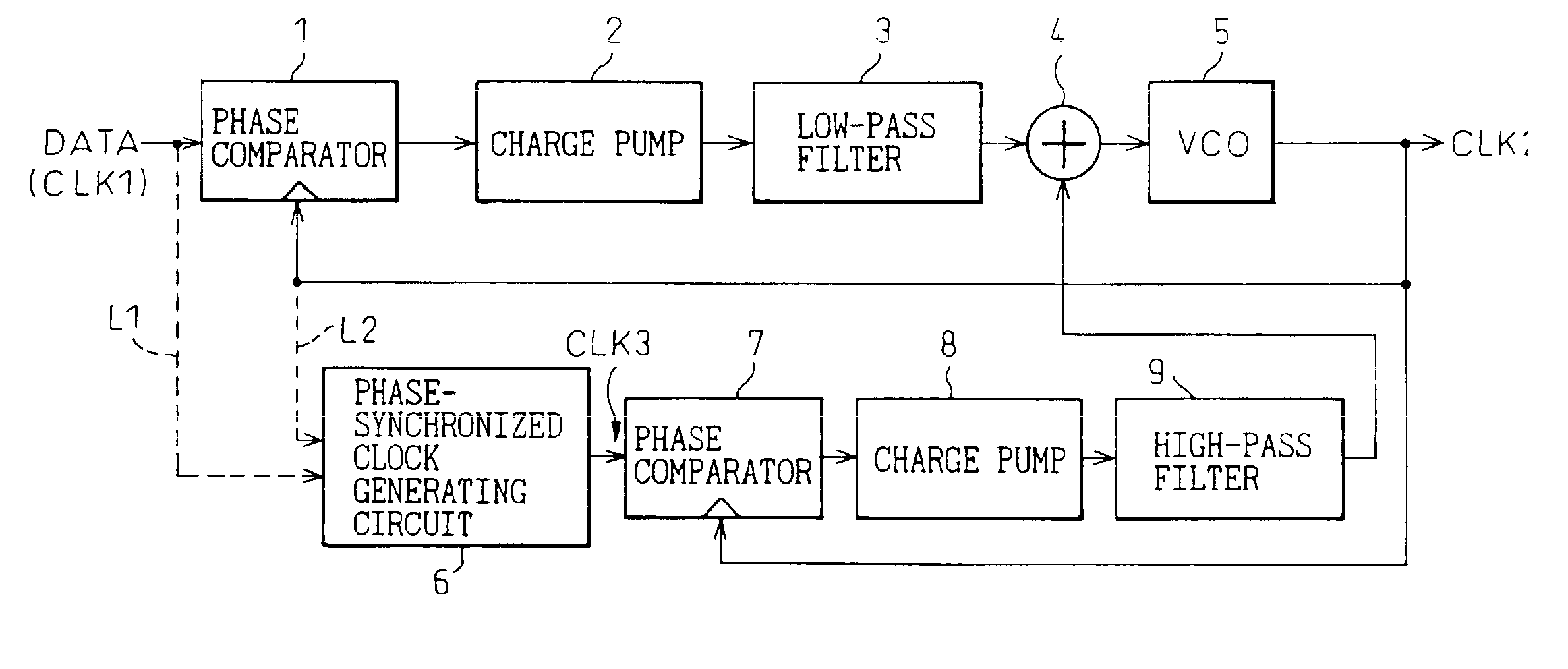

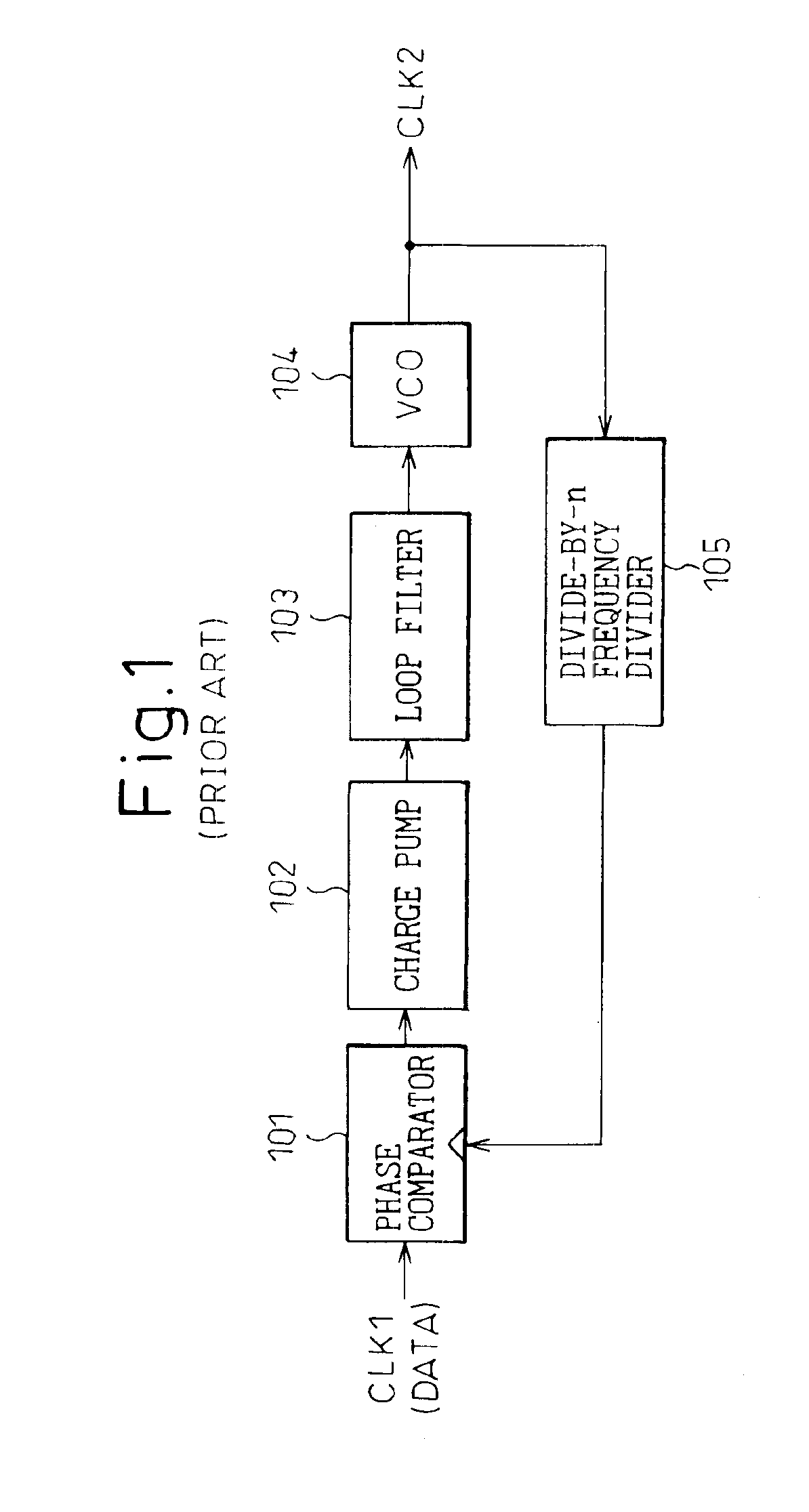

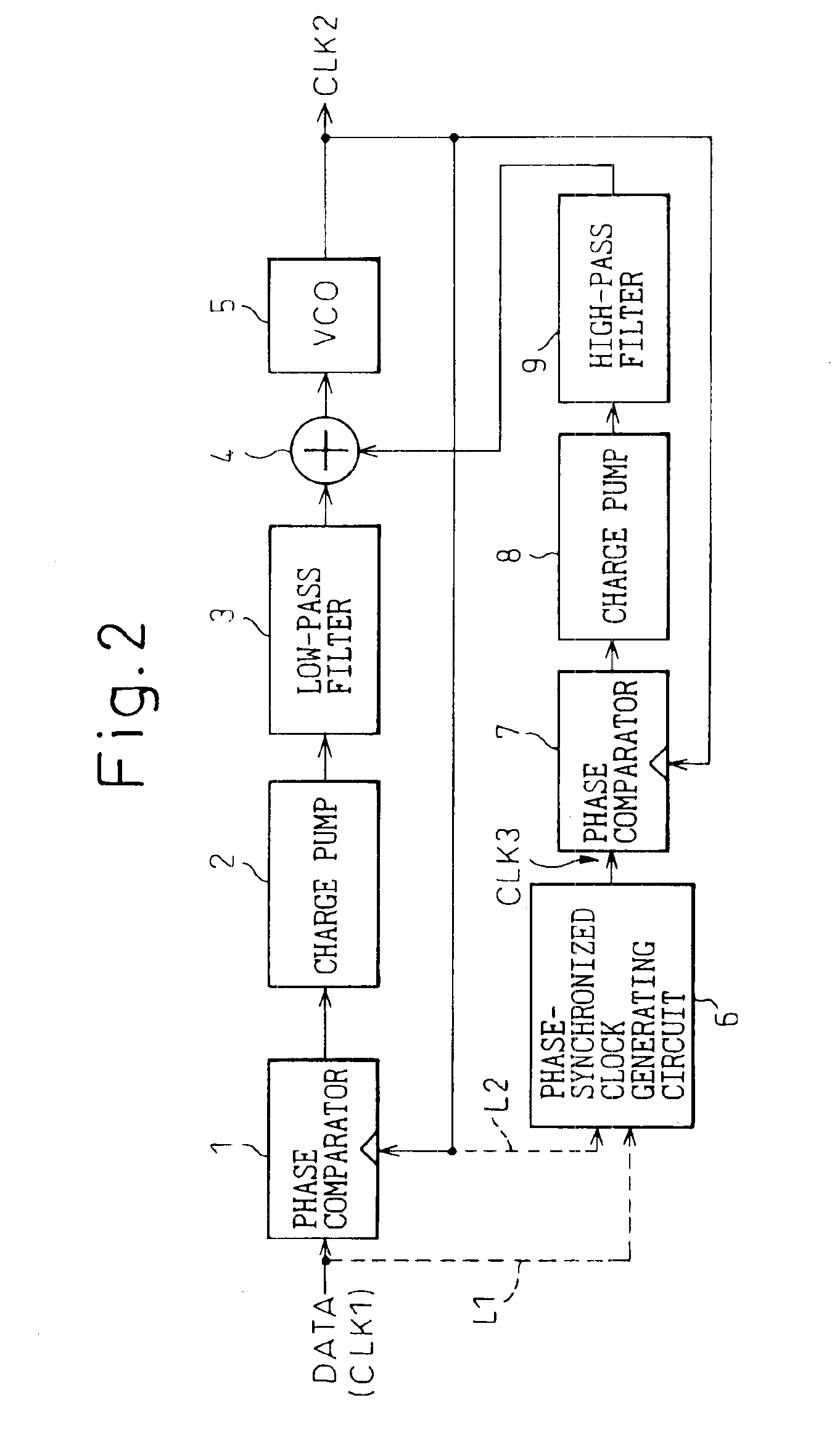

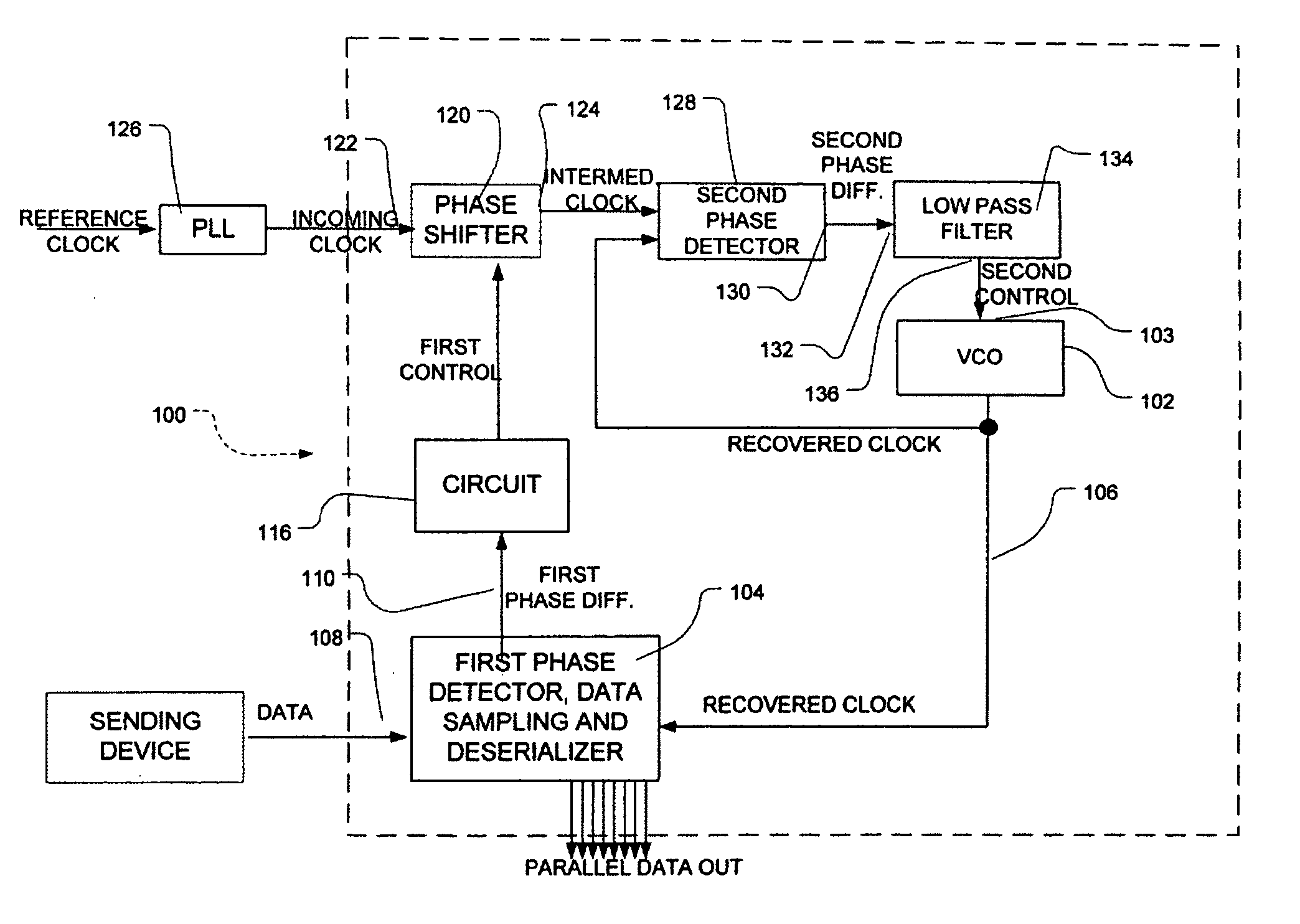

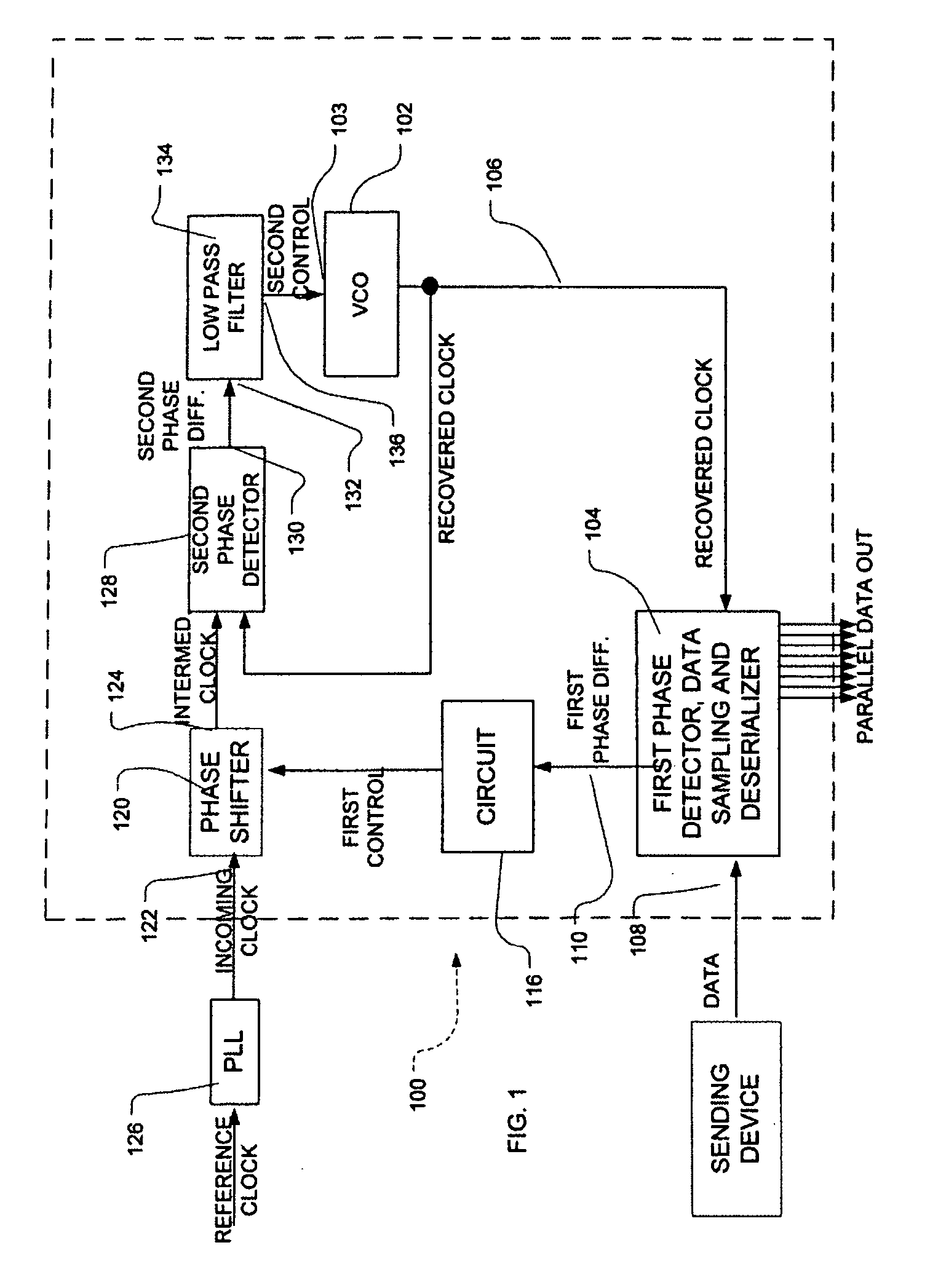

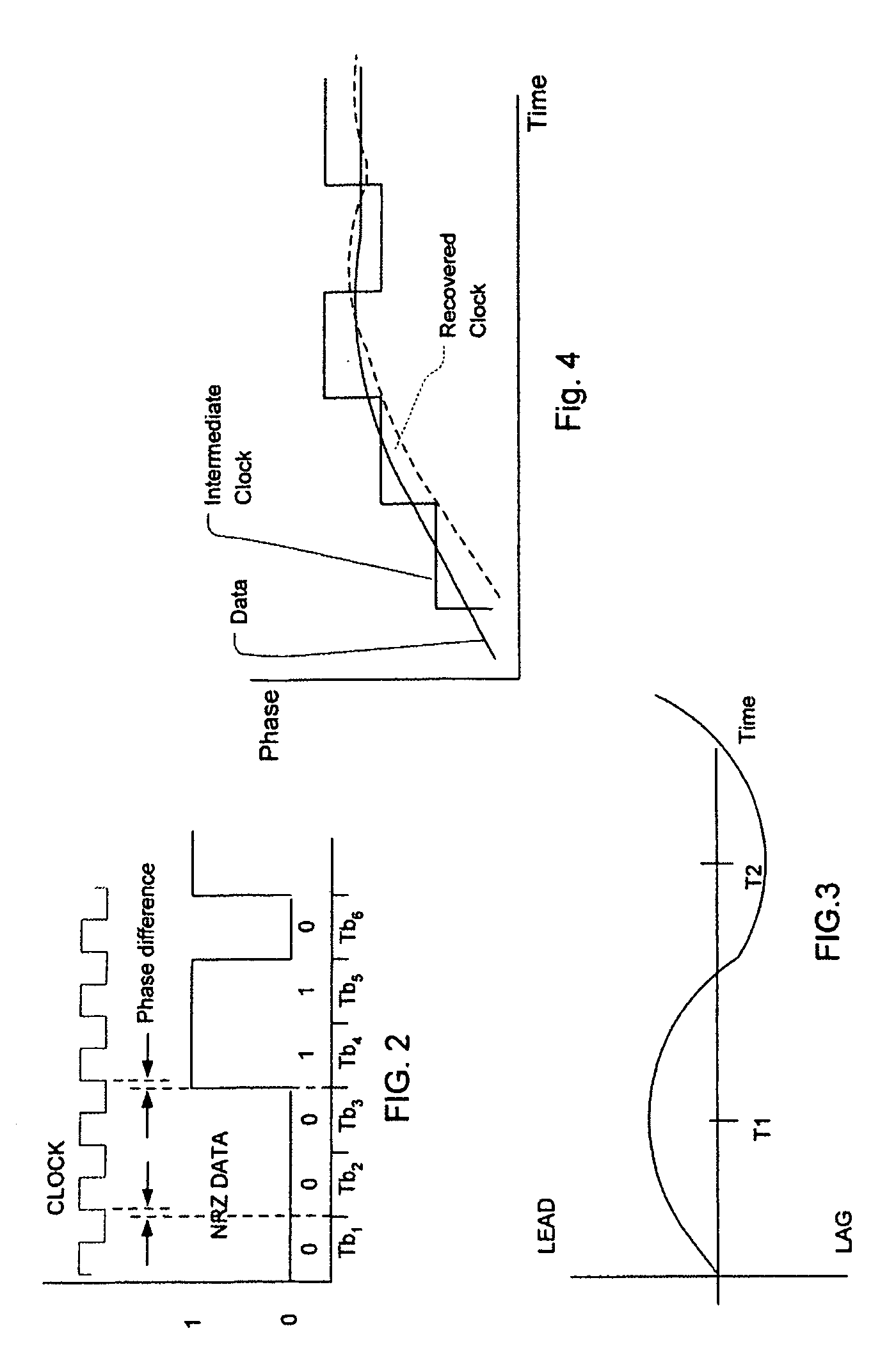

Low jitter clock recovery circuit

ActiveUS20070058768A1Pulse automatic controlOscillations comparator circuitsPhase detectorLow-pass filter

A clock recovery circuit includes a first phase detector for measuring the phase difference between a first clock signal from a voltage controlled oscillator (VCO) and a data signal. A phase shifter responsive to a control signal based on this phase difference adjusts the phase of an incoming clock signal to yield a second clock signal. The phase difference between the first clock signal and the second clock signal is measured and the resulting signal is low-pass filtered to derive a control signal for controlling the VCO. The phase locked loop including the VCO filters out jitter.

Owner:RAMBUS INC

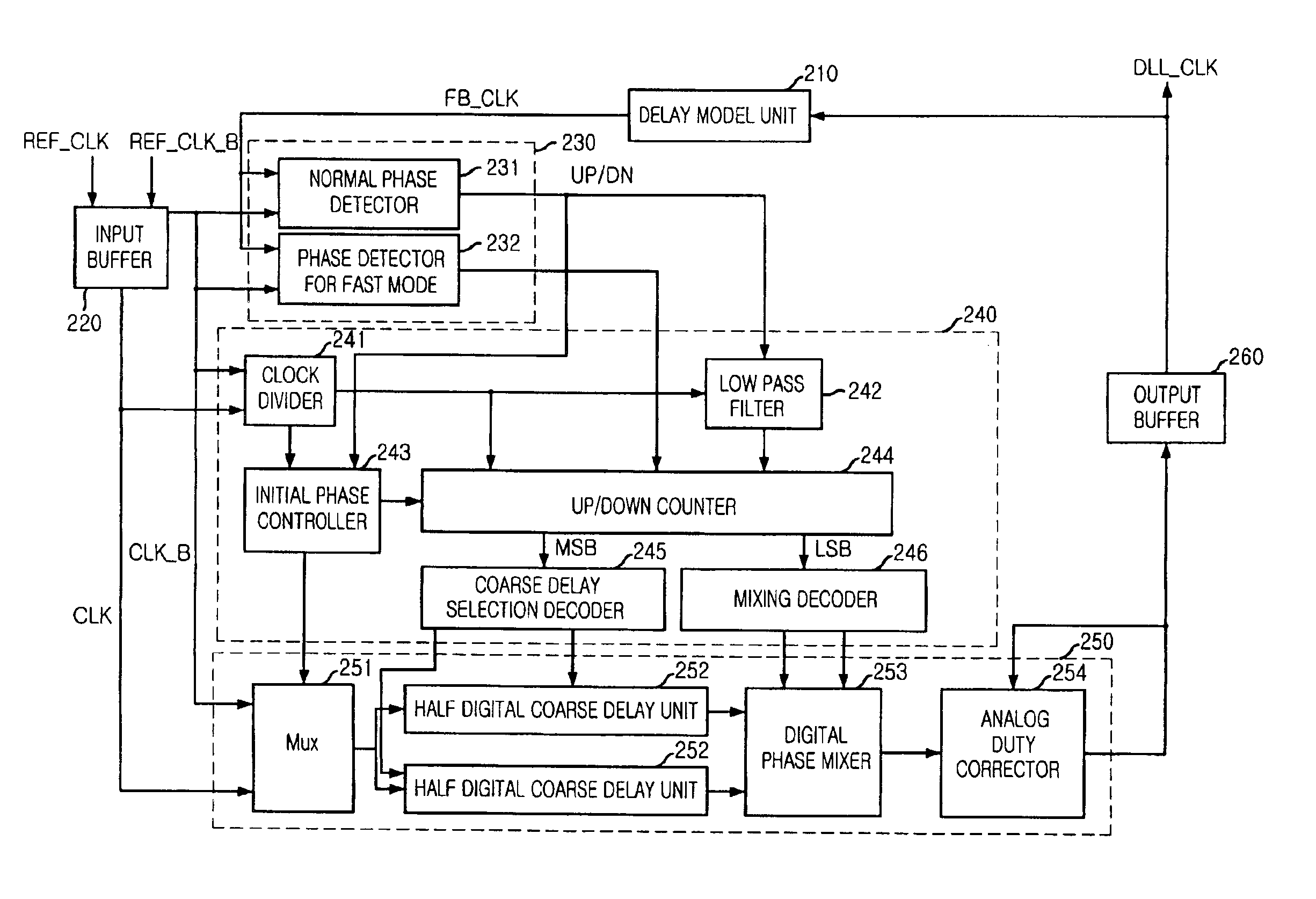

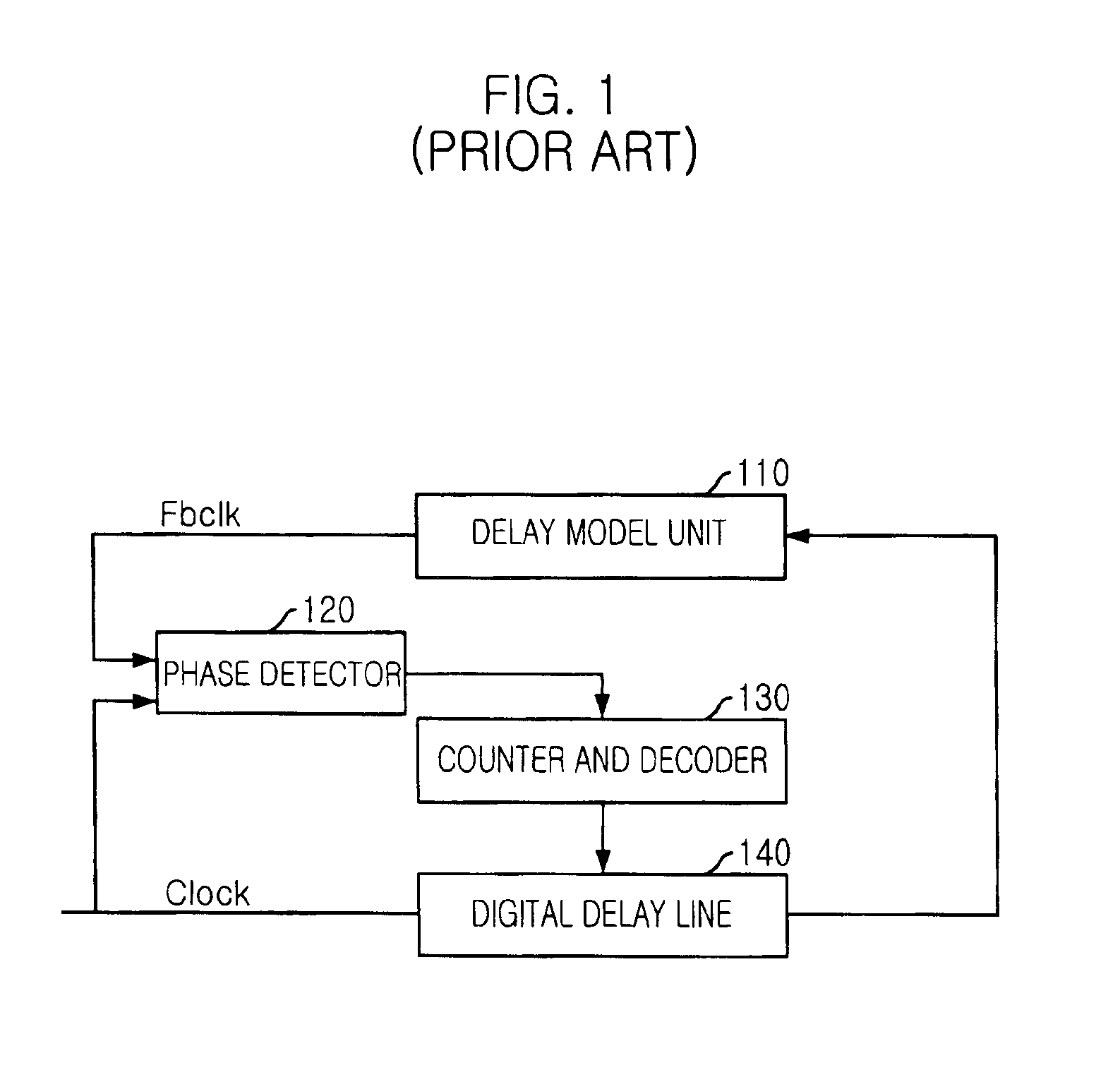

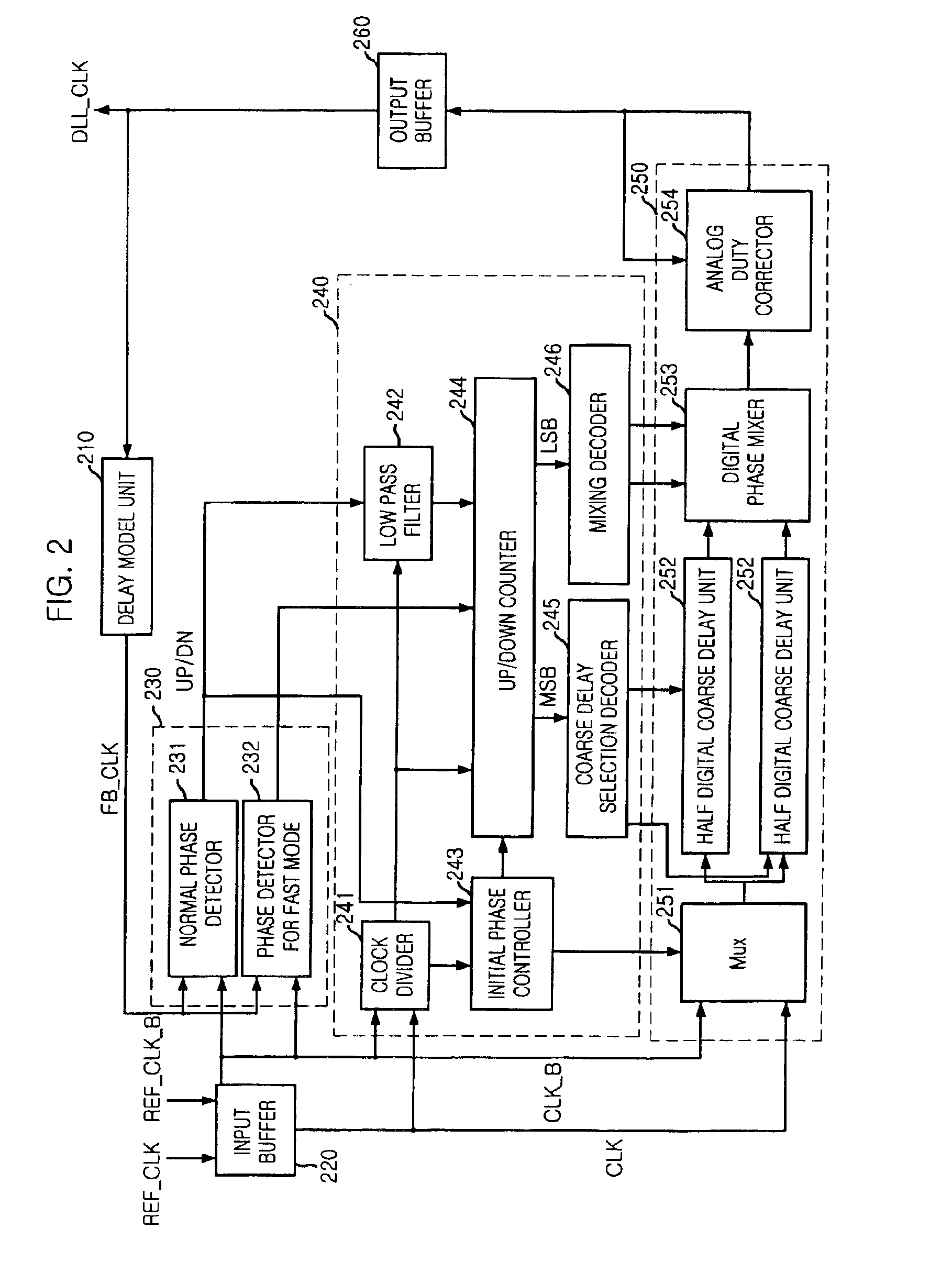

Delay locked loop having low jitter in semiconductor device

InactiveUS6917229B2Reduce jitterPulse automatic controlAngle demodulation by phase difference detectionControl signalDelay-locked loop

A DLL circuit having a low jitter in a semiconductor device, includes a delay model unit for compensating a time difference between an external clock signal and an internal clock signals and generating a compensation signal; an input buffer for receiving a reference clock signal and an inverted clock signal, and for outputting a clock signal and an inverted clock signal activated at each edges of the reference clock signal and the inverted clock signal; a phase detection unit for generating a comparison signal by comparing the compensation signal with the inverted clock signal, and for outputting the comparison signal with a normal mode or a fast mode; a control unit for generating a plurality of control signals by receiving the comparison signal, the inverted clock signal and the clock signal; a delay unit for delaying in response to the plurality of control signals; and an output buffer for outputting a delayed clock signal by receiving an output signal of the duty corrector.

Owner:SK HYNIX INC

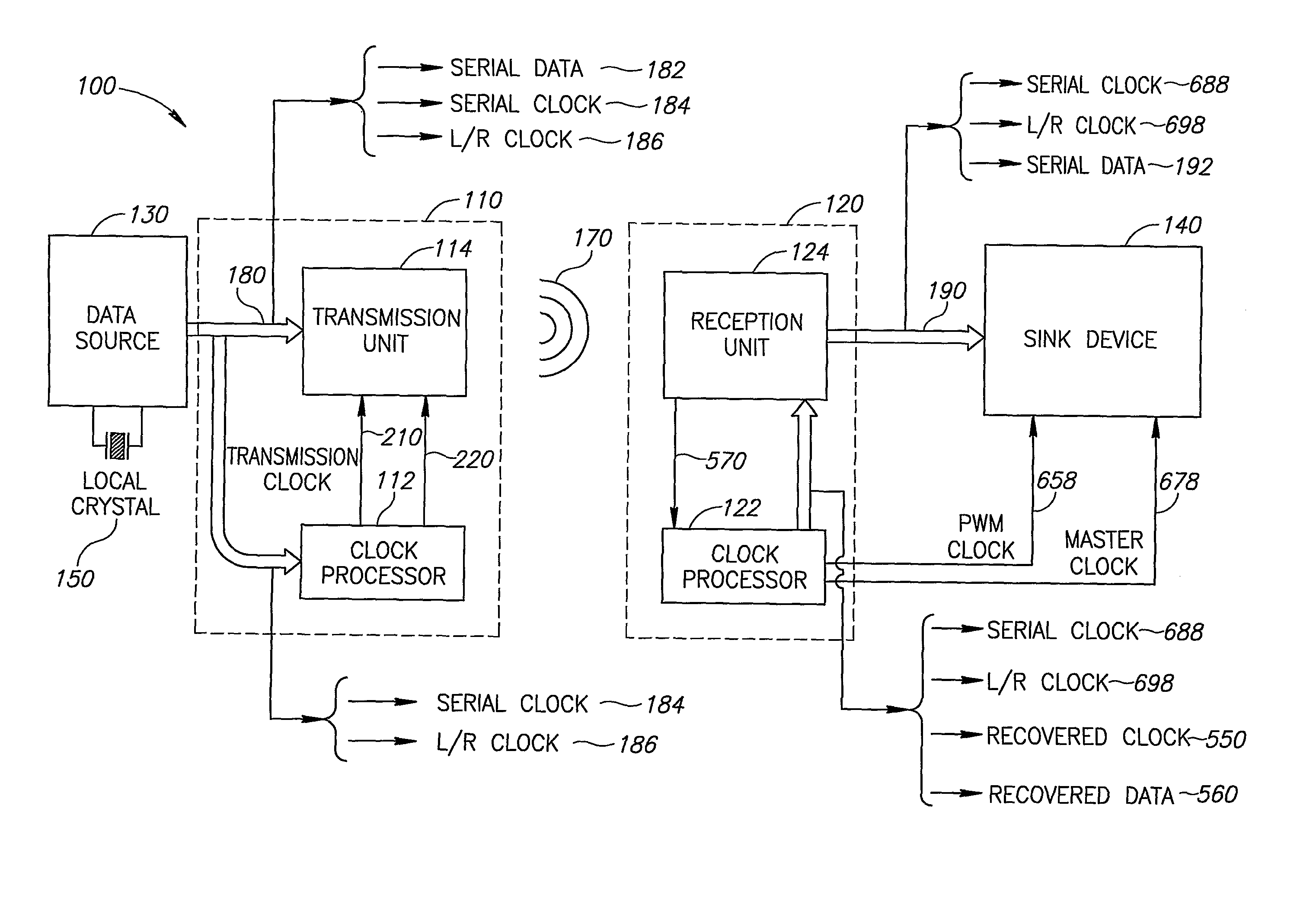

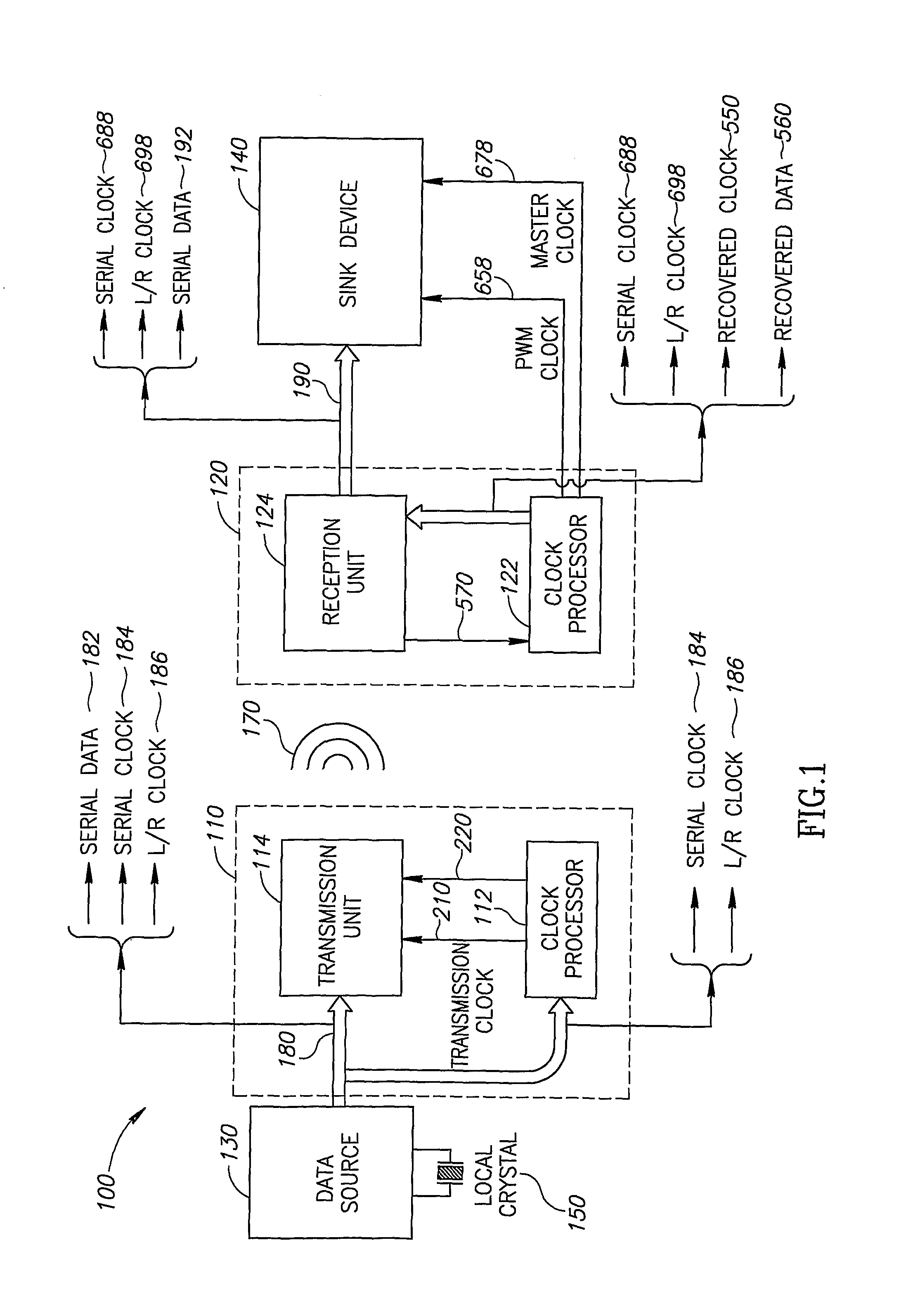

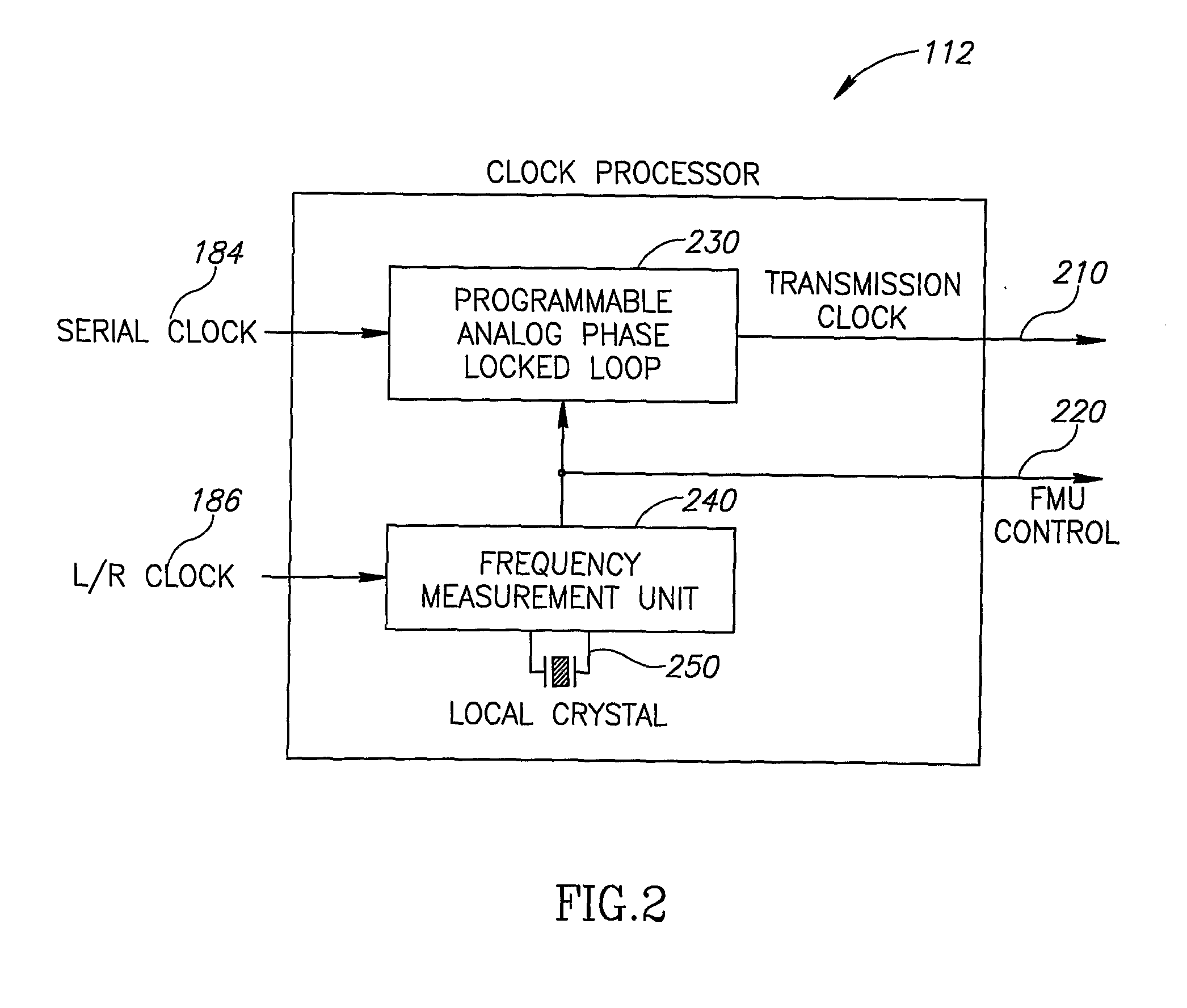

Low Jitter Clock Recovery from a Digital Baseband Data Signal Transmitted Over a Wireless Medium

InactiveUS20080212729A1Synchronisation error detectionCarrier regulationData streamWireless transmission

A system and method of transmitting a data stream from a data source over a baseband wireless communication system to one or more receivers. The receivers simultaneously recover the data and clock signals of the original data stream from the wireless transmitted data so that the data stream can be provided by the receivers to a data sink at the same rate as the original data stream, with low jitter performance.

Owner:INFRA

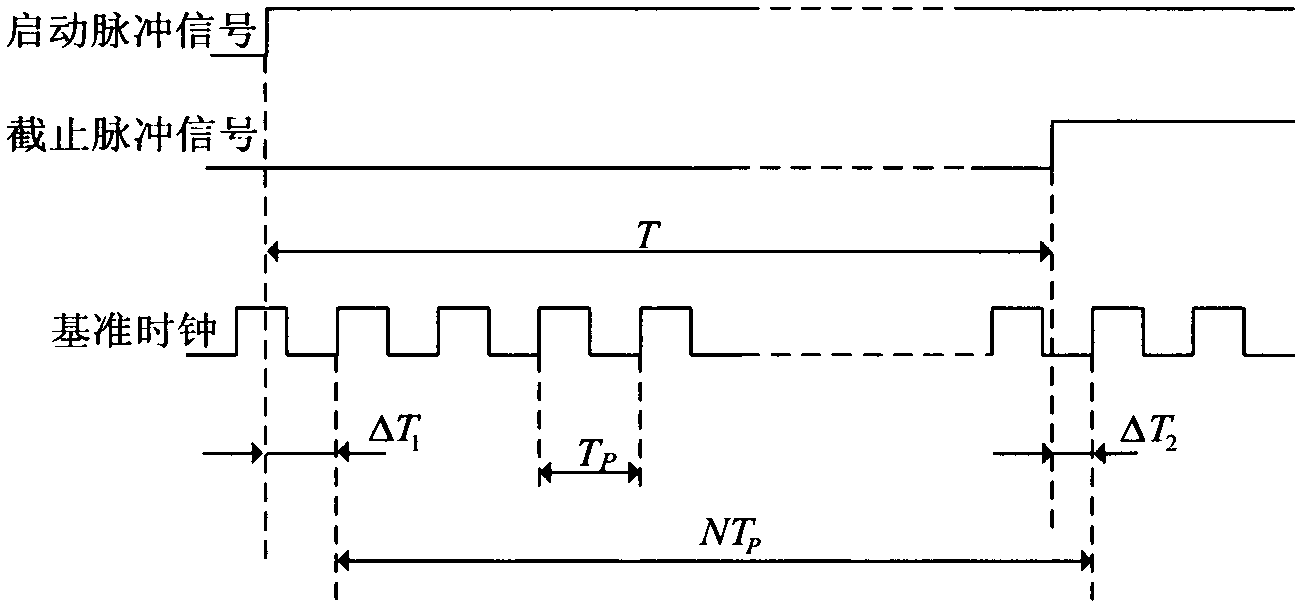

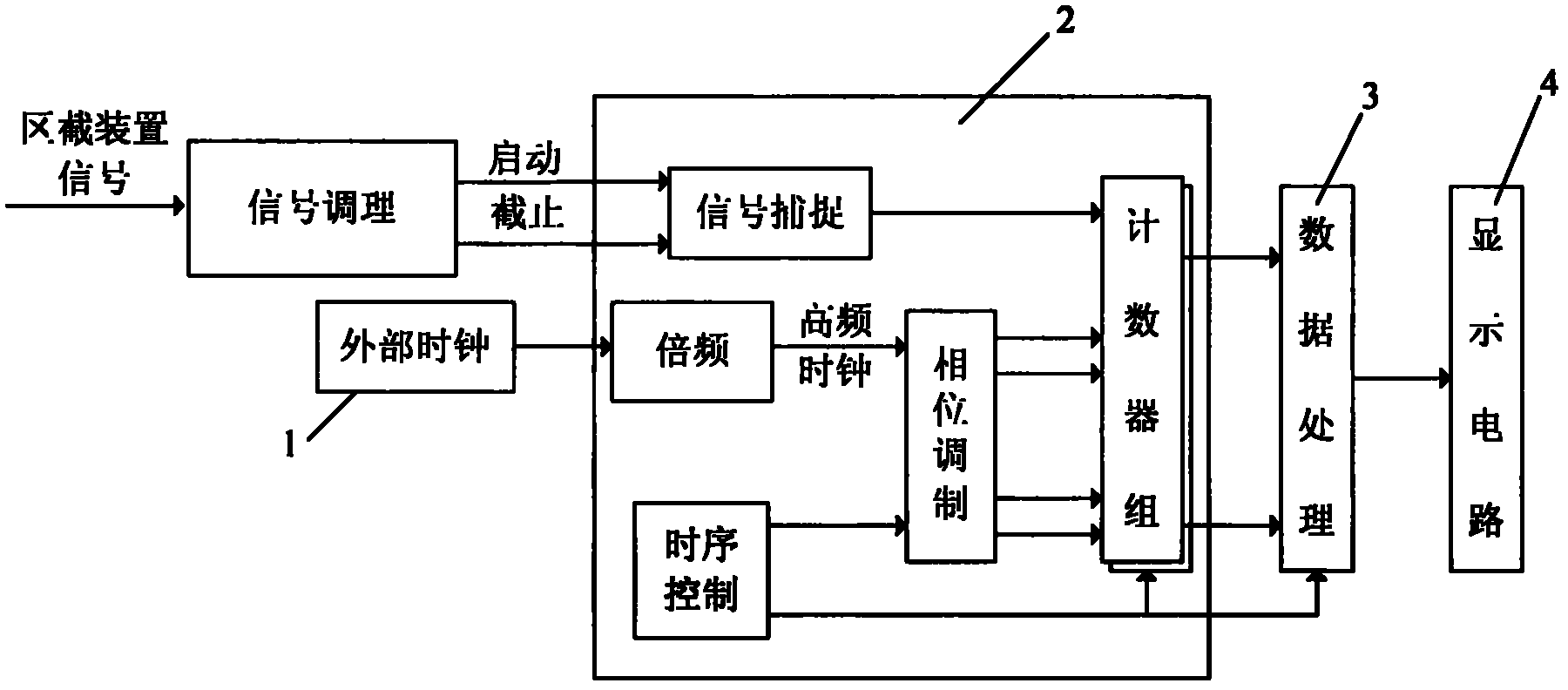

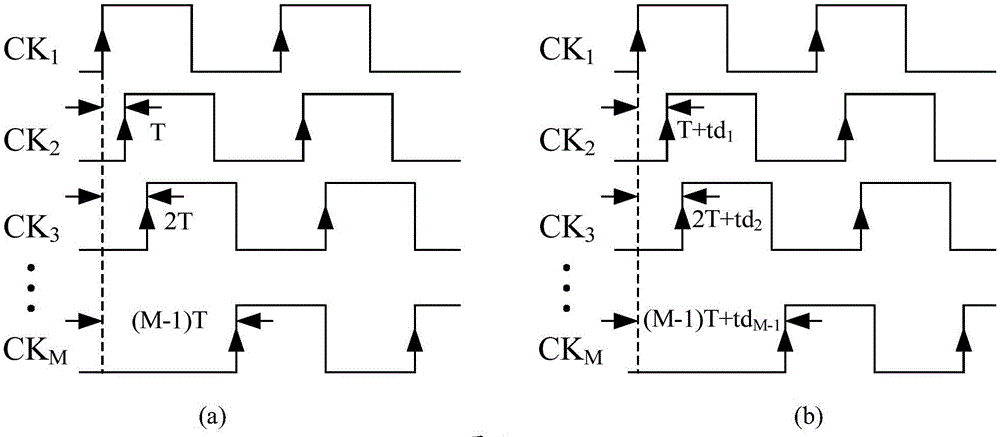

High-precision time interval measurement method based on phase modulation

InactiveCN102540865AMany technical meansEasy to implementElectric unknown time interval measurementObservational errorMeasurement device

The invention discloses a high-precision time interval measurement method based on phase modulation. Under the control of digital clock phase-shift, a path of high-frequency and low-jitter clock is transformed to N paths of clock signals having same frequency and fixed phase difference, and is taken as a counter reference clock; a counter is driven to count respectively in N paths of clock periods; two paths of clock signals, which have the smallest error, are extracted by utilizing the clock phase information; through the combination with the clock period and the counted values, the measurement valve of the time interval is worked out. Compared with the method using a single clock for counting, the high-precision time interval measurement method effectively reduces the measurement principle error, and can improve the measurement resolution ratio to 1 / n of the reference clock. A measurement device is connected with a signal conditioning module, an FPGA module, a singlechip module and a display circuit module sequentially according to the signal processing order, and realizes high measurement precision, high measurement resolution ratio, high measurement speed, real time display, and stable and reliable work under a certain crystal oscillation frequency; and the integration in the FPGA is easy, and the expansion is flexible. The high-precision time interval measurement method can be used for measuring the speed in a high-speed motion.

Owner:XIAN MODERN CHEM RES INST

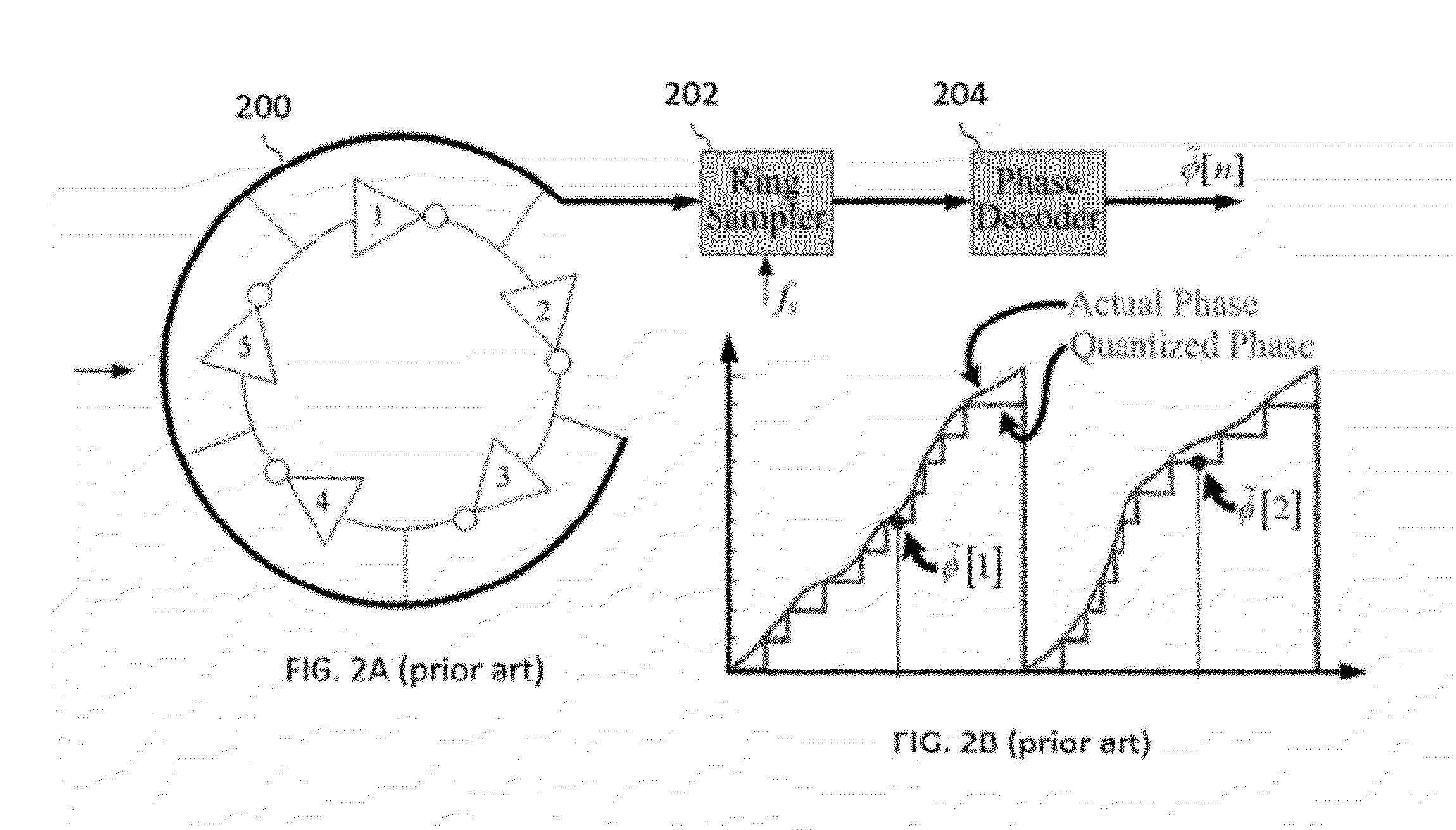

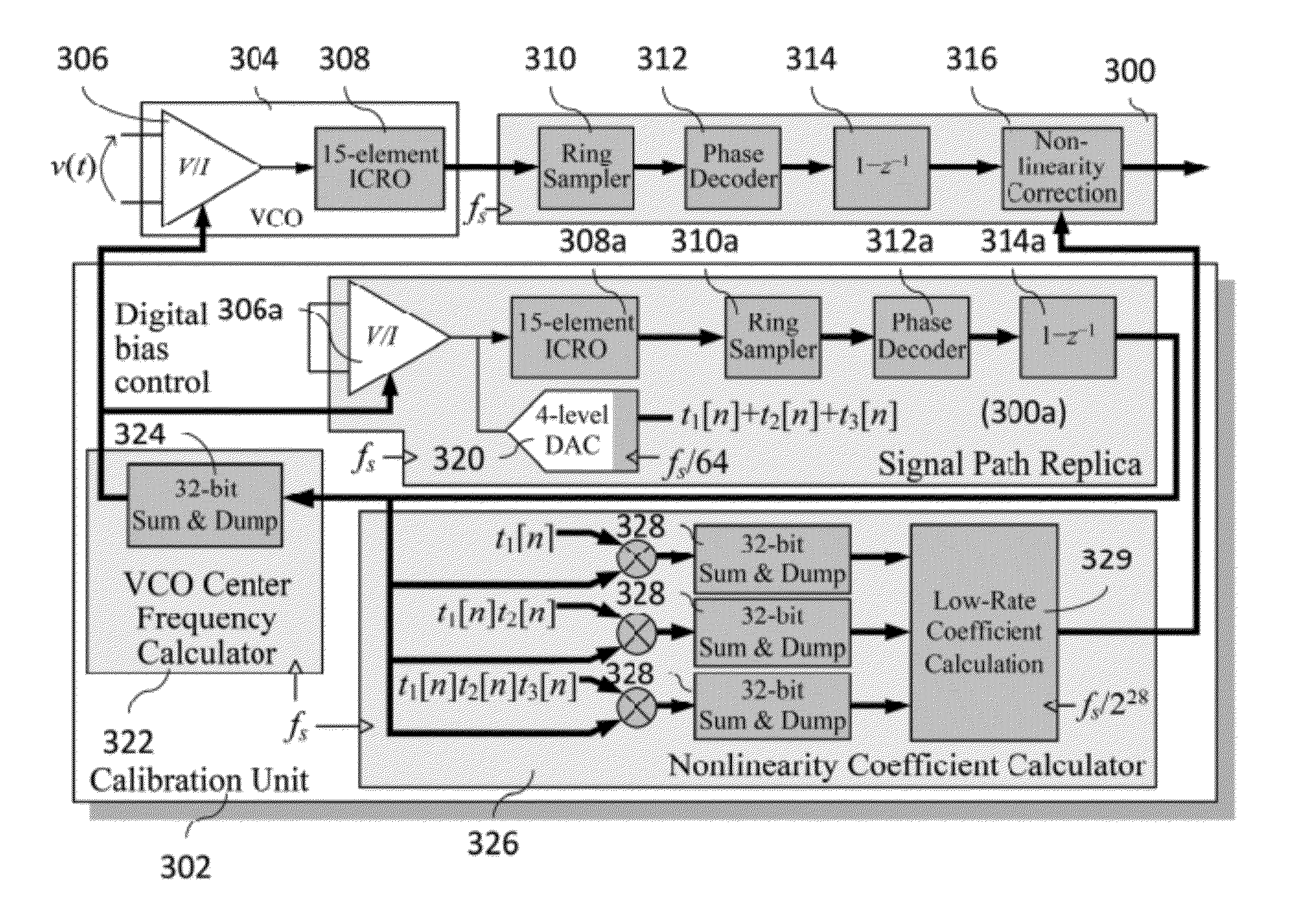

Ring oscillator delta sigma ADC modulator with replica path nonlinearity calibration

ActiveUS20120194369A1Electric signal transmission systemsAnalogue conversionNonlinear distortionIntegrator

An embodiment provides a continuous-time delta-sigma modulator for analog-to-digital conversion. The modulator includes a signal path generating including a ring voltage controlled oscillator driven by an analog input signal. The signal path produces digital values by sampling the ring voltage controlled oscillator. A calibration circuit measures nonlinear distortion coefficients in a replica of the signal path. A nonlinearity corrector corrects the digital values based upon determined nonlinear distortion coefficients. Preferred embodiment ADC ΔΣ modulators do not require any analog integrators, feedback DACs, comparators, or reference voltages, and do not require a low jitter clock.

Owner:RGT UNIV OF CALIFORNIA

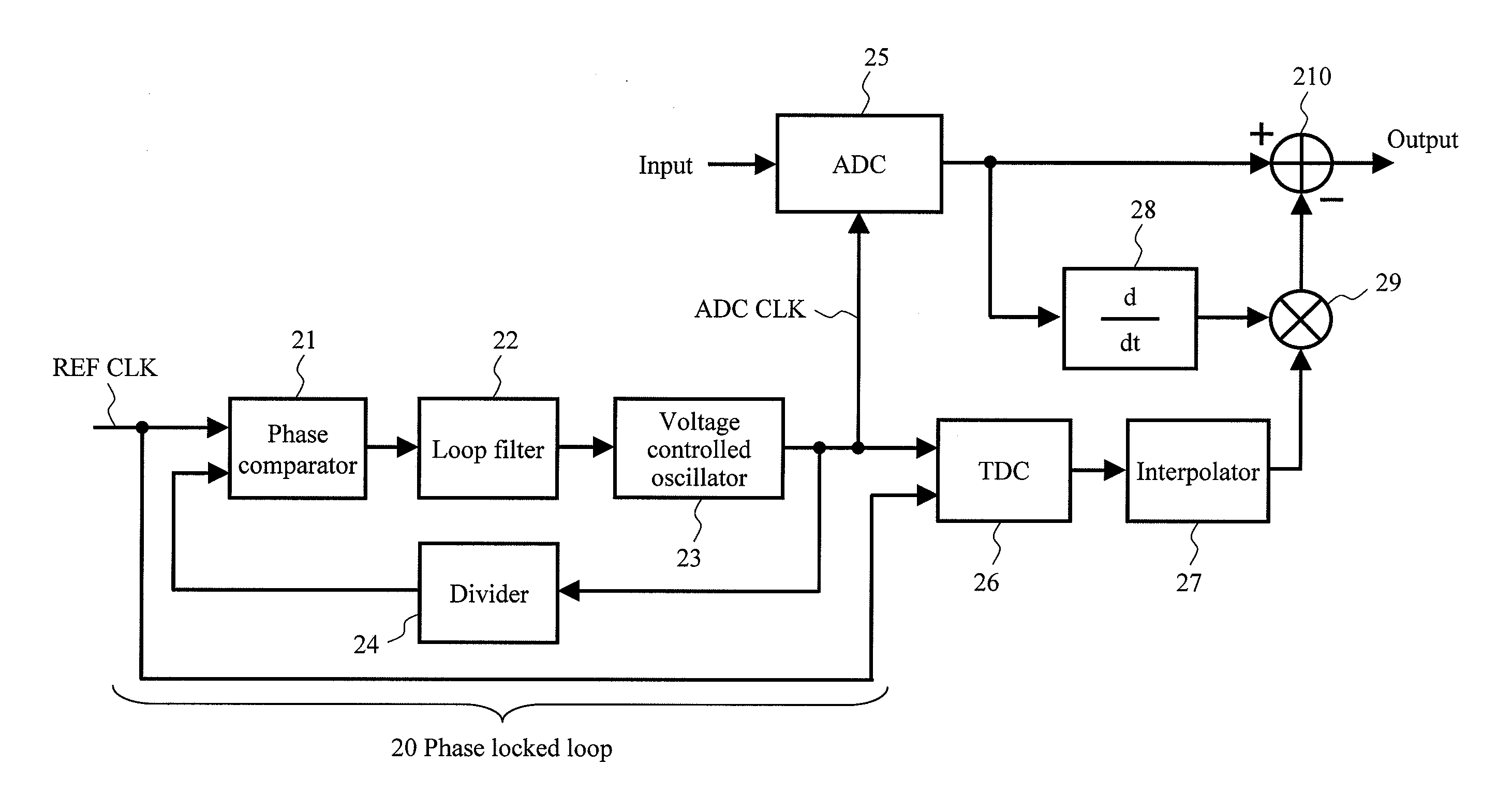

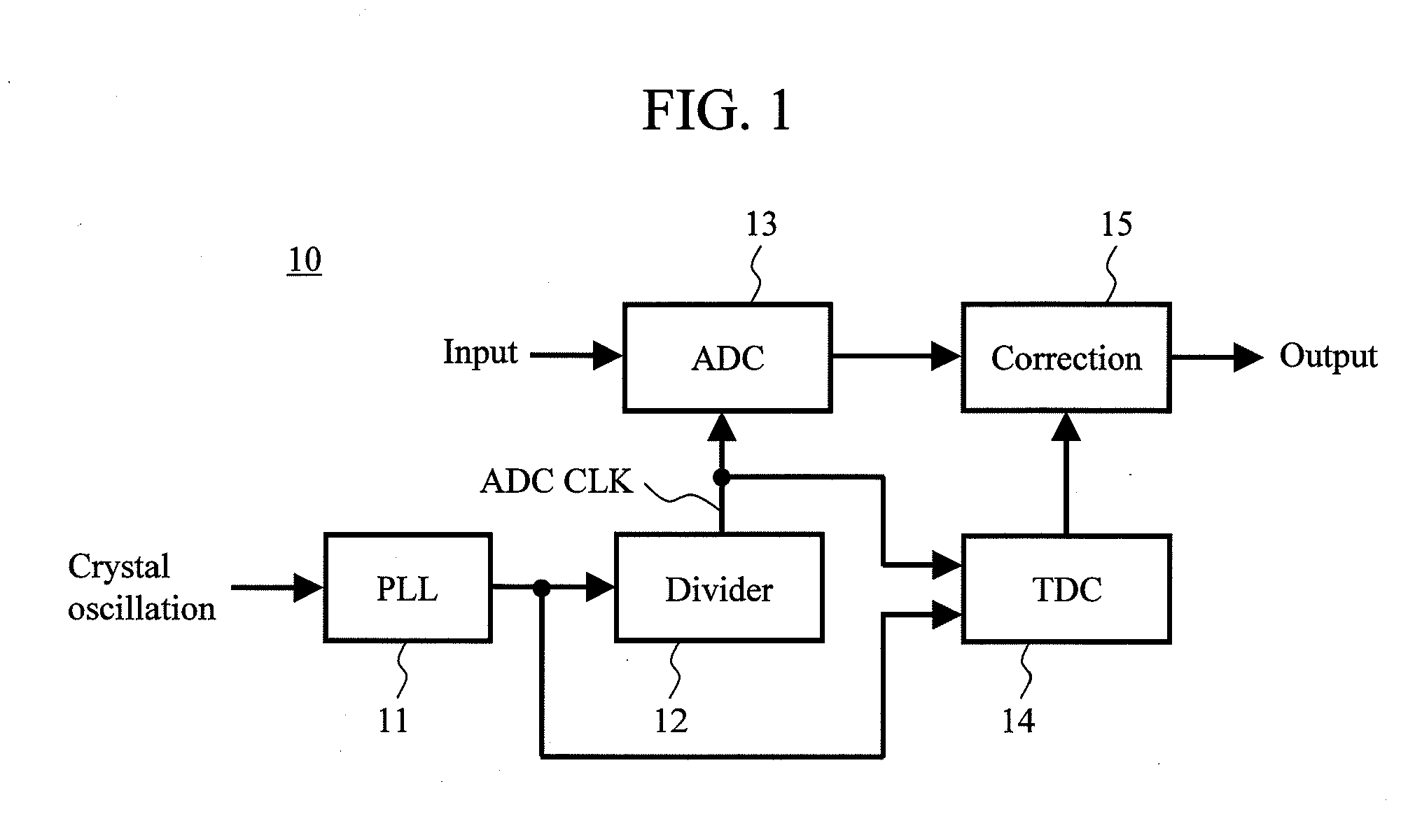

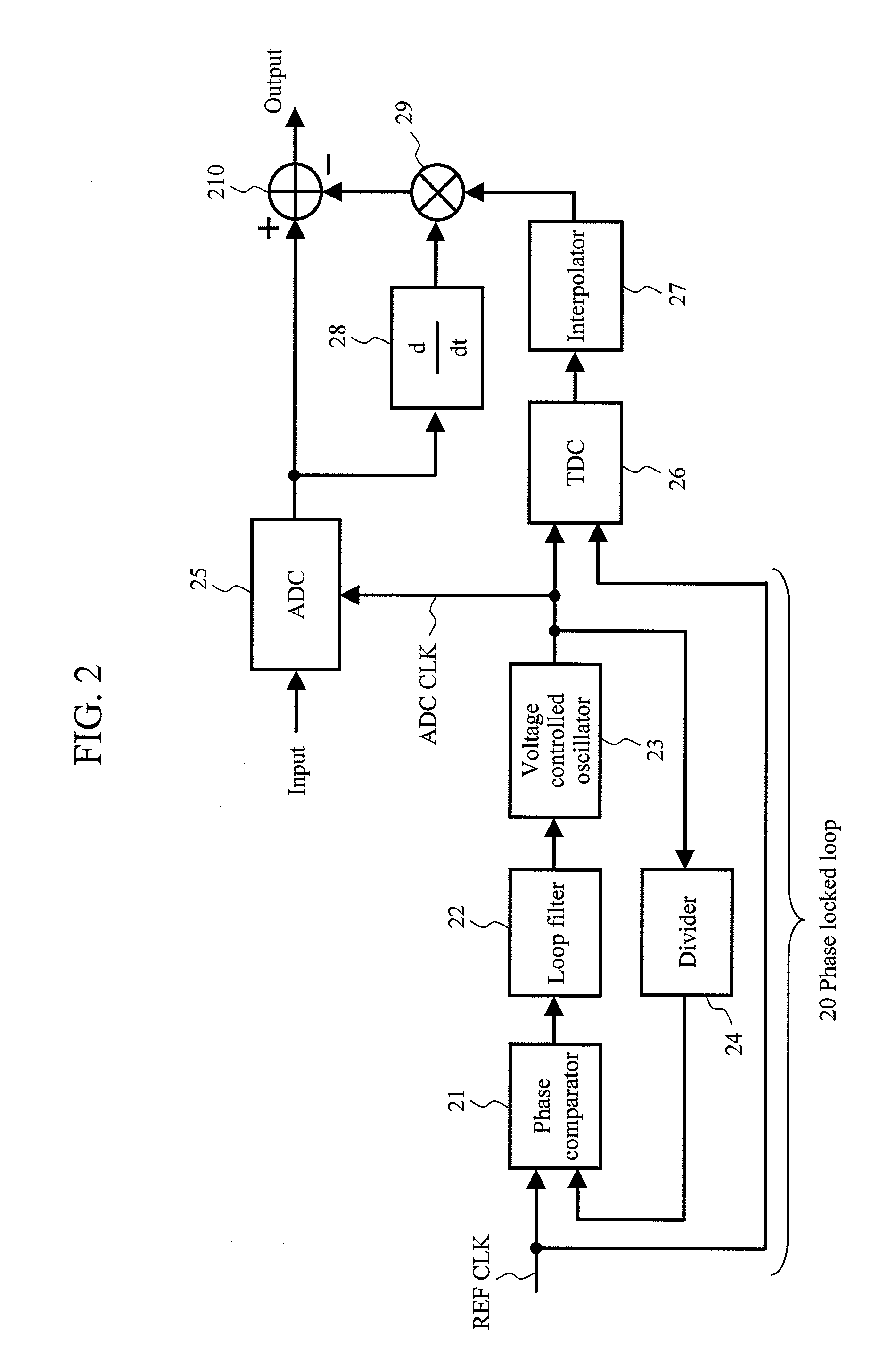

Analog-to-digital converter and wireless receiver

InactiveUS20130058437A1Electric signal transmission systemsModulated-carrier systemsLow jitterEngineering

The influence of a jitter of a sampling clock of an analog-to-digital converter is digitally corrected at low power consumption.The sampling clock of the analog-to-digital converter is generated by a phase locked loop (PLL) using a reference clock, which has a lower frequency and lower jitter than the sampling clock, as a source oscillation. A time-to-digital converter (TDC) converts a timing error at a timing where the sampling clock and the reference clock are synchronized with each other into a digital value. Incidentally, a timing error at a sampling timing where the reference clock is not present is generated by interpolating a detected timing error. Thus, a jitter value of the sampling clock at each sampling timing is obtained. A sampling voltage error is calculated from the jitter value and the output of the analog-to-digital converter is digitally corrected.

Owner:HITACHI LTD

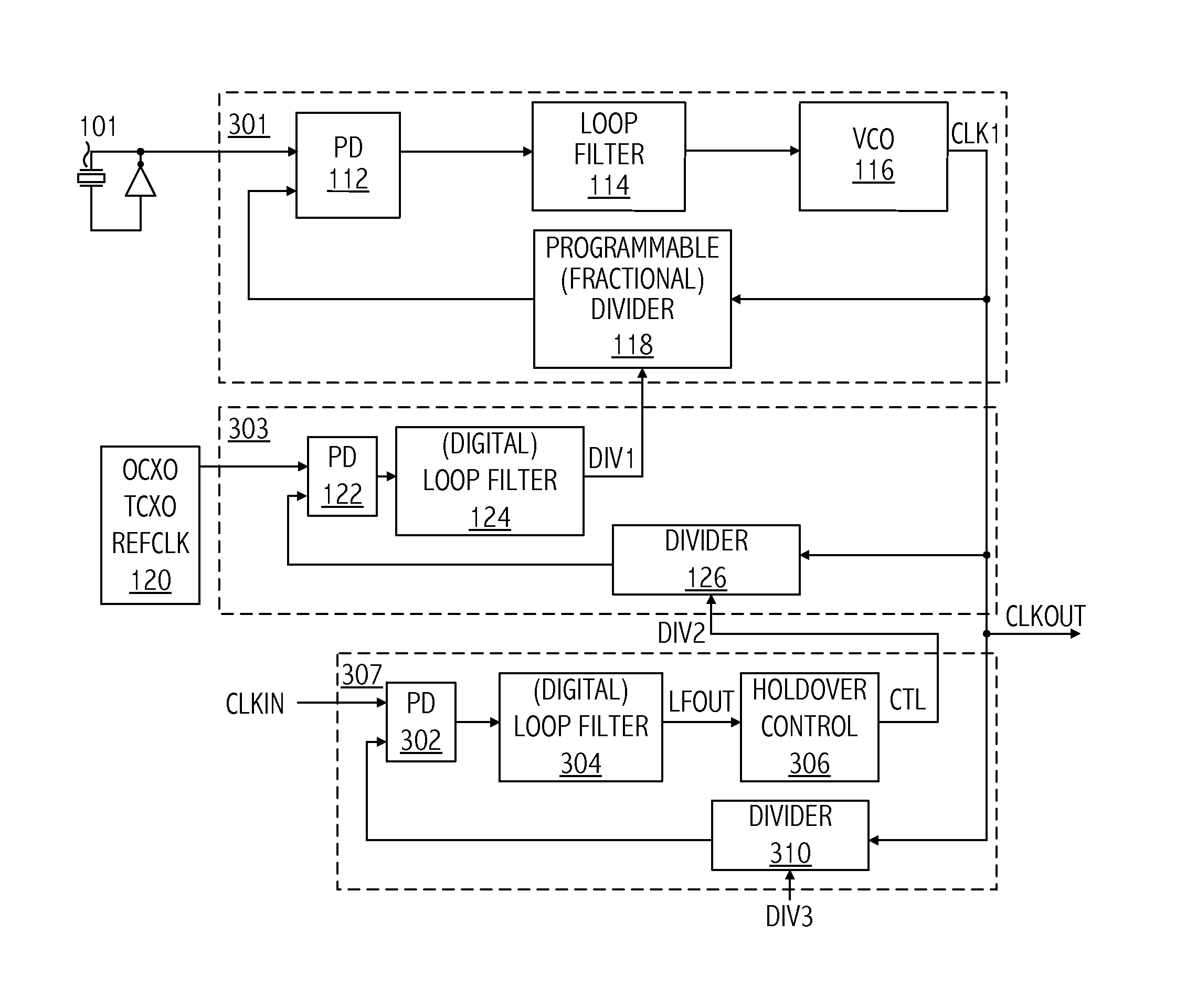

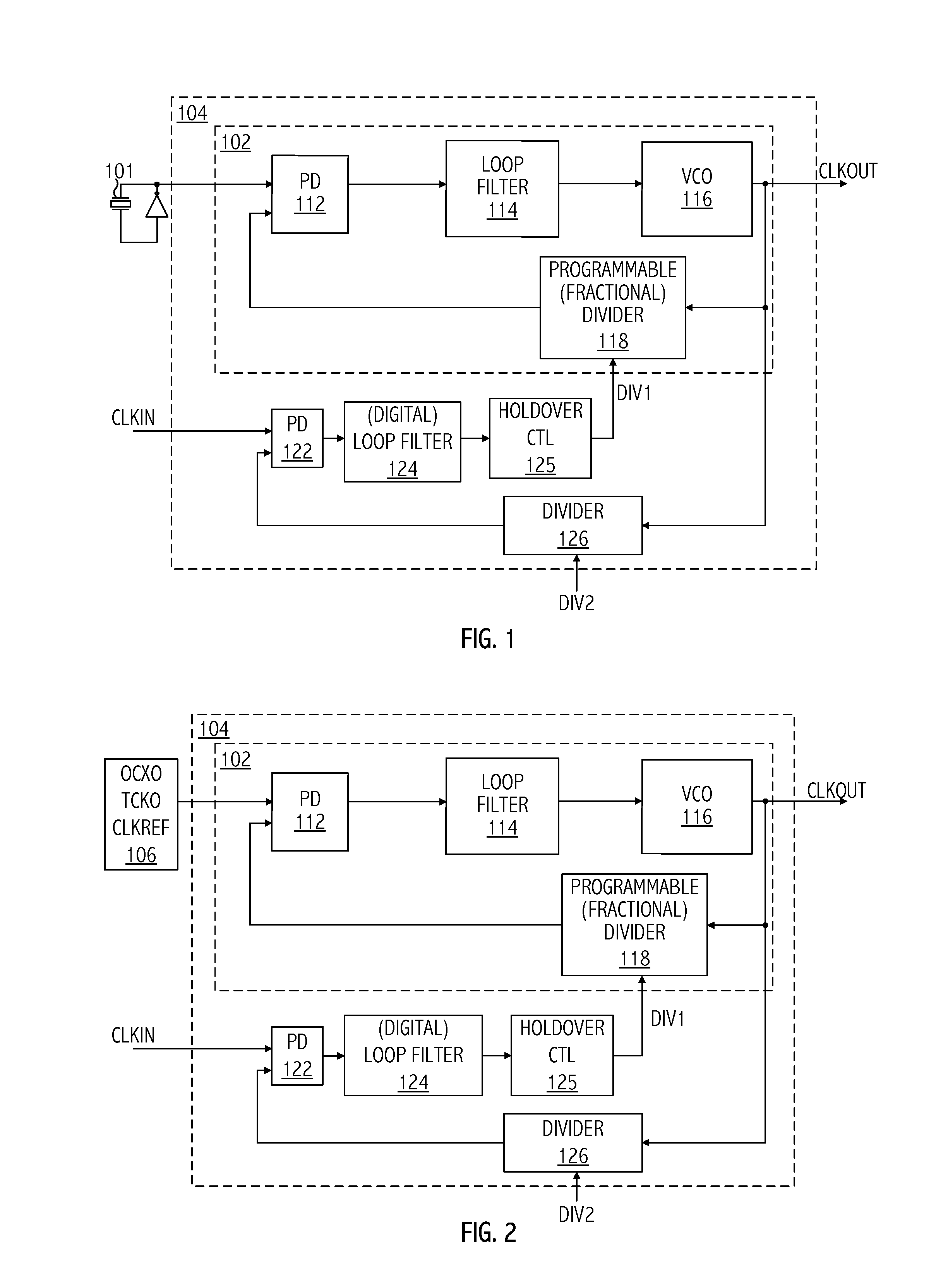

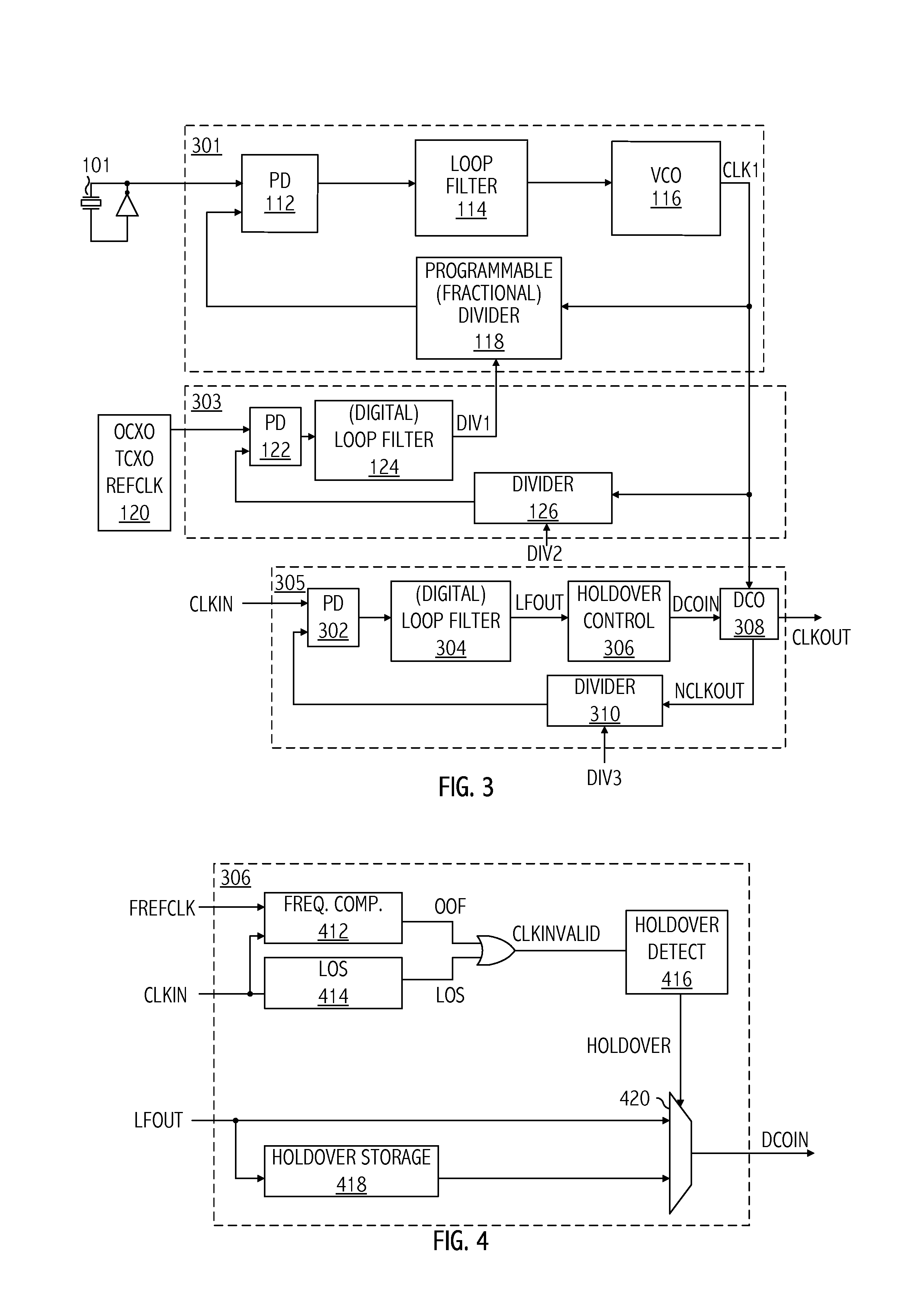

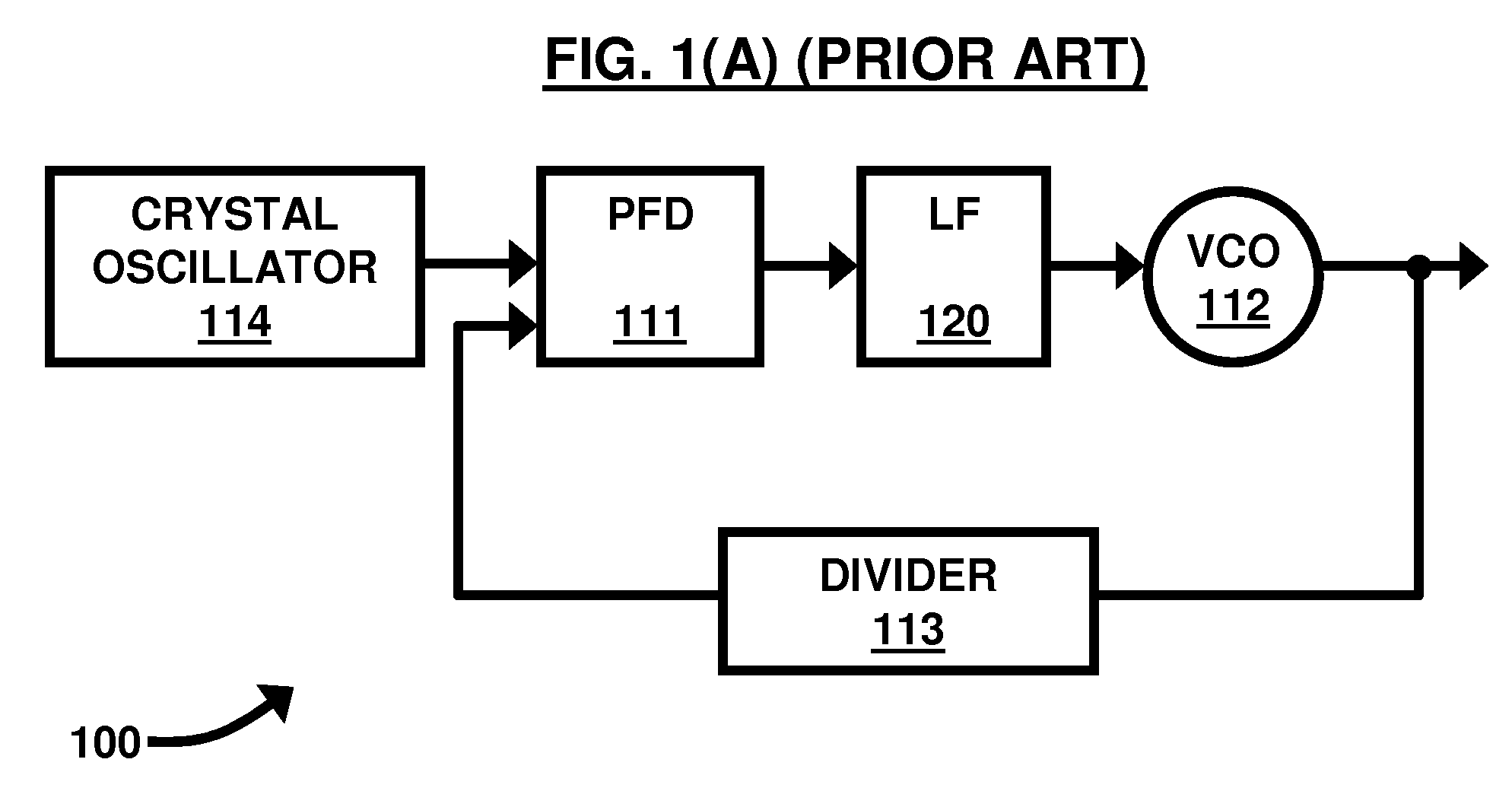

Cascaded PLL for reducing low-frequency drift in holdover mode

ActiveUS8791734B1Reduce frequency driftImproved temperature dependencePulse automatic controlAngle demodulation by phase difference detectionControl signalLow jitter

A cascaded phase-locked loop (PLL) clock generation technique reduces frequency drift of a low-jitter clock signal in a holdover mode. An apparatus includes a first PLL circuit configured to generate a control signal based on a first clock signal and a first divider value. The apparatus includes a second PLL circuit configured to generate the first clock signal based on a low-jitter clock signal and a second divider value. The apparatus includes a third PLL circuit configured to generate the second divider value based on the first clock signal, a third divider value, and a second clock signal. The low-jitter clock signal may have a greater temperature dependence than the second clock signal and the second clock signal may have a higher jitter than the low-jitter clock signal.

Owner:SKYWORKS SOLUTIONS INC

Dual phase locked loop (PLL) architecture for multi-mode operation in communication systems

InactiveUS20080317185A1Reduce adverse effectsImprove accuracyPower managementPulse automatic controlCommunications systemLow jitter

The clock generating portion of a communication system includes a low-power, high-jitter phase locked loop (PLL) and a high-power, low-jitter PLL. Control logic within the chip allows for selective switching between the low-power and high-power PLL for receiving the broadcast signals, such as mobile TV signals. The switching may occur in a manner that is dependent on the conditions of the wireless channel and / or the complexity of the modulation scheme being used. The switching may be used to provide an oscillating signal from one or both of the PLLs to a receiver to be used to receive communication signals. The control logic may power off one of the PLLs to save power when not in use.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

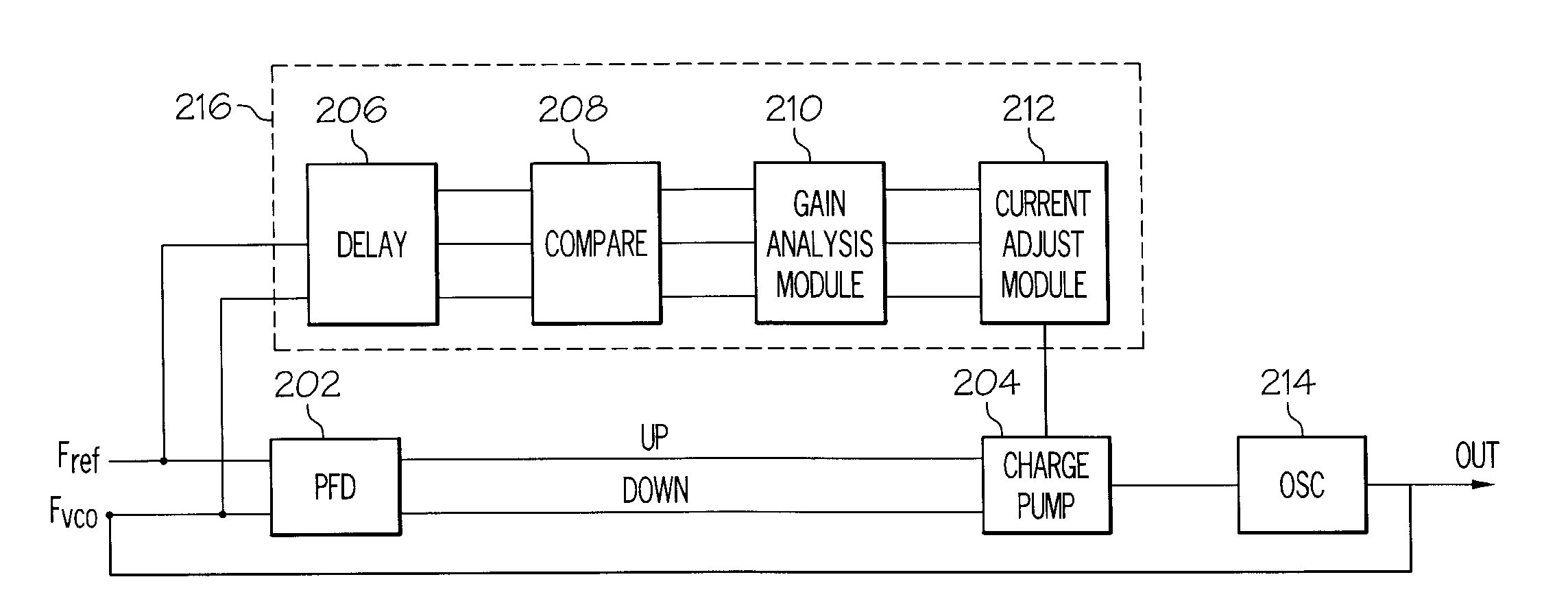

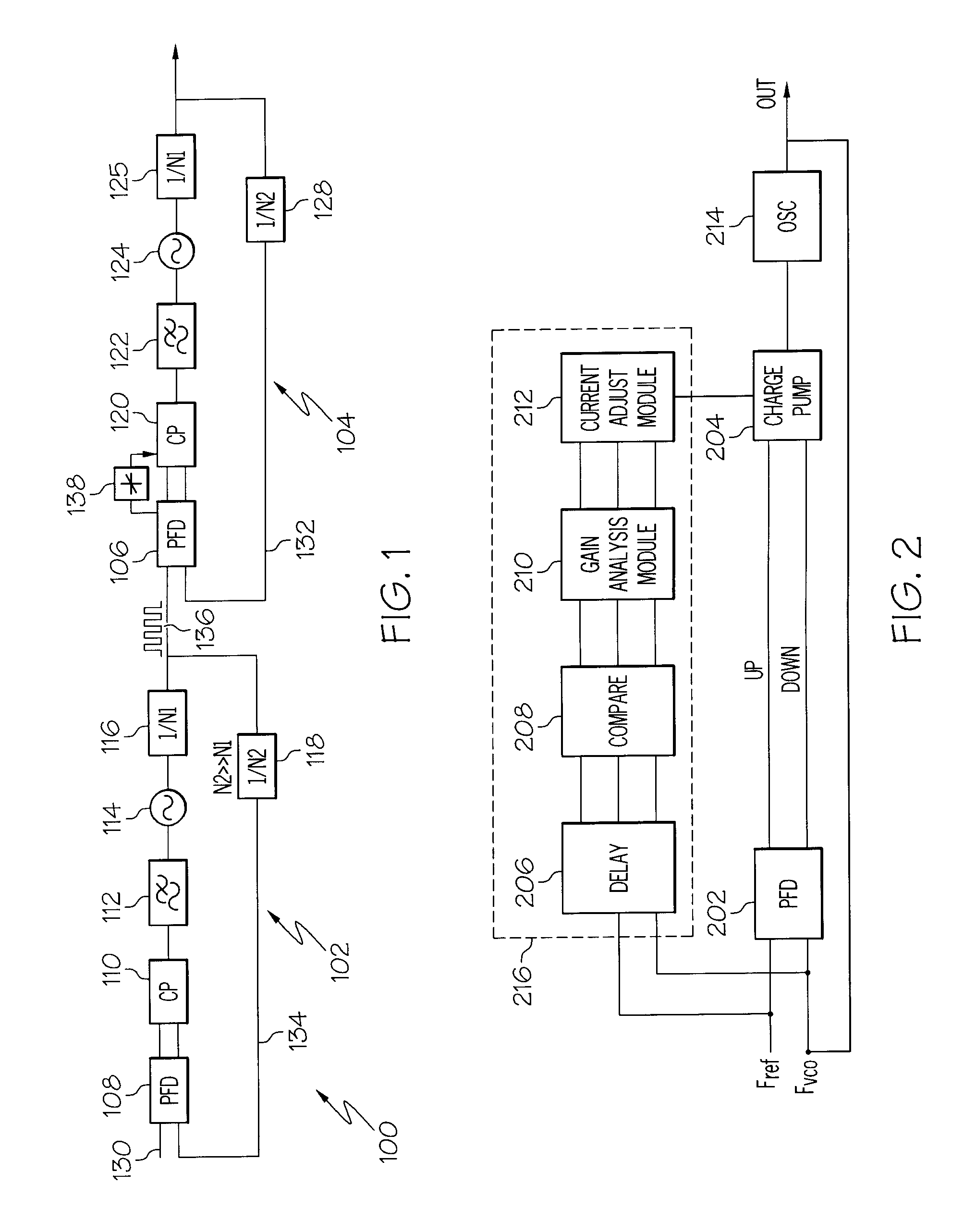

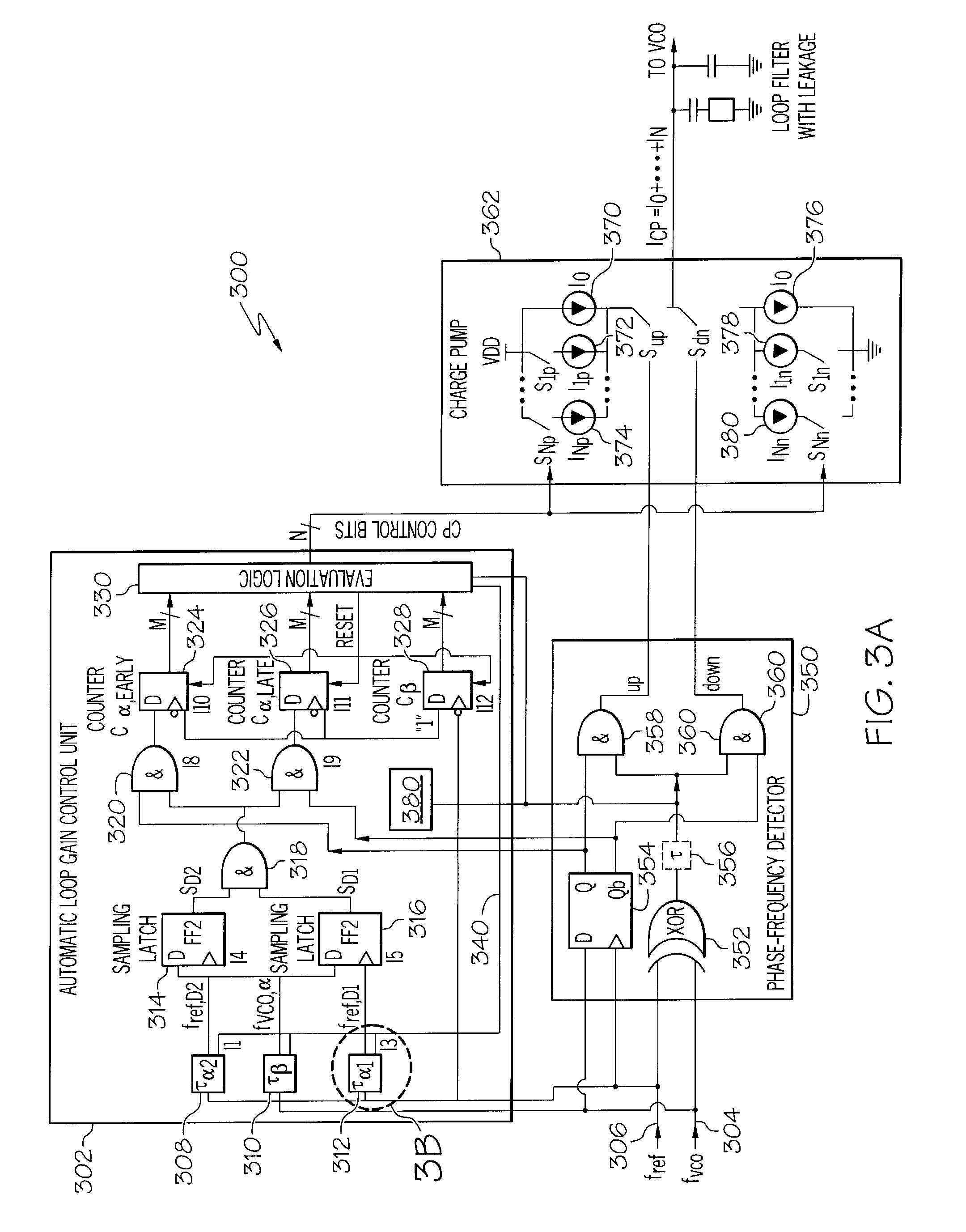

Systems and Arrangements for Controlling Phase Locked Loop

A multi-Gigahertz, low jitter phase locked loop (PLL) with adjustable gain is disclosed. In one embodiment, properties of a fVCO signal of a PLL can be acquired. Properties can include the occurrences of different types of jitter on the fVCO signal and the lock status of the PLL. A gain control module can control at least a portion of the PLL based on an analysis of the acquired properties. For example, when the loop is locked or when there is loop filter leakage, the gain of a charge pump in the PLL can be reduced. When a charge pump mismatch is detected based on the acquired properties, additional control signals can be provided to the charge pump to correct the mismatch.

Owner:IBM CORP

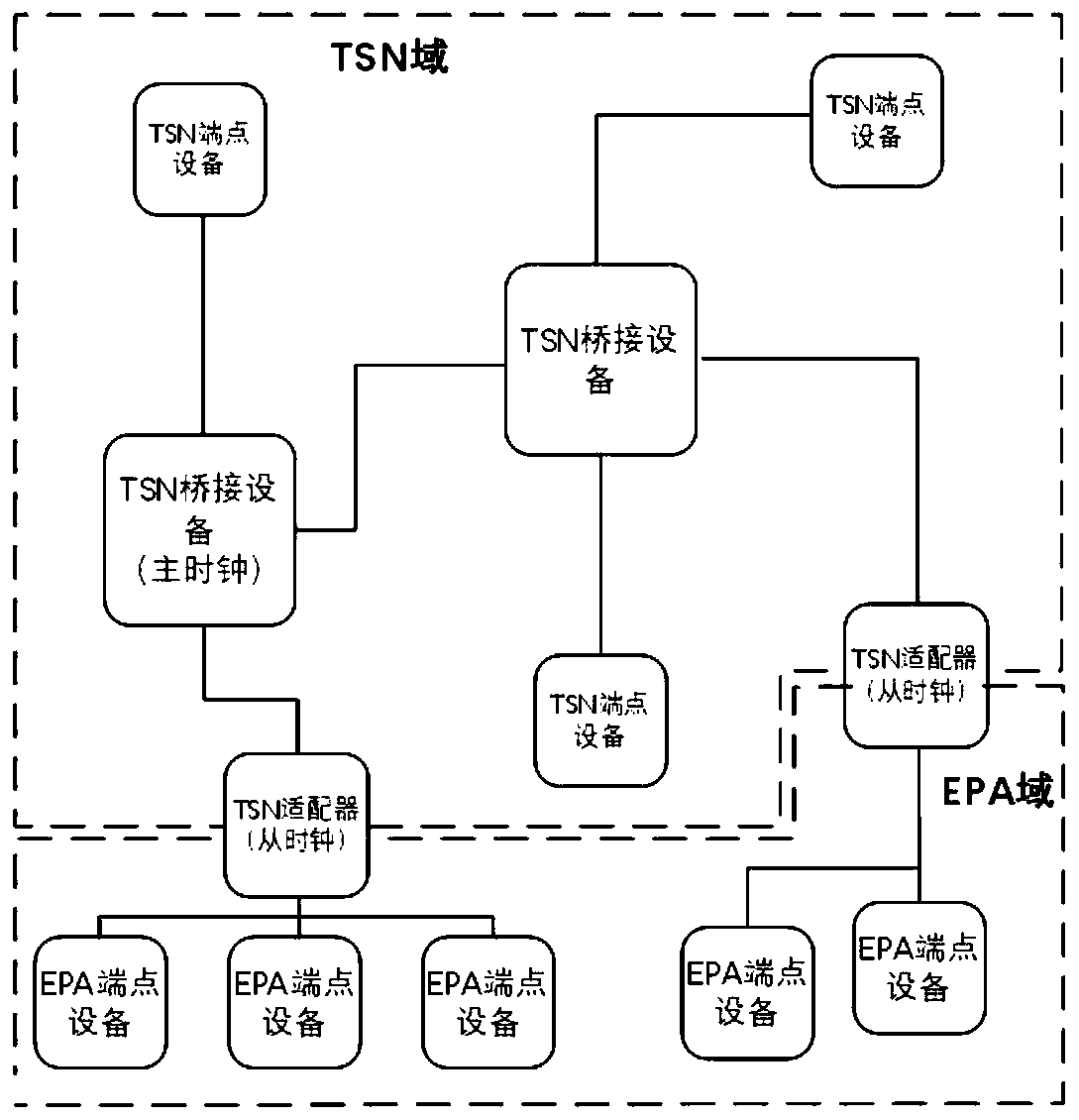

EPA industrial bus and time sensitive network adaptation system and method

ActiveCN110943899AProtect normal transmissionEfficient use ofTime-division multiplexNetworks interconnectionLow jitterLow delay

The invention relates to an EPA industrial bus and time sensitive network adaptation system and method, solves the technical problem that an EPA Ethernet cannot be connected with a time sensitive network in real time to construct a fast channel, and comprises an EPA endpoint device and a TSN endpoint device. The EPA endpoint device is in communication connection with a TSN bridging device througha TSN adapter, and the TSN bridging device is connected with the TSN endpoint device; the TSN adapter receives the time data issued by the main clock from the TSN bridging device, and adds a timestampin the process of receiving or transmitting the clock synchronization data to complete clock synchronization; and the TSN bridging device is used for providing time synchronization, low delay, low jitter and flow bandwidth guarantee, so that the problem is better solved, and the method can be applied to the EPA industrial technology.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

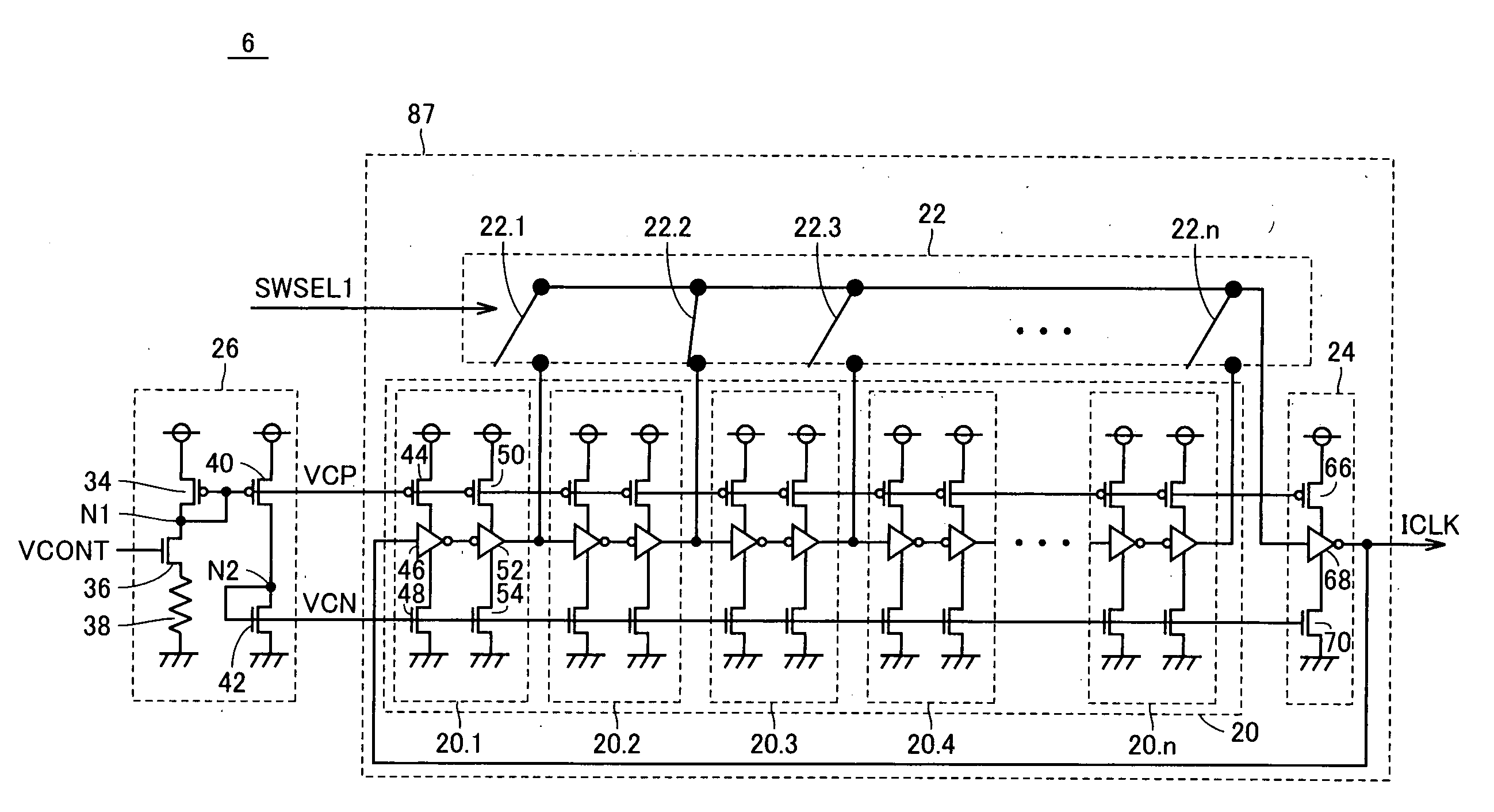

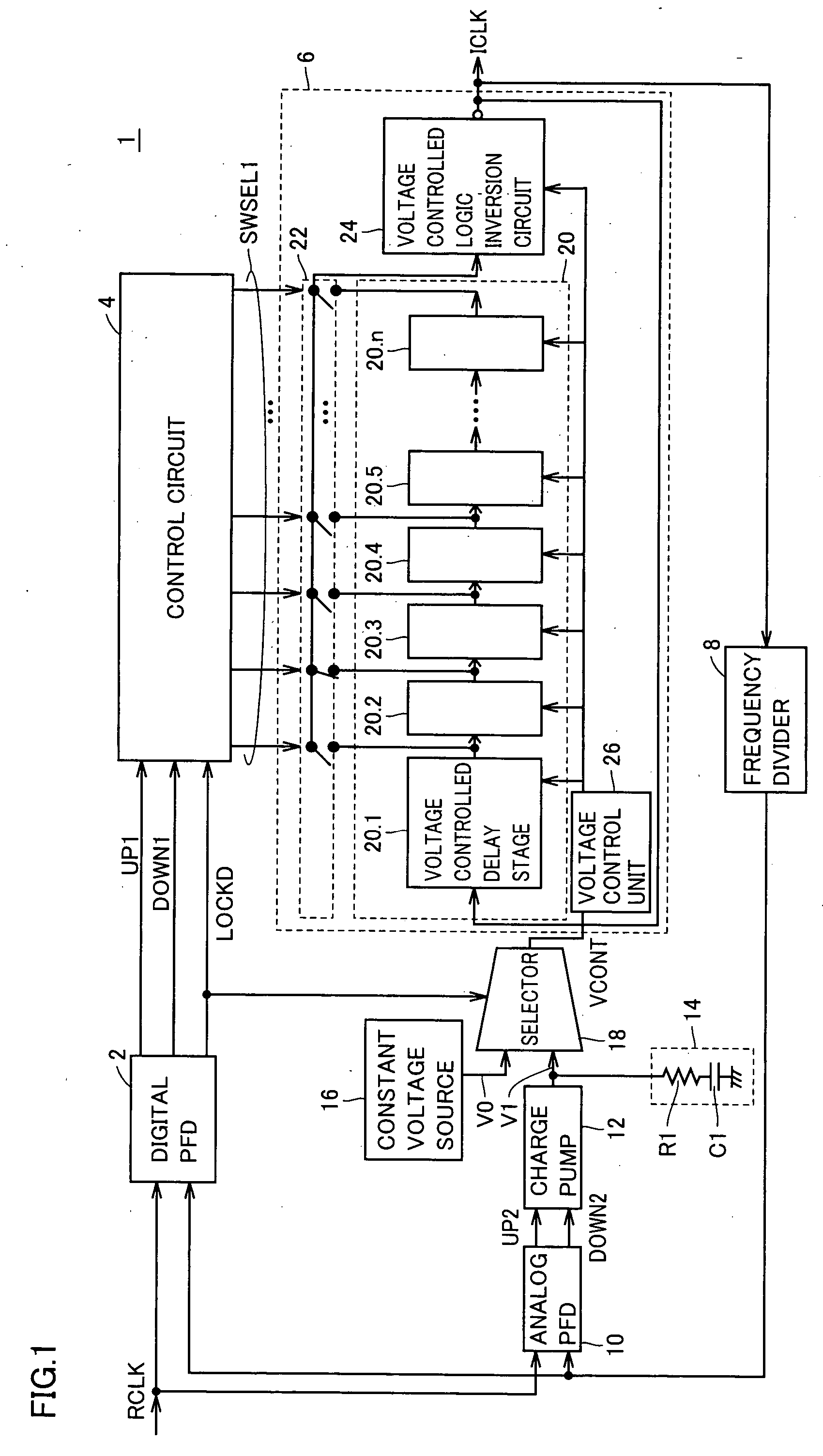

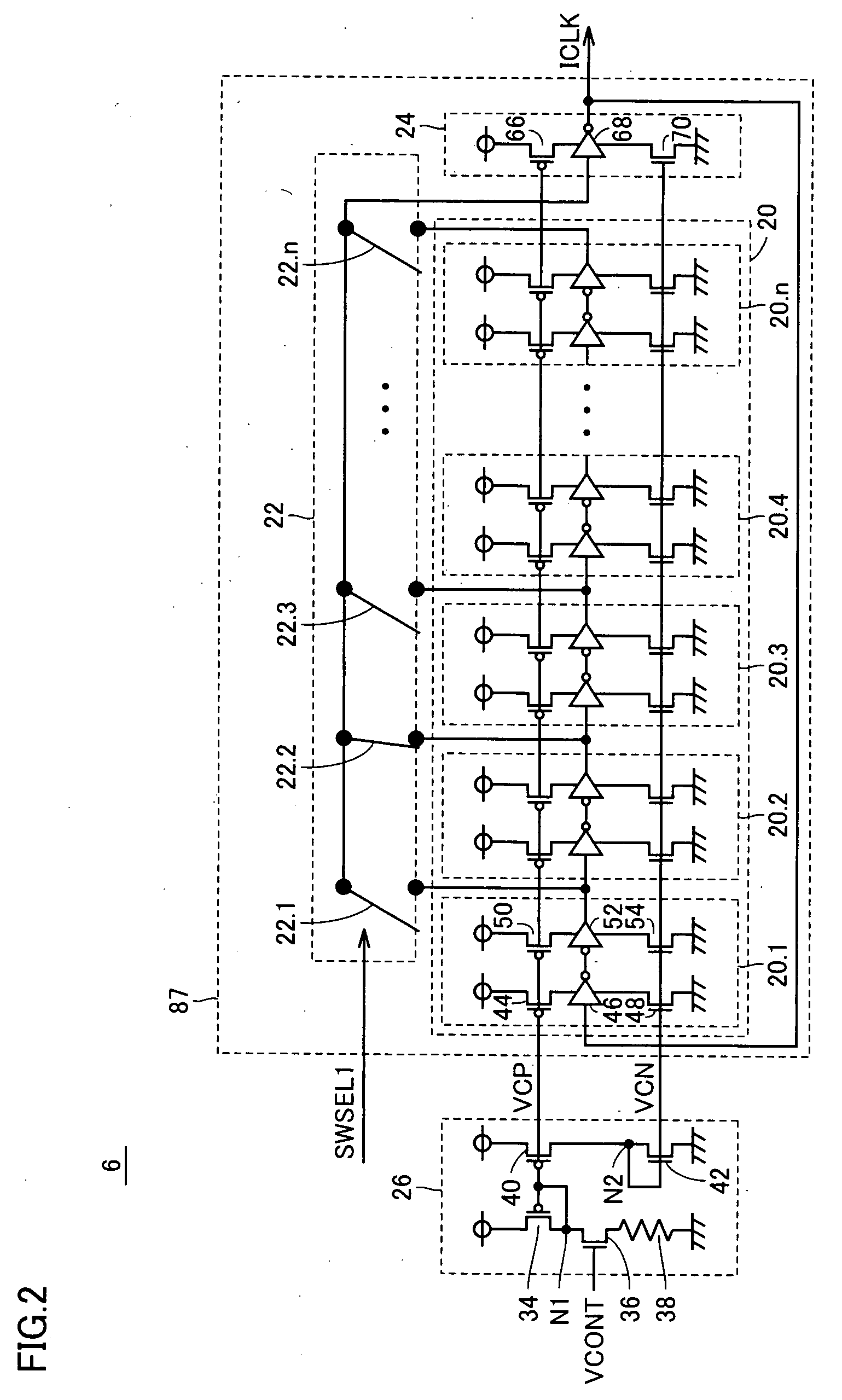

Synchronous clock generation circuit capable of ensuring wide lock-in range and attaining lower jitter

InactiveUS20050046497A1Wide lock-in rangeImprove jitter characteristicsPulse automatic controlPulse generation by logic circuitsLow jitterEngineering

At a first step, in a synchronous clock generation circuit, the number of delay stages serving as a digital PLL circuit is increased / decreased, and an oscillation circuit performs an oscillation operation when an optimal number of delay stages is set. Thereafter, in an operation at a second step, a control voltage is controlled with the optimal number of delay stages being set for serving as an analog PLL circuit, thereby attaining a lock-in state. As the lock-in state is finally maintained under analog control, an excellent jitter characteristic can be obtained. Thus, ensuring a lock-in range that has been a problem in the analog PLL circuit is solved by varying the number of delay stages in the operation at the first step, and a high jitter characteristic that has been a problem in a digital PLL circuit can be solved by analog control in the operation at the second step.

Owner:RENESAS TECH CORP

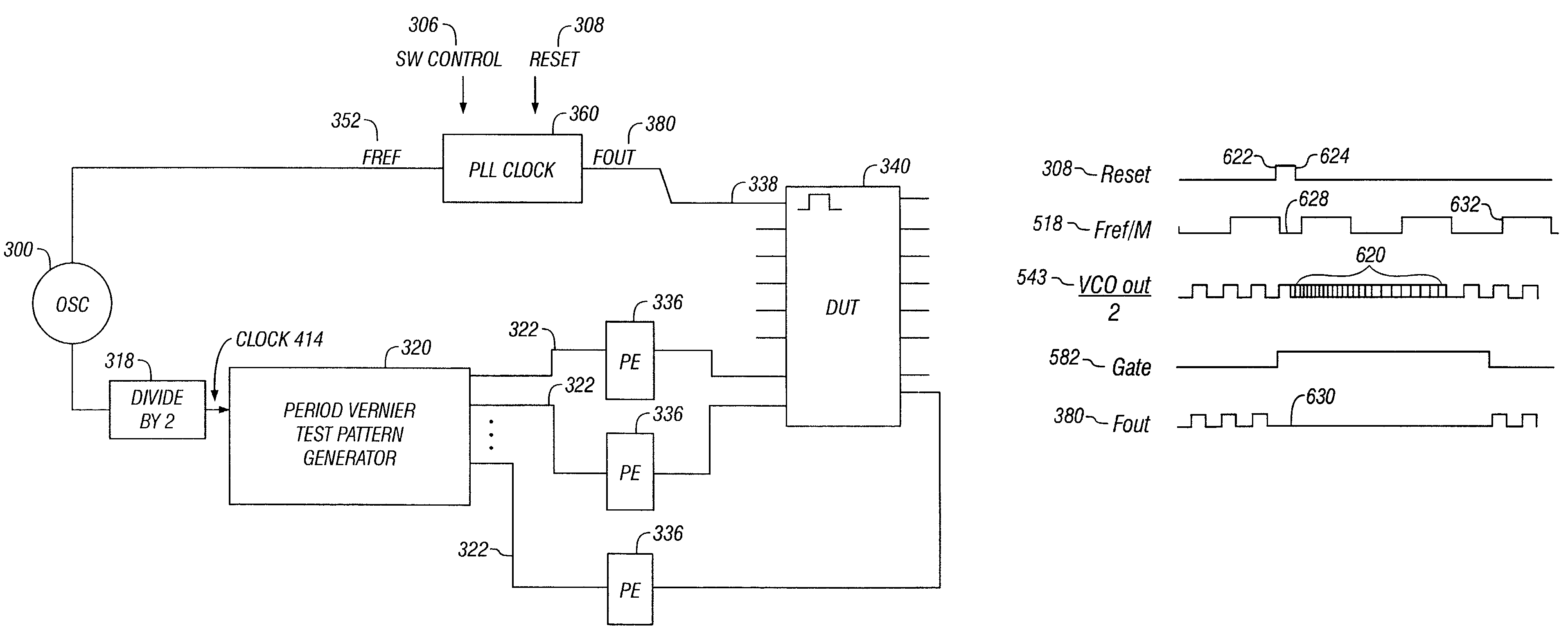

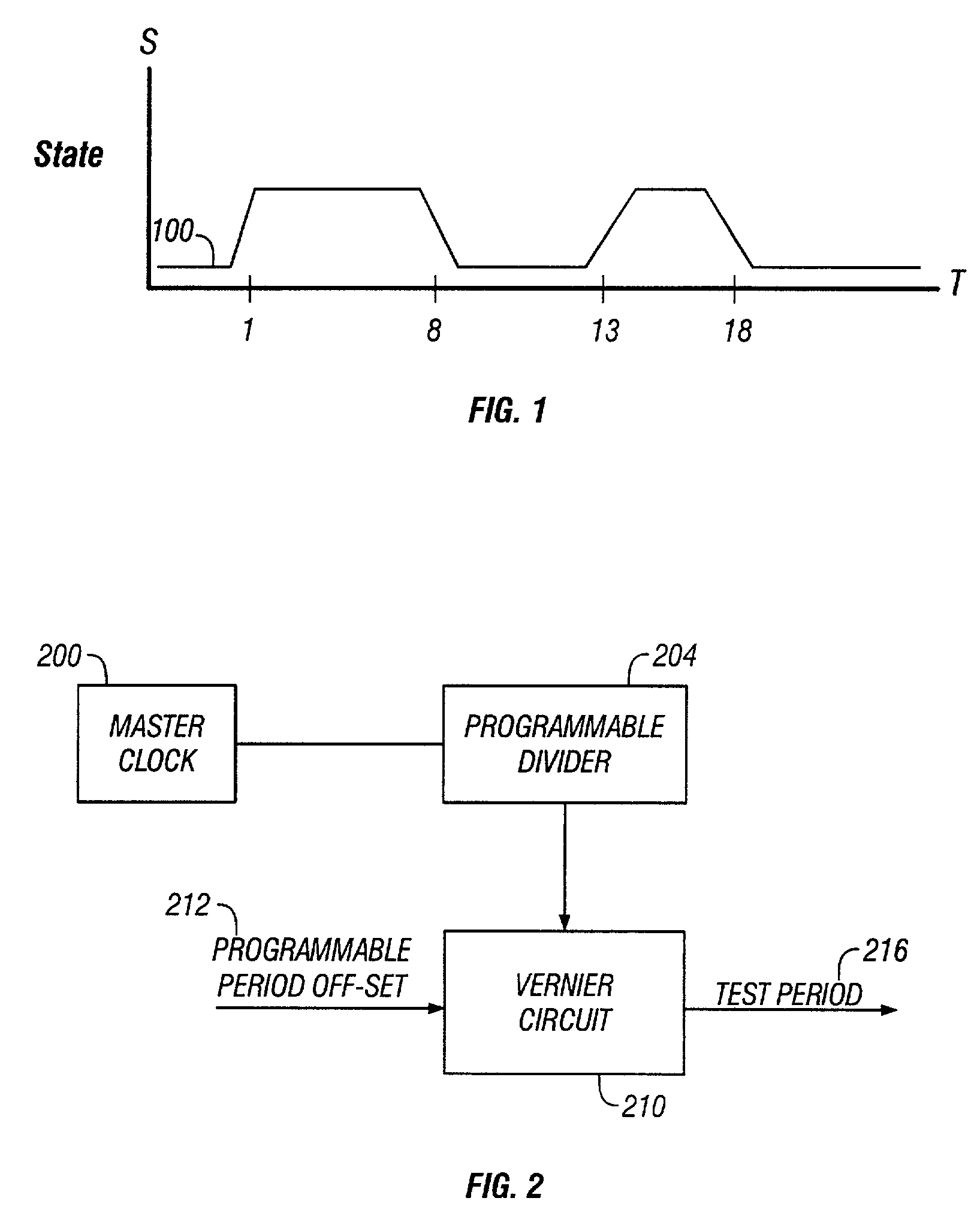

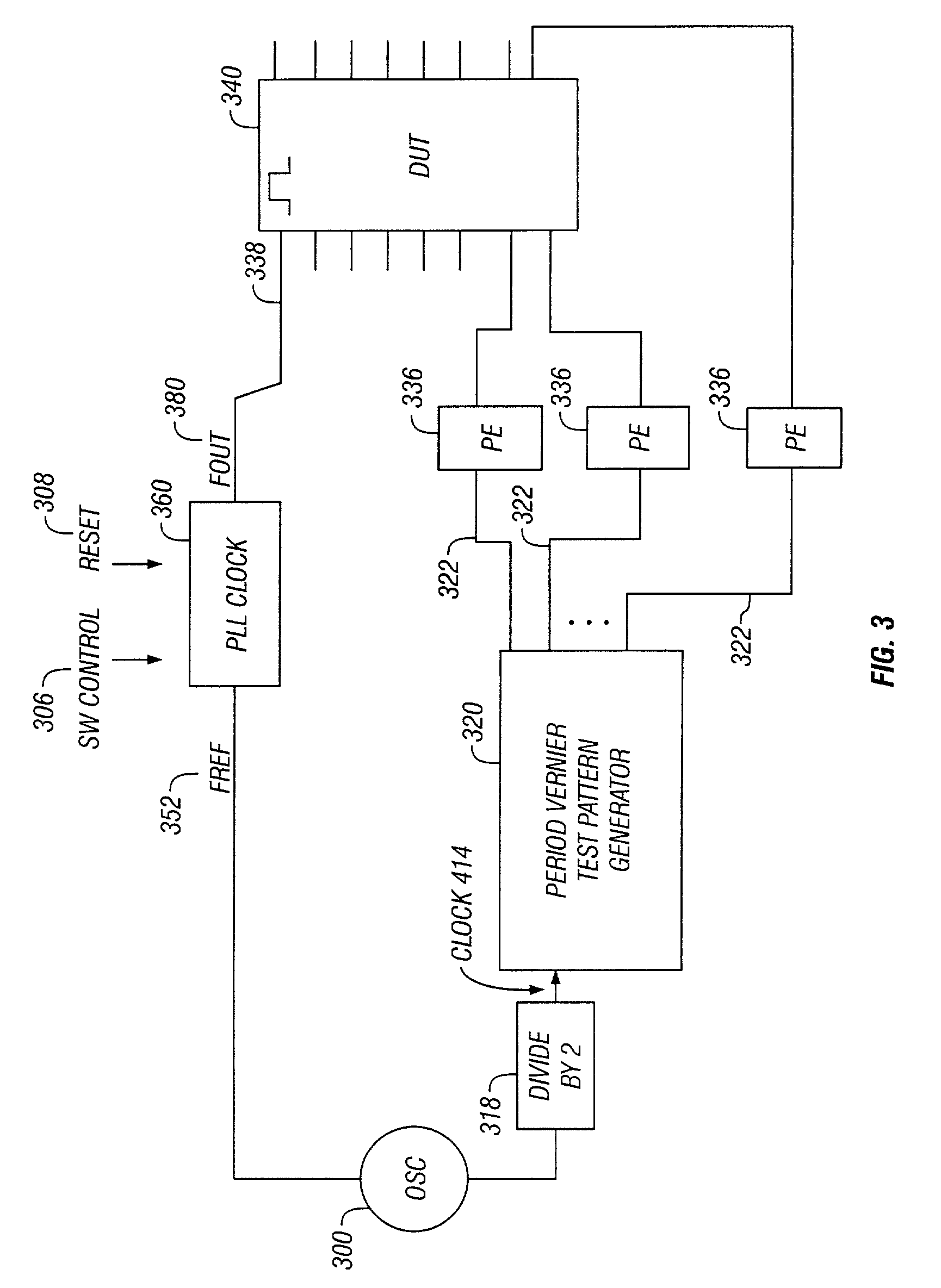

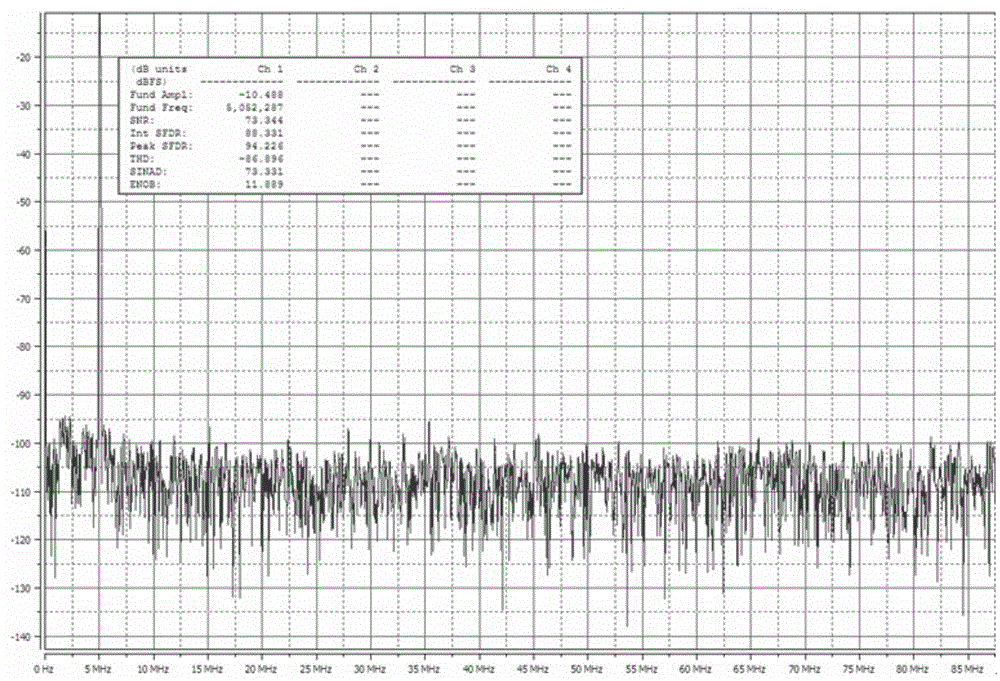

Low-jitter clock for test system

InactiveUS7093177B2Easy to moveOptimize timingDigital circuit testingError detection/correctionLow jitterEngineering

Generating test signals for a device under test (DUT) involves generating a master reference signal, using a vernier technique to generate test pattern signals based on the master reference signal, generating a test clock signal that is phase-matched with and frequency similar to the test pattern signals by providing the master reference signal as input to a phase-locked loop (PLL) and controlling one or more programmable dividers in the PLL to adjust the test clock signal to be a multiple or sub-multiple of a frequency of the test pattern signals, applying the test clock signal to the clock input pin of the DUT, and applying the test pattern signals to data pins of the DUT. When the frequency of the test pattern signals is changed, the test clock signal frequency may be adjusted to calibrate to the changed frequency of the test pattern signals by re-programming the programmable dividers.

Owner:SCHLUMBERGER TECH CORP

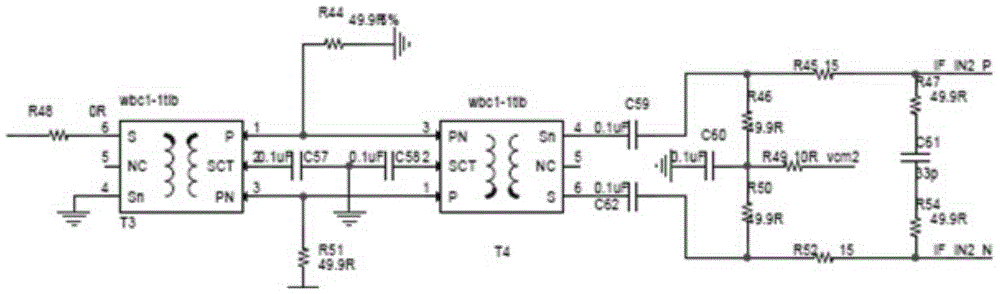

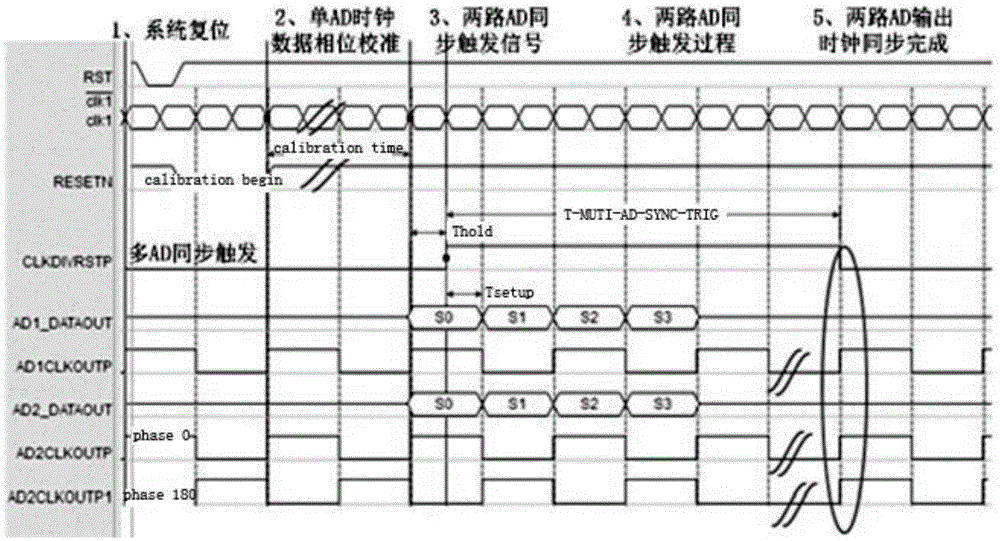

Field programmable gate array (FPGA) based high-speed analog-digital converter (ADC) synchronous acquisition system

InactiveCN104980156AWide applicabilityImprove synchronicityAnalogue-digital convertersPhysical parameters compensation/preventionLow noiseDigital down converter

The invention relates to a field programmable gate array (FPGA) based high-speed analog-digital converter (ADC) synchronous acquisition system, comprising an FPGA based signal processing platform and a high-speed ADC synchronous acquisition daughter board. A clock signal for ADC acquisition, a control signal and date collected by the ADC on the high-speed ADC synchronous acquisition daughter board are transmitted to the FPGA based signal processing platform, and the FPGA based signal processing platform performs subsequent signal processing; the high-speed ADC synchronous acquisition daughter board comprises an ultralow jitter synchronous clock generation circuit, a power supply module, and a plurality of high-speed ADC acquisition circuits; and the front end of each high-speed ADC acquisition circuit is connected with a broadband signal conditioning circuit. Synchronous sampling is performed on the ADC between different channels through a multichannel ADC synchronization technology; the ultralow jitter synchronous clock generation circuit generates multichannel low jitter clocks meeting high-speed ADC signal to noise ratio and synchronism requirements; due to adoption of the two-stage alternating current coupling broadband signal conditioning circuit, the high-speed ADC acquisition circuit can collect middle frequency signals with input frequency between 10kHz and 700MHz; and the power supply module adopts a low noise power supply design.

Owner:PANDA ELECTRONICS GROUP +1

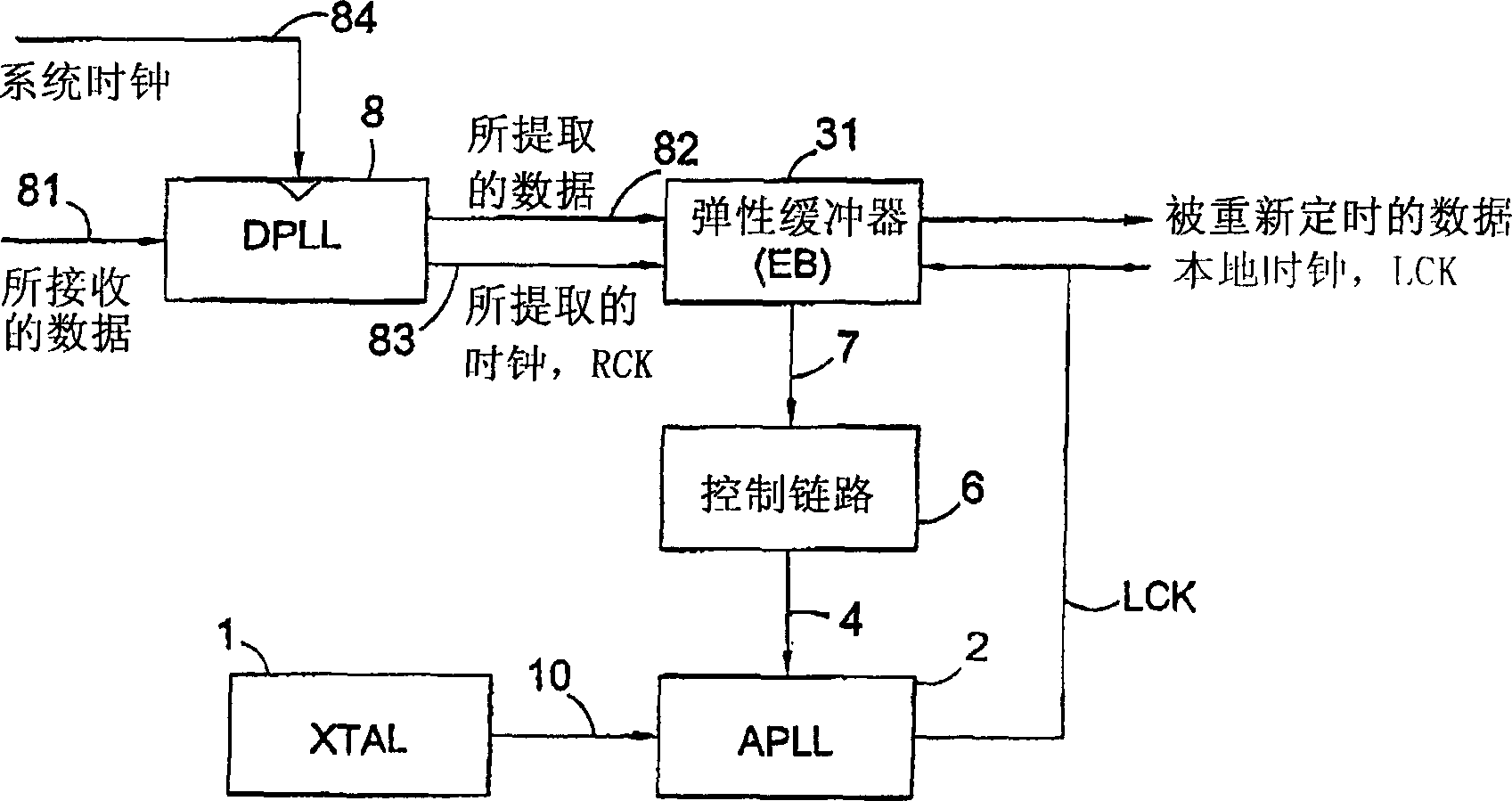

Clock synchronizer and clock and data recovery apparatus and method

A clock synchroniser, and clock and data recovery apparatus incorporating the clock synchroniser, are described, together with corresponding clock synchronisation methods. The clock synchroniser incorporates an elastic buffer. A received clock signal RCK is used to clock data into the buffer, and a locally generated clock LCK is used to clock data out of the buffer. The local clock is synthesised using a PLL, and a fill-level signal from the elastic buffer is used to control to local clock frequency to maintain a desired average quantity of data in the buffer, thereby achieving synchronisation of the received and local clocks. In preferred embodiments the fill-level signal is used to control a variable divider in the feedback path of the PLL, which is supplied with a highly stable reference signal. A synchronised, and low-jitter local clock is thus produced. Preferably, the elastic buffer employs counters of relatively wide word width, and a storage array of much reduced depth, read and write pointers being provided by just a few of the least significant bits of the words.

Owner:CIRRUS LOGIC INT SEMICON

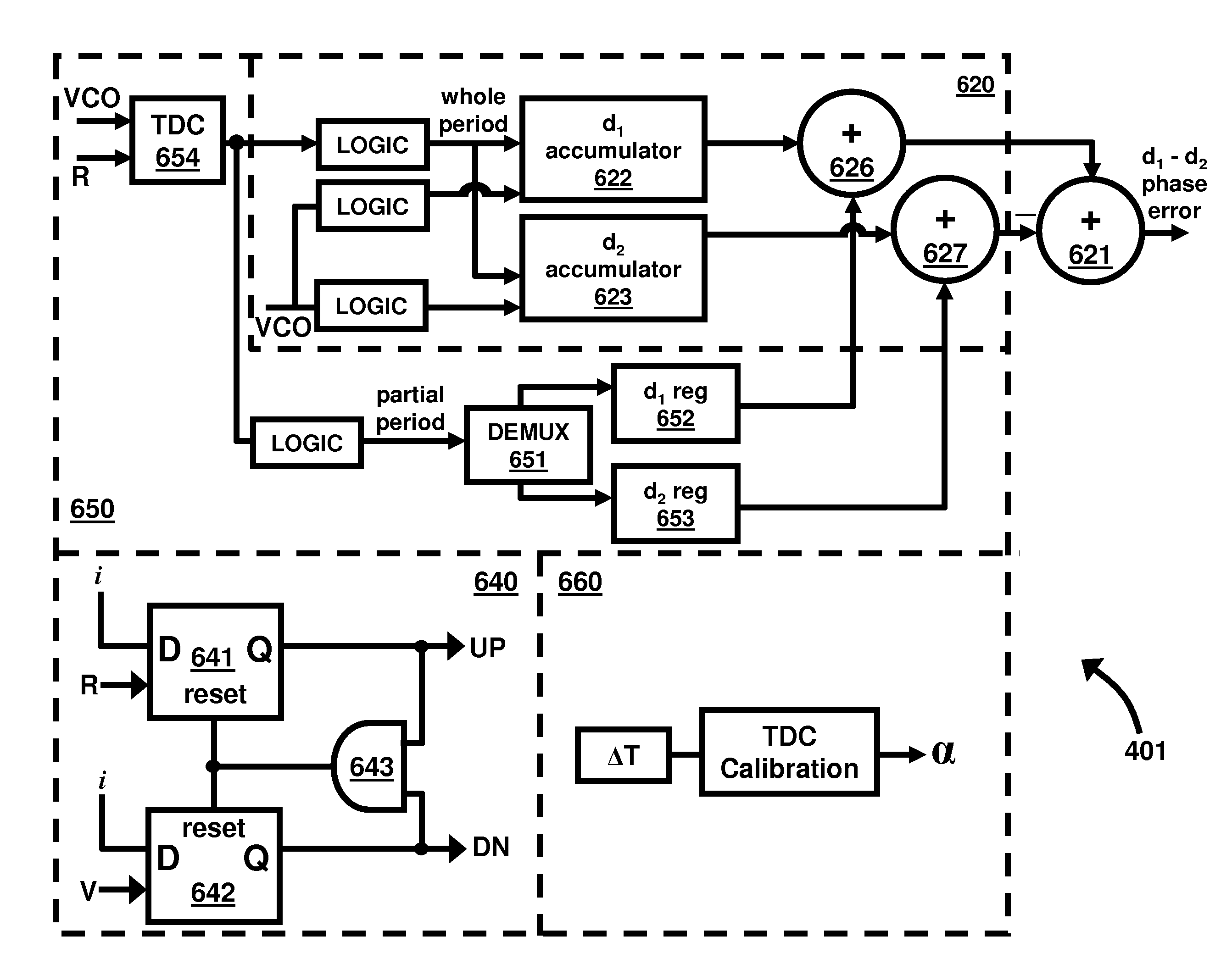

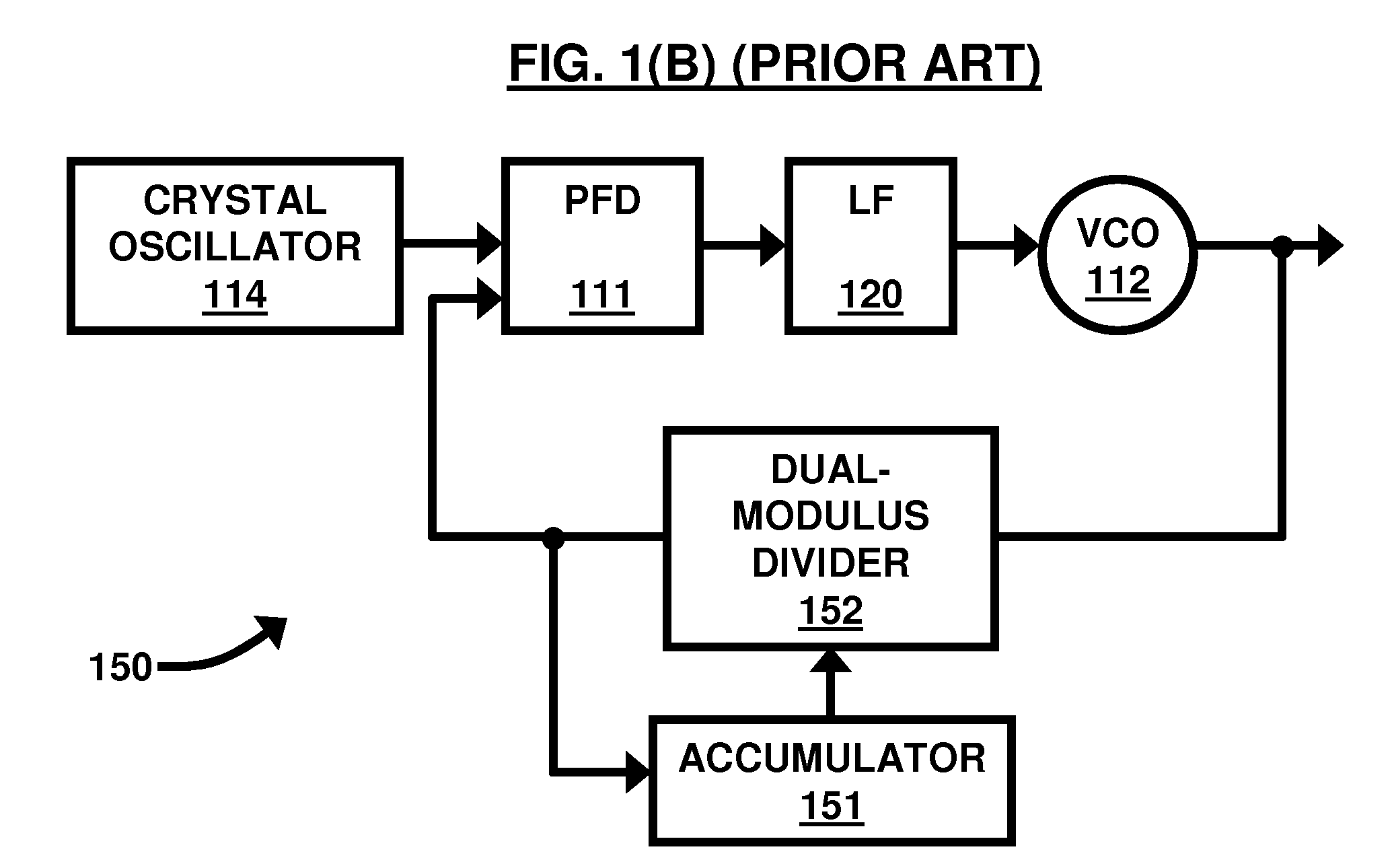

Low-power, low-jitter, fractional-N all-digital phase-locked loop (PLL)

ActiveUS7365607B2Pulse automatic controlAngle demodulation by phase difference detectionLoop filterReference Period

A method for synthesizing frequencies with a low-jitter an all-digital fractional-N phase-locked loop (PLL) electronic circuit adapted to synthesize frequencies with low-jitter, wherein the electronic circuit comprises a digital phase-frequency detector (DPFD) operatively connected to a digital loop filter (DLF), wherein the DPFD adapted to receive a reference signal and a feedback signal; compare a phase and frequency of the reference and feedback signals to determine a phase and frequency error between the reference and feedback signals; and provide a DPFD output comprising a multi-bit output; wherein the DLF is adapted to receive and filter the DPFD output and provide a DLF output, and wherein the DLF output is updated at each reference period.

Owner:ATMEL CORP

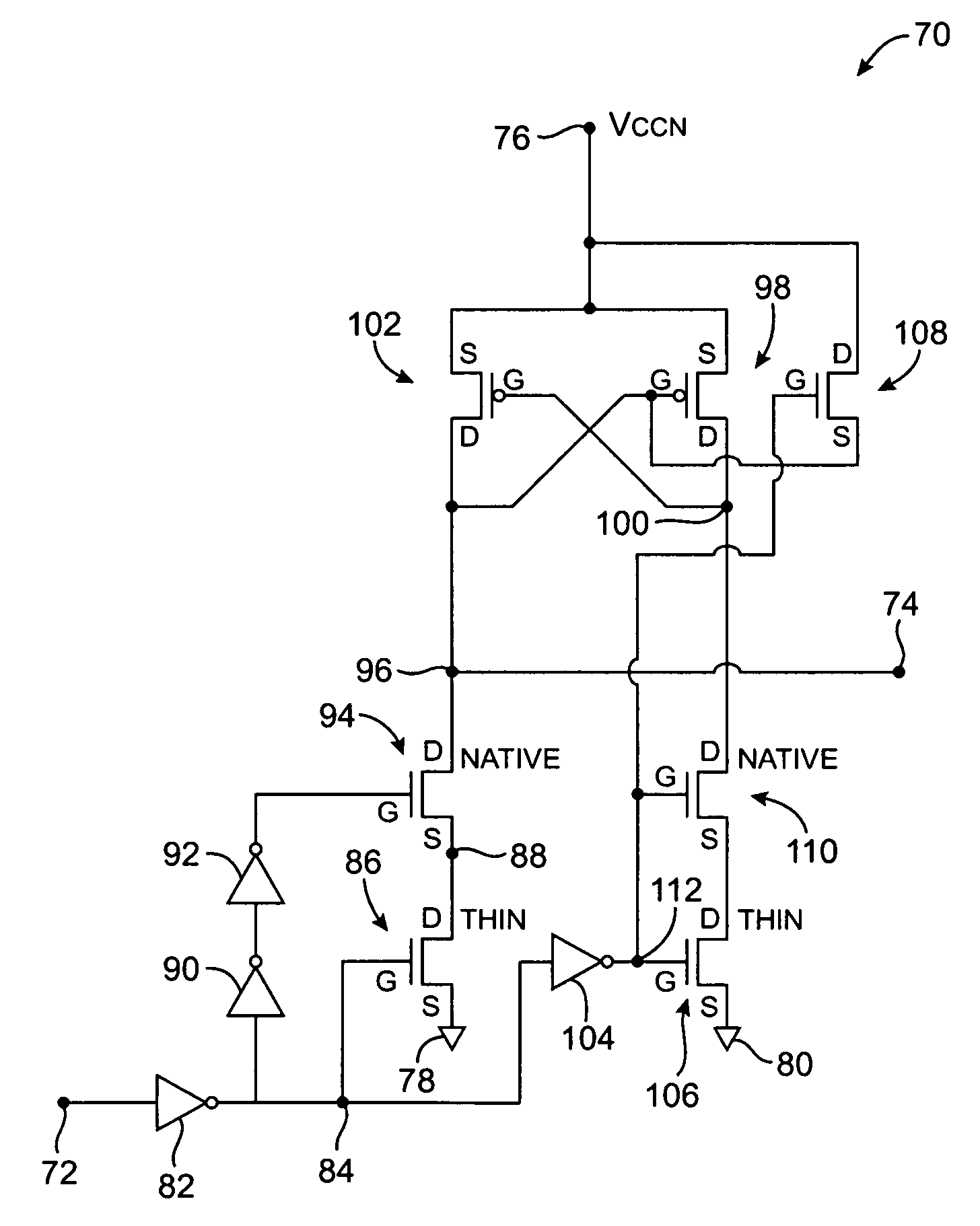

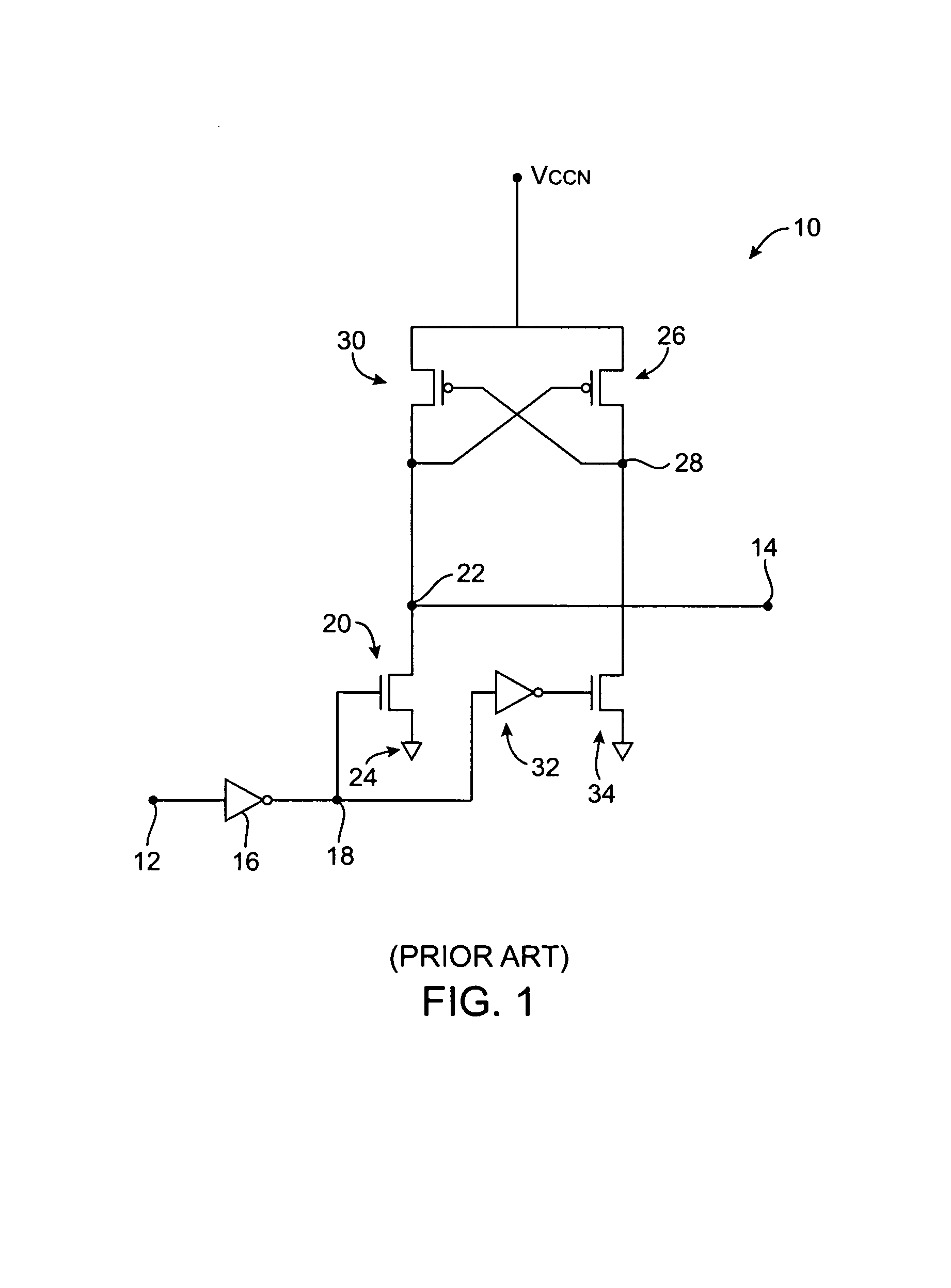

Low-jitter adjustable level shifter with native devices and kicker

InactiveUS7180329B1Reduce jitterFast switching speedElectric pulse generatorLogic circuit coupling/interface arrangementsData terminalThin oxide

An adjustable level shifter with native and kicker transistors is provided. The level shifter provides high switching speeds, adjustable output voltage levels, and low jitter. The level shifter has first and second thick-oxide p-channel metal-oxide-semiconductor (PMOS) transistors, first and second thick-oxide native n-channel metal-oxide-semiconductor (NMOS) transistors, and first and second thin-oxide NMOS transistors. The first PMOS transistor, first native transistor, and first NMOS transistor are connected in series and the second PMOS transistor, second native transistor, and second NMOS transistor are connected in series. An input data signal and an inverted version of the input data signal drive the gates of the thin-oxide NMOS transistors. A node located between the first PMOS transistor and first native transistor is connected to an output data terminal. The kicker transistor is connected in parallel with the first PMOS transistor.

Owner:ALTERA CORP

Network connection device

InactiveUS7453885B2Time-division multiplexData switching by path configurationLow jitterNetwork connectivity

A network connection device bridges a first network that uses a negotiated packet delivery scheduling scheme and a second network that uses an empirically determined packet delivery scheduling scheme. The network connection device translates a request to communicate over the first network into a request to communicate over the second network, thus bridging the two networks. The negotiated packet delivery scheduling scheme permits endpoints to negotiate scheduled delivery times for packets, while the empirically determined packet delivery scheme tests various time interval locations in a network to determine favorable time locations for transmission. The two protocols are bridged by finding compatible overlaps between time interval locations in the two networks. This can provide error-free delivery with low jitter among packets.

Owner:RIVULET COMM INC

Ring oscillator delta sigma ADC modulator with replica path nonlinearity calibration

An embodiment provides a continuous-time delta-sigma modulator for analog-to-digital conversion. The modulator includes a signal path generating including a ring voltage controlled oscillator driven by an analog input signal. The signal path produces digital values by sampling the ring voltage controlled oscillator. A calibration circuit measures nonlinear distortion coefficients in a replica of the signal path. A nonlinearity corrector corrects the digital values based upon determined nonlinear distortion coefficients. Preferred embodiment ADC ΔΣ modulators do not require any analog integrators, feedback DACs, comparators, or reference voltages, and do not require a low jitter clock.

Owner:RGT UNIV OF CALIFORNIA

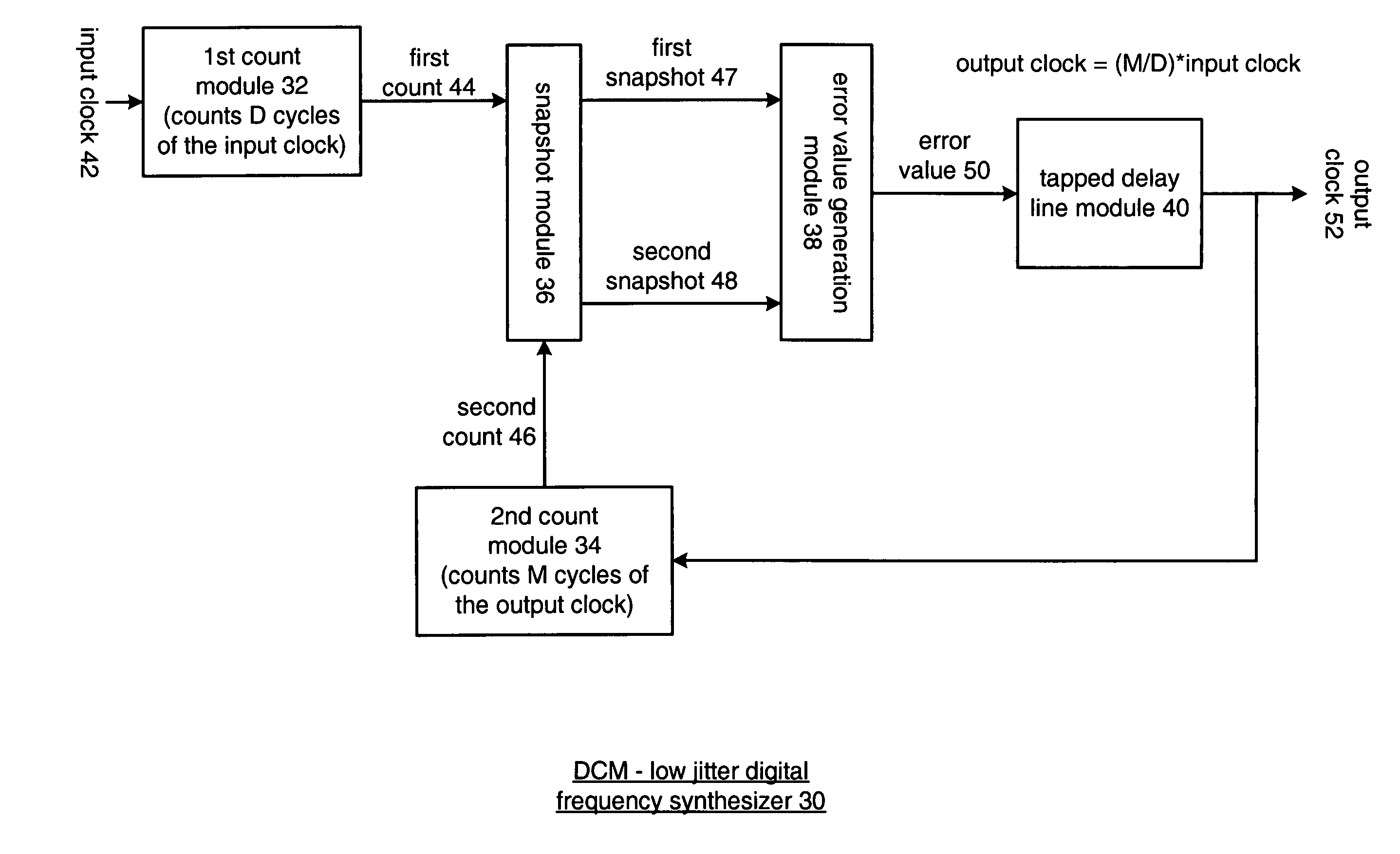

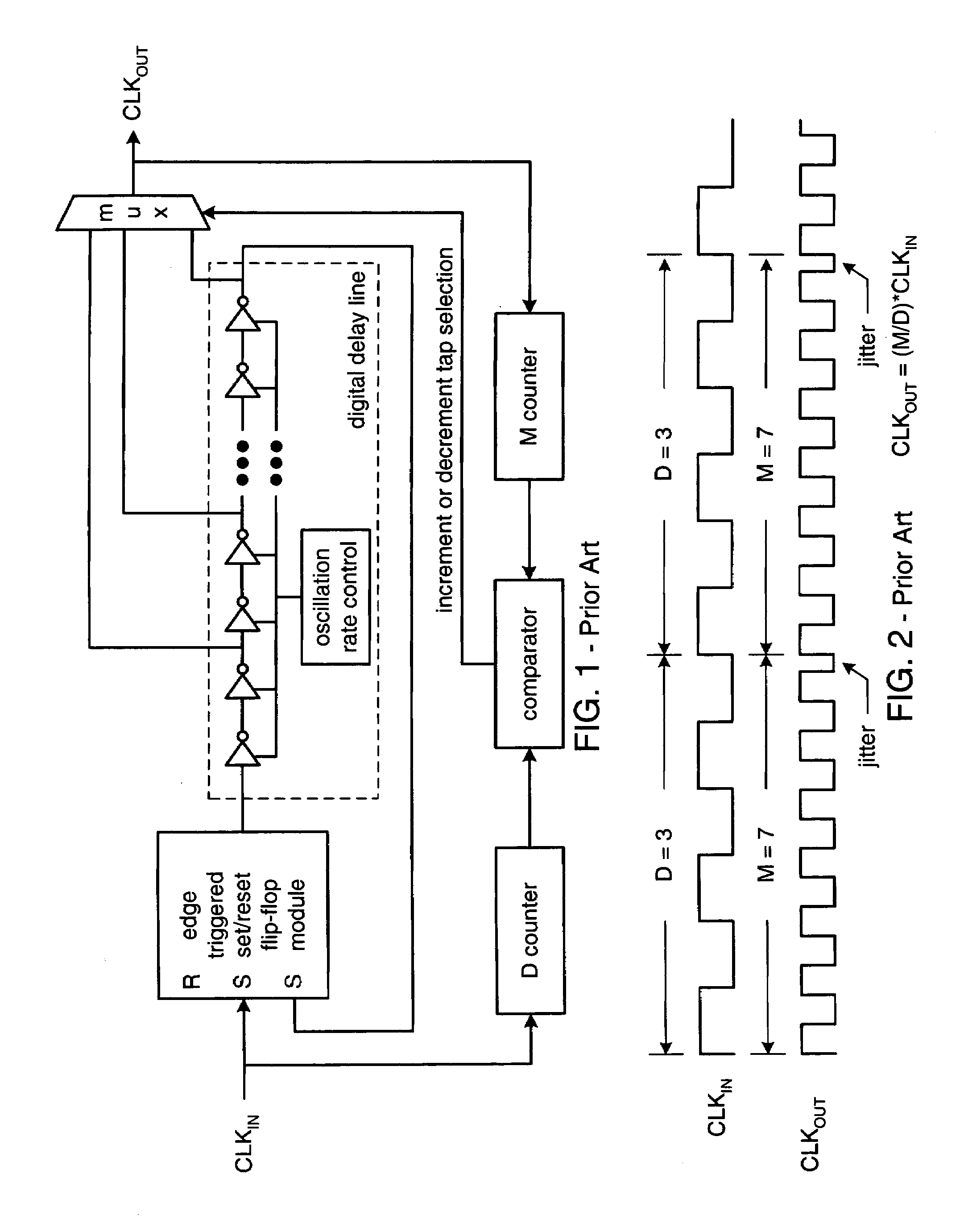

Low jitter digital frequency synthesizer and control thereof

A low jitter digital frequency synthesizer includes a first counter module, a second counter module, a snapshot module, an error value generation module, and a tapped delay line. The first counter module counts intervals of M cycles of an input clock to produce a first count. The second counter module count intervals of D cycles of an output clock to produce a second count, wherein a rate of the output clock corresponds to M / D times a rate of the input clock. The snapshot module periodically takes a snapshot of the first and second counts to produce snapshots. The error value generation module generates an error value based on the snapshots. The tapped delay line module produces the output clock based on the error value.

Owner:XILINX INC

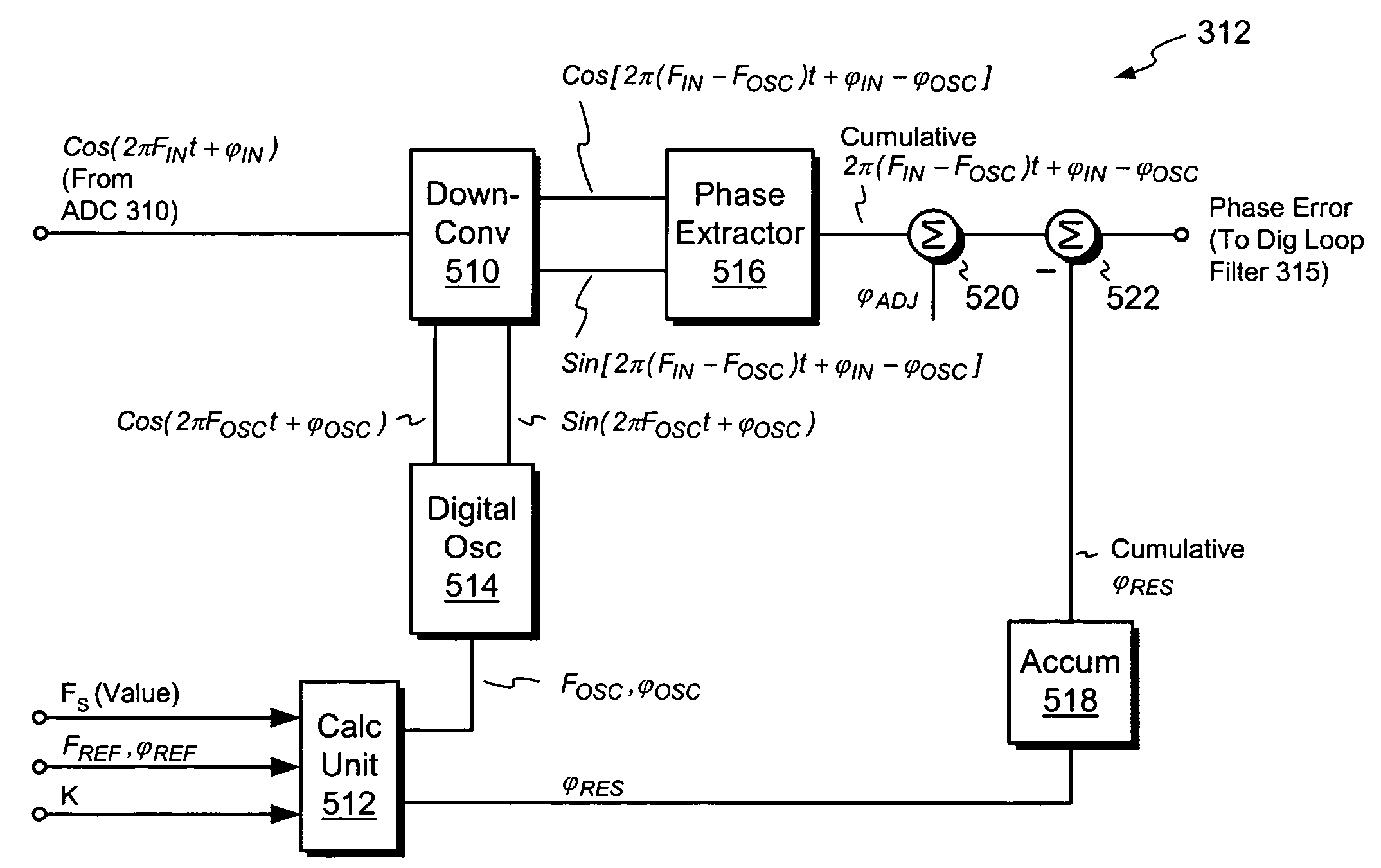

Digital phase detector

A high performance phase detector includes a local digital oscillator for generating a digital reference signal of programmable frequency and phase. The phase detector accumulates a difference in phase between the digital reference signal and a sampled input signal to produce a measure of phase error. The phase detector can be advantageously used in a frequency synthesizer to produce signals with low phase noise and accurate phase control. Synthesizers of this type can further be used to as building blocks in ATE systems and other electronic systems for generating low jitter clocks and waveforms.

Owner:TERADYNE

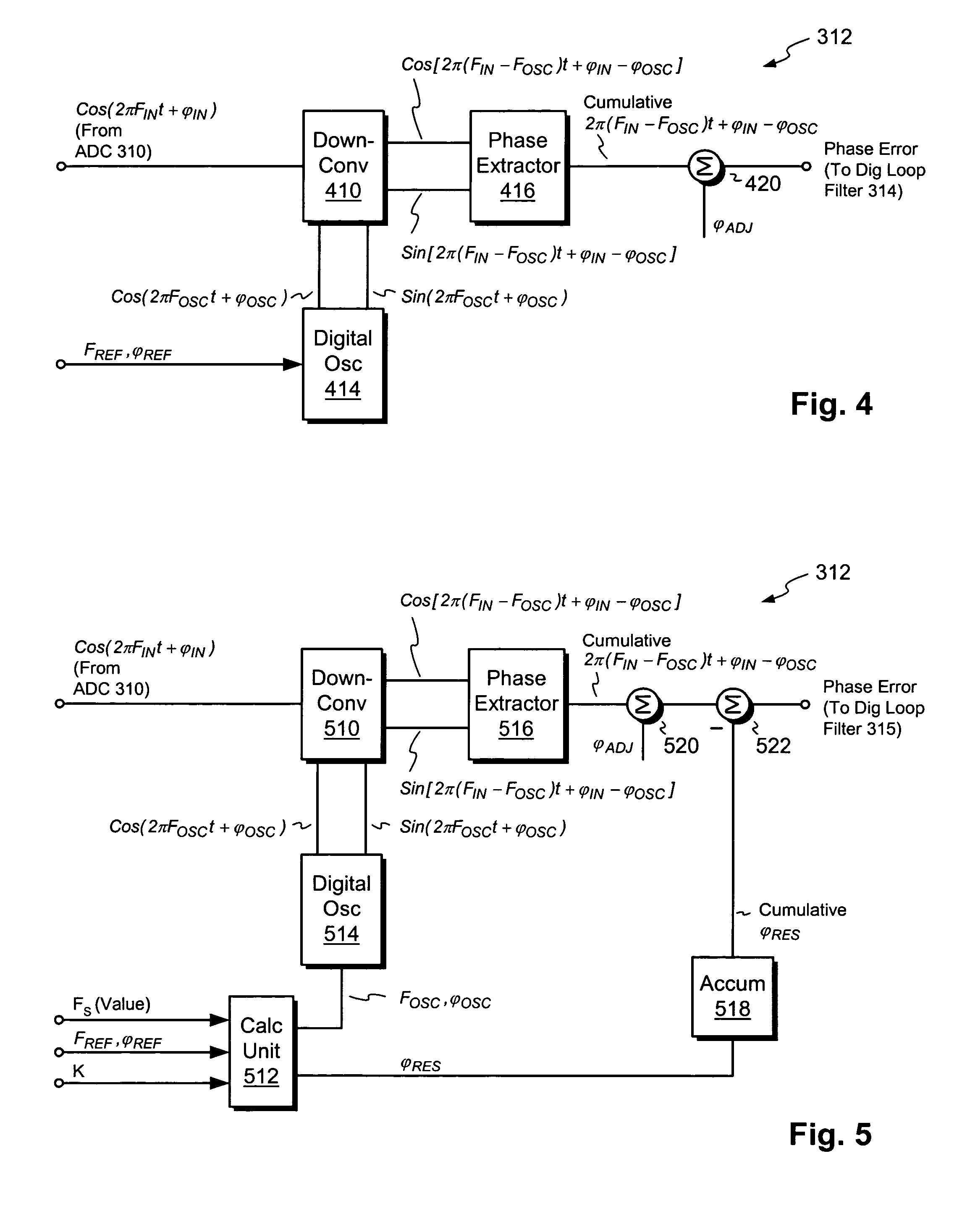

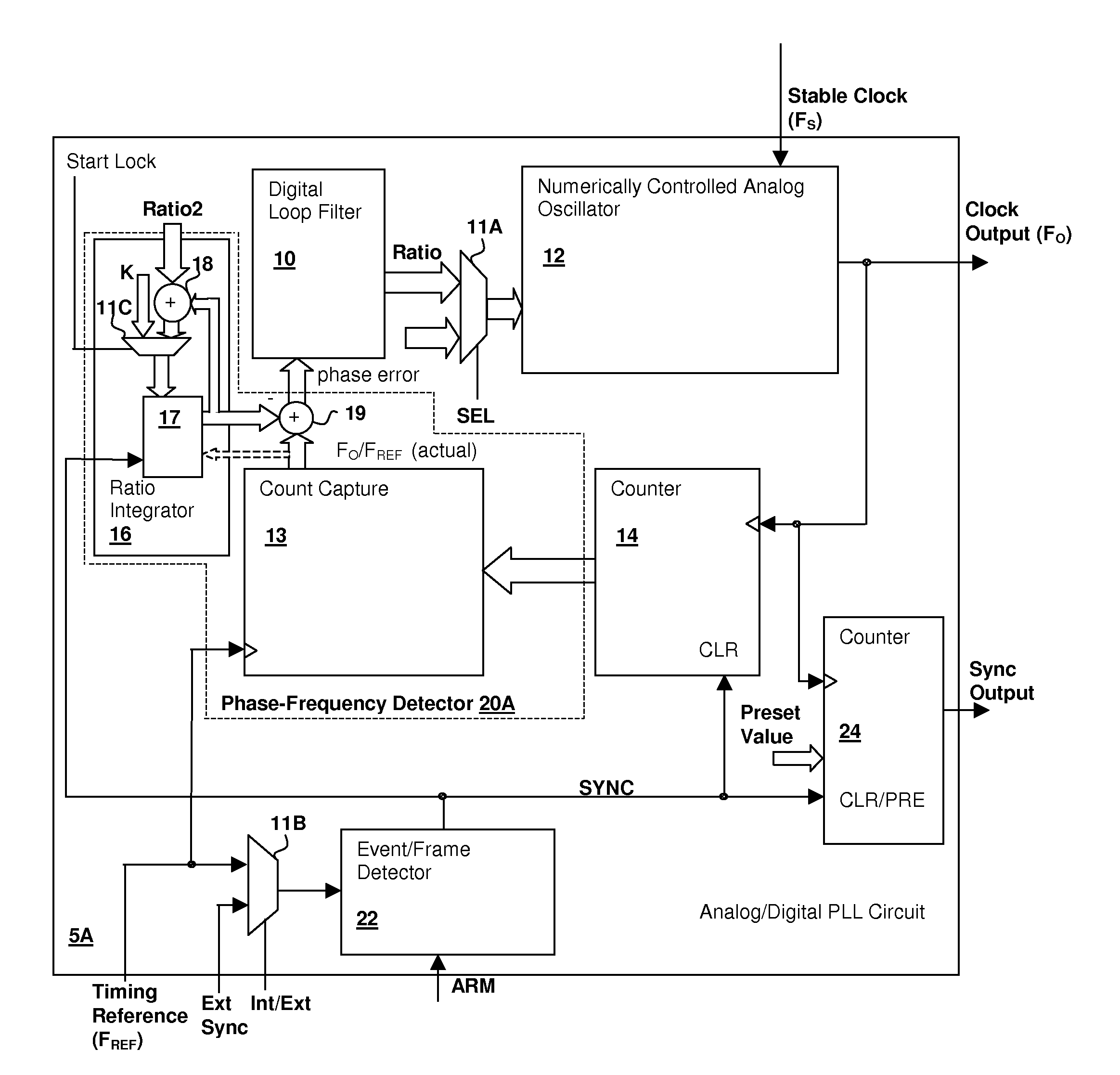

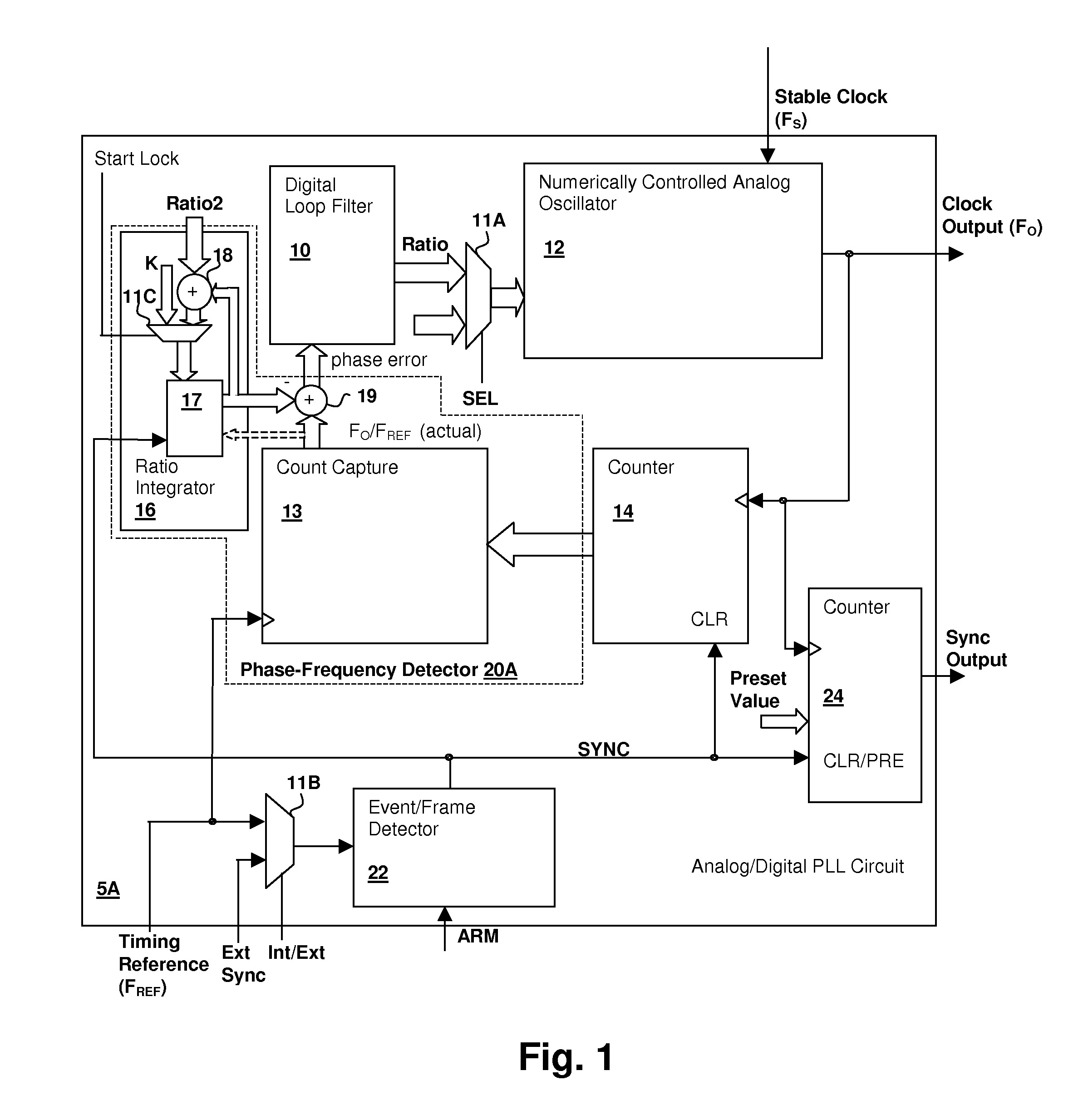

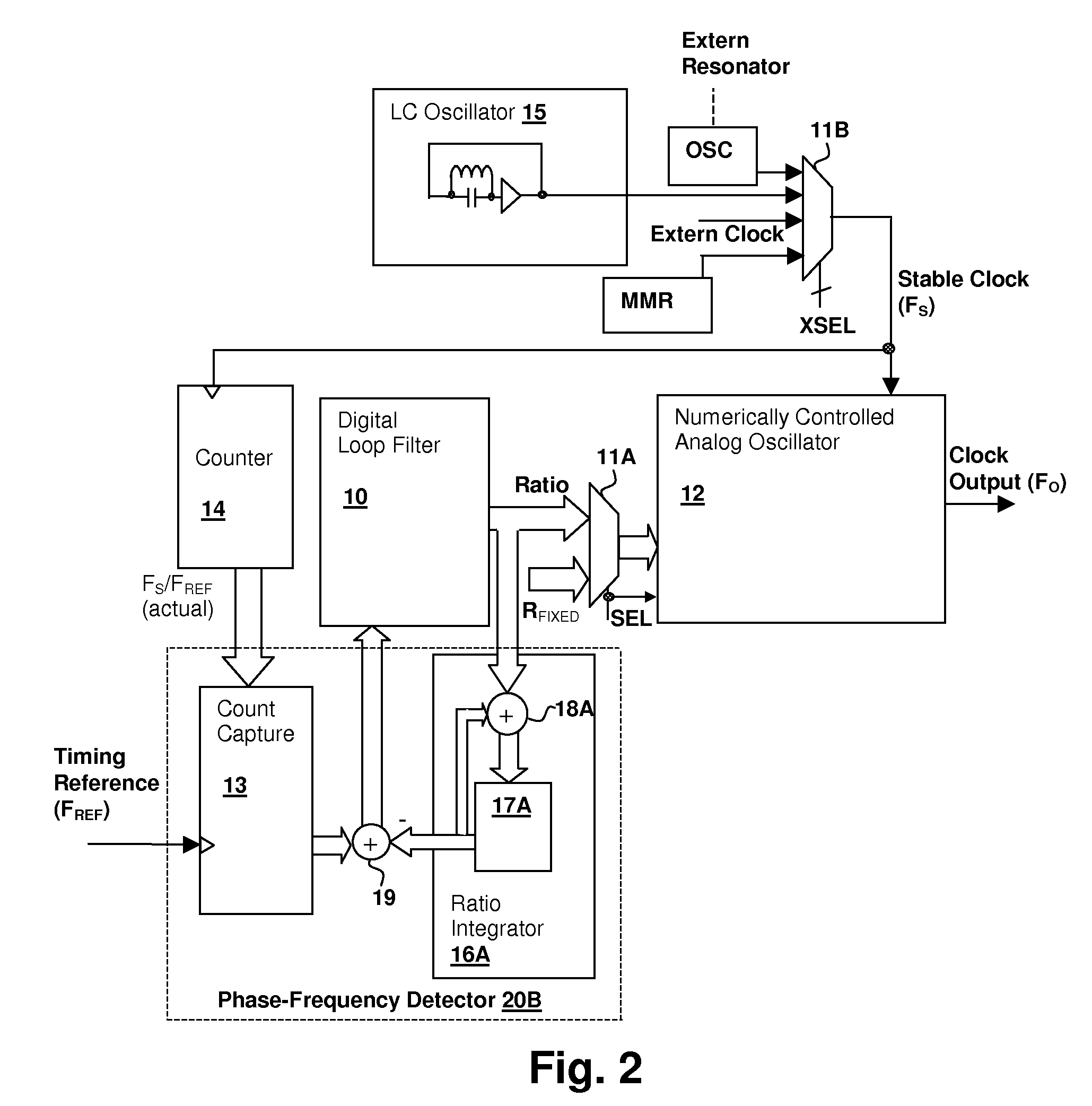

Hybrid analog/digital phase-lock loop with high-level event synchronization

ActiveUS20080075152A1Modulated-carrier systemsPulse automatic controlEvent synchronizationLow jitter

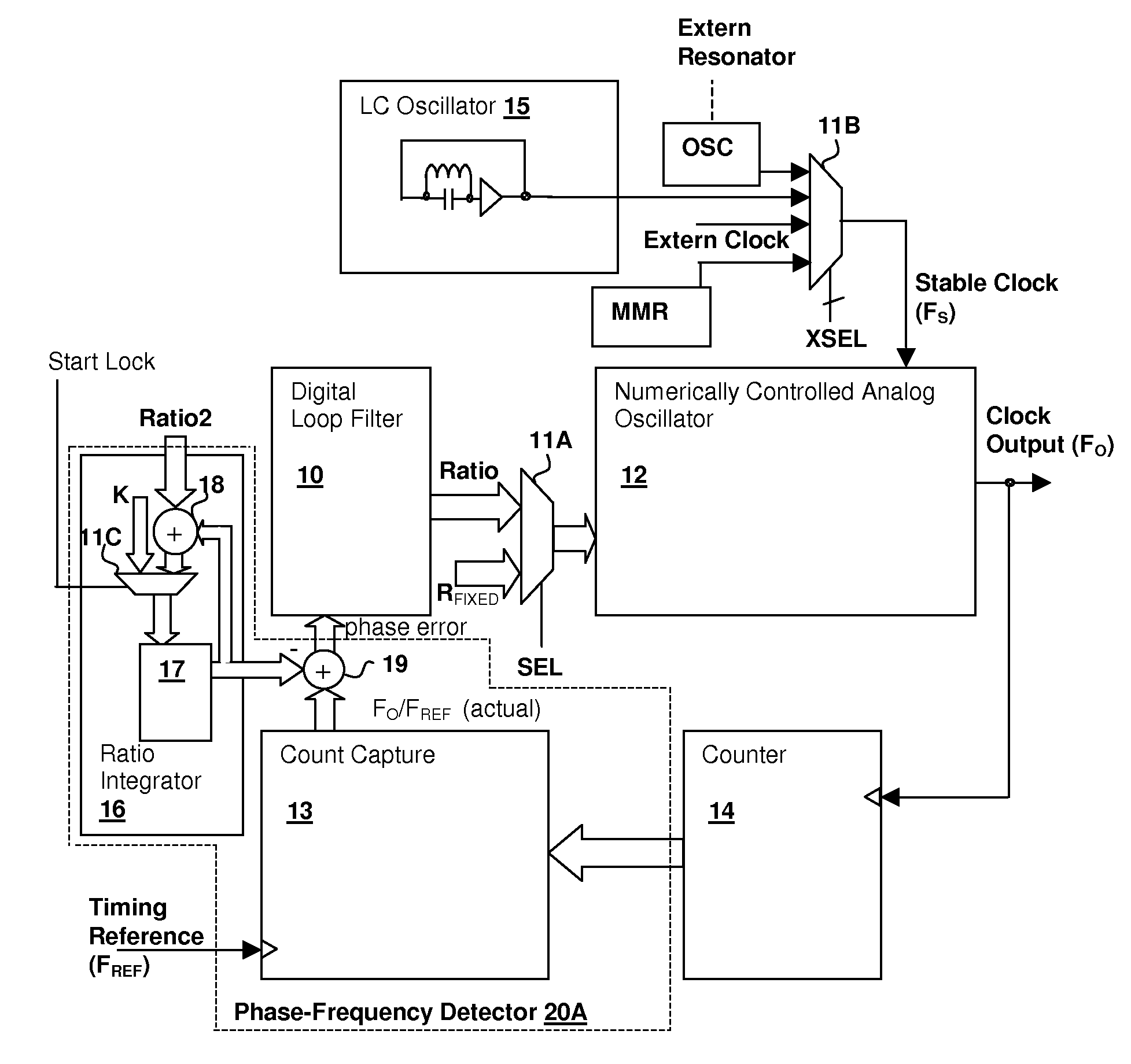

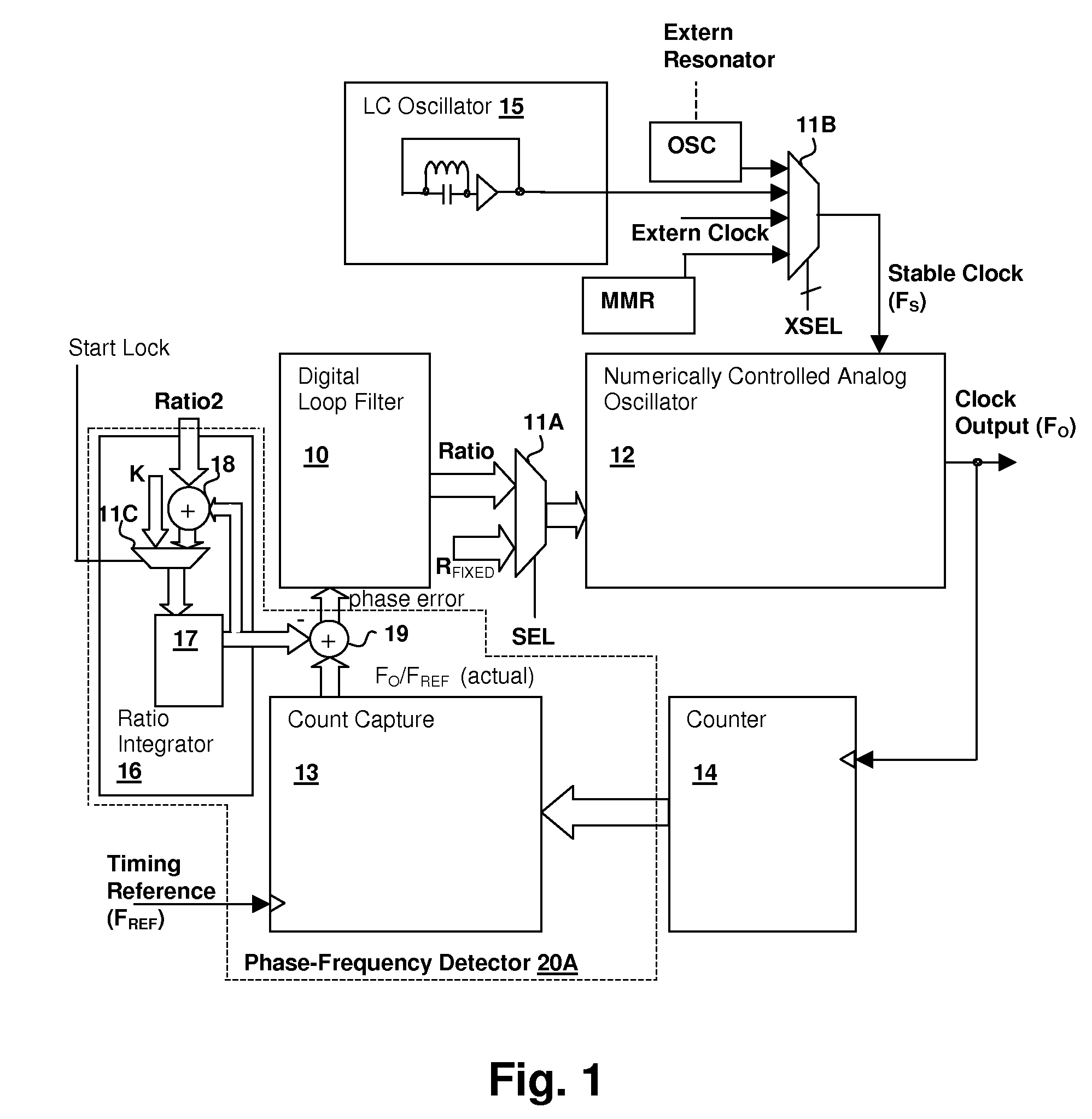

A hybrid analog / digital phase-lock loop with high-level event synchronization provides a mechanism for generating a low-jitter clock from a timing reference that has a high jitter level and synchronizing the output clock to high-level events. A numerically-controlled analog oscillator provides a clock output and a counter divides the frequency of the clock output to provide input to a digital phase-frequency detector for detecting an on-going phase-frequency difference between the timing reference and the output of the counter. A synchronization circuit detects or receives a high-level event signal, and resets the on-going phase-frequency difference and optionally the counter to synchronize the clock output with the events. The synchronization circuit may have an arming input to enable the synchronization circuit to signal a next event. Another clock output divider may be included to generate a timing reference output, and the other clock divider also reset in response to a detected event.

Owner:CIRRUS LOGIC INC

Method and apparatus to schedule packets through a crossbar switch with delay guarantees

ActiveUS8089959B2Multiplex system selection arrangementsData switching by path configurationDifferentiated servicesCrossbar switch

A method for scheduling cell transmissions through a switch with rate and delay guarantees and with low jitter is proposed. The method applies to a classic input-buffered N×N crossbar switch without speedup. The time axis is divided into frames each containing F time-slots. An N×N traffic rate matrix specifies a quantized guaranteed traffic rate from each input port to each output port. The traffic rate matrix is transformed into a permutation with NF elements which is decomposed into F permutations of N elements using a recursive and fair decomposition method. Each permutation is used to configure the crossbar switch for one time-slot within a frame of size F time-slots, and all F permutations result in a Frame Schedule. In the frame schedule, the expected Inter-Departure Time (IDT) between cells in a flow equals the Ideal IDT and the delay jitter is bounded and small. For fixed frame size F, an individual flow can often be scheduled in O(log N) steps, while a complete reconfiguration requires O(N log N) steps when implemented in a serial processor. An RSVP or Differentiated Services-like algorithm can be used to reserve bandwidth and buffer space in an IP-router, an ATM switch or MPLS switch during a connection setup phase, and the proposed method can be used to schedule traffic in each router or switch. Best-effort traffic can be scheduled using any existing dynamic scheduling algorithm to fill the remaining unused switch capacity within each Frame. The scheduling algorithm also supports multicast traffic.

Owner:SZYMANSKI TED HENRYK

Hybrid analog/digital phase-lock loop for low-jitter synchronization

ActiveUS7680236B1Pulse automatic controlAngle demodulation by phase difference detectionLoop filterPhase frequency detector

Owner:CIRRUS LOGIC INC

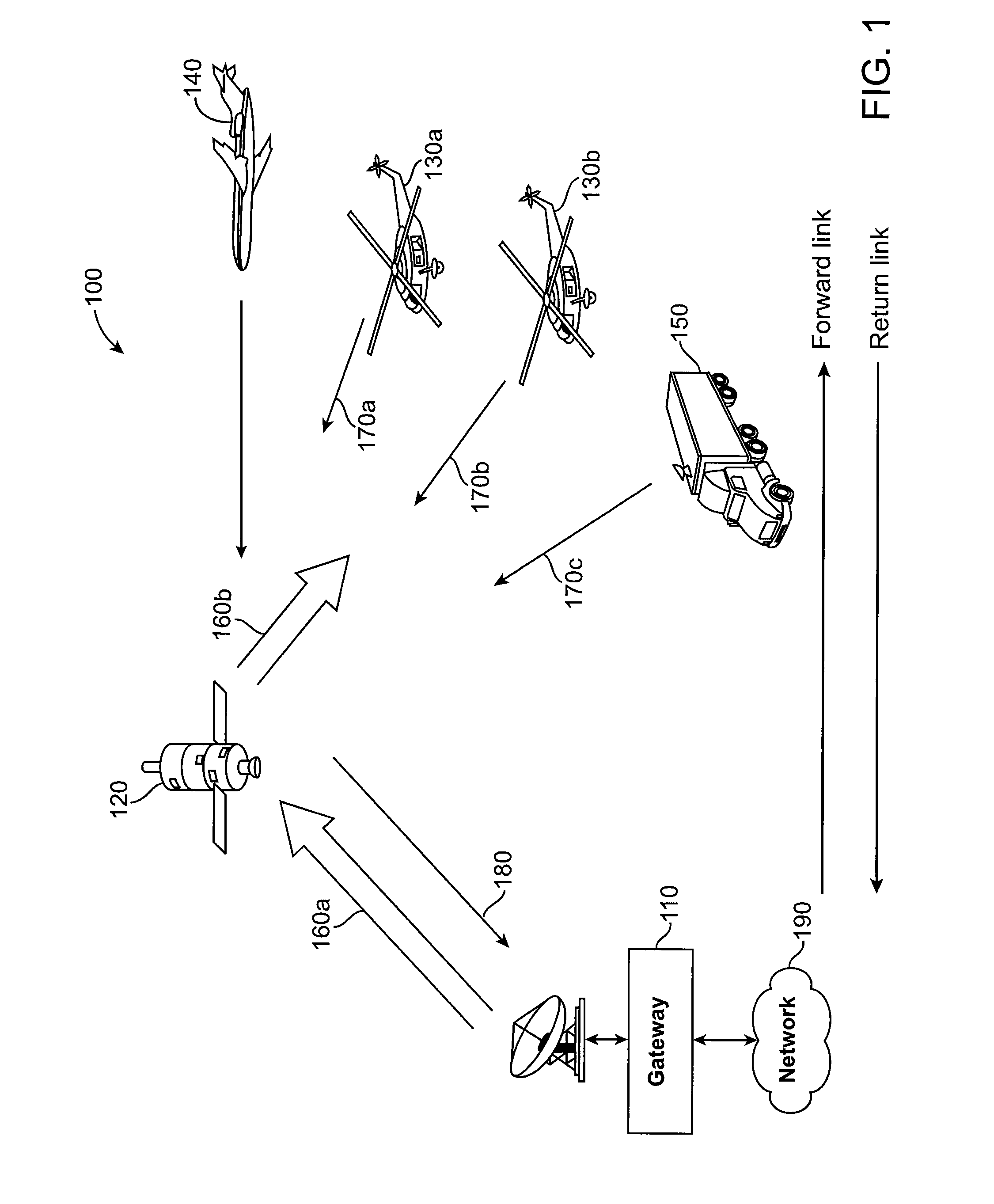

Cyclical obstruction communication system

ActiveUS20100322150A1Radio transmissionError prevention/detection by transmission repeatCommunications systemLow jitter

Techniques for enabling broadband data rates at mobile terminals in a beyond-line-of-sight communication system are disclosed. Forward link time-diversity transmission methods and a time-diversity transmitter based upon blockage characteristics are provided. The transmitter optionally supports selective time-diversity and can operate at Ku-band or higher frequencies. A forward link time-diversity receiver and methods for receiving a forward link time-diversity signal are also disclosed. The forward link time-diversity receiver optionally provides low-jitter or low-delay characteristics. A return link transmitter and return link transmit methods which avoid blockages are also disclosed. The return link transmitter can include a signal presence detector and blockage prediction filter.

Owner:VIASAT INC

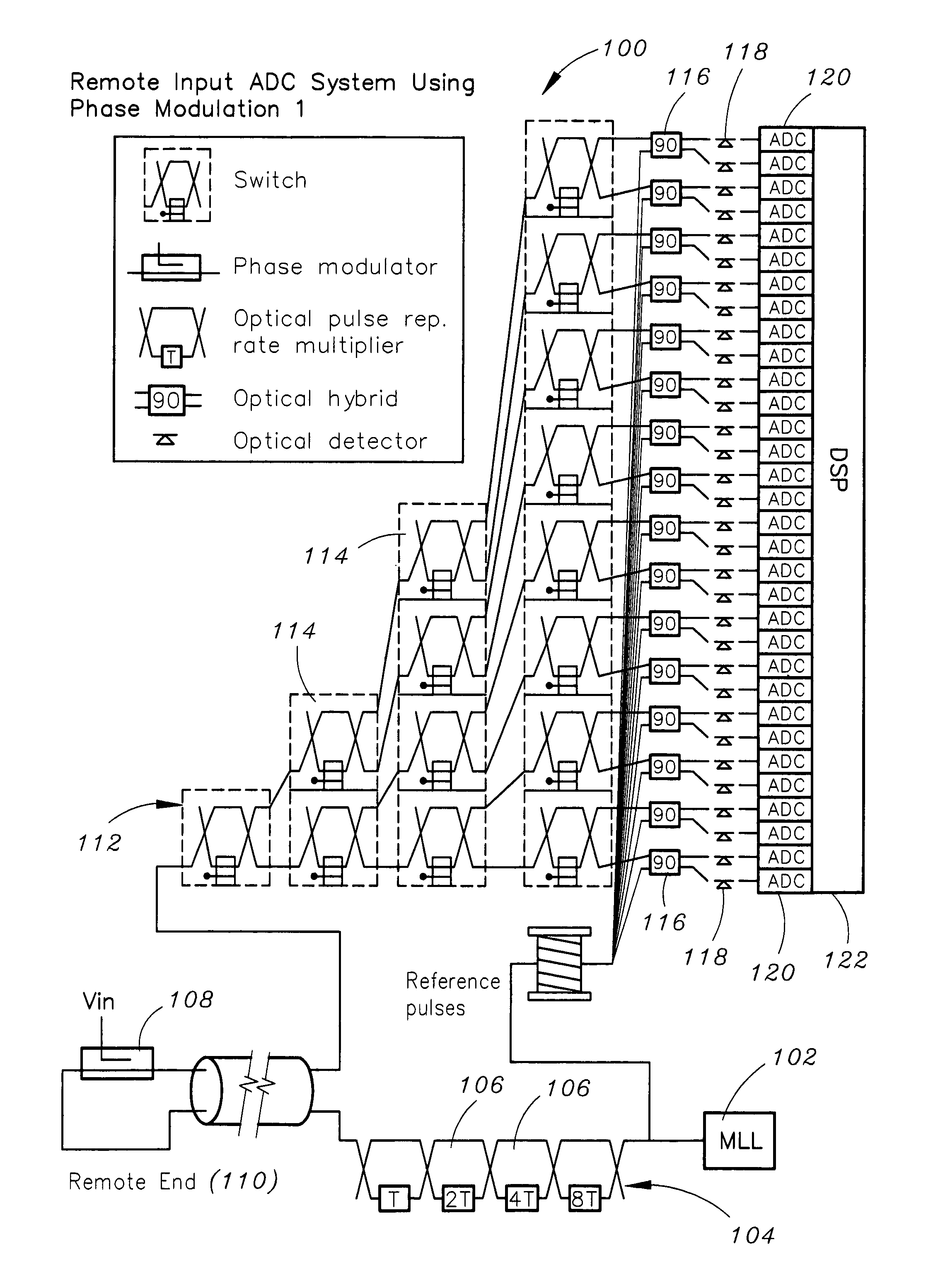

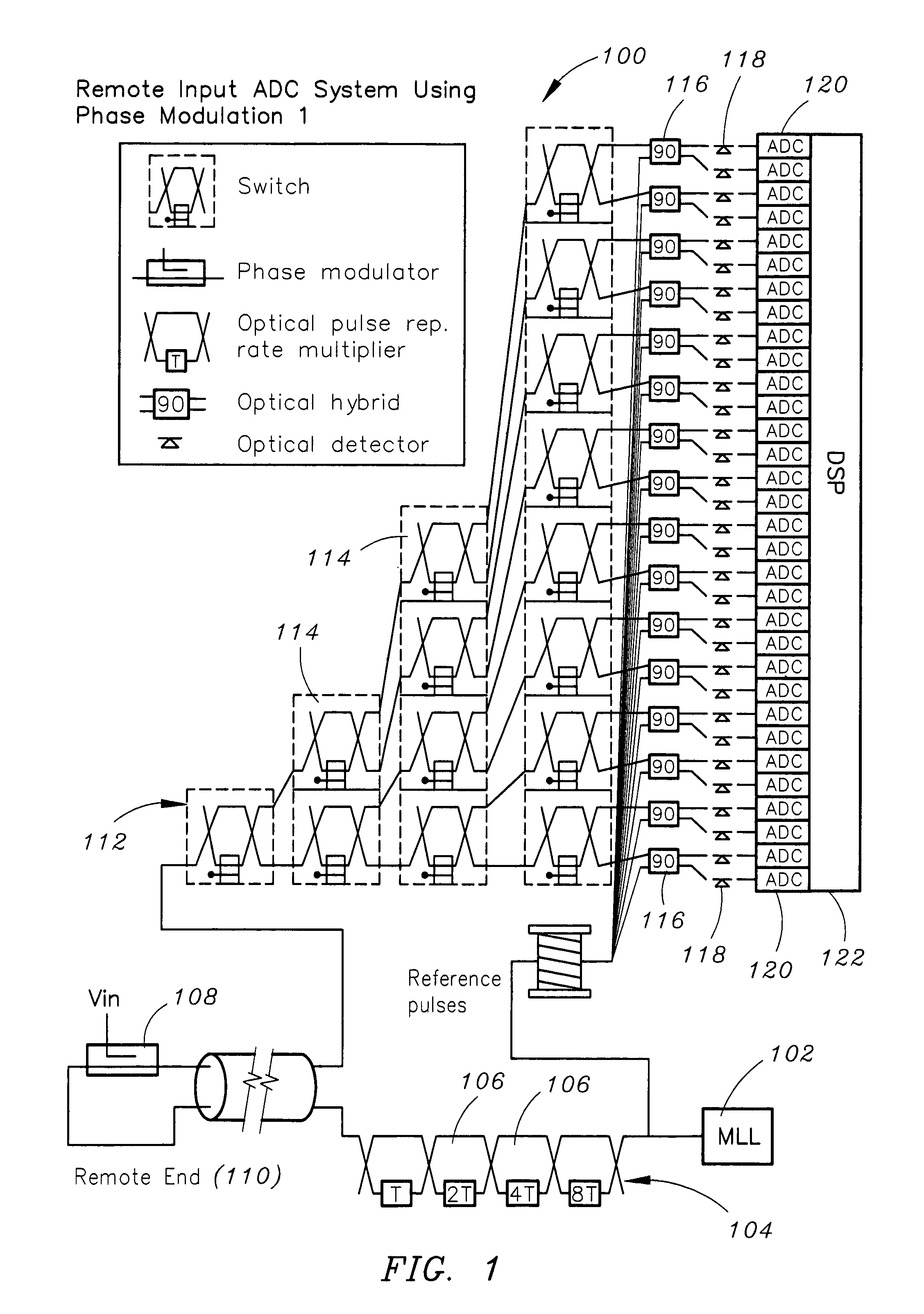

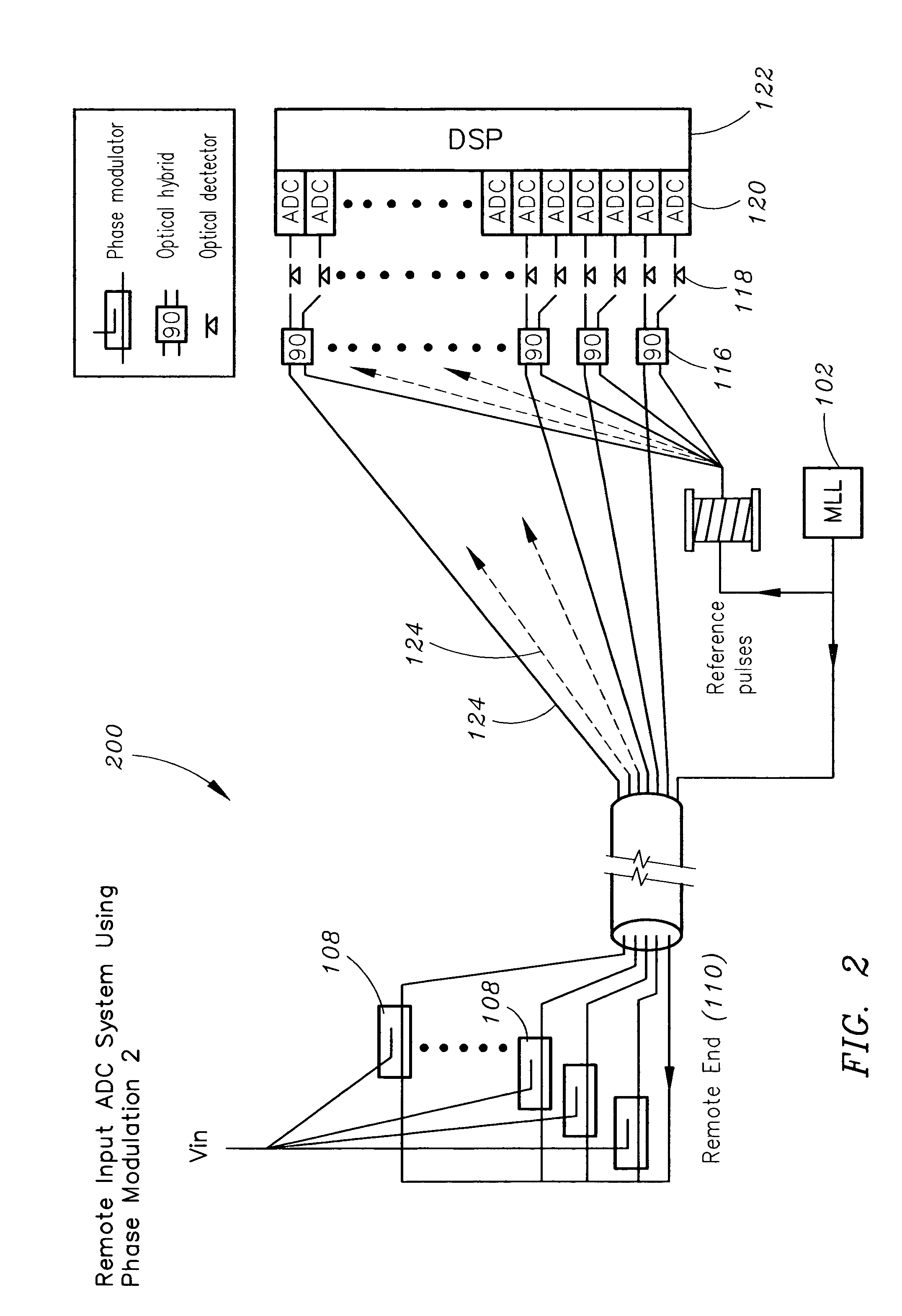

System and method for remoting a photonic analog-to-digital converter

ActiveUS7868799B1Increase sampling rateAnalogue/digital conversionElectric signal transmission systemsDigital down converterPulse stream

The present invention is a remote input analog-to-digital conversion (ADC) system. The system may generate low jitter, short duration optical pulses to allow for high performance sampling of an antenna signal at a remote end of the system. The system may utilize phase modulation and IQ demodulation (with a reference optical pulse stream) using separate analog-to-digital converters for I and Q to overcome linearity limitations. Low sampling rate analog-to-digital converters may be utilized by the system by using parallel, low optical pulse repetition rate paths and / or optical demultiplexer switching trees. The system is an optical fiber system.

Owner:ROCKWELL COLLINS INC

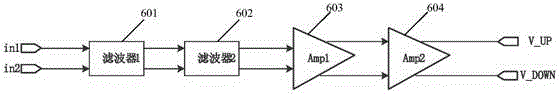

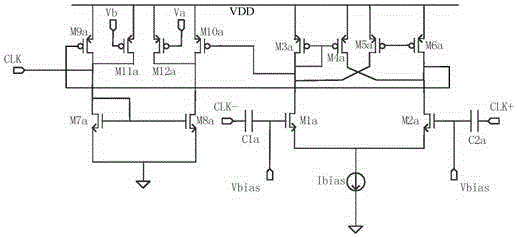

Ultrahigh-speed low-jitter multi-phase clock circuit

ActiveCN106849942AMeet demanding requirementsBreak performance limitsPulse automatic controlElectric pulse generatorDiscriminatorPhase difference

The invention discloses an ultrahigh-speed low-jitter multi-phase clock circuit. The circuit comprises an input clock recovery and duty ratio adjustment module, a phase discriminator module, a charge pump and loop filter module, a variable delay line module, a clock offset error calibration module and a frequency division module, wherein the phase discriminator module is used for detecting a phase relationship between a reference clock and a feedback clock, and correspondingly outputting an 'UP' or 'Down' pulse level to the charge pump; and the charge pump and a loop filter are used for converting pulses output by a phase discriminator into a low-frequency direct-current control level, and controlling the delay amount of a delay chain to adjust a phase difference between the two clocks; when the two clocks are synchronized, the phase discriminator outputs a locking signal; a variable delay line is constructed by serial connection of a plurality of same sub-delay units in order to obtain a multi-phase clock; and the clock offset error calibration module is used for reducing a clock offset error by adopting a multi-phase clock circuit matching calibration technology. The clock signal can meet strict requirements on clock signals in high-frequency applications.

Owner:BEIJING MXTRONICS CORP +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com