Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2830results about How to "Reduce jitter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

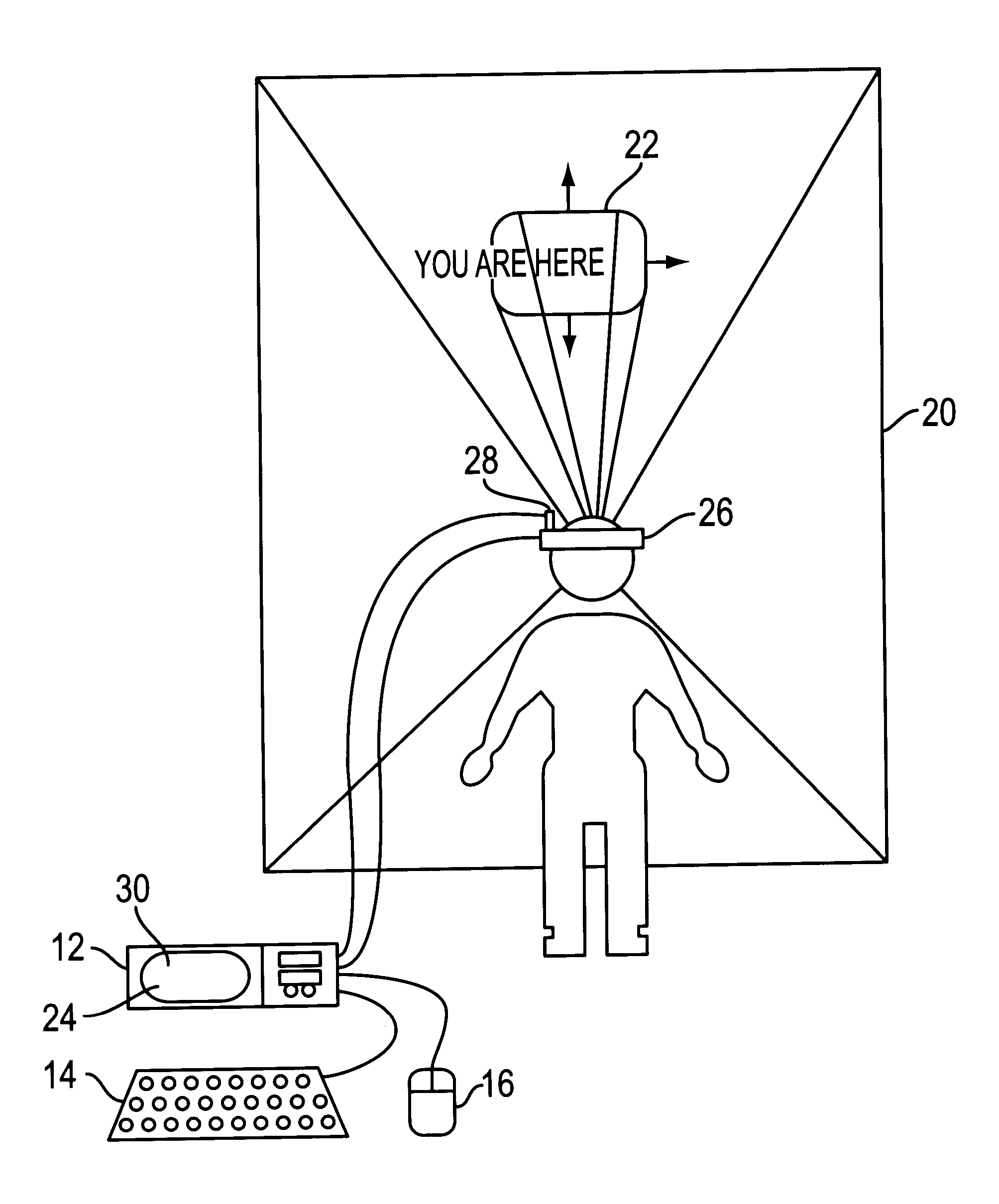

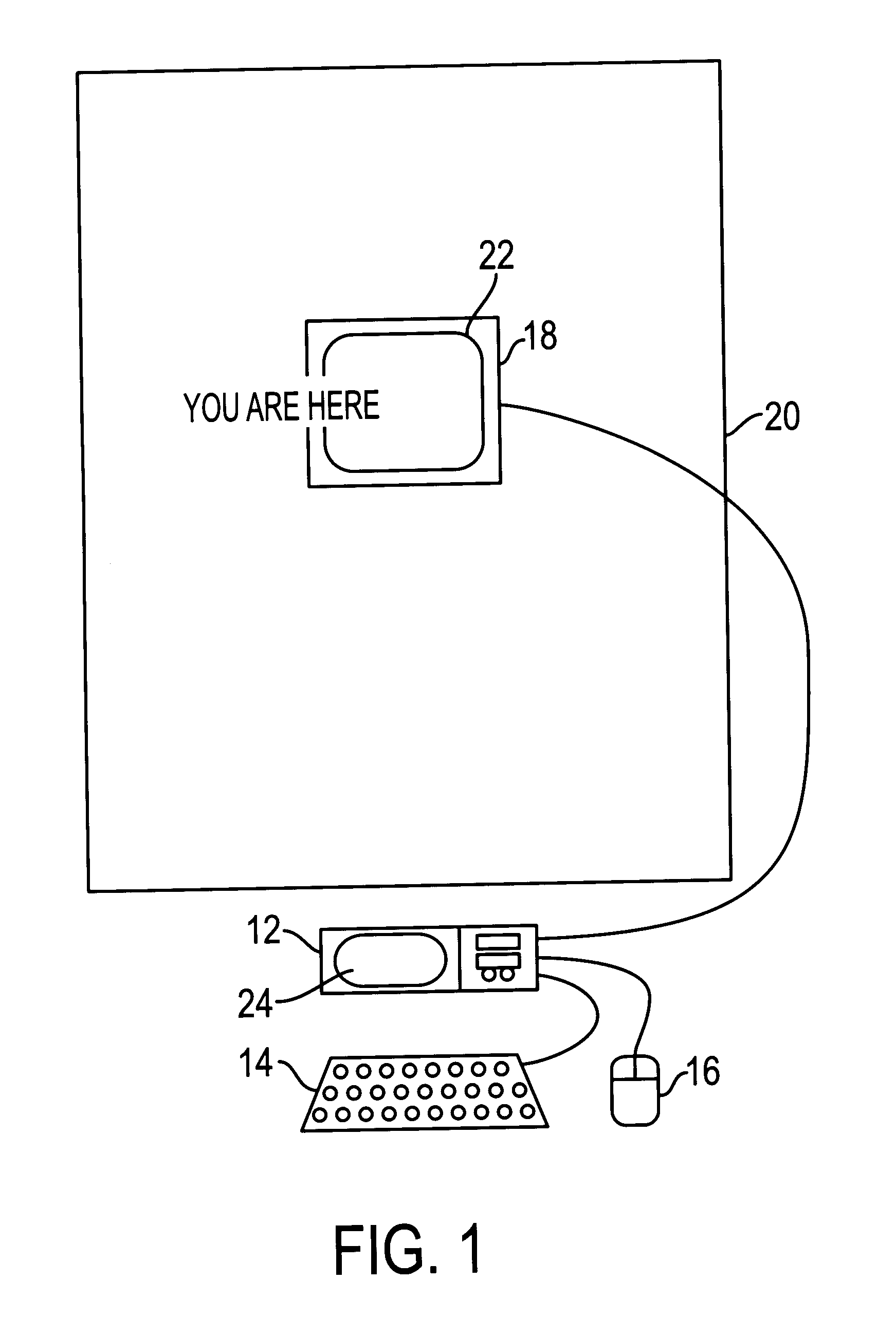

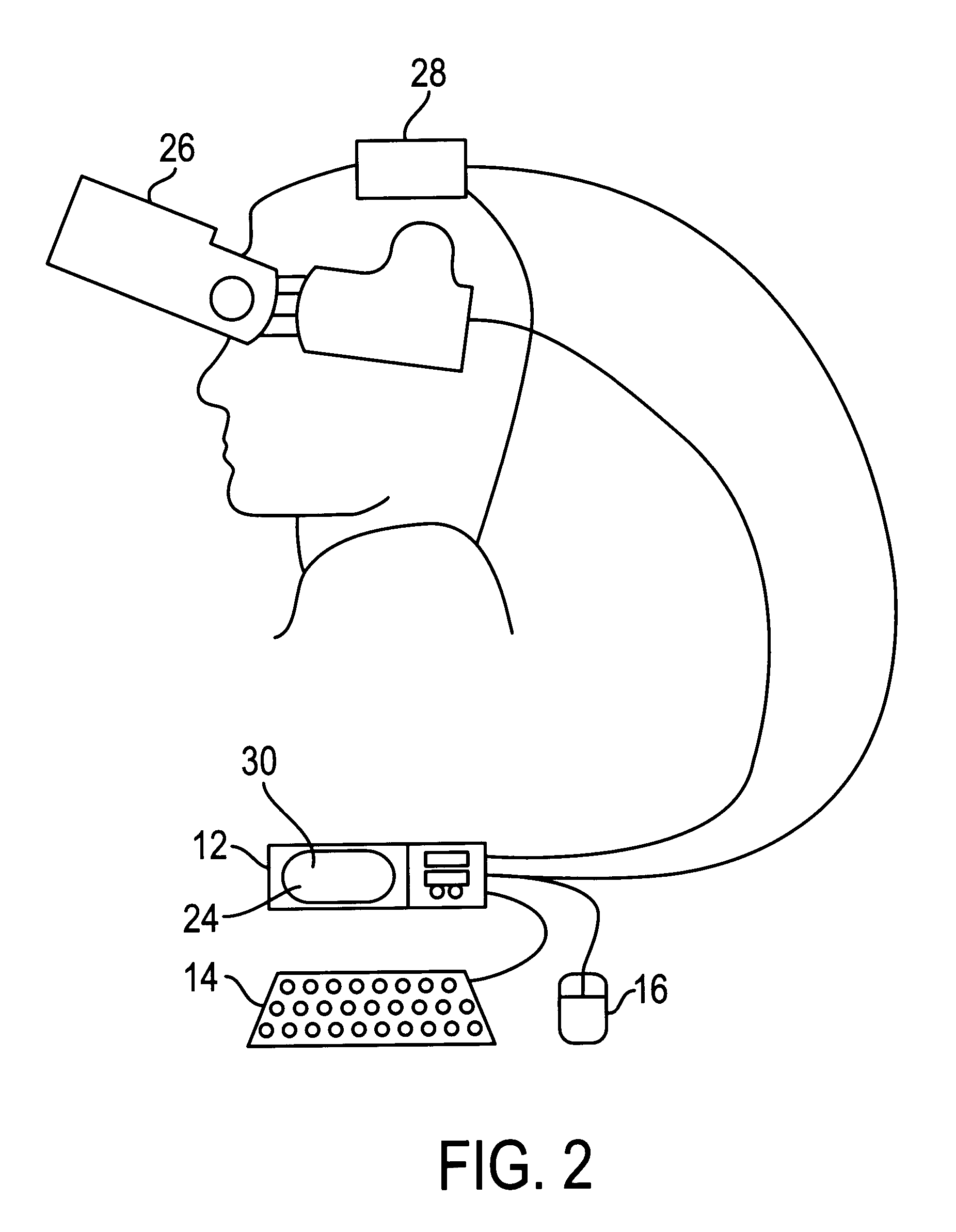

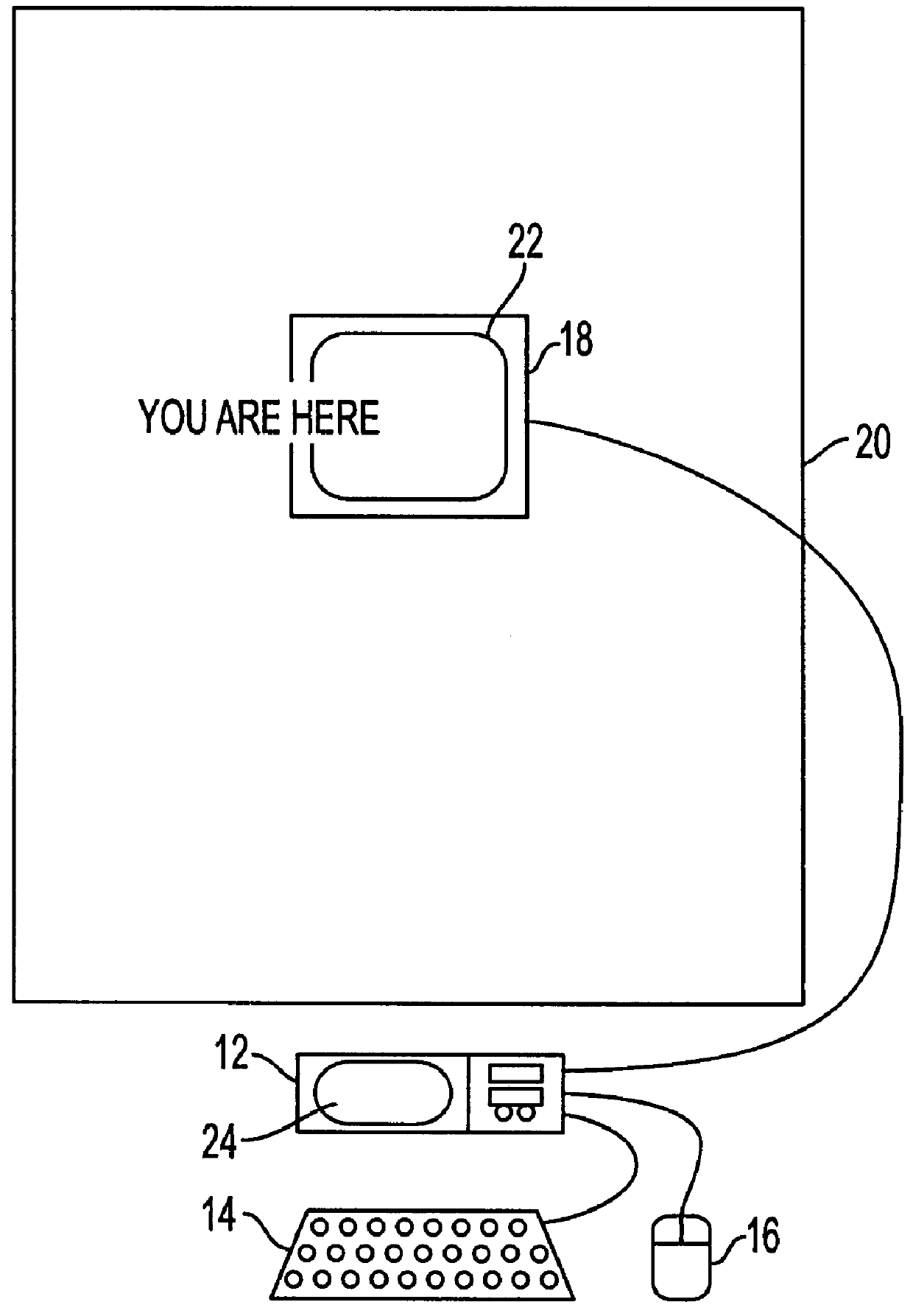

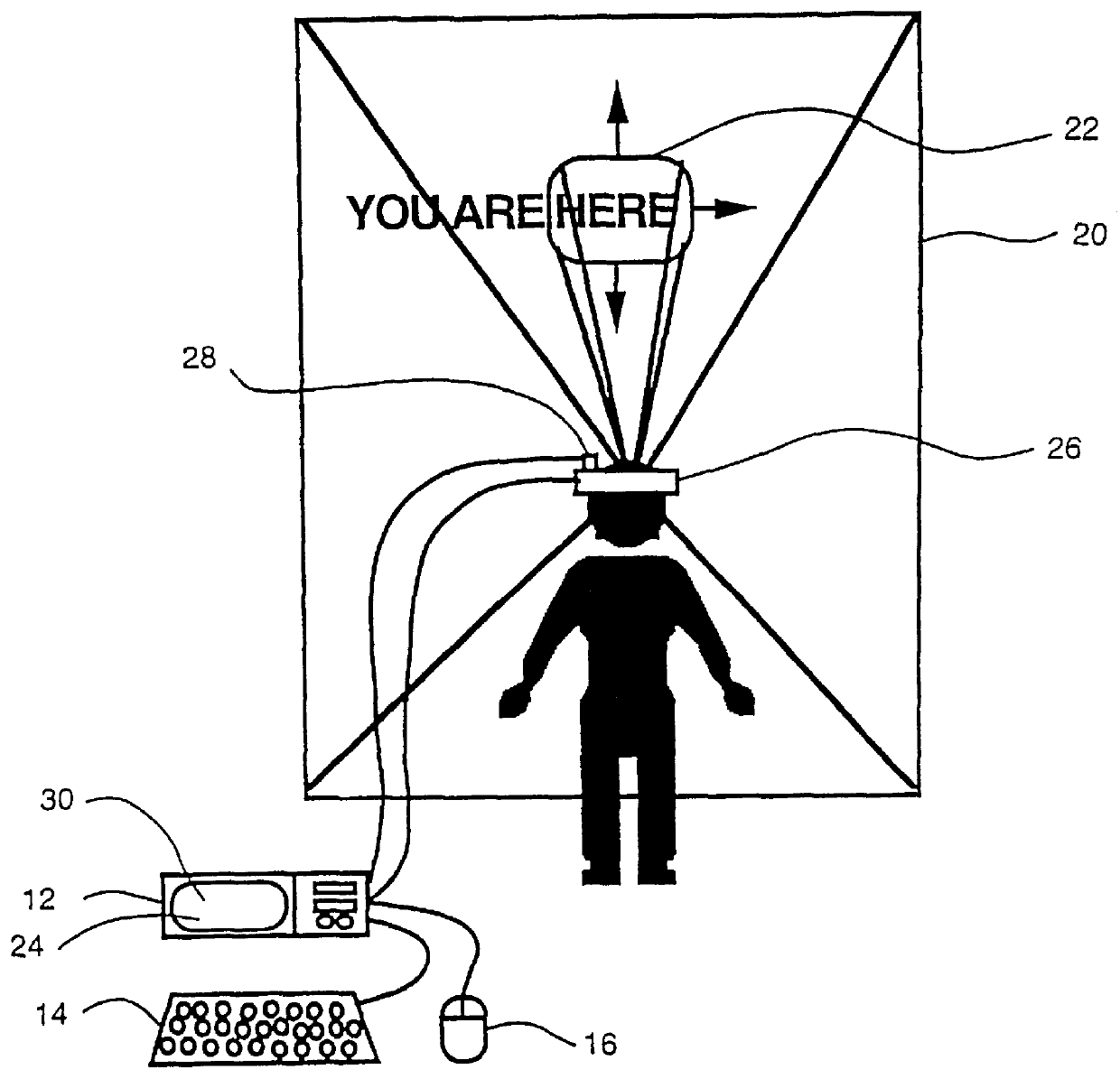

Intuitive control of portable data displays

InactiveUS6184847B1Reduce jitterInput/output for user-computer interactionCathode-ray tube indicatorsVisually impairedData display

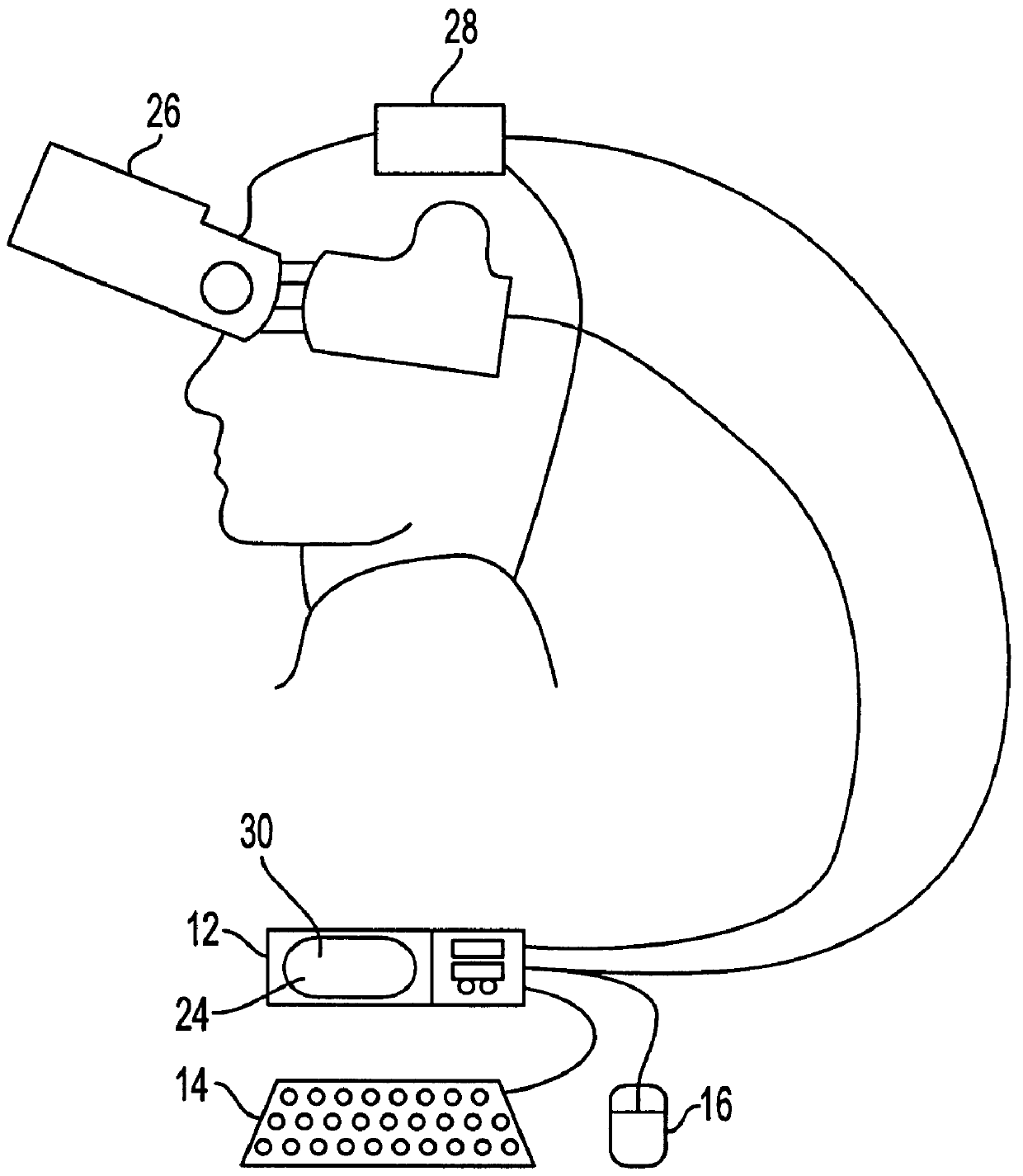

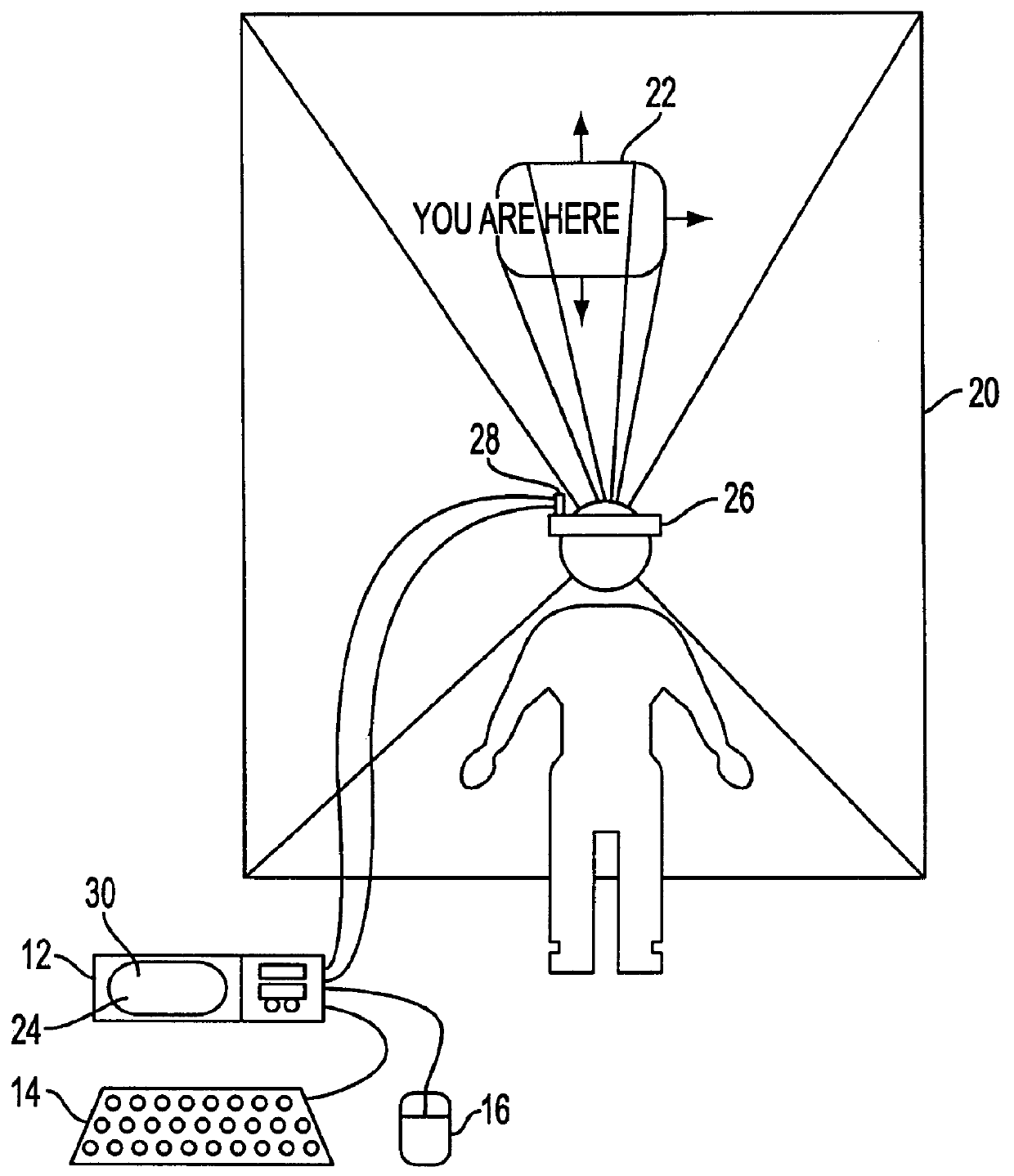

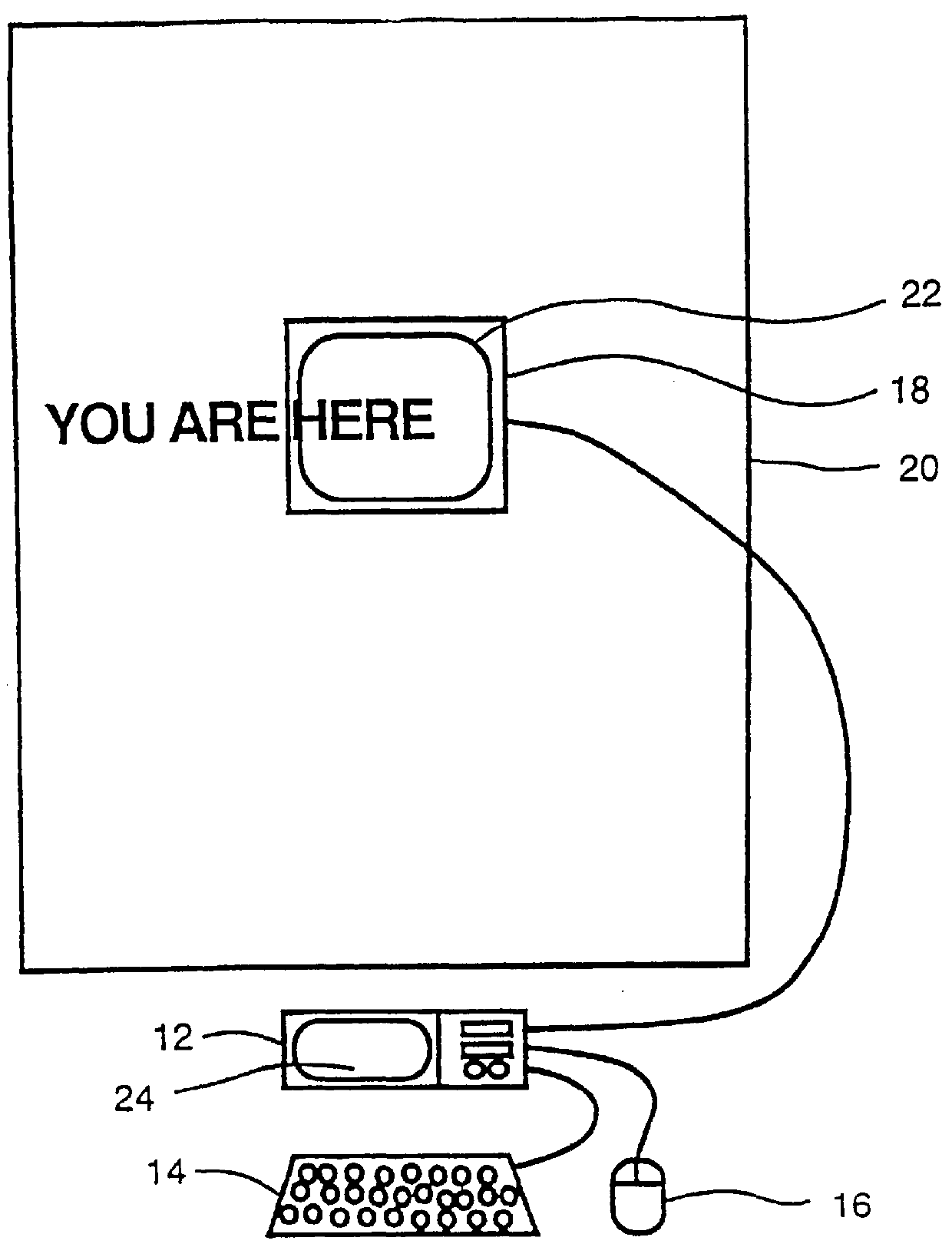

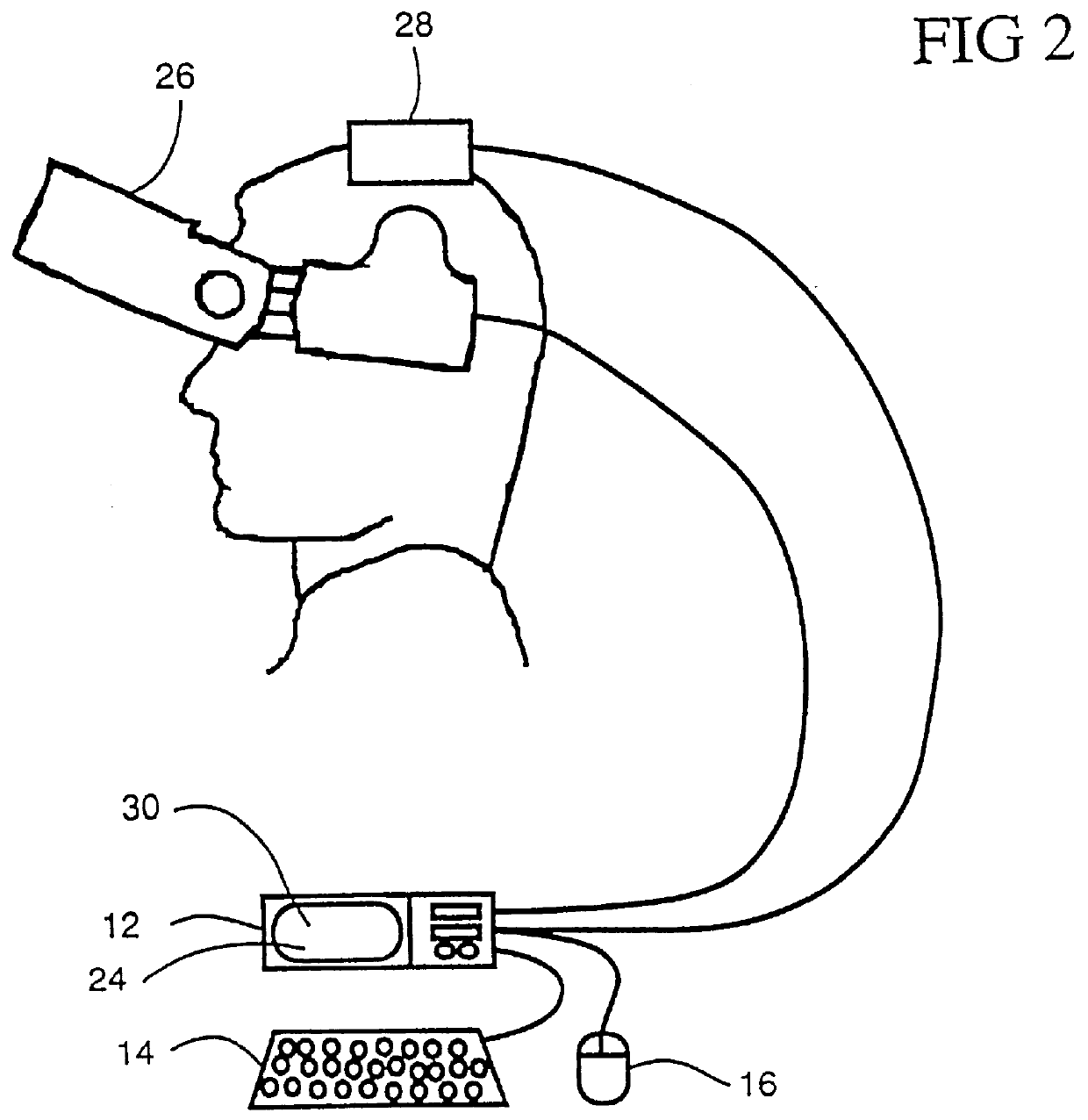

A virtual computer monitor is described which enables instantaneous and intuitive visual access to large amounts of visual data by providing the user with a large display projected virtually in front of the user. The user wears a head-mounted display or holds a portable display containing a head-tracker or other motion tracker, which together allow the user to position an instantaneous viewport provided by the display at any position within the large virtual display by turning to look in the desired direction. The instantaneous viewport further includes a mouse pointer, which may be positioned by turning the user's head or moving the portable display, and which may be further positioned using a mouse or analogous control device. A particular advantage of the virtual computer monitor is intuitive access to enlarged computer output for visually-impaired individuals.

Owner:META PLATFORMS INC +1

Wearable display and methods for controlling same

InactiveUS6127990AReduce jitterCosmonautic condition simulationsColor television detailsComputer monitorDisplay device

A virtual computer monitor is described which enables instantaneous and intuitive visual access to large amounts of visual data by providing the user with a large display projected virtually in front of the user. The user wears a head-mounted display containing a head-tracker, which together allow the user to position an instantaneous viewport provided by the head-mounted display at any position within the large virtual display by turning to look in the desired direction. The instantaneous viewport further includes a mouse pointer, which may be positioned by turning the user's head, and which may be further positioned using a mouse or analogous control device. A particular advantage of the virtual computer monitor is intuitive access to enlarged computer output for visually-impaired individuals.

Owner:REMBRANDT PORTABLE DISPLAY TECH LP

Virtual computer monitor

InactiveUS6084556AReduce jitterCosmonautic condition simulationsCathode-ray tube indicatorsComputer monitorDisplay device

A virtual computer monitor is described which enables instantaneous and intuitive visual access to large amounts of visual data by providing the user with a large display projected virtually in front of the user. The user wears a head-mounted display containing a head-tracker, which together allow the user to position an instantaneous viewport provided by the head-mounted display at any position within the large virtual display by turning to look in the desired direction. The instantaneous viewport further includes a mouse pointer, which may be positioned by turning the user's head, and which may be further positioned using a mouse or analogous control device. A particular advantage of the virtual computer monitor is intuitive access to enlarged computer output for visually-impaired individuals.

Owner:META PLATFORMS INC

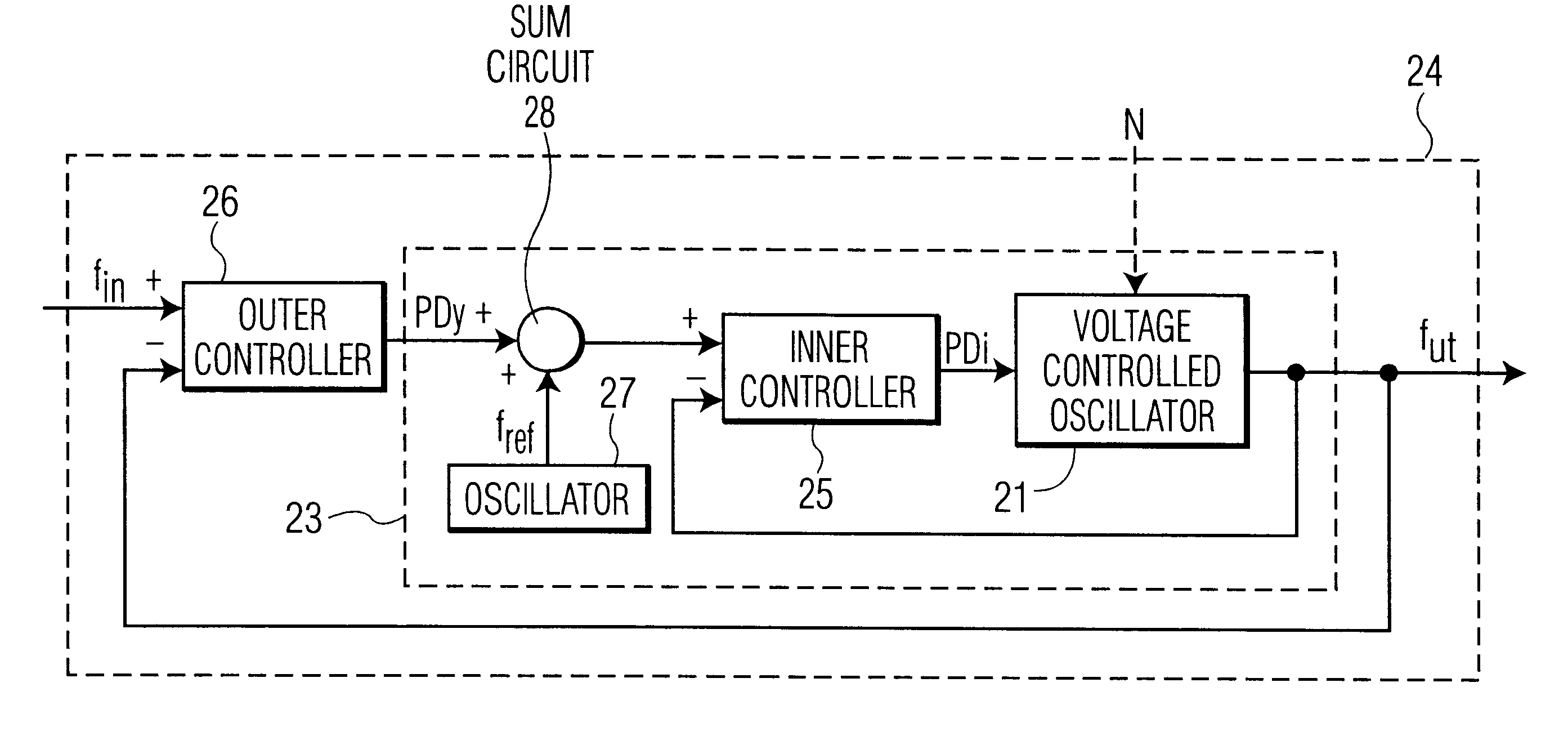

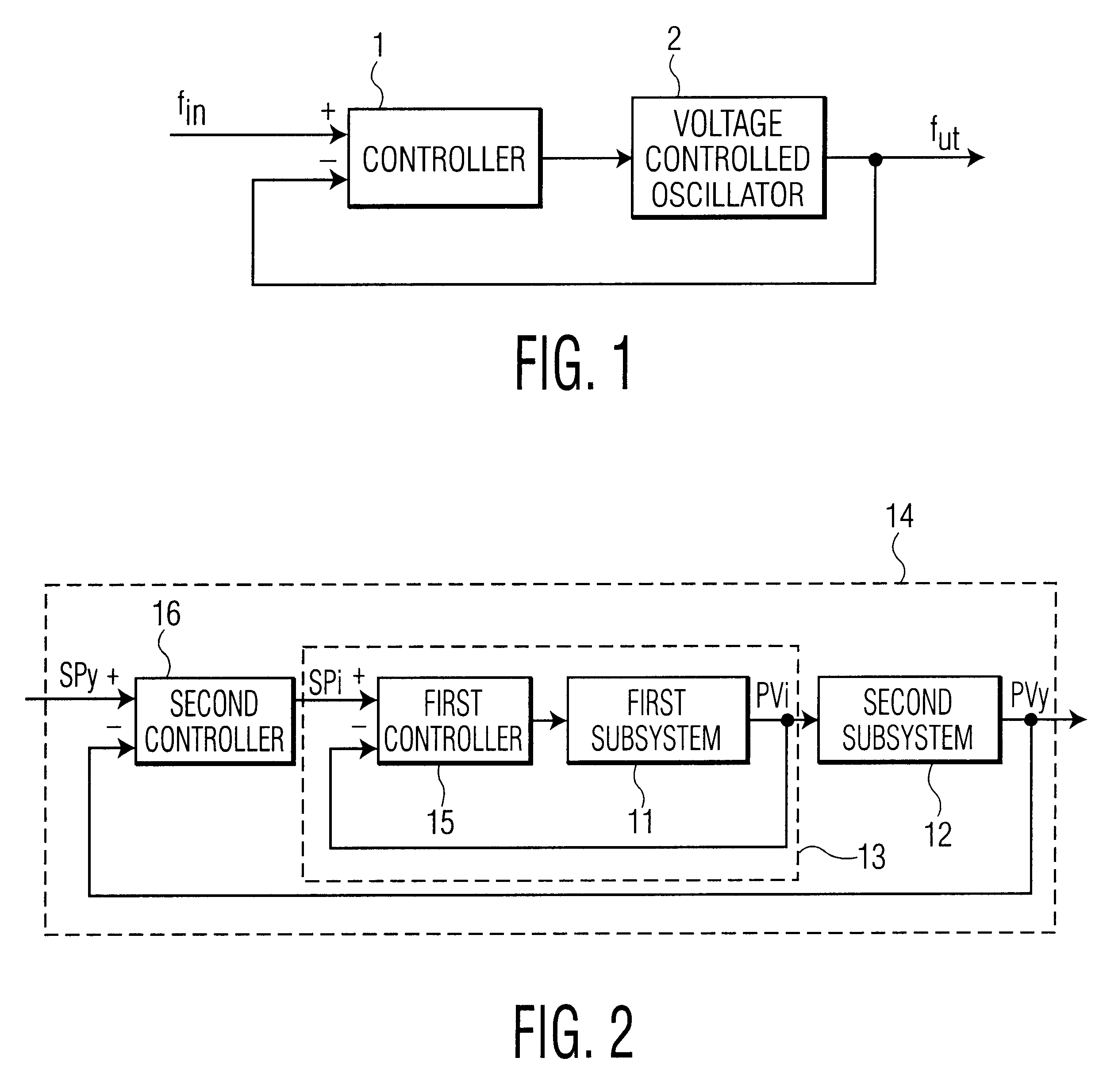

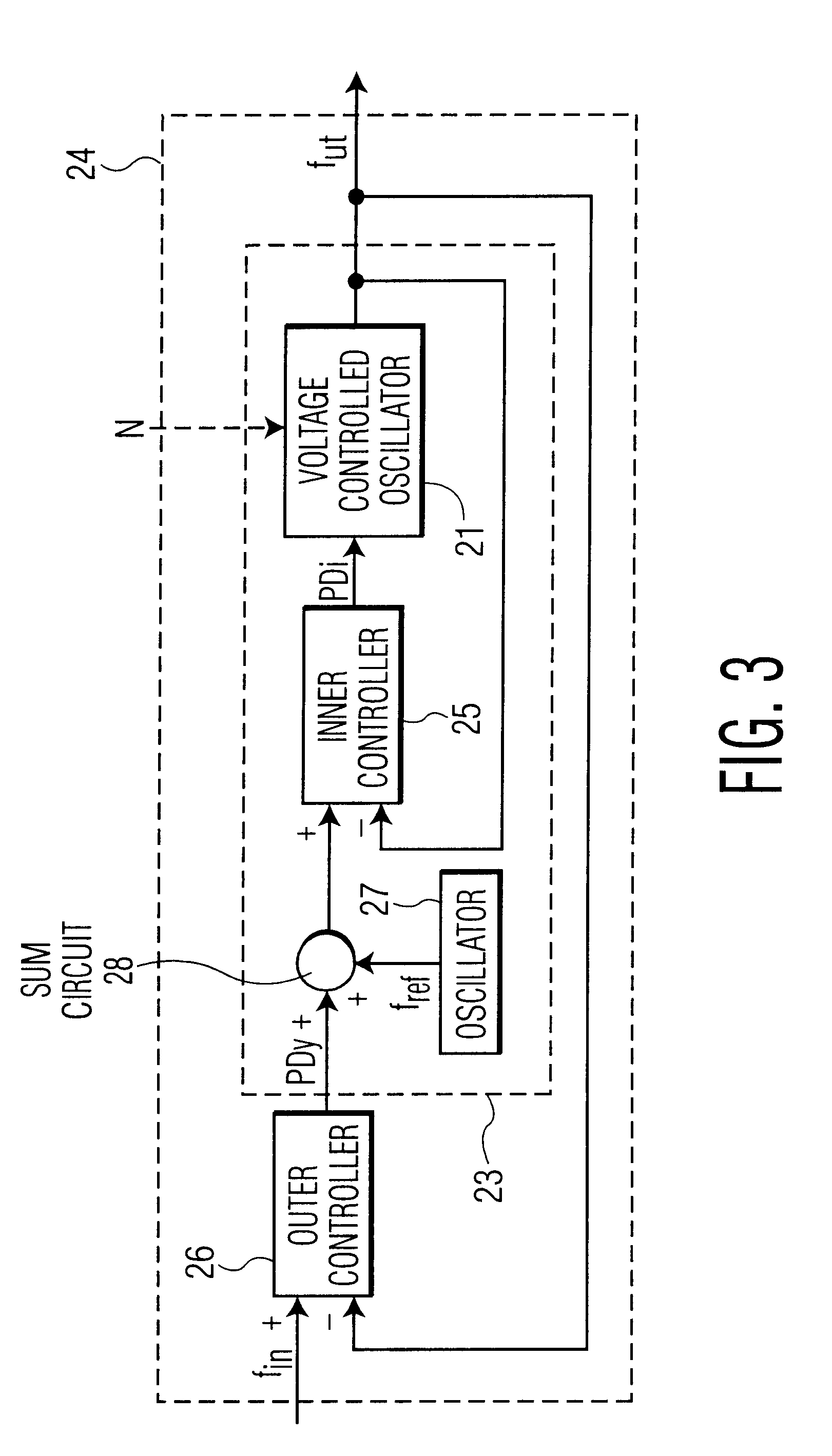

Phase locked loop control via inner and outer feedback control circuits

InactiveUS6384690B1Reduce inputGood frequencyPulse automatic controlNegative feedbackControl circuit

A phase locked loop includes at least one control circuit, where a voltage-controlled oscillator provides an output frequency which is arranged to strive to follow an input frequency. The phase locked loop also includes an outer, slow, negative feedback control circuit, having the input frequency as a setpoint, the output frequency as a process value and an outer output signal. The phase locked loop also includes an inner, fast, negative feedback control circuit, having the sum of a reference frequency from a stable oscillator and the outer output signal as a setpoint, the output frequency as the process value and an inner output signal for controlling the voltage controlled oscillator.

Owner:TELEFON AB LM ERICSSON (PUBL)

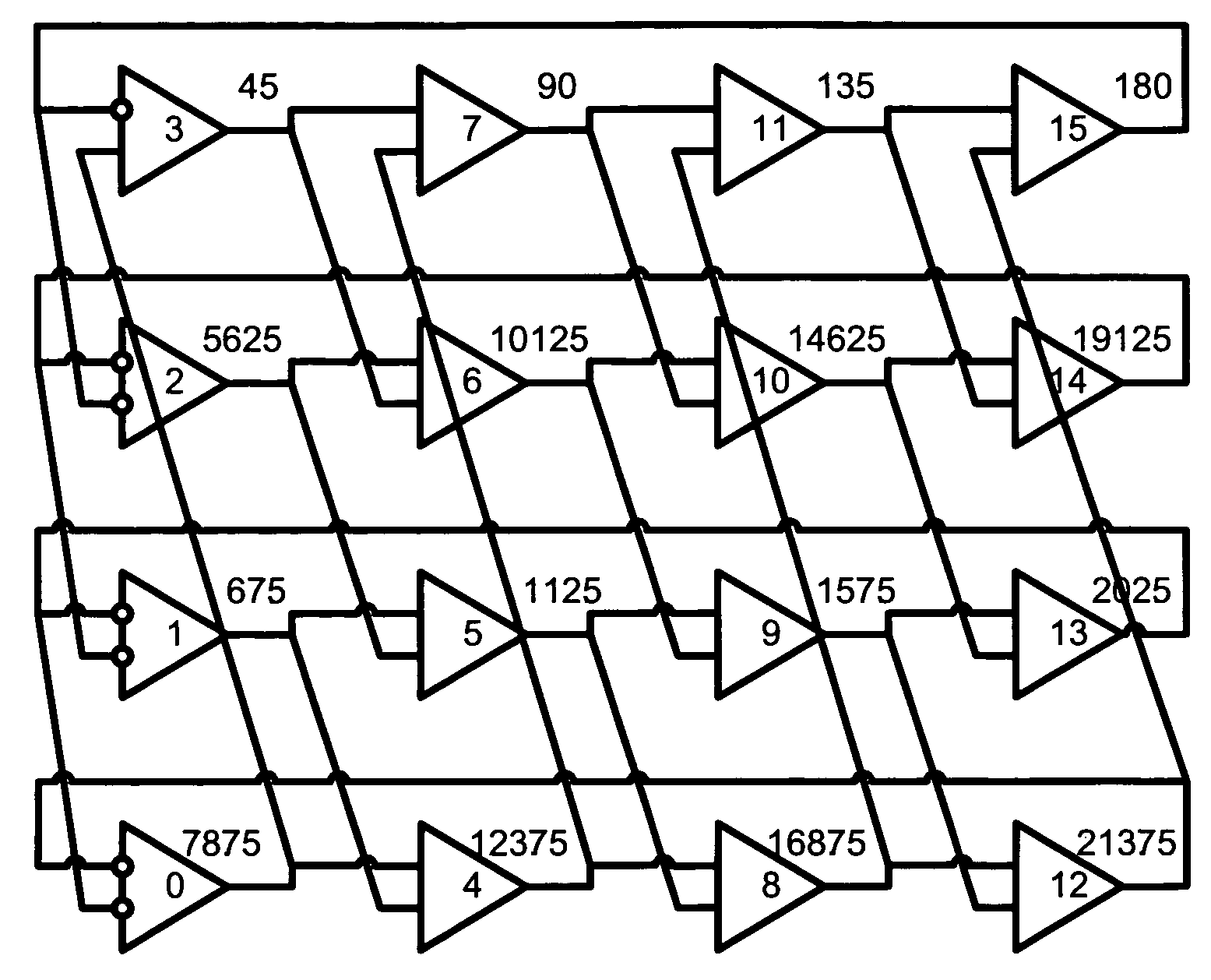

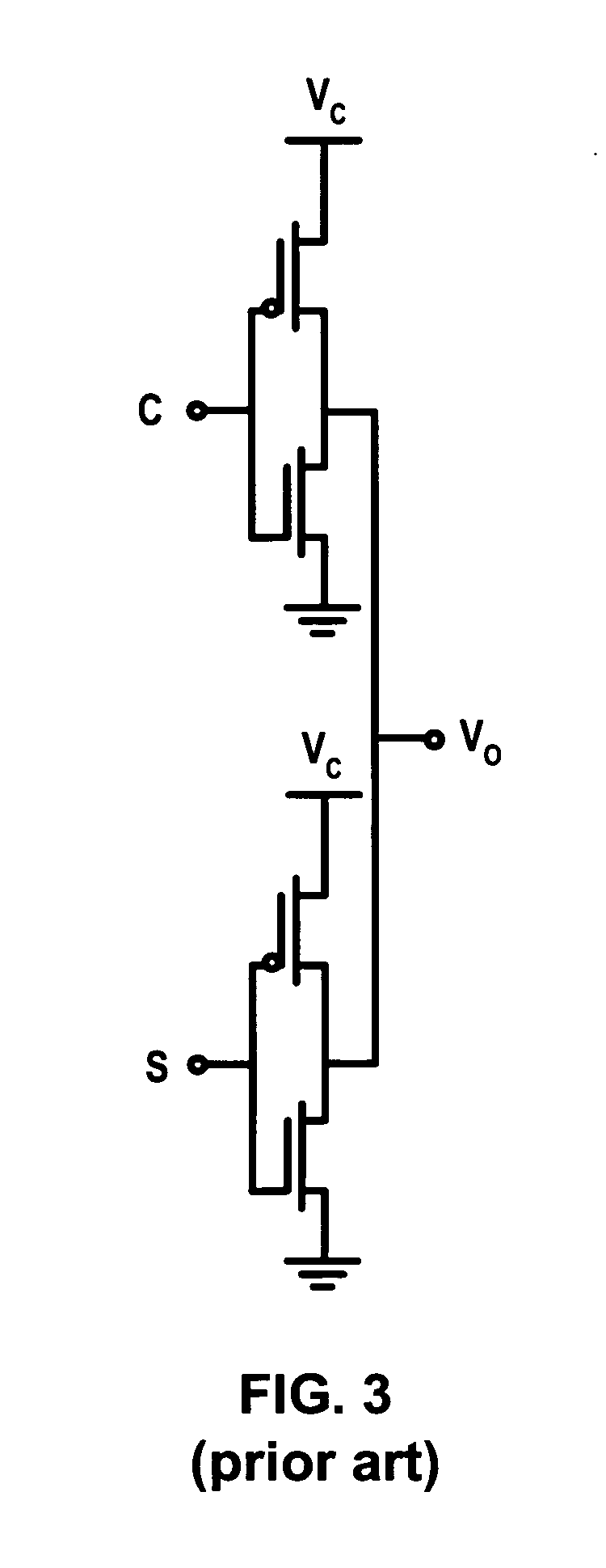

Array oscillator and polyphase clock generator

InactiveUS20060001496A1Increase speedReduce jitterPulse automatic controlPulse generation by logic circuitsMOSFETMultiplexing

The present invention relates generally to array oscillator circuits for use as phase delay generators. More particularly, the present invention relates to a novel array oscillator for providing a plurality of phases which have stable phase relationships. The present invention is particularly applicable to the generation of poly-phase clocks for receivers of very high speed interfaces which employ an over-sampling technique, or multiplexing, and for high speed logic. The array oscillator according to the invention comprises at least one ring oscillator having a plurality of at least two interconnected buffer stages including at least one, or any integer odd number of inverting stages and a series of non-inverting stages, wherein the buffer stages are formed of N-type MOSFET transistors.

Owner:ACUID +1

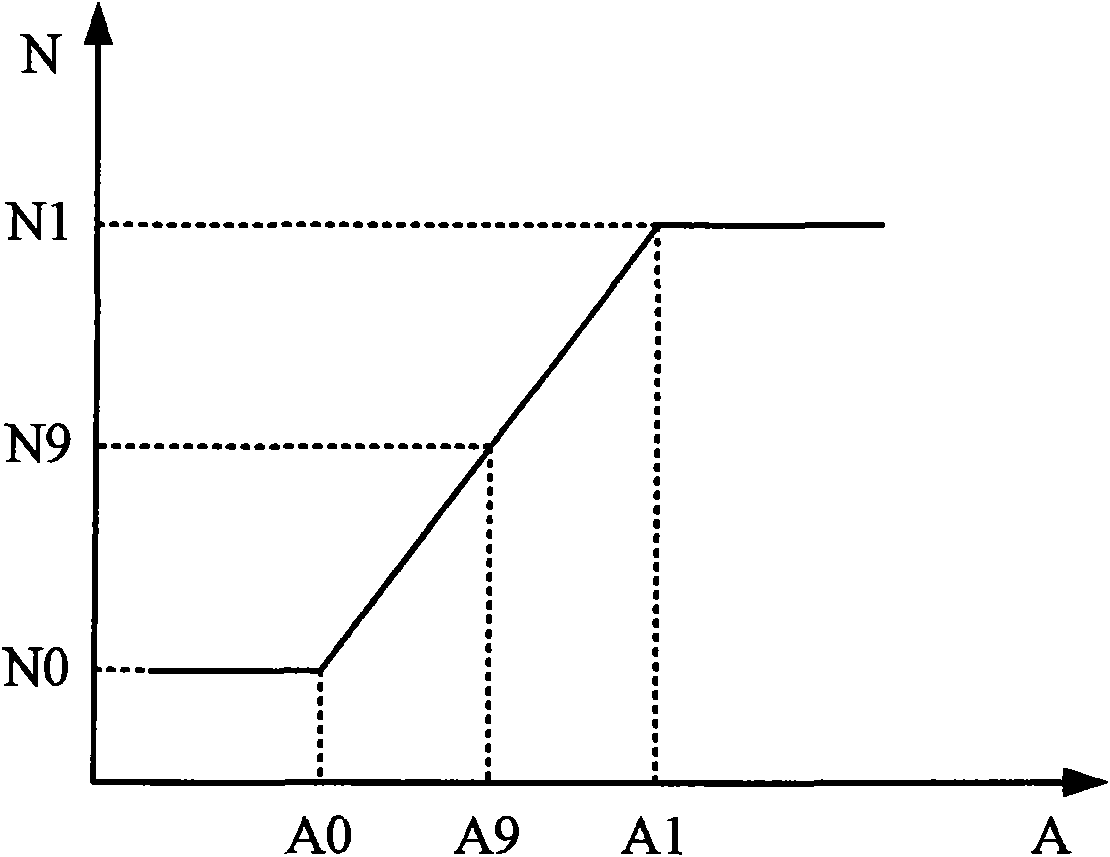

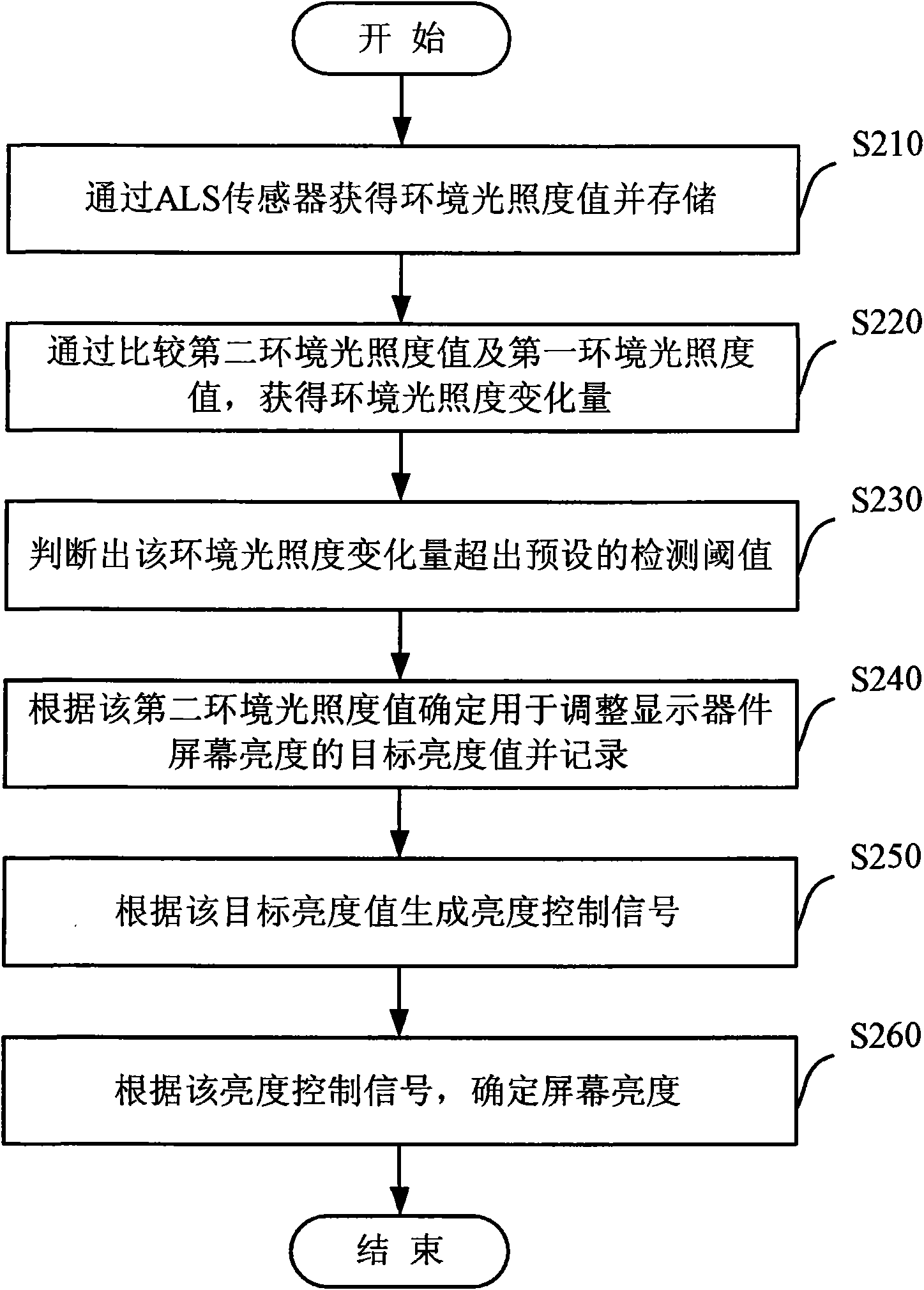

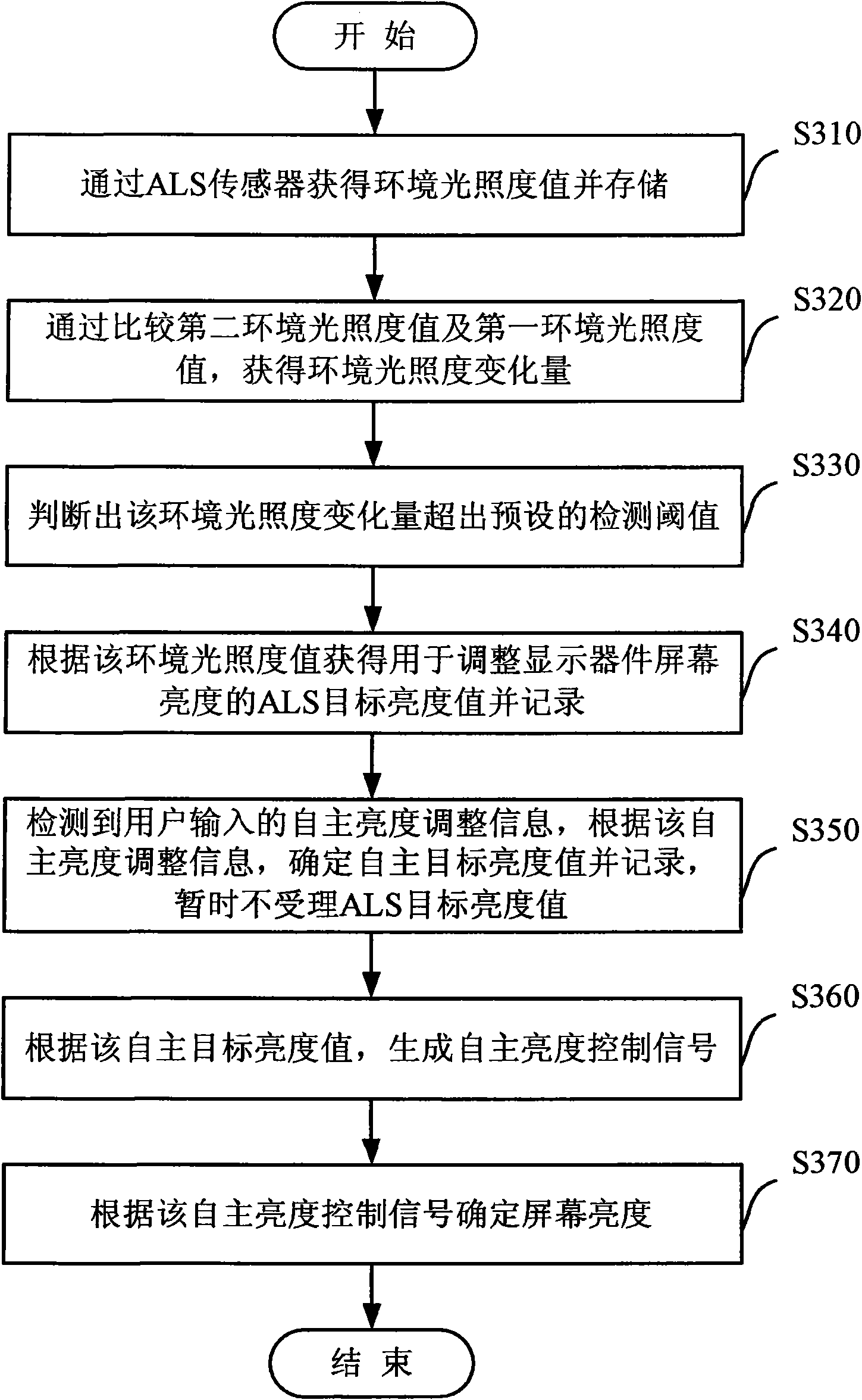

Electronic equipment and display device screen brightness adjusting method thereof

ActiveCN101789230AExtended service lifeImprove experienceCathode-ray tube indicatorsIlluminanceDisplay device

The invention discloses an electronic equipment and display device screen brightness adjusting method thereof, aiming at reducing jitter of the electronic equipment display device screen brightness. The method includes: a first and a second environment illuminance values are obtained, comparison is carried out to obtain an environment illuminance variation, whether the environment illuminance variation is over the preset threshold is judged to produce a judgement result; when the judgement result expresses that the environment illuminance variation is over the threshold, a target brightness value used for adjusting the electronic equipment display device screen brightness is determined according to the second environment illuminance value. The technical scheme of the invention reduces jitter of electronic equipment screen brightness and can prolong service life of screen, save system resource and power consumption and improve user experience.

Owner:LENOVO (BEIJING) CO LTD

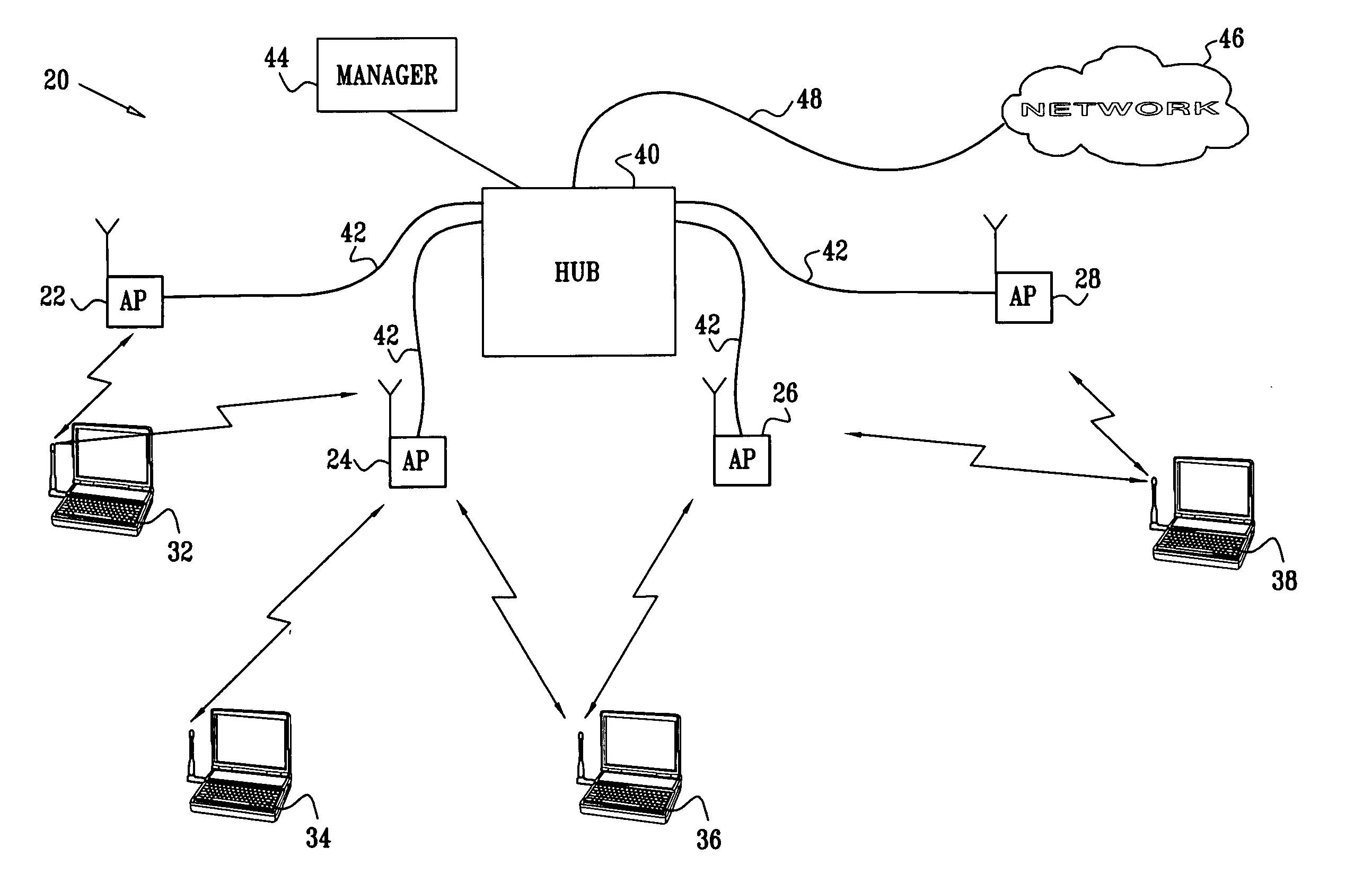

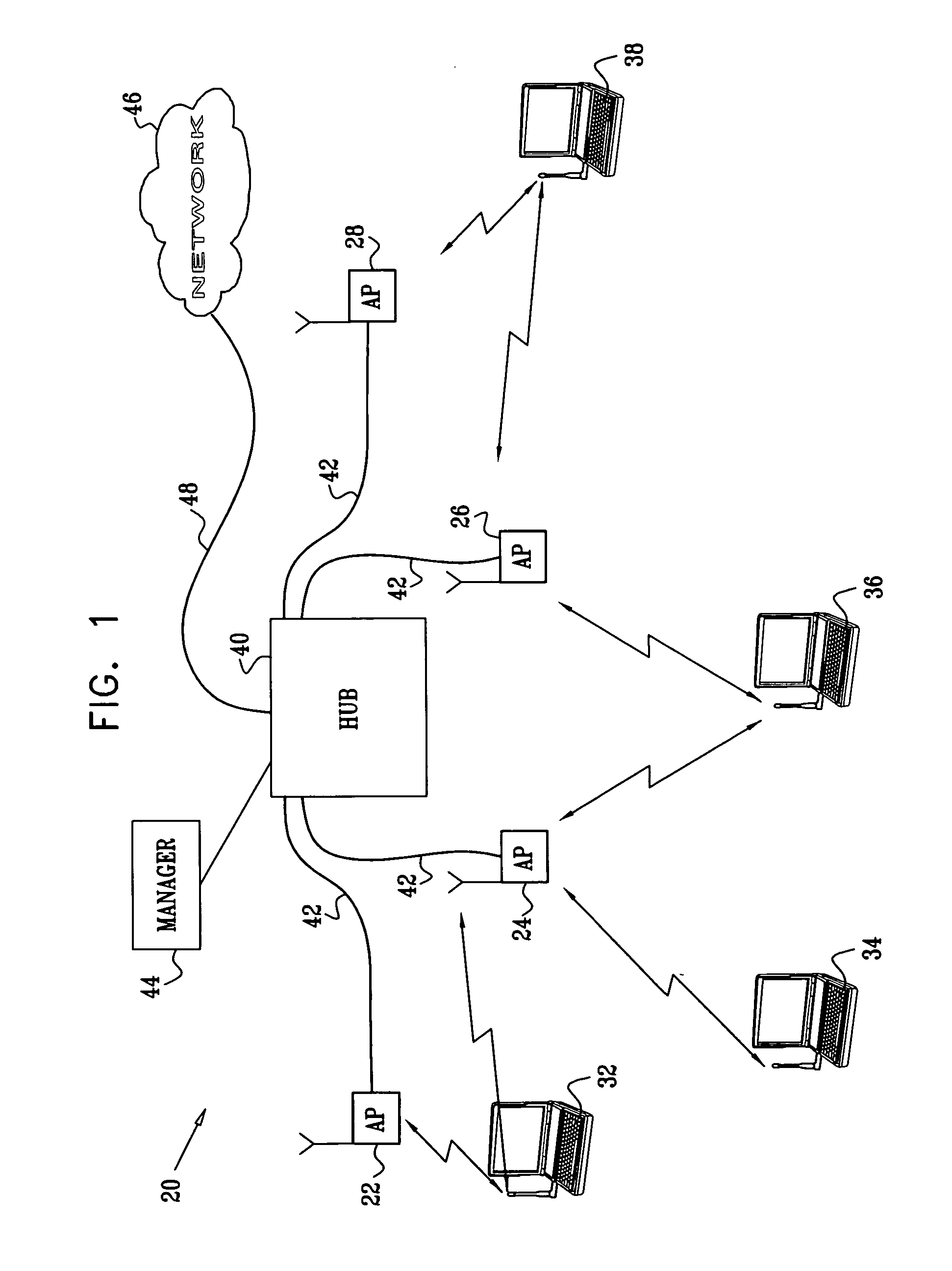

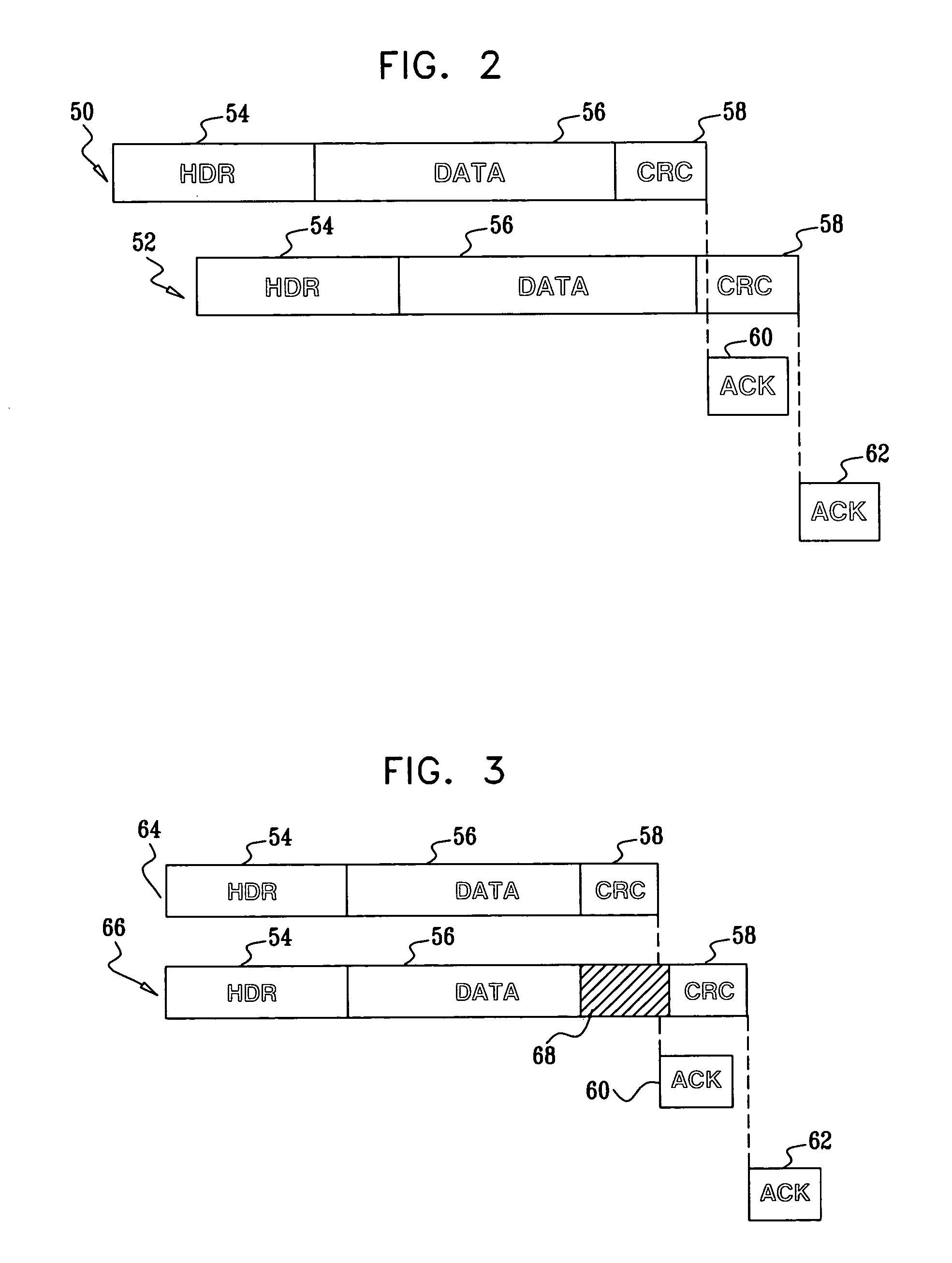

Spatial reuse of frequency channels in a WLAN

InactiveUS20050195786A1Reduce latencyReduce jitterPower managementTransmission control/equalisingSignal responseTelecommunications

A method for communication includes arranging a first plurality of access points, including at least first and second access points, to communicate on a common frequency channel in a wireless local area network (WLAN) with a second plurality of mobile stations, comprising at least first and second mobile stations. The access points are linked to communicate with one another over a communication medium. A message is sent over the communication medium to at least one of the first and second access points so as to cause the first and second access points to simultaneously transmit downlink signals to the first and second mobile stations, respectively. The downlink signals are transmitted simultaneously from the first and second access points responsively to the message.

Owner:ALLIED TELESIS ISRAEL LTD

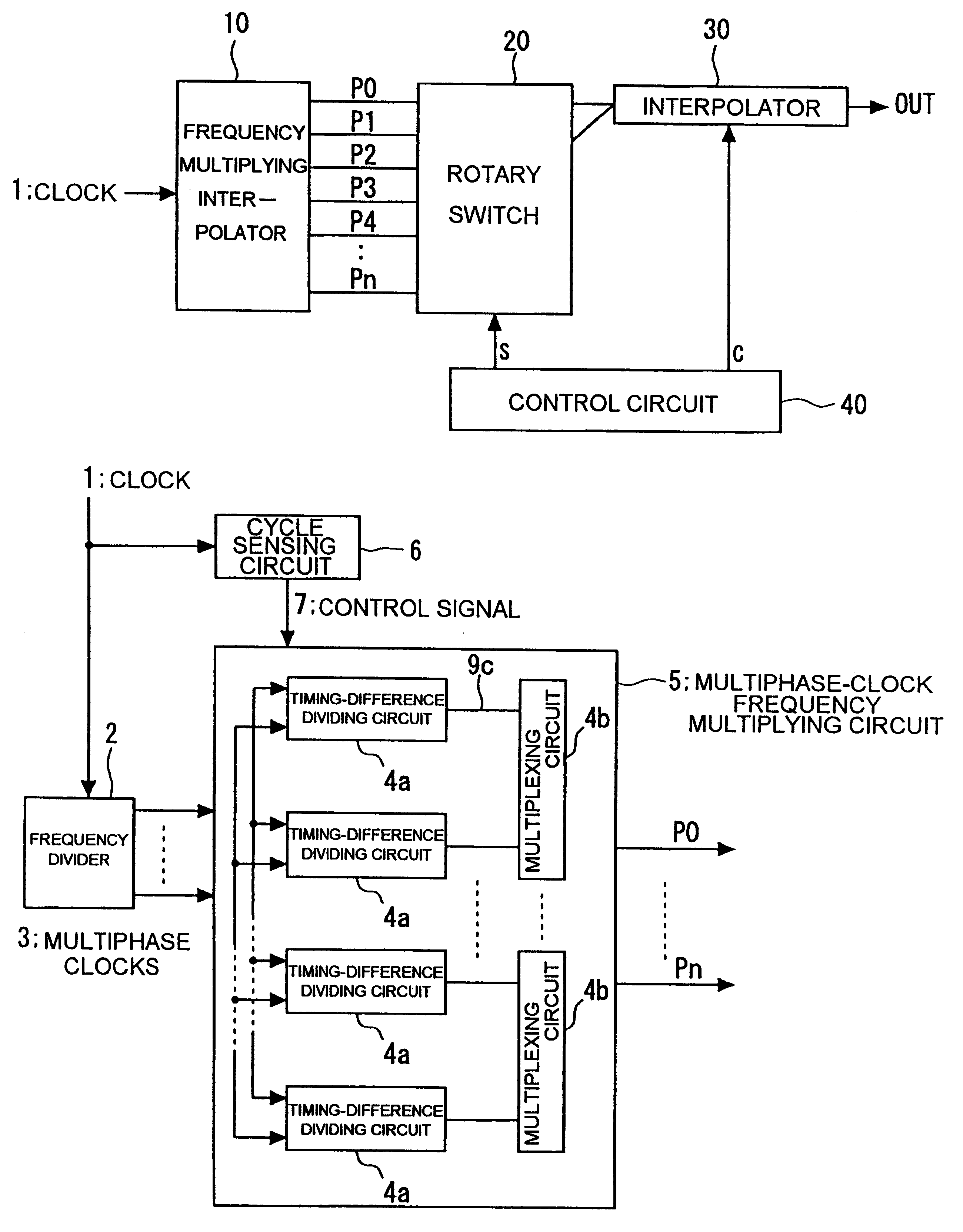

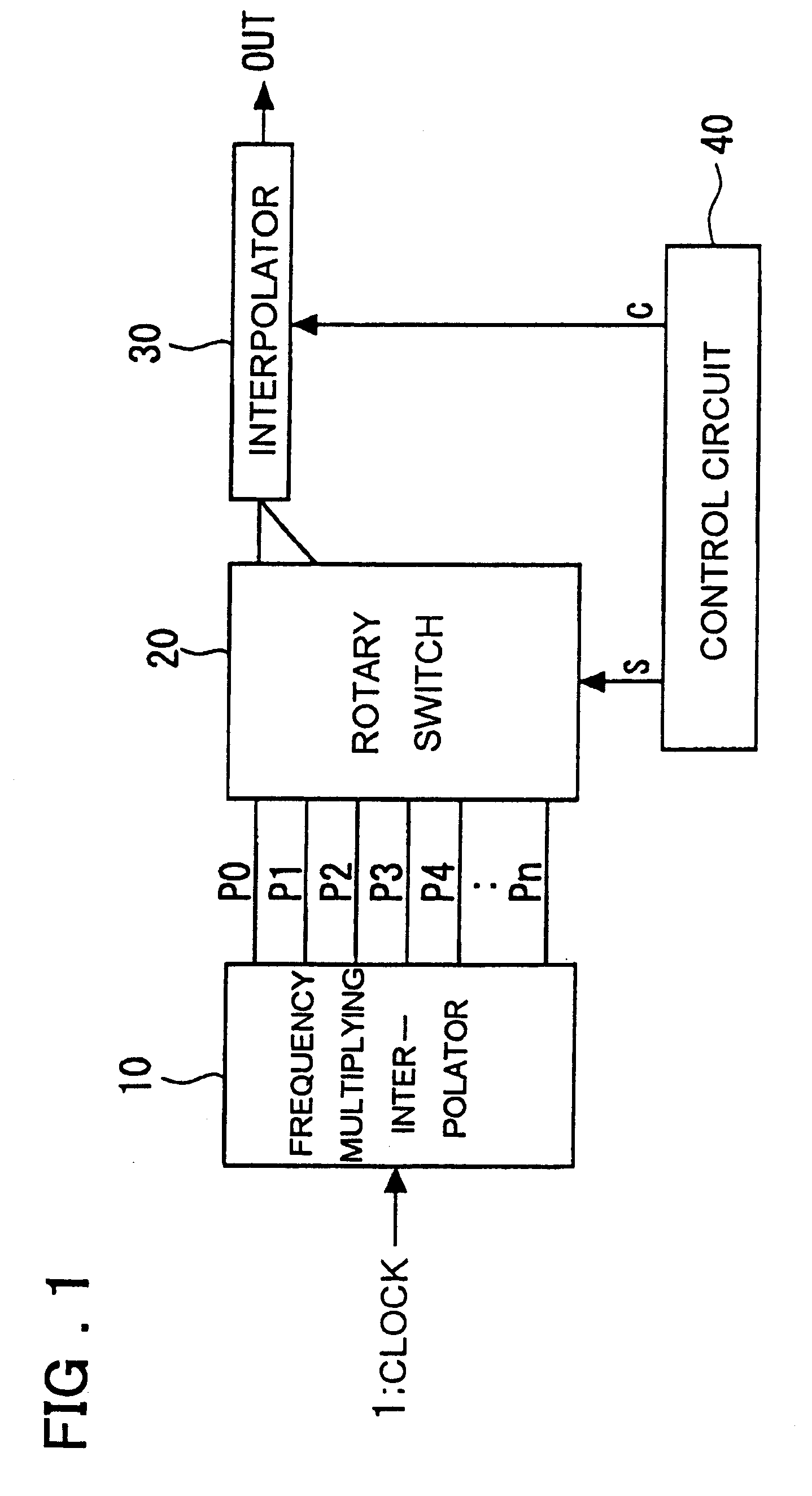

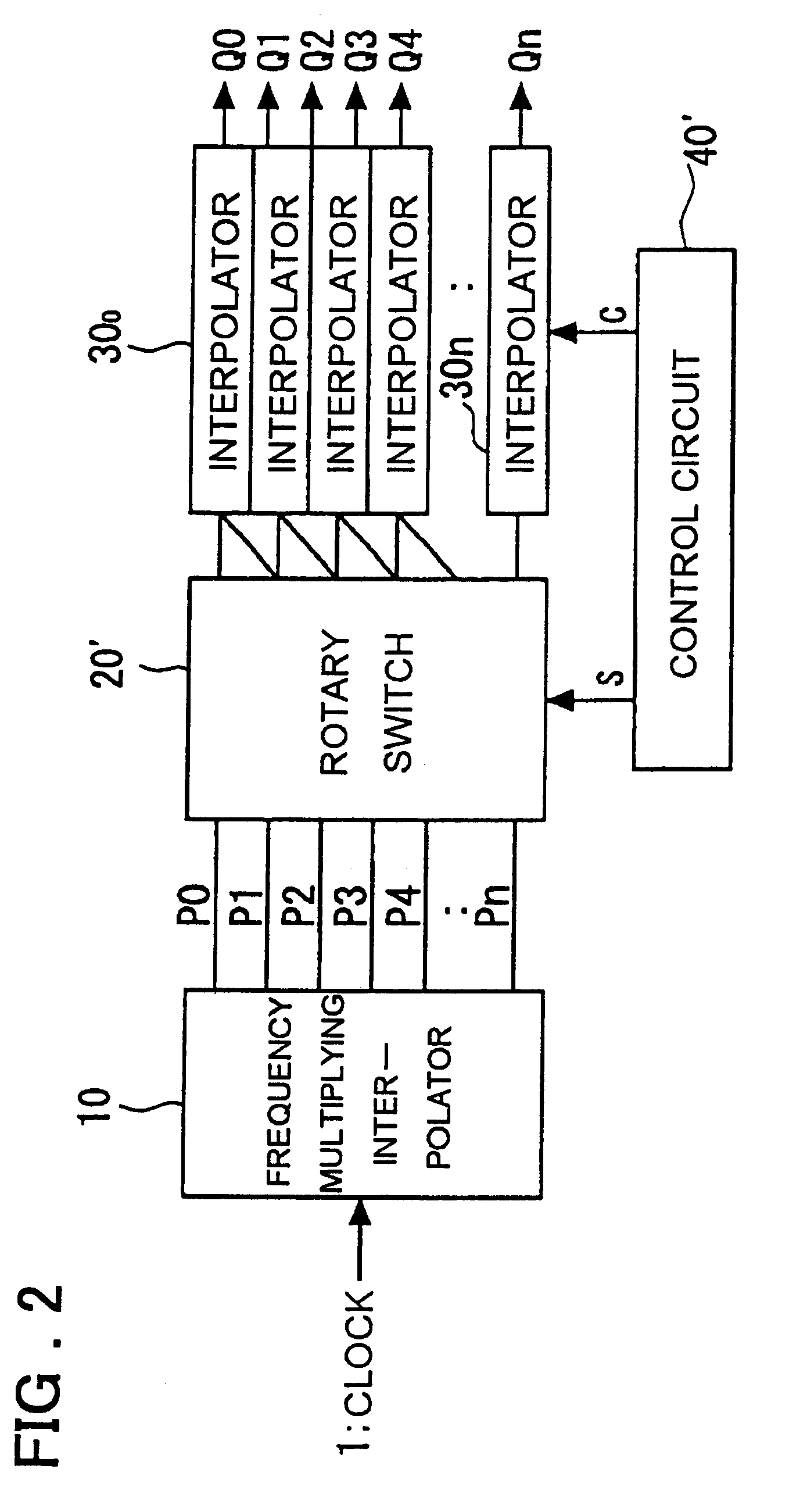

Clock control circuit and clock control method

InactiveUS20010026179A1Reduce errorsEliminate fluctuationsPulse automatic controlContinuous to patterned pulse manipulationControl switchControl theory

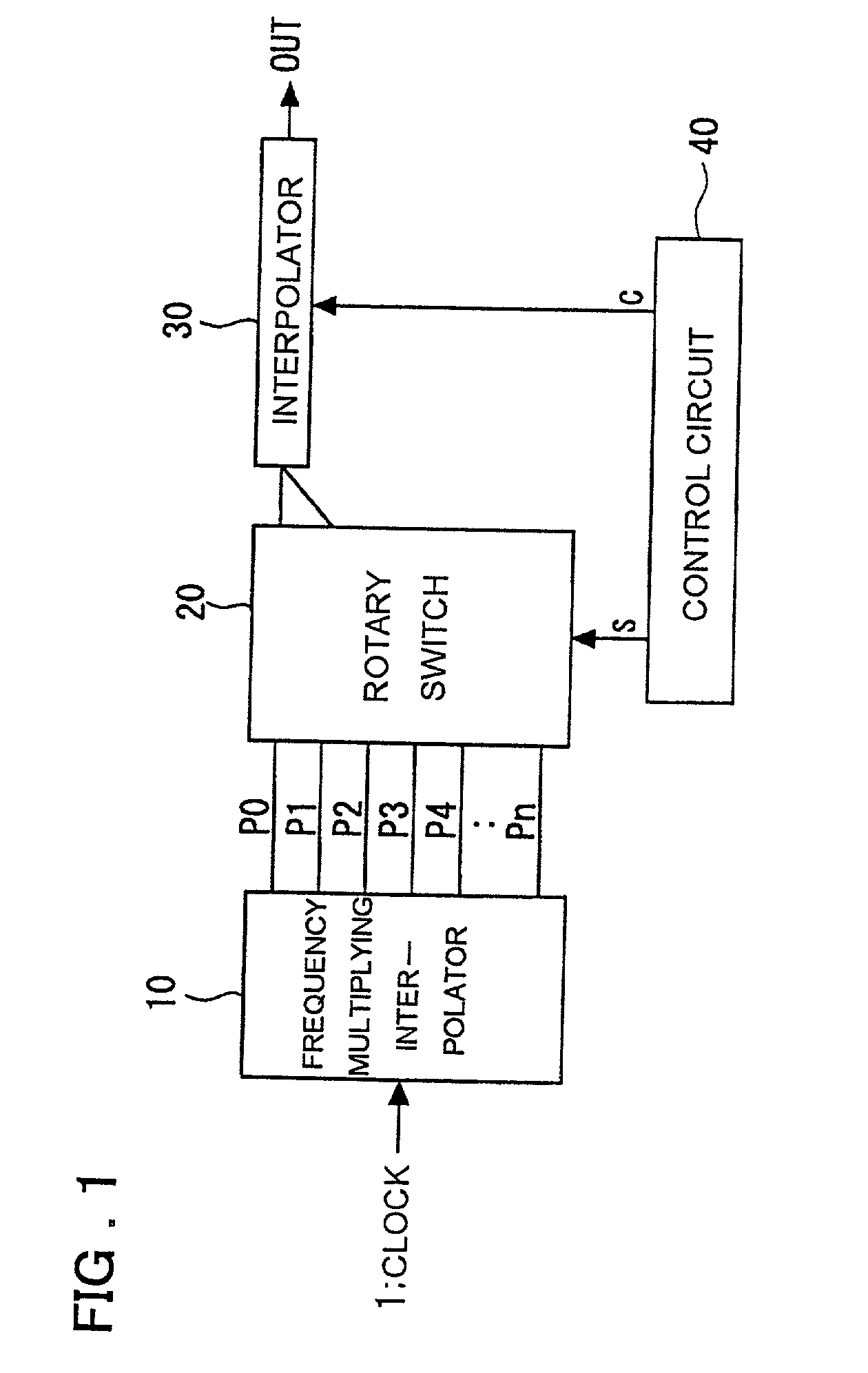

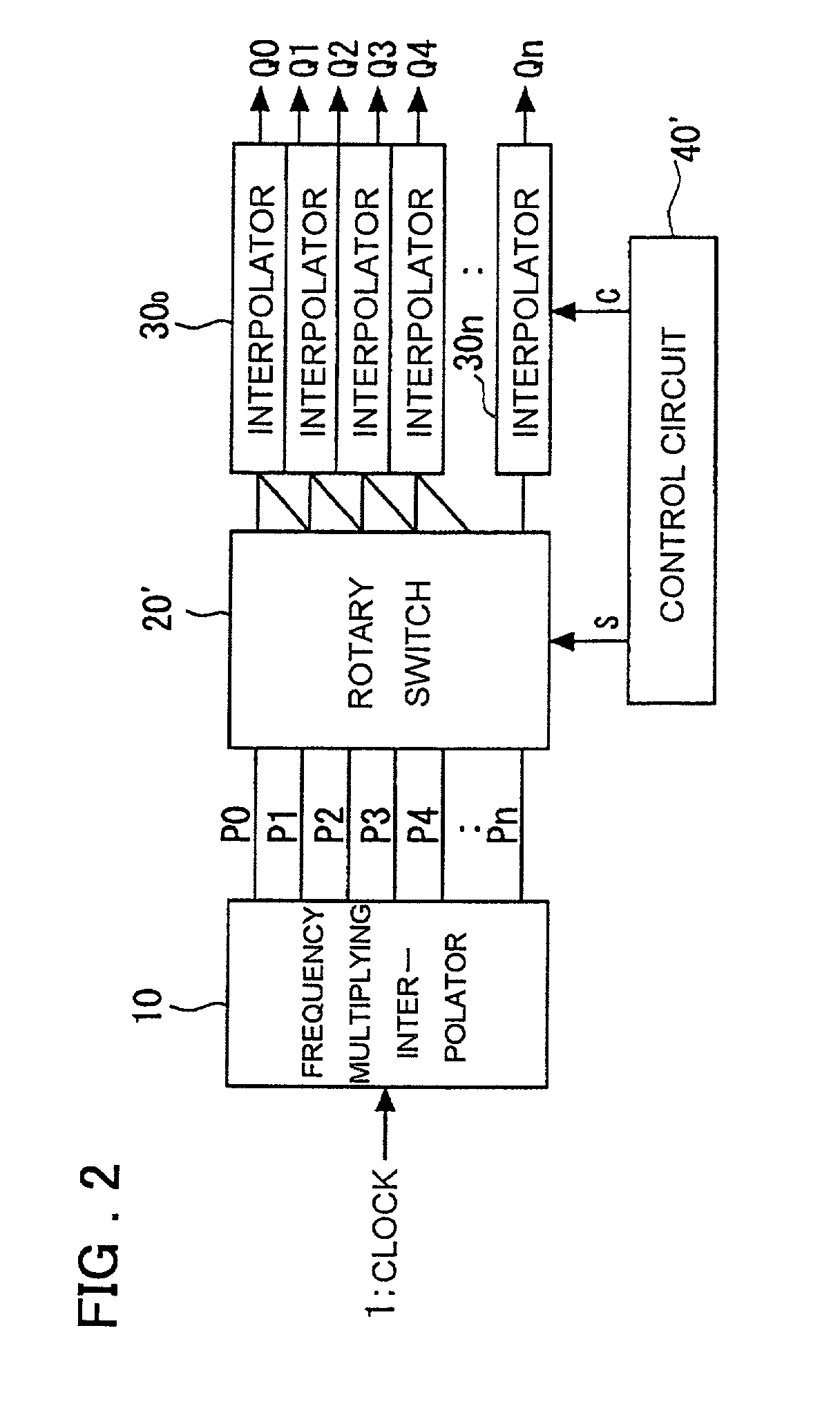

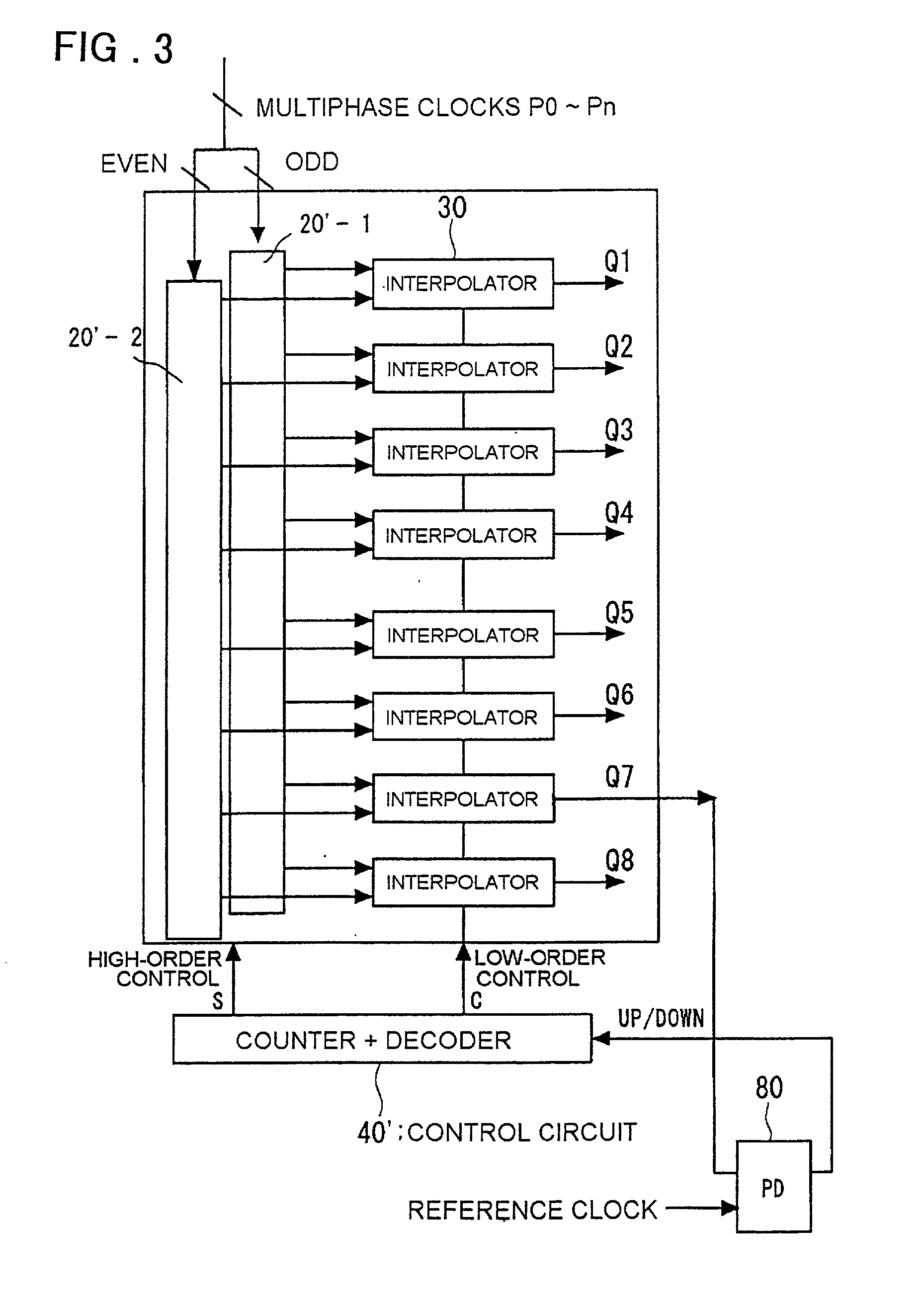

A clock control circuit which includes a frequency multiplying interpolator for generating and outputting multiphase clocks by frequency multiplying an input clock; a switch for outputting two of the multiphase clocks input thereto from the frequency multiplying interpolator; a fine adjusting interpolator, to which the two outputs from the switch are applied, for outputting a signal obtained by internally dividing the phase difference between the two outputs; and a control circuit for controlling the switching of the switch and varying the internal-division ratio of the fine adjusting interpolator.

Owner:RENESAS ELECTRONICS CORP

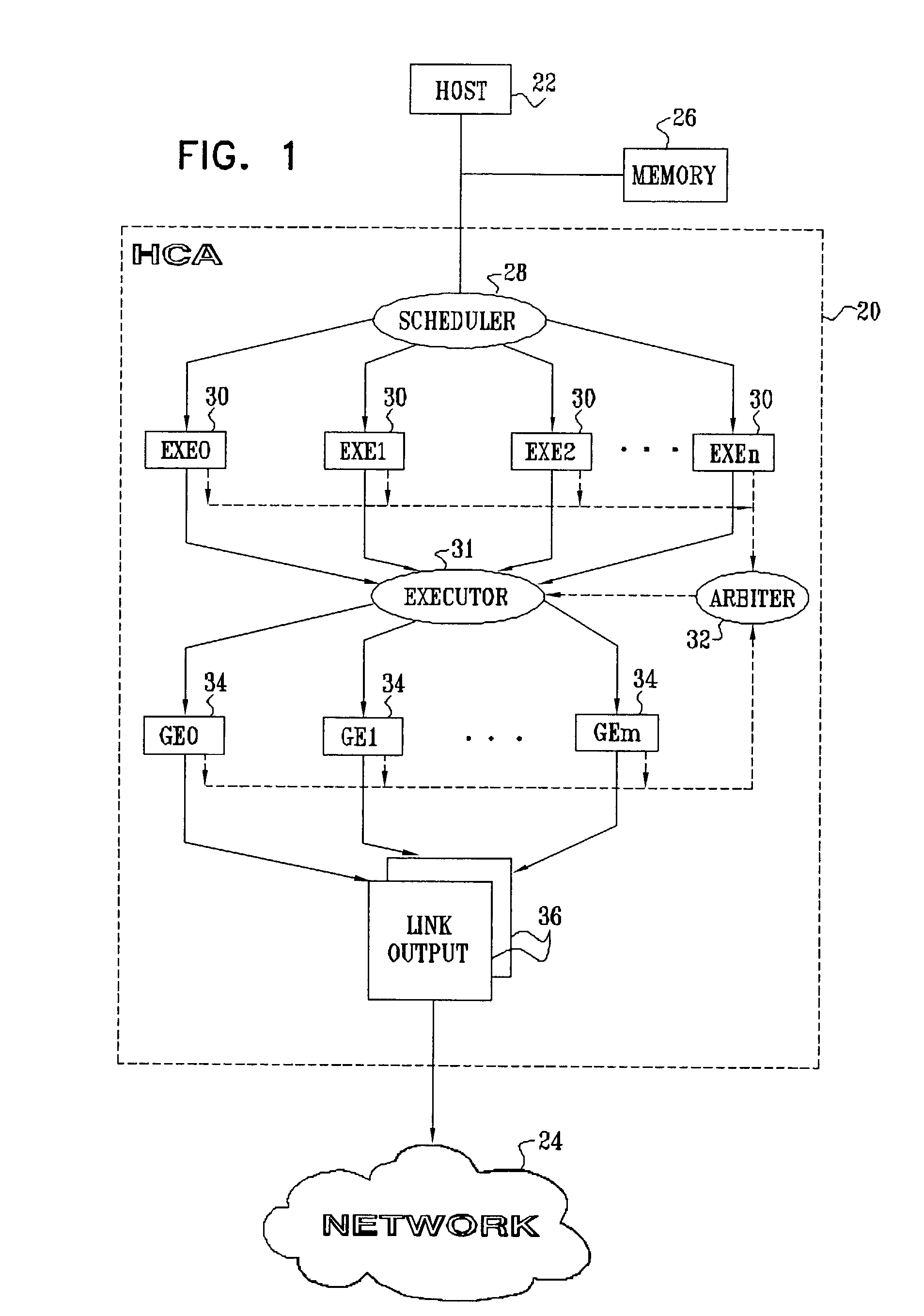

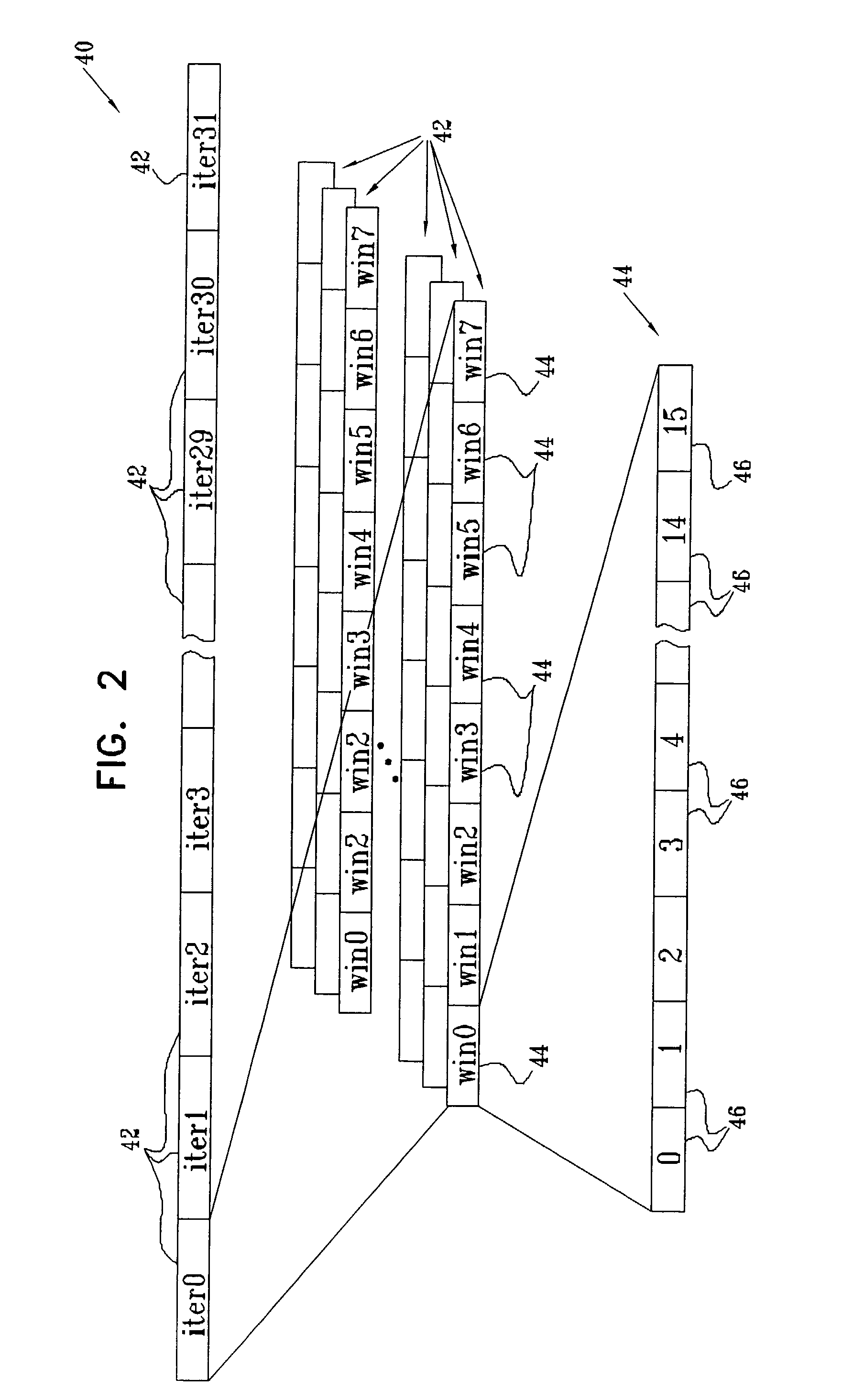

Round-robin arbiter with low jitter

InactiveUS7149227B2Reduce congestionReduced likelihoodTime-division multiplexRadio transmissionMultiplexingComputer network

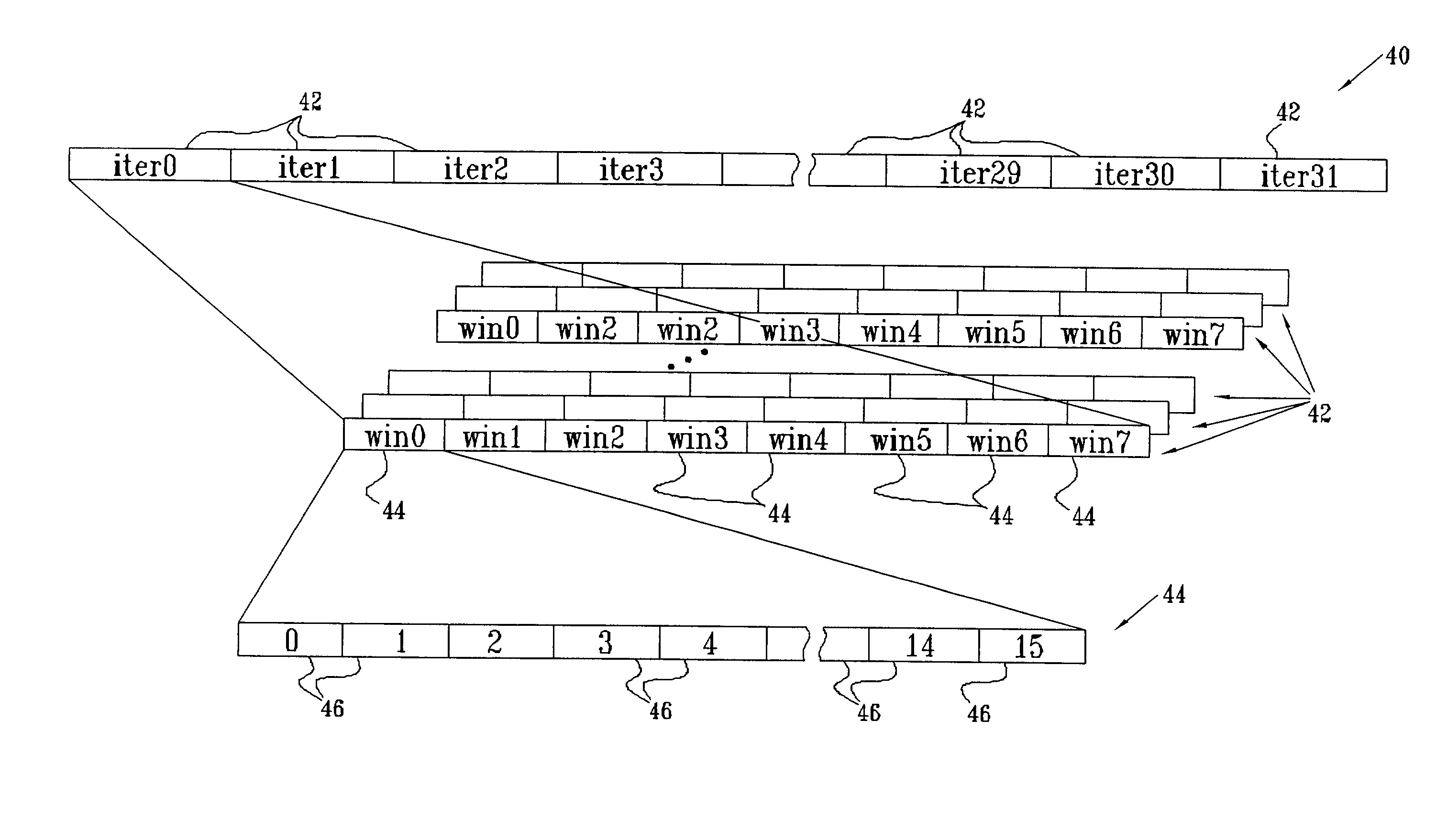

A method for allocating a processing resource among multiple inputs includes defining a sequence of multiplexing iterations, each such iteration including a first plurality of windows, each such window containing a second plurality of time slots. A respective weight is assigned to each of the inputs, and each of the inputs is allotted one of the time slots in each of a respective number of the windows in each of the iterations, the respective number being determined by the respective weight. Each of the inputs is then provided with access to the processing resource during the time slots allotted thereto.

Owner:MELLANOX TECHNOLOGIES LTD

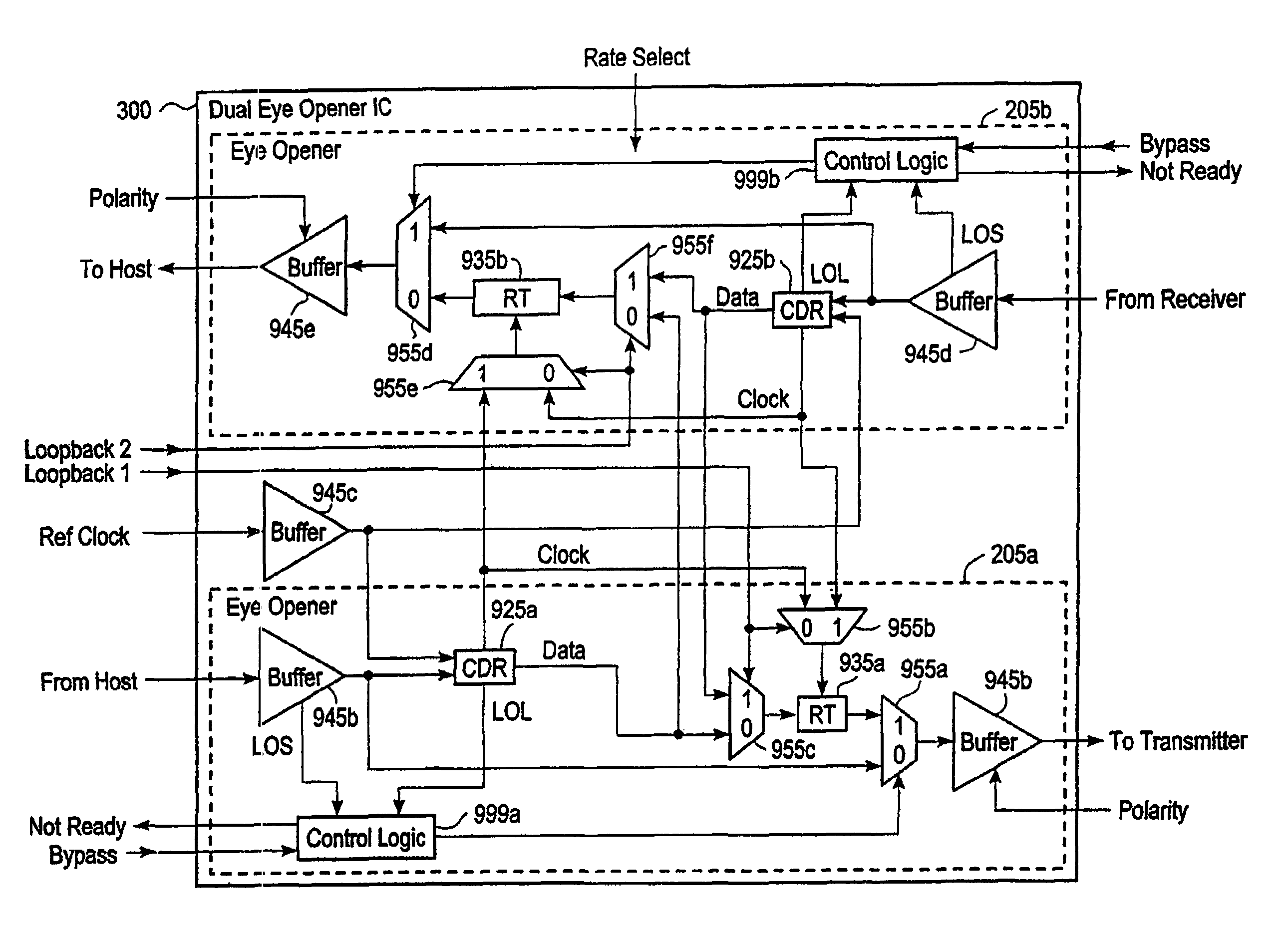

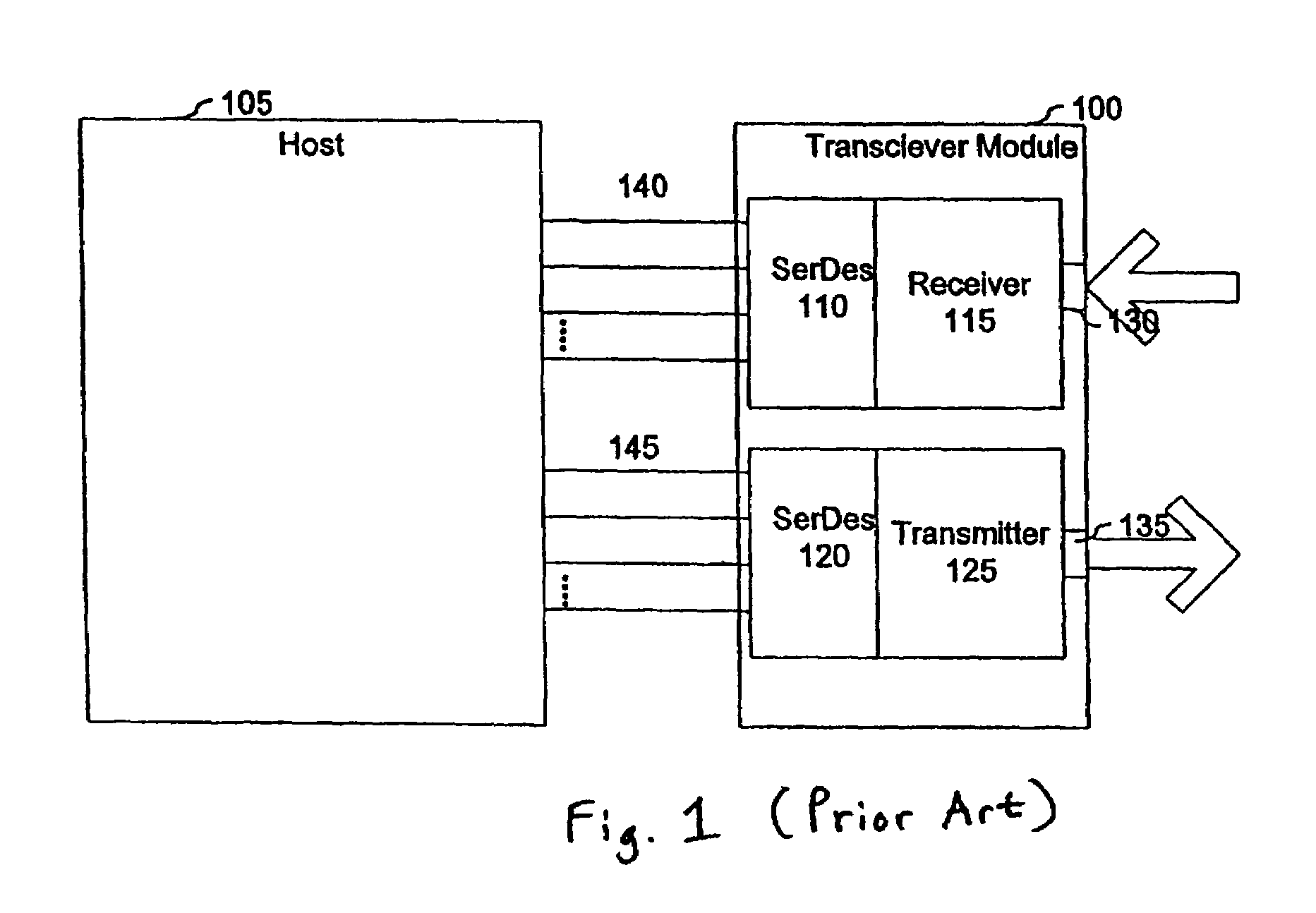

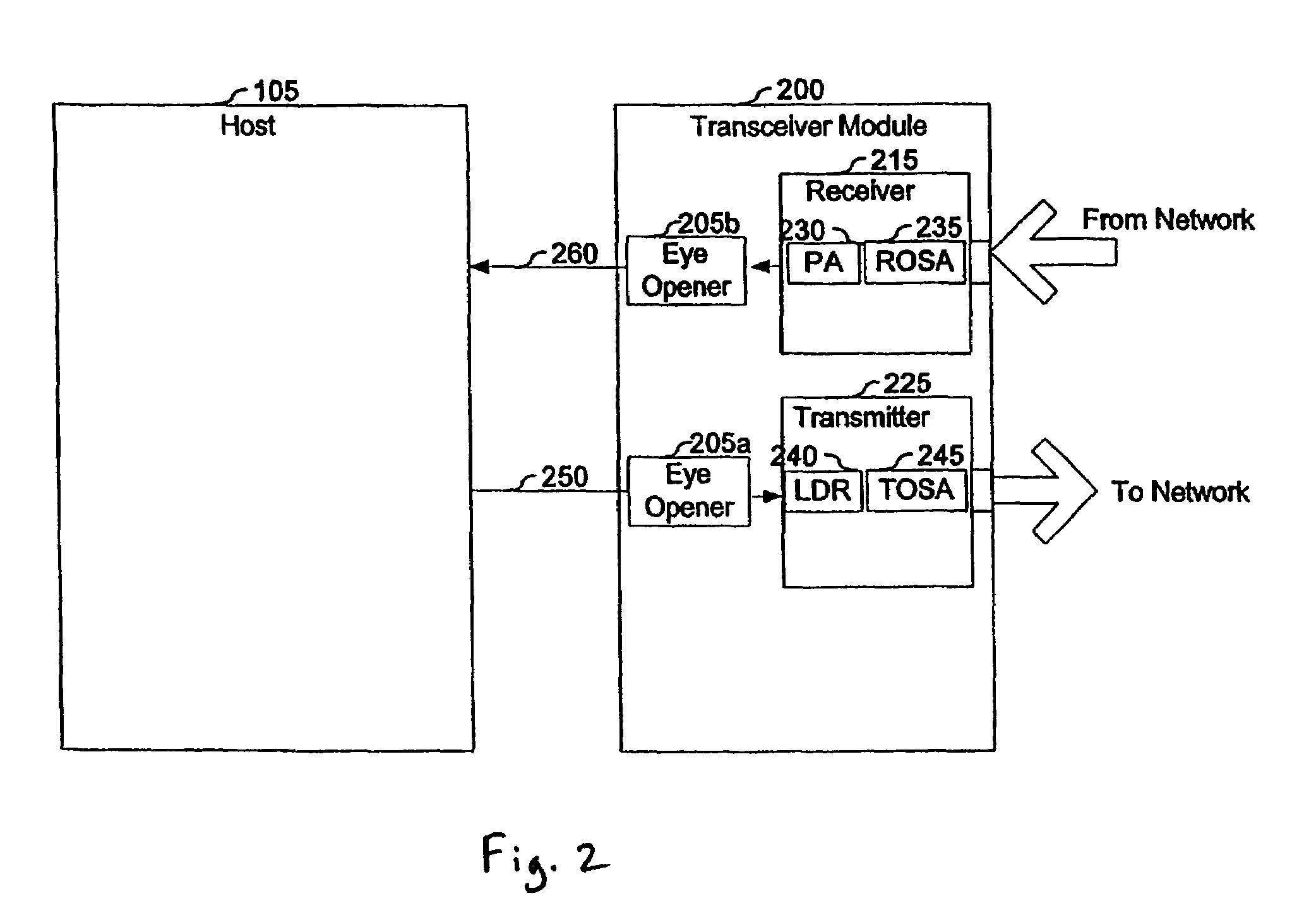

Integrated circuit with dual eye openers

ActiveUS7099382B2Reduce jitterSave energyRepeater/relay circuitsElectromagnetic transceiversTransceiverEngineering

A transceiver module having integrated eye diagram opening functionality for reducing jitter is described. The transceiver module may include a transmitter eye opener and a receiver eye opener integrated in a single circuit. The transceiver module may also include serial control and various other integrated components. Other functionalities that may be integrated on the transceiver module include loopback modes, bypass features, bit error rate testing, and power down modes.

Owner:II VI DELAWARE INC

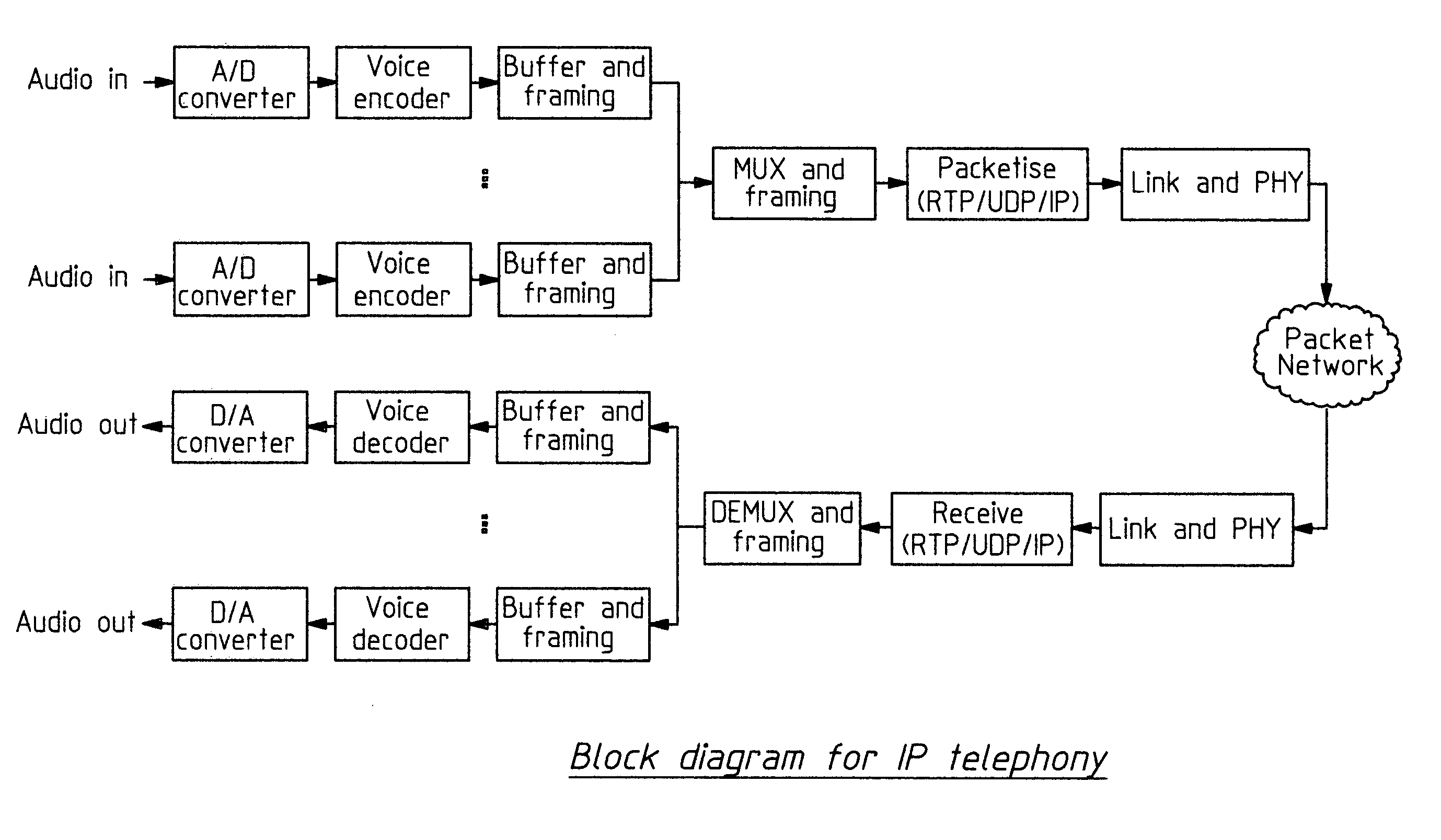

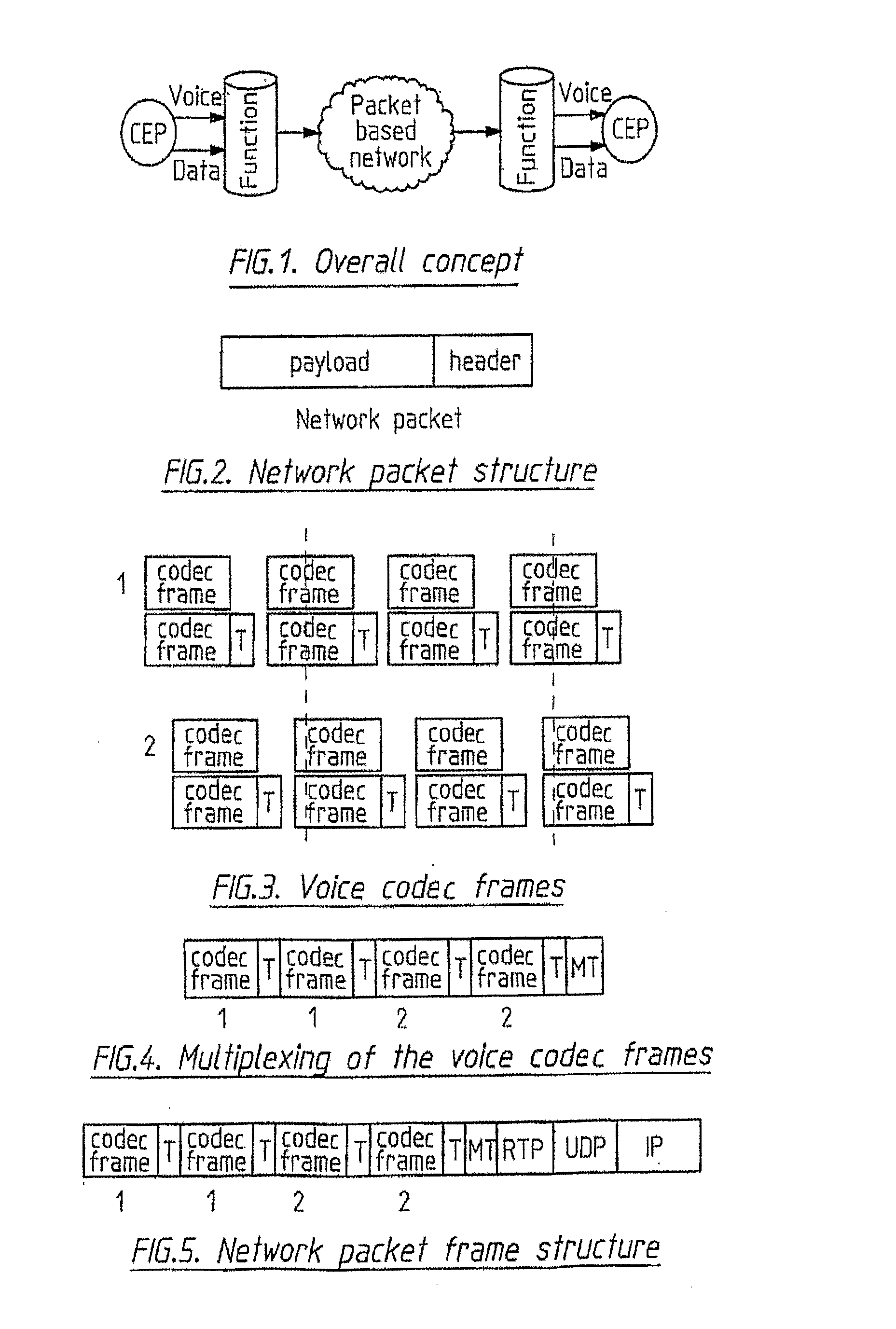

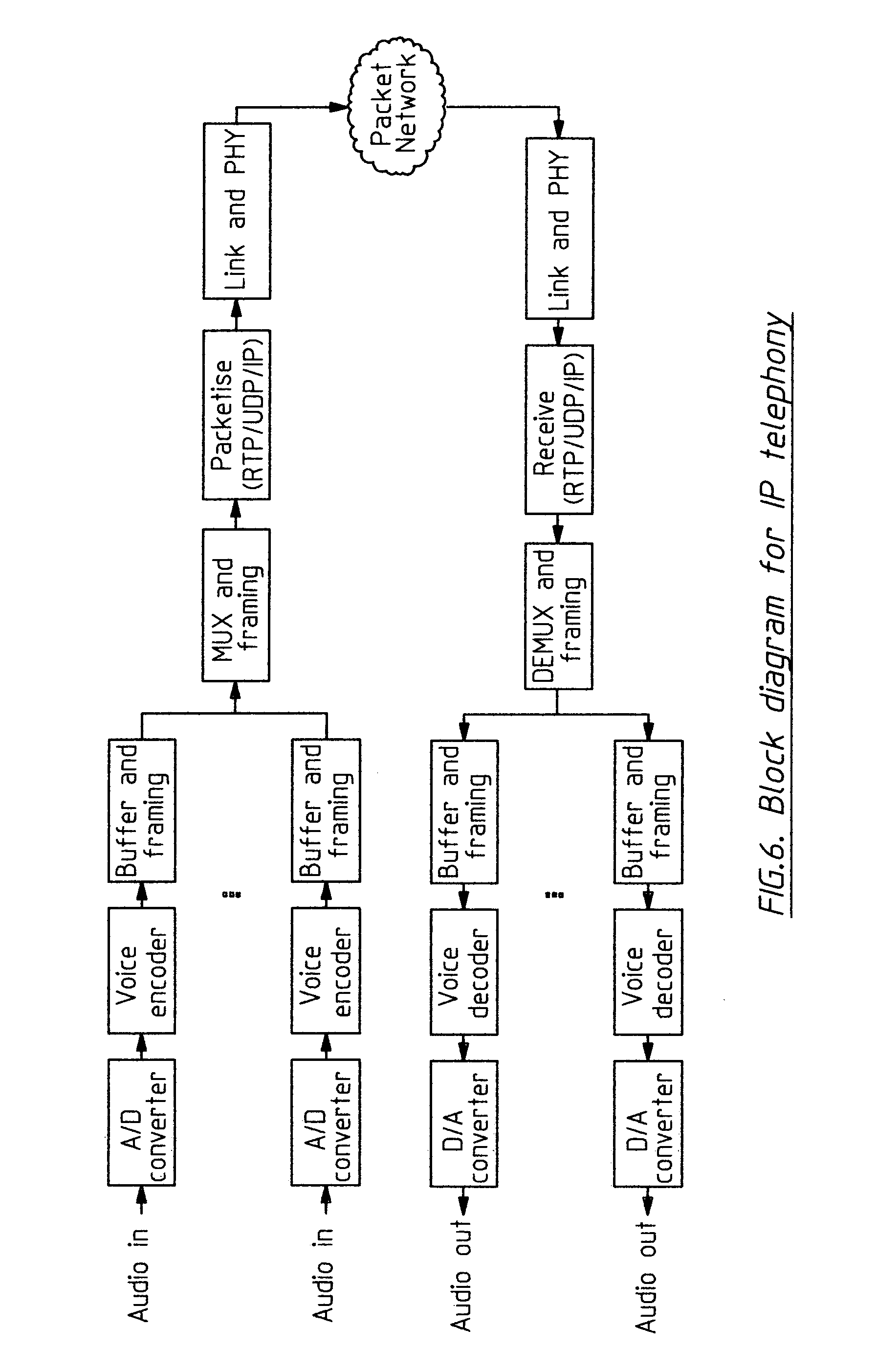

Packet based communications

InactiveUS20100014510A1Raise the ratioImprove efficiencyNetwork connectionsData trafficCommunication endpoint

This invention is applicable to packet based, rate limited radio links, such as satellite or terrestrial wireless digital communications systems. These communications networks concurrently carry time-critical traffic, such as voice or multimedia, and non time-critical traffic, such as generic data traffic, between two or more communication end points. The communication end points may be connected through a number of heterogenous networks and the end to end throughput characteristics may vary over time. A first aspect of the invention concerns a method for generating packets. In other aspects the invention concerns a computer system for use in packet based communications, a computer protocol for packet based communications and a communications packet. The invention involves determining a “time slice” packet size from the link speed and the interval of time extending between the times at which packets are selected for output from a buffer to the transmission interface. It also involves creating a network packet from frames of time-critical data generated during the interval, where the packet is synchronised to both existing timing requirements of the time-critical frames and the link speed. Then, adding non time-critical data to the network packet if its size had not exceeded the determined “time slice” packet size.

Owner:NAT ICT AUSTRALIA

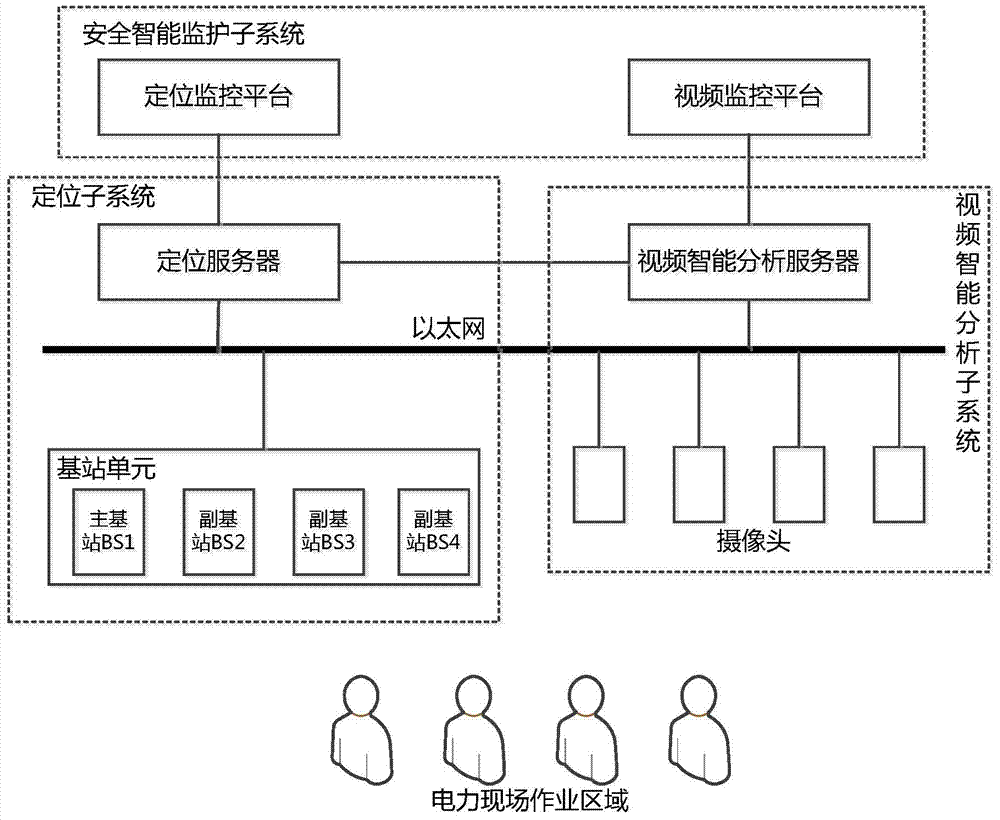

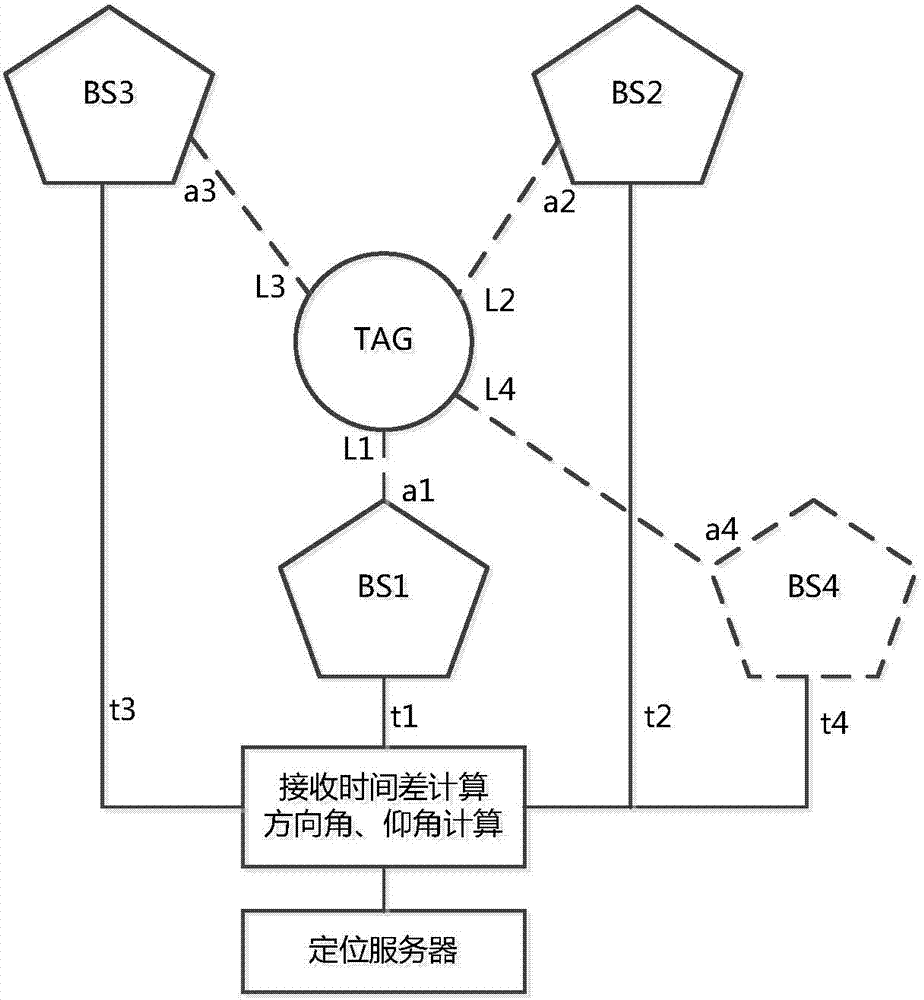

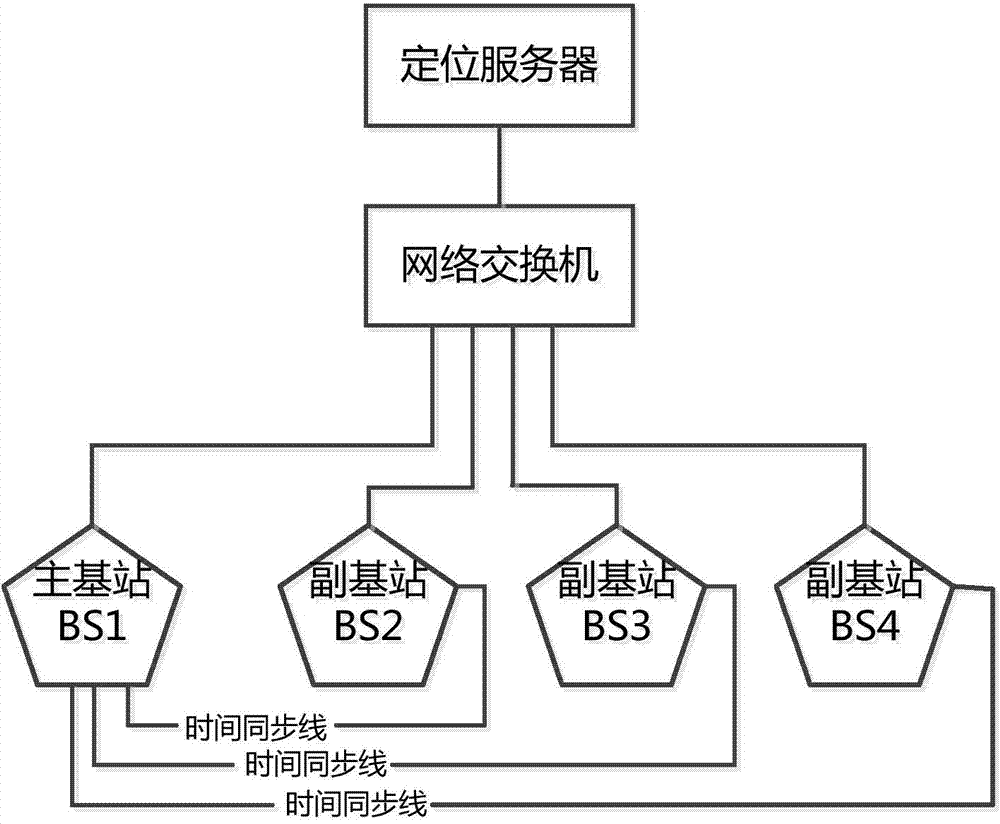

Intelligent safety monitor system of electric power working site

ActiveCN103617699APrecise positioningAccurate monitoringClosed circuit television systemsAlarmsElectric power systemEngineering

The invention provides an intelligent safety monitor system of an electric power working site. The intelligent safety monitor system of the electric power working site comprises a locating sub-system, an intelligent video analysis sub-system and an intelligent safety monitor sub-system. The locating sub-system comprises a locating server, a locating label and a base station unit. The base station unit obtains the position information of the locating label by detecting UWB signals and MAC data sent by the locating label, and sends the position information to the locating server. The intelligent video analysis sub-system analyzes a video stream of the electric power working site so as to monitor the operation actions of working personnel, and gives an alarm according to the analysis result. The intelligent safety monitor sub-system comprises a locating monitor platform and a video monitor platform. Compared with the prior art, the intelligent safety monitor system of the electric power working site can effectively prevent the personnel from breaking rules, prevent or reduce personal injury of an electric power system, and be widely applied to the electric power safety working and electric power construction working site.

Owner:STATE GRID CORP OF CHINA +2

XFP transceiver with 8.5G CDR bypass

ActiveUS20050169585A1Reduce jitterSave energyError preventionFrequency-division multiplex detailsEngineeringXFP transceiver

This disclosure concerns transceivers that include CDR bypass functionality. In one example, a 10 G XFP transceiver module includes integrated CDR functionality for reducing jitter. The 10 G XFP transceiver module also implements CDR bypass functionality so that the CDR can be bypassed at rate less than about 10 Gb / s, such as the Fibre Channel 8.5 Gb / s rate for example.

Owner:II VI DELAWARE INC

Clock control circuit and clock control method

InactiveUS6380774B2Inaccurate to some degreeReduce jitterPulse automatic controlContinuous to patterned pulse manipulationPhase differenceEngineering

A clock control circuit which includes a frequency multiplying interpolator for generating and outputting multiphase clocks by frequency multiplying an input clock; a switch for outputting two of the multiphase clocks input thereto from the frequency multiplying interpolator; a fine adjusting interpolator, to which the two outputs from the switch are applied, for outputting a signal obtained by internally dividing the phase difference between the two outputs; and a control circuit for controlling the switching of the switch and varying the internal-division ratio of the fine adjusting interpolator.

Owner:RENESAS ELECTRONICS CORP

Audio-to-video synchronization system and method for packet-based network video conferencing

InactiveUS7664057B1Overcome disadvantagesReduce jitterMultiplex system selection arrangementsSpecial service provision for substationData synchronizationTimestamp

Synchronizing audio and video streams in packet-based networks requires synchronization of packet timestamps. The present invention provides such synchronization without resort to a network time standard. In one embodiment of the present invention, pairs of timestamp synchronized signals, such as audio and video signals, not having a common timestamp clock are mixed. One of the signals, for example, the audio signals, is mixed first while preserving the original audio timestamps. The preserved timestamp information is then used to synchronize the timestamps of the unmixed signals, in this example the video signals, to provide synchronization of all signals. In another embodiment, the present invention uses packets containing calibration of timestamps to reduce jitter. The present invention also includes specifications for a packet for transmitting timestamp information.

Owner:CISCO TECH INC

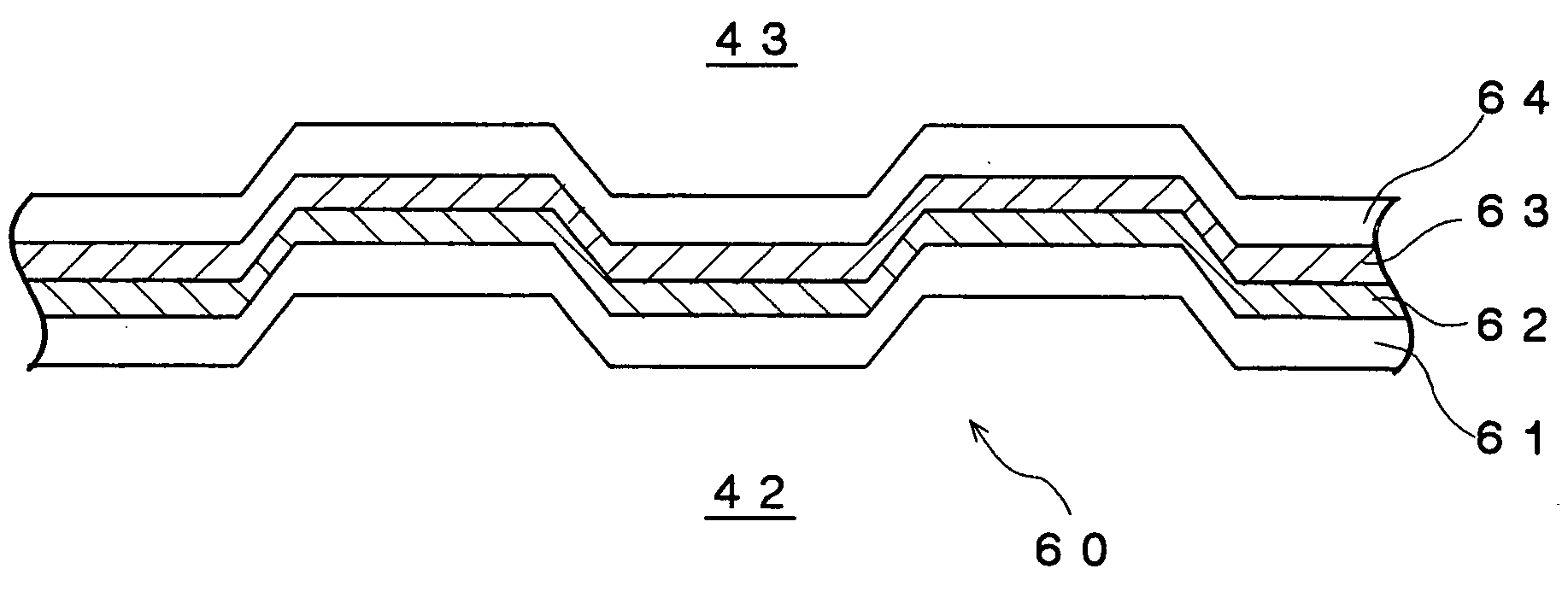

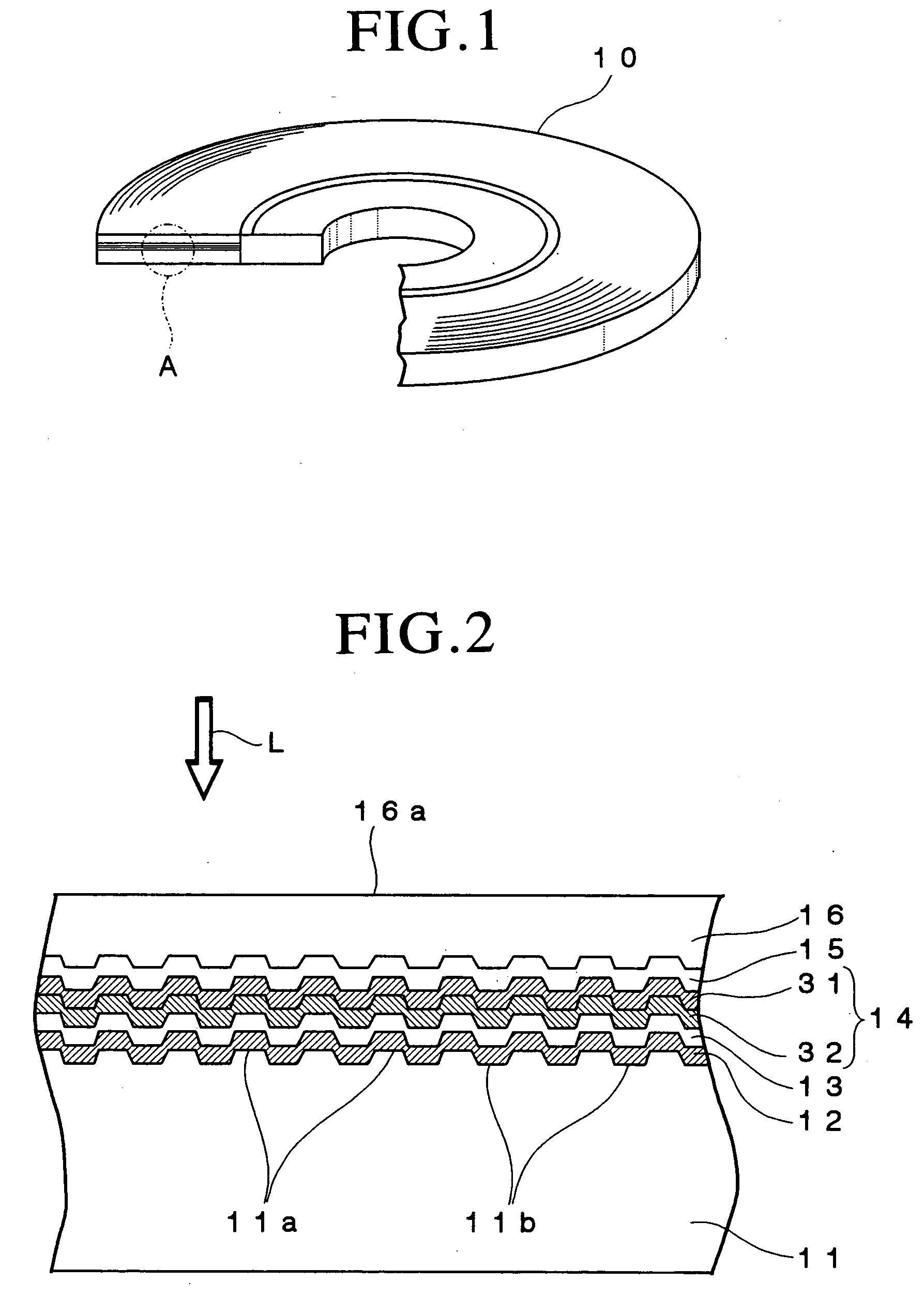

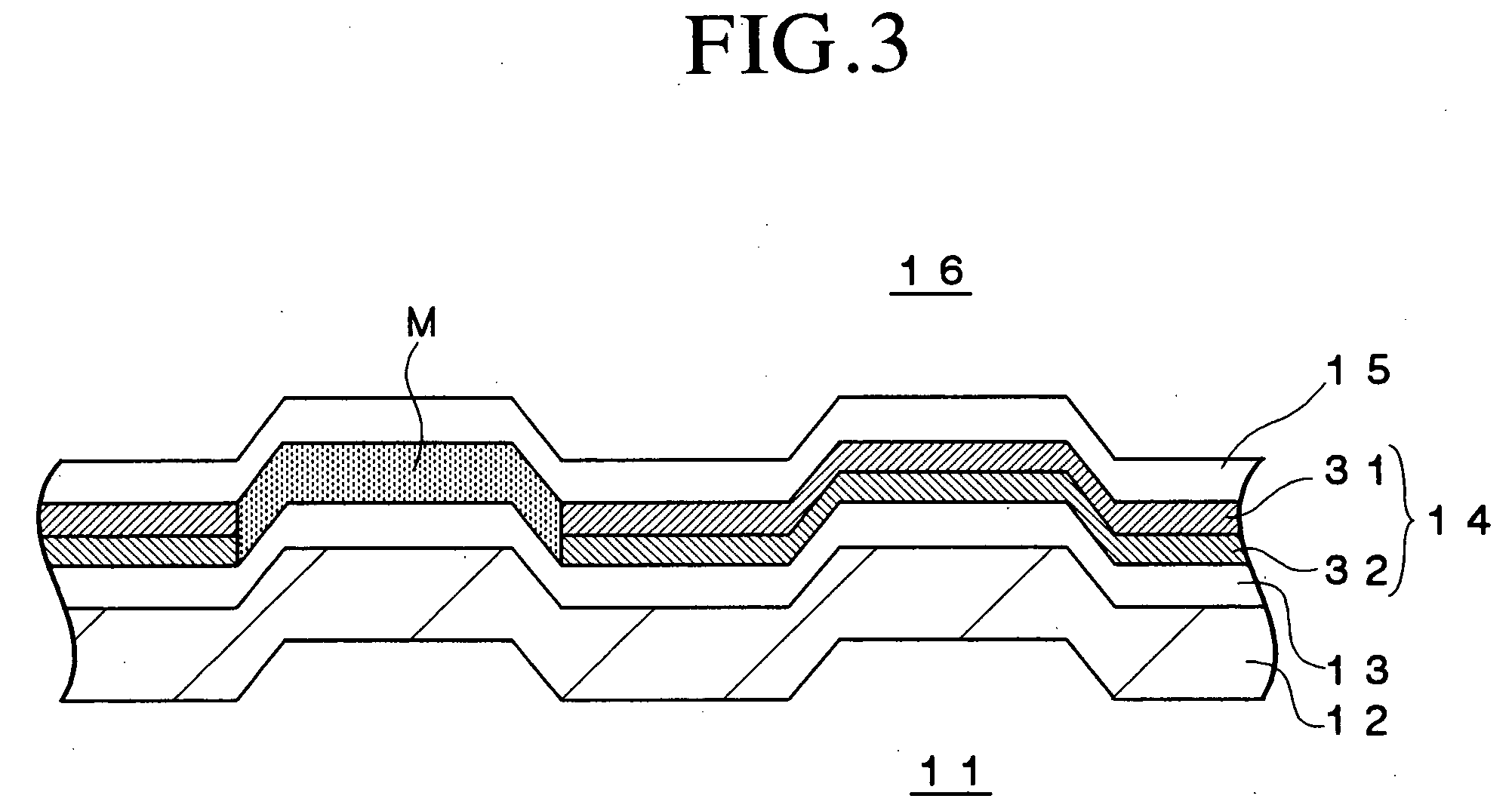

Optical recording medium

InactiveUS20040157158A1High sensitivityReduce reproductionMechanical record carriersPhotomechanical apparatusRecording layerOptical recording

An optical recording medium includes a substrate and a recording layer in which data can be recorded by projecting a laser beam thereonto, the recording layer including a first recording film containing an element selected from the group consisting of Si, Ge, Sn, Mg, In, Zn, Bi and Al as a primary component and a second recording film containing Cu as a primary component and 10 to 30 atomic % of Al as an additive. The thus constituted optical recording medium has an excellent initial recording characteristic and can store recorded data in a good condition over the long term.

Owner:TDK CORPARATION

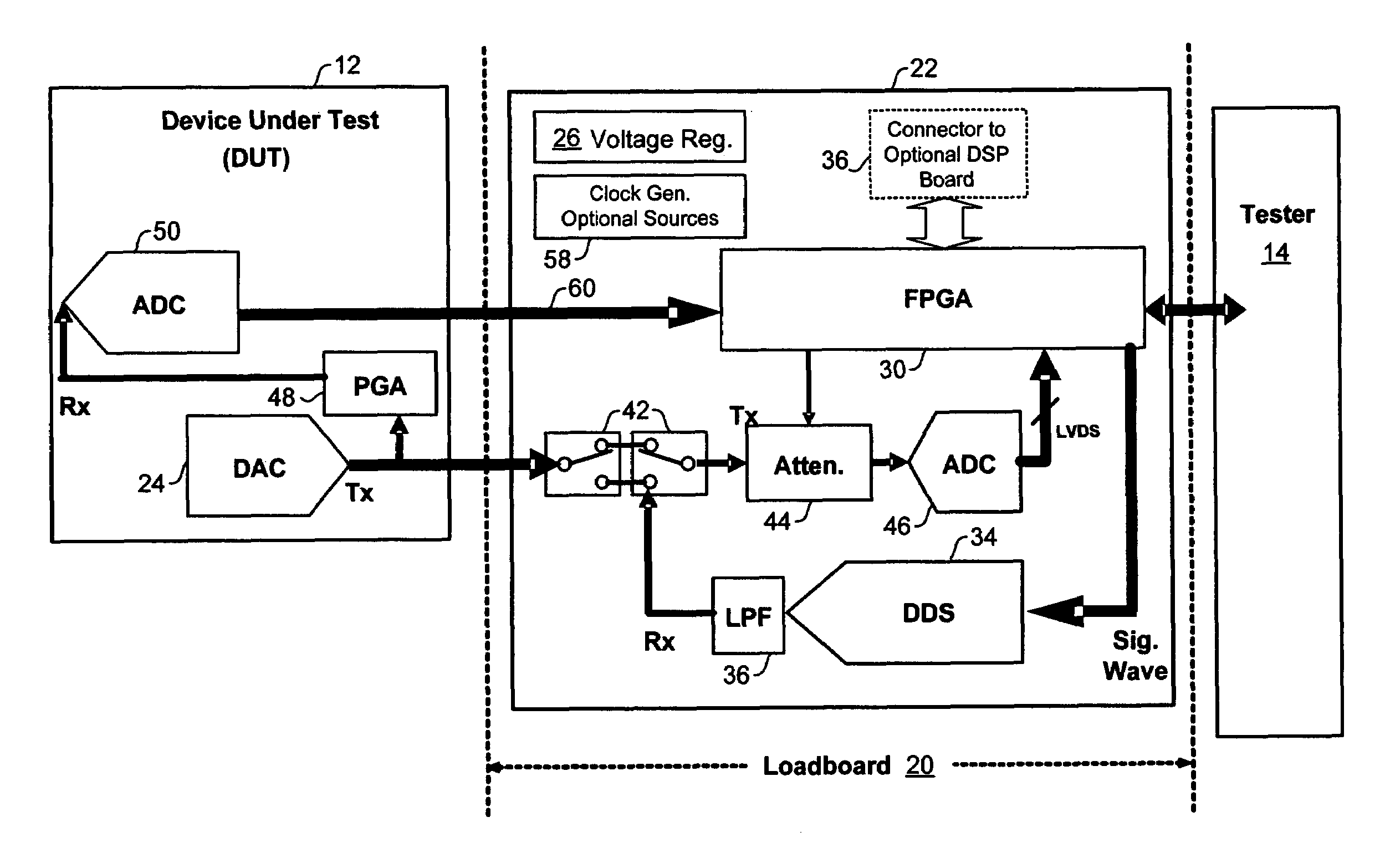

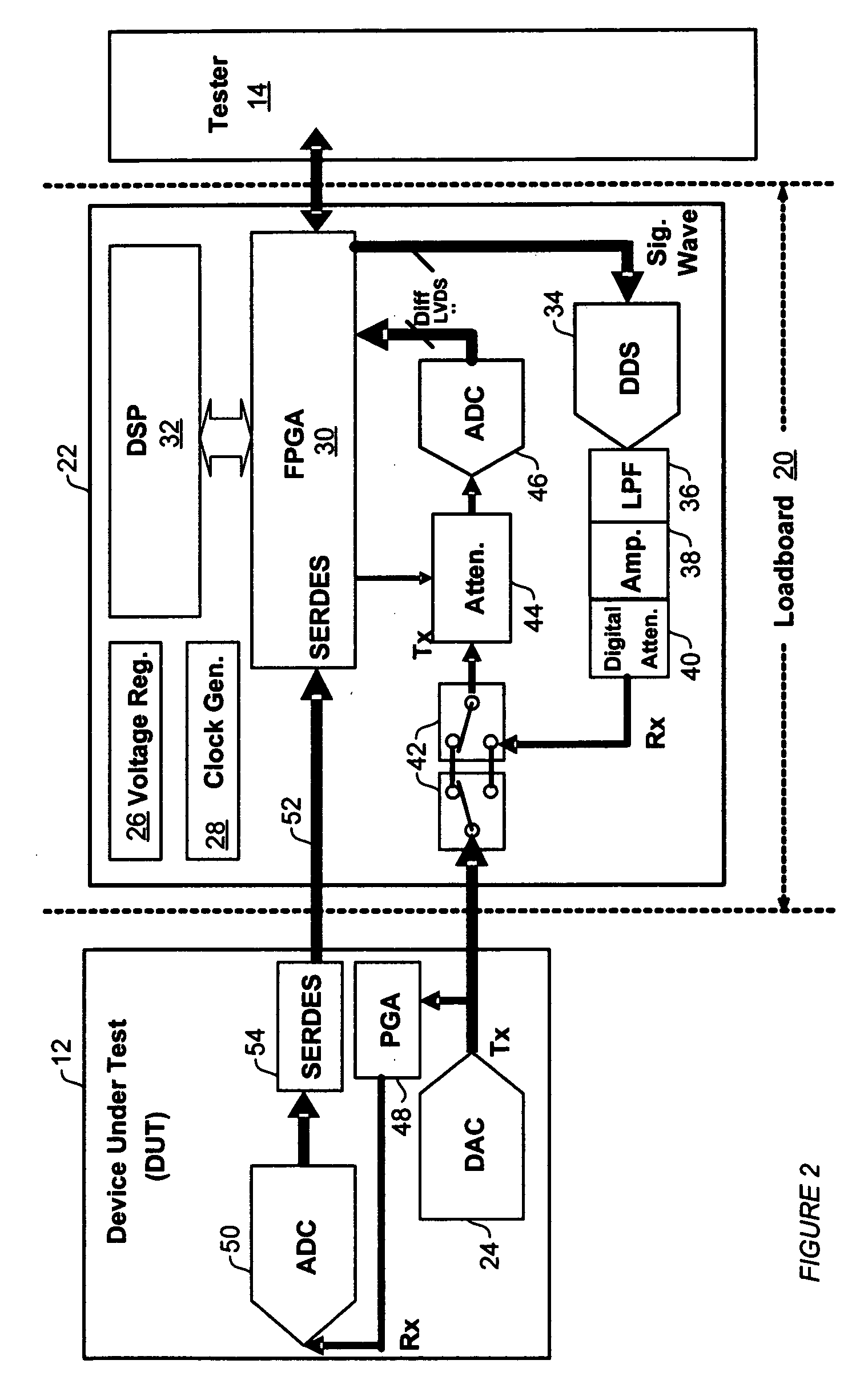

Analog built-in self-test module

ActiveUS7327153B2Quick testImprove efficiencyElectronic circuit testingError detection/correctionOn boardTester device

An analog BIST (Built-in Self-Test) module for a load board in a test system for testing Integrated Chips (IC) and other devices-under-test (DUTs). Components of the test module perform test setup, transmission of analog test signals to a DUT, capture of analog and digital test data from the DUT, and on-board analysis of the test data using DSPs without sending the test data to a tester. Modules may be add-on boards to load boards an contain one or more processors and multiple components to test DUTs in parallel, significantly decreasing test and analysis times of a test system such as a Very Low Cost Tester (VLCT).

Owner:TEXAS INSTR INC

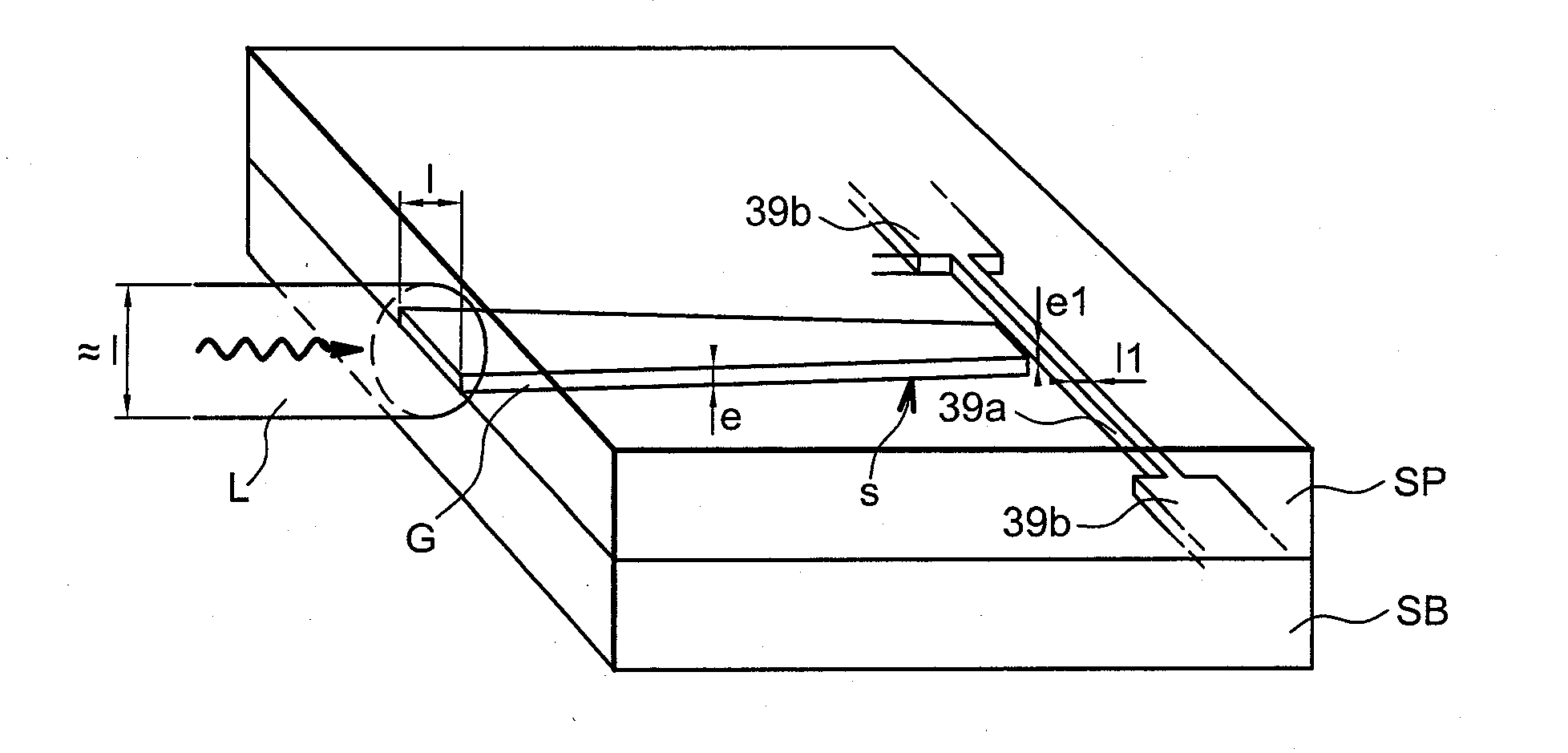

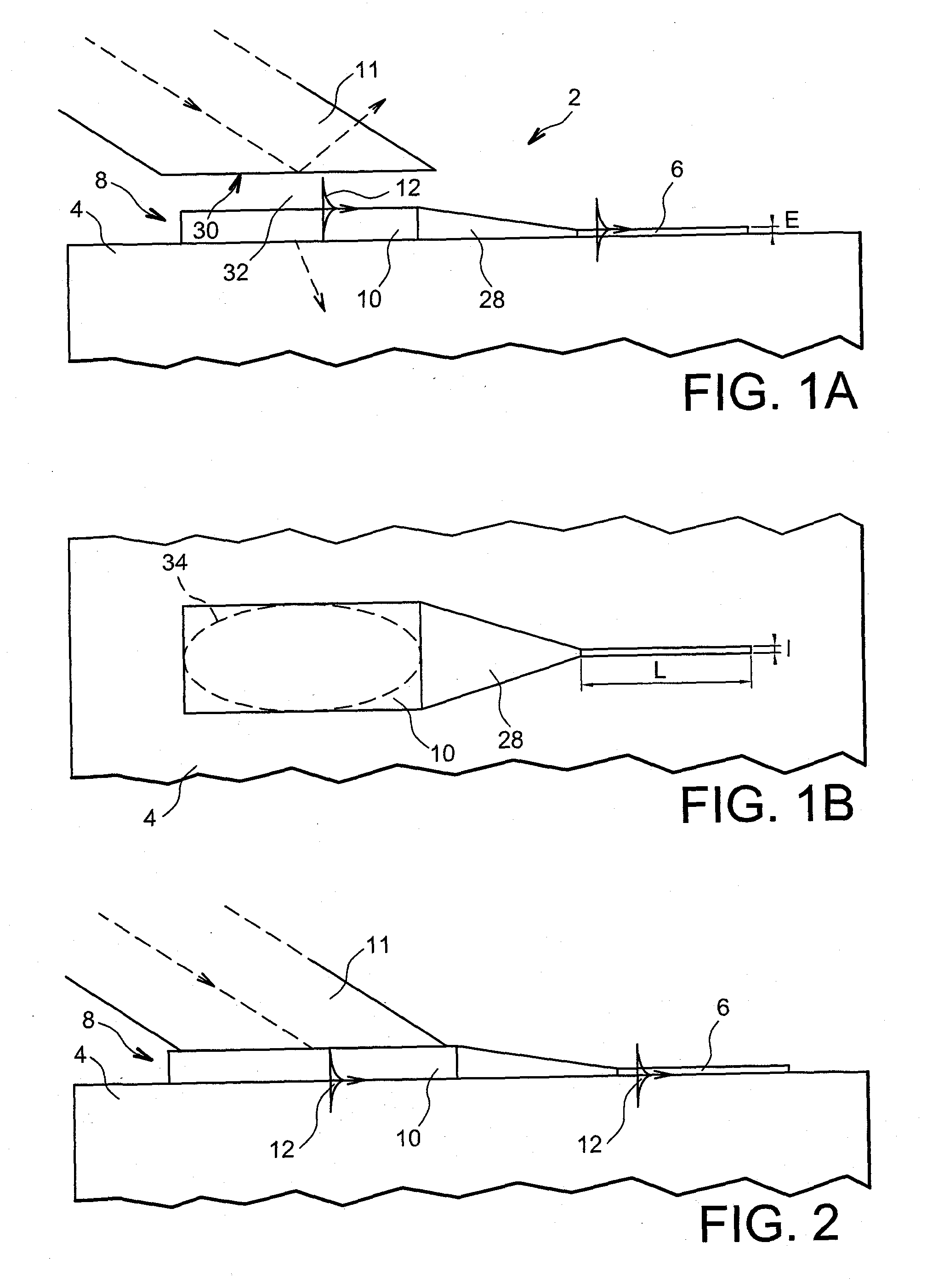

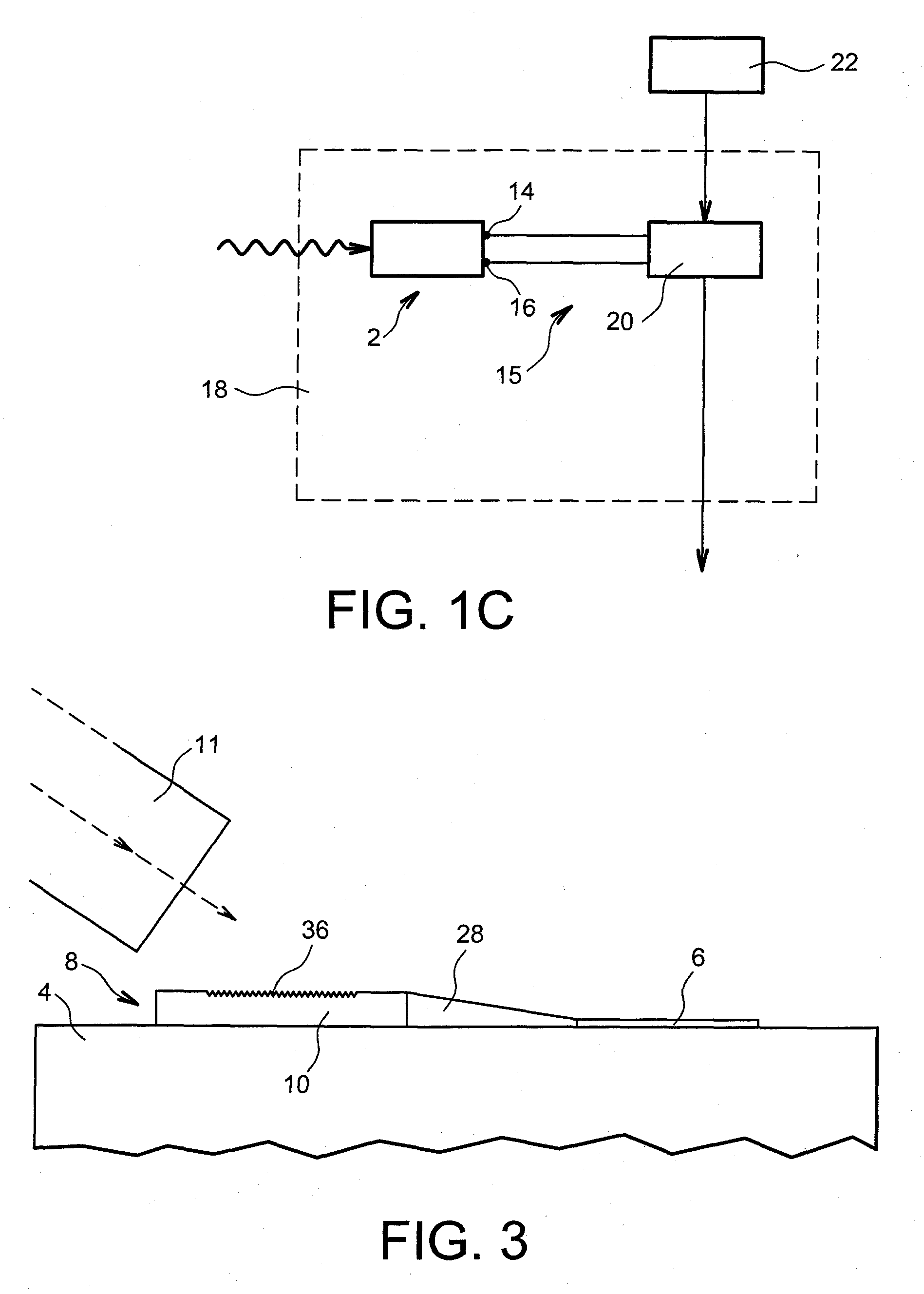

Ultra-Sensitive Optical Detector With High Time Resolution

InactiveUS20080272302A1Increase valueLess phase noiseSolid-state devicesMaterial analysis by optical meansSurface plasmonCoupling

An ultra-sensitive optical detector with large time resolution, using a surface plasmon. The optical detector is configured to detect at least one photon, and including a dielectric substrate, and on the substrate, at least one bolometric detection component, that generates an electrical signal from the energy of received photon(s). Additionally, at least one coupling component is formed on the substrate, distinct from the detection component and including a metal component, and generates a surface plasmon by interaction with the photon(s) and guiding the plasmon right up to the detection component, which then absorbs the energy of the surface plasmon.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

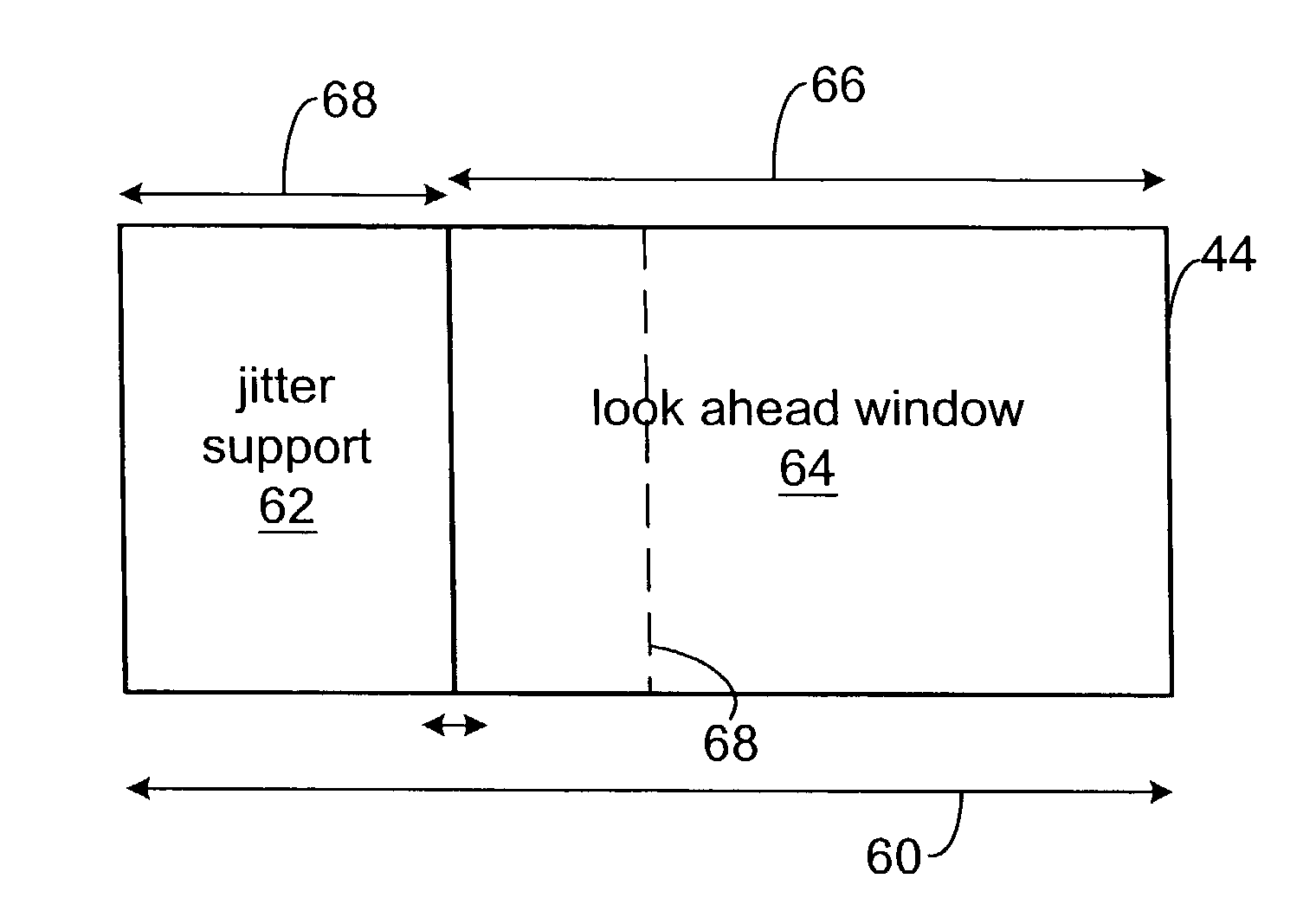

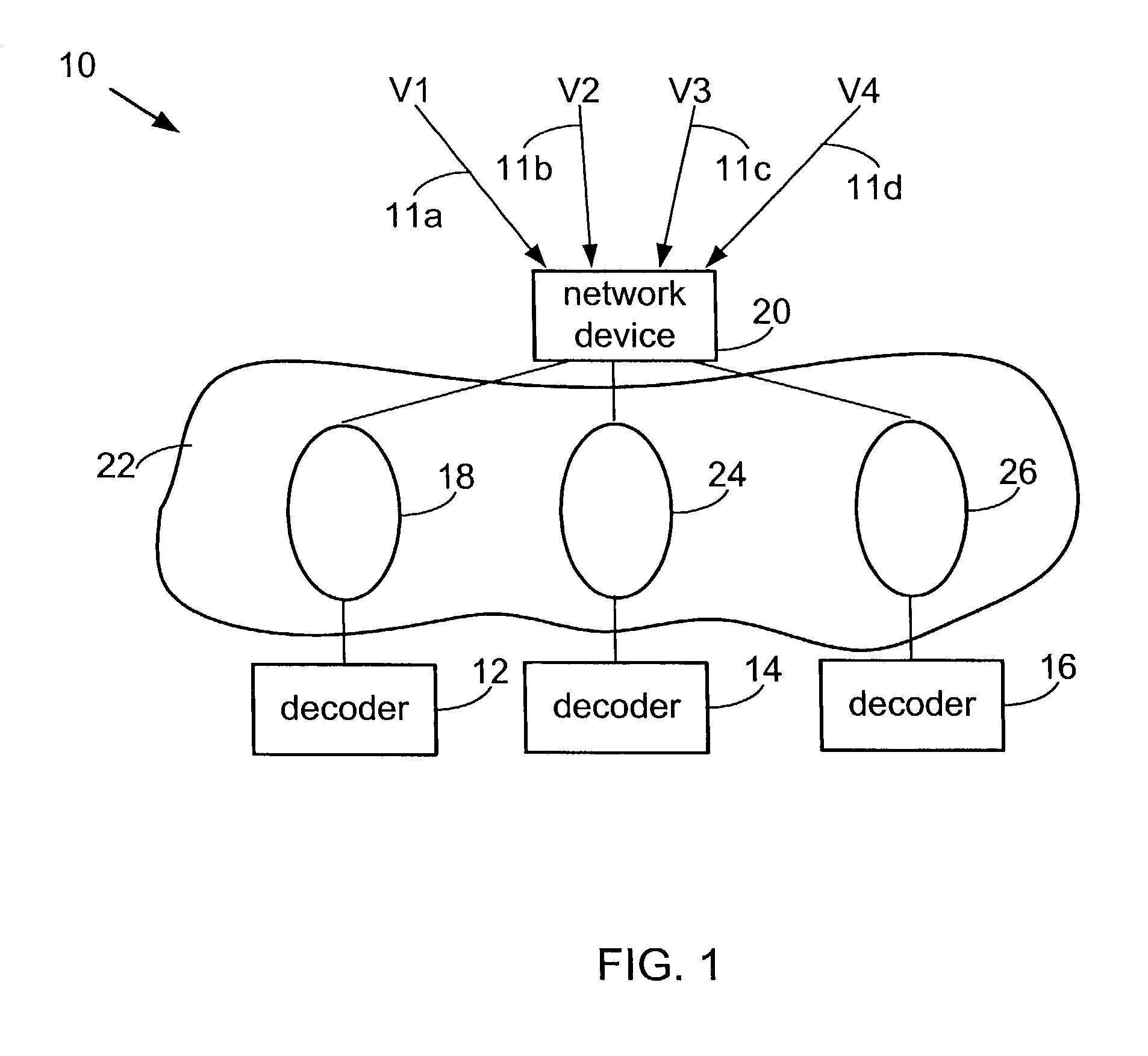

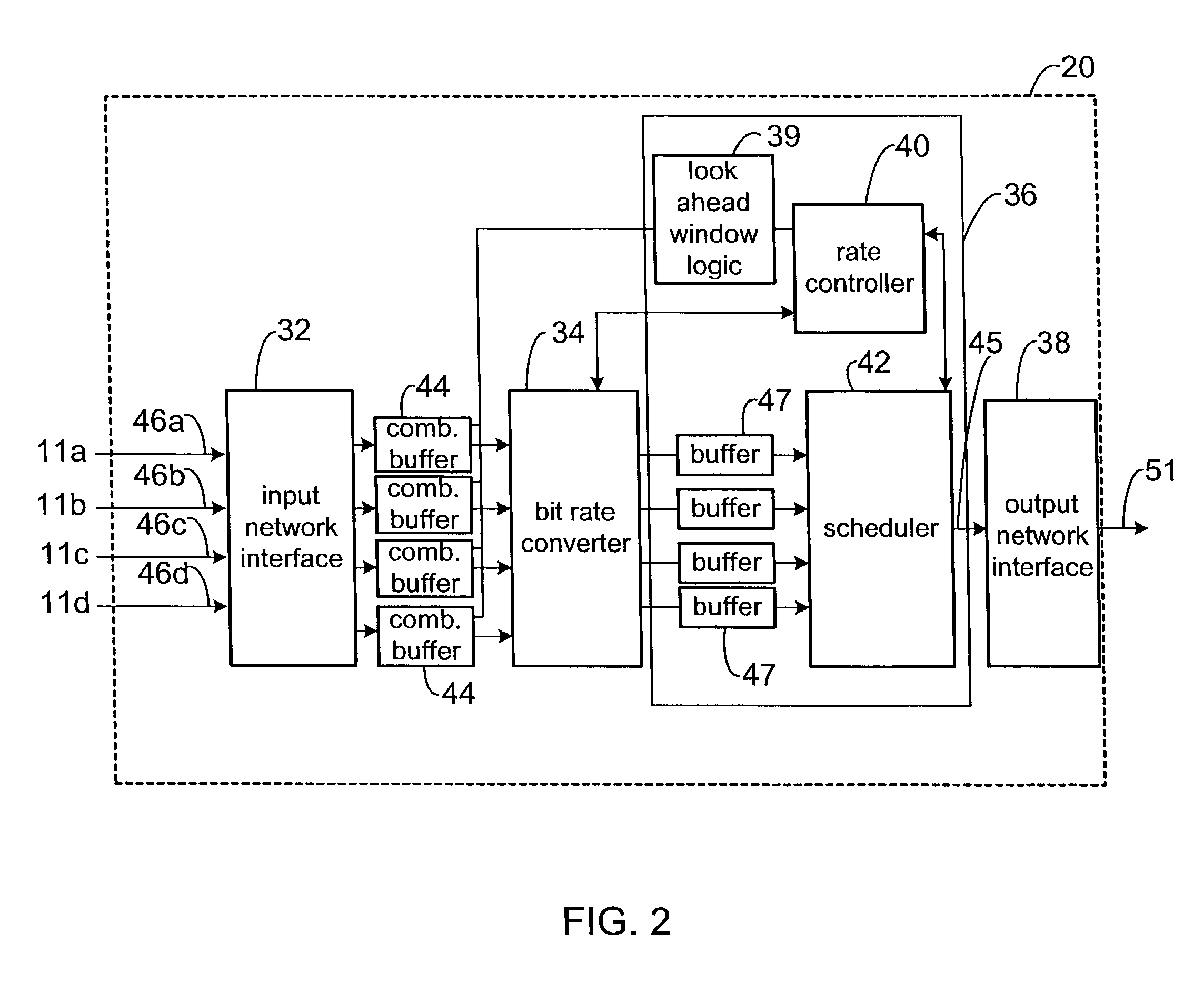

Combined jitter and multiplexing systems and methods

ActiveUS7529276B1Improve performanceIncrease in sizeBroadband local area networksTime-division multiplexMultiplexingBit Rate Reduction

Described herein are systems and methods for processing and transmitting data included in packets with jitter. The systems and methods combine a jitter buffer and a buffer scanned by a look ahead window as a combined buffer. The combined buffer varies look ahead window and performance of a process that uses the look ahead window based on the current jitter support in the buffer. More specifically, the flexible buffering techniques flexibly adapt the size of the look ahead window based on the amount of buffer space used for jitter support. When jitter support requirements are low, the size of the look ahead window is increased. When the look ahead window is implemented with a multiplexer, the multiplexer may benefit from a larger look ahead window and improve multiplexer performance. Improved multiplexer performance may lead to less or more intelligent re-encoding and bit rate reduction for video data transmission applications, leading to improved decoded output video quality.

Owner:CISCO TECH INC

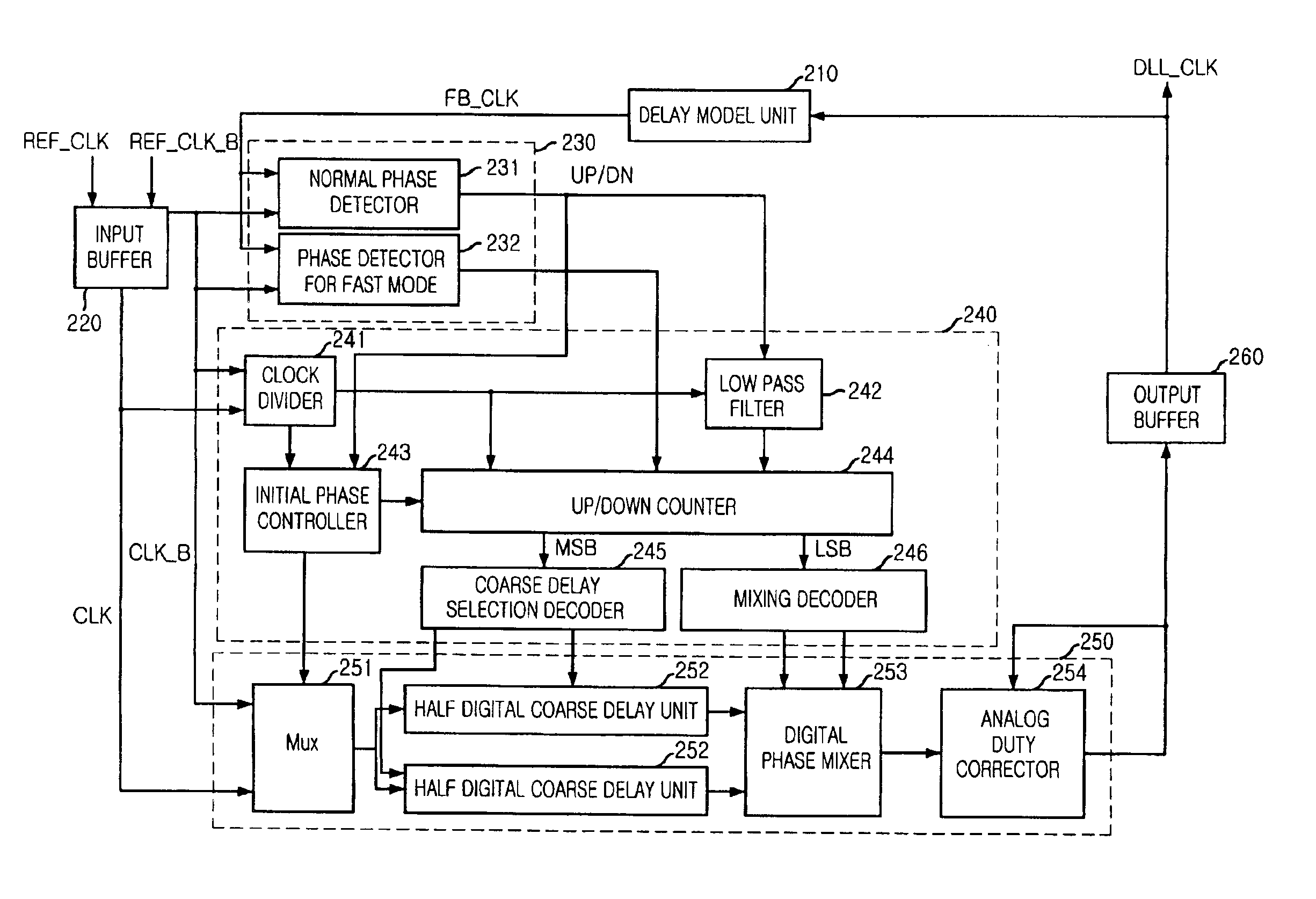

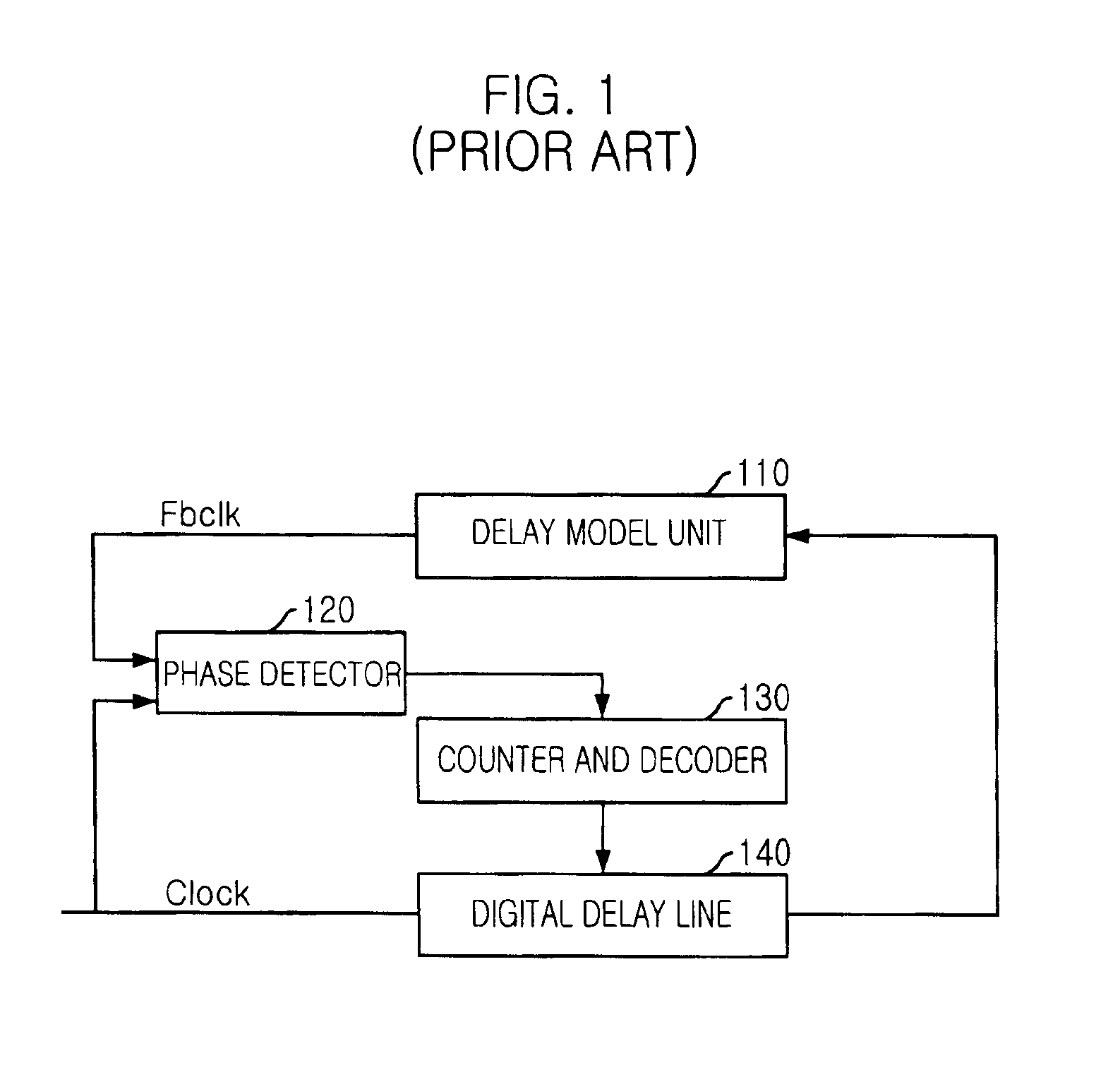

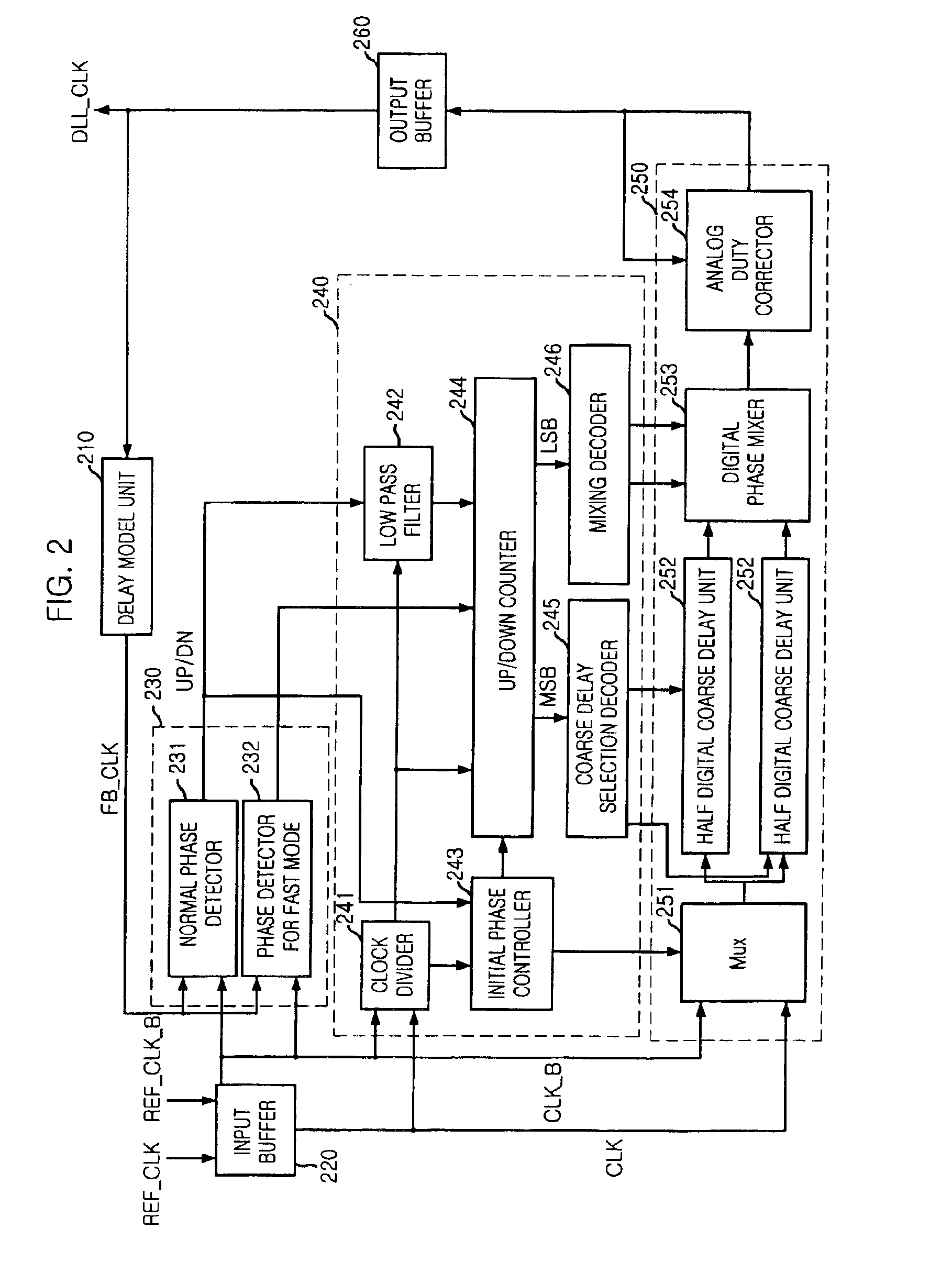

Delay locked loop having low jitter in semiconductor device

InactiveUS6917229B2Reduce jitterPulse automatic controlAngle demodulation by phase difference detectionControl signalDelay-locked loop

A DLL circuit having a low jitter in a semiconductor device, includes a delay model unit for compensating a time difference between an external clock signal and an internal clock signals and generating a compensation signal; an input buffer for receiving a reference clock signal and an inverted clock signal, and for outputting a clock signal and an inverted clock signal activated at each edges of the reference clock signal and the inverted clock signal; a phase detection unit for generating a comparison signal by comparing the compensation signal with the inverted clock signal, and for outputting the comparison signal with a normal mode or a fast mode; a control unit for generating a plurality of control signals by receiving the comparison signal, the inverted clock signal and the clock signal; a delay unit for delaying in response to the plurality of control signals; and an output buffer for outputting a delayed clock signal by receiving an output signal of the duty corrector.

Owner:SK HYNIX INC

Power saving frame transmission method

ActiveUS20060171341A1Reduce jitterSave powerEnergy efficient ICTPower managementPower savingService time

A method that enables the power saving frame transmission comprising an AP informing a plurality of stations within its range in a WLAN about a plurality of scheduled service periods during which the AP has access to a channel in a scheduled service time, receiving the information about the plurality of scheduled service periods by the plurality of stations and deciding about initiating or not initiating a frame transmission, whether or not an acknowledgement and an immediate response expected from other APs pertaining to said WLAN are received prior to a subsequent scheduled service time, wherein the frame is transmitted in a cooperative frame transmission scenario.

Owner:SYMBOL TECH LLC

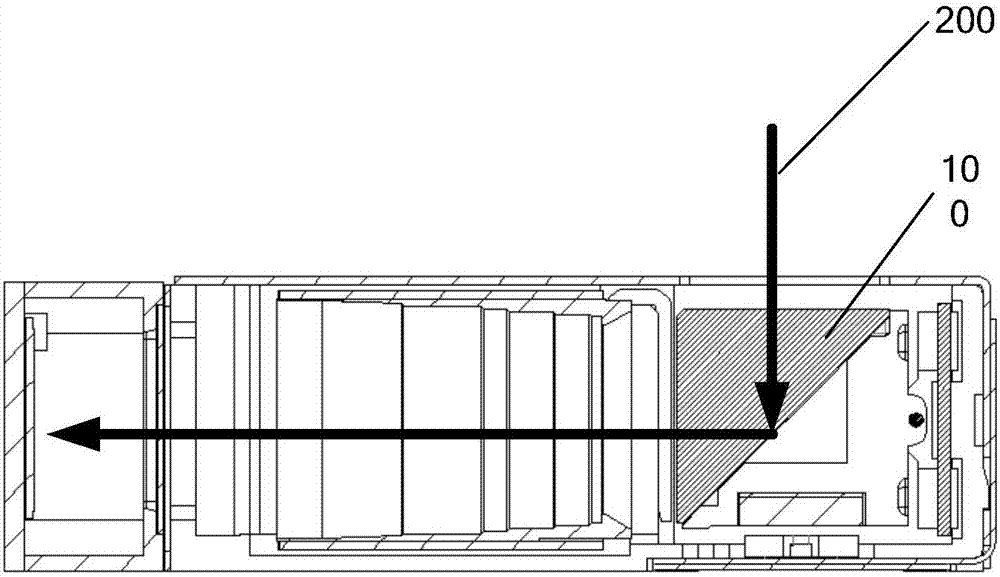

Camera and anti-shake method of the camera

Embodiments of the invention provide a camera and an anti-shake method of the camera and relate to the camera shooting technology field. By using the camera and the method, cost of the camera is reduced and a camera structure is simplified. A total reflection mirror component of the camera comprises a total reflection mirror and a first shape memory alloy metal wire arranged on the total reflection mirror. A lens component comprises a lens. A circuit component comprises an inclination detection instrument and a driving chip. The inclination detection instrument is used for detecting a shaking parameter of total reflection mirror shaking and converting the shaking parameter into a first electric signal so as to transmit. The driving chip is used for receiving the first electric signal, calculating a compensation displacement amount according to the first electric signal and outputting a first current to the first shape memory alloy metal wire after calculation. The first shape memory alloy metal wire is used for generating a first tensile force under a first current effect so as to pull the total reflection mirror to move towards a compensation position.

Owner:VIVO MOBILE COMM CO LTD

Load balance method and system and management server

ActiveCN102055650AReduce emigrationReduce jitterData switching networksQuality of serviceComputer science

An embodiment of the invention relates to a load balance method and a system thereof and a management server; the method comprises the following steps: obtaining the service ability and load information of each memory server in the system, wherein the memory server comprises an original memory server and a new memory server; obtaining the balance values corresponding to different types of files in the system according to the service ability and the load information of the memory server and obtaining the number of the different type of files migrating to the new memory server in the original memory server according to the obtained balance values; and migrating the different type of files requiring to be migrated to the new memory server according to the corresponding number to the new memory server by the original memory server according to the migrating sequence of the files to be migrated to the new memory server. Through the embodiment of the invention, the migration-in and the migration-out data can be quickly balanced and reduced, thereby decreasing the vibration of the system and improving the service quality of the system.

Owner:江苏航天龙梦信息技术有限公司

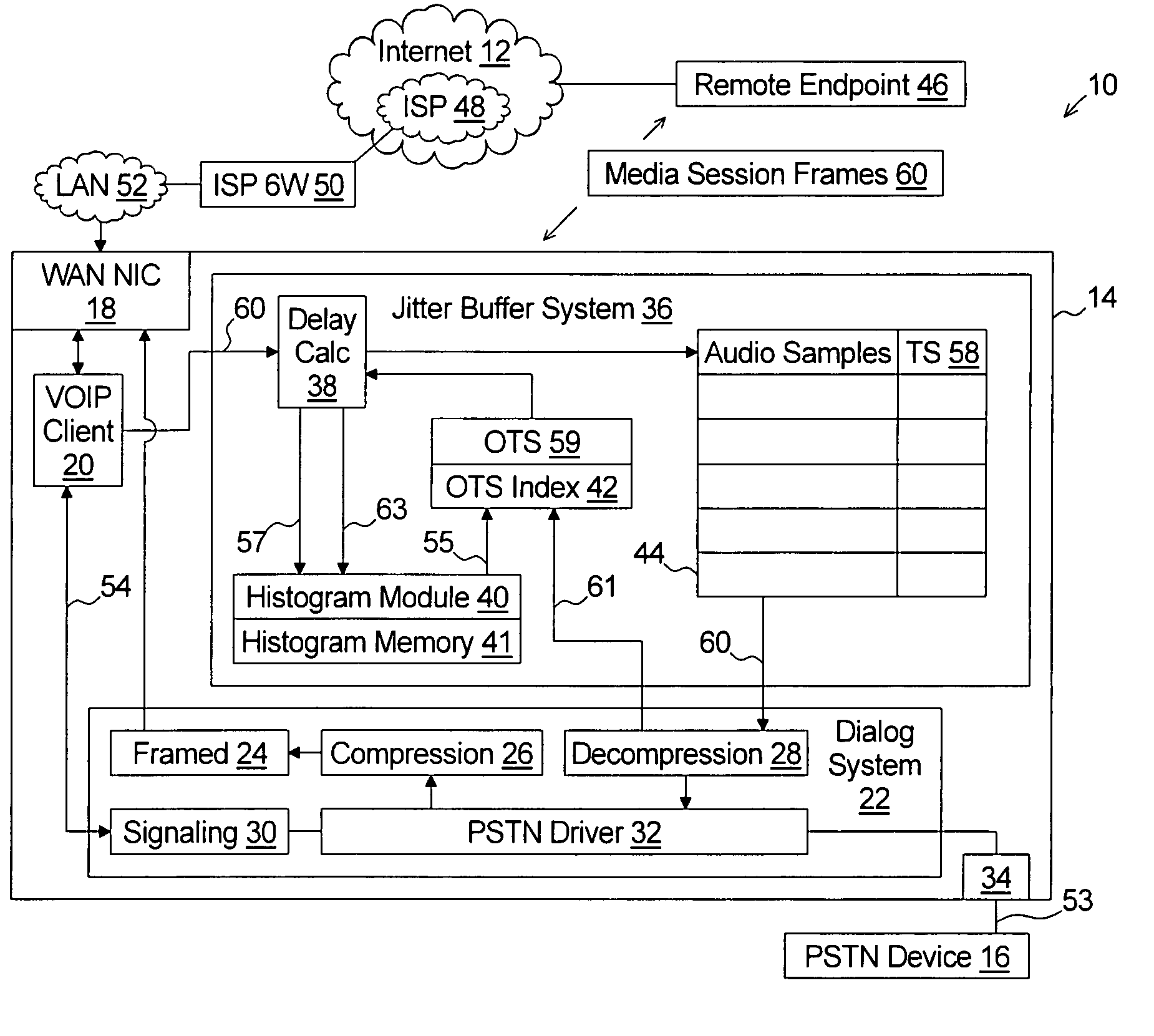

In band signal detection and presentation for IP phone

ActiveUS20050232309A1Reduce jitterTime-division multiplexData switching by path configurationAudio frequencyTime difference

A jitter buffer system for reducing jitter in a packet audio reception device comprises an output time stamp index, a delay calculation module, and a histogram module. The output time stamp index determines an initial output time stamp value upon receipt of a jitter buffer latency value and increments the output time stamp upon release of each of the frames by a jitter buffer. The delay calculation module calculates a delay value for each of the sequence of received frames. The delay value is equal to the time difference between the output time stamp value and a transmission time stamp assigned to the frame by the transmitting system. The histogram module is coupled to each of the output time stamp index and the delay calculation module, the histogram module periodically calculates a target delay value which, based on a buffered history of values representing the delay value of each of a fixed quantity of the most recently received frames from the sequence of receive frames, would have resulted in a predetermined portion of the fixed quantity of frames being dropped, and adjusting the jitter buffer latency value to a value equal to the target value.

Owner:INNOMEDIA PTE

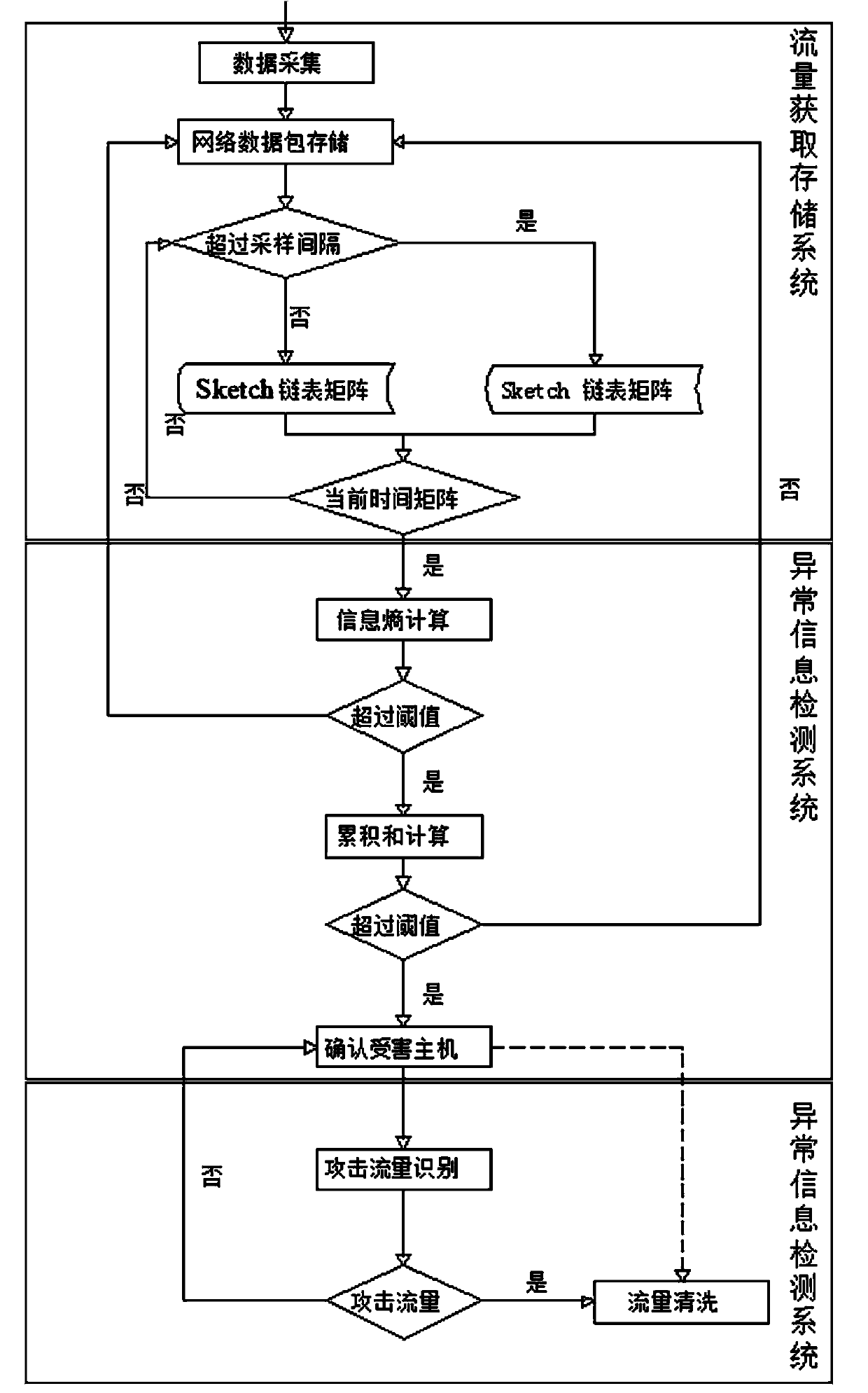

DDoS (distributed denial of service) attach detection method based on information entropy

The invention discloses a DDoS (distributed denial of service) attach detection method based on an information entropy. The method includes the steps of acquiring high-speed network traffic; judging abnormal traffic, to be specific, judging whether or not abnormal traffic occurs at current moment; confirming an attacked host, to be specific, confirming the attacked host mainly through a source IP (internet protocol) address and a target IP address; and recognizing attack traffic. Compared with the prior art, the method has the advantages that detection is timely, accurate and efficient, the occurring moment of the abnormal traffic can be effectively judged, and corresponding measures are taken accordingly before the target host or network resources are exhausted.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

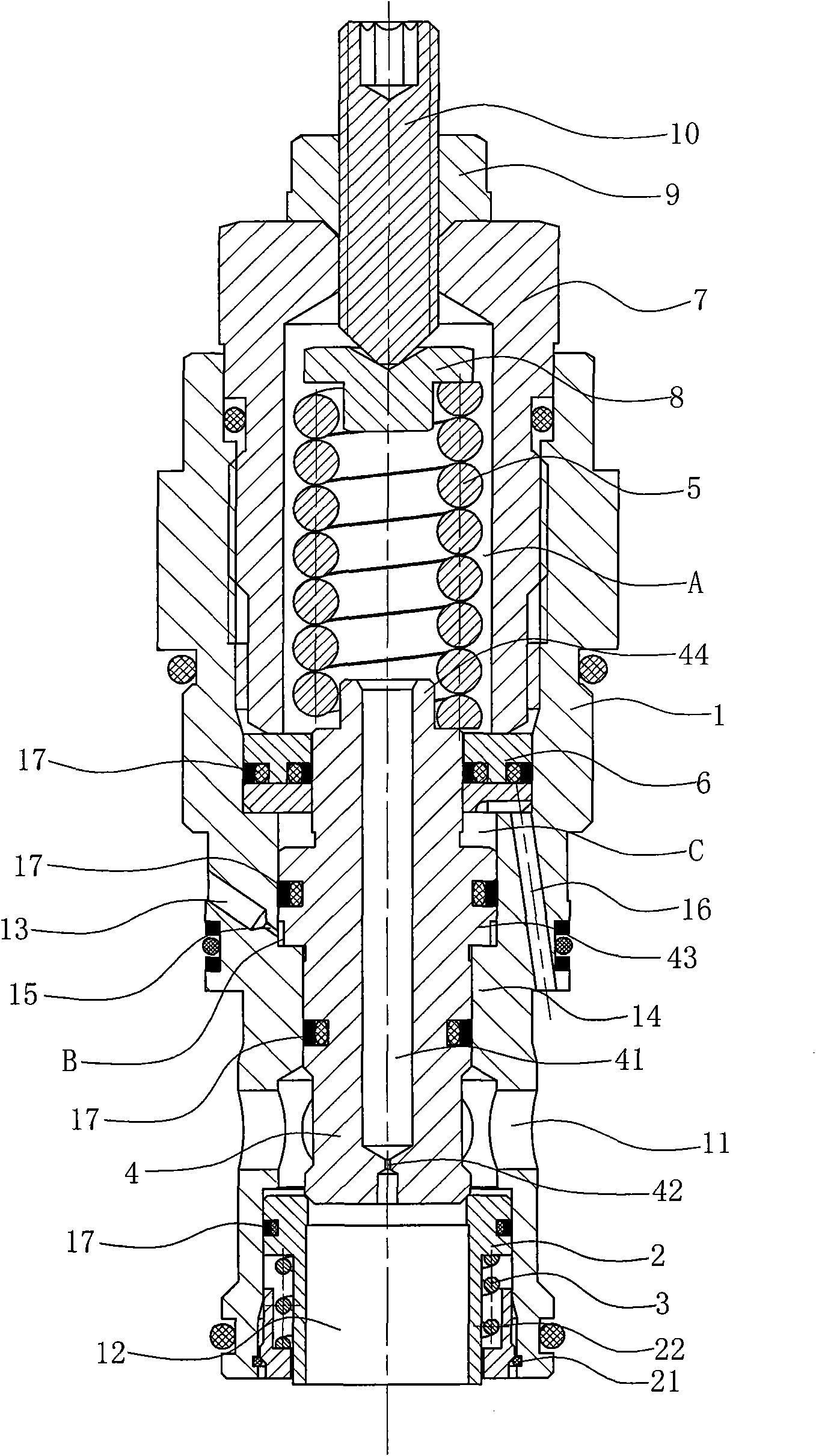

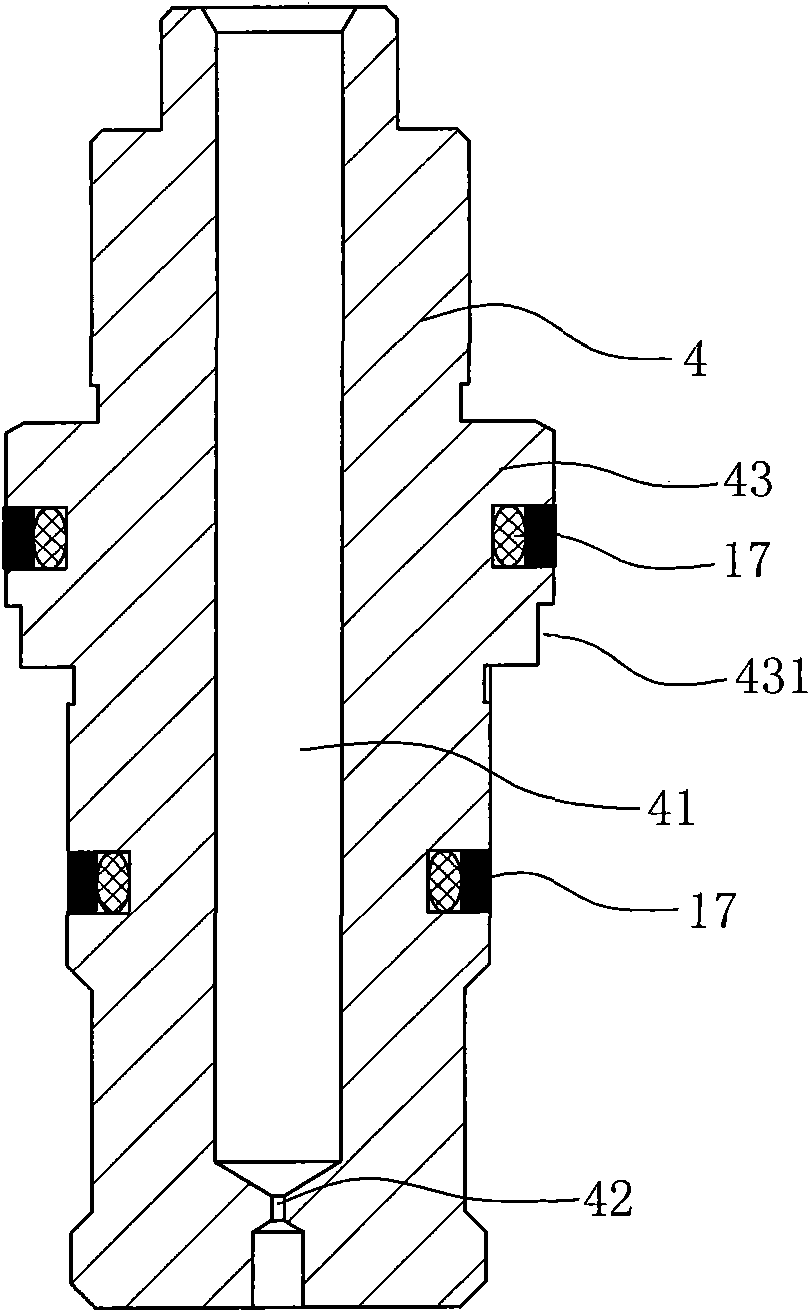

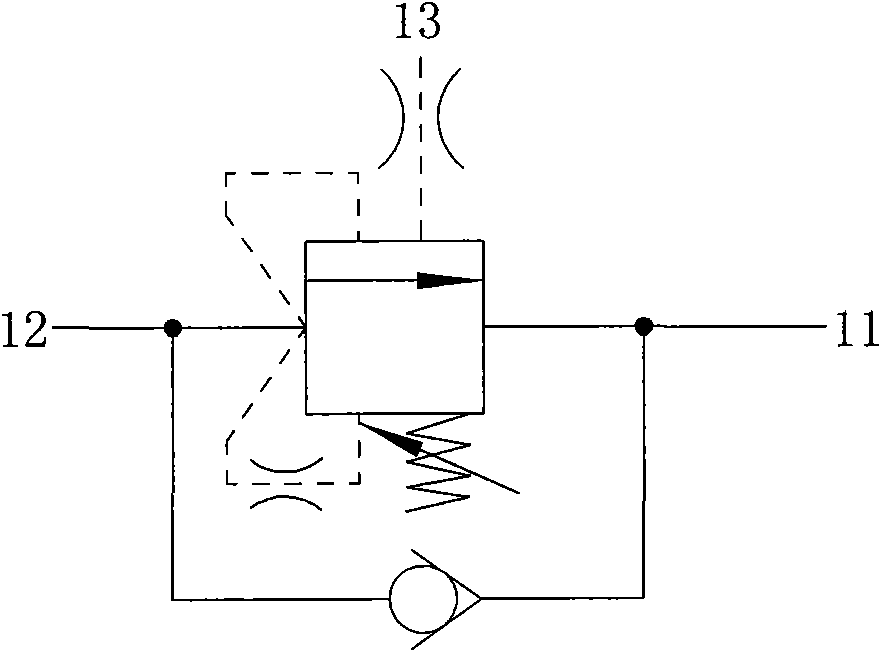

Plug-in type balance valve

InactiveCN101634317AReduce heat treatment requirementsReduce material requirementsServomotor componentsShoulder BladesThermal treatment

The invention relates to a plug-in type balance valve which comprises a valve body, a one-way valve core and a balance valve core, wherein a first oil opening, a second oil opening and a third oil opening are arranged on the valve body; the one-way valve core is arranged at the second oil opening and pushed by a first spring to maintain the trend of axial upward shift; the balance valve core is installed in the valve body and can be matched with a valve opening of the one-way valve core, and a second spring is arranged in a spring cavity of the valve body; the upper part in the balance valve core is provided with an axial passage and a first damping hole; the middle position of the balance valve core is provided with an axial convex shoulder; an annular notch is arranged on the periphery surface of the axial convex shoulder; the inner wall of the valve body is provided with an annular inner shoulder blade; an oil inlet cavity is formed among the annular notch, the inner wall of the valve body and the annular inner shoulder blade; and the third oil opening is communicated with the oil inlet cavity by a second damping hole on the side wall of the valve wall. The balance valve core and the one-way valve core are in an integral structure, and the structure is simple; the balance valve core and the one-way valve core are relatively independent on the relative position relationship, the assembly is convenient, and the requirements on heat treatment and materials of the balance valve core are lowered.

Owner:NINGBO HANSHANG HYDRAULIC

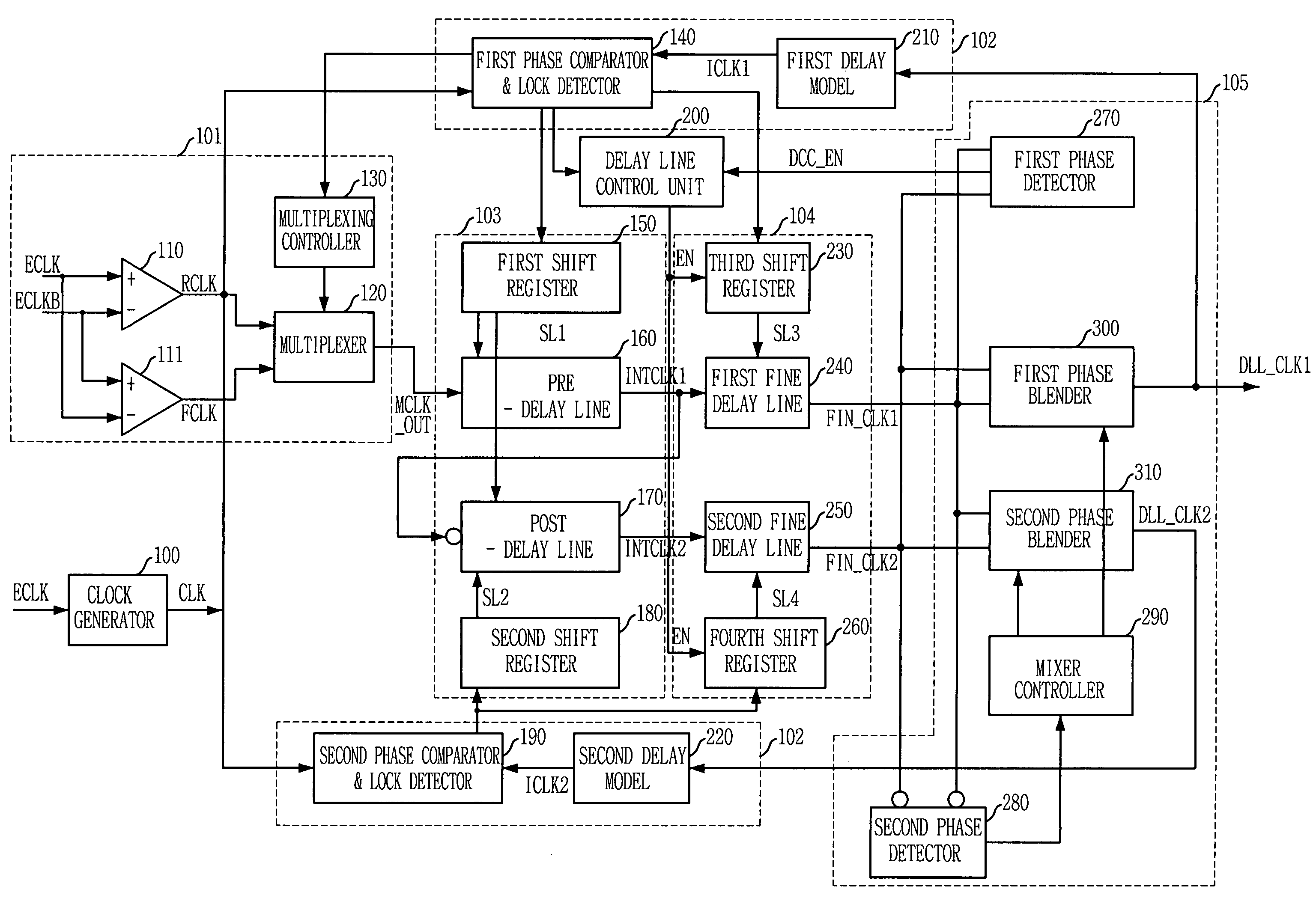

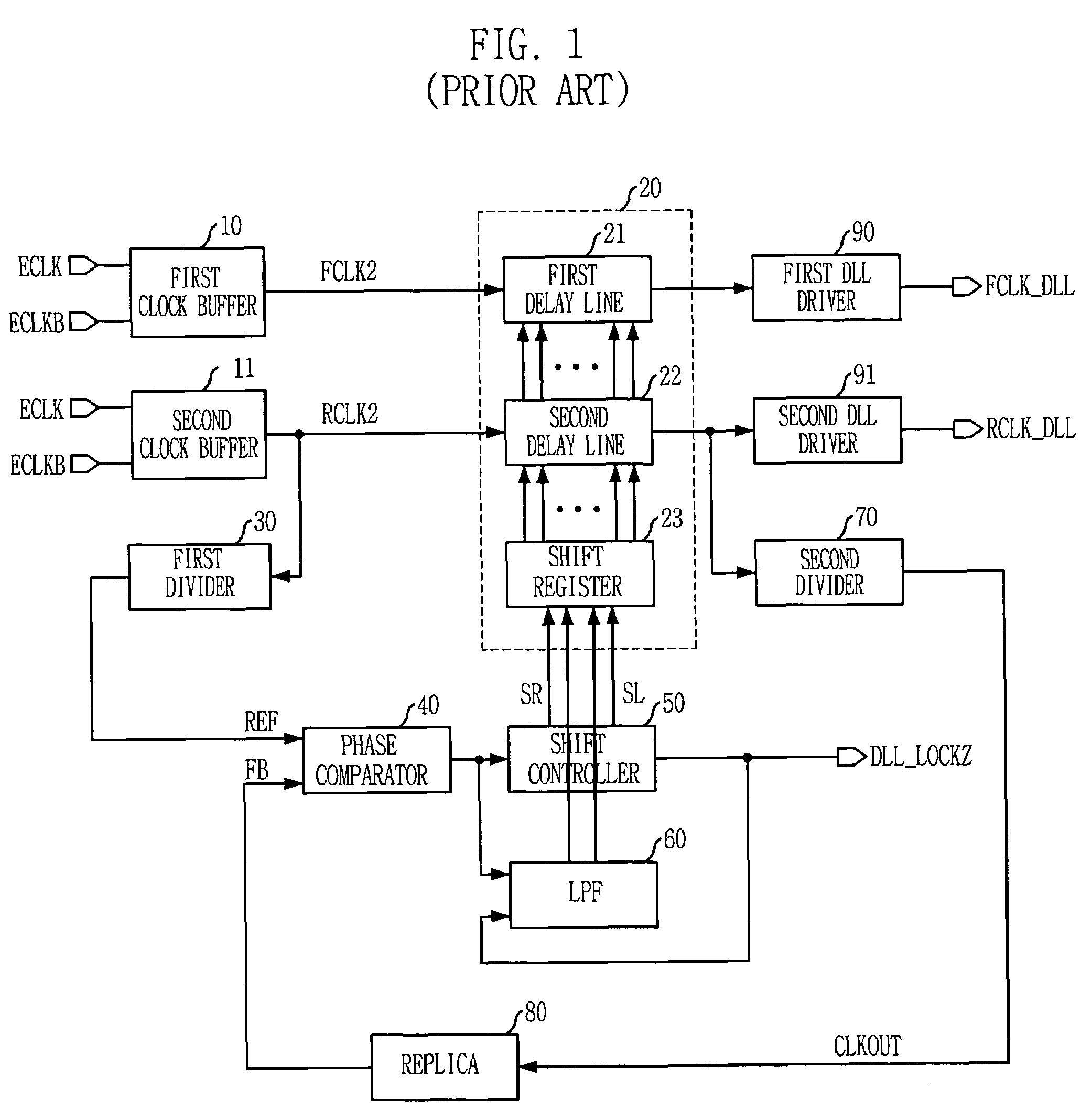

Delay locked loop

InactiveUS7282974B2Reduce jitterPulse automatic controlSingle output arrangementsMultiplexingDelay-locked loop

A DLL for reducing jitter during a high frequency operation by separately controlling a coarse delay and a fine delay. The DLL includes a multiplexing unit for selectively outputting one of the rising clock and the falling clock; a first delay line for generating a first internal clock and a second internal clock; a second delay line for generating a first clock and a second clock; a delay line control unit for controlling the second delay line; a phase control unit for generating a first DLL clock and a second DLL clock by mixing the first clock and the second clock; and a phase comparing unit for comparing the first DLL clock and the second DLL clock with the rising clock to generate a lock signal for controlling an operation timing of the first delay line and the second delay line.

Owner:SK HYNIX INC

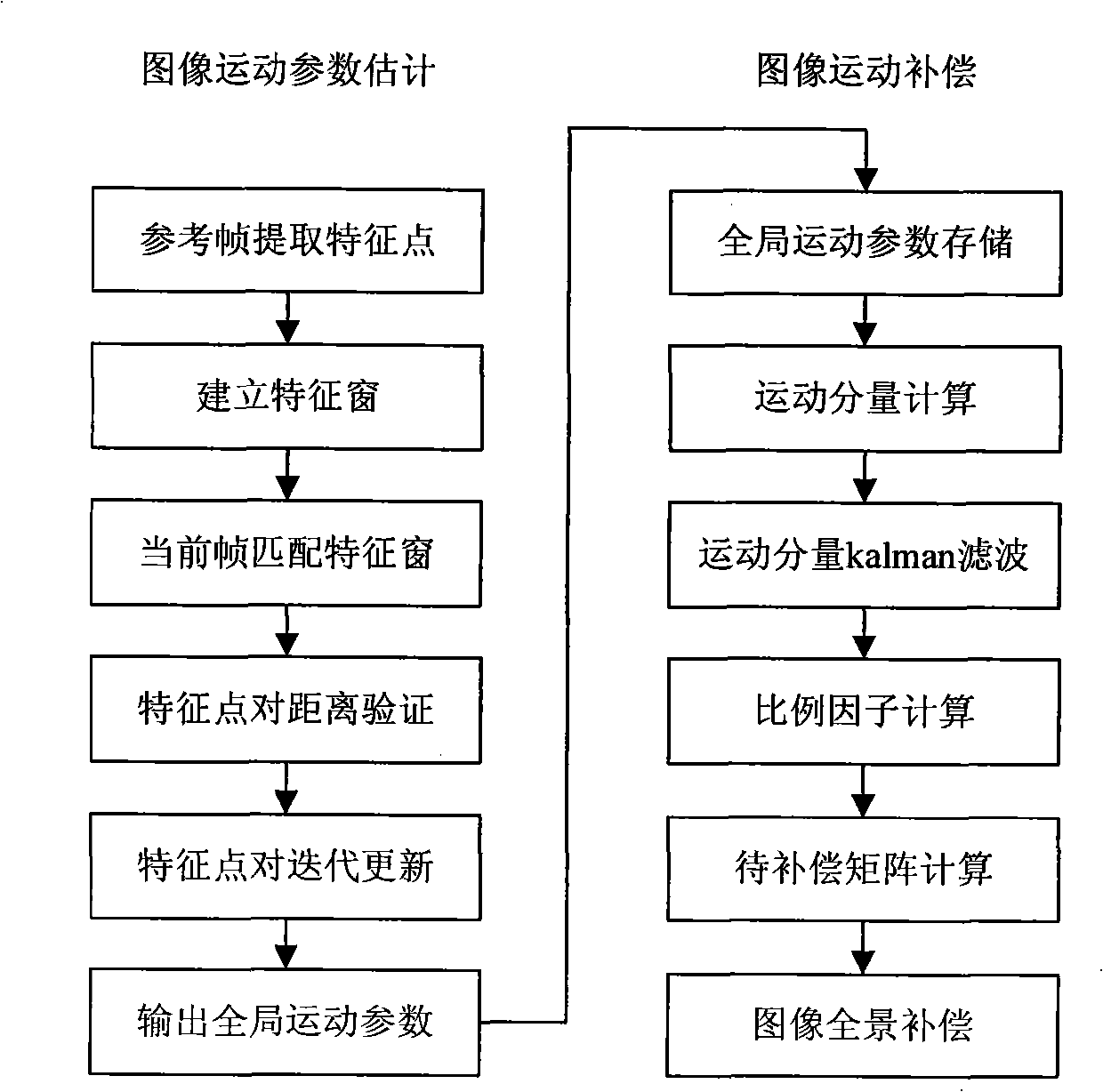

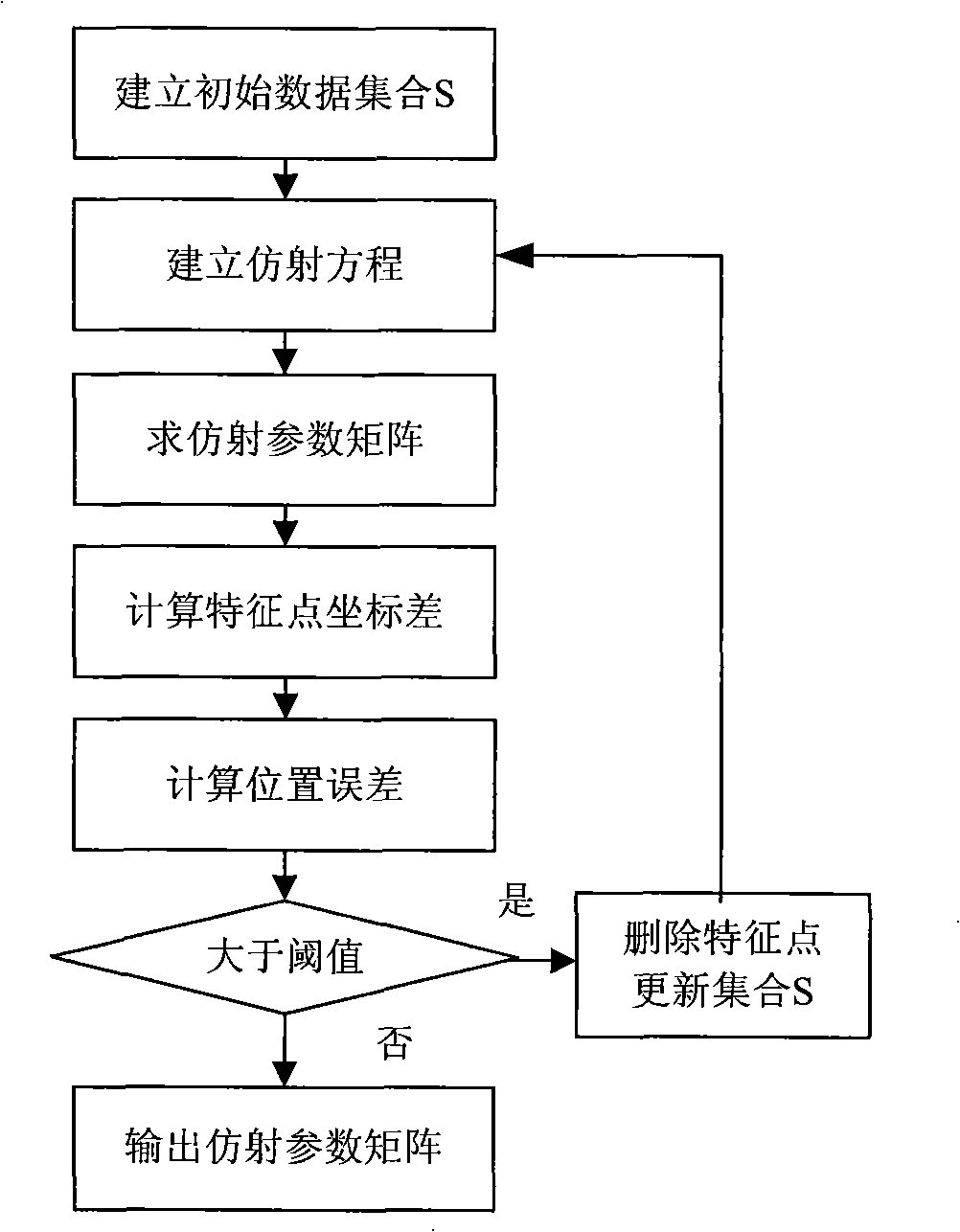

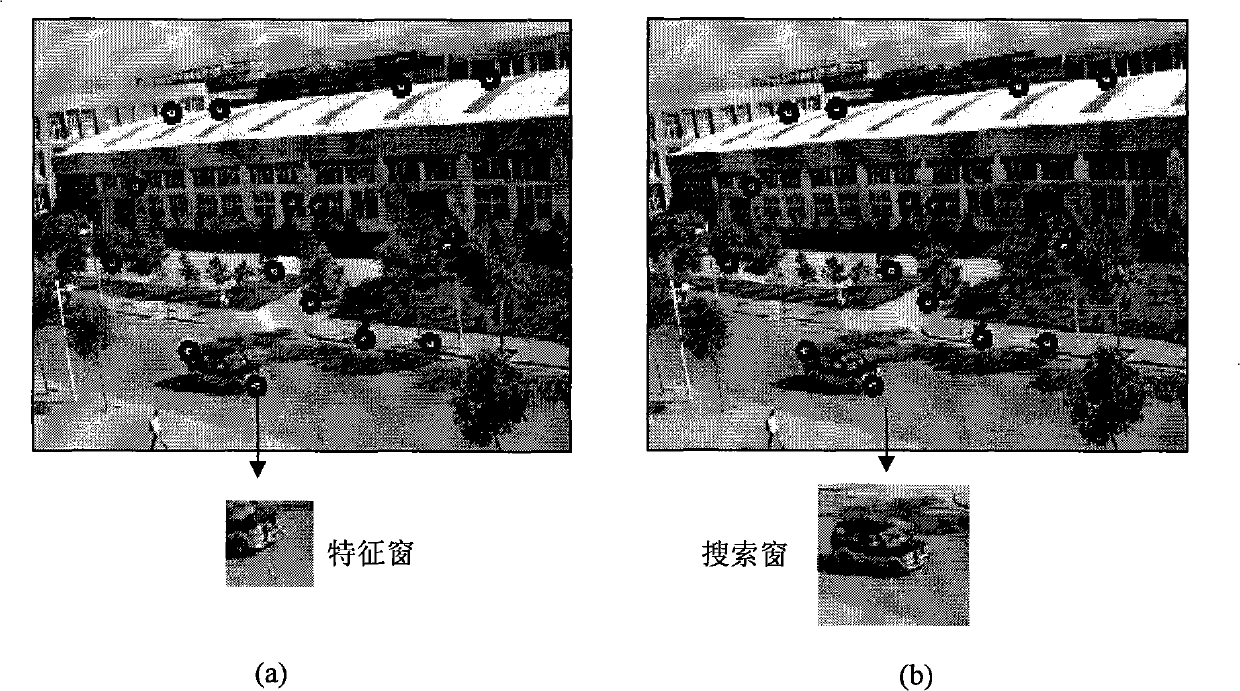

Full view stabilizing method based on global characteristic point iteration

InactiveCN101316368AImprove calculation accuracyHandle translation efficientlyImage analysisTelevision systemsVideo monitoringMotion parameter

The invention discloses a panorama image stabilization method based on the iteration of global characteristic points. The method of the invention includes two parts of the estimation of image motion parameters based on the iteration of characteristic points and the compensation of image motion based on the wave filtering. The estimation of global motion parameters includes that a Harries characteristic point which is the most stable in the image is combined with a characteristic window; local characteristic points are gradually deleted through the identification of the distance consistency and the updating of the iteration of characteristic points so that the global characteristic point set converges rapidly and the global motion parameters can be accurately obtained. The compensation of the motion image includes that the global motion parameters are filtered to acquire dither parameters, and actual dither parameters are compensated and the normal scanning motion of an image pickup system is retained; simultaneously, the image fusion is combined with the compensation to realize the output of a panorama image. The method of the invention can effectively process the dithers such as translation, rotation and zooming, etc., of the image pick-up system and more complex local motion of the scene, and can be used for removing the influence on the video sequence by a motion carrier so as to output a stable video and improve the observation effect of the video monitoring or tracking.

Owner:XIDIAN UNIV

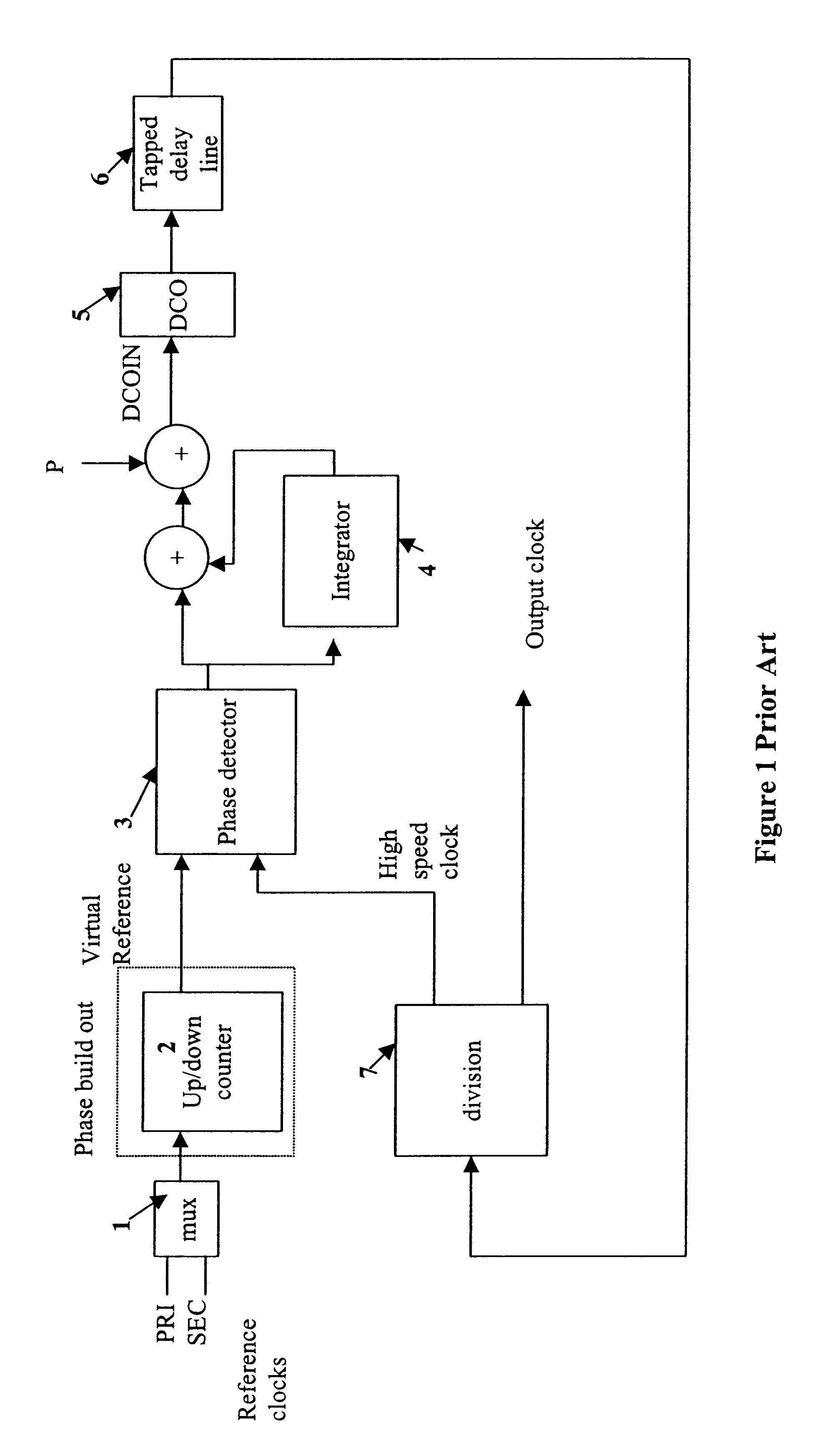

High efficiency active matching electro-optic transducer driver circuit operable with low supply voltages

ActiveUS6965722B1Improve efficiencyImproving Impedance MatchingLaser detailsAmplifier combinationsEngineeringTransistor

An optical transmitter and / or a constituent electro-optic transducer driver that performs active matching. The transducer driver performs active matching using a voltage step down through one base-emitter bipolar transistor, followed by a step up approach through the base-emitter of another bipolar transistor, thereby allowing for lower supply voltages. Furthermore, the voltage drop across the source resistor is minimal by using an operation amplifier in a feedback configuration, thereby further encouraging operability with low supply voltages. The electro-optic transducer driver is also beneficial in that it has high AC-coupling efficiency of the modulation current to the electro-optic transducer, may operate at high speeds with reduced jitter.

Owner:II VI DELAWARE INC

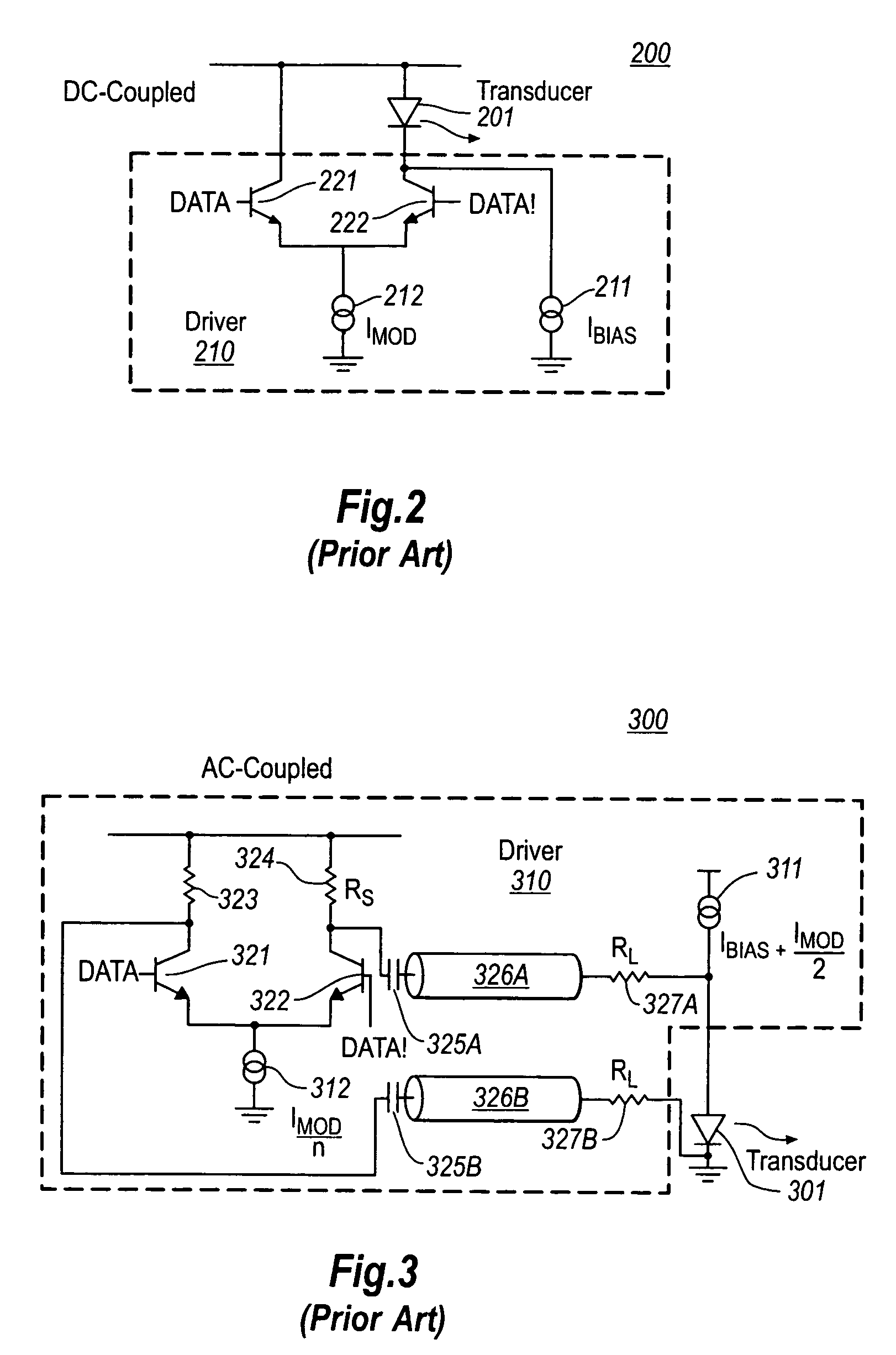

Multiple input phase lock loop with hitless reference switching

InactiveUS6570454B2Reduce jitterPulse automatic controlTime-division multiplexClock recoveryDigital controlled oscillator

Owner:ZARLINK SEMICON LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com