Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1220 results about "Clock recovery" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

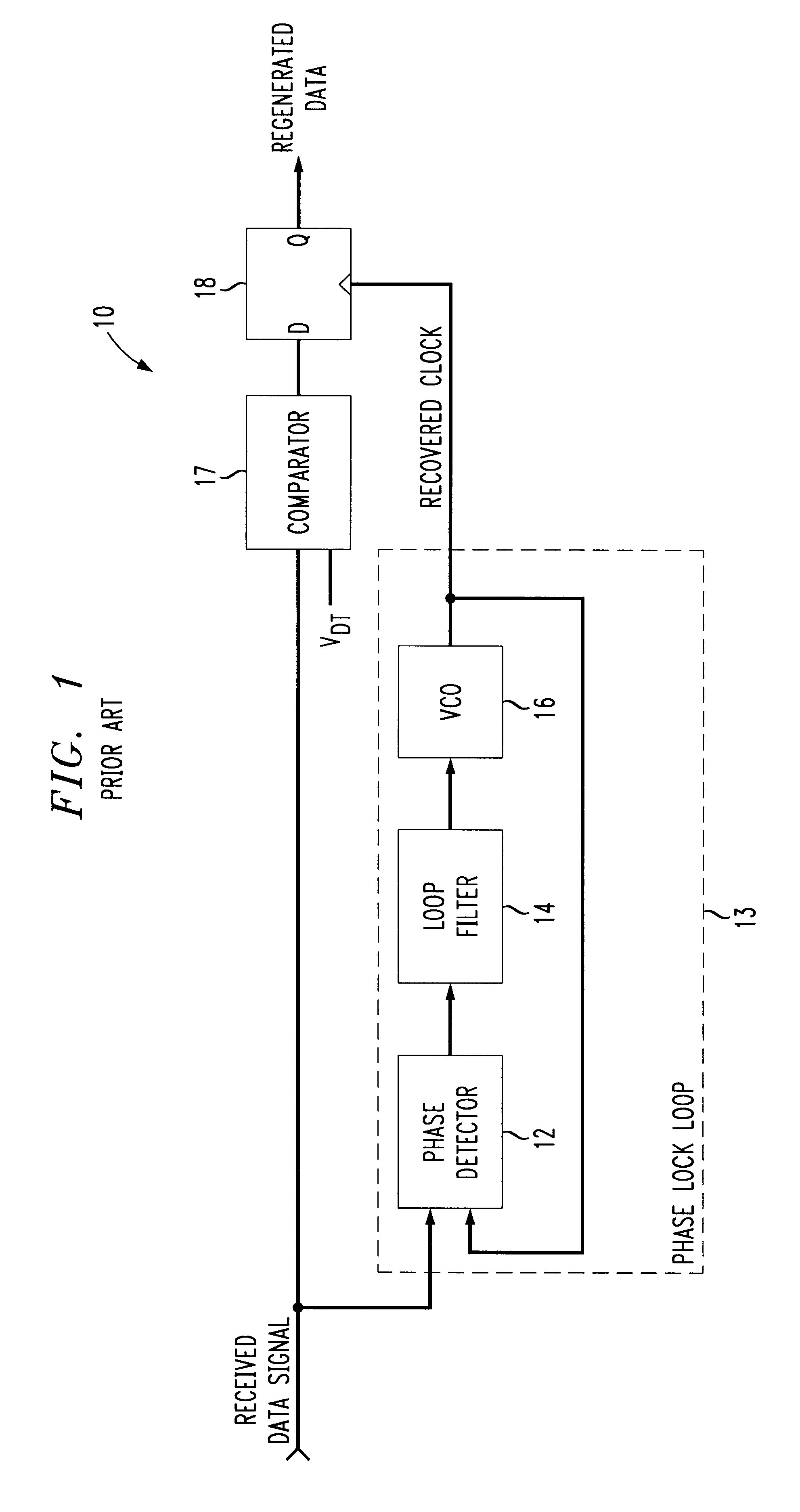

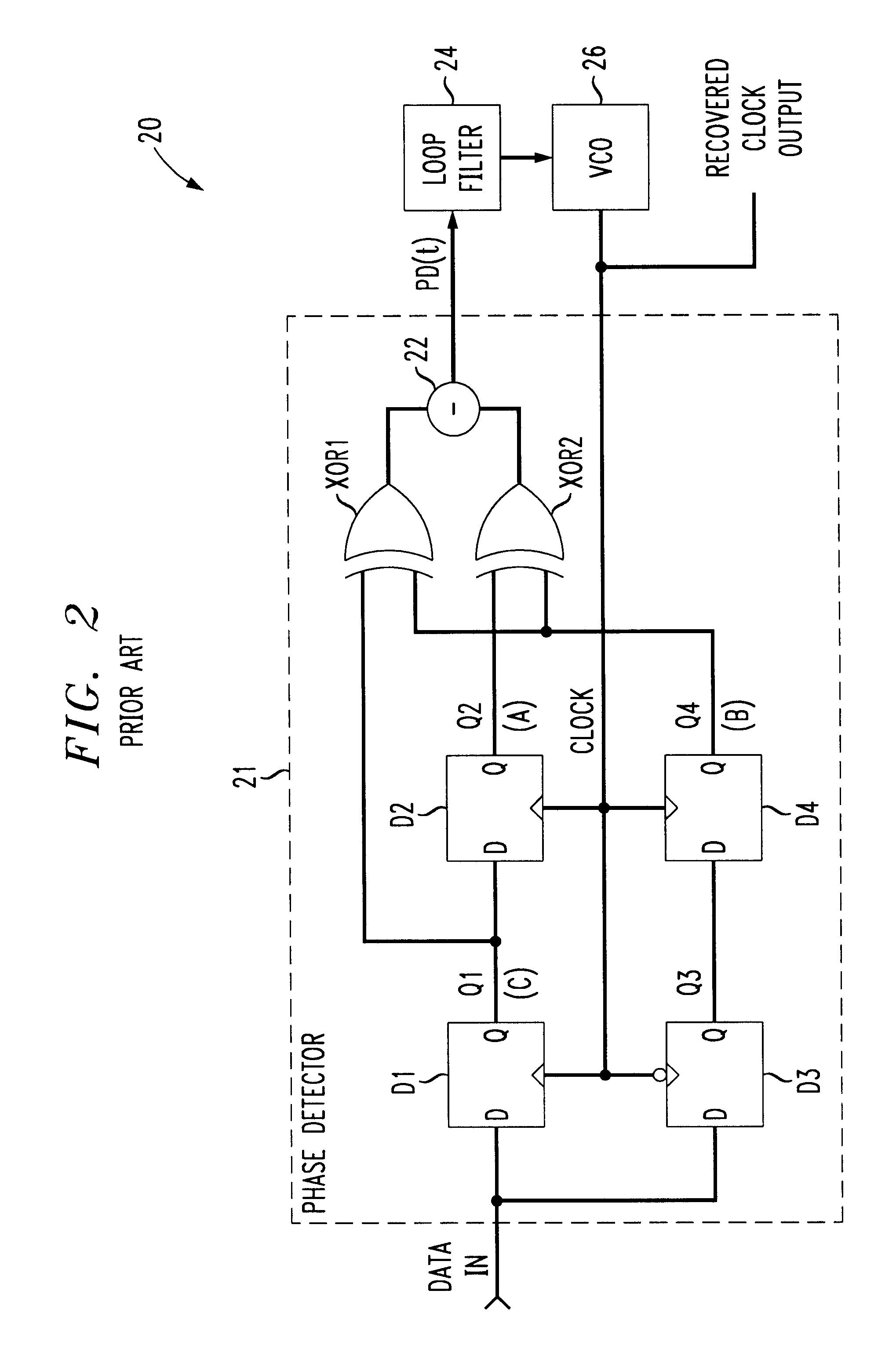

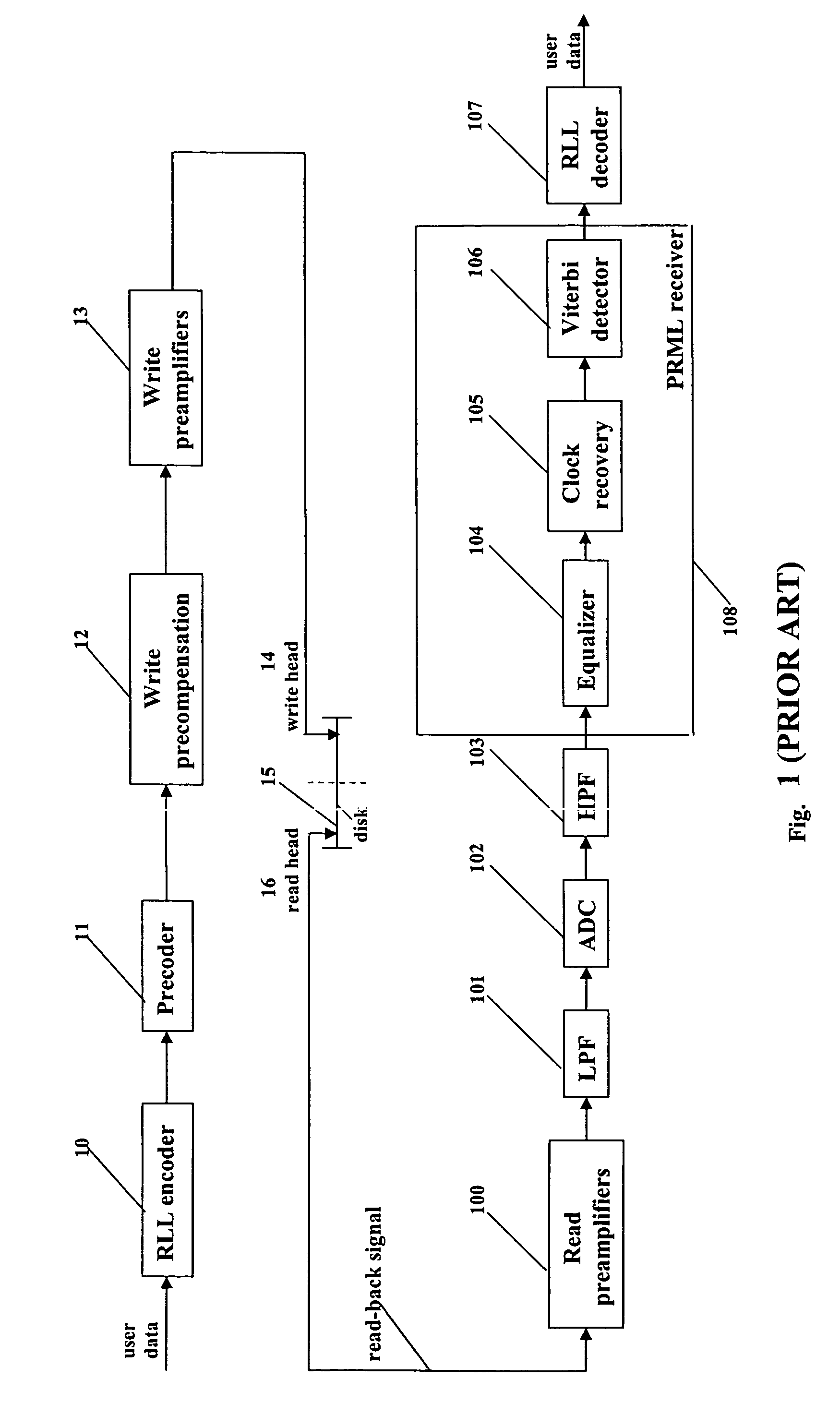

In serial communication of digital data, clock recovery is the process of extracting timing information from a serial data stream to allow the receiving circuit to decode the transmitted symbols. Clock recovery from the data stream is expedited by modifying the transmitted data. Wherever a serial communication channel does not transmit the clock signal along with the data stream, the clock must be regenerated at the receiver, using the timing information from the data stream. Clock recovery is a common component of systems communicating over wires, optical fibers, or by radio.

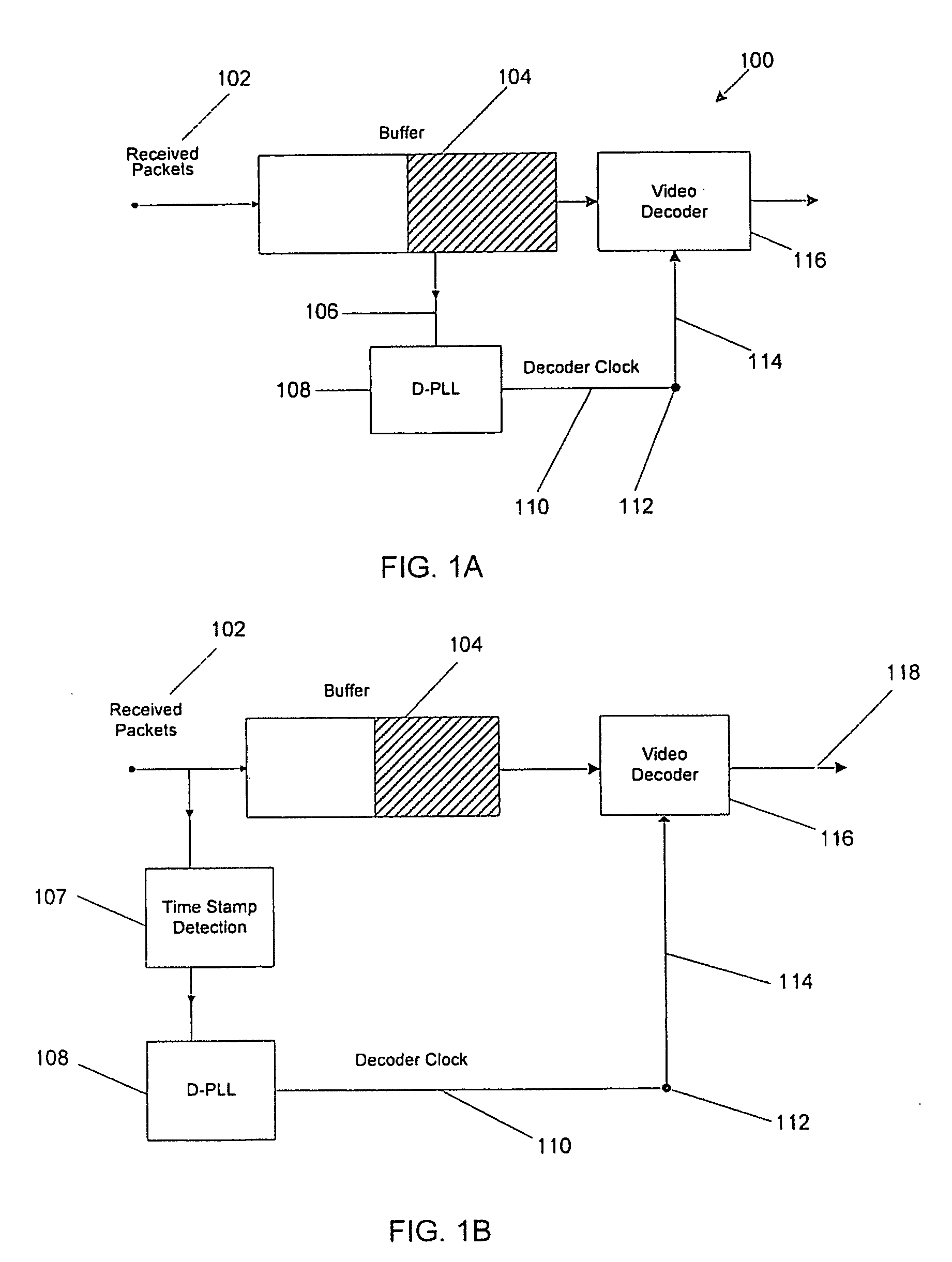

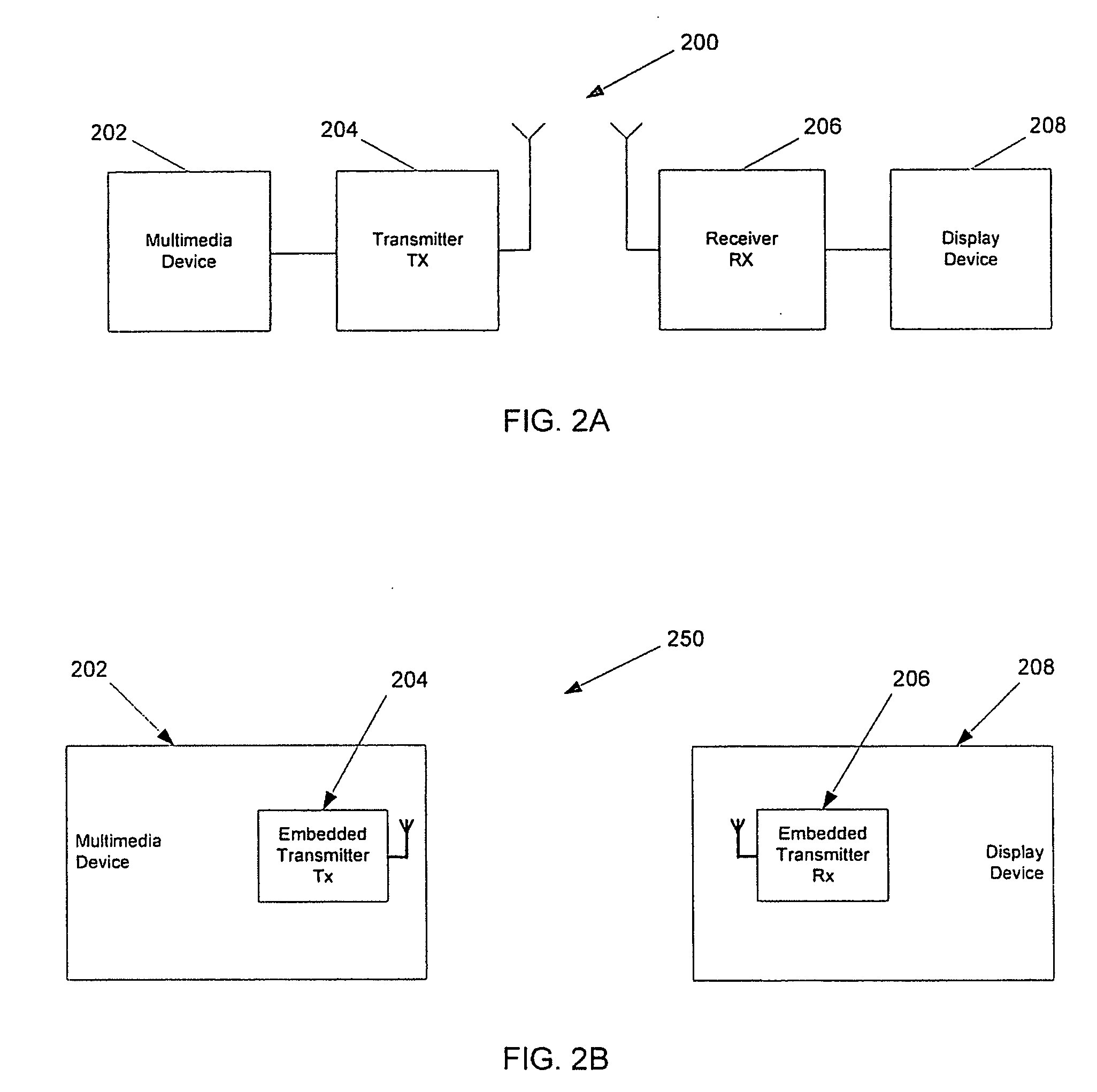

Method and system for providing site independent real-time multimedia transport over packet-switched networks

InactiveUS20060007943A1Minimal latency site-independenceAchieve independenceTime-division multiplexData switching by path configurationData packTimestamp

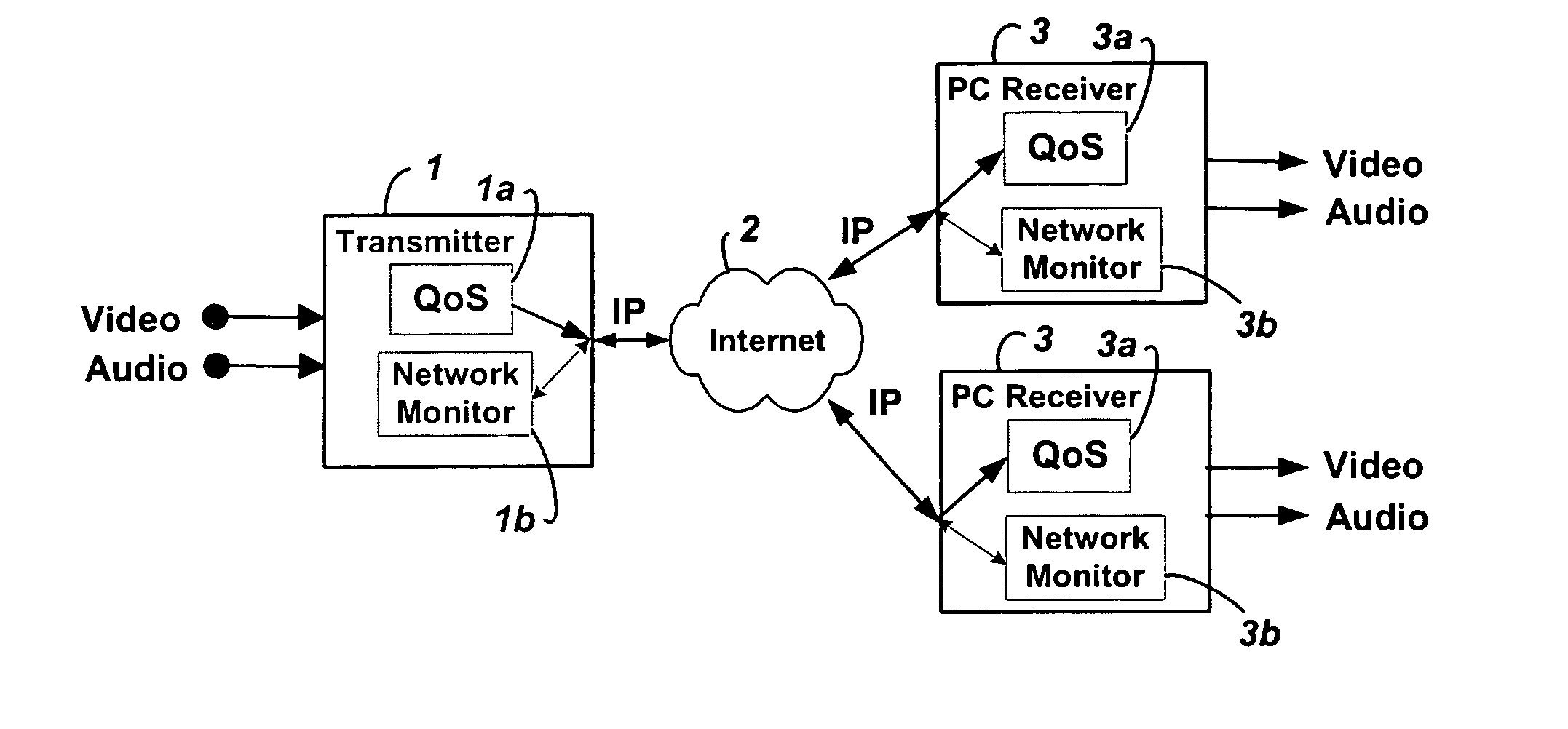

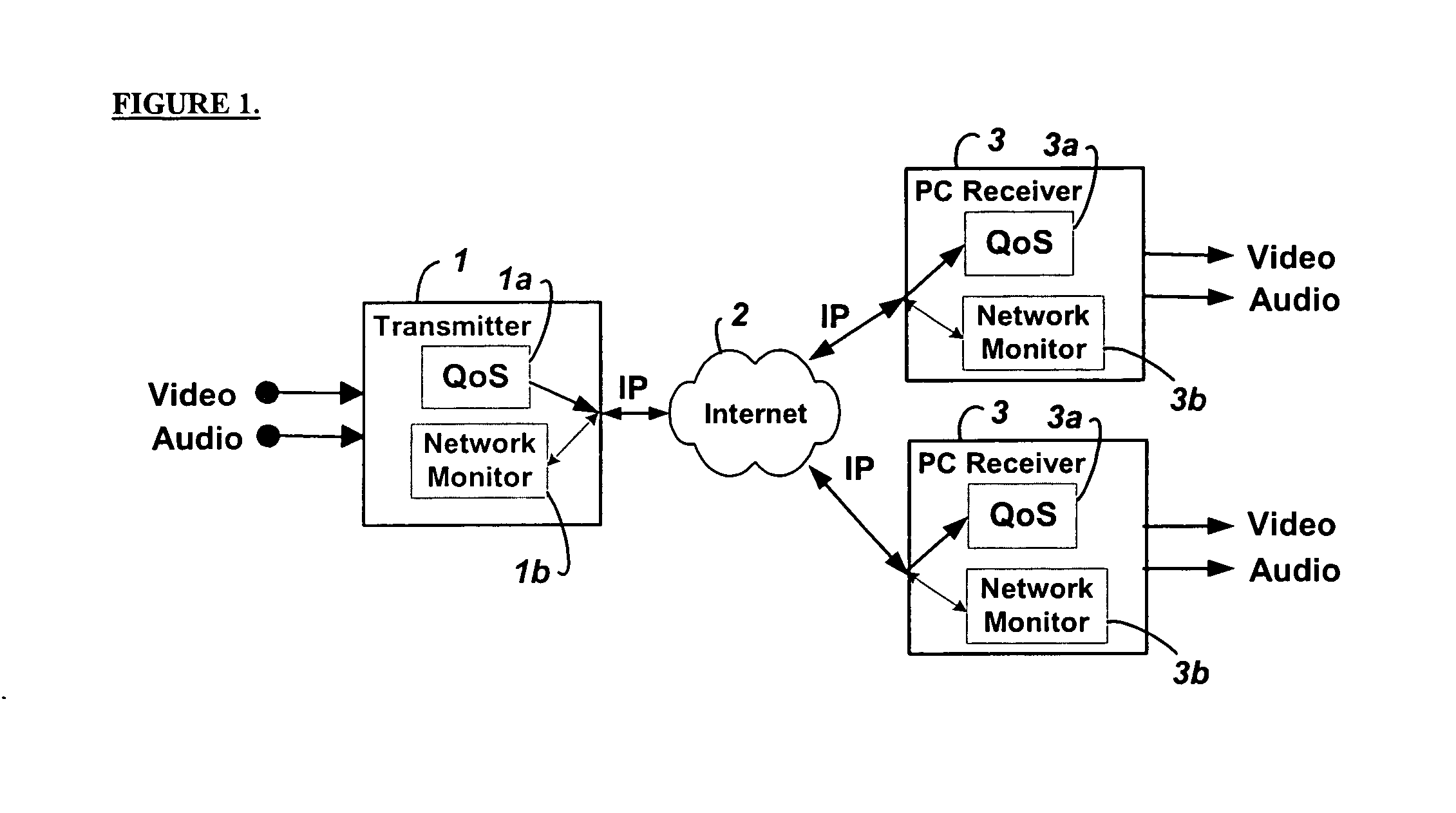

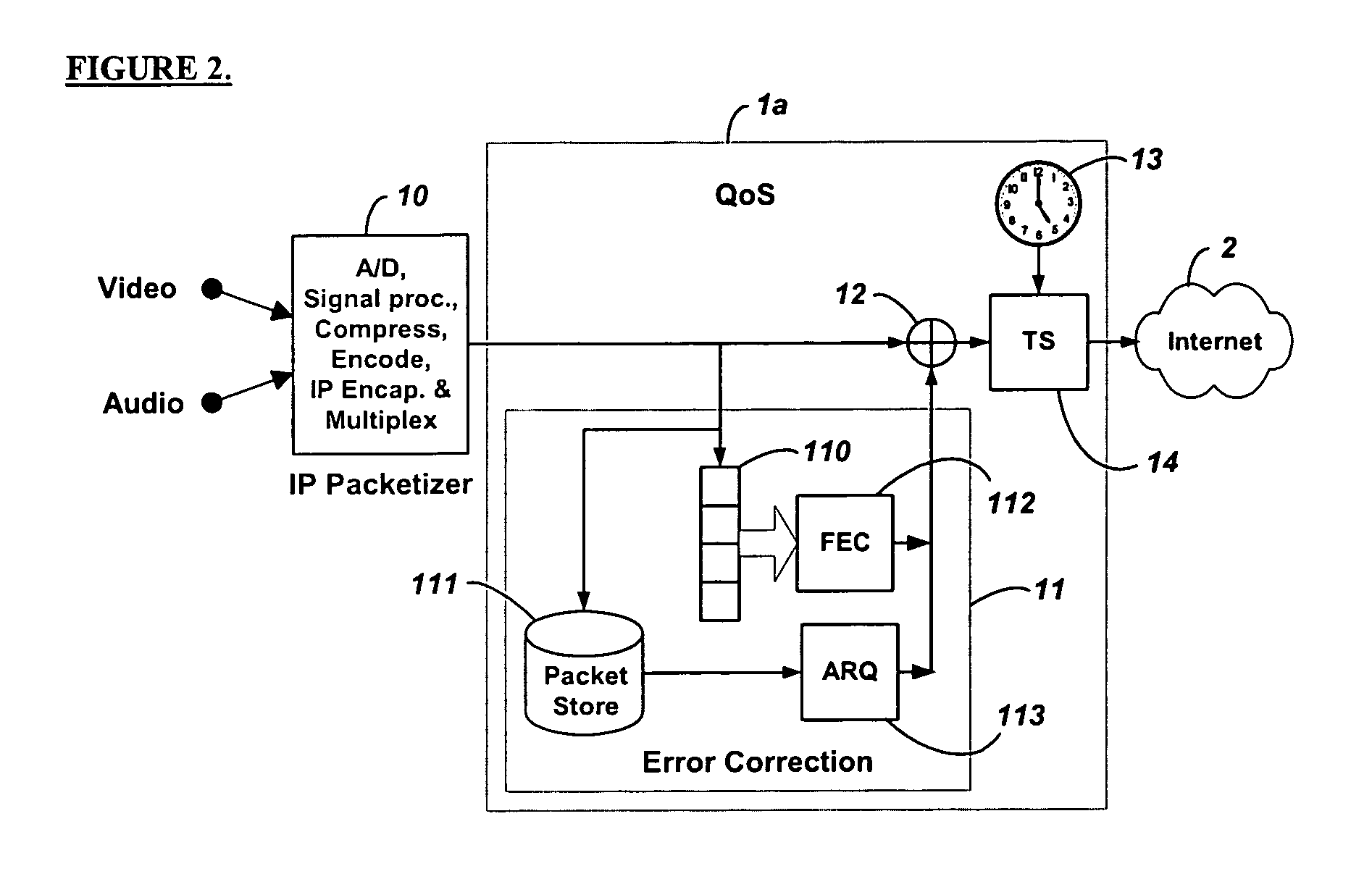

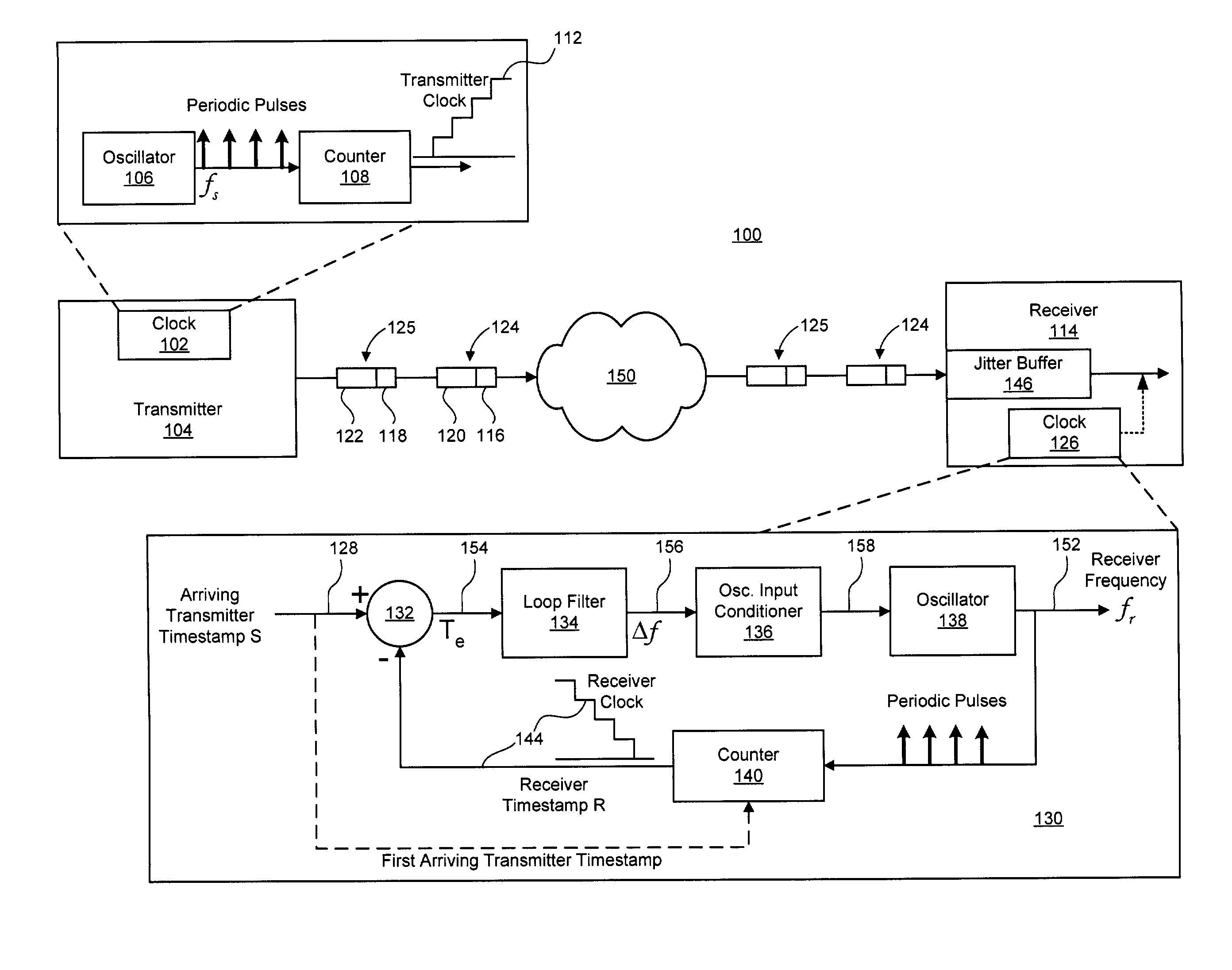

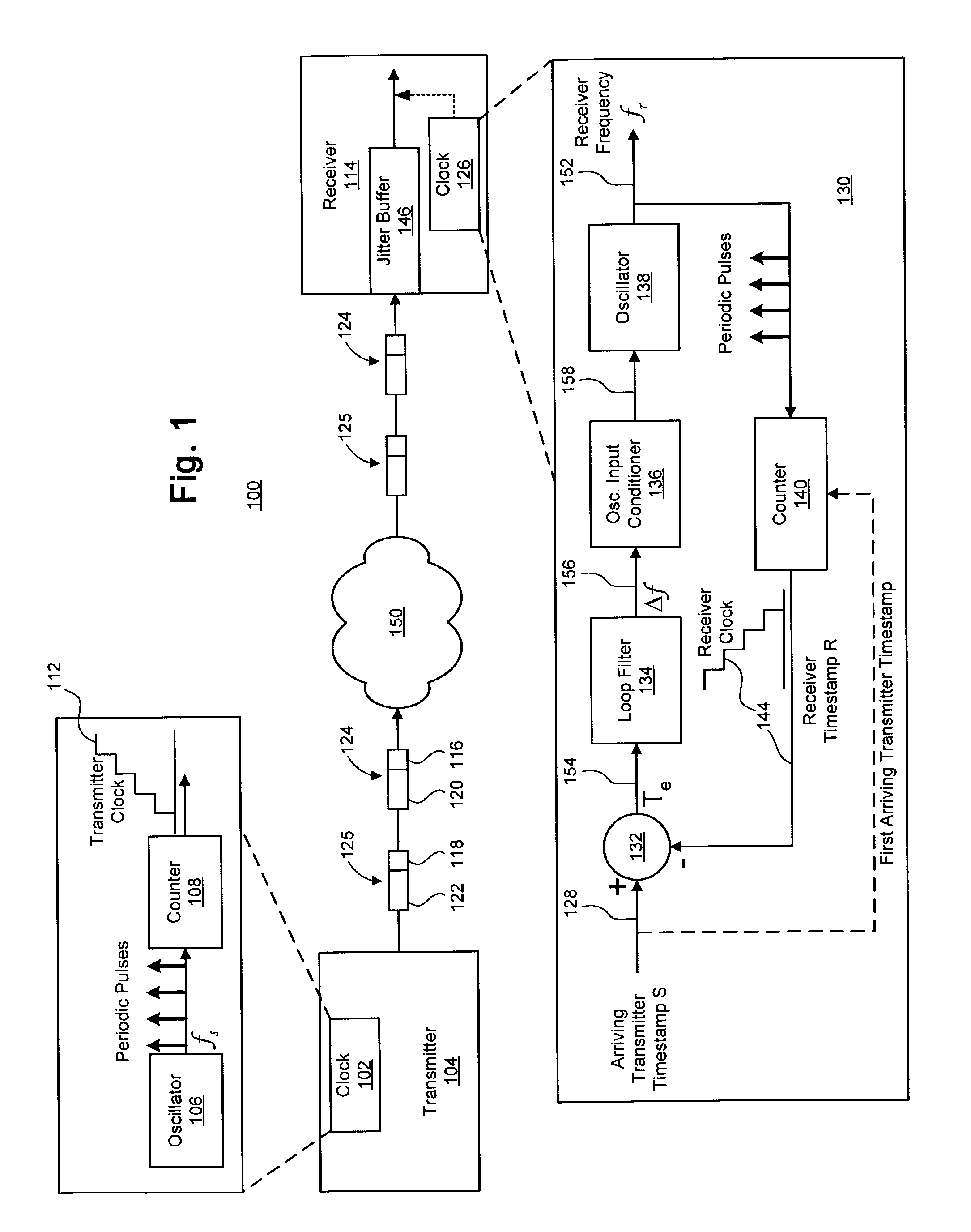

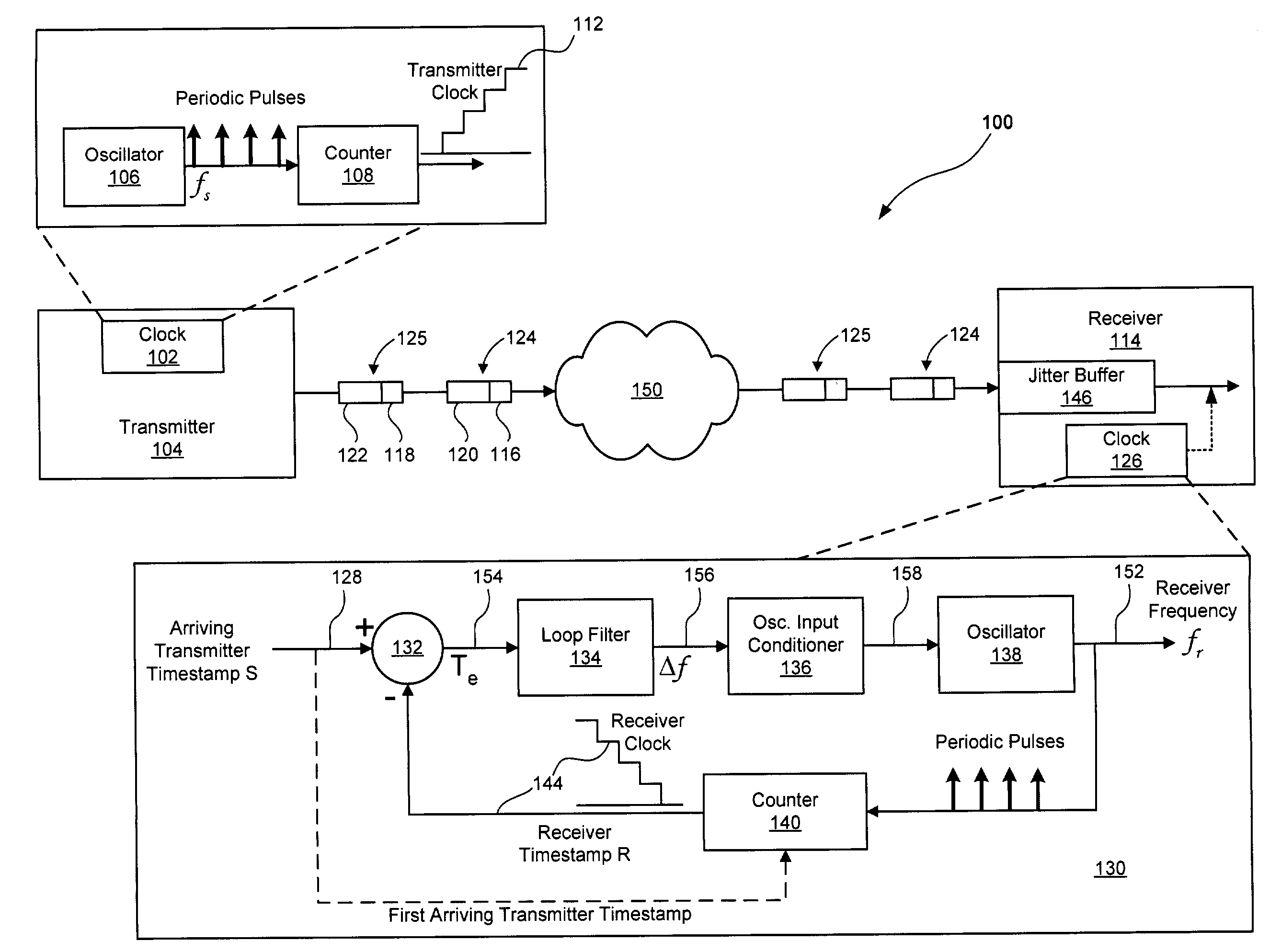

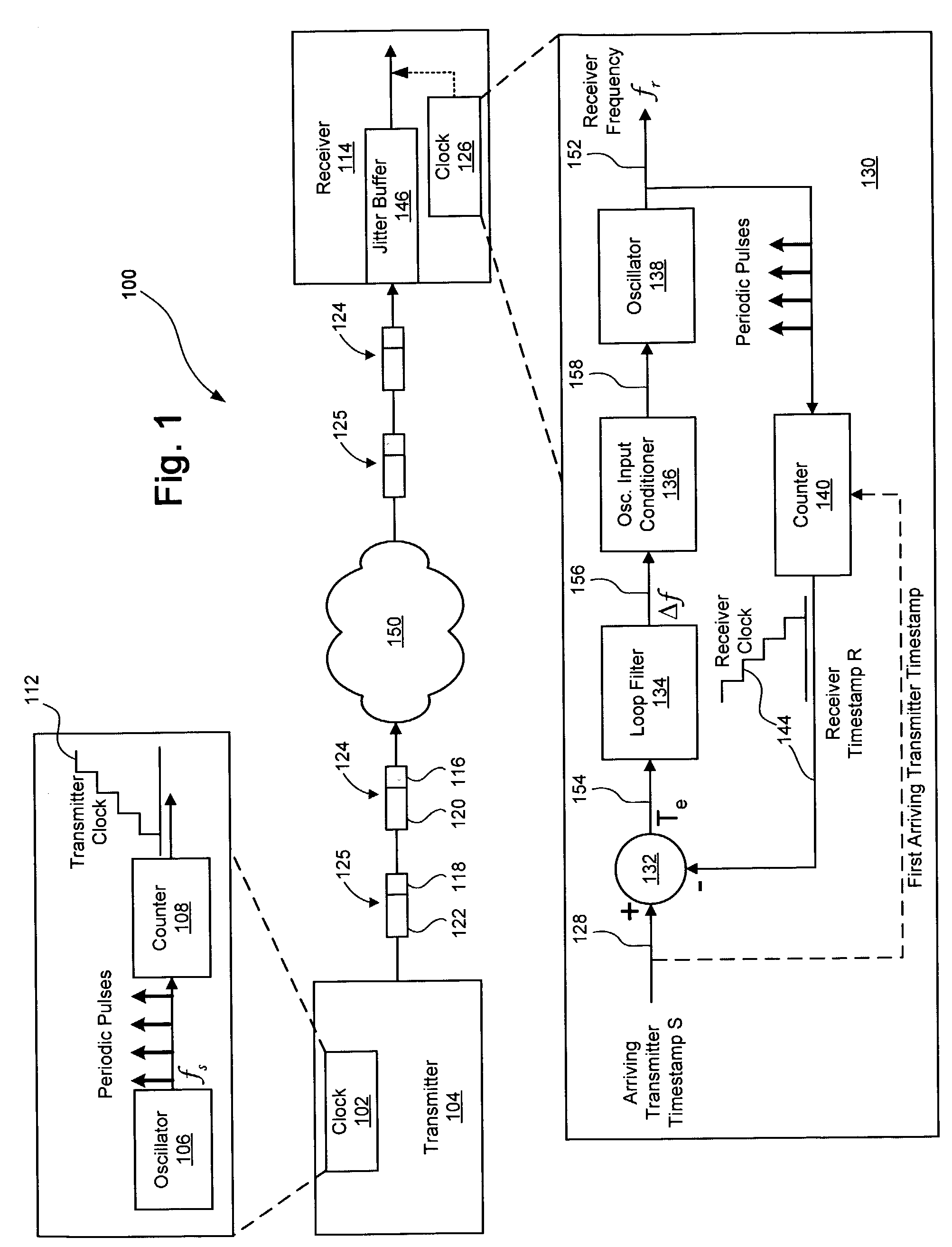

Embodiments of the invention enable minimum latency site independent real-time video transport over packet switched networks. Some examples of real-time video transport are video conferencing and real-time or live video streaming. In one embodiment of the invention, a network node transmits live or real-tine audio and video signals, encapsulated as Internet Protocol (IP) data packets, to one or more nodes on the Internet or other IP network. One embodiment of the invention enables a user to move to different nodes or move nodes to different locations thereby providing site independence. Site independence is achieved by measuring and accounting for the jitter and delay between a transmitter and receiver based on the particular path between the transmitter and receiver independent of site location. The transmitter inserts timestamps and sequence numbers into packets and then transmits them. A receiver uses these timestamps to recover the transmitter's clock. The receiver stores the packets in a buffer that orders them by sequence number. The packets stay in the buffer for a fixed latency to compensate for possible network jitter and / or packet reordering. The combination of timestamp packet-processing, remote clock recovery and synchronization, fixed-latency receiver buffering, and error correction mechanisms help to preserve the quality of the received video, despite the significant network impairments generally encountered throughout the Internet and wireless networks.

Owner:QVIDIUM TECH

Clock recovery using a double-exponential smoothing process

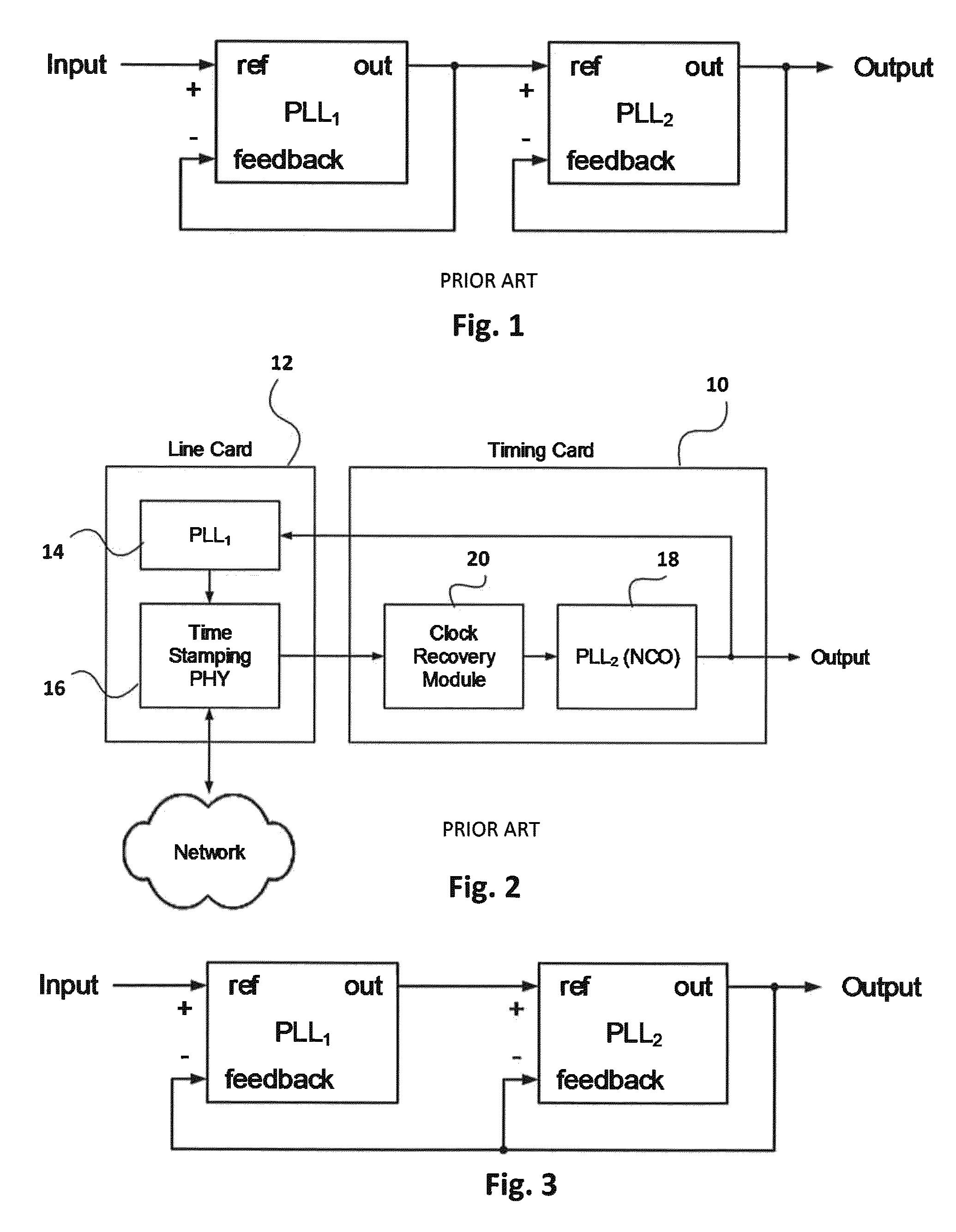

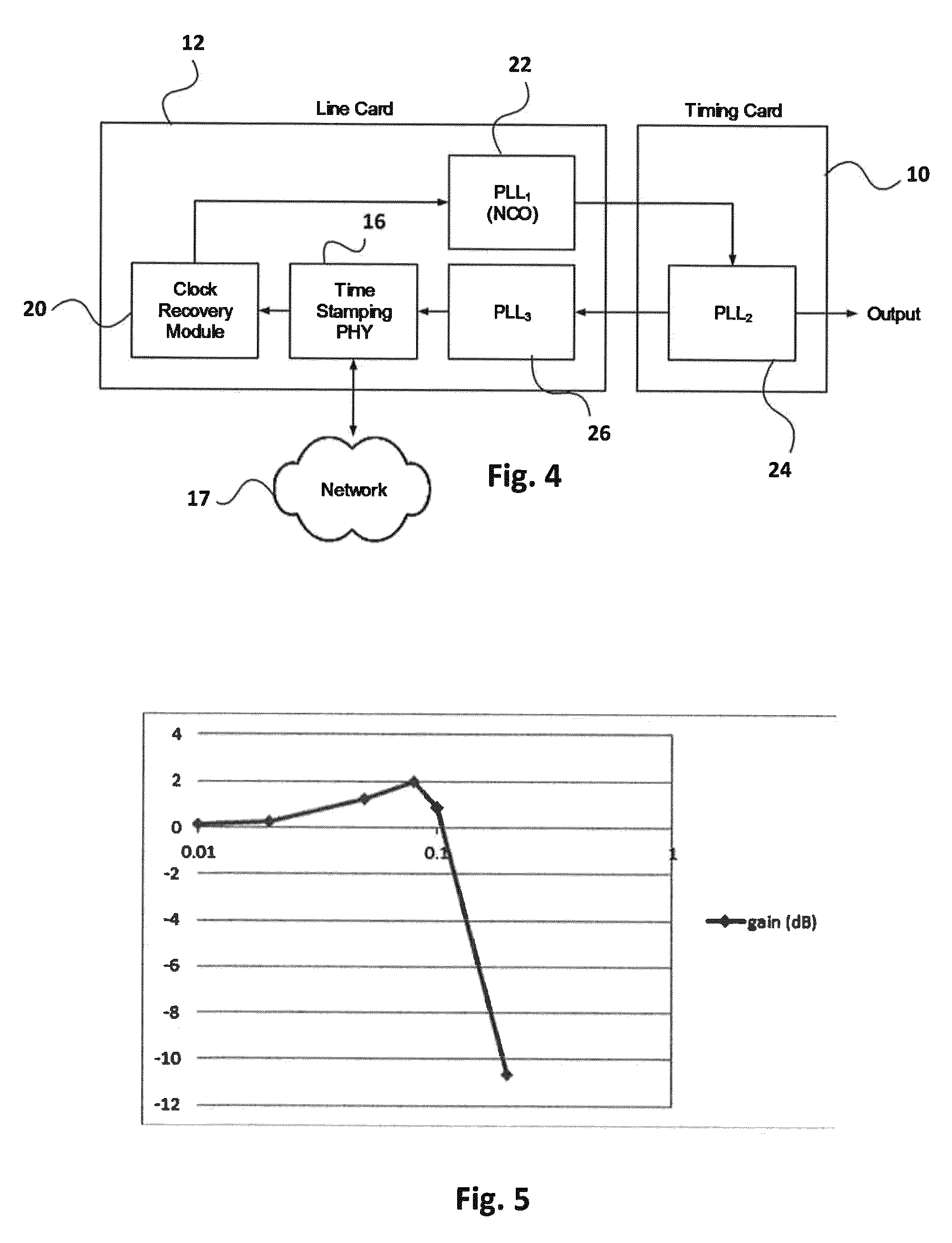

A system and method for synchronizing a local clock to a reference clock using a linear model of the clock error between the local clock and the reference clock is disclosed. In one embodiment, a double-exponential smoothing process is used in conjunction with the linear model to estimate a frequency offset by which the frequency of an oscillator of the local clock is adjusted. Also disclosed herein is a phased-lock loop (PLL) adapted to synchronize a local clock with a reference clock using the double-exponential smoothing process, as well as a system implementing the PLL for timing the playout of data received from a transmitter.

Owner:RPX CLEARINGHOUSE

Clock recovery using a direct smoothing process

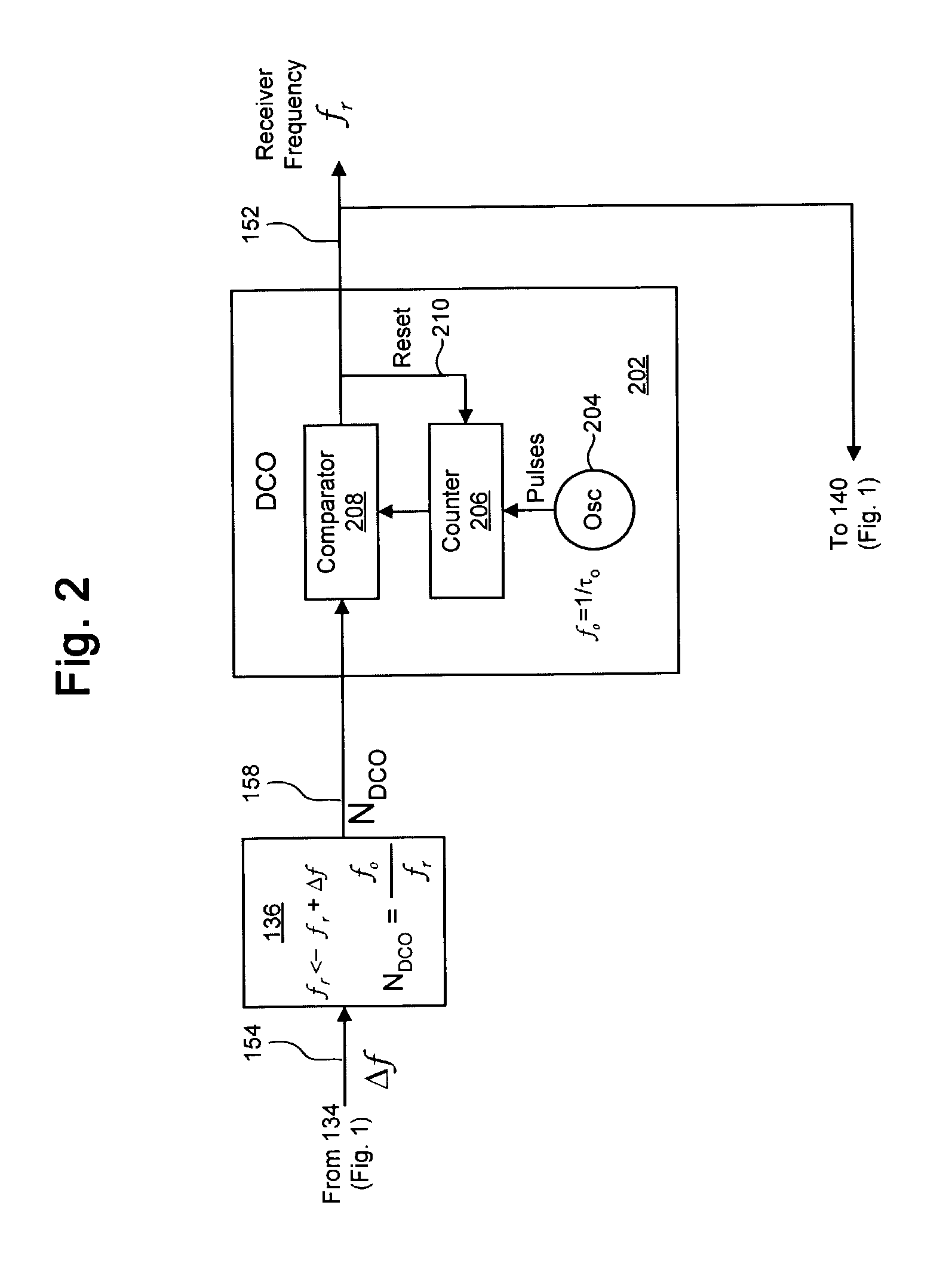

ActiveUS7130368B1Guaranteed maximum utilizationPulse automatic controlModulated-carrier systemsClock recoveryLinear model

A system and method for synchronizing a local clock to a reference clock using a linear model of the error between the local clock and the reference clock is disclosed. In one embodiment, a direct smoothing process is used in conjunction with the linear model to estimate a frequency offset by which the frequency of an oscillator of the local clock is adjusted. Also disclosed herein is a phased-lock loop (PLL) adapted to synchronize a local clock with a reference clock using the direct smoothing process, as well as a system implementing the PLL for timing the playout of data received from a transmitter.

Owner:CIENA

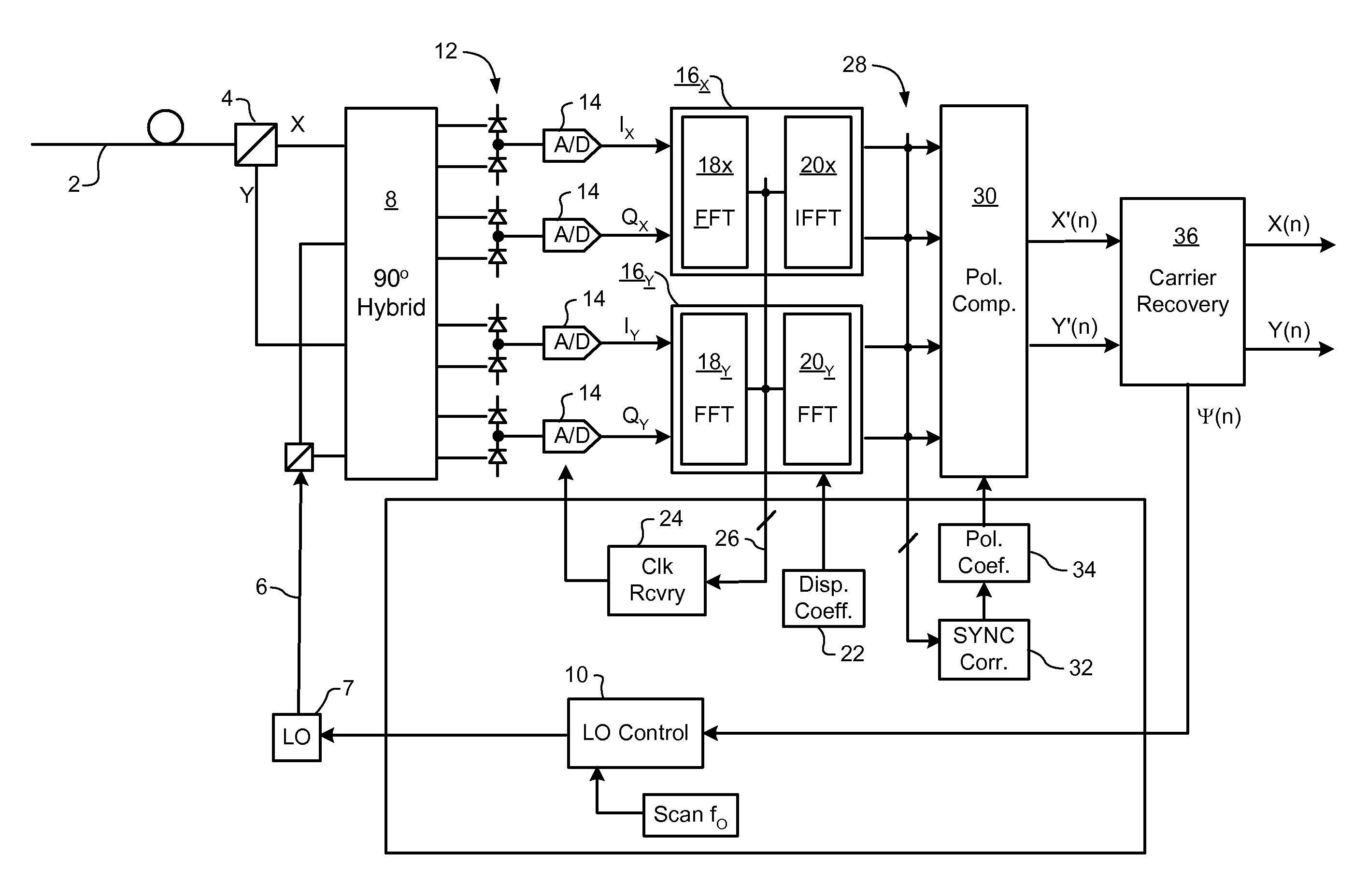

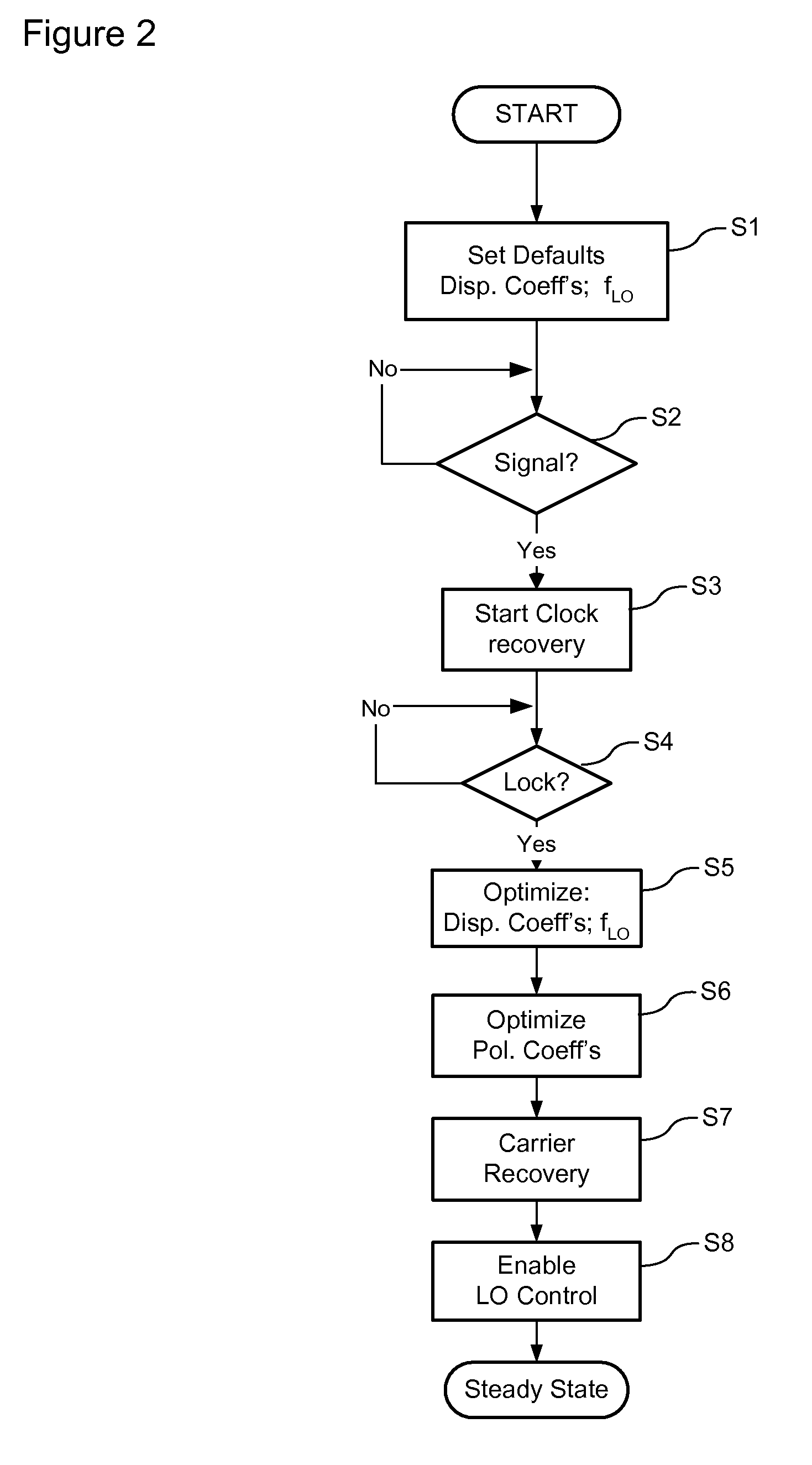

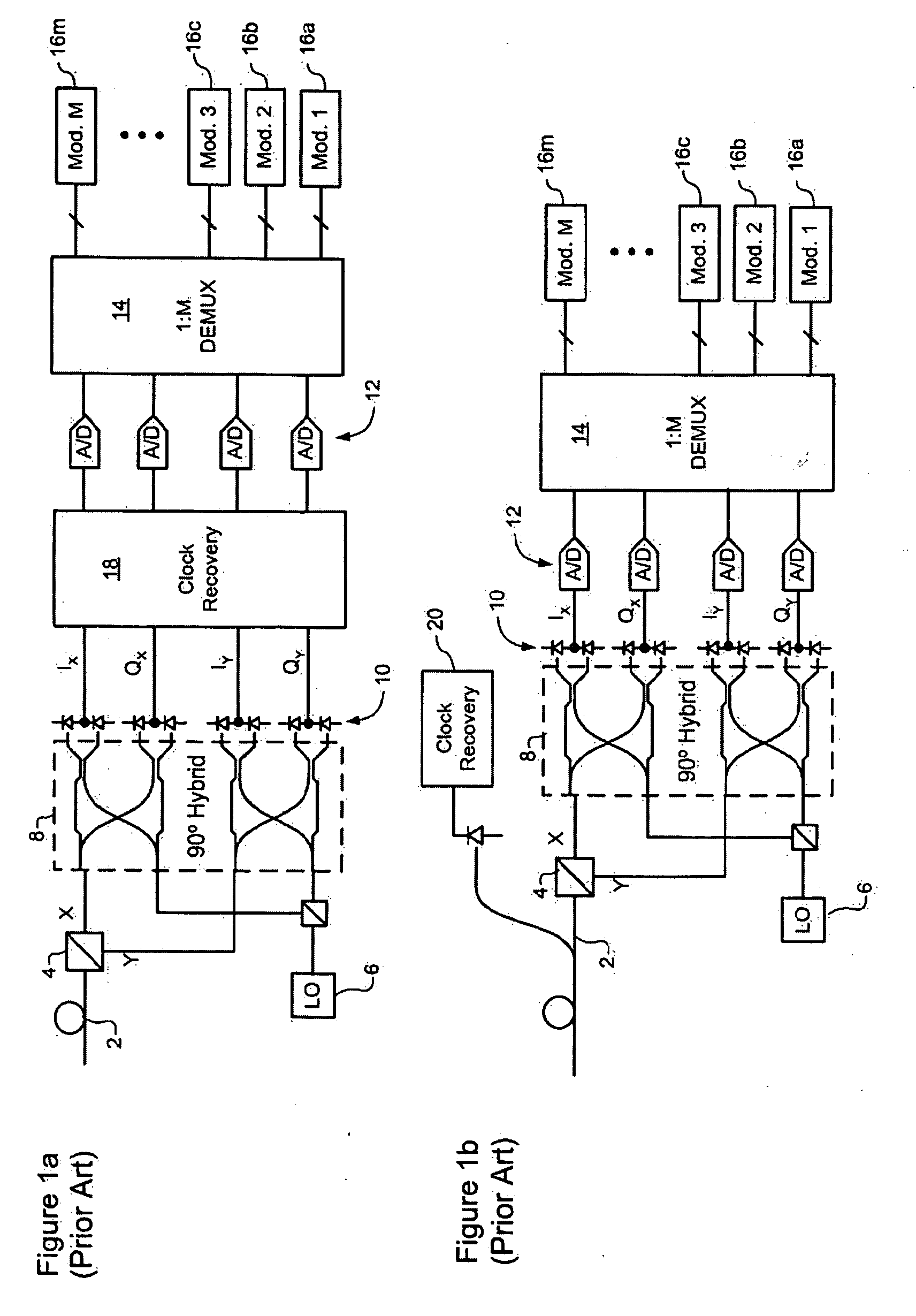

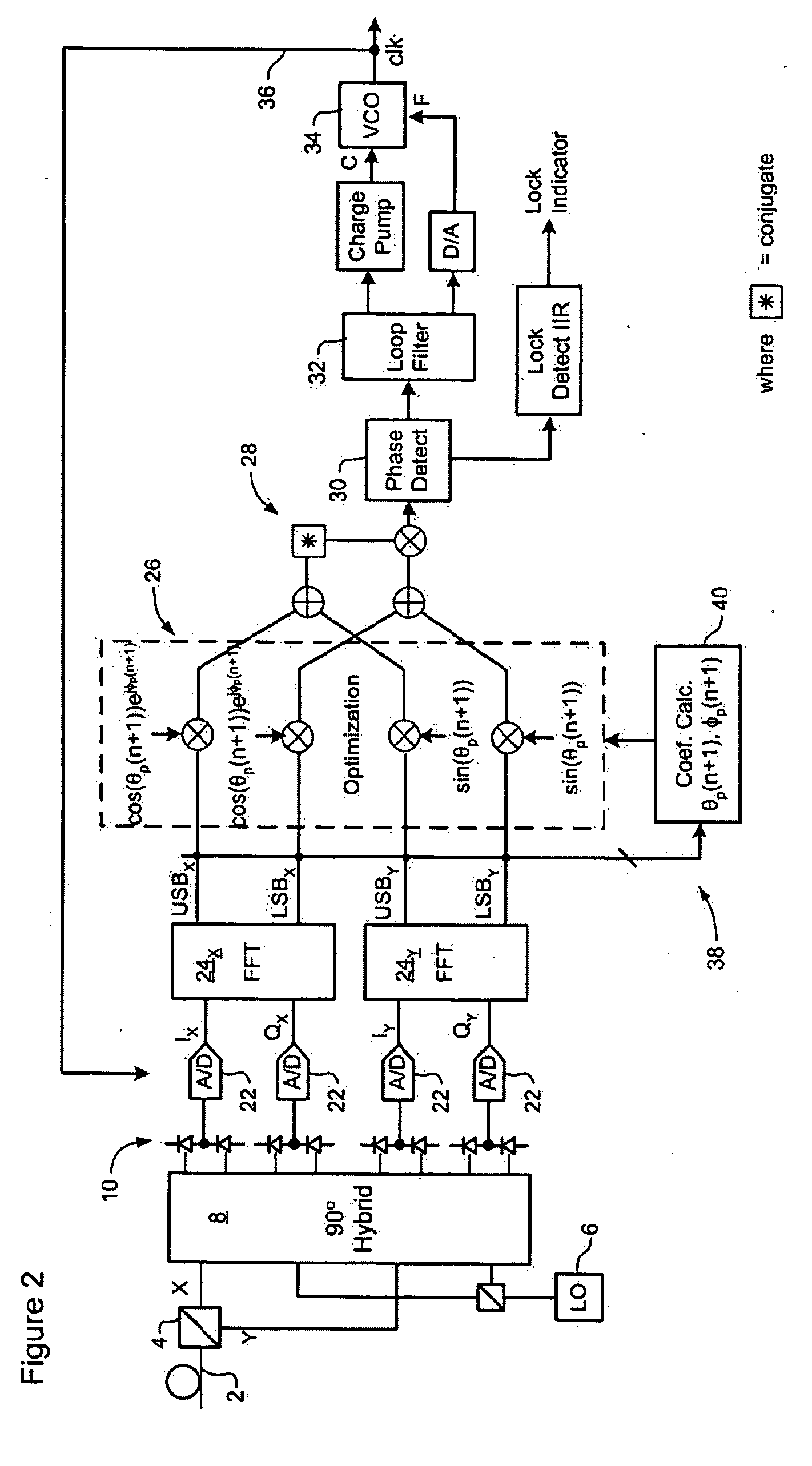

Signal acquisition in a coherent optical receiver

ActiveUS7636525B1Reliably acquire signalSteady-state operationReceiver initialisationSynchronisation by photonic/optical meansClock recoveryEngineering

A method and system for initializing a coherent optical receiver. Upon detection of an optical signal, a multi-bit digital sample stream of the optical signal is digitally processed to initialize each one of a plurality of adaptive control blocks of the coherent optical receiver. The adaptive control blocks include at least a dispersion compensation block and a clock recovery block. The dispersion compensation block is initialized before initializing the clock recovery block.

Owner:CIENA

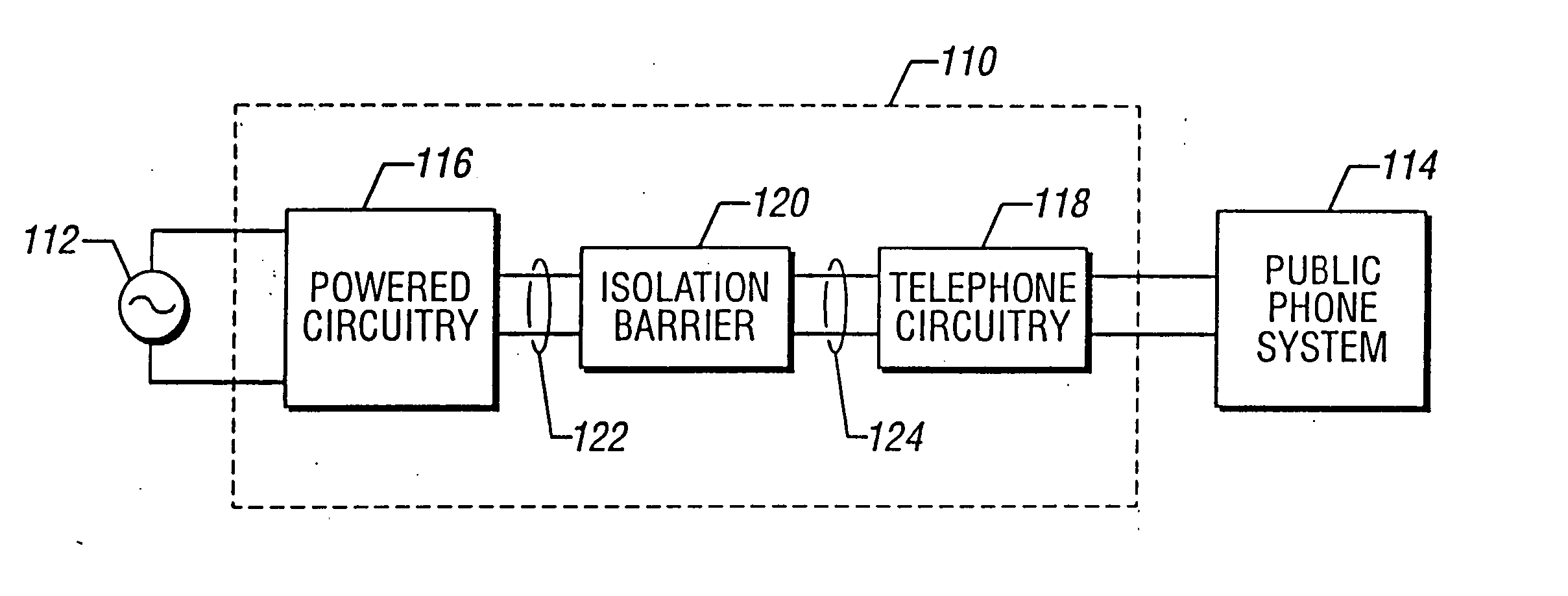

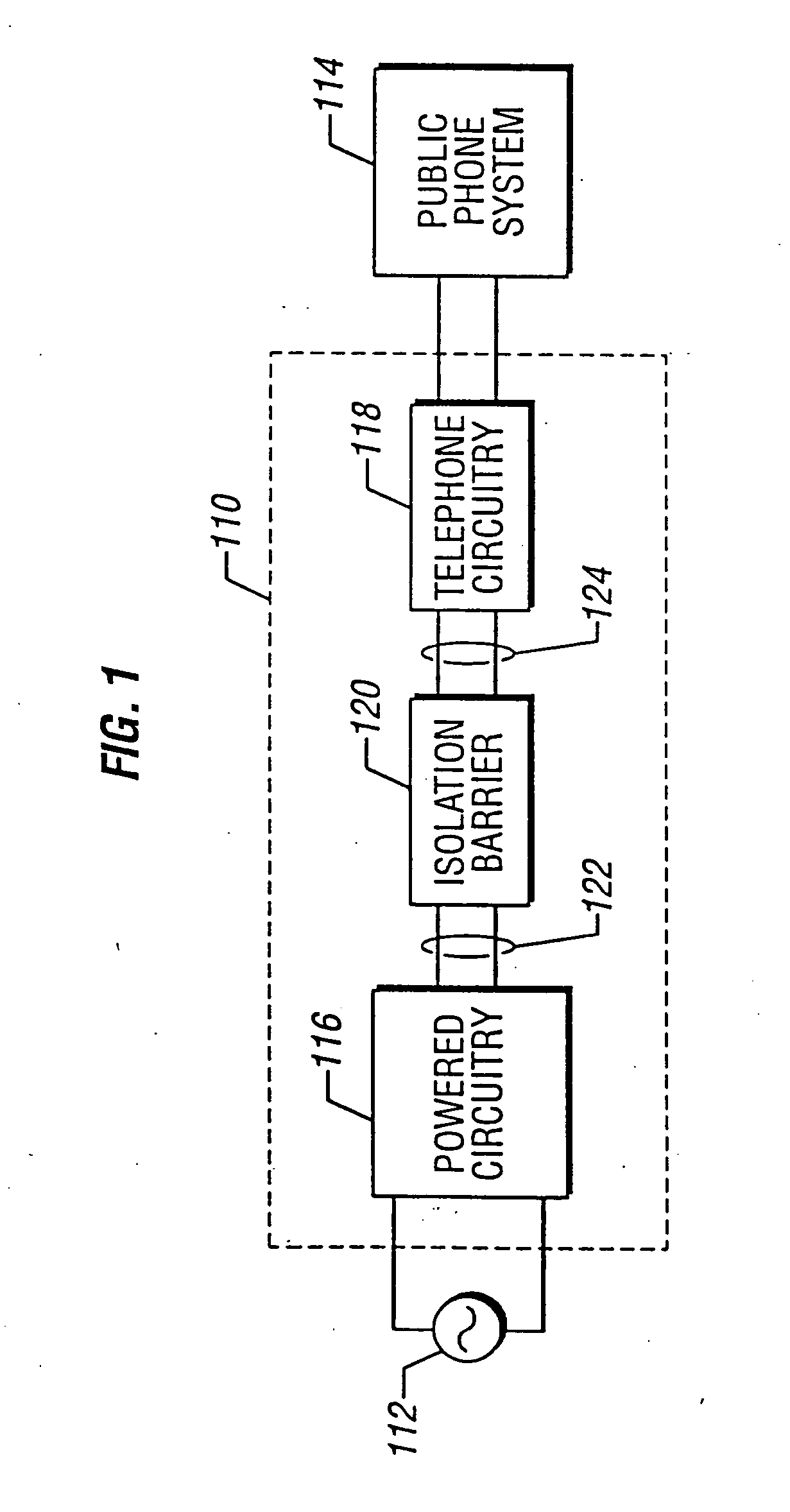

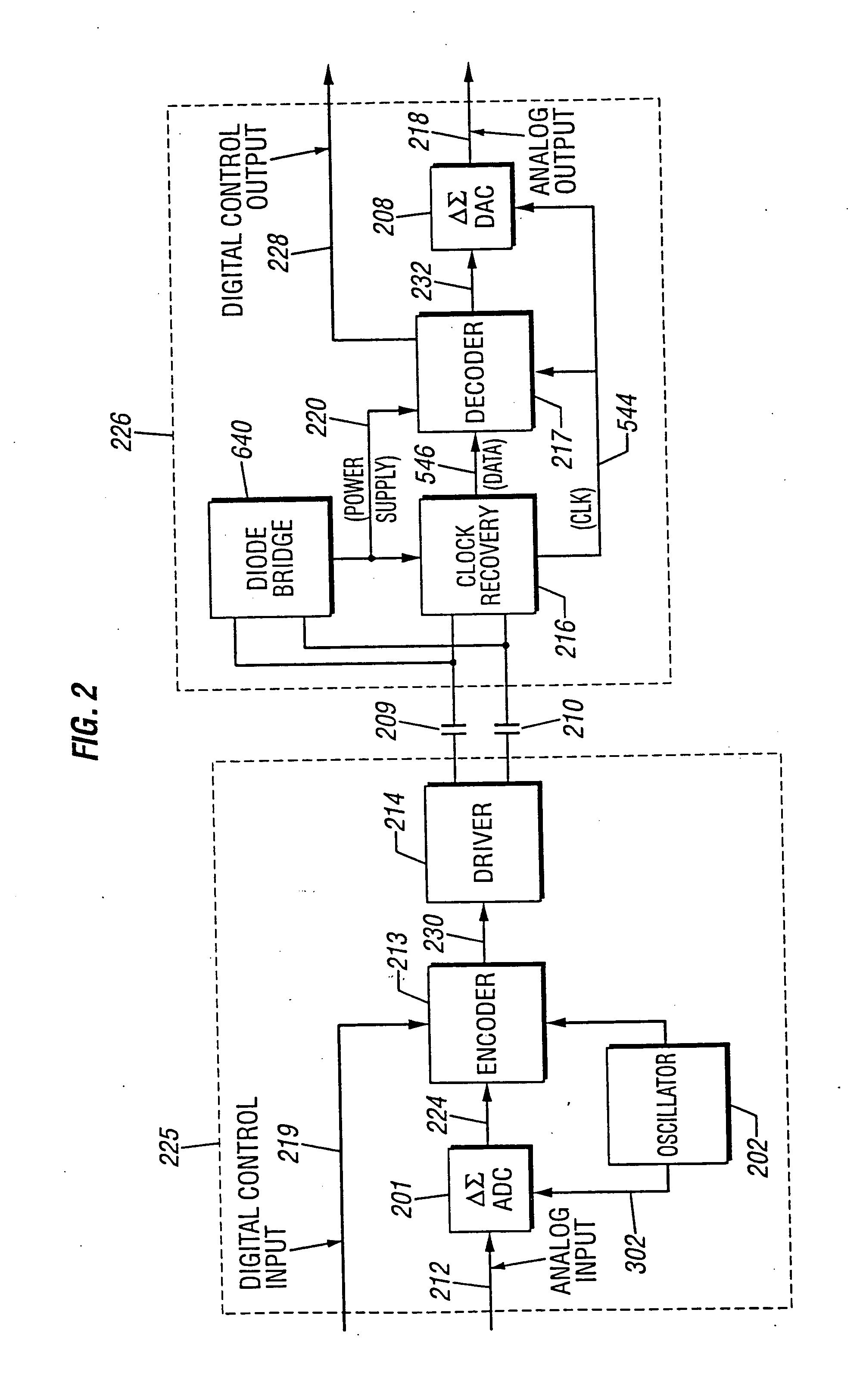

Direct digital access arrangement circuitry and method for connecting DSL circuitry to phone lines

InactiveUS20050036604A1Exact reproductionInterconnection arrangementsDc level restoring means or bias distort correctionCapacitanceDigital data

An isolation system is provided that is suitable for use in telephony, medical instrumentation, industrial process control and other applications. Preferred embodiments of the invention comprise a capacitive isolation barrier across which a digital signal is communicated. The system provides a means of communication across the isolation barrier that is highly immune to amplitude and phase noise interference. Clock recovery circuitry may be employed on one side of the isolation barrier to extract timing information from the digital signal communicated across the barrier, and to filter the effects of phase noise introduced at the barrier. Delta-sigma converters may be disposed on both sides of the isolation barrier to convert signals between analog and digital domains. An isolated power supply may also be provided on the isolated side of the barrier, whereby direct current is generated in response to the digital data received across the isolation barrier. A bidirectional isolation system is provided whereby bidirectional communication of digital signals is accomplished using a single pair of isolation capacitors. In preferred embodiments, the digital data communicated across the barrier consists of digital delta-sigma data signals multiplexed in time with other digital control, signaling and framing information. Finally, the isolation system may include a pulse transformer to accommodate ADSL circuitry, whereby power is transmitted through the pulse transformer.

Owner:SILICON LAB INC

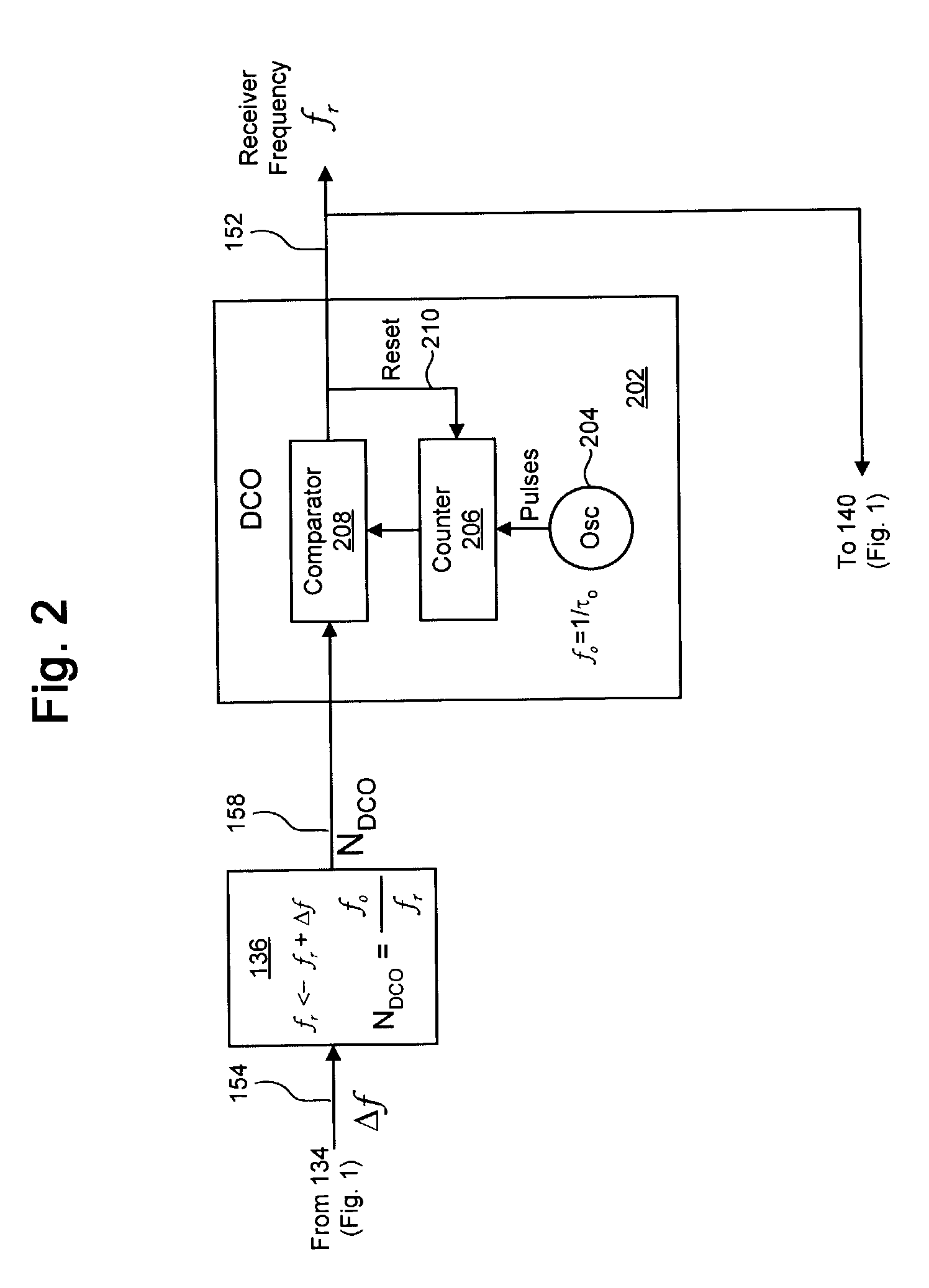

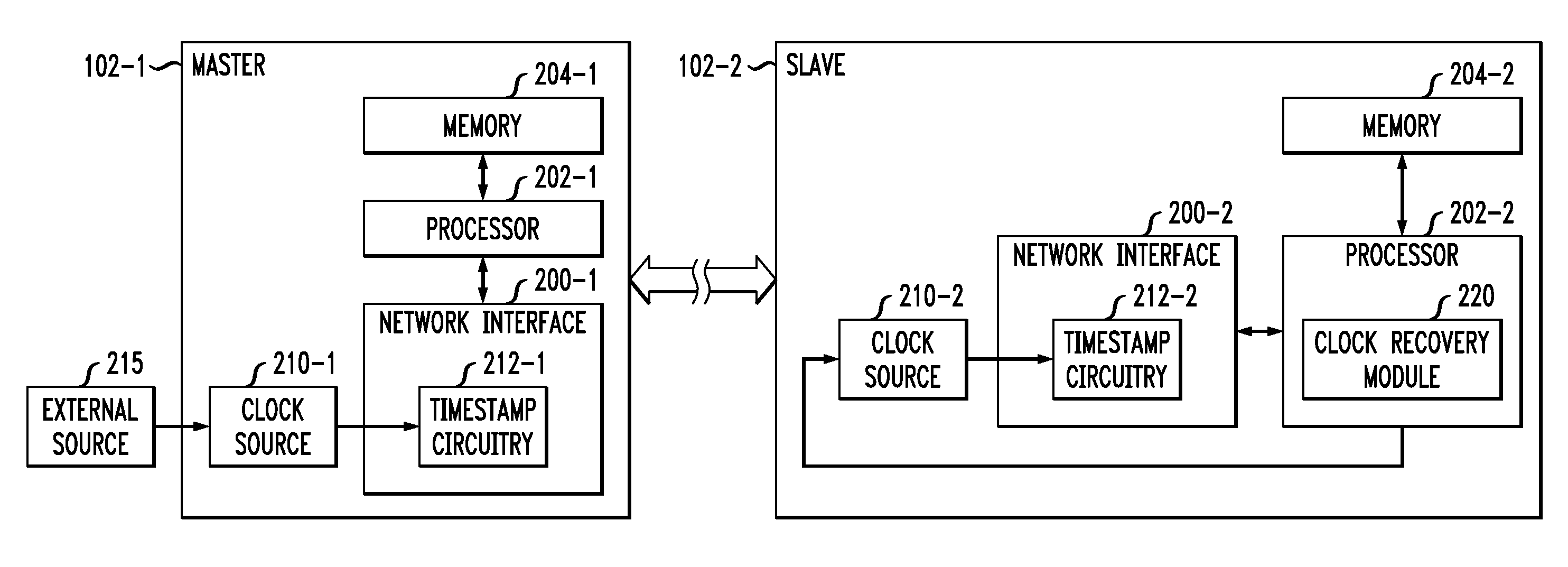

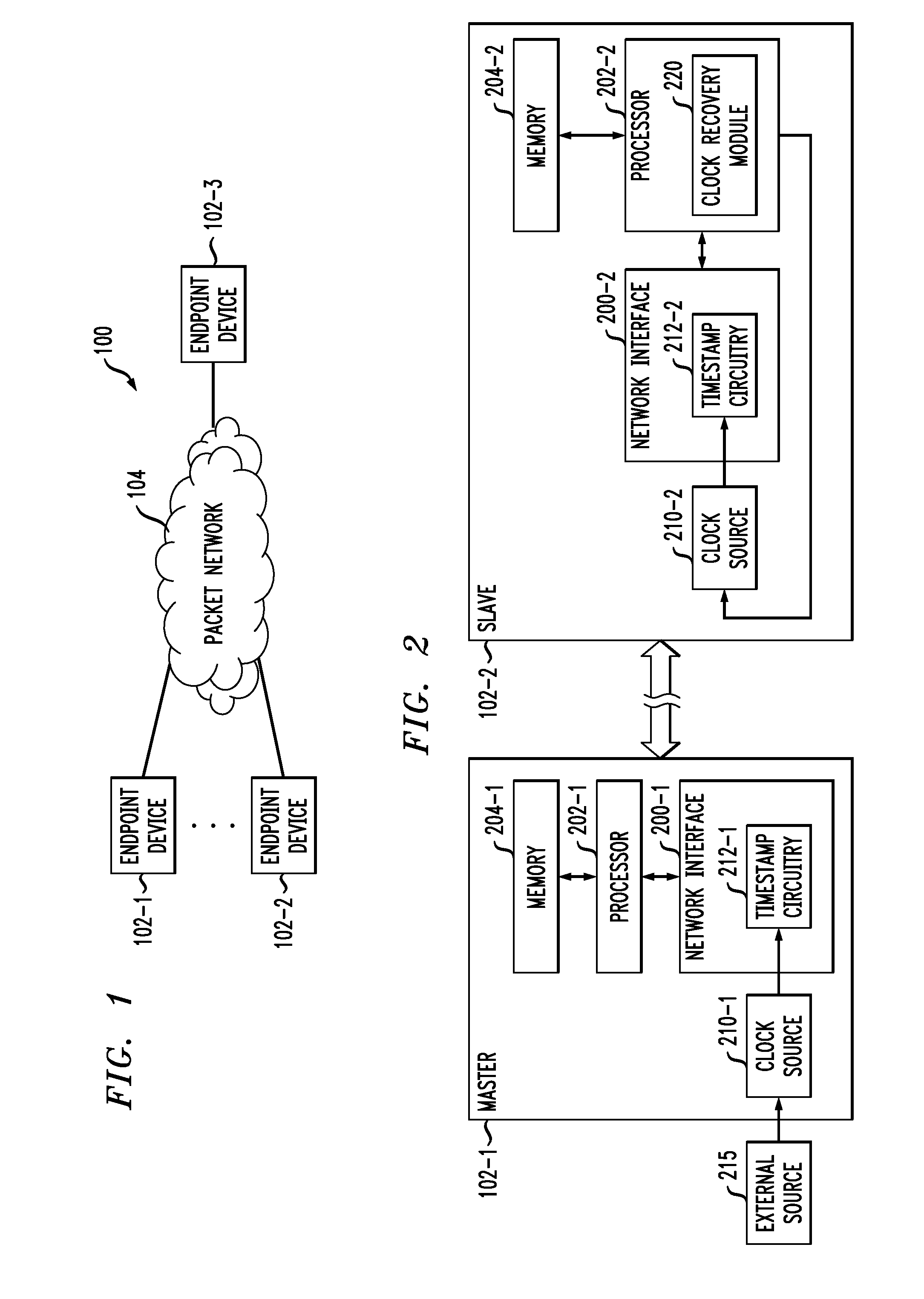

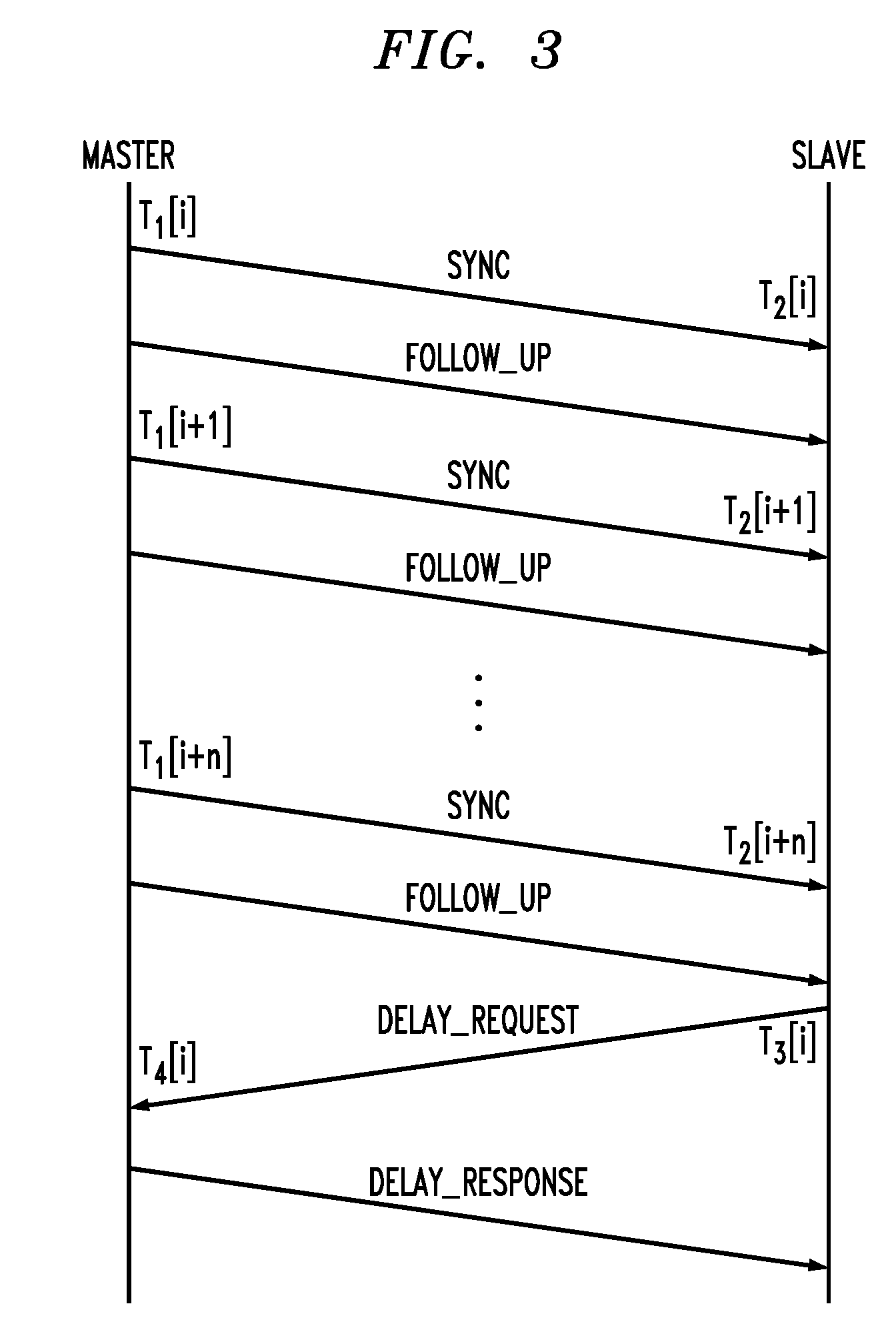

Method, Apparatus and System for Frequency Synchronization Between Devices Communicating over a Packet Network

InactiveUS20100158051A1Simple technologyImprove performancePulse automatic controlTime-division multiplexLoop filterTimestamp

An endpoint or other communication device of a communication system includes a clock recovery module. The communication device is operative as a slave device relative to another communication device that is operative as a master device. The clock recovery module comprises a clock recovery loop configured to control a slave clock frequency of the slave device so as to synchronize the slave clock frequency with a master clock frequency of the master device. The clock recovery loop utilizes a frequency error estimator implemented as a maximum-likelihood estimator with slope fitting based on a sequence of arrival timestamps, and a loop filter implemented as a series combination of an adaptive-bandwidth filter and a proportional-integral controller. The clock recovery module may further comprise a discontinuity detector configured to detect a discontinuity in delays of respective timing messages, and a loop controller operative to place the clock recovery loop in a particular state responsive to detection of the discontinuity.

Owner:PIECE FUTURE PTE LTD

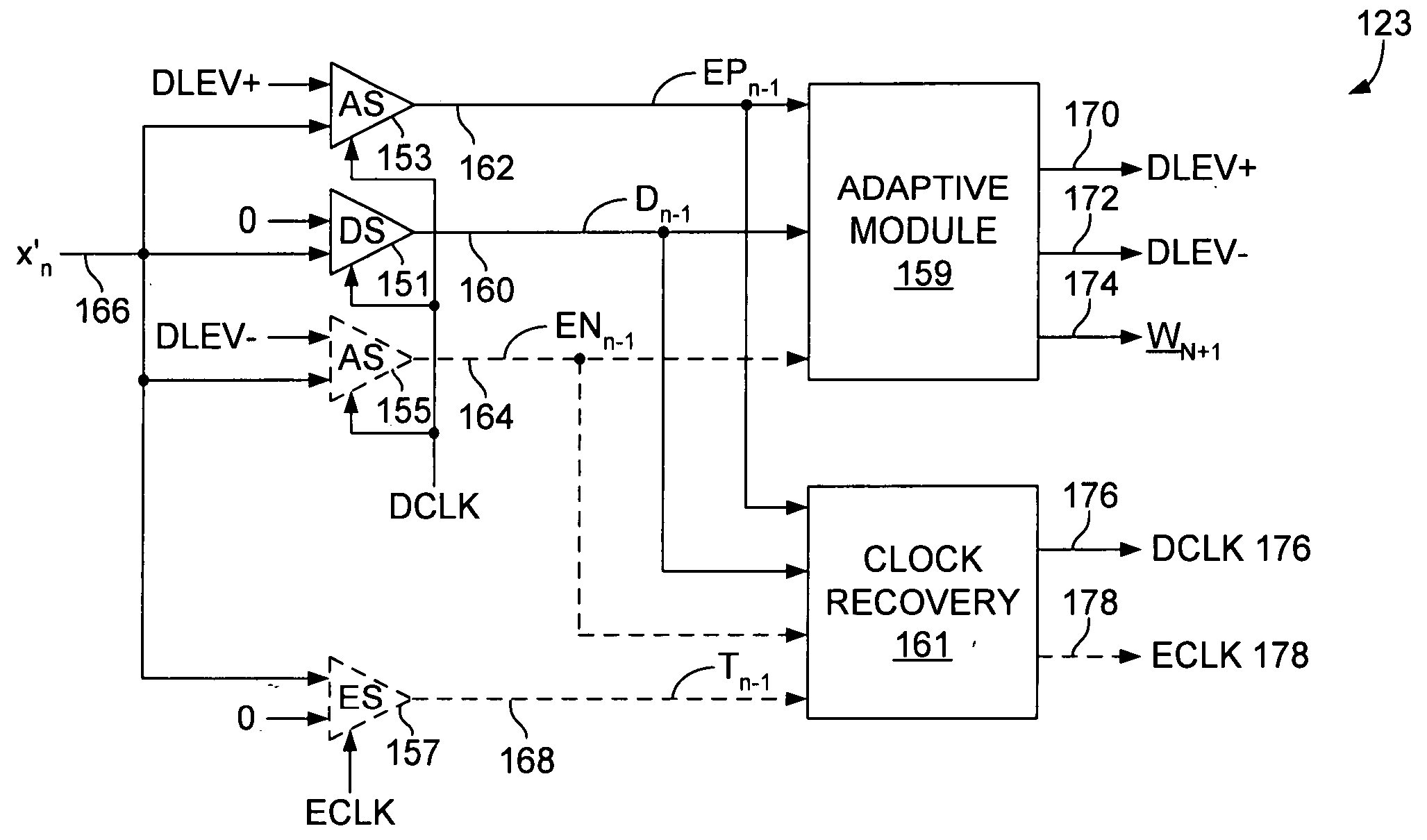

Data-level clock recovery

ActiveUS20050058234A1Angle demodulation by phase difference detectionSynchronising arrangementPattern matchingClock recovery

A circuit for adjusting the phase of a clock signal. A first sampling circuit generates a sequence of data samples in response to transitions of the clock signal, each of the data samples having either a first state or a second state according to whether an incoming signal exceeds a first threshold. An second sampling circuit generates an error sample in response to one of the transitions of the clock signal, the error sample having either the first state or the second state according to whether the incoming signal exceeds a second threshold. A phase adjust circuit adjusts the phase of the clock signal if the sequence of data samples matches a predetermined pattern and based, at least in part, on whether the error sample has the first state or the second state.

Owner:K MIZRA LLC

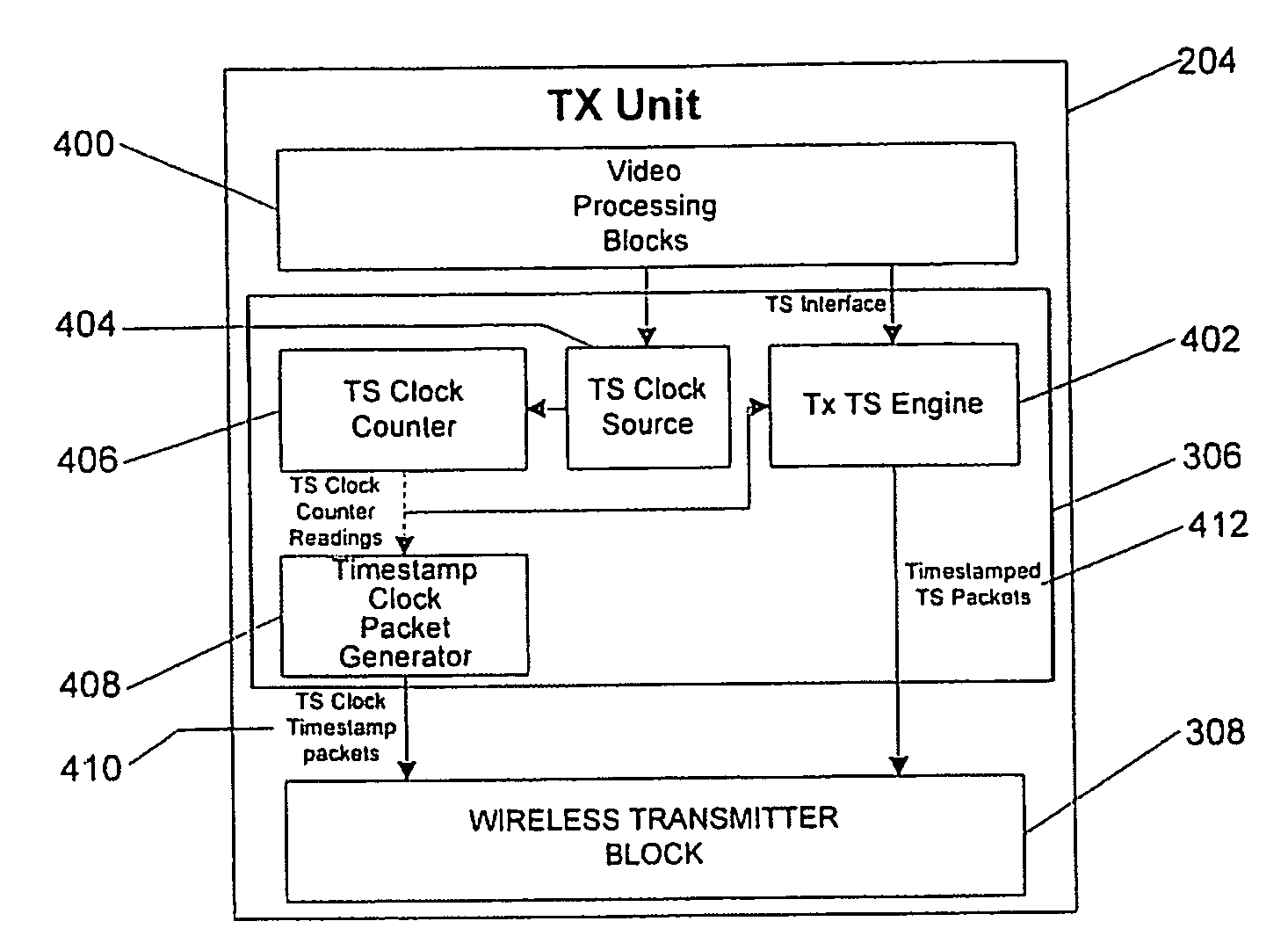

Clock recovery in wireless media streaming

InactiveUS20080019398A1Time-division multiplexSelective content distributionWireless transmissionClock recovery

There is provided, in accordance with some embodiments of the present invention, a system, method and circuit for clock recovery and synchronization in wireless media streaming. More specifically the adverse affect of jitter on the recovery of a wirelessly transmitted MPEG2 Transport Stream (TS) signal at a receiver is addressed through the implementation of algorithms based on observed empirical results, as well as introducing additional timing signals at the transmitter.

Owner:ADIMOS SYSTEMS LTD

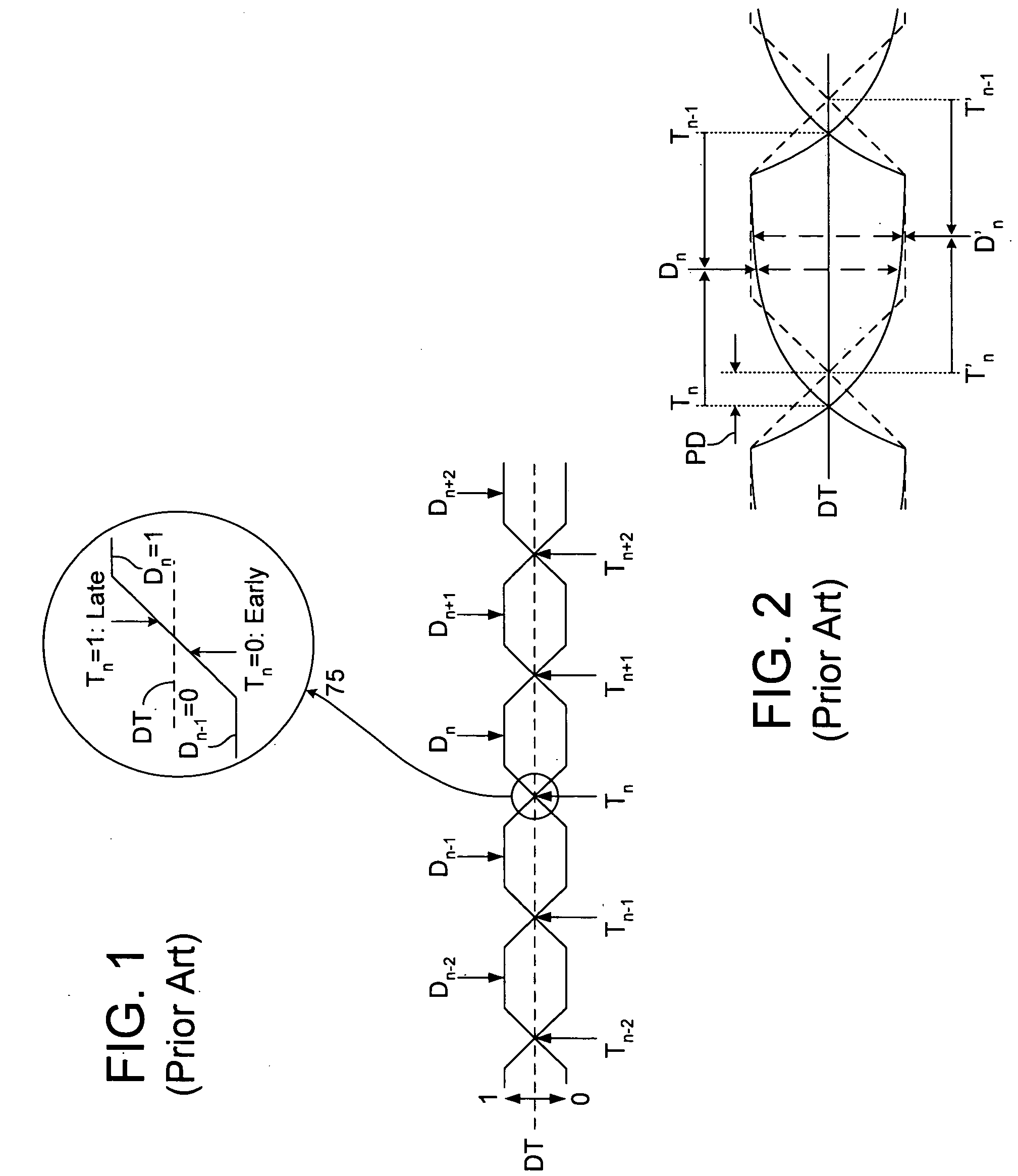

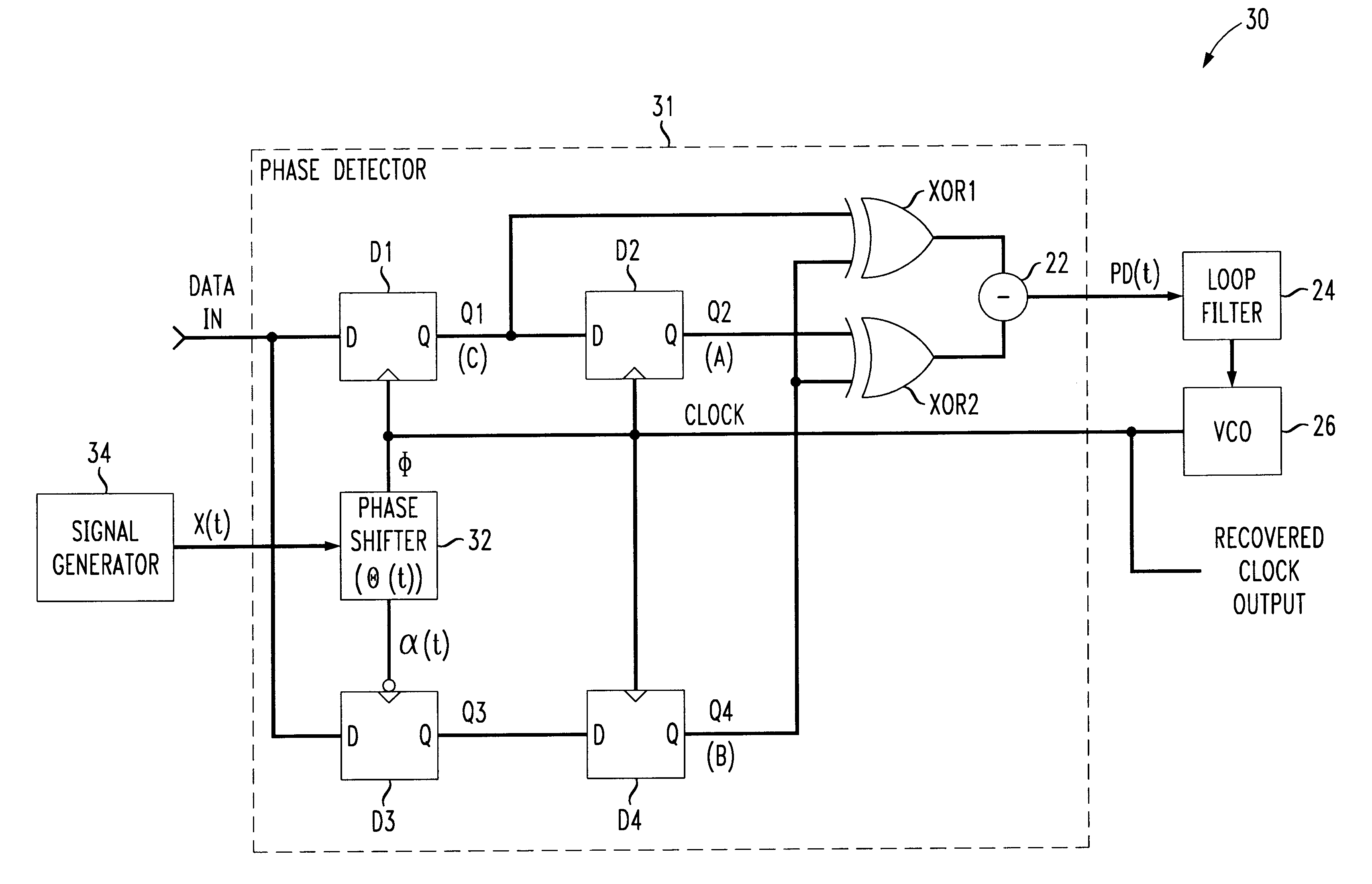

Self-aligned clock recovery circuit with proportional phase detector

InactiveUS6347128B1Pulse automatic controlGenerating/distributing signalsPhase differenceContinuous data

A self-aligned clock recovery circuit for synchronizing a local clock with an input data signal includes a sampling type phase detector for generating an output signal based on the phase difference between the local clock and the data signal timing. The phase detector obtains samples of consecutive data symbols at sampling times corresponding to transitions of the local clock, and obtains a data crossover sample at a sampling instant in between those of the consecutive data symbol samples. A phase shifter is employed to phase shift the local clock by an amount corresponding to a time varying modulation signal so as to obtain each data crossover sample at a variable sampling instant relative to the associated consecutive symbol samples. Logic circuitry determines whether the local clock appears to be early or late based on a comparison of the logic levels of the symbol samples and the associated data crossover sample, and provides a corresponding output signal through a filter to the local clock to adjust the clock accordingly. Since the relative sampling instants of successive data crossover samples are varied with time, the phase detector output signal amplitude is substantially proportional to the amount of phase error between the local clock and the symbol timing, thereby improving jitter properties of the clock recovery circuit.

Owner:AVAGO TECH INT SALES PTE LTD

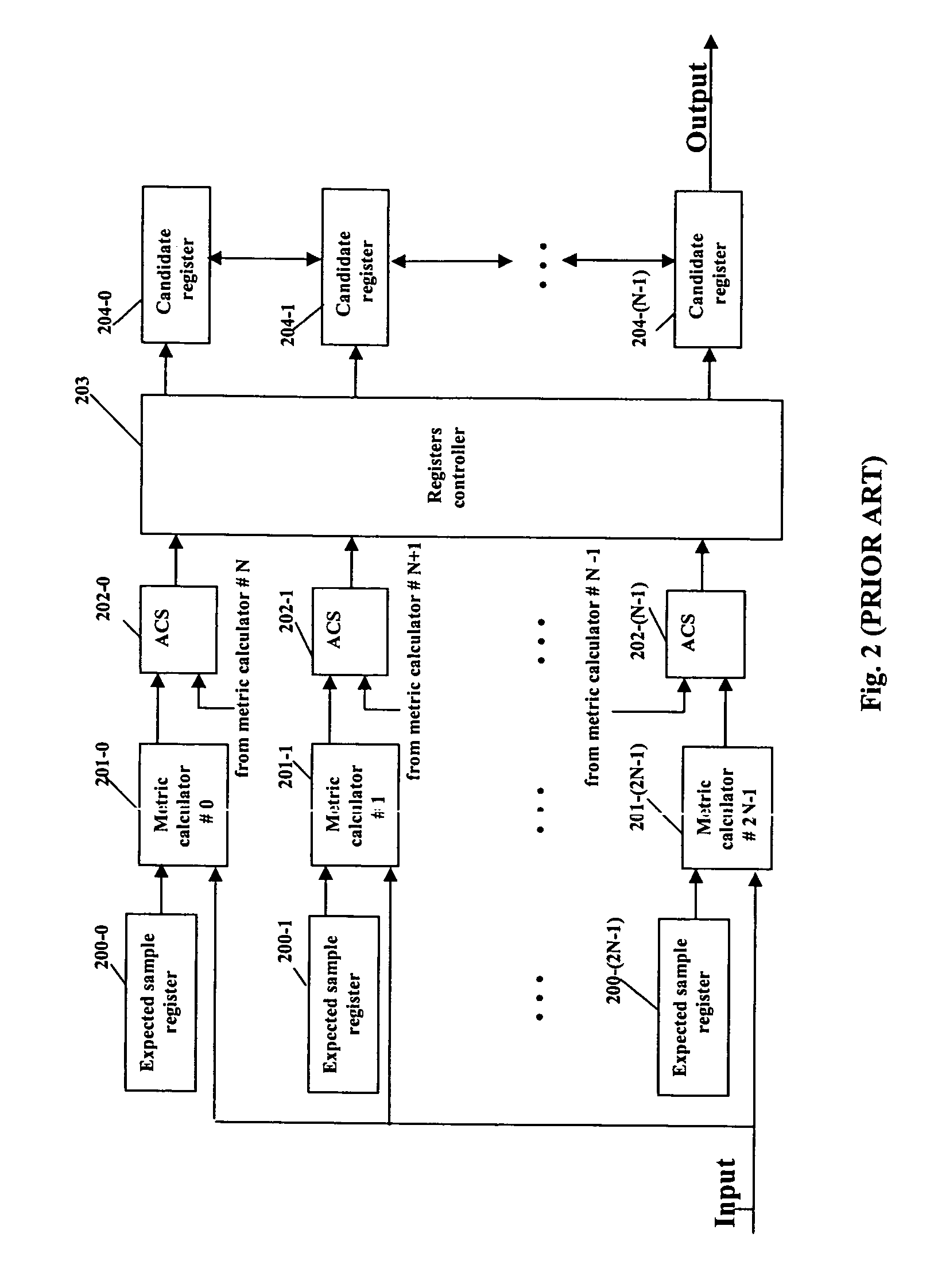

Self-adjusting PRML receiver

Owner:GUZIK TECHN ENTERPRISES

Method and devices for frequency distribution

ActiveUS20150071309A1Good synchronizationHigh-precision synchronizationTime-division multiplexClock recoveryTime Protocol

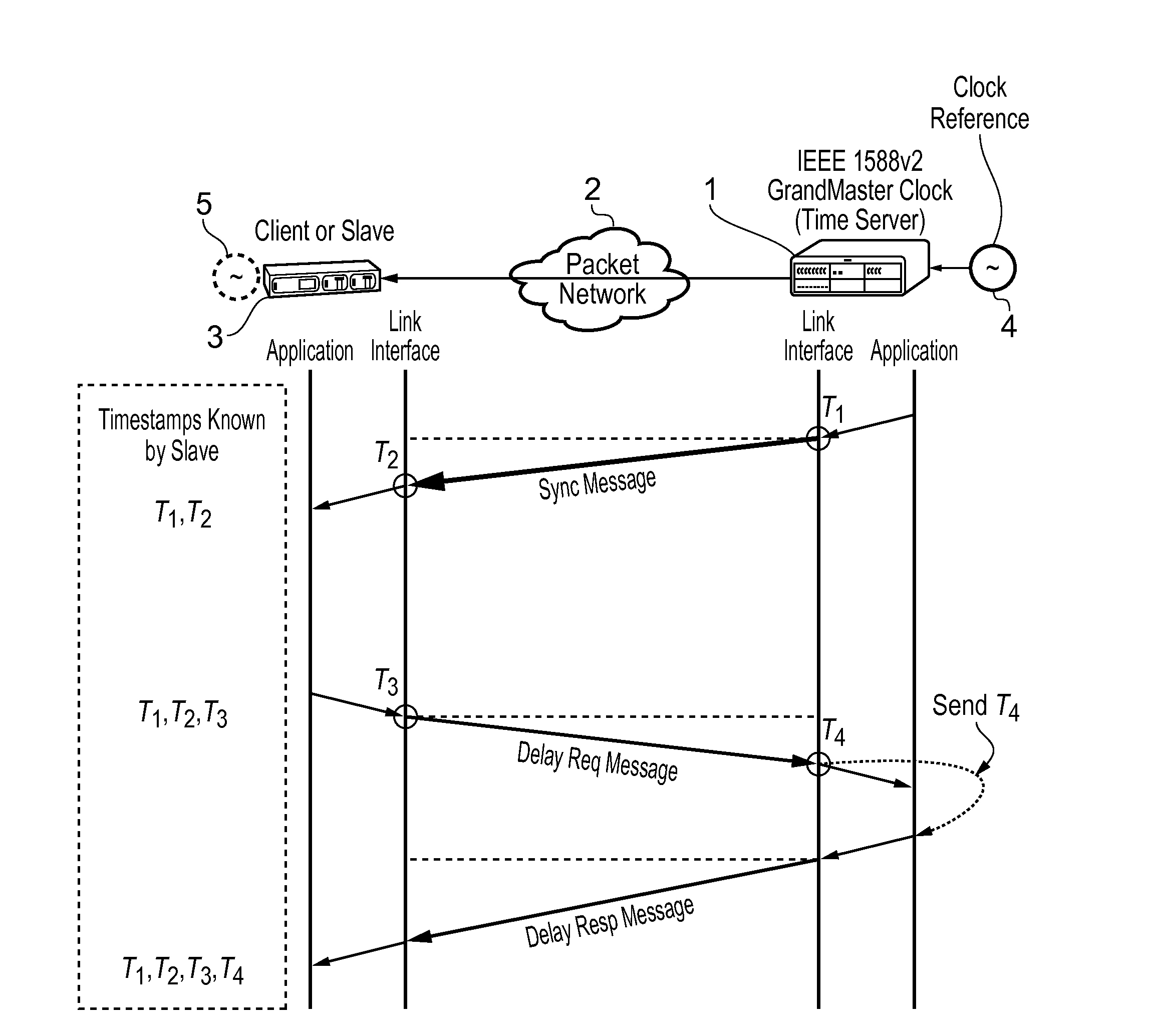

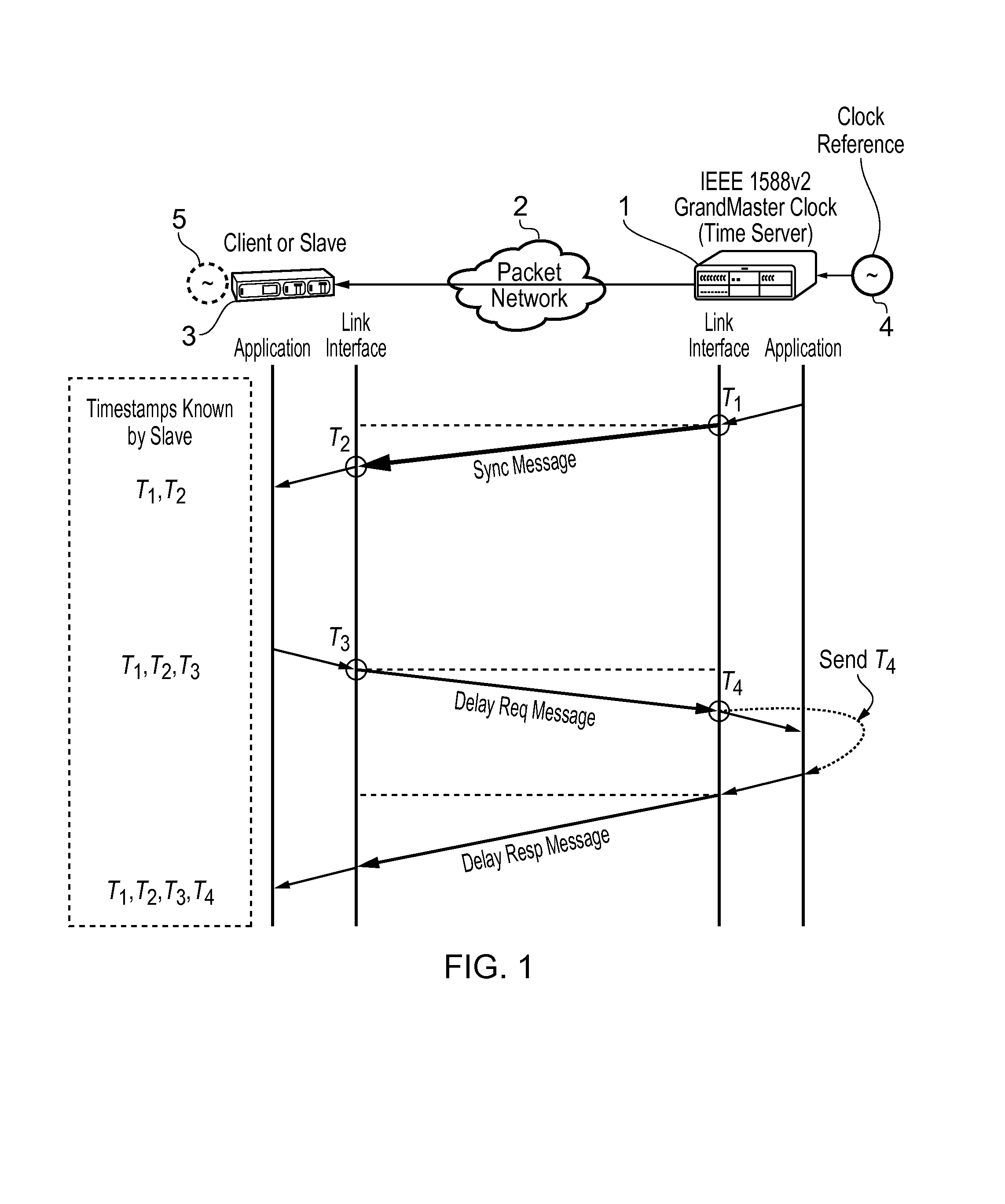

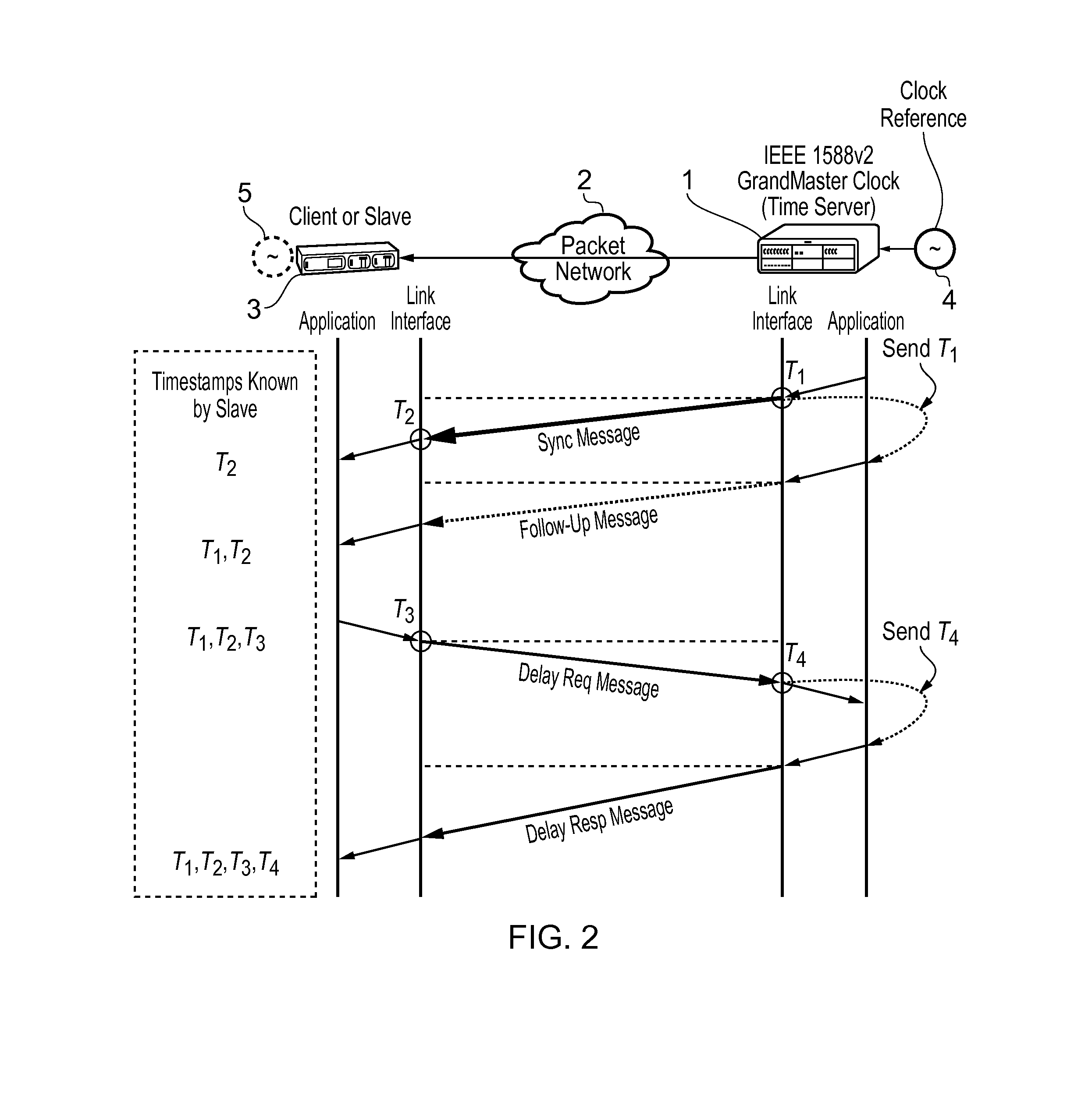

This invention relates to methods and devices for frequency distribution based on, for example, the IEEE 1588 Precision Time Protocol (PTP). Packet delay variation (PDV) is a direct contributor to the noise in the recovered clock and various techniques have been proposed to mitigate its effects. Embodiments of the invention provide a mechanism to directly measure and remove PDV effects in the clock recovery mechanism at a slave clock. One particular embodiment provides a clock recovery mechanism including a phase-locked loop (PLL) with a PDV compensation feature built-in. An aim of the invention is to enable a slave clock to recover the master clock to a higher quality as if the communication path between master and slave is free of PDV. This technique may allow a packet network to provide clock synchronization services to the same level as time division multiplexing (TDM) networks and Global Positioning System (GPS).

Owner:KHALIFA UNIV OF SCI & TECH +2

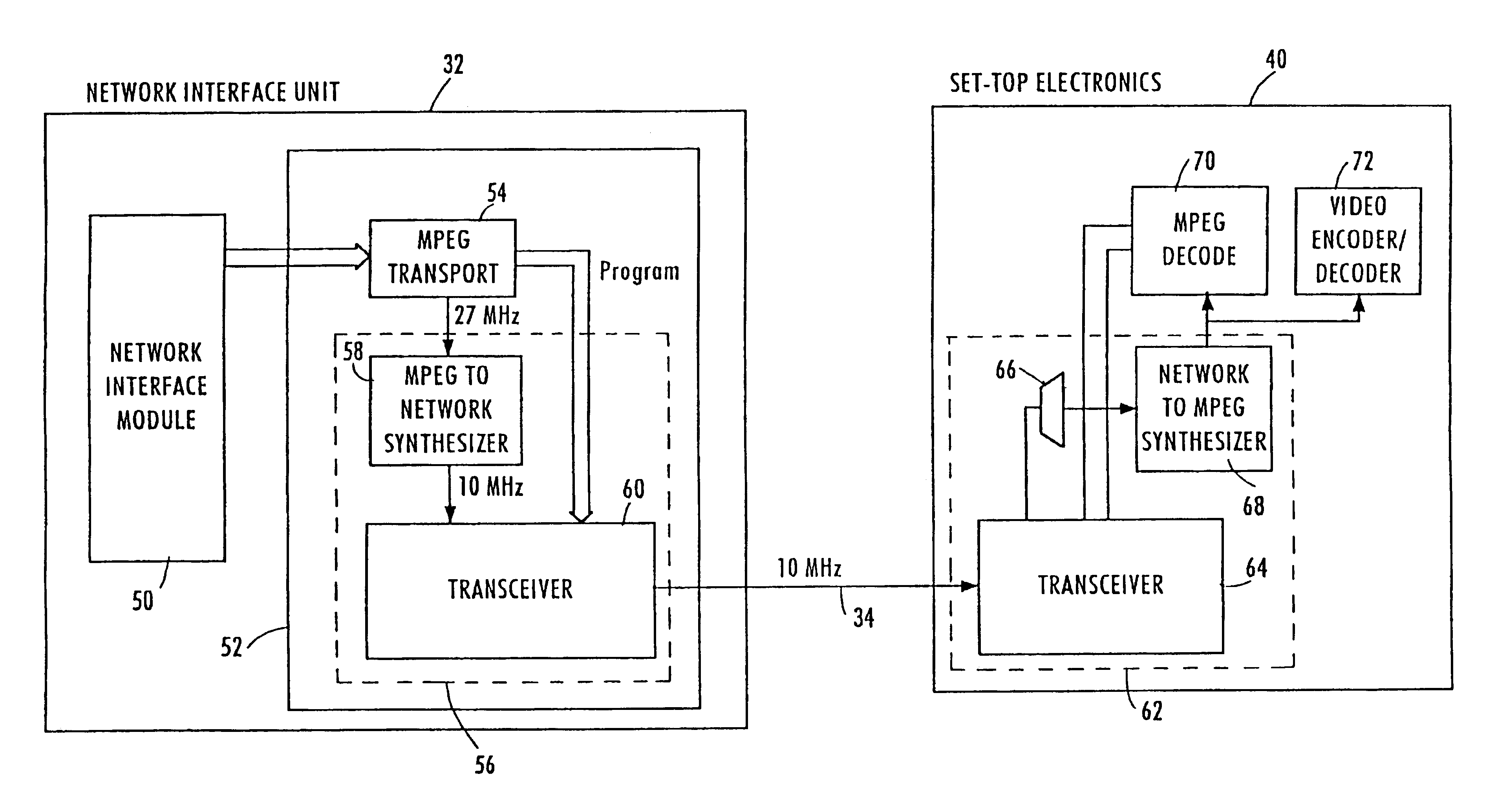

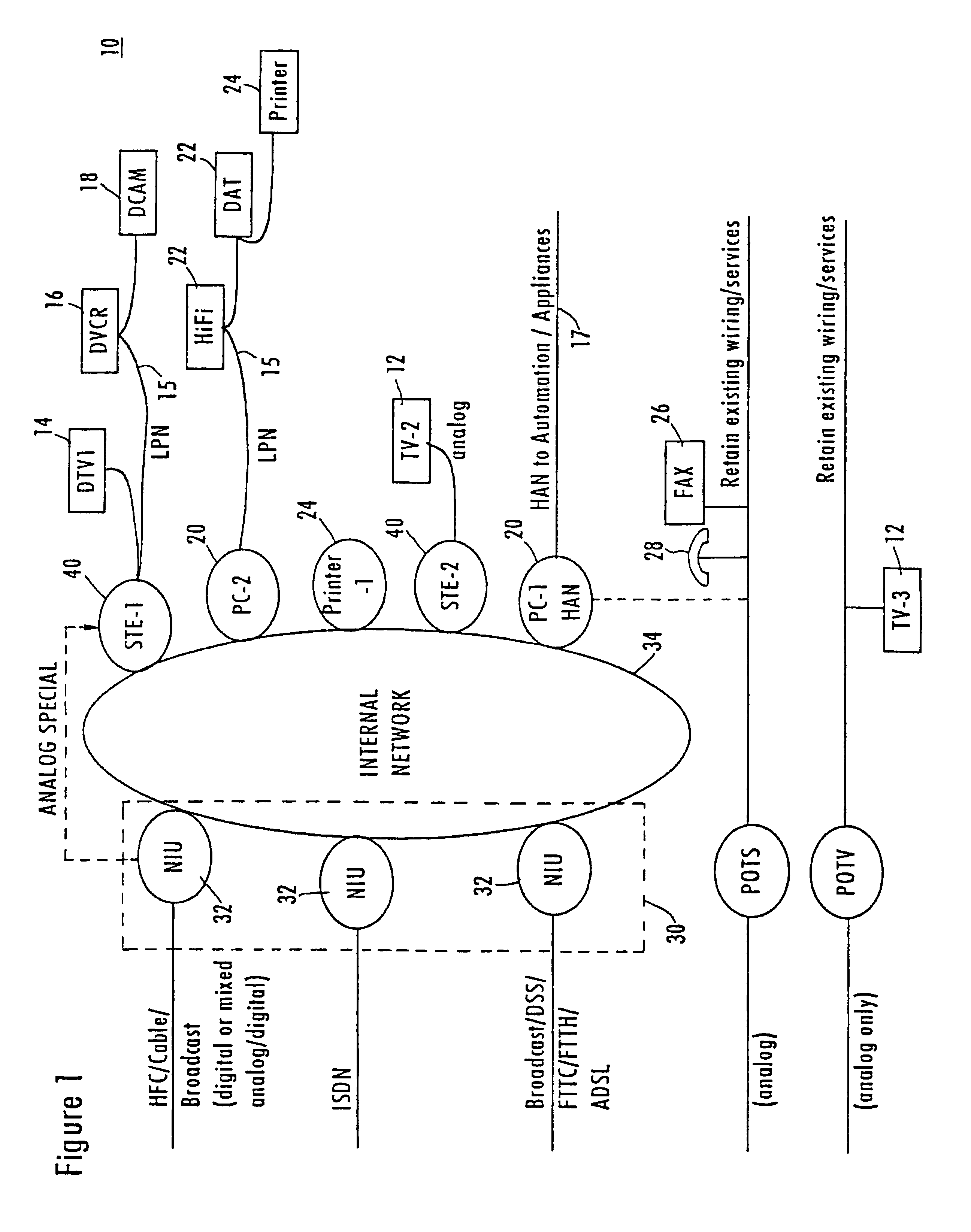

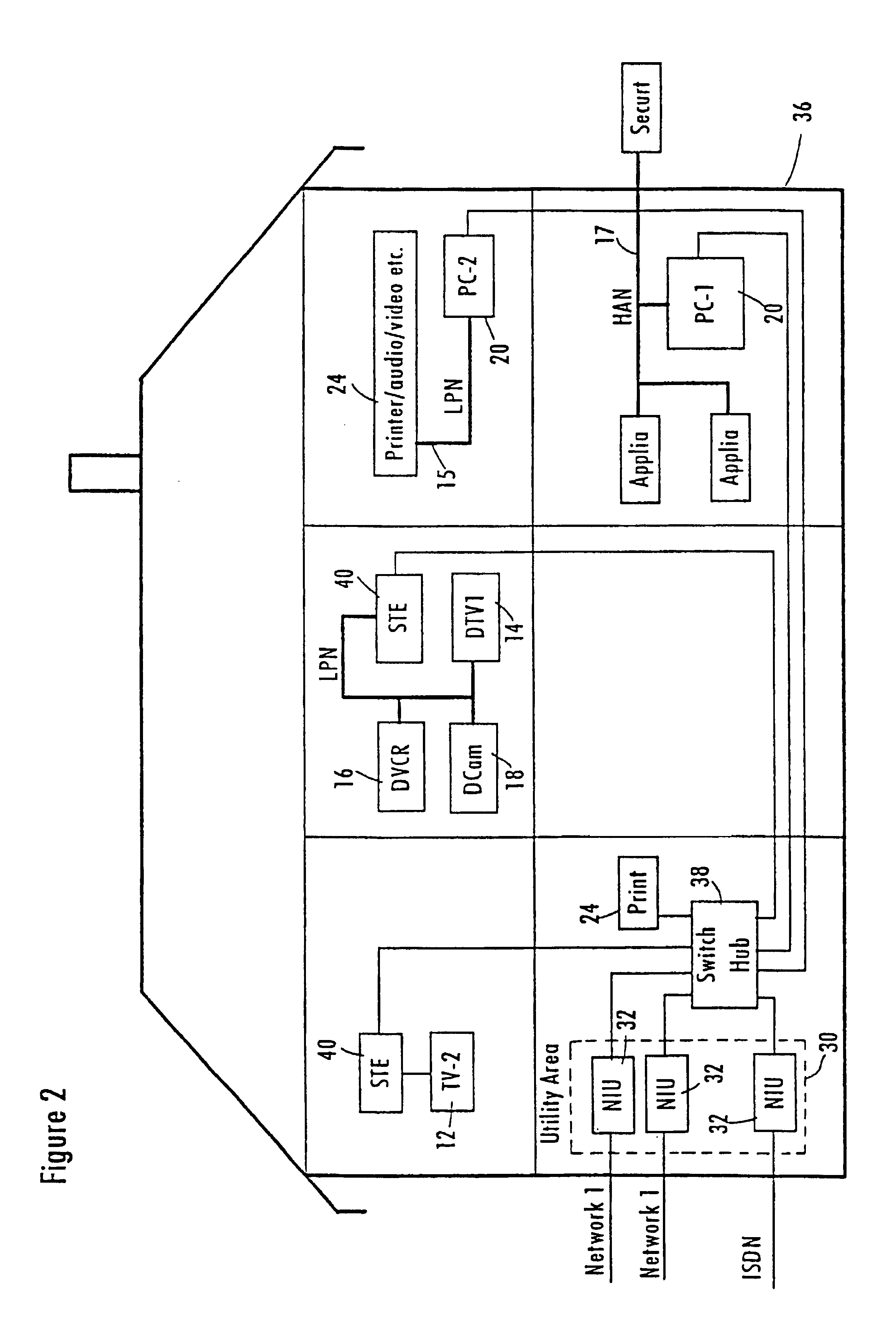

Method and apparatus for recovering data stream clock

InactiveUS7003796B1Without incurring jitterThe process is simple and fastPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningData streamNetwork clock

A home network architecture has an internal digital network interconnecting devices in the home. Entertainment services are introduced into the network through network interface units that are coupled to an external network and to the internal network. The network interface units perform the necessary interfacing between the external and internal networks and perform MPEG clock recovery from an MPEG video data stream. To prevent jitter when the MPEG data stream is transmitted over the internal network to set-top electronics, the recovered MPEG clock is locked by the network interface unit to the internal network clock and then transmitted over the internal network. The set-top electronics then recovers the MPEG clock from the locked MPEG clock transmitted over the internal network. The video data may then be generated using the recovered MPEG clock and displayed on a television, for example.

Owner:SAMSUNG ELECTRONICS CO LTD

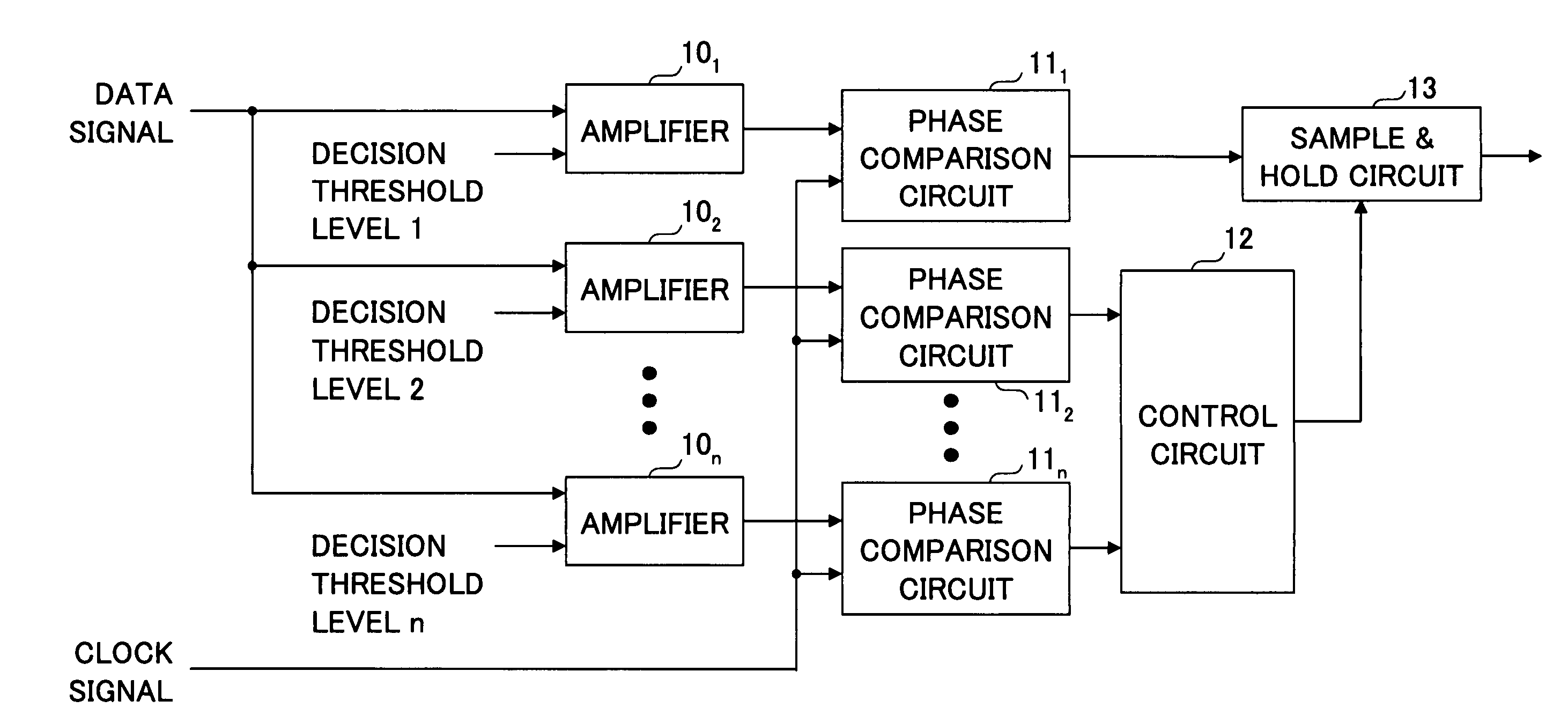

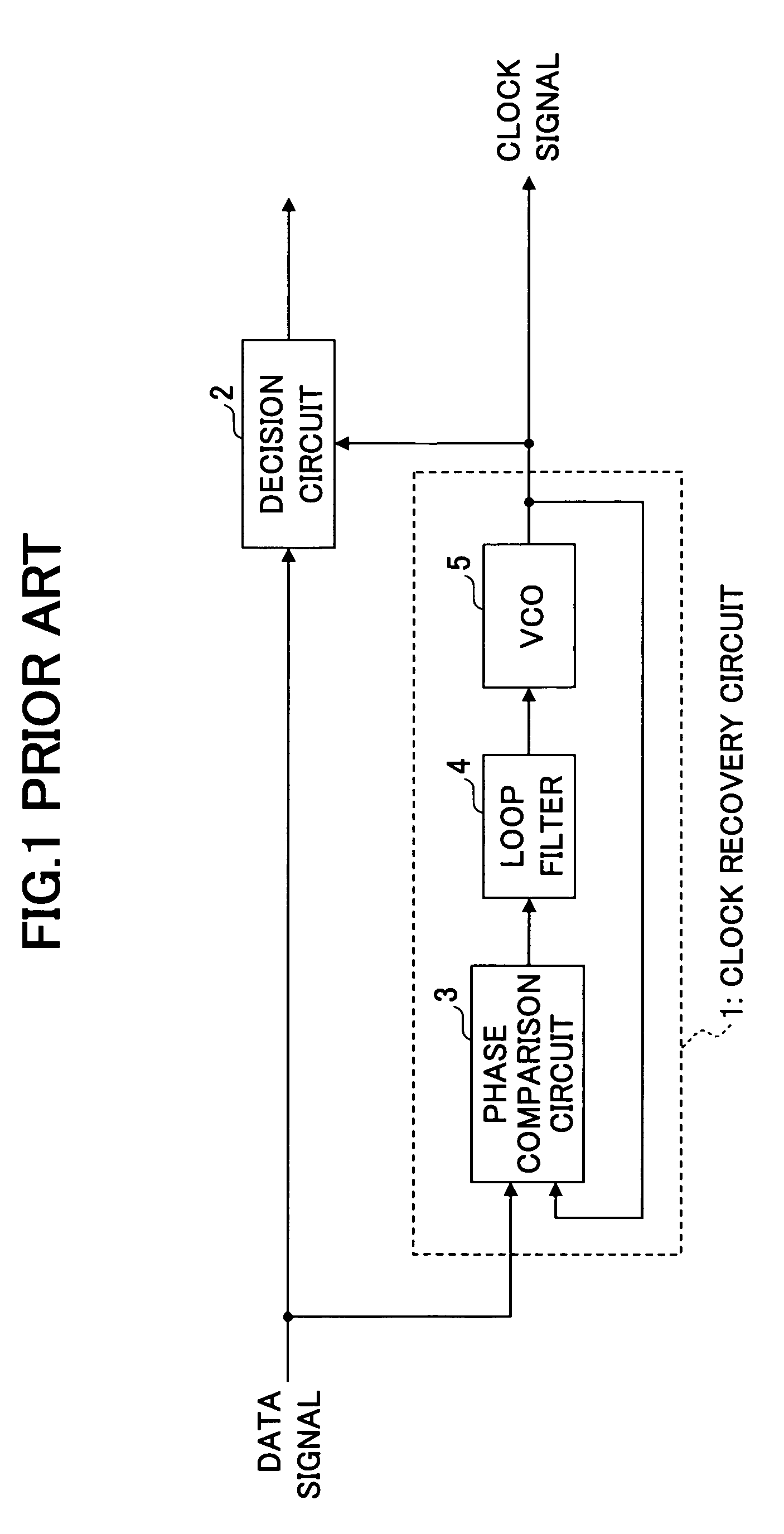

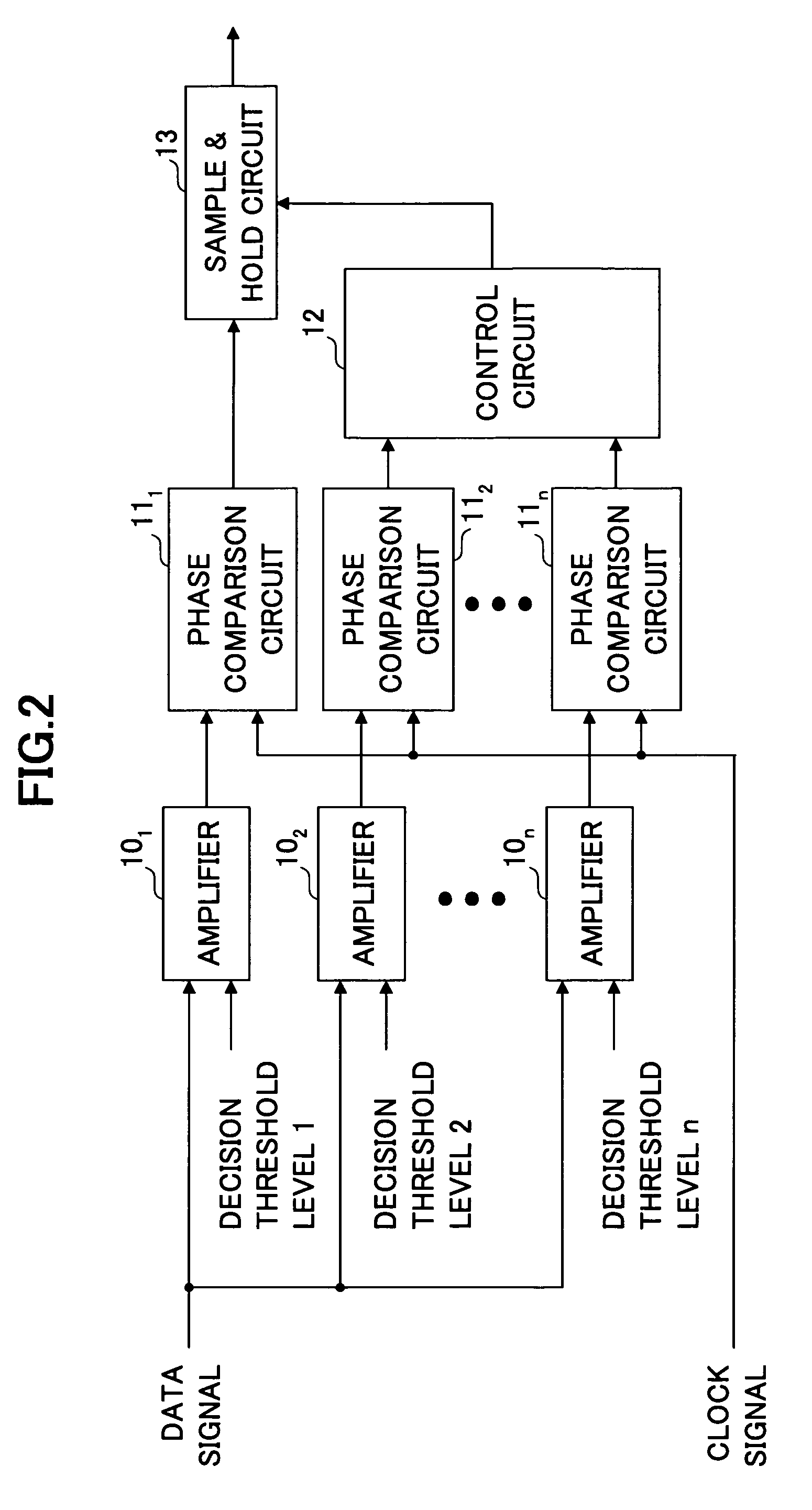

Phase comparison circuit and clock recovery circuit

InactiveUS20050220182A1Correction of phase differenceCancel noiseMultiple input and output pulse circuitsPulse automatic controlPhase differenceClock recovery

A phase comparison circuit for outputting a phase difference signal indicating a phase difference between a data signal and a clock signal is disclosed. The disclosed phase comparison circuit includes: a detection part for outputting a plurality of signals indicating phases of the data signal according to different decision threshold levels; a phase comparison part for outputting phase difference signals each indicating a phase difference between a signal in the plurality of signals output from the detection part and the clock signal; and a control part for determining whether to output a particular phase difference signal in the phase difference signals by using the whole or a part of the phase deference signals.

Owner:FUJITSU LTD

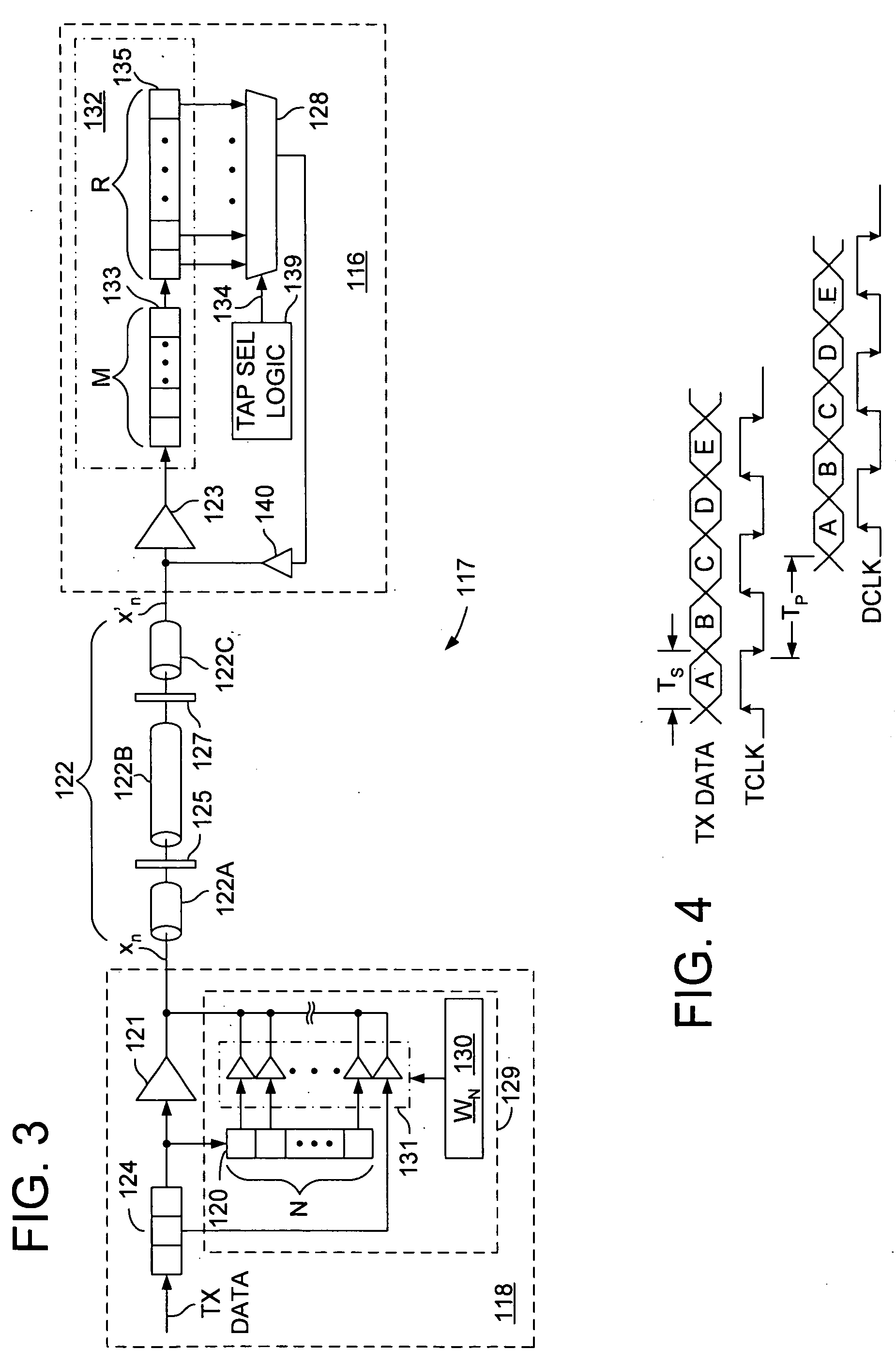

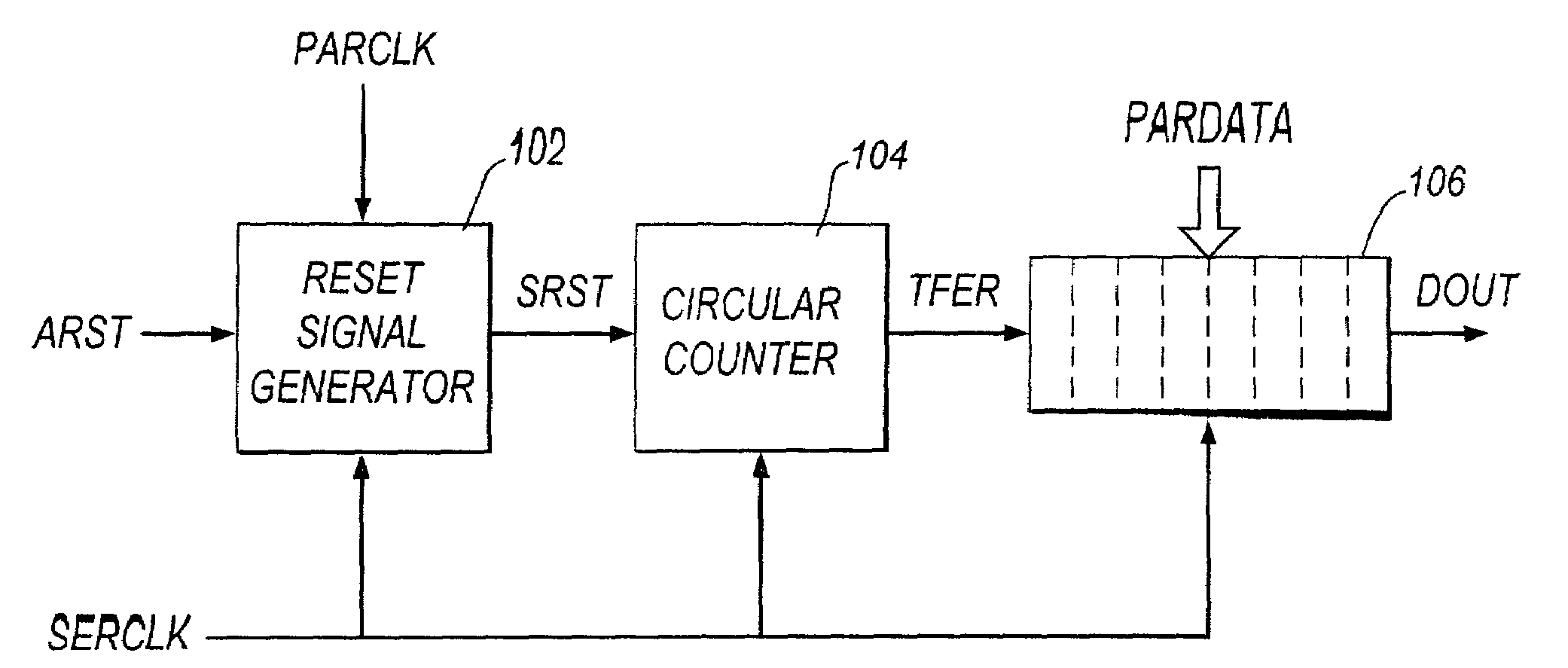

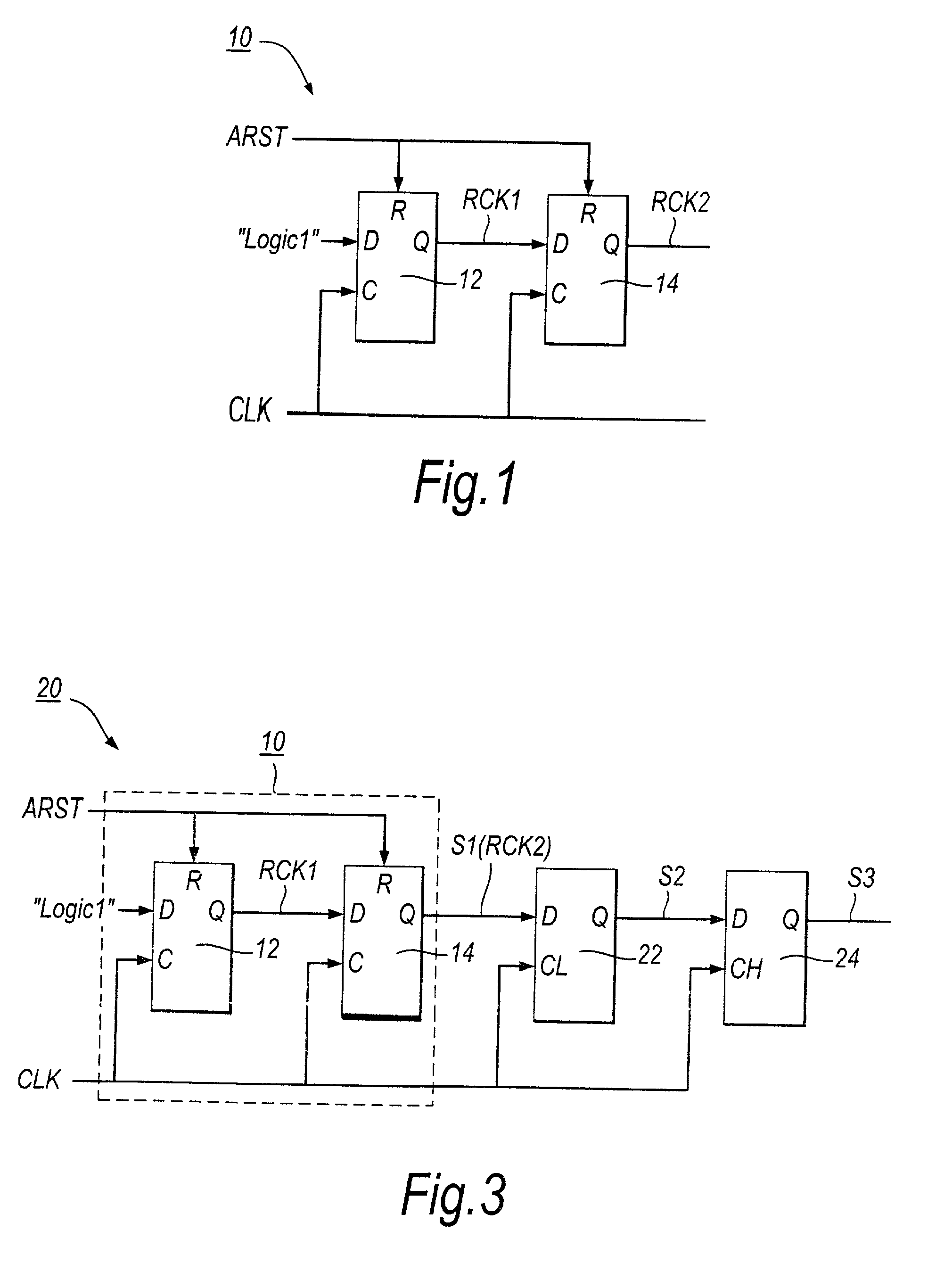

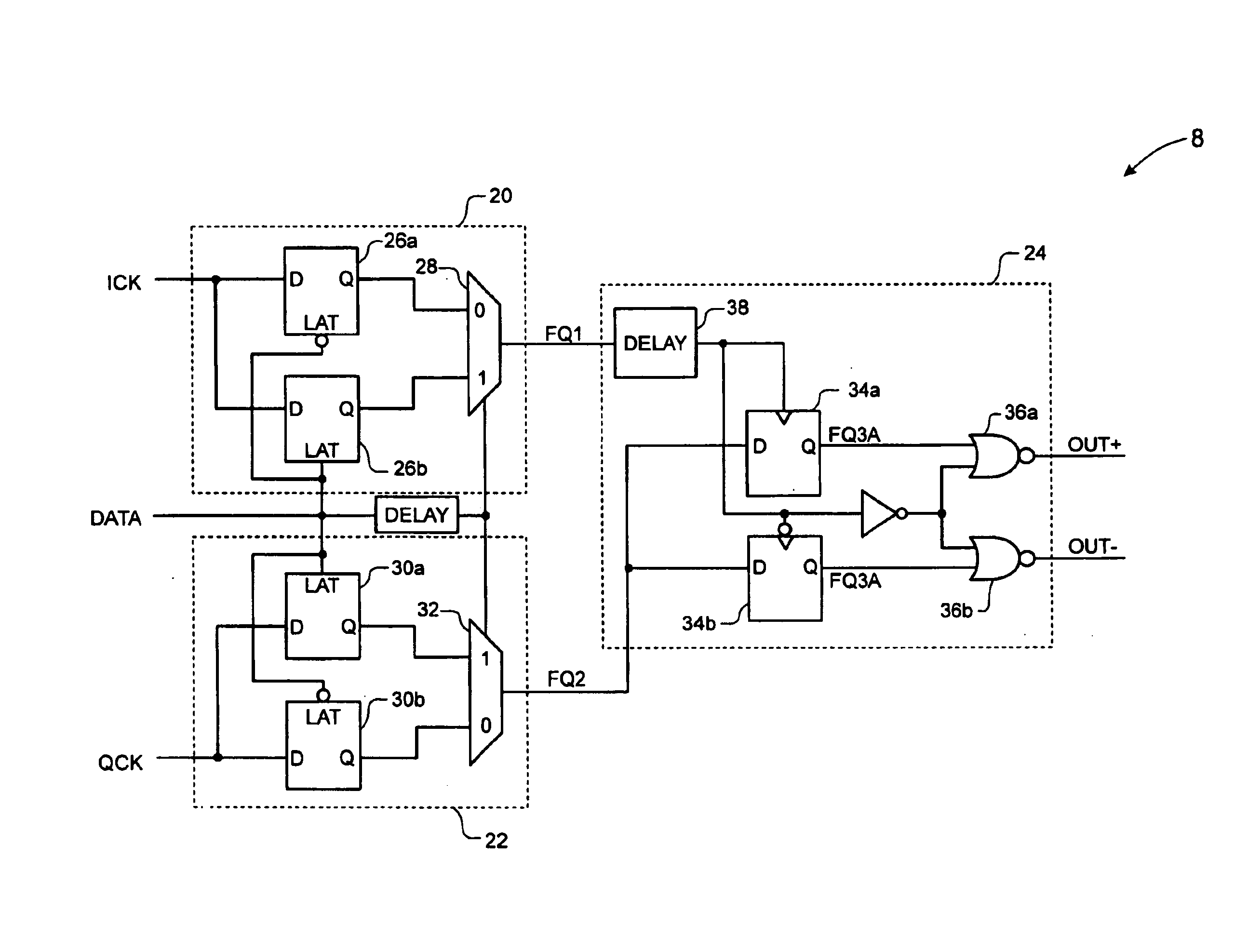

Processing high-speed digital signals

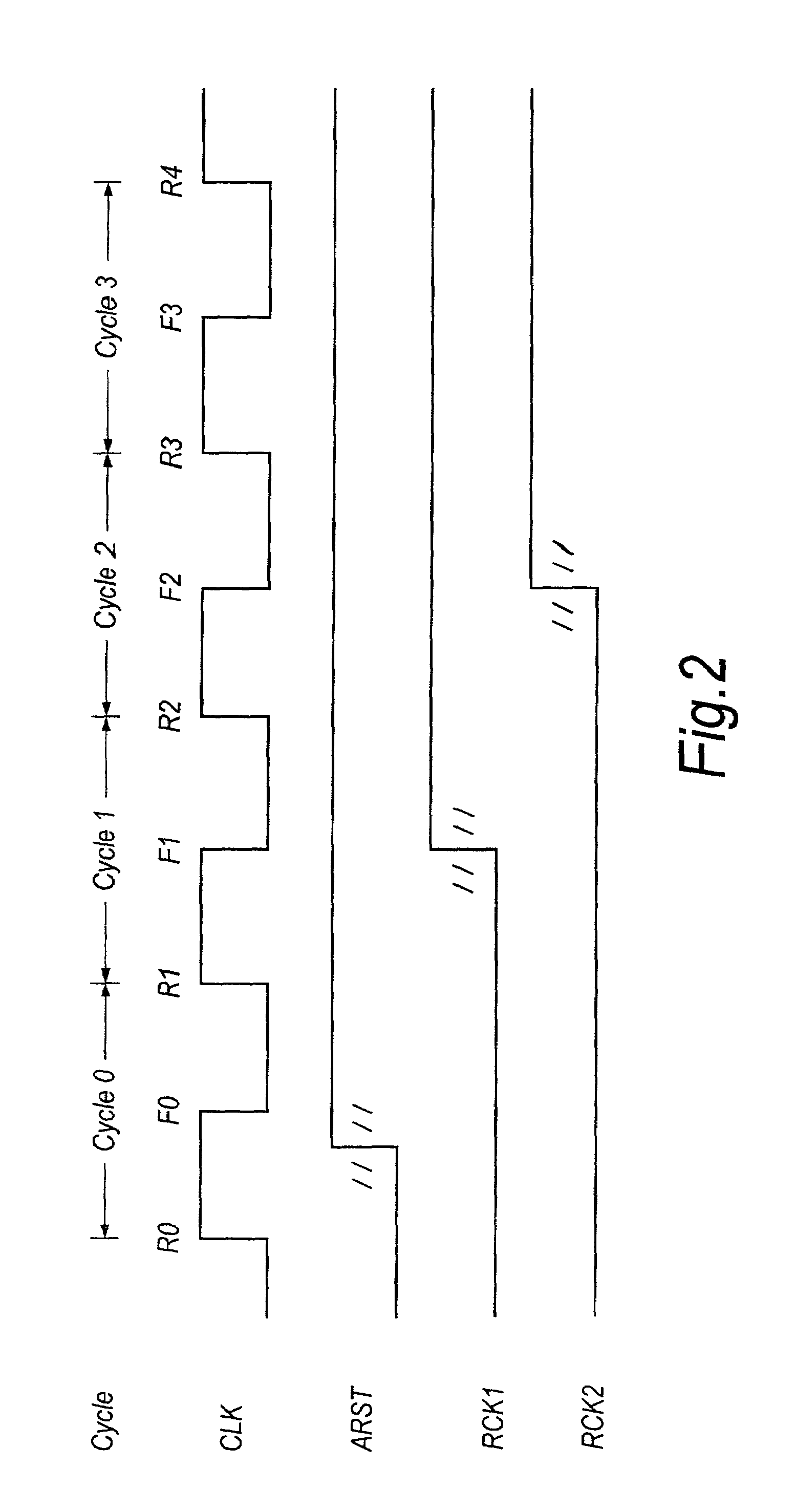

ActiveUS7187738B2Reduce controlMeet high-speed operationChannel dividing arrangementsPulse automatic controlData synchronizationData stream

A first transparent latch receives a first synchronised signal changing its logic state synchronously with respect to a clock signal. A second transparent latch receives a second synchronised signal output by the first latch. When the clock signal has a first logic state the first latch has a non-responsive state and the second latch has a responsive state, and when the clock signal has a second logic state the first latch has the responsive state and the second latch has the non-responsive state. The change in logic state of a third synchronised signal output by the second latch is guaranteed to occur in a particular half-cycle of the clock signal, irrespective of process / voltage / temperature (PVT) variations of the circuitry. Clock recovery circuitry may have rising-edge and falling-edge latches; circulating control pattern verification circuitry; data synchronising circuitry for converting parallel data clocked by a first clock signal into serial data clocked by a second clock signal asynchronous with the first clock signal; and data recovery circuitry for producing an offset clock signal which suits a data eye shape of a received serial data stream.

Owner:SOCIONEXT INC

Clock recovery from an optical signal with polarization impairments

ActiveUS20060285855A1Pulse automatic controlPolarisation multiplex systemsCommunications systemClock recovery

A method of recovering a clock signal from an optical signal received through an optical communications system. A digital sample stream is processed to generate a dispersion compensated signal. The dispersion compensated signal is then tapped to obtain upper side band and lower side, band signals of each received polarization of the optical signal. The upper side band sand lower side band signals are then processed to compensate polarization dependent impairments and the clock recovered from the resulting optimized.

Owner:CIENA

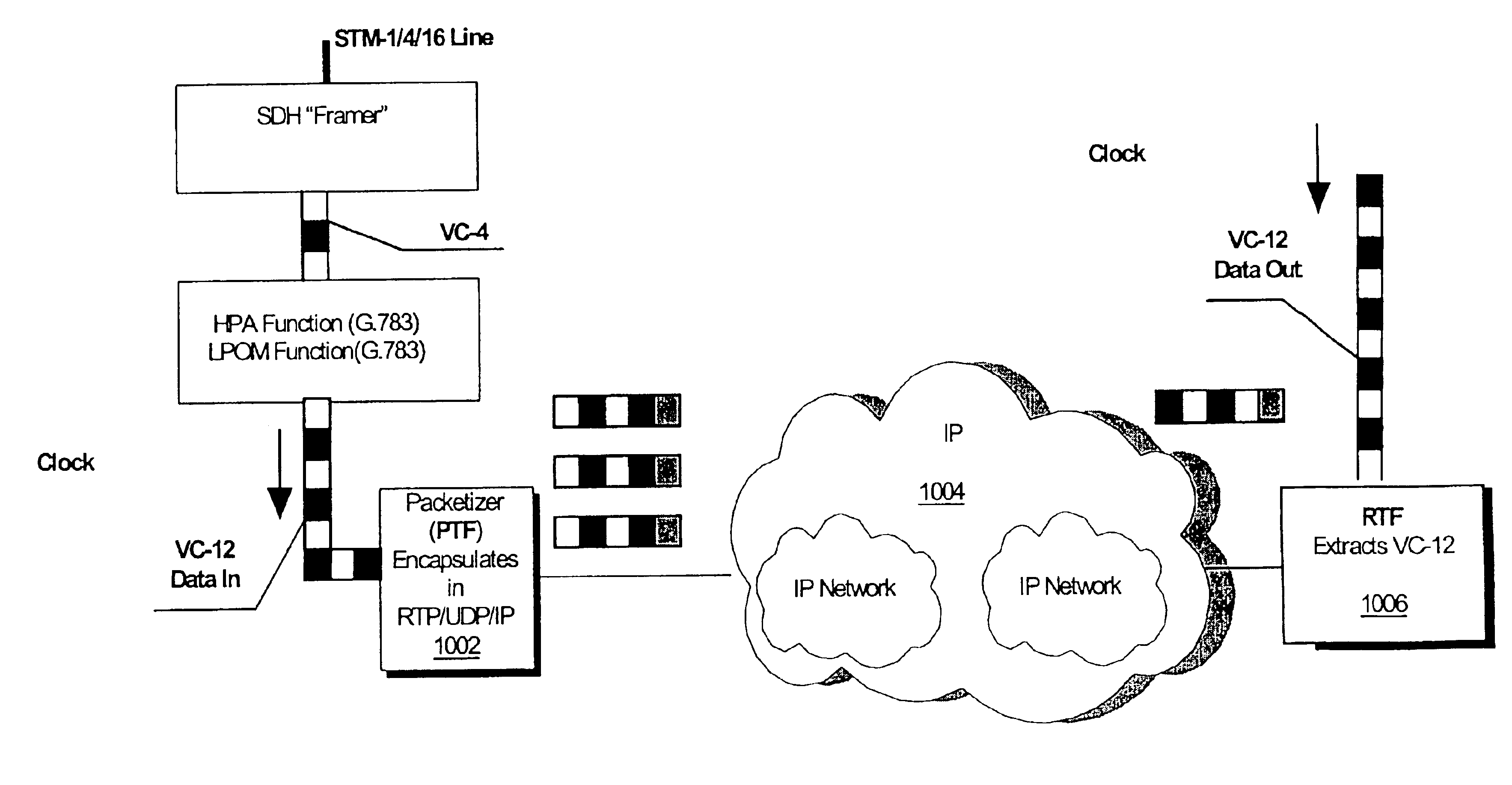

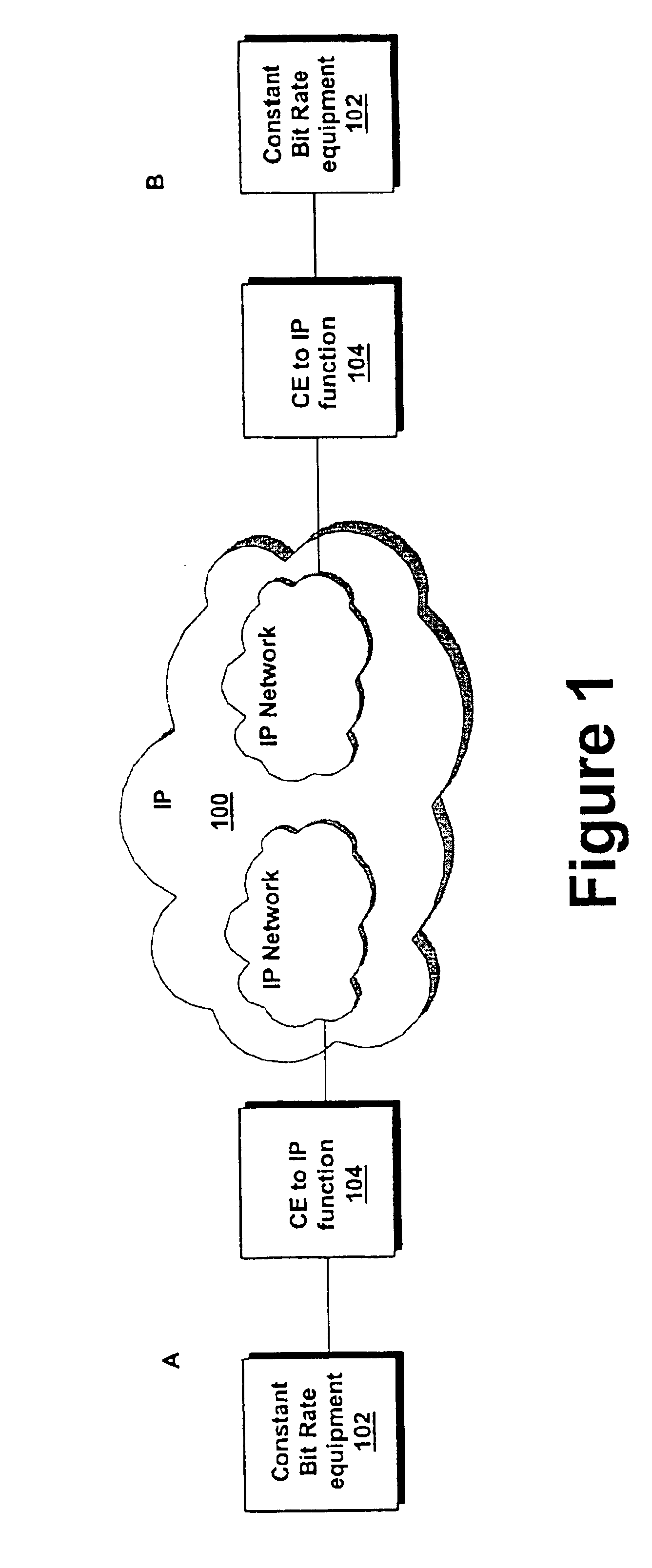

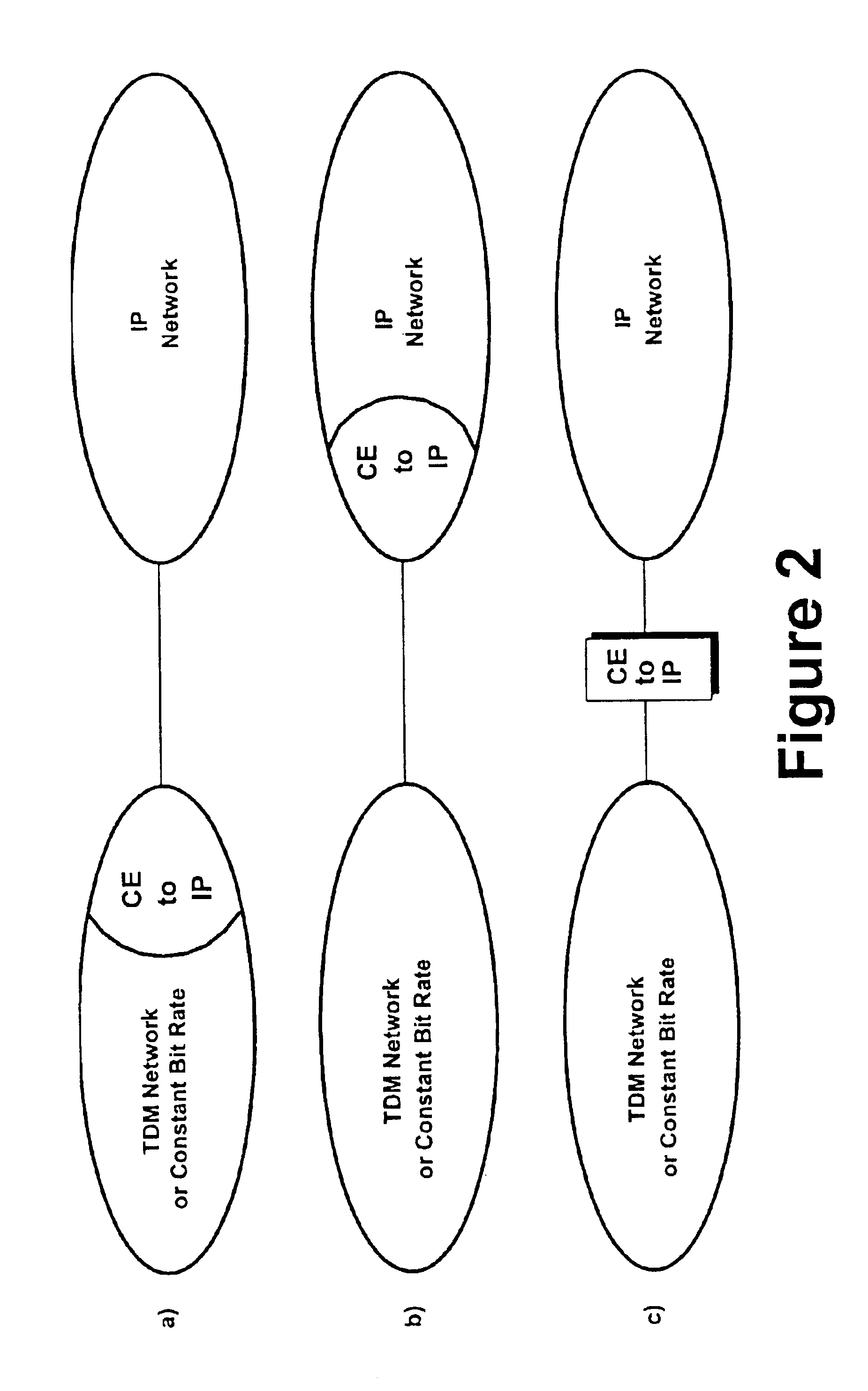

Circuit emulation service (CES) over IP

InactiveUS6898213B1Time-division multiplexTransmissionStructure of Management InformationClock recovery

Streams of data including explicit synchronization patterns (such as entire T1 / E1) are transmitted utilizing an unstructured data format, while streams not containing explicit synchronization patterns (such as fractional T1 / E1) are sent utilizing a structured data format, i.e., the data structure itself provides for circuit alignment at the receiving end. In addition, SDH VC-12 frames are transmitted over the IP network by encapsulating the entire frame (payload and overhead) into an RTP packet. Furthermore, the clock is reconstructed (clock recovery) from the packet stream at the receiver's side.

Owner:AXERRA NETWORKS

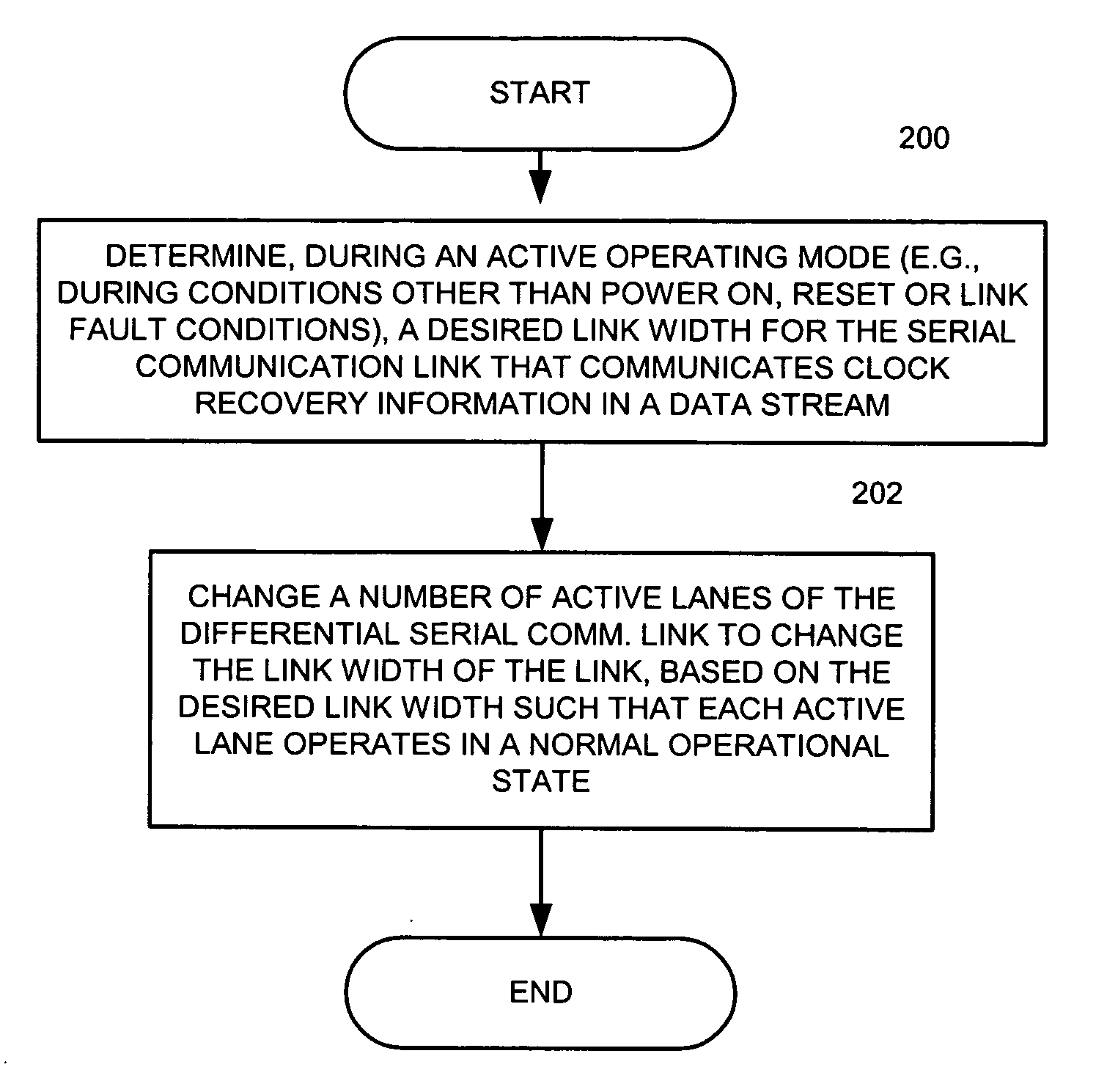

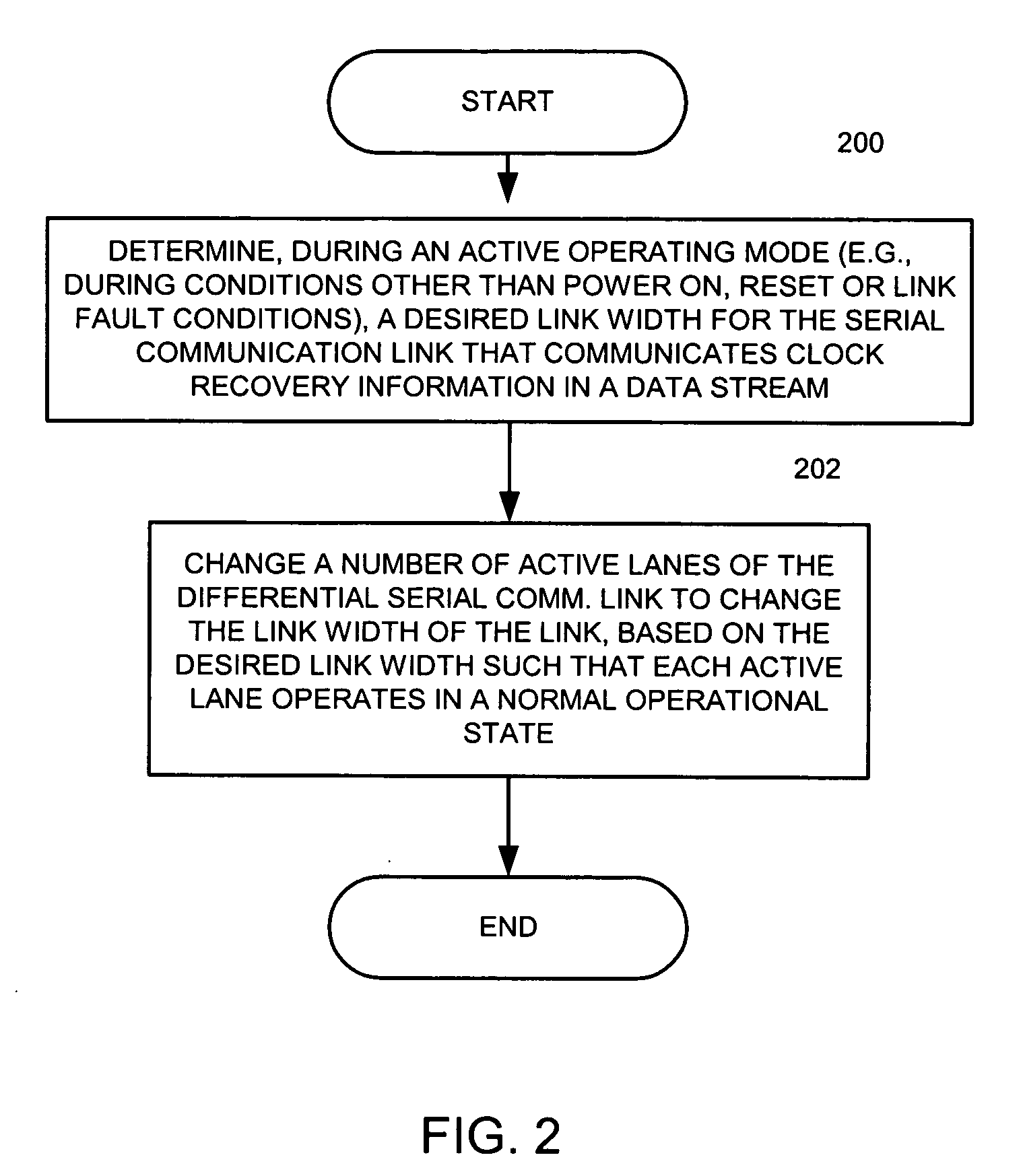

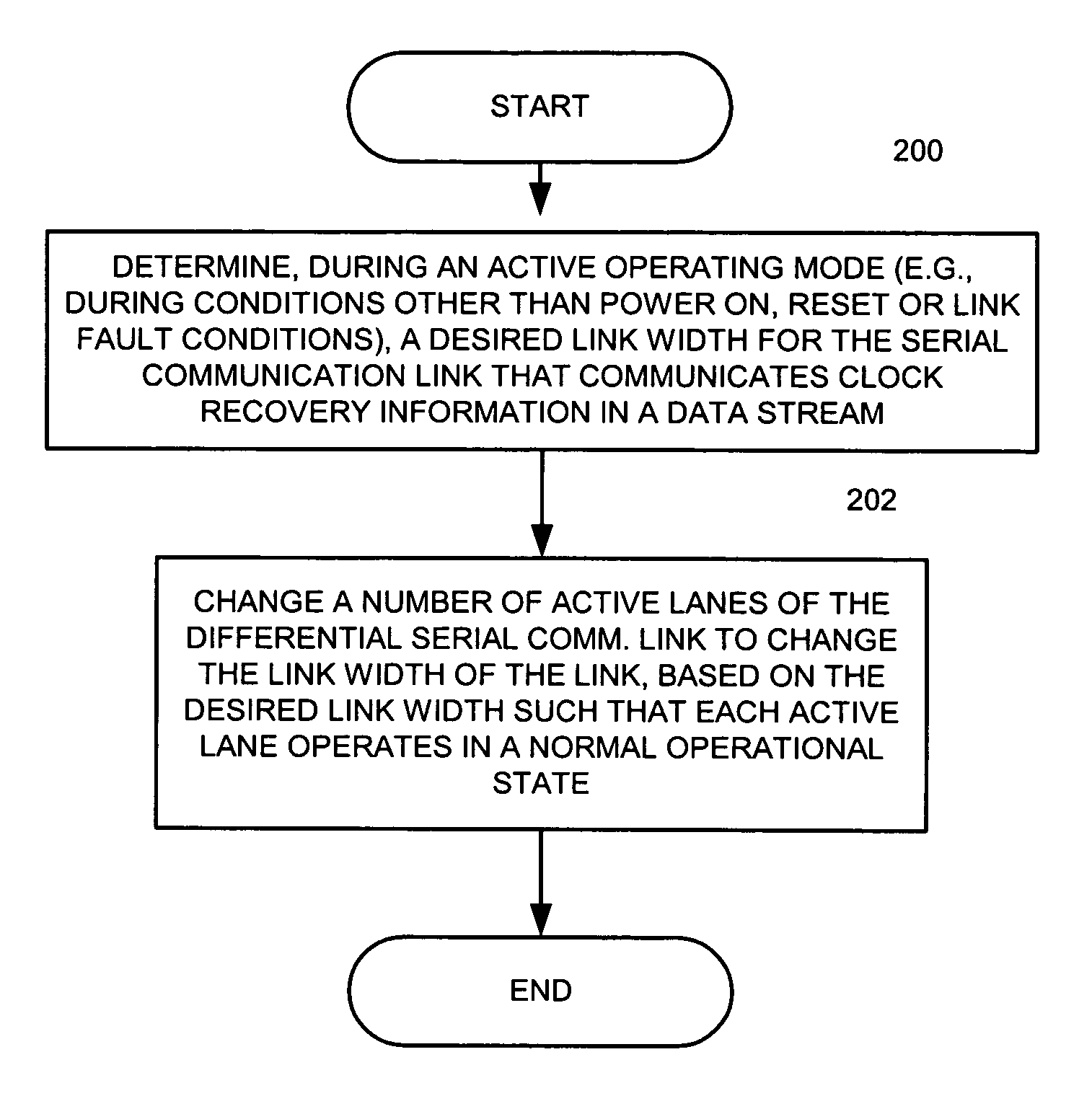

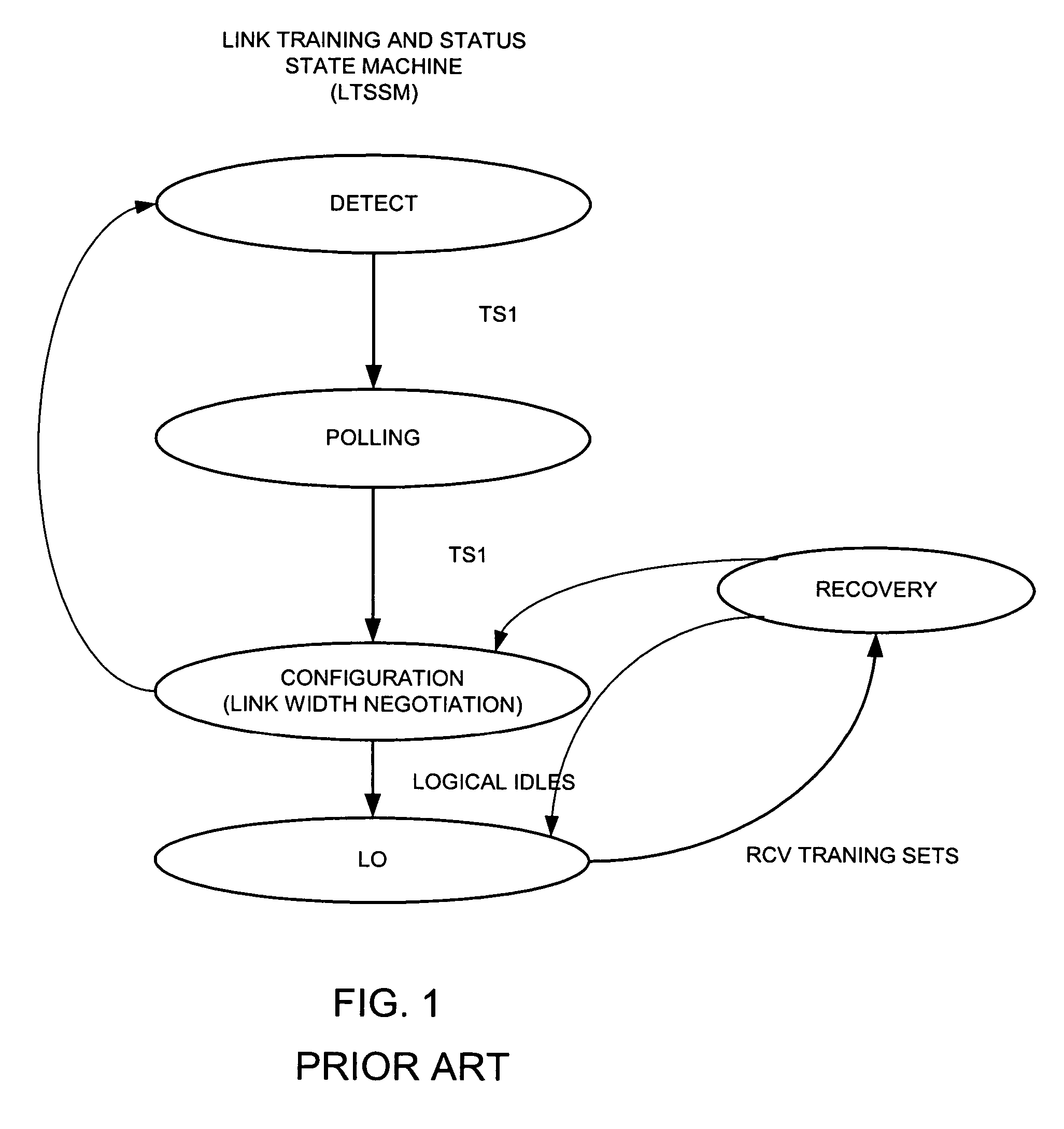

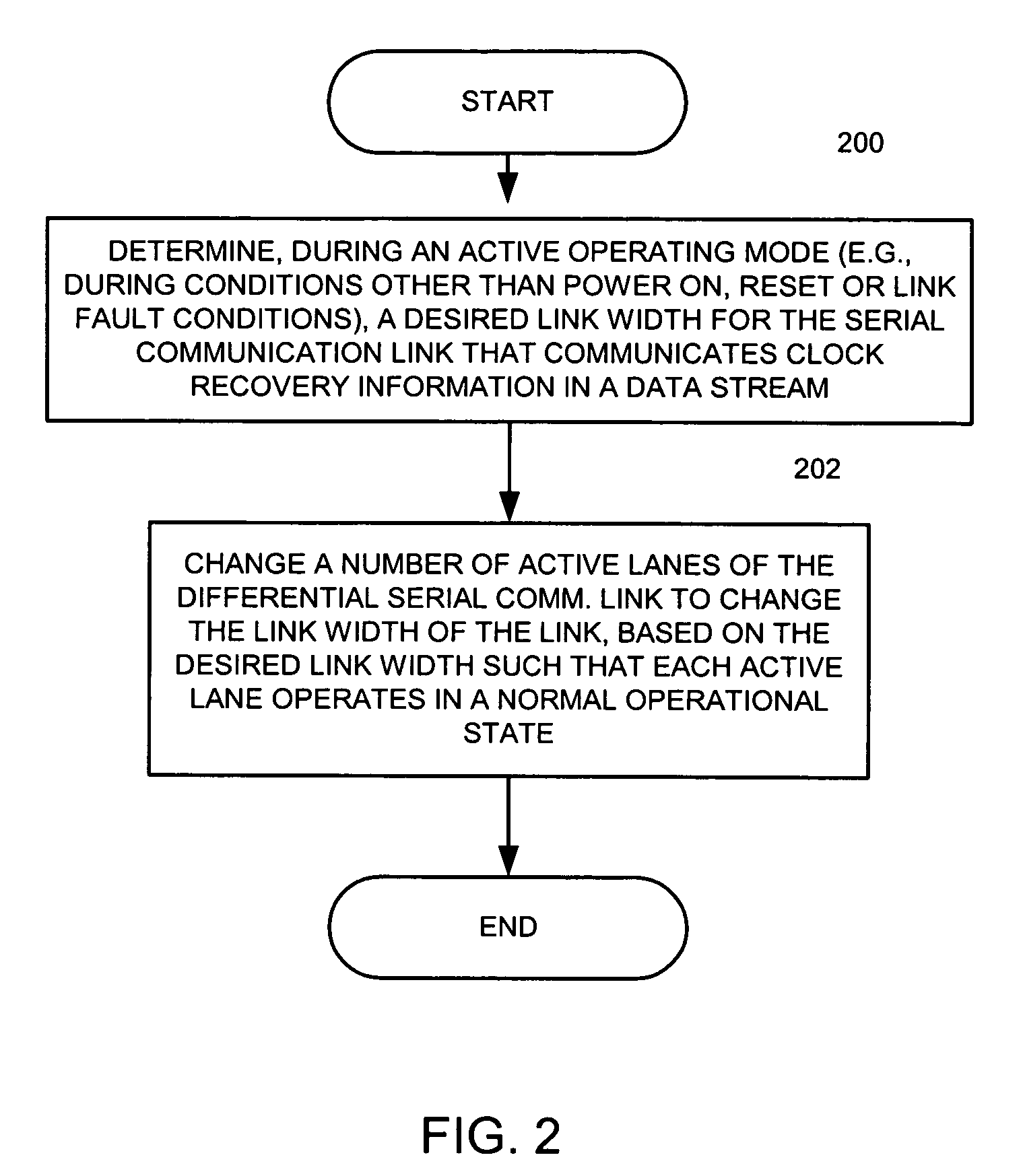

Method and apparatus for managing power consumption relating to a differential serial communication link

Briefly, a method, apparatus and system for managing power corresponding to a differential serial communication link that has a link width defined for example by one or more lanes wherein the lanes are adapted to communicate clock recovery information in a data stream, determines, during normal operating conditions, such as conditions other than power on, reset or link fault conditions, a desired link width for the serial communication link and then changes the link width accordingly.

Owner:ATI TECH INC

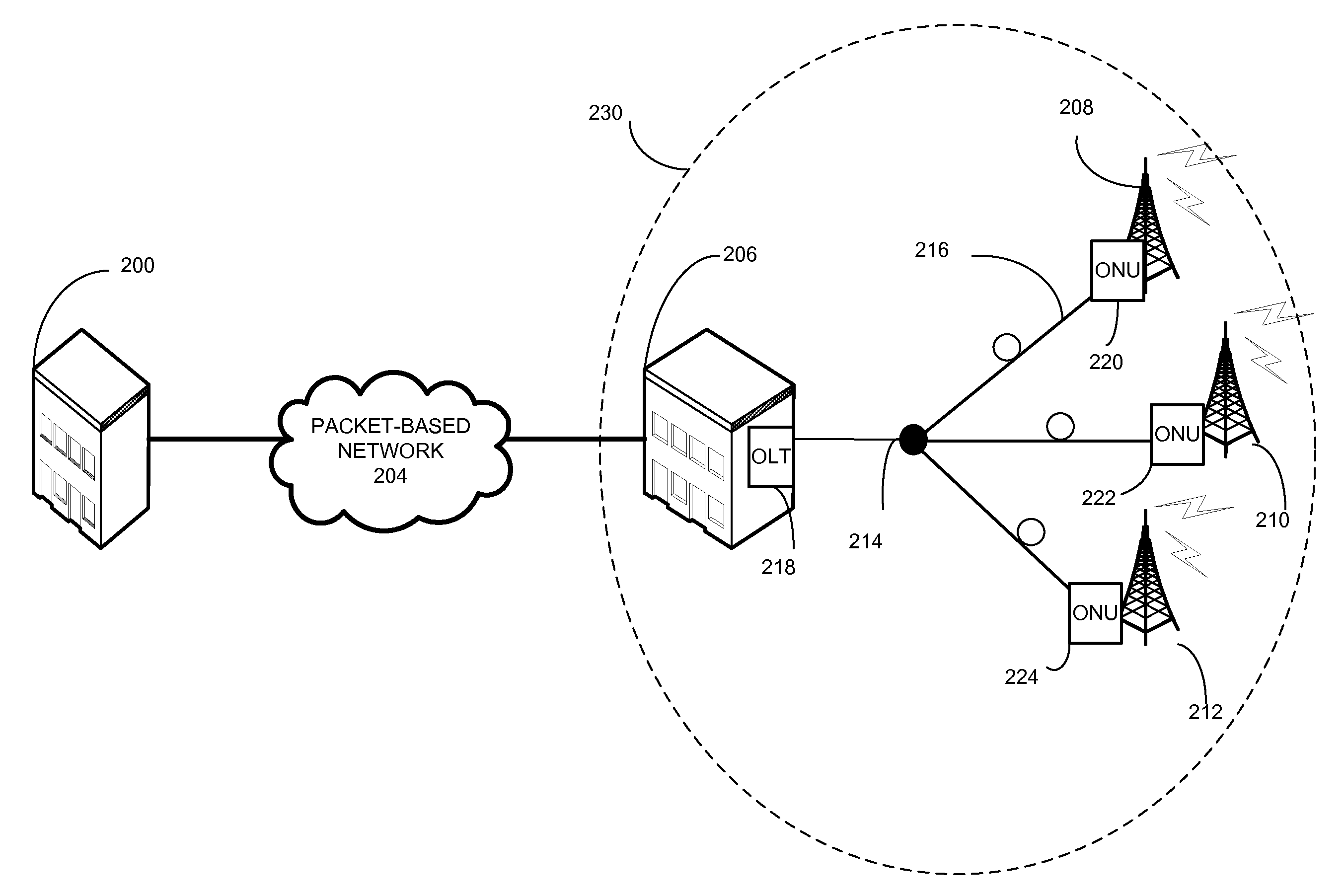

Synchronization transport over passive optical networks

ActiveUS20100098433A1Easy to transportMultiplex system selection arrangementsTime-division multiplexTransceiverClock recovery

One embodiment provides an Ethernet Passive Optical Network (EPON) system for clock transport. The system includes a reference clock configured to generate a frequency-reference signal, an optical line terminal (OLT) coupled to the reference clock, and an optical network unit (ONU). The OLT includes a clock generator configured to generate an OLT clock based on at least the frequency-reference signal. The ONU includes an optical transceiver, a clock recovery module, and a clock output mechanism. The optical transceiver is configured to transmit optical signals to and receive optical signals from the OLT. The clock-recovery module is configured to recover the frequency-reference signal from the received optical signals. The clock output mechanism is configured to output the recovered frequency-reference signal, thus facilitating transport of the frequency-reference signal over the EPON.

Owner:AVAGO TECH INT SALES PTE LTD

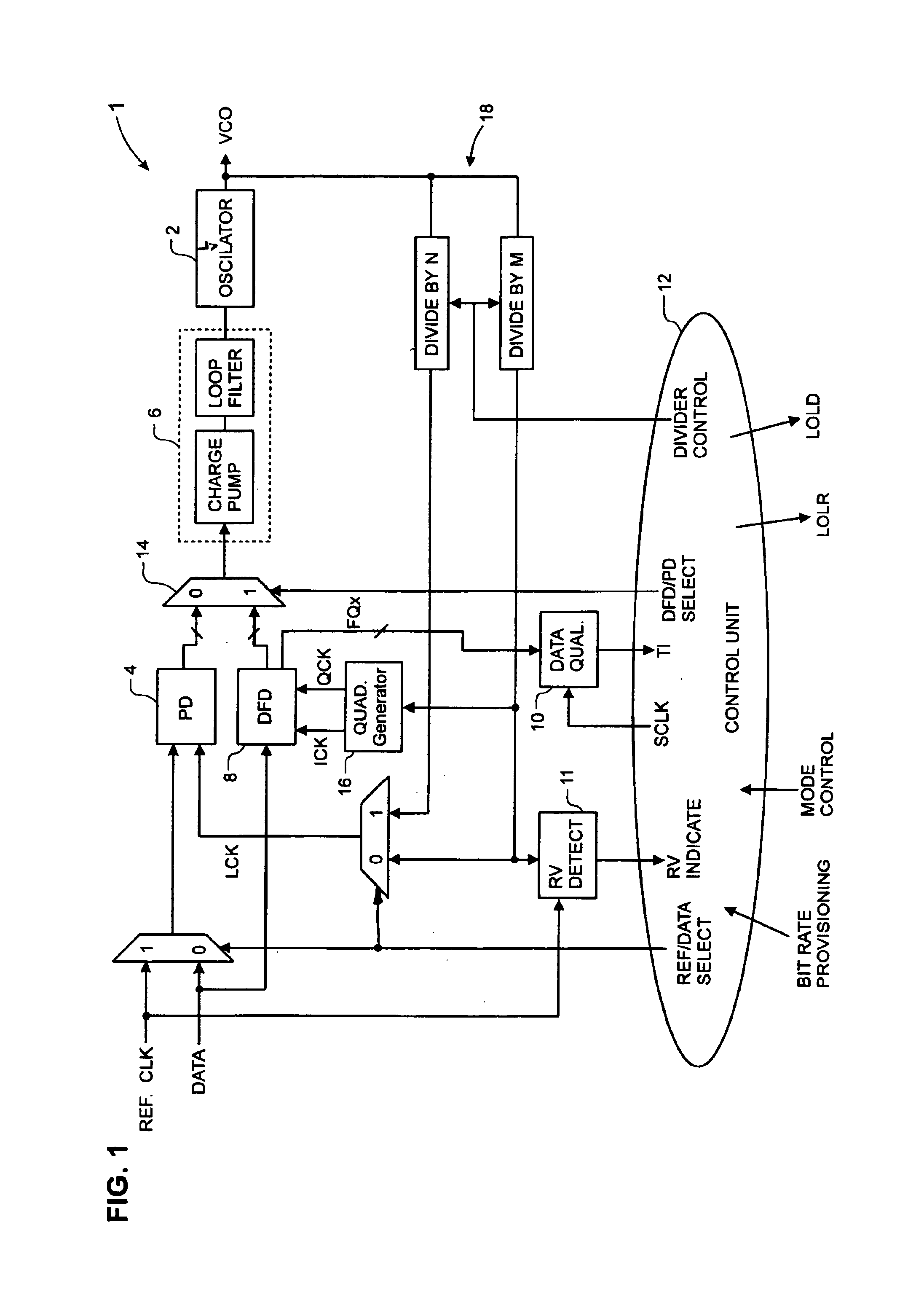

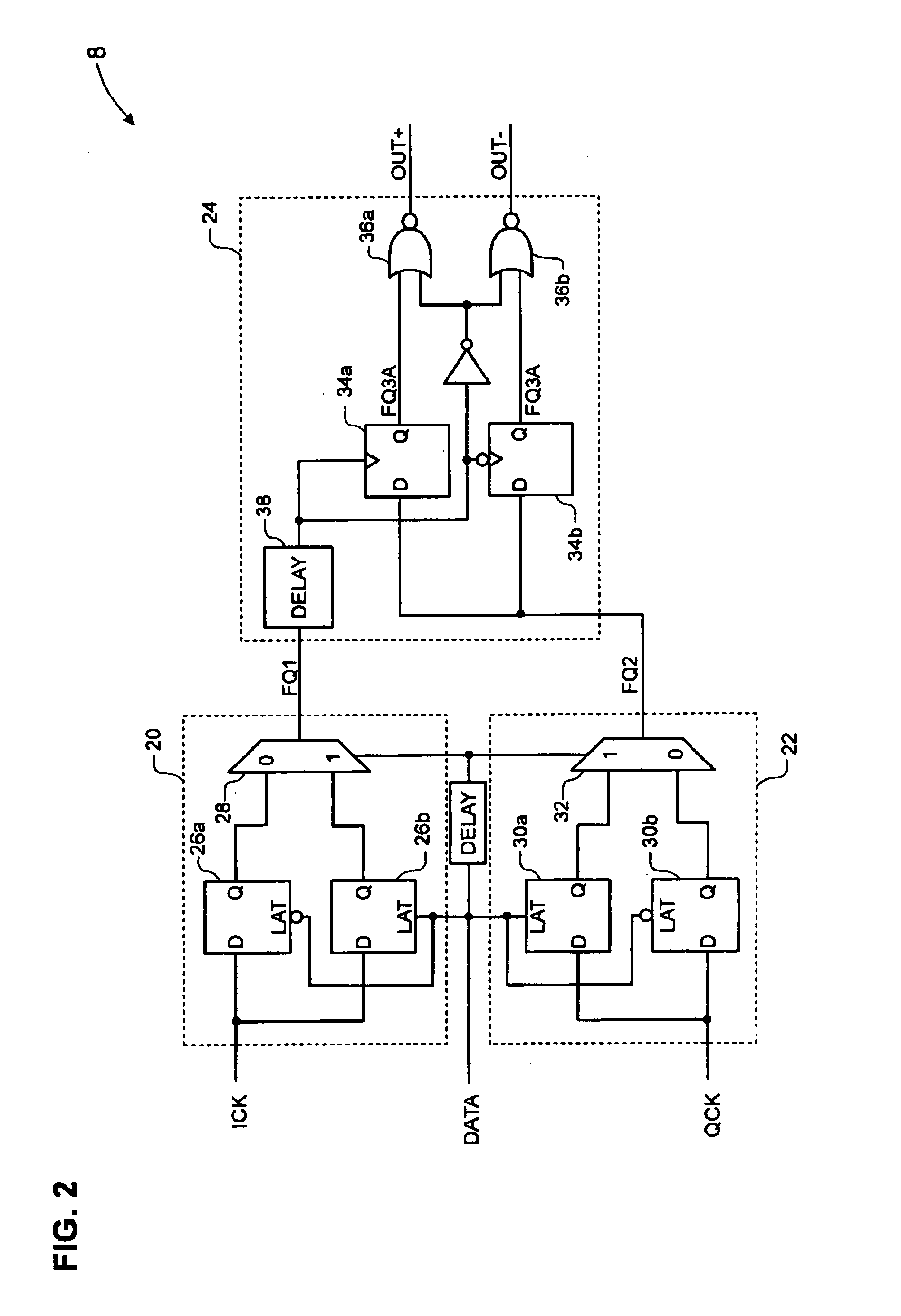

Method and apparatus for clock recovery and data qualification

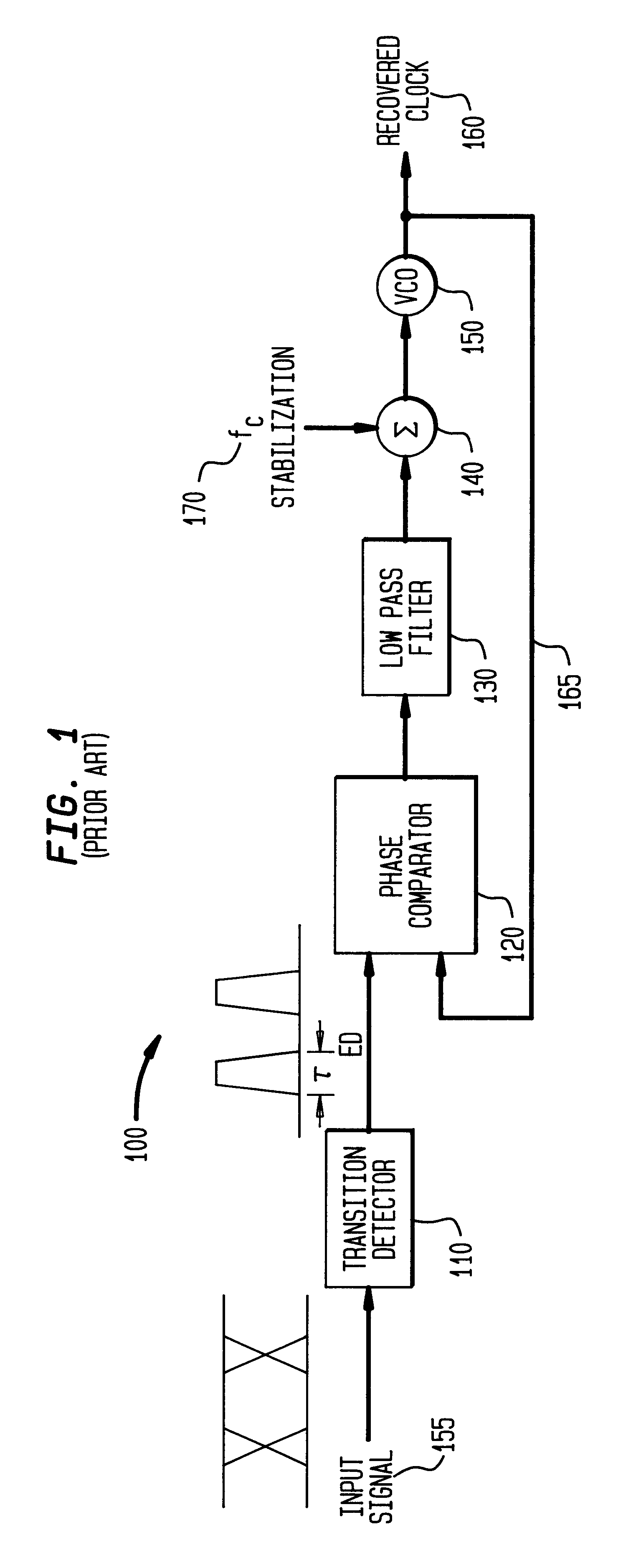

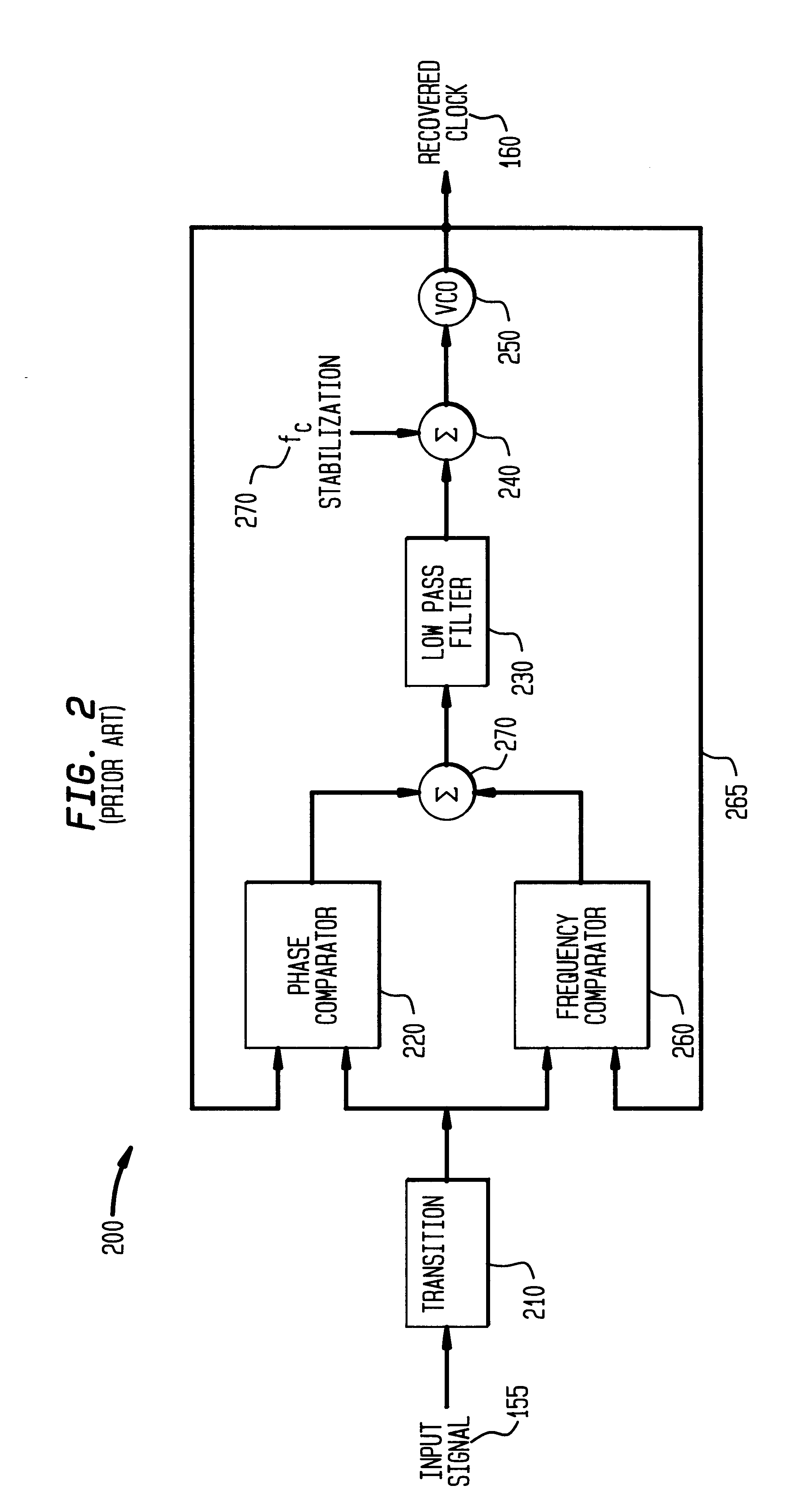

InactiveUS6853696B1Pulse automatic controlAngle demodulation by phase difference detectionSignal onClock recovery

A system for recovering a clock signal from a data signal is described. The system uses an oscillator adapted to generate an oscillator output signal, a first detecting circuit for obtaining a coarse frequency-lock condition between the data signal and a recovered clock signal, a second detecting circuit for obtaining a phase-locked condition between the data signal and the recovered clock signal, a lock-detecting circuit responsive to the first detecting circuit for detecting an out-of-lock condition between the data signal and the recovered clock signal, and a control circuit responsive to the lock-detecting circuits and adapted to control the oscillator to generate an oscillator output signal on the basis of the first detecting circuit during an out-of-lock condition, and otherwise to generate the oscillator output signal on the basis of the second detecting circuit. The advantages include a much wider pull-in range for frequency acquisition, and an accurate and robust measure of a quality of received data.

Owner:NORTEL NETWORKS LTD

Method and apparatus for managing power consumption relating to a differential serial communication link

Briefly, a method, apparatus and system for managing power corresponding to a differential serial communication link that has a link width defined for example by one or more lanes wherein the lanes are adapted to communicate clock recovery information in a data stream, determines, during normal operating conditions, such as conditions other than power on, reset or link fault conditions, a desired link width for the serial communication link and then changes the link width accordingly.

Owner:ATI TECH INC

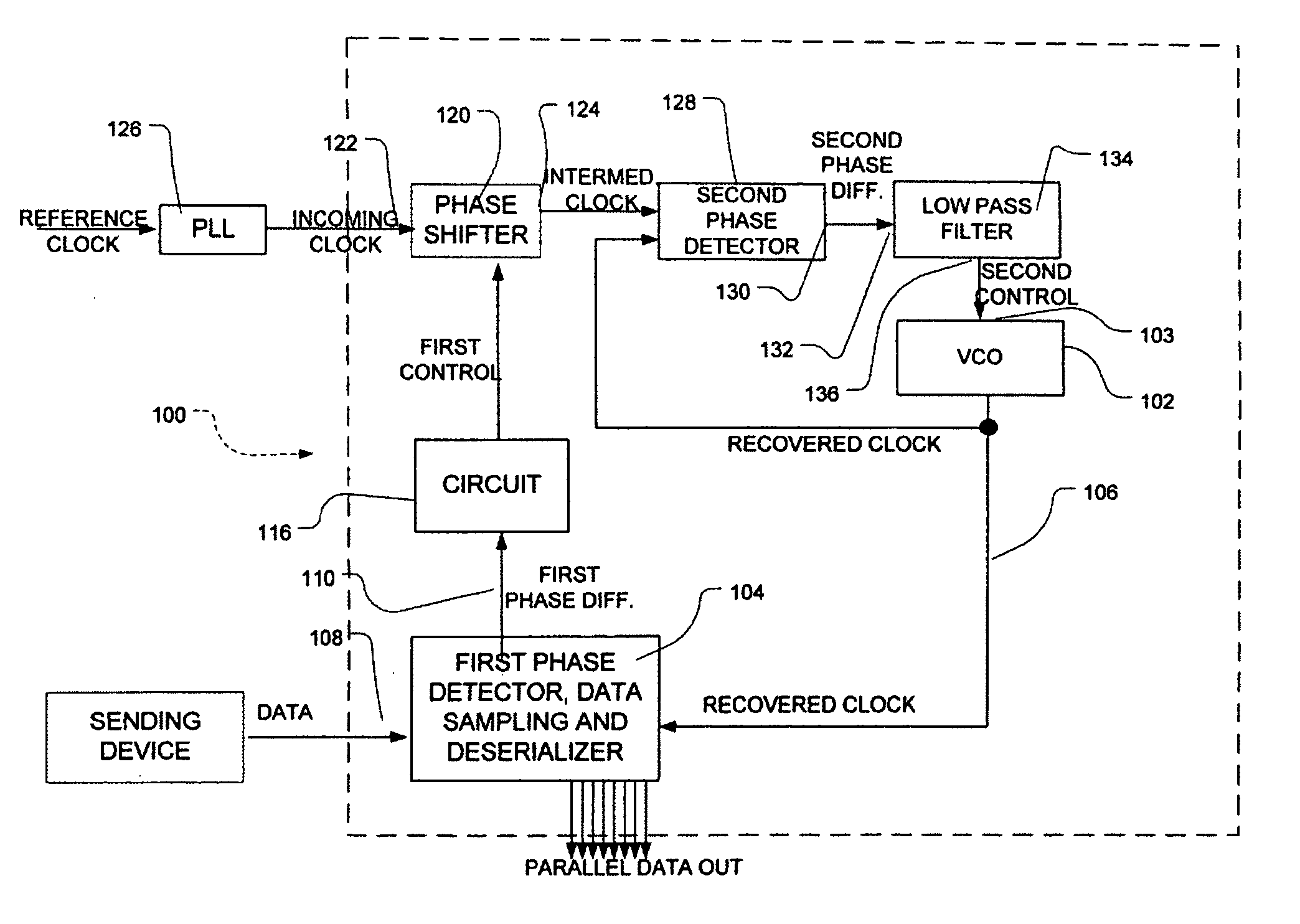

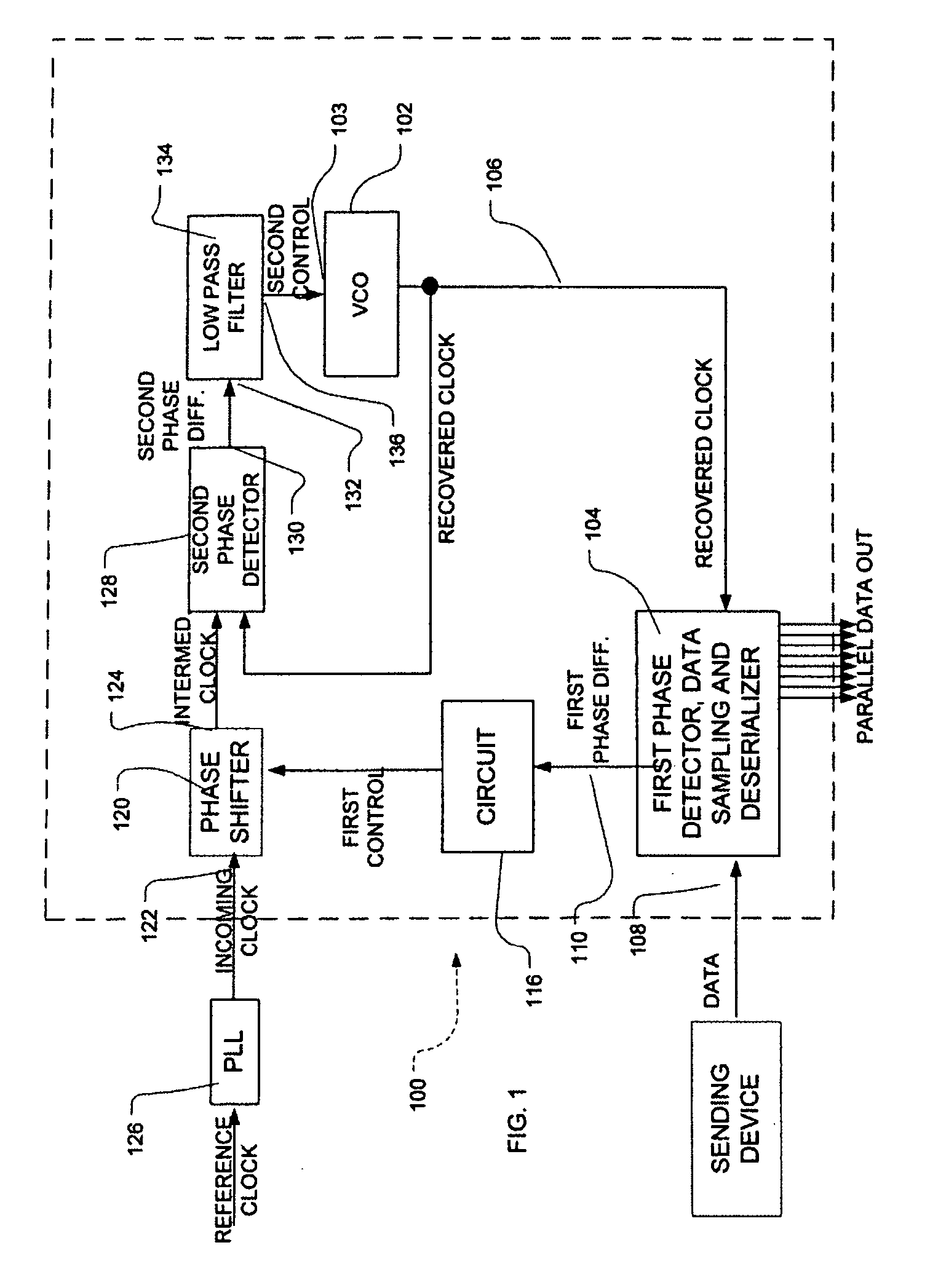

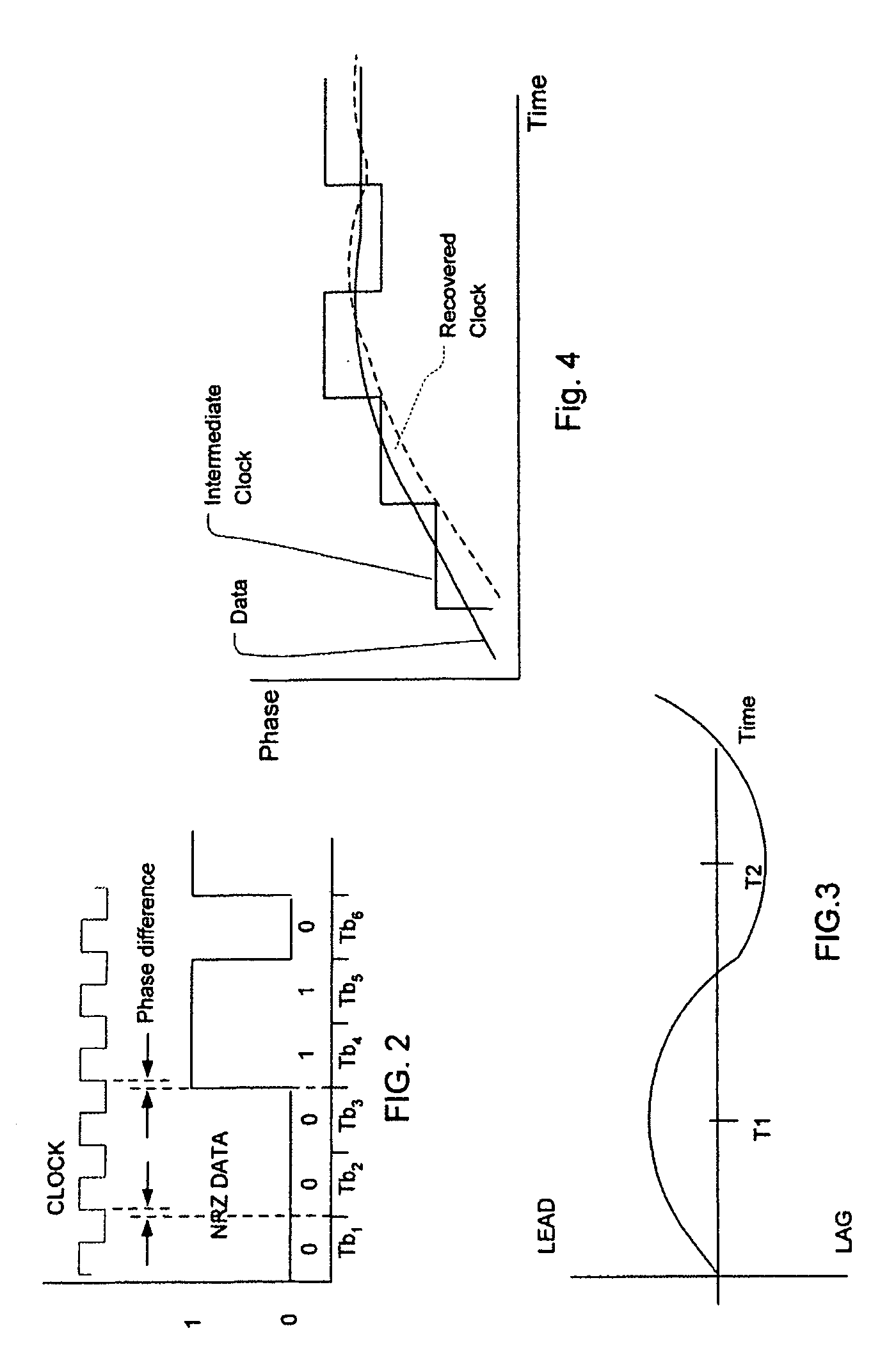

Low jitter clock recovery circuit

ActiveUS20070058768A1Pulse automatic controlOscillations comparator circuitsPhase detectorLow-pass filter

A clock recovery circuit includes a first phase detector for measuring the phase difference between a first clock signal from a voltage controlled oscillator (VCO) and a data signal. A phase shifter responsive to a control signal based on this phase difference adjusts the phase of an incoming clock signal to yield a second clock signal. The phase difference between the first clock signal and the second clock signal is measured and the resulting signal is low-pass filtered to derive a control signal for controlling the VCO. The phase locked loop including the VCO filters out jitter.

Owner:RAMBUS INC

Clock recovery circuitry

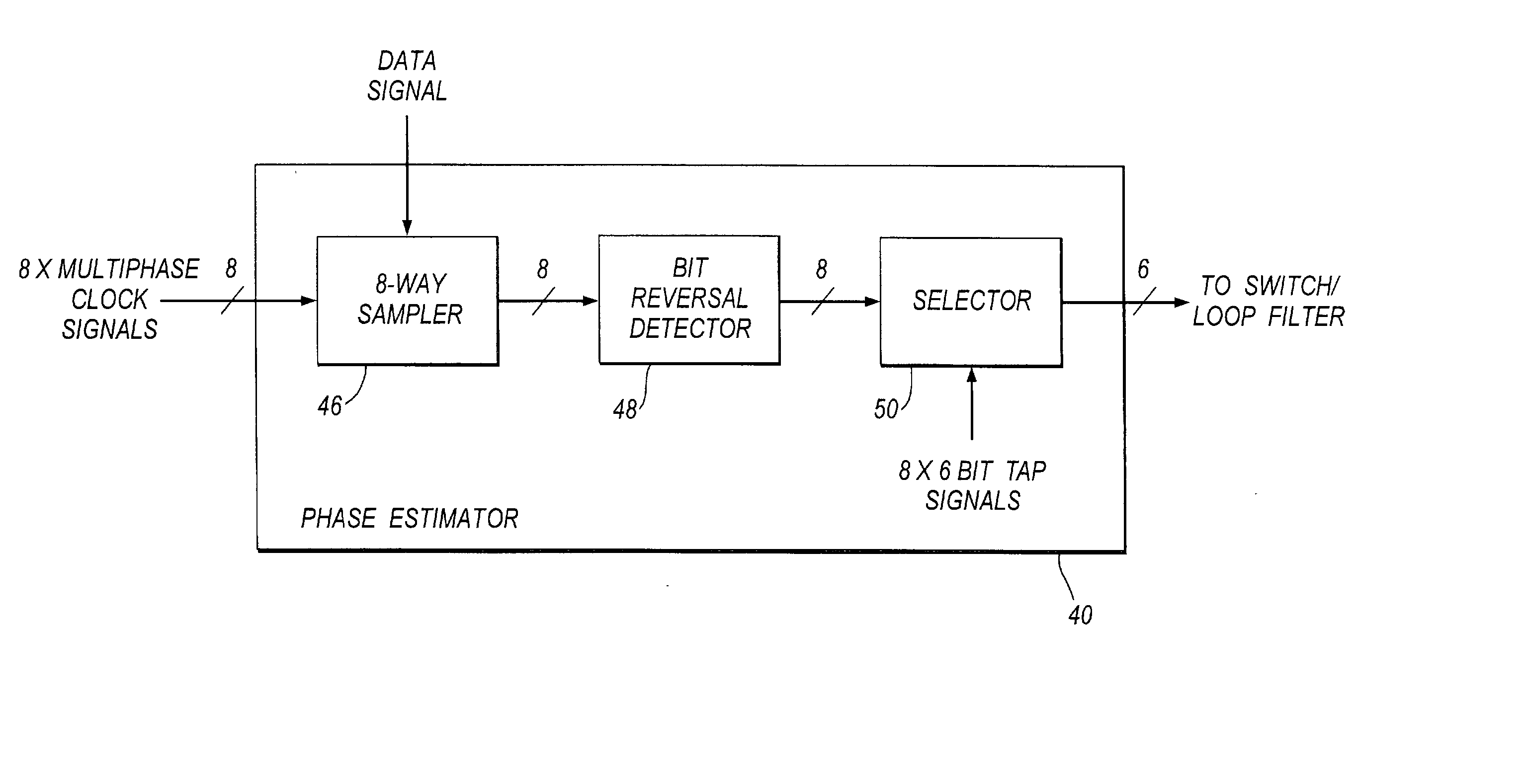

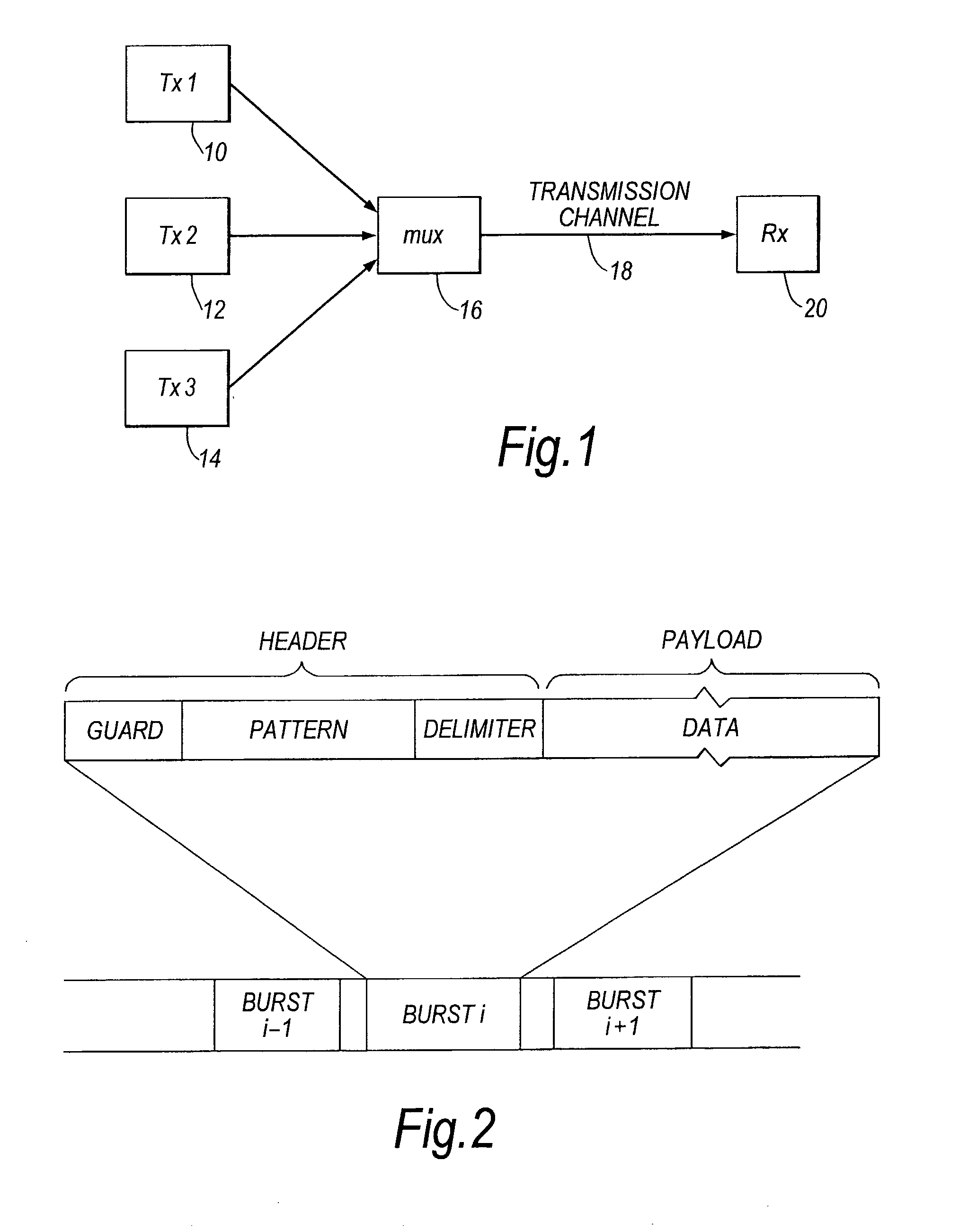

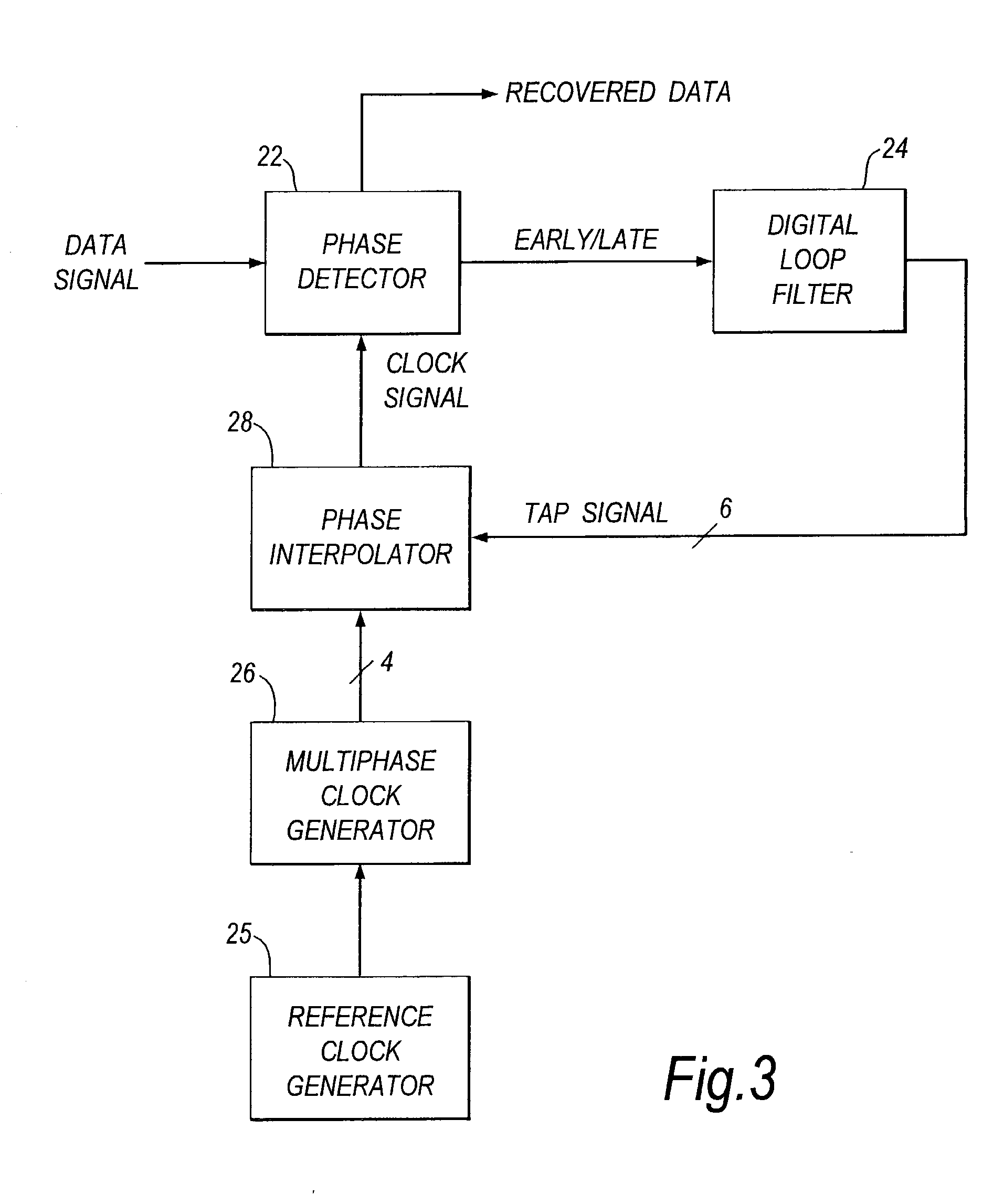

Clock recovery circuitry for recovering a clock signal from a data signal is disclosed. The clock recovery circuitry comprises sampling means (46) for sampling the data signal at a plurality of sampling points, bit reversal detecting means (48) for determining a sampling point at which the data signal changes state, selecting means (50) for selecting a phase from amongst a plurality of candidate phases based on a sampling point at which the data signal is determined to change state, and phase setting means (38) for setting the phase of the clock signal in dependence on the selected phase. The circuitry may be used to produce an estimate of a desired phase of the clock signal for supply to a phase locked loop. This can allow the phase locked loop to be brought quickly into lock.

Owner:SOCIONEXT INC

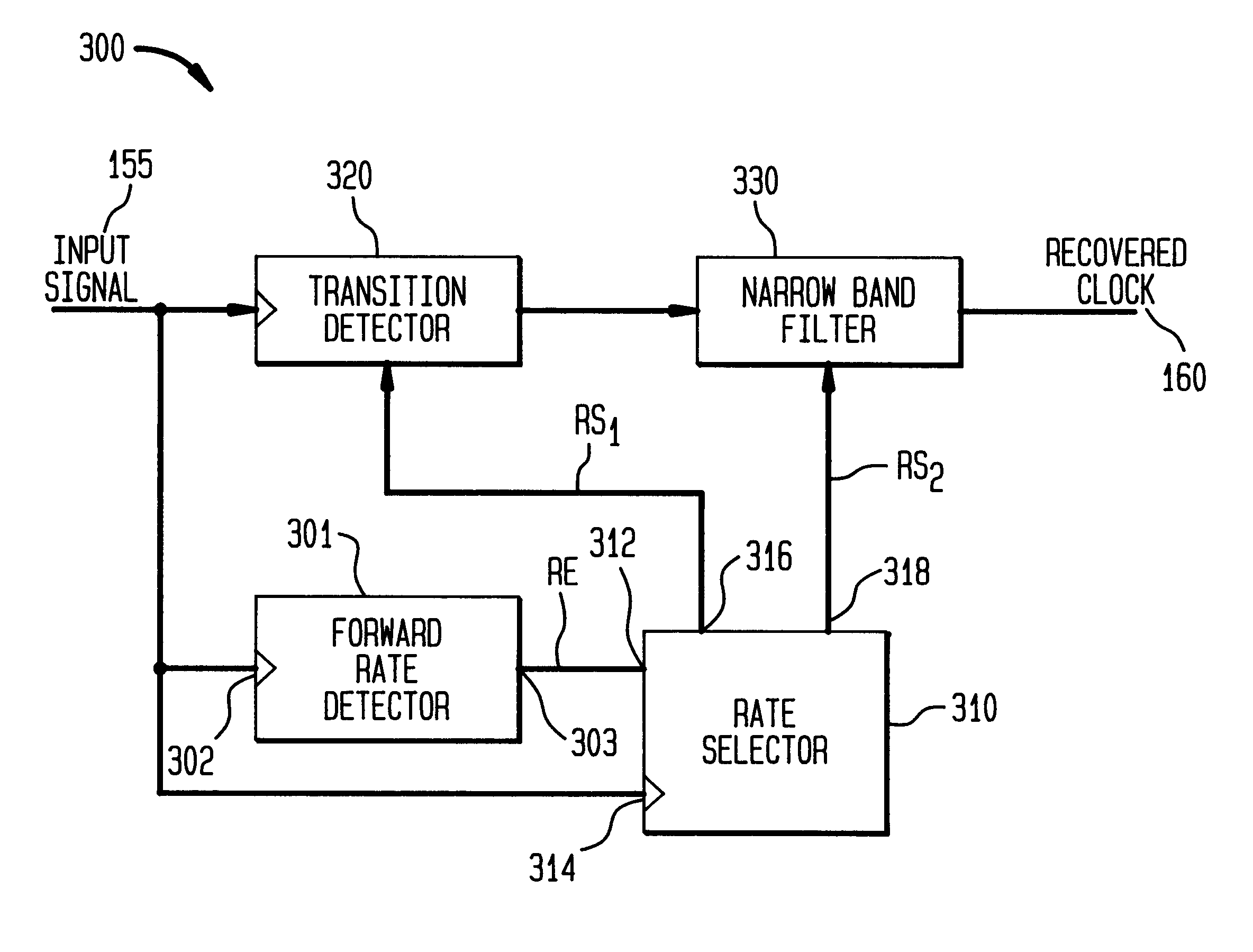

Method and apparatus for variable bit rate clock recovery

Methods and apparatuses consistent with the present invention recover a clock signal from a variable bit rate data signal by estimating, in the time domain, the bit rate of the data signal, and based on the estimated variable bit rate, determining a center frequency of a narrow-band filter for extracting the clock signal from the data signal. A clock recovery circuit consistent with the present invention extracts a clock signal from a variable bit rate data signal by estimating a minimum time interval between transitions in the data signal, generating a plurality of pulses that correspond respectively to transitions in the data signal, adjusting the duration of each of the pulses based on the estimated minimum time interval and inputting into a narrow-band filter the adjusted pulses, determining a center frequency of the narrow-band filter based on the estimated minimum time interval, and extracting in the narrow-band filter the clock signal from the adjusted pulses.

Owner:HANGER SOLUTIONS LLC

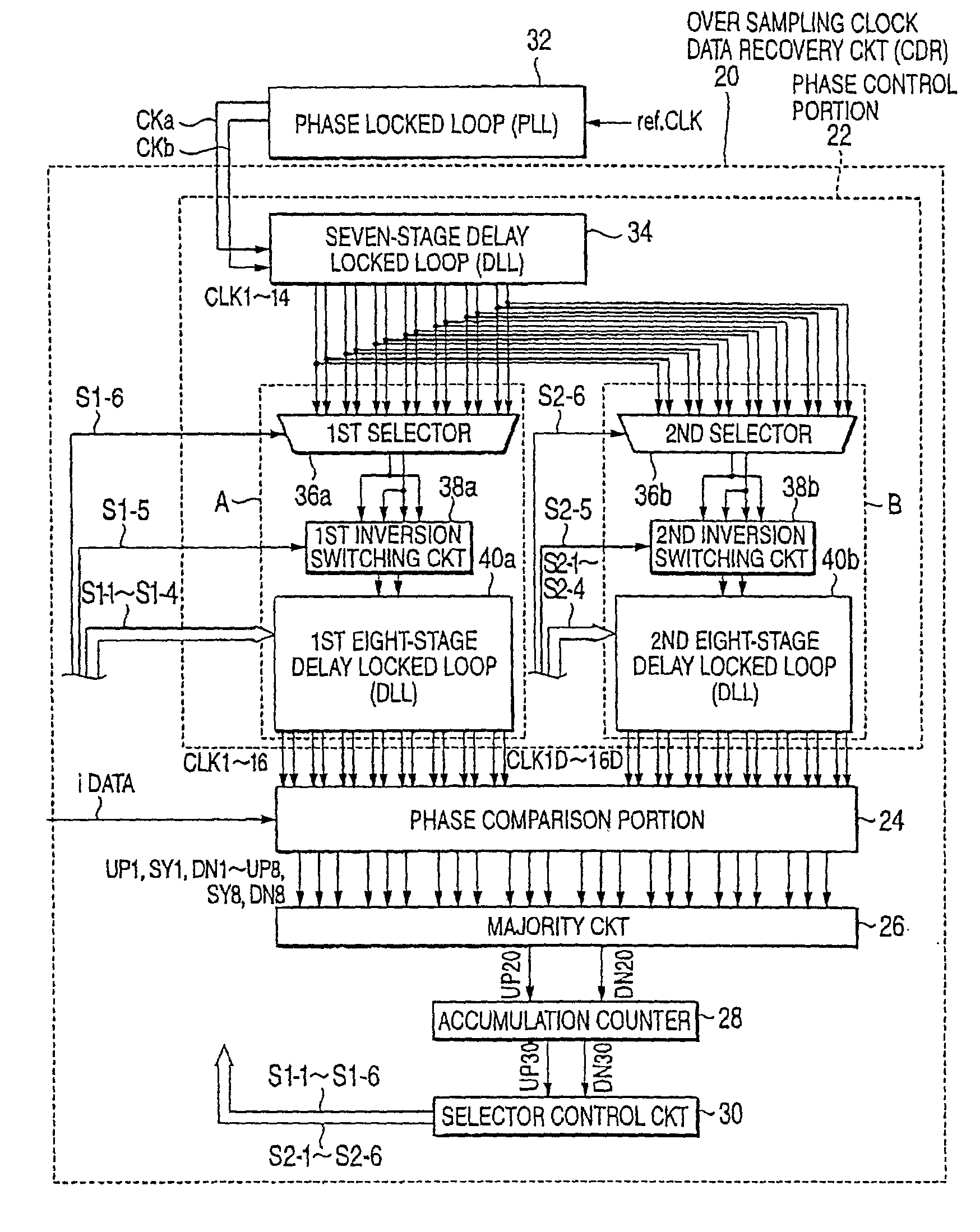

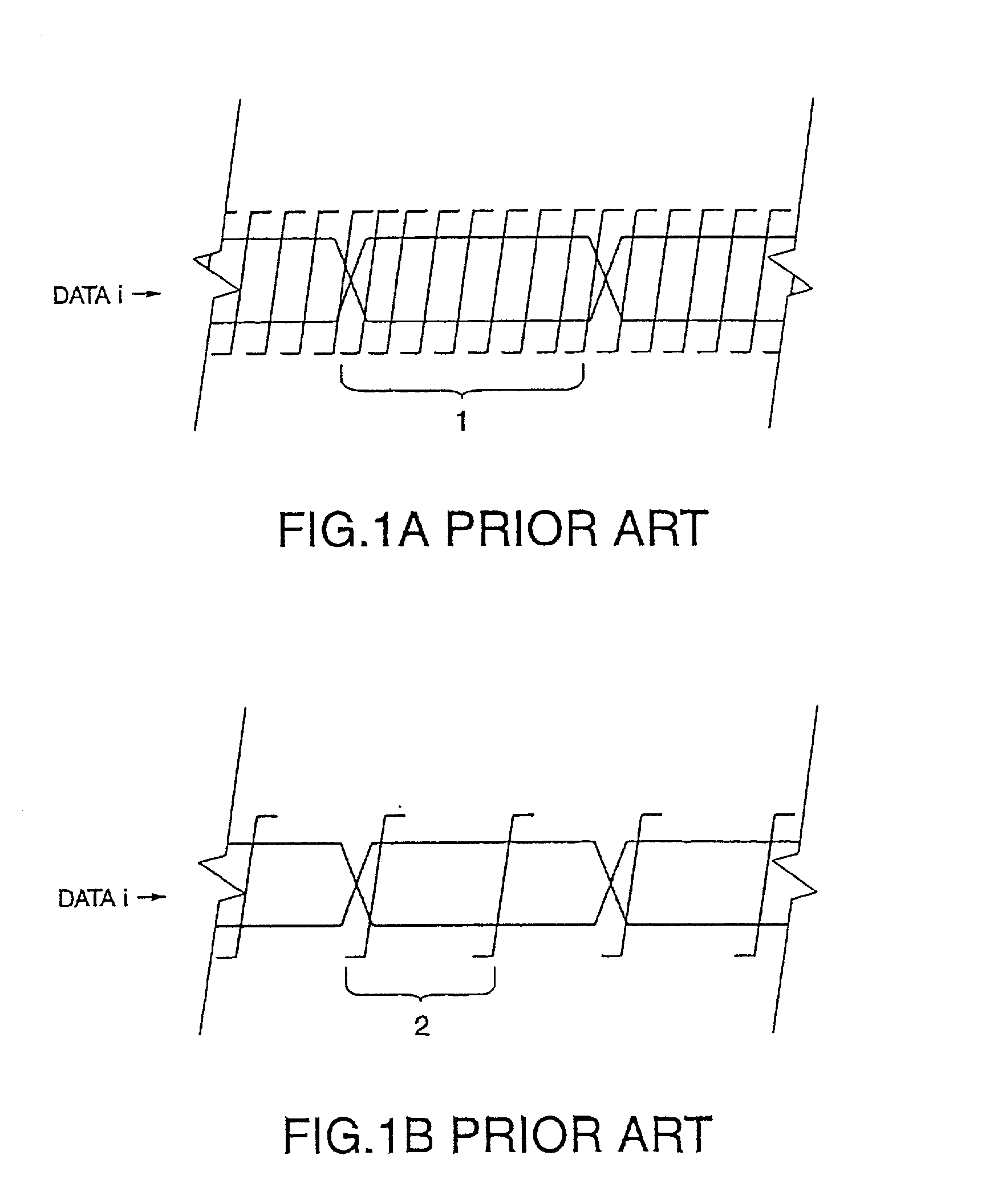

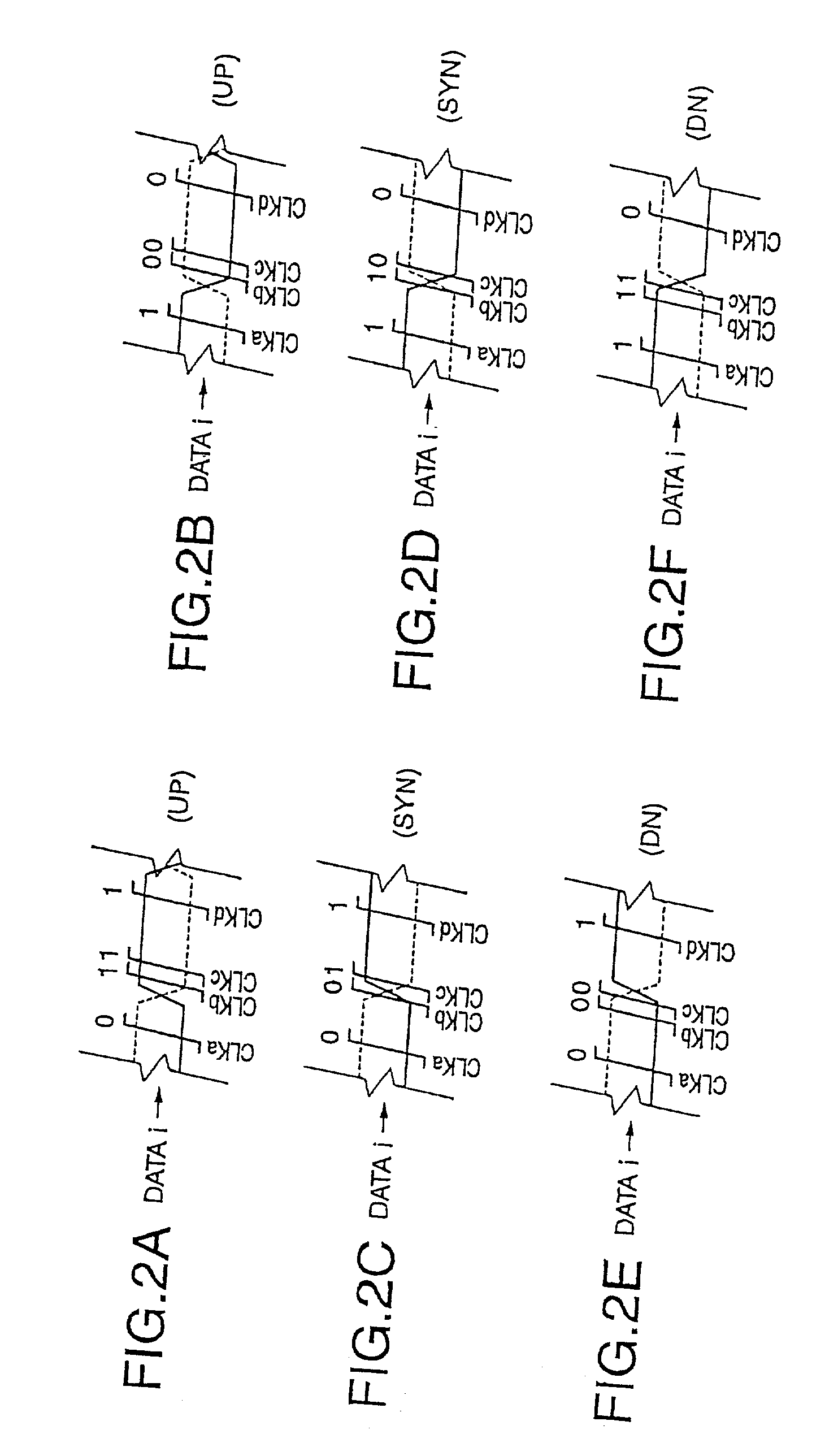

Oversampling clock recovery having a high follow-up character using a few clock signals

InactiveUS7010074B2High follow-up characterReduce the numberPulse automatic controlTime-division multiplexDelay-locked loopClock recovery

An oversampling clock recovery method according to this invention generates non-uniform three-phase clock signals CLKa, CLKb, and CLKc having non-uniform intervals for one bit of an input data i and controls phases of the clock signals so that either phase of two edges of two-phase clock signals CLKb and CLKc having a relatively narrower interval of 57 ps synchronizes with a phase of a transition point of the input data i. By changing clock signals to be phase-locked in three delay locked loops (DLLs), a phase interval of 57 ps is formed.

Owner:RENESAS ELECTRONICS CORP

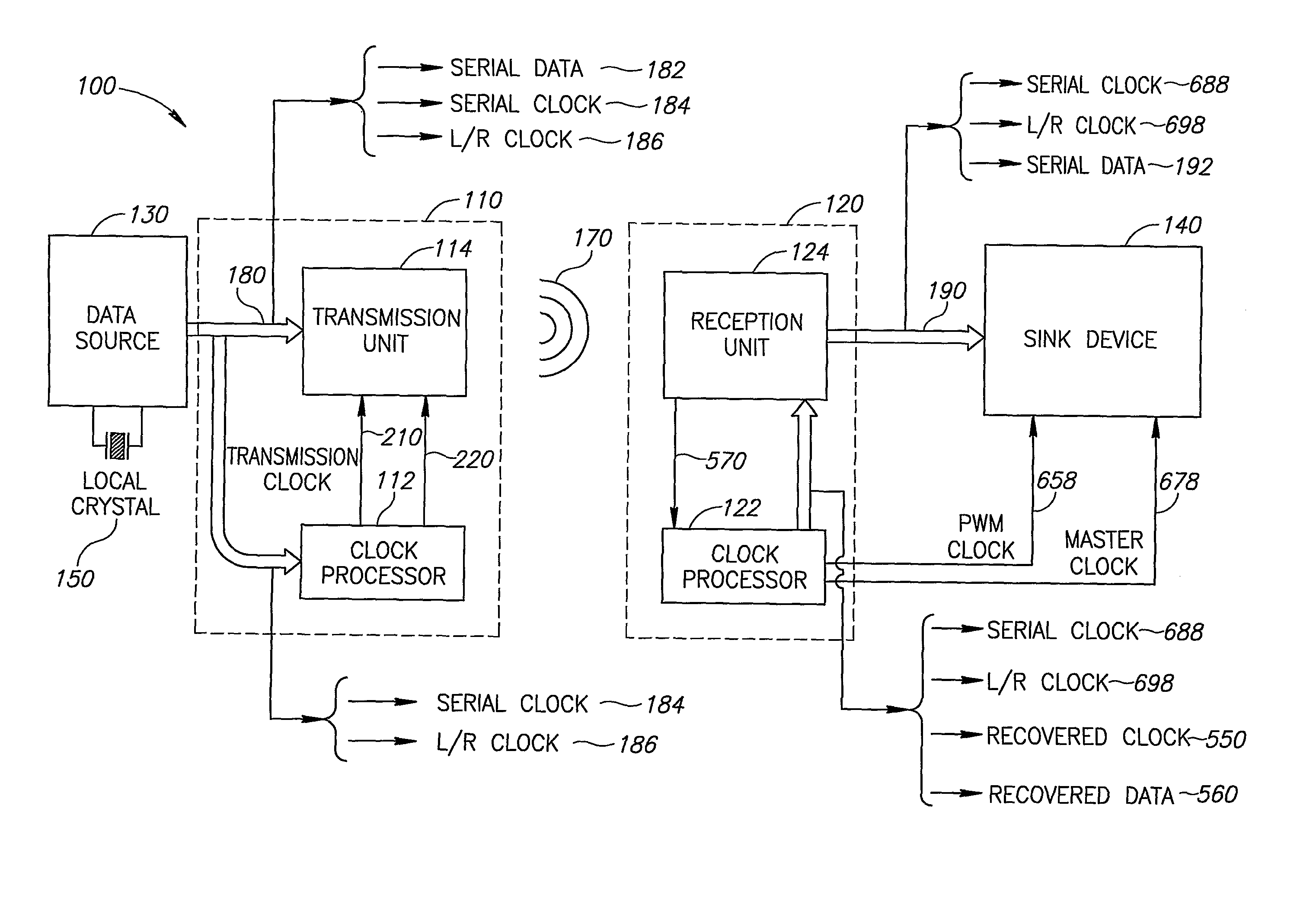

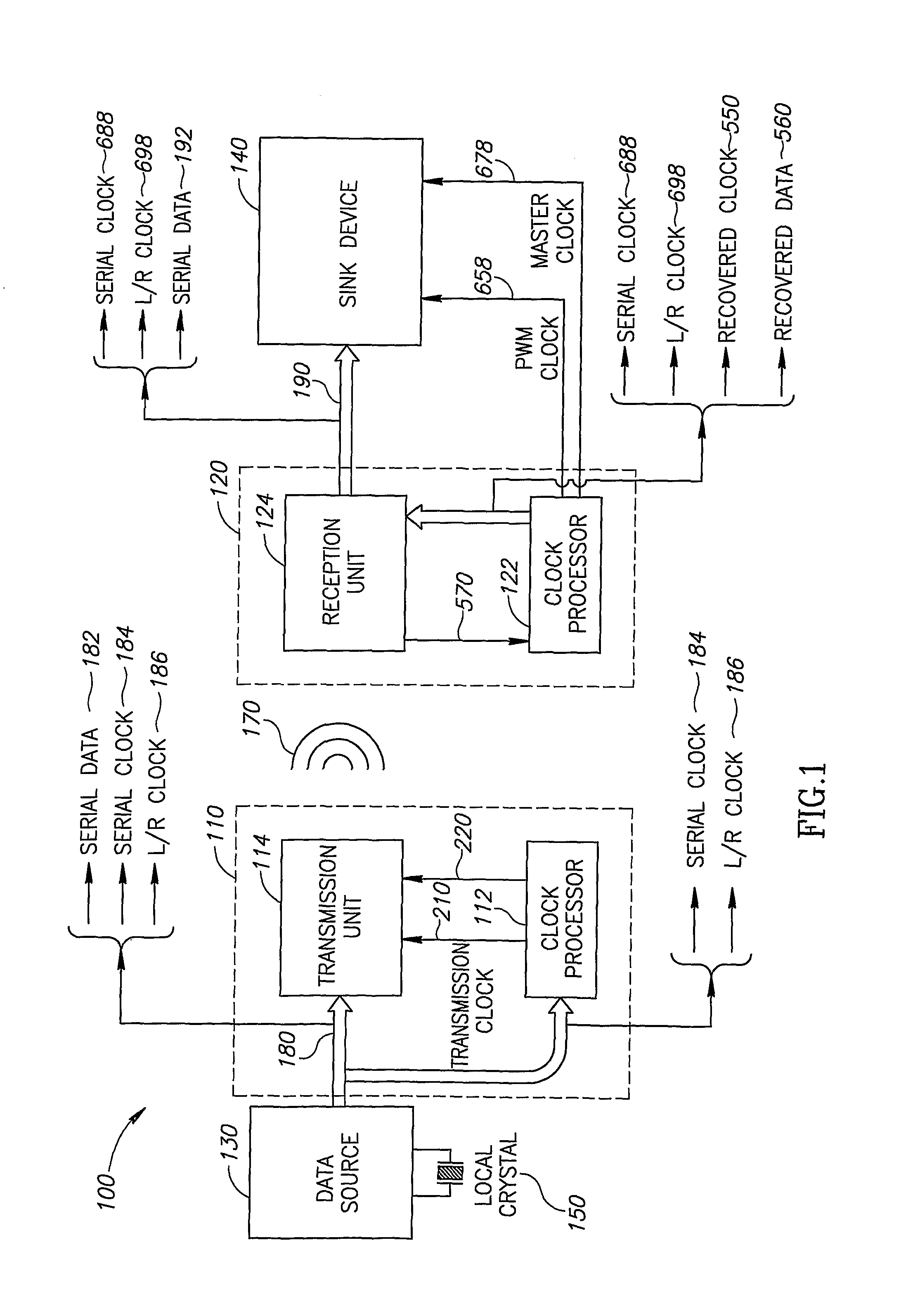

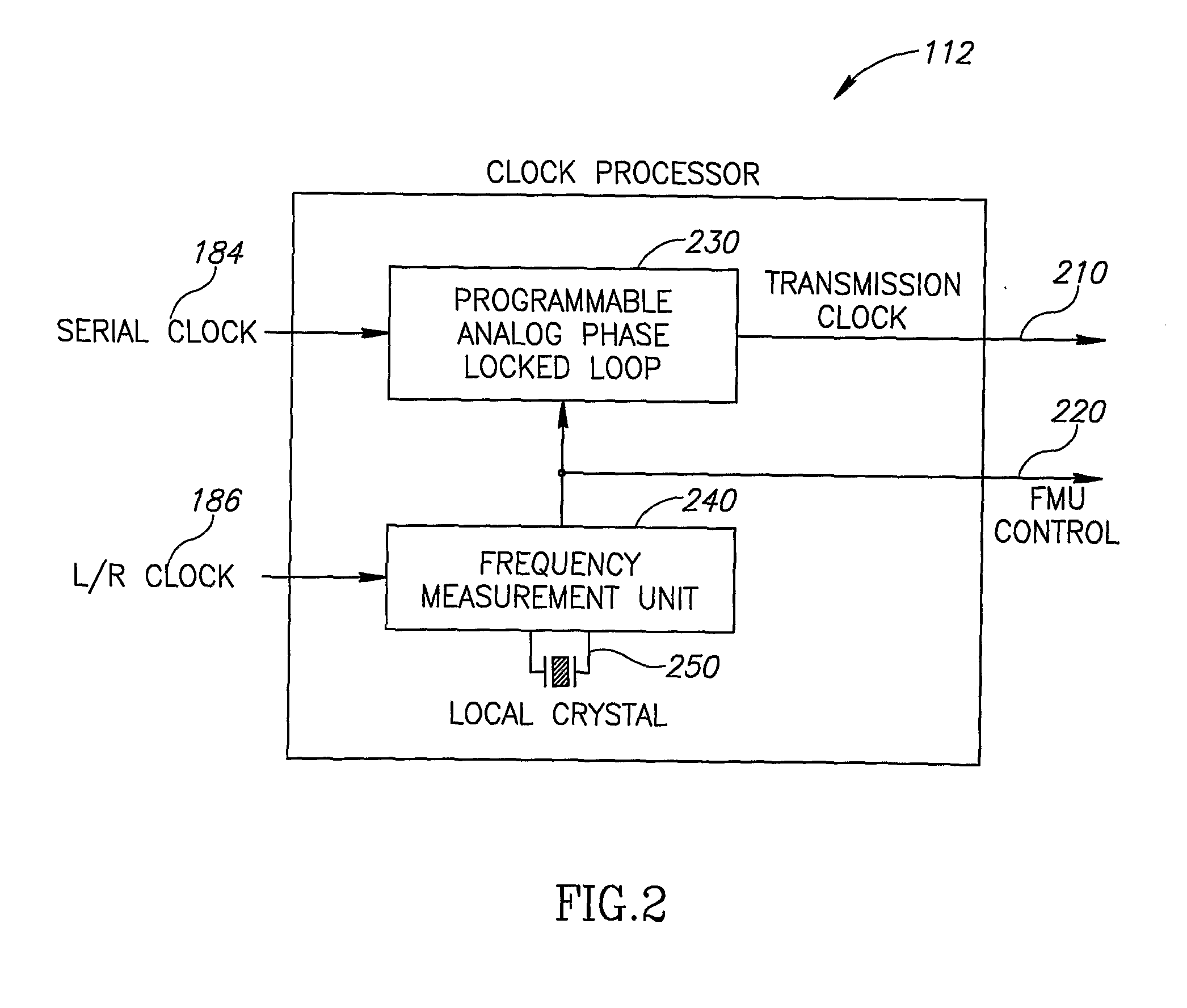

Low Jitter Clock Recovery from a Digital Baseband Data Signal Transmitted Over a Wireless Medium

InactiveUS20080212729A1Synchronisation error detectionCarrier regulationData streamWireless transmission

A system and method of transmitting a data stream from a data source over a baseband wireless communication system to one or more receivers. The receivers simultaneously recover the data and clock signals of the original data stream from the wireless transmitted data so that the data stream can be provided by the receivers to a data sink at the same rate as the original data stream, with low jitter performance.

Owner:INFRA

Multiphase clock recovery using D-type phase detector

InactiveUS6914953B2Increase data rateReduce power consumptionPulse automatic controlTime-division multiplexPhase detectorData stream

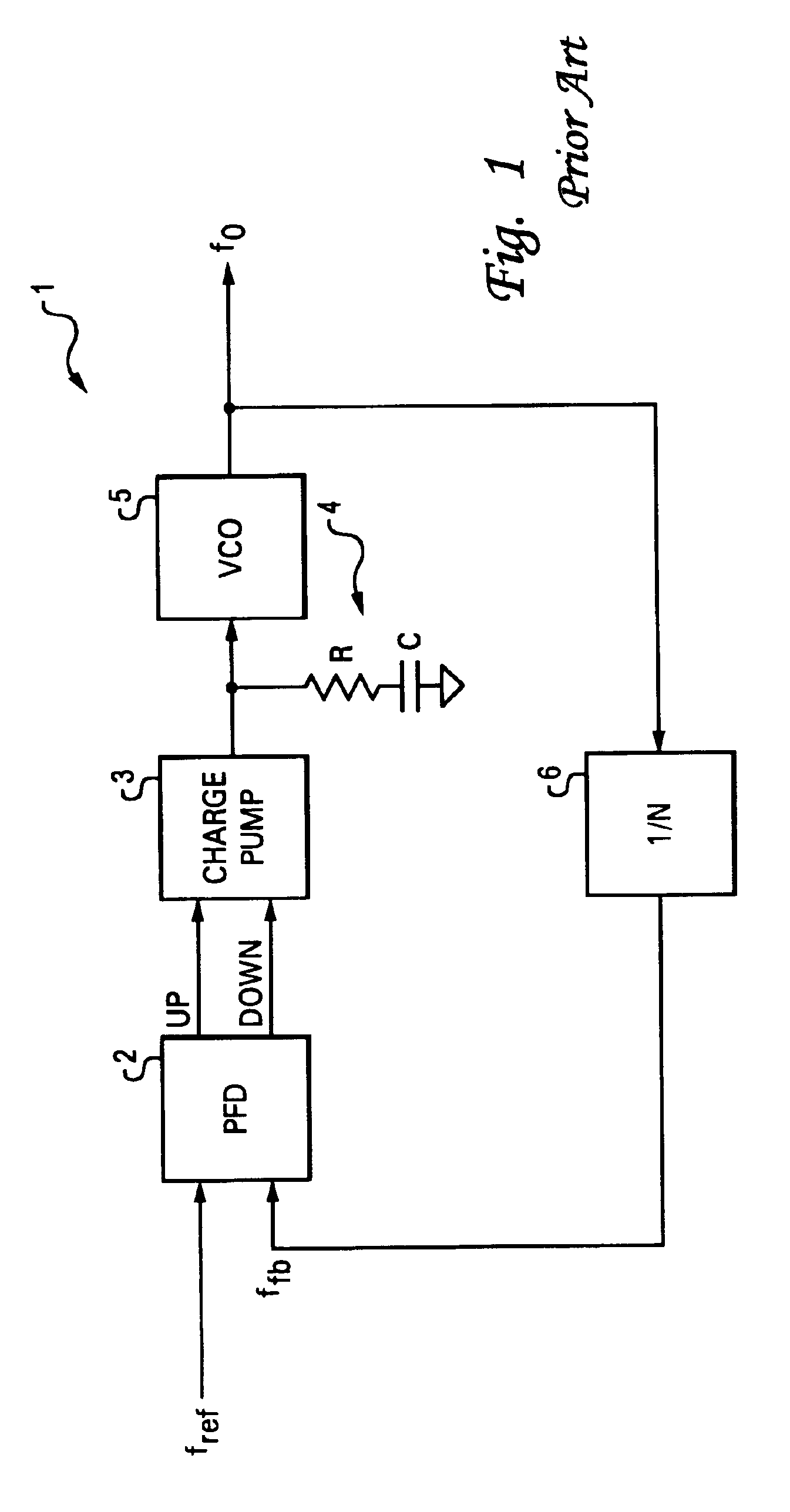

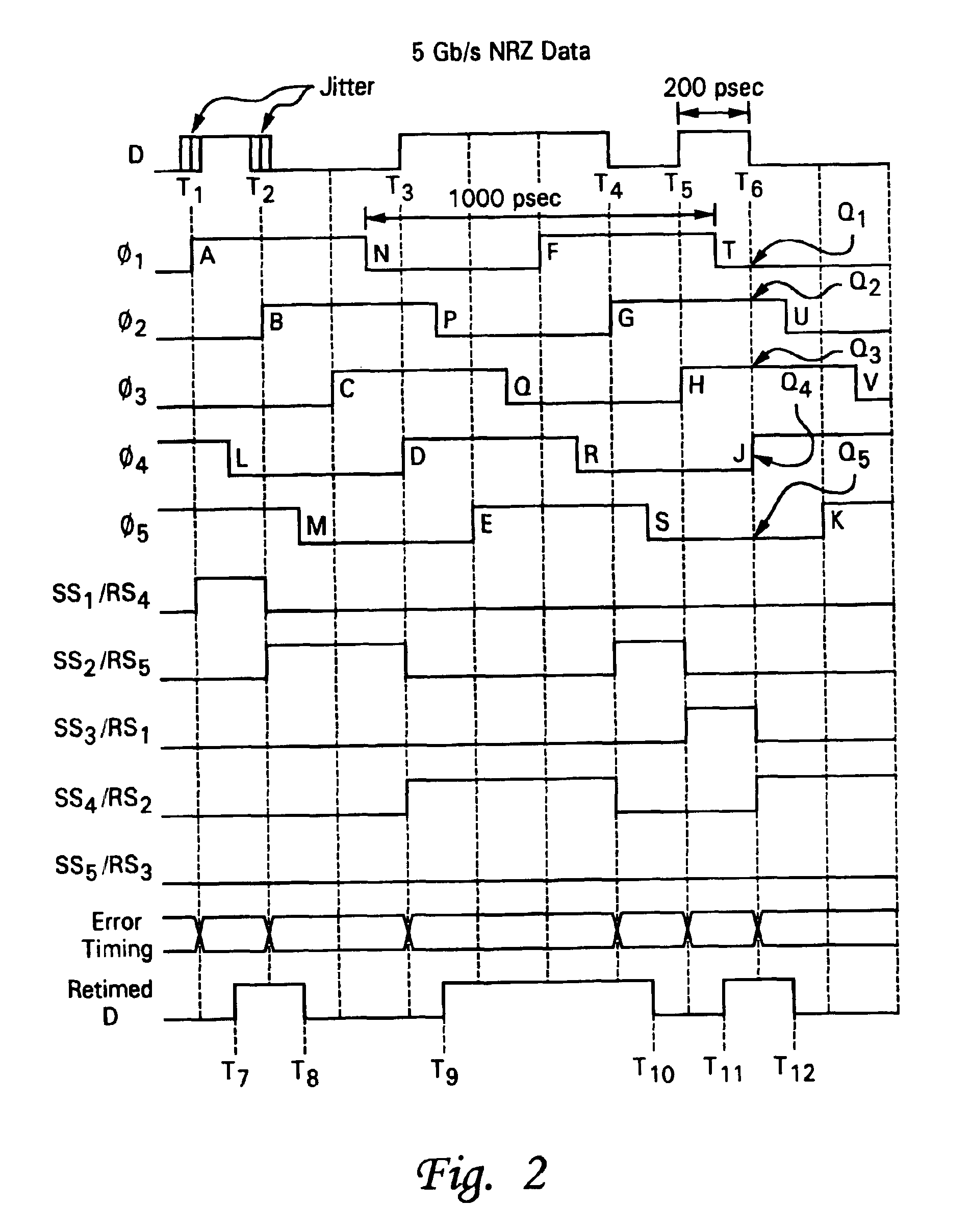

A method of extracting a clock signal from a data stream, by generating a plurality of multiphase clock signals, selecting one of the multiphase signals based on synchronization states identifying which of the multiphase clock signals is most closely aligned with the data stream, and sampling the data stream using the selected multiphase signal to produce a retimed data signal. The multiphase clock signals may be subharmonics of the data stream. The selecting step may include the determination of whether the multiphase clock signals are either early or late with respect to the data stream, particularly using D-type flip-flops. The synchronization states are used to define which of the rising edges of the multiphase clock signals is most closely aligned with an edge of the data stream. A multiphase voltage-controlled oscillator may be used to provide the multiphase clock signals. An error signal is created using the multiphase clock signals and the data stream which is applied to a charge pump, and the multiphase clock signals are corrected using a control voltage output of the charge pump.

Owner:MEDIATEK INC

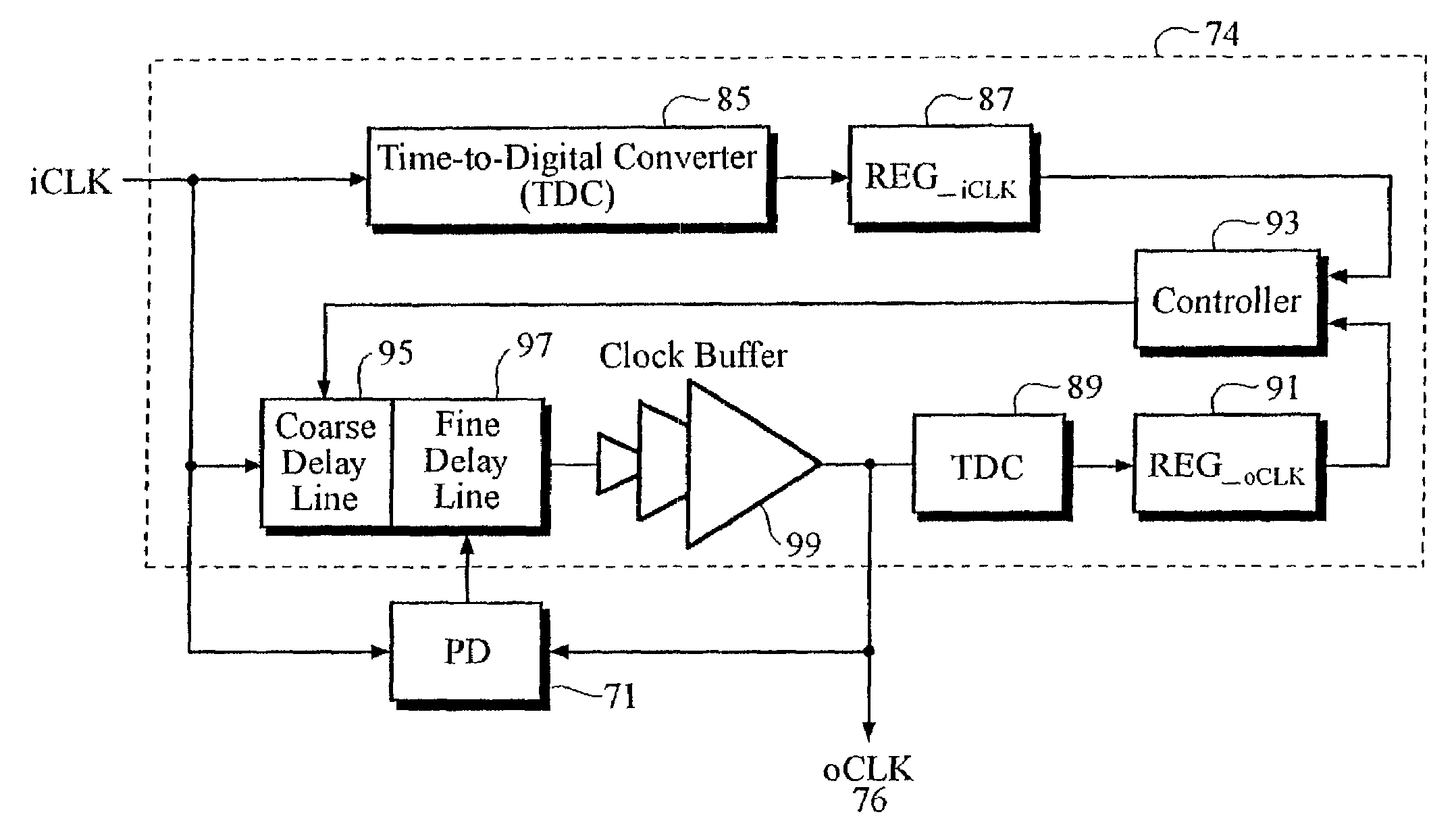

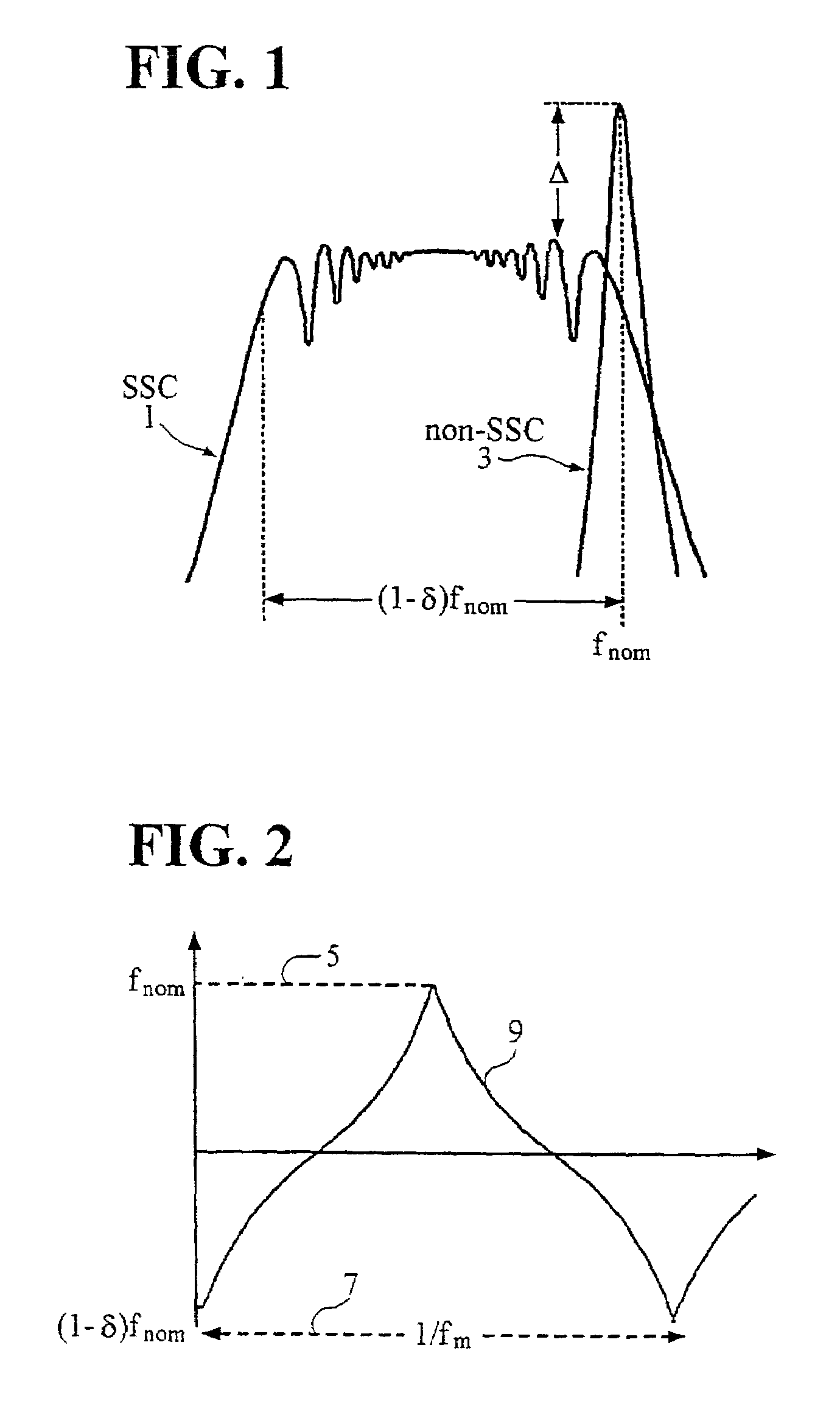

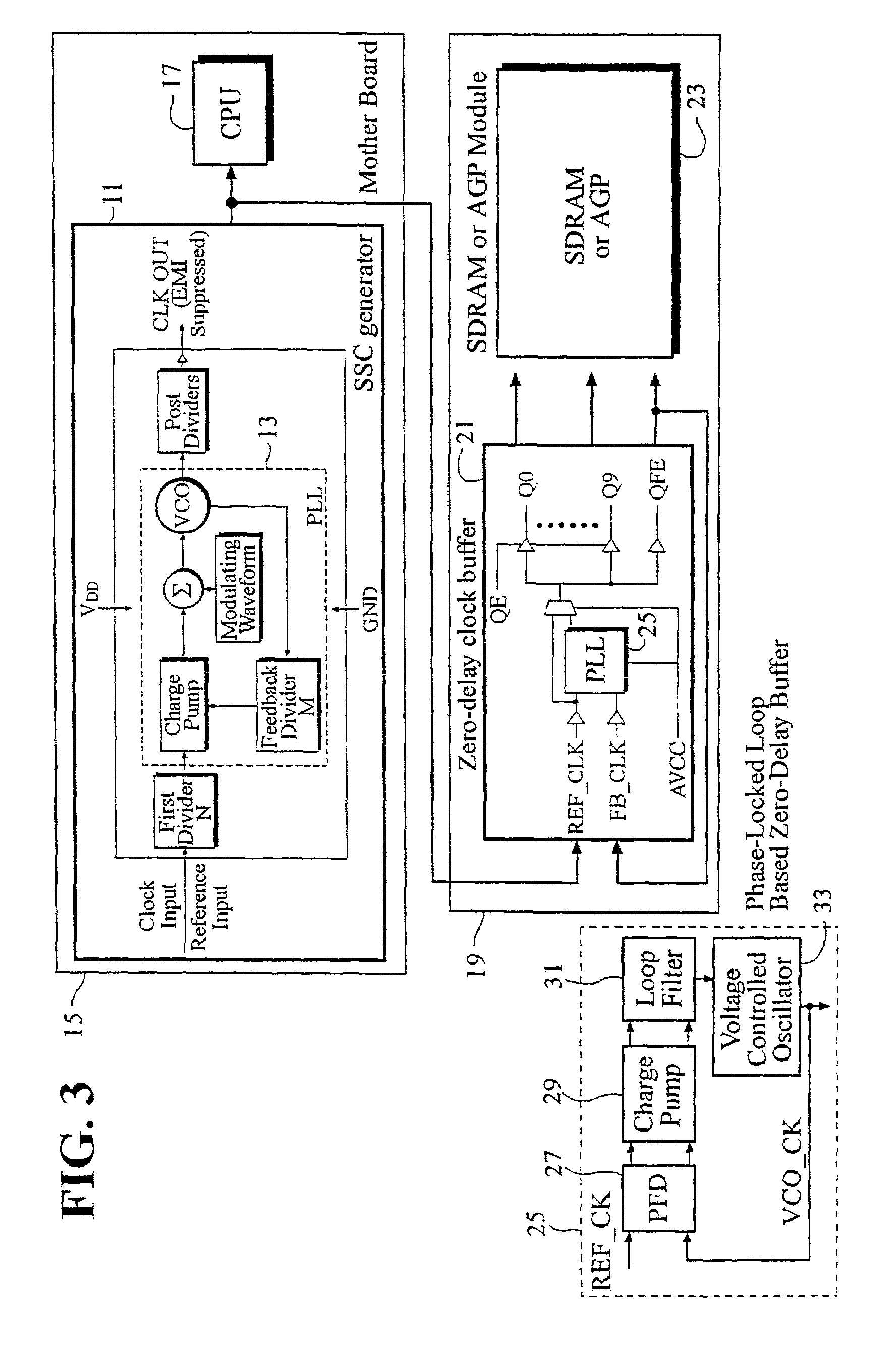

Zero-delay buffer circuit for a spread spectrum clock system and method therefor

InactiveUS6993109B2Improve efficiencyEliminate phase differencePulse automatic controlGenerating/distributing signalsPhase detectorPhase difference

A clock recovery circuit and a method for reducing electromagnetic emission (EMI) and increasing an attainable clock frequency includes a spread spectrum clock (SSC) generator that receives an input clock signal and generates a frequency-modulated clock signal, and a zero-delay buffer circuit that receives and buffers said modulated clock frequency signed to generated an output clock signal. The frequency-modulated clock signal and the output clock signal are phase-aligned such that there is no phase difference between the output clock signal and the modulated frequency clock signal. The clock recovery circuit also includes a delay-locked loop (DLL) circuit that reduces related art jitter and skew characteristics, and a phase detector circuit that eliminates phase ambiguity problems of a related art phase detector.

Owner:ANAPASS

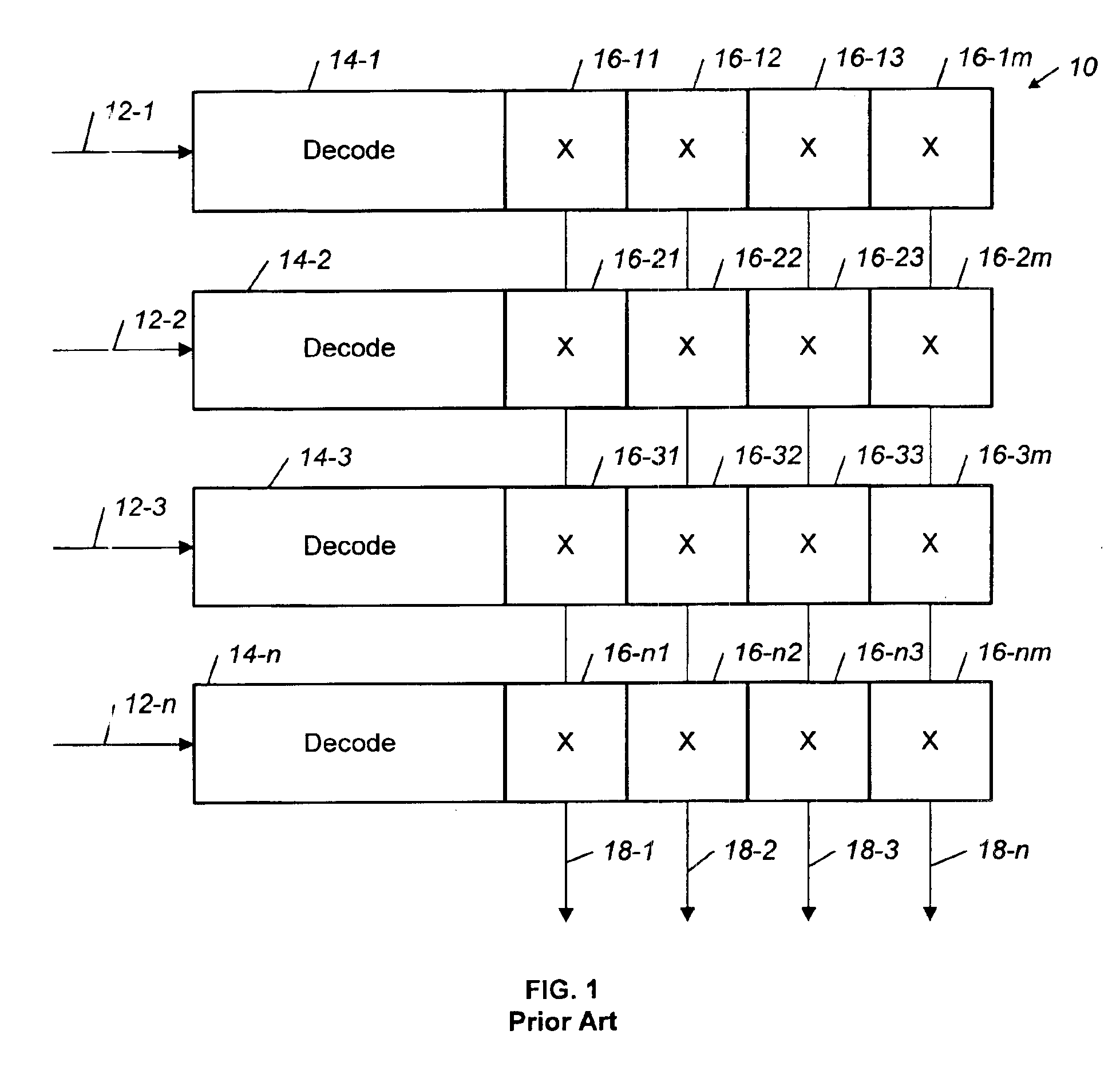

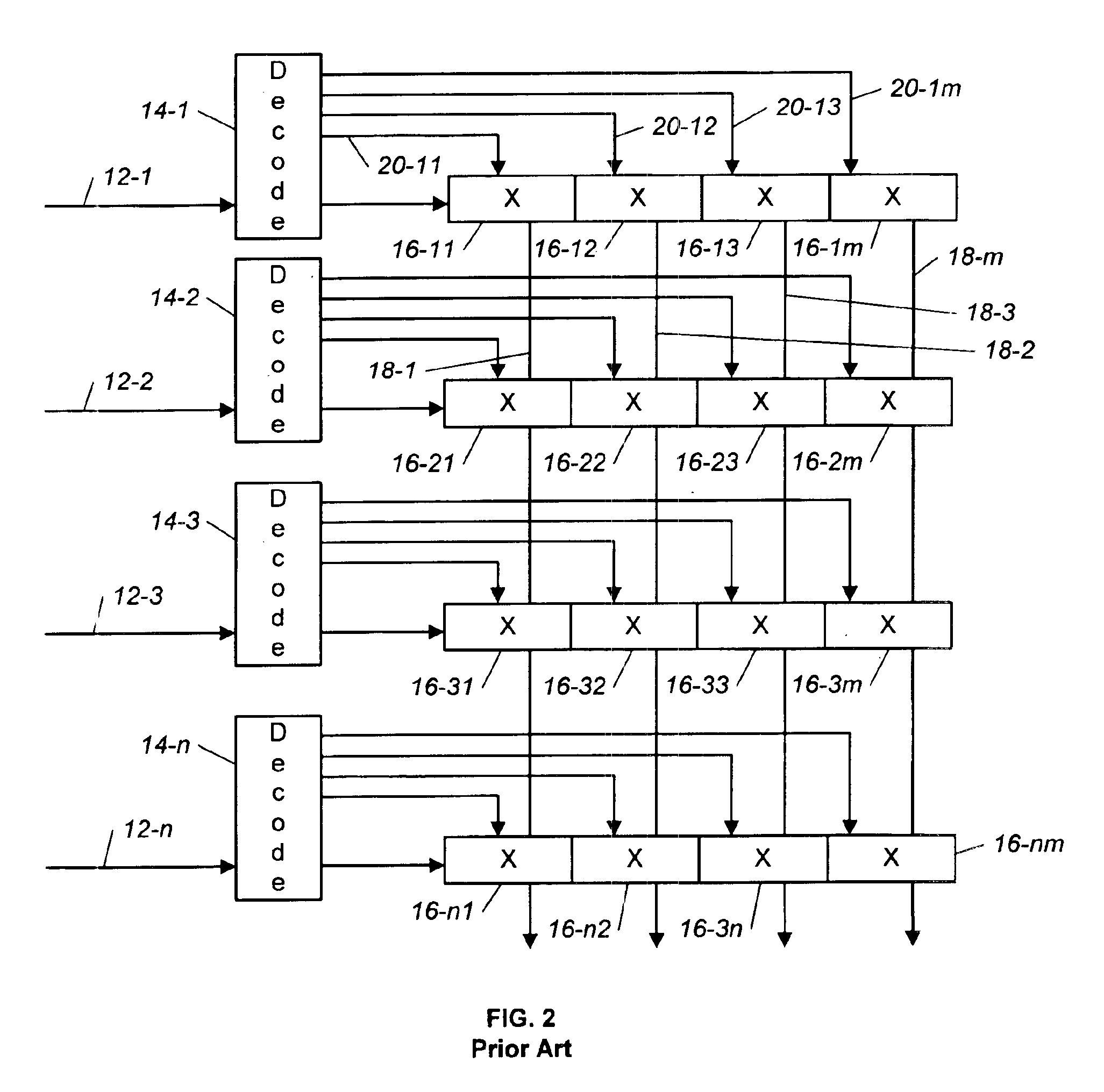

Scalable self-routing superconductor switch

A crossbar switch includes a cross-point matrix with n input rows of cross-points and m output columns of cross-points. The crossbar switch further includes n decoders connected to the n input rows. Each of the n rows includes a single serial address input, a shift input and a data input. A serial address and data enter the address input and the data input in parallel. A shift sequence is transmitted on the single shift input. The data flows before the shift sequence on the shift input is complete. The data is shifted through the crossbar switch using a clock that is generated on-chip using a clock recovery circuit. The decoder converts a binary address input into a serial address and includes an N-bit counter with a plurality of toggle flip-flops. The crossbar switch is implemented using superconductor digital electronics such as rapid single flux quantum (RSFQ) logic.

Owner:NORTHROP GRUMAN CORP

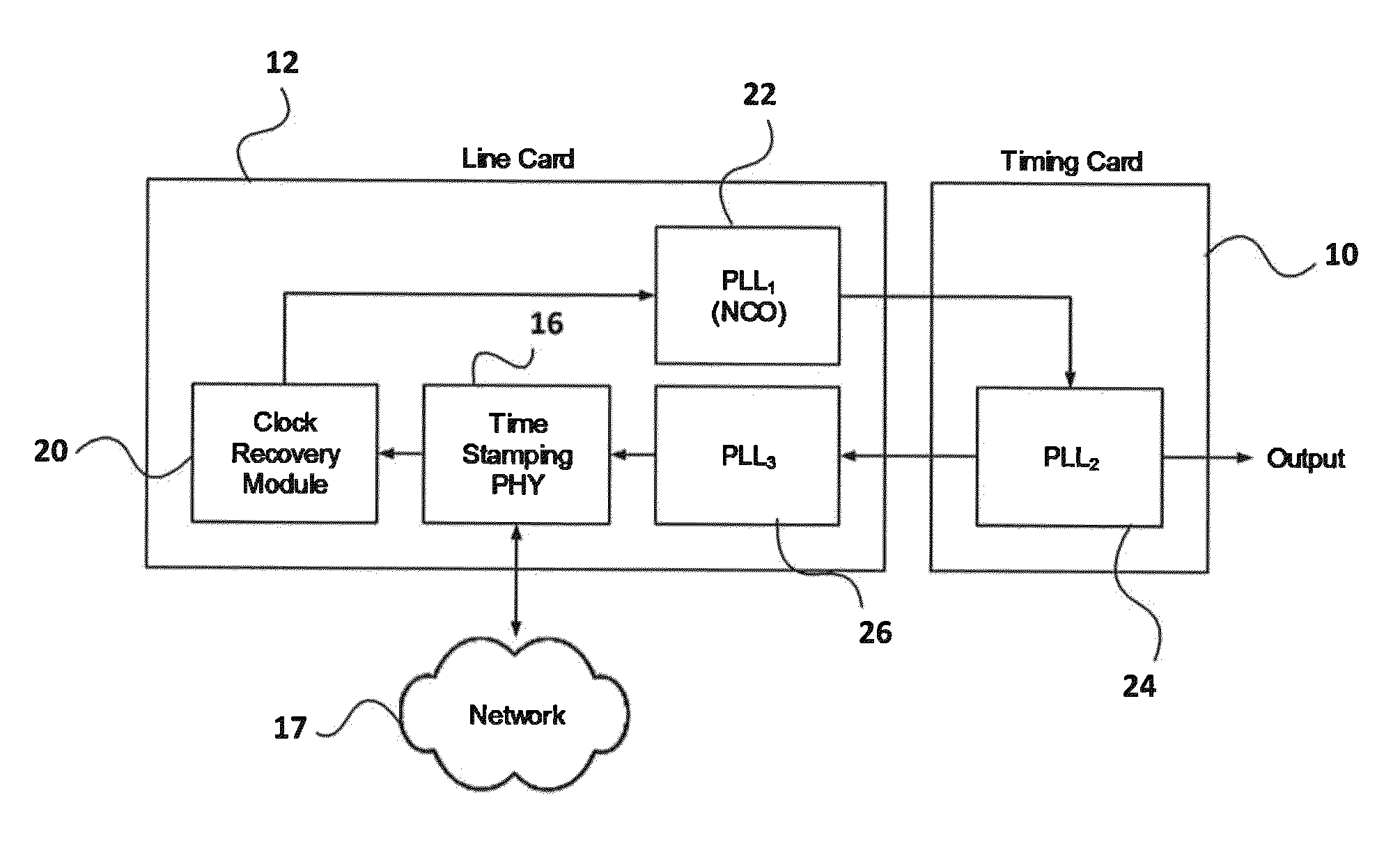

Network interface with clock recovery module on line card

Owner:MICROSEMI SEMICON

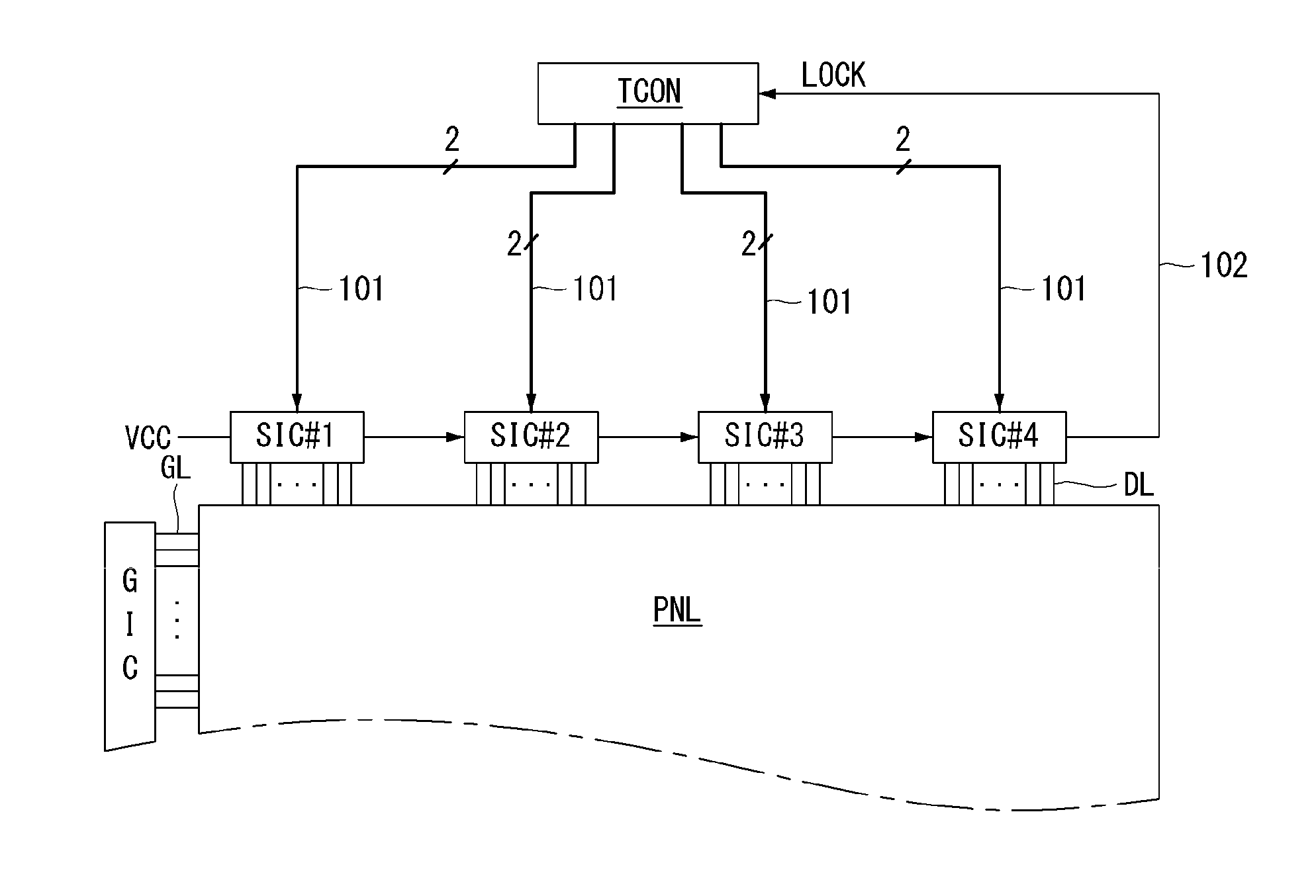

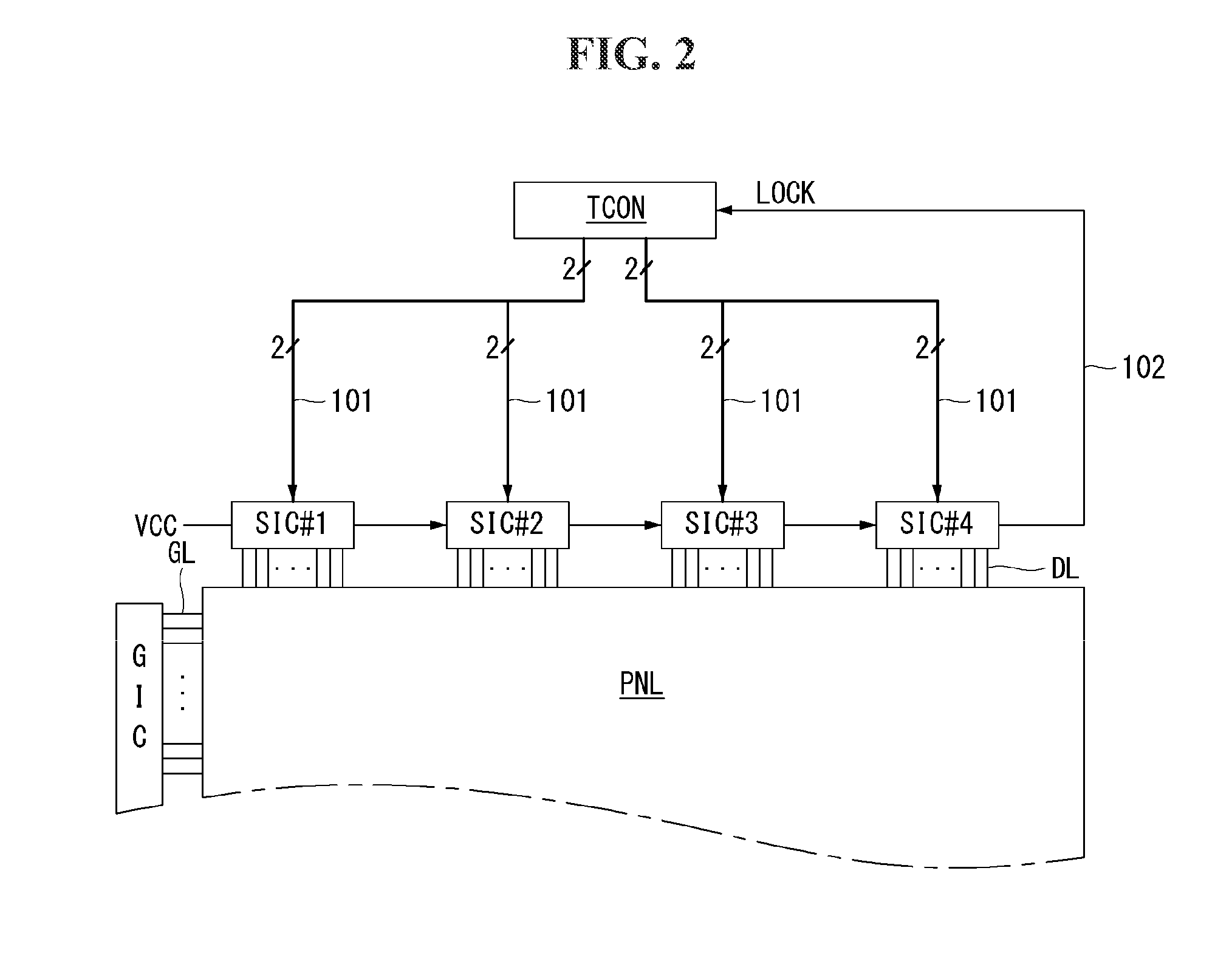

Display device and method for driving the same

A display device includes a source driver integrated circuit (IC) including an equalizer for boosting a data signal received through a pair of signal lines depending on an equalization (EQ) setting value and a clock recovery circuit recovering a clock of the data signal, and a timing controller, which is connected to the source driver IC through the signal line pair and transmits the data signal to the source driver IC. The source driver IC samples the data signal in conformity with a timing of an internal clock output when the clock recovery circuit is in a lock state. The source driver IC further includes an equalizer control circuit for initializing the equalizer when the clock recovery circuit is in an unlock state and the EQ setting value is changed.

Owner:LG DISPLAY CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com