Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5958 results about "Logic circuitry" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A logic circuit is a circuit that performs a processing or controlling function in a computer. This circuit carries out logical operations on information to process it.

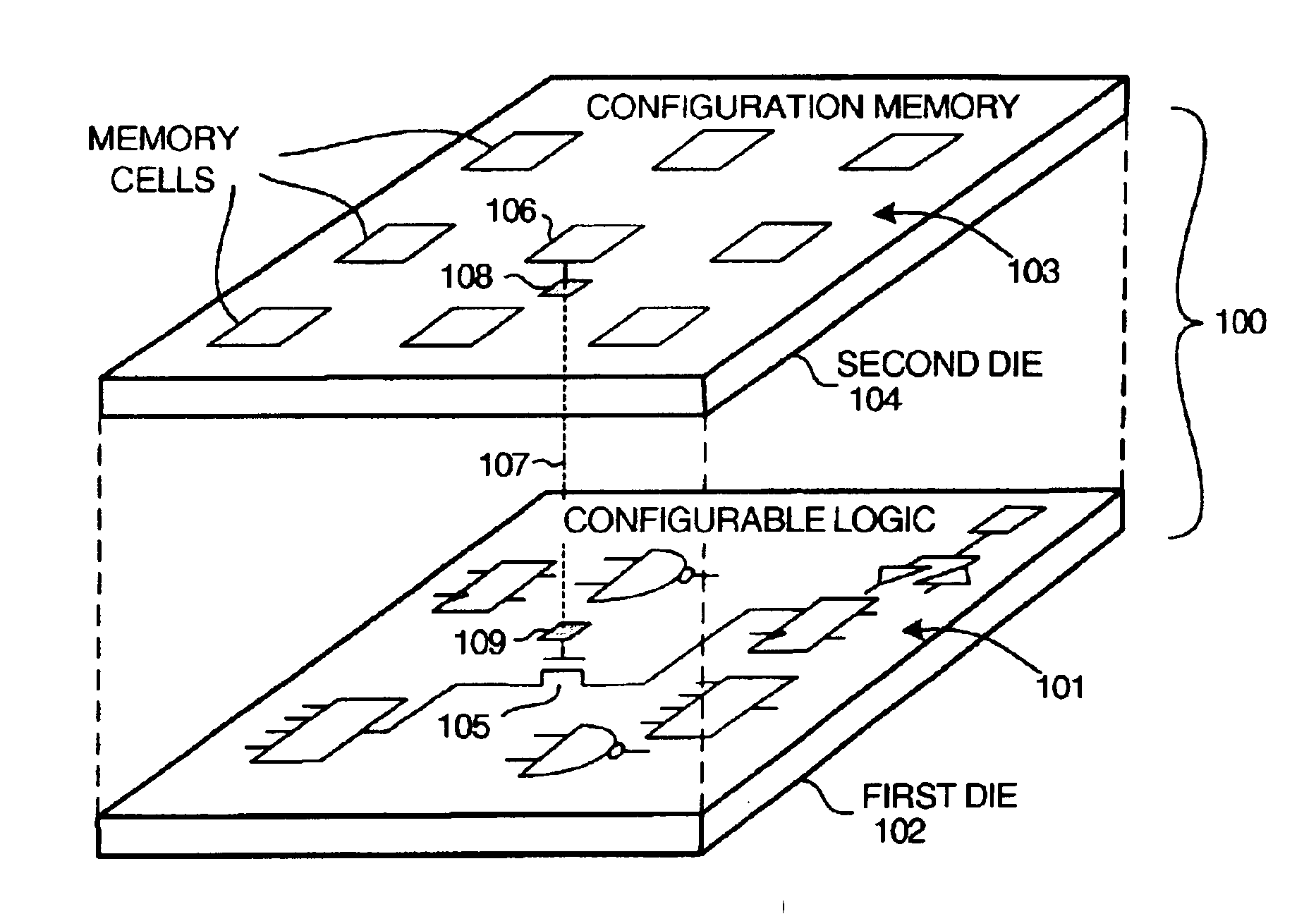

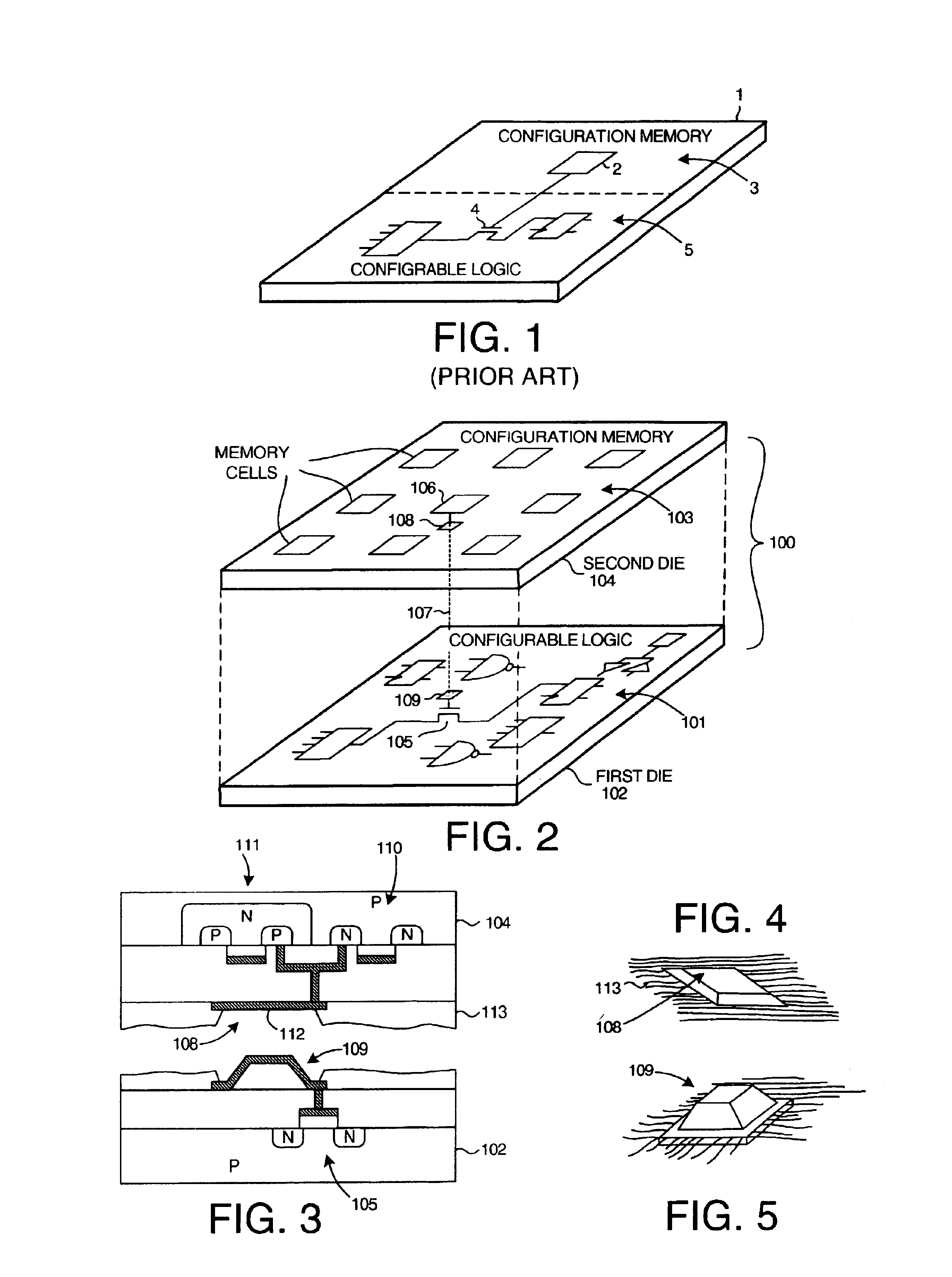

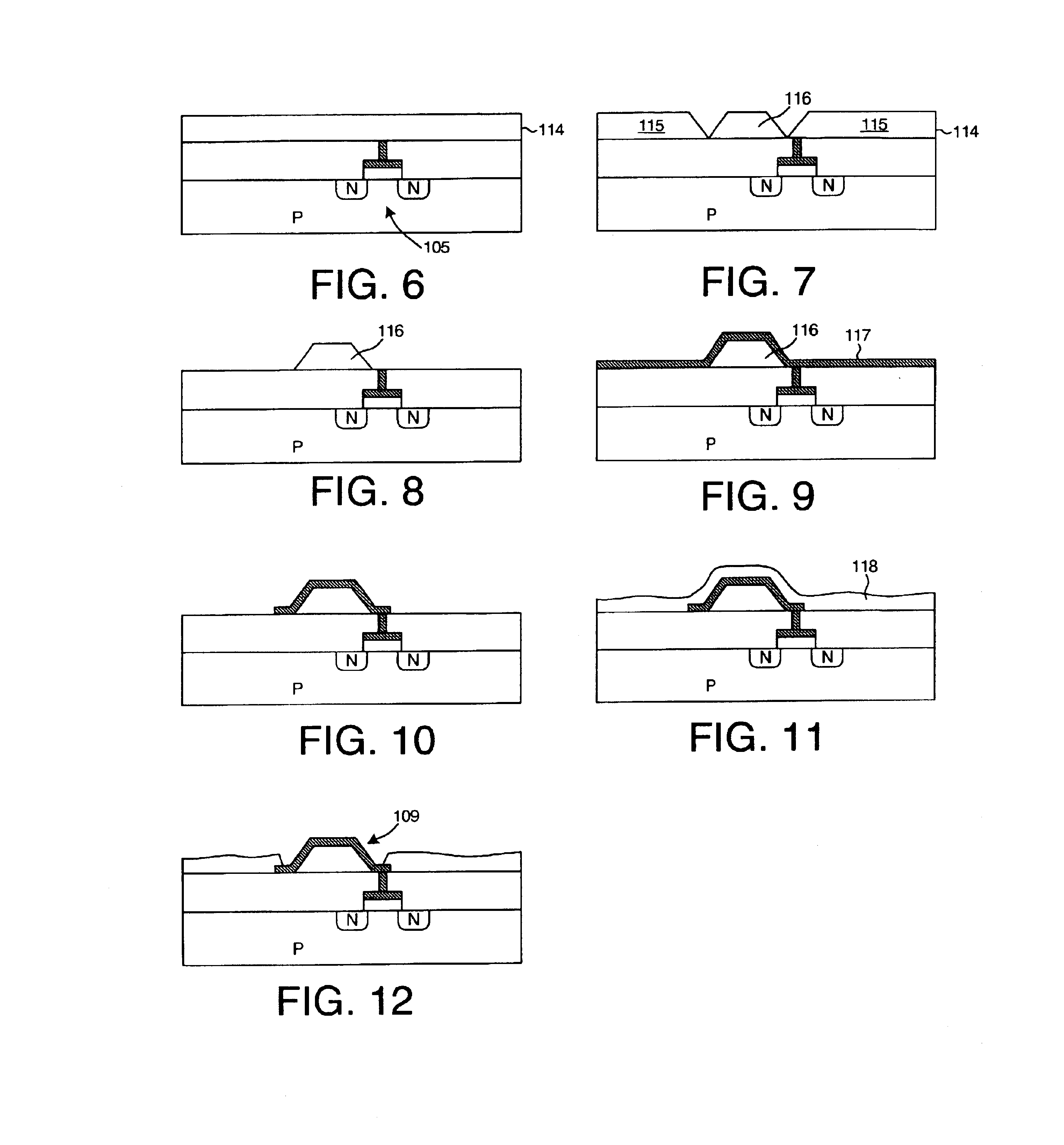

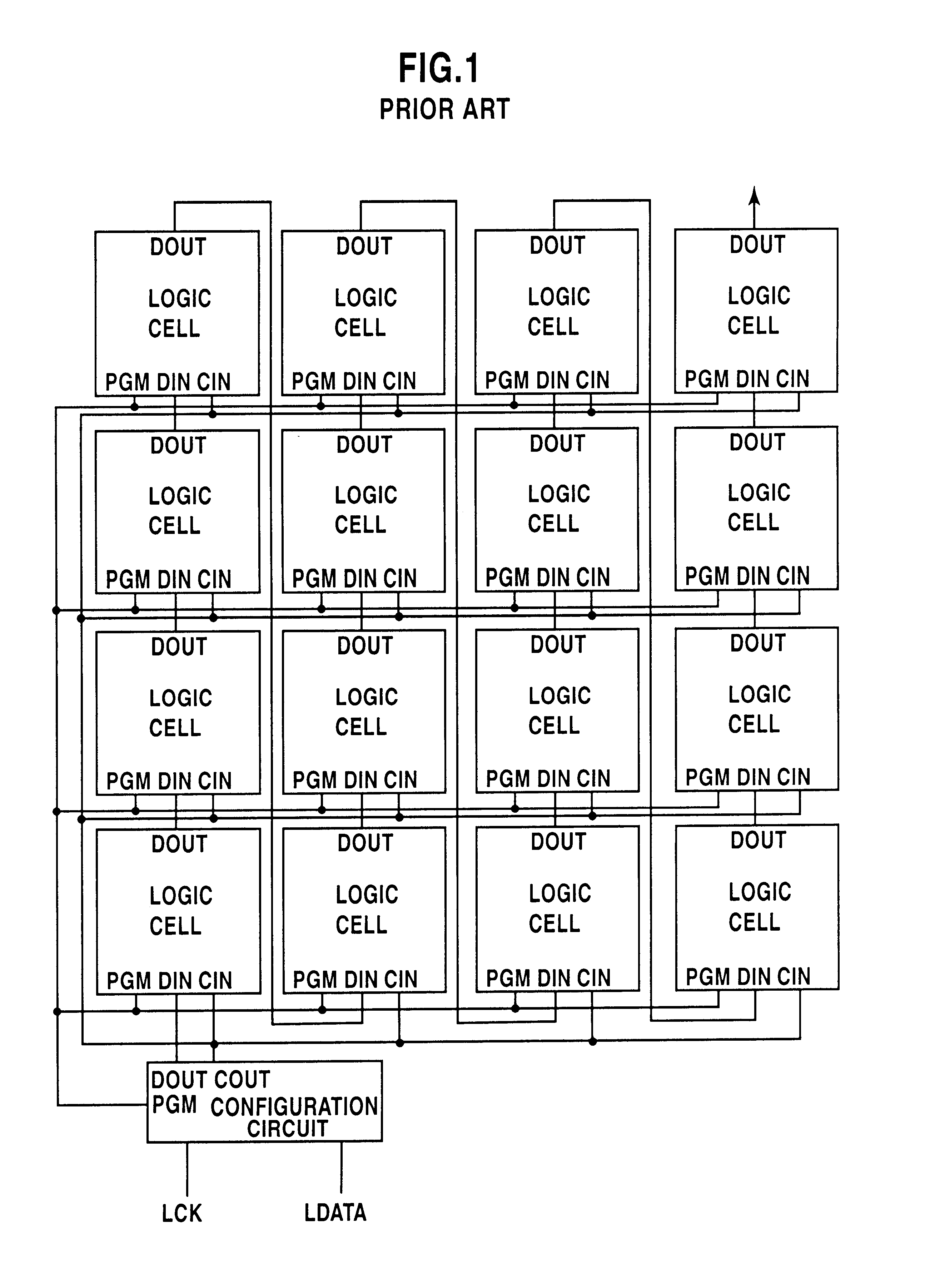

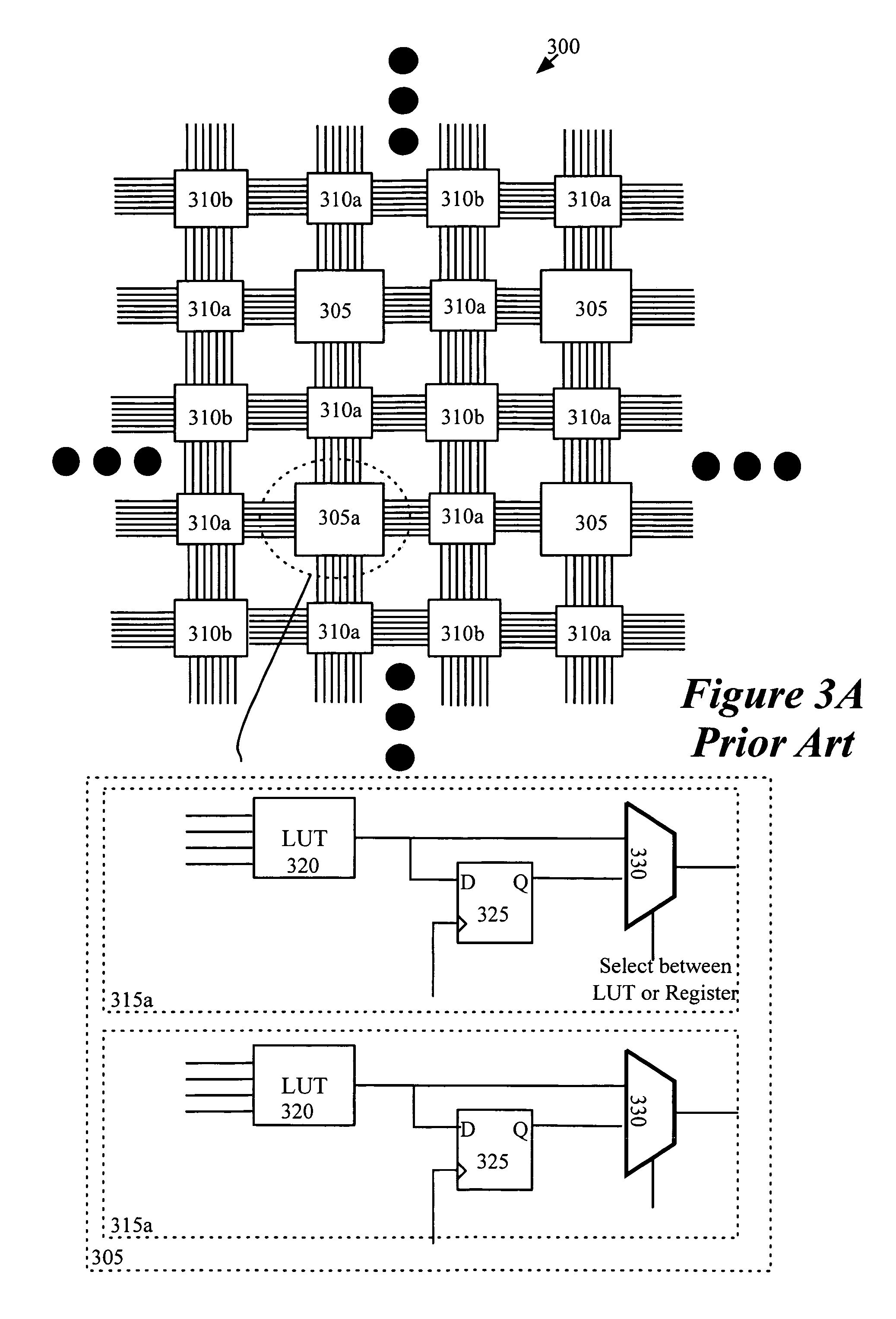

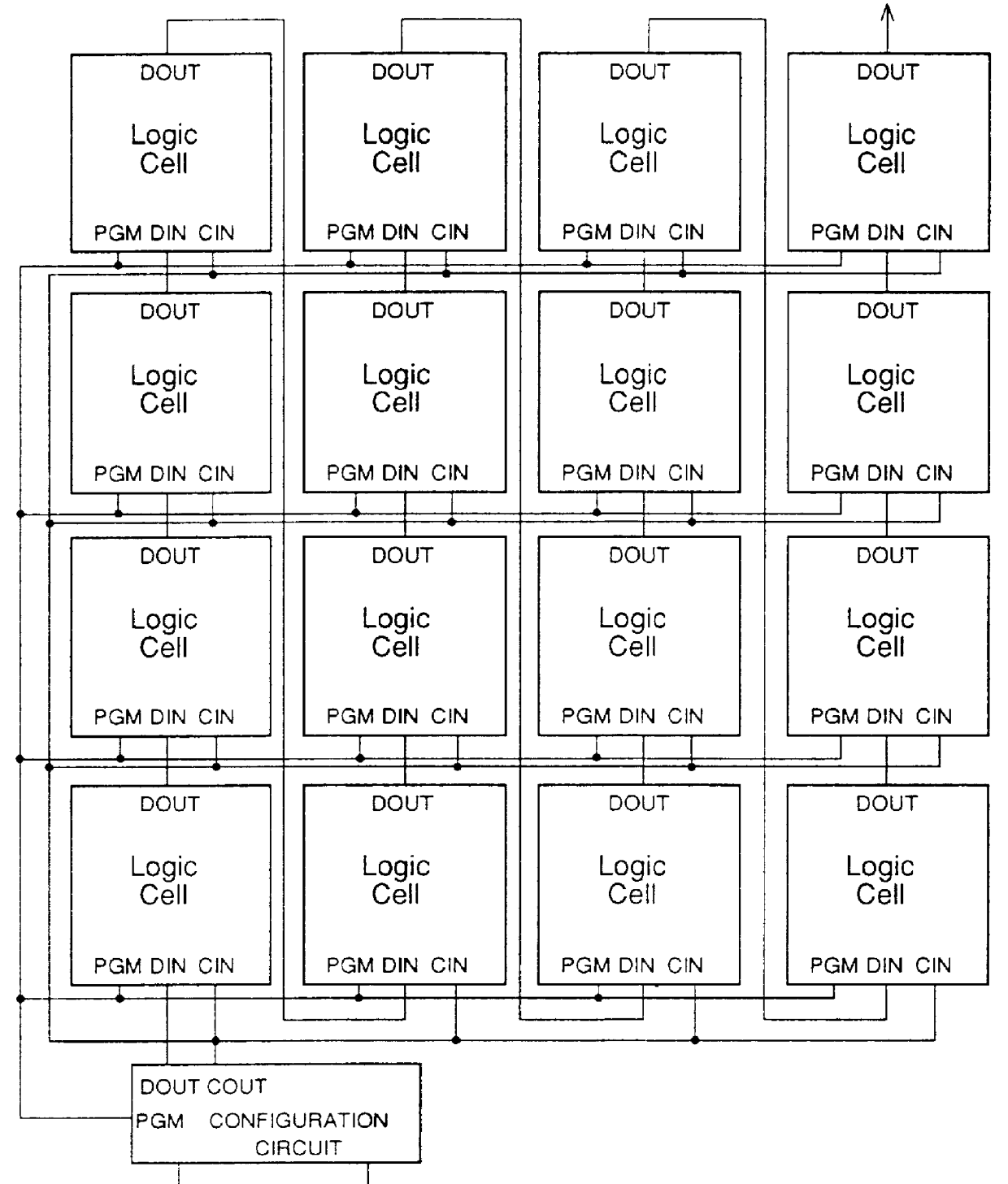

Multi-chip programmable logic device having configurable logic circuitry and configuration data storage on different dice

InactiveUS6917219B2Increase volumeIncrease productionSemiconductor/solid-state device detailsSolid-state devicesProgrammable logic deviceLogical part

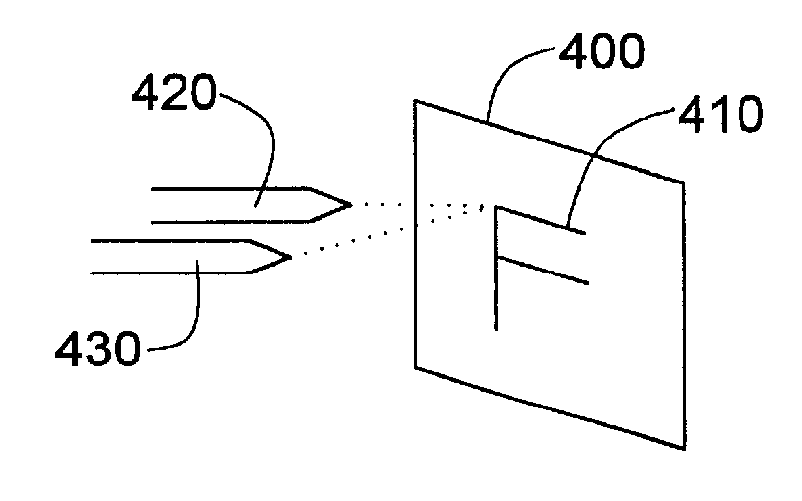

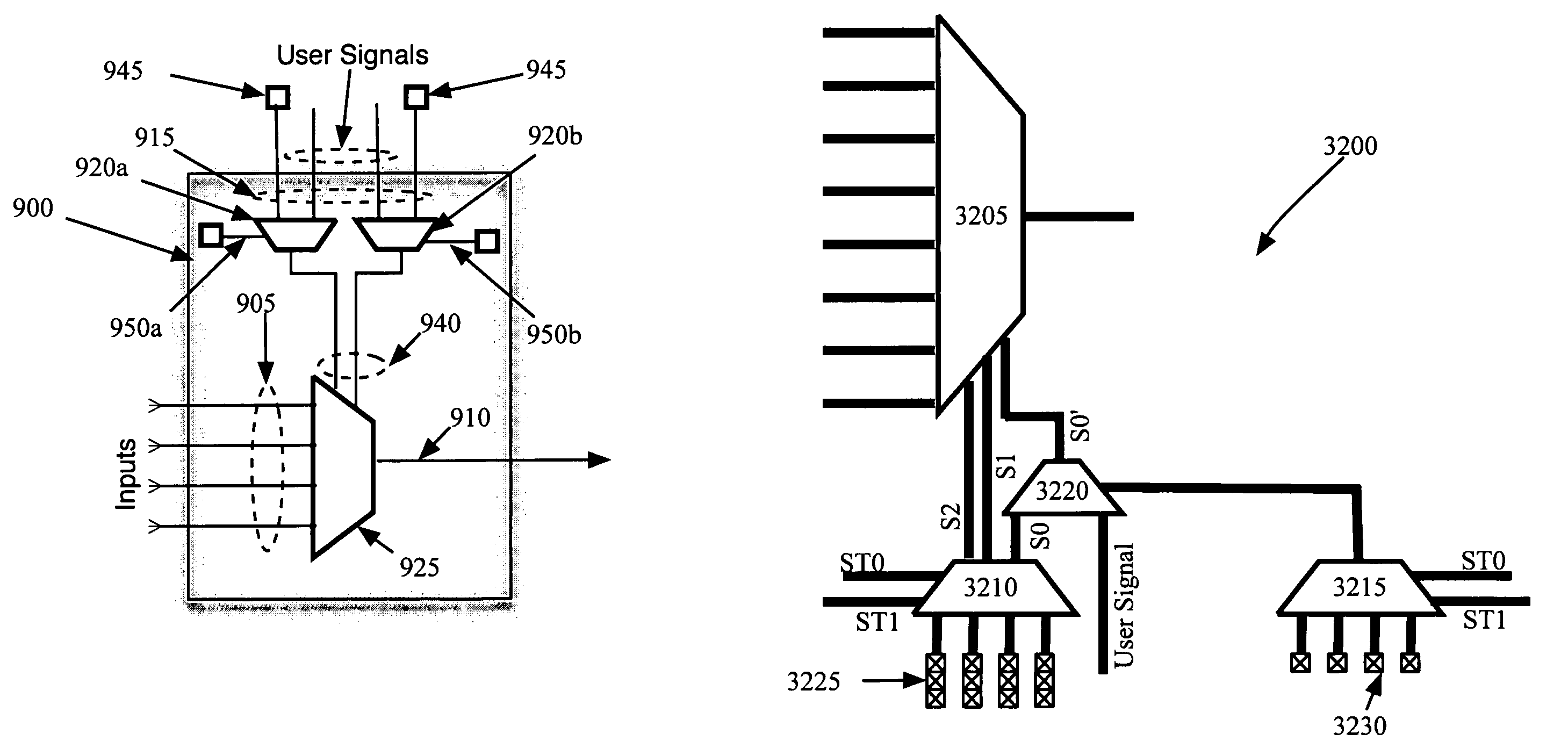

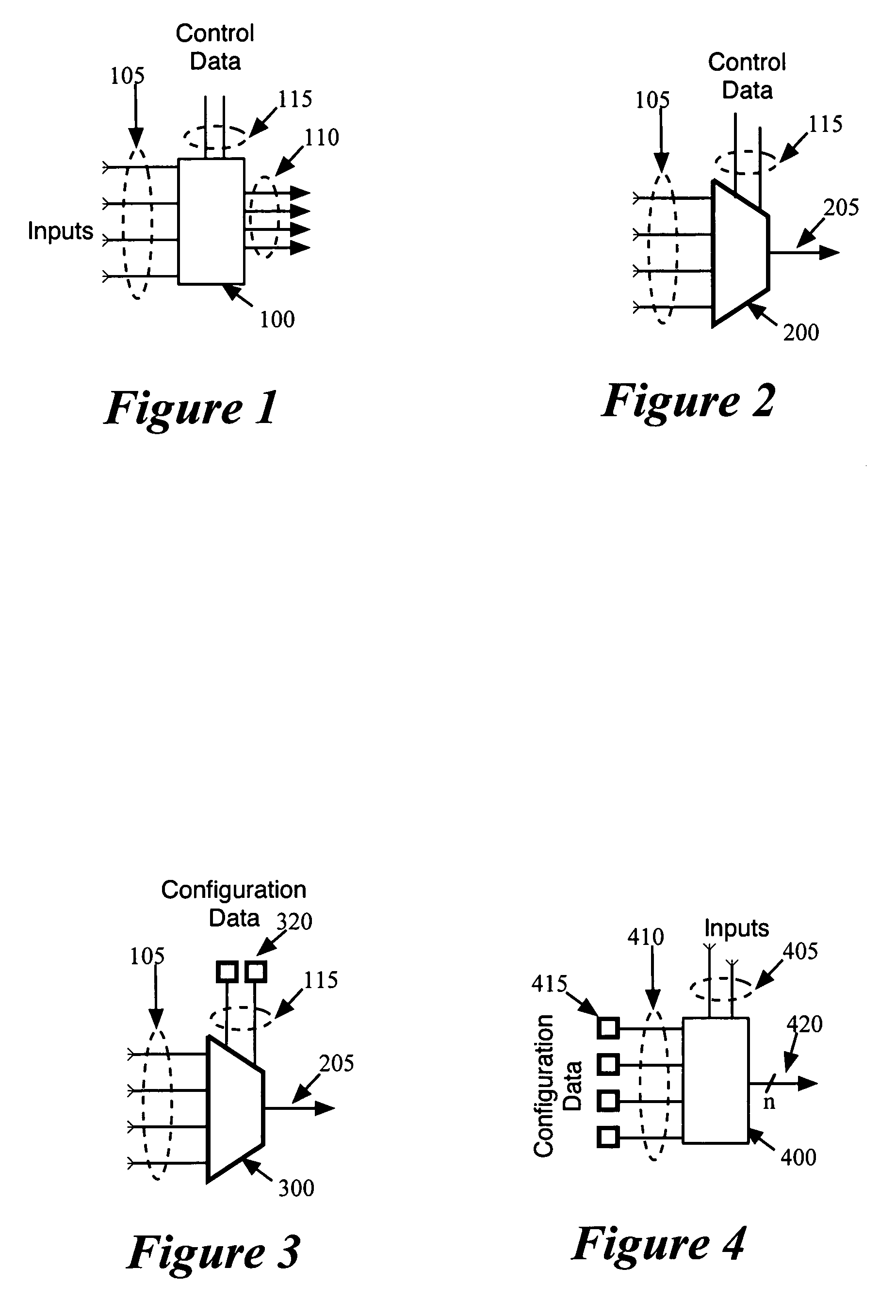

The circuitry of a programmable logic device (for example, an FPGA) includes a configurable logic portion and a configuration memory. The configuration memory stores configuration data that configures the configurable logic portion to realize a user-defined circuit. The configurable logic portion is disposed on a first die whereas the configuration memory is disposed on a second die. The second die is bonded to the first die in stacked relation. Each bit of configuration data passes from the second die to the first die through a pair of micropads. One micropad of the pair is disposed on the first die and the other micropad of the pair is disposed on the second die. When the first die and second die are brought together in face-to-face relation, the two micropads form an electrical connection through which the configuration data bit passes from the second die to the first die.

Owner:XILINX INC

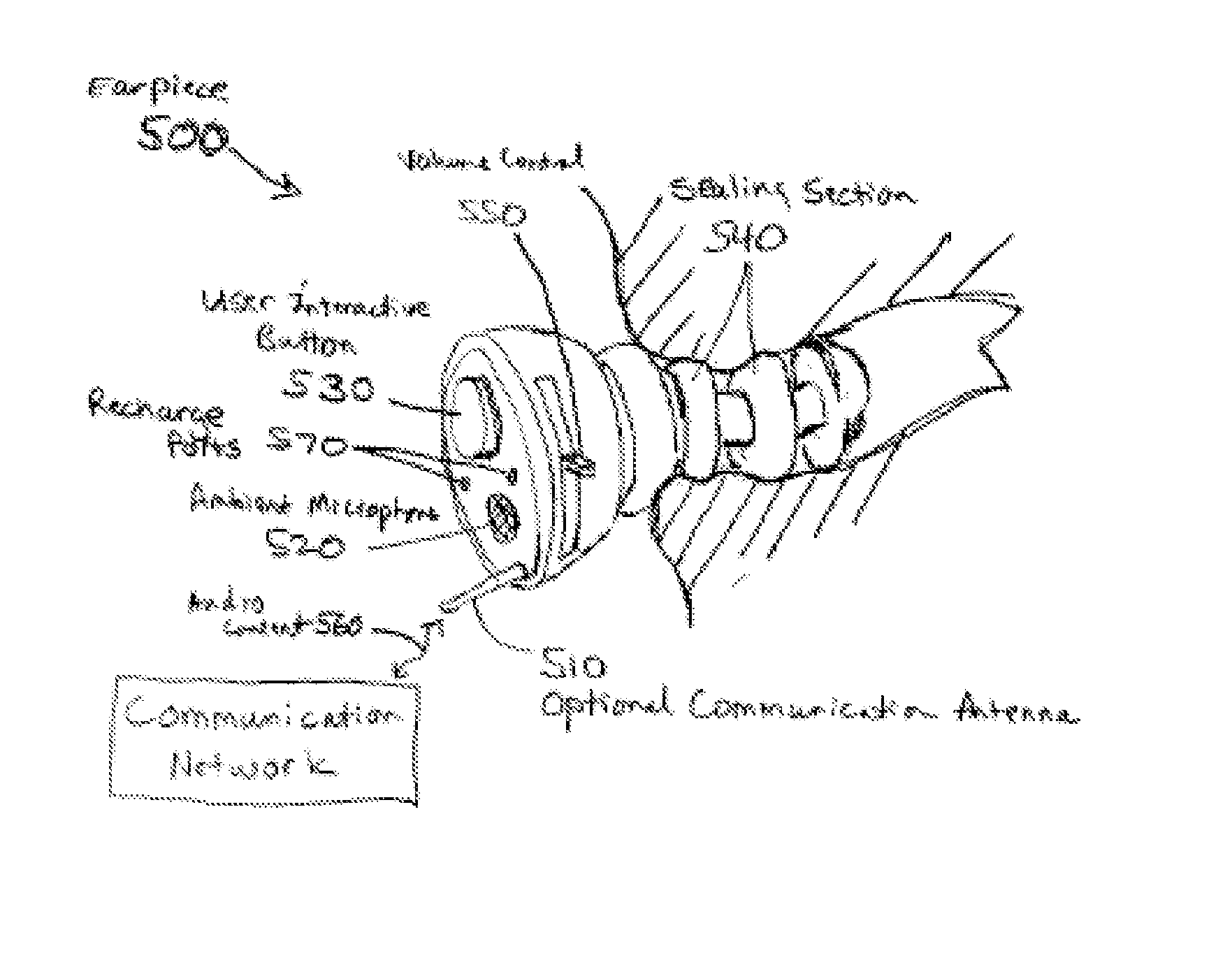

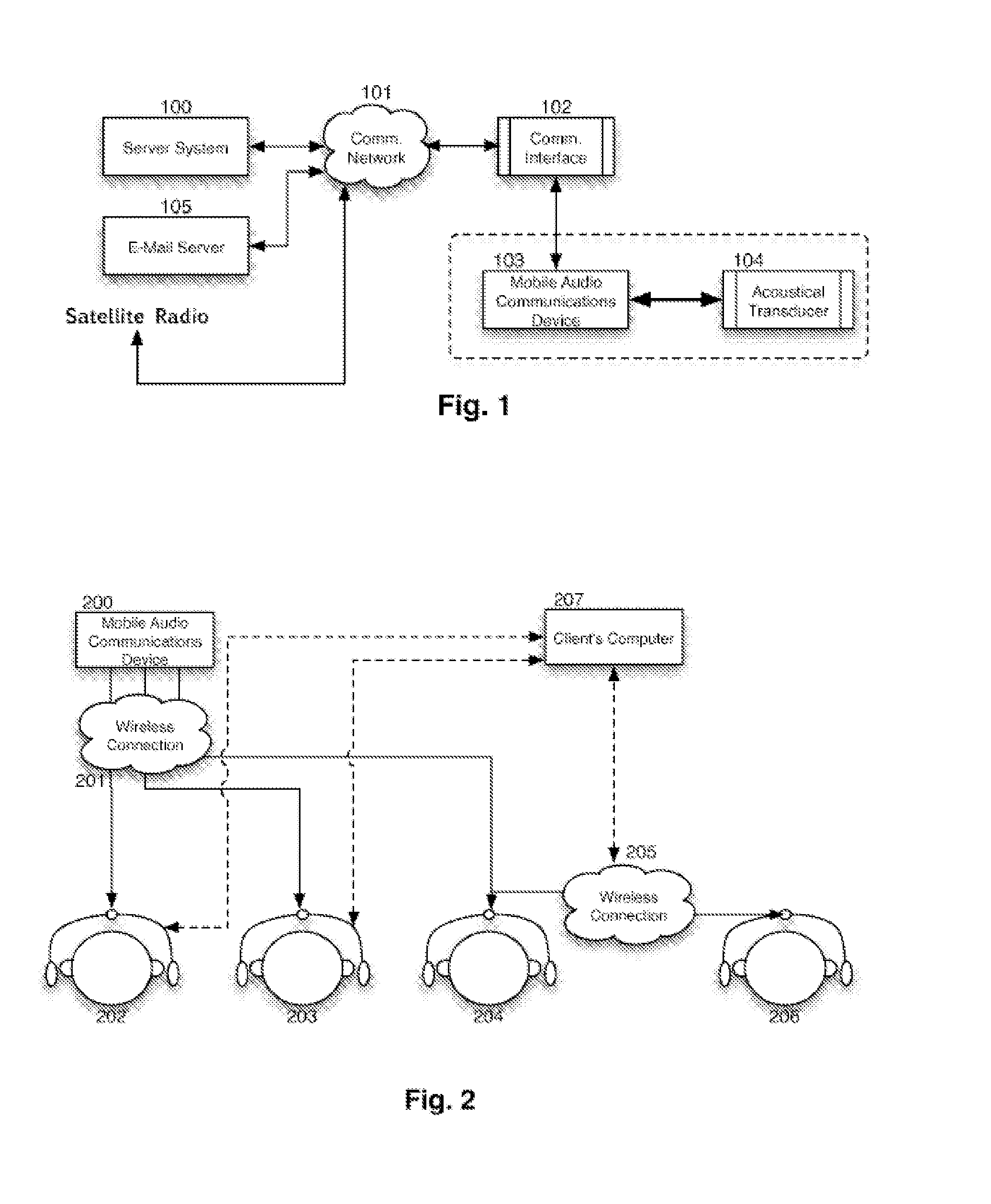

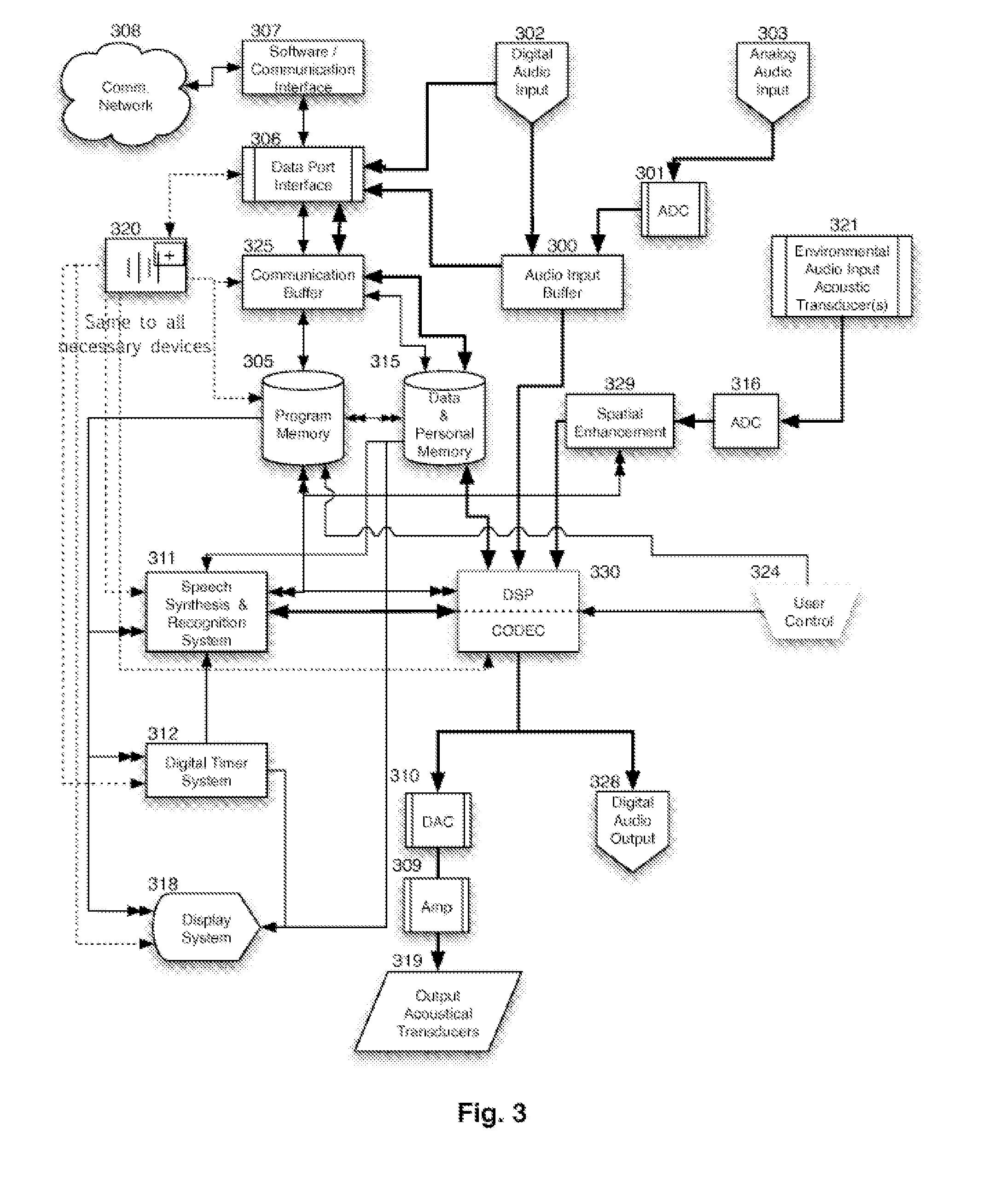

Personal audio assistant device and method

At least one exemplary embodiment is directed to an earpiece comprising: an ambient microphone; an ear canal microphone; an ear canal receiver; a sealing section; a logic circuit; a communication module; a memory storage unit,; and a user interaction element, where the user interaction element is configured to send a play command to the logic circuit when activated by a user where the logic circuit reads registration parameters stored on the memory storage unit and sends audio content to the ear canal receiver according to the registration parameters.

Owner:STATON TECHIYA LLC

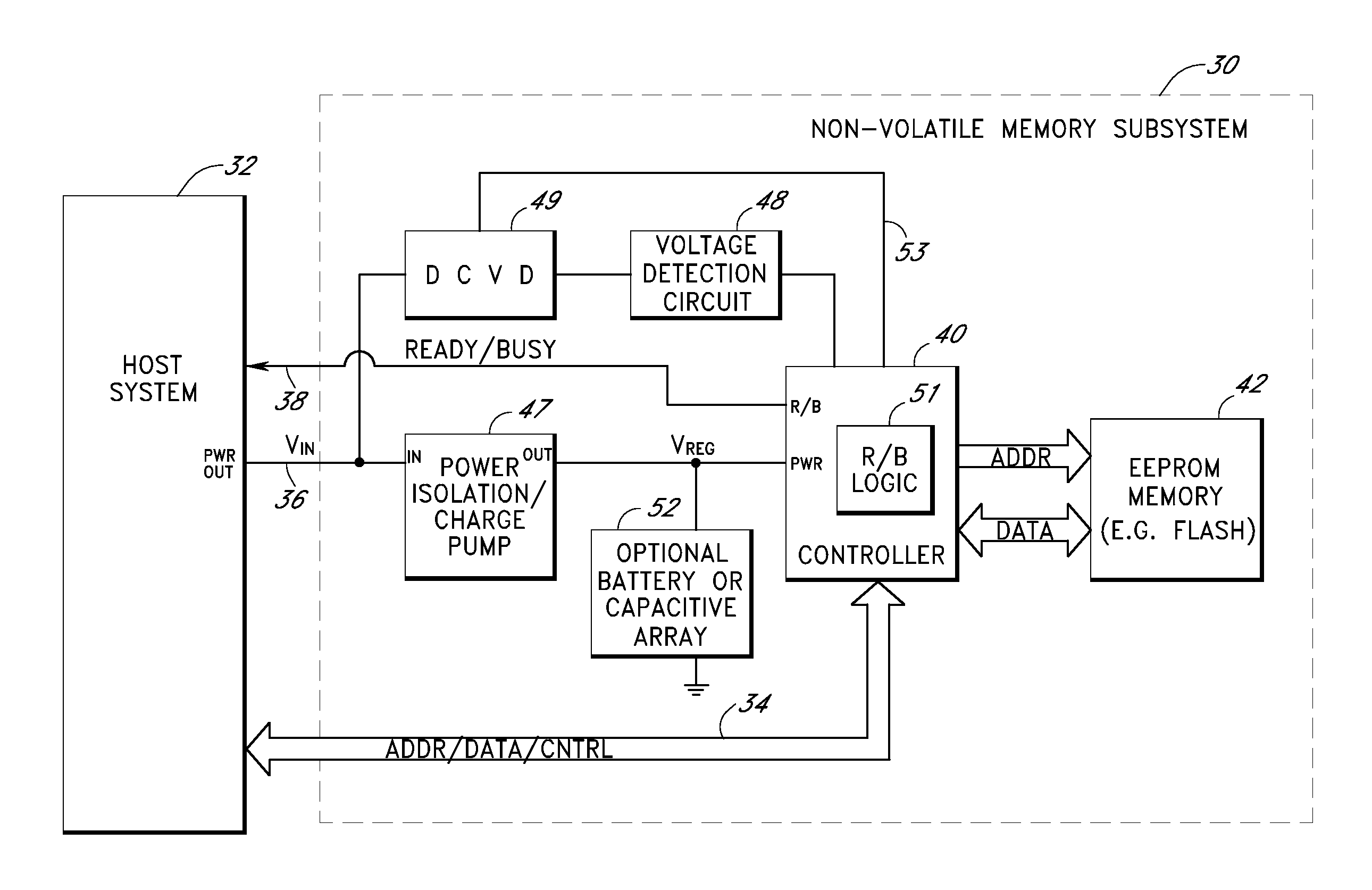

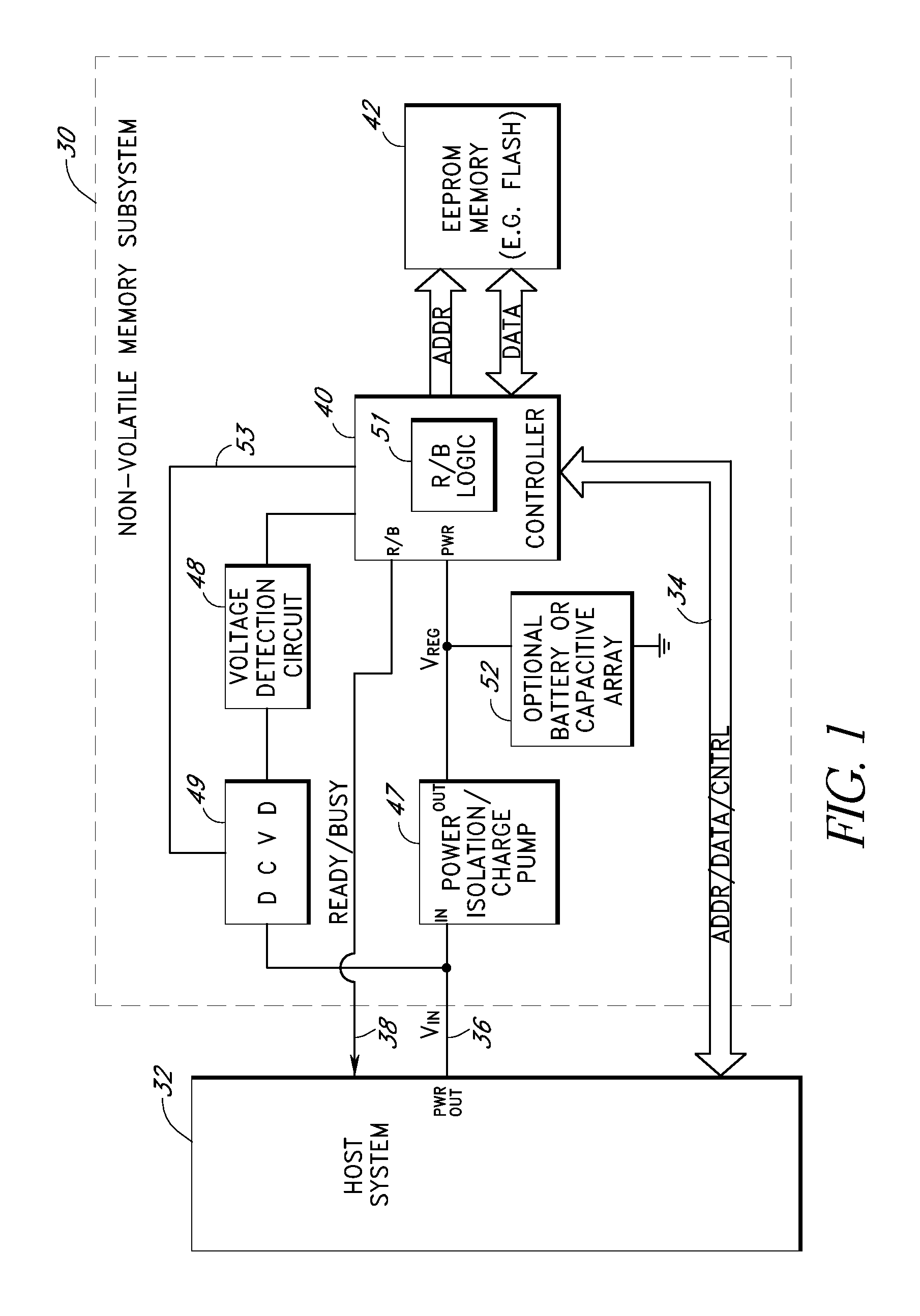

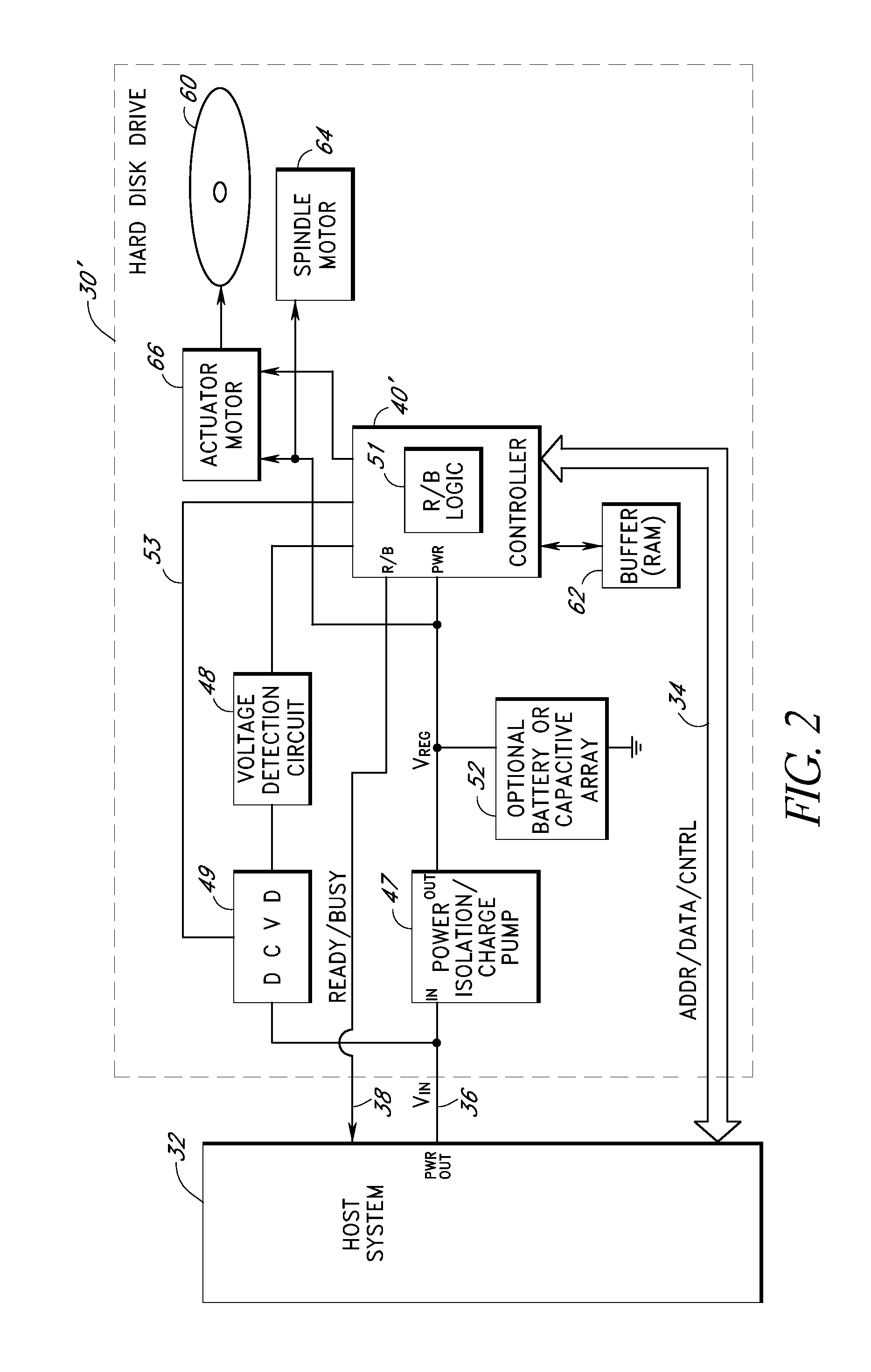

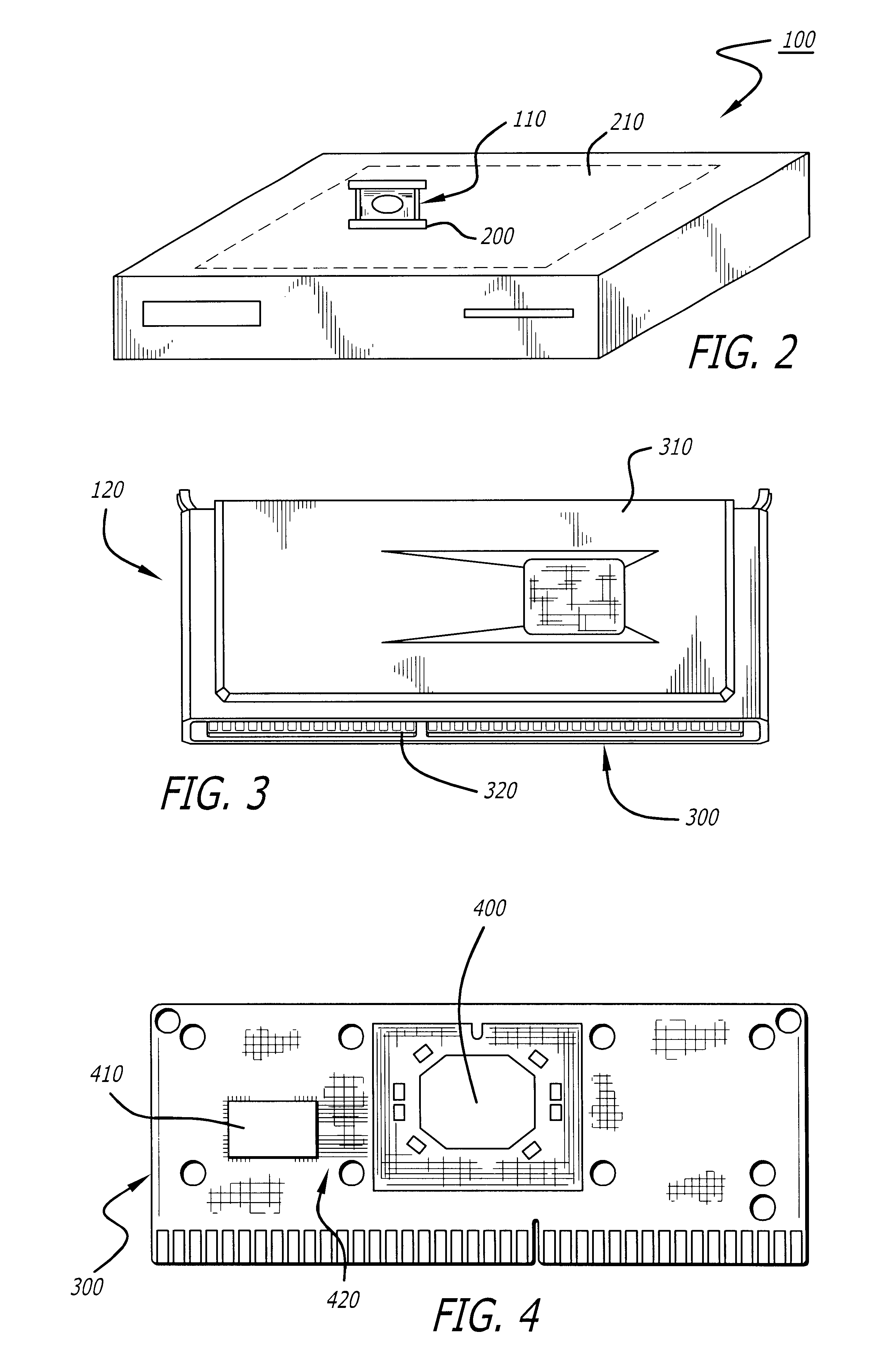

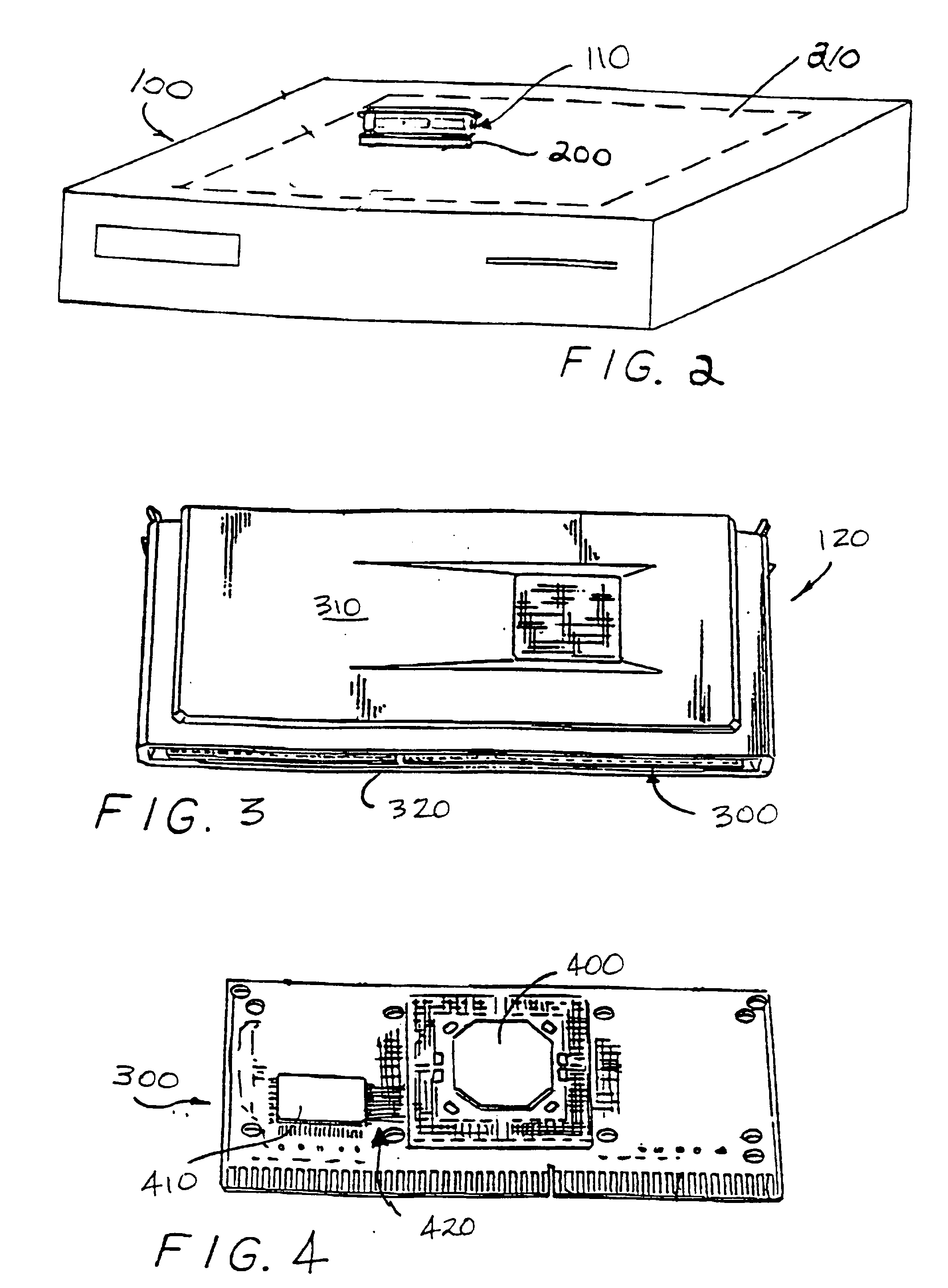

Storage subsystem with embedded circuit for protecting against anomalies in power signal from host

ActiveUS7733712B1Extended runtimeProvide powerRead-only memoriesDigital storageStandby powerEngineering

A storage subsystem includes a charge pump that receives a power signal from a host system, and generates a regulated power signal that is provided to the storage subsystem's controller. When the power signal from the host is interrupted, the charge pump additionally acts as a backup power supply to enable the storage subsystem to continue to operate temporarily, and power isolation circuitry in the storage subsystem prevents power from flowing back to the host system. The storage subsystem further includes a digitally programmable voltage detection circuit that accepts various supply voltages and asserts a busy signal to the controller when an anomaly in the power signal is detected. The controller includes logic circuitry that will block the host system from performing write operations to the storage subsystem either when the voltage detection circuit asserts a busy signal or when the controller is busy executing memory operation commands.

Owner:WESTERN DIGITAL TECH INC

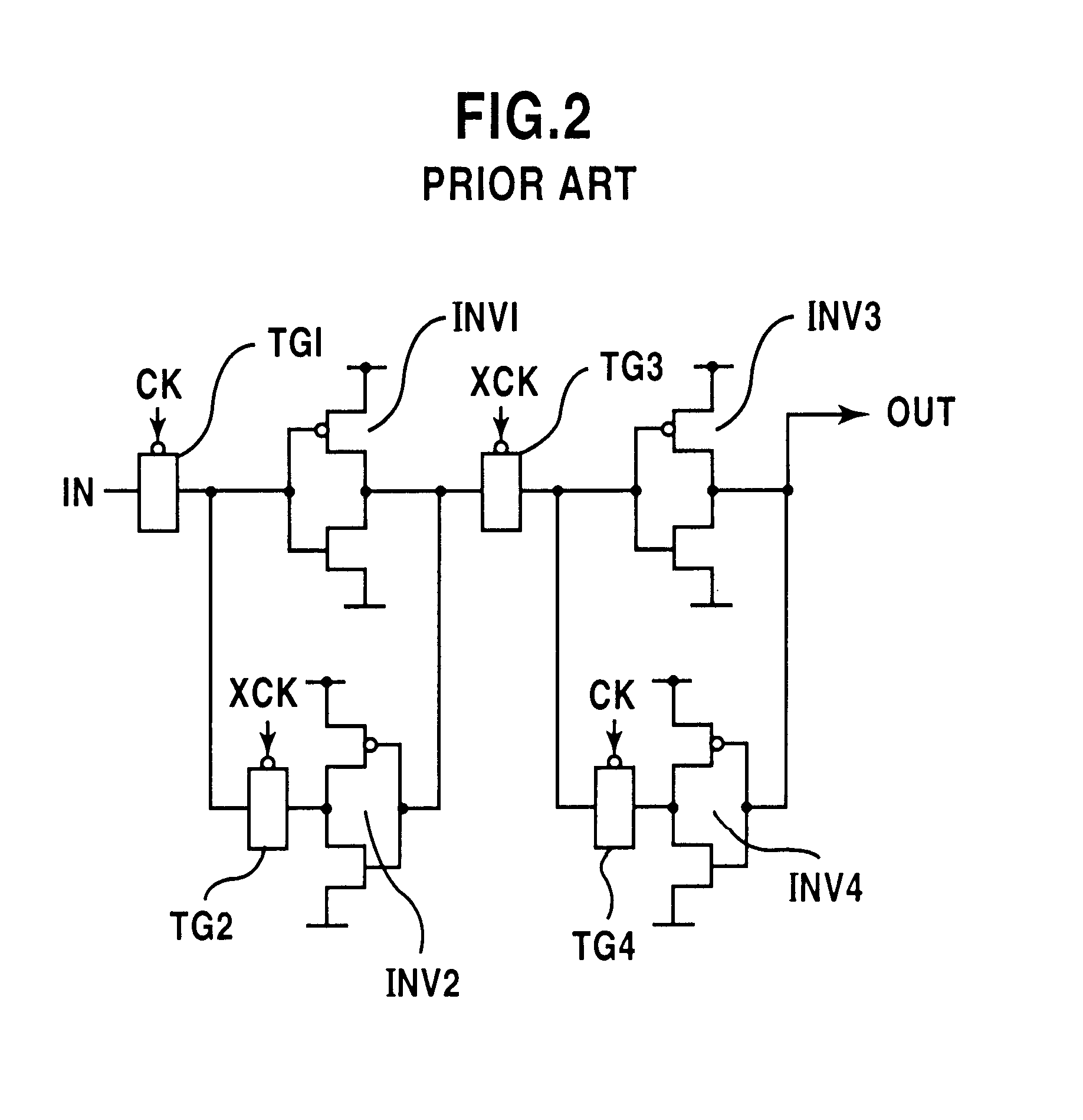

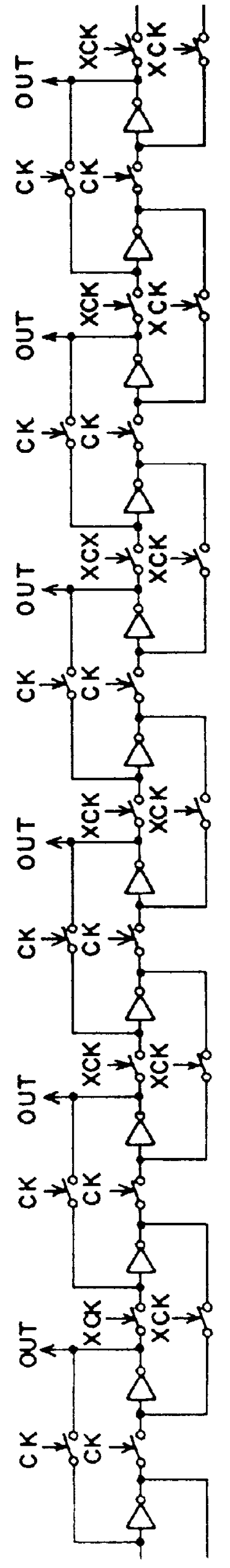

Chain-connected shift register and programmable logic circuit whose logic function is changeable in real time

A shift register having a plurality of circuit cells successively connected in a chain formation is proposed. Each of the circuit cells includes a first inversion gate, a first transmission gate, connected to an output of the first inversion gate, being switched by a clock, and a second inversion gate connected to an output of the first transmission gate. The circuit cell further includes a first P-channel transistor, connected between an output of the second inversion gate and an input of the first inversion gate, being switched by the clock, a second transmission gate, connected to the output of the second inversion gate, being switched by an inversion clock, and a second P-channel transistor, connected to the output of the first transmission gate, being switched by the inversion clock. In the shift register, the plurality of circuit cells are successively connected such that the input of the first inversion gate of the circuit cell is connected to an output of a second transmission gate of a former-stage circuit cell, and the output of the first inversion gate of the circuit cell is connected to an output of a second P-channel transistor of the former-stage circuit cell.

Owner:FUJITSU LTD

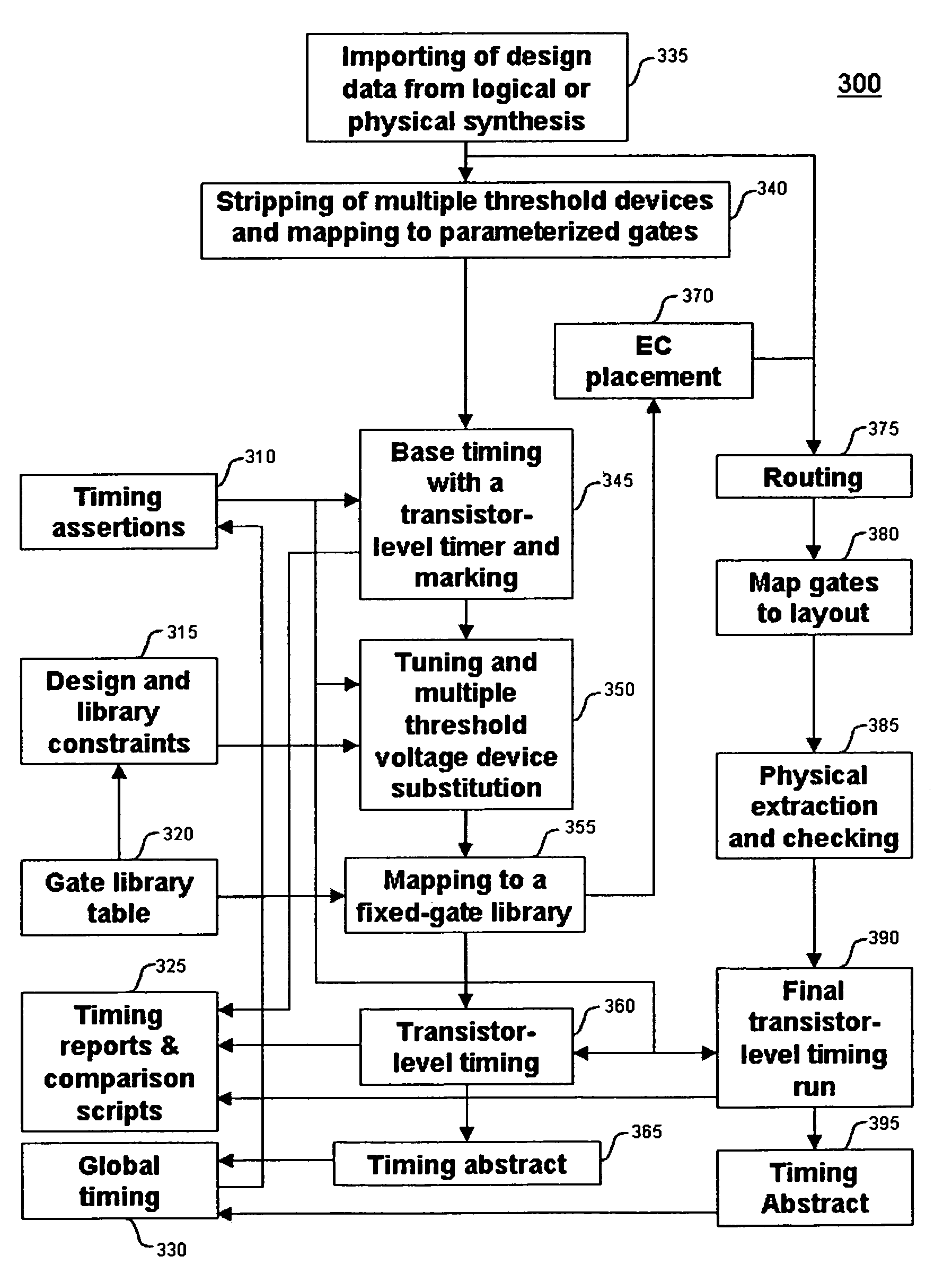

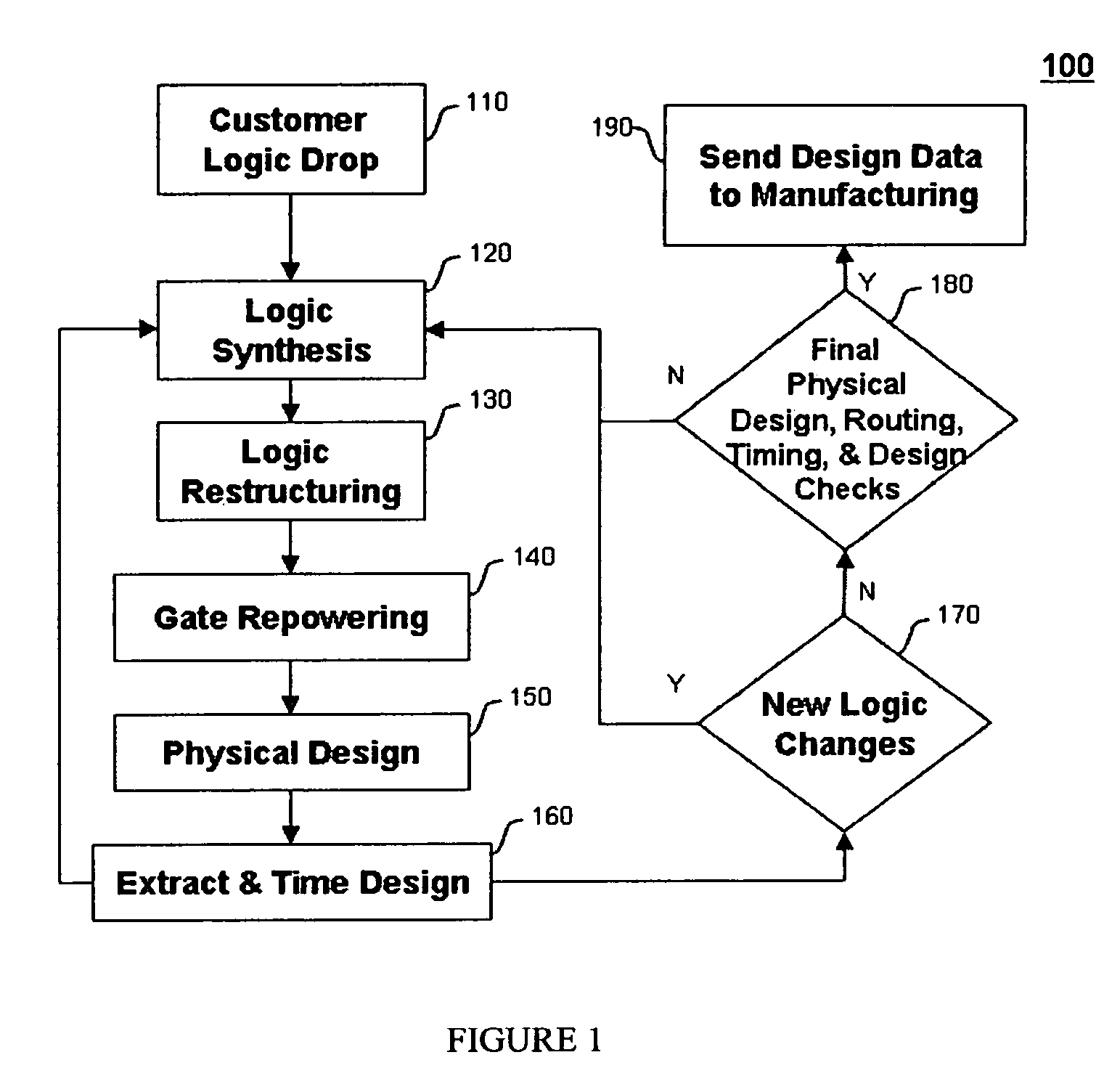

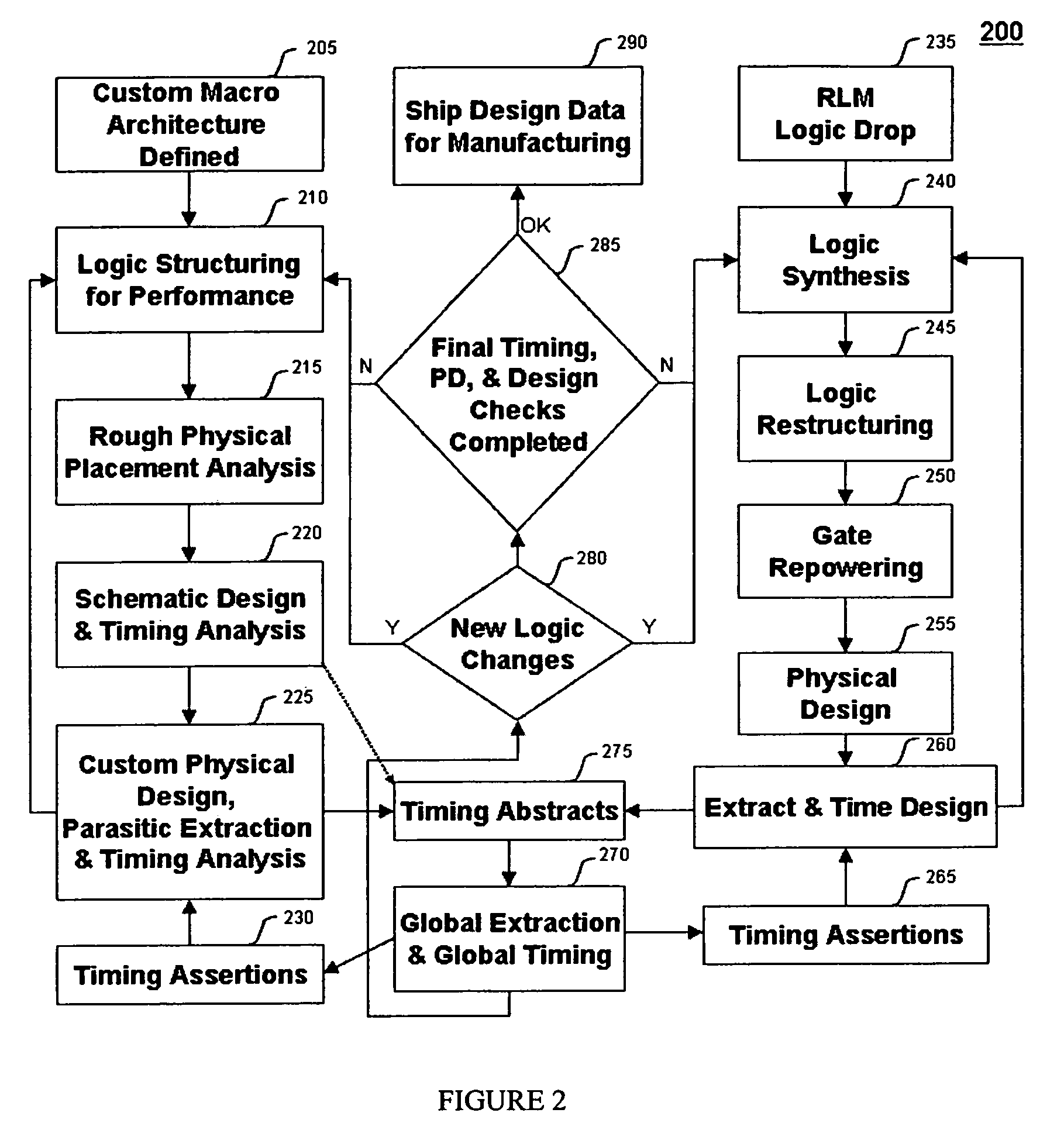

Method for tuning a digital design for synthesized random logic circuit macros in a continuous design space with optional insertion of multiple threshold voltage devices

InactiveUS7093208B2Efficient and effective methodologyError minimizationDigital storageComputer aided designContinuous designCritical section

A Digital Design Method which may be automated is for obtaining timing closure in the design of large, complex, high-performance digital integrated circuits. The methodincludes the use of a tuner on random logic macros that adjusts transistor sizes in a continuous domain. To accommodate this tuning, logic gates are mapped to parameterized cells for the tuning and then back to fixed gates after the tuning. Tuning is constrained in such a way as to minimize “binning errors” when the design is mapped back to fixed cells. Further, the critical sections of the circuit are marked in order to make the optimization more effective and to fit within the problem-size constraints of the tuner. A specially formulated objective function is employed during the tuning to promote faster global timing convergence, despite possibly incorrect initial timing budgets. The specially formulated objective function targets all paths that are failing timing, with appropriate weighting, rather than just targeting the most critical path. Finally, the addition of multiple threshold voltage gates allows for increased performance while limiting leakage power.

Owner:GLOBALFOUNDRIES INC

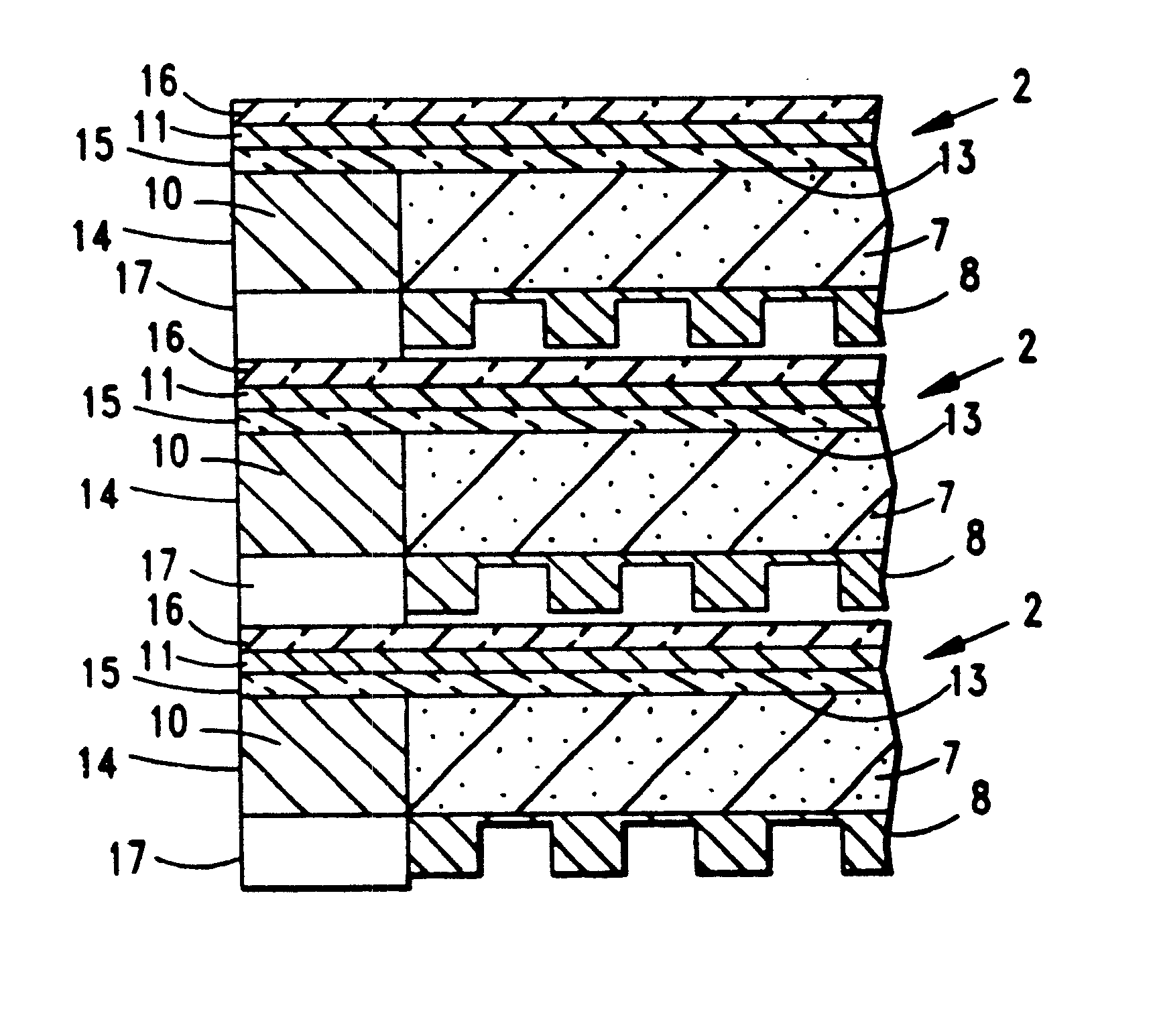

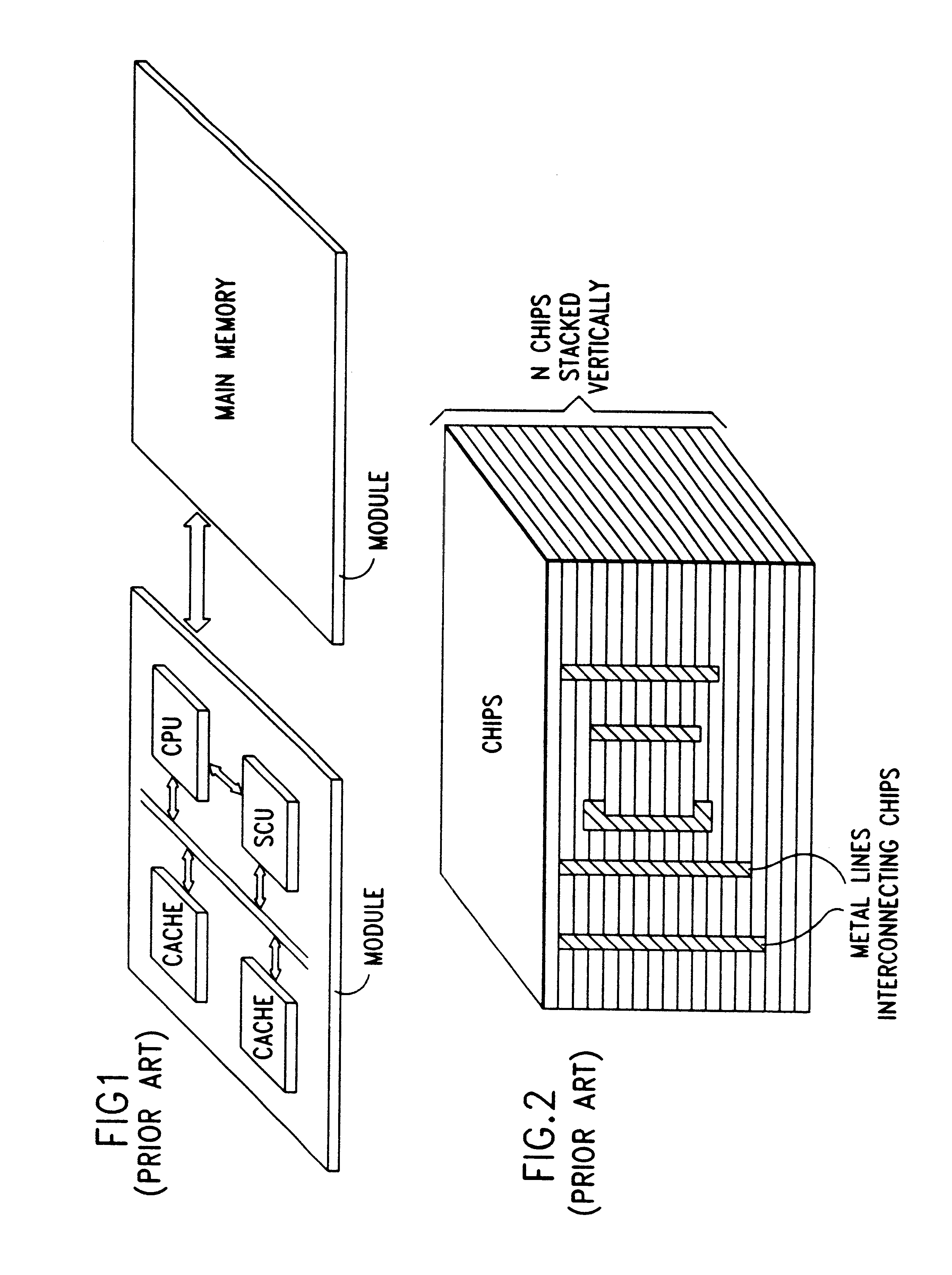

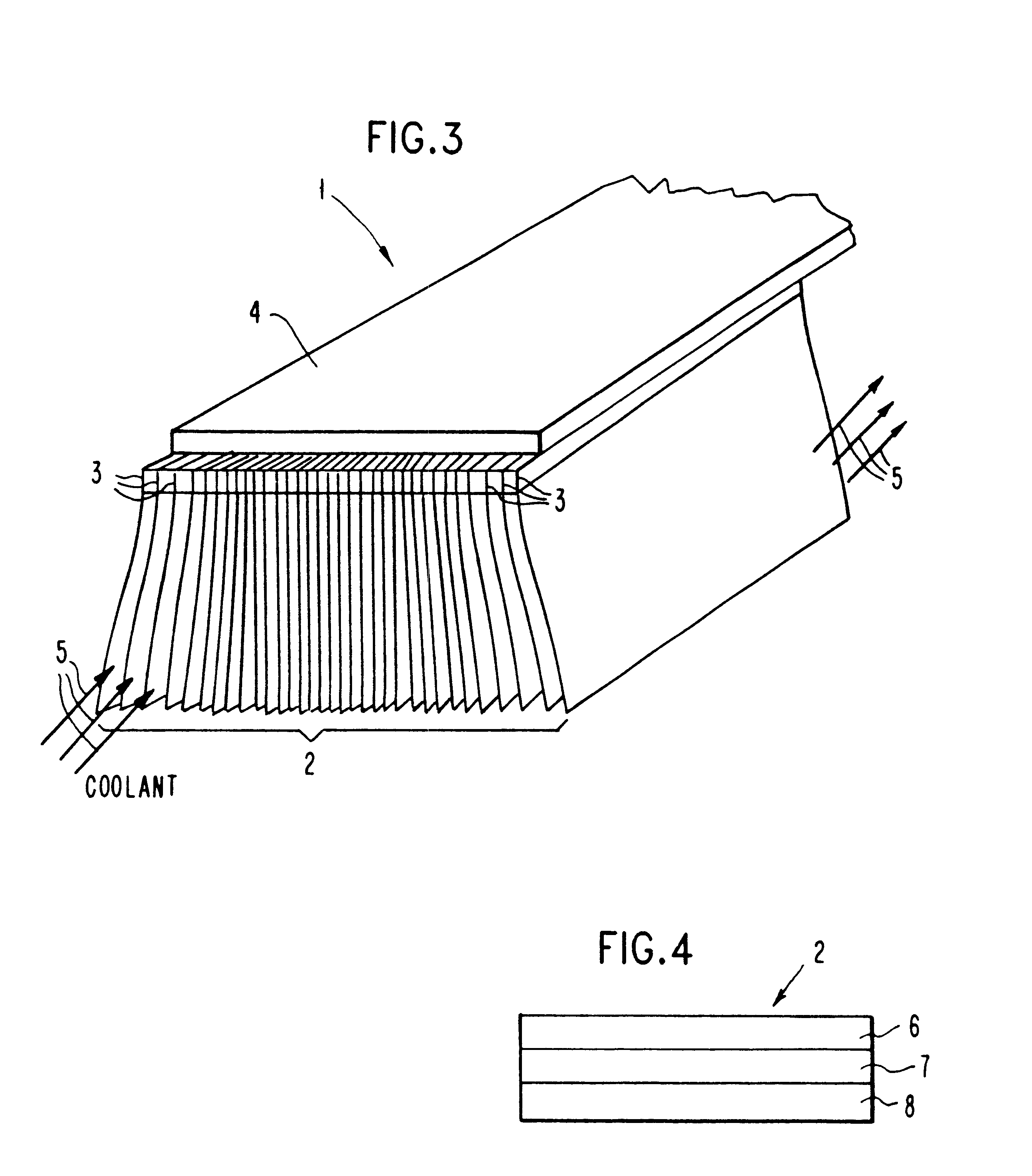

Three-dimensional packaging technology for multi-layered integrated circuits

InactiveUS6355976B1Improve performanceSemiconductor/solid-state device detailsSolid-state devicesPropagation delayEngineering

Disclosed is method and apparatus for packaging multilayered integrated circuit (IC) chips, on which logic circuits and / or memory arrays are disposed and interconnected in a novel way permitting the addressing (i.e. selection) of the logic circuits and / or arrays on these IC chip layers using a minimum number of connections and with the shortest propagation delays.

Owner:REVEO

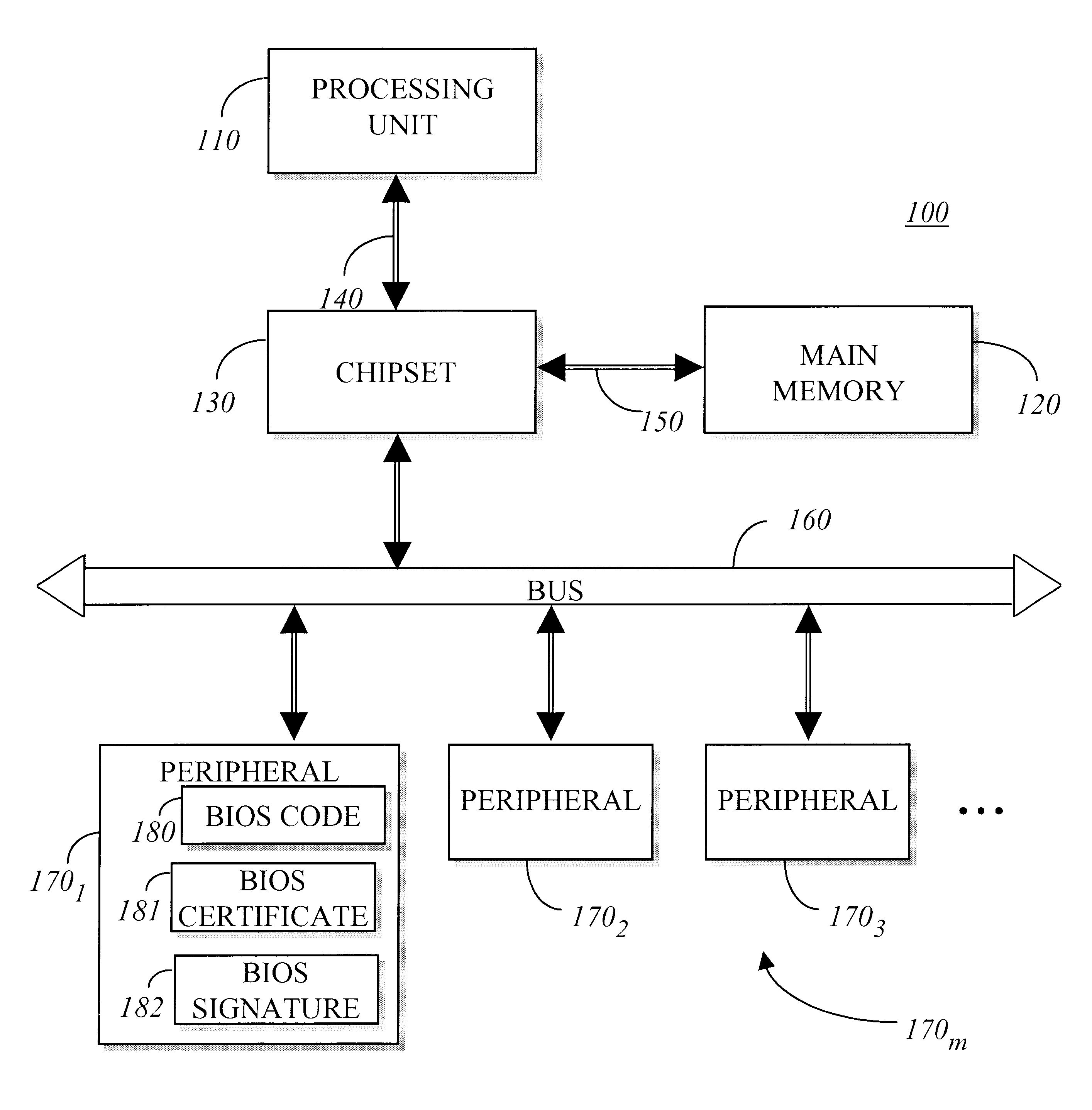

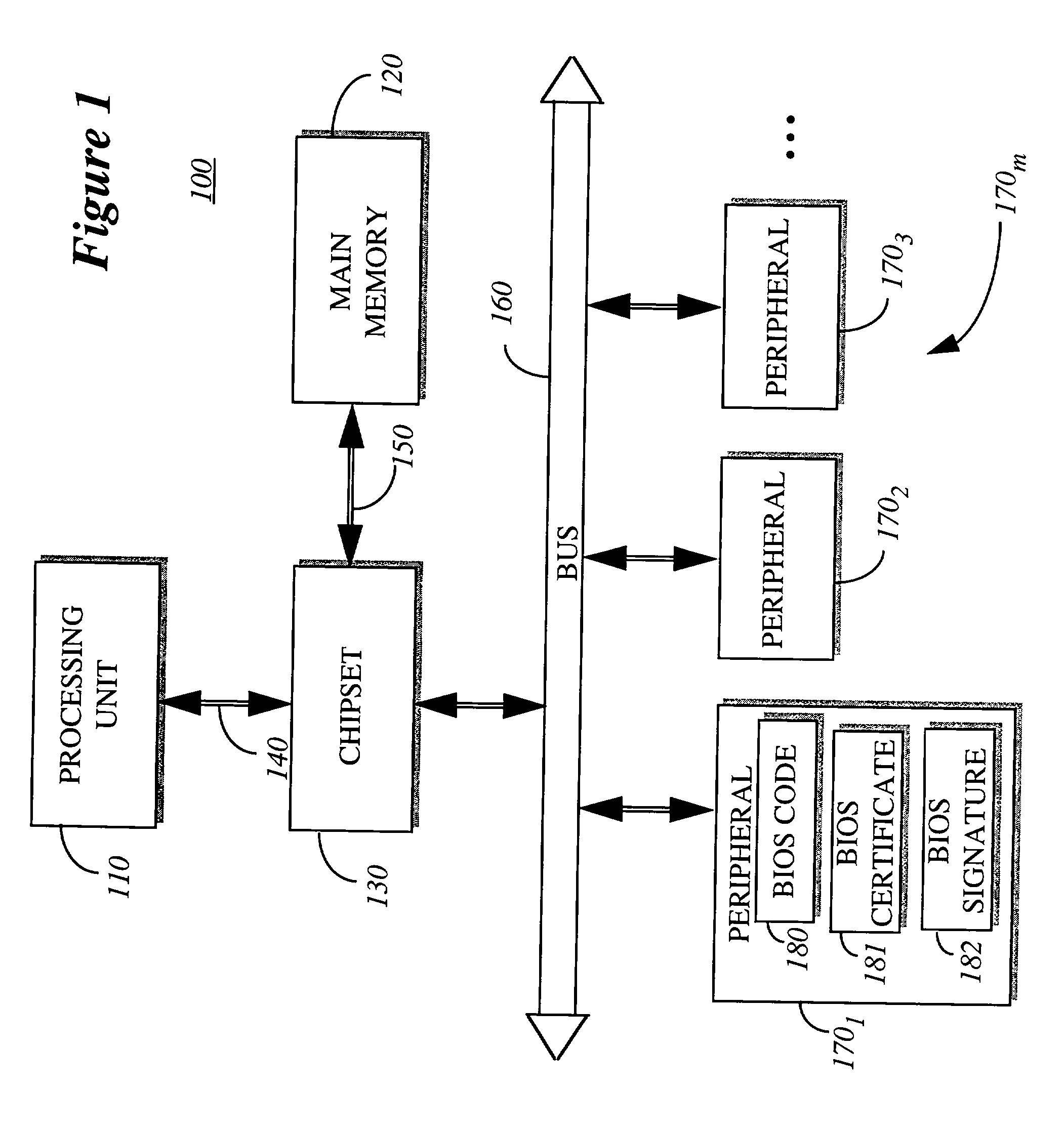

Method for BIOS authentication prior to BIOS execution

InactiveUS6401208B2User identity/authority verificationUnauthorized memory use protectionPower-on resetBIOS

Owner:INTEL CORP

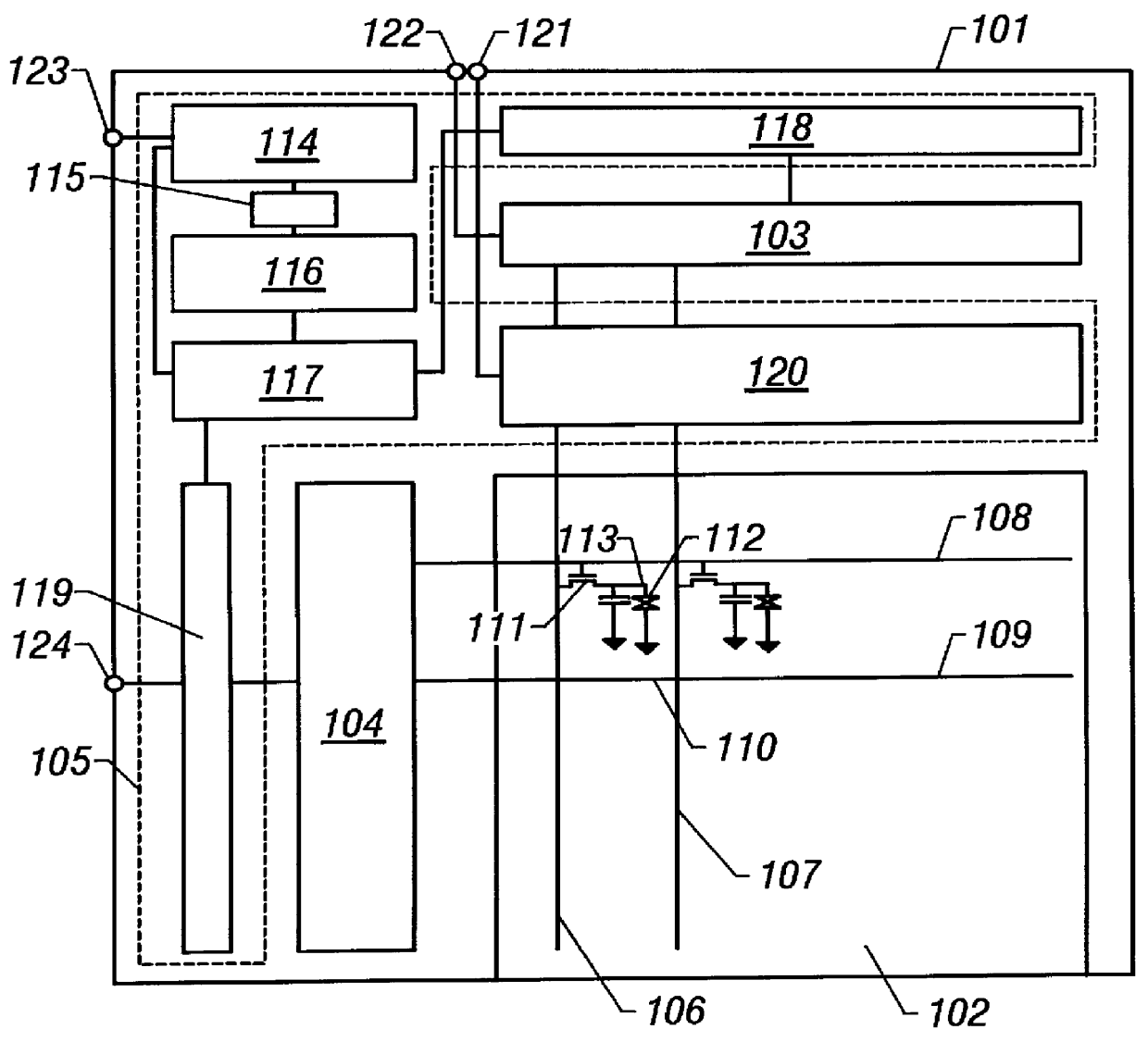

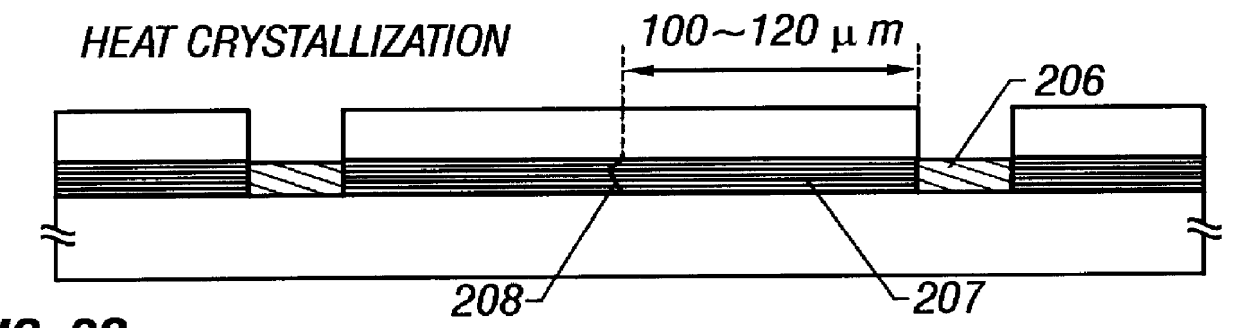

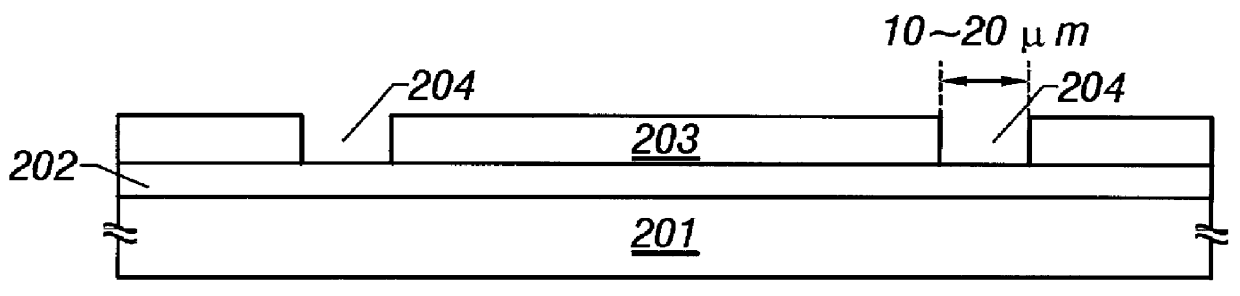

Semiconductor device

InactiveUS6147667ASolid-state devicesSemiconductor/solid-state device manufacturingDriver circuitActive matrix

A systemized active matrix display in which a pixel matrix circuit, a driver circuit and a logic circuit are mounted on the same substrate, is formed. A TFT of the present invention has such characteristics as to be able to operate in a wide driving frequency range of 0.05 to 2 GHz, and by designing a channel length and a film thickness of a gate insulating film of the TFT according to characteristics required by circuits, it is possible to form a high frequency driving circuit and a low frequency driving circuit on the same substrate.

Owner:SEMICON ENERGY LAB CO LTD

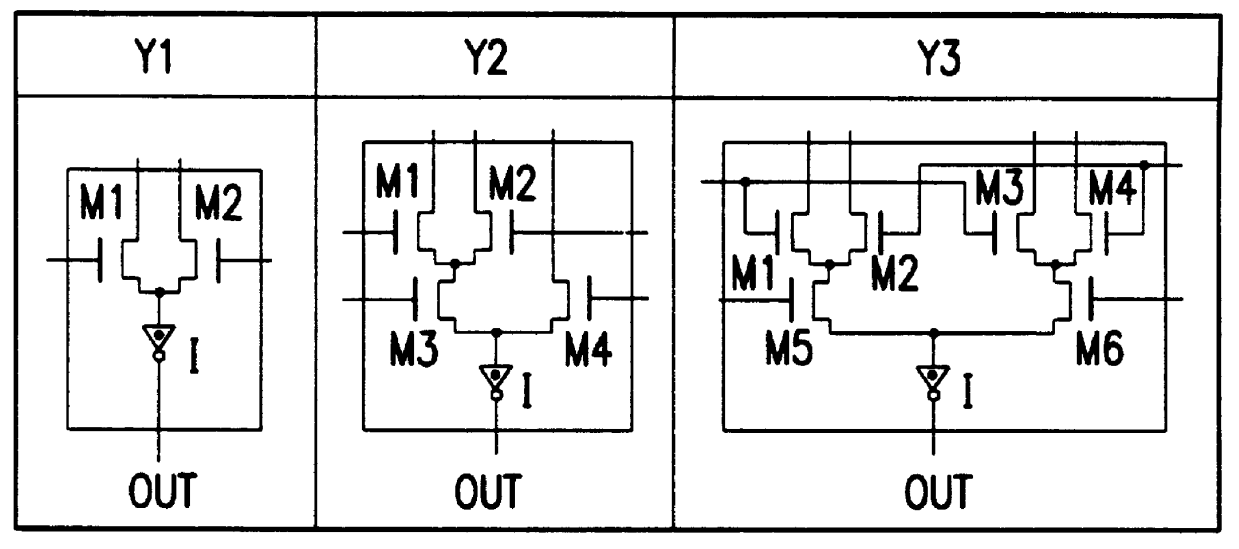

Logic circuit utilizing pass transistors and logic gate

InactiveUS6084437ATransistorReliability increasing modificationsCmos logic circuitsLogical operations

A logic circuit combines a plurality of pass-transistor logic trees and a multiple-input logic gate for receiving intermediate logic signals from the respective pass-transistor logic trees, and can express a complex logical operation while decreasing the number of stages in pass-transistor logic trees and improving operation speed. Even a logical operation that cannot be expressed efficiently by a known or conventional pass-transistor logic circuit can be expressed efficiently with performance higher than that of a known CMOS logic circuit. Furthermore, when a static feedthrough current of the multiple-input logic gate is suppressed, power consumption can be reduced. In some embodiments, since circuitry for suppressing a static feedthrough current of the multiple-input logic gate is arranged so that a probability of occurrence of logical collision with a preceding stage will decrease or will be nil, power consumption can further be reduced.

Owner:KAWASAKI MICROELECTRONICS

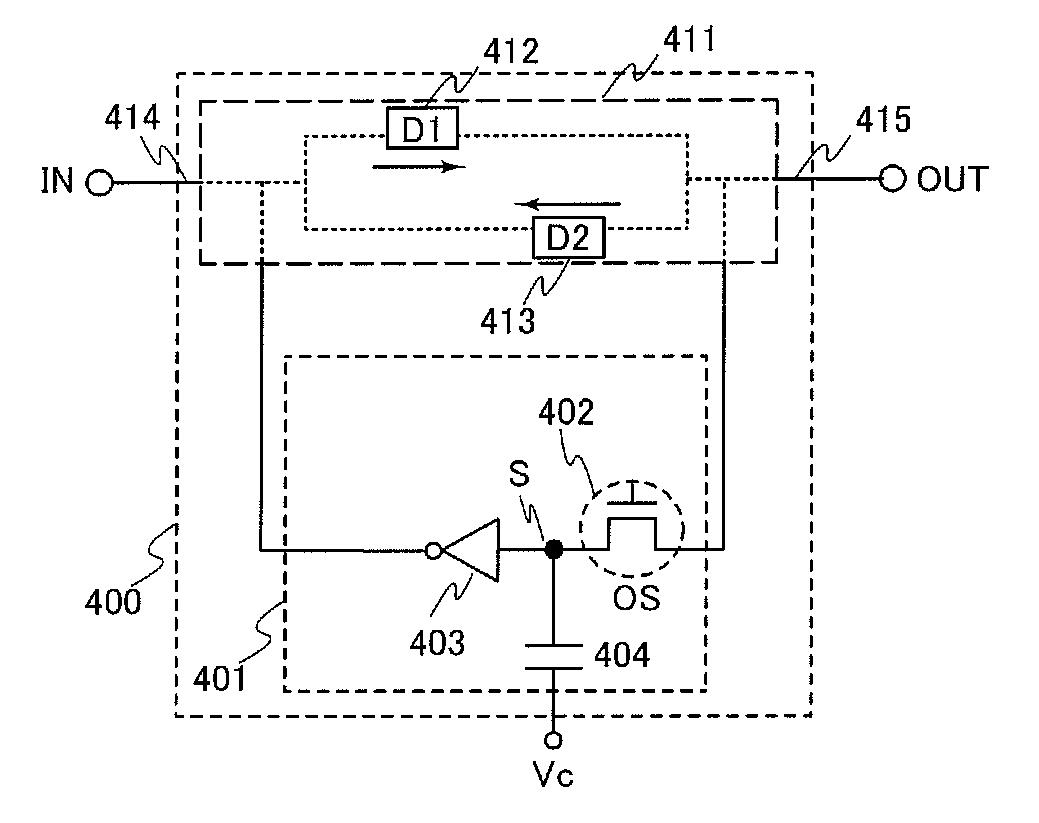

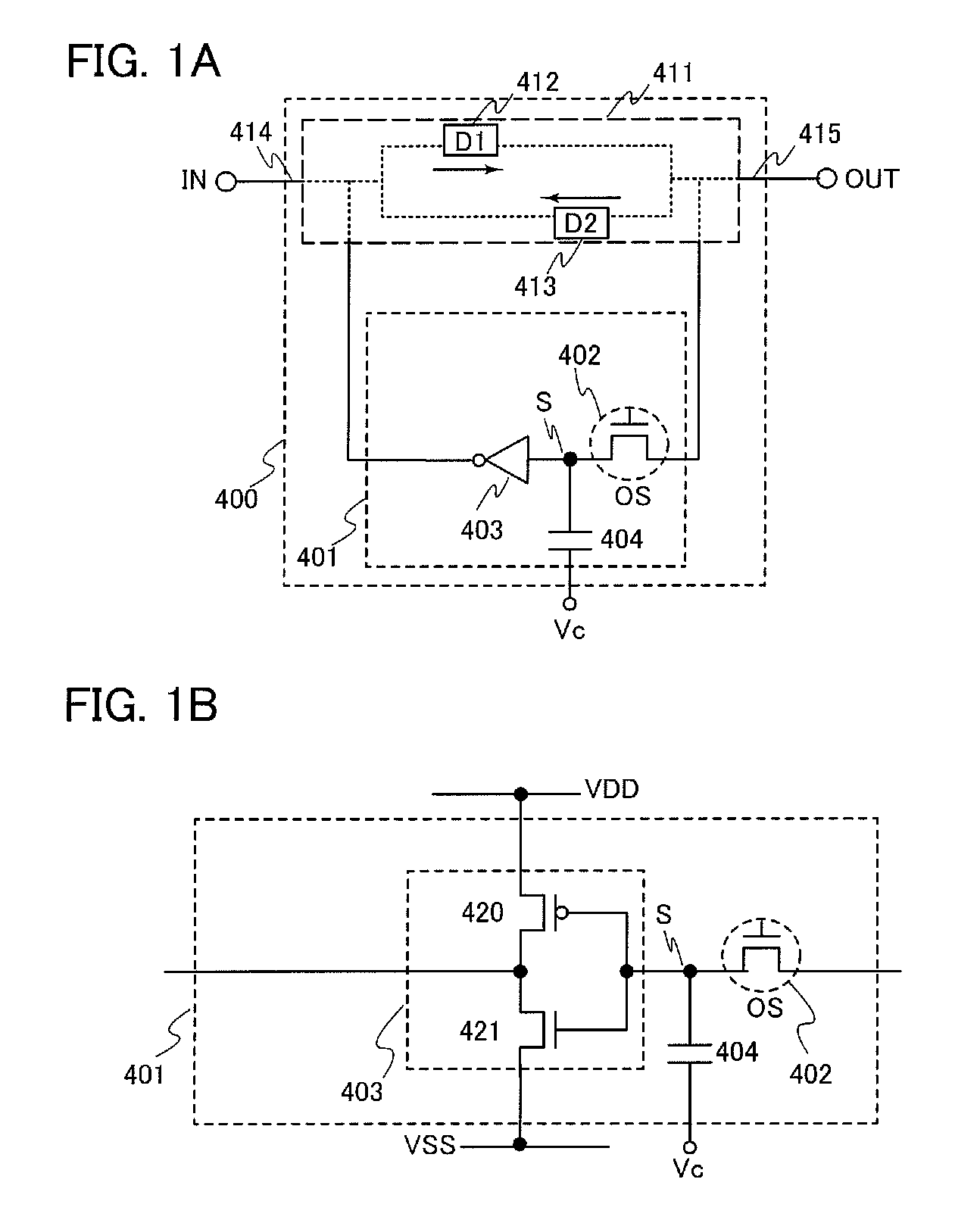

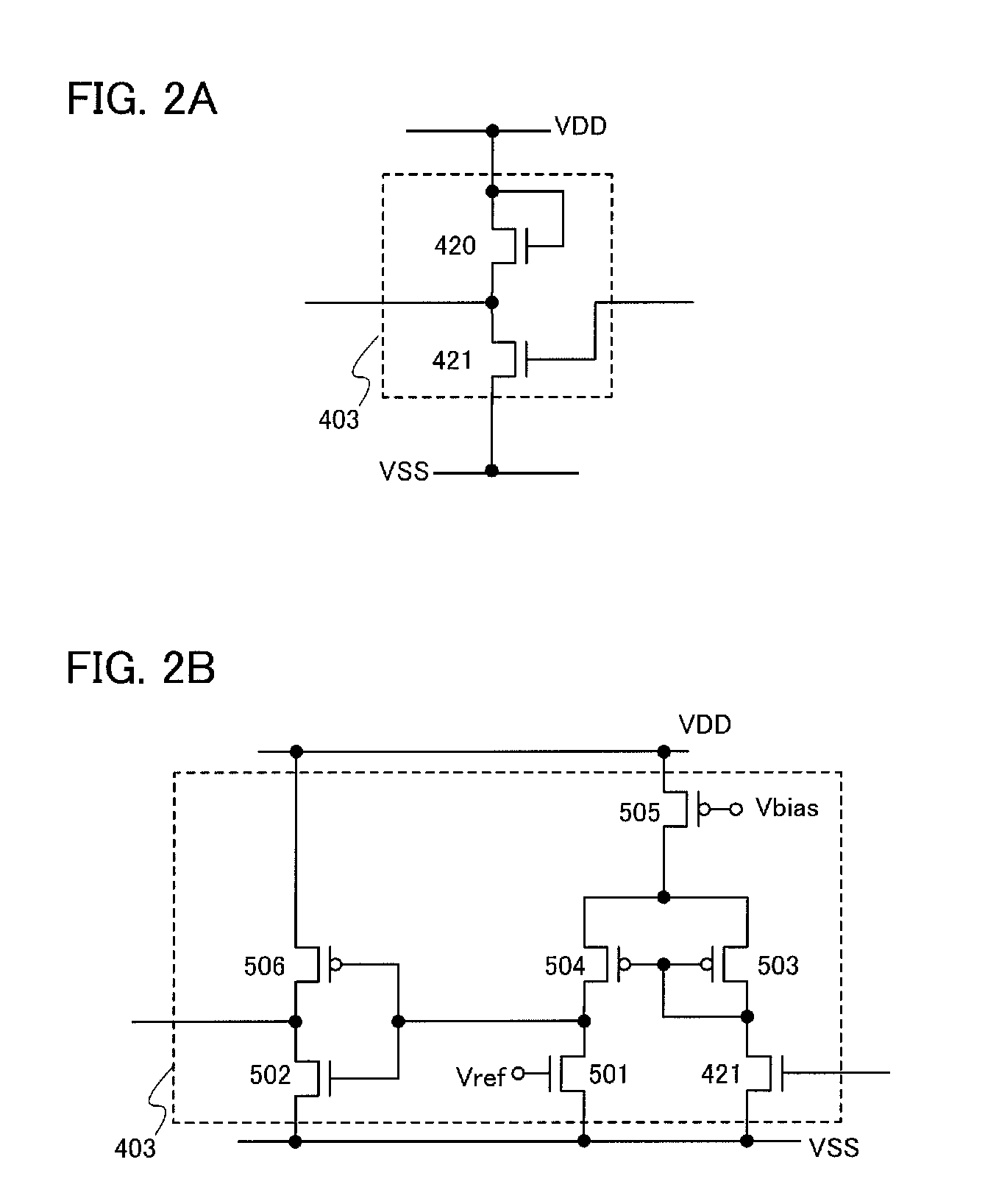

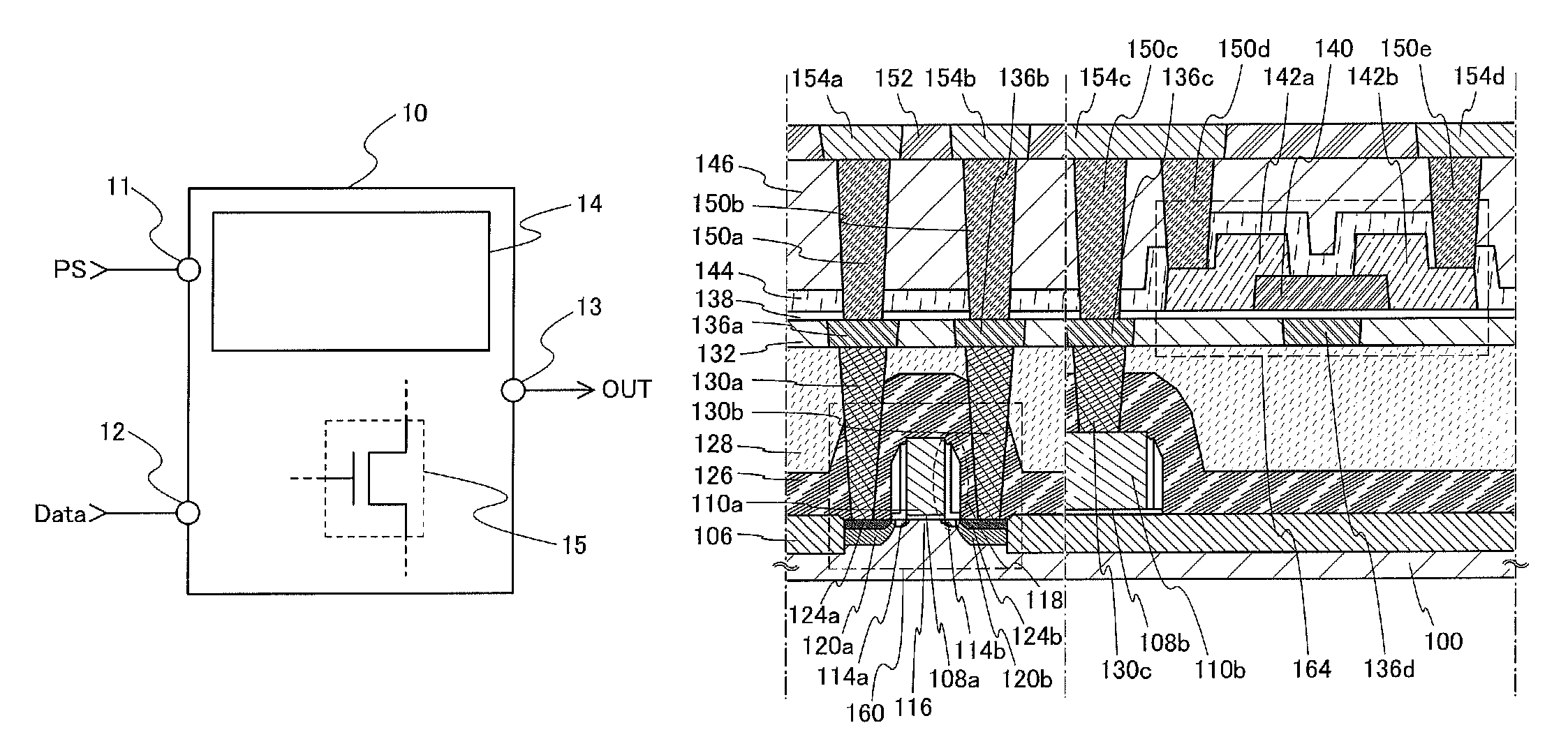

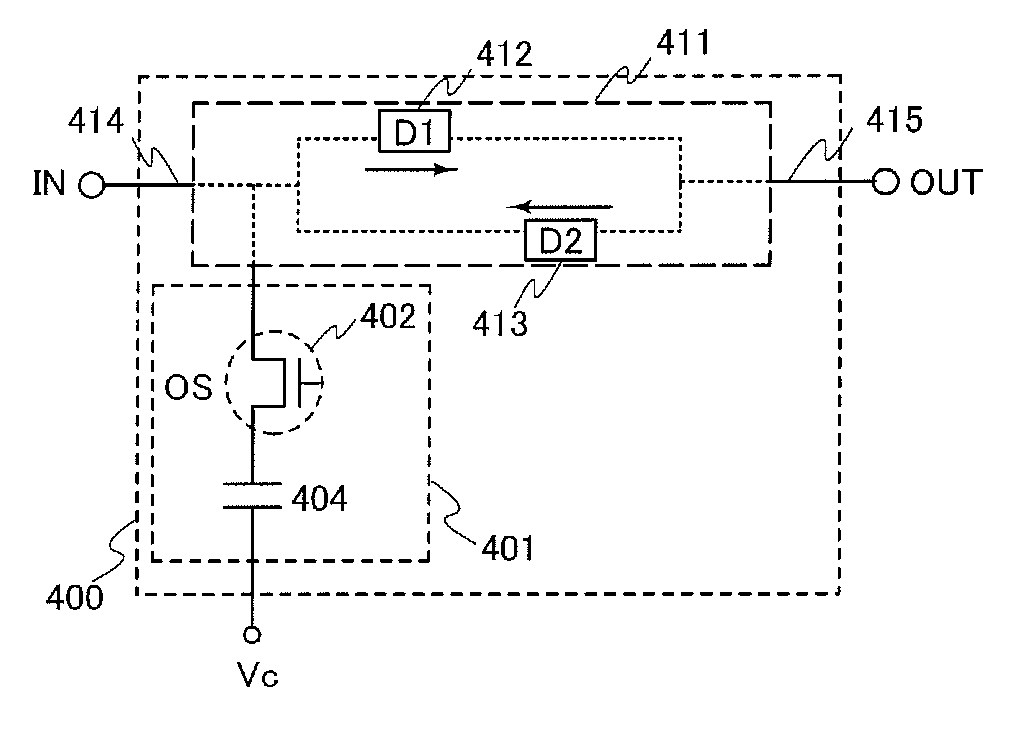

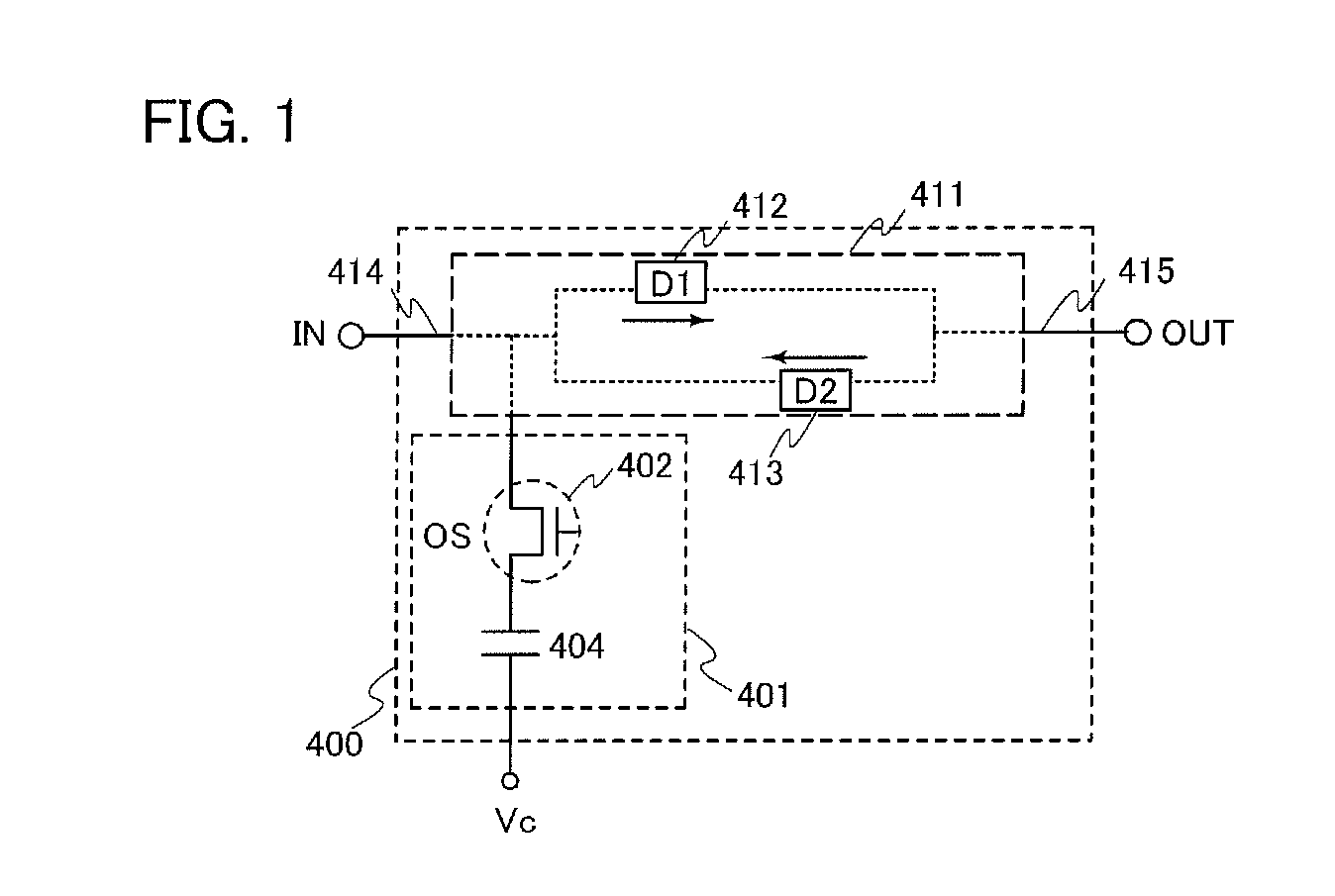

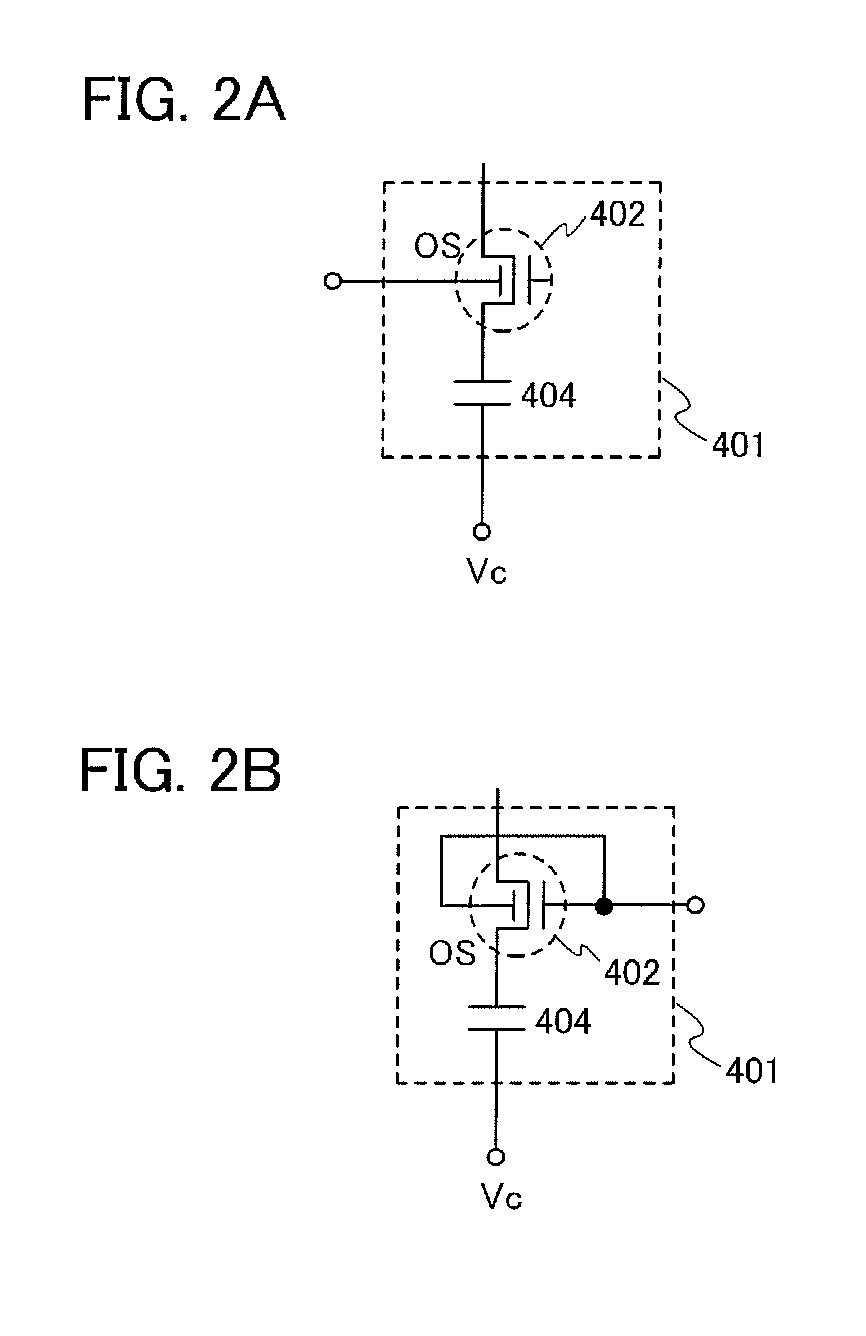

Nonvolatile latch circuit and logic circuit, and semiconductor device using the same

ActiveUS20110121878A1Wide operating temperature rangeGuaranteed uptimeTransistorSolid-state devicesPower semiconductor deviceSemiconductor materials

To provide a novel nonvolatile latch circuit and a semiconductor device using the nonvolatile latch circuit, a nonvolatile latch circuit includes a latch portion having a loop structure where an output of a first element is electrically connected to an input of a second element, and an output of the second element is electrically connected to an input of the first element; and a data holding portion for holding data of the latch portion. In the data holding portion, a transistor using an oxide semiconductor as a semiconductor material for forming a channel formation region is used as a switching element. In addition, an inverter electrically connected to a source electrode or a drain electrode of the transistor is included. With the transistor, data held in the latch portion can be written into a gate capacitor of the inverter or a capacitor which is separately provided.

Owner:SEMICON ENERGY LAB CO LTD

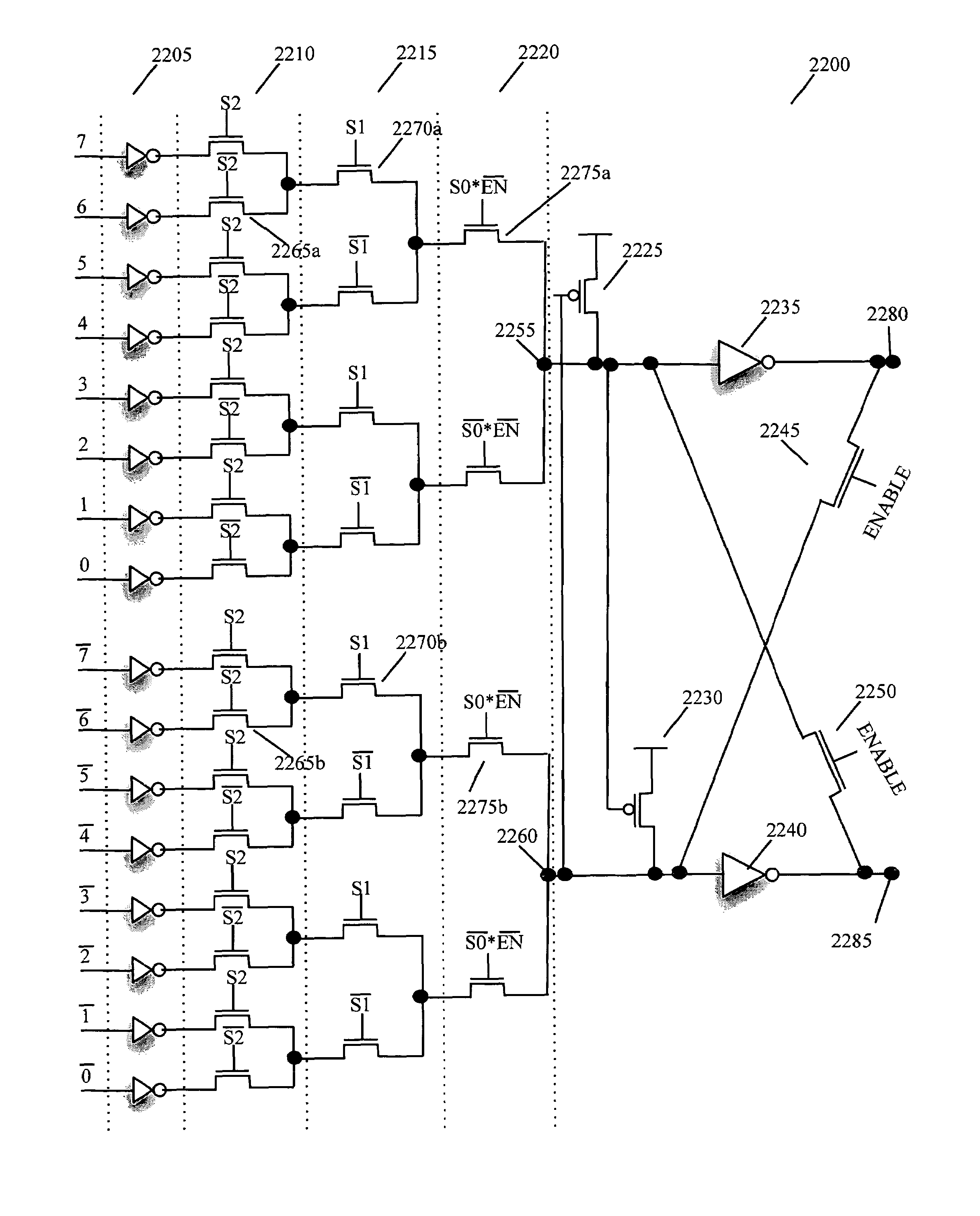

Configurable IC with interconnect circuits that also perform storage operations

InactiveUS7342415B2Logic circuits characterised by logic functionSolid-state devicesComputer scienceLogic circuitry

Owner:ALTERA CORP

Electronically addressable microencapsulated ink and display thereof

InactiveUS20070052757A1Inexpensive displayMechanical clocksVisual indicationsElectrical conductorSemiconductor materials

A system of electronically active inks is described which may include electronically addressable contrast media, conductors, insulators, resistors, semiconductive materials, magnetic materials, spin materials, piezoelectric materials, optoelectronic, thermoelectric or radio frequency materials. We further describe a printing system capable of laying down said materials in a definite pattern. Such a system may be used for instance to: print a flat panel display complete with onboard drive logic; print a working logic circuit onto any of a large class of substrates; print an electrostatic or piezoelectric motor with onboard logic and feedback or print a working radio transmitter or receiver.

Owner:E INK CORPORATION

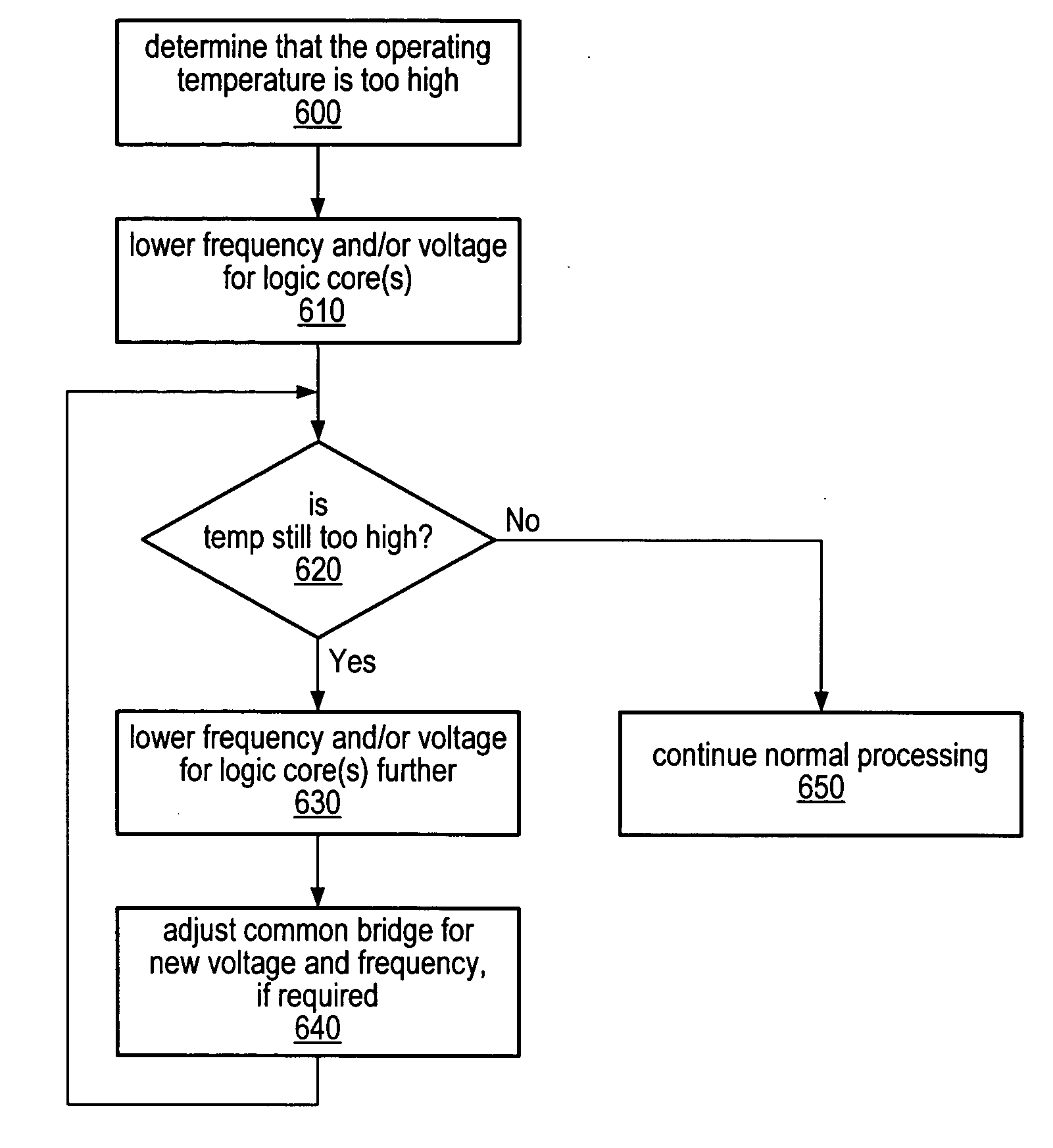

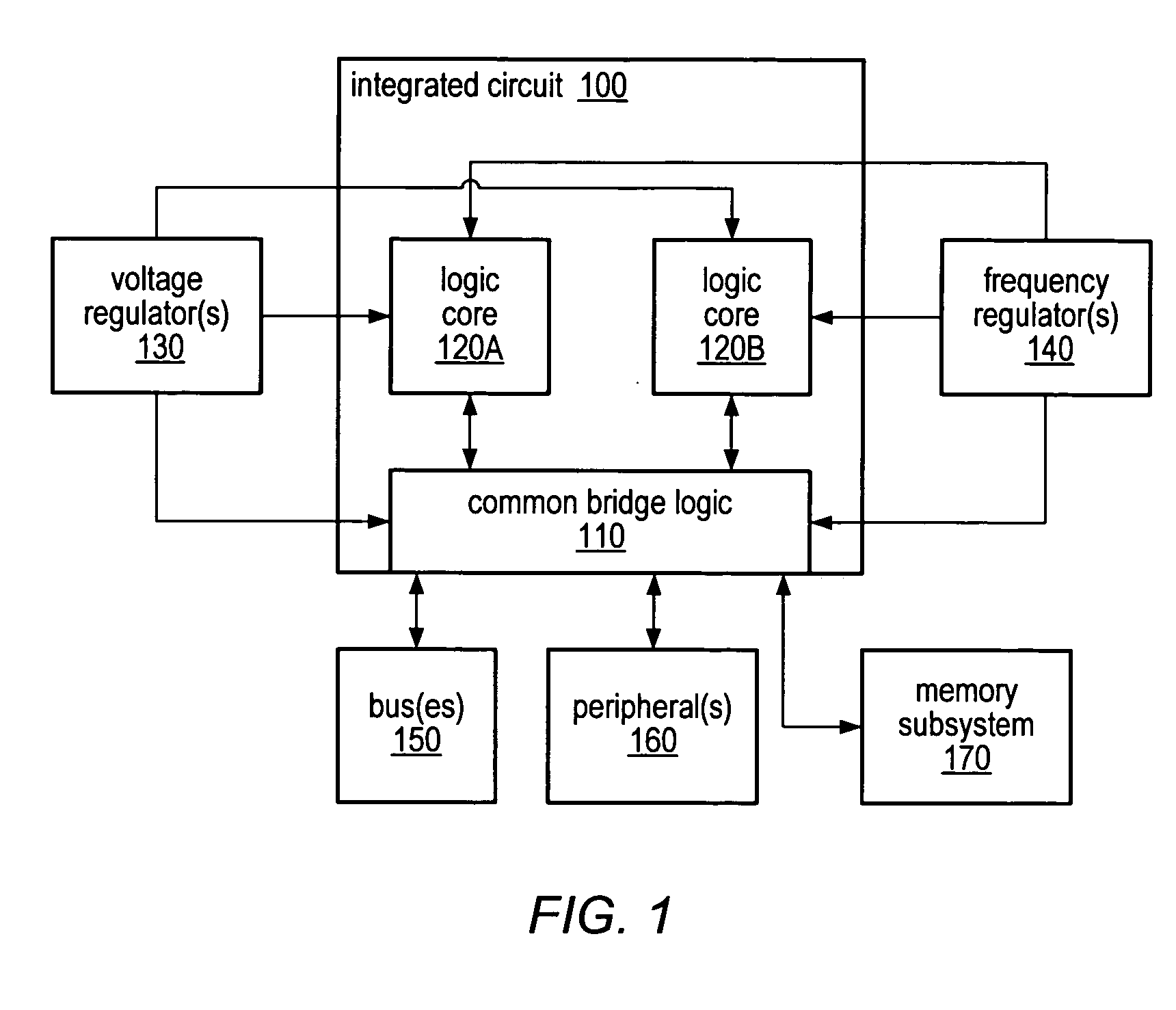

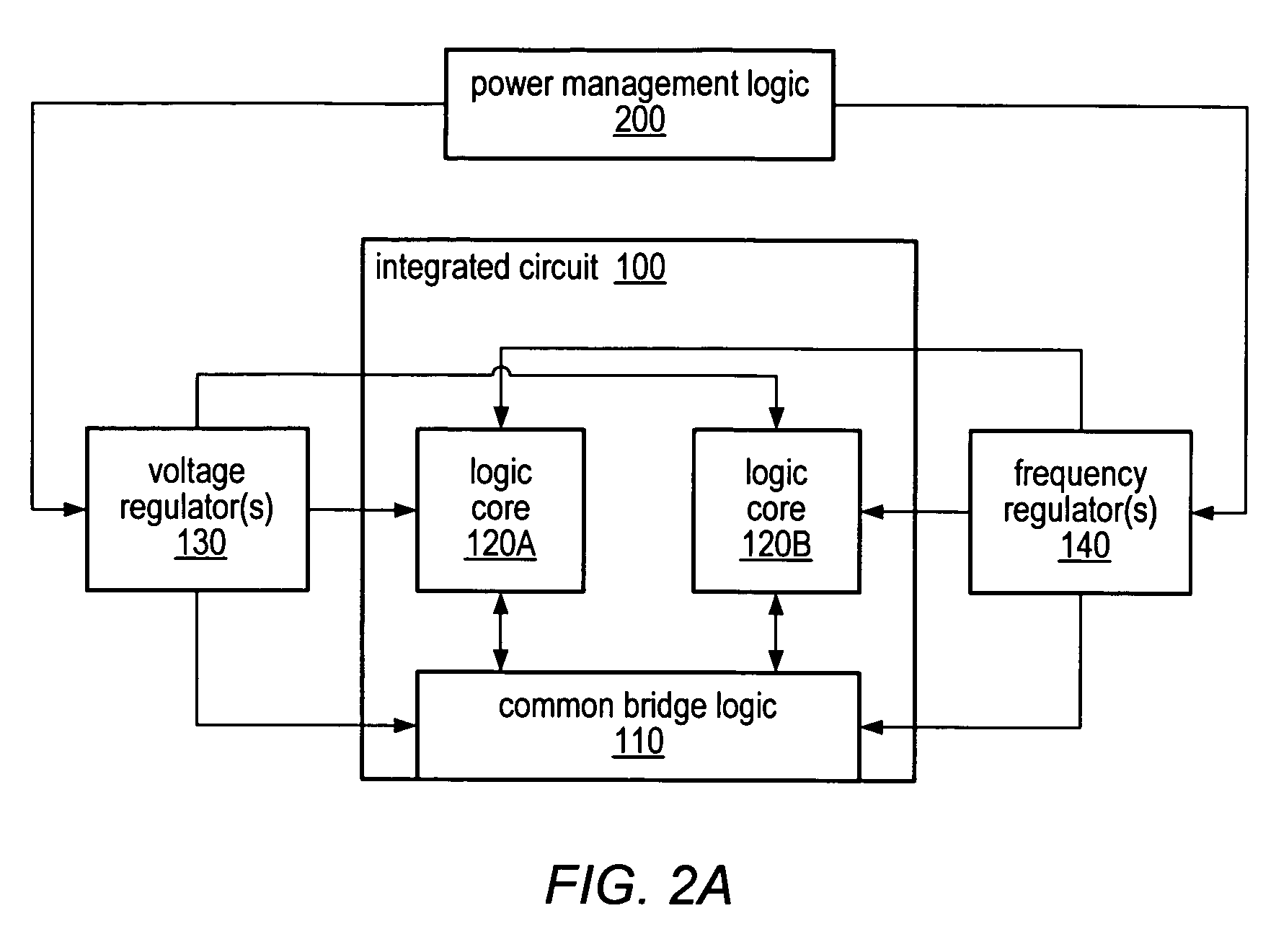

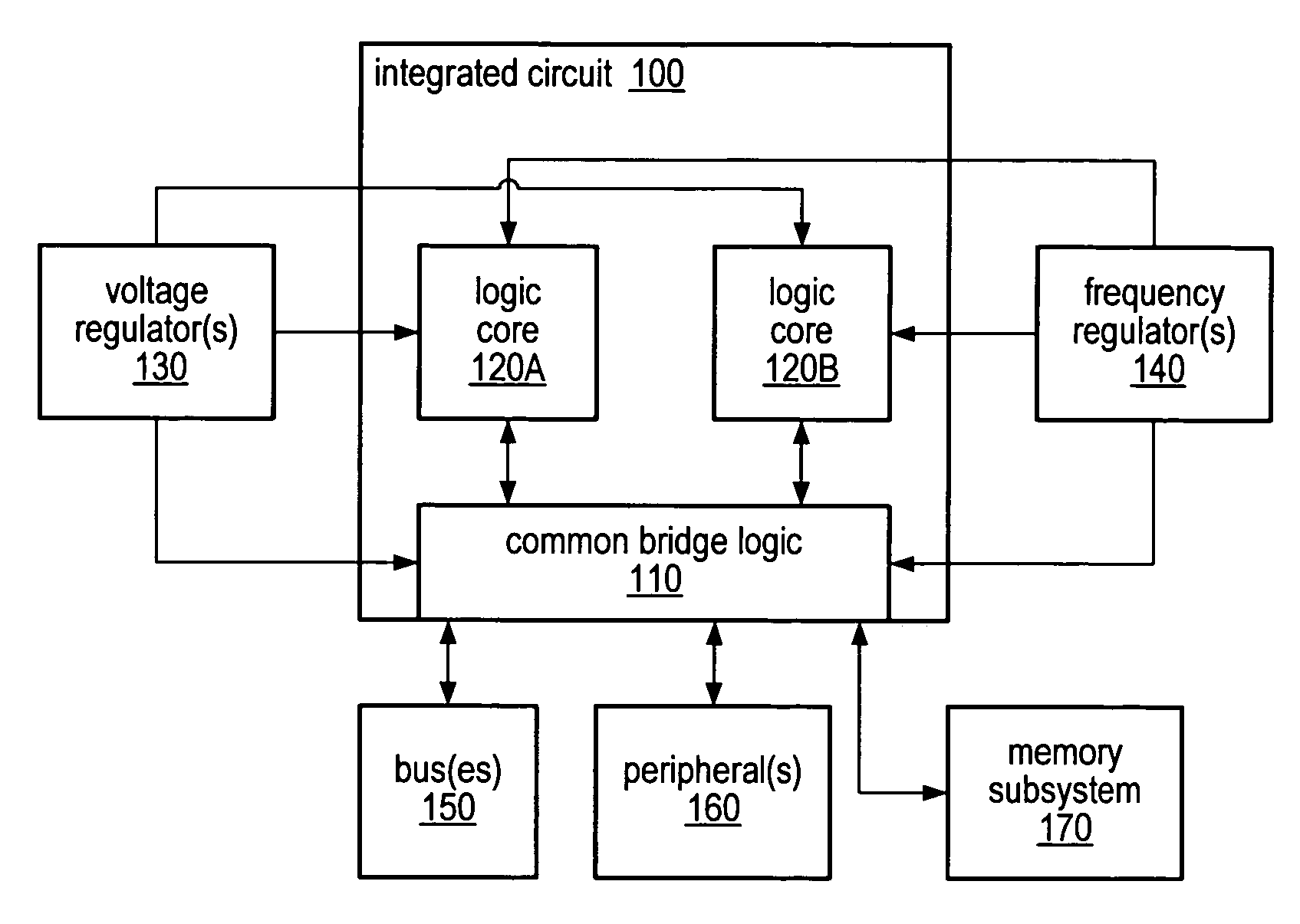

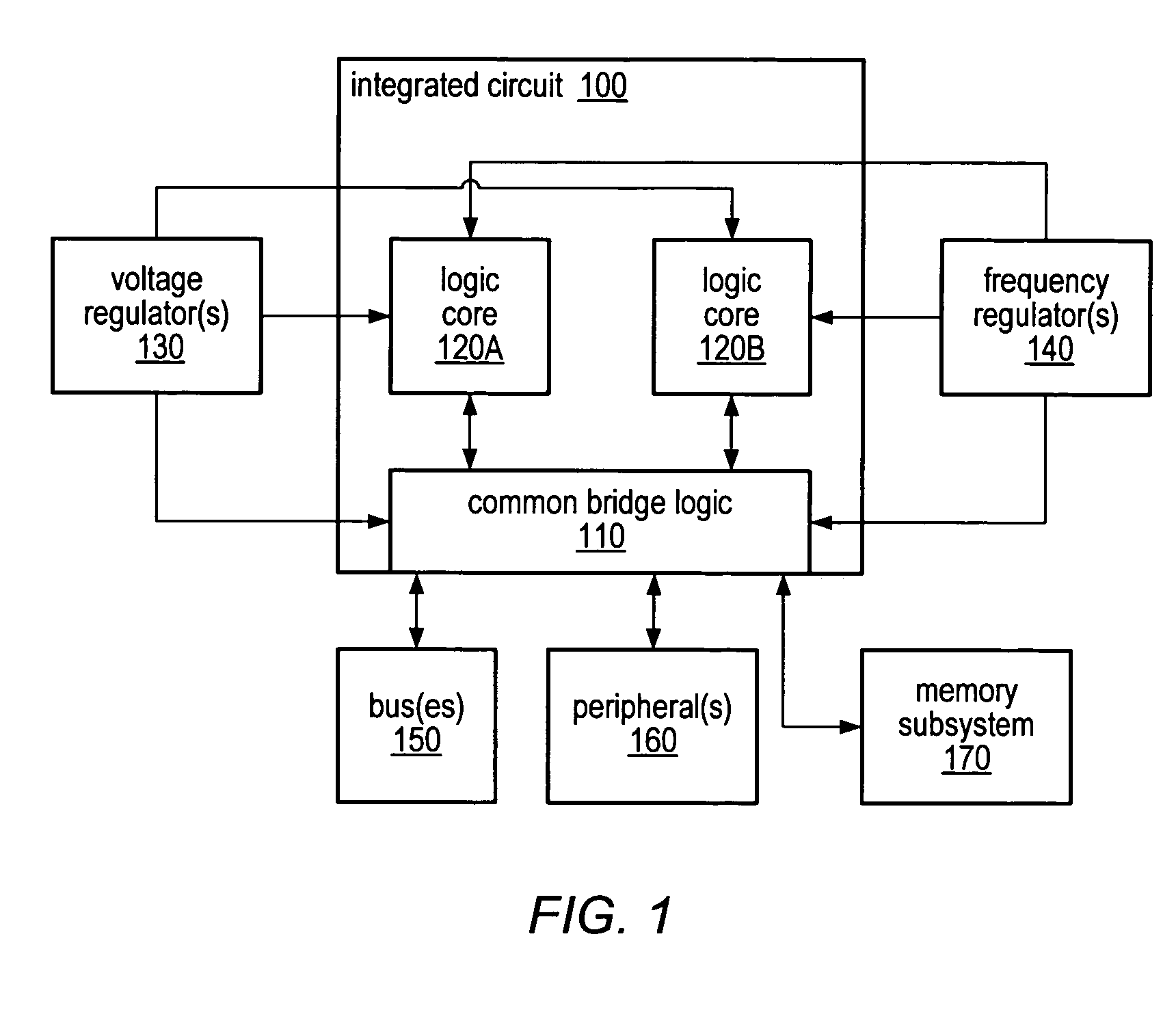

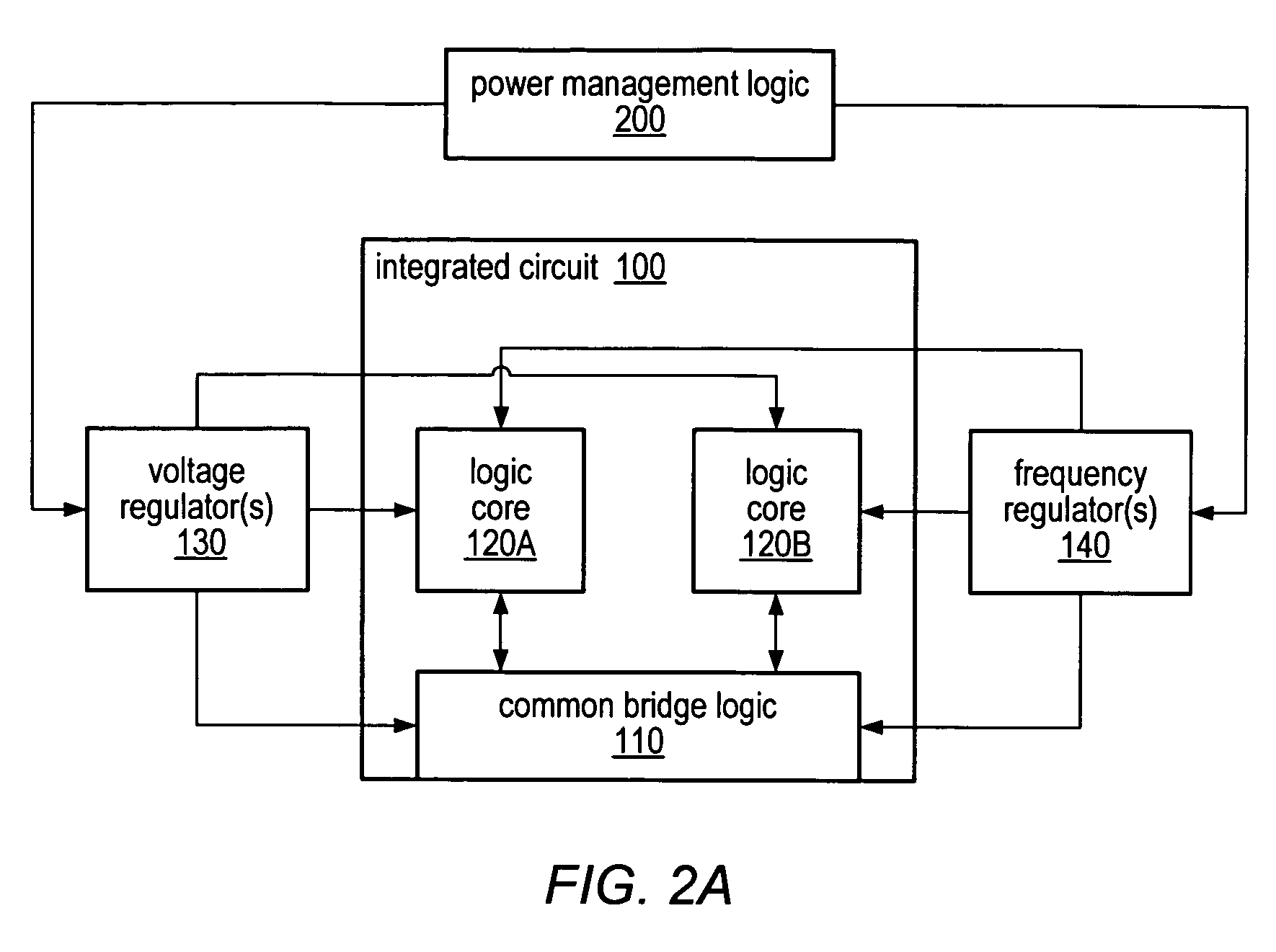

System and method for operating components of an integrated circuit at independent frequencies and/or voltages

ActiveUS20070156370A1Lower operating temperatureReduce power consumptionThermometer detailsEnergy efficient ICTTemperature controlEngineering

Multiple logic cores of integrated circuits and processors may be configured to operate at frequencies and voltages independently of each other. Additionally, other components, such as a common bridge configured to interface with the logic cores, may operate at a voltage and frequency independent of the voltage and frequency at which the logic cores are operating. The operating frequency and / or voltage of a logic core may be independently adjusted for various reasons, including power management and temperature control. Logic circuitry at an interface between the controller and the logic cores may translate logic signals from one voltage and / or frequency to another to enable communication between the bridge and the logic core when the two are operating at different voltages and / or frequencies.

Owner:MEDIATEK INC

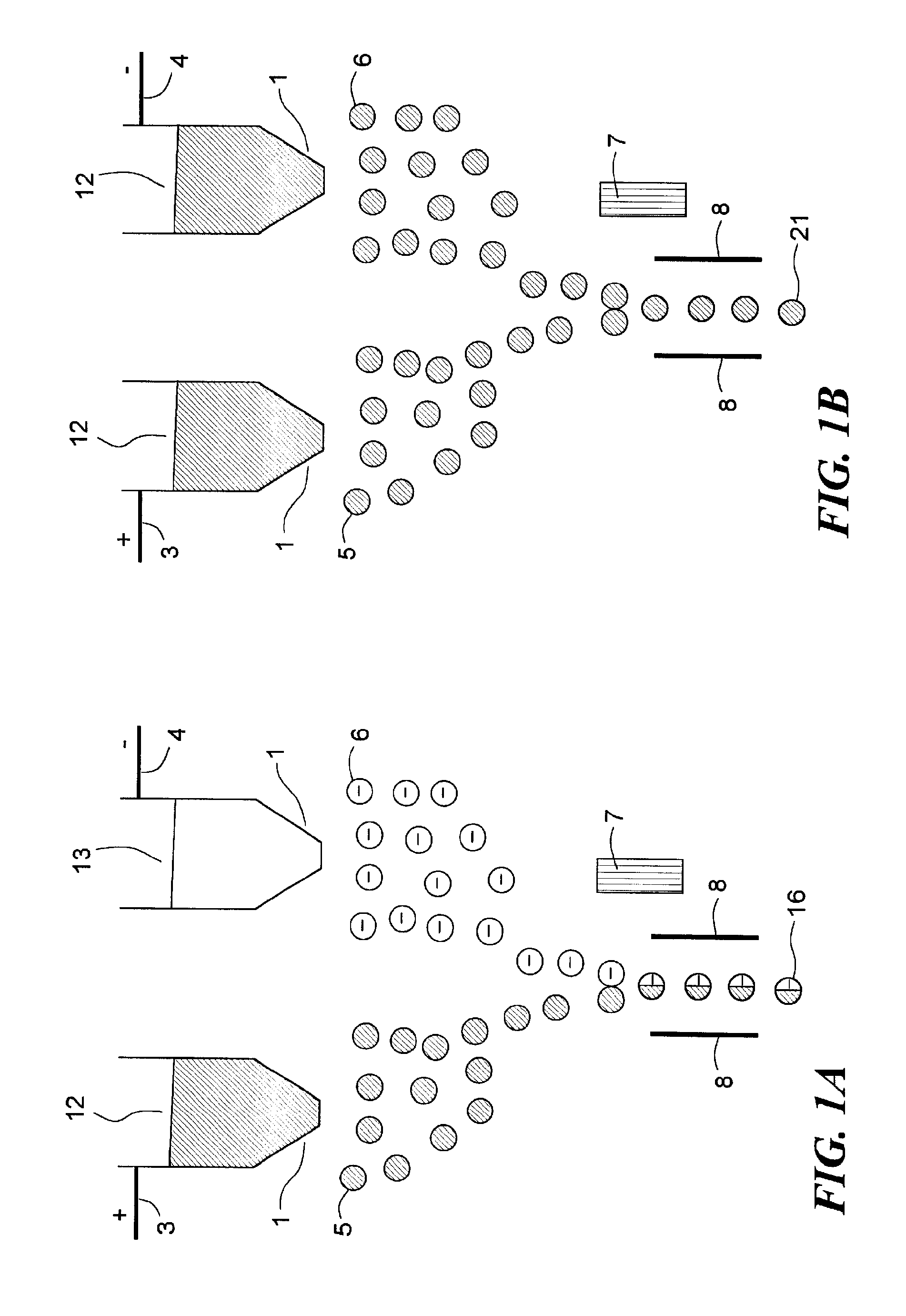

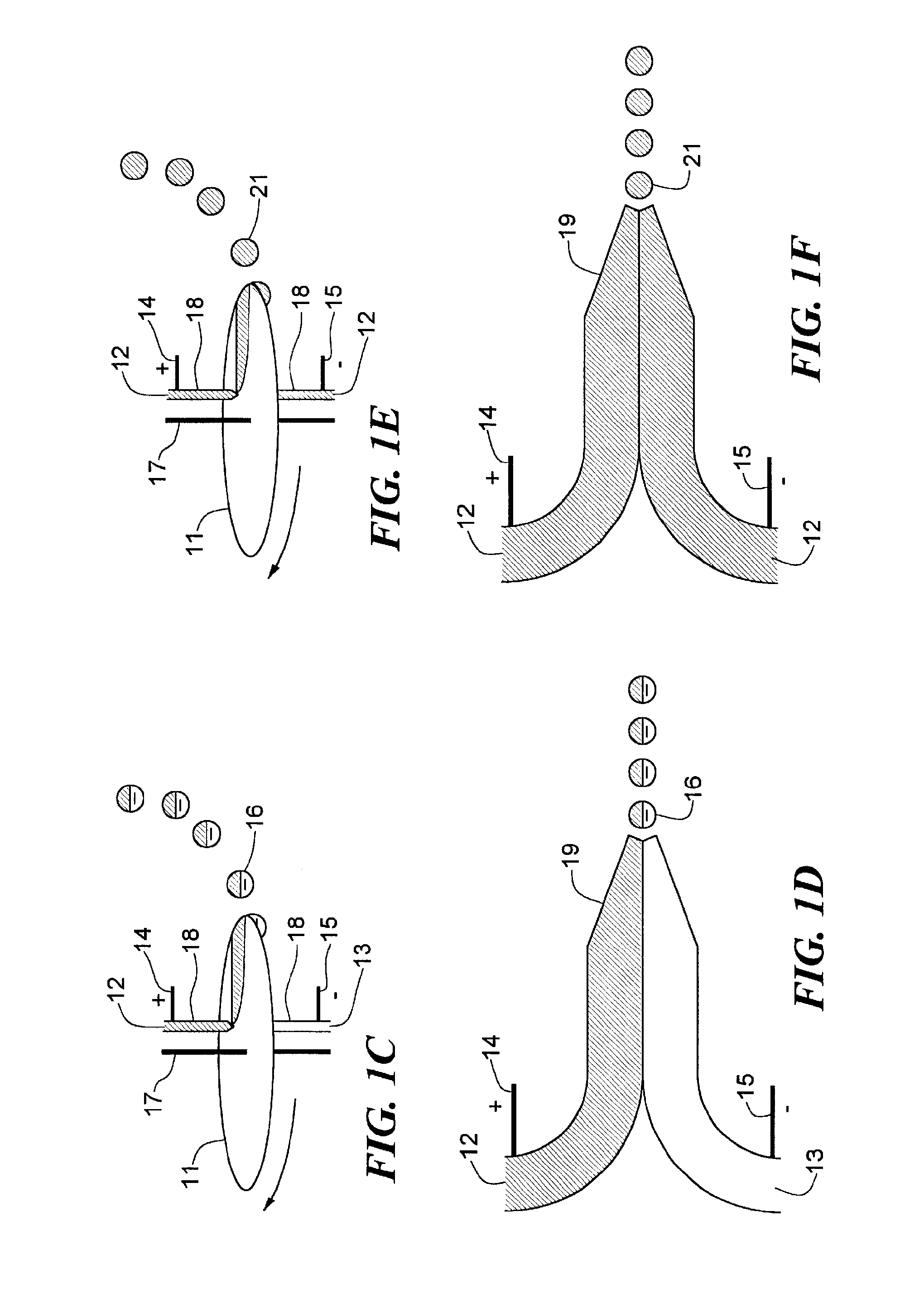

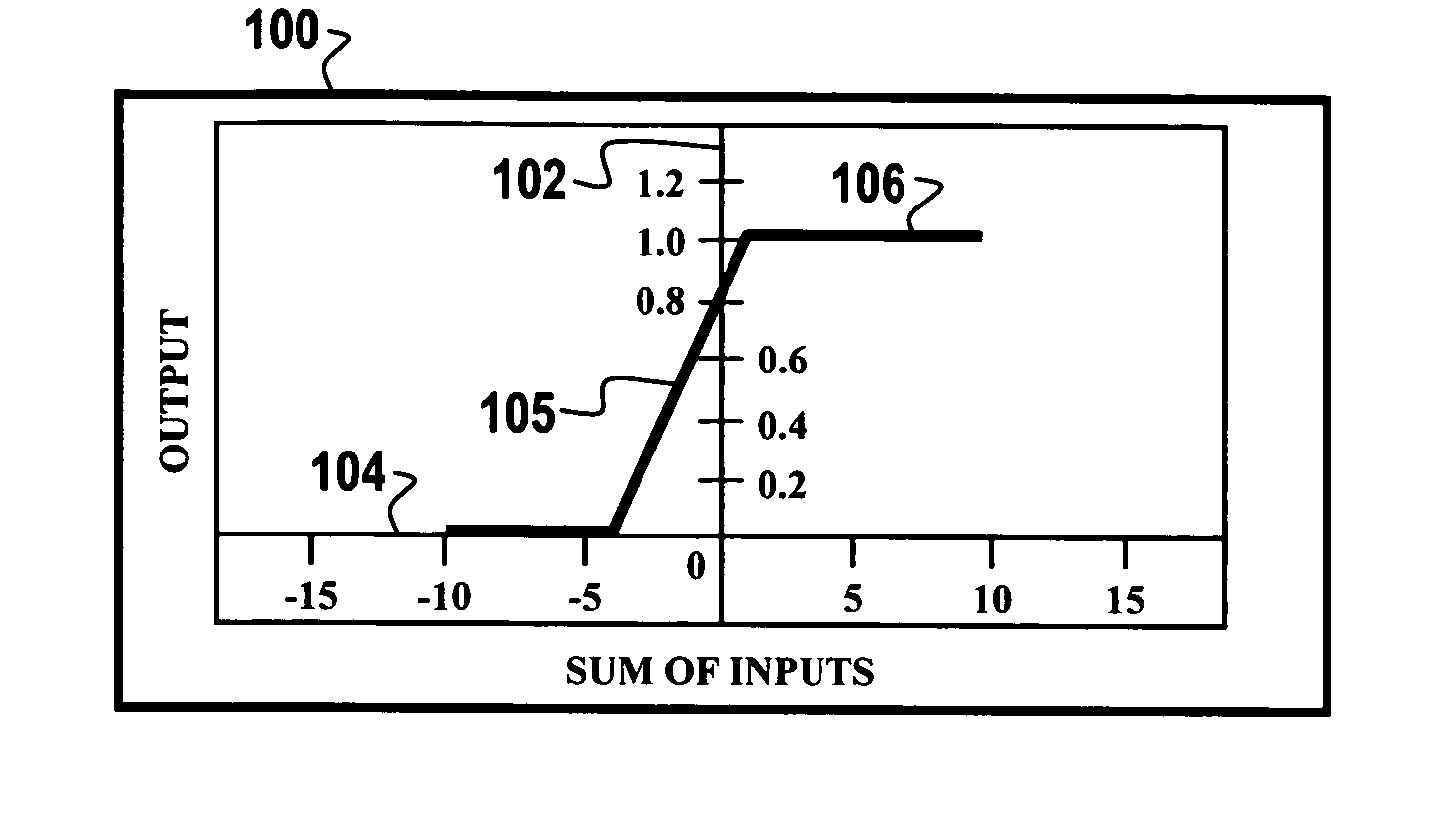

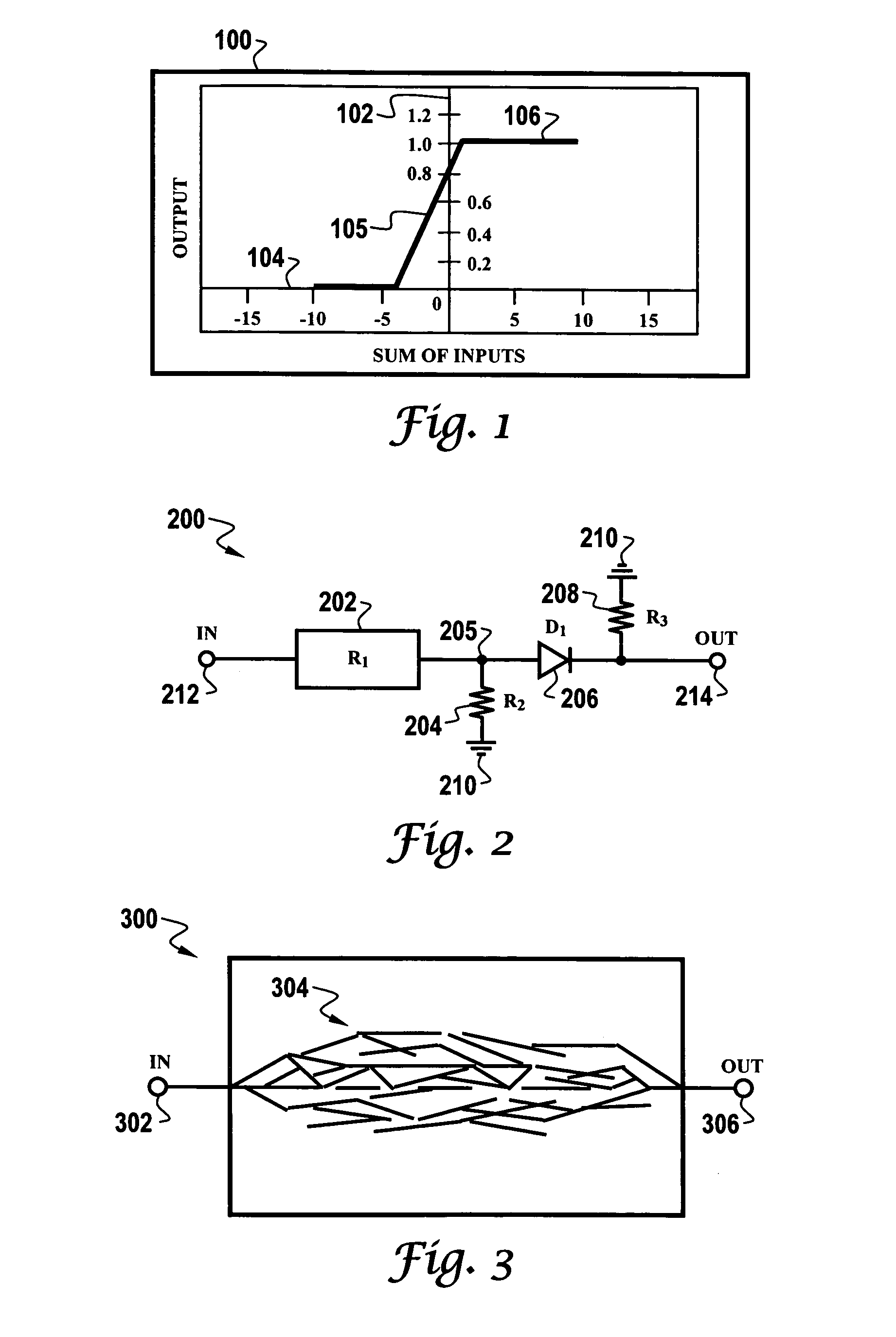

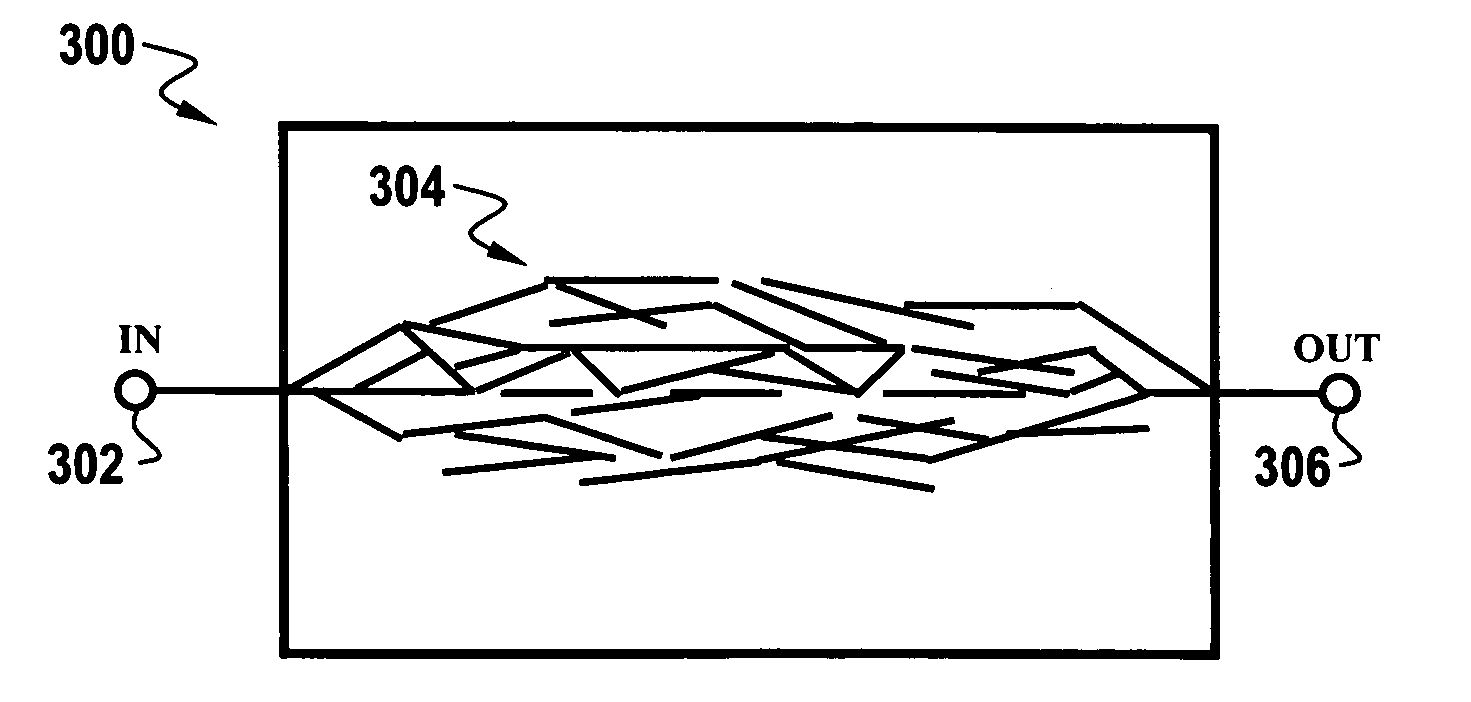

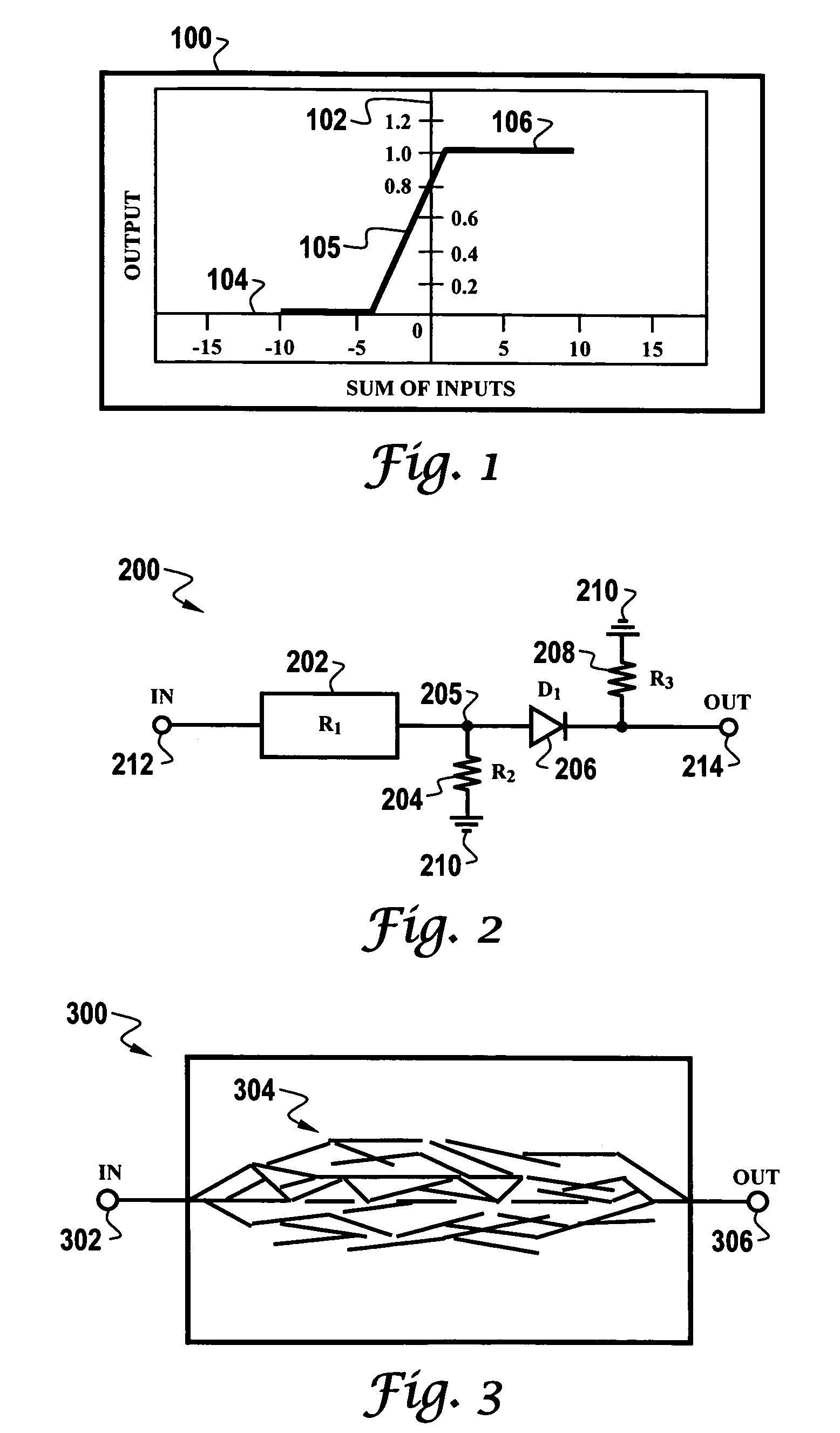

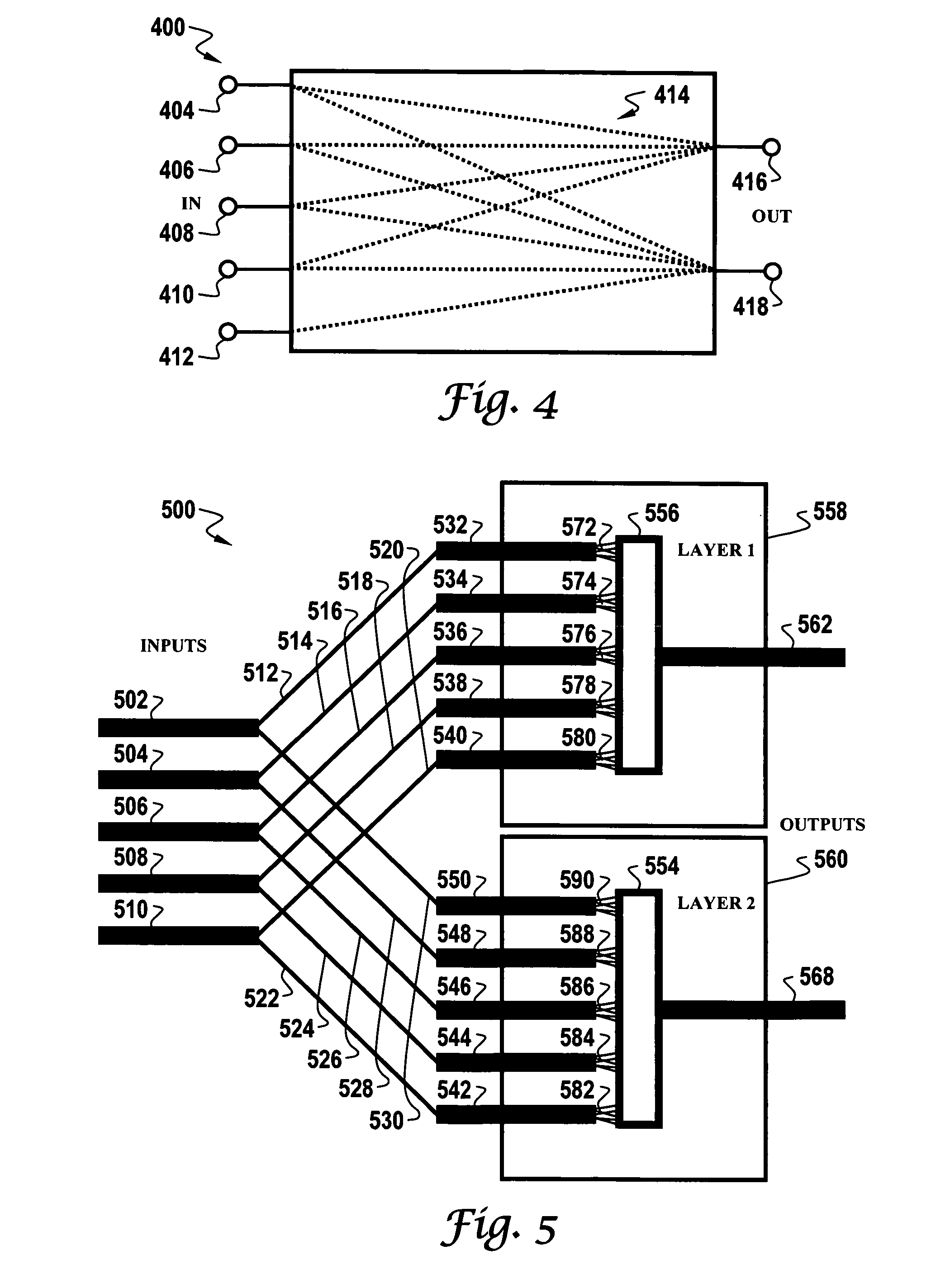

Nanotechnology neural network methods and systems

A physical neural network is disclosed, which includes a connection network comprising a plurality of molecular conducting connections suspended within a connection gap formed between one or more input electrodes and one or more output electrodes. One or more molecular connections of the molecular conducting connections can be strengthened or weakened according to an application of an electric field across said connection gap. Thus, a plurality of physical neurons can be formed from said molecular conducting connections of said connection network. Additionally, a gate can be located adjacent said connection gap and which comes into contact with said connection network. The gate can be connected to logic circuitry which can activate or deactivate individual physical neurons among said plurality of physical neurons.

Owner:KNOWM TECH

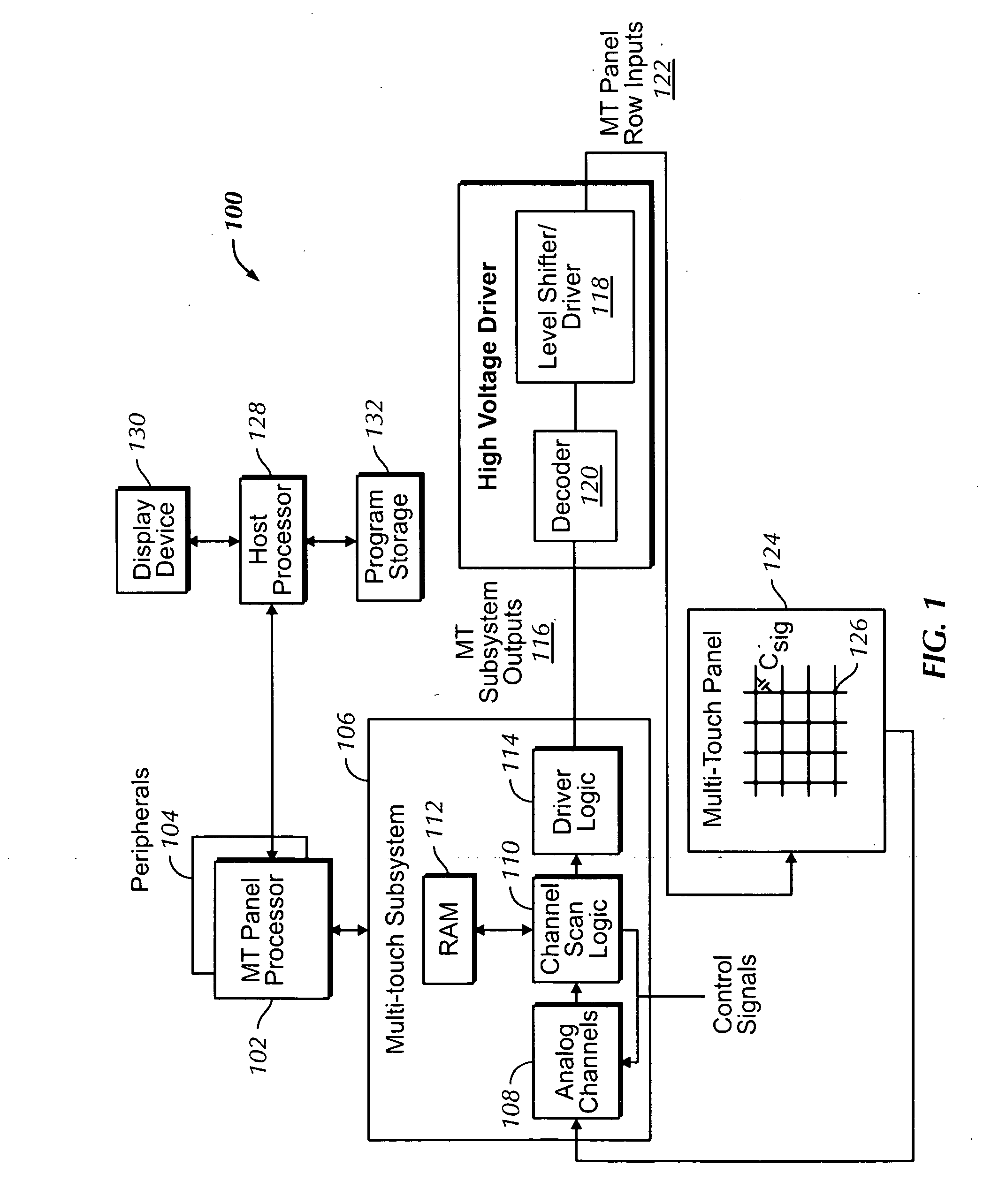

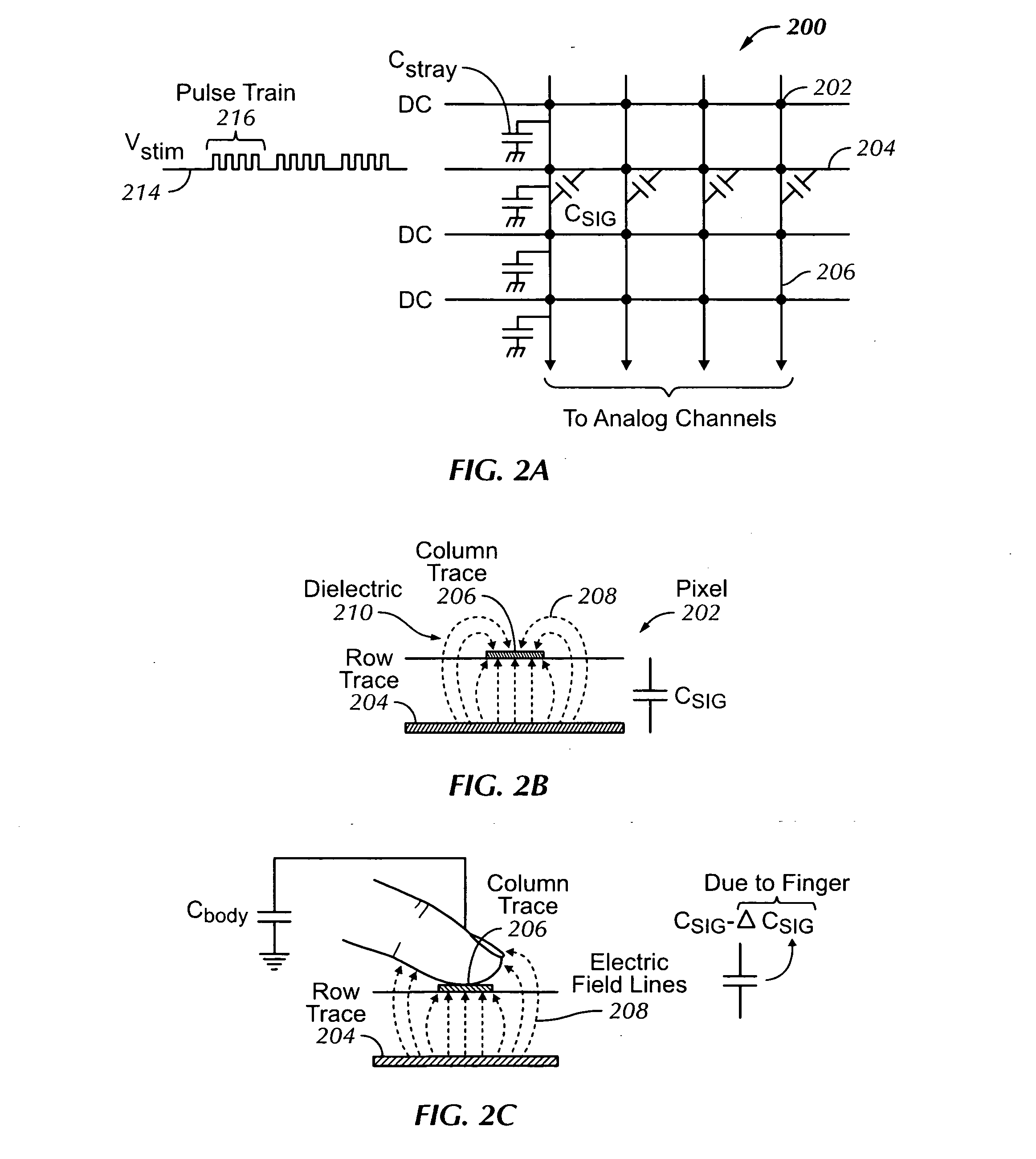

Scan sequence generator

A sensor panel device that can generate and use a stimulus signal having multiple different waveforms for detecting events on or near the sensor panel is disclosed. Among other things, such a stimulus signal can be used to reject environmental noise present in the device. In some embodiments, the stimulus signal has multiple waveforms having different frequencies. Logic circuitry can generate representative values from output of the different waveforms applied to one or more sensing nodes in the sensor panel device. From the representative values, a final value can be generated that represents whether an event occurred at or near the one or more sensing nodes.

Owner:APPLE INC

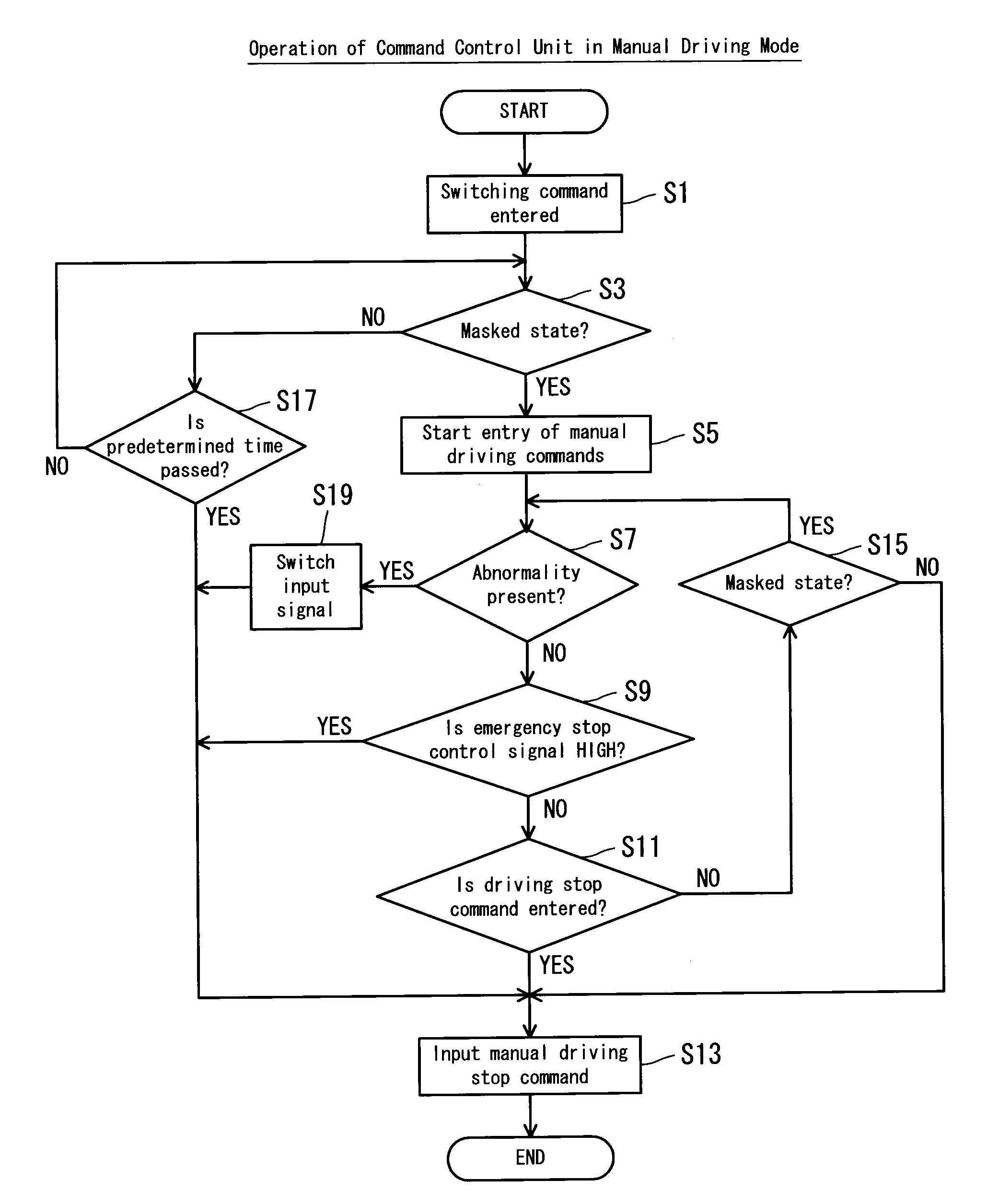

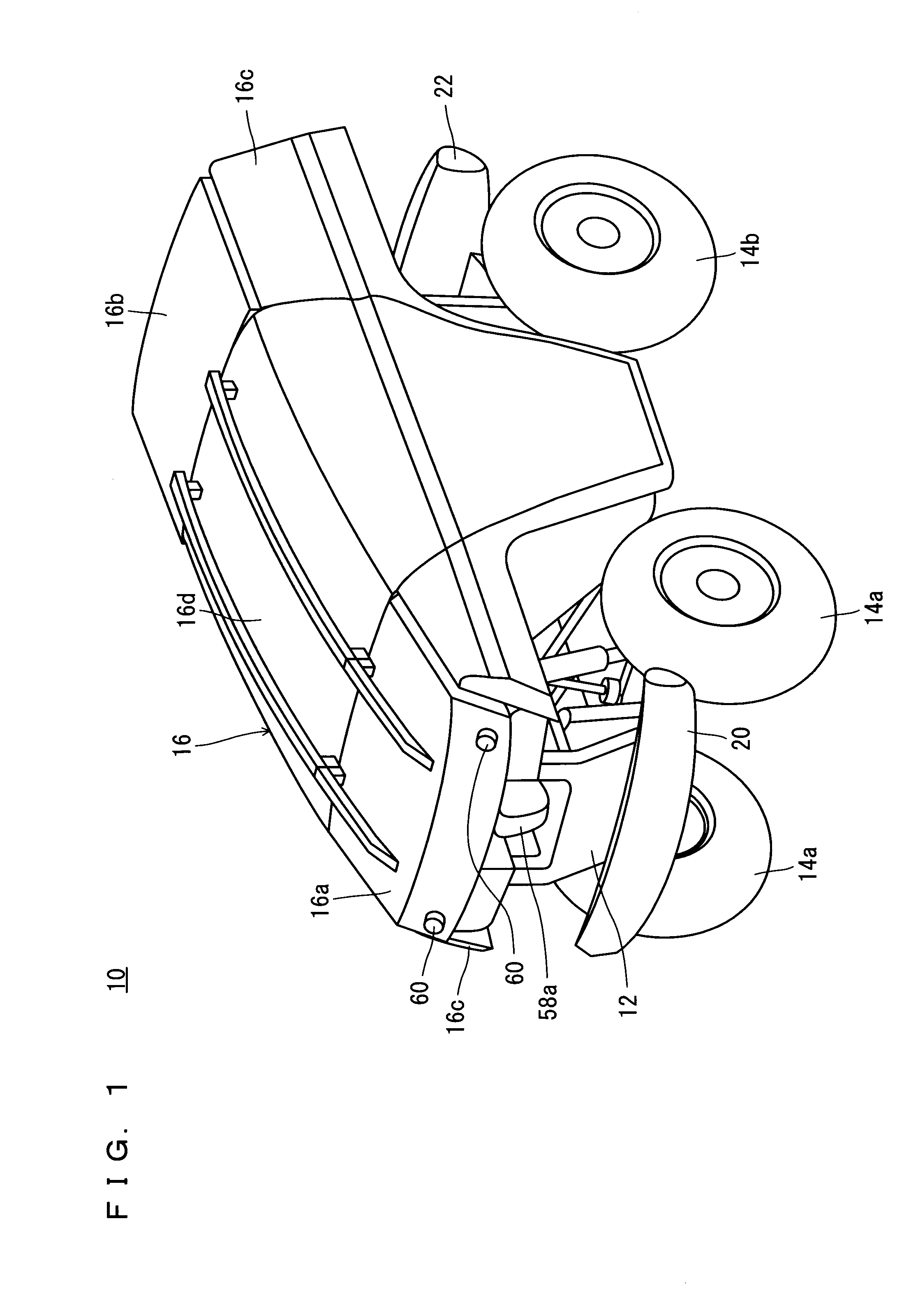

Vehicle

InactiveUS20090248231A1Reliable and goodImprove reliabilityAnti-collision systemsPosition/course control in two dimensionsMicrocomputerControl signal

A vehicle includes a button switch and a remote controller for setting an autonomous or manual driving mode, a microcomputer which outputs a mask control signal that corresponds to the driving mode, a command control unit which inputs a command to the microcomputer to output the mask control signal that corresponds to the driving mode, and a forward obstacle sensor and a rearward obstacle sensor which detect an obstacle and output a detection signal. A first logic circuit generates an emergency stop control signal that indicates a need or no need for an emergency stop of the vehicle based on the mask control signal from the microcomputer and the detection signals from the obstacle sensors. An emergency stopping operation of the vehicle is controlled based on the emergency stop control signal from the first logic circuit.

Owner:YAMAHA MOTOR CO LTD

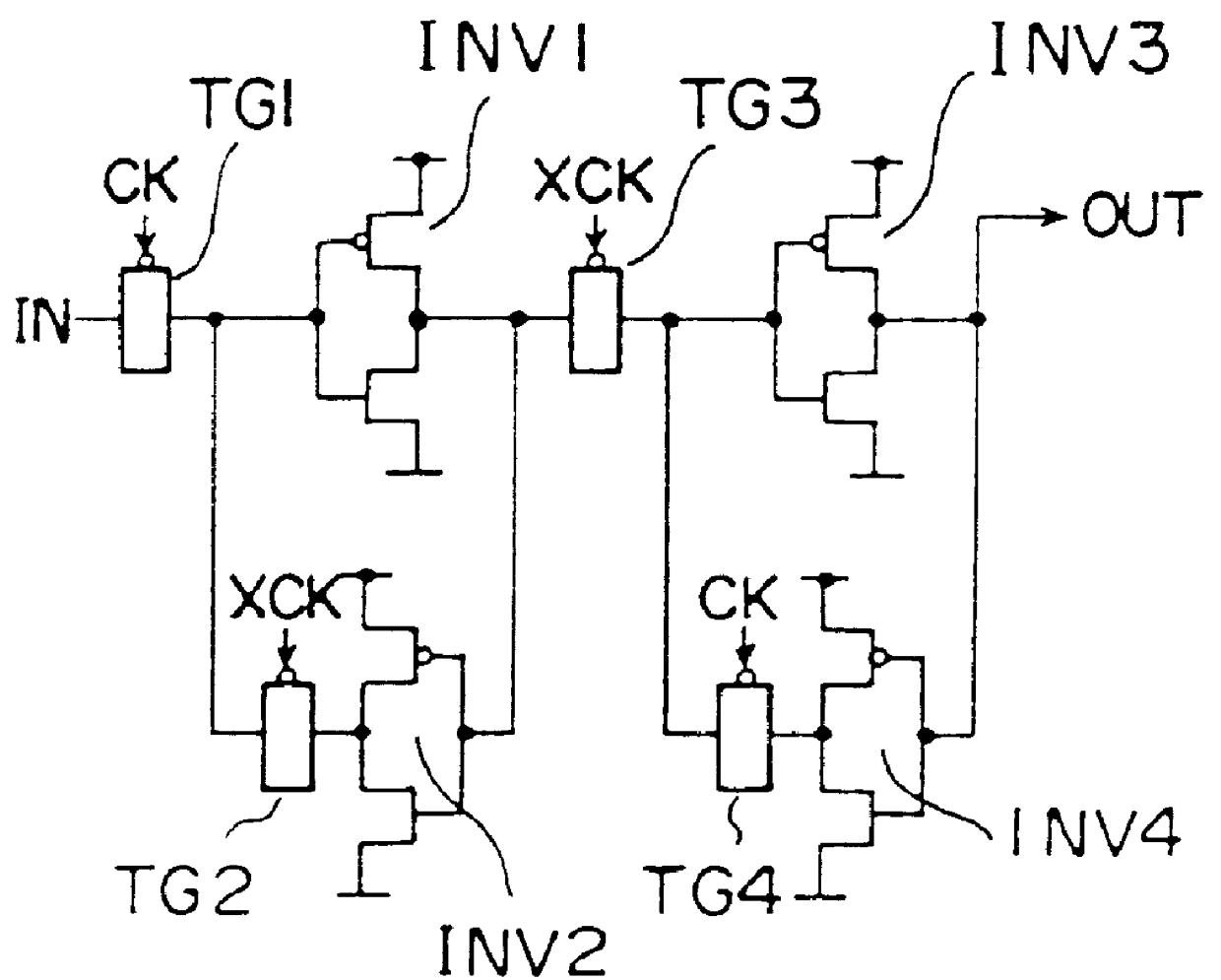

Chain-connected shift register and programmable logic circuit whose logic function is changeable in real time

InactiveUS6018559ADigital storageLogic circuits using elementary logic circuit componentsShift registerTransmission gate

A shift register having a plurality of circuit cells successively connected in a chain formation is proposed. Each of the circuit cells includes a first inversion gate, a first transmission gate, connected to an output of the first inversion gate, being switched by a clock, and a second inversion gate connected to an output of the first transmission gate. The circuit cell further includes a first P-channel transistor, connected between an output of the second inversion gate and an input of the first inversion gate, being switched by the clock, a second transmission gate, connected to the output of the second inversion gate, being switched by an inversion clock, and a second P-channel transistor, connected to the output of the first transmission gate, being switched by the inversion clock. In the shift register, the plurality of circuit cells are successively connected such that the input of the first inversion gate of the circuit cell is connected to an output of a second transmission gate of a former-stage circuit cell, and the output of the first inversion gate of the circuit cell is connected to an output of a second P-channel transistor of the former-stage circuit cell.

Owner:FUJITSU LTD

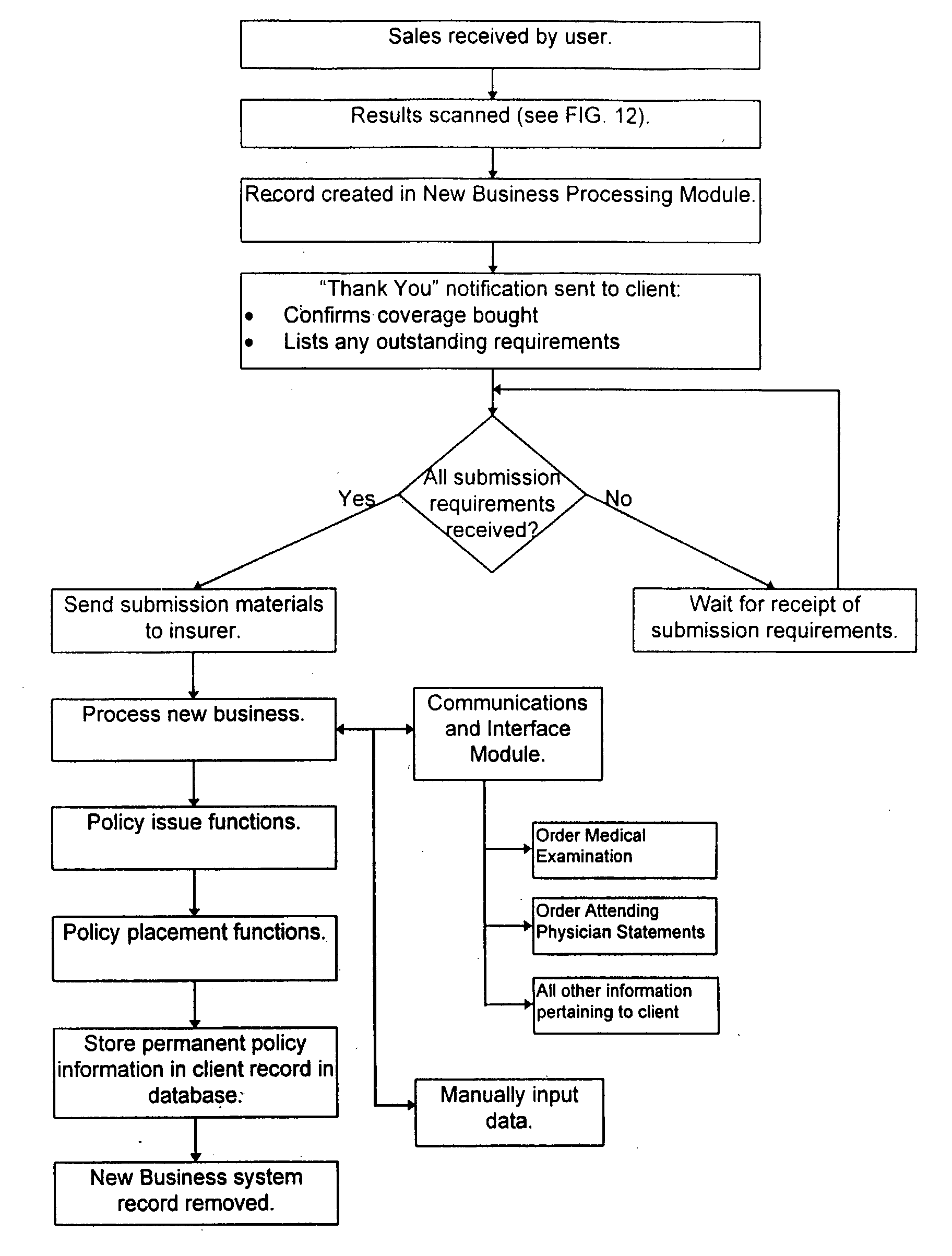

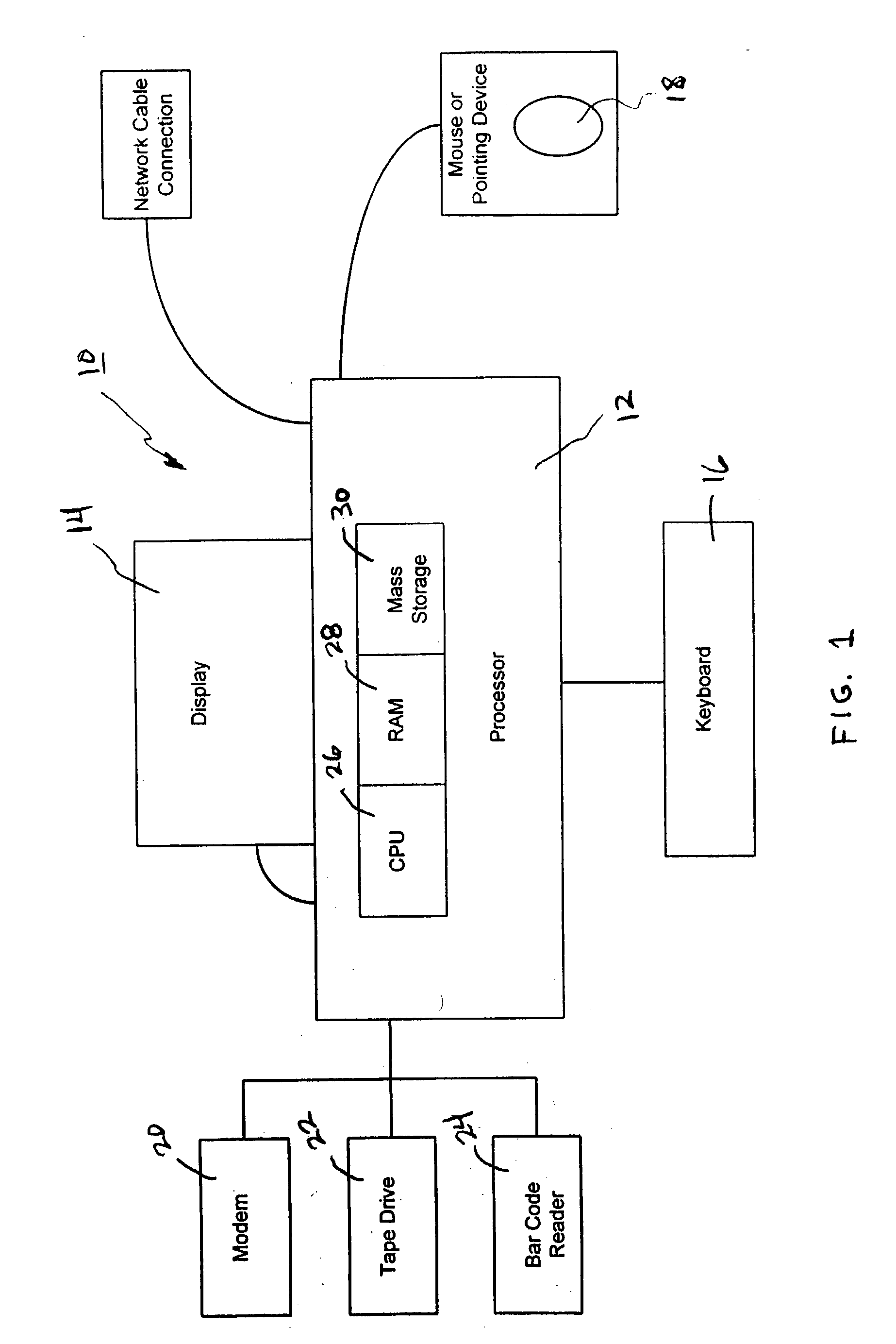

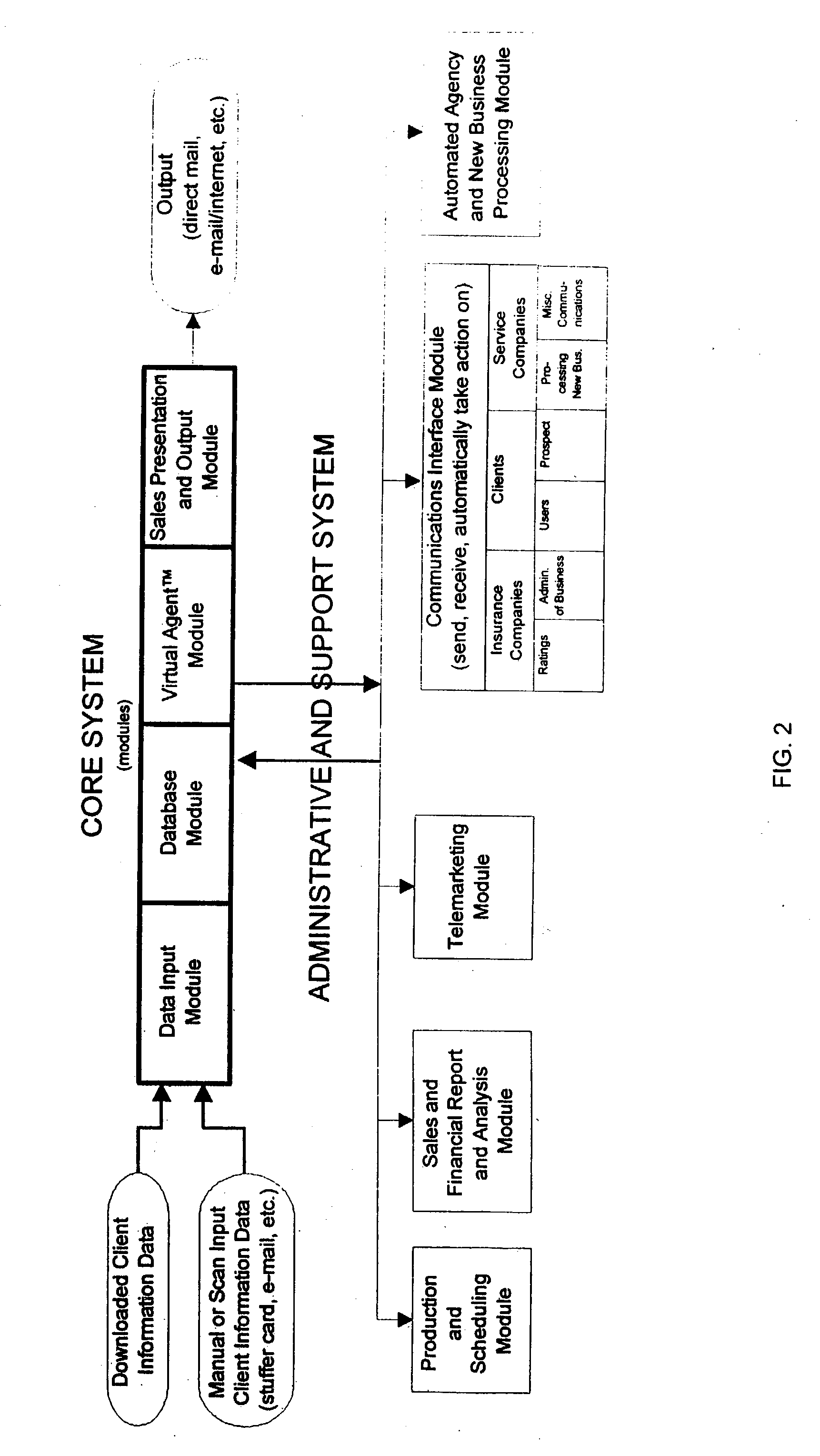

System, method, and computer program product for selecting and presenting financial products and services

InactiveUS20040030626A1Improve automationEffective volumeDiscounts/incentivesFinanceOutput deviceClient-side

An apparatus and method are provided which use client information from a client to automatically select and present financial products appropriate for the client. The apparatus according to one aspect of the invention comprises an input device for inputting client information relevant to a need by the client for the financial products, for inputting information about the financial products, for inputting ancillary data which excludes the client information and the financial products information, and for inputting decision criteria pertaining to selection from among the financial products. The apparatus further includes a storage device for storing the client information, the financial products information, the ancillary information, and the decision criteria. The apparatus still further includes decision making logic circuitry for using the client information, the financial products information, the ancillary information, and the decision criteria to select a subset of the financial products. It further includes an output device for preparing a client communication which identifies the subset of the financial products. The output device incorporates a portion of the client information and a portion of the financial products information into the client communication. The method according to one aspect of the invention comprises inputting client information relevant to a need by the client for the financial products, inputting information about the financial products, inputting ancillary data which excludes the client information and the financial products information, and inputting decision criteria pertaining to selection from among the financial products. The method also includes storing the client information, the financial products information, the ancillary information, and the decision criteria. This method further includes using the client information, the financial products information, the ancillary information, and the decision criteria to select a subset of the financial products. It further includes preparing a client communication which identifies the subset of the financial products. This client communication preparing step includes incorporating a portion of the client information and a portion of the financial products information into the client communication.

Owner:RPX CORP

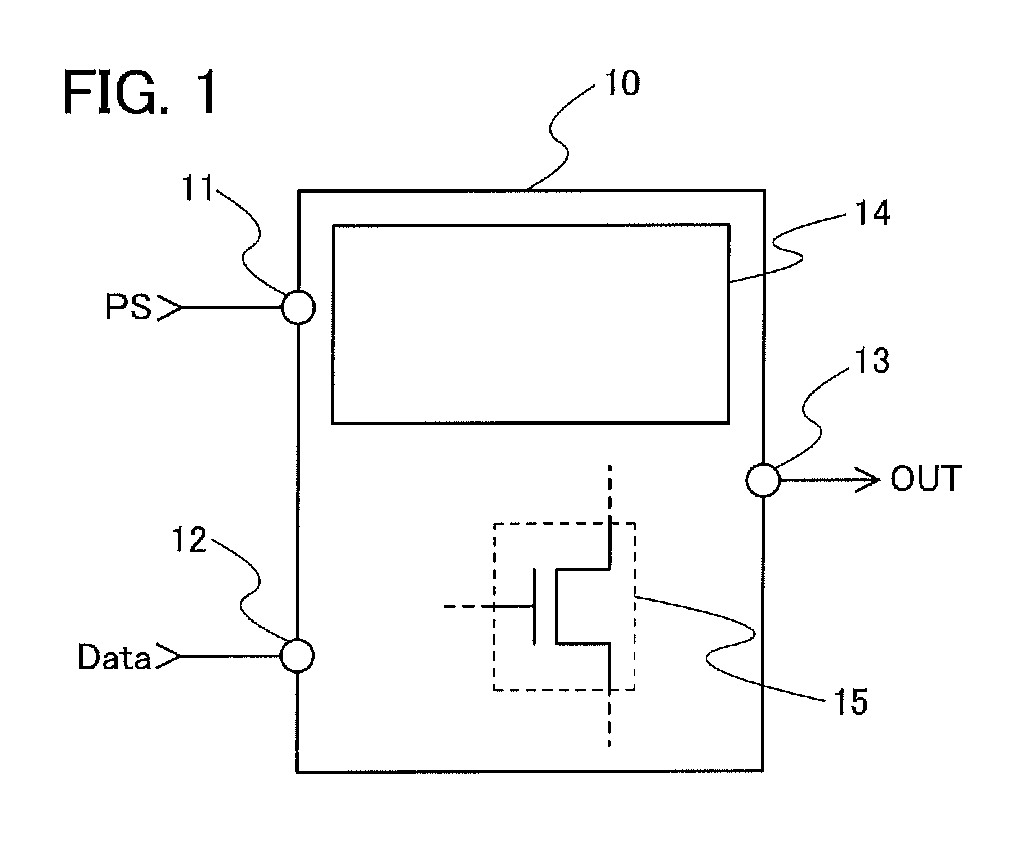

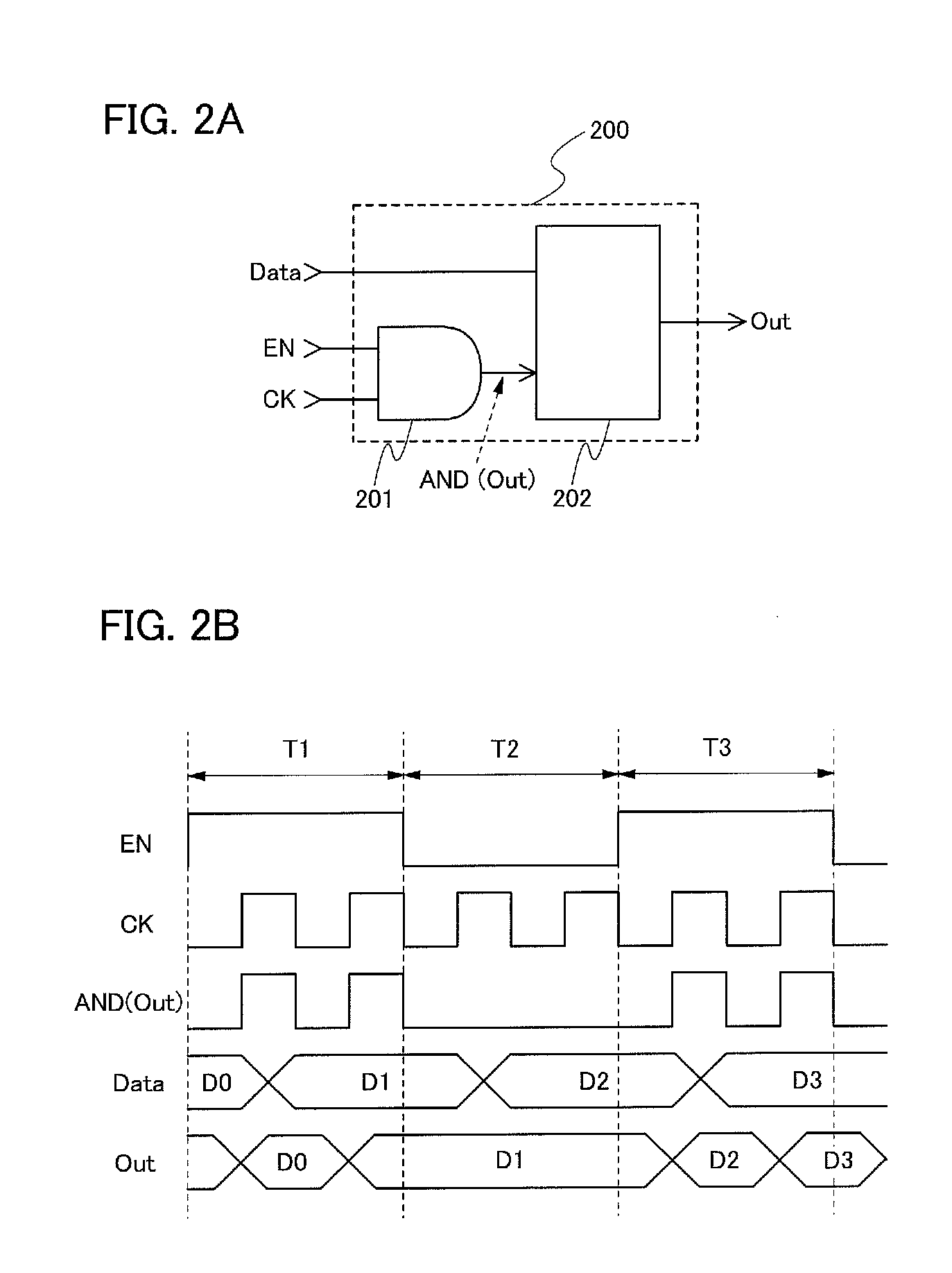

Logic circuit and semiconductor device

ActiveUS8207756B2Reduce dynamic power consumptionLeakage of highTransistorPower reduction by control/clock signalHydrogen concentrationPower semiconductor device

In a logic circuit where clock gating is performed, the standby power is reduced or malfunction is suppressed. The logic circuit includes a transistor which is in an off state where a potential difference exists between a source terminal and a drain terminal over a period during which a clock signal is not supplied. A channel formation region of the transistor is formed using an oxide semiconductor in which the hydrogen concentration is reduced. Specifically, the hydrogen concentration of the oxide semiconductor is 5×1019 (atoms / cm3) or lower. Thus, leakage current of the transistor can be reduced. As a result, in the logic circuit, reduction in standby power and suppression of malfunction can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

Nonvolatile latch circuit and logic circuit, and semiconductor device using the same

ActiveUS20110187410A1Wider range of operating temperatureGuaranteed uptimeSolid-state devicesDigital storageSemiconductor materialsCapacitor

To provide a novel nonvolatile latch circuit and a semiconductor device using the nonvolatile latch circuit, a nonvolatile latch circuit includes a latch portion having a loop structure where an output of a first element is electrically connected to an input of a second element, and an output of the second element is electrically connected to an input of the first element; and a data holding portion configured to hold data of the latch portion. In the data holding portion, a transistor using an oxide semiconductor as a semiconductor material for forming a channel formation region is used as a switching element. In addition, a capacitor electrically connected to a source electrode or a drain electrode of the transistor is included.

Owner:SEMICON ENERGY LAB CO LTD

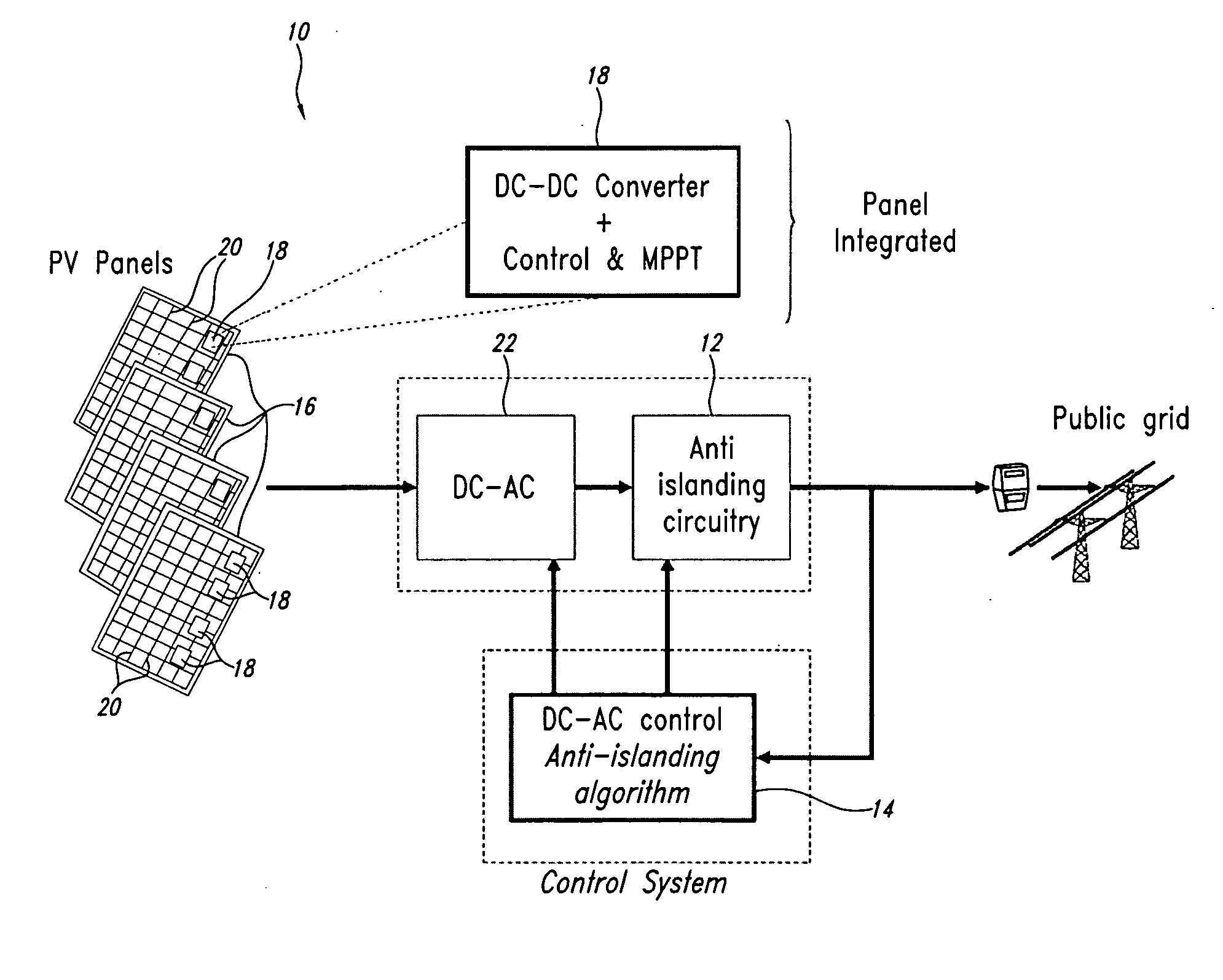

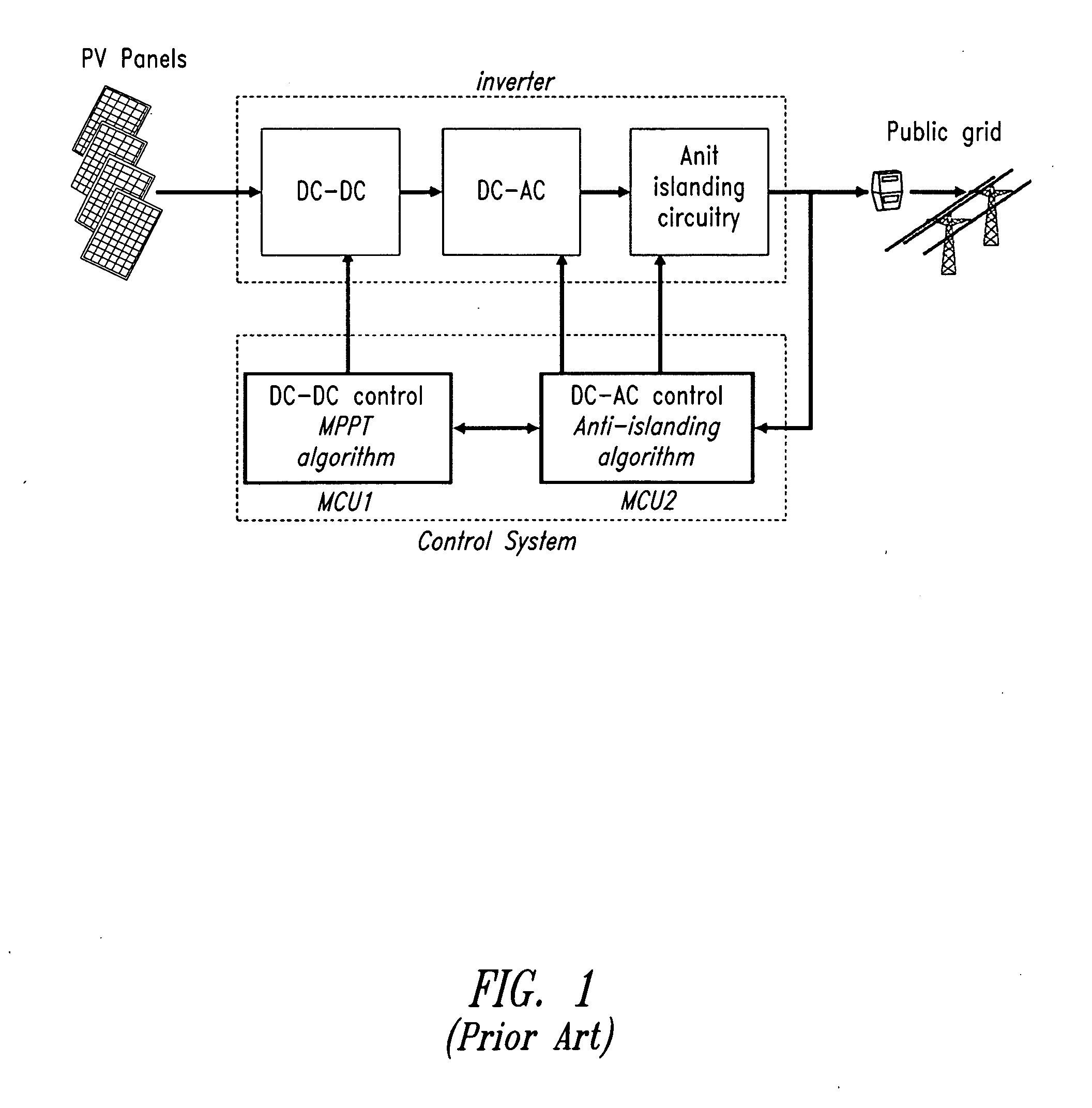

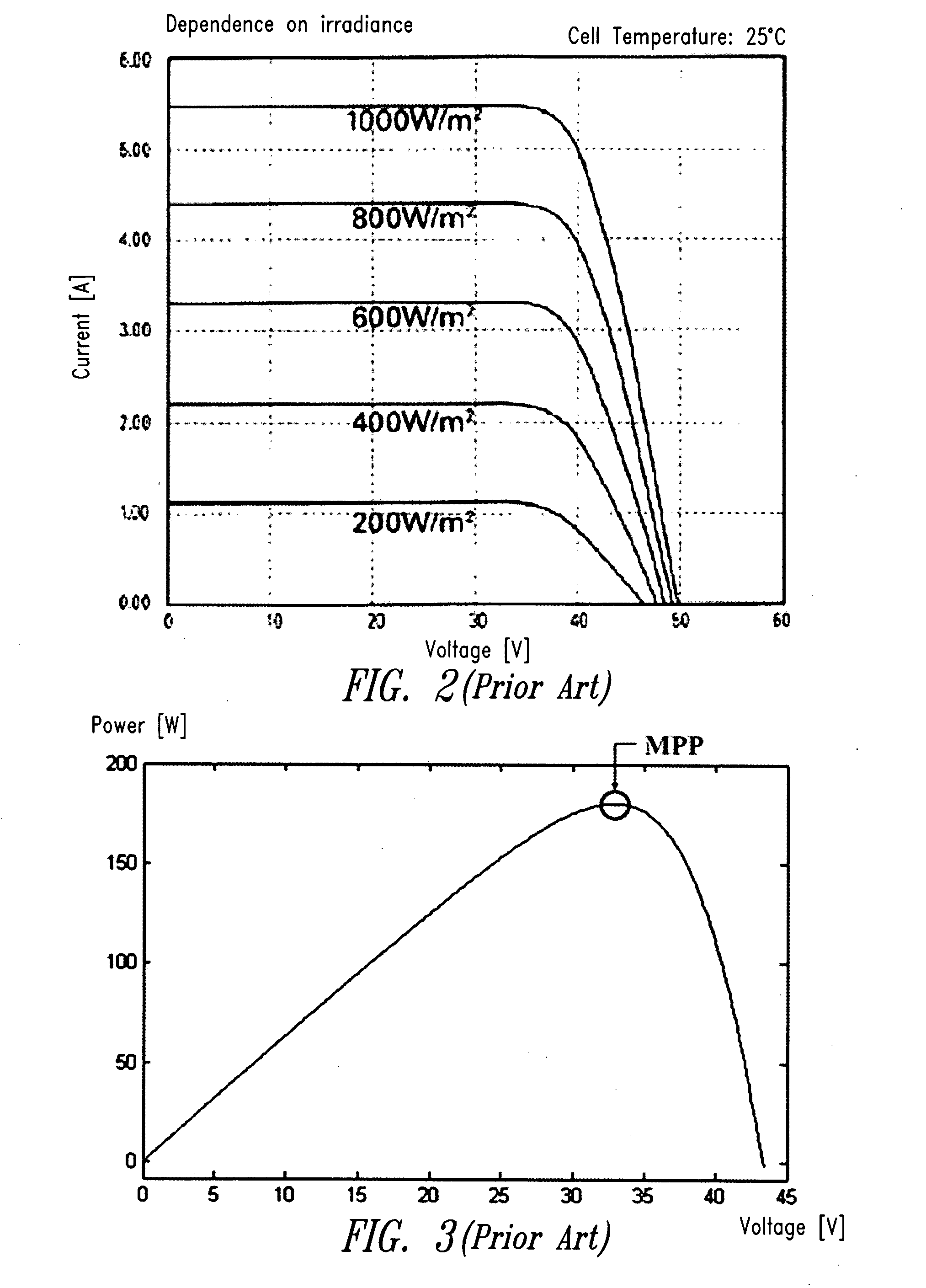

Multi-cellular photovoltaic panel system with dc-dc conversion replicated for groups of cells in series of each panel and photovoltaic panel structure

ActiveUS20090179500A1Improve efficiencySimple processClimate change adaptationDc source parallel operationDc dc converterMppt algorithm

A photovoltaic energy conversion system includes a distributed control structure for groups of cells of each multi-cellular panel, the components of which are entirely physically integrated in the photovoltaic panel. Each multi-cellular photovoltaic panel has a DC bus, supplied in parallel by a plurality of DC-DC converters, each provided with a controller that controls the working point of the photovoltaic cells coupled to the input of the DC-DC converter for a maximum yield of electric power by implementing a relatively simple MPPT algorithm. The controller includes a logic circuit and A / D converters of analog signals representing the input voltage and the input current generated by the group of cells that is coupled to the input of the DC-DC converter and optionally also of the output voltage of the converter, and a relatively simple D / A converter of the drive control signal of the power switch of the DC-DC converter.

Owner:STMICROELECTRONICS SRL

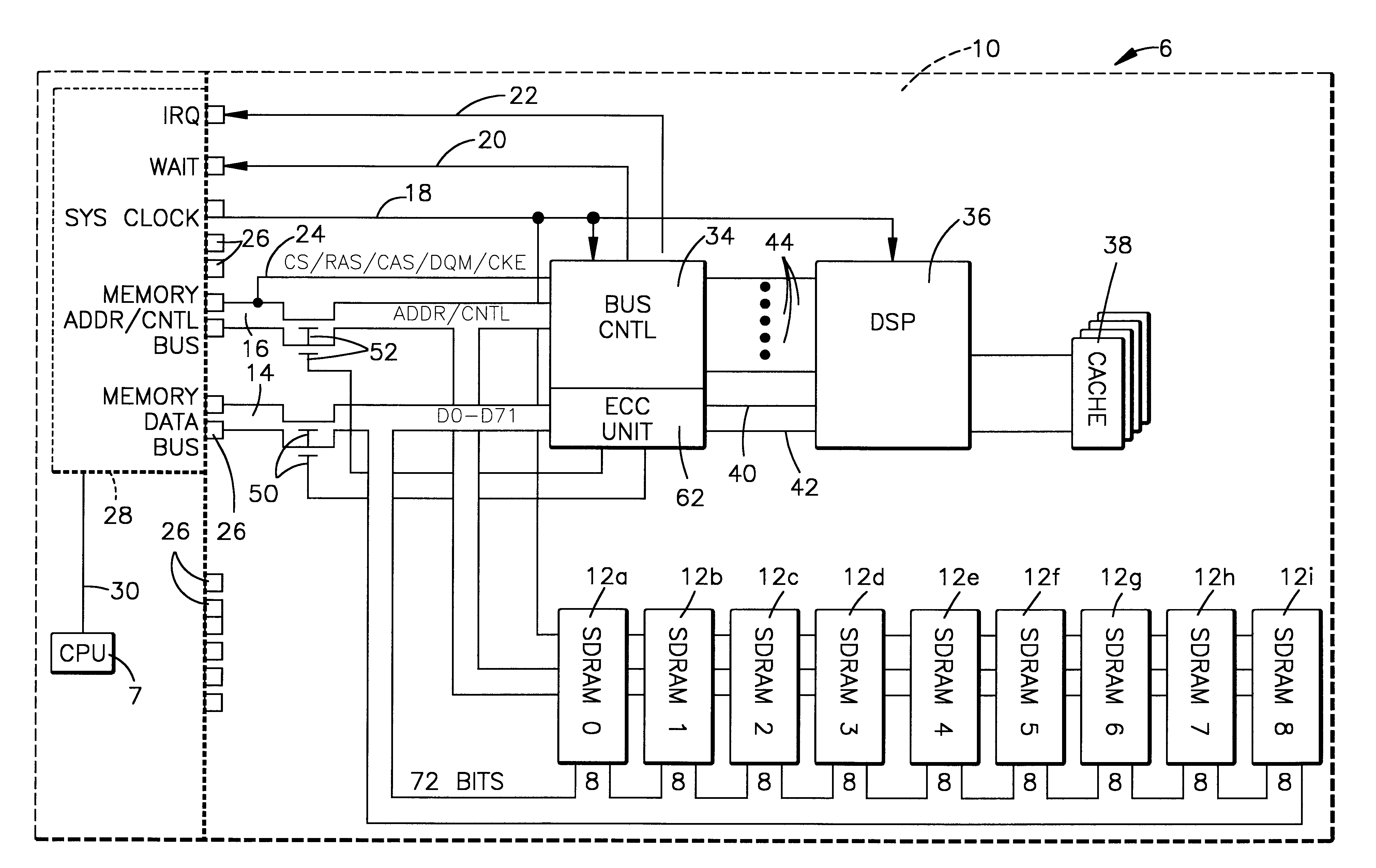

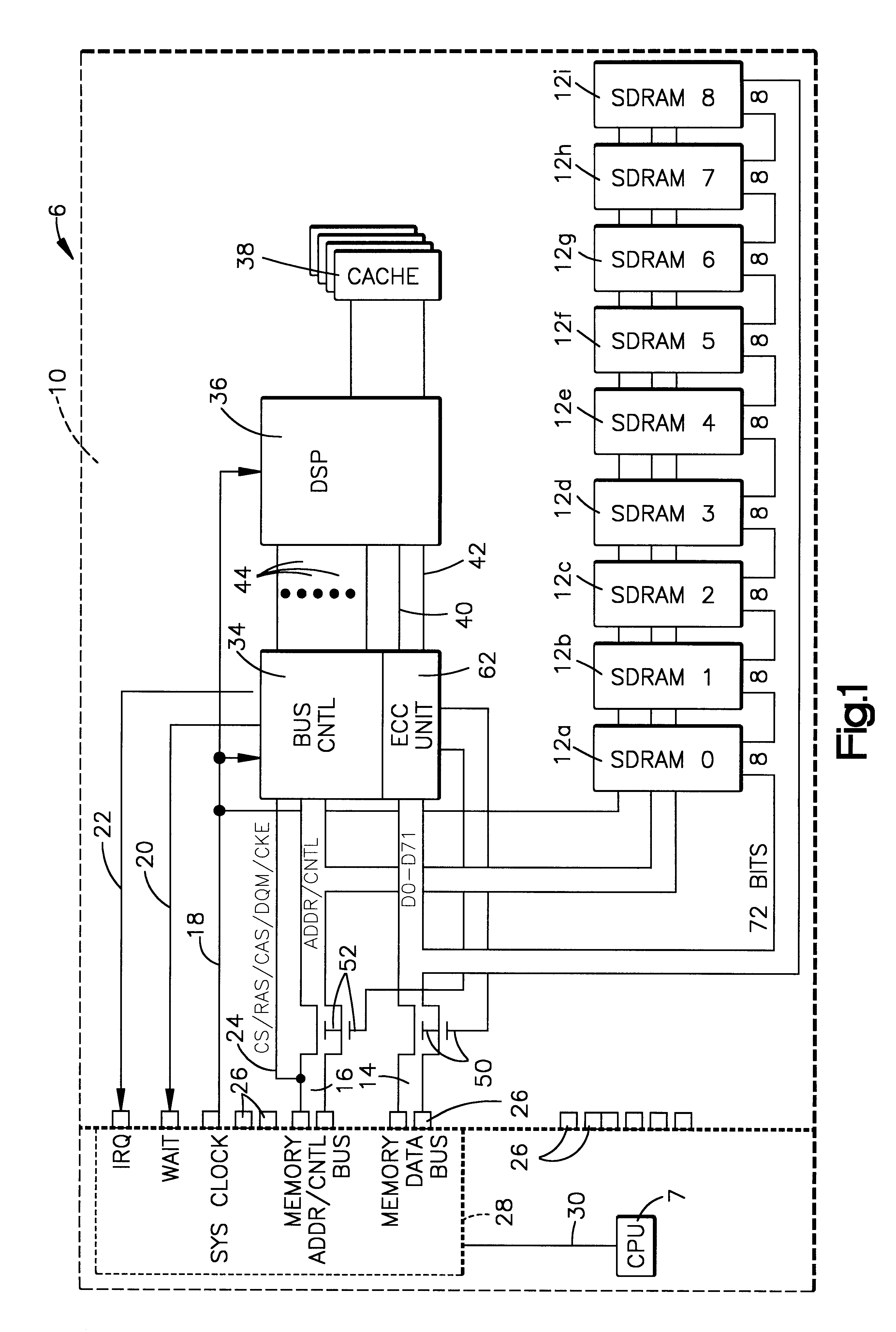

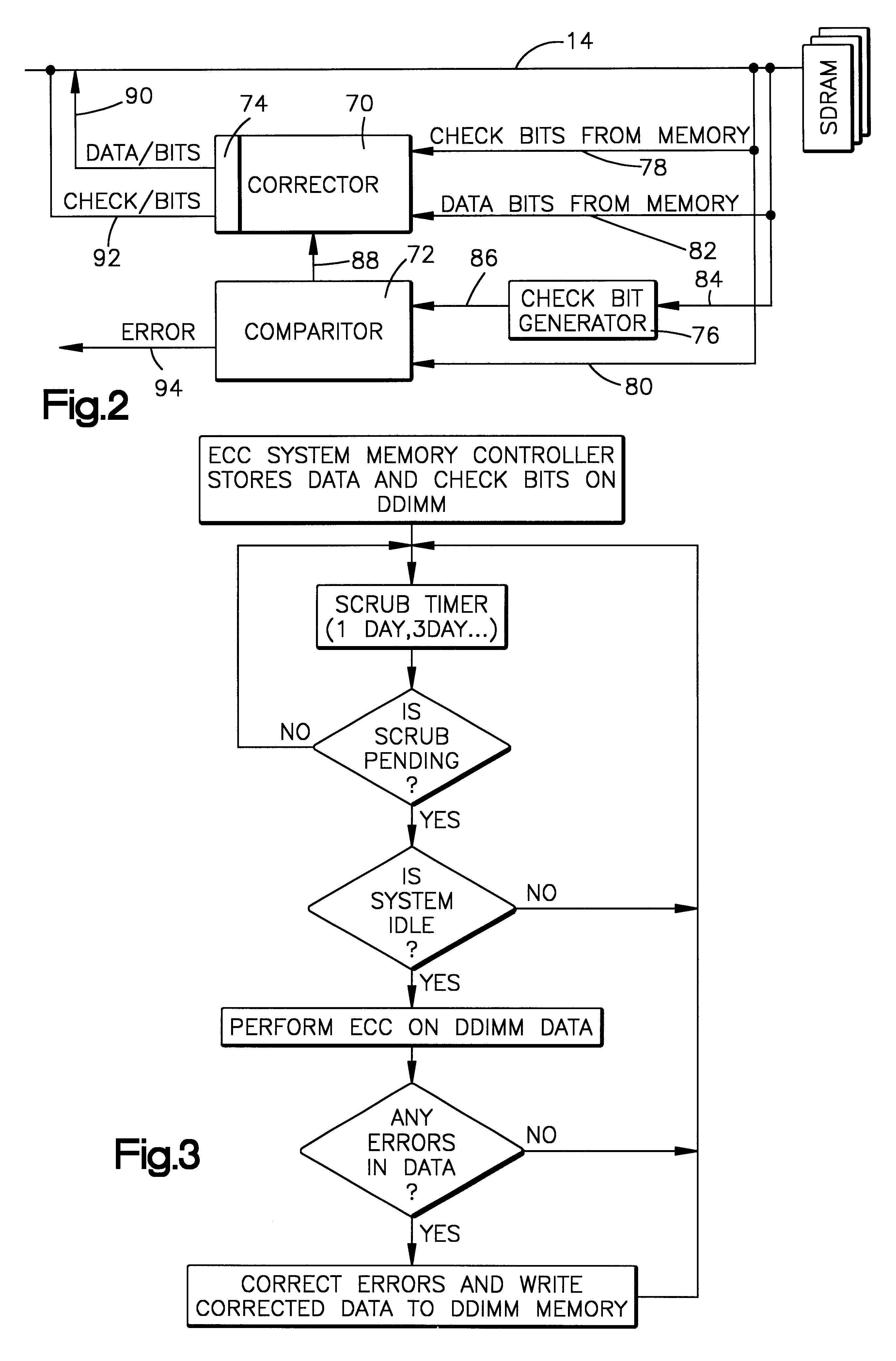

On-board scrubbing of soft errors memory module

A memory module for attachment to a computer system having a memory bus and a method of using the memory module for error correction by scrubbing soft errors on-board the module is provided. The module includes a printed circuit card with memory storage chips on the card to store data bits and associated ECC check bits. Tabs are provided on the circuit card to couple the card to the memory bus of the computer system. Logic circuitry selectively operatively connects and disconnects the memory chip and the memory bus. A signal processor is connected in circuit relationship with the memory chips. The logic circuitry selectively permits the signal processor to read the stored data bits and associated check bits from the memory chips, recalculate the check bits from the read stored data bits, compare the recalculated check bits with the stored check bits, correct all at least one bit errors in the store data bits and stored associated check bits and re-store the correct data bits and associated check bits in the memory chips. When the memory chips and the memory bus are disconnected, single bit soft errors occurring during storage of the data bits and check bits are corrected periodically before the data is read from the memory chips to the data bus on a read operation.

Owner:IBM CORP

Apparatus for reducing power supply noise in an integrated circuit

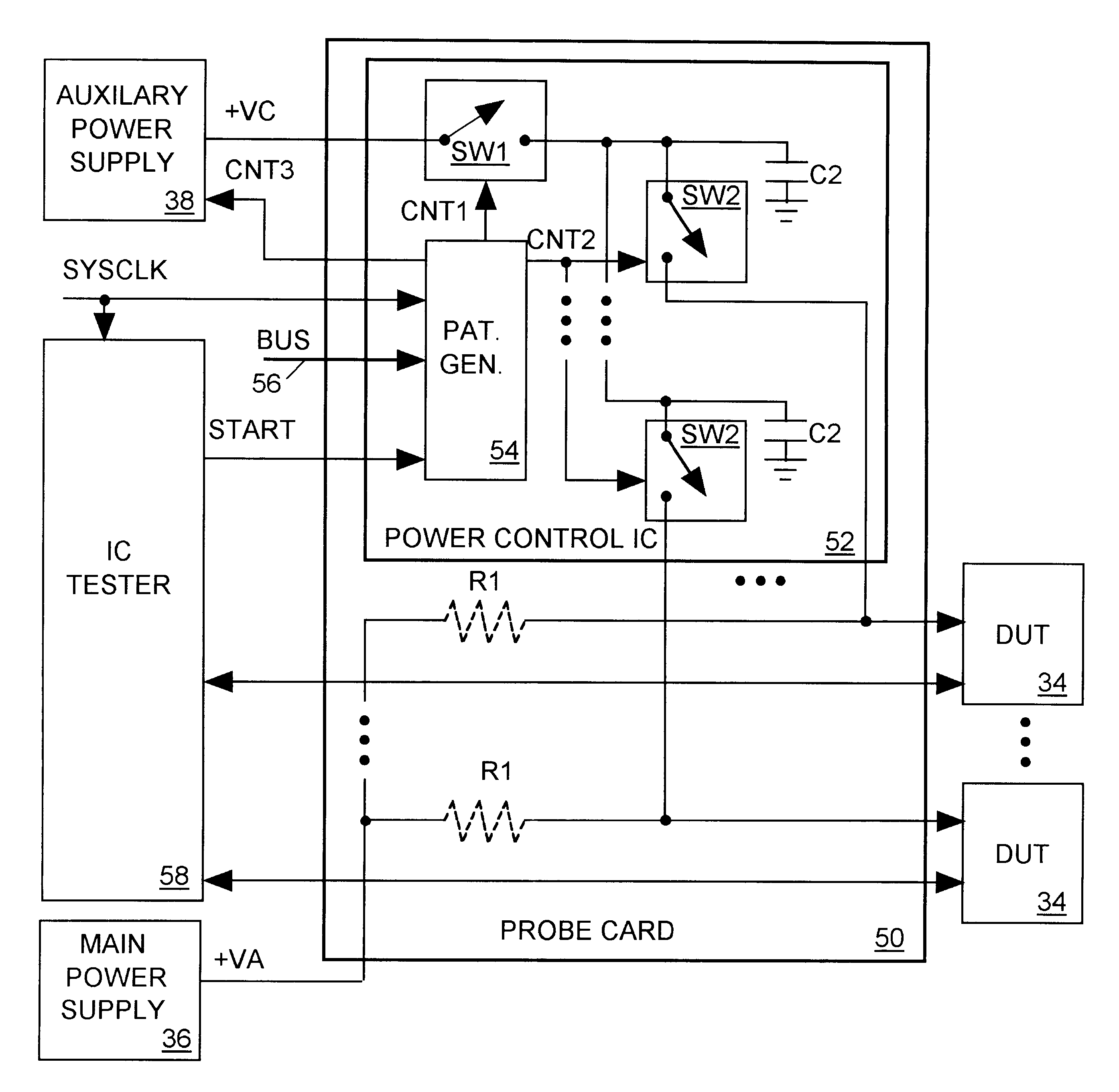

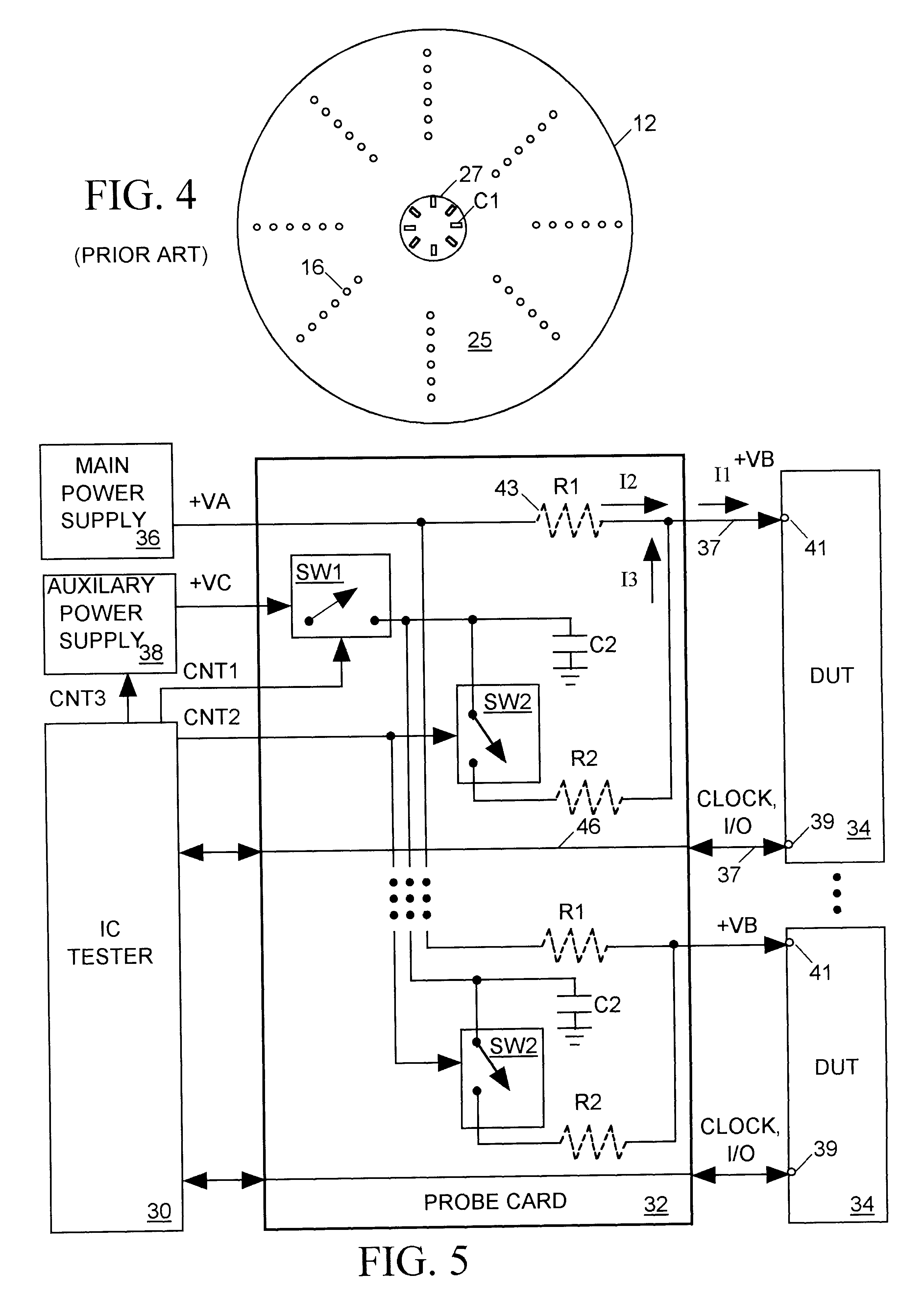

InactiveUS6339338B1Reduce power supply noiseSuppress mutationDigital circuit testingVolume/mass flow measurementCapacitanceState variation

A main power supply continuously provides a current to a power input terminal of an integrated circuit device under test (DUT). The DUT's demand for current at the power input terminal temporarily increases during state changes in synchronous logic circuits implemented within the DUT. To limit variation (noise) in voltage at the power input terminal arising from these temporary increases in current demand, a charged capacitor is connected to the power input terminal during each DUT state change. The capacitor discharges into the power input terminal to supply additional current to meet the DUT's increased demand. Following each DUT state change the capacitor is disconnected from the power input terminal and charged to a level sufficient to meet a predicted increase in current demand during a next DUT state change.

Owner:FORMFACTOR INC

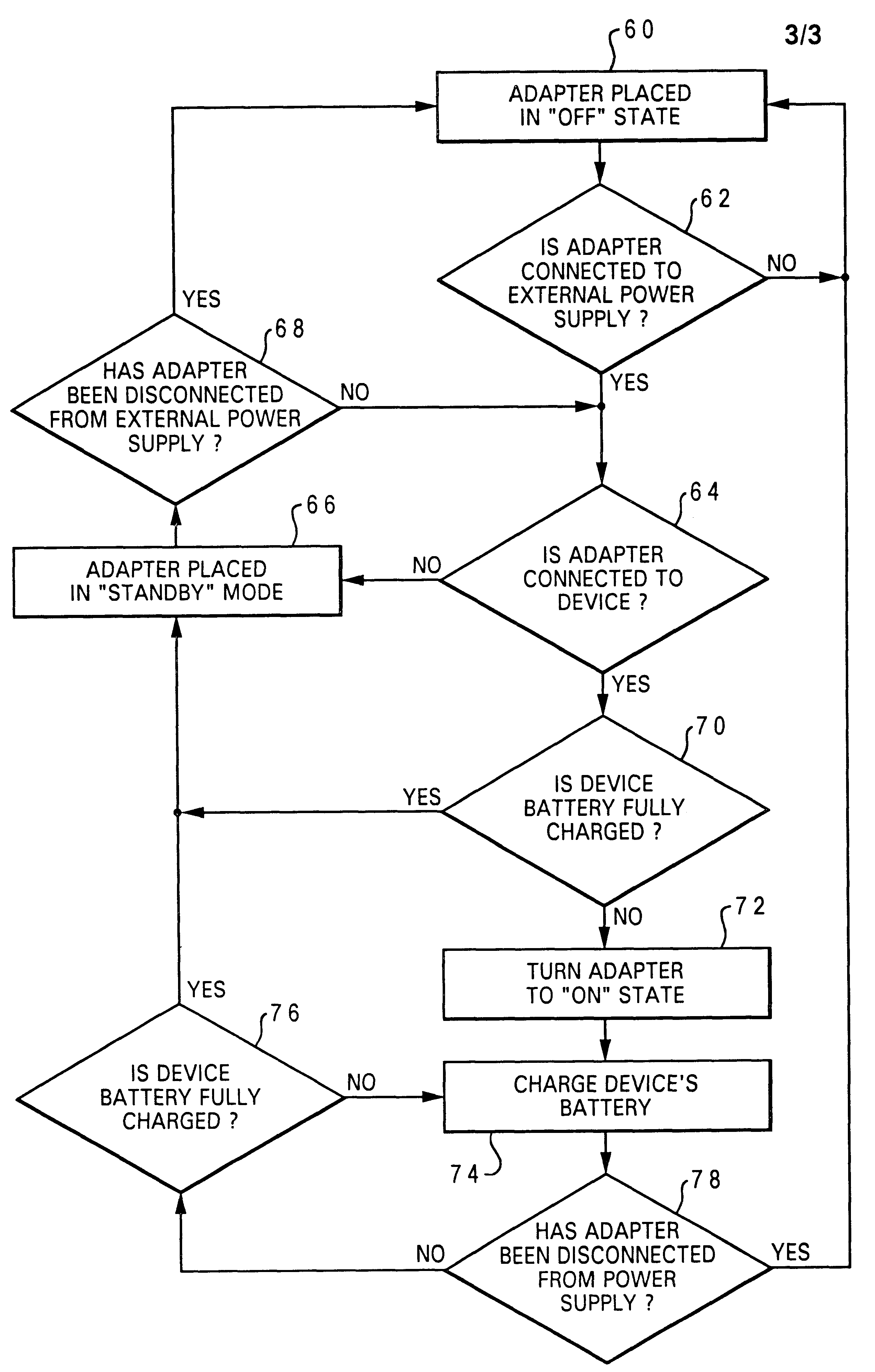

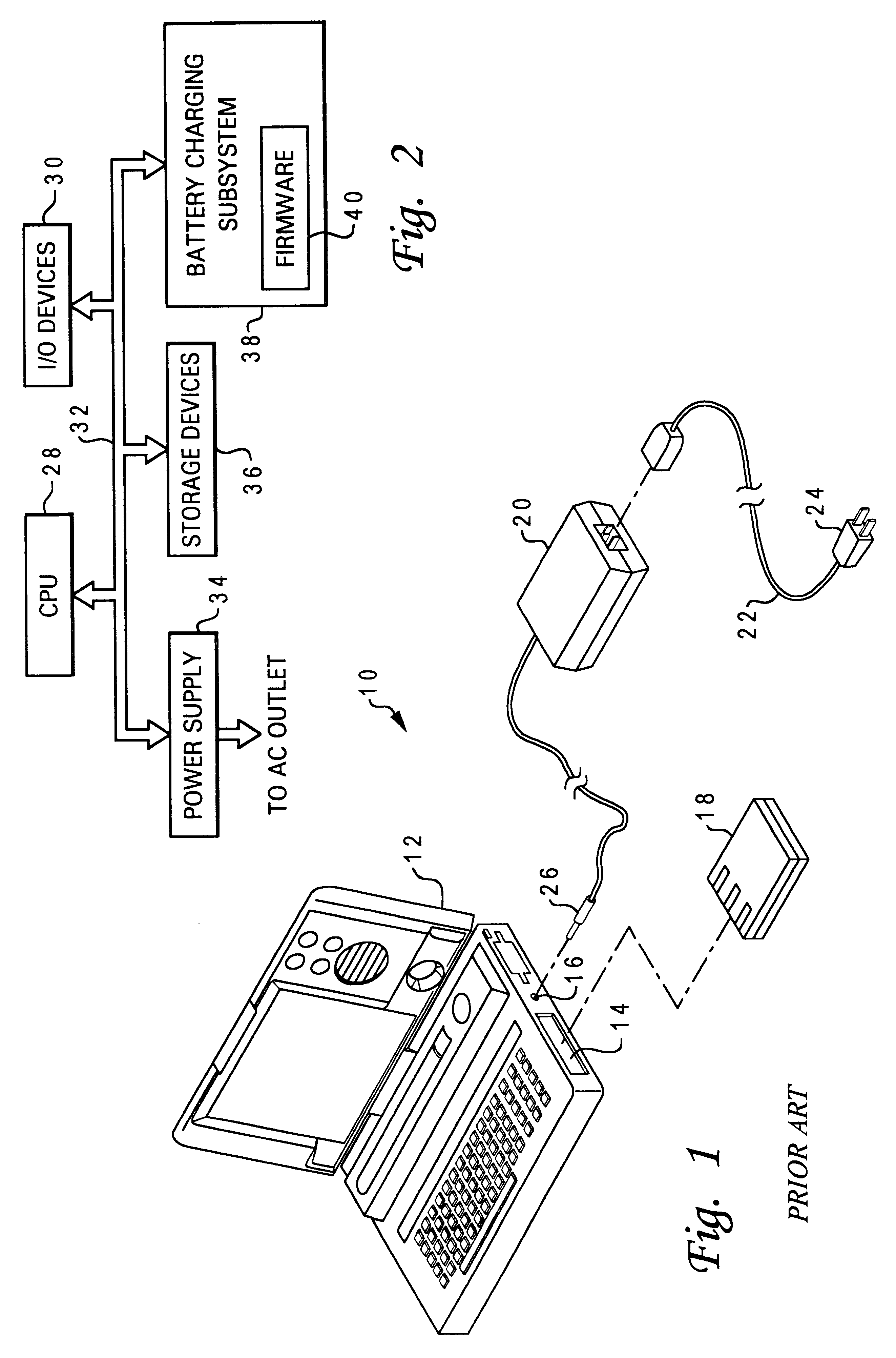

Method and system for remotely supplying power through an automated power adapter to a data processing system

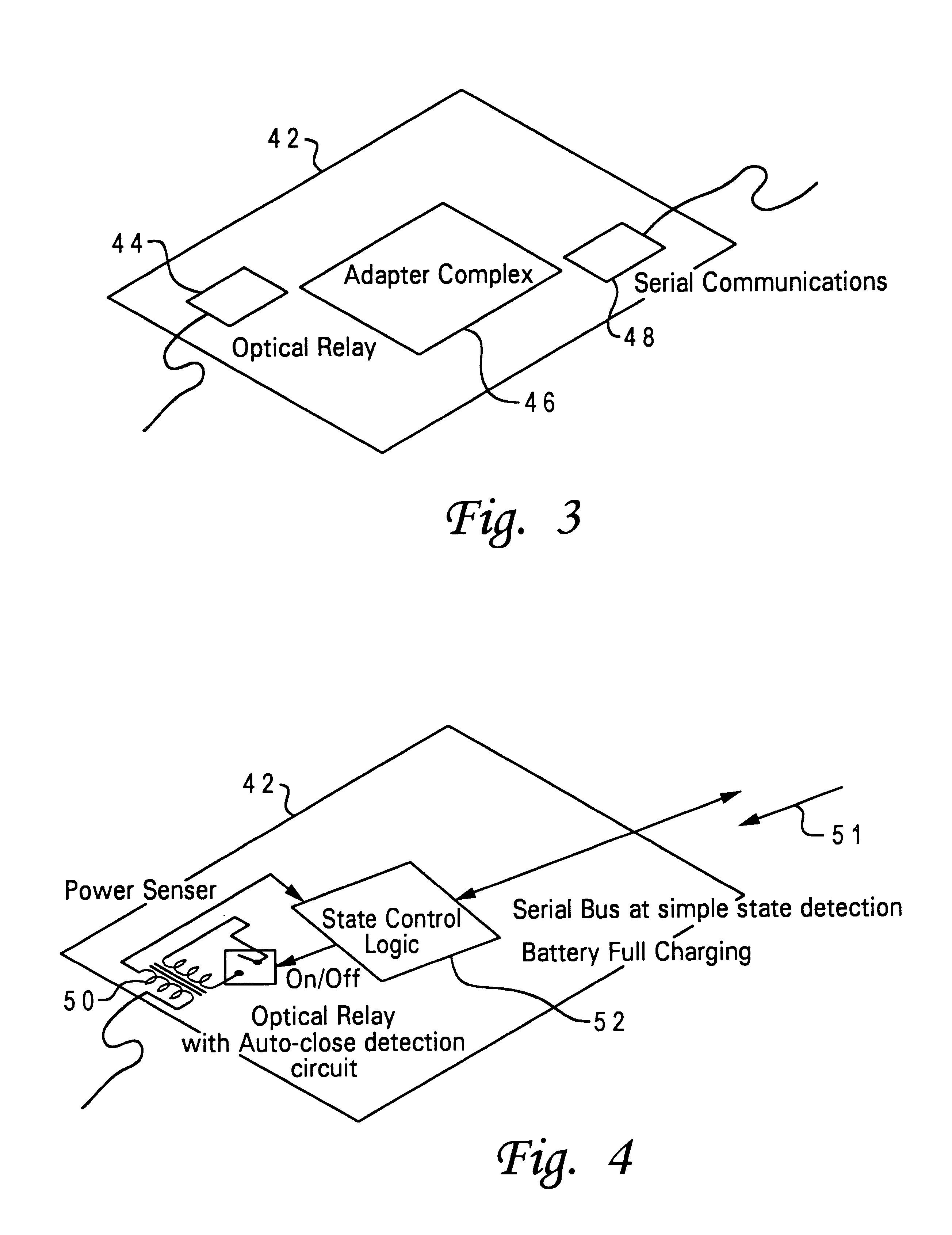

A method and system for supplying external electrical power to charge a battery within a data processing system by utilizing a automated remotely located power adapter is disclosed. The automated remotely located power adapter includes a state control logic circuit for determining when to supply external electrical power to charge the battery and an auto-close detection circuit for automatically shutting on and off the external electrical power in response to the state control logic. The automated remotely located power adapter is connectable between the external power supply and the data processing system for supplying external electrical power to charge the battery within the data processing system and automatically shuts off the external electrical power when the data processing system indicates that the battery is fully charged.

Owner:LENOVO (SINGAPORE) PTE LTD

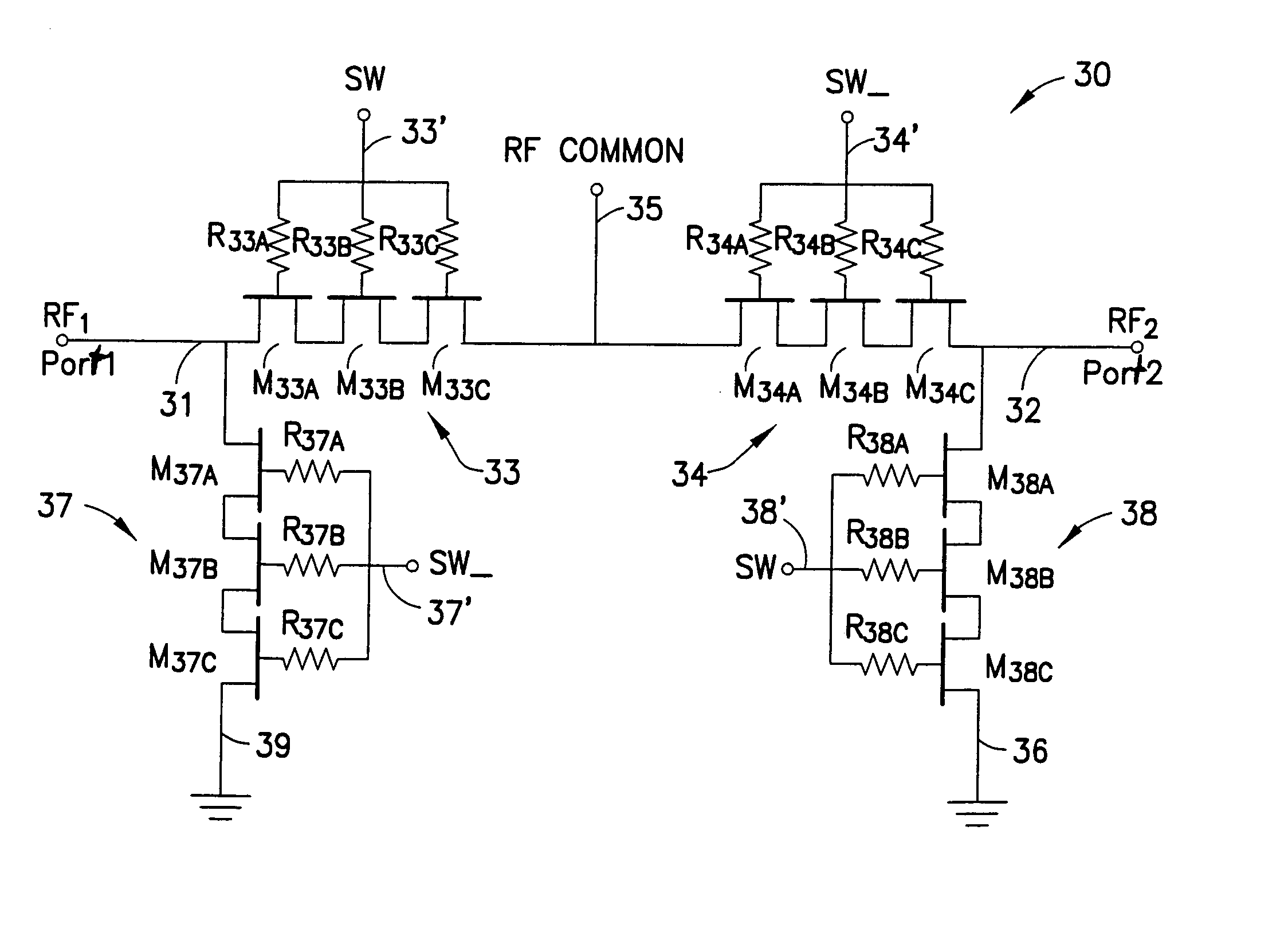

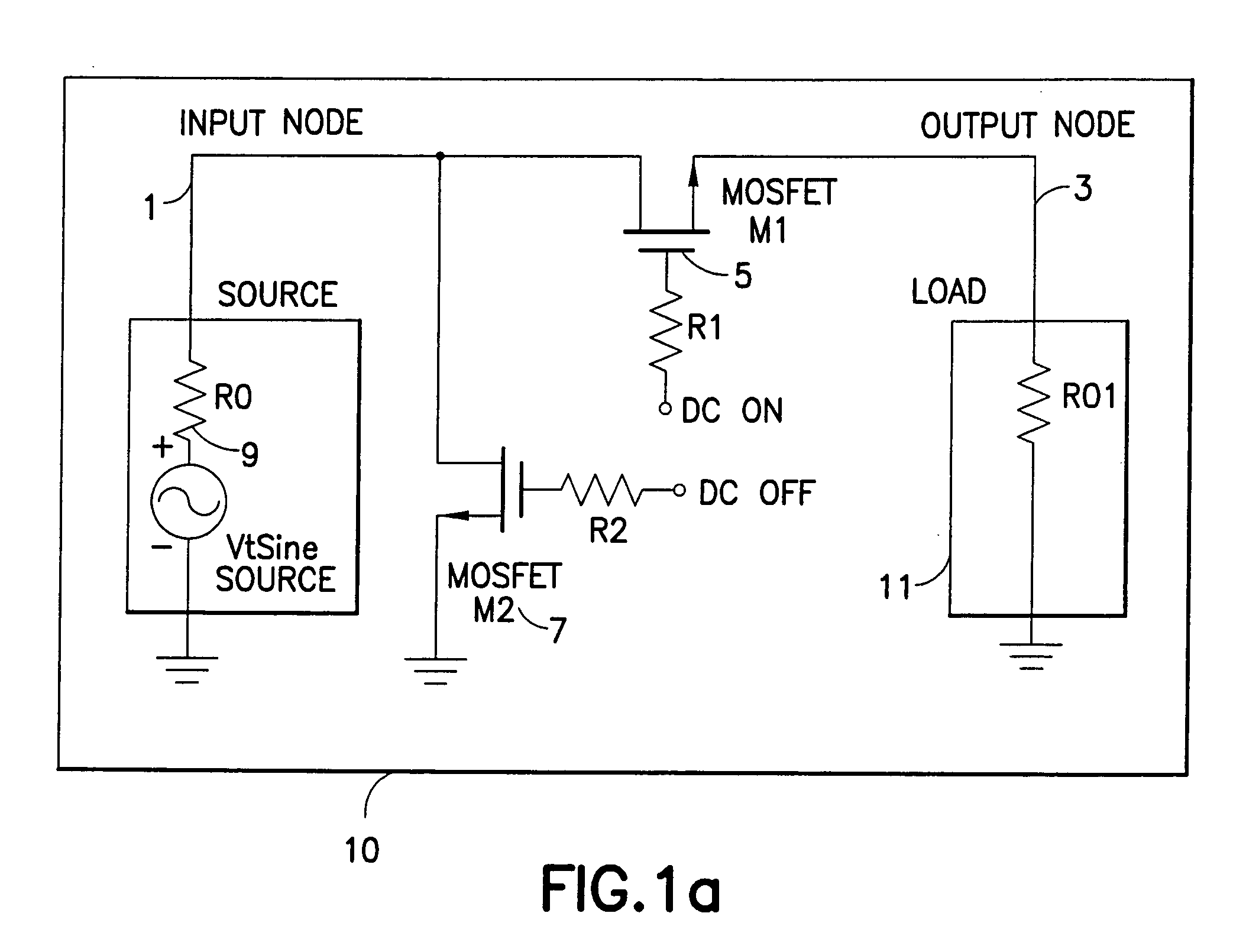

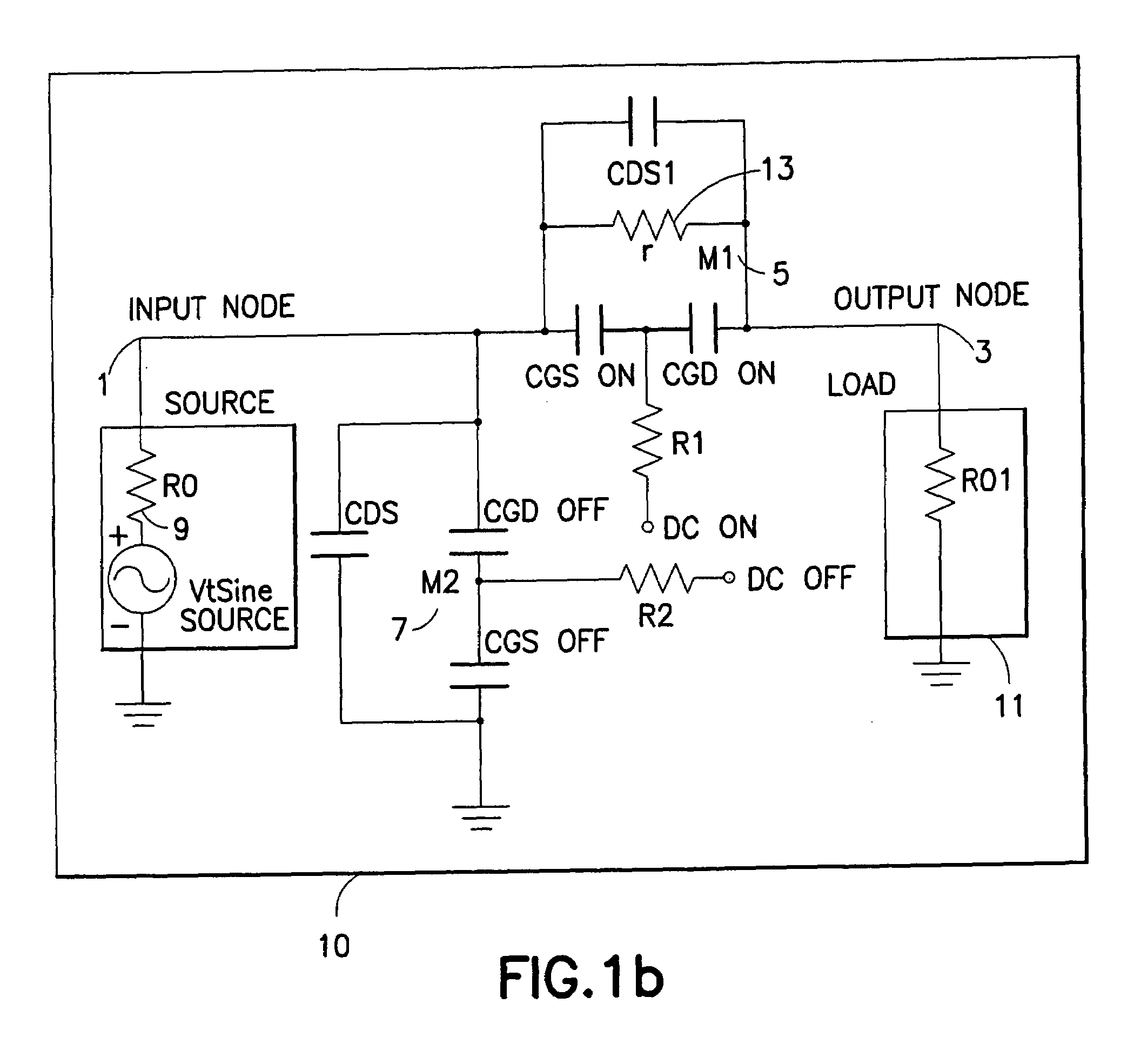

Switch circuit and method of switching radio frequency signals

InactiveUS7123898B2Easy to switchImprove reliabilityTransistorSolid-state devicesMOSFETDigital control

A novel RF buffer circuit adapted for use with an RF switch circuit and method for switching RF signals is described. The RF switch circuit is fabricated in a silicon-on-insulator (SOI) technology. The RF switch includes pairs of switching and shunting transistor groupings used to alternatively couple RF input signals to a common RF node. The switching and shunting transistor grouping pairs are controlled by a switching control voltage (SW) and its inverse (SW_). The switching and shunting transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. The stacking of transistor grouping devices, and associated gate resistors, increase the breakdown voltage across the series connected switch transistors and operate to improve RF switch compression. A fully integrated RF switch is described including digital control logic and a negative voltage generator integrated together with the RF switch elements. In one embodiment, the fully integrated RF switch includes a built-in oscillator, a charge pump circuit, CMOS logic circuitry, level-shifting and voltage divider circuits, and an RF buffer circuit. Several embodiments of the charge pump, level shifting, voltage divider, and RF buffer circuits are described. The inventive RF switch provides improvements in insertion loss, switch isolation, and switch compression.

Owner:PSEMI CORP

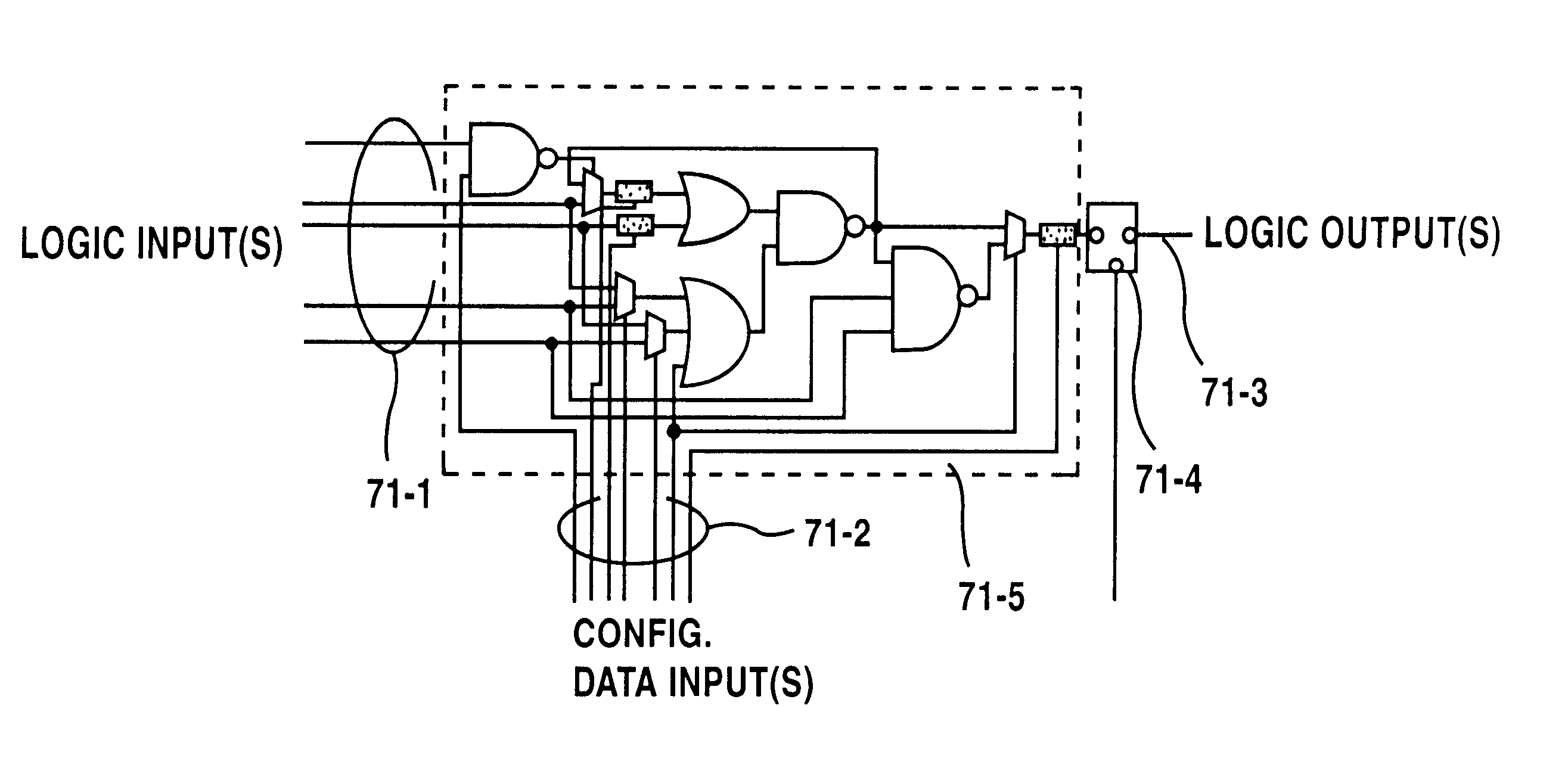

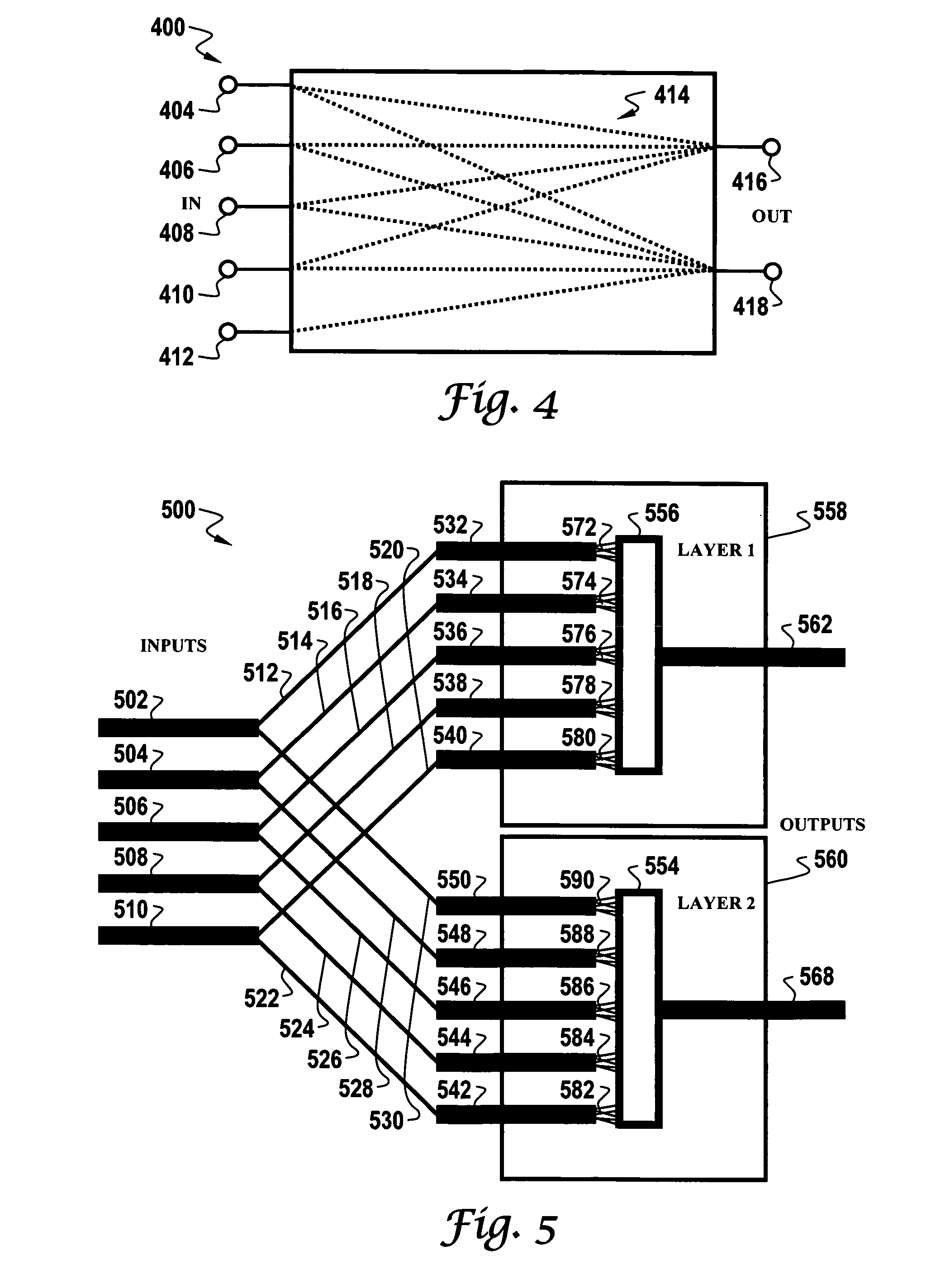

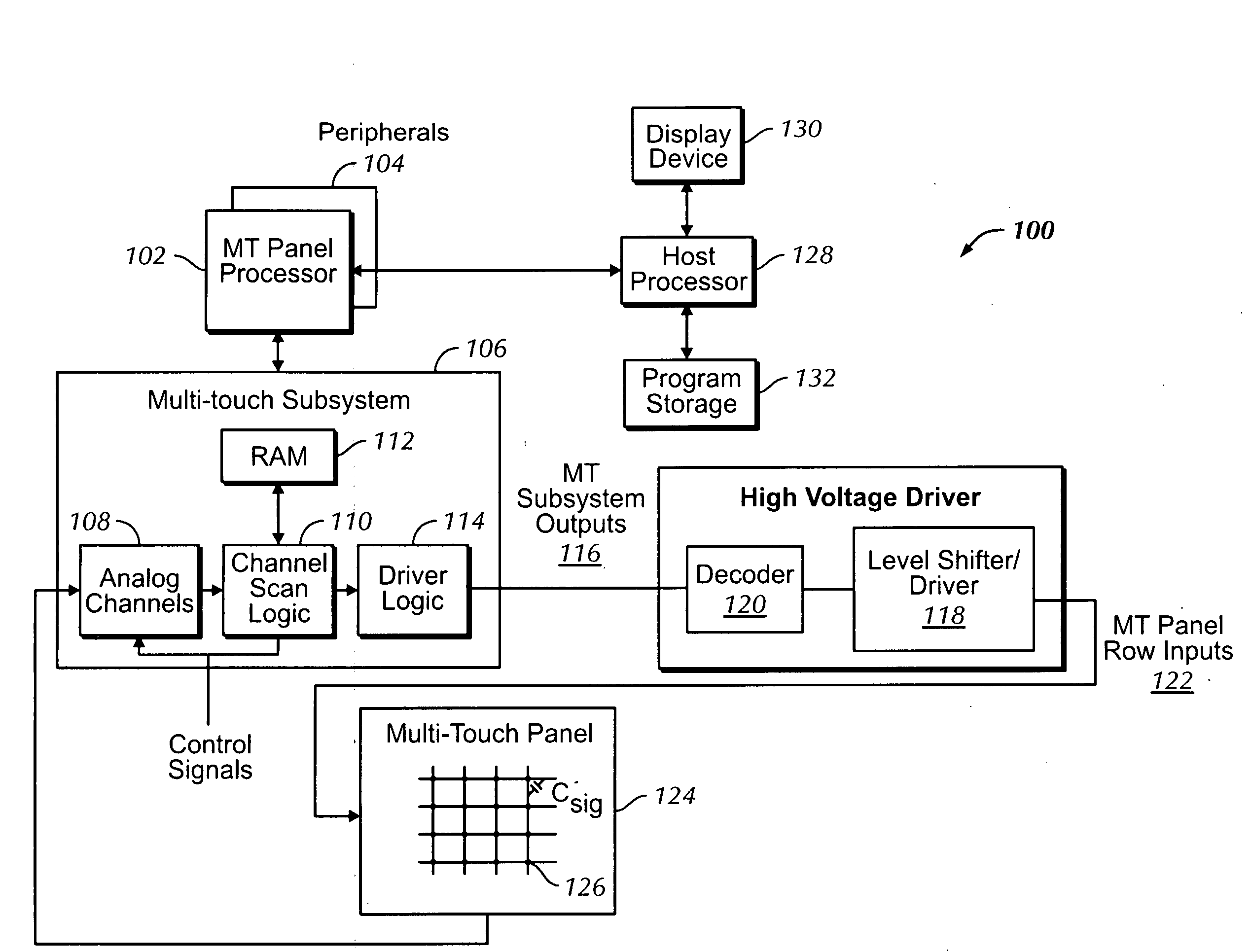

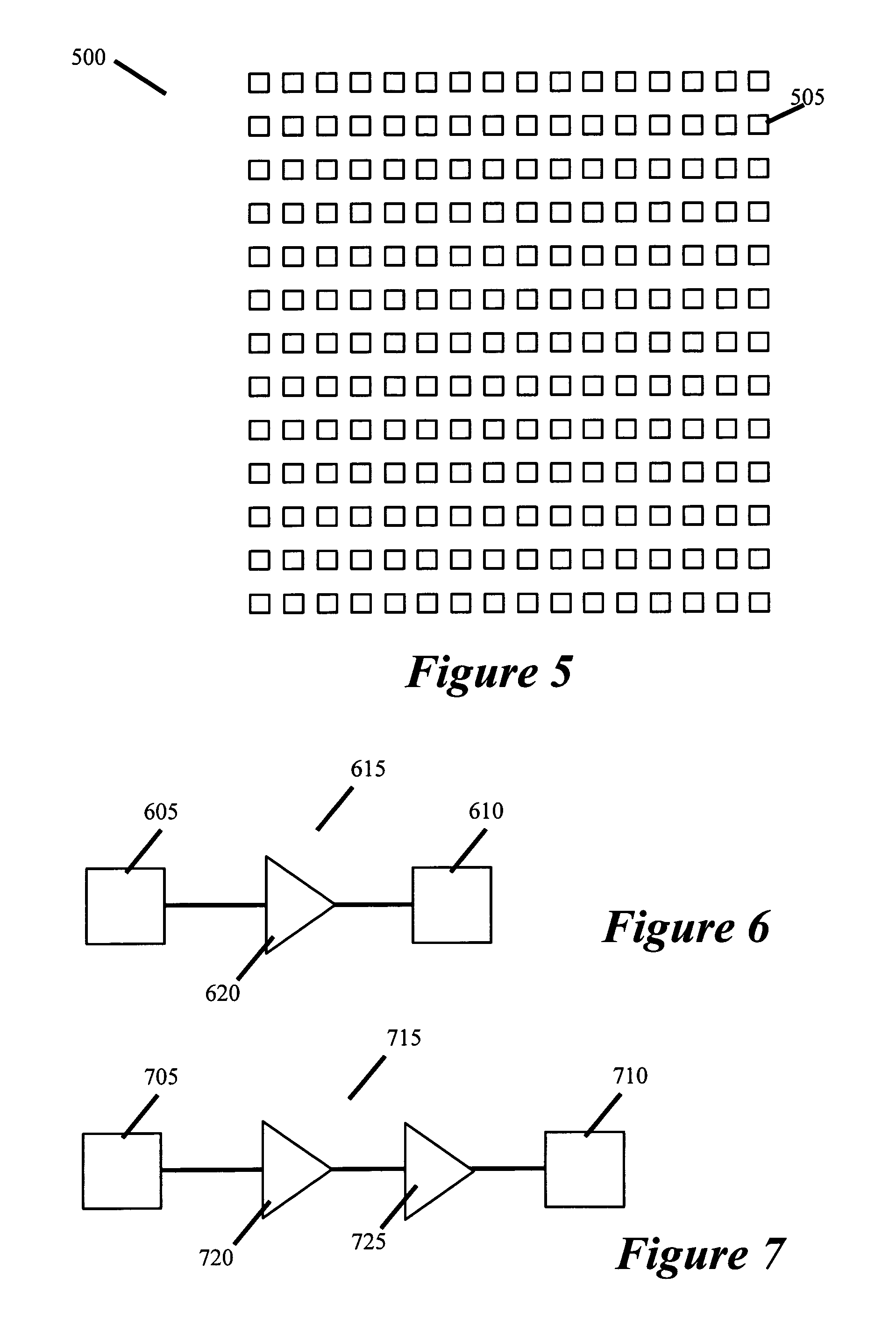

Hybrid configurable circuit for a configurable IC

InactiveUS7224182B1Solid-state devicesLogic circuits using elementary logic circuit componentsComputer scienceLogic circuitry

Some embodiments of the invention provide a configurable integrated circuit (“IC”). This IC includes several configurable logic circuits for receiving configuration data and configurably performing a set of operations based on the configuration data. It also includes several hybrid circuits. Each particular hybrid circuit has: (1) a set of inputs, (2) a set of outputs for selectively connecting to the set of inputs, and (3) a set of select lines for receiving select signals that direct the hybrid circuit to connect the input set to the output set in a particular manner. At least one select signal is for controllably receiving configuration data and at least one select line is for controllably receiving signals generated by the configurable logic circuits.

Owner:ALTERA CORP

System and method for operating components of an integrated circuit at independent frequencies and/or voltages

ActiveUS7263457B2Lower operating temperatureReduce power consumptionThermometer detailsEnergy efficient ICTTemperature controlOperating point

Owner:MEDIATEK INC

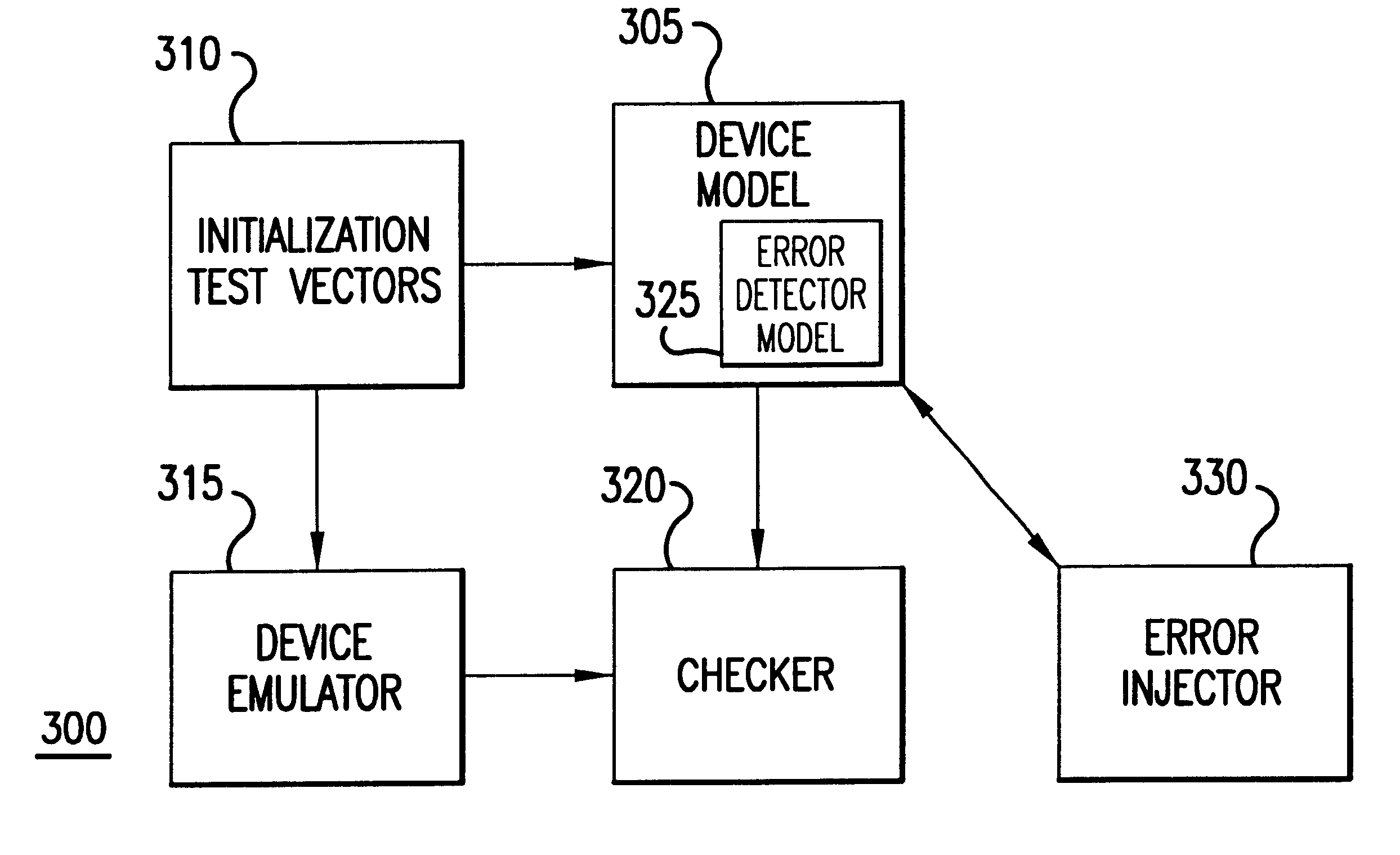

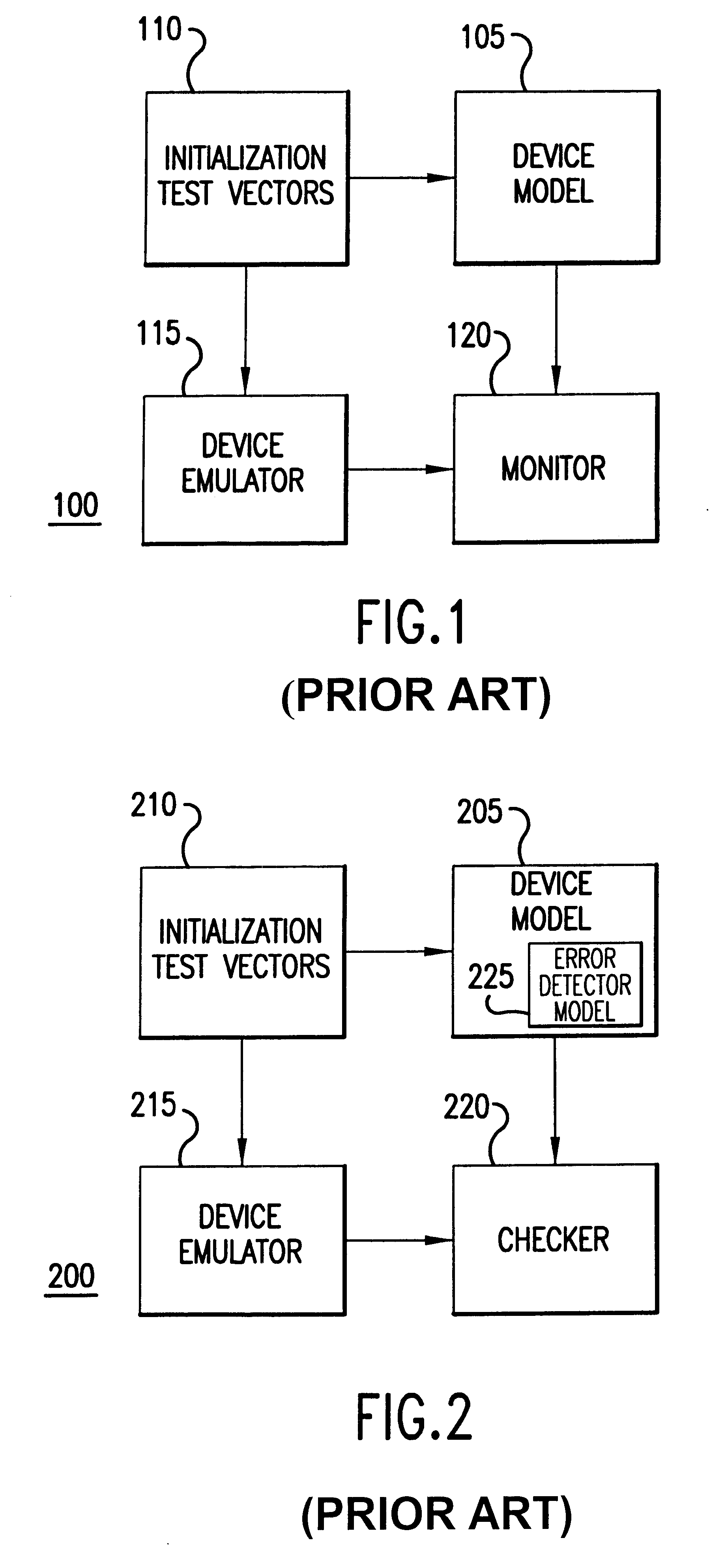

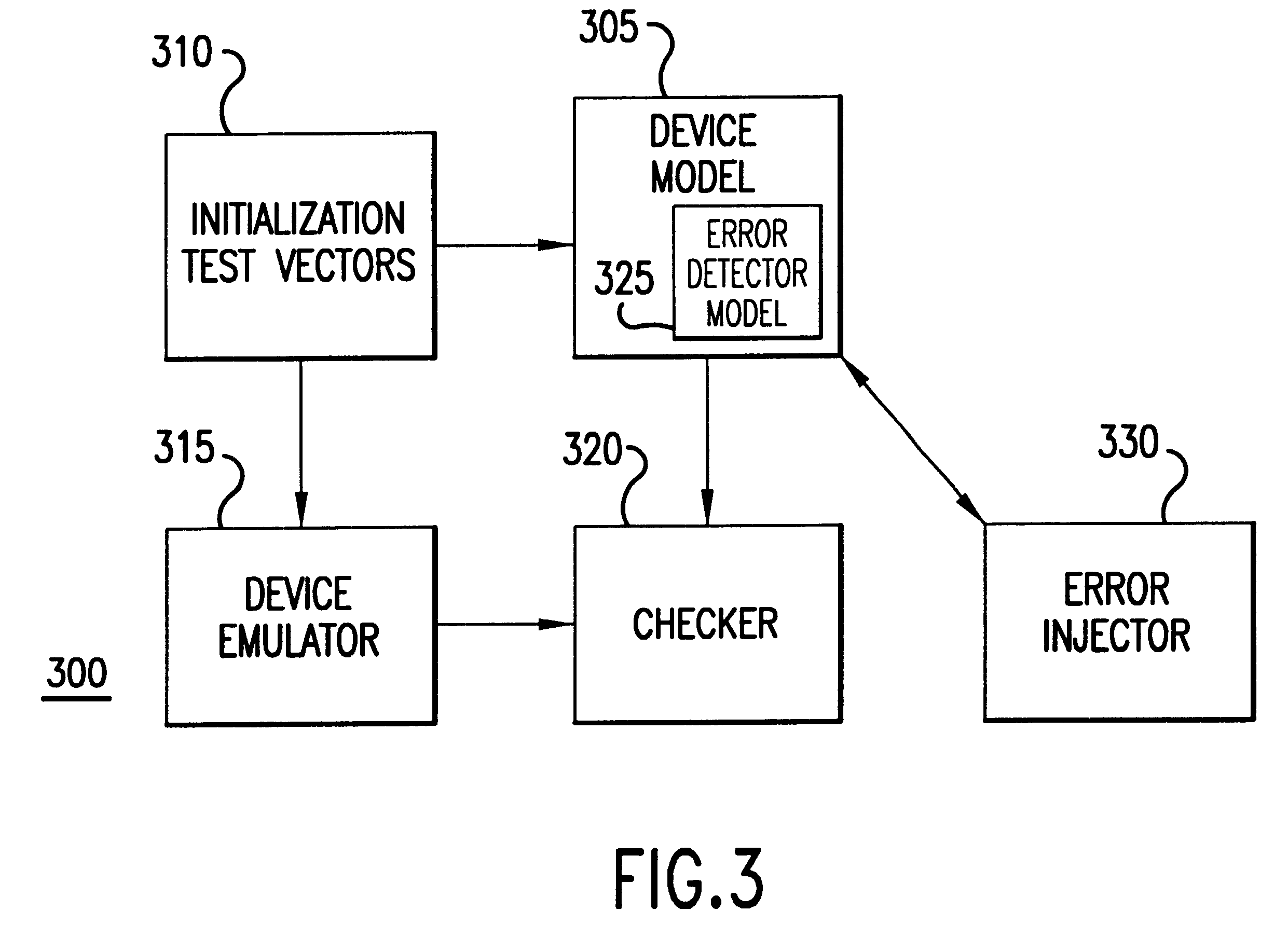

Method and apparatus for testing error detection

InactiveUS6539503B1Easy to testFocusElectronic circuit testingError detection/correctionComputer softwareProcessor design

Disclosed is a device and method for testing of a program or a design of an electronic device comprising digital logic circuitry. The method comprises testing the design of software or an electronic device and injecting, after initiation of the testing step, a predetermined error pattern into a value operated upon by the design of the digital logic circuitry. In a preferred embodiment, the software is a simulation of the design of a processor having a cache with error detection and / or correction circuitry. A triggering condition is preferably a cache hit, in response to which a detectable error is injected into the cache. The simulated operations of the model are observed to determine whether the injected error is detected, as should happen if the processor's error detection circuitry has been designed properly. In another respect, the invention is an apparatus, or computer software embedded on a computer readable medium, for testing a program comprising an error detector. The apparatus or software comprises the program, an error injector module connected to the program; and a checker module connected to the program. The checker module is capable of determining whether the program responds appropriately to an error dynamically produced by the error injector module during execution of the program. By injecting errors dynamically the invention easily facilitates precisely focused testing at any time during simulated operation regardless of initialization conditions.

Owner:SAMSUNG ELECTRONICS CO LTD

Nanotechnology neural network methods and systems

A physical neural network is disclosed, which includes a connection network comprising a plurality of molecular conducting connections suspended within a connection gap formed between one or more input electrodes and one or more output electrodes. One or more molecular connections of the molecular conducting connections can be strengthened or weakened according to an application of an electric field across said connection gap. Thus, a plurality of physical neurons can be formed from said molecular conducting connections of said connection network. Additionally, a gate can be located adjacent said connection gap and which comes into contact with said connection network. The gate can be connected to logic circuitry which can activate or deactivate individual physical neurons among said plurality of physical neurons.

Owner:KNOWM TECH

Method for BIOS authentication prior to BIOS execution

A cryptographic device is implemented in communication with a host processor to prevent the host processor from performing a standard boot-up procedure until a basic input output system (BIOS) code is authenticated. This is accomplished by a cryptographic device which is addressed by the host processor during execution of a first instruction following a power-up reset. The cryptographic device includes a first integrated circuit (IC) device and a second IC device. The first IC device includes a memory to contain firmware and a root certification key. The second IC device includes logic circuitry to execute a software code to authenticate the BIOS code before permitting execution of the BIOS code by the host processor.

Owner:INTEL CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com