Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

250 results about "Network clock" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Synchronous network for digital media streams

InactiveUS6611537B1Avoid collisionPulse modulation television signal transmissionTime-division multiplexData streamNetwork clock

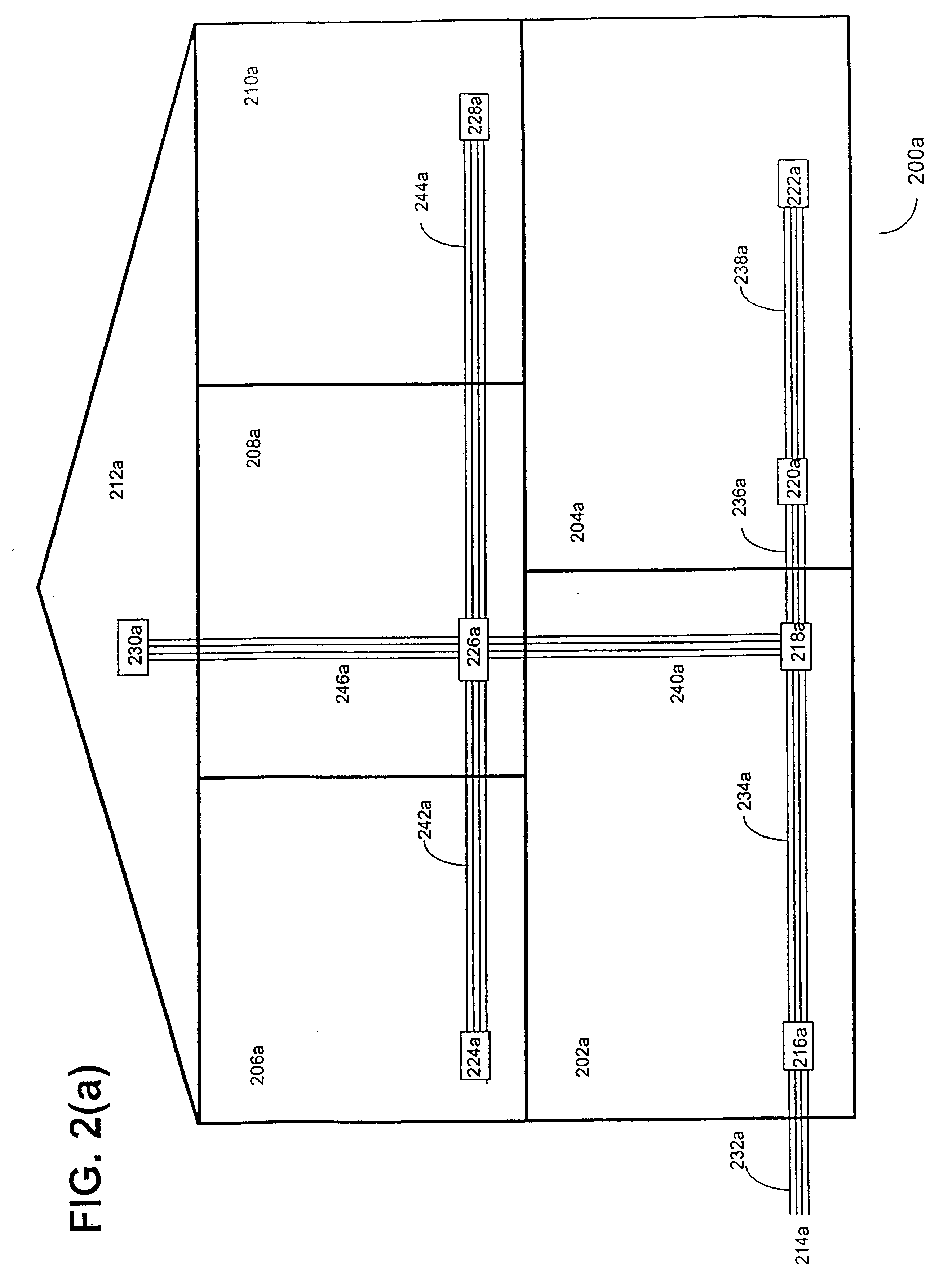

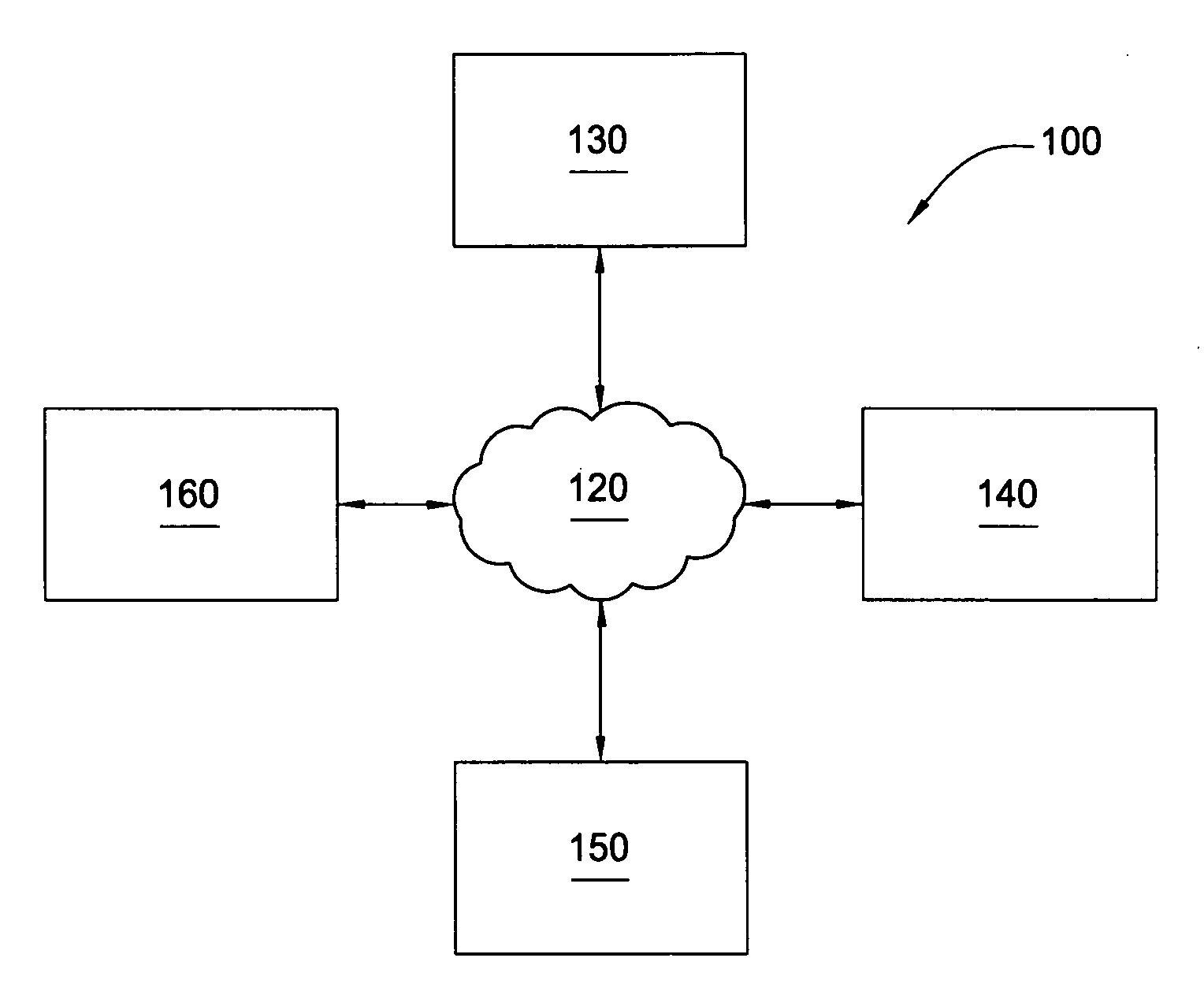

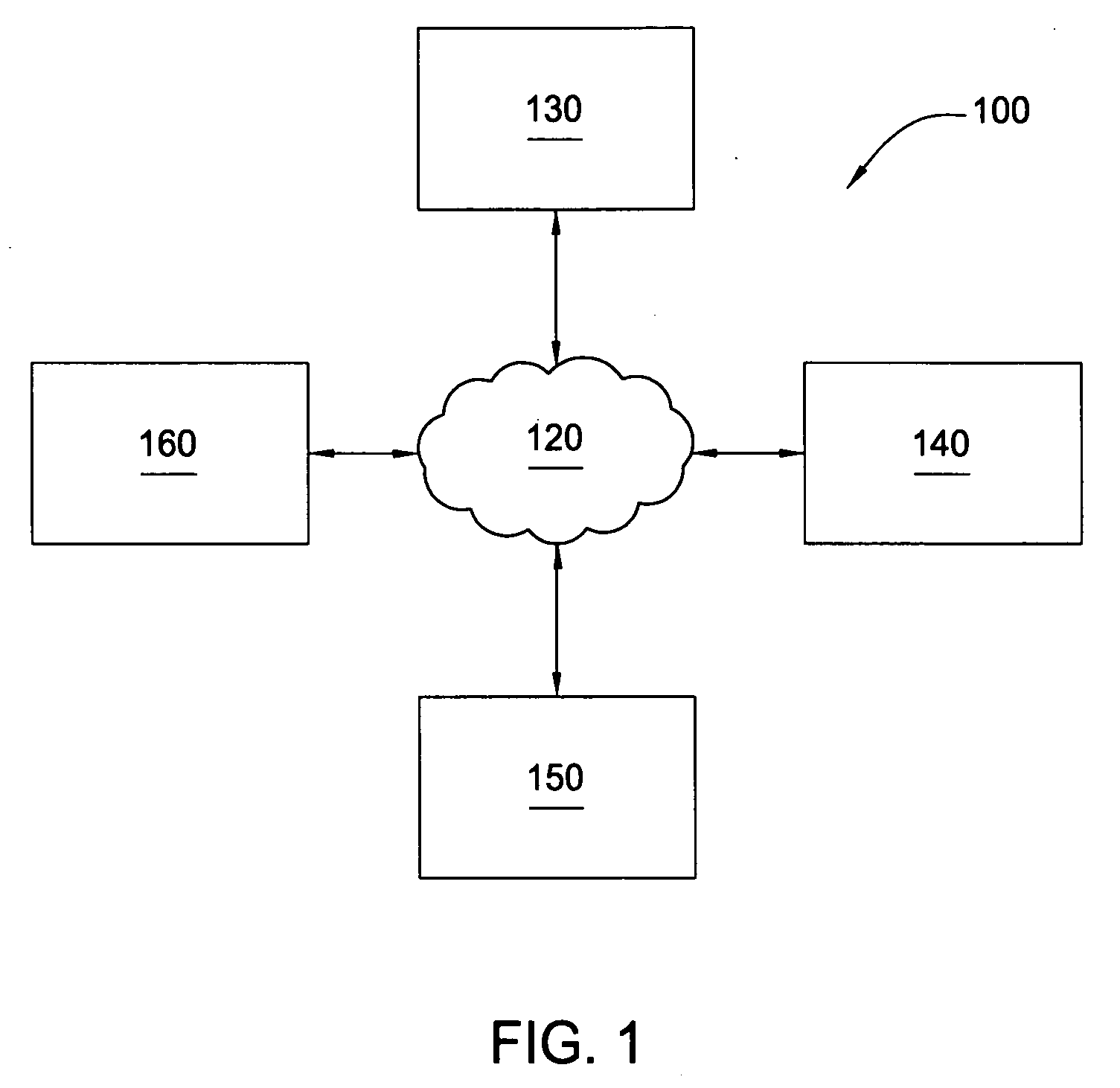

A network adapter for a synchronous logical ring network operates on existing physical twisted-pair telephone topologies. Information propagates around the logical ring, reaching every device on each revolution around the network. Network devices are full-duplex, transmitting and receiving information on every clock cycle. Network devices arbitrate to be elected the network clock device. By synchronizing all network devices to a single reference clock, and providing fixed frames of information propagating around the network at consistent time intervals, the logical ring network ensures that information propagates from one device to another at consistent time intervals. The fixed-length frames are divided into two independent streams: a data stream for the distribution of real-time continuous digital media streams; and a system command stream for the distribution of system commands.

Owner:CENTILLIUM COMM

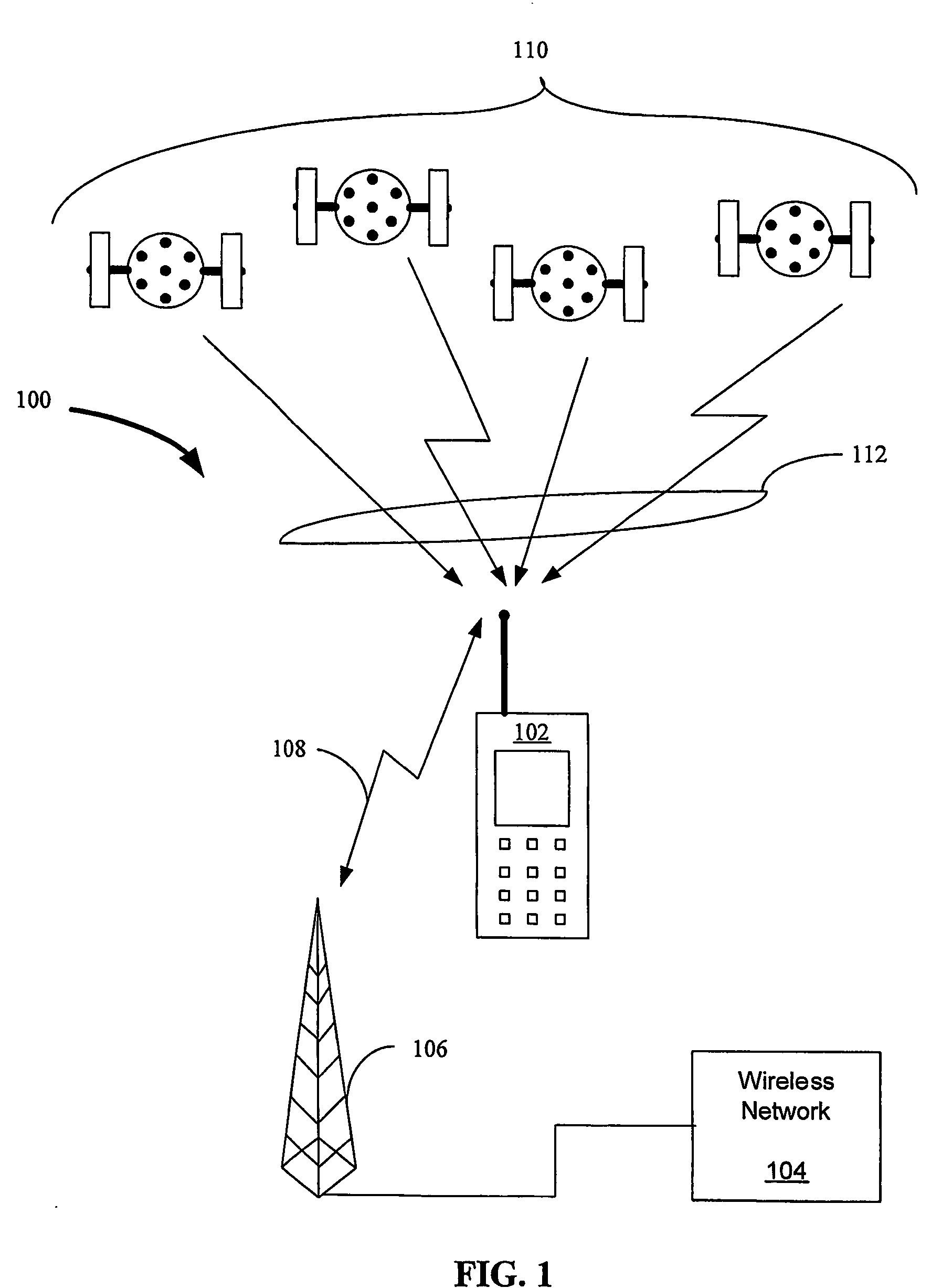

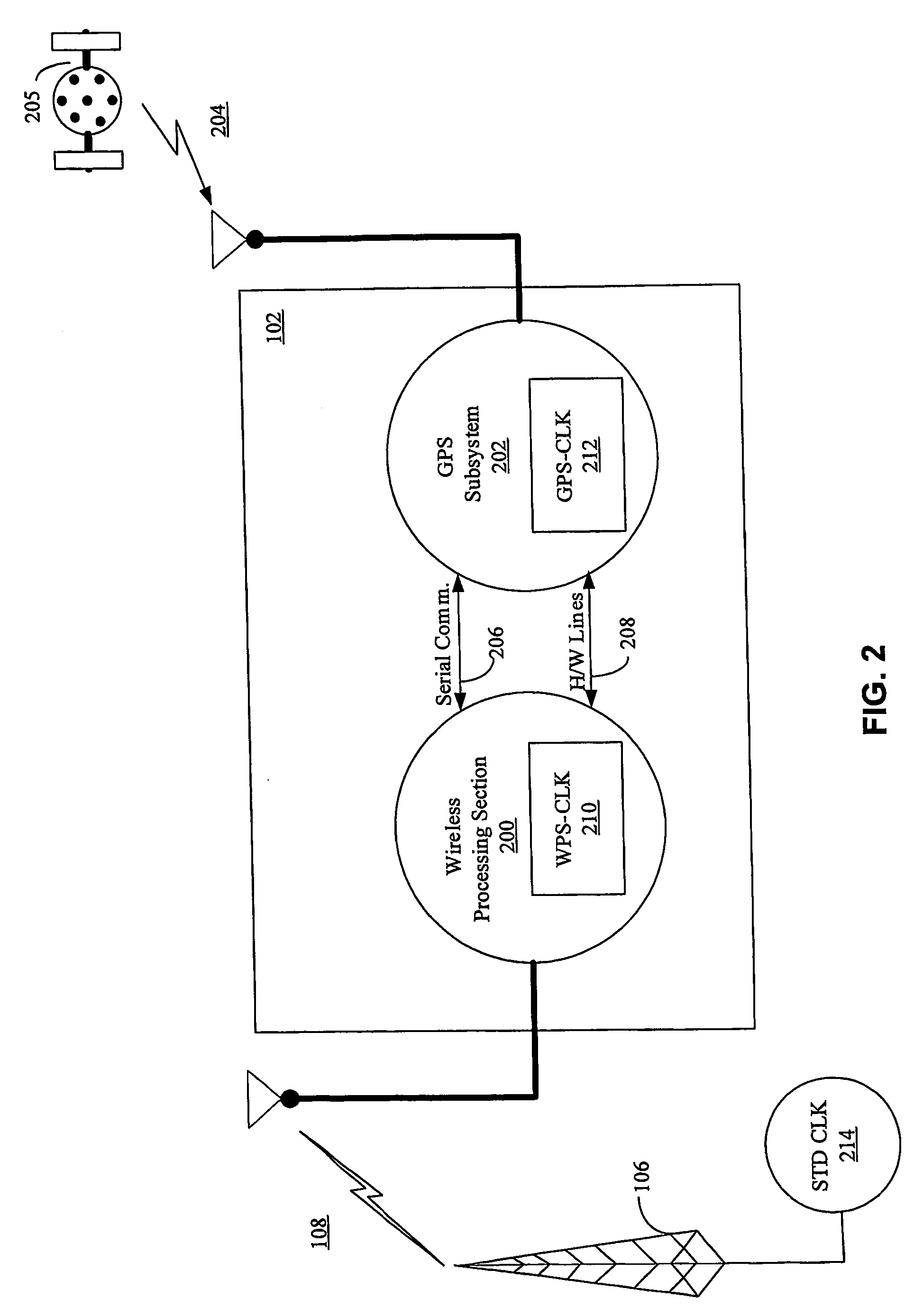

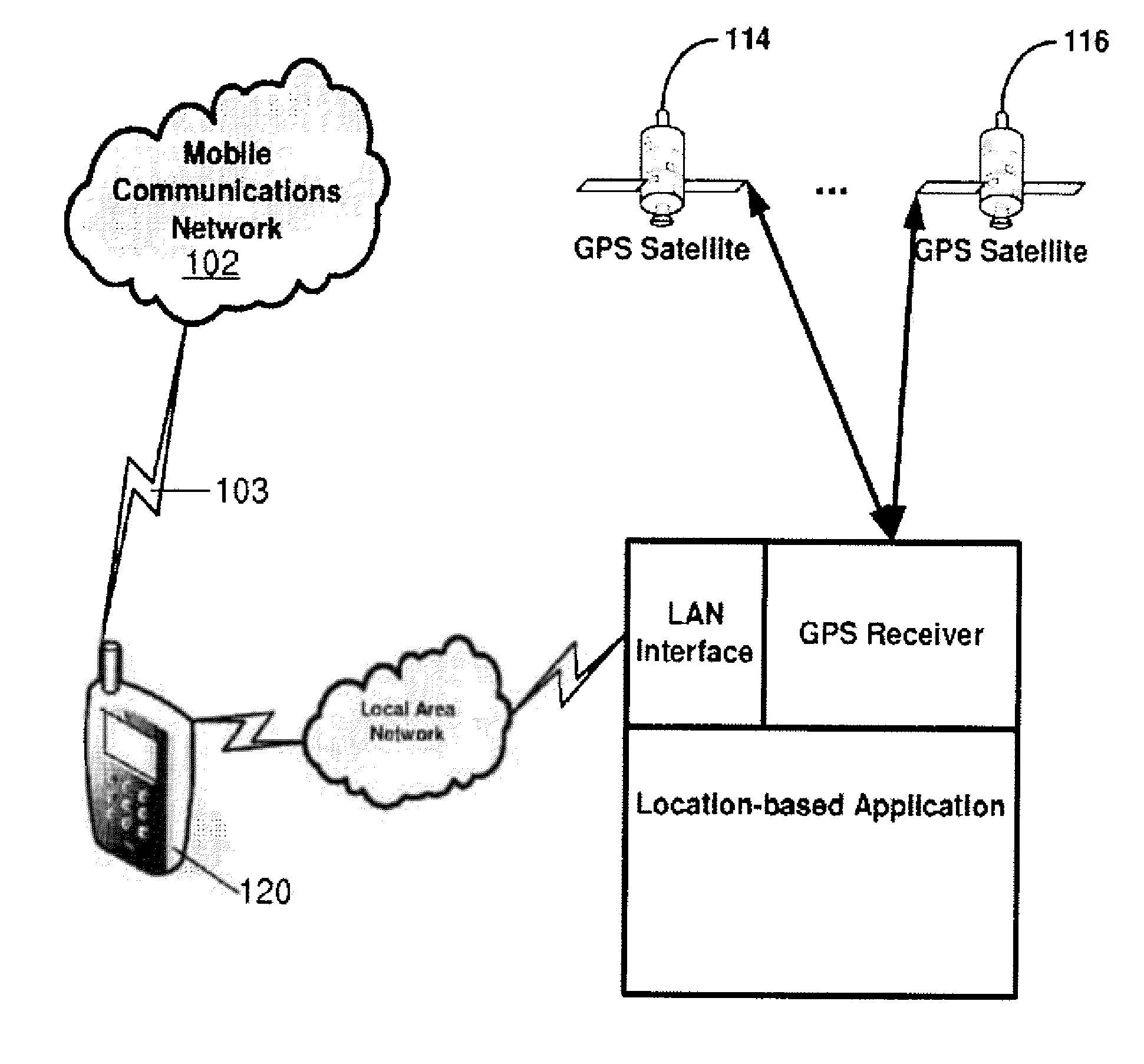

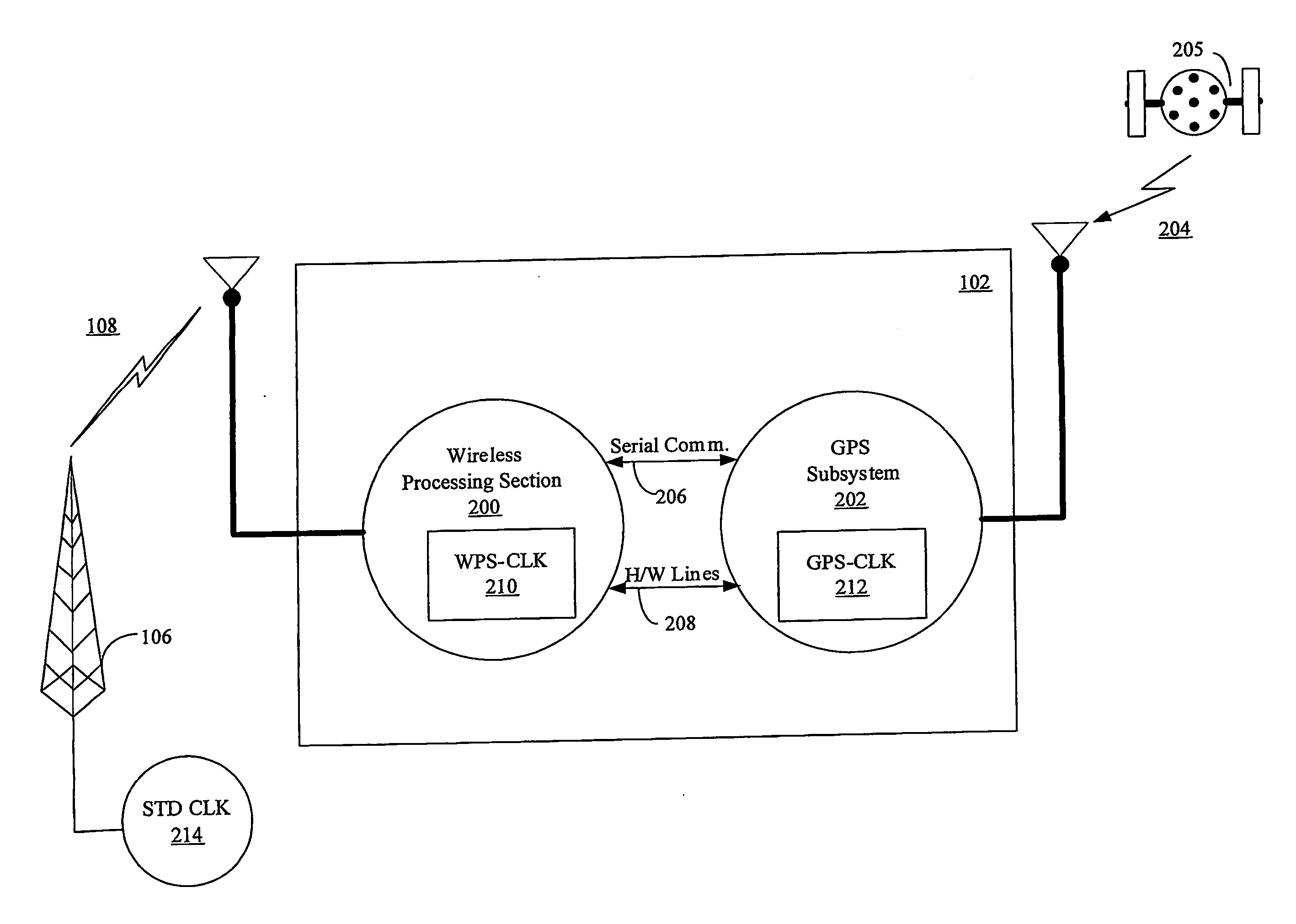

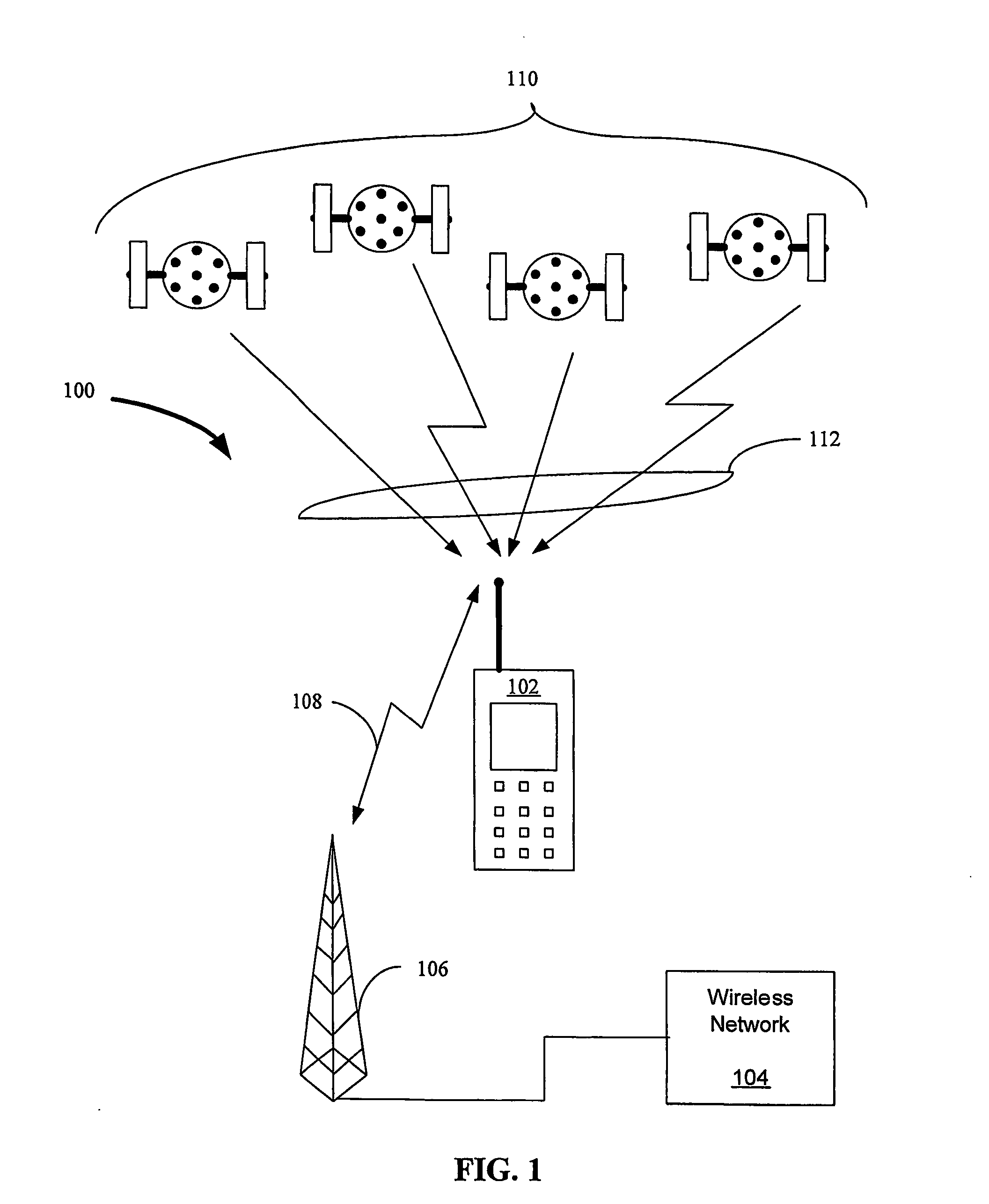

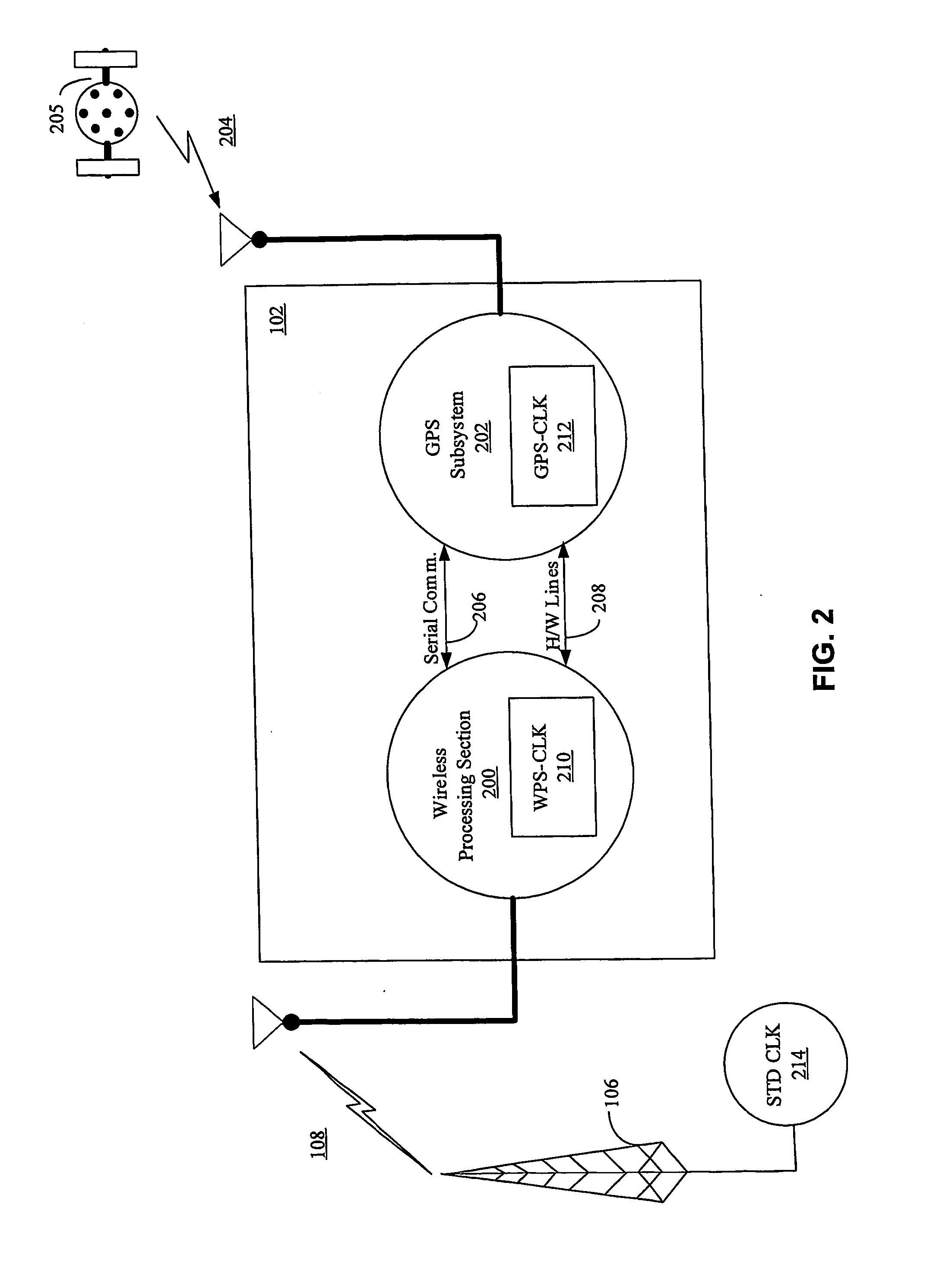

Aiding in a satellite positioning system

InactiveUS7236883B2Broadcast transmission systemsPosition fixationWireless mesh networkNetwork clock

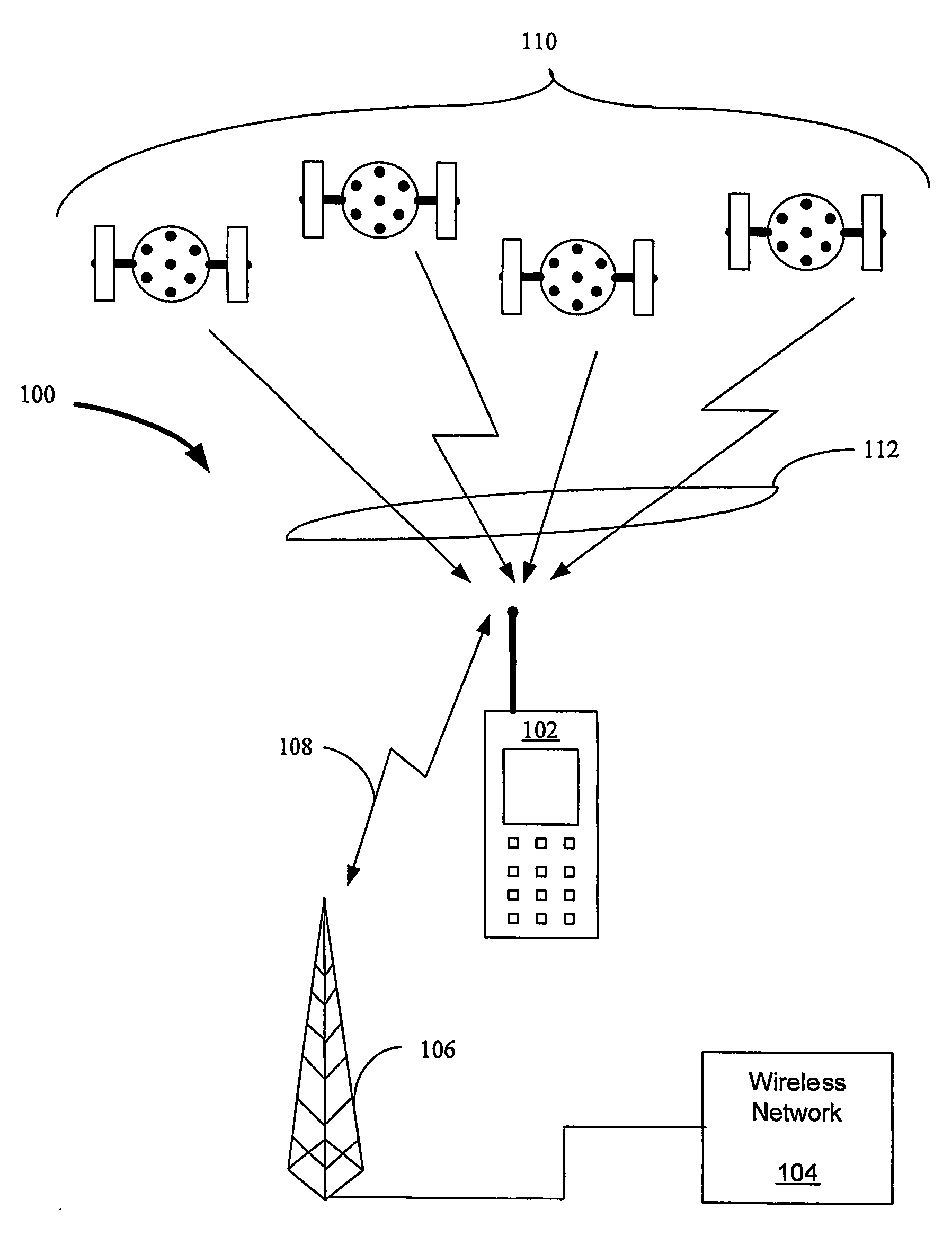

The invention relates to an aided Global Positioning System (GPS) subsystem within a wireless device. The wireless device includes a wireless processing section capable of receiving signals from a wireless network and a GPS subsystem having a radio frequency (RF) front-end capable of receiving a GPS satellite signal. The wireless processing section of the wireless device receives an external clock and determines the offset between the clock in the wireless processing section and that of the external clock. The GPS subsystem then receives the offset information from the wireless processing section, information related to the nominal frequency of the wireless processing section clock and the wireless processing section clock. Using this information and the GPS clock in the GPS subsystem, the GPS subsystem determines an acquiring signal, which is related to a frequency offset between the GPS clock and the network clock. The GPS subsystem then acquires GPS satellite signals in an acquiring unit though the use of the acquiring signal.

Owner:CSR PLC

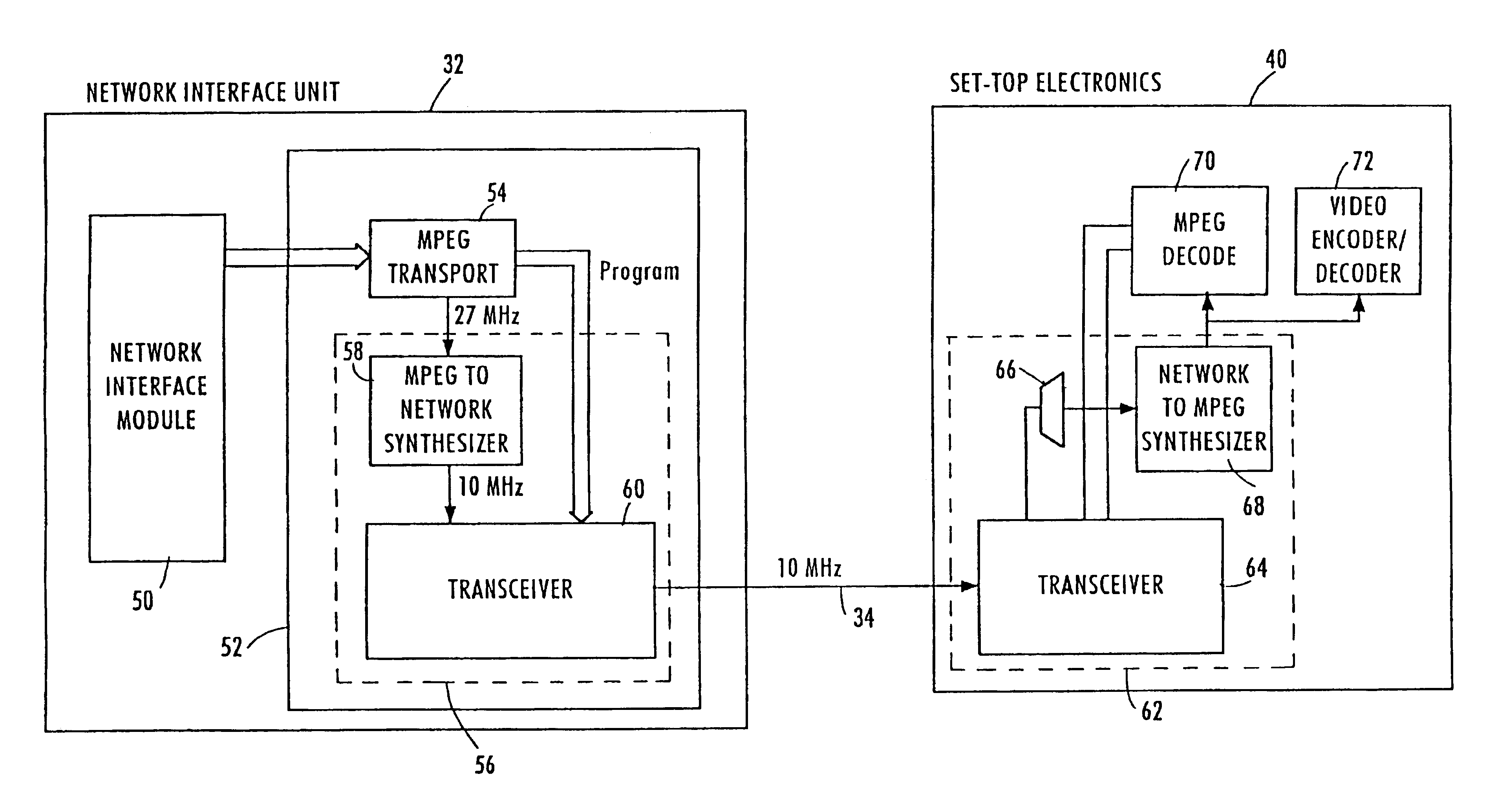

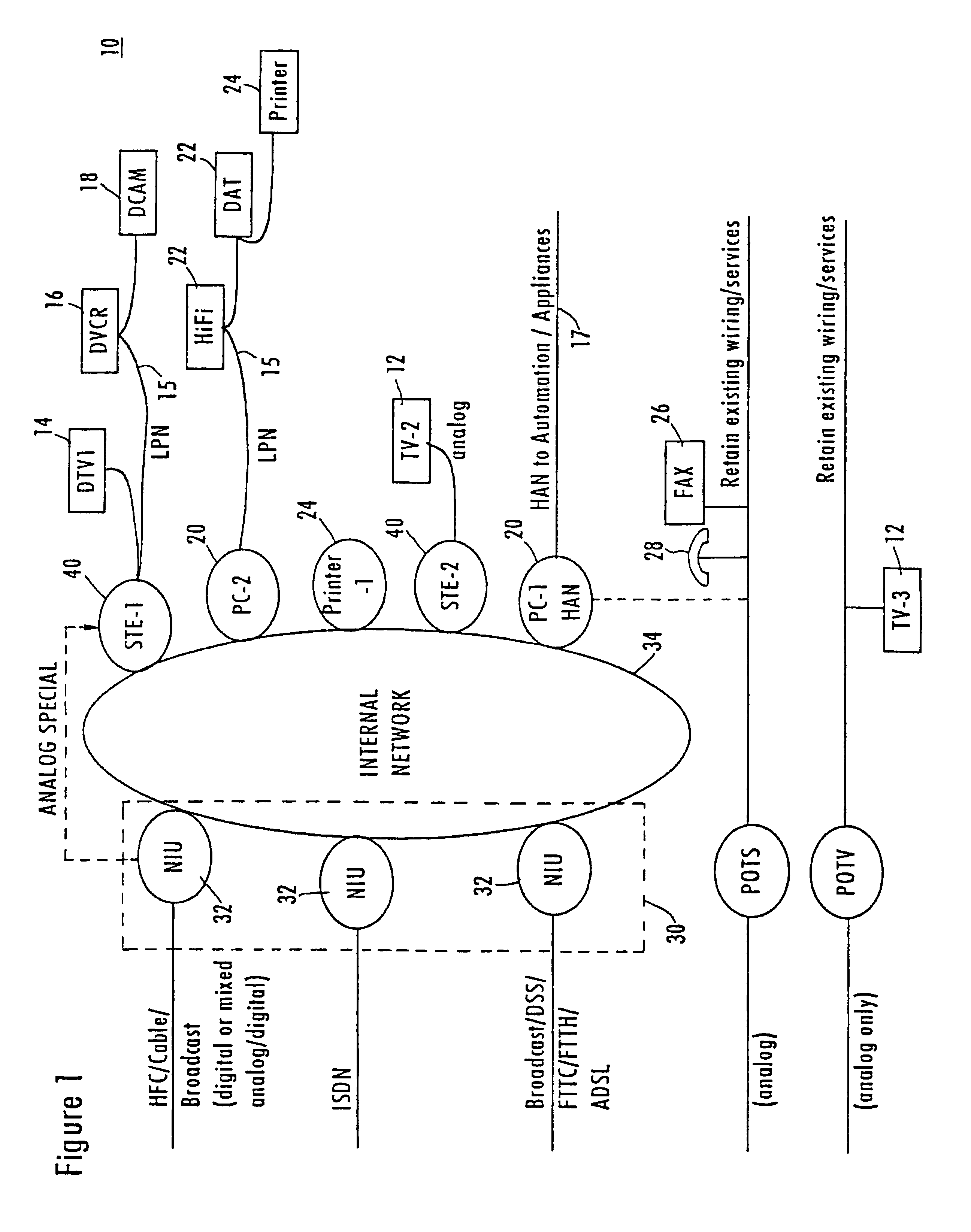

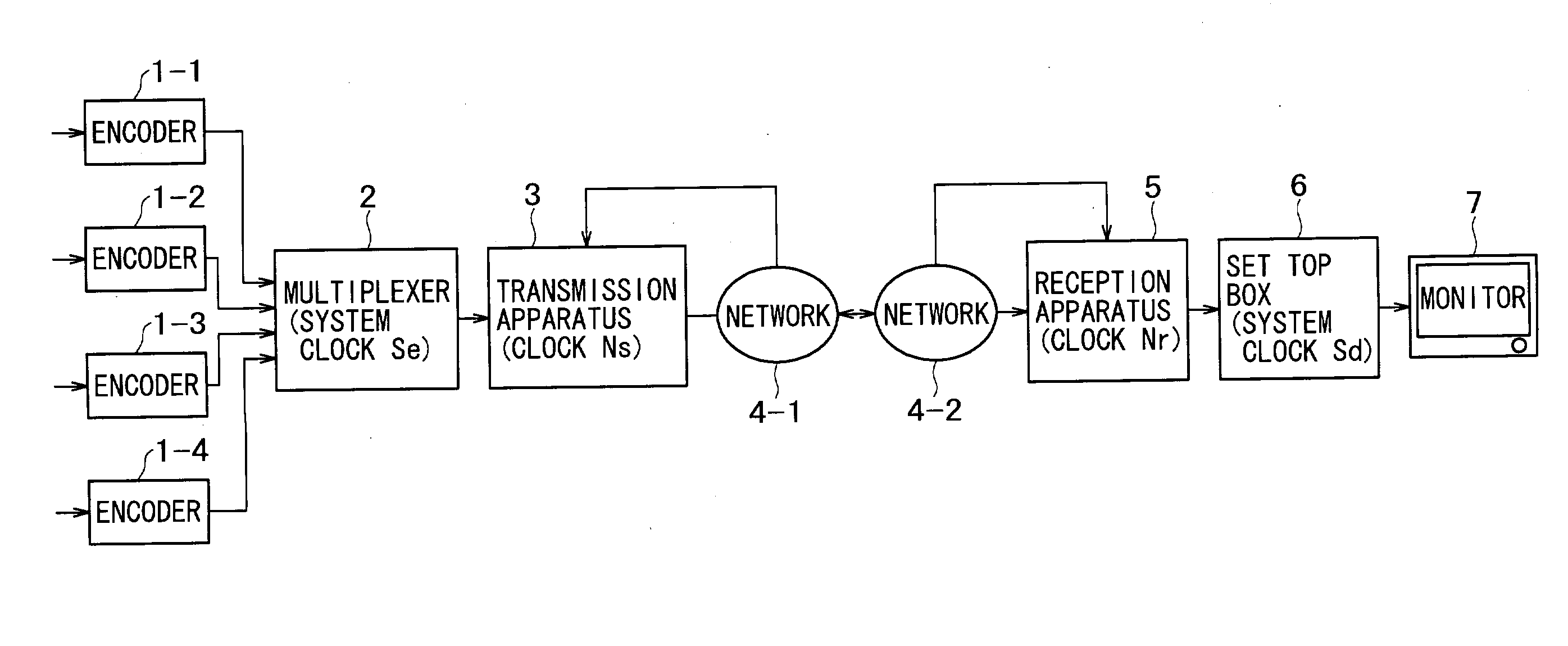

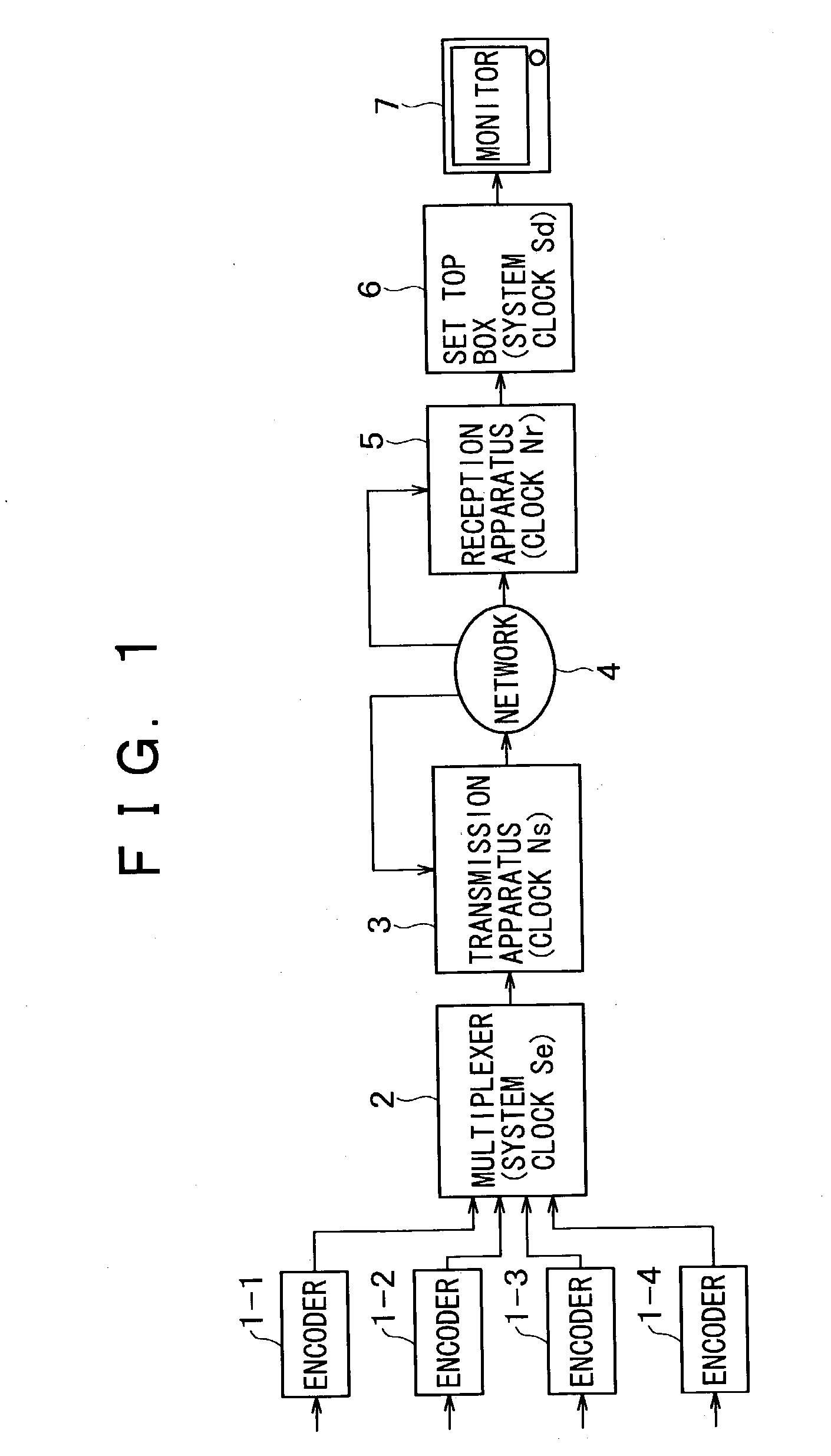

Method and apparatus for recovering data stream clock

InactiveUS7003796B1Without incurring jitterThe process is simple and fastPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningData streamNetwork clock

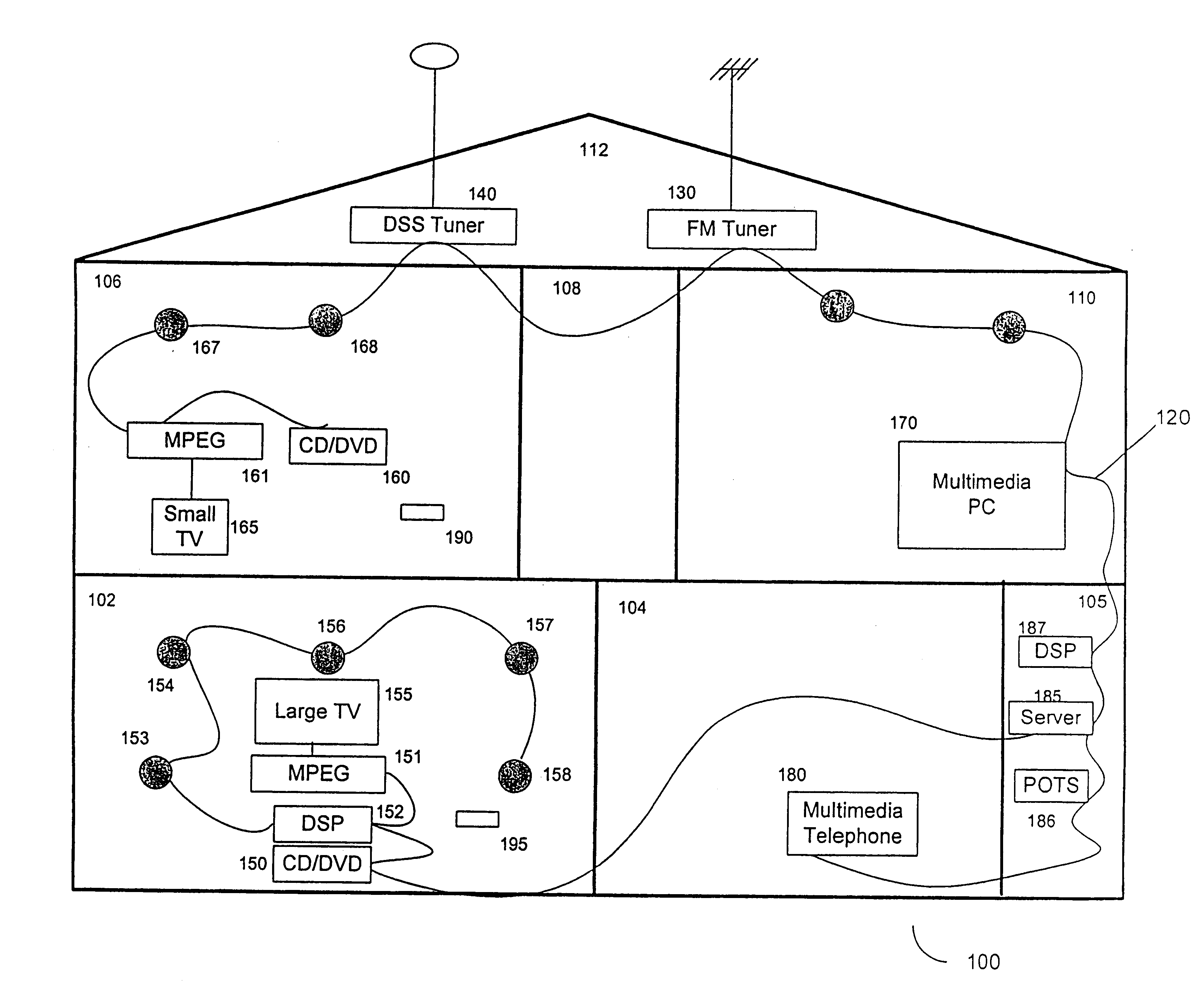

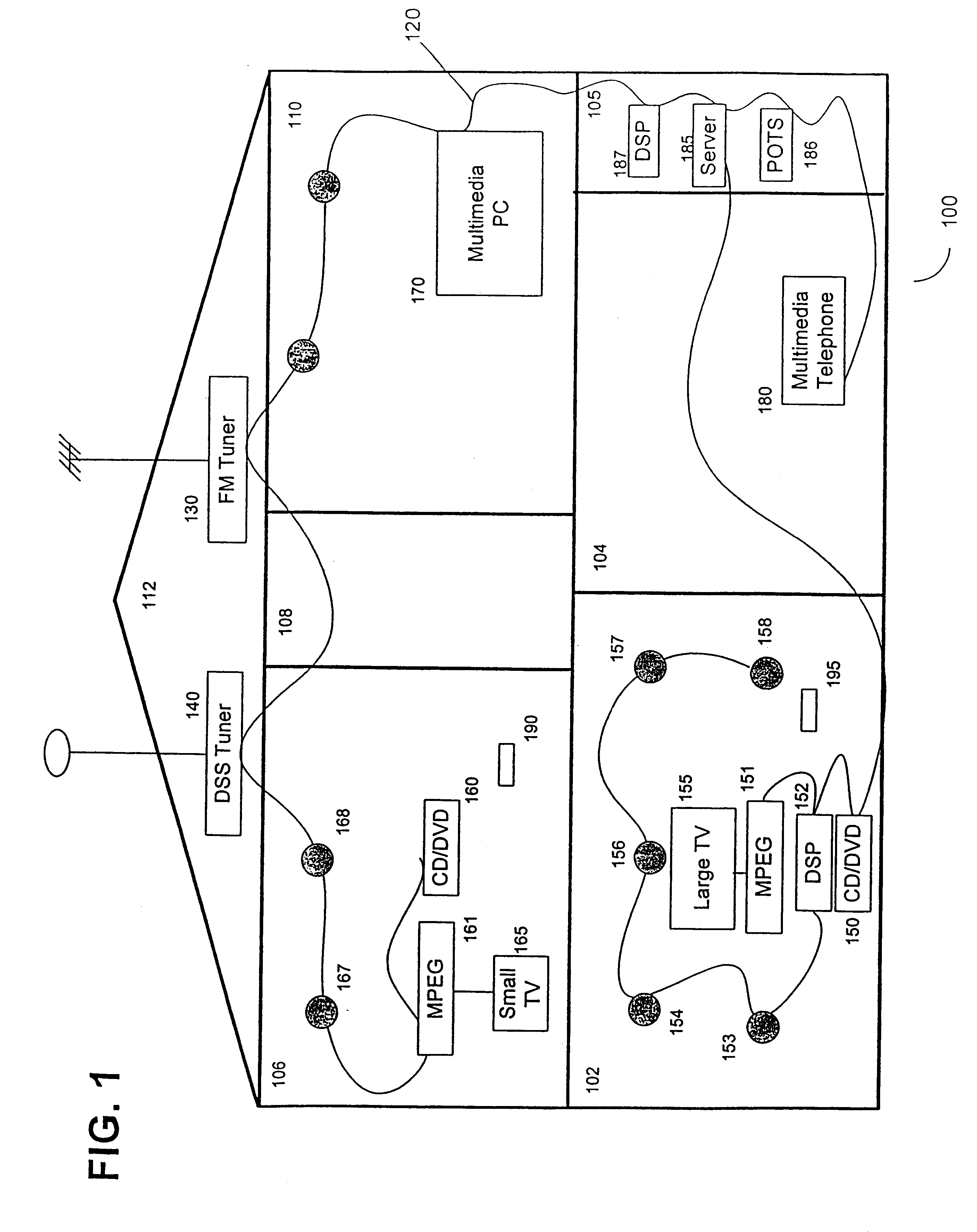

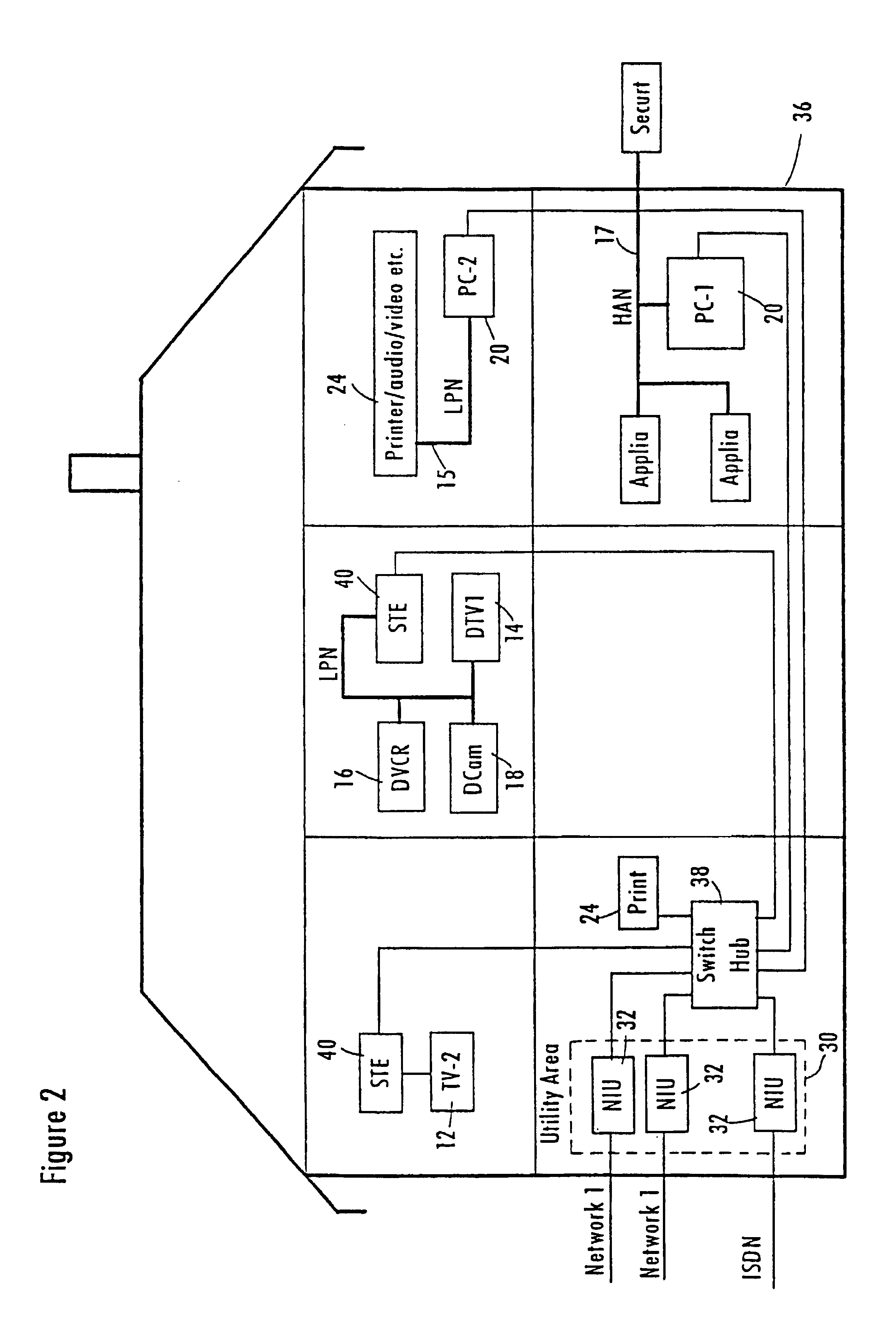

A home network architecture has an internal digital network interconnecting devices in the home. Entertainment services are introduced into the network through network interface units that are coupled to an external network and to the internal network. The network interface units perform the necessary interfacing between the external and internal networks and perform MPEG clock recovery from an MPEG video data stream. To prevent jitter when the MPEG data stream is transmitted over the internal network to set-top electronics, the recovered MPEG clock is locked by the network interface unit to the internal network clock and then transmitted over the internal network. The set-top electronics then recovers the MPEG clock from the locked MPEG clock transmitted over the internal network. The video data may then be generated using the recovered MPEG clock and displayed on a television, for example.

Owner:SAMSUNG ELECTRONICS CO LTD

Circuit for synchronizing CDMA mobile phones

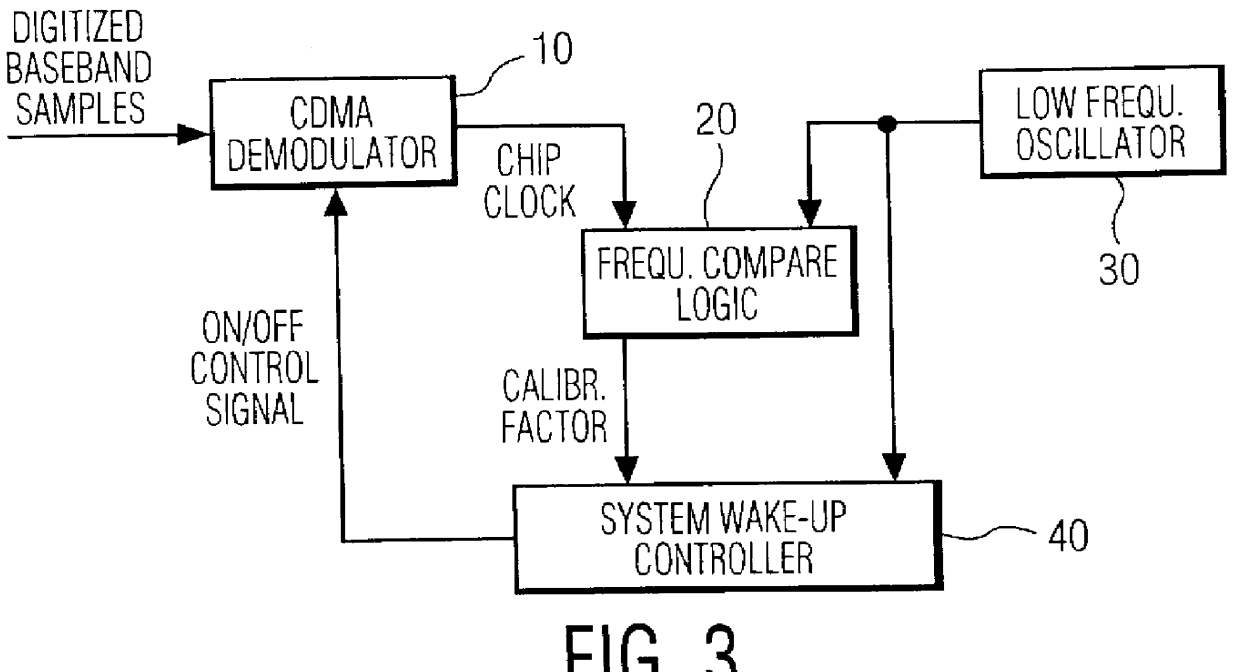

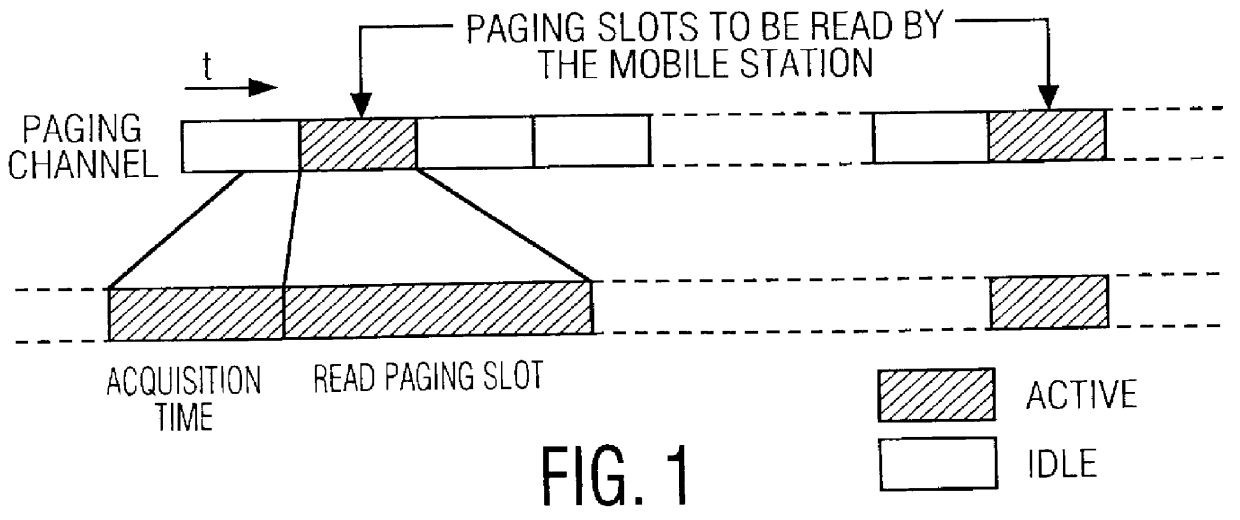

InactiveUS6028855AAccurately reacquireReduce power consumptionPower managementSynchronisation arrangementNetwork clockEngineering

A frequency calibration circuit for use in a spread spectrum receiver. The receiver includes circuitry for receiving a spread spectrum signal from a base station and for recovering a network clock signal therefrom, a low frequency oscillator for producing an oscillator clock signal, and a frequency comparator that takes as inputs the network clock signal and the oscillator clock signal and produces a calibration factor based on the difference between the clock signals. A controller coupled to the low frequency oscillator amd the frequency comparator utilizes the calibration factor together with the low frequency oscillator clock signal to output a accurate and precision timed signal thereby being able to accurately require the timing of the paging channel.

Owner:ST ERICSSON SA

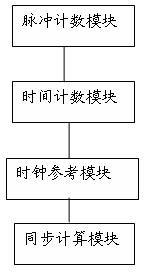

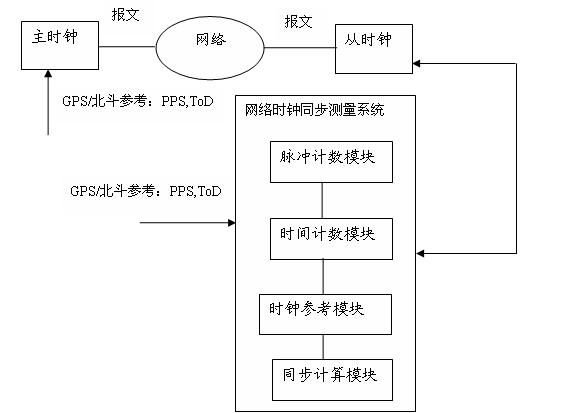

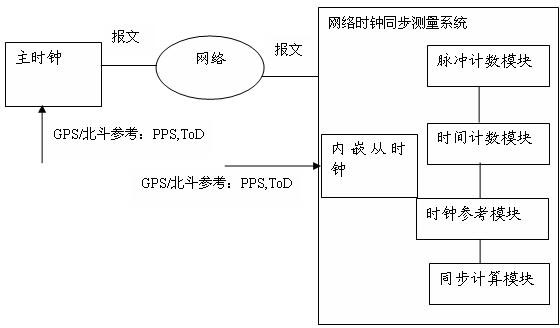

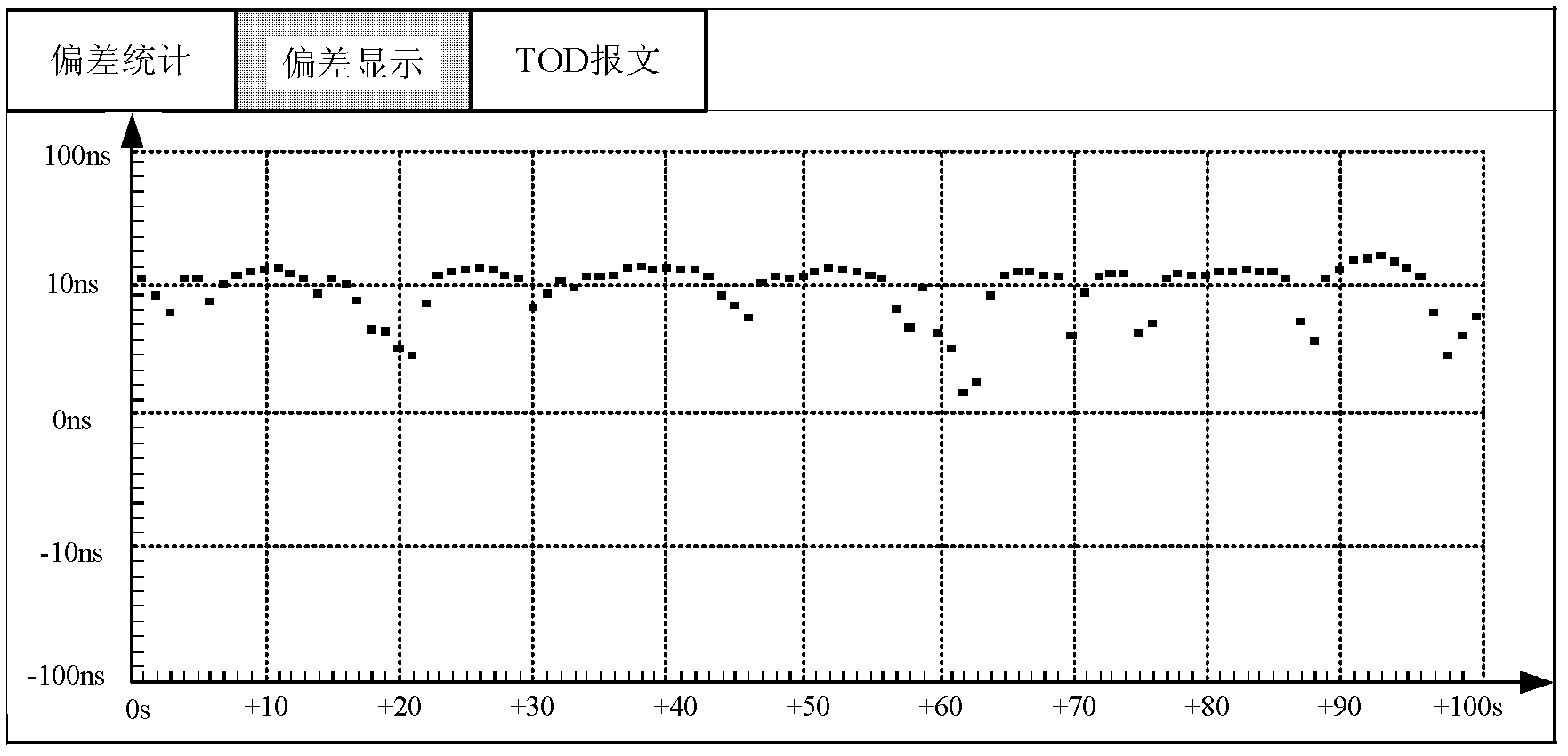

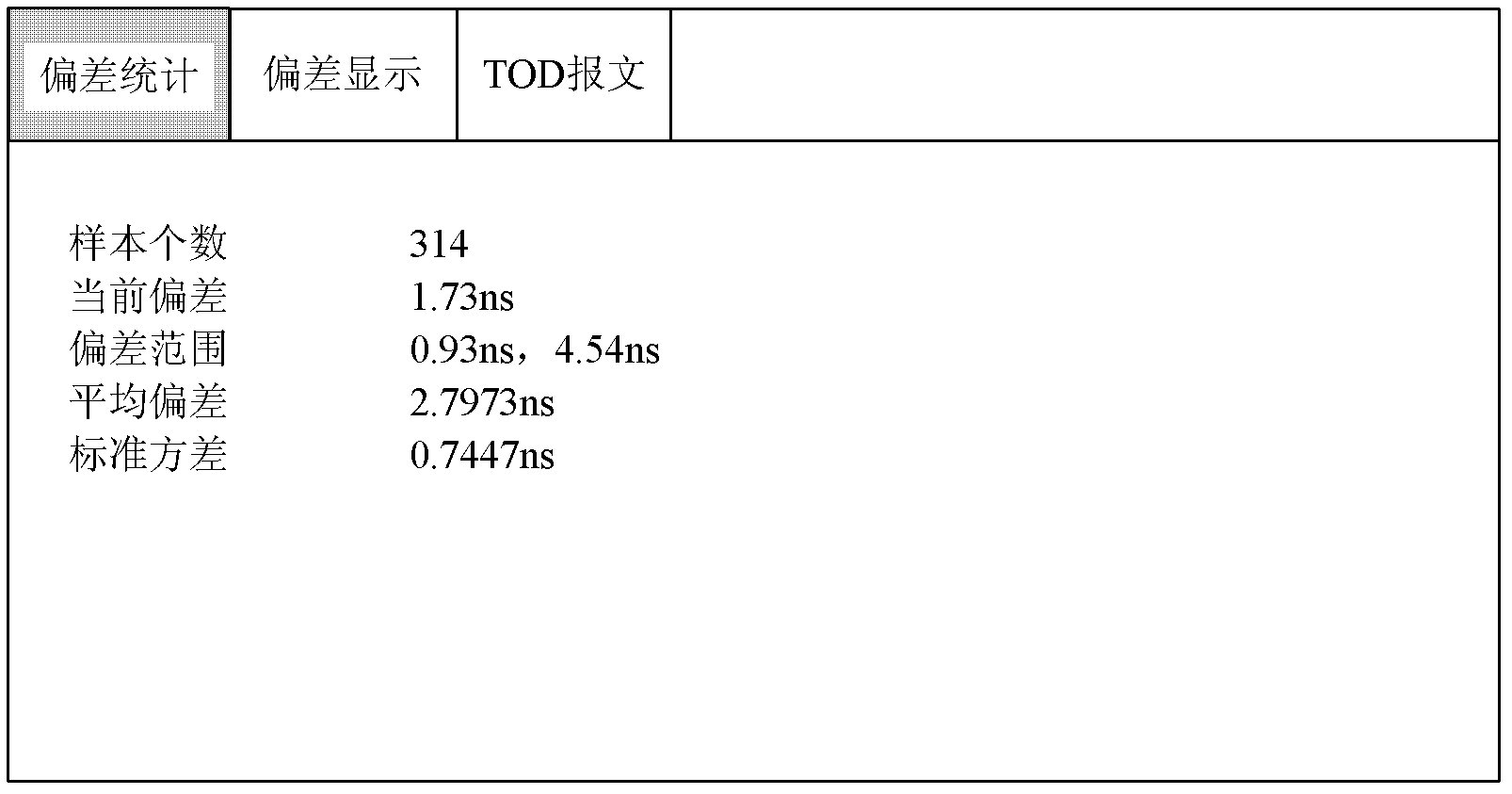

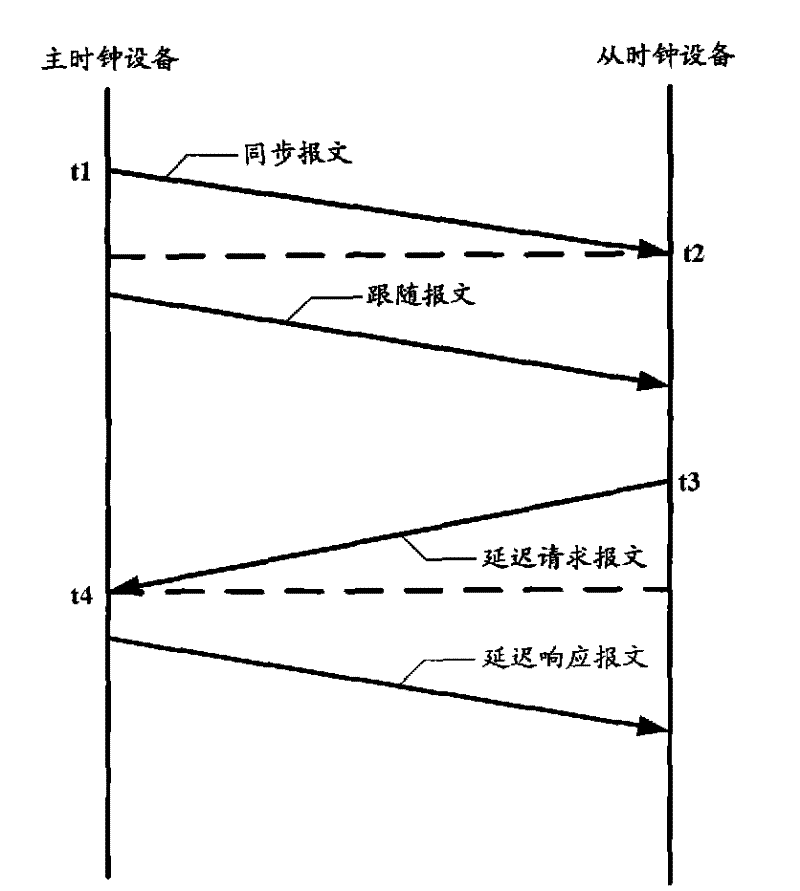

System and method for measuring network clock synchronization

The invention discloses a system for measuring network clock synchronization, is applied to the communication and smart grid fields. The system comprises a pulse countering module, a time counting module, a clock reference module and a synchronization calculation module, wherein the pulse counting module calculates pulse frequency difference between a master clock and a slave clock, the master clock is synchronous with a remote reference clock, and the slave clock is synchronous with the master clock through a network so as to be synchronous with the remote reference clock; the time counting module measures the time difference between the master clock and the slave clock; the clock reference module inputs a reference clock, and the reference clock is synchronous with the remote reference clock; and the synchronization calculating module is used for calculating network clock synchronization parameters according to the time difference and the pulse frequency difference and outputting time synchronization parameters. The system disclosed by the invention can be used for evaluating the clock frequency synchronization accuracy and the time synchronization accuracy which can be reached at each node by an IEEE1588PTP (Institute of Electrical and Electronics Engineers 1588 Peer To Peer) clock synchronous network, and important reference data is provided for clock synchronization network optimization, and performance prediction on application and equipment depending on clock synchronization.

Owner:上海奇微通讯技术有限公司

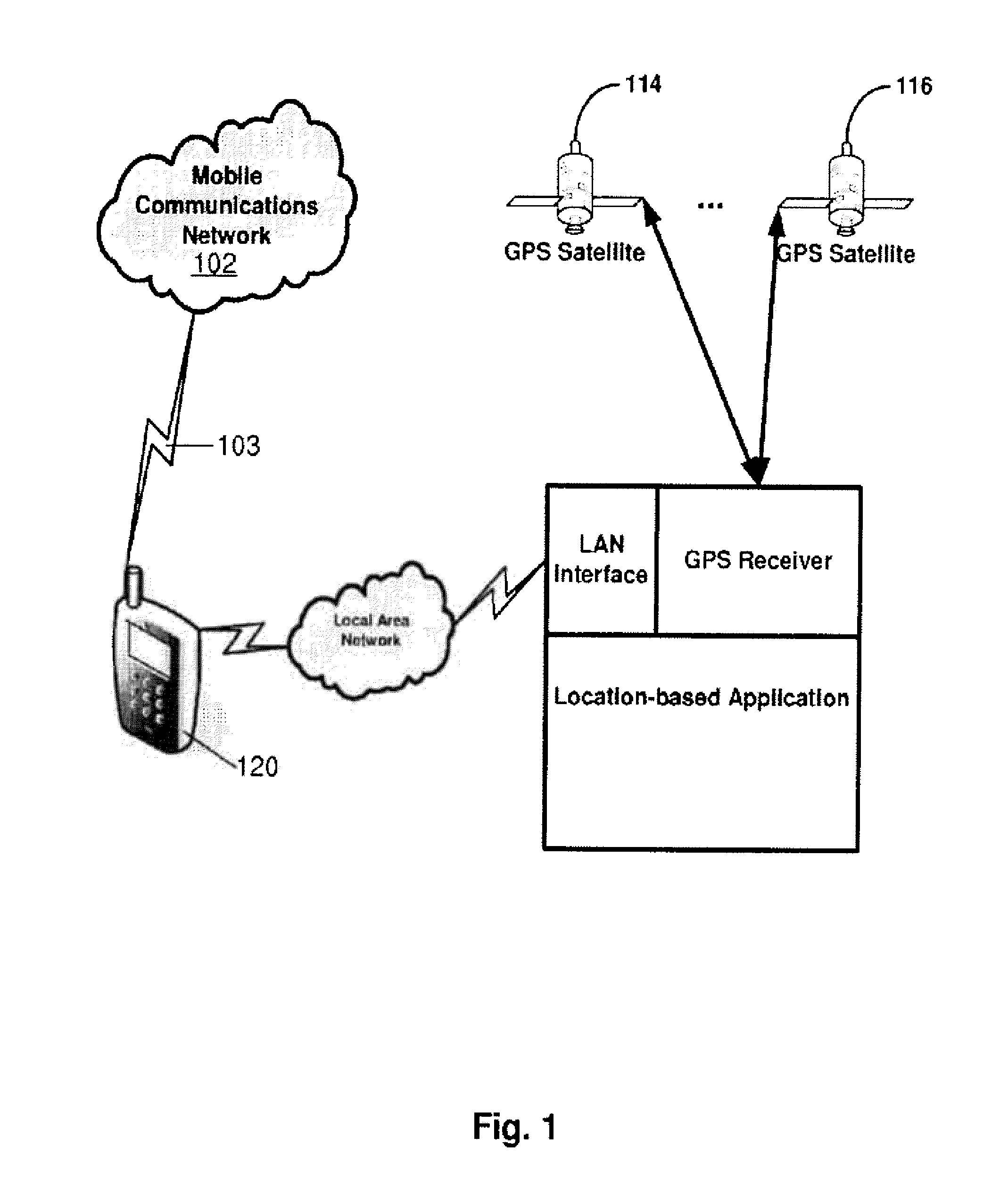

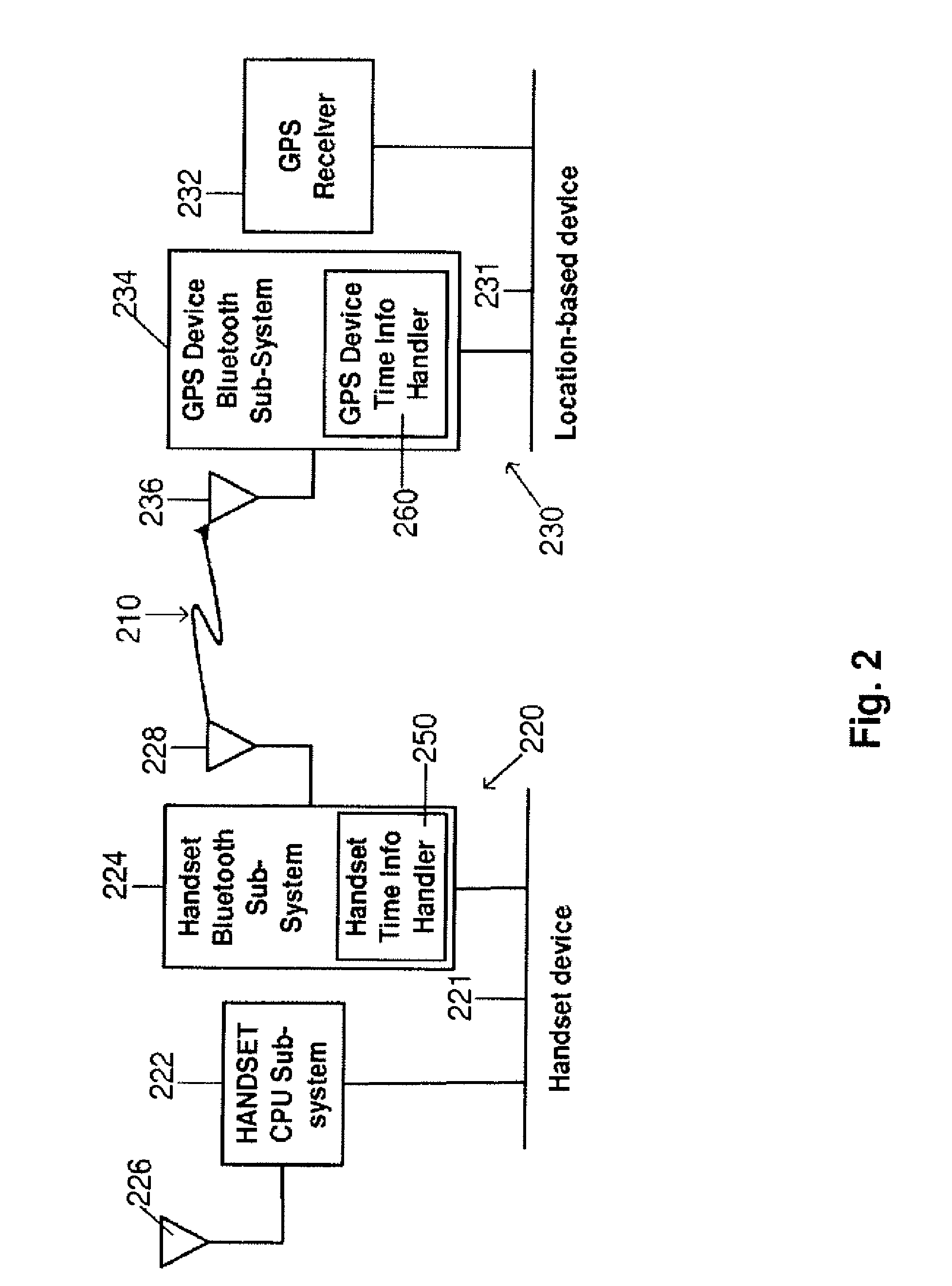

System and method for providing aiding information to a satellite positioning system receiver over short-range wireless connections

InactiveUS7724612B2Synchronous motors for clocksActive radio relay systemsTime informationNetwork clock

Systems and methods for obtaining corrected time information in a GPS-enabled device connected to a mobile handset via a short-range wireless network, such as a Bluetooth™ Piconet™. The mobile handset includes a GPS time and a network clock synchronized with a network clock in a short-range wireless network interface in the GPS-enabled device. The GPS-enabled device may send requests for time information to the mobile handset. The mobile handset receives the request and latches the network clock time and the GPS time. The captured network clock time and GPS times are sent to the GPS-enabled device in response to the request. The GPS-enabled device subtracts the captured network clock time from its own network clock time and adds the difference to the captured GPS time to obtain a corrected GPS time.

Owner:CSR TECH INC

Aiding in a satellite positioning system

InactiveUS20060095206A1Instruments for road network navigationPosition fixationNetwork clockEngineering

The invention relates to an aided Global Positioning System (GPS) subsystem within a wireless device. The wireless device includes a wireless processing section capable of receiving signals from a wireless network and a GPS subsystem having a radio frequency (RF) front-end capable of receiving a GPS satellite signal. The wireless processing section of the wireless device receives an external clock and determines the offset between the clock in the wireless processing section and that of the external clock. The GPS subsystem then receives the offset information from the wireless processing section, information related to the nominal frequency of the wireless processing section clock and the wireless processing section clock. Using this information and the GPS clock in the GPS subsystem, the GPS subsystem determines an acquiring signal, which is related to a frequency offset between the GPS clock and the network clock. The GPS subsystem then acquires GPS satellite signals in an acquiring unit though the use of the acquiring signal.

Owner:CSR PLC

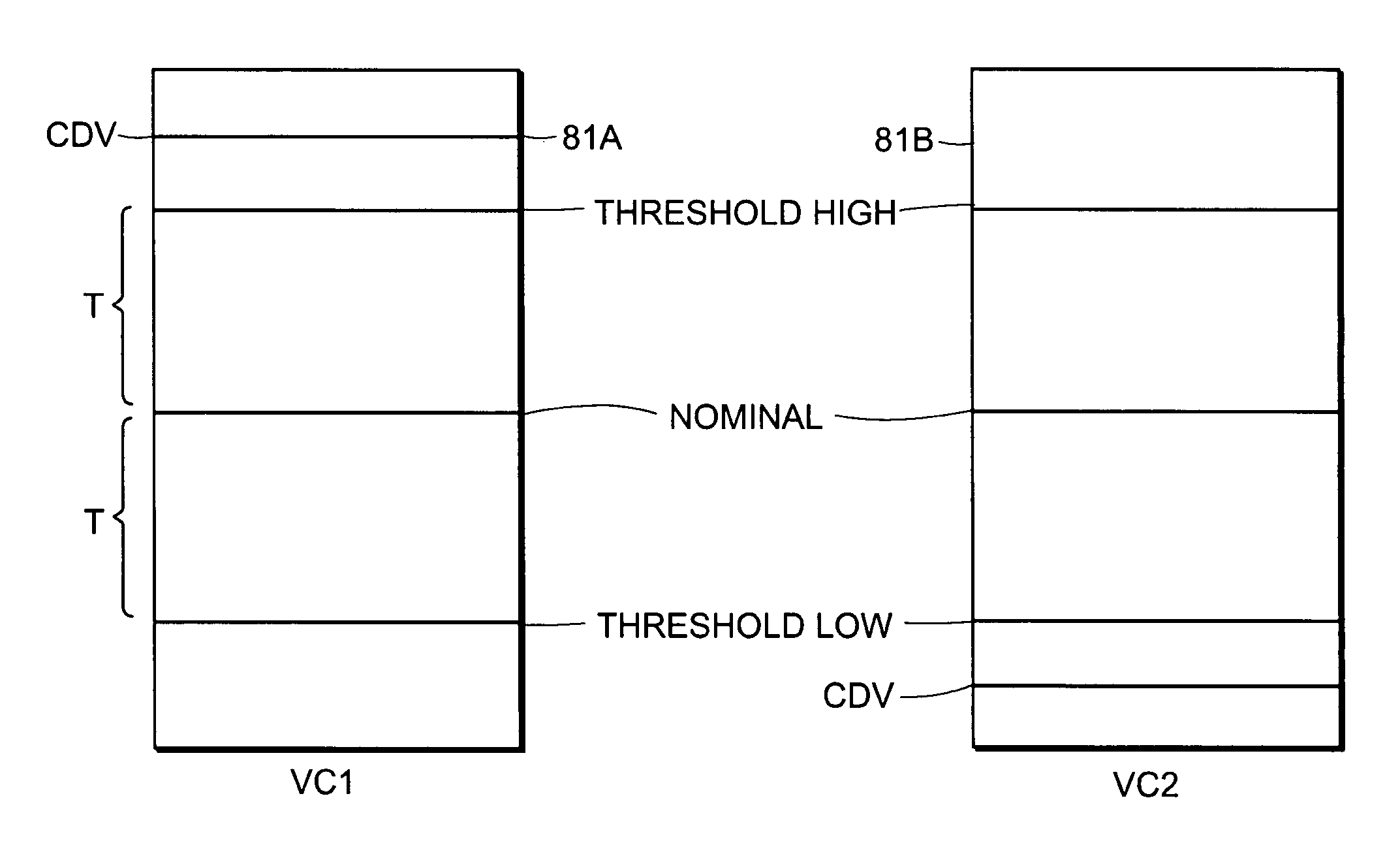

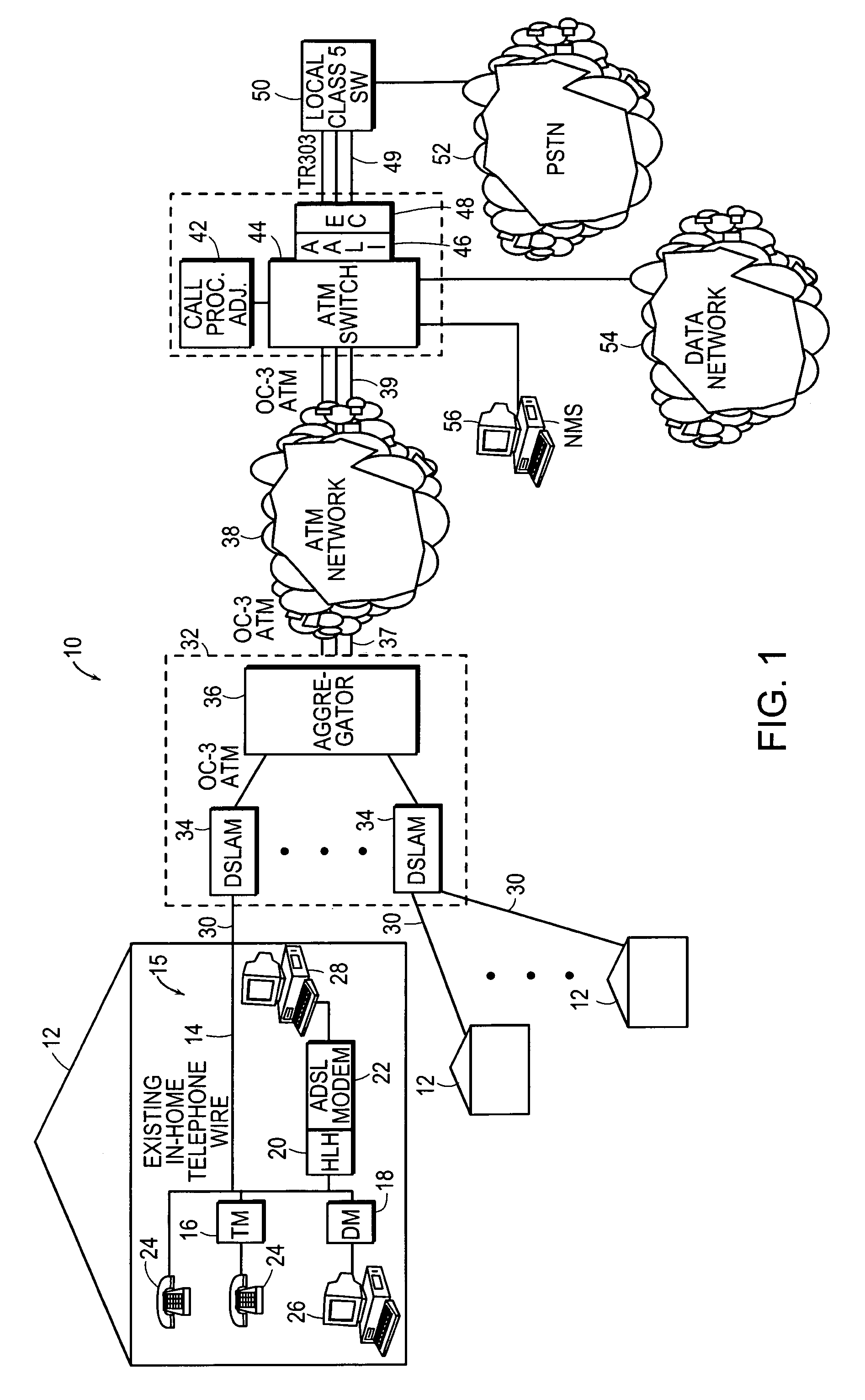

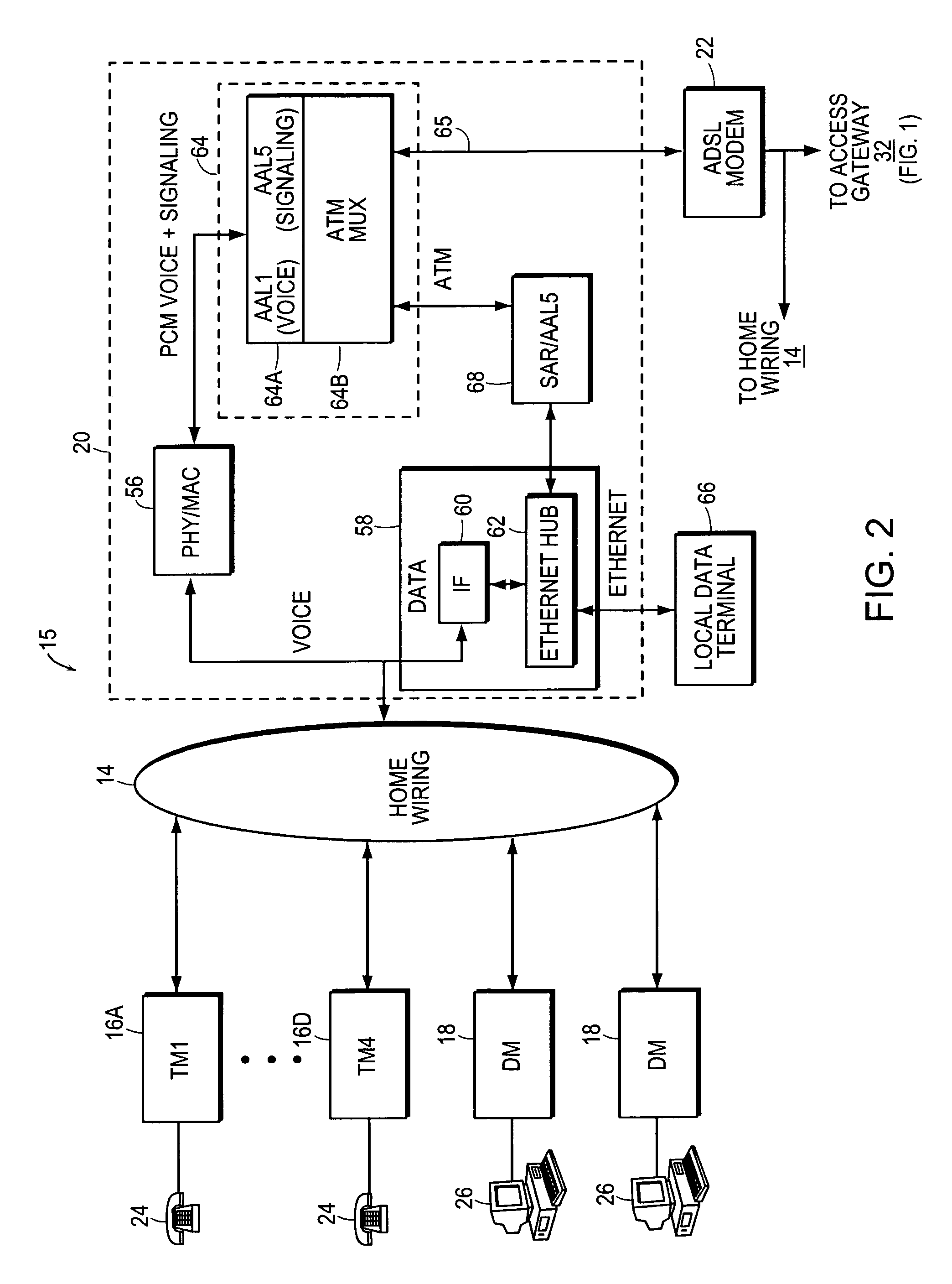

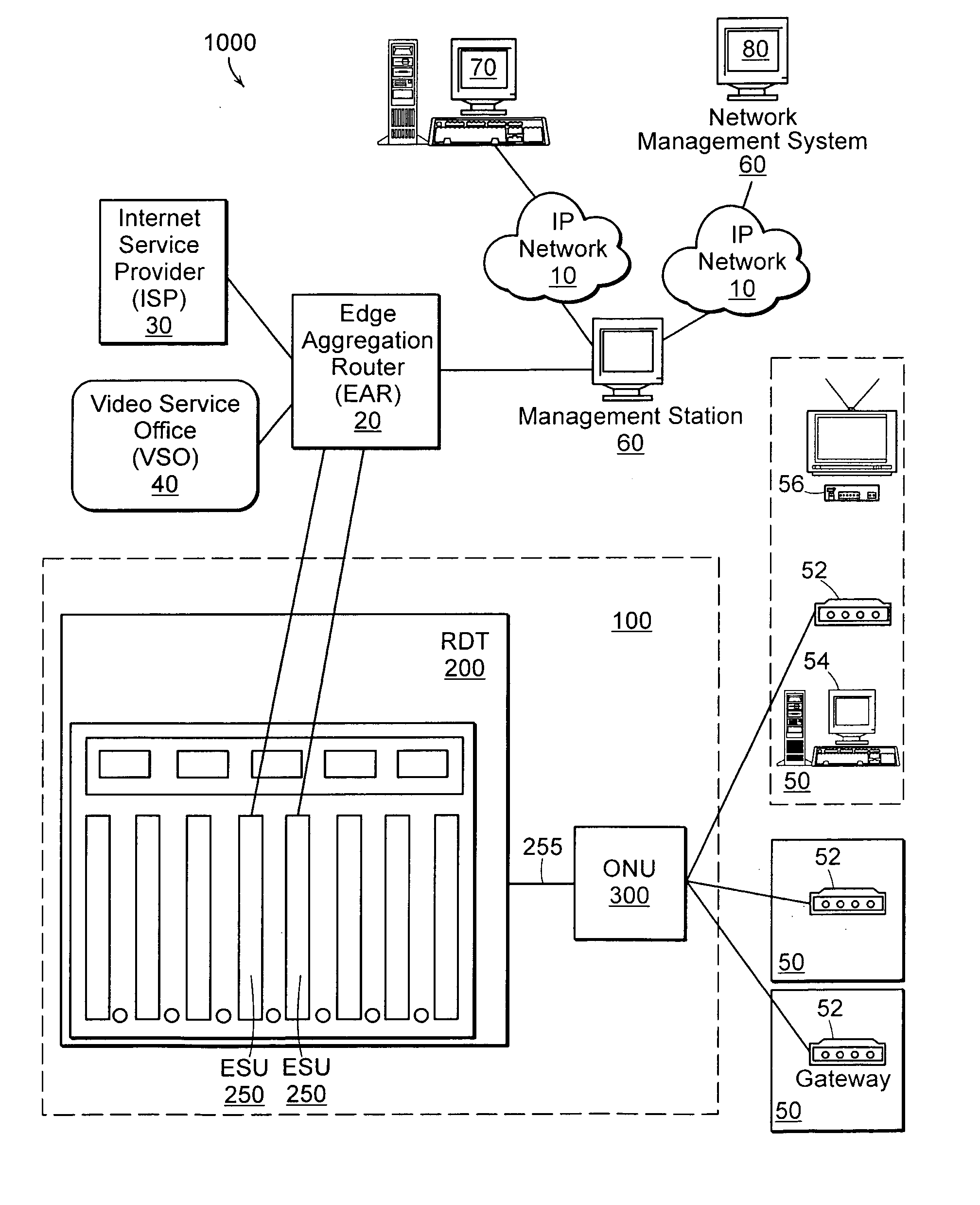

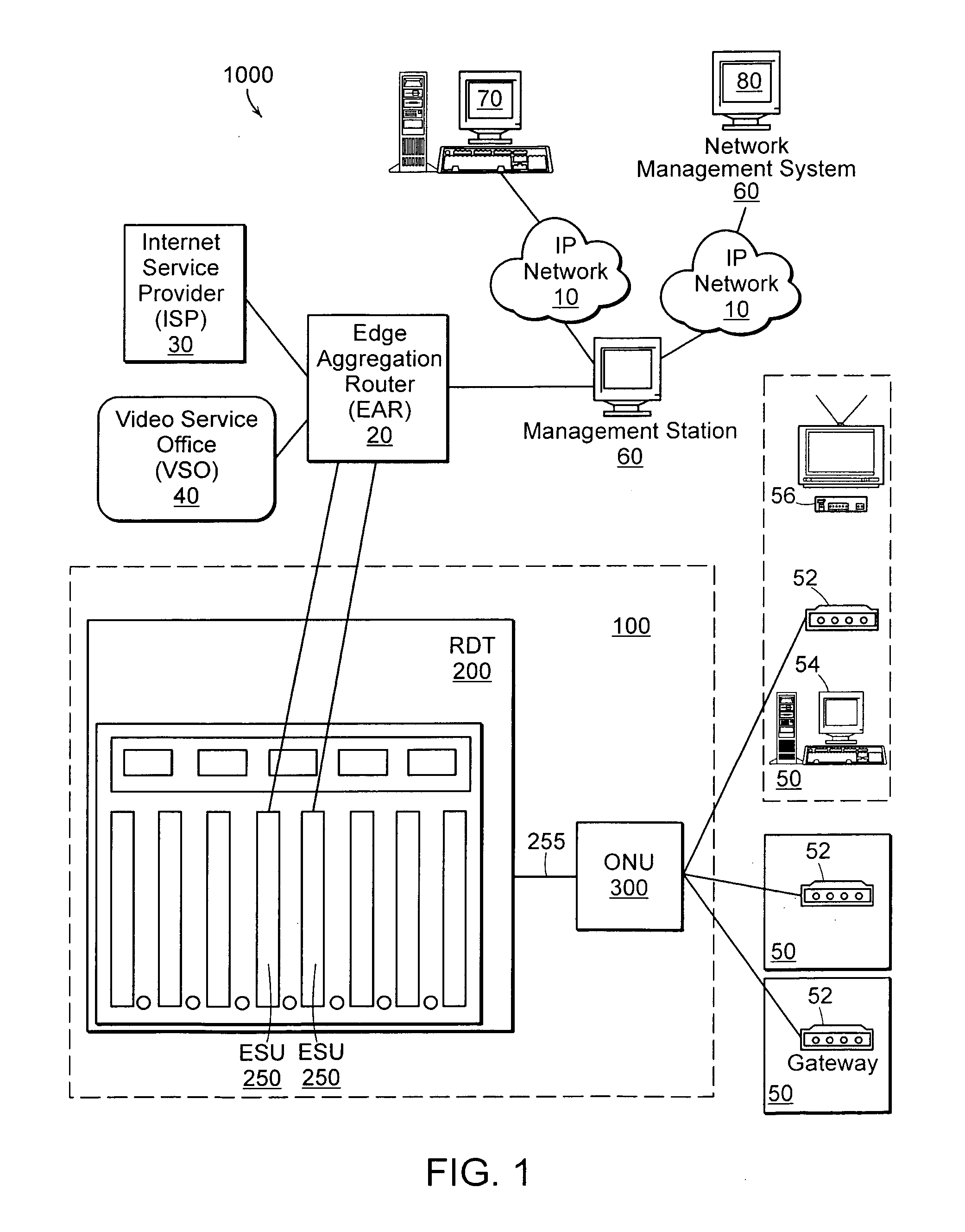

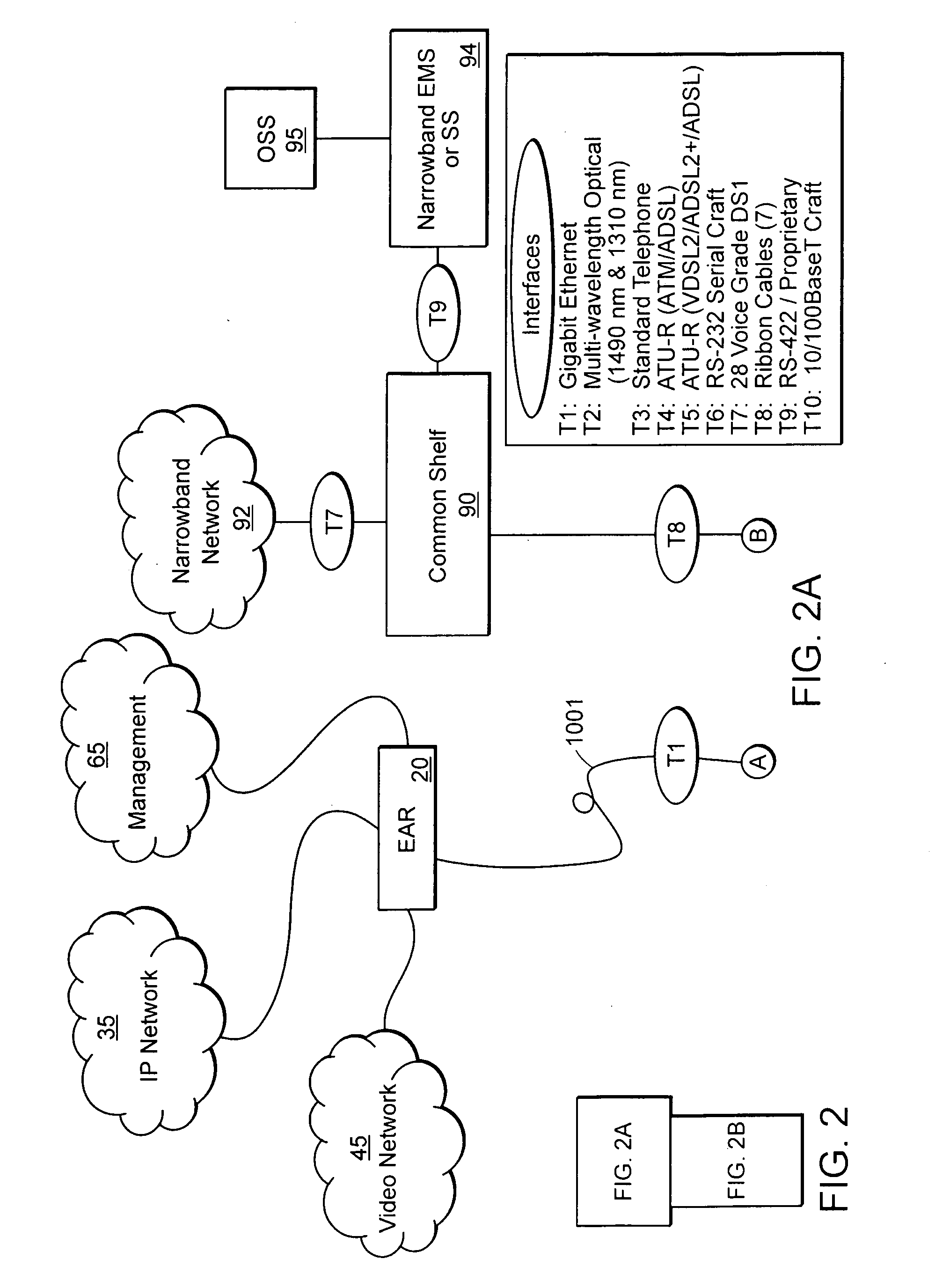

Virtual loop carrier system with network clock recovery

InactiveUS6982993B1Lower unit costGood serviceTime-division multiplexNetwork connectionsClock driftTelecommunications link

A loop carrier system includes a home local area network having plural telephone modules and a hub coupled to in-home telephone wiring. The telephone modules and the hub communicate voice signals over the in-home wiring in a dedicated frequency band above baseband POTS. The hub converts between voice signals and voice packets and is connected to a network access device for transferring the voice packets from the home local area network to a telecommunications network which routes the voice packets to a gateway. The gateway converts between the voice packets and a circuit format compatible with a local digital voice switch. The home local area network includes a timing recovery mechanism which in the absence of a clock that is traceable to the Primary Reference Clock on the public network is robust to clock drift, cell delay variation and cell impairments.

Owner:CISCO TECH INC

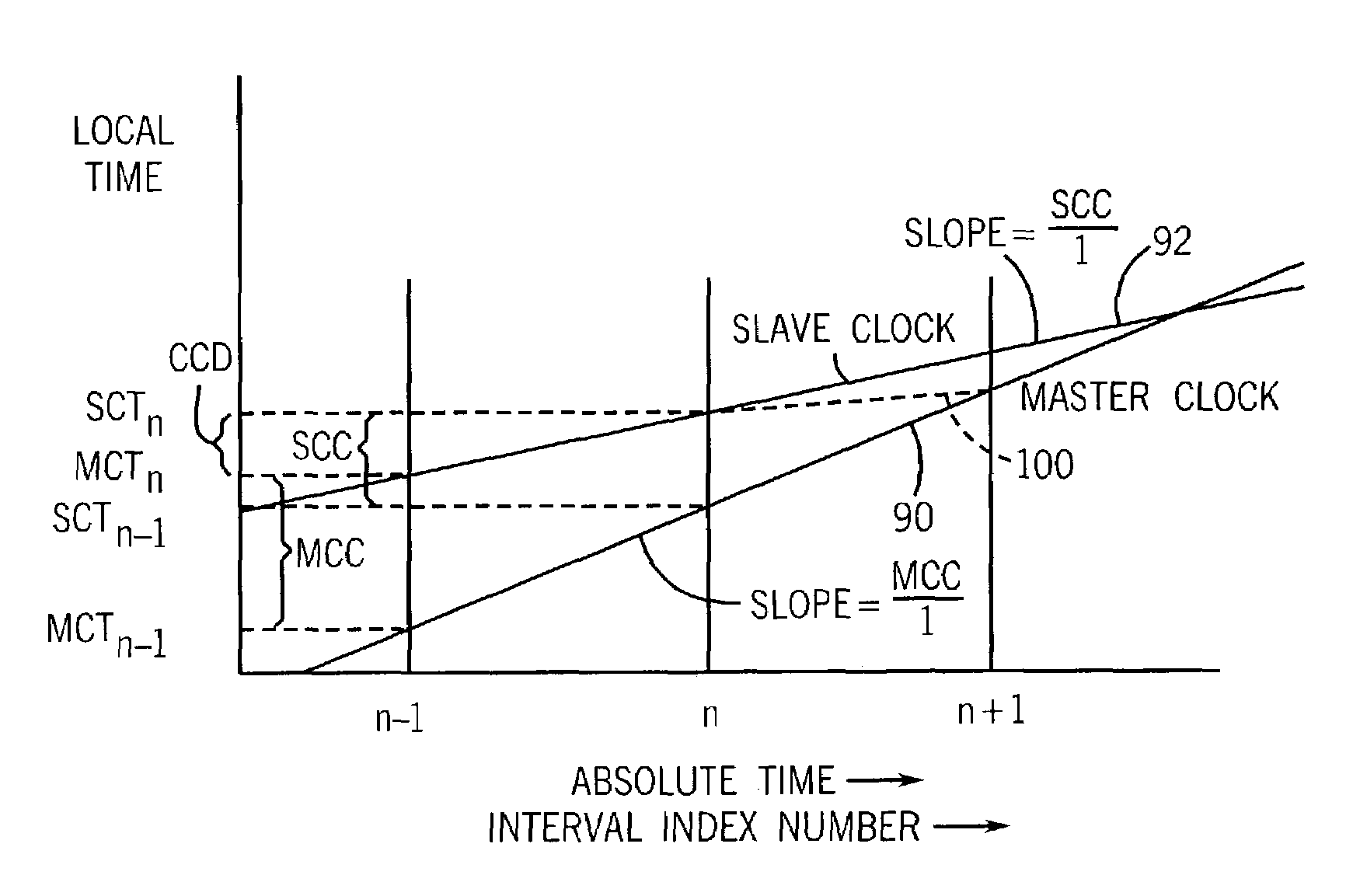

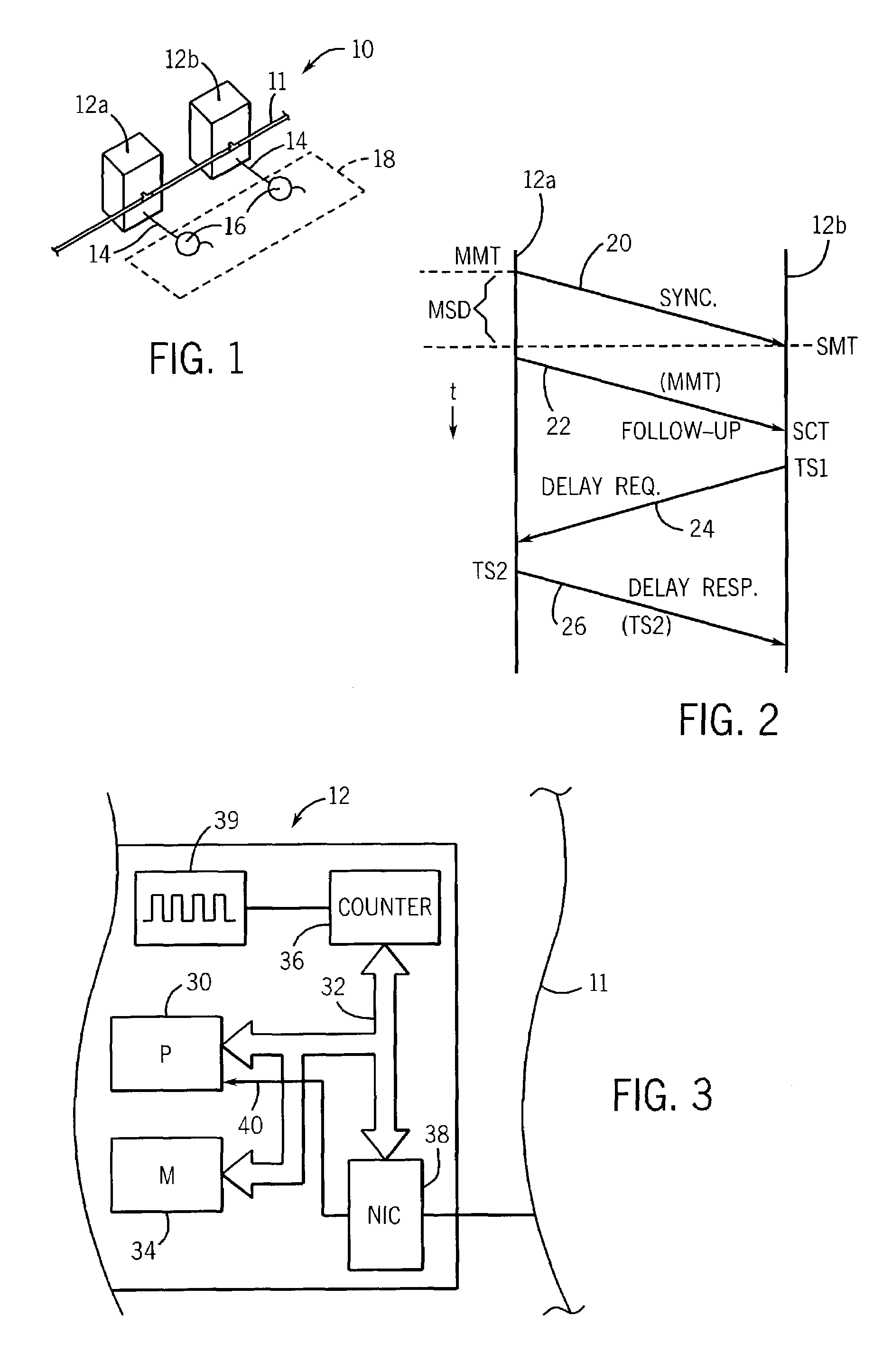

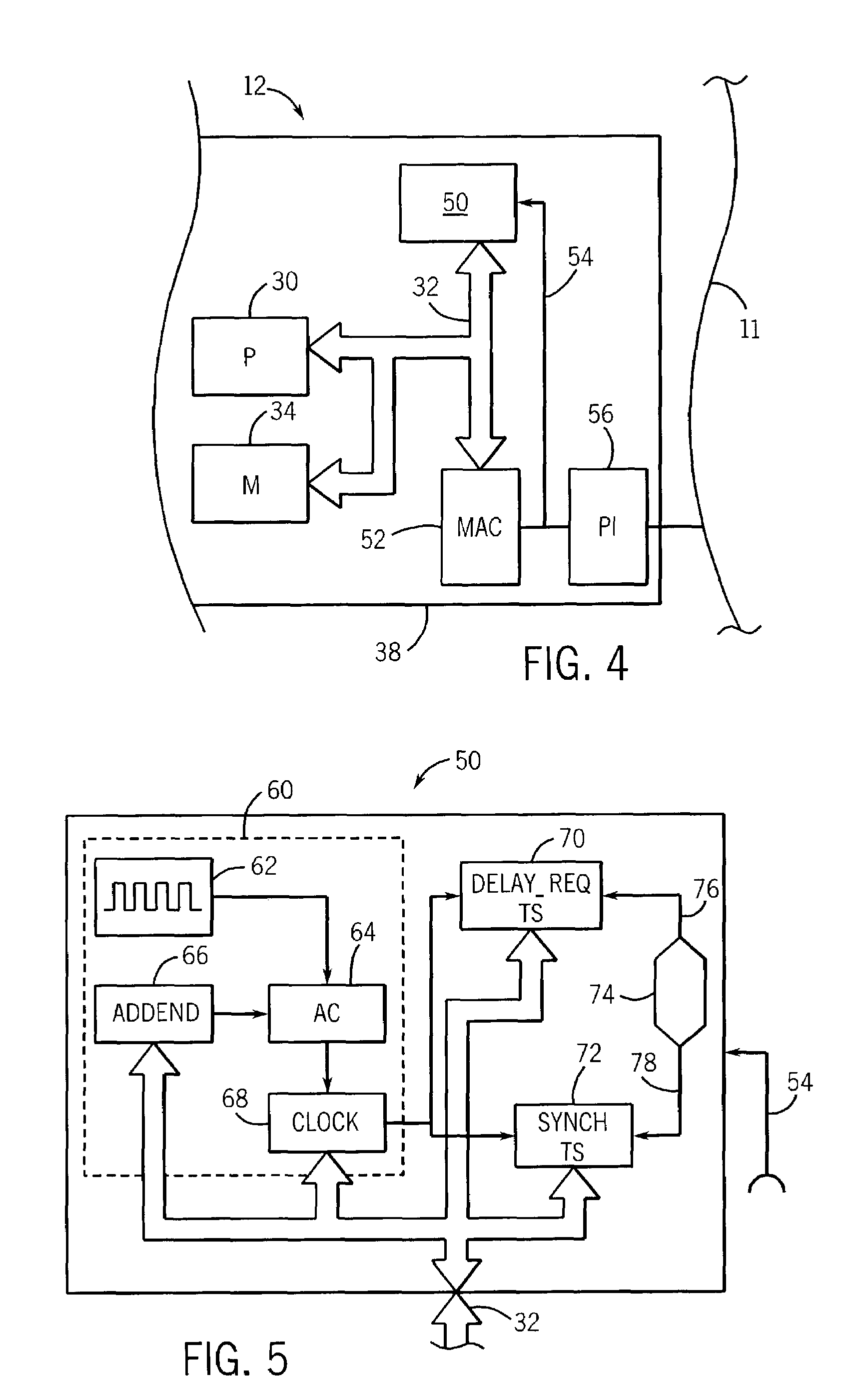

Hardware-based network packet timestamps: improved network clock synchronization

A method and apparatus for synchronizing a real time clock of a slave computer with a real time clock of a master computer. The method includes the steps of: calculating a first time drift value between the real time clock of the slave computer and the real time clock of the master computer, calculating a second time drift value between the real time clock of the slave computer and the real time clock of the master computer, calculating an average time drift value between the real time clock of the slave computer and the real time clock of the master computer using the first time drift value and the second time drift value, and adjusting the real time clock of the slave computer using the average time drift value.

Owner:WESTERNGECO LLC

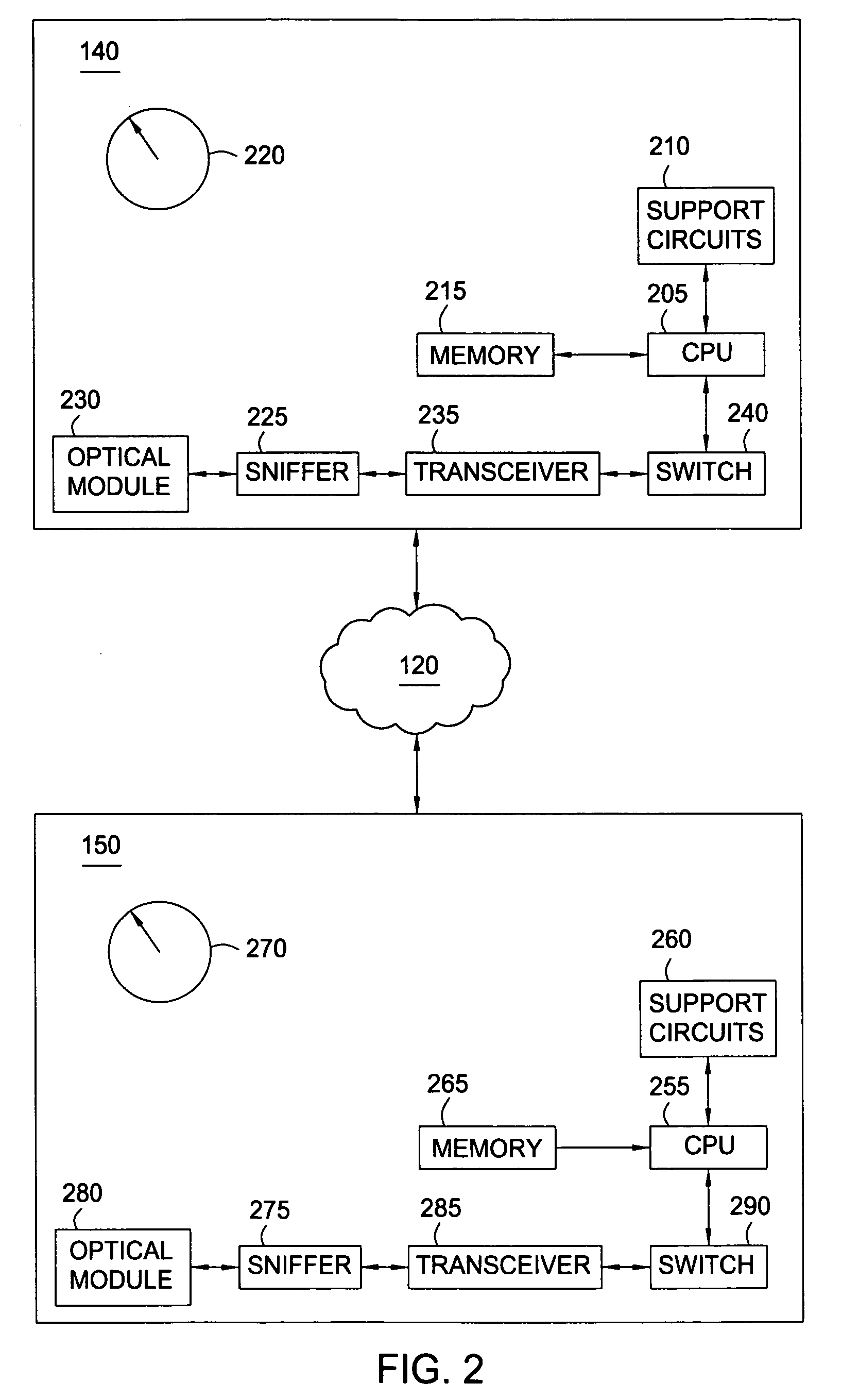

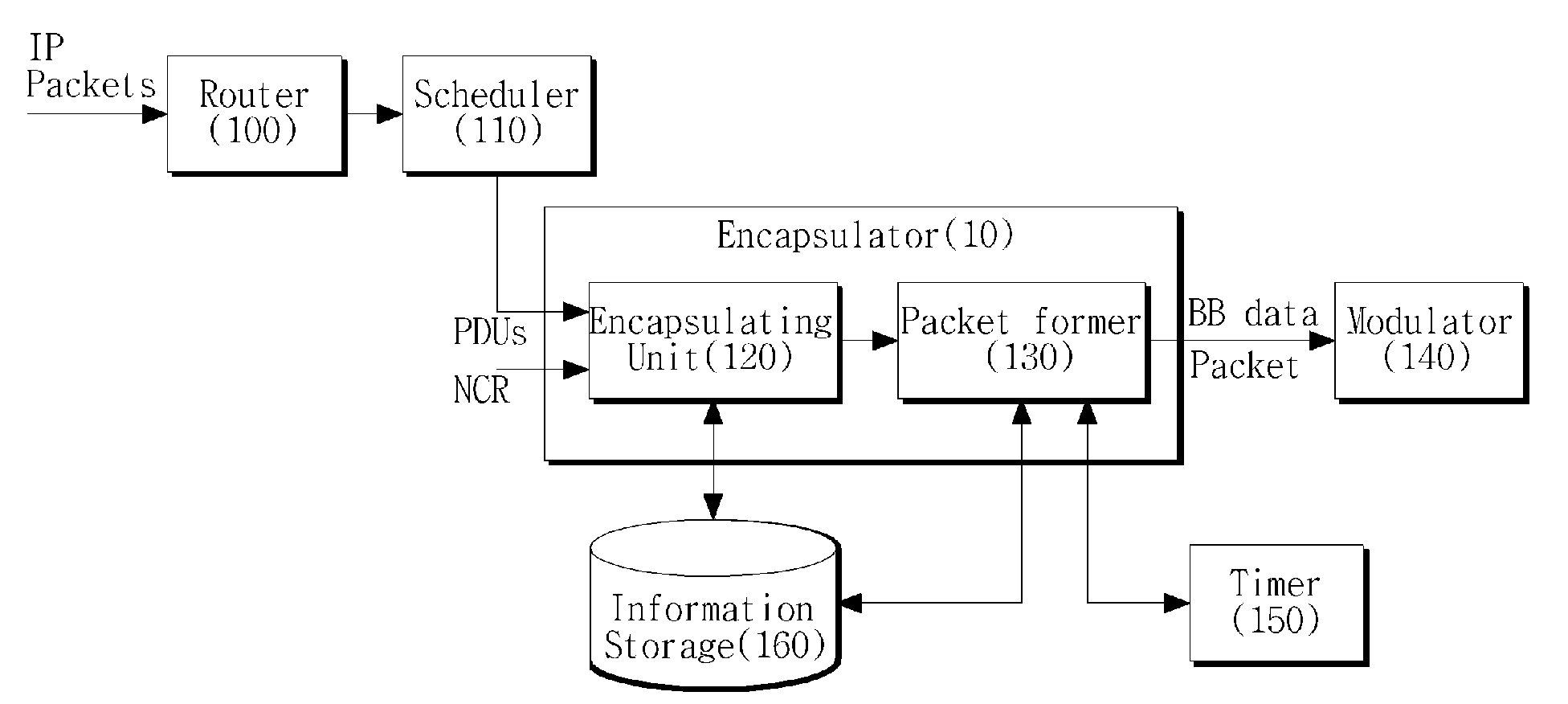

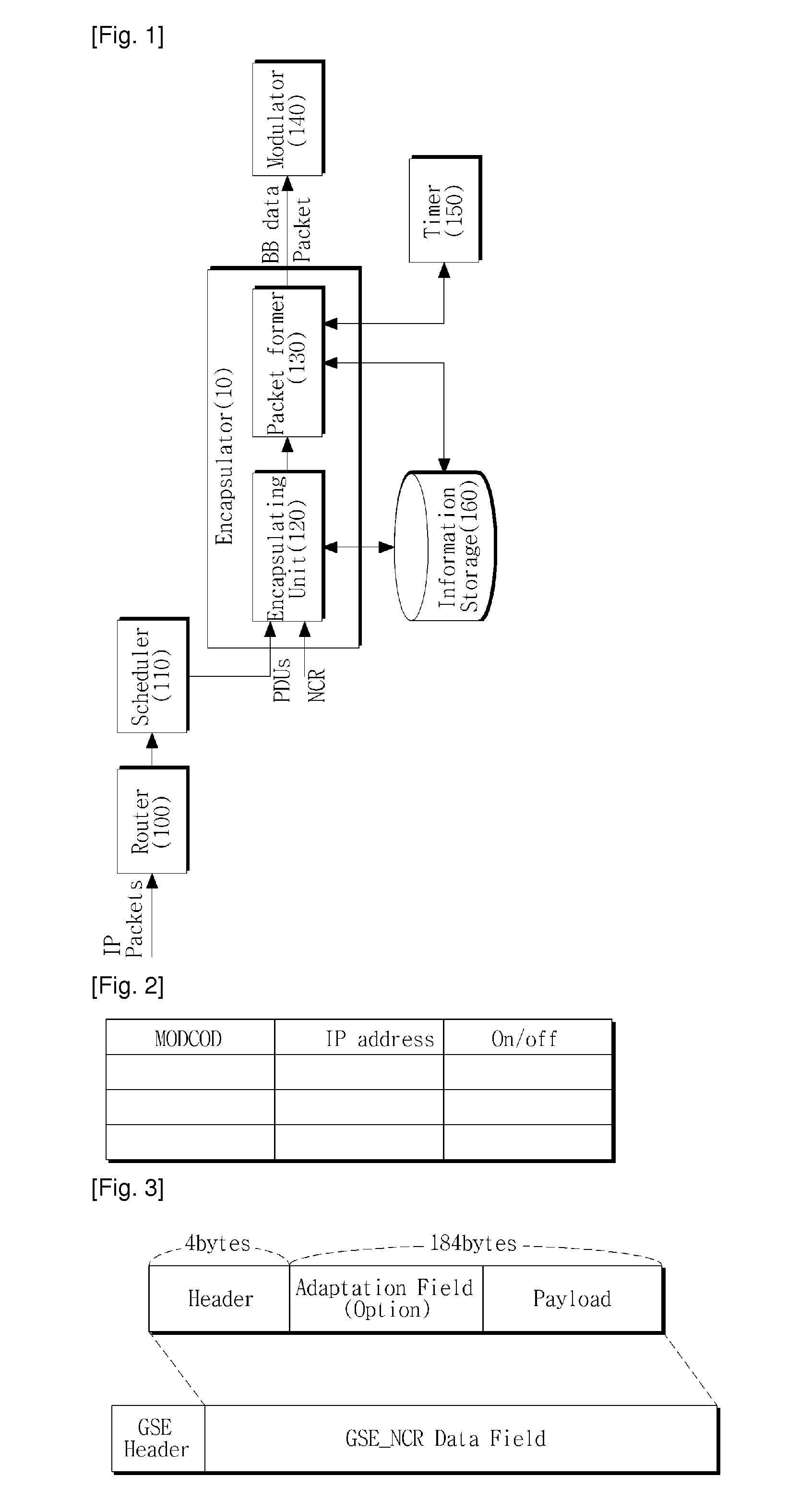

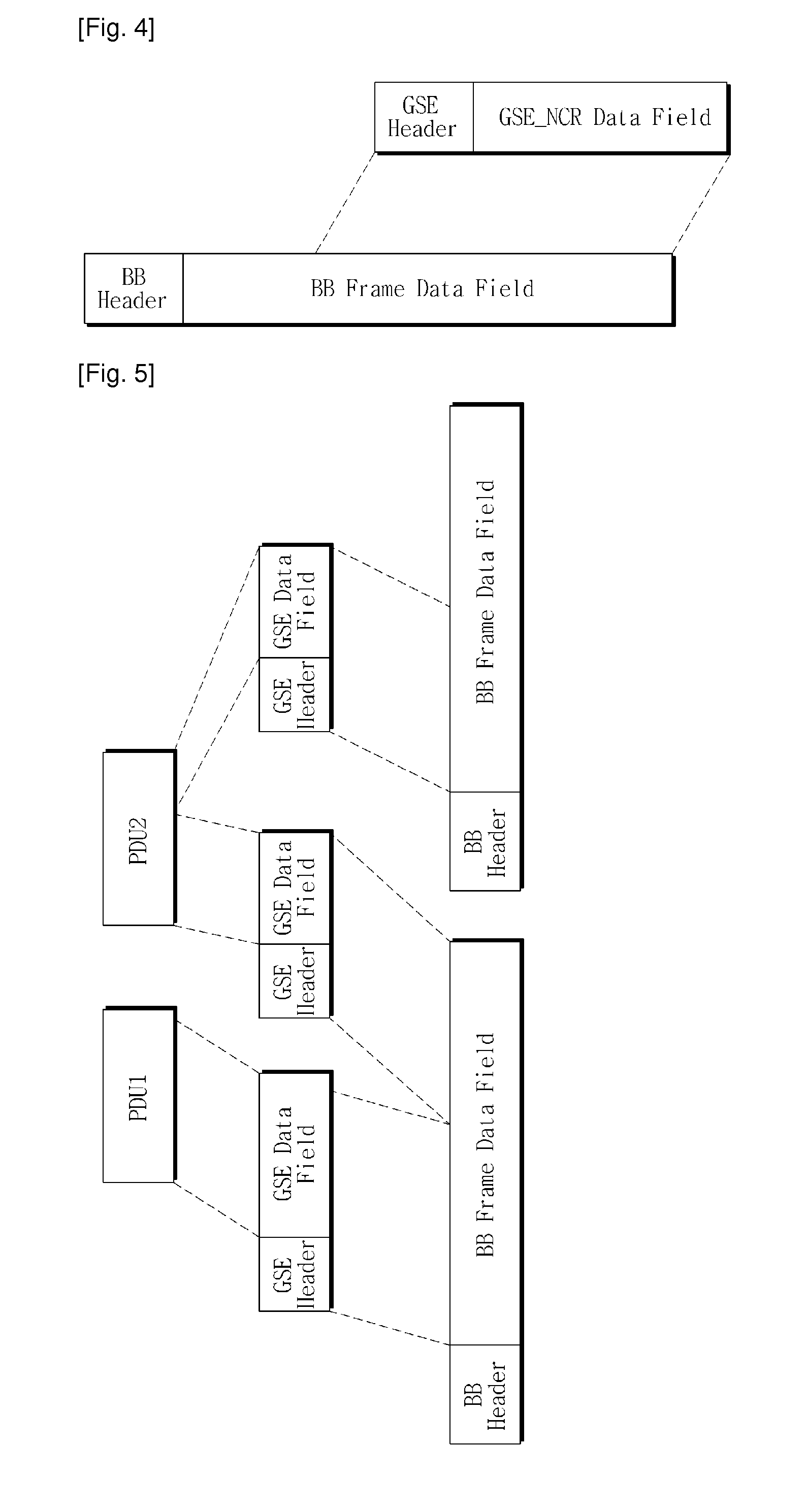

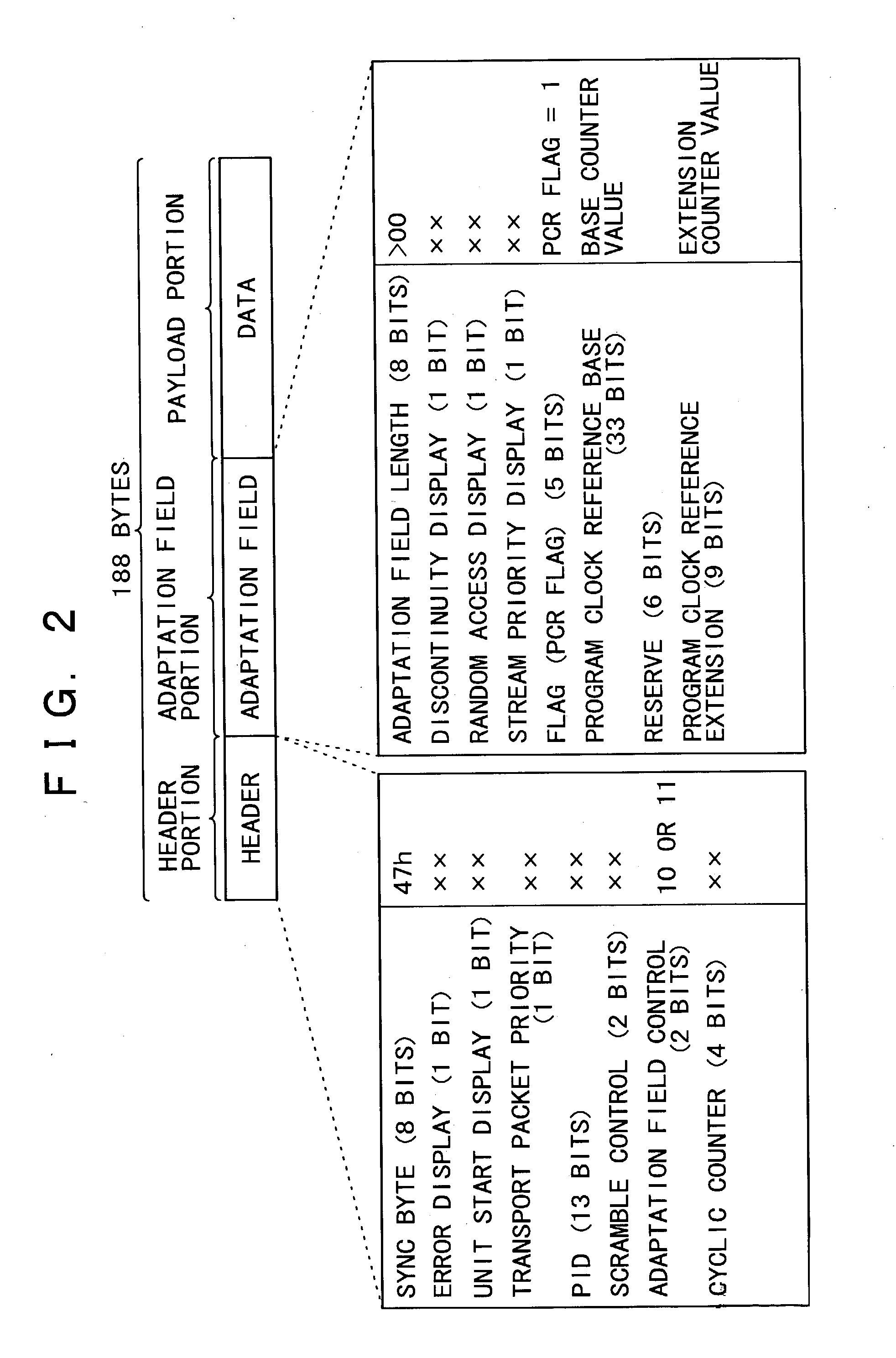

Method of encapsulating data in digital satellite communication system, and data transmission apparatus therefor

InactiveUS20110051745A1Reduce overheadImprove throughputPulse modulation television signal transmissionInformation formatDigital videoTime information

Provided is a satellite network communication system based on Second Generation Digital Video Broad-casting via Satellite (DVB-S2). A method for encapsulating transmission data in a digital satellite communication system includes: determining whether a time at which a reference time information packet has to be inserted into a packet data unit is arrived, in the digital satellite communication system; and if the time at which the reference time information packet has to be inserted into the packet data unit is arrived, transforming the packet data unit in the form of a baseband data packet including the reference time information packet. Therefore, by allowing transmission of Network Clock Reference (NCR) information in a satellite communication environment based on Generic Steam Encapsulation (GSE), bidirectional satellite communications are possible.

Owner:ELECTRONICS & TELECOMM RES INST

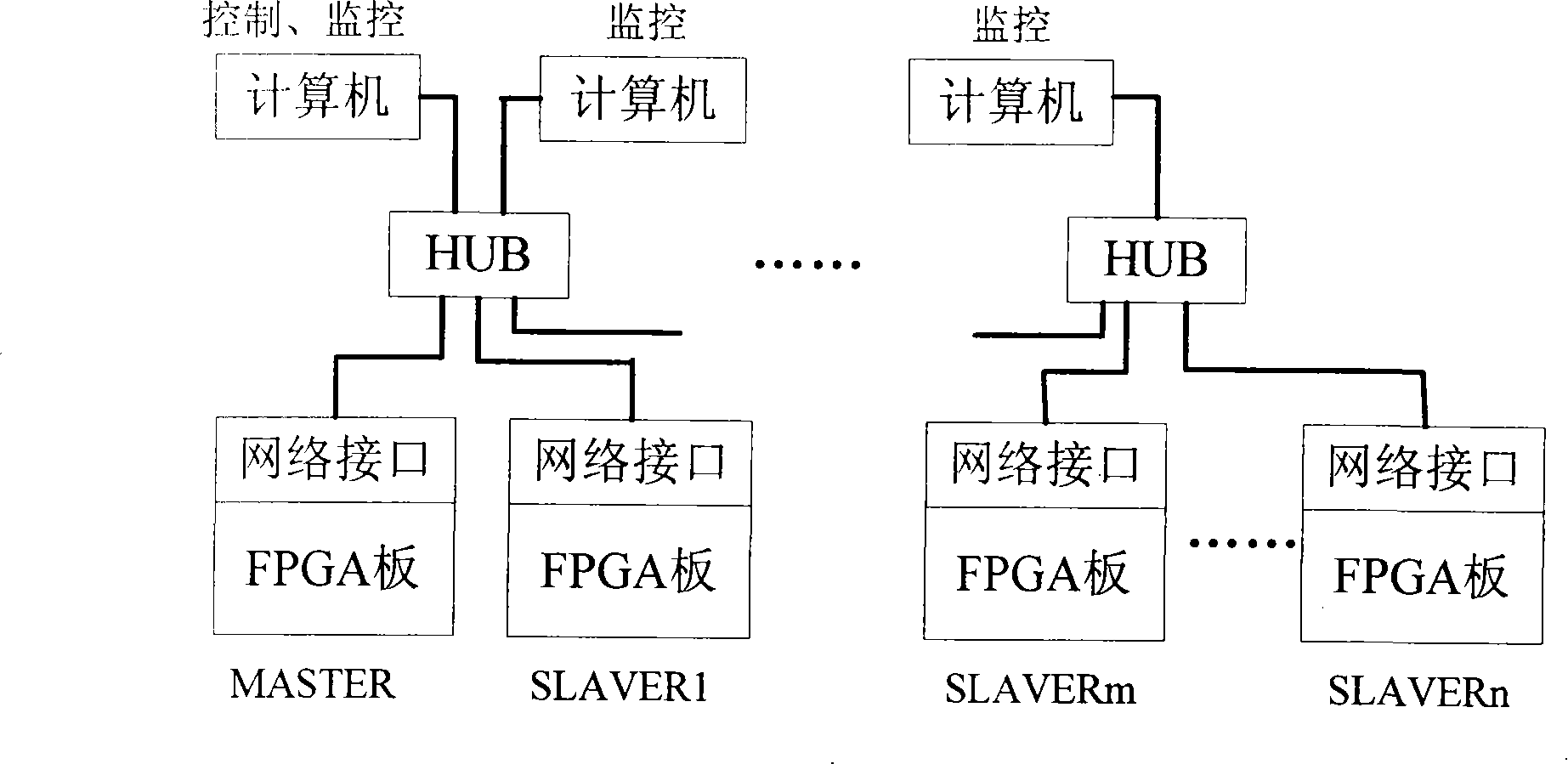

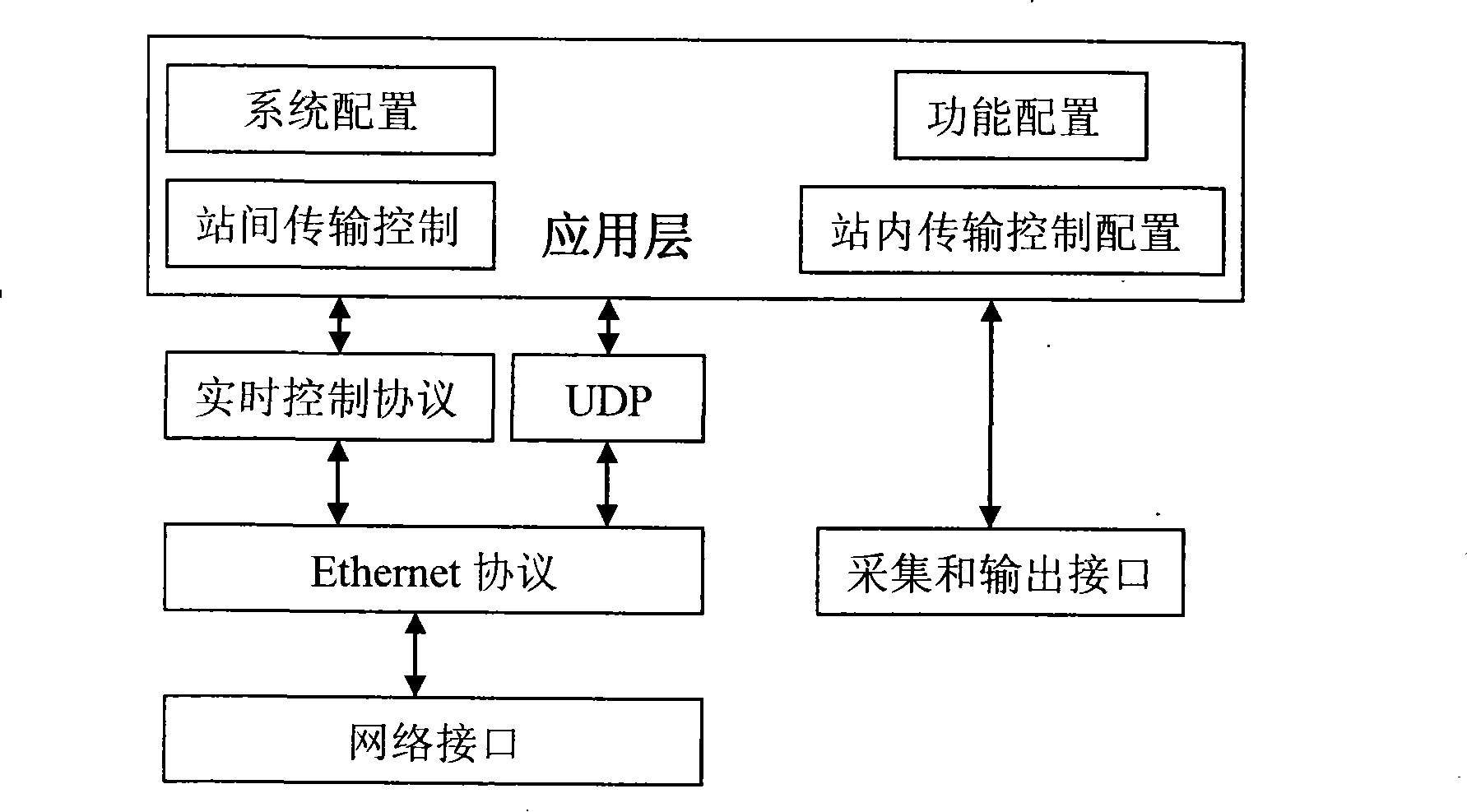

Distributed network clock synchronizing system and method based on FPGA

InactiveCN101252404ASatisfy real-timeMeet the need for controlTime-division multiplexNetwork clockNetworked system

The invention requests to protect a small-size distributed network clock synchronization system based on a field programmable gate array (FPGA), which relates to the distributed network synchronization technique. The synchronization system comprises a PC, a HUB and a distributed unit based on the FPGA; each distributed unit is provided with a general network interface; the fixed synchronization cycle time proposal is adopted to realize the clock synchronization of the small-size distributed network, enabling the system to reach the microsecond grade synchronization. The synchronization mode adopted in the small-size distributed network clock synchronization system is similar to the mode of the IEEE1588 standards; based on the high accuracy synchronization property of the IEEE1588 standards, the initial synchronization speed of the synchronization system is improved so that a distributed system which has the advantages of high initial synchronization speed and high accuracy clock synchronization is realized. The network clock synchronization system provides each composite unit of the distributed network system with synchronization clock used as the reference of the working clock of the system; thereby, the small-size distributed network clock synchronization system is applicable to the distributed network which has high real-time requirement for data transmission.

Owner:CHONGQING UNIV

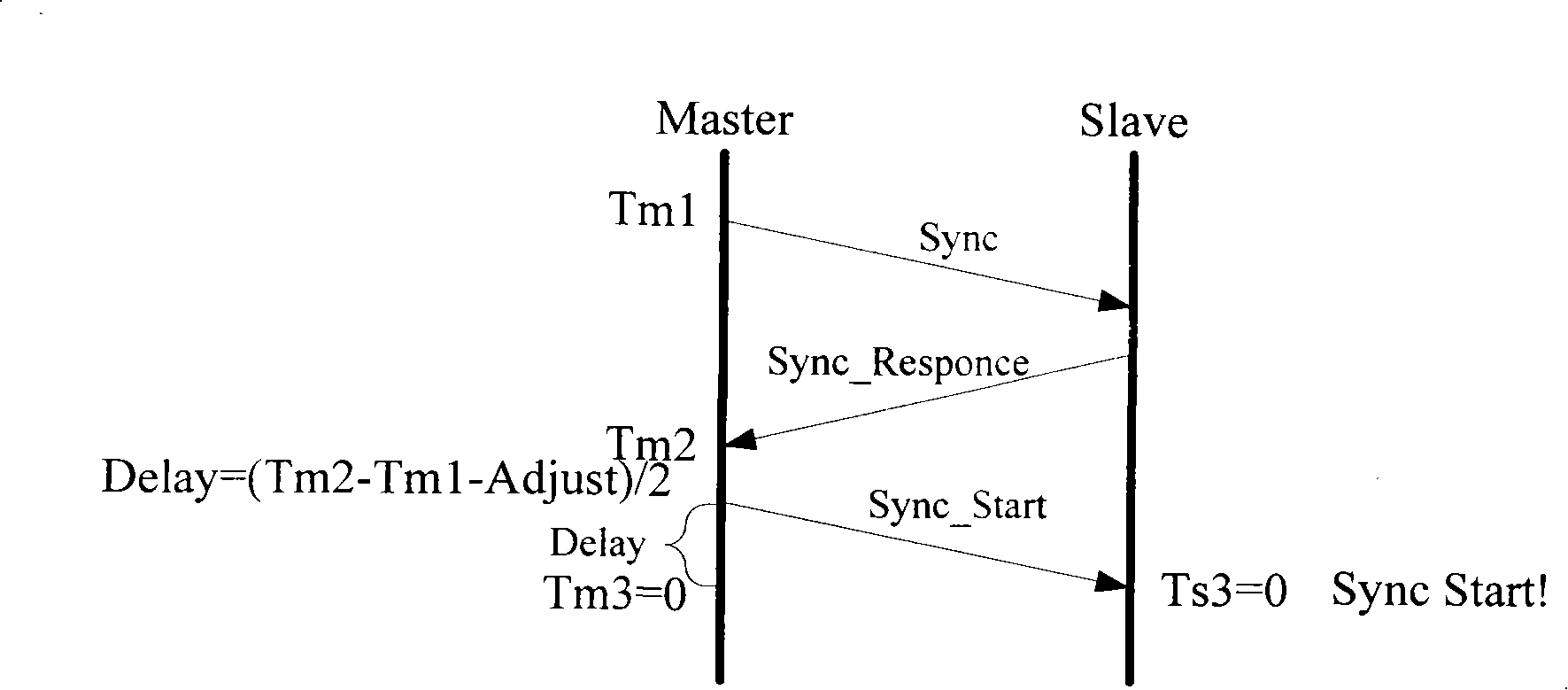

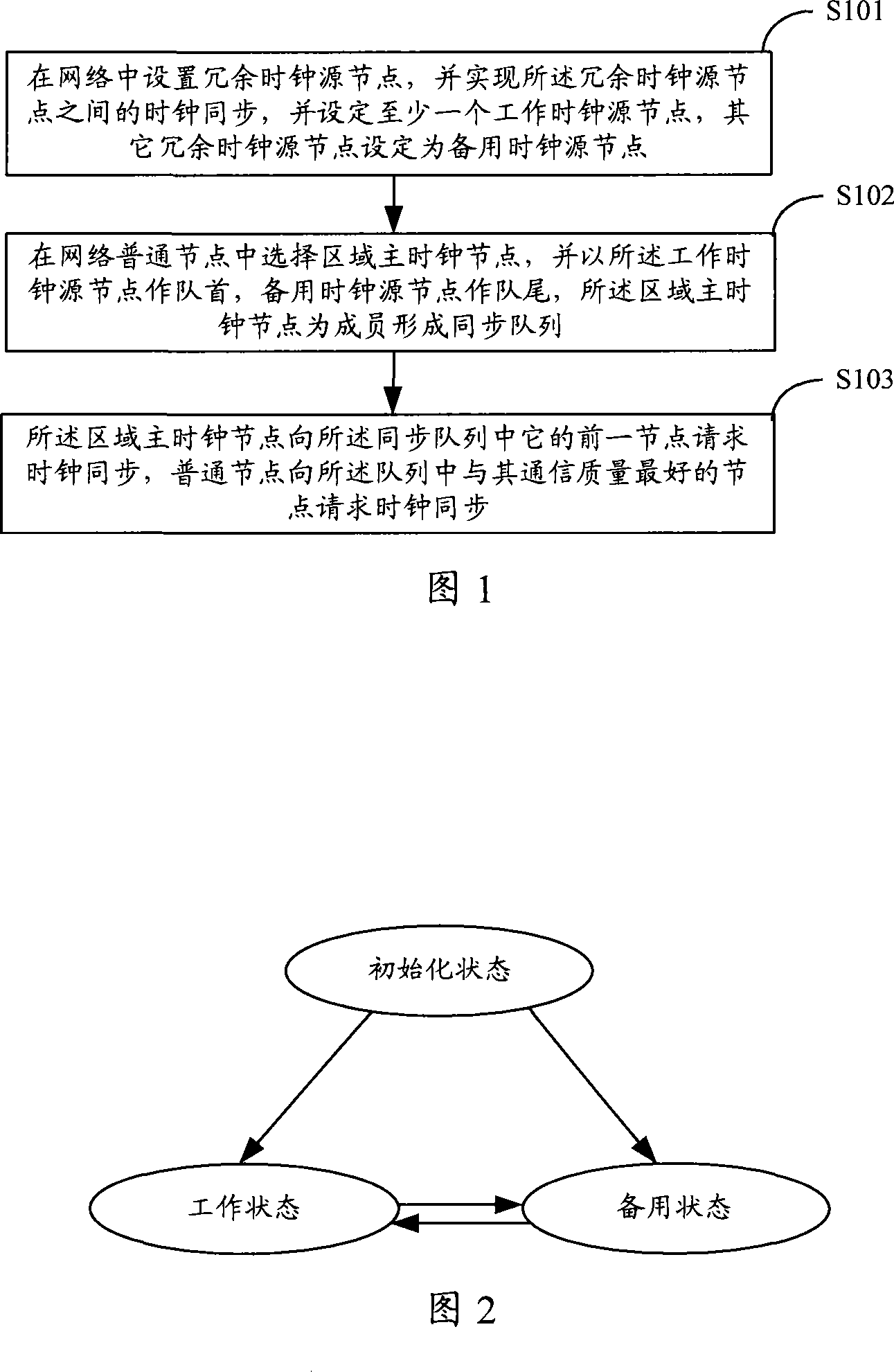

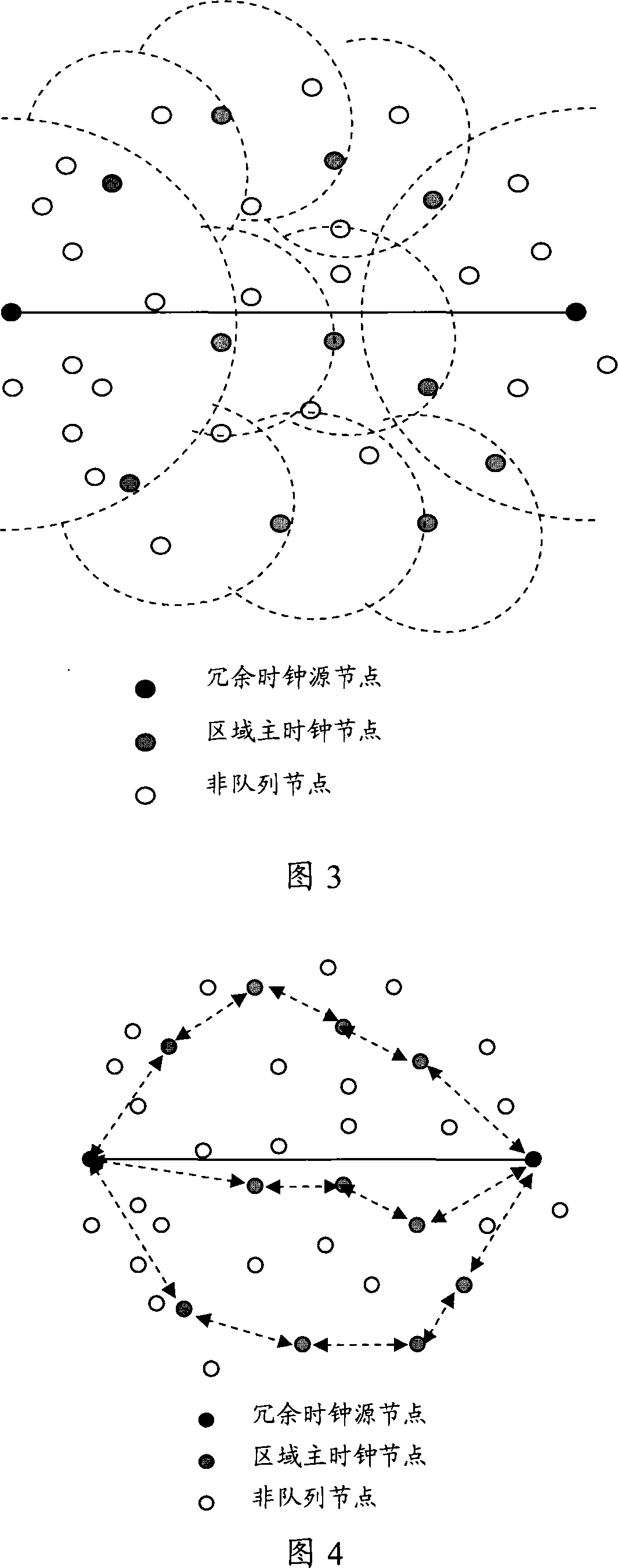

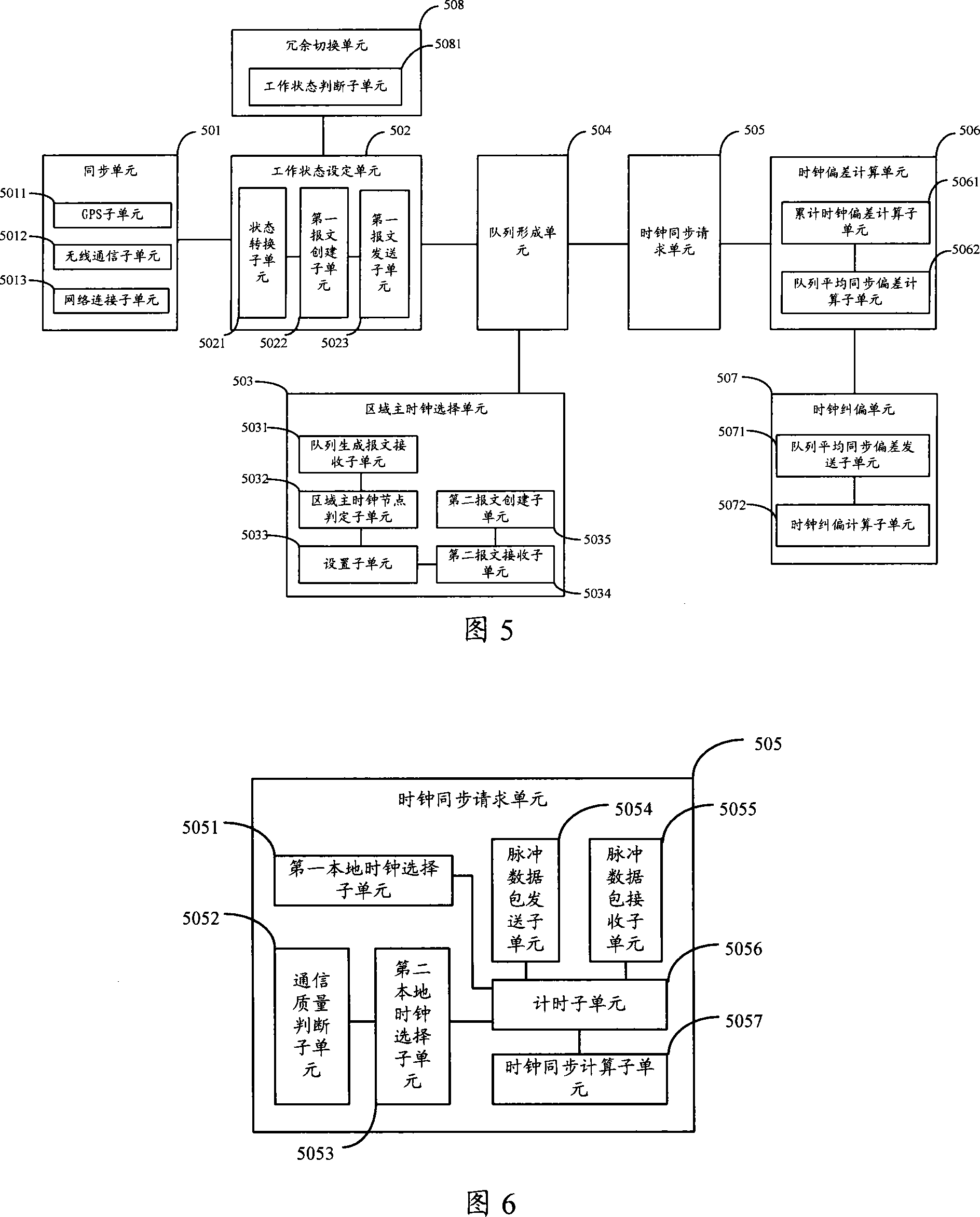

Method and system for network clock synchronous

InactiveCN101090341APrevent crashAchieve synchronizationRadio transmission for post communicationData switching networksNetwork clockWireless sensor networking

This invention discloses a method and a system for synchronizing network clocks, which sets synchronous source nodes with mutual redundance in a wireless sensor network to design them a working clock node and a backup clock source node and selects a regional master clock node in network node to form a synchronous queue, the network node asks for clock synchronization to the nodes in the synchronous queue, the backup clock source node computes the mean queue synchronous clock based on the difference between the local clock and the synchronous clock of the working clock node and sends it to the regional master clock node in the queue so as to realize clock rectification to the regional master clock.

Owner:SUPCON GRP +1

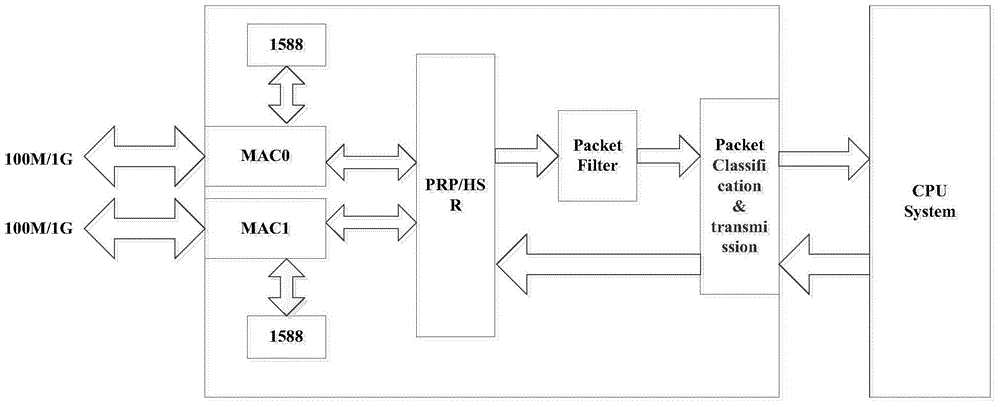

Dual-network-redundancy device hardware architecture in transformer substation and implementation method

ActiveCN104158687AImprove compatibilityReduce the burden onData switching networksHigh-availability Seamless RedundancyTransformer

The invention belongs to the field of internal communication of automatic transformer substation systems for power systems, and specifically discloses dual-network-redundancy device hardware architecture in a transformer substation and an implementation method. The dual-network-redundancy device hardware architecture and the implementation method are characterized in that an MAC (Media Access Control) Ethernet communication module, a PRP&HSR (Parallel Redundancy Protocol and High-availability Seamless Redundancy) module, a packet filter module, a multipath packet transmission control module and a 1588 clock synchronization module are designed on an FPGA (Field Programmable Gate Array) to synergistically finish receiving and transmission of Ethernet packets, IEC61588 accurate network clock synchronization, dual-network-redundancy processing, network storm suppression and packet classification and transmission functions in an automatic transformer substation system. Through adoption of the dual-network-redundancy device hardware architecture and the implementation method, the operation processing demand on a CPU (Central Processing Unit) is lowered greatly, the protection cost on a measurement and control device of the transformer substation is reduced, and the running reliability of the transformer substation system is improved.

Owner:NARI TECH CO LTD +1

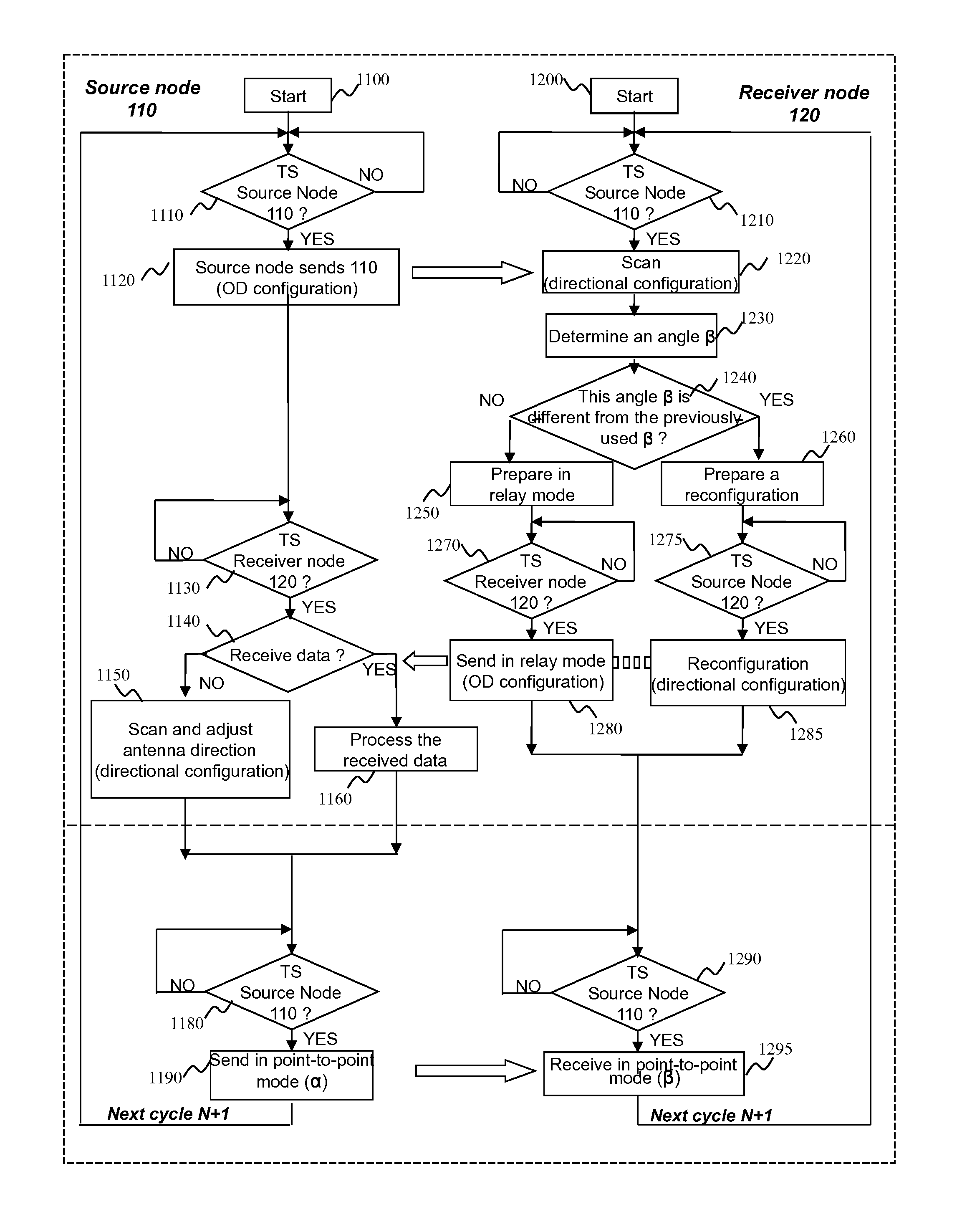

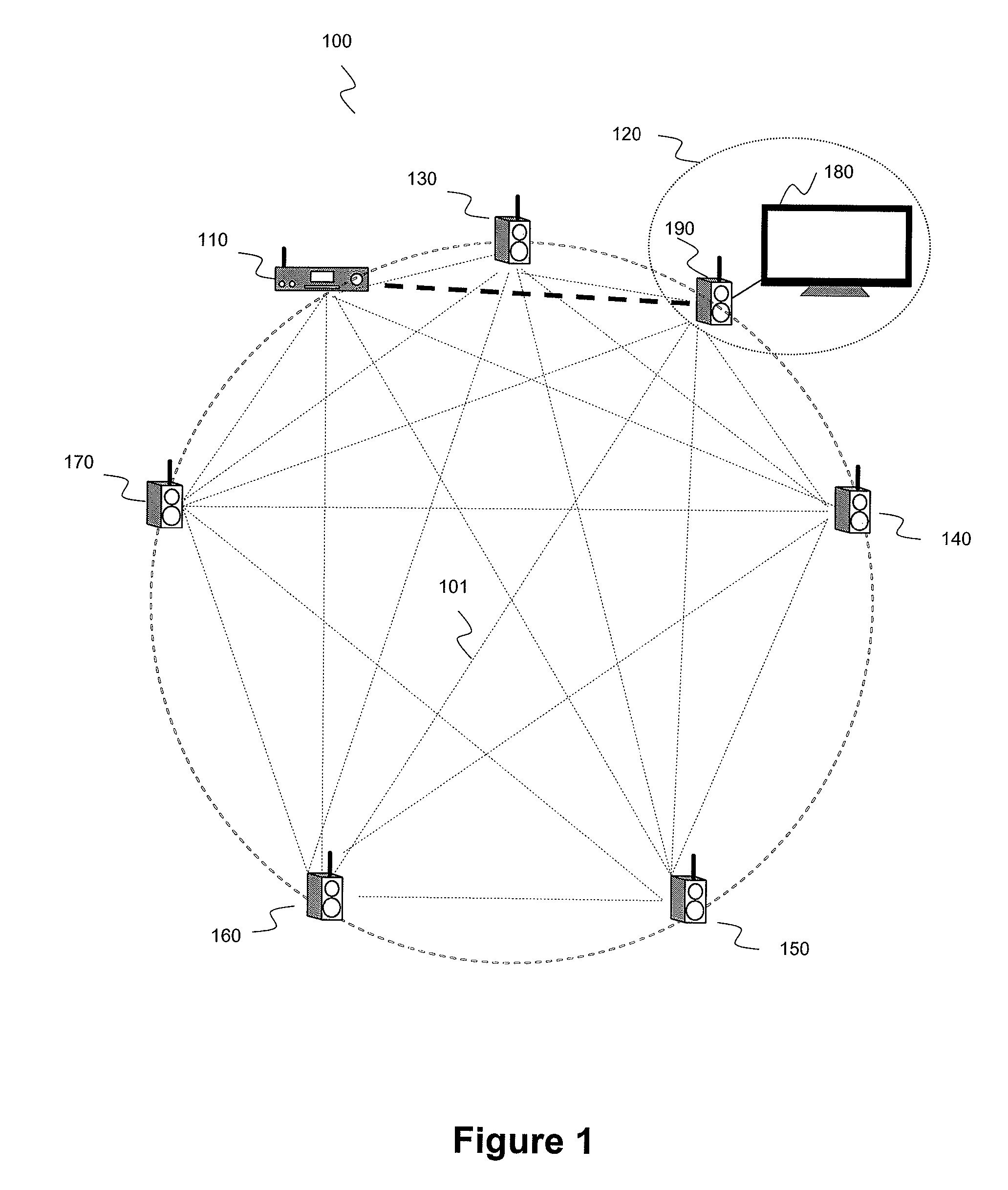

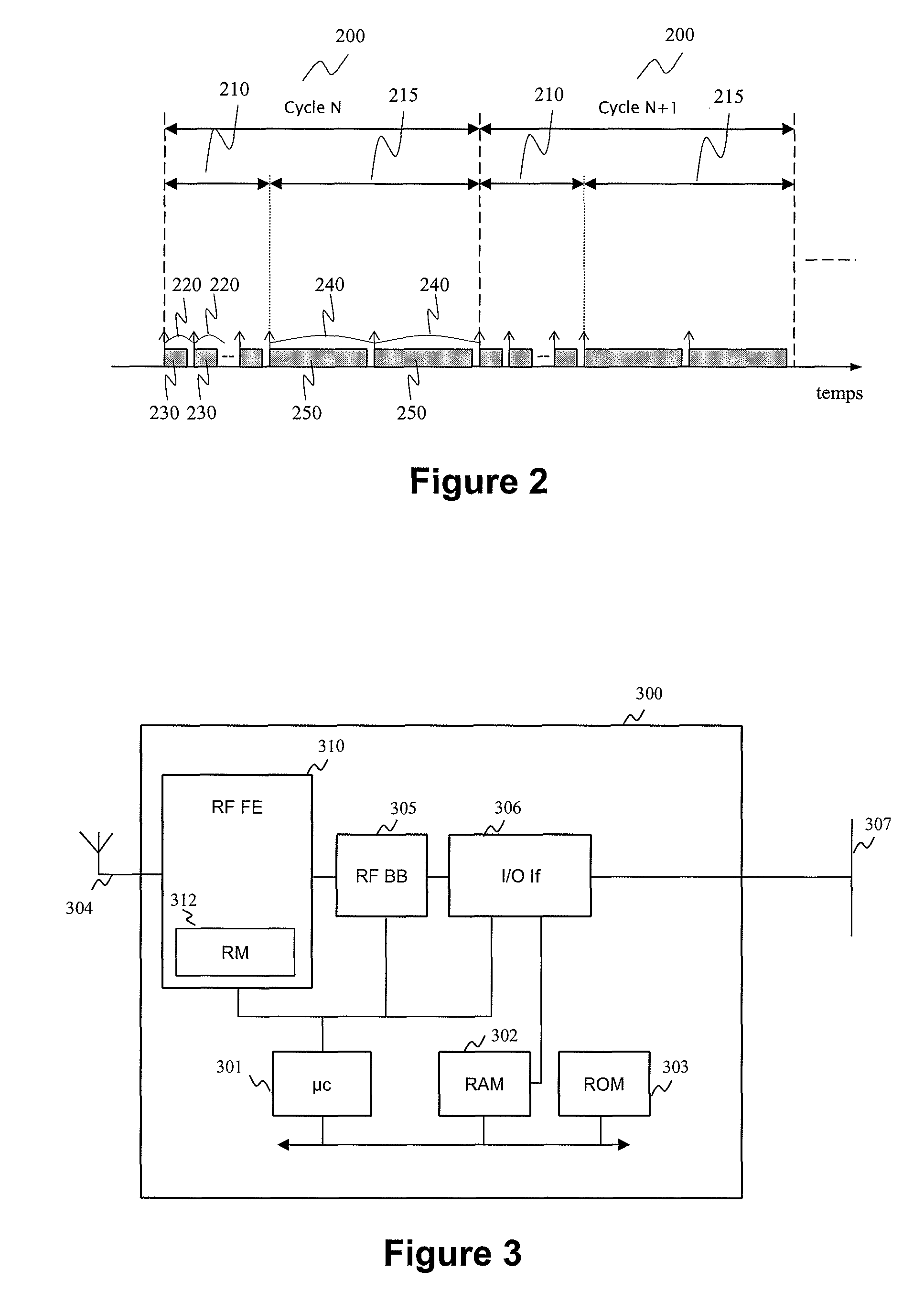

Methods for configuring sender and receiver antennas, corresponding storage means and nodes

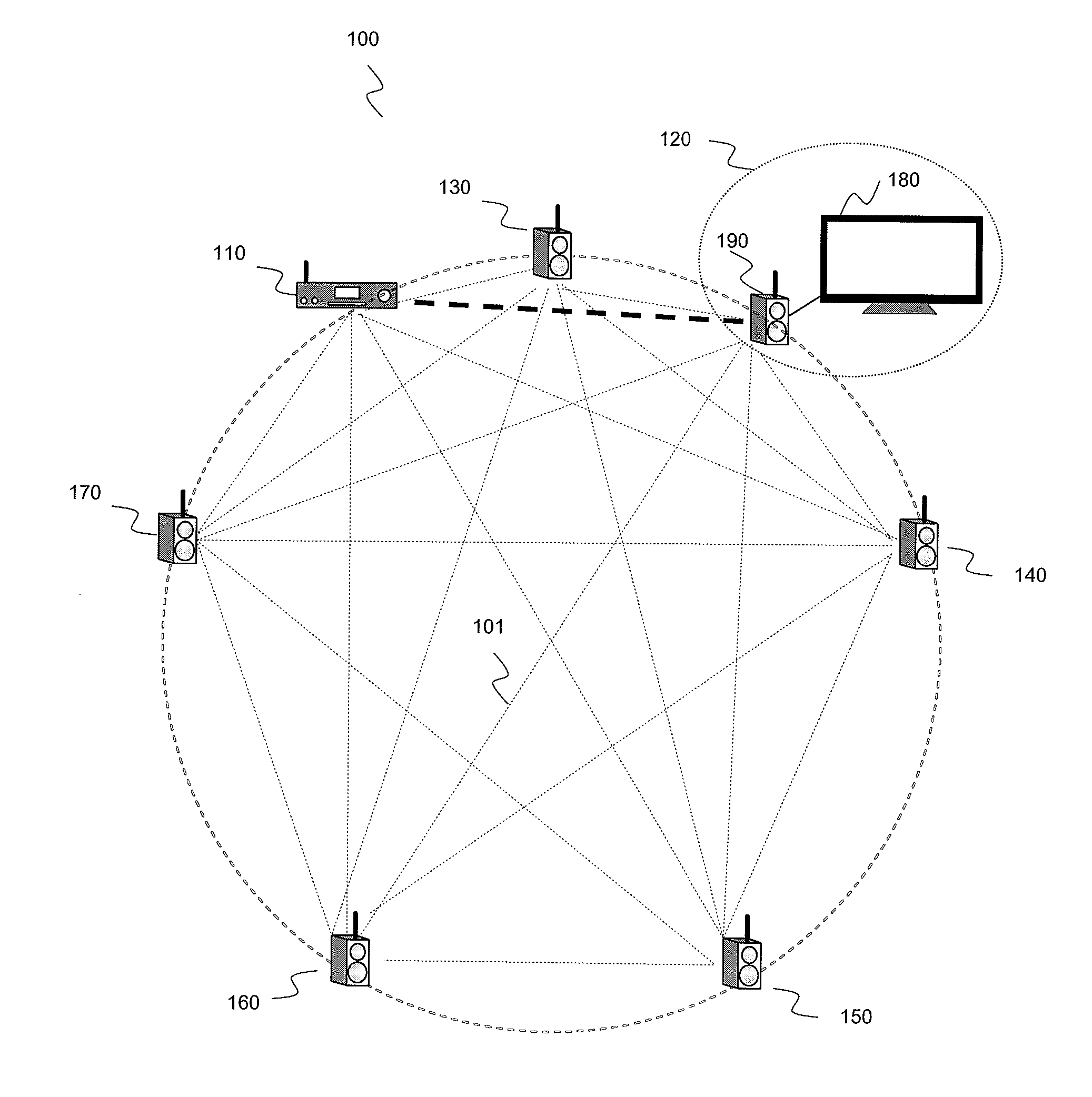

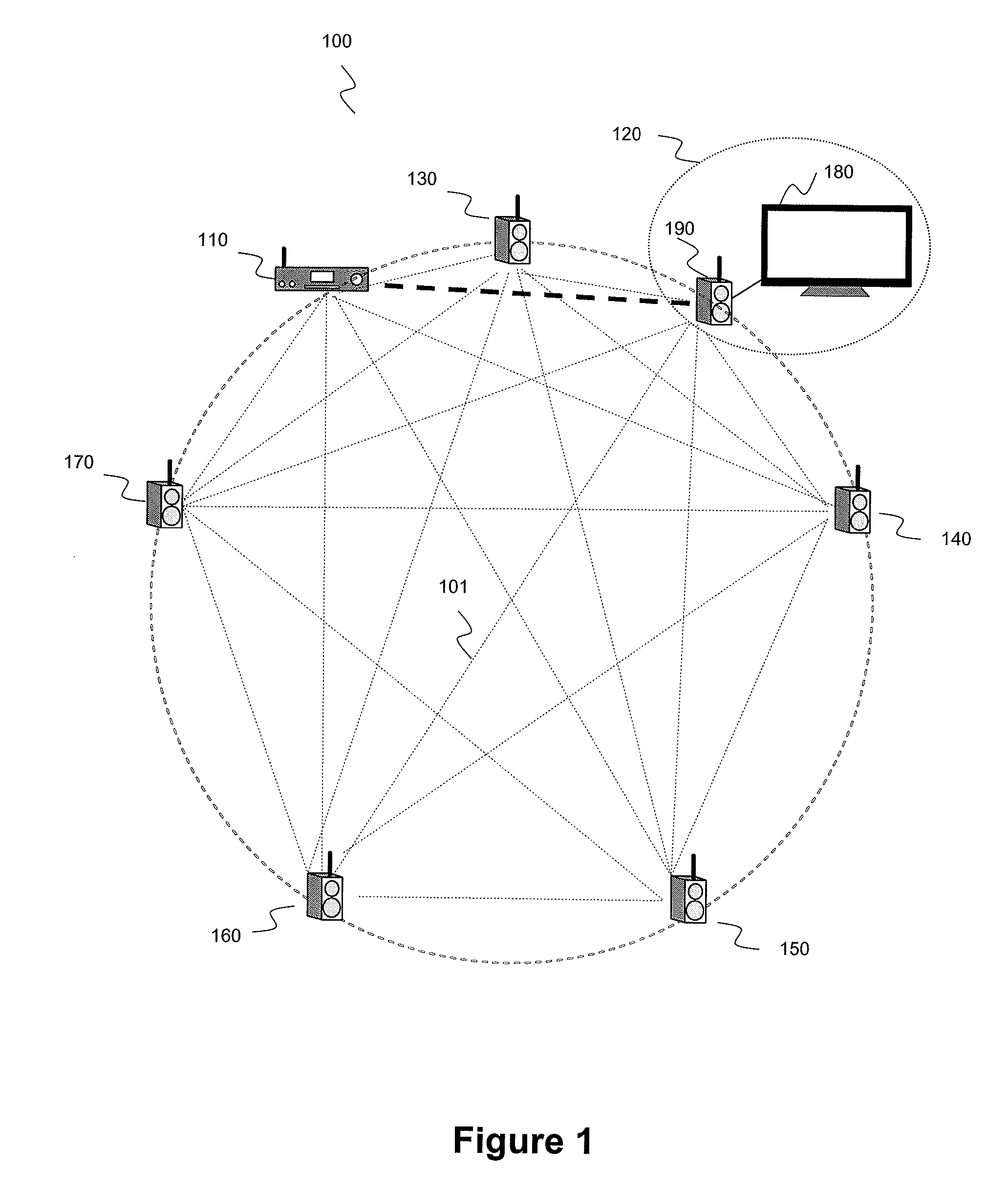

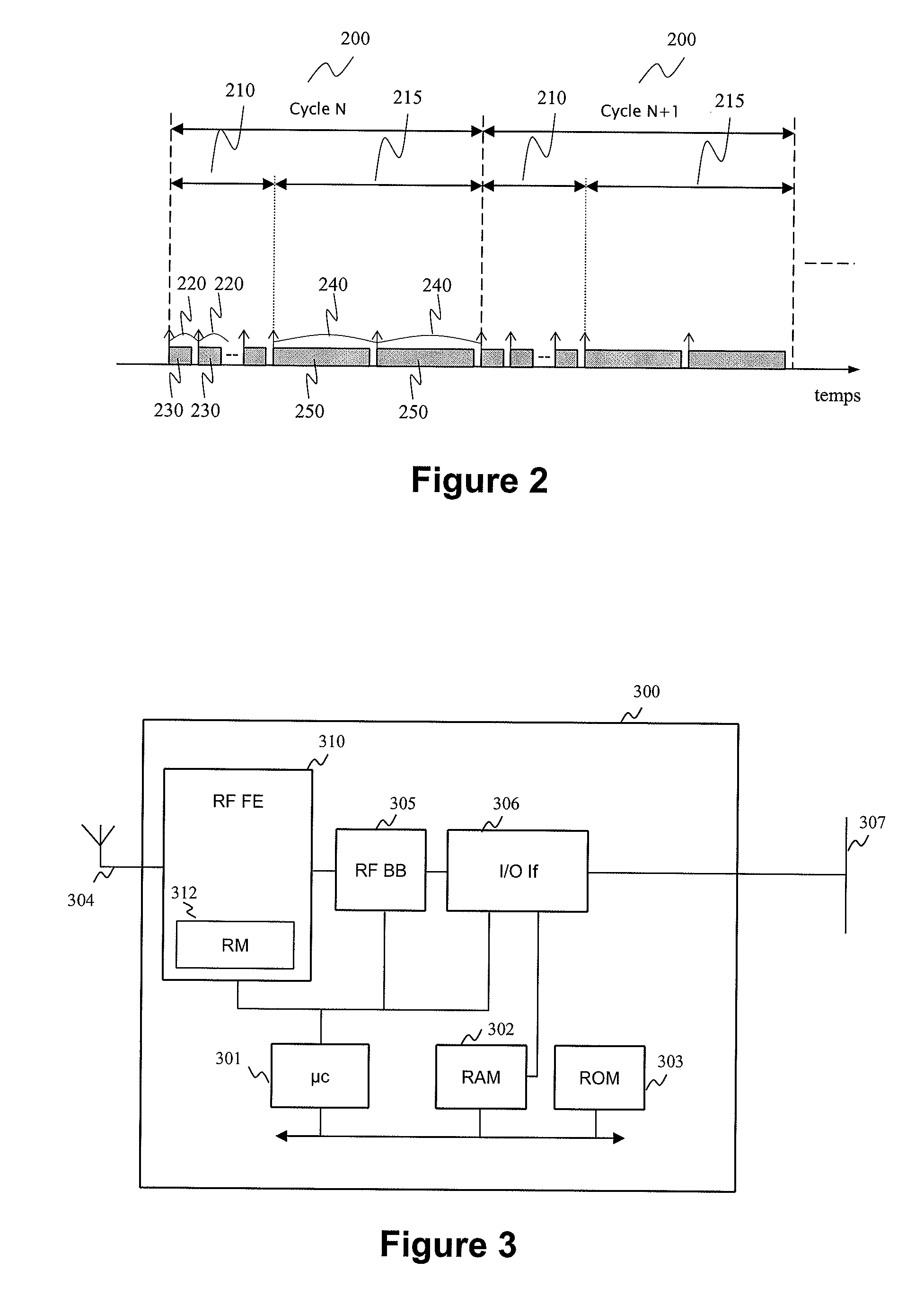

ActiveUS8345578B2Quality improvementImprove robustnessData switching by path configurationRadio transmissionNetwork clockComputer science

Owner:CANON KK

Methods for configuring sender and receiver antennas, corresponding storage means and nodes

ActiveUS20100177664A1Quality improvementImprove robustnessData switching by path configurationRadio transmissionNetwork clockComputer science

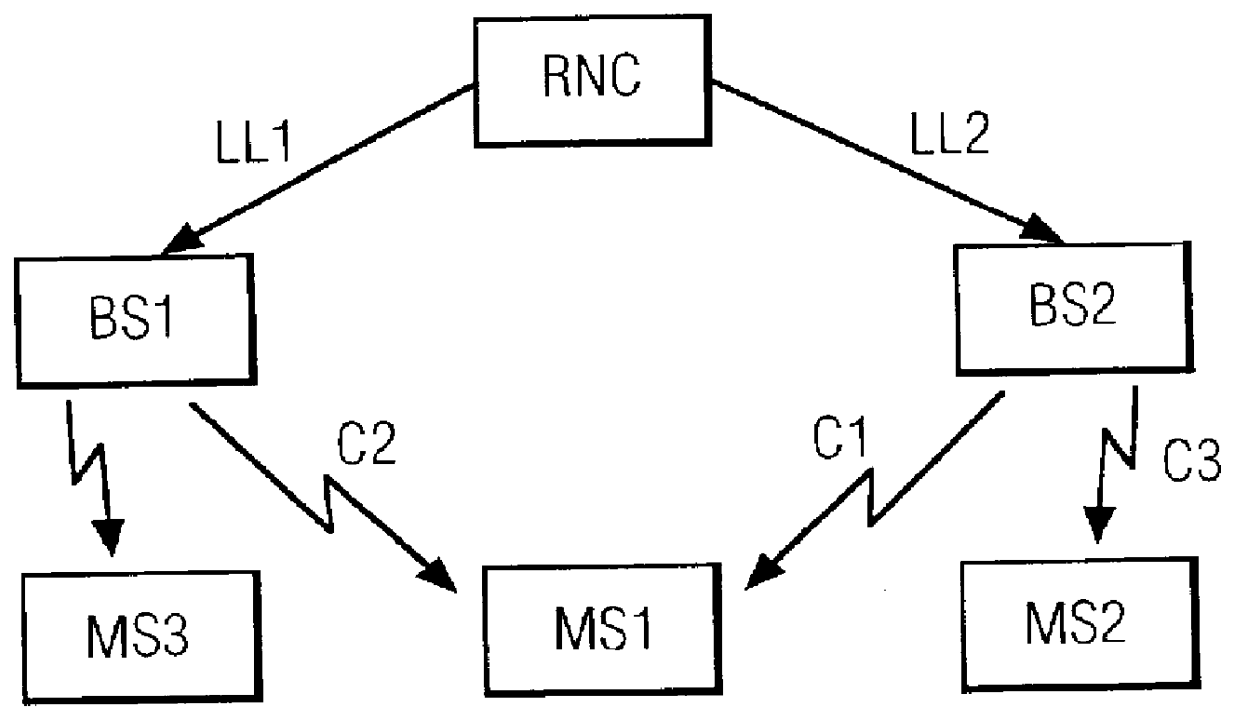

Methods for configuring antennas of first and second nodes of a wireless communications network clocked by transmission cycles, each cycle being divided into time slots, the first node and second nodes having first and second time slots for transmitting data in the first mode, the first node having a third time slot for transmitting data to the second node in a second mode, are proposed. The configuring method, on the second node side, comprises steps of determining a receiving configuration of the antenna of the second node, verifying that the determined receiving configuration is invariant, relative to a receiving configuration previously used for receiving data transmitted from the first node to the second node in the second mode; in the event of negative verification: sending a predetermined signal in the second mode, by using a sending configuration that is determined based on the determined receiving configuration; configuring, during the third time slot, the antenna of the second node by using this determined receiving configuration.

Owner:CANON KK

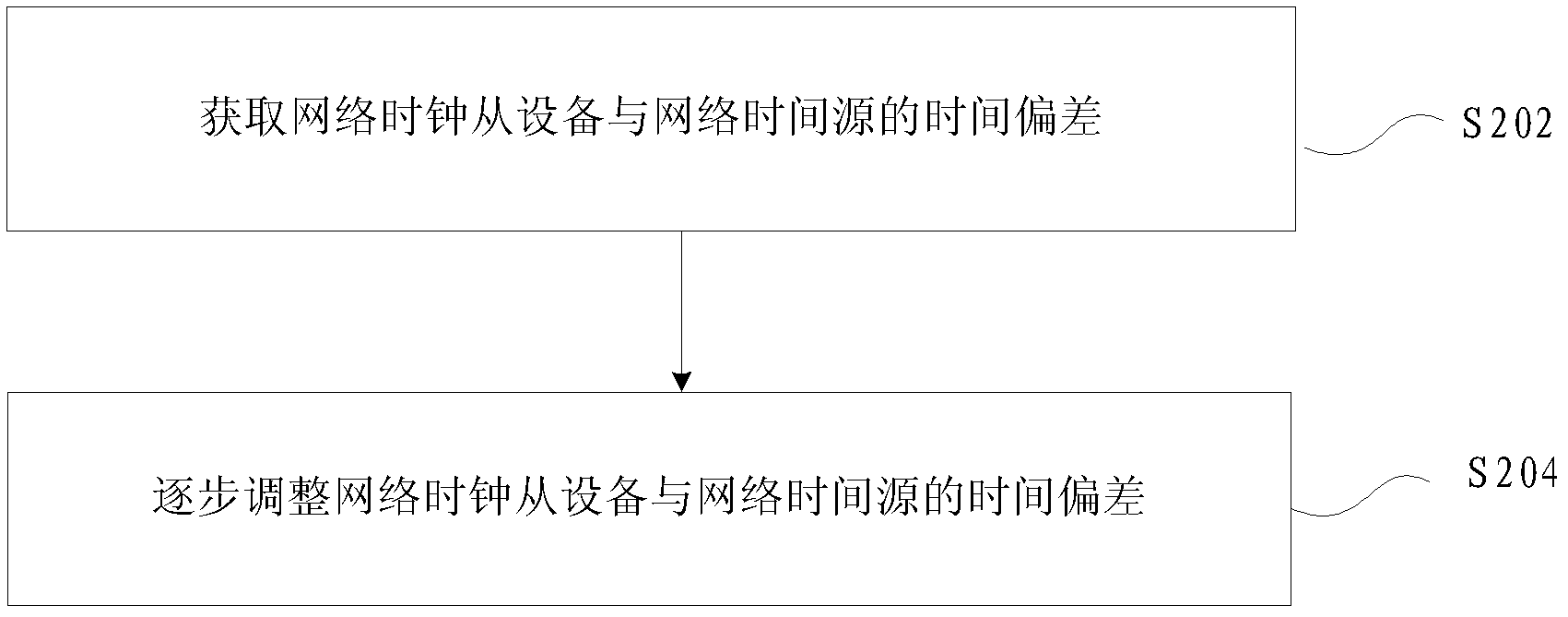

Time synchronization method and device

InactiveCN103138863AQuality improvementImprove stabilityTime-division multiplexTime deviationNetwork clock

The invention discloses a time synchronization method and a device. According to the above method, the time deviation of a network clock from a device and a network time source is obtained; and the time deviation of the network clock from the device and the network time source is adjusted step by step. According to the technical scheme of the time synchronization method and the device, the effect that the reliability and the stability of time synchronization are improved is achieved.

Owner:ZTE CORP

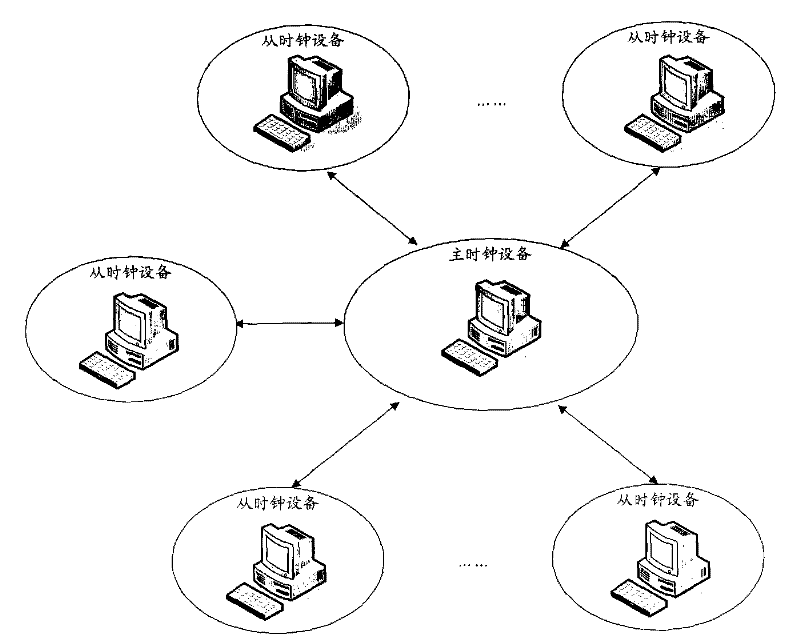

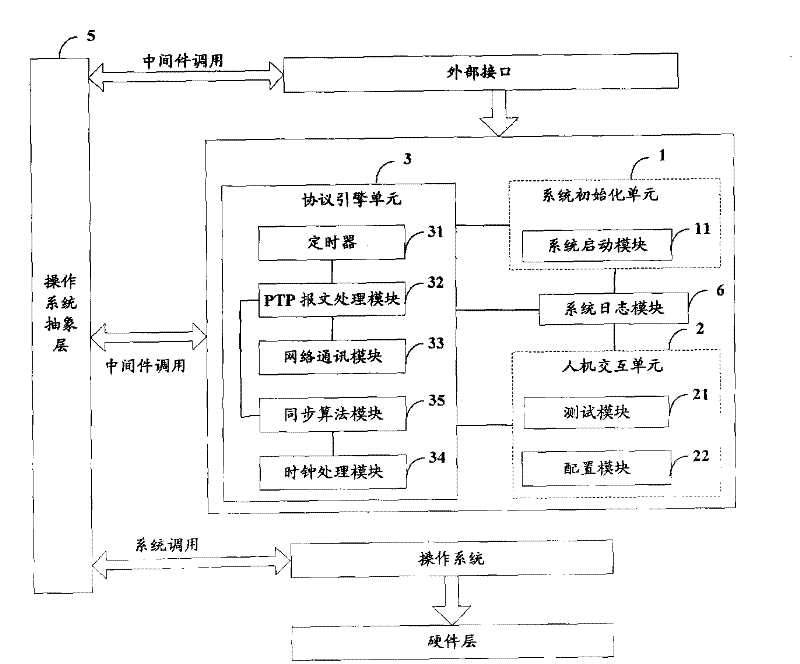

Realizing device of accurate time synchronization protocol

InactiveCN102447553AAchieve high-precision synchronizationResolve out of syncSynchronising arrangementCommunication unitNetwork clock

The invention is applicable in the technical field of network communication, and provides a realizing device of accurate time synchronization protocol, the device comprises a system initialization unit, initializing the realizing device of PTP (precision time protocol), preparing for running of PTP(precision time protocol); a human-computer interaction unit, providing one or more interactive interfaces, providing interact between users and the realizing device of the PTP(precision time protocol); a protocol engine unit, running PTP(precision time protocol); a hardware communication unit, stamping time for all PTP(precision time protocol) messages of engine unit organization of the protocol , transmitting the PTP(precision time protocol) messages with stamp between the master clock device and the vice clock device. The invention of realizing device of PTP(precision time protocol) runs the PTP(precision time protocol) in the network, realizing high-precision synchronization of the network clock, and solving all kinds of problems caused by error of clock synchronization or asynchronization in the current industrial control.

Owner:EVOC INTELLIGENT TECH

Fast frequency adjustment method for synchronizing network clocks

ActiveUS7379480B2Eliminate jumpingEasy to controlTime-division multiplexNetwork clockSynchronization networks

A method of precisely synchronizing clocks held in separate nodes on a communication network is provided that adjusts clock frequency based on a measure of relative clock rates and absolute clock offsets. In one embodiment, clock convergence is obtained with one synchronization session.

Owner:ROCKWELL AUTOMATION TECH

Receivers, methods, and computer program products for an analog modem that receives data signals from a digital modem

InactiveUS7003030B2Efficient implementationEffective synchronizationMultiple-port networksDelay line applicationsModem deviceSignal-to-quantization-noise ratio

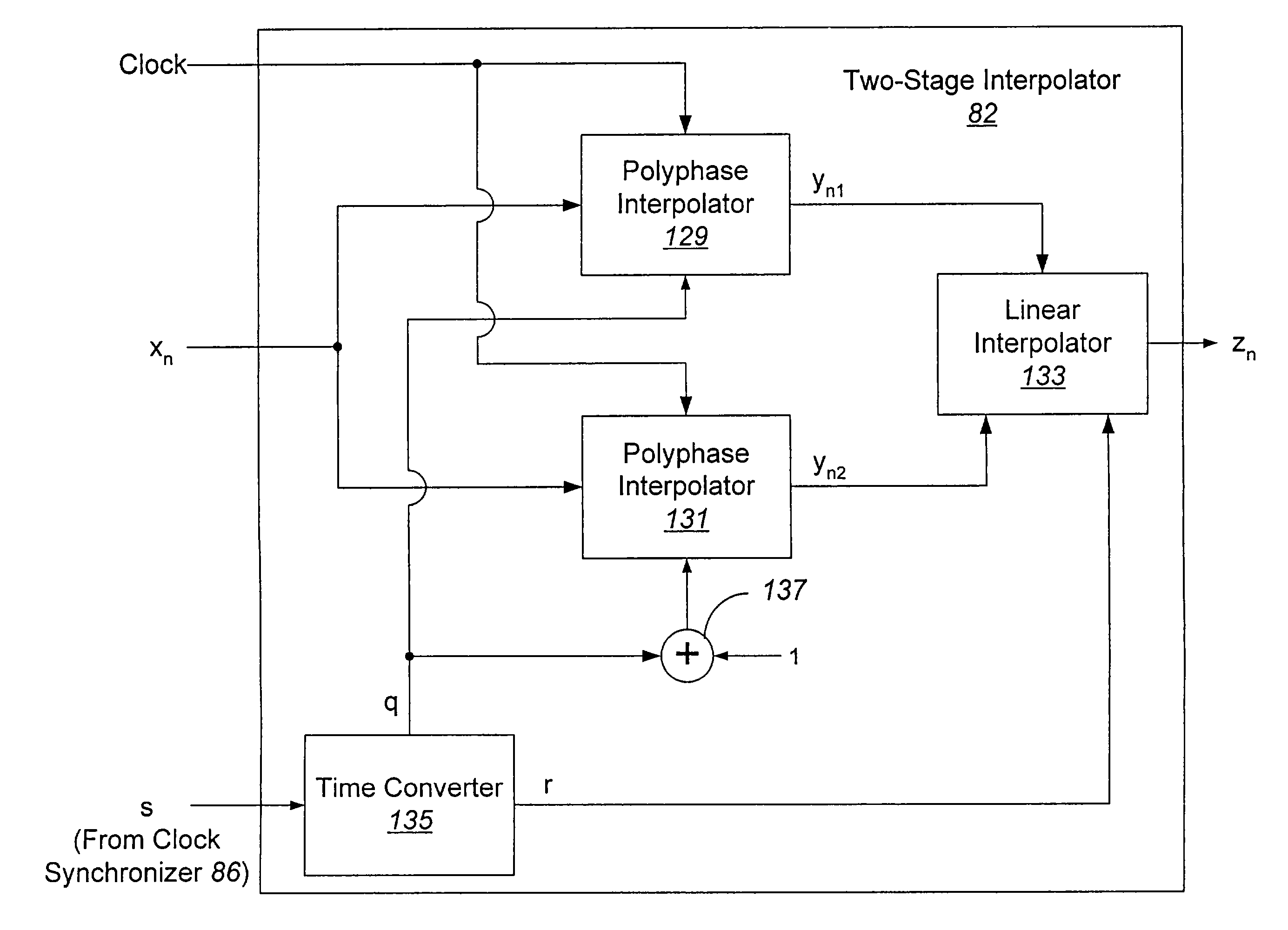

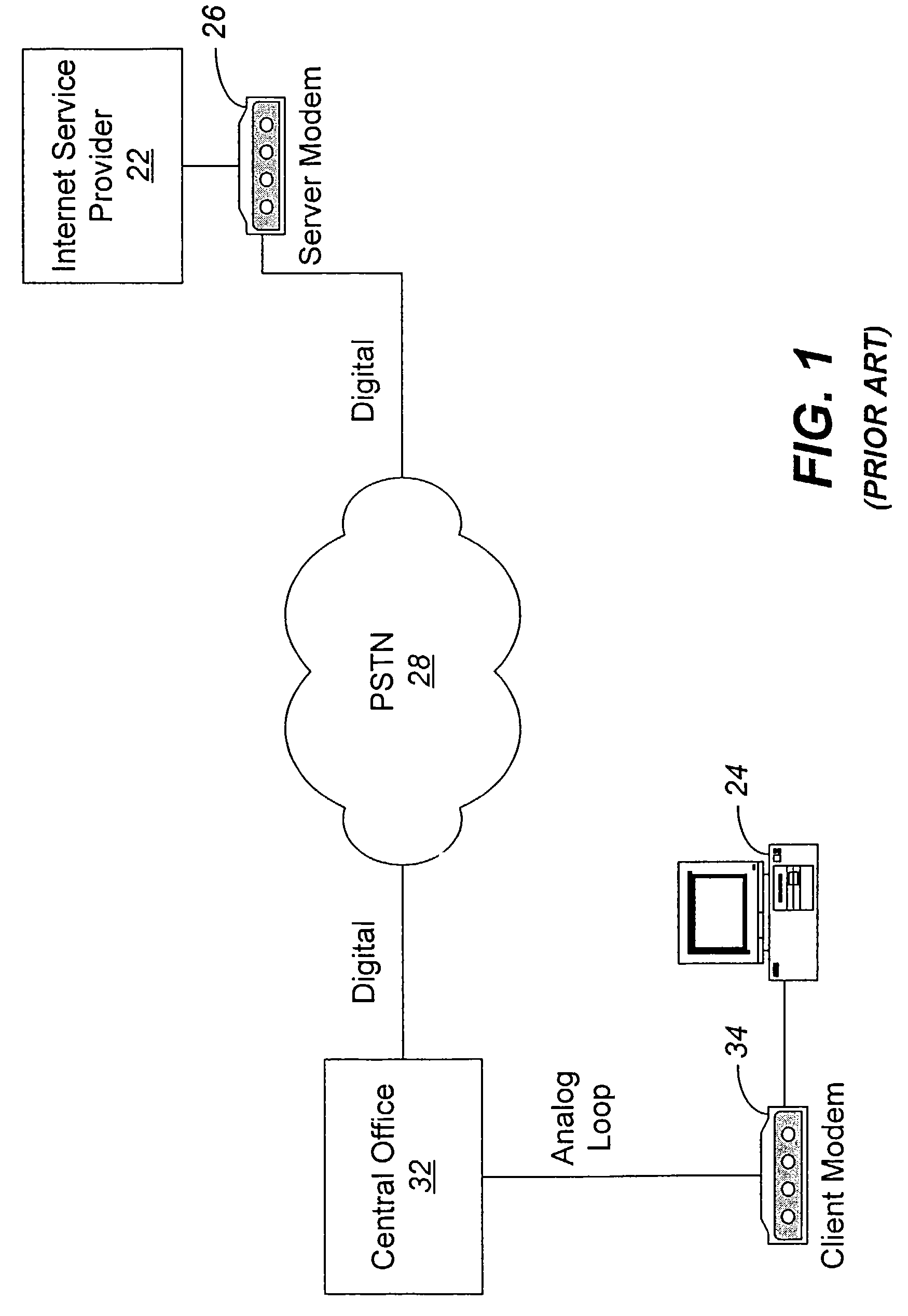

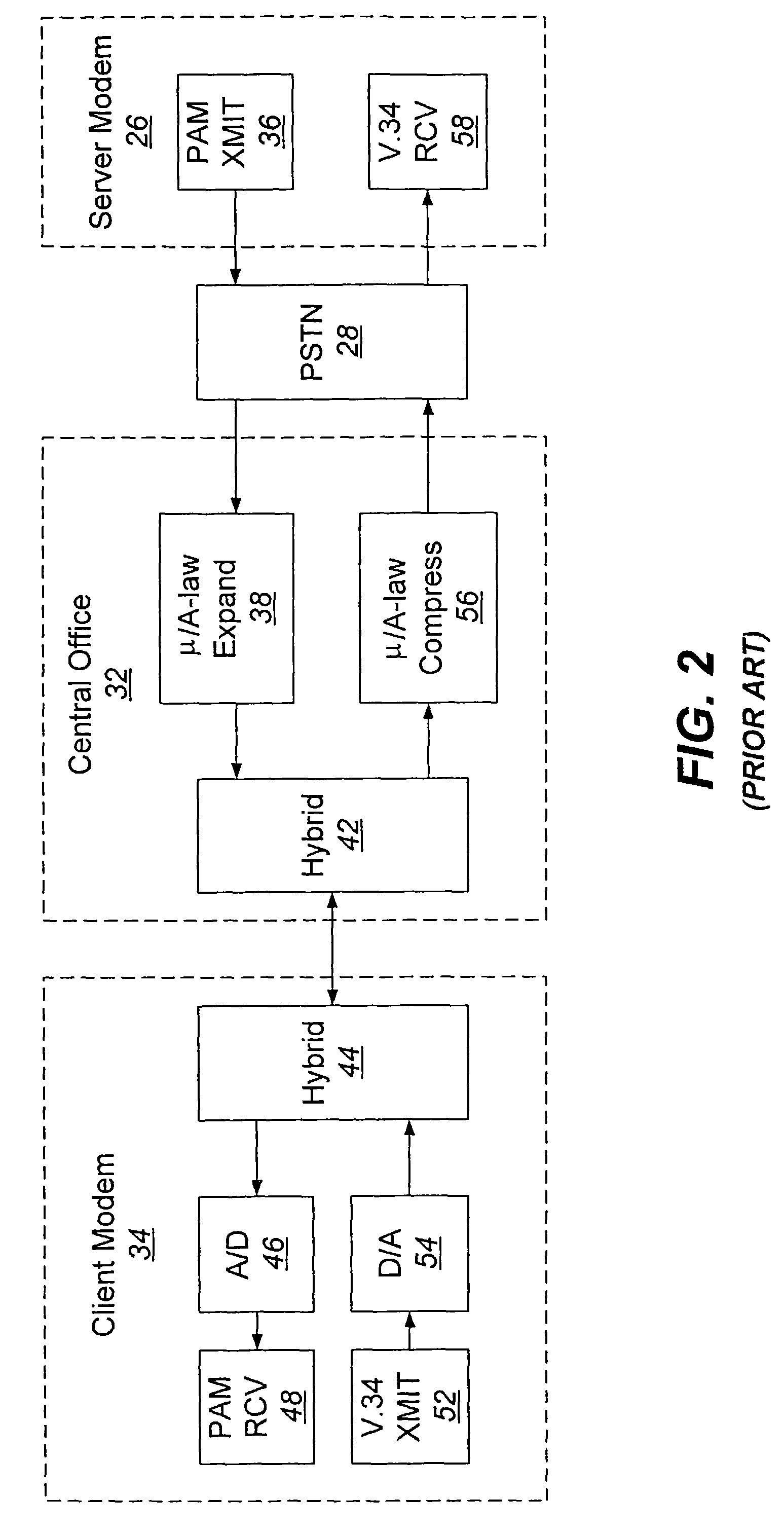

Receivers, methods, and computer program products can be used to demodulate a data signal transmitted from a digital source, which has a network sampling rate that is synchronized with a network clock. In an illustrative embodiment, a receiver includes a two-stage interpolator that receives digital samples of the data signal as an input and produces an interpolated digital sample stream to be filtered by an adaptive fractionally spaced decision feedback equalizer. The digital samples received in the interpolator are synchronized with a local clock; however, the interpolated sample stream is synchronized with the network clock. A slicer generates symbols for the samples output from the decision feedback equalizer by comparing the samples with a reference signaling alphabet. The receiver can be used in a V.90 client modem to demodulate pulse code modulated (PCM) data transmitted as pulse amplitude modulated (PAM) signals from a digital network. In addition, the receiver is compatible with legacy analog modem front ends and transmitters. The two-stage interpolator allows the timing synchronization to be performed with extremely fine granularity, which can be useful in PCM modems that typically require relatively high signal to noise ratios.

Owner:LENOVO (SINGAPORE) PTE LTD

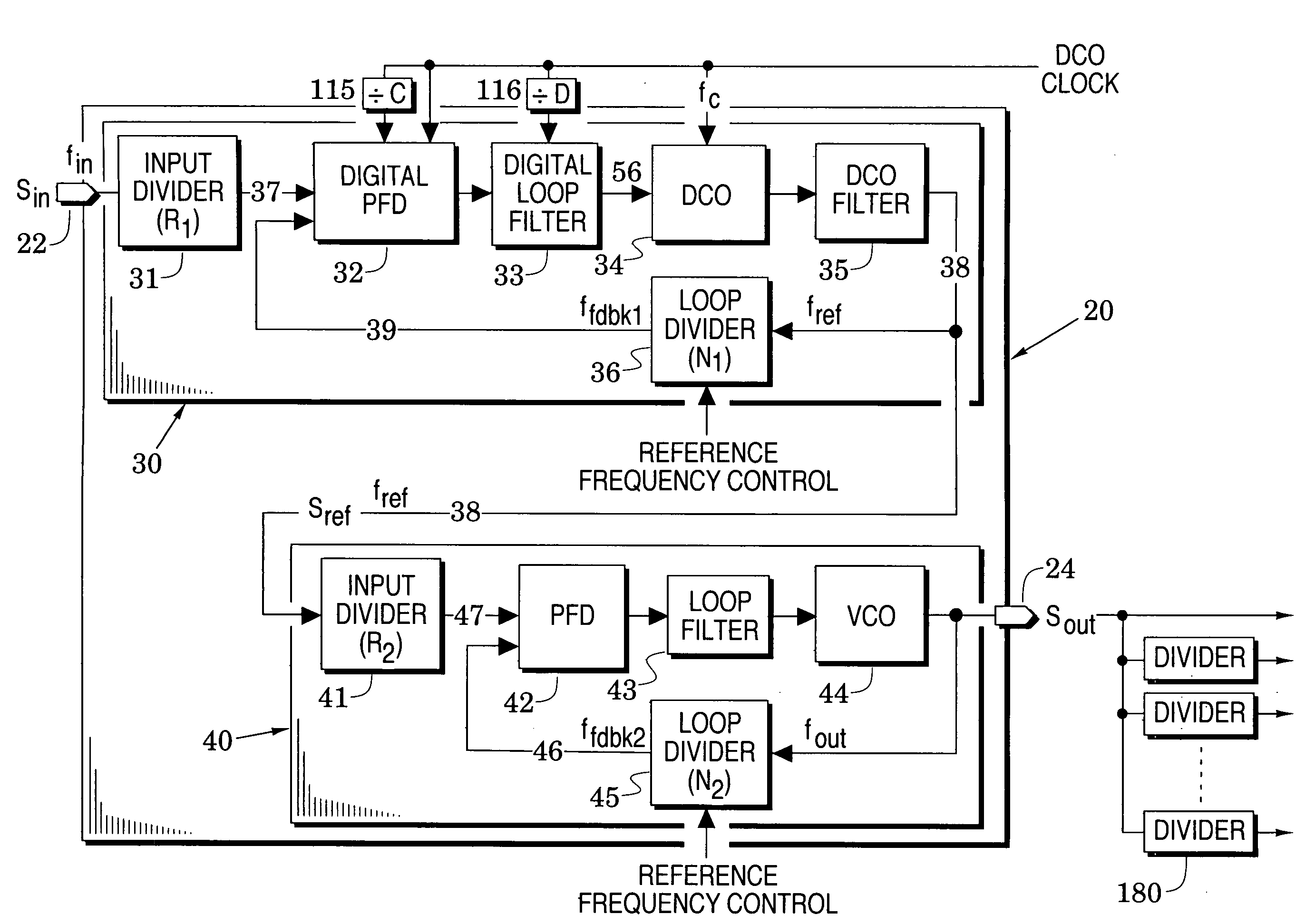

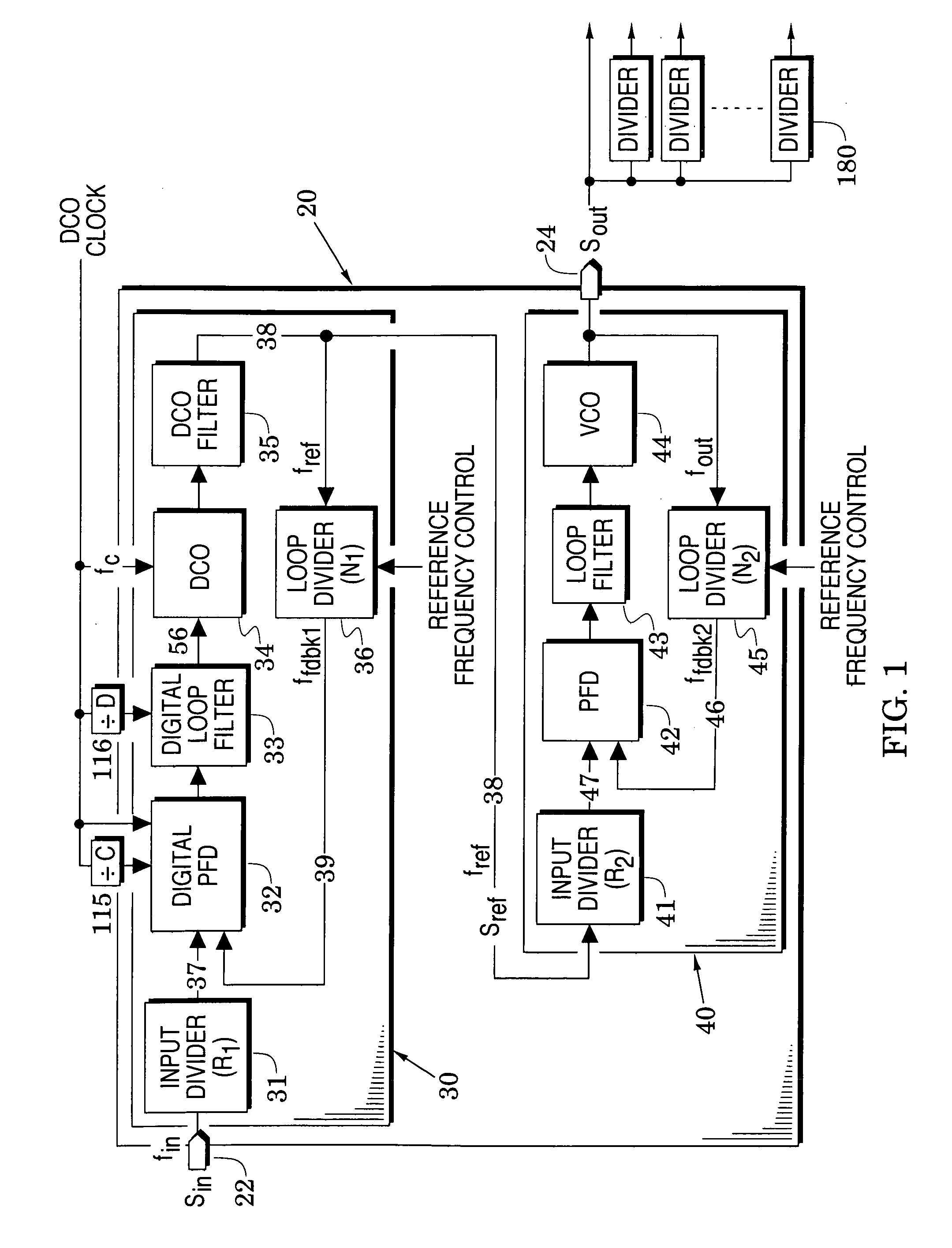

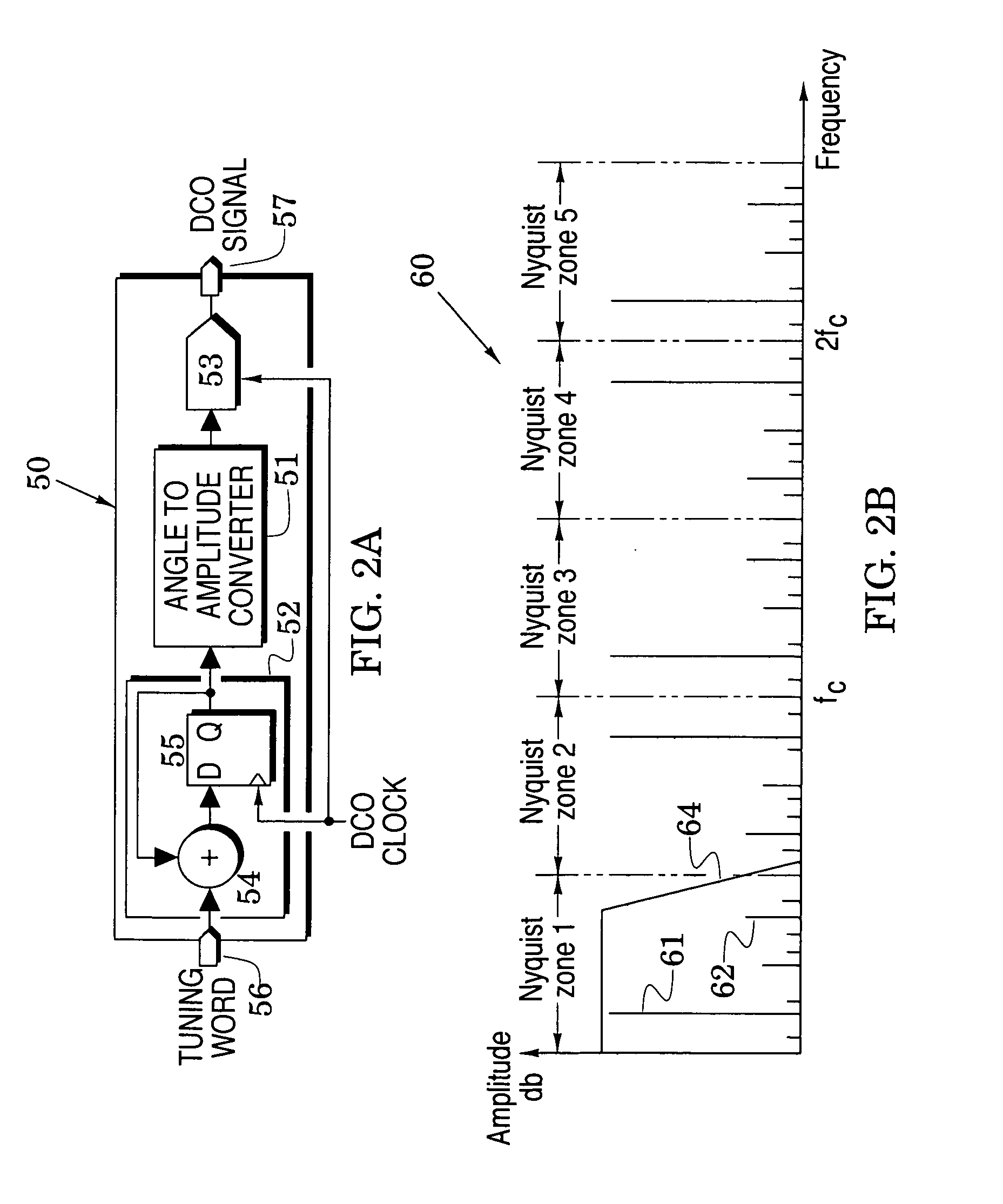

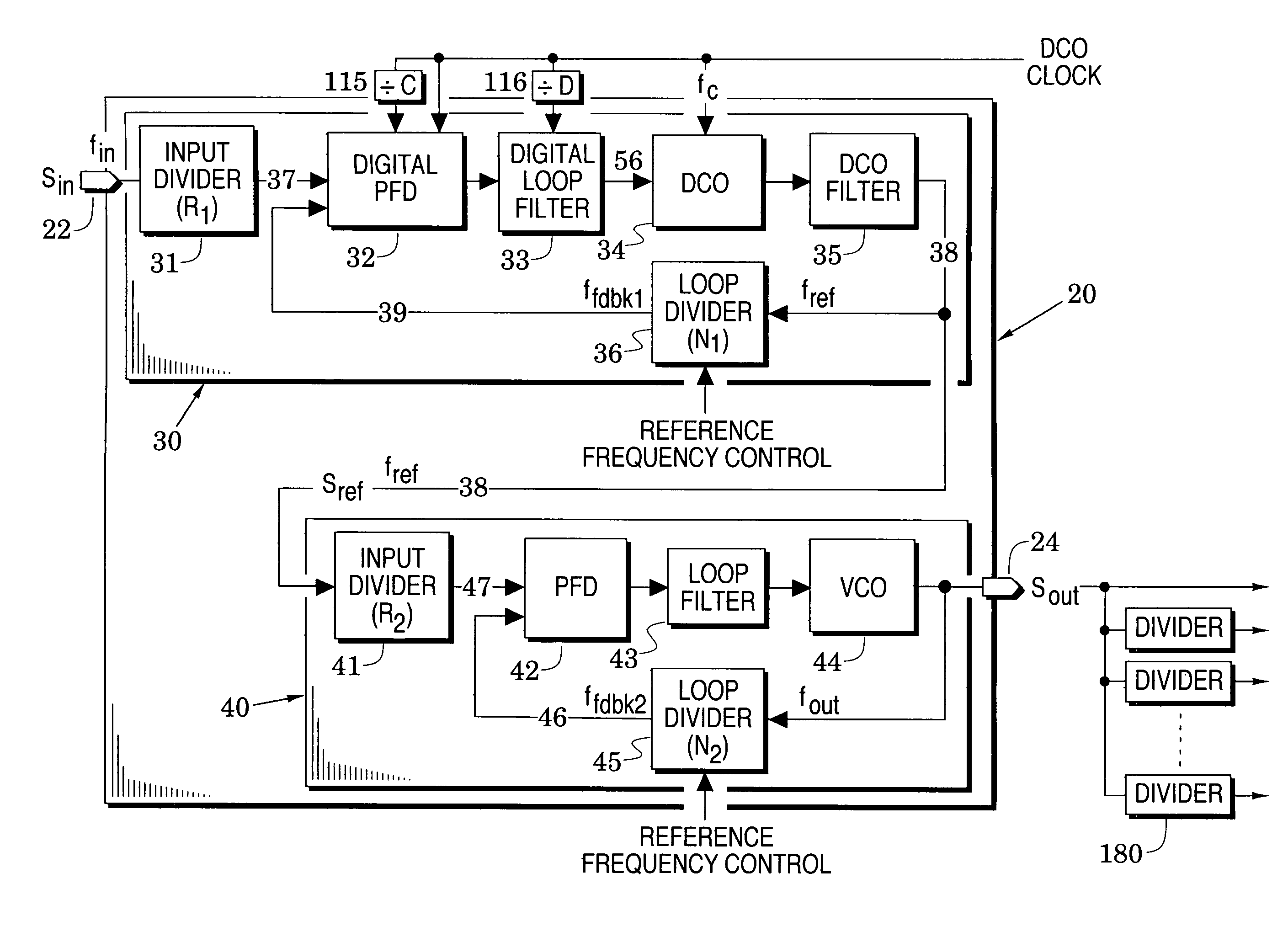

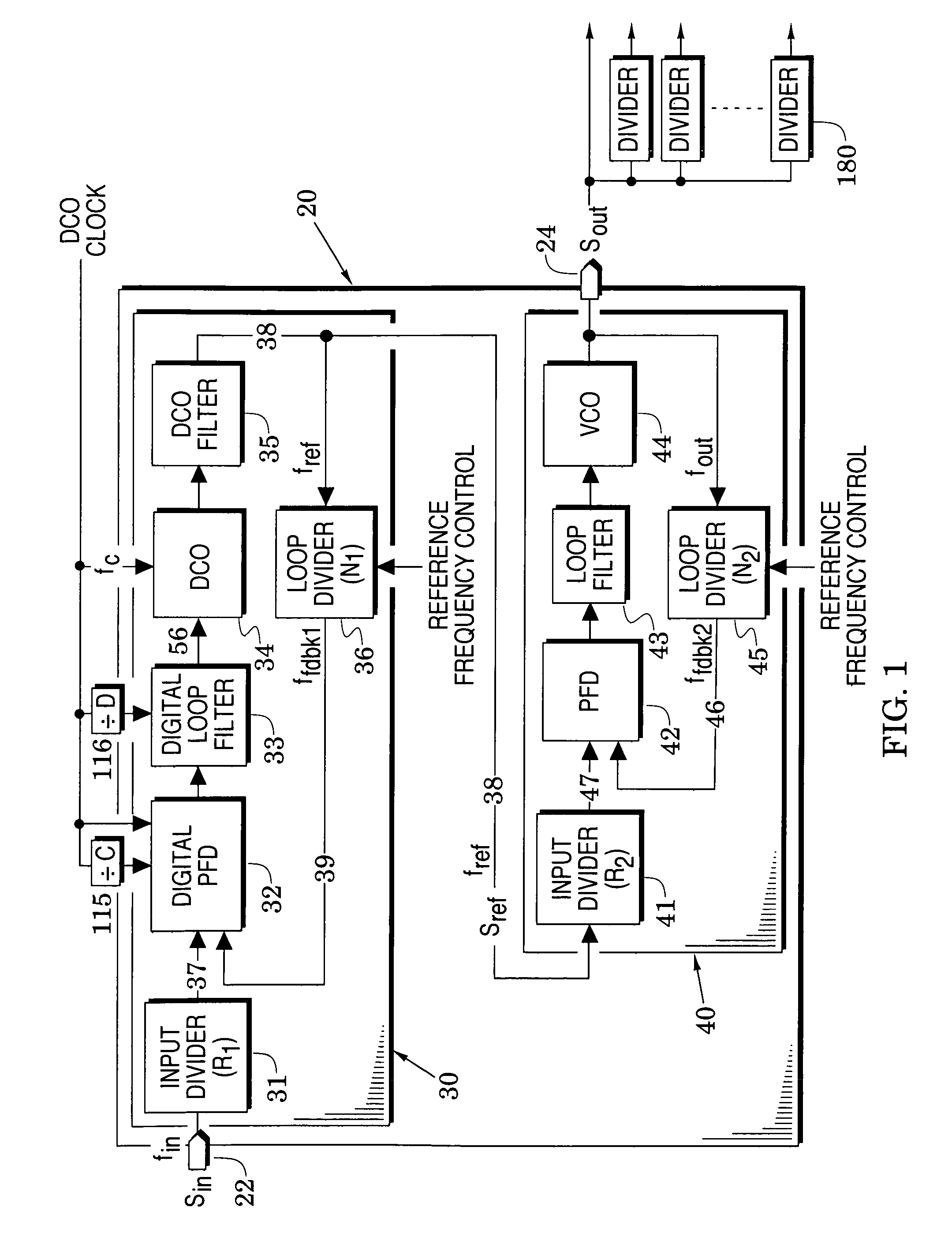

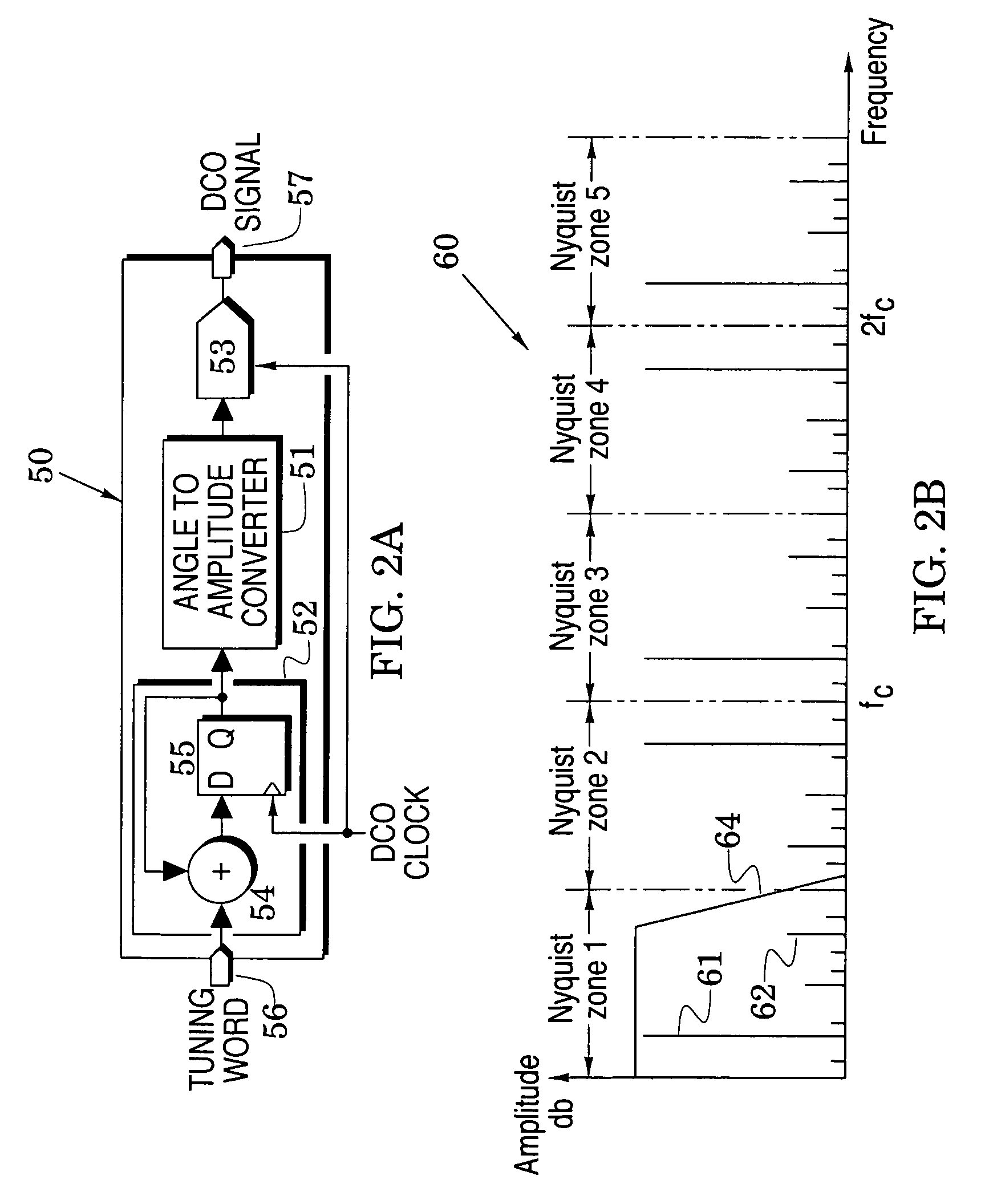

Frequency synthesizers for wireless communication systems

Synthesizers are configured with first and second phase-locked loops (PLL's). The first PLL is arranged to include a digitally-controlled oscillator (DCO) and to respond to an input signal to provide a reference signal with a plurality of selectable reference frequencies. The second PLL is arranged to include a voltage-controlled oscillator (VCO) to thereby provide output signals in response to the reference signal. This synthesizer structure is particularly effective when responding to a noisy input signal as may be the case, for example, in wireless communication systems that provide a network clock to transceivers through lengthy optical links.

Owner:ANALOG DEVICES INC

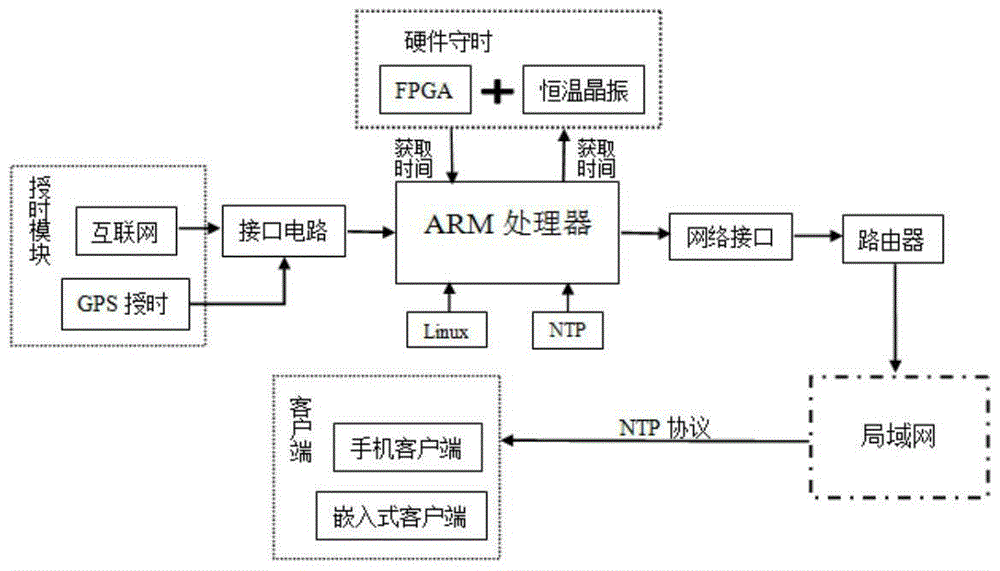

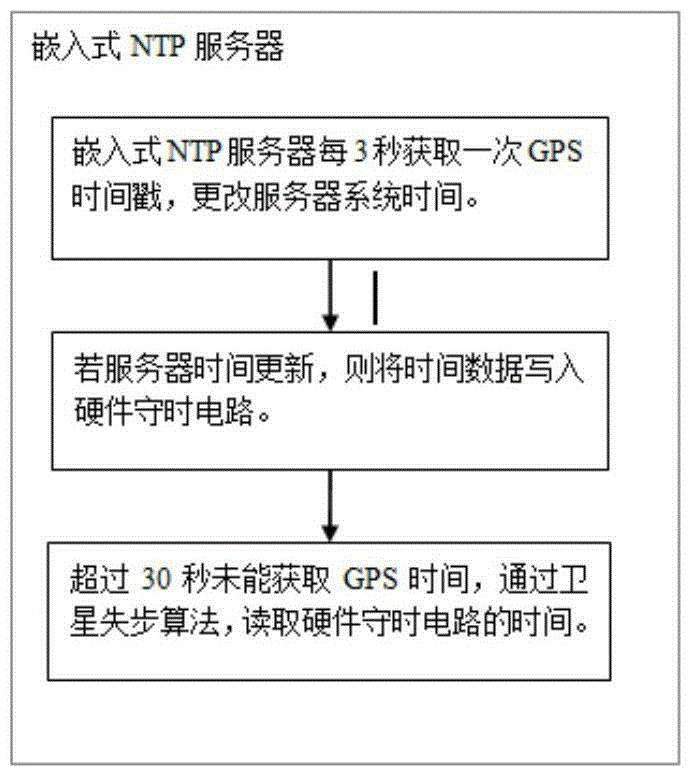

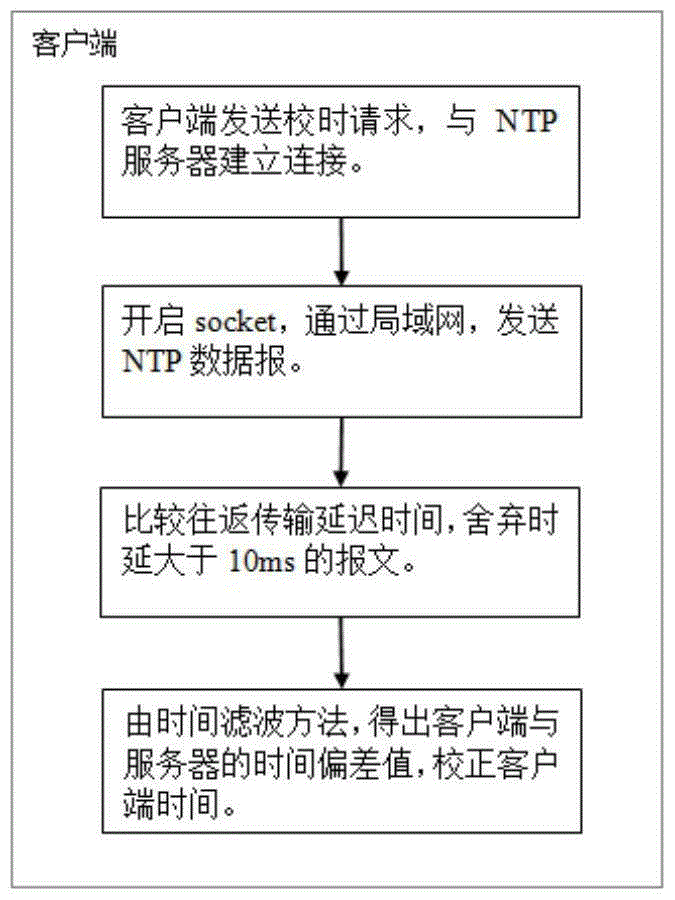

ARM-based network clock synchronization system and method

InactiveCN105187148ASolve the problem of clock out of syncLow costTime-division multiplexTime informationThe Internet

The invention discloses an ARM-based network clock synchronization system and method. The system comprises a GPS (Global Positioning System) satellite time service module, an NTP (Network Time Protocol) server, a hardware time service module and a client module, wherein the GPS satellite time service module is used for acquiring satellite time information in a short time through a satellite; the NTP server is an embedded processor with an operating system, and is used for converting a received time message into a standard format and calibrating local time; the hardware time service module is used for storing time which is recently calibrated by the NTP server; and the client module is used for acquiring server time, and synchronizing local system time. The system and the method are easy to implement. Through adoption of the ARM-based network clock synchronizing system and method, simple, convenient, rapid and accurate time calibration is provided for a distributed clock in a local area network; the phenomena of delay of Internet time in a transmission process and the like are avoided; and the accuracy in time synchronization of all terminal equipment in the local area network is ensured. The system and the method have the characteristics of reasonable design, high reliability, high environment suitability, small size, convenience in use, low power consumption and the like.

Owner:WUHAN UNIV OF TECH

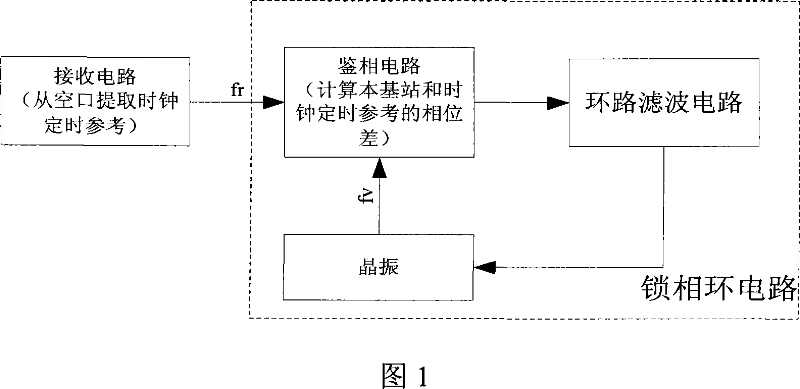

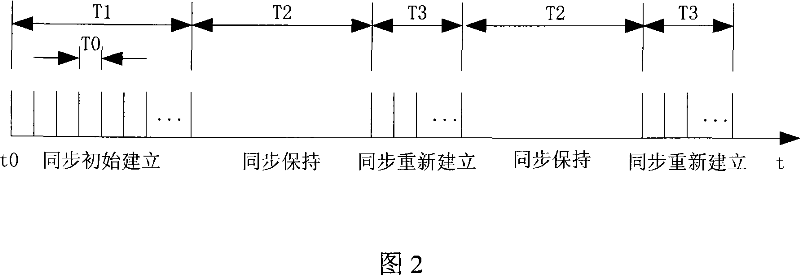

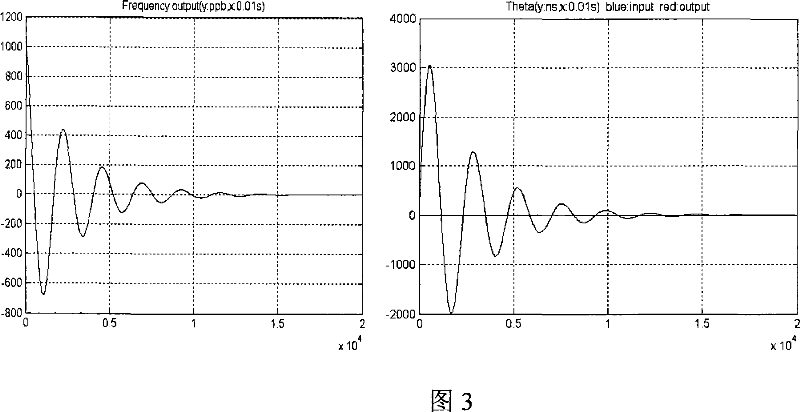

Apparatus and method for empty clock synchronization of wireless mobile communication system base station

InactiveCN101039146AReduce operating costsLow costRadio transmission for post communicationSynchronising arrangementOperational costsNetwork clock

The present invention discloses an air interface clock synchronization device in wireless mobile communication system among base stations, which comprises a receiving circuit and a phase-locked loop circuit. The receiving circuit is used to receive the clock timing reference signal of the neighboring base station from the air interface and send the signal to the phase-locked loop circuit. The phase-locked loop circuit is used to receive the clock timing reference signal and adjust itself basic clock, thus the air interface clock synchronization between itself and the neighboring base station can be realized. The present invention also discloses an air interface clock synchronization method in wireless mobile communication system among base stations. By adopting a simple method to realize the air interface clock synchronization between one basic station and the neighboring base station, the network clock server is no need to use, thus the operation cost of the mobile operating enterprise can be reduced. The invention is helpful to realize new wireless covering means and enrich the content of the wireless network solution.

Owner:ZTE CORP

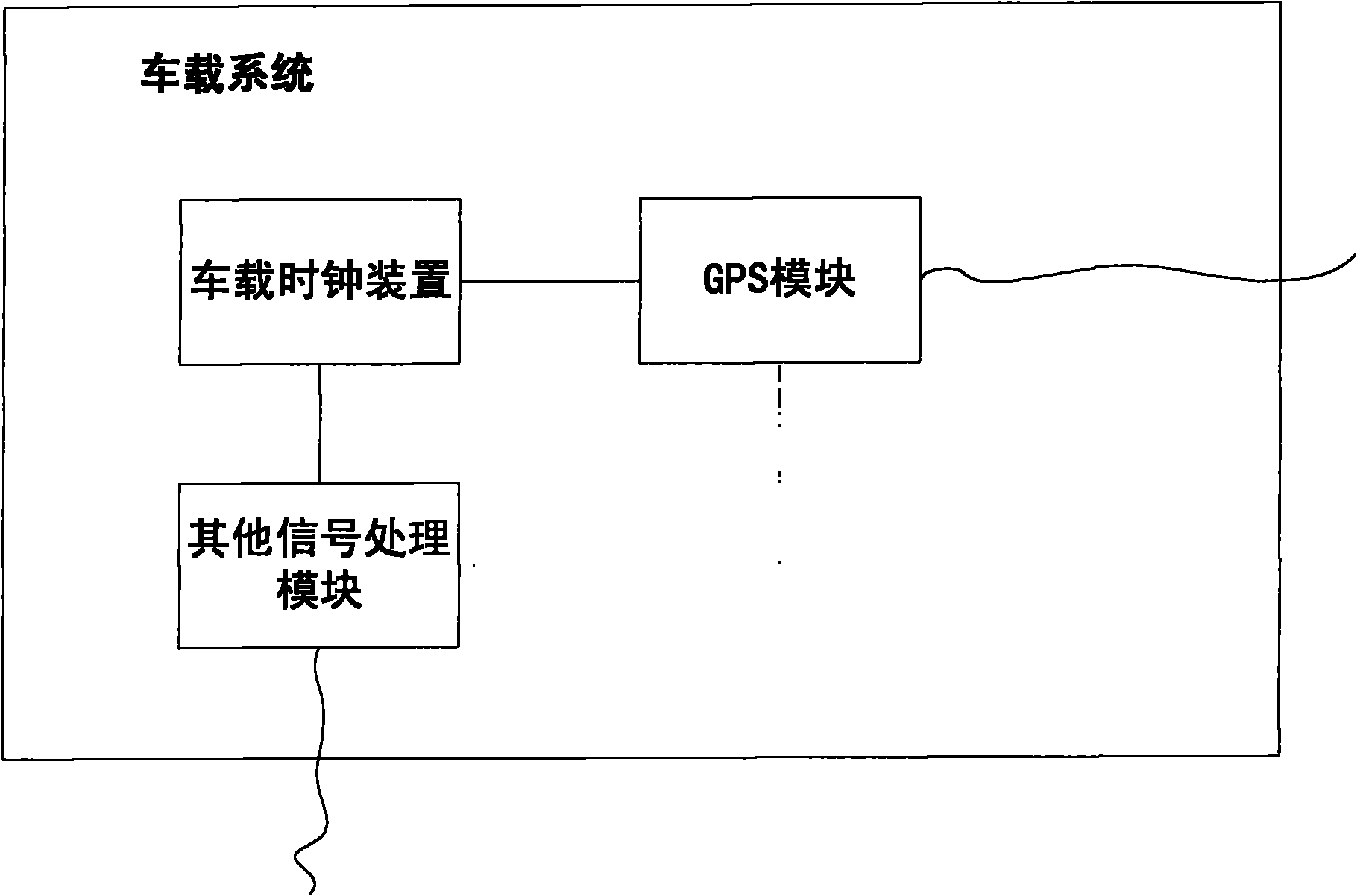

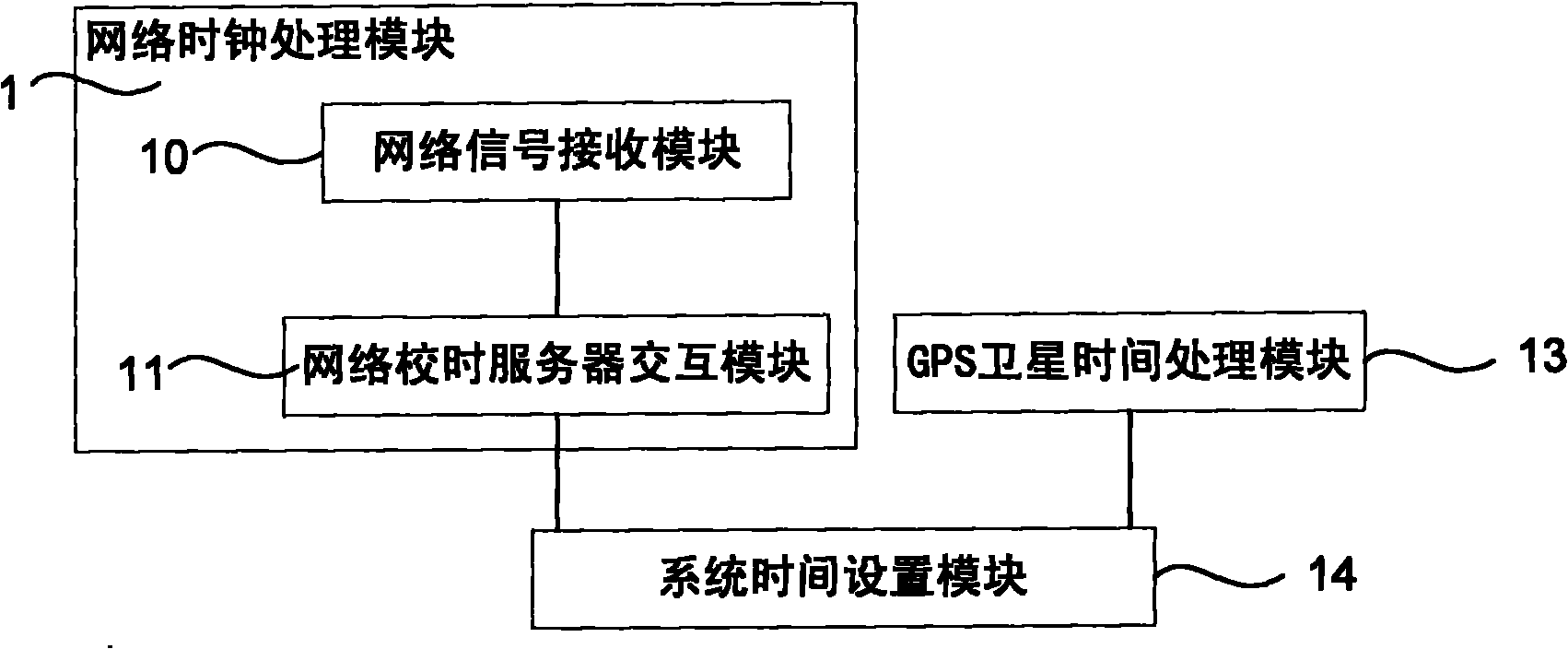

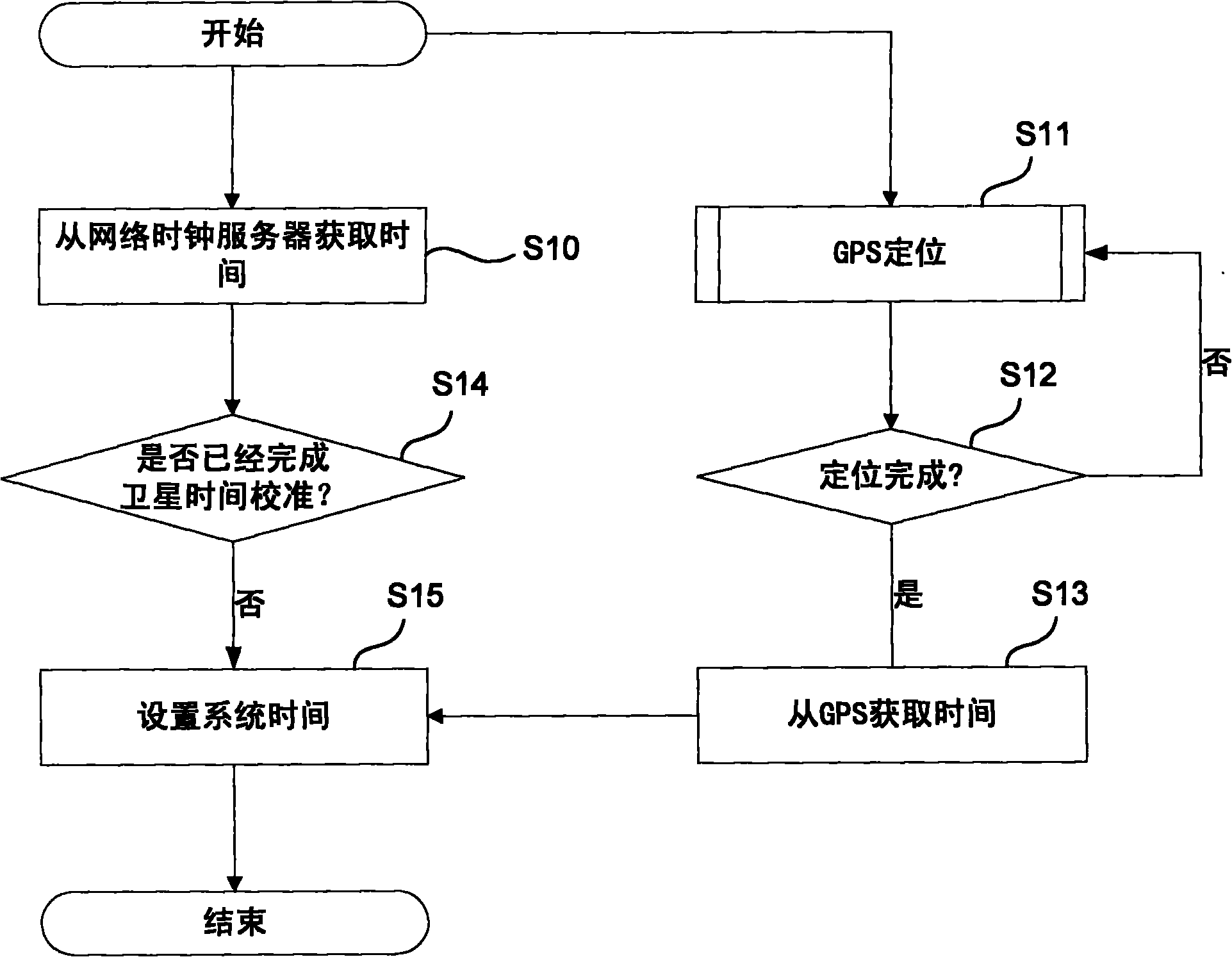

Vehicle-mounted clock device and implementation method thereof

InactiveCN102156403ASolve the problem that the time cannot be displayed immediatelySetting time indicationRadio-controlled time-piecesNetwork clockProcess module

The invention discloses a vehicle-mounted clock device and an implementation method thereof. The current system time can be immediately displayed when a vehicle is started. The invention adopts the technical scheme that: the device comprises a network clock processing module, a global positioning system (GPS) satellite time processing module and a system time setting module, wherein the network clock processing module receives signals from an external network clock server, and calibrates the time by interaction with the network clock server; the GPS satellite time processing module receives GPS satellite time to calibrate the time; and the system time setting module is connected with the network clock processing module and the GPS satellite time processing module, receives the output of the network clock processing module as the system time under the condition that the GPS satellite time processing module has no signal output, and receives the output of the GPS satellite time processing module as the system under the condition that the GPS satellite time processing module has signal output.

Owner:SAIC MOTOR

Method and system of network clock generation with multiple phase locked loops

A method and system generates a network quality clock signal in a communications system by synthesizing a first clock signal based on arrival rate of packets transmitted via a network link at a rate according to a network clock. The system then synthesizes a second clock signal is then synthesized based on the first clock signal. In one embodiment, the second clock signal has a frequency substantially the same as the network clock.

Owner:TELLABS BEDFORD

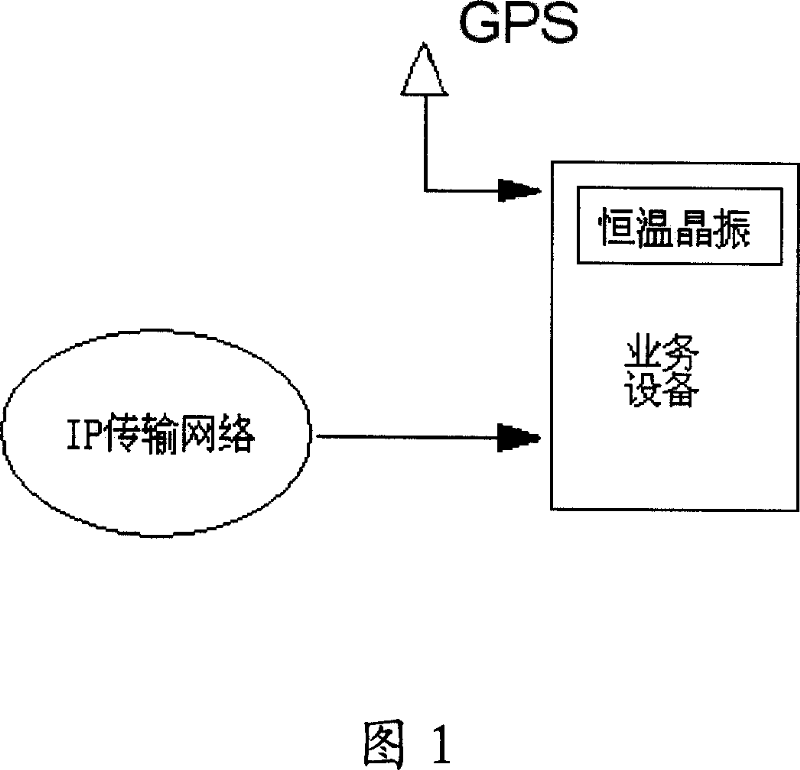

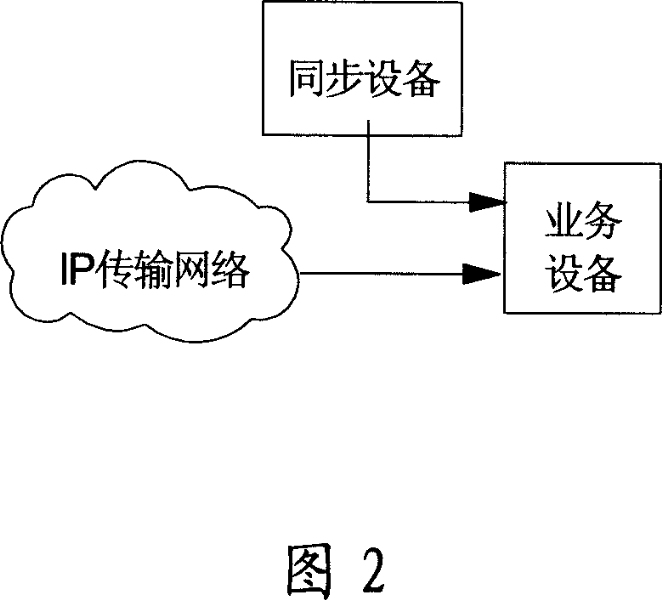

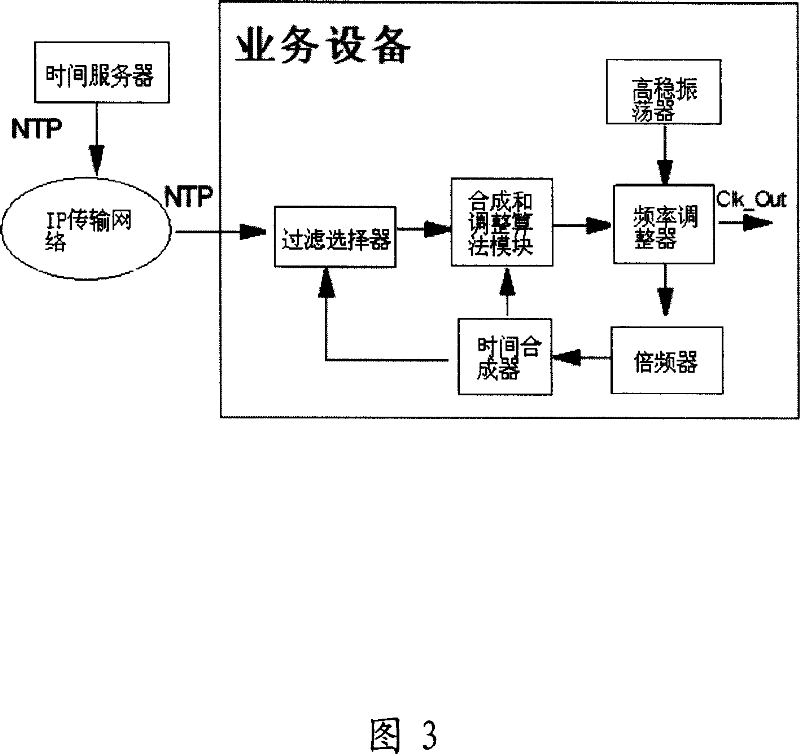

Network clock synchronous device, system and method

InactiveCN101043315AEliminate driftMeet clock synchronization requirementsTime-division multiplexSynchronising arrangementTime deviationTime information

The invention discloses a network time synchronization device, system and method, the method includes following steps: step A: the business device sends the time request to at least one time sever at intervals of time; step B: compares the time samples returned by the time sever, choose the time sample to calculate the time difference between the local time and the time sever; step C: according to obtained time difference data to adjust the frequency regulator in the business device, and locks the time of superior time sever. Using the invention, it can obtain the time information of superior time sever via the transmission network, and according to the time information obtained in different time it can calculate the shift of local oscillator, and it can eliminate the local time shift by adjusting the frequency regulator to satisfy the requirement for the time of business device.

Owner:HUAWEI TECH CO LTD

Frequency synthesizers for wireless communication systems

Synthesizers are configured with first and second phase-locked loops (PLL's). The first PLL is arranged to include a digitally-controlled oscillator (DCO) and to respond to an input signal to provide a reference signal with a plurality of selectable reference frequencies. The second PLL is arranged to include a voltage-controlled oscillator (VCO) to thereby provide output signals in response to the reference signal. This synthesizer structure is particularly effective when responding to a noisy input signal as may be the case, for example, in wireless communication systems that provide a network clock to transceivers through lengthy optical links.

Owner:ANALOG DEVICES INC

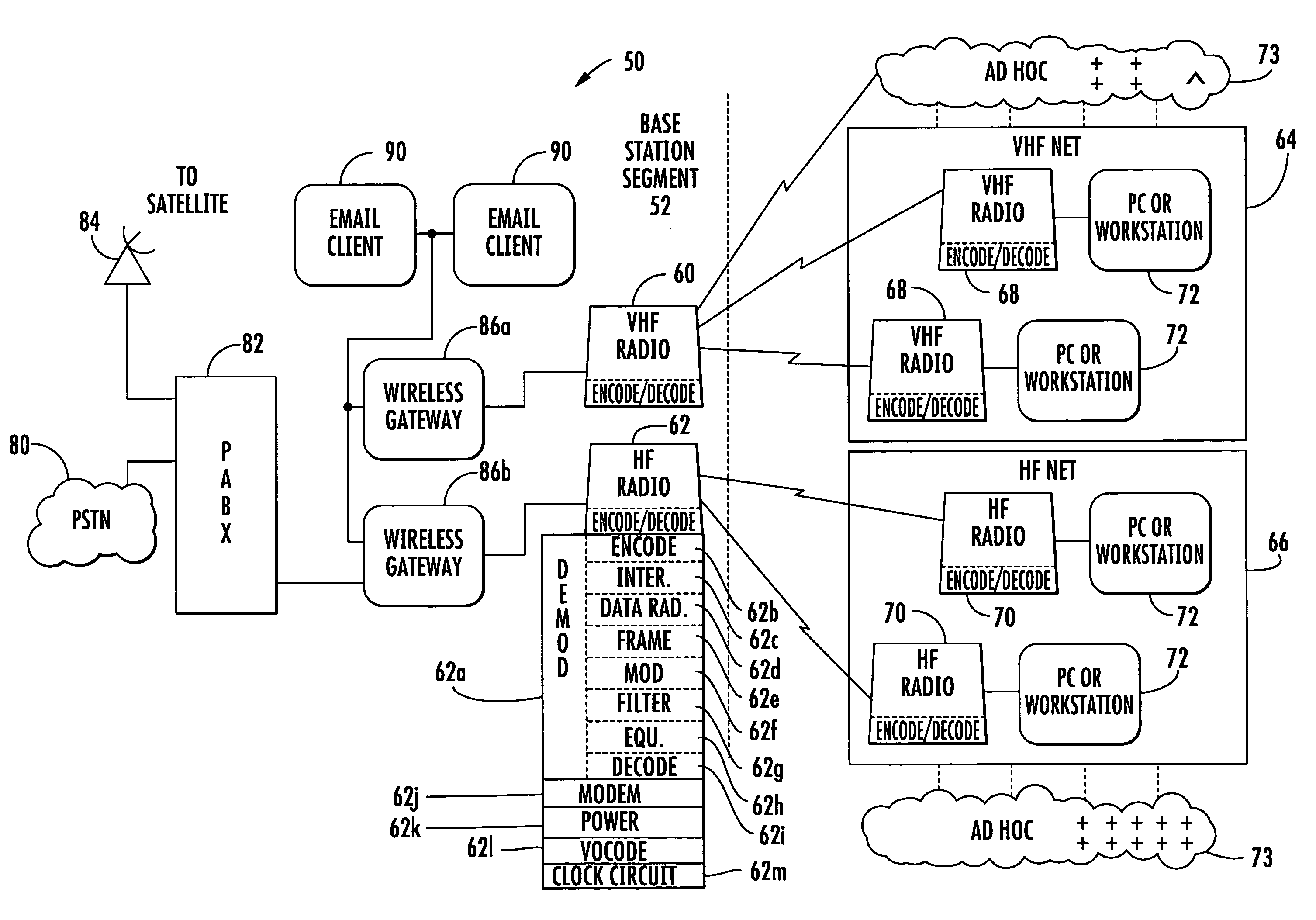

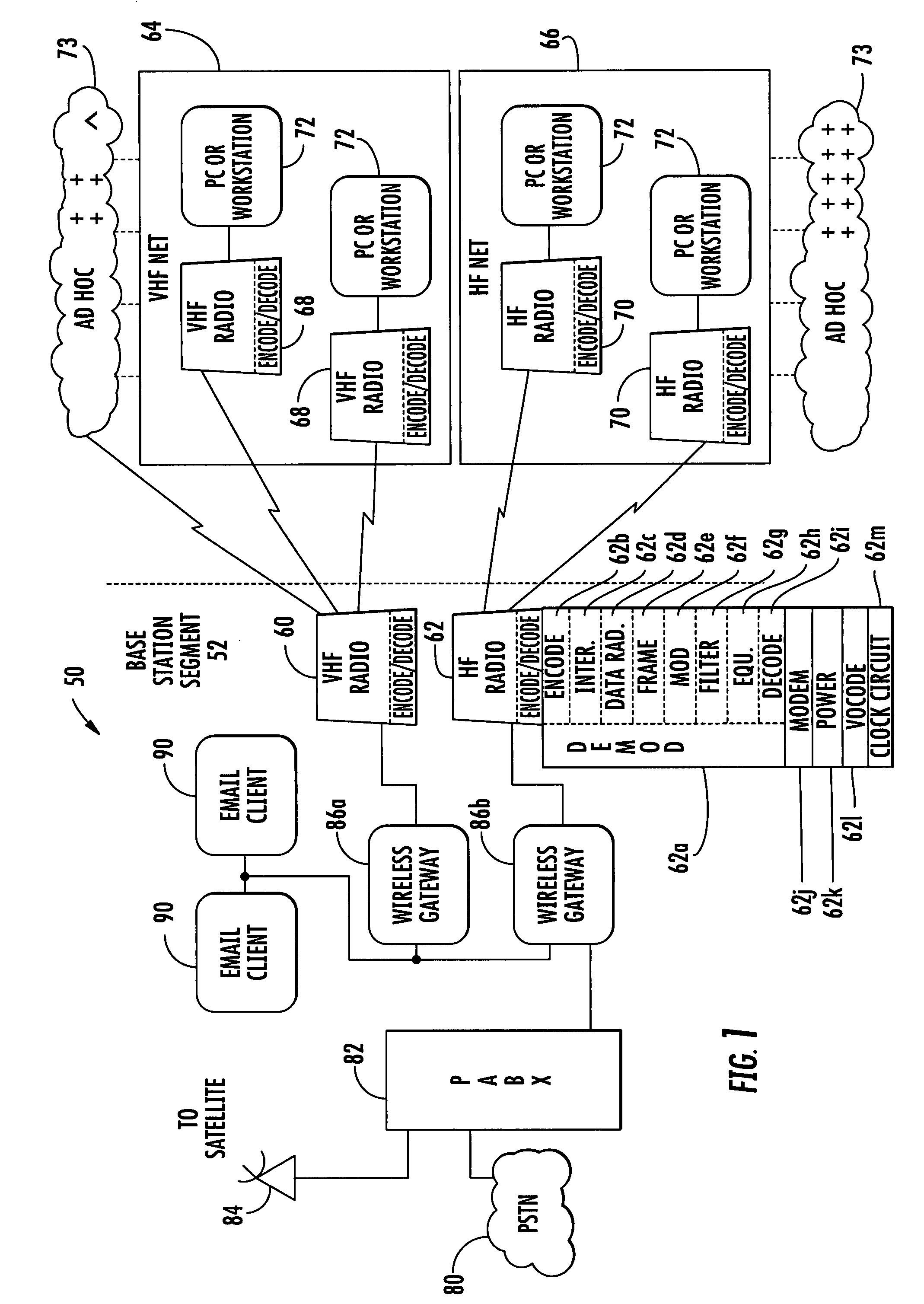

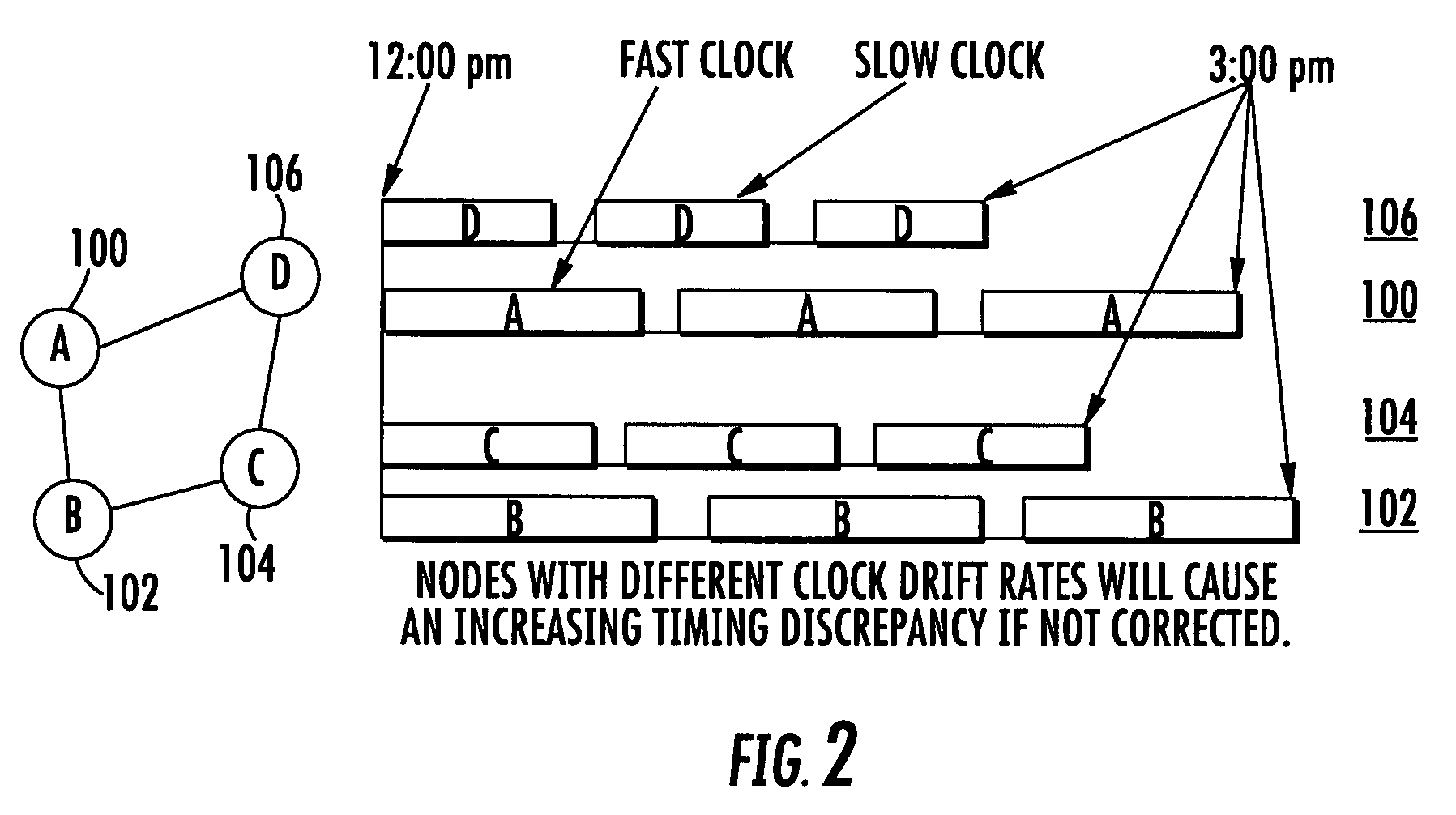

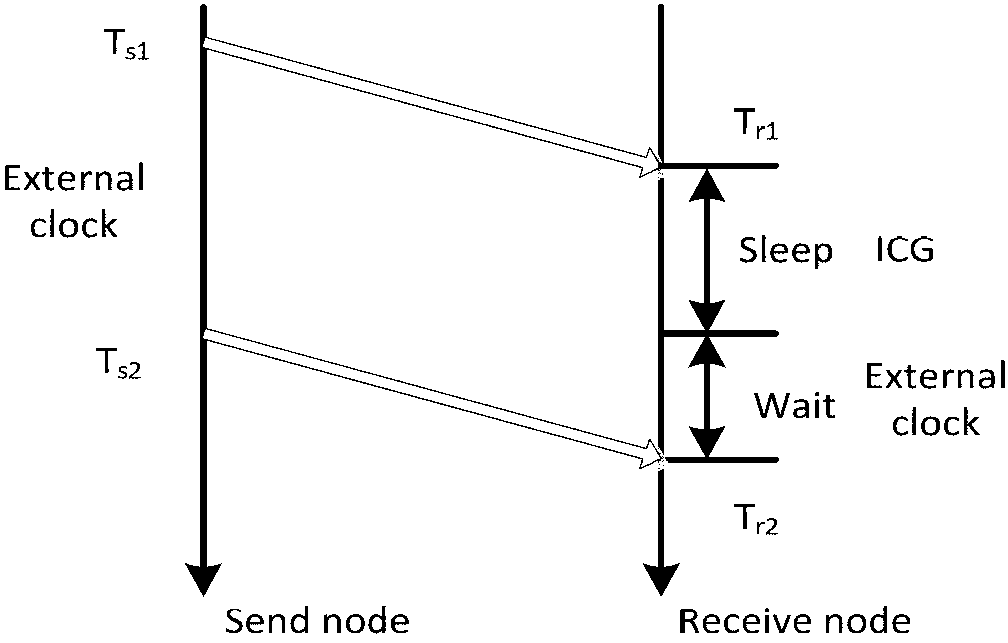

TDMA mobile ad-hoc network (MANET) with second order timing and tracking

InactiveUS20080240050A1Error preventionFrequency-division multiplex detailsTelecommunications linkCommunication link

A communication system includes a plurality of mobile nodes forming a mobile ad-hoc network (MANET) and having a network clock time. A plurality of wireless communications links connects the mobile nodes together. Each mobile node includes a communications device and controller for transmitting and routing data packets wirelessly to other mobile nodes via the wireless communications link using a Time Division Multiple Access (TDMA) data transmission. Each mobile node includes a clock circuit having a digital clock time. A clock circuit is operative for processing a second order internal clock compensation factor as a learned and accumulated value for establishing a virtual clock time to correct any clock timing errors of the physical clock time from the network clock time.

Owner:STINGRAY IP SOLUTIONS LLC

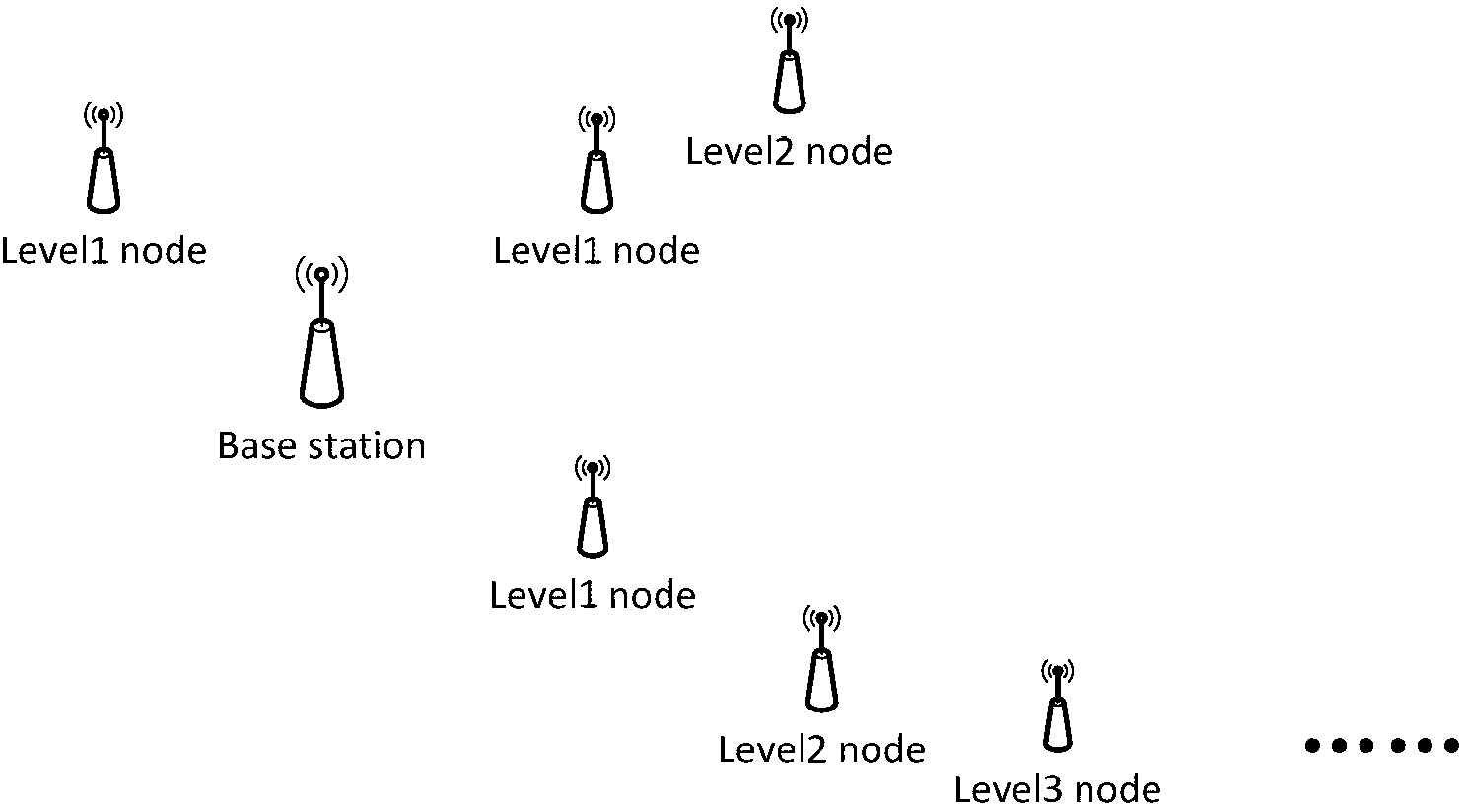

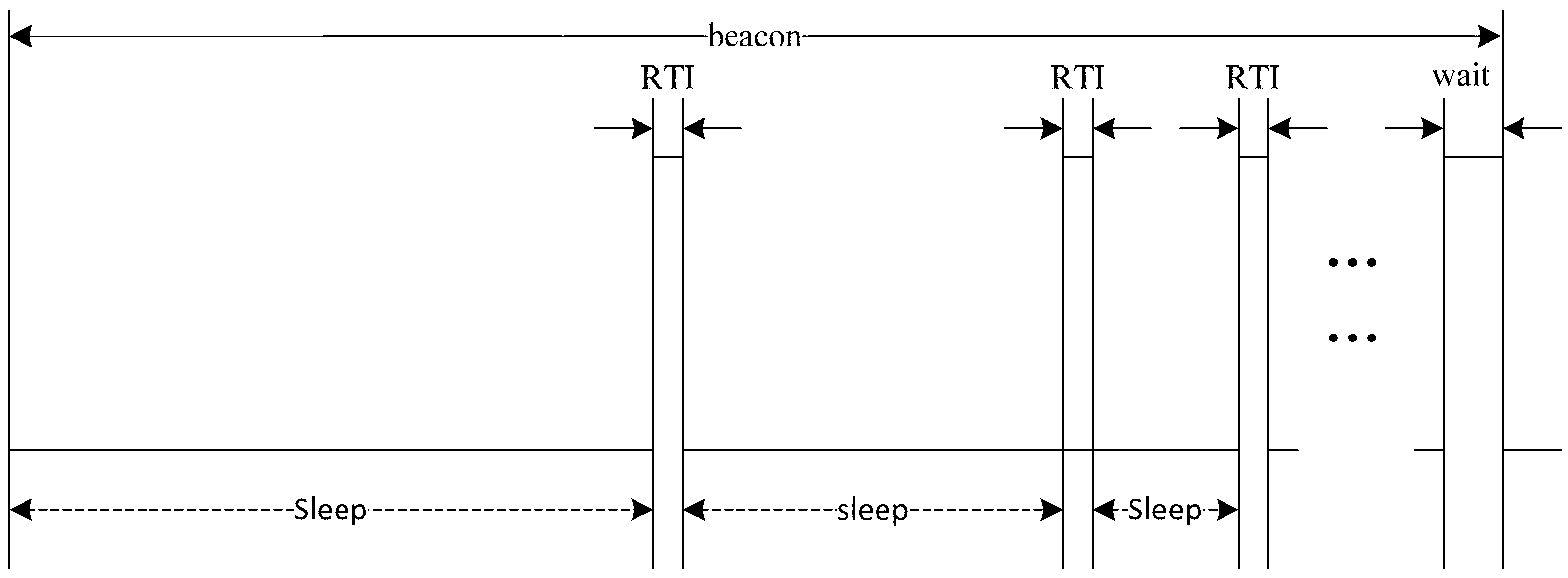

Synchronous method for wireless sensor network node dormancy low power consumption protocol

ActiveCN103327586AEnabling Dual Clock ApplicationsGuaranteed accuracyPower managementSynchronisation arrangementNetwork clockComputer science

The invention discloses a synchronous method for a wireless sensor network node dormancy low power consumption protocol. An MCU used for controlling the work state of each node is arranged on each node. When each MCU is in a work state, a clock is offered by an external crystal oscillator or an external clock source of other modes. When each MCU is in a dormant state, the clock is offered by an internal oscillation circuit. In the process that nodes participate in networking, autonomously layered networking of discrete nodes is achieved through a flooding synchronous mode, and meanwhile, the layered synchronization of a network from the root node to the tail end node is achieved. The synchronous method for the wireless sensor network node dormancy low power consumption protocol can fully guarantee the clock accuracy of the nodes, network clock synchronization and normal use, and meanwhile effectively reduces the power consumption of the nodes and the network.

Owner:SOUTHEAST UNIV

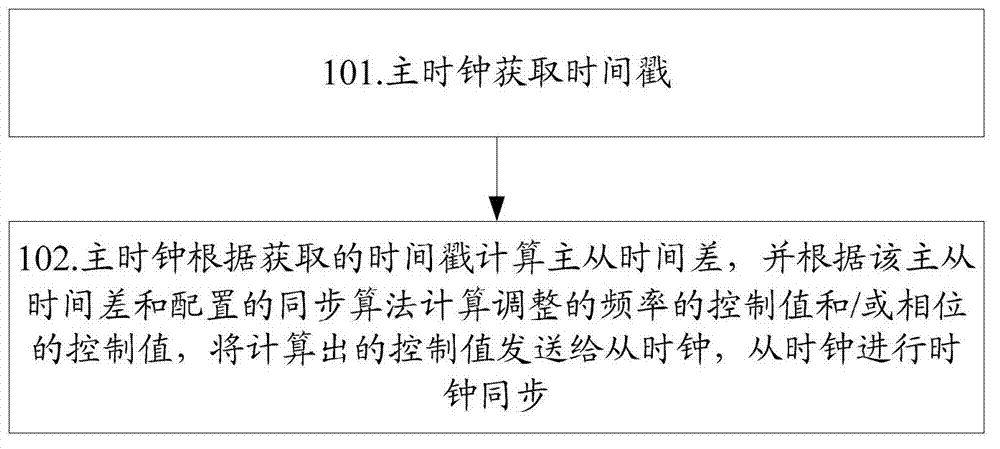

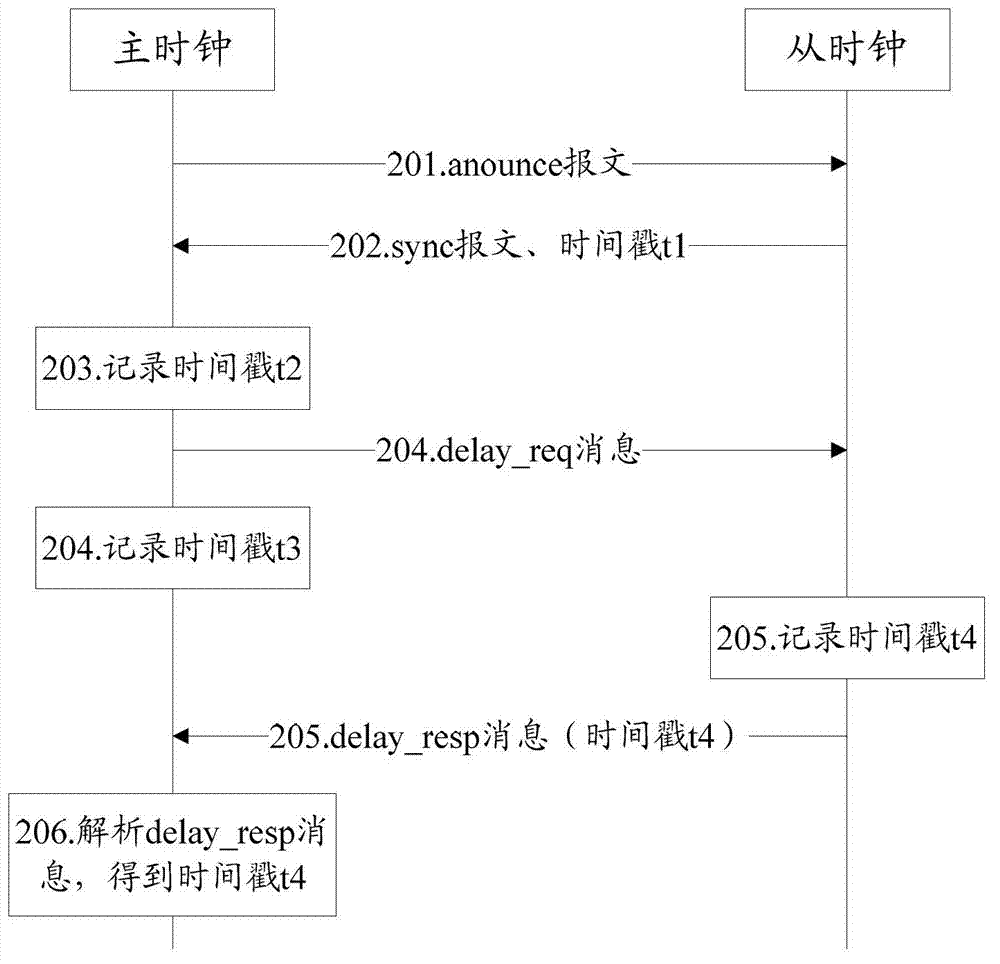

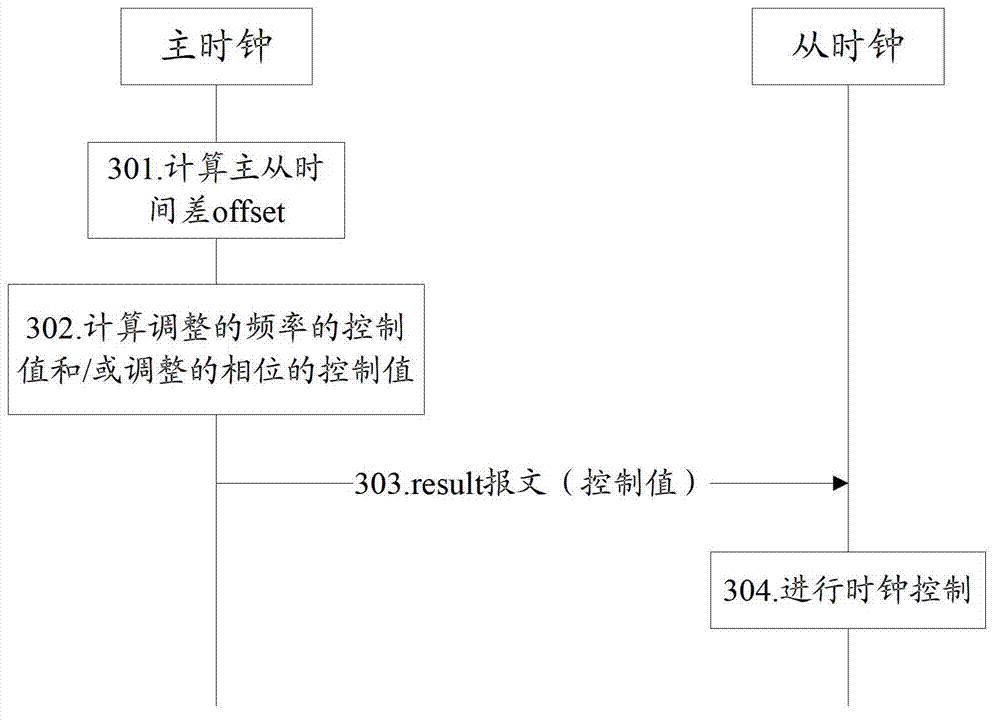

1588 system and method thereof for achieving synchronization

ActiveCN102769504AReduce the difficulty of implementationSynchronous clockTime-division multiplexTimestampNetwork clock

The invention discloses a method of a 1588 system for achieving synchronization, comprising steps that a main clock acquires a timestamp; the main clock calculates a master-slave time difference according to the acquired timestamp; a control value and / or a phase control value of an adjusted frequency is calculated according to the master-slave time difference and a configured synchronization algorithm; the calculated control value is sent to a slave clock; and the slave clock carries out time synchronization. The invention also provides the 1588 system. According to the technical scheme disclosed by the invention, the synchronization precision of the whole-network clocks based on the 1588 system can be improved.

Owner:ZTE CORP

Communication apparatus, communication method and program

Owner:SONY CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com