Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

622 results about "Clock time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

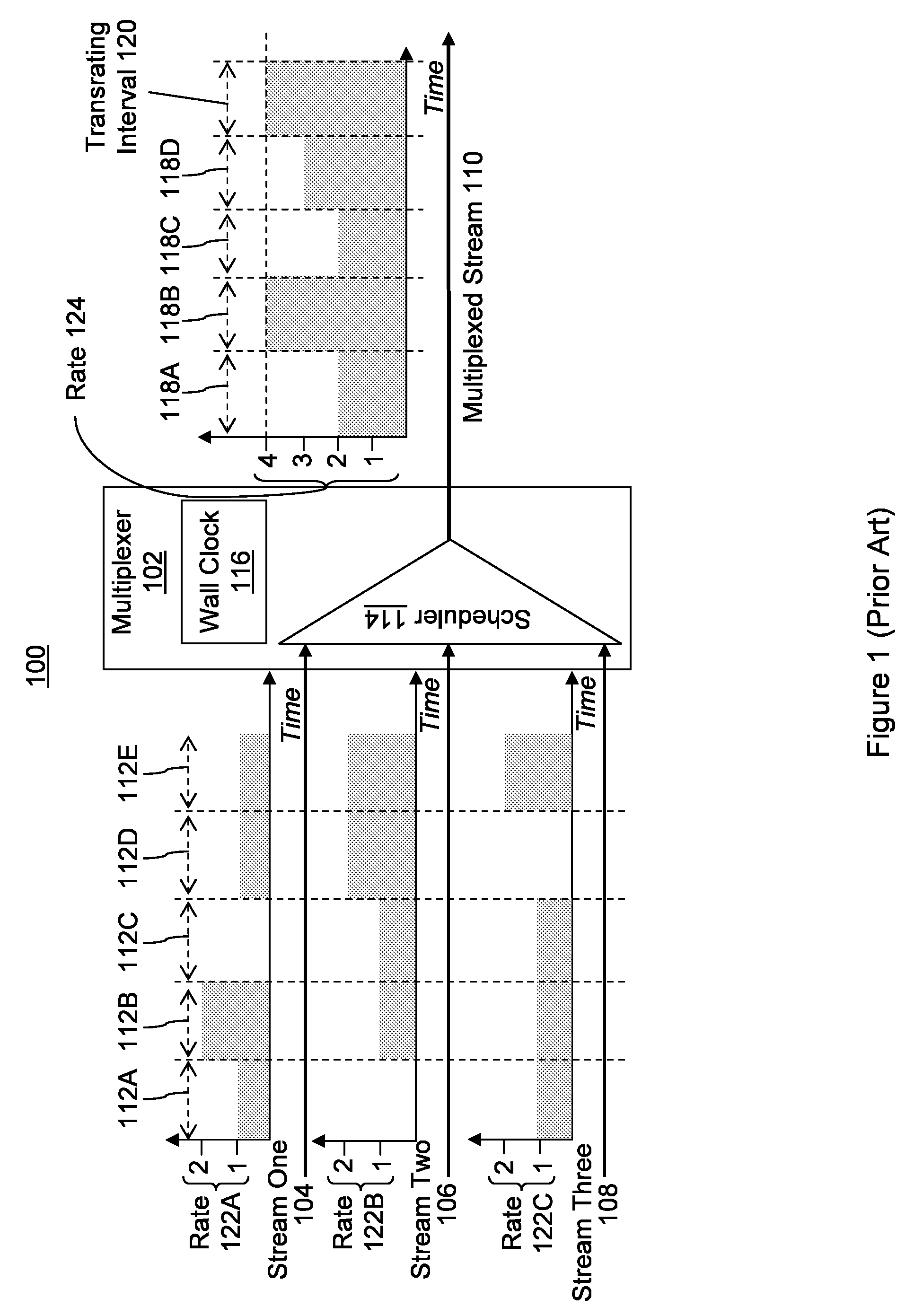

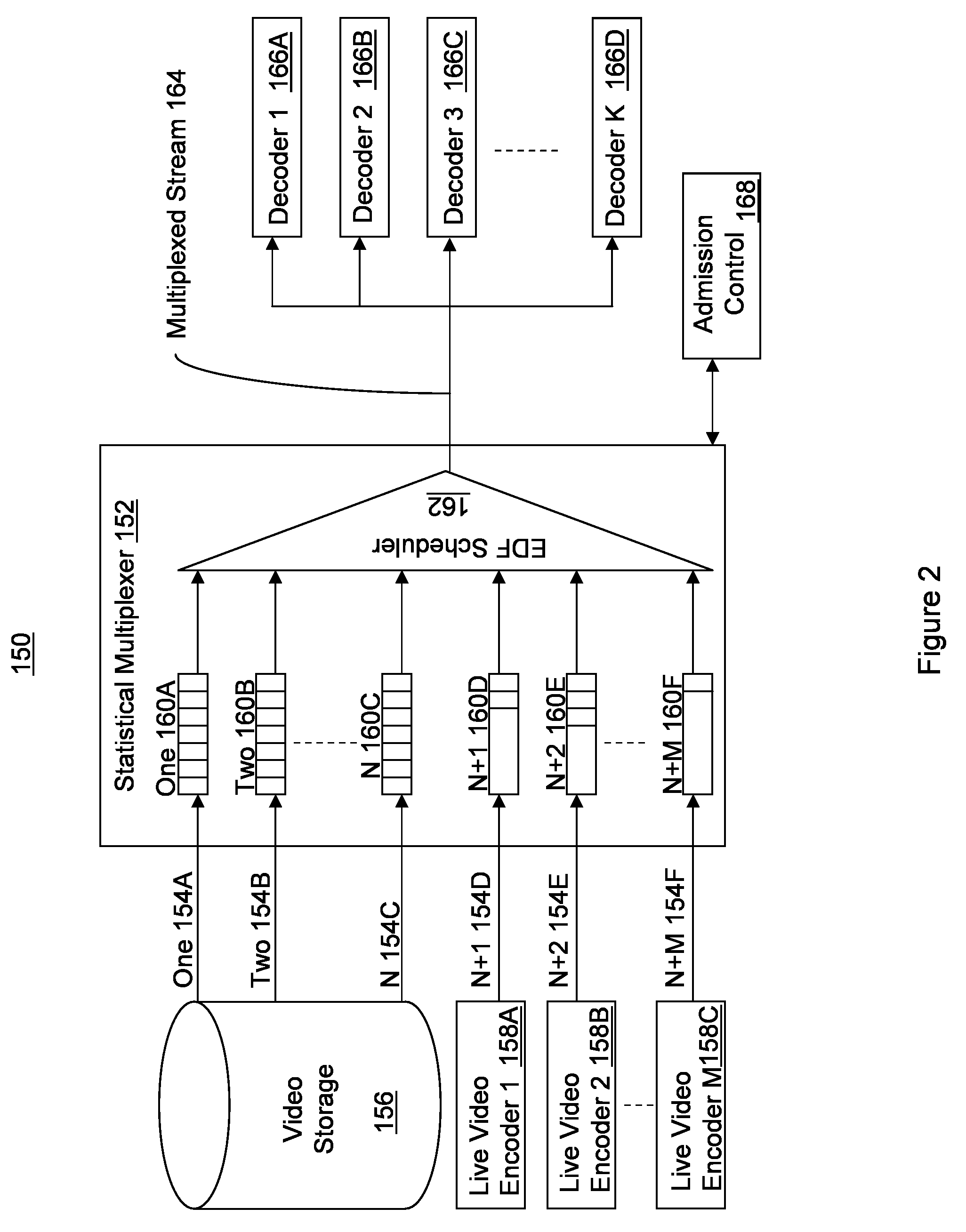

Statistical multiplexing of compressed video streams

InactiveUS20090285217A1Scalable and fashionReduce transmission costsPulse modulation television signal transmissionError preventionMultiplexingProgram clock reference

Described are computer-based methods and apparatuses, including computer program products, for statistical multiplexing of compressed video streams. A deadline of a packet of a compressed video stream is computed based on a program clock reference value of the packet. A plurality of packets, which includes the packet, is sorted based on deadlines corresponding to the packets. A next packet from the sorted plurality of packets is selected, the next packet having a corresponding deadline nearest to a system clock time. The next packet is transmitted.

Owner:VVNET

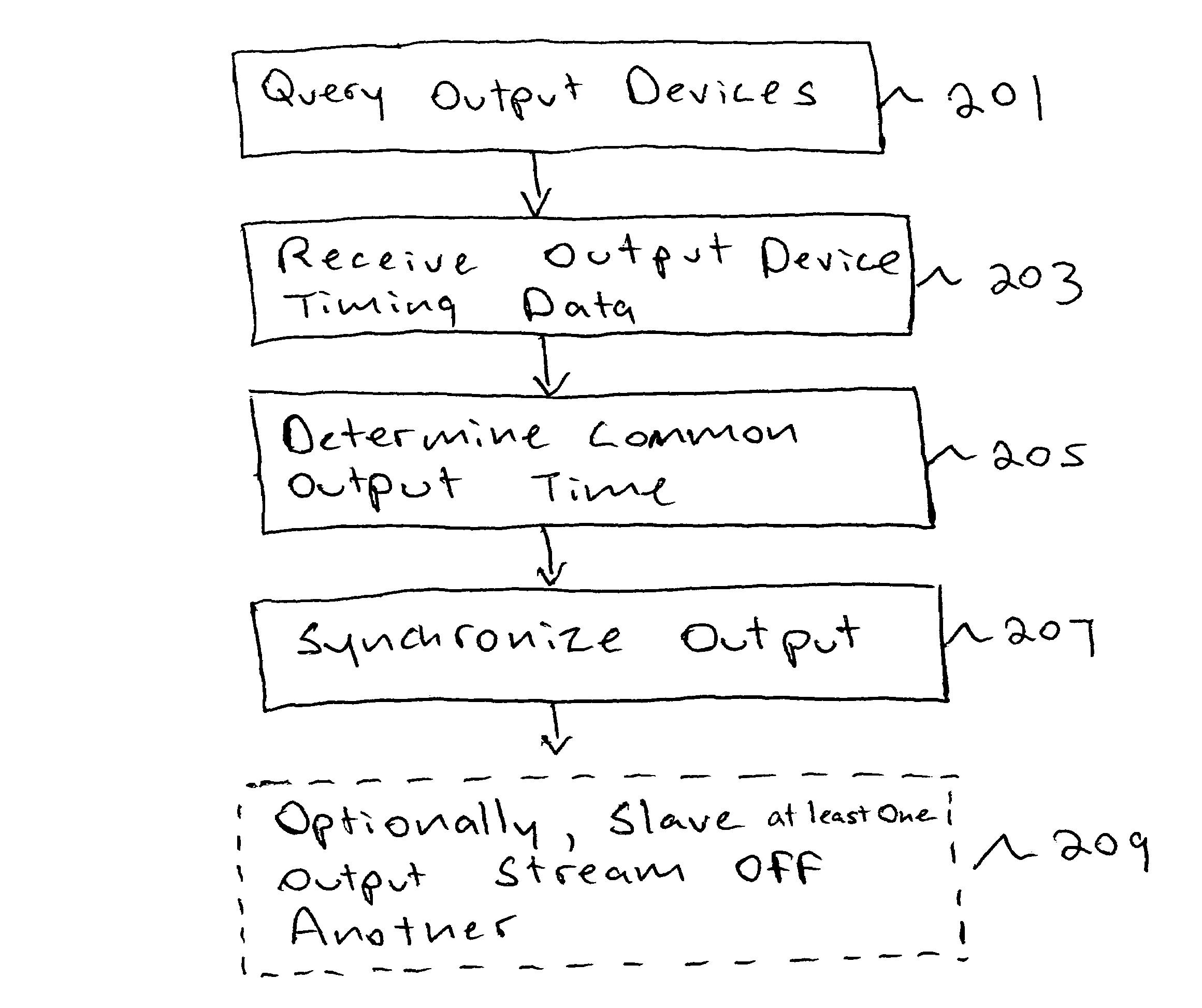

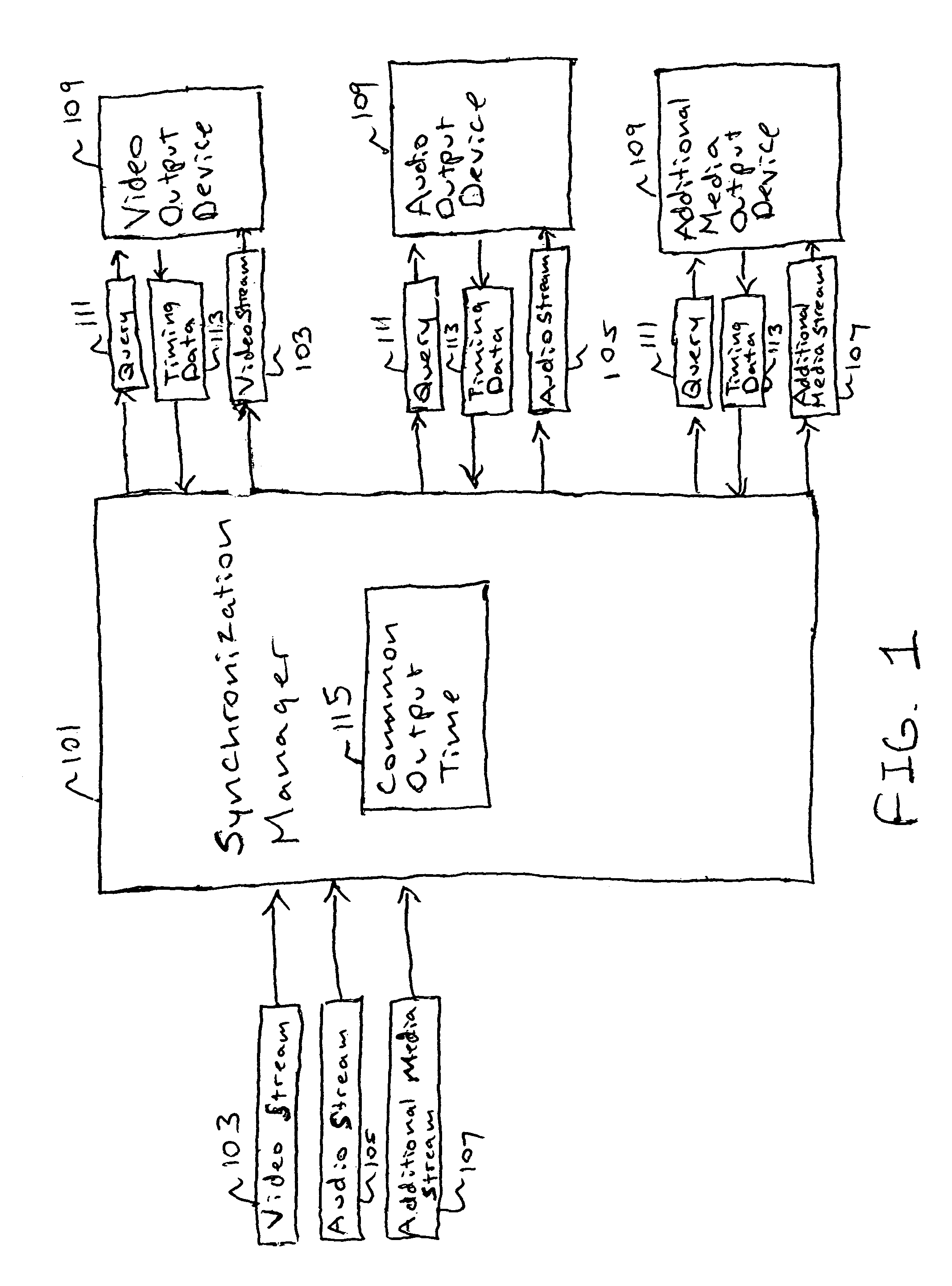

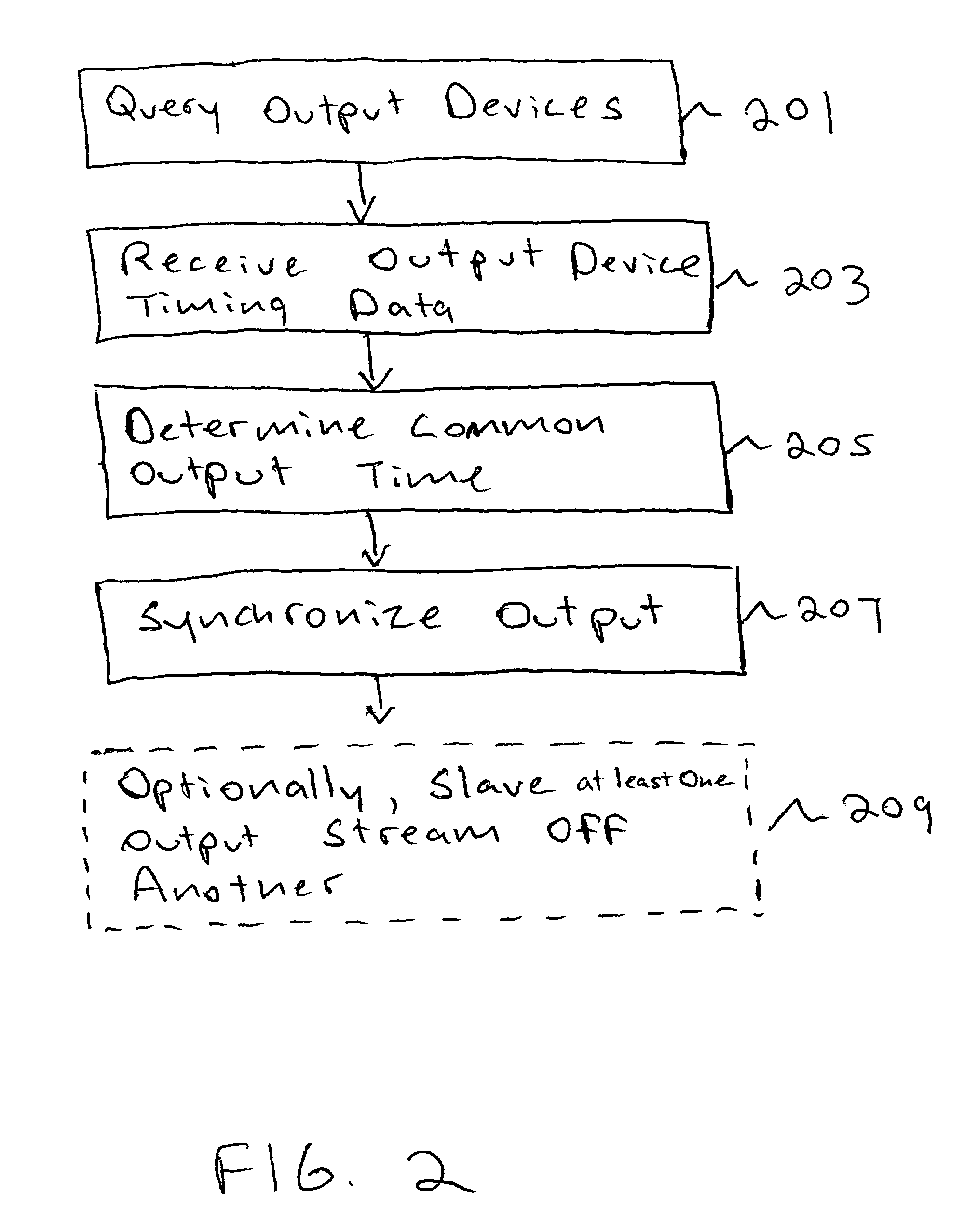

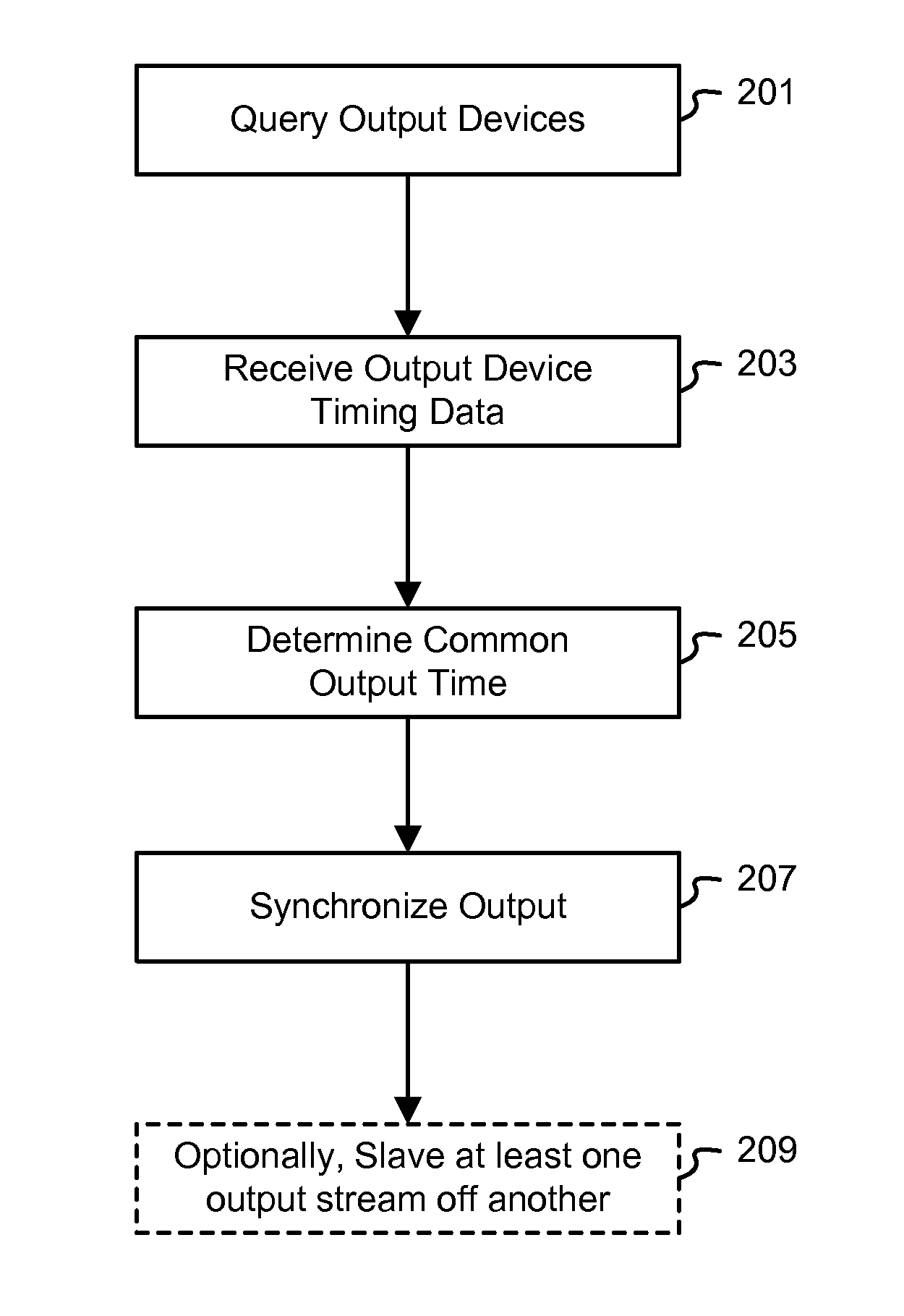

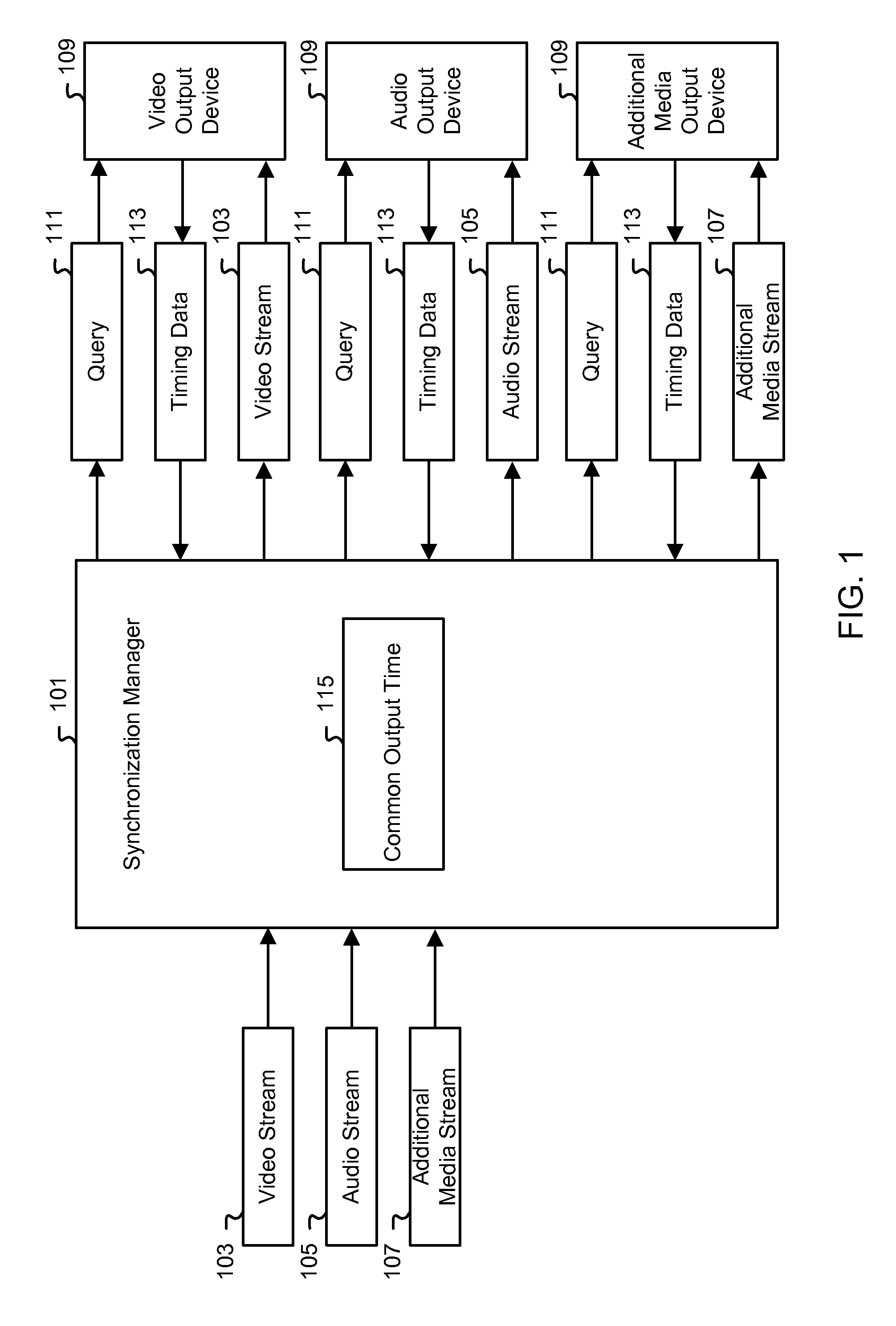

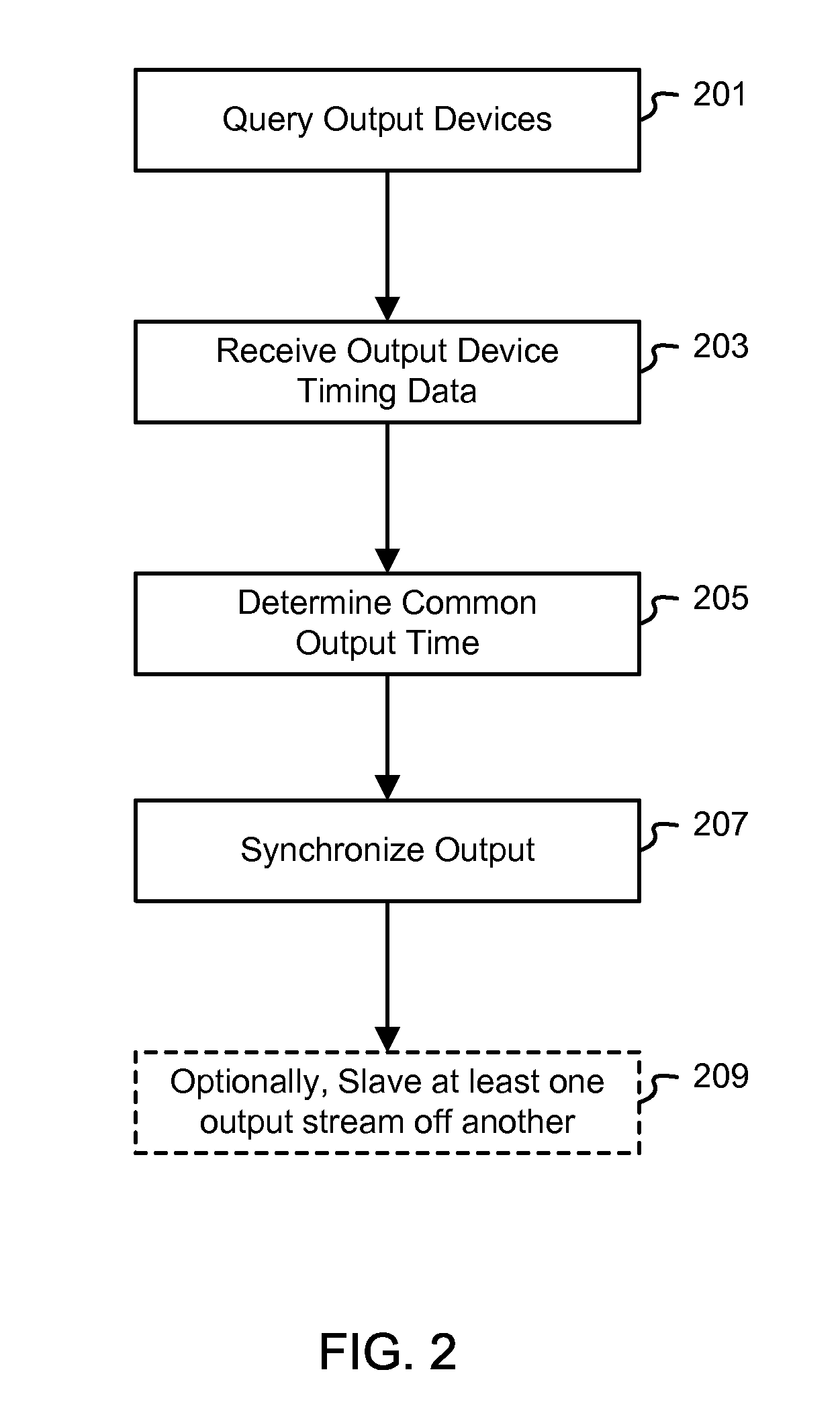

Media stream synchronization using device and host clocks

InactiveUS7669113B1Digital data information retrievalSpecial data processing applicationsClock timeOutput device

A synchronization manager synchronizes multiple media streams. The synchronization manager queries a media stream output device associated with each media stream to synchronize, and in response receives the current device clock time of each device, each device's next available media stream output time, and each device's delta between available media stream output times. The synchronization manager uses this timing information to determine an earliest available media stream output time common to each media stream output device, and synchronizes the output of the media streams by providing each stream to its associated output device at the earliest available common output time.

Owner:APPLE INC

Media stream synchronization using device and host clocks

ActiveUS8239748B1Digital data information retrievalSpecial data processing applicationsClock timeOutput device

A synchronization manager synchronizes multiple media streams. The synchronization manager queries a media stream output device associated with each media stream to synchronize, and in response receives the current device clock time of each device, each device's next available media stream output time, and each device's delta between available media stream output times. The synchronization manager uses this timing information to determine an earliest available media stream output time common to each media stream output device, and synchronizes the output of the media streams by providing each stream to its associated output device at the earliest available common output time.

Owner:APPLE INC

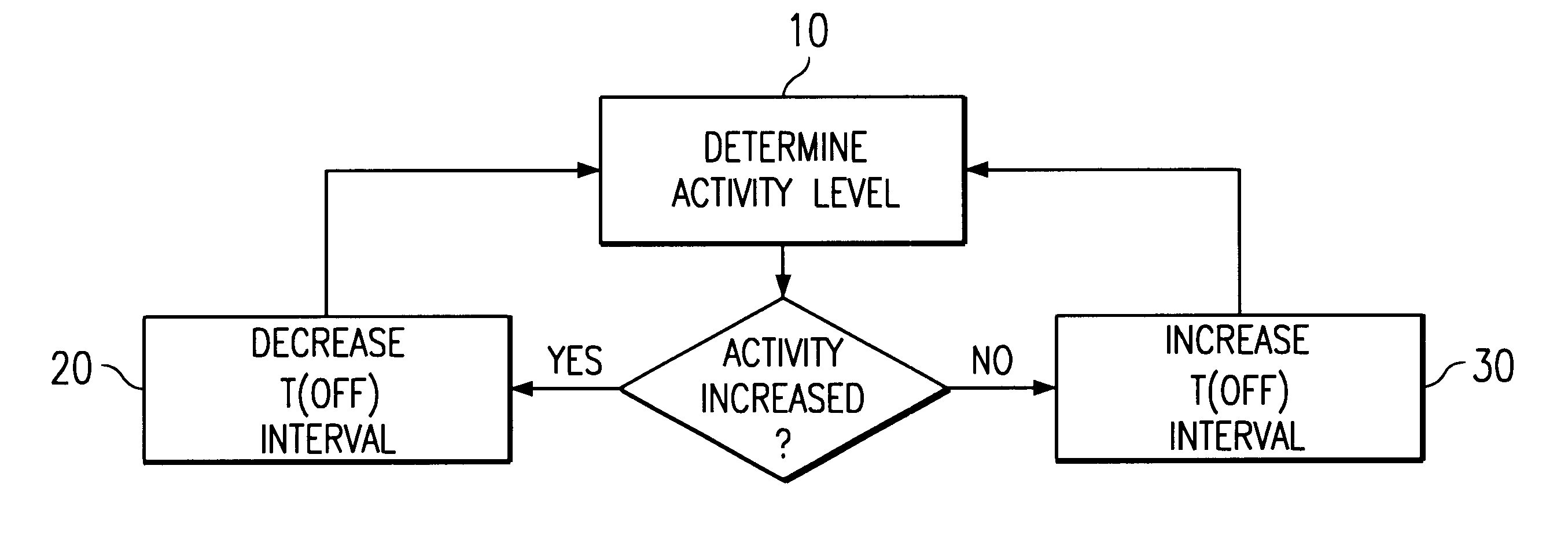

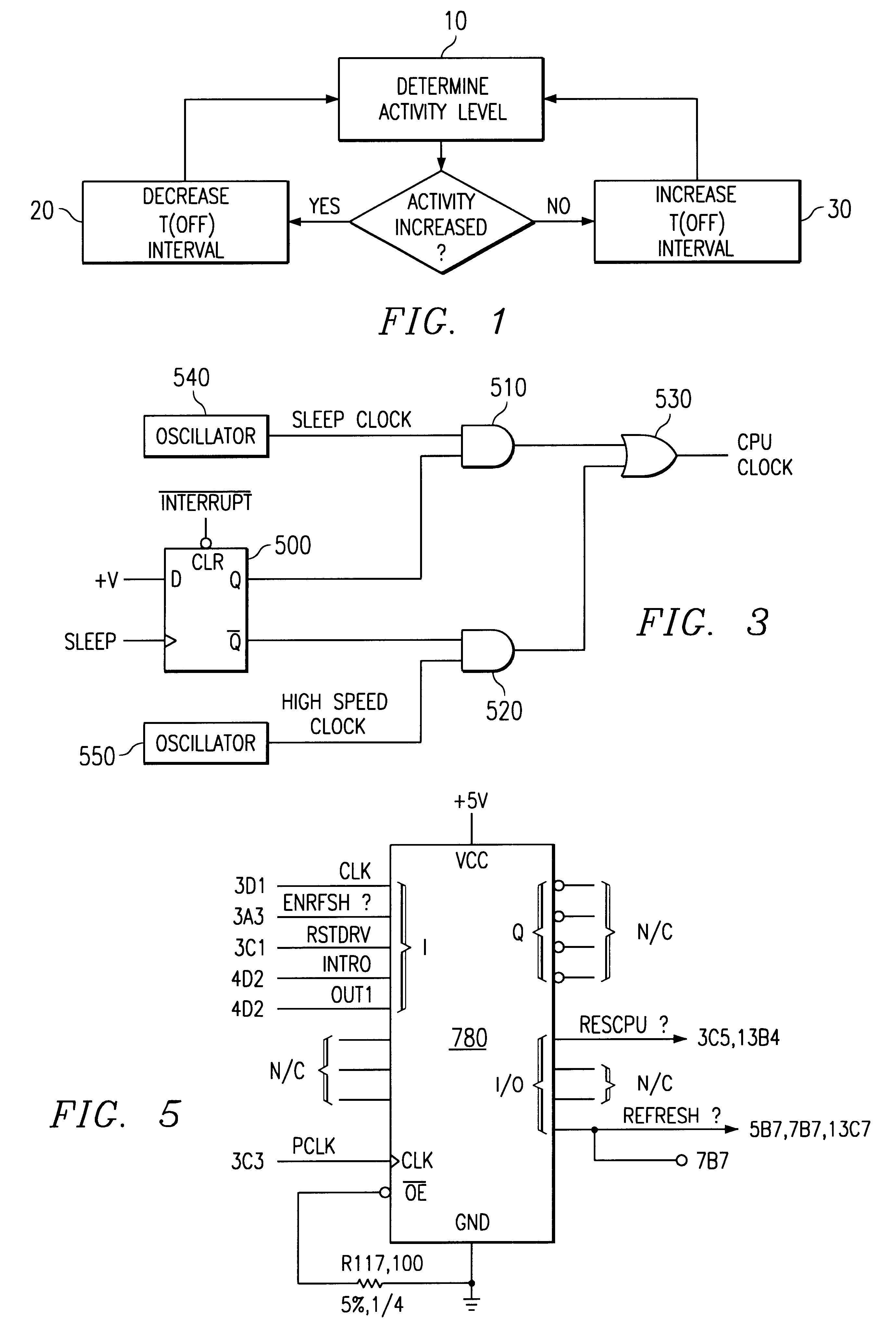

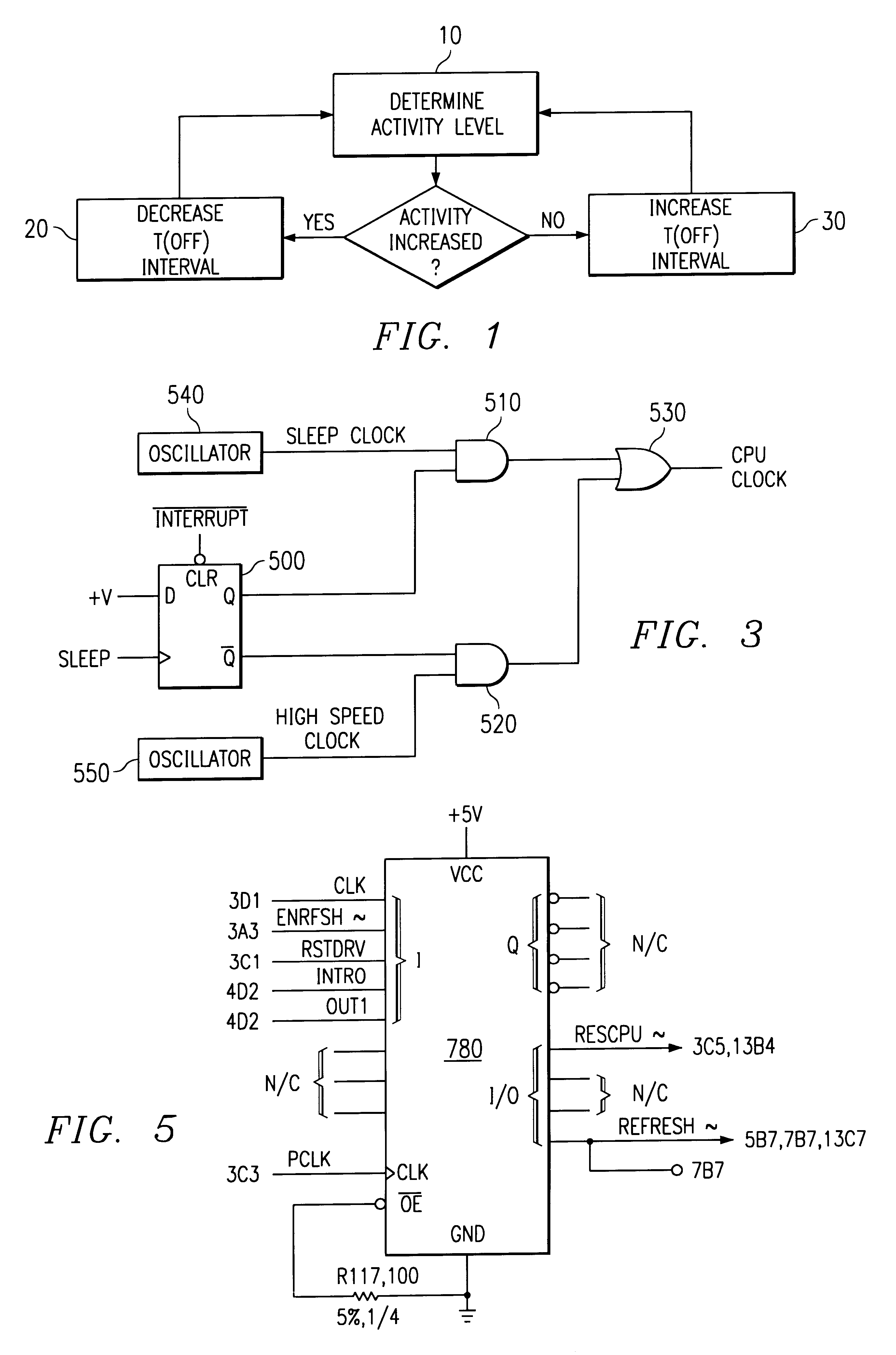

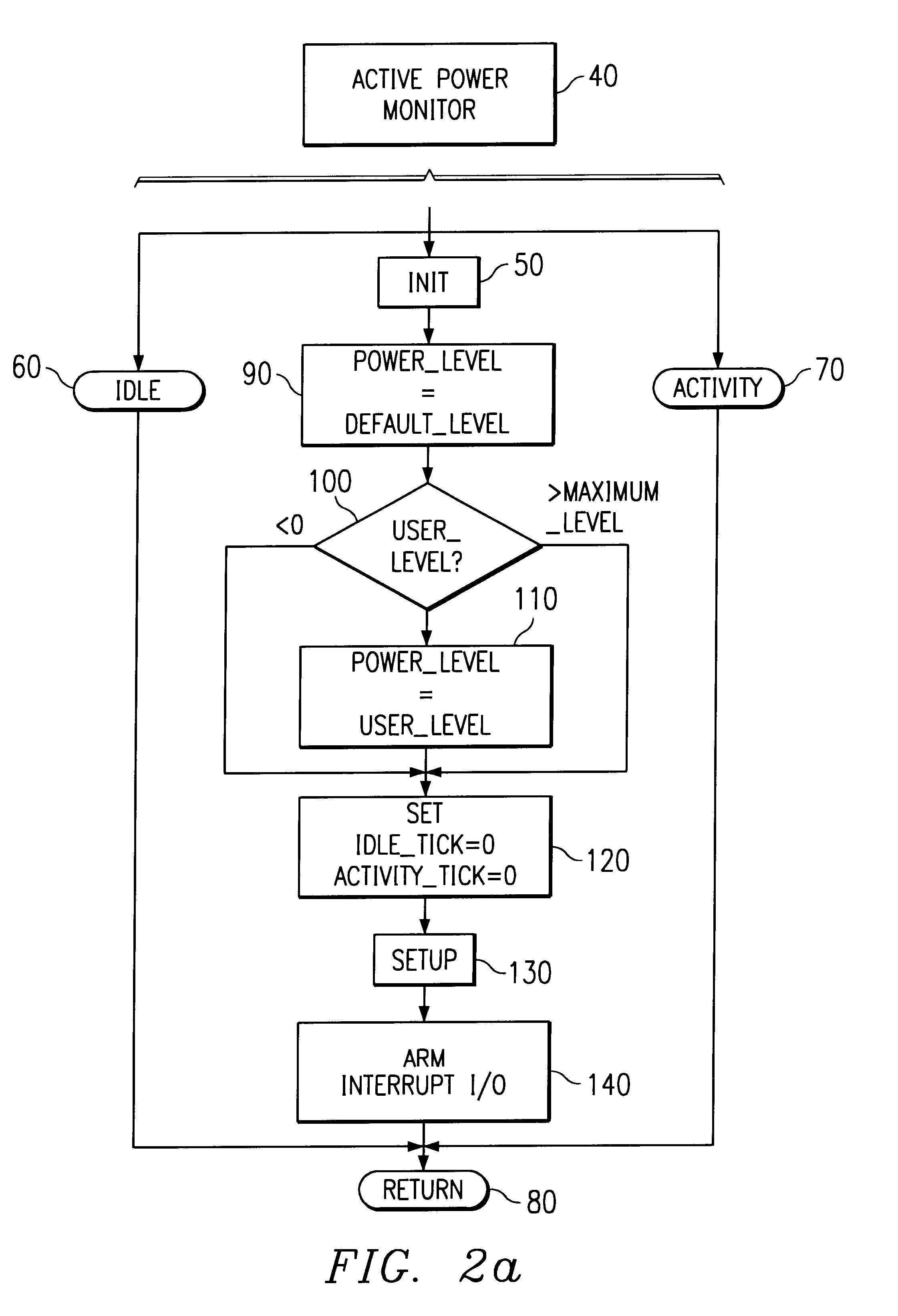

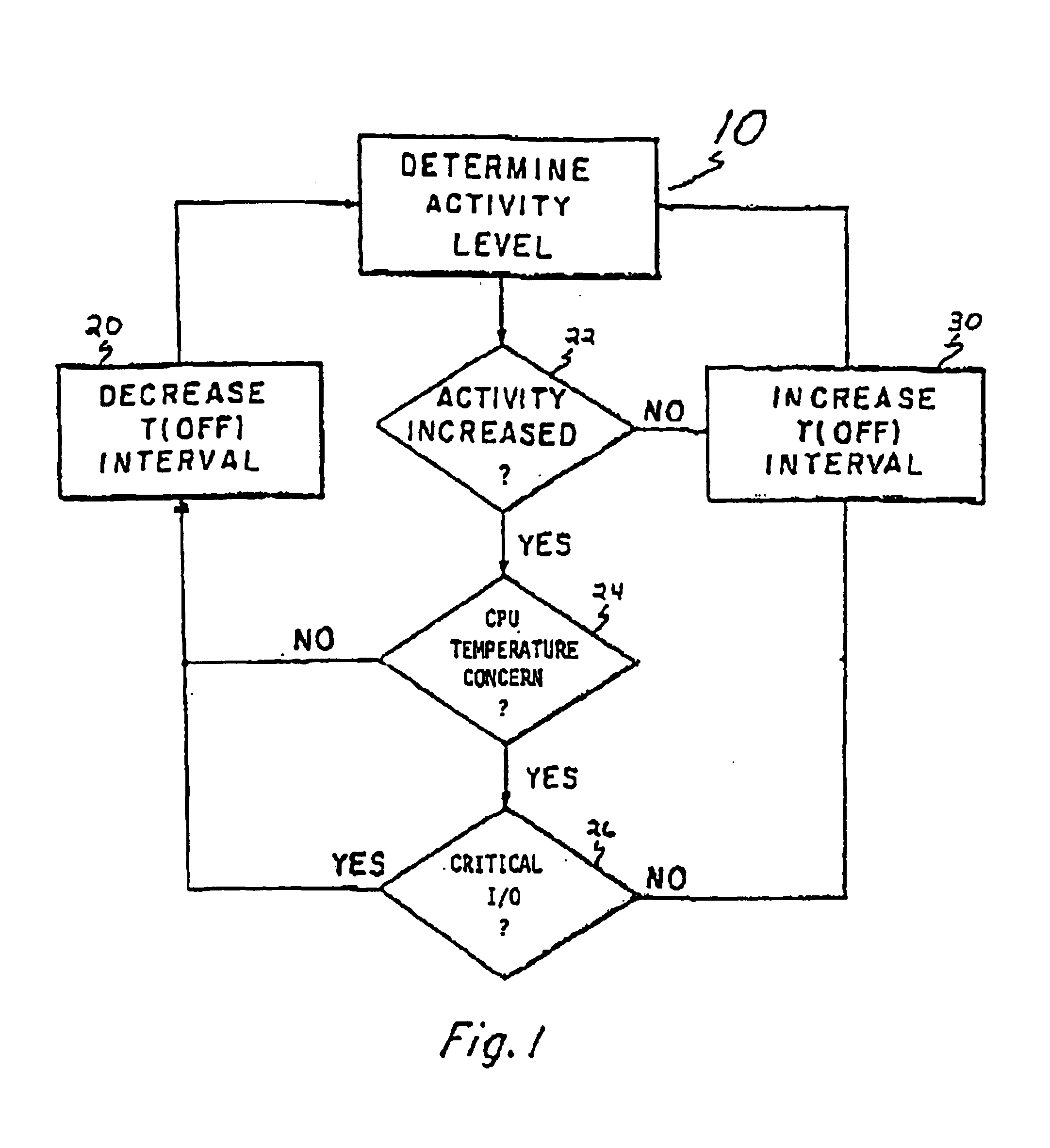

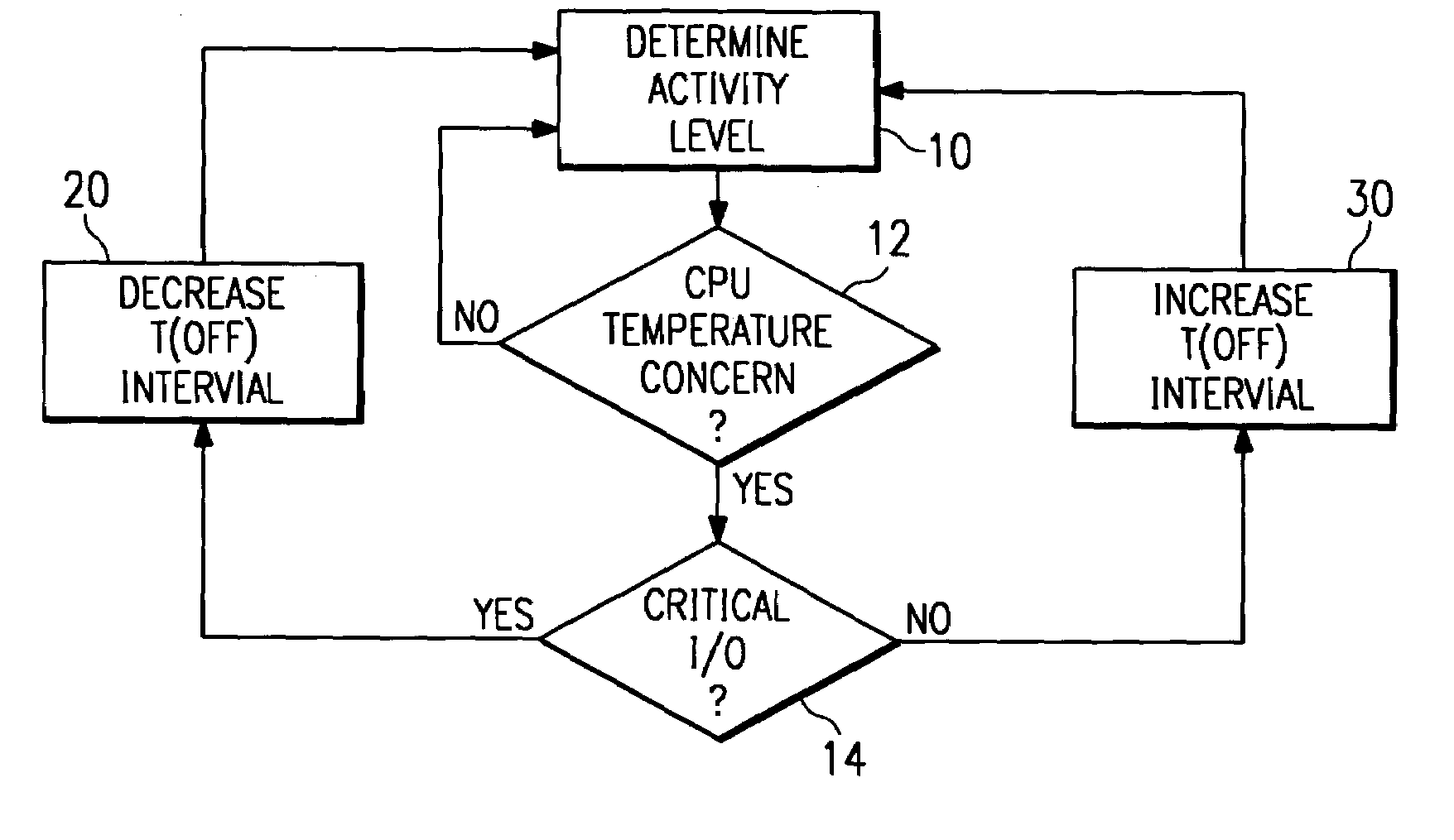

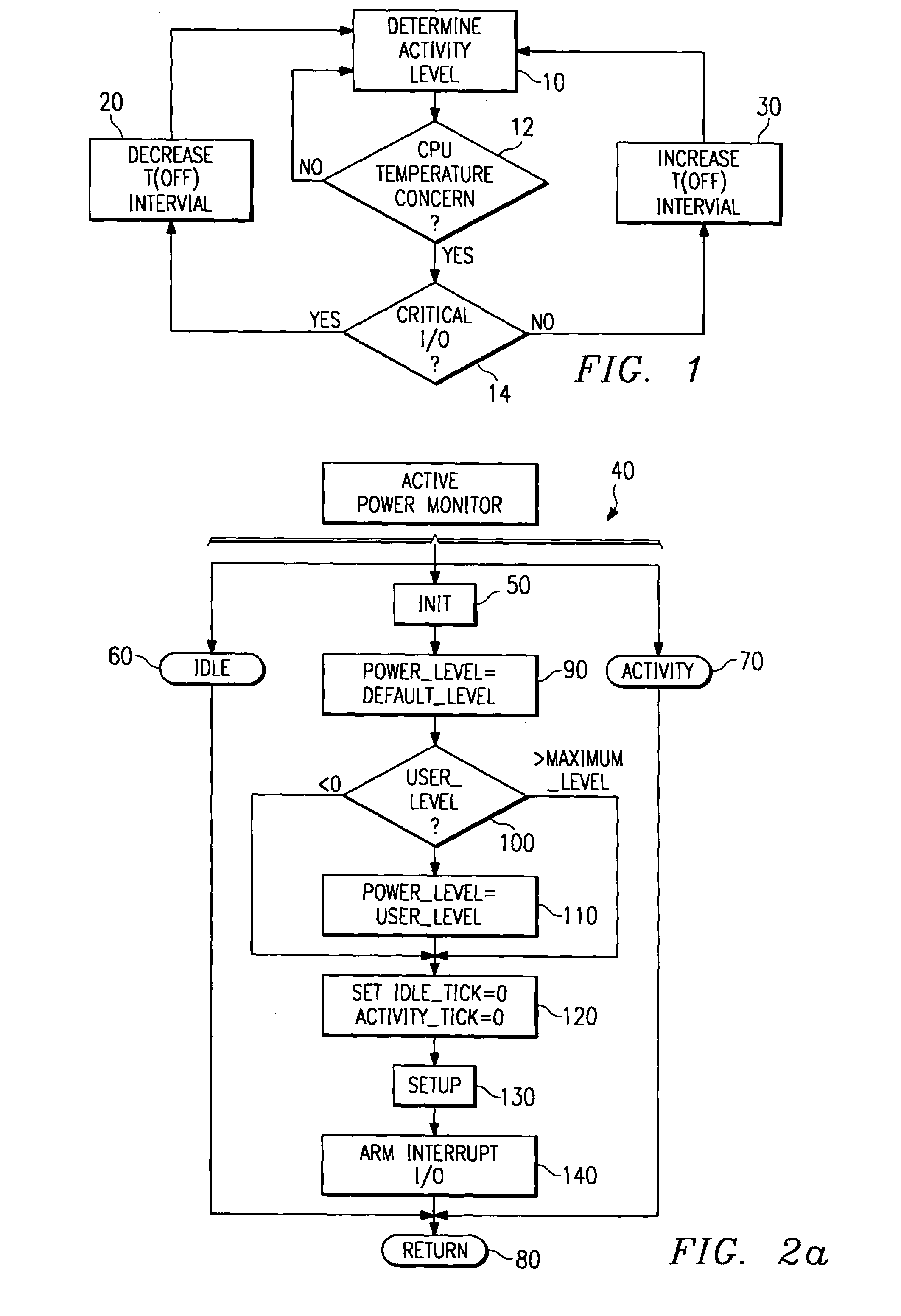

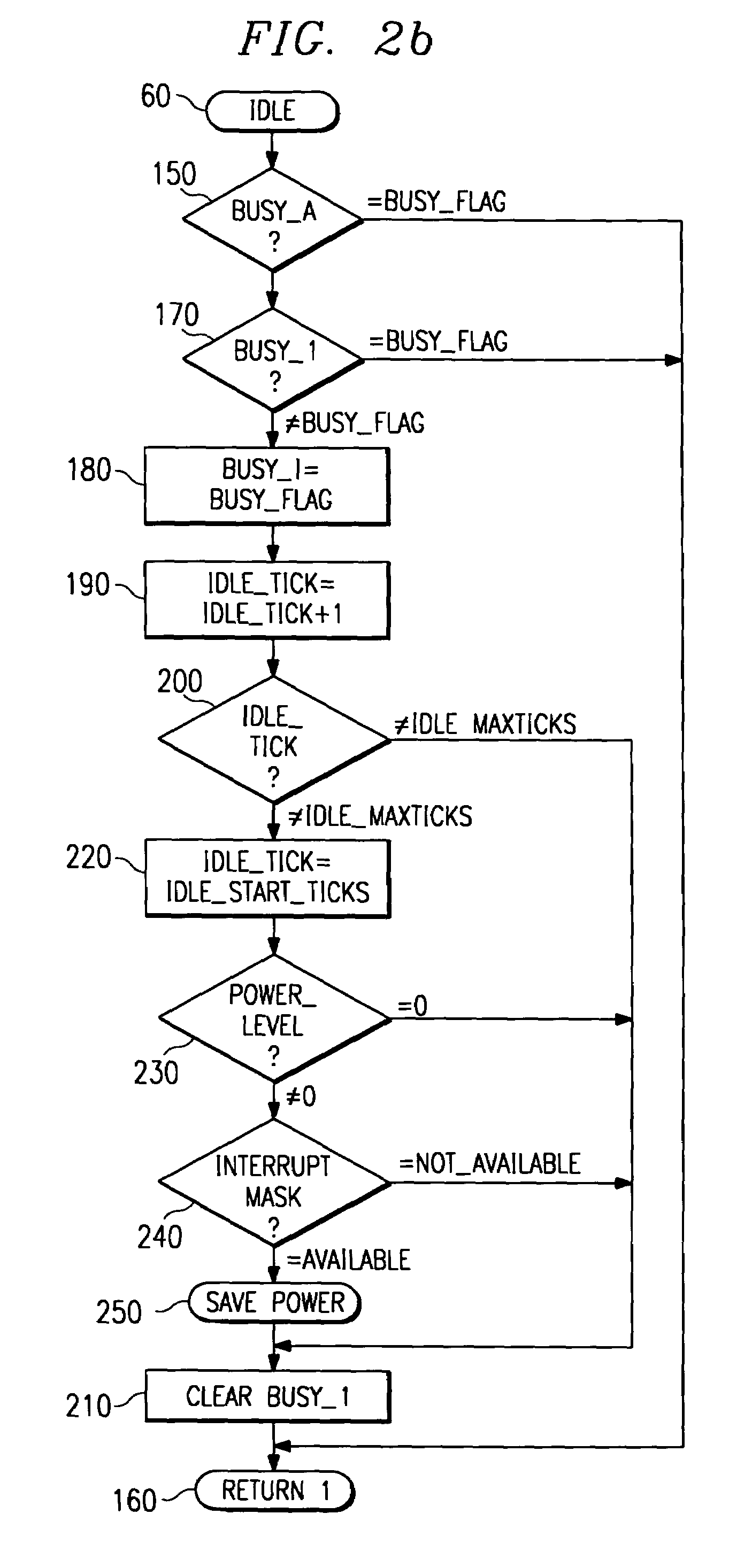

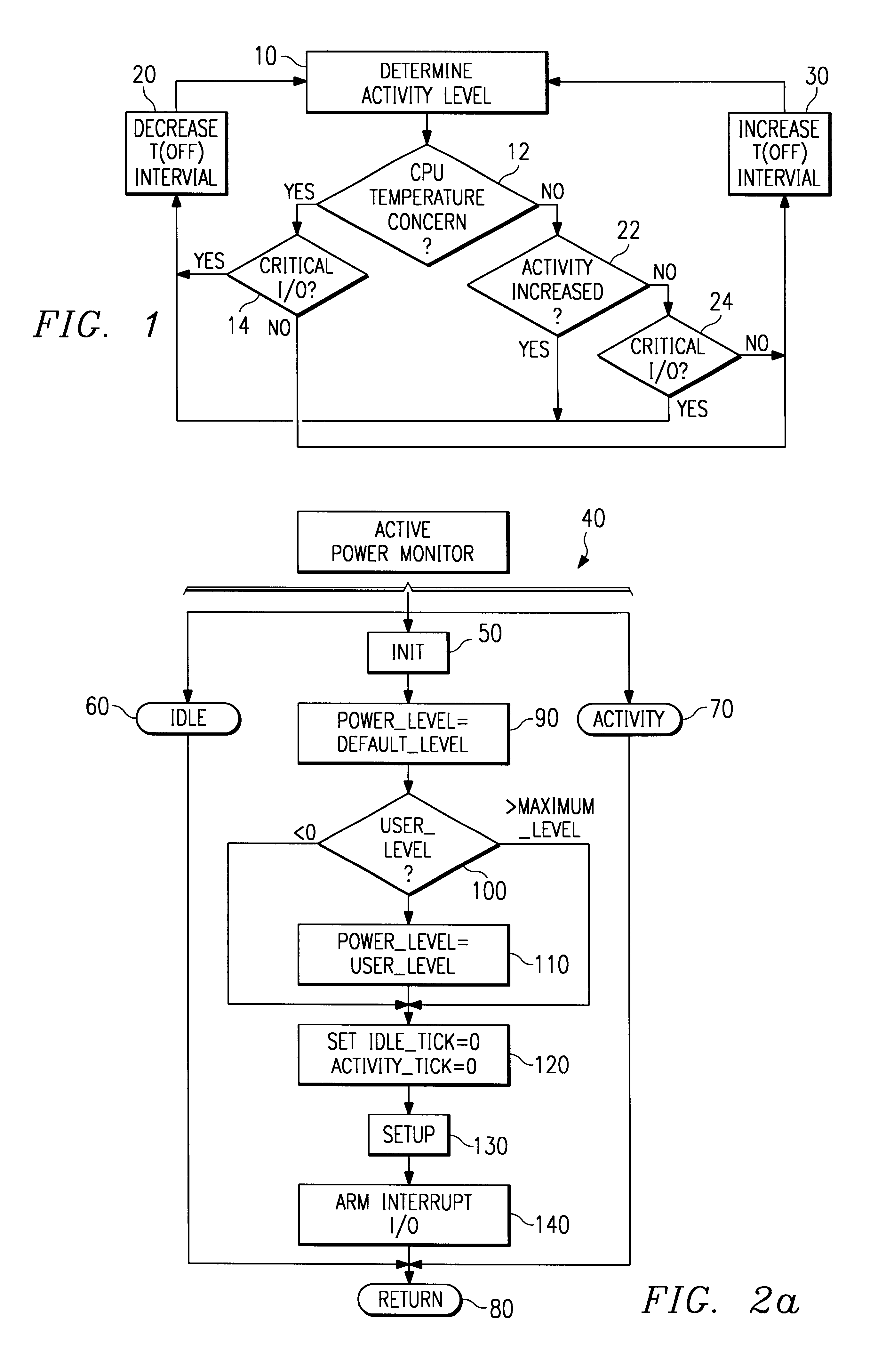

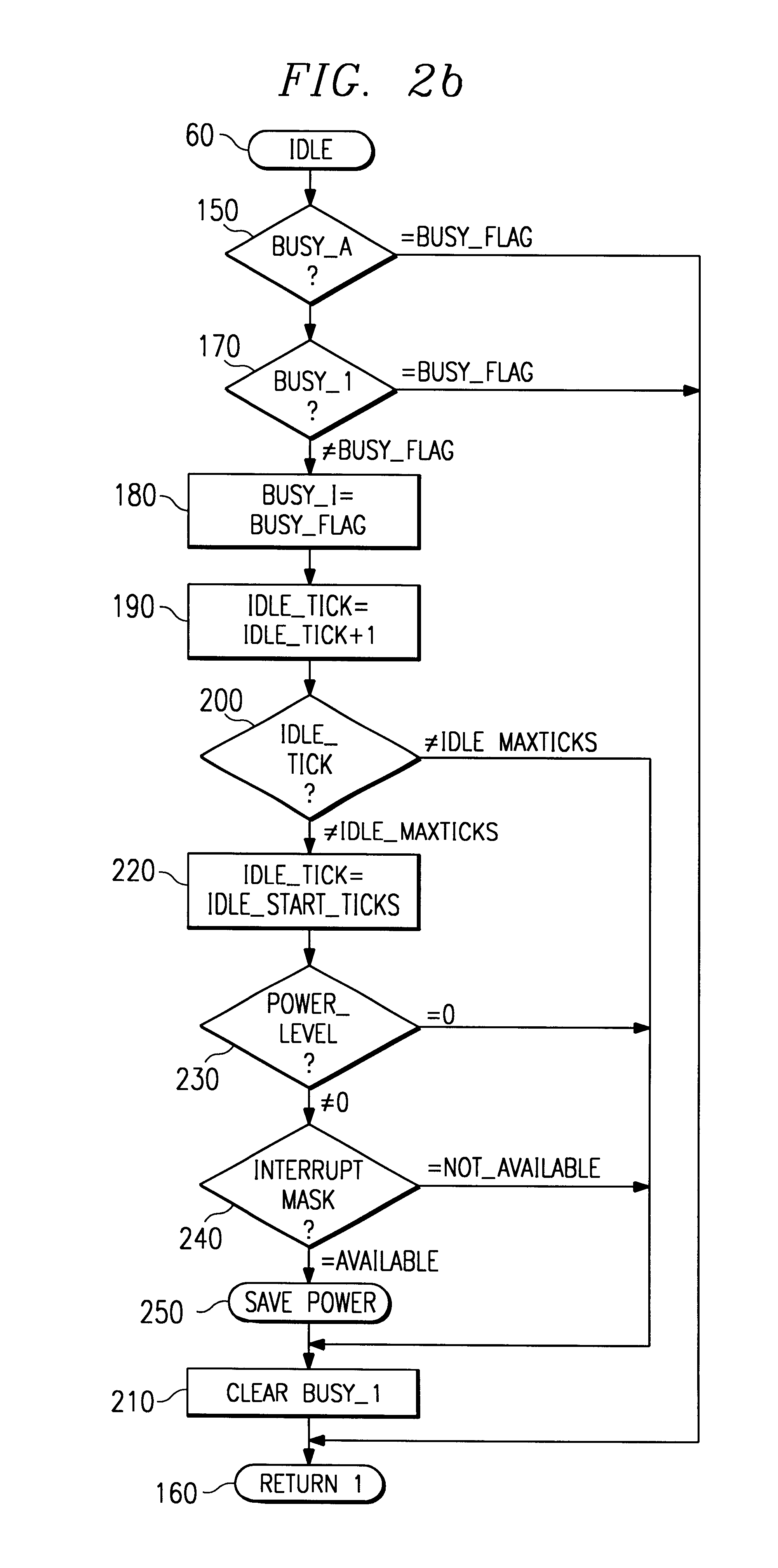

Real-time power conservation for electronic device having a processor

InactiveUS6397340B2Reduce power consumptionWithout perceived performanceEnergy efficient ICTDigital computer detailsClock timeApplication software

A real-time power conservation apparatus and method for portable computers employs a monitor to determine whether a CPU may rest based upon a real-time sampling of the CPU activity level and to activate a hardware selector to carry out the monitor's determination. If the monitor determines the CPU may rest, the hardware selector reduces CPU clock time; if the CPU is to be active, the hardware selector returns the CPU to its previous high speed clock level. Switching back into full operation from its rest state occurs without a user having to request it and without any delay in the operation of the computer while waiting for the computer to return to a "ready" state. Furthermore, the monitor adjusts the performance level of the computer to manage power conservation in response to the real-time sampling of CPU activity. Such adjustments are accomplished within the CPU cycles and do not affect the user's perception of performance and do not affect any system application software executing on the computer.

Owner:TEXAS INSTR INC

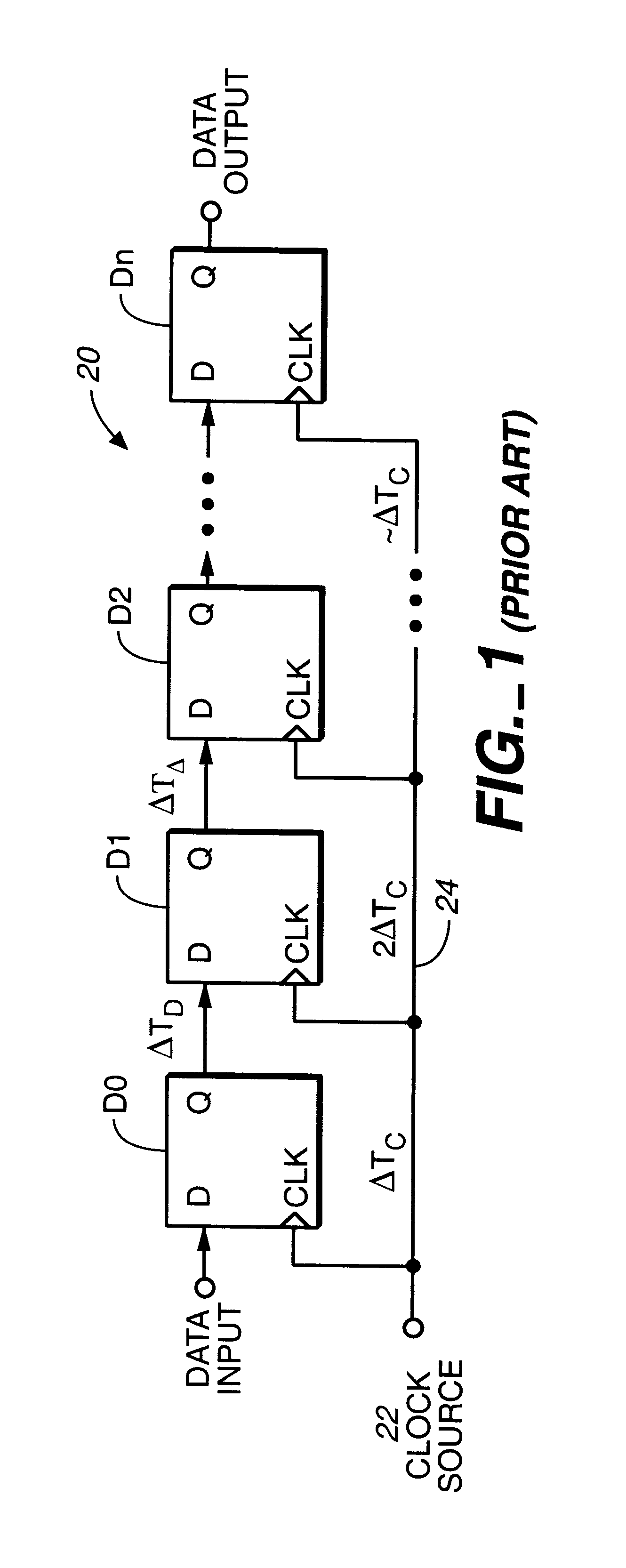

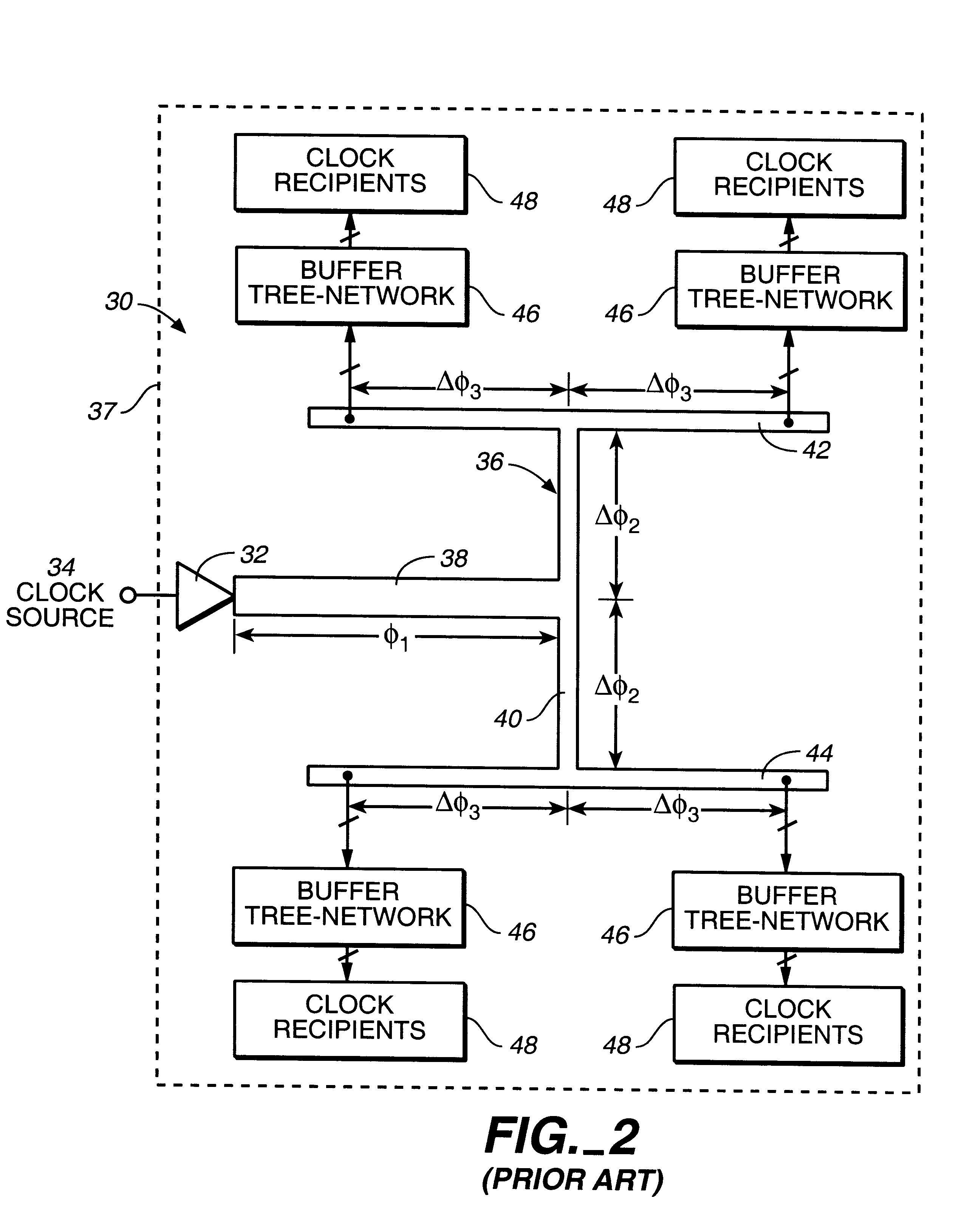

Clock distribution network planning and method therefor

InactiveUS6305001B1Reduce adverse effectsReduce noiseCAD circuit designGenerating/distributing signalsClock timeComputer science

A method for planning the clock distribution network in the conceptual design phase of an ASIC device is provided herein that comprises partitioning the technology-independent description of the device into partitioned groups based on the clocking time of the clock recipients in each of the partitioned groups. In addition, a clock budgeting plan is generated by creating target timing groups and assigning each of the partitioned groups to one of the target timing groups based on the clocking time of the clock recipients in each of the partitioned groups. The clock recipients in each of the target timing groups clock at a substantially same time and clock recipients in different target groups clock at different times. The clock distribution network is created based on the clock budgeting plan such that the clock distribution network provides a clock signal to clock recipients in each of the target timing groups in a manner that the clock recipients in each of the target timing groups are clocked together at a substantially same time.

Owner:BELL SEMICON LLC

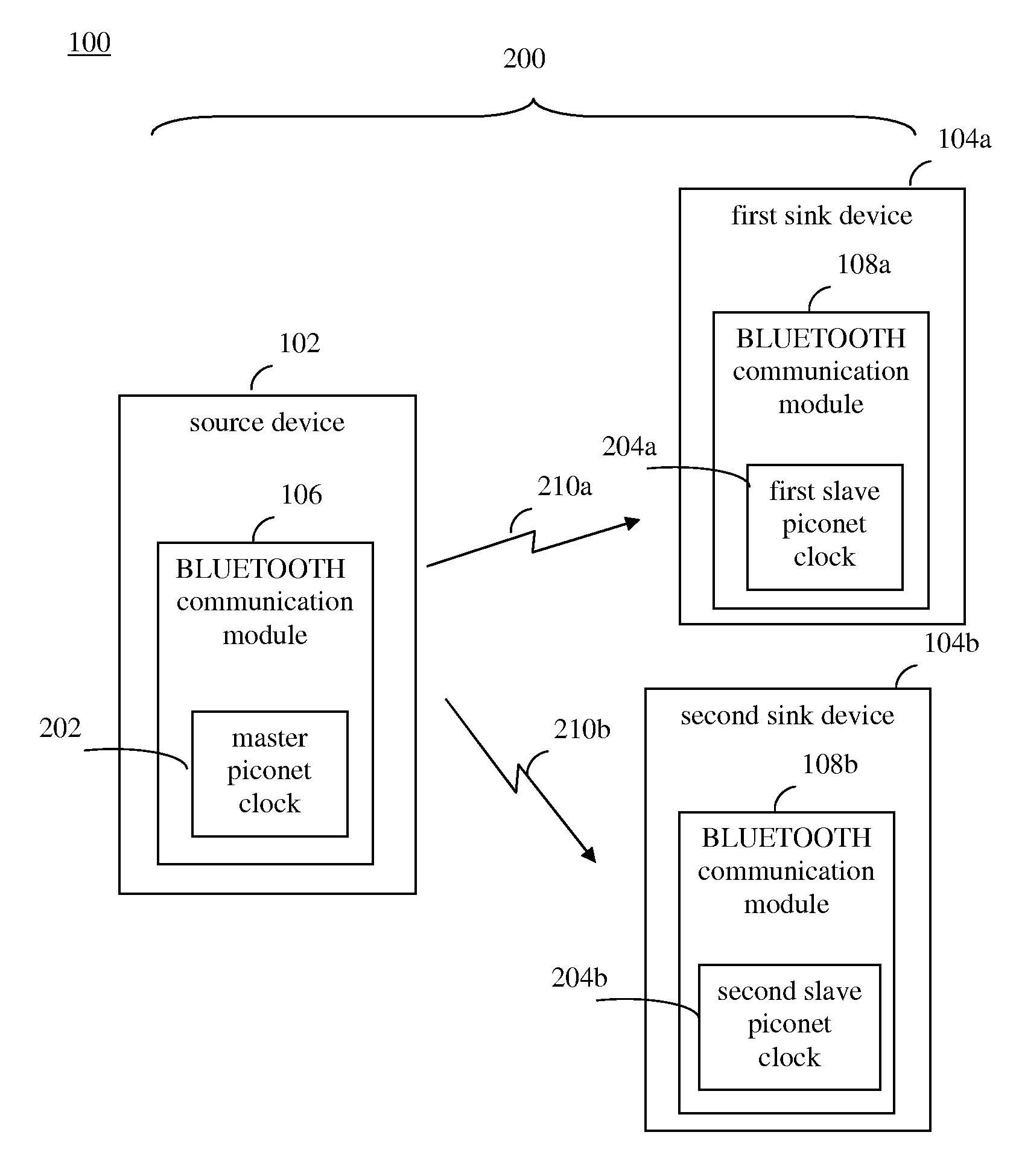

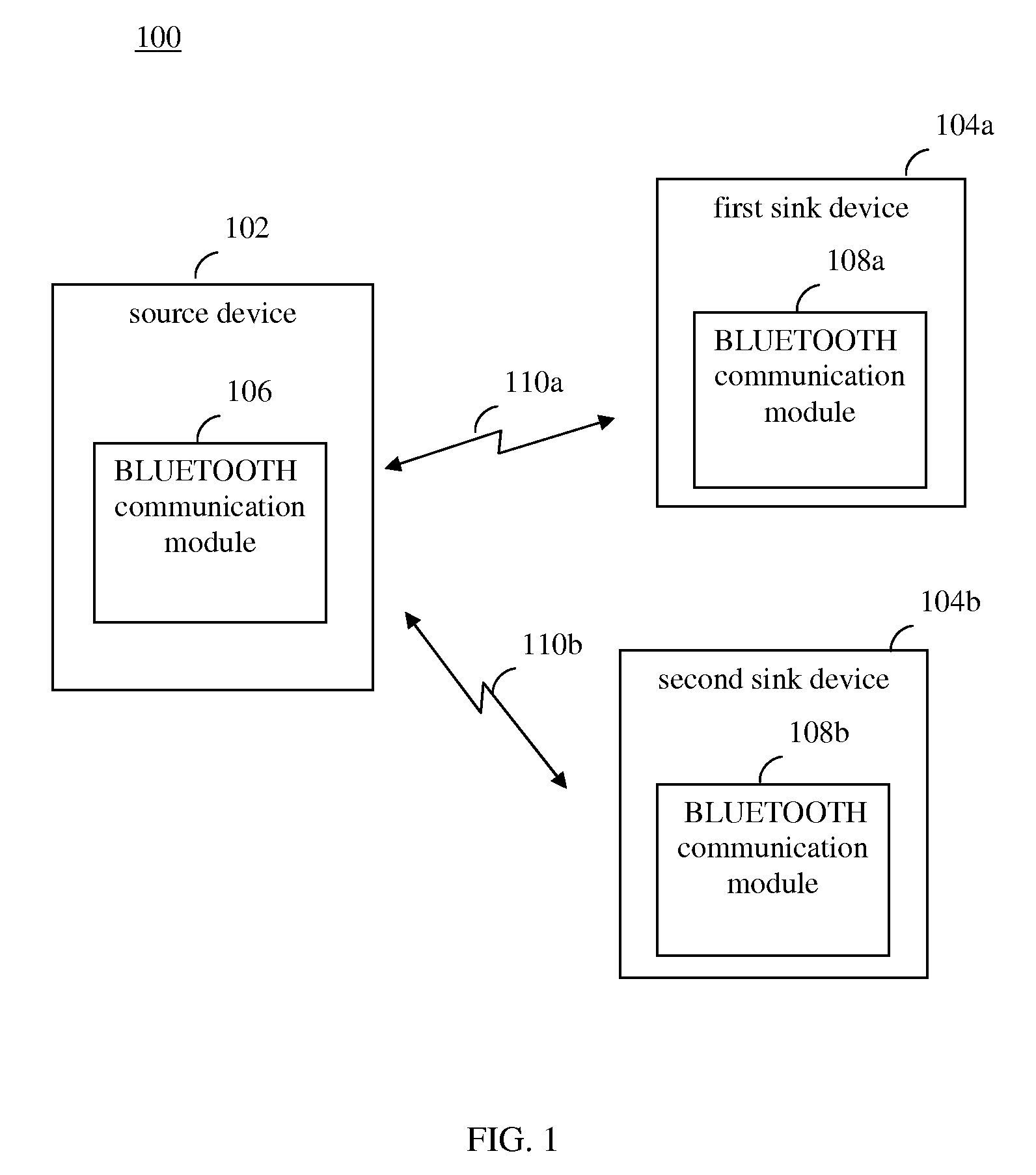

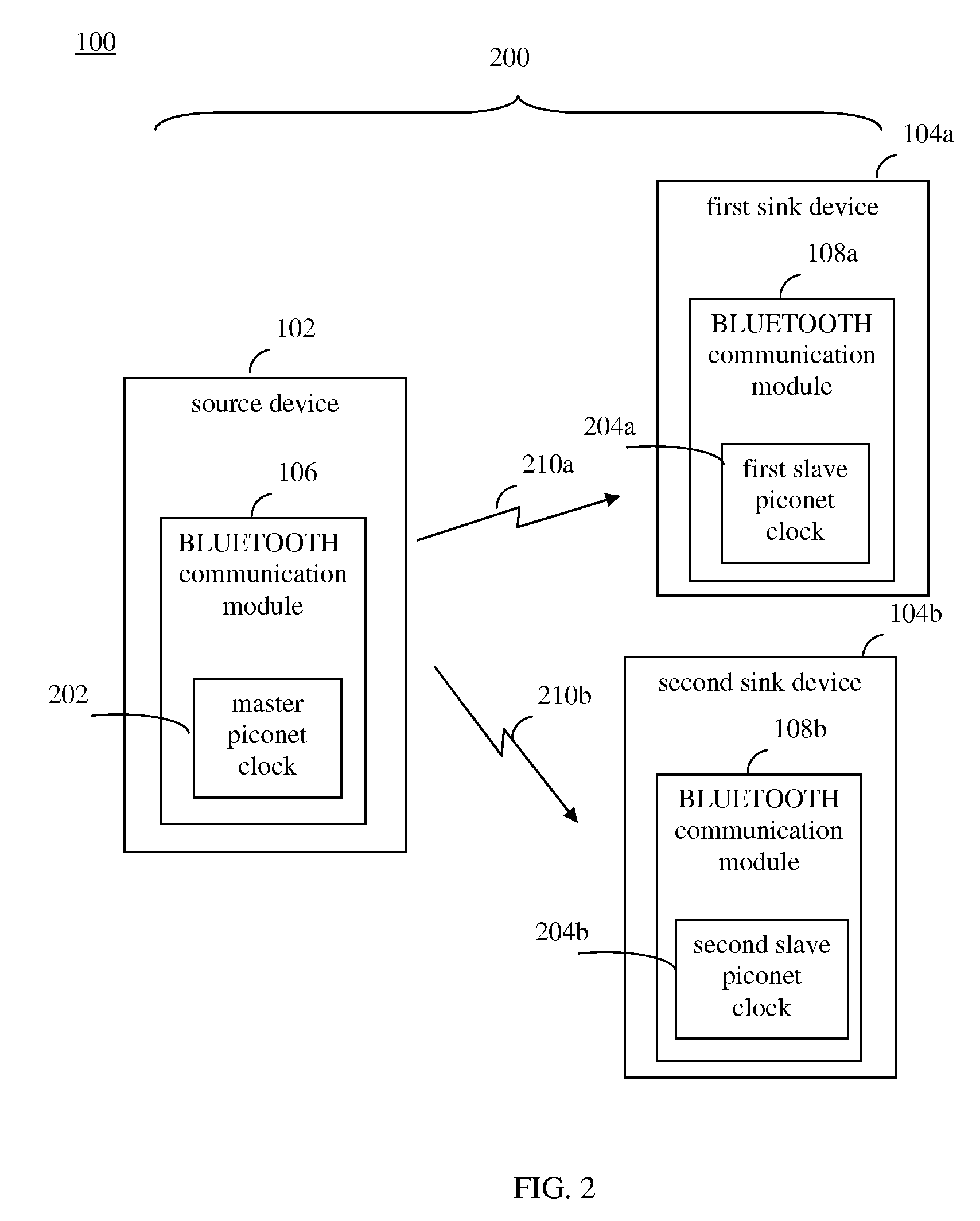

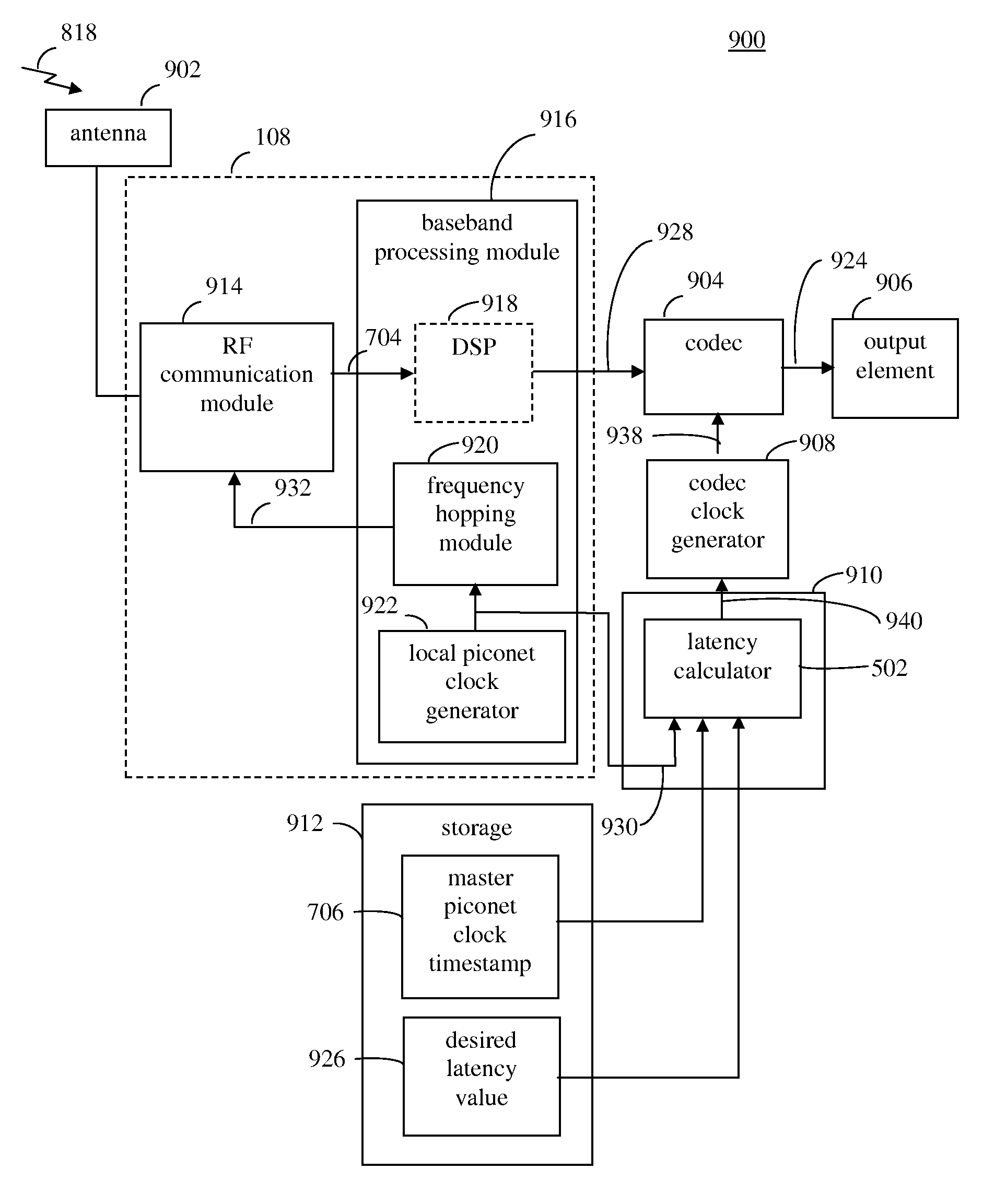

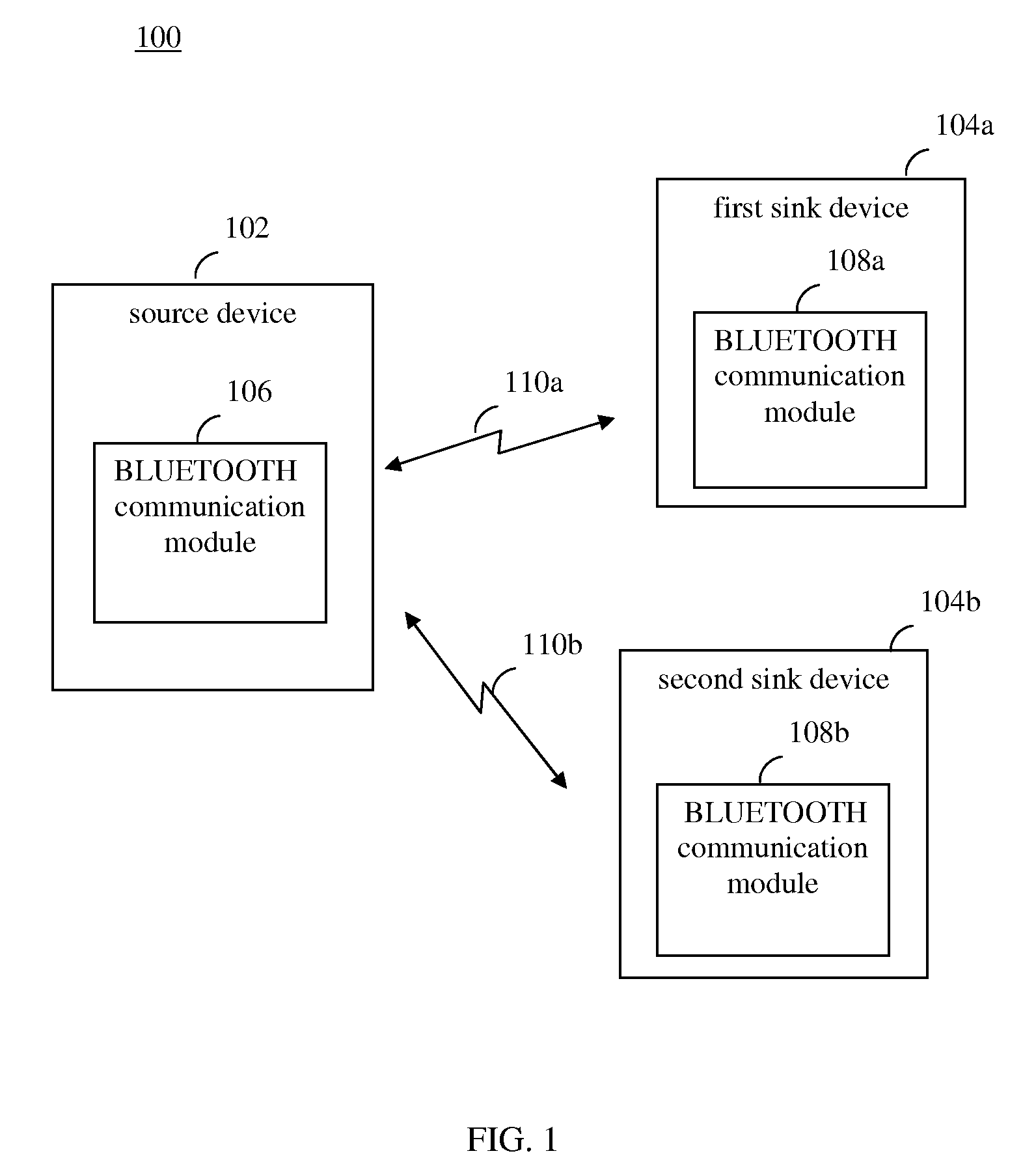

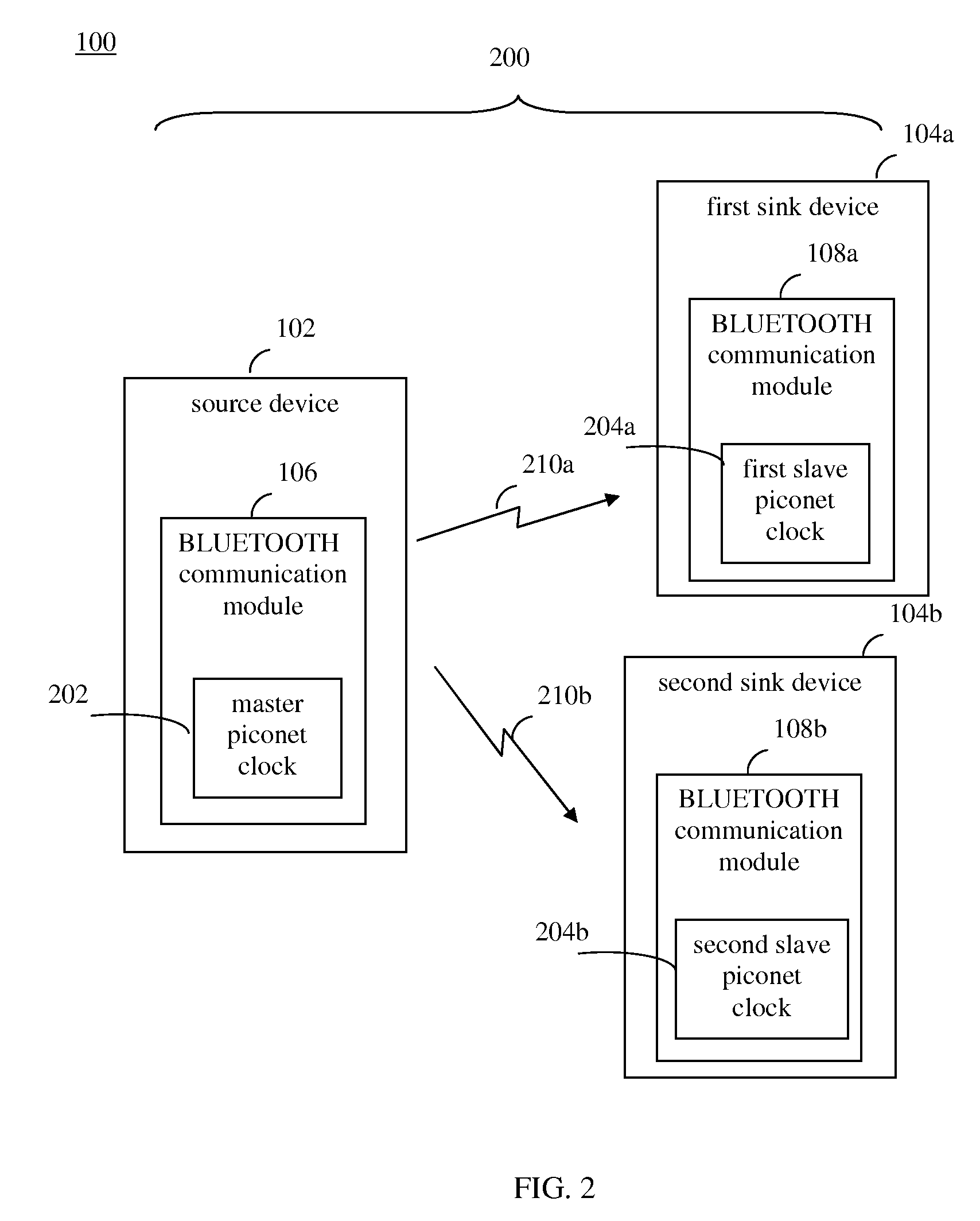

Synchronization Of A Split Audio, Video, Or Other Data Stream With Separate Sinks

ActiveUS20080291891A1Synchronisation arrangementNetwork traffic/resource managementClock timeData stream

Methods, systems, and apparatuses for synchronizing one or more output / sink devices are described. In each sink device, a communication packet is received from a source device. The communication packet includes data and a source clock timestamp. A local clock signal is generated that is synchronized with a source clock signal of the source device. The data is decoded using a codec. At least one delay and the source clock timestamp are subtracted from a current value of the local clock signal to generate a local latency value. A difference between a desired latency value and the local latency value is determined. A rate of a clock signal of the codec is adjusted according to the determined difference. Because each sink device adjusts its latency to a common desired latency value, the sink devices are thereby synchronized.

Owner:AVAGO TECH INT SALES PTE LTD

Real-time power conservation for electronic device having a processor

InactiveUS6173409B1Reduce power consumptionWithout perceived performanceEnergy efficient ICTDigital computer detailsClock timeApplication software

A real-time power conservation apparatus and method for portable computers employs a monitor to determine whether a CPU may rest based upon a real-time sampling of the CPU activity level and to activate a hardware selector to carry out the monitor's determination. If the monitor determines the CPU may rest, the hardware selector reduces CPU clock time; if the CPU is to be active, the hardware selector returns the CPU to its previous high speed clock level. Switching back into full operation from its rest state occurs without a user having to request it and without any delay in the operation of the computer while waiting for the computer to return to a "ready" state. Furthermore, the monitor adjusts the performance level of the computer to manage power conservation in response to the real-time sampling of CPU activity. Such adjustments are accomplished within the CPU cycles and do not affect the user's perception of performance and do not affect any system application software executing on the computer.

Owner:TEXAS INSTR INC

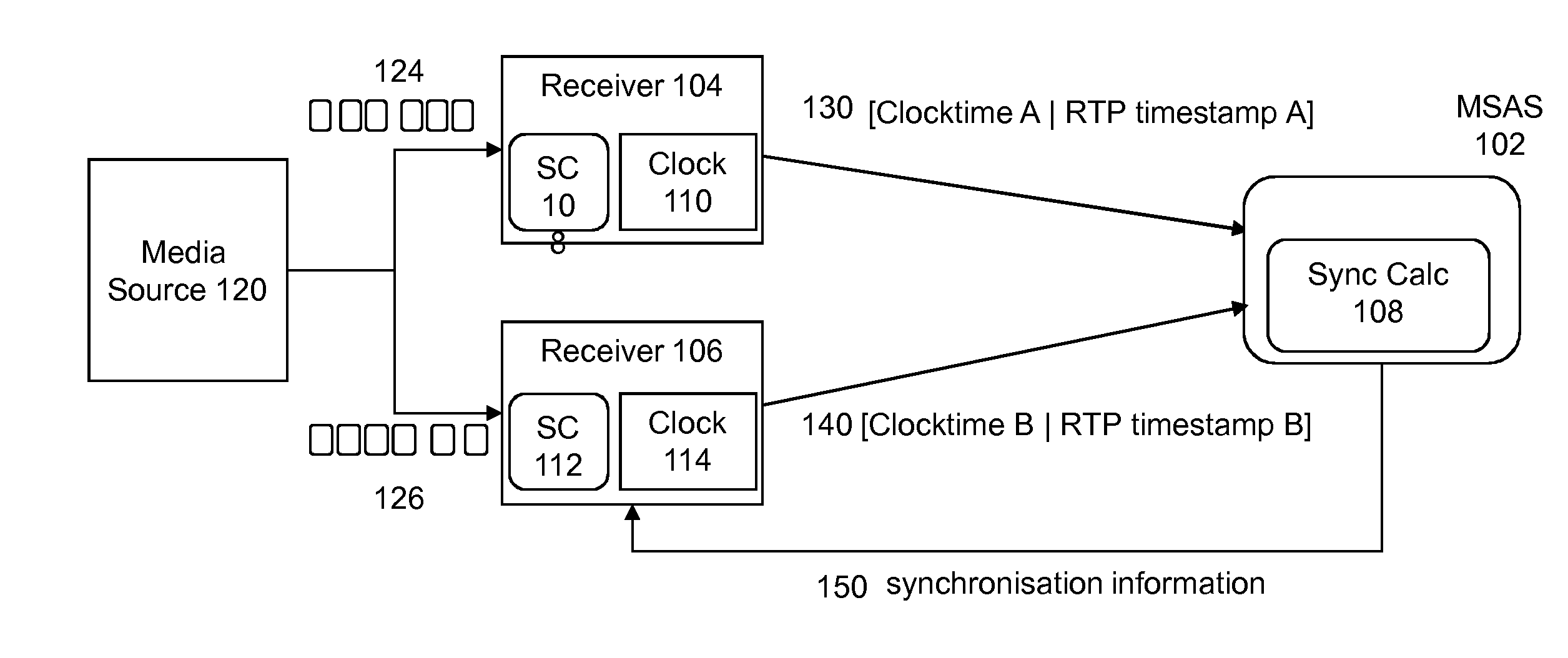

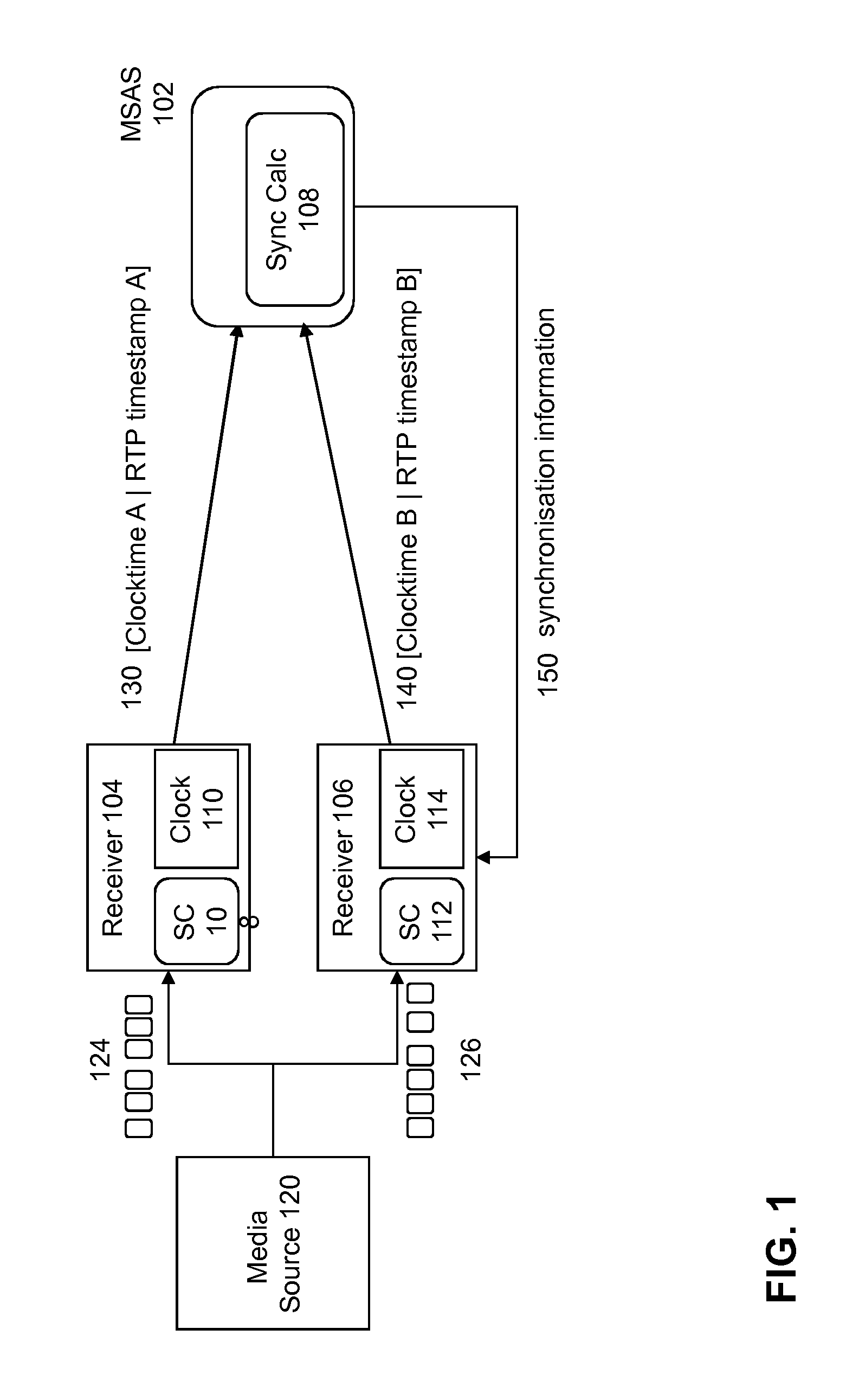

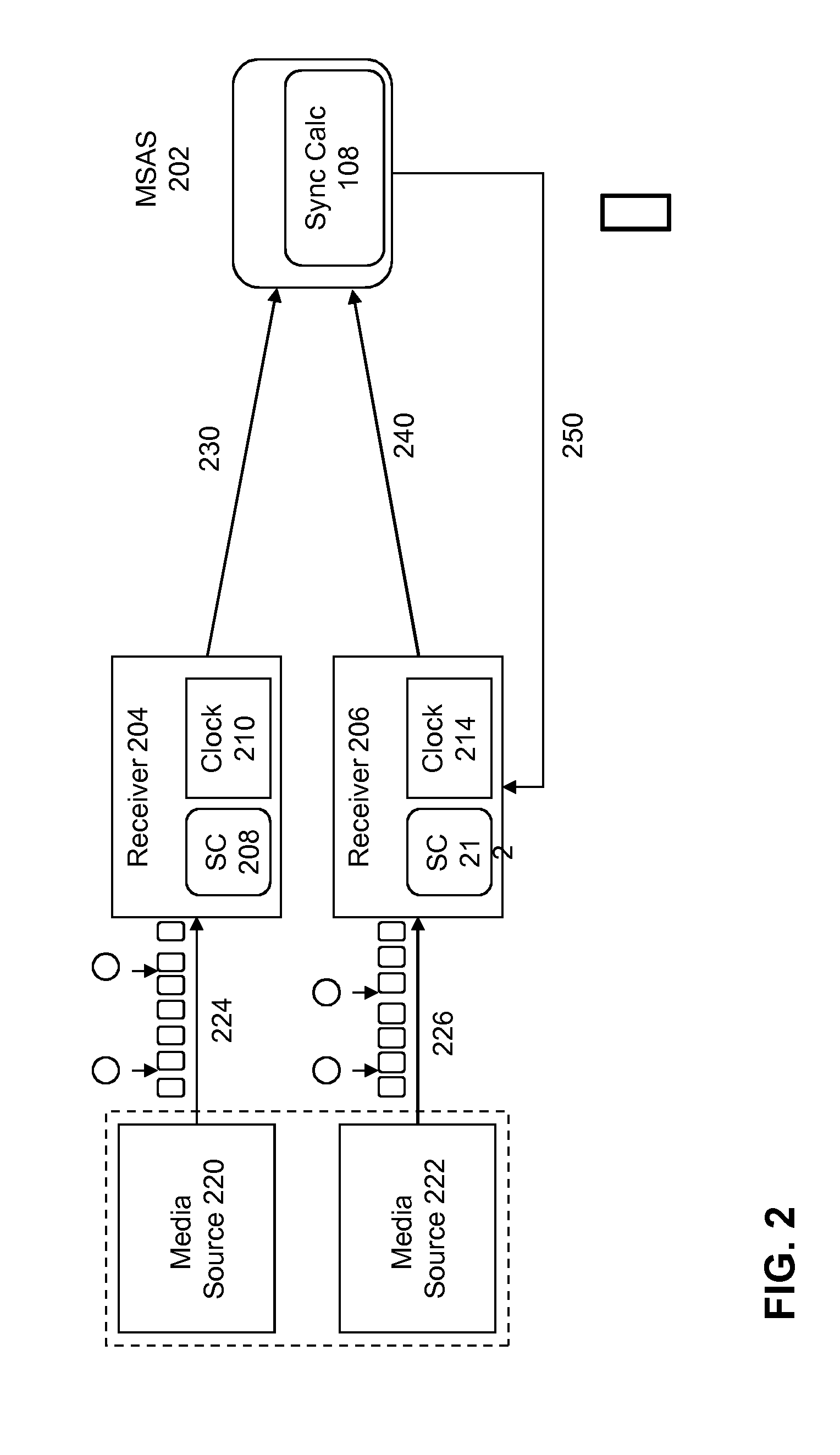

Marker-Based Inter-Destination Media Synchronization

ActiveUS20150052571A1Effective synchronizationTwo-way working systemsSelective content distributionClock timeReal-time computing

A method and a system enabling inter-destination synchronization of processing of content of at least a first and second media stream, wherein said first and second media stream are associated with one or more markers for marking one or more content parts of said first and second media streams respectively. The method comprises the steps of: detecting a first marked content part in said first media stream and a second marked content part in said second media stream, said first and second market content part being associated with a first and second marker respectively; associating first timing information, preferably comprising a first clock time, with said detected first marked content part and associating second timing information, preferably comprising a second clock time, with said detected second marked content part; determining a timing difference on the basis of said first and second timing information; and, generating on the basis of said timing difference synchronization information for enabling a first and / or second synchronization client to adjust the processing of said first and / or second media stream respectively.

Owner:KONINK KPN NV +1

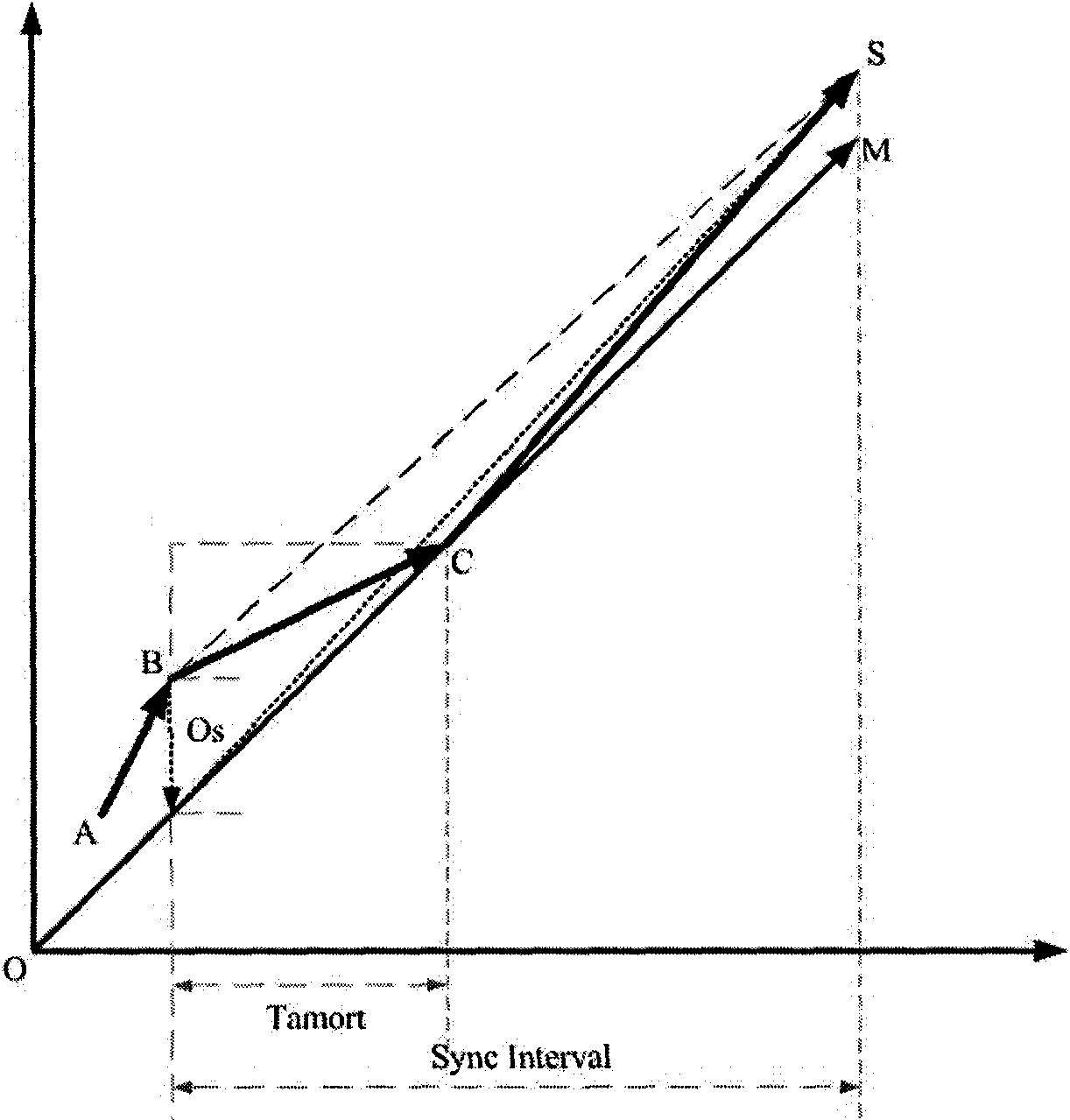

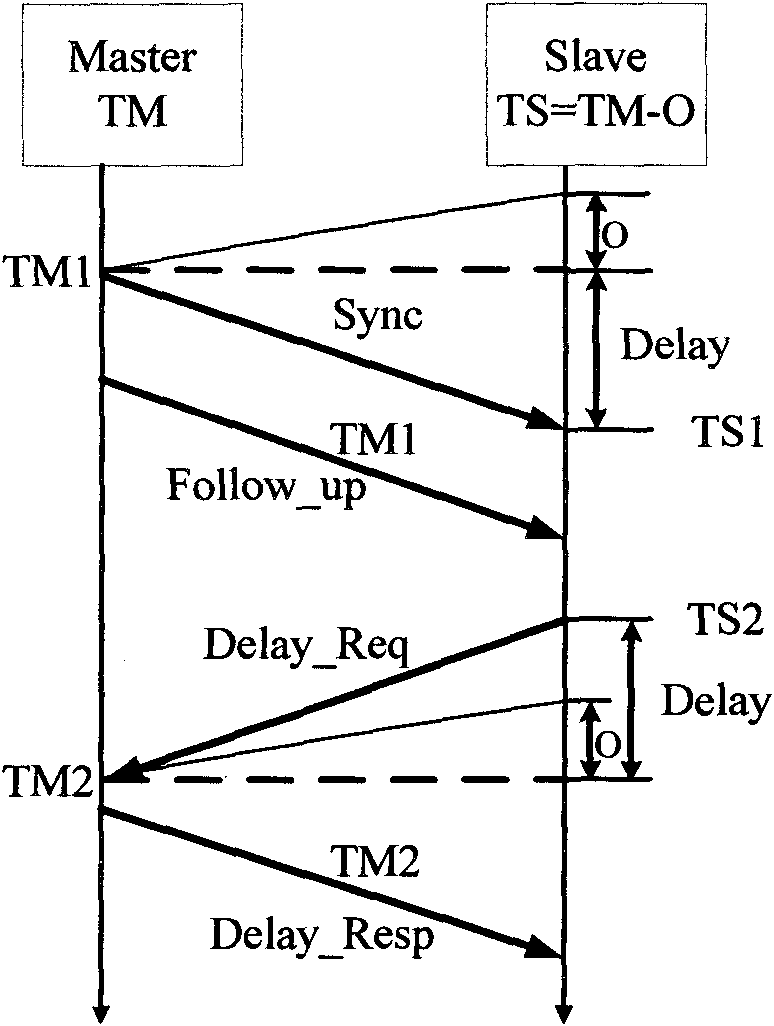

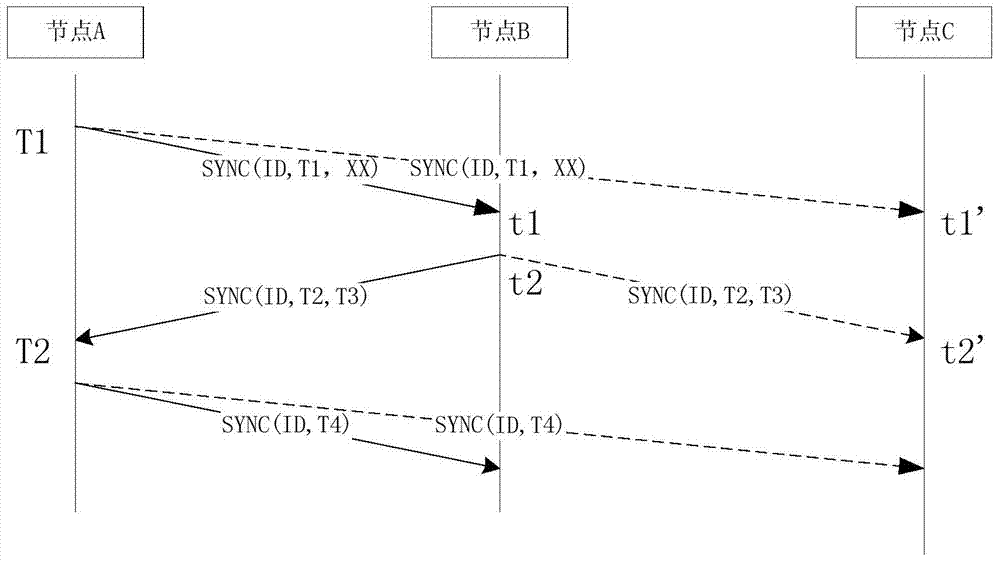

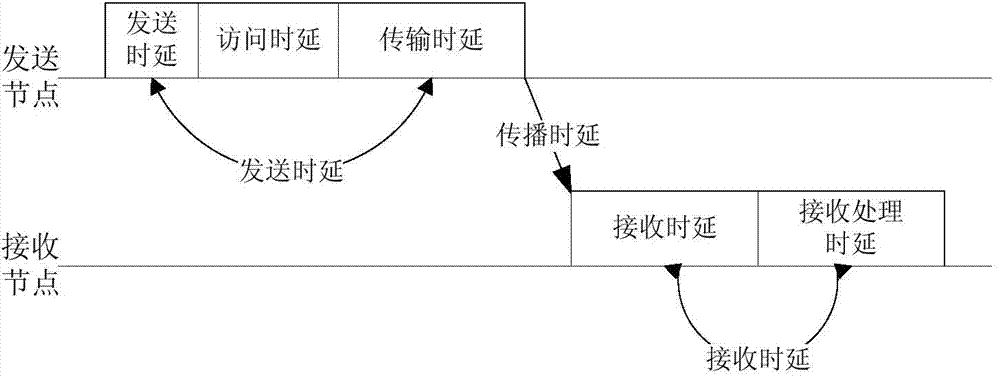

Method for realizing accurate time synchronization by utilizing IEEE1588 protocol

The invention discloses a method for realizing accurate time synchronization by utilizing an IEEE1588 protocol, comprising the following steps: a) a Sync message is transmitted to a slave clock by a master clock, a transmission timestamp TM1 and a receiving timestamp TS1 of the message are acquired by the slave clock; b) a Delay_Req message is transmitted to the master clock by the slave clock, and a transmission timestamp TM2 and a receiving timestamp TS2 of the message are acquired by the slave clock; c) transmission delay and time offset are calculated by the slave clock according to the timestamp; and d) the calculated Offset is corrected in a fixed adjustment frequency in the correction time by the slave clock. The invention realizes accurate time synchronization, calculates time offset and self-compensate through the slave time clock in a packet based network, and leads the slave clock to lock the master clock whether in clock frequency or on the clock time in a shorter time, and occupies little hardware resources.

Owner:ZHEJIANG UNIV

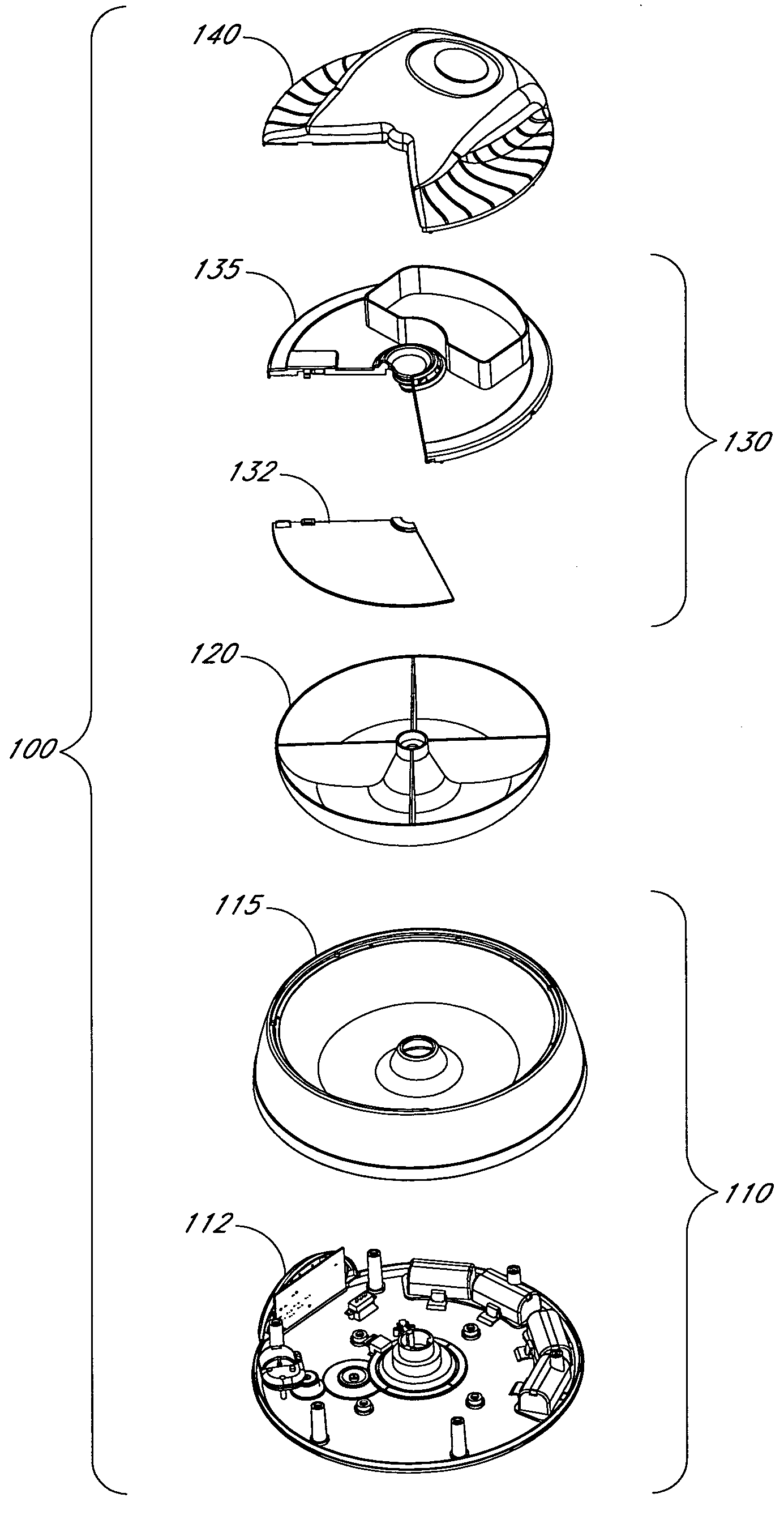

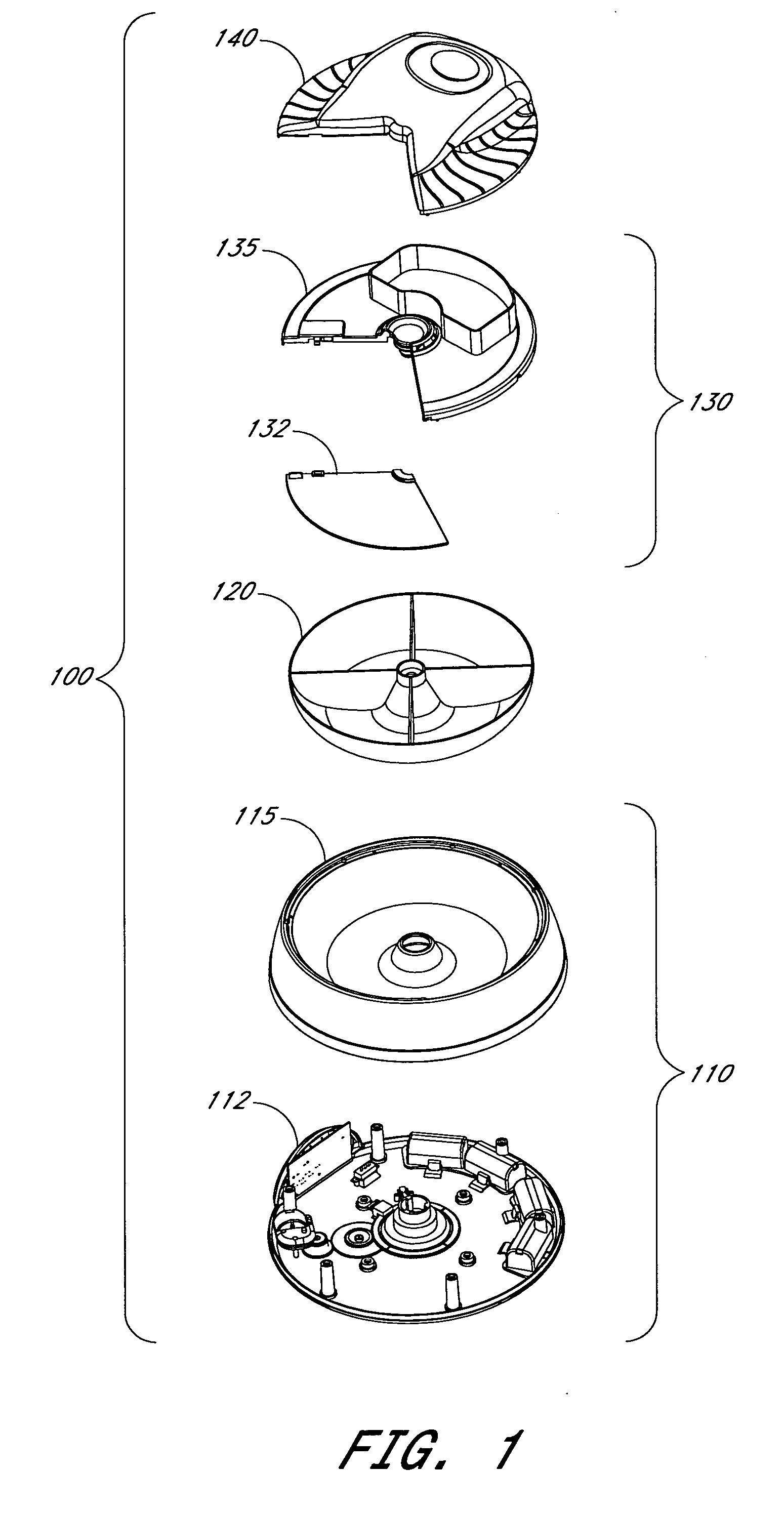

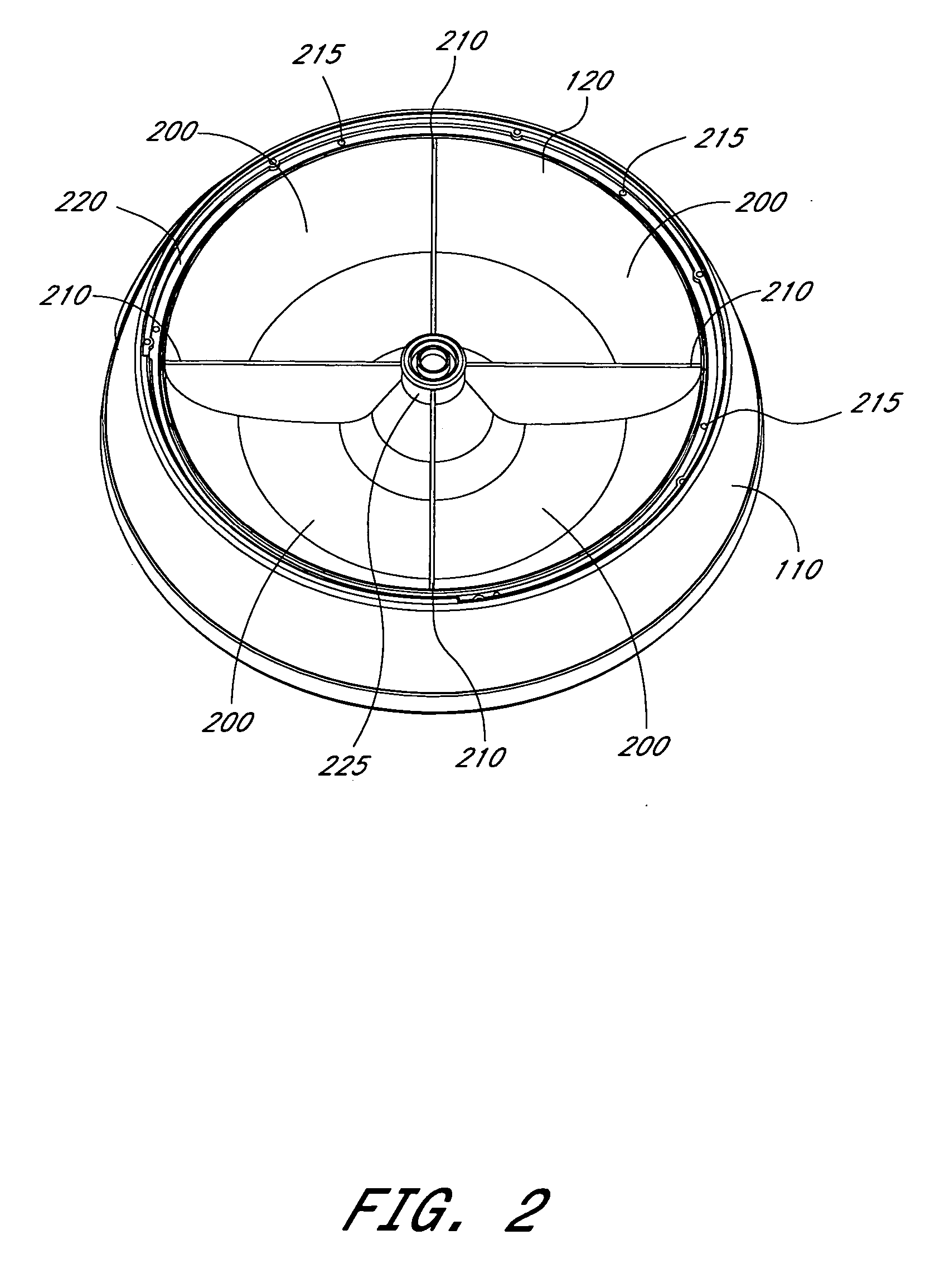

Automated pet feeder

InactiveUS20050066905A1Reduce needOptimize locationAnimal feeding devicesAnimal housingClock timeReady to use

An automated pet feeder is described that allows portions of pet food to be placed into cavities in a rotatable food bowl and to be made accessible to a pet at predetermined feeding times. A lid with an opening for exposing one of the cavities is positioned above the bowl. A base unit that supports the bowl is configured to rotate the bowl while the lid remains stationary and to monitor the position of the bowl. A timing mechanism controls rotation of the bowl and sequentially positions a next cavity under the opening at feeding times that may be set to occur at various time intervals or clock times that may be pre-programmed by a user. A sound system allows a user to record a voice or other sound recording that may be played at feeding times. In some embodiments, a reservoir may hold ice or an ice pack or other cooling material or apparatus to help keep the pet food fresh until it is made accessible, or the reservoir may be used to hold drinking water. Inserts may be used that are configured to fit into the cavities allow for the convenient use of disposable pet food packs and greatly reduce the need for washing the food bowl after use.

Owner:MOROSIN ROSE CHAN +1

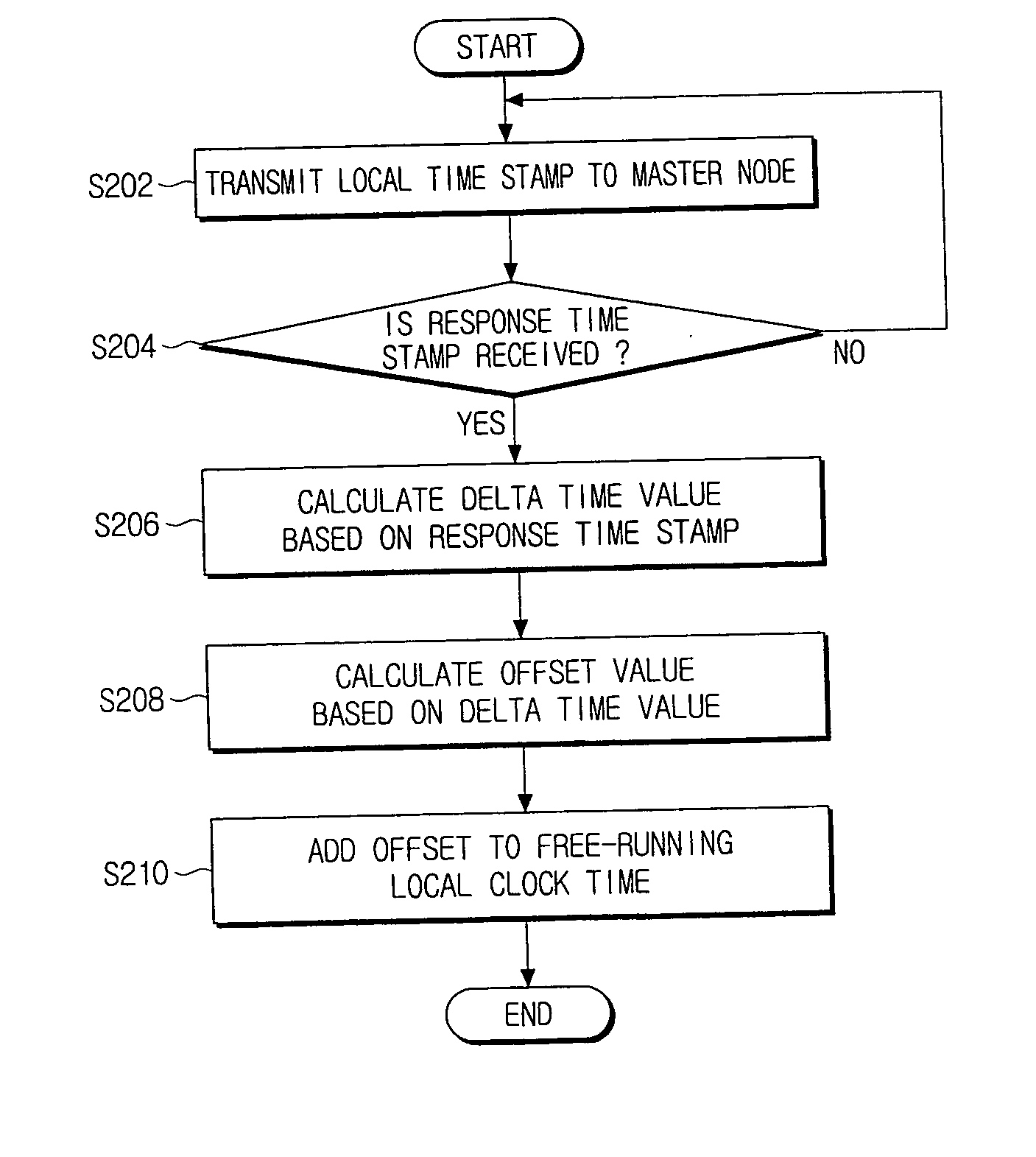

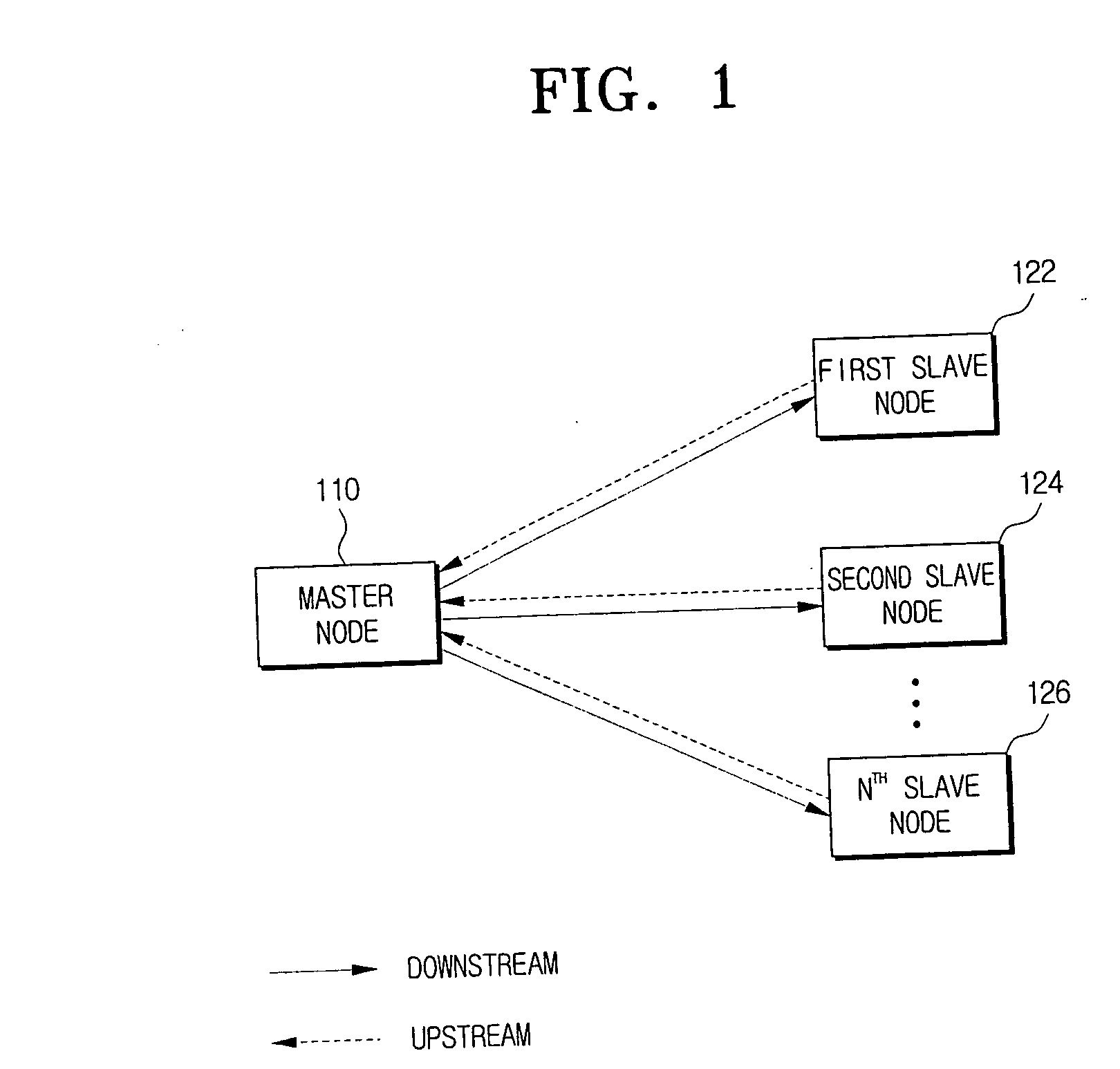

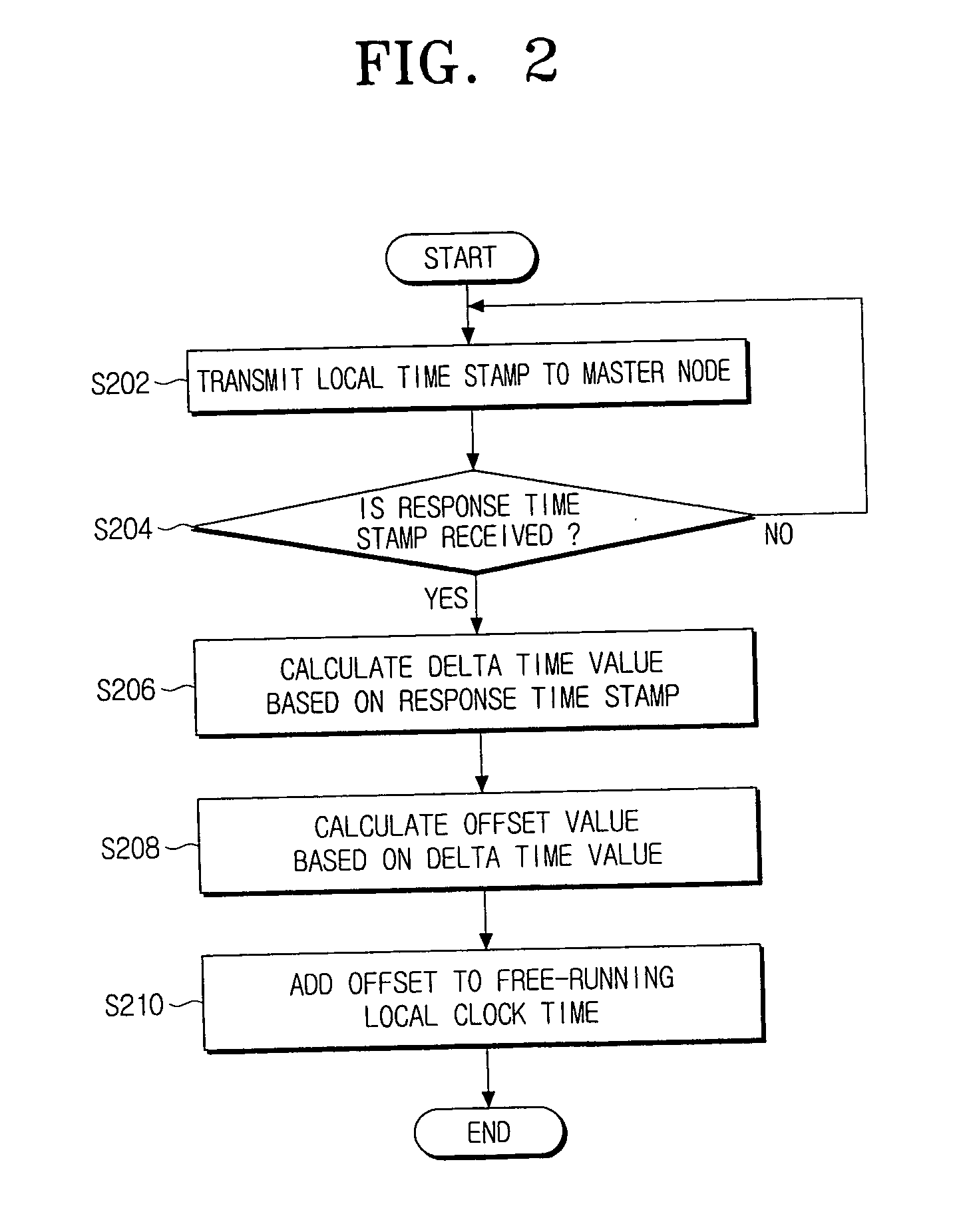

Time synchronizing method and apparatus based on time stamp

InactiveUS20070025481A1Shorten the timeIncrease blockingTime-division multiplexSynchronising arrangementClock timeClock rate

Provided are a time synchronizing method and apparatus based on a time stamp. The time synchronizing method includes: transmitting a local time stamp based on a free-running local clock to a master node; receiving a response time stamp from the master node; calculating a delta time value based on the response time stamp; filtering the delta-time using a digital low pass filter running at the free-running local clock rate; and adjusting a local clock time based on the filtered delta time value.

Owner:SAMSUNG ELECTRONICS CO LTD

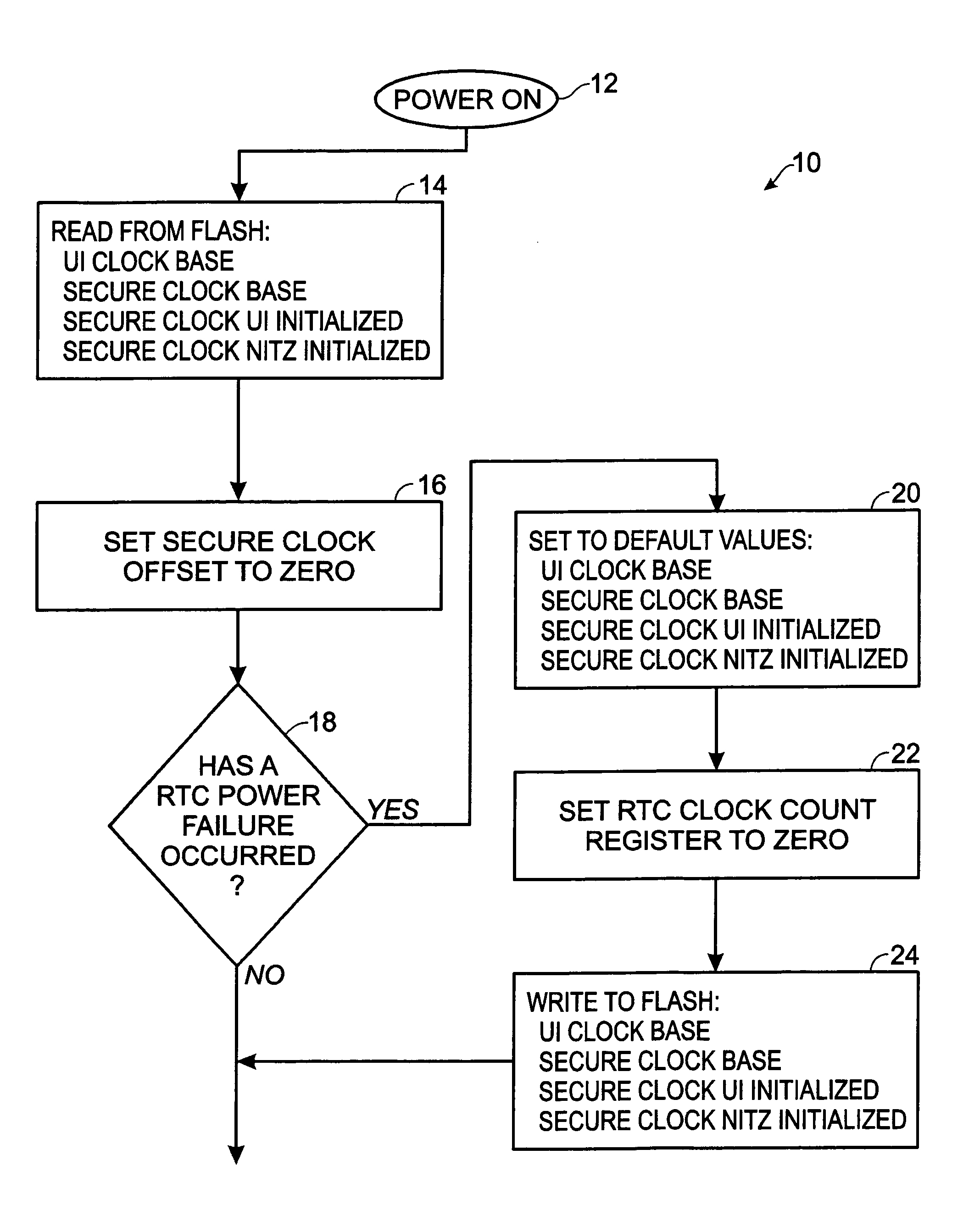

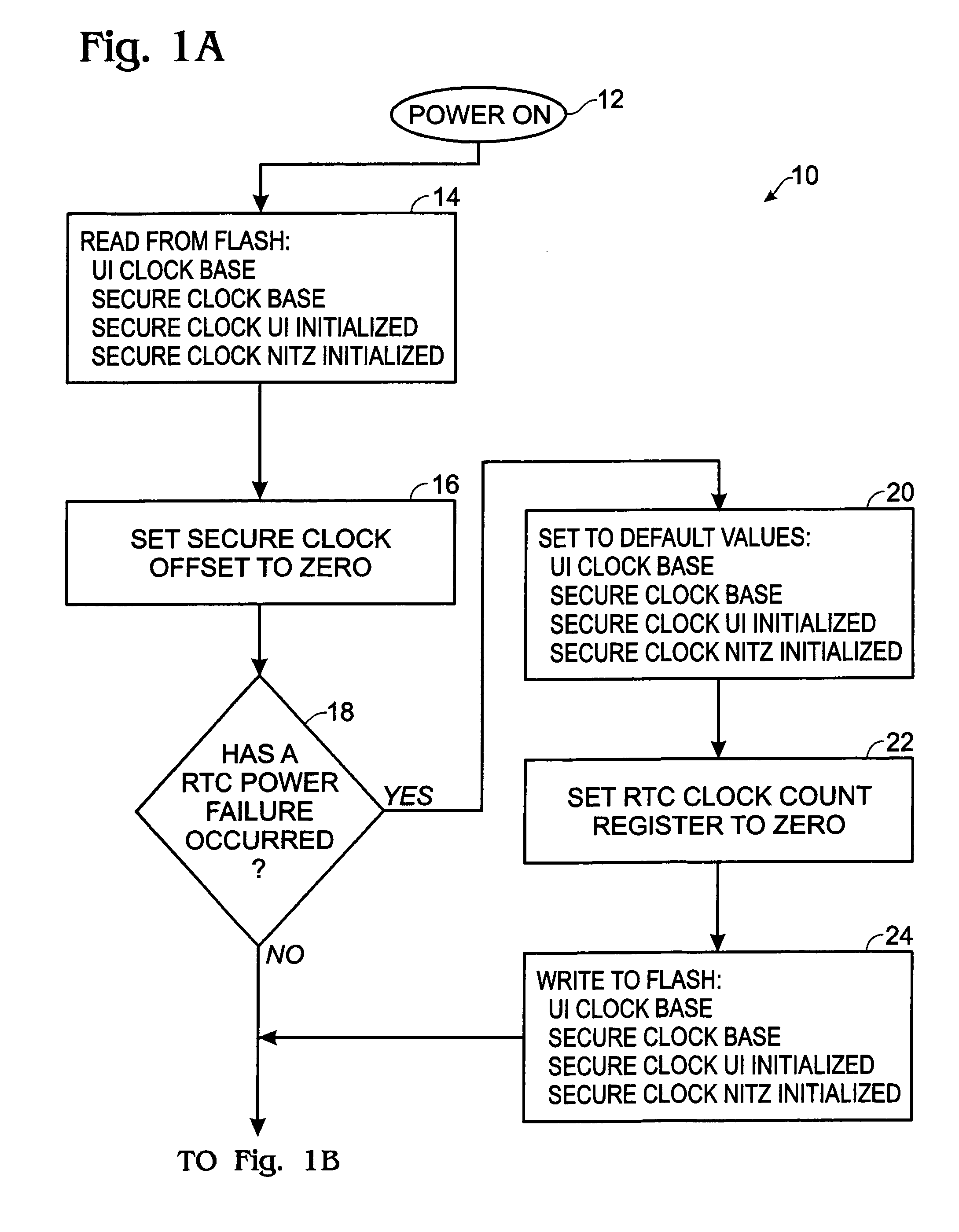

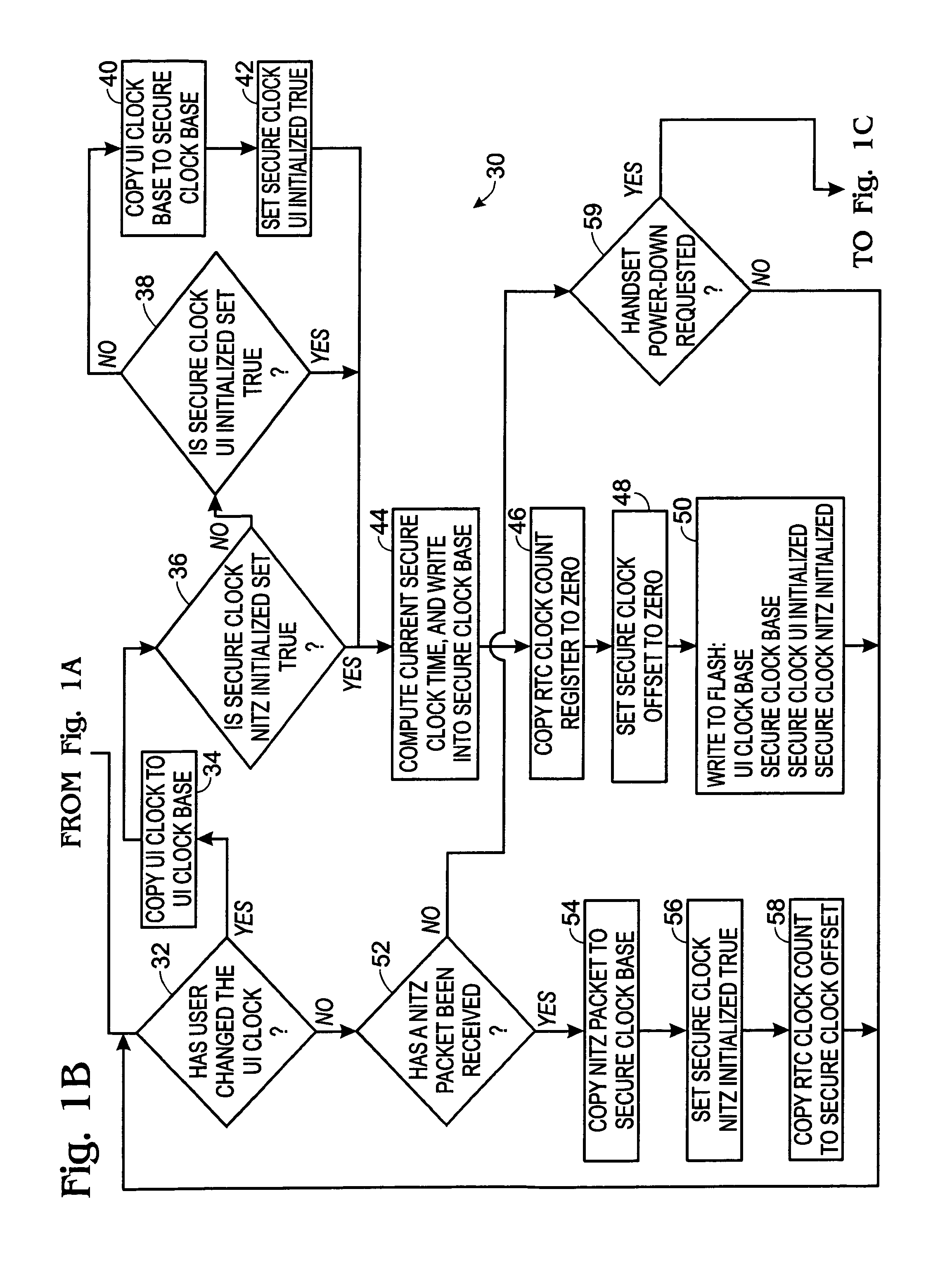

Wireless device having a secure clock authentication method and apparatus

ActiveUS7116969B2Cannot be arbitrarily altered by a userUnauthorised/fraudulent call preventionEavesdropping prevention circuitsClock timeCommunications system

Owner:SHARP KK

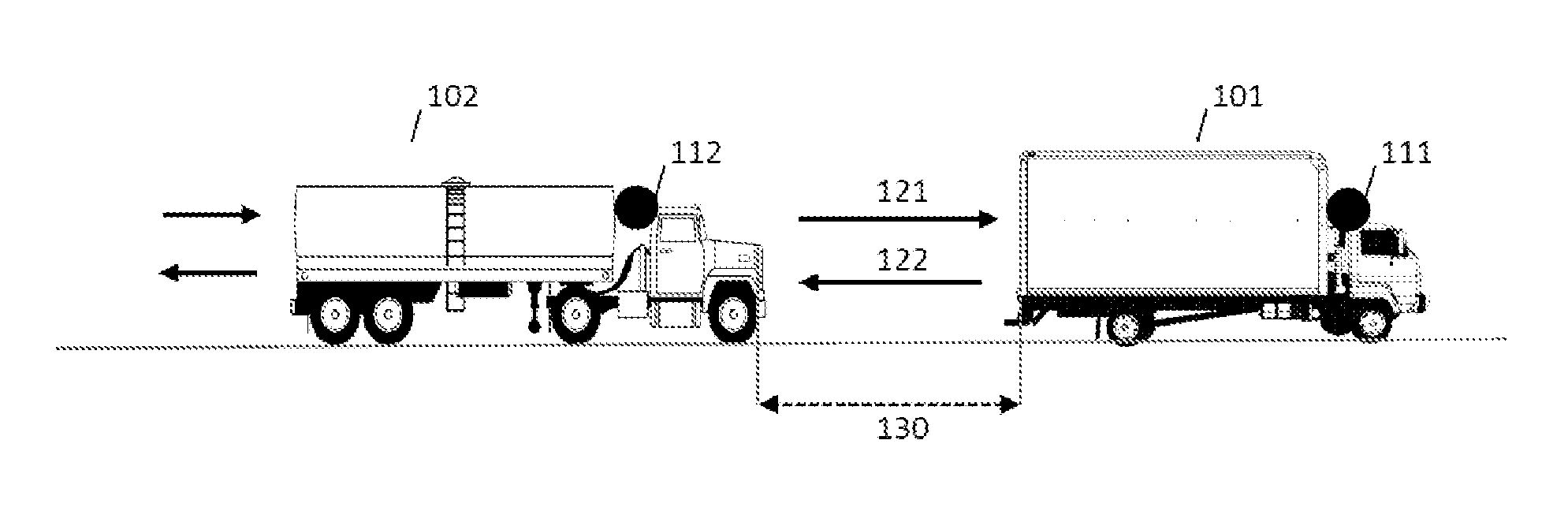

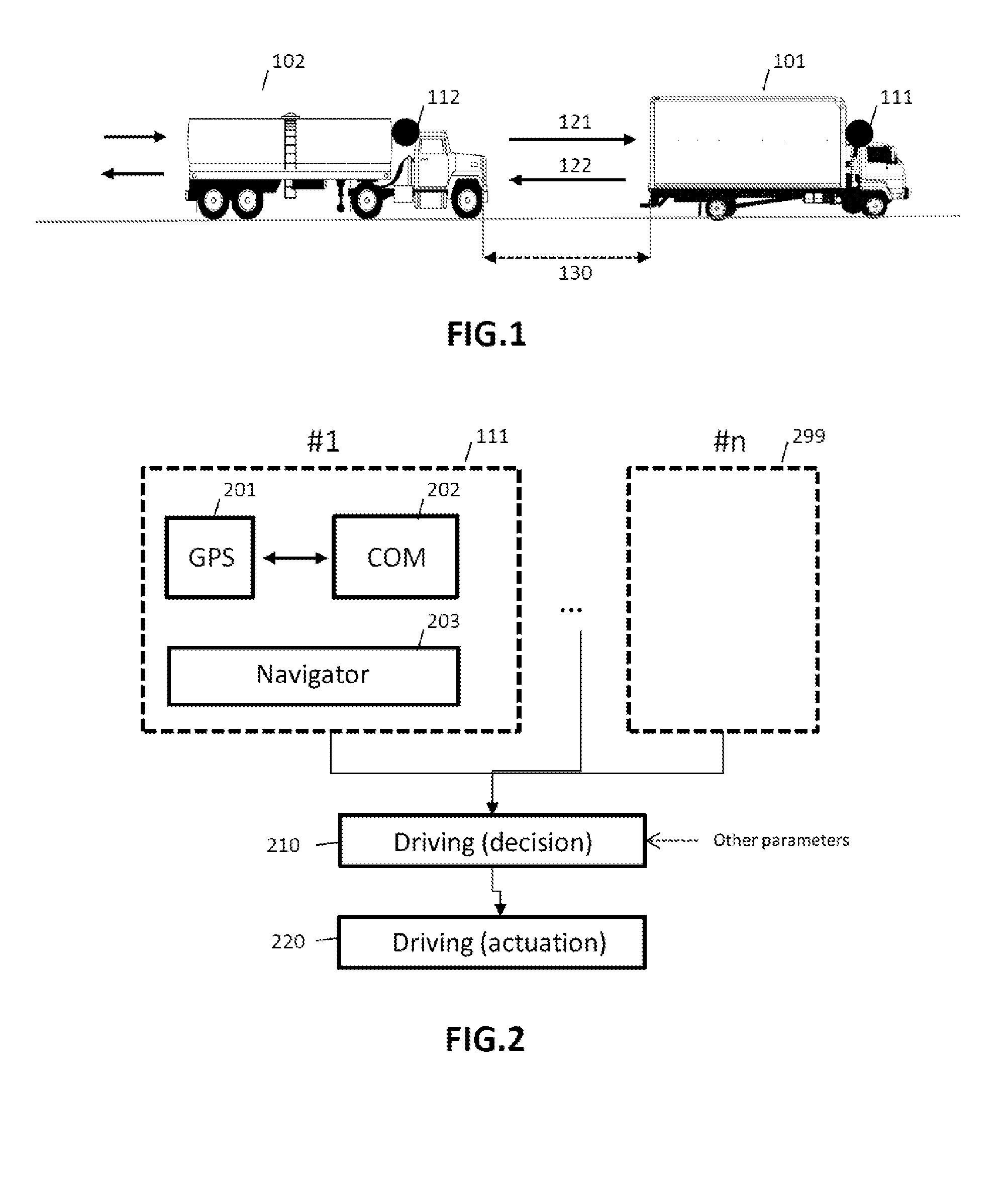

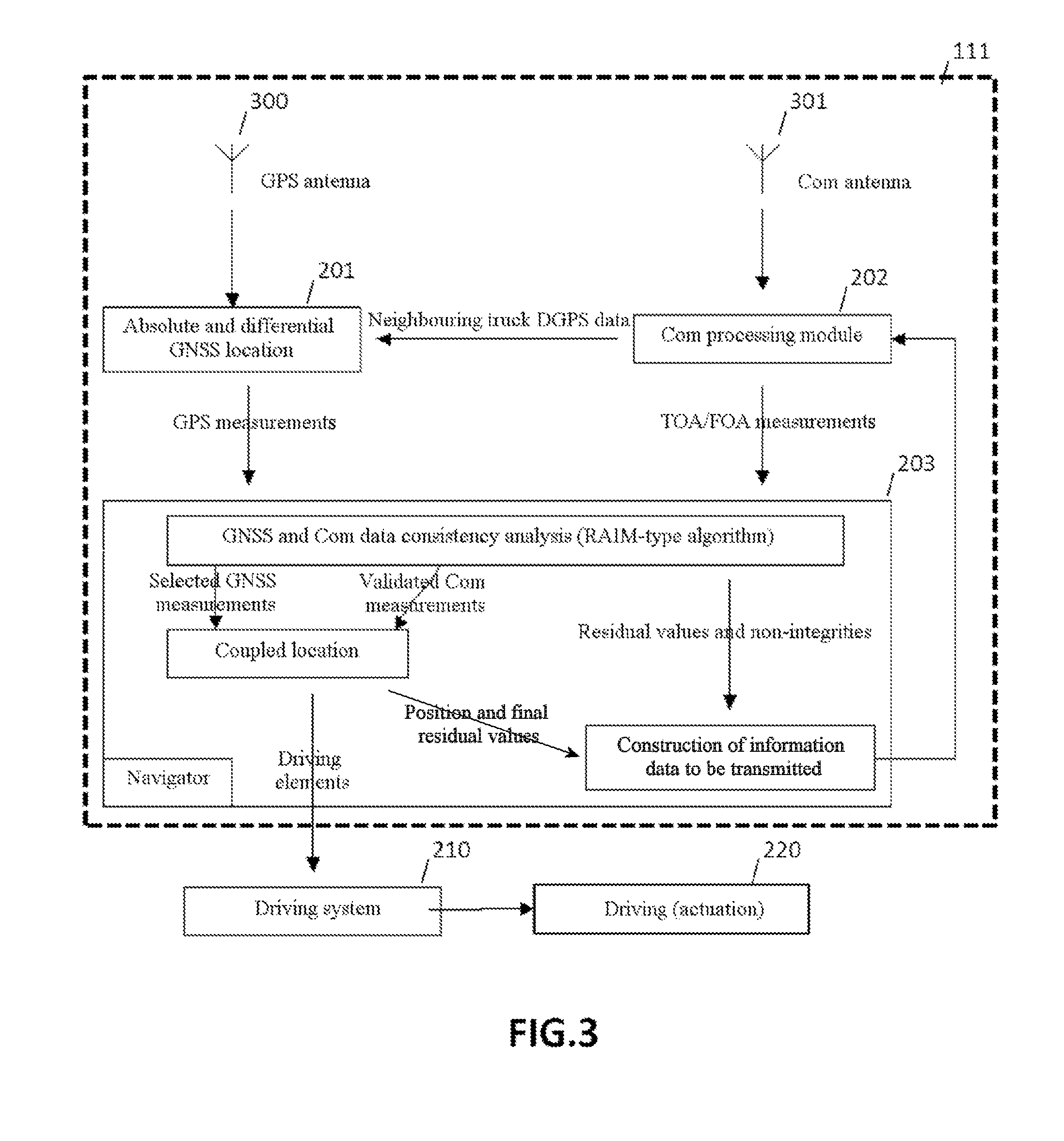

Driving vehicles in convoy

ActiveUS20150269845A1Good propagation time measurement qualityExternal condition input parametersSatellite radio beaconingEngineeringSignal-to-quantization-noise ratio

A method is implemented by computer for the management of a convoy comprising at least two vehicles, each of the at least two vehicles comprising satellite positioning means and vehicle-to-vehicle communication means, the method comprising the determination of the relative positioning of the vehicles, the determination comprising the measurement of the propagation time of a signal between vehicles by the communication means, the clocks associated with the communication means being synchronized via satellite positioning means at a reference clock time. Developments comprise the communication between the vehicles of various data (e.g. measurement uncertainties, signal-to-noise ratios, residual values), the determination of absolute locations, the use of an SBAS-type system, the use of differential GPS, the use of Doppler measurements for the turns or even the exclusion of a failing satellite. A computer program product and associated systems are described.

Owner:THALES SA

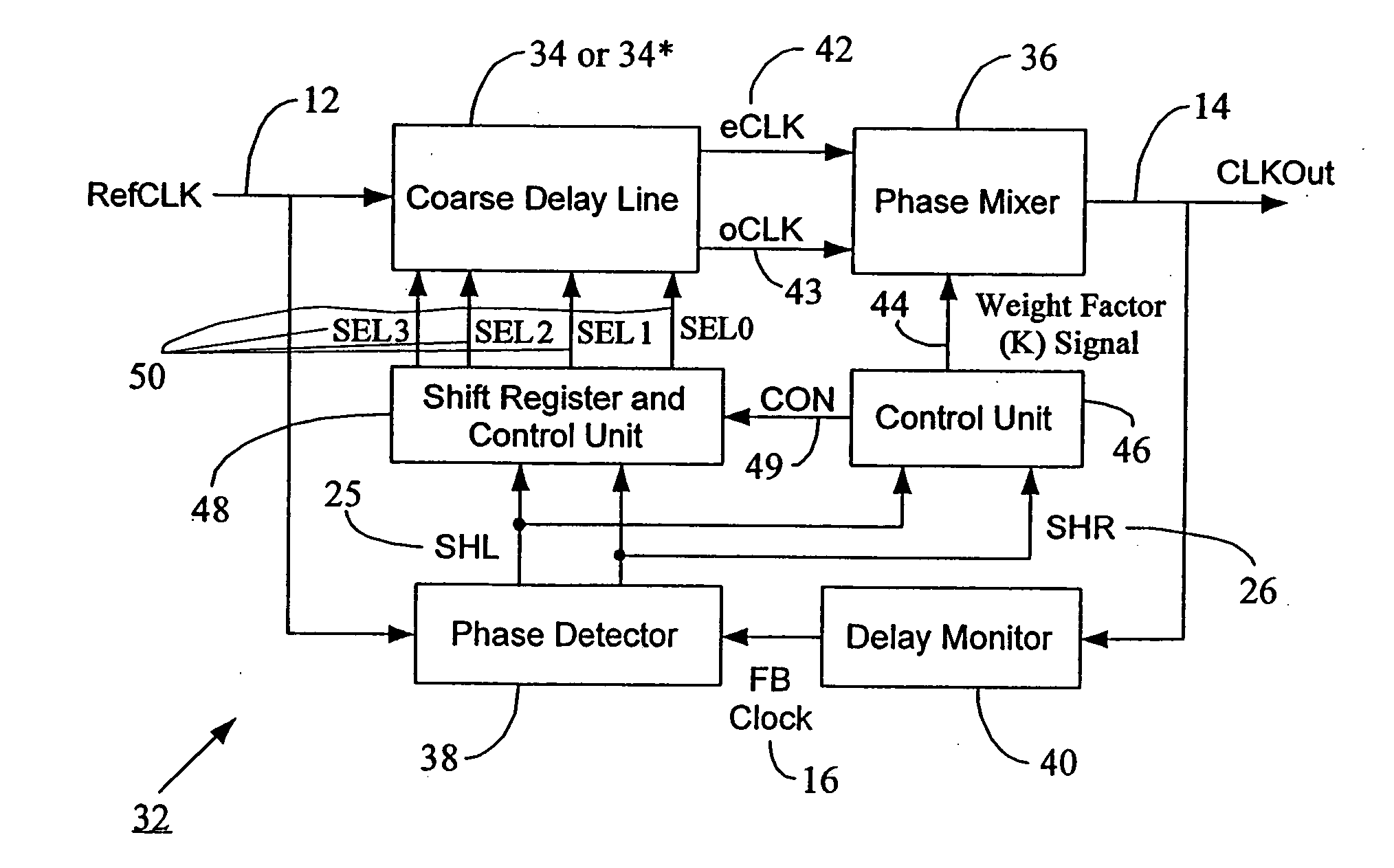

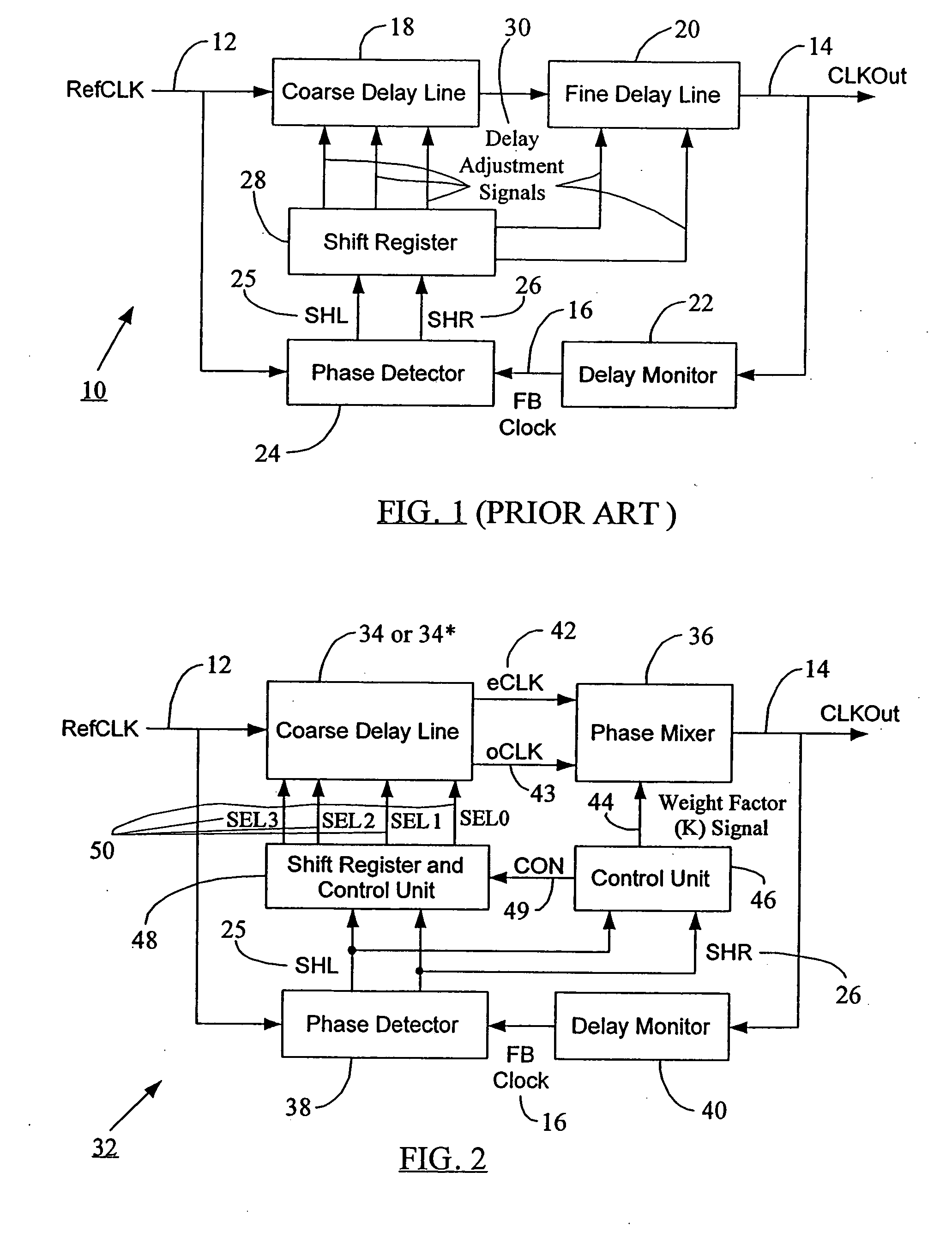

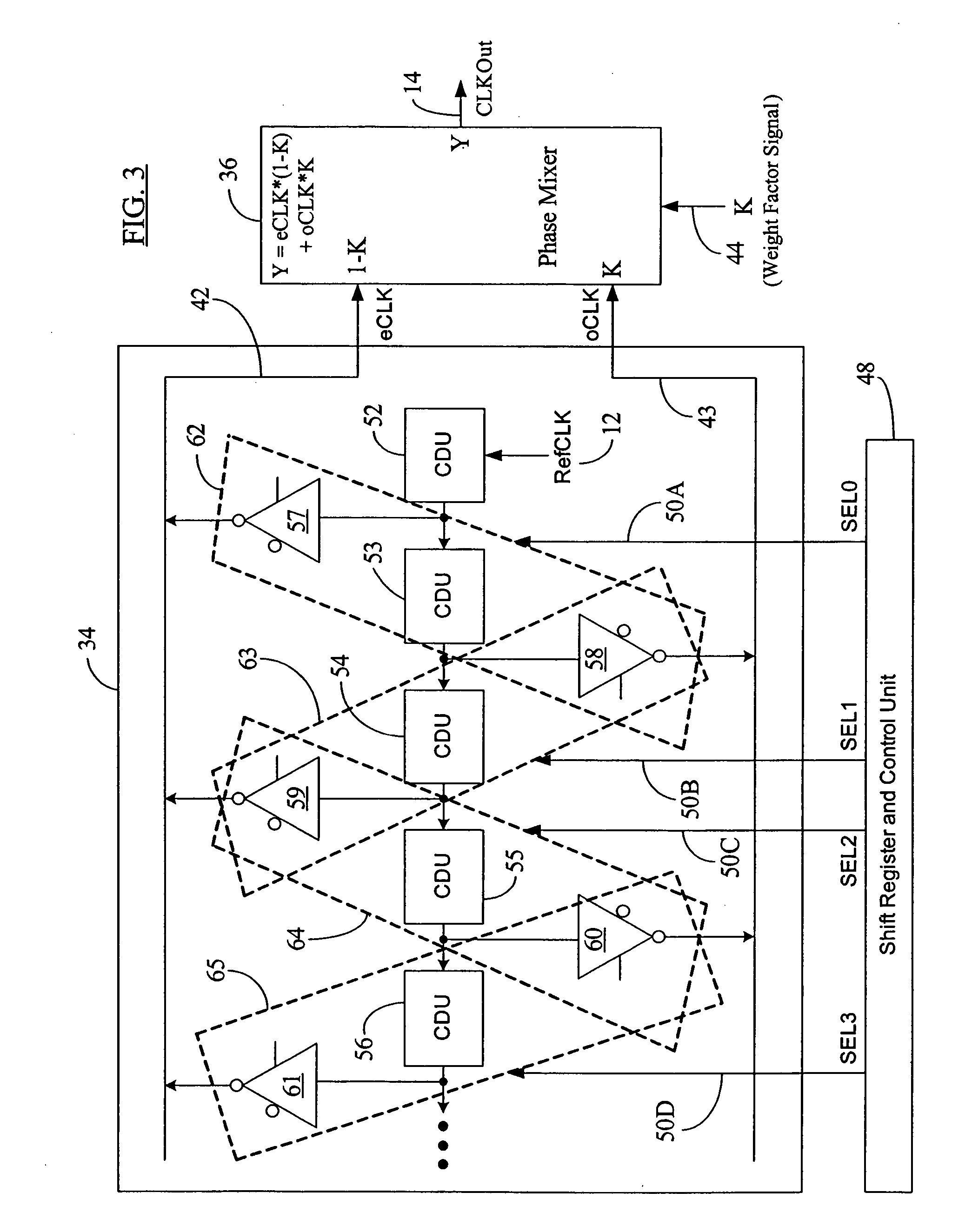

Seamless coarse and fine delay structure for high performance DLL

ActiveUS20070030753A1Smooth phase transitionDelay problemPulse automatic controlCounting chain pulse countersClock timePhase difference

A clock synchronization system and method avoids output clock jitter at high frequencies and also achieves a smooth phase transition at the boundary of the coarse and fine delays. The system may use a single coarse delay line configured to generate two intermediate clocks from the input reference clock and having a fixed phase difference therebetween. The coarse delay line may have a hierarchical or a non-hierarchical structure. A phase mixer receives these two intermediate clocks and generates the final output clock having a phase between the phases of the intermediate clocks. The coarse shifting in the delay line at high clock frequencies does not affect the phase relationship between the intermediate clocks fed into the phase mixer. The output clock from the phase mixer is time synchronized with the input reference clock and does not exhibit any jitter or noise even at high clock frequency inputs. Because of the rules governing abstracts, this abstract should not be used to construe the claims.

Owner:MICRON TECH INC

Synchronization of a split audio, video, or other data stream with separate sinks

Owner:AVAGO TECH INT SALES PTE LTD

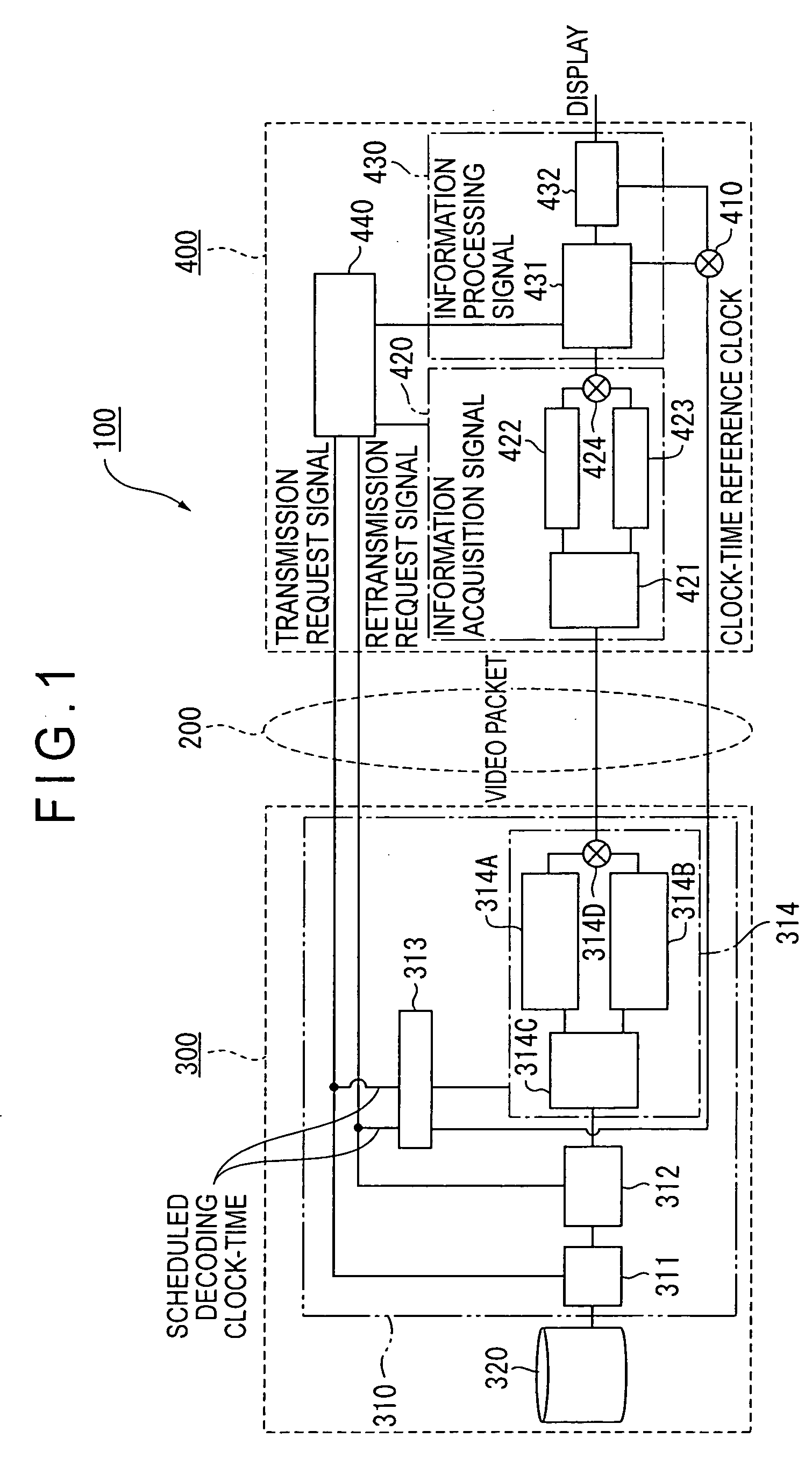

Information processing device, its system, its method, its program, and recording medium storing the program

InactiveUS20050050424A1Receive information efficientlyTransmit information efficientlyError prevention/detection by using return channelTransmission systemsTemporal informationClock time

In a server unit (300), a clock-time comparator (313) acquires the scheduled decoding clock-time information for decoding a video packet and RTT for transferring the video packet to a client unit (400) via a network and computes the time necessary for retransmitting the video packet on the basis of RTT. If the clock-time comparator (313) determines that it cannot meet the scheduled decoding clock-time information when the video packet is retransmitted, a processing unit (314) adds an error correction code to the video packet and transmits it. If, on the other hand, the clock-time comparator (313) determines that it can meet the scheduled decoding clock-time information, the processing unit (314) adds an error detection code to the video packet and transmits it. Thus, either way can be selected depending on the status of transmission and hence it is possible to reduce the load of transmitting video data in order to output video data on a stable basis and improve the processing efficiency.

Owner:PIONEER CORP

GPS receiver using stored navigation data bits for a fast determination of GPS clock time

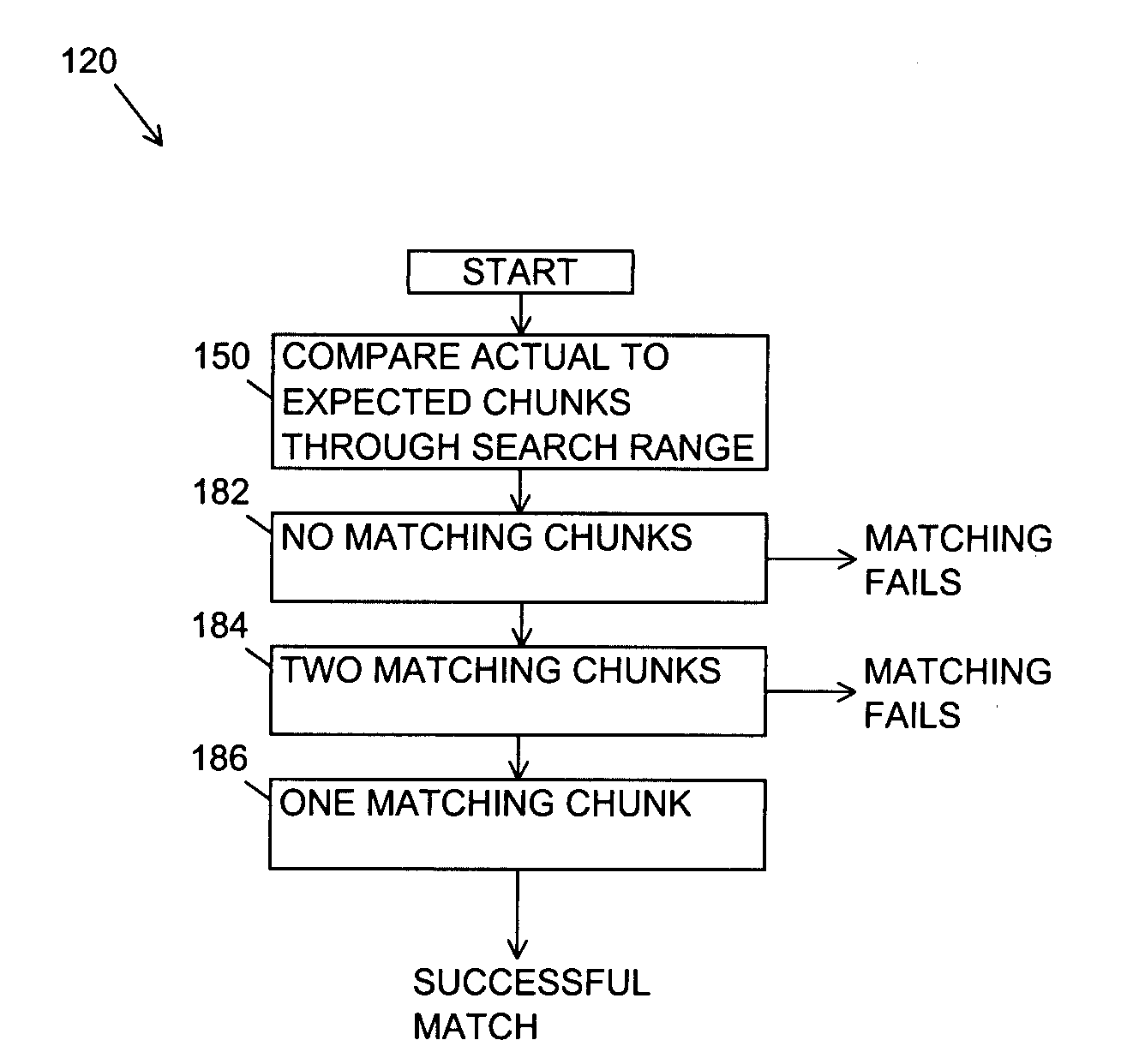

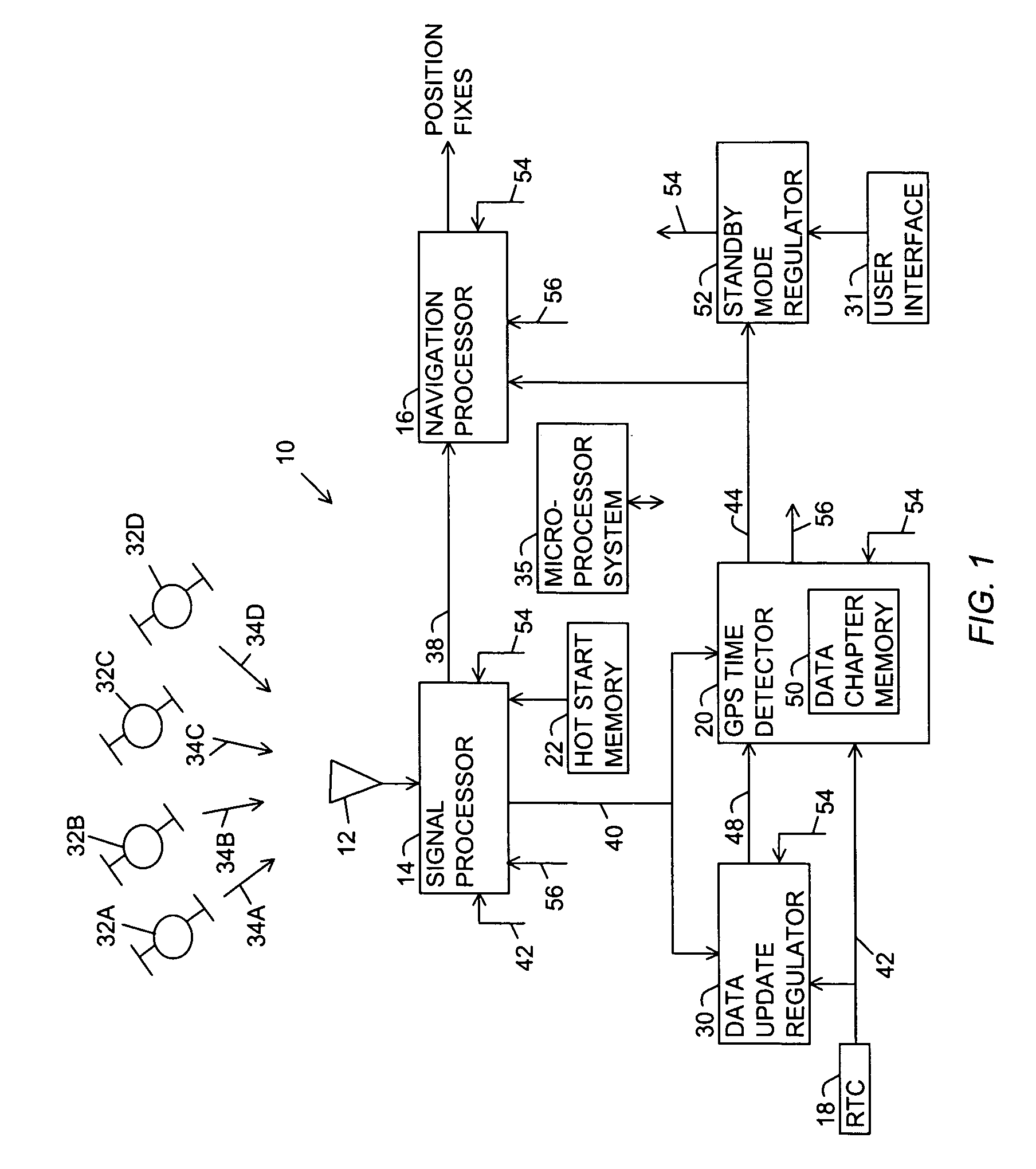

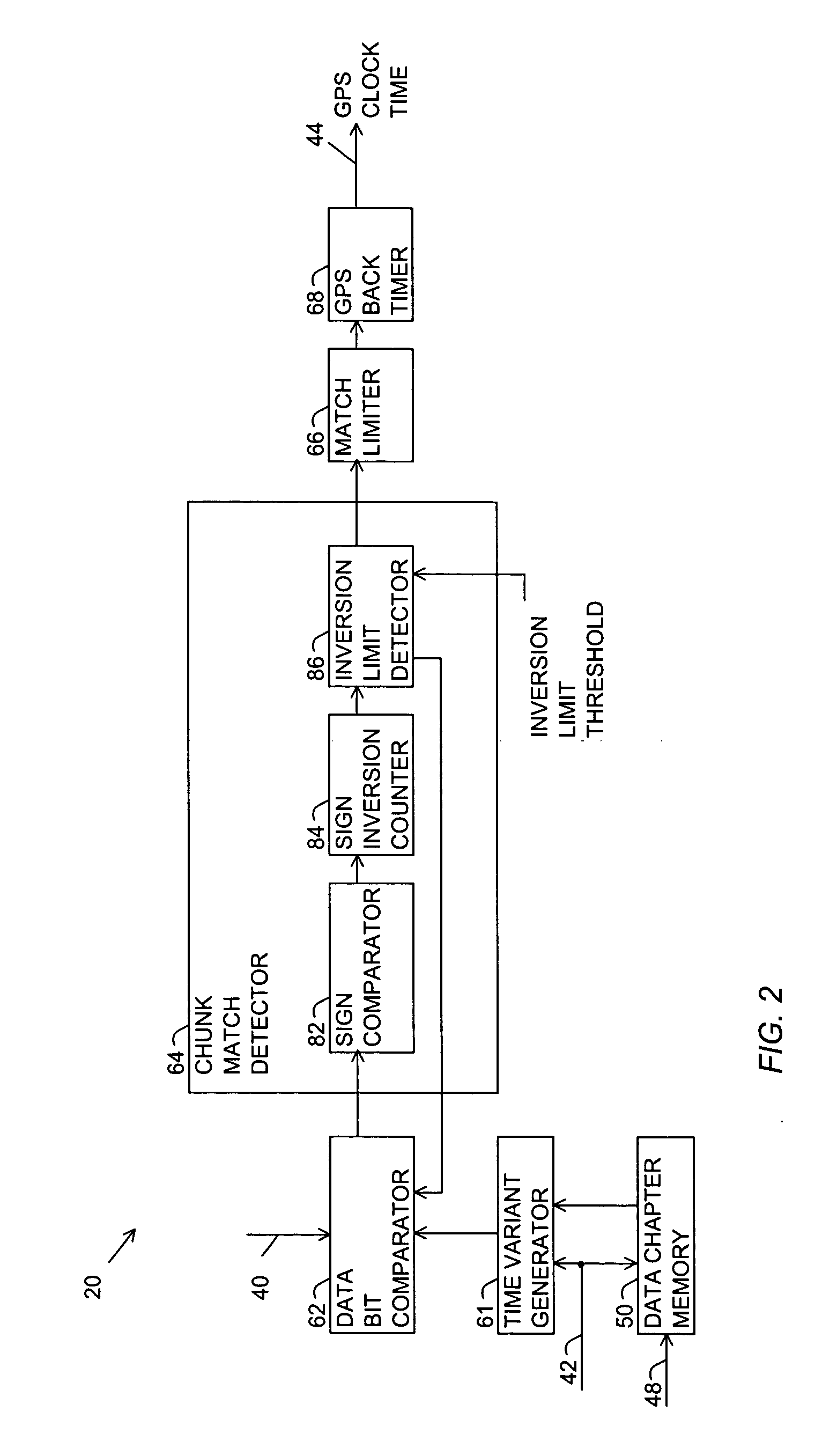

ActiveUS20070063894A1Fast time to fixFast time to lowPosition fixationSatellite radio beaconingOperation modeEntry time

A GPS receiver having a fast method for determining GPS clock time. The GPS receiver includes a signal processor for receiving GPS signals from GPS satellites and detecting current GPS data bits carried by the respective GPS signals, a chapter memory for storing a block of expected GPS data bits for the respective GPS satellites, and a GPS time detector for detecting a successful match when a chunk of the expected data bits within a selected search range within the block matches a chunk of the current data bits, and using the successful match for determining the GPS clock time. In an anytime embodiment the GPS receiver enters an operation mode at any time in order to minimize user request latency. In a focused embodiment the GPS receiver enters the operation mode at a prescribed time-of-entry in order to minimize power consumption for cycles of standby and operation modes.

Owner:TRIMBLE NAVIGATION LTD

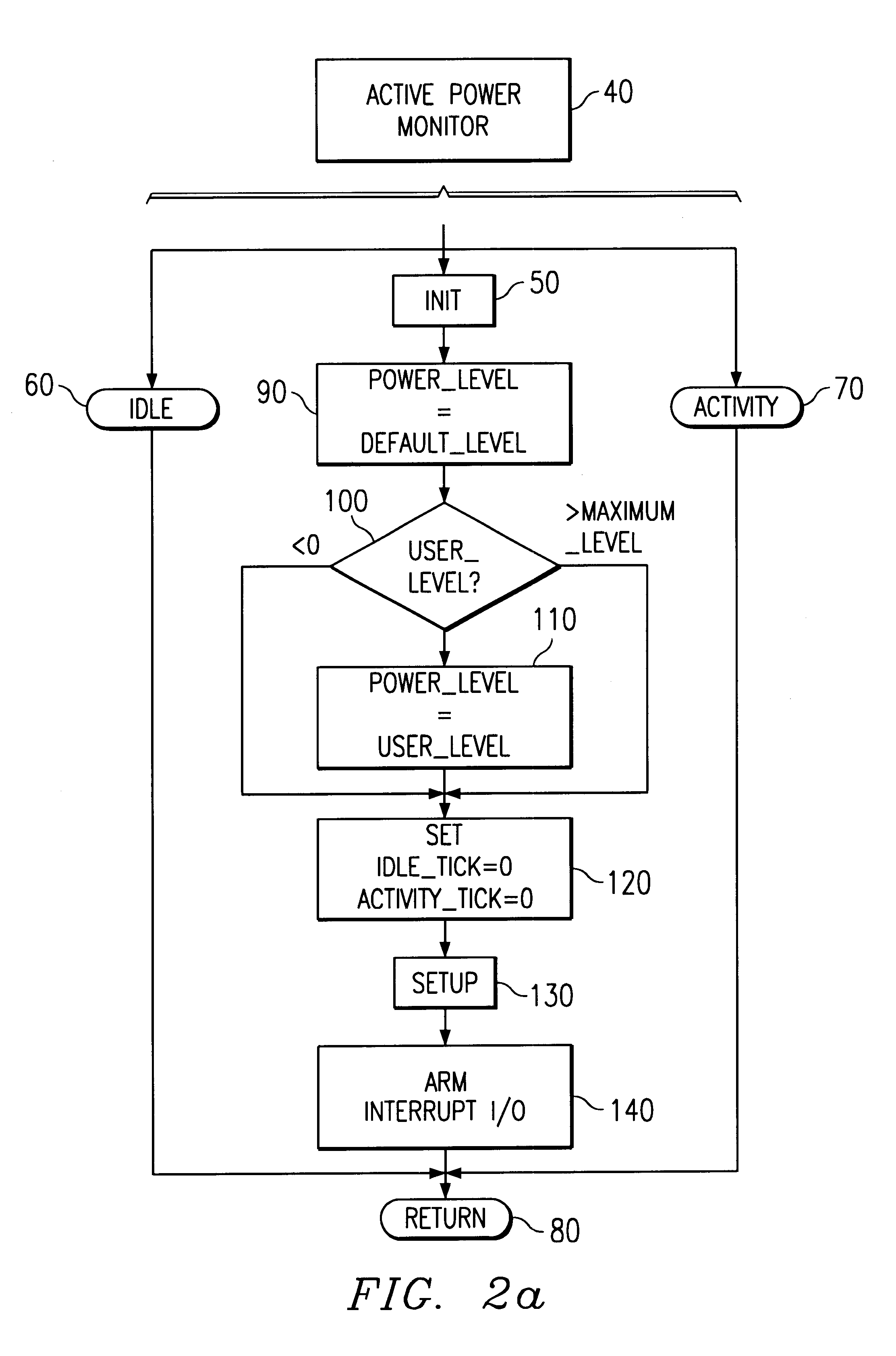

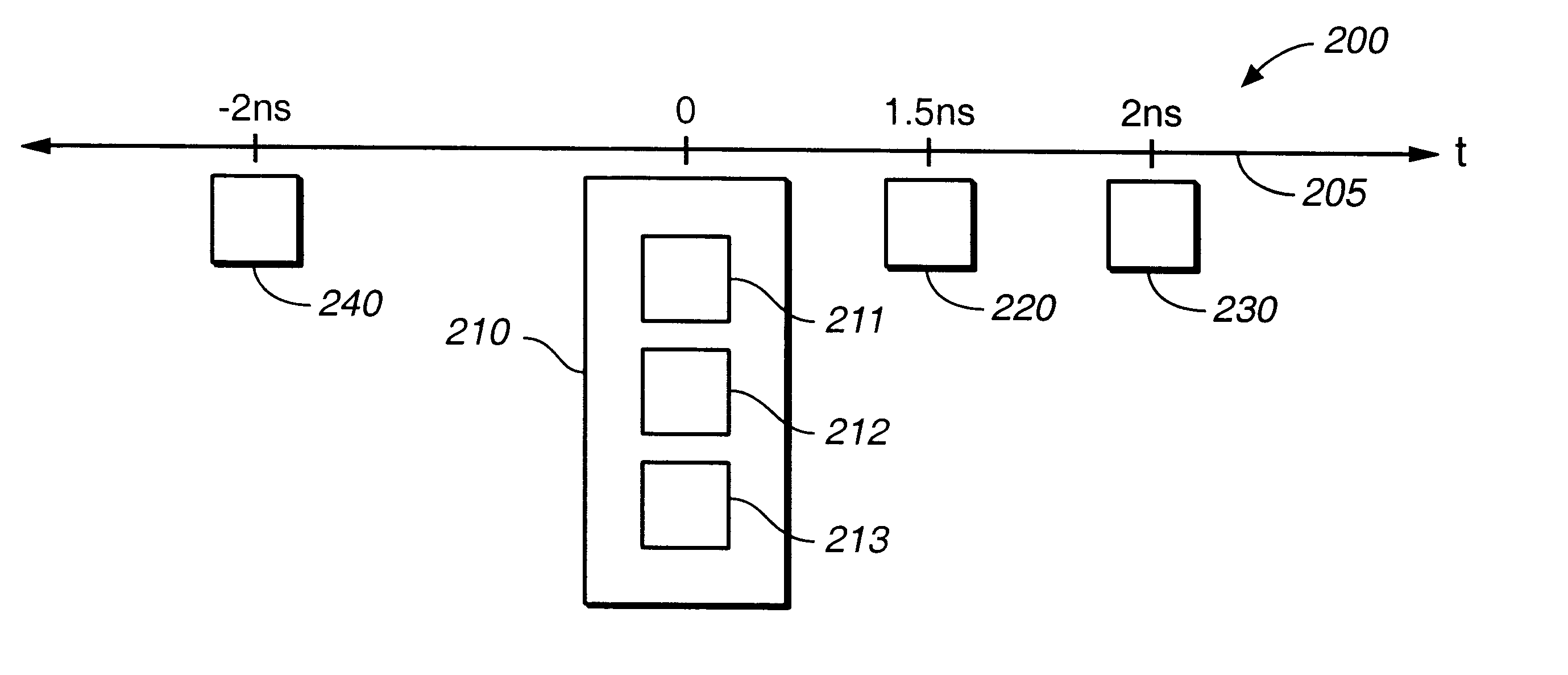

Processor having real-time power conservation and thermal management

InactiveUS6901524B2Reduce power consumptionWithout perceived performanceThermometer detailsEnergy efficient ICTClock timeApplication software

A real-time power conservation and thermal management apparatus and method for portable computers employs a monitor (40) to determine whether a CPU may rest based upon a real-time sample of the CPU activity and temperature levels and to activate a hardware selector(500, 510, 520, 530) to carry out the monitor's determination. If the monitor determines the CPU may rest, the hardware selector reduces CPU clock time (280); if the CPU is to be active, the hardware selector returns the CPU to its previous high speed clock level (330). Switching back into full operation from its rest state occurs without a user having to request it and without any delay in the operation of the computer while waiting for the computer to return to a “ready” state. Furthermore, the monitor adjusts the performance level of the computer to manage power conservation and thermal management in response to the real-time sampling of CPU activity (10) and temperature (24). Such adjustments are accomplished within the CPU cycles and do not affect the user's perception of performance and do not affect any system application software executing on the computer.

Owner:TEXAS INSTR INC

Real-time thermal management for computers

A real-time thermal management apparatus and method for a computer employs a monitor (40) to determine whether a CPU may rest based upon real-time sampling of temperature levels and CPU activity levels within the computer. The monitor activates a hardware selector to carry out the monitor's determination. If the monitor determines the CPU may rest, the hardware selector reduces CPU clock time; if the CPU is to be active, the hardware selector returns the CPU to its previous high speed clock level. Switching back into full operation from its rest state occurs without a user having to request it and without any delay in the operation of the computer while waiting for the computer to return to a “ready” state. Furthermore, the monitor (40) adjusts the performance level of the computer in response to the real-time sampling of CPU activity and temperature levels. Such adjustments are accomplished within the CPU cycles and do not affect the user's perception of performance and do not affect any system application software executing on the computer.

Owner:TEXAS INSTR INC

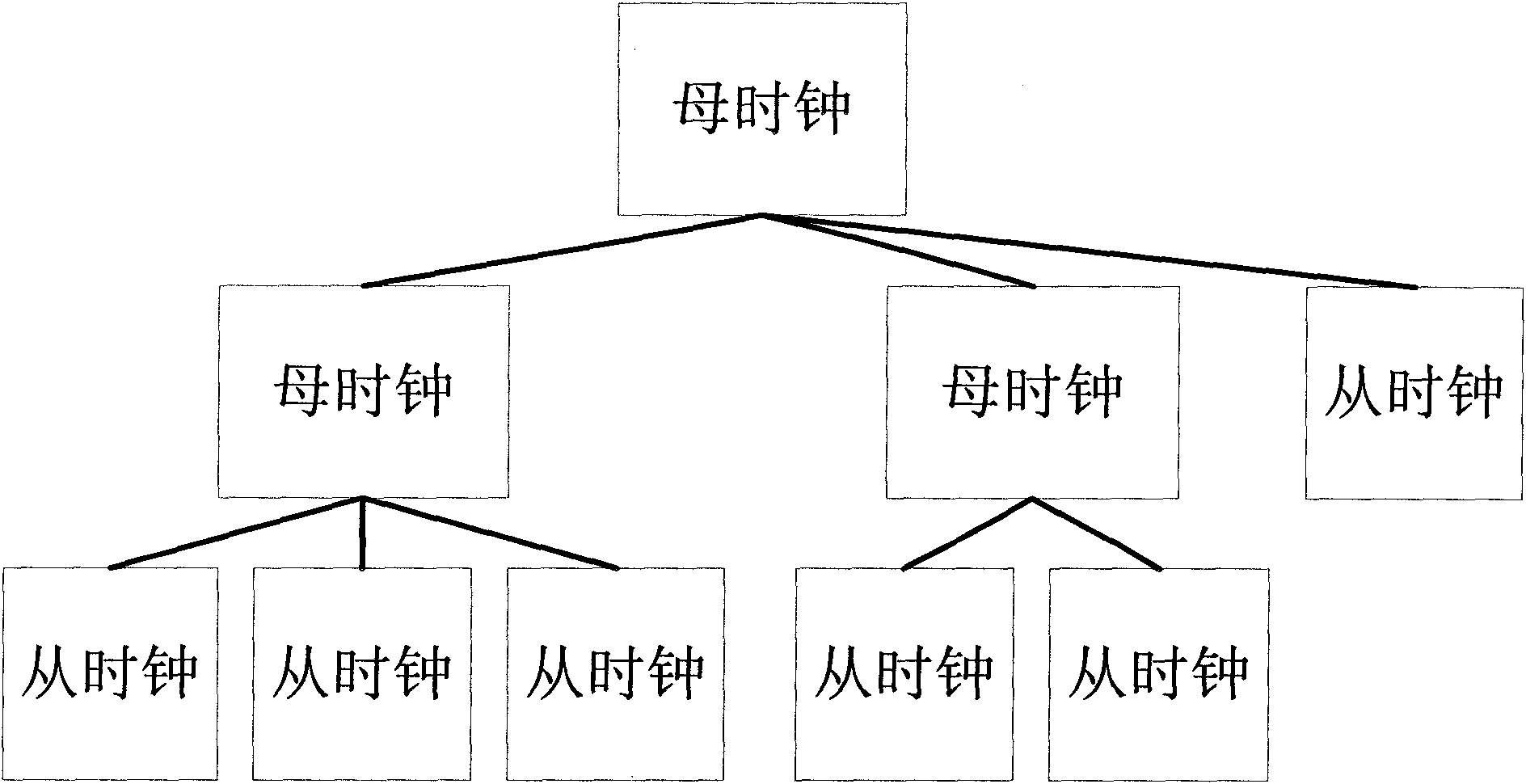

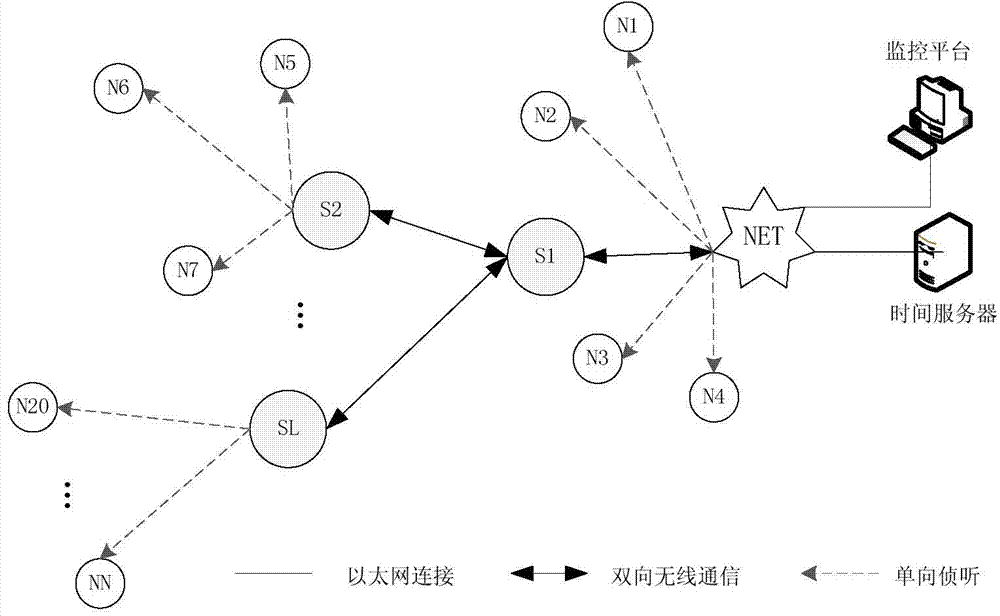

Hierarchical structure based wireless sensor network time synchronization method

InactiveCN103945525ALower energy billsReduce interactionSynchronisation arrangementNetwork topologiesBroadcast packetData synchronization

The invention provides a hierarchical structure based wireless sensor network time synchronization method. According to the hierarchical structure based wireless sensor network time synchronization method, gateway nodes and aggregation nodes are distributed in a monitoring site in advance and sensor nodes are carried by operators; the gateway nodes send hierarchy establishment broadcast data packages with time stamps; the aggregation nodes and the sensor nodes within the communication distance range extract hierarchy information after receiving the data packages, hierarchies of the aggregation nodes and the sensor nodes are changed by adding one to the current hierarchies, and local clocks are modified according to the time stamps; the gateway nodes are served as global time after network hierarchies are built, the timed polling sends time synchronization data packages to aggregation sub-nodes and the aggregation nodes synchronize the local clock time and the global time through the time synchronization algorithm; the sensor nodes perform time synchronization on the local clocks by intercepting time synchronization mutual data package information. The hierarchical structure based wireless sensor network time synchronization method achieves high accuracy time synchronization and improves the wireless sensor network channel utilization rate and the network life cycle.

Owner:STATE GRID CORP OF CHINA +2

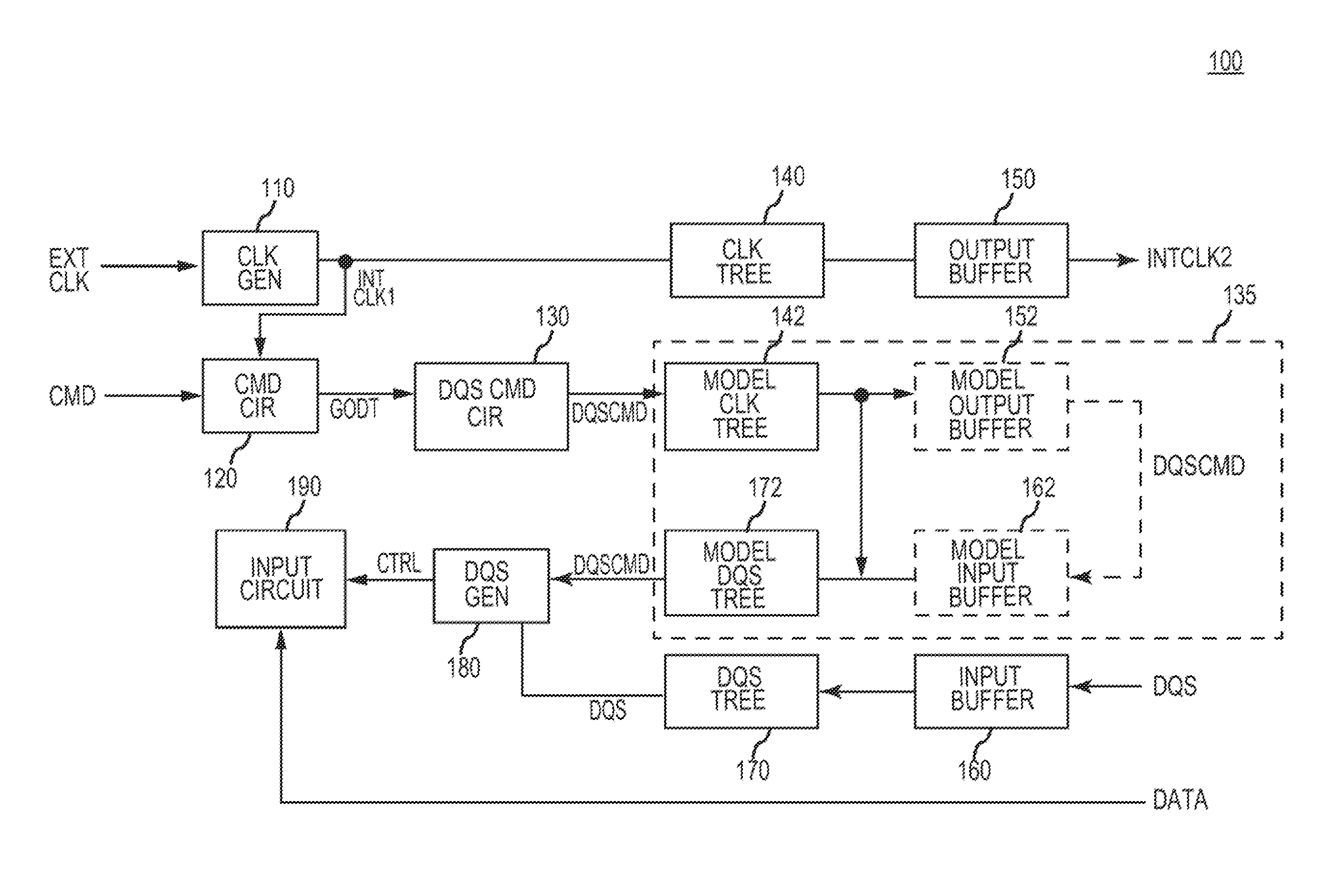

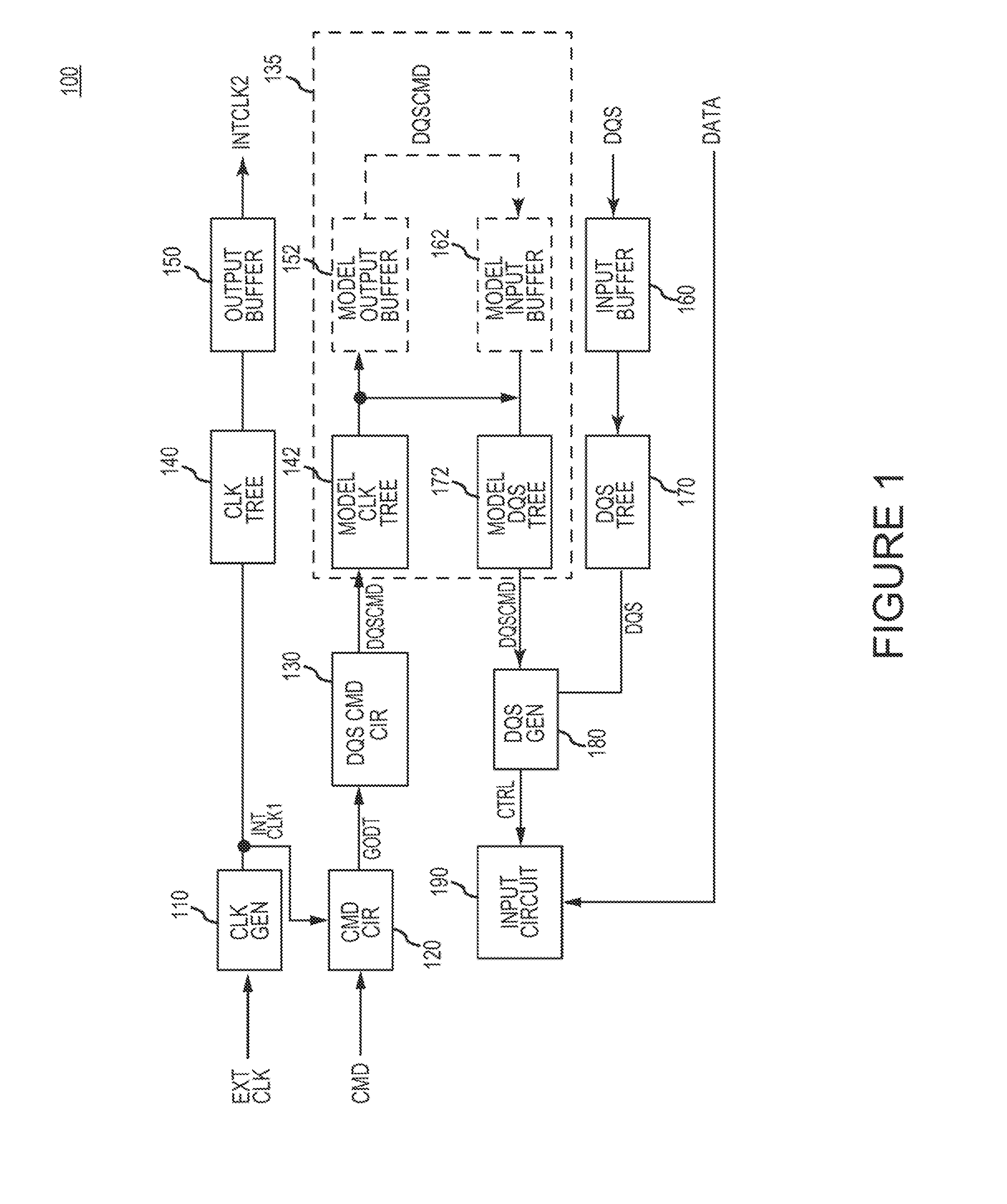

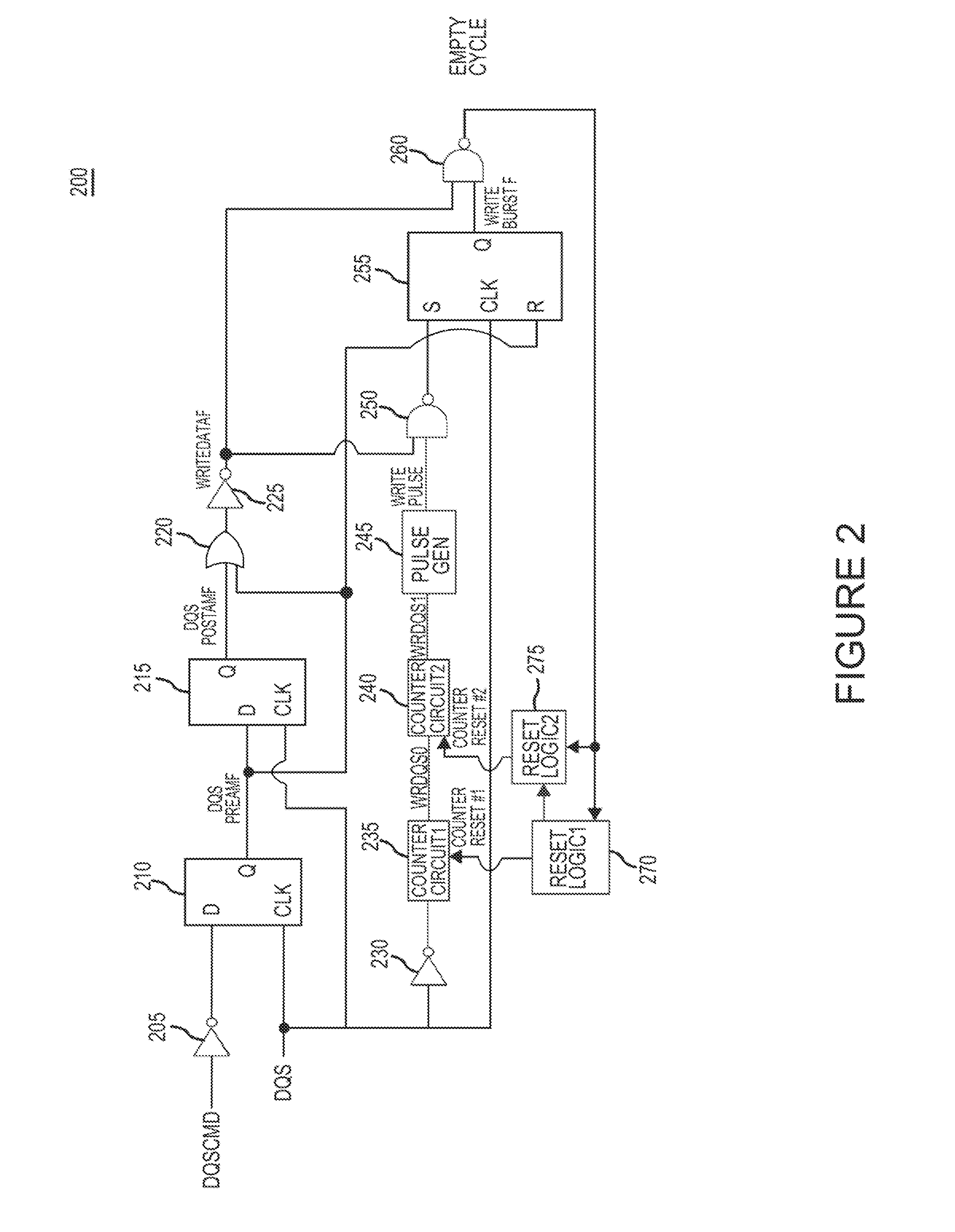

Apparatuses and methods for timing provision of a command to input circuitry

Apparatuses and methods for providing a command to a data block are described. An example apparatus includes a command circuit configured to provide a command signal in an internal clock time domain based at least in part on a memory access command received in an external clock time domain. The example apparatus further includes a command path delay configured to delay the command signal. The example apparatus further includes a data strobe generator circuit configured to receive the command signal and a data strobe signal. A plurality of clock edges of the data strobe signal correspond to received data bits associated with the memory access command. The data strobe generator circuit is configured to control input circuitry to capture the data associated with the memory access command based at least in part on the data strobe signal and the command signal.

Owner:MICRON TECH INC

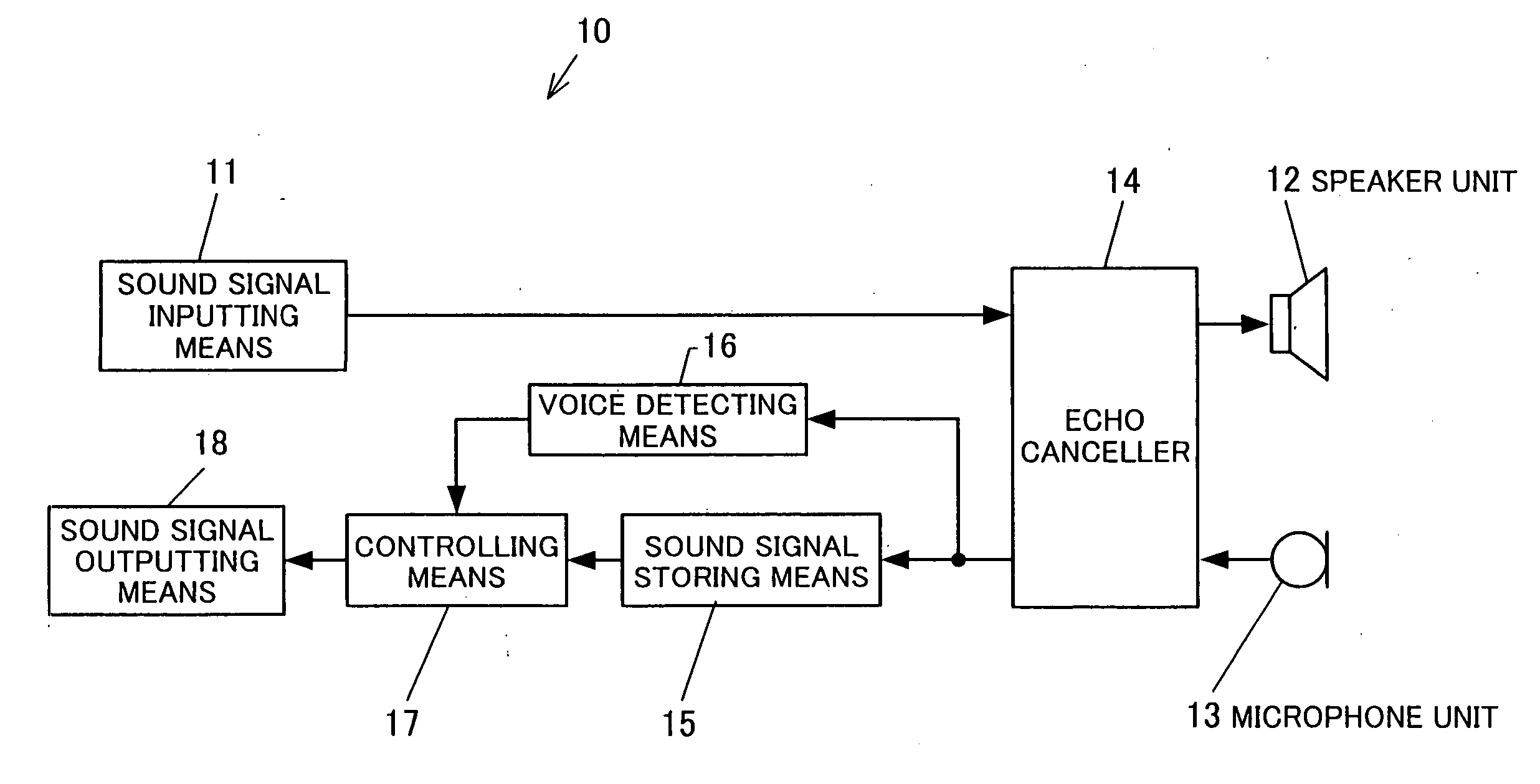

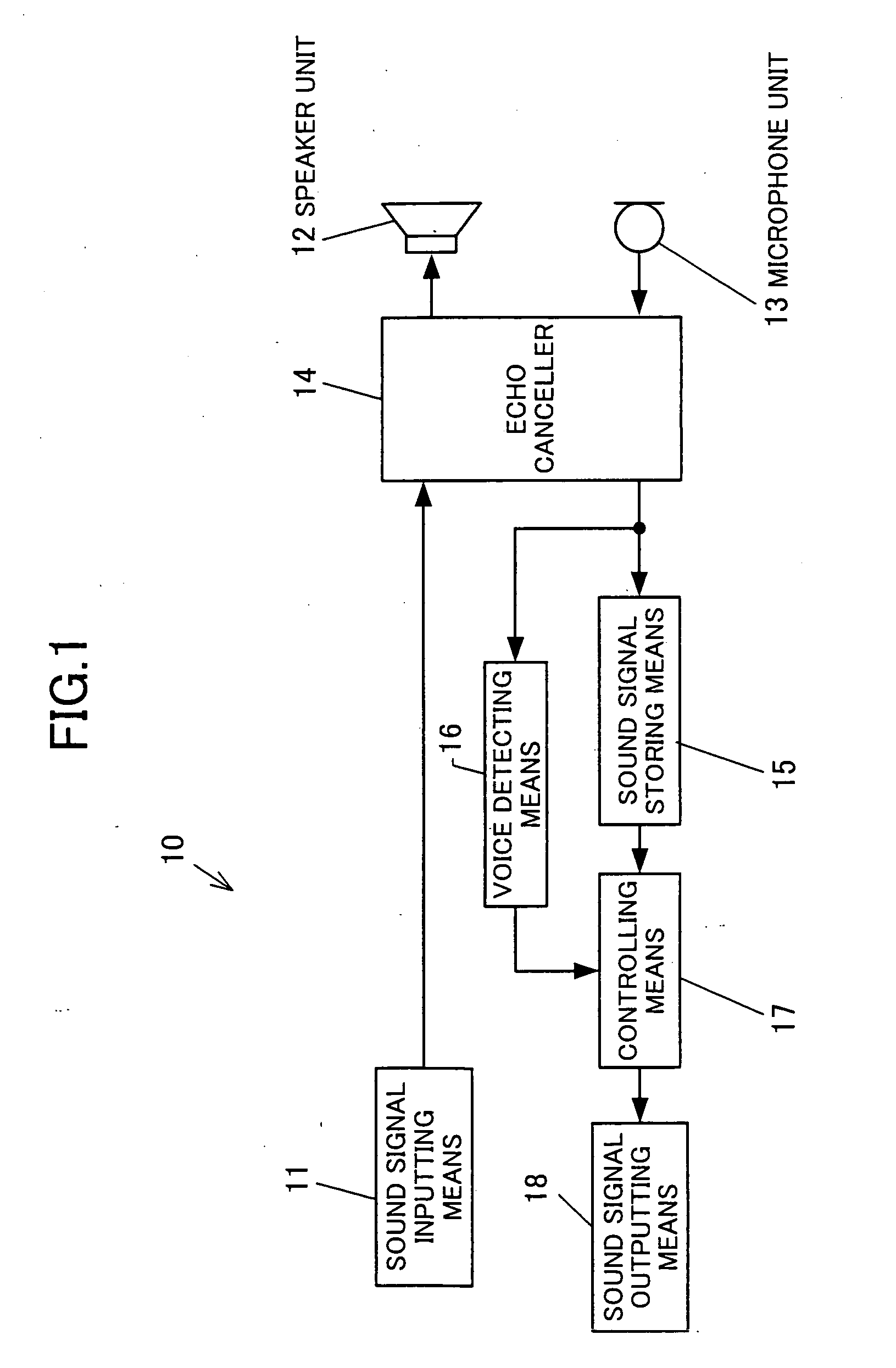

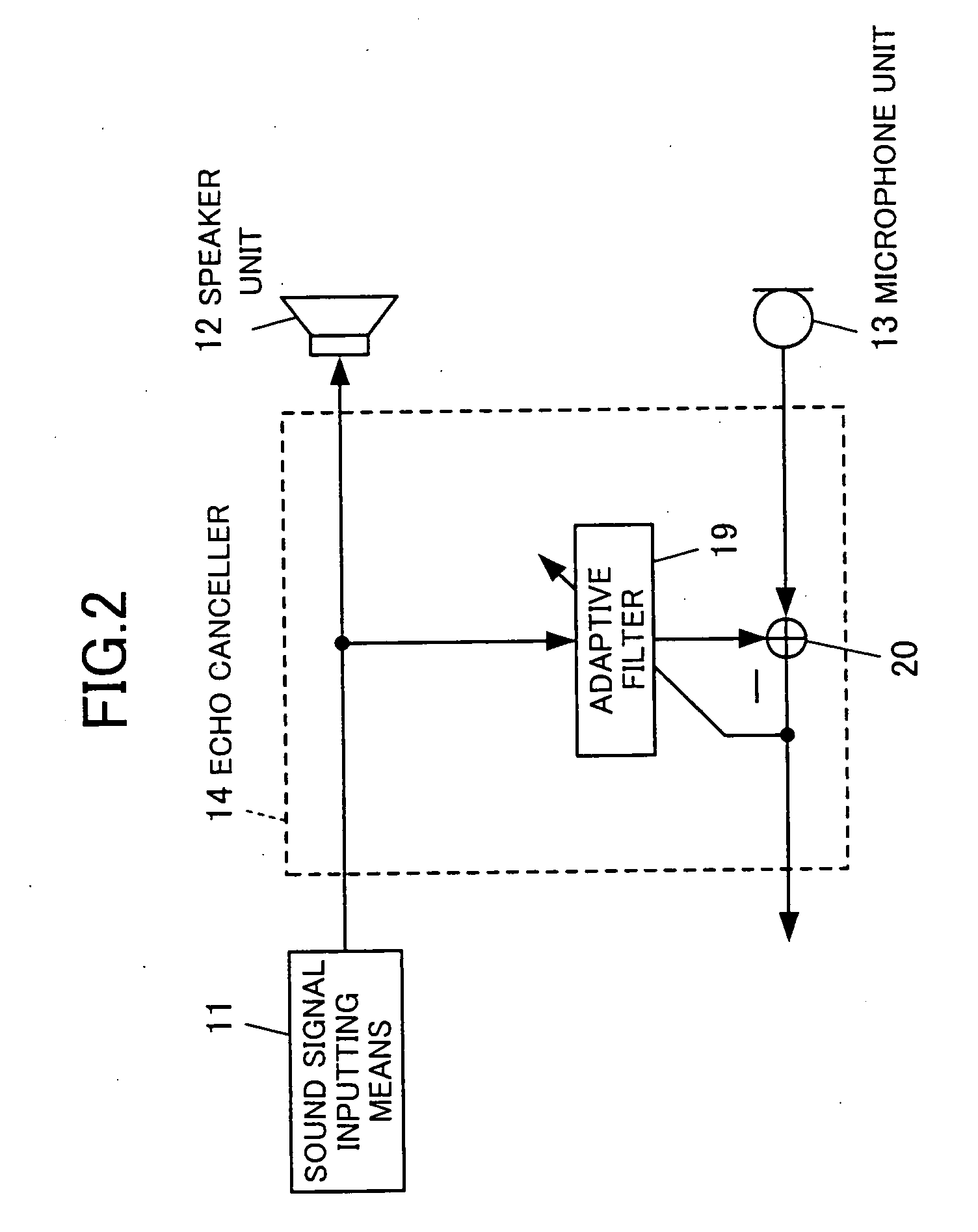

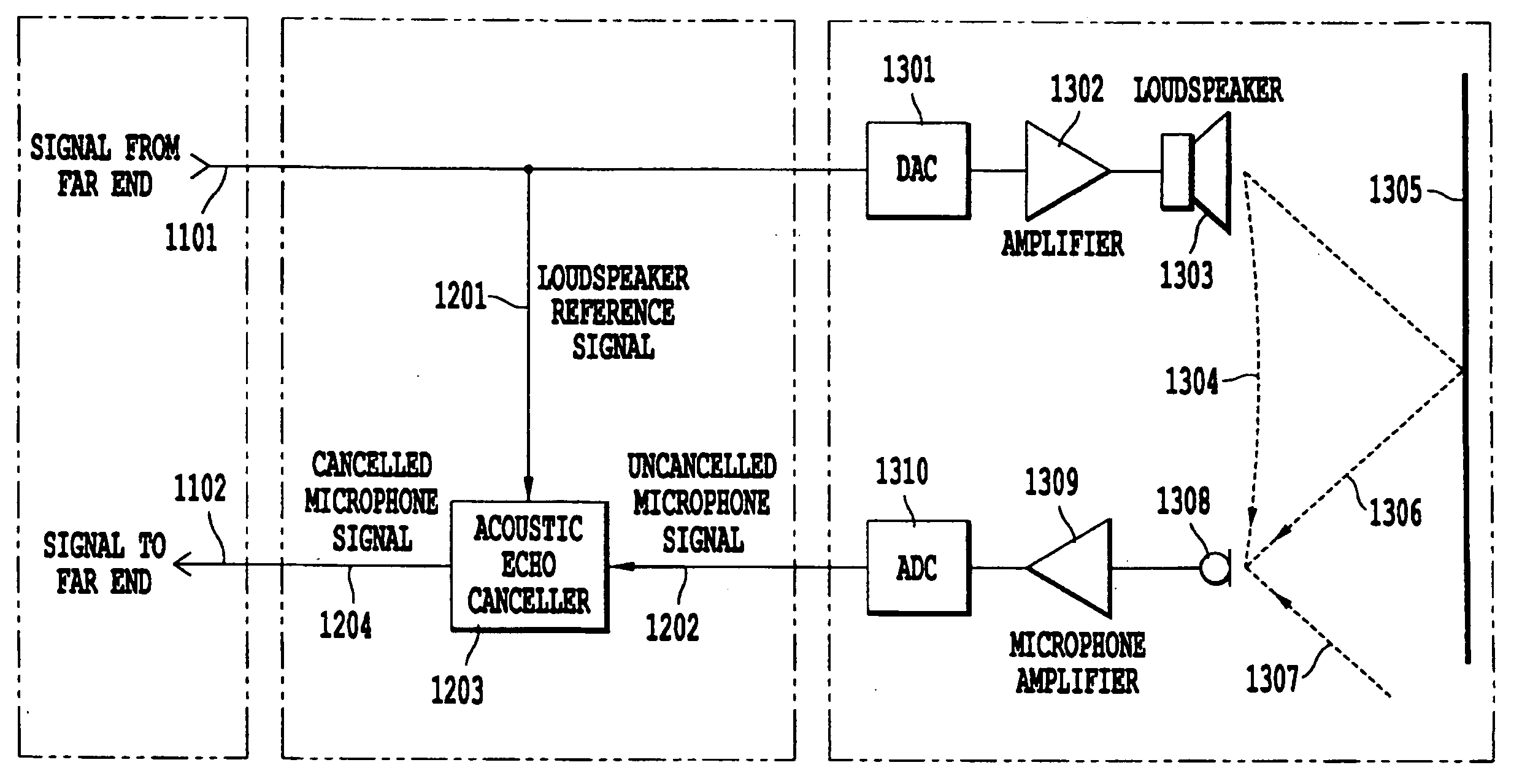

Acoustic processing system, acoustic processing device, acoustic processing method, acoustic processing program, and storage medium

InactiveUS20060182291A1Shorten the time periodImprove accuracyInterconnection arrangementsDigital technique networkClock timeSignal on

Herein disclosed is a sound signal processing apparatus (10), comprising: a speaker unit (12) for converting a first sound signal to a first sound; sound signal producing means (13) for producing a second sound signal constituted by at least two different components including an echo component indicative of the sound outputted by the speaker unit (12), and a voice component indicative of one's voice having a least one leading end; echo component suppressing means (14) for suppressing the echo component of the second sound signal on the basis of the first and second sound signals to output, as a third sound signal, the suppressed second sound signal; sound signal storing means (15) for storing the third sound signal outputted by the echo component suppressing means (14); voice detecting means (16) for detecting the leading end of the speaker's voice on the basis of the third sound signal outputted by the echo component suppressing means (14); and controlling means (17) for controlling the sound signal storing means (15) to have the sound signal storing means (15) output, as a fourth sound signal, said third sound signal stored in the time period when said voice is detected on the basis of said third sound signal outputted by said echo component suppressing means, the controlling means (17) being operative to specify two different clock times on the basis of a predetermined time difference, the clock times including a first clock time at which the leading end of the voice is detected by the voice detecting means (16), and a second clock time prior to the first clock time, the controlling means (17) being operative to have the sound signal storing means (15) start to output the third sound signal stored after the second clock time.

Owner:PANASONIC CORP

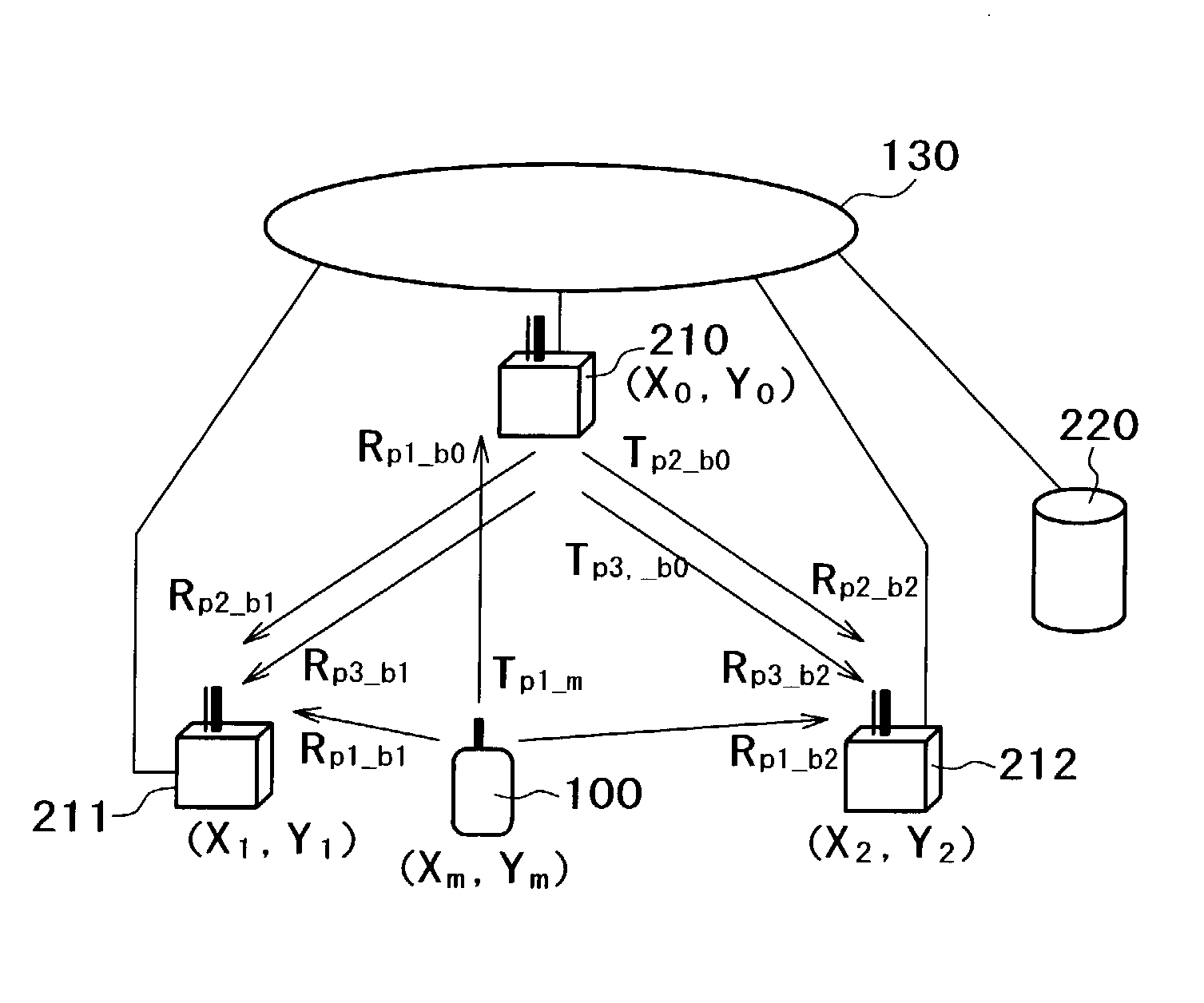

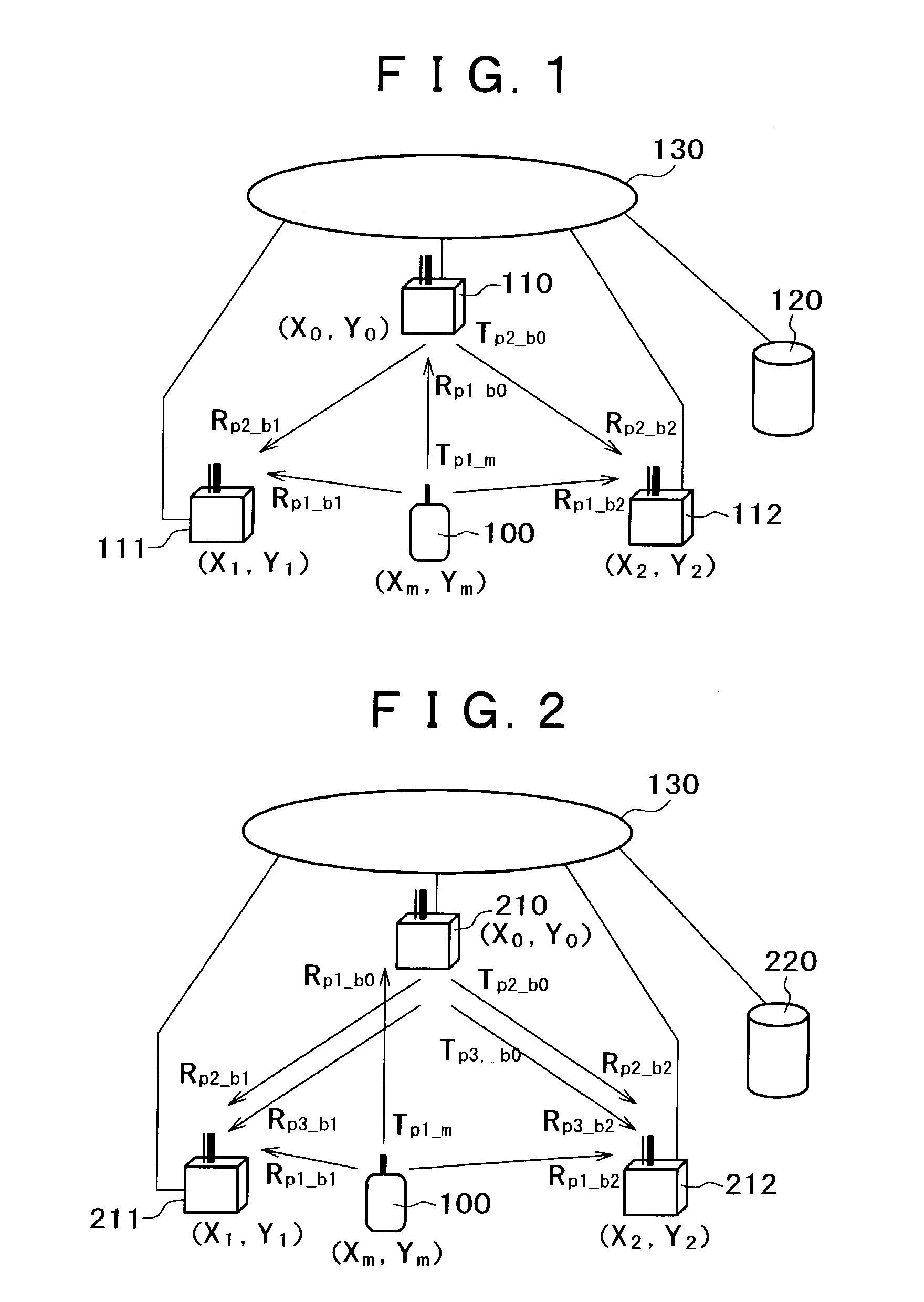

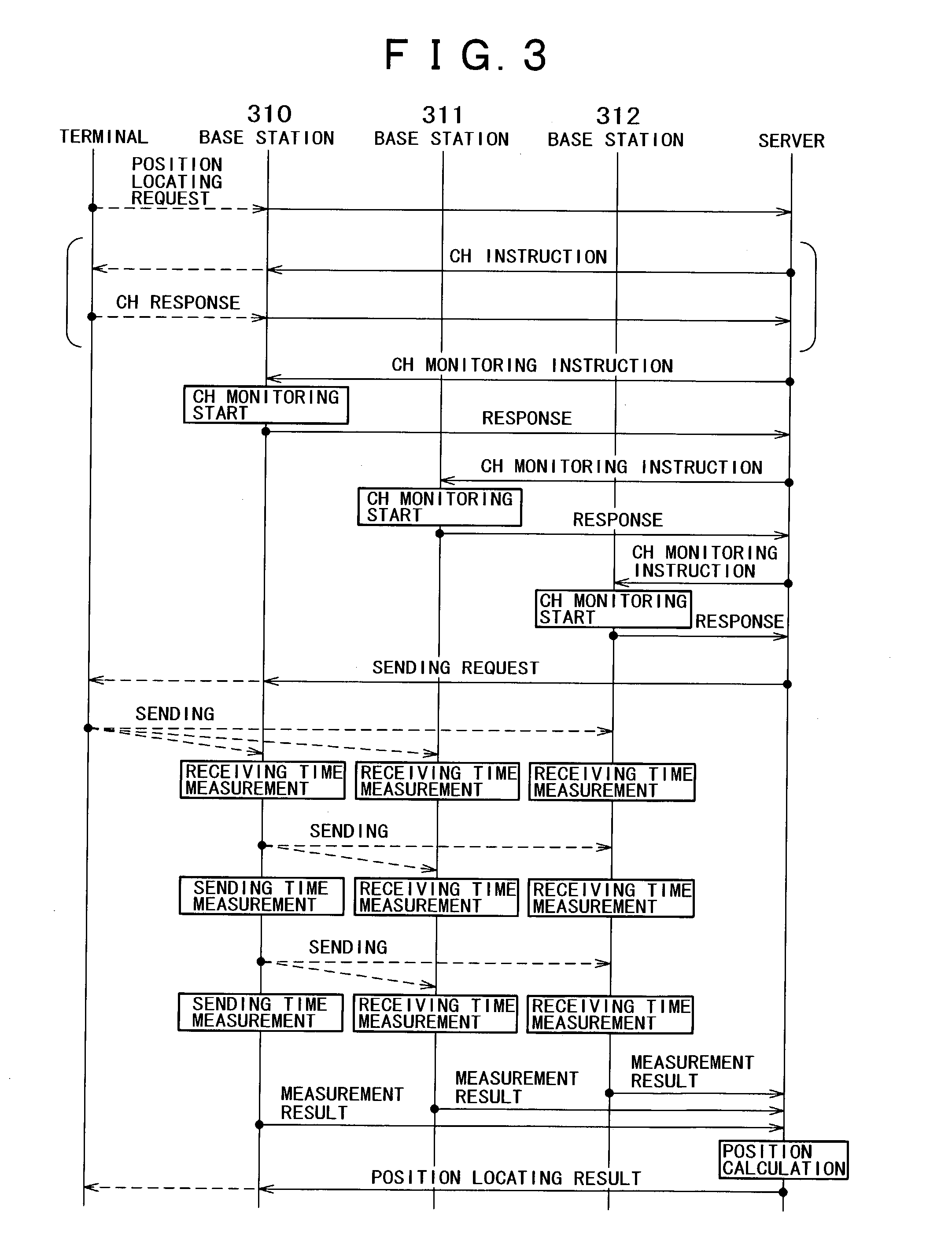

Method, system, and apparatus for detecting a position of a terminal in a network

InactiveUS7167712B2Precise positioningSynchronisation arrangementPosition fixationClock timeGps receiver

A method, system, and apparatus are provided for detecting a position of a terminal in a network accurately without a GPS receiver. In one example, a method for locating a position of a terminal includes calculating a position of a base station; detecting a clock time difference between the base station and another base station; measuring a reception timing of a signal received by the base station from the terminal; and locating the position of the terminal using at least the position of the base station, the clock time difference, and the reception timing.

Owner:HITACHI LTD

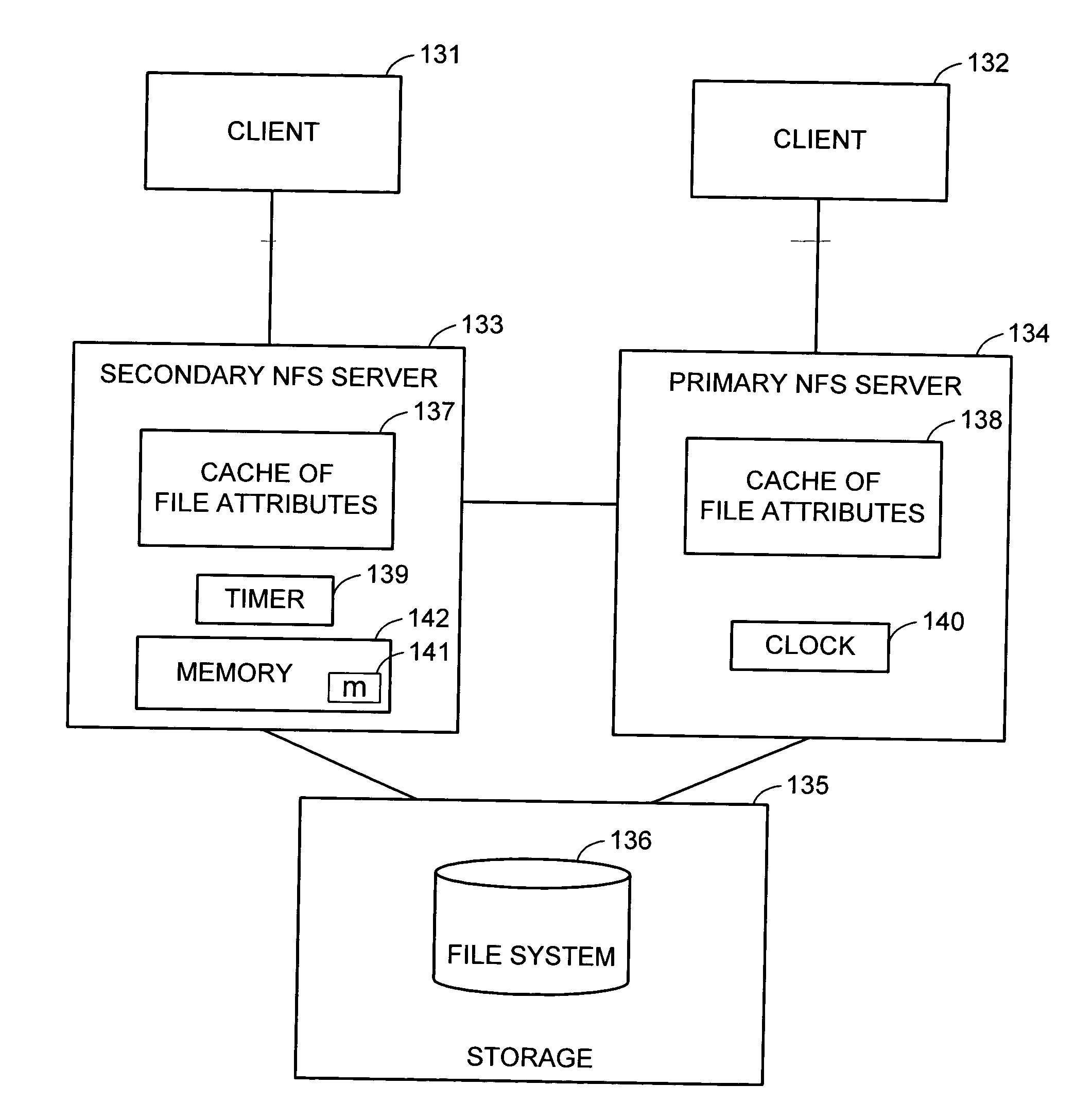

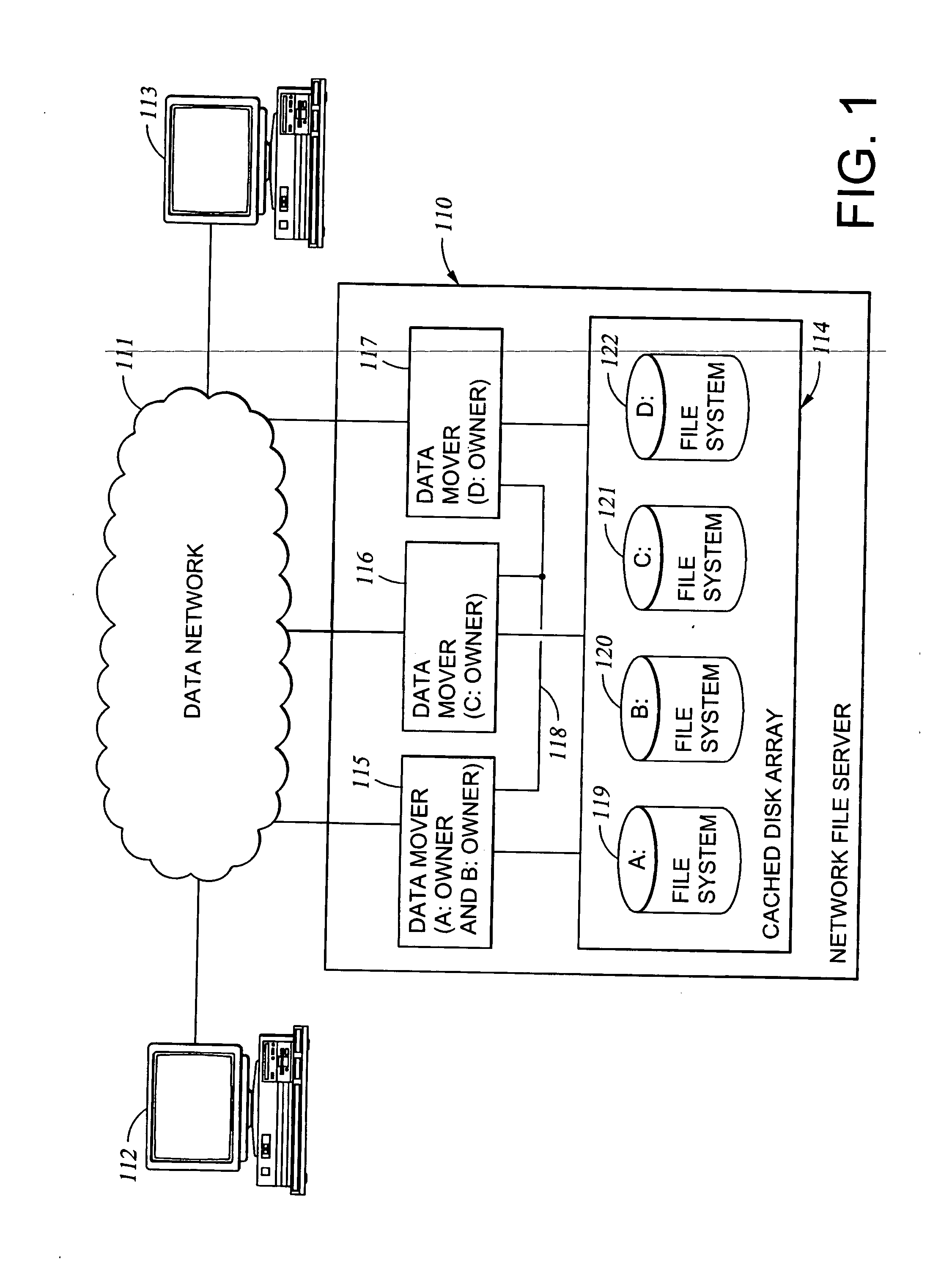

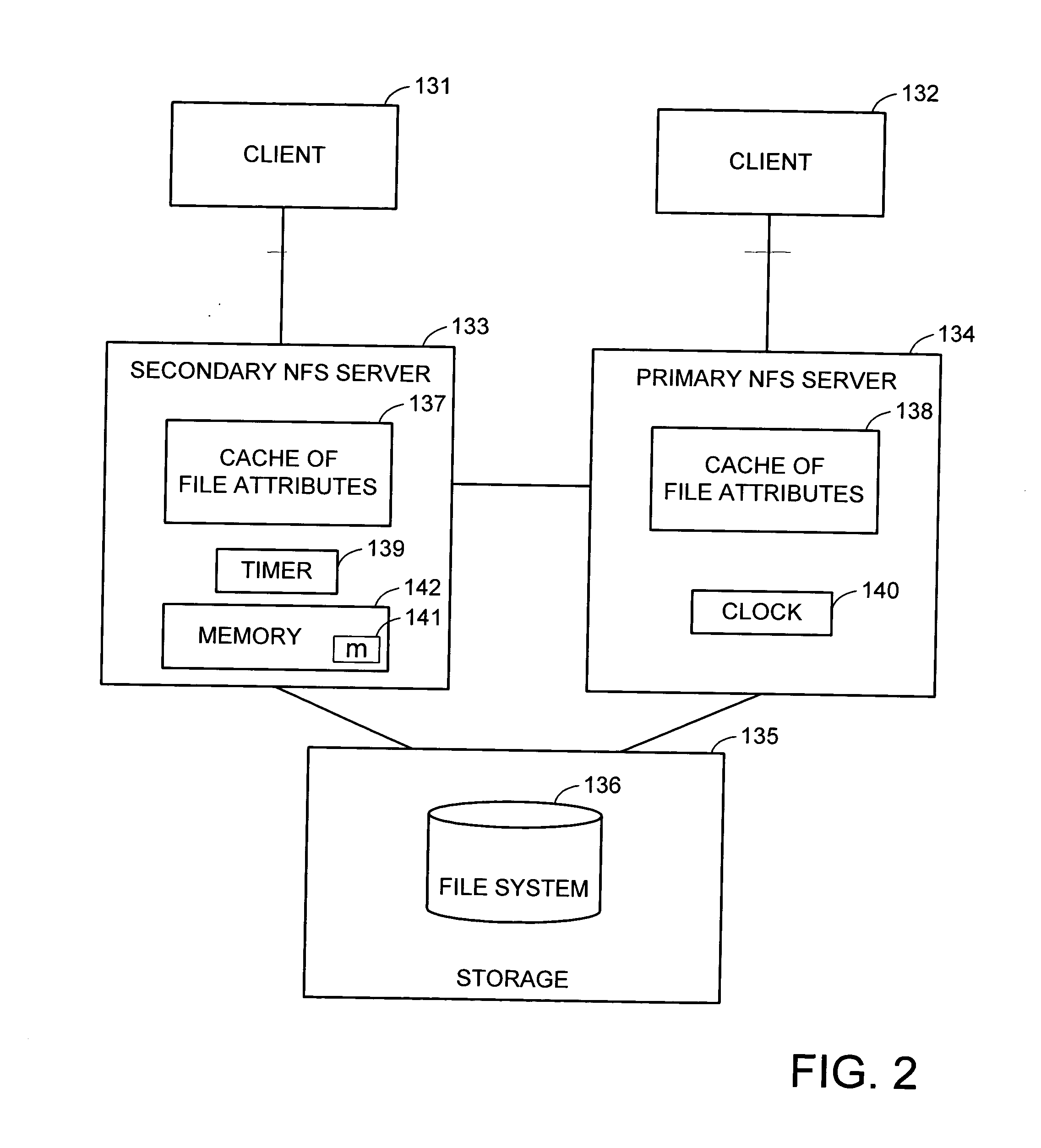

Management of the file-modification time attribute in a multi-processor file server system

ActiveUS20050044080A1Multiple digital computer combinationsSpecial data processing applicationsClock timeMulti processor

To permit multiple unsynchronized processors to update the file-modification time attribute of a file during concurrent asynchronous writes to the file, a primary processor having a clock manages access to metadata of the file. A number of secondary processors service client request for access to the file. Each secondary processor has a timer. When the primary processor grants a range lock upon the file to a secondary, it returns its clock time (m). Upon receipt, the secondary starts a local timer (t). When the secondary modifies the file data, it determines a file-modification time that is a function of the clock time and the timer interval, such as a sum (m+t). When the secondary receives an updated file-modification time (mp) from the primary, if mp>m+t, then the secondary updates the clock time (m) to (mp) and resets its local timer.

Owner:EMC IP HLDG CO LLC

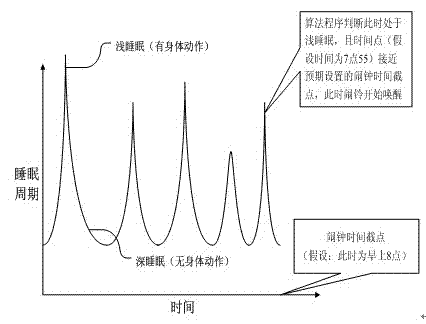

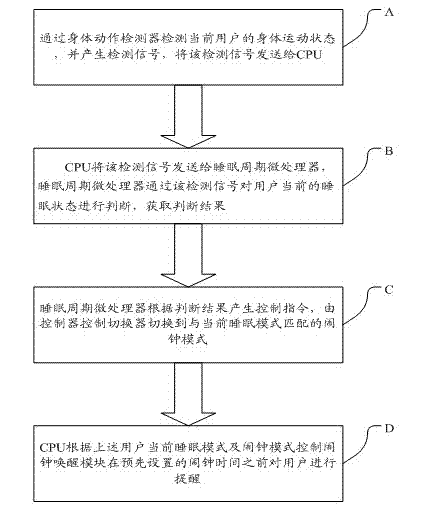

System and method of mobile phone clock for automatically waking up user based on sleep depth period

The invention discloses a system and a method of a mobile phone clock for automatically waking up a user based on a sleep depth period. The method includes that A, a body motion state of the user at current is detected through a body movement detector, and a detection signal is produced and sent to a central processing unit (CPU); B, the detection signal is sent to a sleep period microprocessor by the CPU, judgment for a sleep state of the user at current is carried out by the sleep period microprocessor through the detection signal, and a judgment result is obtained; C, a control command is produced by the sleep period microprocessor according to the judgment result, and a switcher is controlled by a controller to be in a clock mode matched with a sleep mode at current; and D, and the CPU controls a clock wake-up module to remind the user before a preset clock time according to the sleep mode of the user at current and the clock mode. Compared with the prior art, the system and the method greatly guarantee time and the state of deep sleep of the user, are scientized and humanized, can naturally wake up the user in a sleep state, and enable the user to feel relaxed and full of energy and to be in good mood.

Owner:SHENZHEN GIONEE COMM EQUIP

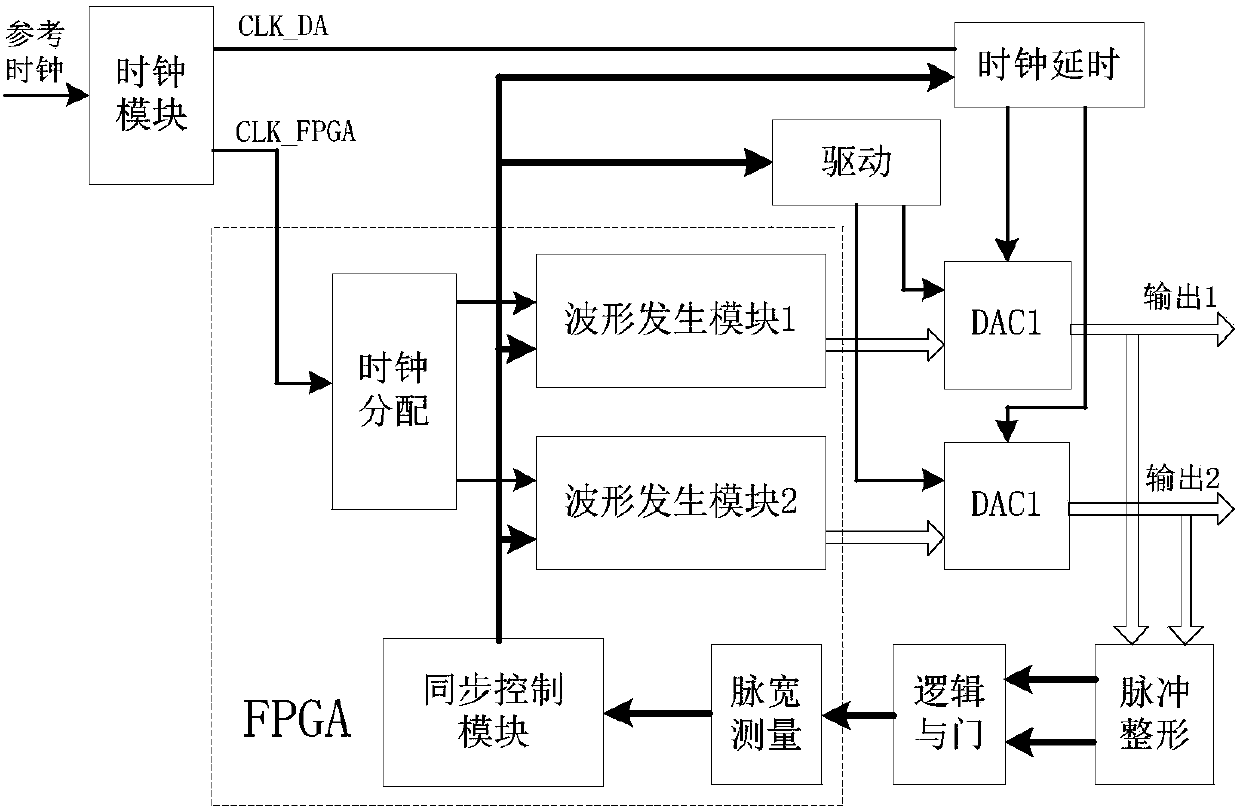

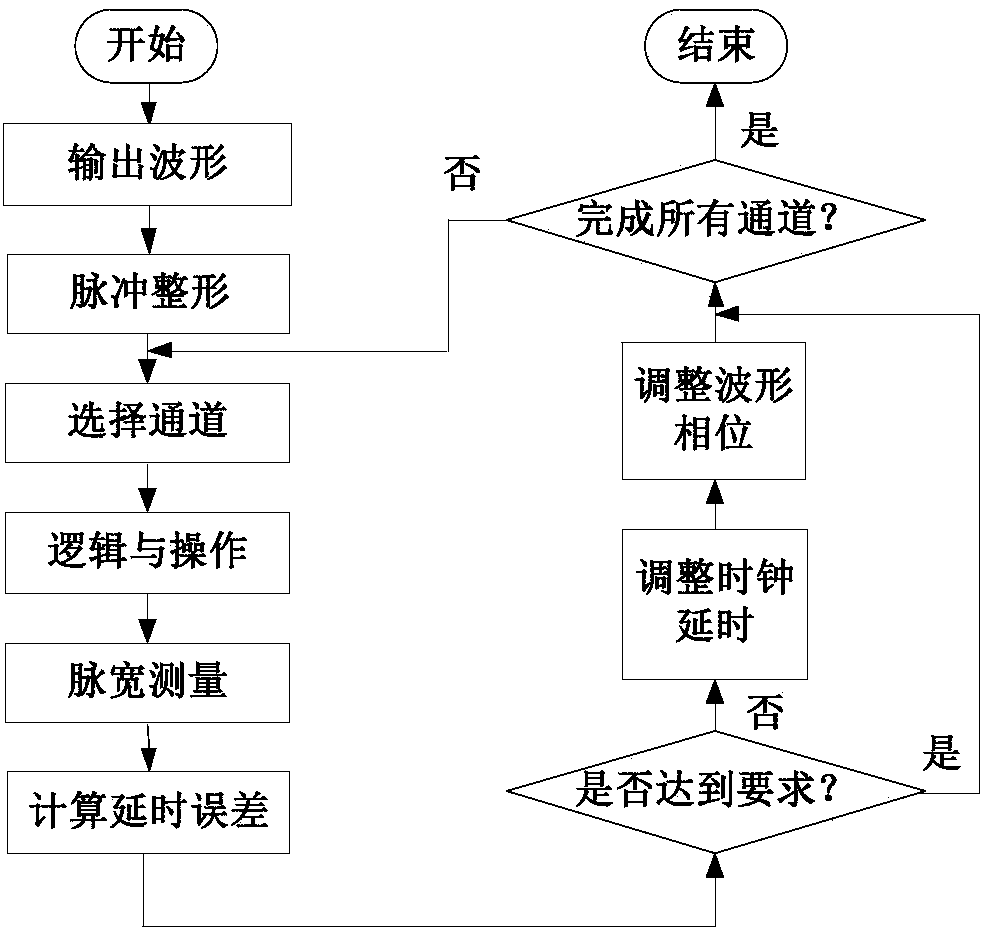

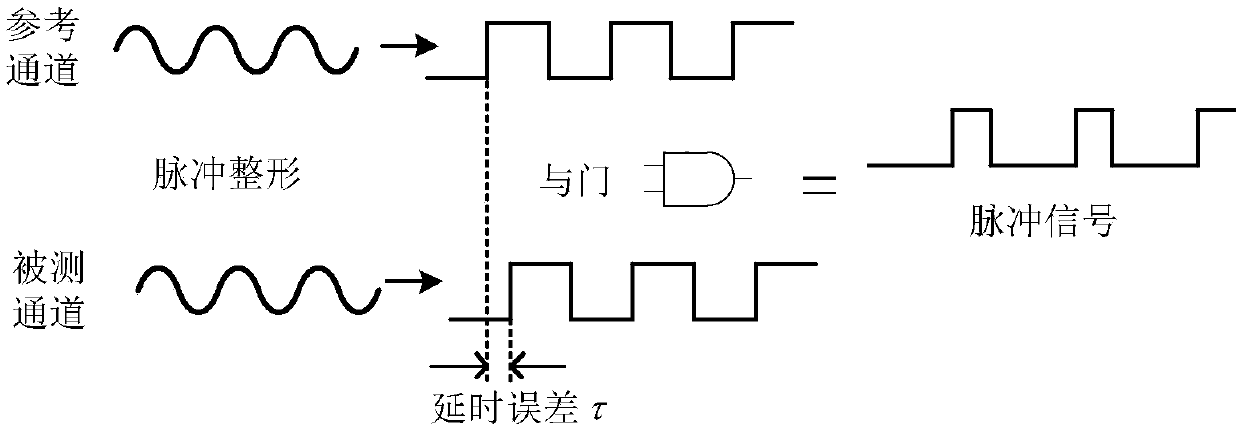

Multichannel synchronous output calibrating apparatus and method

ActiveCN107863967AImprove consistencySimple structureLogic circuits characterised by logic functionAnalogue conversionClock timeObservational error

The invention discloses a multichannel synchronous output calibrating apparatus and method. The calibrating apparatus includes a clock module, a clock time delay module, a waveform generation module,a pulse shaping module, a logic AND gate module, a pulse width measurement module and a synchronous control module, wherein an inter-channel synchronous time delay error is obtained by adopting the pulse shaping module, the logic AND gate module and the pulse width measurement module. The circuit structure is simple, the hardware implementation is easy, the complex calculation is avoided, an ADC circuit and a high-performance calculation module do not need and the cost is low; when the error is corrected, the calibrating apparatus adjusts a time delay and a waveform phase of a sampling block sequentially via the clock time delay module and the waveform generation module until the inter-channel synchronous time delay error reaches to a designed requirement, so the precision is high and thechannel consistency is good; and in additional, since a cooperative manner of precise time delay adjustment and edge inspection is adopted by the pulse width measurement module, a pulse width measurement error is effectively reduced.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

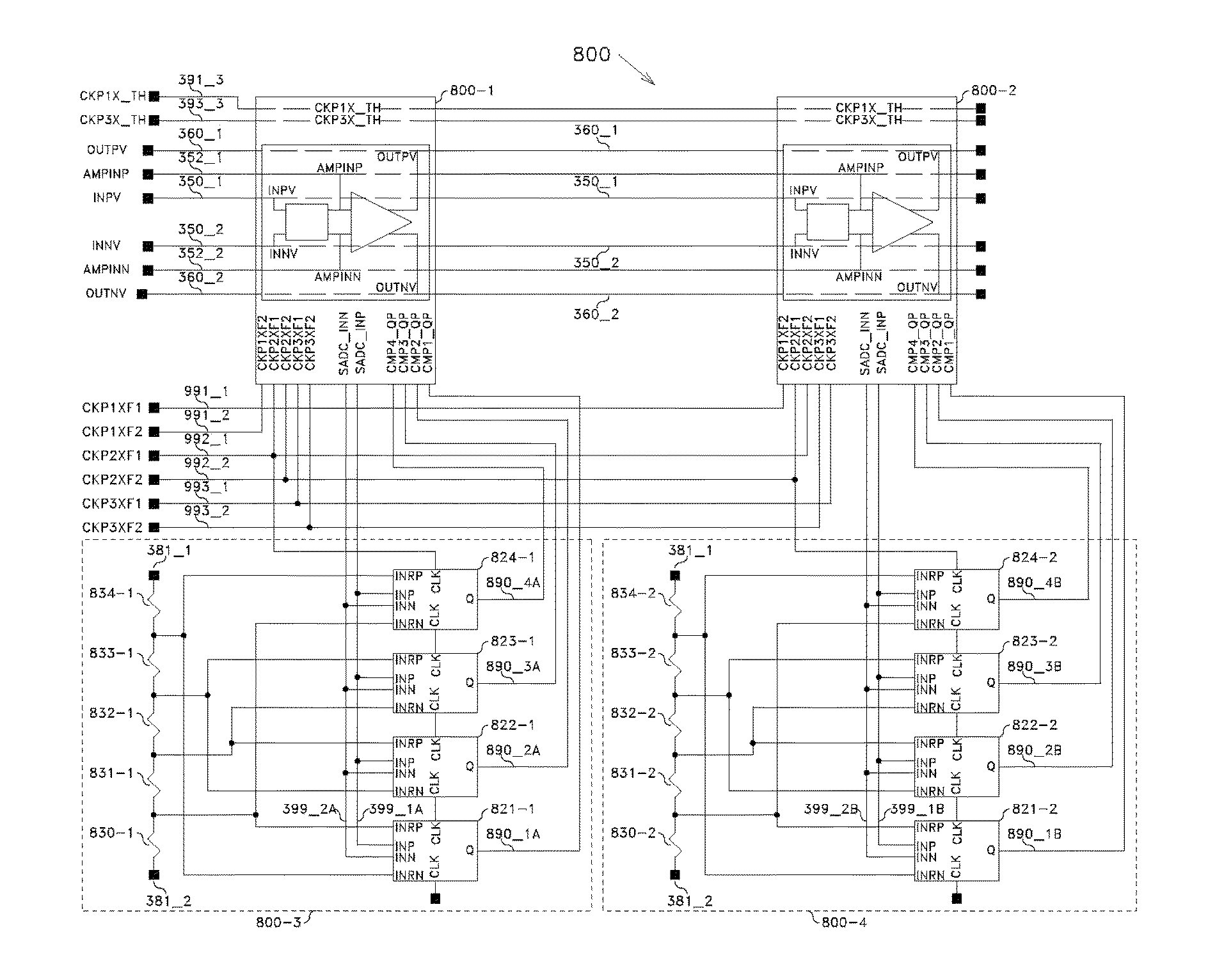

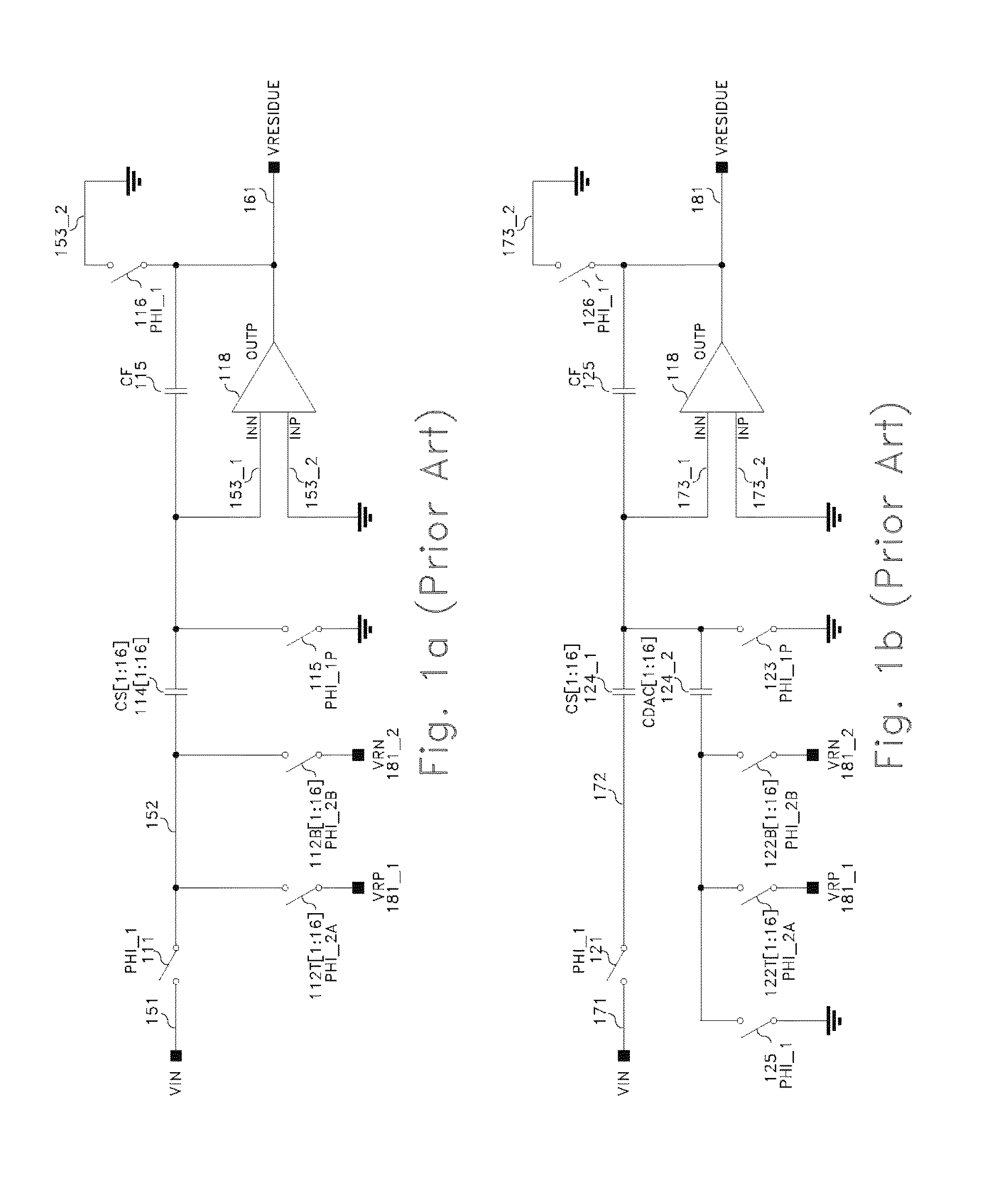

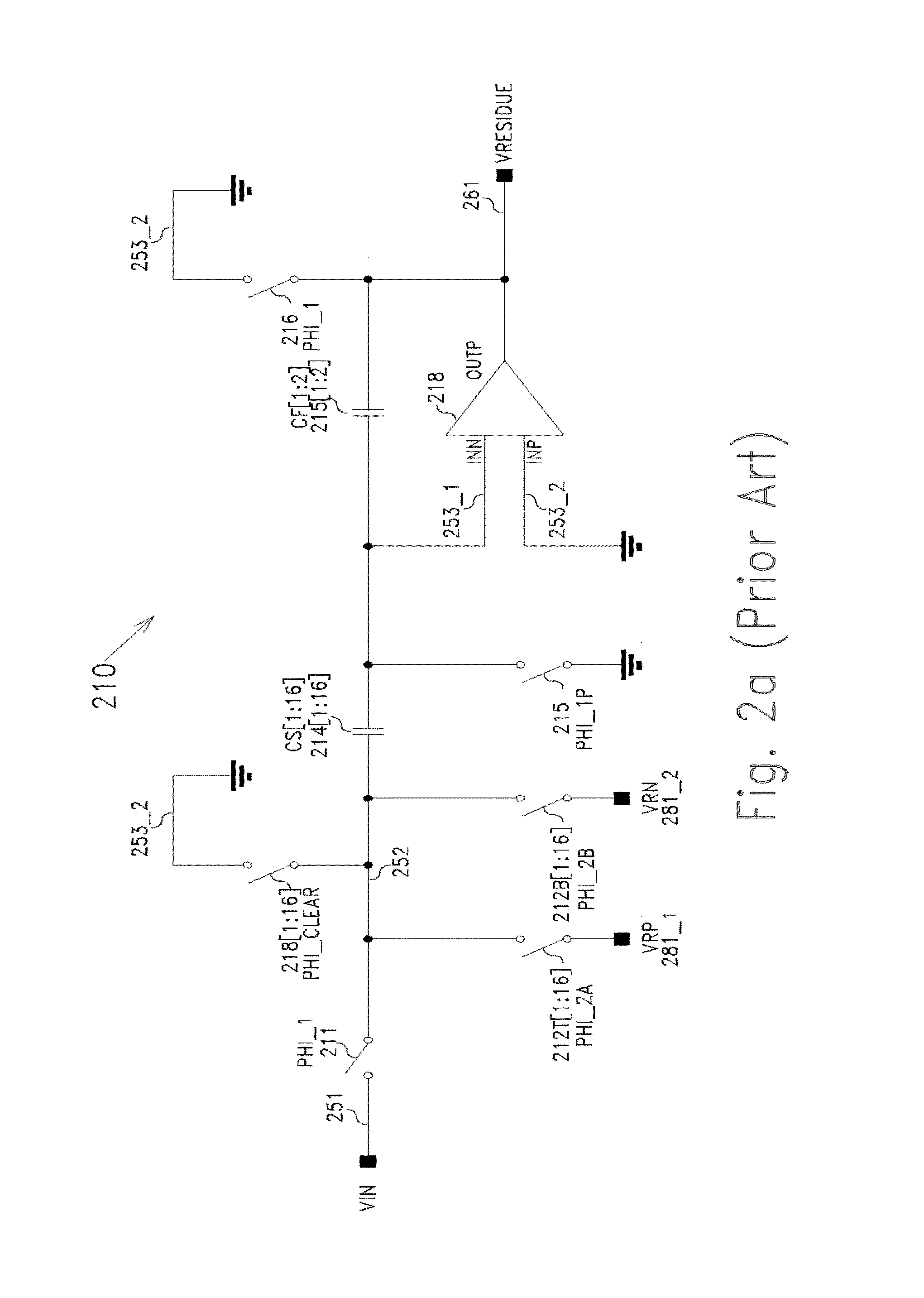

ADC first stage combining both sample-hold and ADC first stage analog-to-digital conversion functions

ActiveUS8604962B1Analogue/digital conversionElectric signal transmission systemsCapacitanceEngineering

A first stage circuit for a pipeline ADC first stage combines the functions of an input sample-and-hold-plus-amplifier (SHA) stage, and the functions of the first analog-to-digital conversion stage of an ADC, including a multiplying DAC (MDAC), stage-flash ADC (SFADC) comparators, and residue opamp (RAMP). The ADC first stage is duplicated, inputs and outputs are connected, and an autozero circuit using a switched-capacitor filter feedback loop controls the RAMP bias circuitry to reduce 1 / f noise and DC offsets. The sampling capacitors may be connected to the ADC input for one full sample clock time period and are disconnected from the analog input period before connecting the sampling capacitors to an amplifier voltage output or voltage reference, thereby sampling the input and allowing sufficient time for the SFADC comparators to resolve and control the MDAC capacitor settings with a low metastability error rate.

Owner:LEWYN CONSULTING

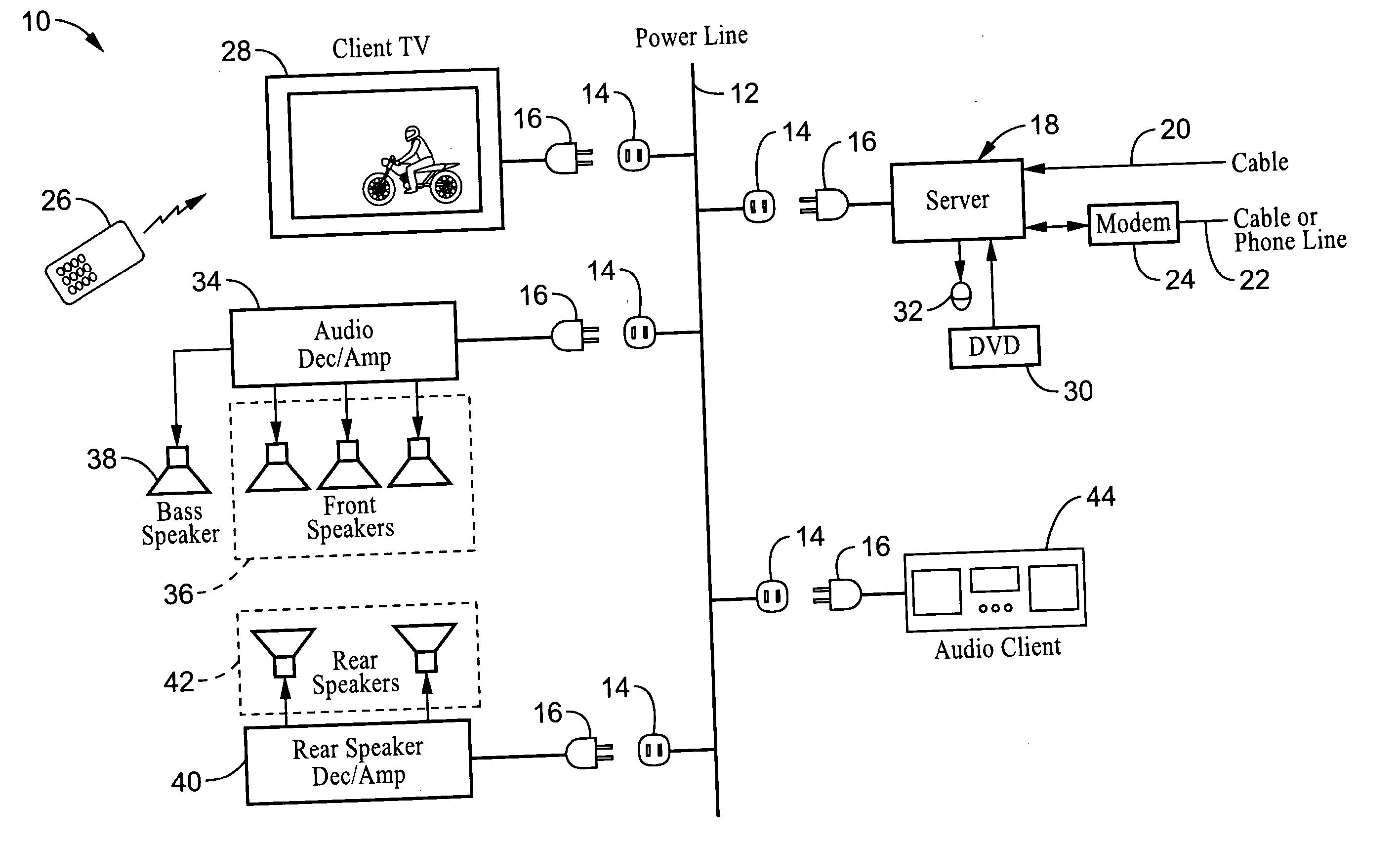

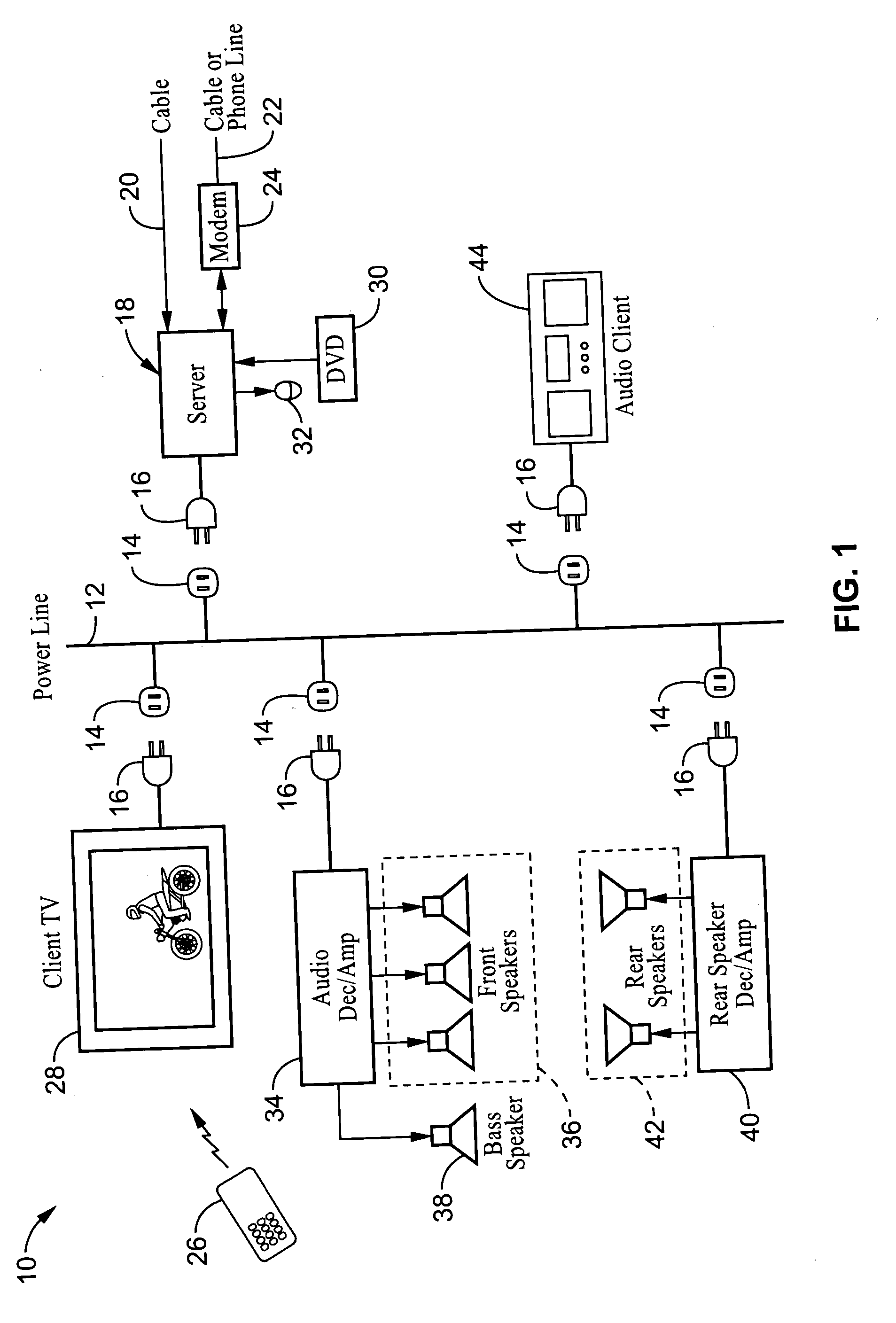

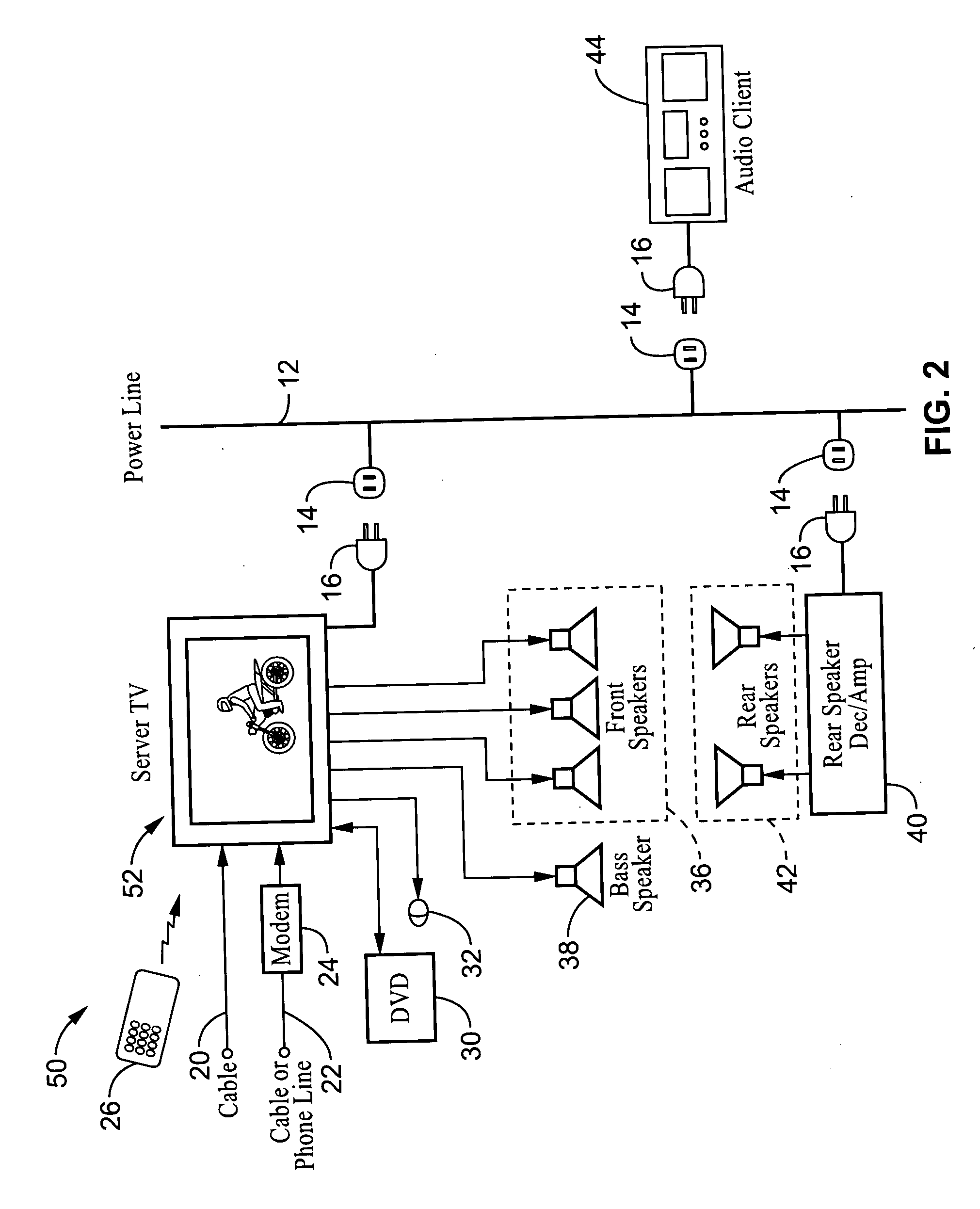

System and method for synchronizing audio-visual devices on a power line communications (PLC) network

ActiveUS20060072695A1Minimum delayMinimize divergenceTime-division multiplexWireless systems/telephoneComputer hardwareClock time

A method and apparatus for synchronizing streaming media devices within a PLC network. Output synchronization errors exceeding ˜30 ms become noticeable when multiple streaming media devices are outputting an audio stream. The present invention provides a system and method for isochronously sending periodic reference clocks from a master device to client devices coupled to the PLC network. The client devices set their clocks based on the reference clock. In addition the clients adjust their system clock time base in response to the average divergence of the system clock with the reference clock, or a count of the number of clocks between beacon frames. In this way the client clock is adjusted to closely track the server clock so that synchronization is maintained between each of the devices. Streaming audio shared between servers and client devices is thus output across the network with high fidelity due to the accurate synchronization.

Owner:SONY CORP +1

Method and system for clock drift compensation

ActiveUS20090185695A1Solve problemsTwo-way loud-speaking telephone systemsEar treatmentClock timeTime domain

Different sampling rates between a playout unit and a capture unit are compensated for via a system, method and computer program product. The playout unit receives samples from a computational unit, and the capture unit sends samples to the computational unit. A playout FIFO buffer operates in a playout time domain, and a capture FIFO buffer operates in a capture time domain. The computational unit is synchronized to a common clock. A first relationship is calculated between the common clock and a playout fifo buffer read pointer, and a second relationship is calculated between the common clock and a capture FIFO buffer write pointer. For each sample in the playout time domain a corresponding sample in the samples from said computational unit is found and sent to the playout FIFO buffer. For each sample in the common clock time domain the corresponding sample in the capture time domain is found and sent to the computational unit.

Owner:CISCO TECH INC

Real-time computer thermal management and power conservation

InactiveUS6848054B1Reduce power consumptionWithout perceived performanceEnergy efficient ICTPower supply for data processingClock timeApplication software

A real-time thermal management and power conservation apparatus and method for computers employs a monitor to determine whether a CPU may rest based upon a real-time sampling of temperature and CPU activity levels and activates a hardware selector to carry out the monitor's determination. If the monitor determines the CPU may rest, the hardware selector reduces or stops CPU clock time; if the CPU is to be active, the hardware selector returns the CPU to its previous high speed clock level. Switching back into full operation from its rest state occurs without a user having to request it and without any delay in the operation of the computer while waiting for the computer to return to a “ready” state. Furthermore, the monitor adjusts the performance level of the computer to manage power conservation and thermal management in response to the real-time sampling of temperature and CPU activity levels. Such adjustments are accomplished within the CPU cycles and do not affect the user's perception of performance and do not affect any system application software executing on the computer.

Owner:MOTOROLA INC +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com