Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

129results about How to "Delay problem" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

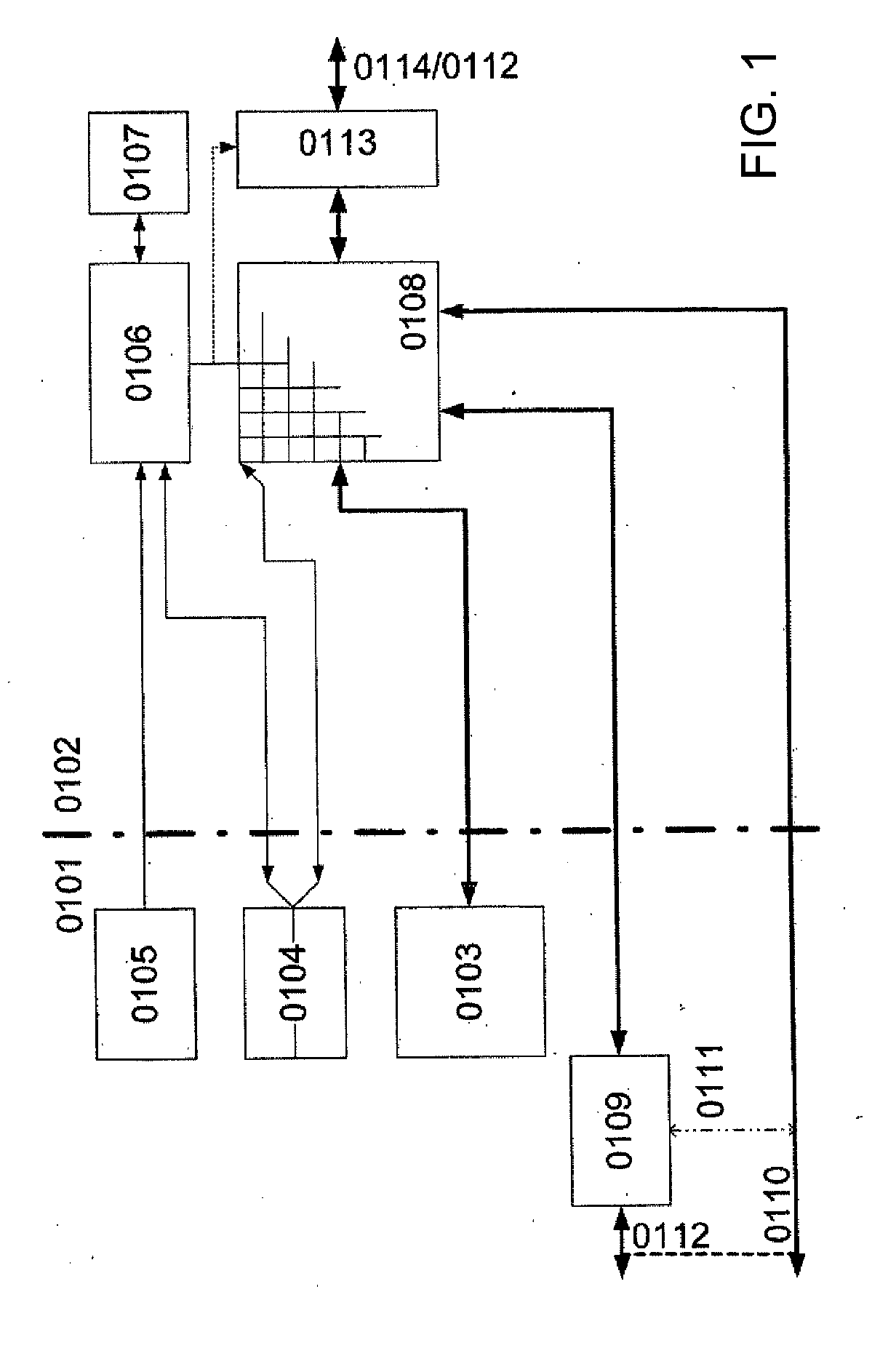

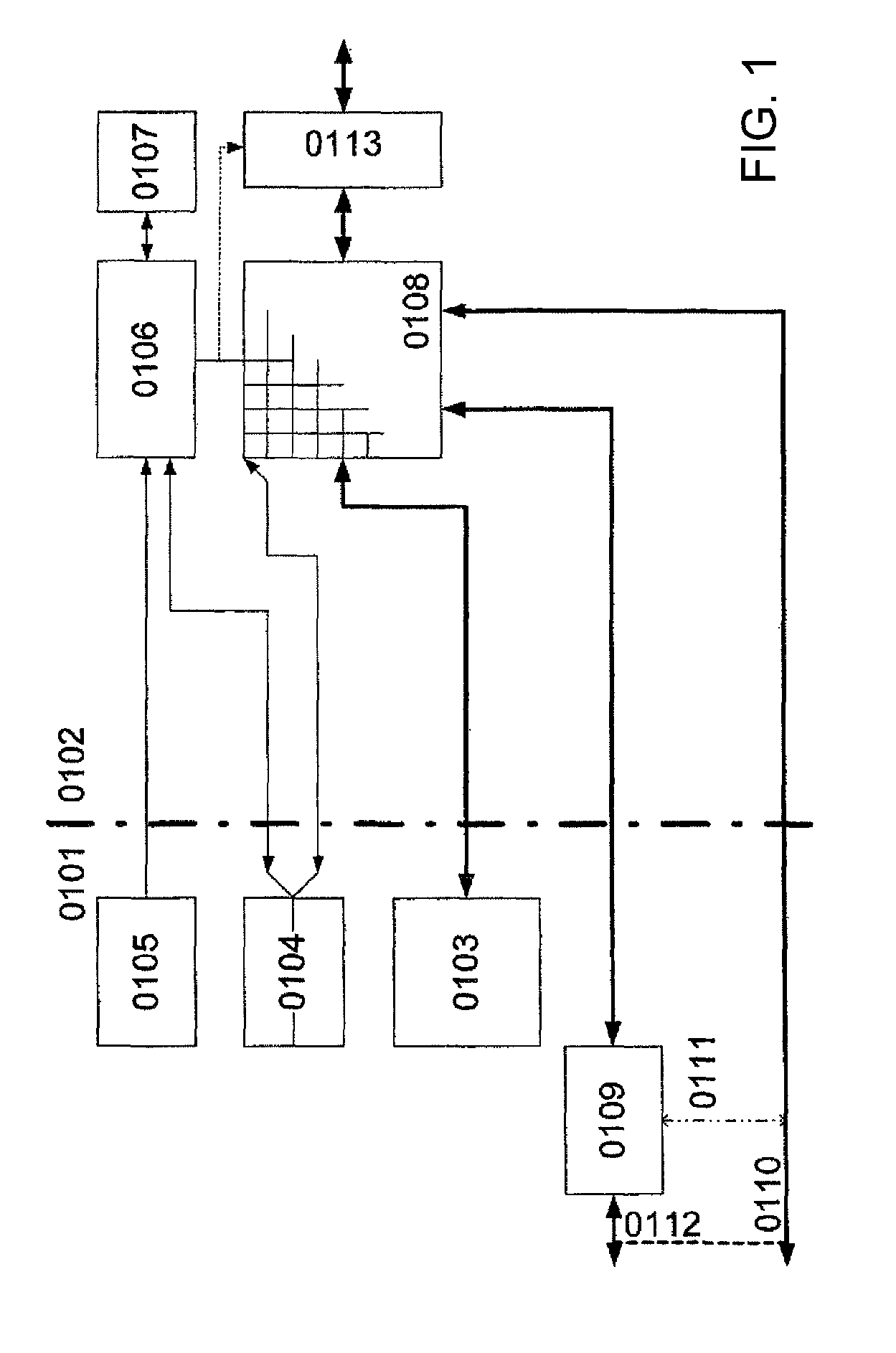

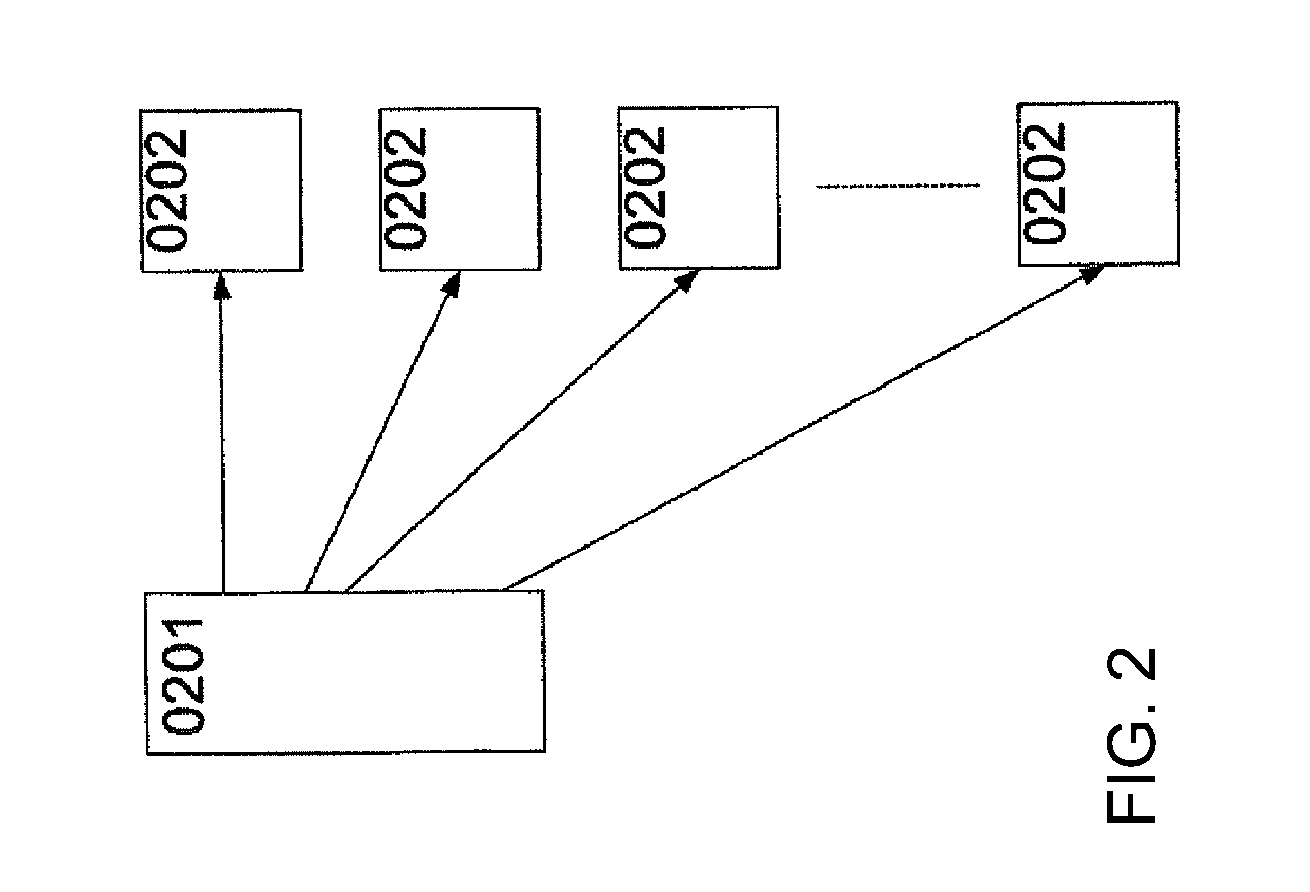

Data processing method and device

ActiveUS20070050603A1Improve data throughputDelay problemMemory adressing/allocation/relocationConcurrent instruction executionParallel computingData processing

In a data-processing method, first result data may be obtained using a plurality of configurable coarse-granular elements, the first result data may be written into a memory that includes spatially separate first and second memory areas and that is connected via a bus to the plurality of configurable coarse-granular elements, the first result data may be subsequently read out from the memory, and the first result data may be subsequently processed using the plurality of configurable coarse-granular elements. In a first configuration, the first memory area may be configured as a write memory, and the second memory area may be configured as a read memory. Subsequent to writing to and reading from the memory in accordance with the first configuration, the first memory area may be configured as a read memory, and the second memory area may be configured as a write memory.

Owner:SCIENTIA SOL MENTIS AG

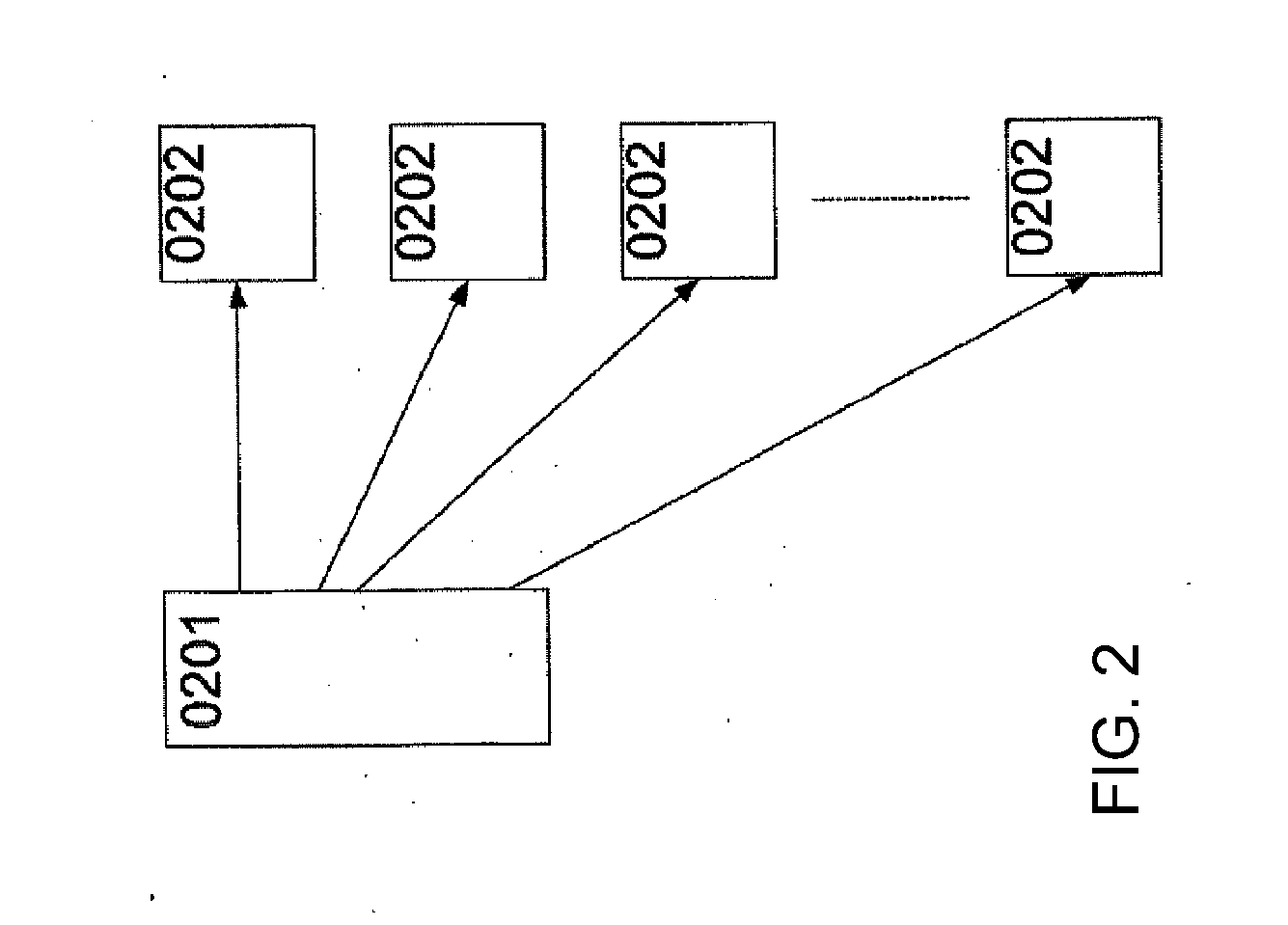

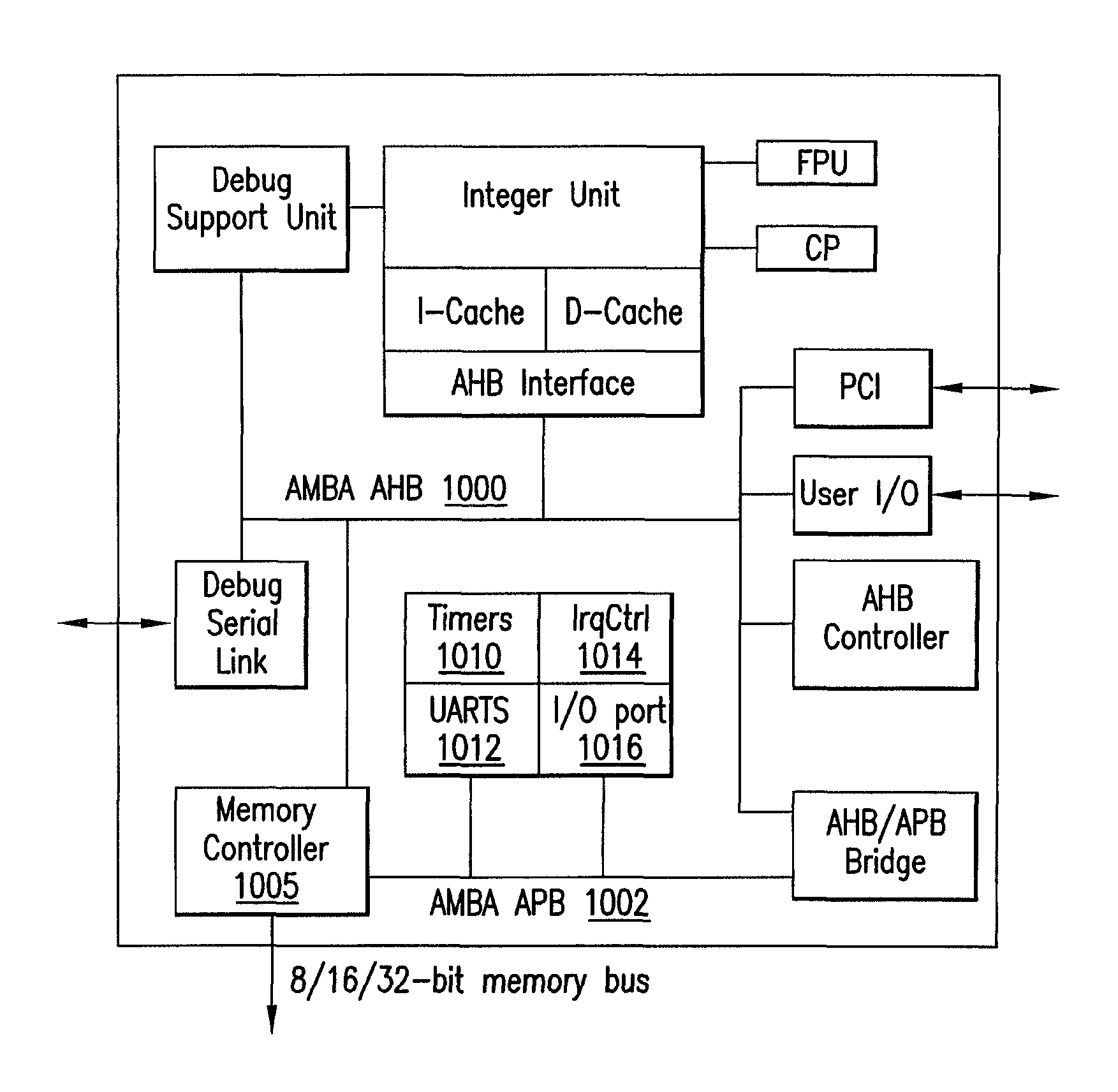

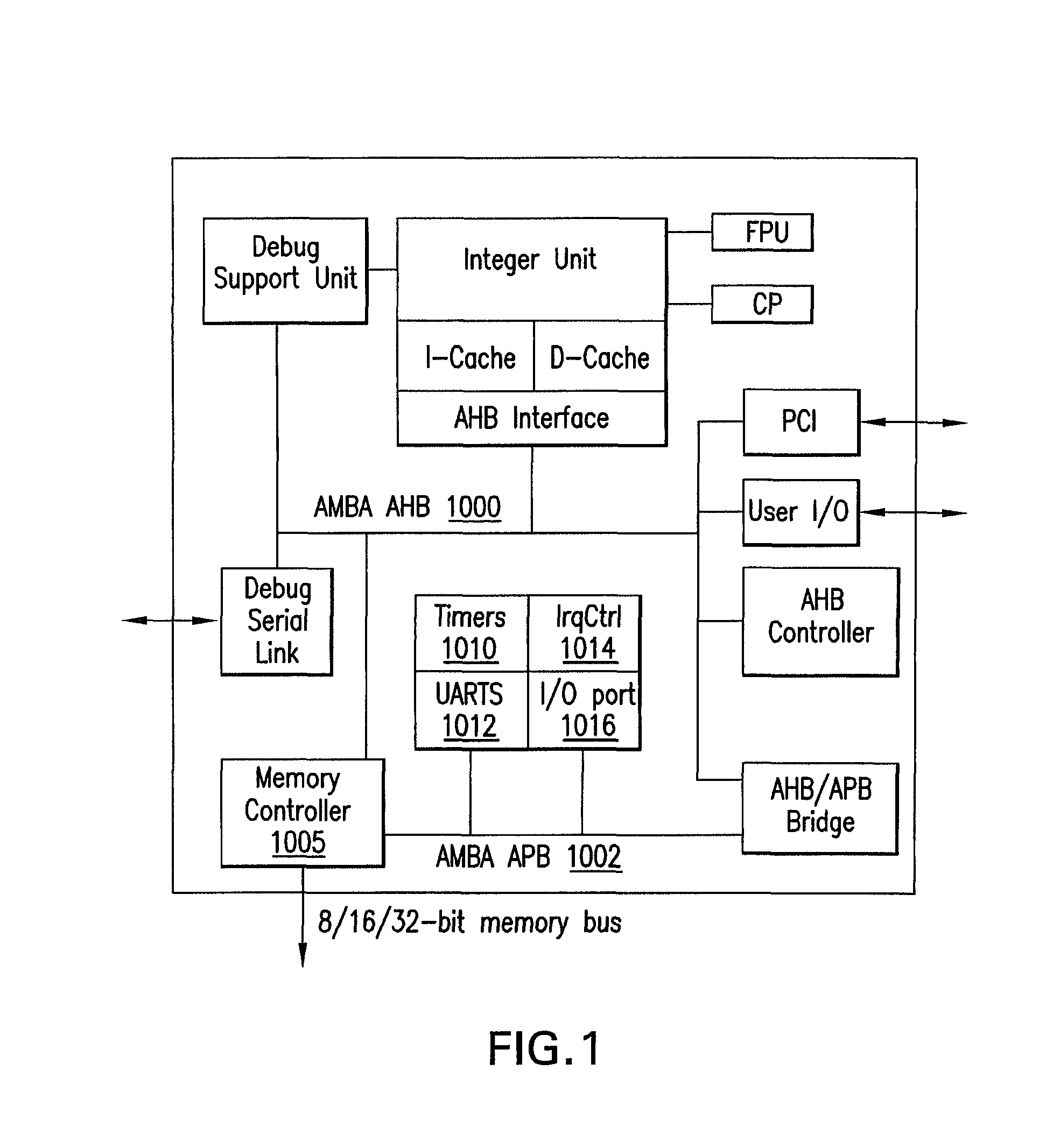

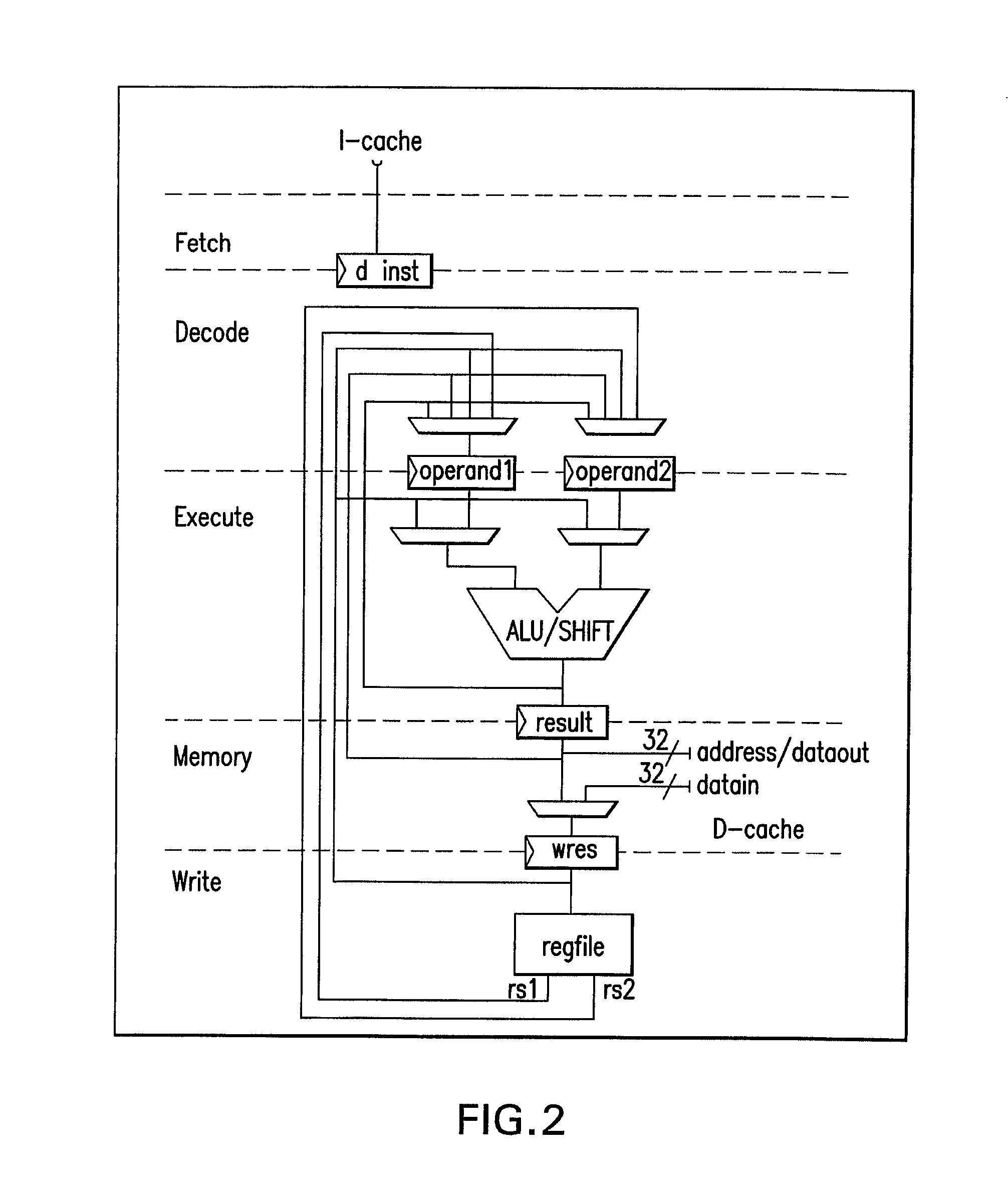

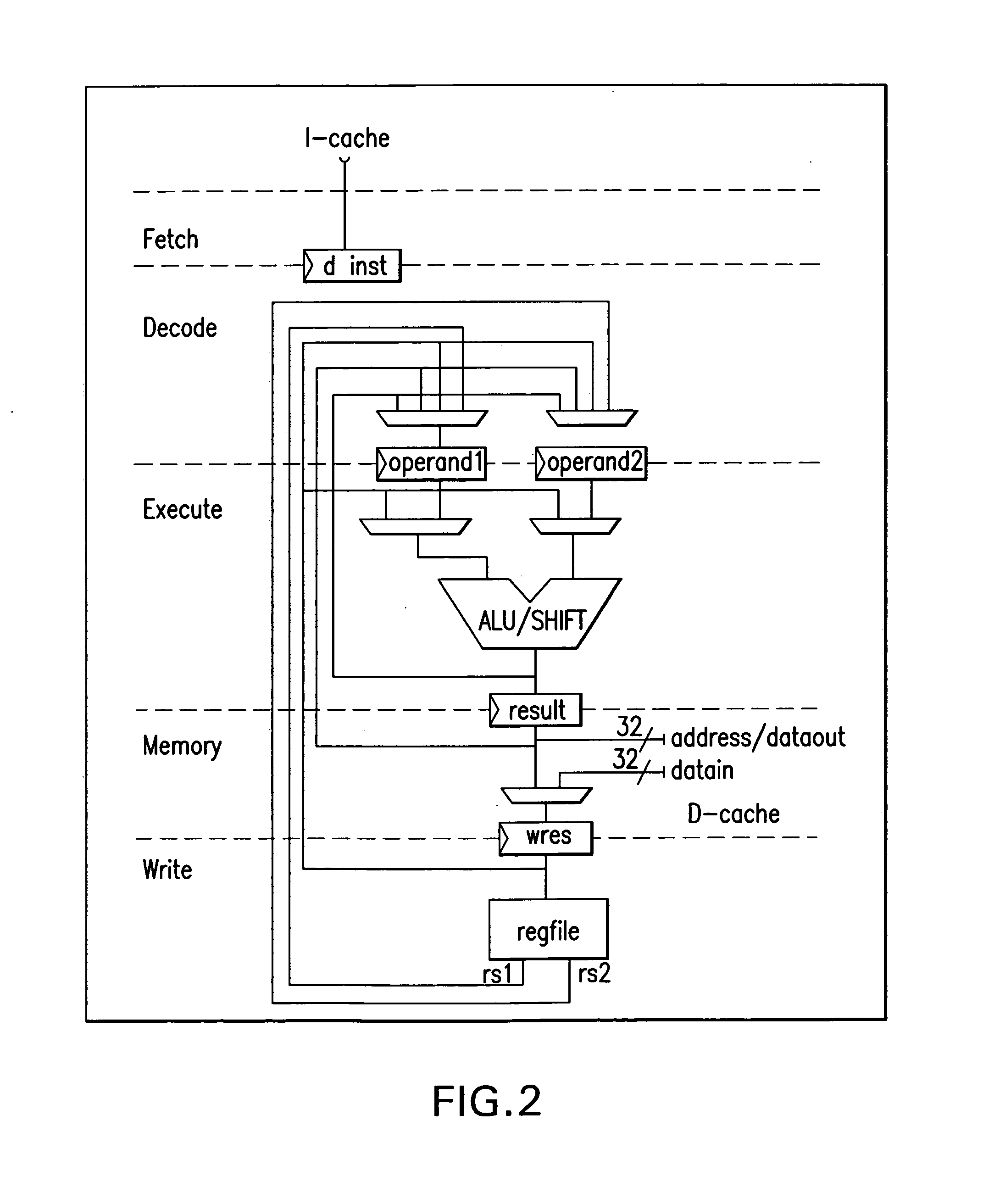

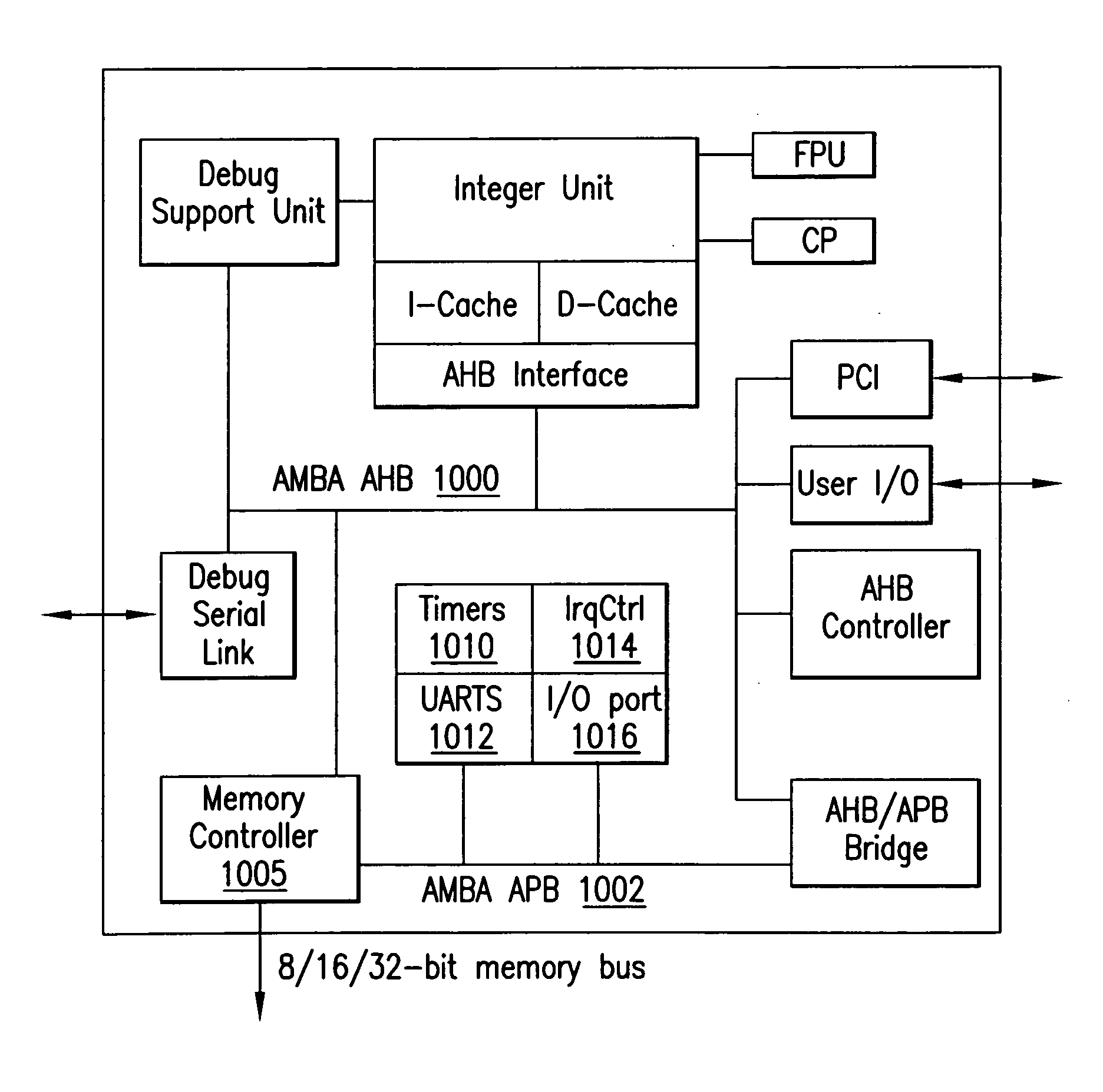

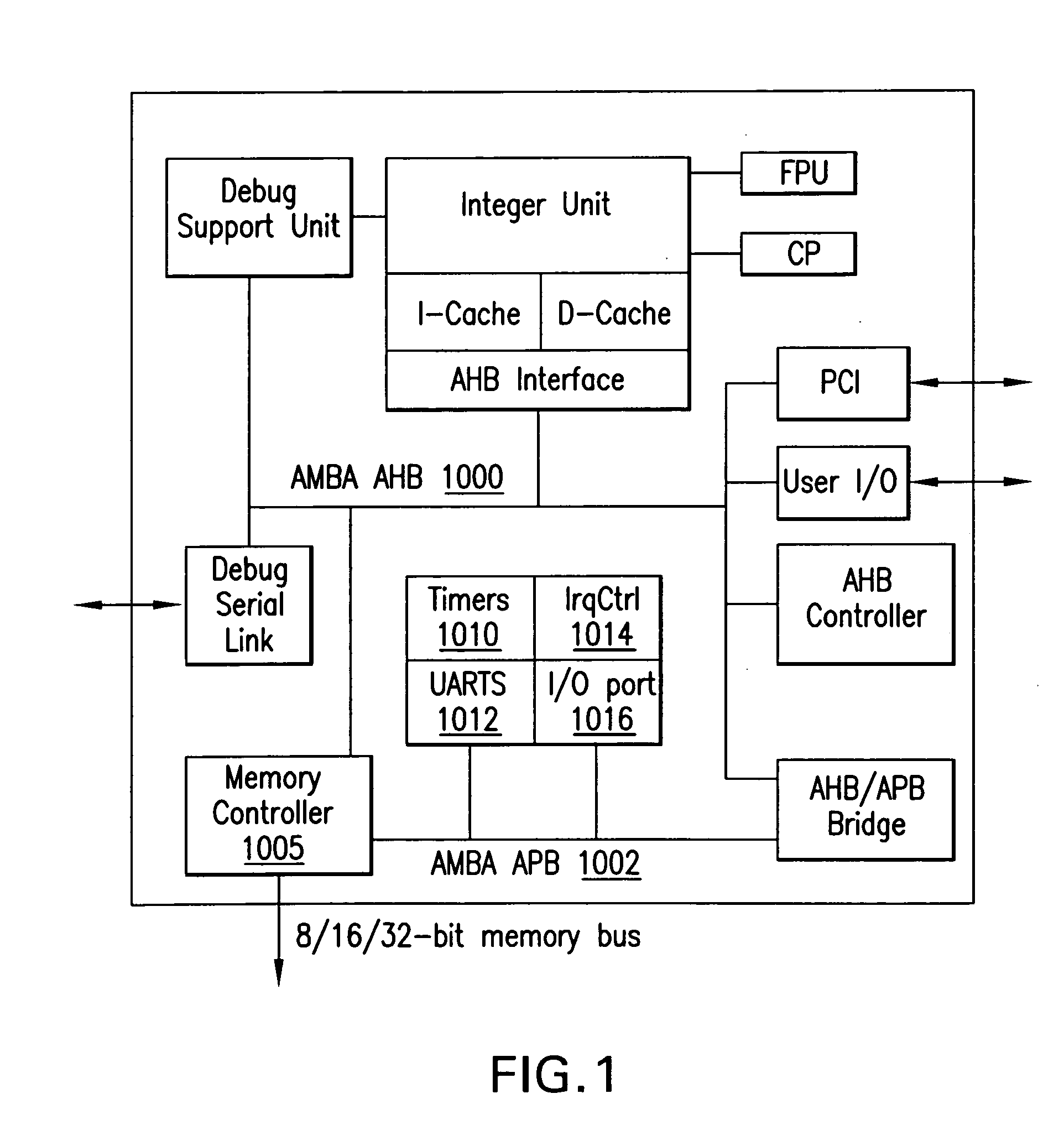

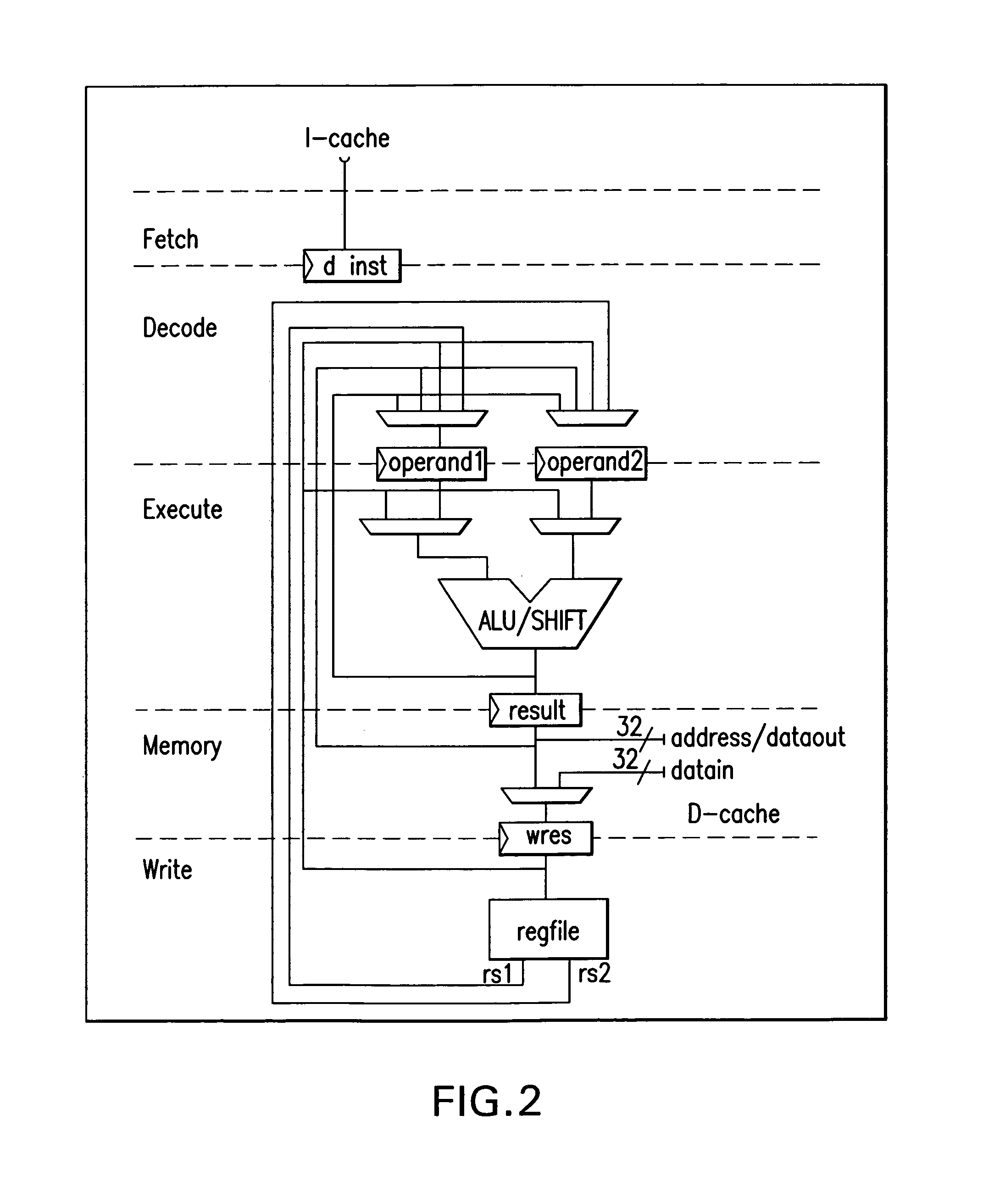

Data Processing System Having Integrated Pipelined Array Data Processor

InactiveUS20150106596A1Improve executionImprove performanceMemory architecture accessing/allocationInstruction analysisData processing systemParallel computing

A data processing system having a data processing core and integrated pipelined array data processor and a buffer for storing list of algorithms for processing by the pipelined array data processor.

Owner:SCIENTIA SOL MENTIS AG

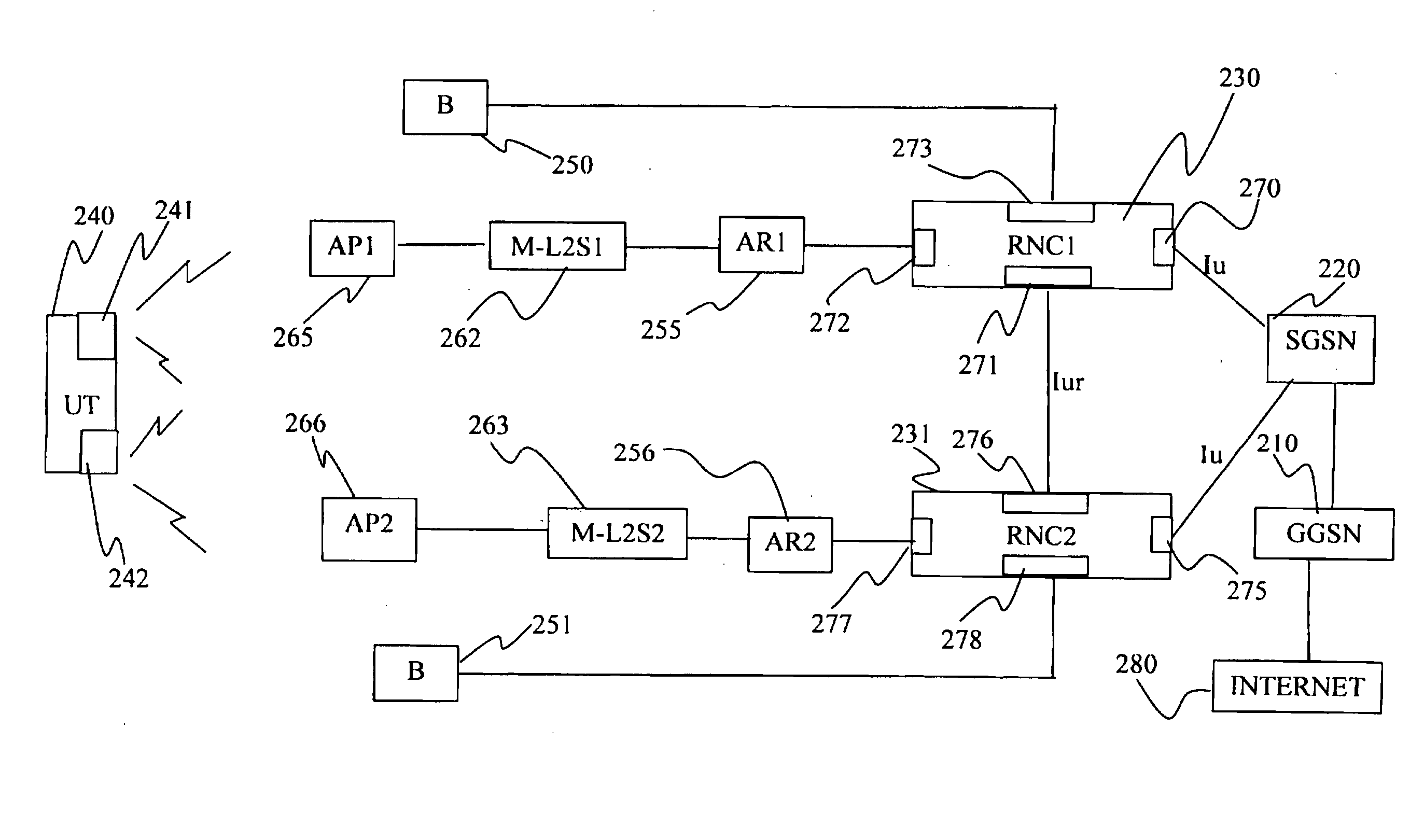

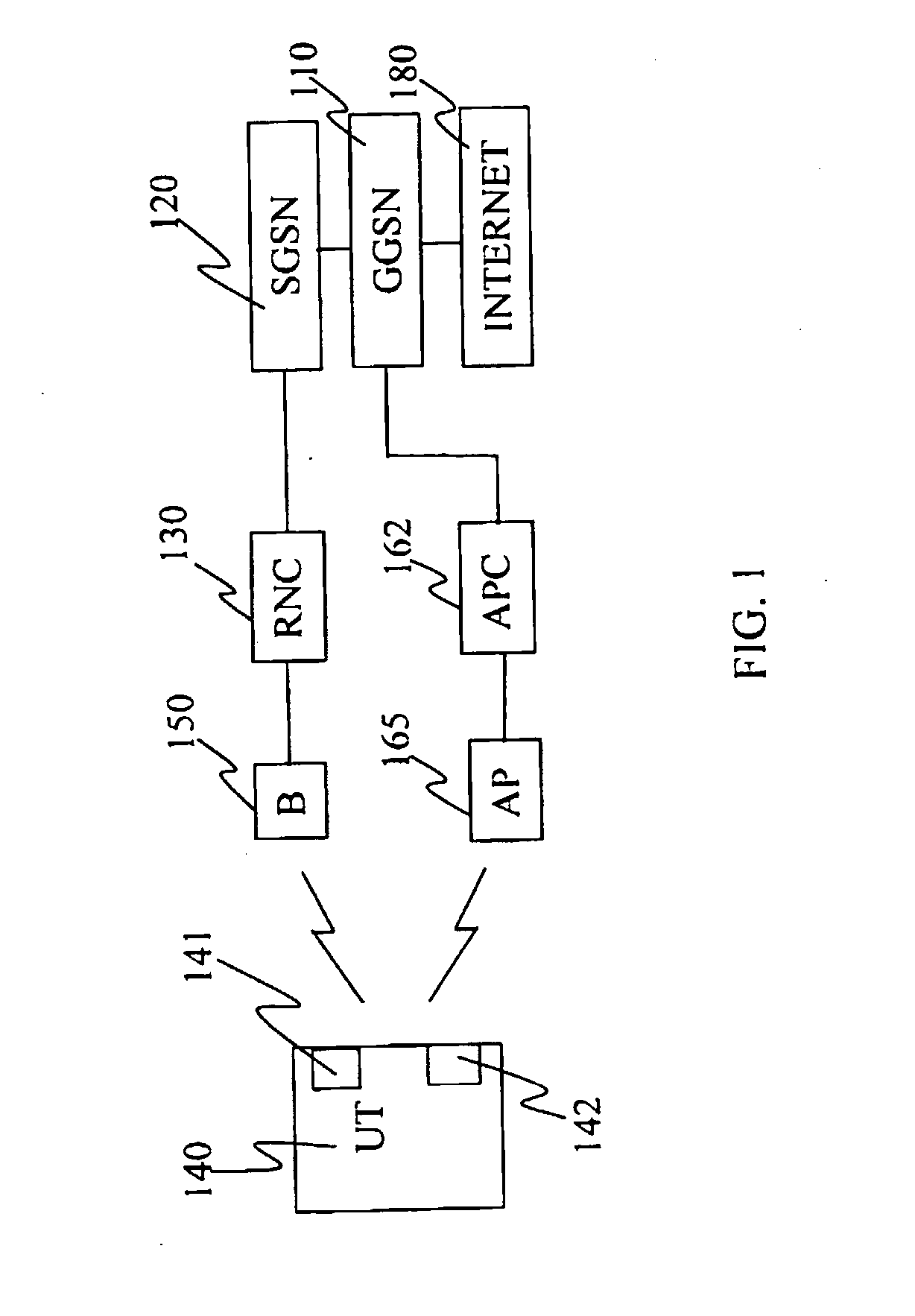

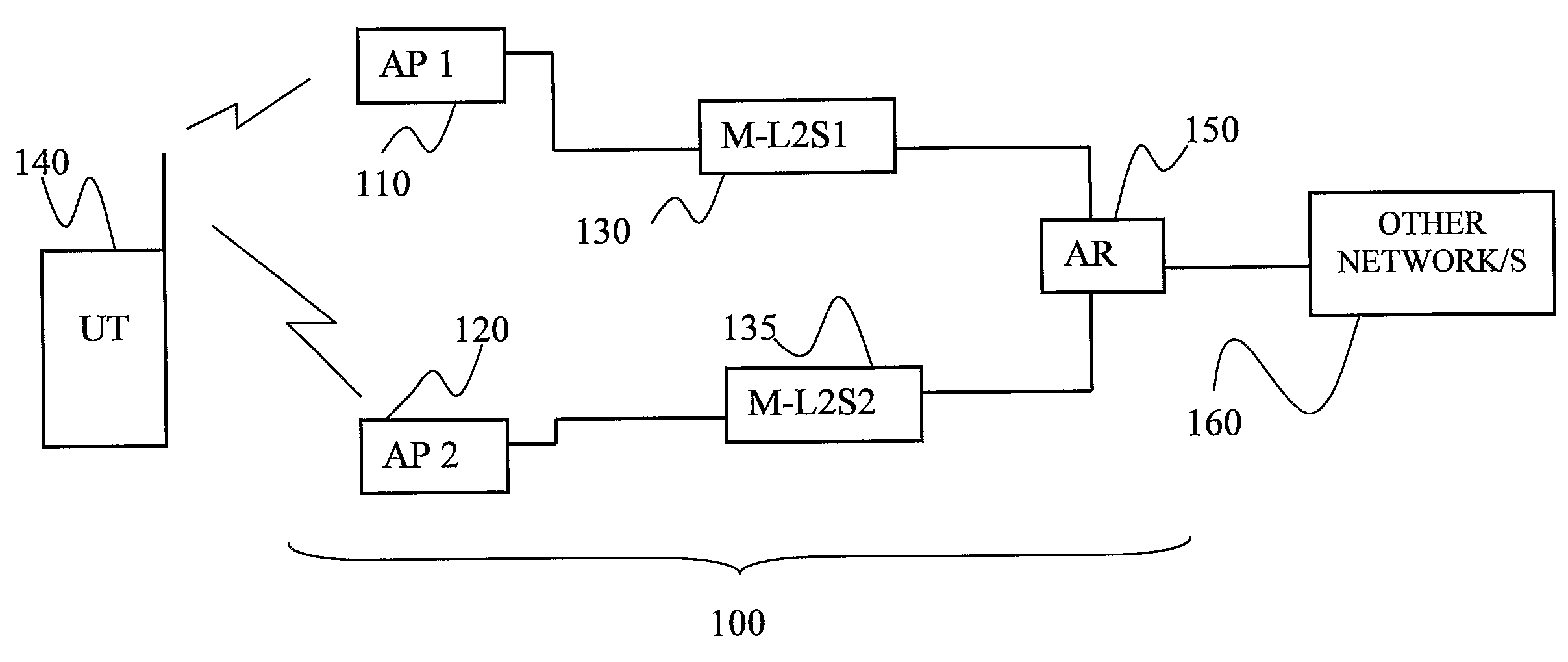

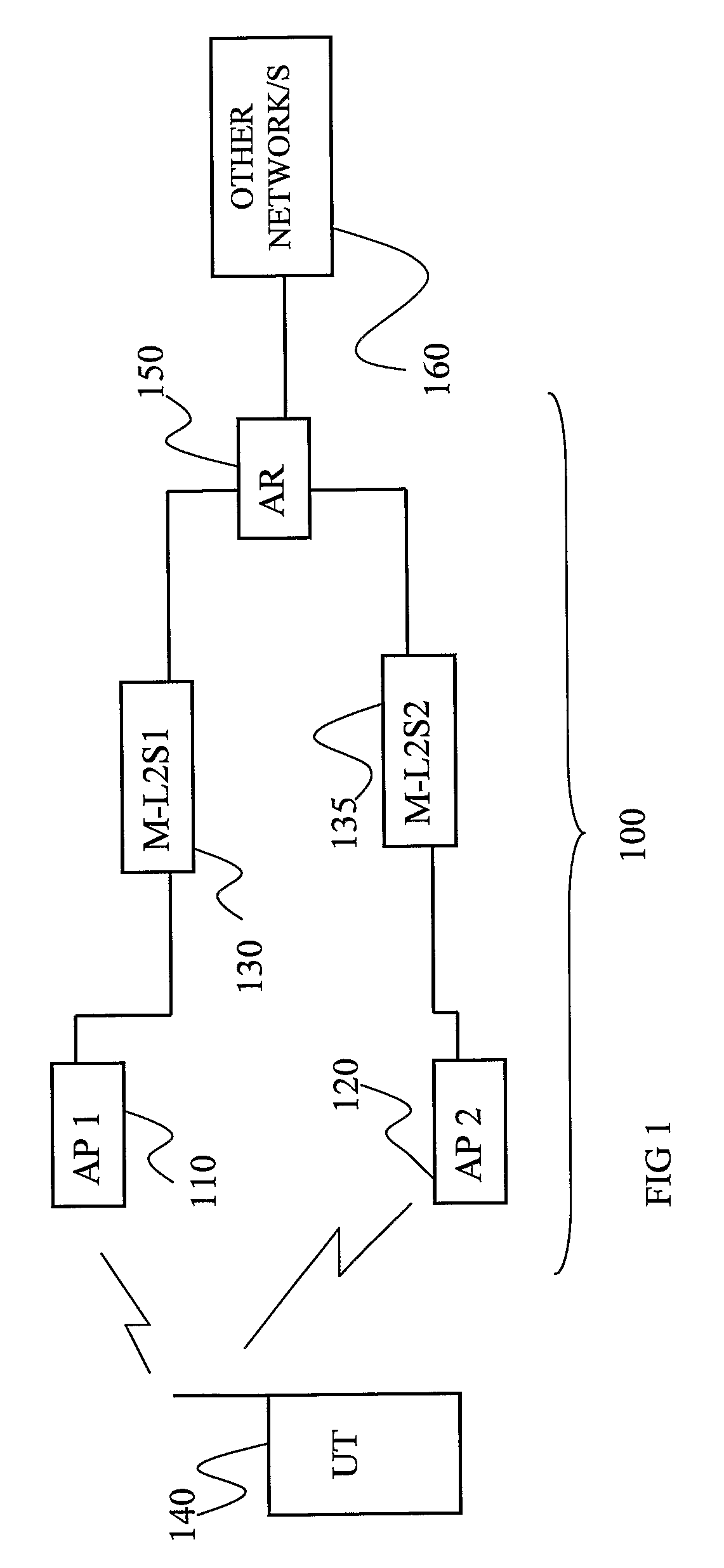

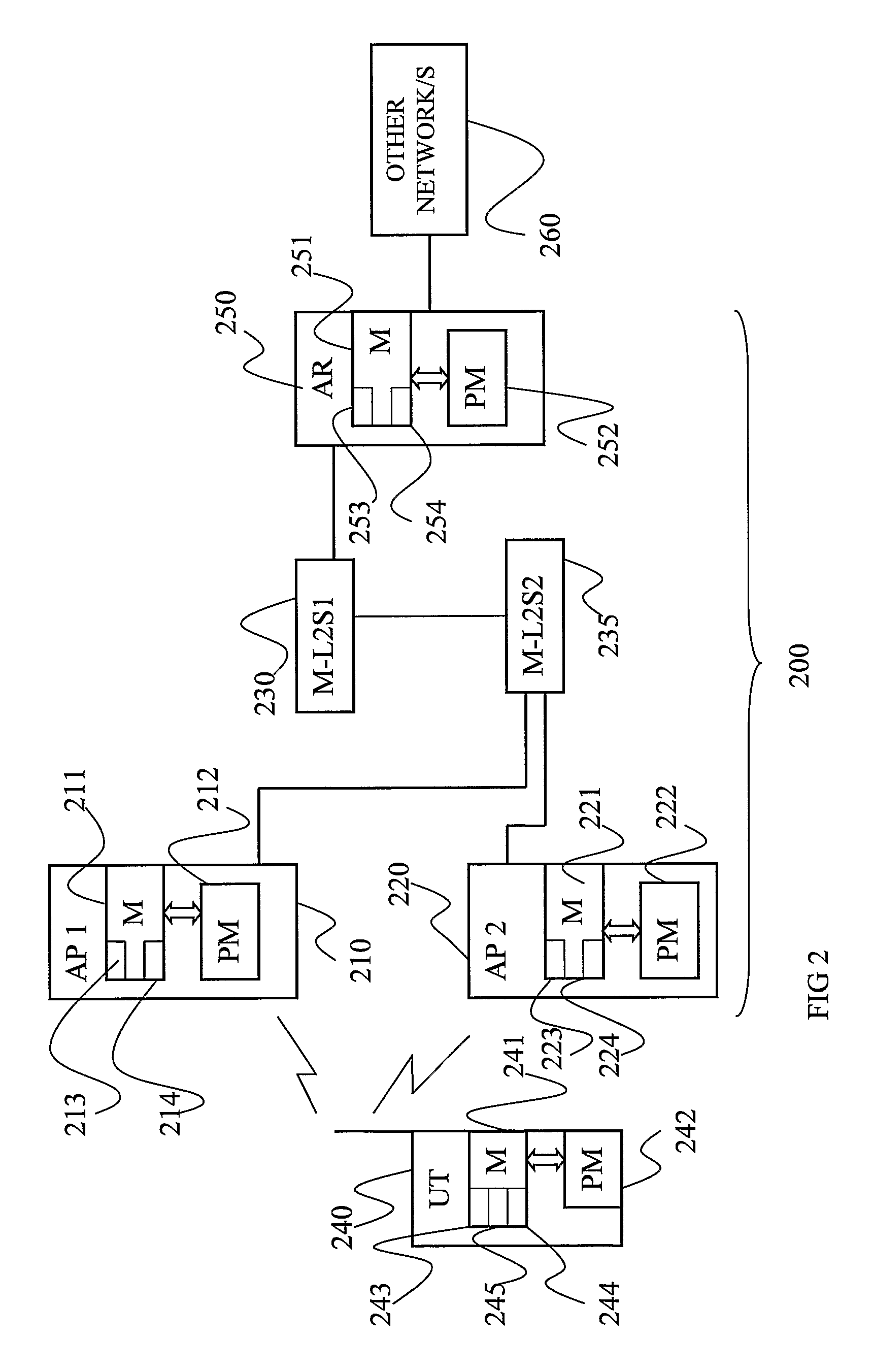

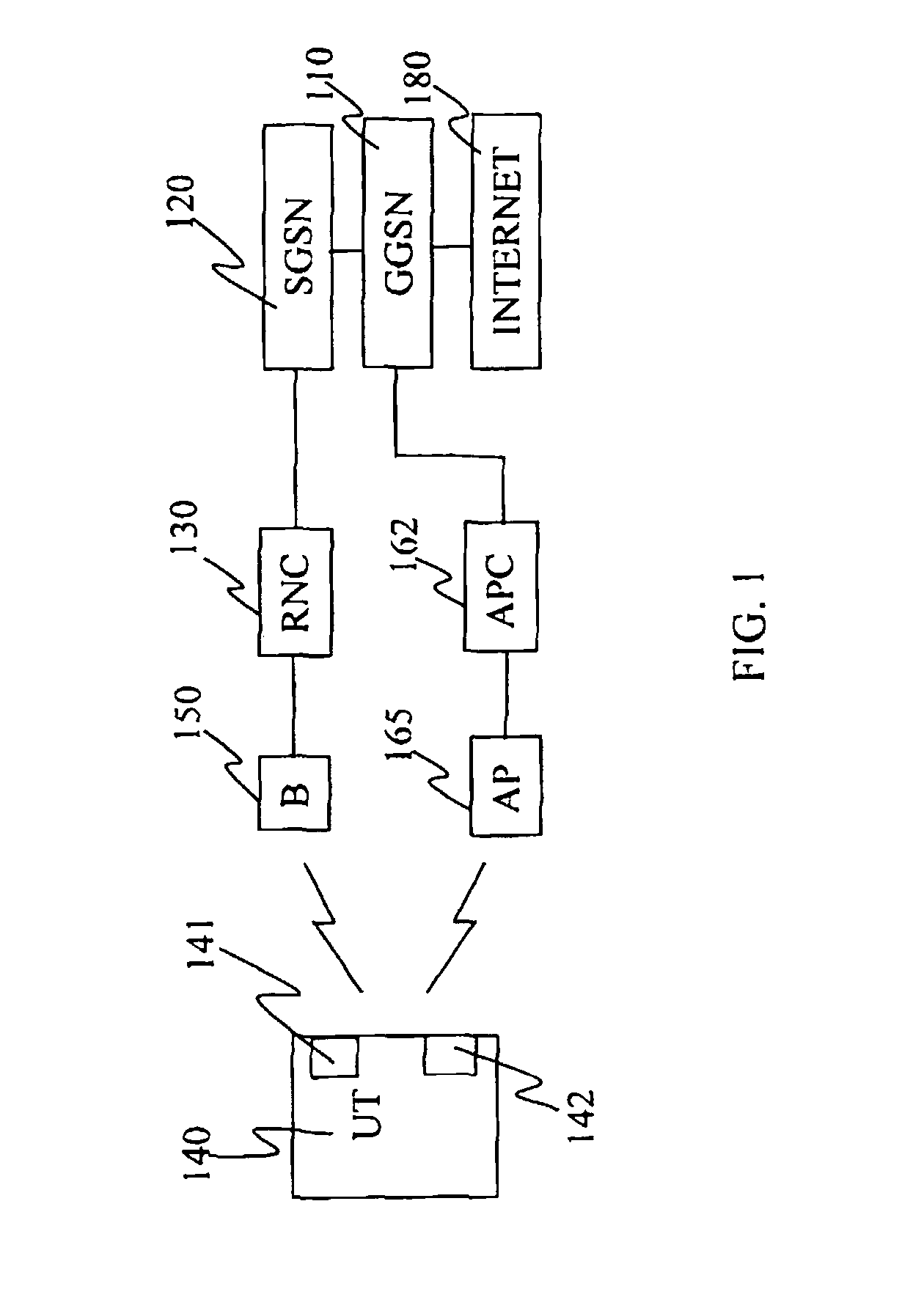

Means and Methods for Improving the Handover Characteristics of Integrated Radio Access Networks

InactiveUS20080205345A1Improve switching characteristicsMinimize data lossRadio/inductive link selection arrangementsWireless commuication servicesMessage typeRadio access network

The invention provides a method for assisting handover of a user terminal's, UT's, communication session in an integrated multi RAT network, said method to be carried out by an RNCI being installed in said network, said method comprising the following steps:— receiving a “Handover Candidate” message comprising a message type identifier information element identifying said message as being a “Handover Candidate” message and which message identifies said session and which message further identifies a candidate RNC of said network, wherein said candidate RNC constitutes an RNC handover candidate for said session,— establishing the identity of said RNC by investigating said message,— associating said communication session with said candidate RNC identified in the previous step. The invention provides an RNC1, RNC2, and software, realising the method according to the invention.

Owner:TELEFON AB LM ERICSSON (PUBL)

Data processing method and device

ActiveUS8156284B2Improve executionImprove performanceMemory adressing/allocation/relocationConcurrent instruction executionParallel computingRead-write memory

In a data-processing method, first result data may be obtained using a plurality of configurable coarse-granular elements, the first result data may be written into a memory that includes spatially separate first and second memory areas and that is connected via a bus to the plurality of configurable coarse-granular elements, the first result data may be subsequently read out from the memory, and the first result data may be subsequently processed using the plurality of configurable coarse-granular elements. In a first configuration, the first memory area may be configured as a write memory, and the second memory area may be configured as a read memory. Subsequent to writing to and reading from the memory in accordance with the first configuration, the first memory area may be configured as a read memory, and the second memory area may be configured as a write memory.

Owner:SCIENTIA SOL MENTIS AG

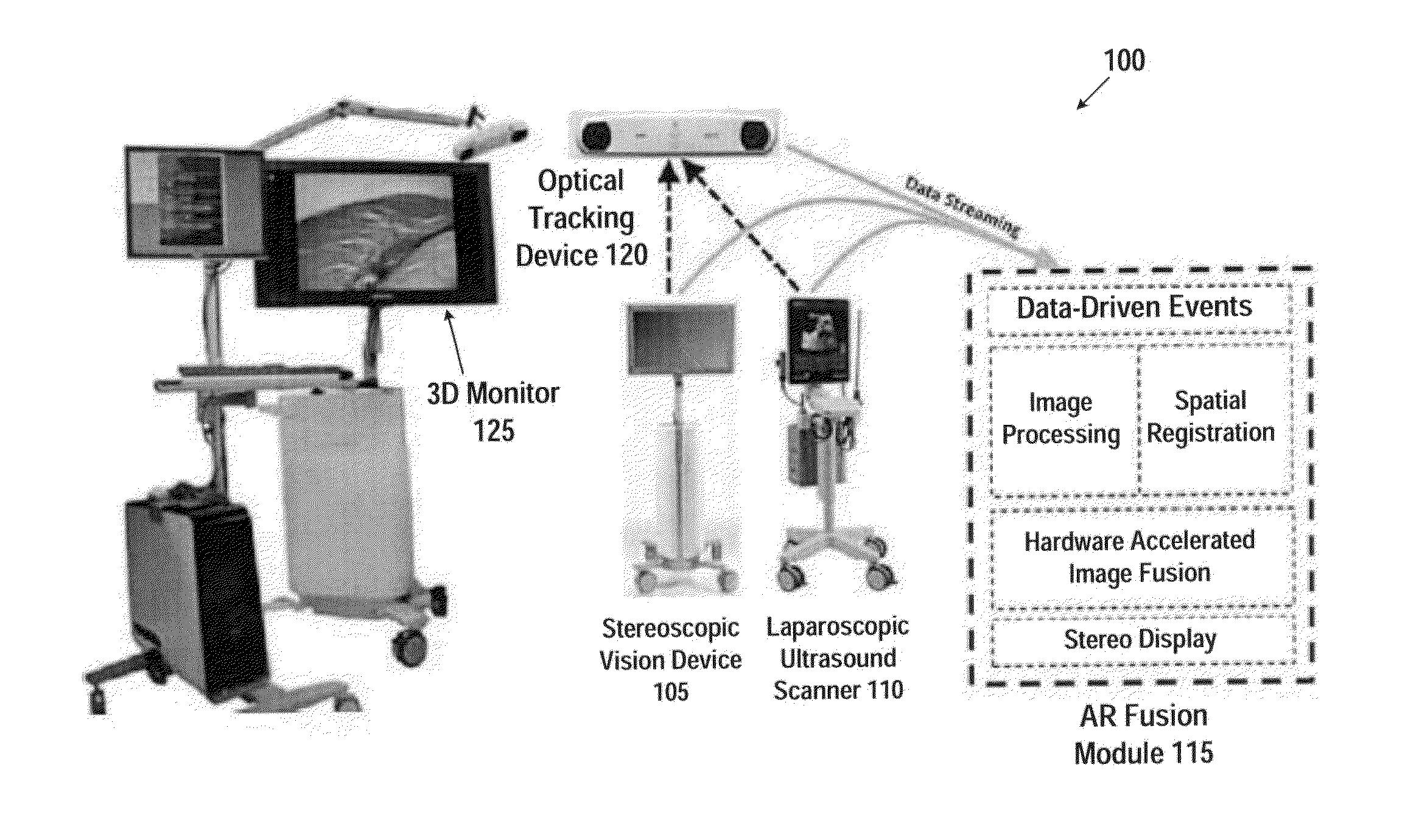

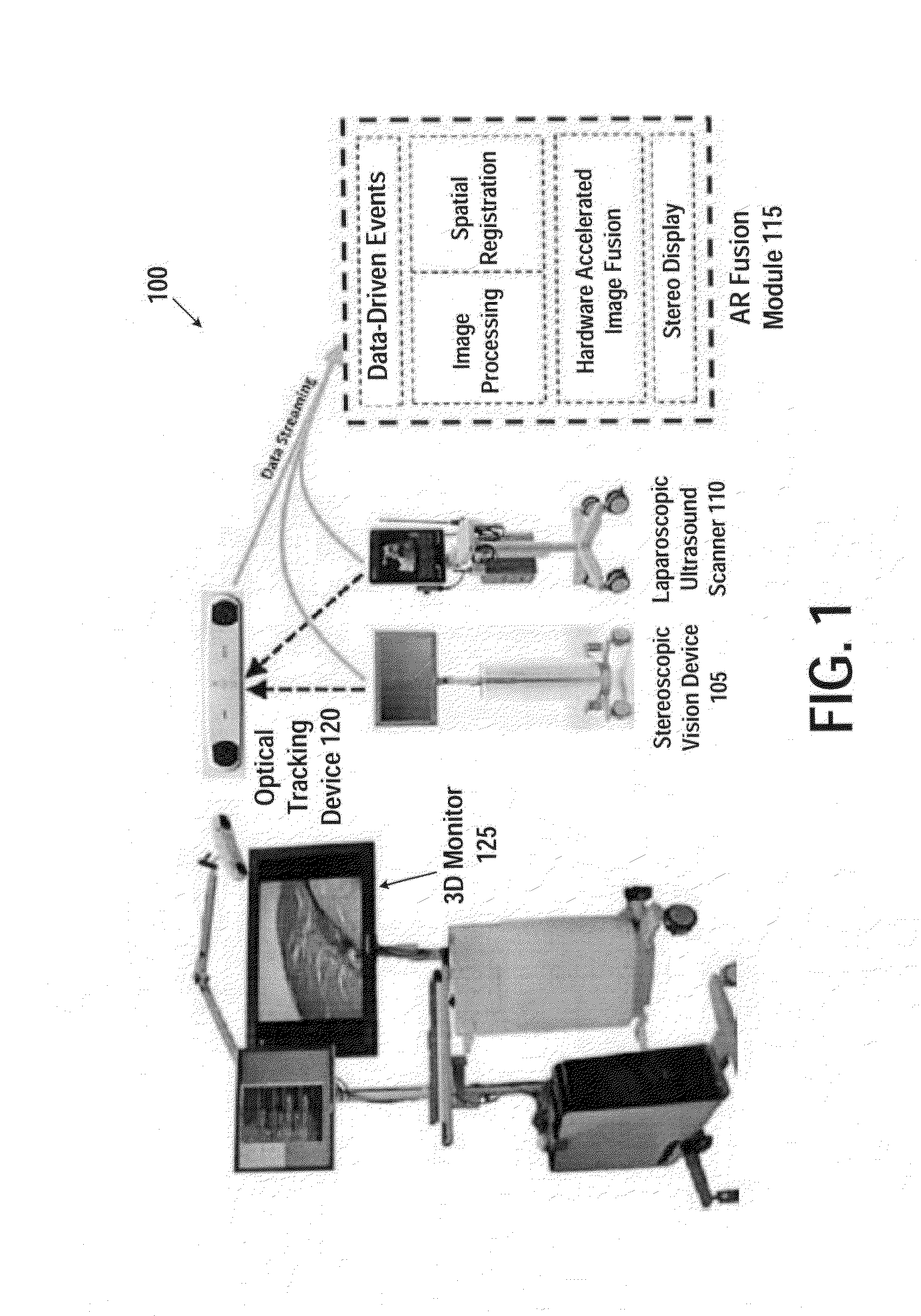

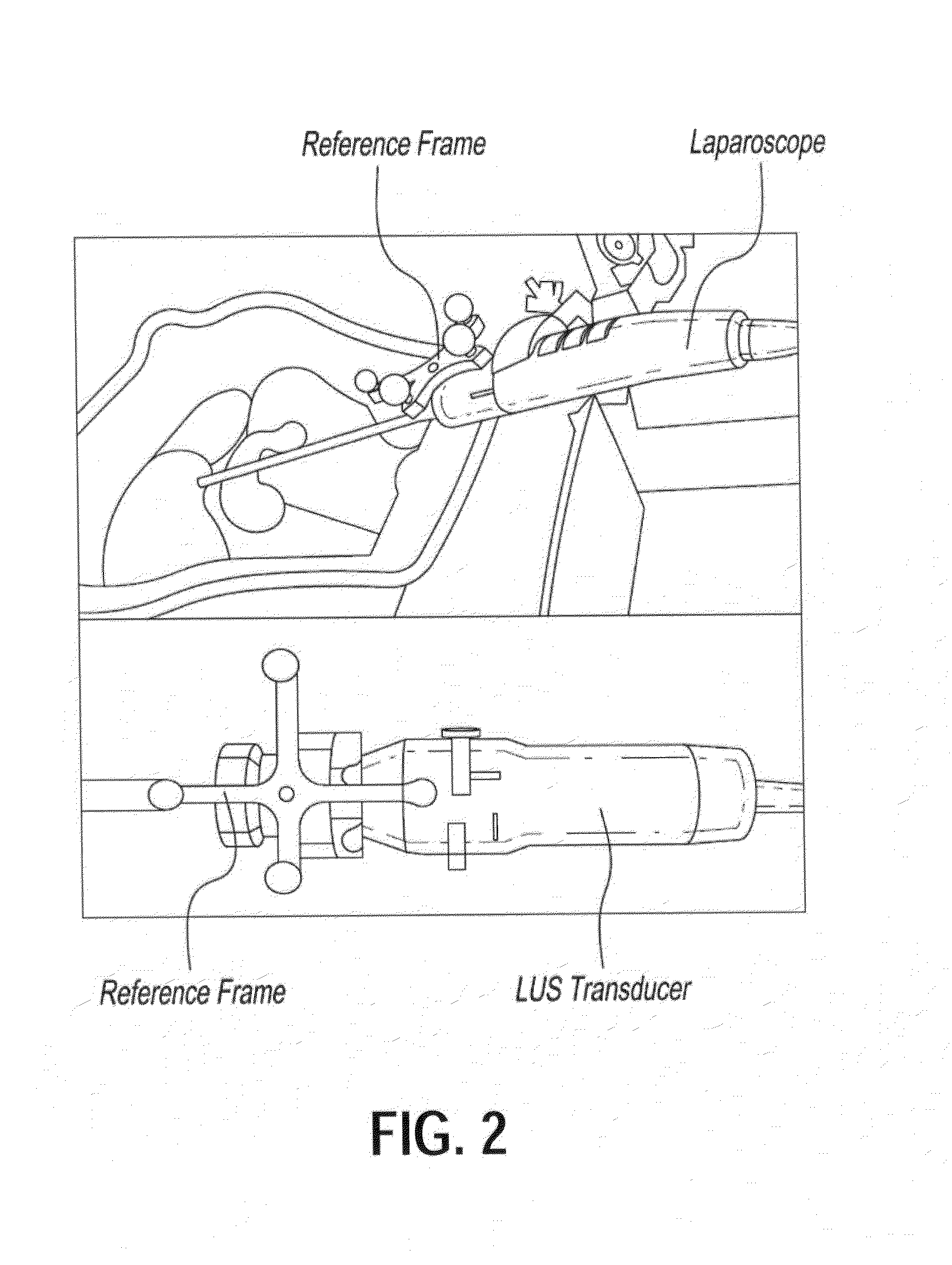

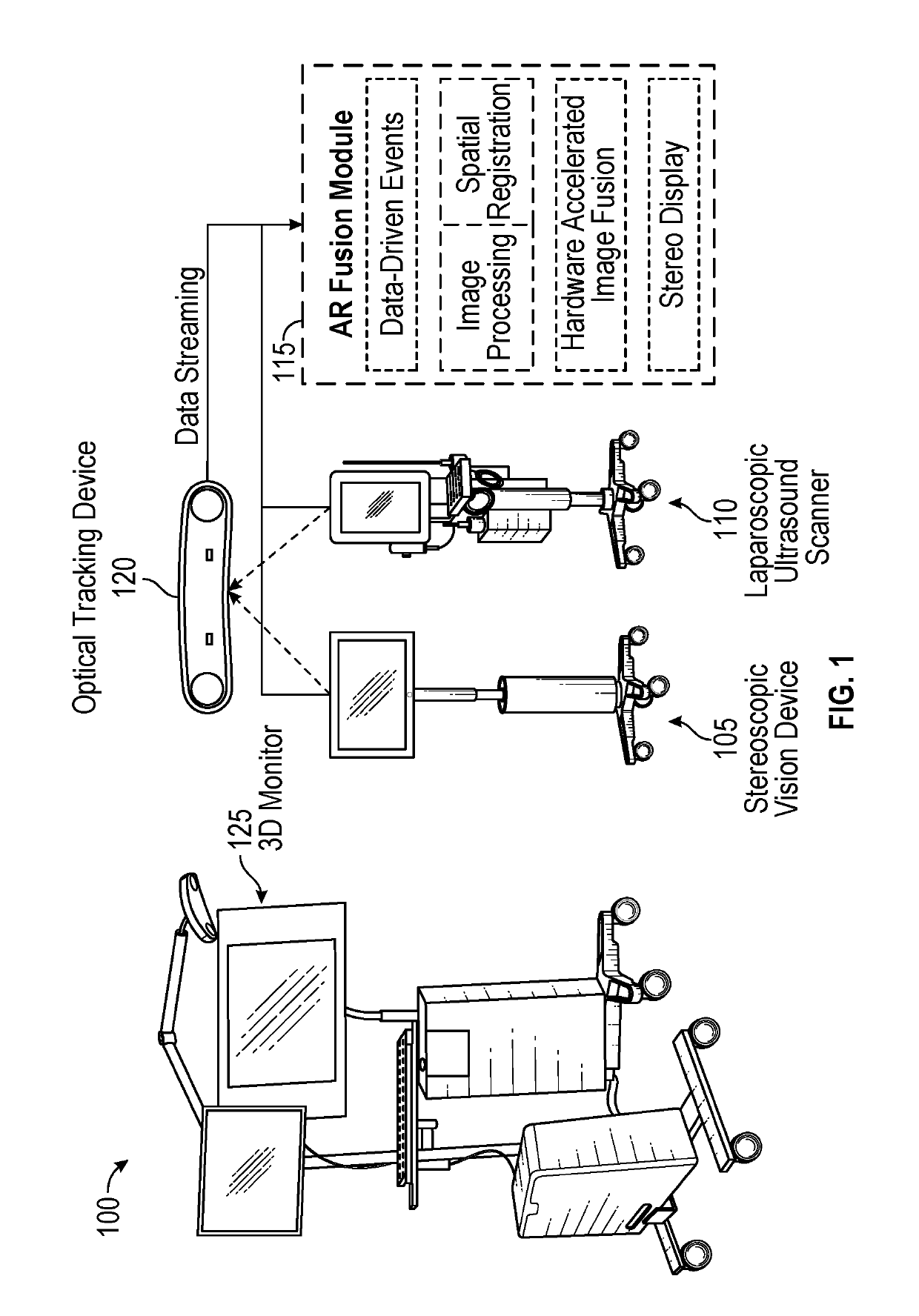

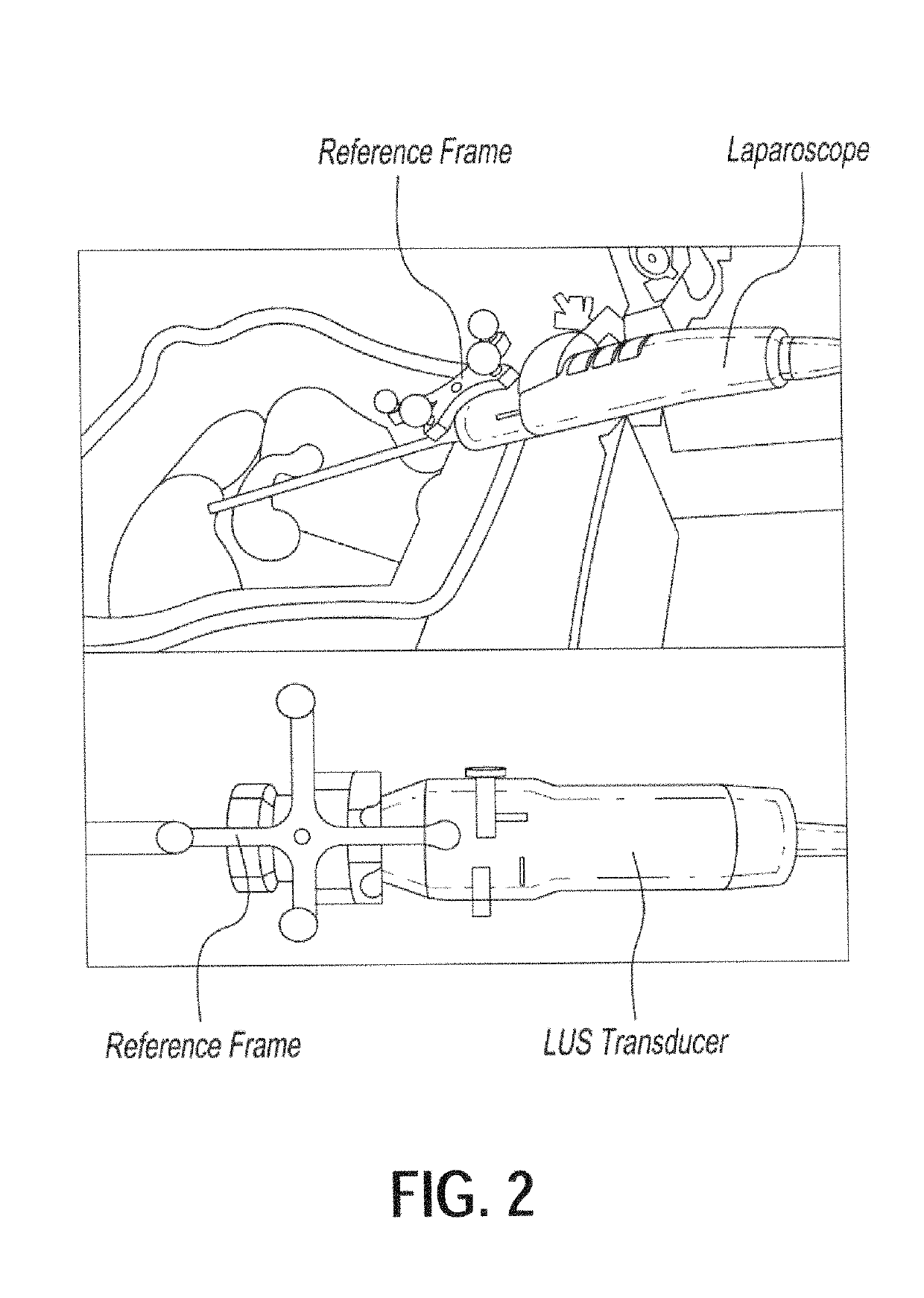

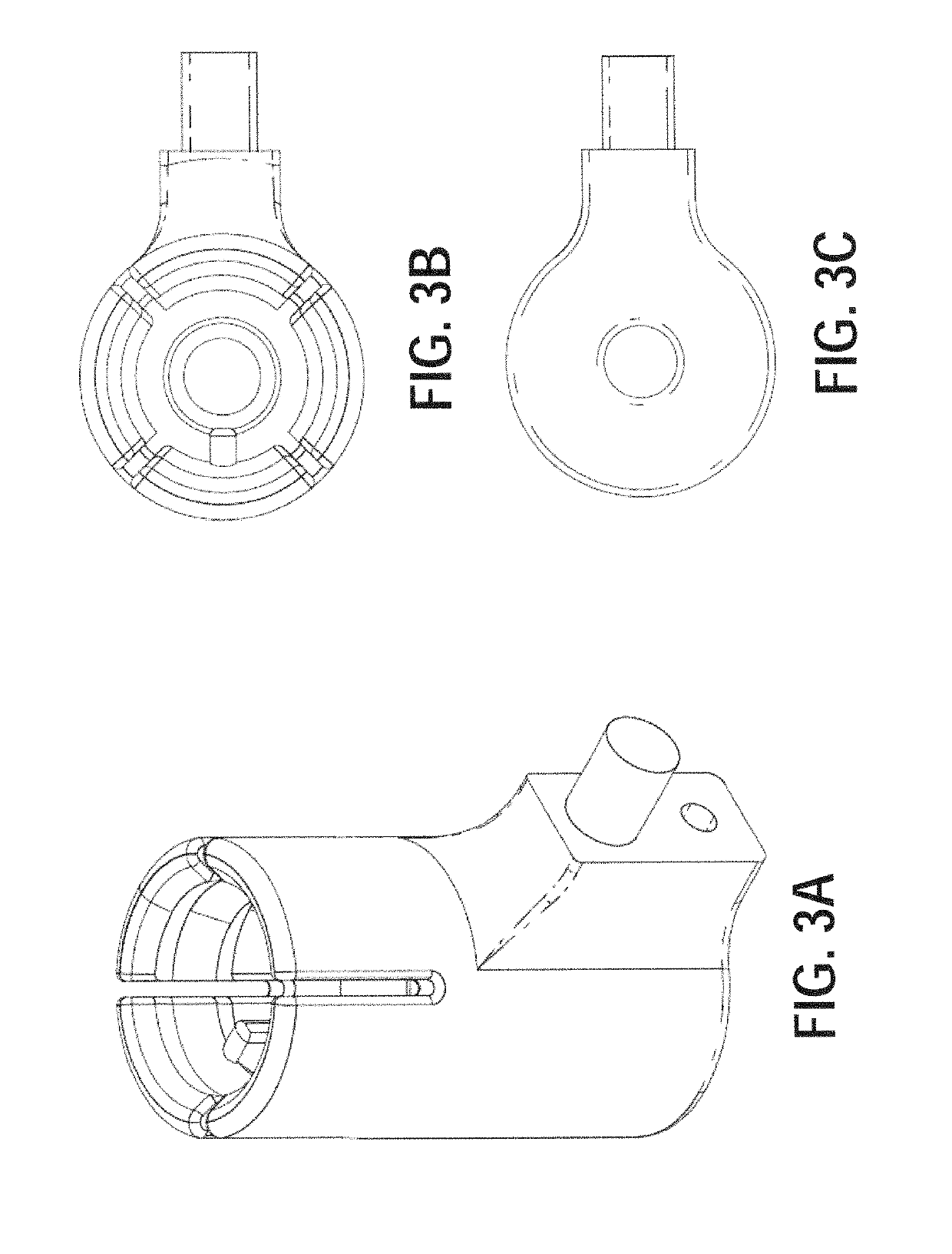

Device and method for generating composite images for endoscopic surgery of moving and deformable anatomy

ActiveUS20140303491A1Improve understandingImprove surgical efficiencyUltrasonic/sonic/infrasonic diagnosticsImage enhancementIntra operativeTomographic image

A device for generating composite images of dynamically changing surgical anatomy includes circuitry configured to receive, from an endoscopic imaging device, endoscopic image data. The circuitry is configured to receive, from a tomographic imaging device, intra-operative tomographic image data. The circuitry is configured to receive, from a tracking device, spatial tracking data corresponding to the endoscopic imaging device and the tomographic imaging device. The circuitry is configured to generate real-time dynamically changing composite image data by overlaying, based on the spatial tracking data, the intra-operative tomographic image data on the endoscopic image data. The circuitry is configured to output the composite image data to a display.

Owner:CHILDRENS NAT MEDICAL CENT

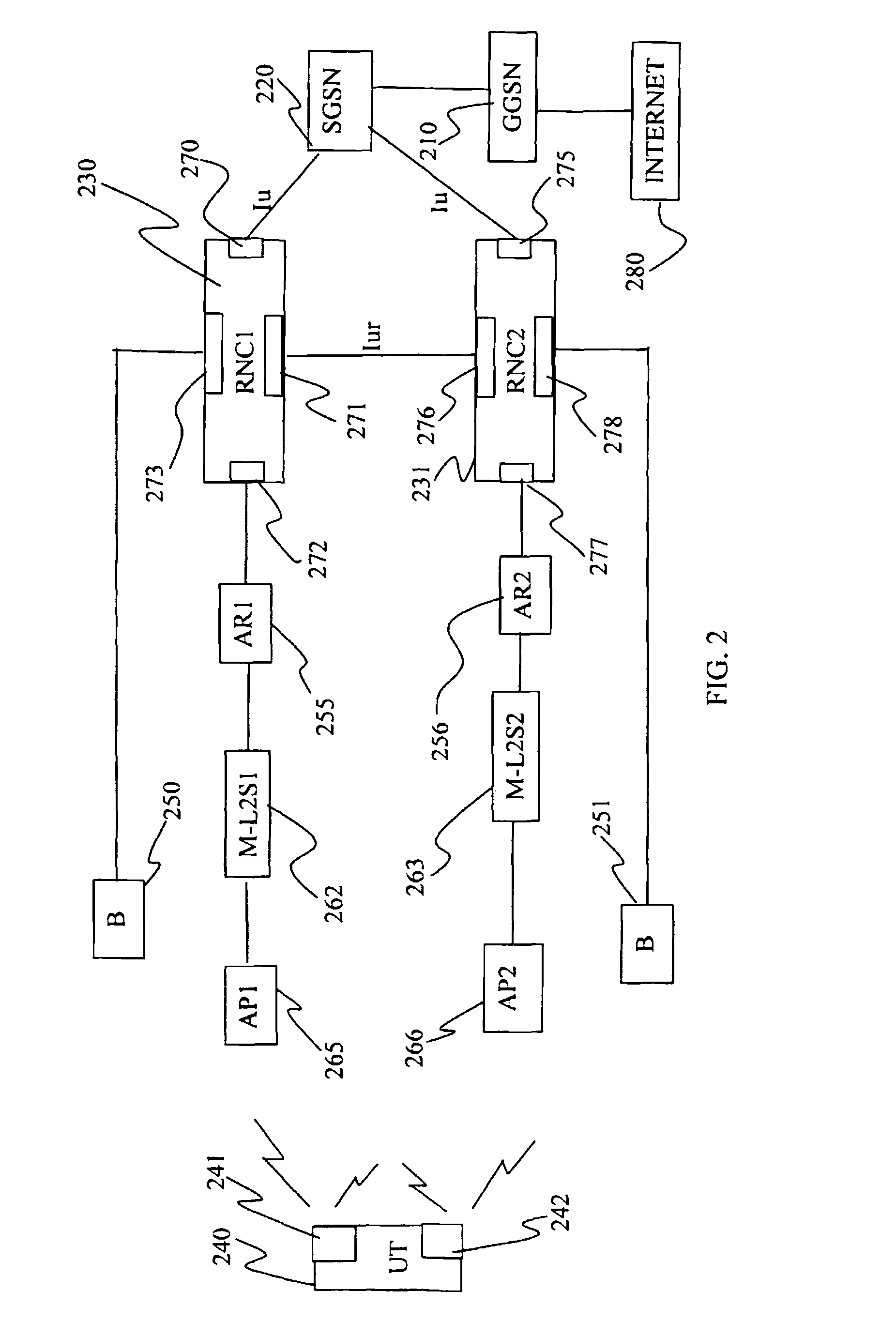

Handover Optimisation in a Wlan Radio Access Network

ActiveUS20080192696A1Improve switching characteristicsMinimize data lossRadio/inductive link selection arrangementsWireless commuication servicesAccess networkRadio access network

The invention provides a method for assisting handover of a communication session associated with a UT from a first radio access point, AP1, to a second radio access point, AP2, in a radio access network, said method to be carried out by said AP1 and comprising the steps of:—receiving a handover intention notify message comprising a session identifier identifying said session and indicating that said UT intends to perform a session handover,—assigning said session a buffer memory space in a memory of said AP1,—buffering downlink data packets addressed to said UT in said buffer memory as a response on receiving said handover intention notify message. The invention further provides a UT, an AP1, AP2, an AR, and software program / s co-operating and / or realizing the method according to the invention. The invention provides a smoother handover.

Owner:TELEFON AB LM ERICSSON (PUBL)

Data processing method and device

ActiveUS20100153654A1Ease memory access problemIncrease data throughputMemory adressing/allocation/relocationDigital computer detailsData processingRead-write memory

In a data-processing method, first result data may be obtained using a plurality of configurable coarse-granular elements, the first result data may be written into a memory that includes spatially separate first and second memory areas and that is connected via a bus to the plurality of configurable coarse-granular elements, the first result data may be subsequently read out from the memory, and the first result data may be subsequently processed using the plurality of configurable coarse-granular elements. In a first configuration, the first memory area may be configured as a write memory, and the second memory area may be configured as a read memory. Subsequent to writing to and reading from the memory in accordance with the first configuration, the first memory area may be configured as a read memory, and the second memory area may be configured as a write memory.

Owner:SCIENTIA SOL MENTIS AG

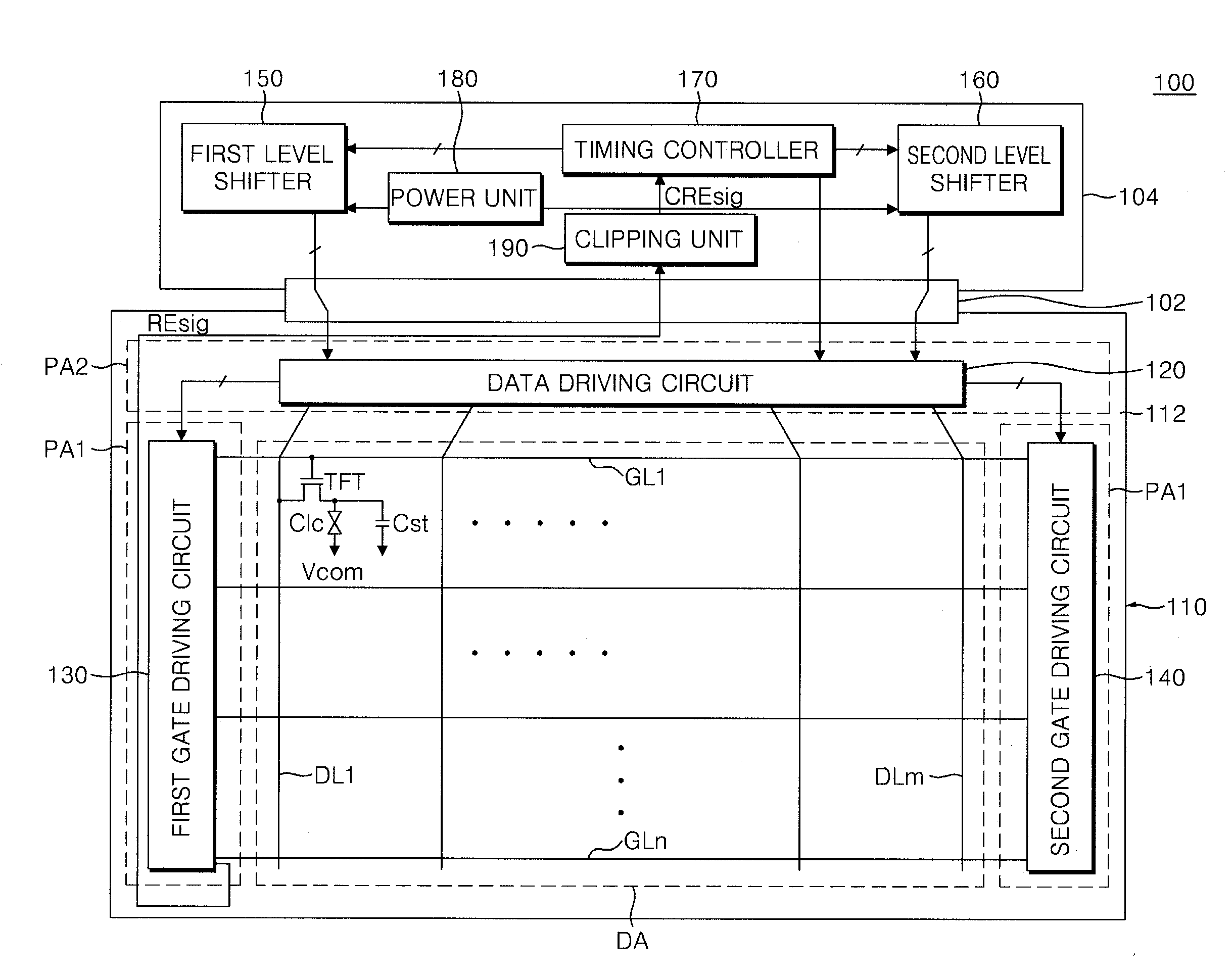

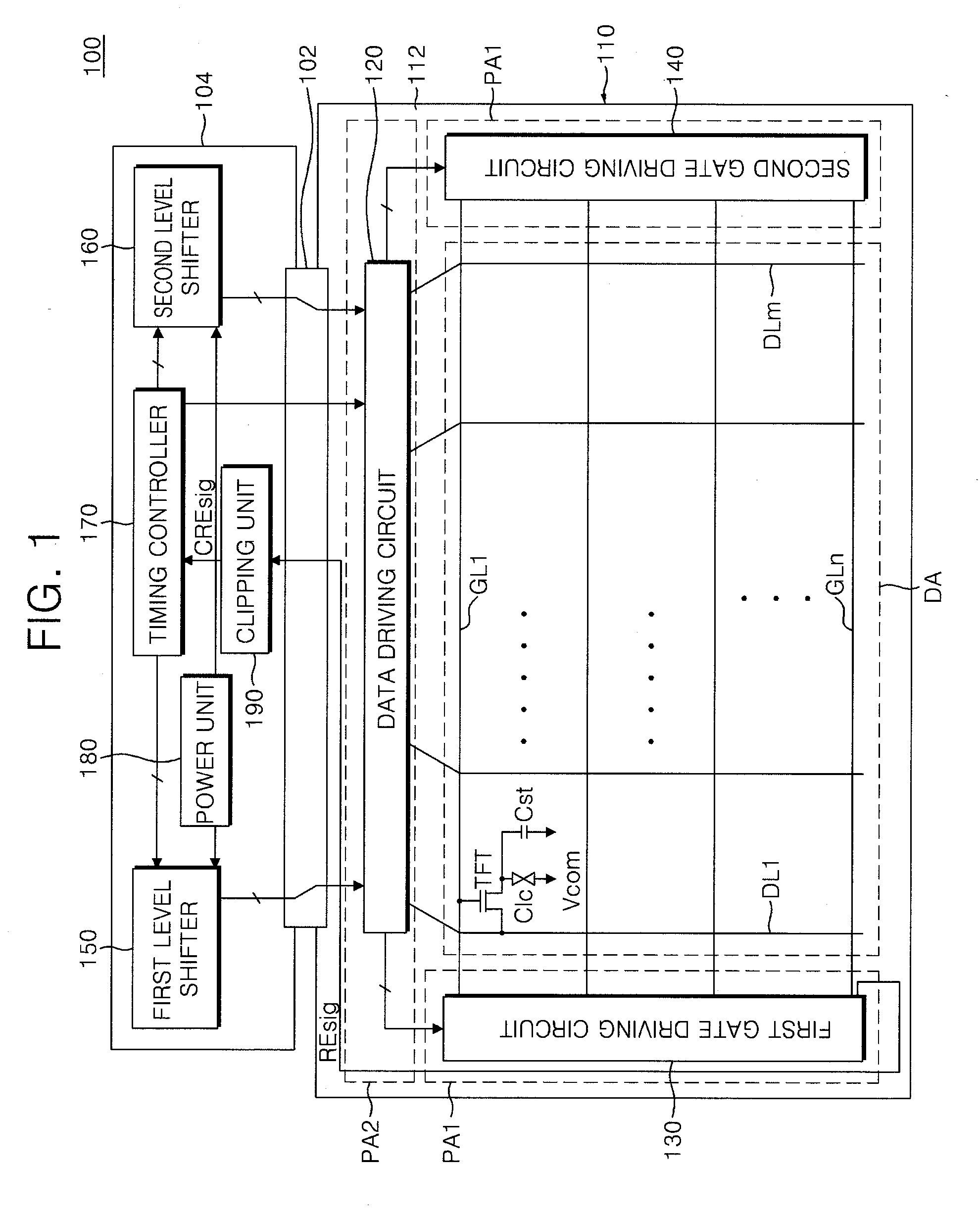

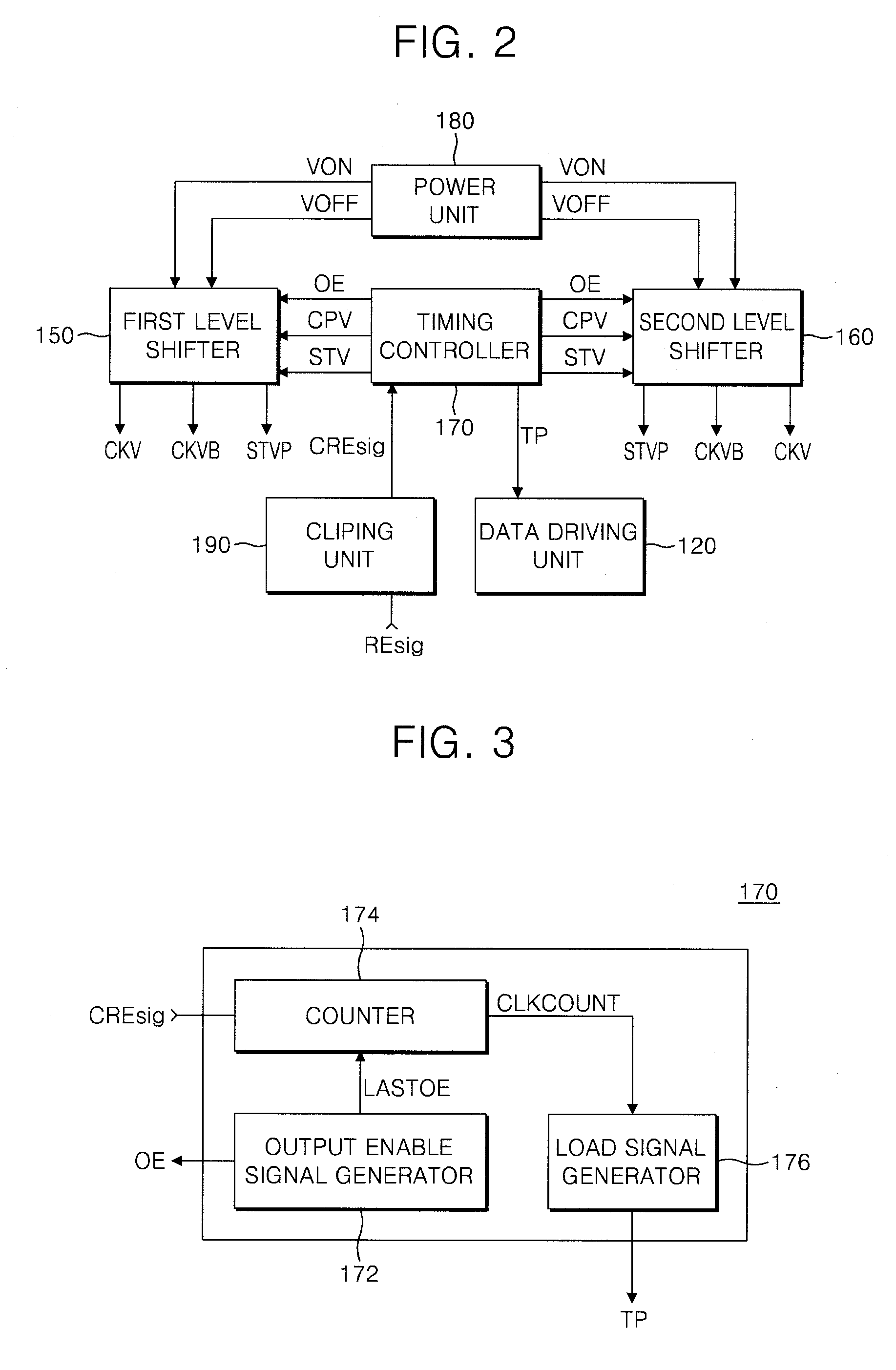

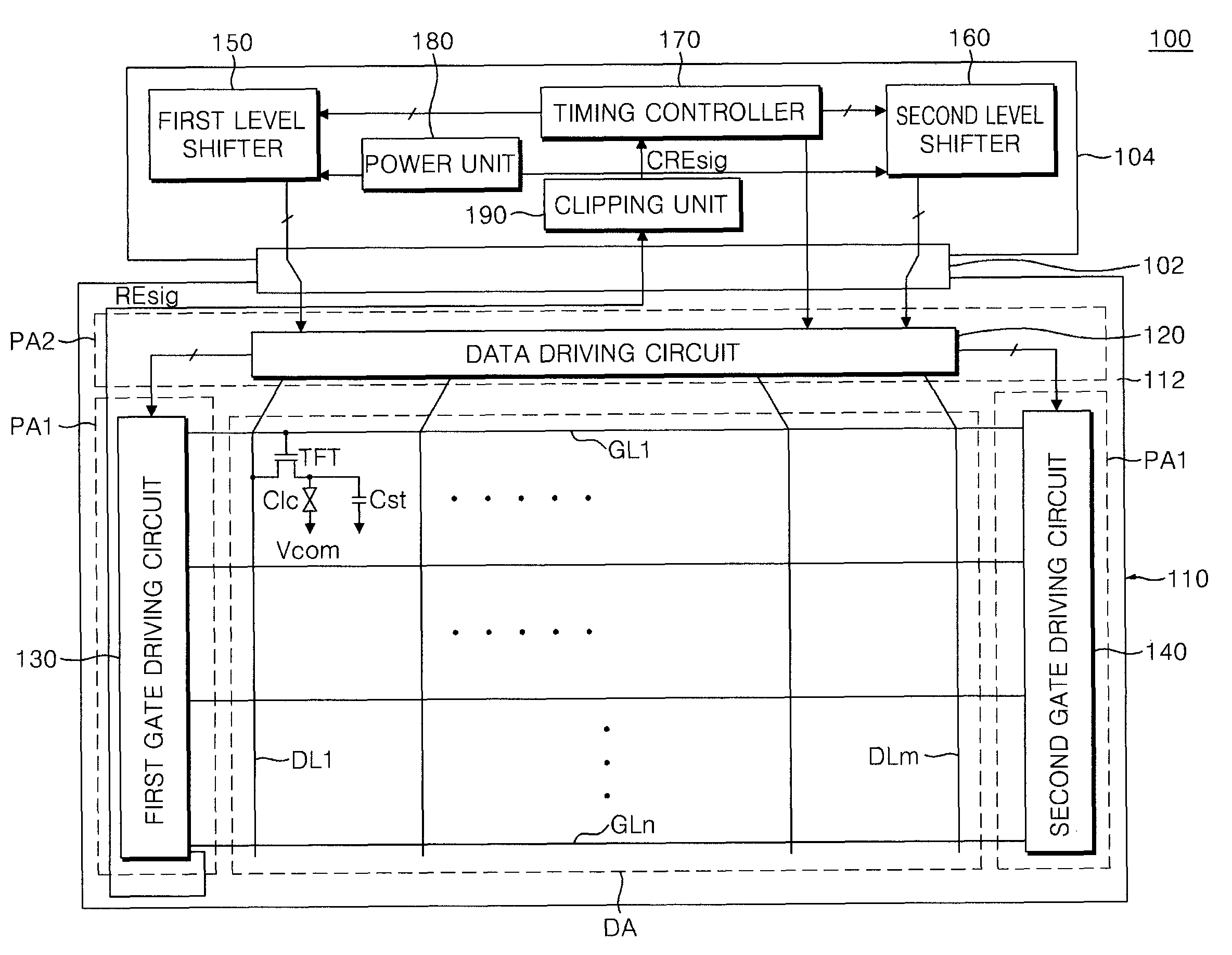

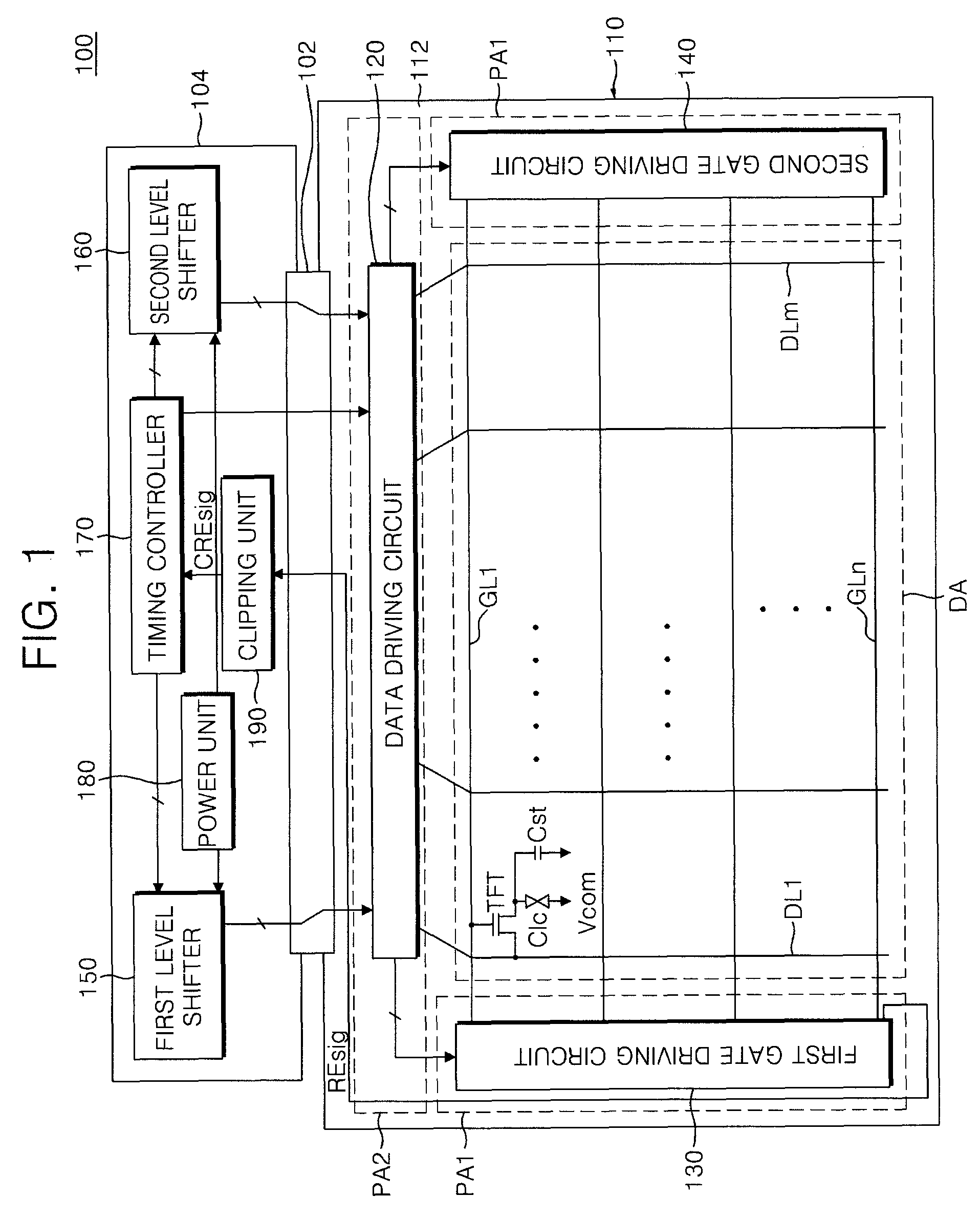

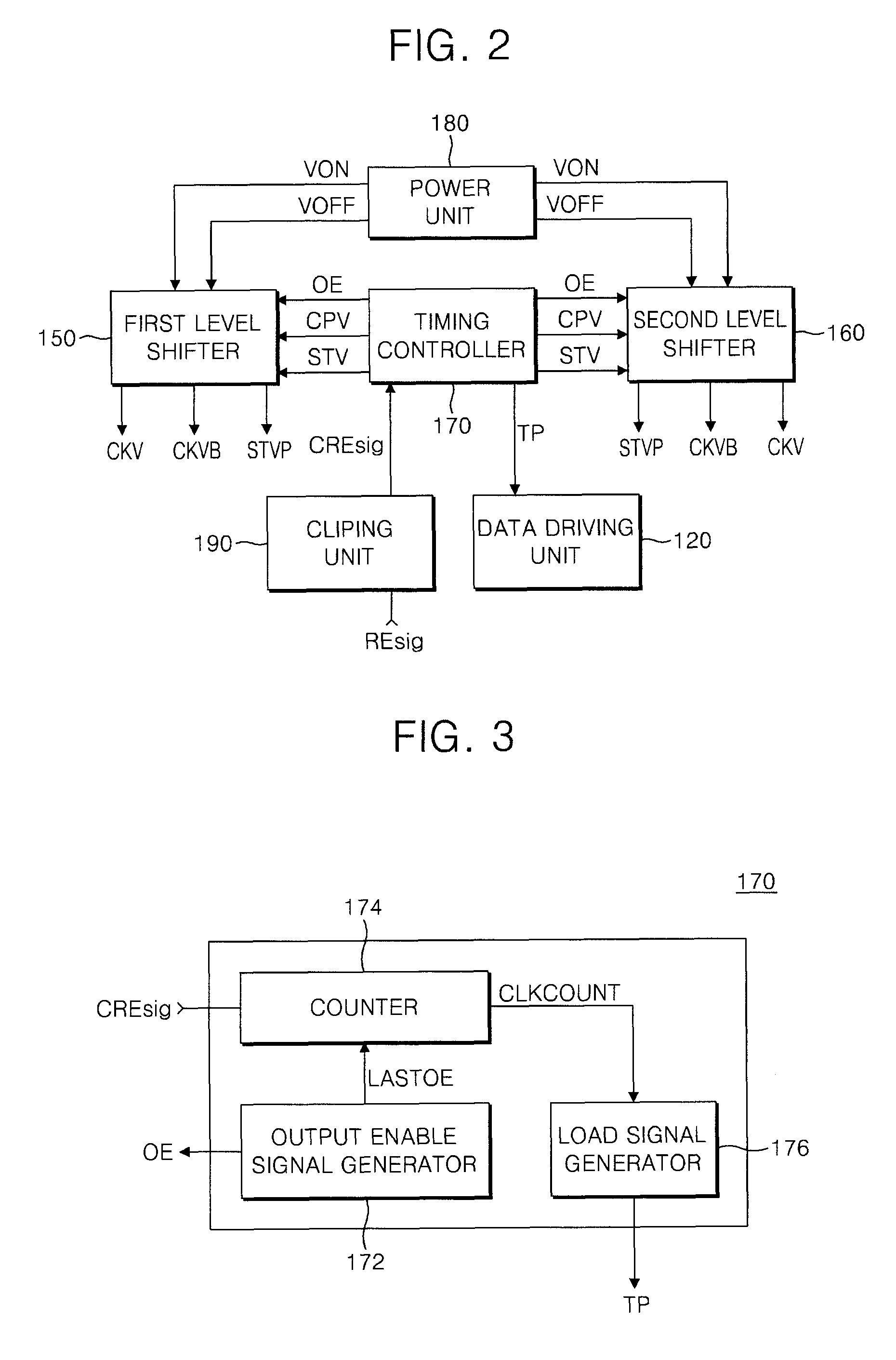

Liquid crystal display device, system and methods of compensating for delays of gate driving signals thereof

ActiveUS20080136756A1Delay problemCathode-ray tube indicatorsNon-linear opticsShift registerLiquid-crystal display

A liquid crystal display device includes a gate driving shift register having symmetrically split circuit portions by which each of plural gate lines is dually driven from both ends of the gate line during ripple-through scanning of rows of the LCD device. The LCD device includes a timing controller generating an output enable signal and a gate clock, where the timing controller adjusts a timing of a load signal for deciding a data output timing point when data will be loaded into a currently activated display row. The data output timing point is a function of a delay measuring feedback signal that is used to measure the cumulative delays of the sequentially connected stages of the shift register.

Owner:SAMSUNG DISPLAY CO LTD

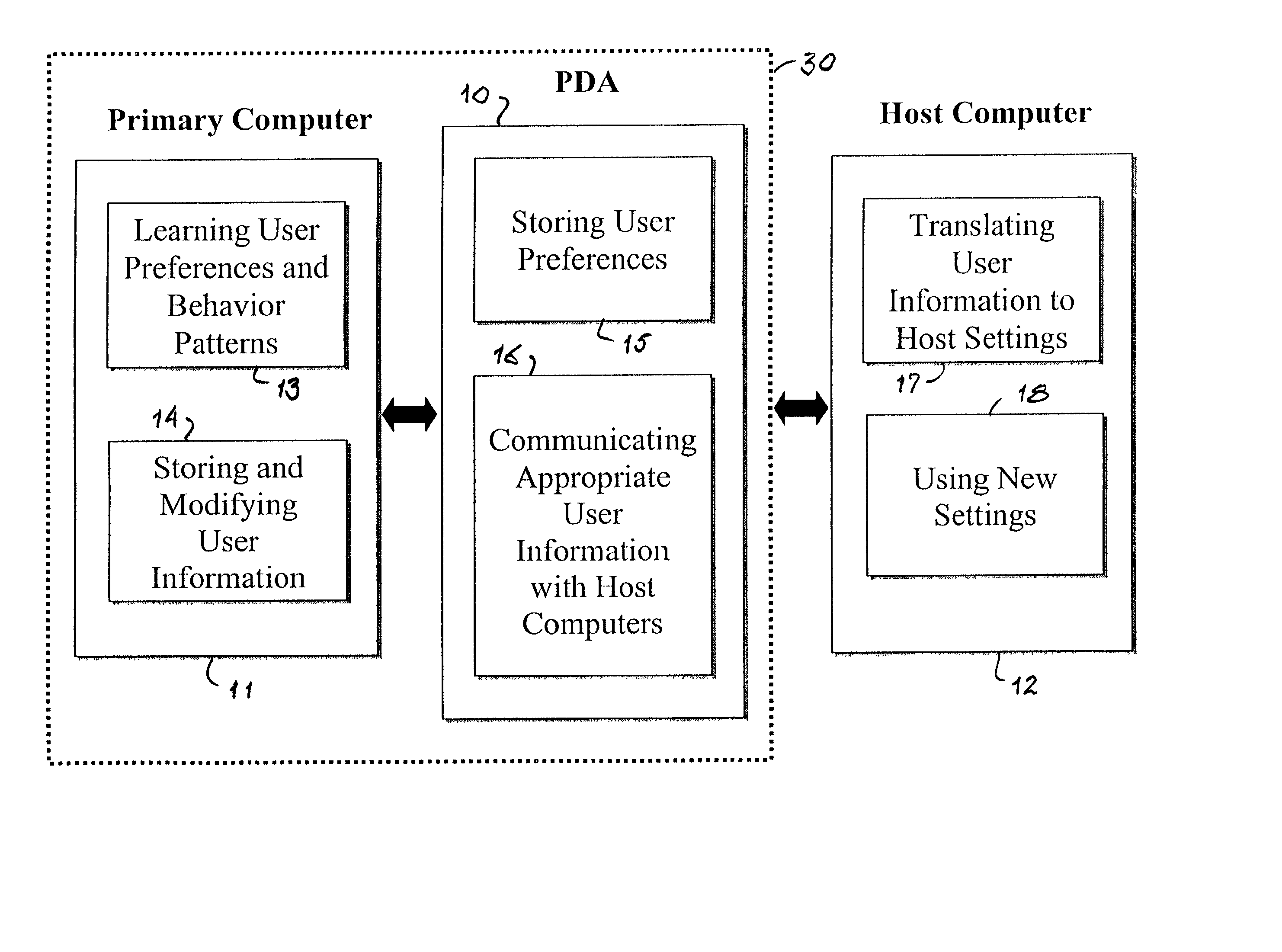

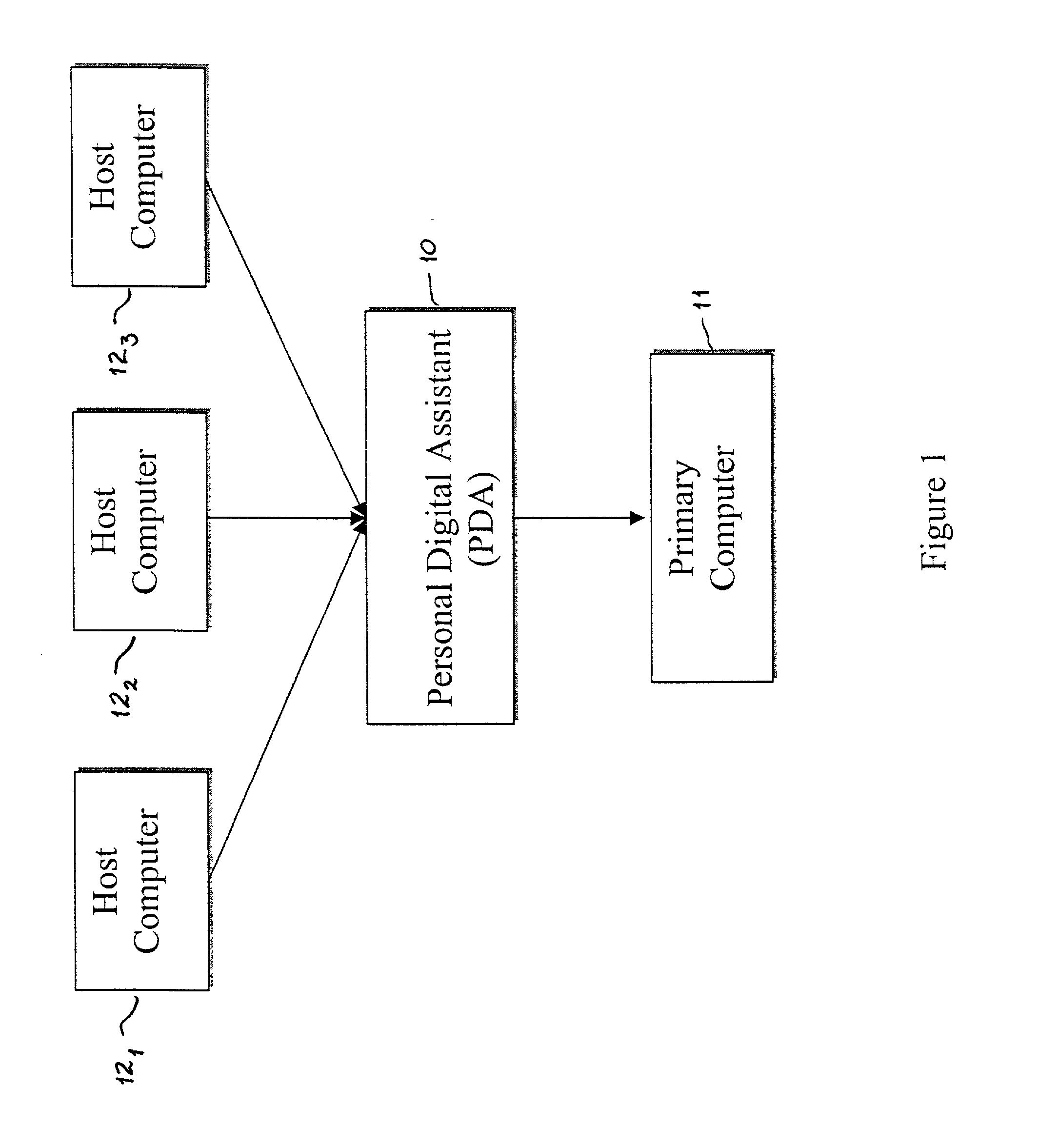

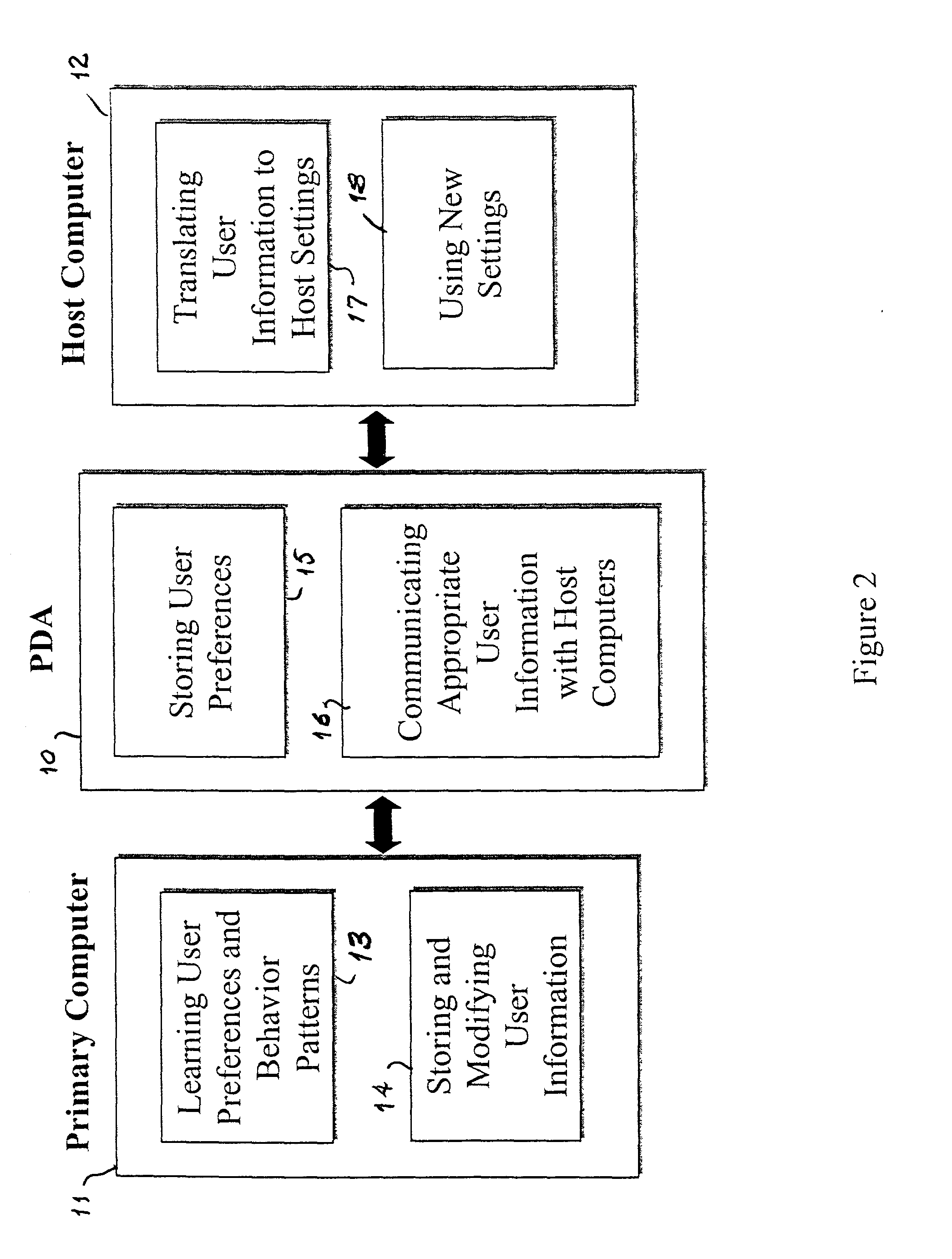

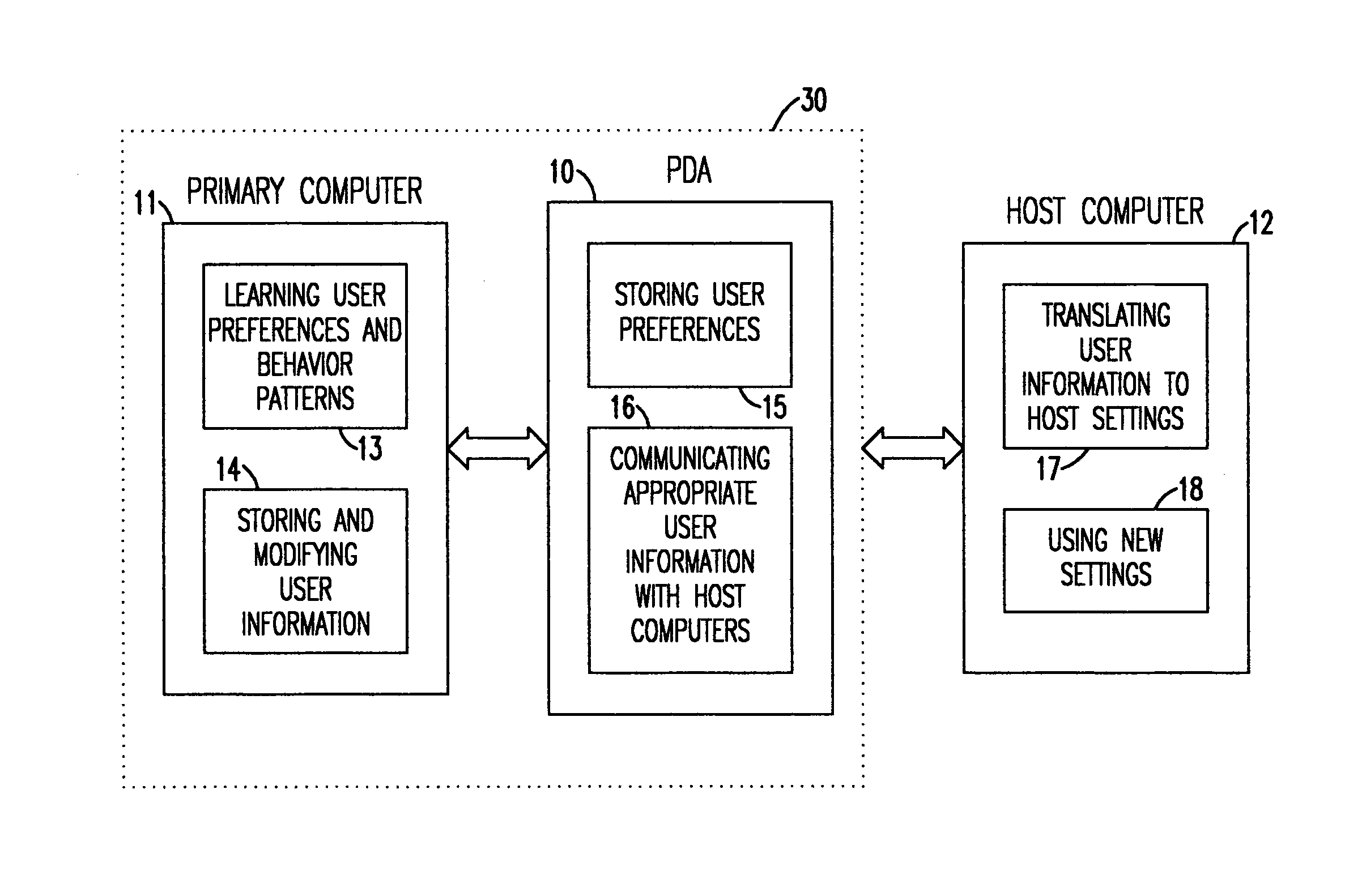

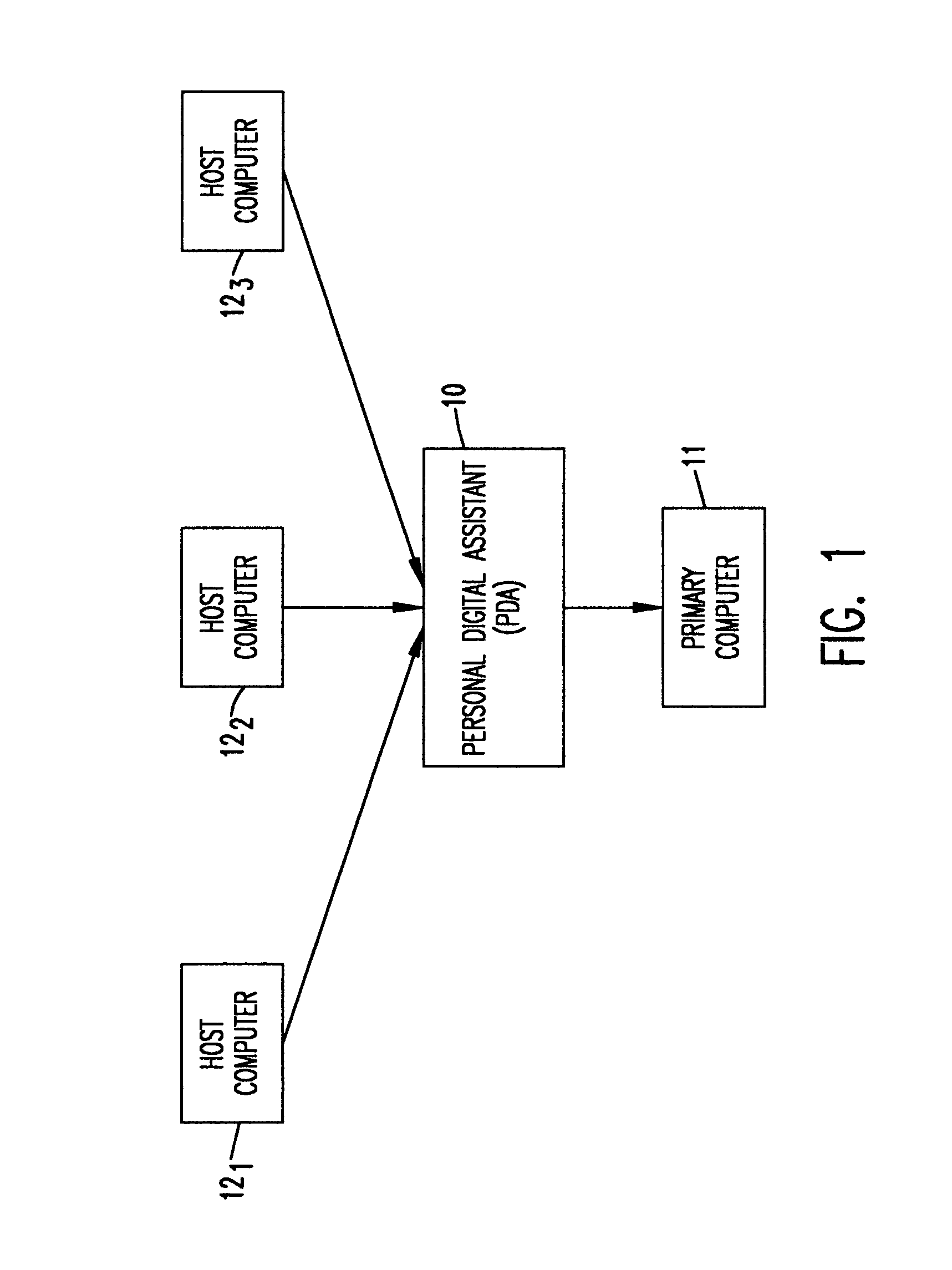

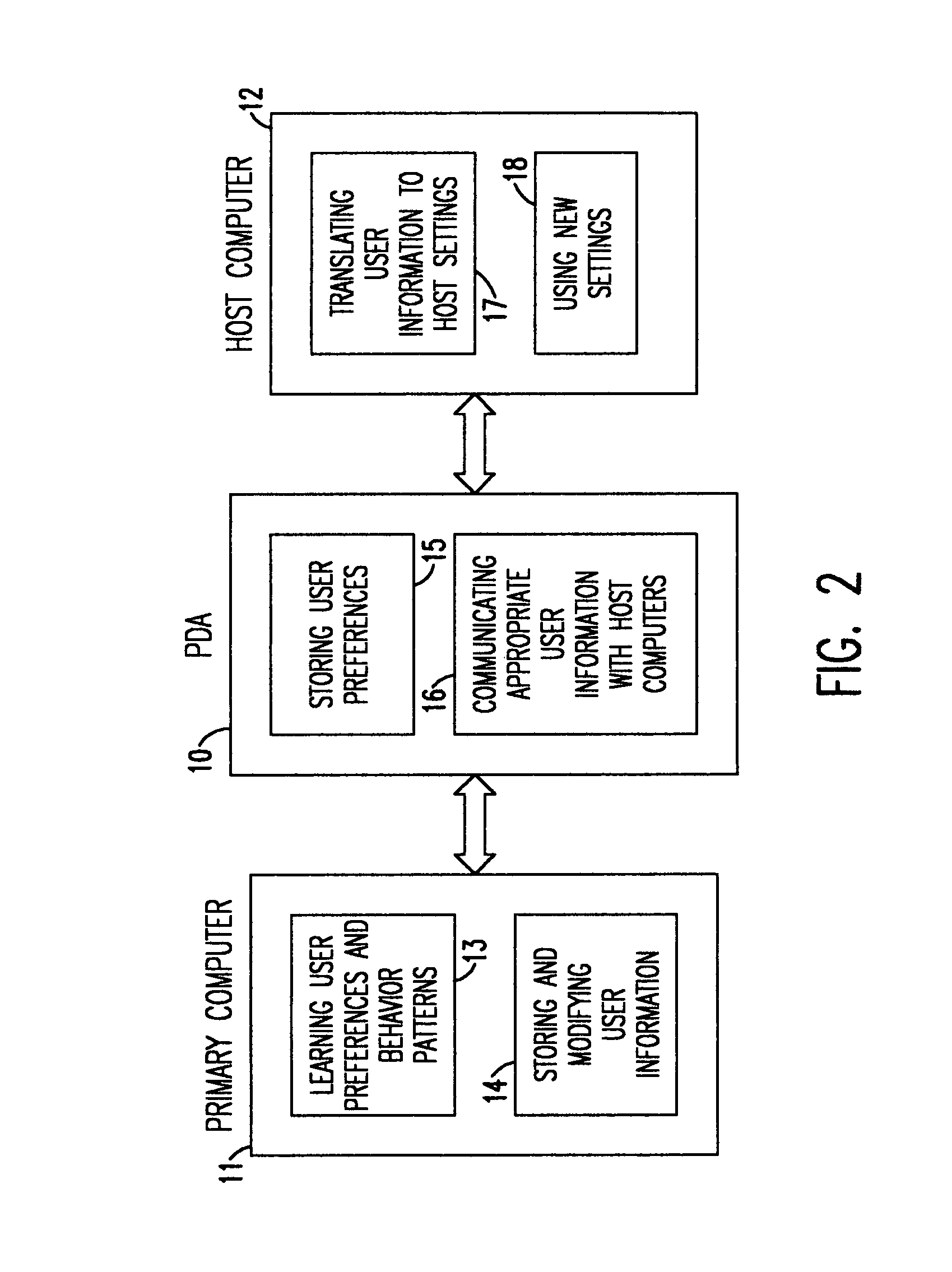

Personalizing user interfaces across operating systems

InactiveUS20020118223A1Improve accessibilityDelay problemDigital computer detailsBiological neural network modelsPersonalizationOperational system

A user-centered interface agent eases the problem of unfamiliar user interfaces on host computers. The agent operates by learning user preferences and typical behaviors and predicting the user's preferred user interface for different types of host computers. Most of the agent's learning is through observation, requiring minimal-initialization by the user. The interface agent consists of a learning program which operates on the user's primary computer, a shadow program which is installed on a Personal Digital Assistant (PDA), and a remote program which operates on host computers. The role of the PDA includes the transfer of data between the primary and remote machines, and the PDA can also be the user's primary computer. On the primary computer, the agent learns a user's preference by observing the user's actions. The user may run agent-training module or directly query and modify the agent's current state of knowledge, but the user is not forced to explicitly teach the agent. The learning algorithm may be statistical, rule-based, case-based, neural network, or employ any other technique for reasoning under uncertainty. The automated way of reaching a usable configuration has a particular advantage for individuals with disabilities who require configuration before they can use a new computer system.

Owner:IBM CORP

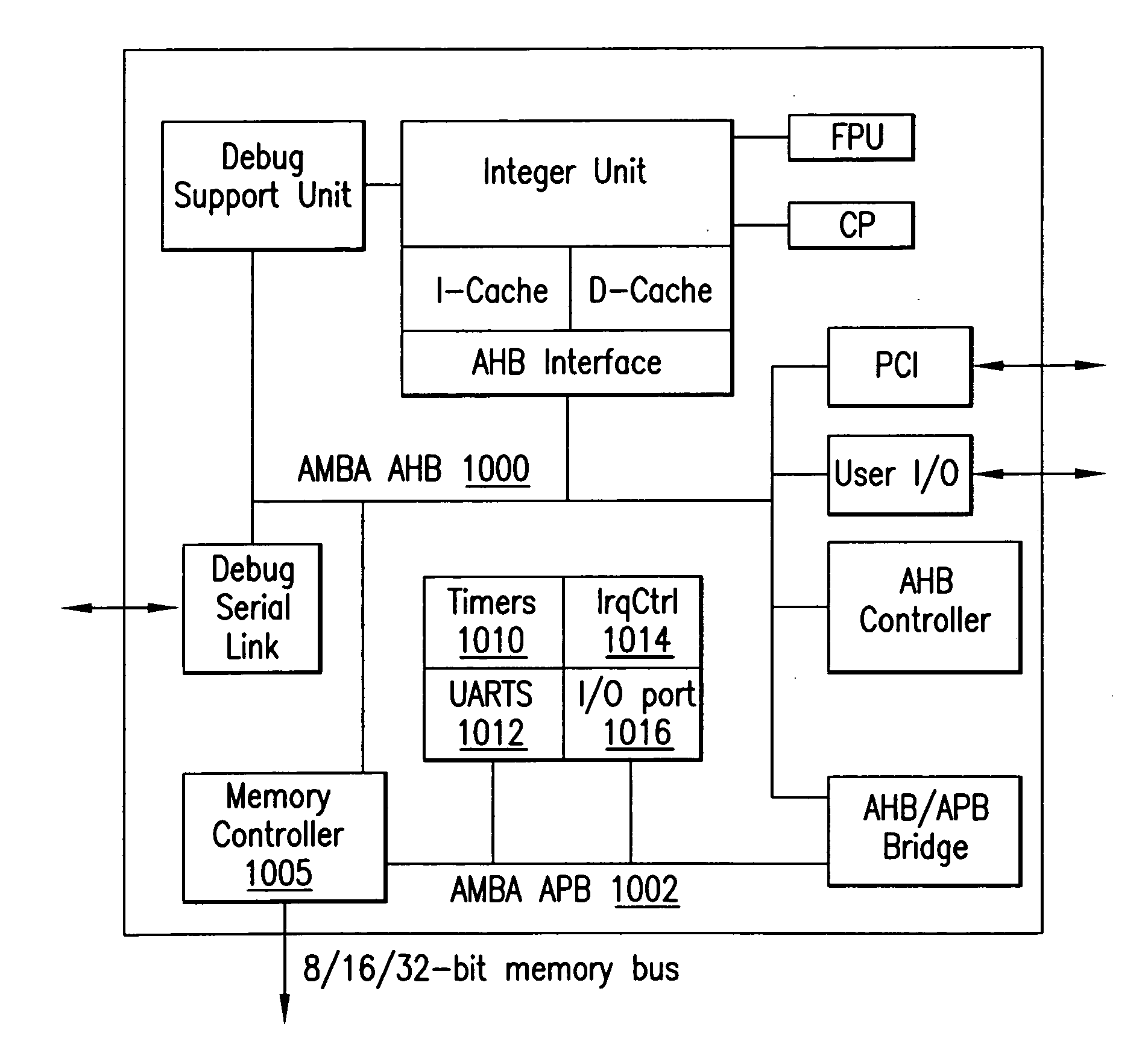

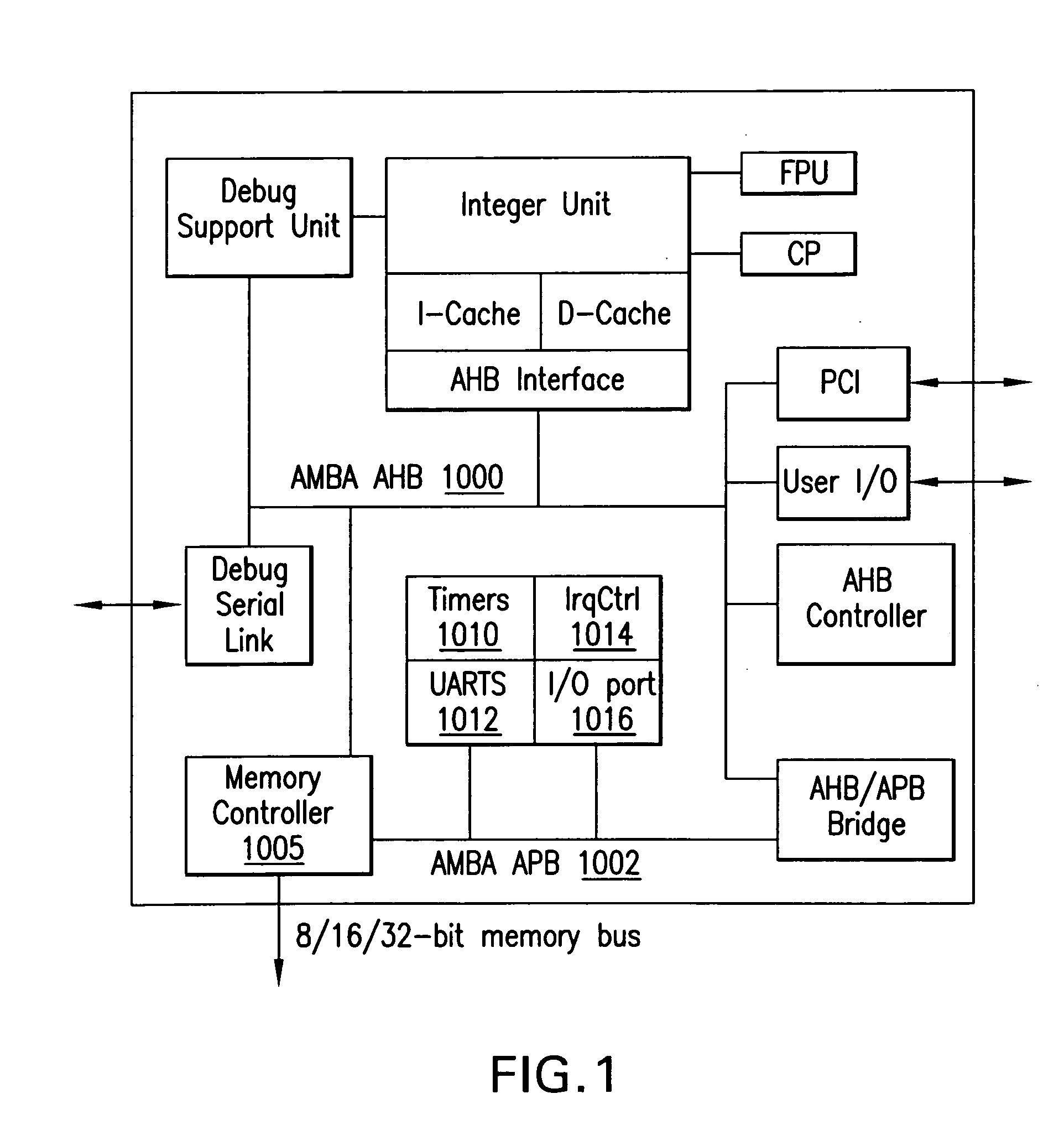

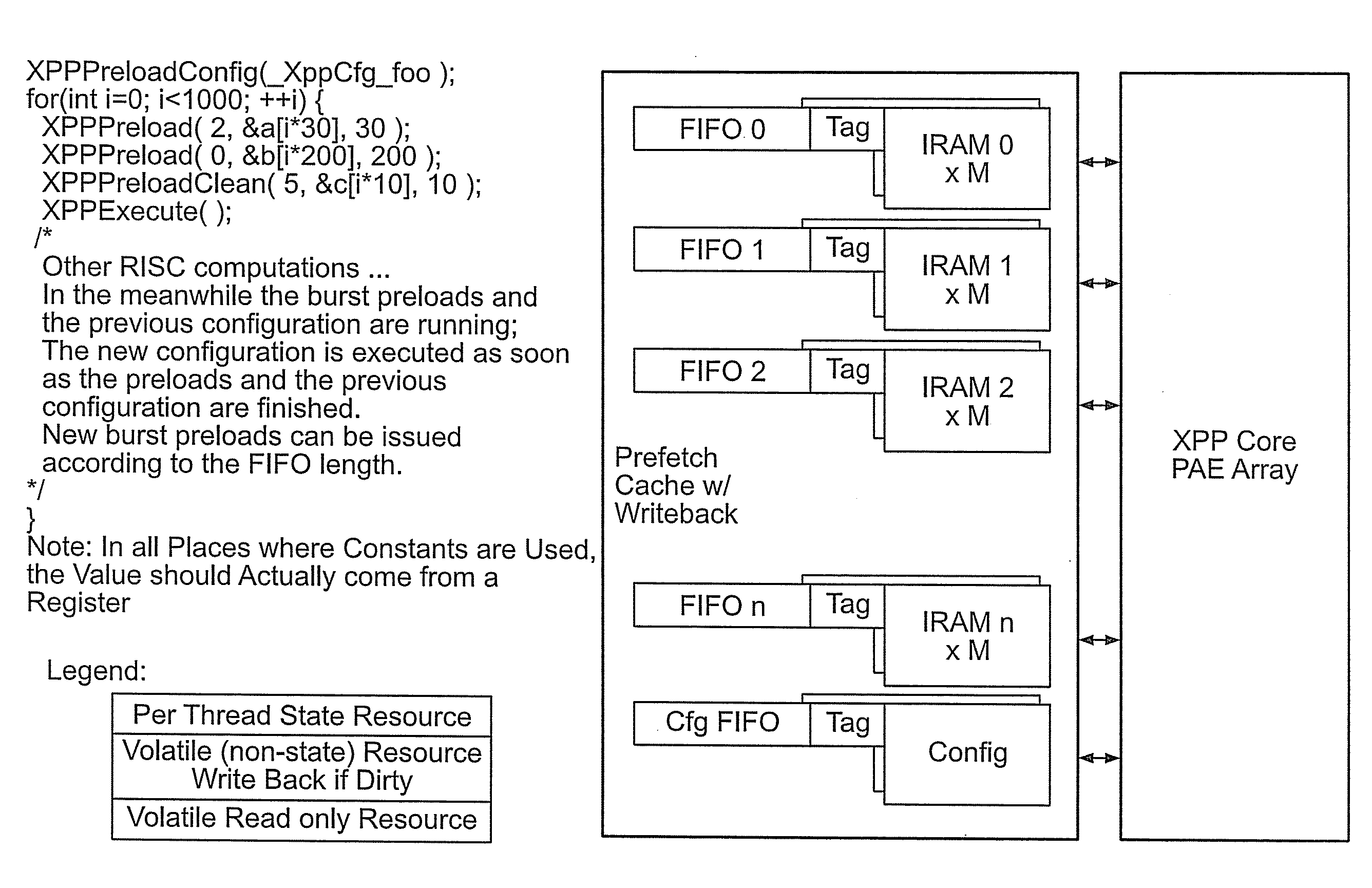

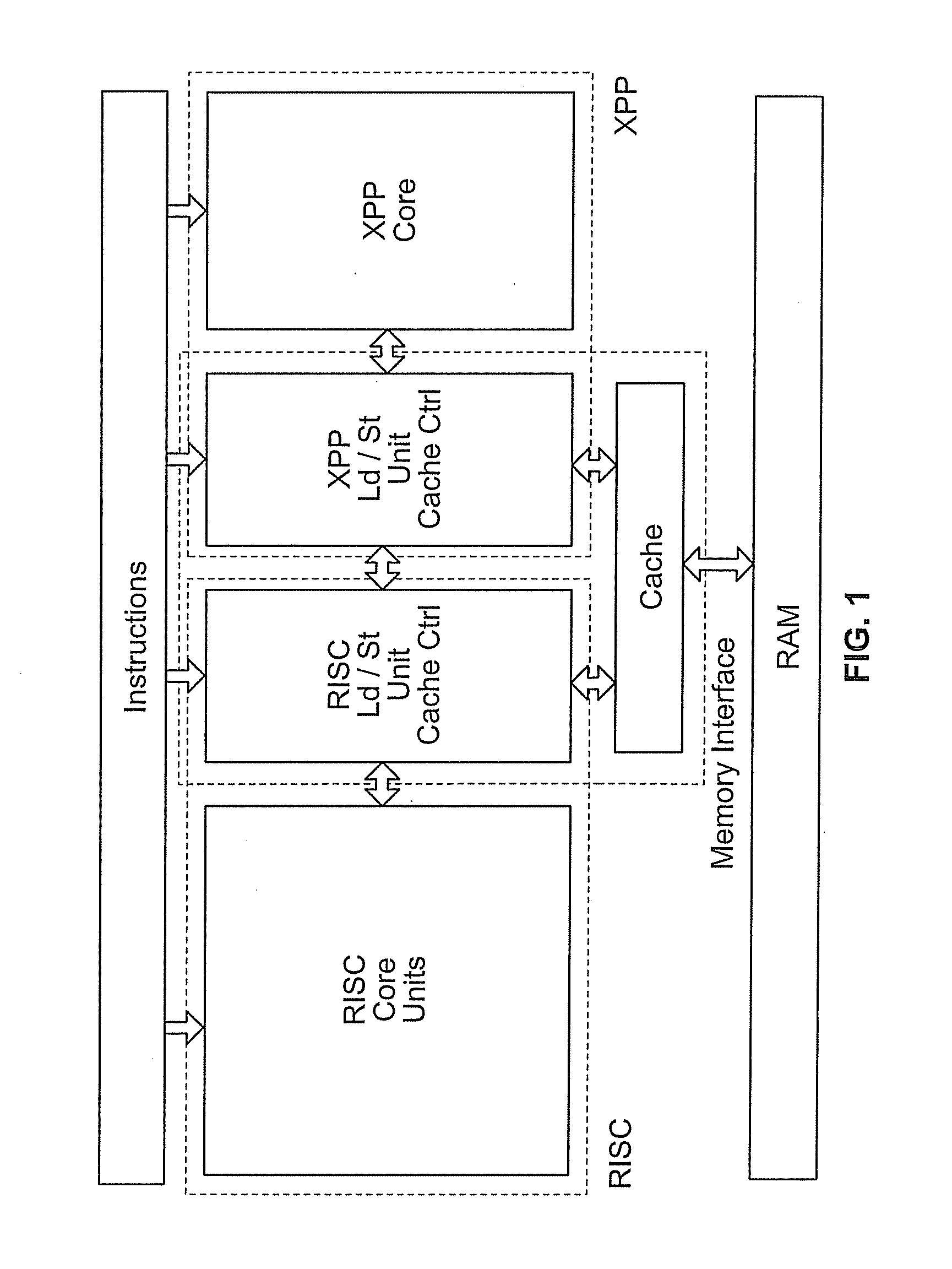

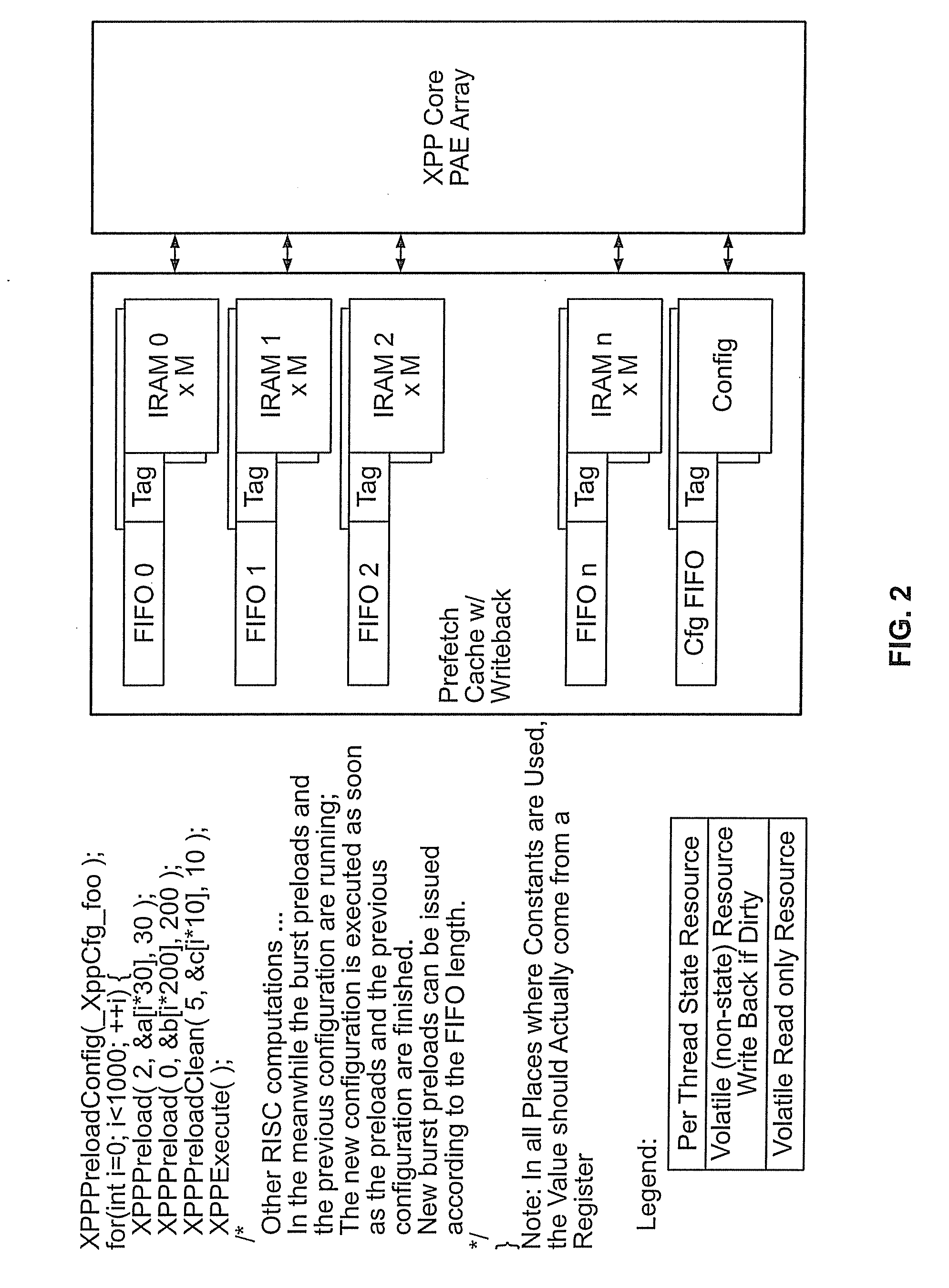

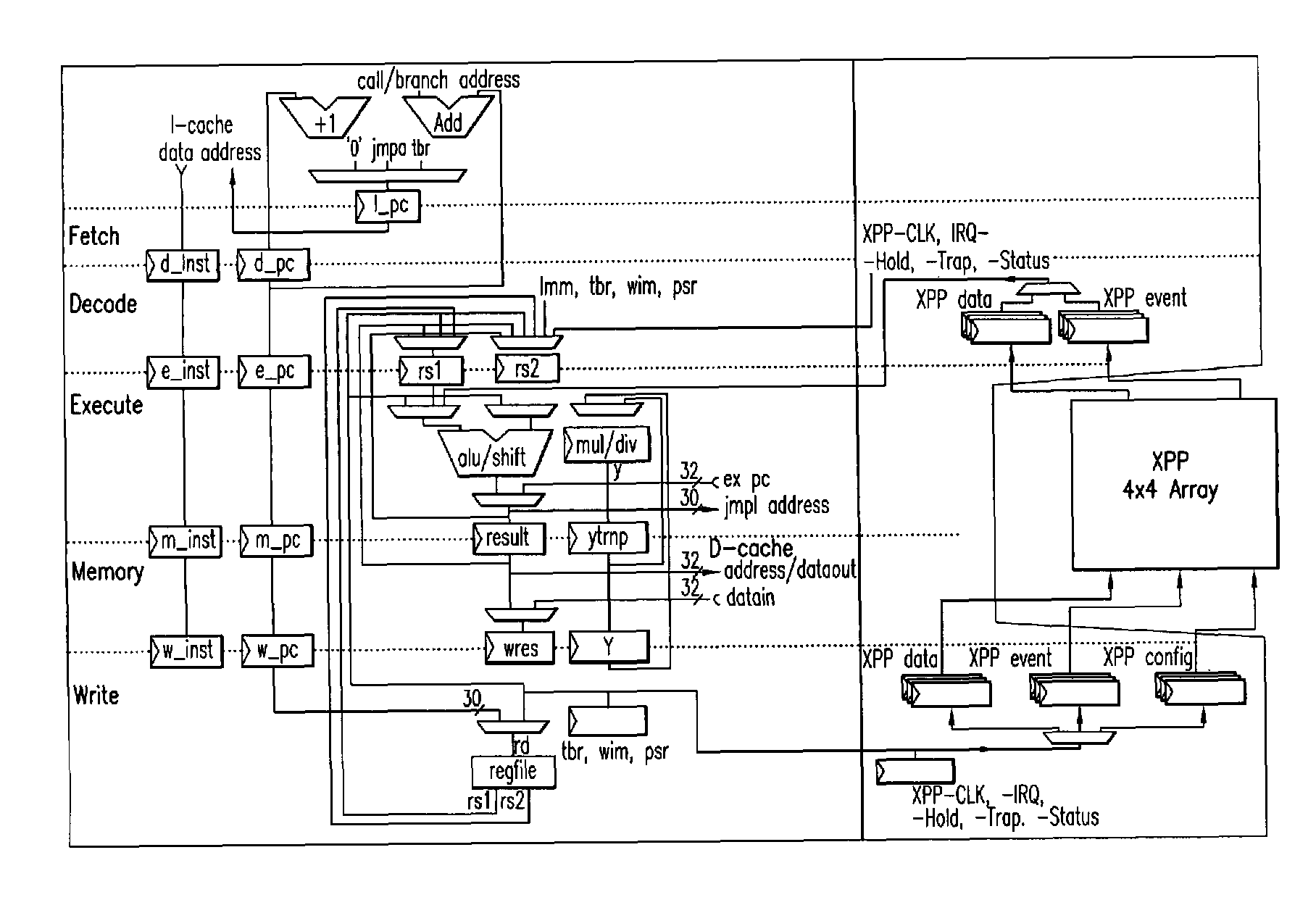

Method and device for coupling a data processing unit and a data processing array

InactiveUS20110238948A1Ease memory access problemIncrease data throughputProgram control using stored programsGeneral purpose stored program computerRAID processing unitData processing

The present invention relates to a method of coupling at least one (conventional) unit processing data in a sequential manner, e.g. a CPU, von-Neumann-Processor and / or microcontroller, the (conventional) unit for data processing comprising an instruction pipeline, and an array for processing data comprising a plurality of data processing cells, e.g. a preferably coarse grain and / or preferably runtime reconfigurable data processor, FPGA, DFP, DSP, XPP or chaemeleon-technology-like data processing fabric, wherein the array is coupled to the instruction pipeline.

Owner:PACT XPP TECH

Data processing system having integrated pipelined array data processor

InactiveUS9170812B2Improve executionImprove performanceMemory architecture accessing/allocationInstruction analysisData processing systemParallel computing

A data processing system having a data processing core and integrated pipelined array data processor and a buffer for storing list of algorithms for processing by the pipelined array data processor.

Owner:SCIENTIA SOL MENTIS AG

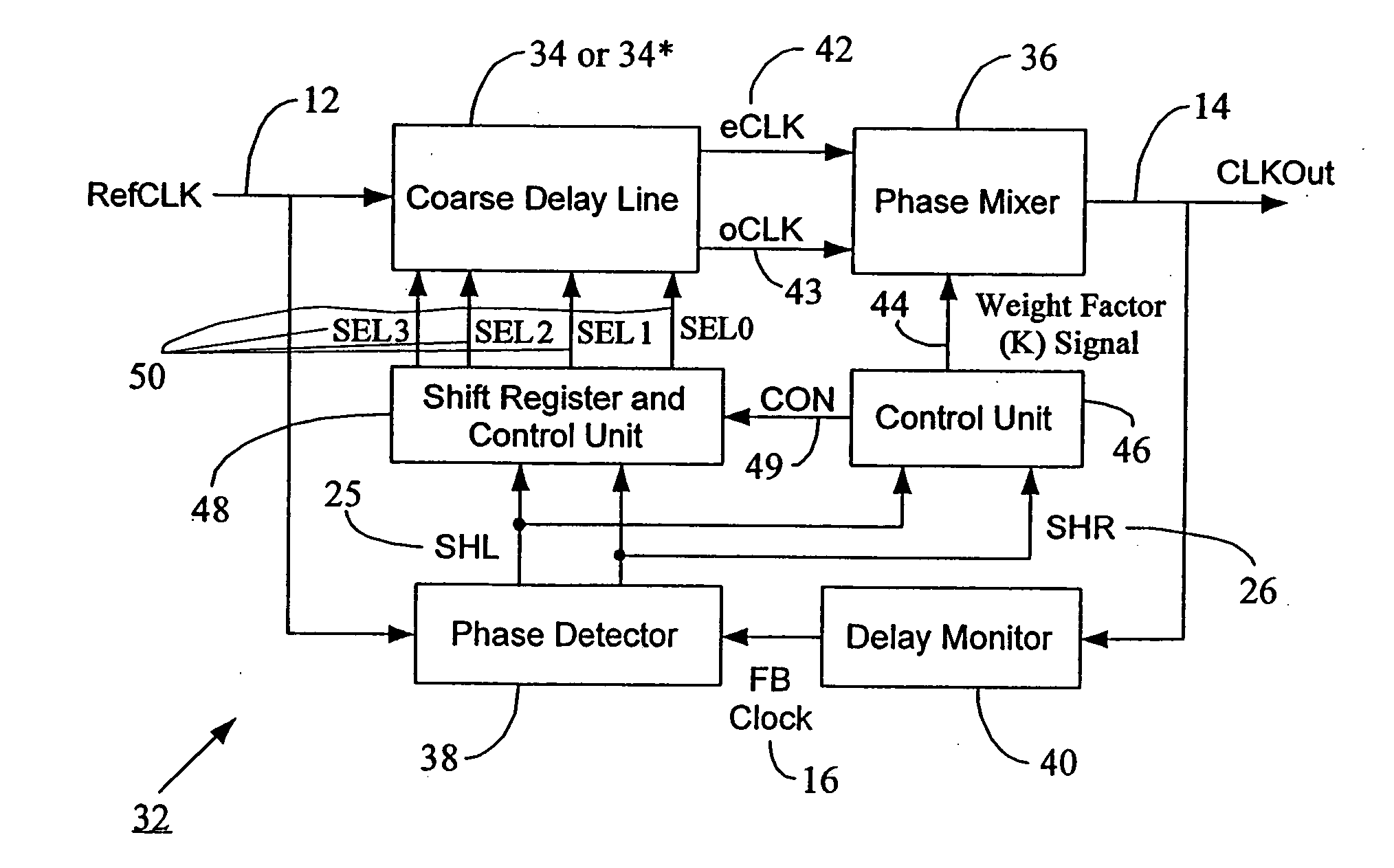

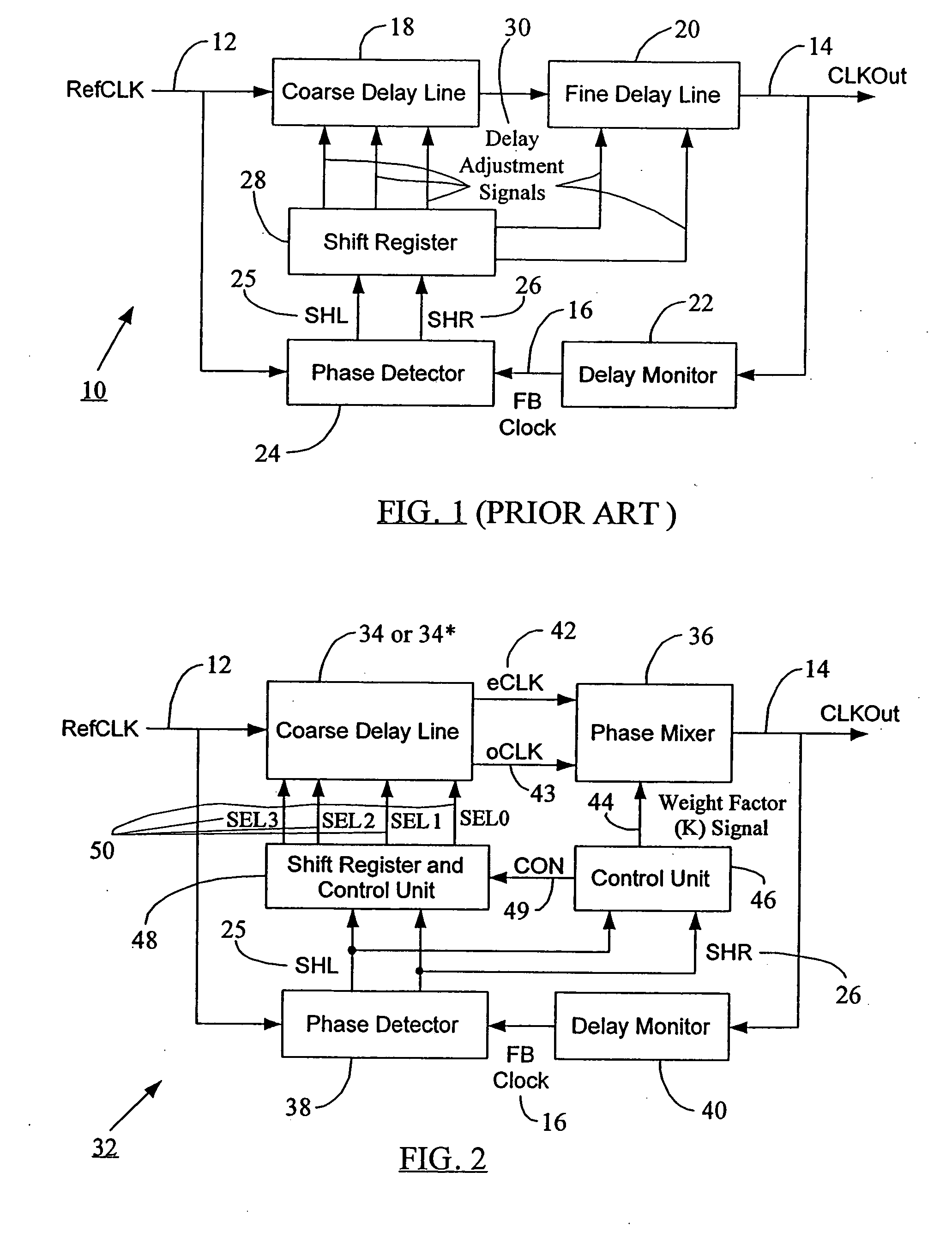

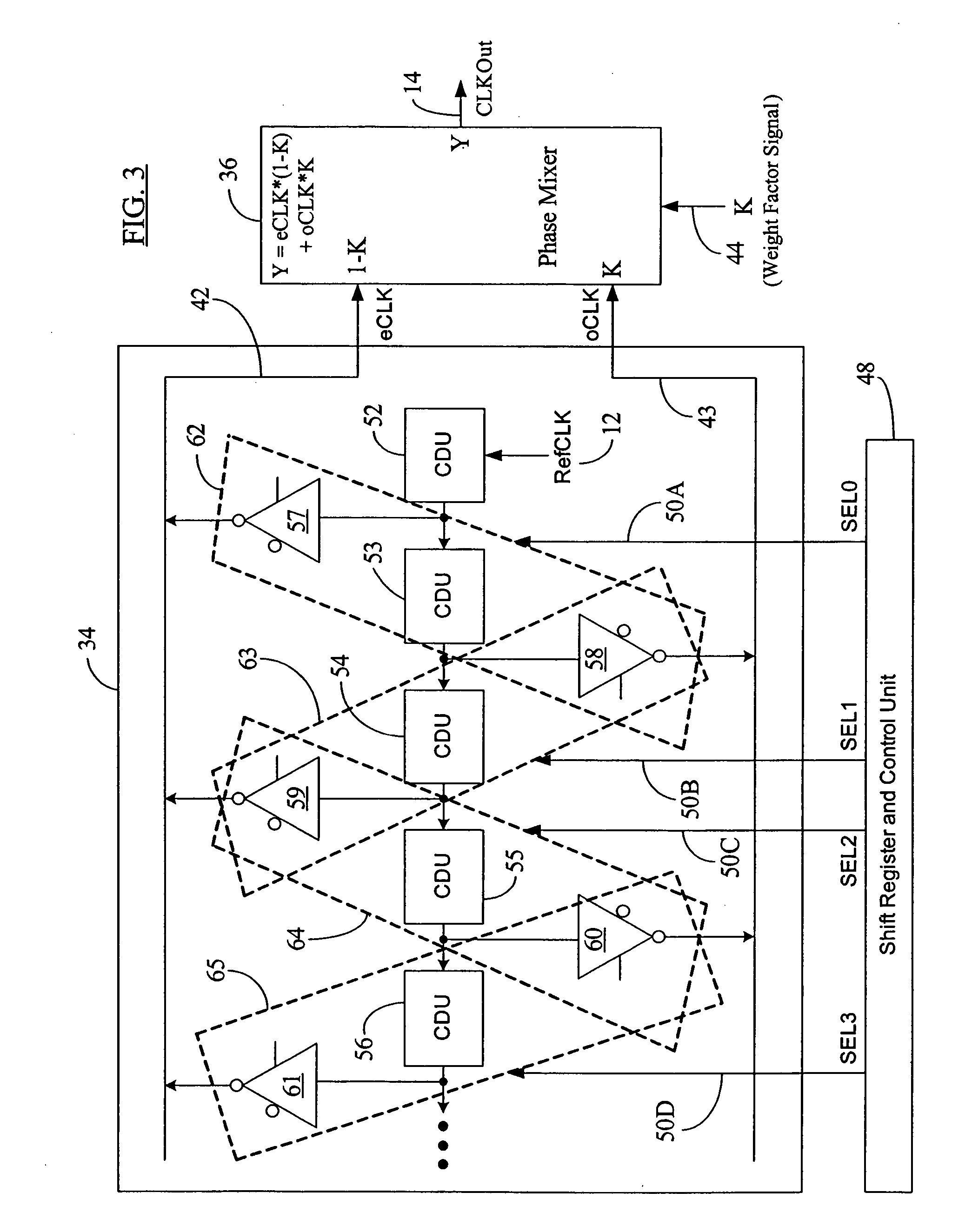

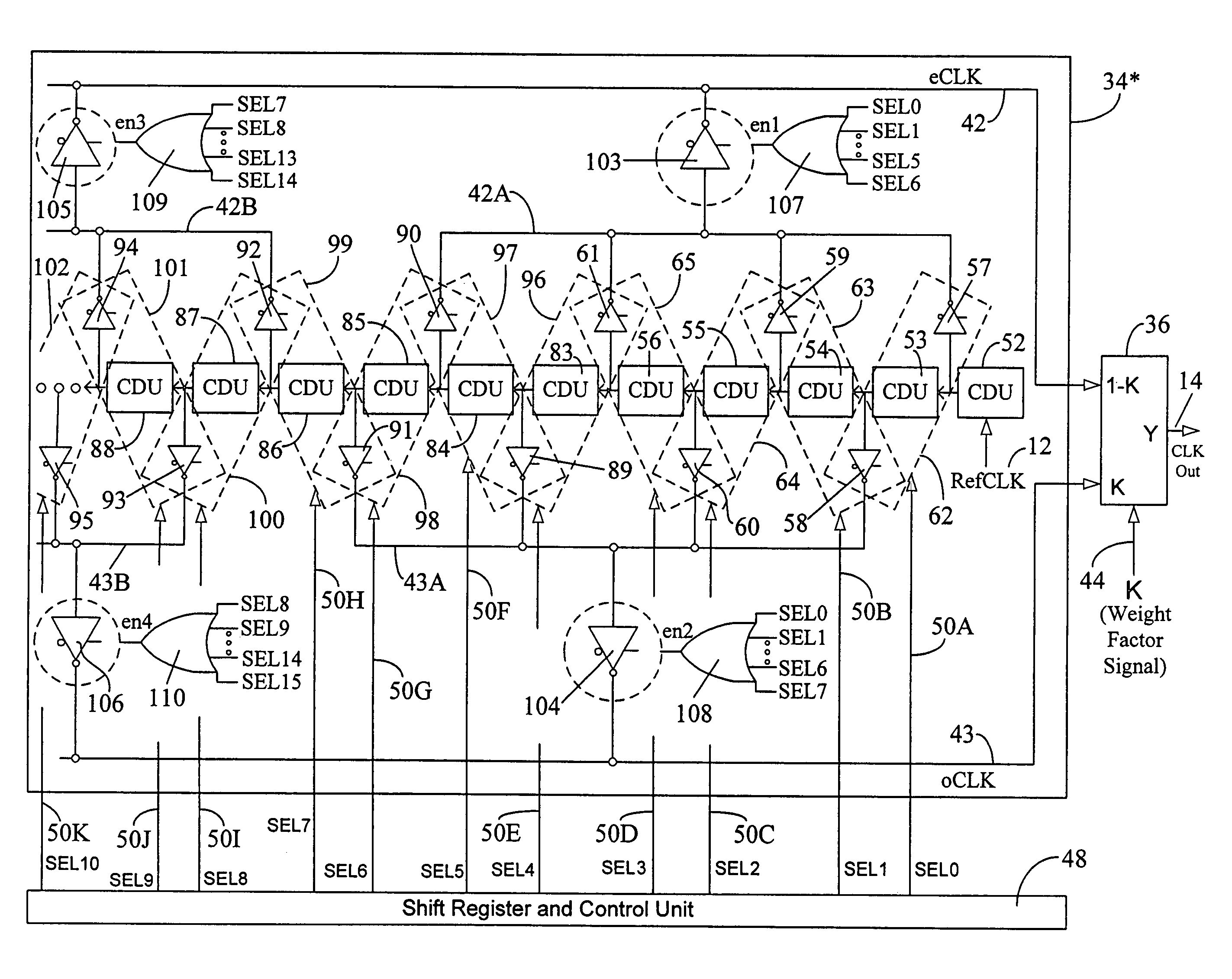

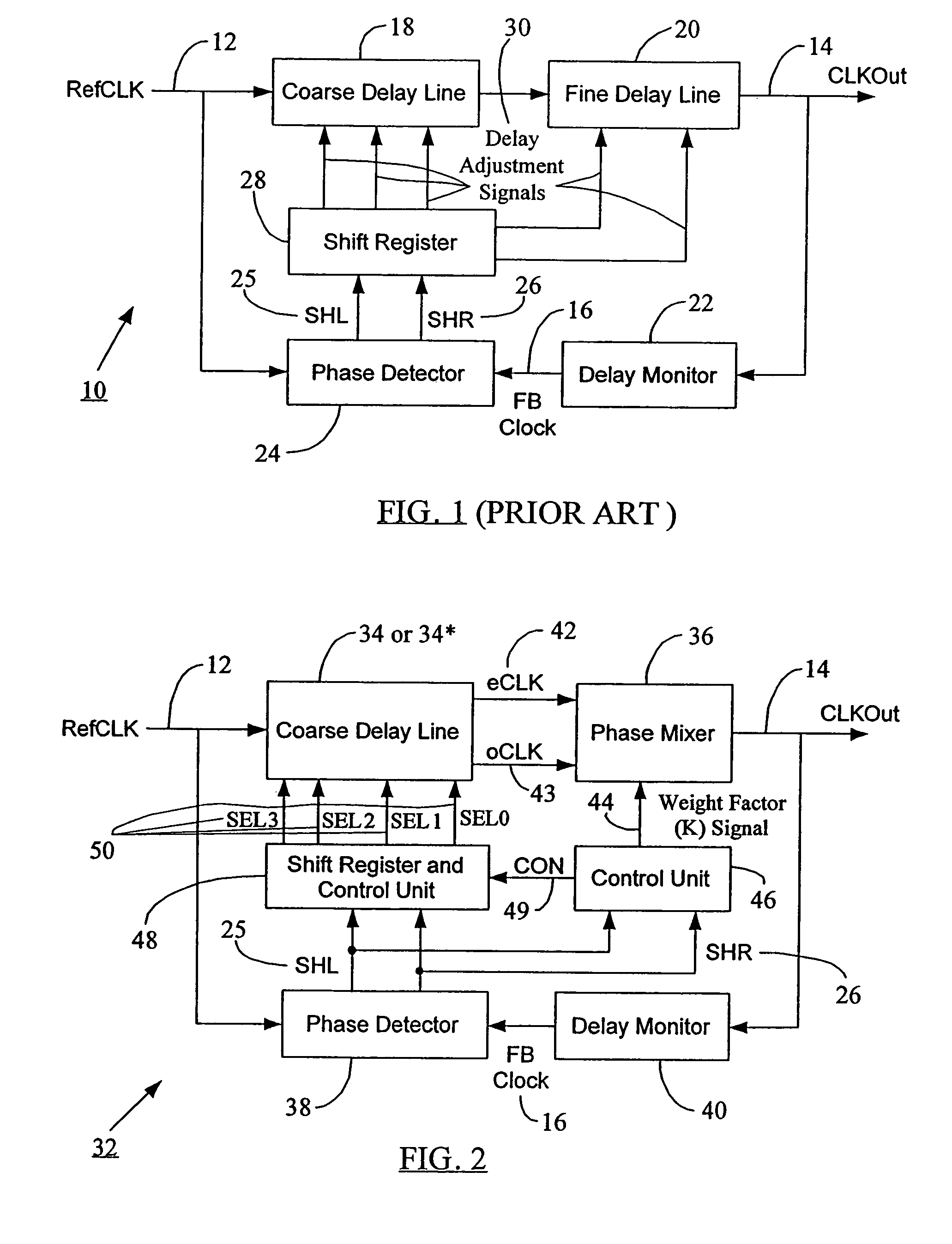

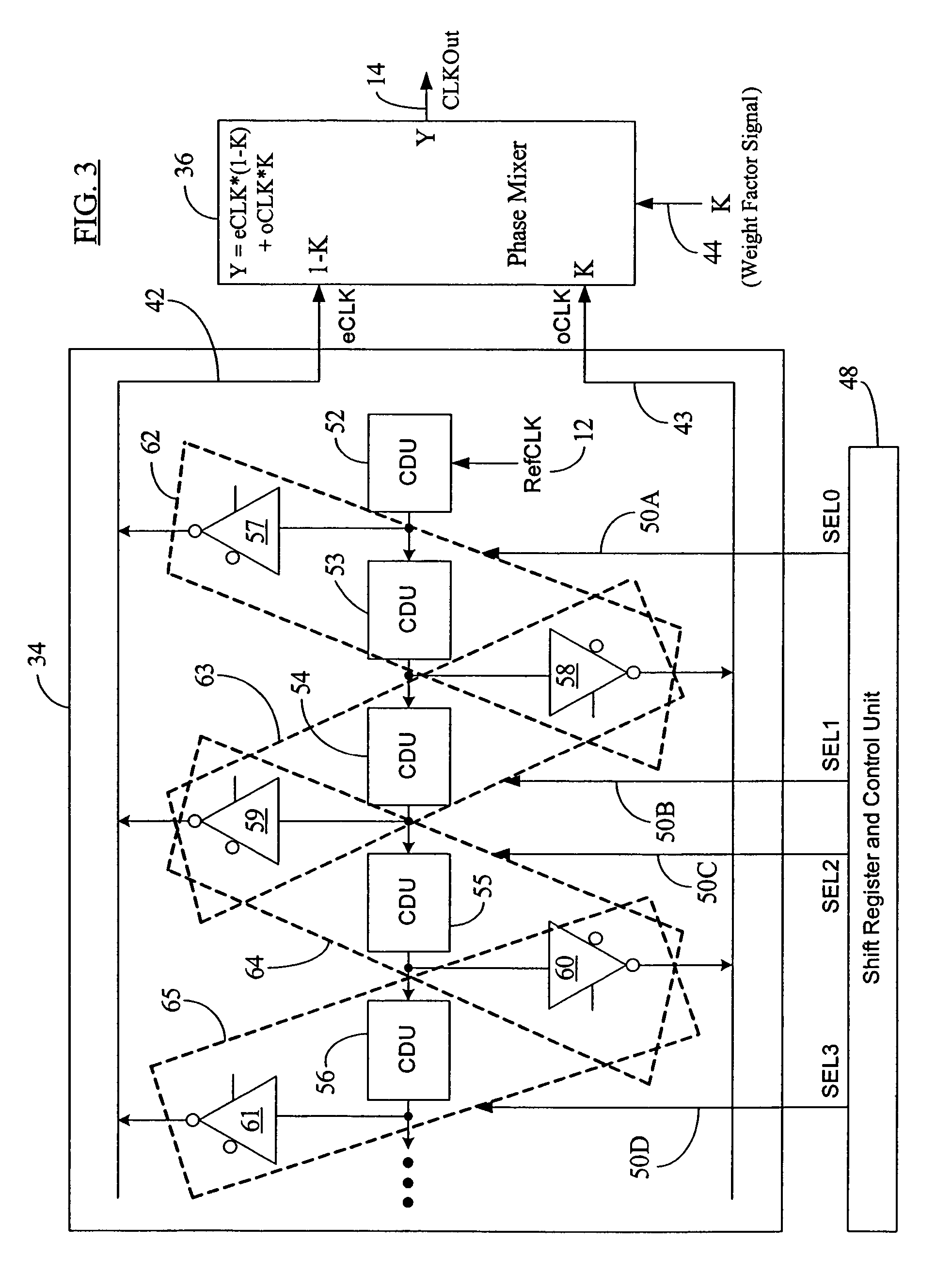

Seamless coarse and fine delay structure for high performance DLL

ActiveUS20070030753A1Smooth phase transitionDelay problemPulse automatic controlCounting chain pulse countersClock timePhase difference

A clock synchronization system and method avoids output clock jitter at high frequencies and also achieves a smooth phase transition at the boundary of the coarse and fine delays. The system may use a single coarse delay line configured to generate two intermediate clocks from the input reference clock and having a fixed phase difference therebetween. The coarse delay line may have a hierarchical or a non-hierarchical structure. A phase mixer receives these two intermediate clocks and generates the final output clock having a phase between the phases of the intermediate clocks. The coarse shifting in the delay line at high clock frequencies does not affect the phase relationship between the intermediate clocks fed into the phase mixer. The output clock from the phase mixer is time synchronized with the input reference clock and does not exhibit any jitter or noise even at high clock frequency inputs. Because of the rules governing abstracts, this abstract should not be used to construe the claims.

Owner:MICRON TECH INC

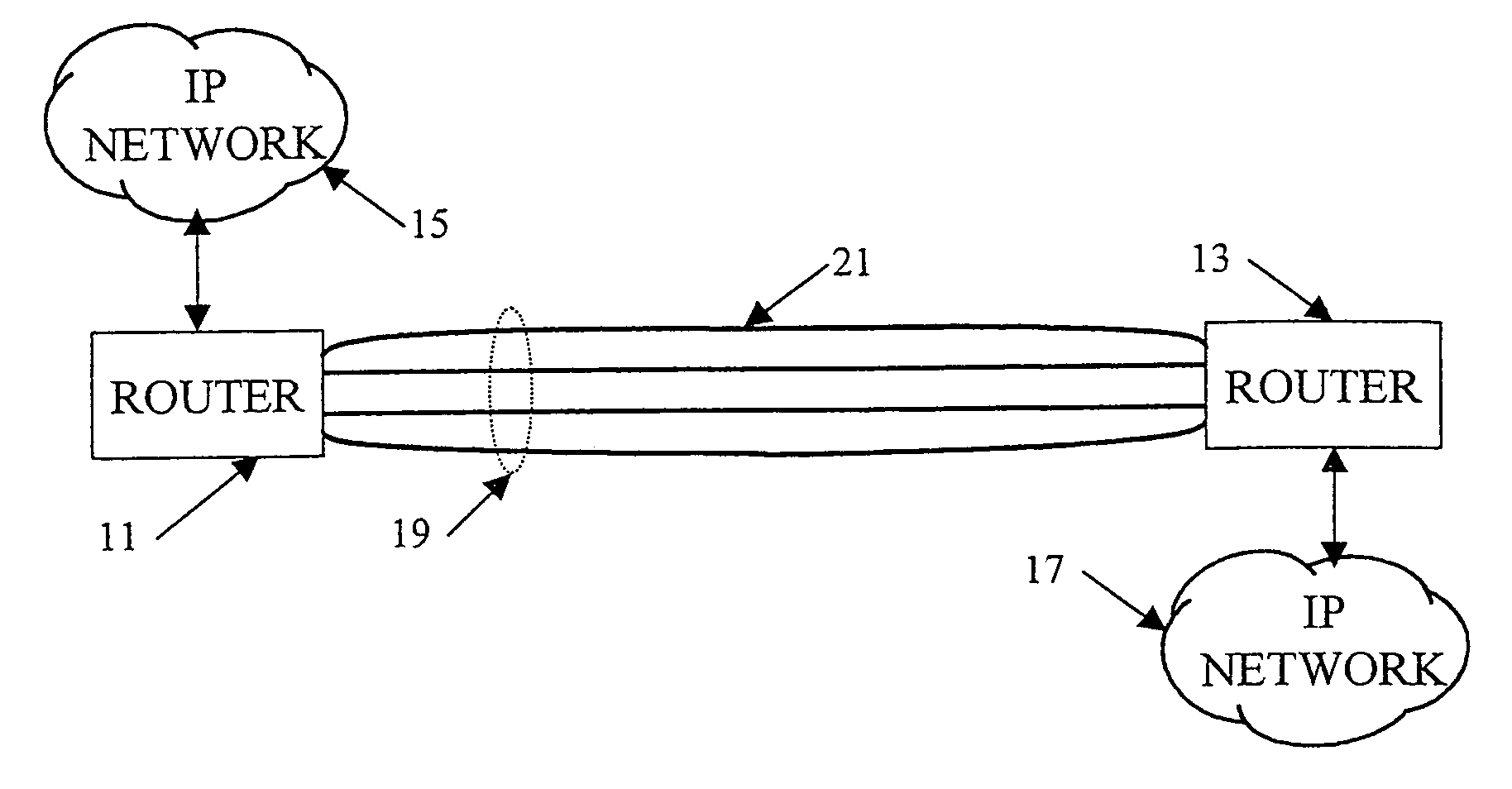

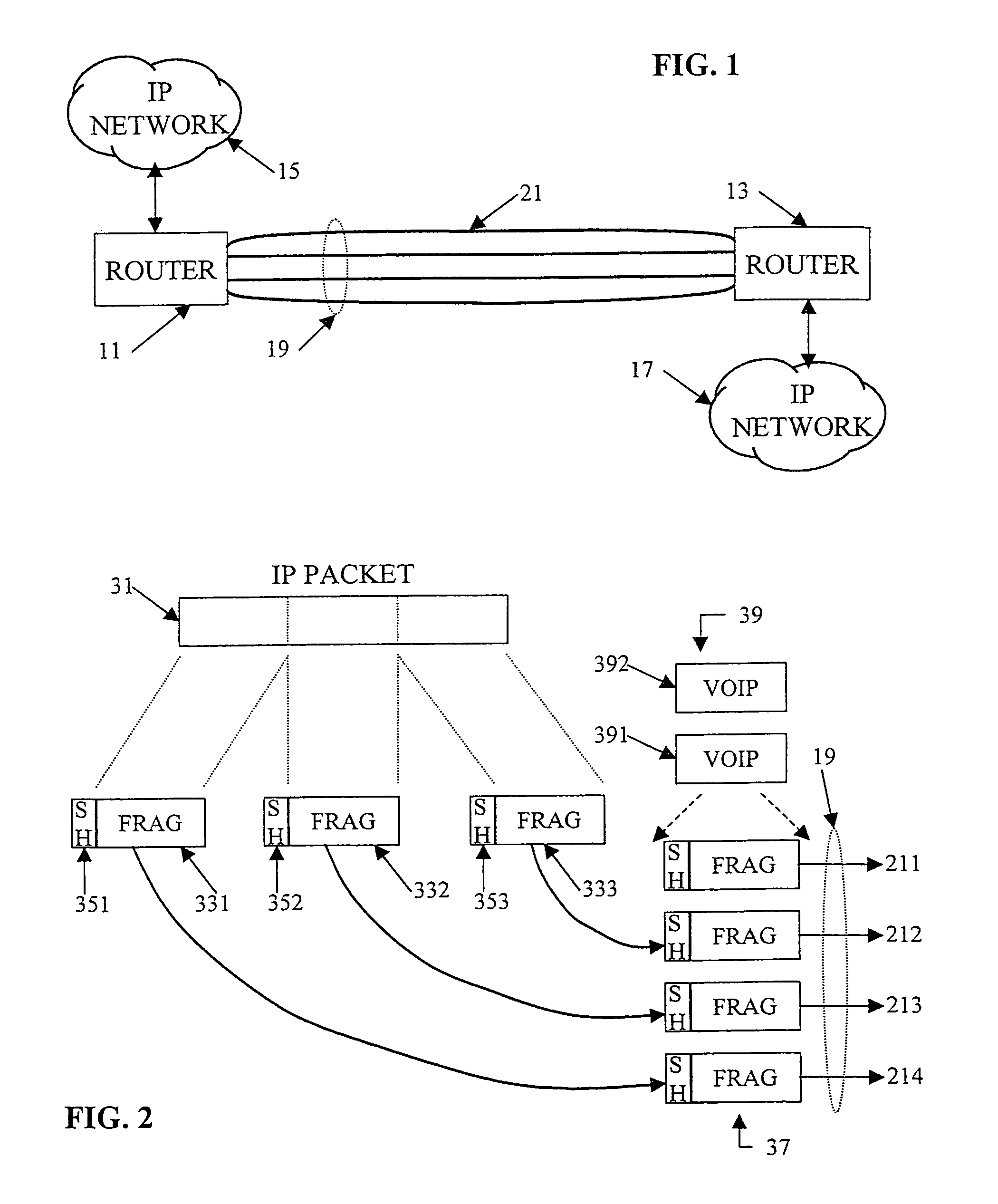

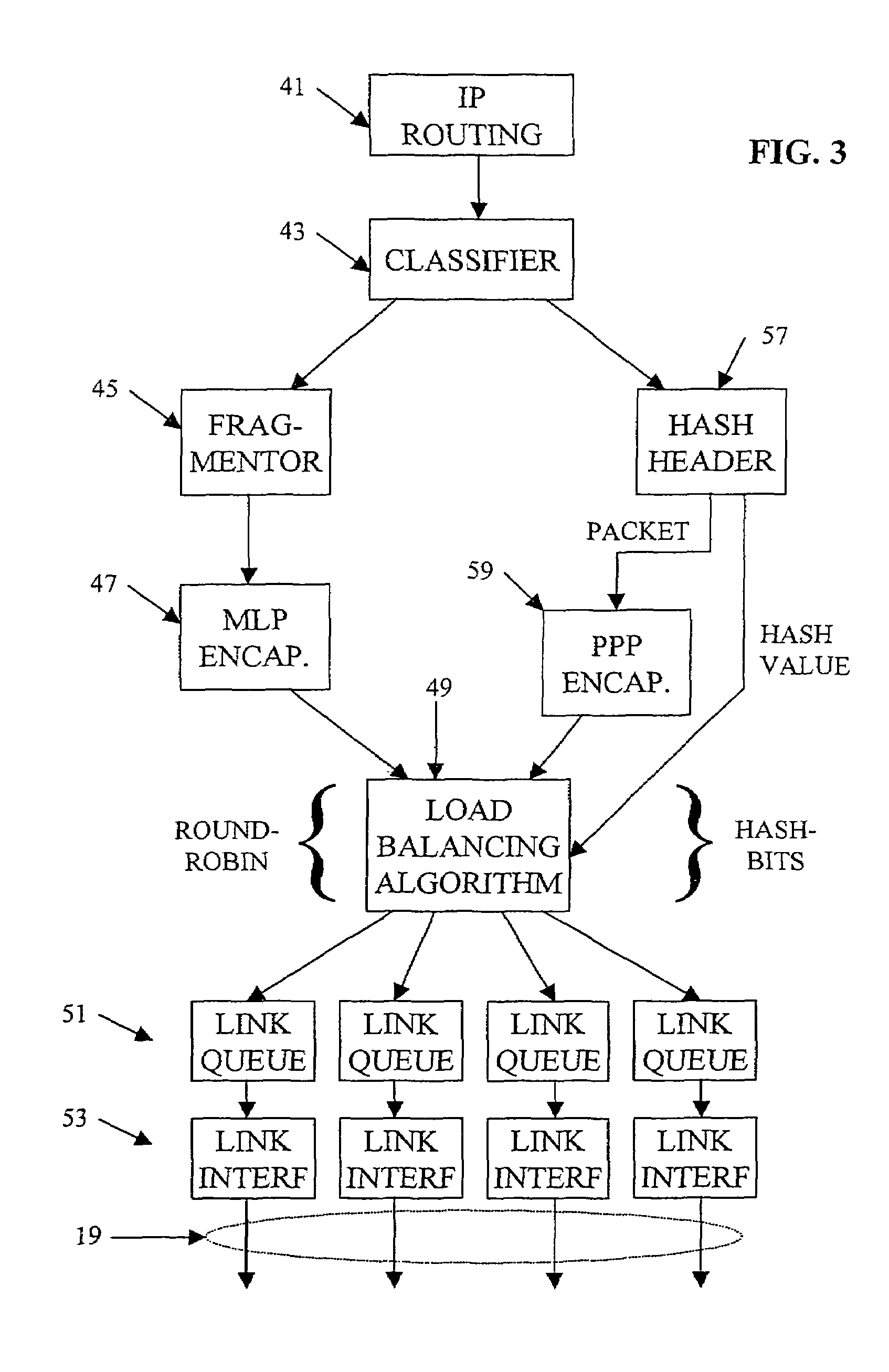

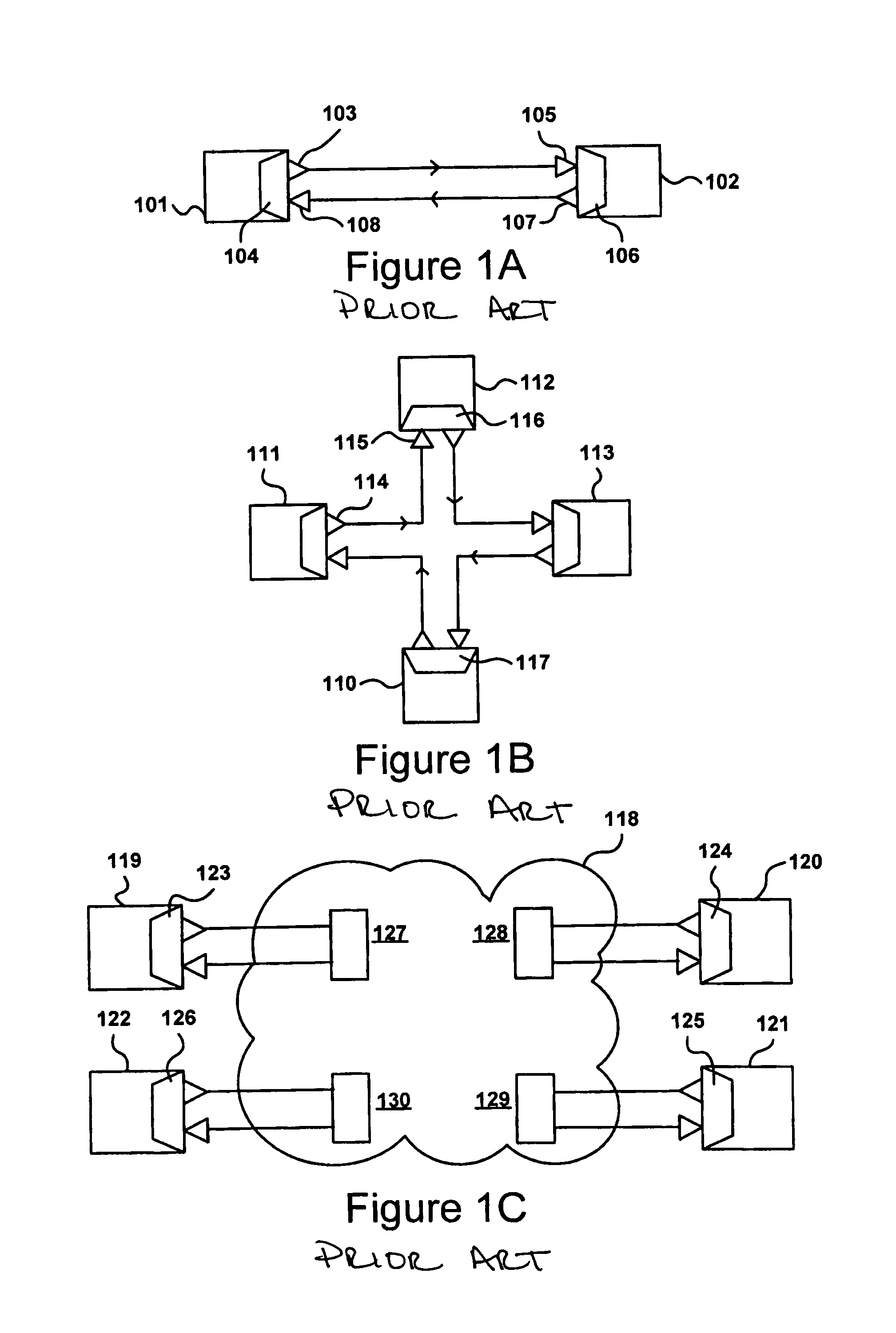

Combining multilink and IP per-destination load balancing over a multilink bundle

InactiveUS7613110B1Prevents differential delayAvoid uneven loadEnergy efficient ICTError preventionTraffic capacityProtocol processing

Load balanced transport of best efforts traffic together with delay-bounded traffic over a multilink bundle combines fragmentation and fragment distribution for best efforts packets with per-flow balancing for delay-bounded traffic. In the preferred embodiments, the best efforts packets receive Multilink Protocol treatment, including fragmentation and addition of sequence headers. Fragments of packets for one such communication go over the various links within the bundle, as appropriate for load balancing on the links. For each delay-bounded flow, such as for a VOIP service, the sending node hashes the packet header data and applies all packets for the flow to one of the links, assigned as a function of the hash value. Different flow headers produce different hash results; therefore the node sends different flows over the different links in a substantially balanced manner.

Owner:CISCO TECH INC

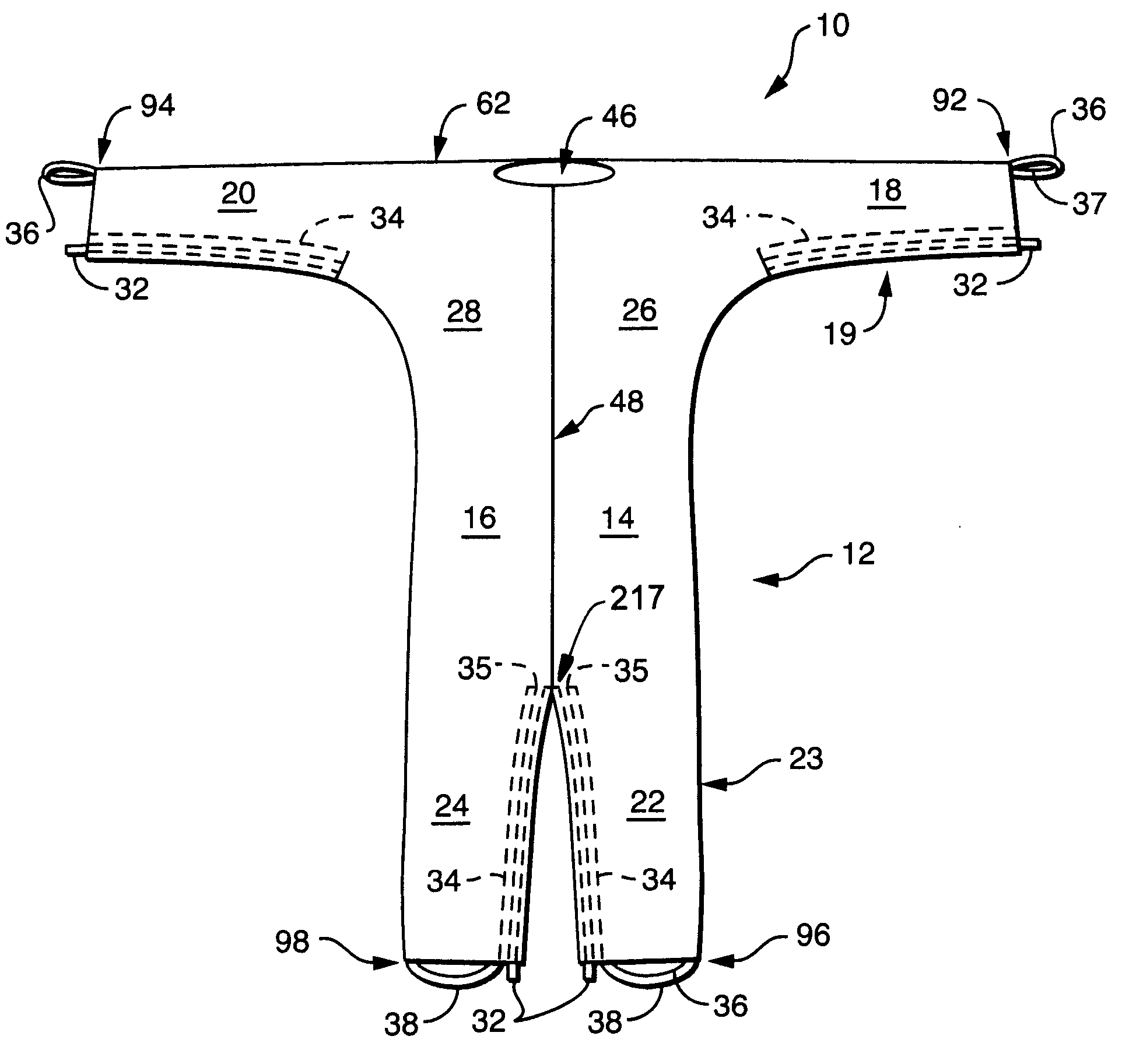

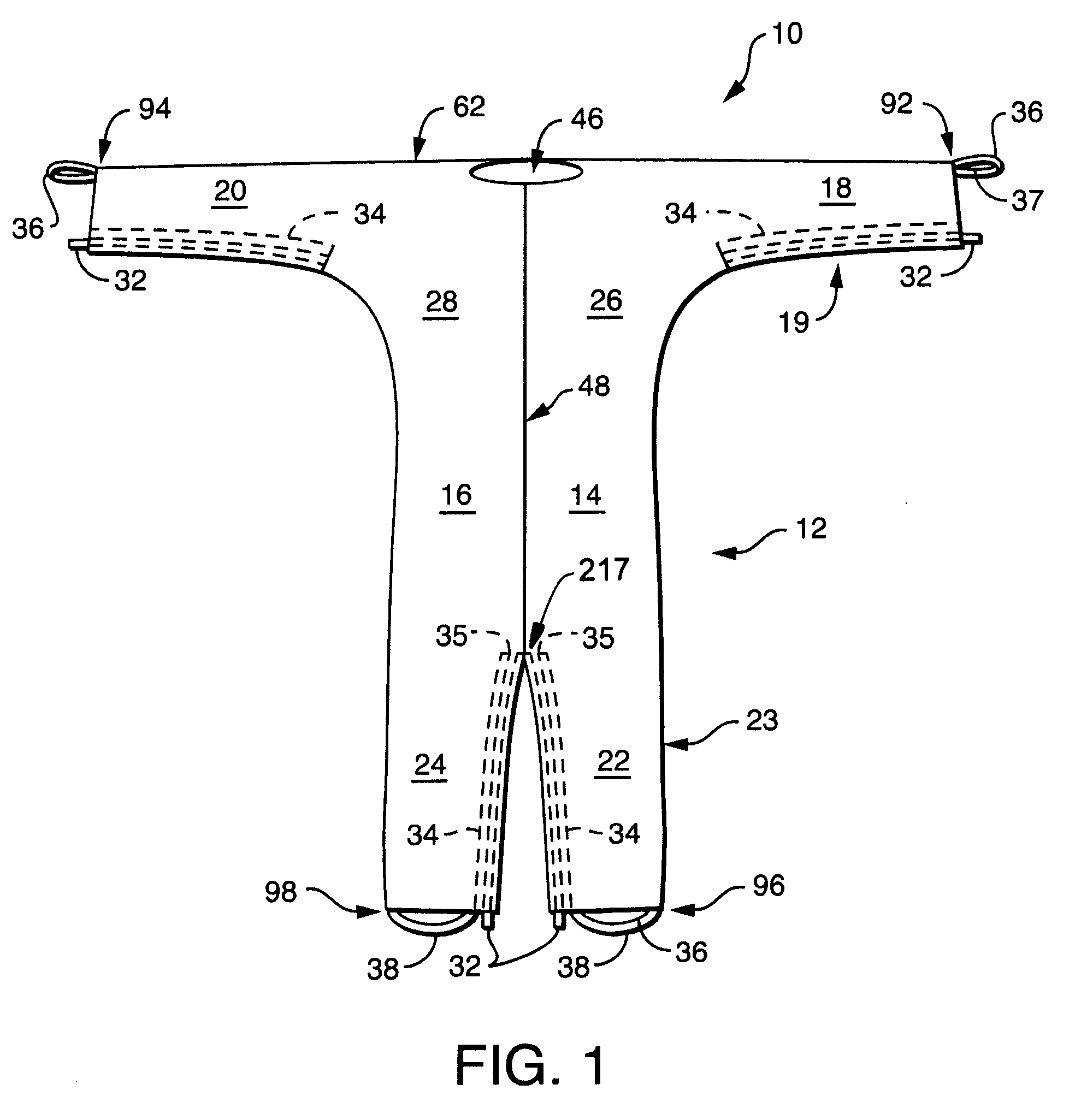

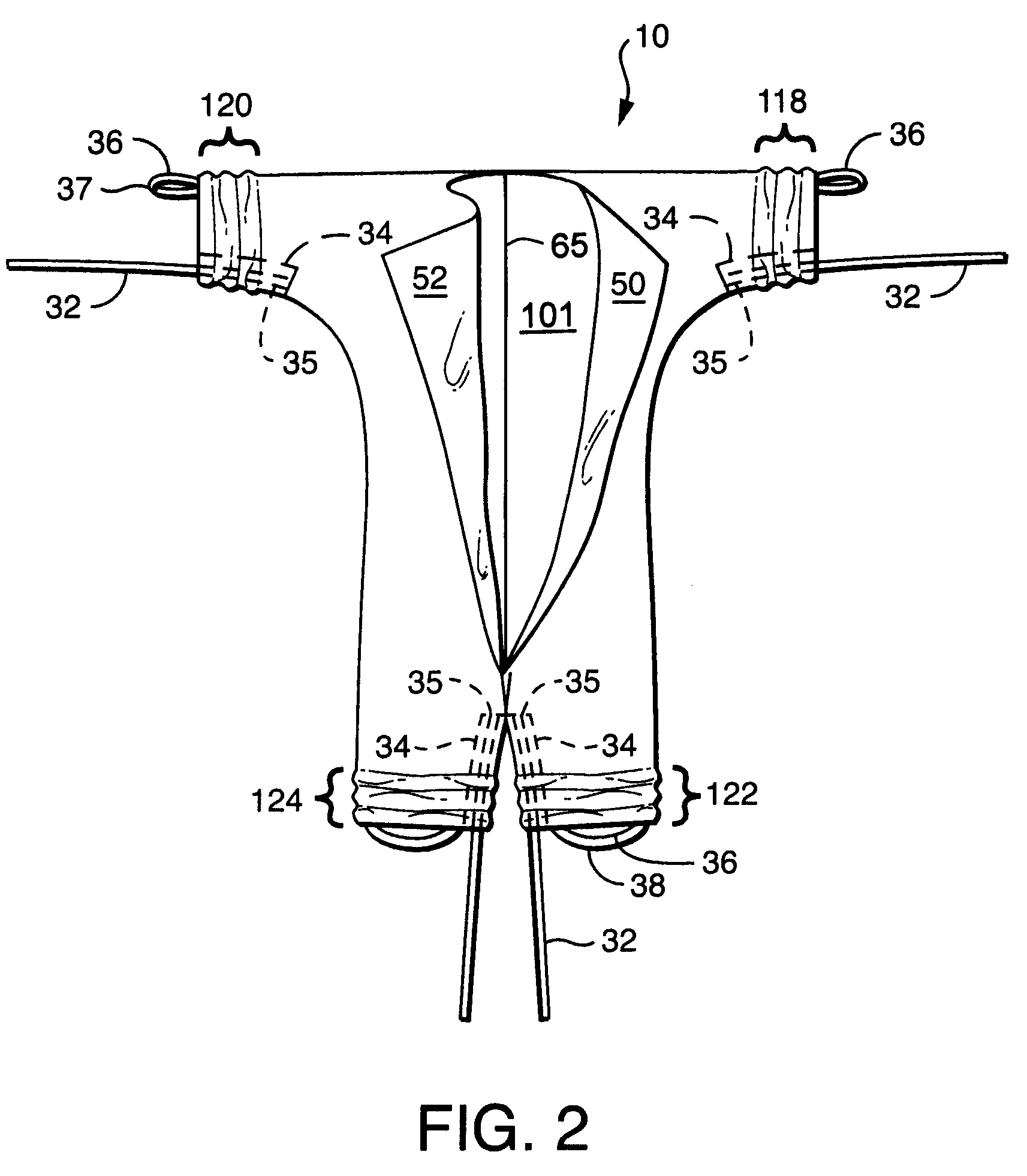

Easy Donning Garment

ActiveUS20090019616A1Easily don garmentPrevent surfaceGarment special featuresConvertible garmentEngineeringProtective Garment

A protective garment configured to facilitate easy donning of the garment is described. The sleeves and legs are shorted and held in a donning configuration by releaseably affixing at least a portion of upper and lower segments of the interior surface of each limb. This allows the garment to be handled and donned by the wearer, without the wearer touching an exterior surface of the garment. A method of preparing a protective garment for donning and a method of donning such a garment is also disclosed.

Owner:KIMBERLY-CLARK WORLDWIDE INC

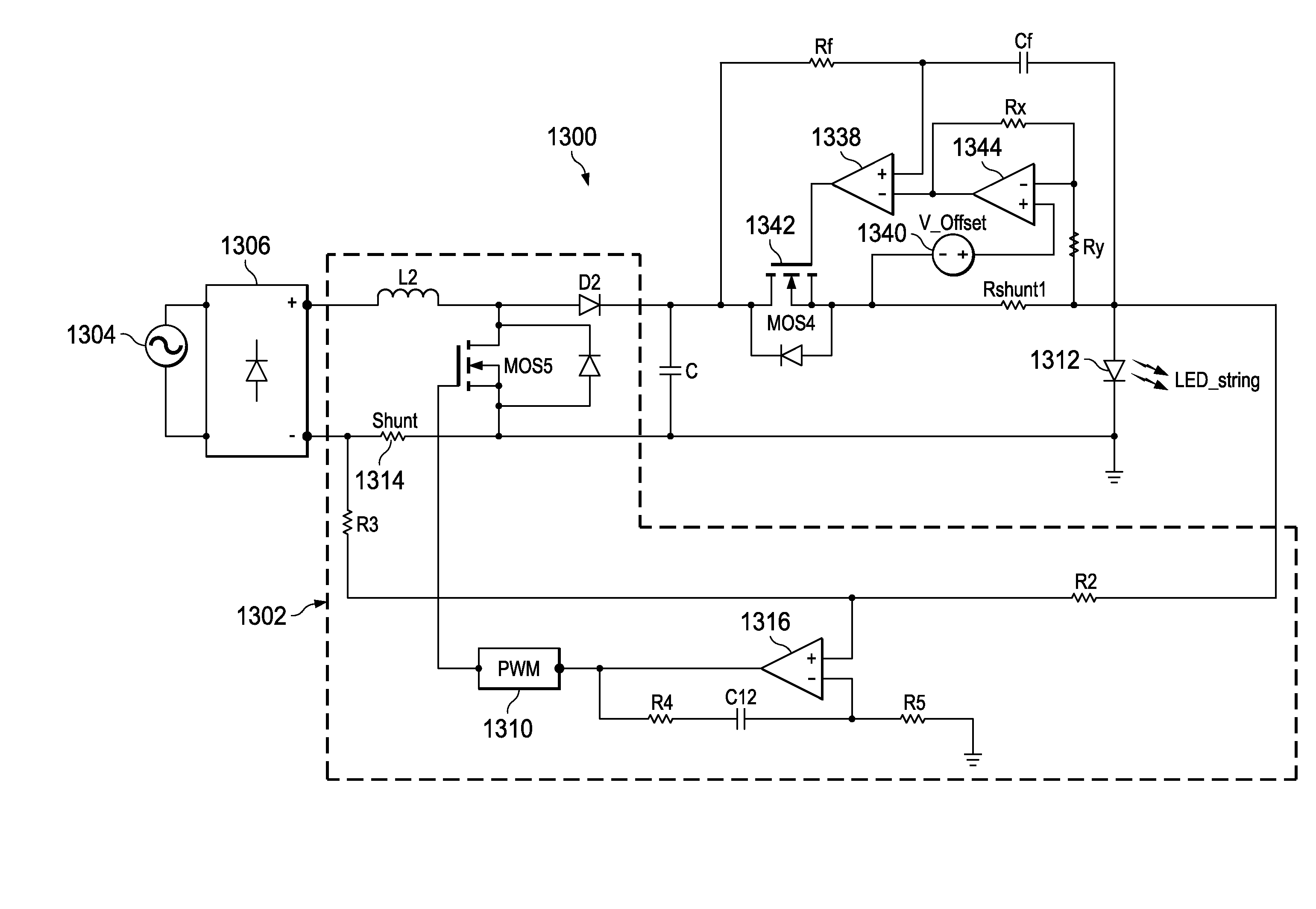

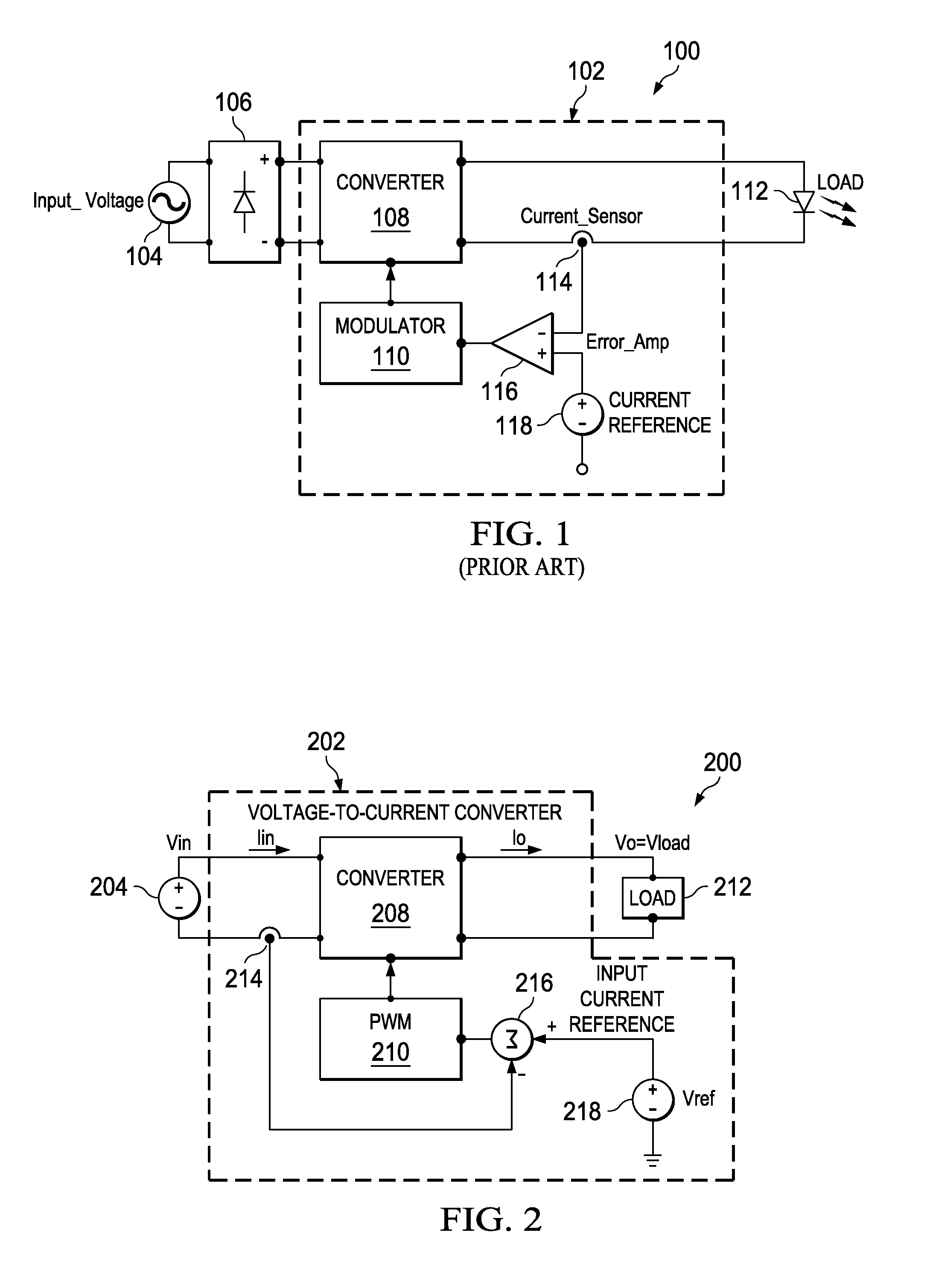

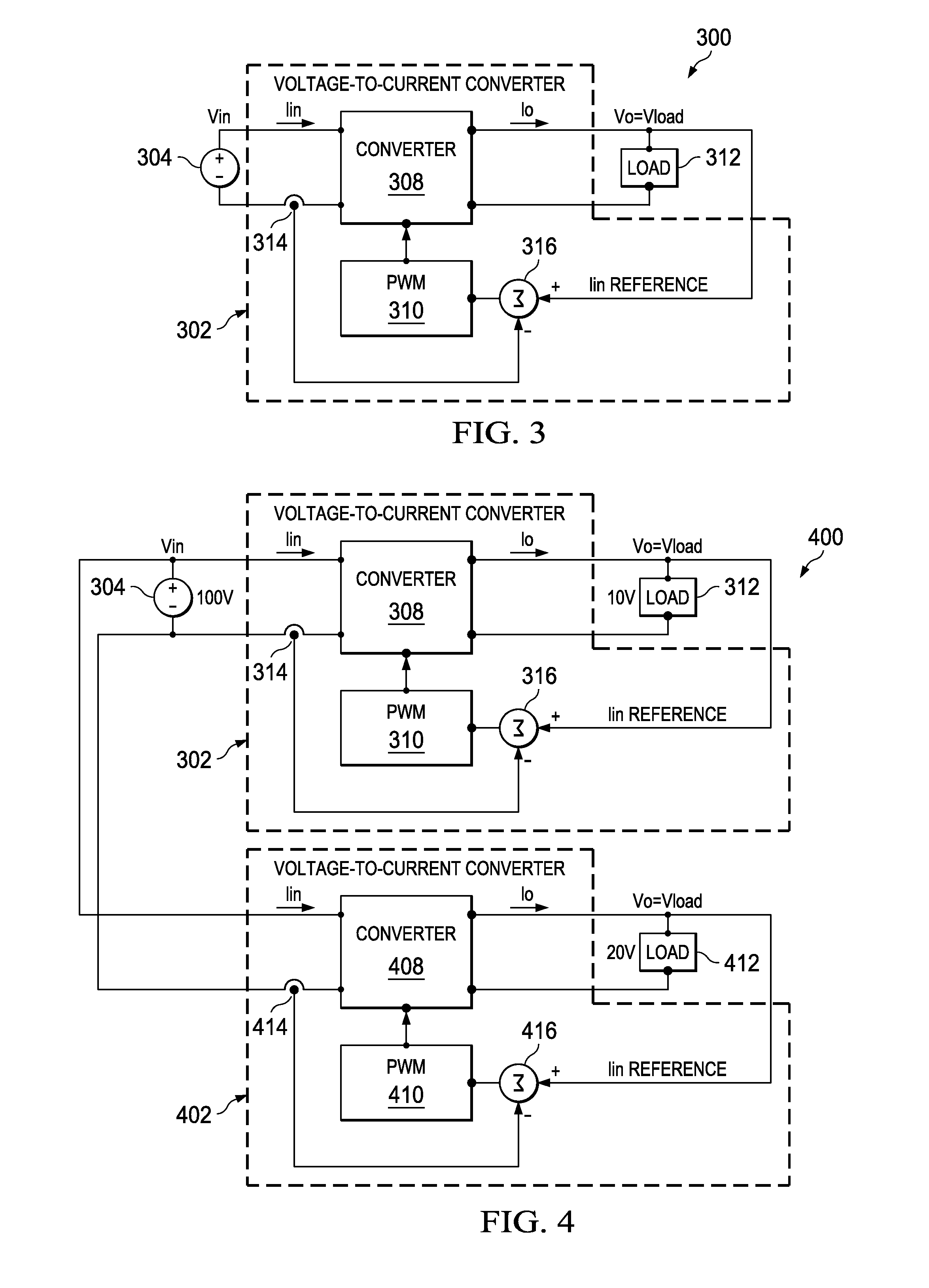

Feed forward controlled voltage to current source for LED driver

InactiveUS20130082611A1Efficient driveDelay problemEfficient power electronics conversionConversion with intermediate conversion to dcCurrent sensorControl circuit

A DC to DC converter receives a DC input voltage and generates an output DC voltage. A current sensor measures a DC input current. A control circuit is coupled to the current sensor for controlling the DC to DC converter to have a constant DC input current.

Owner:TEXAS INSTR INC

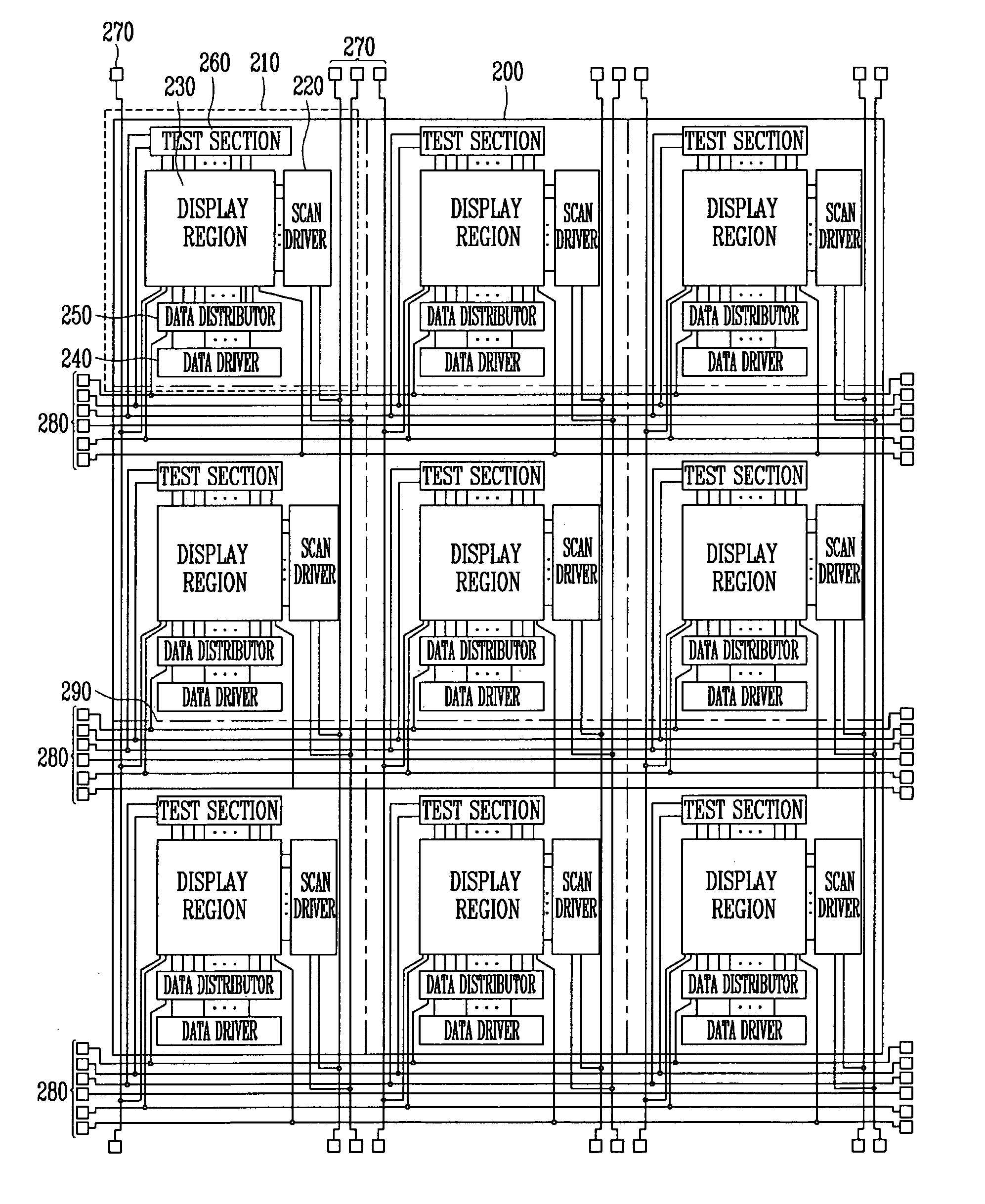

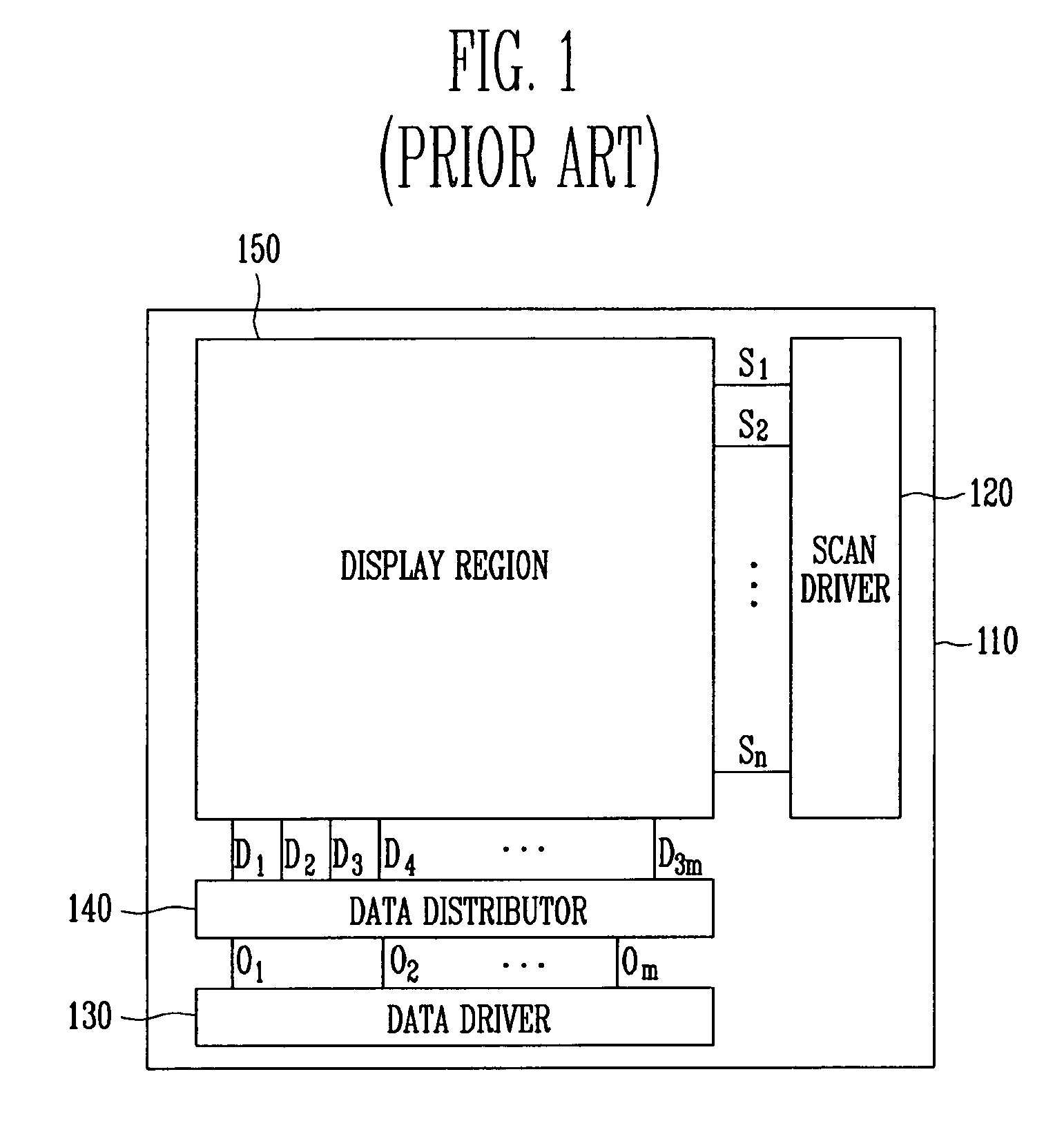

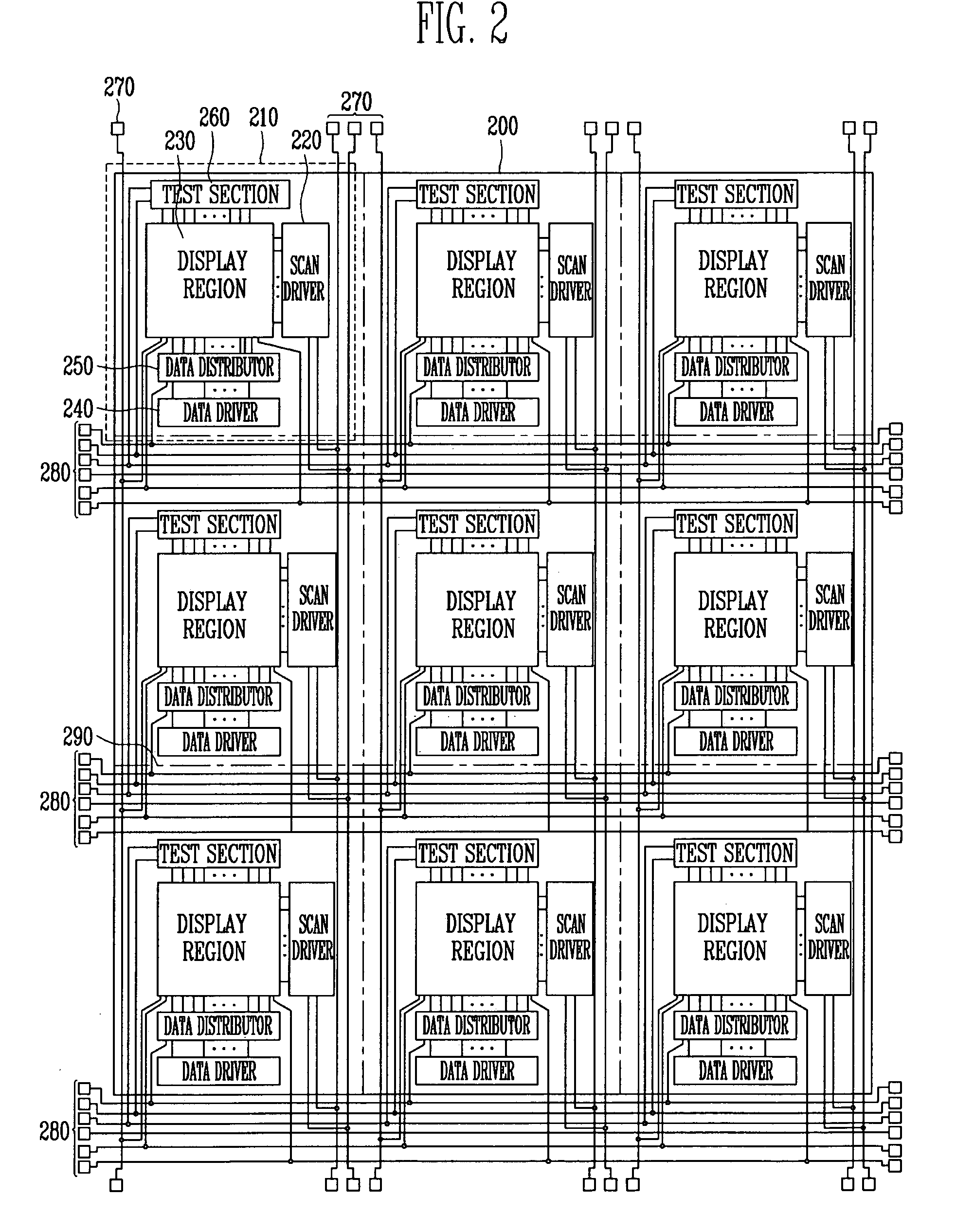

Organic light emitting display device and mother substrate for performing sheet unit test and testing method thereof

ActiveUS20070139312A1Delay problemDischarge tube luminescnet screensSemiconductor/solid-state device testing/measurementScan lineData signal

The present invention relates to an organic light emitting display device, a mother substrate, and a testing method, in which a sheet unit test is performed by directly supplying a test signal to a display region, rather than passing through a data distributor. The organic light emitting display device includes: a display region including pixels coupled to scan lines and data lines; a scan driver for supplying scan signals to the scan lines; a data driver for supplying data signals to output lines; a data distributor for supplying data signals to the data lines; a transistor group including transistors each coupled to one or more of the data lines; and a first wire group and a second wire group, wherein one of the wires included in the first wire group and the second wire group is coupled to gate electrodes of various transistors in the transistor group.

Owner:SAMSUNG DISPLAY CO LTD

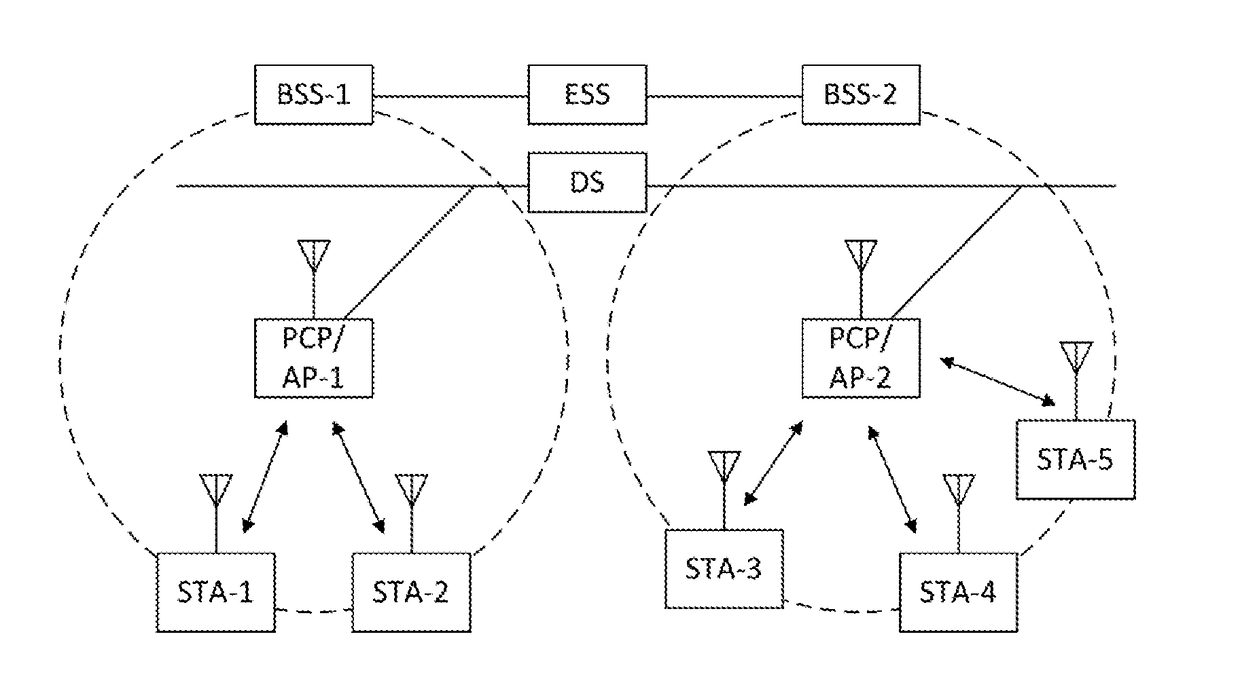

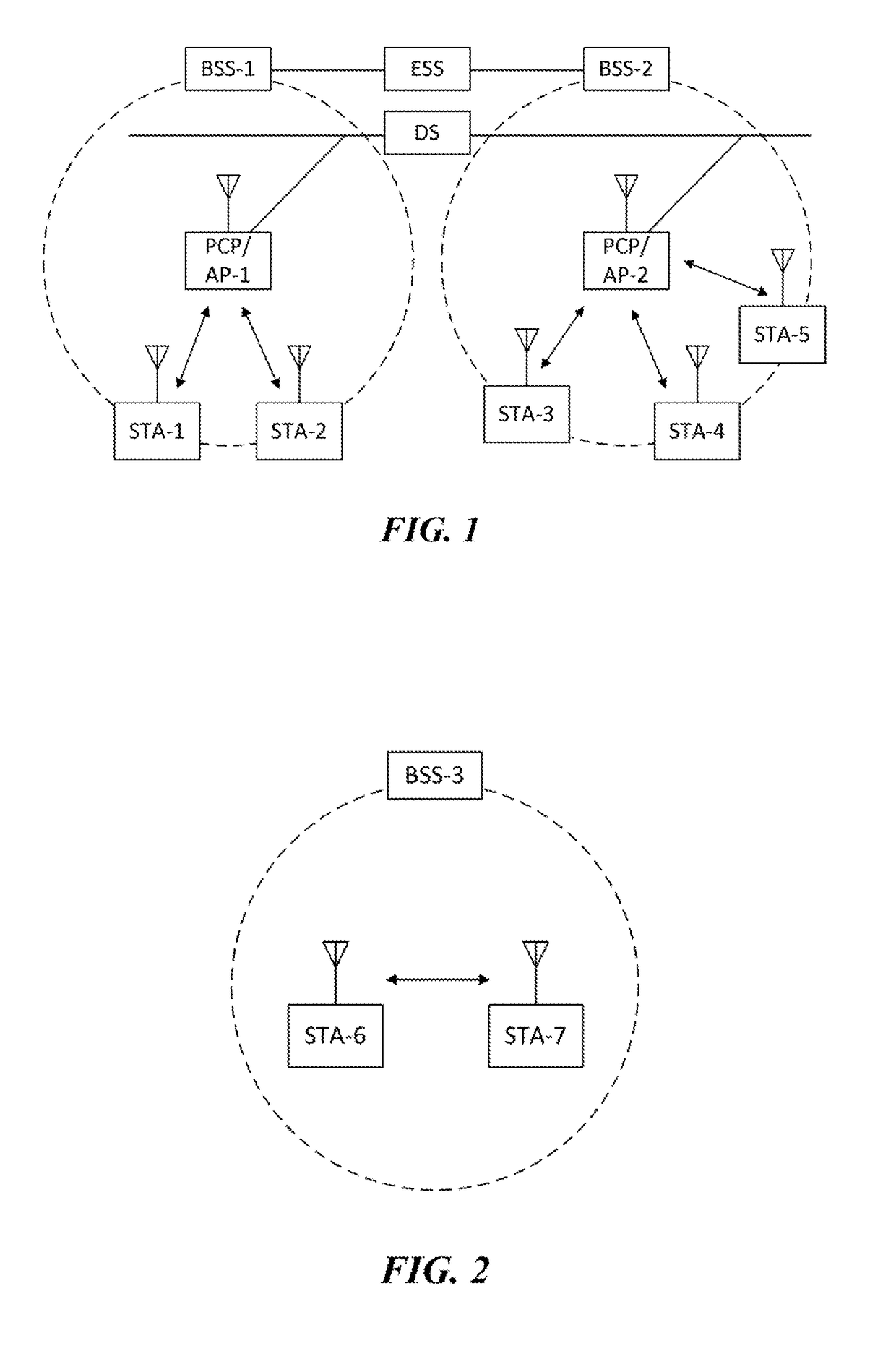

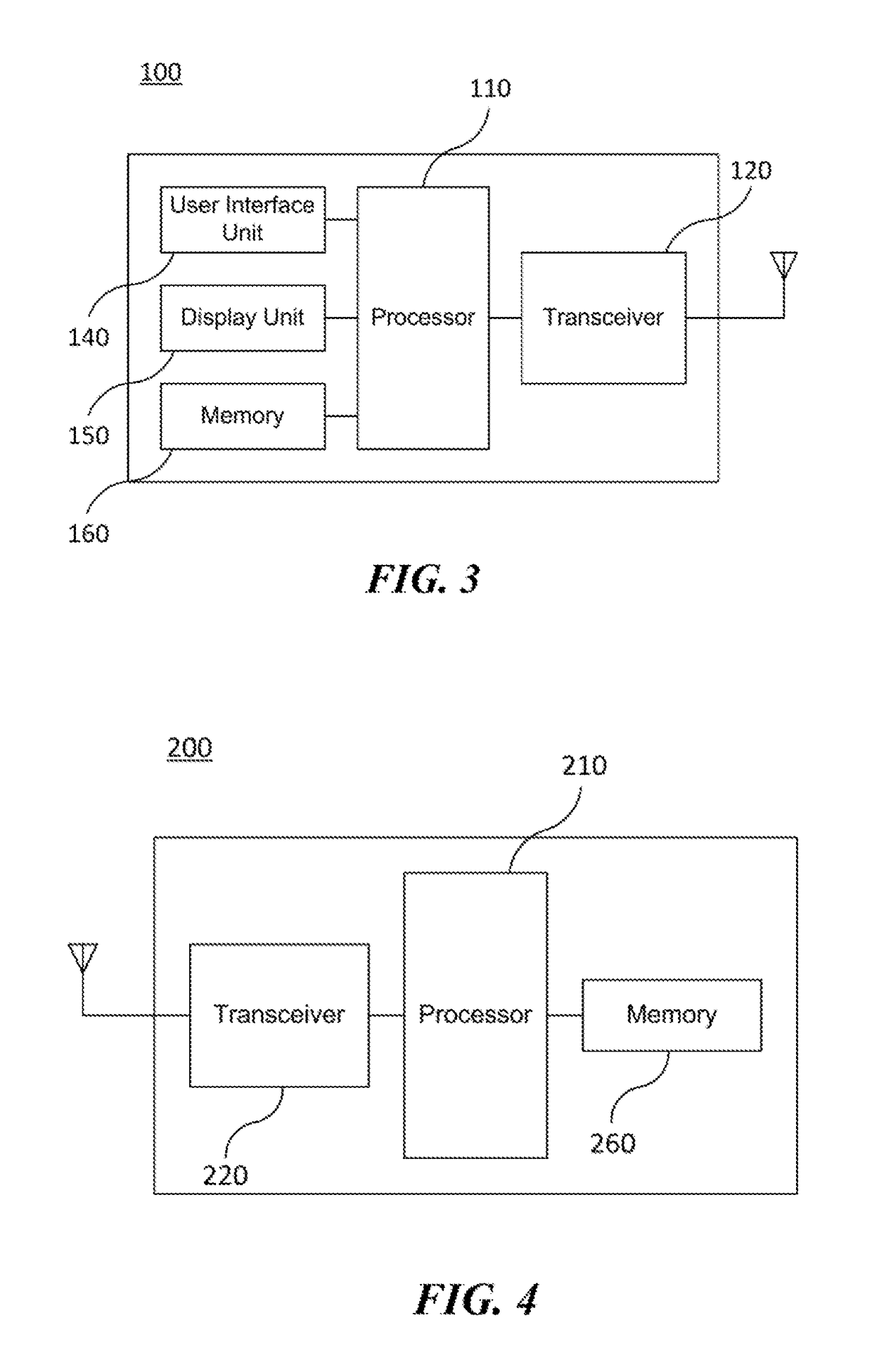

Wireless communication method for simultaneous data communication, and wireless communication terminal using same

ActiveUS20170164406A1Efficiently determinedMinimize time delayNetwork topologiesTransmission monitoringCompletion timeCommunications system

The present invention relates to a wireless communication method for simultaneous data communication and a wireless communication terminal using the same, and more particularly, to a wireless communication method for suppressing interference between terminals and ensuring fairness when performing data simultaneous communication for spatial reuse of communication system and wireless communication terminal using the same.For this, provided are a wireless communication method and a wireless communication terminal using the same. The method includes: receiving a wireless signal of a specific channel; extracting basic service set (BSS) identifier information of the received wireless signal; extracting length information from the wireless signal wherein the length information represents information relating to a transmission completion time point of the wireless signal; and adjusting a data transmission period of the terminal based on the extracted length information, when the BSS identifier information of the wireless signal is different from BSS identifier information of the terminal.

Owner:WILUS INST OF STANDARDS & TECH +1

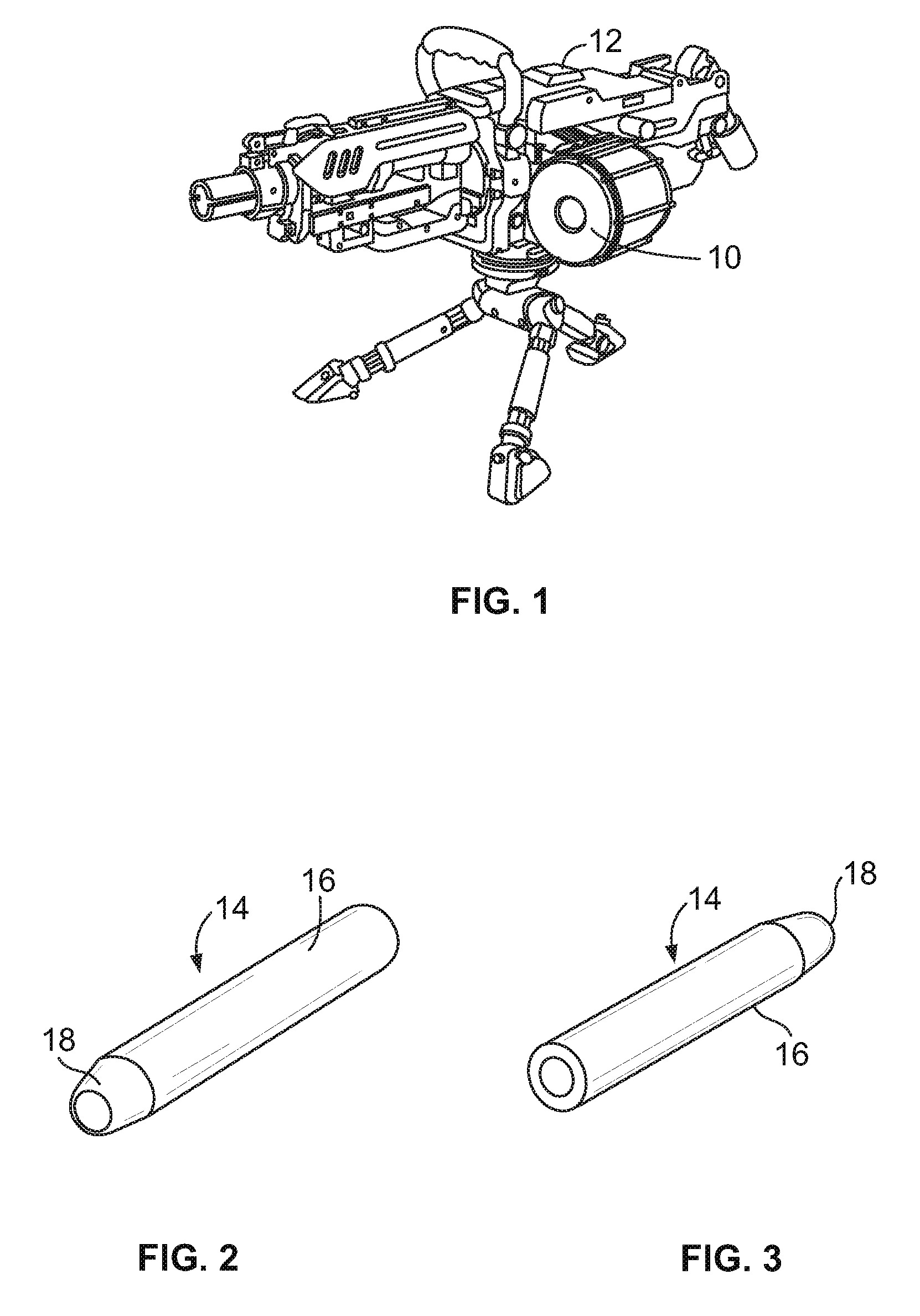

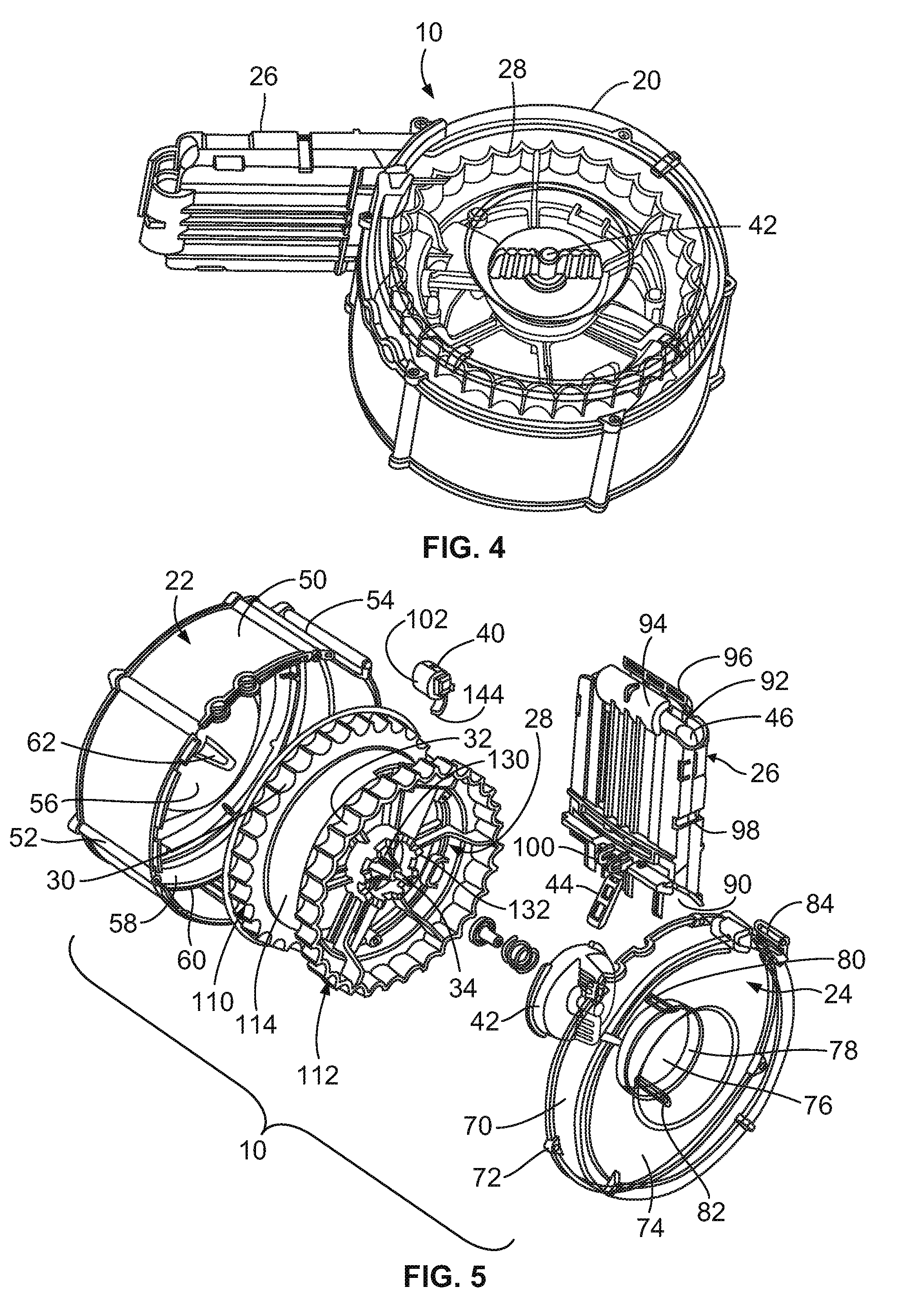

Toy dart magazine apparatus

ActiveUS8402958B2Simple structureReliable manufacturingFriction-wheel launchersAmmunition loadingEngineeringConstant-force spring

The wheel also includes an opening in the third portion leading to a chamber in a hollow support of the wheel. A spring-biased knob is mounted on a shaft that also mounts the wheel. Both the knob and the wheel have axially align protrusions that may engage each other to allow the wheel to be rotationally adjusted to correct any jam or misalignment of the darts stored on the wheel. A flexible arm and a pusher structure are also included with the magazine apparatus and are connected to a constant force spring, where the flexible arm and a portion of the constant force spring are lodged in the chamber of the hollow support during a dart loading process of the wheel, and the constant force spring uncoils when the wheel is rotated during the loading process. The constant force spring biases the wheel to feed the darts from both the drum and the clip to a firing position at the end of the clip located in the launcher, but the constant force spring is insufficient to discharge the darts when the magazine is not connected to the launcher.

Owner:HASBRO INC

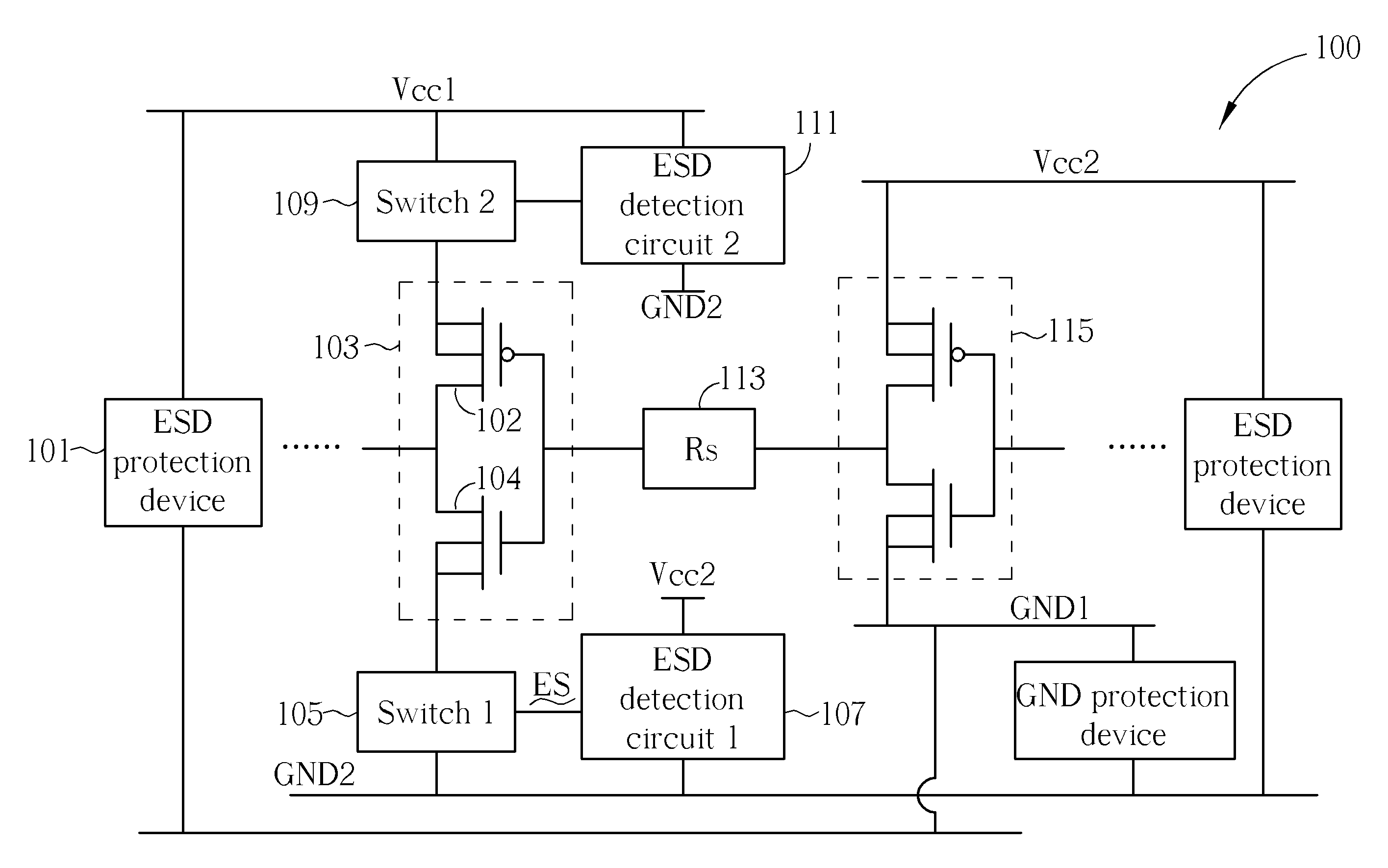

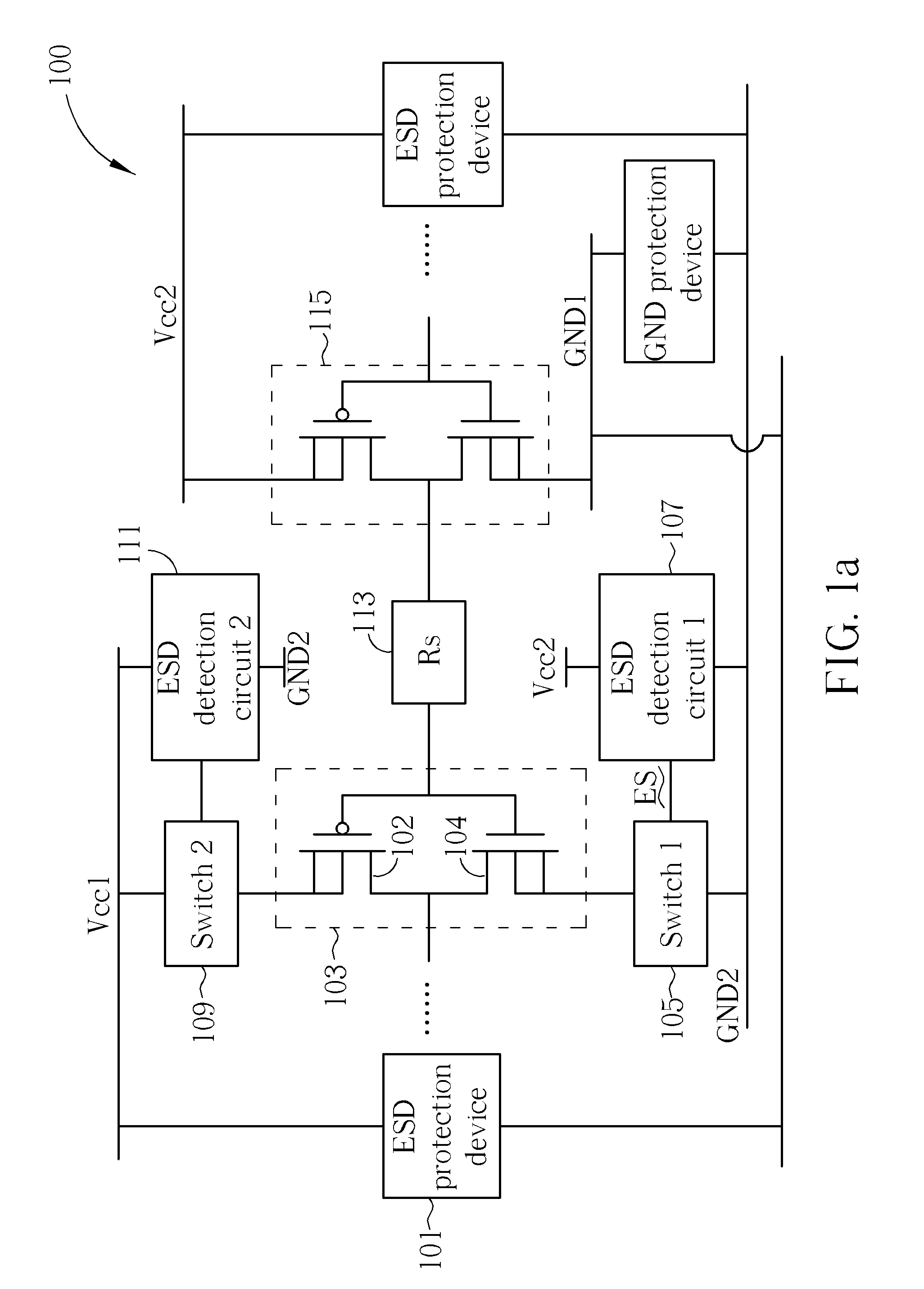

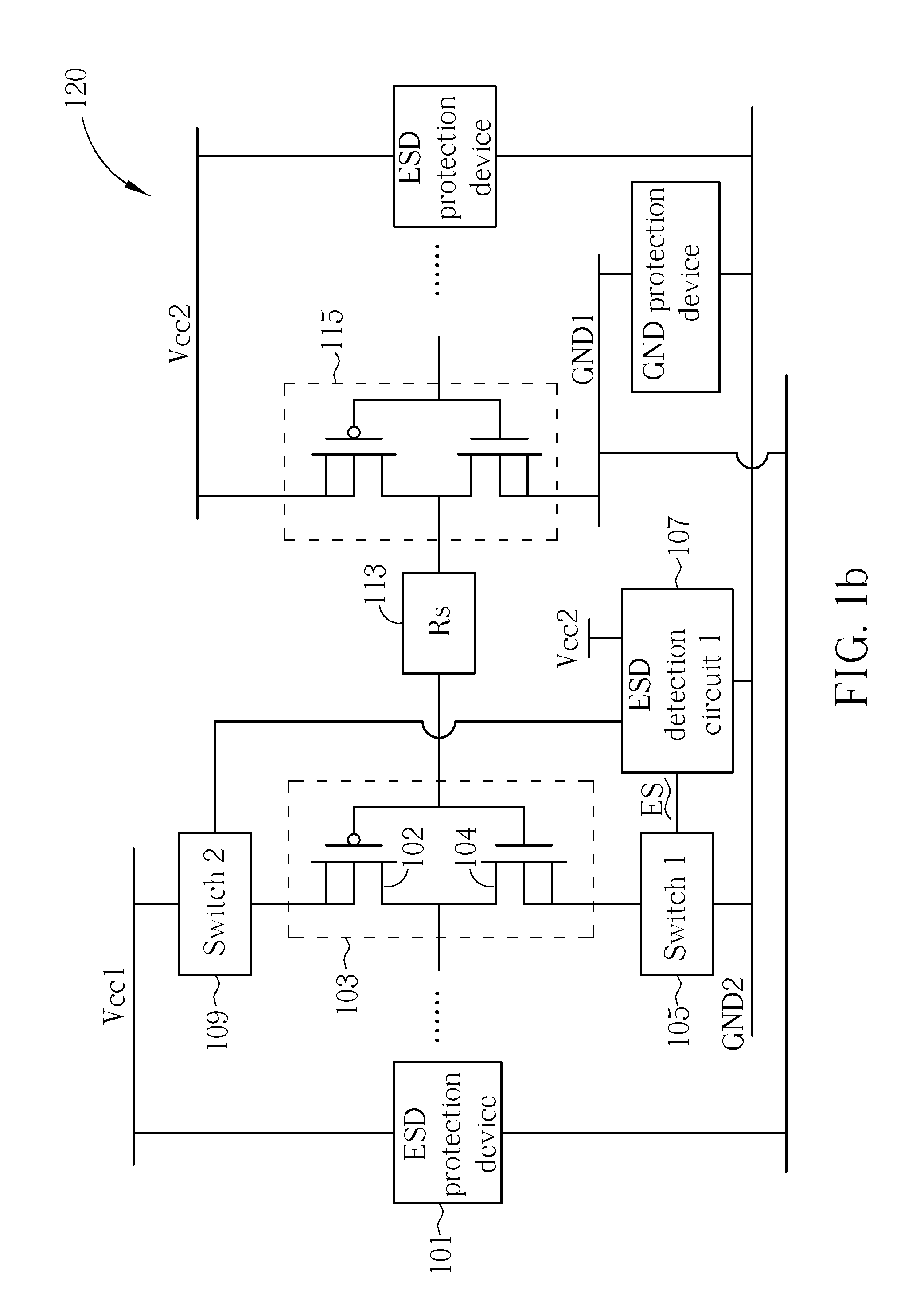

Electrostatic discharge circuit for integrated circuit with multiple power domain

ActiveUS20110255200A1Delay problemAvoid problemEmergency protective arrangements for limiting excess voltage/currentArrangements responsive to excess voltageElectrostatic dischargeIntegrated circuit

An ESD protection circuit with multiple domains, which comprises: an ESD protection device, coupled between a first power supplying line and a first ground line; a first internal circuit, having a first terminal coupled to the first power supplying line; a first switch, coupled between a second terminal of the first internal circuit and a second ground line; and a first ESD detection circuit, coupled to the first switch, for detecting an ESD signal, and controls the first switch to be non-conductive when the ESD signal occurs.

Owner:FARADAY TECH CORP

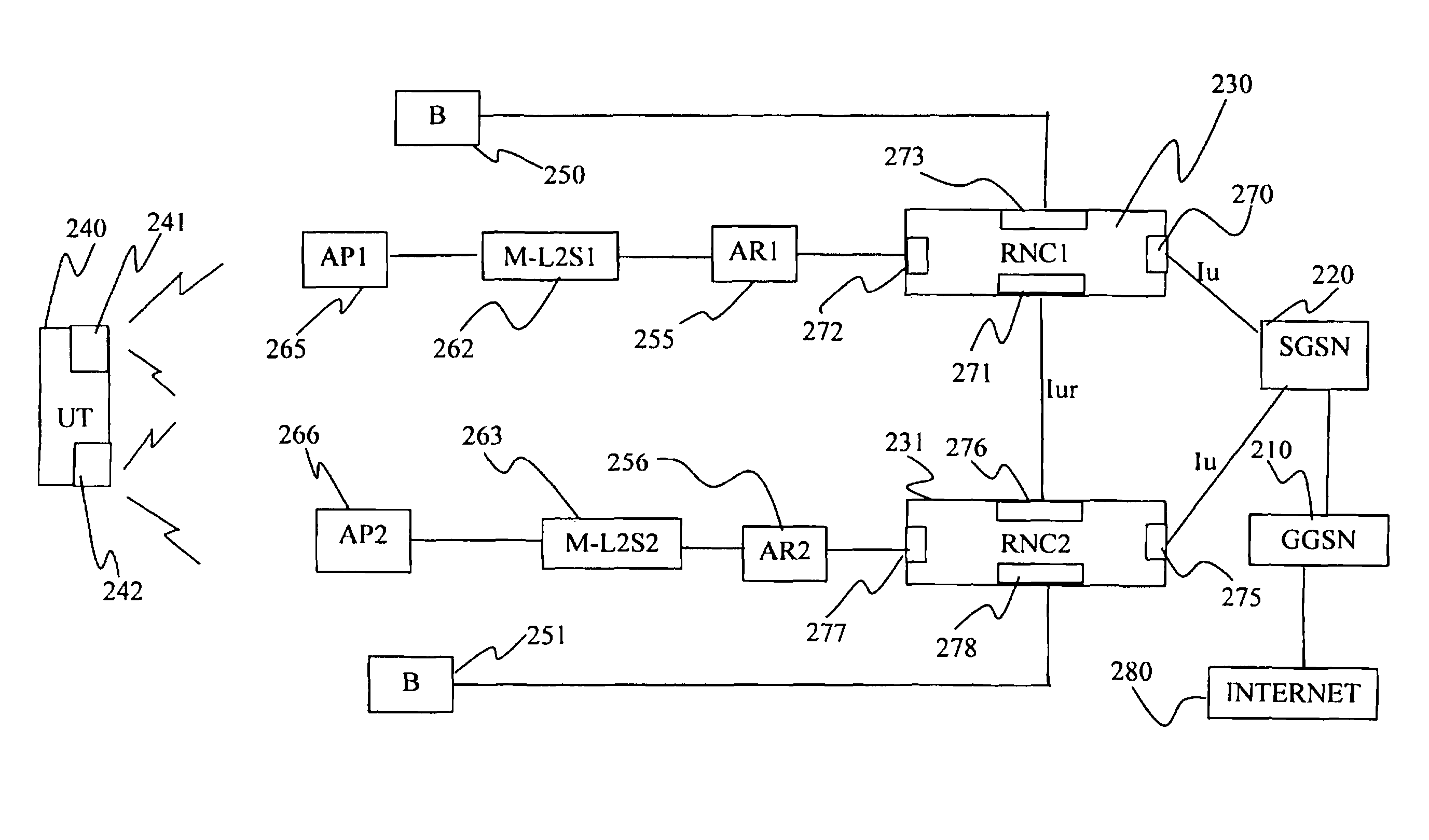

Means and Methods for Improving the Handover Characteristics of Integrated Radio Access Networks

InactiveUS8019346B2Minimize data lossReduce distractionsWireless commuication servicesMessage typeRadio access network

Owner:TELEFON AB LM ERICSSON (PUBL)

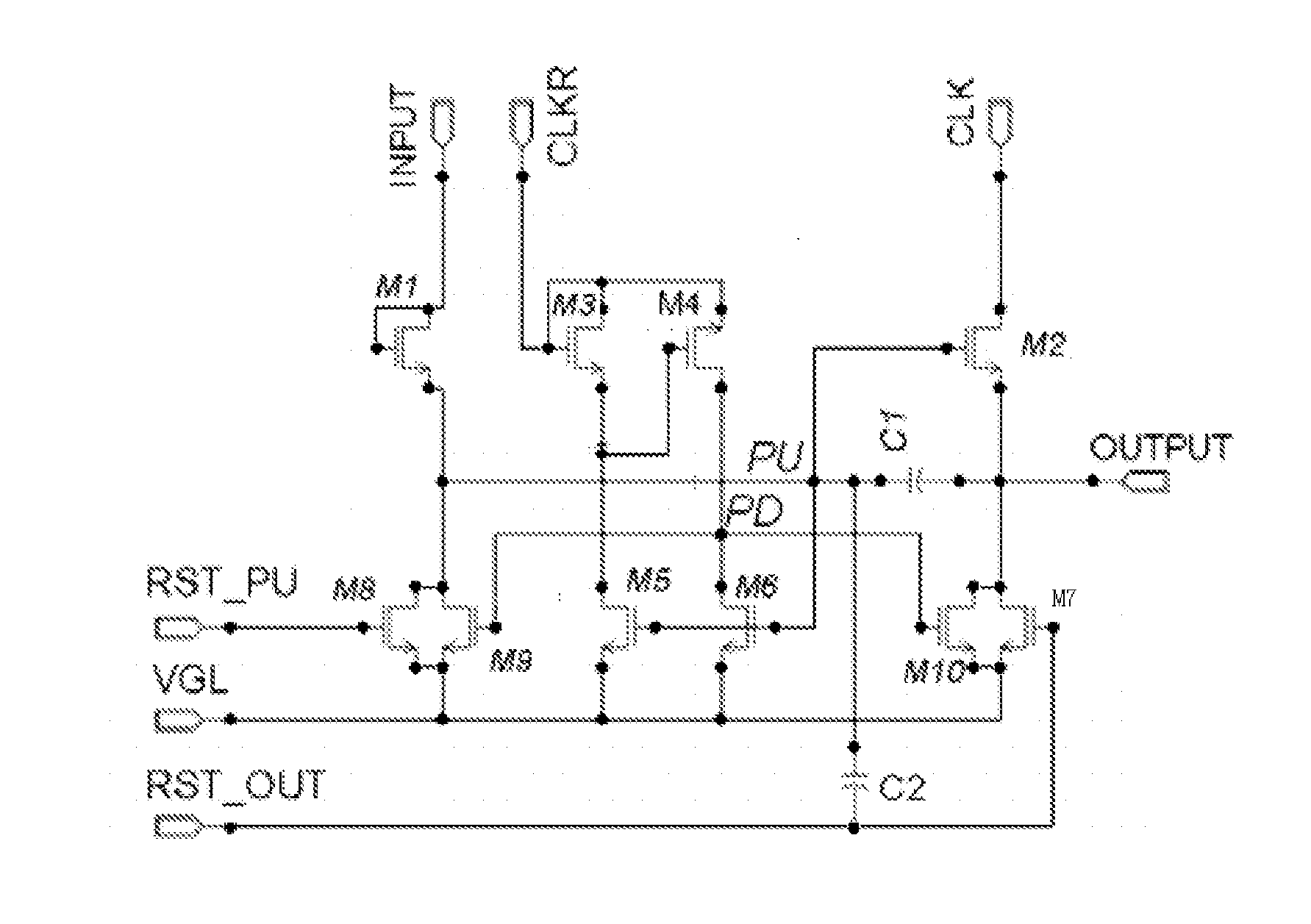

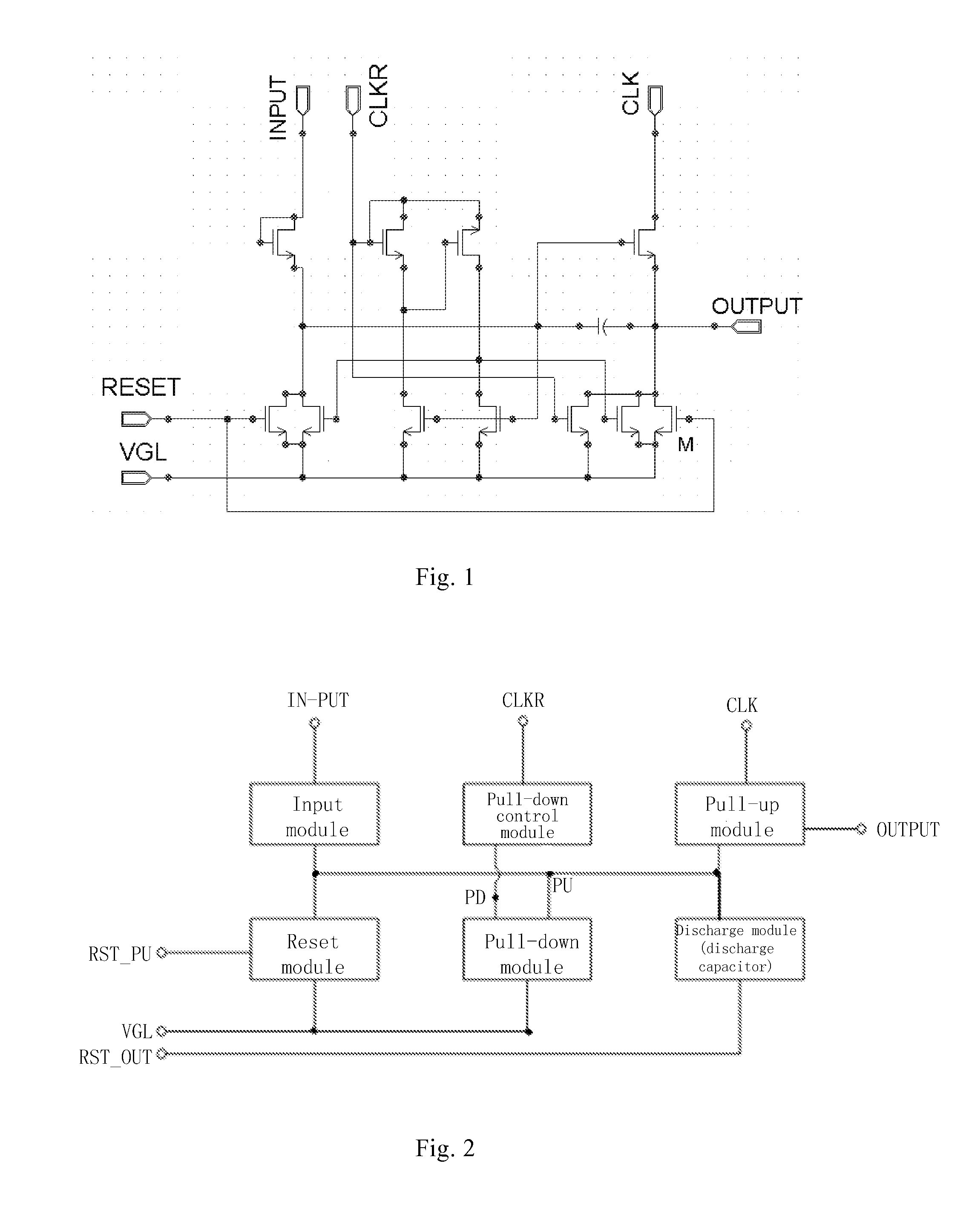

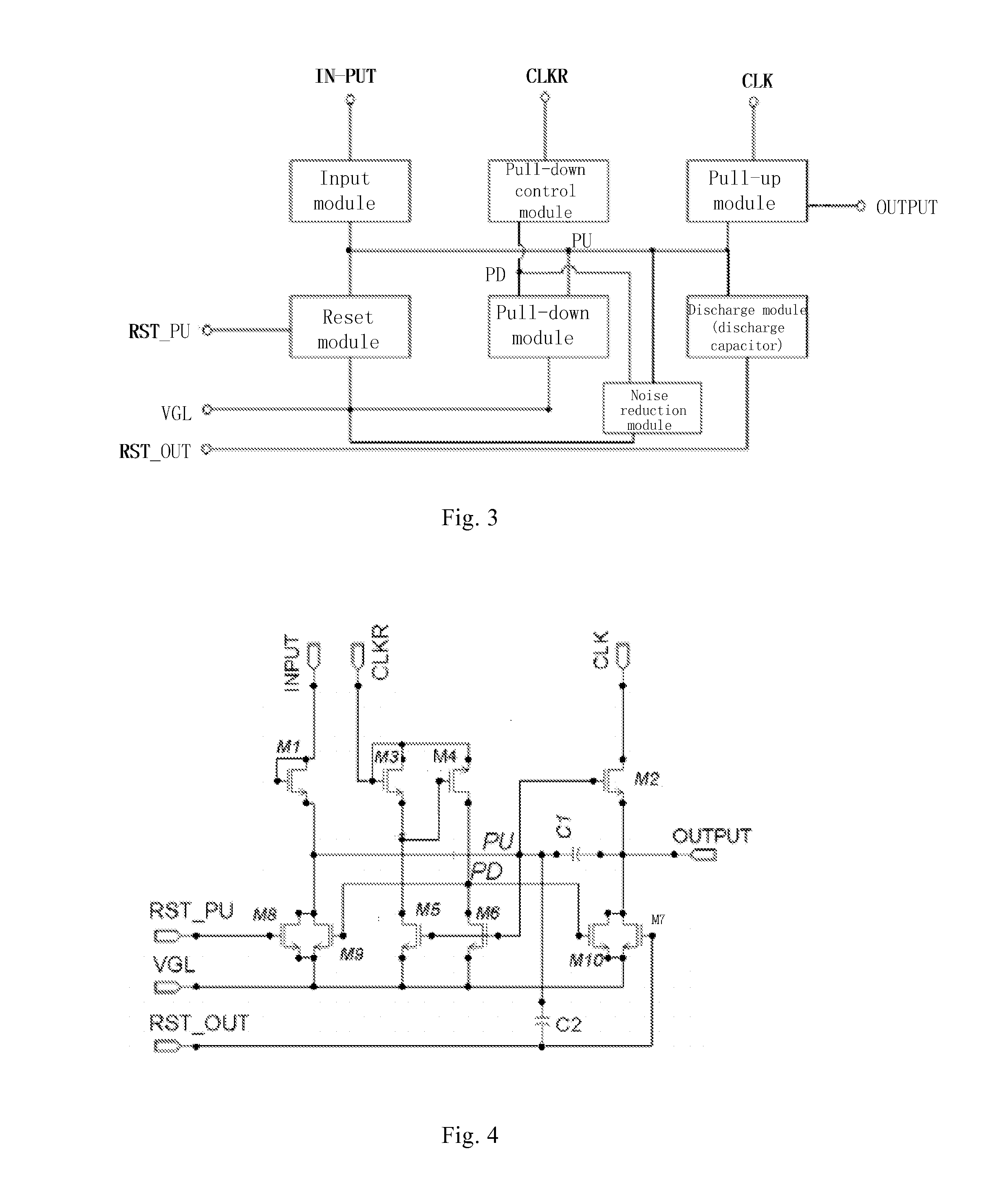

Shift register unit, gate driving circuit and display device

ActiveUS20160300542A1Cancel noiseSimple structureStatic indicating devicesDigital storageShift registerDisplay device

The present invention provides a shift register unit, a gate driving circuit and a display device, which belongs to the field of display technology. The shift register unit of the present invention comprises: an input module, a pull-up module, a pull-down control module, a pull-down module, a reset module and a discharge module.

Owner:BOE TECH GRP CO LTD

Seamless coarse and fine delay structure for high performance DLL

ActiveUS7629819B2Delay problemPulse automatic controlCounting chain pulse countersPhase differenceClock rate

A clock synchronization system and method avoids output clock jitter at high frequencies and also achieves a smooth phase transition at the boundary of the coarse and fine delays. The system may use a single coarse delay line configured to generate two intermediate clocks from the input reference clock and having a fixed phase difference therebetween. The coarse delay line may have a hierarchical or a non-hierarchical structure. A phase mixer receives these two intermediate clocks and generates the final output clock having a phase between the phases of the intermediate clocks. The coarse shifting in the delay line at high clock frequencies does not affect the phase relationship between the intermediate clocks fed into the phase mixer. The output clock from the phase mixer is time synchronized with the input reference clock and does not exhibit any jitter or noise even at high clock frequency inputs.

Owner:MICRON TECH INC

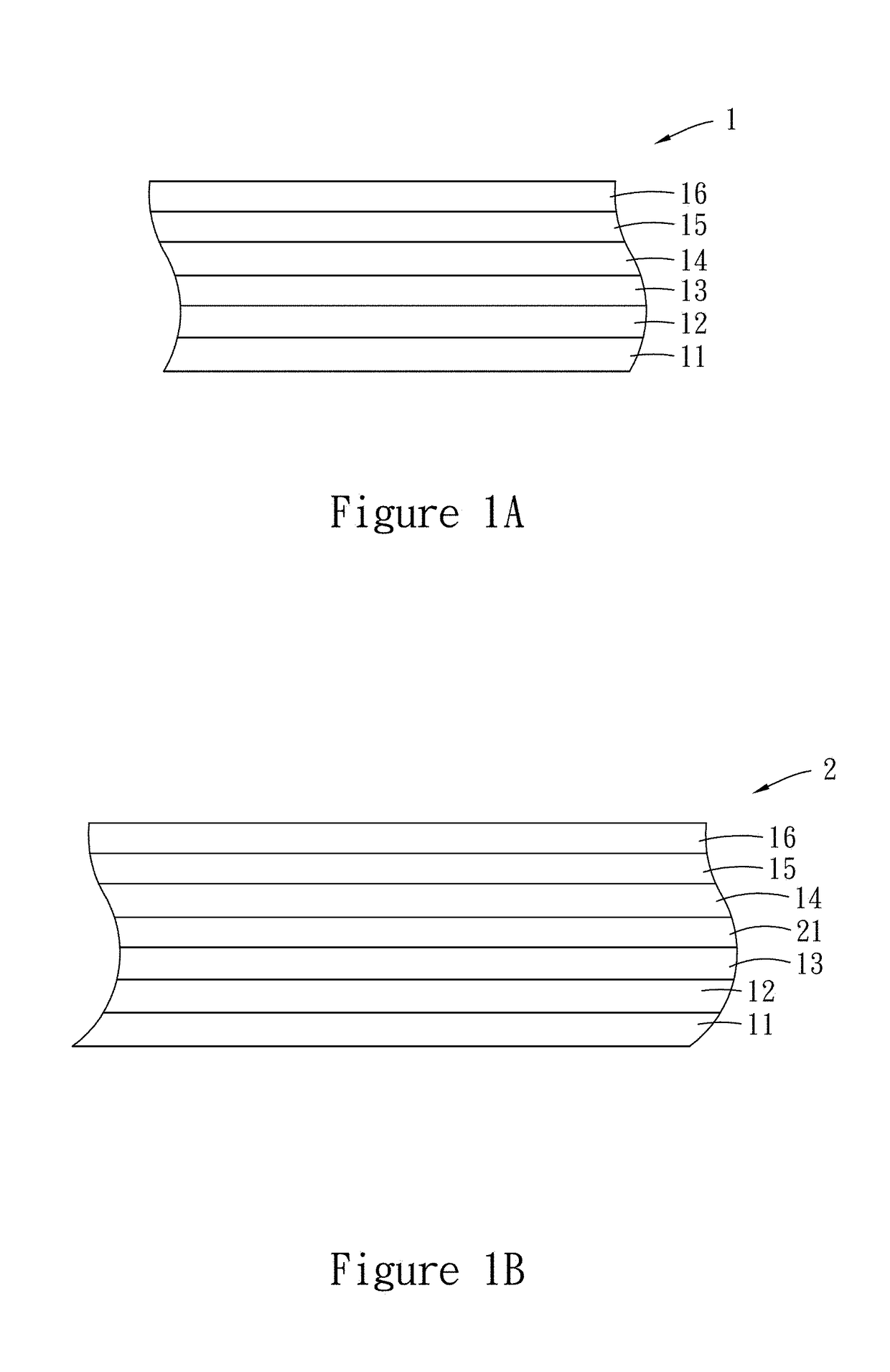

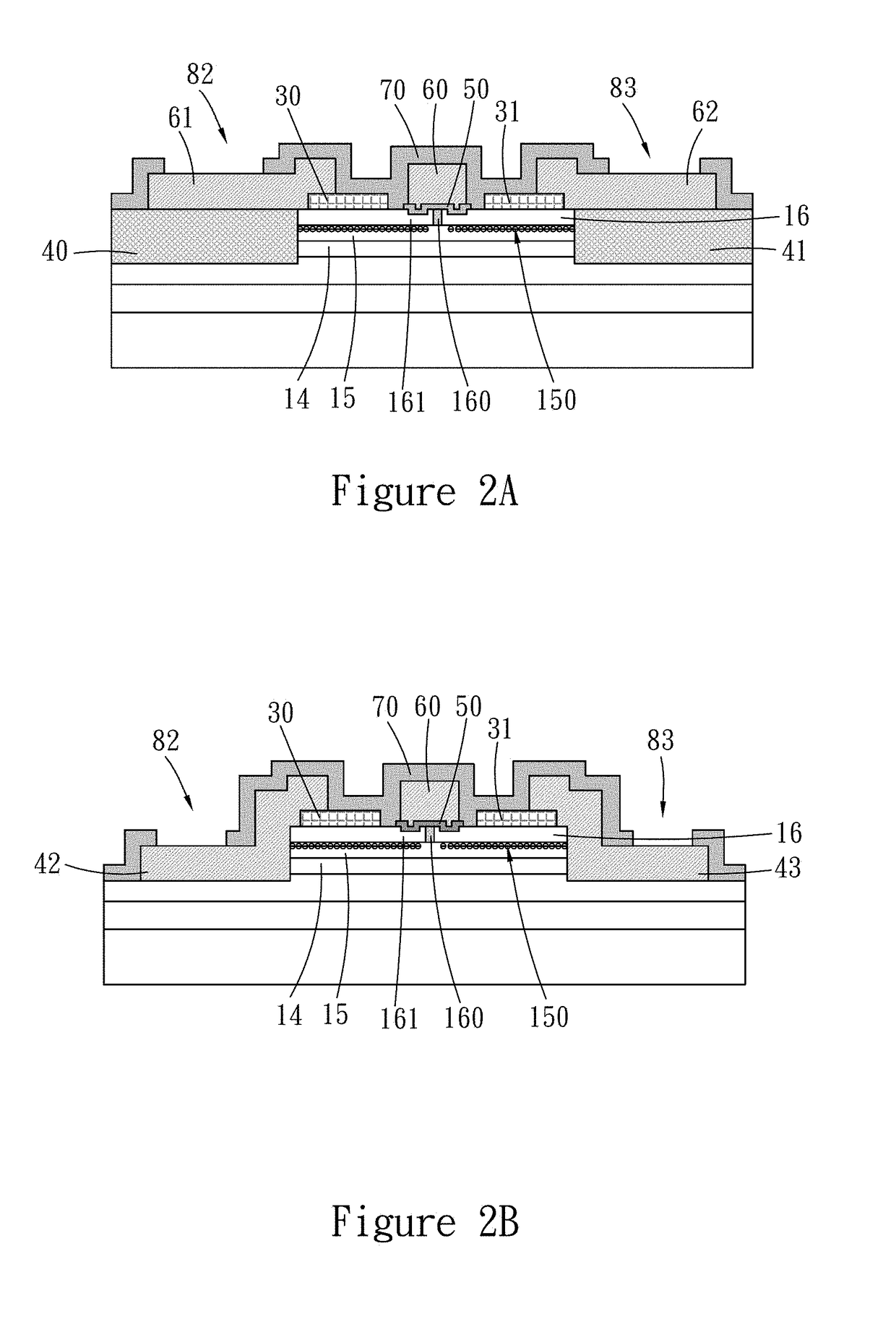

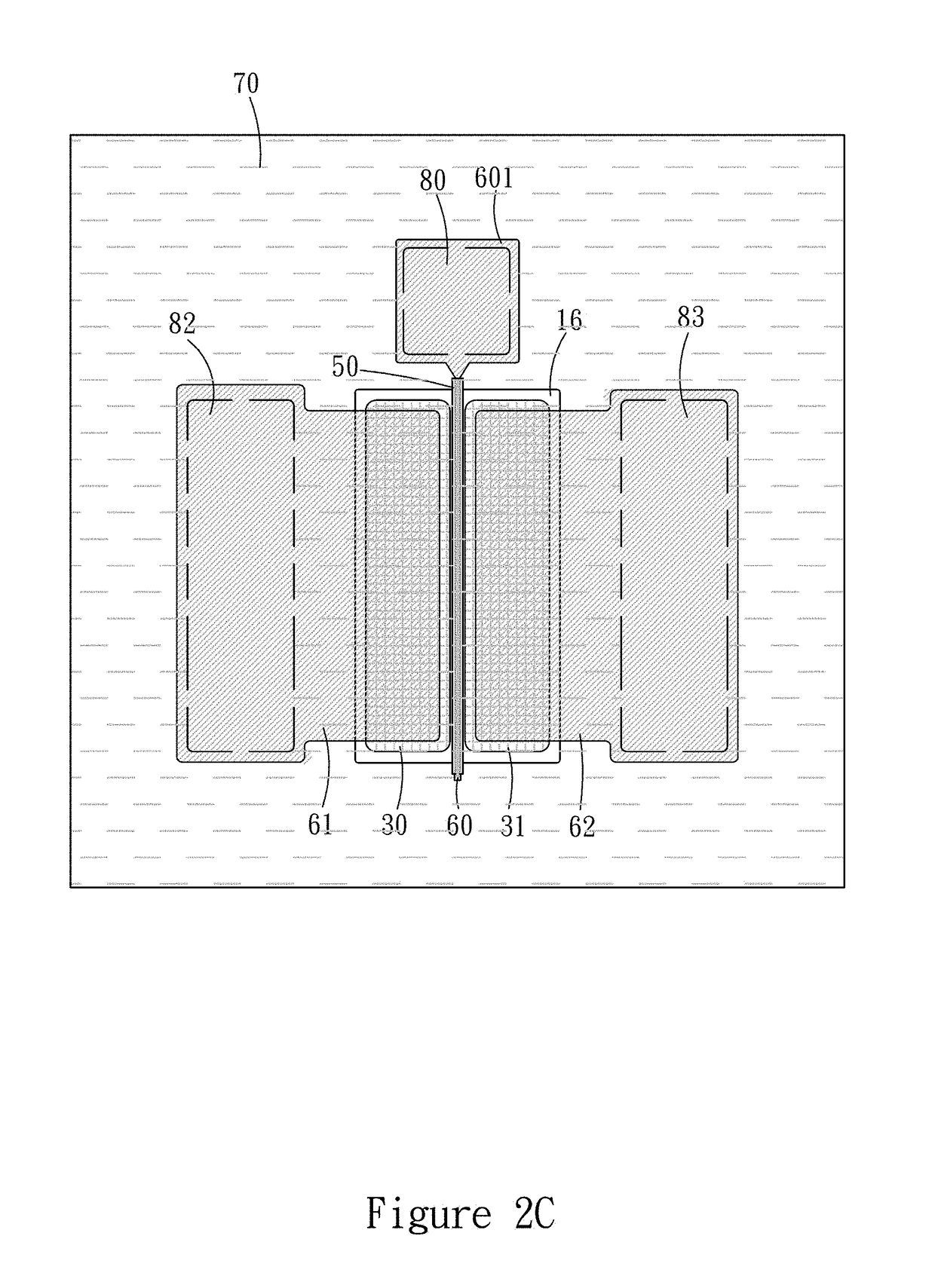

Epitaxial structure of n-face group iii nitride, active device, and method for fabricating the same with integration and polarity inversion

ActiveUS20180350944A1Maintain integrityAdditional drawbackTransistorPolycrystalline material growthSBDSElectrical polarity

The present invention provides an epitaxial structure of N-face group III nitride, its active device, and the method for fabricating the same. By using a fluorine-ion structure in device design, a 2DEG in the epitaxial structure of N-face group III nitride below the fluorine-ion structure will be depleted. Then the 2DEG is located at a junction between a i-GaN channel layer and a i-AlyGaN layer, and thus fabricating GaN enhancement-mode AlGaN / GaN high electron mobility transistors (HEMTs), hybrid Schottky barrier diodes (SBDs), or hybrid devices. After the fabrication step for polarity inversion, namely, generating stress in a passivation dielectric layer, the 2DEG will be raised from the junction between the i-GaN channel layer and the i-AlyGaN layer to the junction between the i-GaN channel layer and the i-AlxGaN layer.

Owner:HUANG CHIH SHU

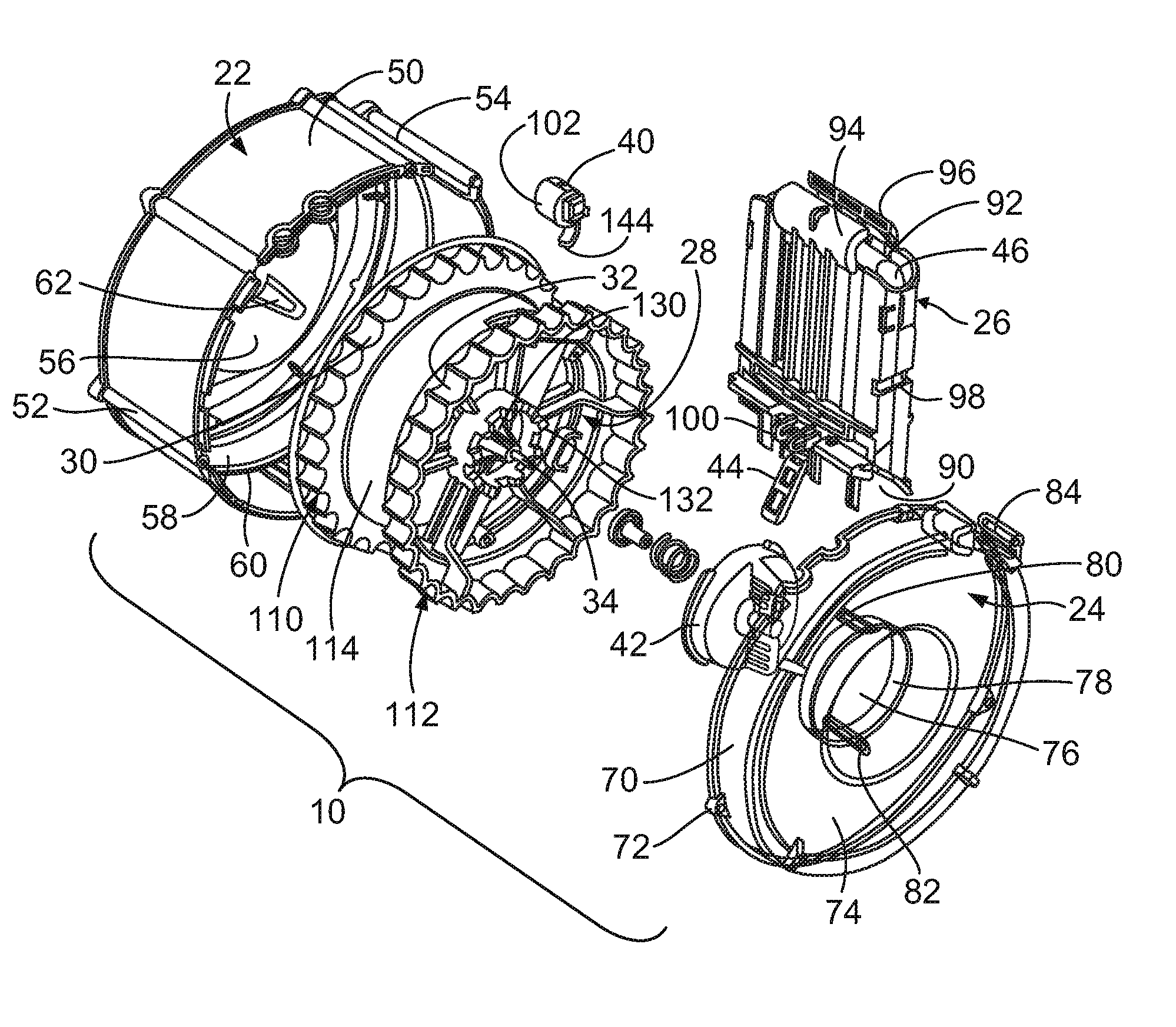

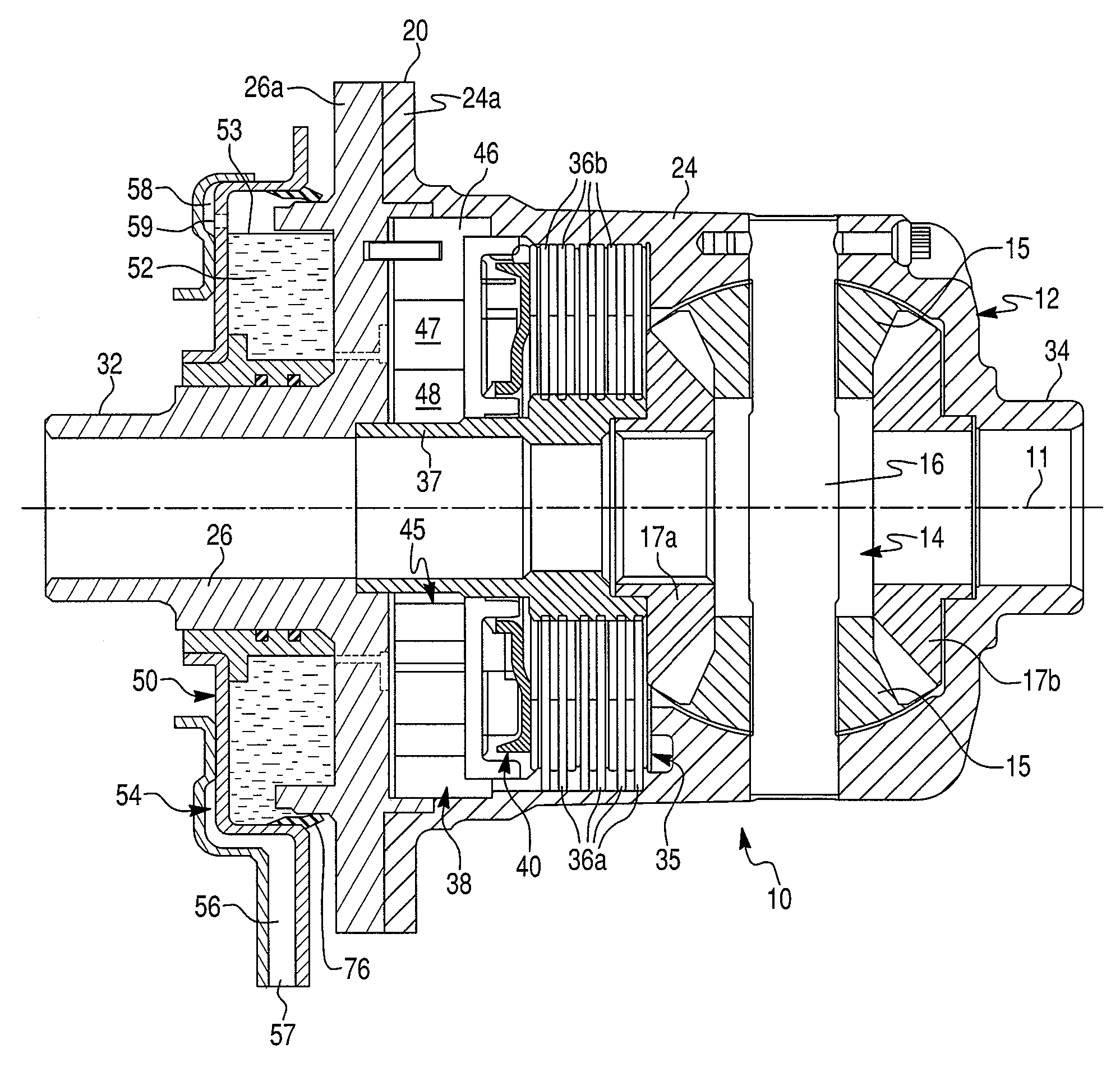

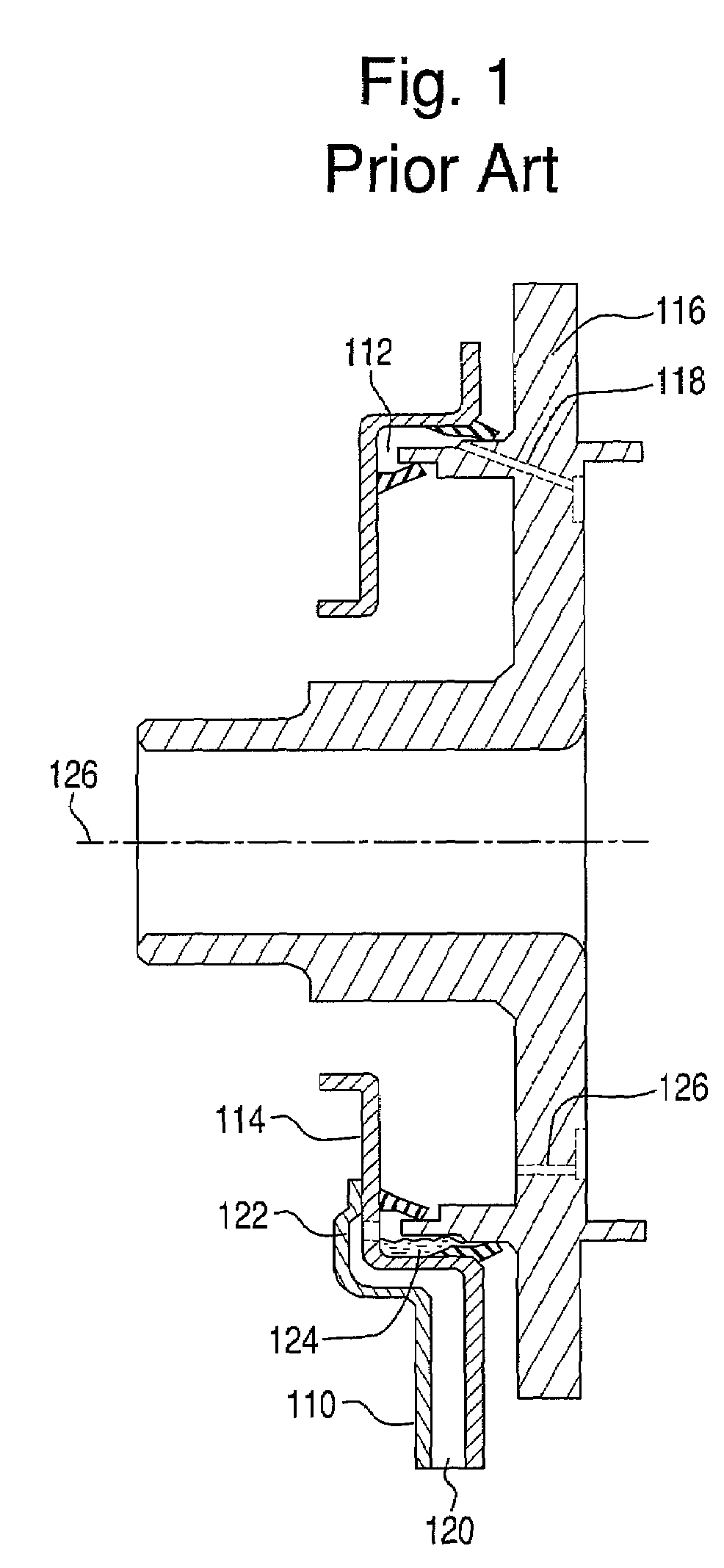

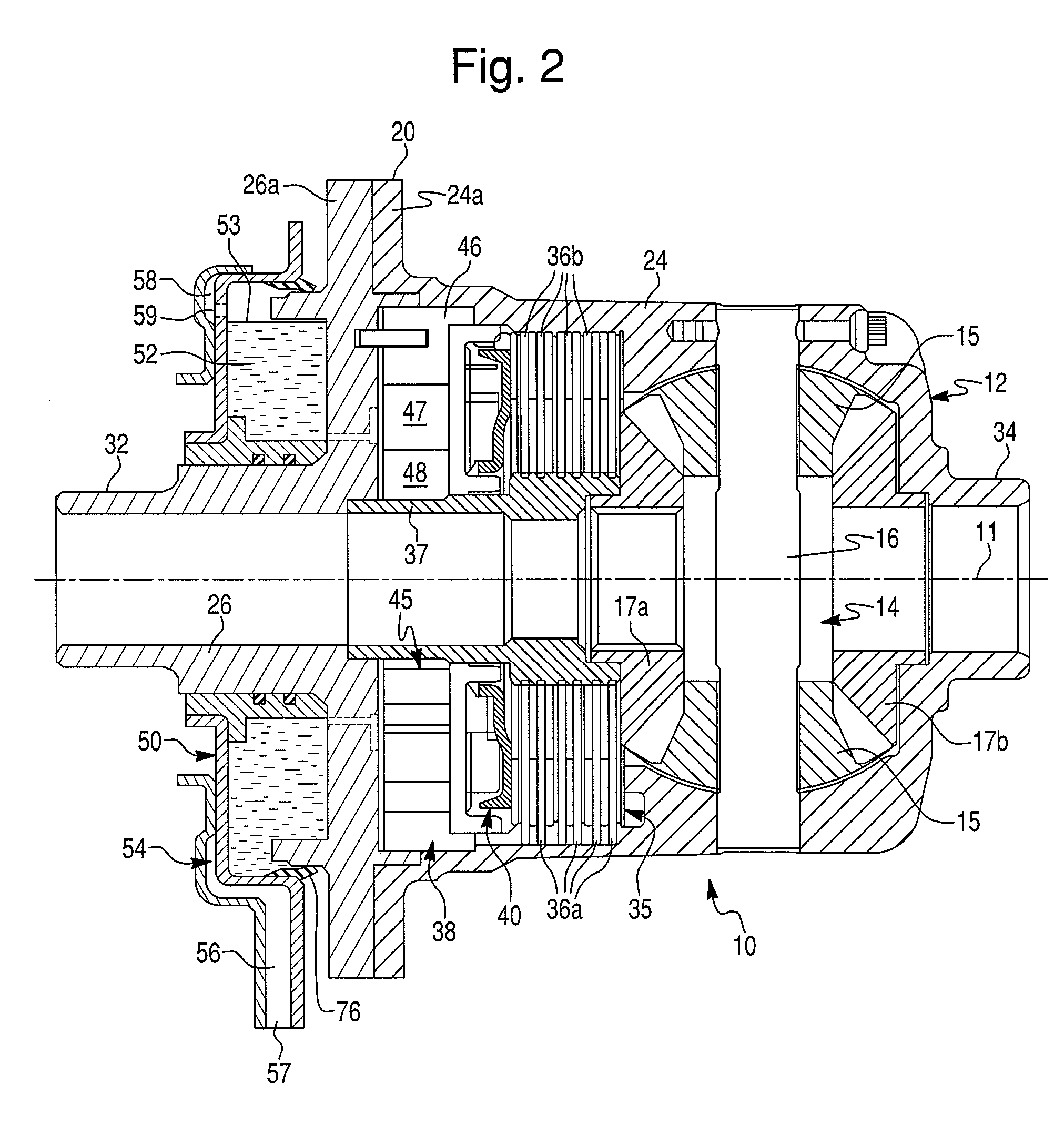

Hydraulic fluid plenum plate assembly

A hydraulic fluid plenum plate assembly in a torque-coupling assembly, non-rotatably mounted to a rotatable coupling case thereof so as to form a plenum chamber between the plenum plate assembly and the coupling case. The coupling case has an inlet port fluidly connecting the plenum chamber with a hydraulic pump disposed within the coupling case. The plenum plate assembly comprises a pickup tube for supplying a hydraulic fluid from a fluid reservoir to the plenum chamber. The pickup tube has inlet and outlet ends. The inlet end has an inlet opening submerged in the hydraulic fluid in the fluid reservoir. The outlet end has an outlet opening fluidly connecting the pickup tube with the plenum chamber. The outlet opening is disposed above the inlet port in the coupling case at any angular position of the coupling case relative to the plenum plate assembly.

Owner:DANA AUTOMOTIVE SYST GRP LLC

Personalizing user interfaces across operating systems

InactiveUS7089499B2Improve accessibilityDelay problemDigital computer detailsBiological neural network modelsPersonalizationOperational system

A user-centered interface agent learns user preferences and typical behaviors and, based on what is learned, predicts the user's preferred user interface for different types of host computers. The interface agent consists of a learning program which operates on the user's primary computer, a shadow program which is installed on a Personal Digital Assistant (PDA), and a remote program which operates on host computers. The PDA transfers data between the primary and remote machines, and can also be used as the user's primary computer. On the primary computer, the agent learns a user's preferences automatically by observing the user's actions, requiring minimal initialization by the user. The learning algorithm may be statistical, rule-based, case-based, neural network, or employ any other technique for reasoning under uncertainty. The automated personalizing of a user interface configuration has a particular advantage for individuals with disabilities who require configuration before they can use a new computer system.

Owner:INT BUSINESS MASCH CORP

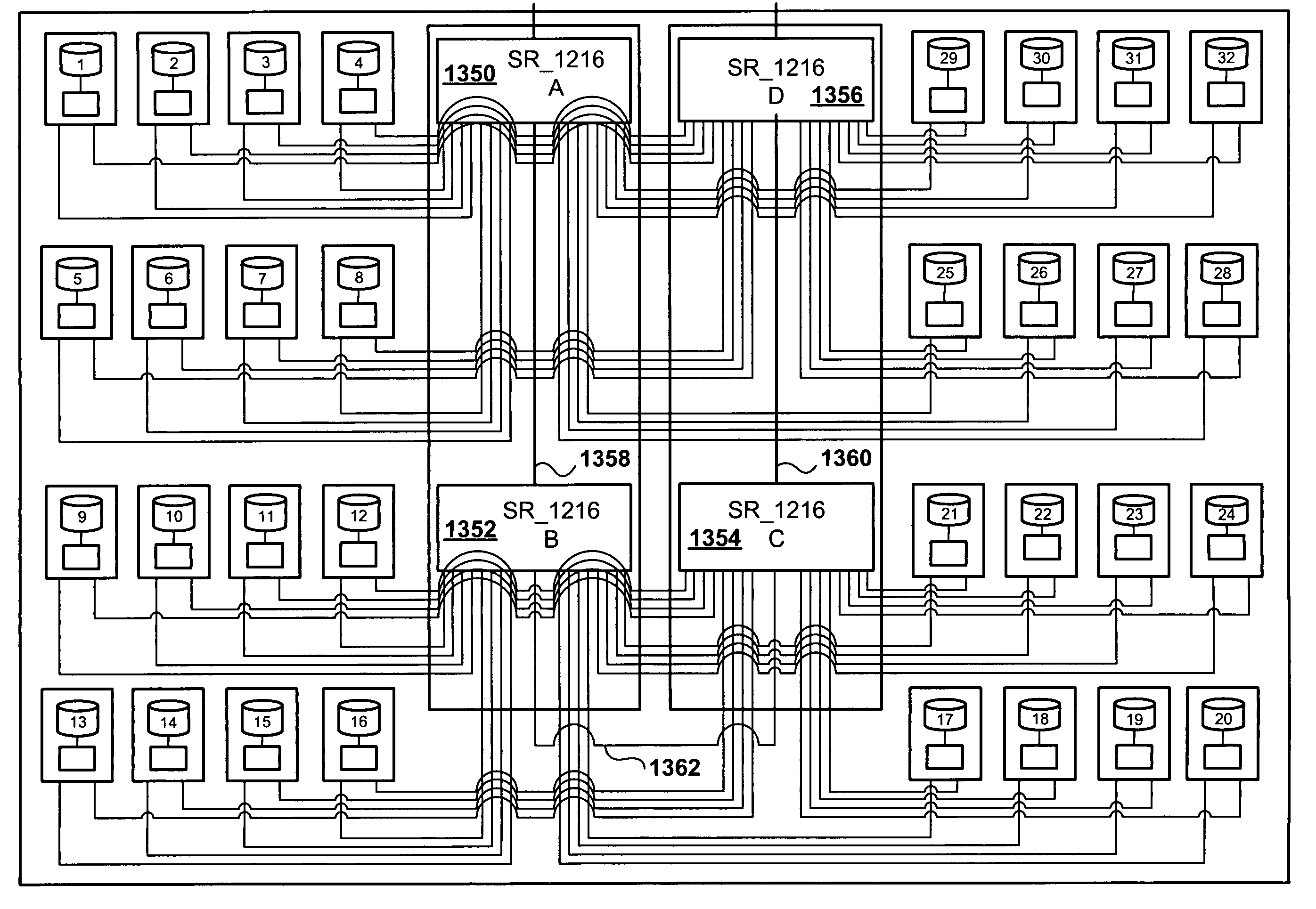

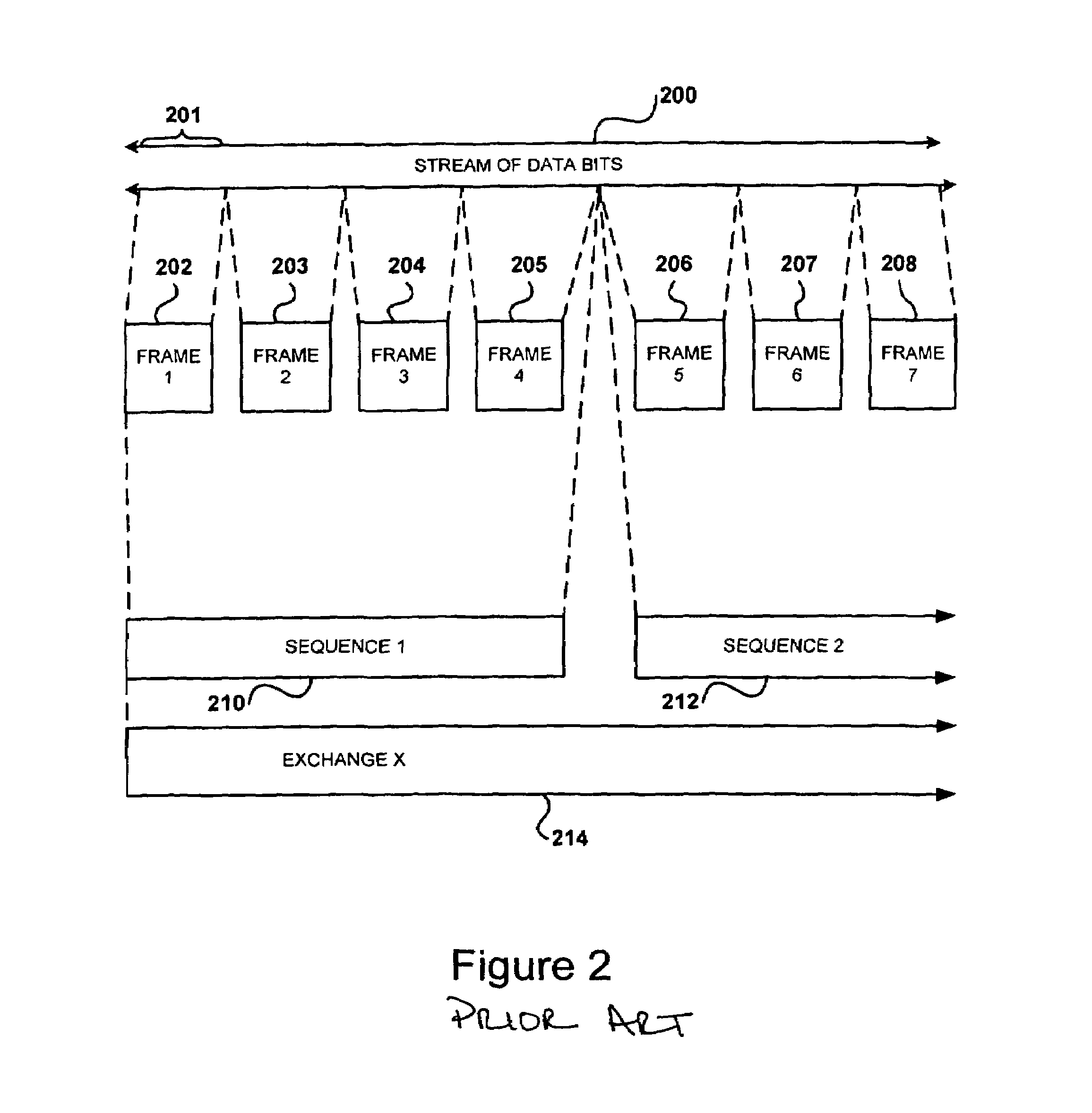

Integrated-circuit implementation of a storage-shelf router and a path controller card for combined use in high-availability mass-storage-device shelves that may be incorporated within disk arrays

ActiveUS7353321B2Eliminates cumulative node delay problemHigh operating requirementsInput/output to record carriersError detection/correctionMass storageNetwork Communication Protocols

An integrated circuit implementing a storage-shelf router used alone, or in combination with other storage-shelf routers, and in combination with path controller cards, to interconnect the disks within a storage shelf or disk array to a high-bandwidth communications medium, such as an FC arbitrated loop, through which data is exchanged between the individual disk drives of the storage shelf and a disk-array controller. A set of interconnected storage-shelf routers within a storage shelf can be accessed through a single port of an FC arbitrated loop or other high-bandwidth communications medium. Because, in one implementation, eight storage-shelf routers can be interconnected within a storage shelf to provide highly available interconnection of sixty-four disk drives within the storage shelf to an FC arbitrated loop via a single FC-arbitrated-loop port, a single FC arbitrated loop including a disk-array controller, may interconnect 8,000 individual disk drives to the disk-array controller within a disk array. The storage-shelf router can serve to translate FC-based communications protocols into one or more communication protocols appropriate to the internal links, providing for use of less expensive, non-FC-compatible disk drives within the storage shelf.

Owner:SIERRA LOGIC

System for generating composite images for endoscopic surgery of moving and deformable anatomy

InactiveUS10426345B2Improve understandingImprove efficiencyImage enhancementImage analysisDisplay deviceEndoscopic surgery

A device for generating composite images of dynamically changing surgical anatomy includes circuitry configured to receive, from an endoscopic imaging device, endoscopic image data. The circuitry is configured to receive, from a tomographic imaging device, intra-operative tomographic image data. The circuitry is configured to receive, from a tracking device, spatial tracking data corresponding to the endoscopic imaging device and the tomographic imaging device. The circuitry is configured to generate real-time dynamically changing composite image data by overlaying, based on the spatial tracking data, the intra-operative tomographic image data on the endoscopic image data. The circuitry is configured to output the composite image data to a display.

Owner:CHILDRENS NAT MEDICAL CENT

Data processing method and device

ActiveUS8914590B2Improve executionImprove performanceMemory adressing/allocation/relocationConcurrent instruction executionParallel computingRead-write memory

Owner:SCIENTIA SOL MENTIS AG

Liquid crystal display device, system and methods of compensating for delays of gate driving signals thereof

ActiveUS8232941B2Delay problemCathode-ray tube indicatorsNon-linear opticsShift registerLiquid-crystal display

A liquid crystal display device includes a gate driving shift register having symmetrically split circuit portions by which each of plural gate lines is dually driven from both ends of the gate line during ripple-through scanning of rows of the LCD device. The LCD device includes a timing controller generating an output enable signal and a gate clock, where the timing controller adjusts a timing of a load signal for deciding a data output timing point when data will be loaded into a currently activated display row. The data output timing point is a function of a delay measuring feedback signal that is used to measure the cumulative delays of the sequentially connected stages of the shift register.

Owner:SAMSUNG DISPLAY CO LTD

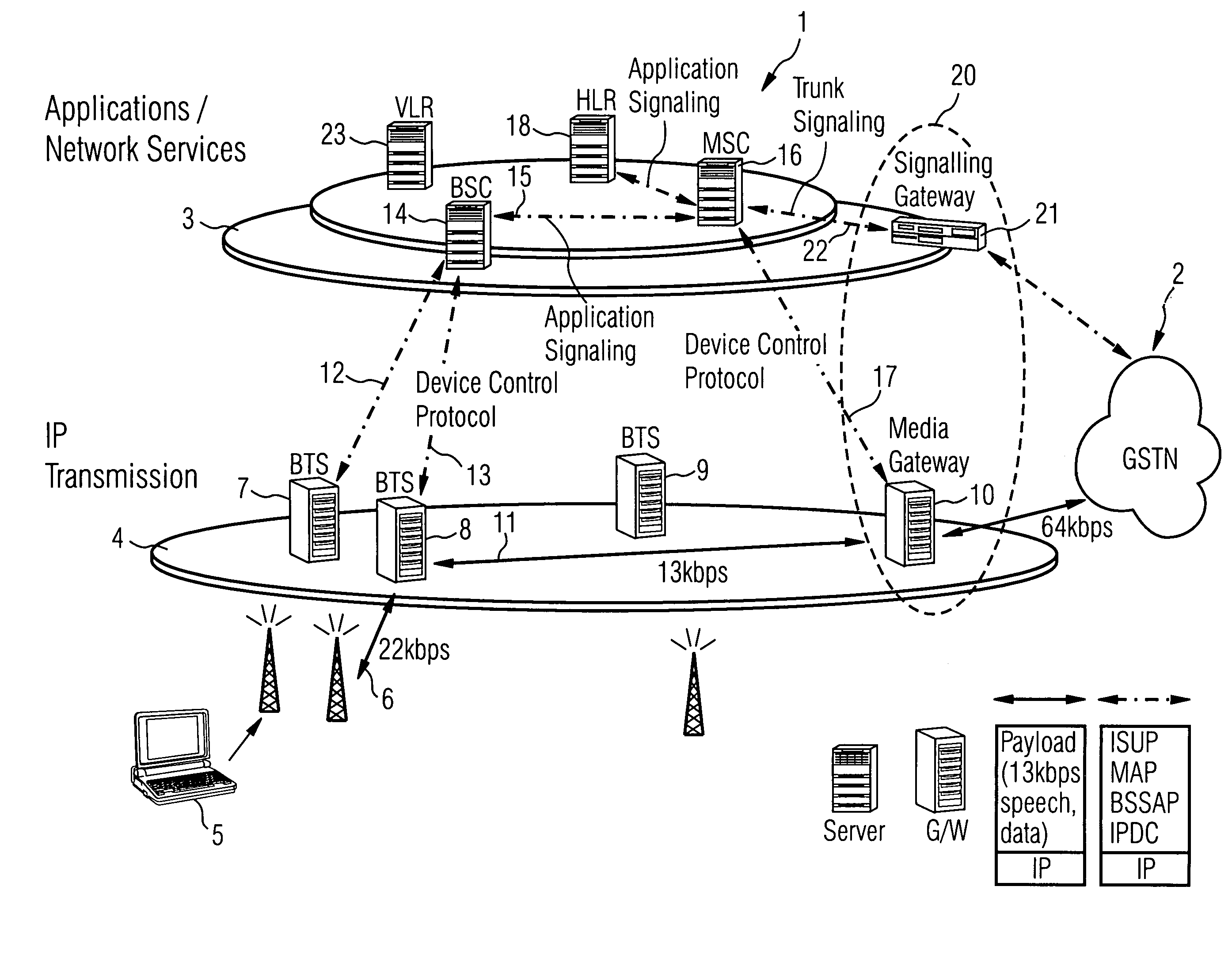

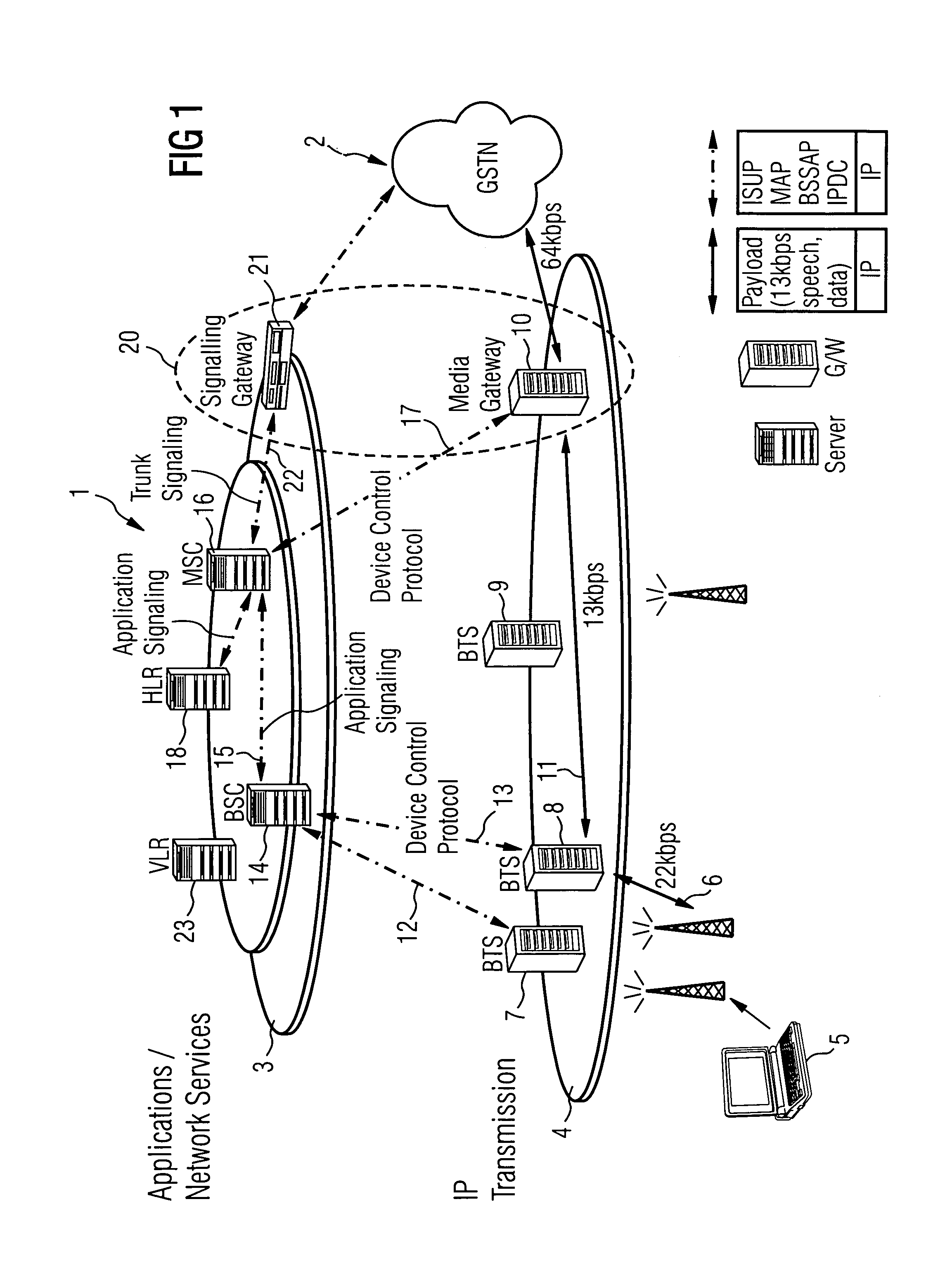

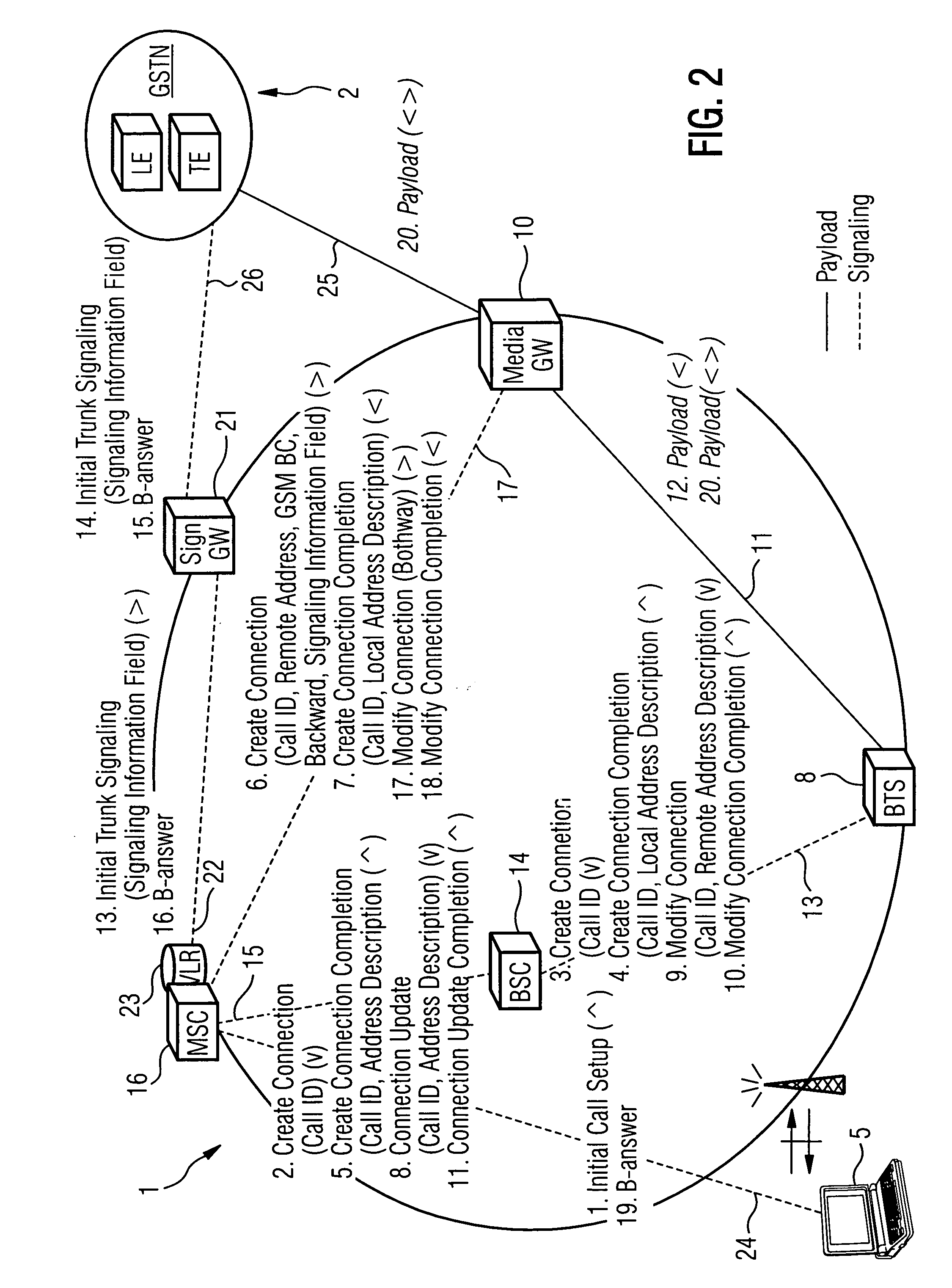

Basic architecture for packet switched protocol based GSM networks

InactiveUS6928067B1Minimise delay problemMinimise bandwidth requirementTime-division multiplexData switching by path configurationTelephone networkNetwork processing

Communication network and a corresponding method are disclosed for operating the communication network that has a packet switched protocol based cellular telephone network comprising a first layer for transferring signalling information assigned to a telephone call being processed by the communication network, a second layer for transferring payload information assigned to the telephone call and an interface for coupling the cellular telephone network to a further network, the interface comprising a signalling information exchange function between the cellular telephone network and the further network and a payload information exchange function between the cellular telephone network and the further network, the first layer and the second layer of the cellular telephone network being coupled to the interface, wherein the second layer of the cellular telephone network transfers the payload information of the telephone call to and from the interface on a direct route assigned to the telephone call within the second layer.

Owner:TELEFON AB LM ERICSSON (PUBL)

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com