Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1667 results about "Protocol processing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

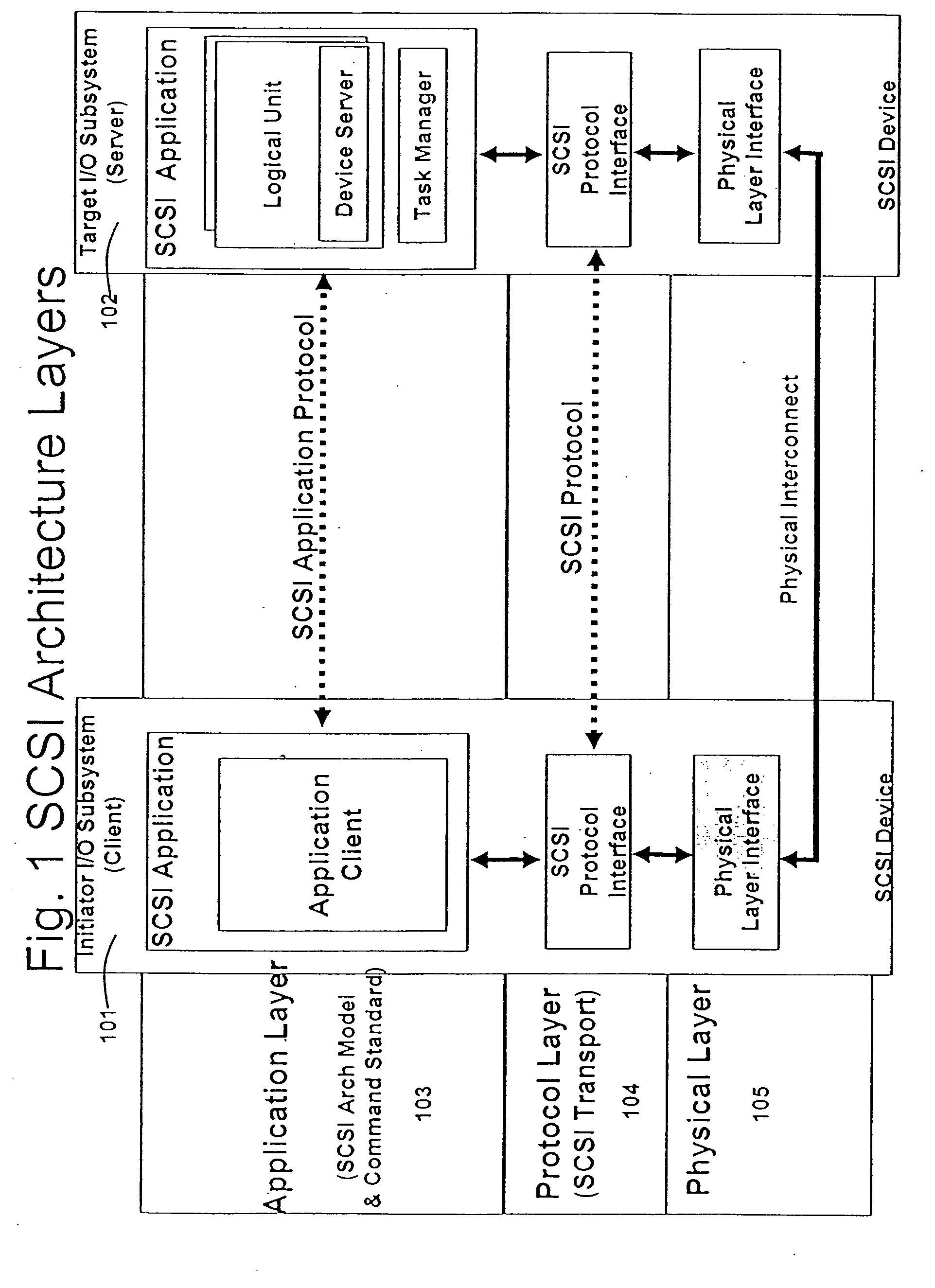

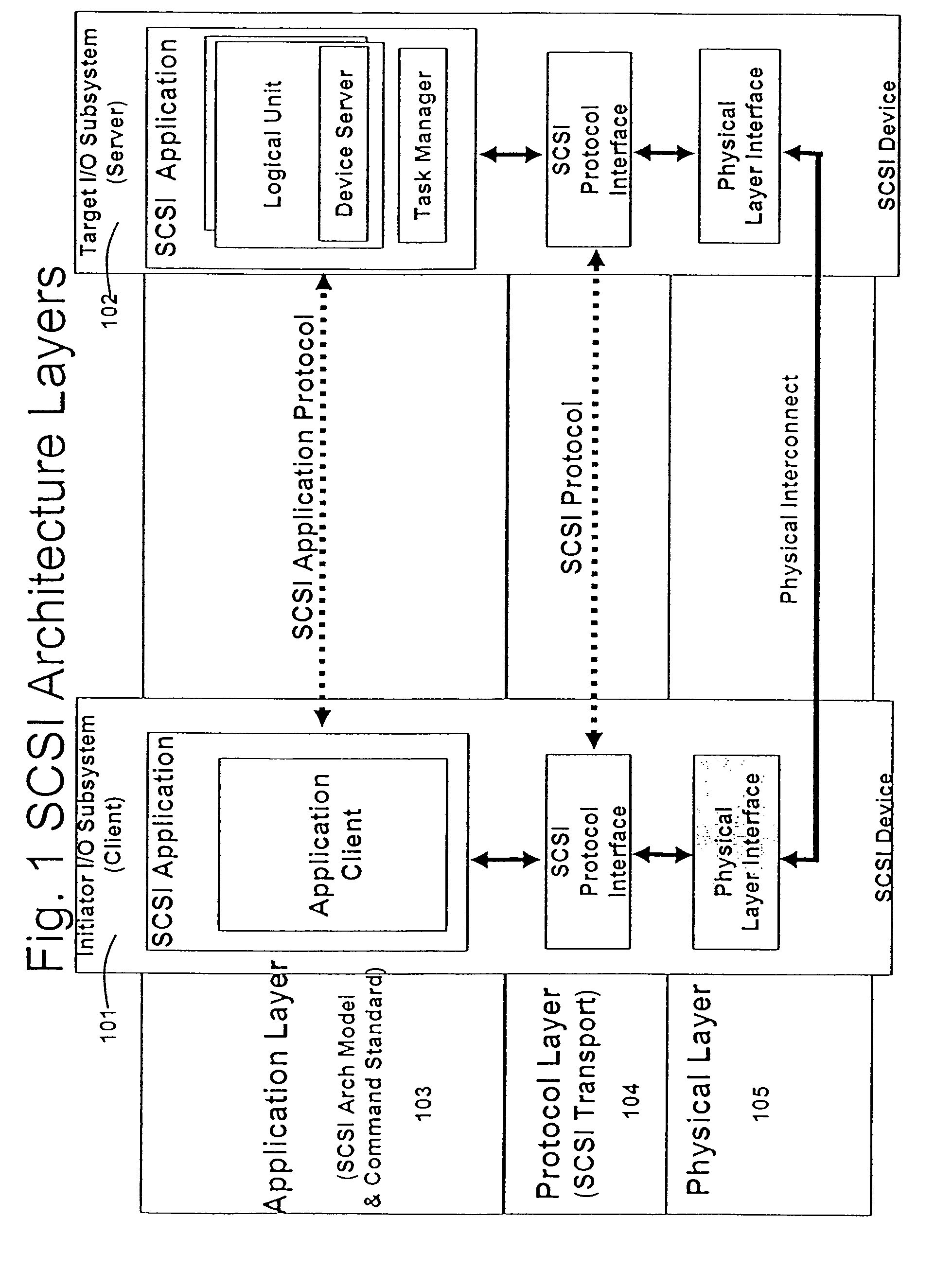

Protocol processing is slightly more complex for a reliable, flow-controlled protocol such as TCP. As in the original architecture, data written by an application is queued in the socket queue. Some data may be transmitted immediately in the context of the user process performing the send system call.

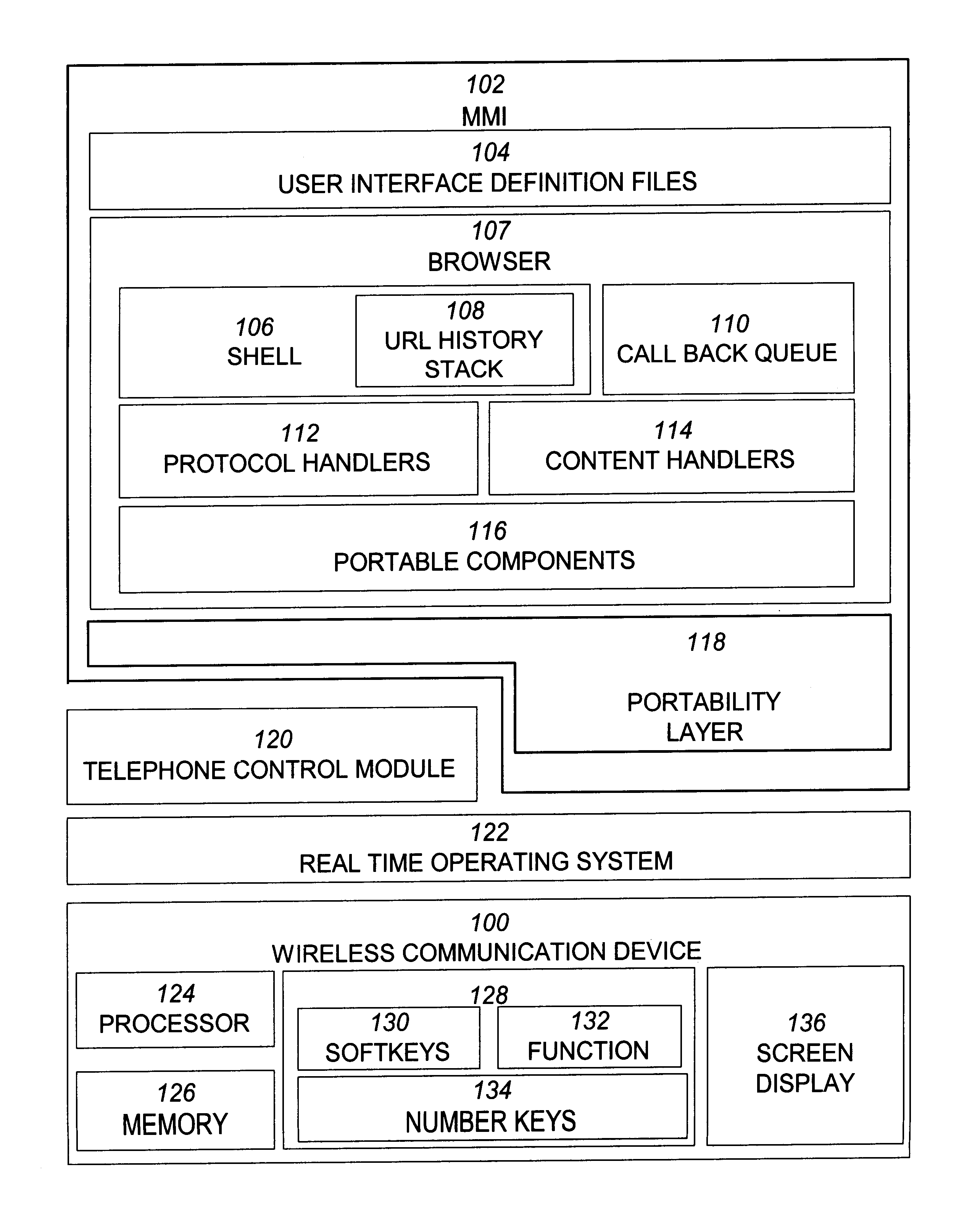

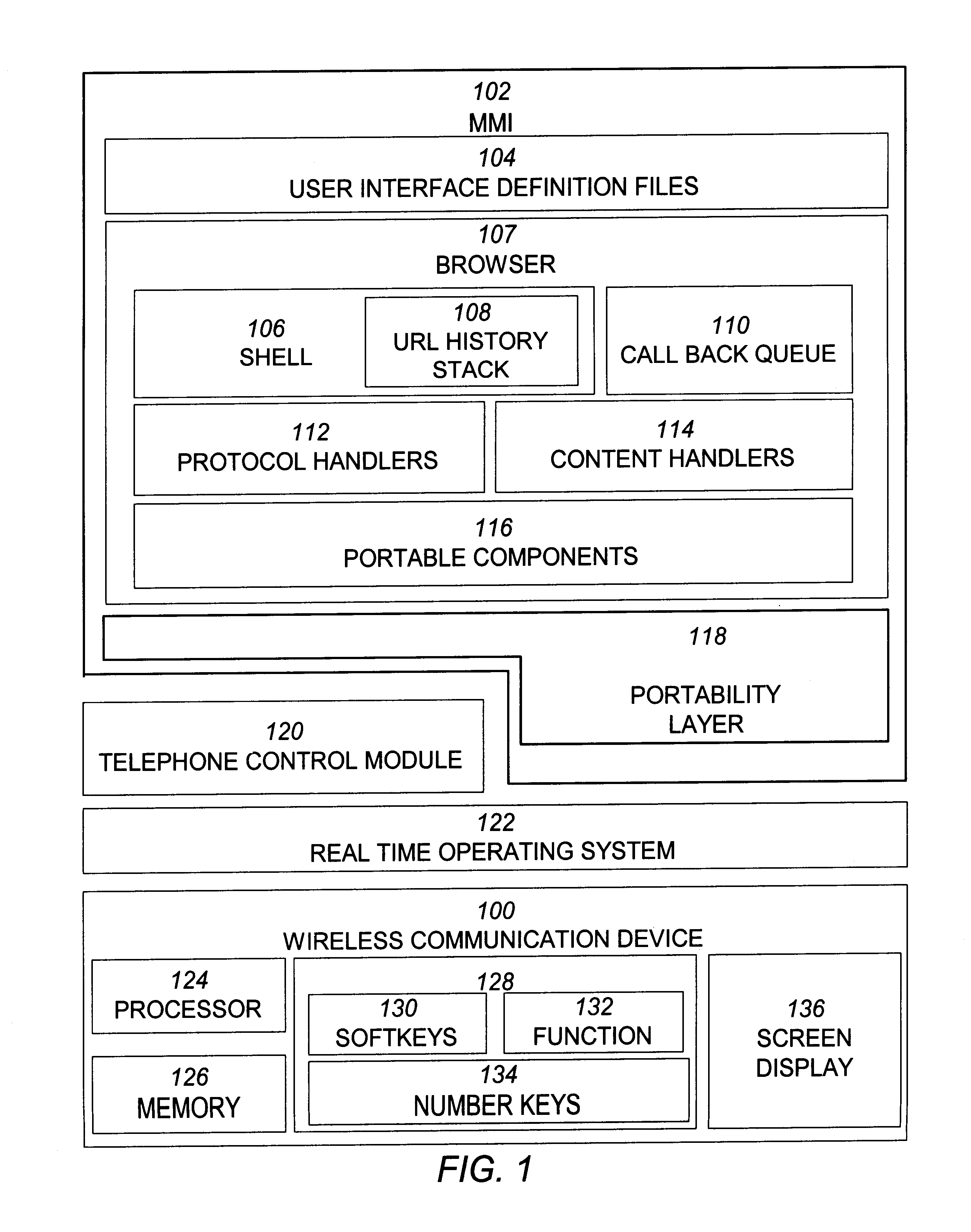

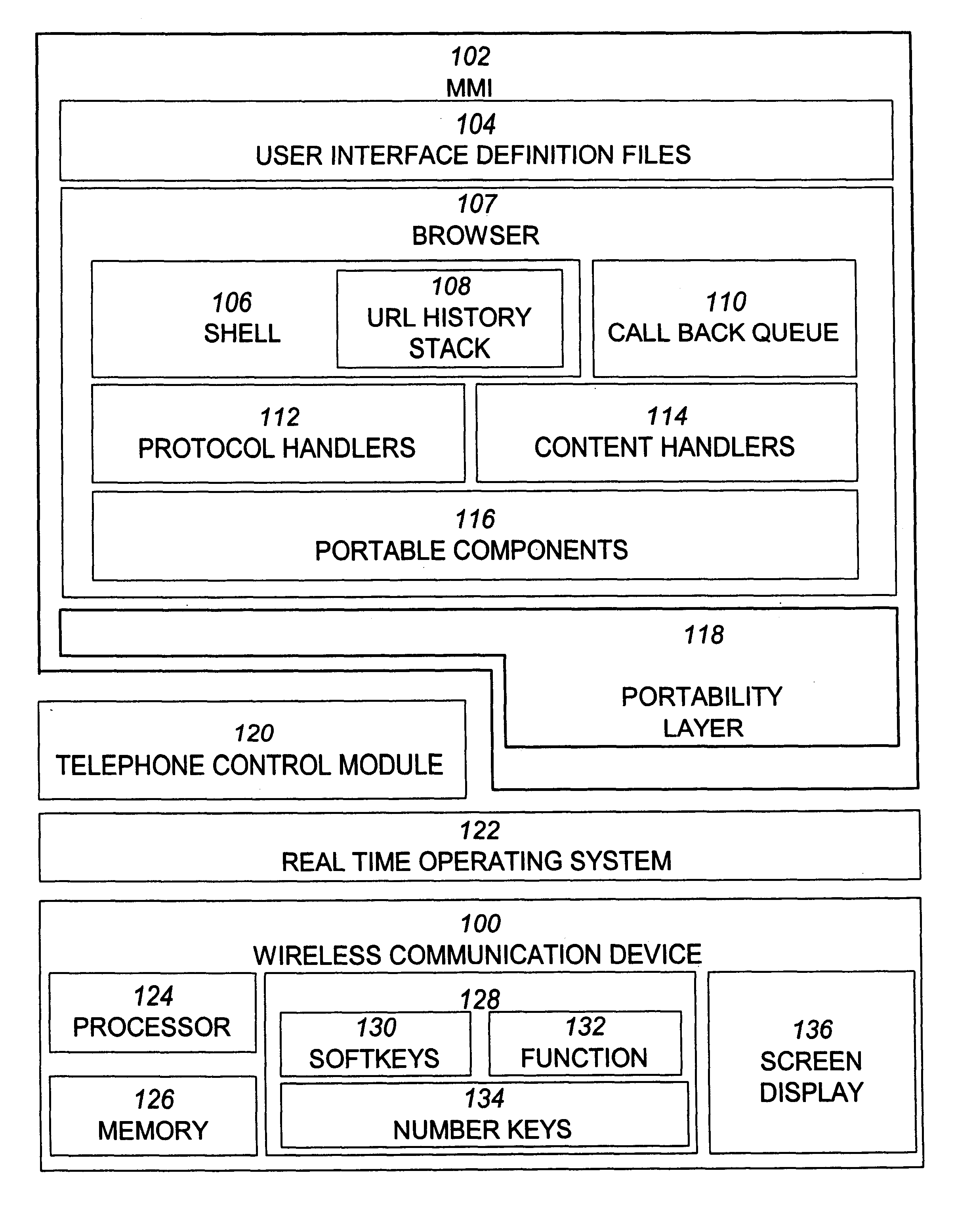

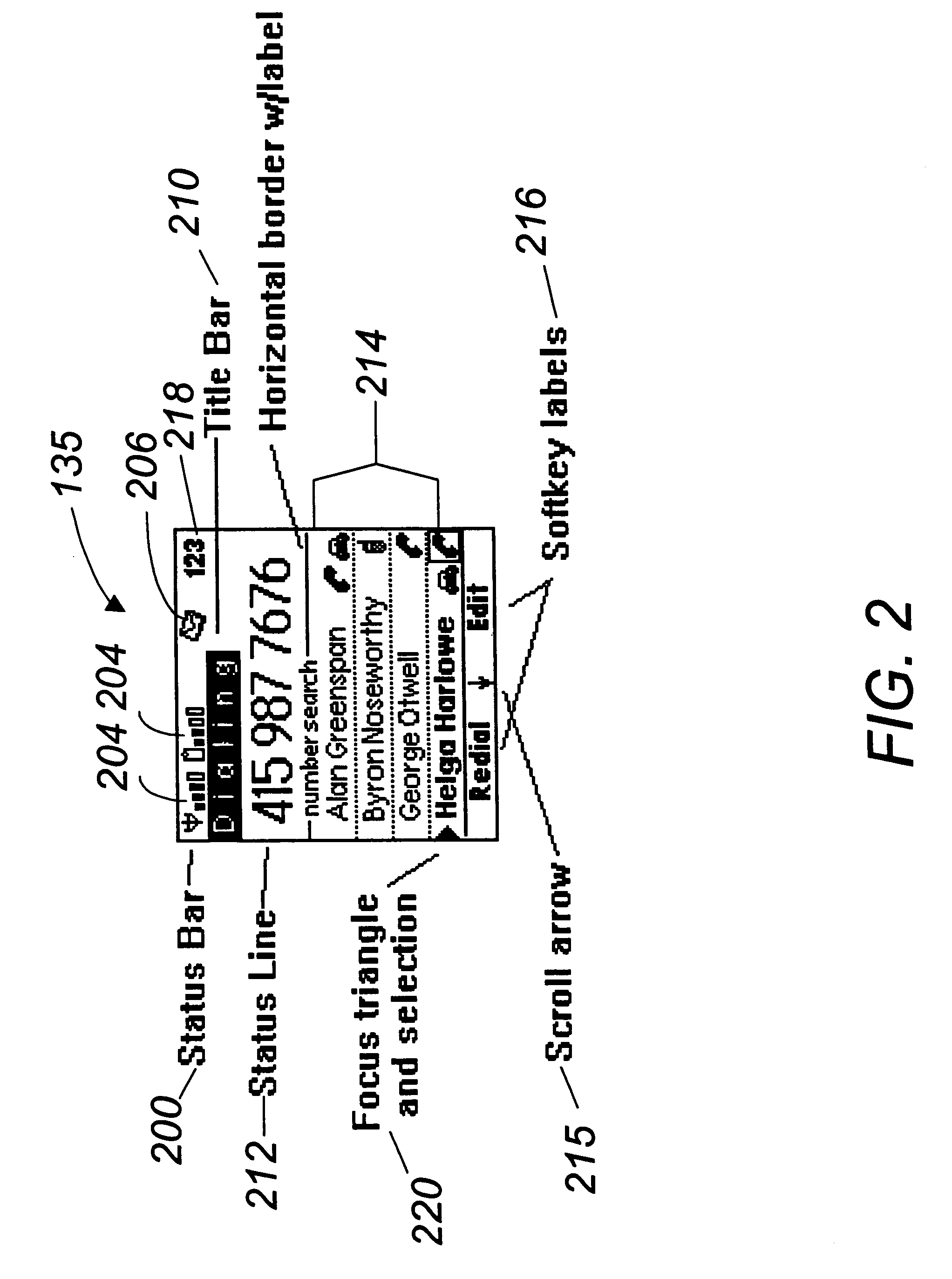

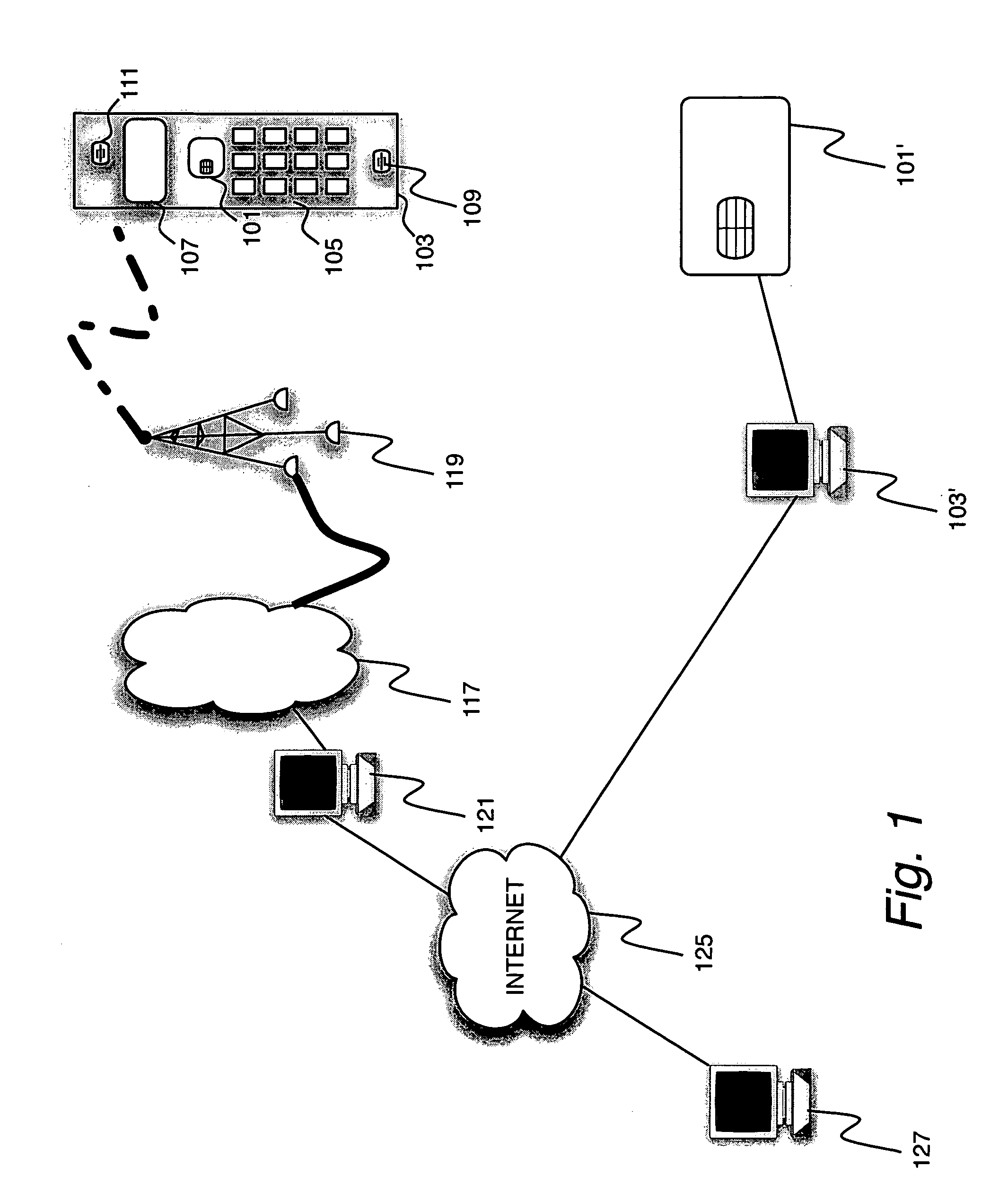

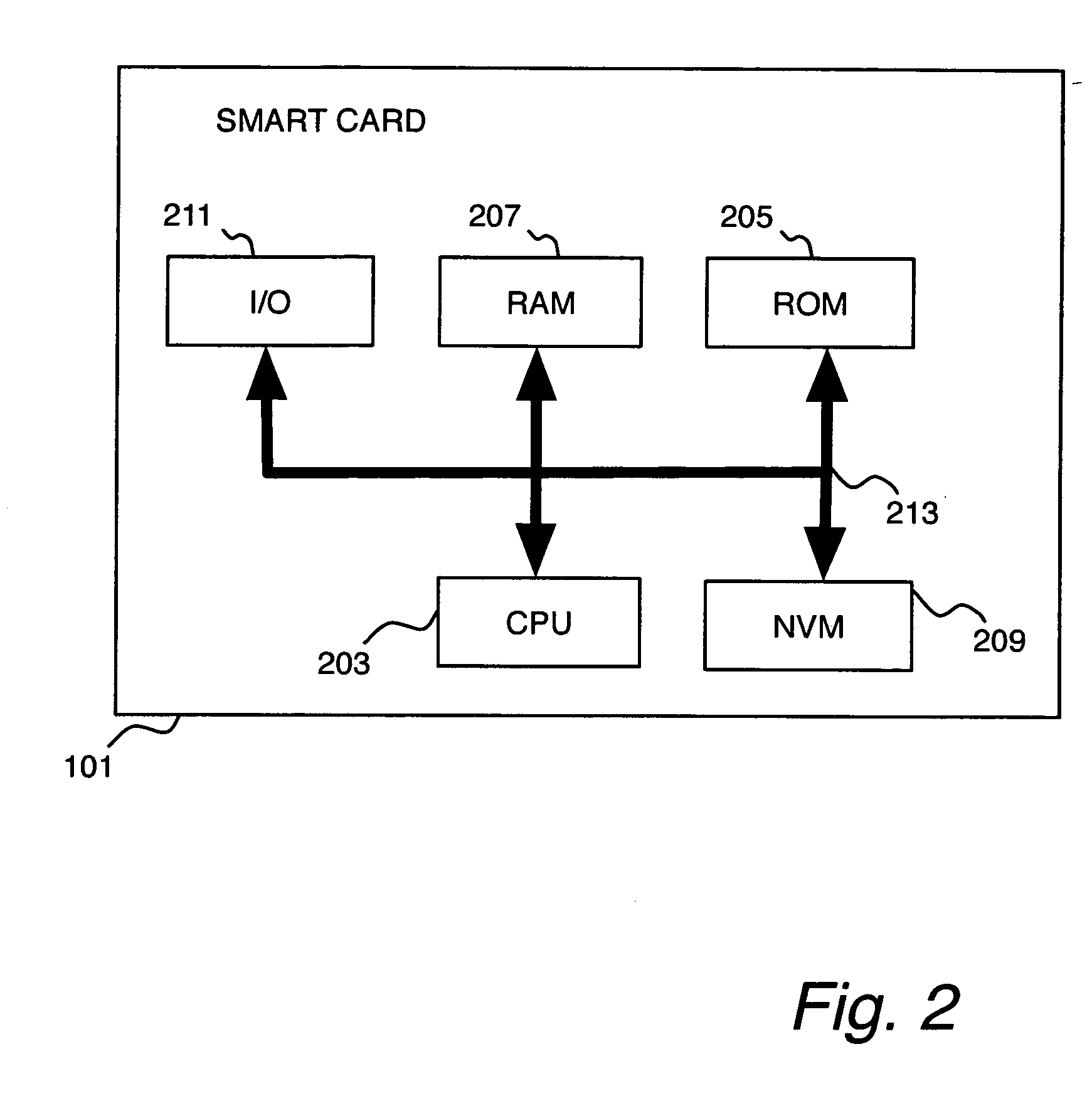

Wireless communication device with markup language based man-machine interface

A system, method, and software product provide a wireless communications device with a markup language based man-machine interface. The man-machine interface provides a user interface for the various telecommunications functionality of the wireless communication device, including dialing telephone numbers, answering telephone calls, creating messages, sending messages, receiving messages, establishing configuration settings, which is defined in markup language, such as HTML, and accessed through a browser program executed by the wireless communication device. This feature enables direct access to Internet and World Wide Web content, such as Web pages, to be directly integrated with telecommunication functions of the device, and allows Web content to be seamlessly integrated with other types of data, since all data presented to the user via the user interface is presented via markup language-based pages. The browser processes an extended form of HTML that provides new tags and attributes that enhance the navigational, logical, and display capabilities of conventional HTML, and particularly adapt HTML to be displayed and used on wireless communication devices with small screen displays. The wireless communication device includes the browser, a set of portable components, and portability layer. The browser includes protocol handlers, which implement different protocols for accessing various functions of the wireless communication device, and content handlers, which implement various content display mechanisms for fetching and outputting content on a screen display.

Owner:ACCESS

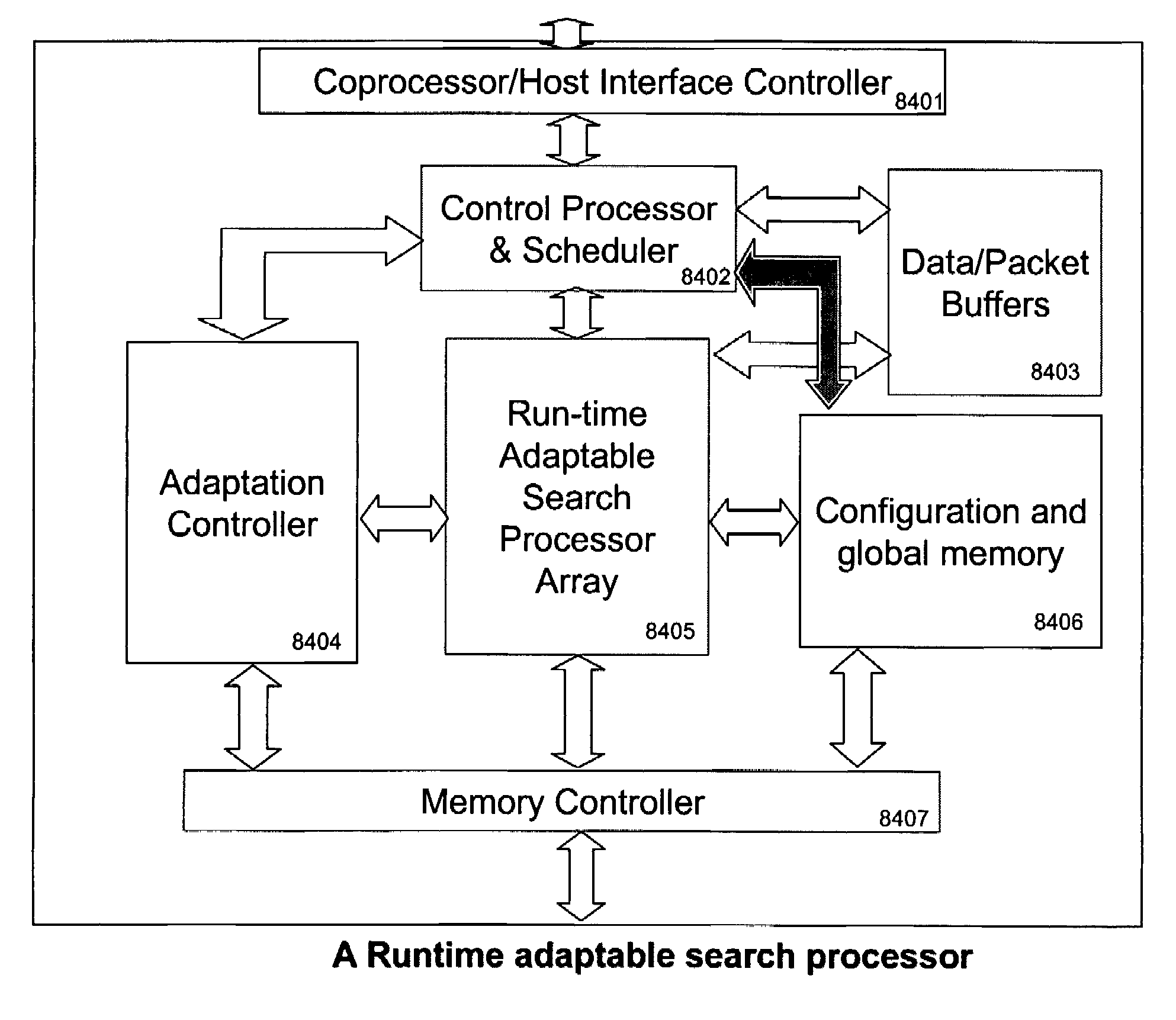

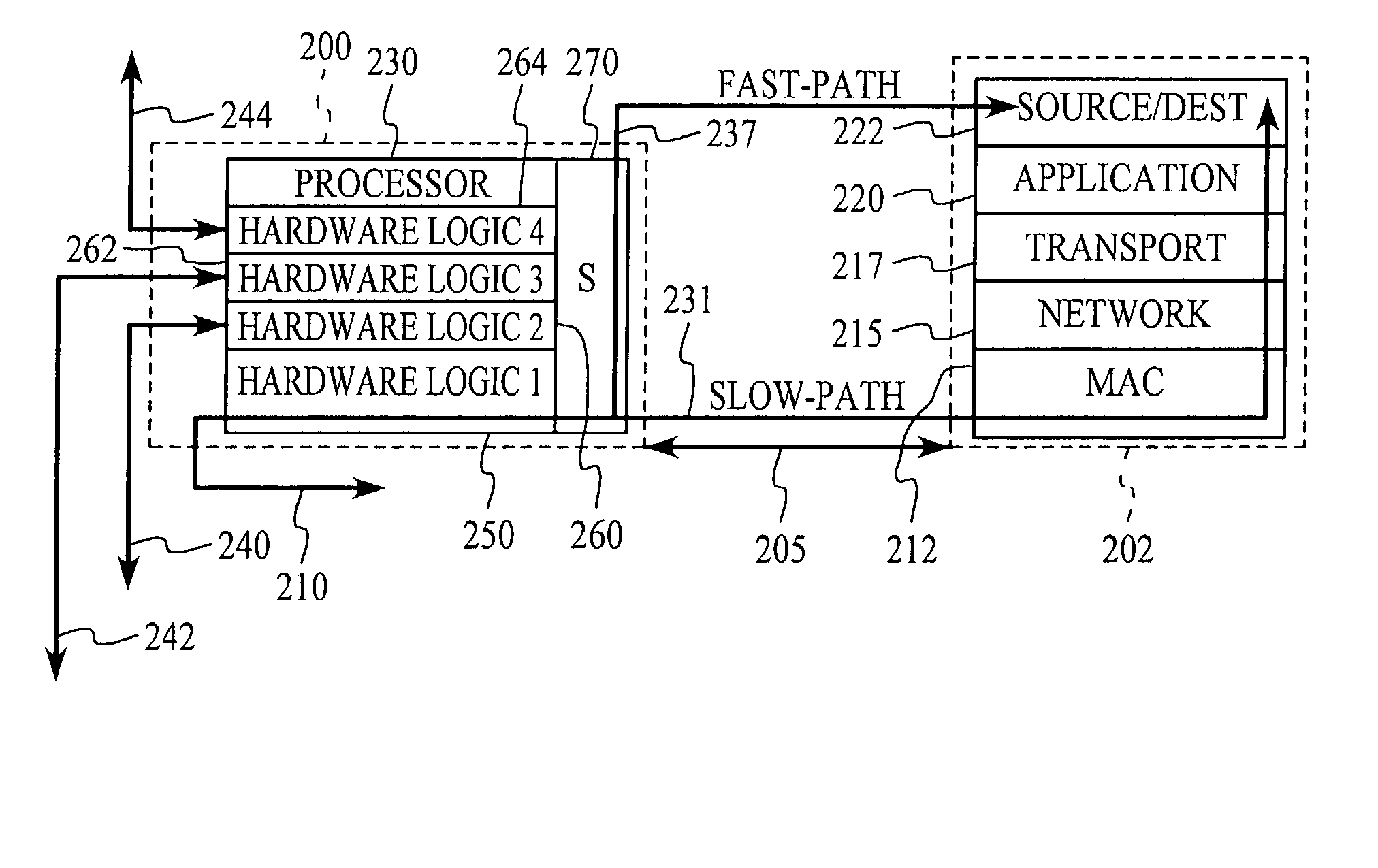

Runtime adaptable search processor

ActiveUS20060136570A1Reduce stacking processImproving host CPU performanceWeb data indexingMultiple digital computer combinationsData packInternal memory

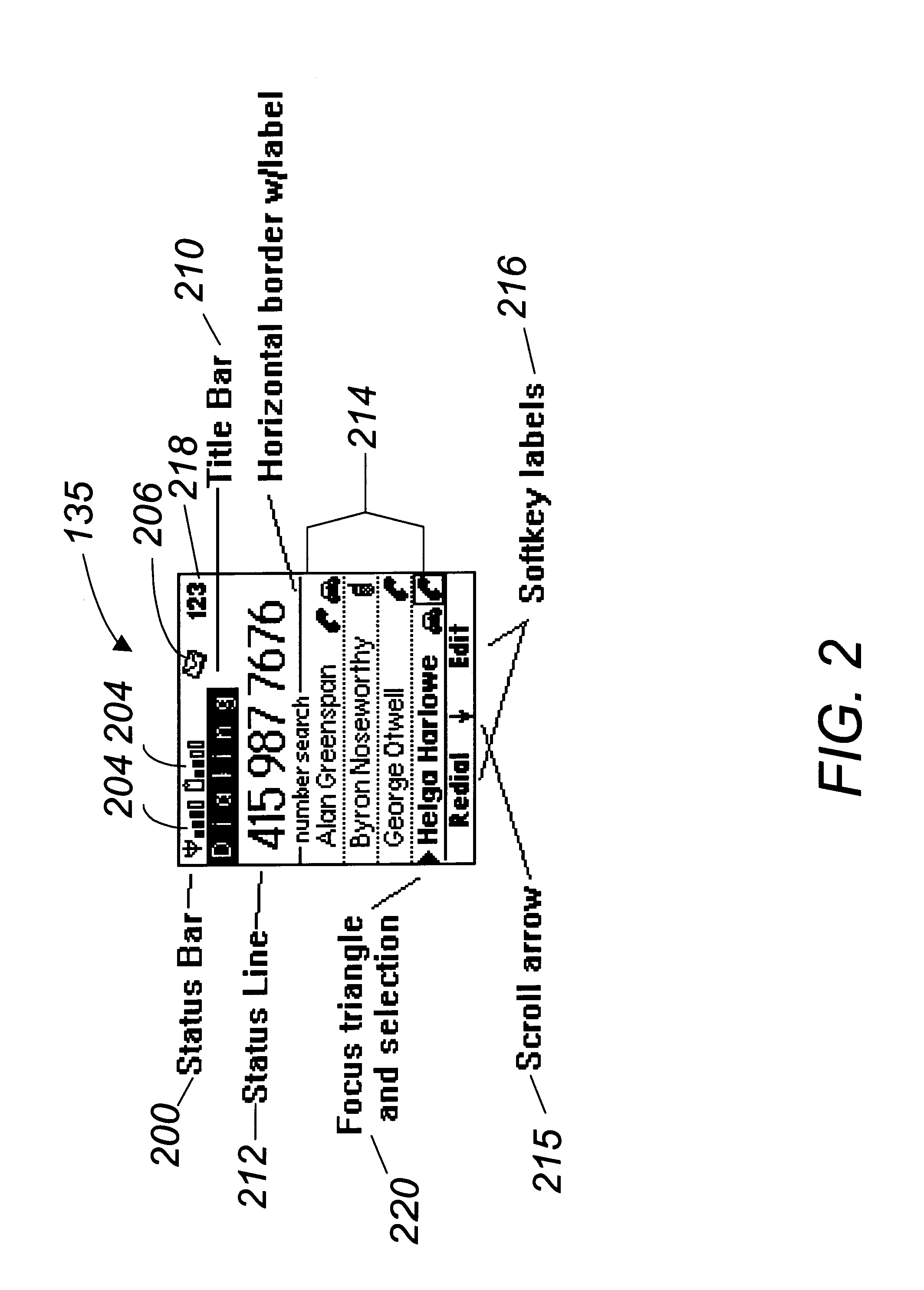

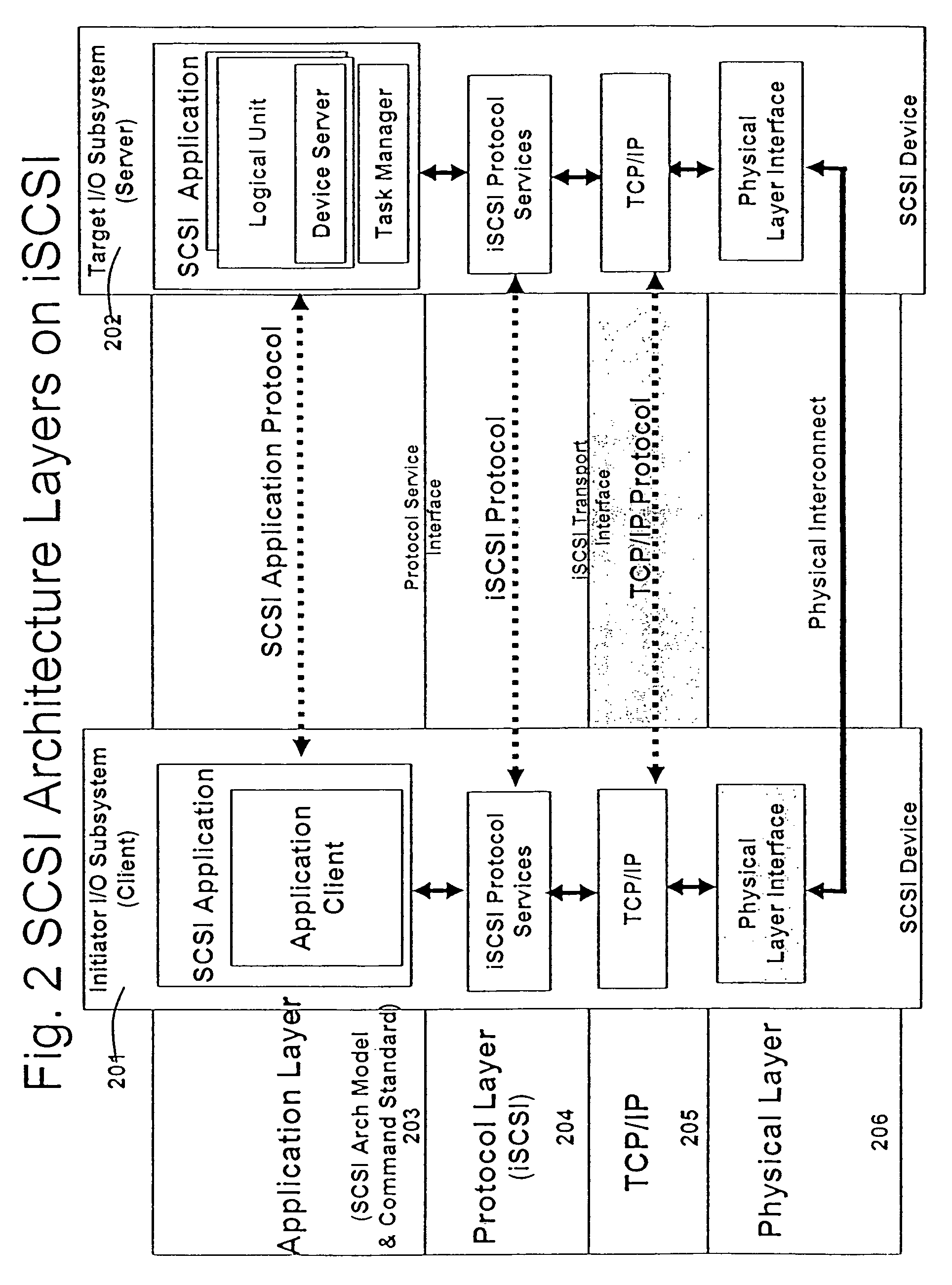

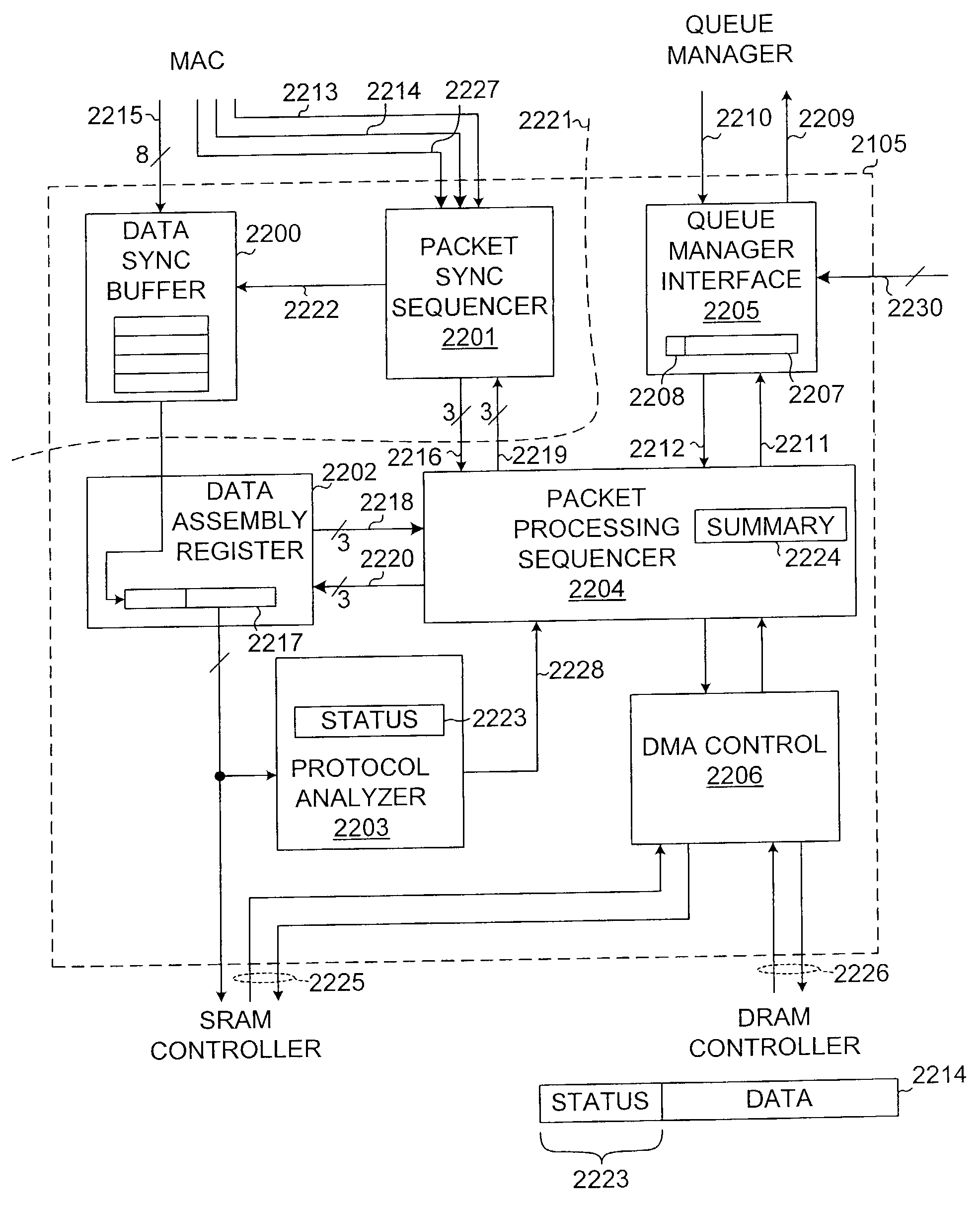

A runtime adaptable search processor is disclosed. The search processor provides high speed content search capability to meet the performance need of network line rates growing to 1 Gbps, 10 Gbps and higher. he search processor provides a unique combination of NFA and DFA based search engines that can process incoming data in parallel to perform the search against the specific rules programmed in the search engines. The processor architecture also provides capabilities to transport and process Internet Protocol (IP) packets from Layer 2 through transport protocol layer and may also provide packet inspection through Layer 7. Further, a runtime adaptable processor is coupled to the protocol processing hardware and may be dynamically adapted to perform hardware tasks as per the needs of the network traffic being sent or received and / or the policies programmed or services or applications being supported. A set of engines may perform pass-through packet classification, policy processing and / or security processing enabling packet streaming through the architecture at nearly the full line rate. A high performance content search and rules processing security processor is disclosed which may be used for application layer and network layer security. scheduler schedules packets to packet processors for processing. An internal memory or local session database cache stores a session information database for a certain number of active sessions. The session information that is not in the internal memory is stored and retrieved to / from an additional memory. An application running on an initiator or target can in certain instantiations register a region of memory, which is made available to its peer(s) for access directly without substantial host intervention through RDMA data transfer. A security system is also disclosed that enables a new way of implementing security capabilities inside enterprise networks in a distributed manner using a protocol processing hardware with appropriate security features.

Owner:MEMORY ACCESS TECH LLC

Multiple network protocol encoder/decoder and data processor

InactiveUS6034963AReduce system costLow costTime-division multiplexData switching by path configurationRaw socketByte

A multiple network protocol encoder / decoder comprising a network protocol layer, data handler, O.S. State machine, and memory manager state machines implemented at a hardware gate level. Network packets are received from a physical transport level mechanism by the network protocol layer state machine which decodes network protocols such as TCP, IP, User Datagram Protocol (UDP), PPP, and Raw Socket concurrently as each byte is received. Each protocol handler parses and strips header information immediately from the packet, requiring no intermediate memory. The resulting data are passed to the data handler which consists of data state machines that decode data formats such as email, graphics, Hypertext Transfer Protocol (HTTP), Java, and Hypertext Markup Language (HTML). Each data state machine reacts accordingly to the pertinent data, and any data that are required by more than one data state machine is provided to each state machine concurrently, and any data required more than once by a specific data state machine, are placed in a specific memory location with a pointer designating such data (thereby ensuring minimal memory usage). Resulting display data are immediately passed to a display controller. Any outgoing network packets are created by the data state machines and passed through the network protocol state machine which adds header information and forwards the resulting network packet via a transport level mechanism.

Owner:NVIDIA CORP

Runtime adaptable search processor

ActiveUS7685254B2Improve application performanceLarge capacityWeb data indexingMemory adressing/allocation/relocationPacket schedulingSchema for Object-Oriented XML

A runtime adaptable search processor is disclosed. The search processor provides high speed content search capability to meet the performance need of network line rates growing to 1 Gbps, 10 Gbps and higher. The search processor provides a unique combination of NFA and DFA based search engines that can process incoming data in parallel to perform the search against the specific rules programmed in the search engines. The processor architecture also provides capabilities to transport and process Internet Protocol (IP) packets from Layer 2 through transport protocol layer and may also provide packet inspection through Layer 7. Further, a runtime adaptable processor is coupled to the protocol processing hardware and may be dynamically adapted to perform hardware tasks as per the needs of the network traffic being sent or received and / or the policies programmed or services or applications being supported. A set of engines may perform pass-through packet classification, policy processing and / or security processing enabling packet streaming through the architecture at nearly the full line rate. A high performance content search and rules processing security processor is disclosed which may be used for application layer and network layer security. Scheduler schedules packets to packet processors for processing. An internal memory or local session database cache stores a session information database for a certain number of active sessions. The session information that is not in the internal memory is stored and retrieved to / from an additional memory. An application running on an initiator or target can in certain instantiations register a region of memory, which is made available to its peer(s) for access directly without substantial host intervention through RDMA data transfer. A security system is also disclosed that enables a new way of implementing security capabilities inside enterprise networks in a distributed manner using a protocol processing hardware with appropriate security features.

Owner:MEMORY ACCESS TECH LLC

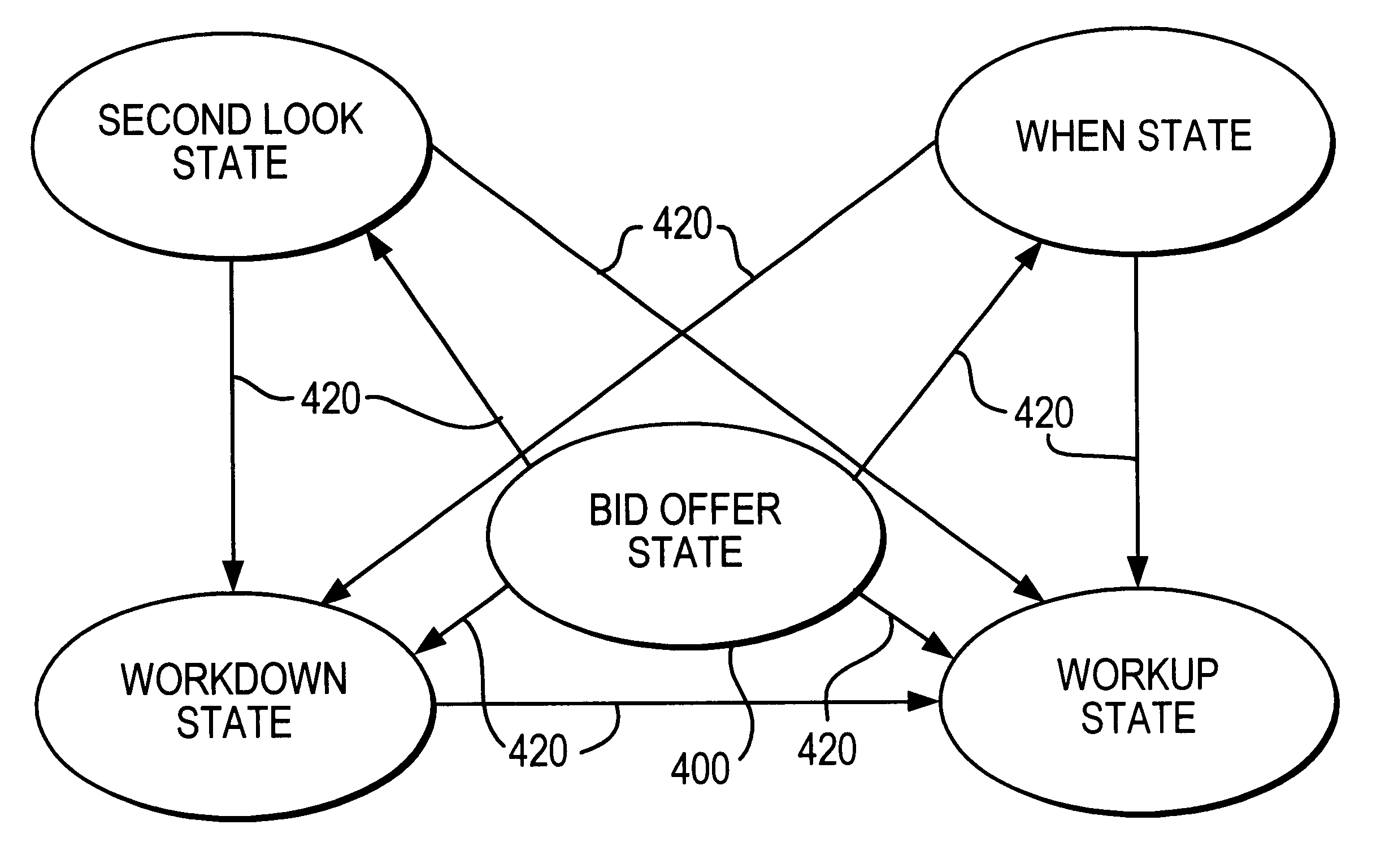

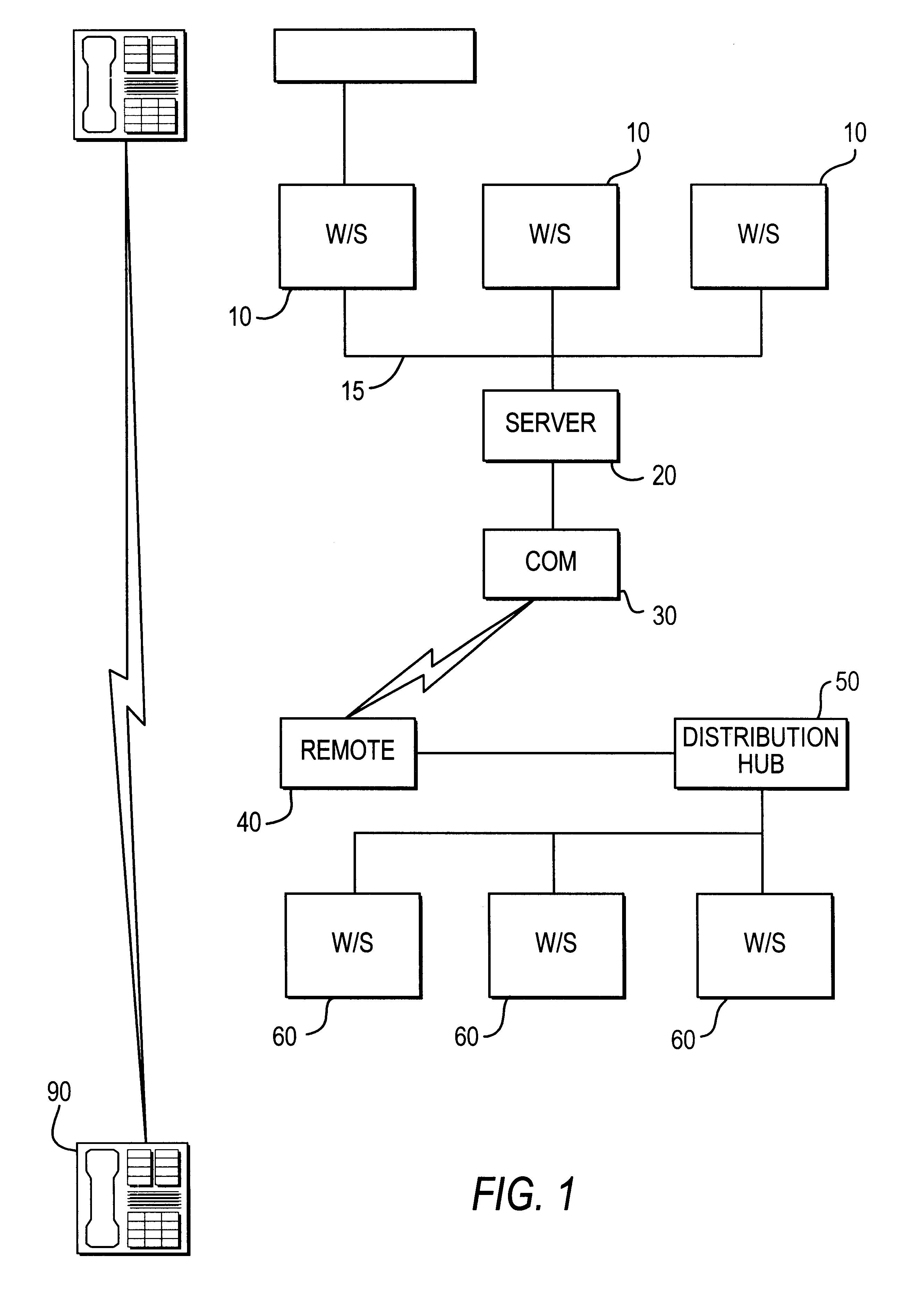

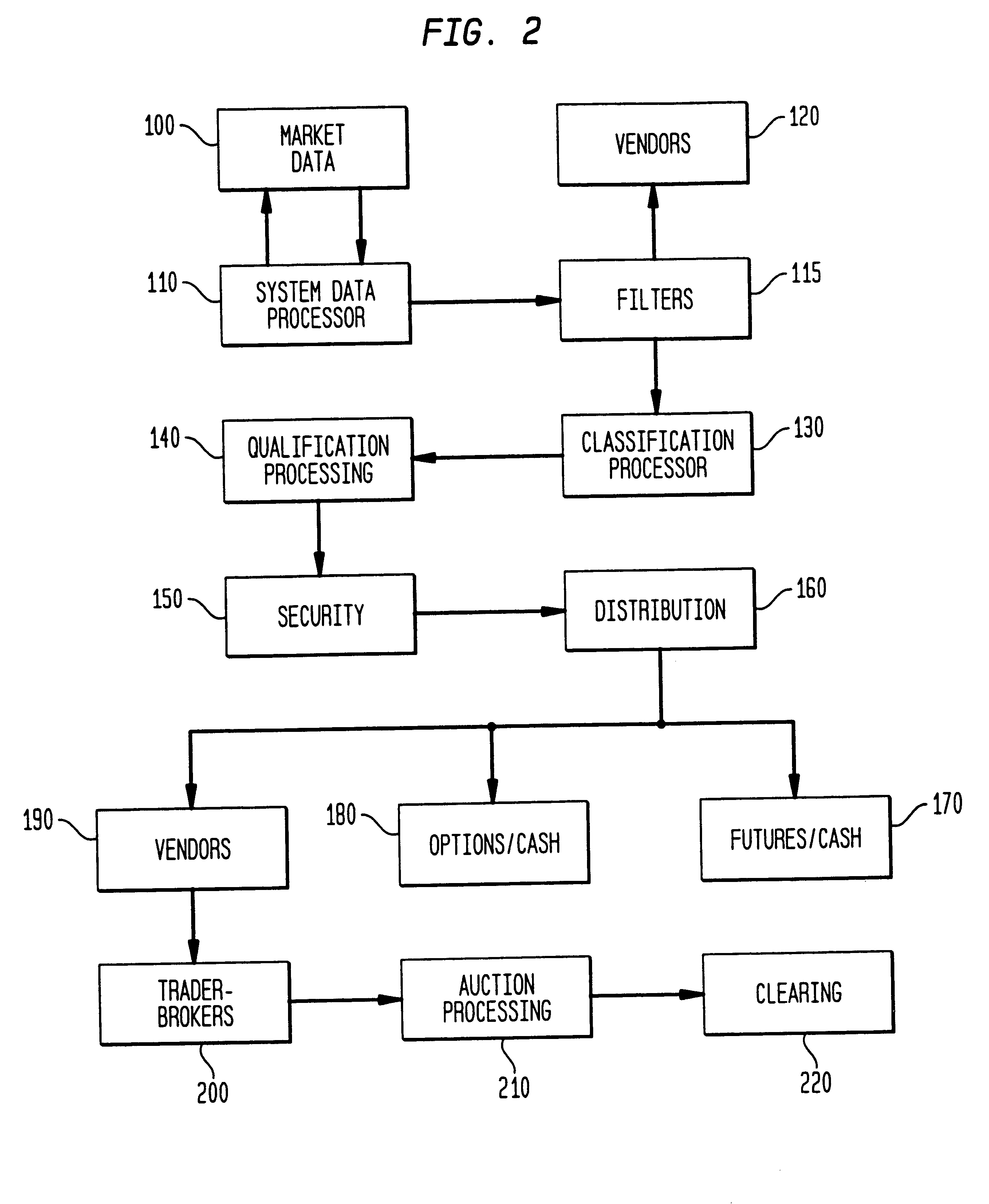

Automated price improvement protocol processor

InactiveUS6850907B2Distribute quicklyFast exchangeFinanceBuying/selling/leasing transactionsData processing systemProtocol processing

A data processing system for implementing transaction management of auction-based trading for specialized items such as fixed income instruments. The data processing system provides a highly structured trading protocol implemented through a sequence of trading paradigms. The system employs a distributed computer processing network linking together a plurality of commonly configured program controlled workstations. The protocol and its program controlling logic enhances trading efficiency, rewards market Makers, and fairly distributes market opportunity to system users.

Owner:CANTOR FITZGERALD LP +1

Runtime adaptable security processor

InactiveUS20050108518A1Improve performanceReduce overheadSecuring communicationInternal memoryPacket scheduling

A runtime adaptable security processor is disclosed. The processor architecture provides capabilities to transport and process Internet Protocol (IP) packets from Layer 2 through transport protocol layer and may also provide packet inspection through Layer 7. Further, a runtime adaptable processor is coupled to the protocol processing hardware and may be dynamically adapted to perform hardware tasks as per the needs of the network traffic being sent or received and / or the policies programmed or services or applications being supported. A set of engines may perform pass-through packet classification, policy processing and / or security processing enabling packet streaming through the architecture at nearly the full line rate. A high performance content search and rules processing security processor is disclosed which may be used for application layer and network layer security. A scheduler schedules packets to packet processors for processing. An internal memory or local session database cache stores a session information database for a certain number of active sessions. The session information that is not in the internal memory is stored and retrieved to / from an additional memory. An application running on an initiator or target can in certain instantiations register a region of memory, which is made available to its peer(s) for access directly without substantial host intervention through RDMA data transfer. A security system is also disclosed that enables a new way of implementing security capabilities inside enterprise networks in a distributed manner using a protocol processing hardware with appropriate security features.

Owner:MEMORY ACCESS TECH LLC

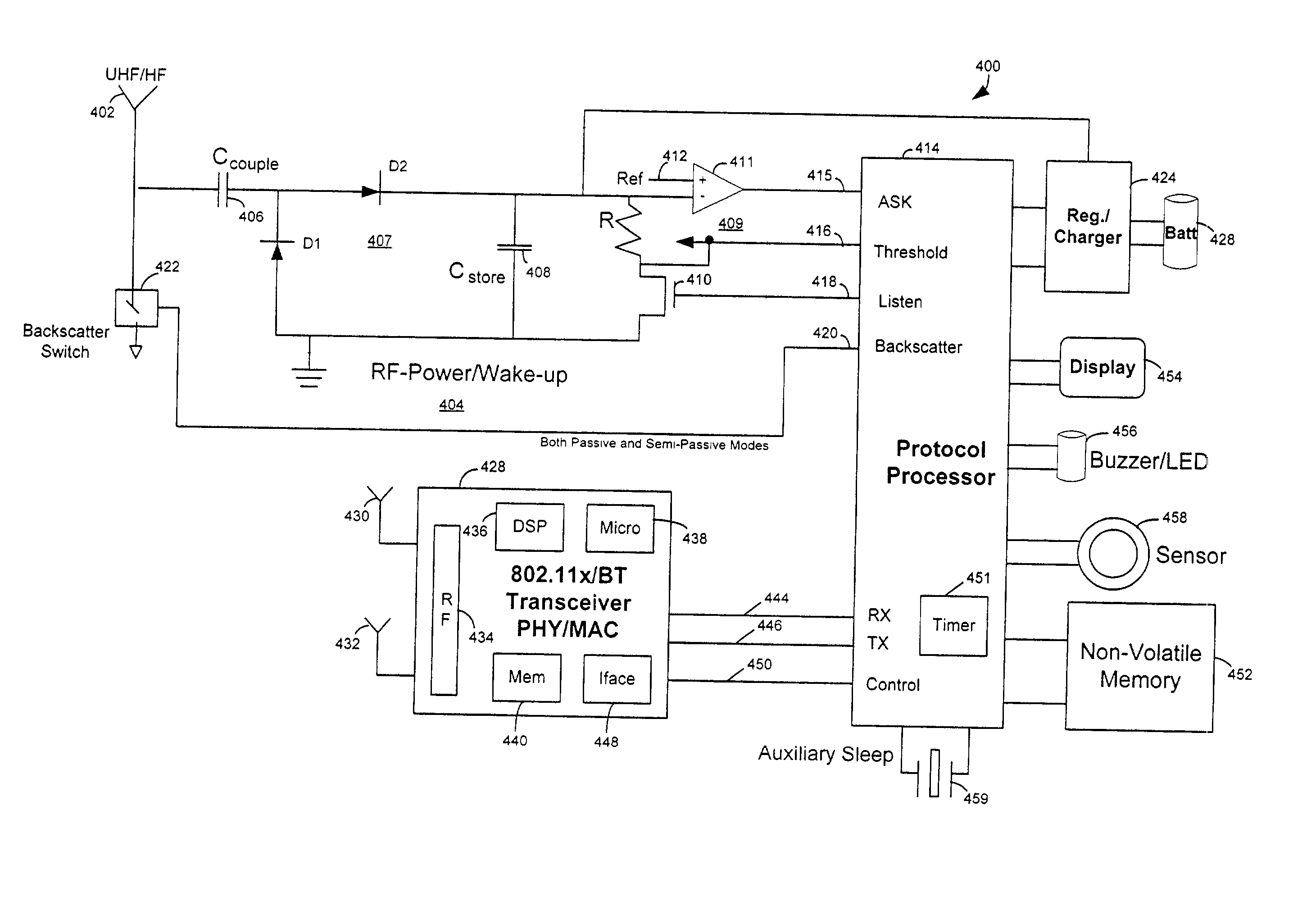

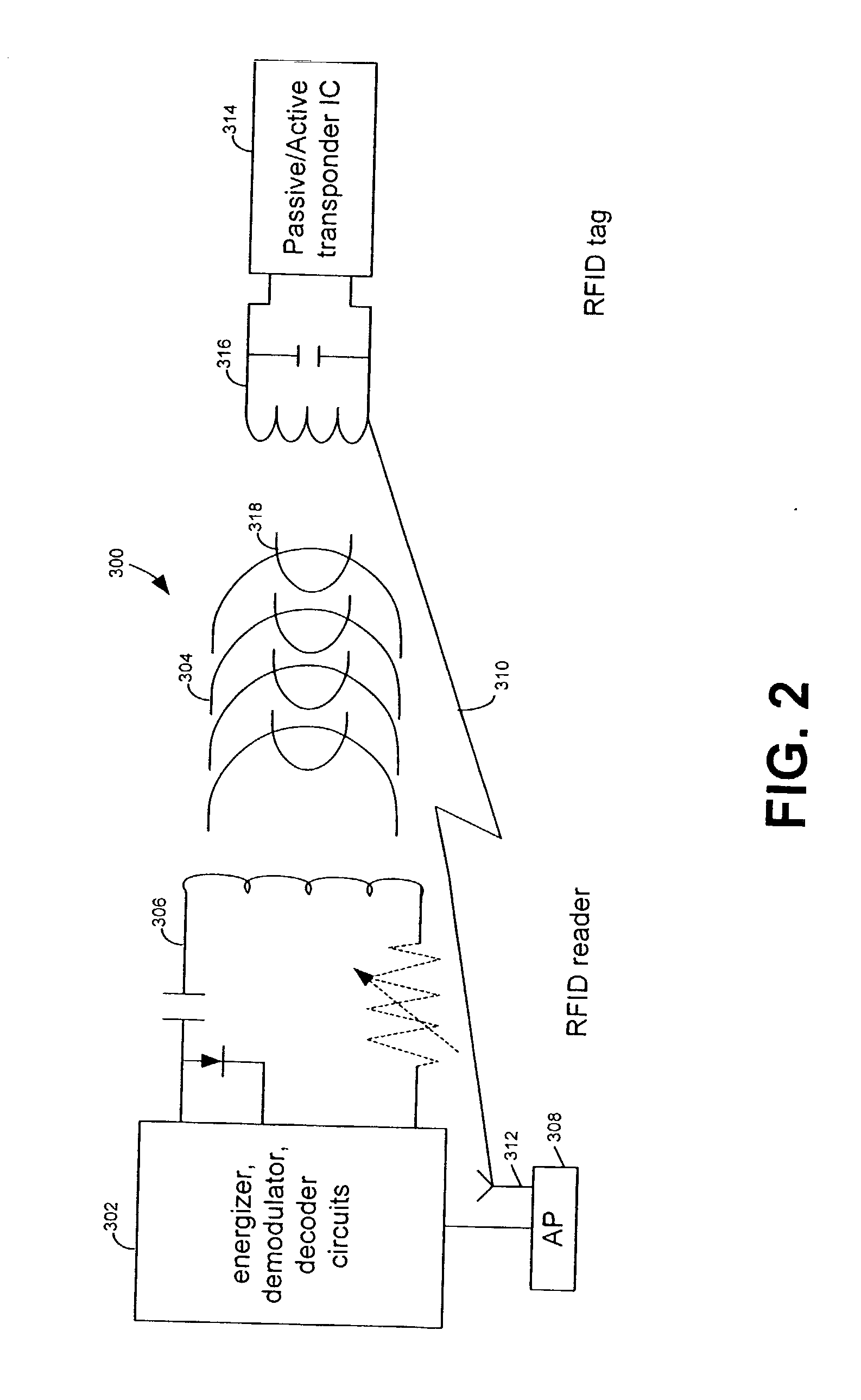

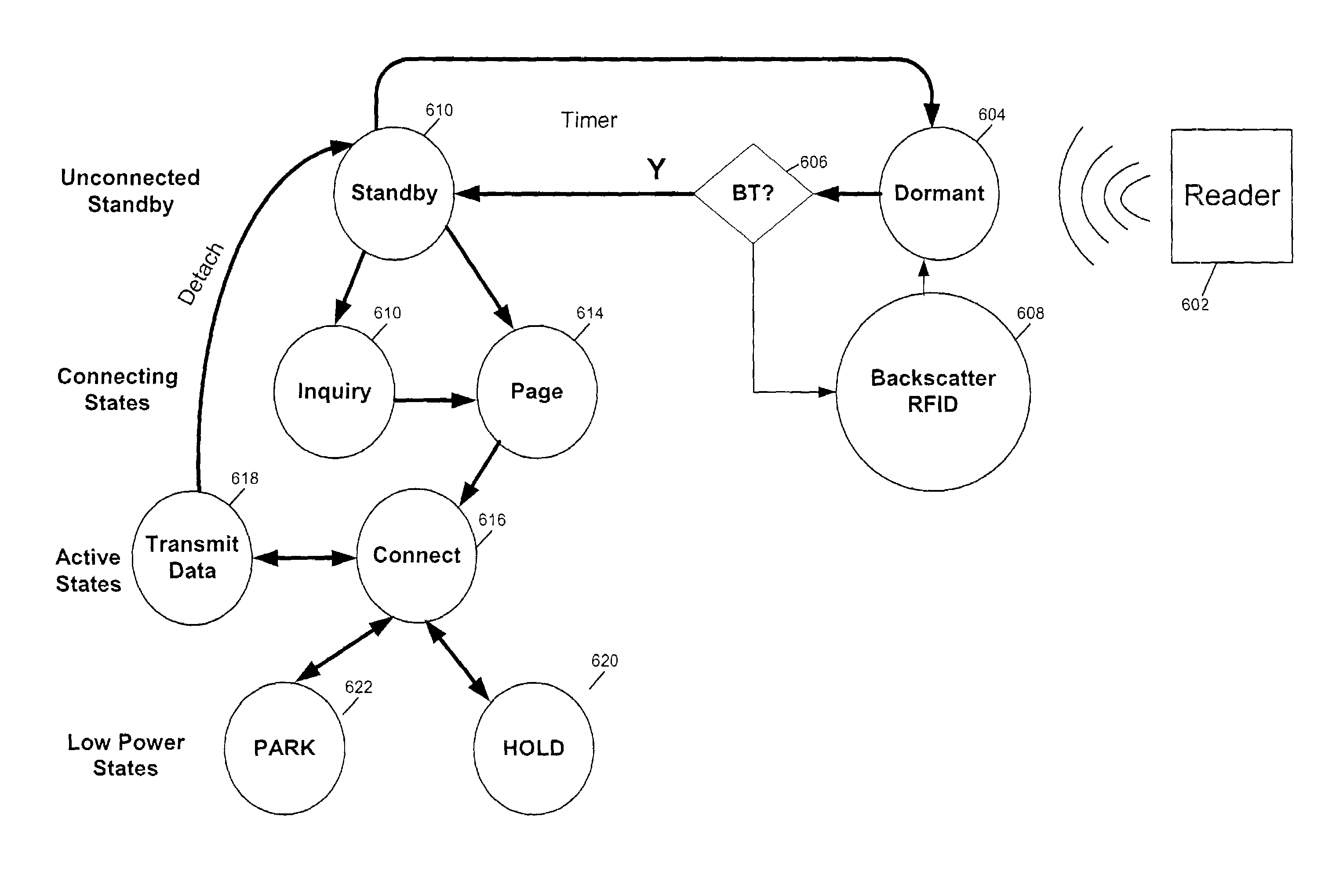

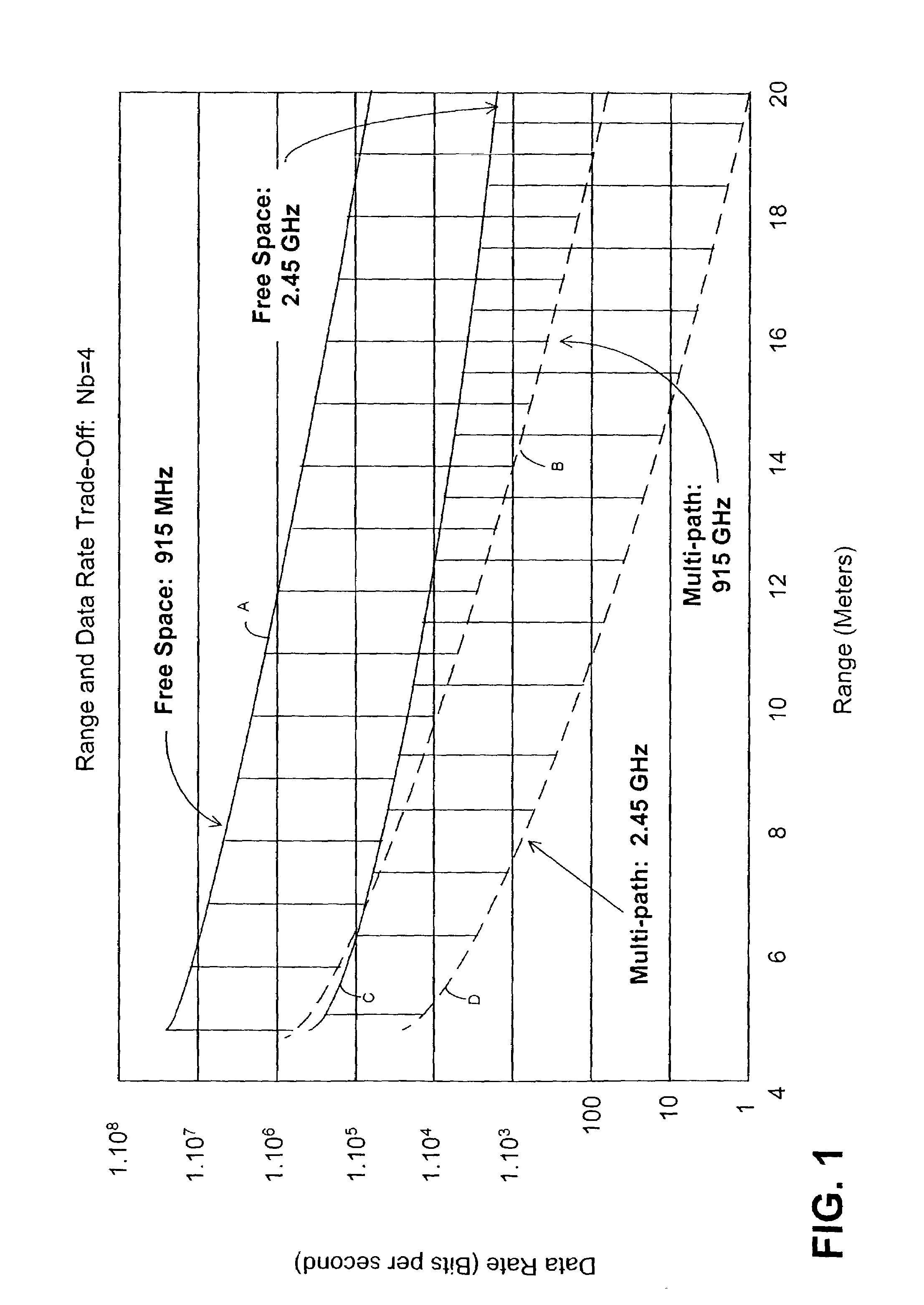

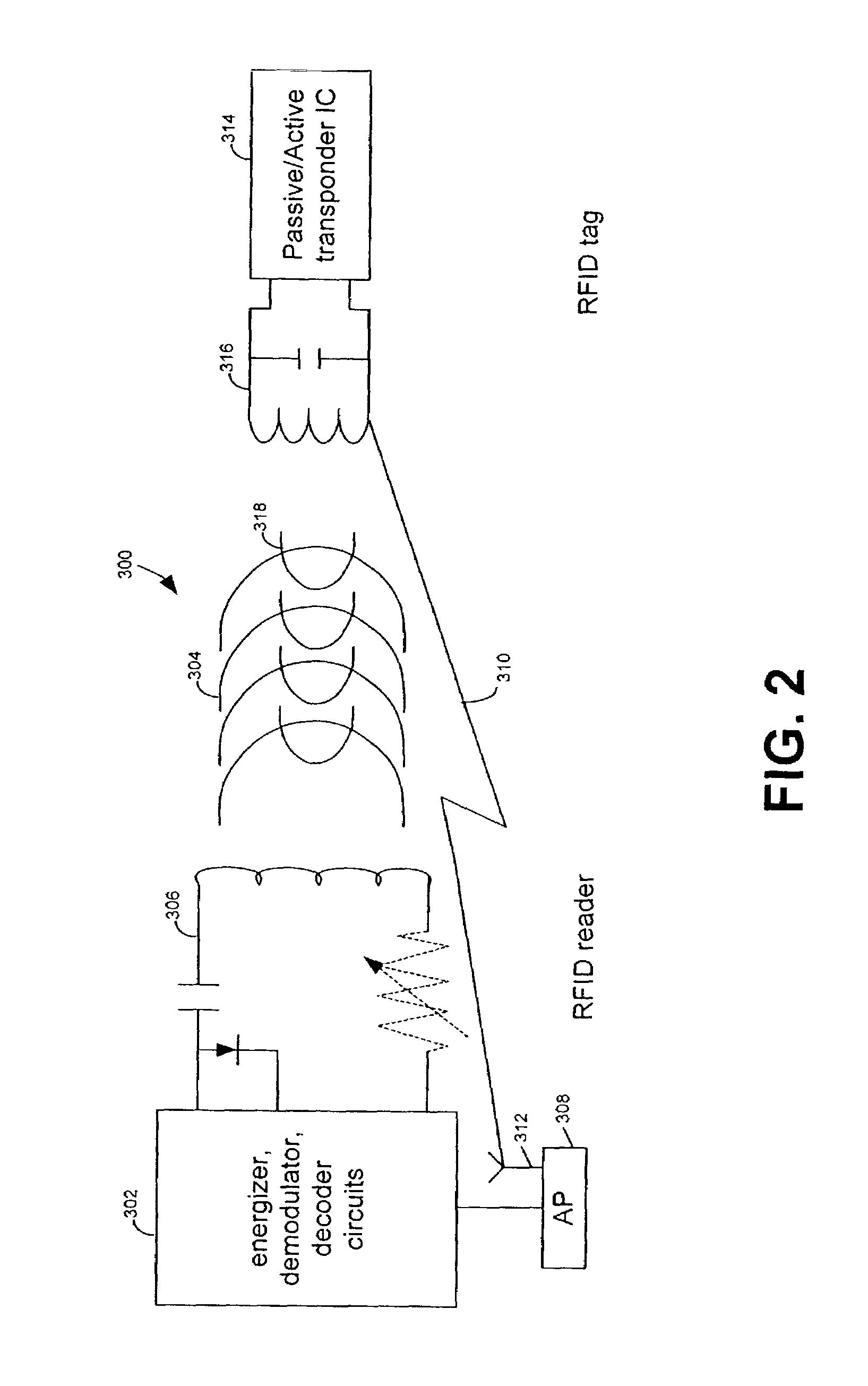

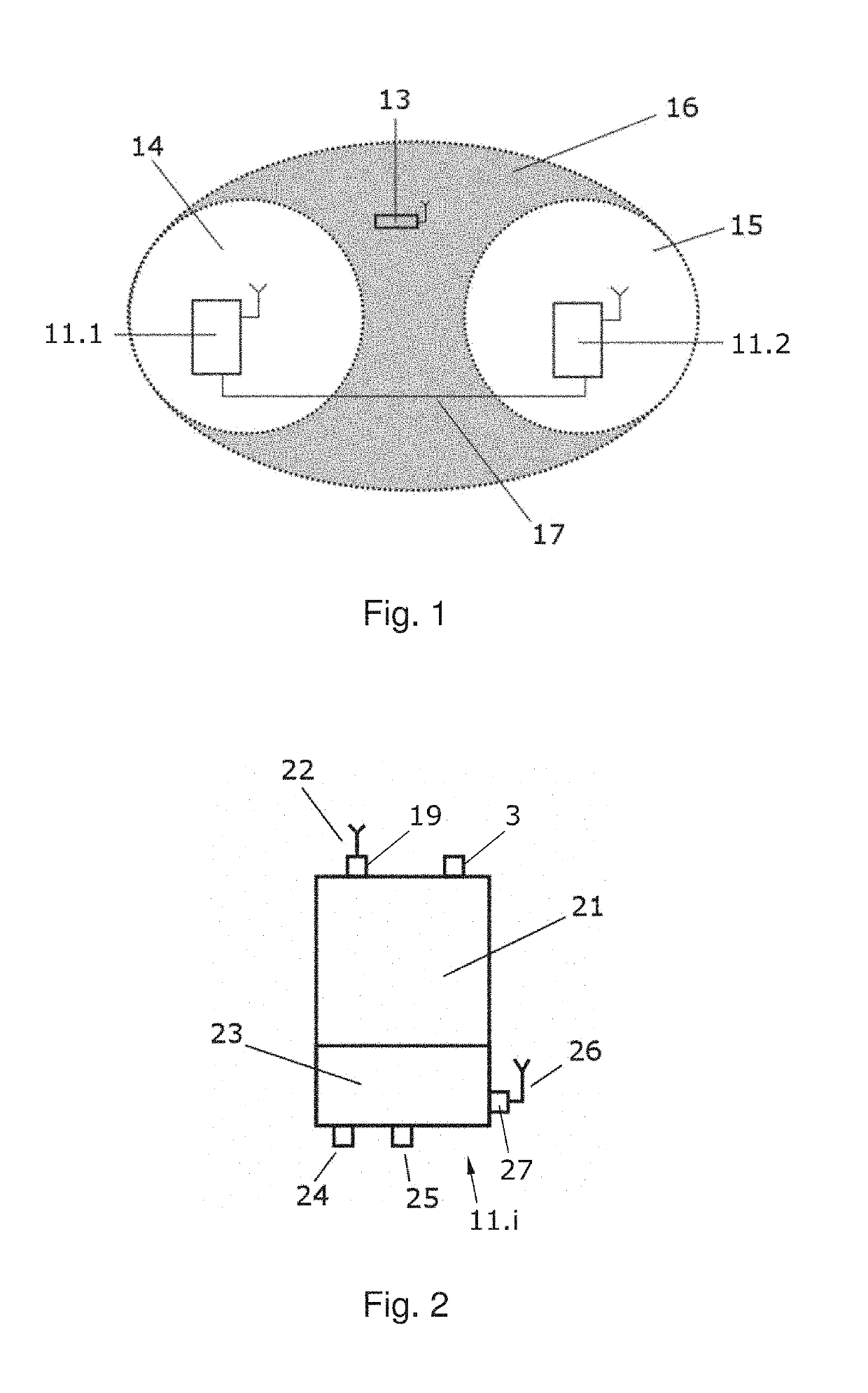

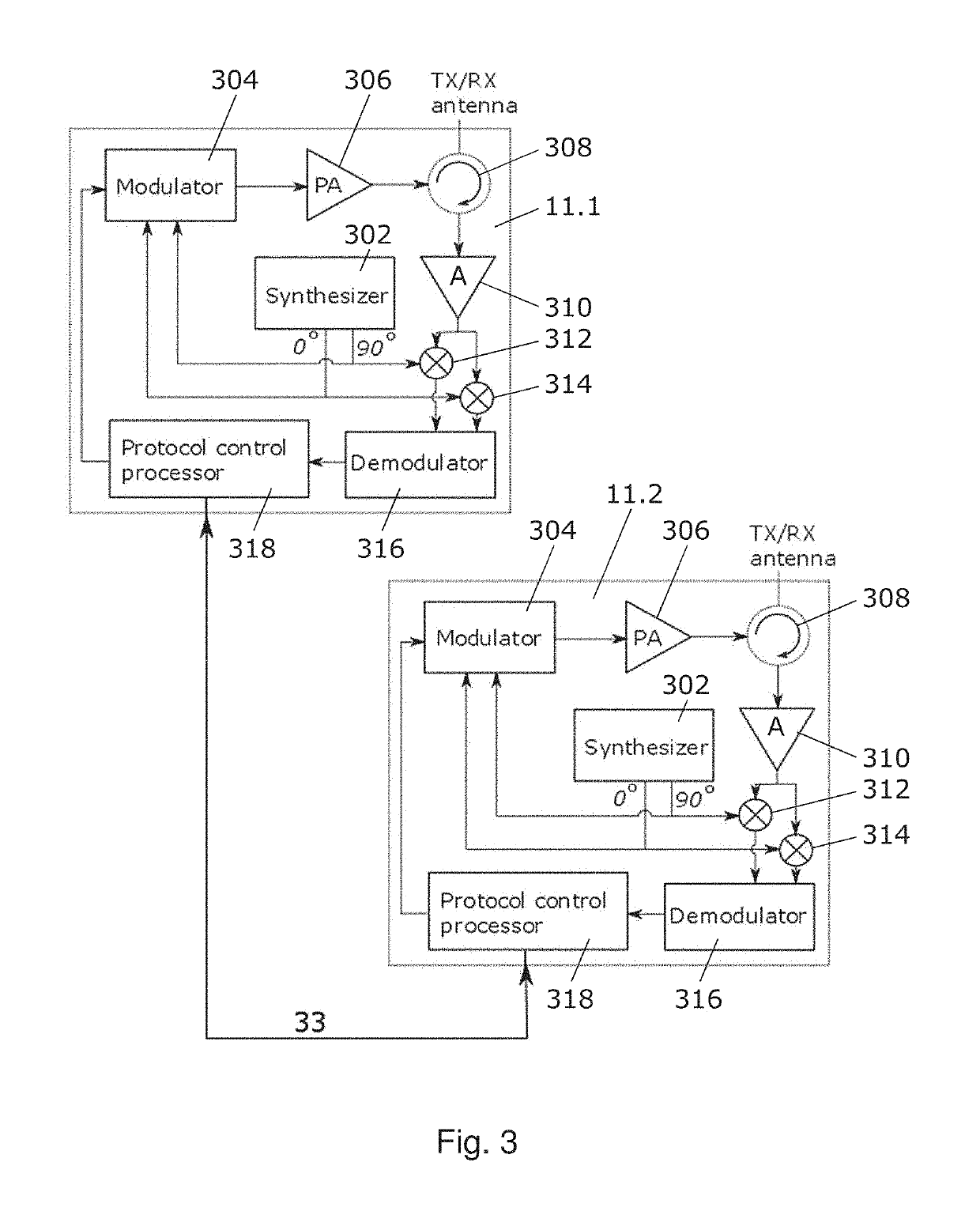

RFID device, system and method of operation including a hybrid backscatter-based RFID tag protocol compatible with RFID, bluetooth and/or IEEE 802.11x infrastructure

ActiveUS20030104848A1Near-field transmissionMemory record carrier reading problemsTransceiverAntenna impedance

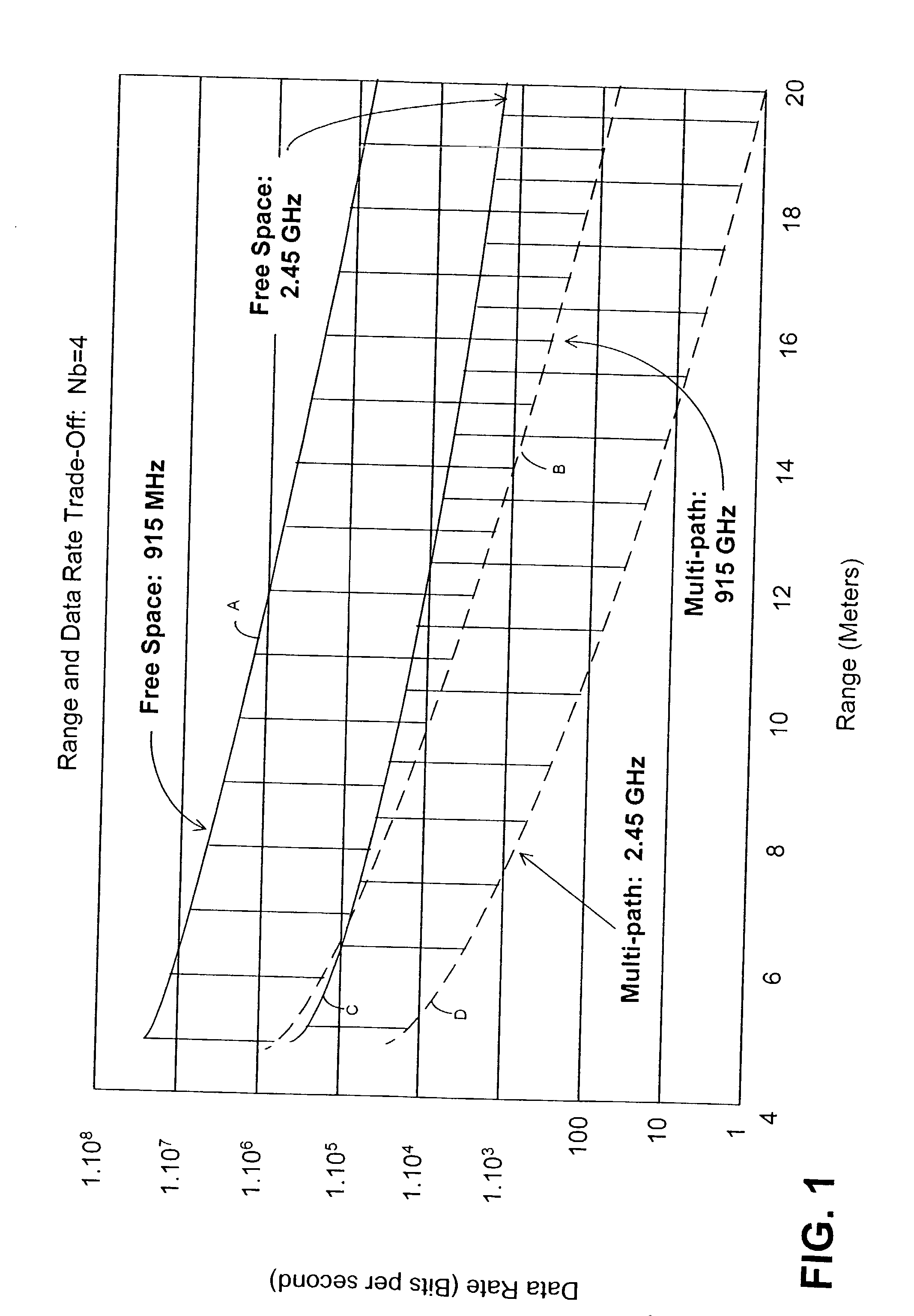

An RFID system includes a hybrid backscatter-based RFID tag protocol-compatible with existing 802.11x / Bluetooth Standards as well as RFID standards. The tag is linked to a multi-protocol Interrogator via a generated RF Continuous Wave (CW) field. The tag includes an antenna coupled to an RFID and a Bluetooth / 802.11x transceiver section. A Protocol Processor services RFID and transceiver sections and is coupled to the antenna via a backscatter switch. The Interrogator can switch the tag to an RFID backscatter radiation mode where the processor switches the antenna impedance to reflect the CW signal. For transceiver operation the processor switches antenna impedance in synchronization with a frame organized bit stream. For reception, the RFID section utilizes demodulation techniques, typically Amplitude Shift Keying (ASK), and provides a wake up mode within a predetermined distance of the Interrogator. The transceiver may operate in a backscatter or regular mode as directed by an Access Point.

Owner:GOOGLE TECH HLDG LLC

Wireless communication device with markup language based man-machine interface

A system, method, and software product provide a wireless communications device with a markup language based man-machine interface. The man-machine interface provides a user interface for the various telecommunications functionality of the wireless communication device, including dialing telephone numbers, answering telephone calls, creating messages, sending messages, receiving messages, establishing configuration settings, which are defined in markup language, such as HTML, and accessed through a browser program executed by the wireless communication device. This feature enables direct access to Internet and World Wide Web content, such as Web pages, to be directly integrated with telecommunication functions of the device, and allows Web content to be seamlessly integrated with other types of data, since all data presented to the user via the user interface is presented via markup language-based pages. The browser processes an extended form of HTML that provides new tags and attributes that enhance the navigational, logical, and display capabilities of conventional HTML, and particularly adapt HTML to be displayed and used on wireless communication devices with small screen displays. The wireless communication device includes the browser, a set of portable components, and portability layer. The browser includes protocol handlers, which implement different protocols for accessing various functions of the wireless communication device, and content handlers, which implement various content display mechanisms for fetching and outputting content on a screen display.

Owner:ACCESS

RFID device, system and method of operation including a hybrid backscatter-based RFID tag protocol compatible with RFID, bluetooth and/or IEEE 802.11x infrastructure

ActiveUS7215976B2Near-field transmissionMemory record carrier reading problemsTransceiverAntenna impedance

Owner:GOOGLE TECHNOLOGY HOLDINGS LLC

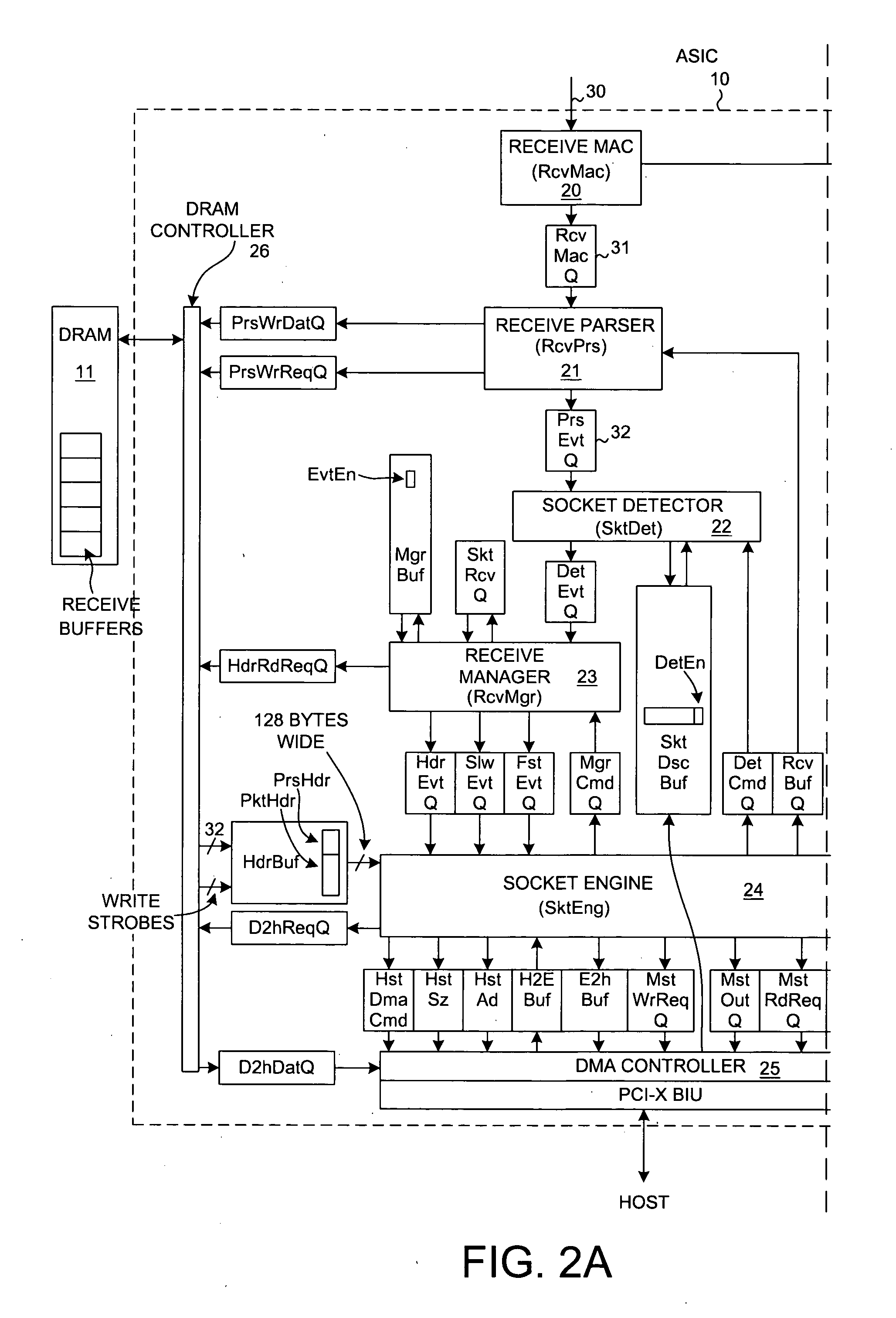

TCP/IP offload device with reduced sequential processing

ActiveUS6996070B2Block valueNarrow structureError preventionTransmission systemsProtocol processingState variable

A TCP Offload Engine (TOE) device includes a state machine that performs TCP / IP protocol processing operations in parallel. In a first aspect, the state machine includes a first memory, a second memory, and combinatorial logic. The first memory stores and simultaneously outputs multiple TCP state variables. The second memory stores and simultaneously outputs multiple header values. In contrast to a sequential processor technique, the combinatorial logic generates a flush detect signal from the TCP state variables and header values without performing sequential processor instructions or sequential memory accesses. In a second aspect, a TOE includes a state machine that performs an update of multiple TCP state variables in a TCB buffer all simultaneously, thereby avoiding multiple sequential writes to the TCB buffer memory. In a third aspect, a TOE involves a state machine that sets up a DMA move in a single state machine clock cycle.

Owner:ALACRITECH

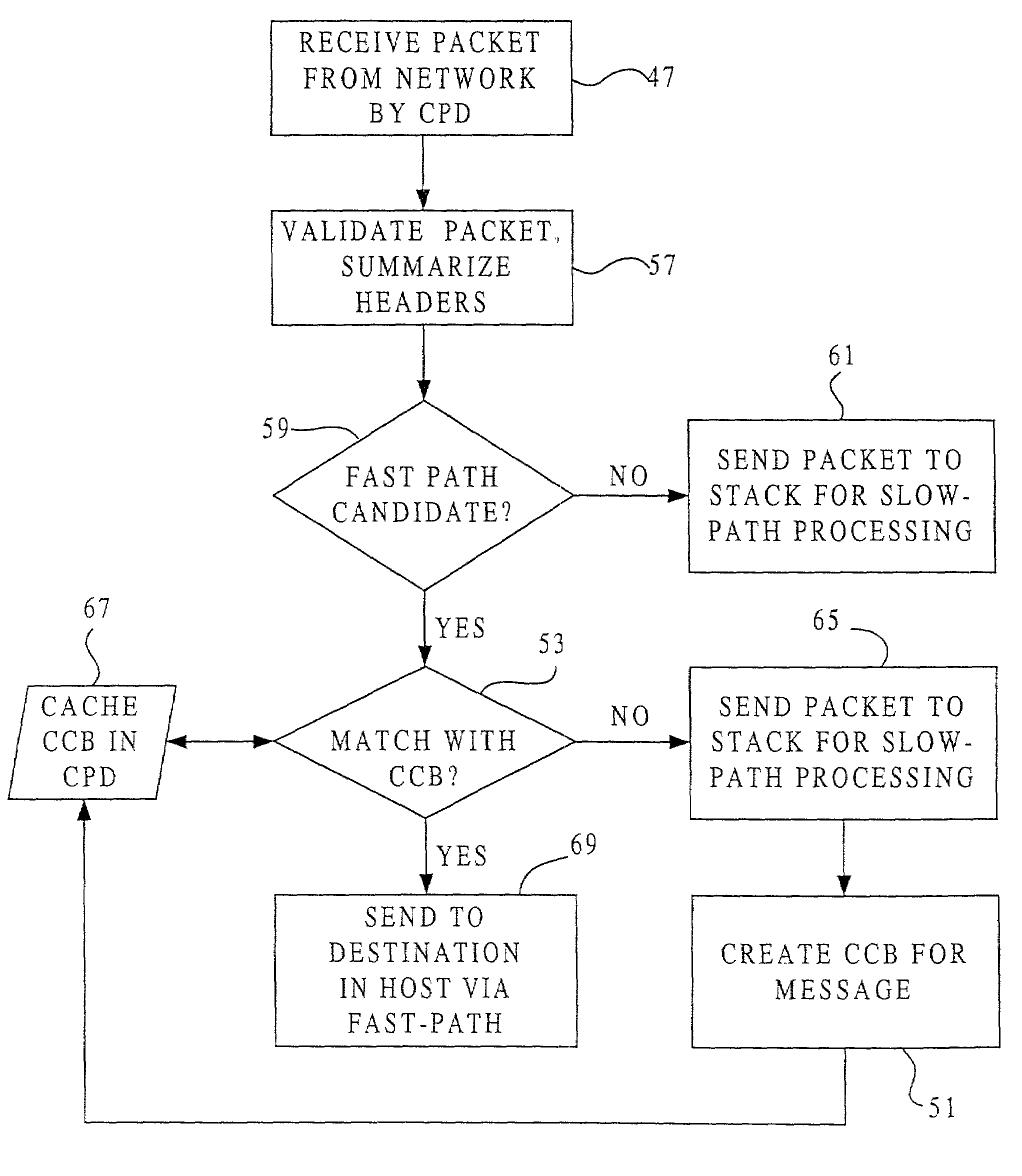

Fast-path processing for receiving data on TCP connection offload devices

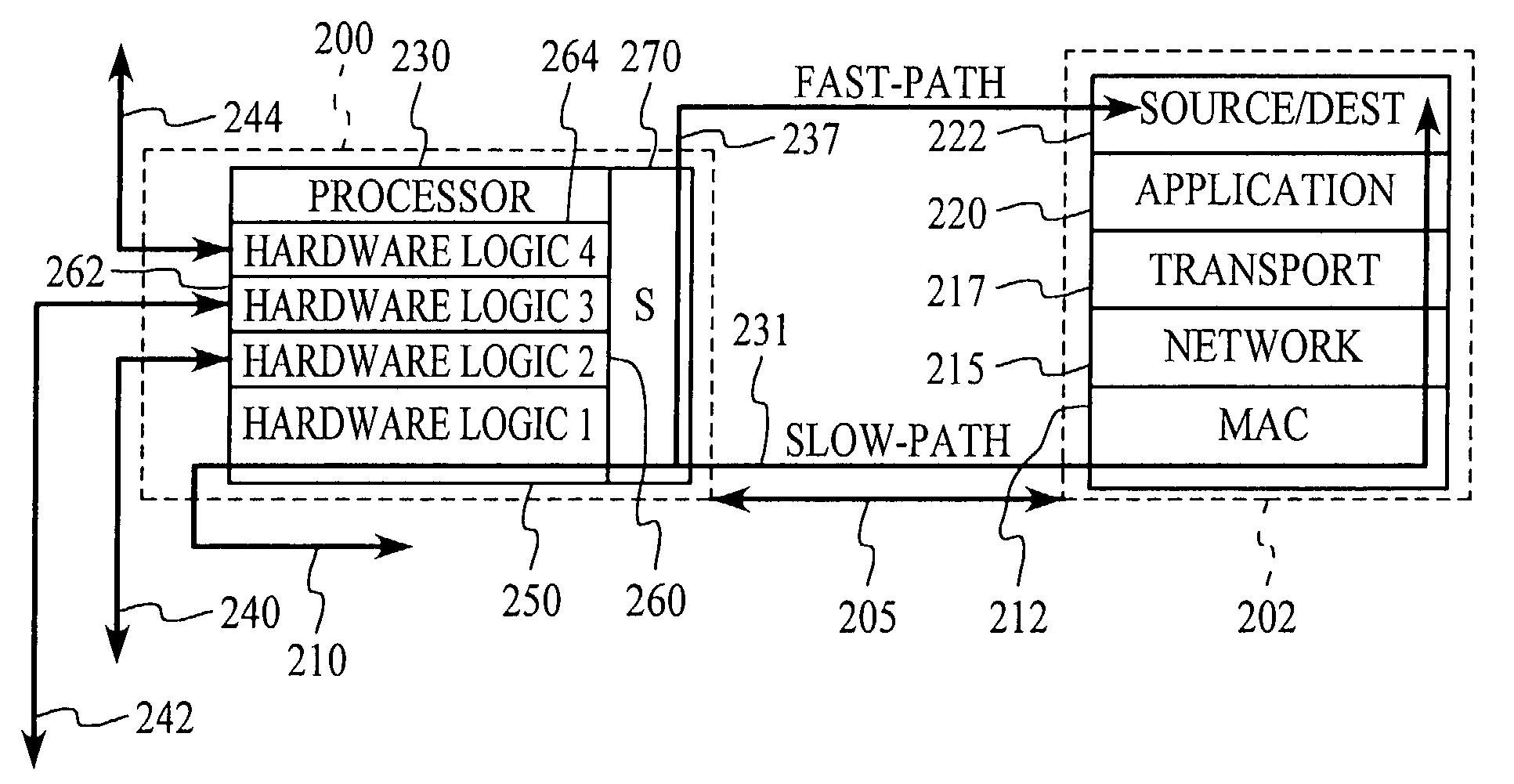

ActiveUS7089326B2Negligibly effectMove quicklyMultiple digital computer combinationsData switching networksFast pathProtocol processing

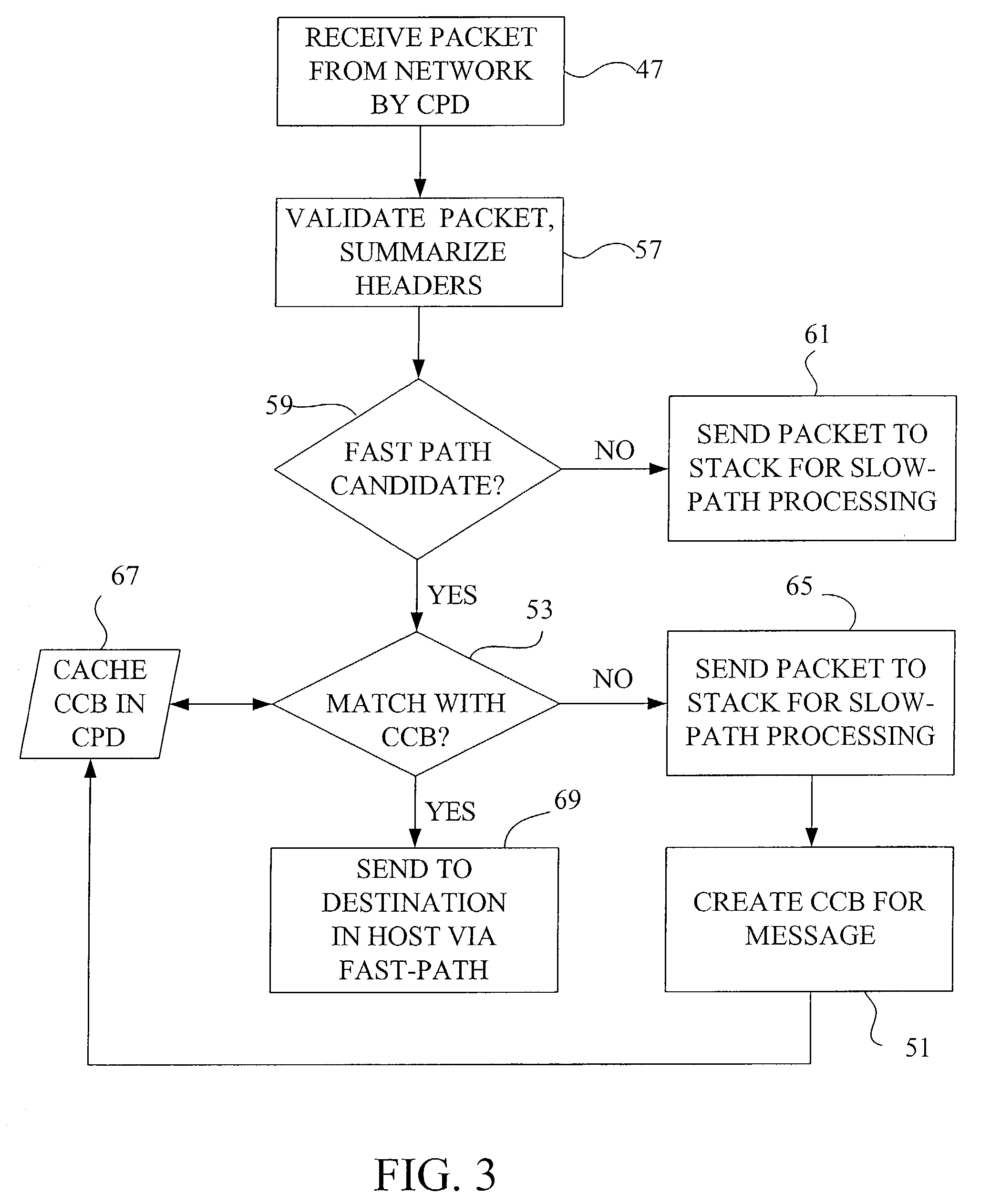

A network interface device provides a fast-path that avoids most host TCP and IP protocol processing for most messages. The host retains a fallback slow-path processing capability. In one embodiment, generation of a response to a TCP / IP packet received onto the network interface device is accelerated by determining the TCP and IP source and destination information from the incoming packet, retrieving an appropriate template header, using a finite state machine to fill in the TCP and IP fields in the template header without sequential TCP and IP protocol processing, combining the filled-in template header with a data payload to form a packet, and then outputting the packet from the network interface device by pushing a pointer to the packet onto a transmit queue. A transmit sequencer retrieves the pointer from the transmit queue and causes the corresponding packet to be output from the network interface device.

Owner:ALACRITECH

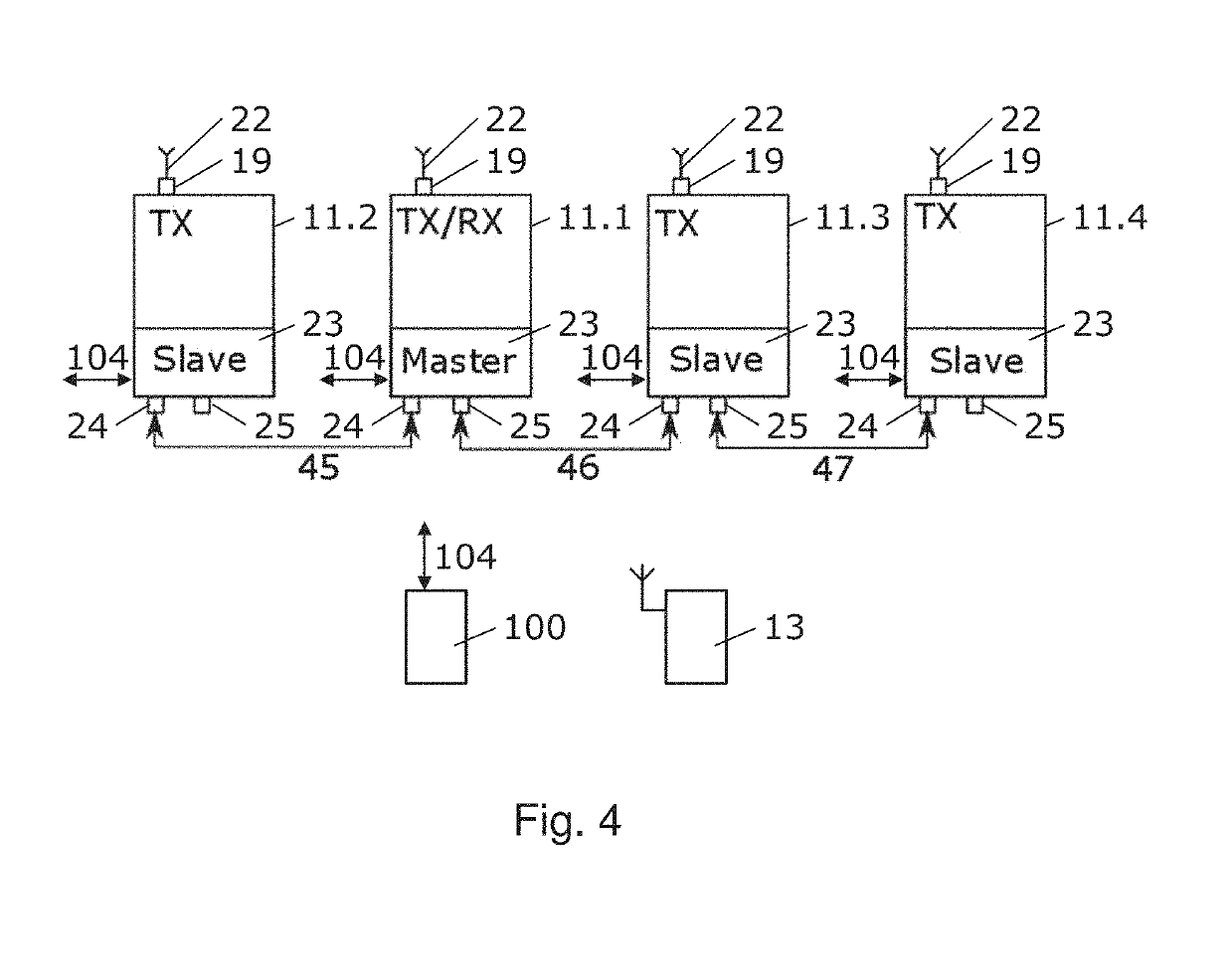

System of RFID reader units transmitting synchronized modulation using asynchronous carrier waves

ActiveUS20190138770A1Efficiently enhancing coverage area and read performanceLess complicated and expensive hardwareSensing by electromagnetic radiationTransceiverProtocol processing

A UHF RFID system is disclosed in which an RFID transponder or tag can be simultaneously powered and interrogated by multiple RFID transceivers. The architecture of the system is such that each transceiver generates its own carrier wave, with a frequency that might be equal to or different from the other units, and the interrogation data is distributed throughout a network of transceivers and modulated by each transceiver unit onto their own carrier waves. During an interrogation period, one or more of the transceivers will be configured as the master unit, generating and distributing the protocols commands. The other units can be configured as transmitters, receivers or transceivers. After each period the units may be given different roles. The proposed setup yields a system with the capability to power and interrogate RFID tags with multiple readers, without compromising the required modulation depth and protocol handling.

Owner:N V NETHERLANDSCHE APPNFAB NEDAP

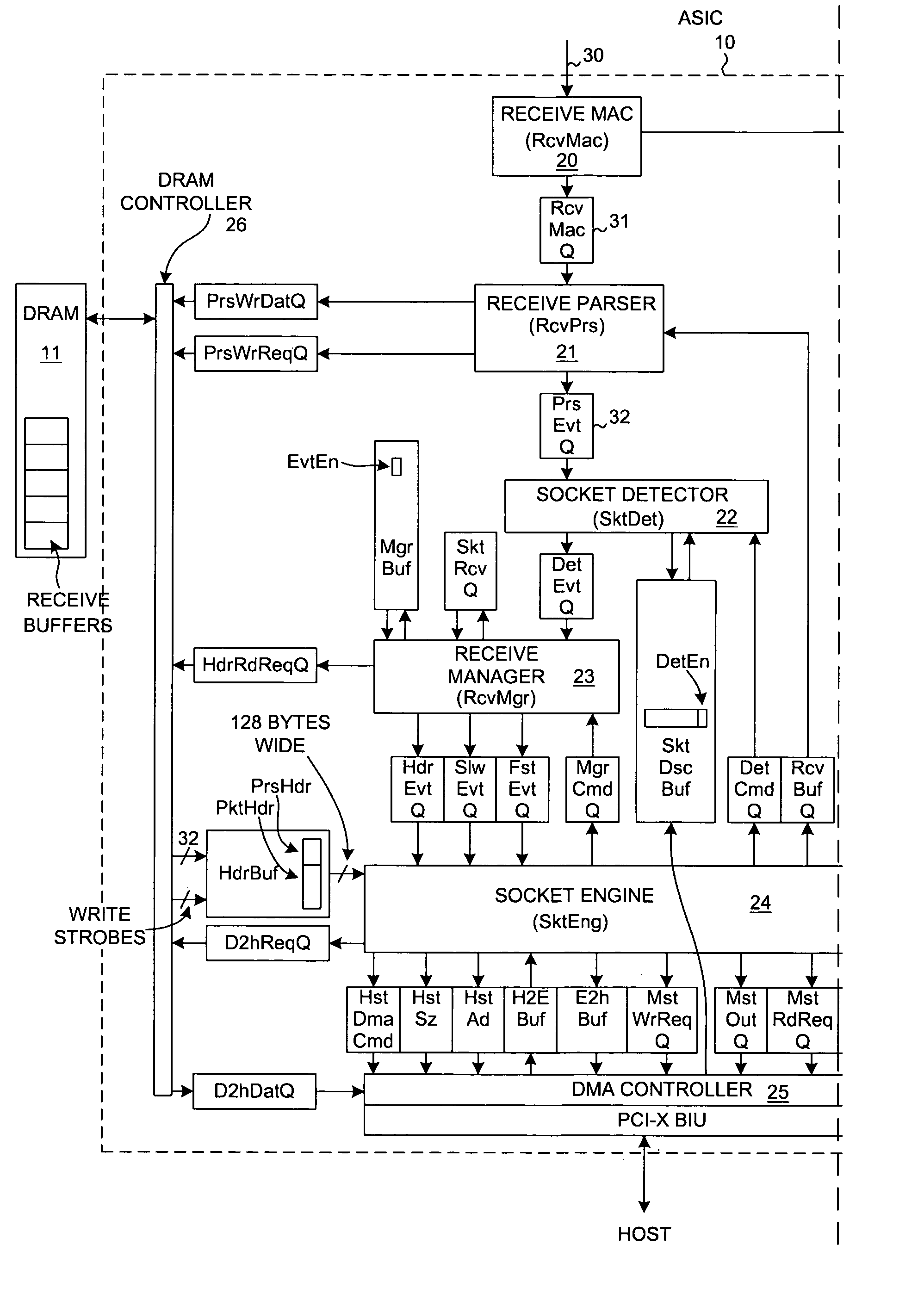

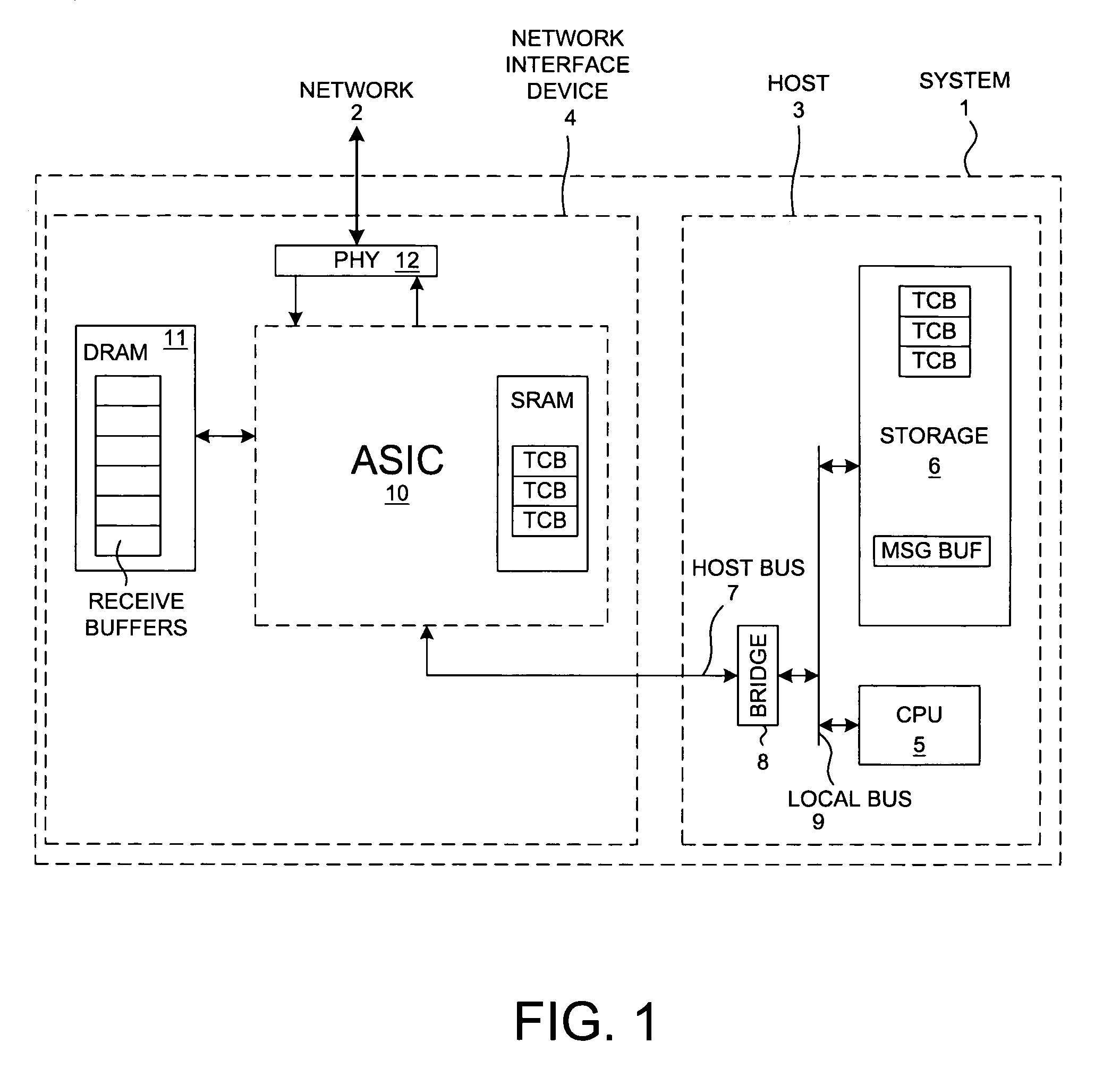

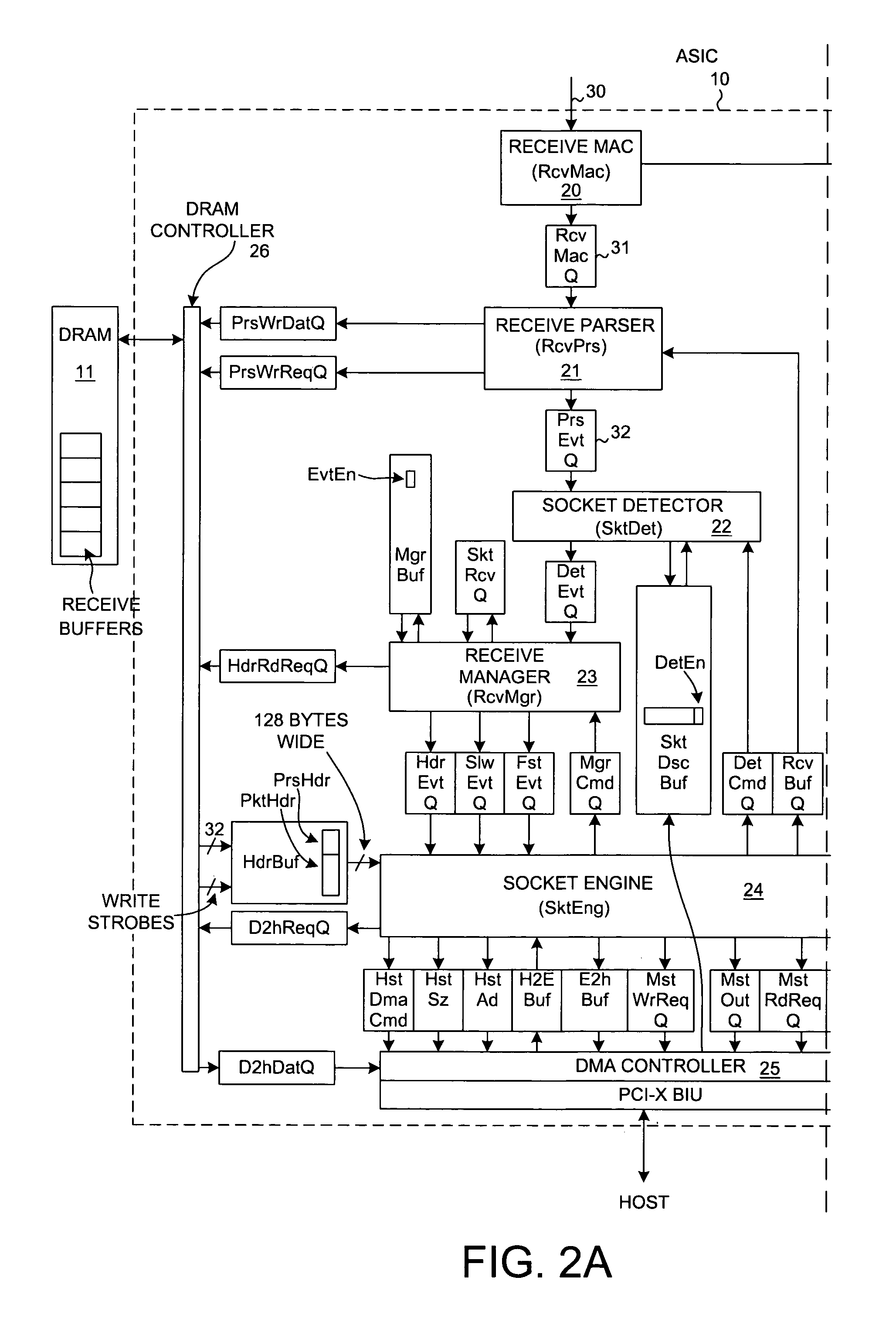

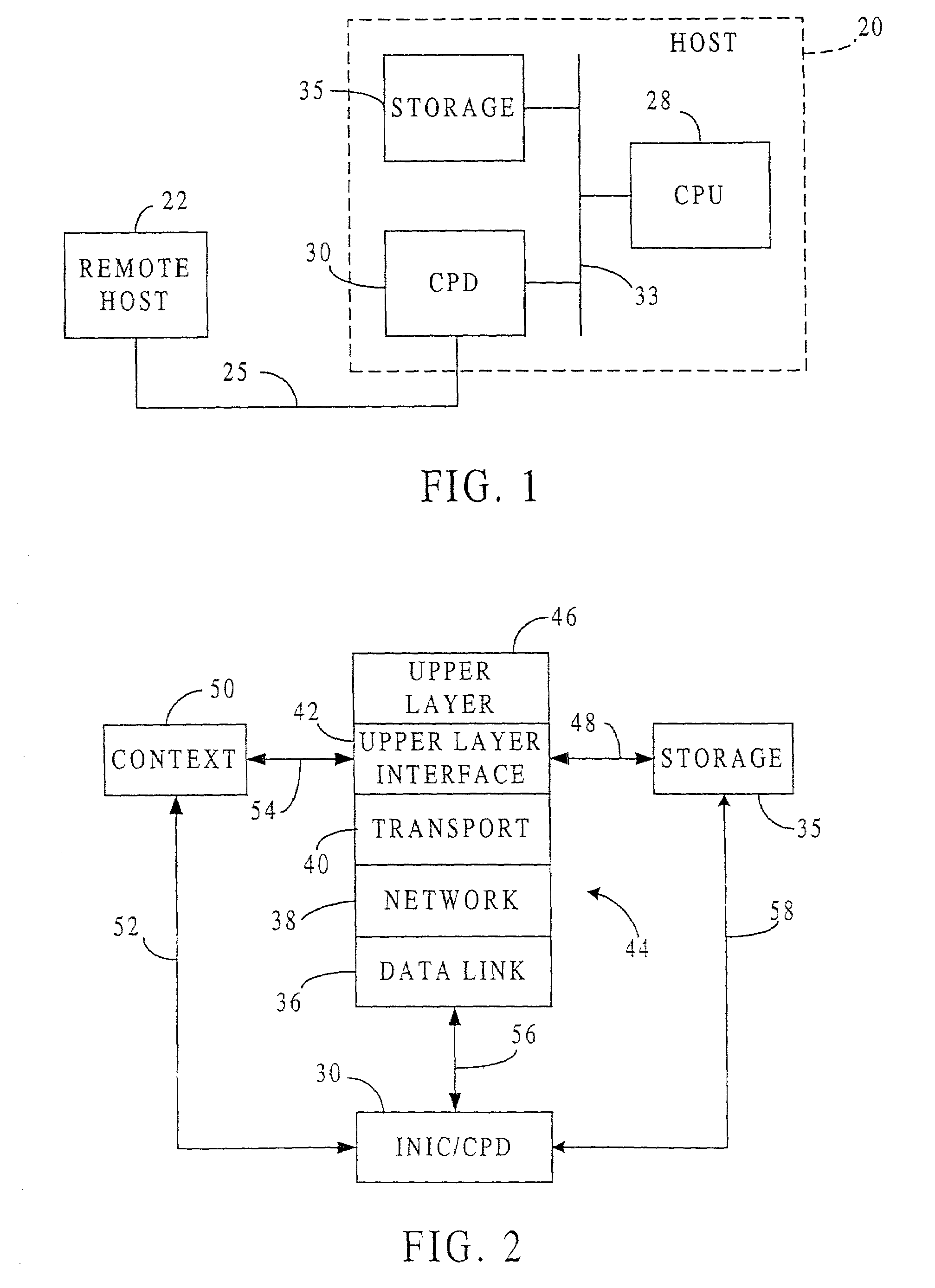

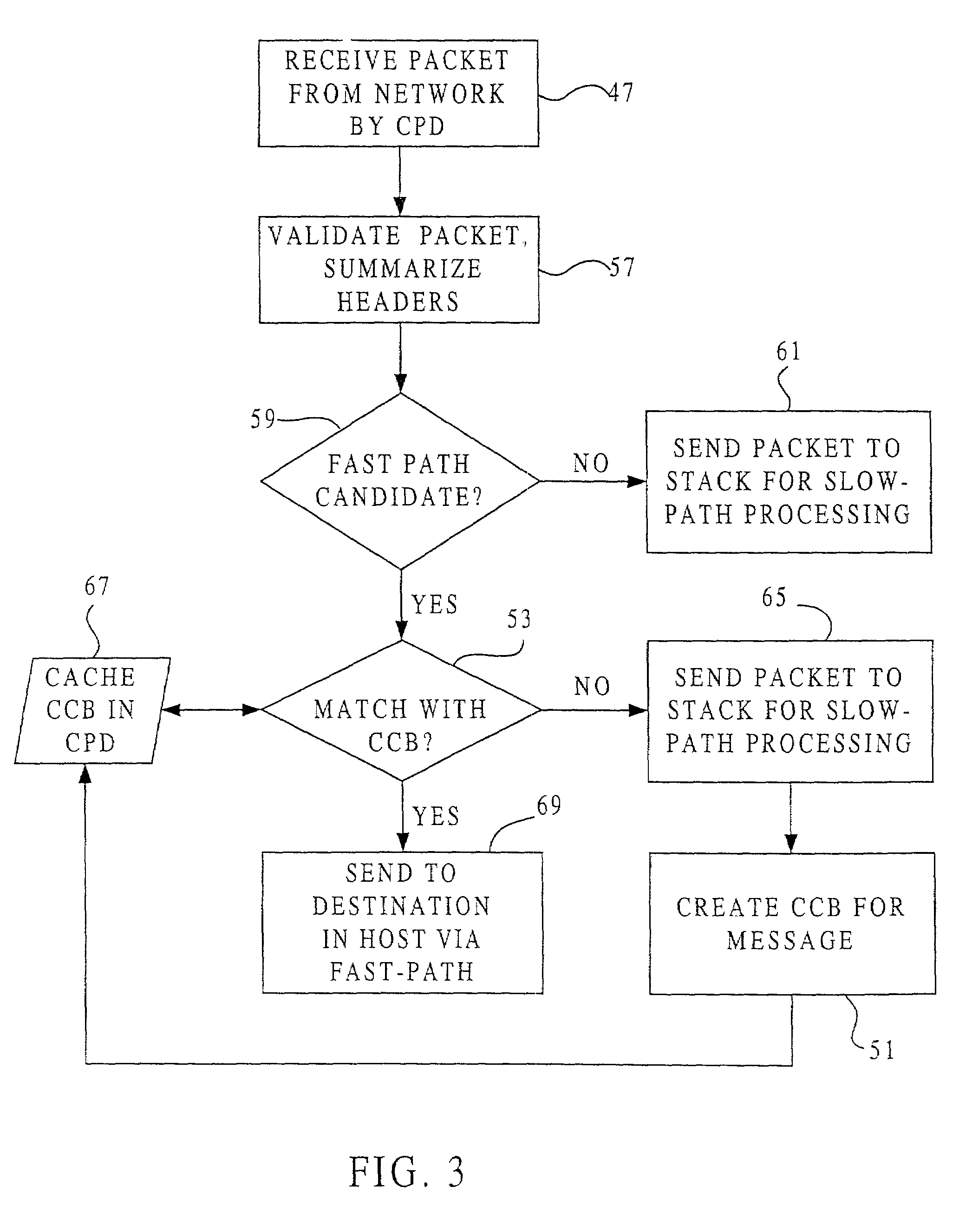

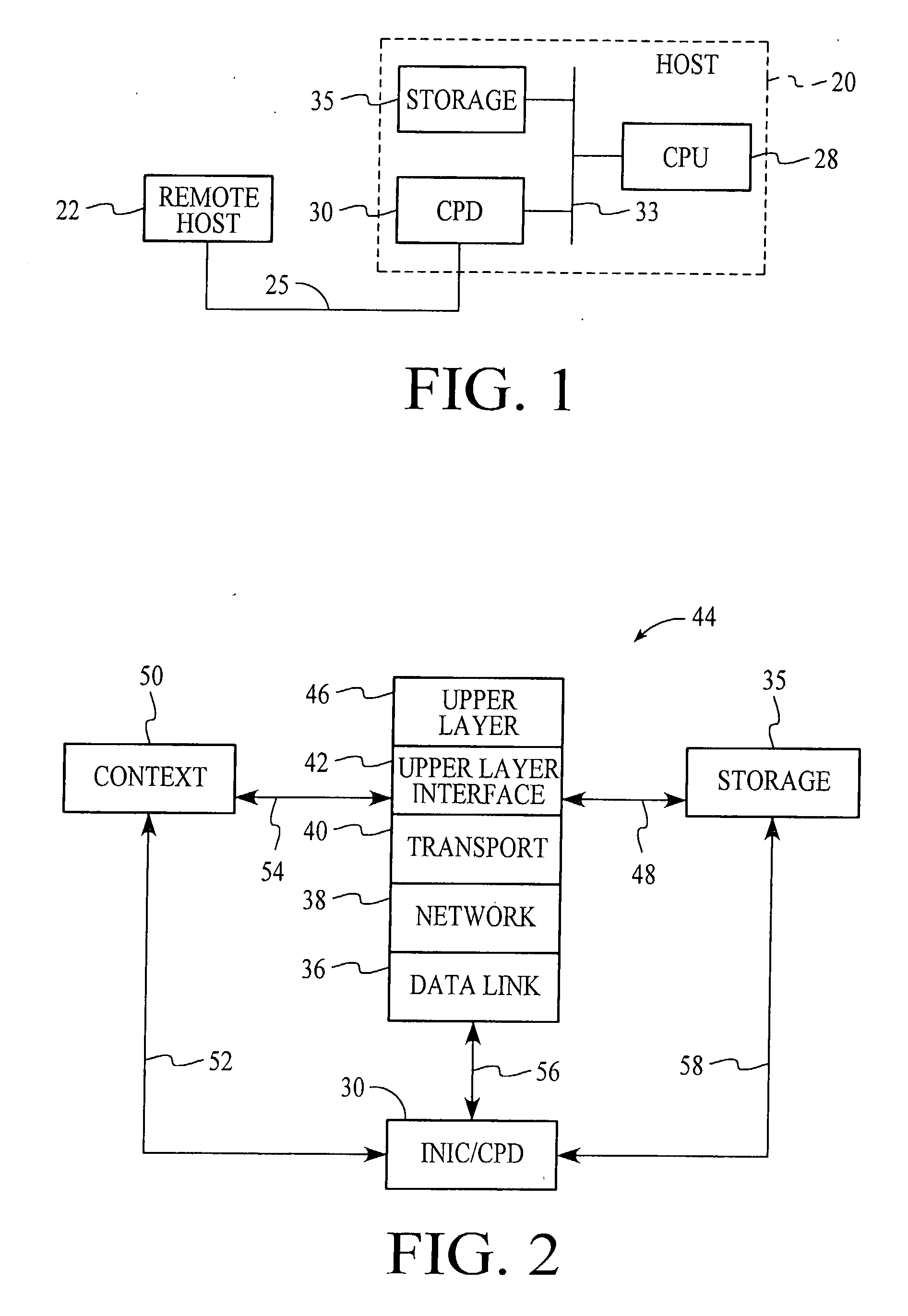

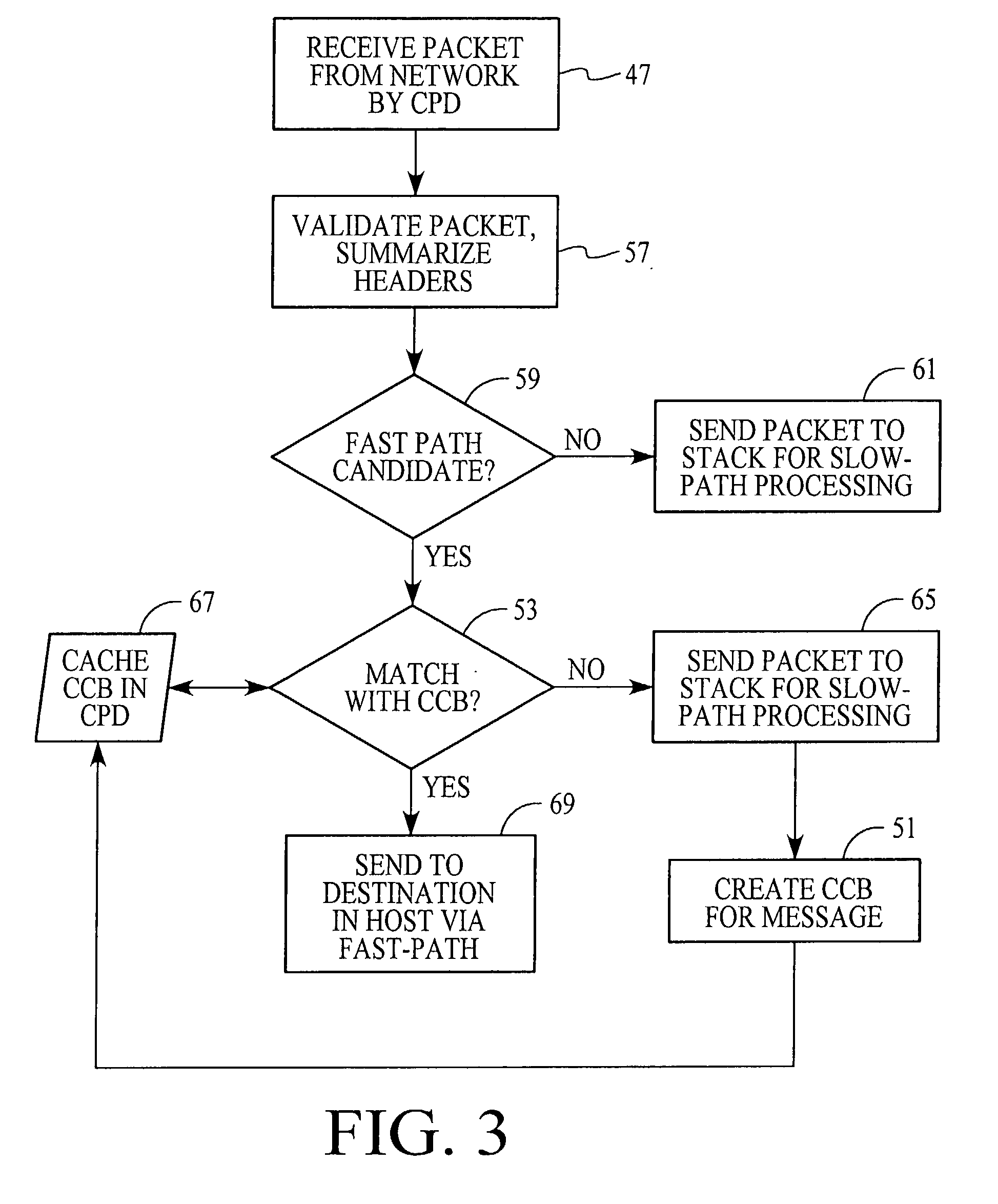

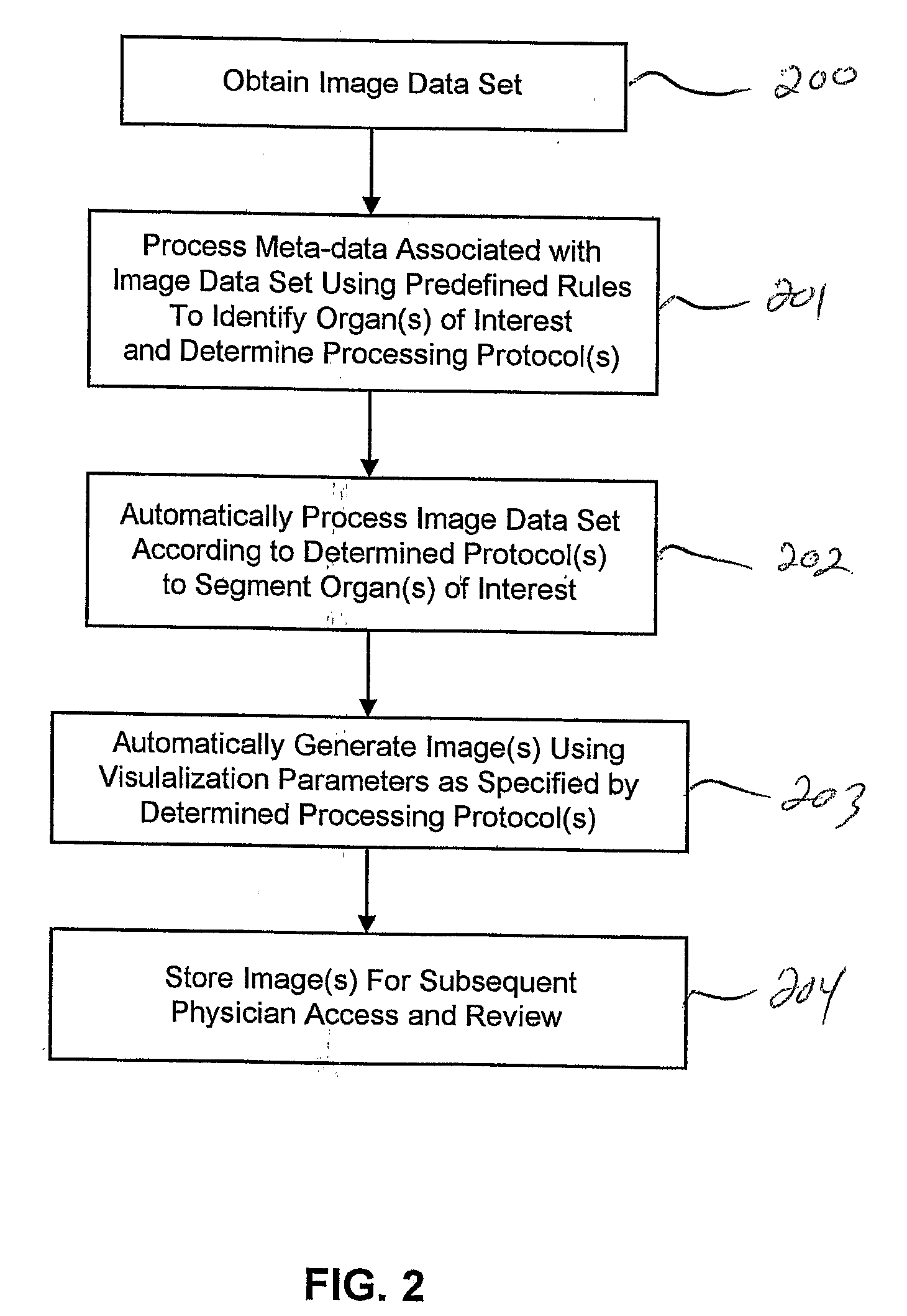

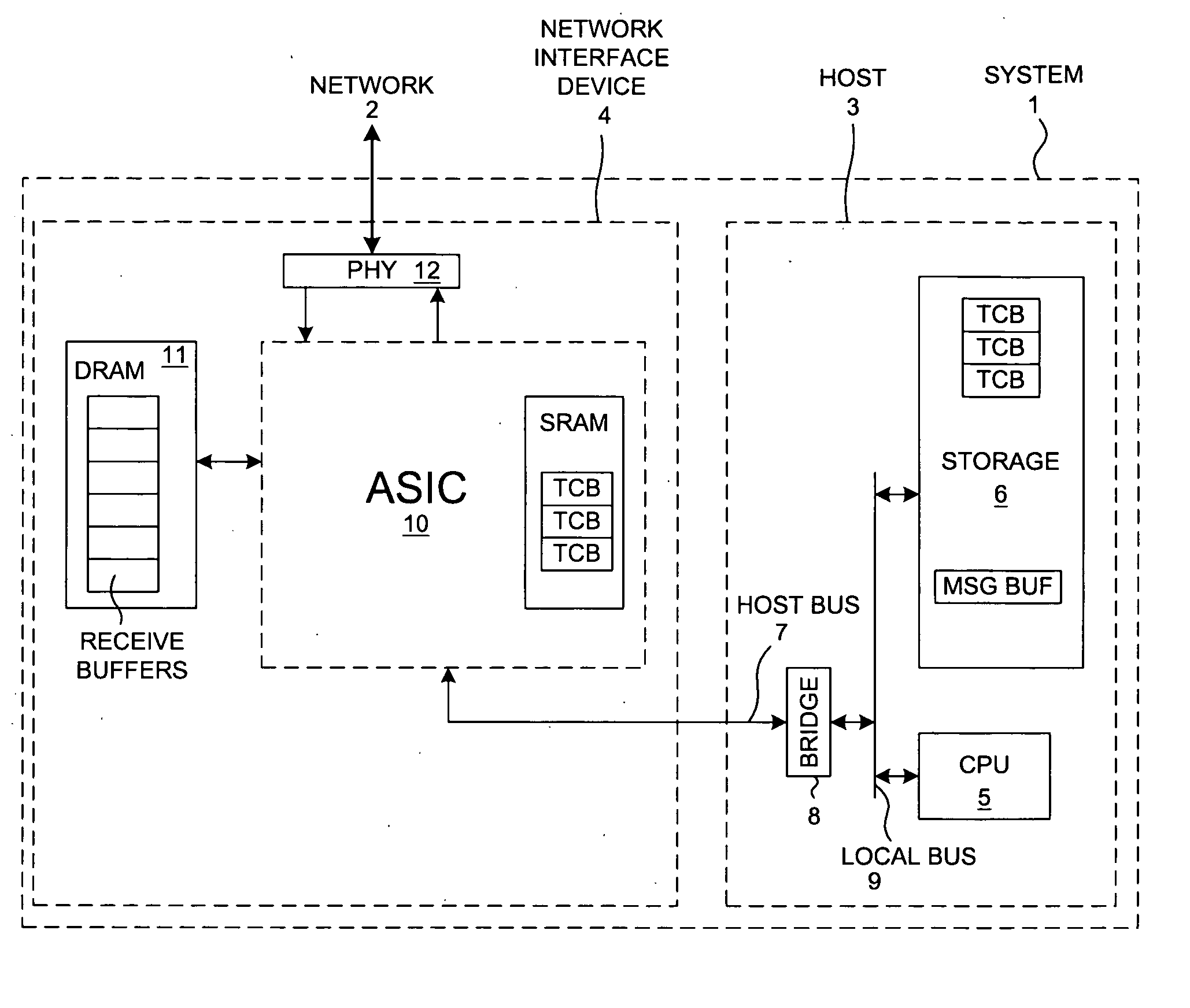

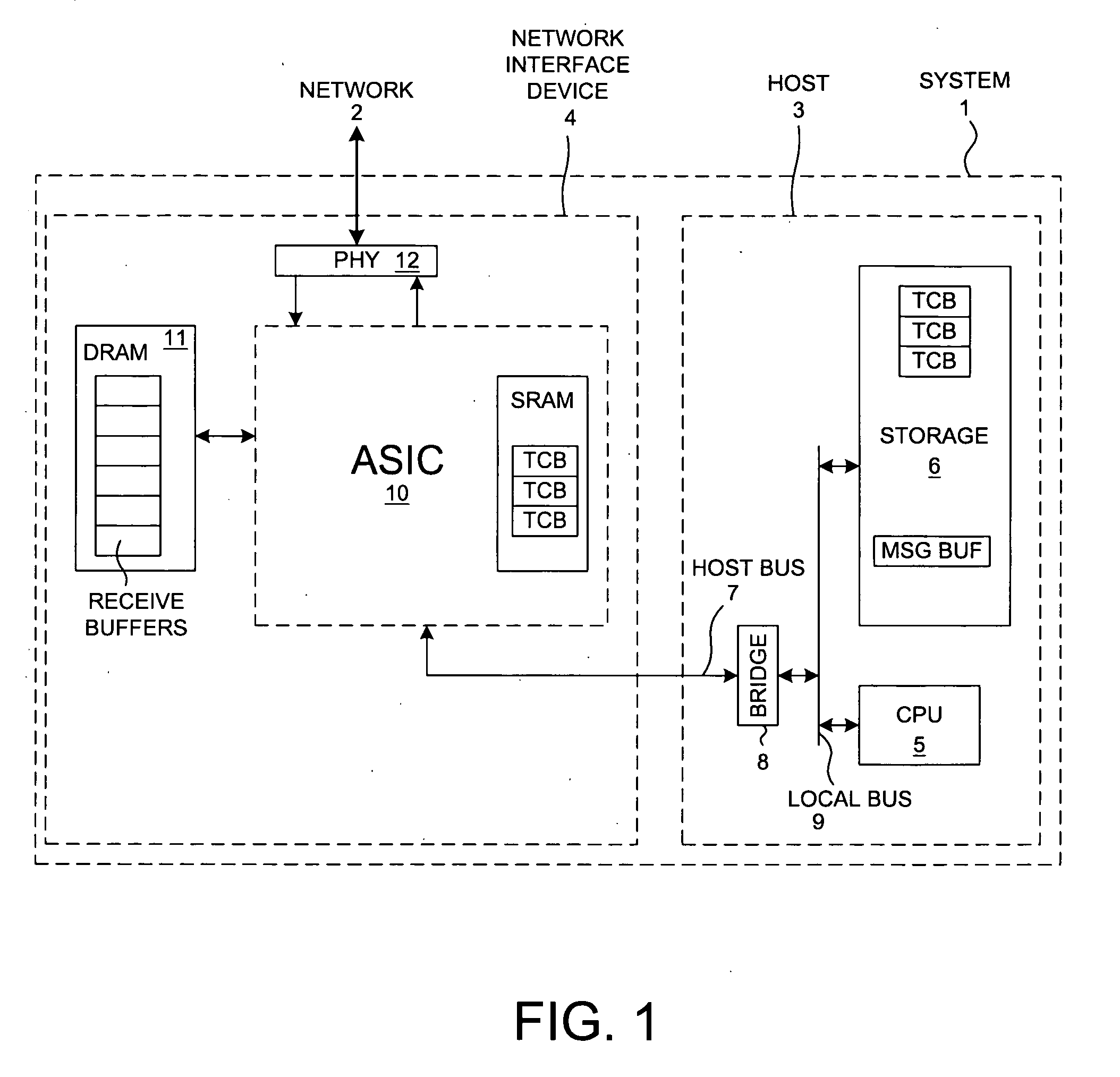

TCP/IP offload network interface device

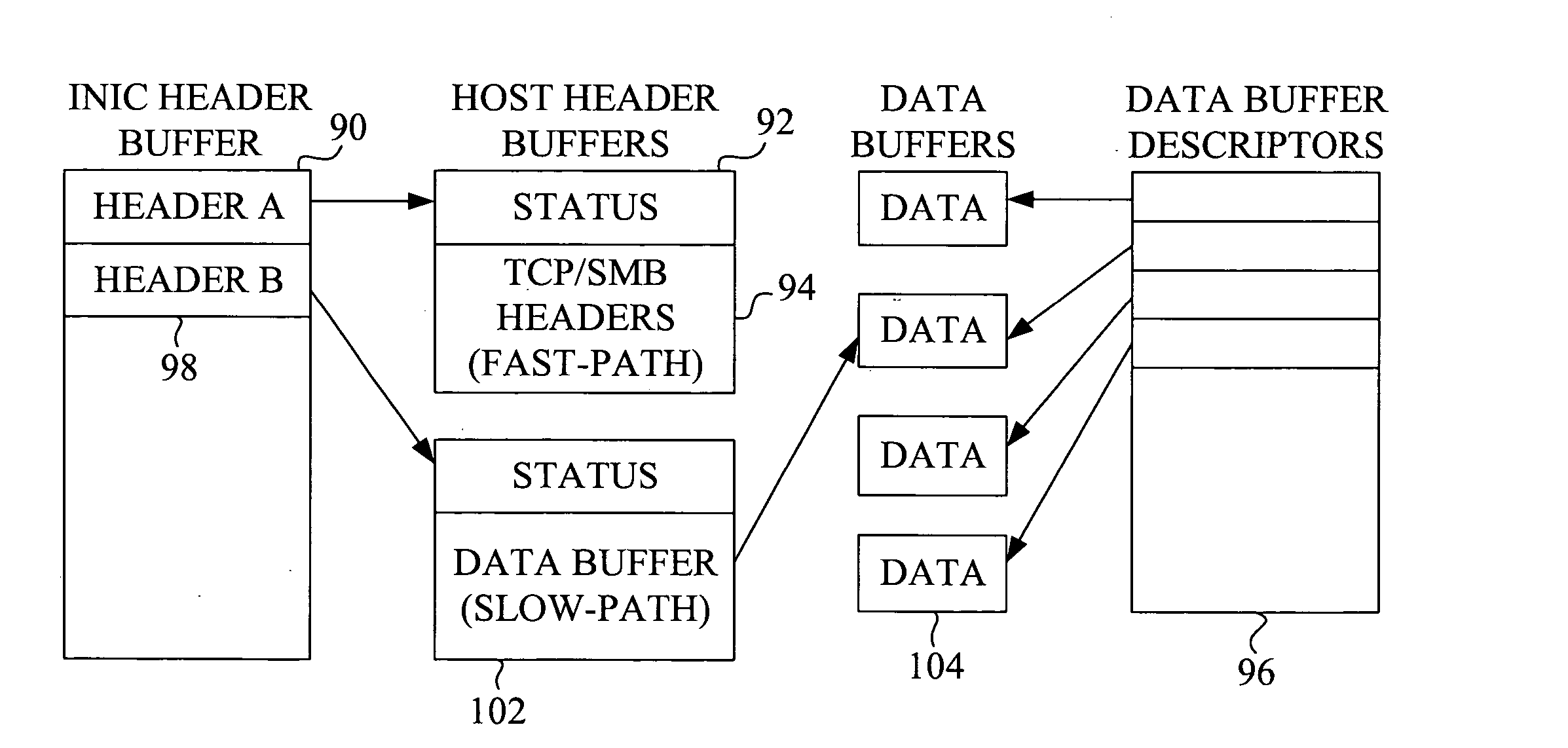

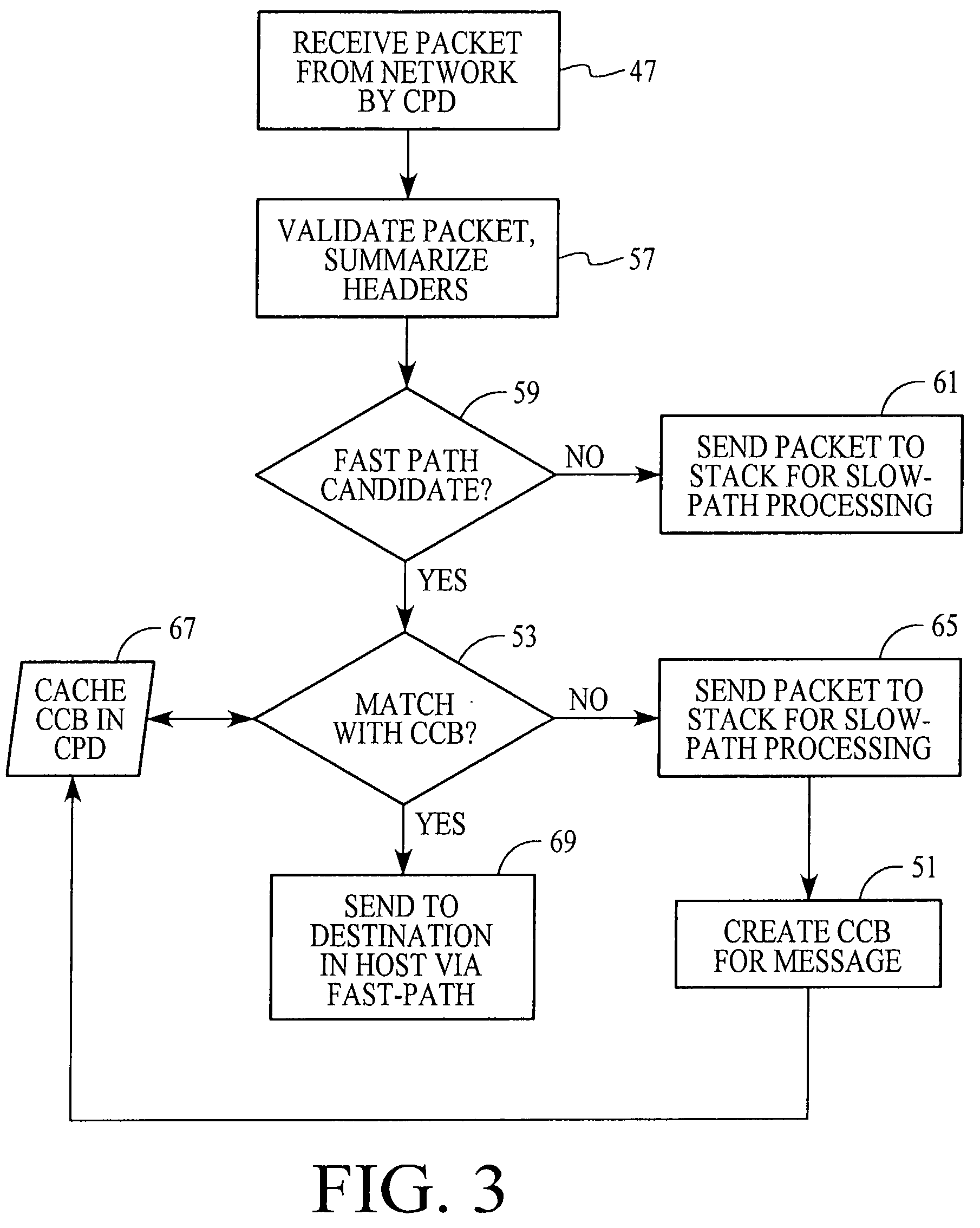

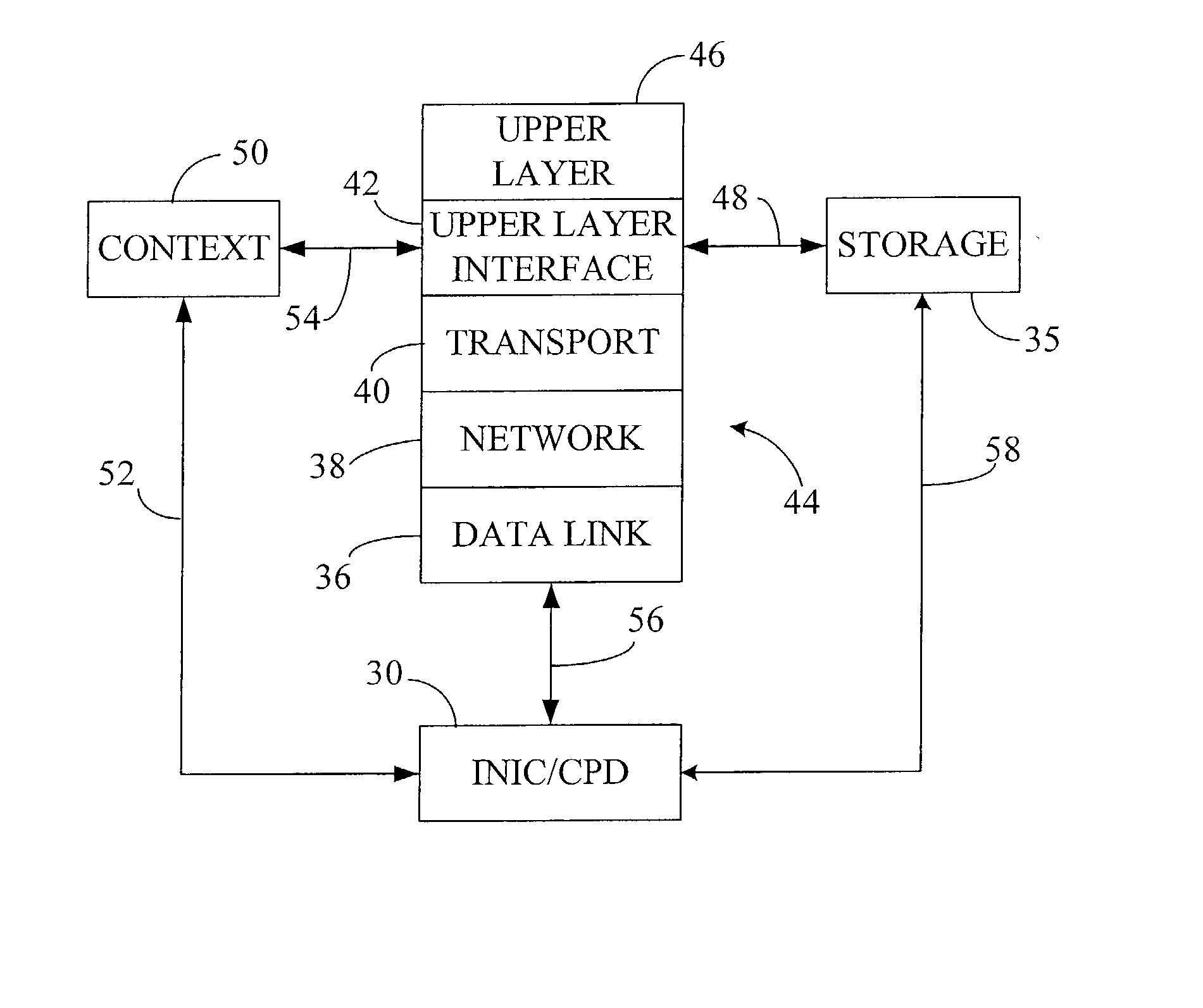

InactiveUS20020156927A1Negligibly effectMove quicklyMultiple digital computer combinationsNetwork connectionsFast pathGeneral purpose

A system for protocol processing in a computer network has a TCP / IP Offload Network Interface Device (TONID) associated with a host computer. The TONID provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The TONID also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the TONID to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the TONID as a communication control block (CCB) that can be passed back to the host for message processing by the host. The TONID contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

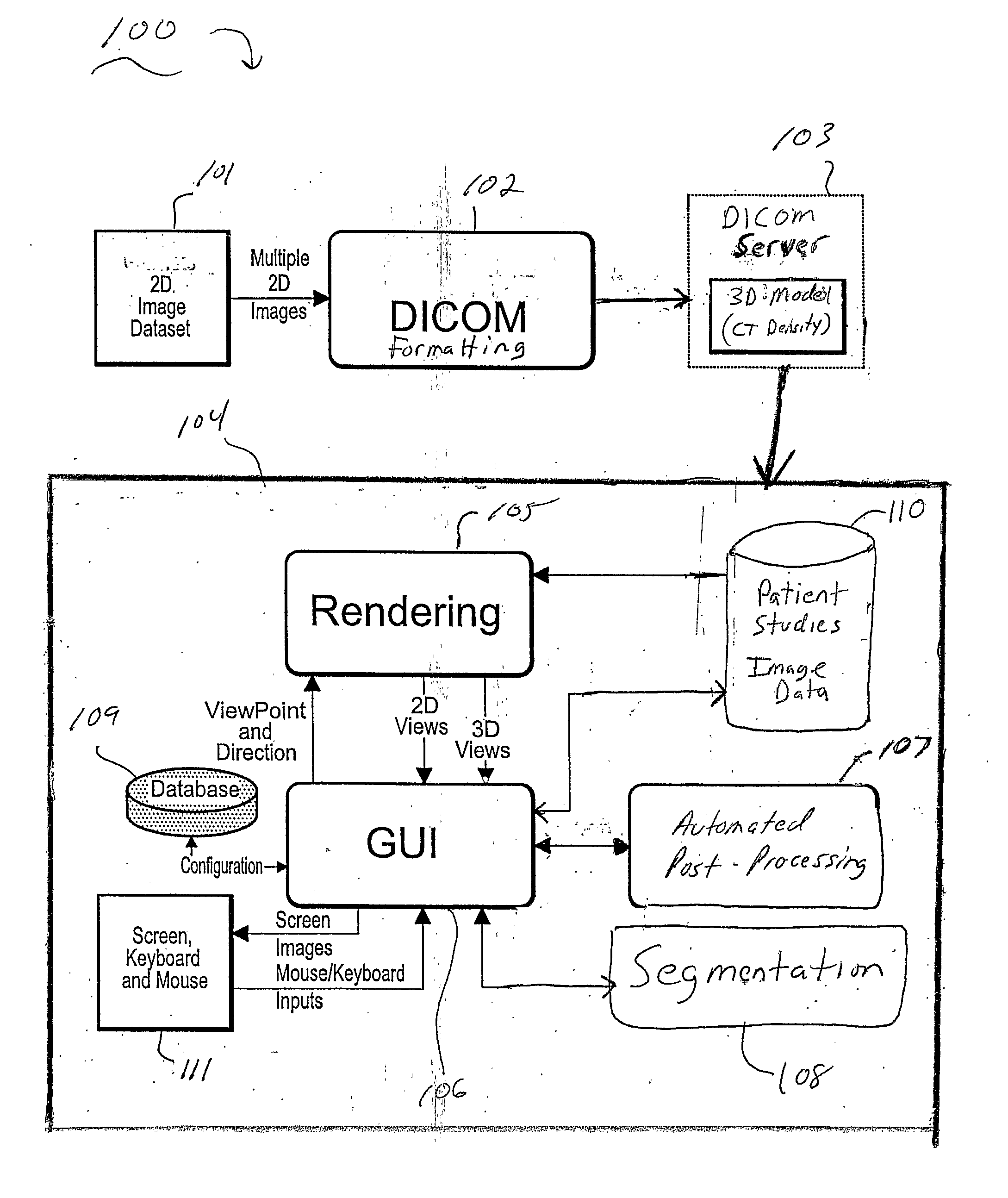

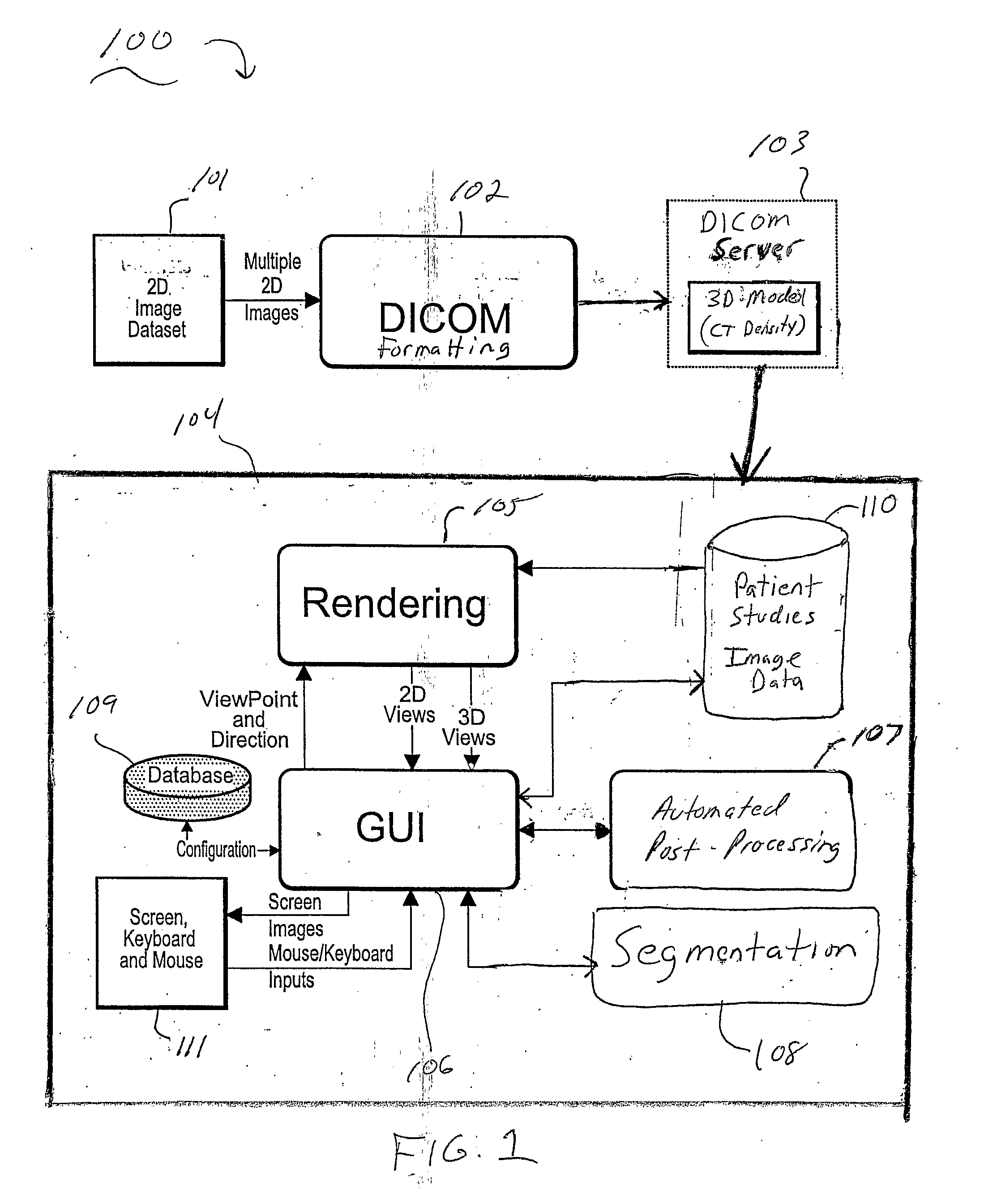

Systems and Methods for Automated Segmentation, Visualization and Analysis of Medical Images

An imaging system for automated segmentation and visualization of medical images (100) includes an image processing module (107) for automatically processing image data using a set of directives (109) to identify a target object in the image data and process the image data according to a specified protocol, a rendering module (105) for automatically generating one or more images of the target object based on one or more of the directives (109) and a digital archive (110) for storing the one or more generated images. The image data may be DICOM-formatted image data (103), wherein the imaging processing module (107) extracts and processes meta-data in DICOM fields of the image data to identify the target object. The image processing module (107) directs a segmentation module (108) to segment the target object using processing parameters specified by one or more of the directives (109).

Owner:VIATRONIX

Transmit fast-path processing on TCP/IP offload network interface device

InactiveUS6965941B2Little and no performance benefitMove quicklyMultiplex system selection arrangementsMultiple digital computer combinationsFast pathProtocol processing

Owner:ALACRITECH

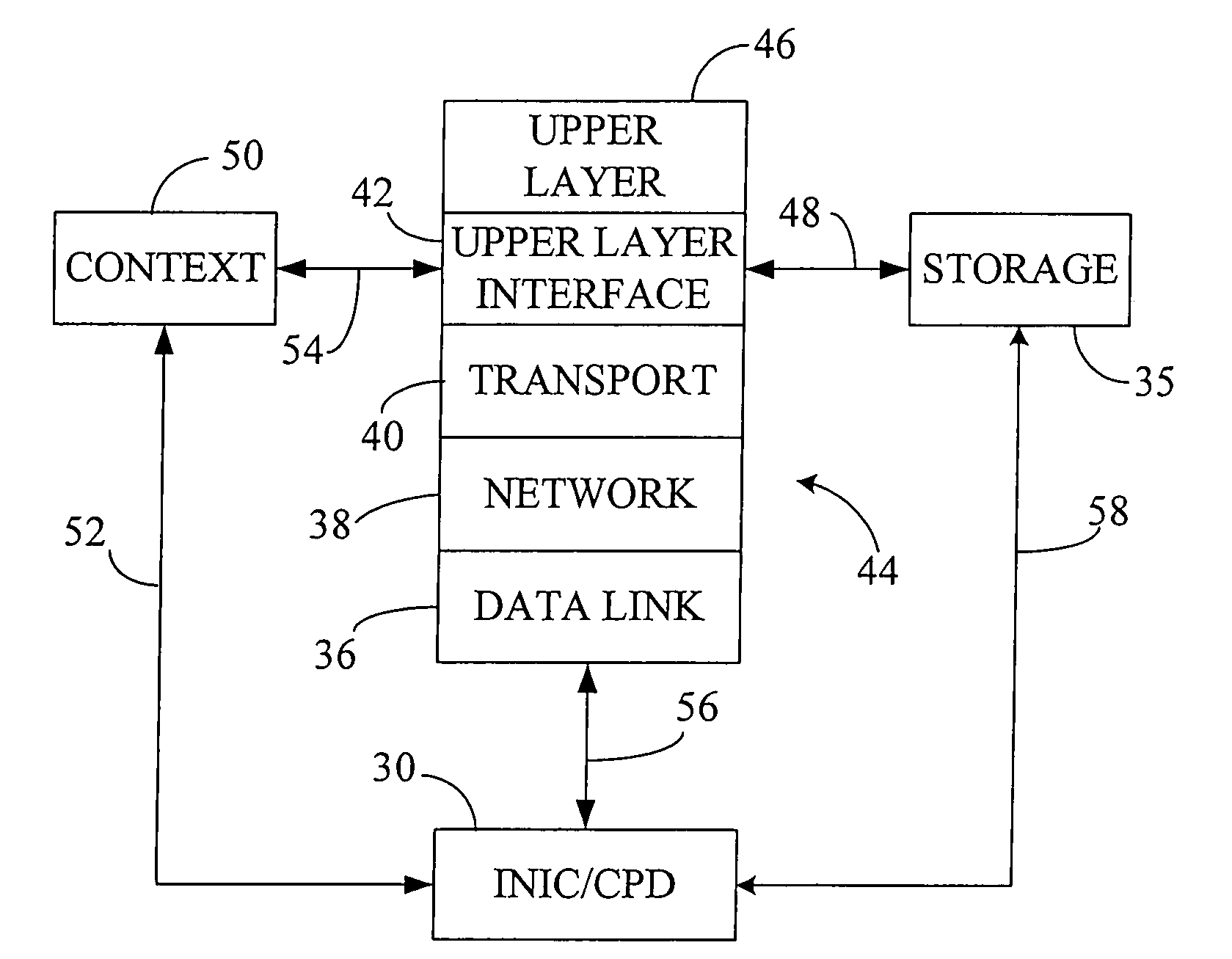

Fast-path apparatus for receiving data corresponding to a TCP connection

ActiveUS7337241B2Little and no performance benefitMove quicklyMultiple digital computer combinationsSecuring communicationFast pathGeneral purpose

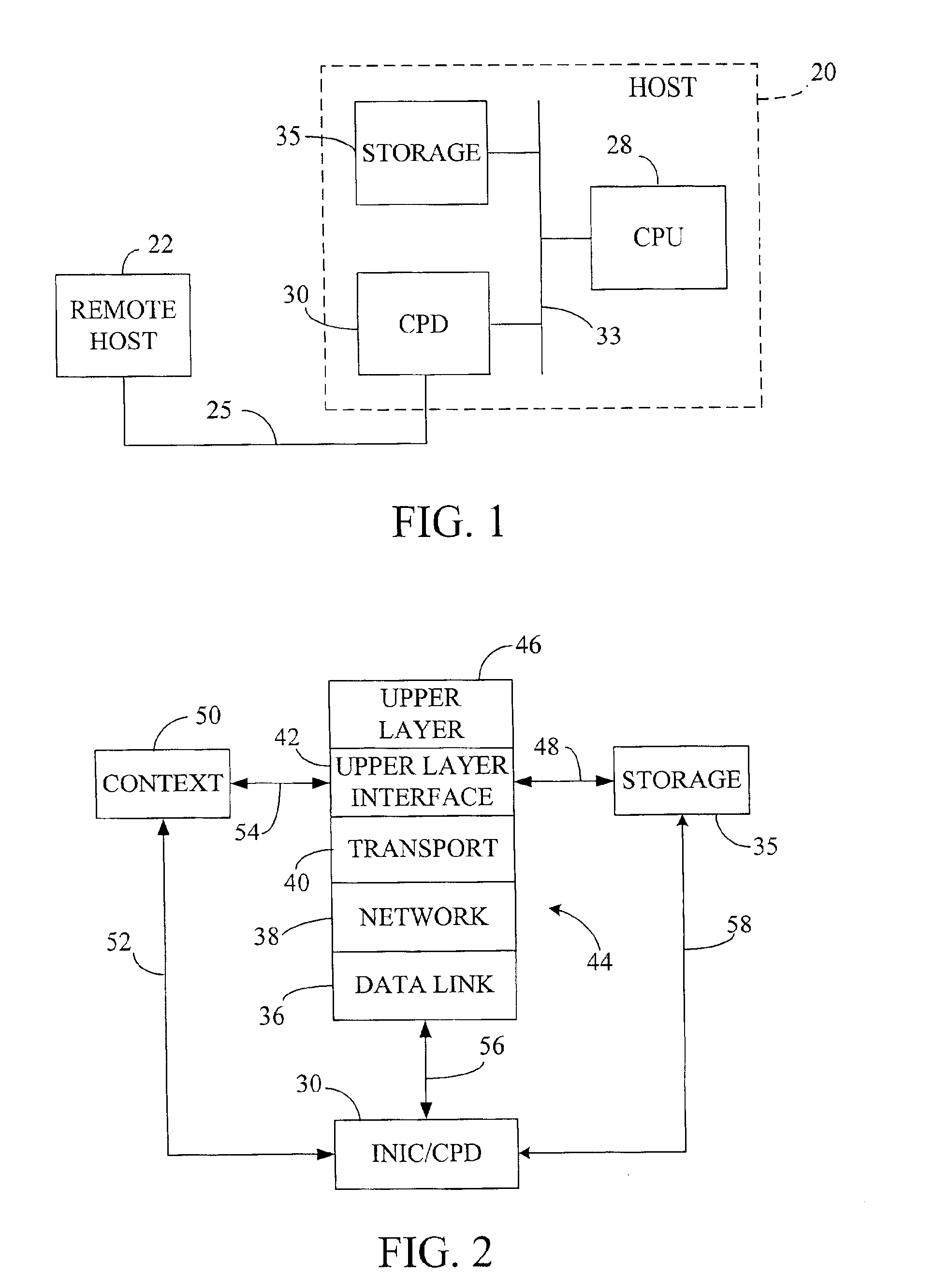

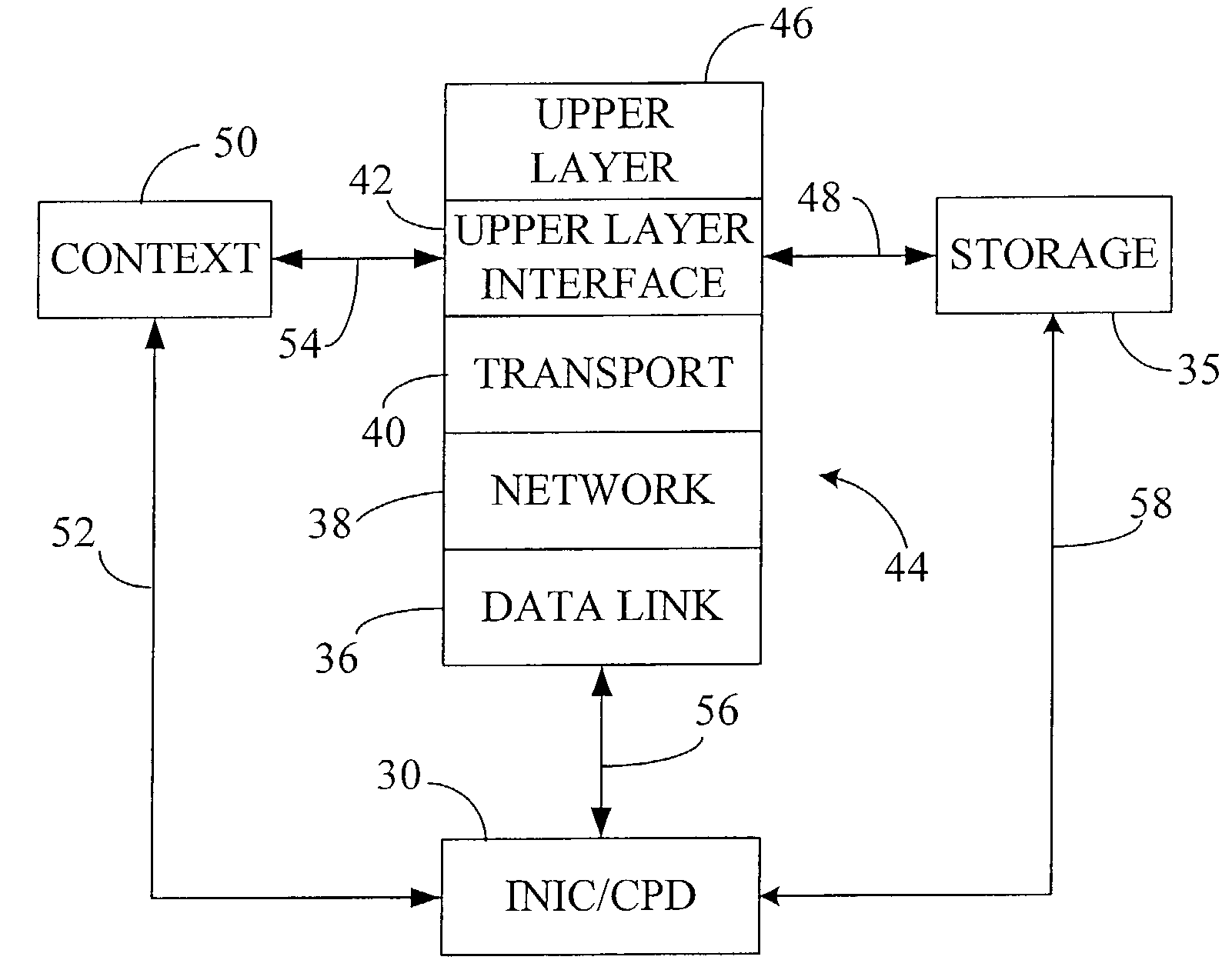

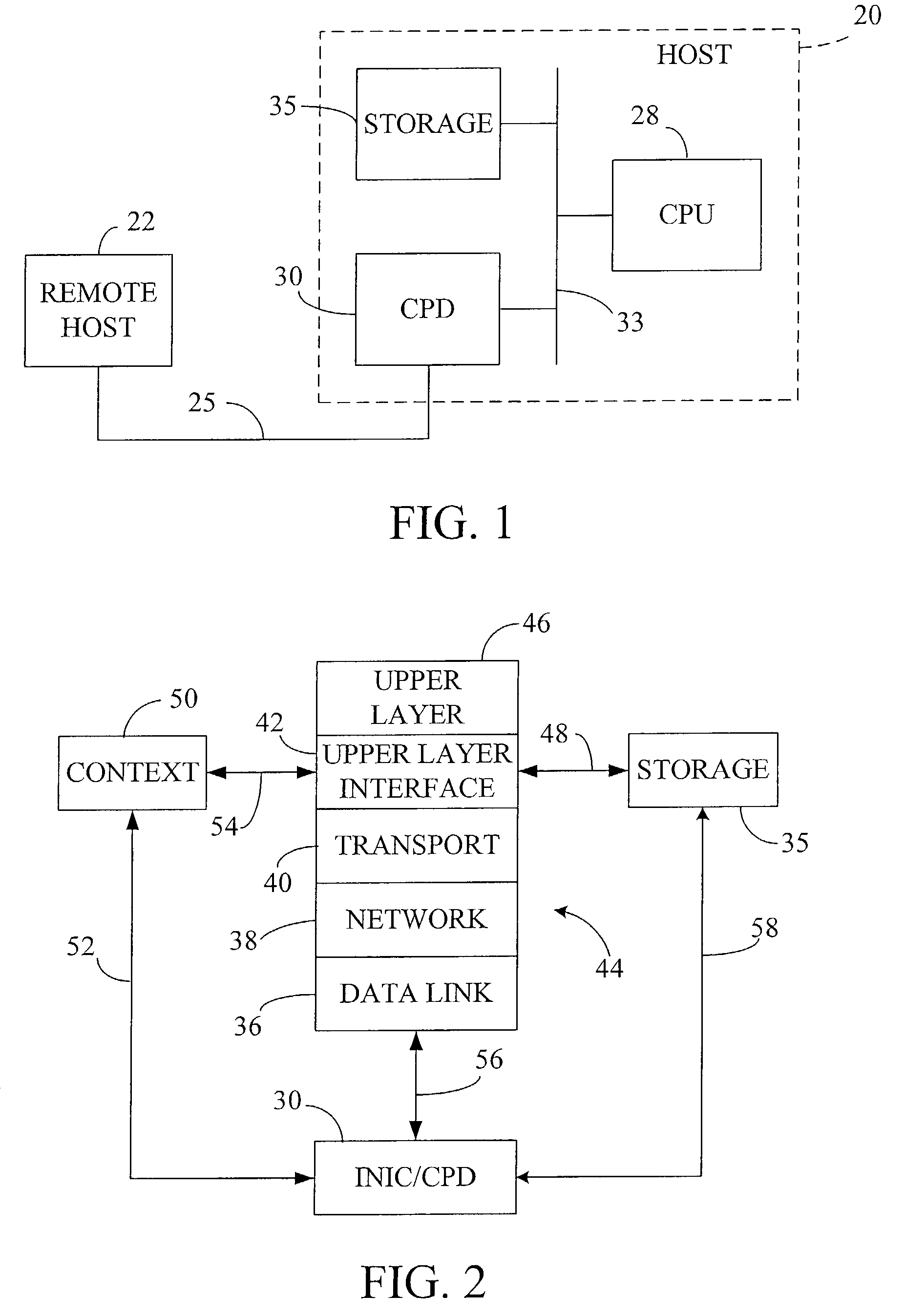

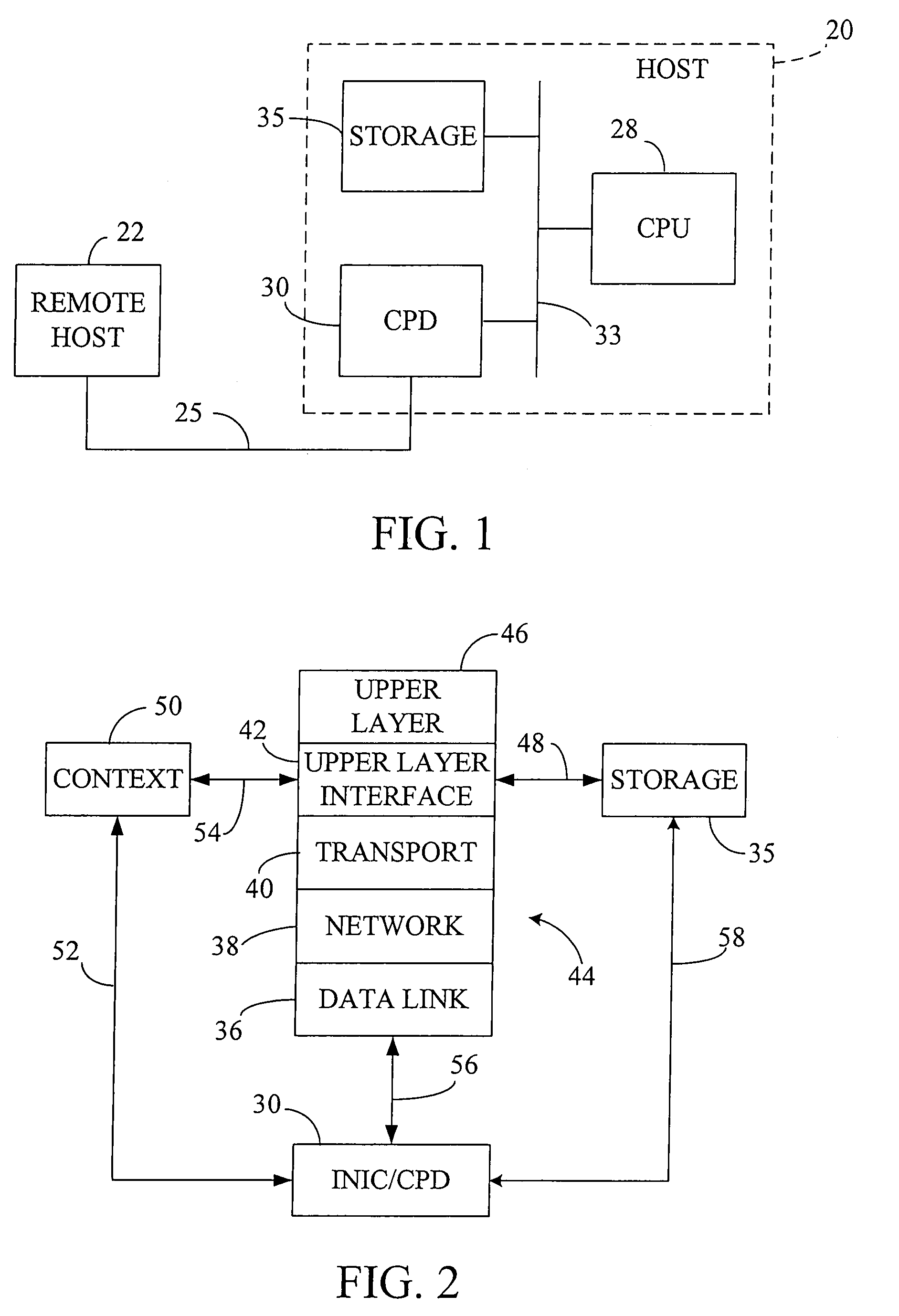

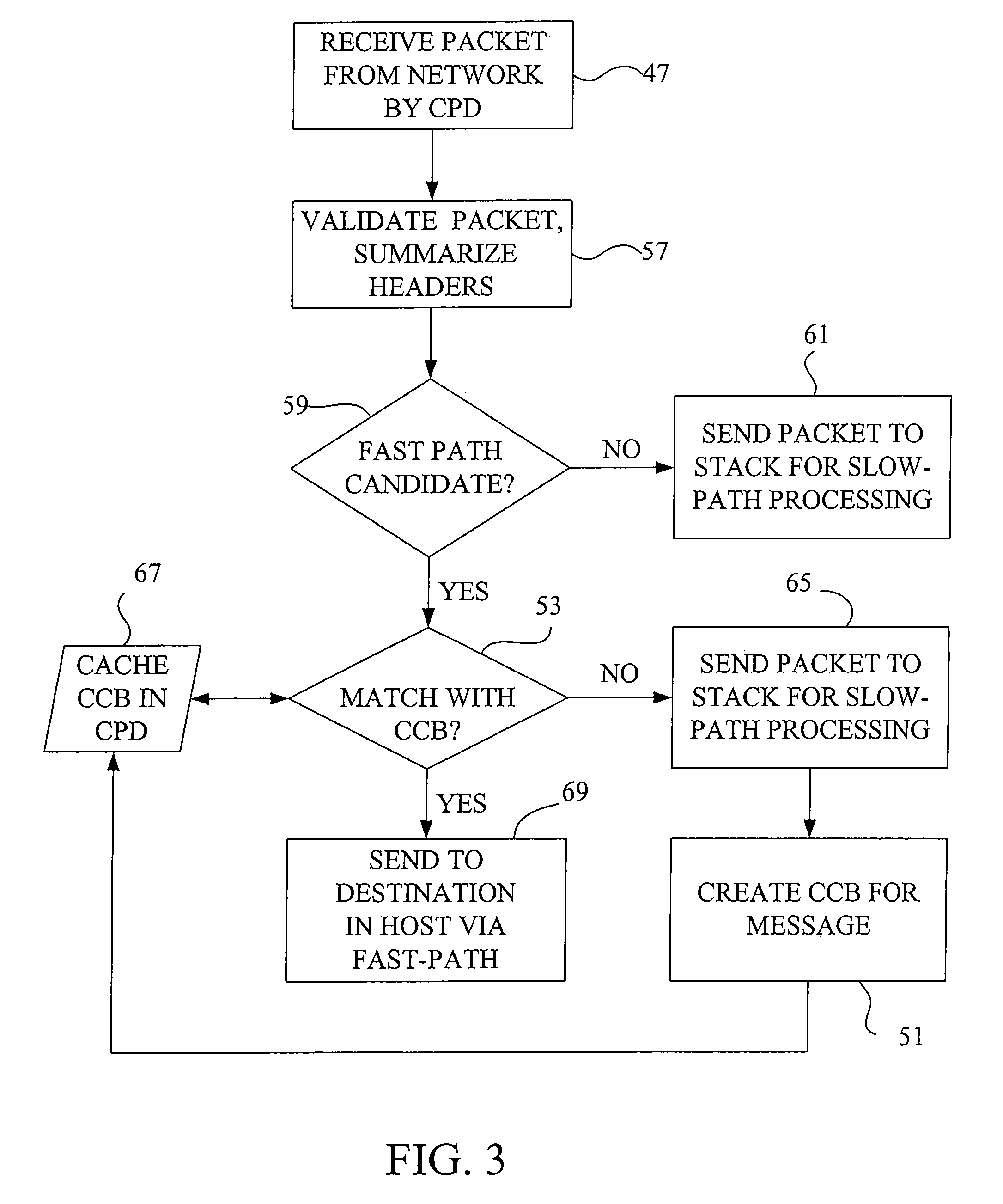

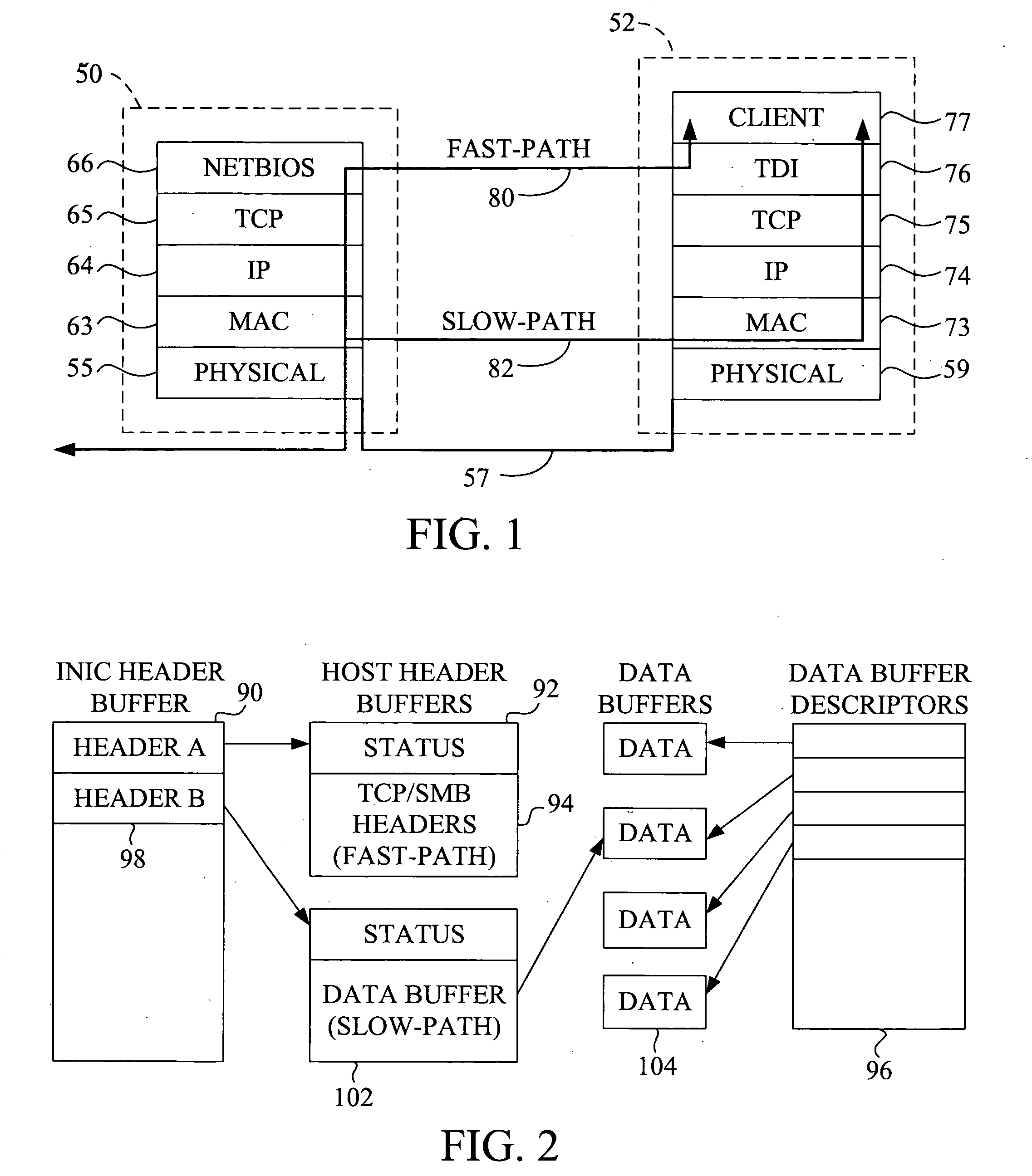

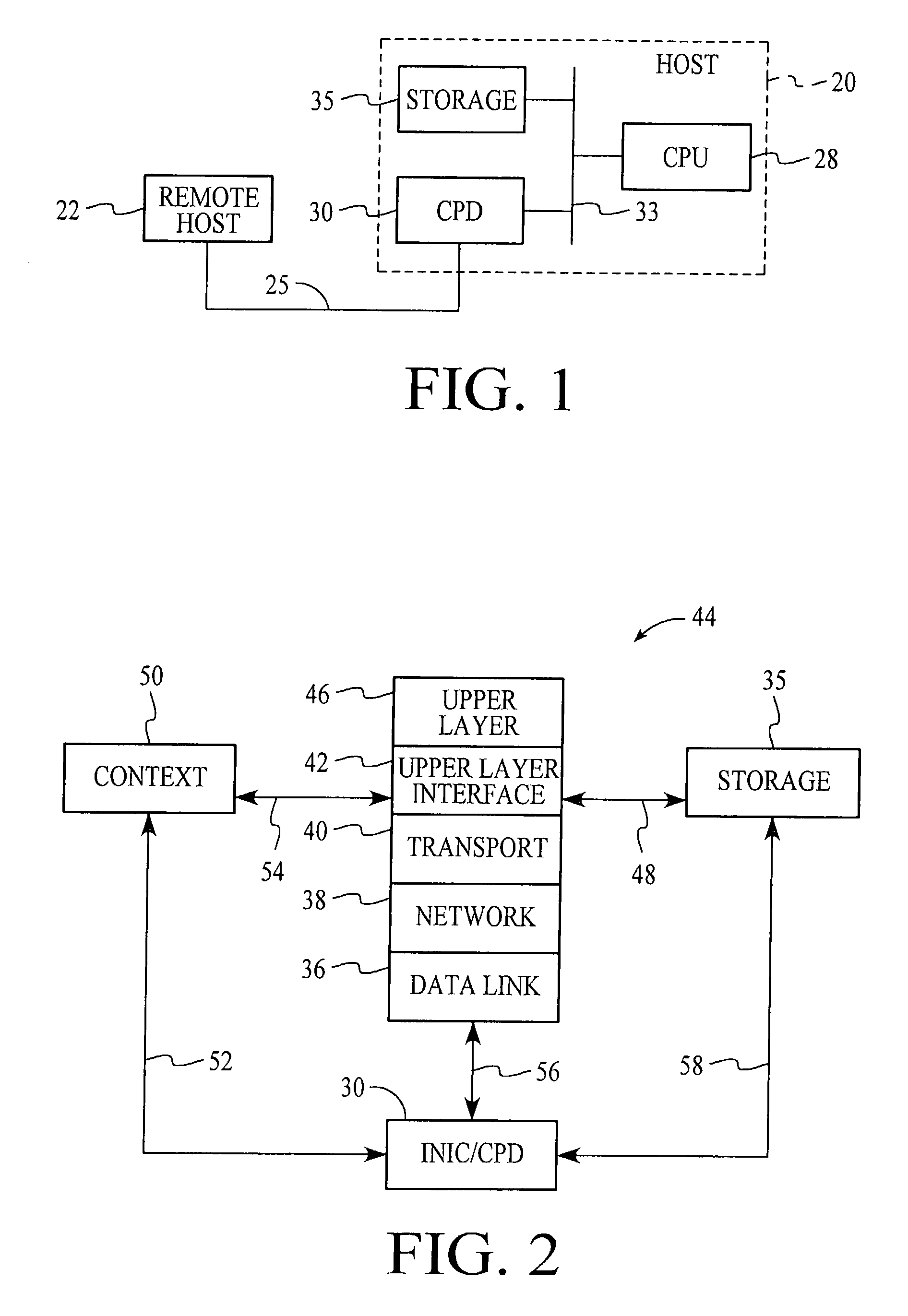

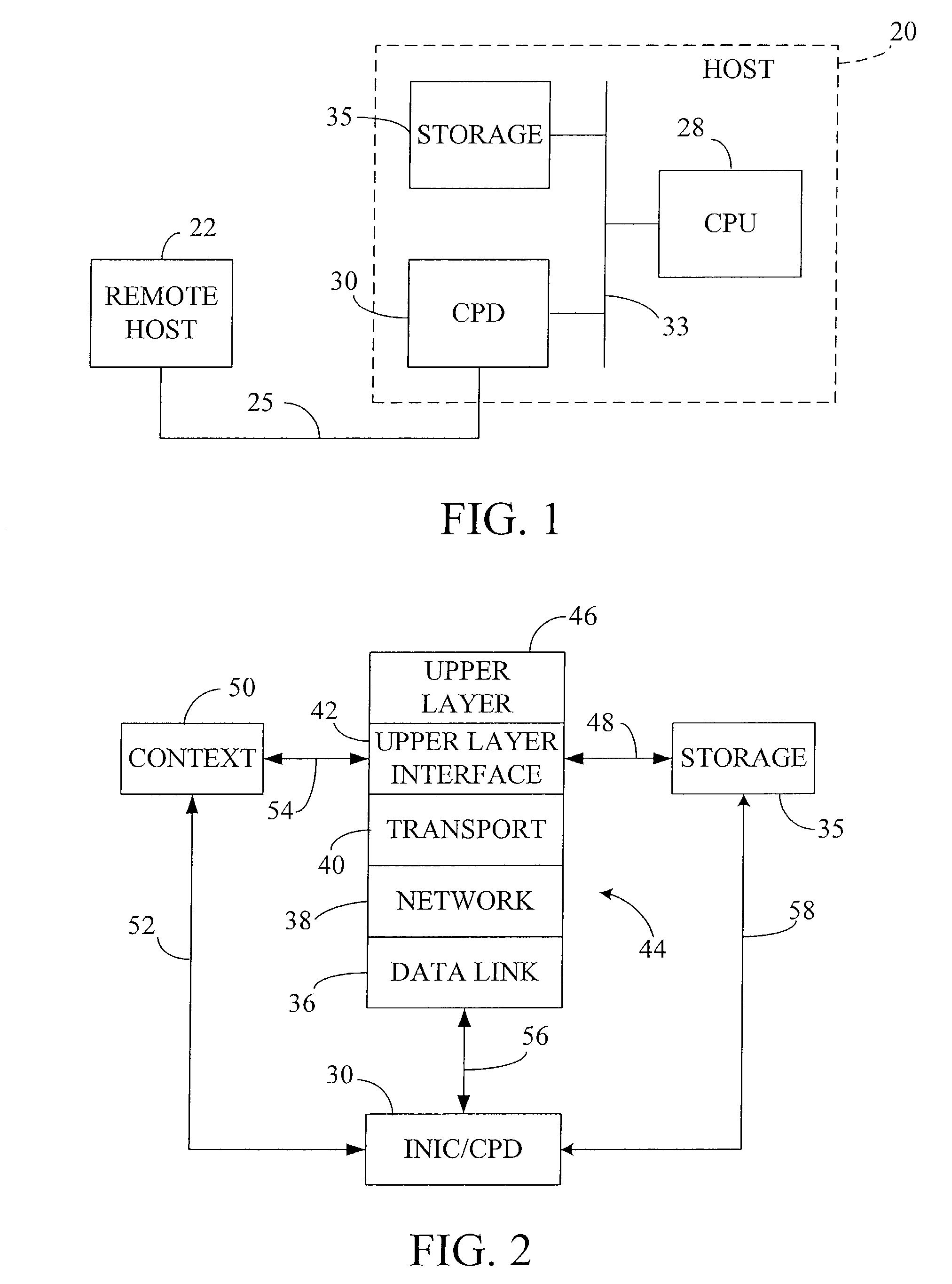

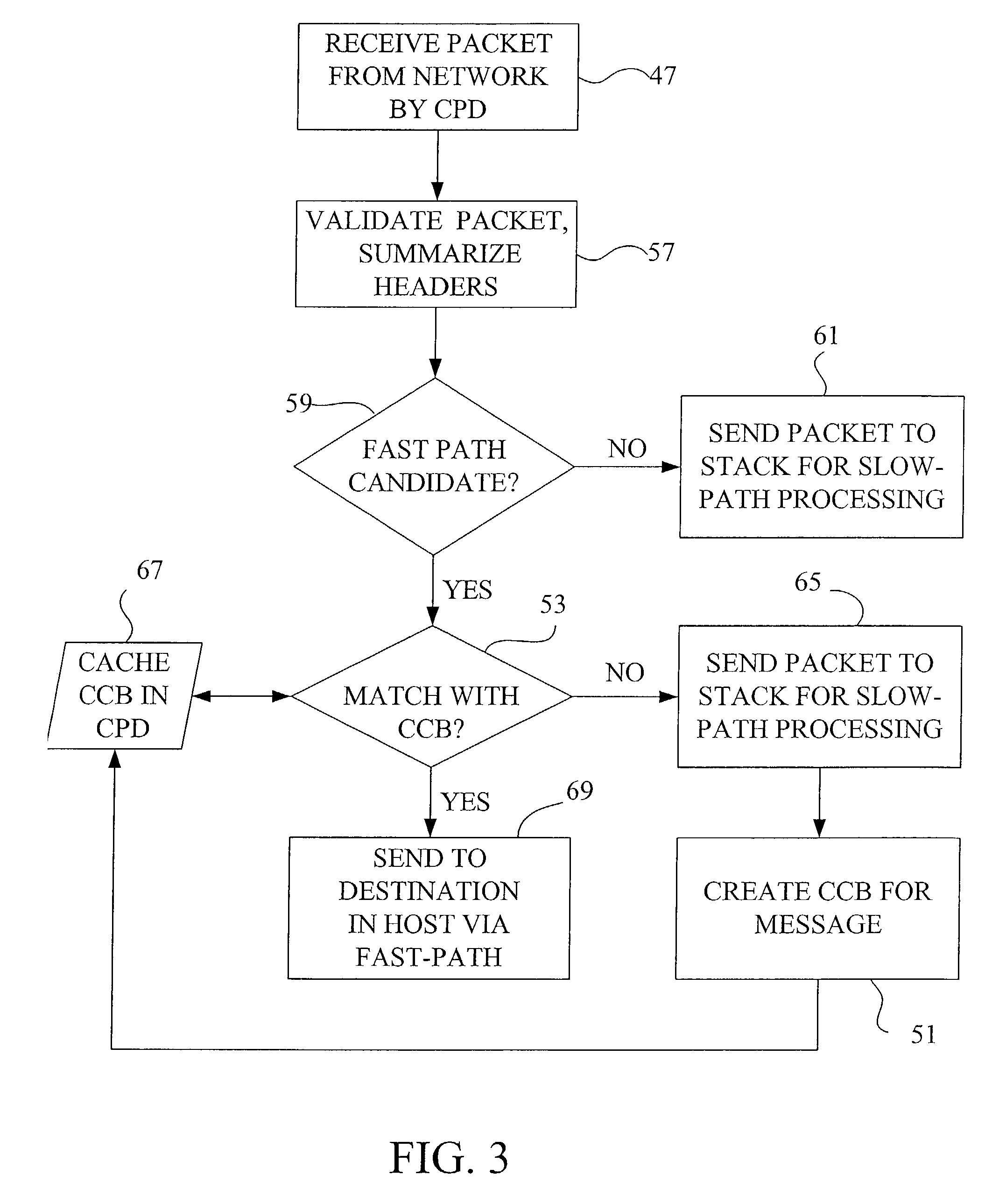

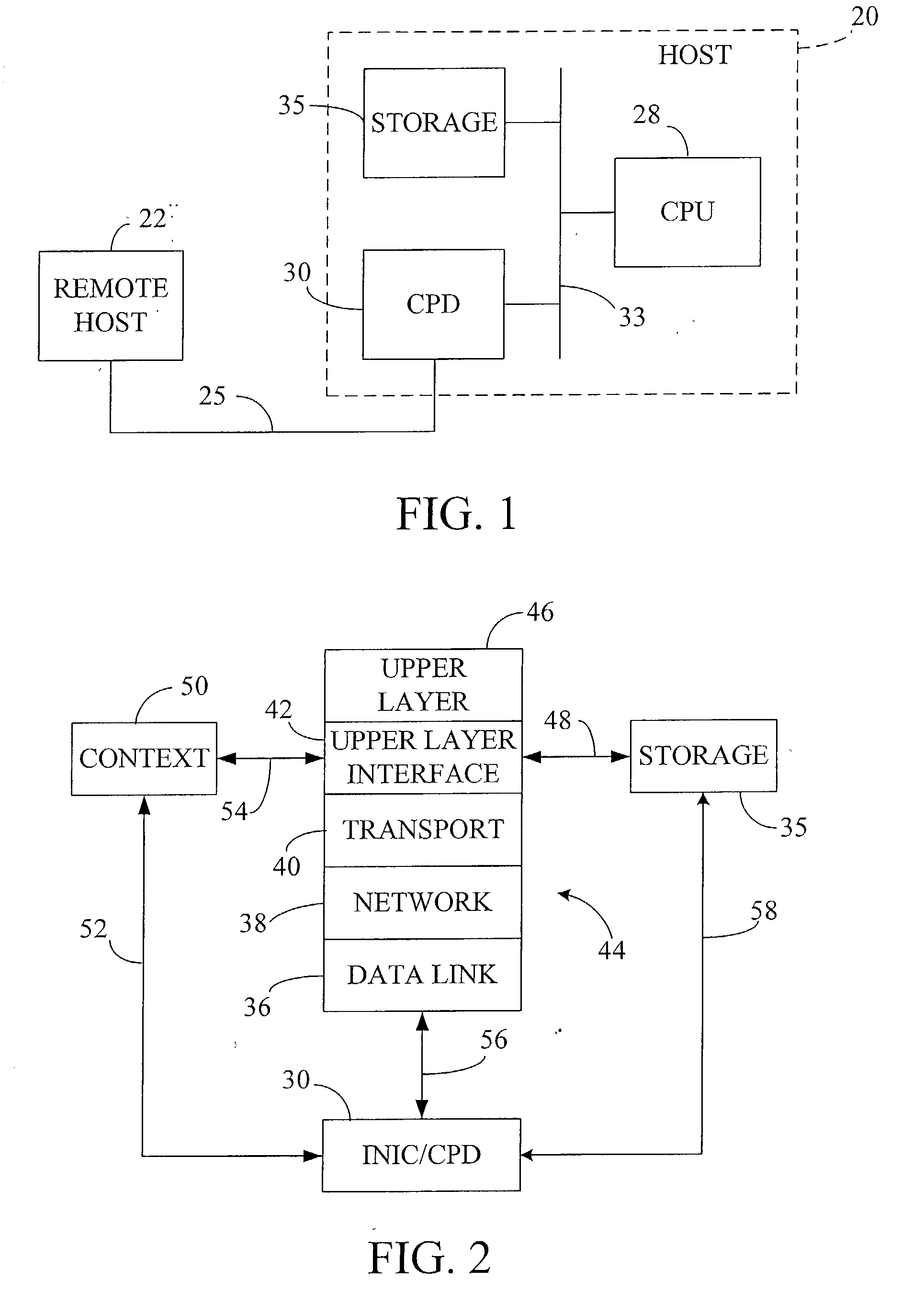

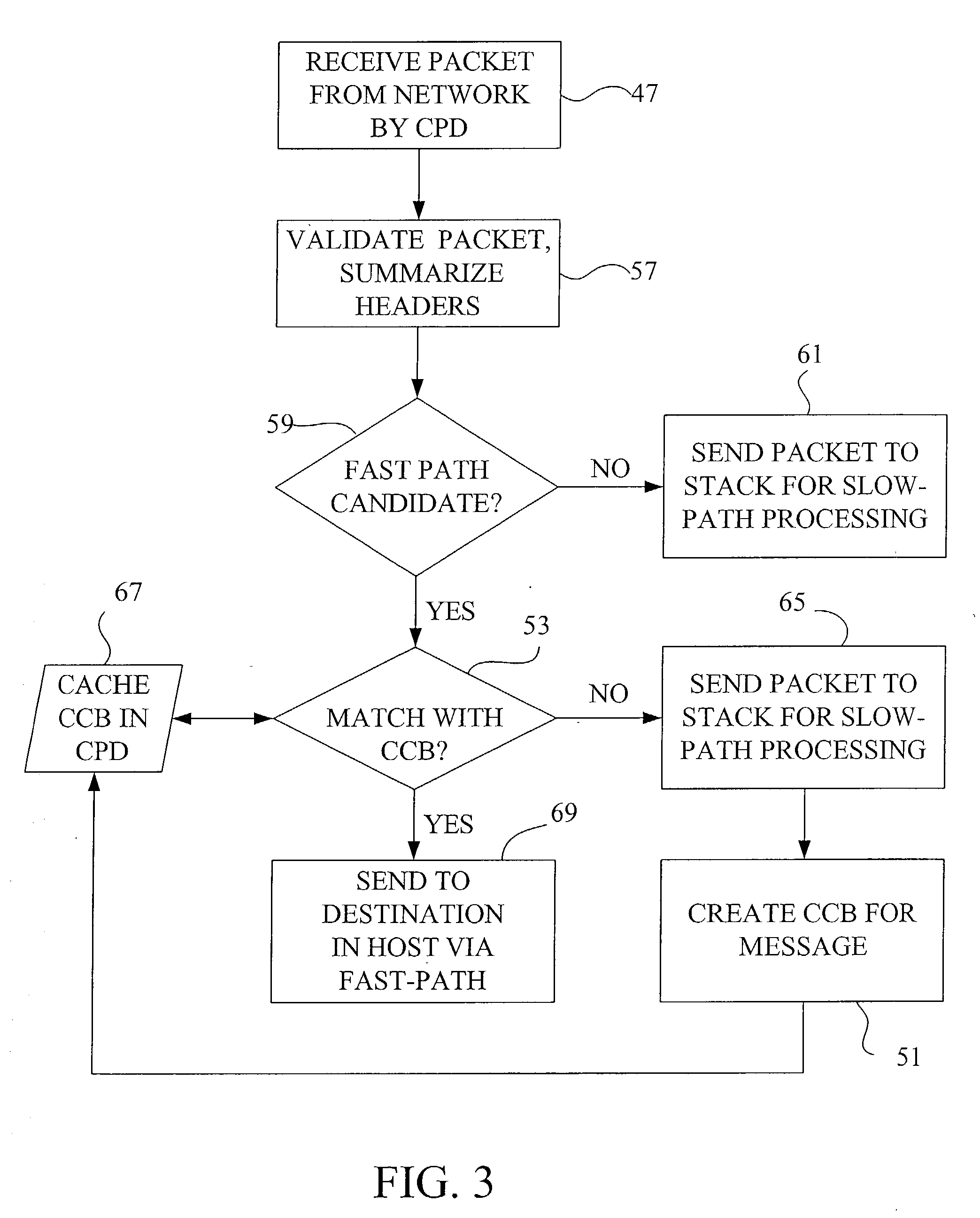

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

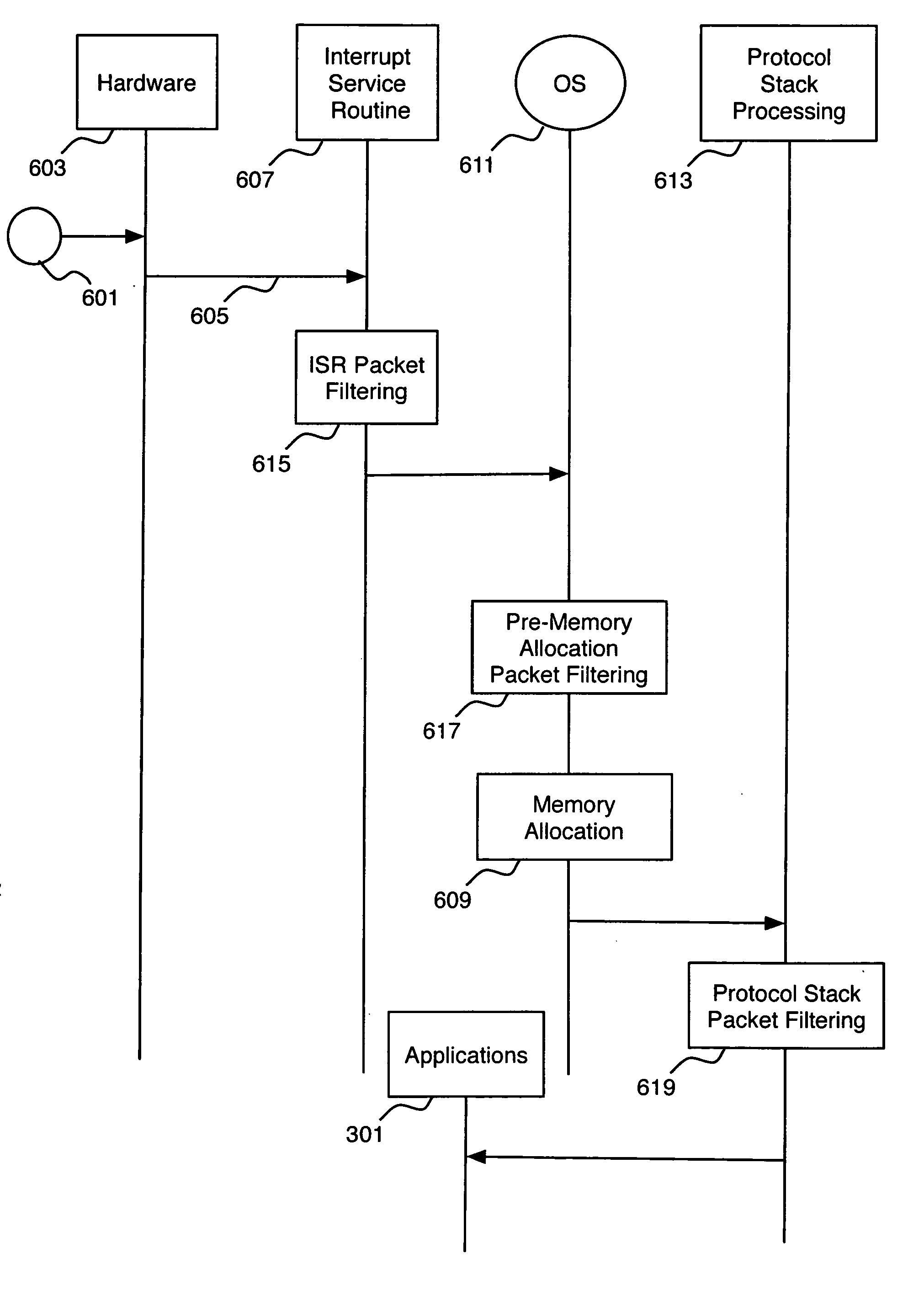

System and method for multi-stage packet filtering on a networked-enabled device

InactiveUS20070083924A1Avoiding allocating memory resourceAvoid resourcesMultiple digital computer combinationsProgram controlData packProtocol processing

A multi-stage packet filtering method and system. The multi-stage packet filtering according to the invention applies a set of filtering rules early in the processing of incoming communications packets by filtering incoming data packets using the filtering rules in a plurality of stages wherein the first stage is triggered by the receipt of a data packet by the device. Filtering rules that cannot be applied in the first stage may be deferred to a pre-memory allocation stage. Thus, preferable leaving only rules that must be executed in conjunction with protocol processing to be filtered at a filtering stage executed in a protocol processing filtering stage.

Owner:LU HONGQIAN KAREN

Fast-path apparatus for transmitting data corresponding to a TCP connection

InactiveUS7673072B2Little and no performance benefitMove quicklyError preventionFrequency-division multiplex detailsGeneral purposeFast path

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

Method and apparatus for data re-assembly with a high performance network interface

InactiveUS20050204058A1Avoid header processing and data copying and checksummingCost-effectiveMultiple digital computer combinationsData switching networksFast pathGeneral purpose

An intelligent network interface card (INIC) or communication processing device (CPD) works with a host computer for data communication. The device provides a fast-path that avoids protocol processing for most messages, greatly accelerating data transfer and offloading time-intensive processing tasks from the host CPU. The host retains a fallback processing capability for messages that do not fit fast-path criteria, with the device providing assistance such as validation even for slow-path messages, and messages being selected for either fast-path or slow-path processing. A context for a connection is defined that allows the device to move data, free of headers, directly to or from a destination or source in the host. The context can be passed back to the host for message processing by the host. The device contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors devoted to transmit, receive and utility processing, providing full duplex communication for four Fast Ethernet nodes.

Owner:ALACRITECH

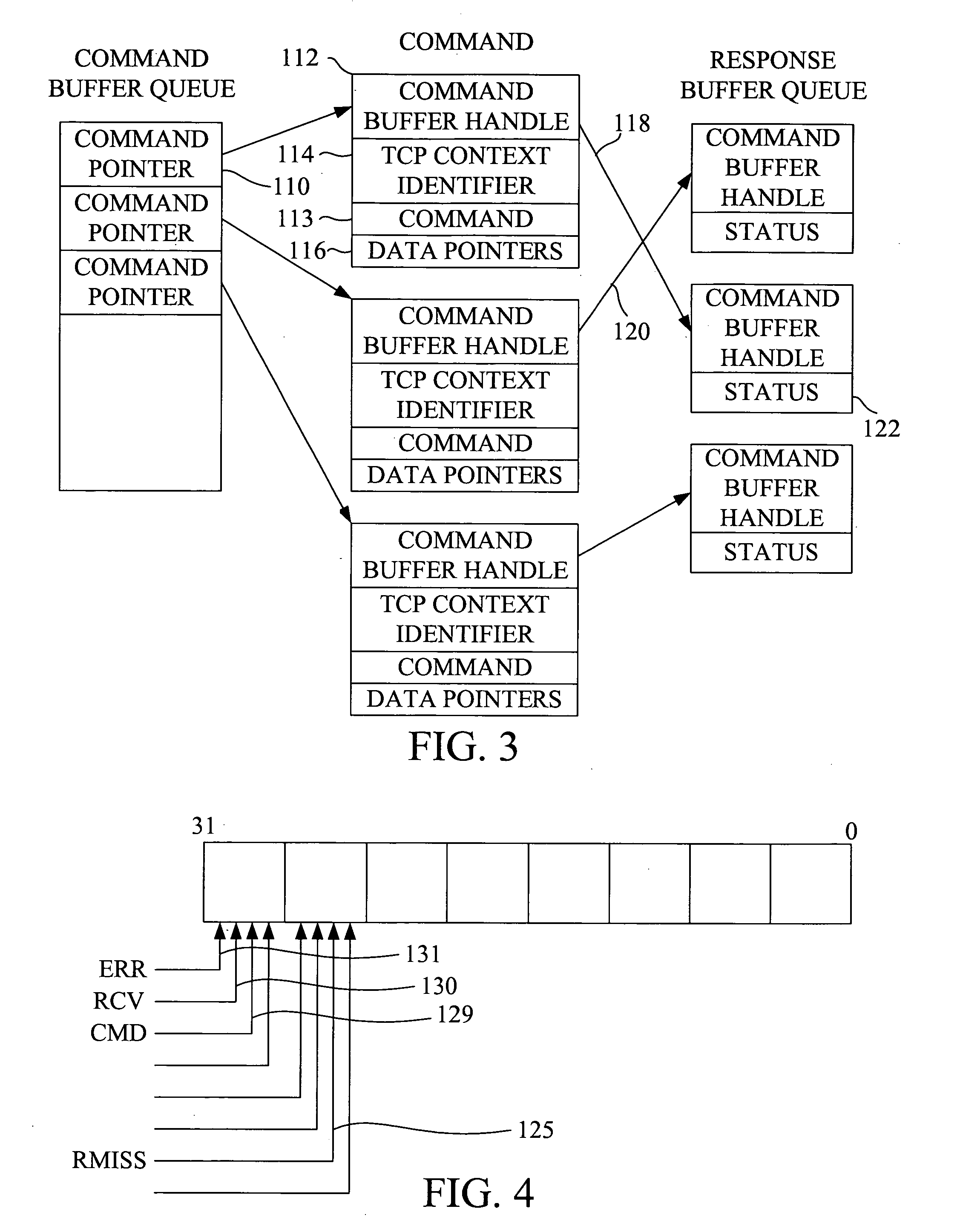

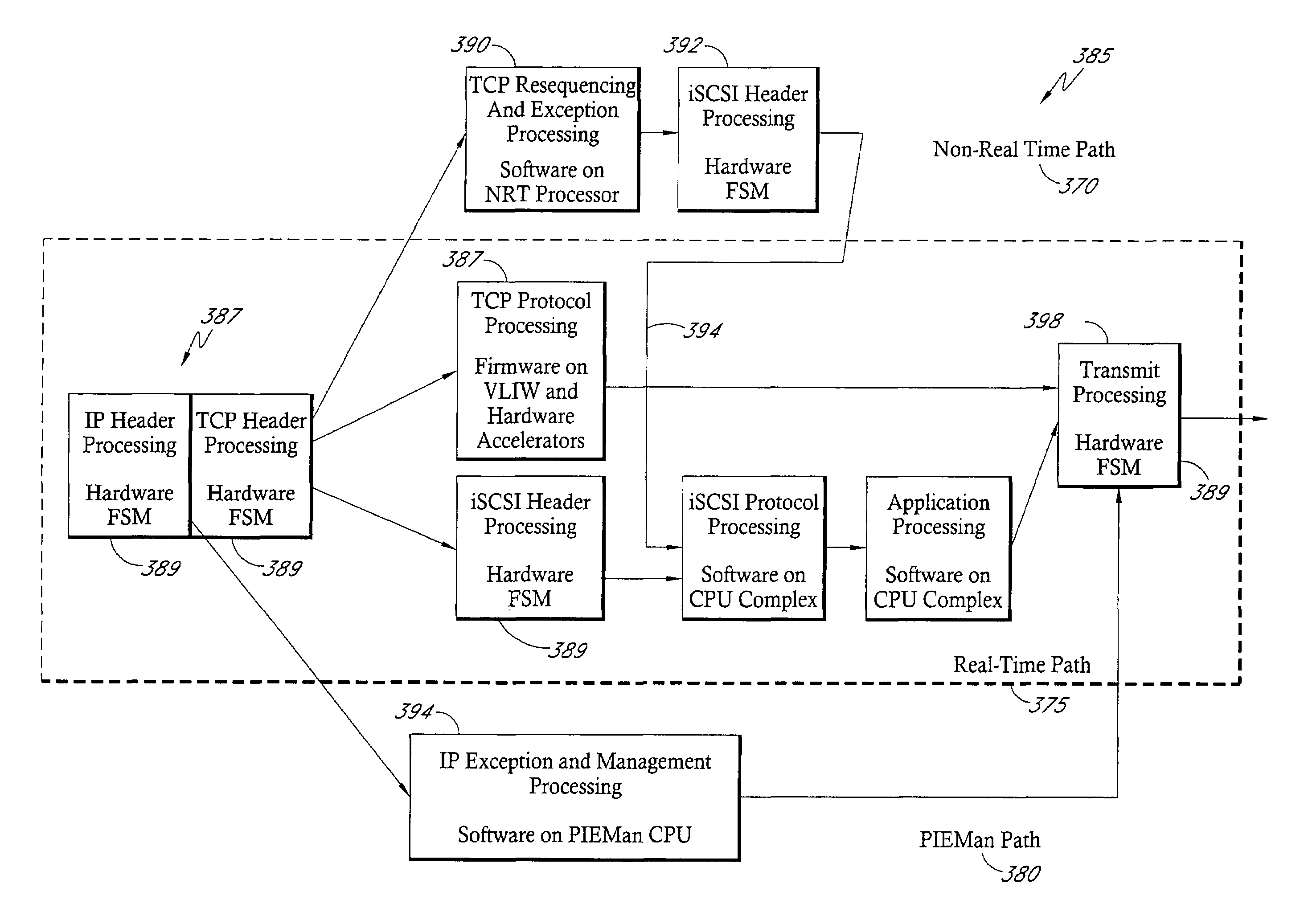

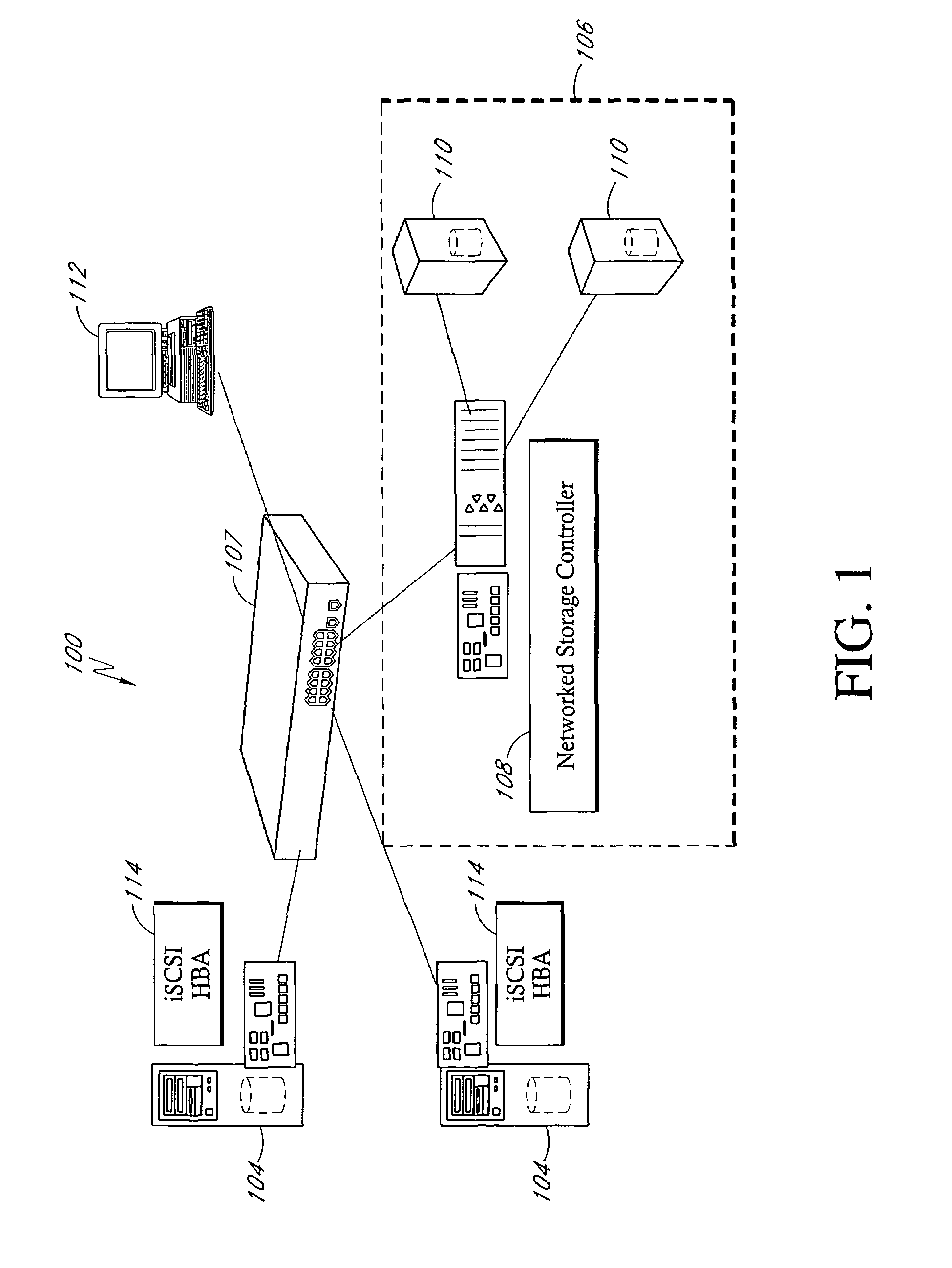

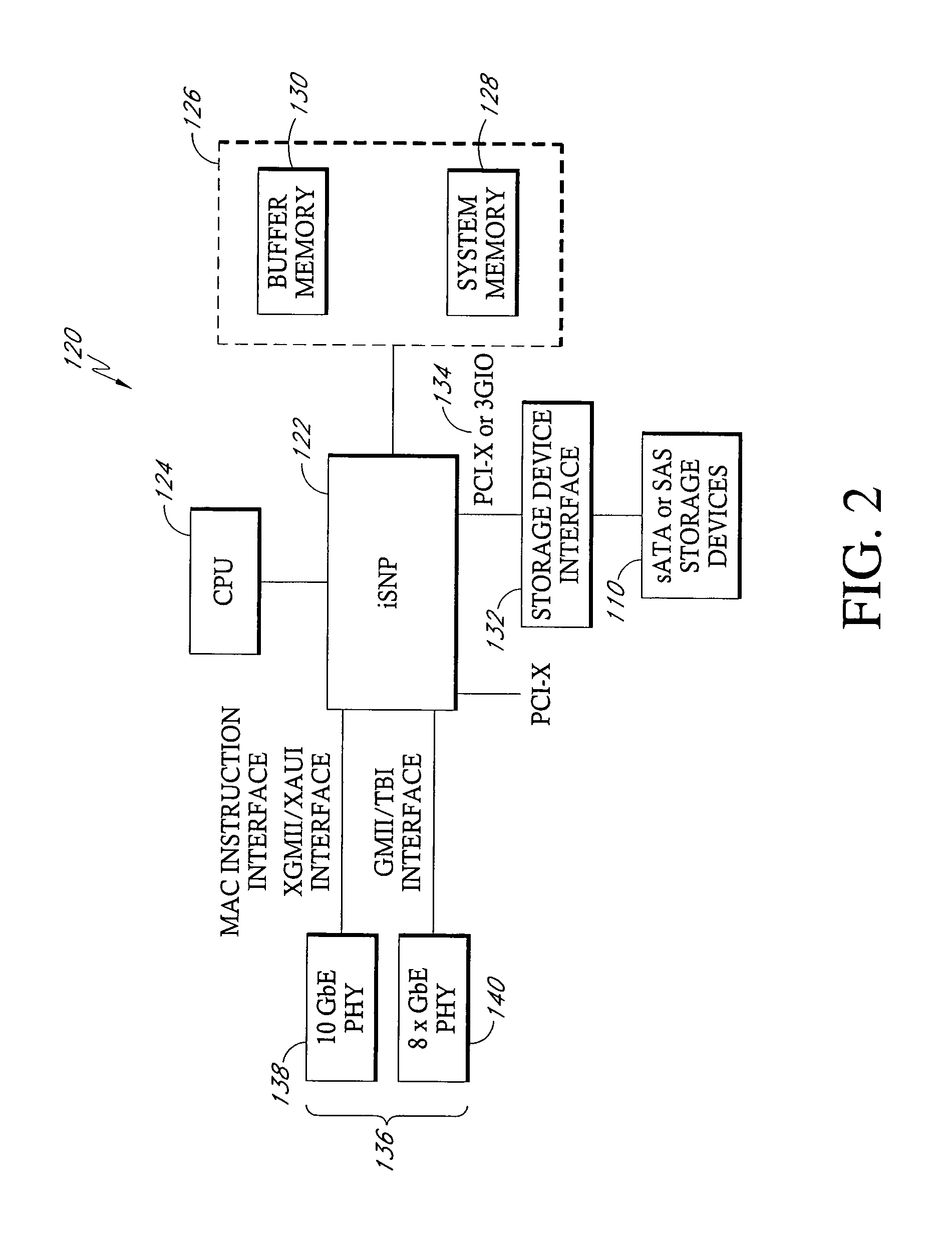

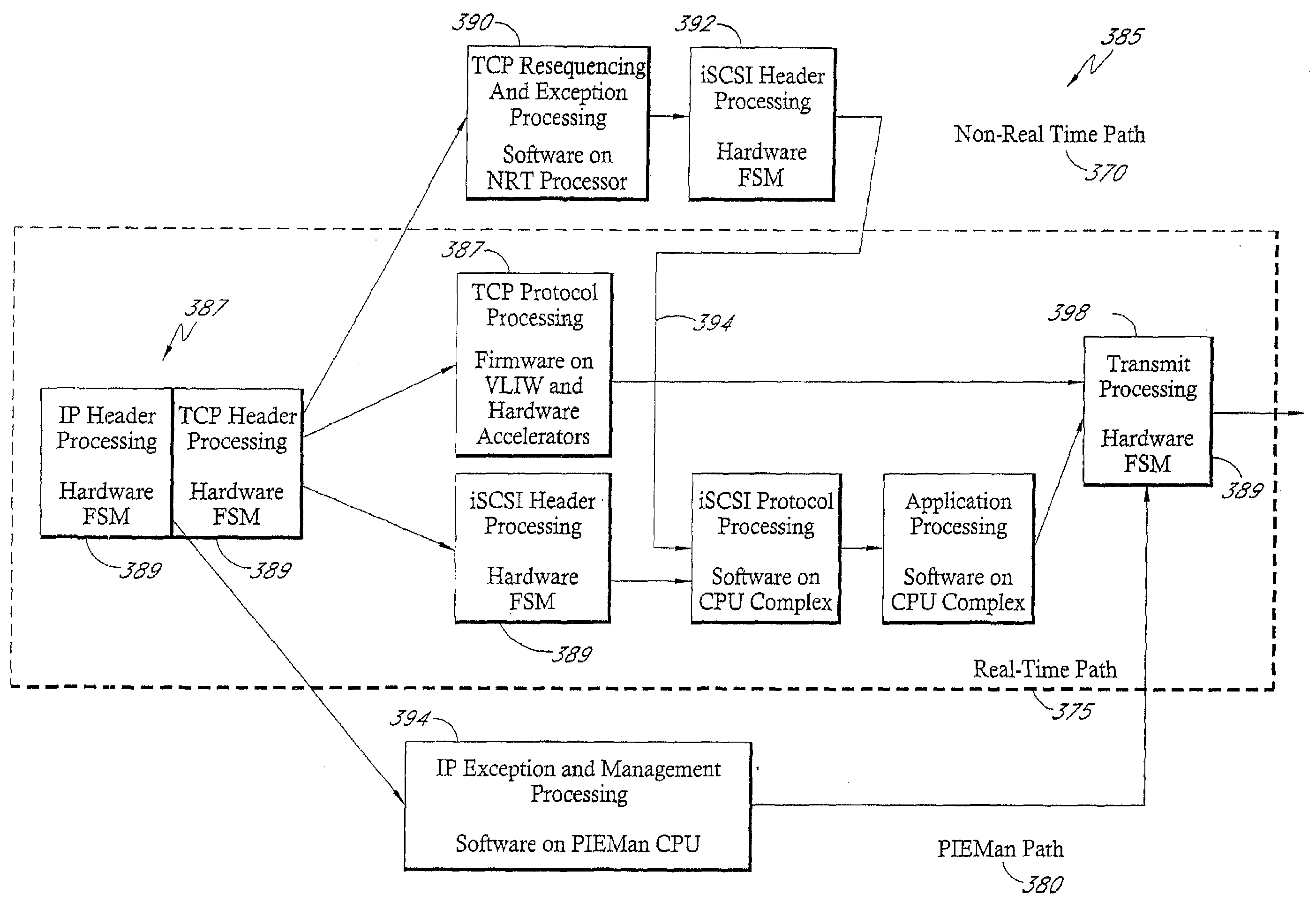

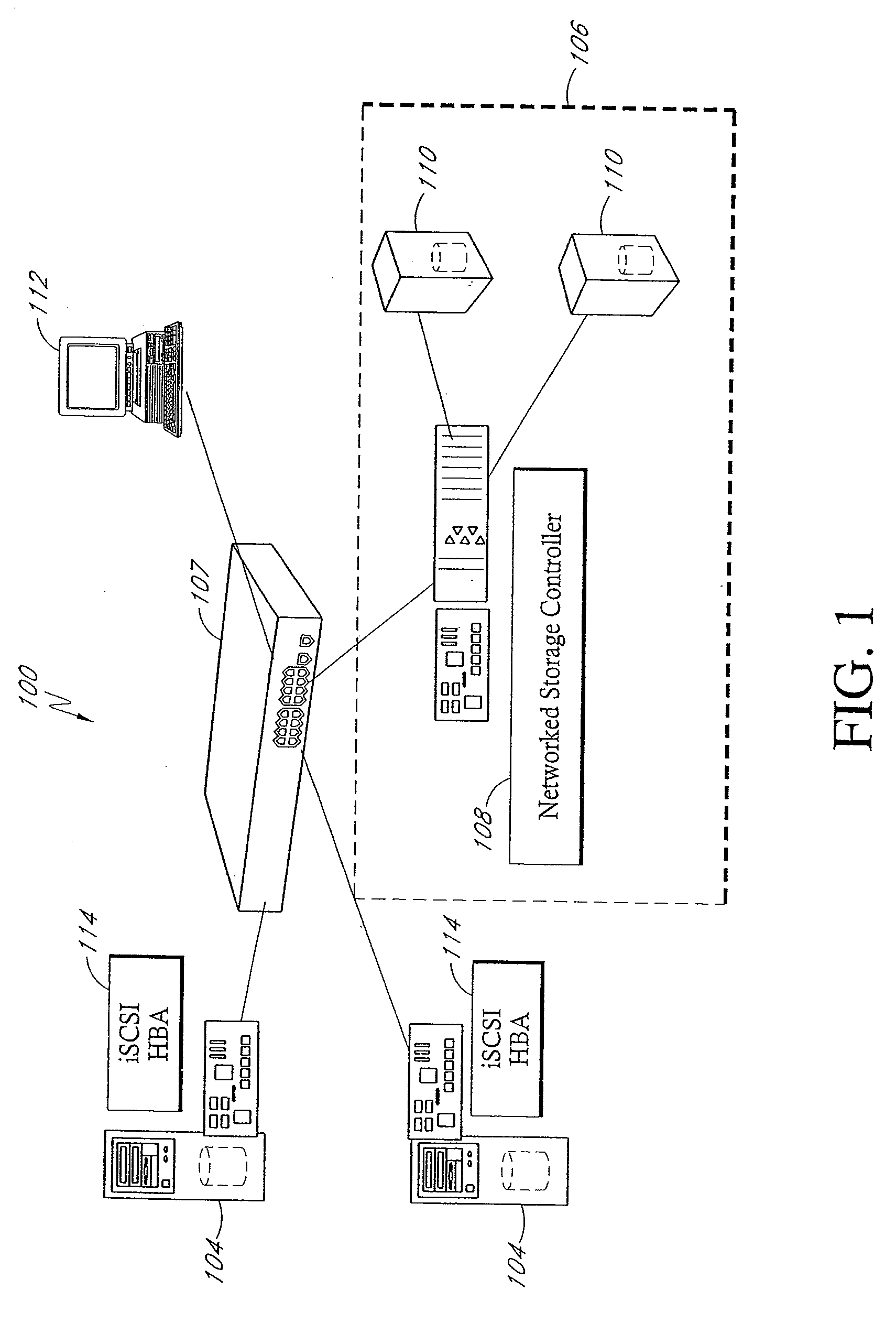

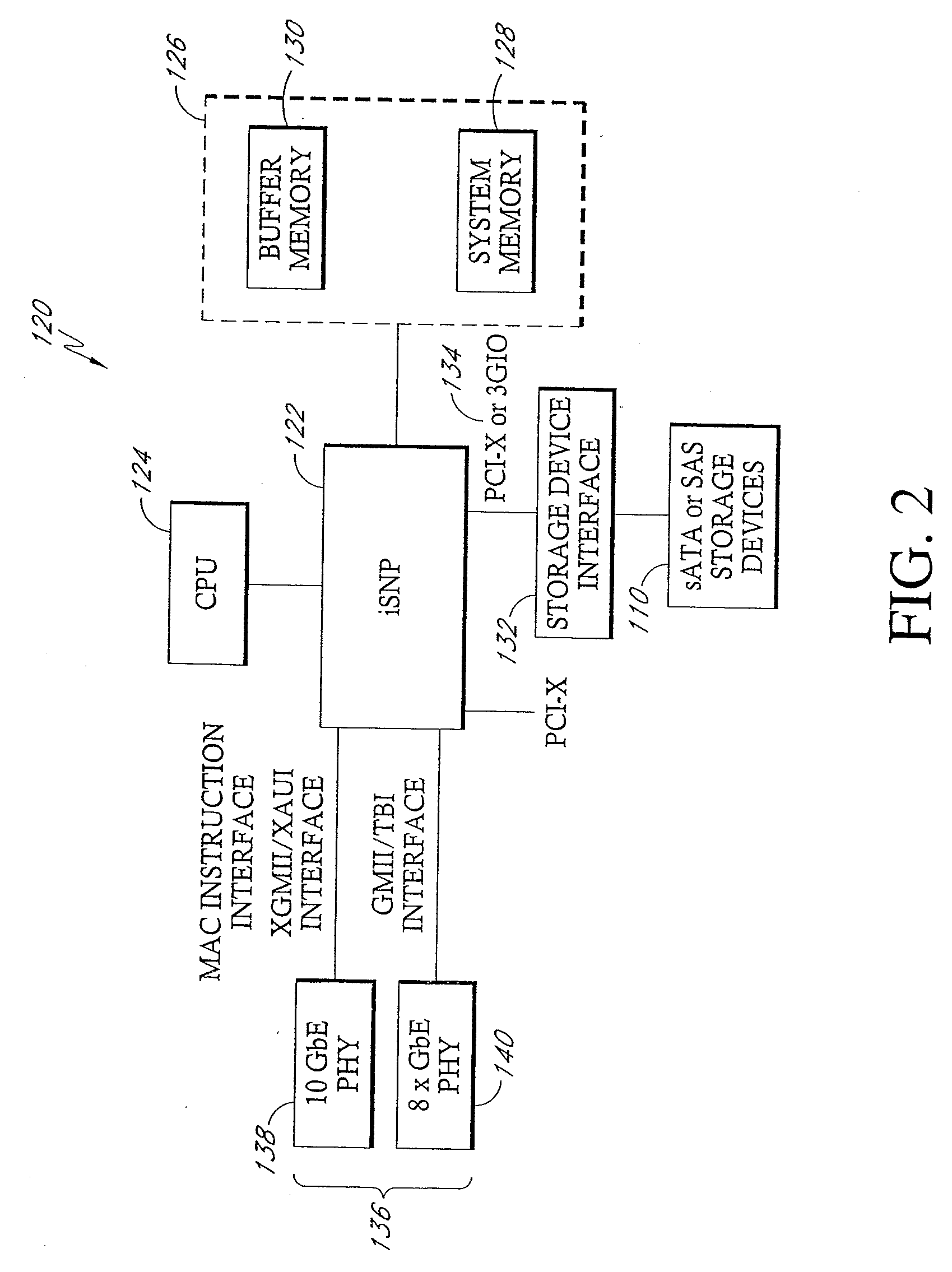

System and methods for high rate hardware-accelerated network protocol processing

InactiveUS7389462B1Improve network performanceImprove storage performanceError prevention/detection by using return channelTransmission systemsTraffic capacityHigh rate

Disclosed is a system and methods for accelerating network protocol processing for devices configured to process network traffic at relatively high data rates. The system incorporates a hardware-accelerated protocol processing module that handles steady state network traffic and a software-based processing module that handles infrequent and exception cases in network traffic processing.

Owner:PROMISE TECHNOLOGY

TCP/IP offload network interface device

InactiveUS7174393B2Little and no performance benefitMove quicklyMultiple digital computer combinationsData switching networksGeneral purposeFast path

A system for protocol processing in a computer network has a TCP / IP Offload Network Interface Device (TONID) associated with a host computer. The TONID provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The TONID also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the TONID to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the TONID as a communication control block (CCB) that can be passed back to the host for message processing by the host. The TONID contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

Fast-path apparatus for receiving data corresponding to a TCP connection

InactiveUS7191241B2Little and no performance benefitMove quicklyMultiple digital computer combinationsTransmissionFast pathGeneral purpose

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

Fast-path apparatus for receiving data corresponding to a TCP connection

ActiveUS20040064578A1Negligibly effectMove quicklyMultiple digital computer combinationsSecuring communicationGeneral purposeFast path

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

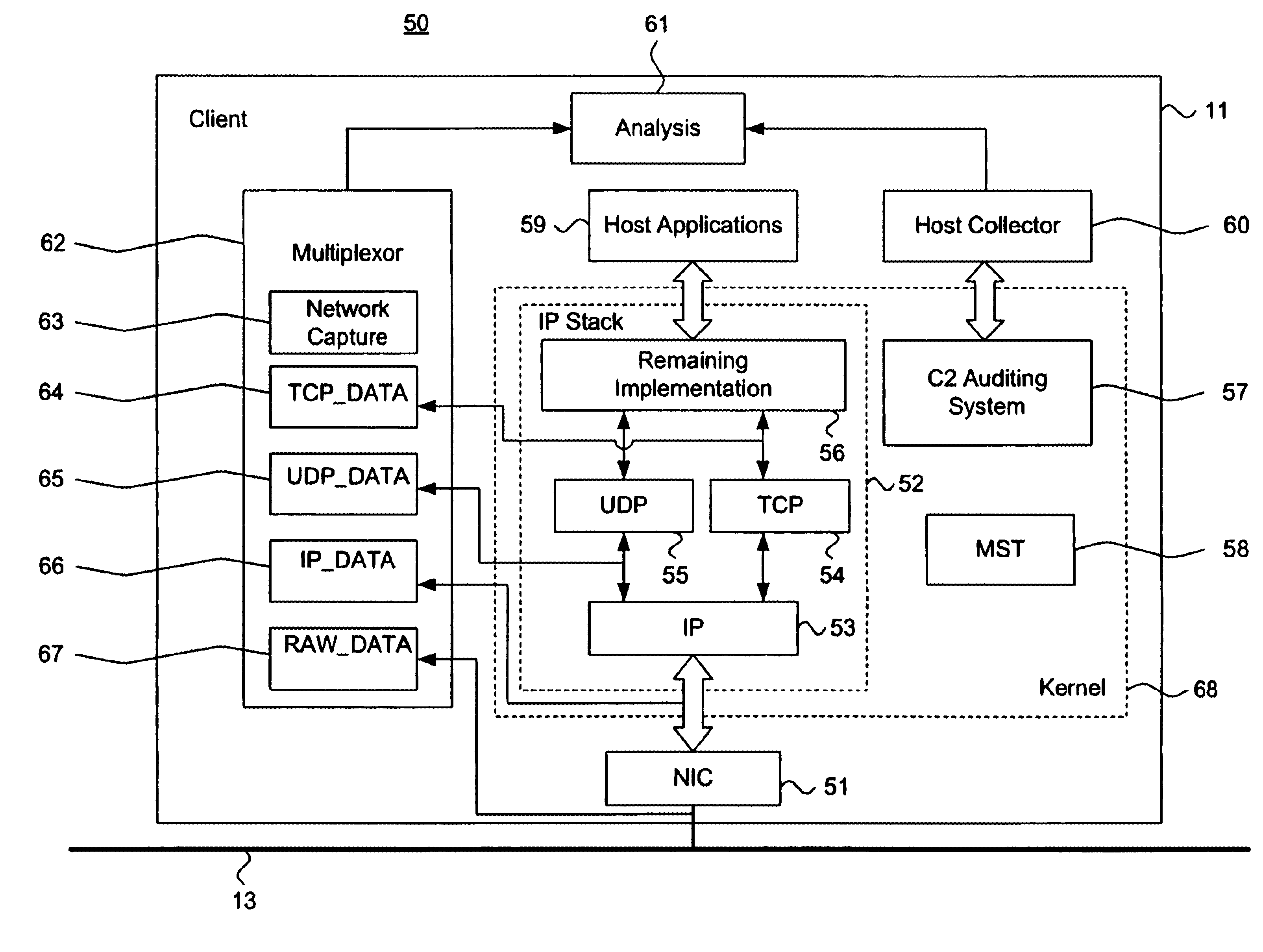

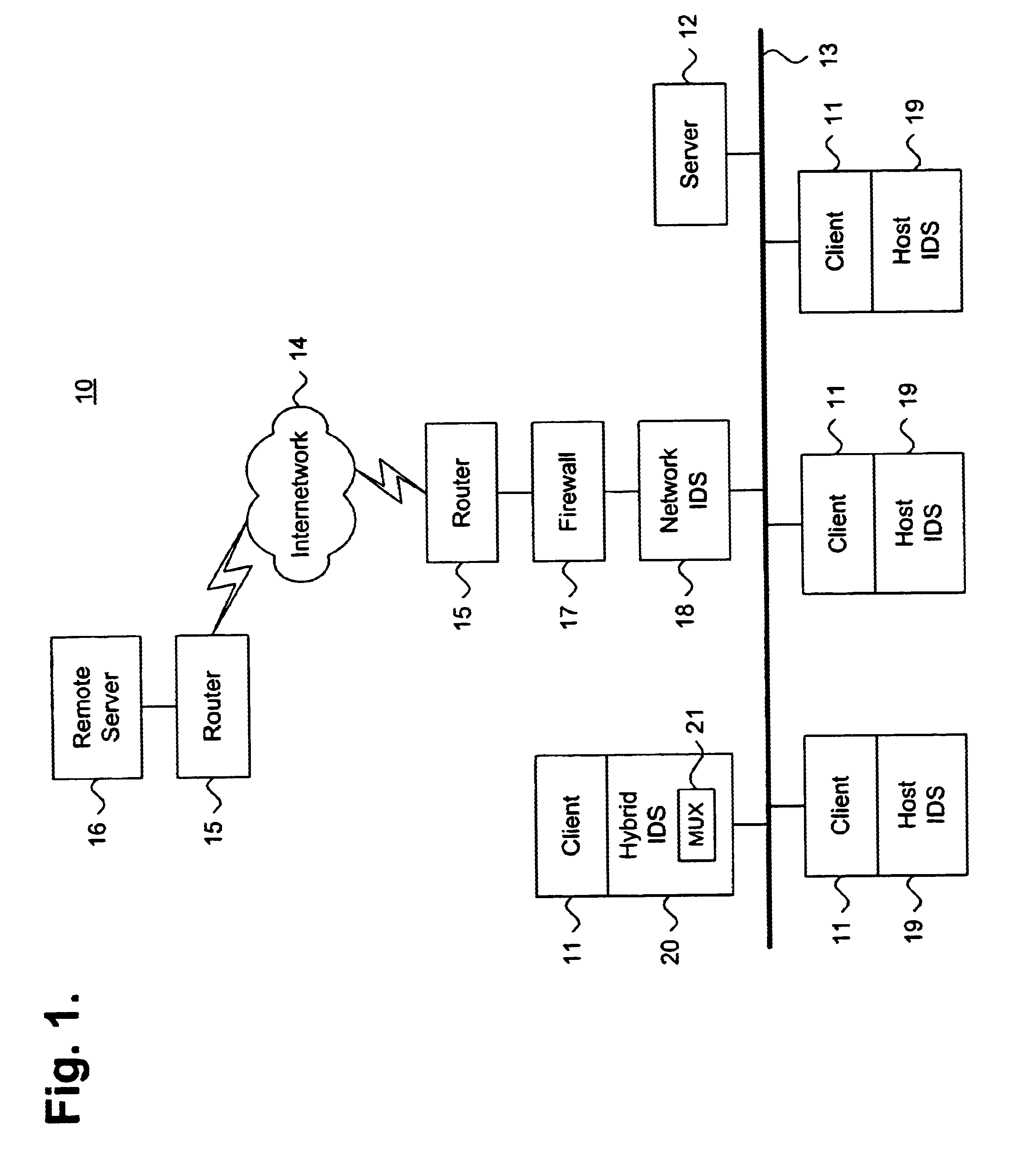

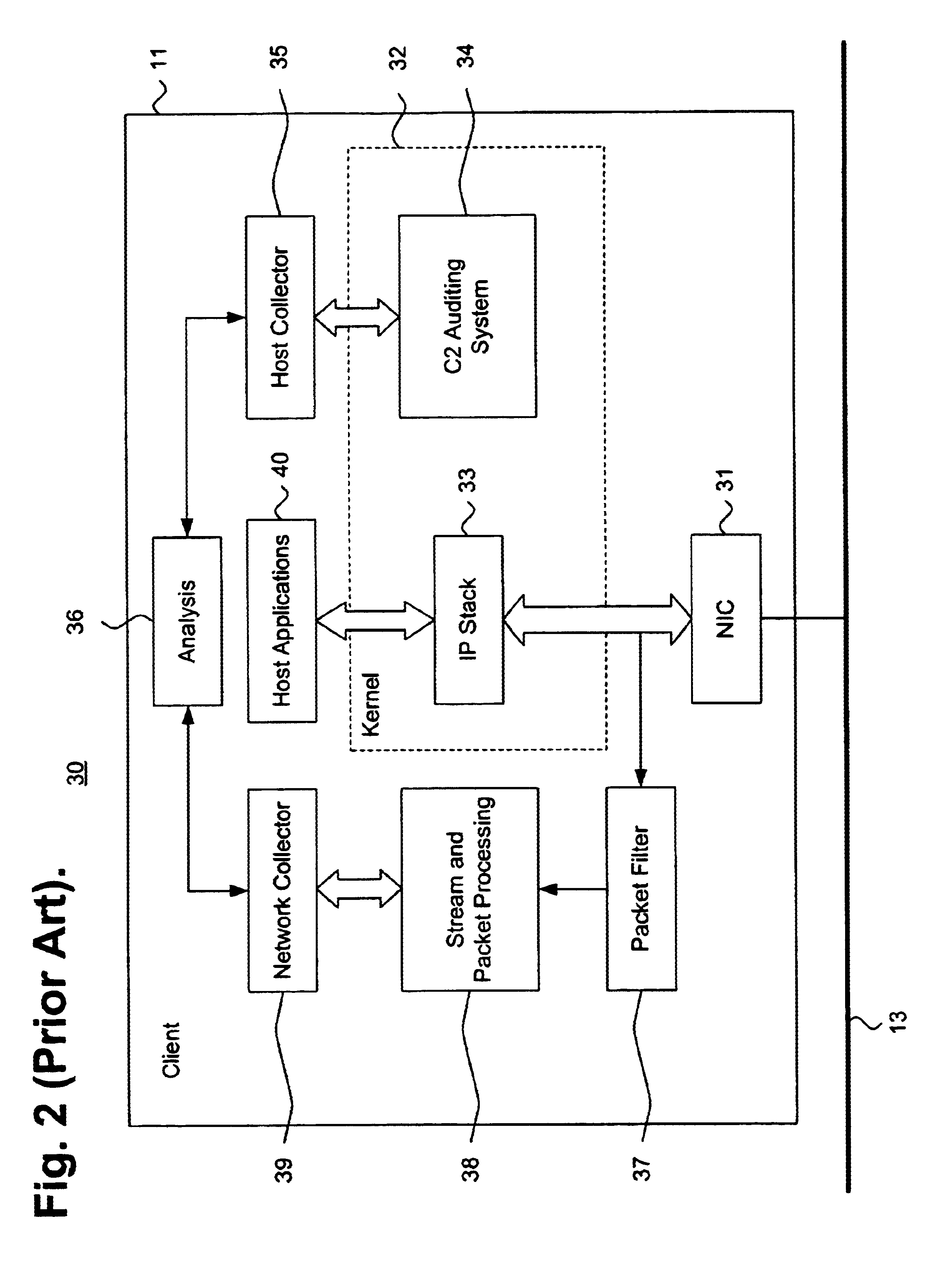

System and method for intrusion detection data collection using a network protocol stack multiplexor

InactiveUS6851061B1Memory loss protectionDigital computer detailsProtocol processingNetworking protocol

A system and method for detecting network intrusions using a protocol stack multiplexor is described. A network protocol stack includes a plurality of hierarchically structured protocol layers. Each such protocol layer includes a read queue and a write queue for staging transitory data packets and a set of procedures for processing the transitory data packets in accordance with the associated protocol. A protocol stack multiplexor is interfaced directly to at least one such protocol layer through a set of redirected pointers to the processing procedures of the interfaced protocol layer. A data packet collector references at least one of the read queue and the write queue for the associated protocol layer. A data packet exchanger communicates a memory reference to each transitory data packet from the referenced at least one of the read queue and the write queue for the associated protocol layer. An analysis module receives the communicated memory reference and performs intrusion detection based thereon.

Owner:MCAFEE LLC

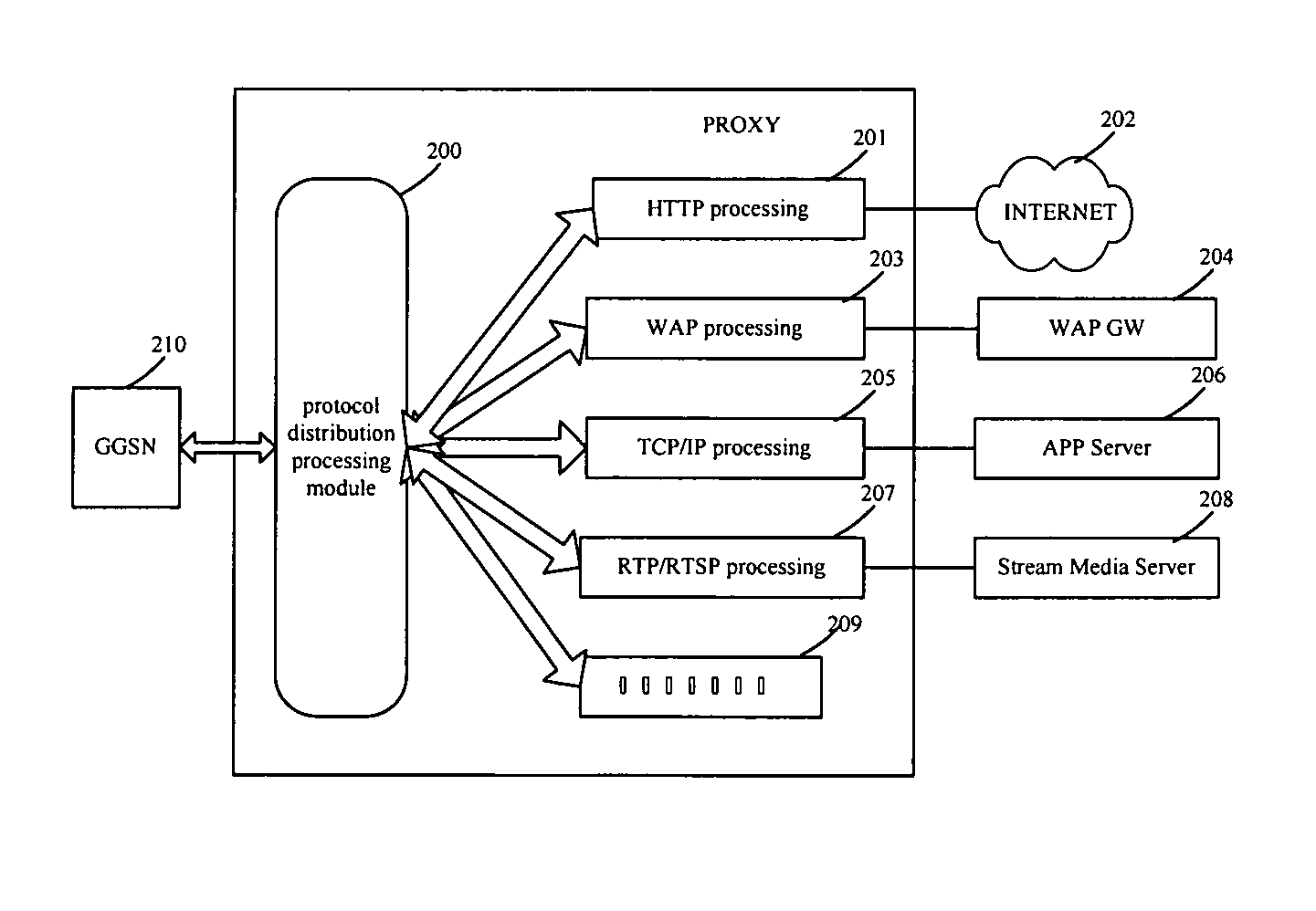

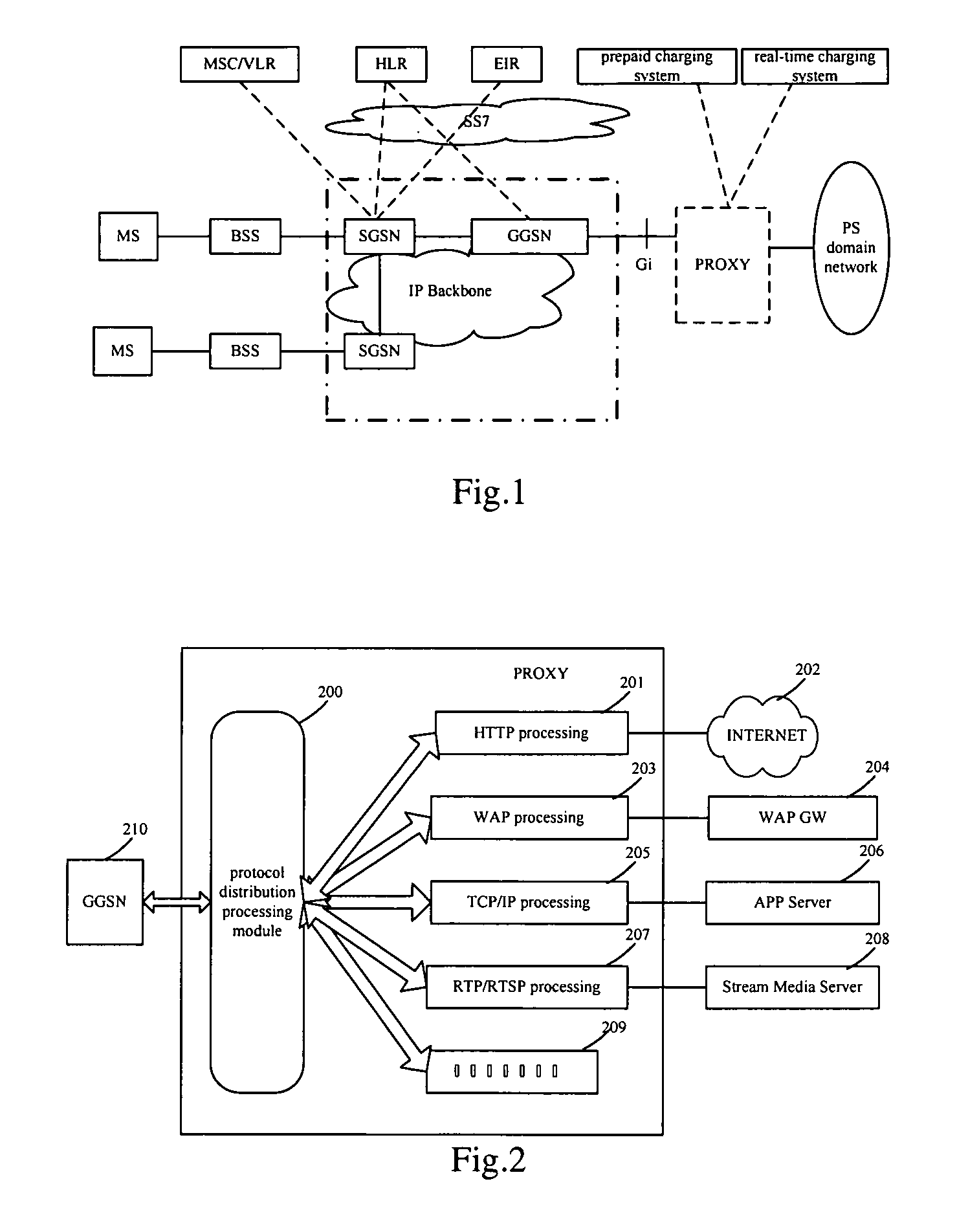

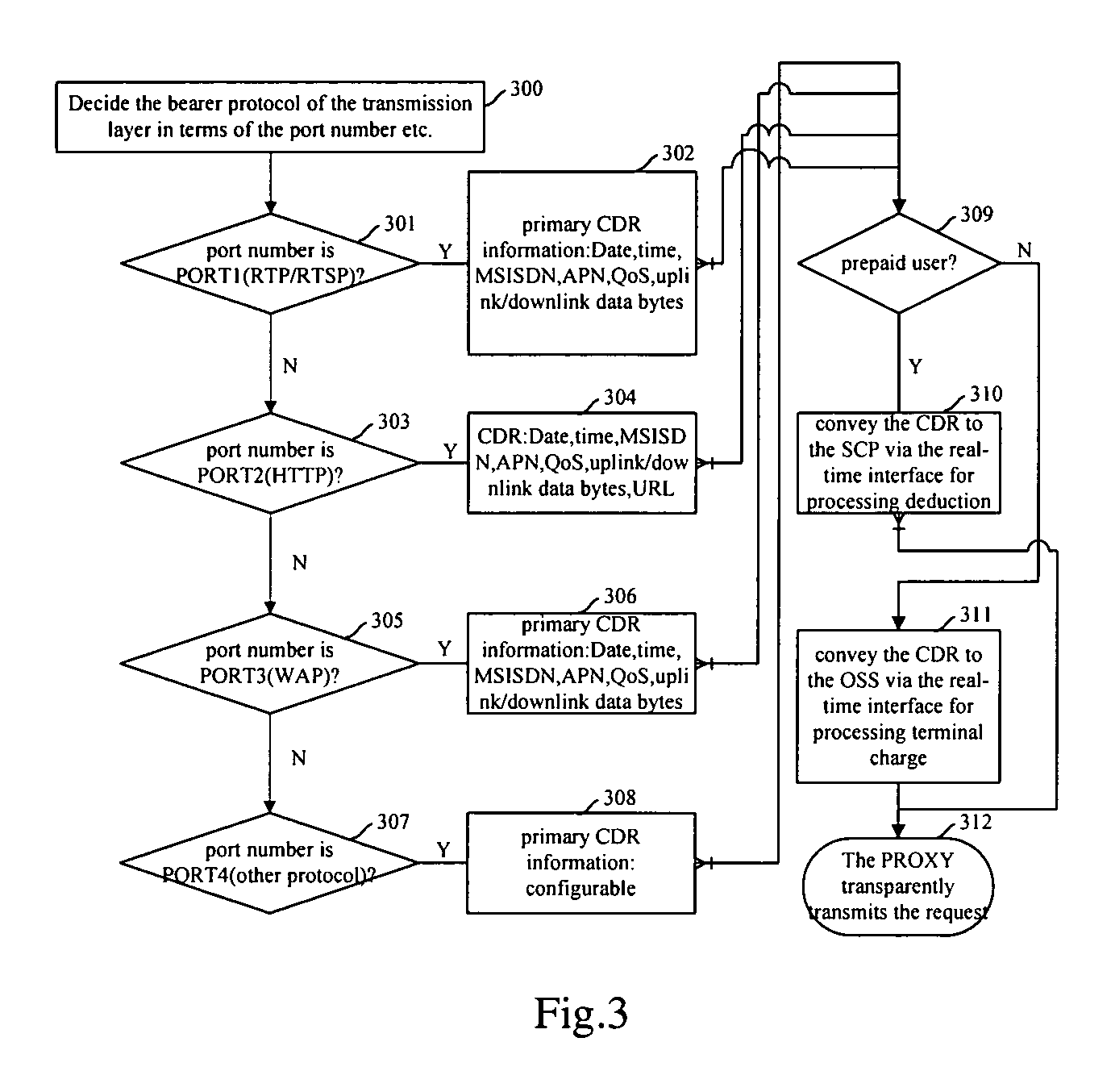

Apparatus for collecting charging information of a data service and charging method thereof

ActiveUS8488597B2Uniform collectionMetering/charging/biilling arrangementsNumber-allocation/character-counting for messagesProtocol processingPacket switched

The present invention discloses an apparatus for collecting charging information of data service and charging method thereof. The apparatus comprises: a protocol distribution processing module, for classifying service data received from a gateway service node in the wireless network by the protocol type, and sending the classified service data to a protocol processing module of the corresponding protocol type; receiving service data from said one or more than one protocol processing module and sending the service data to the gateway service node; at least one protocol processing module, for receiving the classified service data from the protocol distribution processing module, obtaining charging information of the service data and sending the charging information to a charging system, and transparently transmitting the service data to a packet switched domain network; receiving the service data from a packet switched domain network, obtaining the charging information of the service data and sending the charging information to the charging system, and transparently transmitting the service data to the protocol distribution processing module. This invention can accurately collect the charging information of service data of various classes.

Owner:HUAWEI TECH CO LTD

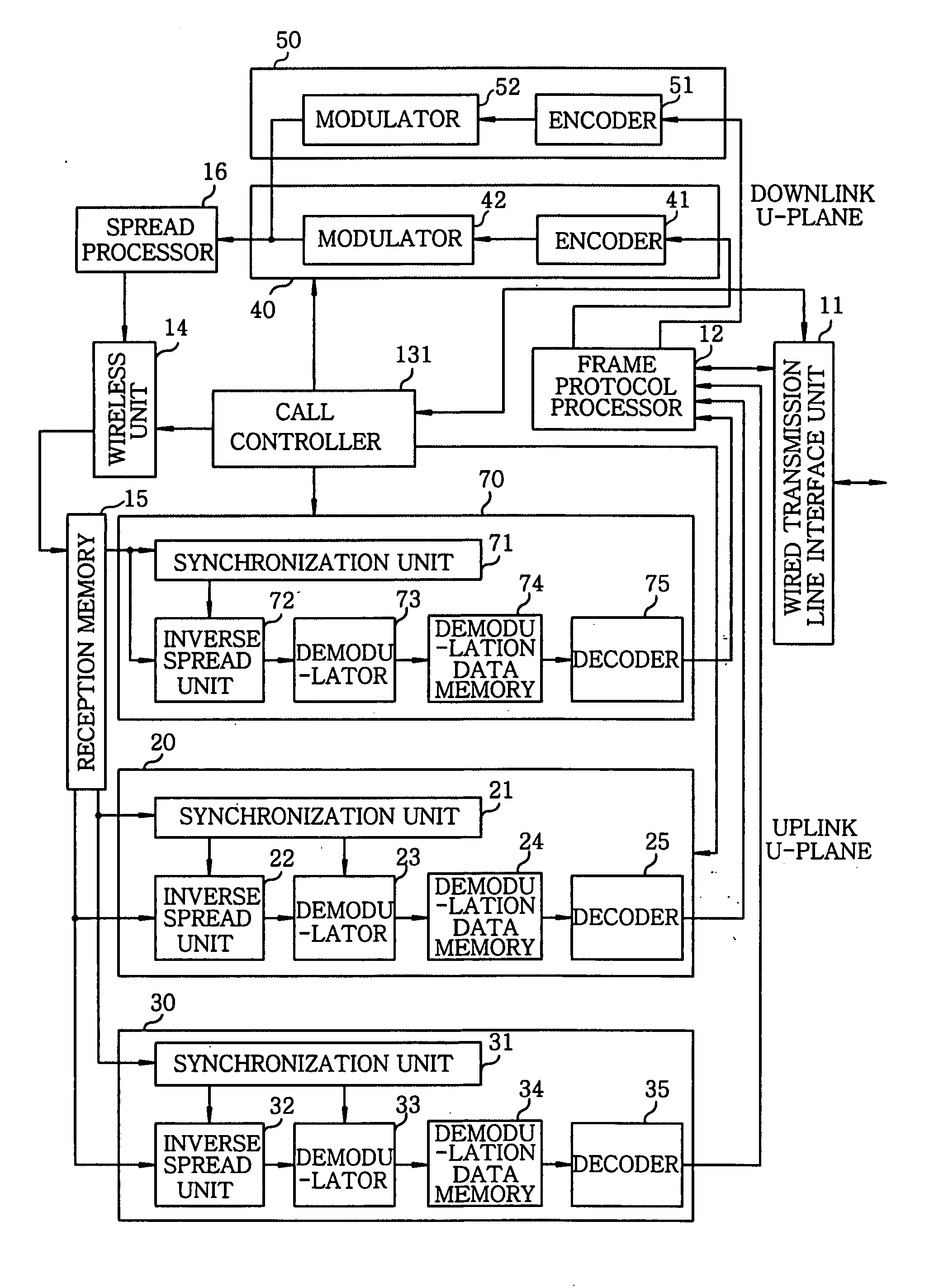

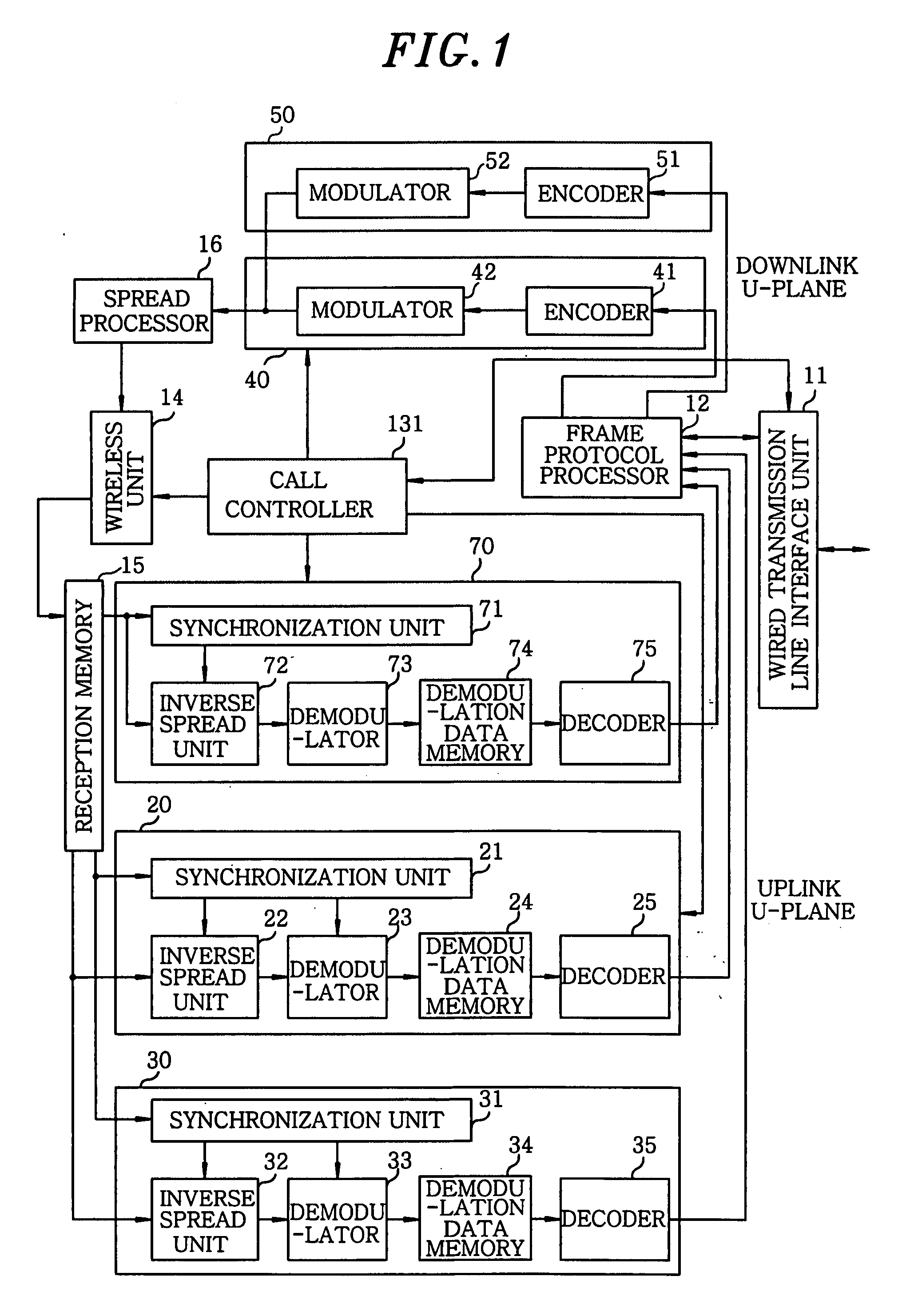

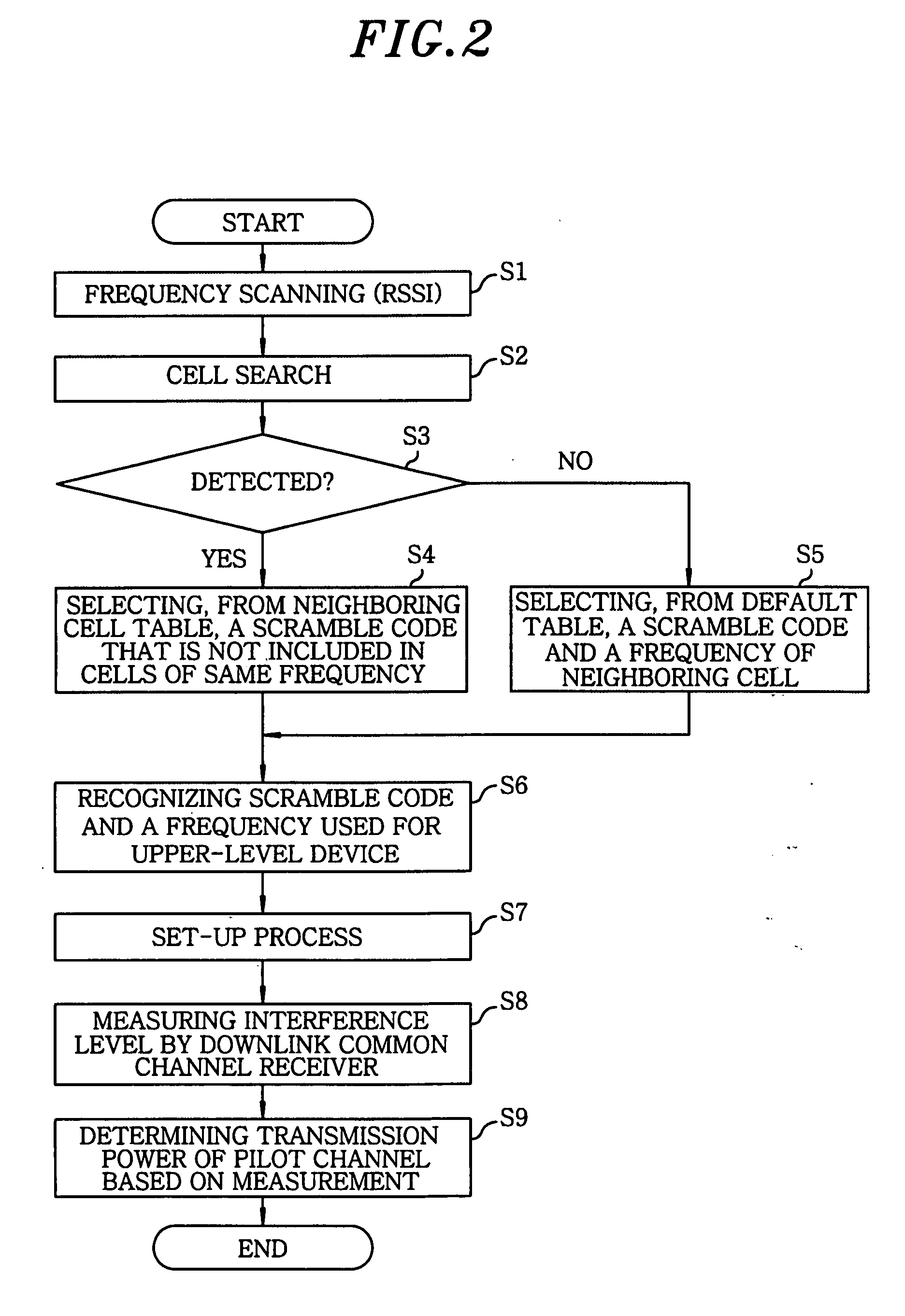

Wireless base station device

InactiveUS20070287501A1Efficient use ofMultiplex system selection arrangementsPower managementFrequency spectrumProtocol processing

A wireless base station device includes a wireless unit for performing wireless communications with a mobile station; a reception memory unit for storing therein reception spectrum spread data as reception data; a baseband reception unit for processing and decoding the reception data stored in the reception memory unit; a common downlink channel reception unit for receiving a downlink signal of other base station devices; a frame protocol processing unit for converting a transmission channel format; a baseband transmission unit for outputting encoded data; a spread processing unit for outputting spread-modulated data to the wireless unit; and a call controller for controlling an allocation of processing resources. Parameters including a spreading code and a transmission power required for installing the wireless base station device are automatically set by operating the common downlink channel reception unit to detect notification information and signal levels of neighboring base station devices.

Owner:KOKUSA ELECTRIC CO LTD

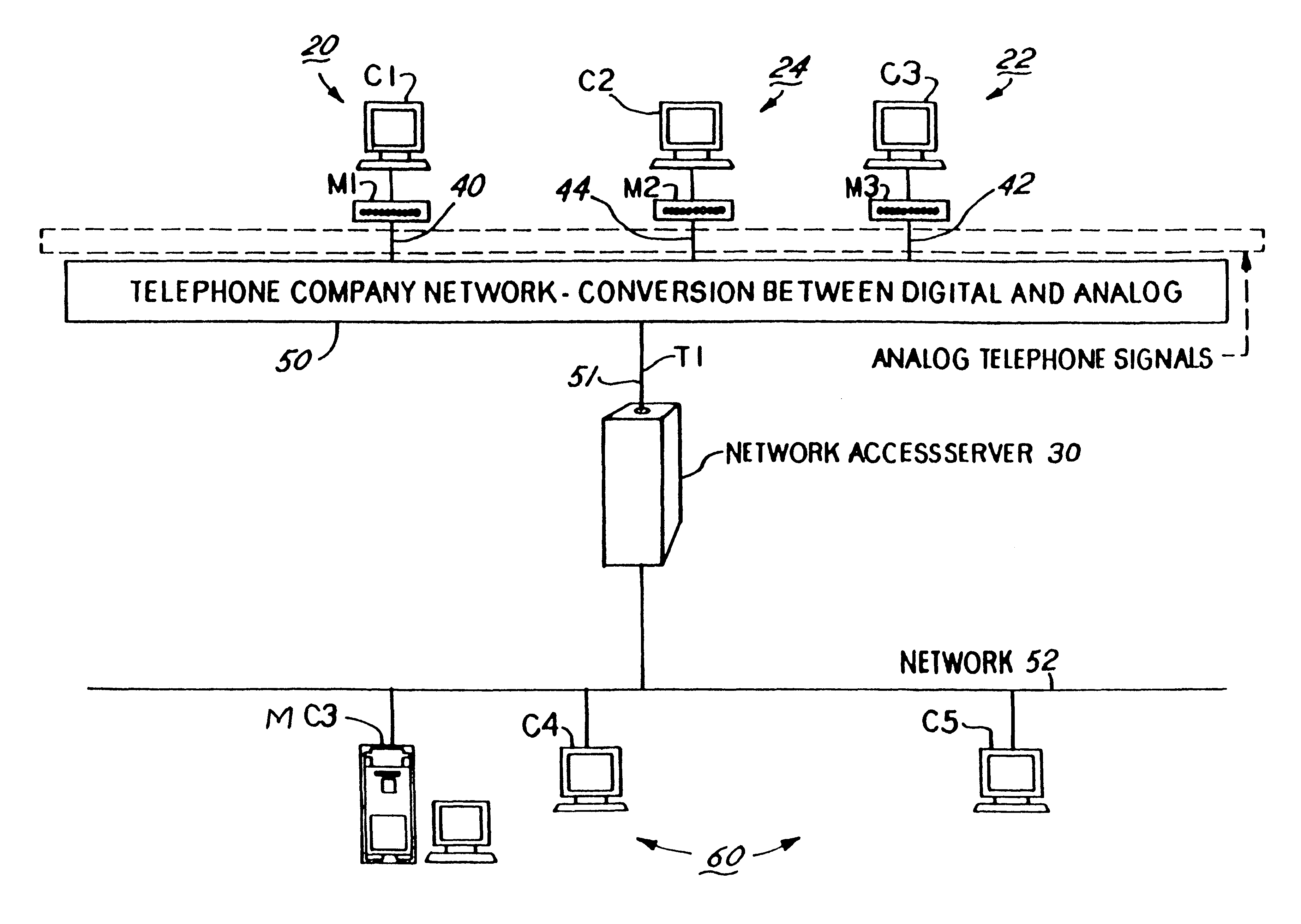

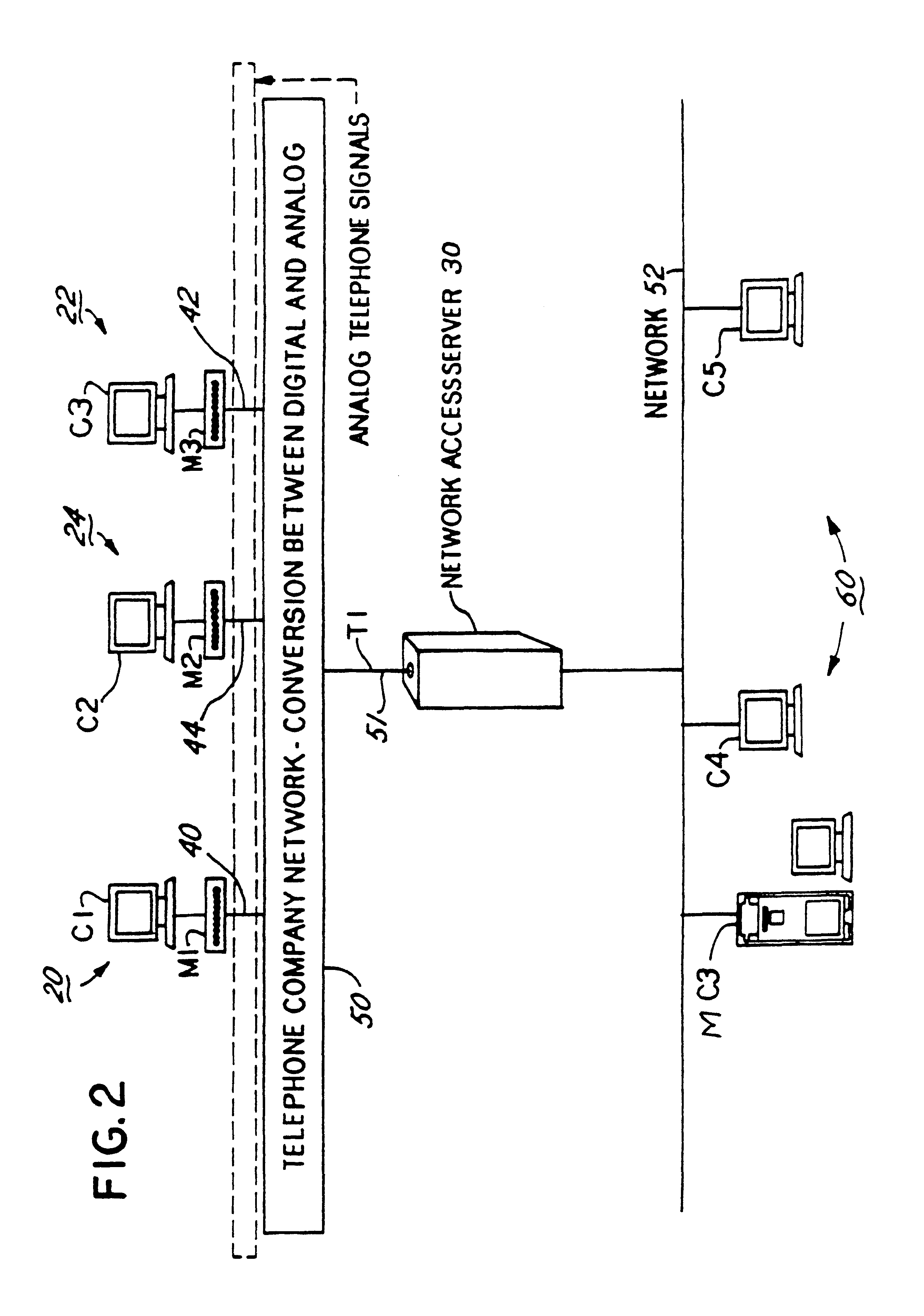

Distributed processing of high level protocols, in a network access server

InactiveUS6304574B1Introduces latency and delayHeavy loadTelephone data network interconnectionsTime-division multiplexNetwork access serverModem device

A method and apparatus for distributing protocol processing among a plurality of computing platforms. Data communications equipment such as Remote Access Devices, Communication Servers, Terminal Servers, and Dial-up Routers provide single user or large-scale multiple user communication access to various computing environments. The equipment costs and performance of such access equipment is related to the amount of CPU processing capability and memory required to support the desired number of serial communication links. It is common to use protocols that terminate in their entirely in the same processing machine. This invention encompasses methods developed to increase the cost / performance capabilities of the communication equipment that supports these serial links, primarily by means of distributing the protocol processing for higher level protocols across multiple computing platforms, including devices such as modems. Examples of such higher level protocols include PPP, SLIP and RTP.

Owner:UTSTARCOM INC

TCP/IP offload device with reduced sequential processing

ActiveUS20050122986A1Reduce power consumptionLess-expensive memoryError preventionTransmission systemsProtocol processingState variable

A TCP Offload Engine (TOE) device includes a state machine that performs TCP / IP protocol processing operations in parallel. In a first aspect, the state machine includes a first memory, a second memory, and combinatorial logic. The first memory stores and simultaneously outputs multiple TCP state variables. The second memory stores and simultaneously outputs multiple header values. In contrast to a sequential processor technique, the combinatorial logic generates a flush detect signal from the TCP state variables and header values without performing sequential processor instructions or sequential memory accesses. In a second aspect, a TOE includes a state machine that performs an update of multiple TCP state variables in a TCB buffer all simultaneously, thereby avoiding multiple sequential writes to the TCB buffer memory. In a third aspect, a TOE involves a state machine that sets up a DMA move in a single state machine clock cycle.

Owner:ALACRITECH

System and methods for high rate hardware-accelerated network protocol processing

InactiveUS20090063696A1Improve performanceError prevention/detection by using return channelTransmission systemsTraffic capacityHigh rate

Disclosed is a system and methods for accelerating network protocol processing for devices configured to process network traffic at relatively high data rates. The system incorporates a hardware-accelerated protocol processing module that handles steady state network traffic and a software-based processing module that handles infrequent and exception cases in network traffic processing.

Owner:PROMISE TECHNOLOGY

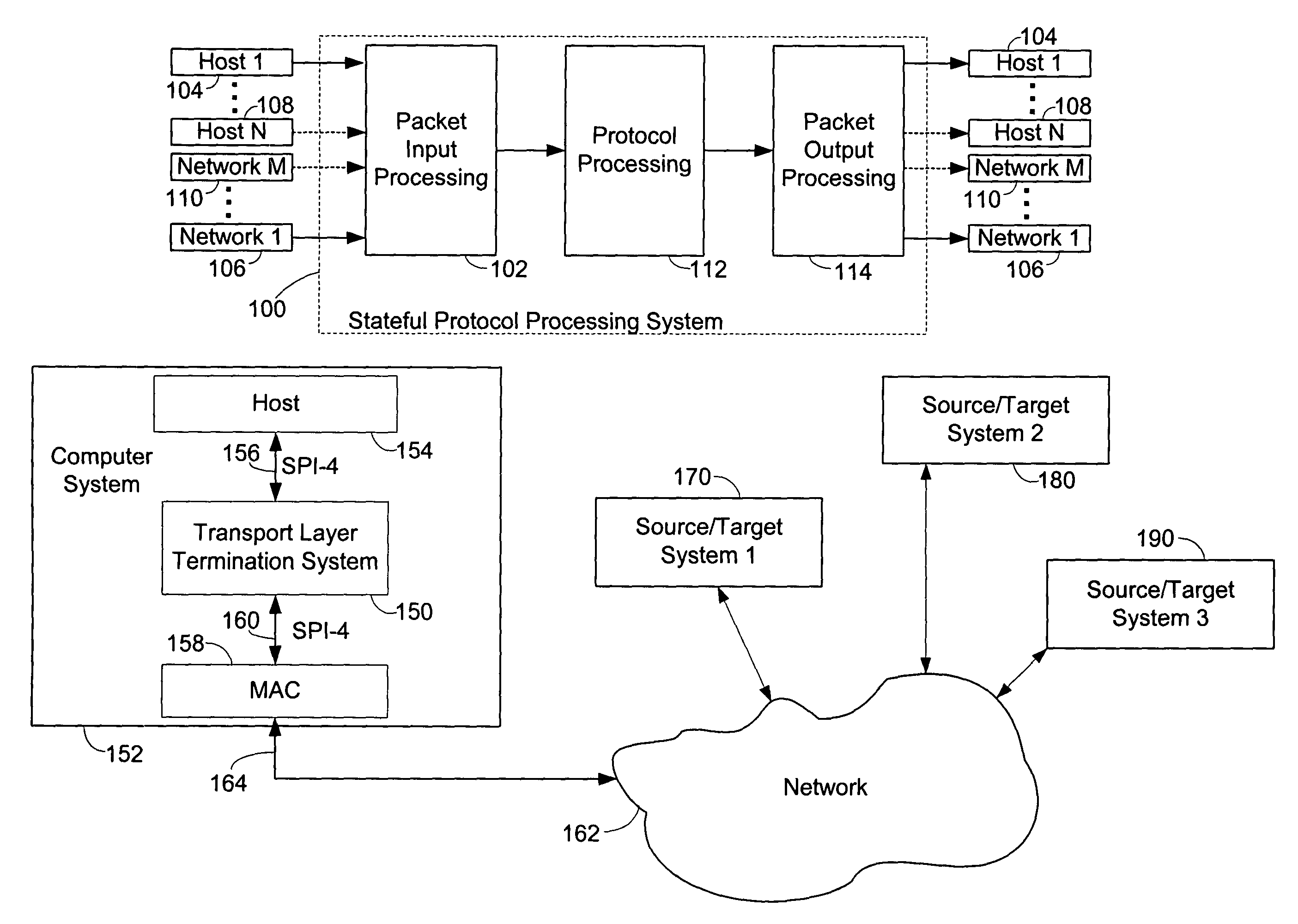

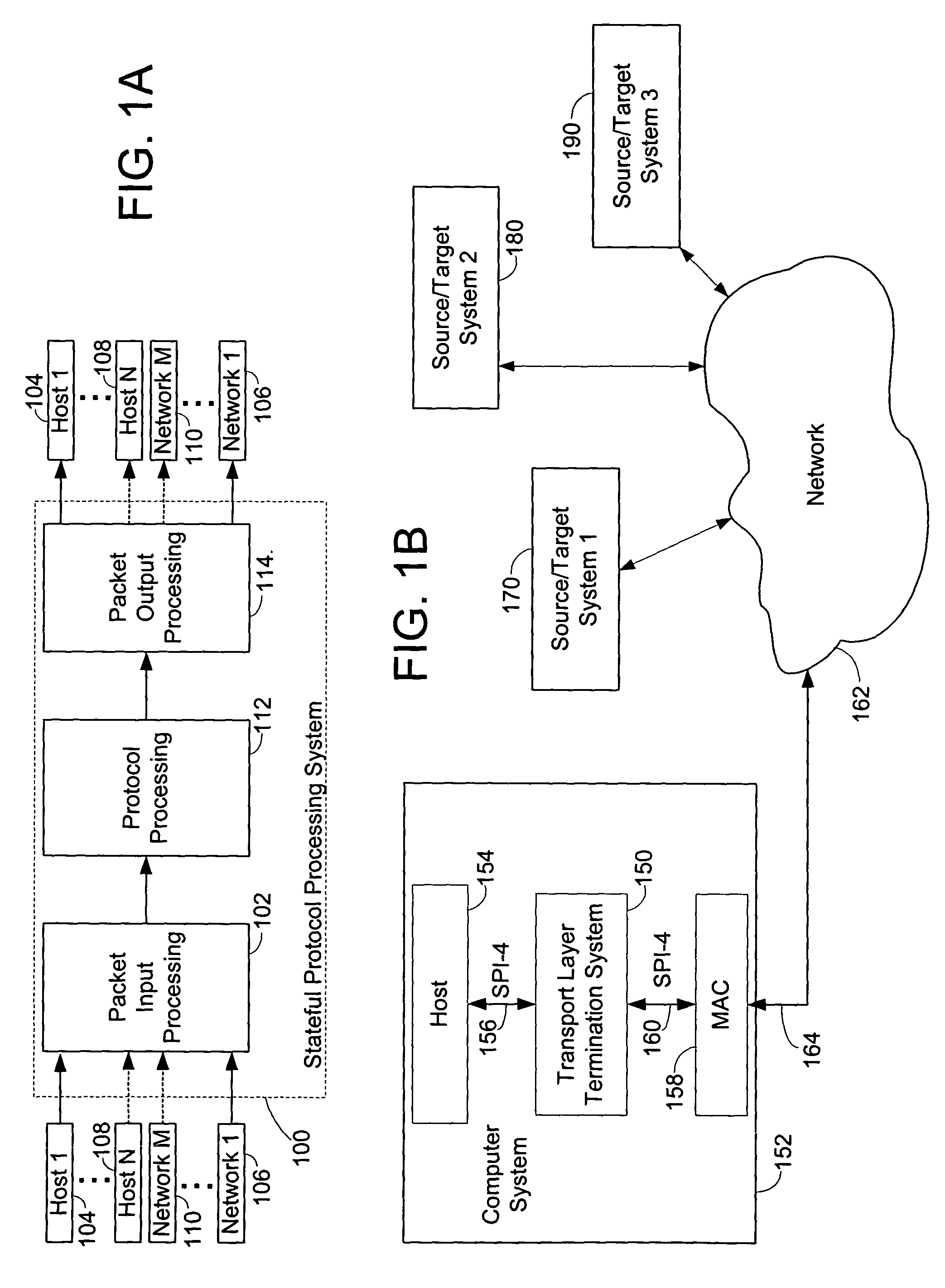

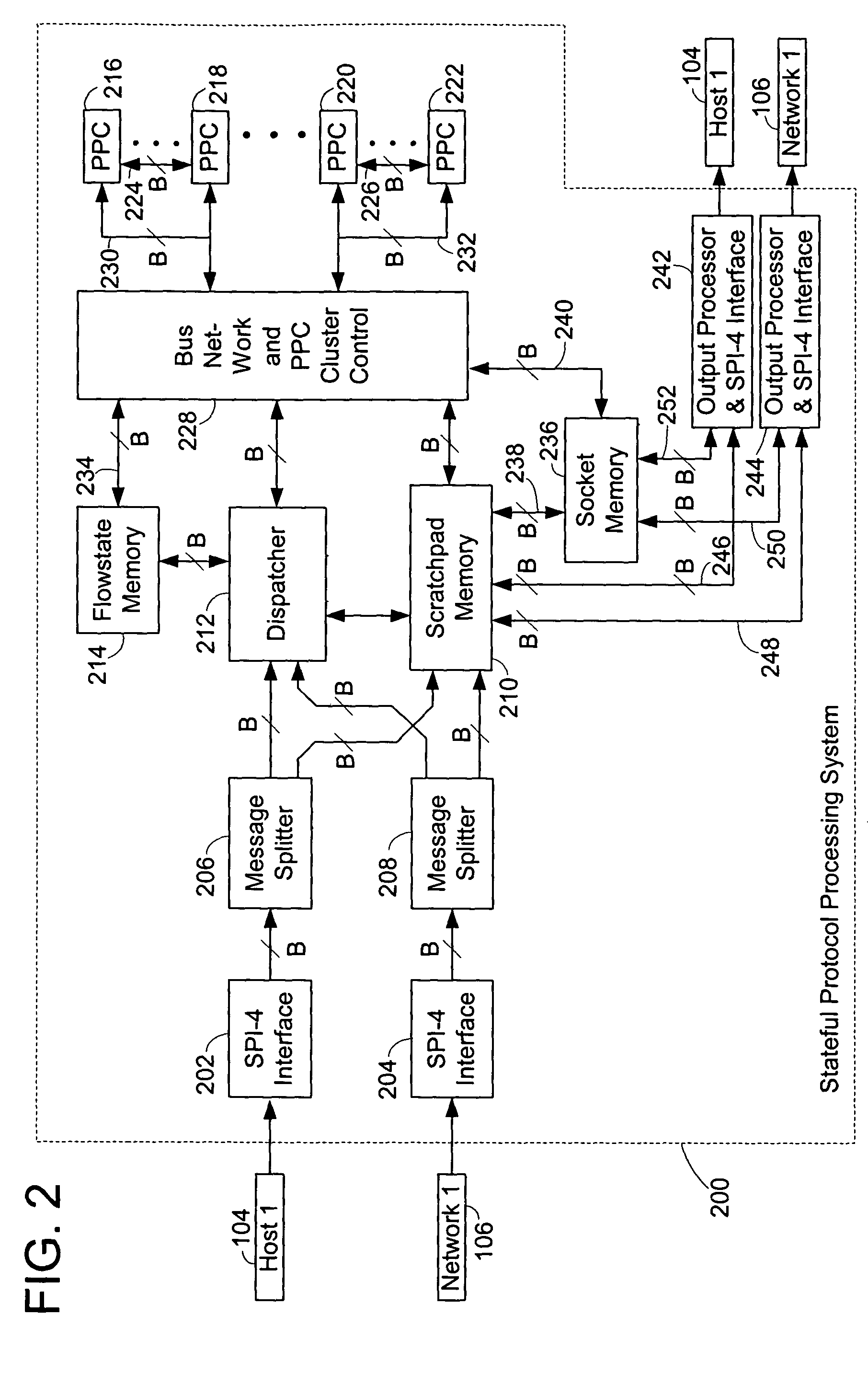

Multi-protocol and multi-format stateful processing

InactiveUS7814218B1Multiple digital computer combinationsTransmissionProtocol processingProcessing core

A system and method of processing data in a stateful protocol processing system (“SPPS”) configured to process a multiplicity of flows of messages is disclosed herein. The method includes receiving a first plurality of messages belonging to a first of the flows comporting with a first stateful protocol. In addition, a second plurality of messages belonging to a second of the flows comporting with a second stateful protocol are also received. Various events of at least first and second types associated with the first flow are then derived from the first plurality of received messages. The method further includes assigning a first protocol processing core to process the events of the first type in accordance with the first stateful protocol. A second protocol processing core is also assigned to process the events of the second type in accordance with the first stateful protocol.

Owner:IKANOS COMMUNICATIONS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com