Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

666results about "Continuous to patterned pulse manipulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

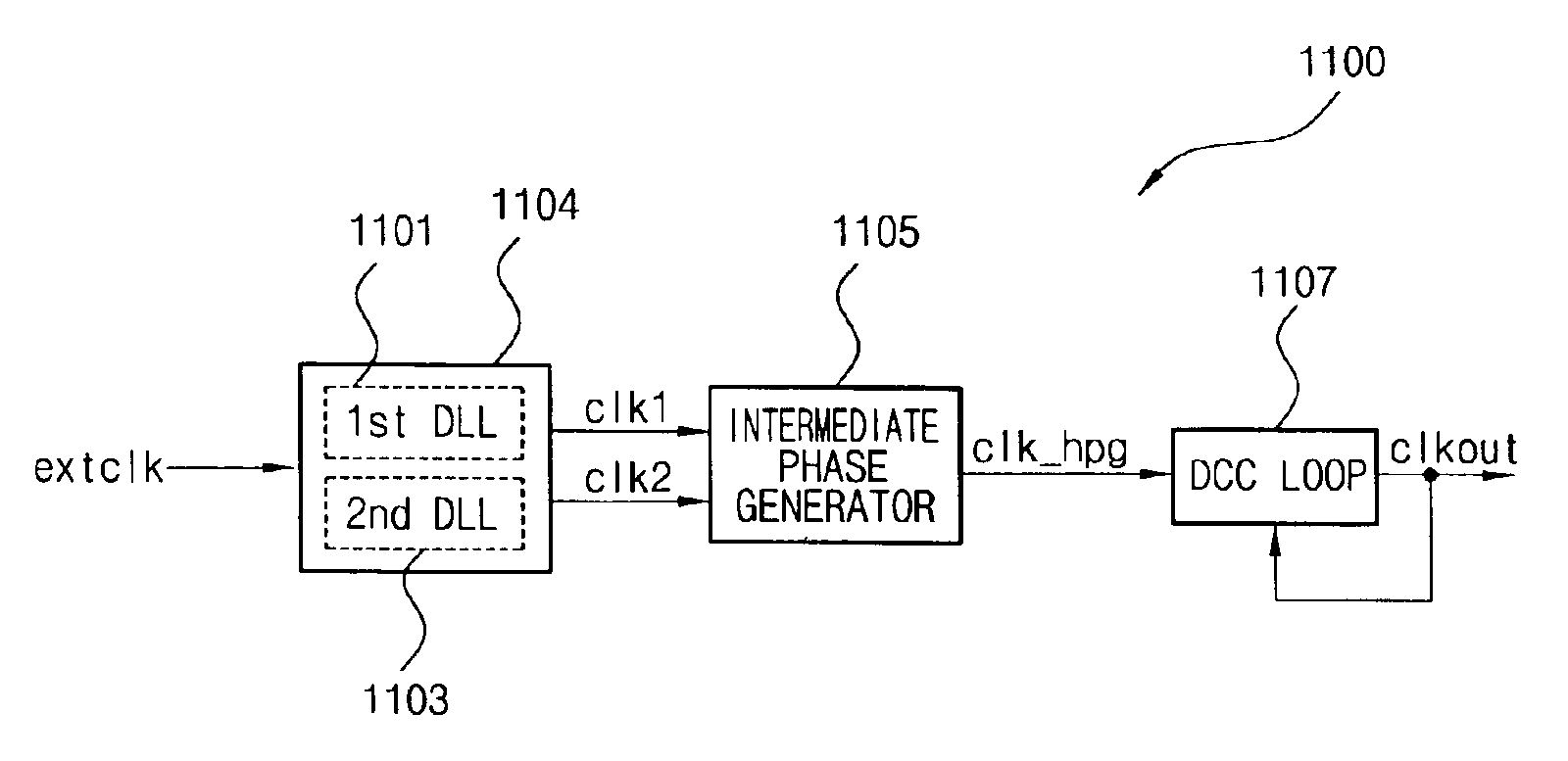

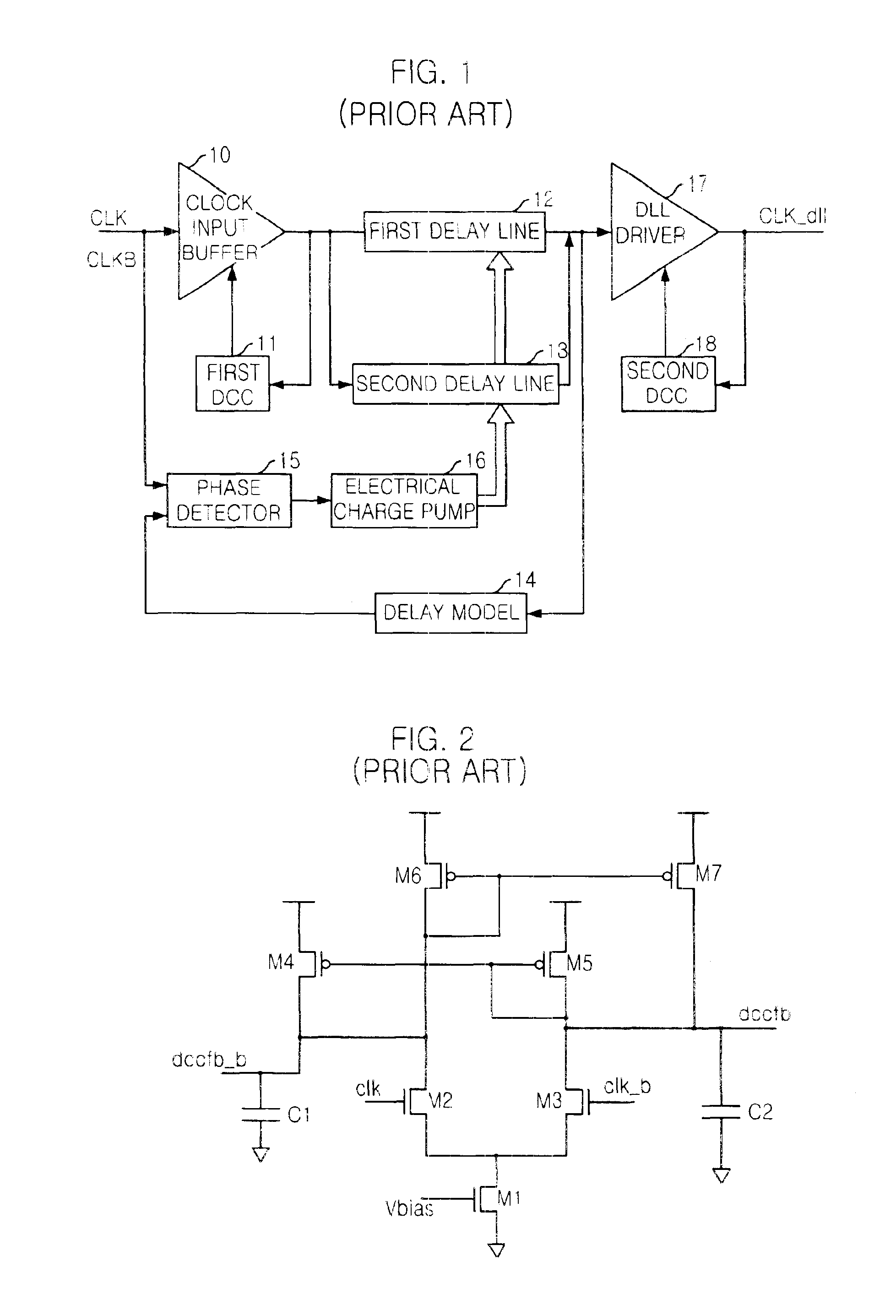

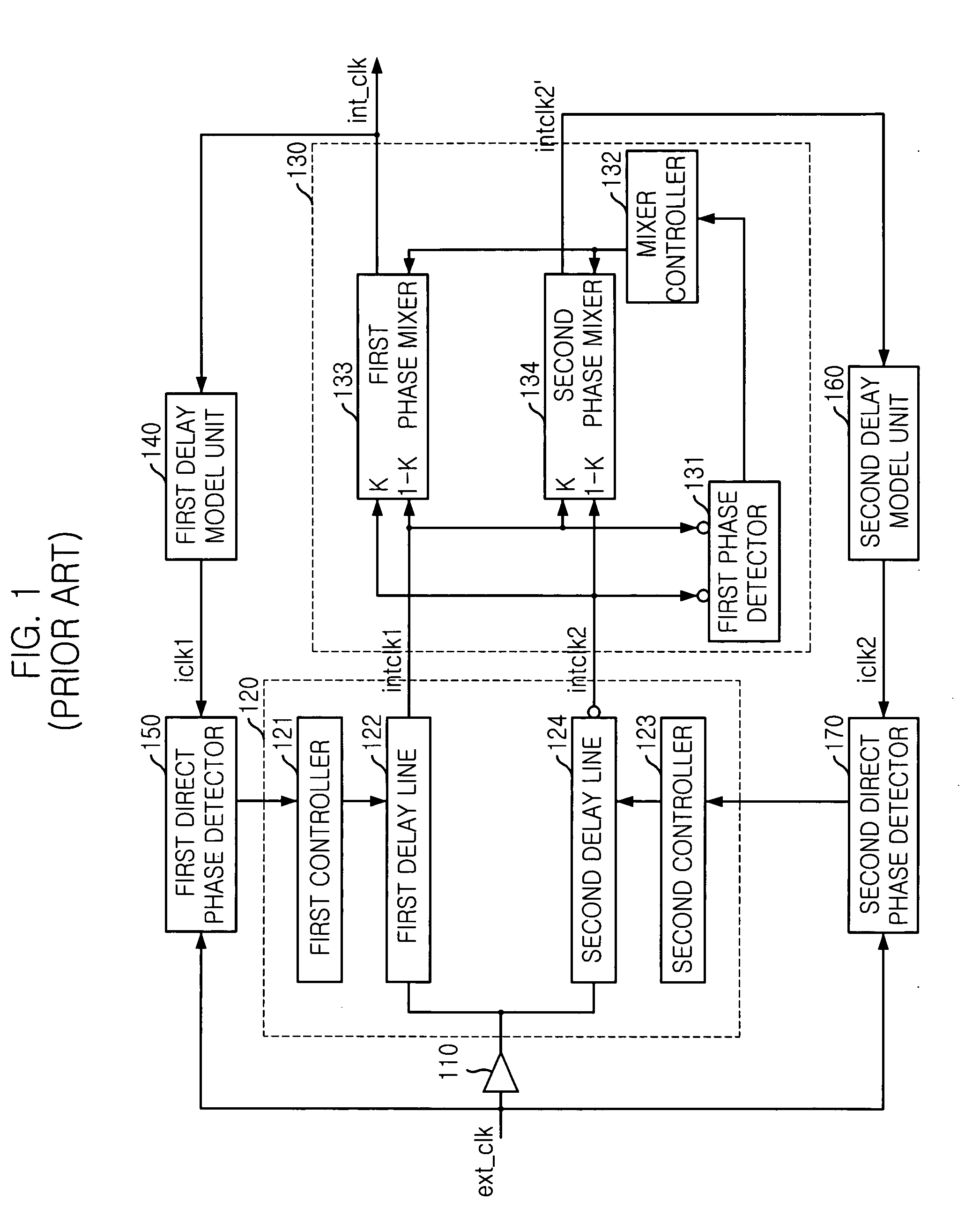

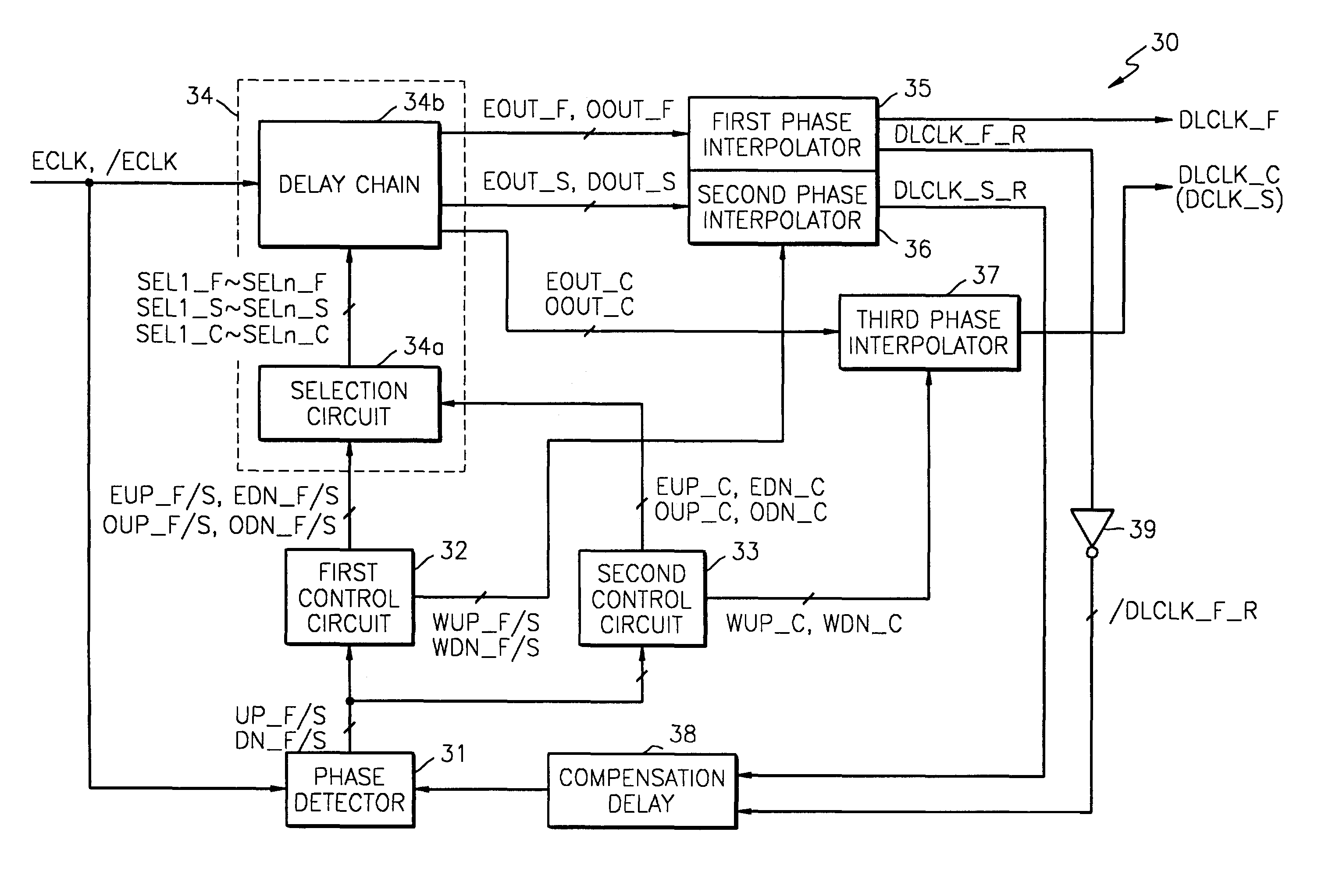

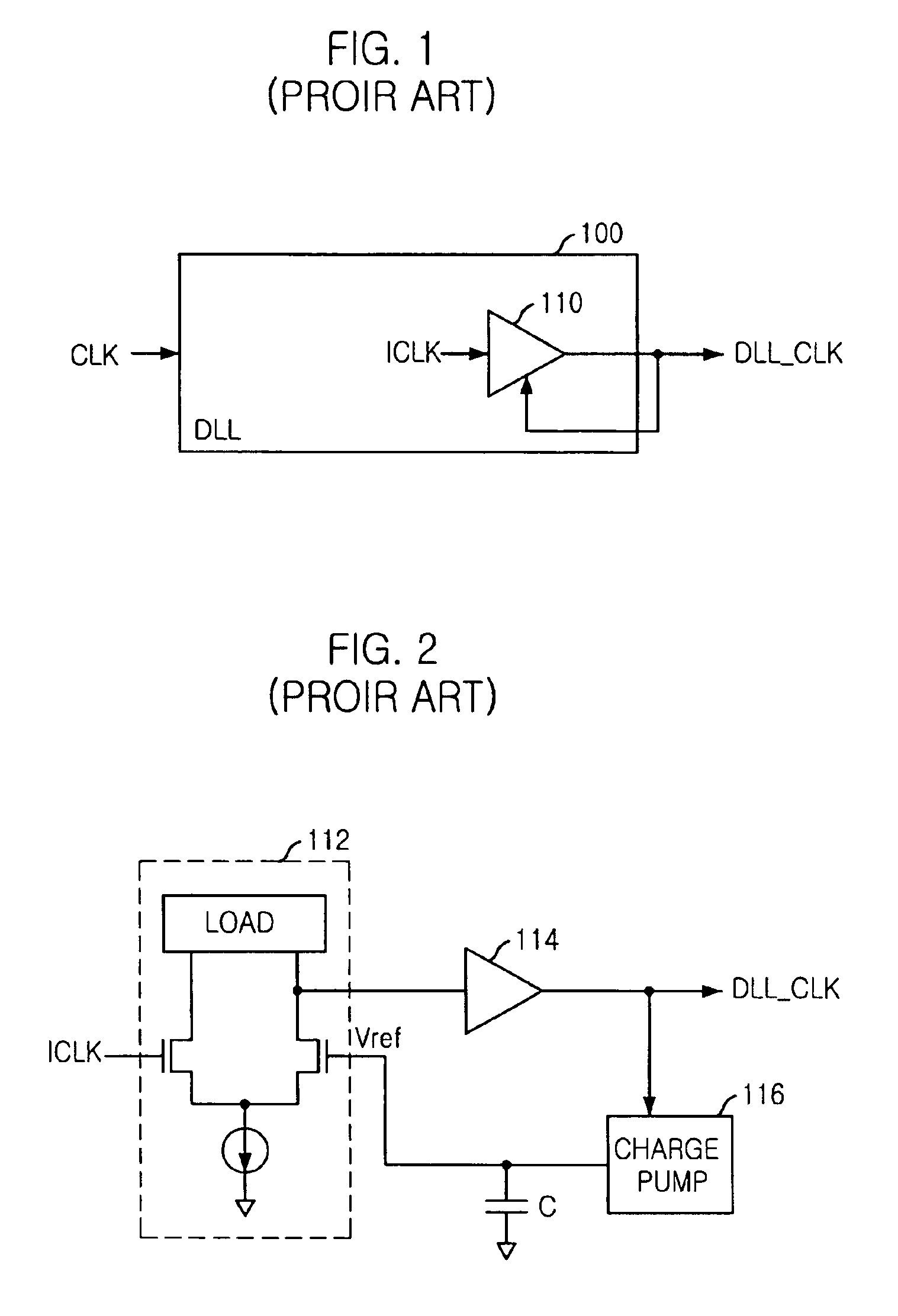

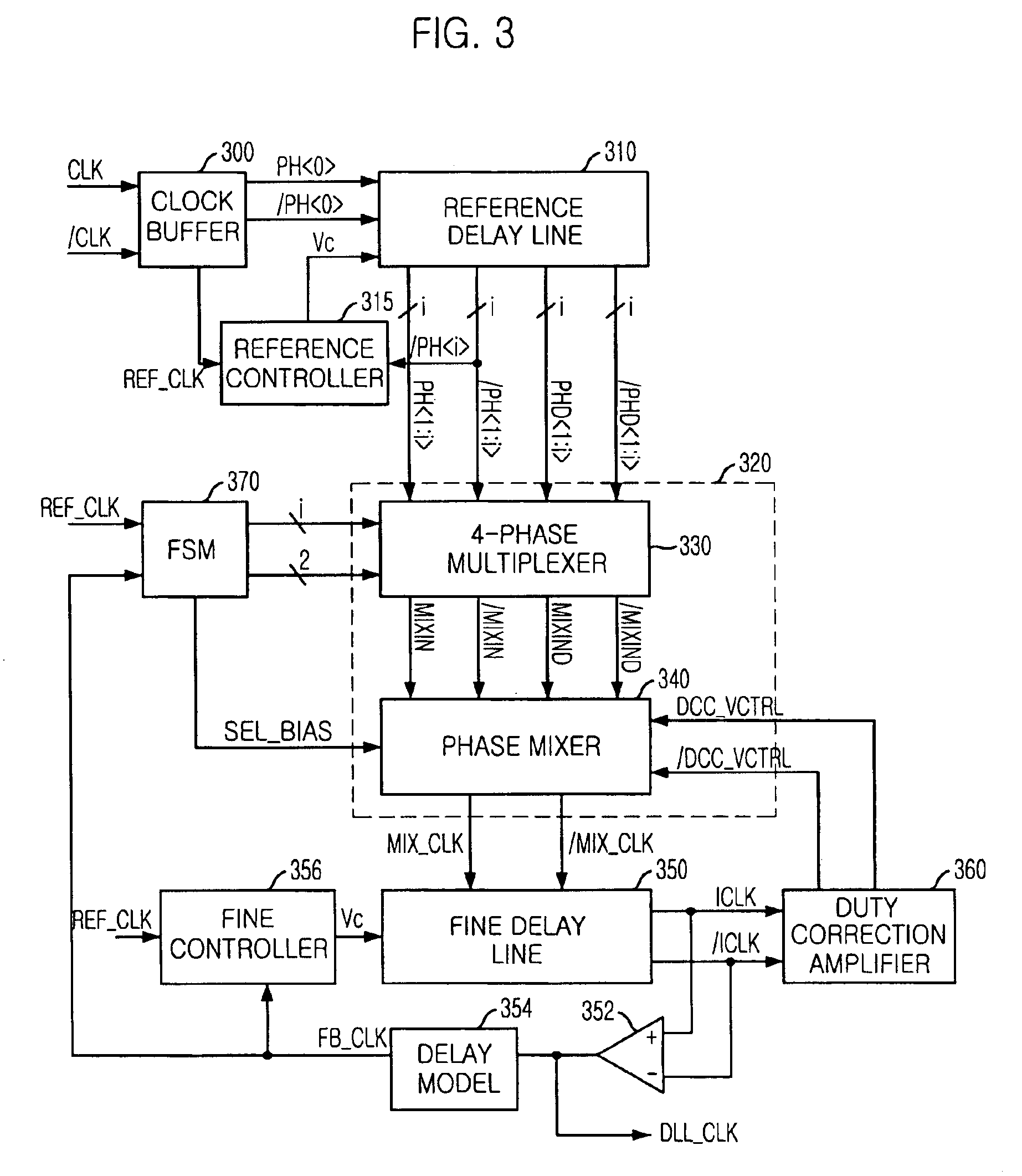

Delay locked loop circuit with duty cycle correction function

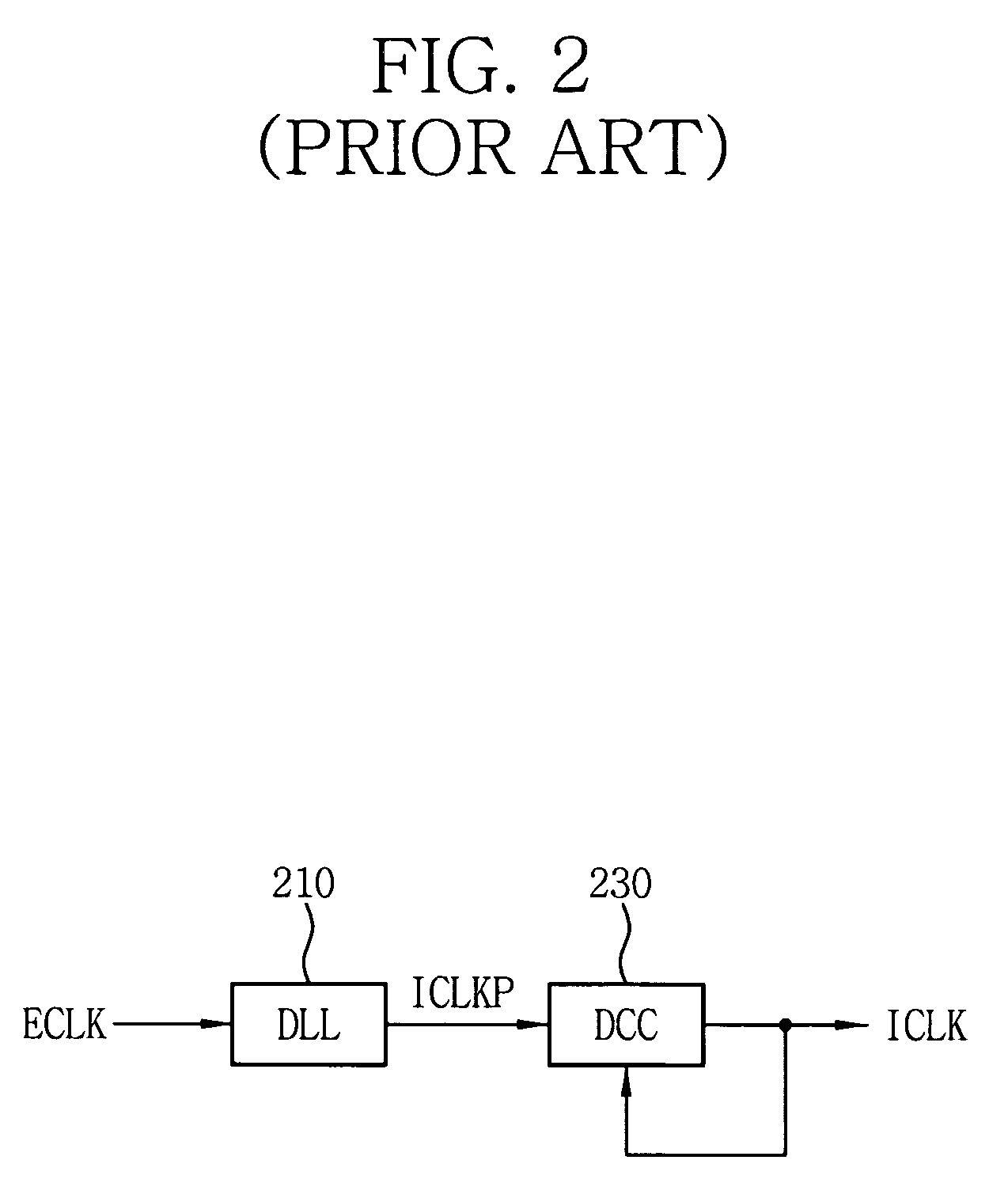

InactiveUS6853225B2Improve accuracyShort lock timePulse automatic controlContinuous to patterned pulse manipulationNegative feedbackDelay-locked loop

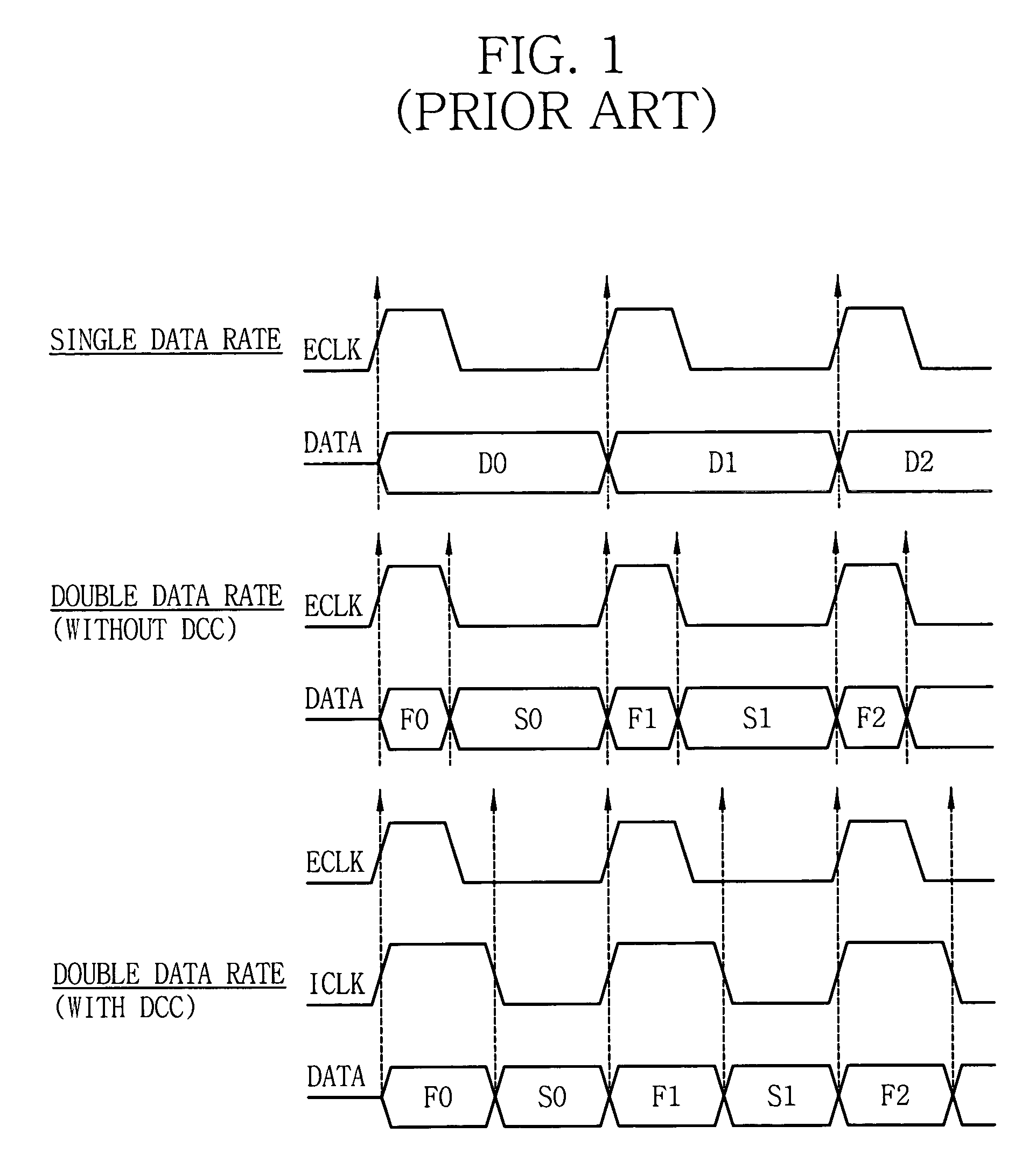

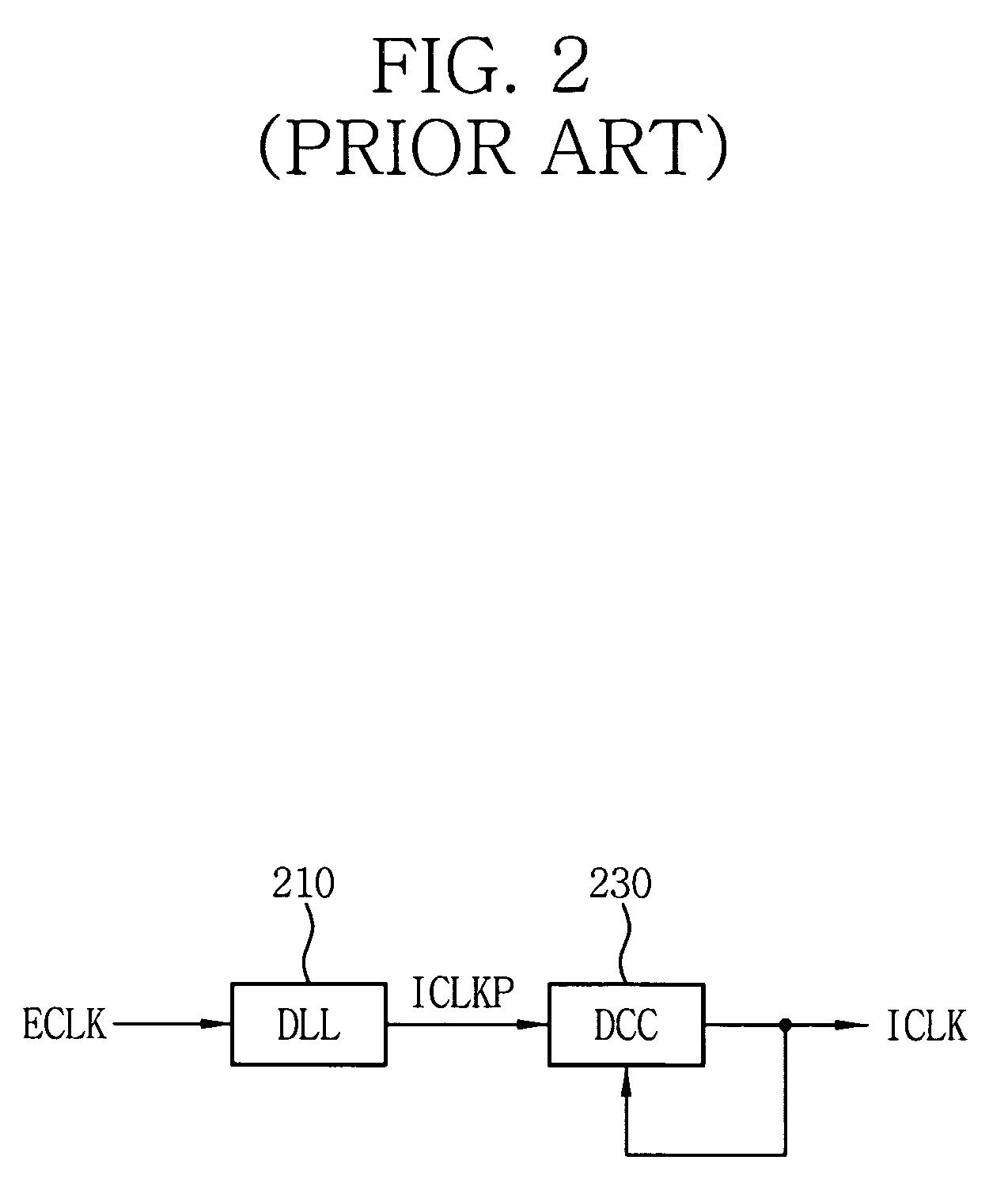

A delay locked loop (DLL) circuit having a structure in which a method of performing duty cycle correction (DCC) using two DLLs and an intermediate phase composer and a method of performing DCC by forming a closed loop using a negative feedback are combined with each other is provided. The DLL circuit includes a first DLL for receiving an external clock signal and generating a first clock signal and a second DLL for receiving an external clock signal and generating a second clock signal. The first clock signal and the second clock signal are synchronized with an external clock signal. The DLL circuit further includes an intermediate phase generation circuit for receiving the first and second clock signals and generating an intermediate phase clock signal and a DCC loop for receiving the intermediate phase clock signal and generating an output clock signal. The intermediate phase clock signal has an intermediate phase between the phases of the first and second clock signals. The output clock signal is generated through correction of the duty cycle of the intermediate phase clock signal using a value obtained by integrating the output clock signal.

Owner:SK HYNIX INC

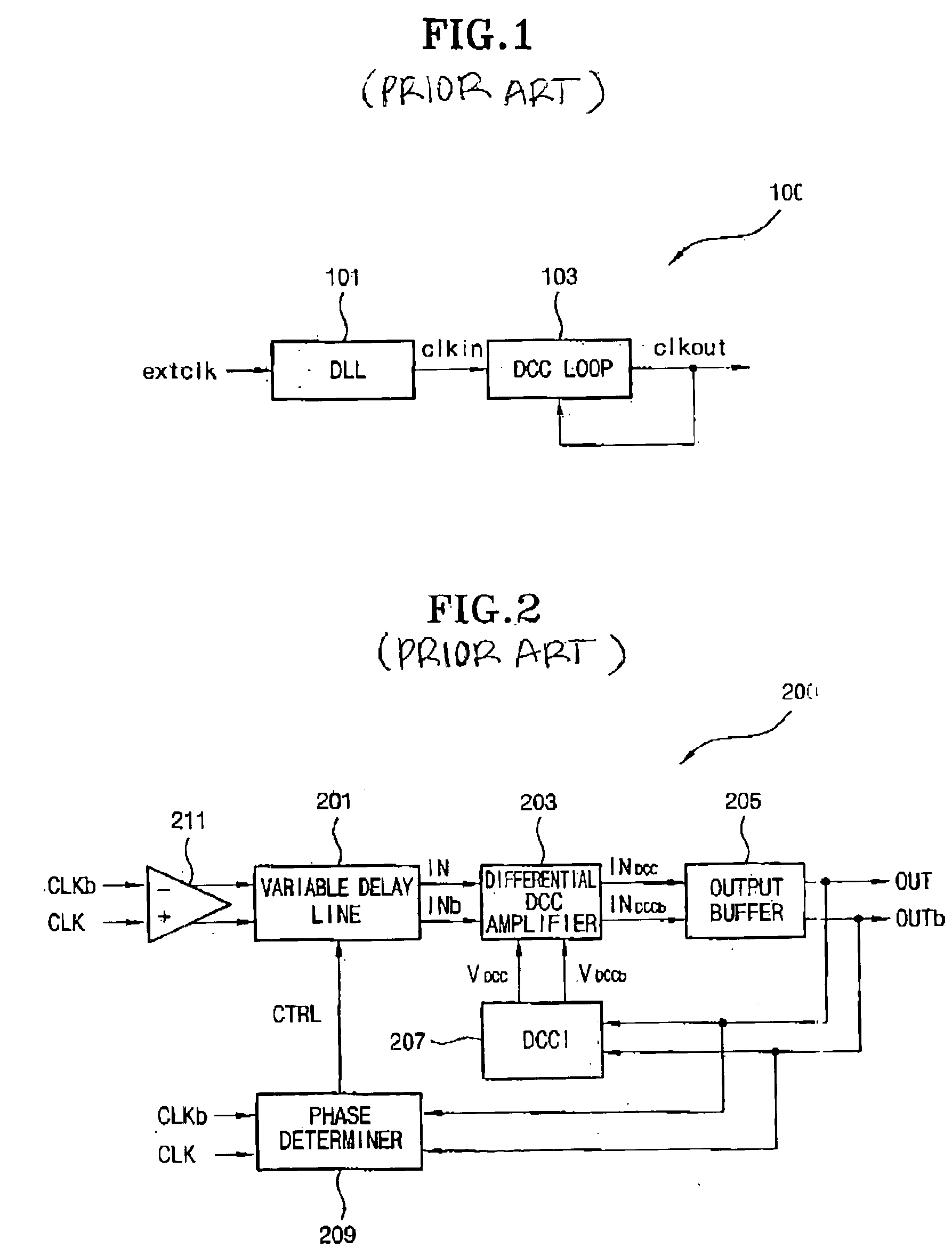

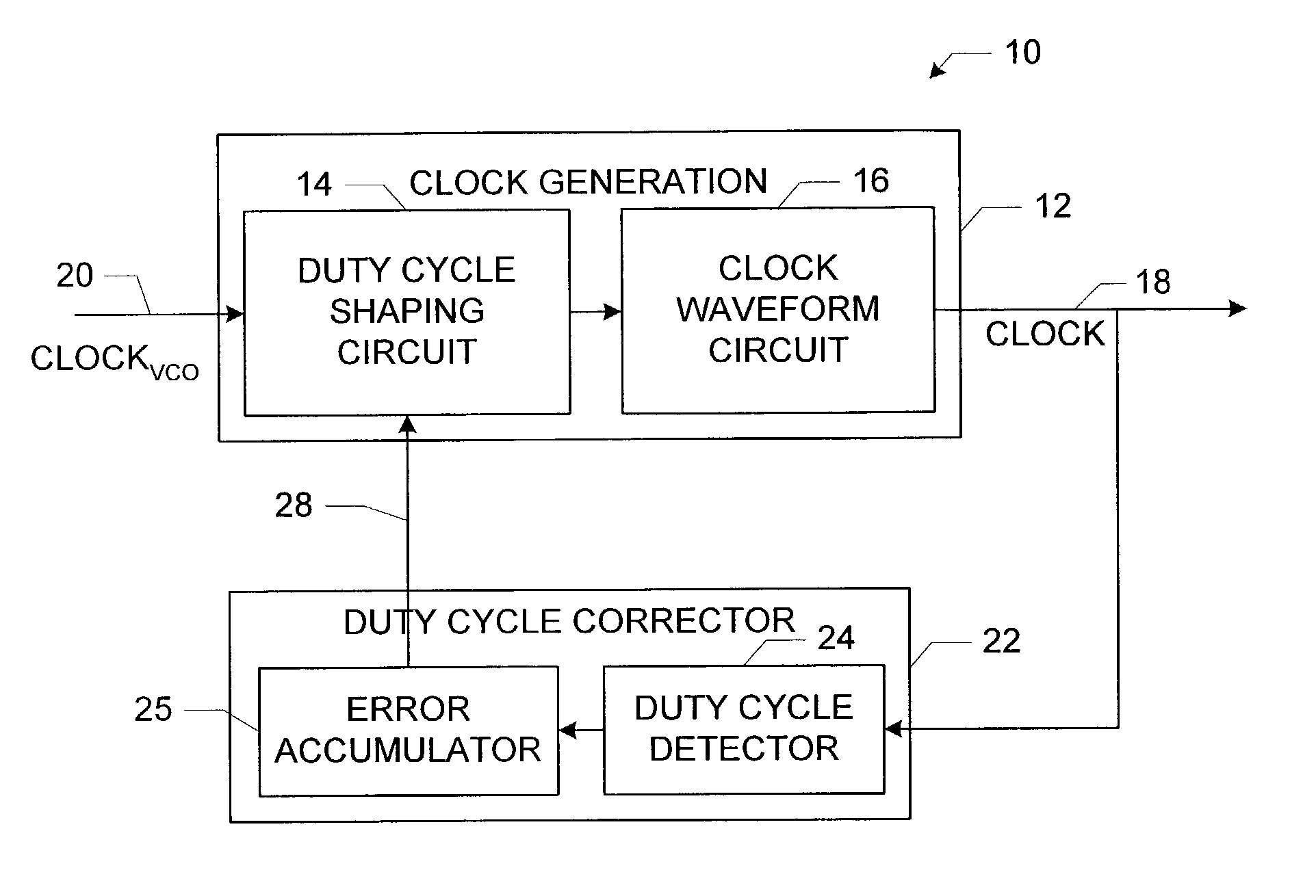

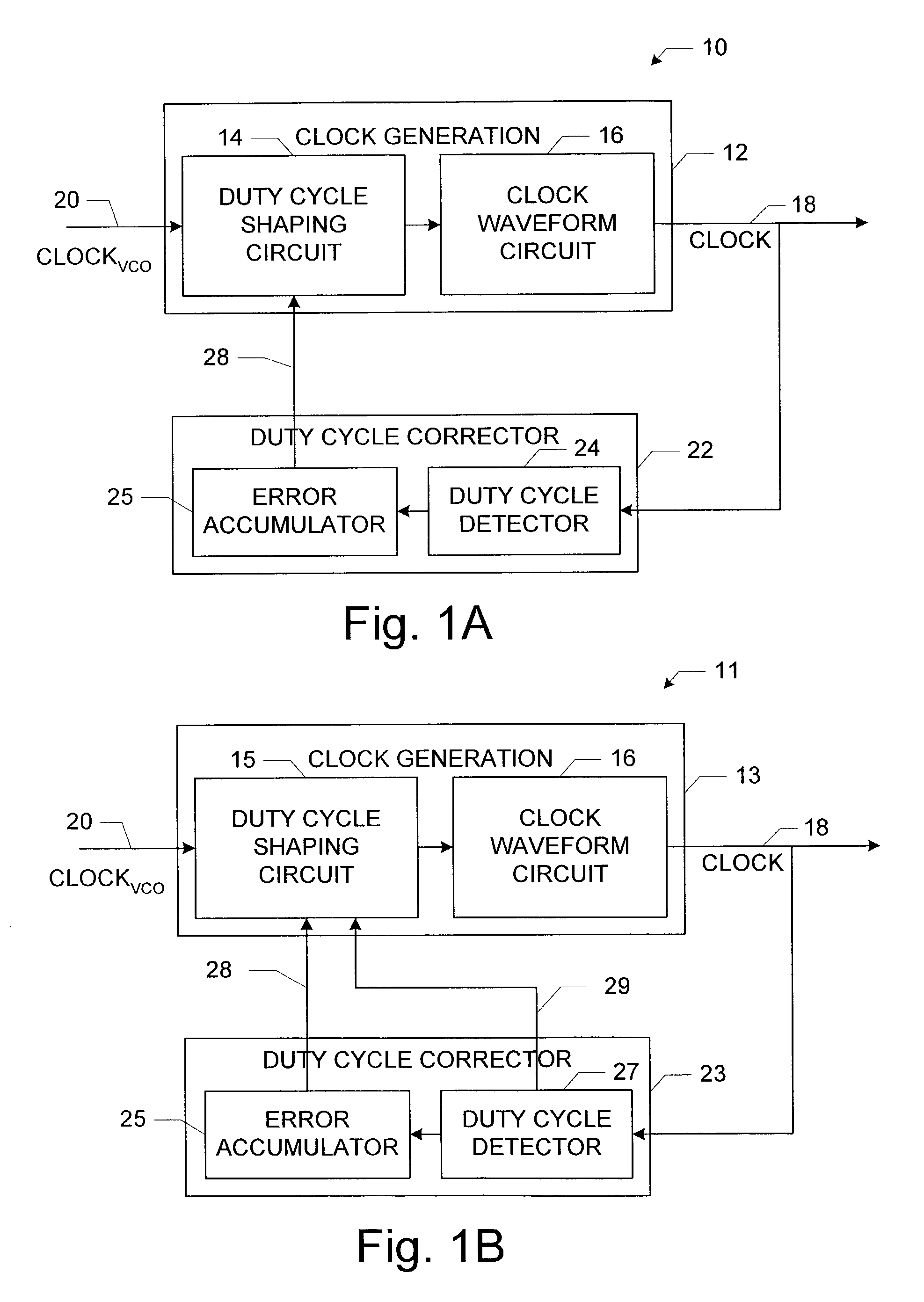

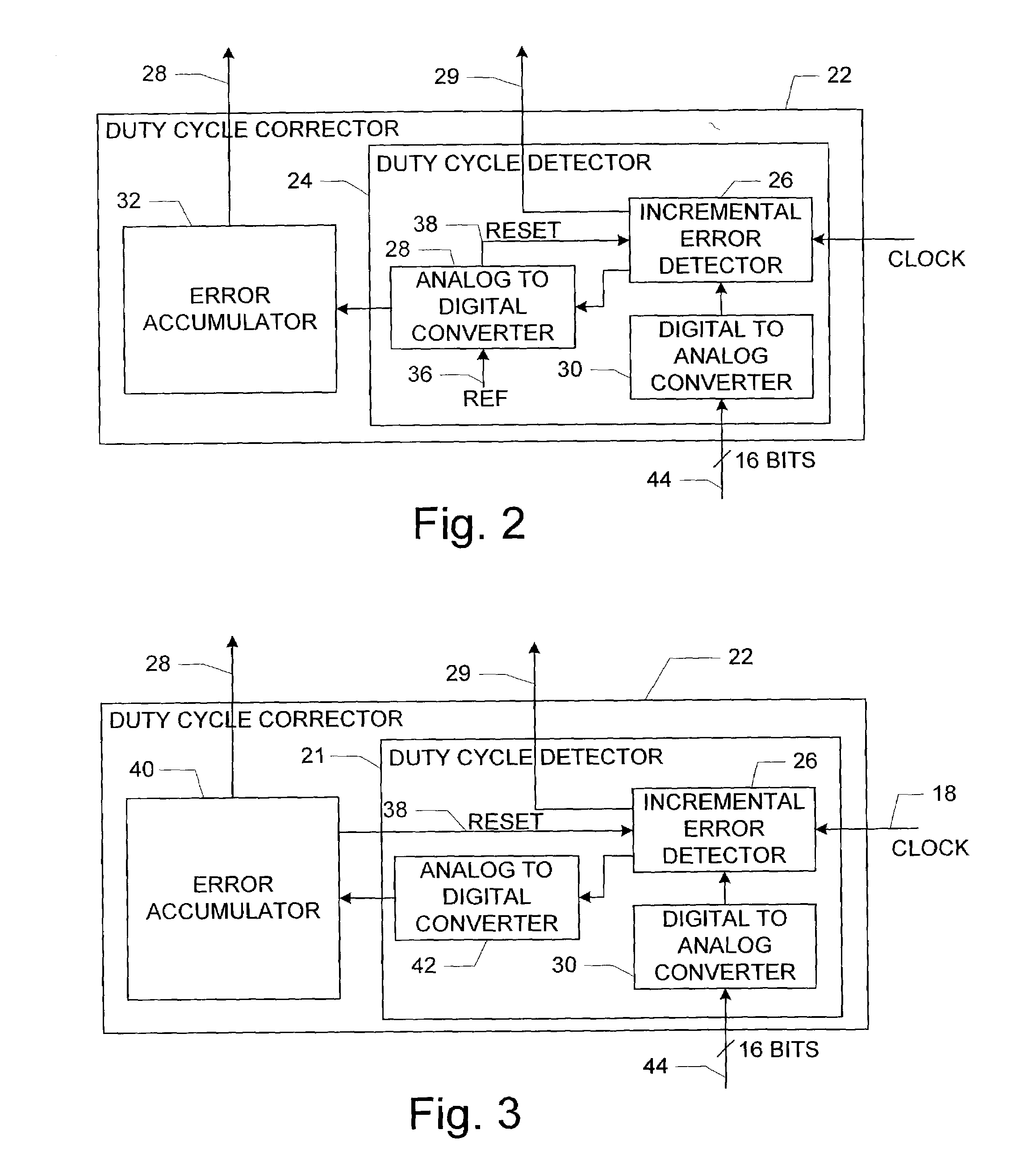

Method and apparatus for digital duty cycle adjustment

InactiveUS6967514B2Reliability increasing modificationsContinuous to patterned pulse manipulationError signalClock signal

Adjusting a clock duty cycle. An incremental error signal is generated in response to the clock signal. A cumulative error signal is generated in response to the incremental error signal. The incremental error signal is reset and the duty cycle of the clock signal is adjusted in response to the cumulative error signal.

Owner:RAMBUS INC

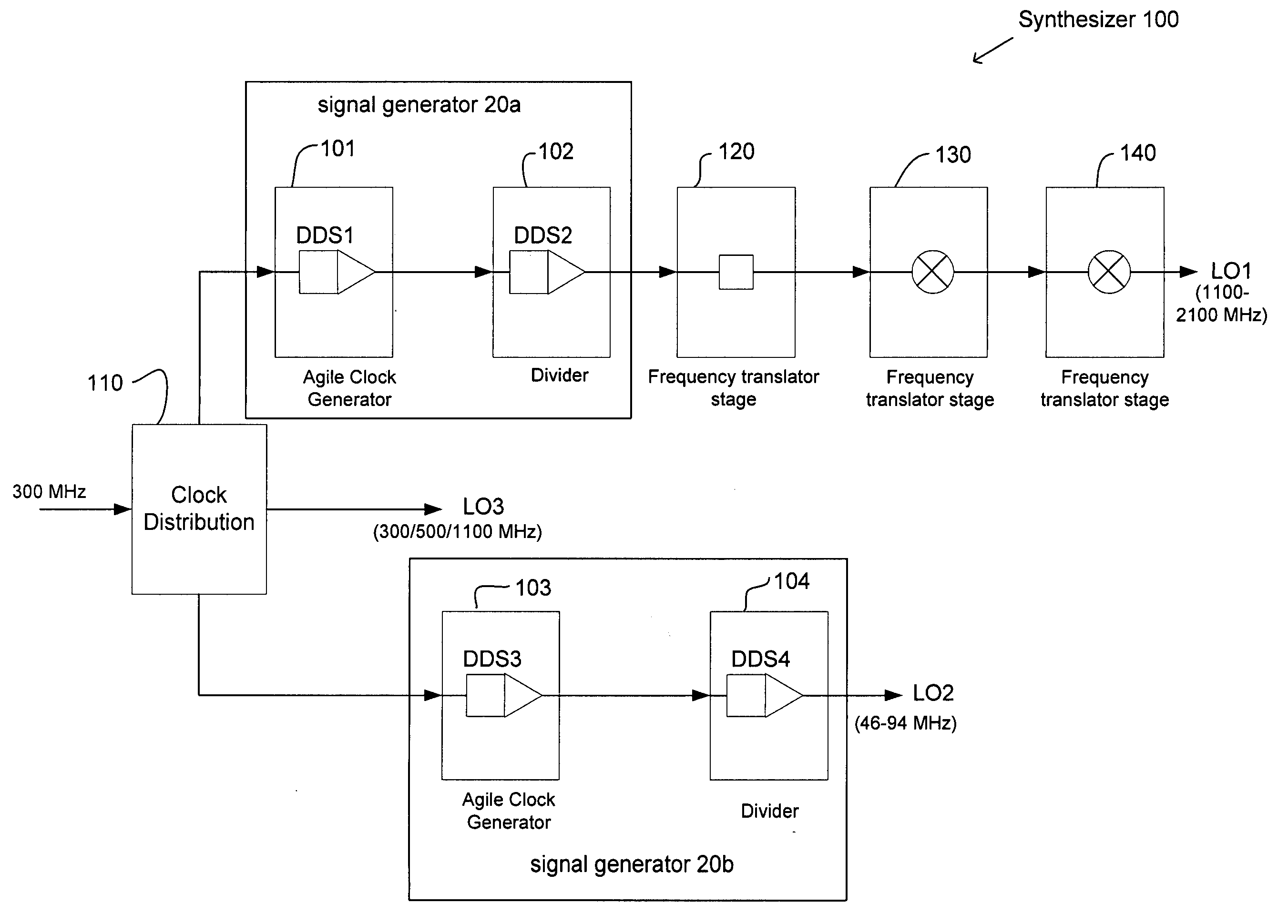

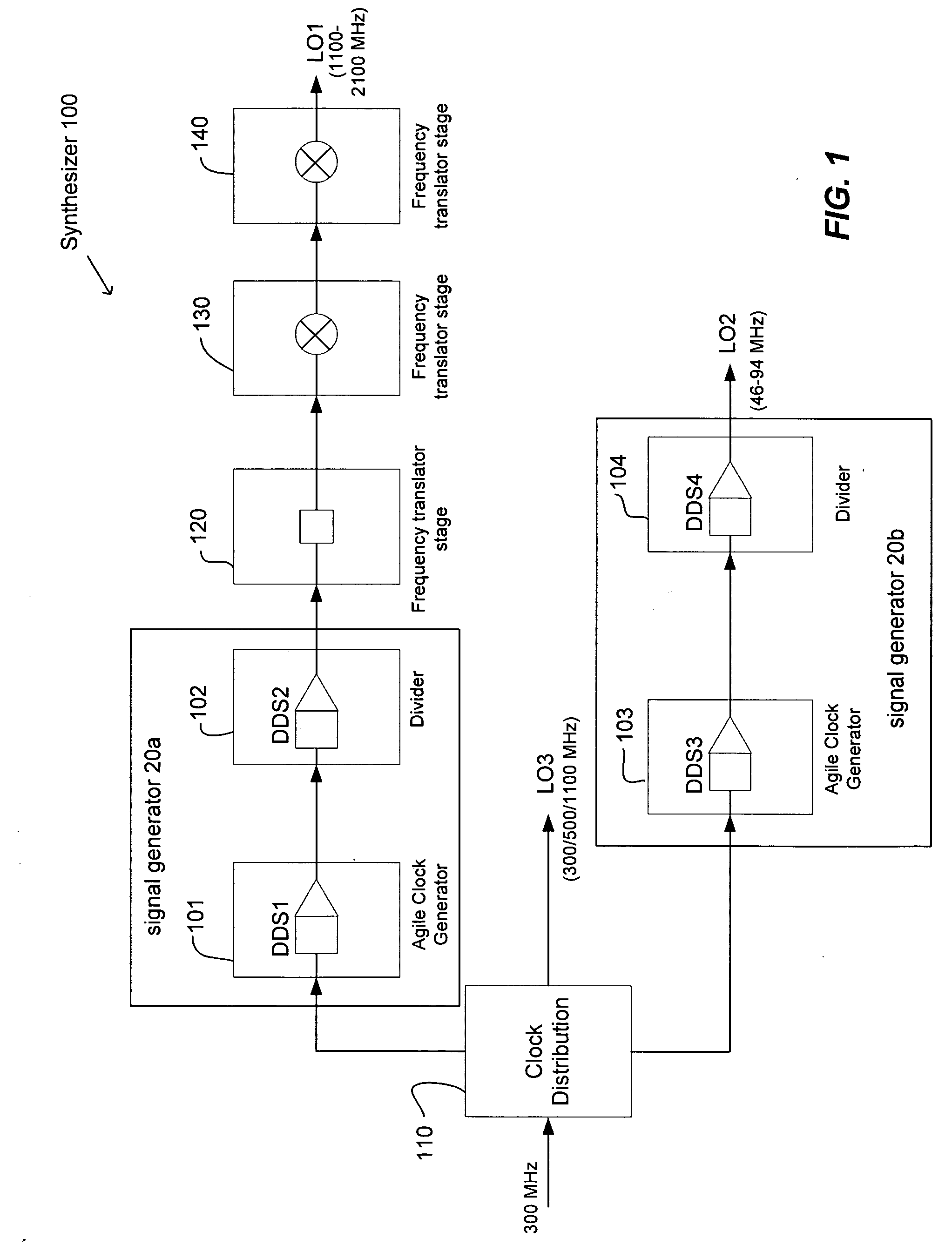

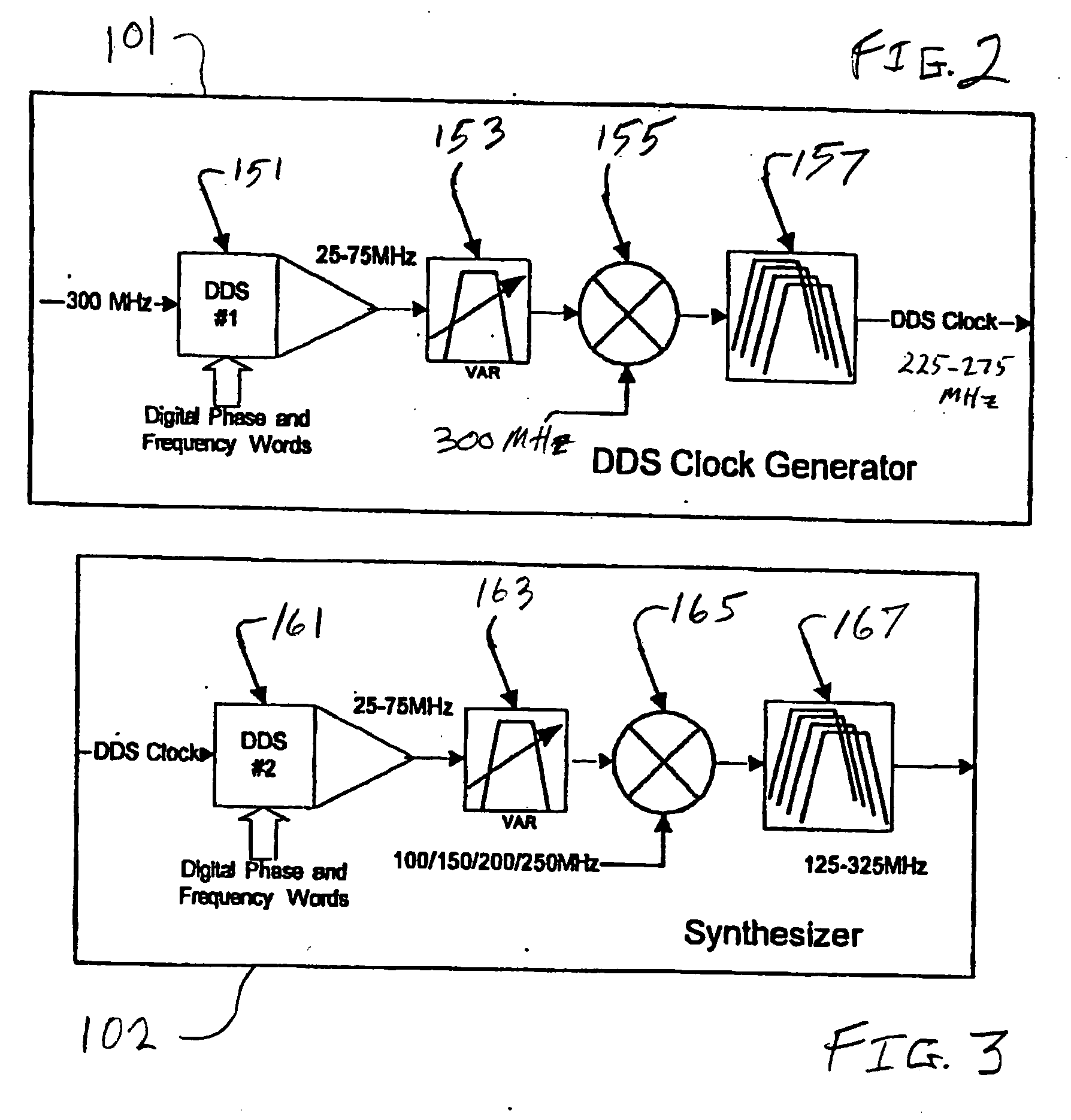

Wideband signal generators, measurement devices, methods of signal generation, and methods of signal analysis

ActiveUS20050003785A1Small sizeReducing or avoiding spurious DDS responsesPulse automatic controlContinuous to patterned pulse manipulationMeasurement deviceSignal analyzer

A wideband signal generator according to one embodiment of the invention includes a variable frequency source and a direct digital synthesizer. Local oscillators, signal analyzers, modulators, demodulators, and other equipment including one or more such generators are also disclosed.

Owner:MERCURY SISTEMS INC

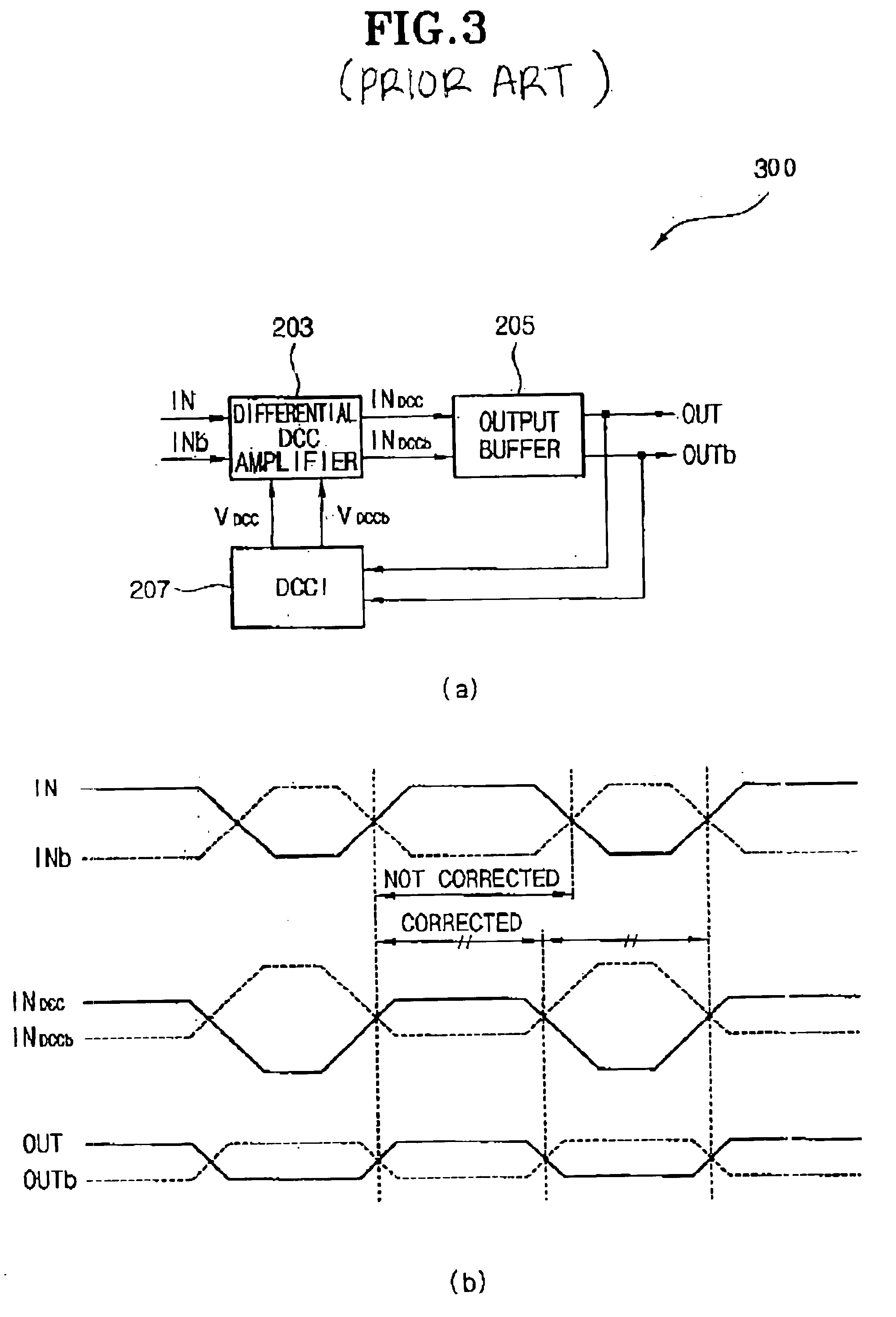

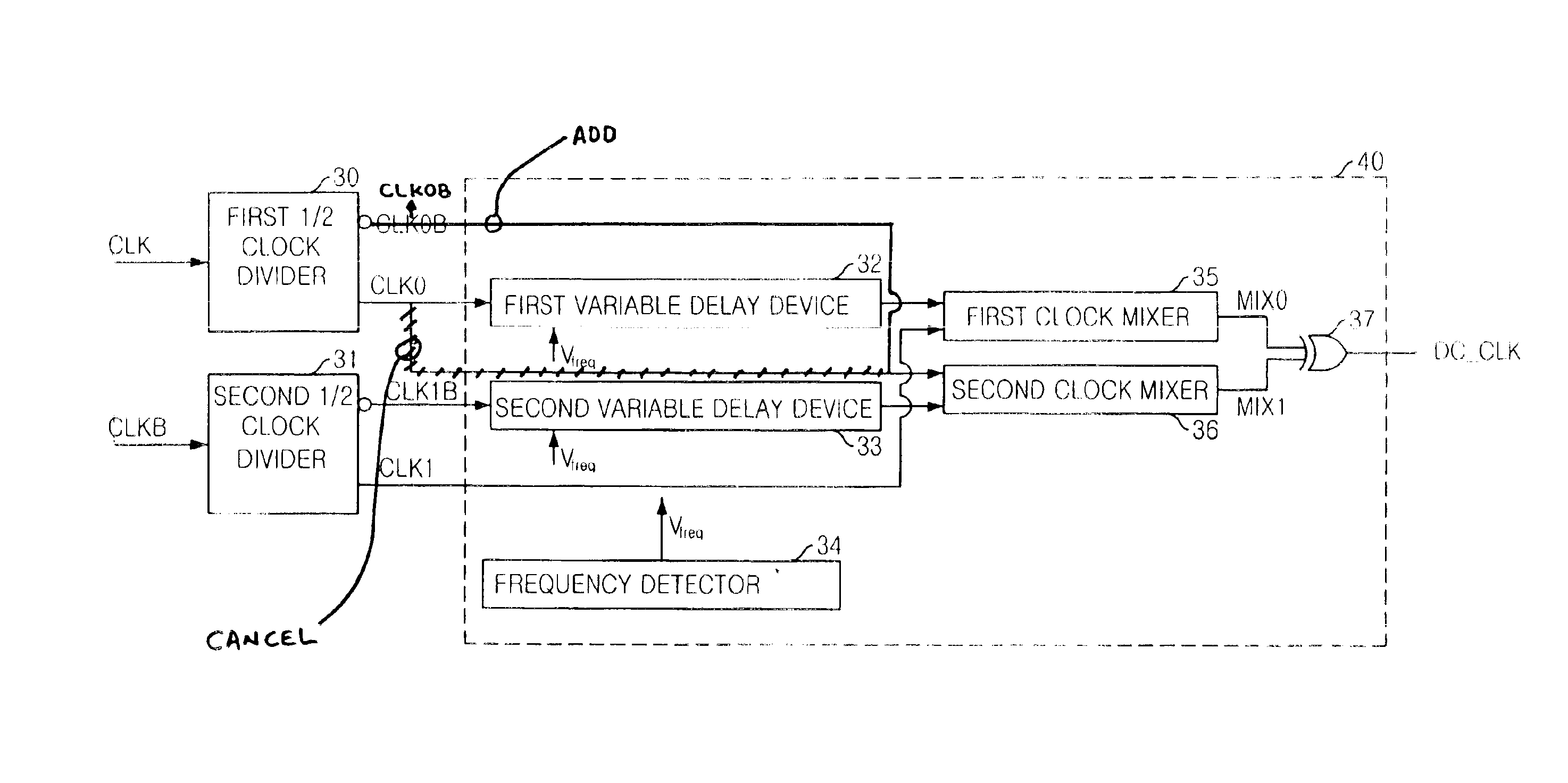

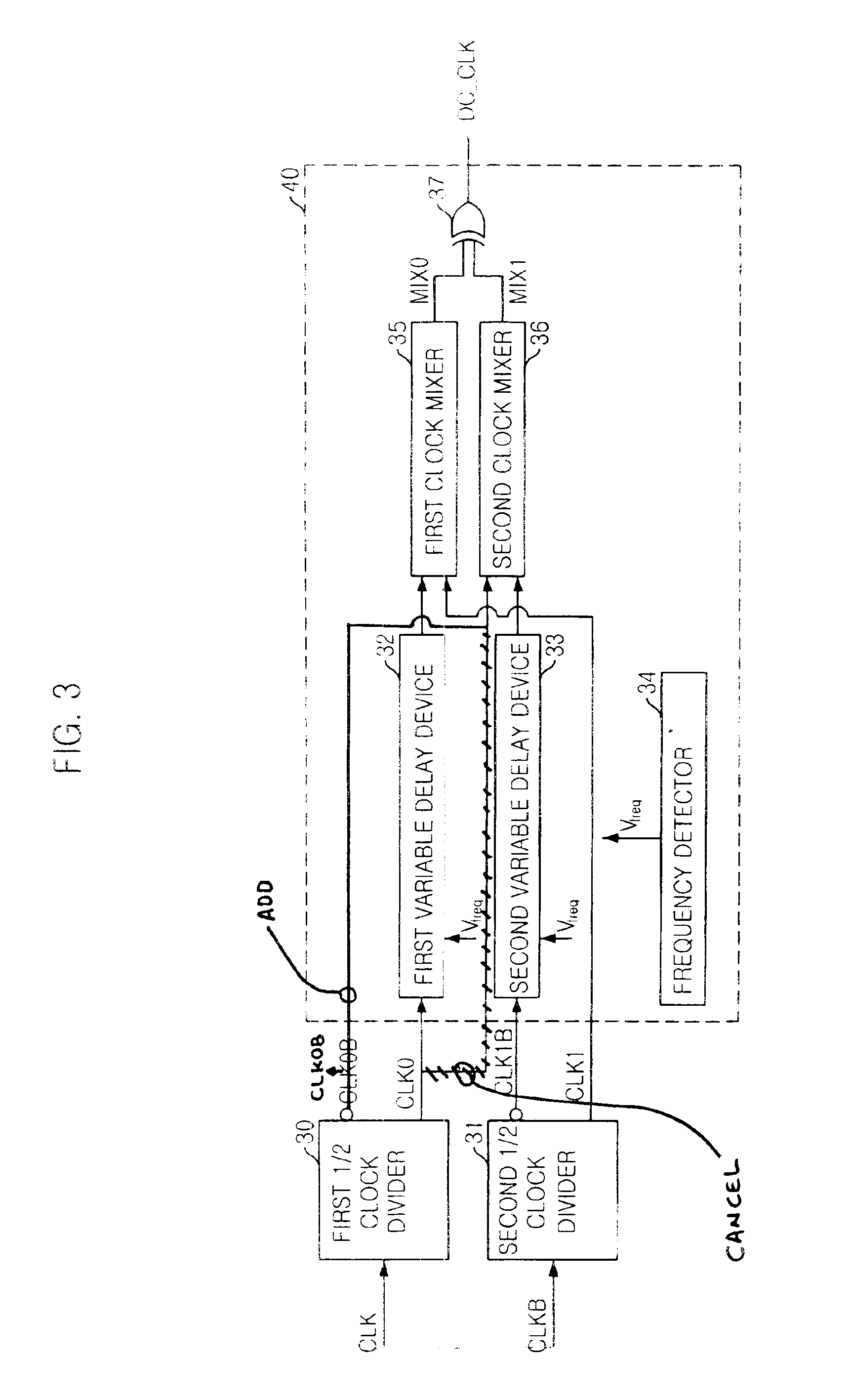

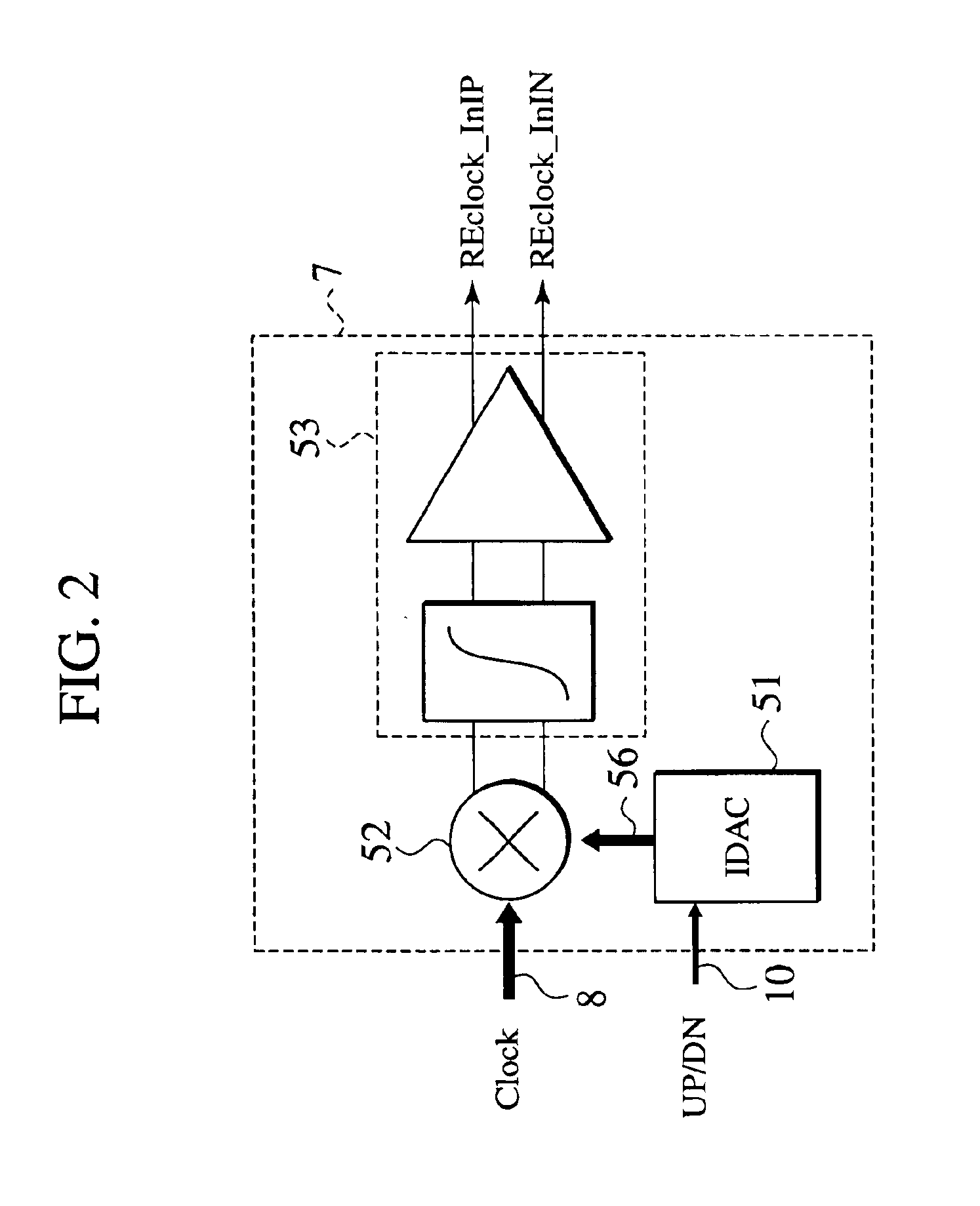

Duty cycle correction circuit and delay locked loop having the same

InactiveUS6859081B2Reduce power consumptionPulse automatic controlContinuous to patterned pulse manipulationClock rateFrequency mixer

A duty cycle correction (DCC) circuit including first and second clock dividers for dividing ordinary and sub-input clocks. Optional first and second variable delay devices delay the divided clocks. First and second mixers mix an optionally delayed ordinary divided clock and sub-ordinary divided clock, or an ordinary divided clock and an optionally delayed sub-ordinary divided clock. A logic combination device is included to produce a clock at the same frequency as the ordinary and sub-input clocks, with a corrected duty cycle.

Owner:CONVERSANT INTPROP MANAGEMENT INC

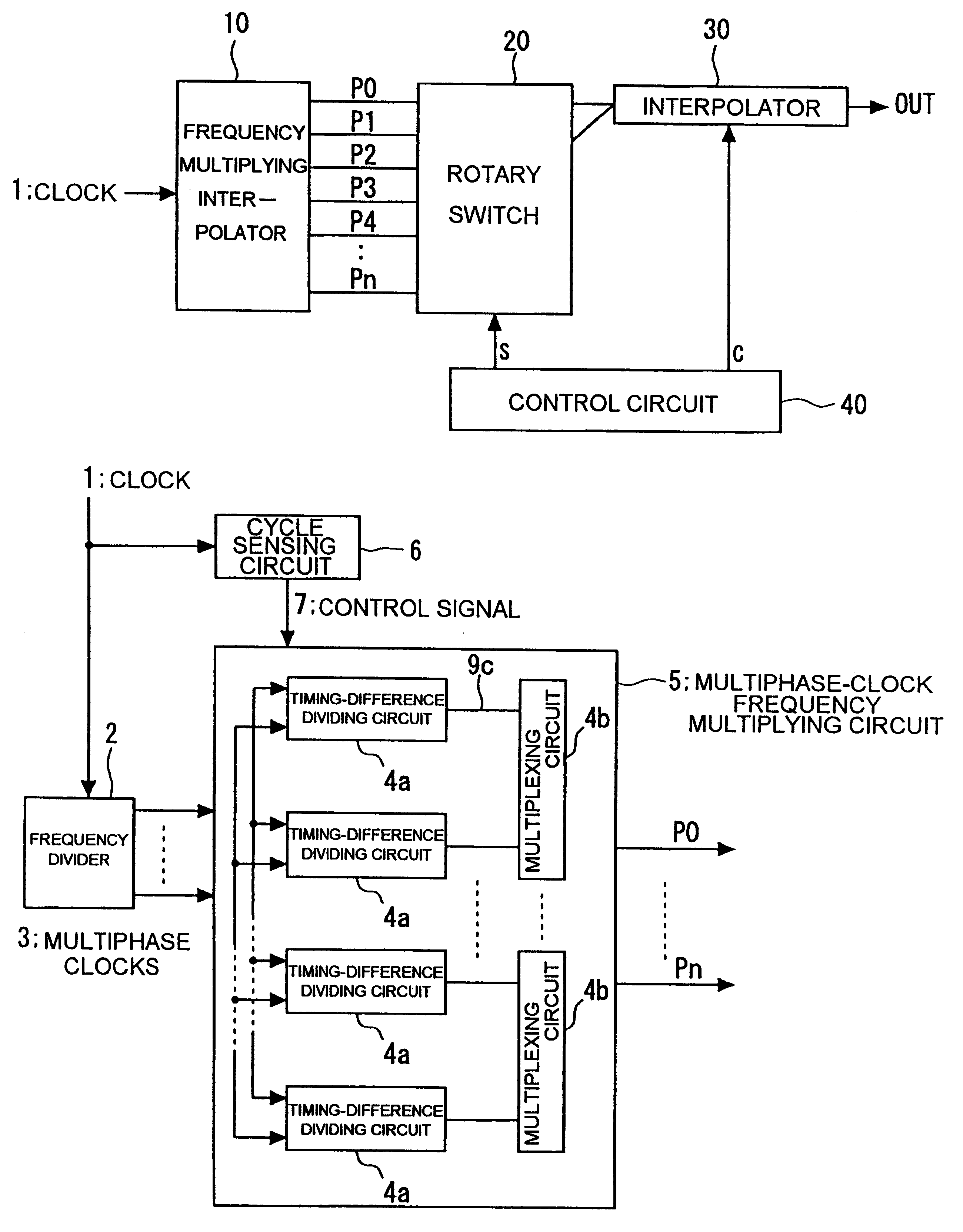

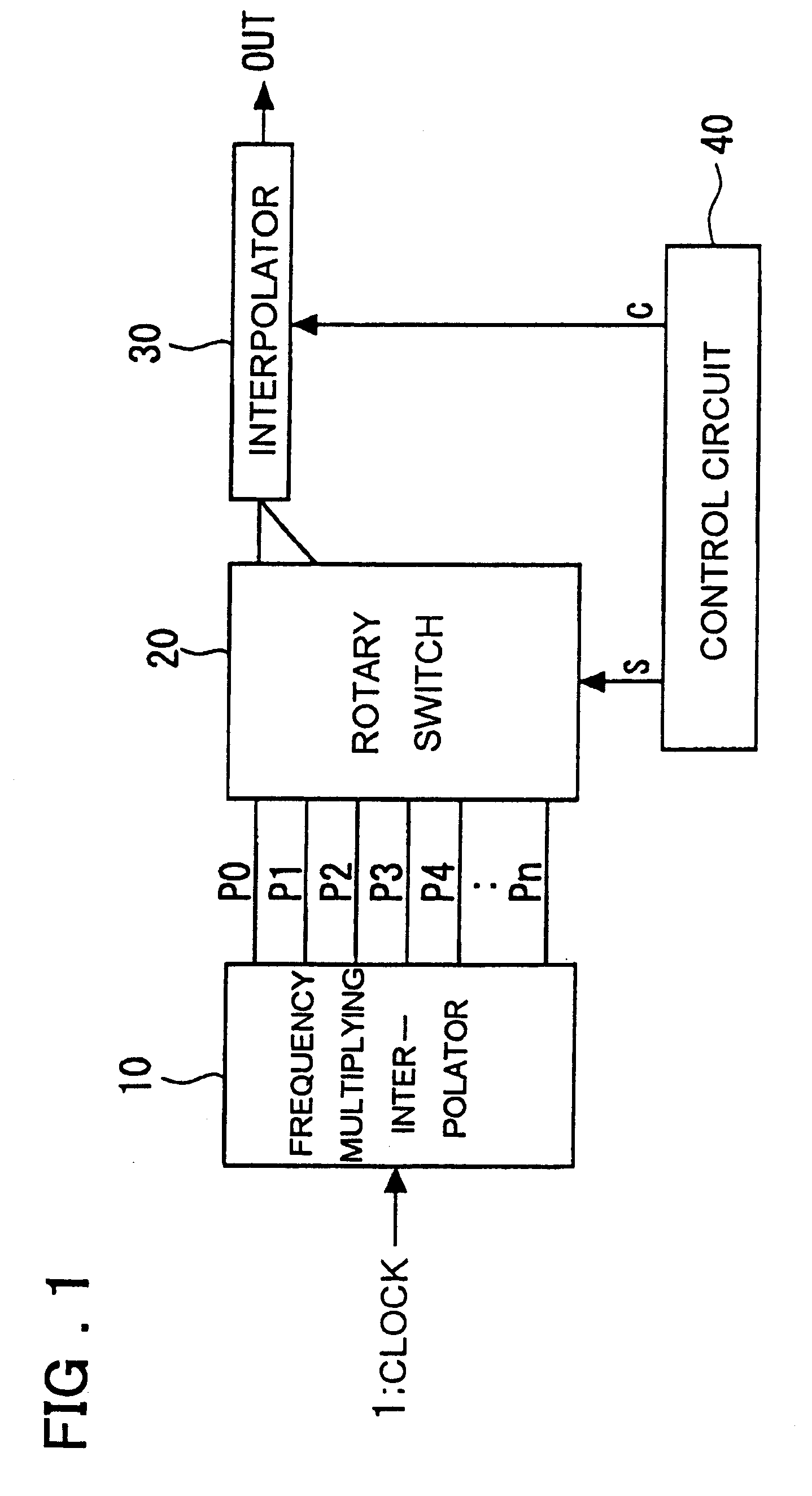

Clock control circuit and clock control method

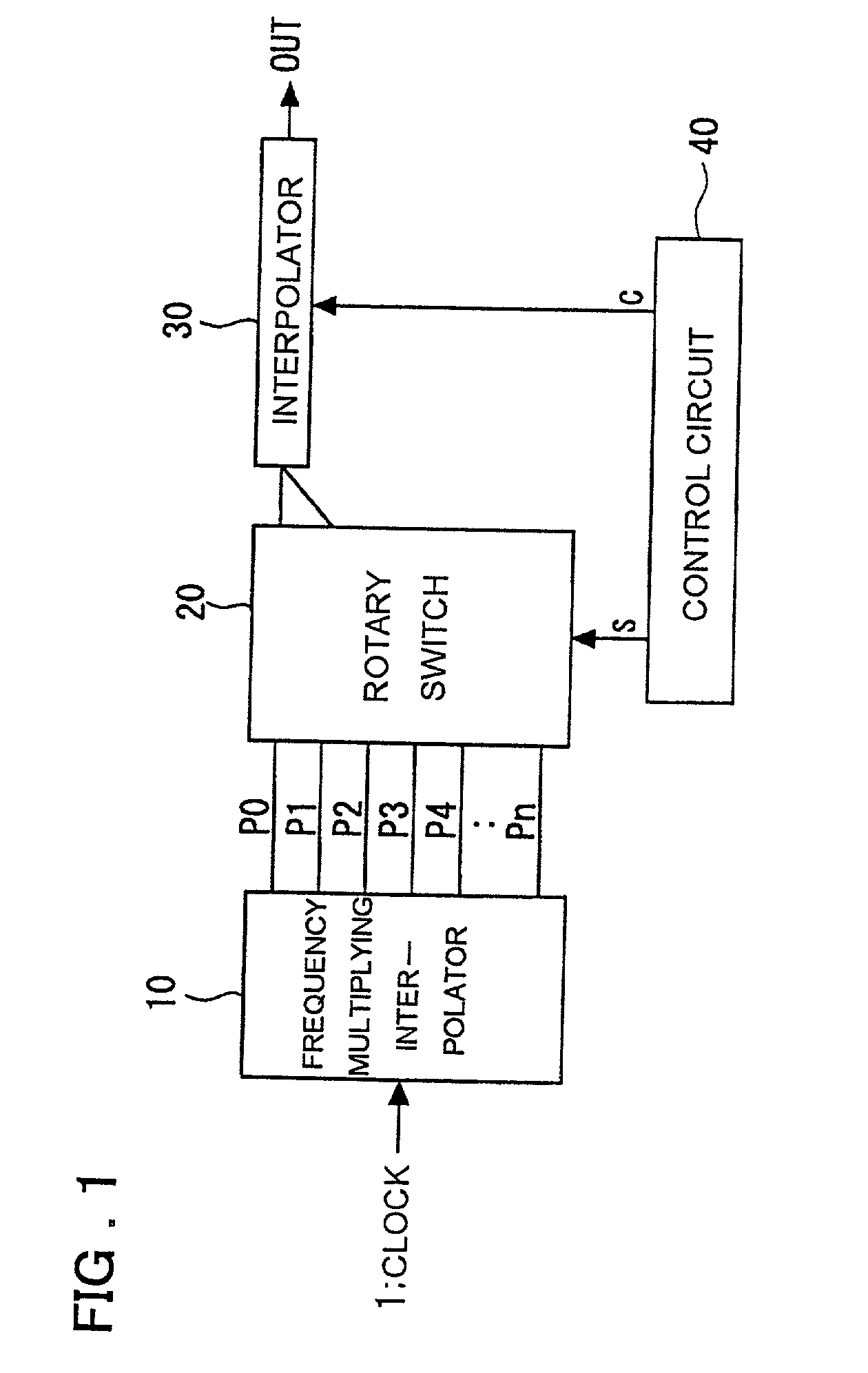

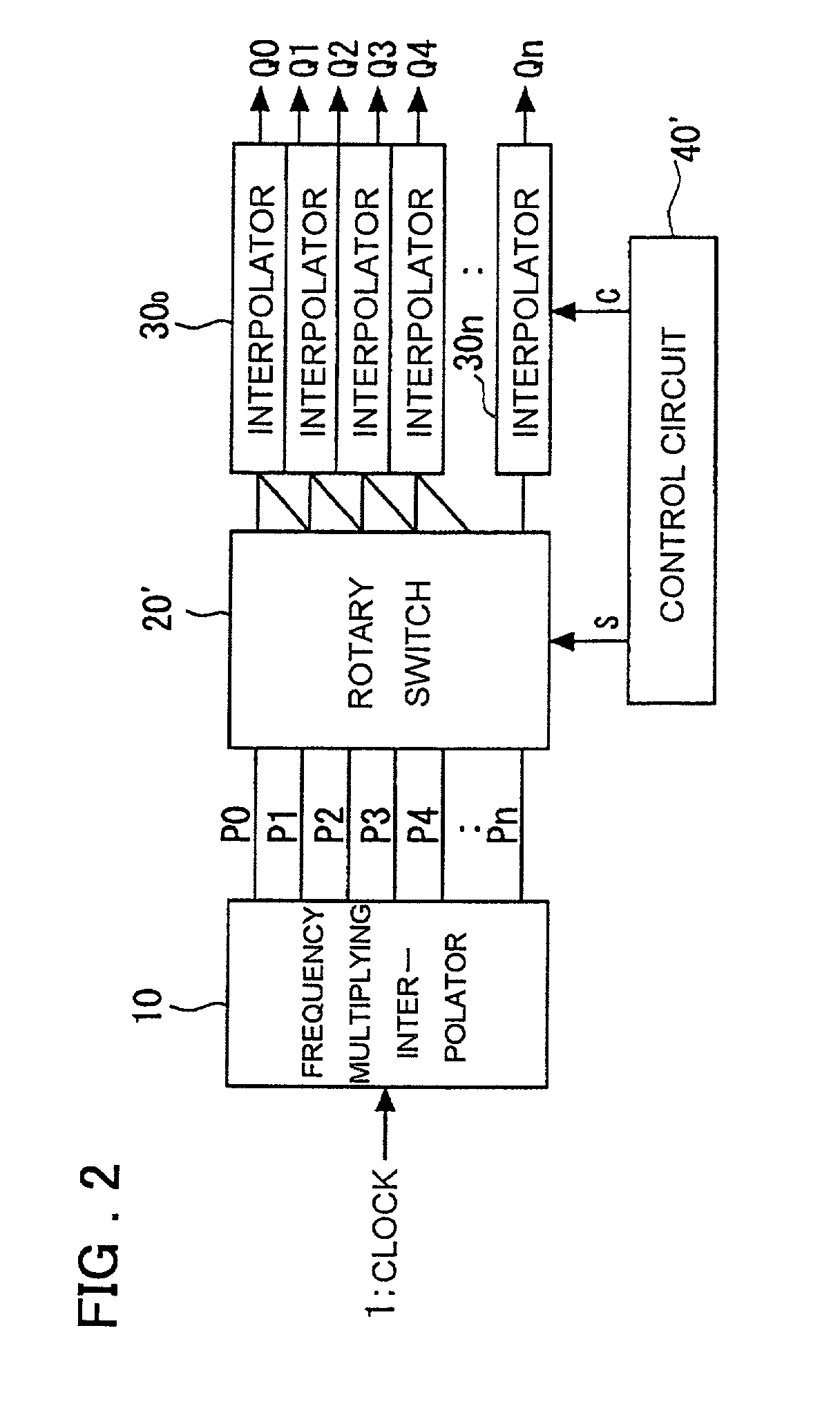

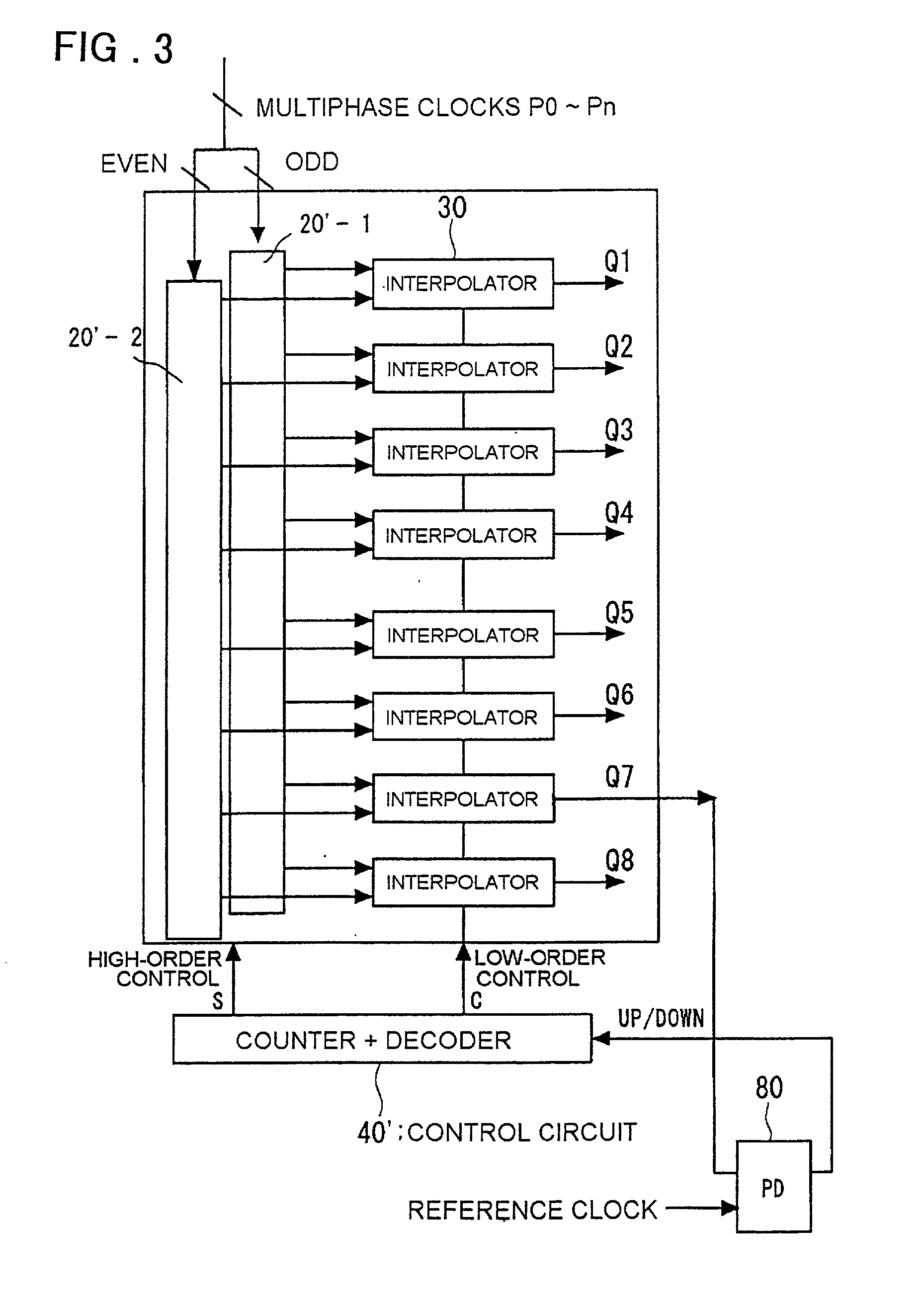

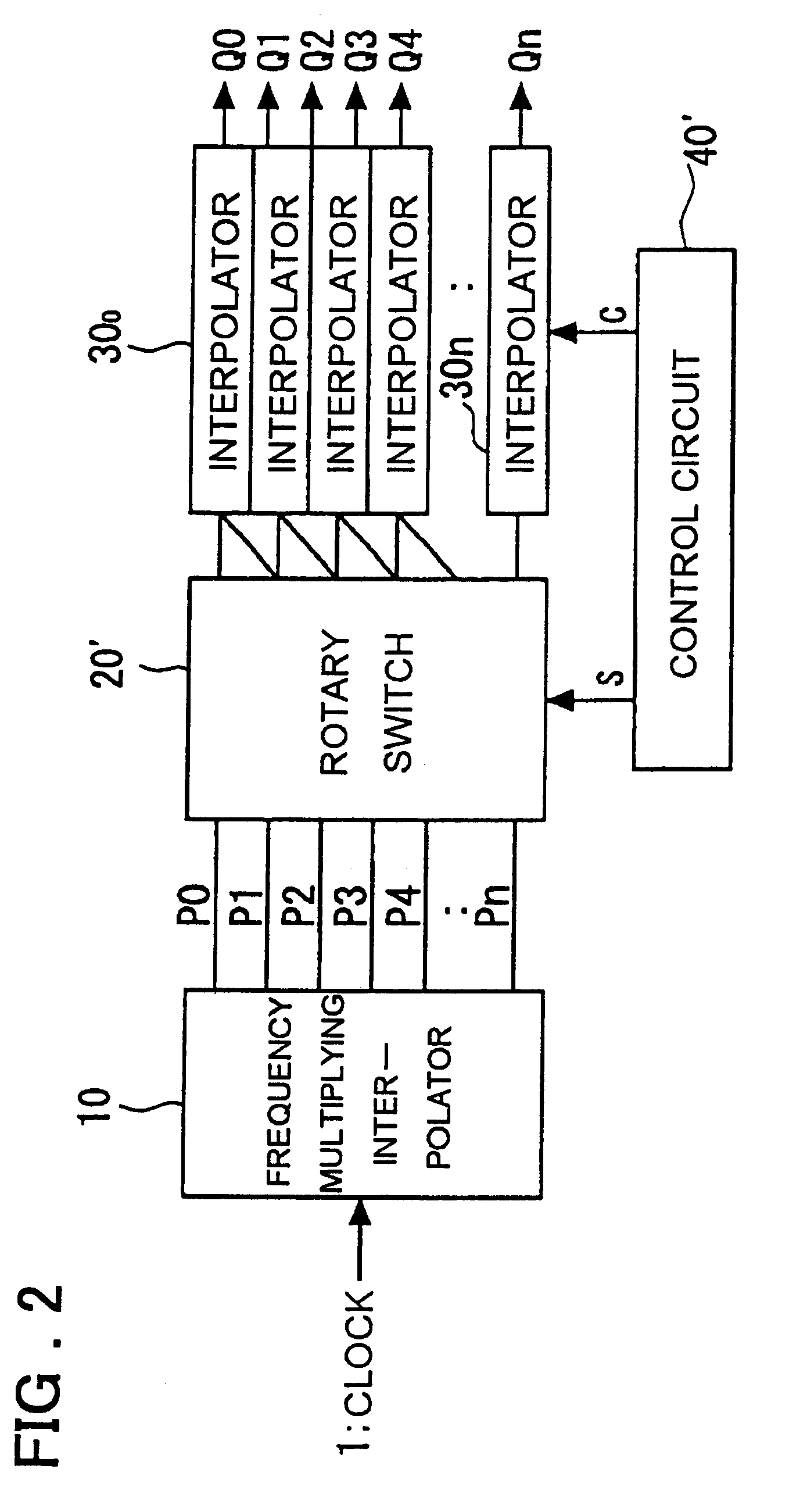

InactiveUS20010026179A1Reduce errorsEliminate fluctuationsPulse automatic controlContinuous to patterned pulse manipulationControl switchControl theory

A clock control circuit which includes a frequency multiplying interpolator for generating and outputting multiphase clocks by frequency multiplying an input clock; a switch for outputting two of the multiphase clocks input thereto from the frequency multiplying interpolator; a fine adjusting interpolator, to which the two outputs from the switch are applied, for outputting a signal obtained by internally dividing the phase difference between the two outputs; and a control circuit for controlling the switching of the switch and varying the internal-division ratio of the fine adjusting interpolator.

Owner:RENESAS ELECTRONICS CORP

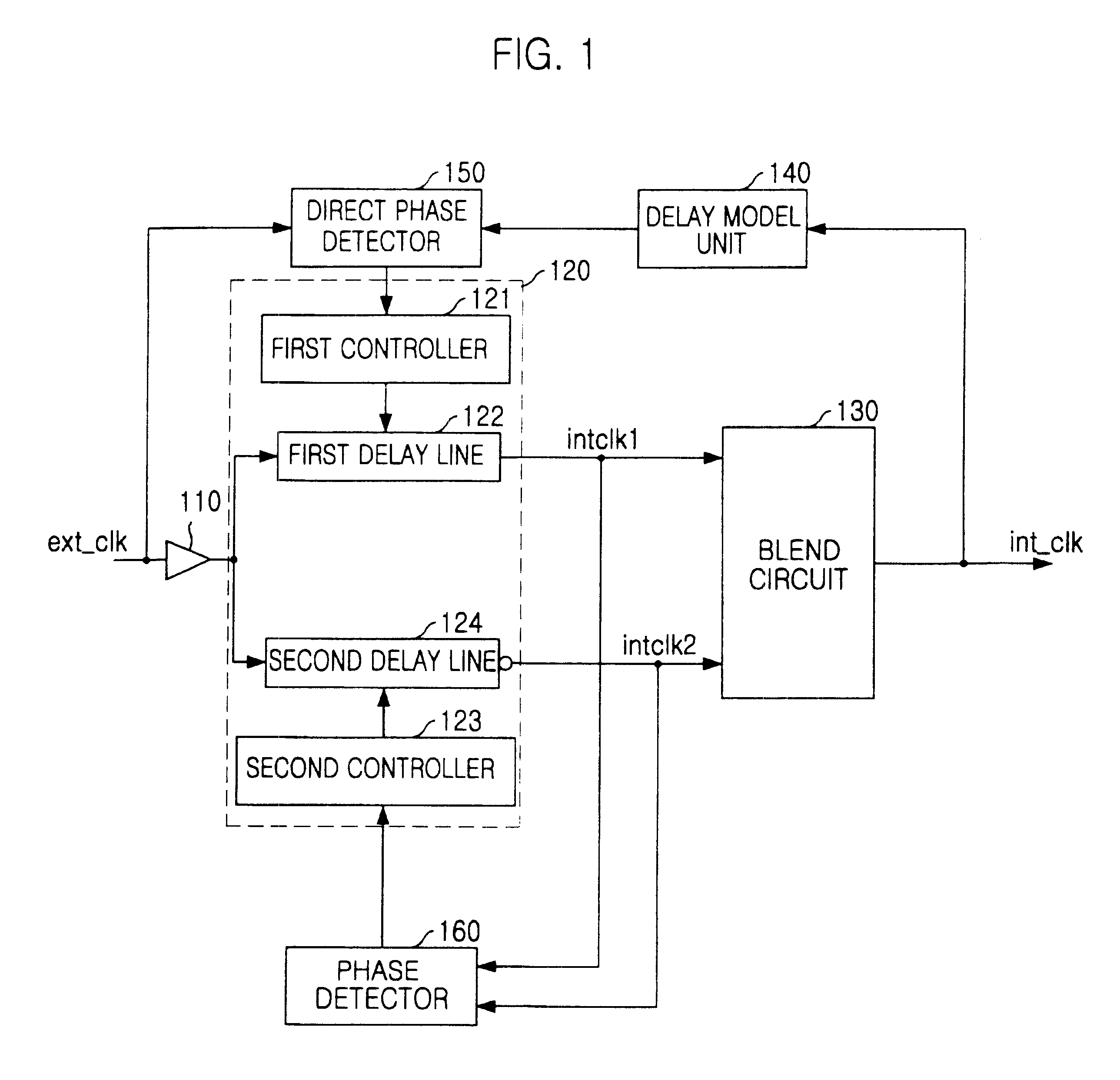

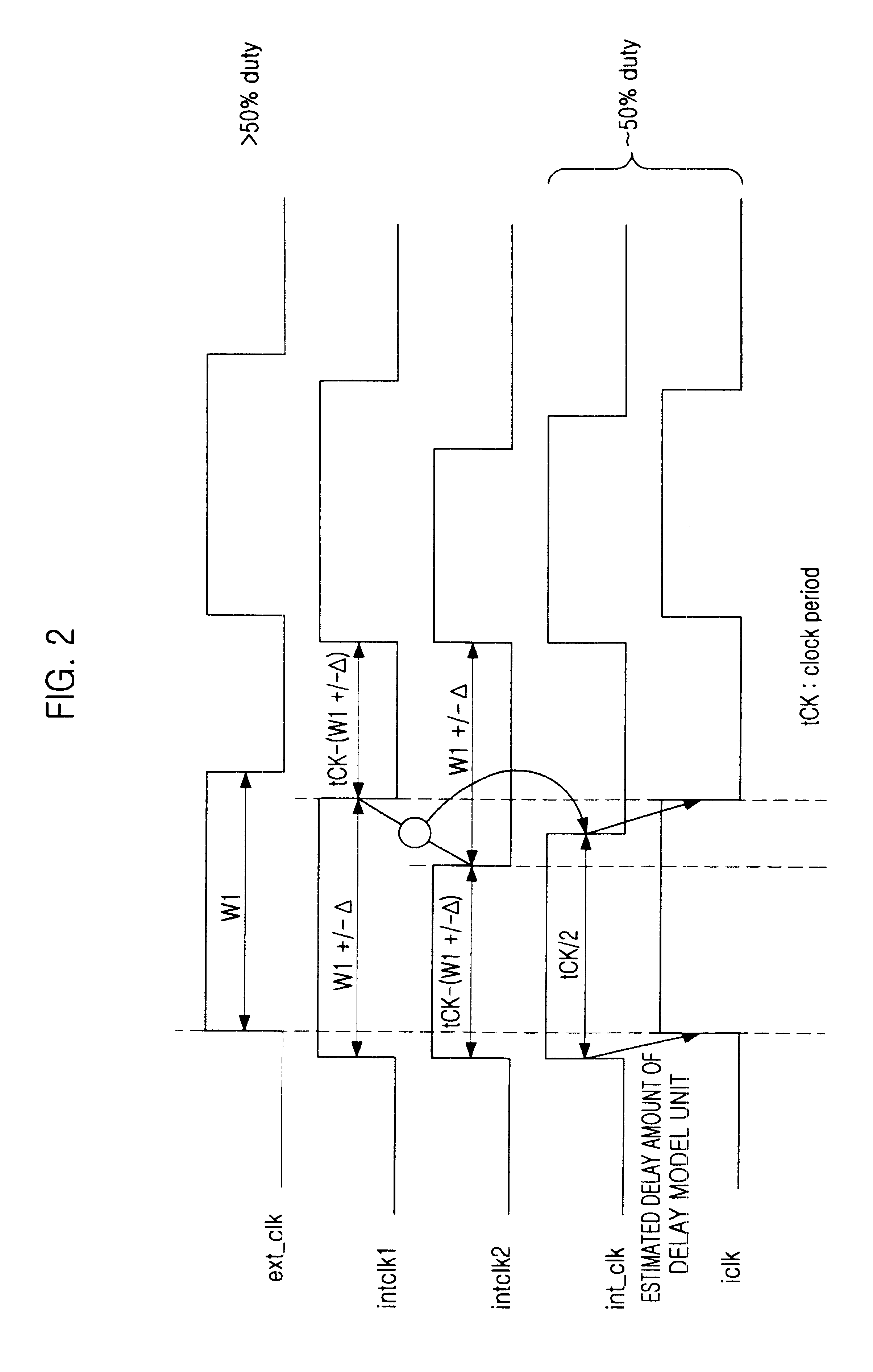

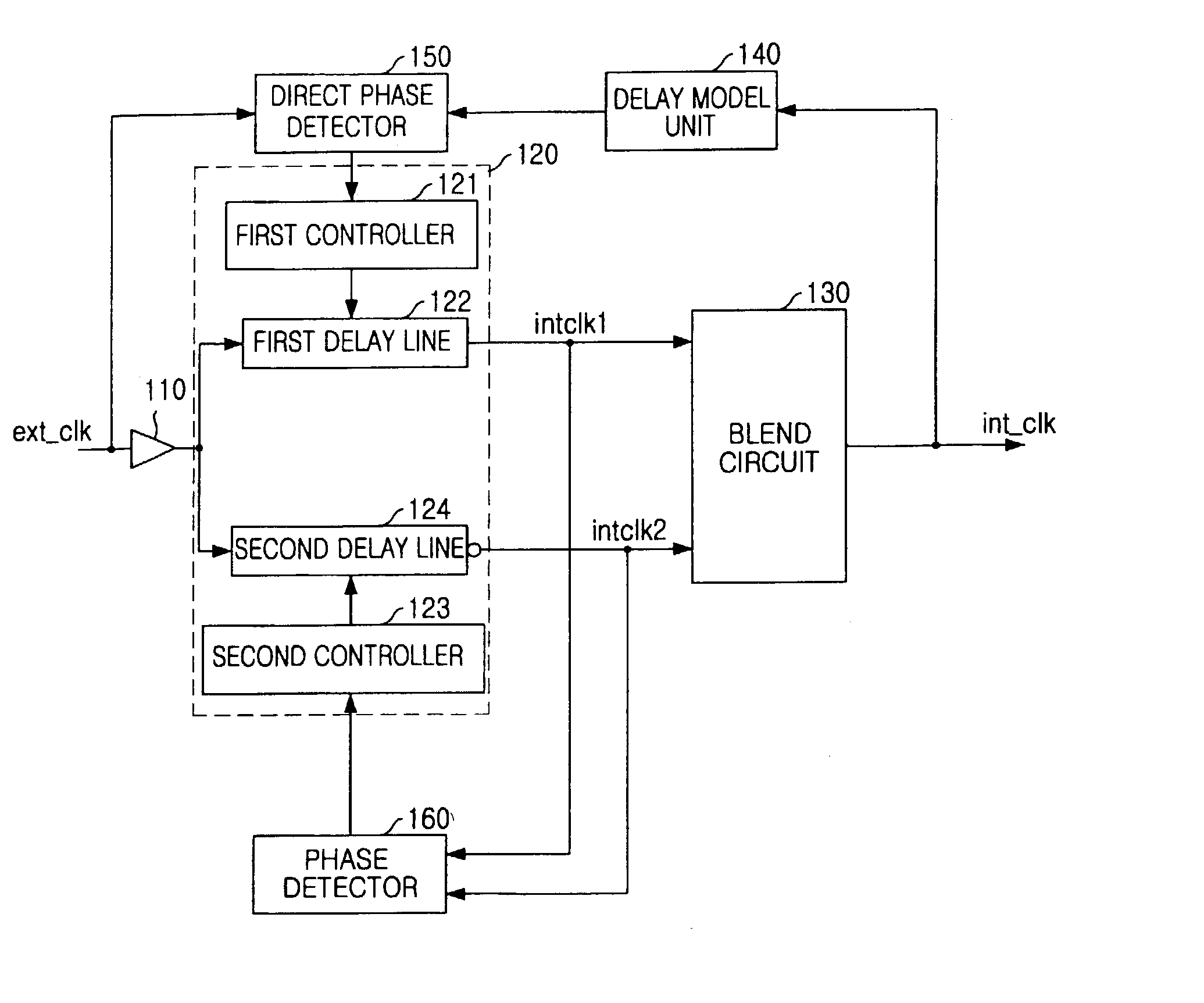

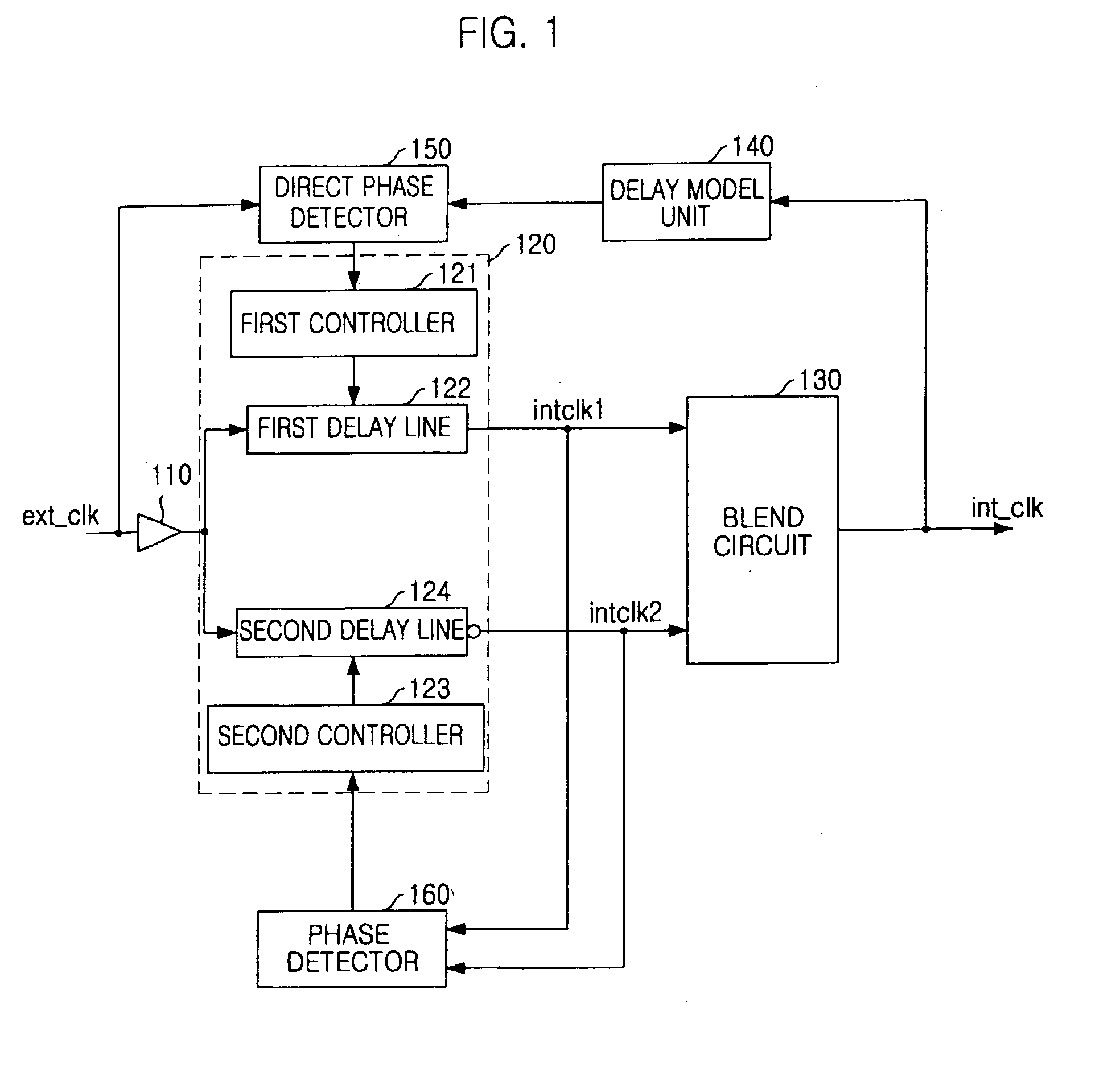

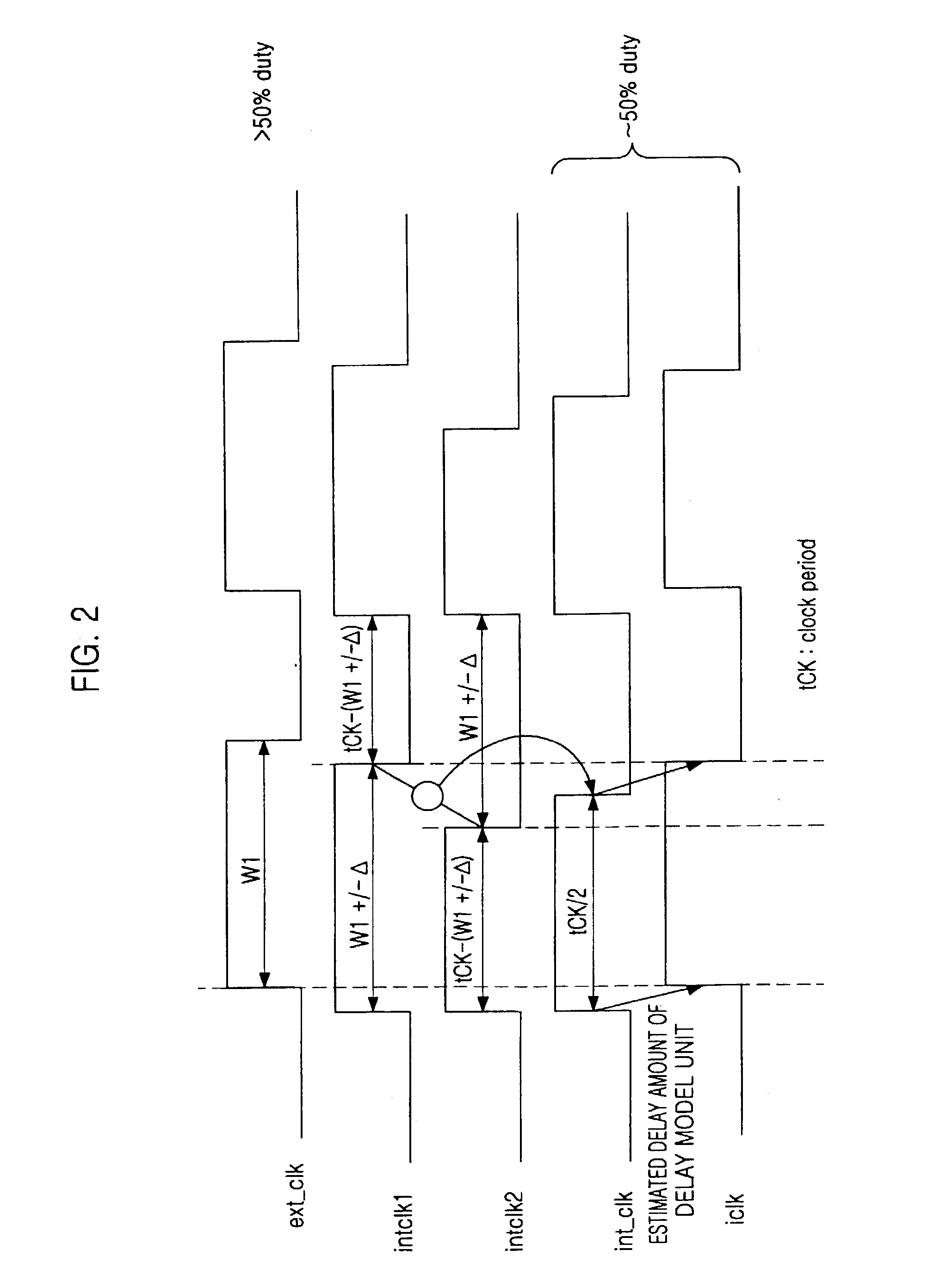

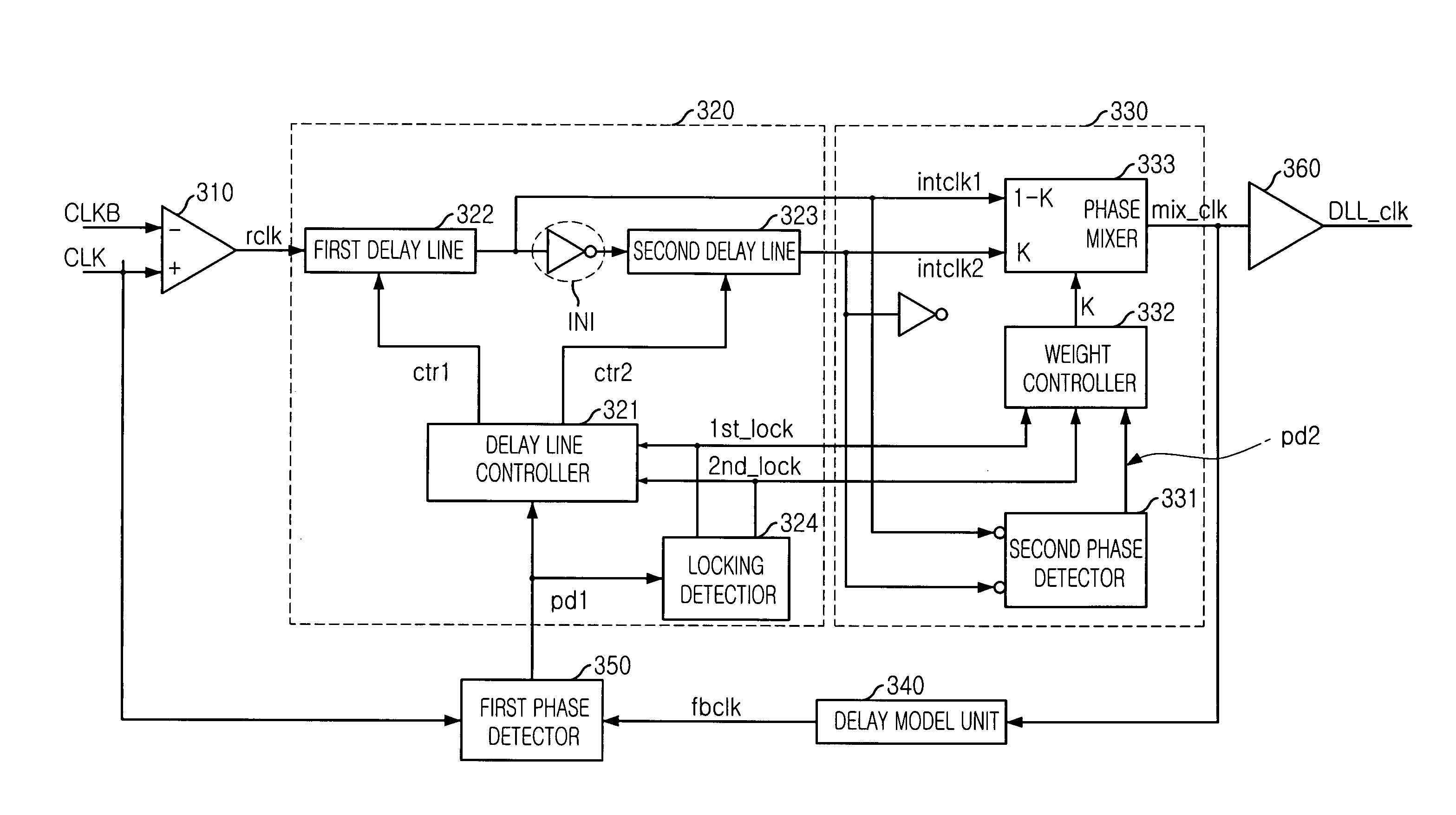

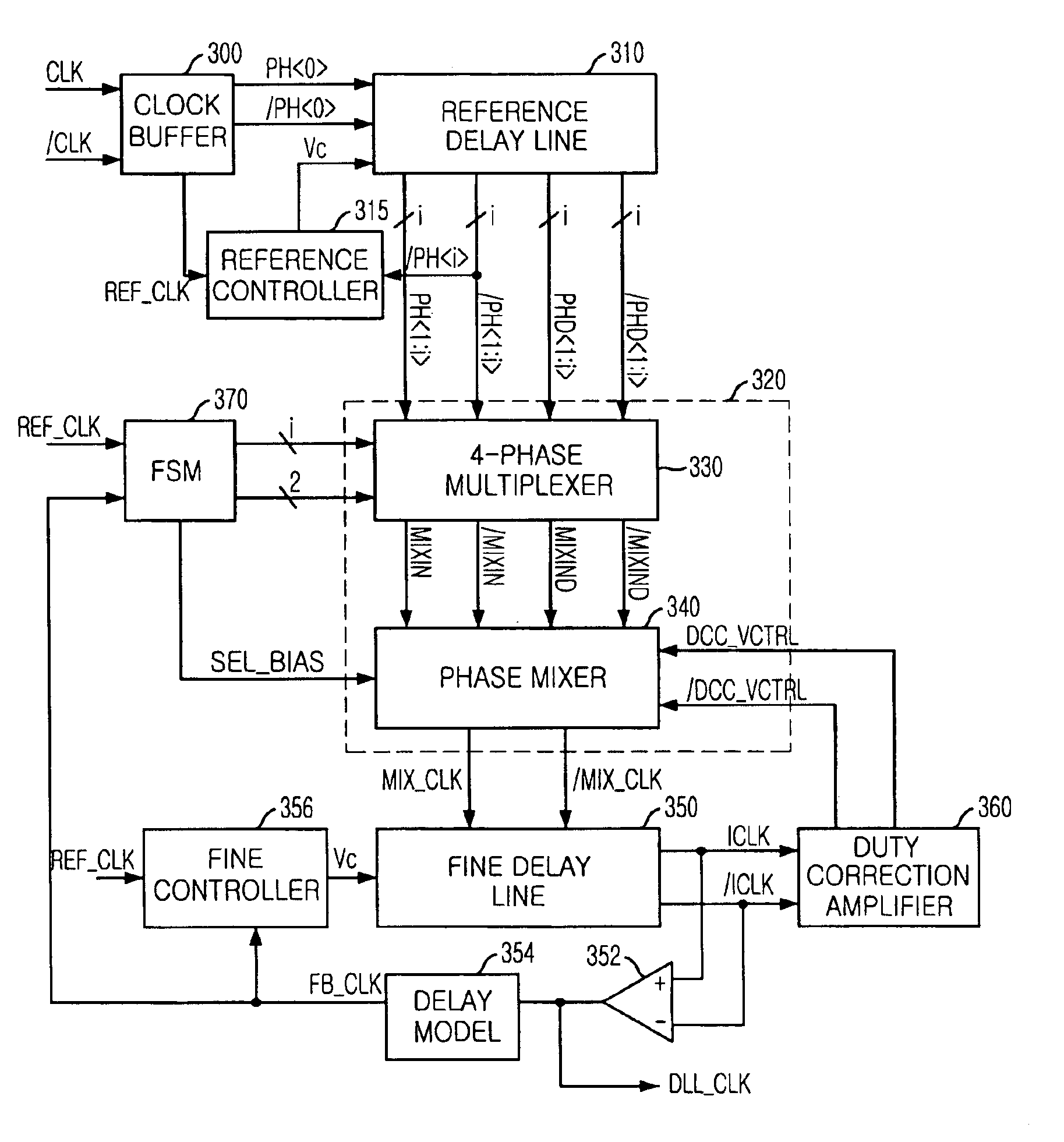

Digital DLL apparatus for correcting duty cycle and method thereof

InactiveUS6677792B2Pulse automatic controlContinuous to patterned pulse manipulationPhase detectorEngineering

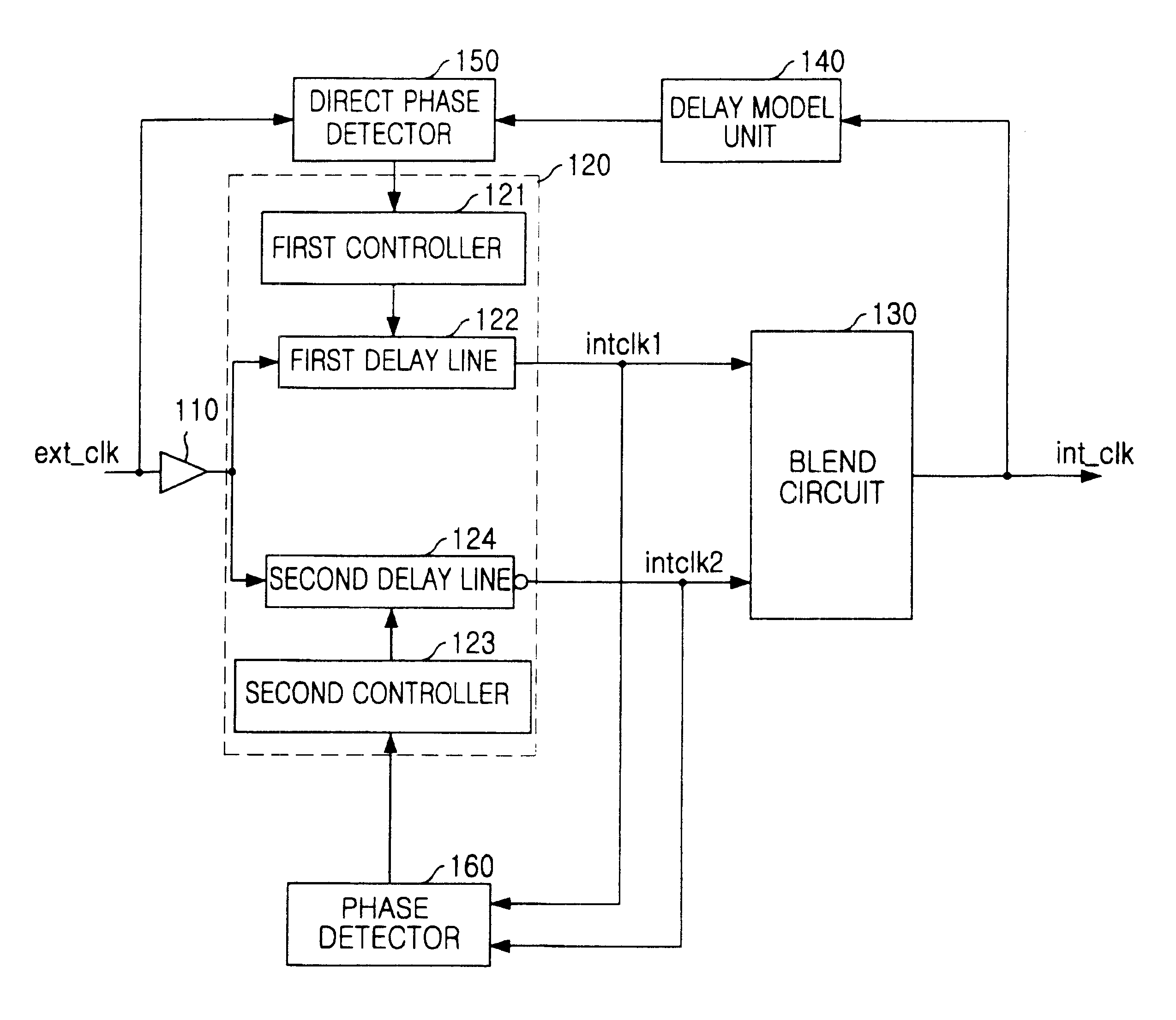

A digital DLL apparatus and a method for correcting a duty cycle are disclosed. The digital DLL apparatus for correcting a duty cycle, includes: a buffer for producing a clock input signal; a delay line unit for receiving / delaying the clock input signal and outputting the clock input signal; a blend circuit for bypassing the first clock signal or producing a blended clock signal; a delay model unit for compensating a time difference of an external clock and an internal clock and generating a compensate clock signal; a direct phase detector for generating a first comparison signal; and a phase detector for generating a second comparison signal. The disclosed apparatus can correct the duty error by using the blend circuit and generate an internal clock signal having 50% of duty cycle.

Owner:SK HYNIX INC

Clock control circuit and clock control method

InactiveUS6380774B2Inaccurate to some degreeReduce jitterPulse automatic controlContinuous to patterned pulse manipulationPhase differenceEngineering

A clock control circuit which includes a frequency multiplying interpolator for generating and outputting multiphase clocks by frequency multiplying an input clock; a switch for outputting two of the multiphase clocks input thereto from the frequency multiplying interpolator; a fine adjusting interpolator, to which the two outputs from the switch are applied, for outputting a signal obtained by internally dividing the phase difference between the two outputs; and a control circuit for controlling the switching of the switch and varying the internal-division ratio of the fine adjusting interpolator.

Owner:RENESAS ELECTRONICS CORP

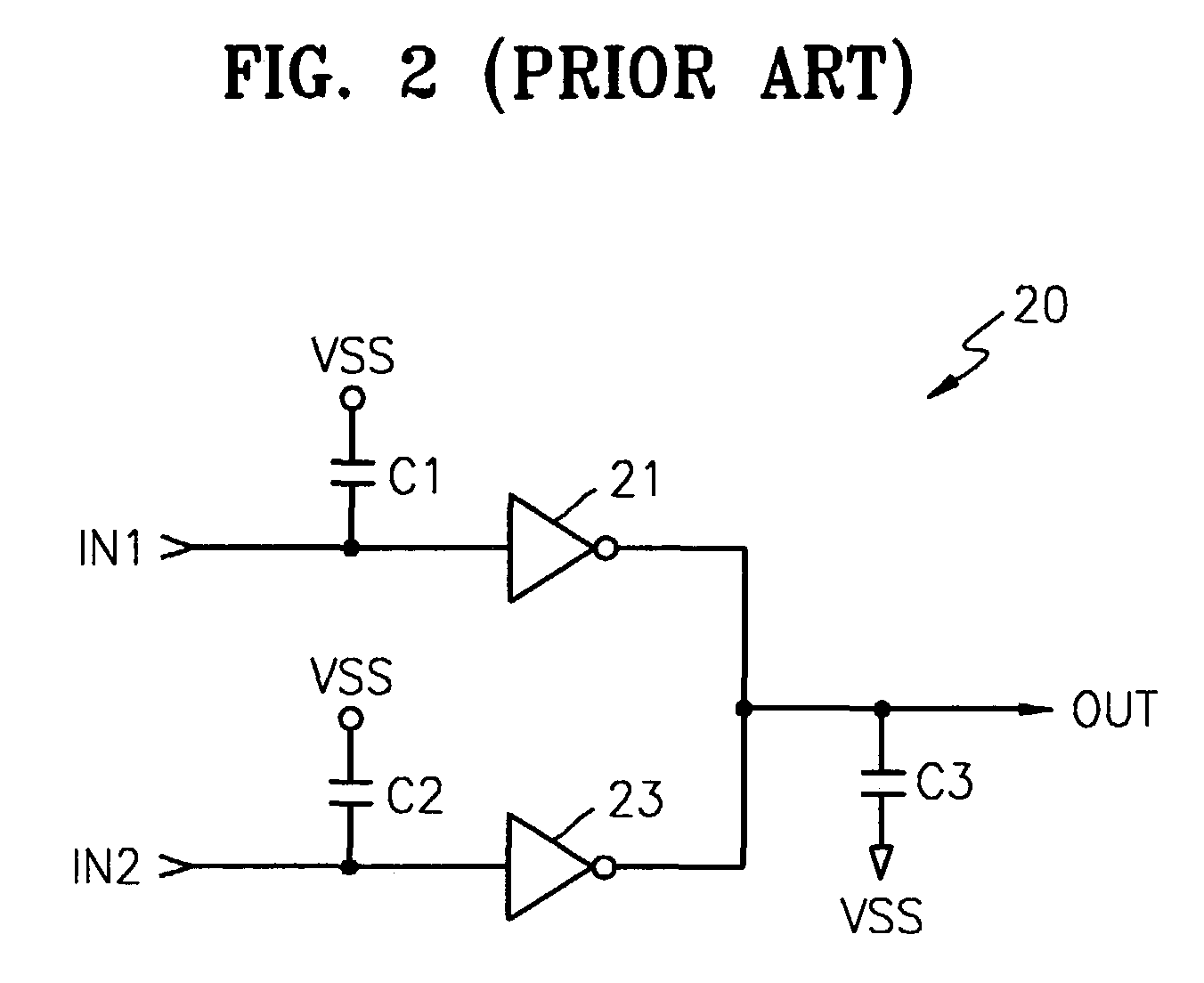

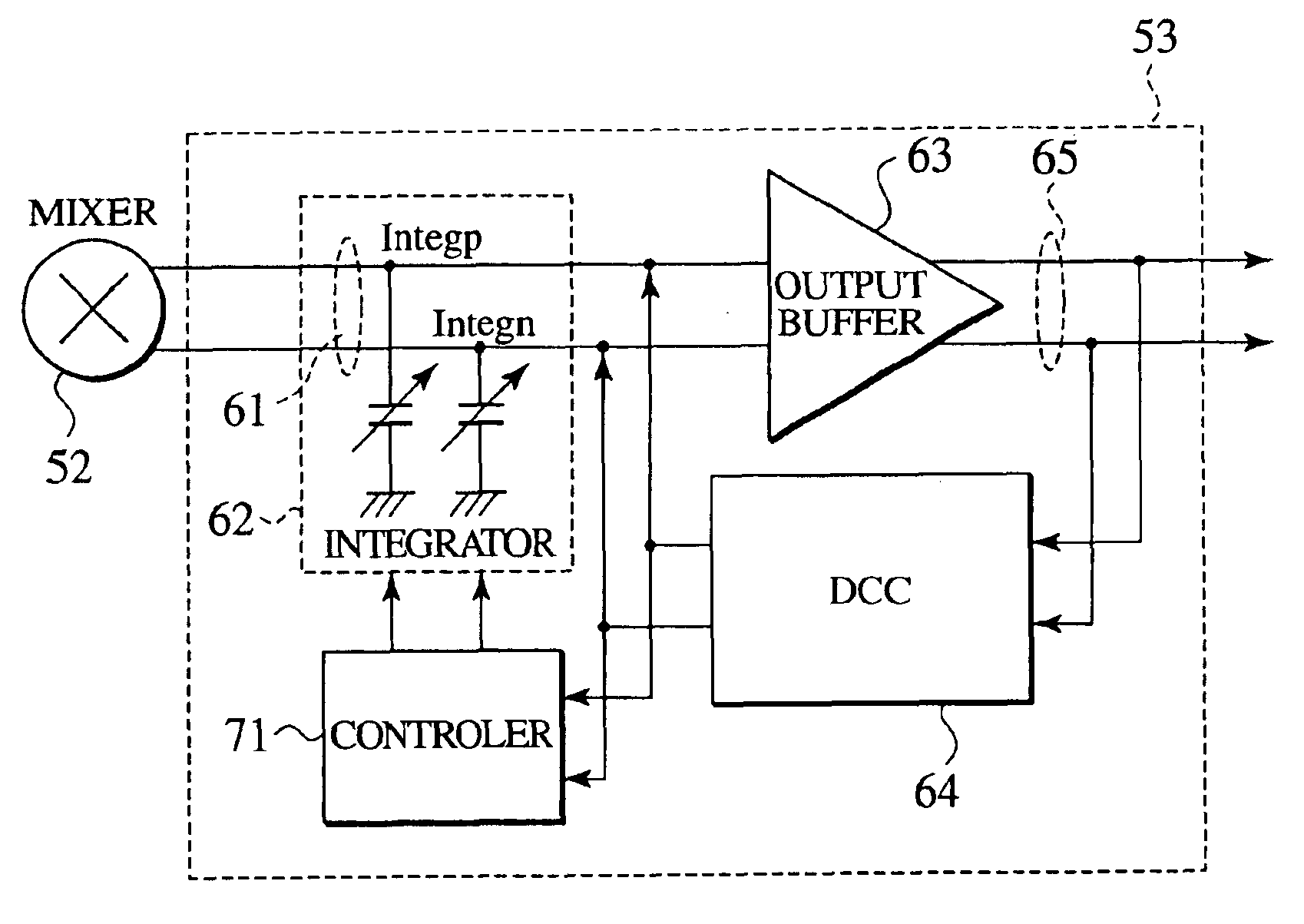

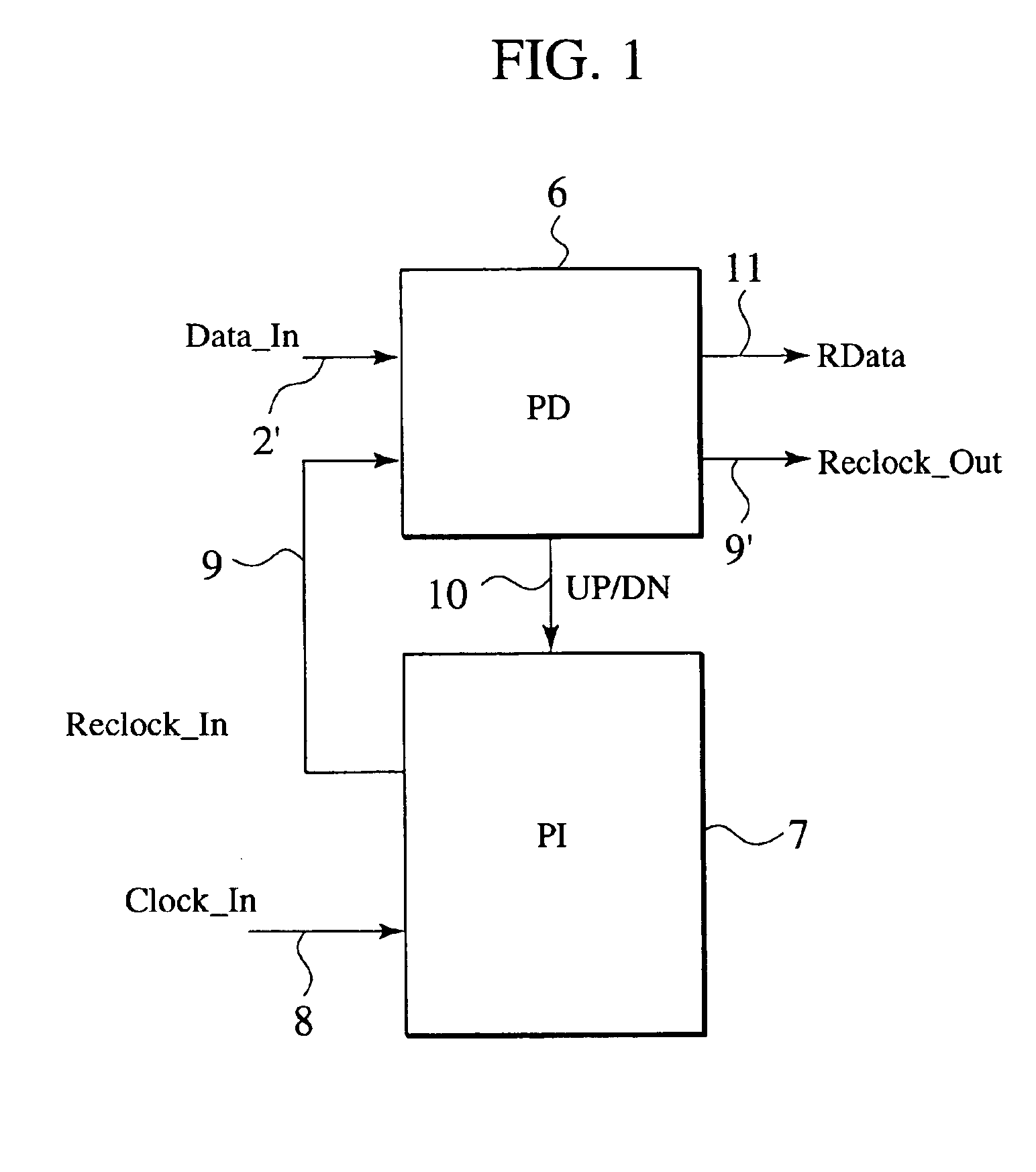

Phase interpolator and receiver

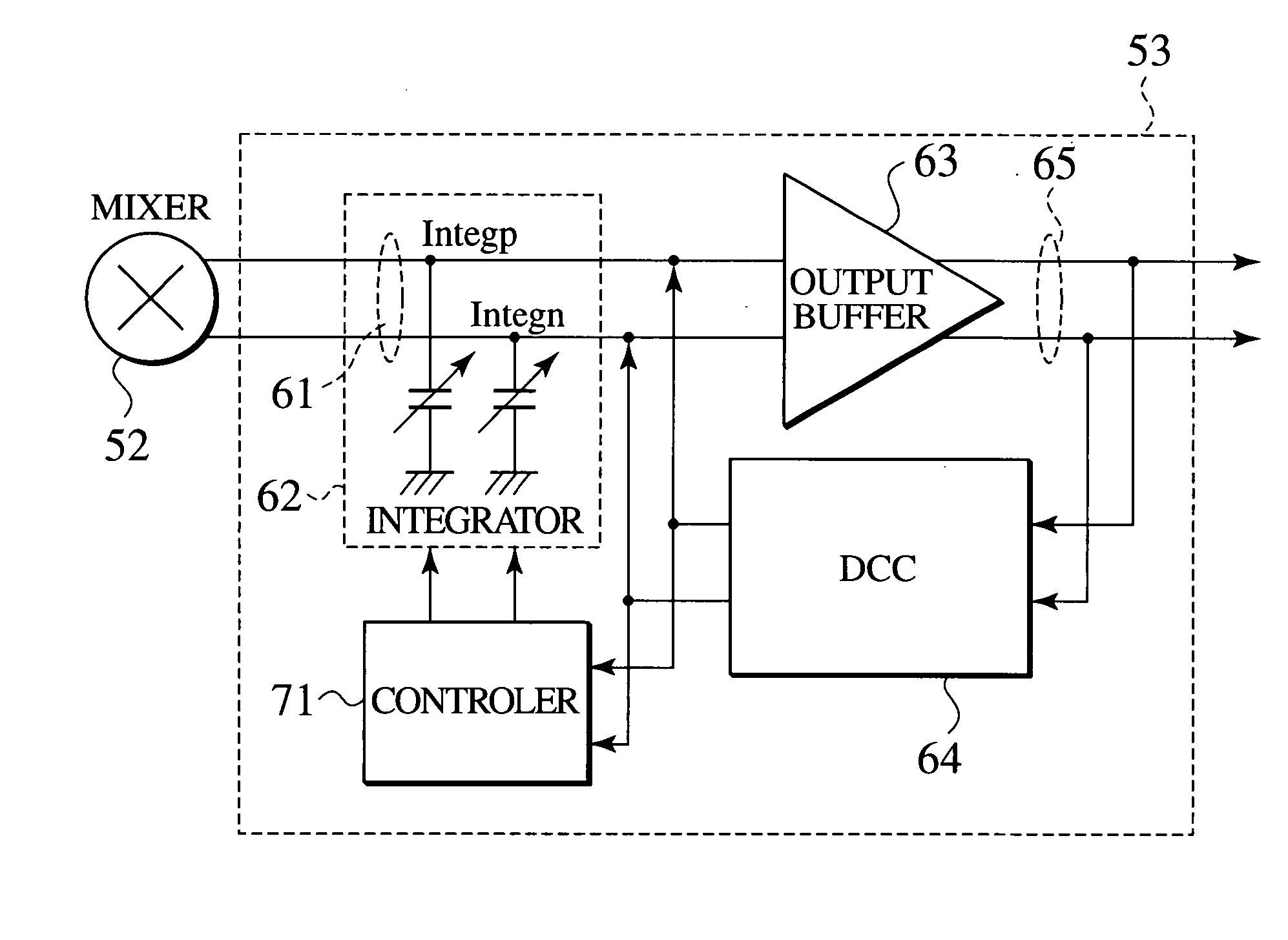

InactiveUS20040189363A1Pulse automatic controlContinuous to patterned pulse manipulationIntegratorEngineering

An aspect of the present invention provides a phase interpolator for adjusting a phase of differential clock signals of a receiver to a phase of a data from a transmitter that includes, an integrator configured to slew edges of differential clock signals adjusted to the phase of the data from the transmitter, a output buffer configured to amplify an output of the integrator, a duty cycle correction circuit configured to feed duty correction signals back to the adjusted differential clock signals, and a controller configured to ensure operations of an amplitude of the output buffer and a data read circuit to adjust the swings and duties of the adjusted differential clock signals.

Owner:KK TOSHIBA

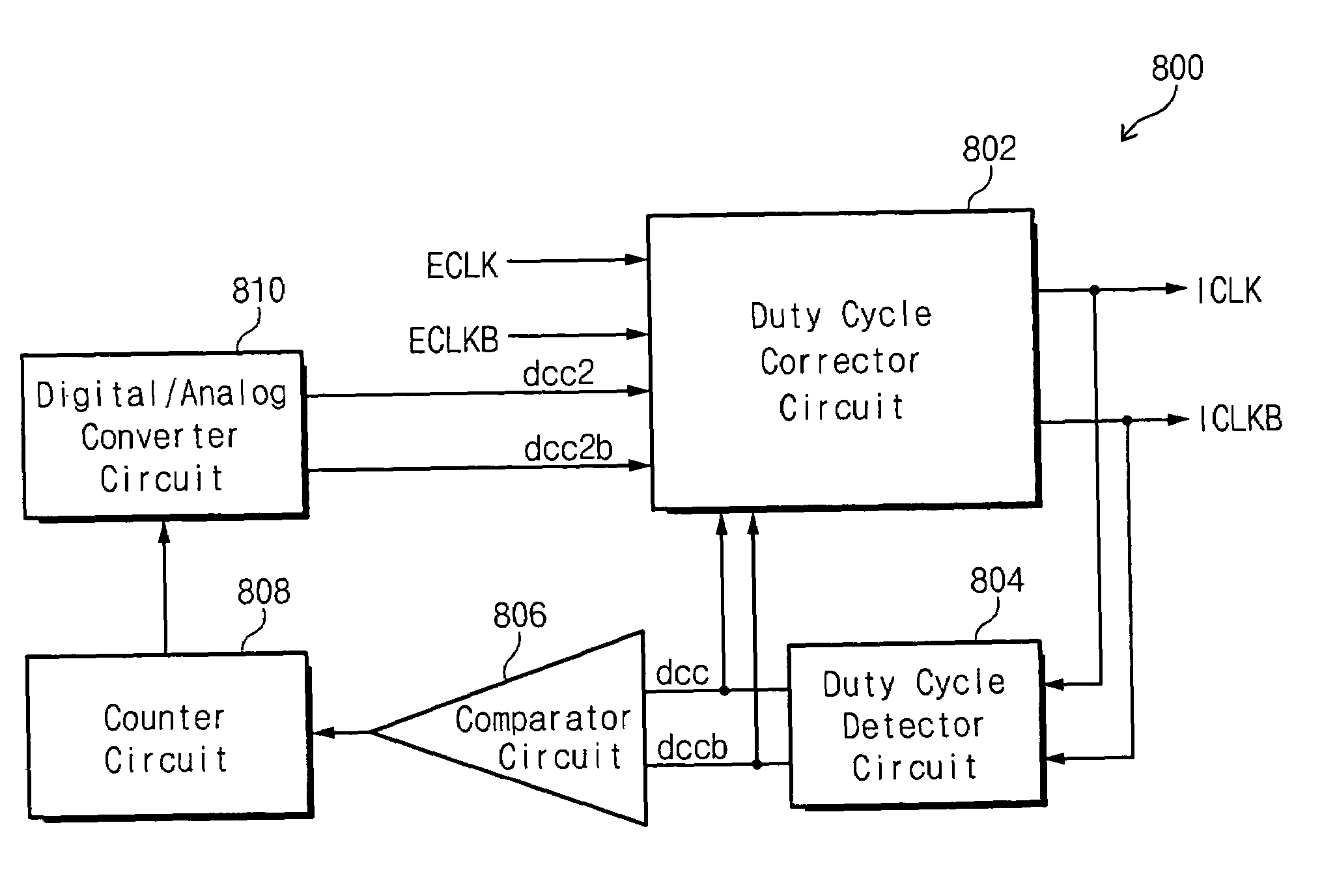

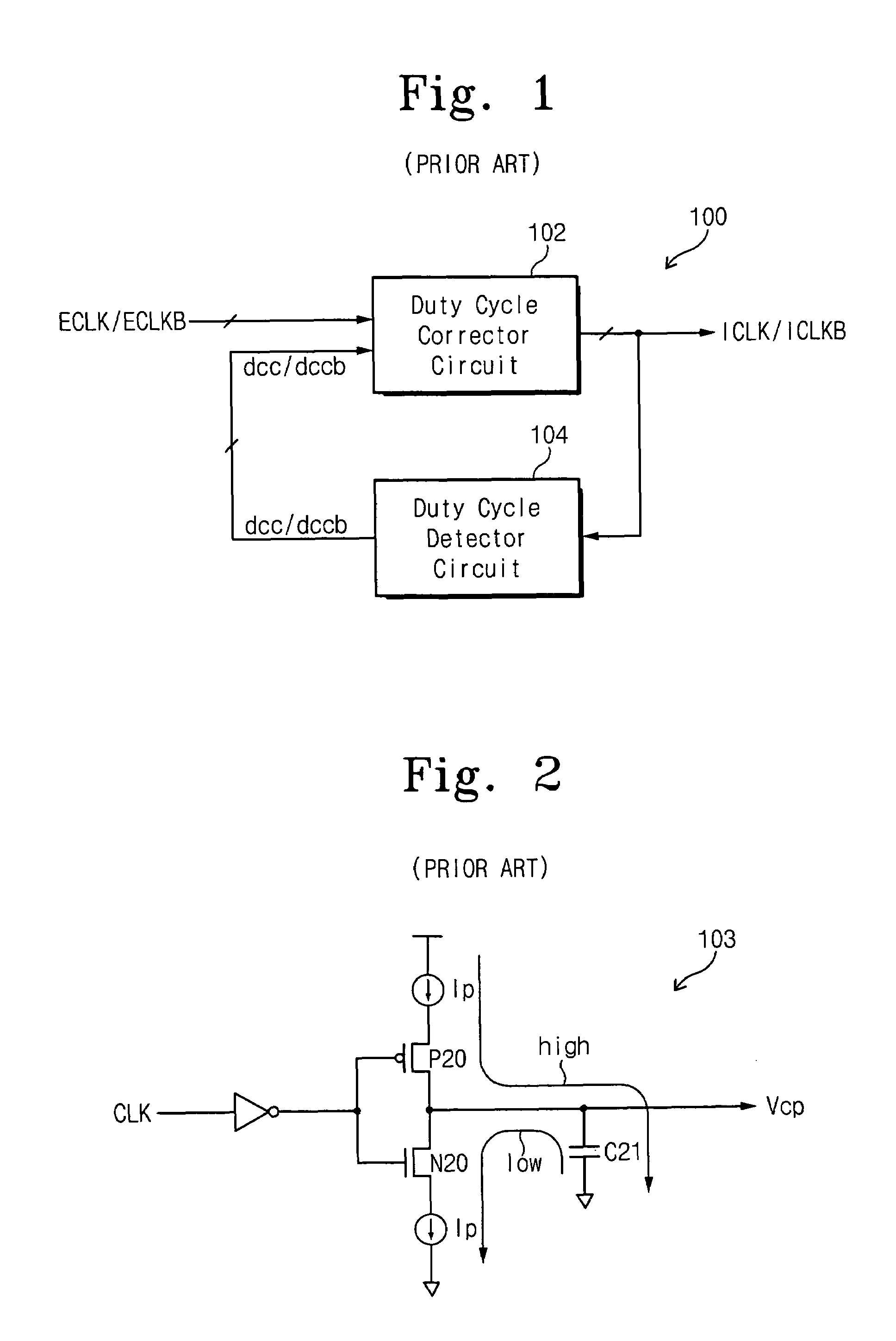

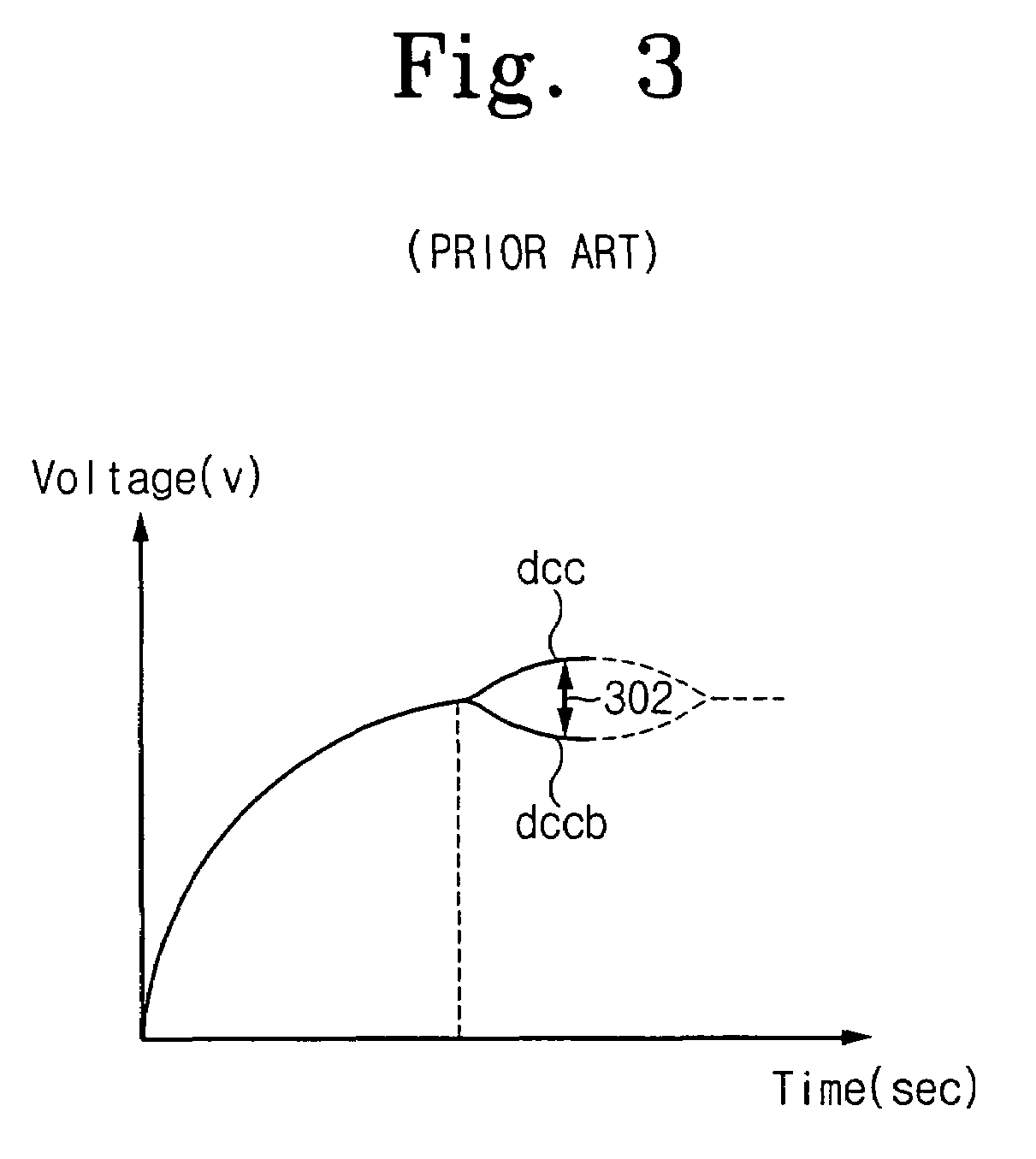

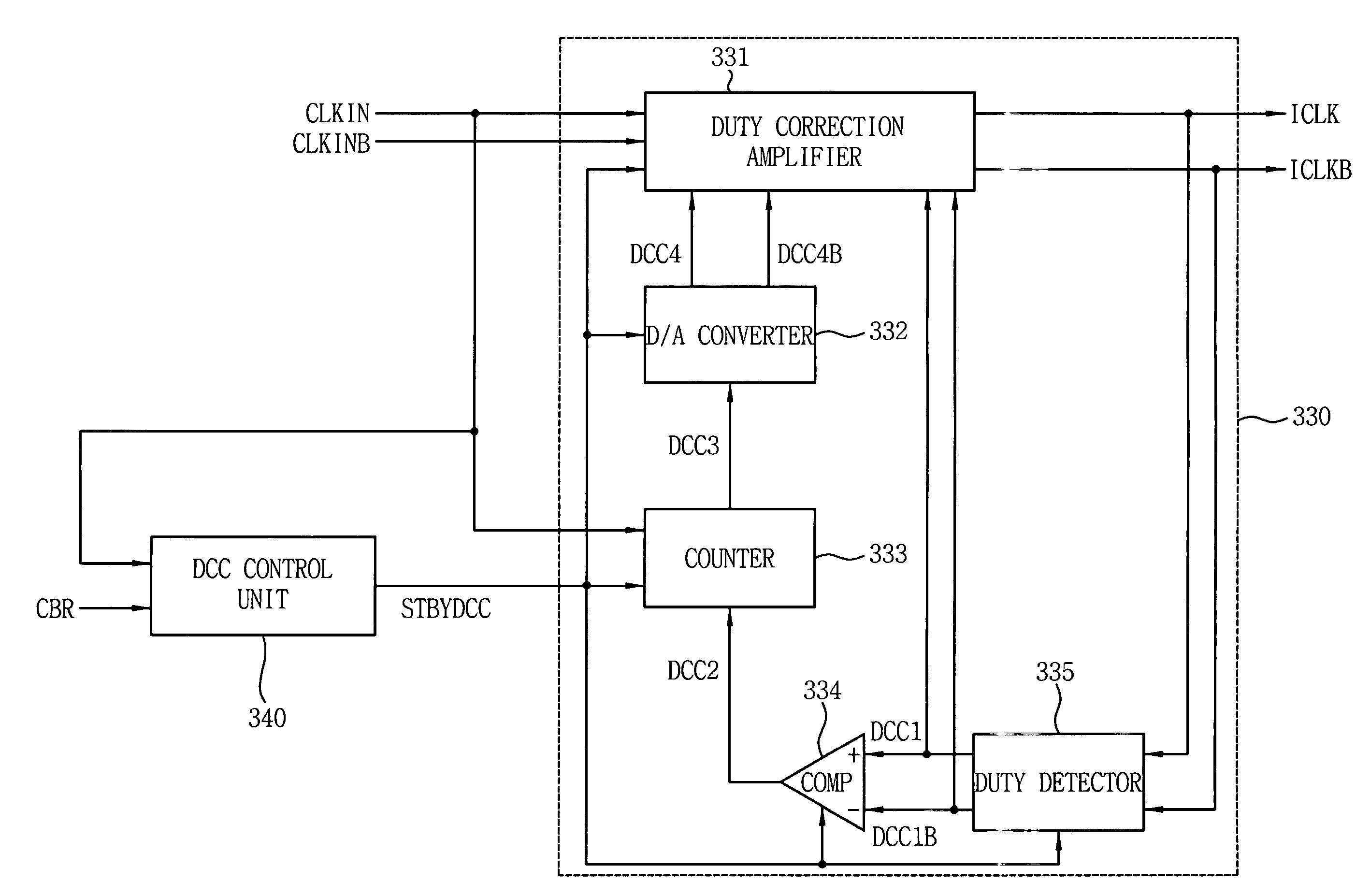

Integrated circuit devices having duty cycle correction circuits that receive control signals over first and second separate paths and methods of operating the same

InactiveUS7015739B2Pulse automatic controlContinuous to patterned pulse manipulationDigital analog converterDetector circuits

Digital duty cycle correction circuits are provided including a duty cycle detector circuit configured to generate first and second control values associated with a first internal clock signal and a second internal clock signal, respectively. A comparator circuit is also provided and is configured to compare the first control value to the second control value and provide a comparison result. A counter circuit is configured to perform an addition and / or a subtraction operation responsive to the comparison result to provide a digital code. A digital to analog converter is configured to generate third and fourth control values responsive to the digital code. Finally, a duty cycle corrector circuit is configured to receive first and second external clock signals and the first through fourth control values and generate the first and second internal clock signals having a corrected duty cycle. The first and second control values are received over a first path and the third and fourth control values are received over a second path, different from the first path. Related methods of operating duty cycle correction circuits are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

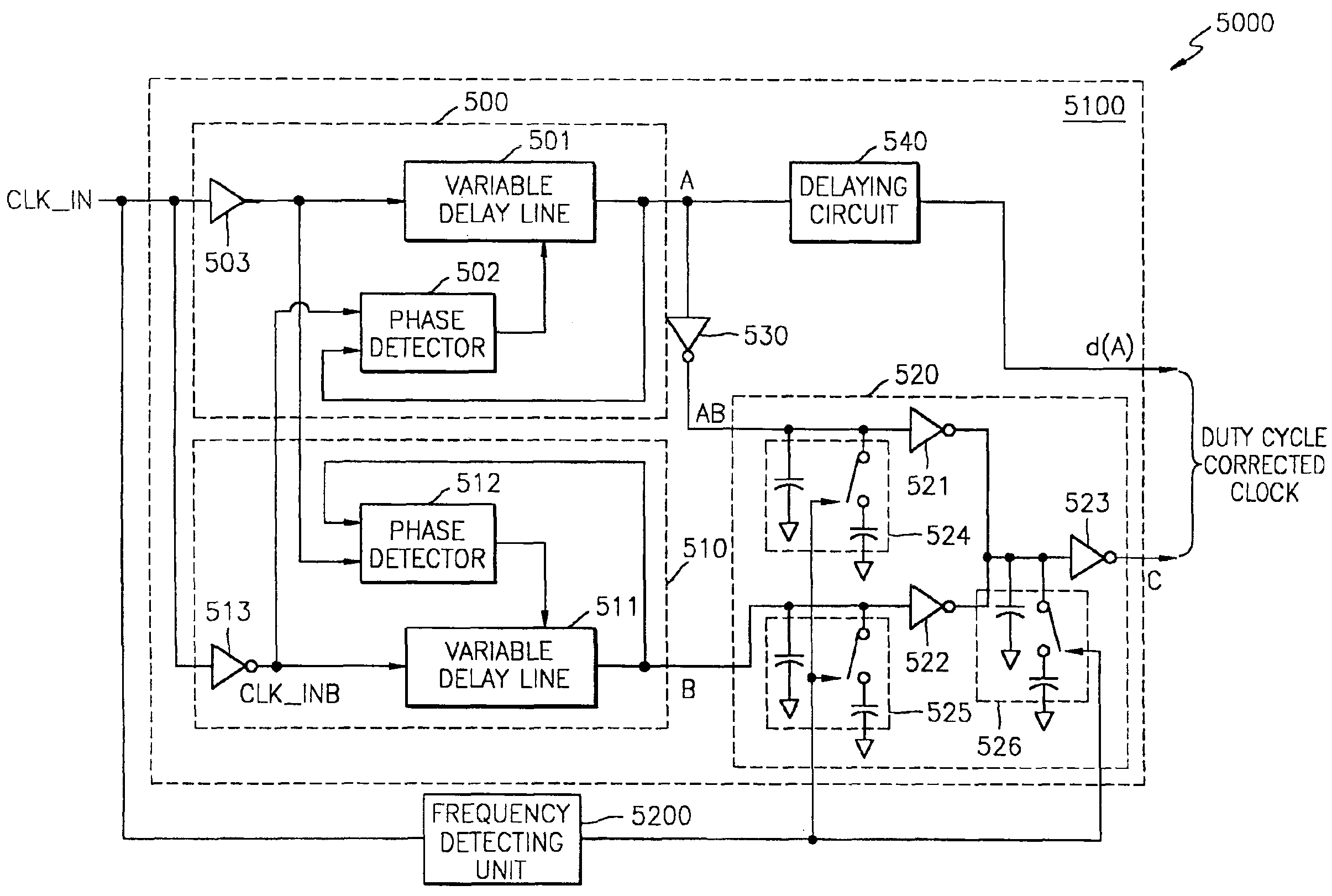

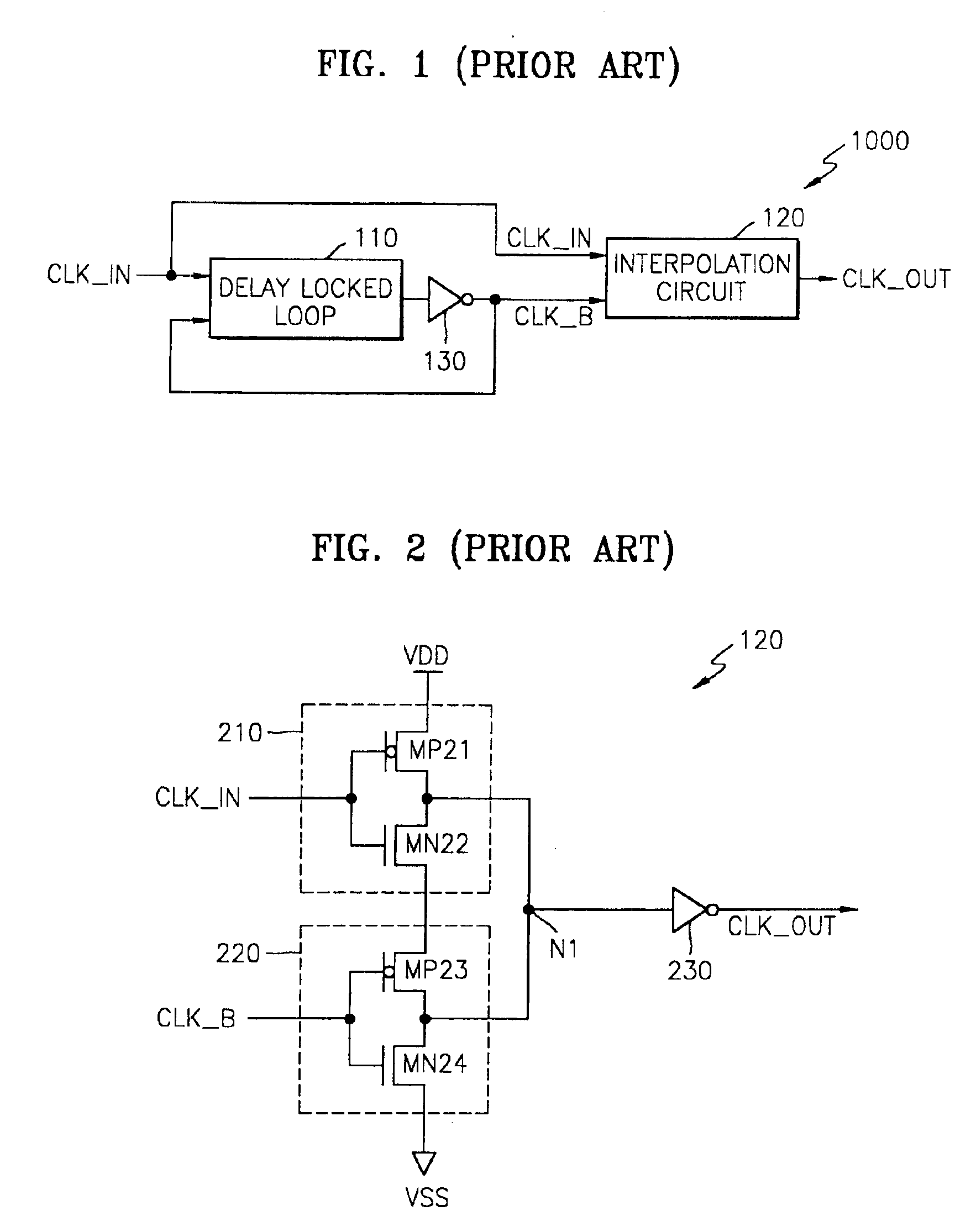

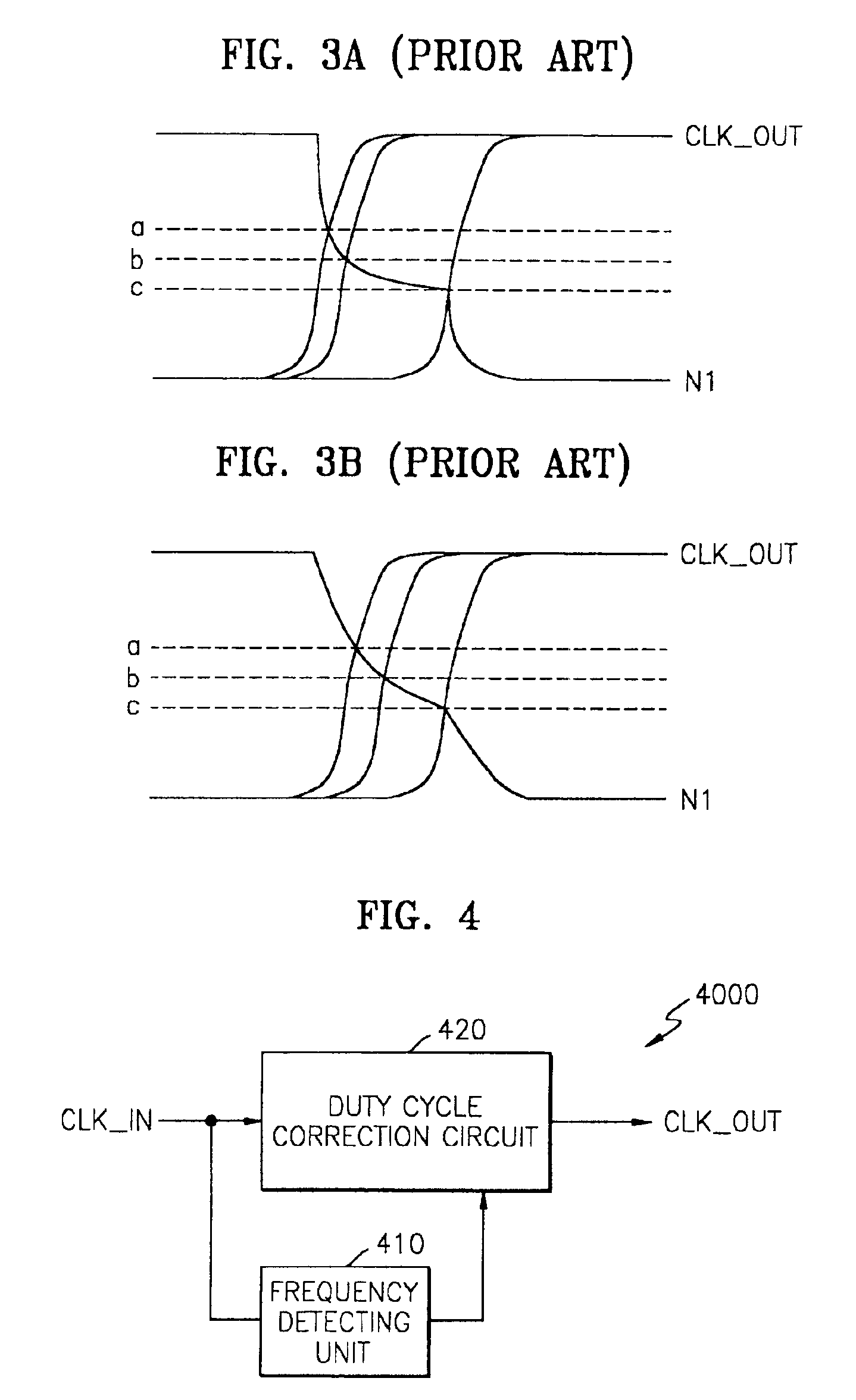

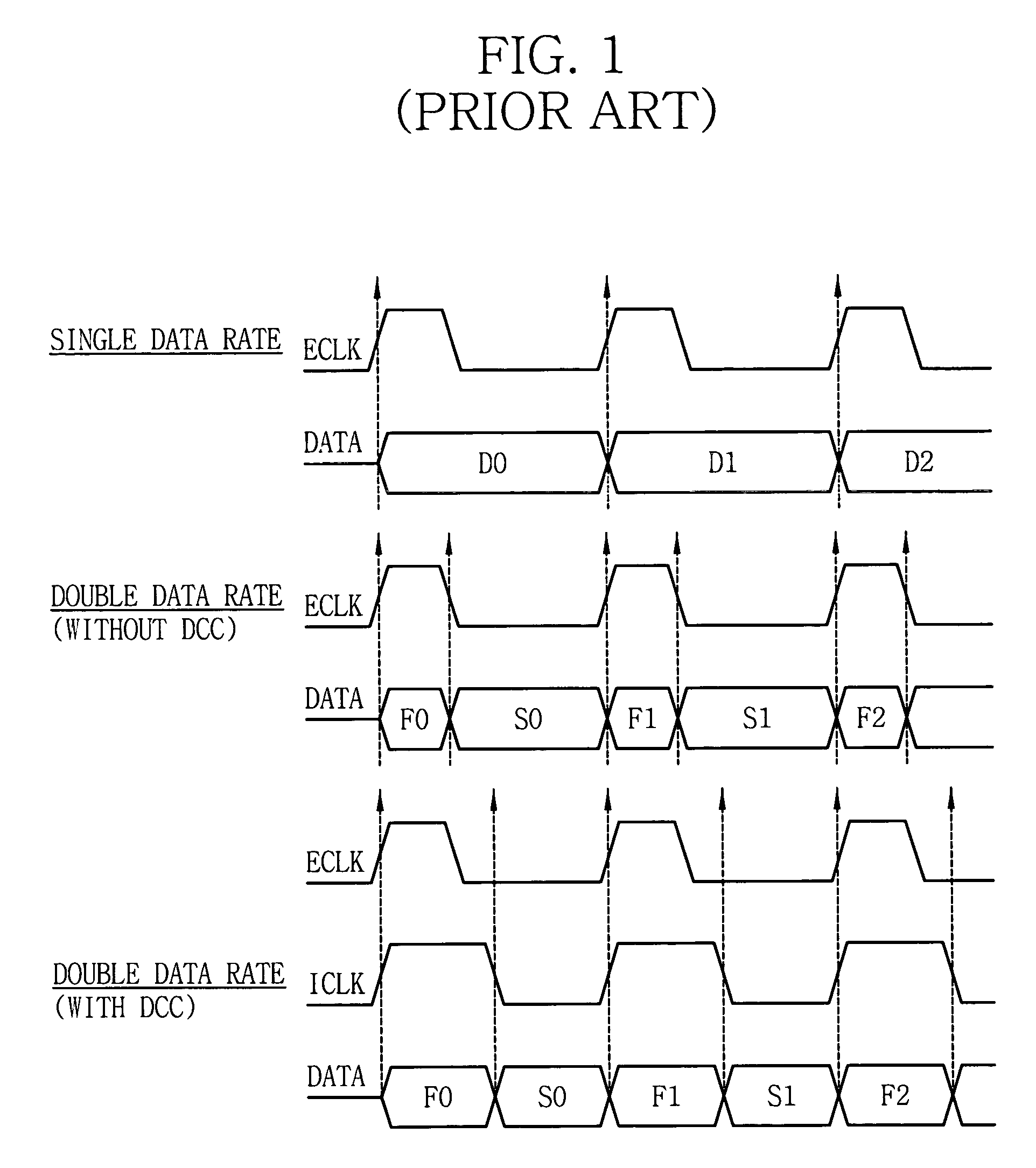

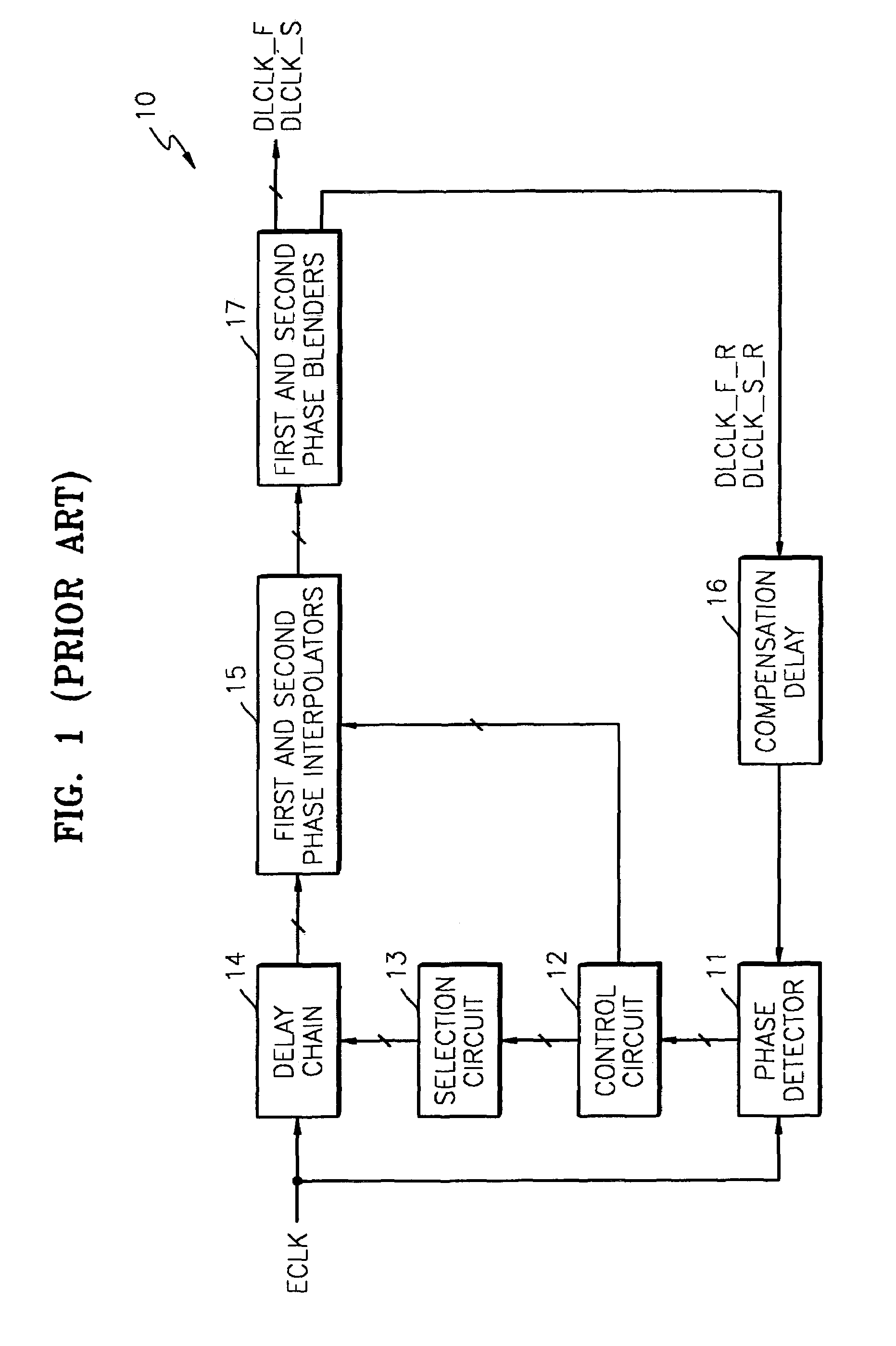

Semiconductor memory device having duty cycle correction circuit and interpolation circuit interpolating clock signal in the semiconductor memory device

ActiveUS6934215B2Small capacitanceLarge capacitanceContinuous to patterned pulse manipulationDigital storageClock rateDelay-locked loop

A semiconductor memory device having a duty cycle correction circuit and an interpolating circuit interpolating a clock signal in the semiconductor memory device are disclosed. The semiconductor memory device comprises a duty cycle correction circuit, which receives an external clock, corrects the duty cycle of the external clock, and outputs the corrected duty cycle. The duty cycle correction circuit comprises a first delay locked loop that receives the external clock, inverts the external clock, synchronizes the external clock with the inverted external clock, and outputs the synchronized clock; a second delay locked loop that receives the inverted external clock, synchronizes the inverted external clock with the external clock and outputs the synchronized clock; an inverting circuit that inverts the output signal of the first delay locked loop; an interpolation circuit that interpolates the output signal of the inverting circuit with the output signal of the second delay locked loop, and outputs the interpolated signal; and a control circuit that controls the interpolation circuit in response to the clock frequency information of the external clock.

Owner:SAMSUNG ELECTRONICS CO LTD

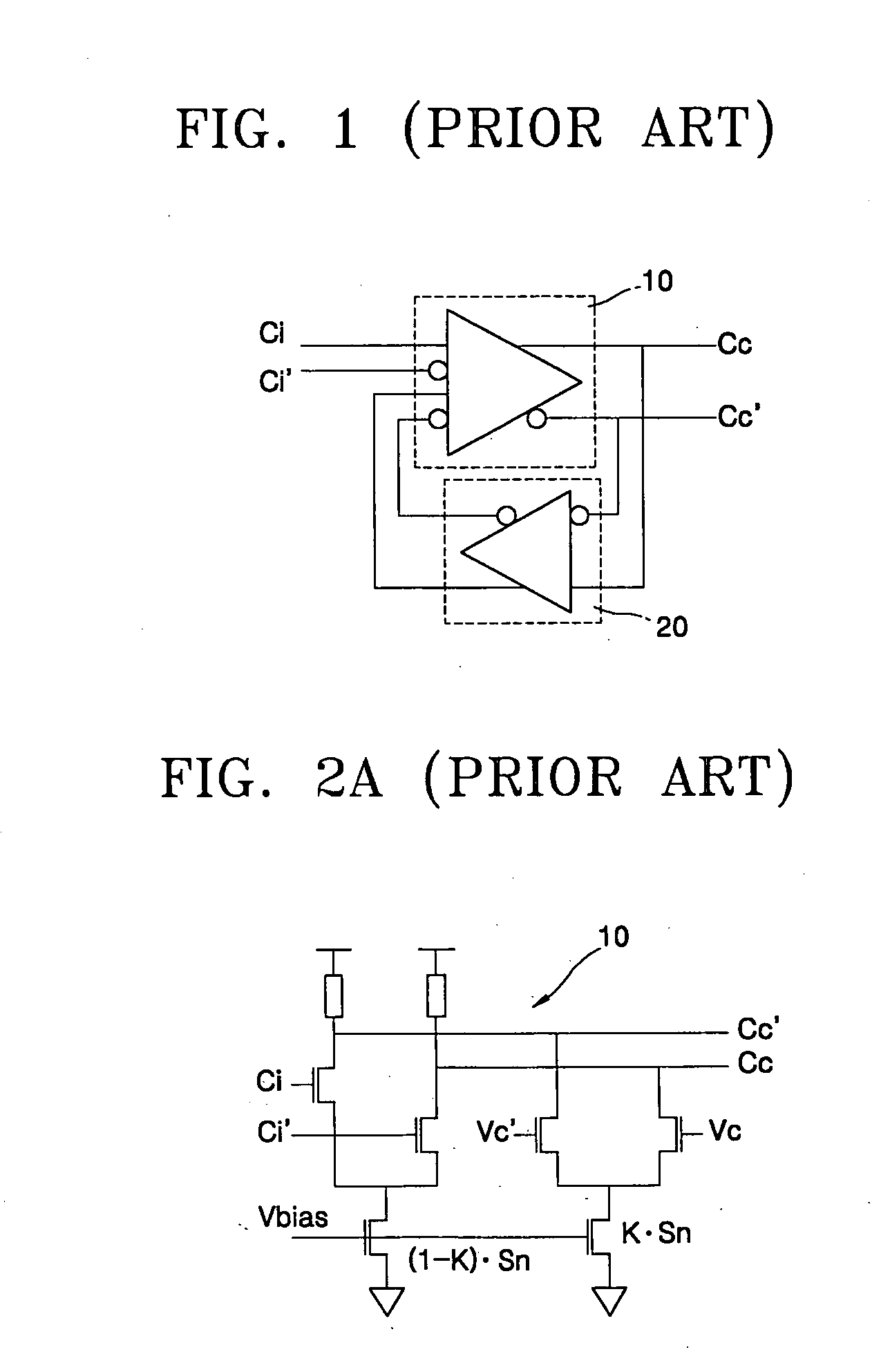

Duty cycle correction circuits suitable for use in delay-locked loops and methods of correcting duty cycles of periodic signals

InactiveUS7199634B2Pulse automatic controlContinuous to patterned pulse manipulationControl signalDelay-locked loop

Delay-locked loop integrated circuits include a duty cycle correction circuit. This duty cycle correction circuit generates at least one output clock signal having a substantially uniform duty cycle in response to at least one input clock signal having a non-uniform duty cycle. The duty cycle correction circuit is also responsive to a standby control signal that synchronizes timing of power-saving duty cycle update operations within the duty cycle correction circuit. These update operations reset the set point of the correction circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

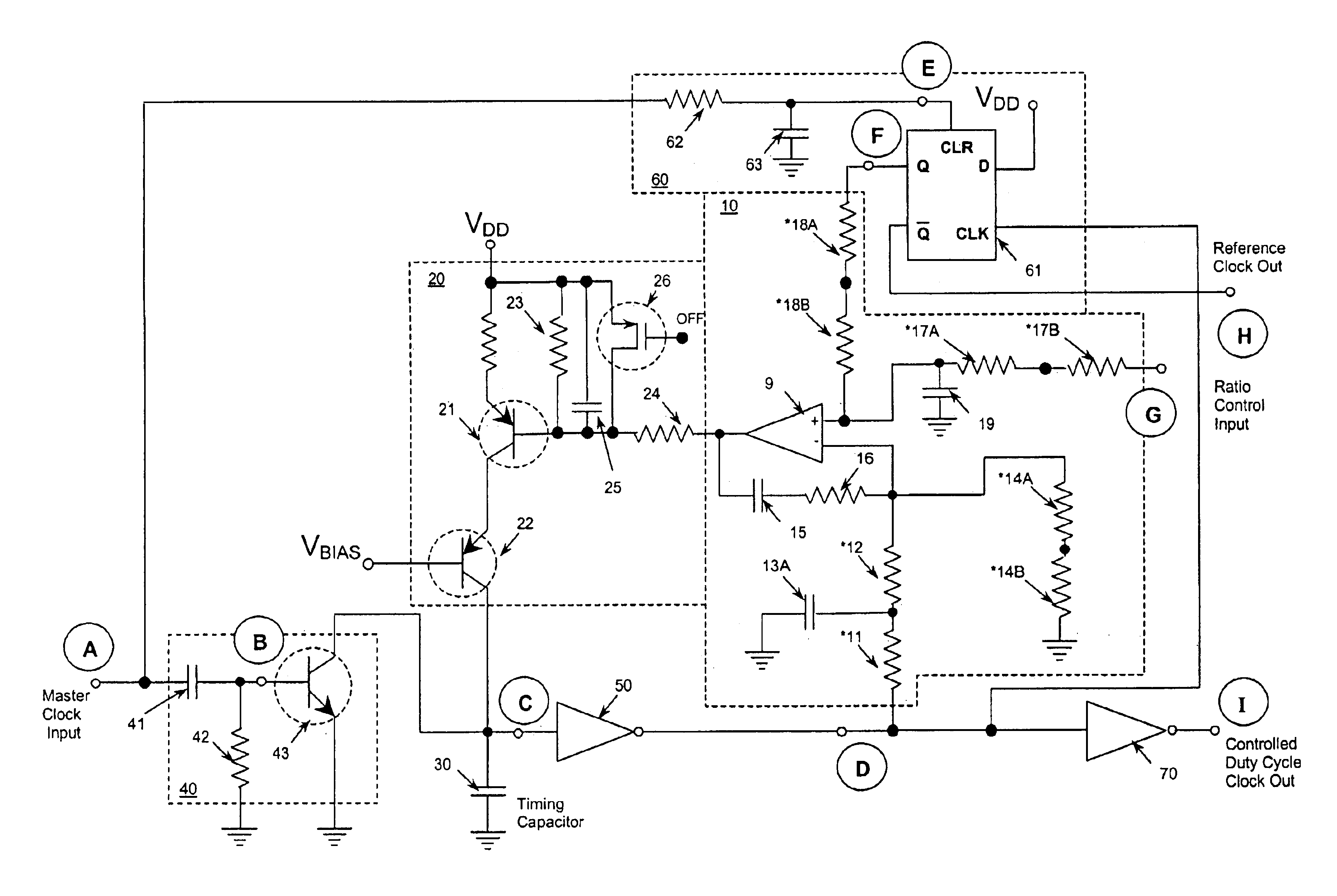

Methods and apparatus for duty cycle control

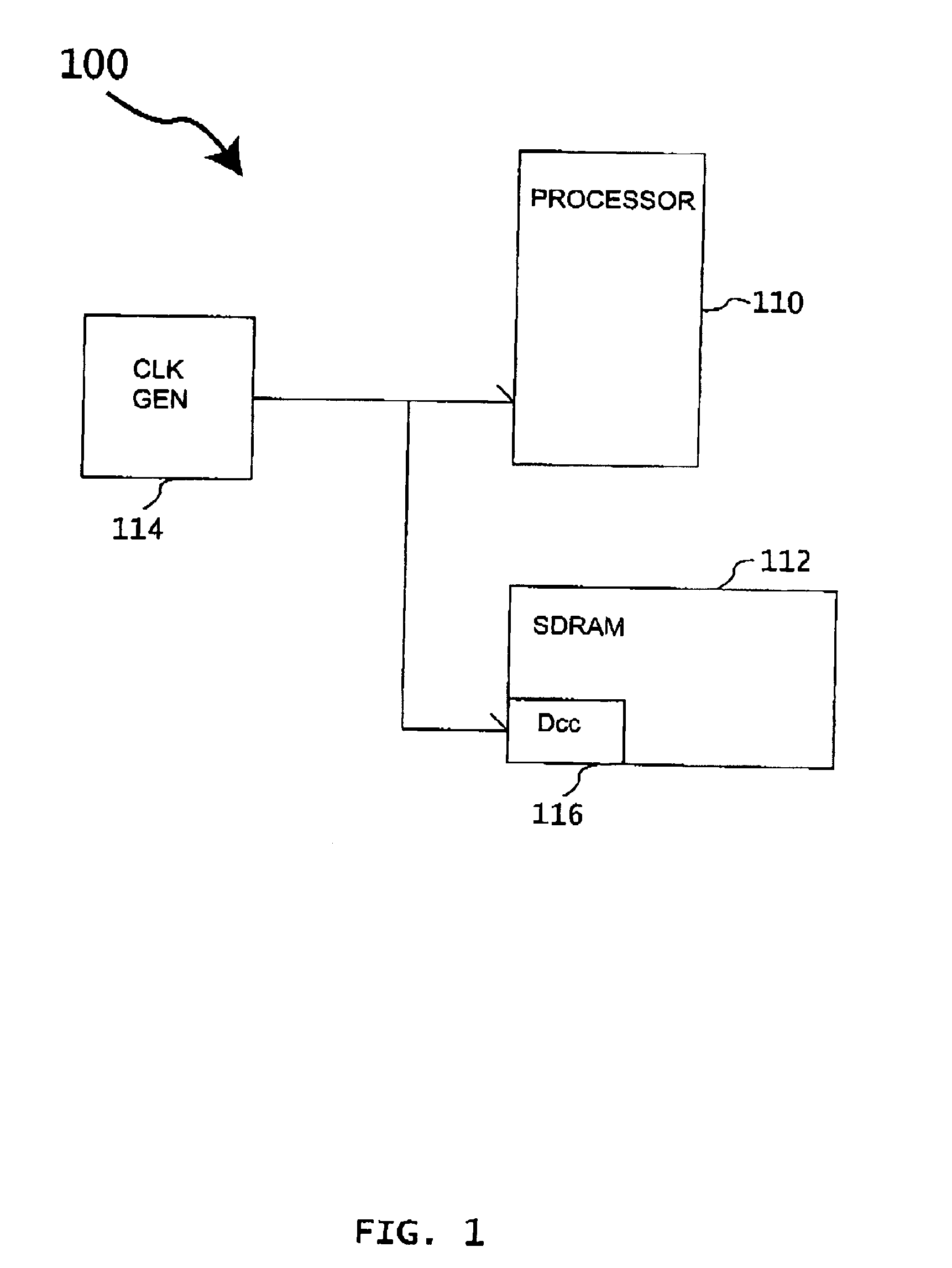

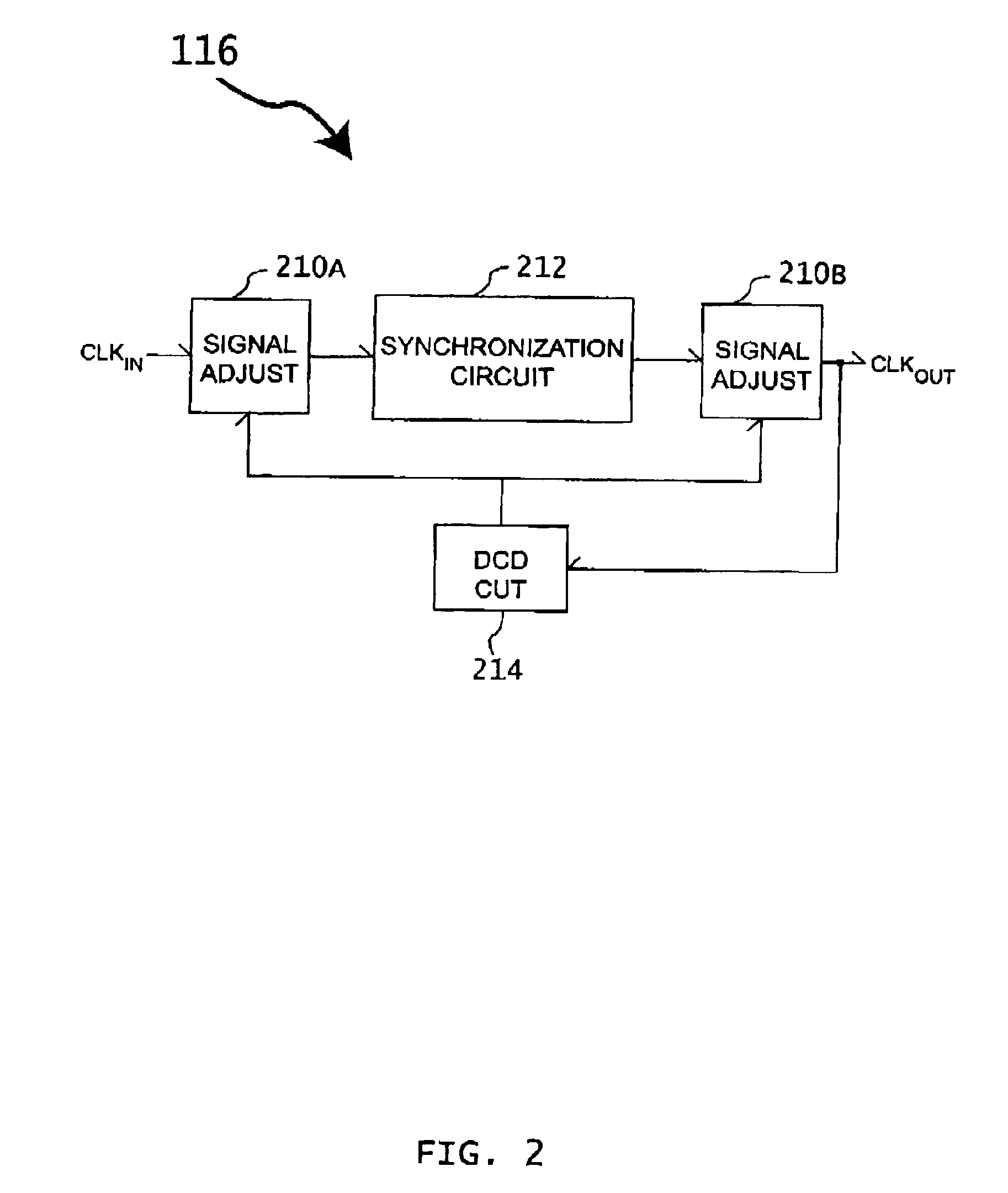

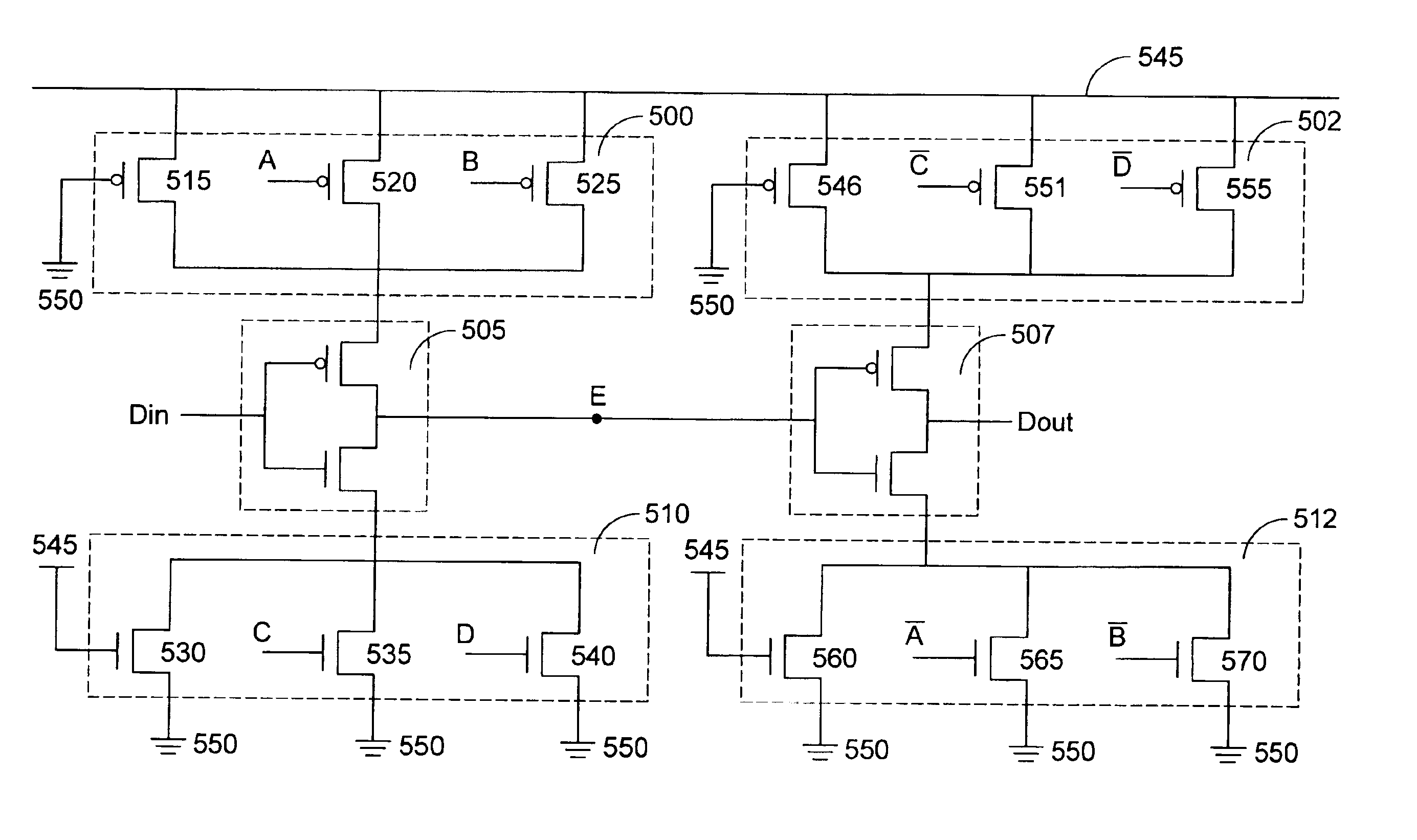

InactiveUS6940328B2Continuous to patterned pulse manipulationElectric pulse generatorElectronic systemsControl signal

An electronic system according to various aspects of the present invention comprises a signal generator configured to generate a first signal and a duty cycle correction circuit configured to be responsive to the first signal and provide a corrected signal having a corrected duty cycle. The duty cycle correction circuit may include a duty cycle detection circuit and a signal adjustment circuit. The duty cycle detection circuit is suitably configured to identify a disparity between a corrected duty cycle of the corrected signal and a target duty cycle. In one embodiment, the duty cycle detection circuit includes a self-bias circuit configured to generate a control signal according to the disparity between the corrected duty cycle and the target duty cycle. The signal adjustment circuit may be responsive to the control signal and configured to provide the corrected signal having the corrected duty cycle according to the control signal.

Owner:MOSAID TECH

Duty-cycle adjustable buffer and method and method for operating same

ActiveUS6897696B2Increase the number ofContinuous to patterned pulse manipulationElectric pulse generatorClock treeEngineering

A duty-cycle adjustable buffer and a method for operating such buffer can be applied to a clock tree circuit for providing an adjustable duty cycle. The duty-cycle adjustable buffer includes a first inverter and a second inverter connected with each other in series. Each of the first inverter and the second inverter includes a plurality of controlled current charging paths and a plurality of controlled current discharging paths, wherein at least one controlled current charging path and at least one controlled current discharging path of the first inverter and the second inverter are conducted. The timing of the rising edge and falling edge of a clock signal is dynamically adjusted so as to dynamically altering the duty cycle of the clock signal.

Owner:VIA TECH INC

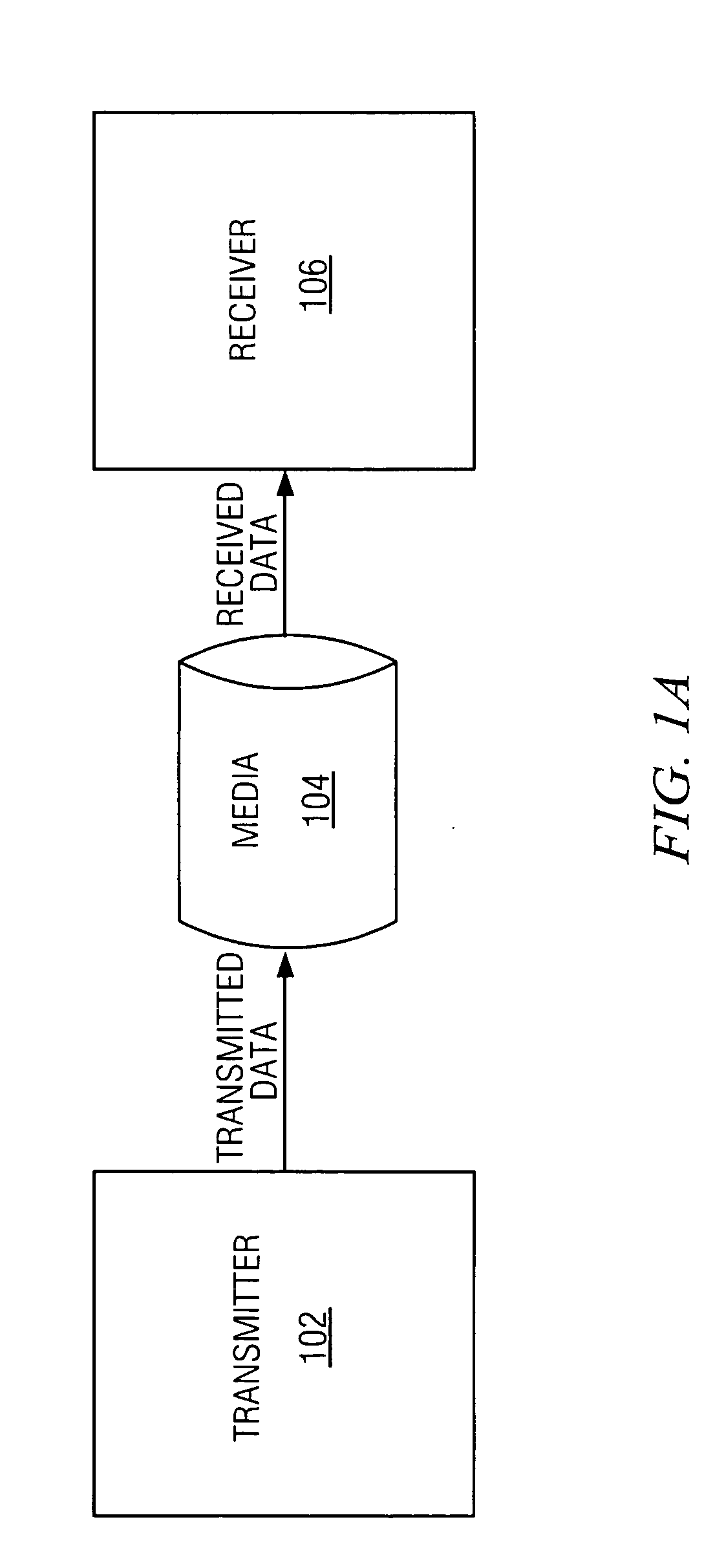

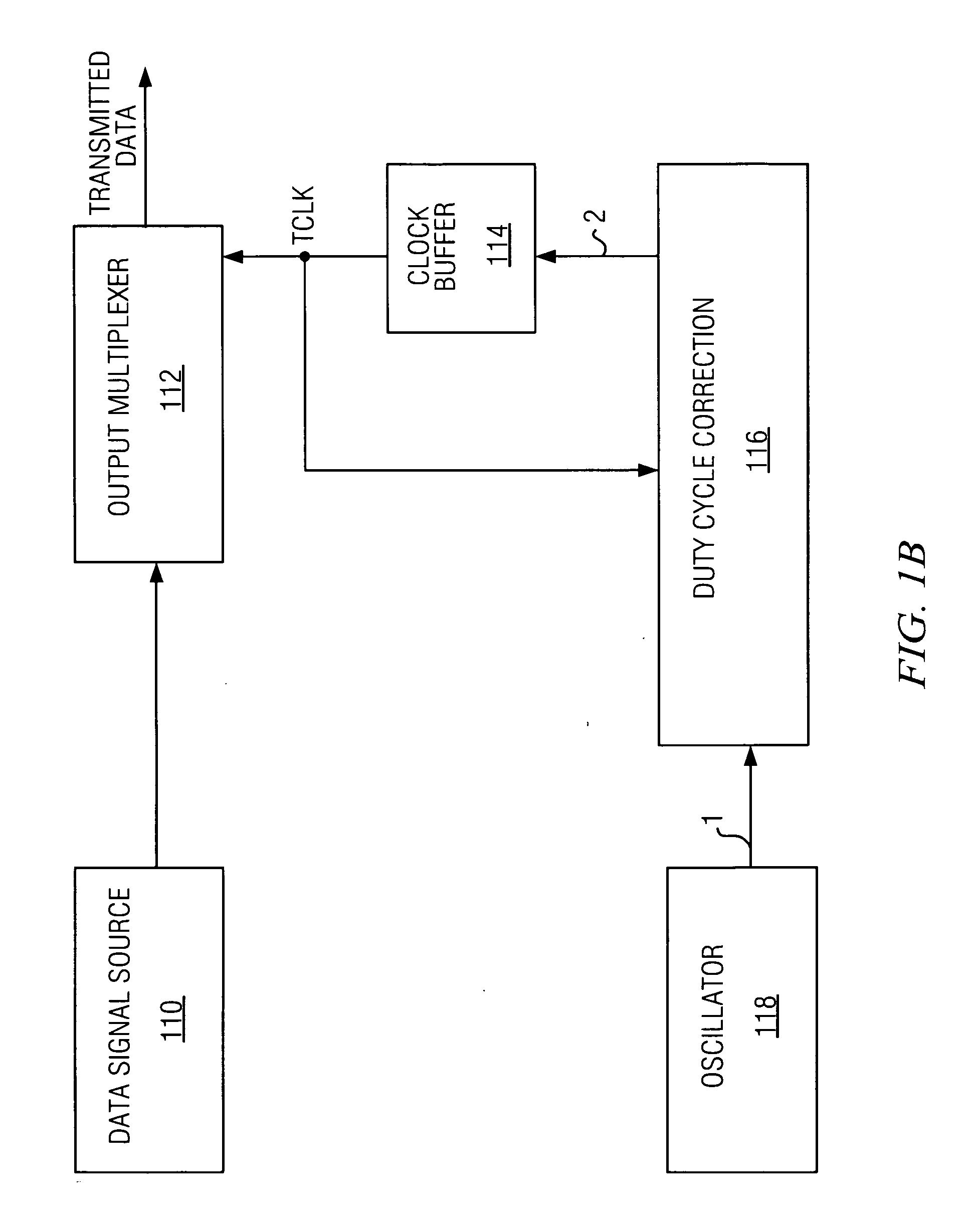

Systems and methods of performing duty cycle control

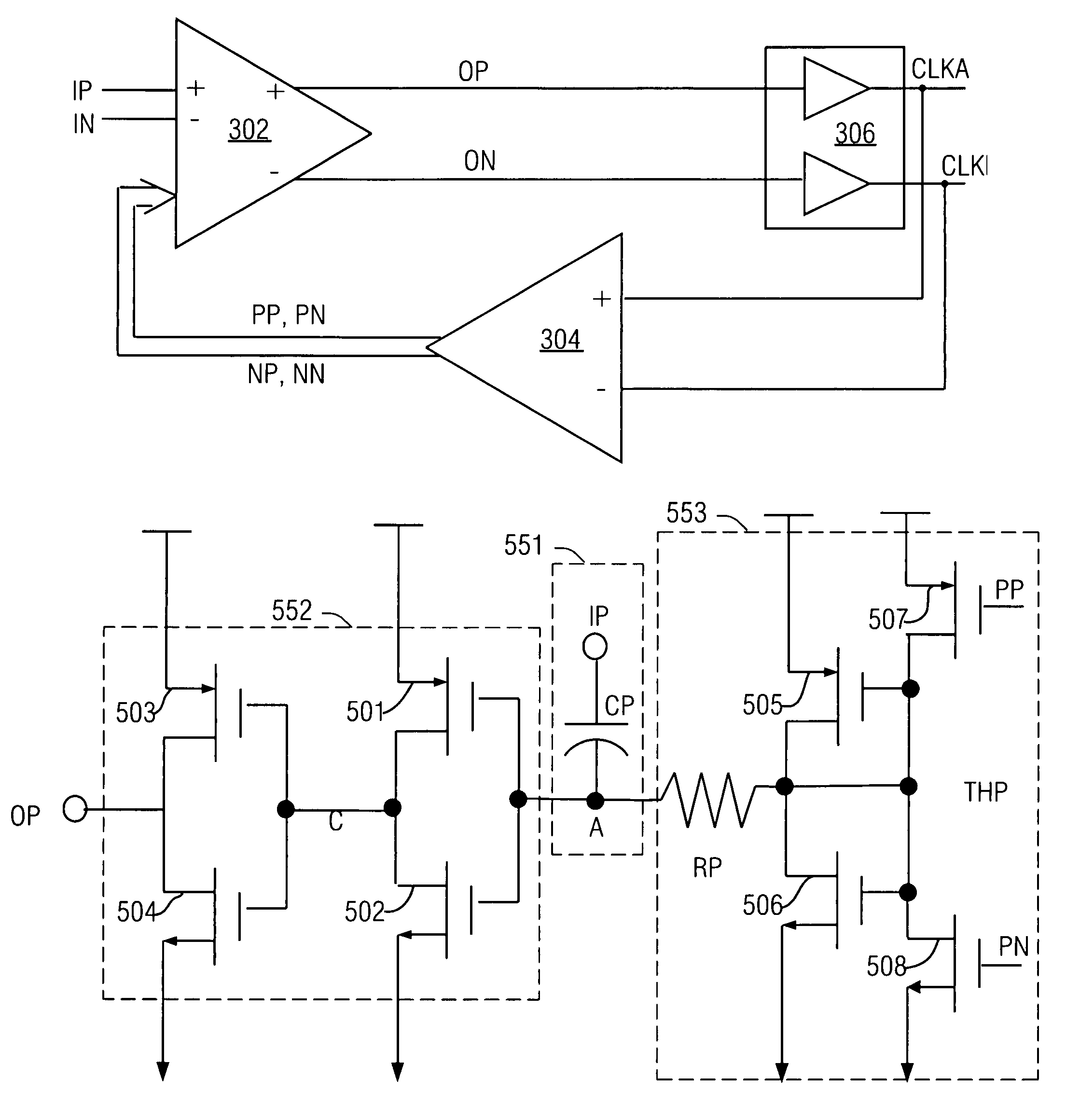

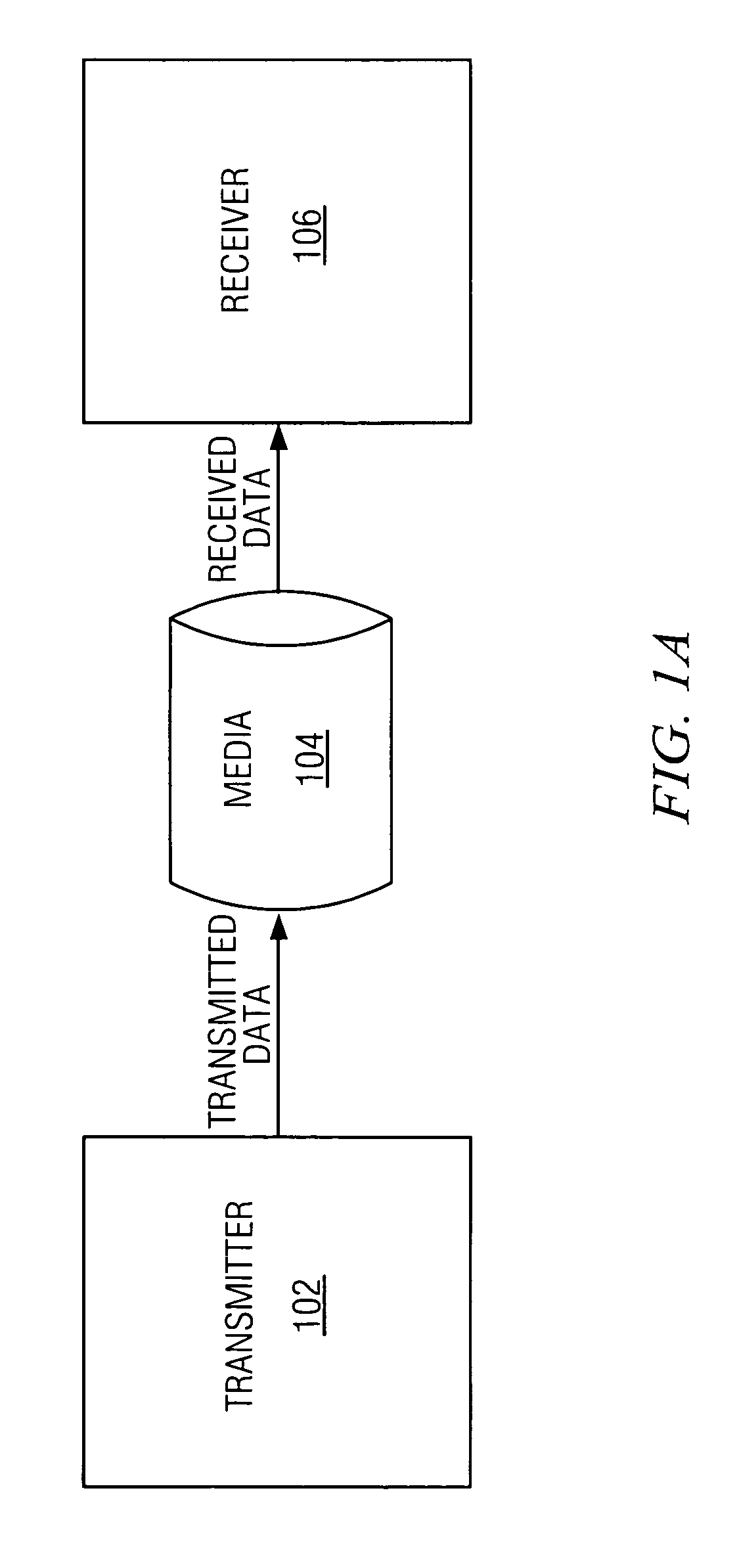

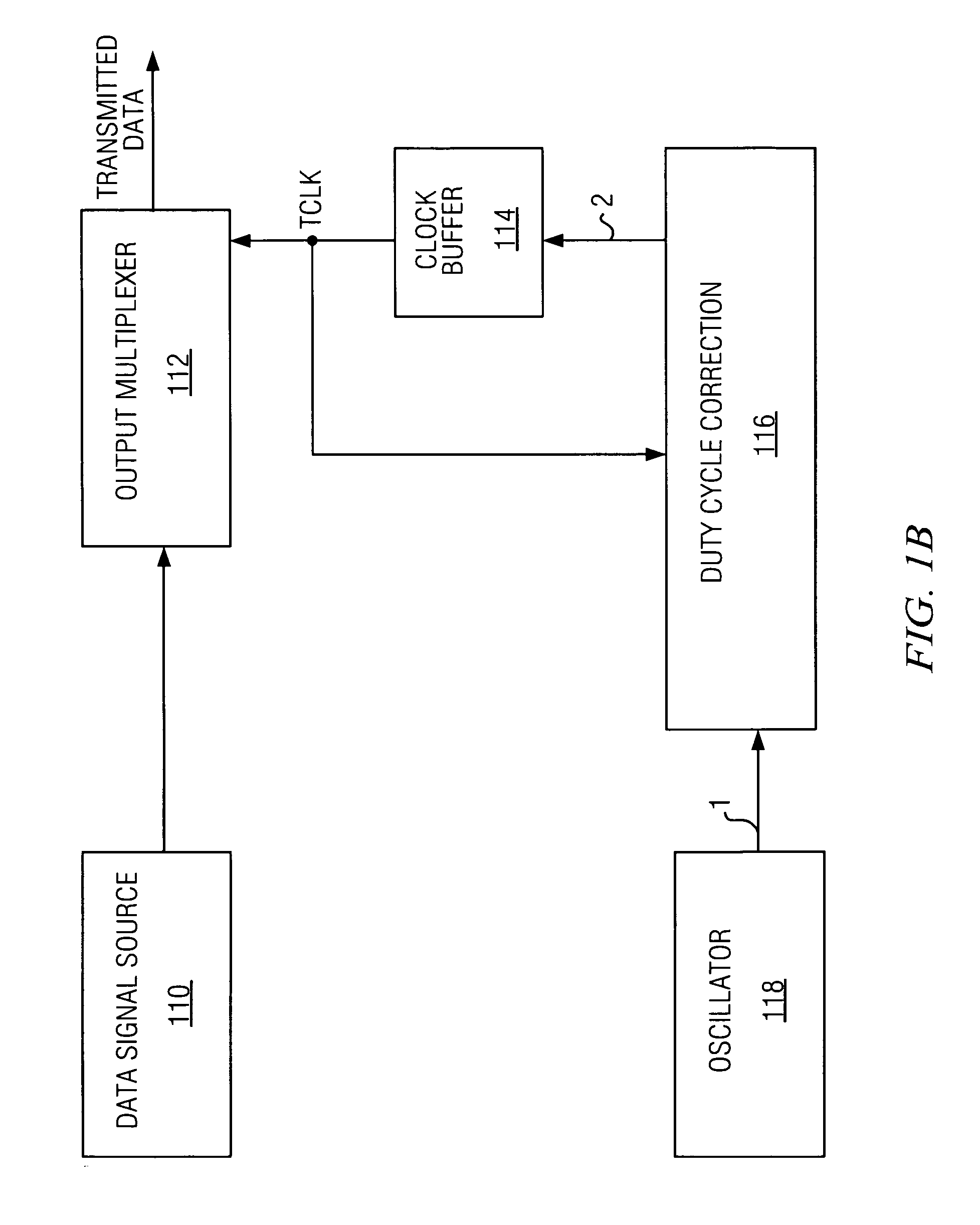

ActiveUS6933759B1Reduce error rateFacilitate communicationContinuous to patterned pulse manipulationManipulation where pulse delivered at different timesMultiplexingCycle control

The present invention facilitates serial communication by performing duty cycle correction. A duty cycle correction component 302 performs duty cycle corrections on a pair of differential sinusoidal signals according to a pair of adjustment signals and, as a result, generates a differential pair of square wave signals. A cross coupled buffer 306 buffers the differential pair of square wave signals and provides the buffered signals to a feedback circuit 304 that measures duty cycles of the signals and generates the pair of adjustment signals accordingly. The buffer 306 can also remove skew from the signals. In a transmitter 102, the buffered signals are also generally provided to a multiplexer 112 or encoder and in a receiver 106, the buffered signals are also generally provided to a sampling component 122.

Owner:TEXAS INSTR INC

Duty cycle correcting circuits having a variable gain and methods of operating the same

InactiveUS7180346B2Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringClock signal

Duty cycle correcting circuits having a gain adjusting circuit that selects one of a plurality of gains of the duty cycle correcting circuit based on a frequency of an input signal. An output circuit outputs a duty cycle corrected output signal based on the input signal and the selected one of the plurality of gains. The input signal may be an input clock signal and the output signal may be a corrected clock signal. Methods are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

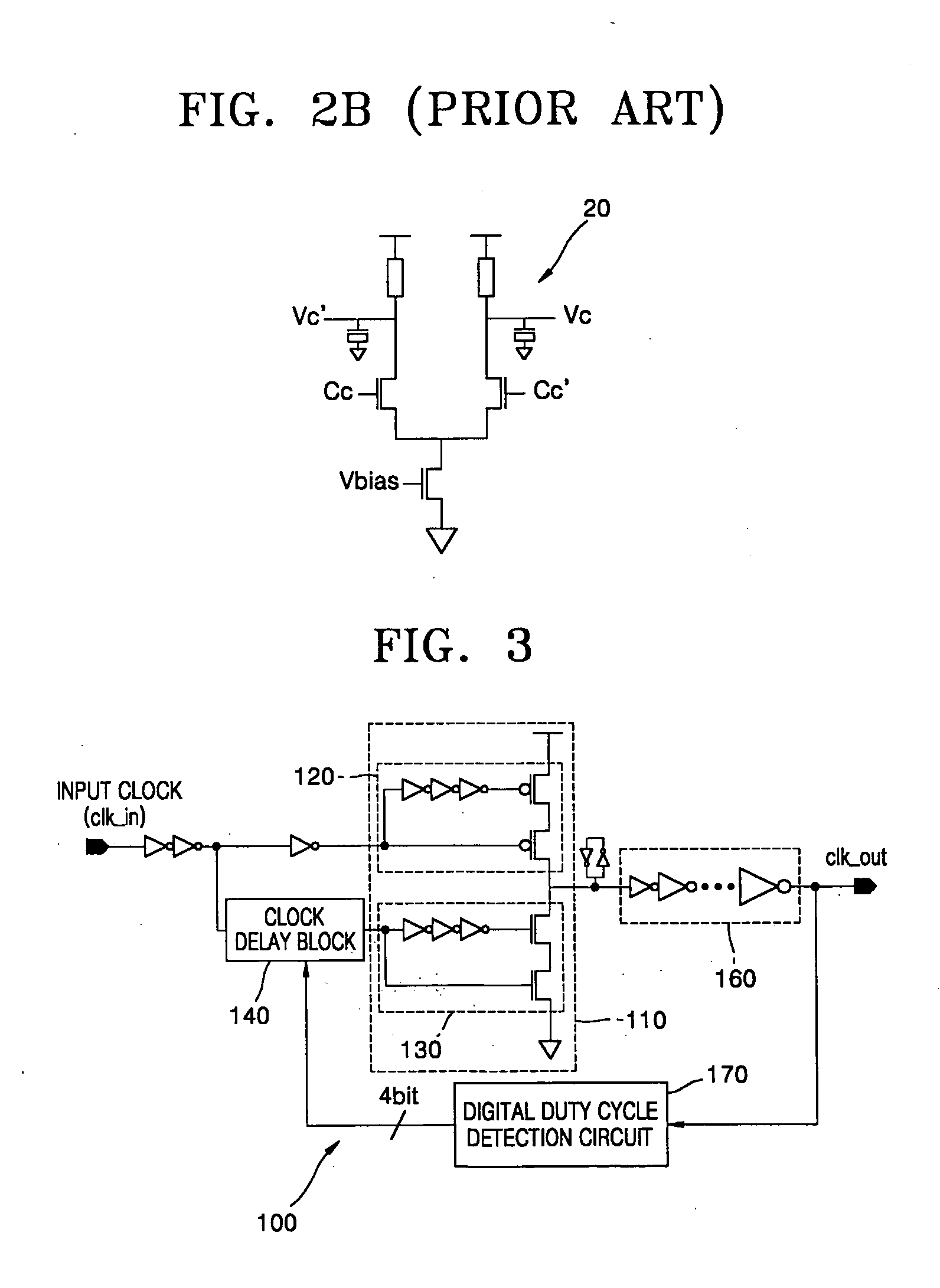

Digital duty cycle correction circuit and method for multi-phase clock

InactiveUS20050007168A1Not affectContinuous to patterned pulse manipulationElectric pulse generatorIntegratorShunt capacitors

Provided is a digital duty cycle correction circuit and method for a multi-phase clock, in which duty cycle correction information of an input clock signal is stored in a power save state of a system by adopting a digital correction method in a duty cycle correction method for a multi-phase clock and phase information of the input clock signal is held constant during duty cycle correction of the input clock signal by correcting duty cycles of the input clock signal by changing the falling edge of the clock without changing the rising edge of the input clock signal during duty cycle correction of the input clock signal, thereby correcting the multi-phase clock. To this end, the digital duty cycle correction circuit includes a clock delay means that takes the form of a shunt capacitor-inverter, a clock generation means including a clock rising edge generation circuit and a clock falling edge generation circuit, and a digital duty cycle detection means including integrators, a comparator, and a counter / register.

Owner:POSTECH ACAD IND FOUND

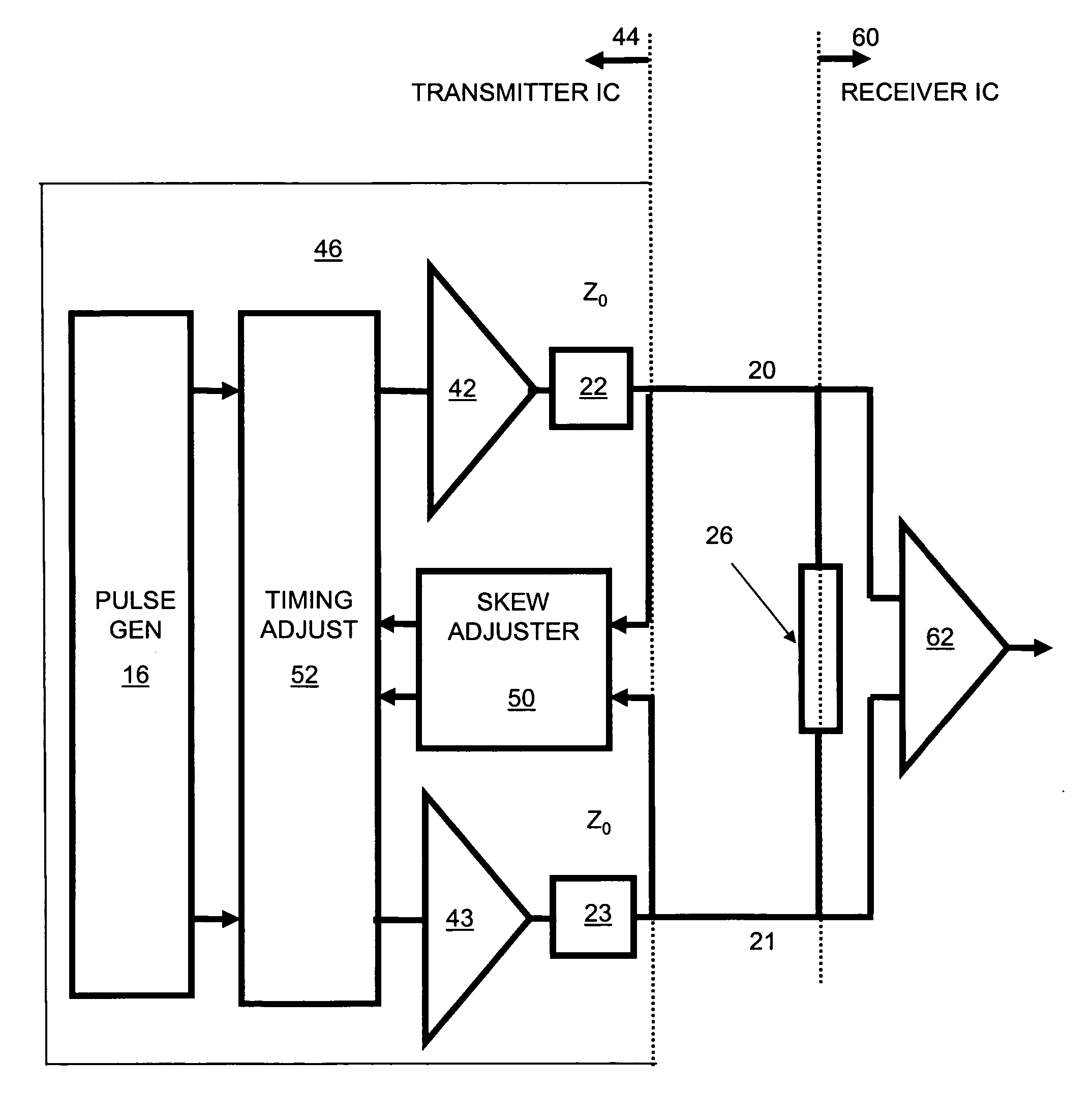

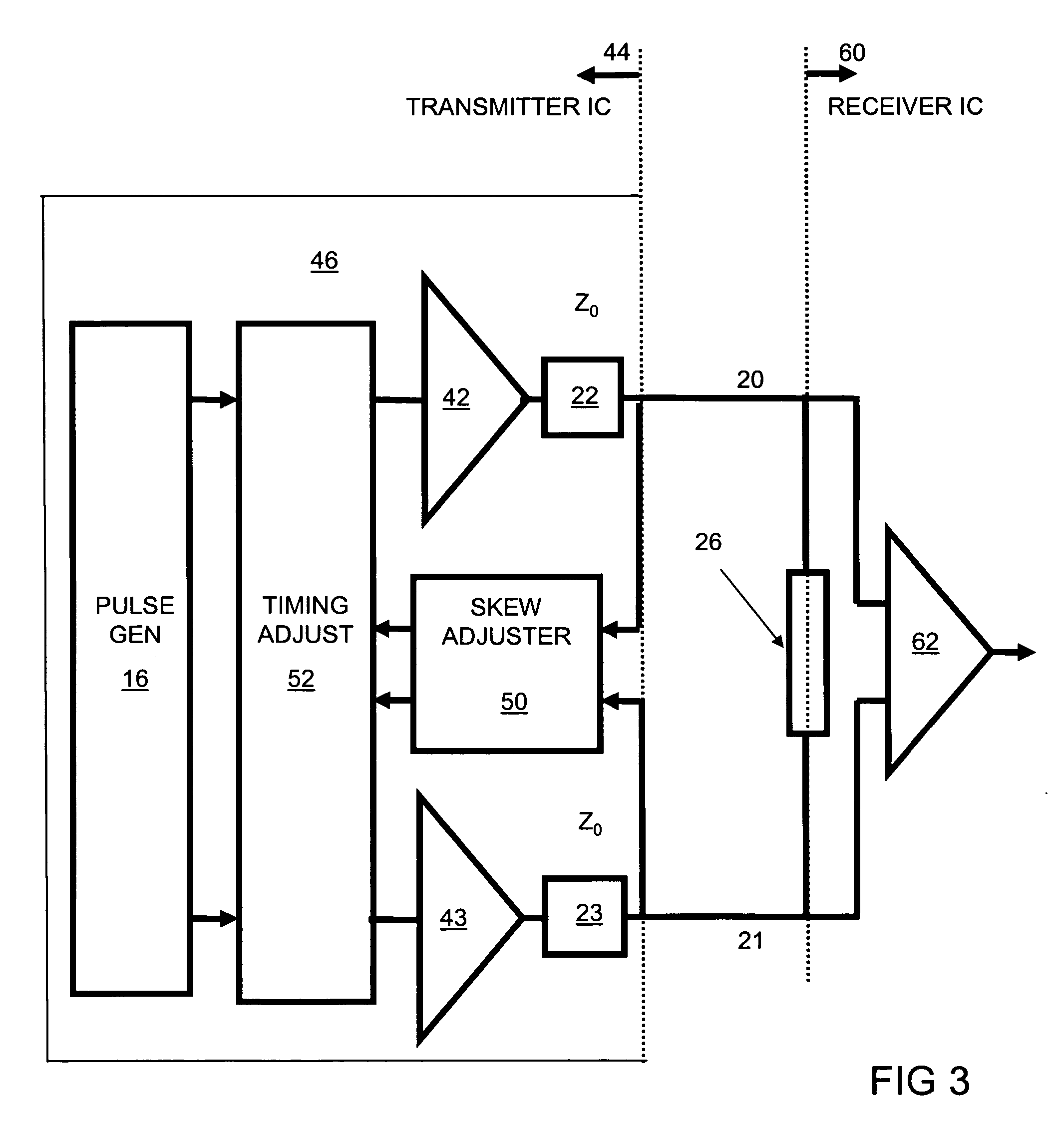

Automatic skew correction for differential signals

InactiveUS20060256880A1Reduce skewReliability increasing modificationsElectrical testingSignal onSignal monitoring

A skew correction system incorporated into a transmitter forwarding a differential signal on a differential lane monitors returning signal reflections when the receiving end of the differential lane is appropriately terminated. Based on an analysis of the reflections, the skew correction system adjusts the relative timing of complementary edges of the differential signal departing the transmitter so as to substantially eliminate skew at the receiving end of the differential lane.

Owner:WARPSPEED CHIPS

Digital DLL apparatus for correcting duty cycle and method thereof

InactiveUS20030218486A1Pulse automatic controlContinuous to patterned pulse manipulationPhase detectorEngineering

A digital DLL apparatus and a method for correcting a duty cycle are disclosed. The digital DLL apparatus for correcting a duty cycle, includes: a buffer for producing a clock input signal; a delay line unit for receiving / delaying the clock input signal and outputting the clock input signal; a blend circuit for bypassing the first clock signal or producing a blended clock signal; a delay model unit for compensating a time difference of an external clock and an internal clock and generating a compensate clock signal; a direct phase detector for generating a first comparison signal; and a phase detector for generating a second comparison signal. The disclosed apparatus can correct the duty error by using the blend circuit and generate an internal clock signal having 50% of duty cycle.

Owner:SK HYNIX INC

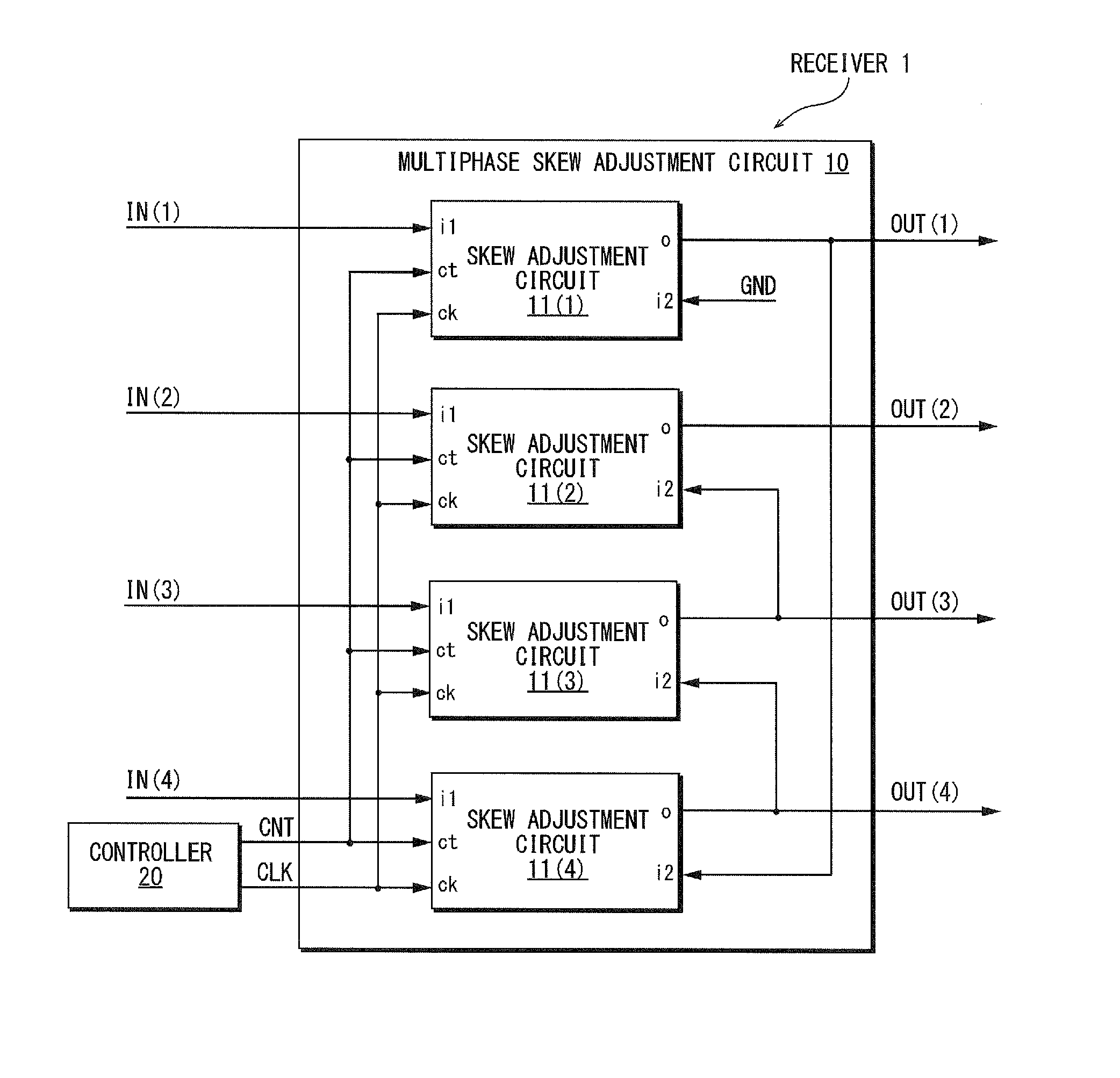

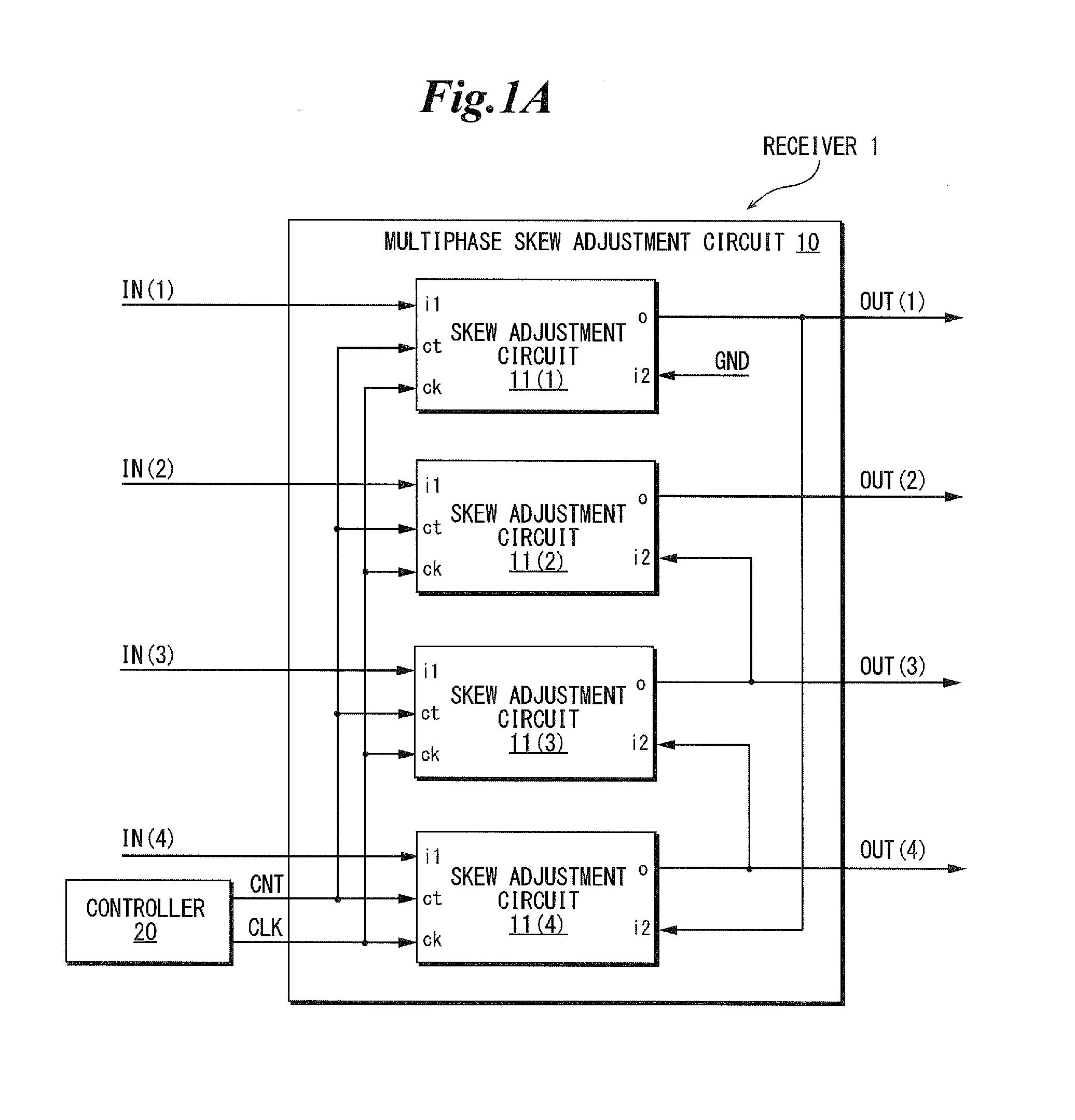

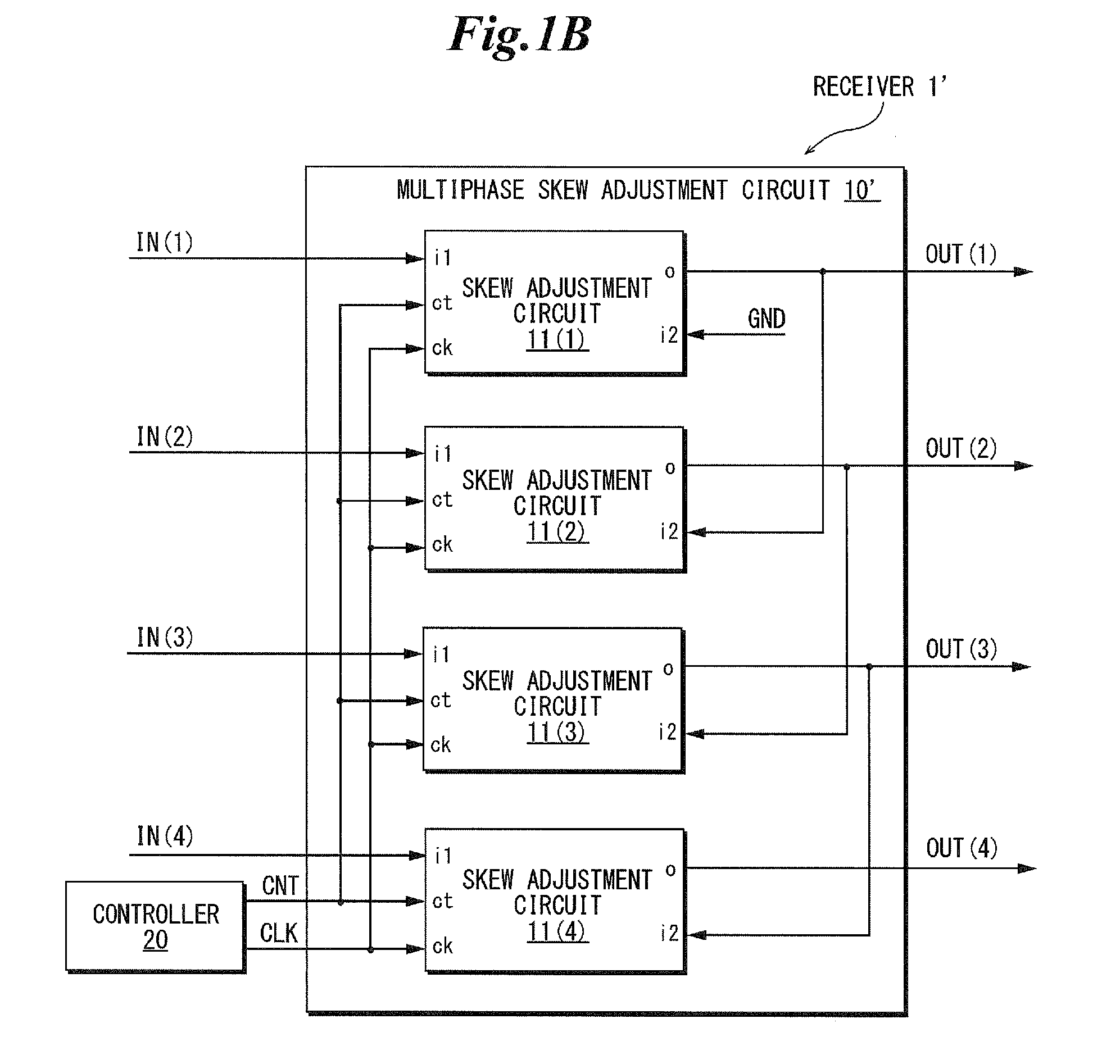

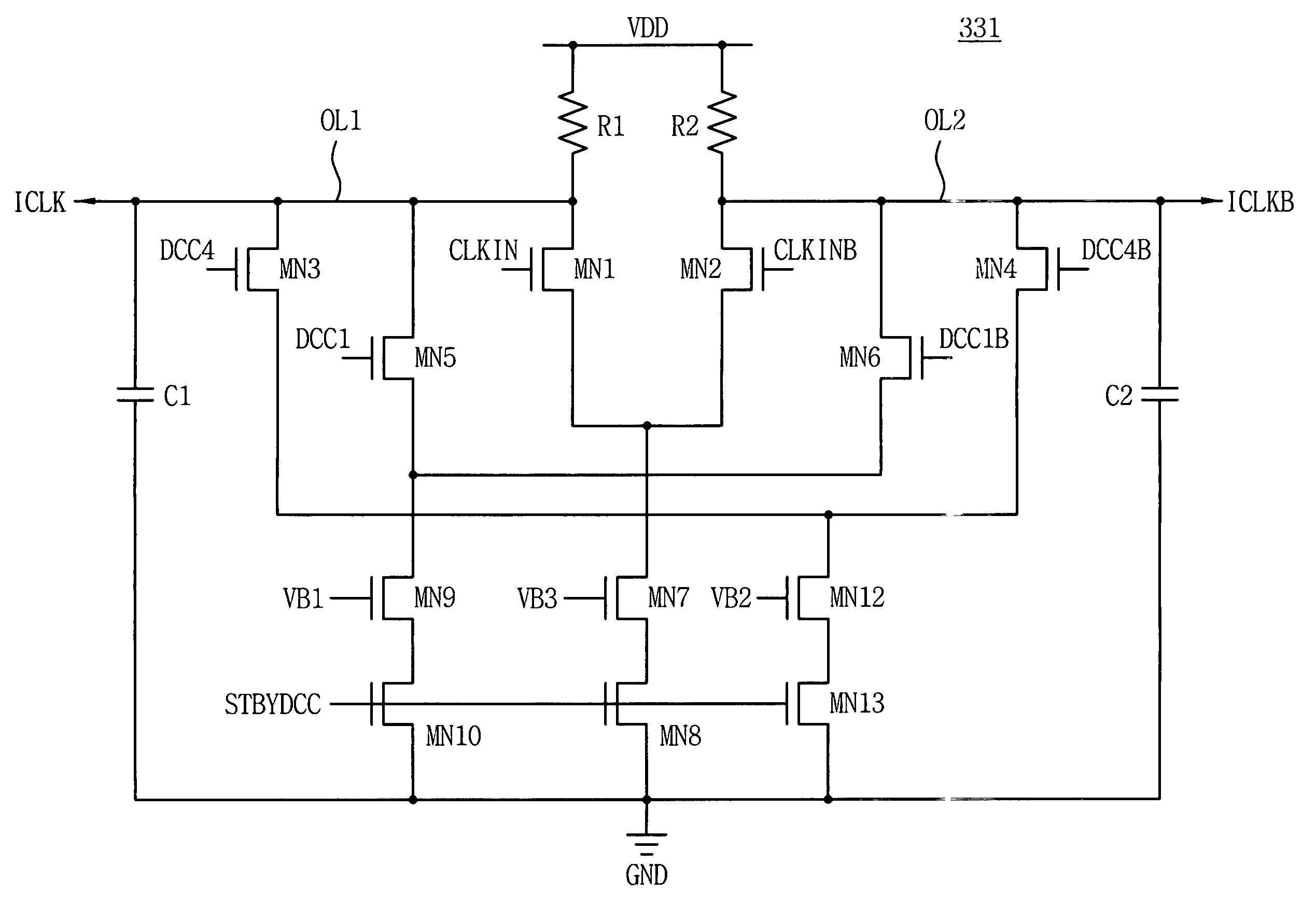

Skew adjustment circuit and skew adjustment method

ActiveUS20160134267A1Improve accuracyIncrease speedDelay line applicationsContinuous to patterned pulse manipulationExecution controlVoltage reference

A skew adjustment circuit comprises a phase adjustment circuit that adjusts a phase of a first input clock based on a predetermined phase control signal, and outputs it as an output clock, a logical circuit that performs a logical operation between signals that are input, an integral circuit that generates a predetermined voltage signal, based on a result of the logical operation by the logical circuit, a comparator that compares an electric potential of the predetermined voltage signal and an electric potential of a predetermined reference voltage signal, a first controller that generates the predetermined phase control signal based on a result of the comparison by the comparator, and a second controller that performs control for selecting a signal that is to be input to the logical circuit. The second controller, in a first mode, performs the control such that the output clock and a second input clock are selected.

Owner:MEGACHIPS

Duty cycle correction circuits suitable for use in delay-locked loops and methods of correcting duty cycles of periodic signals

InactiveUS20050122149A1Pulse automatic controlContinuous to patterned pulse manipulationControl signalDelay-locked loop

Delay-locked loop integrated circuits include a duty cycle correction circuit. This duty cycle correction circuit generates at least one output clock signal having a substantially uniform duty cycle in response to at least one input clock signal having a non-uniform duty cycle. The duty cycle correction circuit is also responsive to a standby control signal that synchronizes timing of power-saving duty cycle update operations within the duty cycle correction circuit. These update operations reset the set point of the correction circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

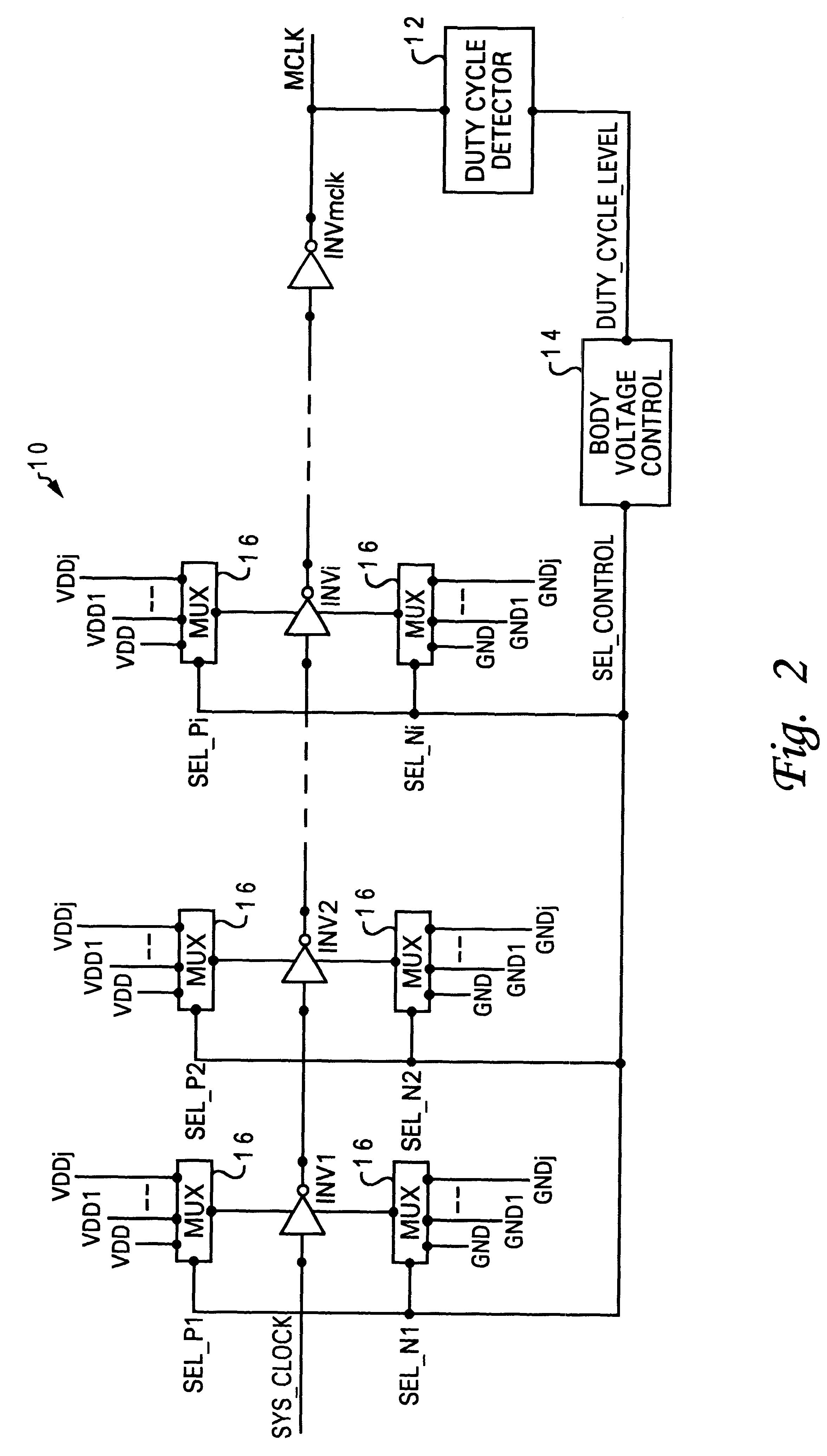

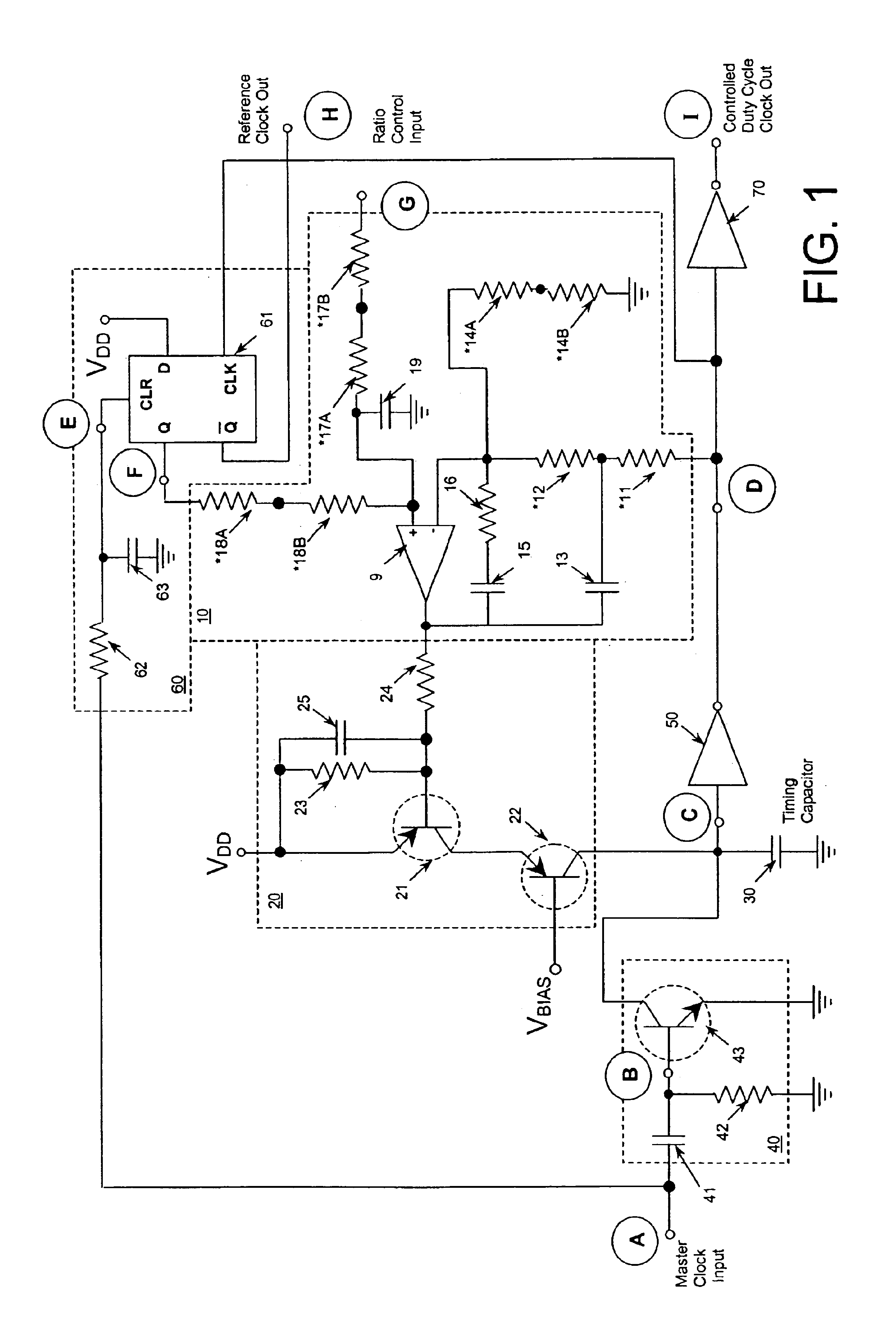

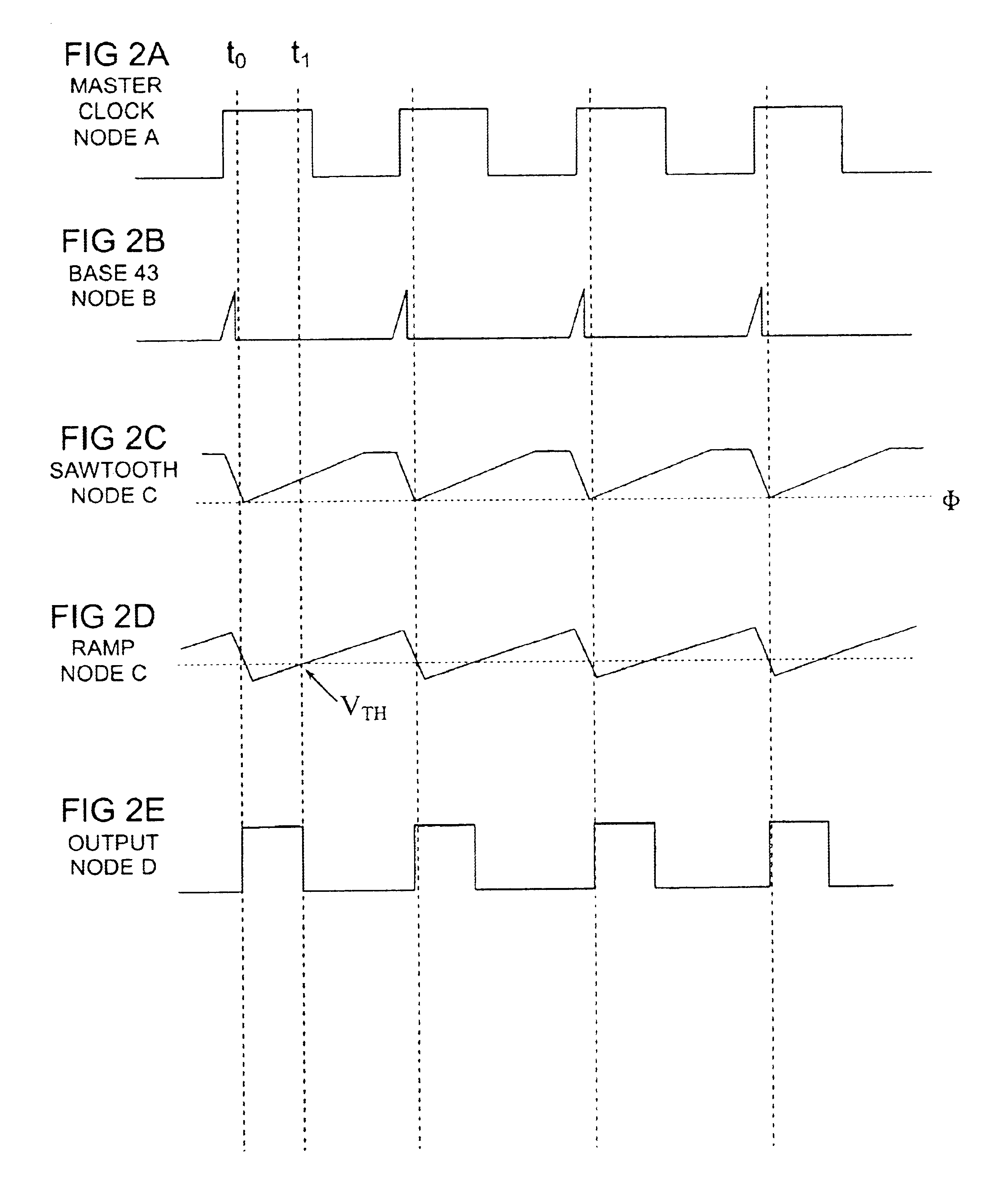

Dynamic duty cycle adjuster

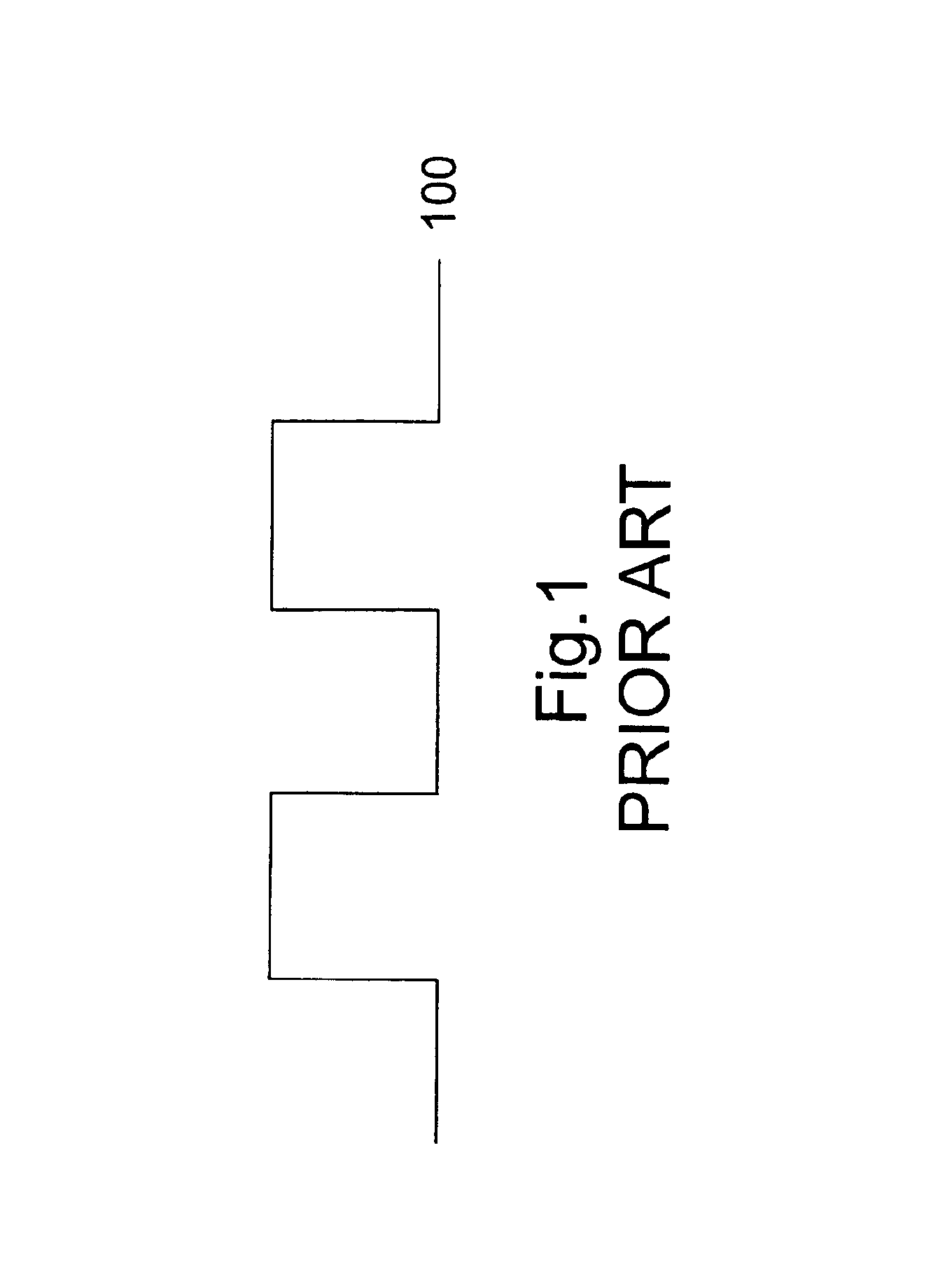

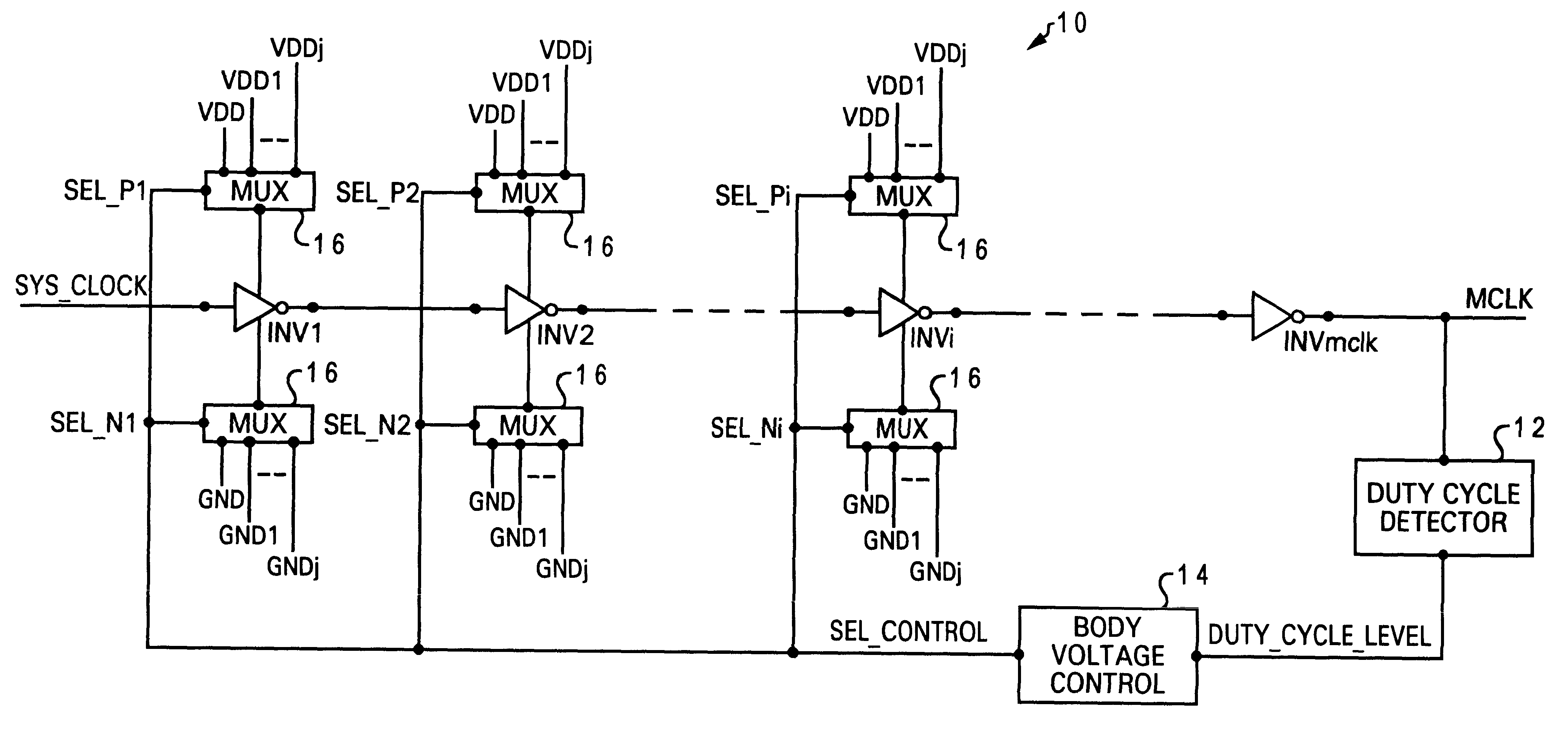

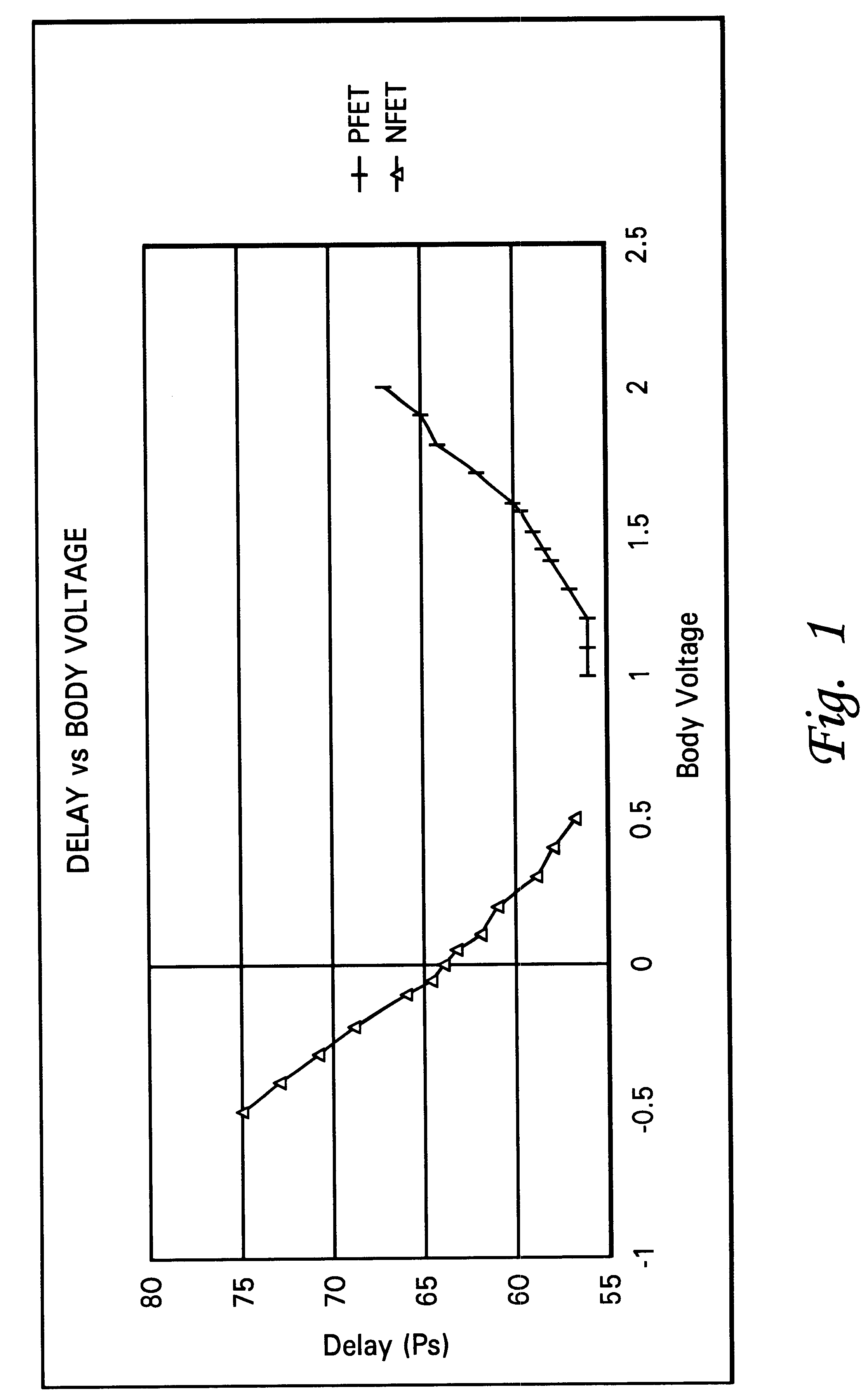

InactiveUS6501313B2Reduce cycle variationAdding significant expenseContinuous to patterned pulse manipulationElectric pulse generator detailsBody contactMultiplexer

Owner:LINKEDIN

Delay locked loop and its control method for correcting a duty ratio of a clock signal

ActiveUS7142026B2Small sizeReduce power consumptionPulse automatic controlContinuous to patterned pulse manipulationPhase detectorDelay-locked loop

A delay locked loop (DLL) capable of correcting a duty ratio including: a clock buffer for receiving an external clock signal and an inverted external clock signal to generate a rising edge clock signal; a delay unit for delaying the rising edge clock signal based on a first comparison signal in order to generate a first internal clock signal, a second internal clock signal, a first delay locking signal and a second delay locking signal; a duty correction unit for receiving the first and the second internal clock signals and the first and the second delay locking signals to generate a mixed clock signal; a delay model unit for delaying the mixed clock signal to generate a feed-backed clock signal; and a first phase detector for receiving the external clock signal and the feed-backed clock signal to generate the first comparison signal.

Owner:SK HYNIX INC

Systems and methods of performing duty cycle control

ActiveUS20050174156A1Facilitates serial communicationReduce error rateContinuous to patterned pulse manipulationManipulation where pulse delivered at different timesMultiplexingSquare waveform

The present invention facilitates serial communication by performing duty cycle correction. A duty cycle correction component 302 performs duty cycle corrections on a pair of differential sinusoidal signals according to a pair of adjustment signals and, as a result, generates a differential pair of square wave signals. A cross coupled buffer 306 buffers the differential pair of square wave signals and provides the buffered signals to a feedback circuit 304 that measures duty cycles of the signals and generates the pair of adjustment signals accordingly. The buffer 306 can also remove skew from the signals. In a transmitter 102, the buffered signals are also generally provided to a multiplexer 112 or encoder and in a receiver 106, the buffered signals are also generally provided to a sampling component 122.

Owner:TEXAS INSTR INC

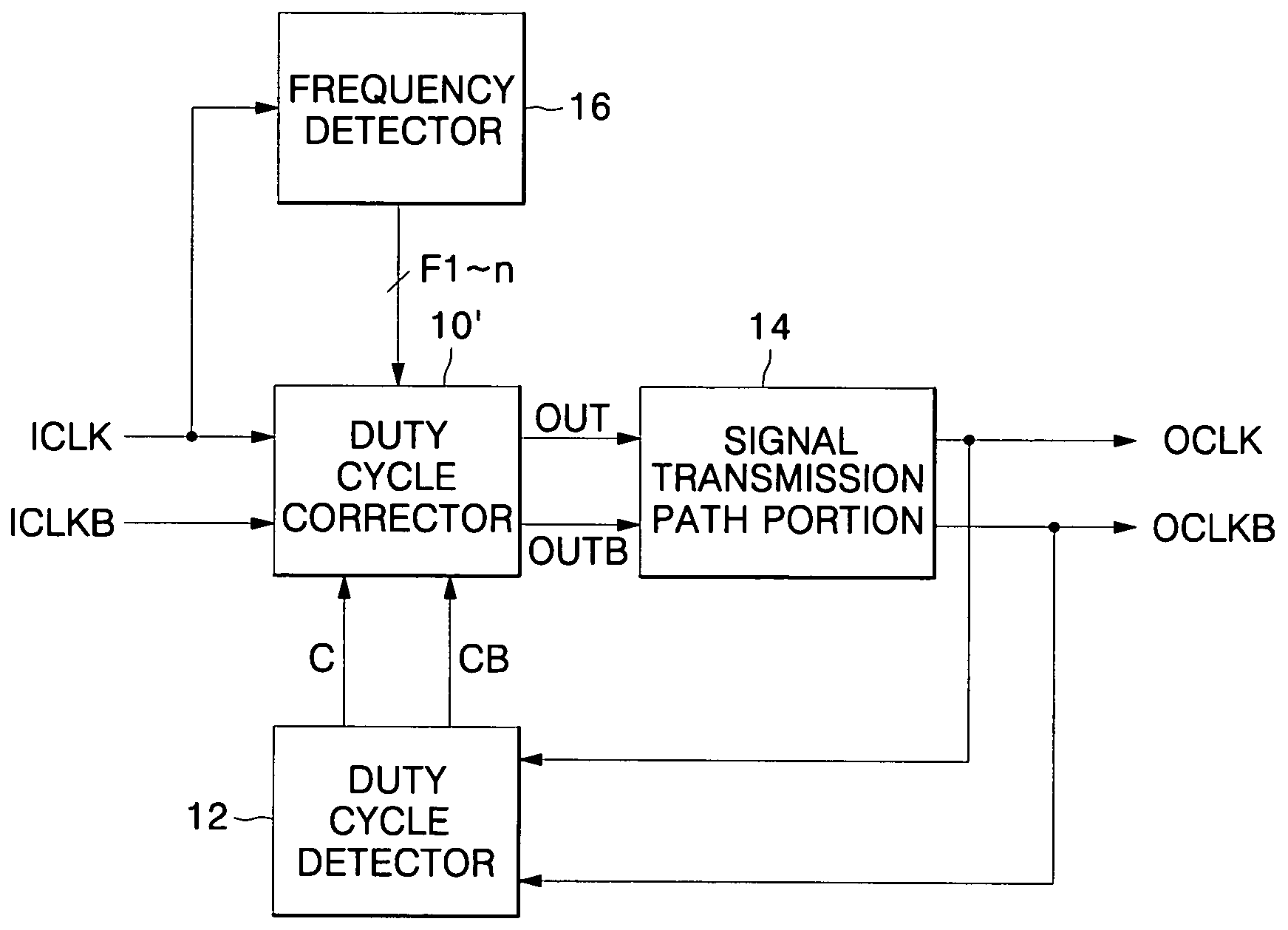

Delay locked loop circuit for internally correcting duty cycle and duty cycle correction method thereof

InactiveUS7184509B2Solve the large consumptionReduce restrictionsPulse automatic controlContinuous to patterned pulse manipulationDelay-locked loopEngineering

A delay locked loop (DLL) circuit having a duty cycle corrector (DCC) that has a broad range of duty cycle correction, consumes only a small amount of power, has few restrictions on operating frequency, and improves the characteristics of a memory device is described. The delay locked loop circuit includes an additional loop for duty cycle correction as well as loops for controlling a rising edge and a falling edge of output signals. Thus, the delay locked loop circuit can internally correct the duty cycle without the use of a phase blender.

Owner:SAMSUNG ELECTRONICS CO LTD

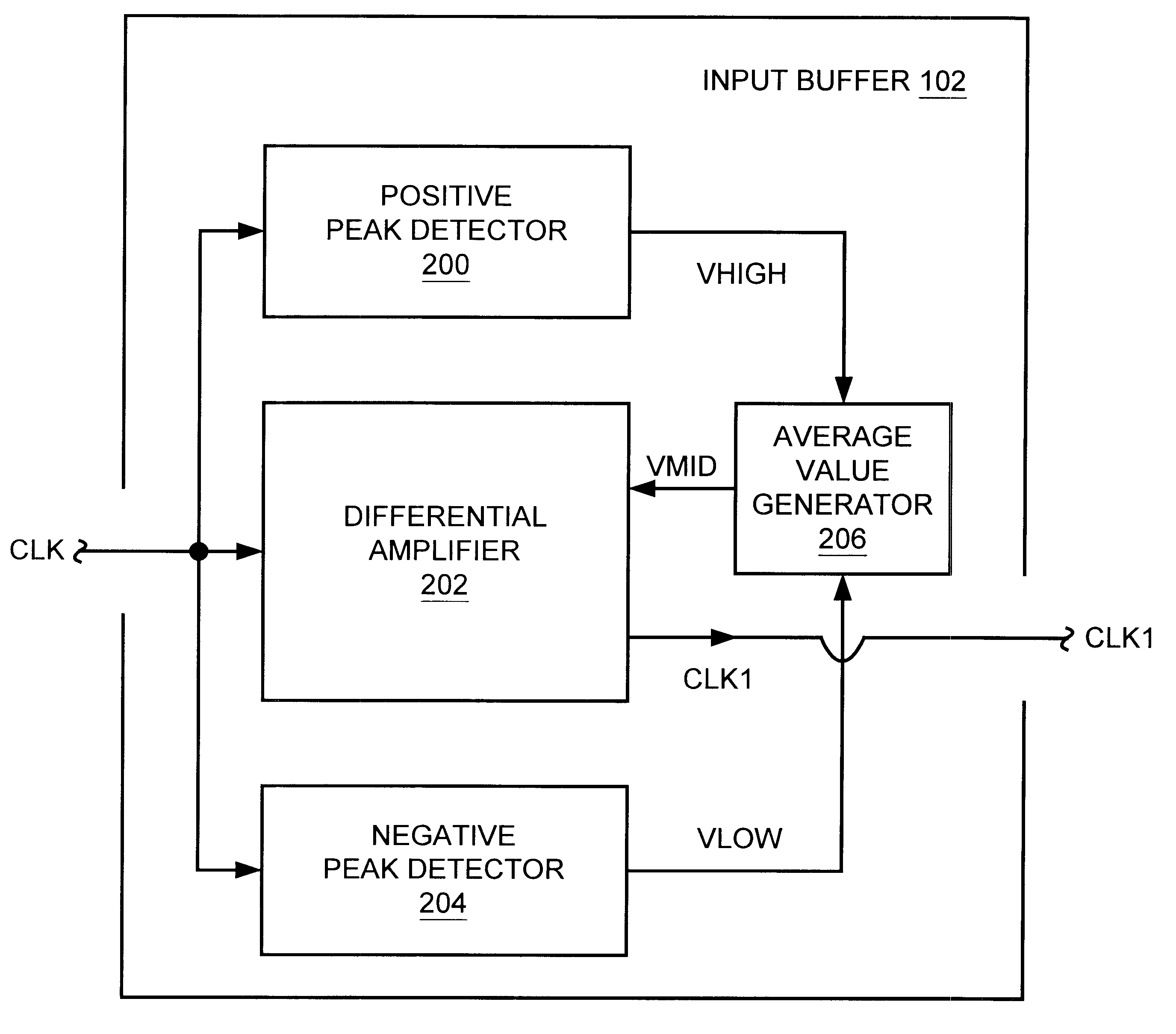

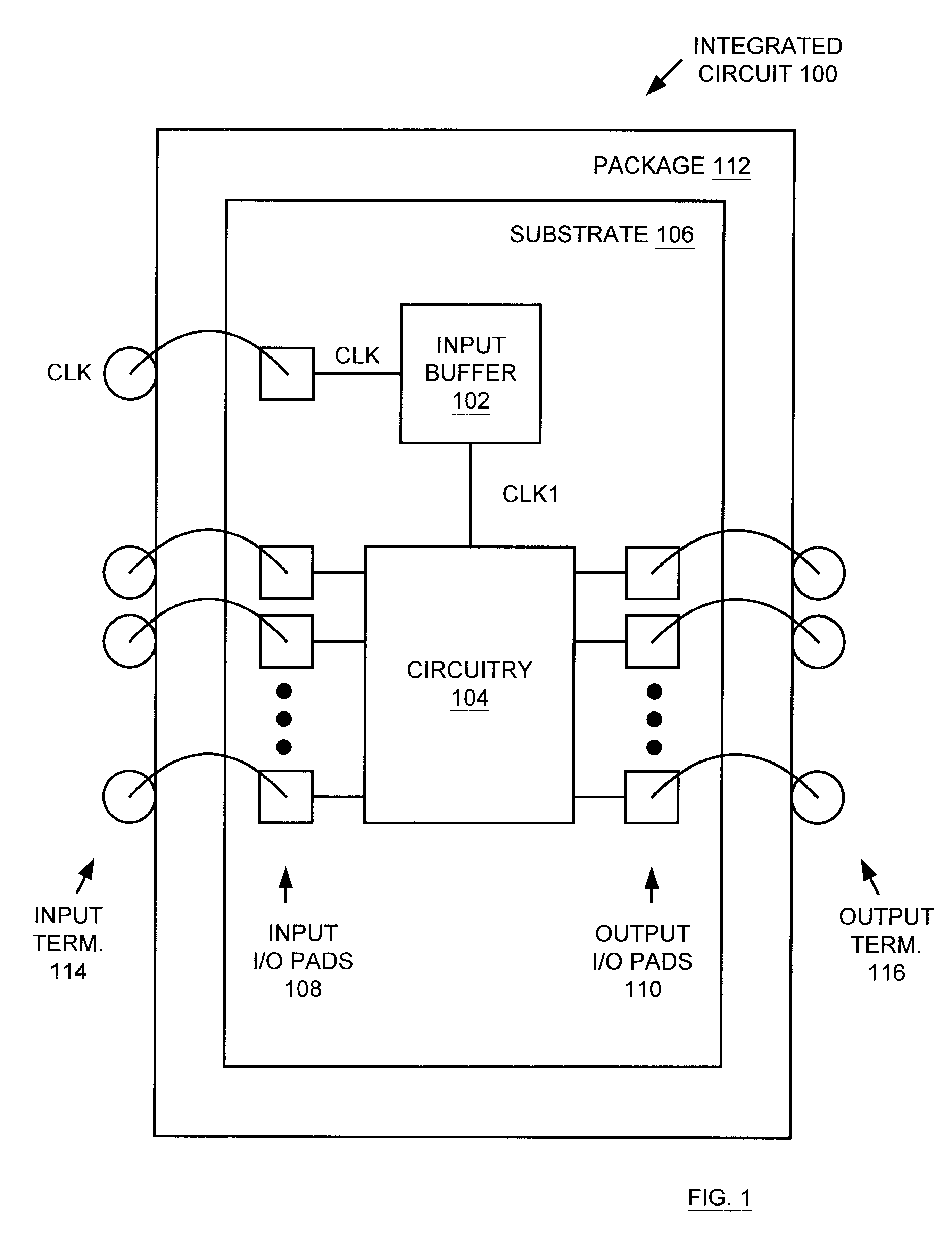

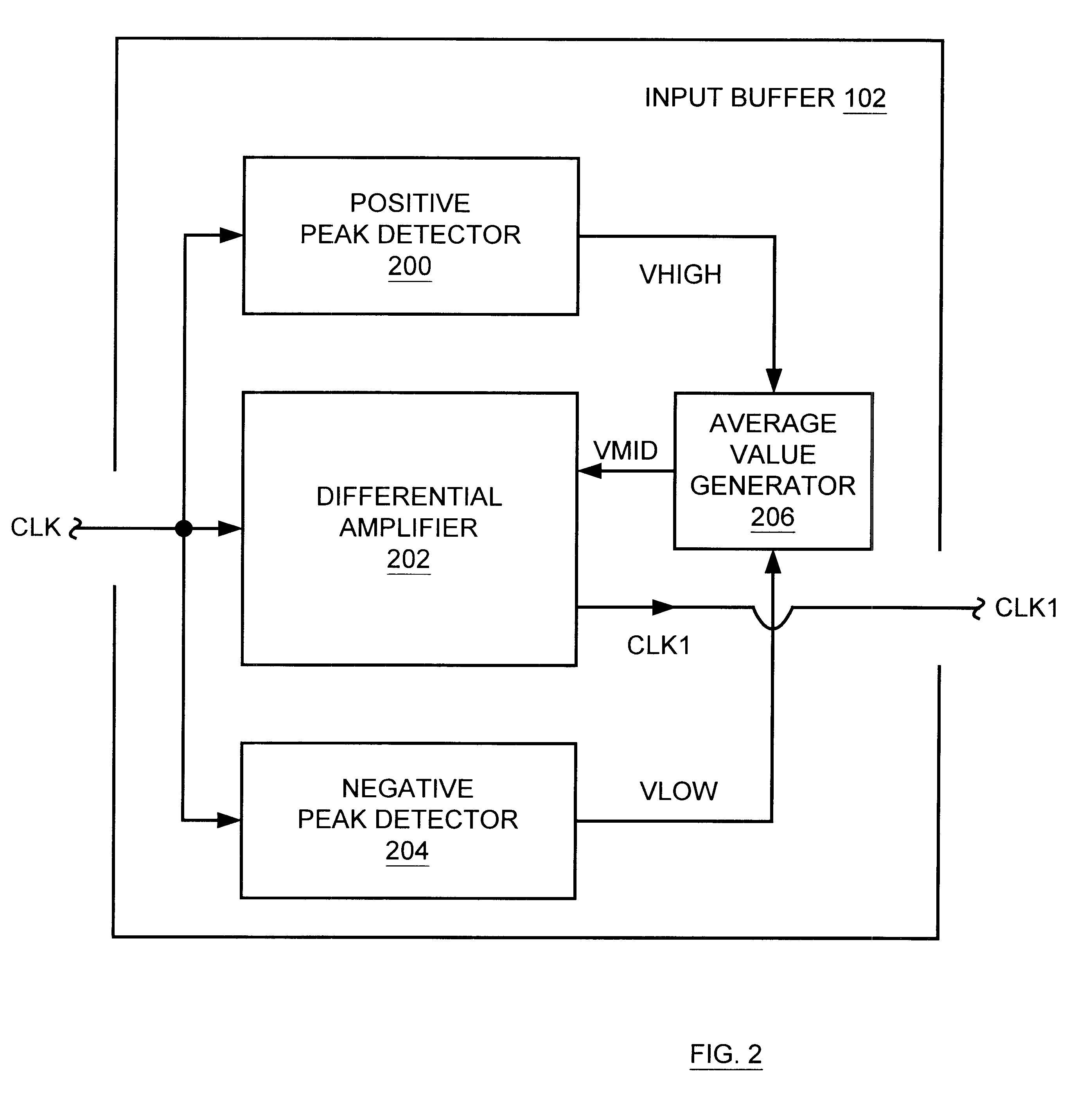

Input buffer with automatic switching point adjustment circuitry, and synchronous DRAM device including same

InactiveUS6522160B1Reliability increasing modificationsMultiple input and output pulse circuitsVoltage amplitudeDetector circuits

An input buffer is presented for buffering an input signal having a voltage magnitude which alternates between a first voltage level and a second voltage level, where the first and second voltage levels may vary over time. In one embodiment, the input buffer includes a first and second detector circuits, an average generator circuit, and a differential amplifier. The first detector circuit receives the input signal and produces a first signal having a magnitude indicative of the first voltage level. The second detector circuit receives the input signal and produces a second signal having a magnitude indicative of the second voltage level. The average generator circuit receives the first and second signals, and uses the magnitudes of the first and second signals to produce a third signal having a magnitude indicative of a third voltage level substantially mid way between the first voltage level and the second voltage level. The third voltage level defines a variable an automatically adjusted "switching point". The differential amplifier receives the input signal, the third signal, and a first and second power supply voltages. The differential amplifier amplifies a difference between the voltage magnitude of the input signal and the third voltage level in order to produce an output signal which alternates between the first and second power supply voltages. An integrated circuit is described including the input buffer coupled between one of a set of input / output pads and circuitry, wherein the circuitry may be synchronous dynamic random access memory (SDRAM) circuitry.

Owner:MICRON TECH INC

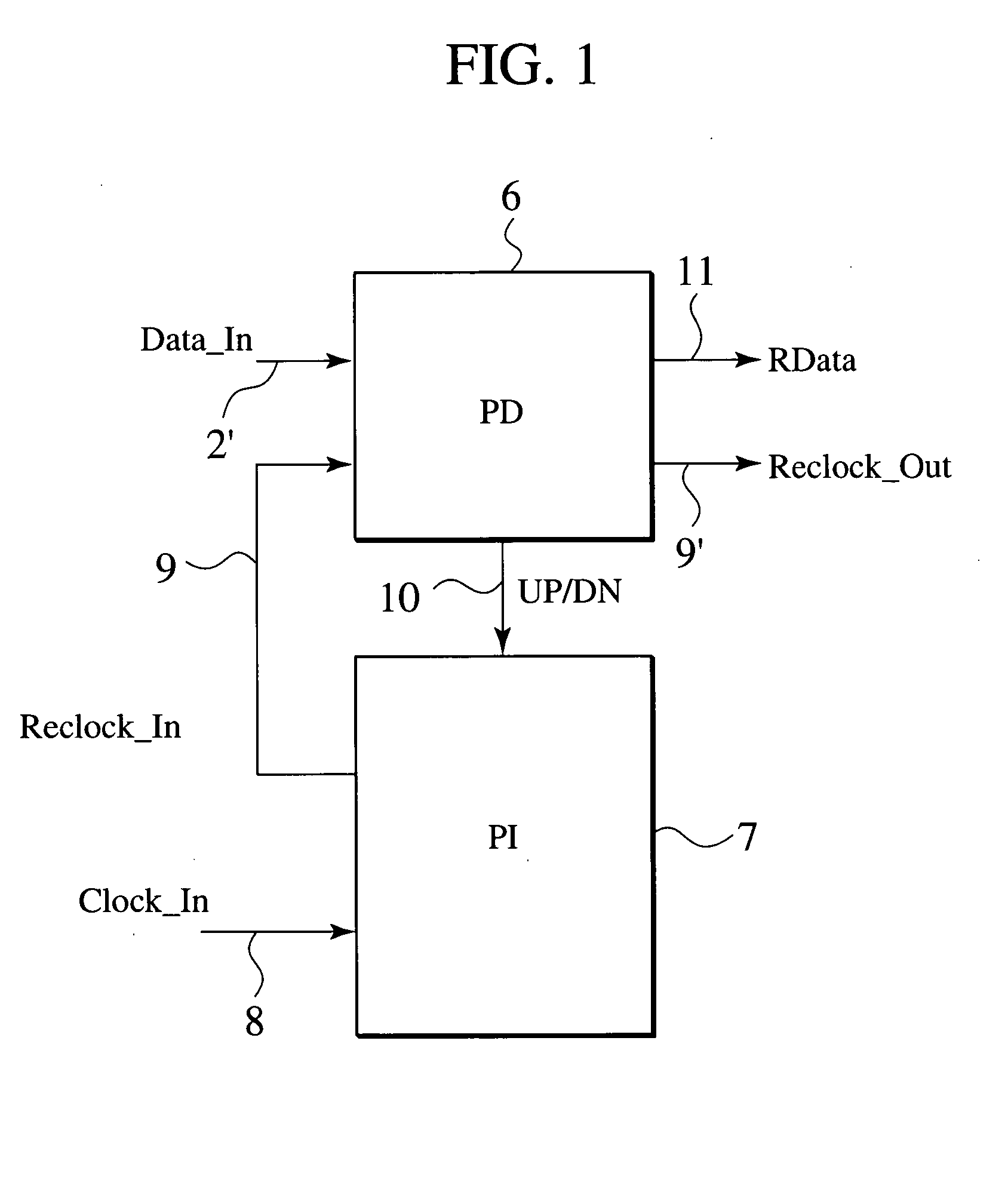

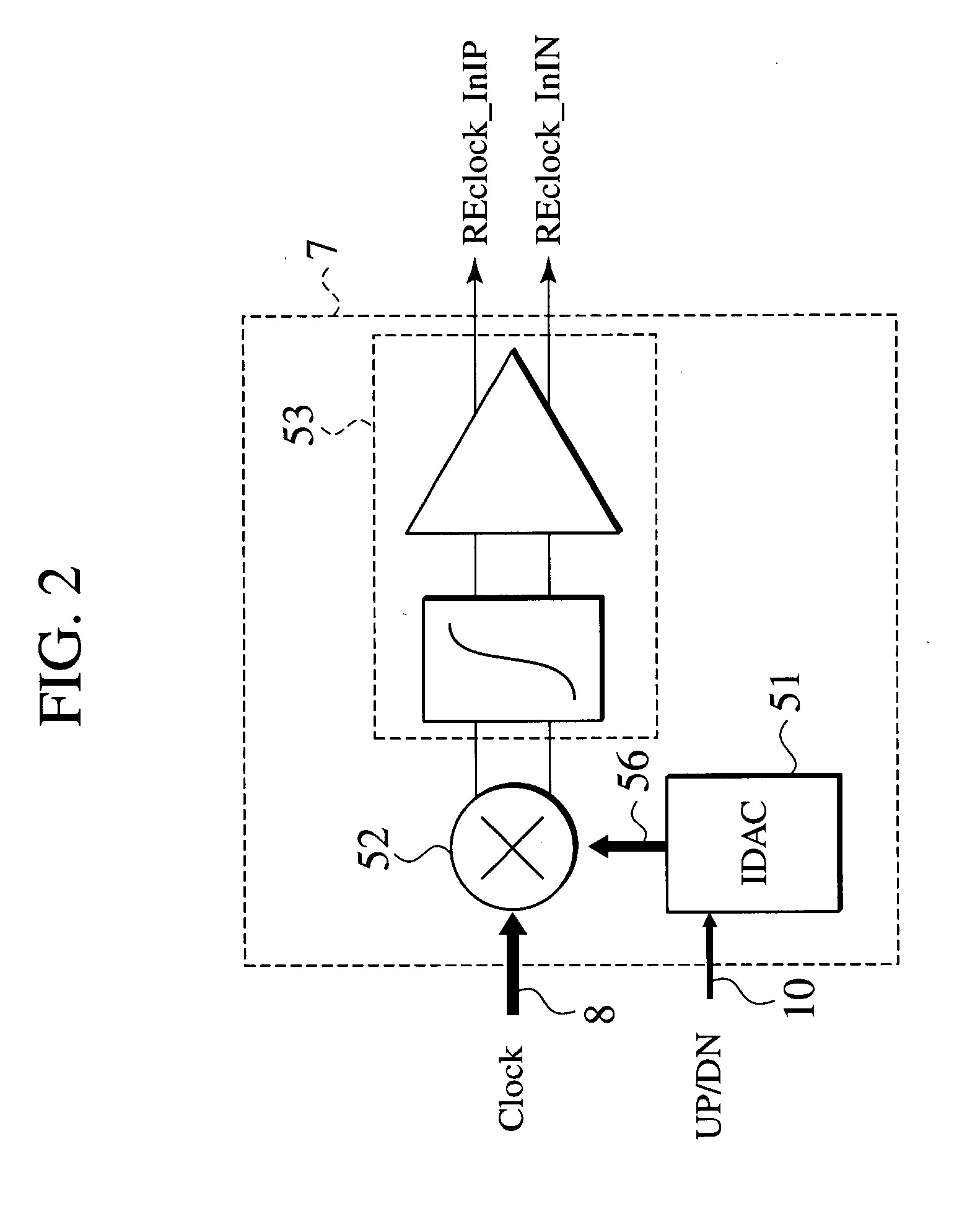

Phase interpolator and receiver for adjusting clock phases into data phases

InactiveUS6900681B2Pulse automatic controlContinuous to patterned pulse manipulationIntegratorEngineering

Owner:KK TOSHIBA

Analog delay locked loop having duty cycle correction circuit

InactiveUS7078949B2Correct wide rangeReduce initial timePulse automatic controlContinuous to patterned pulse manipulationAnalog delay lineDelay-locked loop

An analog delay locked loop device includes a first block for receiving an internal clock signal and a reference clock signal to generate normal multi phase clock signal pairs and dummy multi phase clock signal pairs; and a second block for receiving the reference clock signal to generate a delay locked internal clock signal having a corrected duty cycle based on the normal multi phase clock signal pairs and the dummy multi phase clock signal pairs.

Owner:SK HYNIX INC

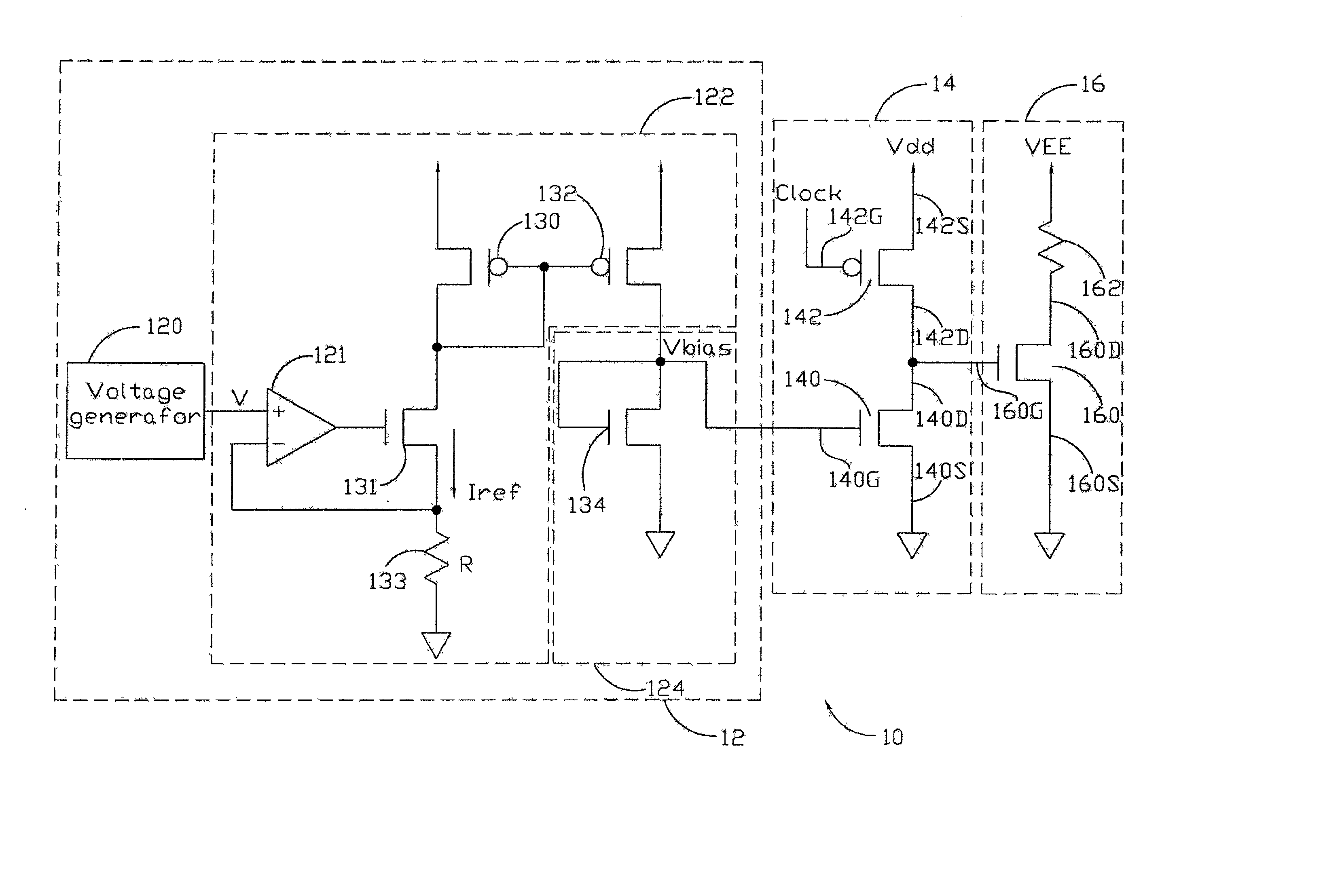

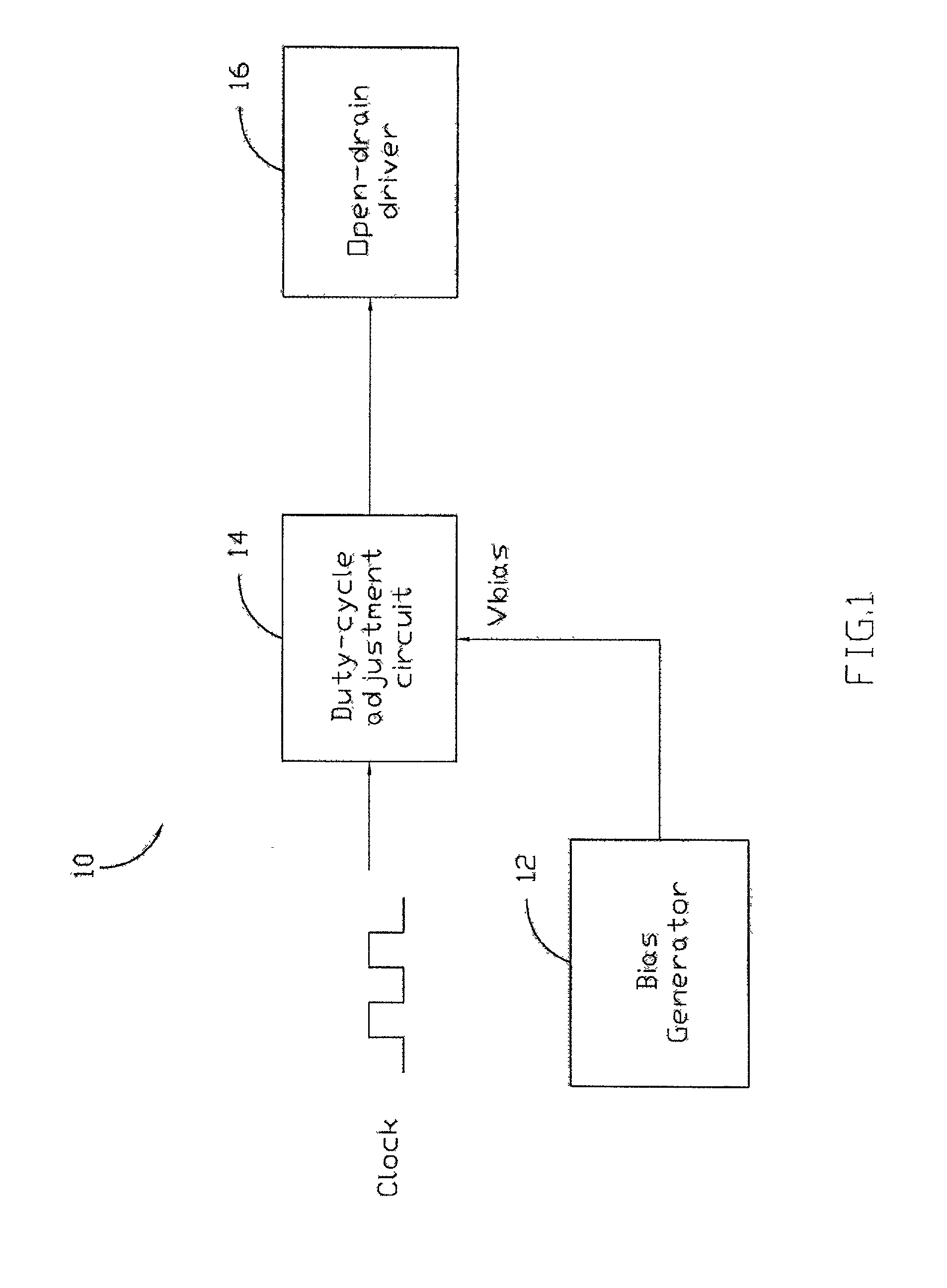

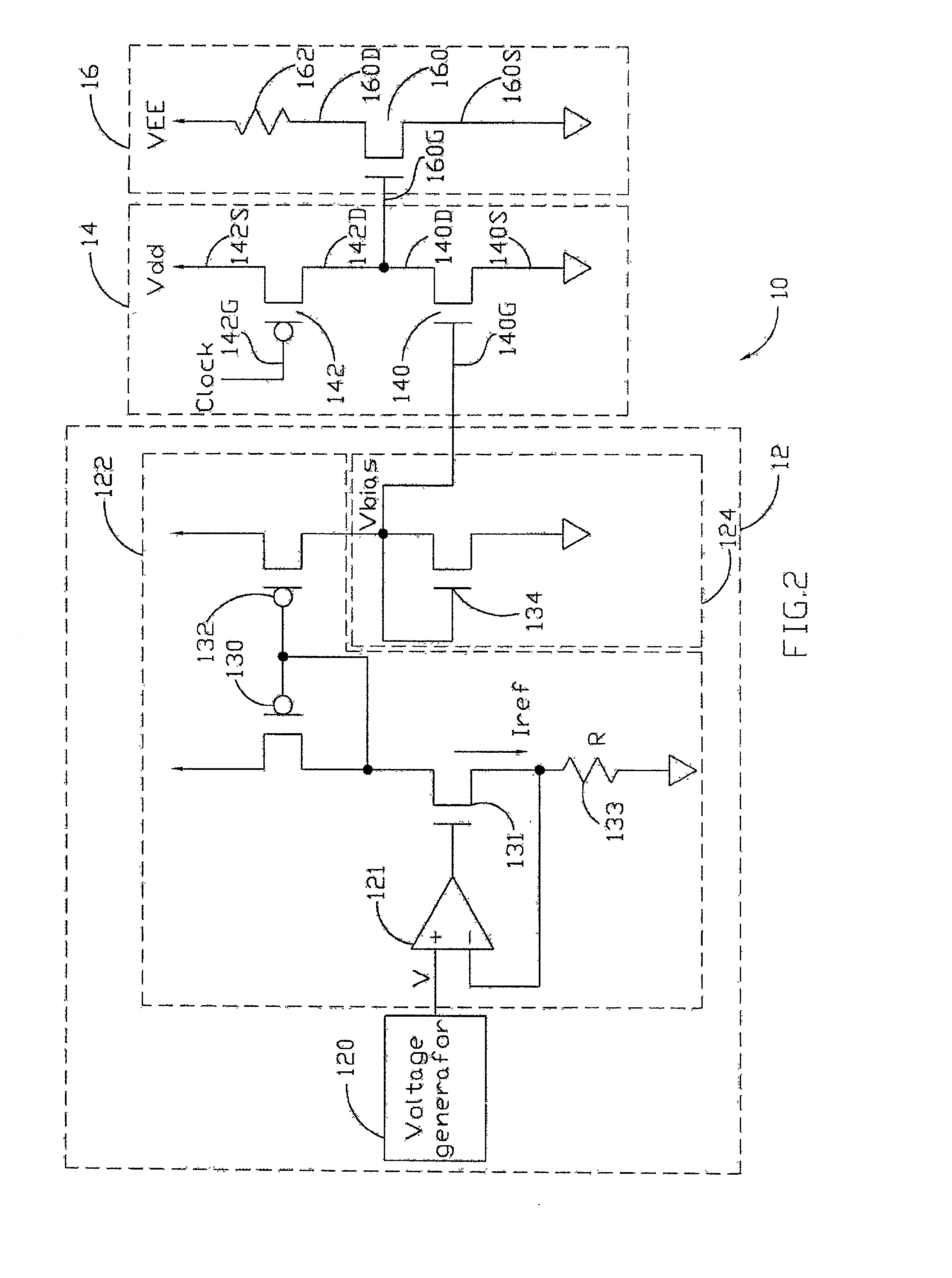

Clock duty cycle control circuit

InactiveUS20020125929A1Reduce varianceEasy to controlContinuous to patterned pulse manipulationElectric pulse generatorEngineeringVoltage reference

A clock duty cycle control circuit comprises a reference voltage circuit and a constant current generator connected to the reference voltage circuit. A duty-cycle adjustment circuit is used to receive a clock signal and controlled by the bias voltage of the bias voltage generating circuit which is connected to constant current generator. Accordingly, by a method of controlling duty-cycle adjustment circuit, the bias voltage has capability for adjusting a charging time and a discharging time of the clock signal. Finally, an open-drain driver with open-drain output is connected to the duty-cycle adjustment circuit, and thereby substantially stabilizing the output duty cycle of the clock signal.

Owner:CHEN PI FEN +1

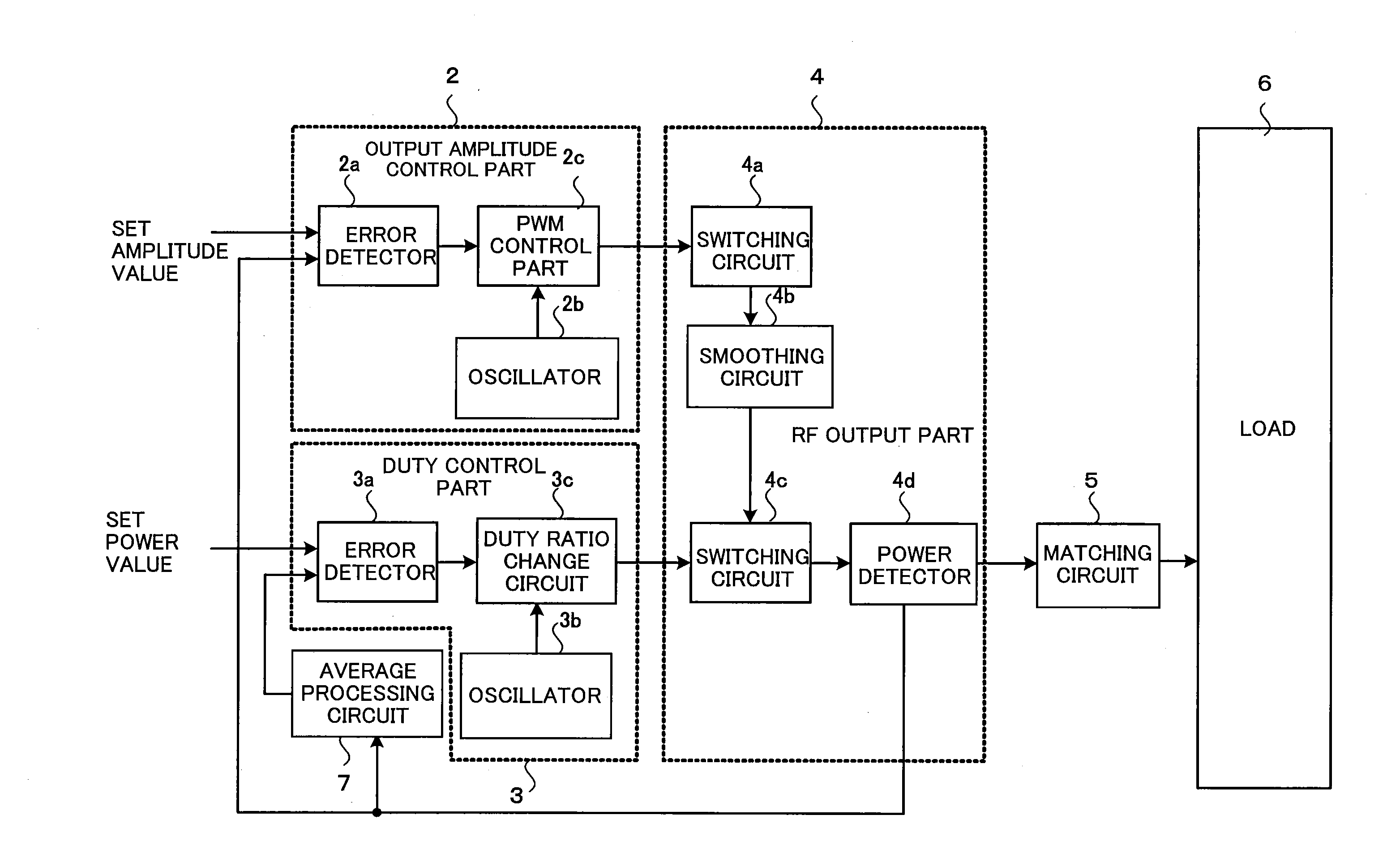

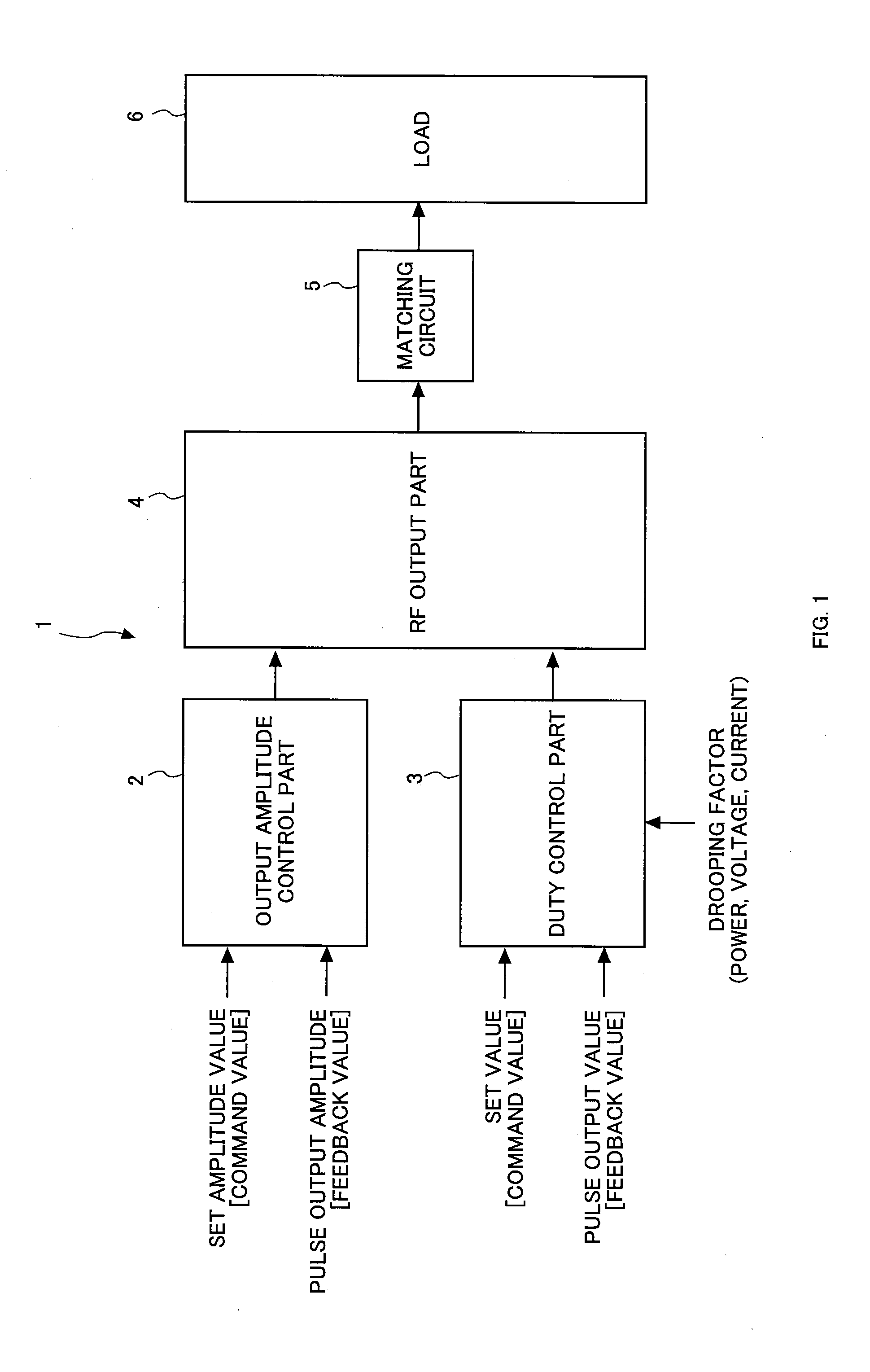

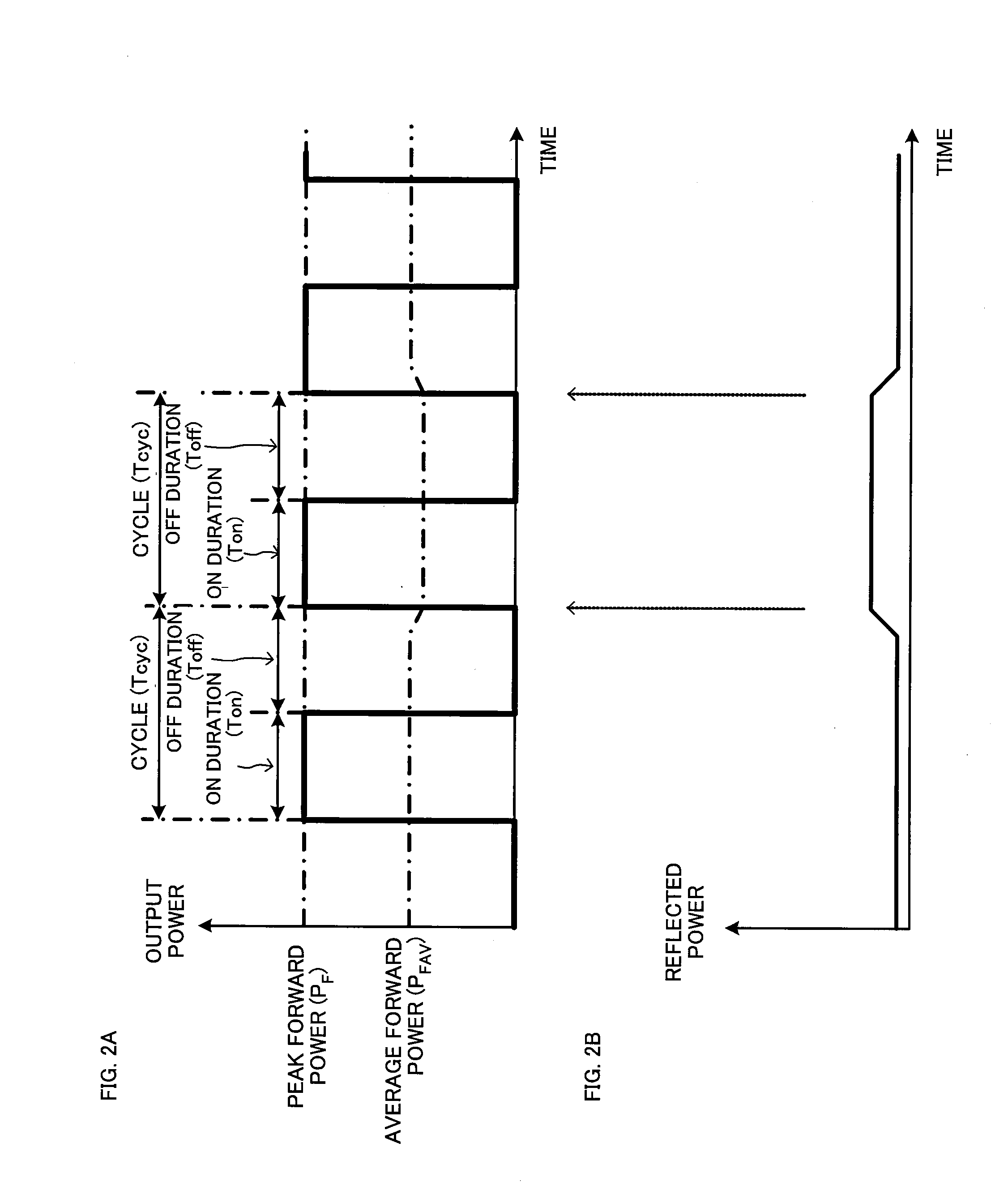

Pulse modulated RF power control method and pulse modulated RF power supply device

ActiveUS20110032047A1Improve homogeneityStabilizing plasma loadElectric discharge tubesAmplifier with semiconductor-devices/discharge-tubesAmplitude controlPower control

The pulse modulated RF power control method includes an output amplitude control step for controlling amplitude of a pulse output, and a duty control step for controlling a duty ratio of the pulse output. The output amplitude control step performs a constant amplitude control to control an amplitude value of the pulse output so that the amplitude value becomes equal to a set amplitude value. The constant amplitude control according to the output amplitude control, for instance, gives a feedback of the amplitude value of the pulse output outputted by the power control, obtains a difference value between the feedback value and the set amplitude value, and controls the amplitude value of the pulse output so that the difference value becomes zero.

Owner:KYOSAN ELECTRIC MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com