Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

949results about "Electric pulse generator details" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

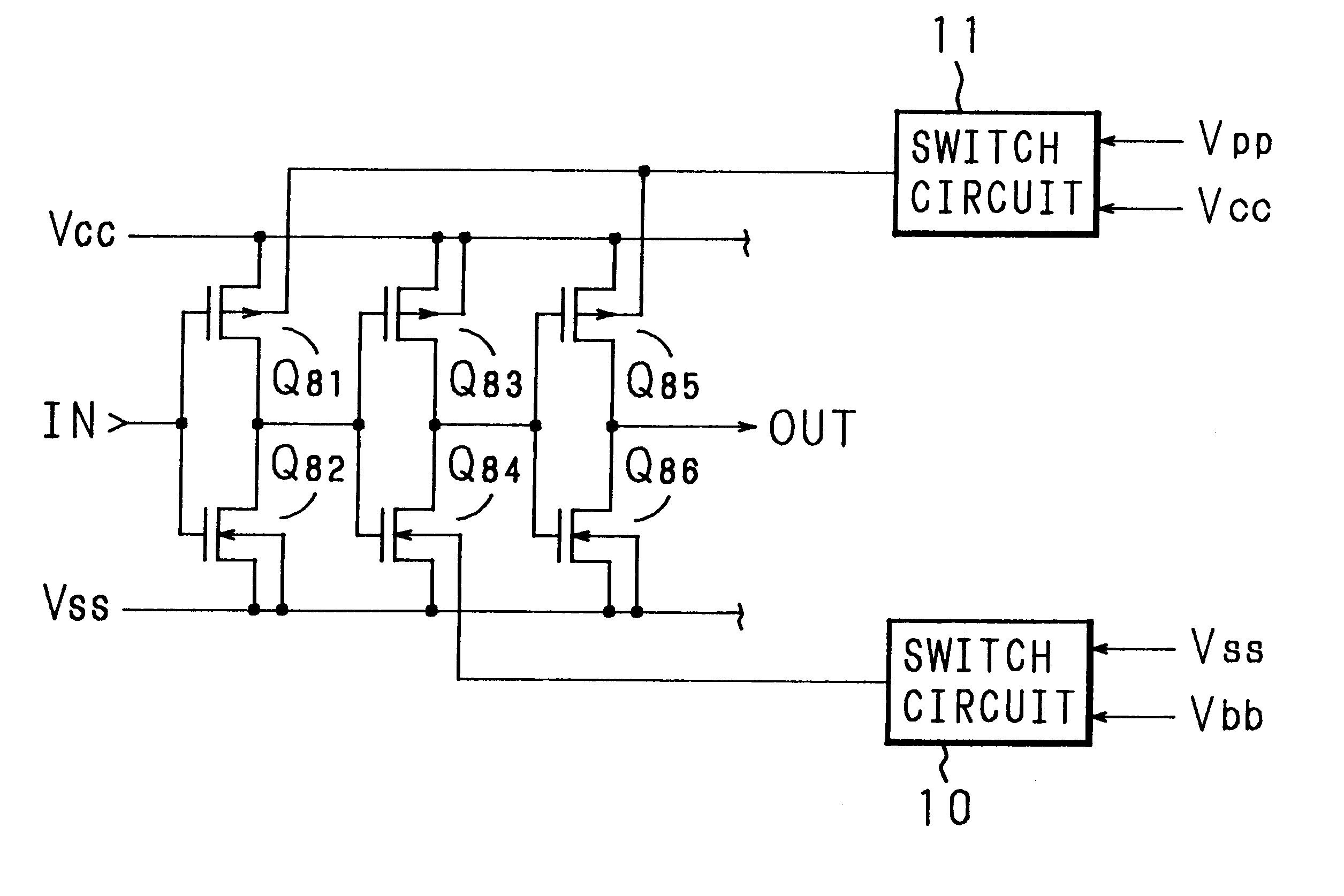

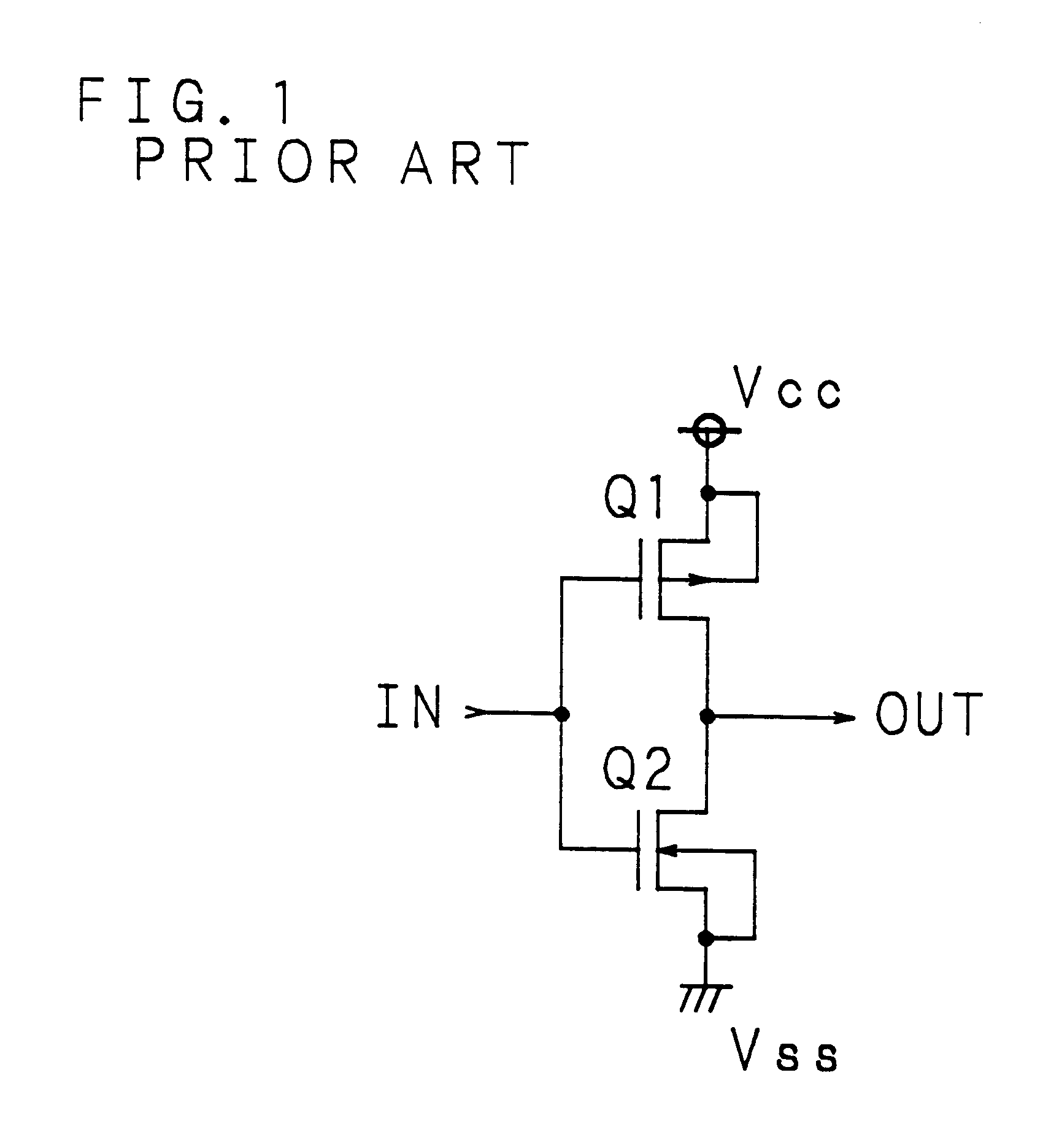

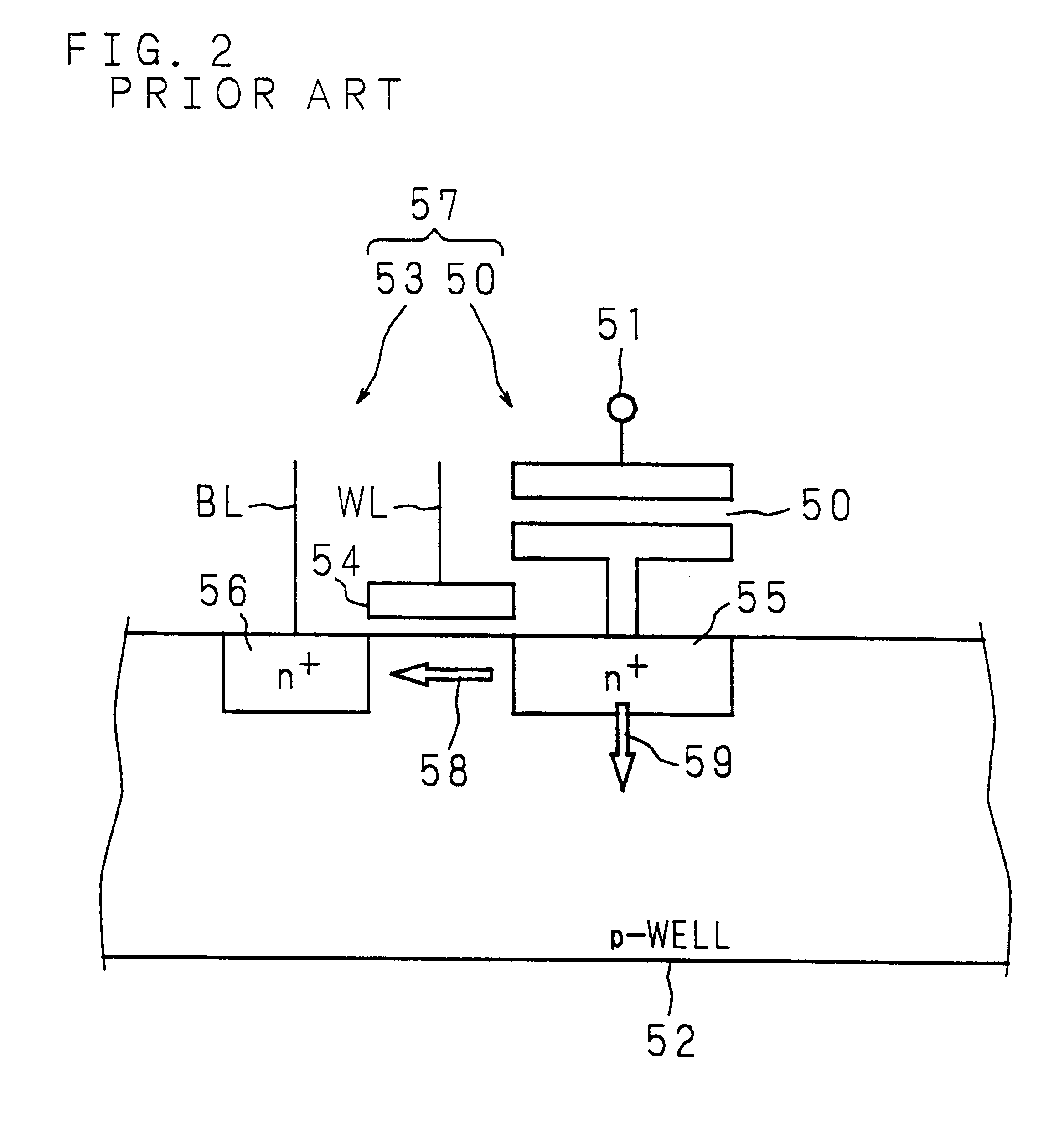

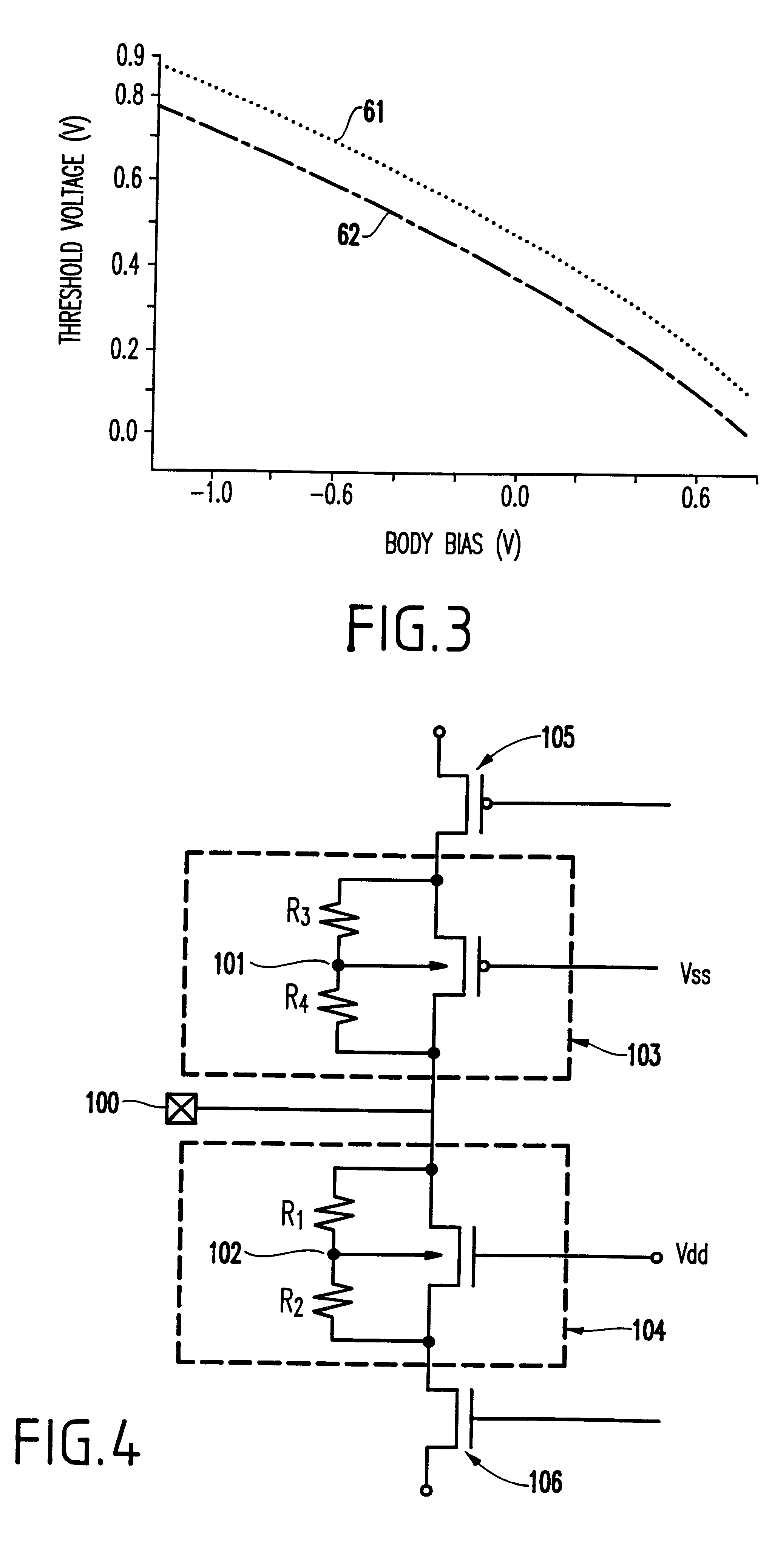

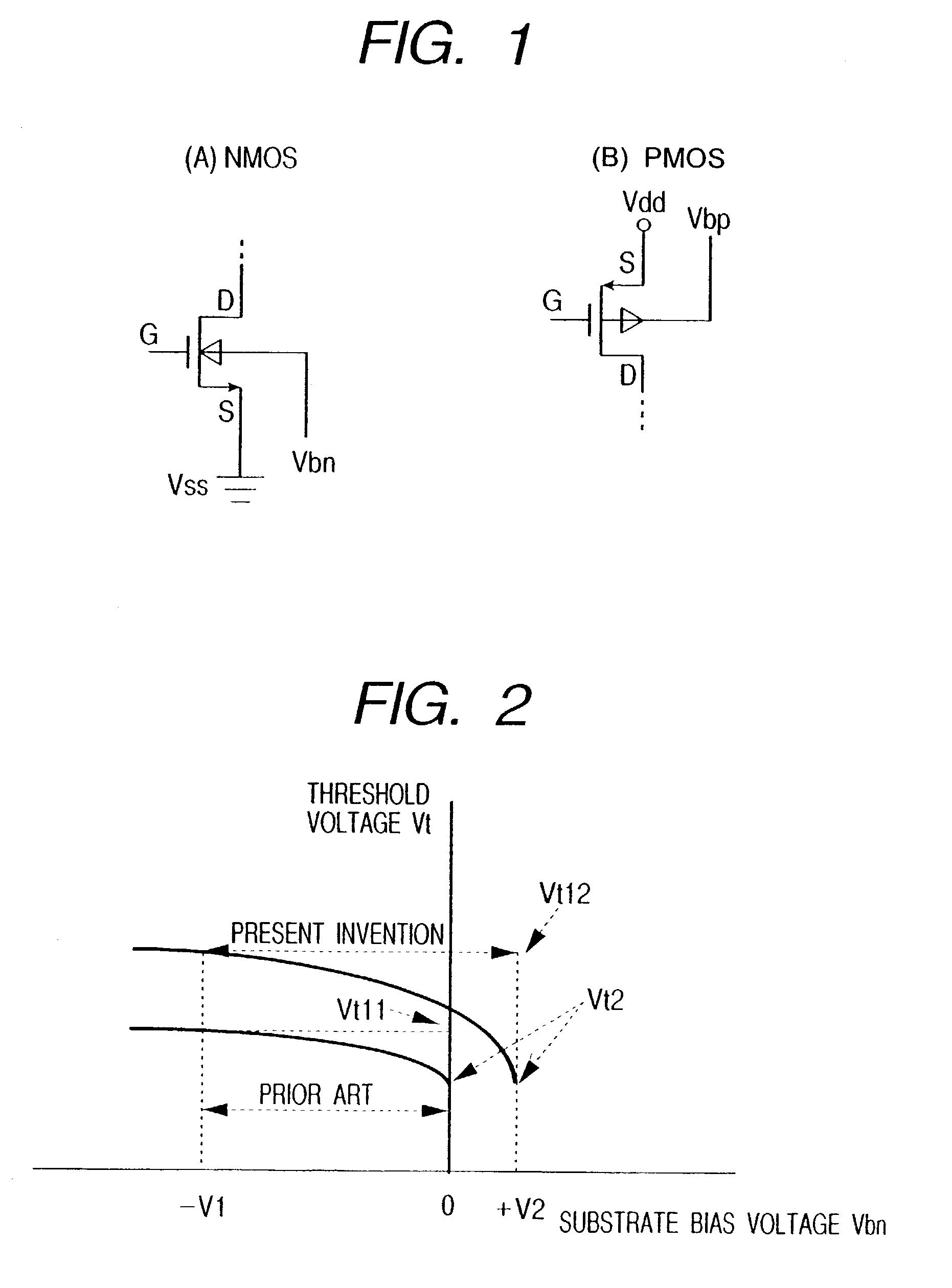

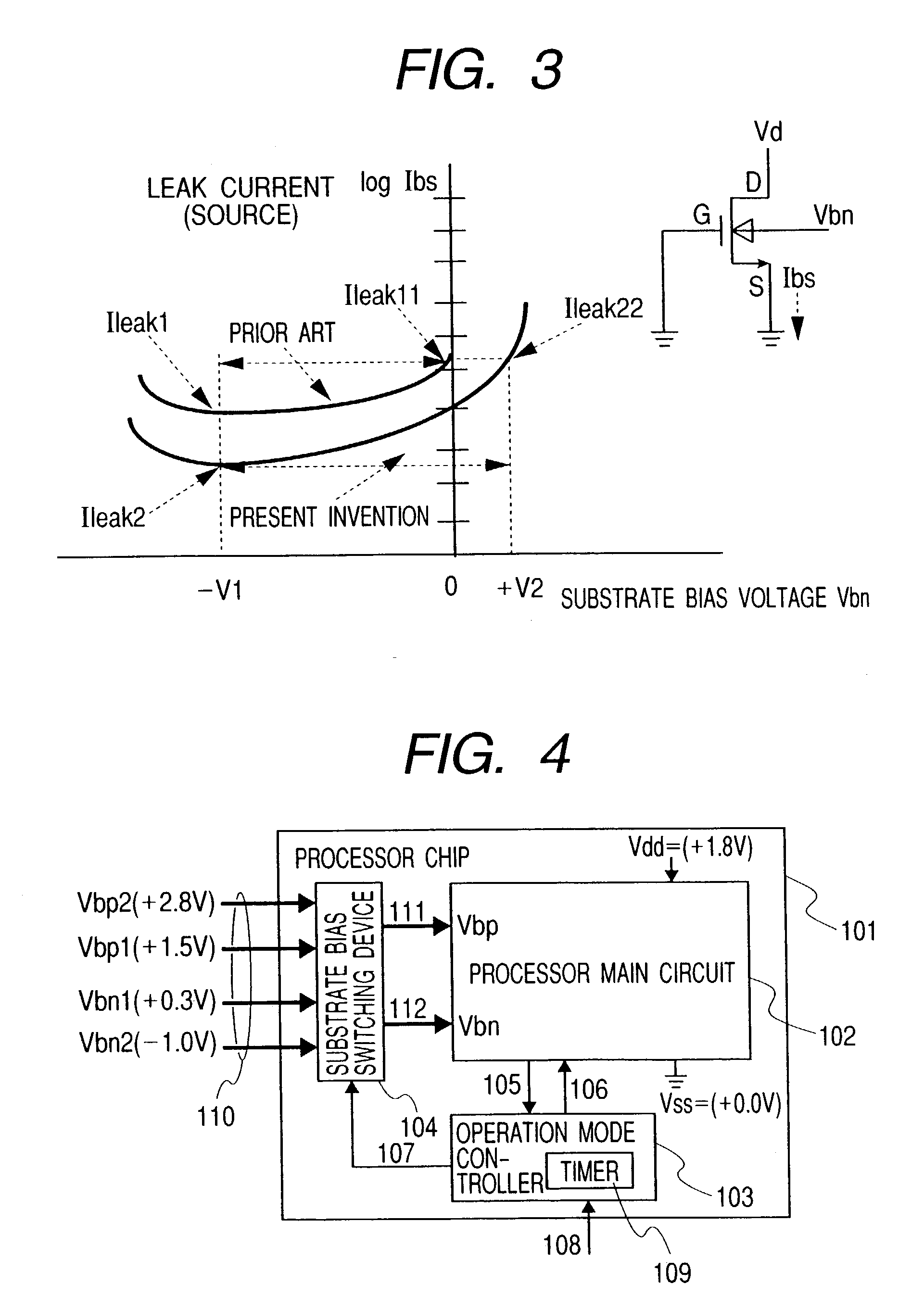

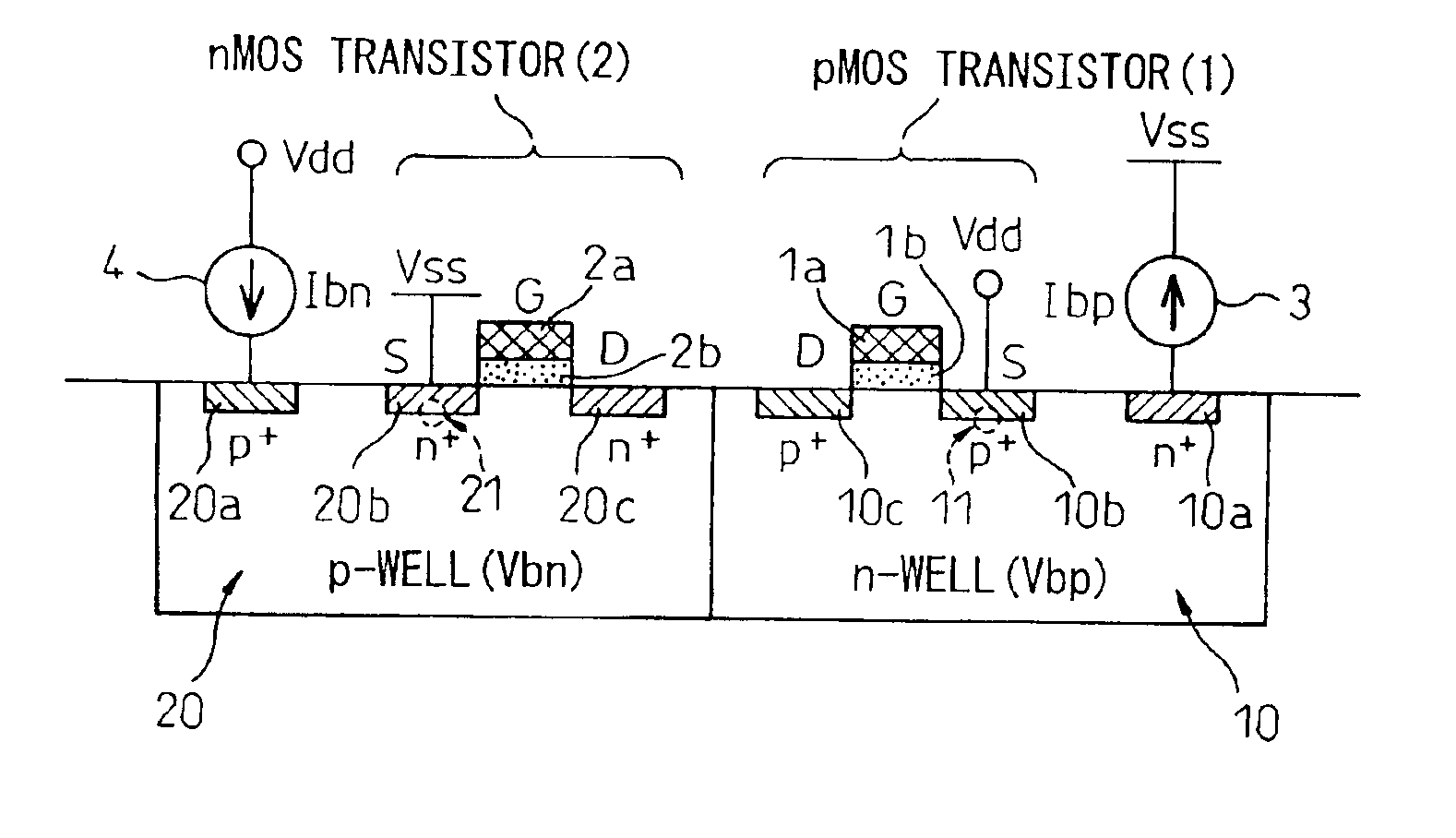

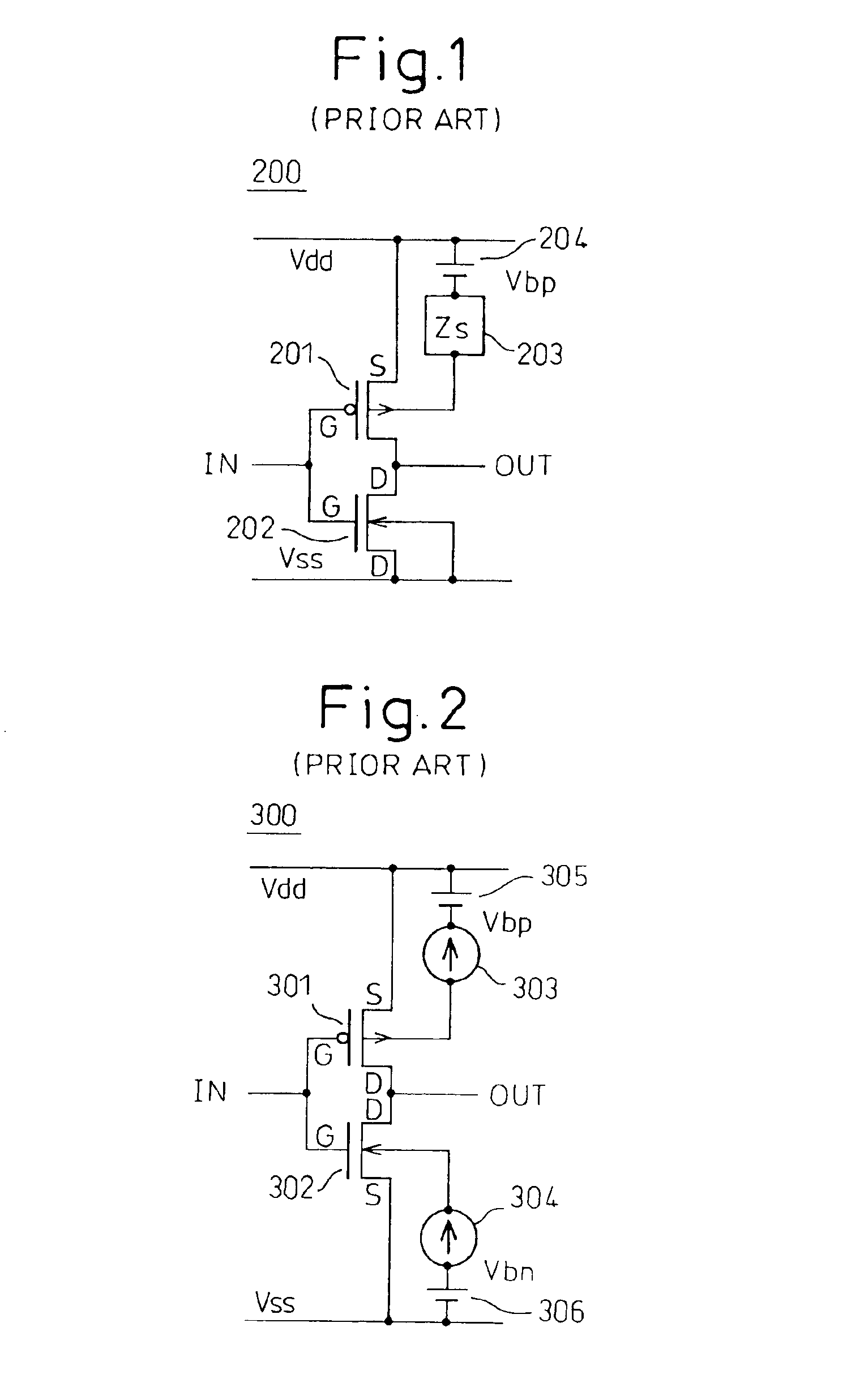

Switched backgate bias for FET

InactiveUS6232793B1Reliability increasing modificationsPower reduction by control/clock signalHemt circuitsEngineering

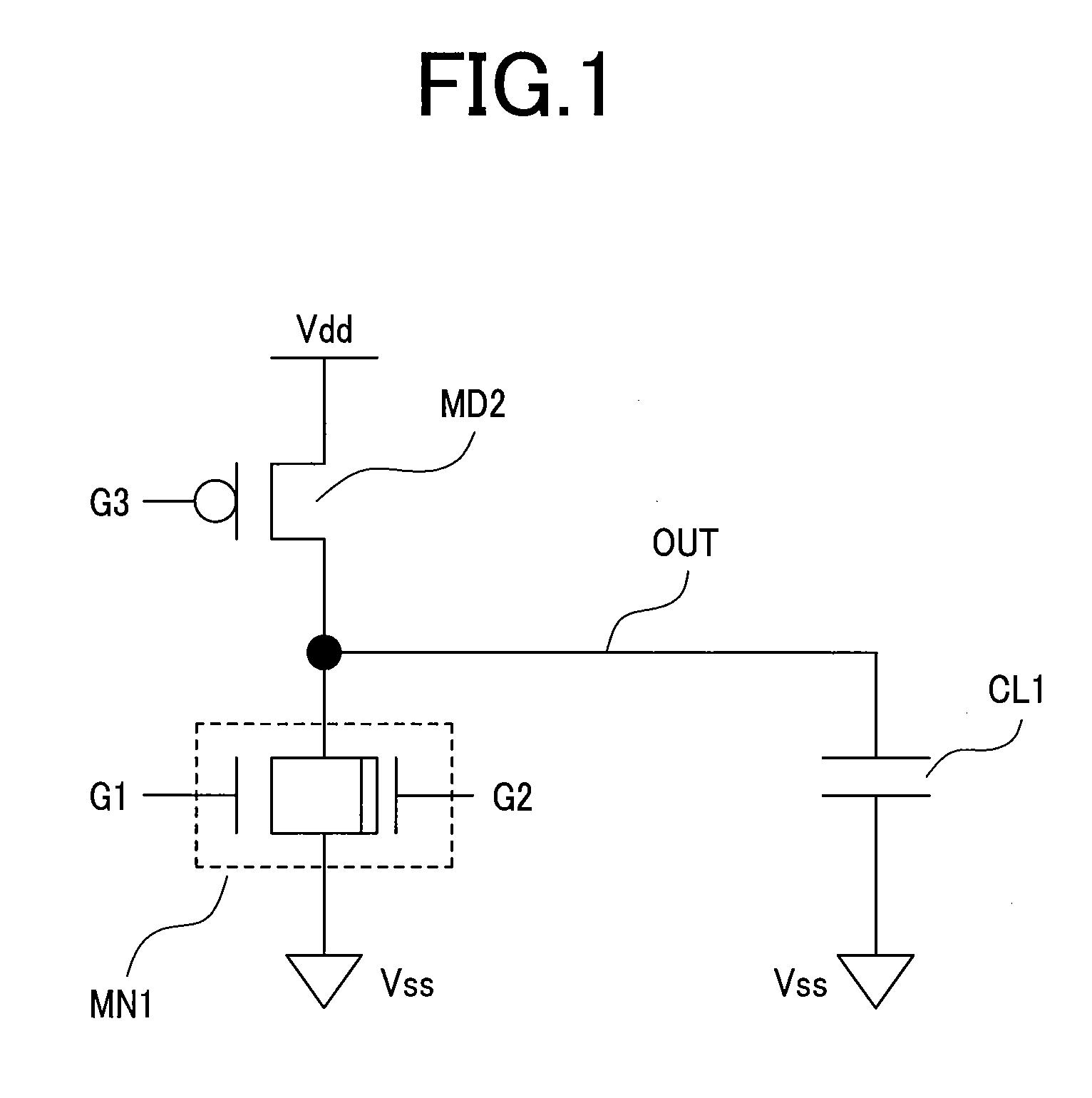

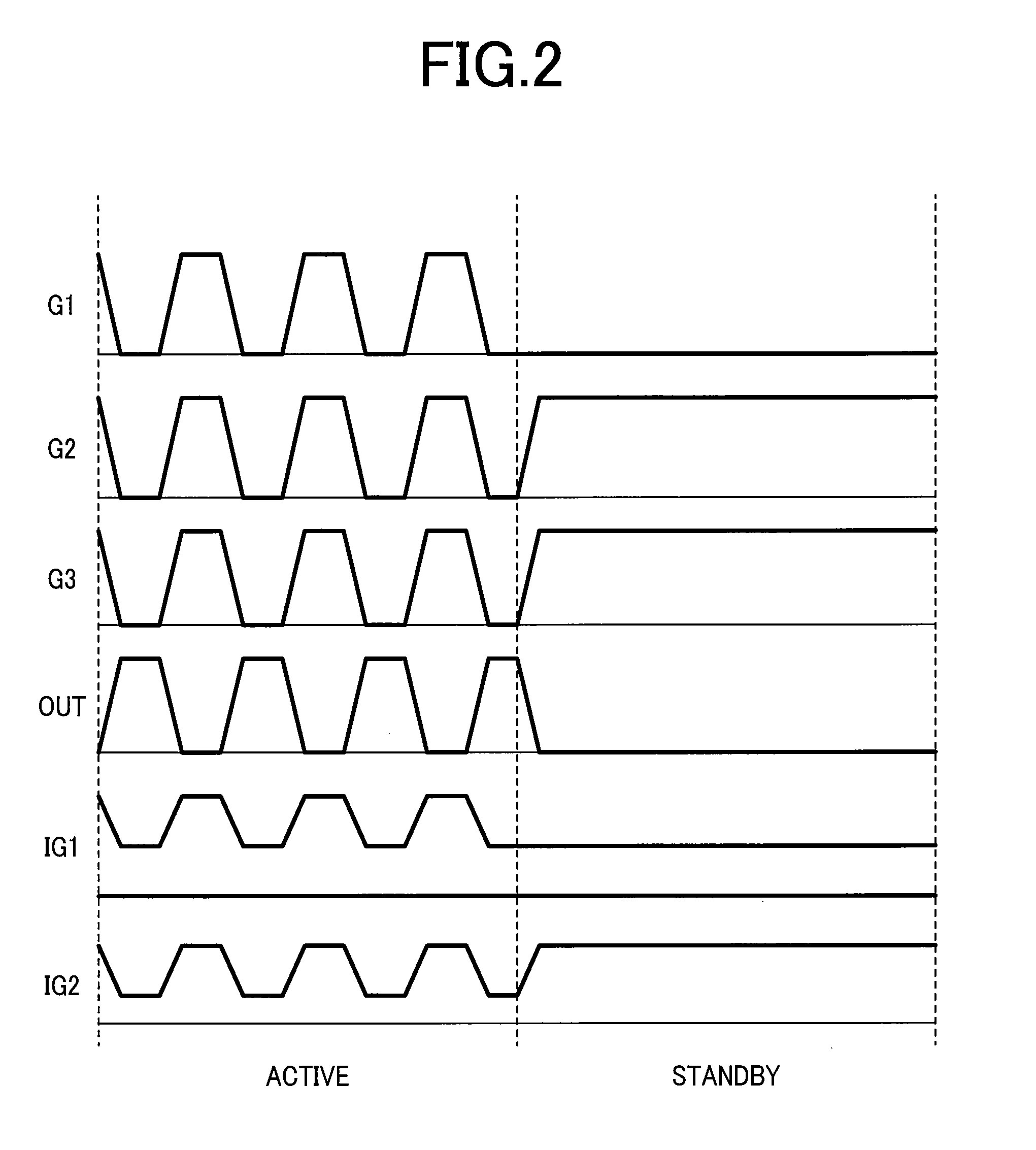

A semiconductor circuit or a MOS-DRAM wherein converting means is provided that converts substrate potential or body bias potential between two values for MOS-FETs in a logic circuit, memory cells, and operating circuit of the MOS-DRAM, thereby raising the threshold voltage of the MOS-FETs when in the standby state and lowering it when in active state. The converting means includes a level shift circuit and a switch circuit. The substrate potential or body bias potential is controlled only of the MOS-FETs which are nonconducting in the standby state; this configuration achieves a reduction in power consumption associated with the potential switching. Furthermore, in a structure where MOS-FETs of the same conductivity type are formed adjacent to each other, MOS-FETs of SOI structure are preferable for better results.

Owner:RENESAS ELECTRONICS CORP

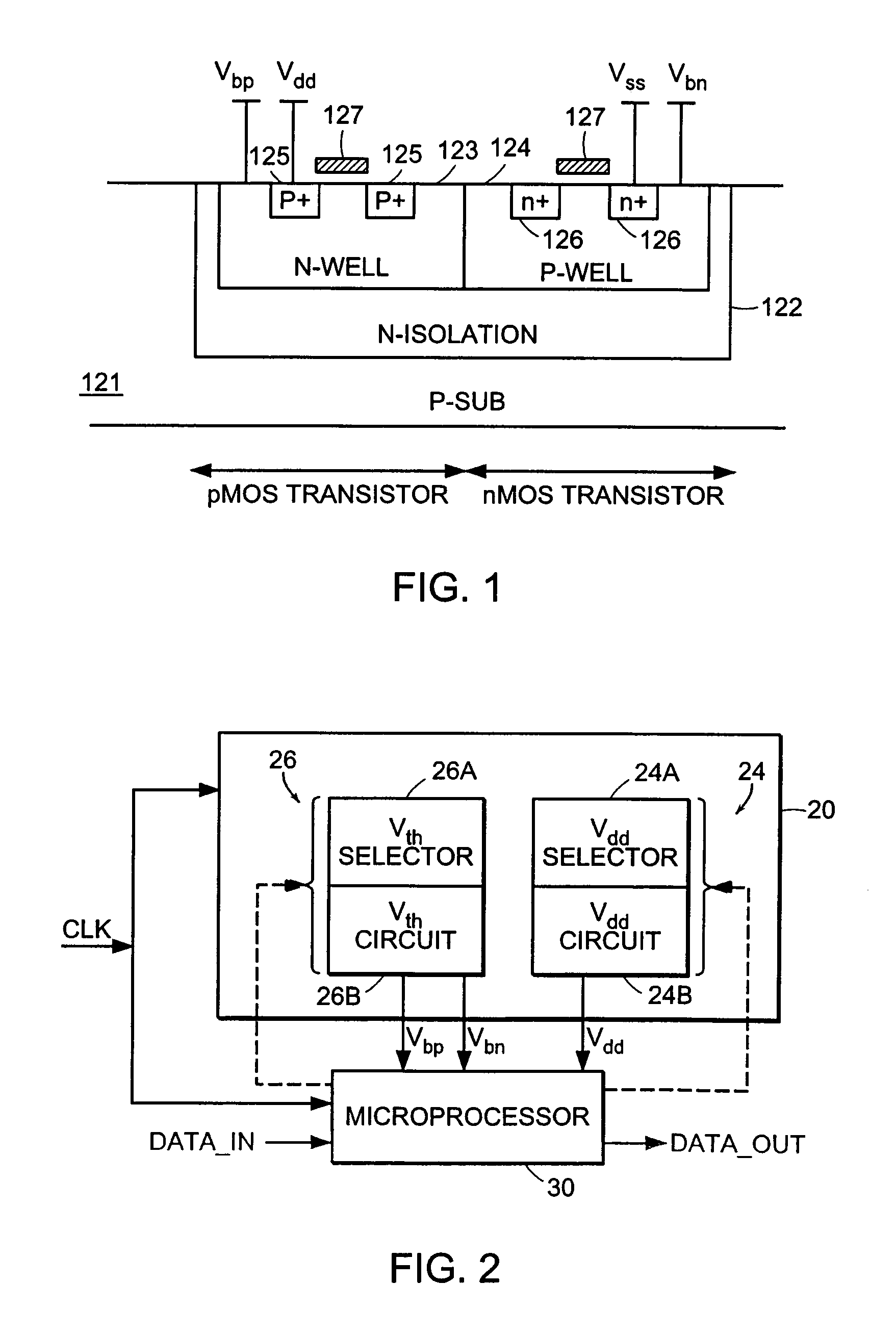

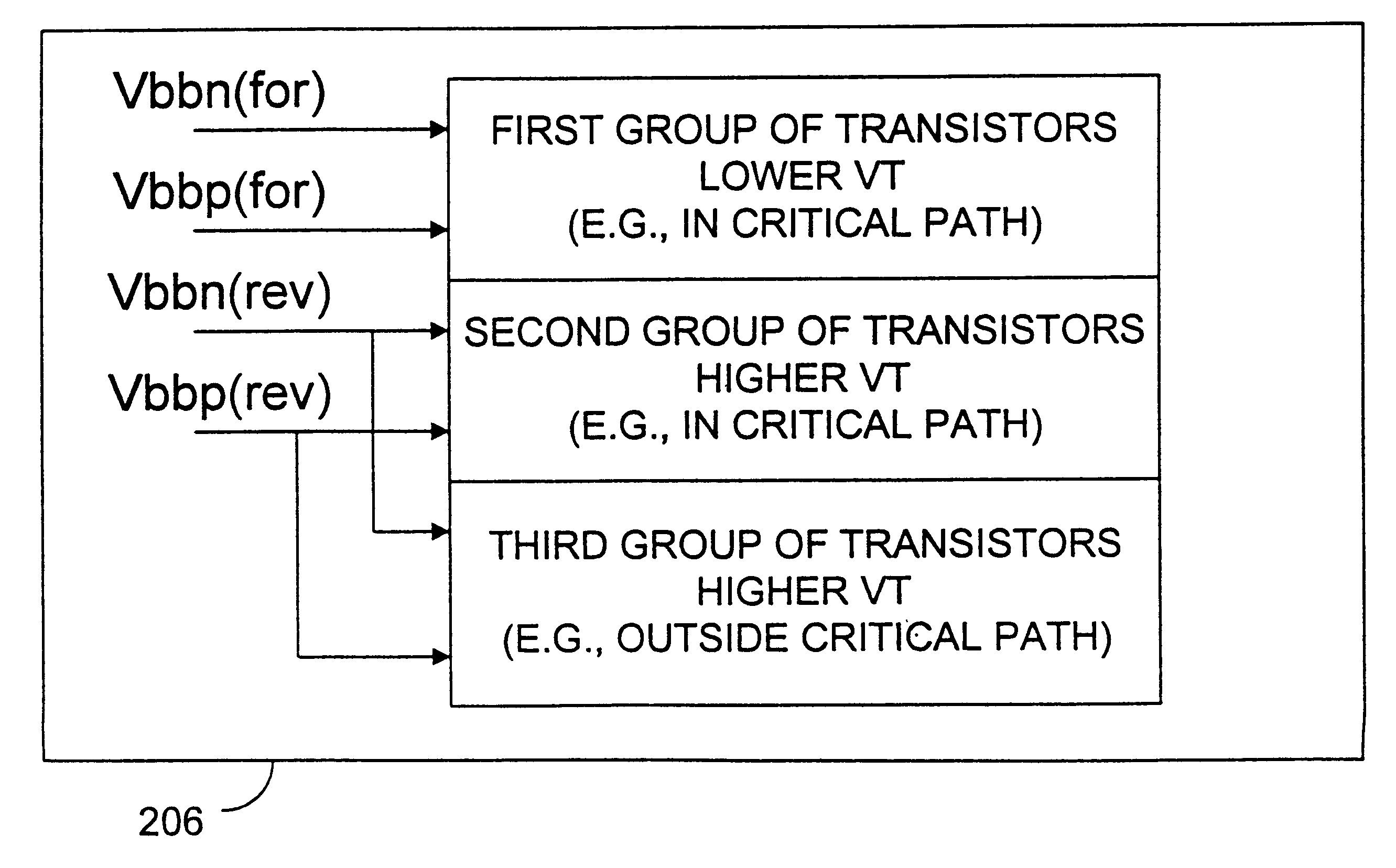

Adaptive power supply and substrate control for ultra low power digital processors using triple well control

InactiveUS6967522B2Improve power efficiencyMinimize power consumptionElectric pulse generator detailsElectric variable regulationEngineeringSelf adaptive

A system for improving the power efficiency of an electronic device includes a threshold voltage selector and a supply voltage selector. The threshold voltage selector selects a value of a threshold voltage for operation of the device in response to a present operating condition of the device. The supply voltage selector selects a value of a supply voltage to be applied to the device in response to the present operating condition of the device. The value of the threshold voltage and the value of the supply voltage control a power consumption of the device.

Owner:MASSACHUSETTS INST OF TECH

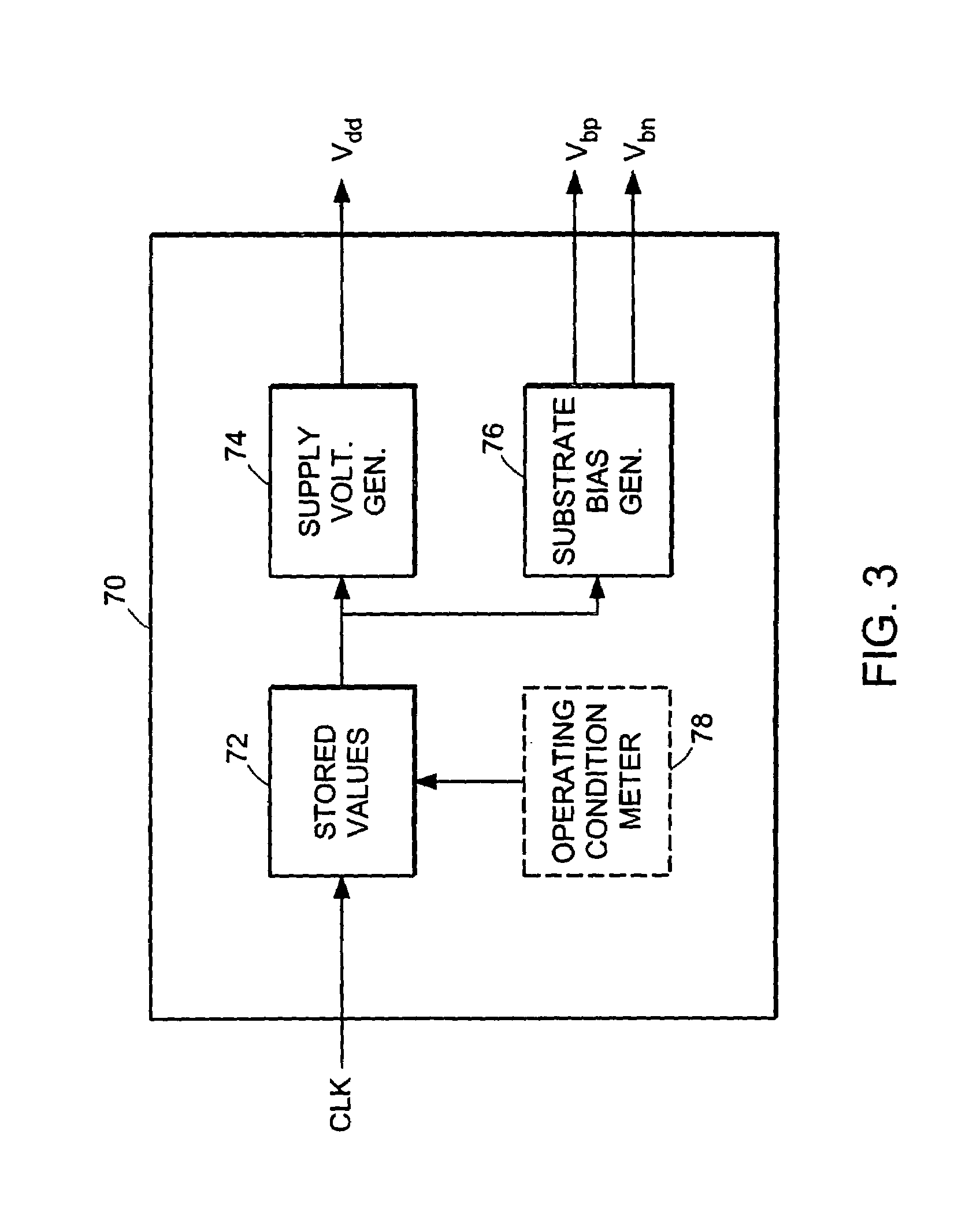

Adaptive control of operating and body bias voltages

ActiveUS7562233B1Adaptive control of operatingOperating bias voltageEnergy efficient ICTError detection/correctionEngineeringSelf adaptive

Adaptive control of operating and body bias voltages. In accordance with a first embodiment of the present invention, a desirable operating frequency for the microprocessor is determined. Information stored within and specific to the microprocessor is accessed. The information can comprise coefficients of a quadratic approximation of a frequency-voltage characteristic of the microprocessor for a set of body biasing conditions. An efficient voltage for operating the microprocessor at the desirable operating frequency is computed. The microprocessor is operated at the efficient voltage and the set of body biasing conditions.

Owner:META PLATFORMS INC

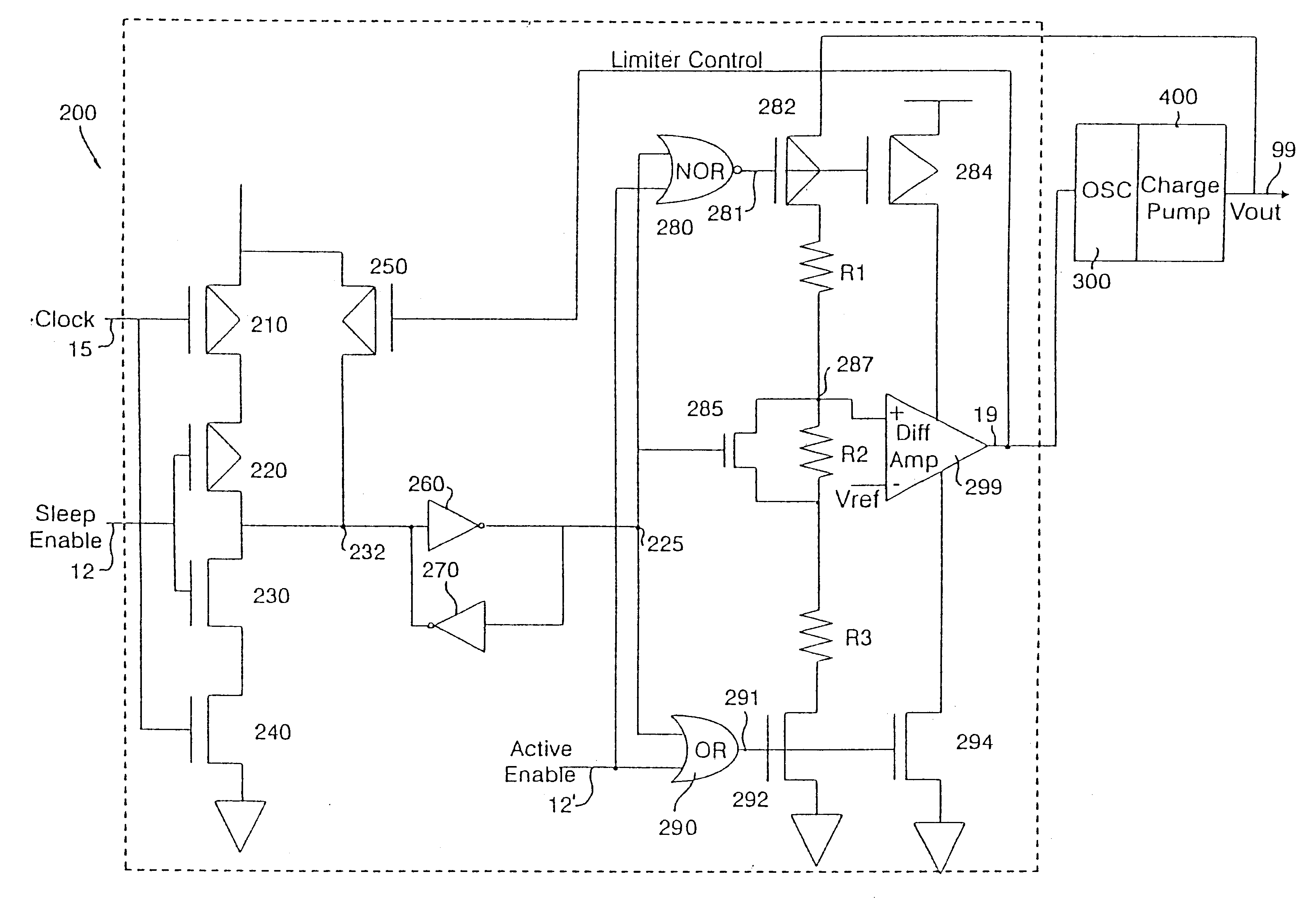

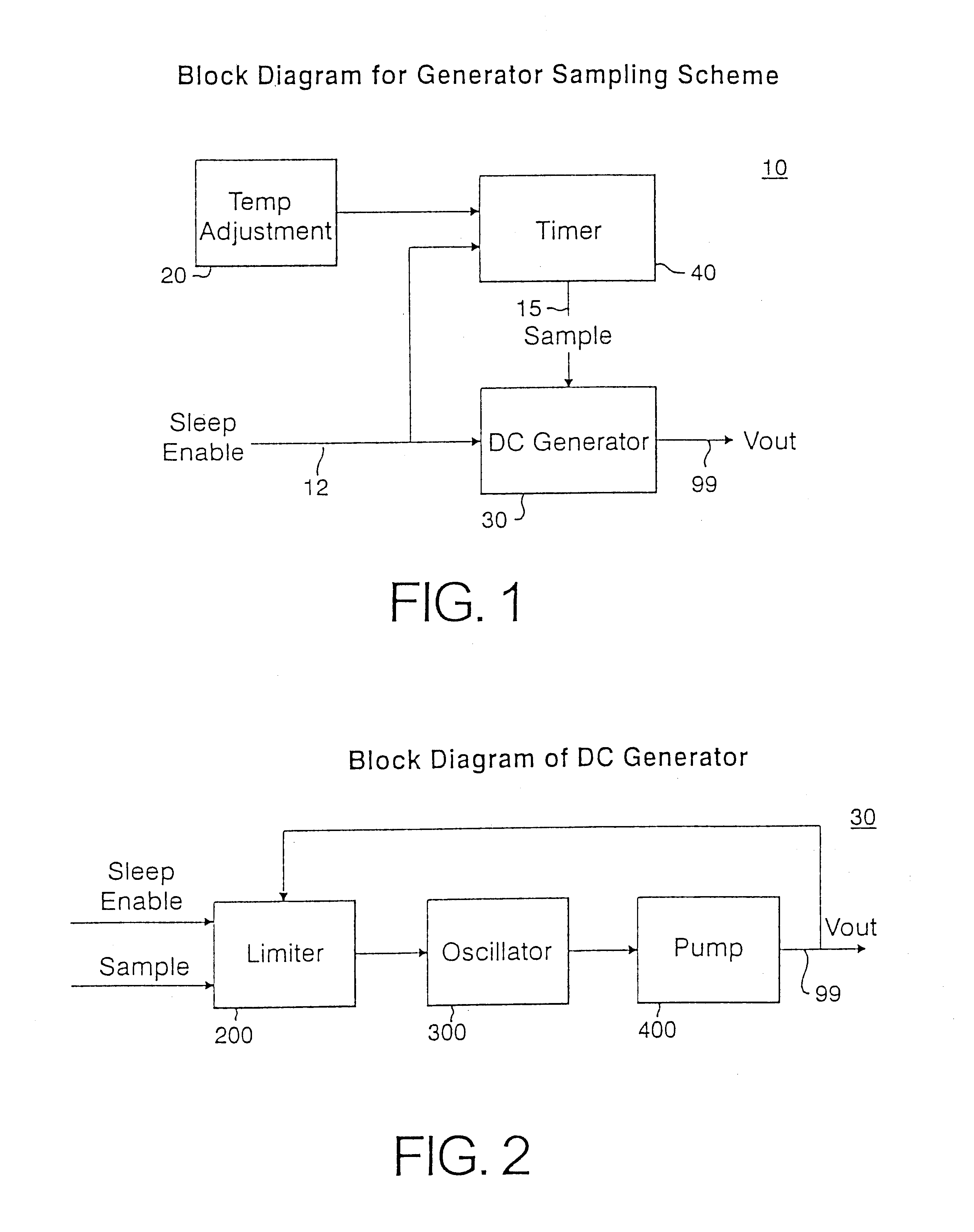

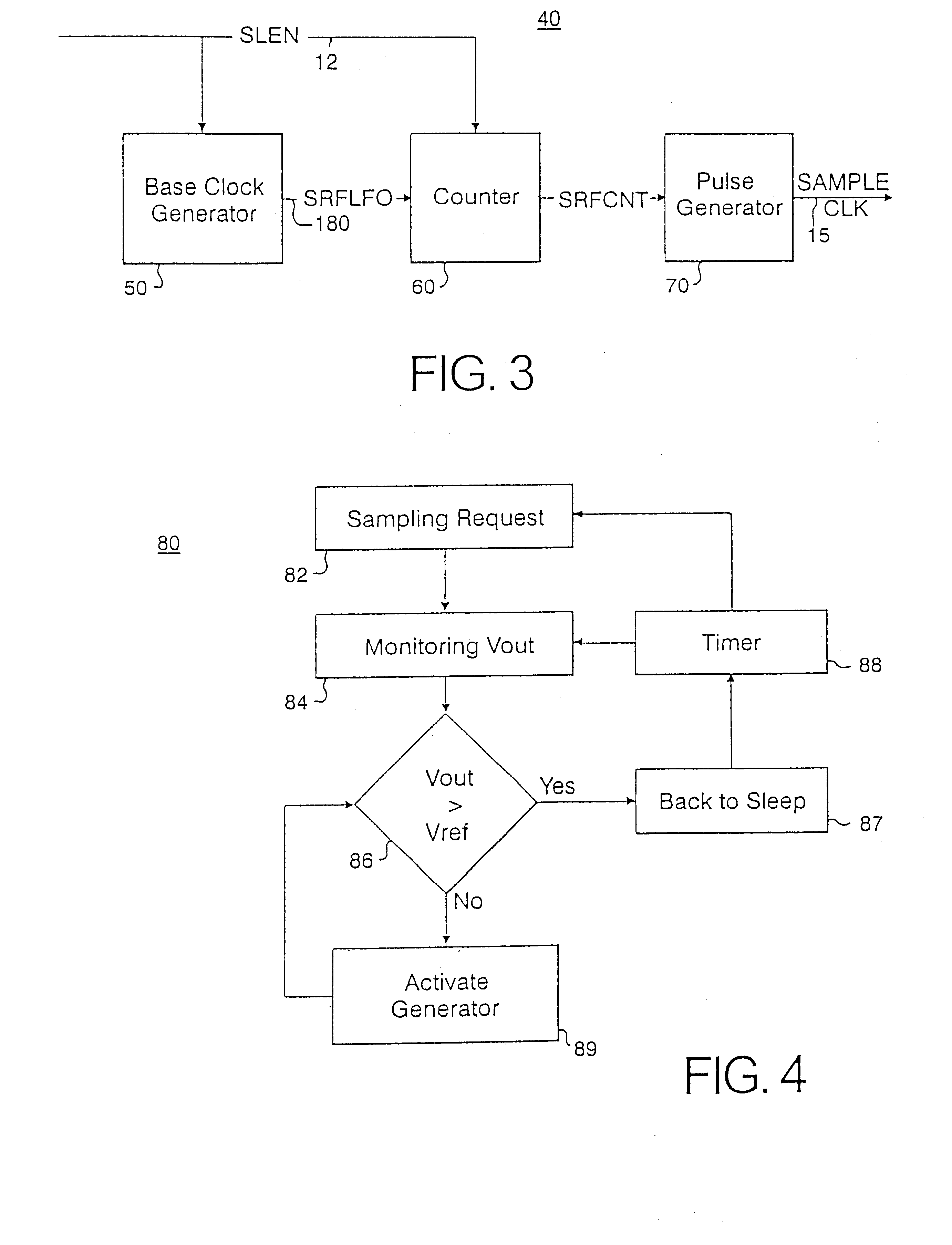

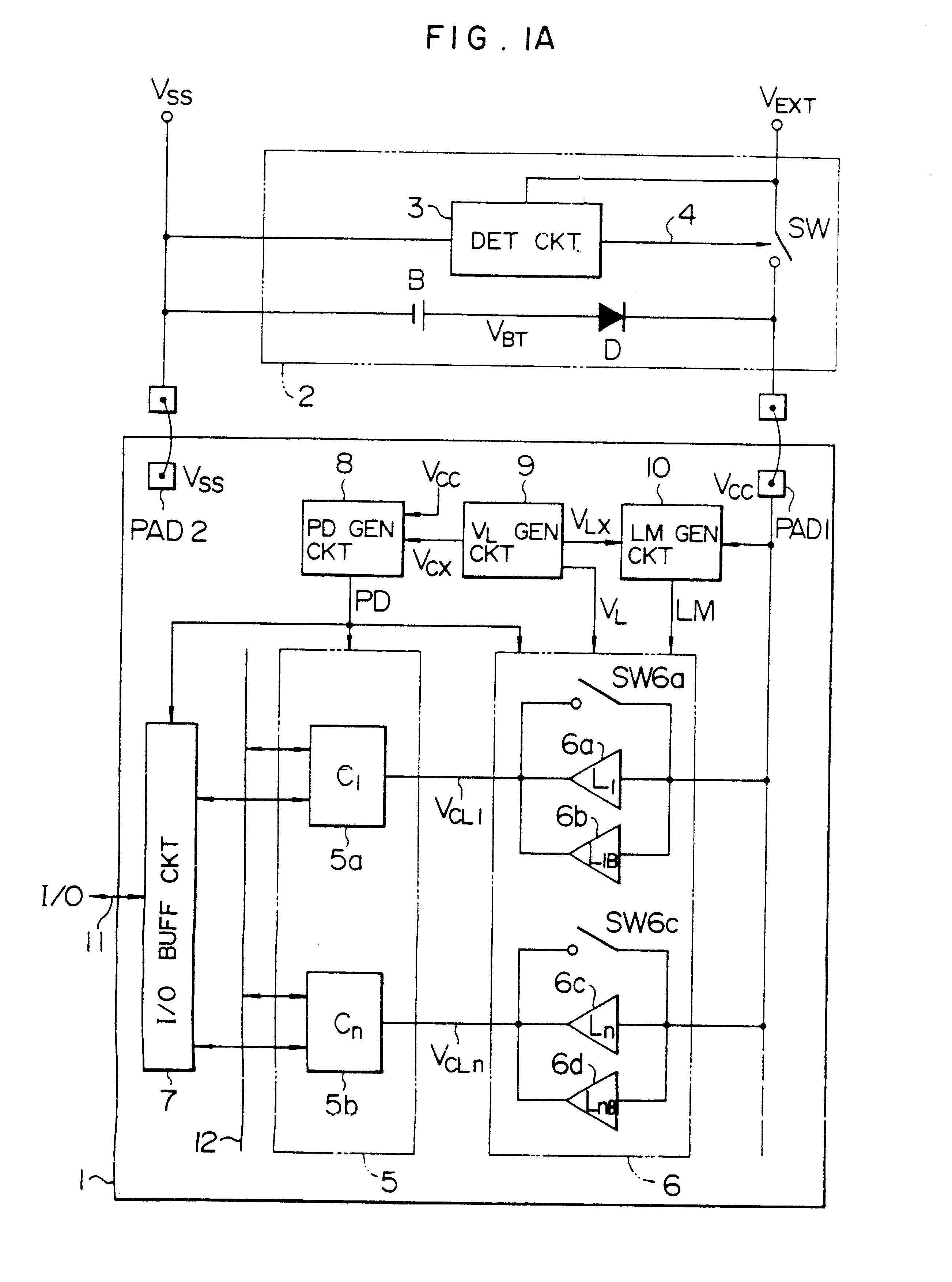

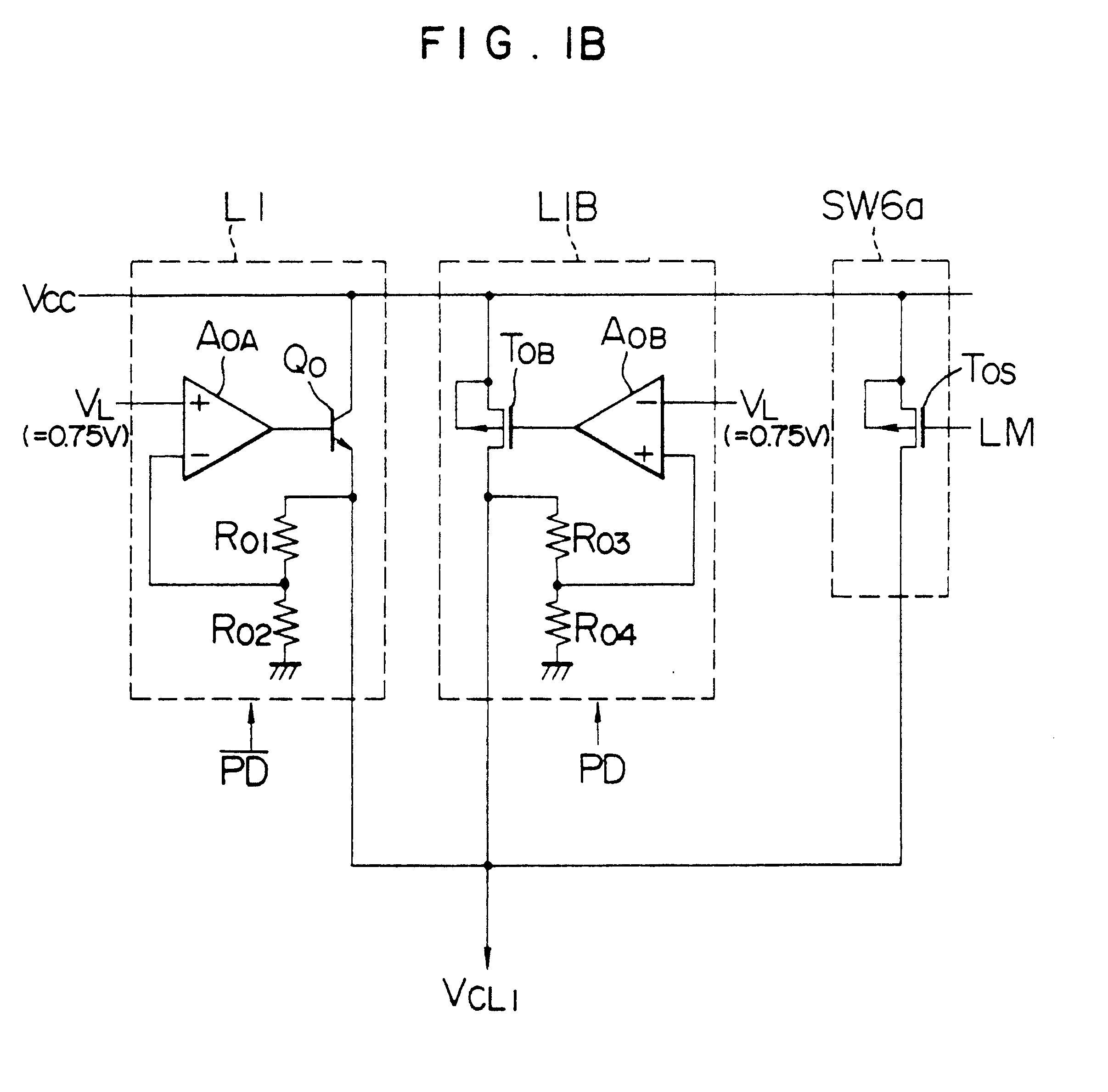

Self-refresh on-chip voltage generator

InactiveUS6411157B1Lower Level RequirementsReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingElectricityVoltage generator

A voltage control system and methodology for maintaining internally generated voltage levels in a semiconductor chip. The method comprises the steps of intermittently sampling an internal voltage supply level during a low power or "sleep" mode of operation; comparing the internal voltage supply level against a predetermined voltage reference level; and, activating a voltage supply generator for increasing the internal voltage supply level when the internal voltage supply level falls below the predetermined voltage reference level. The voltage supply generator is subsequently deactivated when the voltage supply level is restored to the predetermined voltage reference level. The sampling cycle may be appropriately tailored according to chip condition, chip temperature, and chip size. In one embodiment, the voltage control system and methodology is implemented in DRAM circuits during a refresh operation. The voltage levels that are suitable for sampling including DRAM band-gap reference voltage, boost wordline line voltage, wordline low voltage, bitline high voltage and bitline equalization voltages.

Owner:IBM CORP

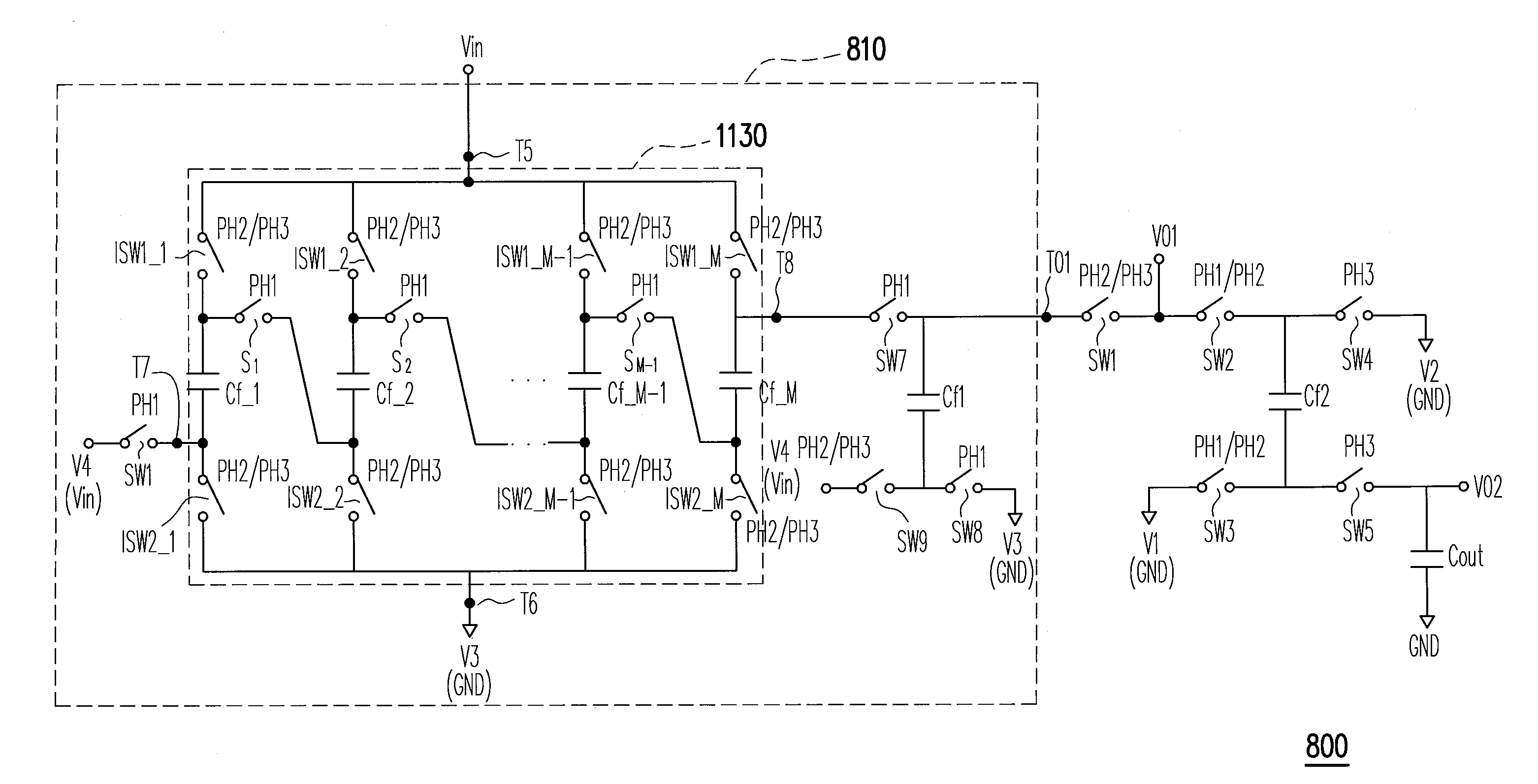

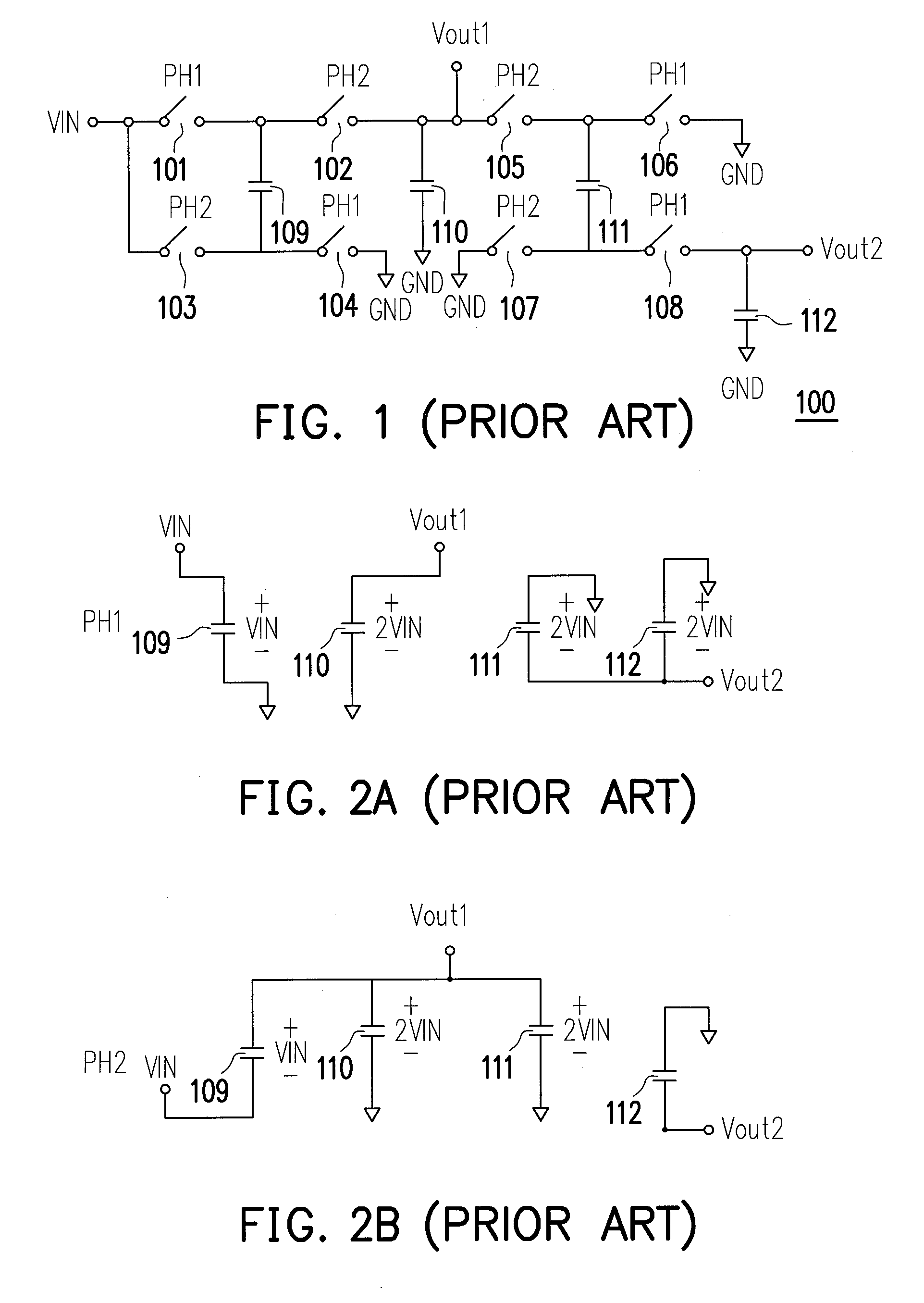

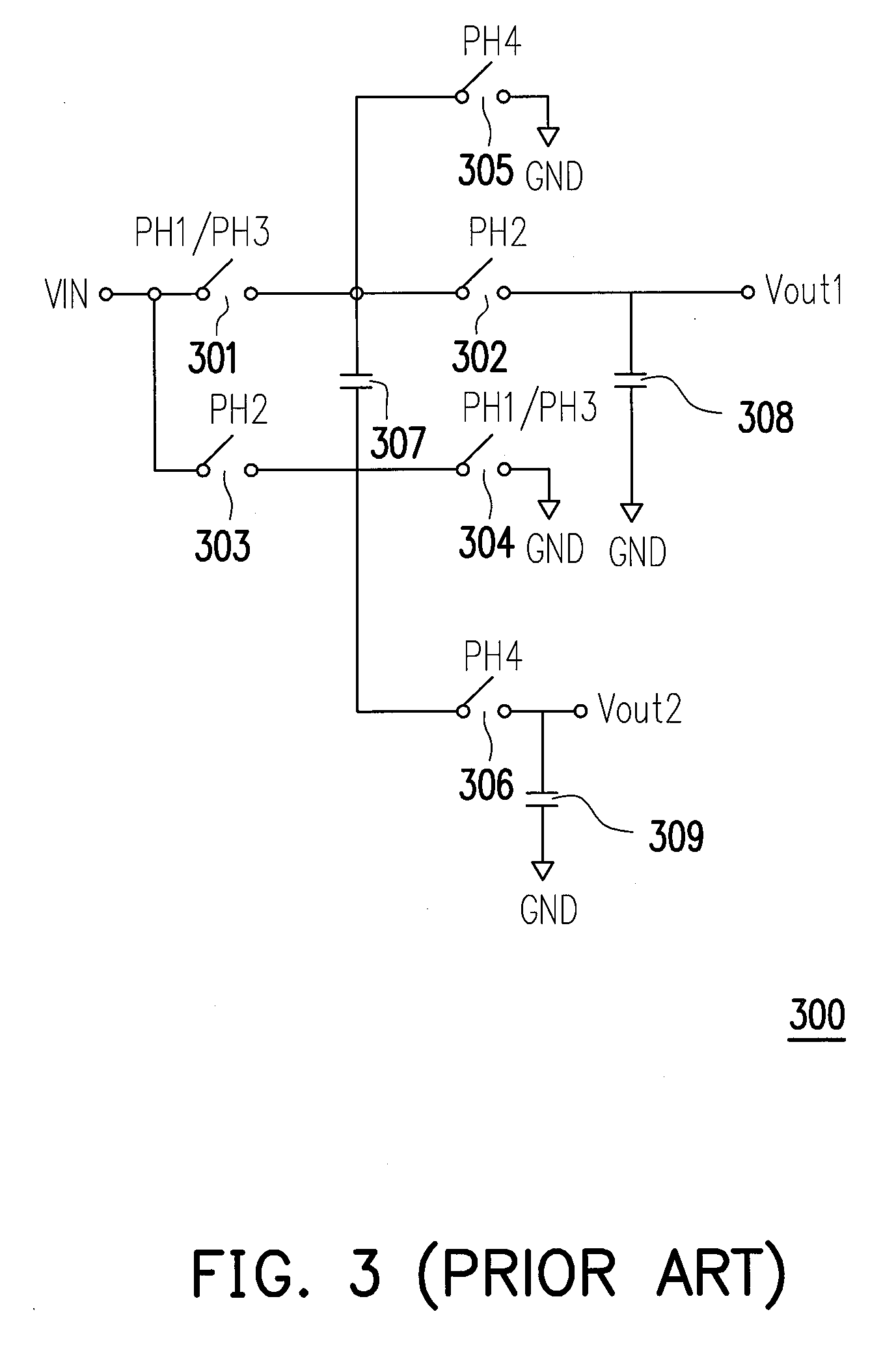

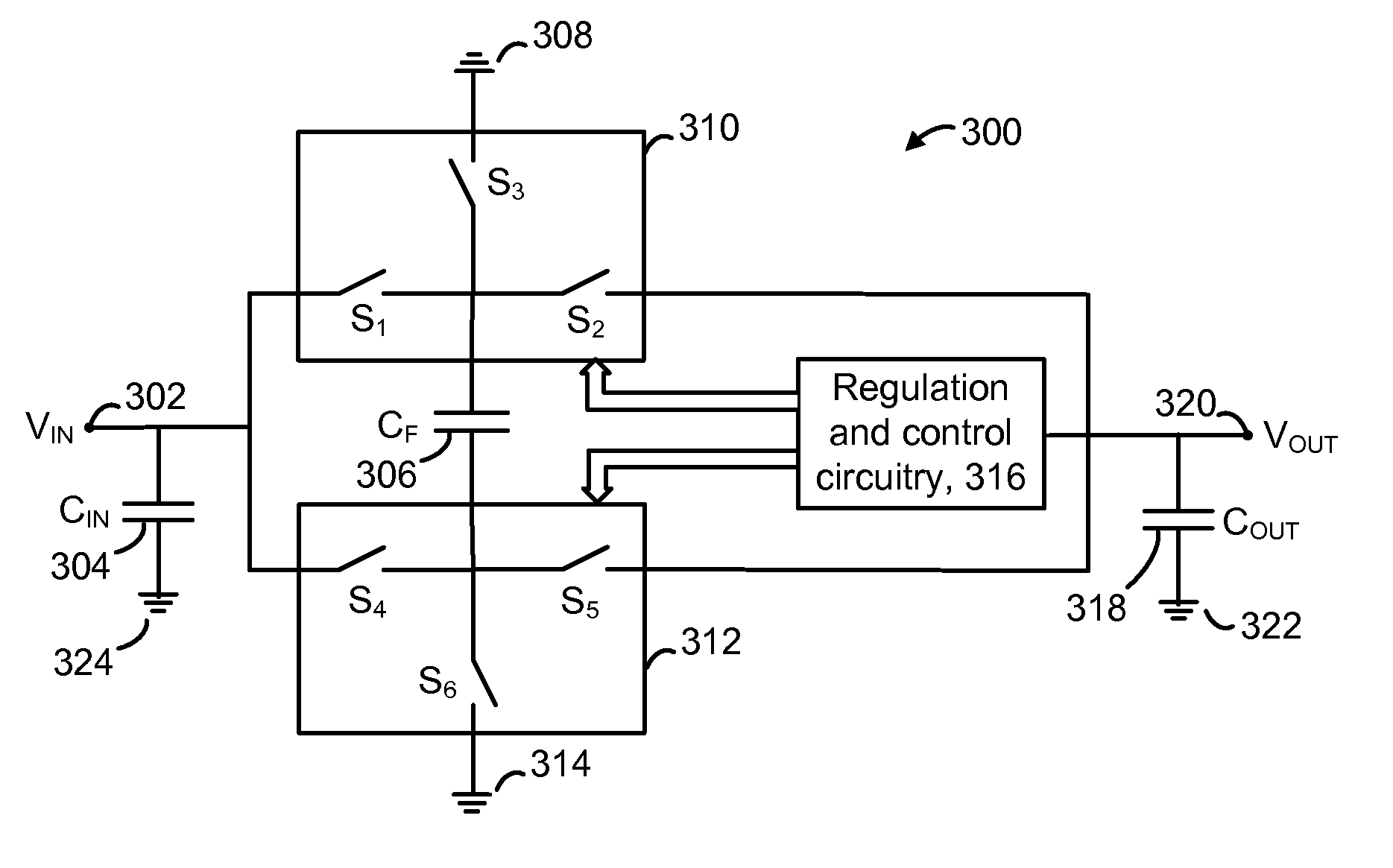

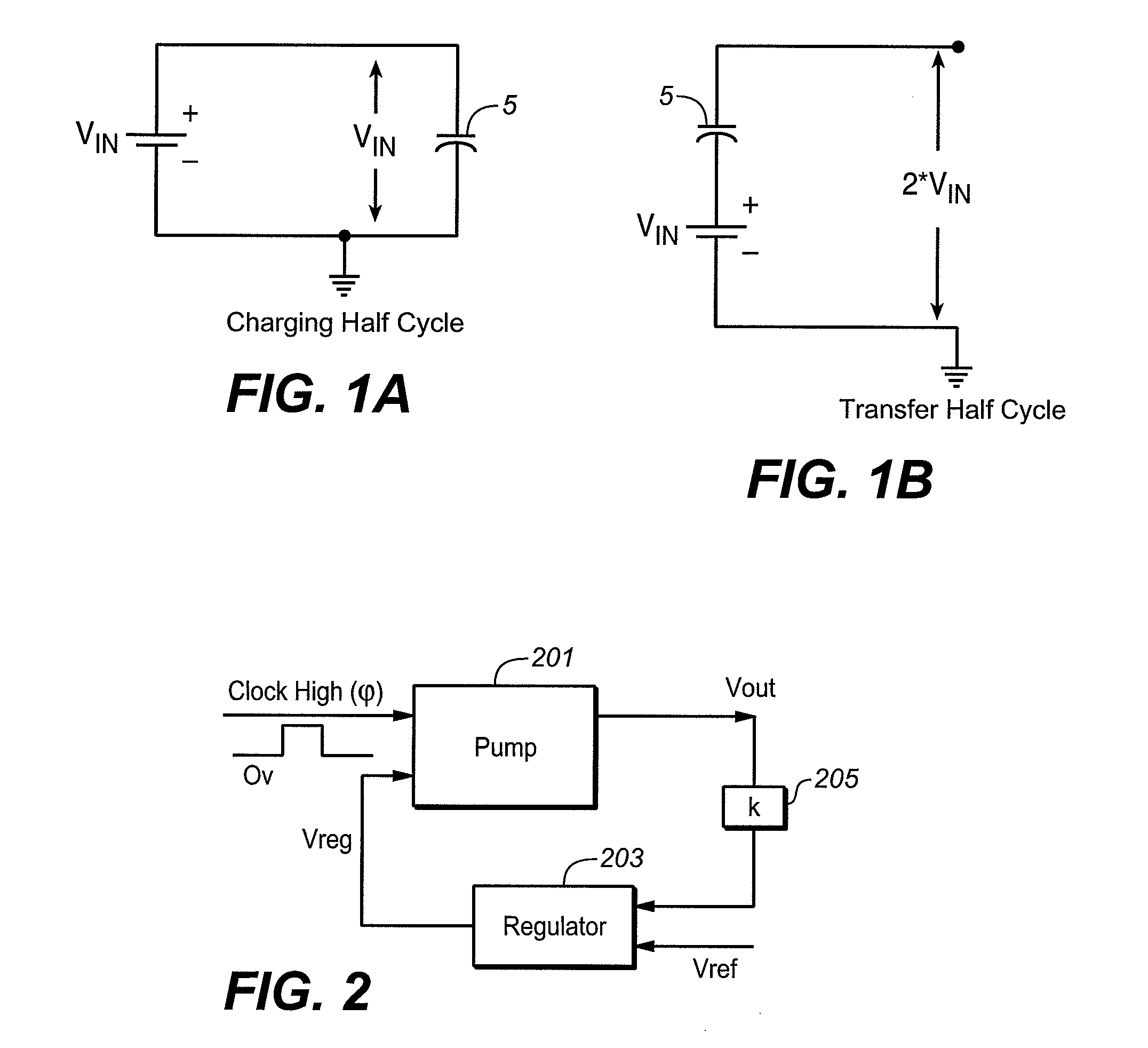

Charge pump circuit

InactiveUS20090174466A1Improve efficiencyLarge maximum load currentApparatus without intermediate ac conversionElectric pulse generator detailsEngineeringCharge pump

A charge pump circuit is provided. The charge pump circuit includes a pump unit, first through sixth switches, a fly capacitor and an output capacitor. In a first period, an input voltage and a first voltage charge at least one internal capacitor of the pump unit via a first terminal and a second terminal of the pump unit. In the second period, the internal capacitor of the pump unit provides charges to the fly capacitor via the second switch and generates a first output voltage. In the third period, the fly capacitor supplies the charges to the output capacitor via the fourth switch to generate a second output voltage.

Owner:NOVATEK MICROELECTRONICS CORP

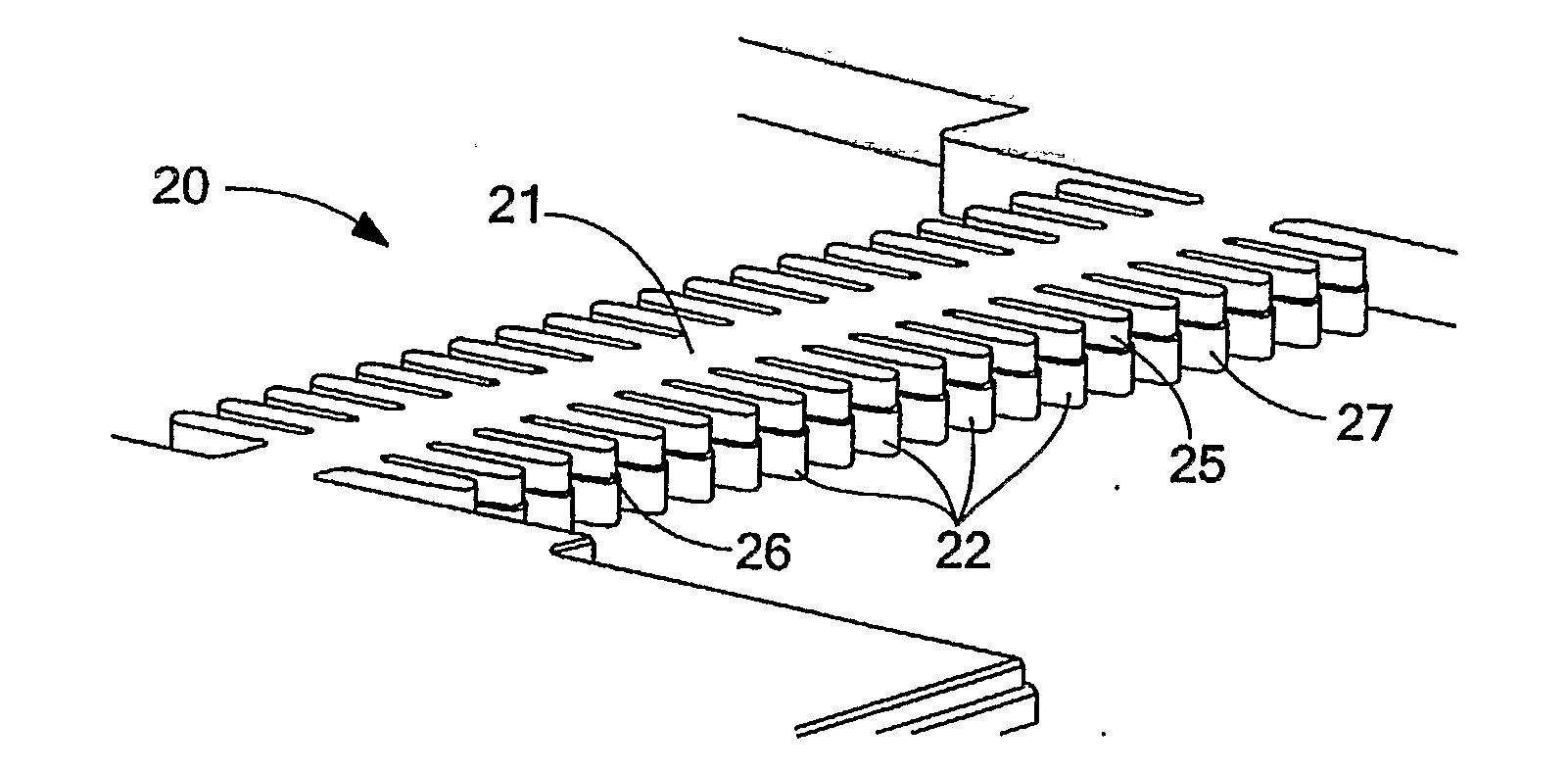

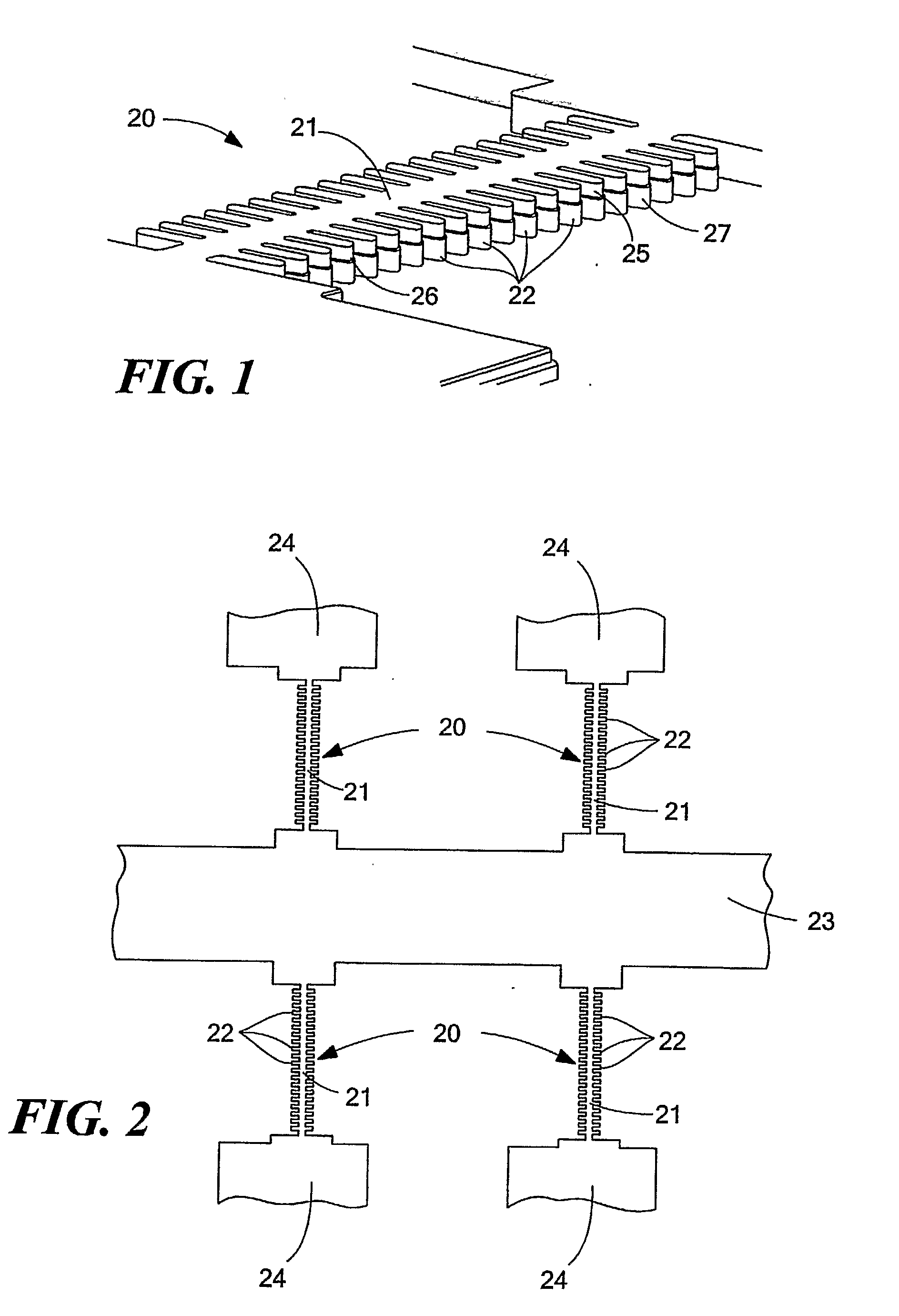

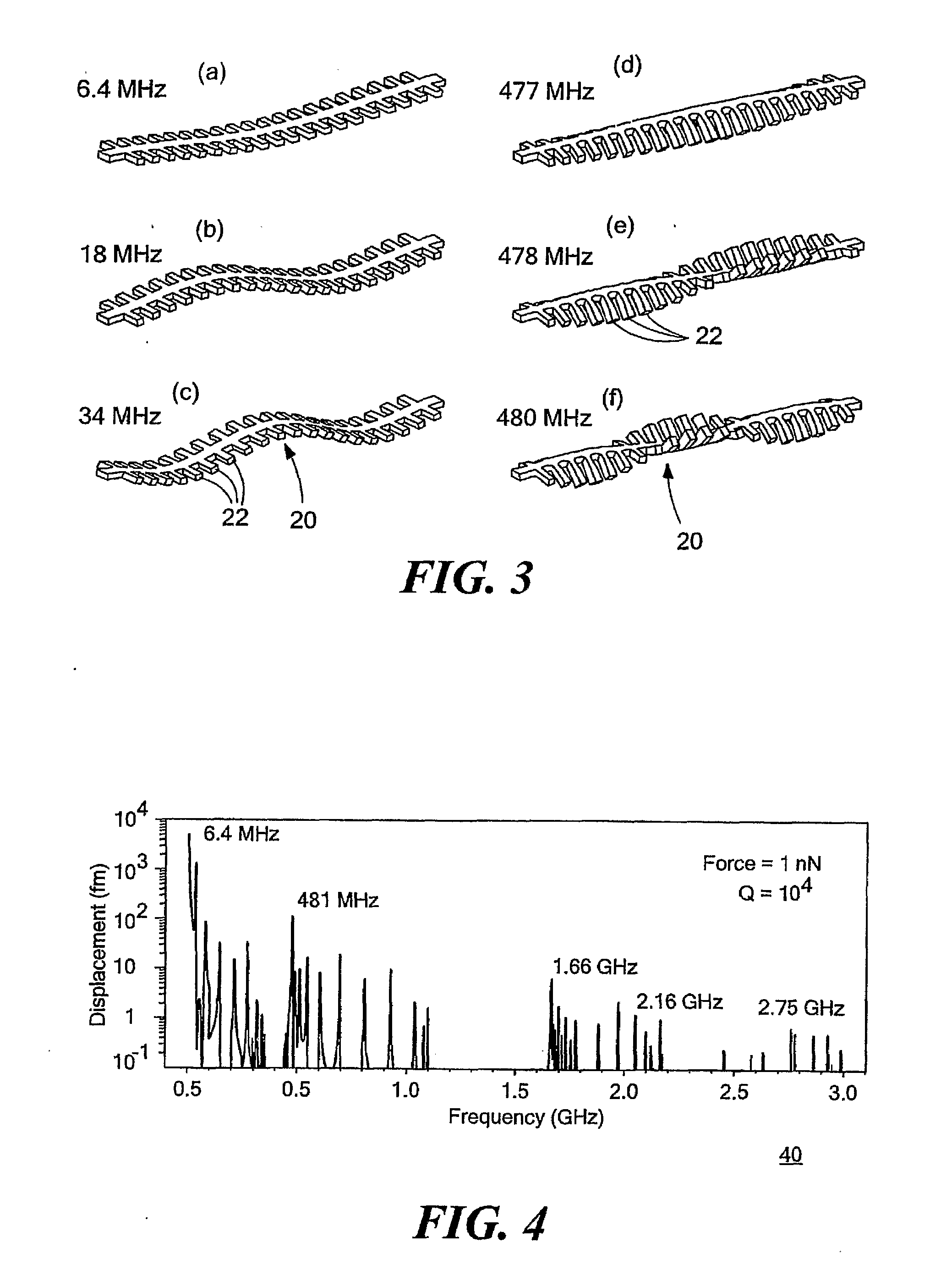

Nanomechanical Oscillator

ActiveUS20090294638A1Easy to detectHigh-frequency oscillationSolid-state devicesMaterial analysis by optical meansResonanceFrequency oscillation

A mechanical oscillator has components with dimensions in a sub-micron range to produce resonance mode oscillations in a gigahertz range. A major element is coupled to a minor, sub-micron element to produce large amplitude gigahertz frequency oscillation that is detected with readily available techniques. The mechanical structure can be formed according to a number of geometries including beams and rings and is excited with electrostatic, magnetic and thermal related forces, as well as other excitation techniques. The mechanical structure can be arranged in arrays for applications such as amplification and mixing and is less sensitive to shock and radiative environments than electrical or optical counterparts.

Owner:TRUSTEES OF BOSTON UNIV

Charge coupled pump-efficient charge pump regulator with MOS capacitor

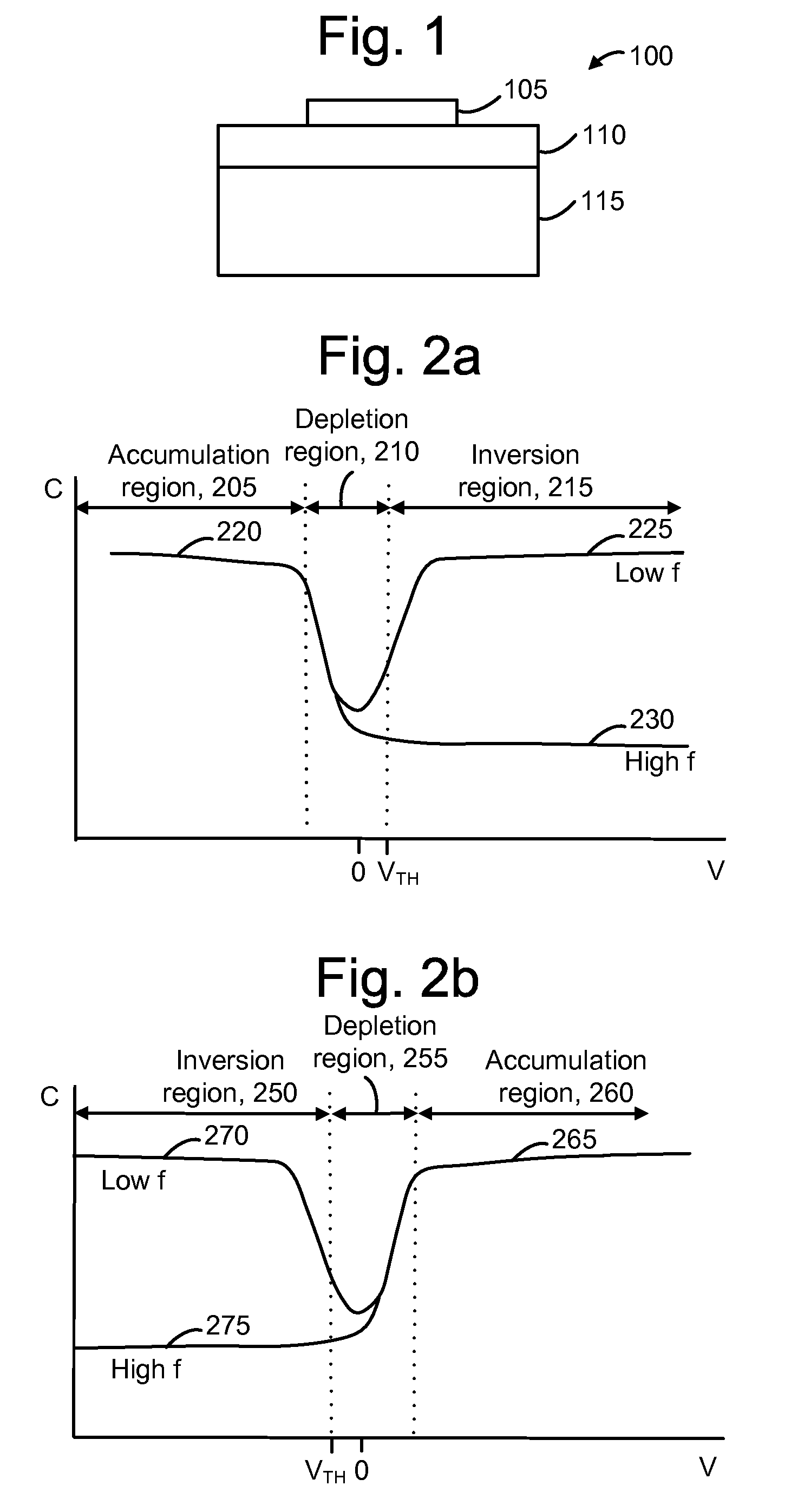

ActiveUS8040174B2Easy to operateCurrent/voltage measurementInstant pulse delivery arrangementsCapacitanceVoltage multiplier

A charge pump with a MOS-type capacitor, where the MOS-type capacitor is operated in an inversion region in which capacitance varies as a function of the frequency of the applied signal. The charge pump is switched to transfer charge from an input node to the capacitor and from the capacitor to an output node. During a transition interval, a relatively high frequency switching signal is used to lower the capacitance and increase efficiency. During a settling interval, a relatively low frequency switching signal is used, in which case the capacitance is higher, but similar to a level which would be seen if the capacitor was operated in an accumulation region. MOS capacitor dimensions and switching intervals are mutually optimized to provide high efficiency and required throughput. The charge pump may be configured as a voltage multiplier, divider, inverter or follower, for instance.

Owner:WESTERN DIGITAL ISRAEL LTD

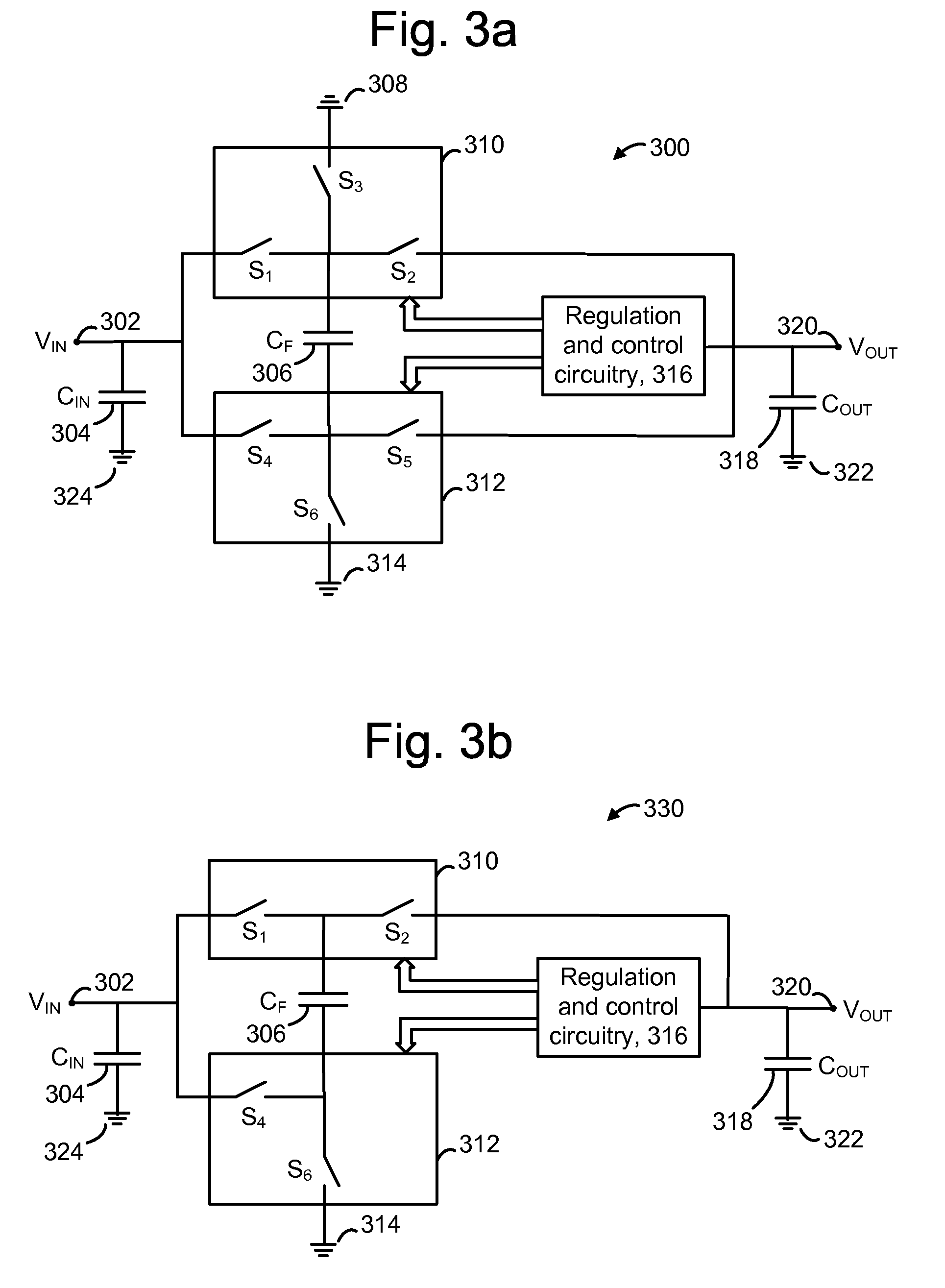

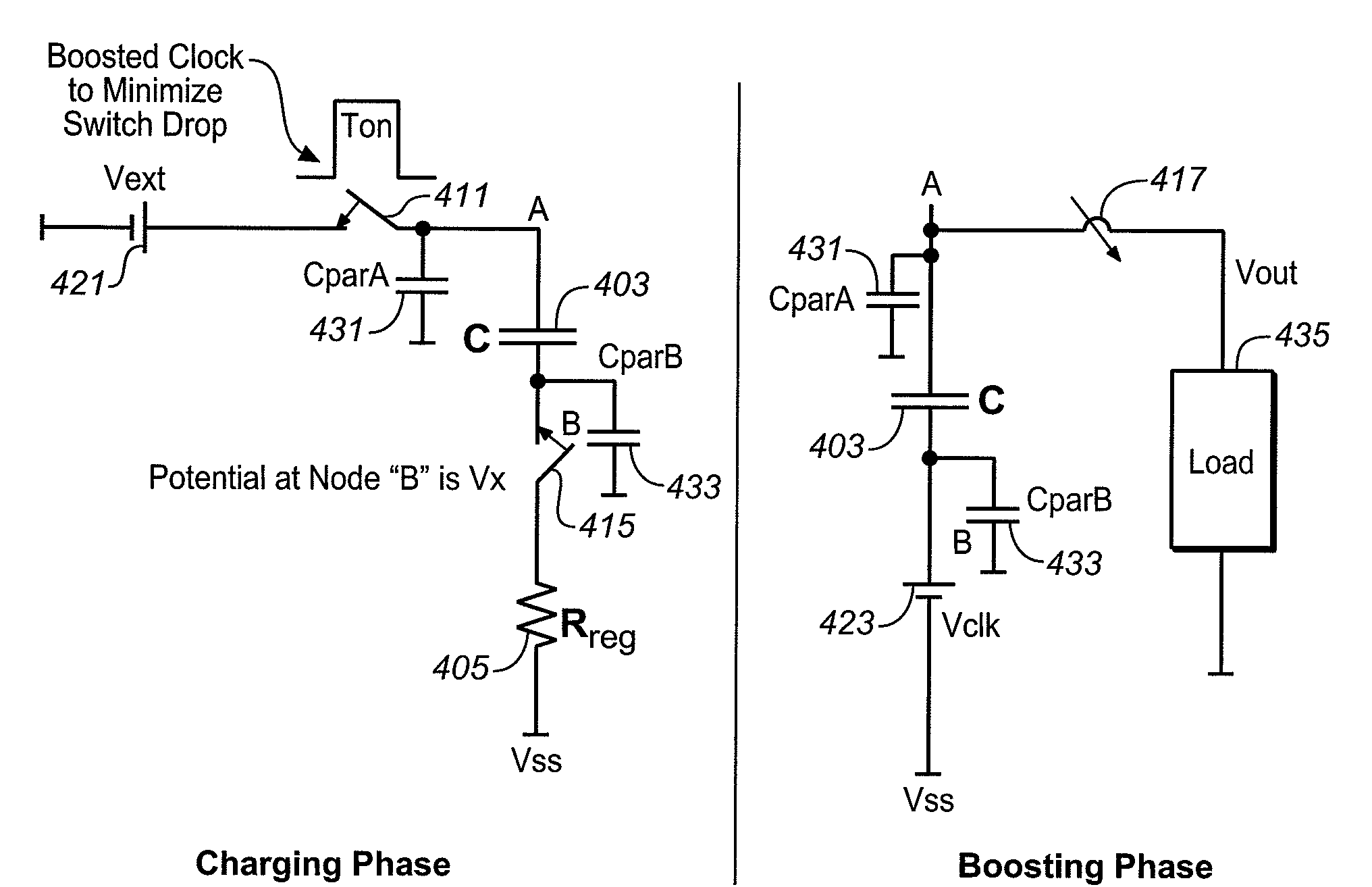

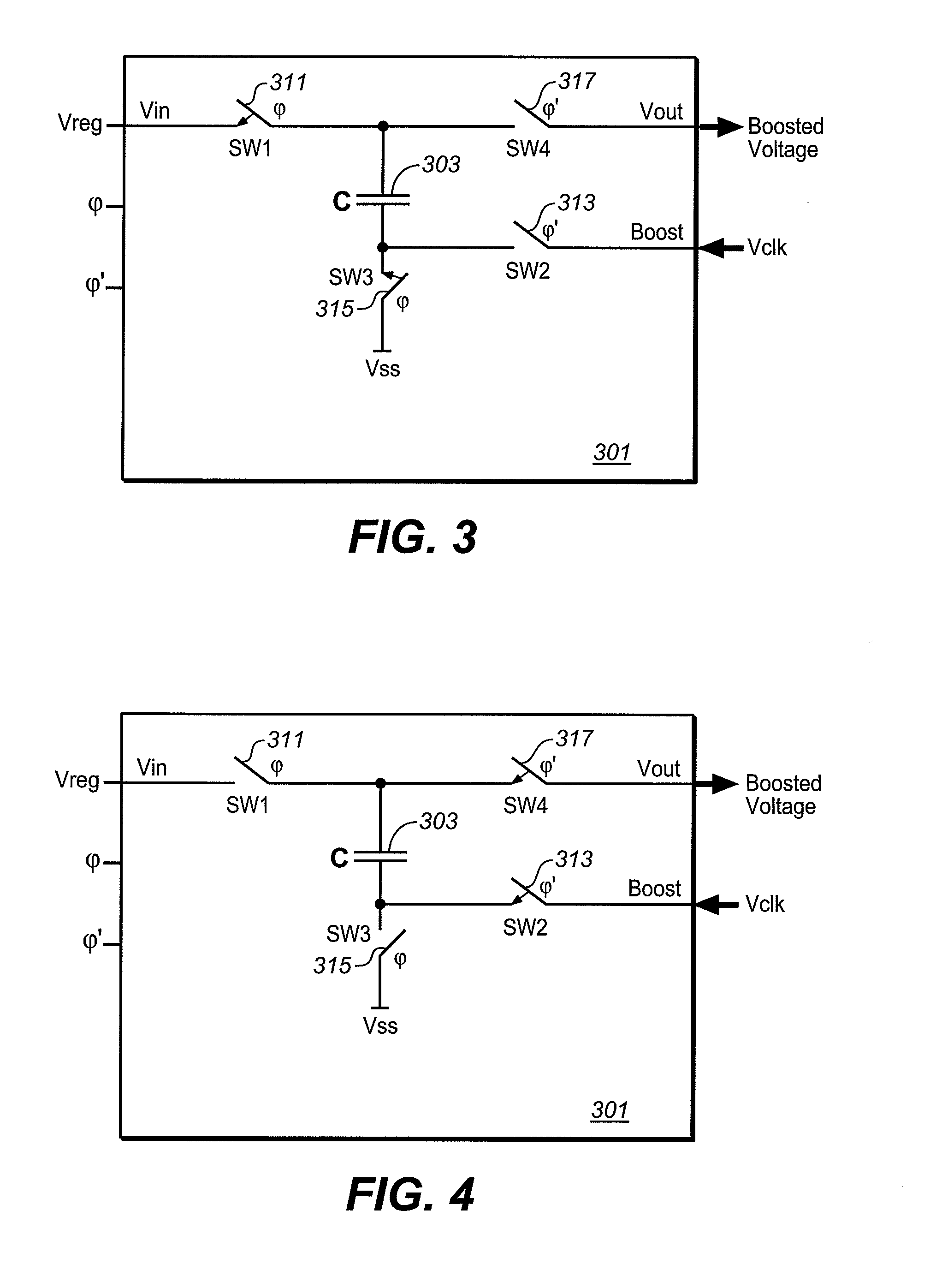

Bottom Plate Regulation of Charge Pumps

ActiveUS20090058506A1Apparatus without intermediate ac conversionElectric pulse generator detailsEngineeringCapacitor

Techniques of operating a charge pump are described. The charge pump is connectable to receive a clock signal and a regulating voltage and provide an output voltage. The charge pump can have one or multiple stages, each of the stages will include a capacitor. During the charging phase, the regulating voltage is used to regulate the potential of the capacitor's bottom plate. During the boosting phase, the capacitor's top plate is connected to supply the output for the stage and the bottom plate is connected to receive the stage's input. Each stage will also have a set of switching elements, allowing the capacitor to be alternately connected in the charging and boosting phases. For the first stage, the input is derived from the clock signal, and for any subsequent stages, the input will be the output of the preceding stage. The last stage provides the output voltage of the pump.

Owner:SANDISK TECH LLC

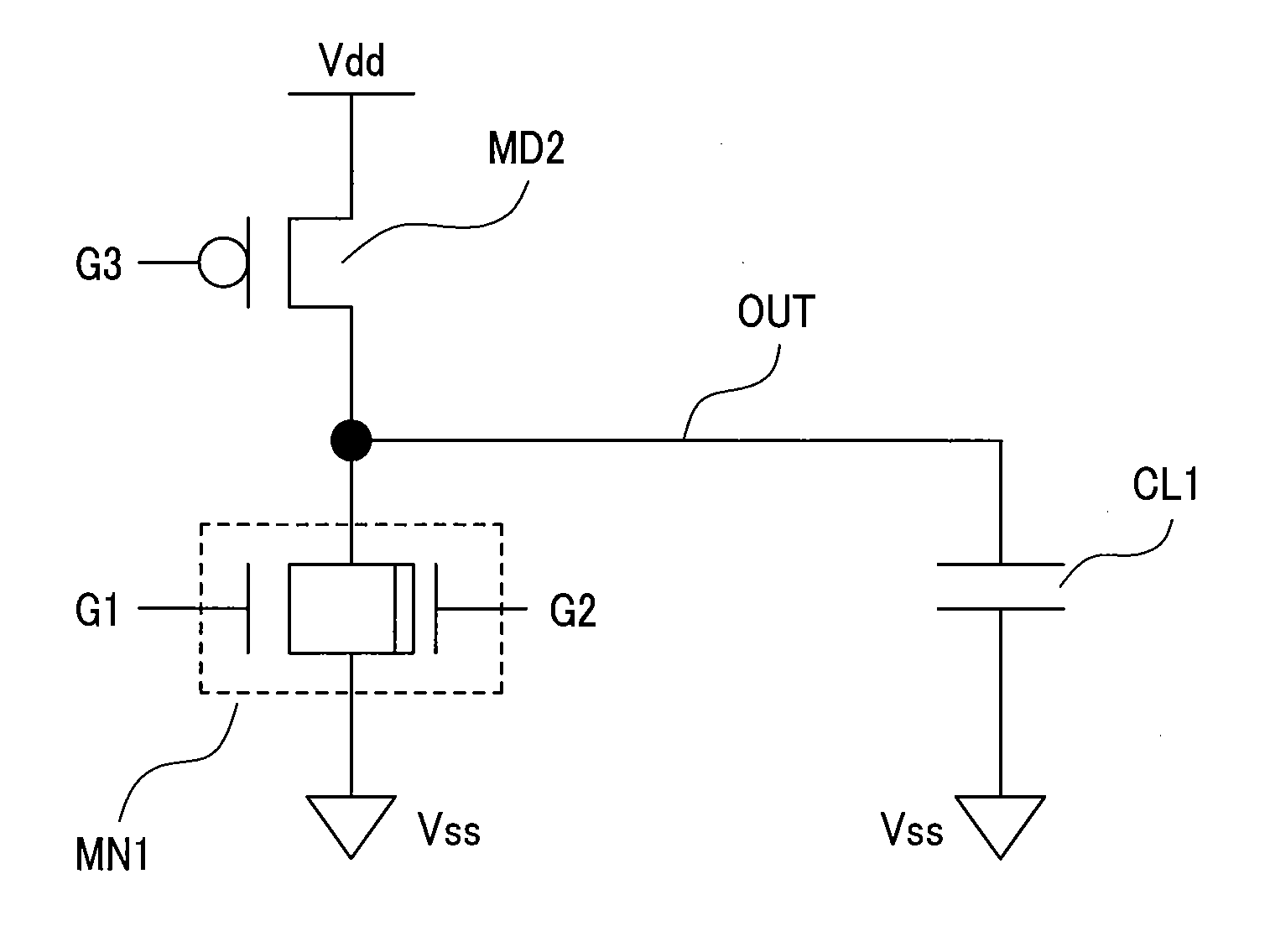

Low power SOI ESD buffer driver networks having dynamic threshold MOSFETS

A method and structure for a body coupled driver circuit includes a pull-up stage having a first transistor and a pull-down stage having a second transistor. The first transistor and the second transistor have bodies coupled to either a reference voltage or a pad node.

Owner:GLOBALFOUNDRIES INC

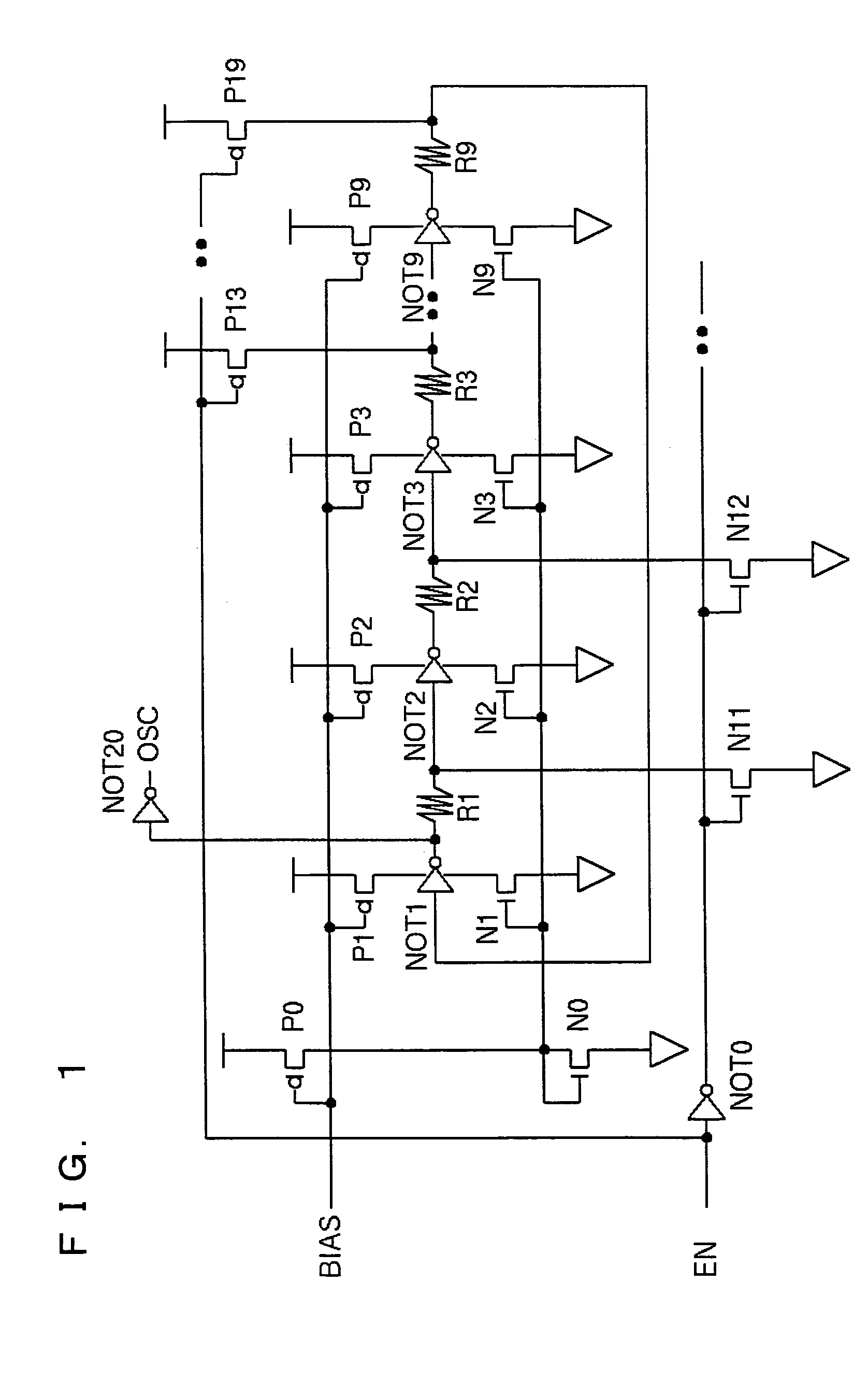

Oscillating circuit, booster circuit, nonvolatile memory device, and semiconductor device

InactiveUS7180794B2Suppress the variation in the oscillating frequencies of an output signalChange in resistancesSolid-state devicesRead-only memoriesPower inverterEngineering

In a ring oscillator constituting an oscillating circuit, resistor circuits are used as delay circuits to be connected to respective inverters. That is, the inverters and the resistors are connected in series so that the resistor is provided between the adjacent inverters. With the arrangement, it is possible to provide an oscillating circuit which is less dependent on any of power supply voltages, temperatures, and manufacturing variations, while maintaining a characteristic in which the oscillating frequency decreases as an output voltage of a booster circuit increases.

Owner:TAMIRAS PER PTE LTD LLC

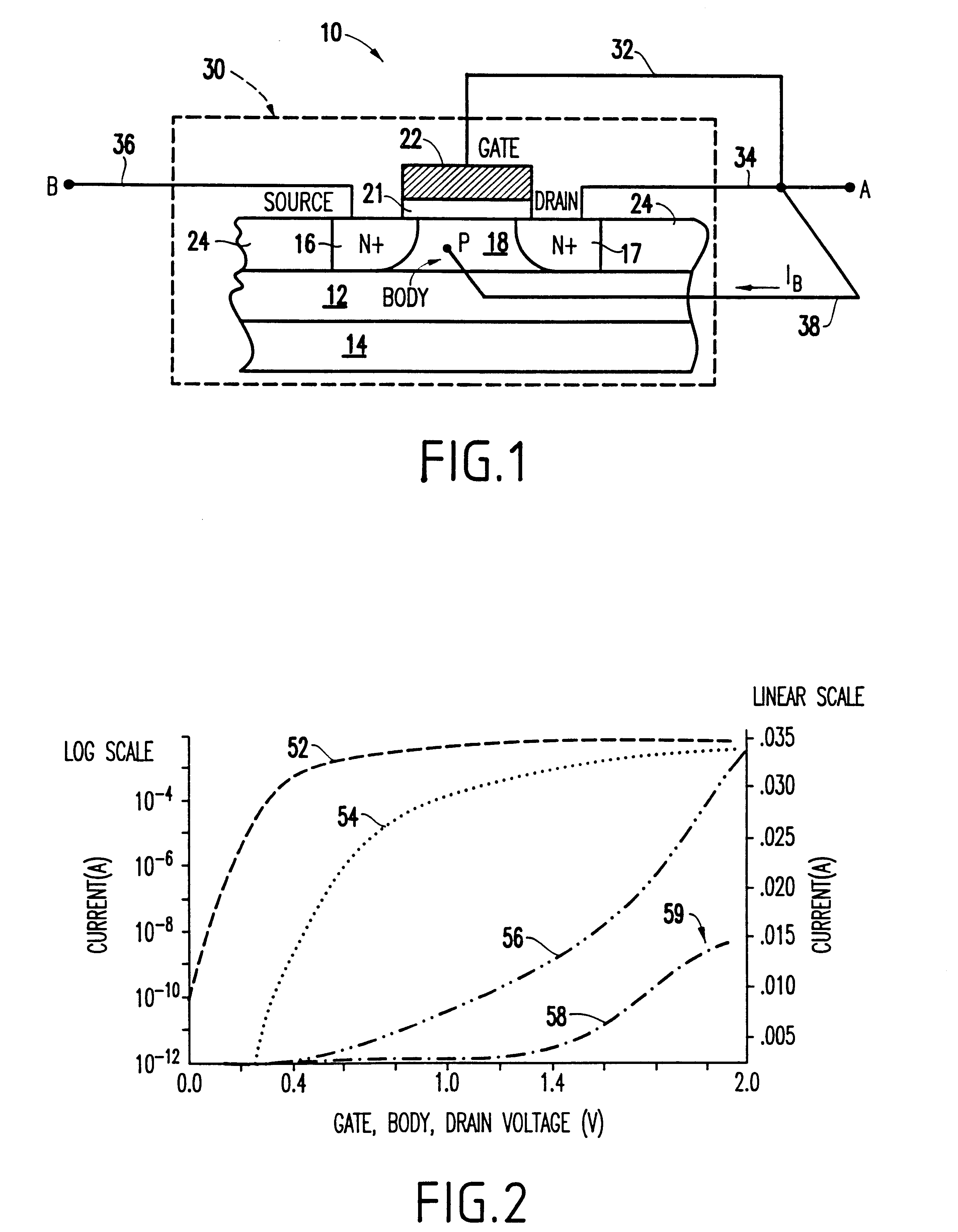

Forward body biased field effect transistor providing decoupling capacitance

In one embodiment of the invention, a semiconductor circuit includes a first group of field effect transistors that are forward body biased and have threshold voltages and a second group of field effect transistors that are not forward body biased and have threshold voltages that are higher than the threshold voltages of the first group of field transistors. In another embodiment of the invention, a semiconductor circuit includes first and second groups of field effect transistors. The circuit includes voltage source circuitry to provide voltage signals to bodies of the first group of field effect transistors to forward body bias the transistors of the first group. When the voltage signals are applied, the transistors of the first group have lower threshold voltages than do the transistors of the second group, except that there may be unintentional variations in threshold voltages due to parameter variations. Other aspects of the invention include forward biased decoupling transistors and a method of testing for leakage.

Owner:INTEL CORP

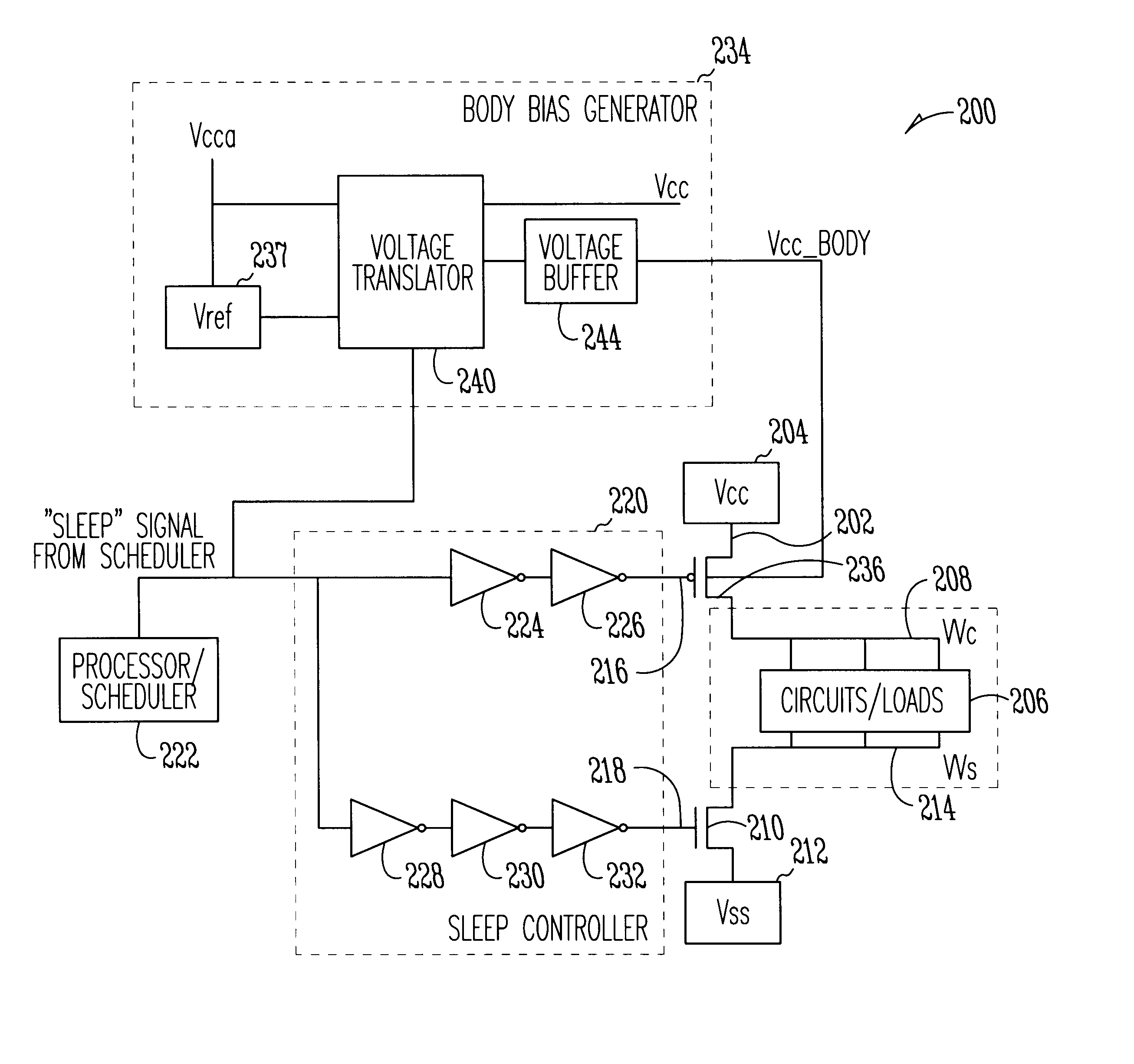

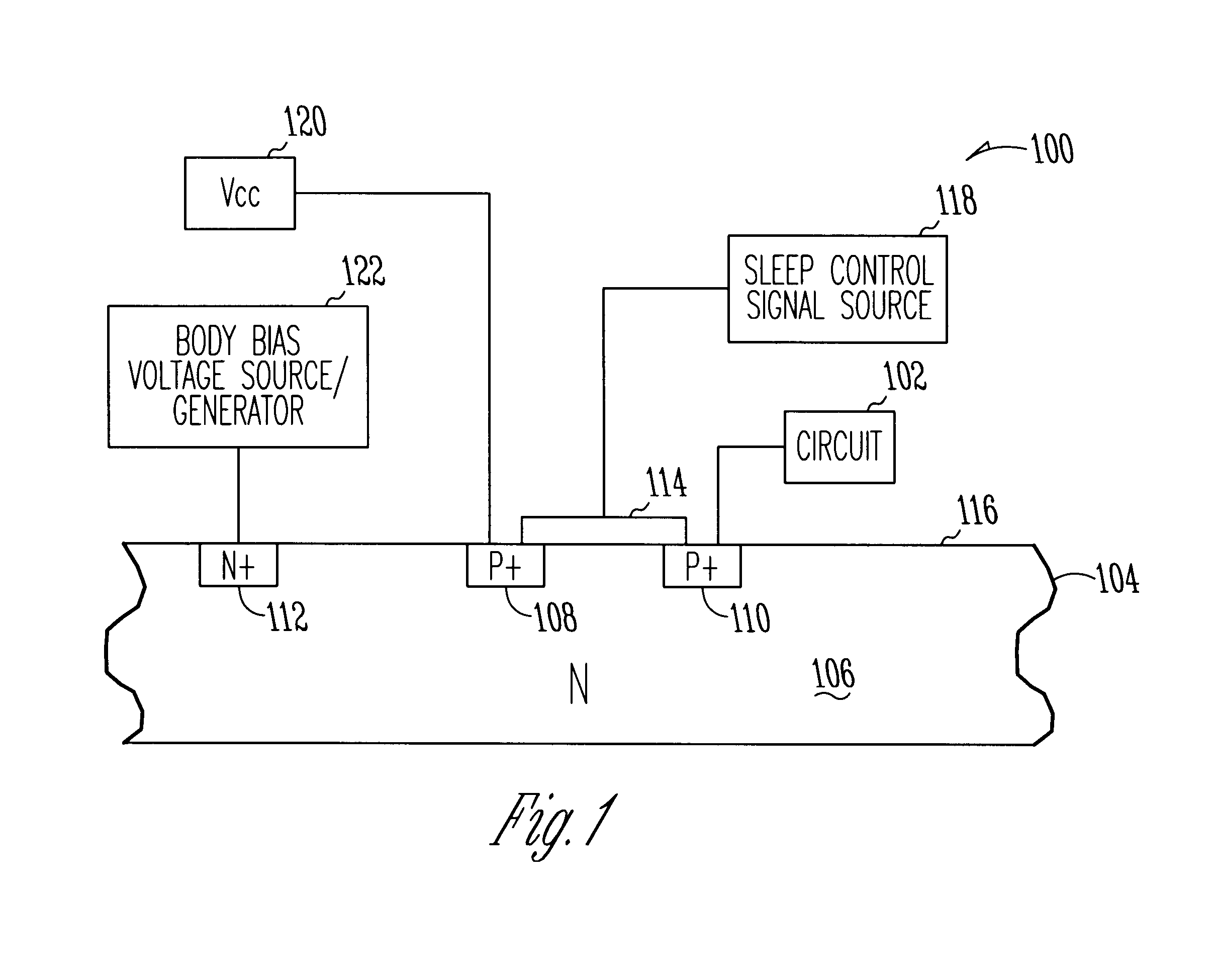

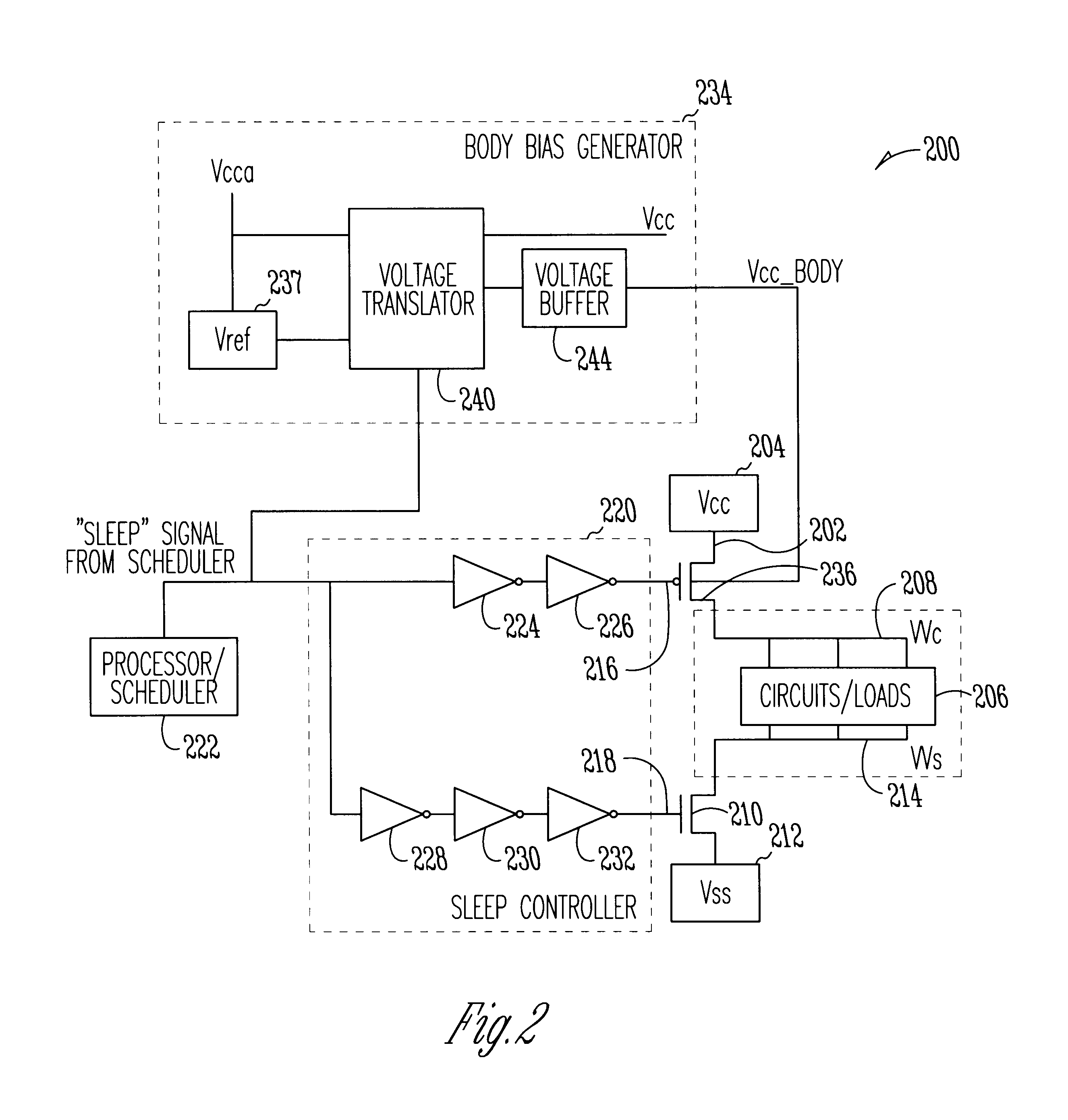

System using body-biased sleep transistors to reduce leakage power while minimizing performance penalties and noise

InactiveUS6744301B1Electric pulse generator detailsElectric variable regulationSleep controlVoltage generator

A system and method to reduce leakage power while minimizing performance penalties and noise is disclosed. In accordance with one embodiment of the invention, the system includes at least one sleep transistor operatively coupleable between a system power supply and at least one circuit powered by the system power supply to control the application of power to the circuit. The sleep transistor is also operatively coupleable to receive a sleep control signal to turn the sleep transistor on and off. A body bias voltage generator is operatively coupleable to a body of the at least one sleep transistor to substantially reduce leakage current when the sleep transistor is non-operational or idle and to improve the operational characteristics of the sleep transistor when the transistor is operational by reducing the performance penalty of the sleep transistor and by reducing impact of noise on the circuit and other devices.

Owner:INTEL CORP

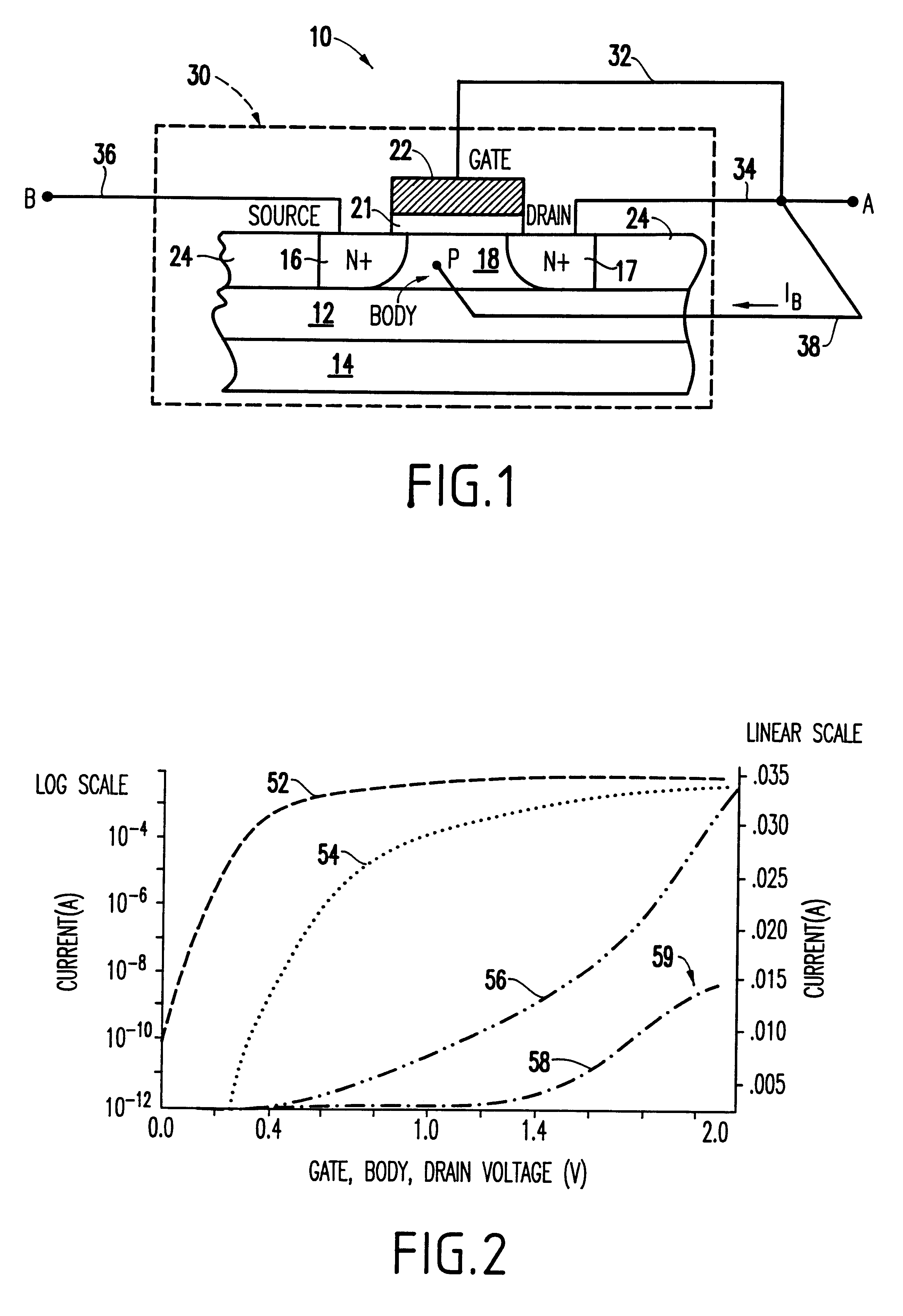

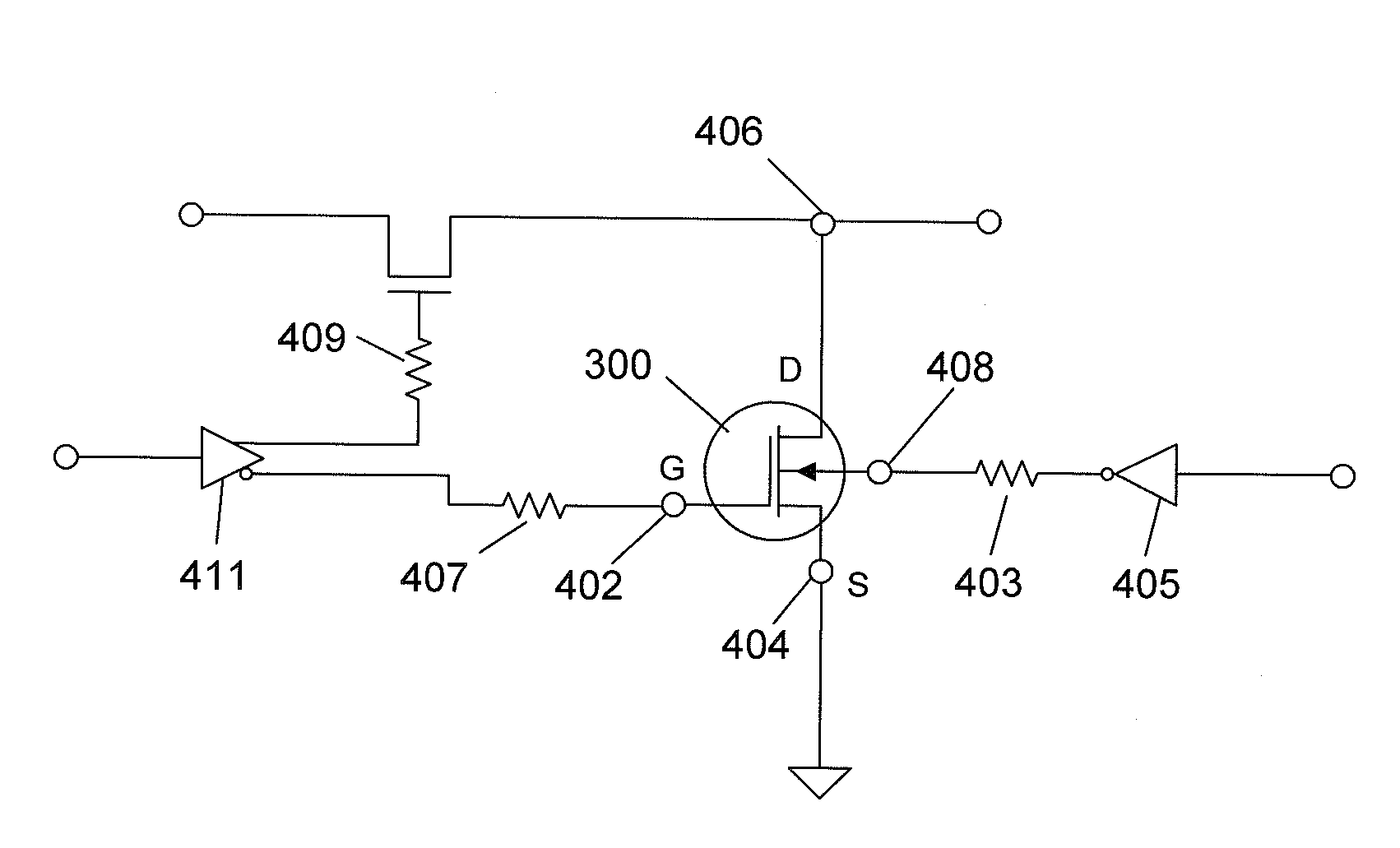

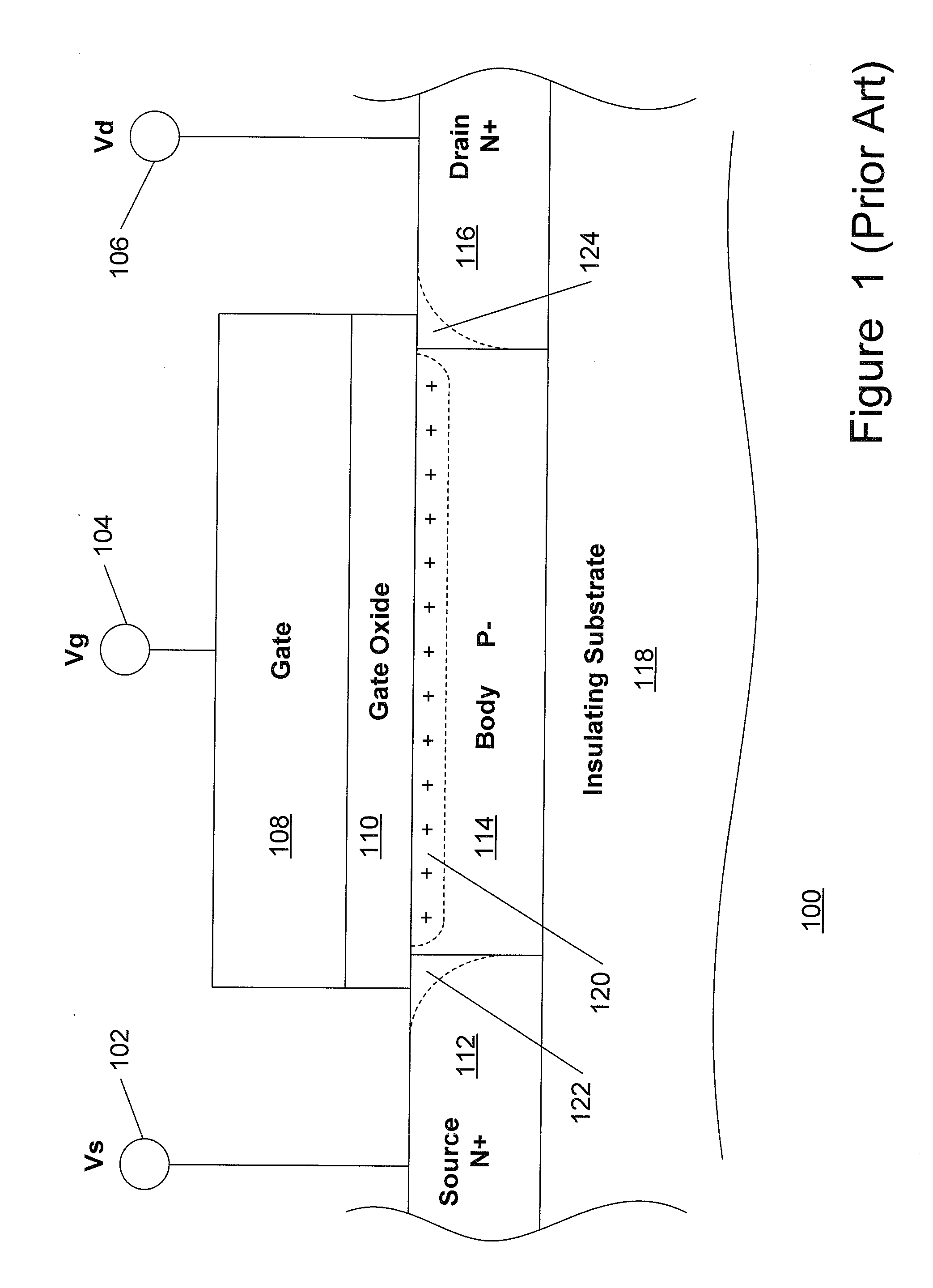

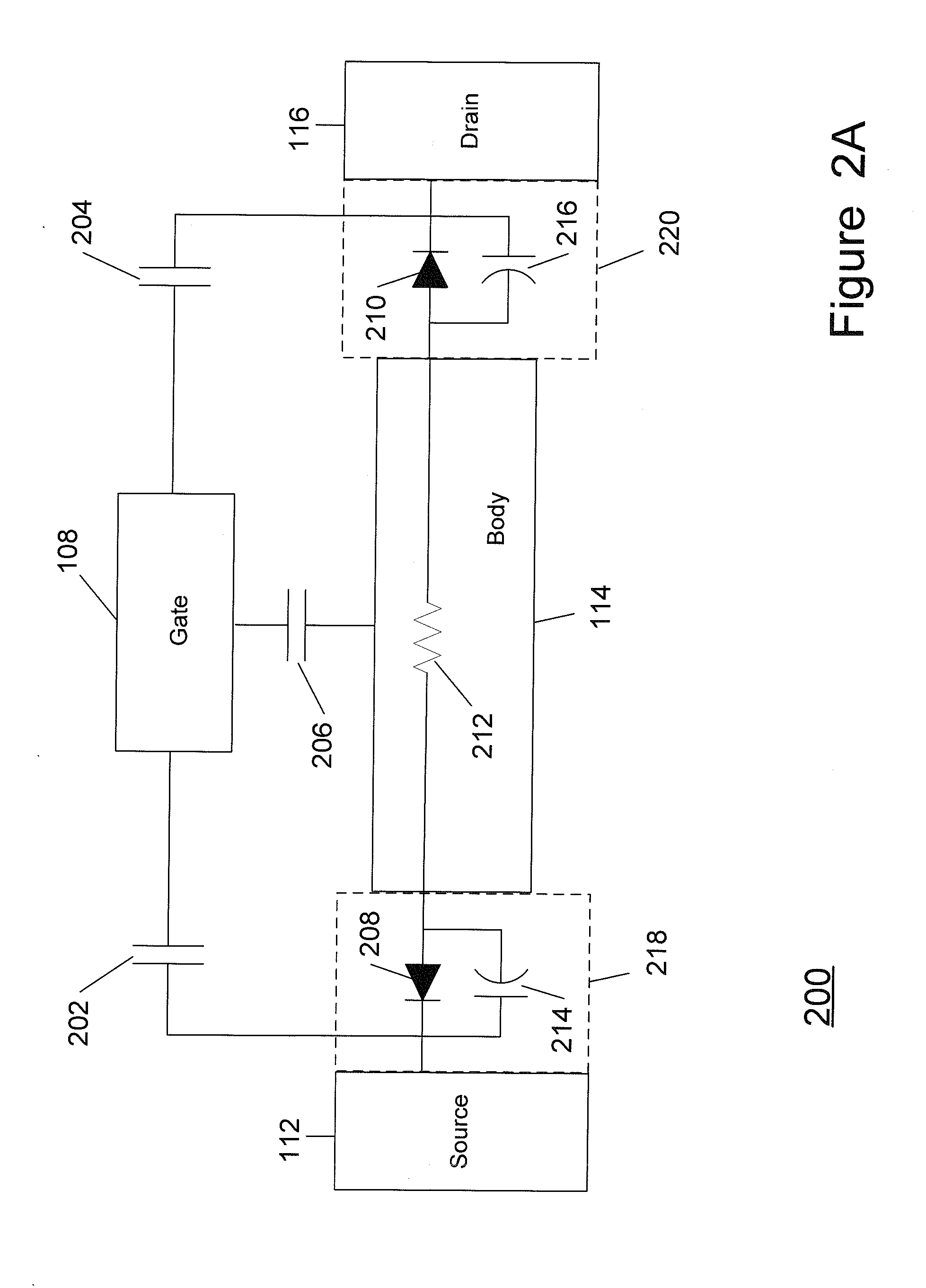

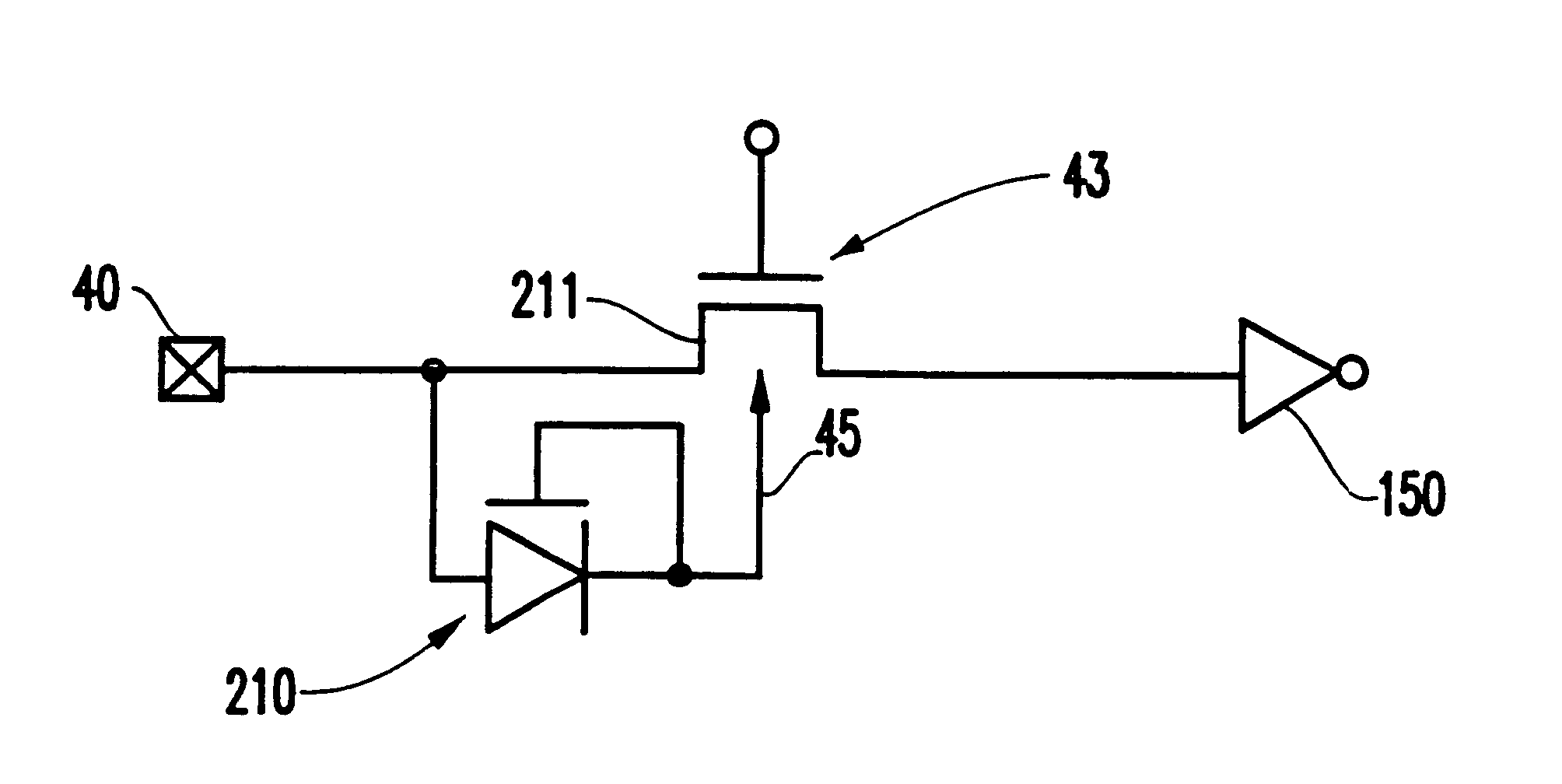

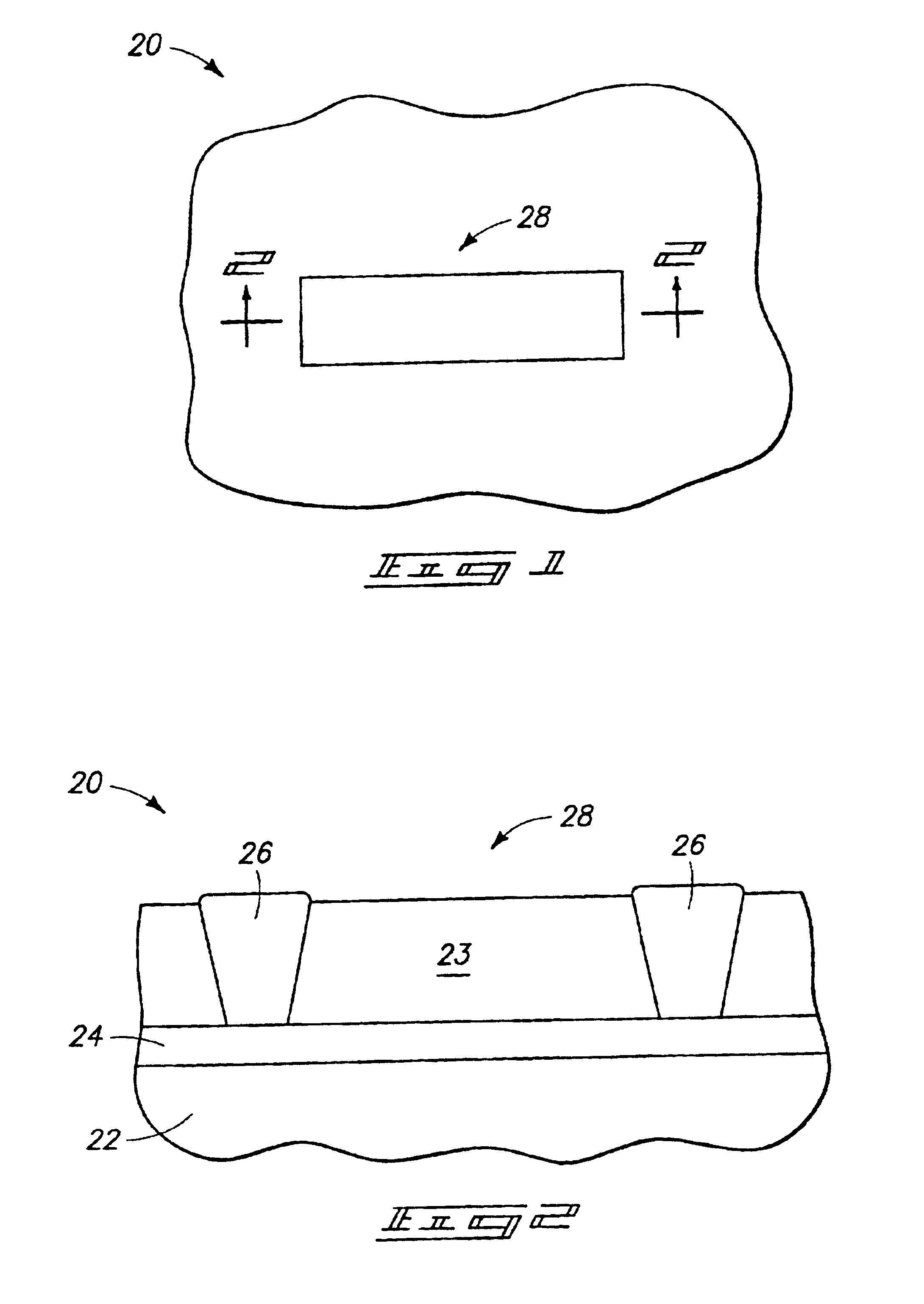

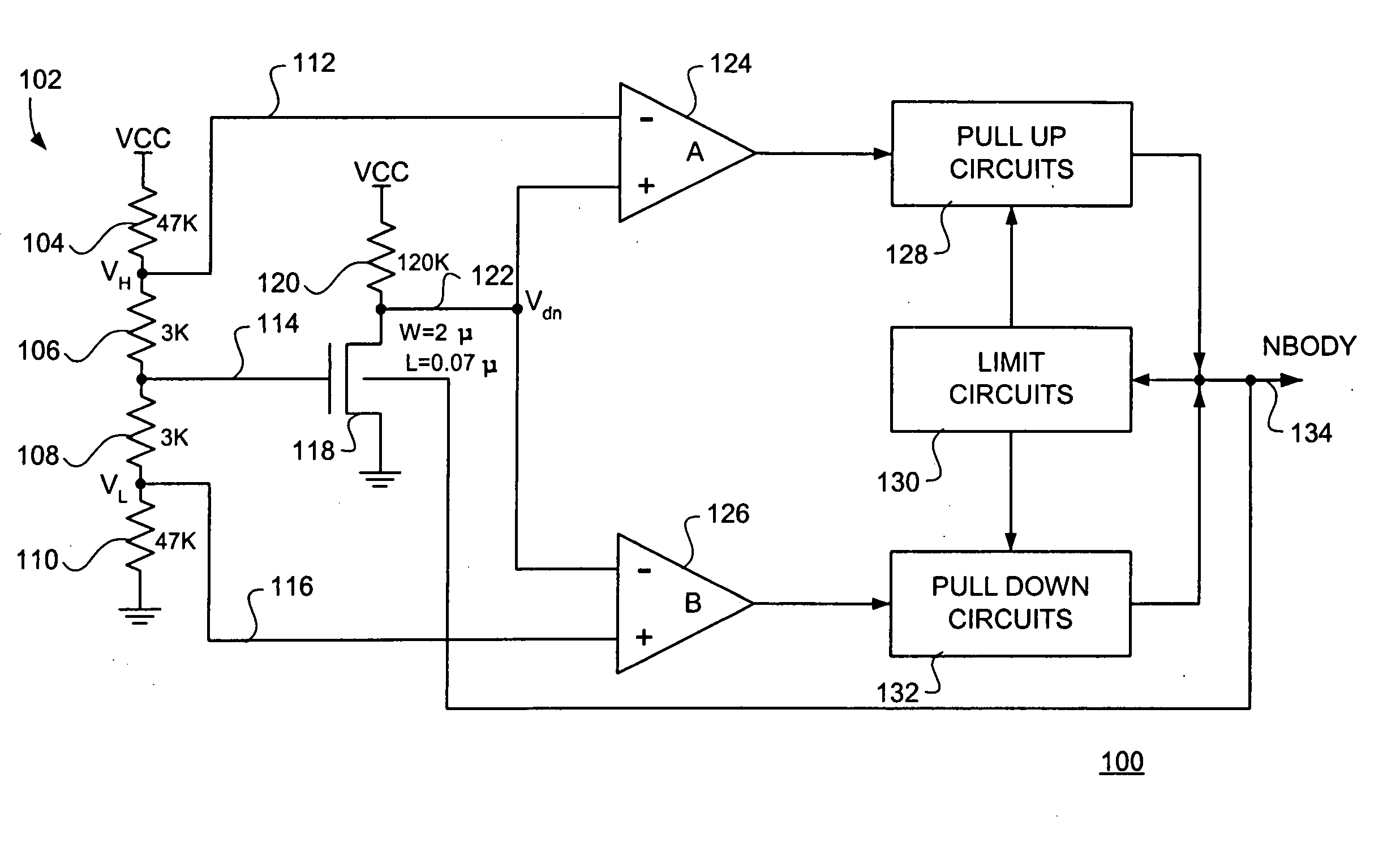

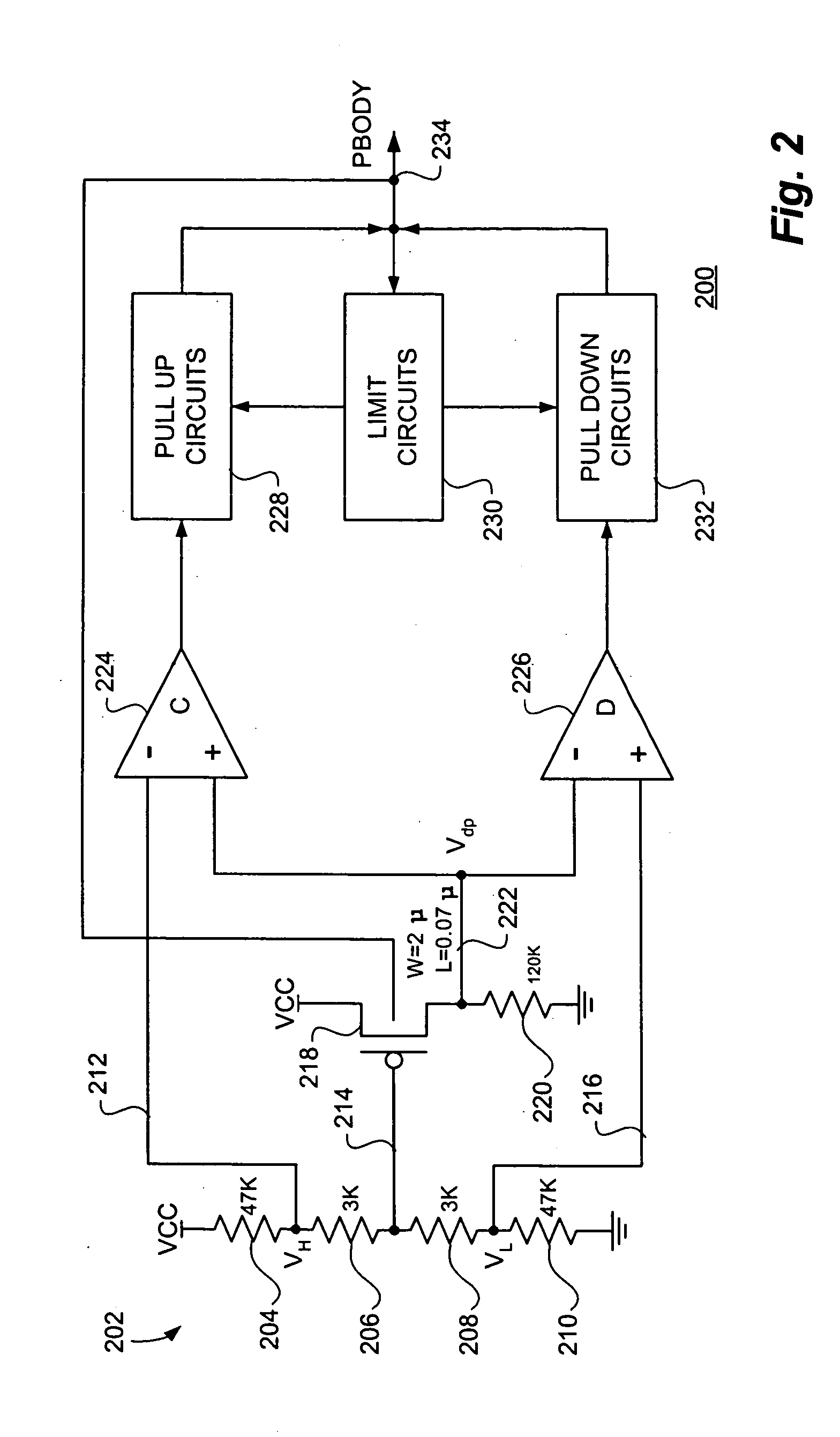

Method and Apparatus for Use in Improving Linearity of MOSFETs Using an Accumulated Charge Sink

ActiveUS20110169550A1Improving nonlinear responses and harmonic and intermodulaton distortion effectsReduce non-linearitySolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceMOSFET

A method and apparatus for use in improving the linearity characteristics of MOSFET devices using an accumulated charge sink (ACS) are disclosed. The method and apparatus are adapted to remove, reduce, or otherwise control accumulated charge in SOI MOSFETs, thereby yielding improvements in FET performance characteristics. In one exemplary embodiment, a circuit having at least one SOI MOSFET is configured to operate in an accumulated charge regime. An accumulated charge sink, operatively coupled to the body of the SOI MOSFET, eliminates, removes or otherwise controls accumulated charge when the FET is operated in the accumulated charge regime, thereby reducing the nonlinearity of the parasitic off-state source-to-drain capacitance of the SOI MOSFET. In RF switch circuits implemented with the improved SOI MOSFET devices, harmonic and intermodulation distortion is reduced by removing or otherwise controlling the accumulated charge when the SOI MOSFET operates in an accumulated charge regime.

Owner:PSEMI CORP

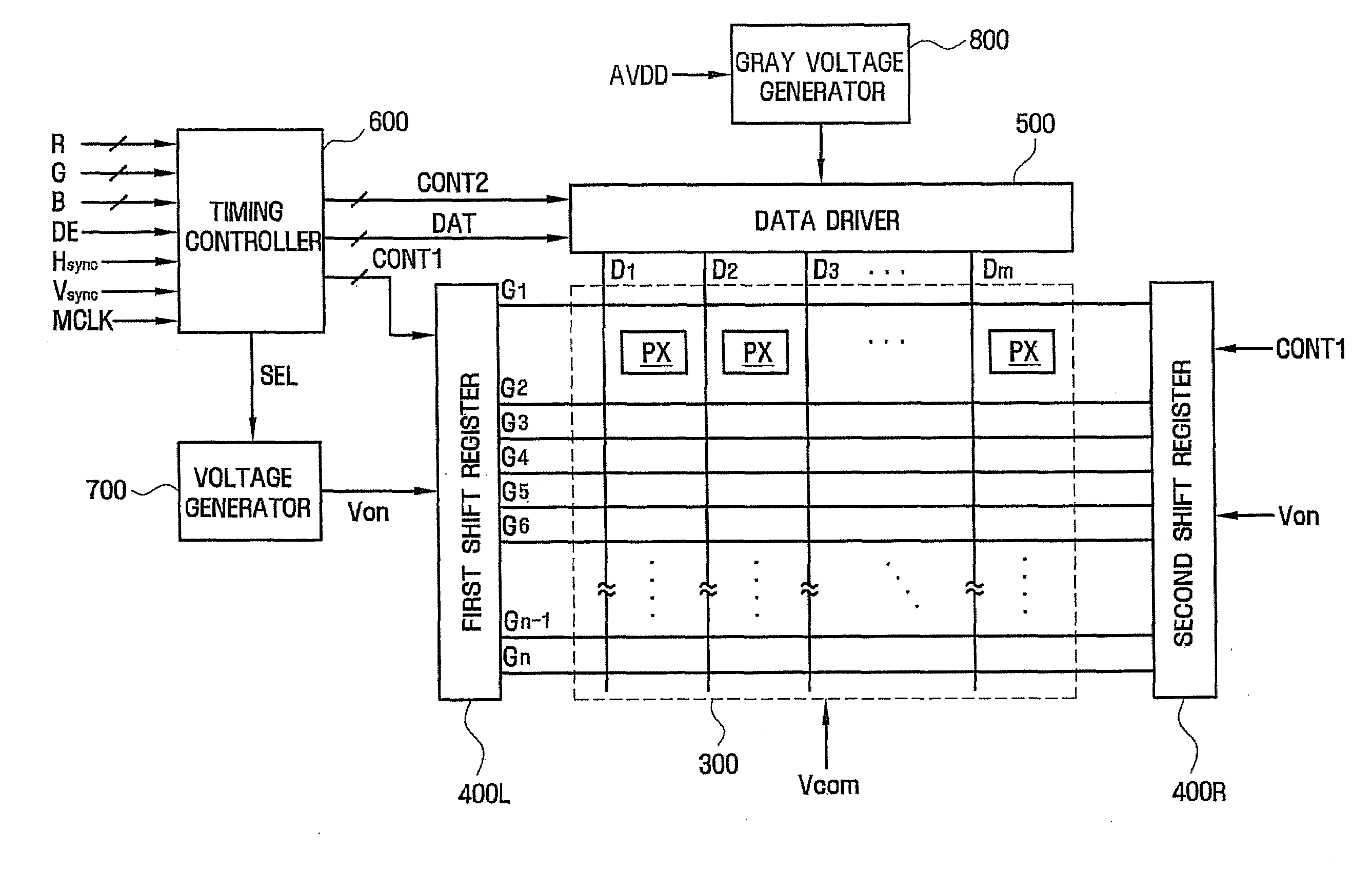

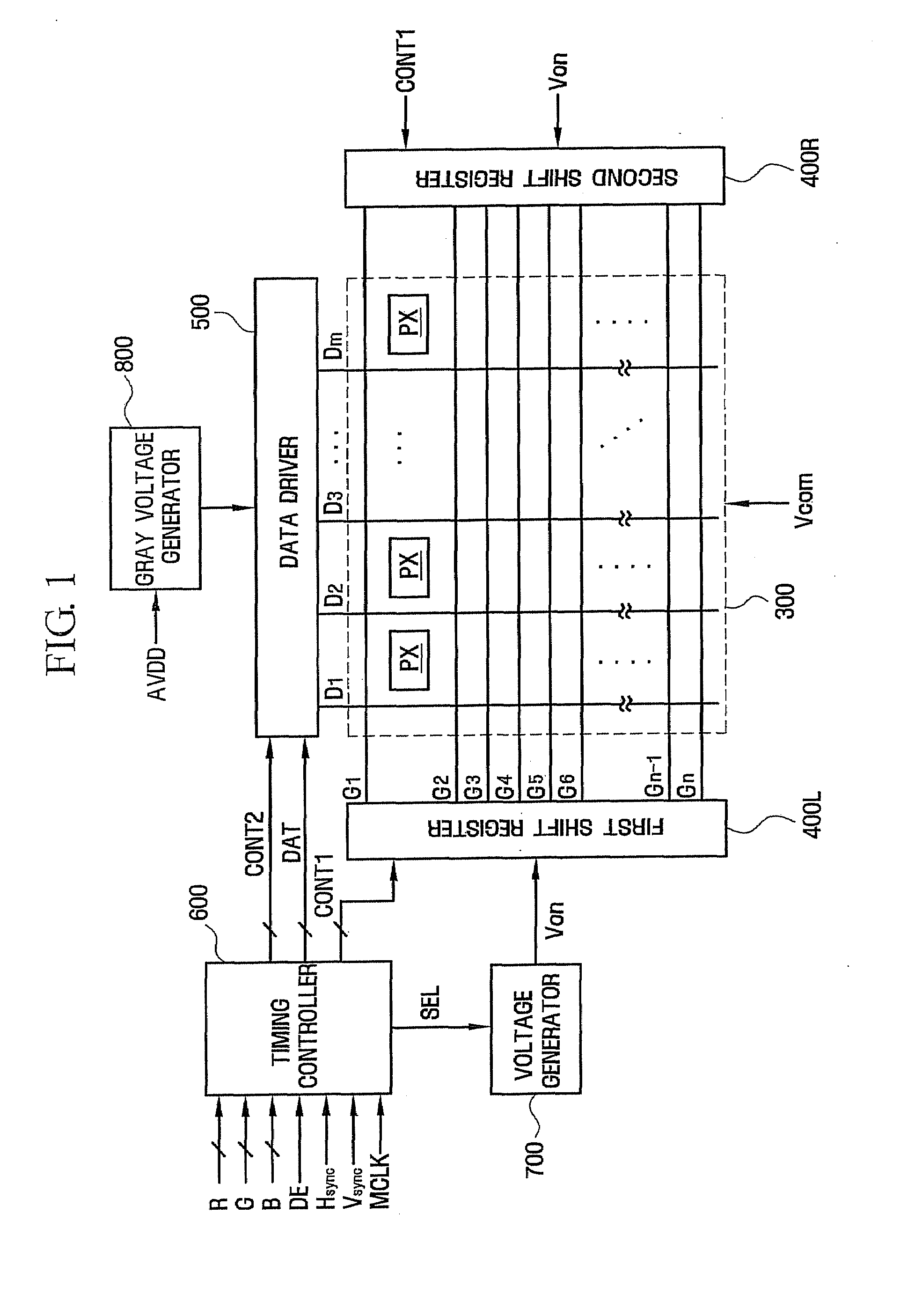

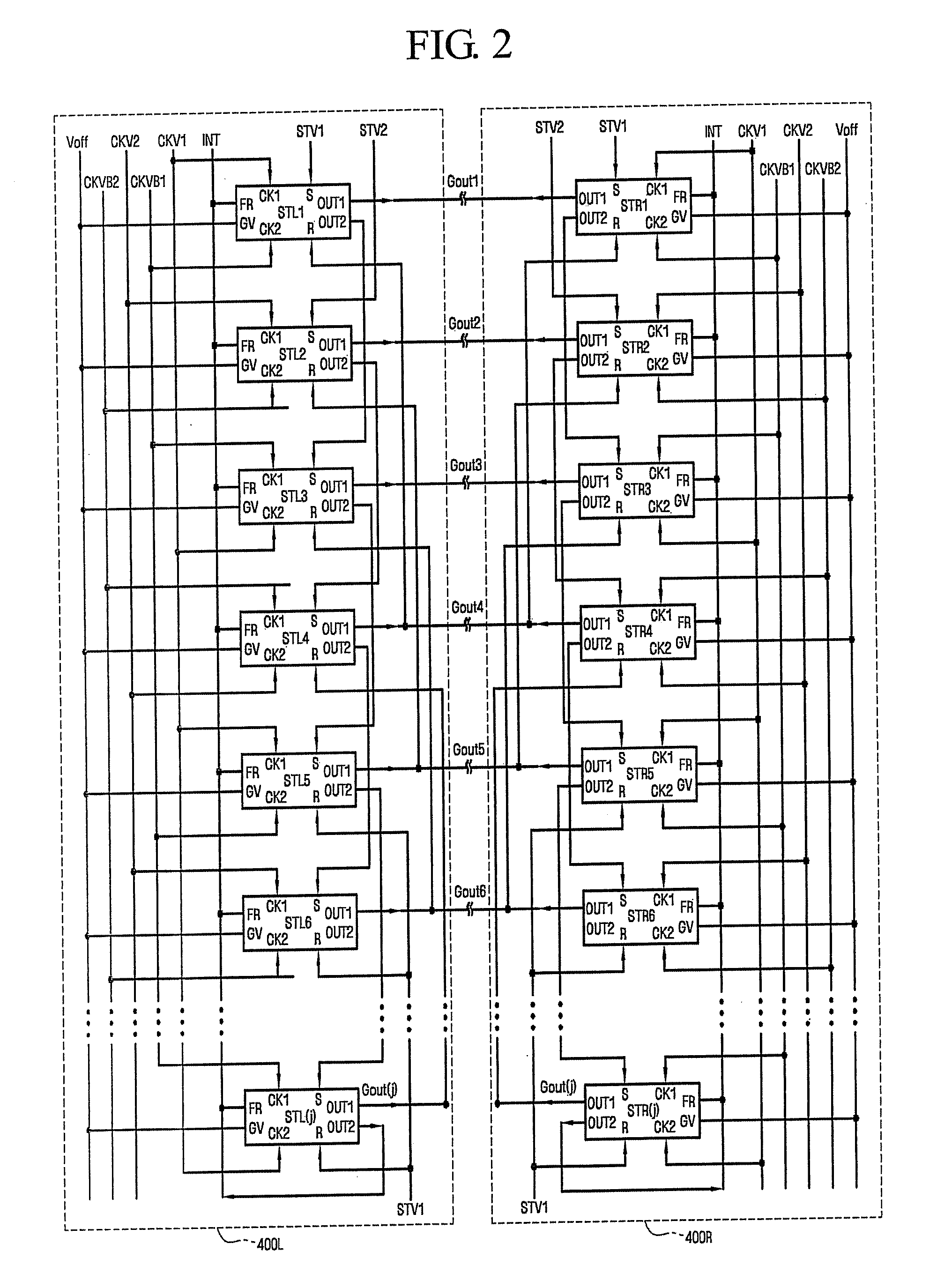

Gate driving circuit and liquid crystal display having the same

ActiveUS20080266477A1Small sizeStatic indicating devicesDigital storageLiquid-crystal displayControl signal

A gate driving circuit has a first stage which includes: a pull-up driving unit which receives a first carry signal from a second stage and outputs a control signal having first, second, third and fourth voltages to a first node during a preliminary period, a gate active period, a first gate inactive period and a second gate inactive period, respectively; a pull-up unit which receives the control signal and outputs a gate-on signal to a second node during the gate active period; a carry output unit which receives the control signal and outputs a second carry signal to a third stage during the gate active period; and a pull-down unit which receives a gate-off signal and the second carry signal from the second stage and outputs the control signal having the fourth voltage level to the first node during the second gate inactive period.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

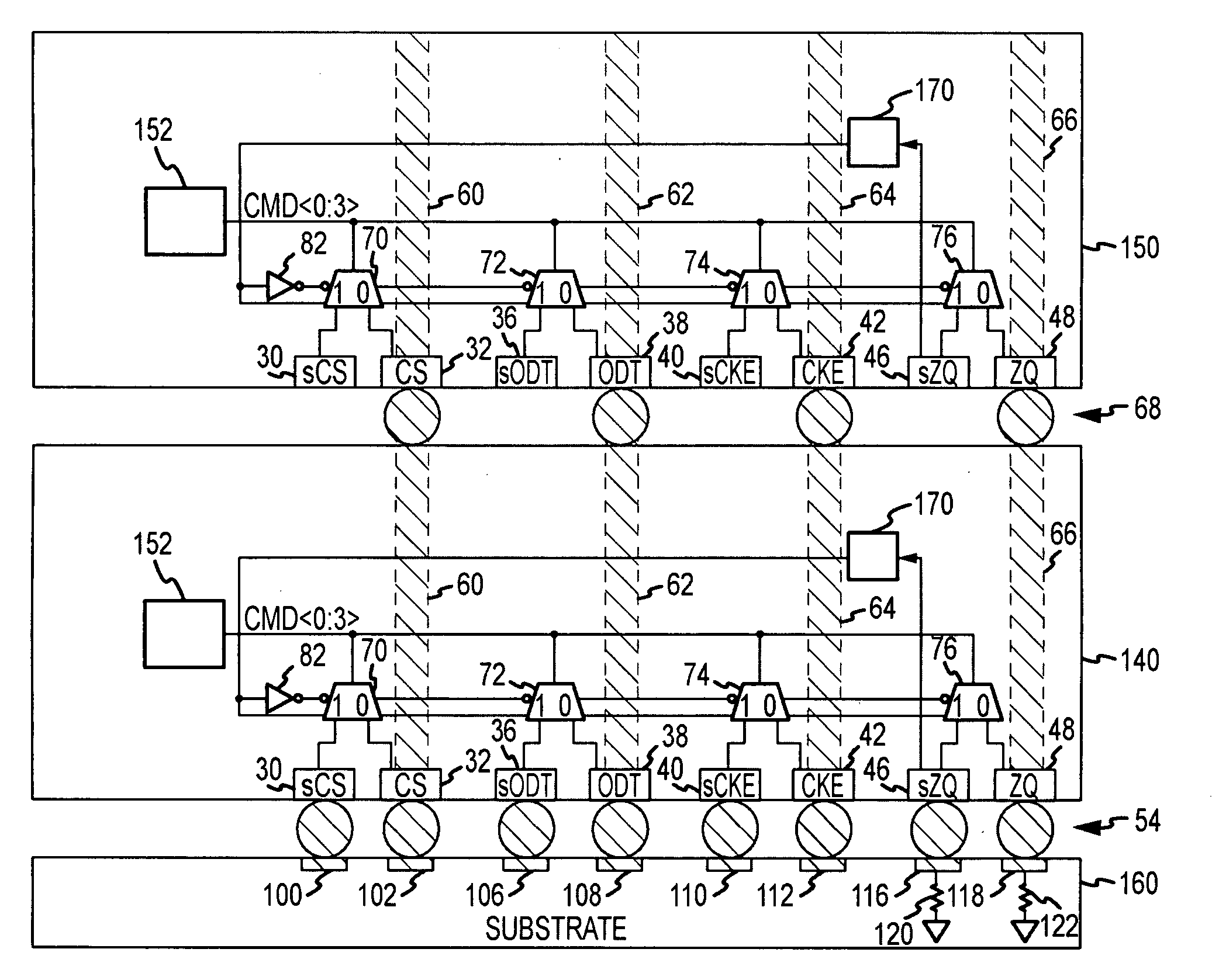

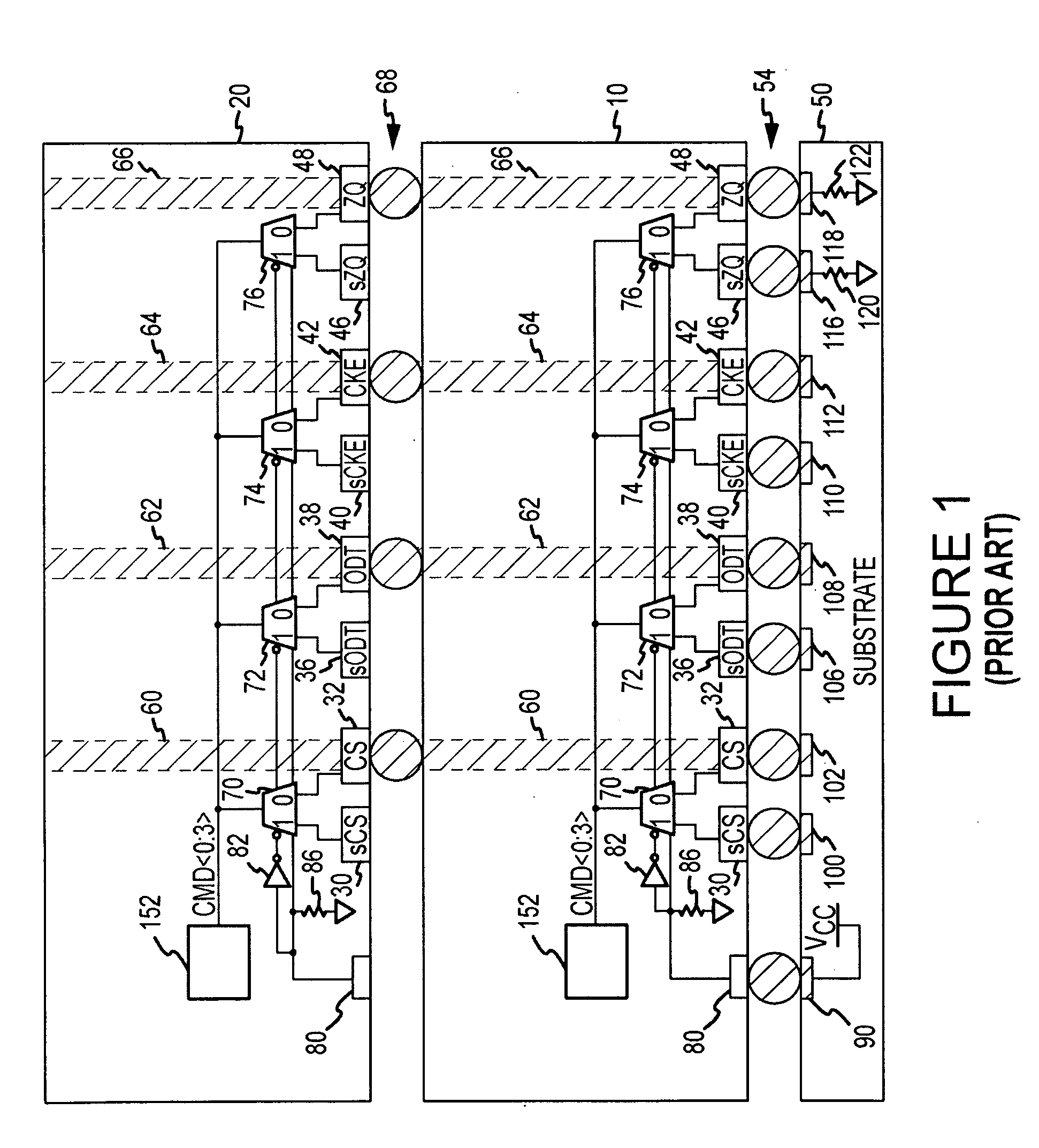

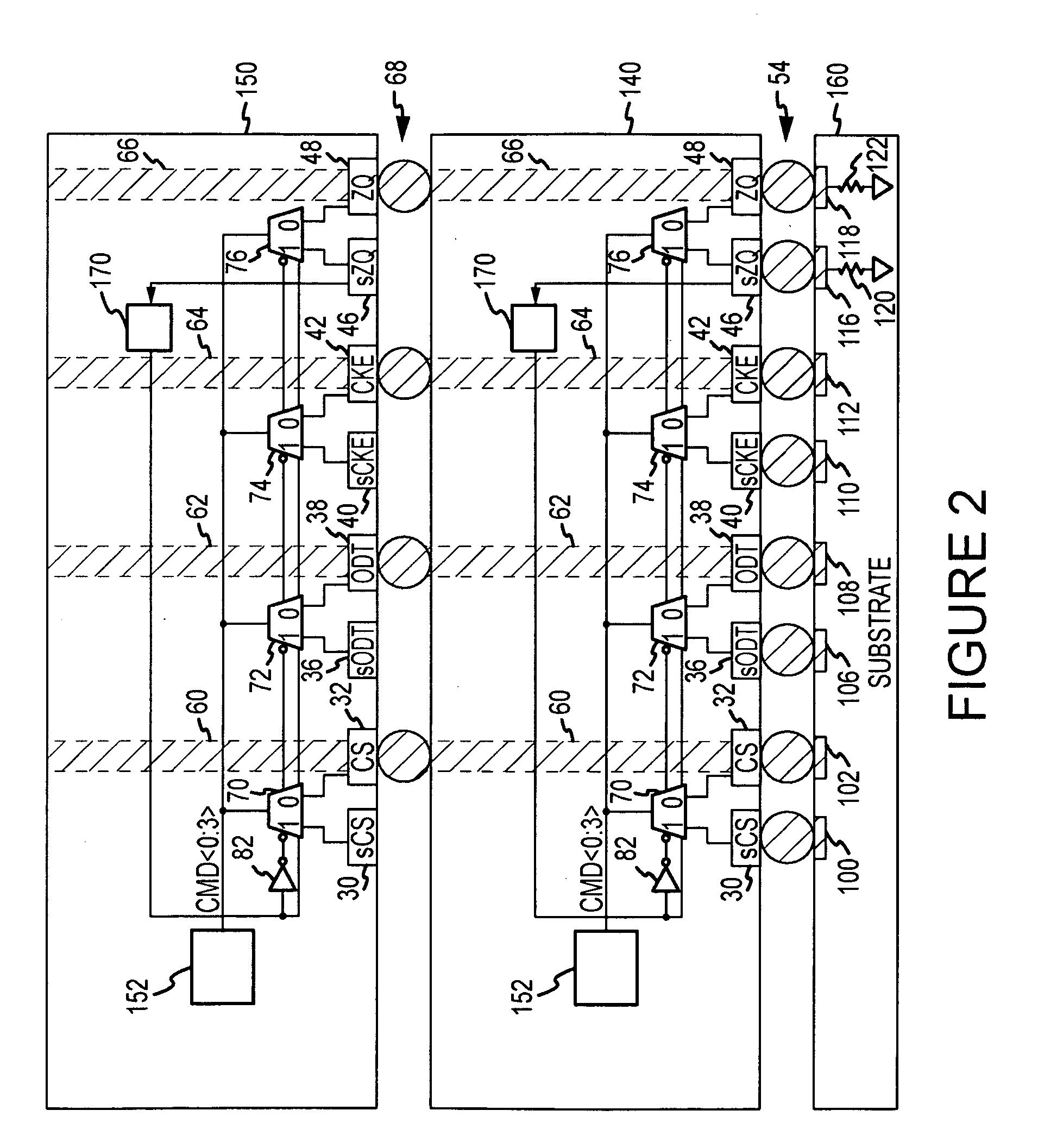

Structure and method for coupling signals to and/or from stacked semiconductor dies

Signals are coupled to and from stacked semiconductor dies through first and second sets of external terminals. The external terminals in the second set are connected to respective conductive paths extending through each of the dies. Signals are coupled to and from the first die through the first set of external terminals. Signals are also coupled to and from the second die through the conductive paths in the first die and the second set of external terminals. The external terminals in first and second sets of each of a plurality of pairs are connected to an electrical circuit through respective multiplexers. The multiplexers in each of the dies are controlled by respective control circuits that sense whether a die in the first set is active. The multiplexers connect the external terminals in either the first set or the second set depending on whether the bonding pad in the first set is active.

Owner:MICRON TECH INC

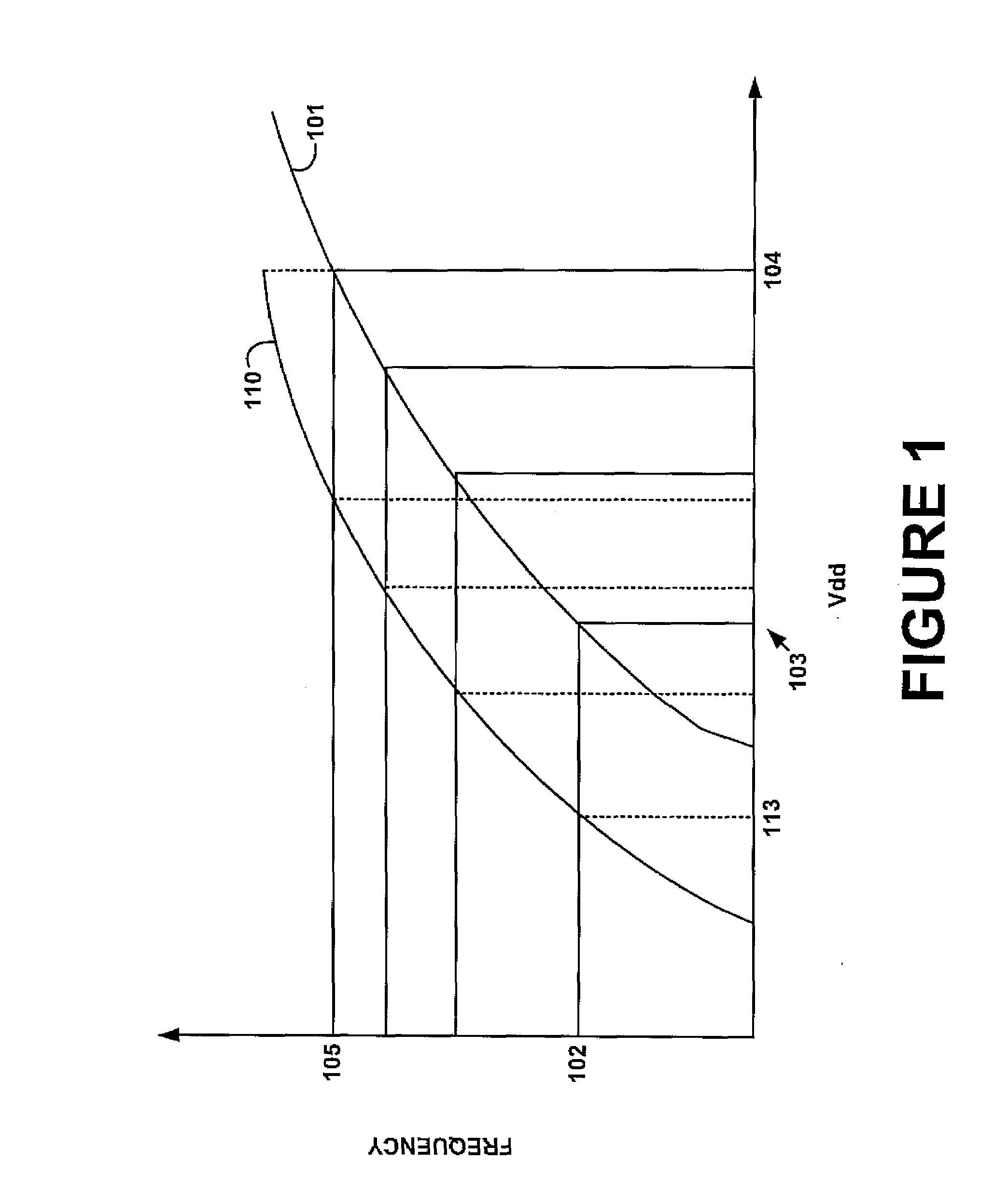

Semiconductor integrated circuit

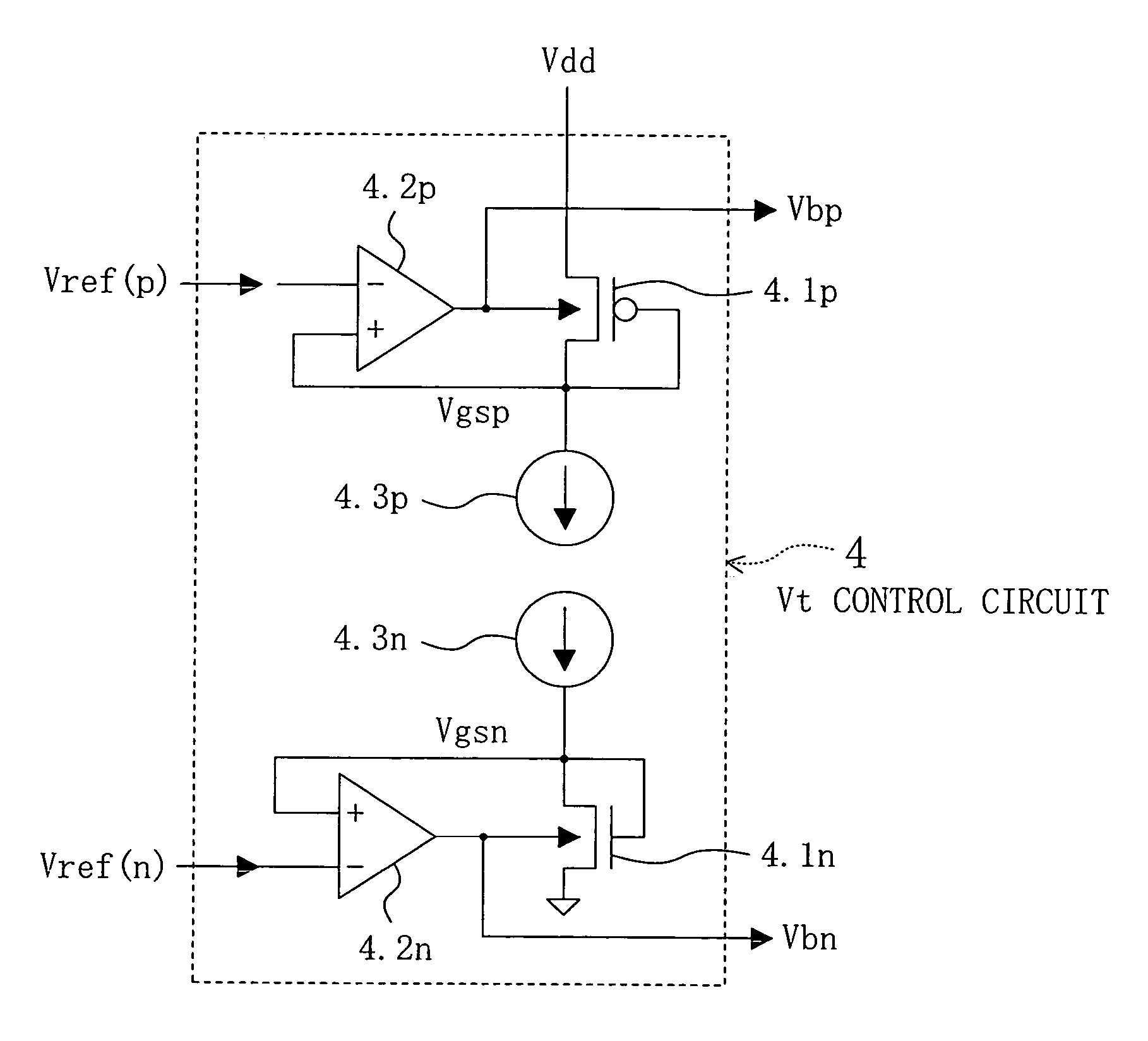

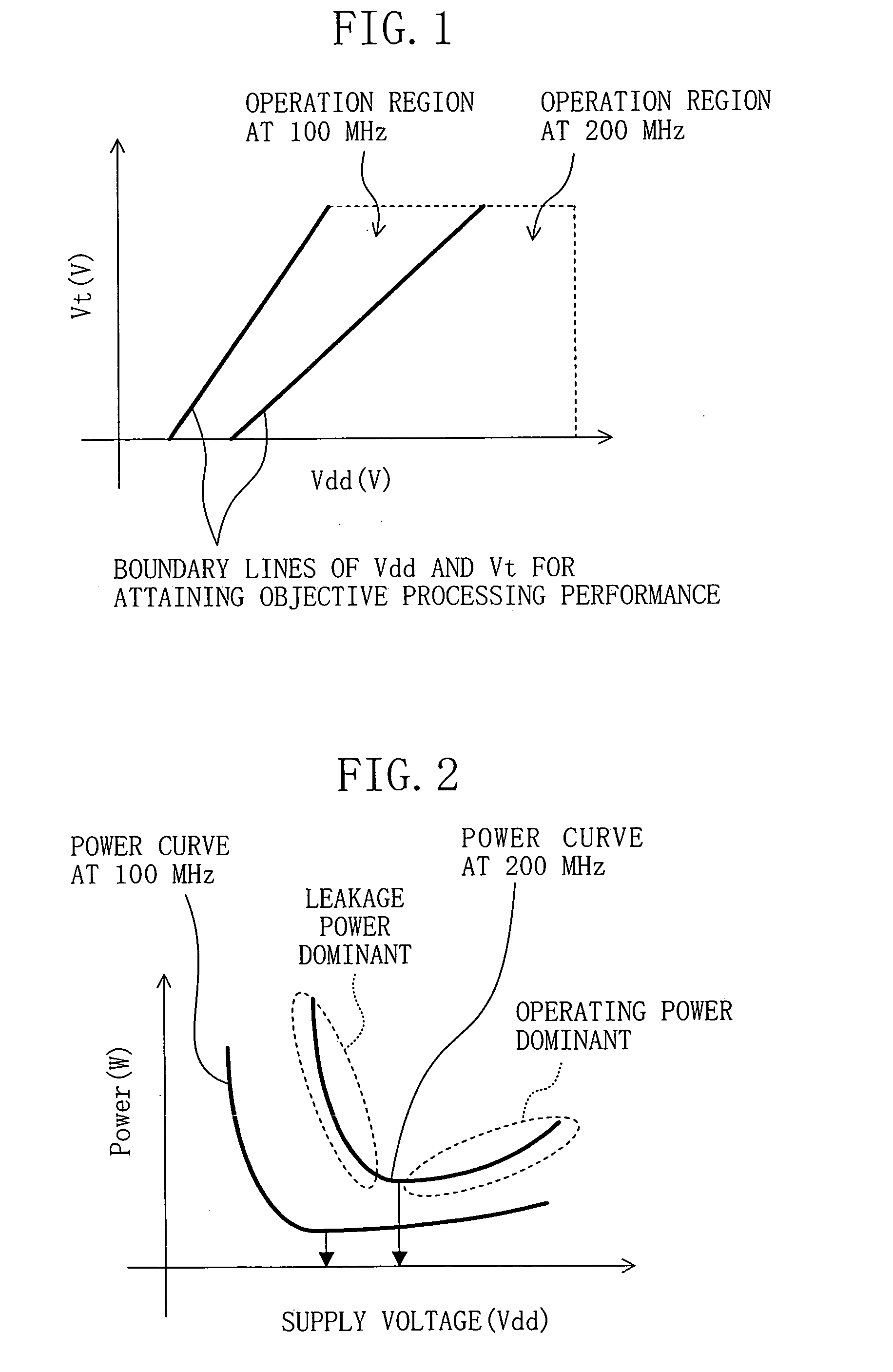

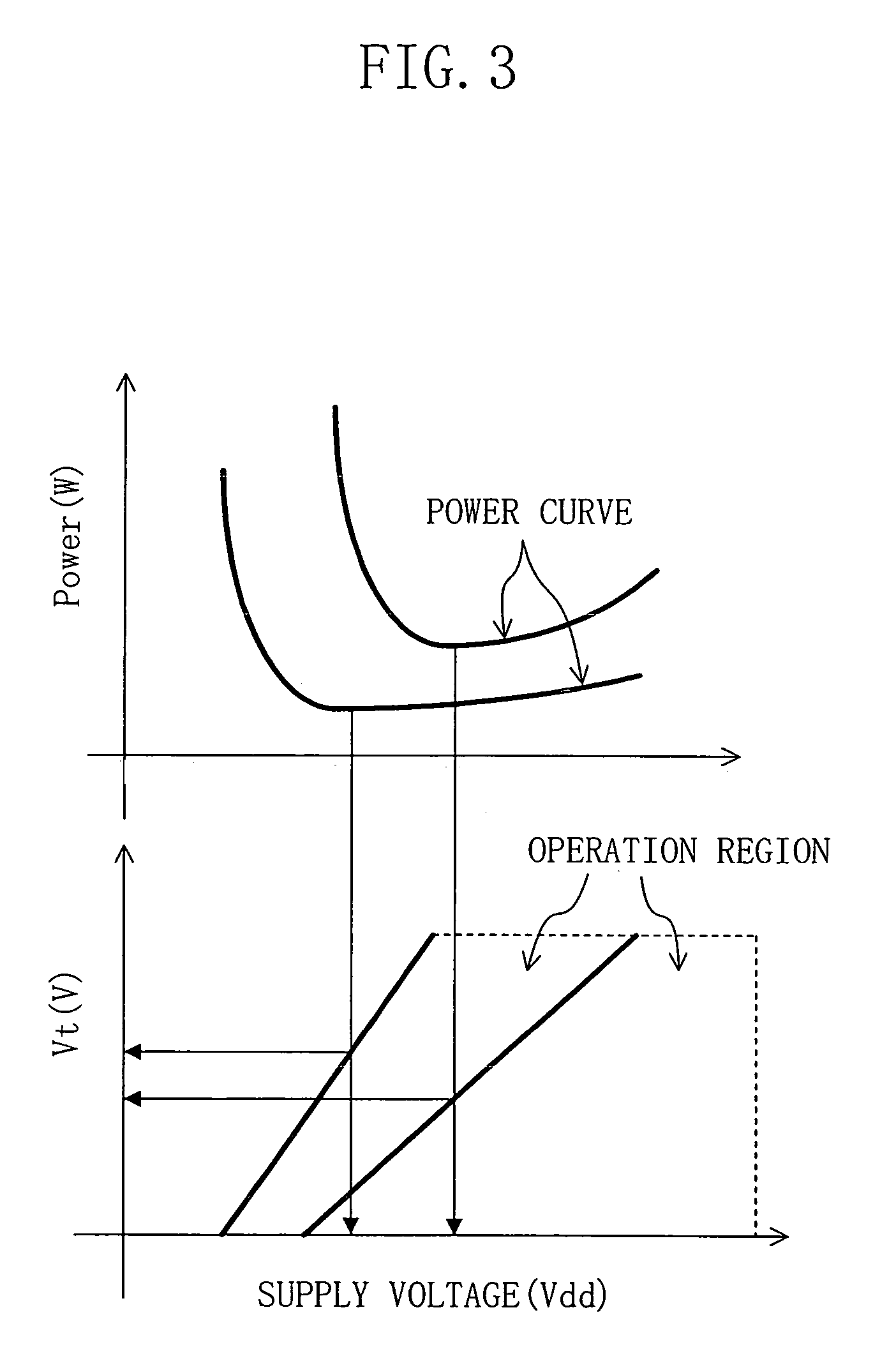

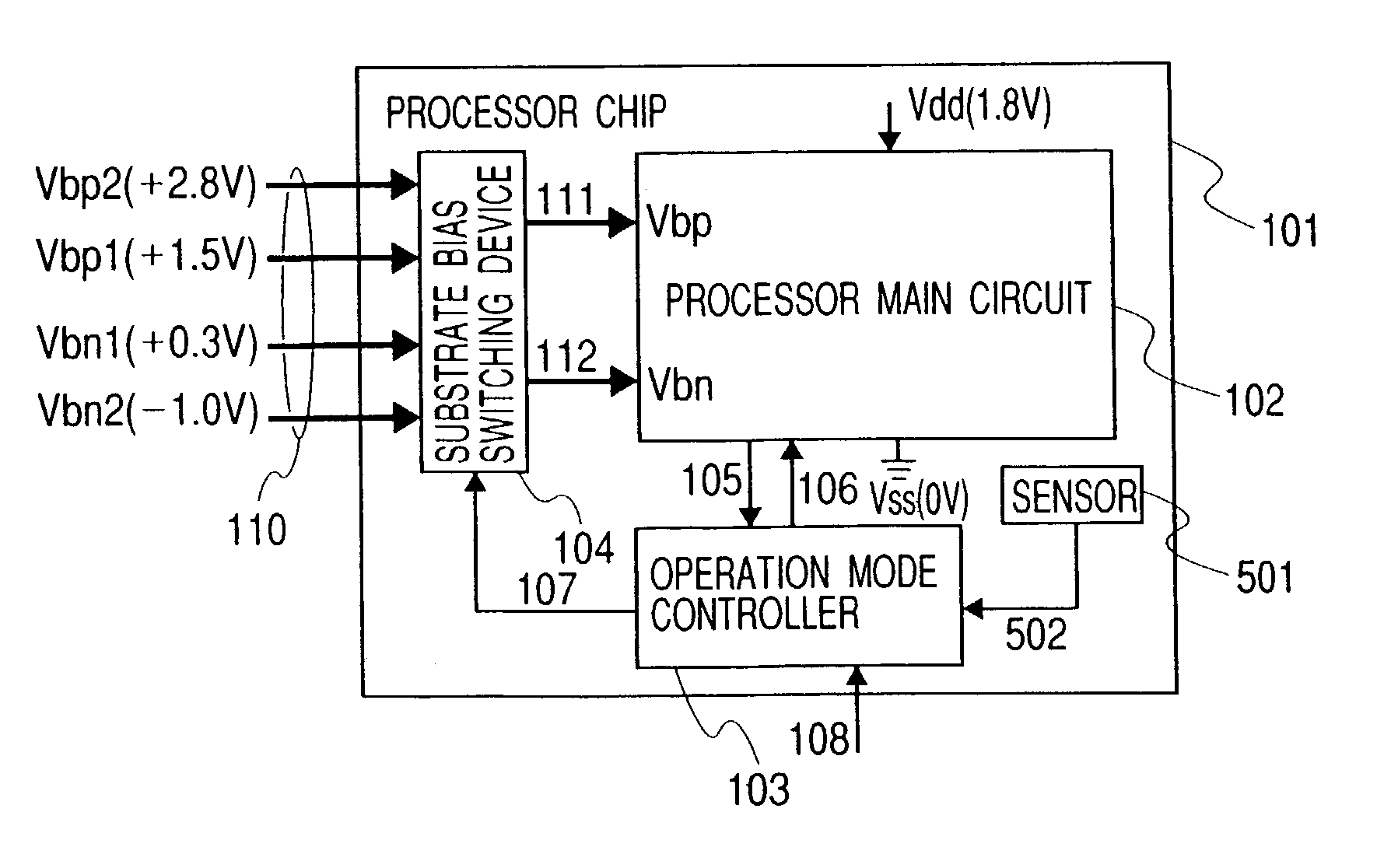

InactiveUS20050116765A1Increase probabilityReduce power consumptionTransistorPower reduction in field effect transistorsEngineeringControl circuit

In a semiconductor integrated circuit, respective semiconductor circuits are disposed in different regions partitioned in accordance with their operation probabilities per unit time, and a supply voltage and a threshold voltage are correlatively controlled in each region. A target value for controlling the threshold voltage is determined in accordance with the operation probability of the semiconductor circuit. A threshold voltage control circuit controls substrate voltages of p-type and n-type MOS transistors included in the semiconductor circuit so that the threshold voltage can be constant at the target value regardless of the temperature change occurring in use. Simultaneously, a supply voltage control circuit controls the supply voltage for the semiconductor circuit so that an objective operating frequency can be attained. As a result, a semiconductor integrated circuit with low power consumption can be obtained.

Owner:PANASONIC CORP

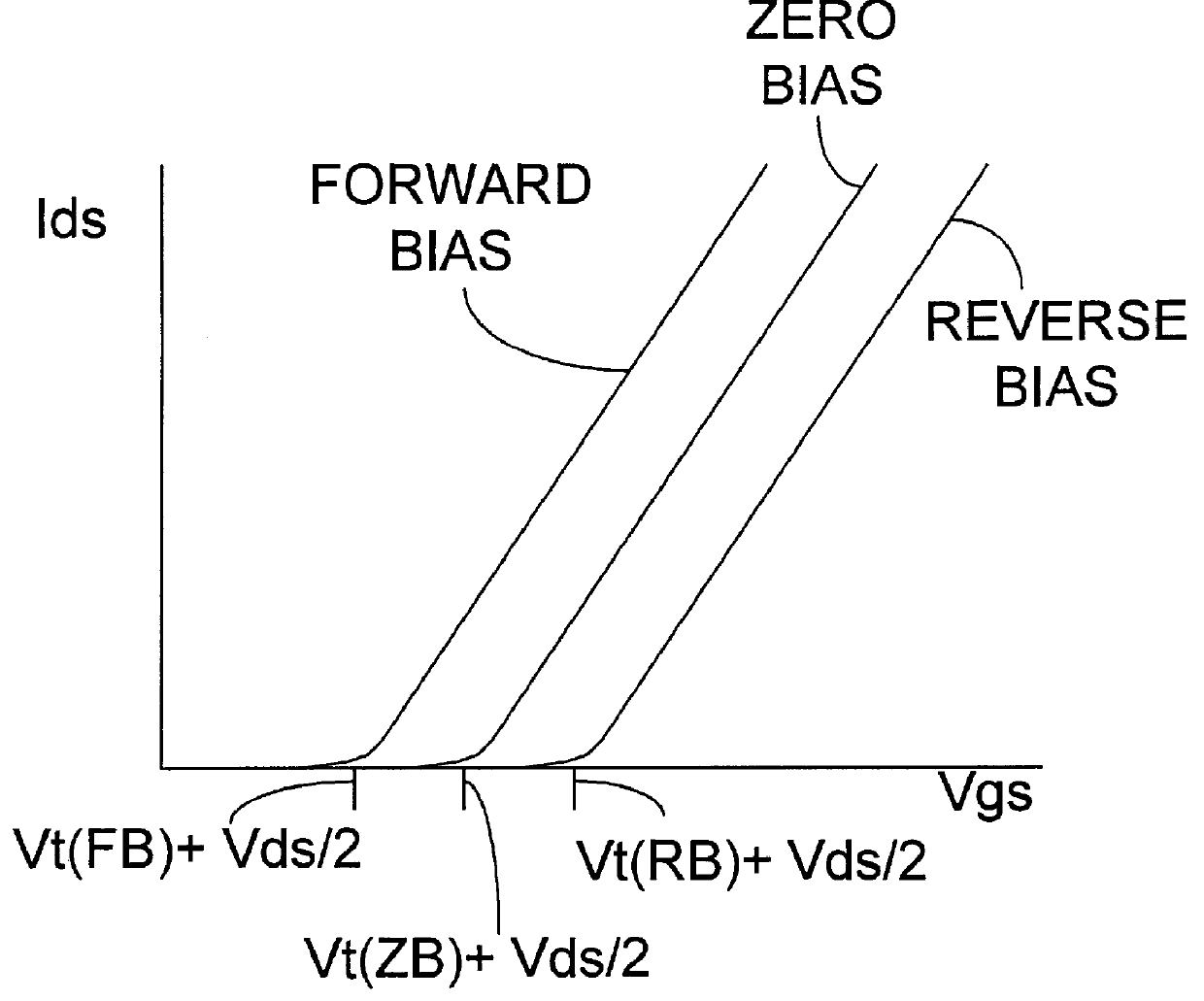

Method of setting back bias of MOS circuit, and MOS integrated circuit

In a MOS circuit comprising a plurality of MOSFETs constituting a digital circuit, an input signal is supplied to the digital circuit, and a first back bias voltage is supplied to a semiconductor substrate or a semiconductor well region in which the MOSFETs are formed, so that a pn junction between the semiconductor substrate or the semiconductor well region and a source region is brought to a forward voltage. In a non-operating state in which a circuit operation is suspended by the input signal supplied to the digital circuit as a fixed level, a second back bias voltage is applied to the semiconductor substrate or the semiconductor well region so that the pn junction between the semiconductor substrate or the semiconductor well region and the source region is brought to a reverse voltage.

Owner:RENESAS ELECTRONICS CORP

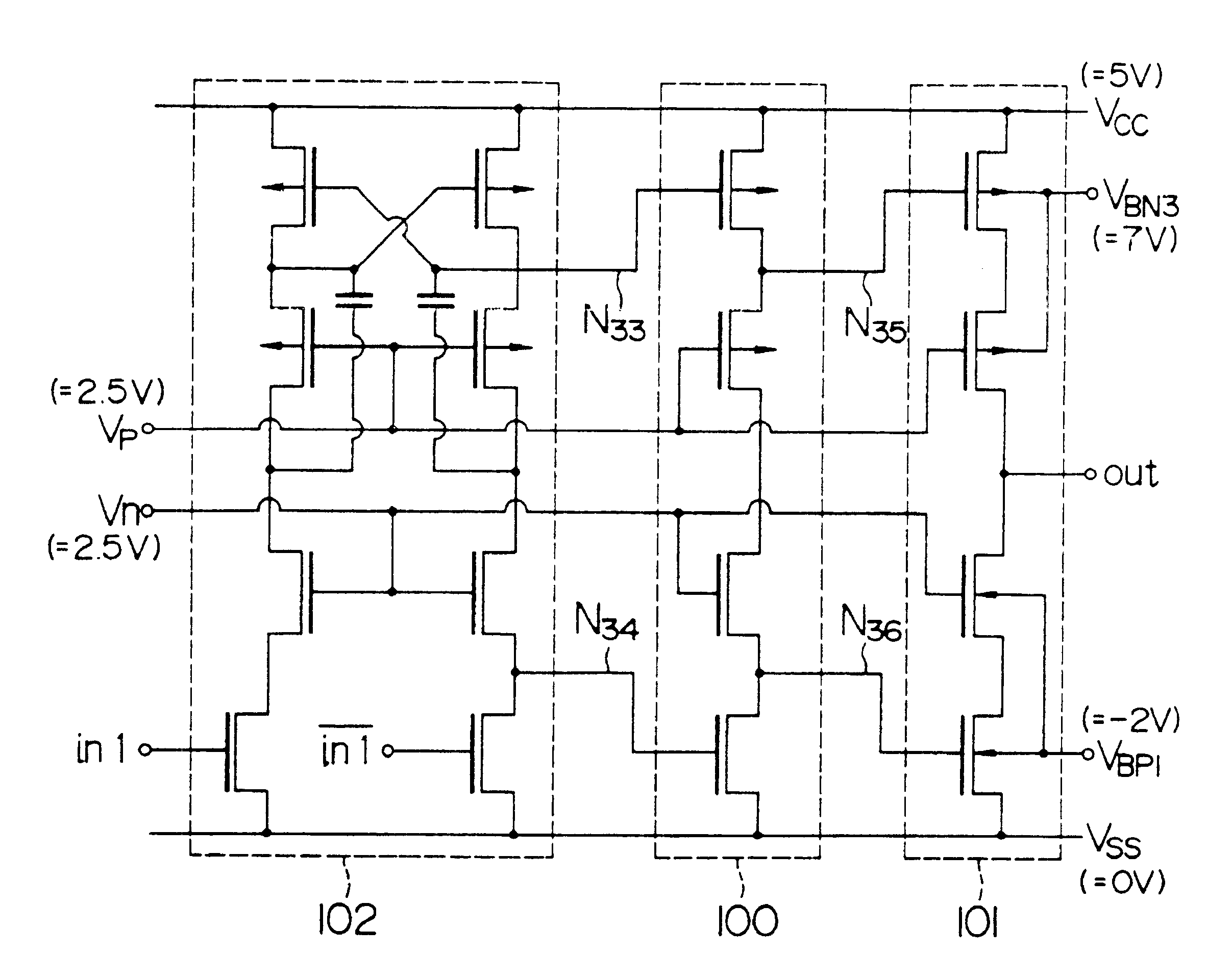

Large scale integrated circuit with sense amplifier circuits for low voltage operation

InactiveUSRE37593E1Low working voltageEasy to operateSingle network parallel feeding arrangementsDigital storageLow voltageHemt circuits

Disclosed is a one-chip ULSI which can carry out the fixed operation in a wide range of power supply voltage (1 V to 5.5 V). This one-chip ULSI is composed of a voltage converter circuit(s) which serves to a fixed internal voltage for a wide range of power supply voltage, an input / output buffer which can be adapted to several input / output levels, a dynamid RAM(s) which can operate at a power supply voltage of 2 V or less, etc. This one-chip ULSI can be applied to compact and portable electronic devices such as a lap-top type personal computer, an electronic pocket note book, a solid-state camera, etc.

Owner:PS4 LUXCO SARL

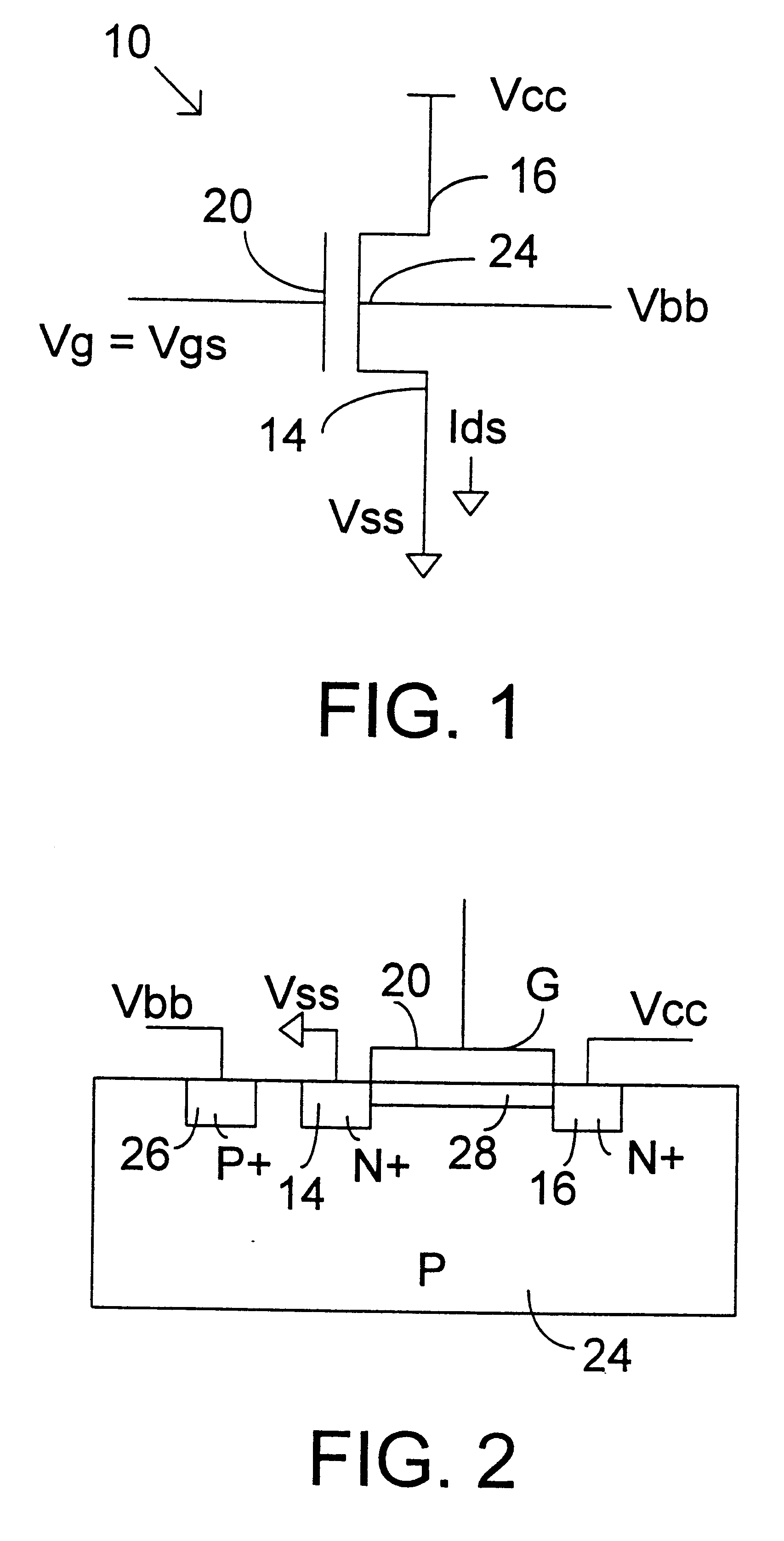

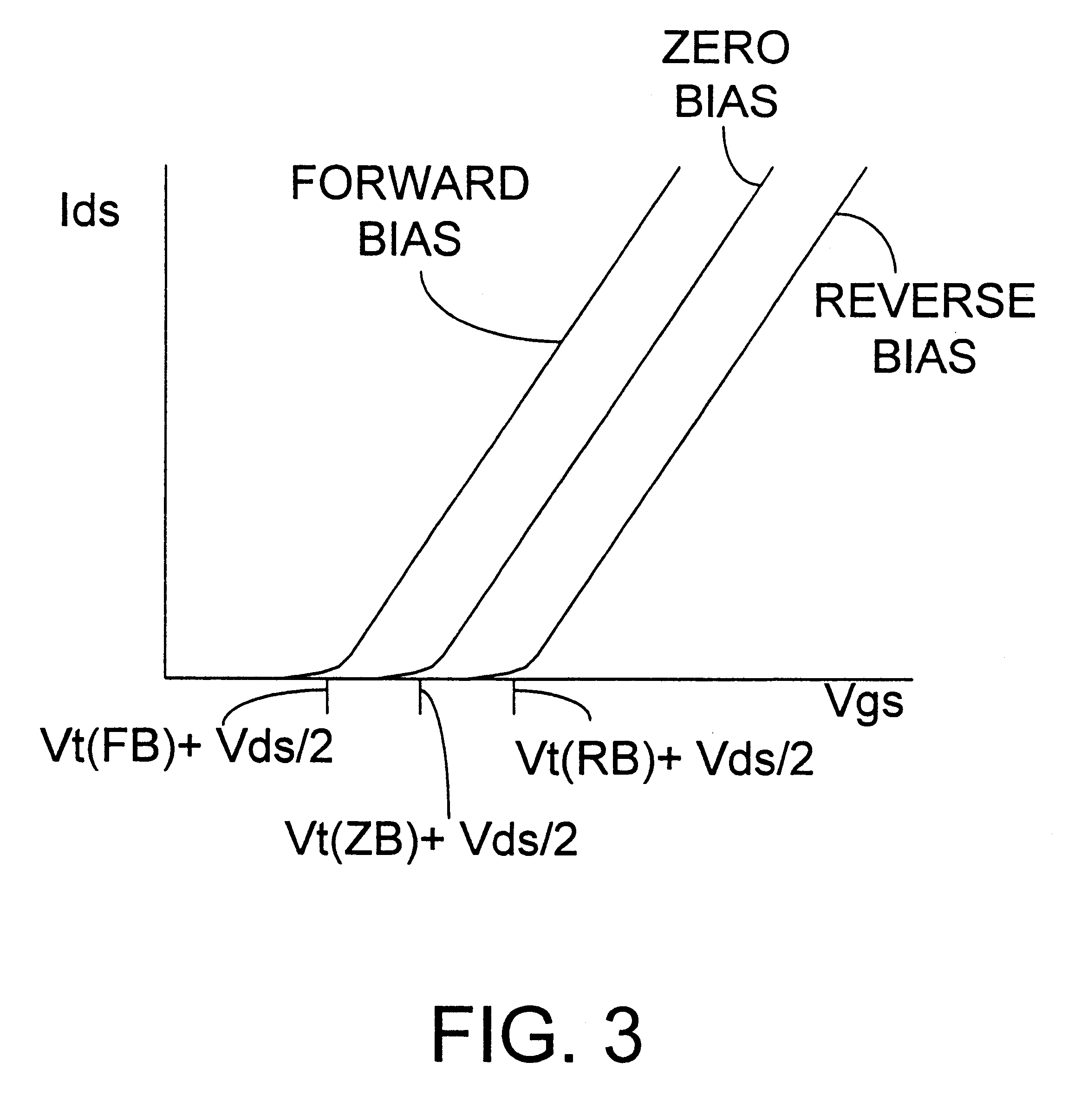

Transistors providing desired threshold voltage and reduced short channel effects with forward body bias

In one embodiment, a semiconductor circuit includes a first group of field effect transistors having a body and parameters including a net channel doping level DL1. The circuit also includes a conductor to provide a first voltage to the body to forward body bias the first group of transistors, the first group of transistors having a forward body bias threshold voltage (VtFBB) when forward body biased, wherein DL1 is at least 25% higher than a net channel doping level in the first group of transistors that would result in a zero body bias threshold voltage equal to VtFBB, with the parameters other than the net channel doping level being unchanged. In another embodiment, the semiconductor circuit includes a first circuit including a first group of field effect transistors having a body. The circuit also includes a first voltage source to provide a first voltage to the body such that the field effect transistors have a forward body bias, the first voltage being at a level leading to the circuit experiencing a reduced rate of soft error failures as compared to when the circuit is not forward biased.

Owner:INTEL CORP

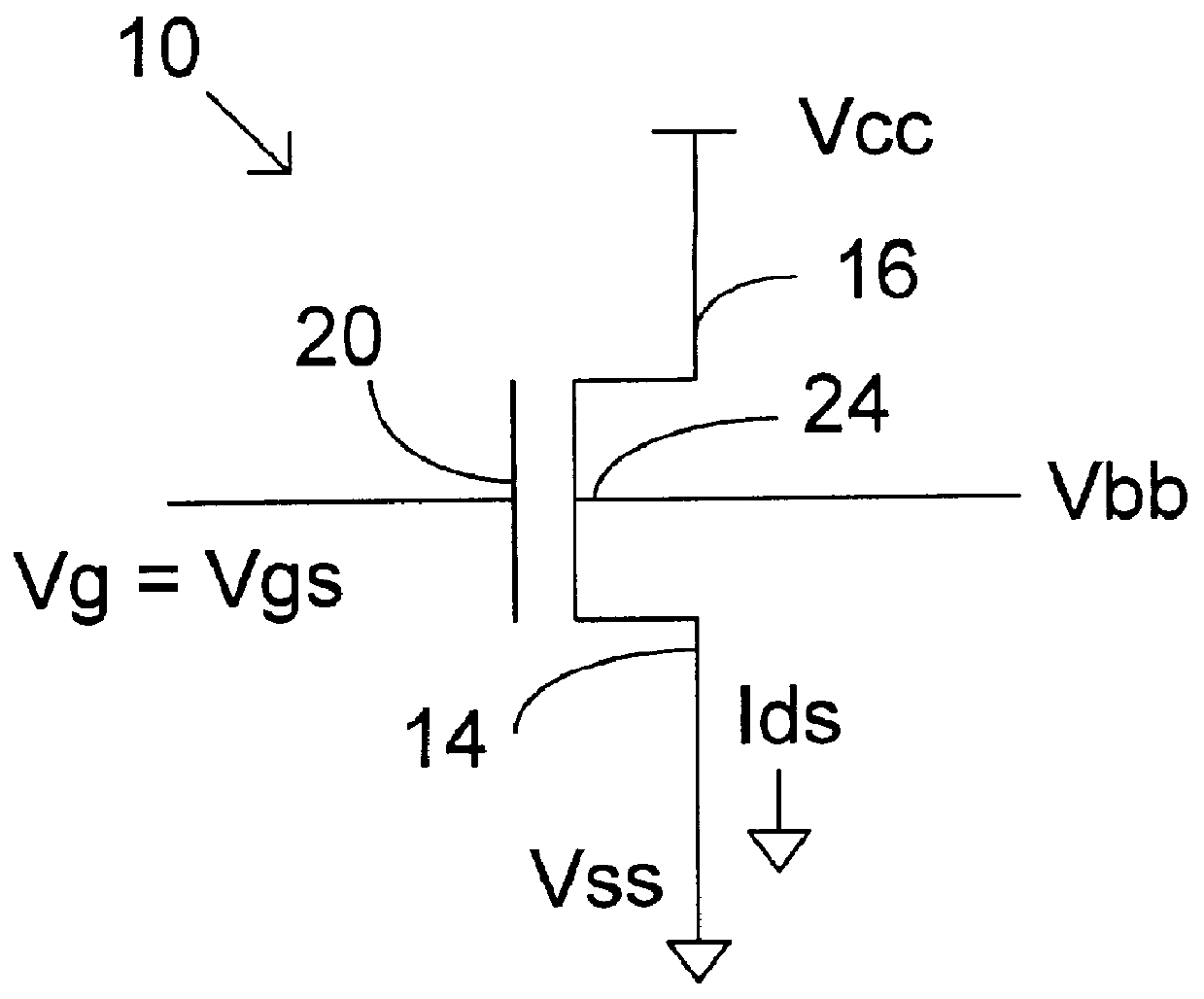

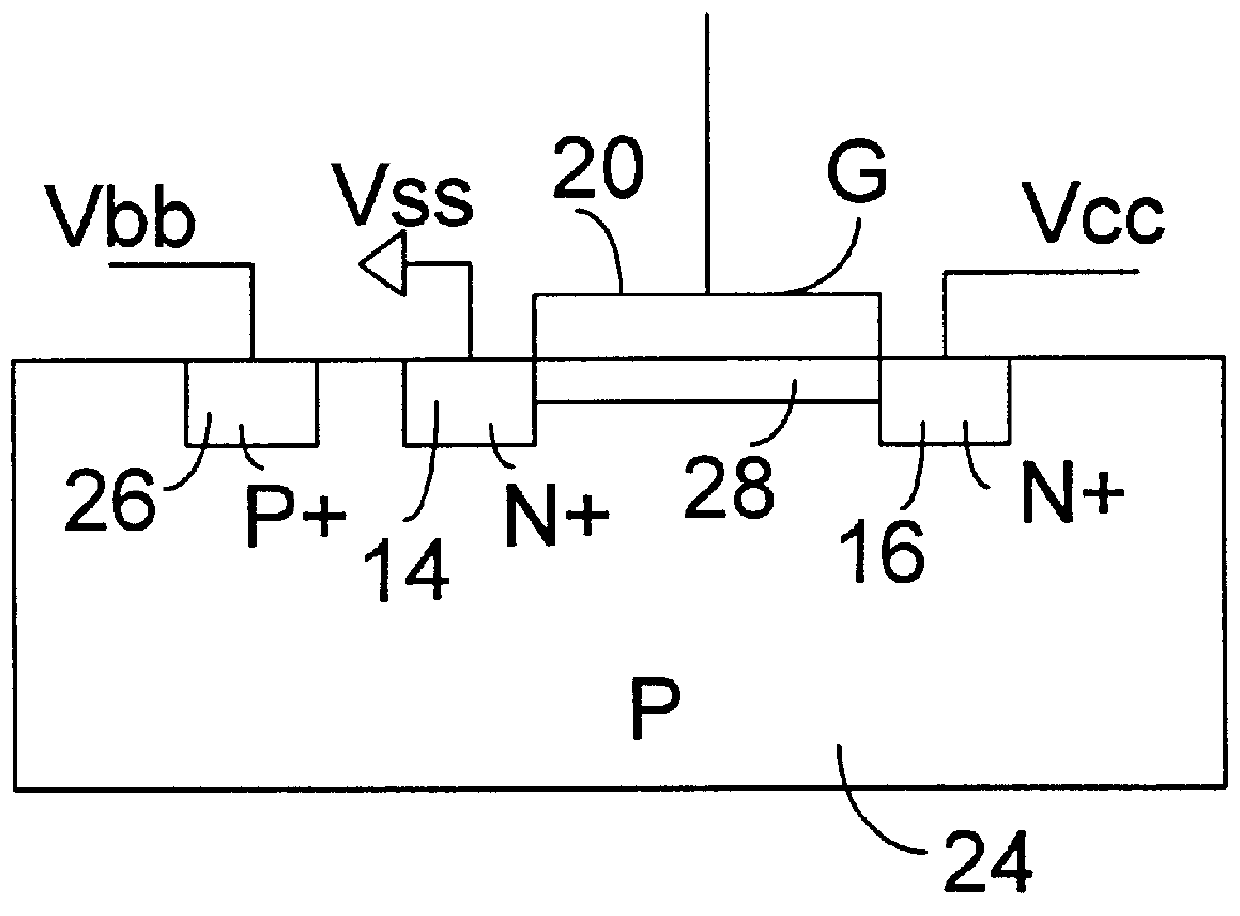

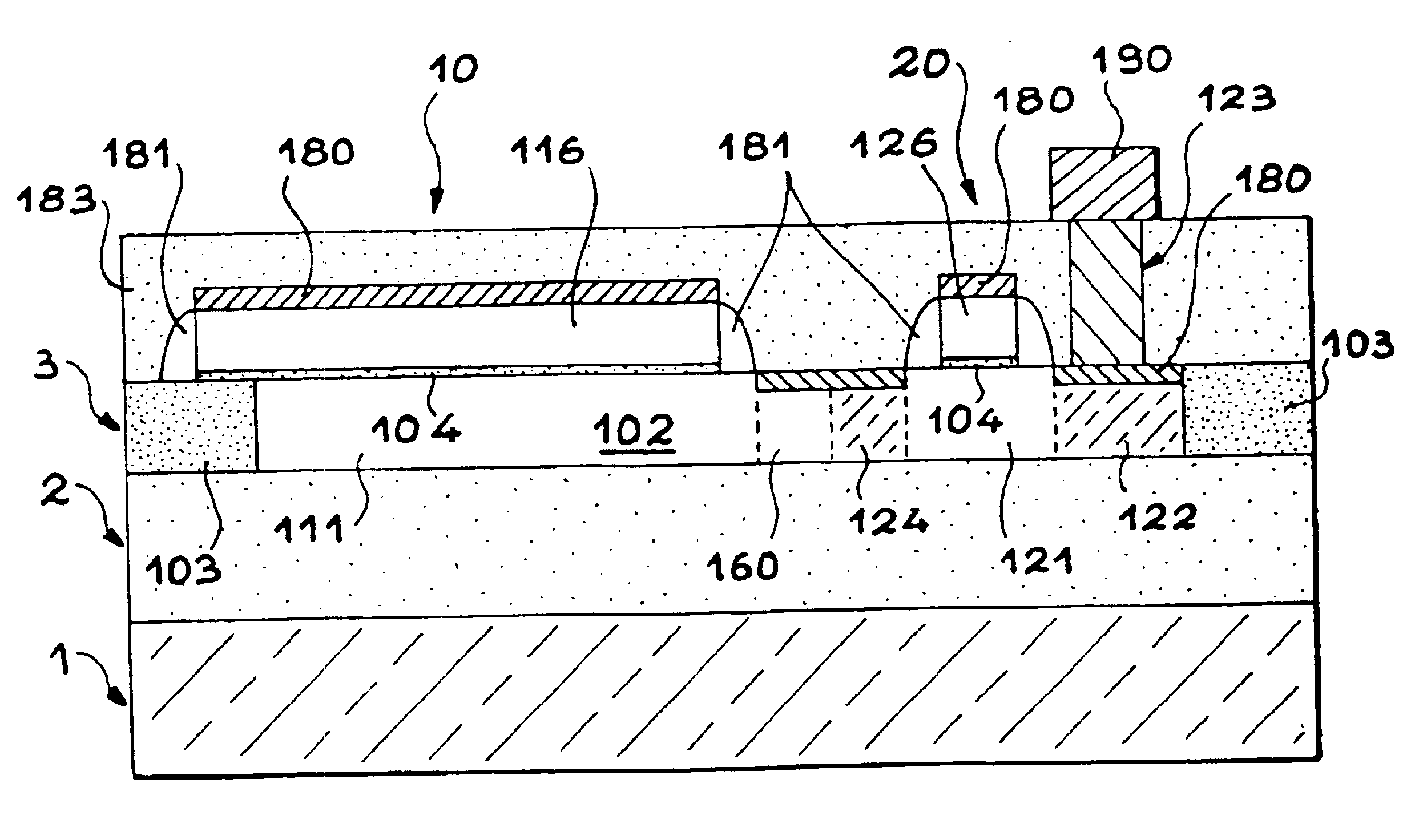

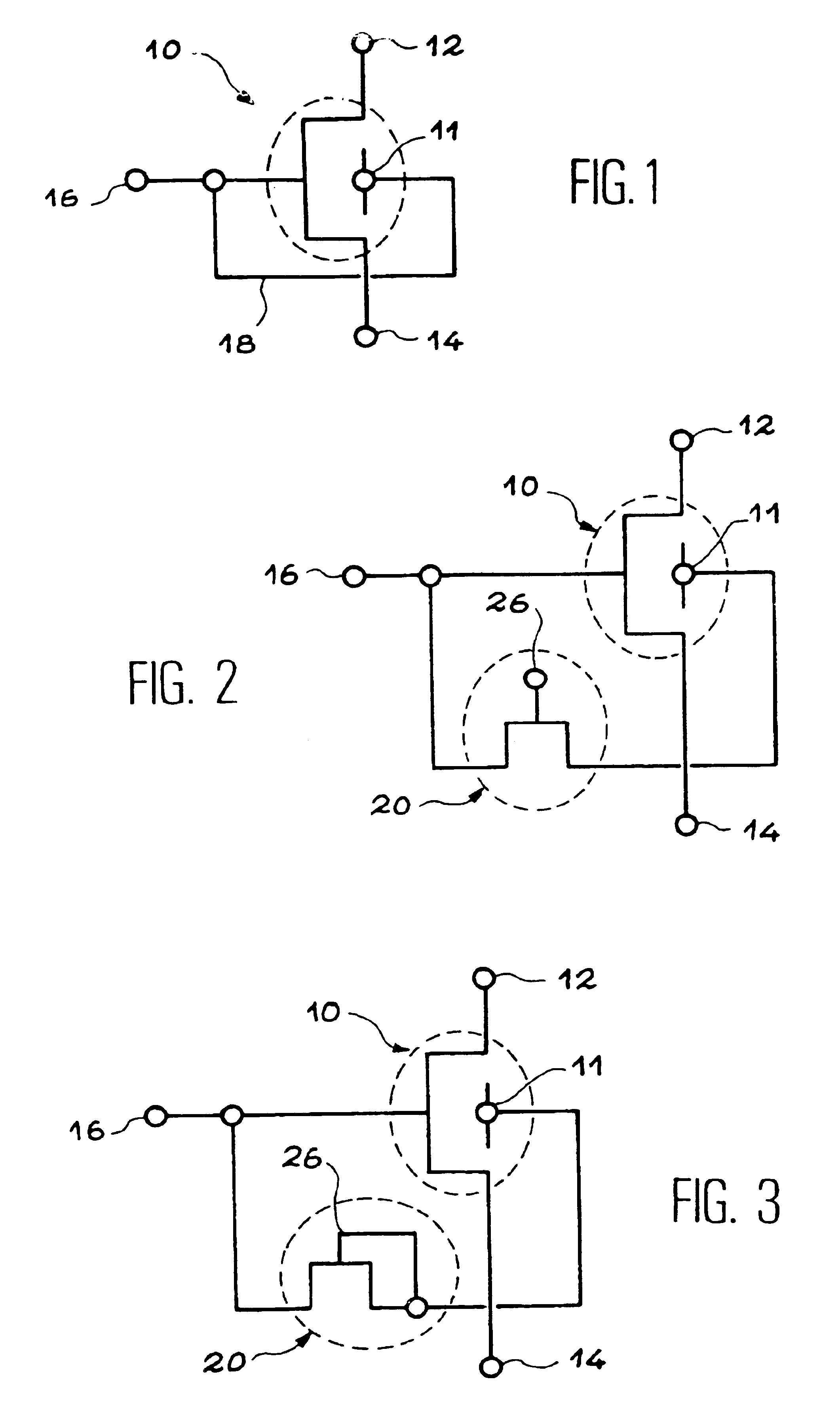

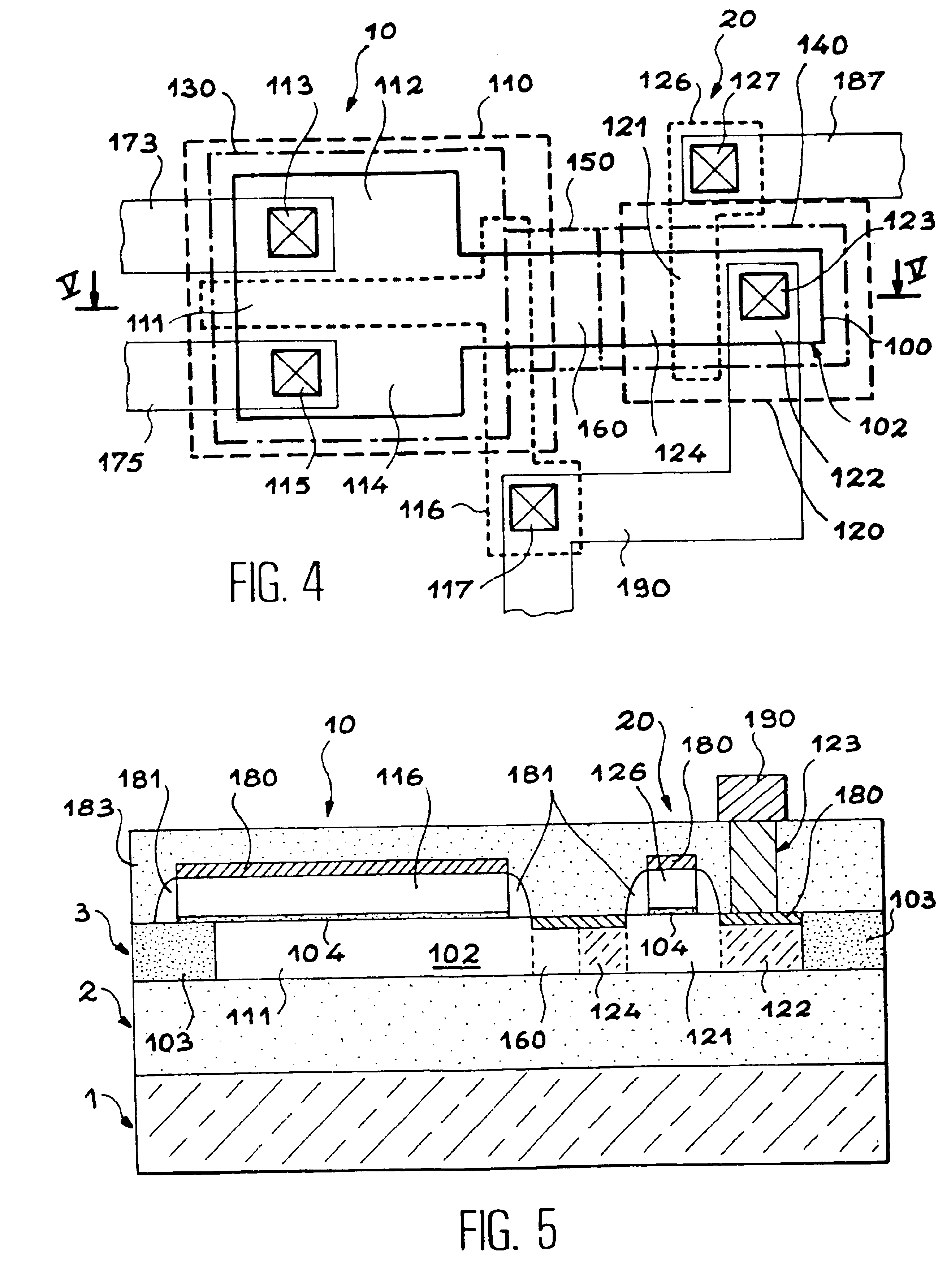

Dynamic threshold voltage MOS transistor fitted with a current limiter

The invention concerns a semi-conductor device comprising on a substrate:a first dynamic threshold voltage MOS transistor (10), with a gate (116), and a channel (111) of a first conductivity type, anda current limiter means (20) connected between the gate and the channel of said first transistor.In accordance with the invention, this first transistor is fitted with a first doped zone (160) of the first conductivity type, connected to the channel, and the current limiter means comprises a second doped zone (124) of a second conductivity type, placed against the first doped zone and electrically connected to the first zone by an ohmic connection.Application to the manufacture of CMOS circuits.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

Semiconductor integrated circuit device

ActiveUS20070139072A1Reduce leakage currentReduce power consumptionReliability increasing modificationsPower reduction by control/clock signalDrain currentDouble gate

An object of the present invention is to provide a technique of reducing the leakage current of a drive circuit for driving a circuit that must retain a potential (or information) when in its standby state. A semiconductor integrated circuit device of the present invention includes a drive circuit for driving a circuit block. This drive circuit is made up of a double gate transistor with gates having different gate oxide film thicknesses. When the circuit block is in its standby state, the gate of the double gate transistor having a thinner gate oxide film is turned off and that having a thicker gate oxide film is turned on. This arrangement allows a reduction in the leakage currents of both the circuit block and the drive circuit while allowing the drive circuit to deliver or cut off power to the circuit block.

Owner:RENESAS ELECTRONICS CORP

SOI voltage-tolerant body-coupled pass transistor

A method and device for A pass transistor device which includes a source; a drain opposite the source, a body between the source and the drain, and a circuit control network connected between the drain and the source, wherein the circuit control network controls a potential voltage of the body and provides overvoltage protection to the pass transistor.

Owner:GOOGLE LLC

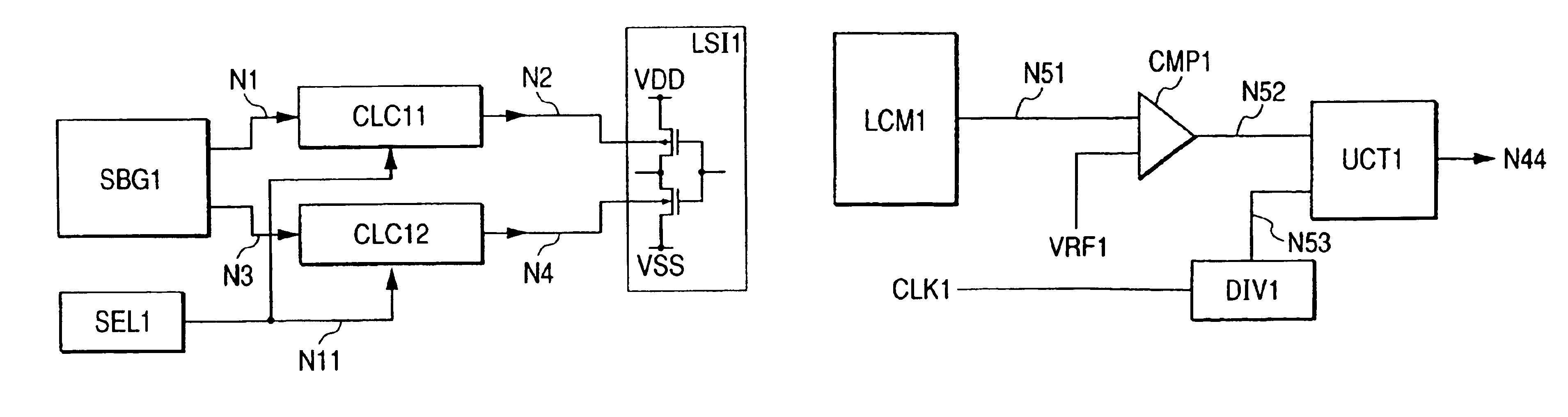

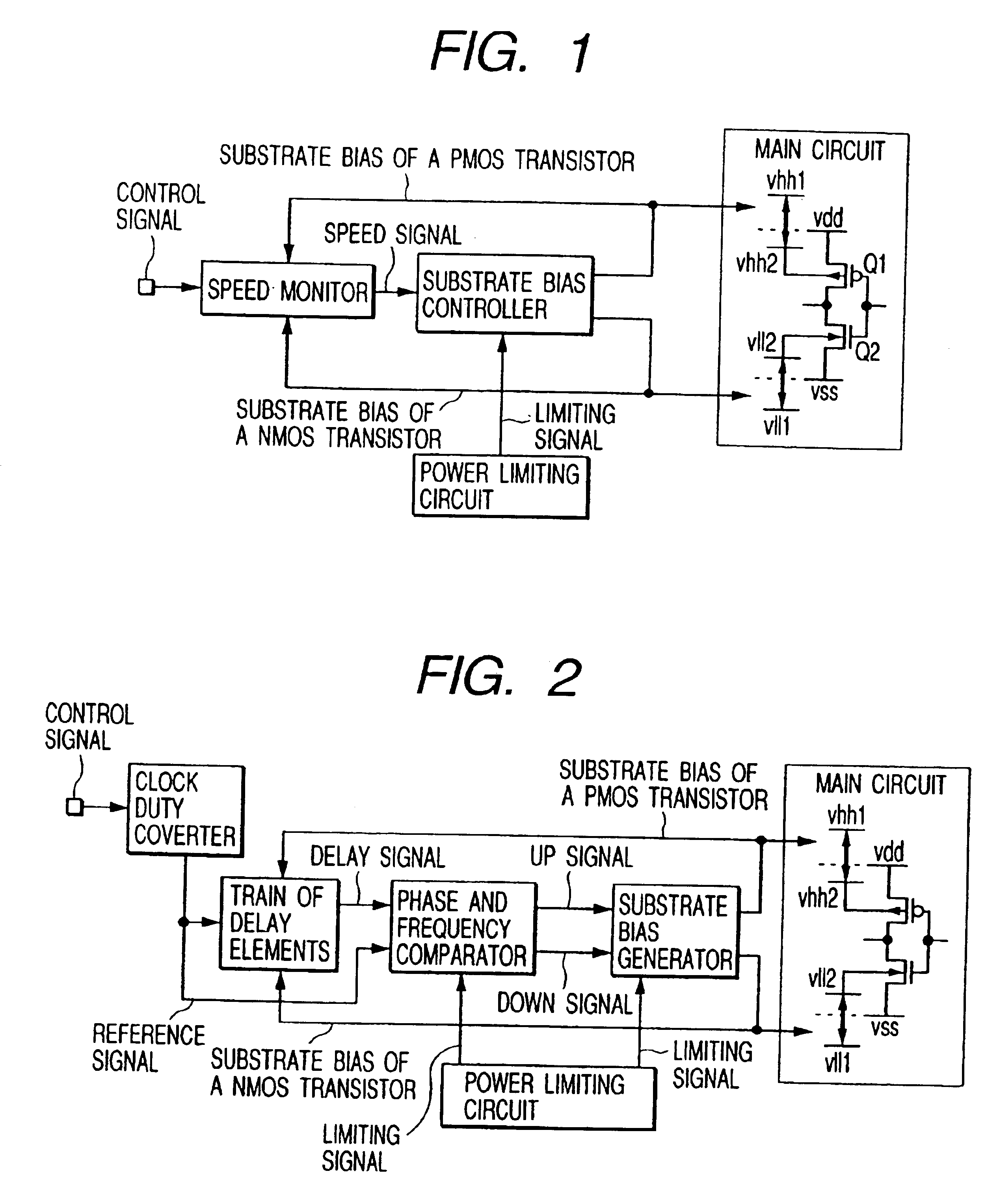

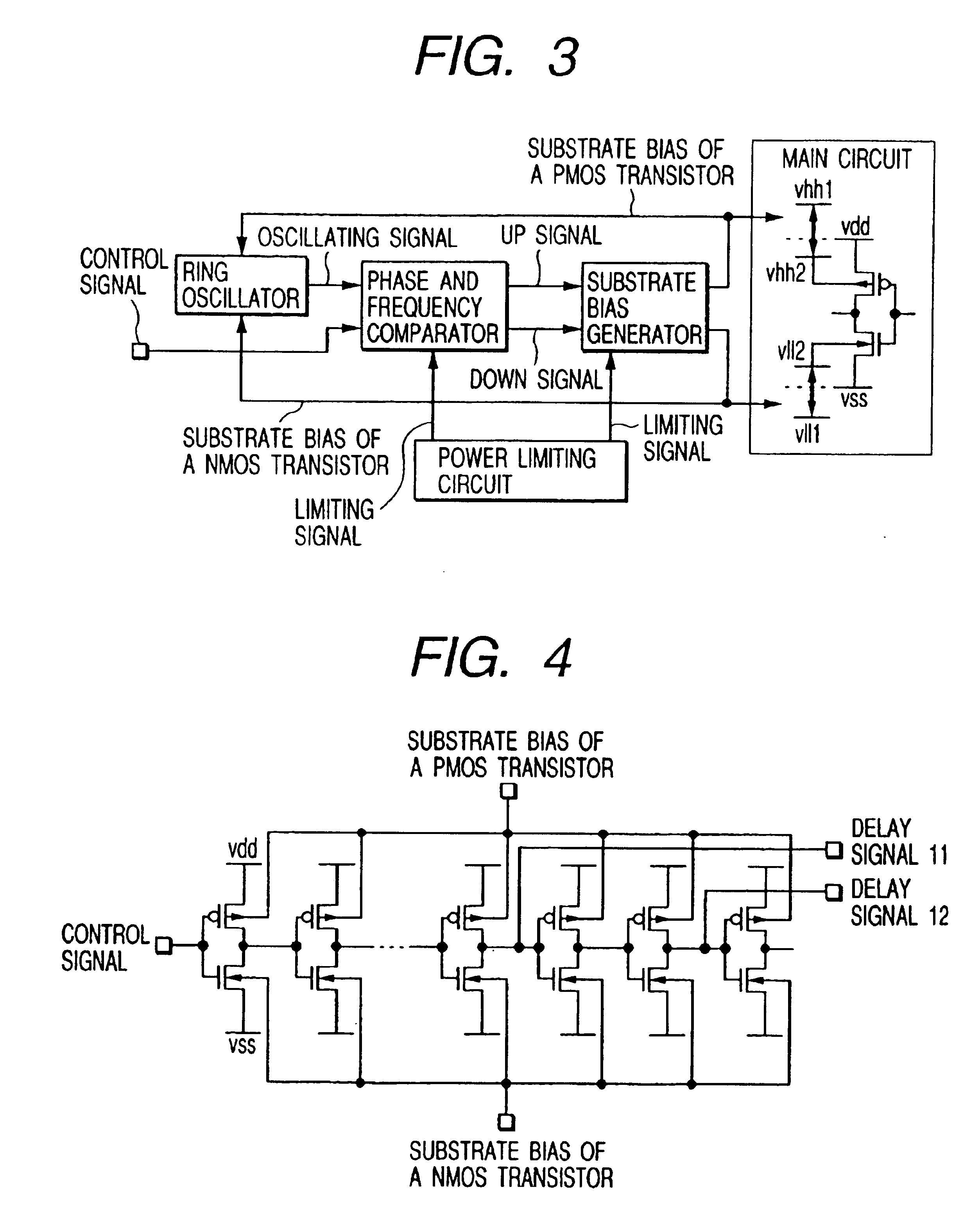

Semiconductor integrated circuit device including a substrate bias controller and a current limiting circuit

In a semiconductor integrated circuit device, for realizing high speed, as well as superior product yield rate and usability, while reducing circuit scale and improving on product yield rate and reliability thereof, a main circuit, constructed with CMOS elements, is coupled to a speed monitor circuit for forming a speed signal corresponding to an operating speed thereof and to a substrate bias controller for supplying corresponding substrate bias voltages to the main circuit in response to the speed monitor circuit. A current limiting circuit is also provided in conjunction with the substrate bias controller to prevent an overflow of current due to bias voltage.

Owner:RENESAS ELECTRONICS CORP

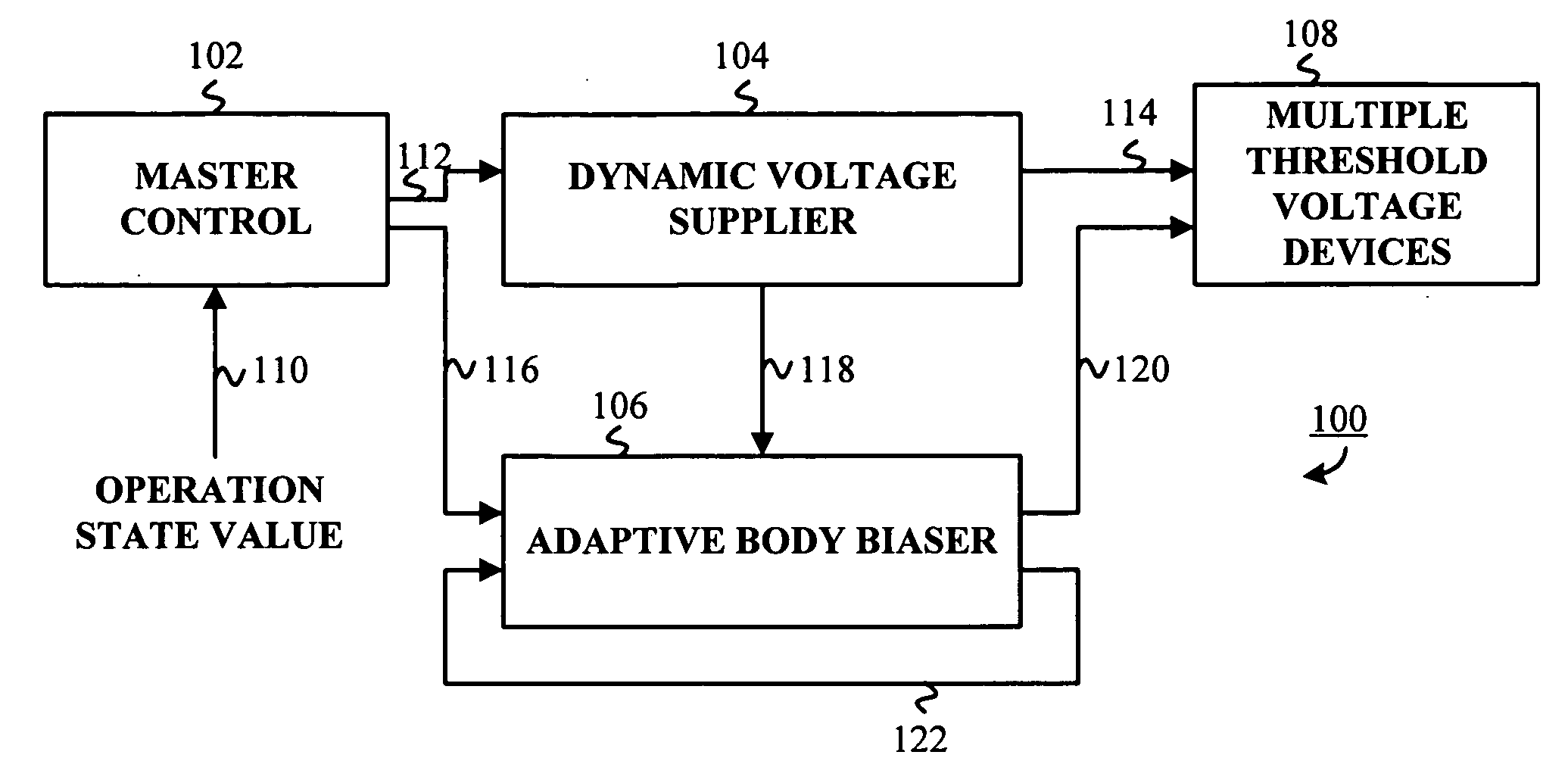

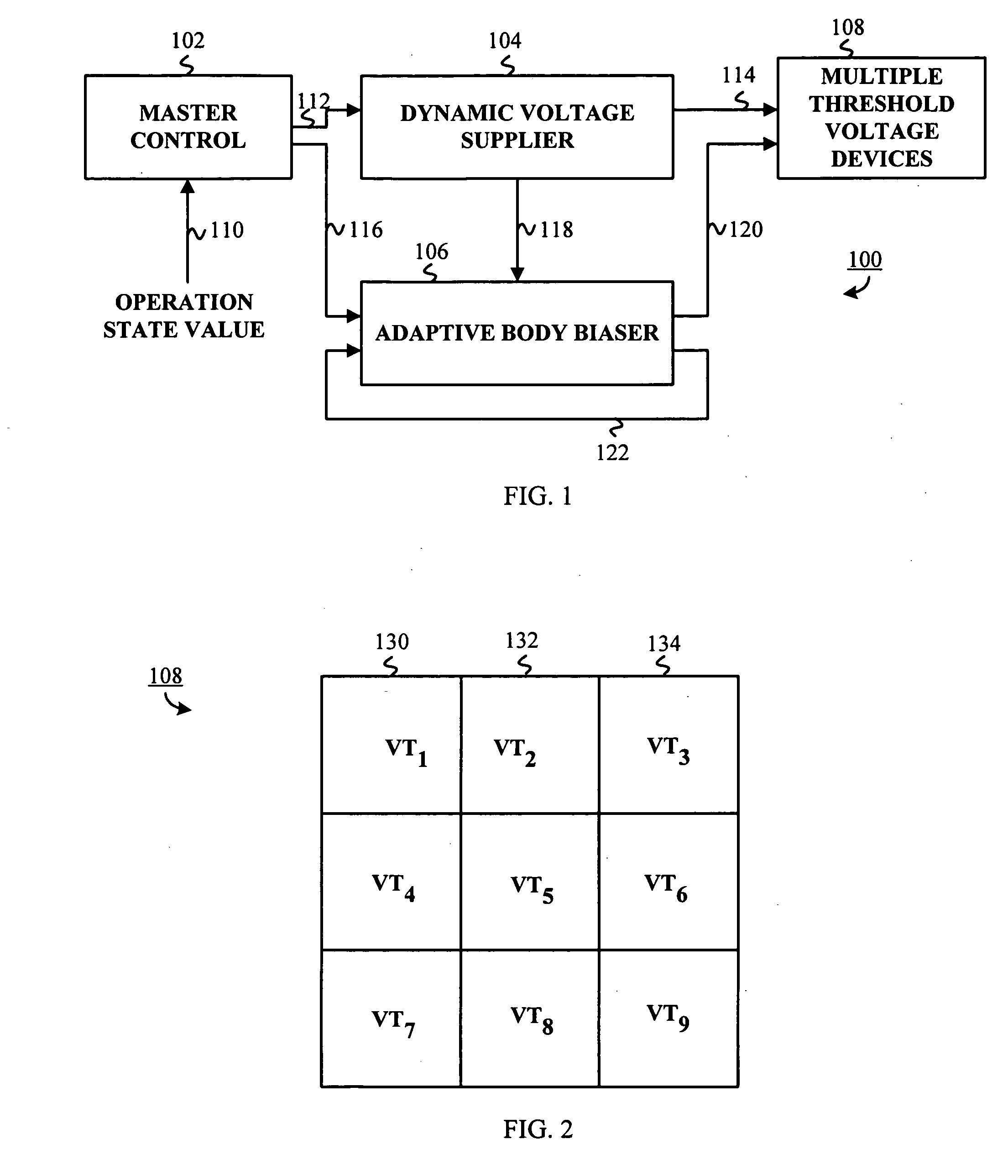

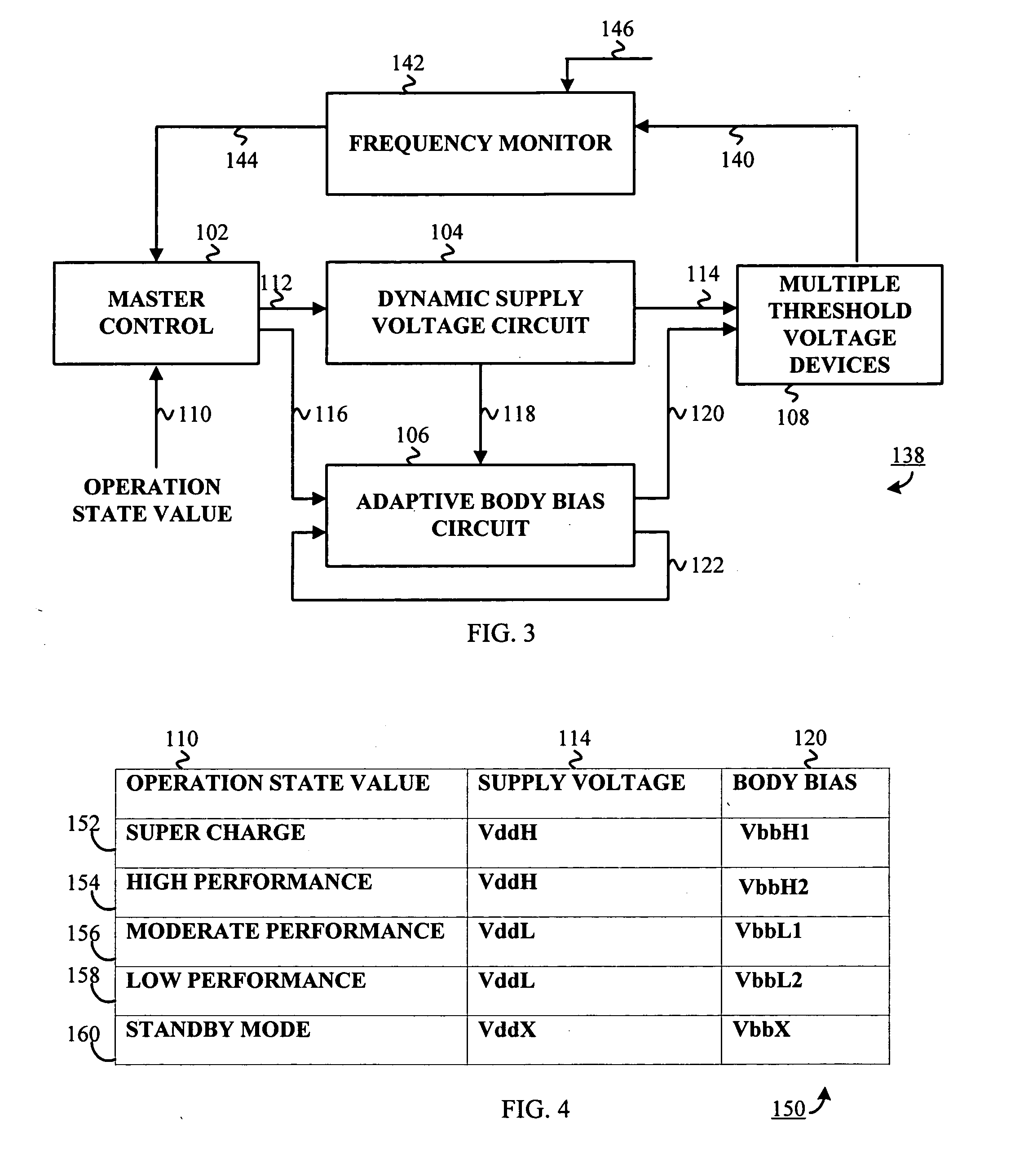

Adaptive supply voltage body bias apparatus and method thereof

InactiveUS20050225376A1Power reduction in field effect transistorsPower reduction by control/clock signalMaster controllerSelf adaptive

An adaptive supply voltage and body bias apparatus includes a master controller including an operation state value. The apparatus and method includes a dynamic voltage supplier coupled to the master controller operative to receive a supply voltage indicator. The apparatus and method includes an adaptive body biaser coupled to the master controller operative to receive a body bias indicator. Furthermore, the apparatus and method includes a plurality of computing devices each having one of a plurality of threshold voltages. The plurality of computing devices are operative to receive the supply voltage from the dynamic voltage supplier and a bias voltage from the adaptive body biaser for optimized power supply in conjunction with reduction of power leakage in view of the varying threshold voltage of the computing devices.

Owner:ATI TECH INC

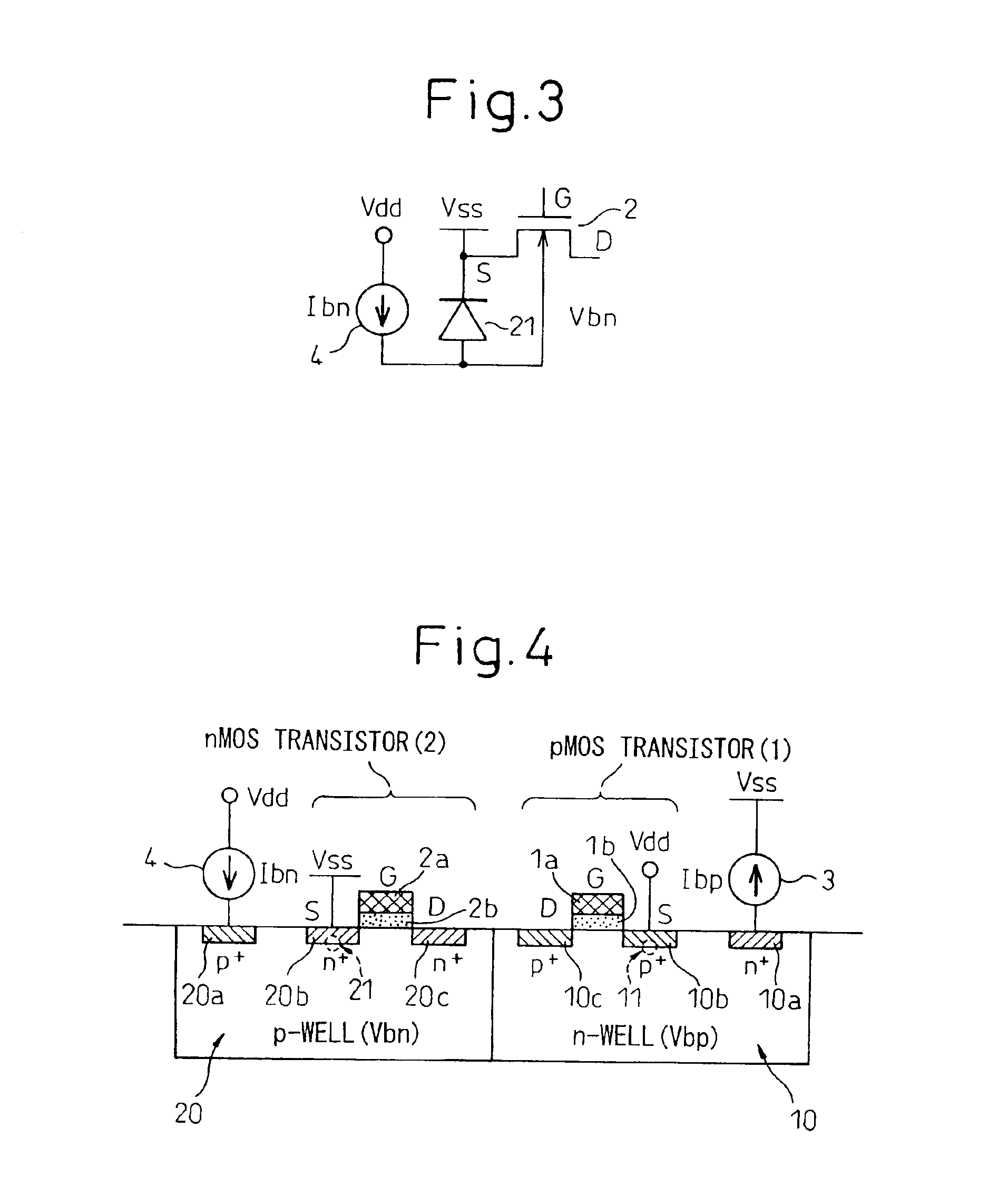

Semiconductor integrated circuit device having body biasing circuit for generating forward well bias voltage of suitable level by using simple circuitry

InactiveUS6864539B2Simple circuitTransistorSwitching accelaration modificationsSemiconductorSimple circuit

A semiconductor integrated circuit device has a MISFET and a body biasing circuit. The MISFET has a source electrode and a drain electrode of a first conductivity type and a gate electrode, and the MISFET is formed in a well of a second conductivity type. The body biasing circuit generates a voltage in the well by passing a prescribed current in a forward direction into a diode which is formed from the well and the source electrode of the MISFET.

Owner:RENESAS ELECTRONICS CORP

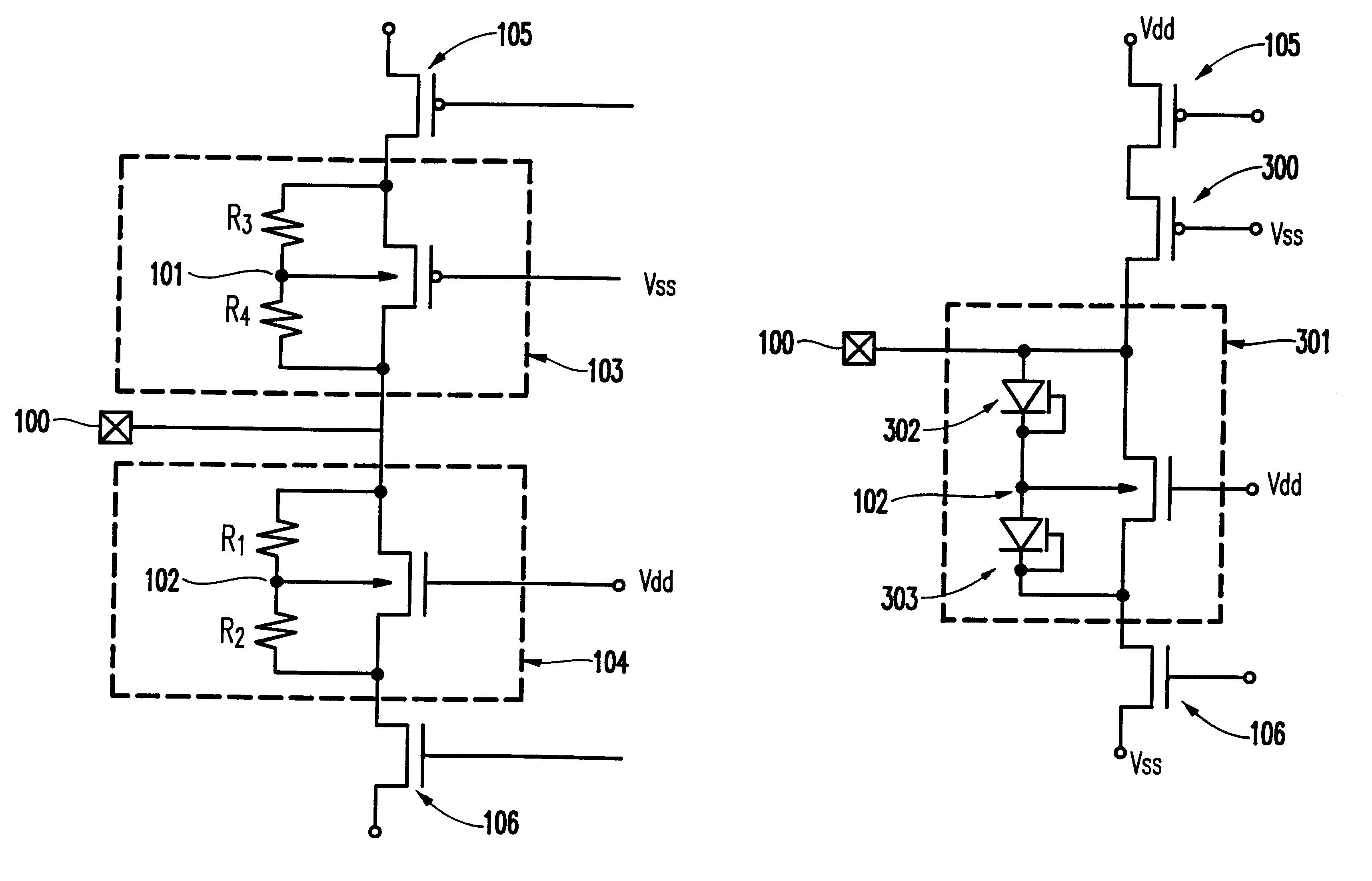

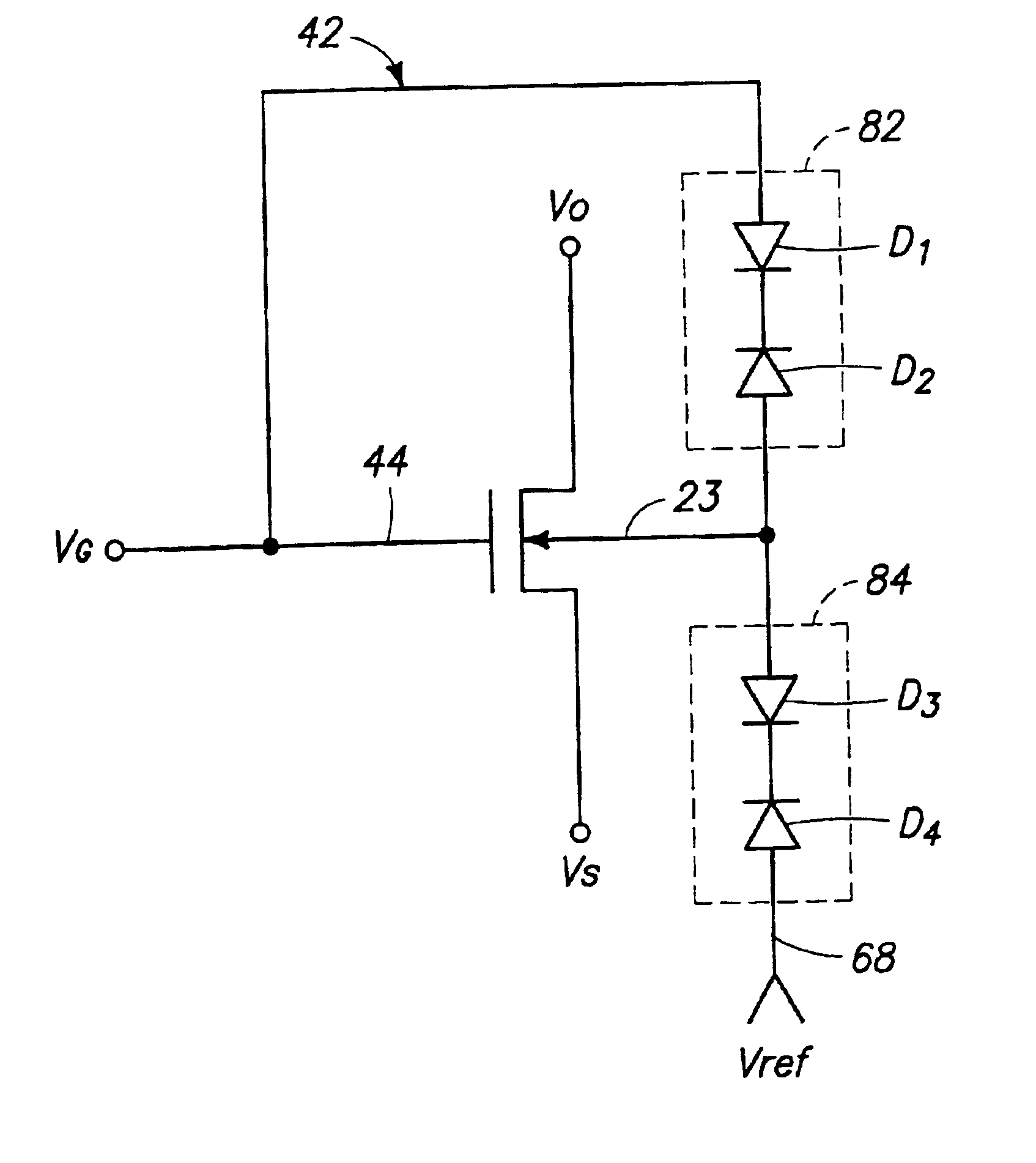

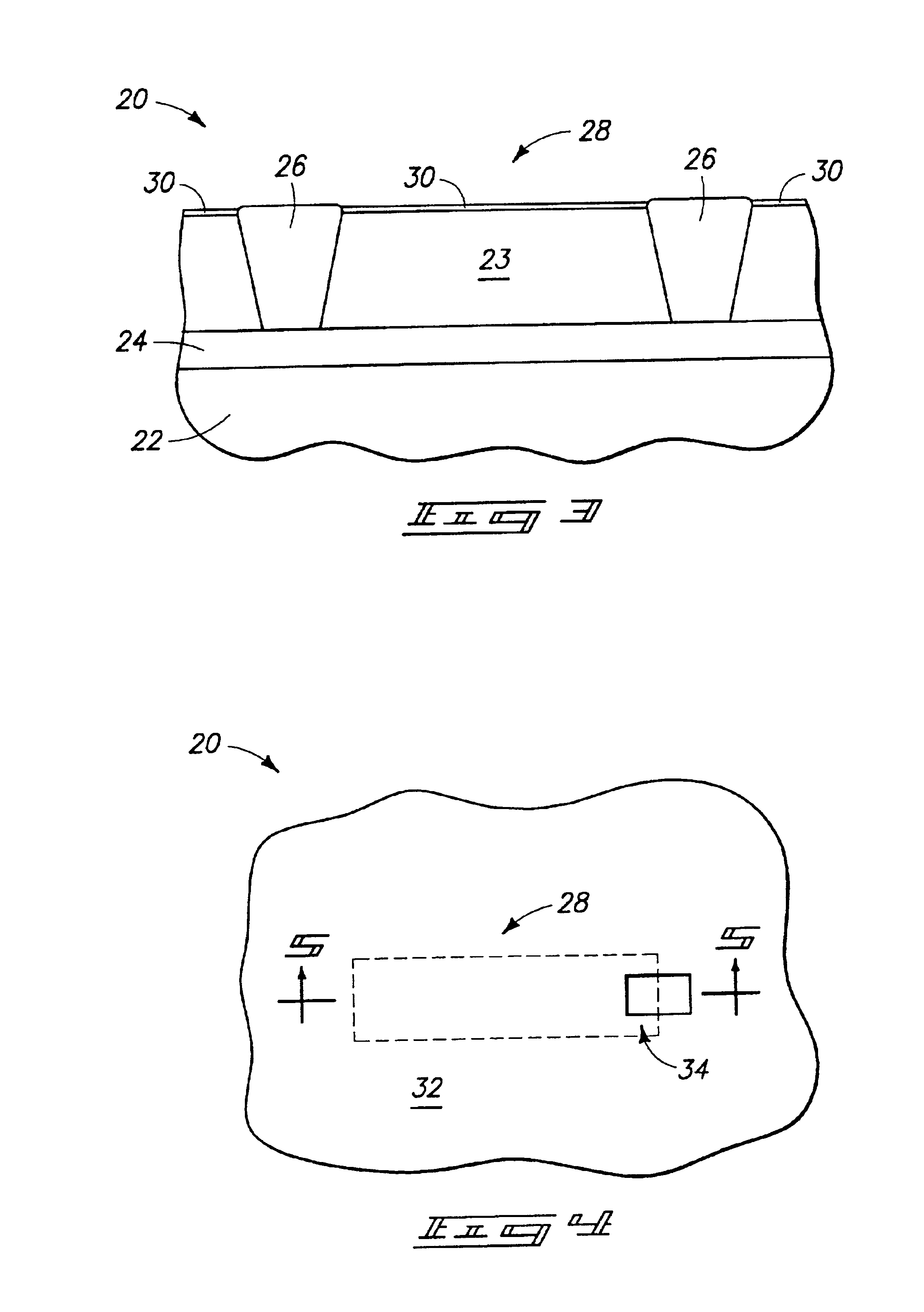

Methods of forming field effect transistors and field effect transistor circuitry

InactiveUS6958519B2Logic circuits characterised by logic functionSemiconductor/solid-state device detailsVoltage referenceTransistor circuits

Methods of forming field effect transistors and resultant field effect transistor circuitry are described. In one embodiment, a semiconductive substrate includes a field effect transistor having a body. A first resistive element is received by the substrate and connected between the transistor's gate and the body. A second resistive element is received by the substrate and connected between the body and a reference voltage node. The first and second resistive elements form a voltage divider which is configured to selectively change threshold voltages of the field effect transistor with state changes in the gate voltage. In a preferred embodiment, first and second diode assemblies are positioned over the substrate and connected between the gate and body, and the body and a reference voltage node to provide the voltage divider.

Owner:MICRON TECH INC

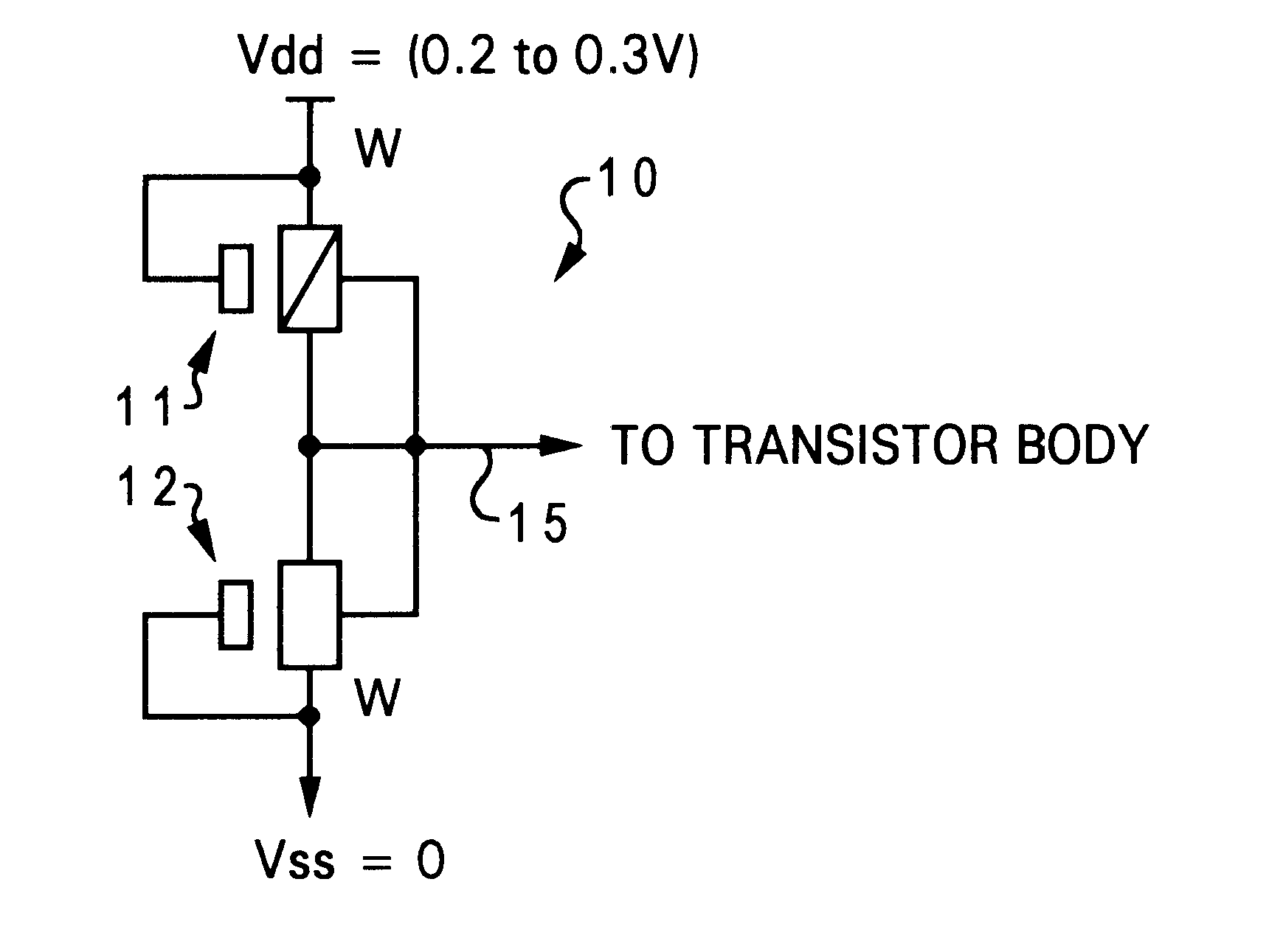

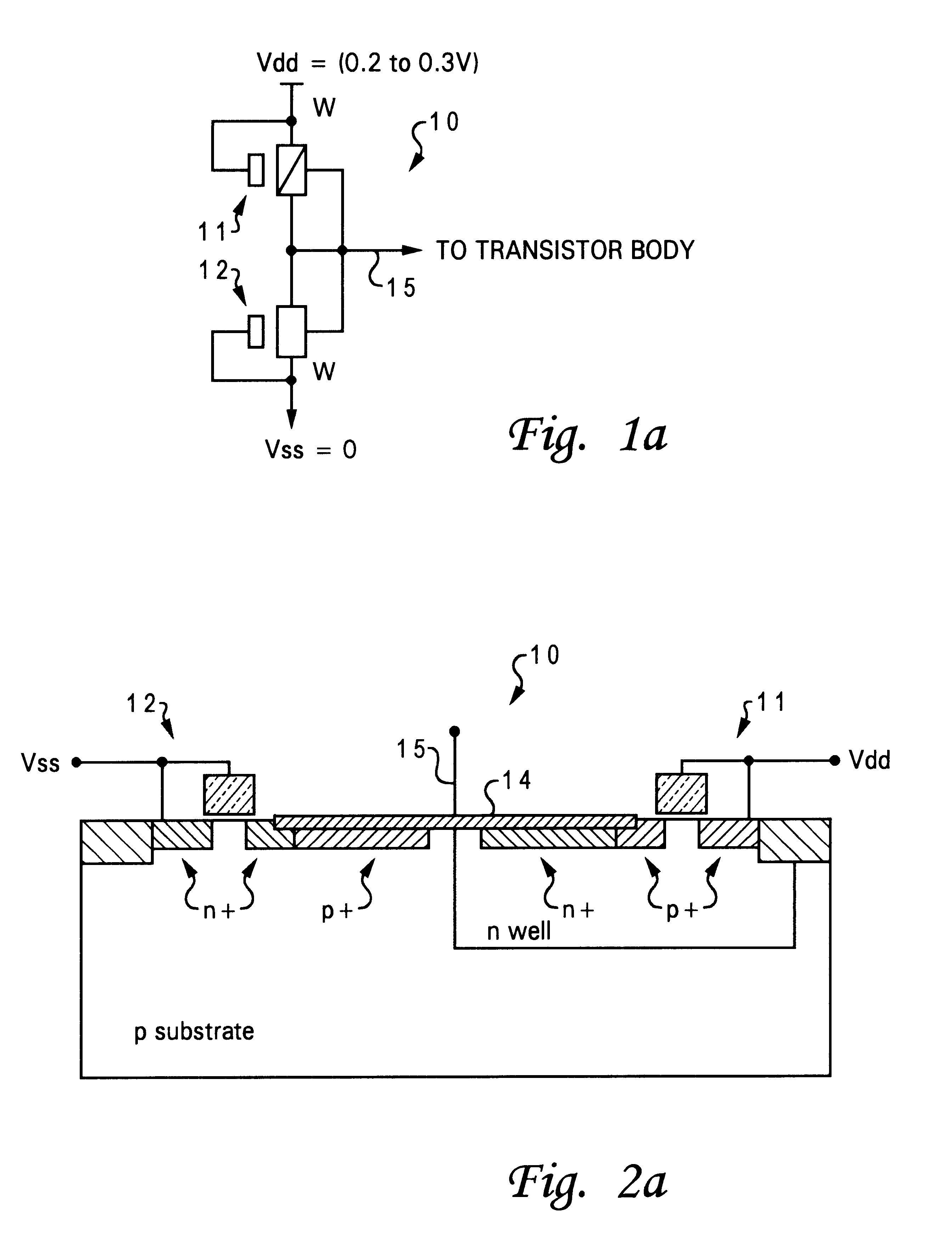

Apparatus for biasing ultra-low voltage logic circuits

An apparatus for biasing ultra-low voltage logic circuits is disclosed. An integrated circuit device includes multiple transistors and a global body bias circuit. The global body bias circuit includes a first transistor and second transistors connected in series between a power supply and a second power supply or ground. The gate and source of the first transistor are connected to the first power supply. The gate and source of the second transistor are connected to the second power supply. The drains and bodies of the first and second transistors are connected together to form an output connected to the bodies of the other transistors within the integrated circuit device.

Owner:INT BUSINESS MASCH CORP

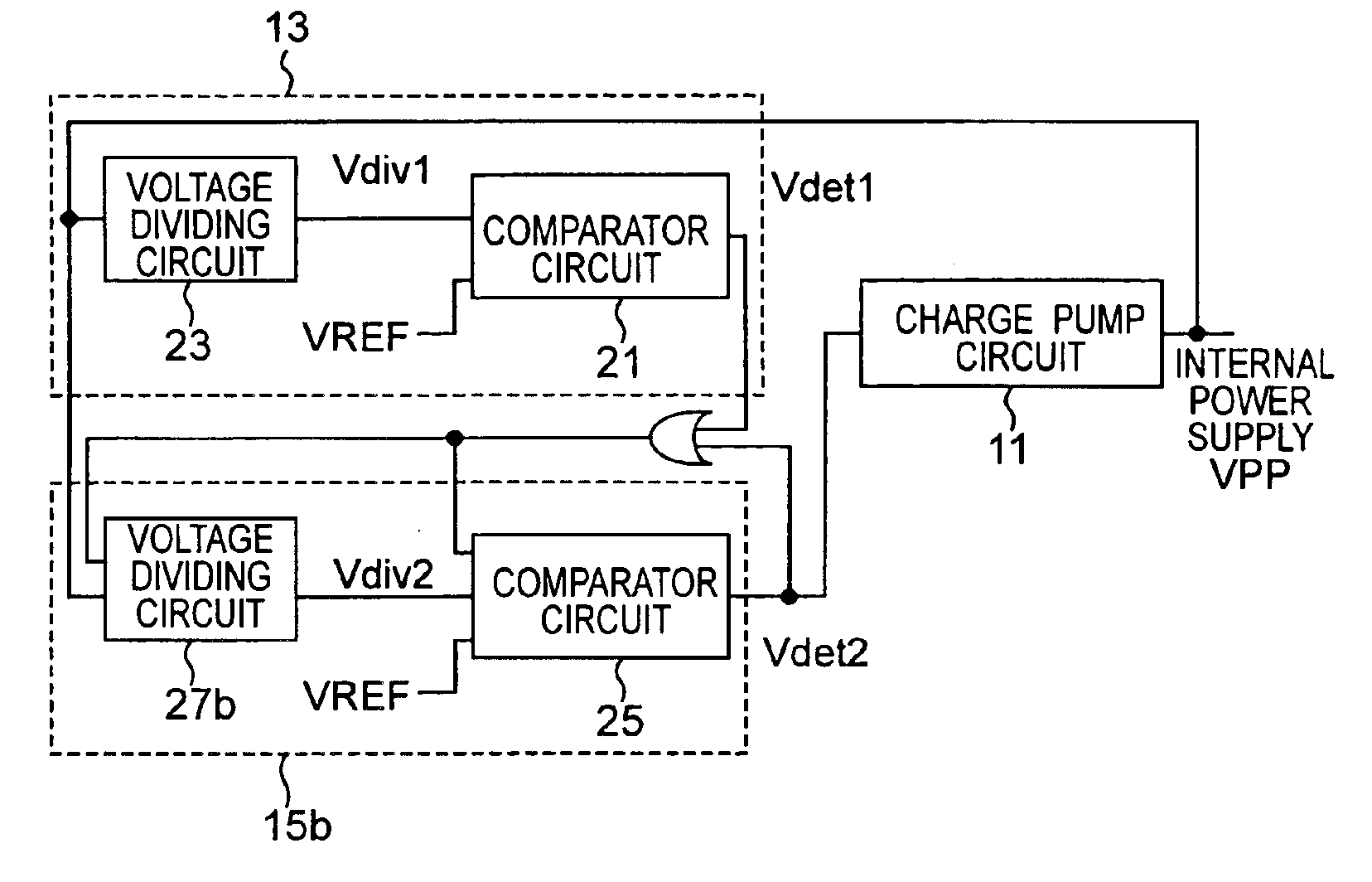

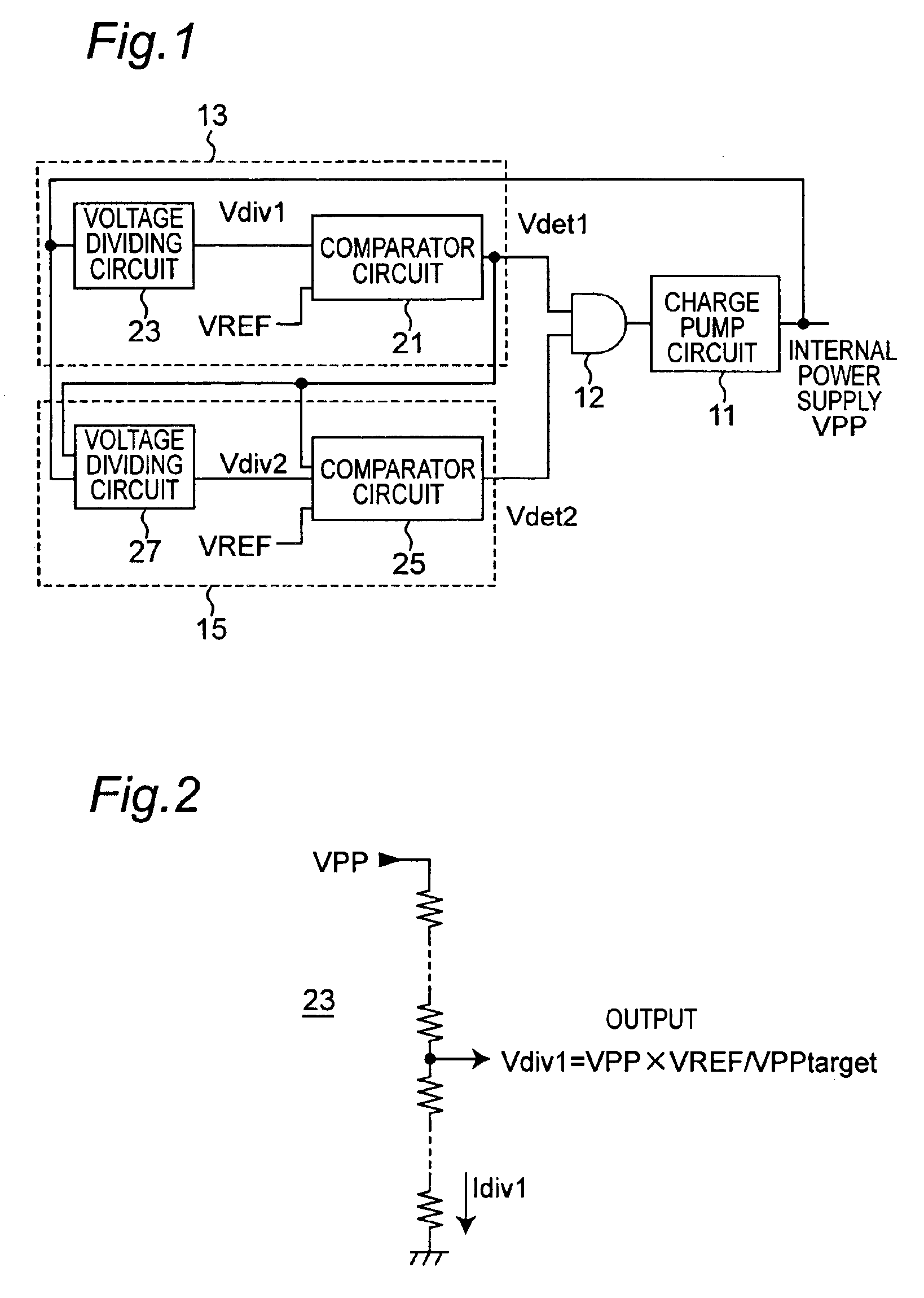

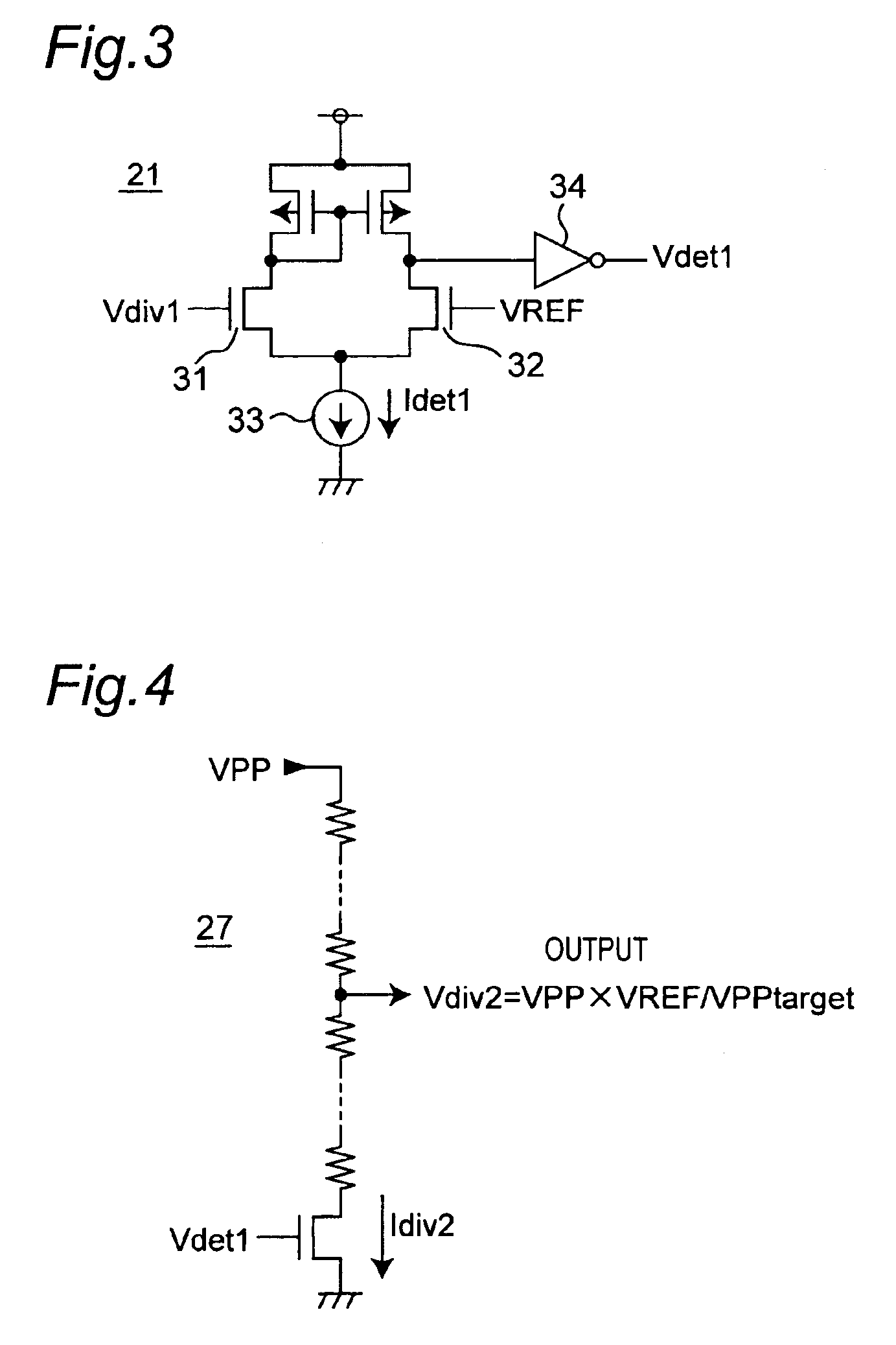

Semiconductor device having a boosting circuit to suppress current consumption

InactiveUS6927620B2Small voltage changeEasy to operateSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceDc current

A semiconductor device includes a boosting circuit for supplying a power supply voltage during a standby state of the semiconductor device. The boosting circuit includes a charge pump circuit and first and second detection circuits for detecting an output voltage of the charge pump circuit. The second detection circuit is operated by a DC current greater than that of the first detection circuit, and is activated by an output (Vdet1) from the first detection circuit. The charge pump circuit is activated based on at least an output (Vdet2) from the second detection circuit.

Owner:RENESAS ELECTRONICS CORP

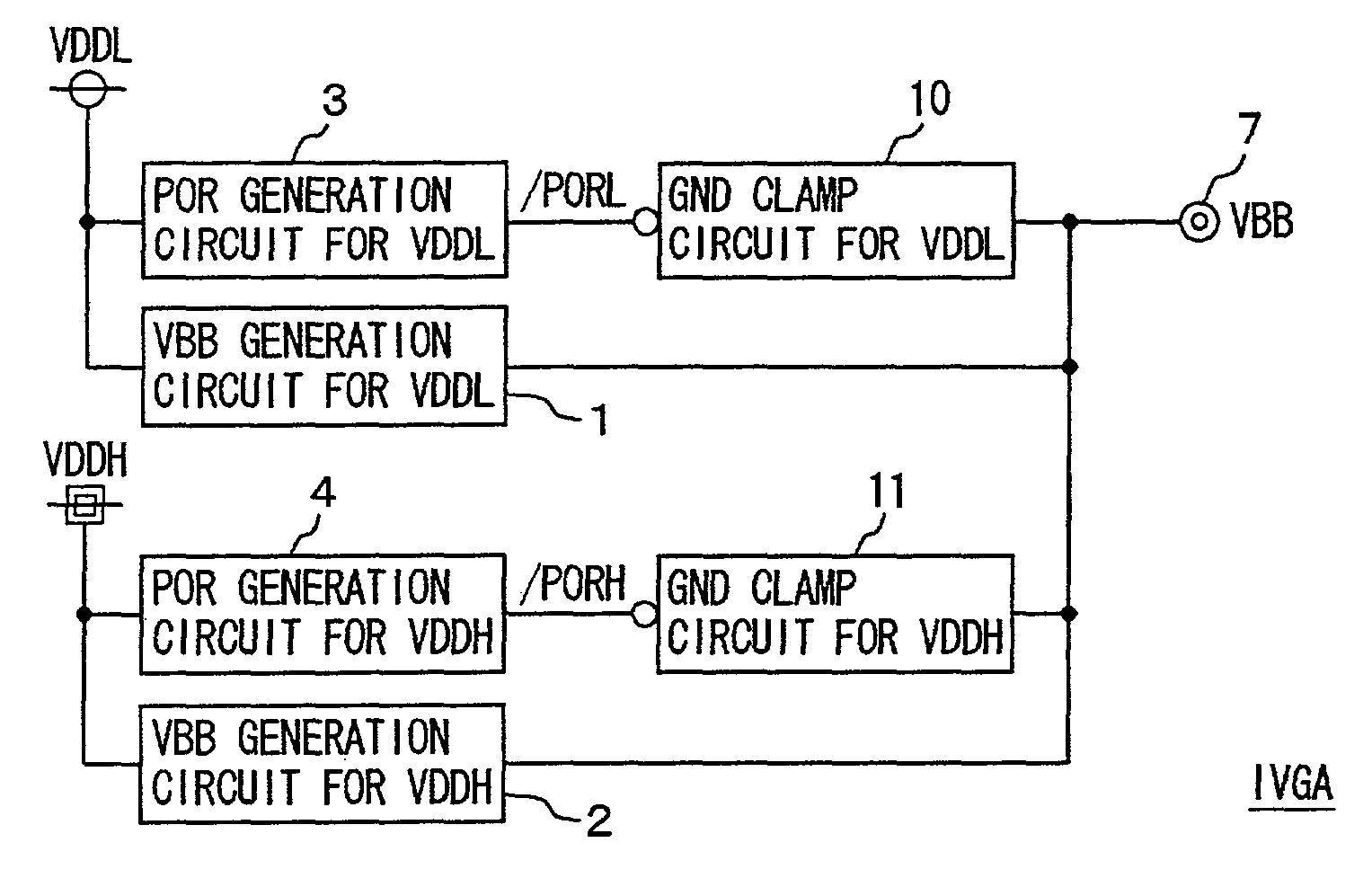

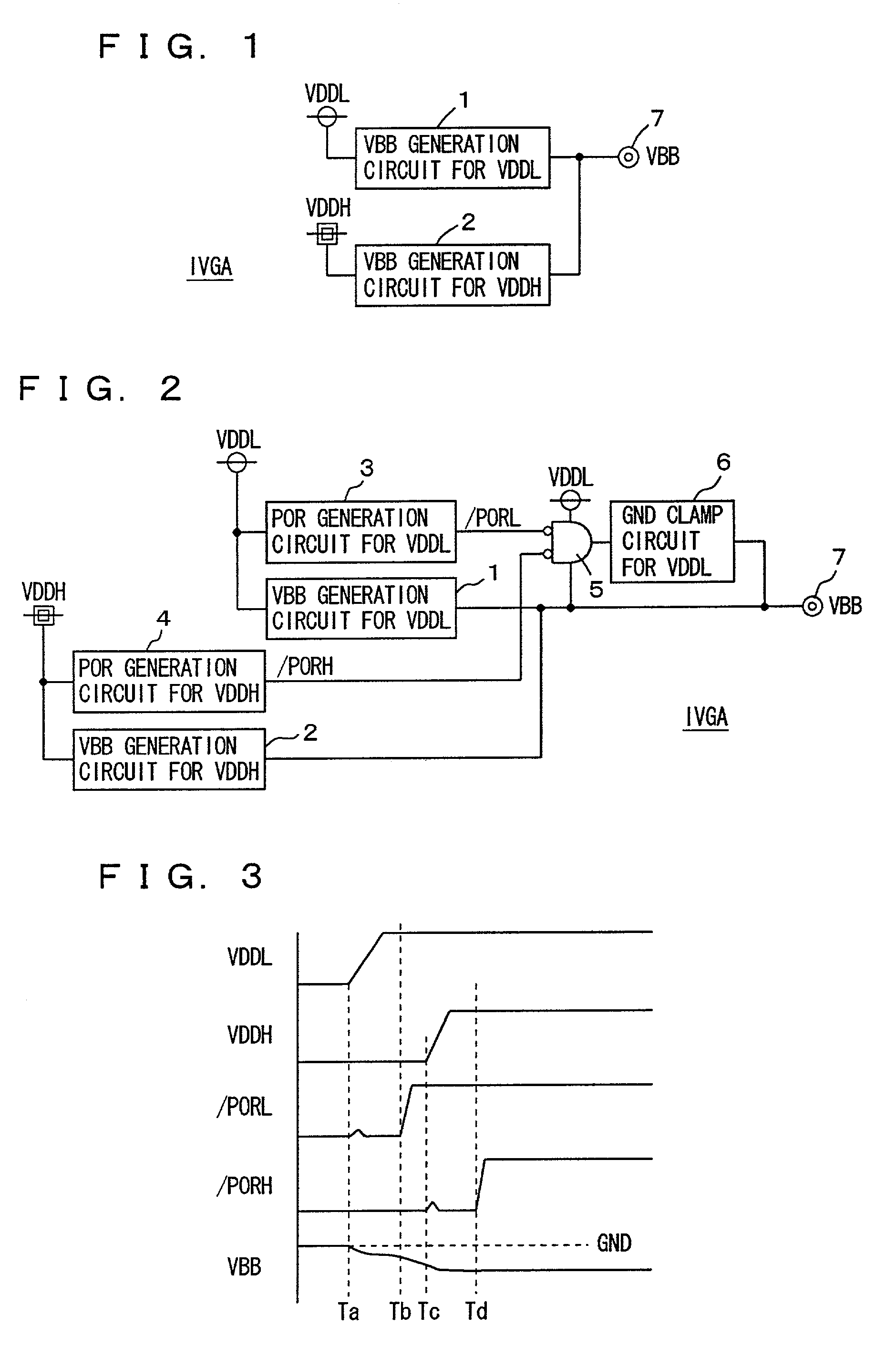

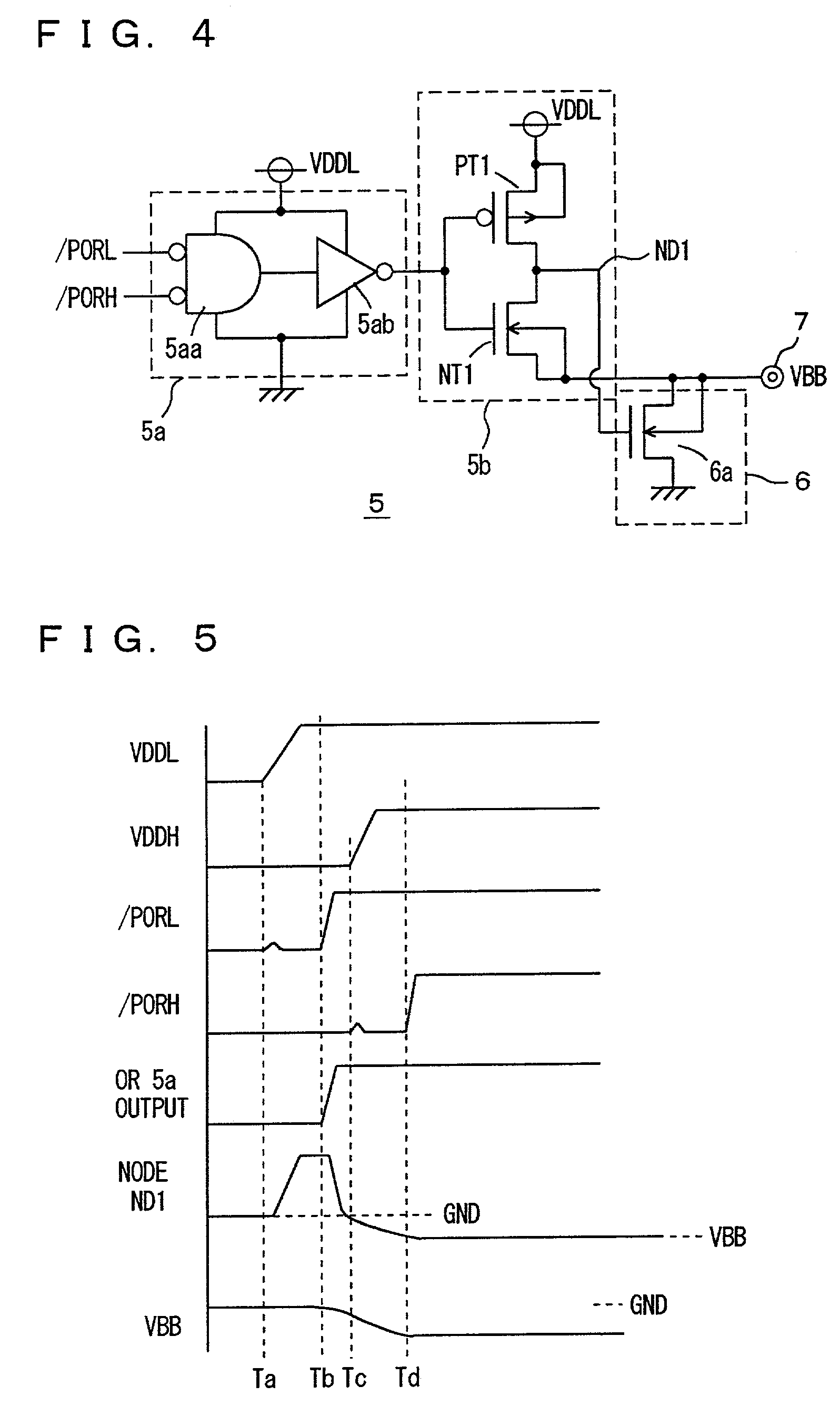

Semiconductor device with multiple power sources

InactiveUS7030681B2Low costTotal current dropPulse automatic controlSolid-state devicesPower semiconductor deviceEngineering

Well bias voltages are generated in accordance with a logic power supply voltage and a memory power supply voltage. The transistor included in a control circuit in a memory core is constituted of a logic transistor manufactured through the same manufacturing steps as those for the transistors of a logic formed on the same semiconductor substrate. Well bias voltages (VBB, VPP) are applied to a back gate of this logic transistor. A memory integrated with a logic on a common semiconductor substrate is provided which allows a transistor of a control circuit therein to be manufactured through the same manufacturing process as that of the logic and allows reduction of current consumption.

Owner:RENESAS TECH CORP

Integrated circuit transistor body bias regulation circuit and method for low voltage applications

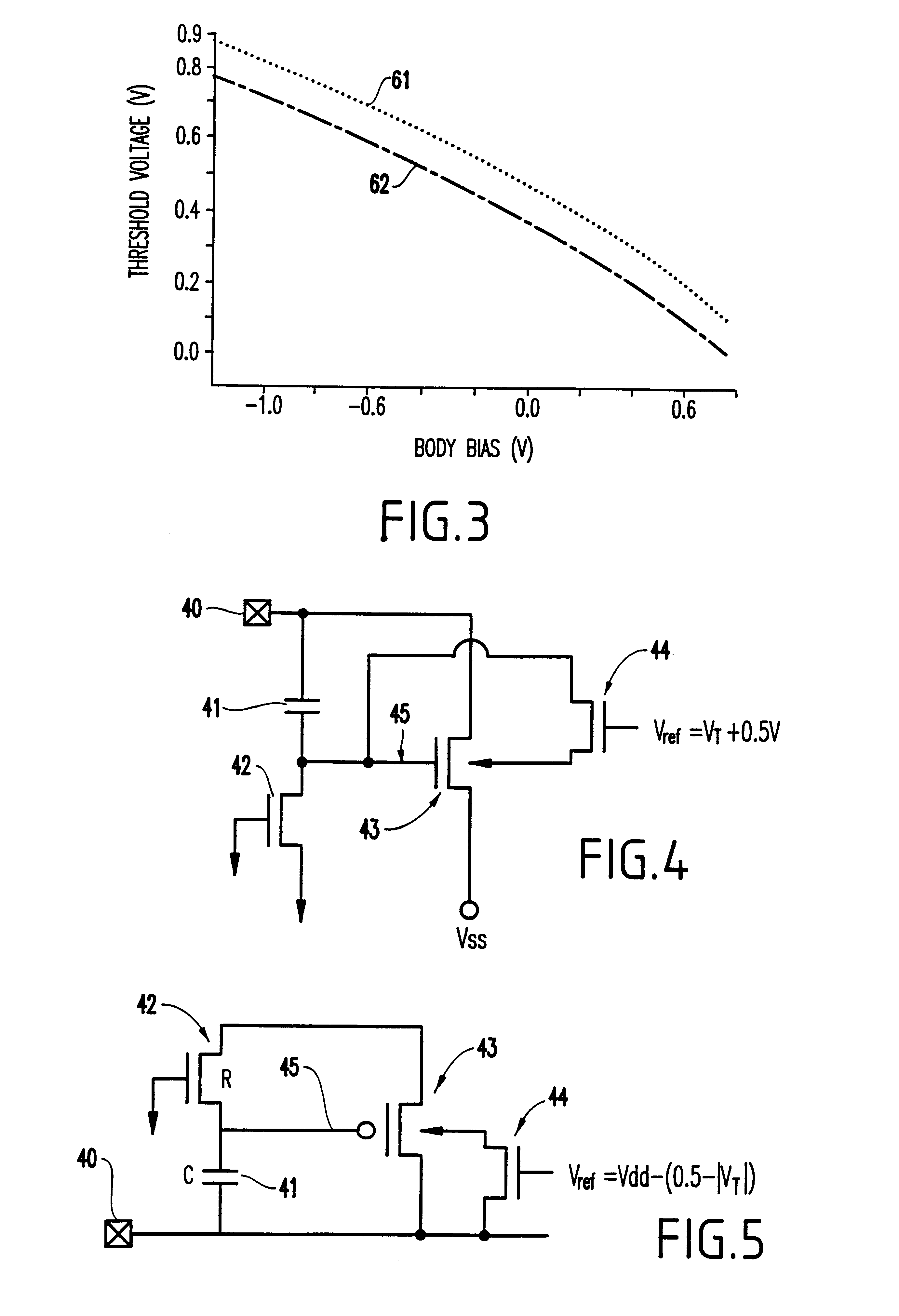

InactiveUS20050052219A1Reduce leakage currentMinimizing speed variationSolid-state devicesSemiconductor/solid-state device manufacturingLow voltageEngineering

An integrated circuit transistor body bias regulation circuit and method of especial applicability with respect to low voltage applications wherein the threshold voltage (Vt) of certain transistors is lowered at low power supply voltage (VCC) levels, low temperature and / or high Vt process conditions to assure adequate transistor drive but may also be raised at high VCC levels, high temperature and / or low Vt process conditions to reduce leakage current. In this manner, circuit speed that is closer to constant (versus VCC, temperature and process variation) is thereby achieved.

Owner:UNITED MEMORIES +1

Popular searches

Logic circuit coupling/interface arrangements Logic circuits using dielectric elements Semiconductor devices Volume/mass flow measurement Power supply for data processing Energy efficient computing Electric winding Oscillations generators Flexible microstructural devices Beam/ray focussing/reflecting arrangements

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com