Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4974results about "Logic circuit coupling/interface arrangements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

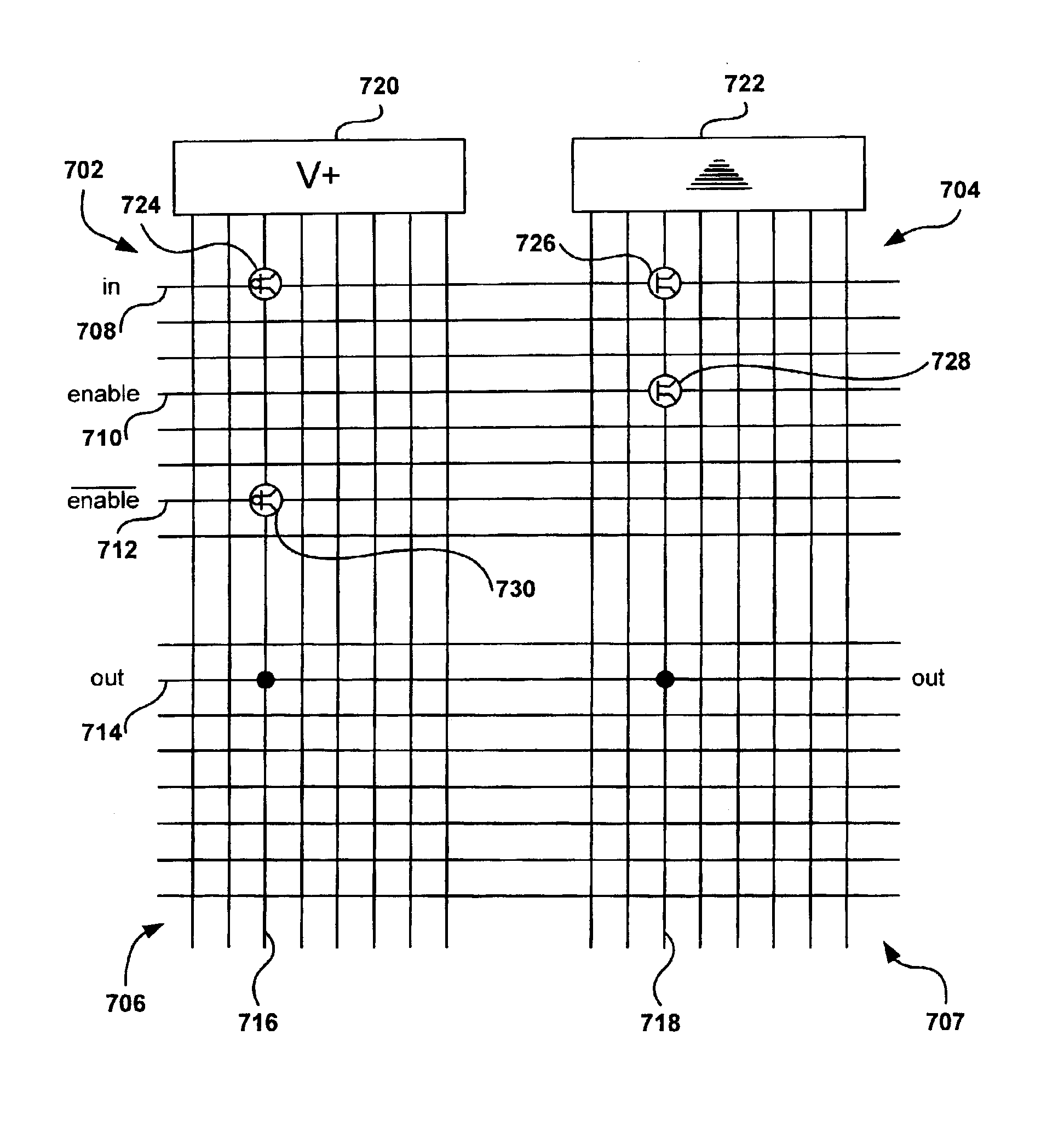

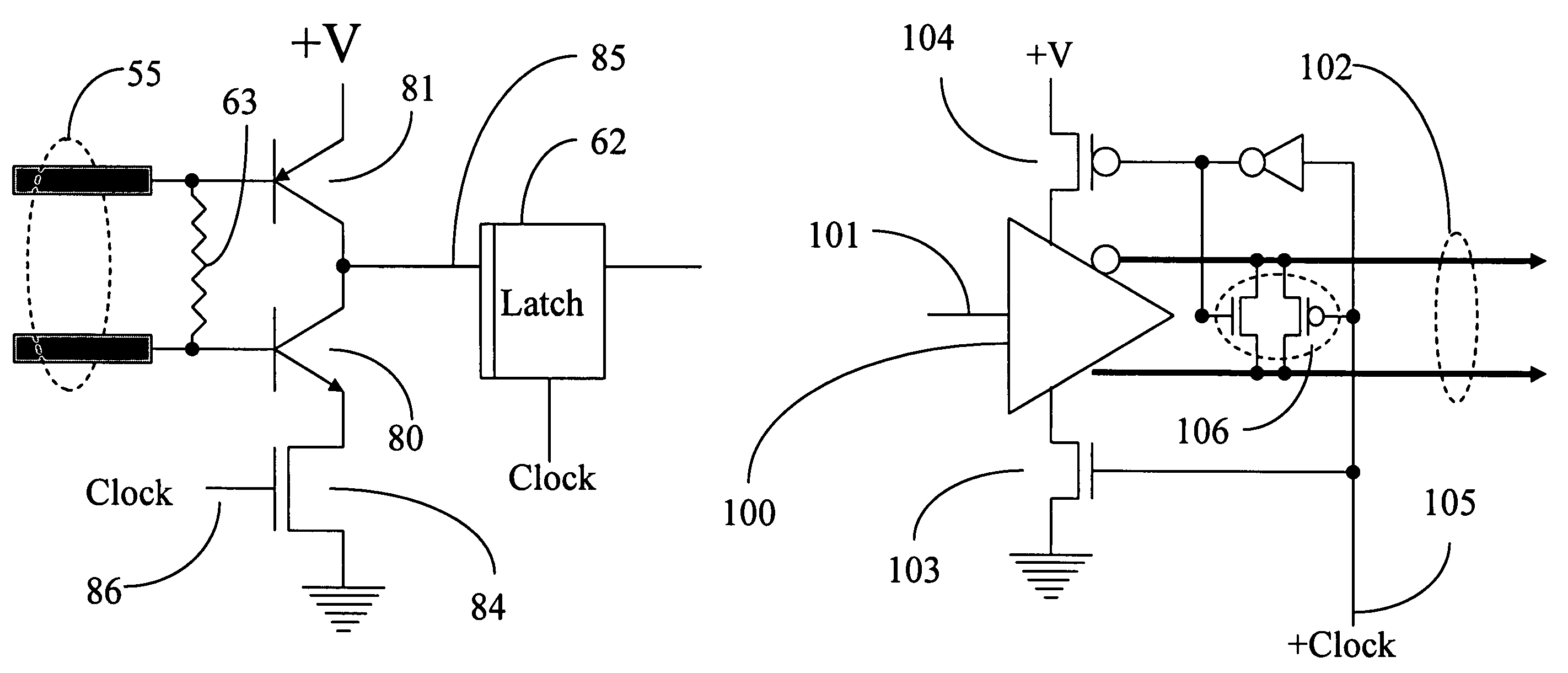

Molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits, and more complex circuits composed, in part, from molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits

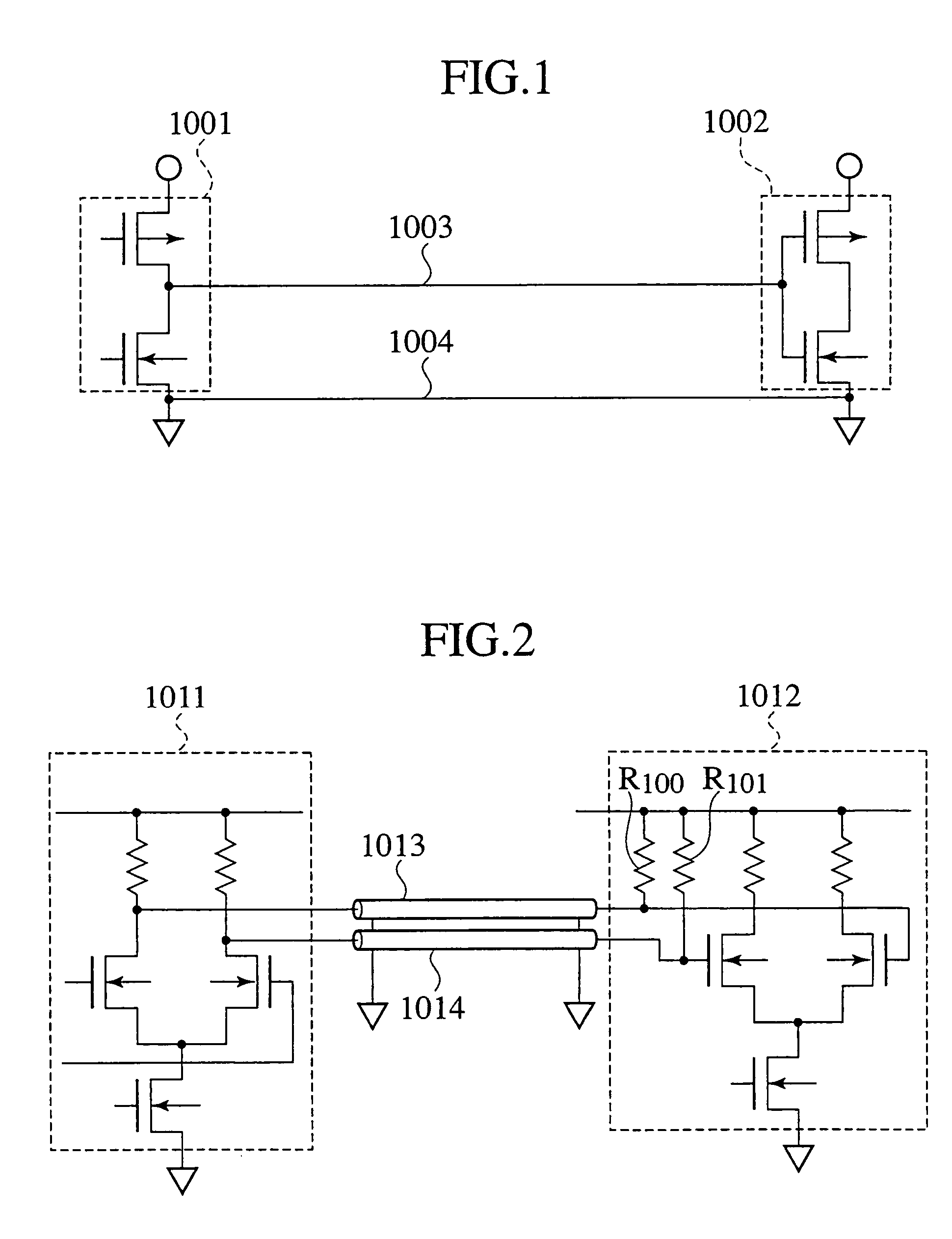

InactiveUS6919740B2High densityLittle powerLogic circuits characterised by logic functionNanoinformaticsCrossbar switchNanowire

Methods for implementing familiar electronic circuits at nanoscale sizes using molecular-junction-nanowire crossbars, and nanoscale electronic circuits produced by the methods. In one embodiment of the present invention, a 3-state inverter is implemented. In a second embodiment of the present invention, two 3-state inverter circuits are combined to produce a transparent latch. The 3-state inverter circuit and transparent-latch circuit can then be used as a basis for constructing additional circuitry, including master / slave flip-flops, a transparent latch with asynchronous preset, a transparent latch with asynchronous clear, and a master / slave flip-flop with asynchronous preset. 3-state inverters can thus be used to compose latches and flip-flops, and latches and flip-flops can be used, along with additional Boolean circuitry, to compose a wide variety of useful, state-maintaining circuits, all implementable within molecular-junction-nanowire crossbars by selectively configuring junctions within the molecular-junction-nanowire crossbars.

Owner:HEWLETT PACKARD DEV CO LP

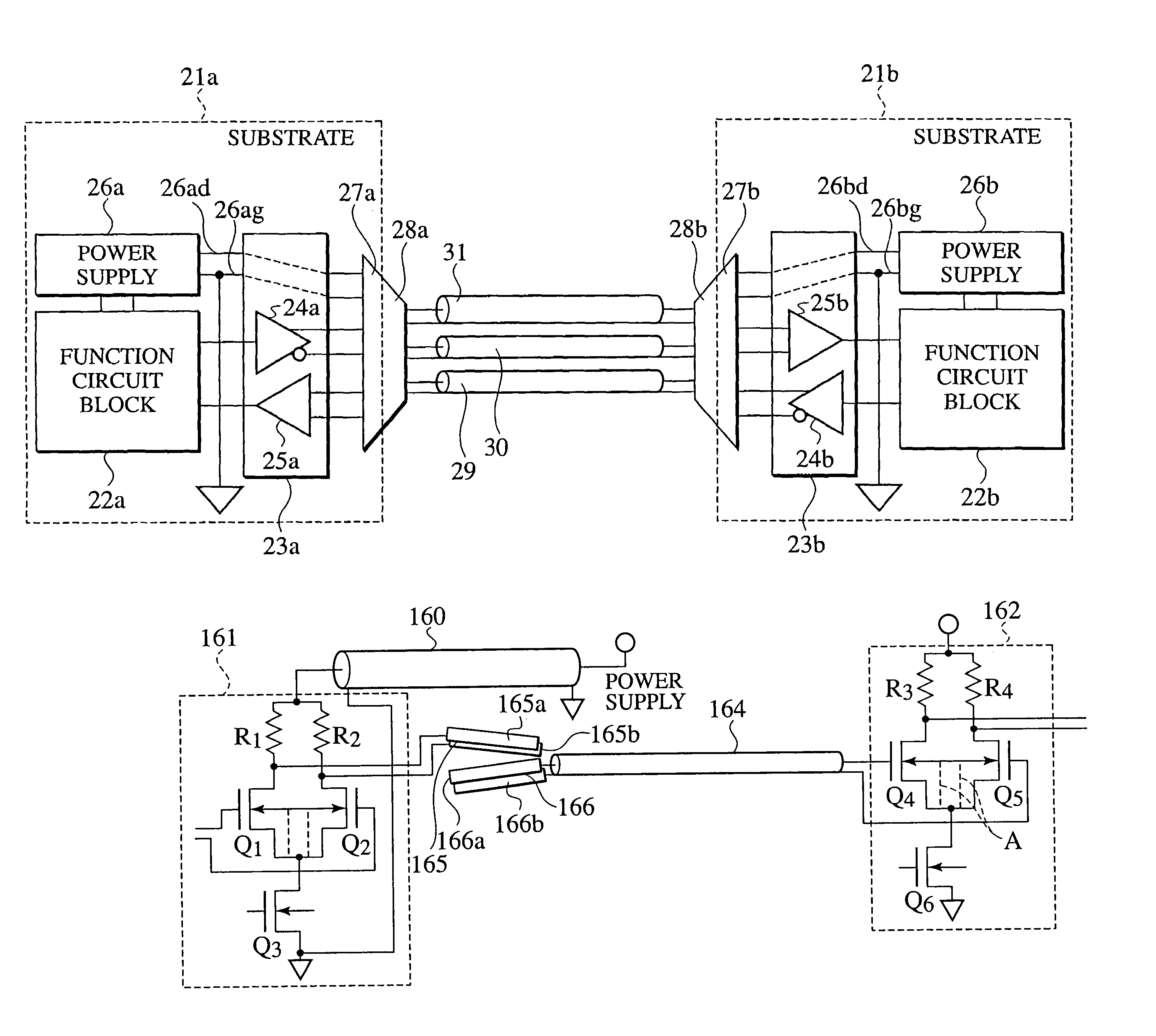

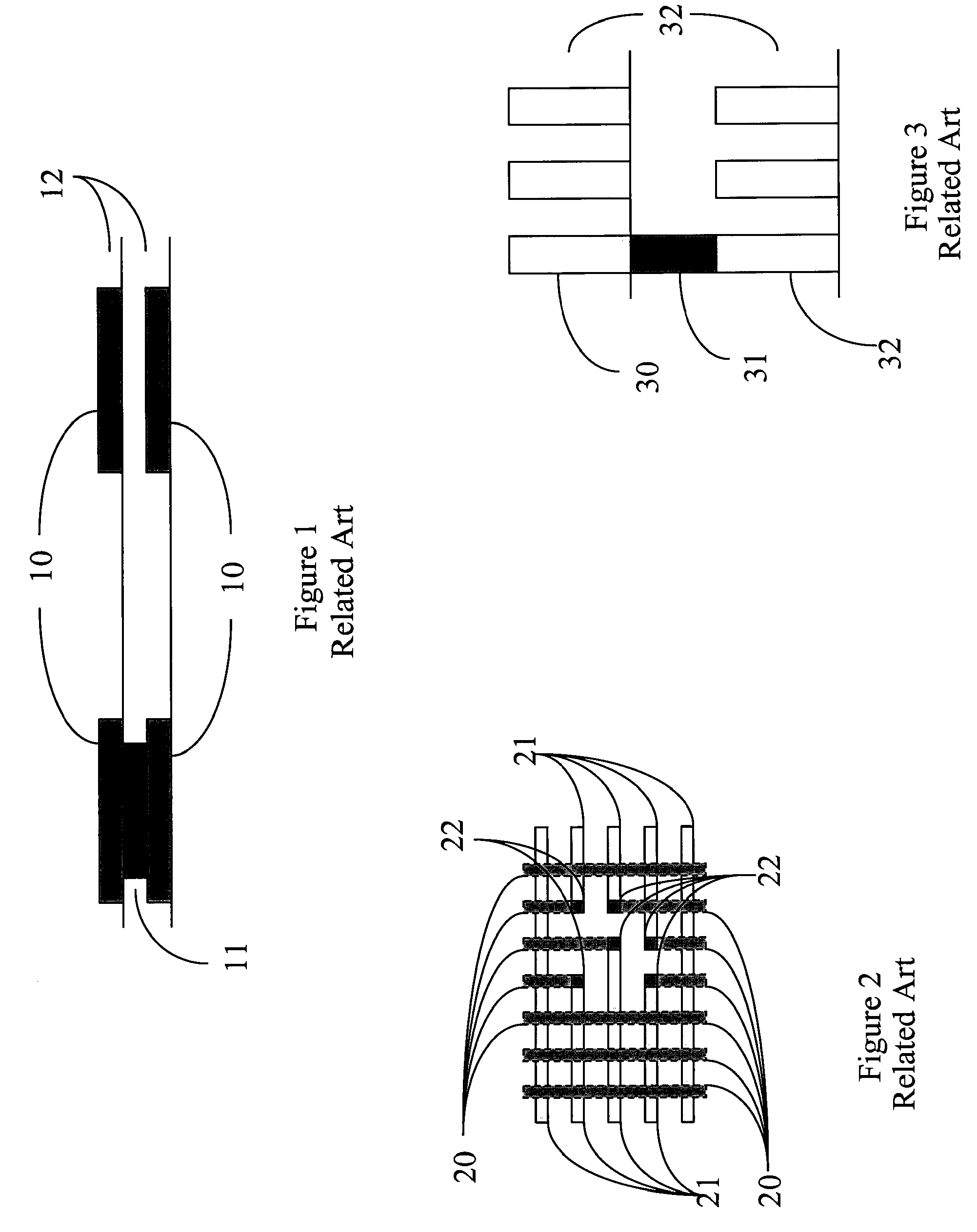

Transmission cable structure for GHz frequency band signals and connector used for transmission of GHz frequency band signals

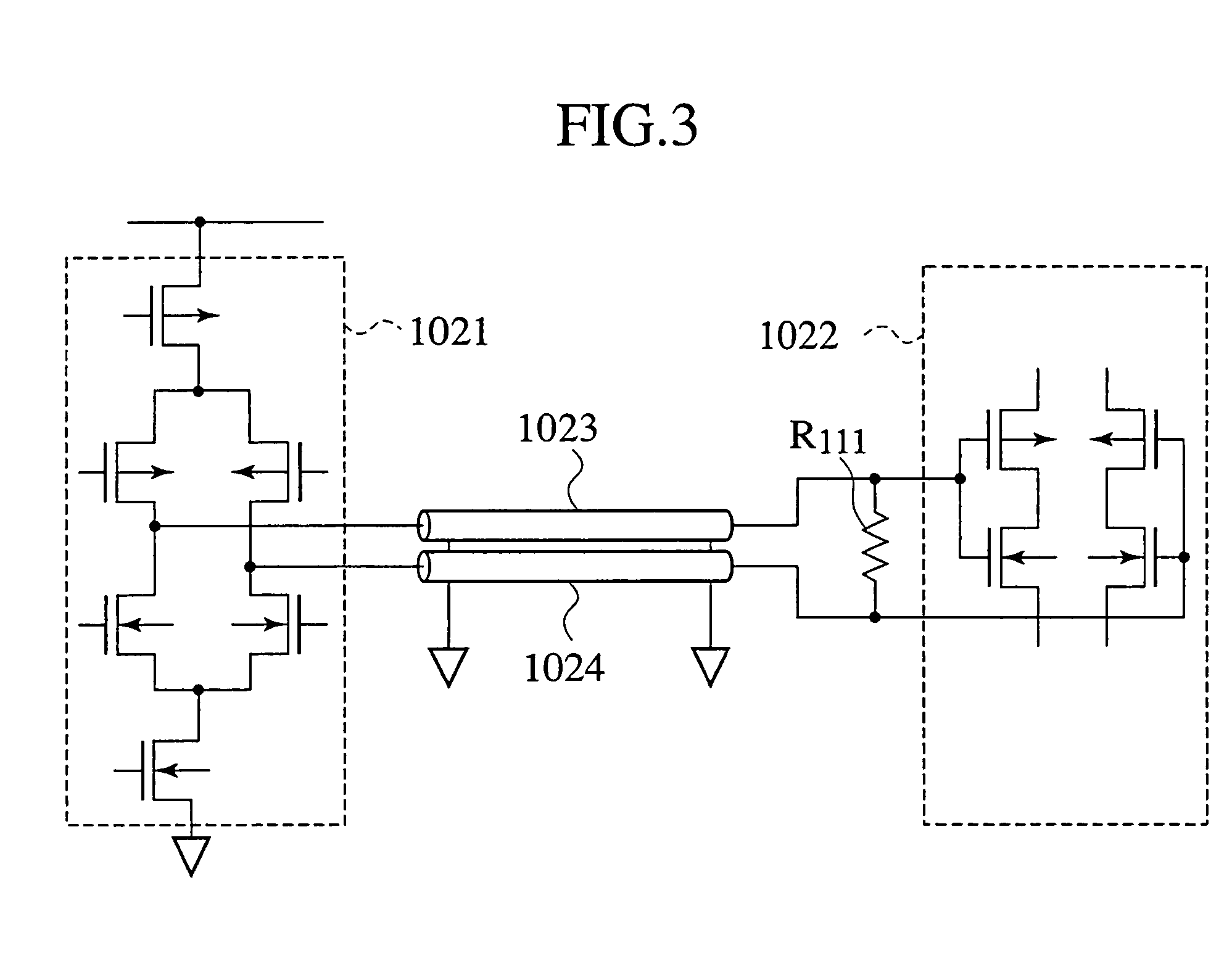

InactiveUS7113002B2Containment leakReduce couplingMultiple-port networksElectrically conductive connectionsDriver circuitDifferential signaling

A differential signal transmission cable structure for transmitting differential signals having GHz frequency band in the present invention is provided with a differential signal transmission pair cable 30 connecting a driver circuit 23a and a receiver circuit 23b, for transmitting differential signals having GHz frequency band, and a power supply ground transmission pair cable 31 connecting ground and a first power supply 26a connected to the driver circuit and ground and a second power supply 26b connected to the receiver circuit. Further characteristic impedance of the differential signal transmission pair cable is matched to that of the driver circuit and the receiver circuit, thereby enabling TEM waves of differential signals having GHz frequency band transmission mode to be maintained when the differential signals are transmitted.

Owner:THE FUJIKURA CABLE WORKS LTD

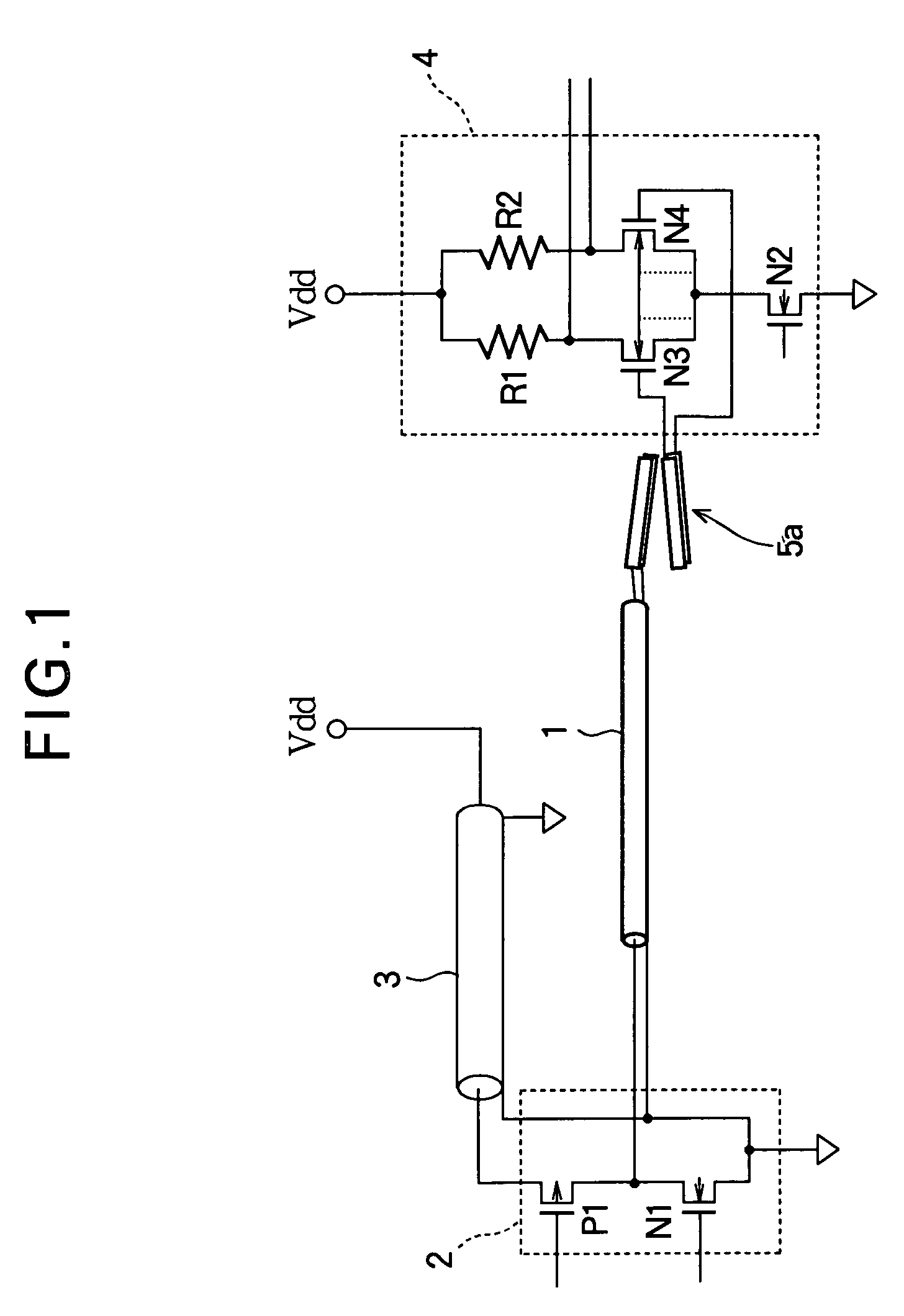

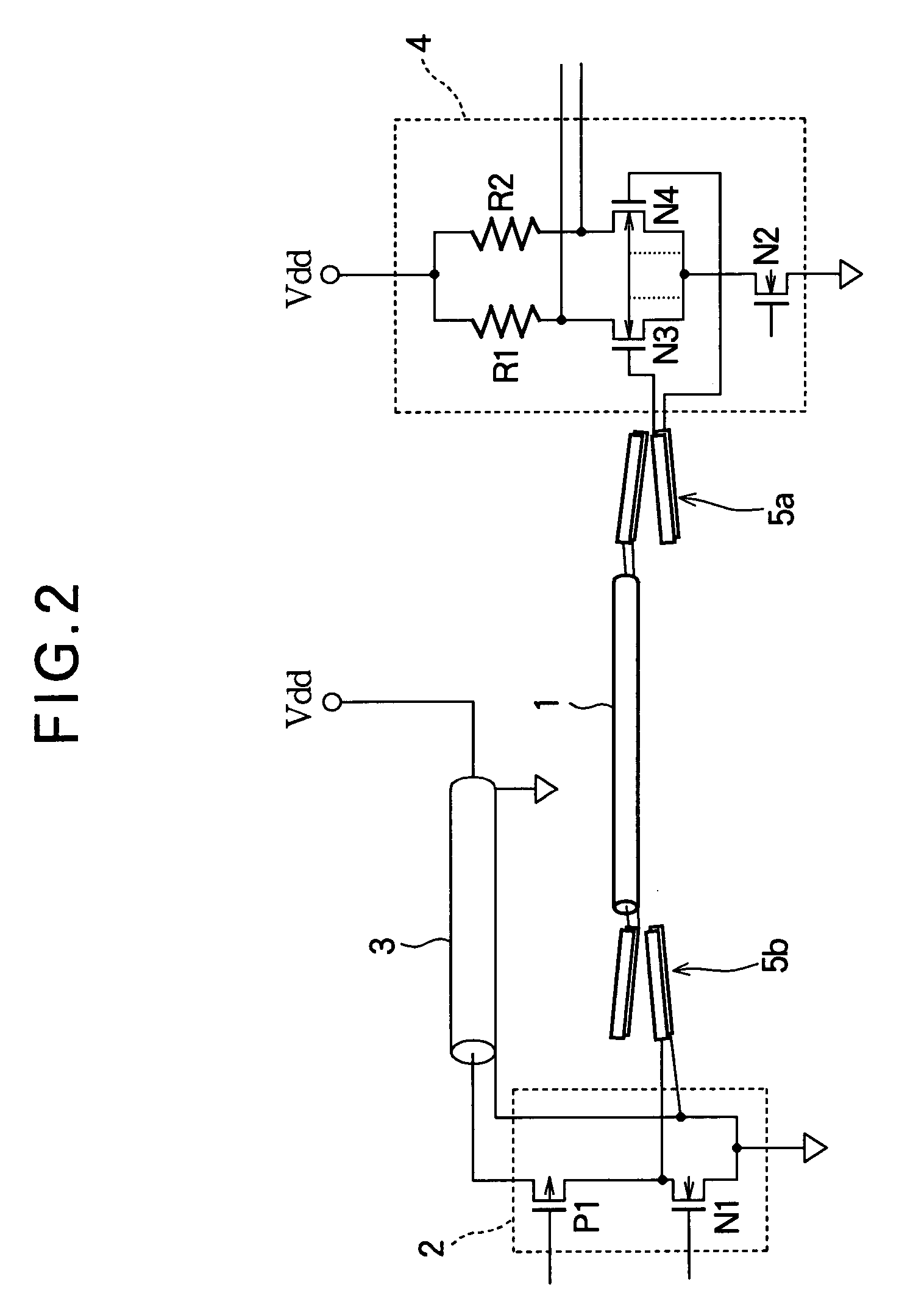

Pseudo-differential interfacing device having a switching circuit

InactiveUS7884648B2Reduce couplingReduced unwanted couplingReliability increasing modificationsElectronic switchingDifferential transmissionEngineering

The invention relates to an interfacing device for pseudo-differential transmission through interconnections used for sending a plurality of electrical signals. The interfacing device of the invention includes signal terminals and a common terminal. A transmitting circuit receives the input signals of the transmitting circuit coming from a source. The output of the transmitting circuit delivers, when the transmitting circuit is in the activated state, voltages between one of the signal terminals and the reference terminal (ground). A receiving circuit delivers, when the receiving circuit is in the activated state, output signals of the receiving circuit determined each by the voltage between one of the signal terminals and the common terminal, to the destination. In the closed state, the common terminal switching circuit is, for the common terminal, equivalent to a voltage source delivering a constant voltage, connected in series with a passive two-terminal circuit element presenting a low impedance.

Owner:ZXNOISE LLC

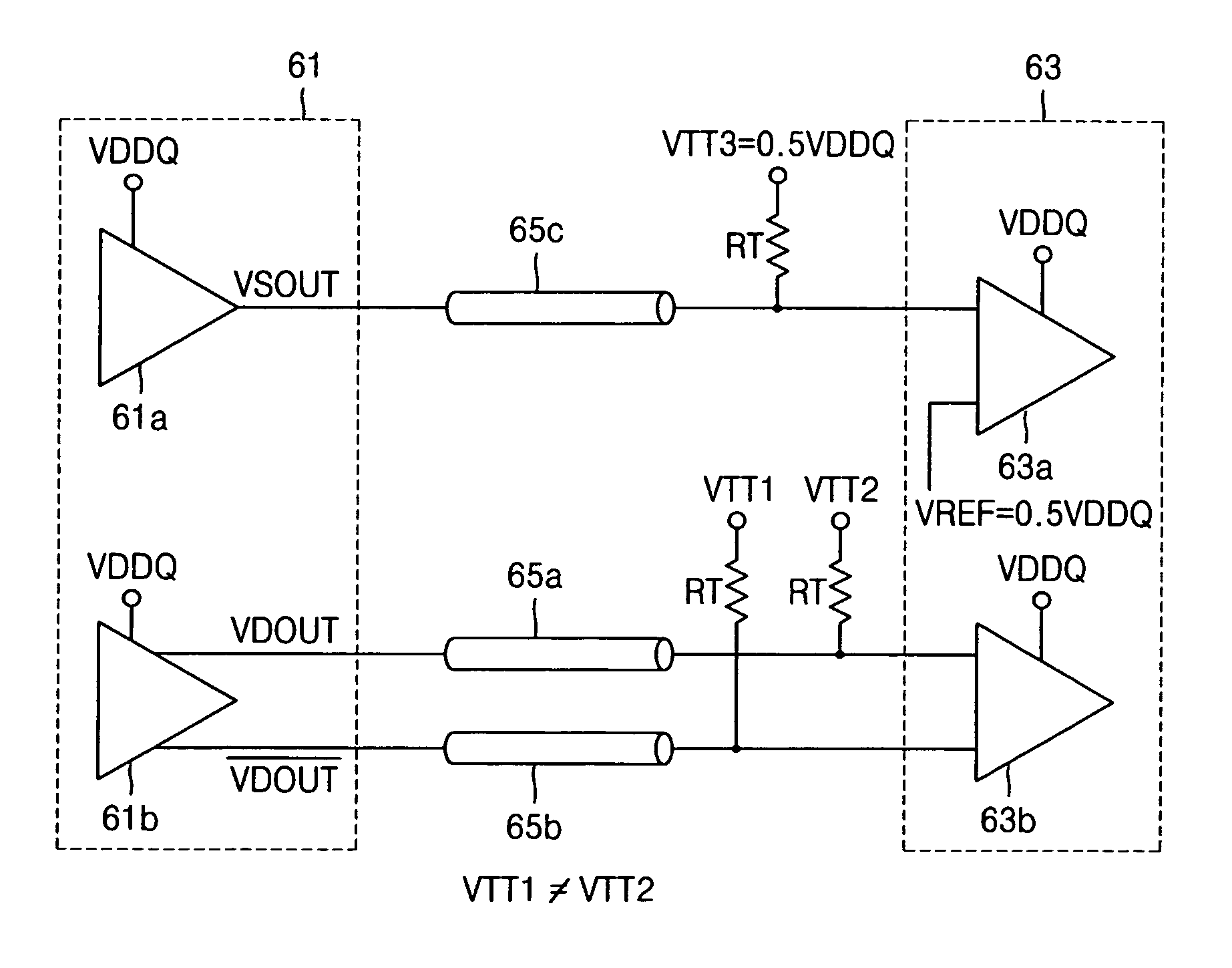

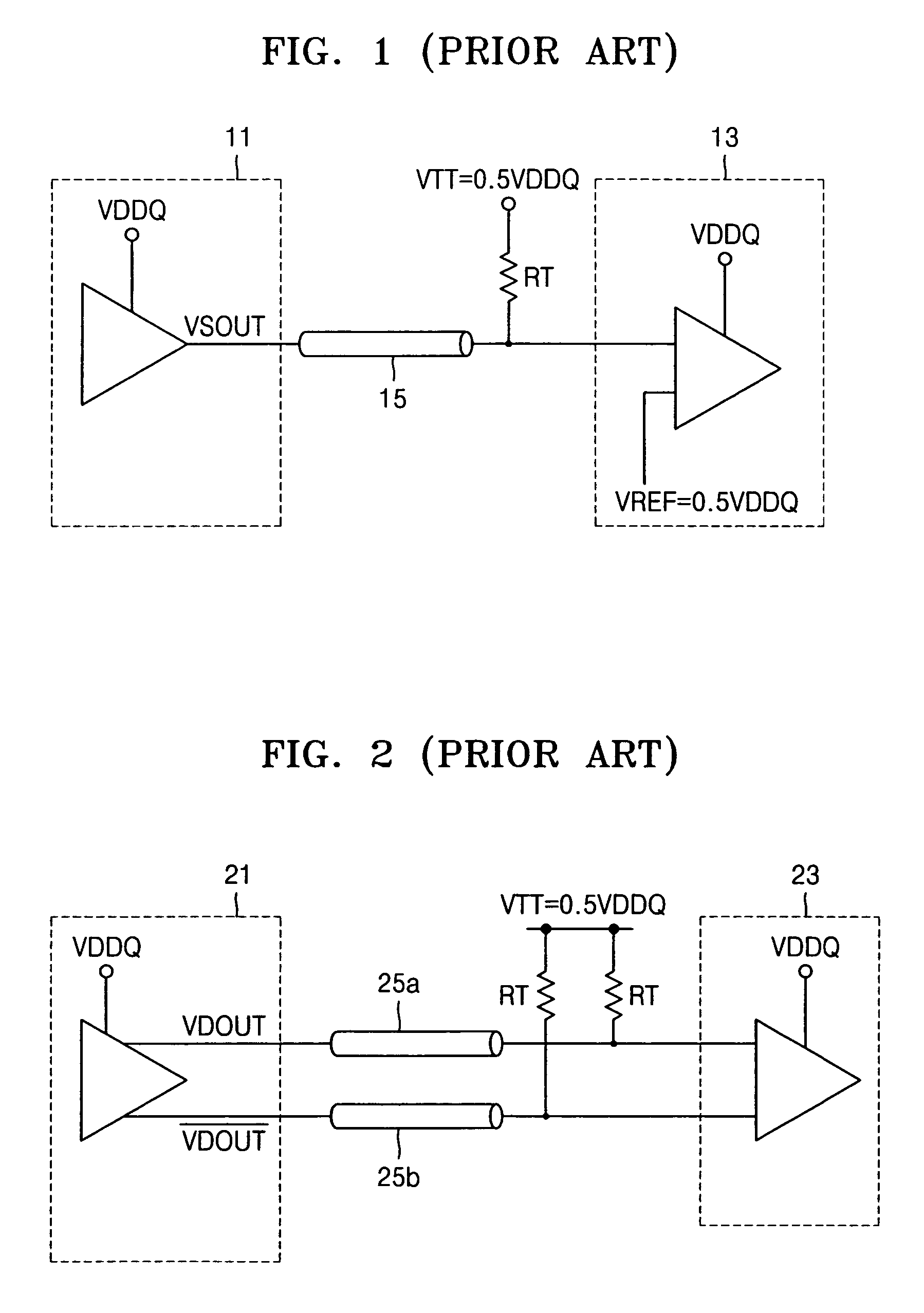

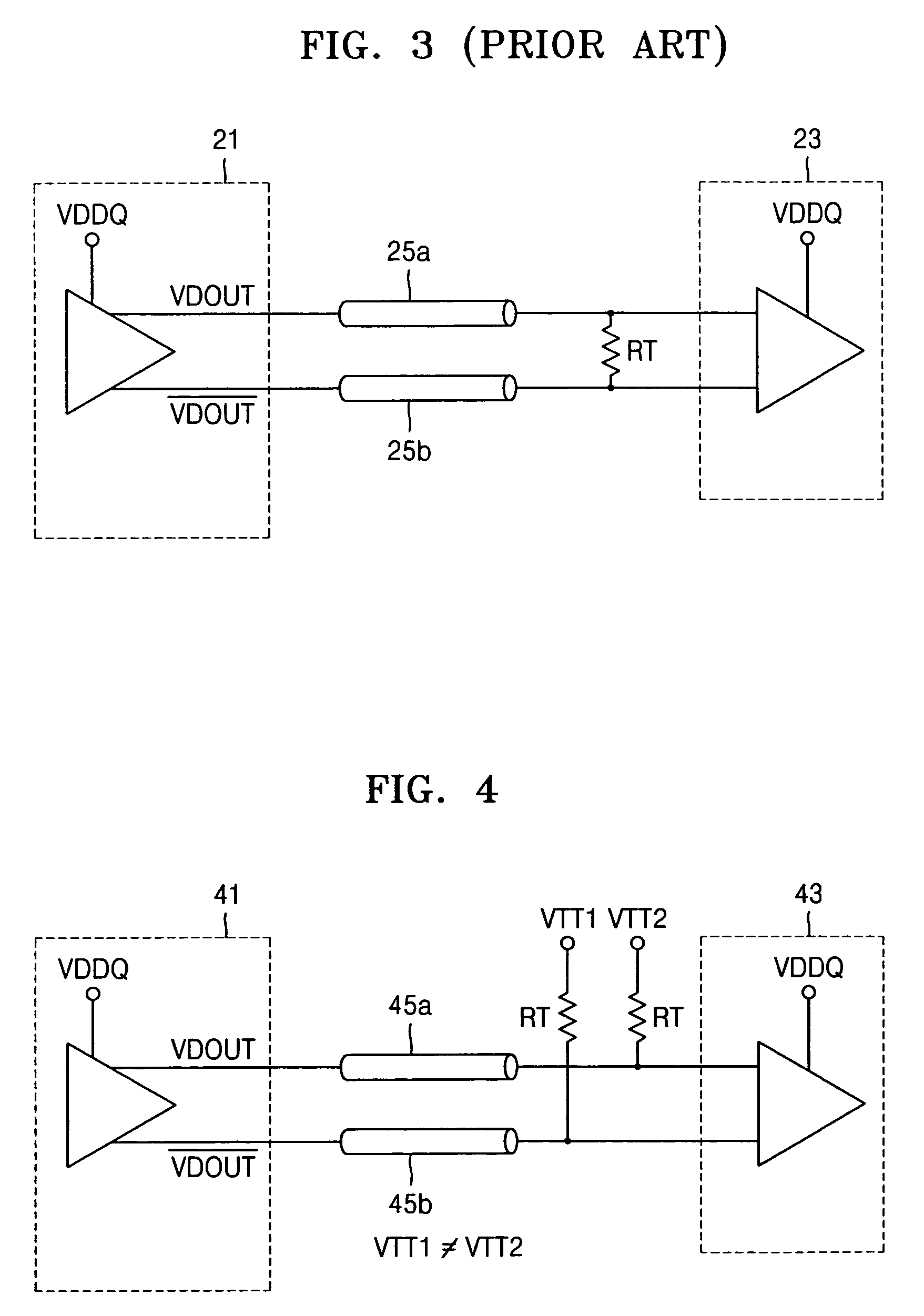

Memory system with stable termination of a pair of differential signals transmitted via a pair of transmission lines

InactiveUS7456650B2Avoid instabilityReliability increasing modificationsBaseband system detailsEngineeringTransmitter

Provided is a memory system in which a pair of differential signals transmitted via a pair of transmission lines are prevented from being terminated at the same voltage during a standby mode, thereby preventing a receiver from entering an unstable state. The memory system includes a pair of transmission lines, a transmitter that outputs a pair of differential signals to the pair of transmission lines, and a receiver that receives the pair of differential signals via the pair of transmission lines. A first termination voltage is applied to one of the pair of transmission lines, and a second termination voltage is applied to the other transmission line. The first termination voltage is determined to be different from the second termination voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

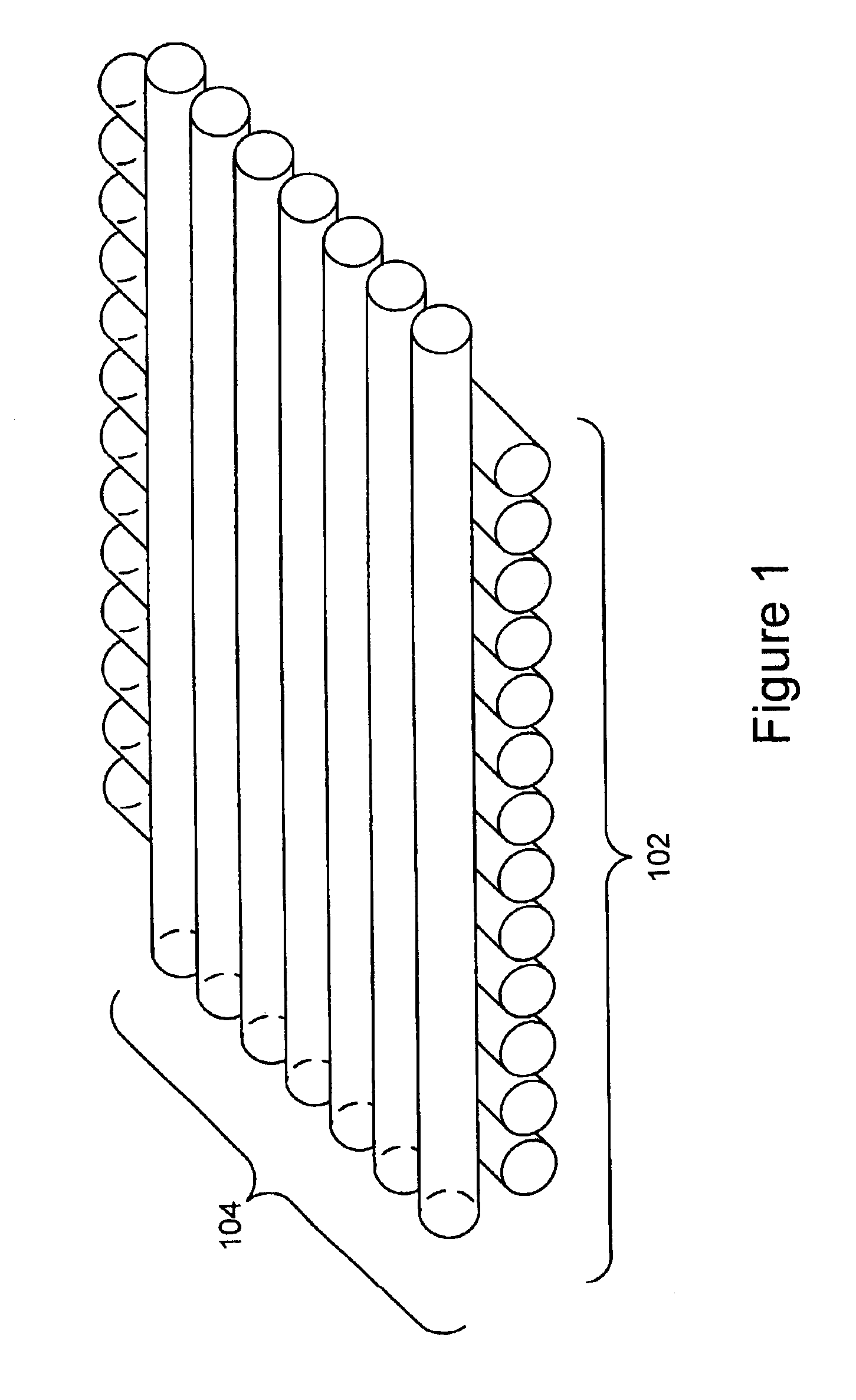

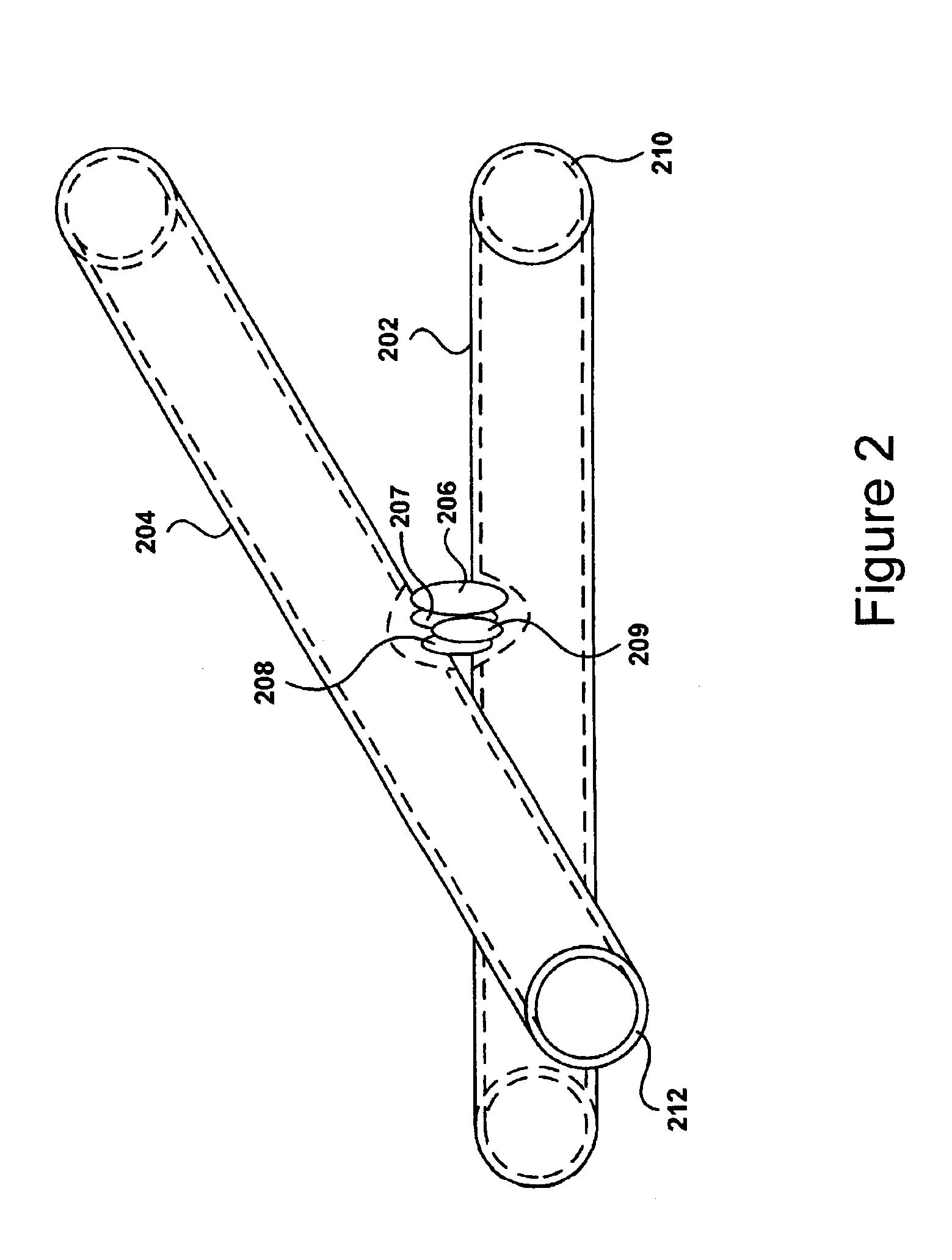

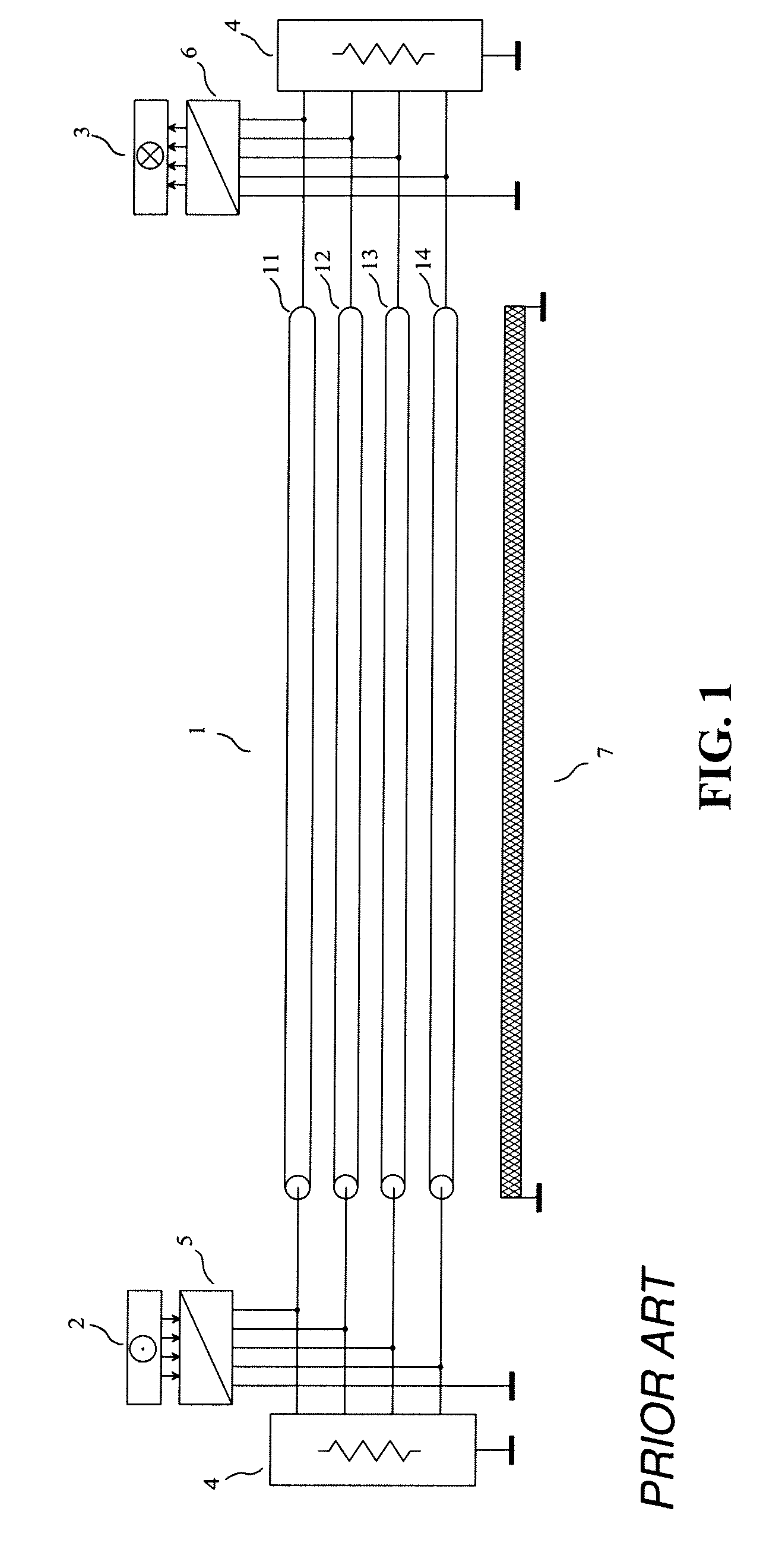

Differential transmission line connector

InactiveUS8027391B2Constant length of the signal linesLittle unwanted radiation noiseCurrent interference reductionCoupling device detailsIsoetes triquetraDifferential signaling

A differential transmission line connector with little unwanted radiation noise is provided. A connector connects a differential transmission pattern for multiple transmission of a group of three differential signals and a differential transmission cable. The differential transmission pattern is provided with three signal lines, and the differential transmission cable also is provided with three signal lines. In a plane that is perpendicular to the longitudinal direction of the differential transmission pattern and the differential transmission cable, the signal lines are positioned at the apexes of an equilateral triangle. The connector is provided with three signal lines that connect, at identical lengths, the signal lines of the differential transmission pattern and the signal lines of the differential transmission cable, between a predetermined first plane of the planes that perpendicularly intersect the longitudinal direction of the differential transmission pattern and a predetermined second plane of the planes that perpendicularly intersect the longitudinal direction of the differential transmission cable.

Owner:PANASONIC CORP

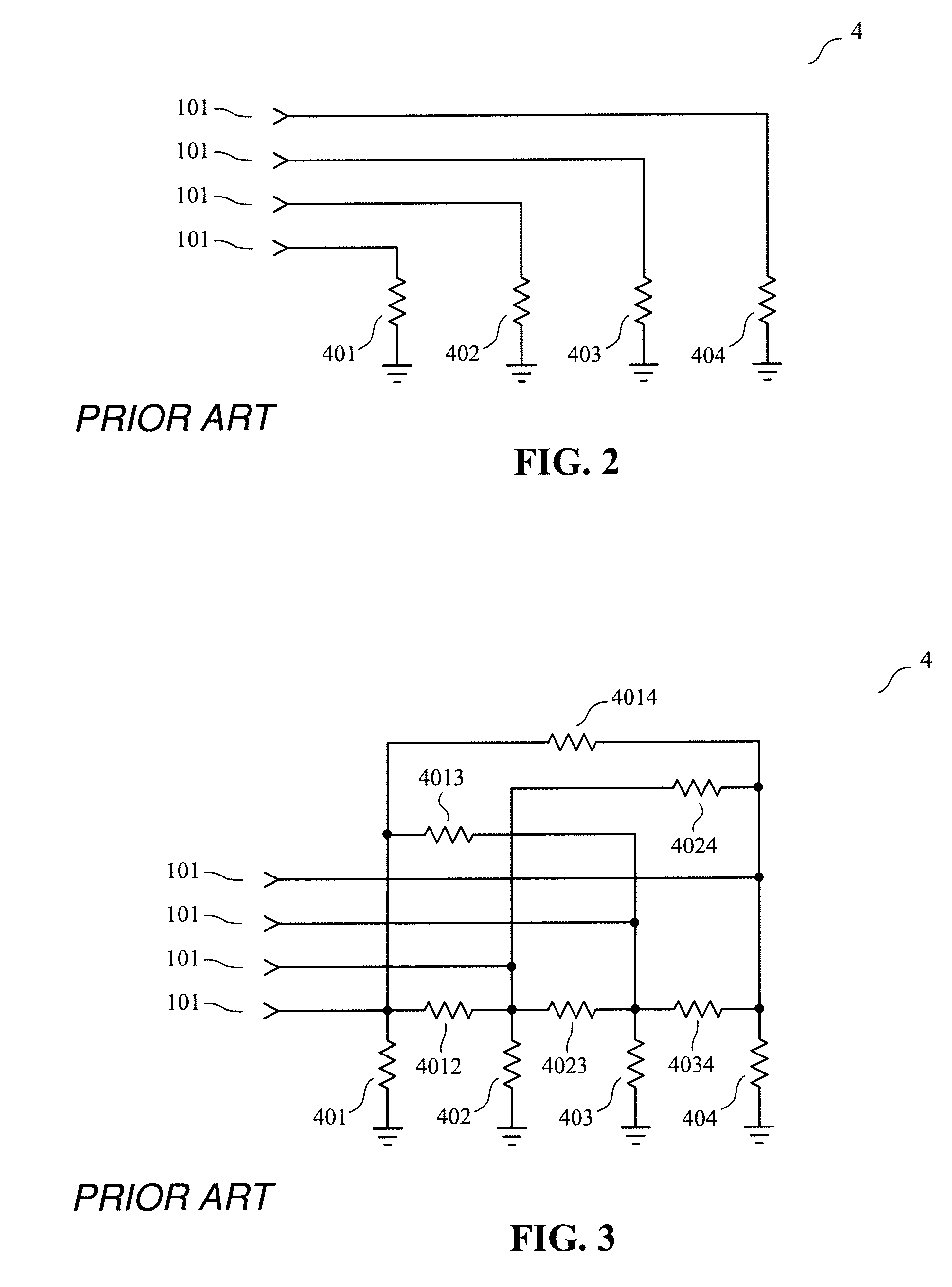

Multichannel interfacing device having a termination circuit

InactiveUS8222919B2Reduce reflectionReduce inductanceMultiple-port networksReliability increasing modificationsDiagonal matrixInterconnection

The invention relates to an interfacing device for transmission through interconnections used for sending a plurality of electrical signals.The interfacing device of the invention comprises signal terminals and a common terminal. A receiving circuit delivers, when the receiving circuit is in the activated state, “output signals of the receiving circuit” determined each by a linear combination of the voltages between one of the signal terminals and the common terminal, to the destination. A termination circuit is such that, when it is in the activated state, it is approximately equivalent, for the signal terminals and the common terminal, to a (m+1)-terminal network such that, for small signals, the impedance matrix, with respect to the common terminal, of the (m+1)-terminal network is equal to a wanted non-diagonal matrix of size m×m.

Owner:ZXNOISE LLC

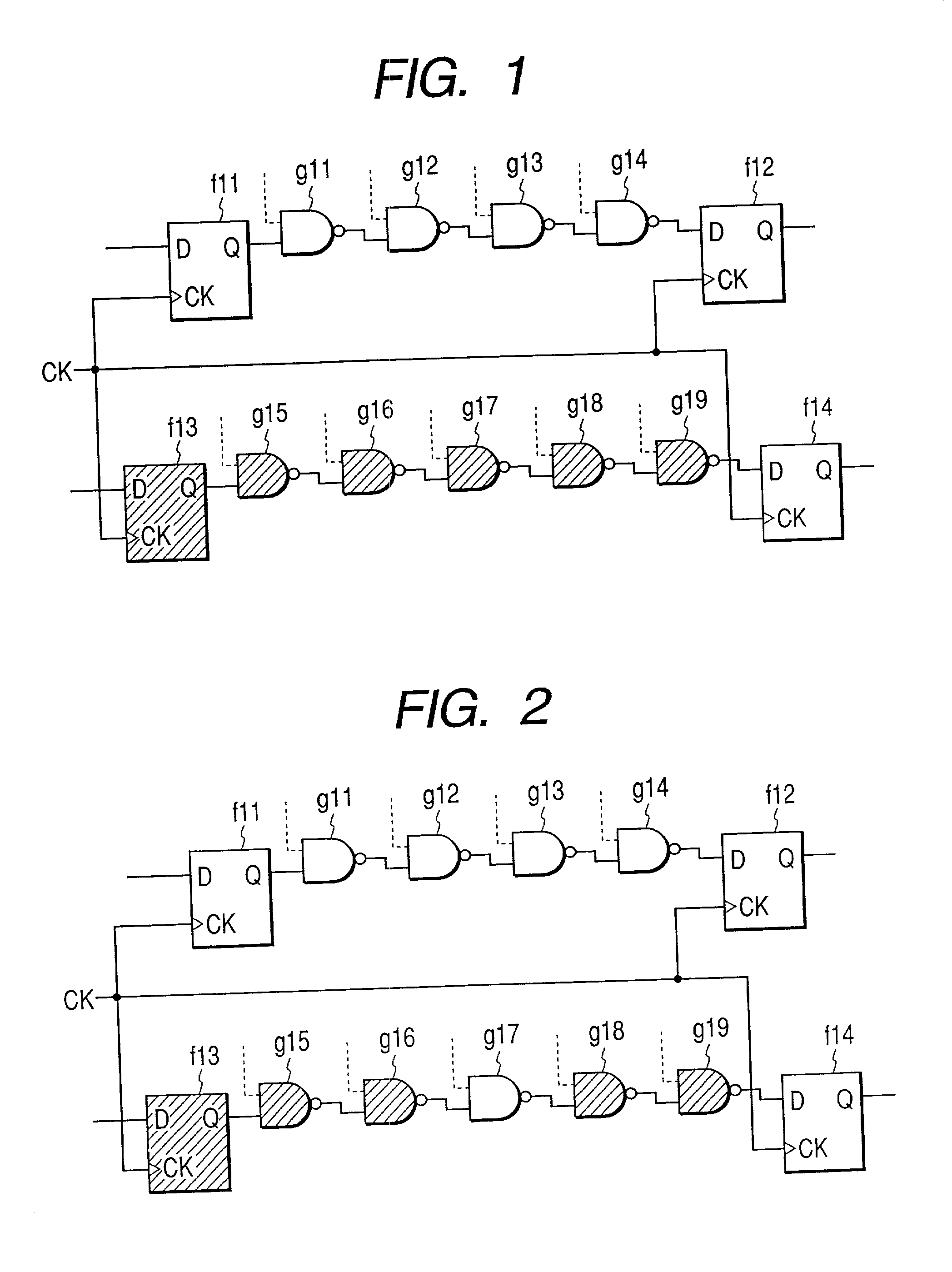

Logic circuit utilizing pass transistors and logic gate

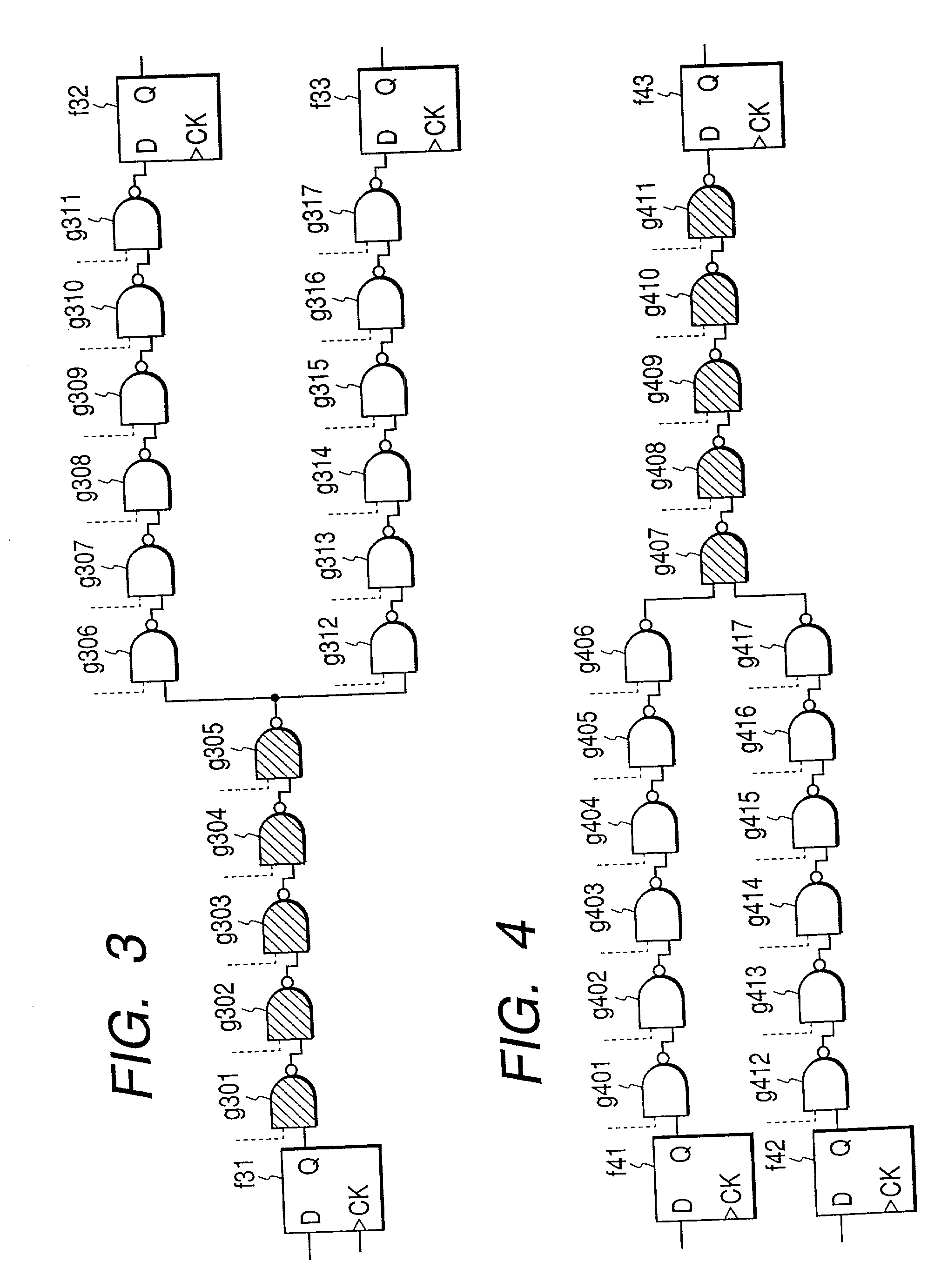

InactiveUS6084437ATransistorReliability increasing modificationsCmos logic circuitsLogical operations

A logic circuit combines a plurality of pass-transistor logic trees and a multiple-input logic gate for receiving intermediate logic signals from the respective pass-transistor logic trees, and can express a complex logical operation while decreasing the number of stages in pass-transistor logic trees and improving operation speed. Even a logical operation that cannot be expressed efficiently by a known or conventional pass-transistor logic circuit can be expressed efficiently with performance higher than that of a known CMOS logic circuit. Furthermore, when a static feedthrough current of the multiple-input logic gate is suppressed, power consumption can be reduced. In some embodiments, since circuitry for suppressing a static feedthrough current of the multiple-input logic gate is arranged so that a probability of occurrence of logical collision with a preceding stage will decrease or will be nil, power consumption can further be reduced.

Owner:KAWASAKI MICROELECTRONICS

Integrated circuit communication techniques

ActiveUS7439773B2Reduce the required powerReduce power consumptionReliability increasing modificationsPower reduction by control/clock signalEngineeringSemiconductor

Owner:TAHOE RES LTD

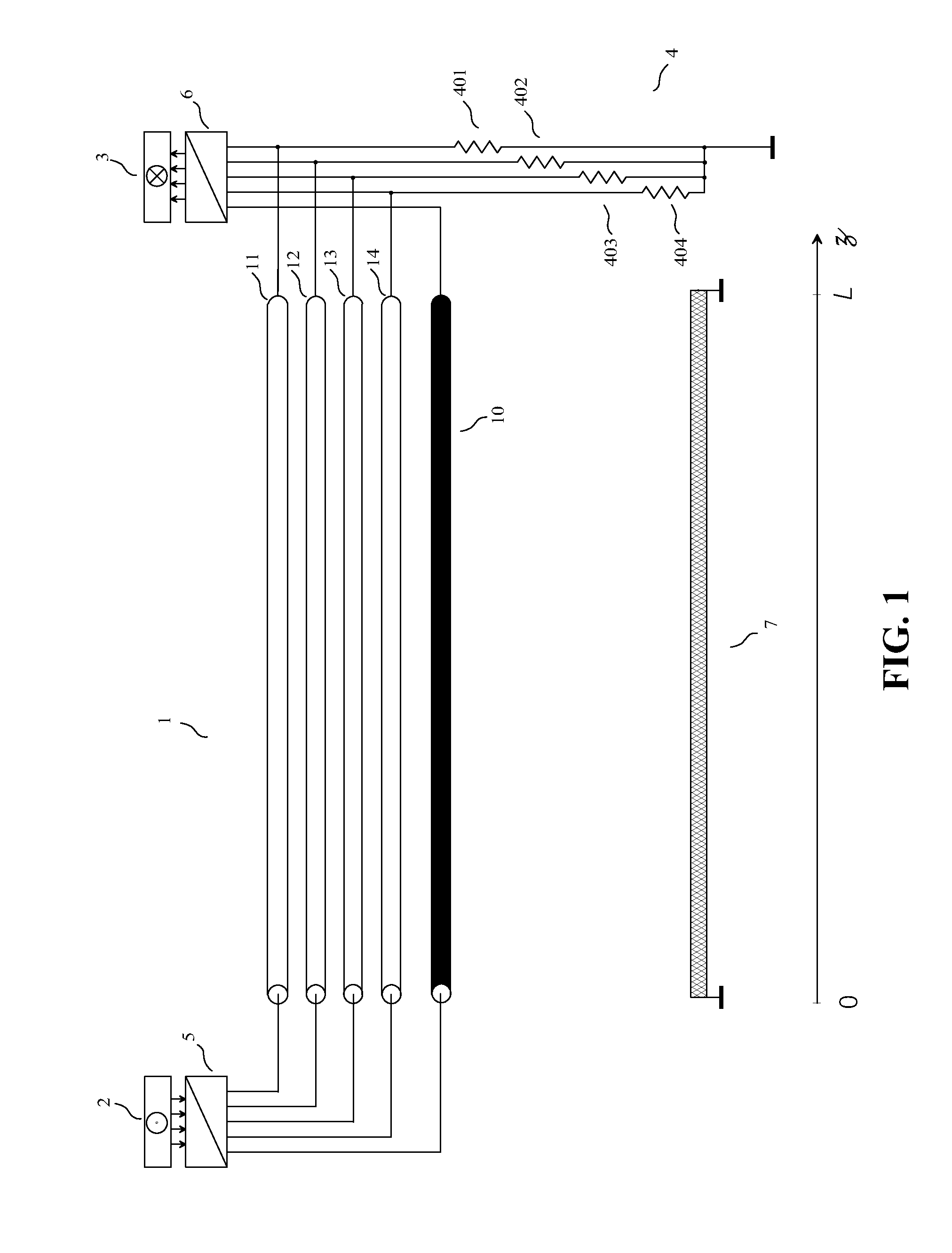

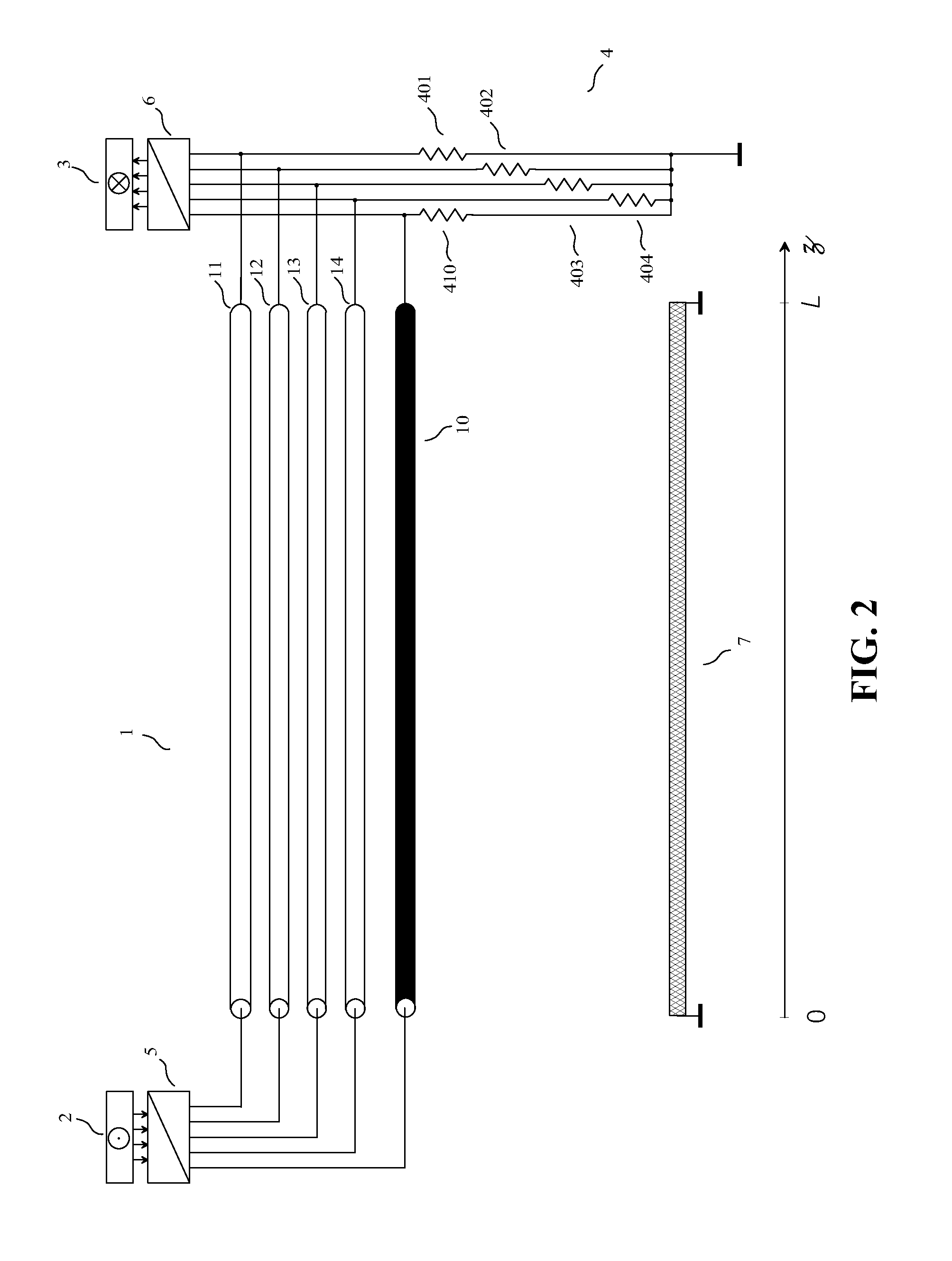

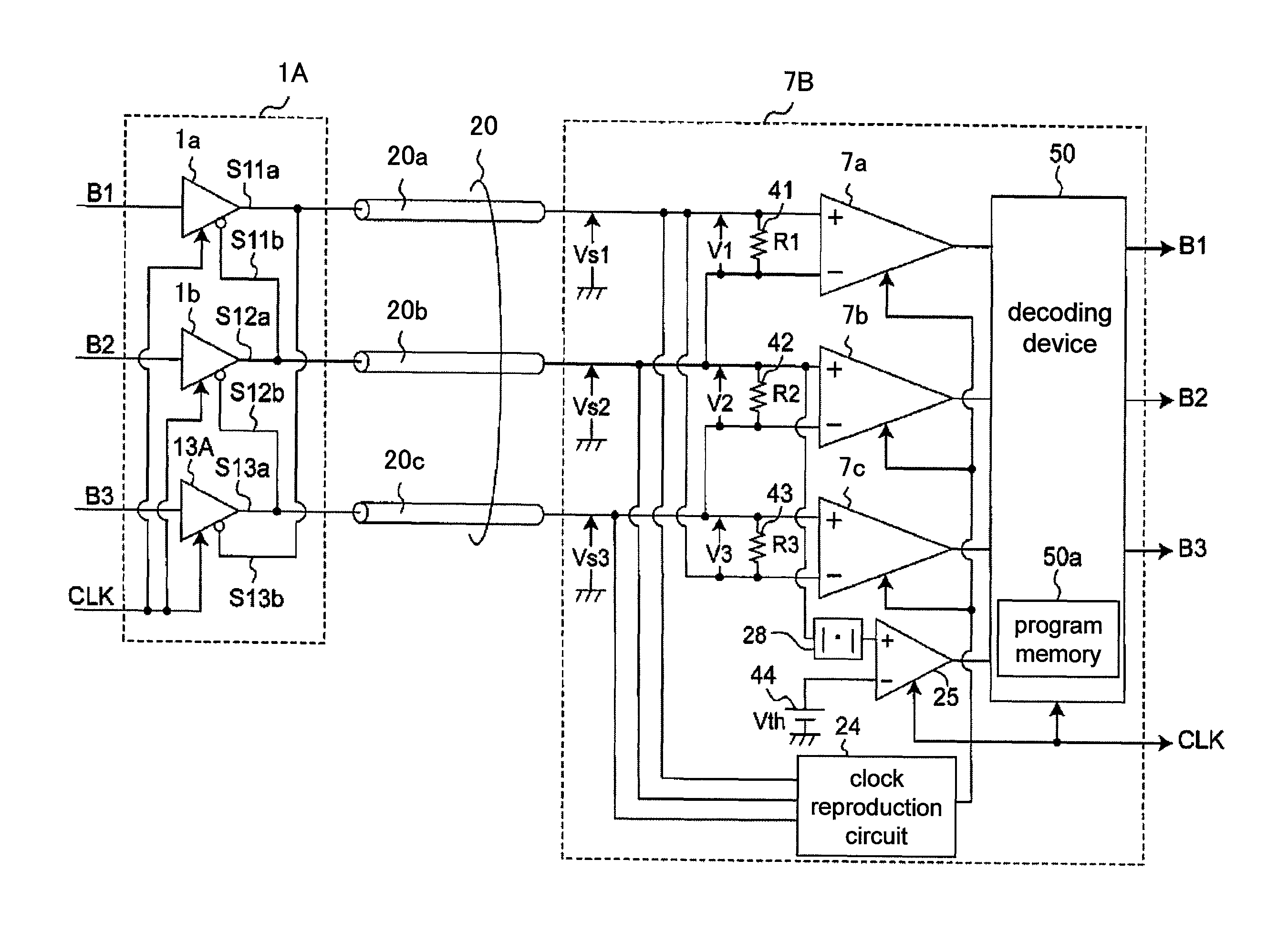

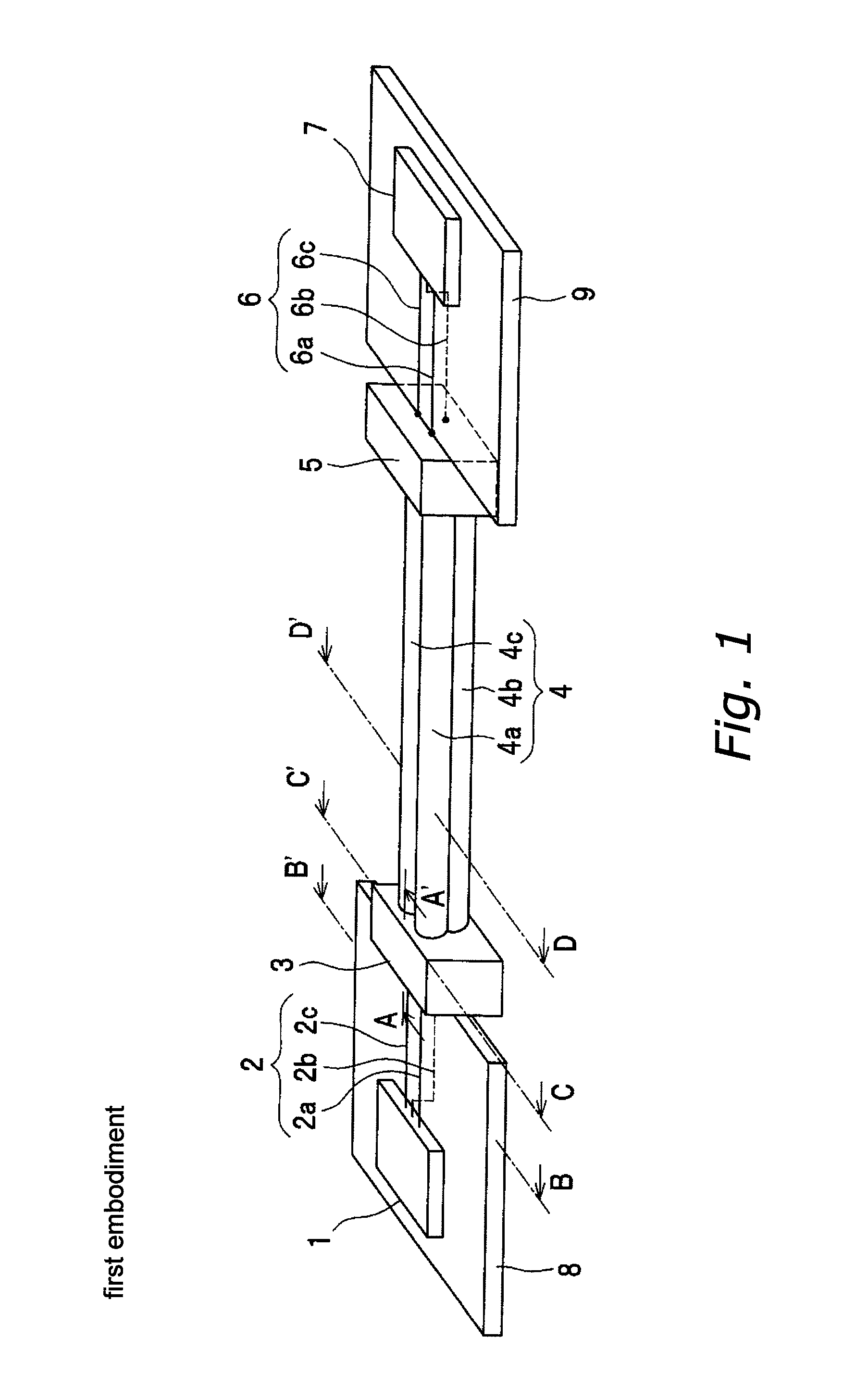

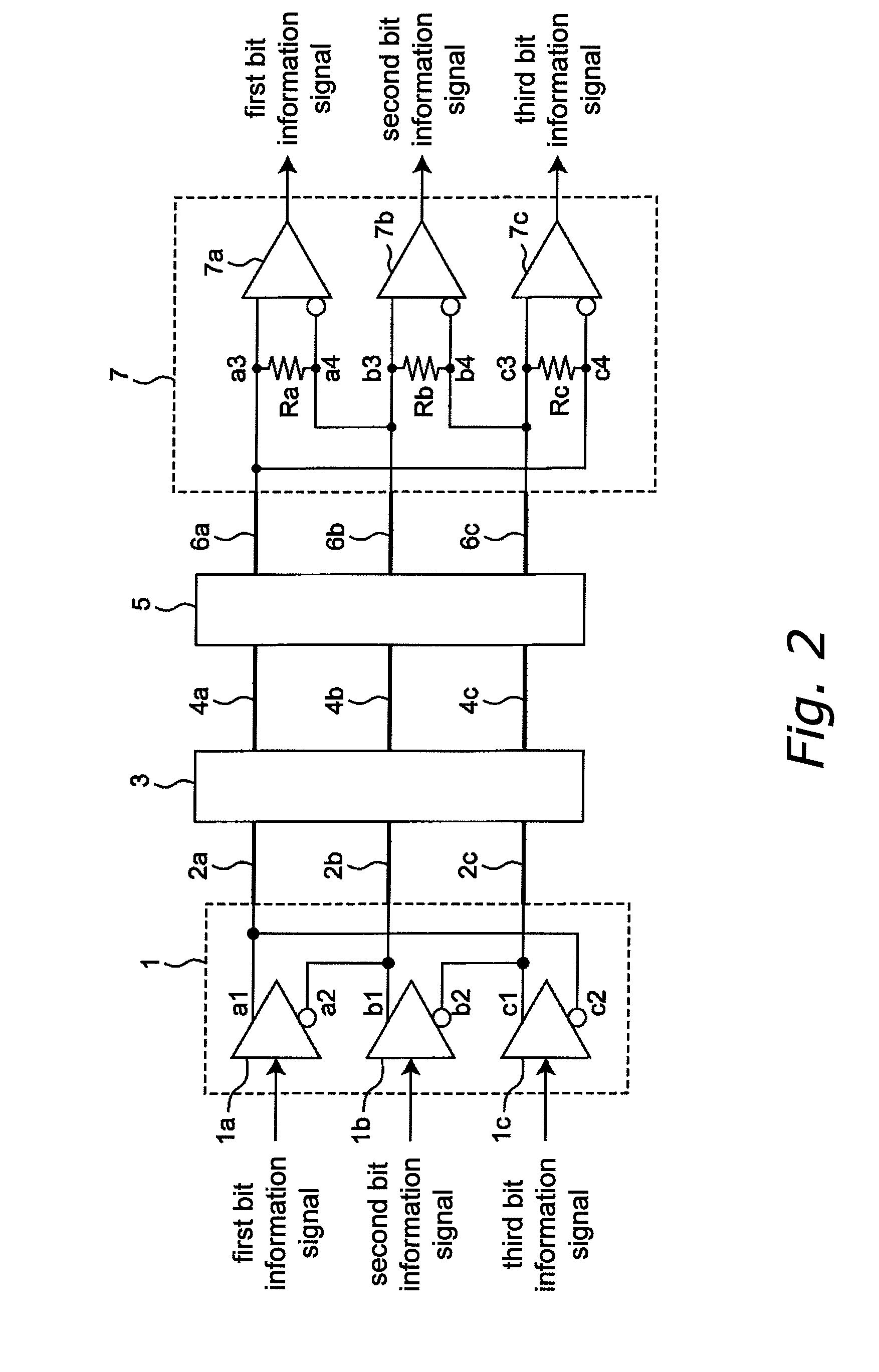

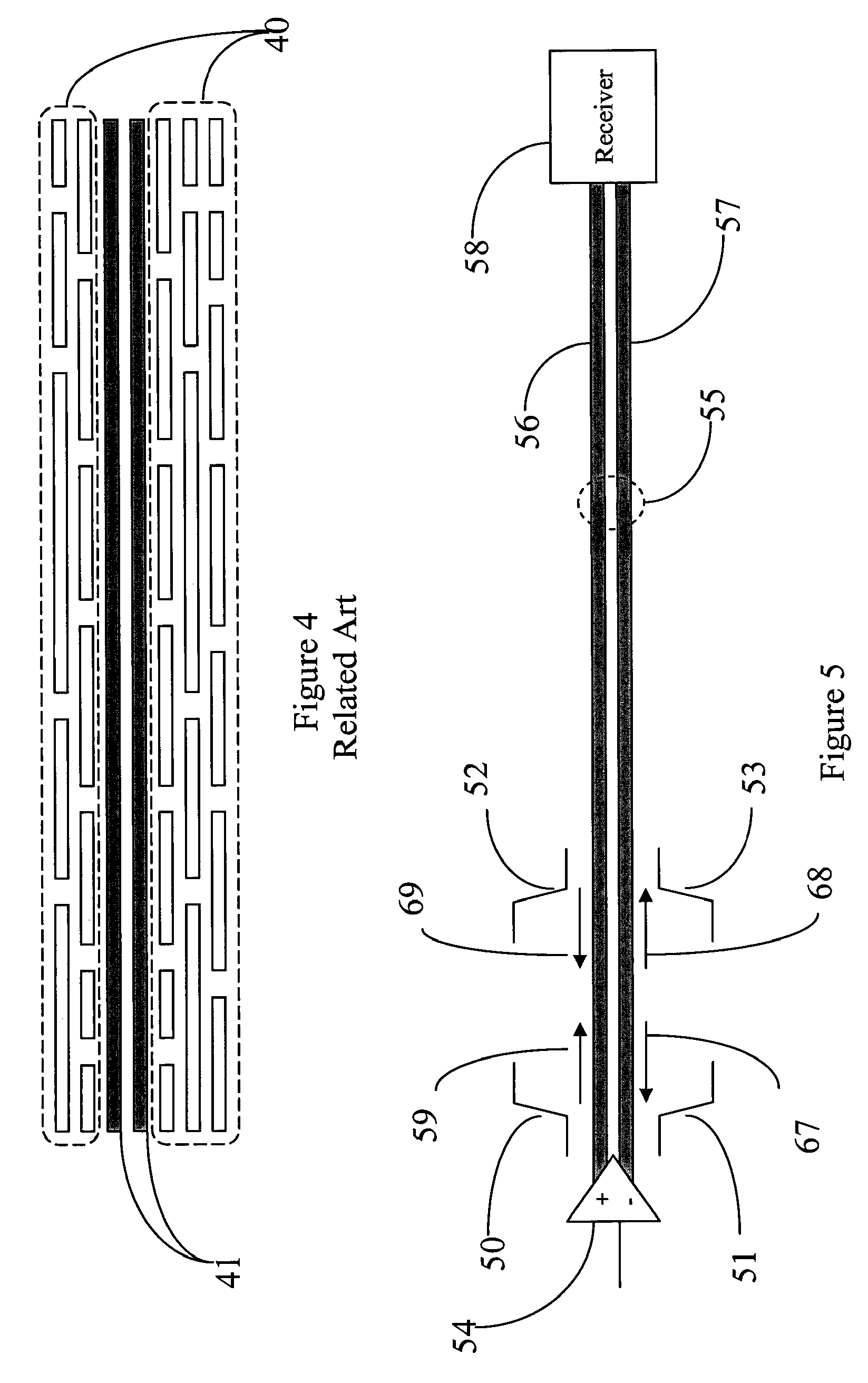

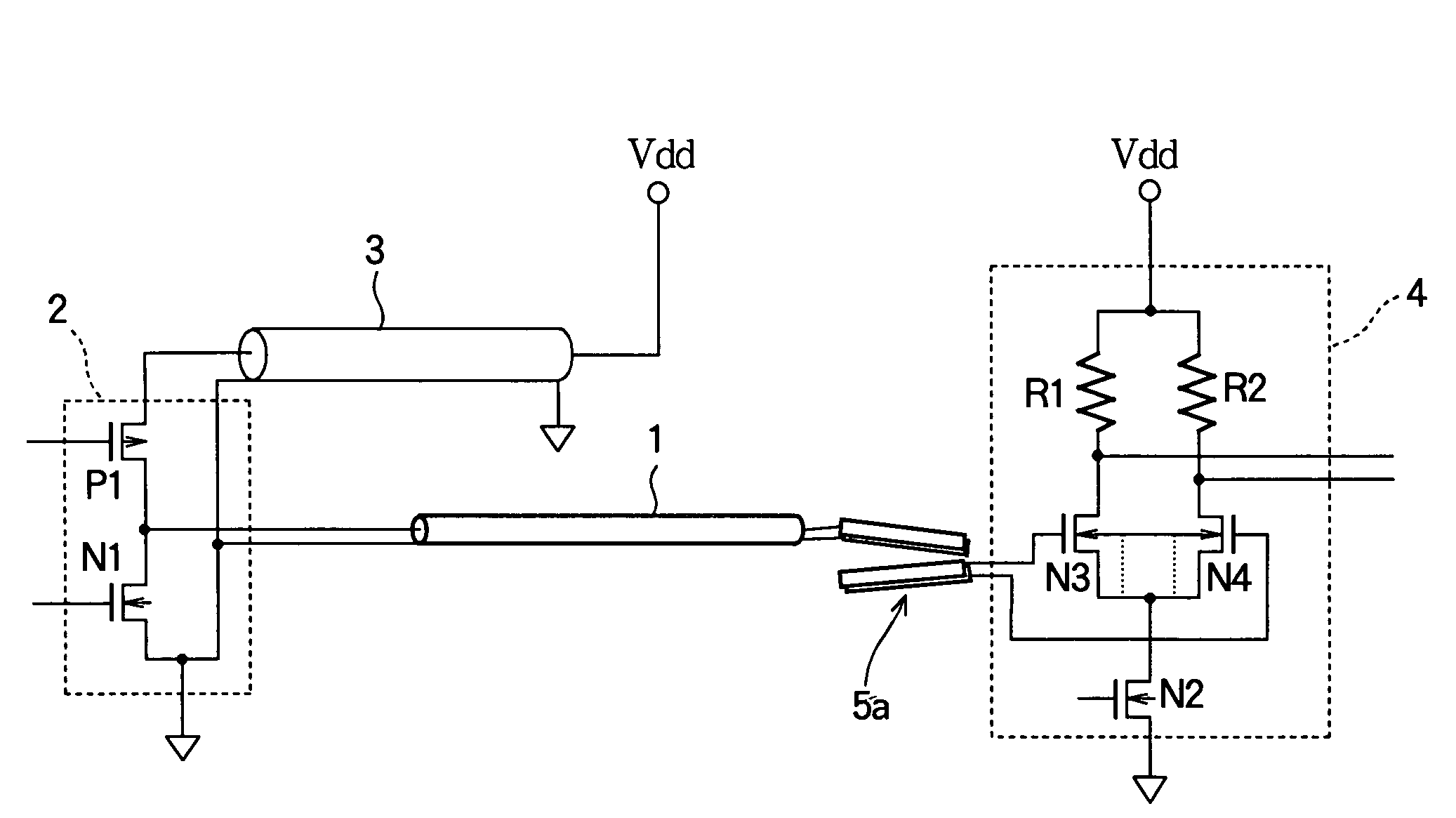

Signal transmission apparatus and interconnection structure

ActiveUS7446567B2Sufficient capabilitySimple and scalableReliability increasing modificationsBatteries circuit arrangementsLine pairHarmonic

Apparatus for transmitting a digital signal within, for example, an integrated circuit includes a signal transmission line with a directional coupler at one or both ends. The directional coupler blocks the direct-current component of the digital signal while transmitting the alternating-current component, including enough higher harmonics to transmit a well-defined pulse waveform. A suitable directional coupler consists of two adjacent line pairs in materials with different dielectric constants. The apparatus may also include a driver of the inverter type, a receiver of the differential amplifier type, a terminating resistor, and a power-ground transmission line pair for supplying power to the driver. An all-metallic transmission-line structure is preferably maintained from the output interconnections in the driver to the input interconnections in the receiver.

Owner:PANASONIC CORP +11

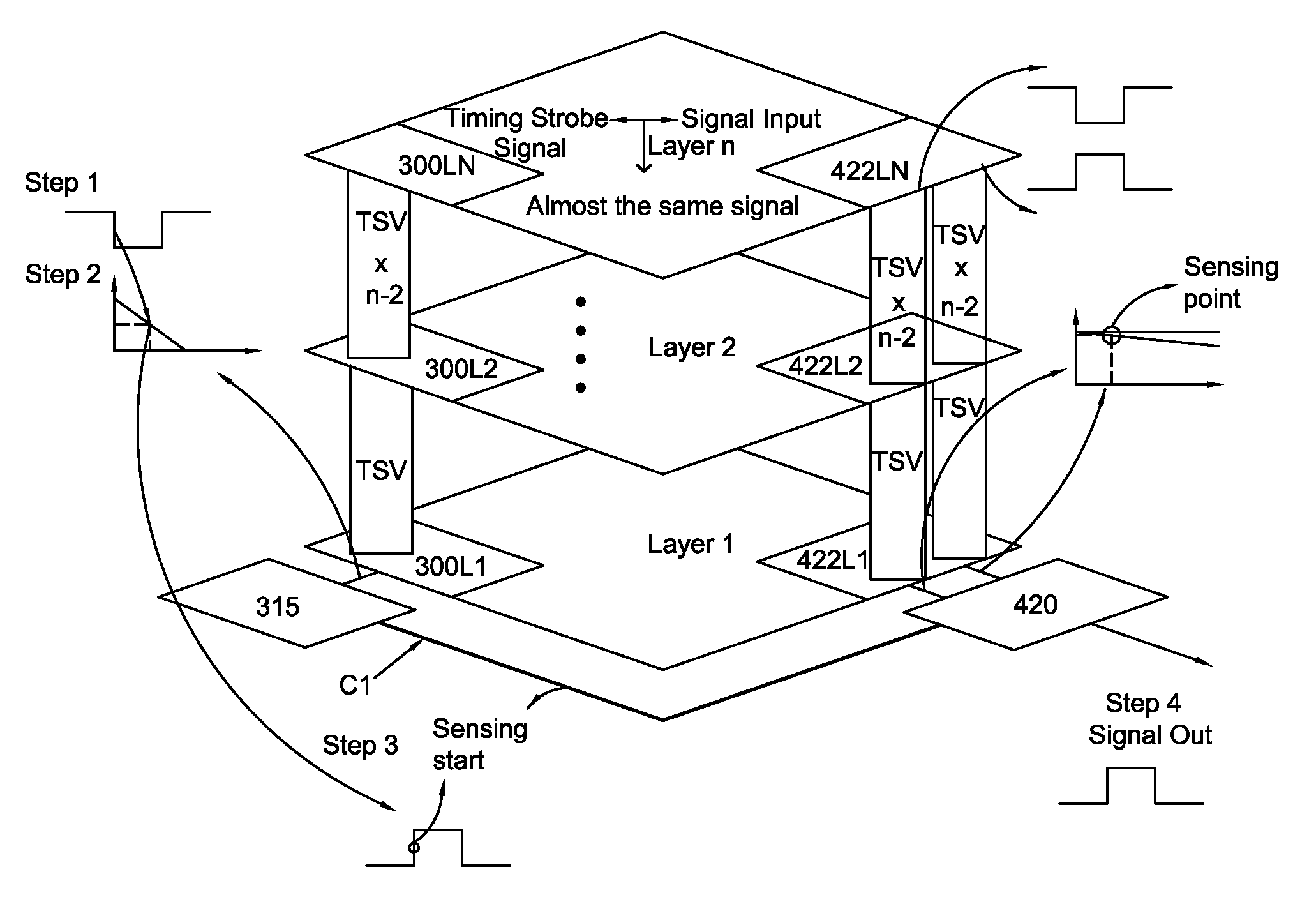

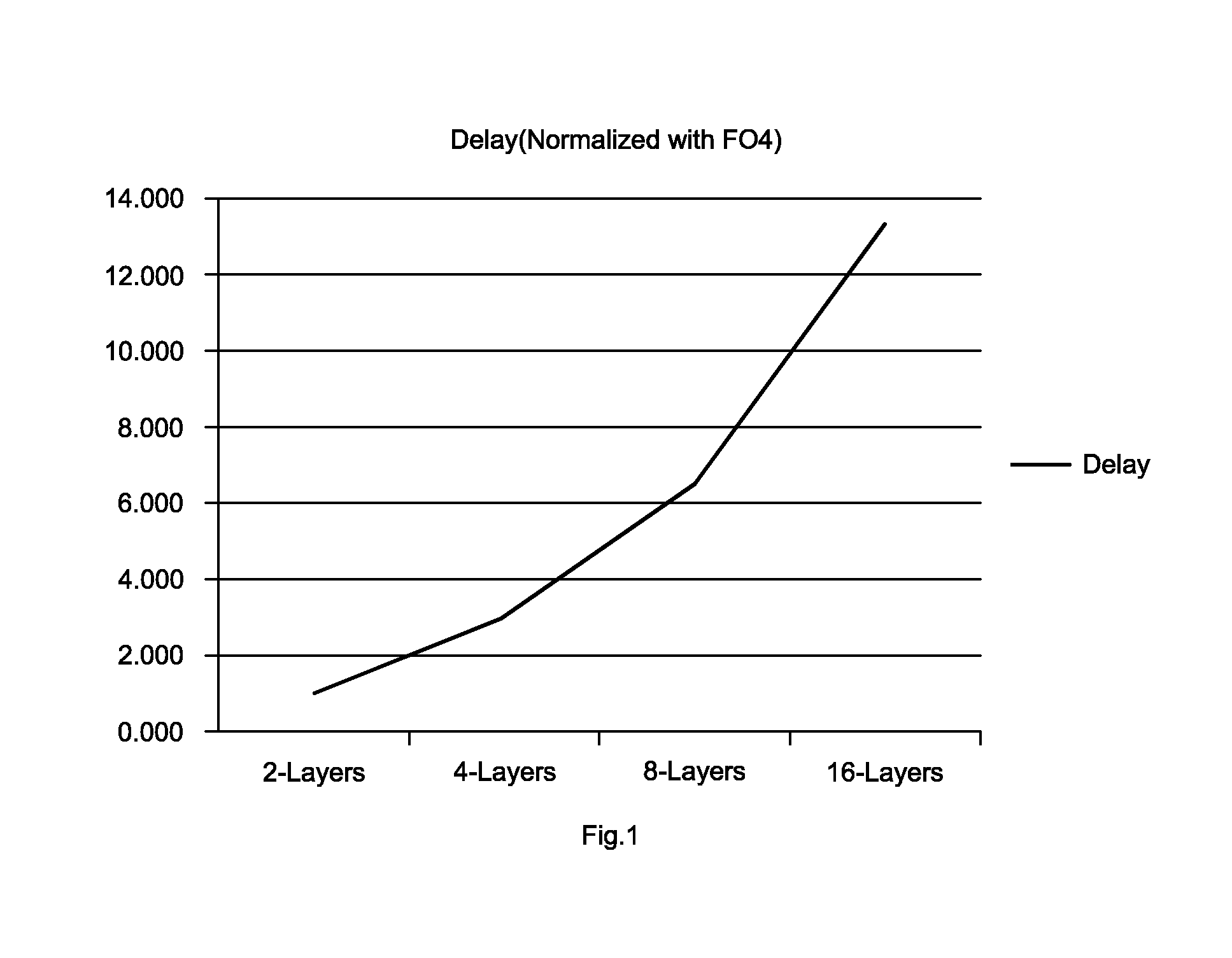

Differential sensing and TSV timing control scheme for 3D-IC

ActiveUS7969193B1Improve signal transmission speedSemiconductor/solid-state device detailsSolid-state devicesDummy loadHigh ability

This disclosure uses a differential sensing and TSV timing control scheme for 3D-IC, which includes a first chip layer of the stacked device having a detecting circuits and a relative high ability driver horizontally coupled to the detecting circuits. A sensing circuit is coupled to the detecting circuits by a horizontal line, a first differential signal driver is coupled to the sensing circuit, horizontally. The Nth chip layer of the stacked device includes a Nth relative high ability driver and a Nth differential signal driver formed on the Nth chip layer. The Nth relative high ability driver is vertically coupled to the first relative high ability driver through one relative low loading TSV and (N−2) TSVs to act as dummy loadings. The TSV and (N−2) TSVs penetrate the stacked device from Nth chip layer to first chip layer. The TSV shares same configuration with the (N−2) TSVs. The Nth differential signal driver is vertically coupled to the first differential signal driver through a pair of TSVs and (N−2) pairs of TSVs, vertically. The pair of TSVs and the (N−2) TSVs penetrate the stacked device from the Nth chip layer to the first chip layer. Each of TSV is formed between a first and a second chip layers. Each of TSV is formed between any adjacent two chip layers of the stacked device.

Owner:NATIONAL TSING HUA UNIVERSITY

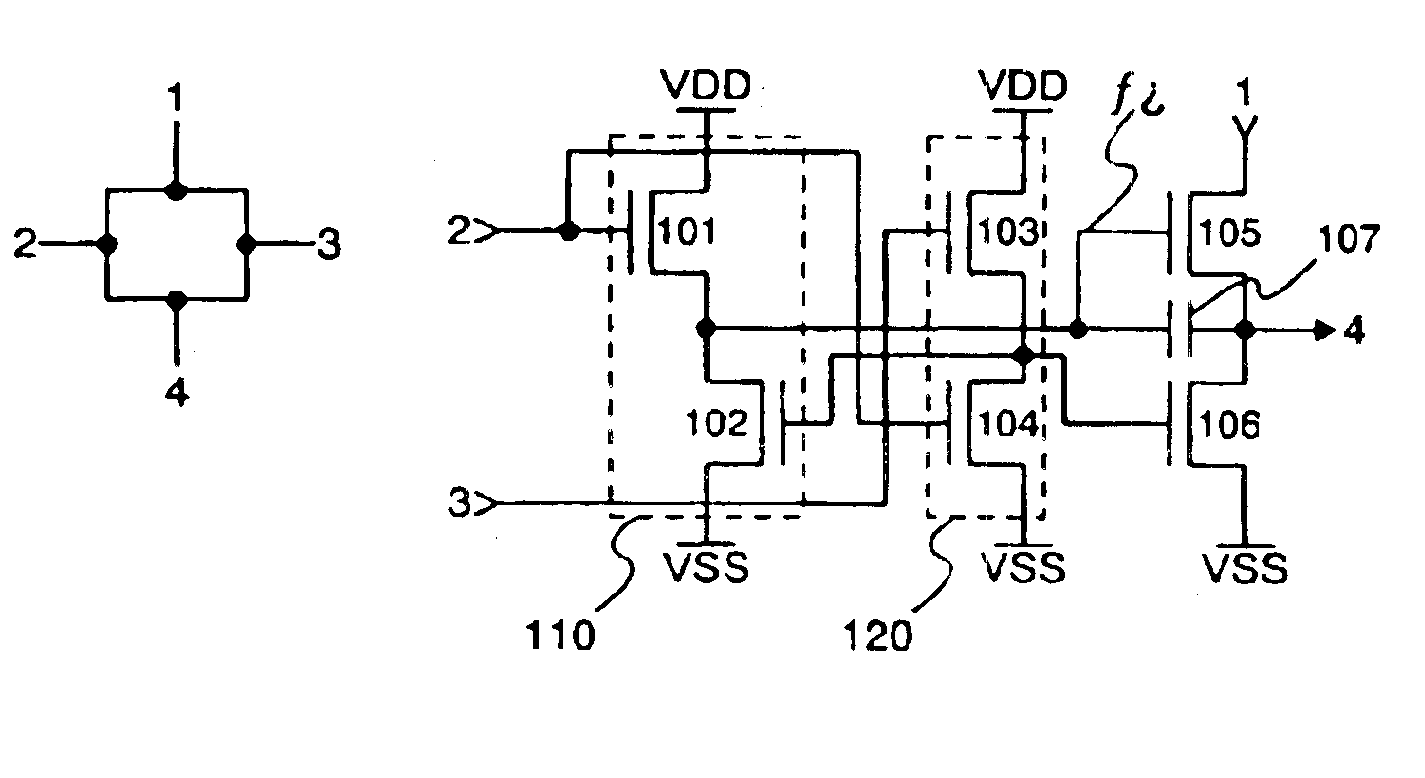

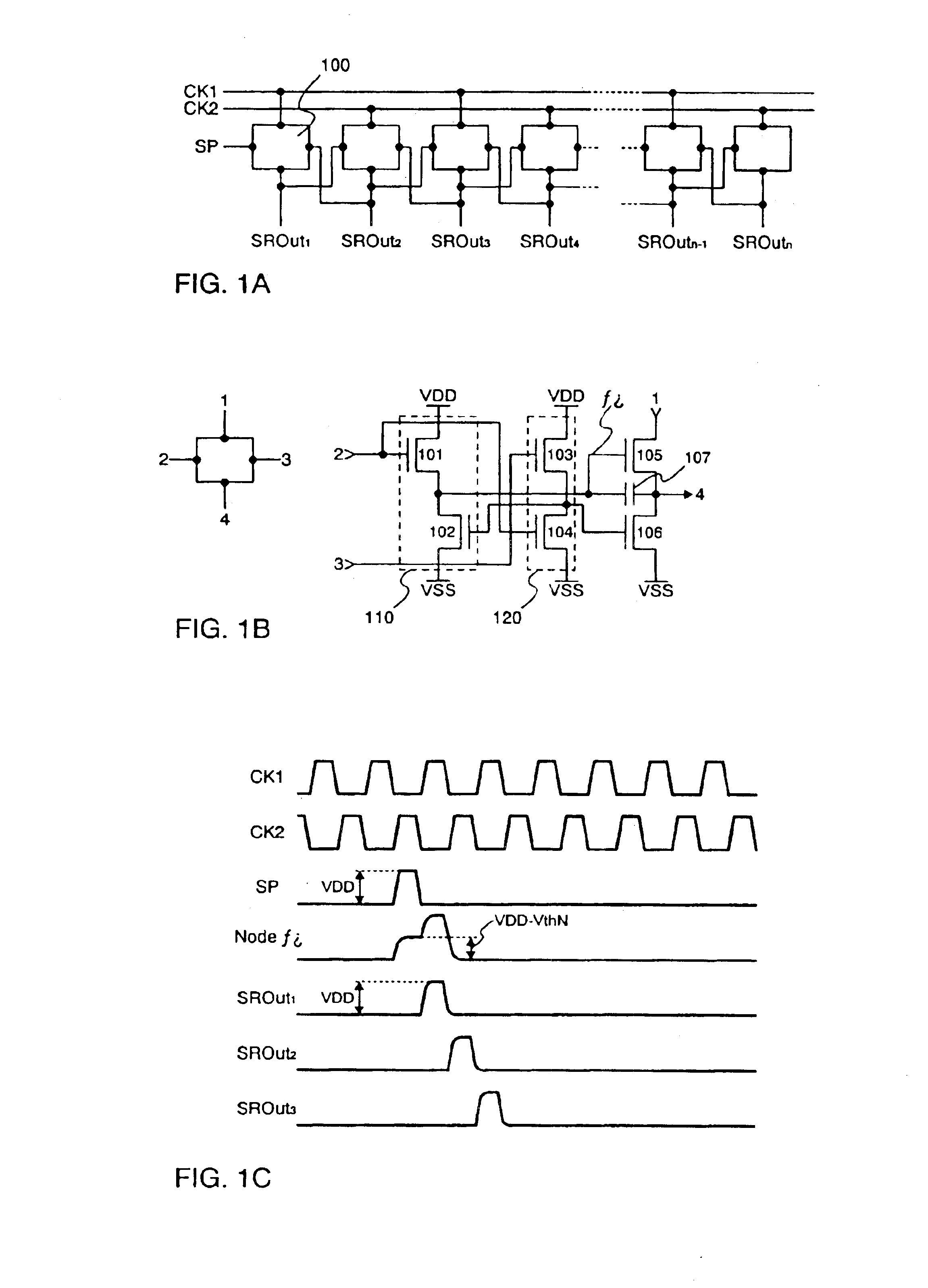

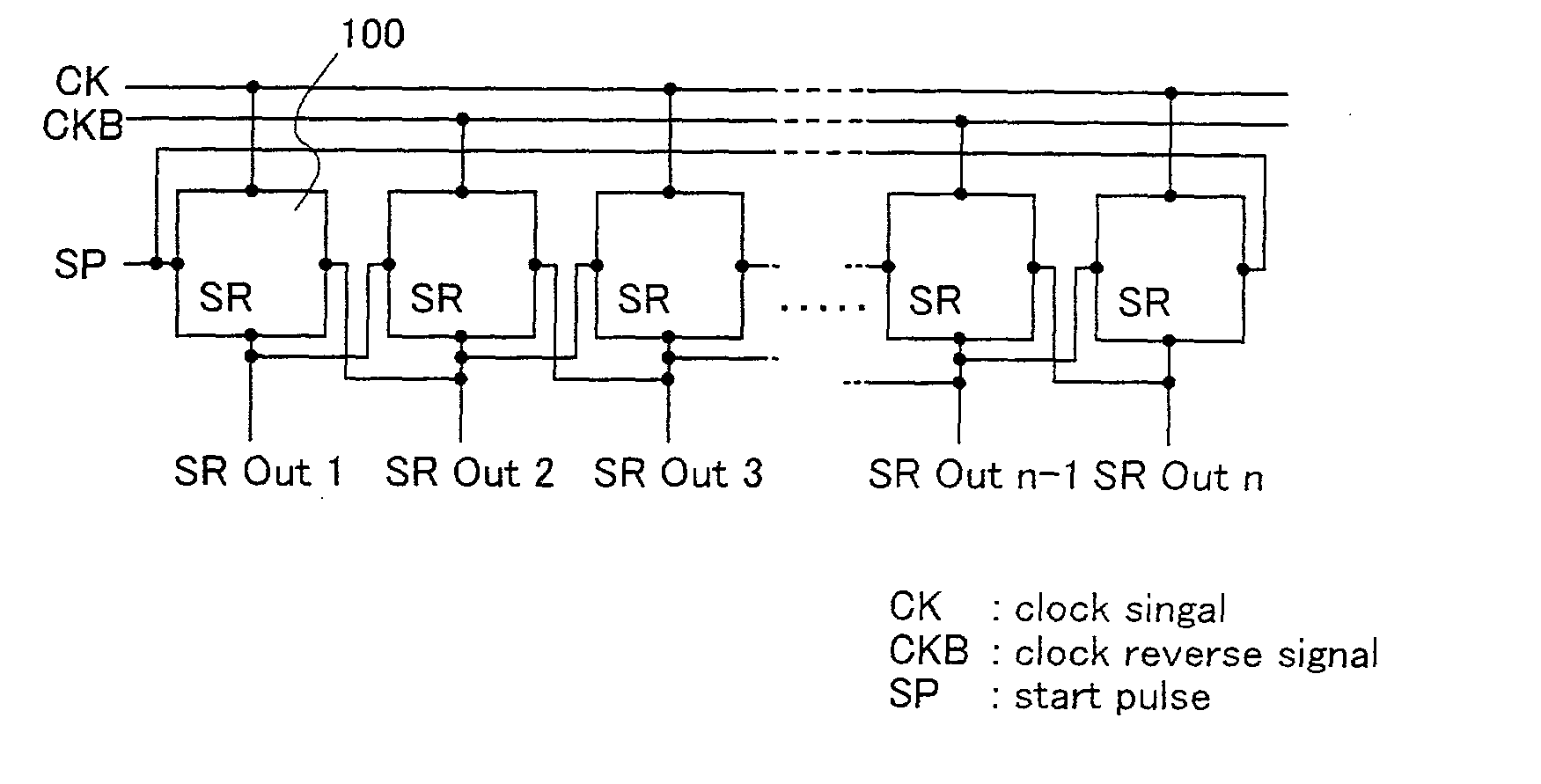

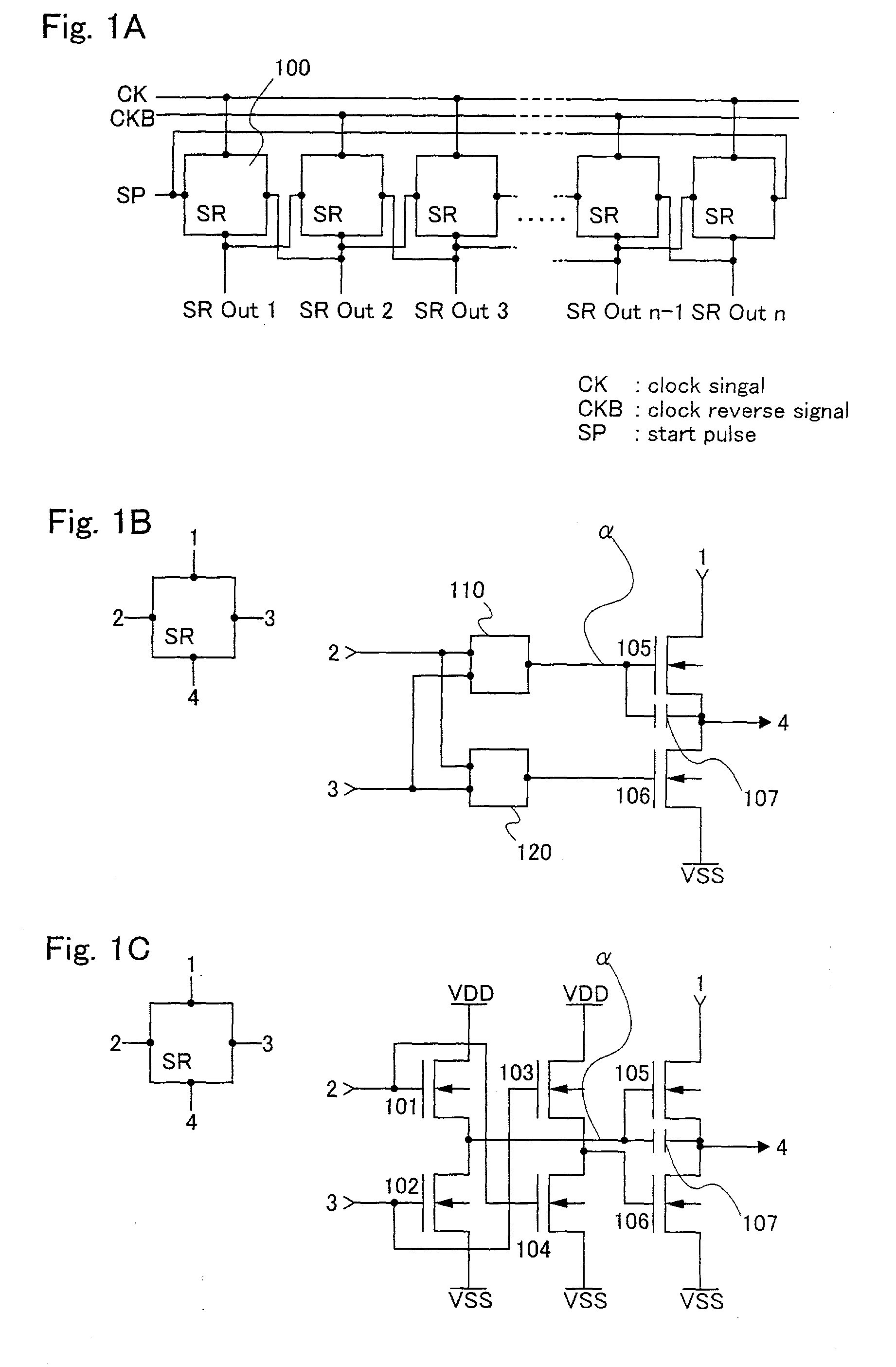

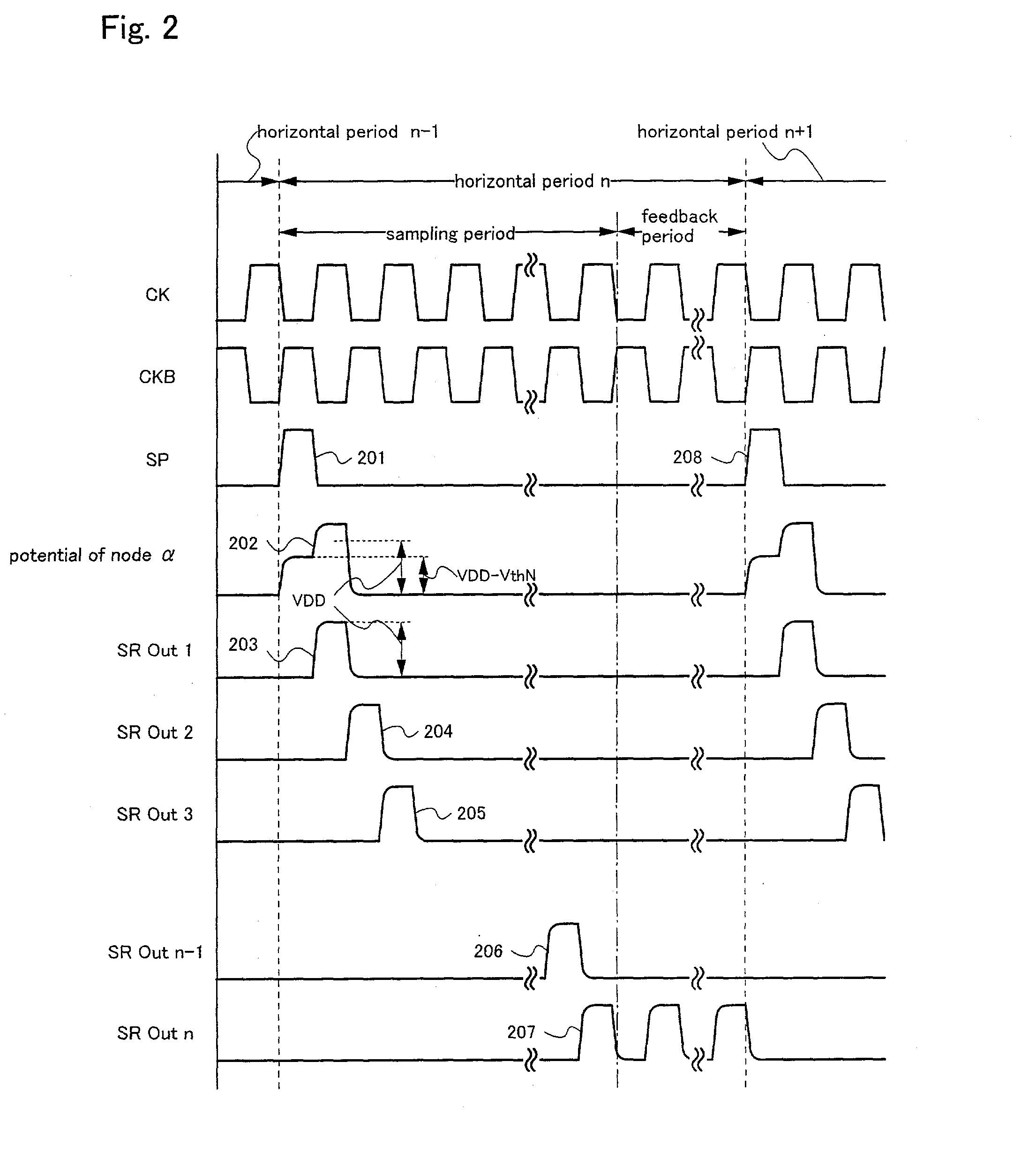

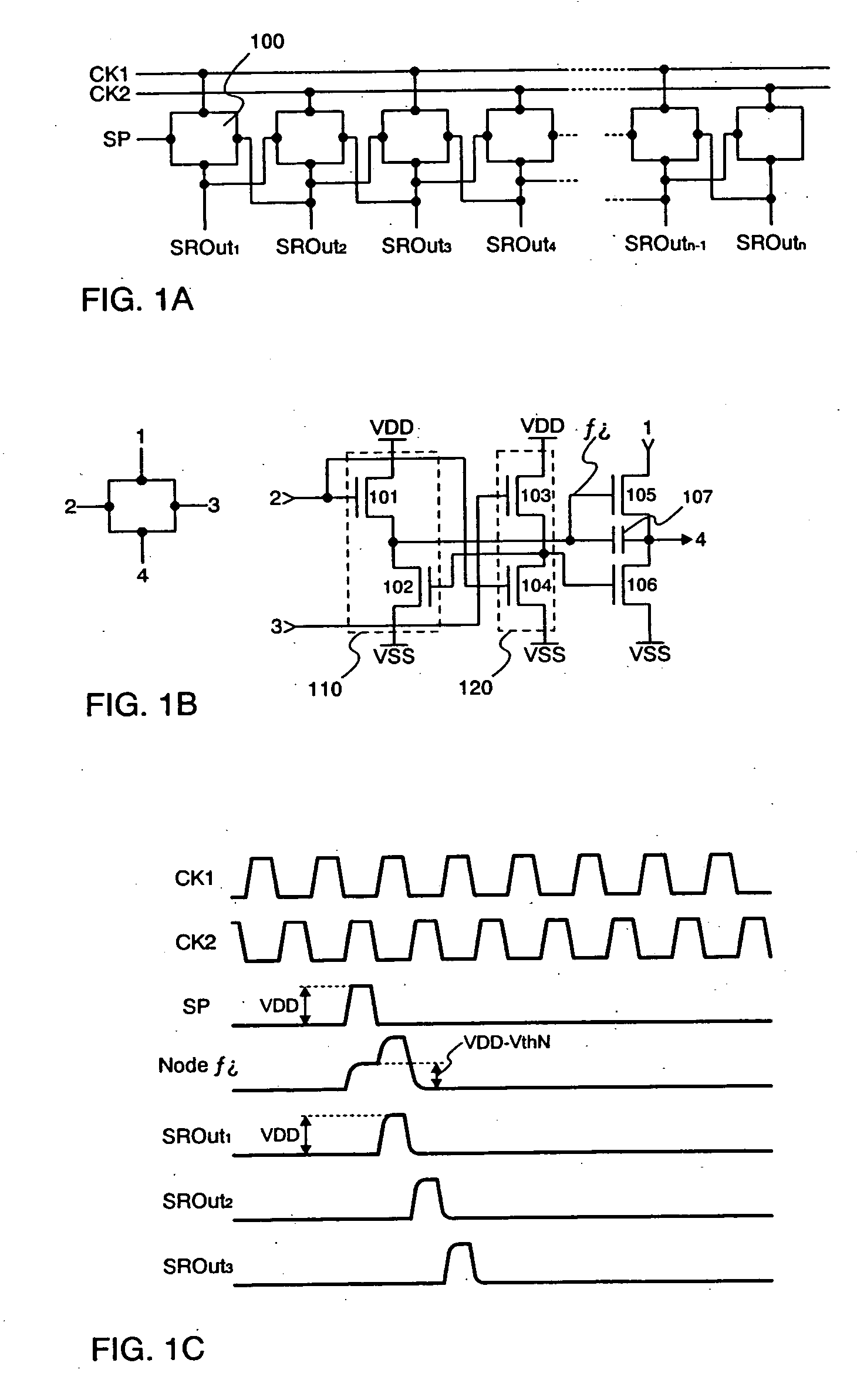

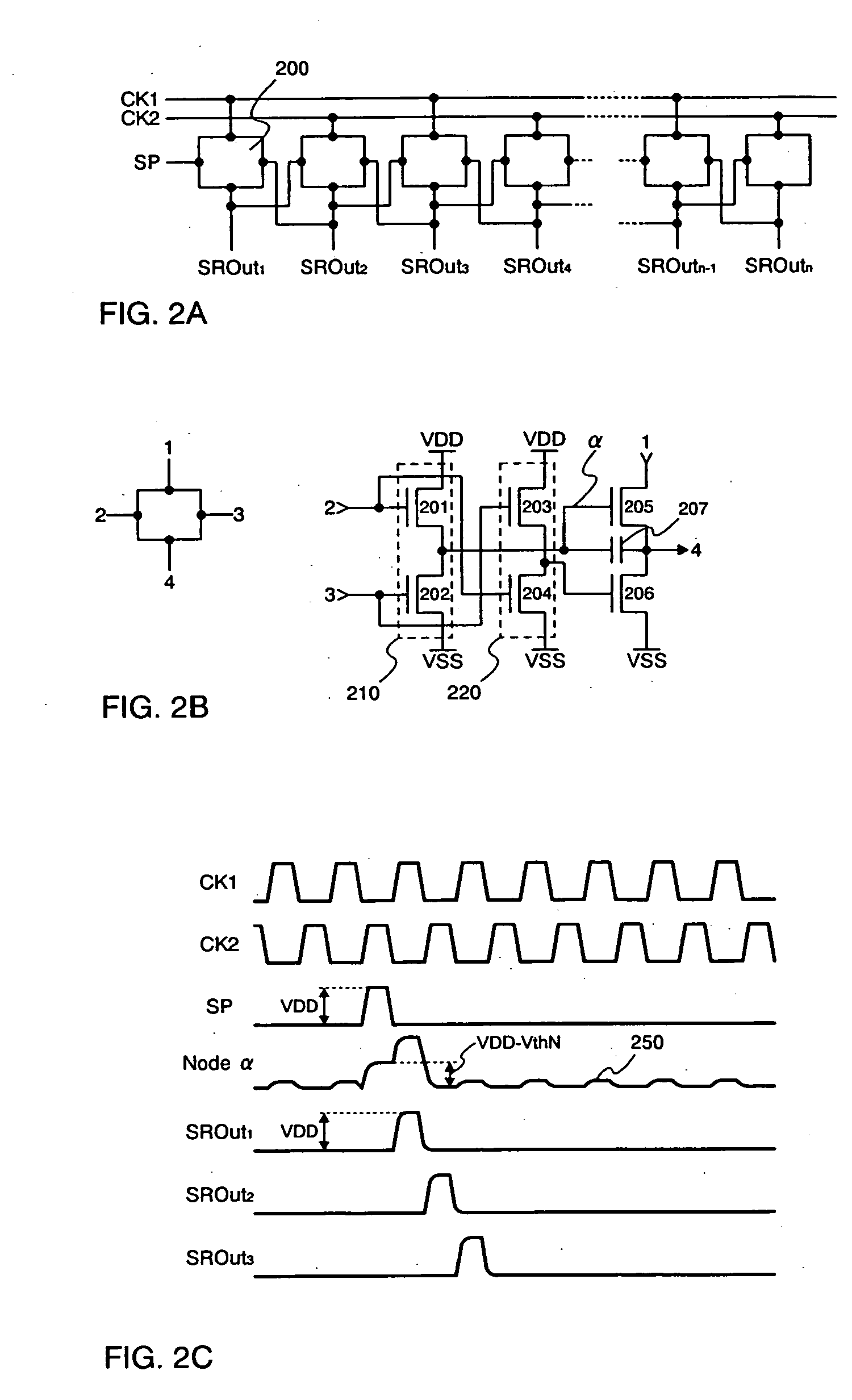

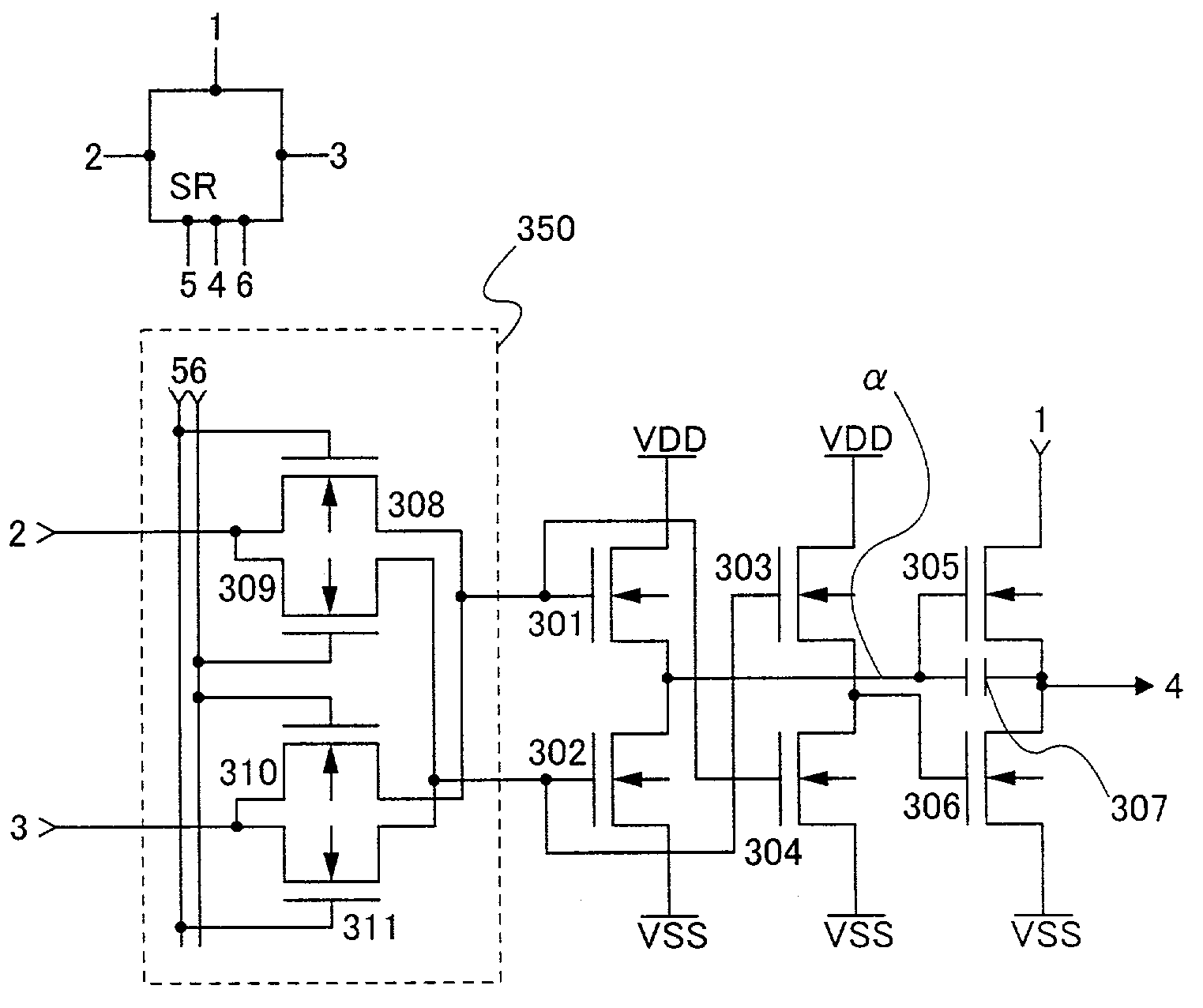

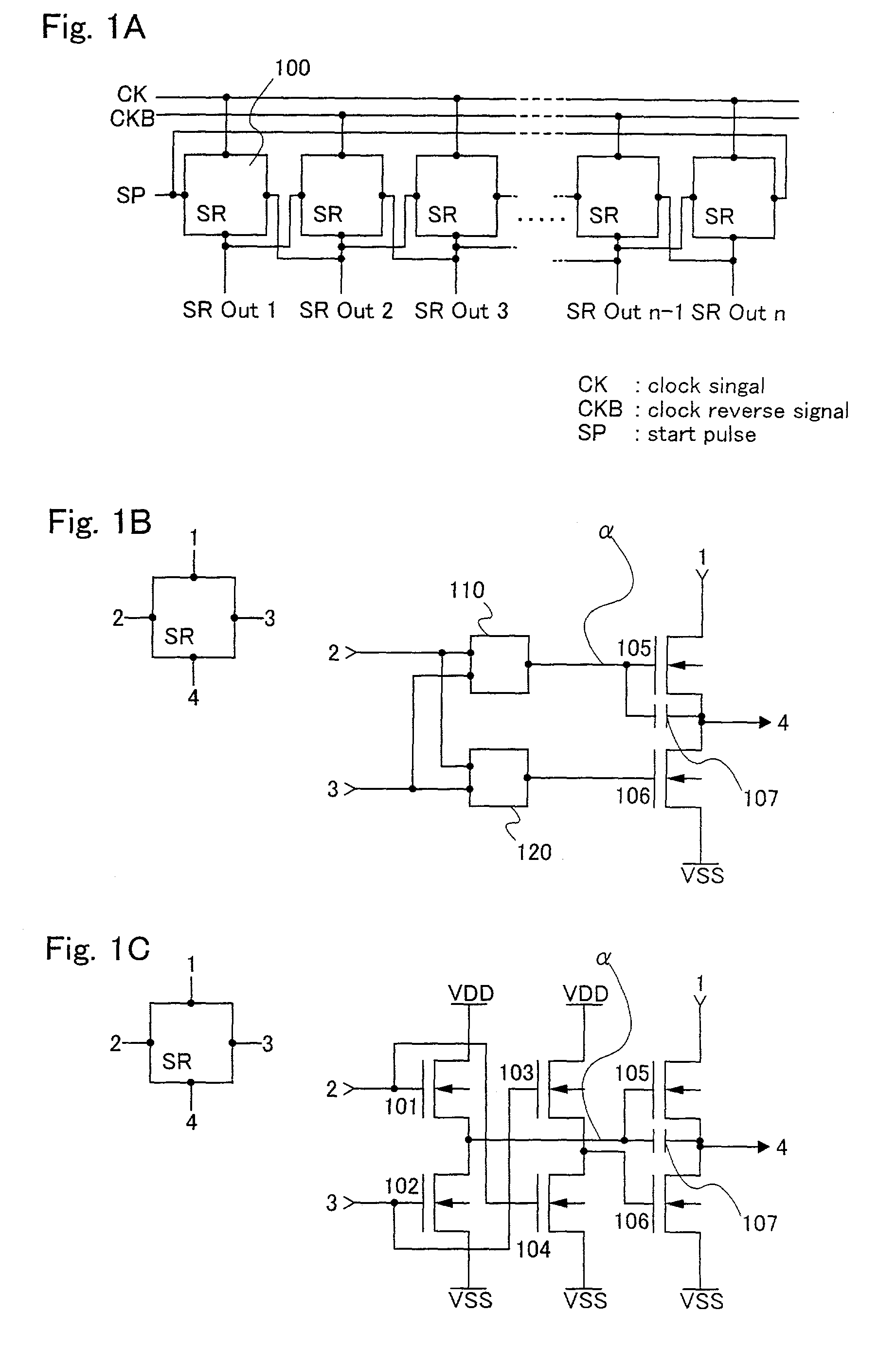

Pulse output circuit, shift register and electronic equipment

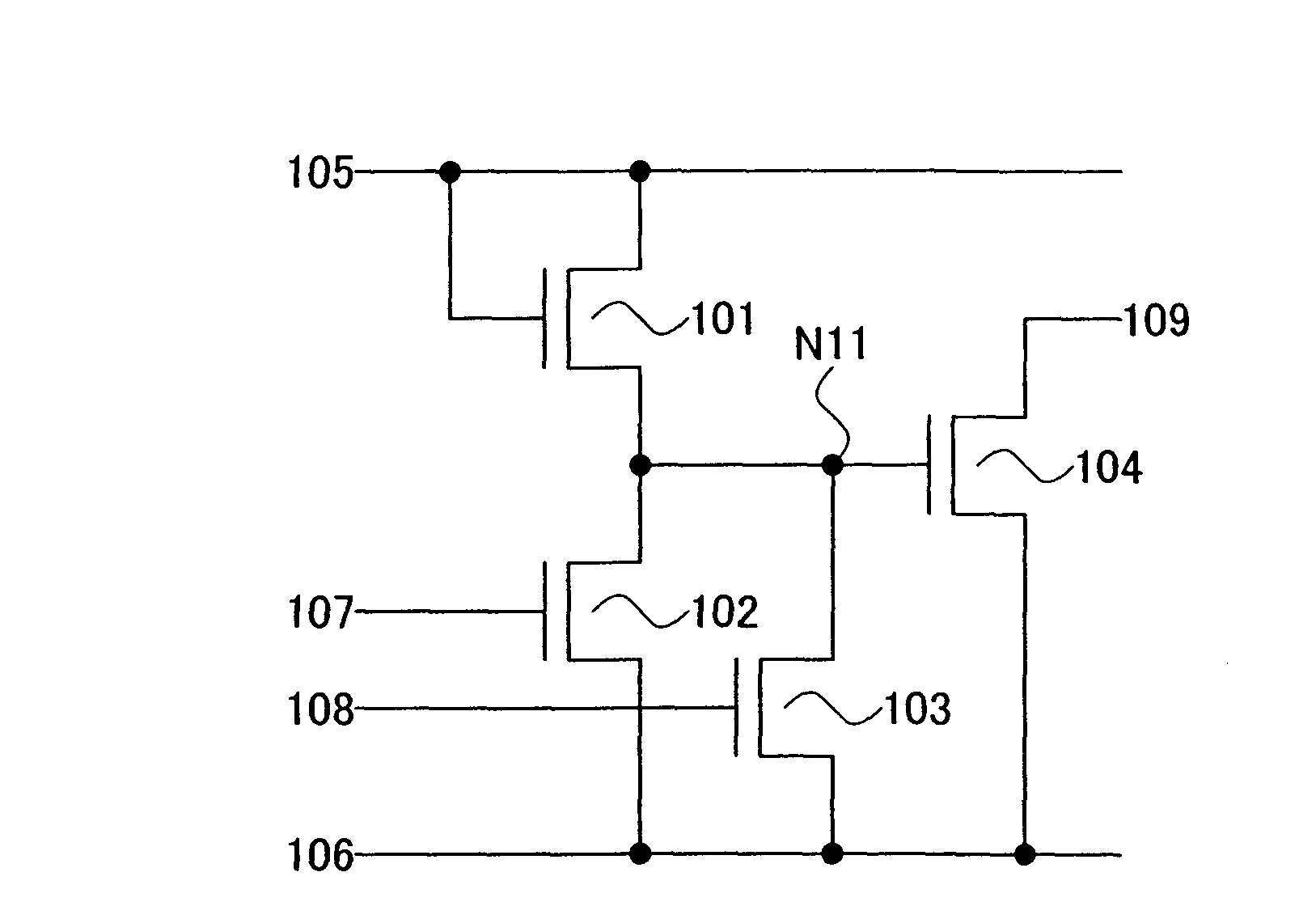

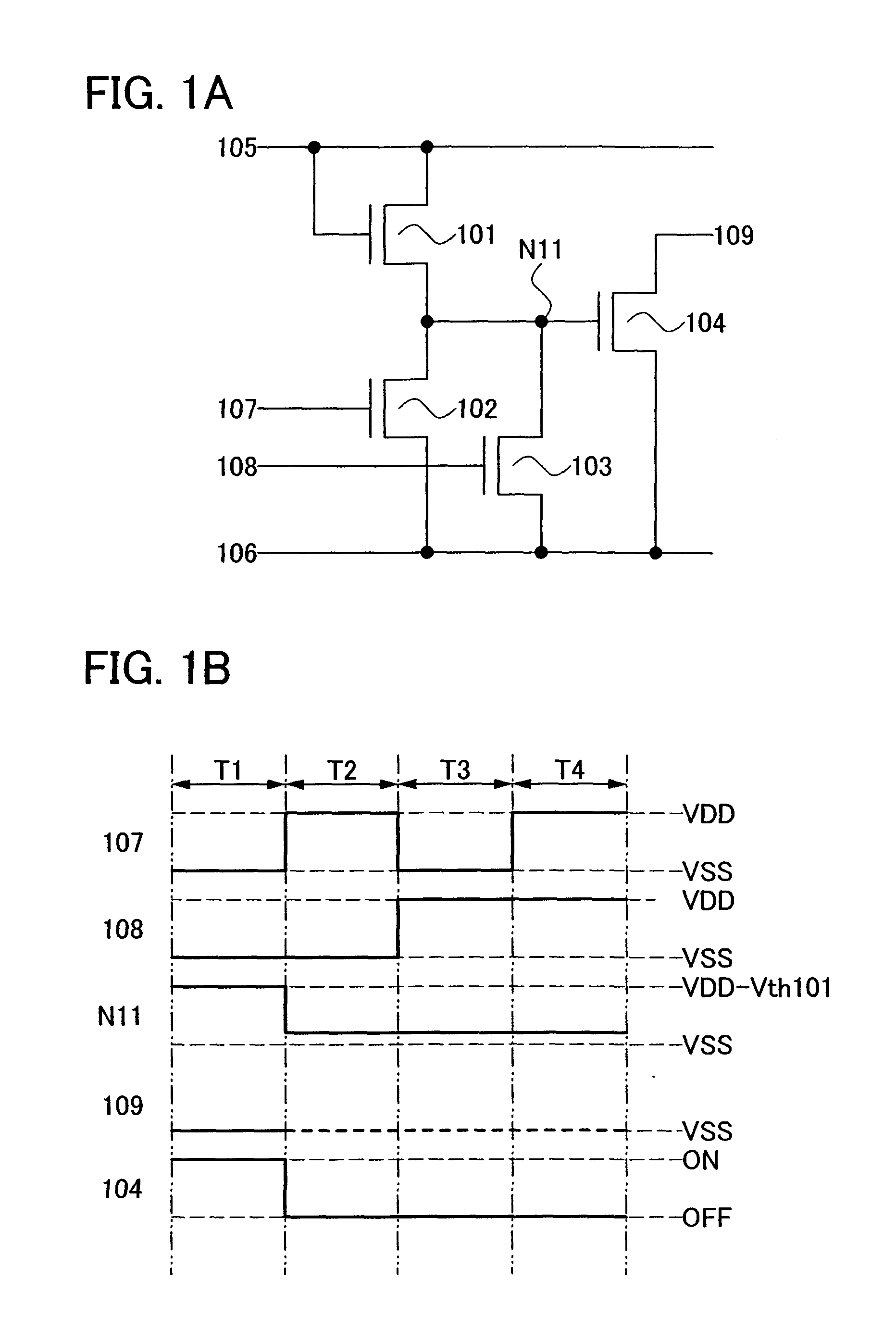

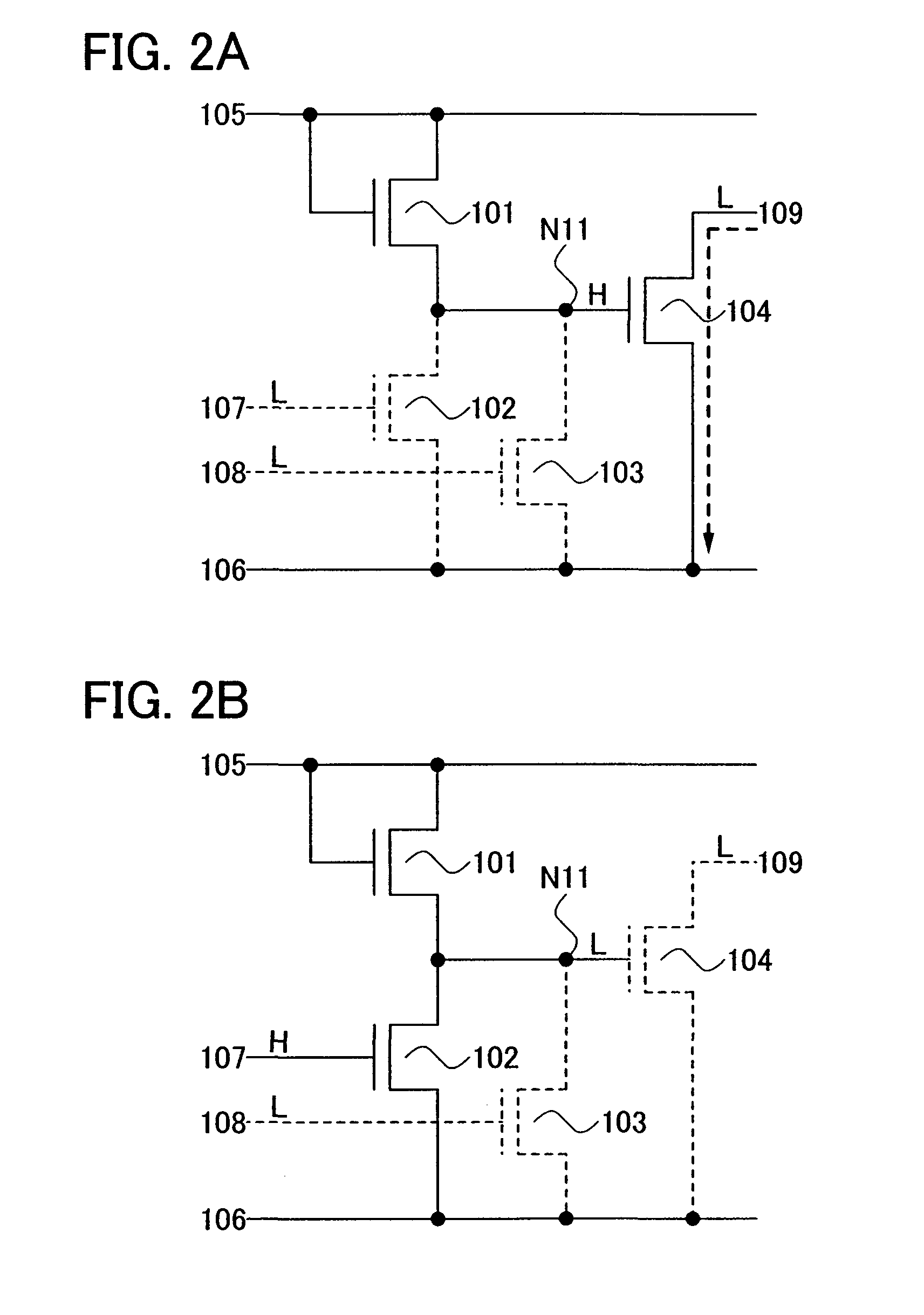

A driver circuit of a display device, which includes TFTs of a single conductivity type and outputs an output signal with normal amplitude. A pulse is inputted to TFTs 101 and 104 to turn ON the TFTs and a potential of a node alpha is raised. When the potential of the node alpha reaches (VDD-VthN), the node alpha becomes in a floating state. Accordingly, a TFT 105 is turned ON and a potential of an output node is raised as a clock signal becomes High level. On the other hand, a potential of a gate electrode of the TFT 105 is further raised due to an operation of a capacitance means 107 as the potential of the output node is raised, so that the potential of the gate electrode of the TFT 105 becomes higher than (VDD+VthN). Thus, the potential of the output node is raised to VDD without causing a voltage drop due to a threshold voltage of the TFT 105. An output at the subsequent stage is then inputted to a TFT 103 to turn the TFT 103 On, while the potential of the node alpha of TFTs 102 and 106 is dropped to turn the TFT 105 OFF. As a result, the potential of the output node becomes Low level.

Owner:SEMICON ENERGY LAB CO LTD

Cross point switch

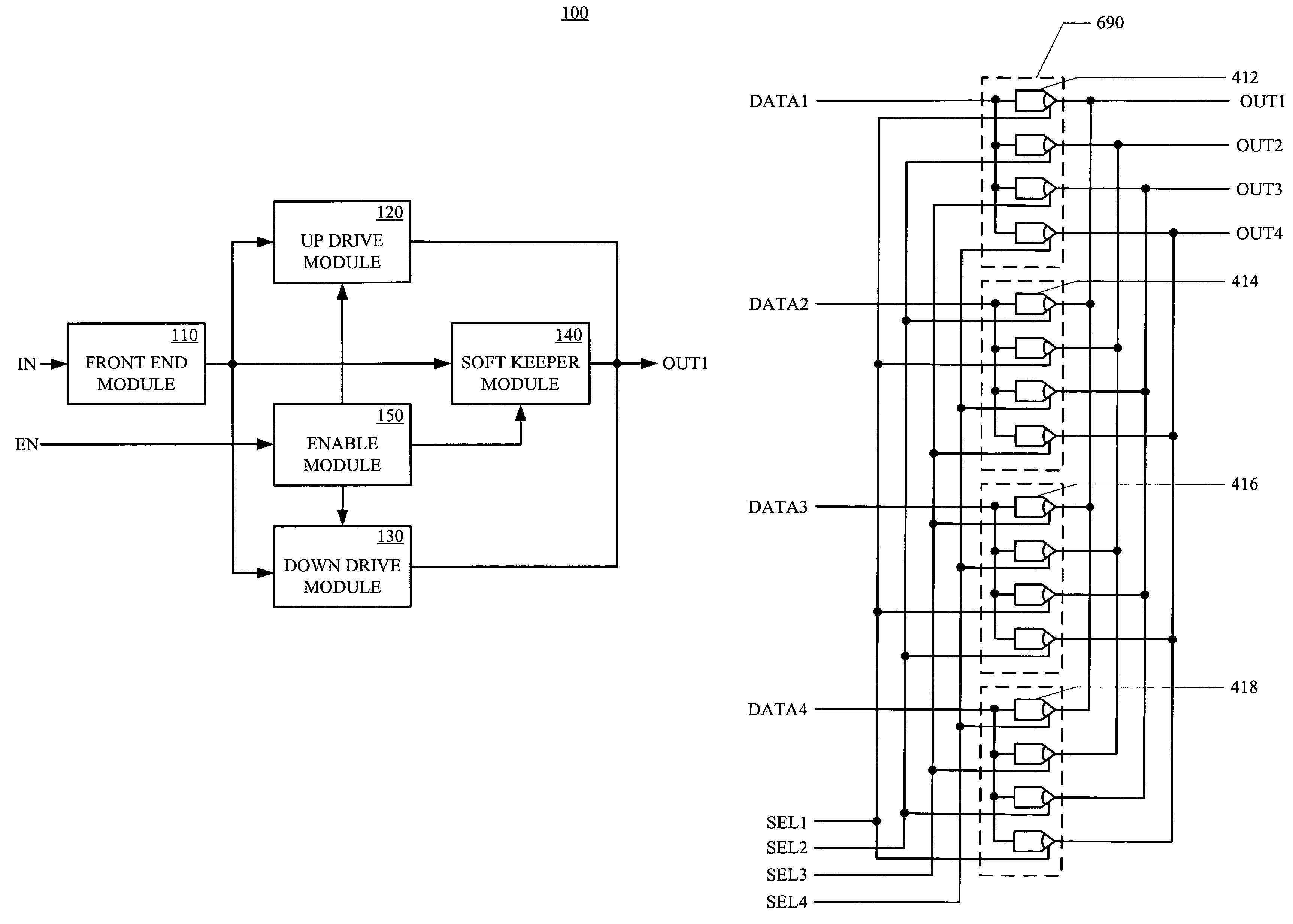

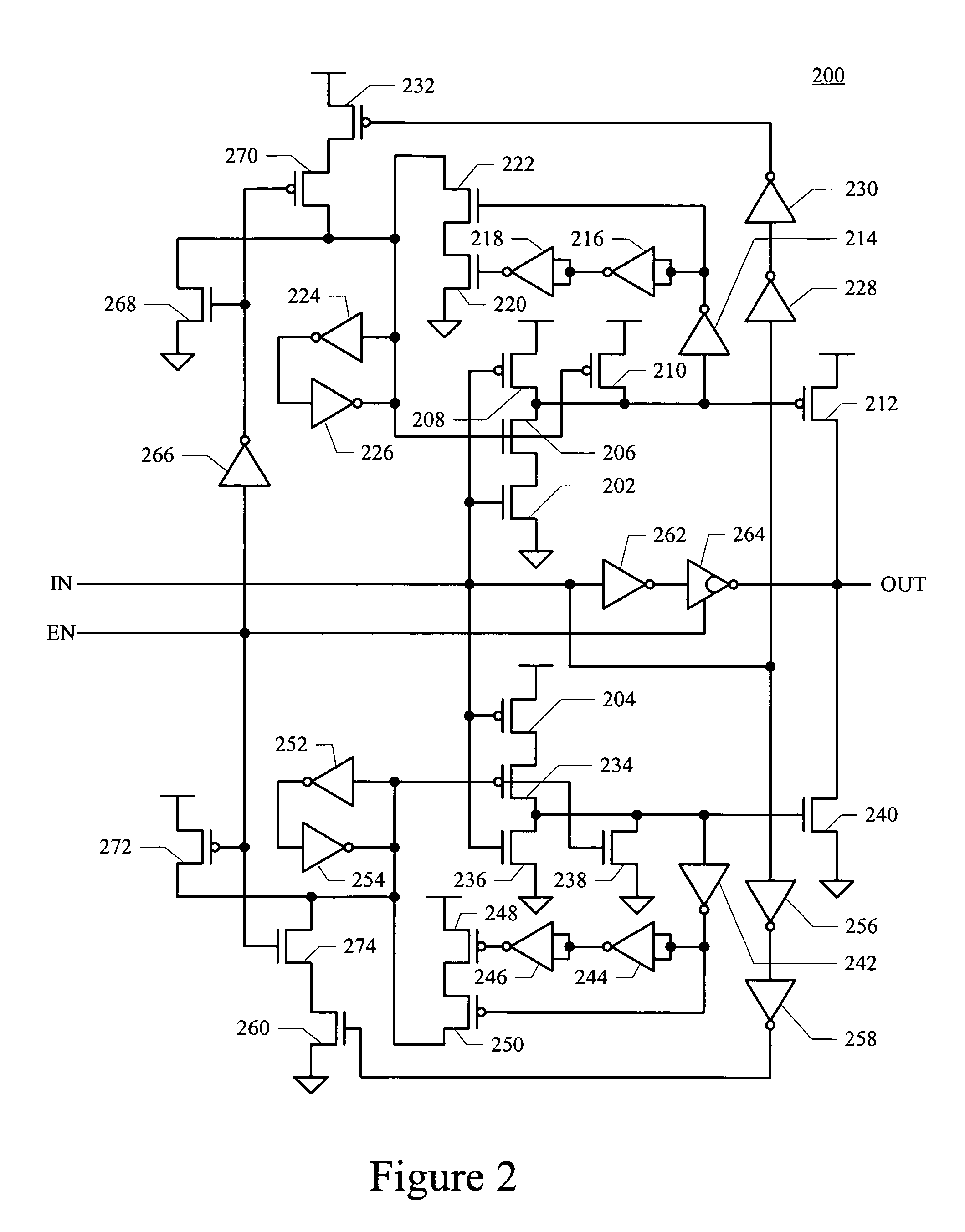

ActiveUS7710153B1Reduce delaysElectronic switchingLogic circuit coupling/interface arrangementsCapacitanceMultiplexer

A cross point switch, in accordance with one embodiment of the present invention, includes a plurality of tri-state repeaters coupled to form a plurality of multiplexers. Each set of corresponding tri-state repeaters in the plurality of multiplexers share a front end module such that delay through the cross point switch due to input capacitance is reduced as compared to conventional cross point switches.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

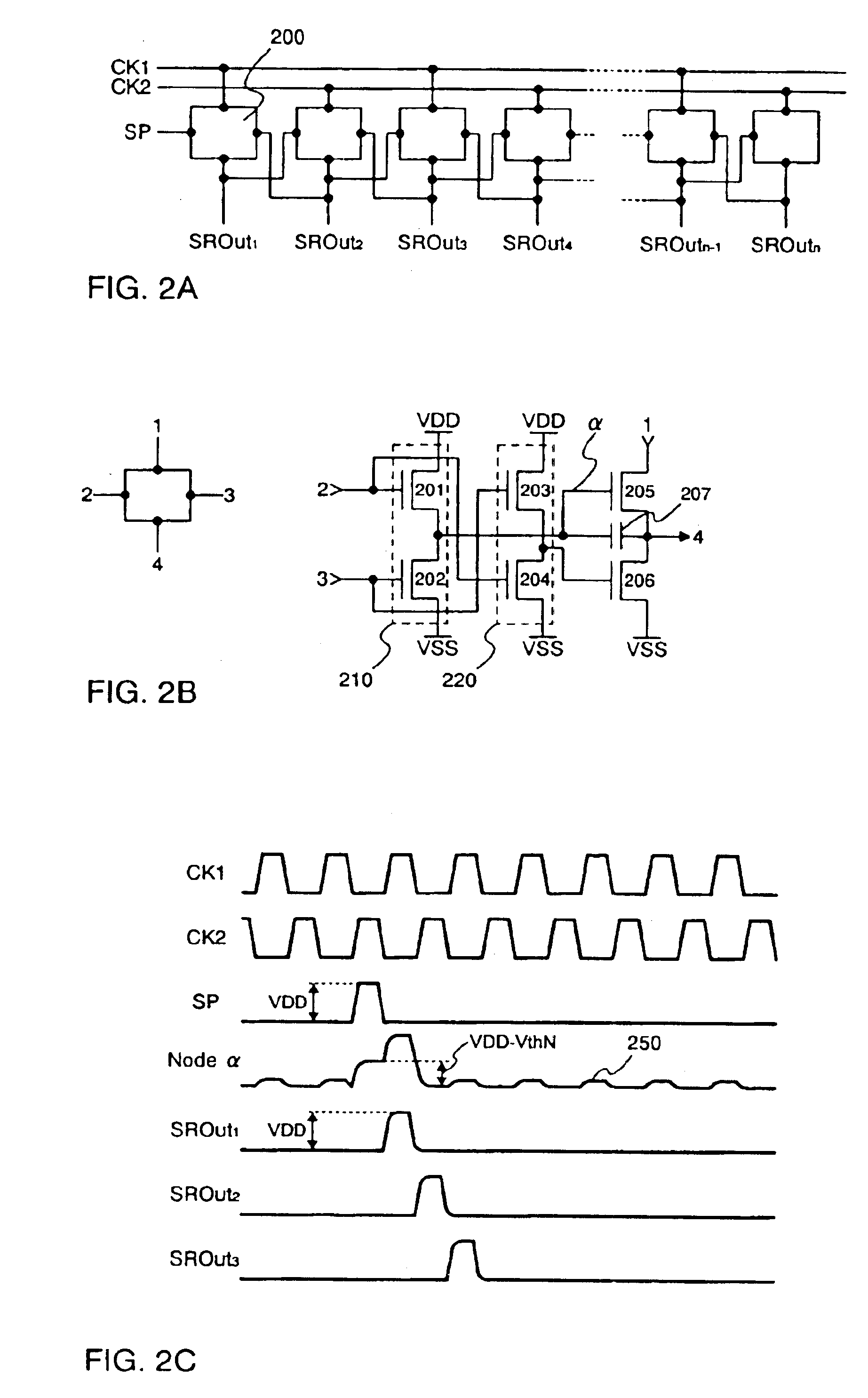

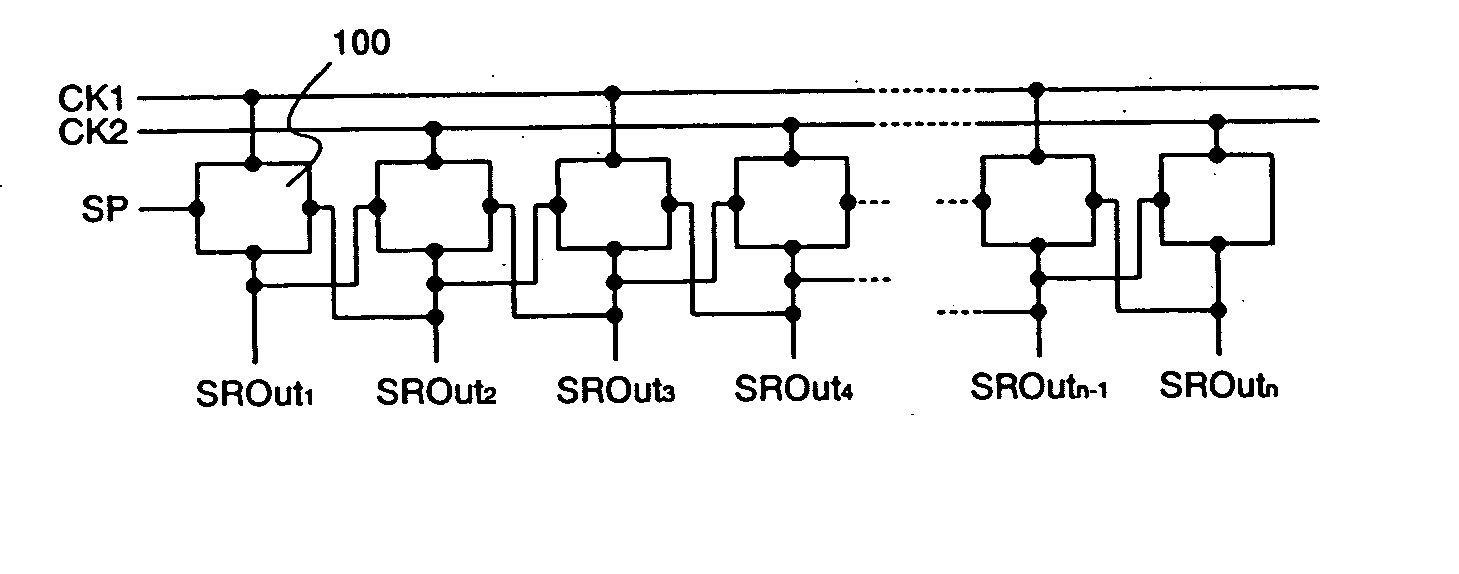

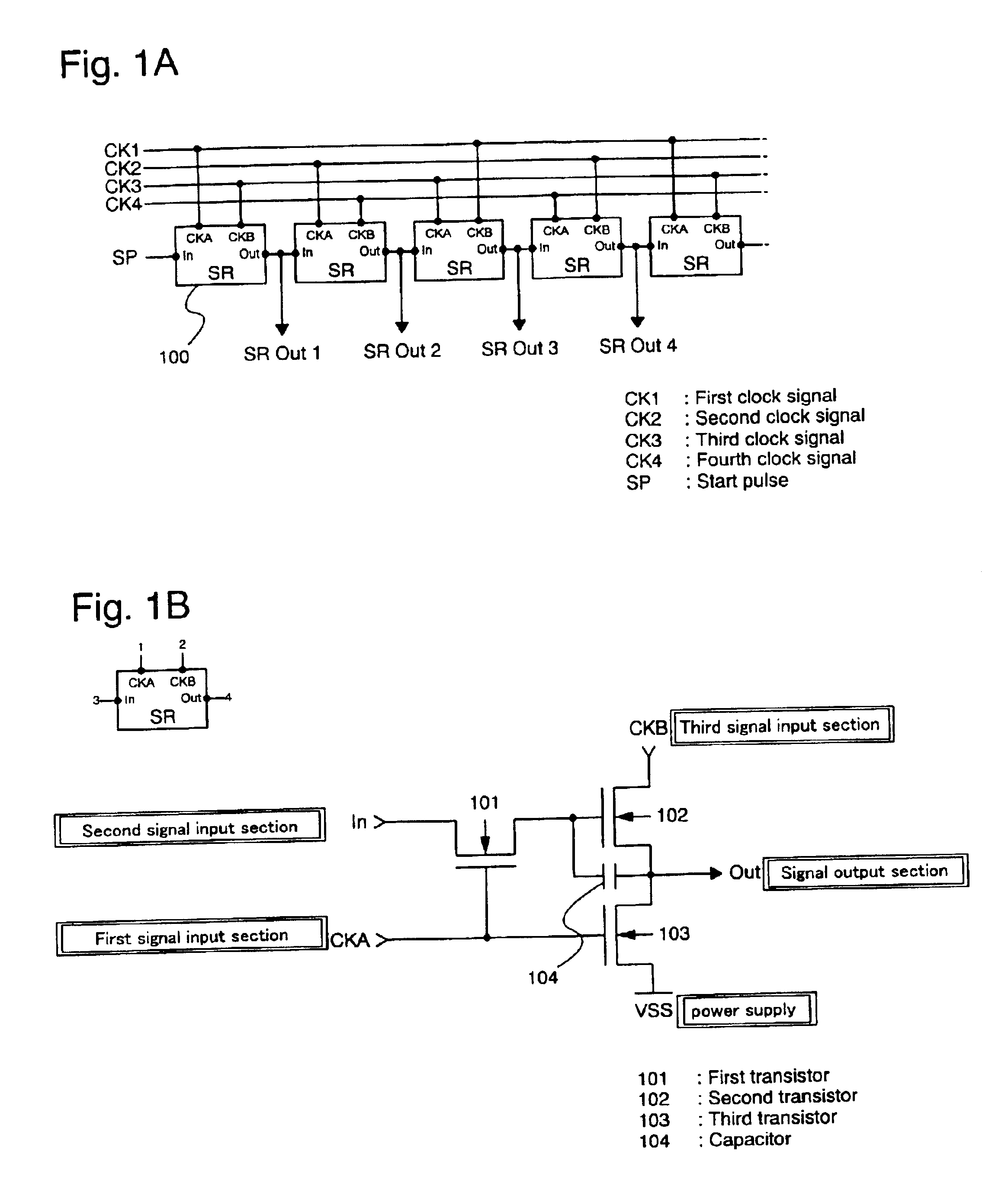

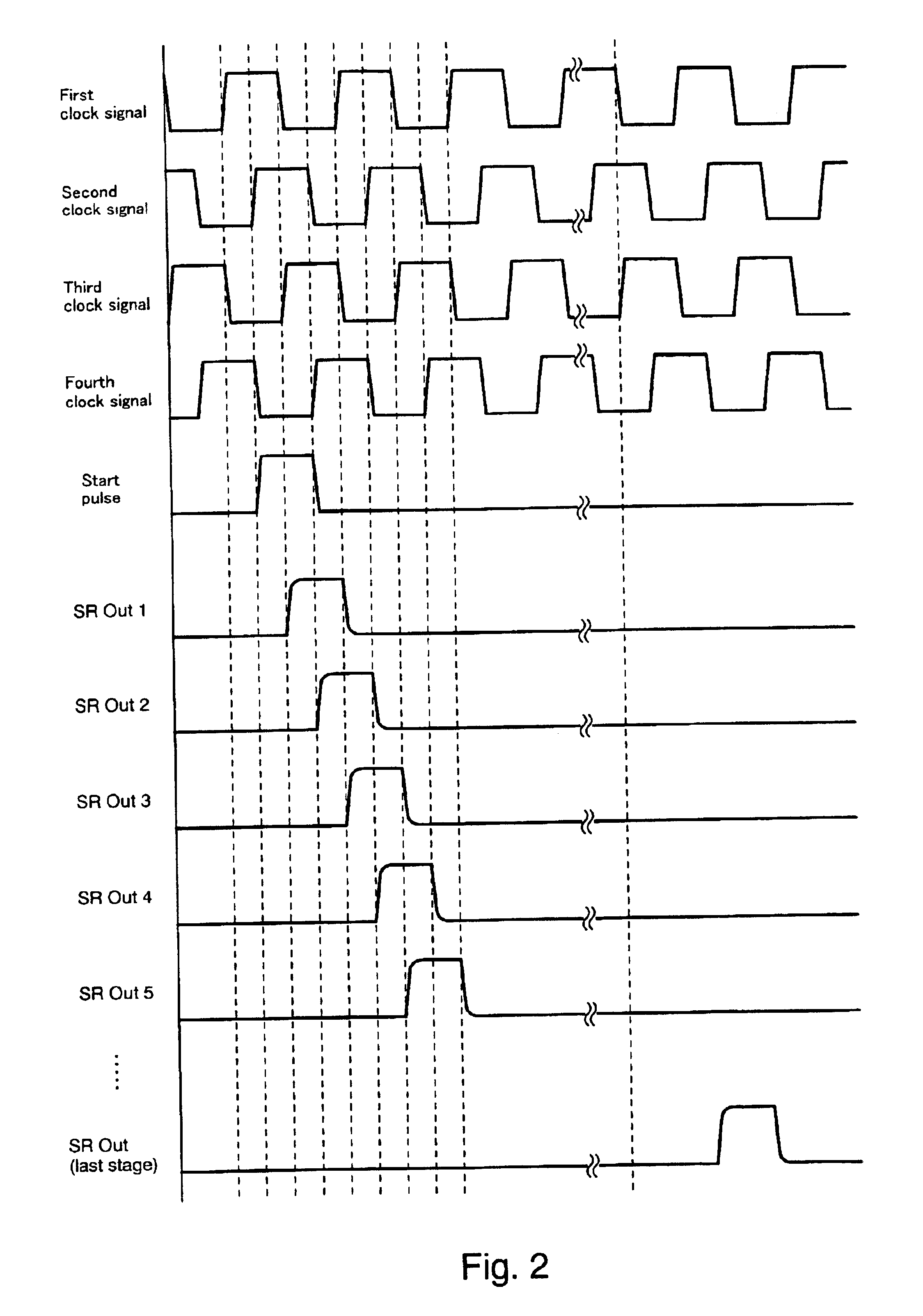

Pulse output circuit, shift register and display device

A drive circuit of a display device, which comprise only single conductive TFTs and in which amplitude of an output signal is normal, is provided. A pulse is inputted to TFTs 101 and 104 so that the TFTs would turn ON and then potential of a node á rises. When the potential of the node á reaches (VDD-VthN), the node á became in a floating state. Accordingly, a TFT 105 then turns ON, and potential of an output node rises as a clock signal reaches the level H. On the other hand, potential of a gate electrode of the TFT 105 further rises due to an operation of capacitance 107 as the potential of the output node rises, so that the potential of the output node would be higher than (VDD+VthN). Thus, the potential of the output node rises to VDD without voltage drop caused by a threshold of the TFT 105. An output at the subsequent stage is then inputted to TFTs 102 and 103 to turn the TFTs 102 and 103 ON, while the potential of the node á drops down to turn the TFT 105 OFF. A TFT 106 turns ON at the same time so that the potential of the output node would reach the level L.

Owner:SEMICON ENERGY LAB CO LTD

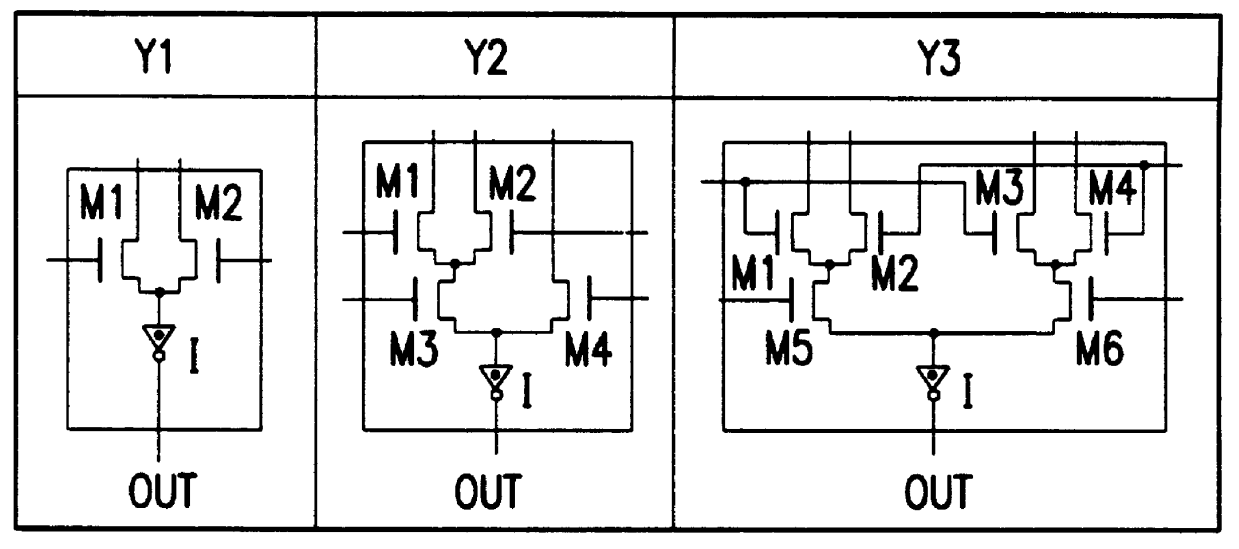

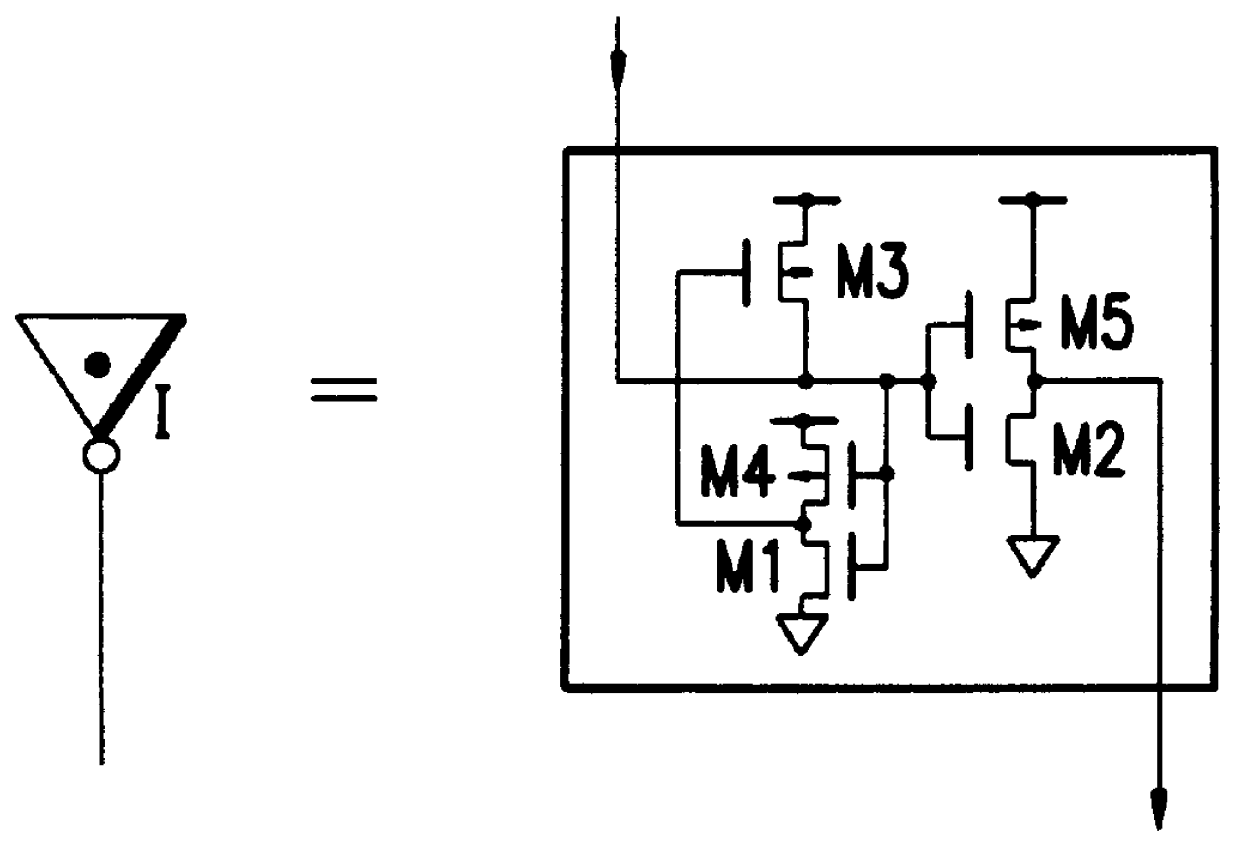

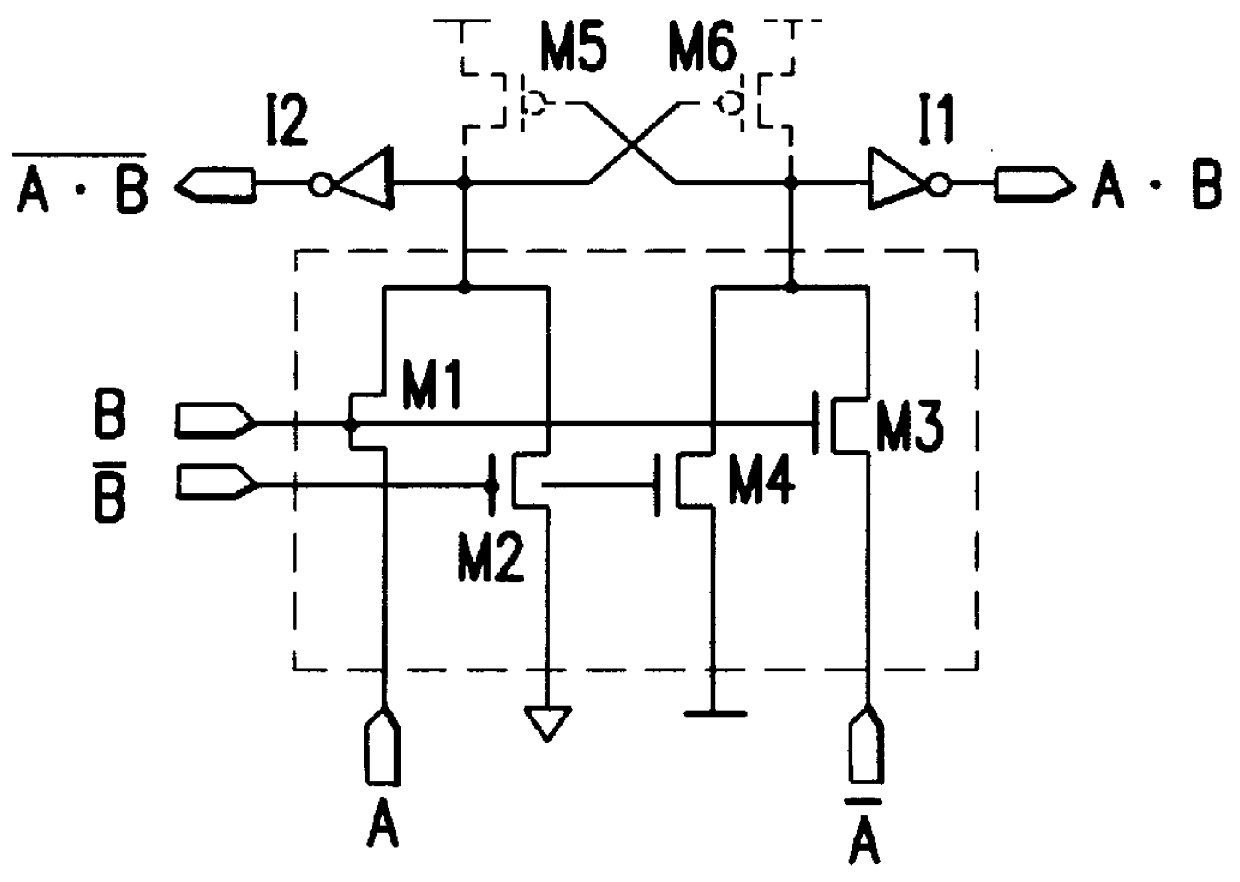

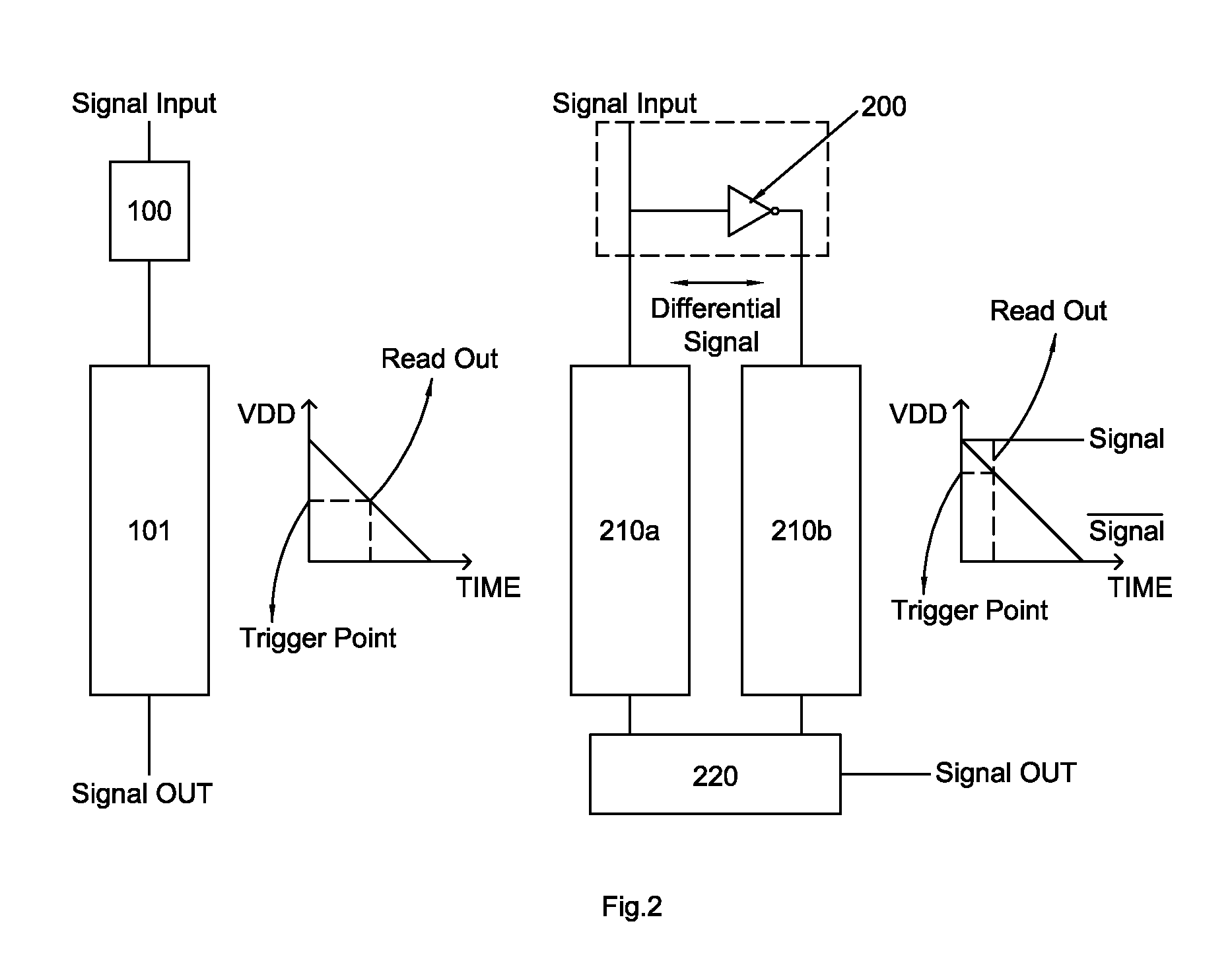

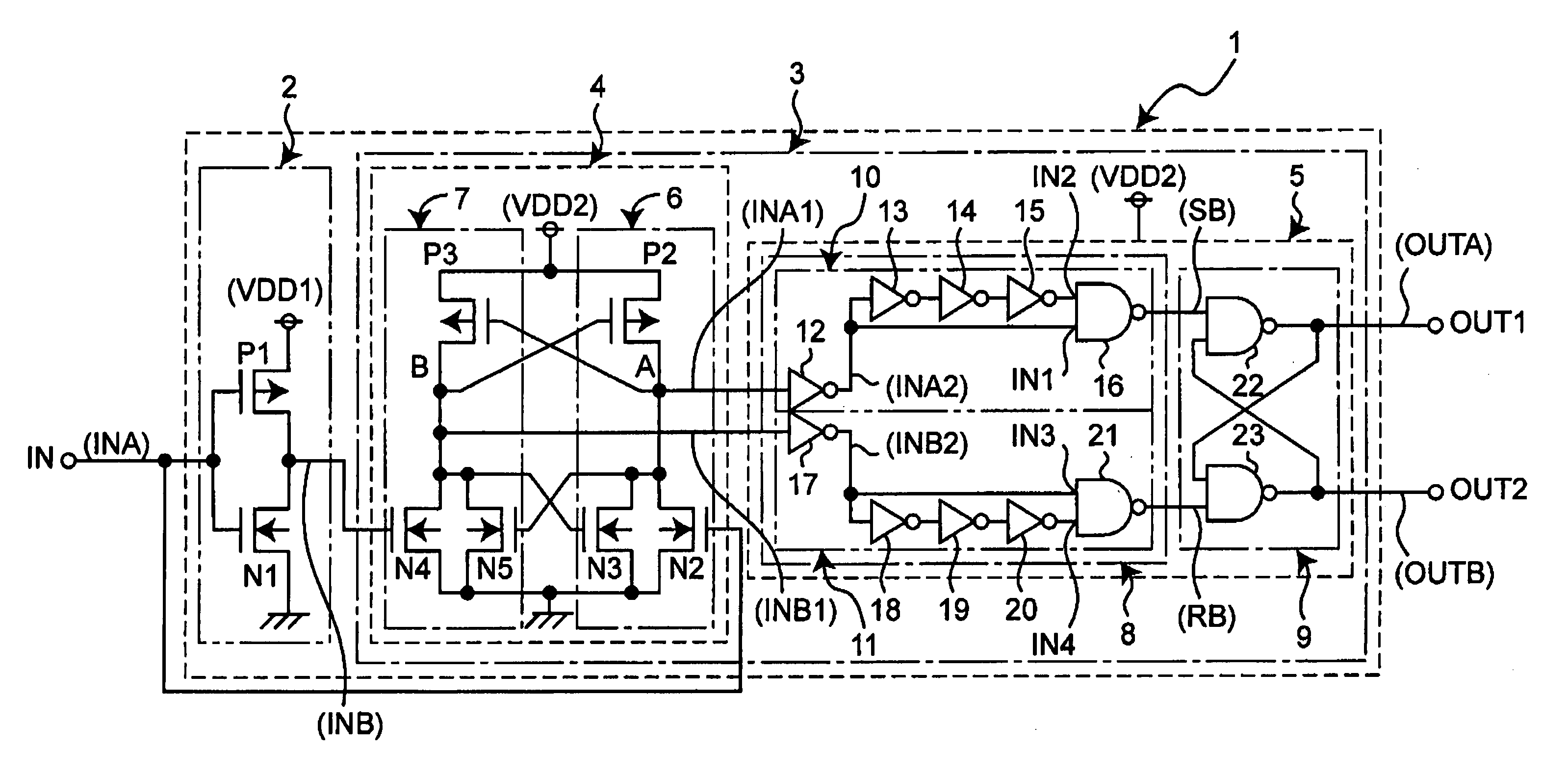

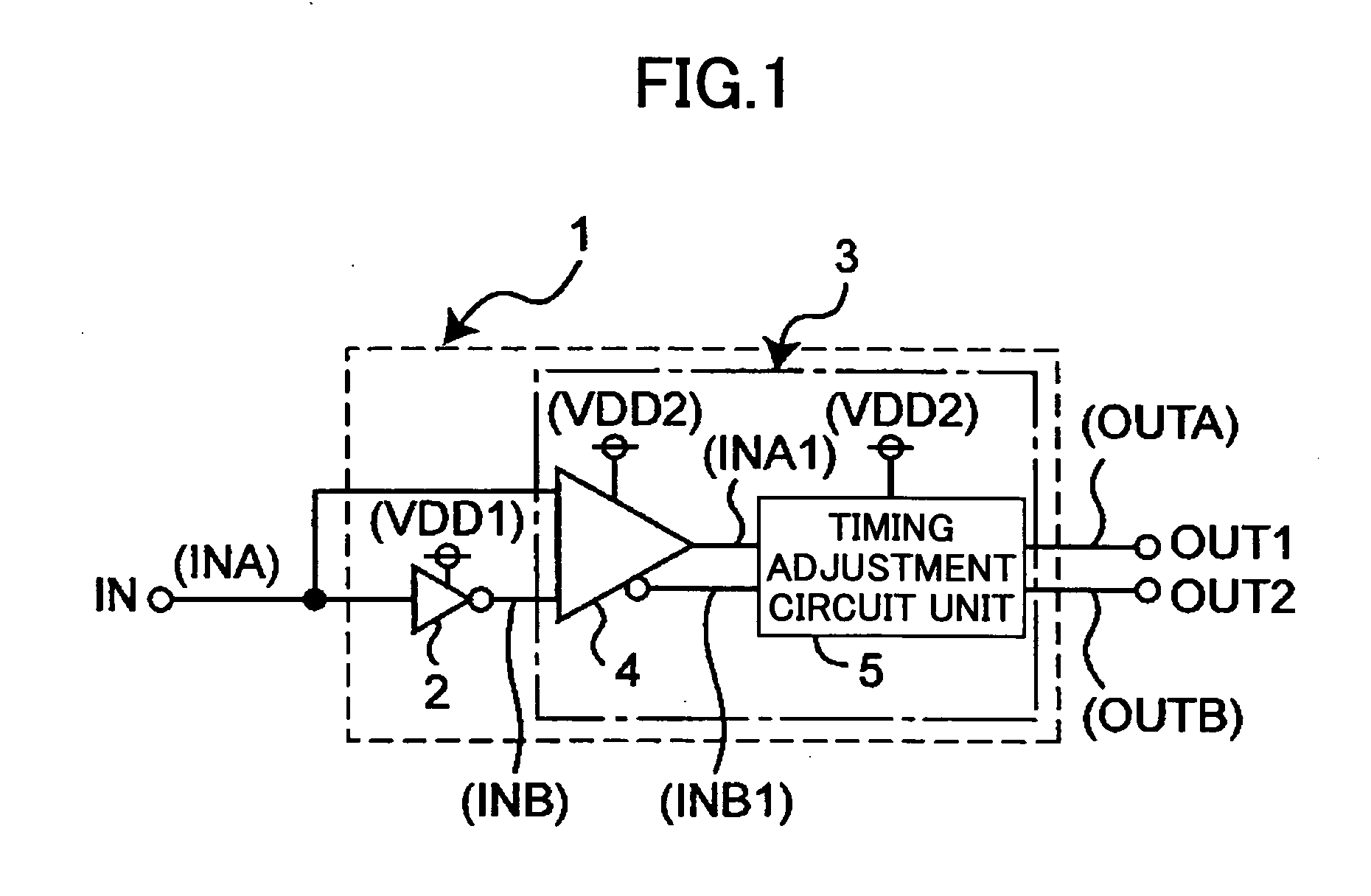

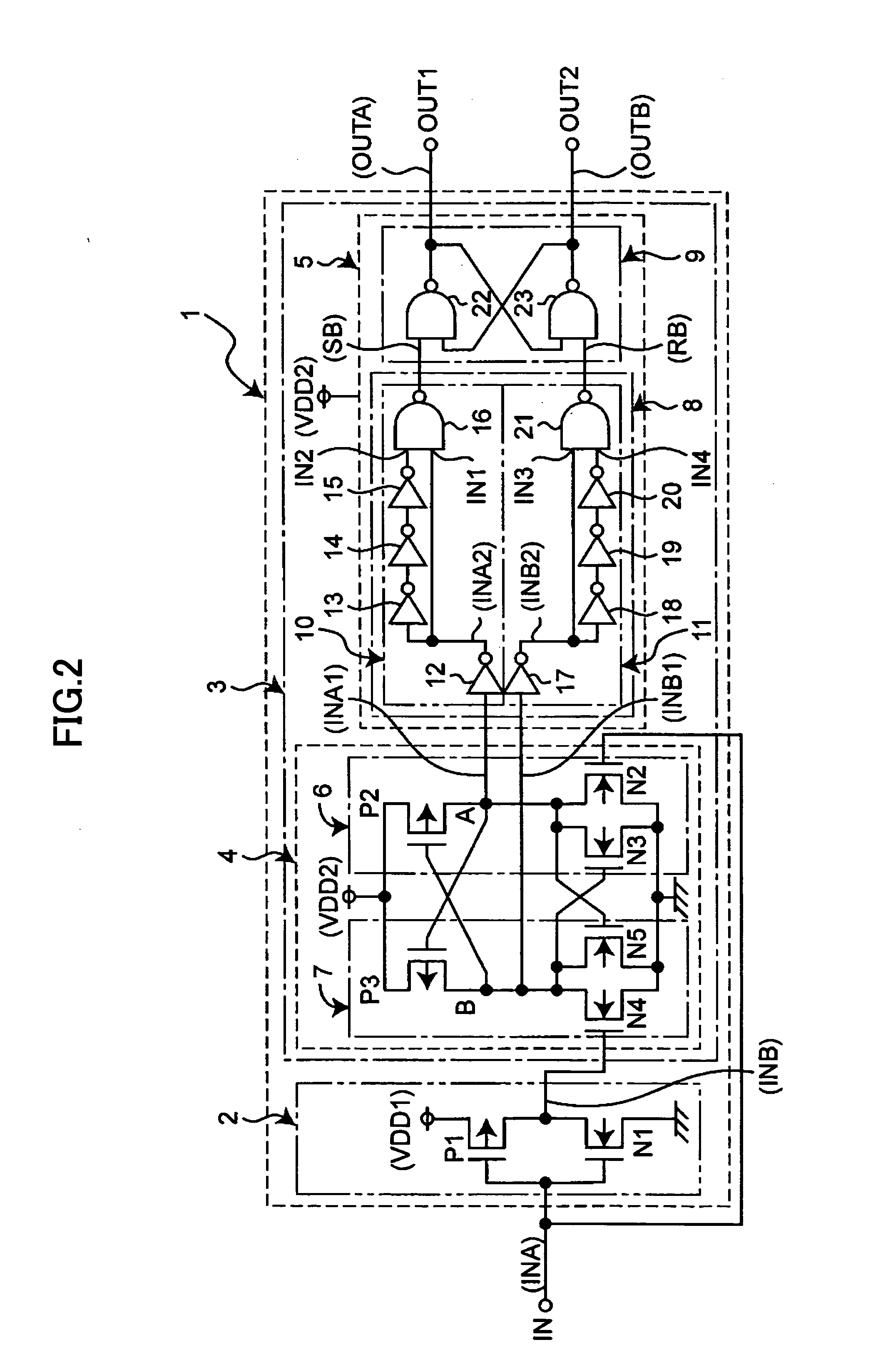

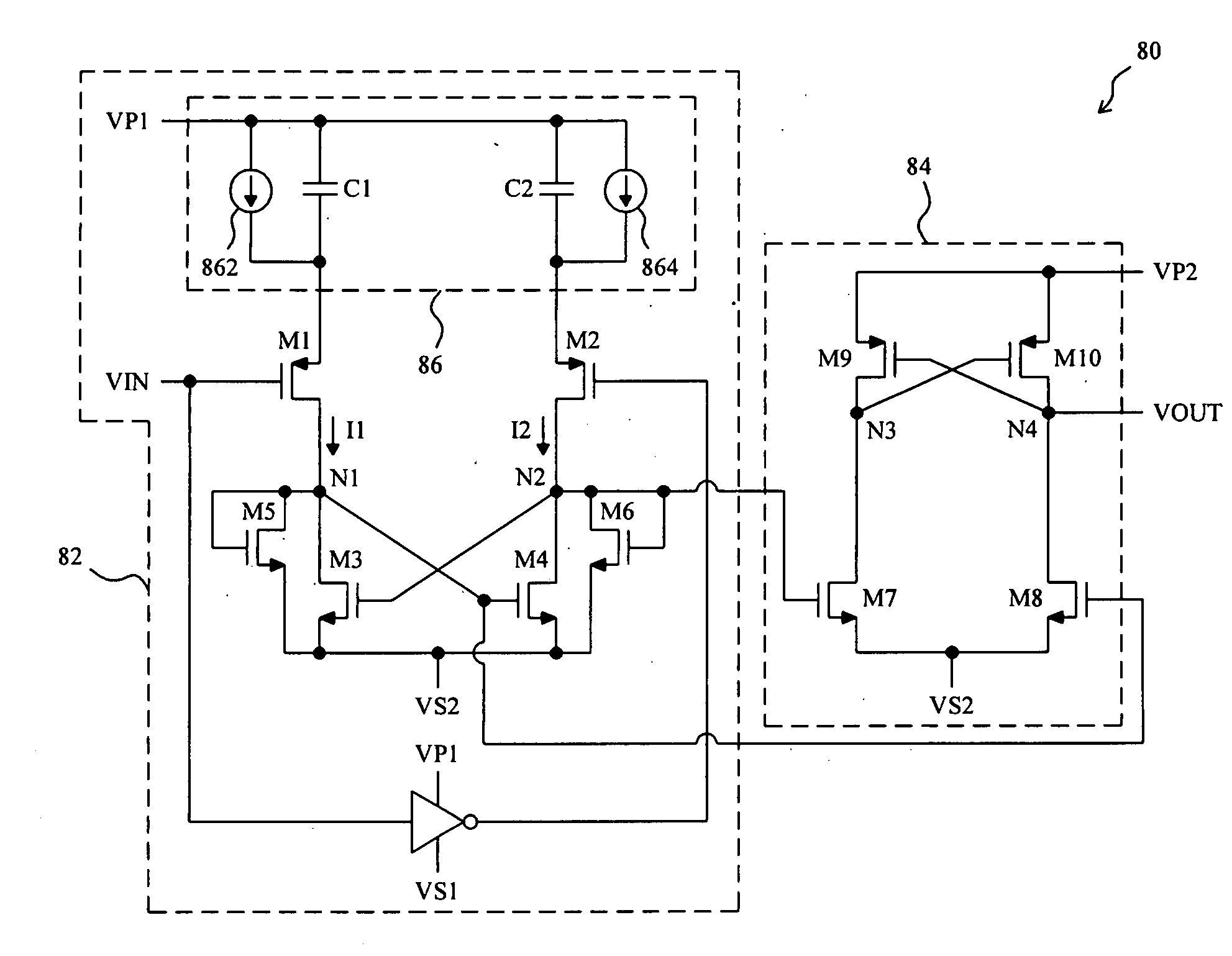

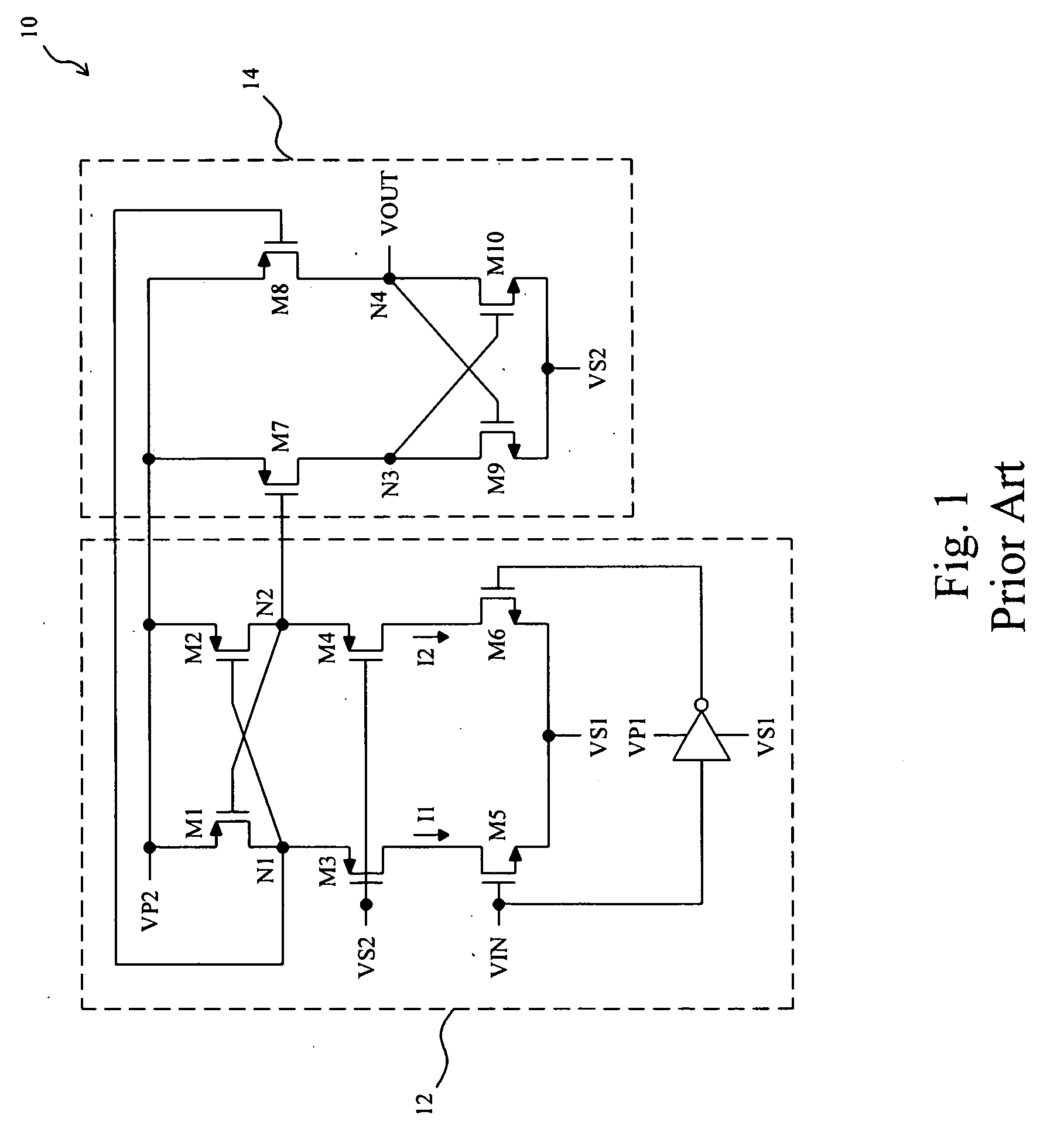

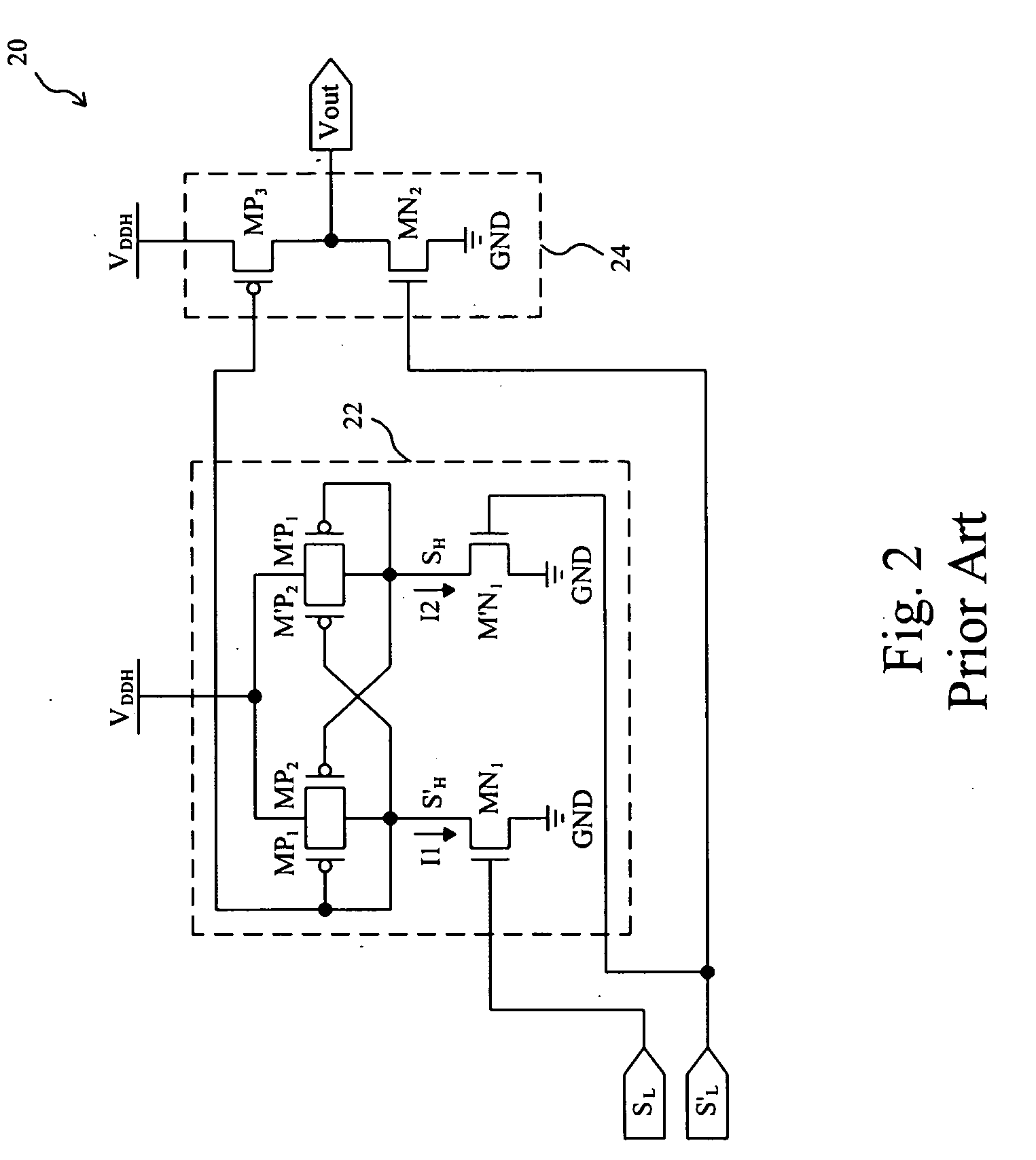

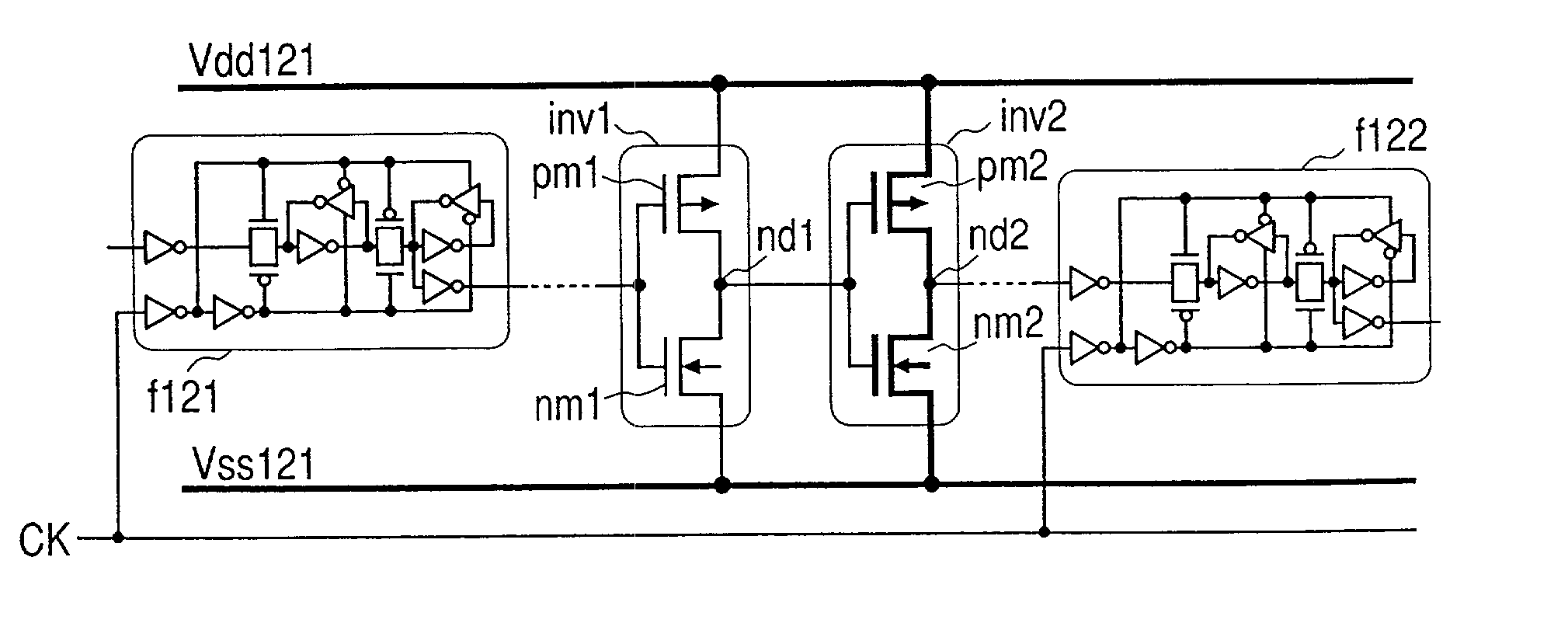

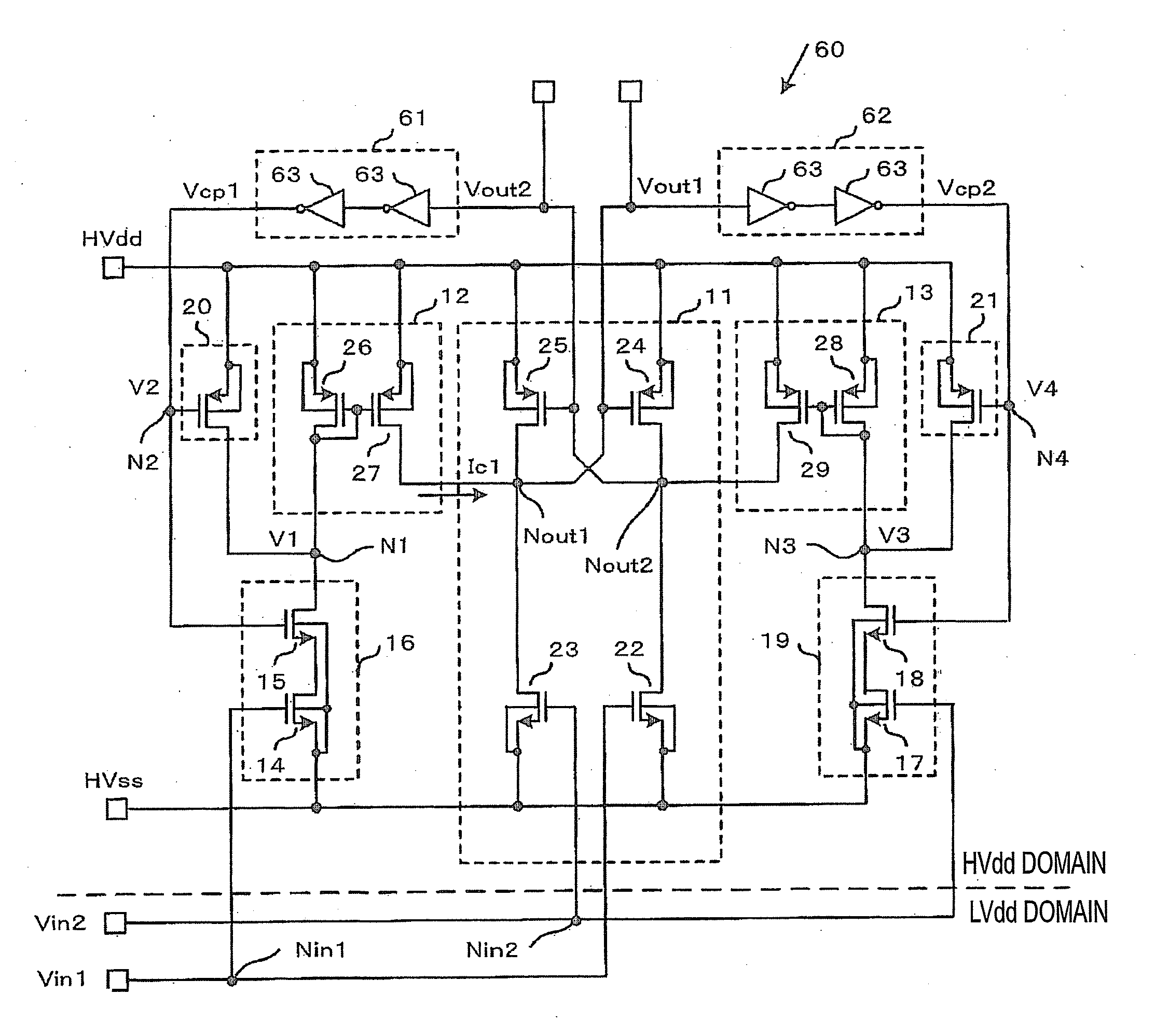

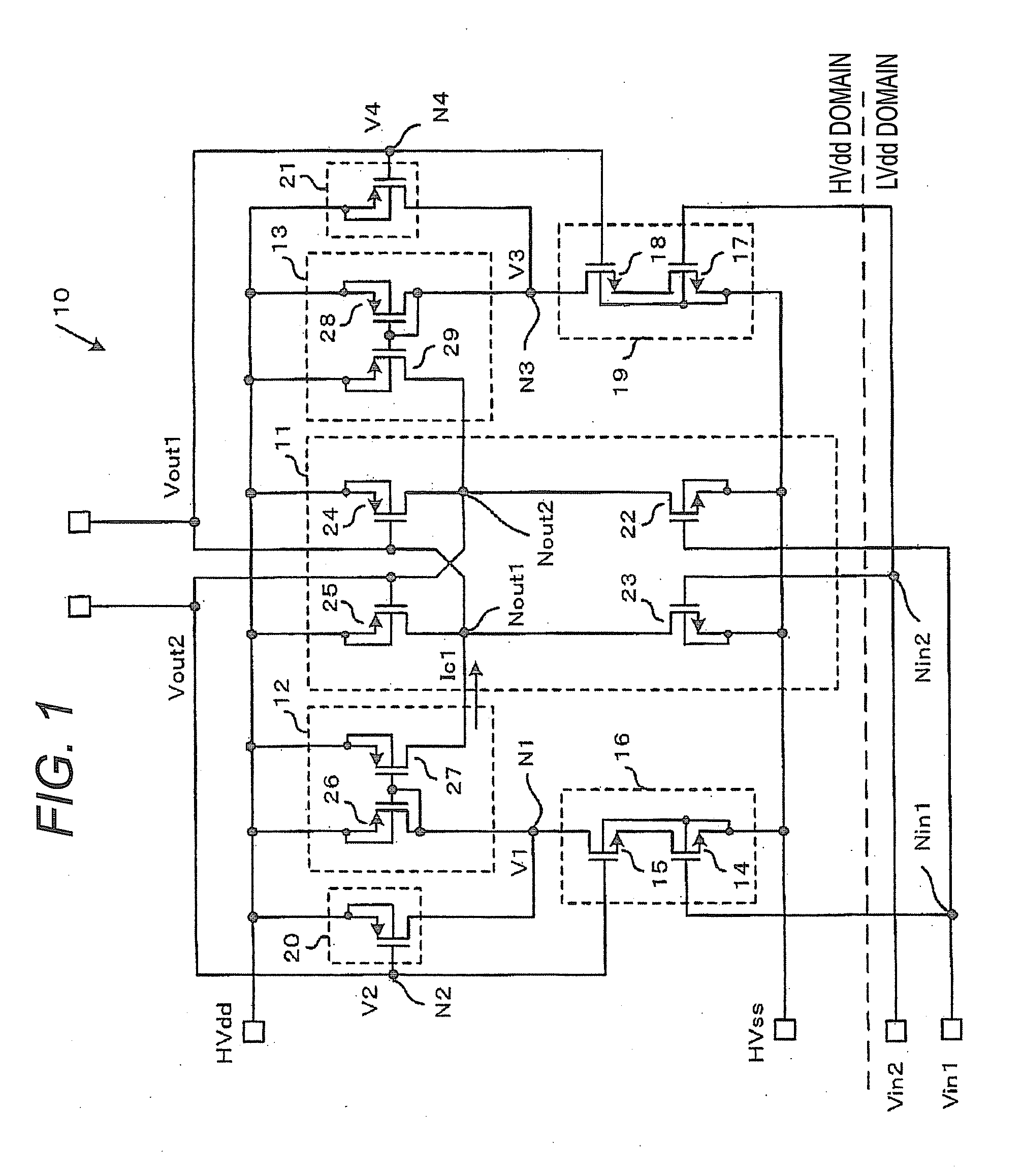

Level shift circuit having timing adjustment circuit for maintaining duty ratio

InactiveUS20060066349A1Accurate operationReliability increasing modificationsElectronic switchingEngineeringVoltage range

A level shift circuit for shifting levels of a pair of binary input signals having a first voltage range to produce a pair of binary output signals having a second voltage range includes a first circuit to shift a level of a first one of the binary input signals thereby to produce a first signal having the second voltage range, a second circuit to shift a level of a second one of the binary input signals thereby to produce a second signal having the second voltage range, and a timing adjustment circuit to produce the binary output signals by adjusting a pulse width thereof in response to the first and second signals such that the pulse width is equal to a time interval from when one of the first and second circuits stops level shift operation to when another one of the first and second circuits stops level shift operation.

Owner:RICOH ELECTRONIC DEVICES CO LTD

Level shift circuit

ActiveUS20090066399A1Fast processReduce layoutPulse automatic controlElectric pulse generatorLevel shiftingStable status

A level shift circuit includes an input stage and an output stage coupled to each other by two nodes. The input stage changes the voltages on the nodes according to an input signal, and the output stage determines an output signal according to the voltages on the two nodes. In a transition state, the input stage provides a large current to charge or discharge the first node or the second node so as to quickly change the voltage thereon. In a steady state, the input stage lowers the current so as to reduce power consumption.

Owner:RICHTEK TECH

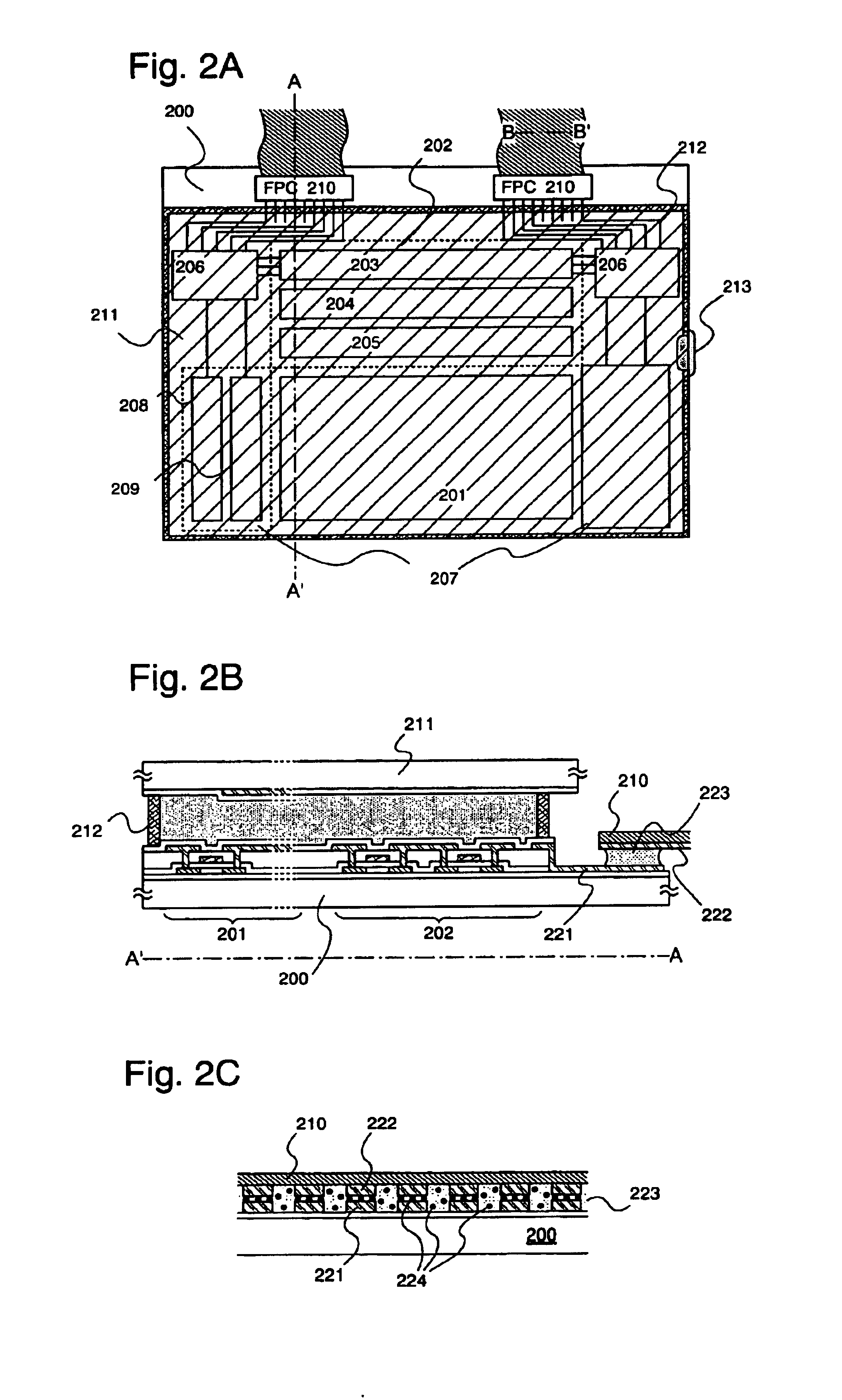

Liquid crystal display device and electronic device

ActiveUS20080007296A1Optimize layoutMaintain good propertiesStatic indicating devicesSolid-state devicesShift registerLiquid-crystal display

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor integrated circuit device, storage medium on which cell library is stored and designing method for semiconductor integrated circuit

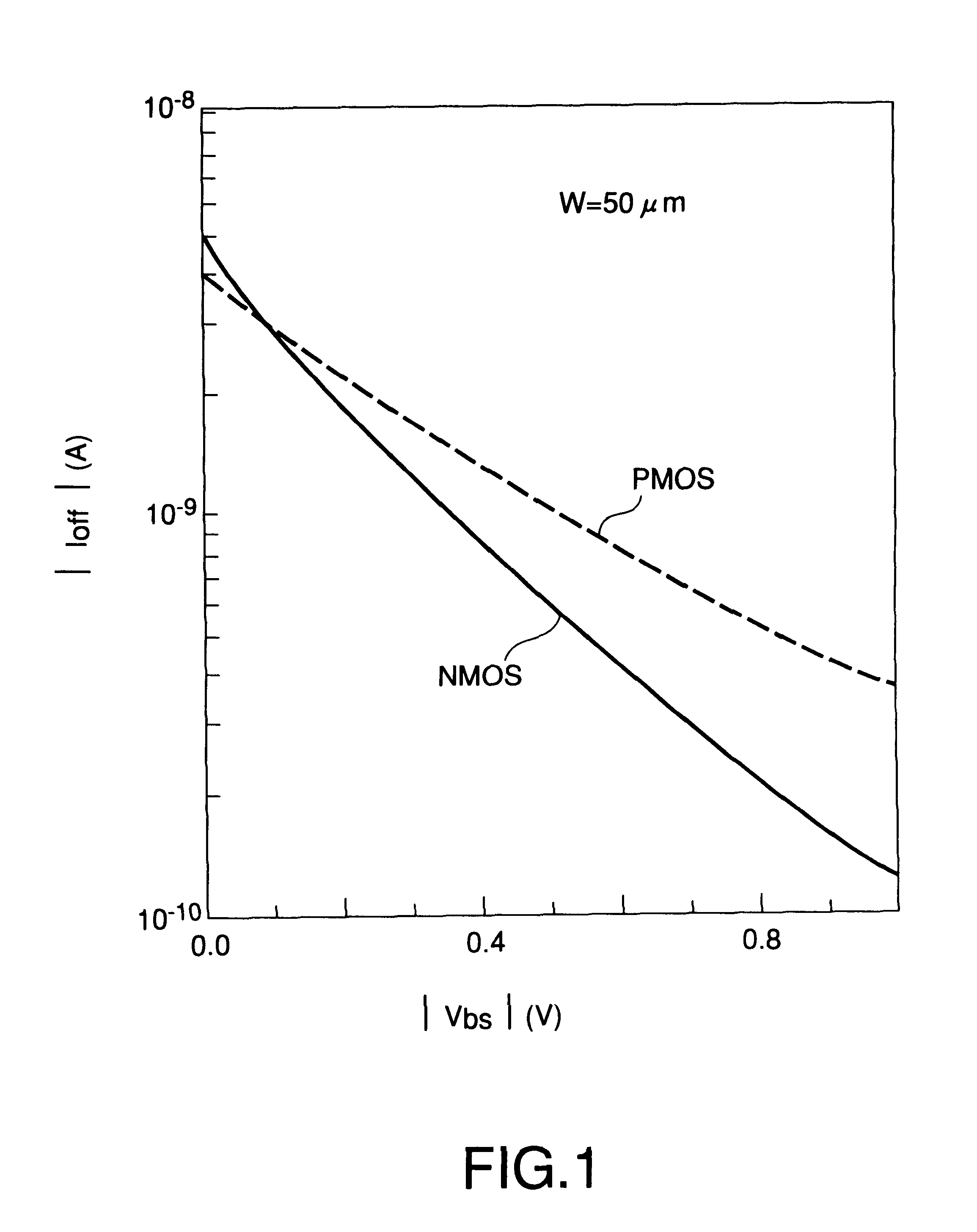

InactiveUS20020079927A1Power reduction in field effect transistorsSolid-state devicesMOSFETDrain current

Owner:RENESAS ELECTRONICS CORP

Semiconductor integrated device

InactiveUS20090224817A1Pulse automatic controlElectric pulse generatorSemiconductorIntegrated devices

According to an aspect of the present invention, there is provided a semiconductor integrated device including: a level-shifting circuit including: a first and a second input nodes; and a first and a second output nodes; a first current mirror circuit connected with the first output node; a second current mirror circuit connected with the second output node; a first switch circuit series-connected with an input-side of first current mirror circuit; a second switch circuit series-connected with an input-side of the second current mirror circuit; a fifth switching element parallel-connected with the input-side of the first current mirror circuit; and a sixths switching element parallel-connected with the input-side of the second current mirror circuit.

Owner:KK TOSHIBA

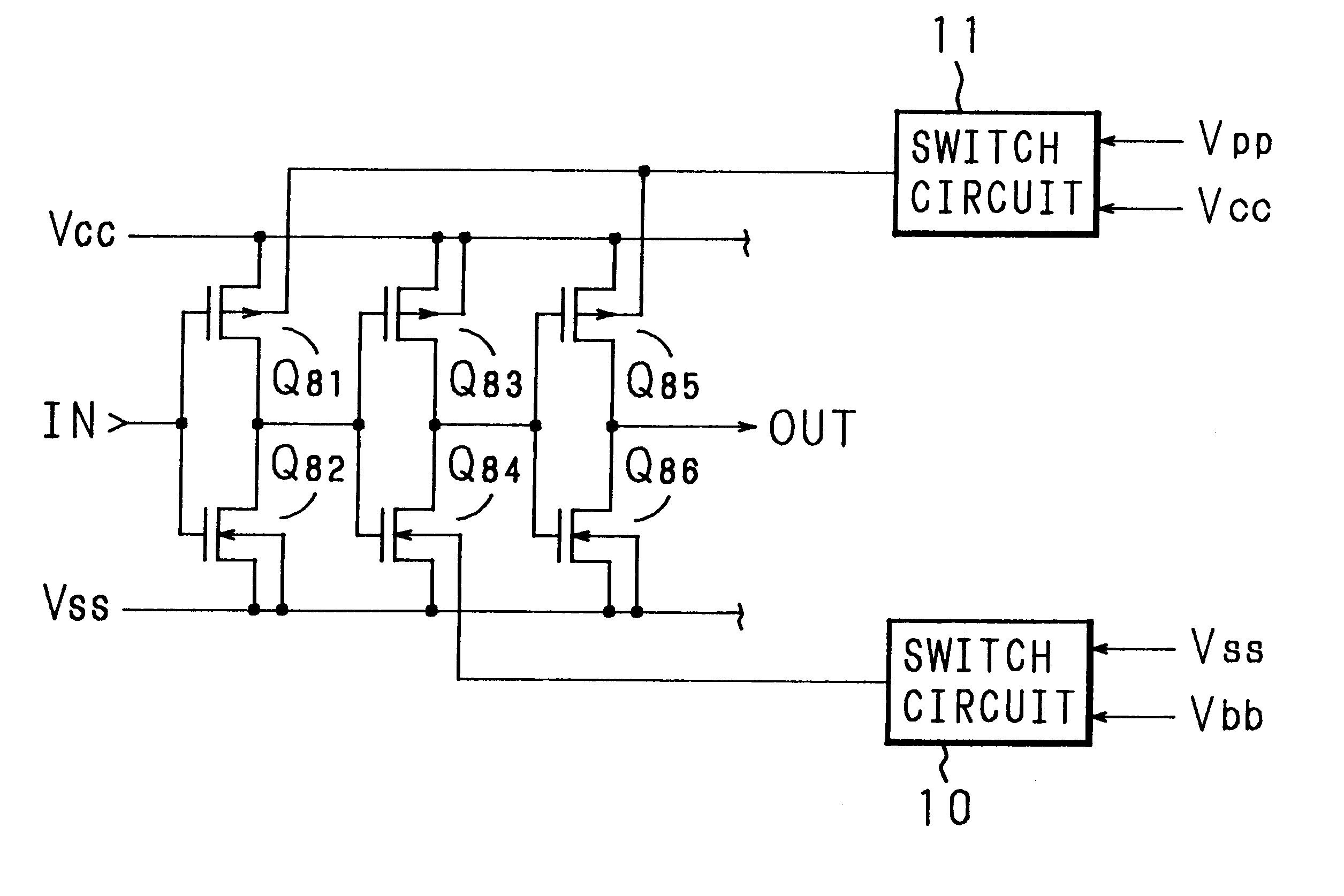

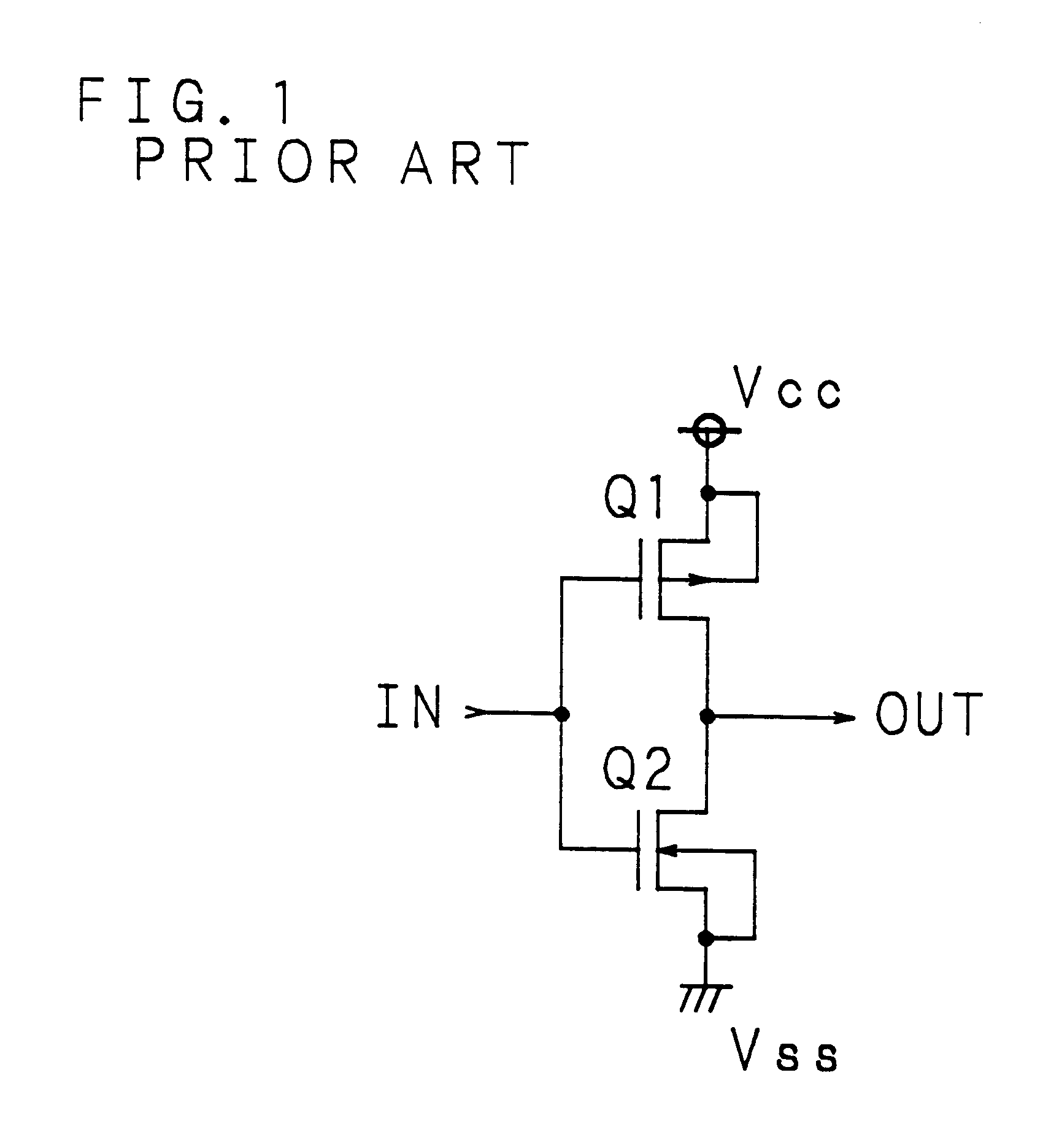

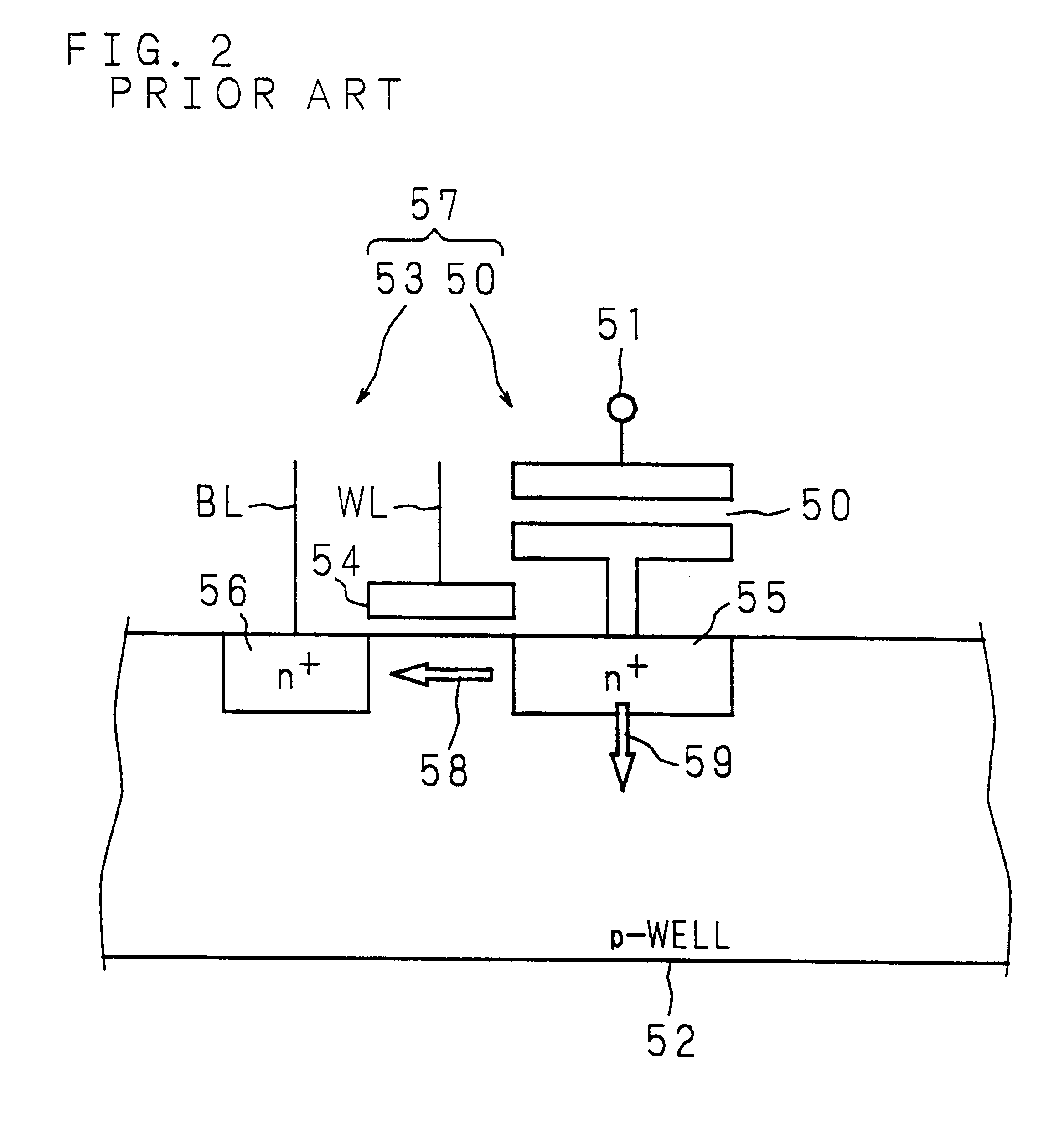

Switched backgate bias for FET

InactiveUS6232793B1Reliability increasing modificationsPower reduction by control/clock signalHemt circuitsEngineering

A semiconductor circuit or a MOS-DRAM wherein converting means is provided that converts substrate potential or body bias potential between two values for MOS-FETs in a logic circuit, memory cells, and operating circuit of the MOS-DRAM, thereby raising the threshold voltage of the MOS-FETs when in the standby state and lowering it when in active state. The converting means includes a level shift circuit and a switch circuit. The substrate potential or body bias potential is controlled only of the MOS-FETs which are nonconducting in the standby state; this configuration achieves a reduction in power consumption associated with the potential switching. Furthermore, in a structure where MOS-FETs of the same conductivity type are formed adjacent to each other, MOS-FETs of SOI structure are preferable for better results.

Owner:RENESAS ELECTRONICS CORP

Pulse output circuit, shift register and electronic equipment

A driver circuit of a display device, which includes TFTs of a single conductivity type and outputs an output signal with normal amplitude. A pulse is inputted to TFTs 101 and 104 to turn ON the TFTs and a potential of a node alpha is raised. When the potential of the node alpha reaches (VDD-VthN), the node alpha becomes in a floating state. Accordingly, a TFT 105 is turned ON and a potential of an output node is raised as a clock signal becomes High level. On the other hand, a potential of a gate electrode of the TFT 105 is further raised due to an operation of a capacitance means 107 as the potential of the output node is raised, so that the potential of the gate electrode of the TFT 105 becomes higher than (VDD+VthN). Thus, the potential of the output node is raised to VDD without causing a voltage drop due to a threshold voltage of the TFT 105. An output at the subsequent stage is then inputted to a TFT 103 to turn the TFT 103 ON, while the potential of the node alpha of TFTs 102 and 106 is dropped to turn the TFT 105 OFF. As a result, the potential of the output node becomes Low level.

Owner:SEMICON ENERGY LAB CO LTD

Pulse output circuit, shift register, and display device

InactiveUS6928136B2Low costReduce manufacturing stepsTransistorLogic circuits characterised by logic functionElectricityShift register

A circuit is provided which is constituted by TFTs of one conductivity type, and which is capable of outputting signals of a normal amplitude. When an input clock signal CK1 becomes a high level, each of TFTs (101, 103) is turned on to settle at a low level the potential at a signal output section (Out). A pulse is then input to a signal input section (In) and becomes high level. The gate potential of TFT (102) is increased to (VDD−V thN) and the gate is floated. TFT (102) is thus turned on. Then CK1 becomes low level and each of TFTs (101, 103) is turned off. Simultaneously, CK3 becomes high level and the potential at the signal output section is increased. Simultaneously, the potential at the gate of TFT (102) is increased to a level equal to or higher than (VDD+V thN) by the function of capacitor (104), so that the high level appearing at the signal output section (Out) becomes equal to VDD. When SP becomes low level; CK3 becomes low level; and CK1 becomes high level, the potential at the signal output section (Out) becomes low level again.

Owner:SEMICON ENERGY LAB CO LTD

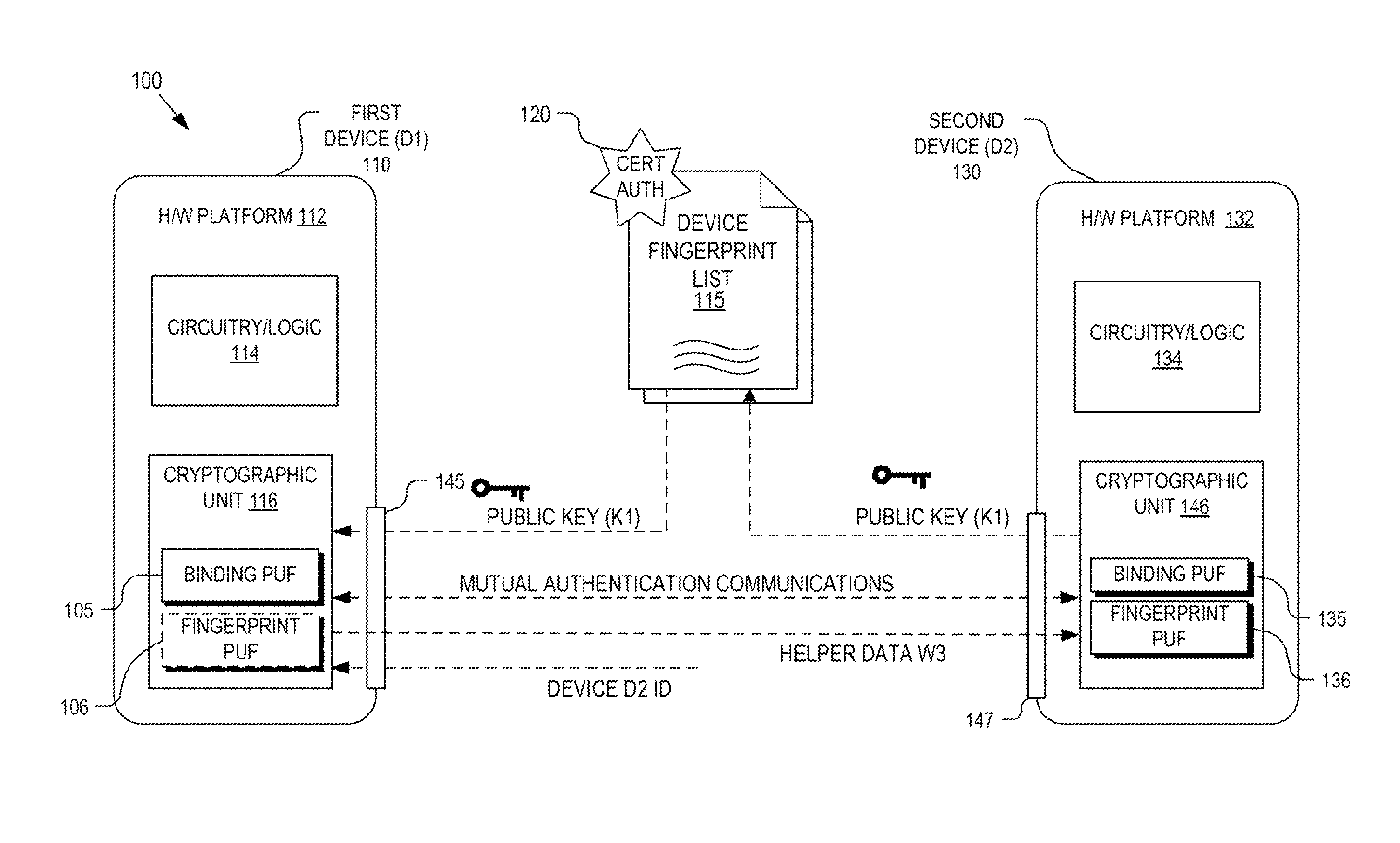

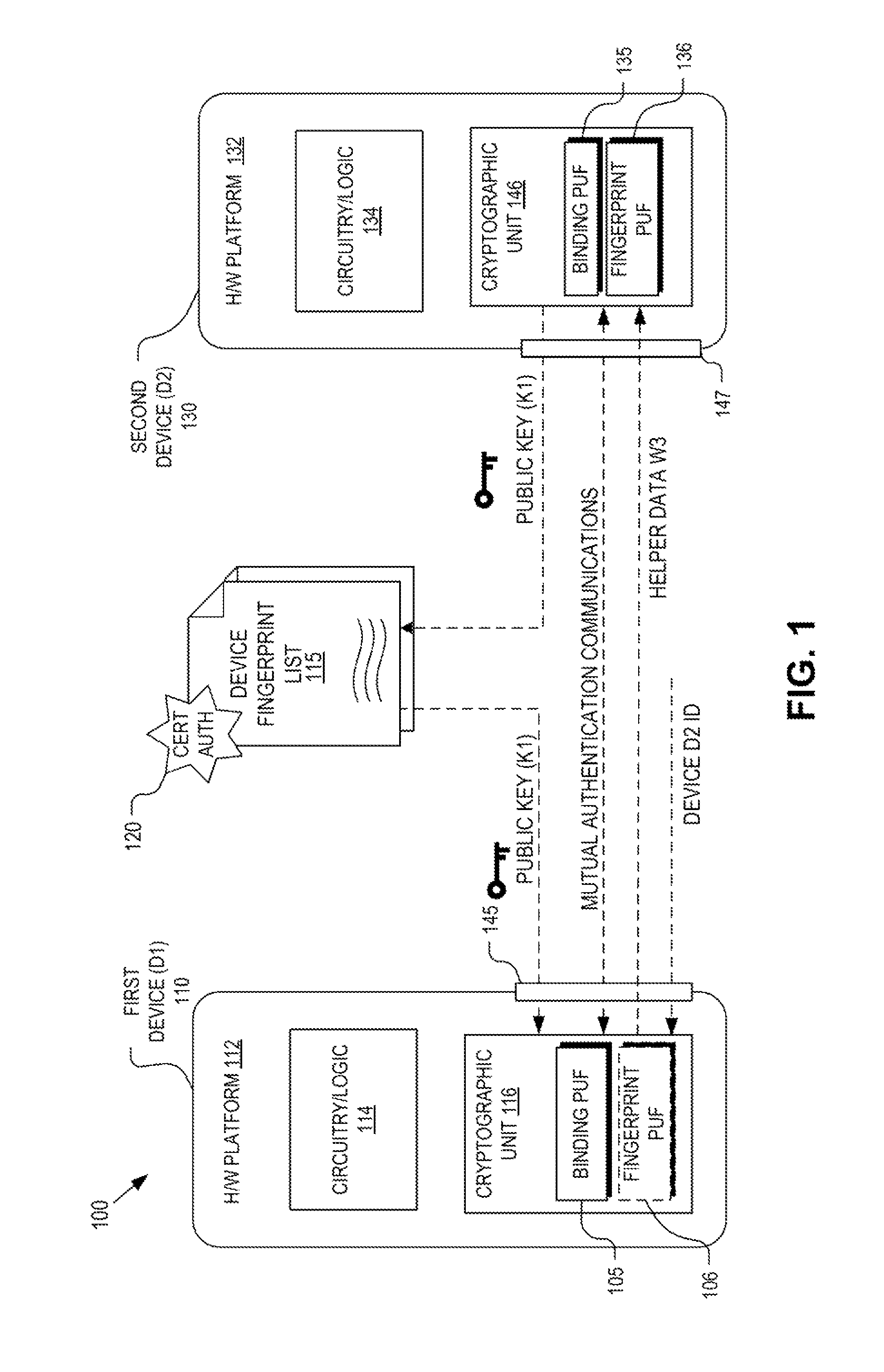

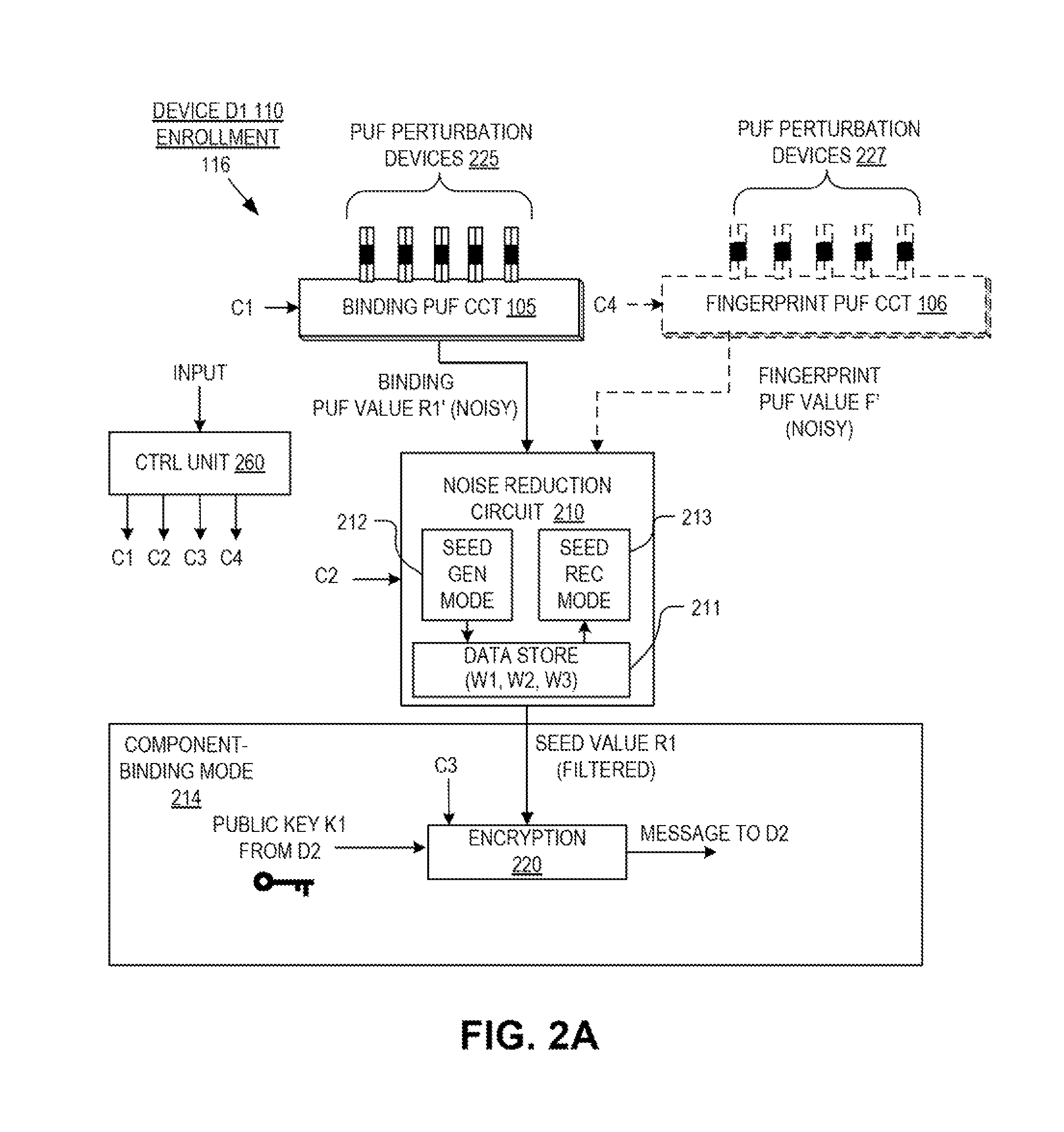

Hardware device binding and mutual authentication

ActiveUS8667265B1Digital data authenticationSecuring communicationComputer hardwarePhysical unclonable function

Detection and deterrence of device tampering and subversion by substitution may be achieved by including a cryptographic unit within a computing device for binding multiple hardware devices and mutually authenticating the devices. The cryptographic unit includes a physically unclonable function (“PUF”) circuit disposed in or on the hardware device, which generates a binding PUF value. The cryptographic unit uses the binding PUF value during an enrollment phase and subsequent authentication phases. During a subsequent authentication phase, the cryptographic unit uses the binding PUF values of the multiple hardware devices to generate a challenge to send to the other device, and to verify a challenge received from the other device to mutually authenticate the hardware devices.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

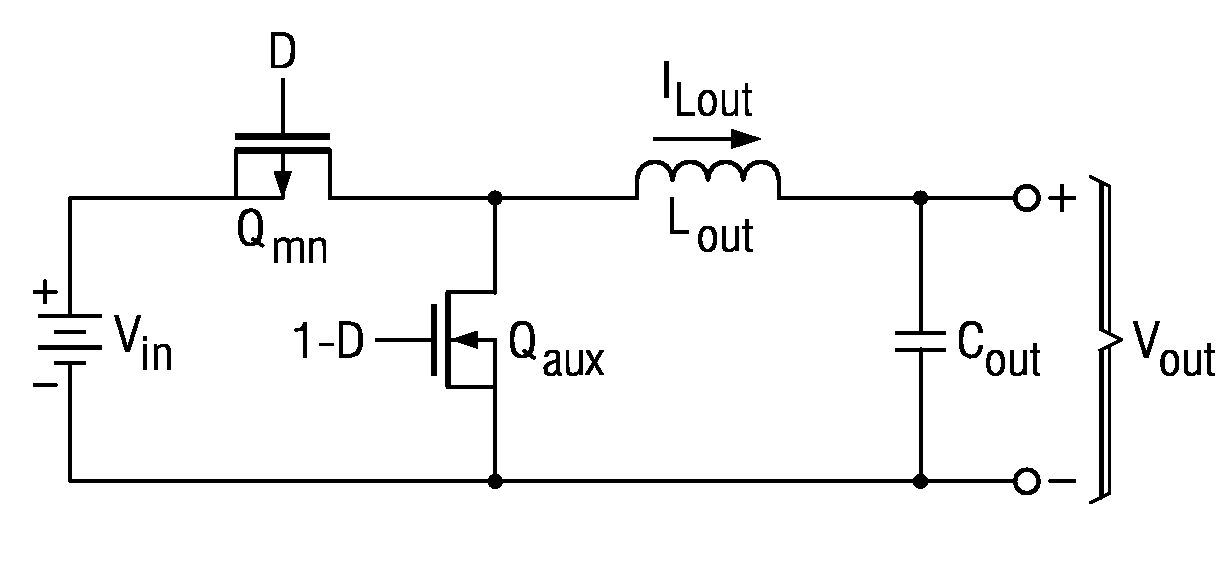

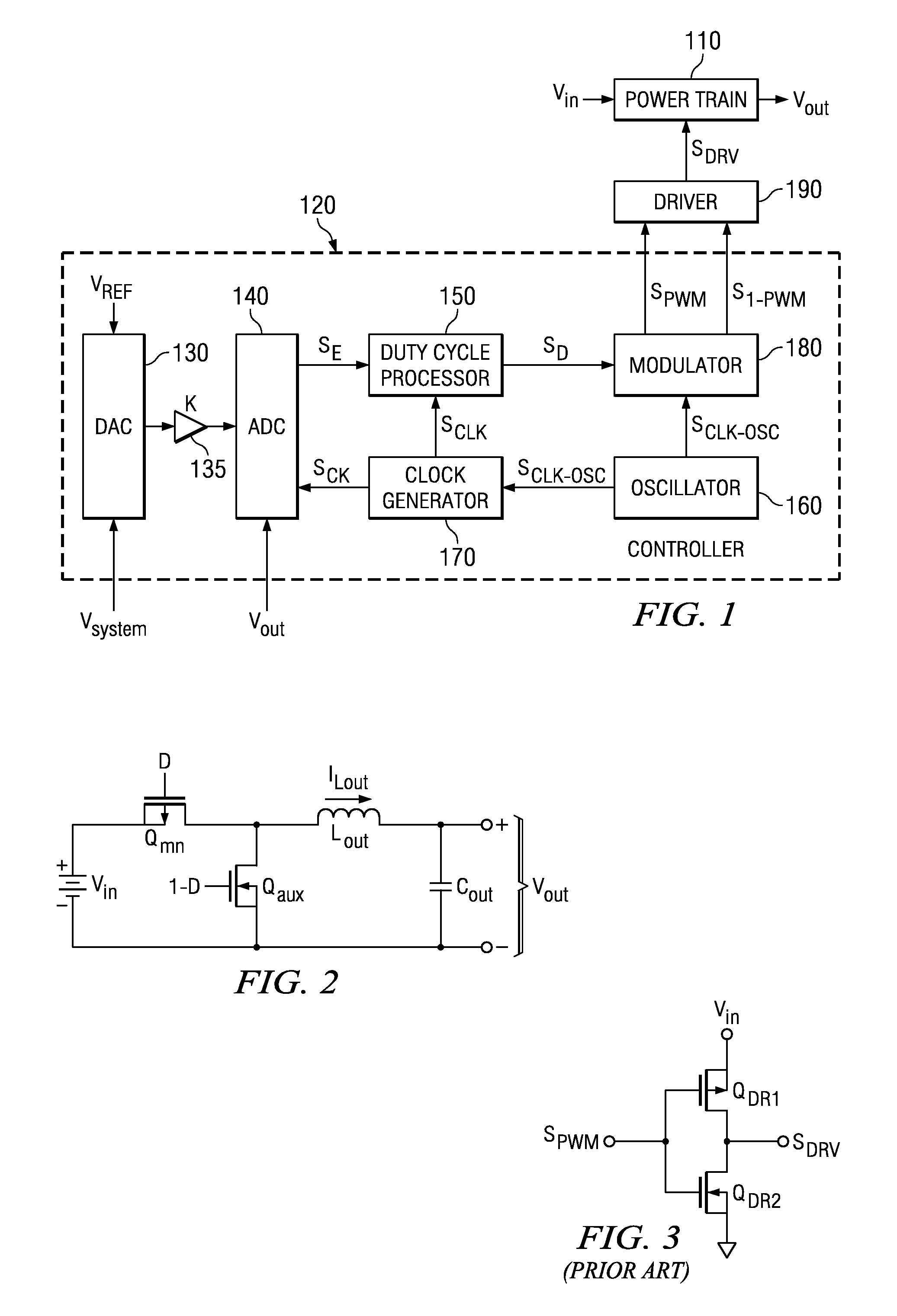

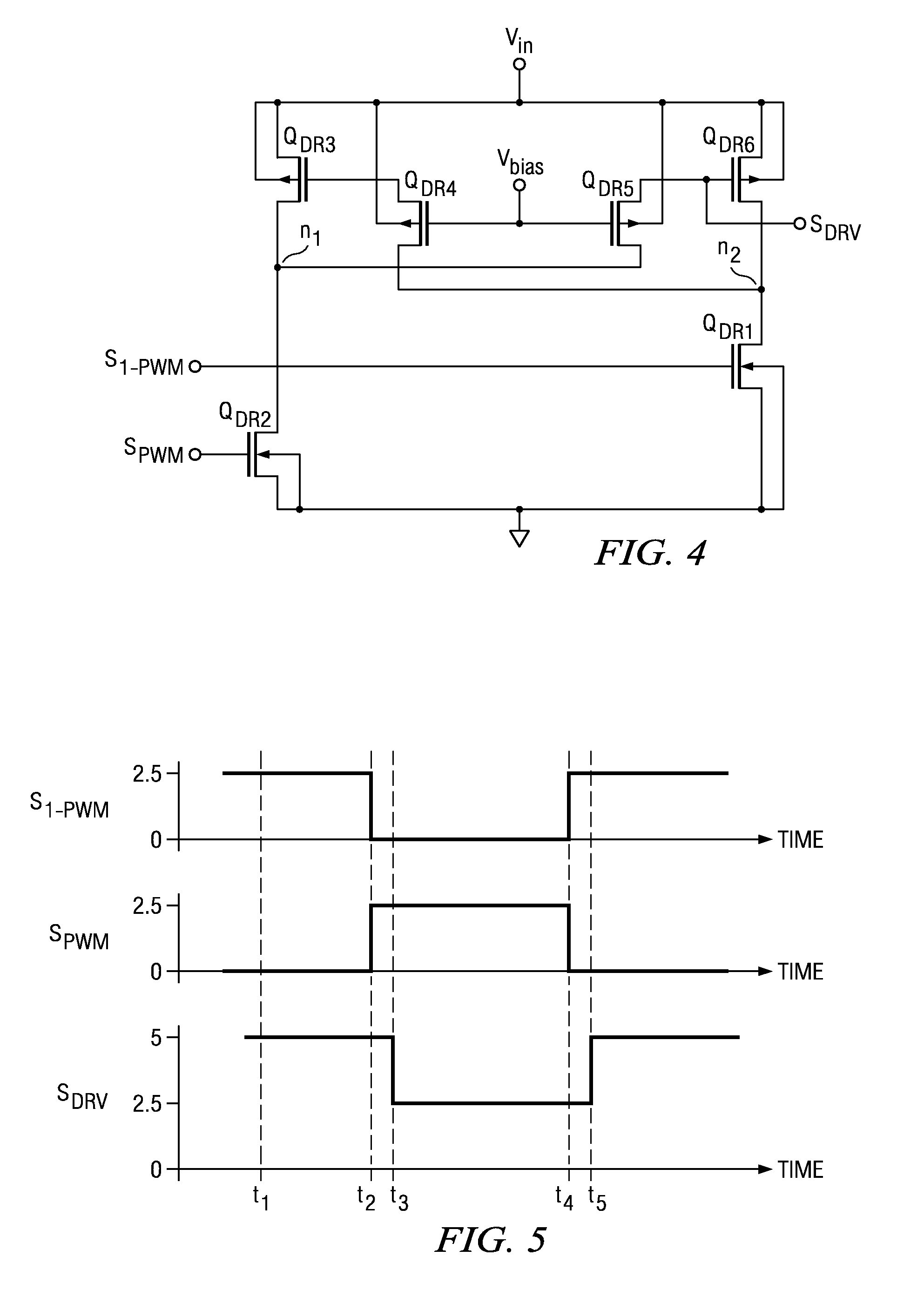

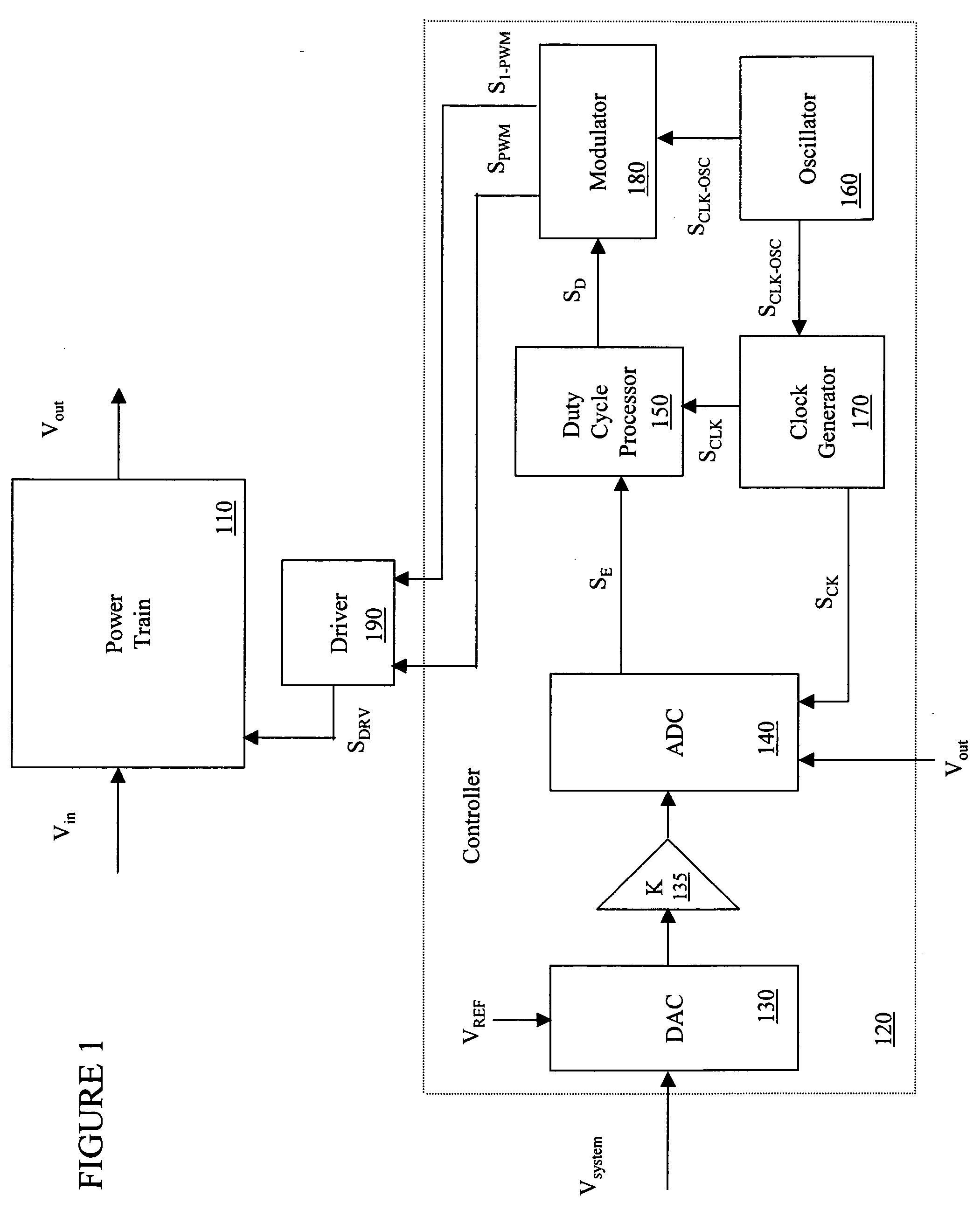

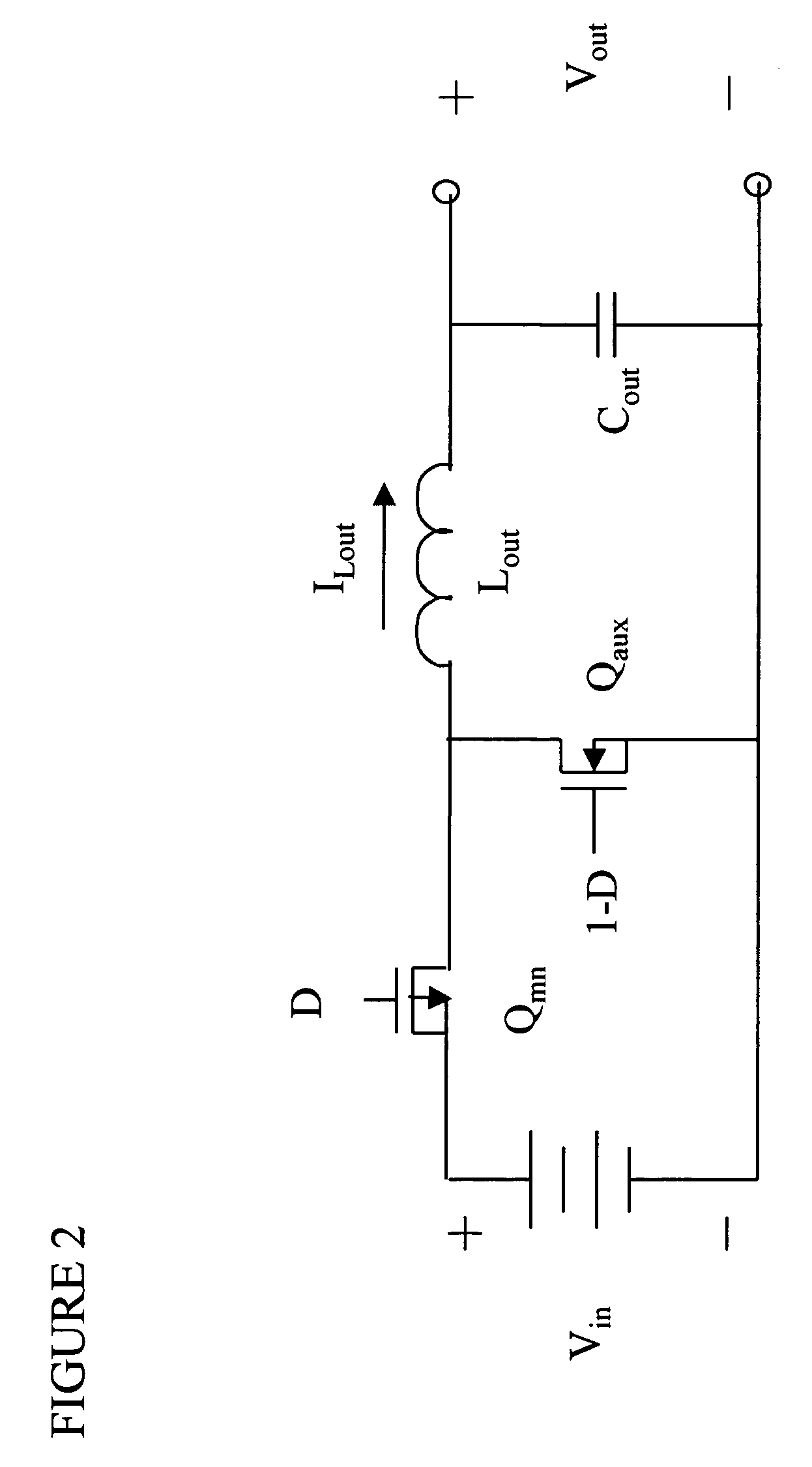

Driver for a power converter and a method of driving a switch thereof

A driver for a power converter, method of driving a switch thereof, and a power converter employing the same. In one embodiment, the driver includes switching circuitry referenced to a voltage level and configured to provide a drive signal for a switch referenced to another voltage level and subject to a control voltage limit. In a related, but alternative embodiment, the driver is employable with a power converter couplable to a source of electrical power adapted to provide an input voltage thereto. The power converter includes a power train having a switch referenced to the input voltage and subject to a control voltage limit. The driver includes switching circuitry referenced to a voltage level different from the input voltage and configured to provide a drive signal for the switch within the control voltage limit of the switch.

Owner:INTEL CORP

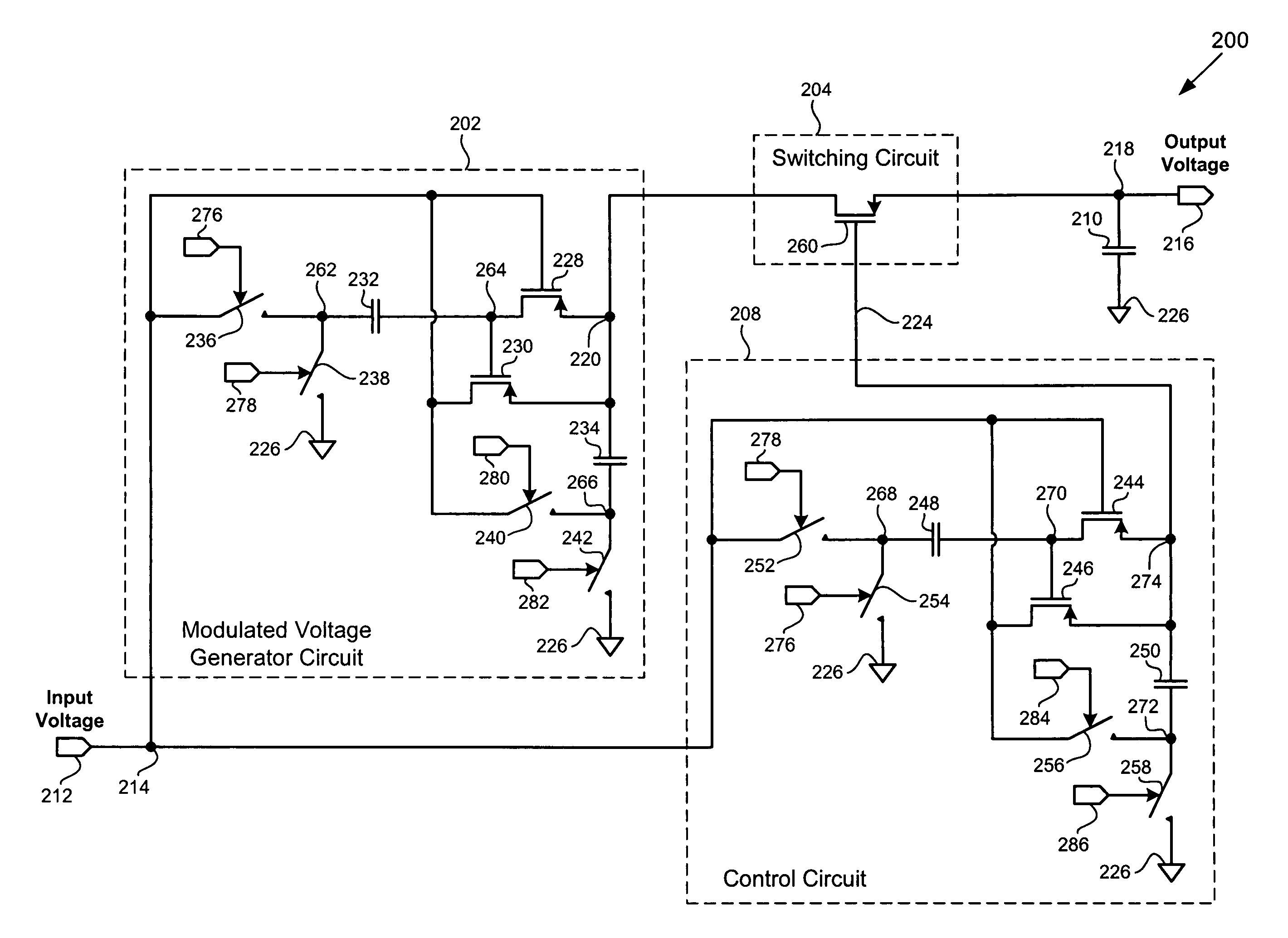

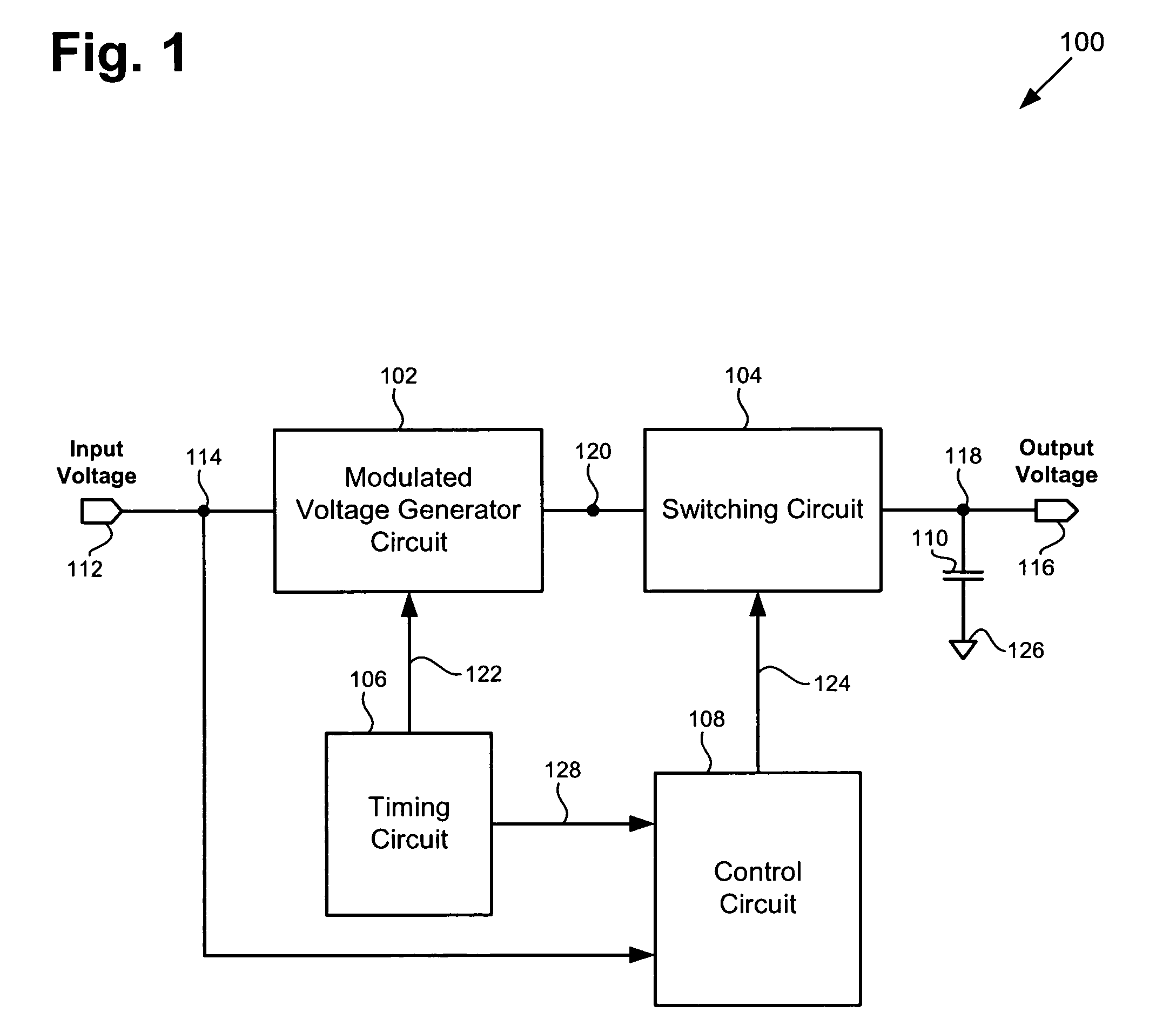

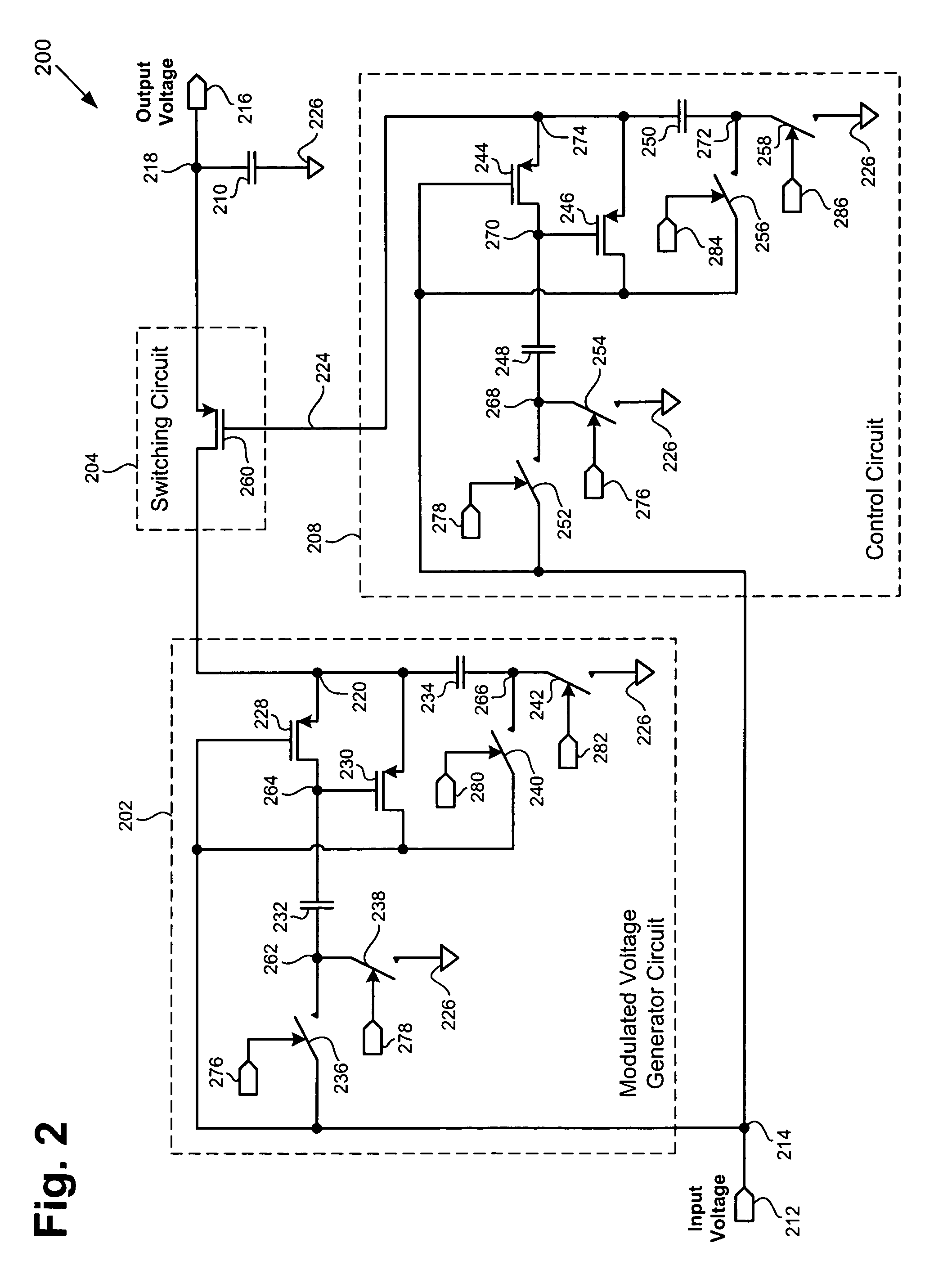

Voltage up-conversion circuit using low voltage transistors

ActiveUS7408330B2Low costApparatus without intermediate ac conversionLogic circuit coupling/interface arrangementsVoltage generatorLow voltage

According to one exemplary embodiment, a voltage up-conversion circuit includes a modulated voltage generator circuit, where the modulated voltage generator circuit is configured to receive an input voltage and generate a modulated voltage, and where the modulated voltage generator circuit includes at least one transistor. The voltage up-conversion circuit further includes a switching circuit coupled to the modulated voltage generator circuit, where the switching circuit is configured to couple the modulated voltage to a load capacitor when the modulated voltage is at a high level and decouple the modulated voltage to the load capacitor when the modulated voltage is at a low level. In the voltage up-conversion circuit, the load capacitor reaches a voltage greater a breakdown voltage of the at least one transistor in the modulated voltage generator circuit. The breakdown voltage can be a reliability breakdown voltage.

Owner:SKYWORKS SOLUTIONS INC

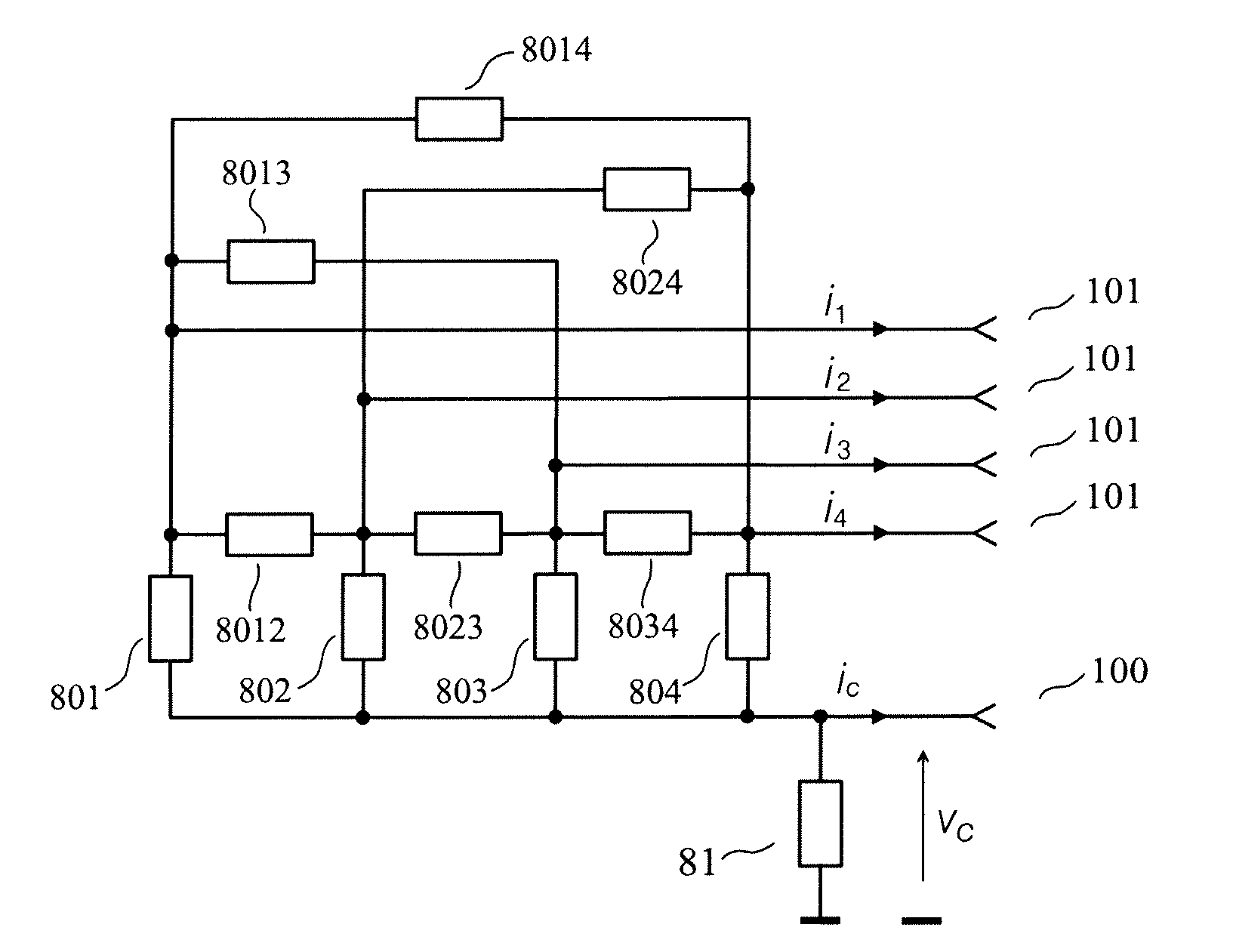

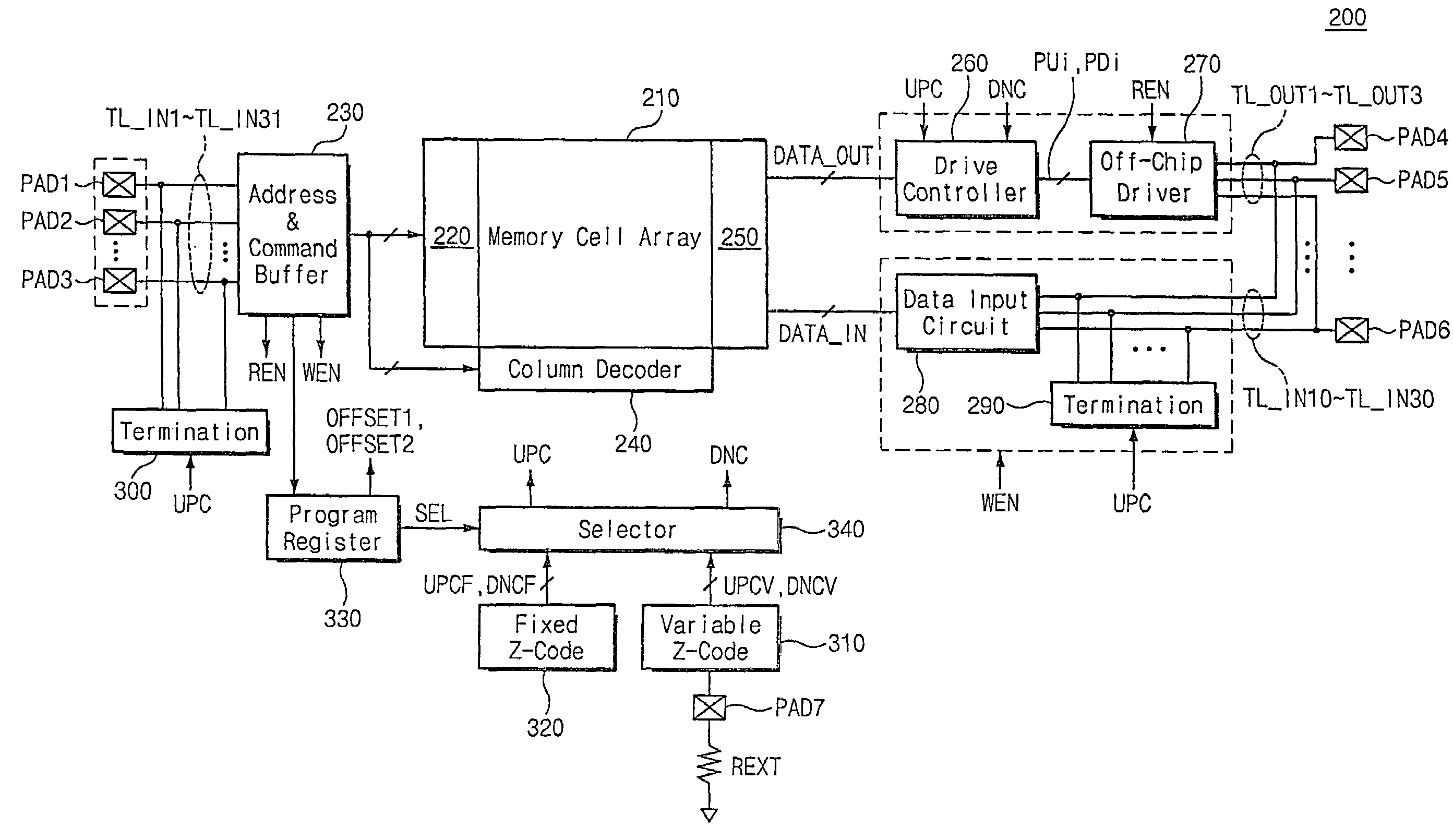

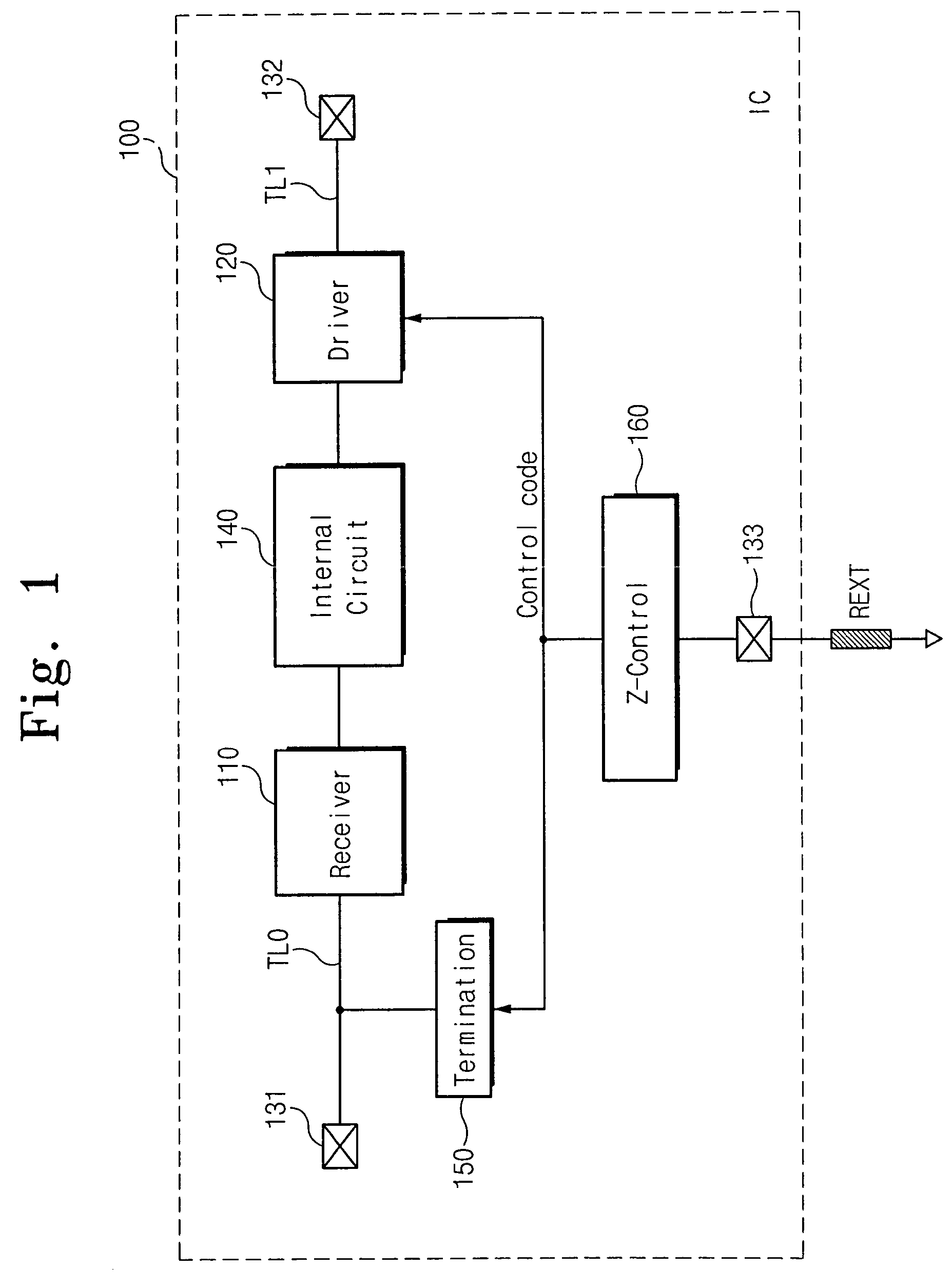

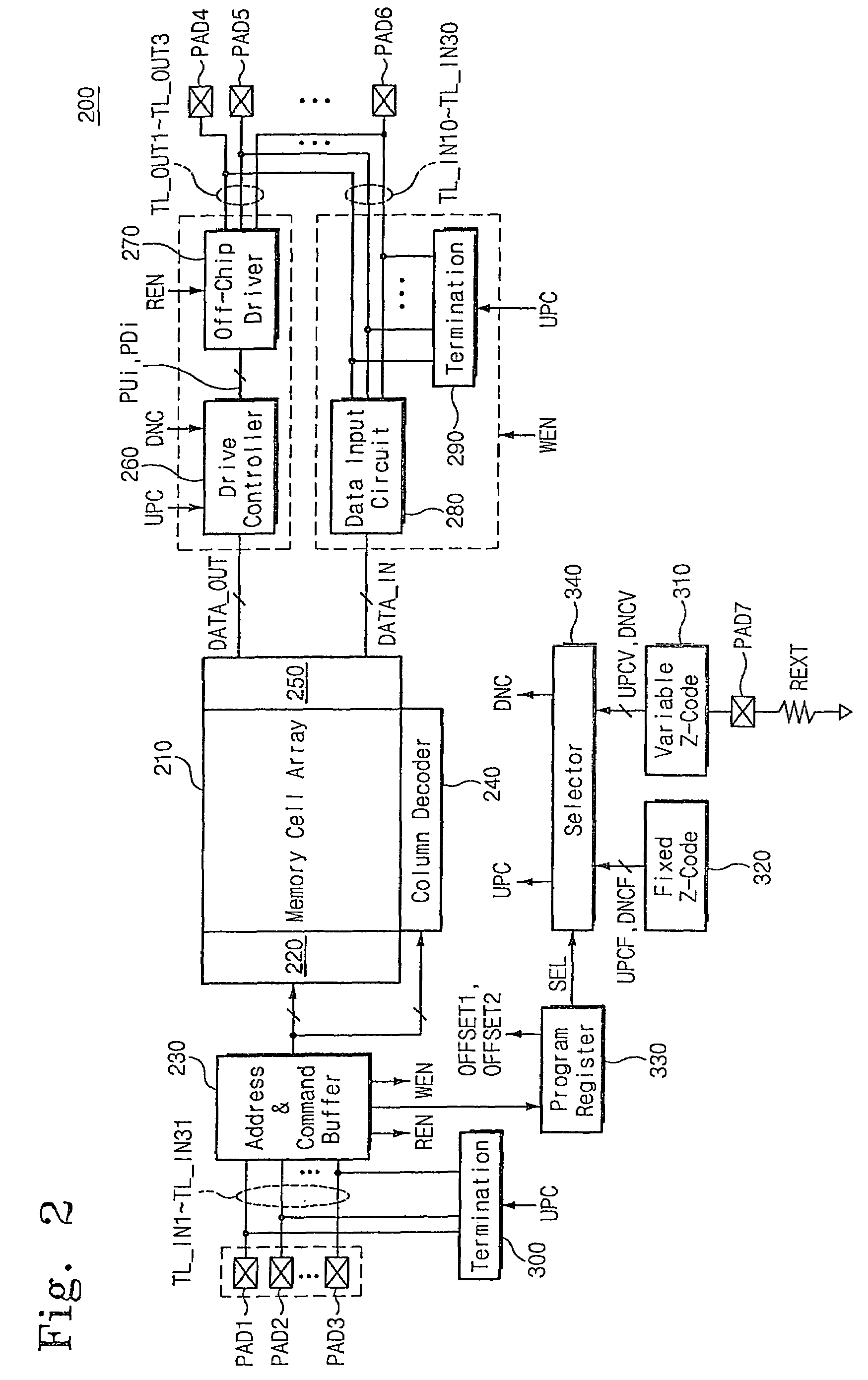

Semiconductor integrated circuit device capable of controlling impedance

ActiveUS7148721B2Input/output impedence modificationReliability increasing modificationsExternal referenceSemiconductor

A semiconductor integrated circuit device is connected to an external reference resistor, including an impedance control circuit for generating impedance control codes variable with impedances established by the external reference resistor. An input circuit receives an external signal through an input transfer line and forwards the external signal to an internal circuit. A termination circuit terminates the input transfer line in response to at least one of the impedance control code. An output circuit drives an output transfer line in accordance with an output signal. Impedance is variable with the control codes.

Owner:SAMSUNG ELECTRONICS CO LTD

Driver for a power converter and a method of driving a switch thereof

A driver for a power converter, method of driving a switch thereof, and a power converter employing the same. In one embodiment, the driver includes switching circuitry referenced to a voltage level and configured to provide a drive signal for a switch referenced to another voltage level and subject to a control voltage limit. In a related, but alternative embodiment, the driver is employable with a power converter couplable to a source of electrical power adapted to provide an input voltage thereto. The power converter includes a power train having a switch referenced to the input voltage and subject to a control voltage limit. The driver includes switching circuitry referenced to a voltage level different from the input voltage and configured to provide a drive signal for the switch within the control voltage limit of the switch.

Owner:INTEL CORP

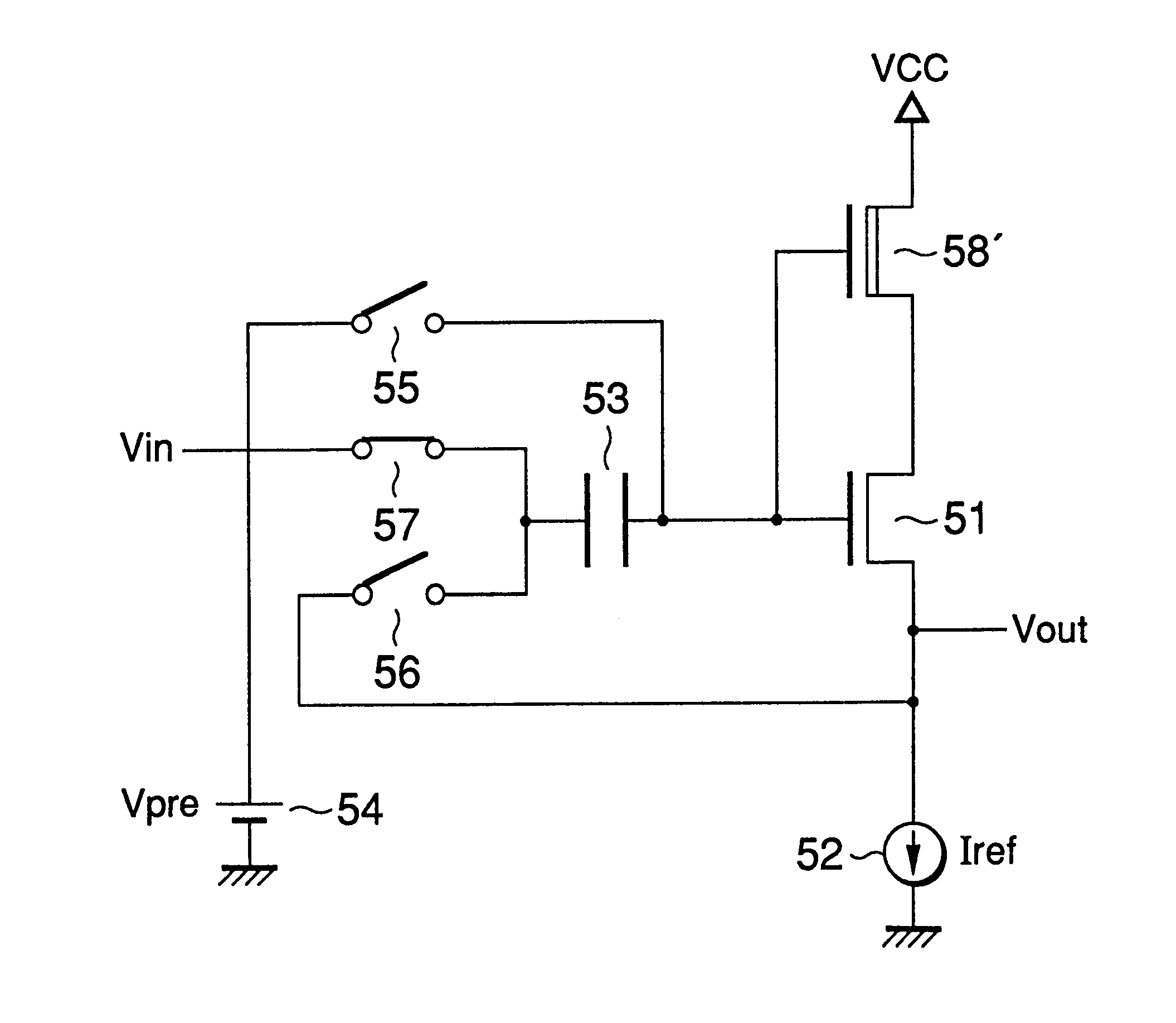

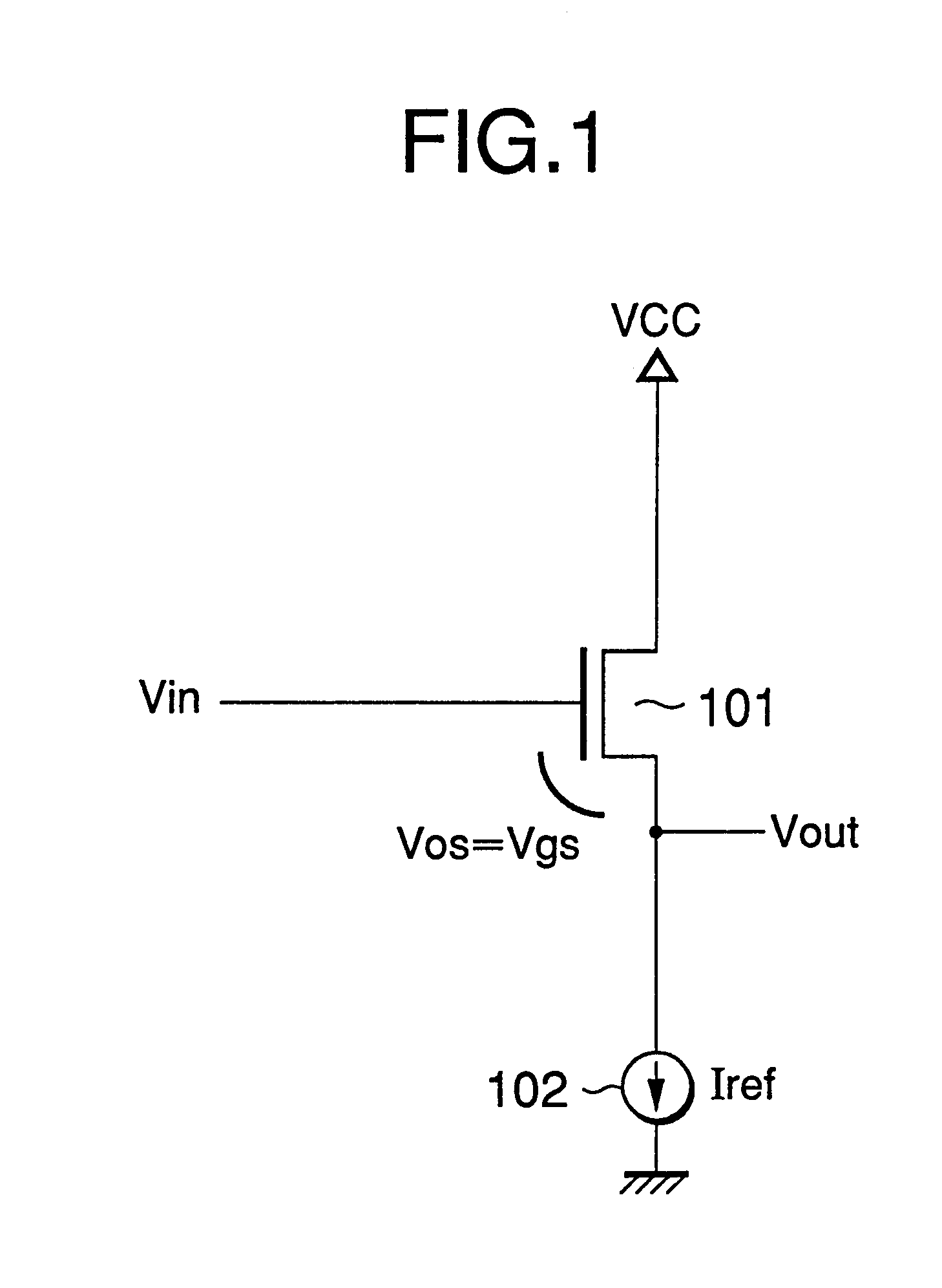

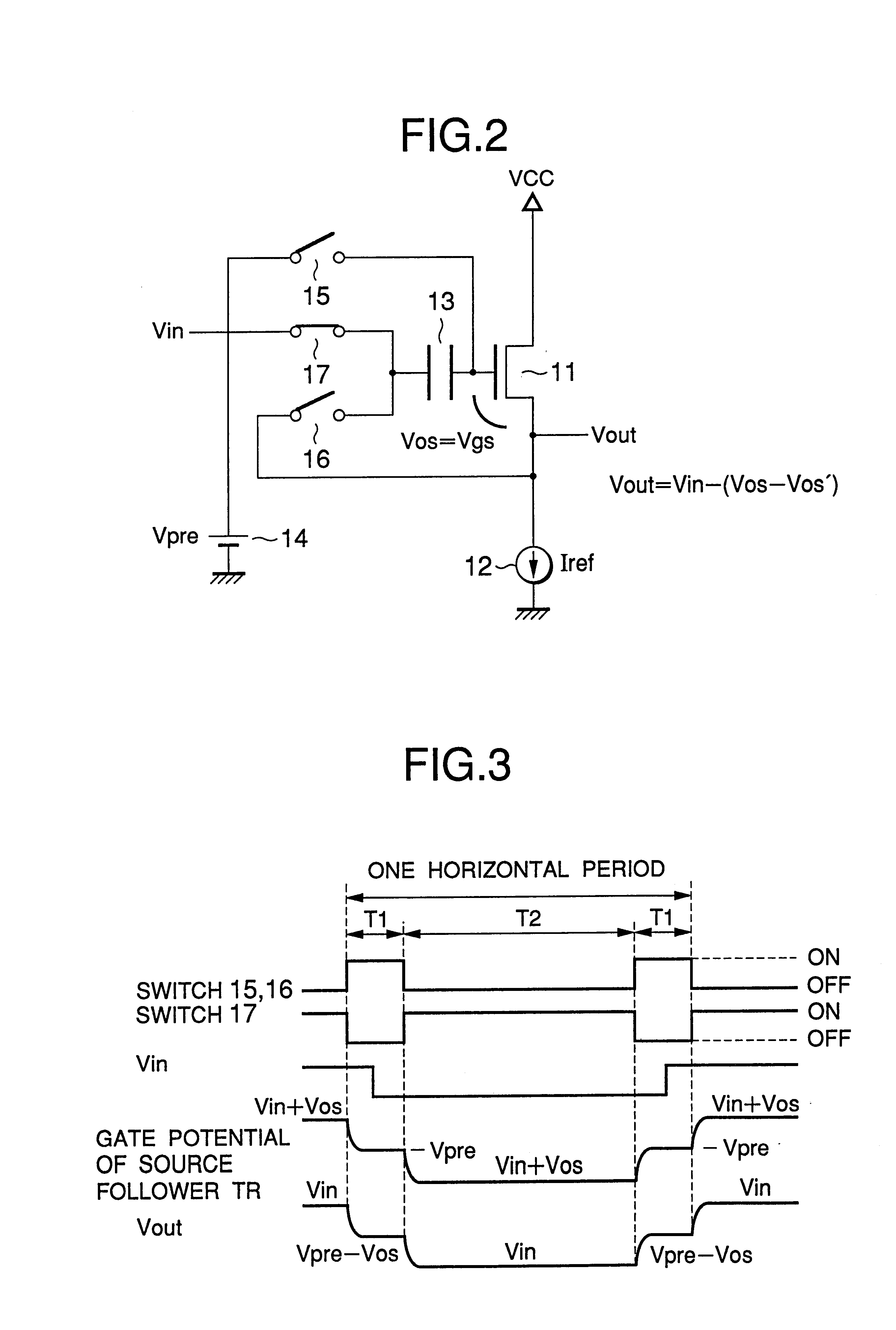

Liquid crystal display device

InactiveUS6313819B1Large variation in amountVariation in outputStatic indicating devicesAmplifiers with impedence circuitsLiquid-crystal displayEngineering

In a source follower circuit having an NMOS source follower transistor with a drain thereof connected to a power supply and a current supply connected across the source of this transistor and earth, one end of a capacitor is connected to the gate of the transistor, the first analog switch is connected across the gate of the transistor and a precharge supply, the second analog switch is connected across the other end of the capacitor and the source of the transistor, and the third analog switch is connected across the other end of the capacitor and a signal source.

Owner:SONY CORP

Semiconductor integrated circuit device with low power consumption and simple manufacturing steps

InactiveUS6208171B1Reduce manufacturing stepsProduction costPower reduction by control/clock signalLogic circuits characterised by logic functionPotential clampBack bias

In a semiconductor integrated circuit, a control transistor 4 and a potential clamp circuit 9 are arranged between a power supply line 2 and a virtual power supply line 3. Even in a sleeve mode where the control transistor 4 is turned off, the potential clamp circuit 9-1 clamps the virtual power supply line 3 at a certain potential to hold a potential state (high level or low level) of each node of a logical circuit. At this time, each FET forming the logical circuit is applied with a back bias so that a threshold voltage Vt becomes higher than that in an active mode. Therefore, a leakage current can be decreased. In the semiconductor integrated circuit, the threshold voltage Vt of the control transistor 4 can be selected to be equal to that of one FET of the complementary FET forming the logical circuit. Therefore, the layout area and the number of manufacturing steps can be reduced.

Owner:NEC CORP

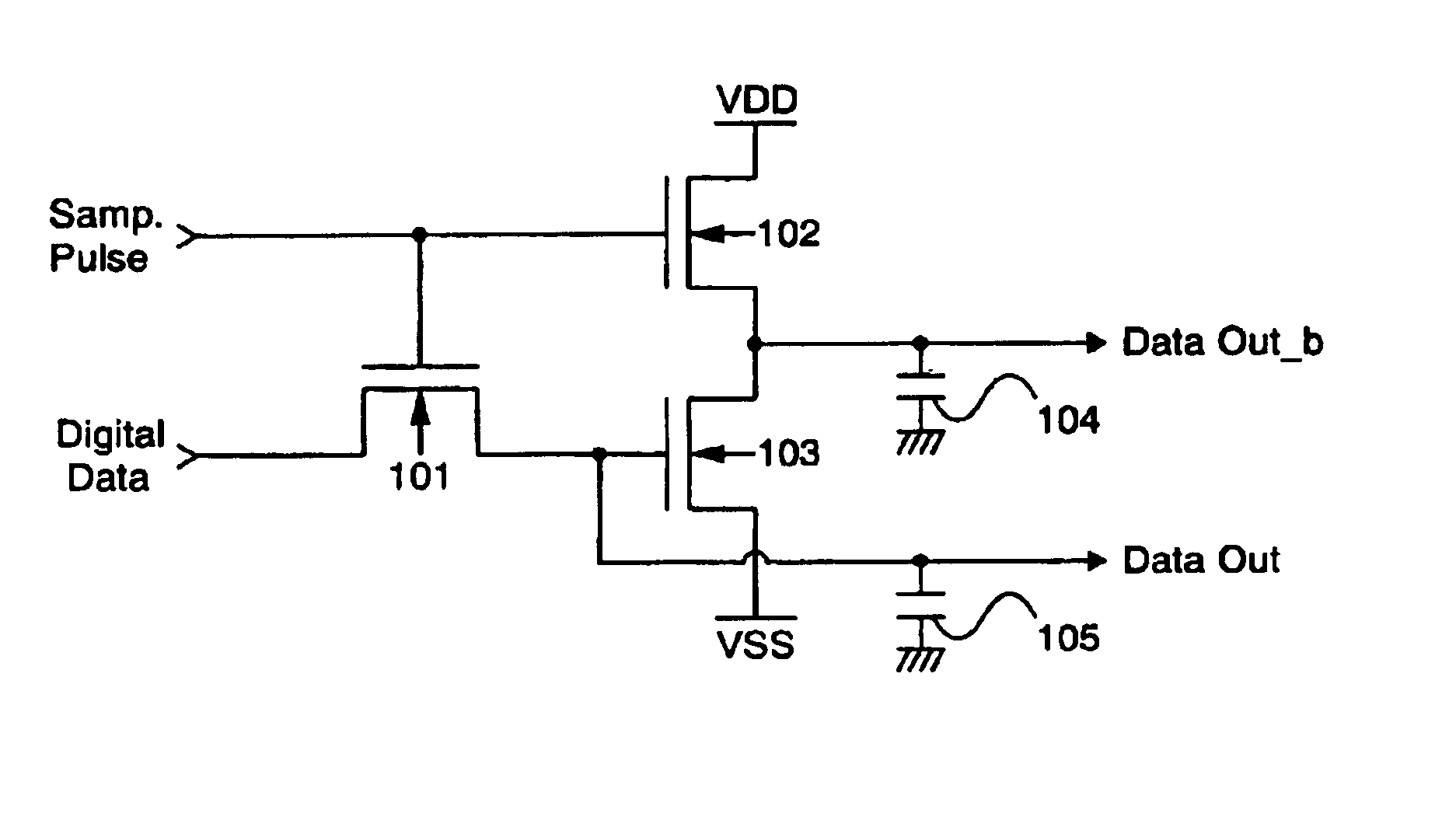

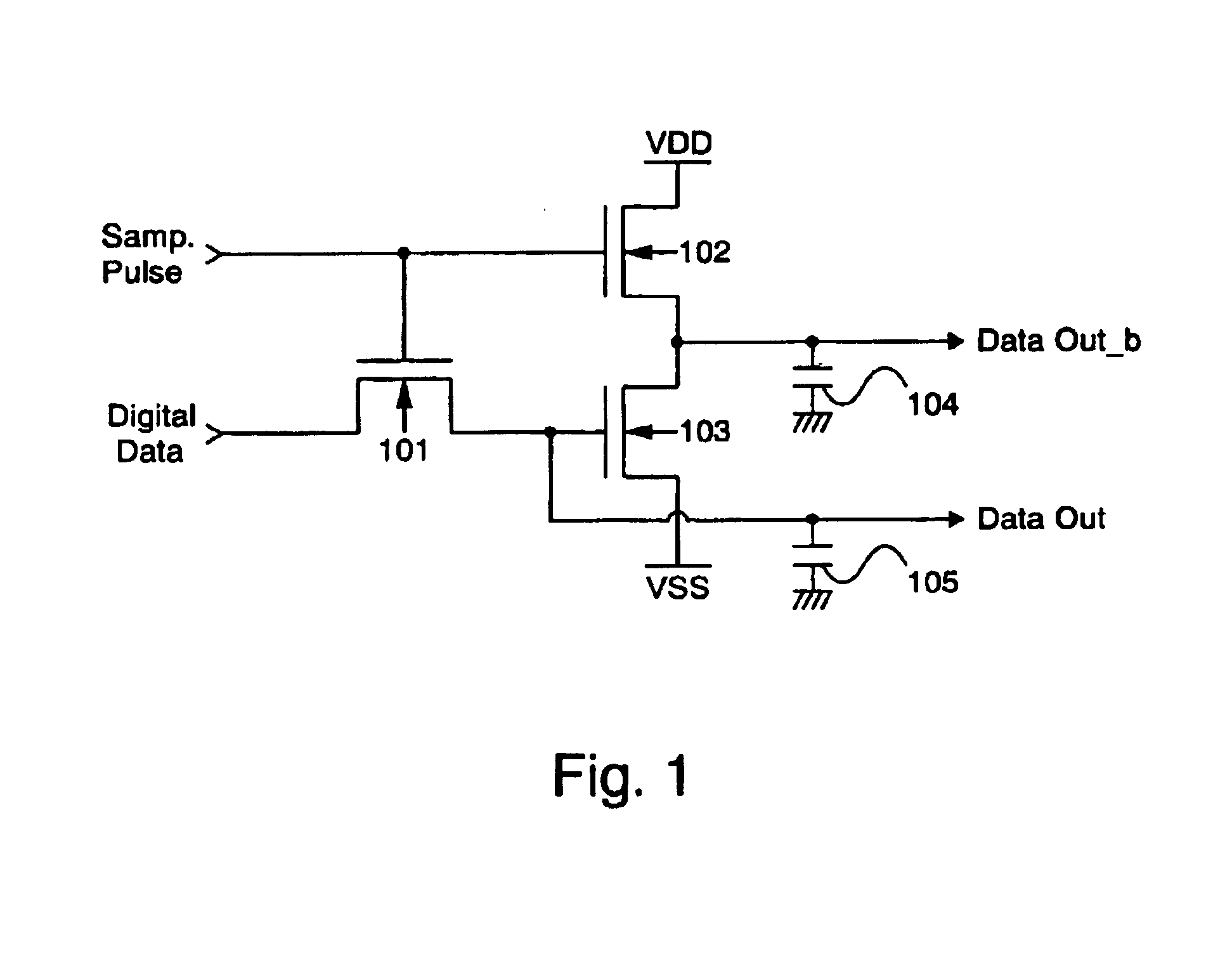

Semiconductor device and display device

InactiveUS7068076B2Obstruction is producedPower reduction in field effect transistorsLogic circuits characterised by logic functionDigital videoDevice material

A circuit capable of reducing a consumption current is provided for a digital display device composed of unipolar TFTs. There is provided a latch circuit for holding a digital video signal. According to the latch circuit, when the digital video signal is inputted to an input electrode of a TFT (101), a non-inverting output signal is outputted from an output electrode of the TFT (101) and an inverting output signal is outputted from output electrodes of TFTs (102 and 103). Two line outputs of non-inversion and inversion are obtained. Thus, when a buffer located in a subsequent stage is operated, a period for which a direct current path is produced between a high potential and a low potential of a power source can be shortened, thereby contributing to reduction in a consumption current.

Owner:SEMICON ENERGY LAB CO LTD

Pulse output circuit, shift register and display device

InactiveUS7057598B2Low priceReduce weightStatic indicating devicesSolid-state devicesCapacitanceShift register

A drive circuit of a display device, which comprise only single conductive TFTs and in which amplitude of an output signal is normal, is provided.A pulse is inputted to TFTs 101 and 104 so that the TFTs would turn ON and then potential of a node á rises. When the potential of the node á reaches (VDD−VthN), the node á became in a floating state. Accordingly, a TFT 105 then turns ON, and potential of an output node rises as a clock signal reaches the level H. On the other hand, potential of a gate electrode of the TFT 105 further rises due to an operation of capacitance 107 as the potential of the output node rises, so that the potential of the output node would be higher than (VDD+VthN). Thus, the potential of the output node rises to VDD without voltage drop caused by a threshold of the TFT 105. An output at the subsequent stage is then inputted to TFTs 102 and 103 to turn the TFTs 102 and 103 ON, while the potential of the node á drops down to turn the TFT 105 OFF. A TFT 106 turns ON at the same time so that the potential of the output node would reach the level L.

Owner:SEMICON ENERGY LAB CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com