Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1083results about How to "Reduce inductance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

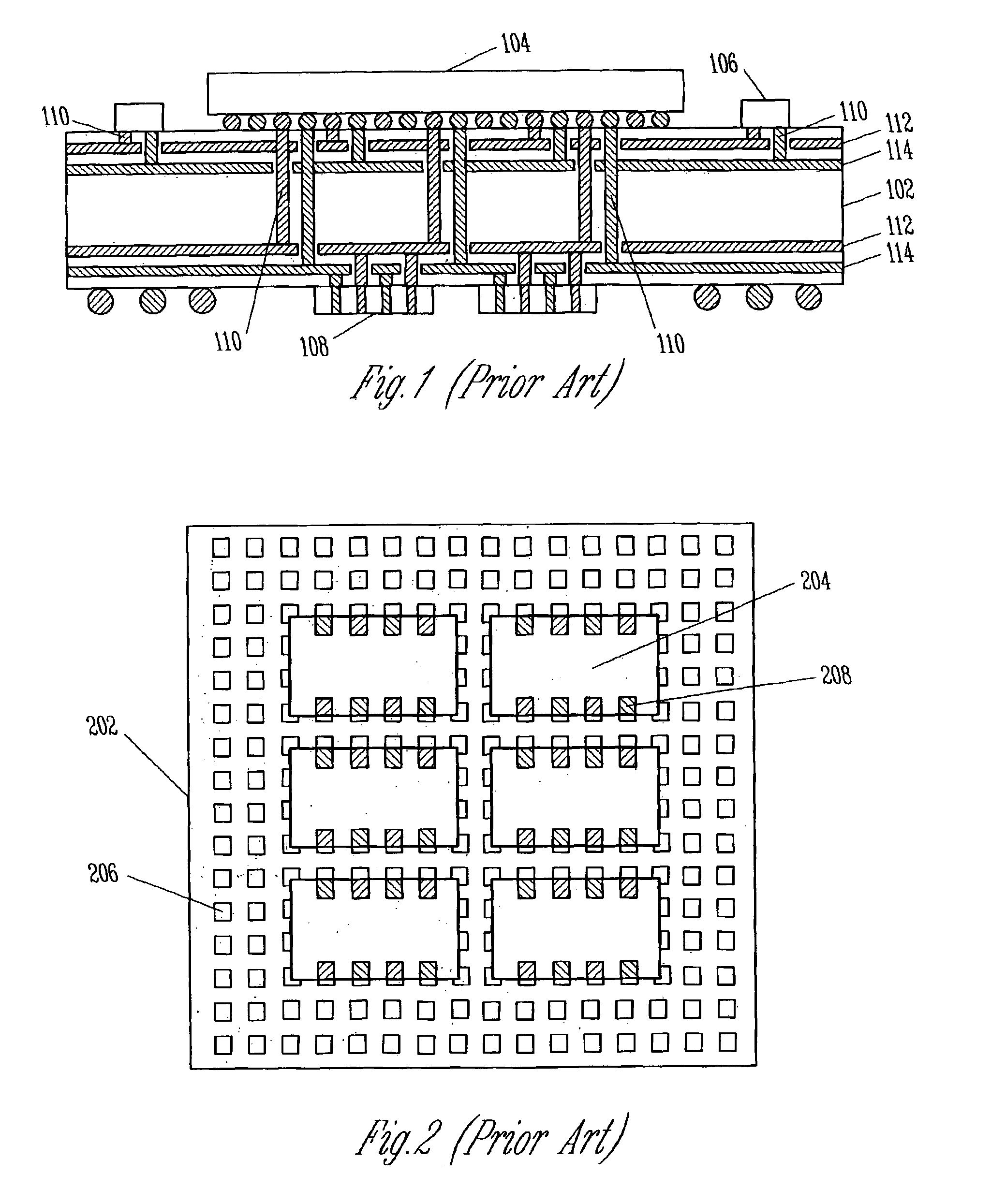

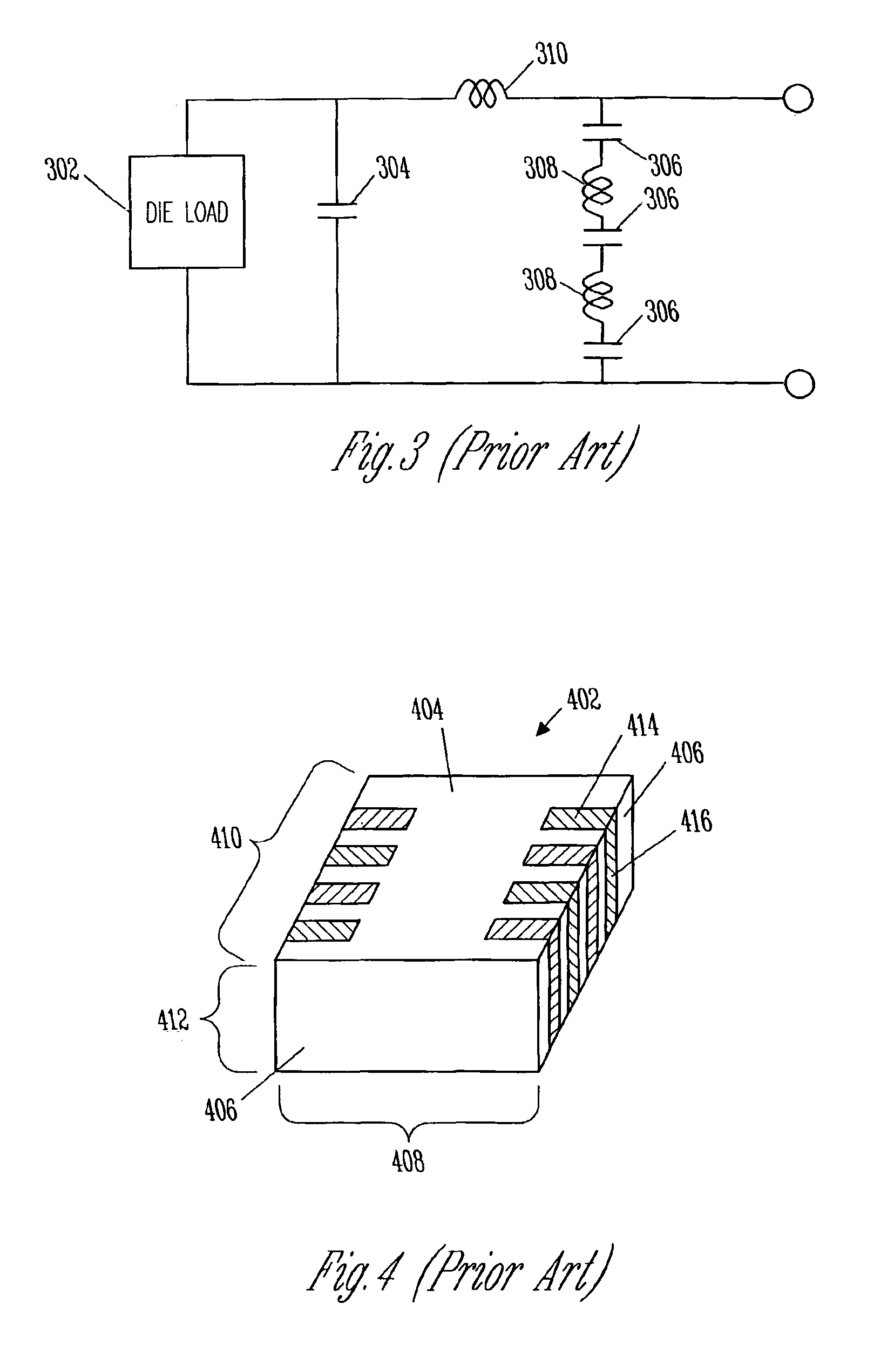

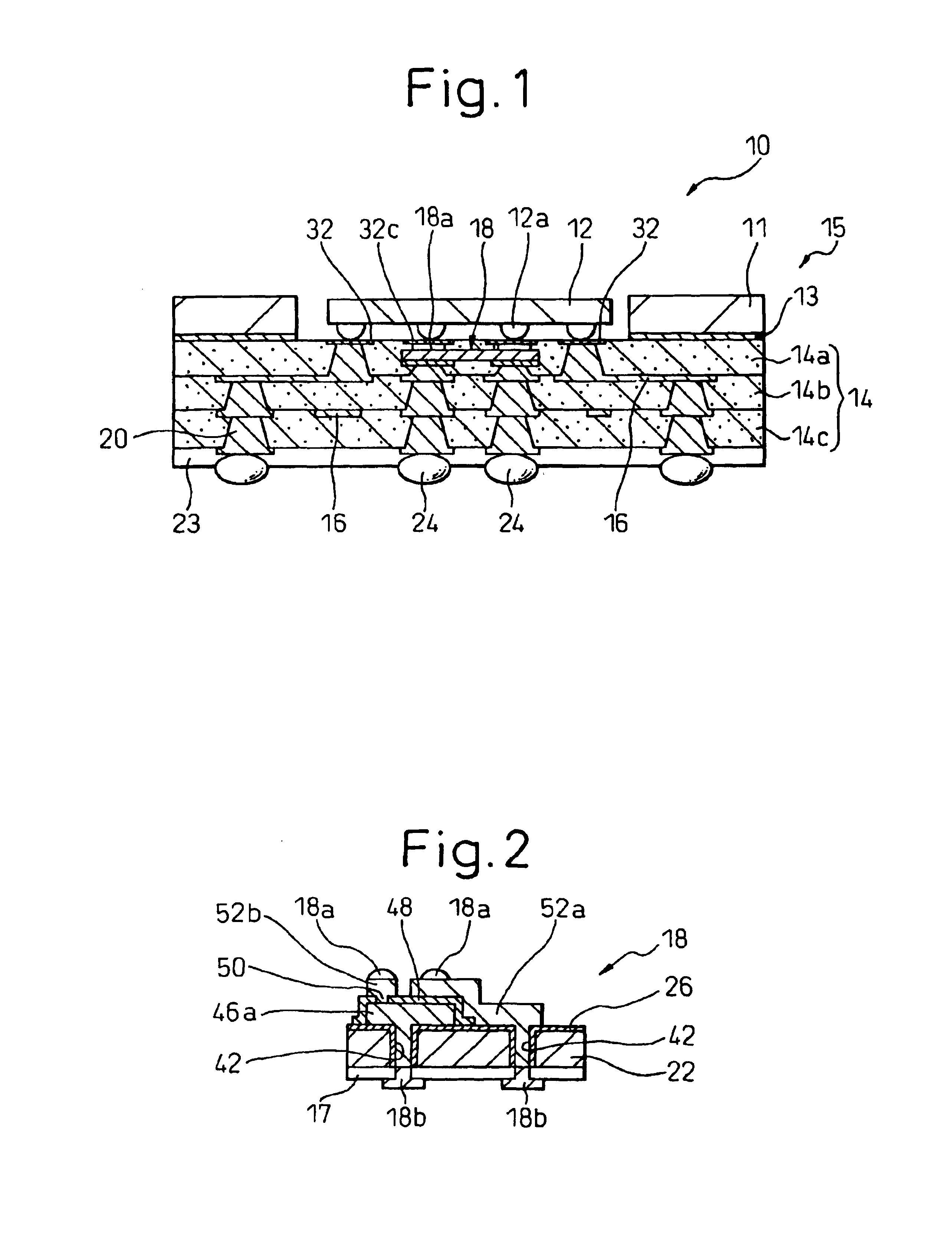

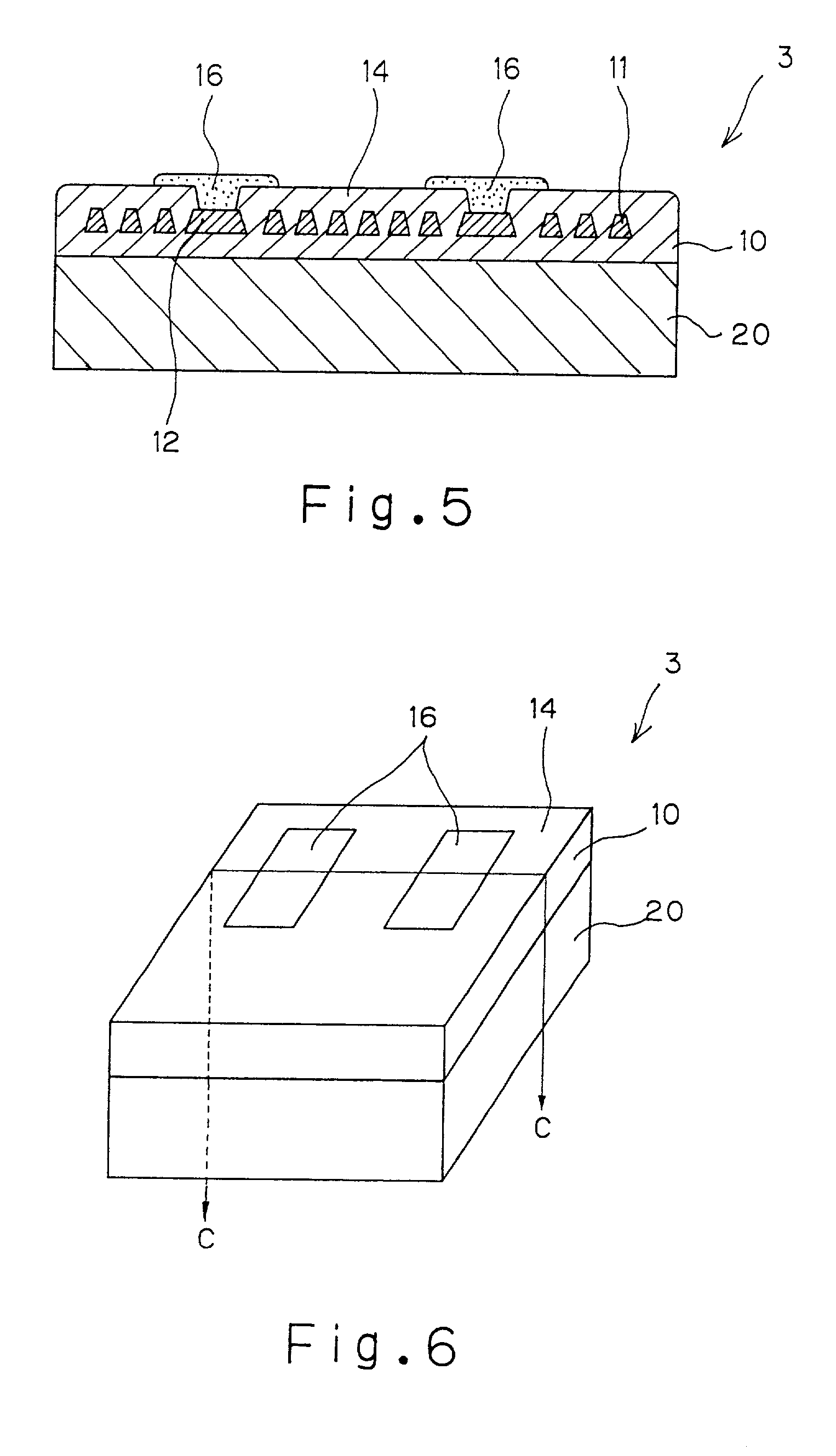

High density chip carrier with integrated passive devices

InactiveUS6962872B2Reduce inductanceEasy accessSemiconductor/solid-state device detailsPrinted circuit aspectsHigh densityEngineering

Owner:GLOBALFOUNDRIES U S INC

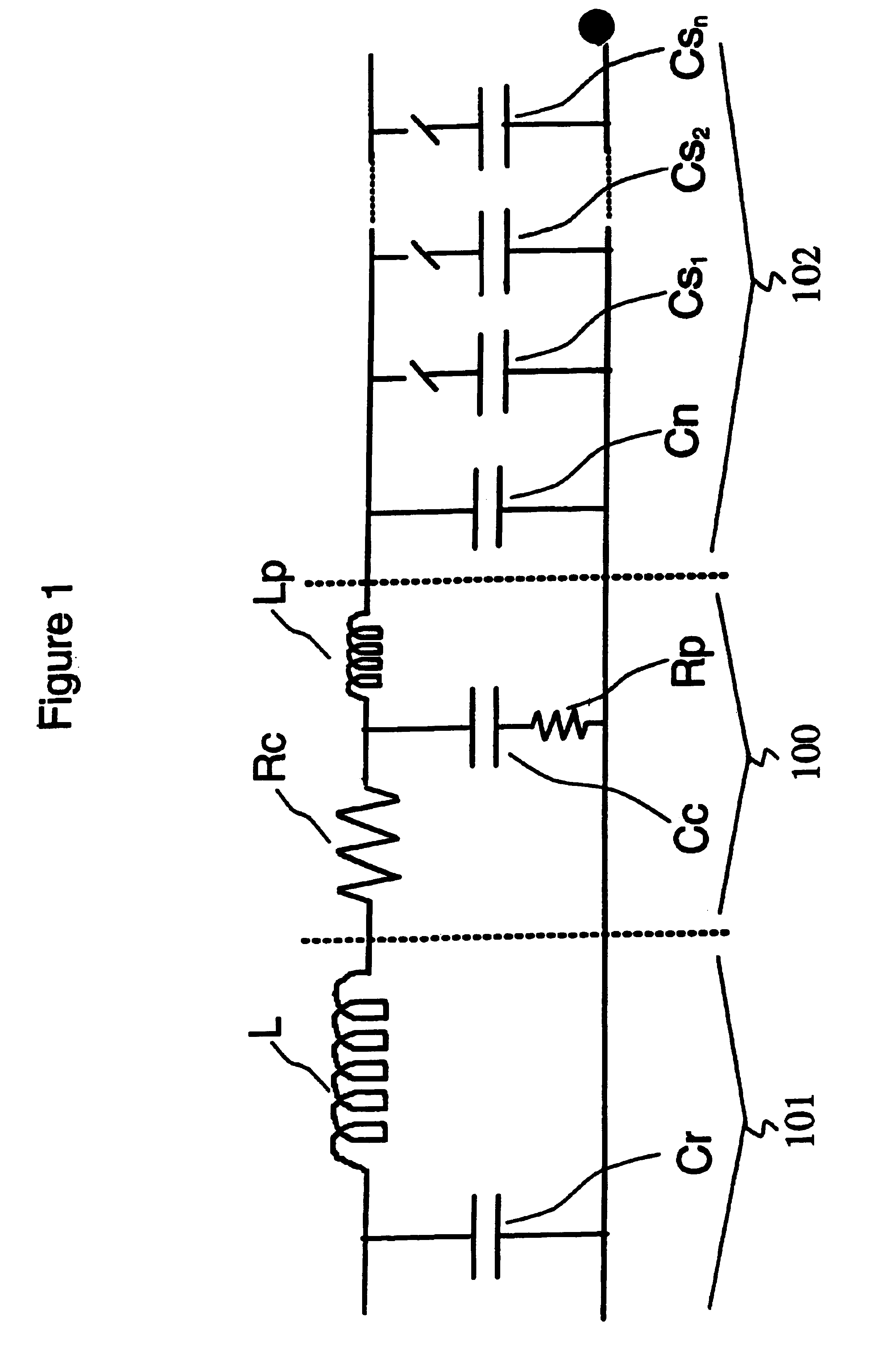

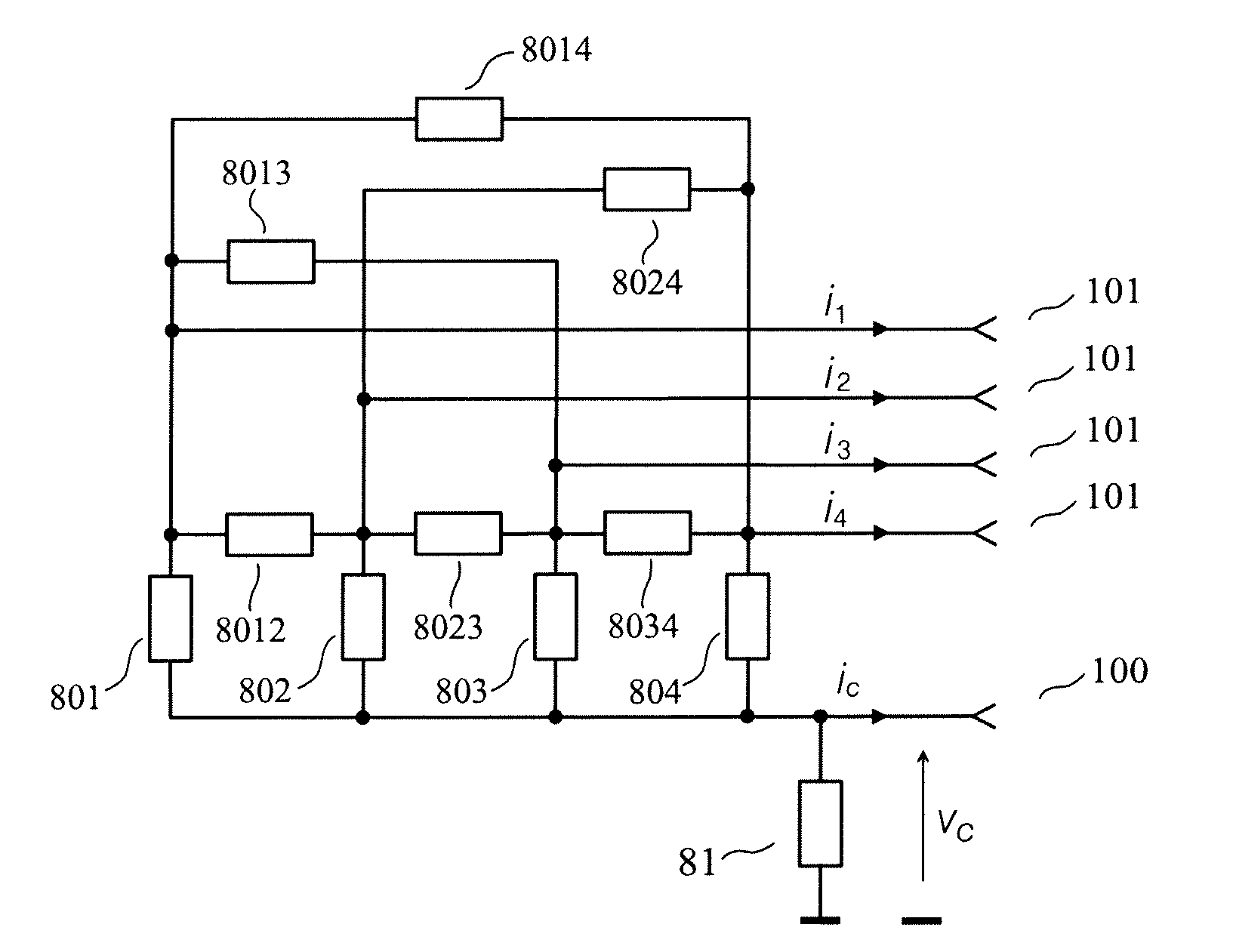

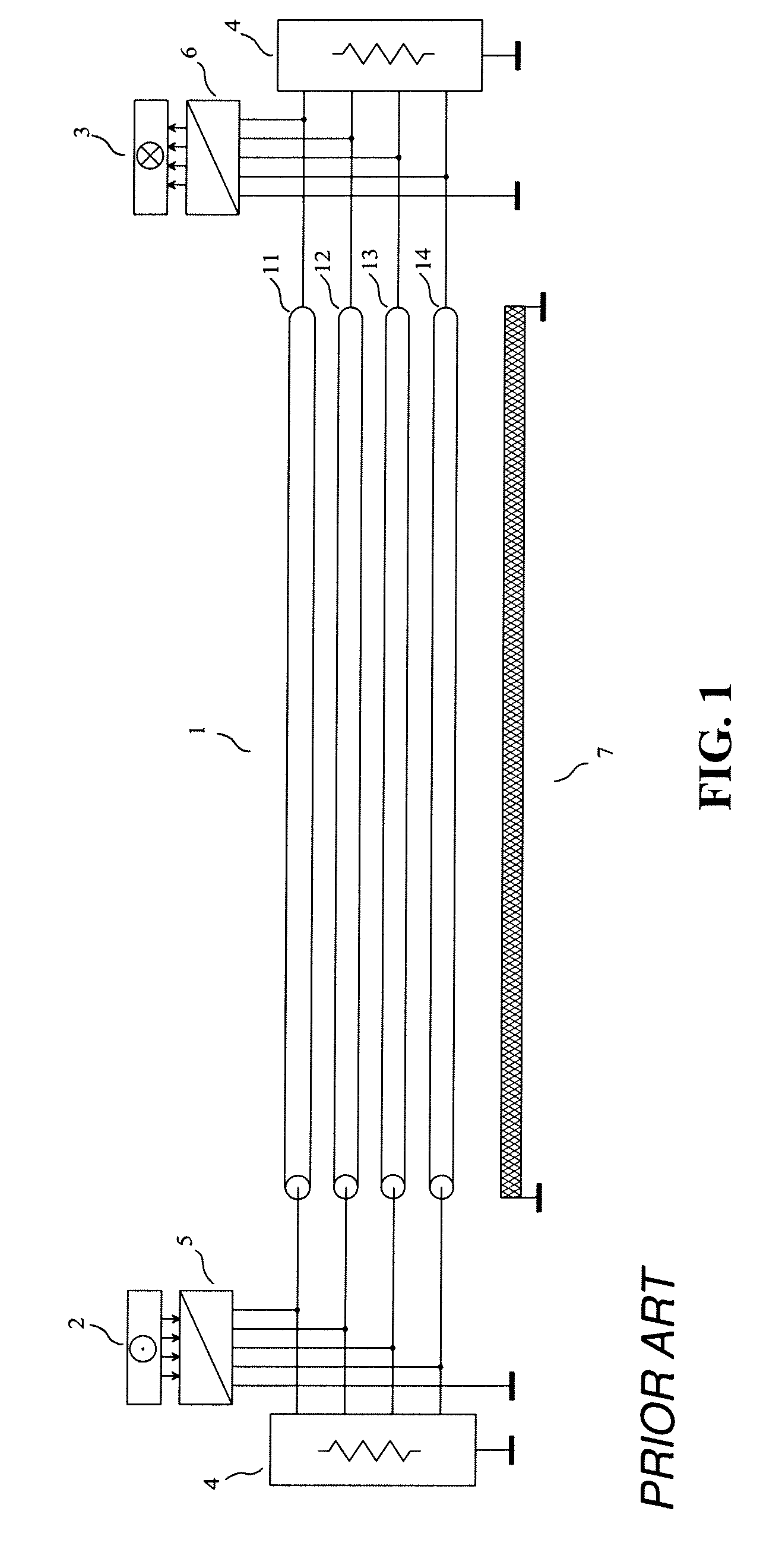

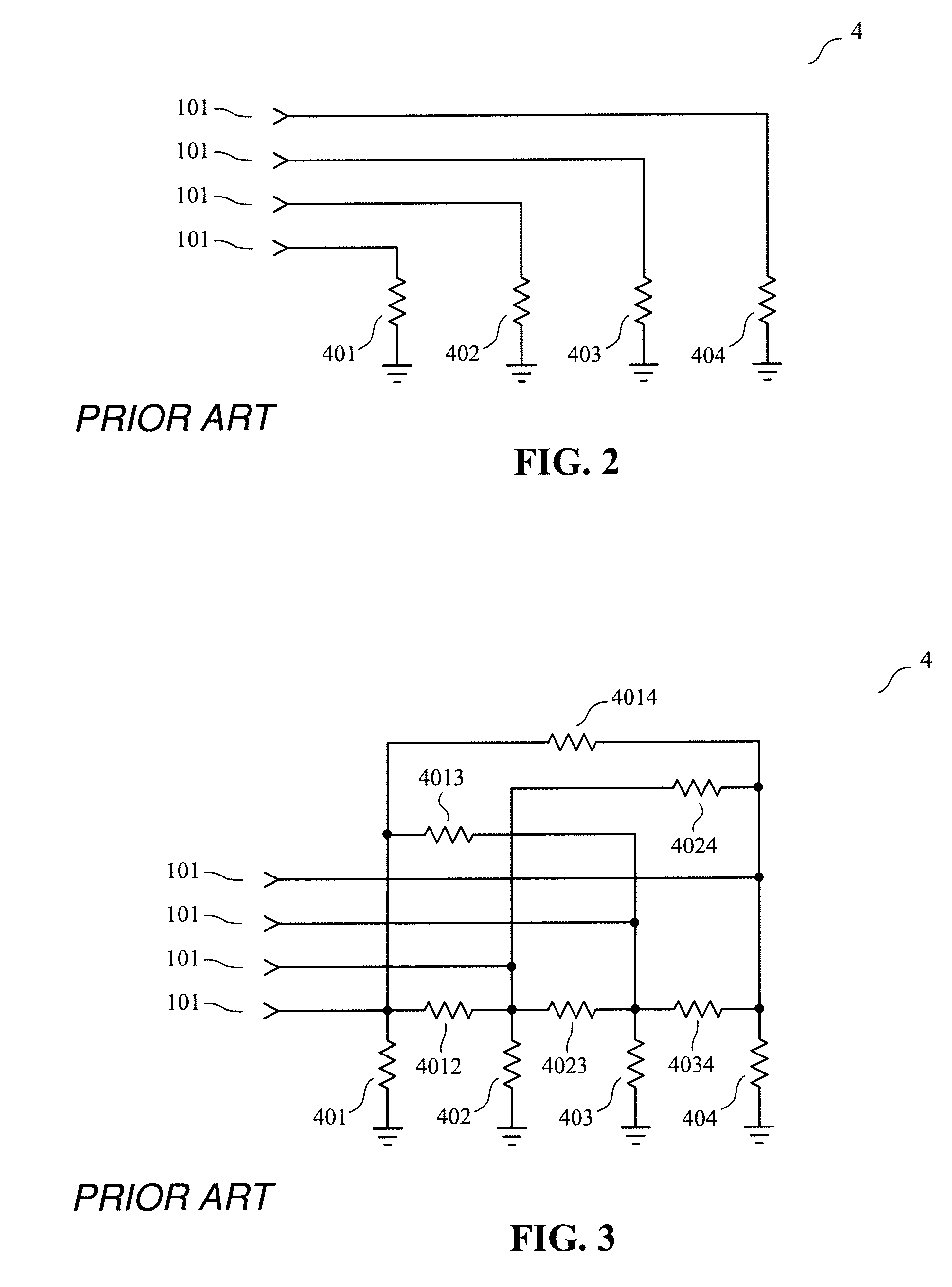

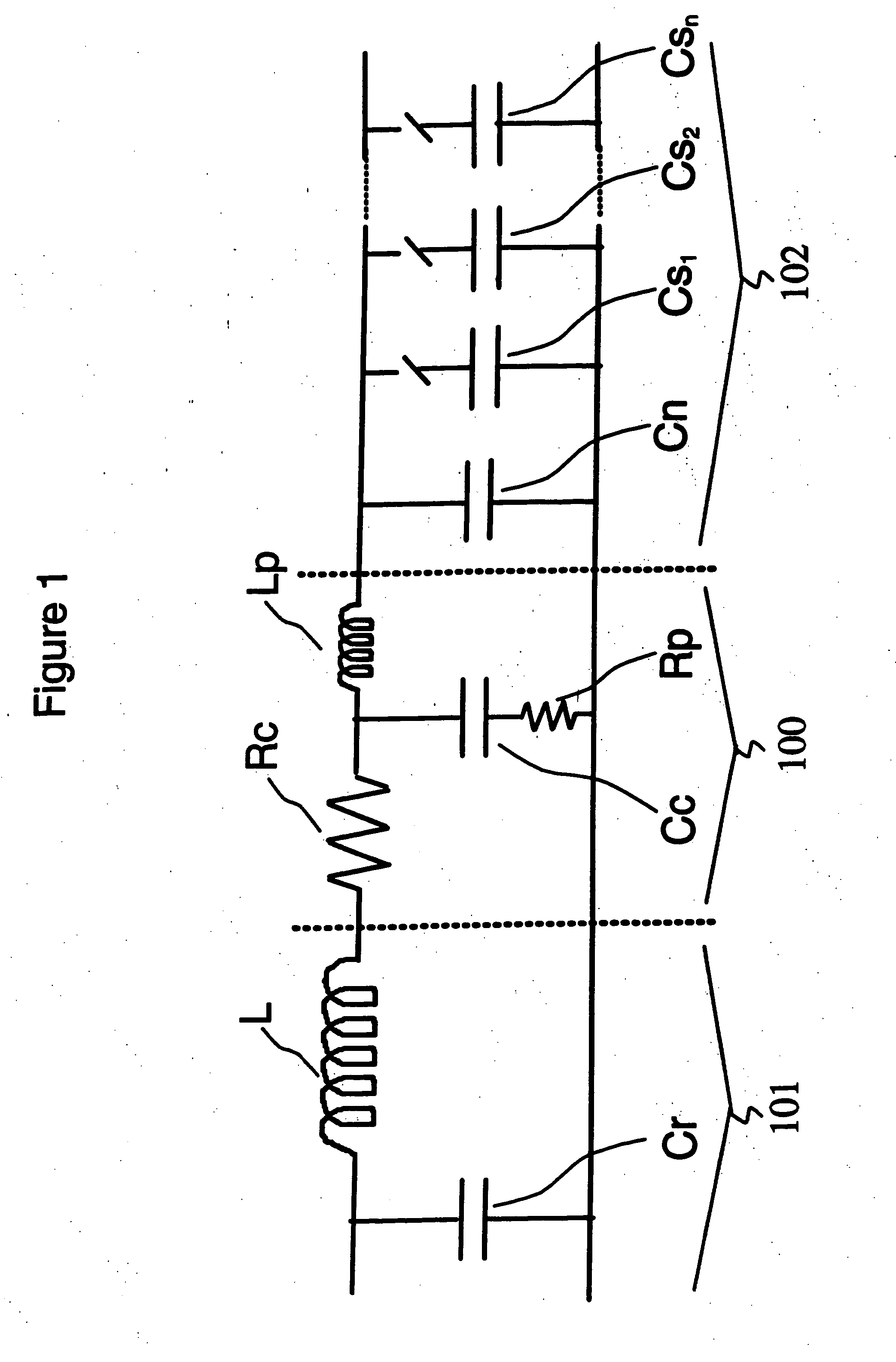

Multichannel interfacing device having a termination circuit

InactiveUS8222919B2Reduce reflectionReduce inductanceMultiple-port networksReliability increasing modificationsDiagonal matrixInterconnection

The invention relates to an interfacing device for transmission through interconnections used for sending a plurality of electrical signals.The interfacing device of the invention comprises signal terminals and a common terminal. A receiving circuit delivers, when the receiving circuit is in the activated state, “output signals of the receiving circuit” determined each by a linear combination of the voltages between one of the signal terminals and the common terminal, to the destination. A termination circuit is such that, when it is in the activated state, it is approximately equivalent, for the signal terminals and the common terminal, to a (m+1)-terminal network such that, for small signals, the impedance matrix, with respect to the common terminal, of the (m+1)-terminal network is equal to a wanted non-diagonal matrix of size m×m.

Owner:ZXNOISE LLC

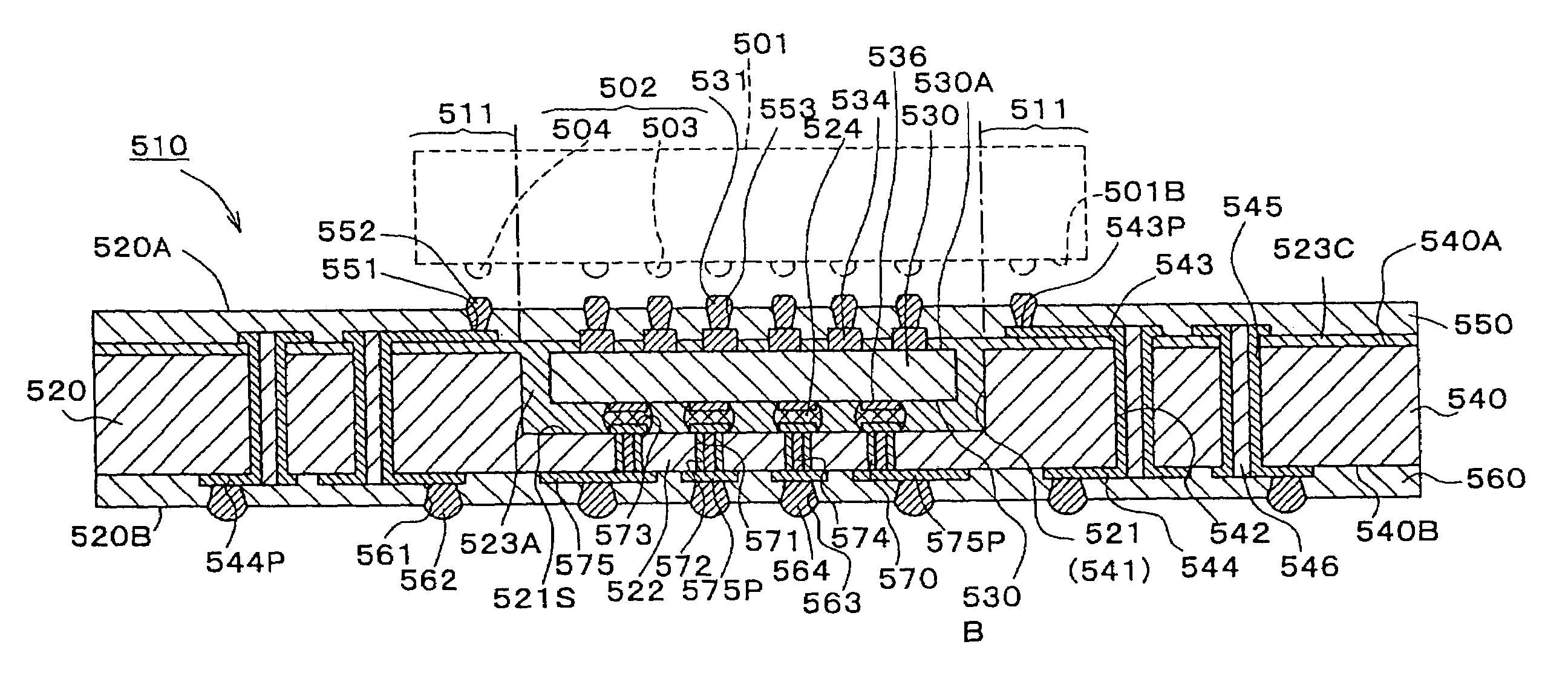

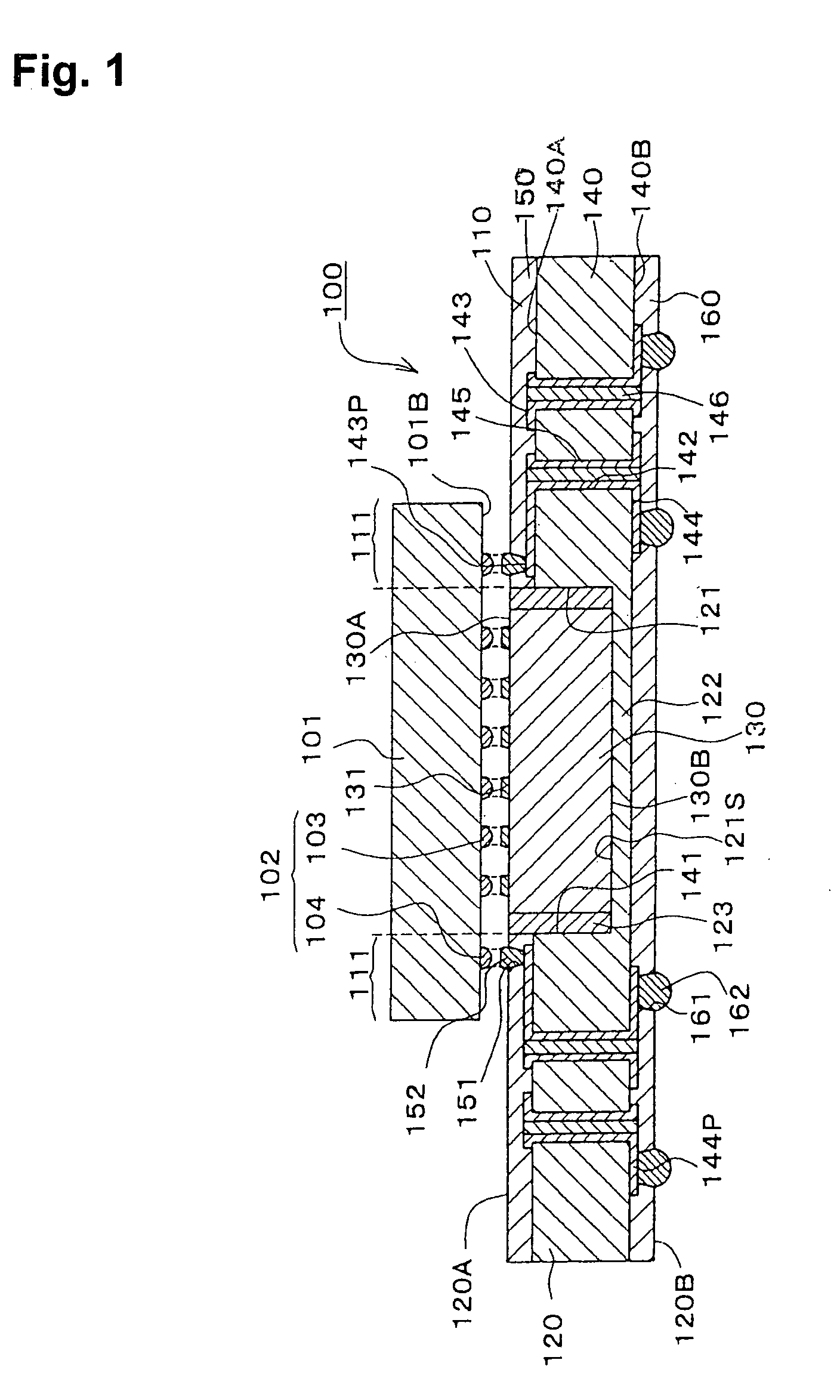

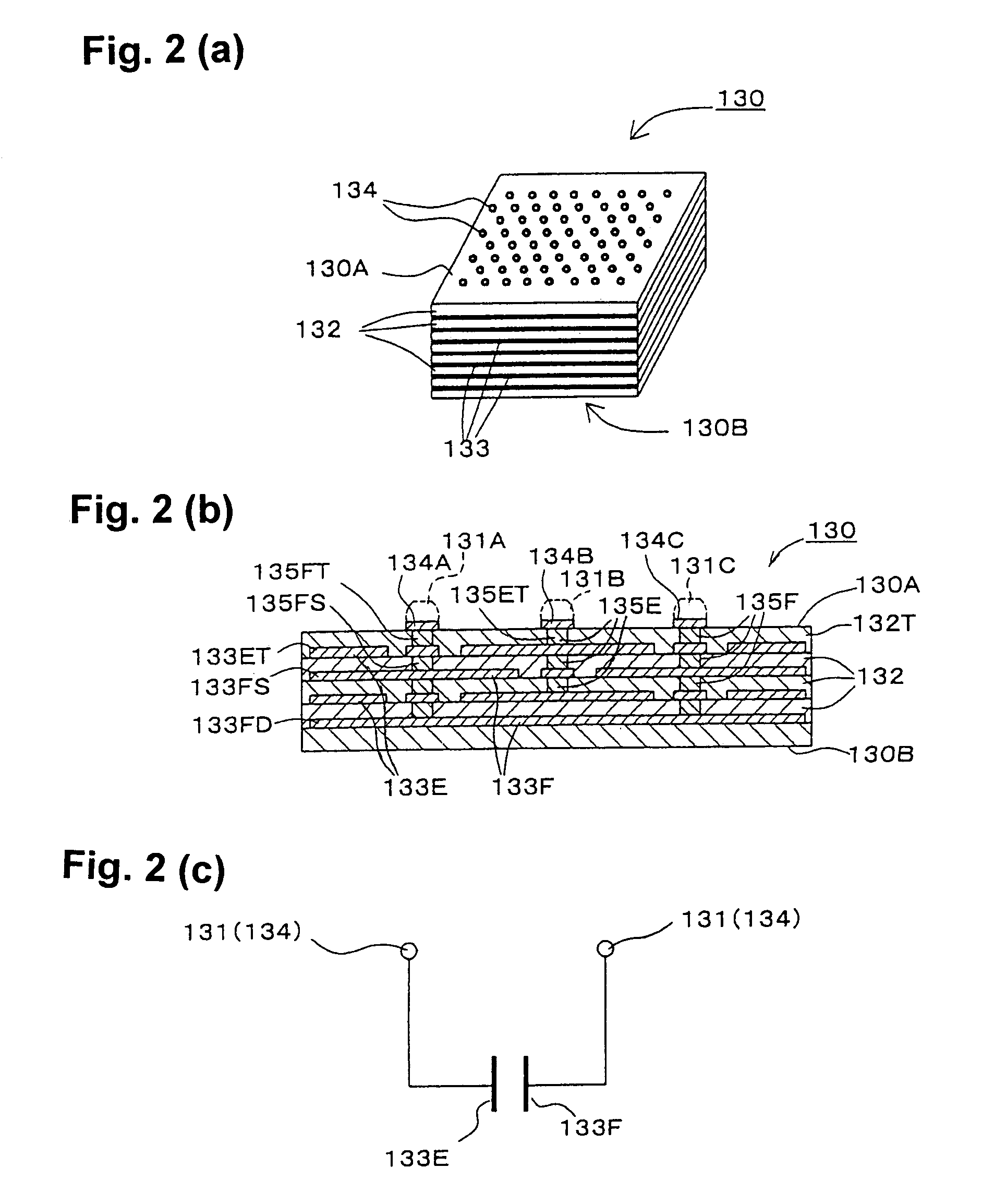

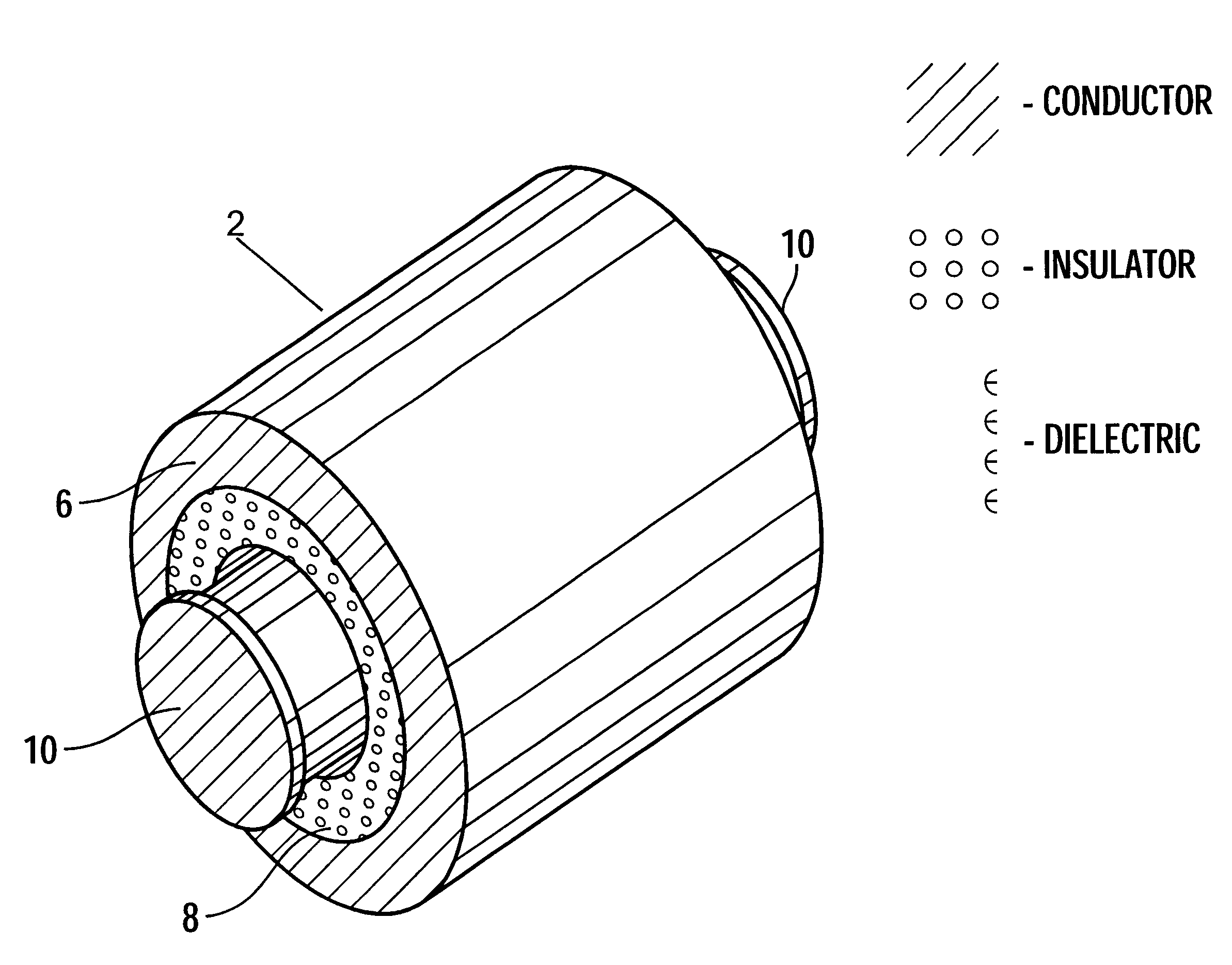

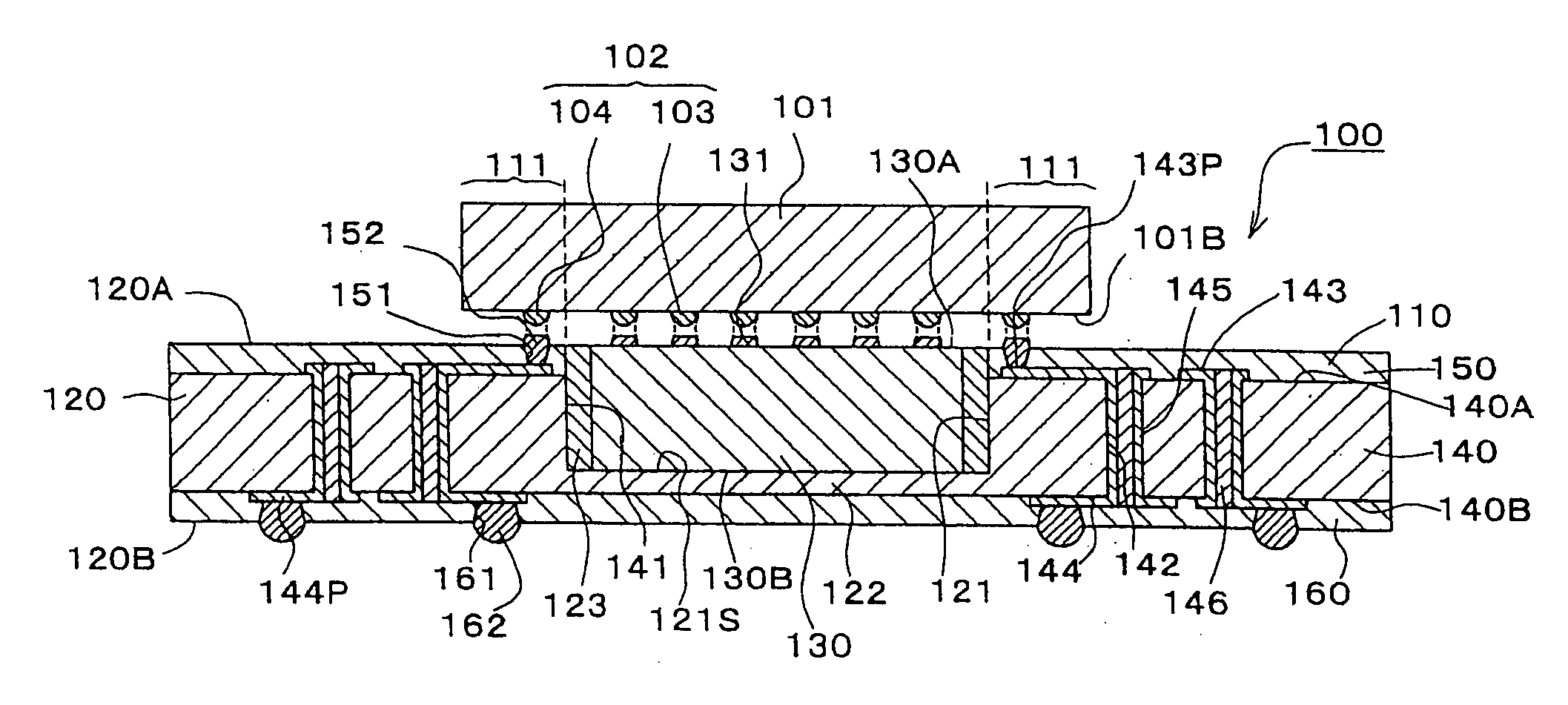

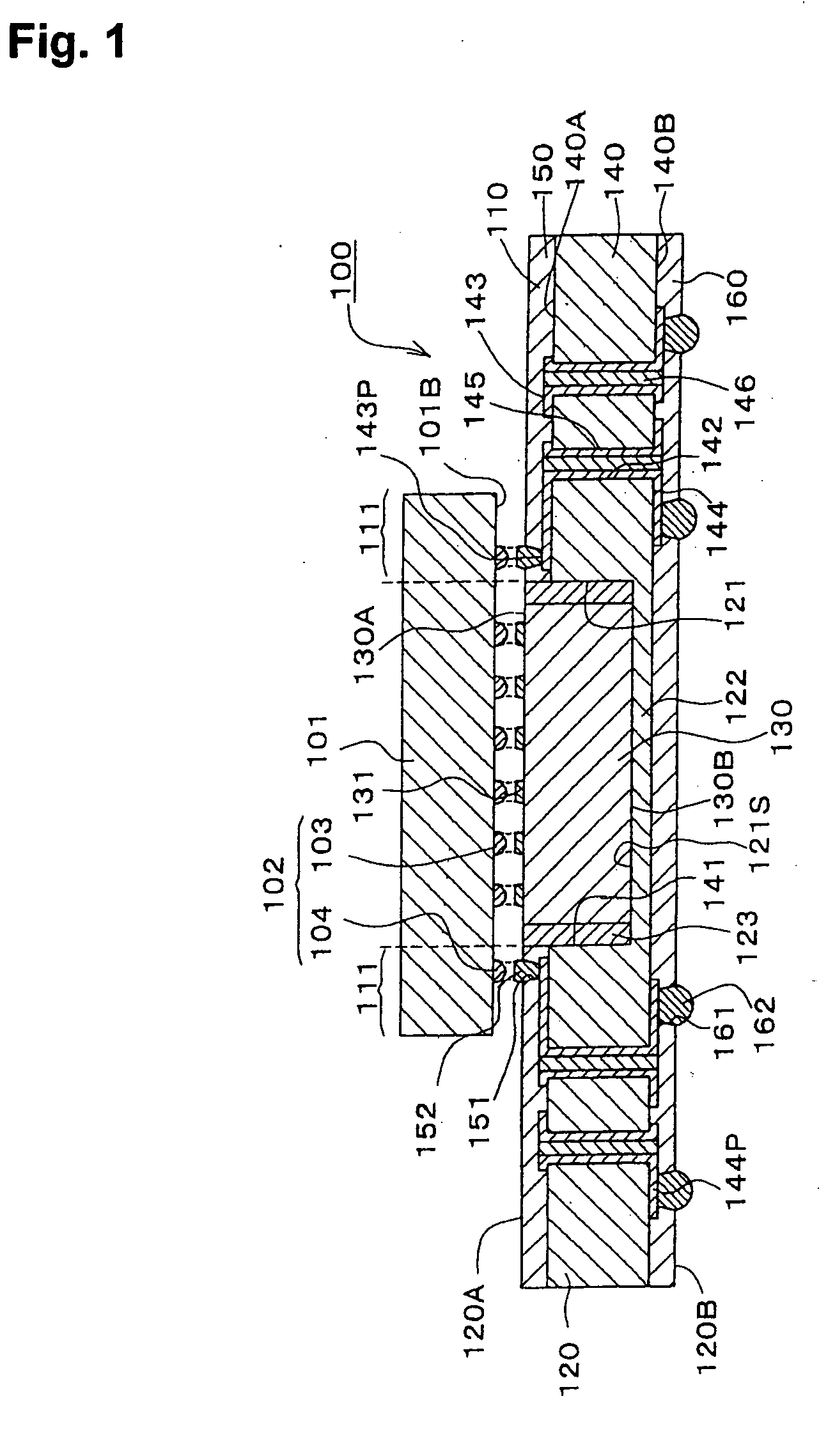

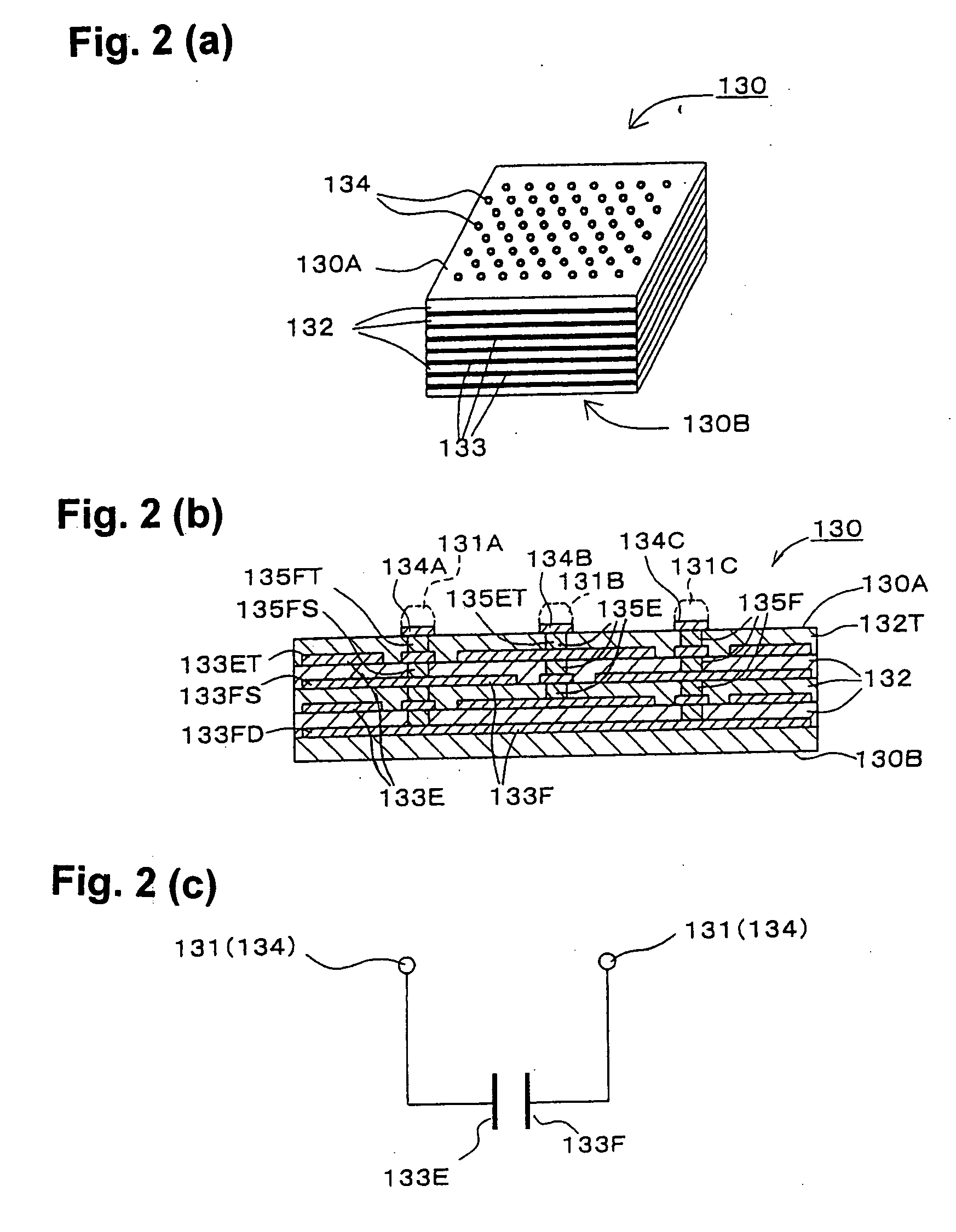

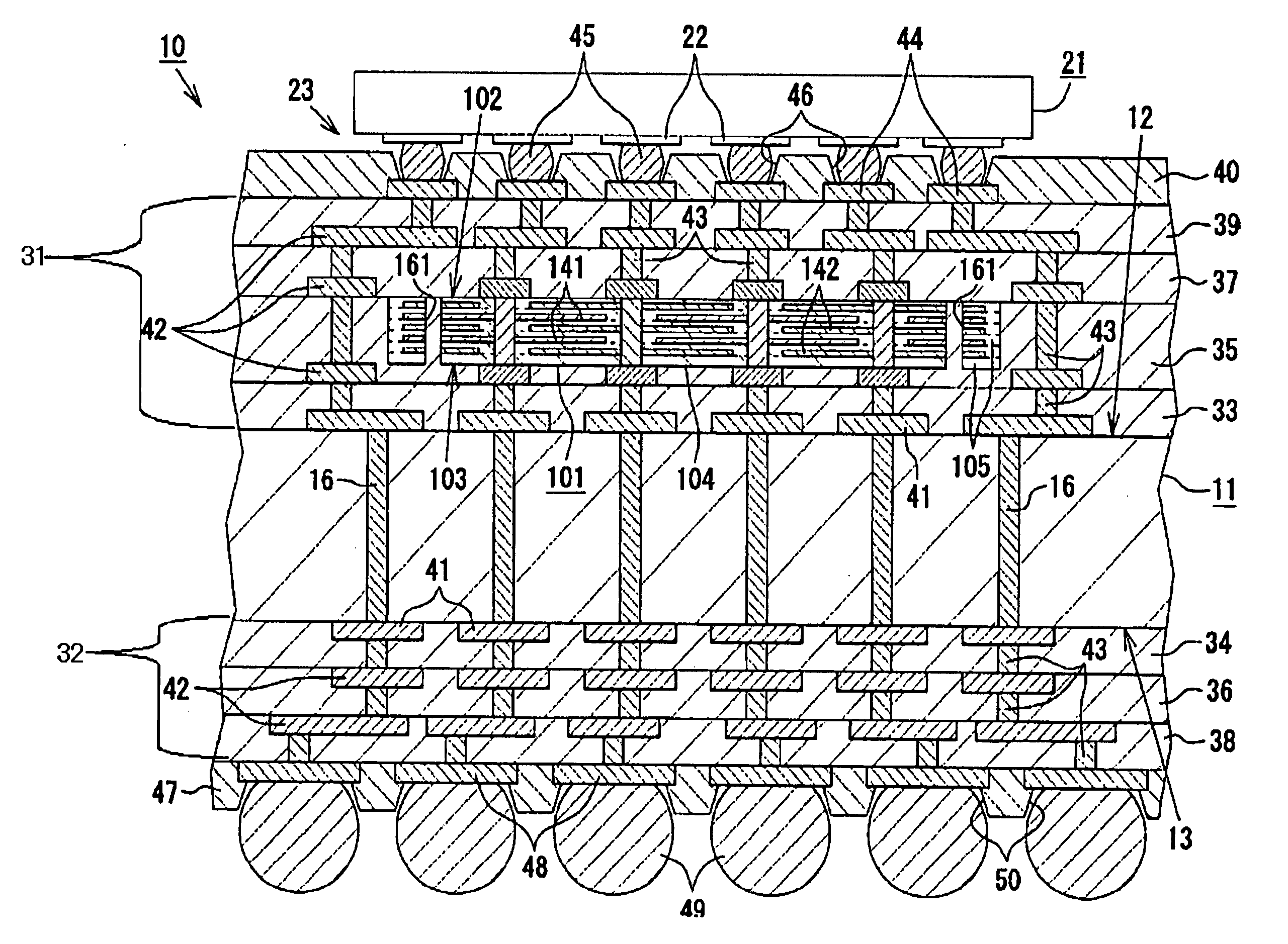

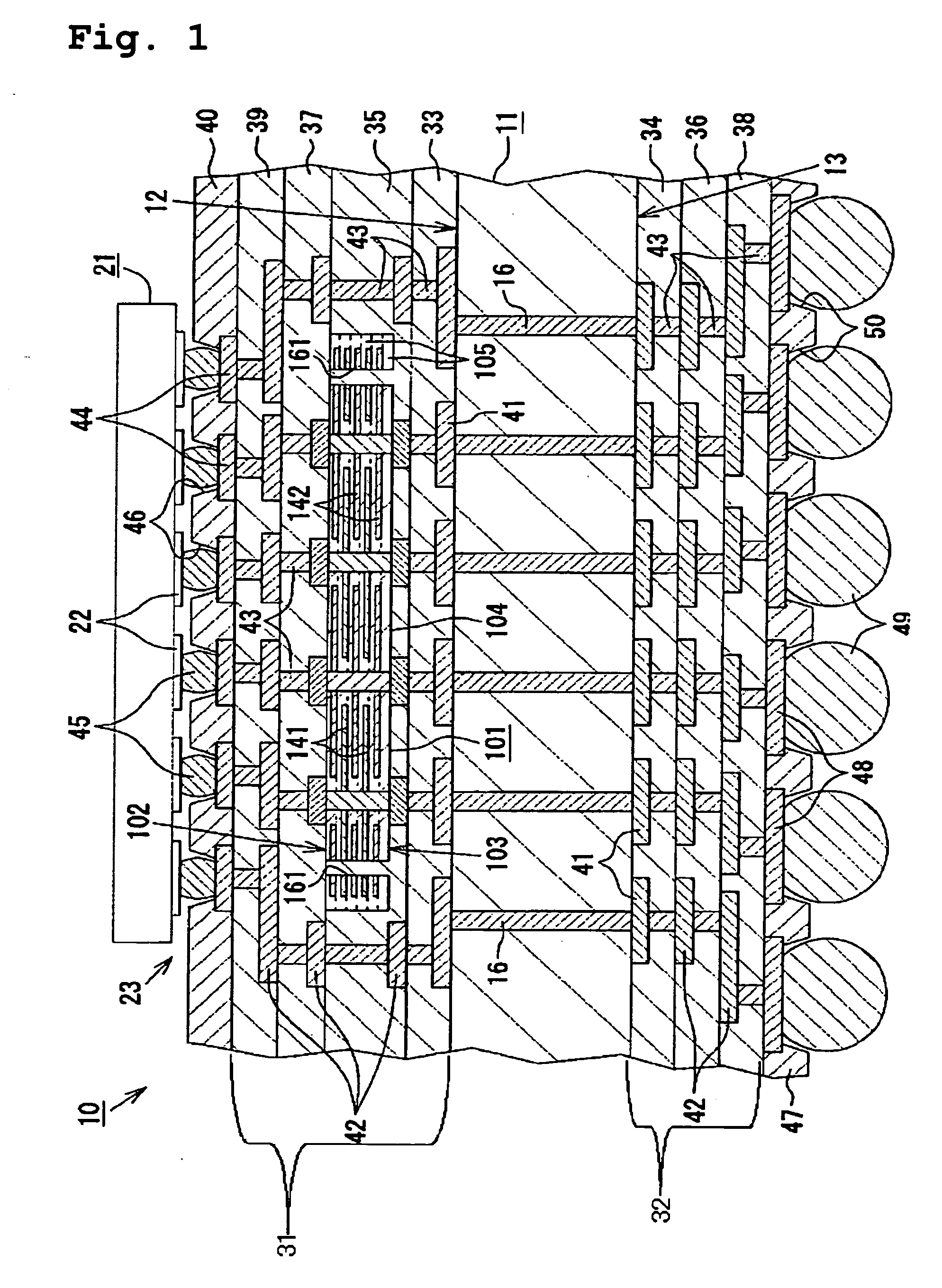

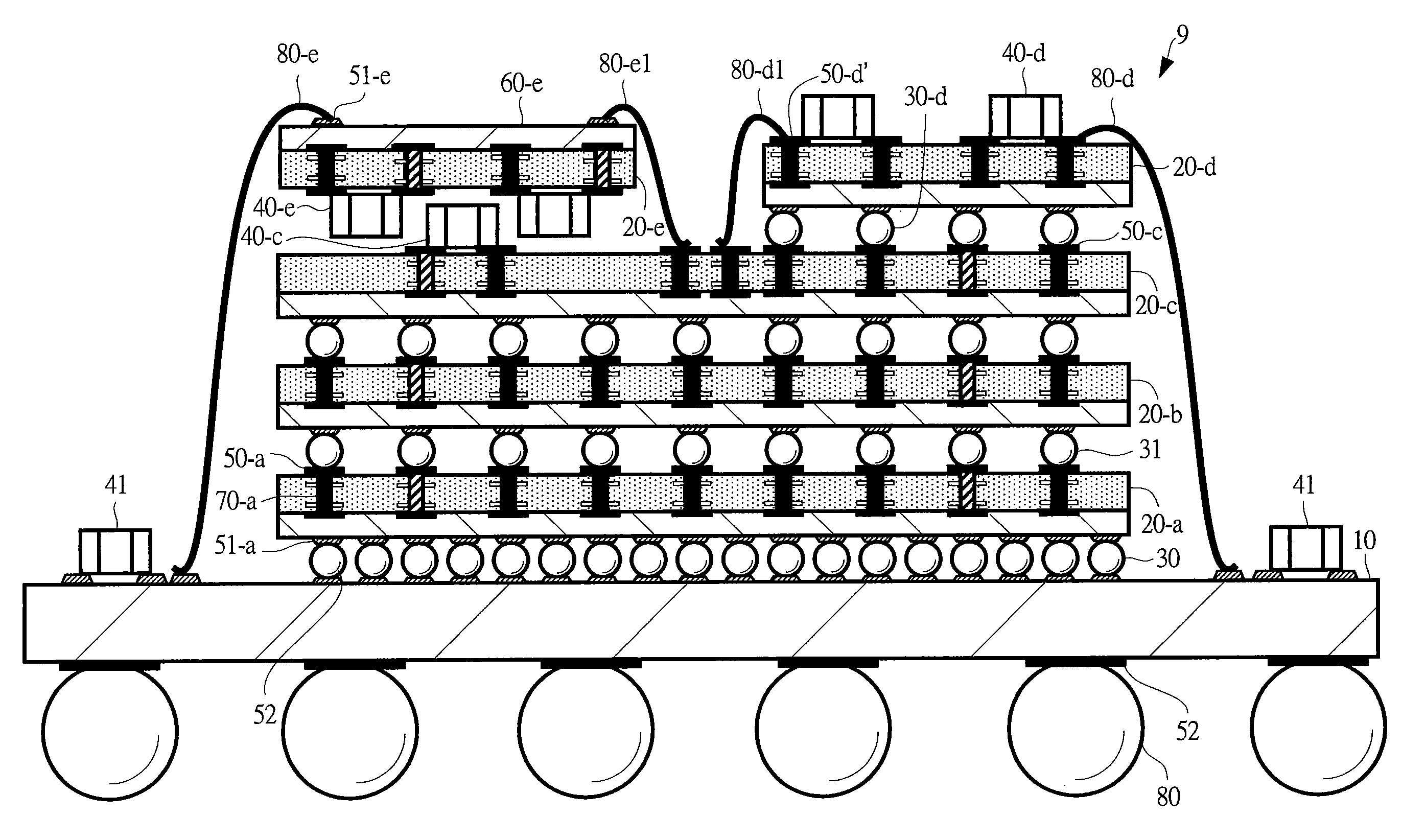

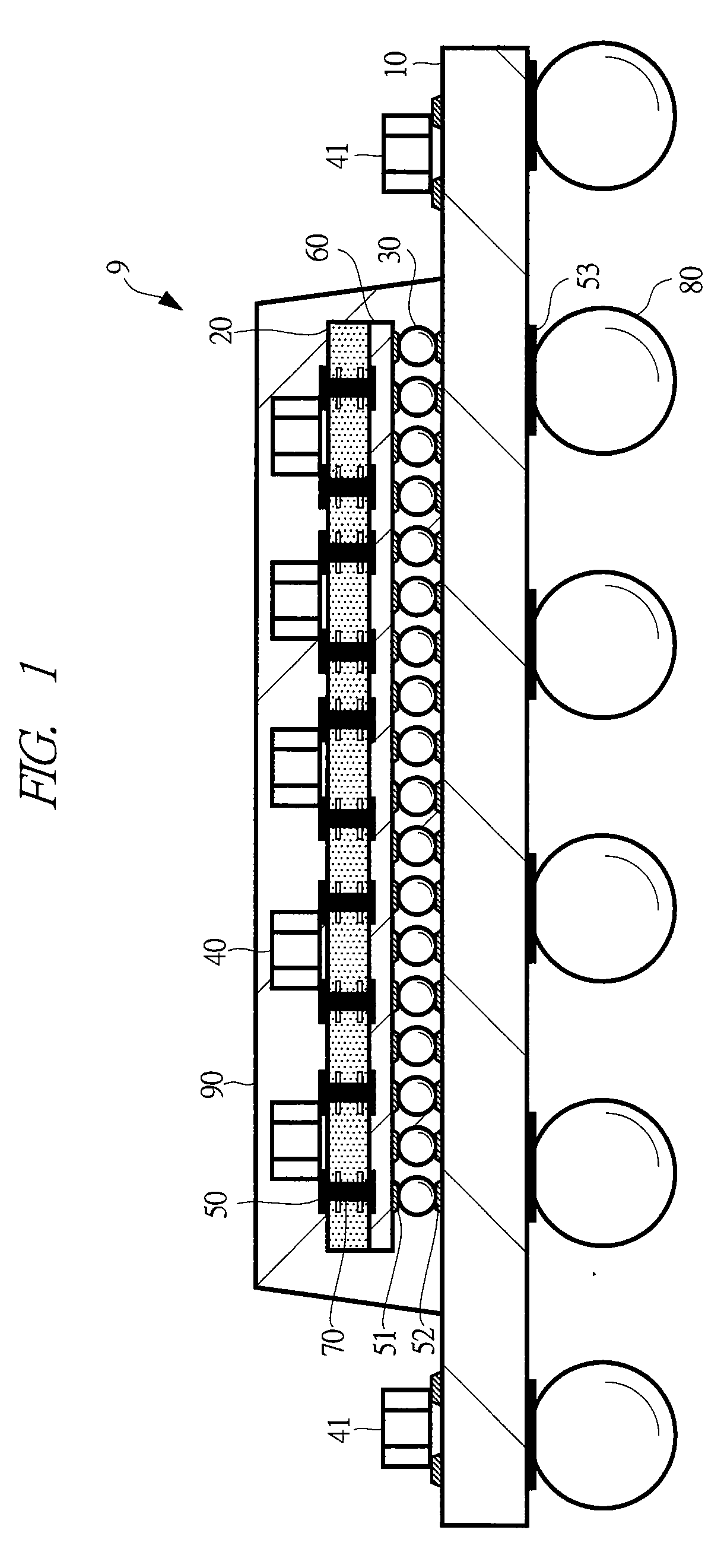

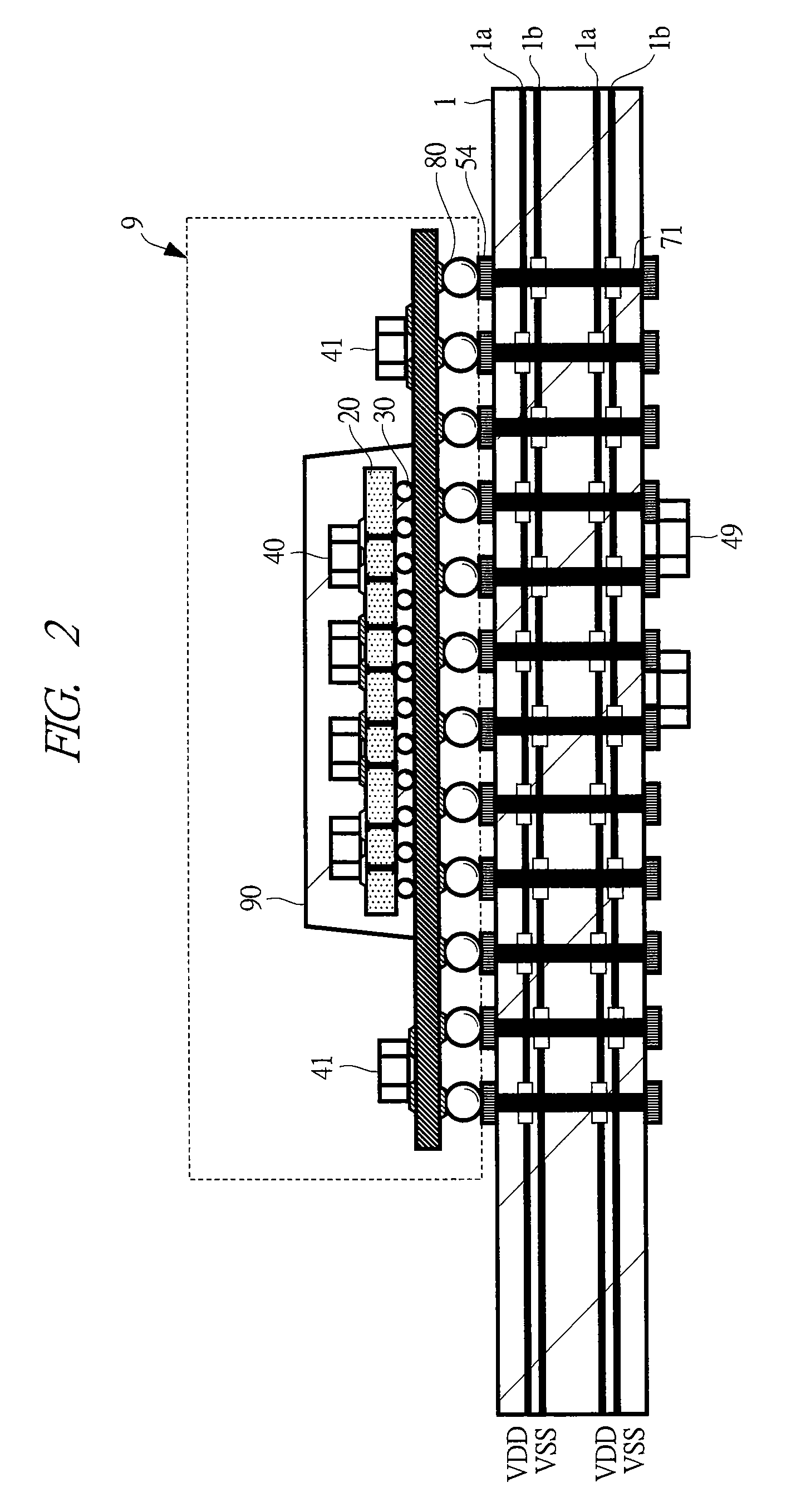

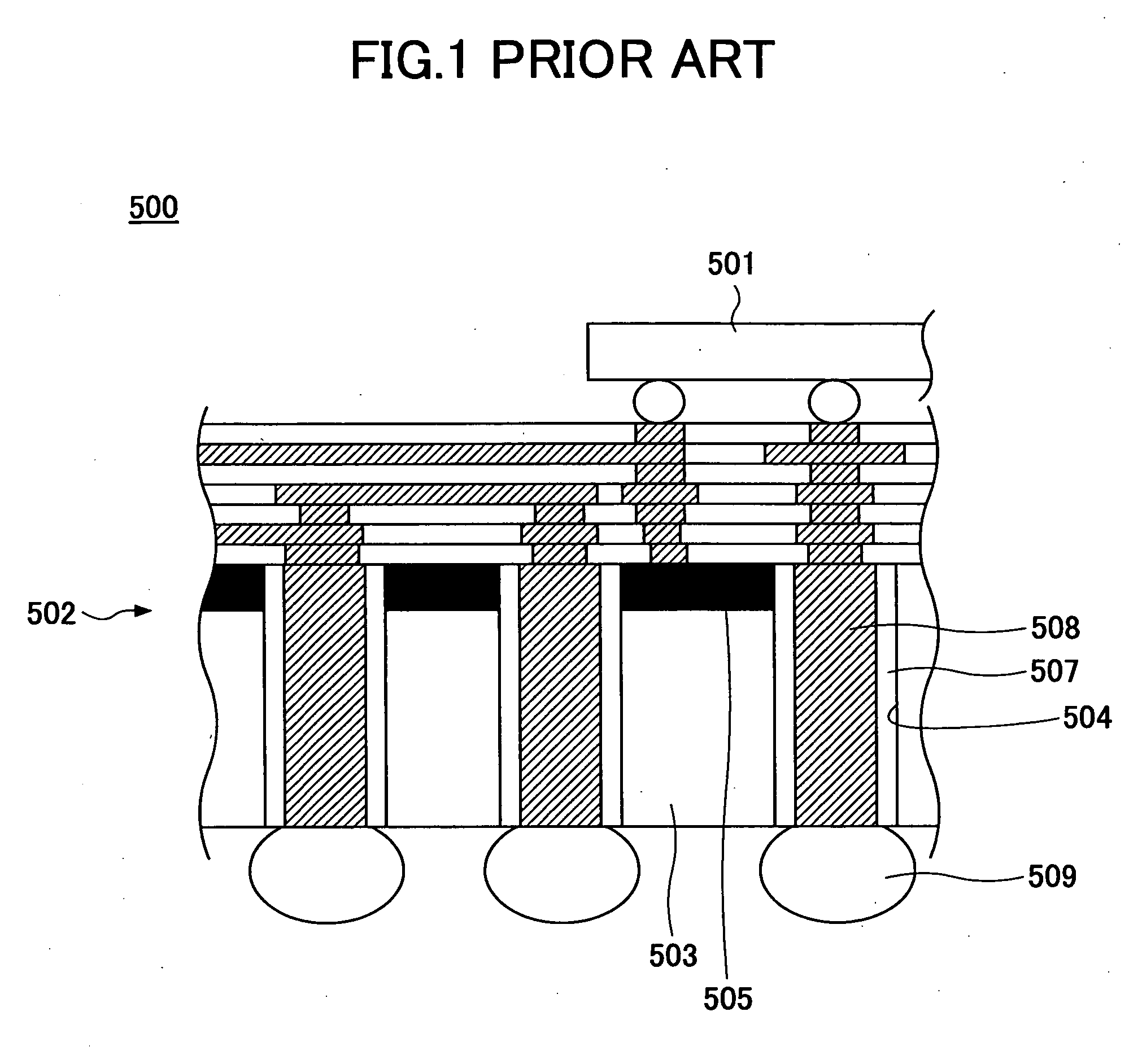

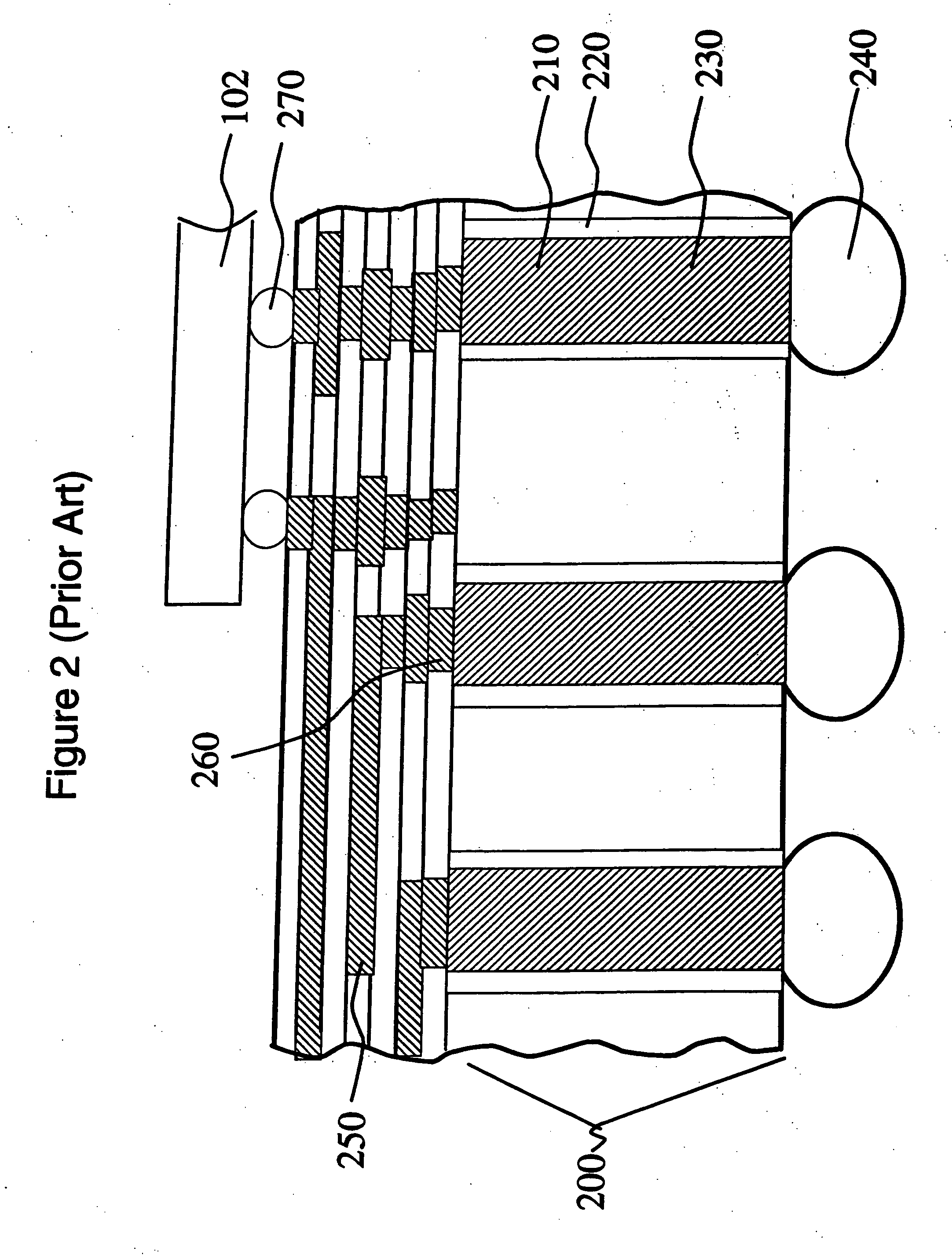

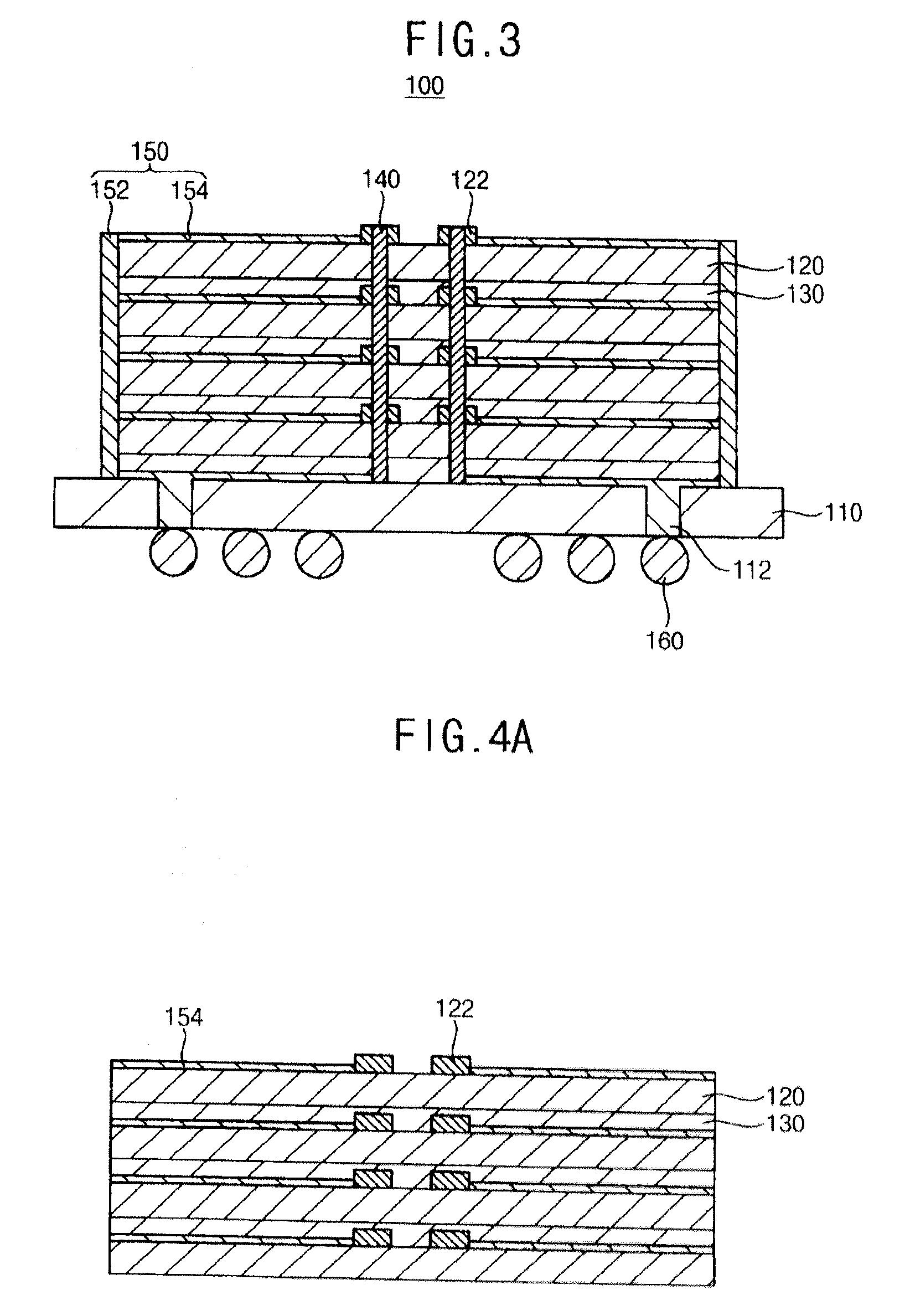

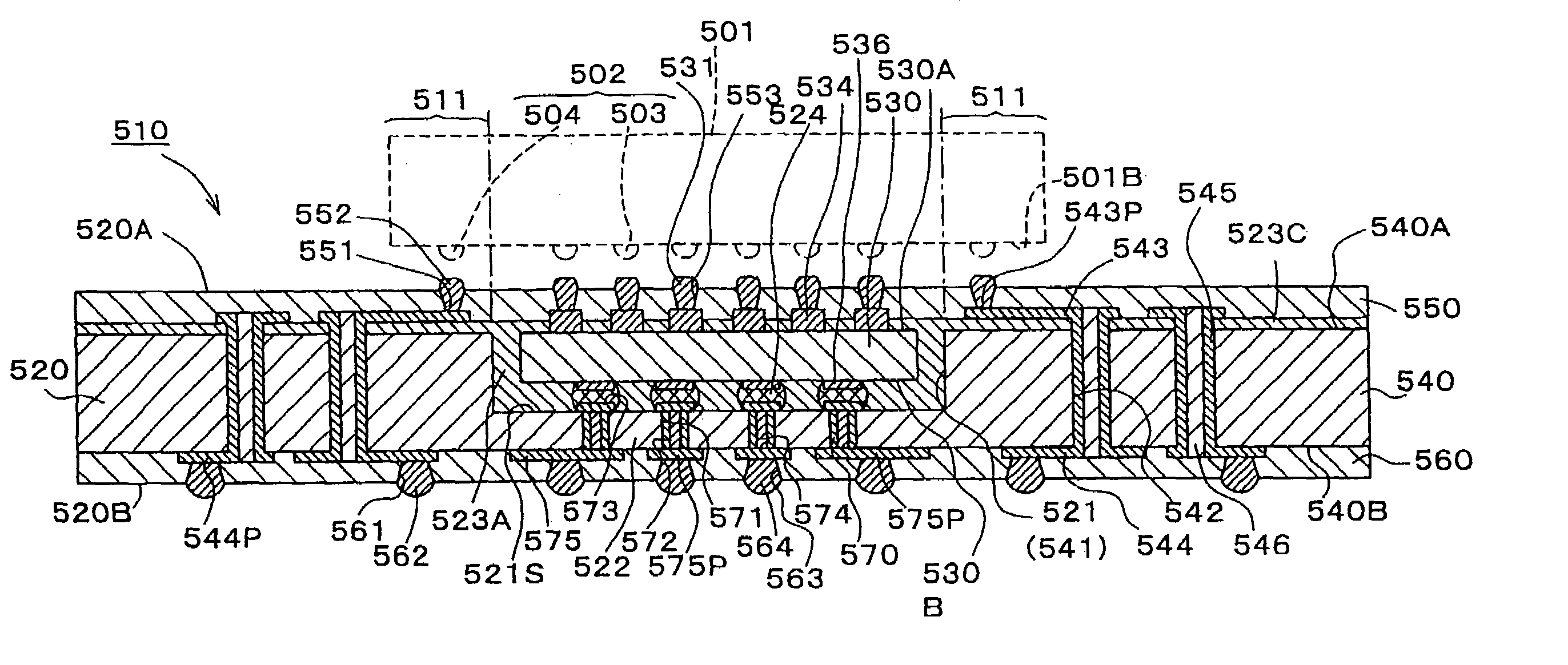

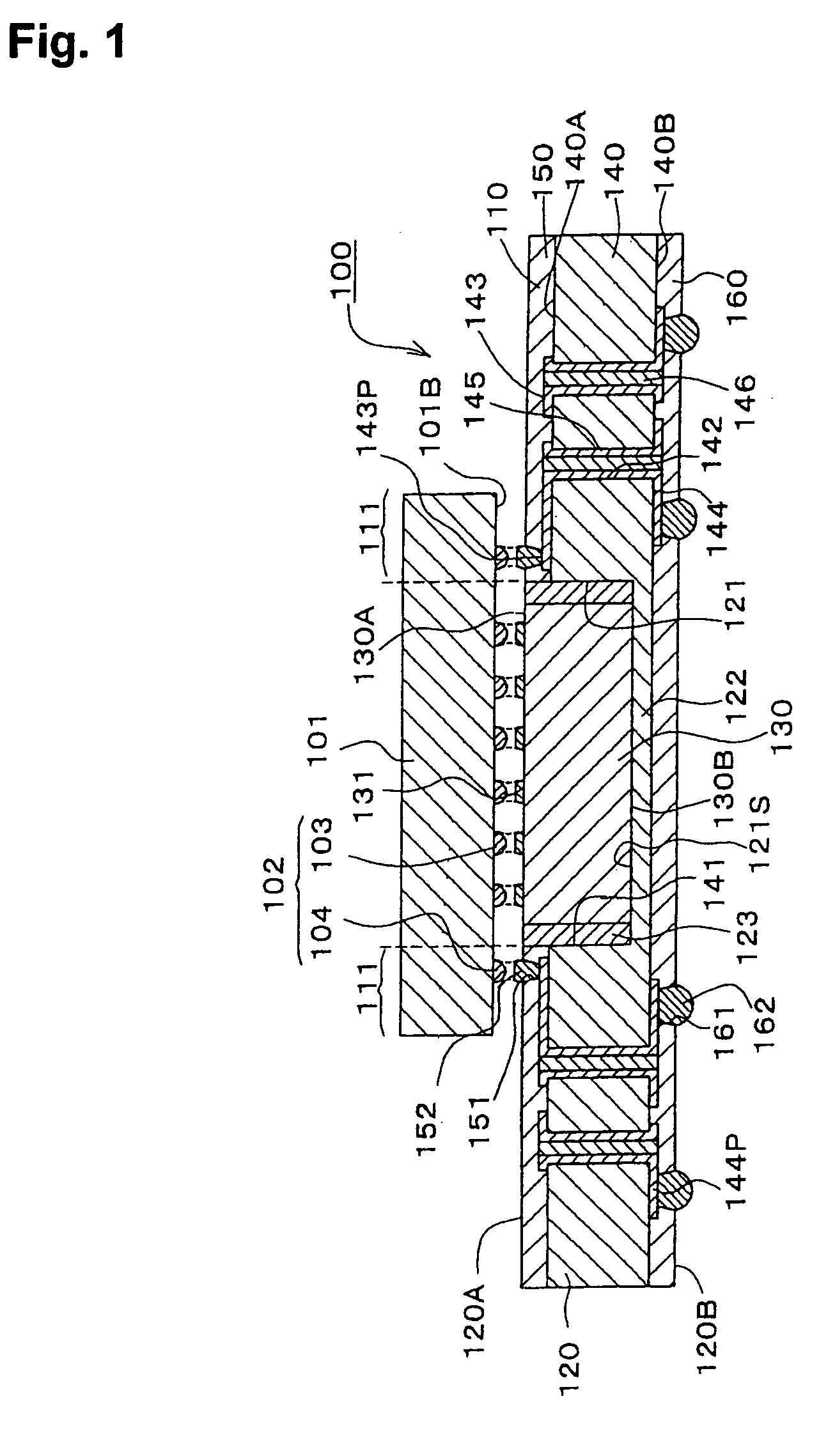

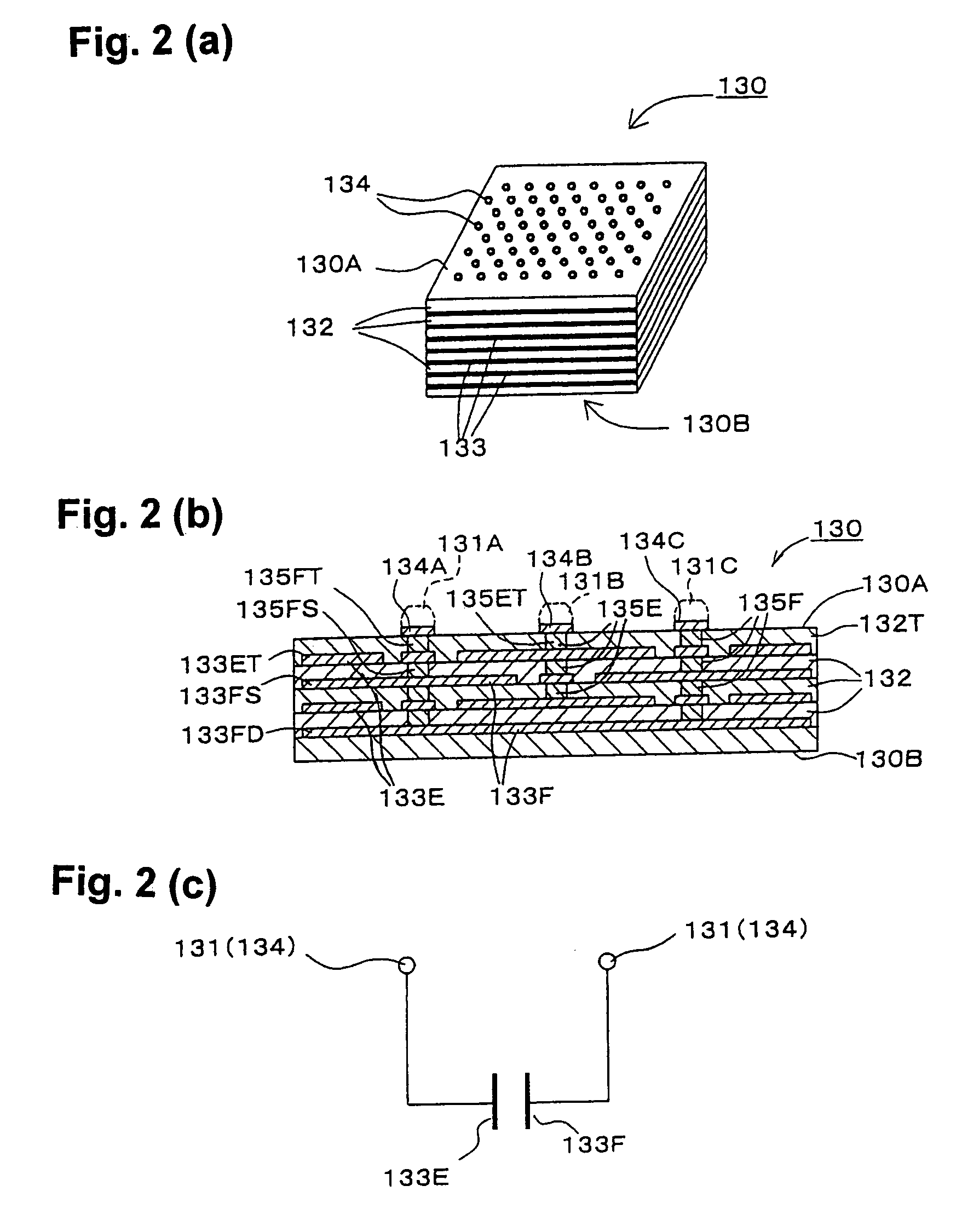

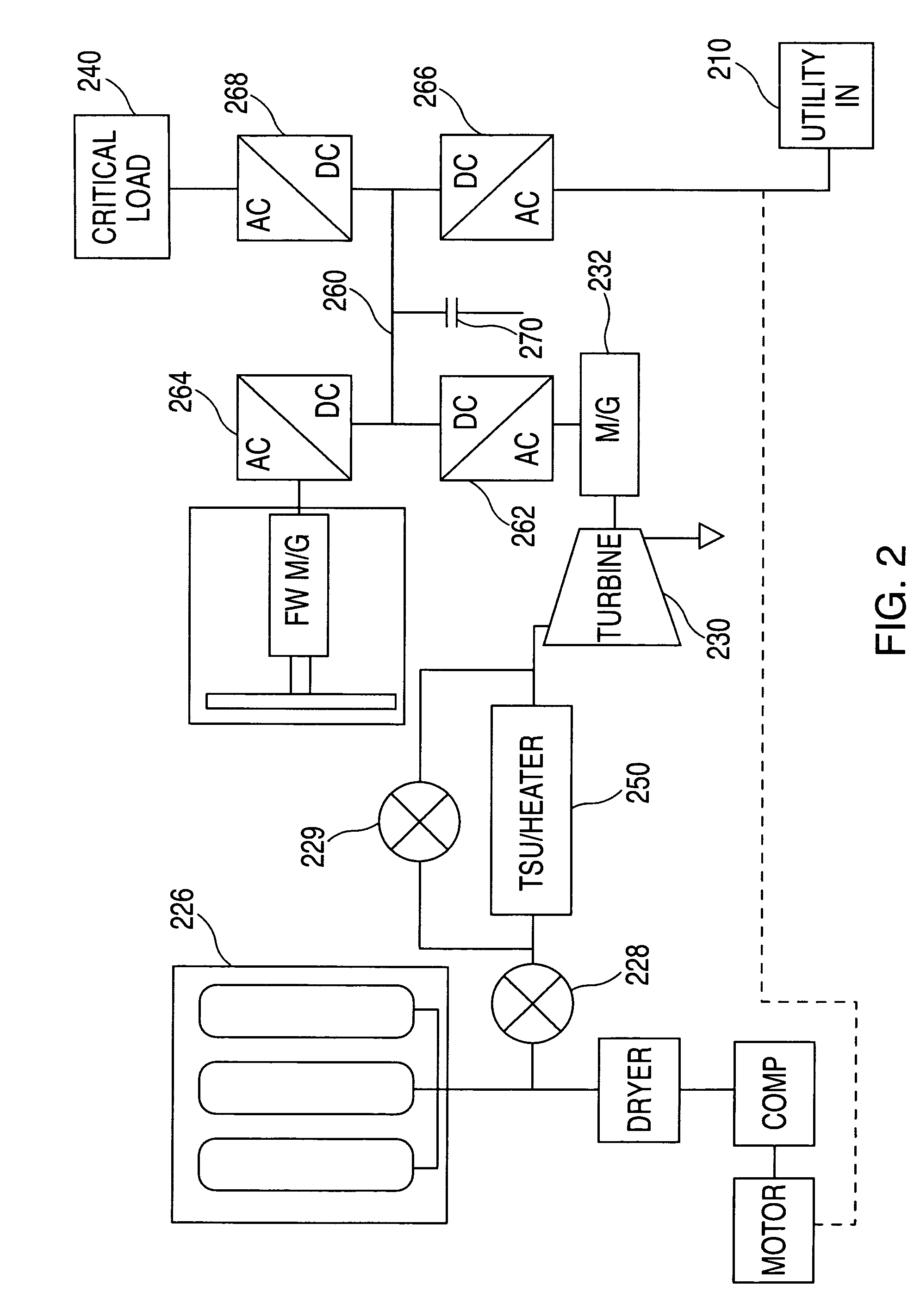

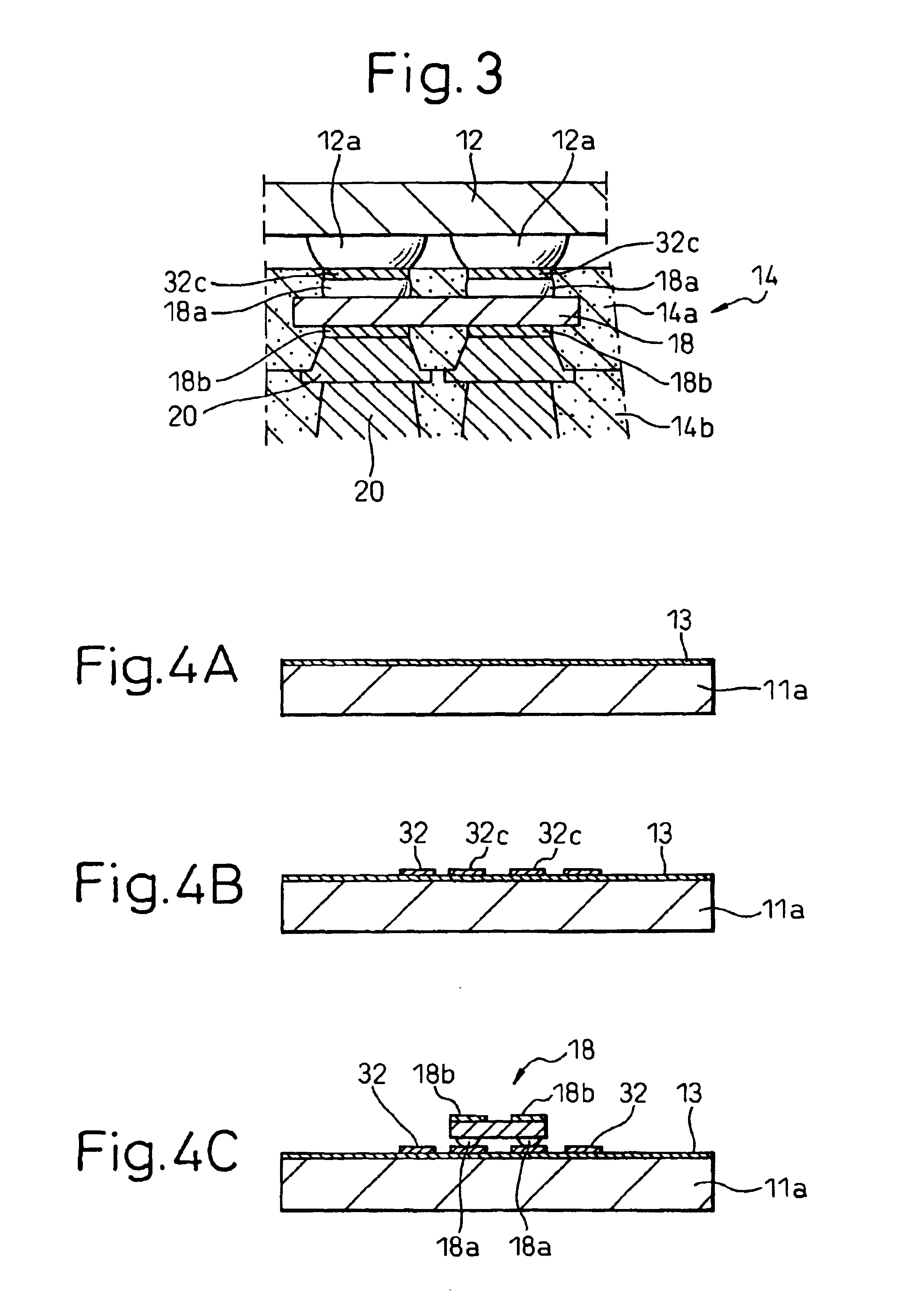

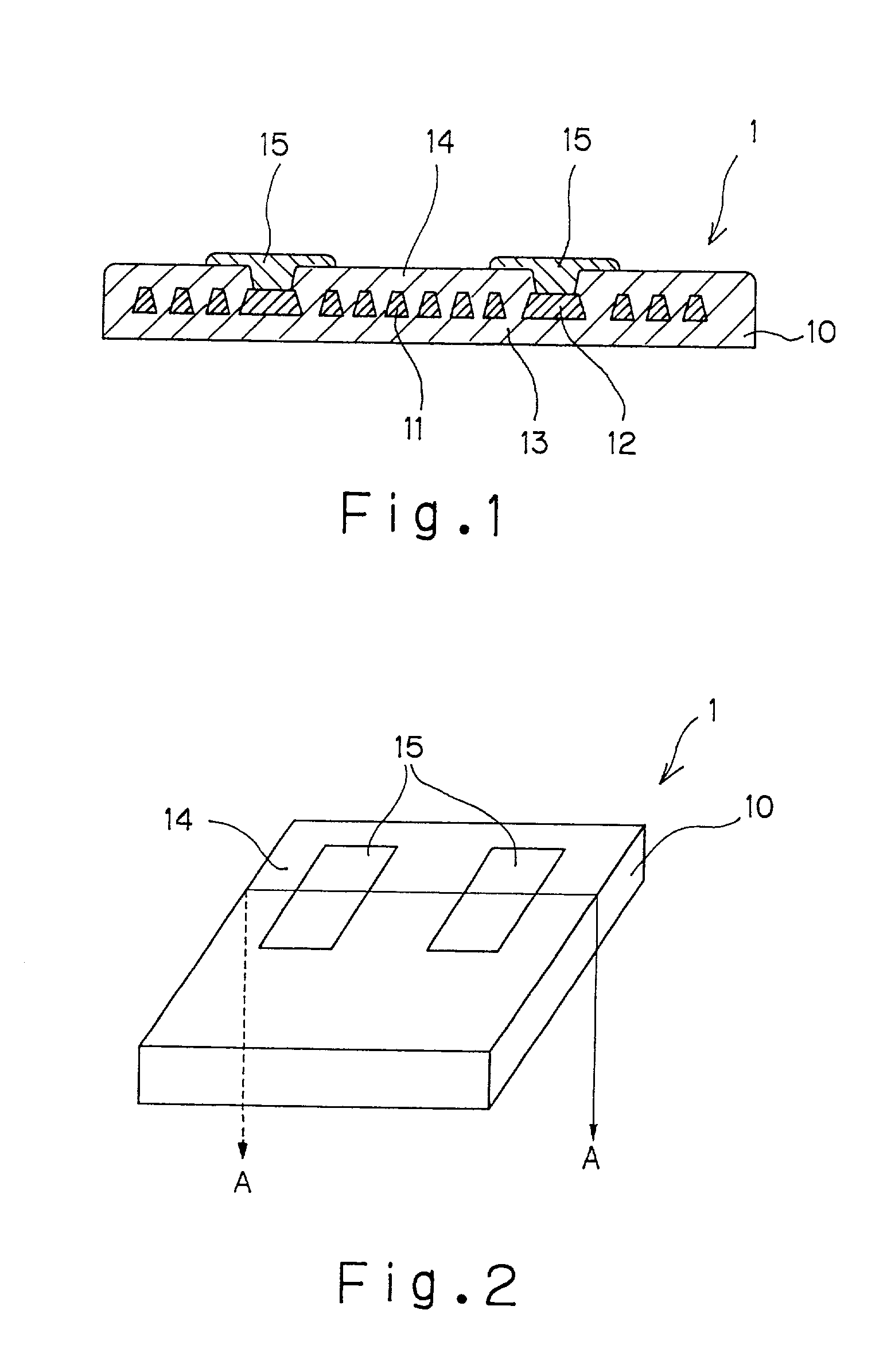

Capacitor-built-in type printed wiring substrate, printed wiring substrate, and capacitor

InactiveUS6952049B1Firmly connectedReliably eliminate noiseCross-talk/noise/interference reductionSemiconductor/solid-state device detailsLow inductanceEngineering

A capacitor-built-in-type printed wiring substrate which can reliably eliminate noise and attain extremely low resistance and low inductance in connections between an IC chip and the capacitor, and a printed wiring substrate and capacitor for use in the same. A capacitor-built-in-type printed wiring substrate 100 on which an IC chip is mounted includes a capacitor-built-in-type printed wiring substrate 110 and an IC chip 101 mounted on the capacitor-built-in-type printed wiring substrate 110. A printed wiring substrate 120 includes a number of connection-to-IC substrate bumps 152 and a closed-bottomed capacitor accommodation cavity 121 formed therein. A capacitor 130 is disposed in the cavity 121 and includes a pair of electrode groups 133E and 133F and a number of connection-to-IC capacitor bumps 131 connected to either one of the paired electrode groups 133E and 133F. The connection-to-IC capacitor bumps 131 are flip-chip-bonded to corresponding connection-to-capacitor bumps 103 on the IC chip 101. The connection-to-IC substrate bumps 152 are flip-chip-bonded to corresponding connection-to-substrate bumps 104 on the IC chip 101.

Owner:NGK SPARK PLUG CO LTD

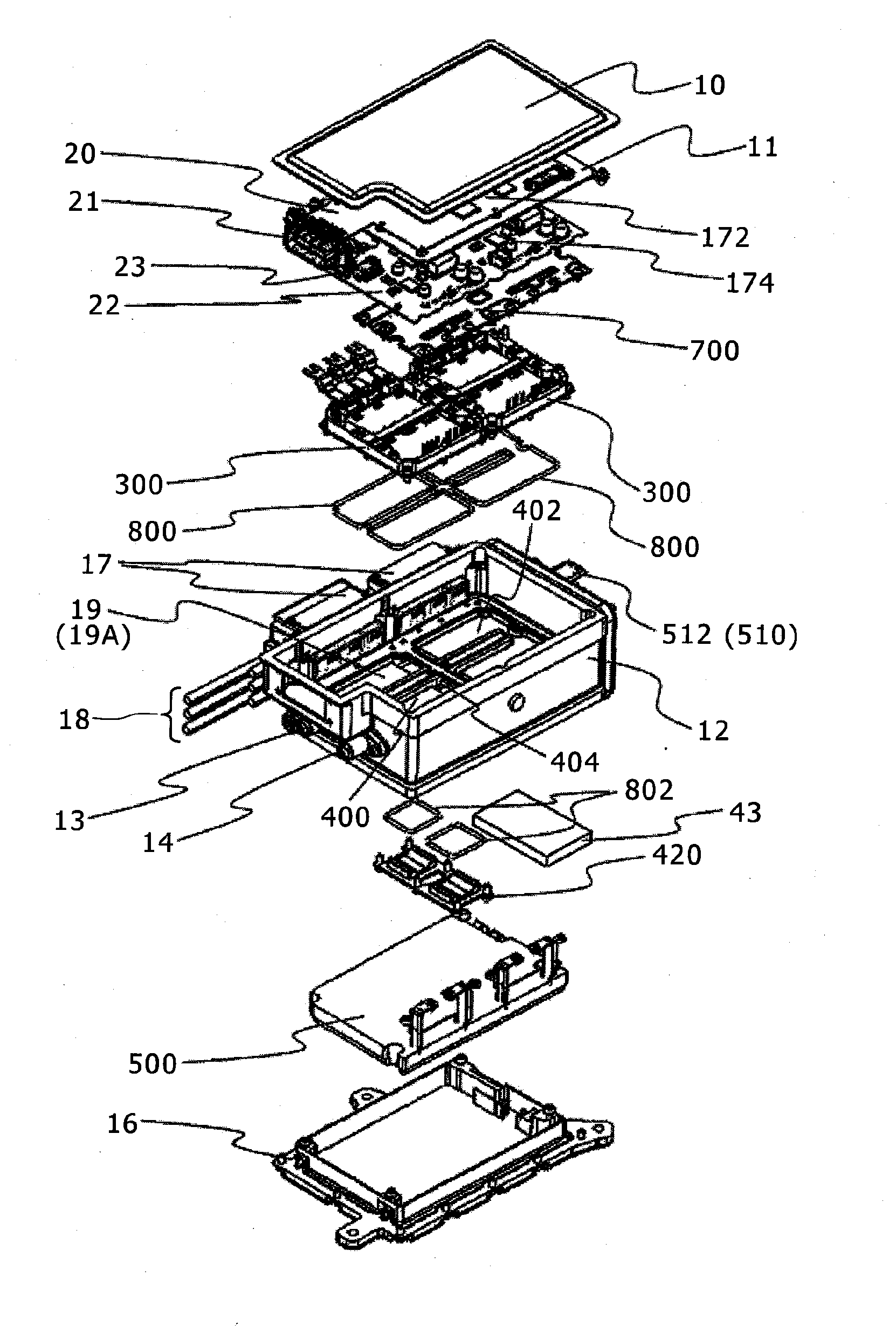

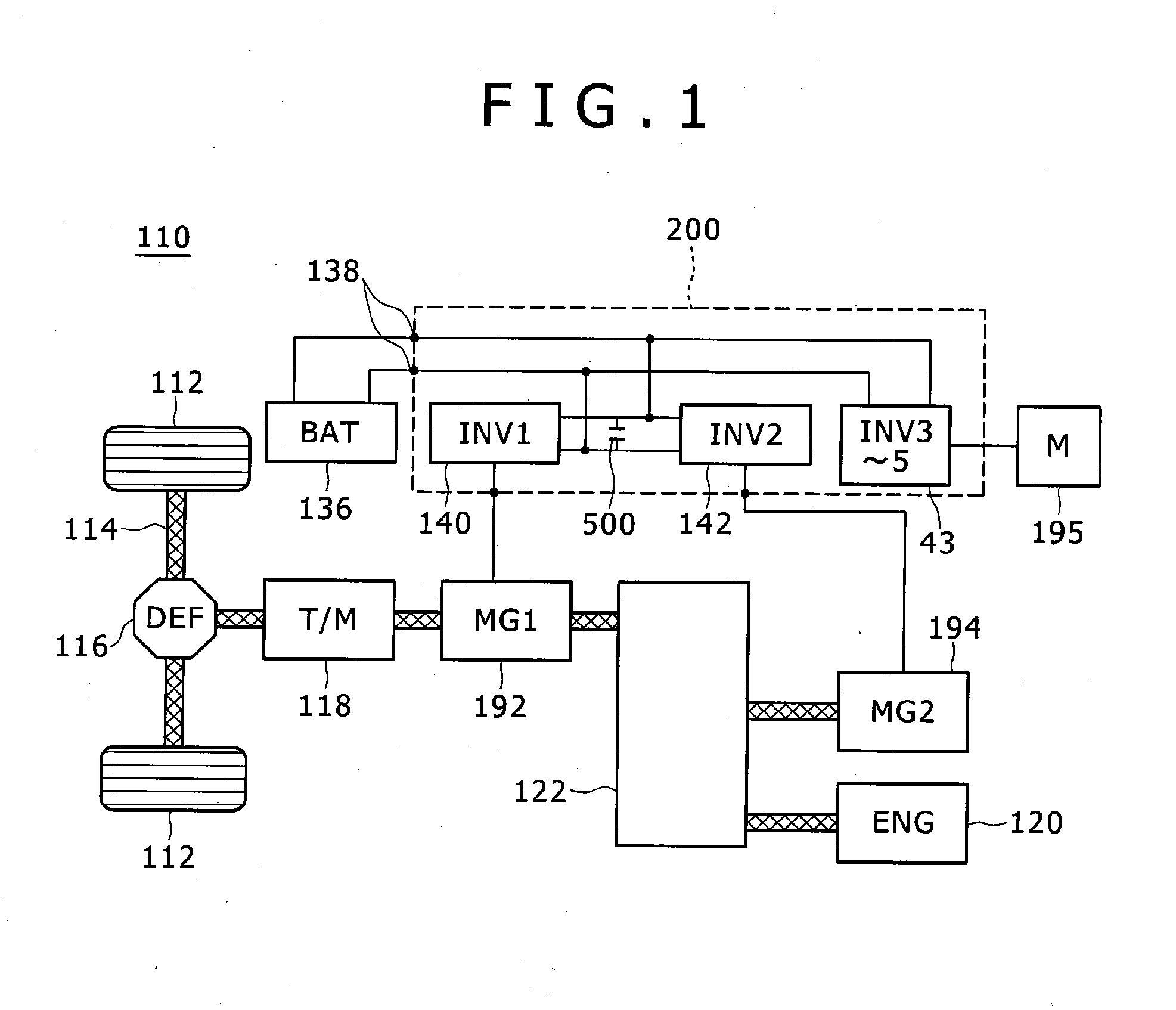

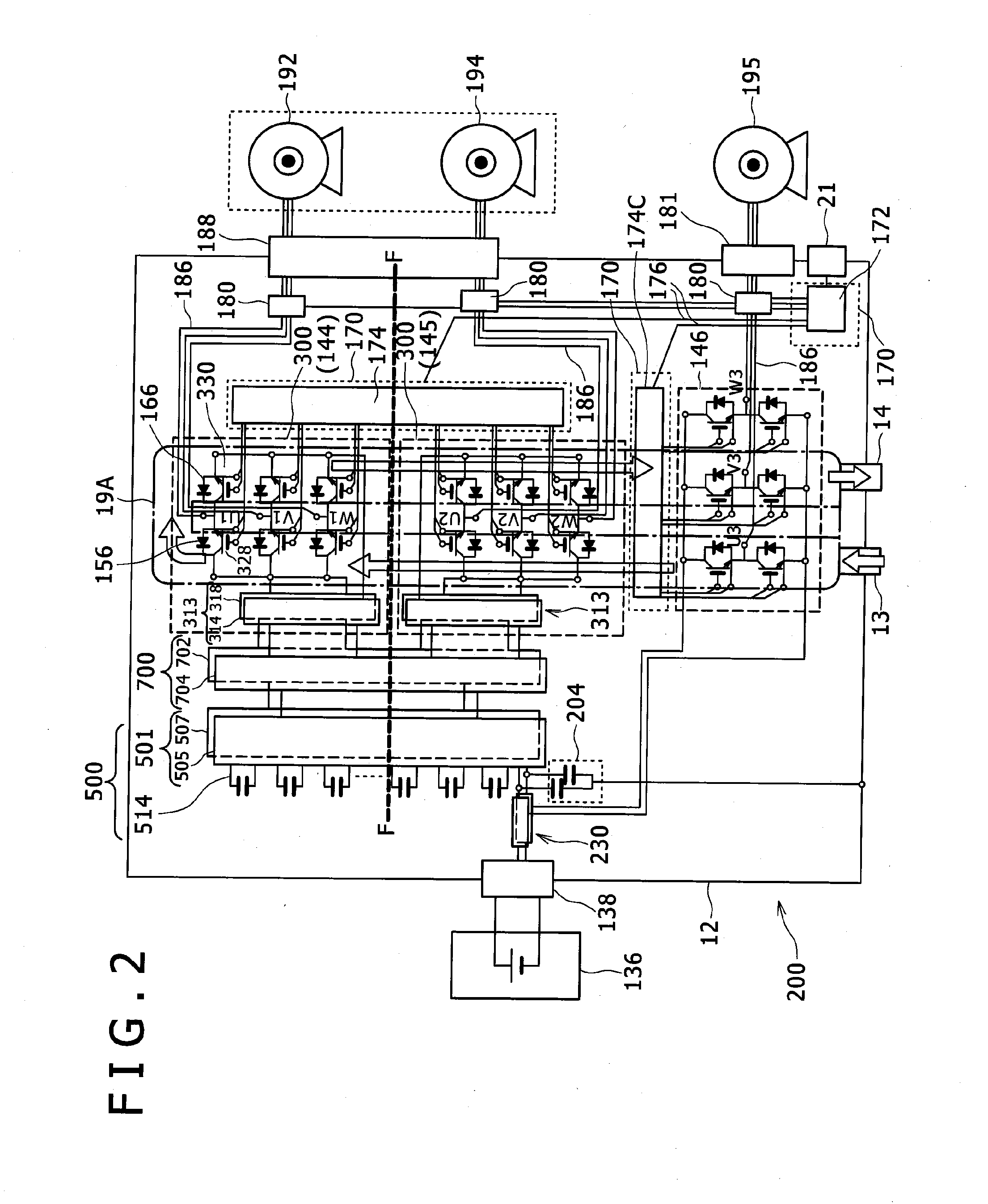

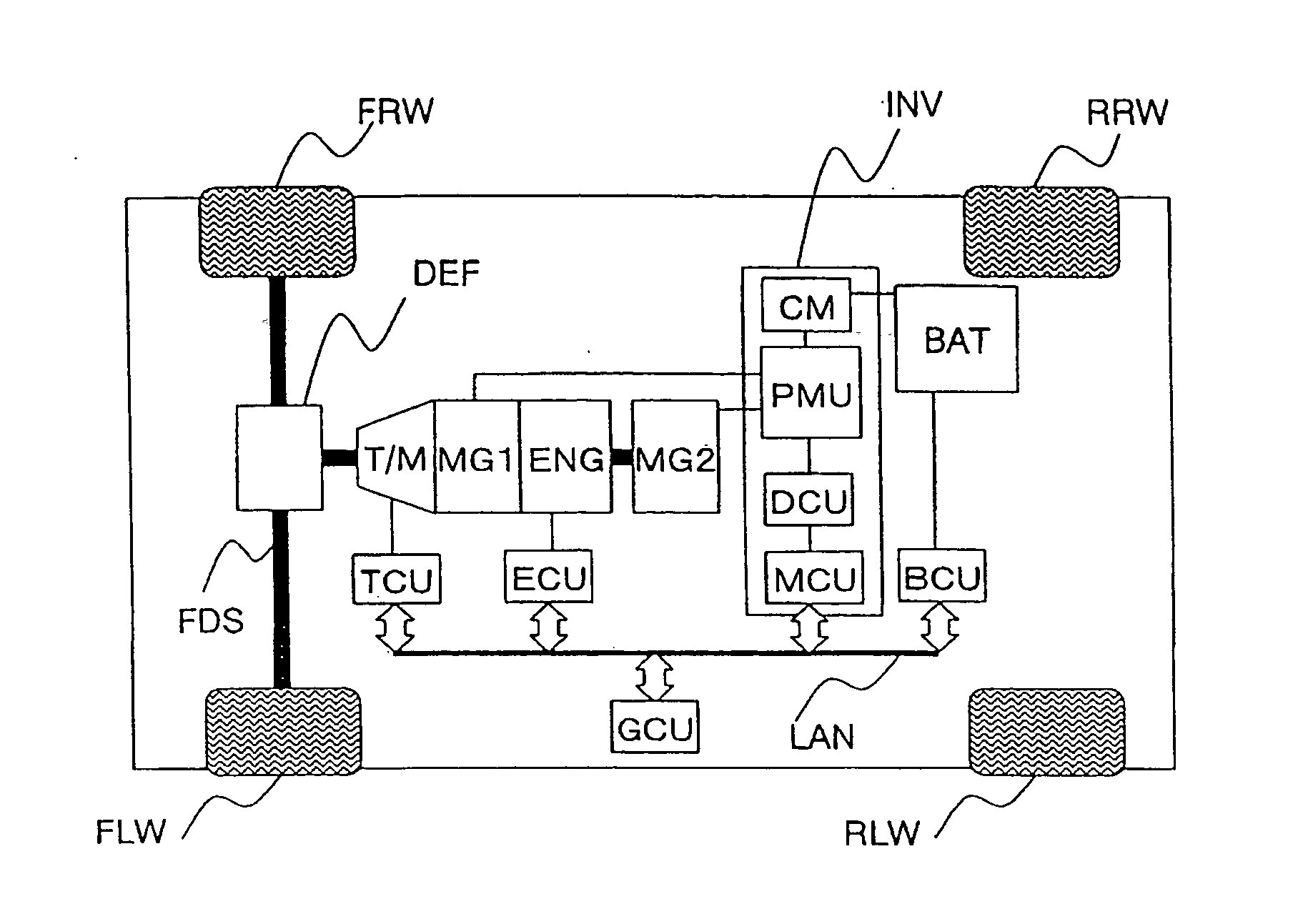

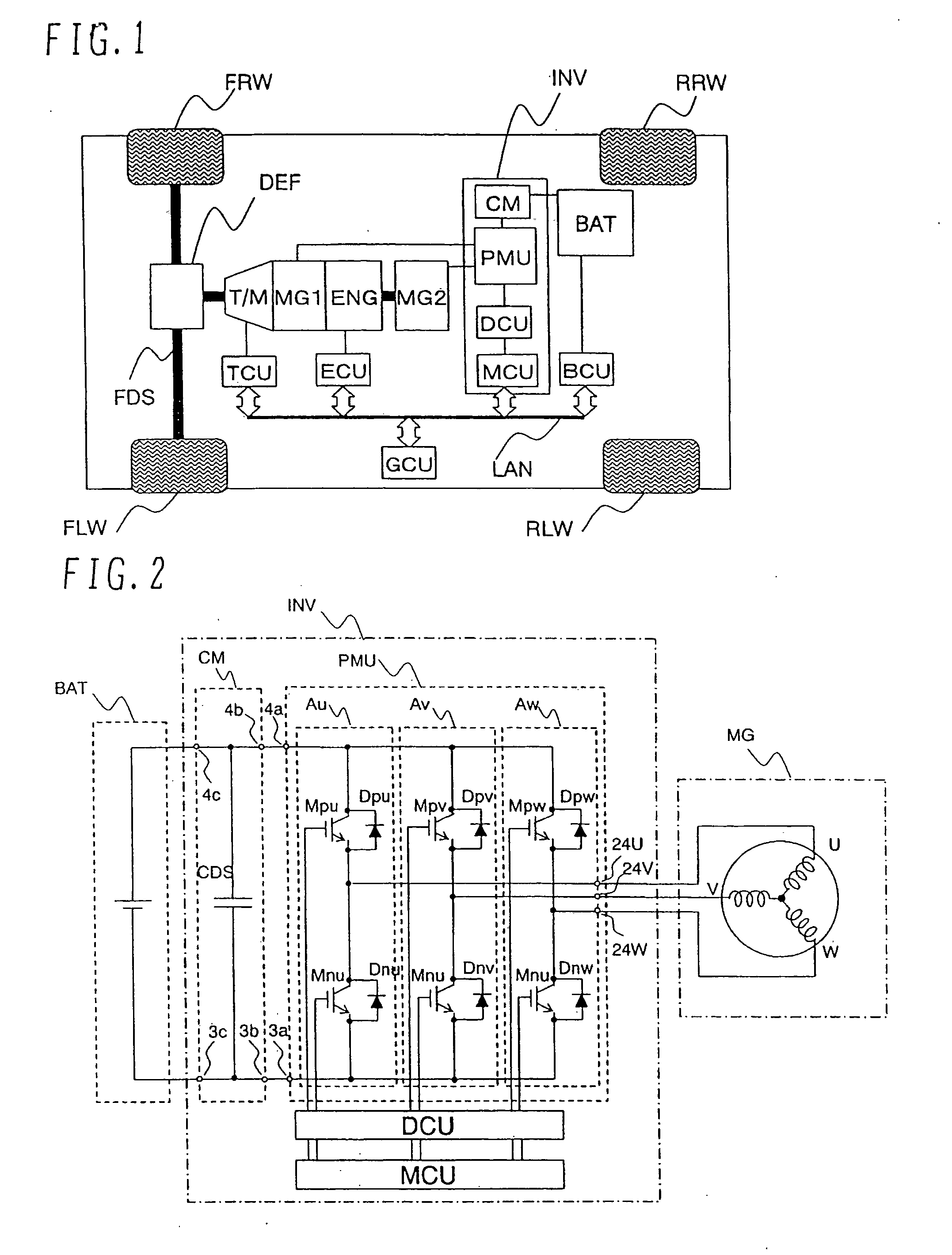

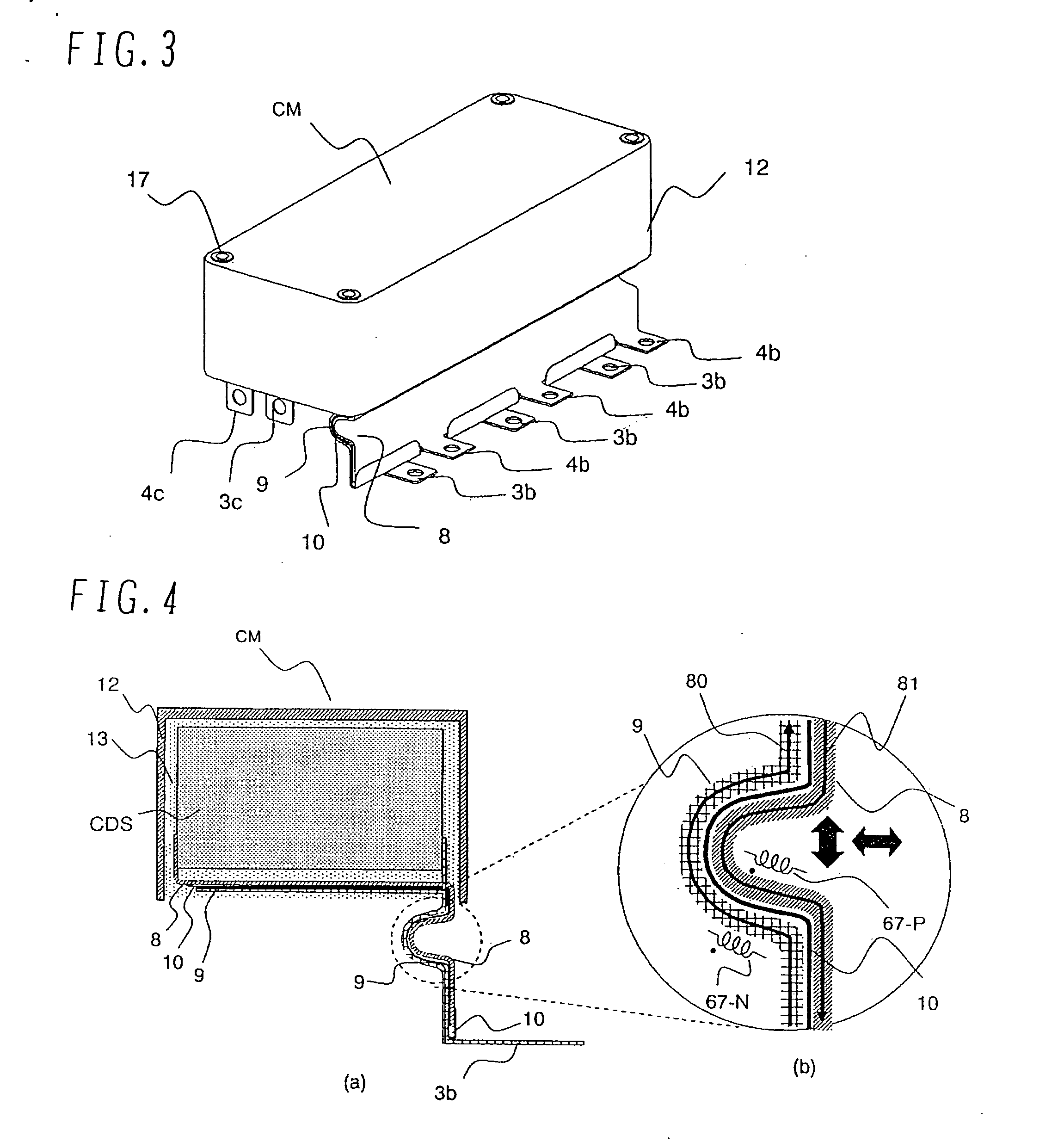

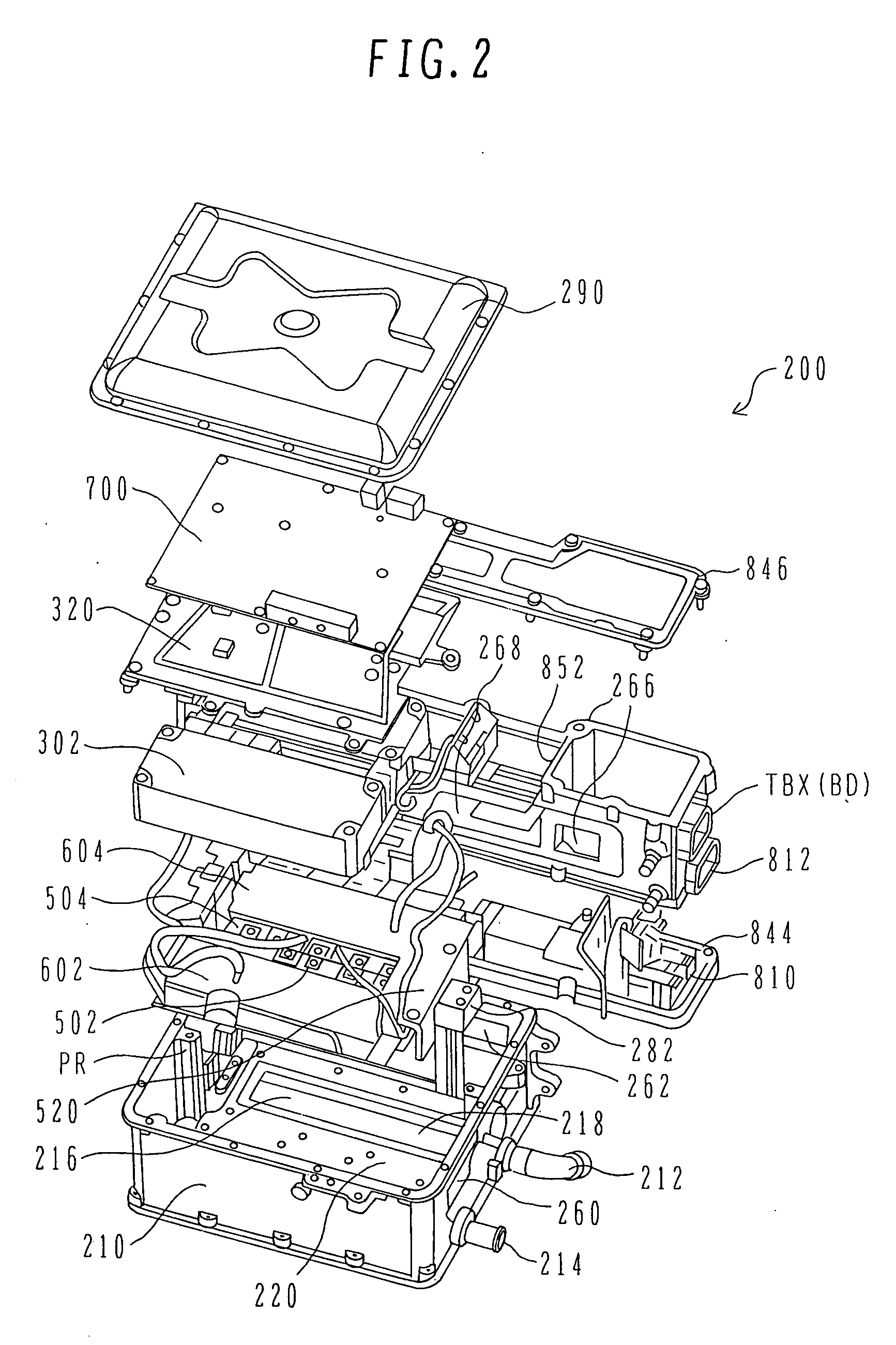

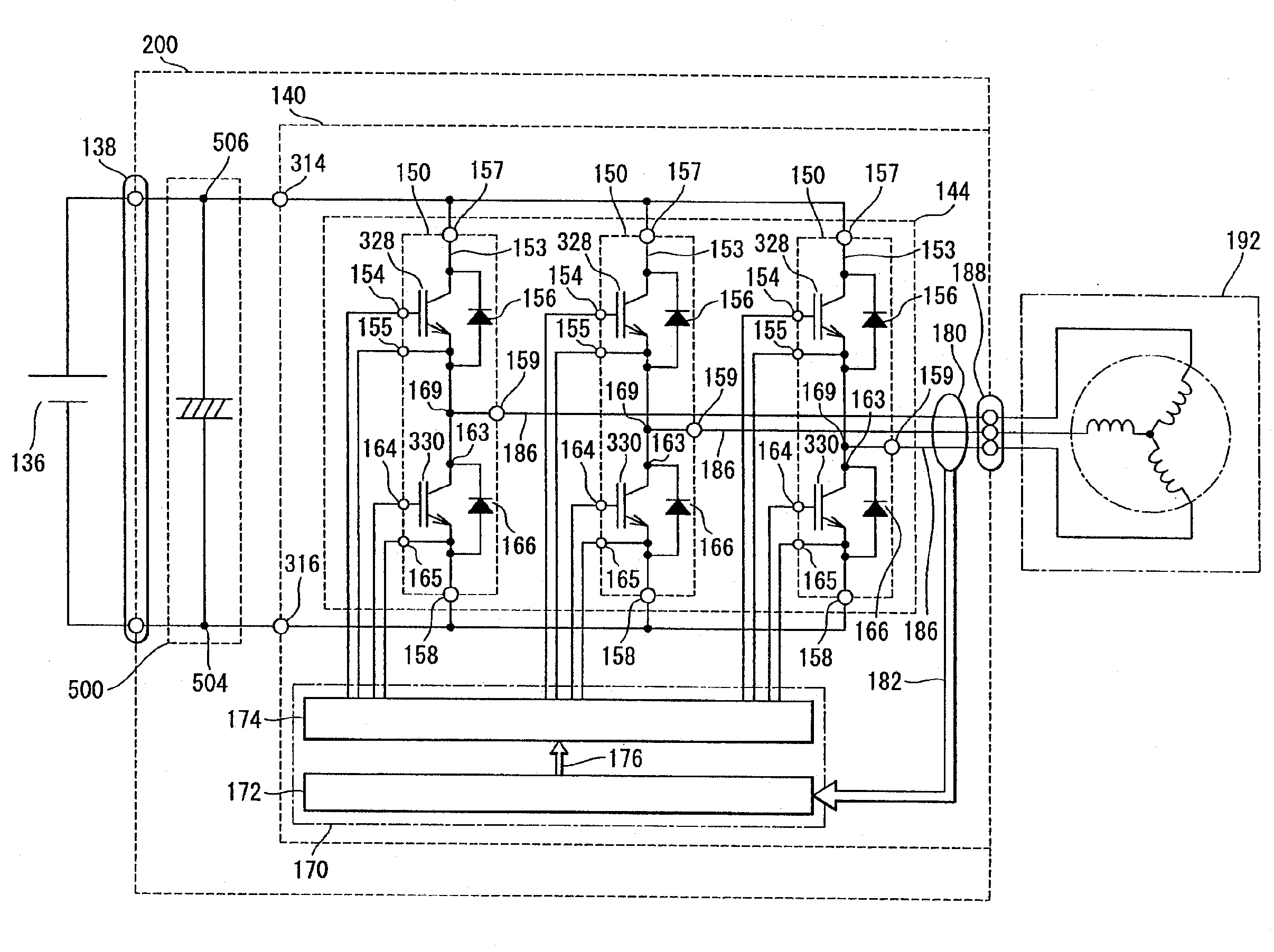

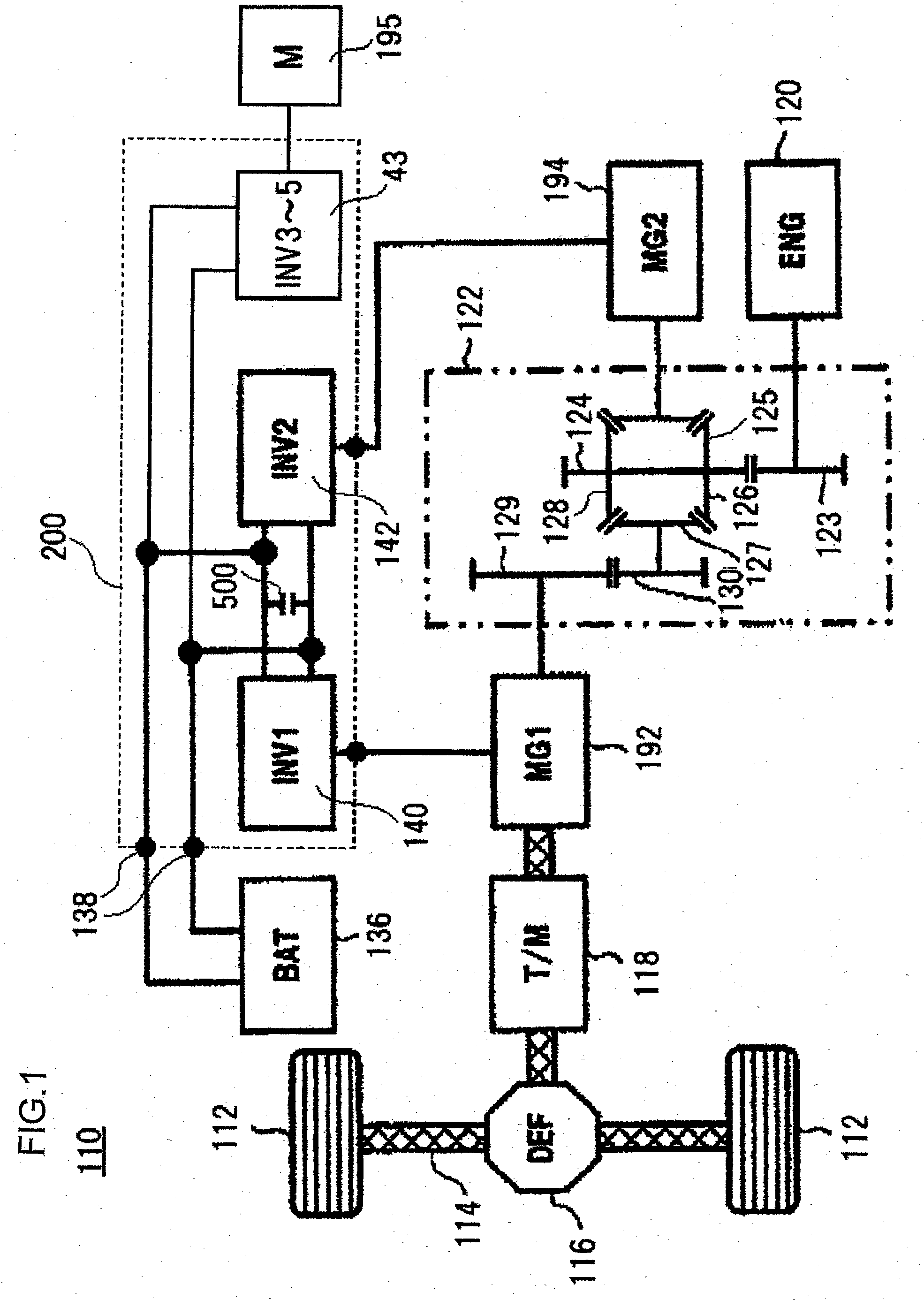

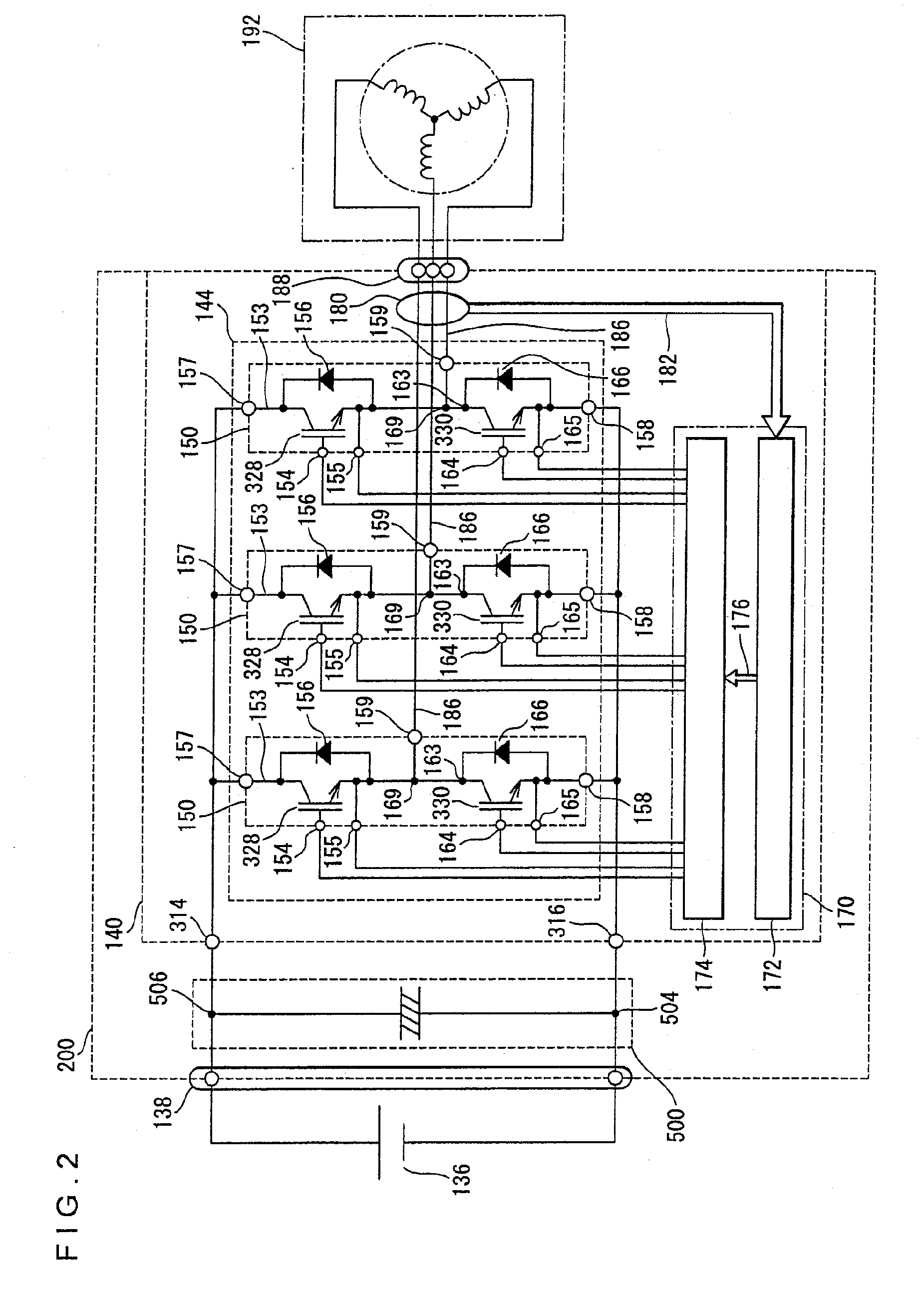

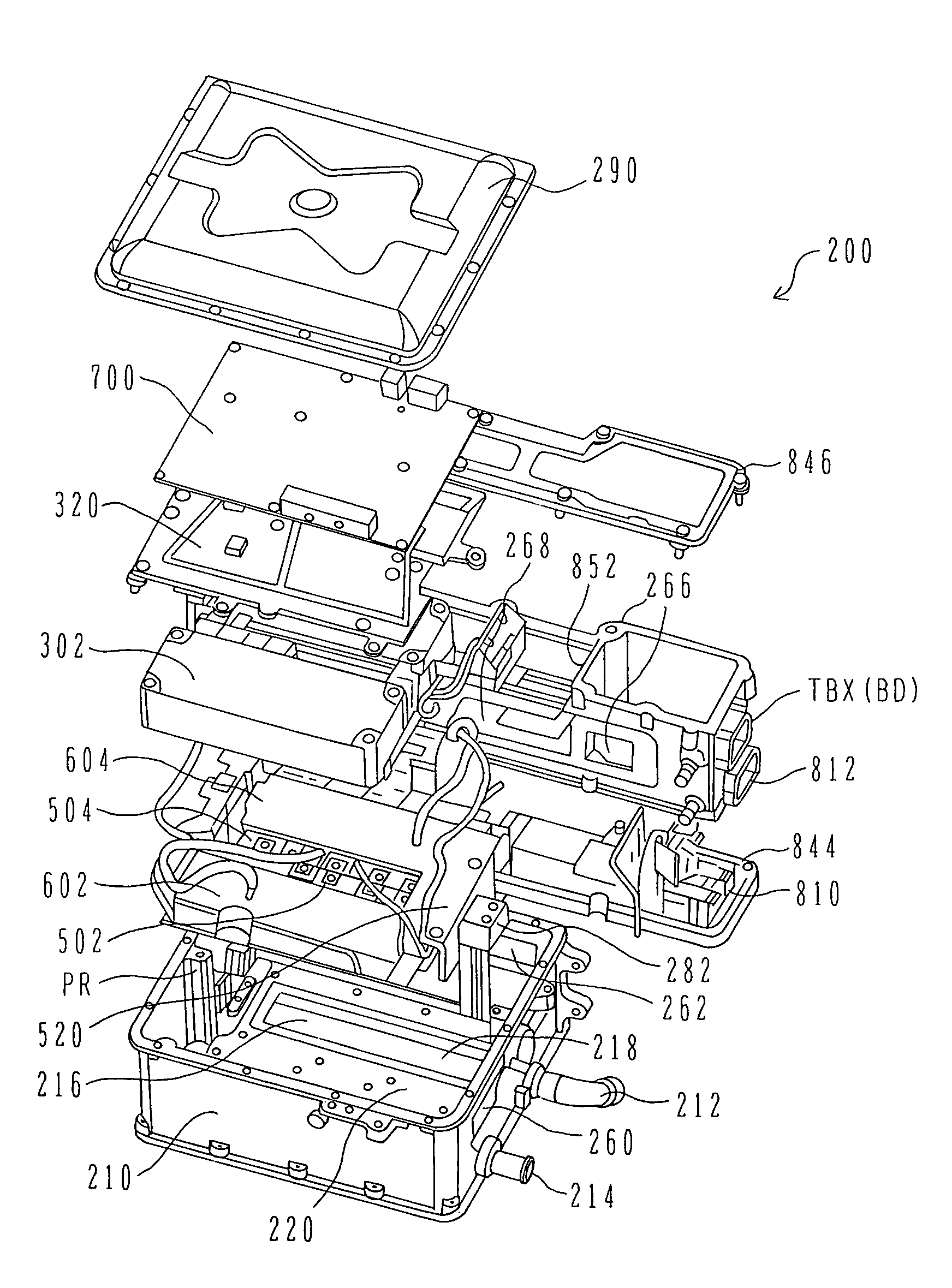

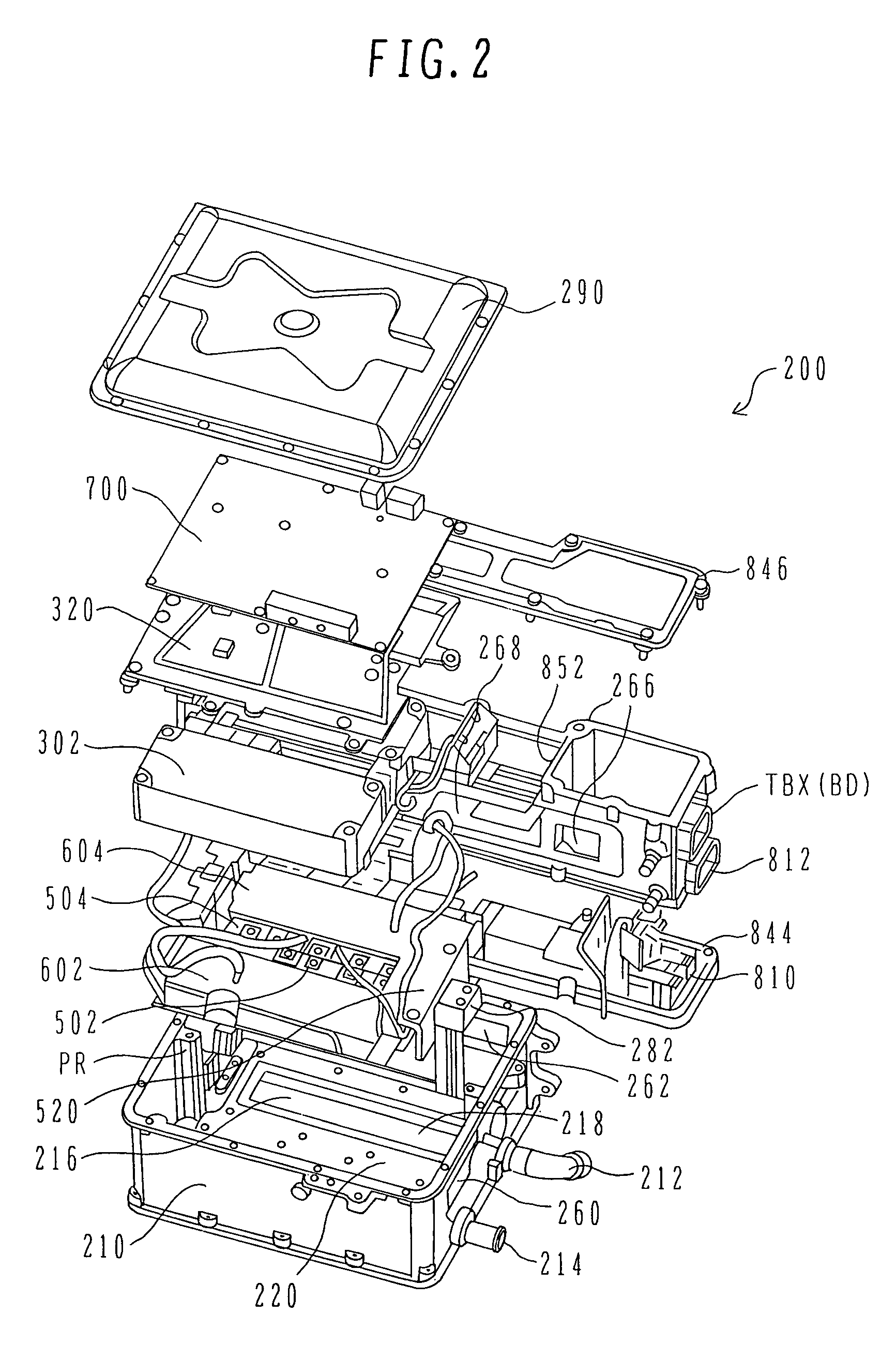

Power Conversion Apparatus and Electric Vehicle

ActiveUS20100025126A1Reduce inductanceImprove cooling effectCasings with connectors and PCBConversion constructional detailsDriver circuitComputer module

The metallic case of a power conversion apparatus includes a casing having a side wall, as well as an upper case and a lower case, a first area being formed between a cooling jacket provided at the inner periphery of the side wall and the lower case, the metal base plate dividing the first area between the cooling jacket and the upper case into a lower side second area and an upper side third area, first and second power modules being fastened to a top surface and a capacitor module being provided in the first area, driving circuits that drive inverter circuits of the power modules respectively being provided in the second area, and a control circuit that controls the driver circuits being provided in the third area.

Owner:HITACHI ASTEMO LTD

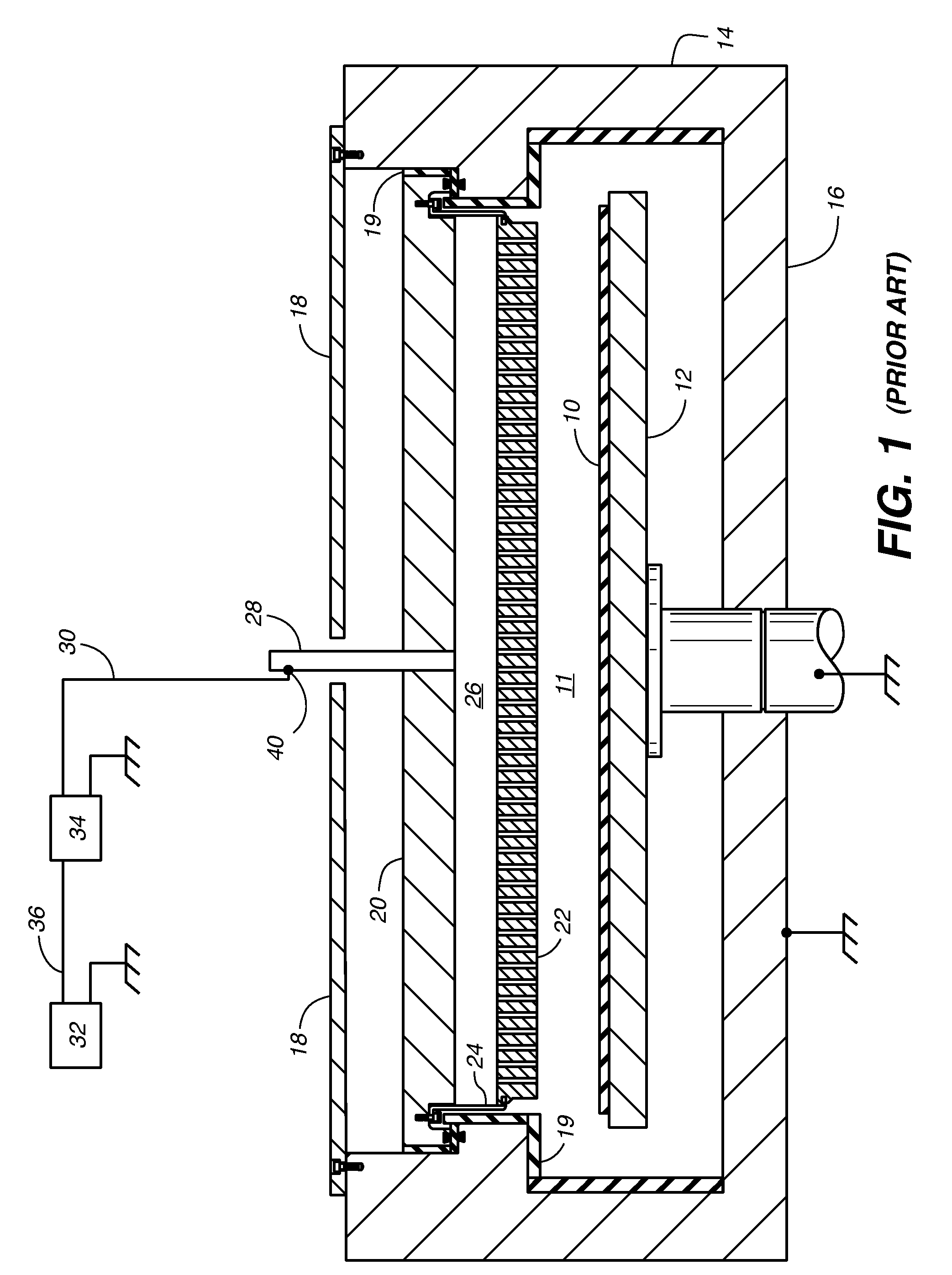

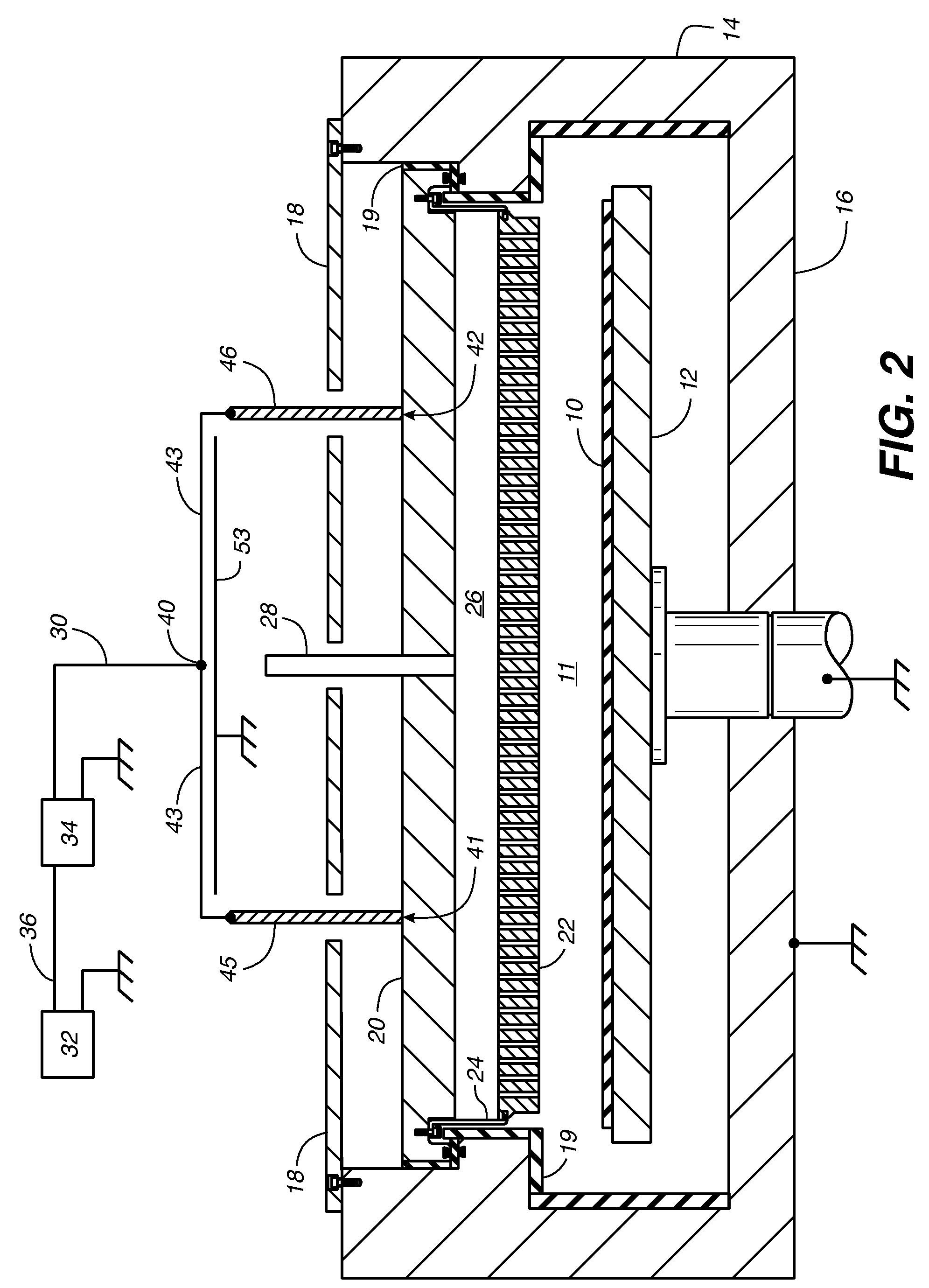

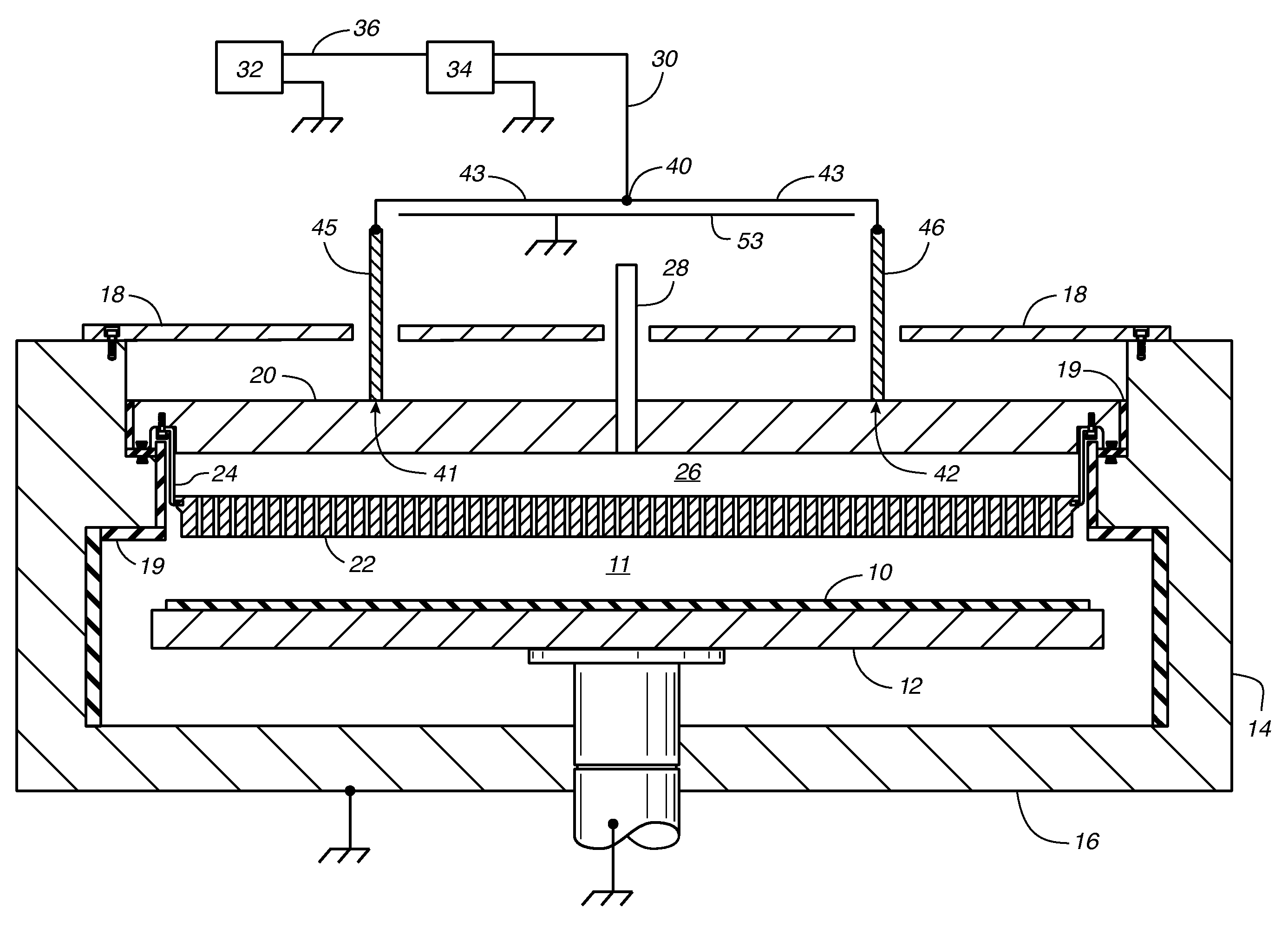

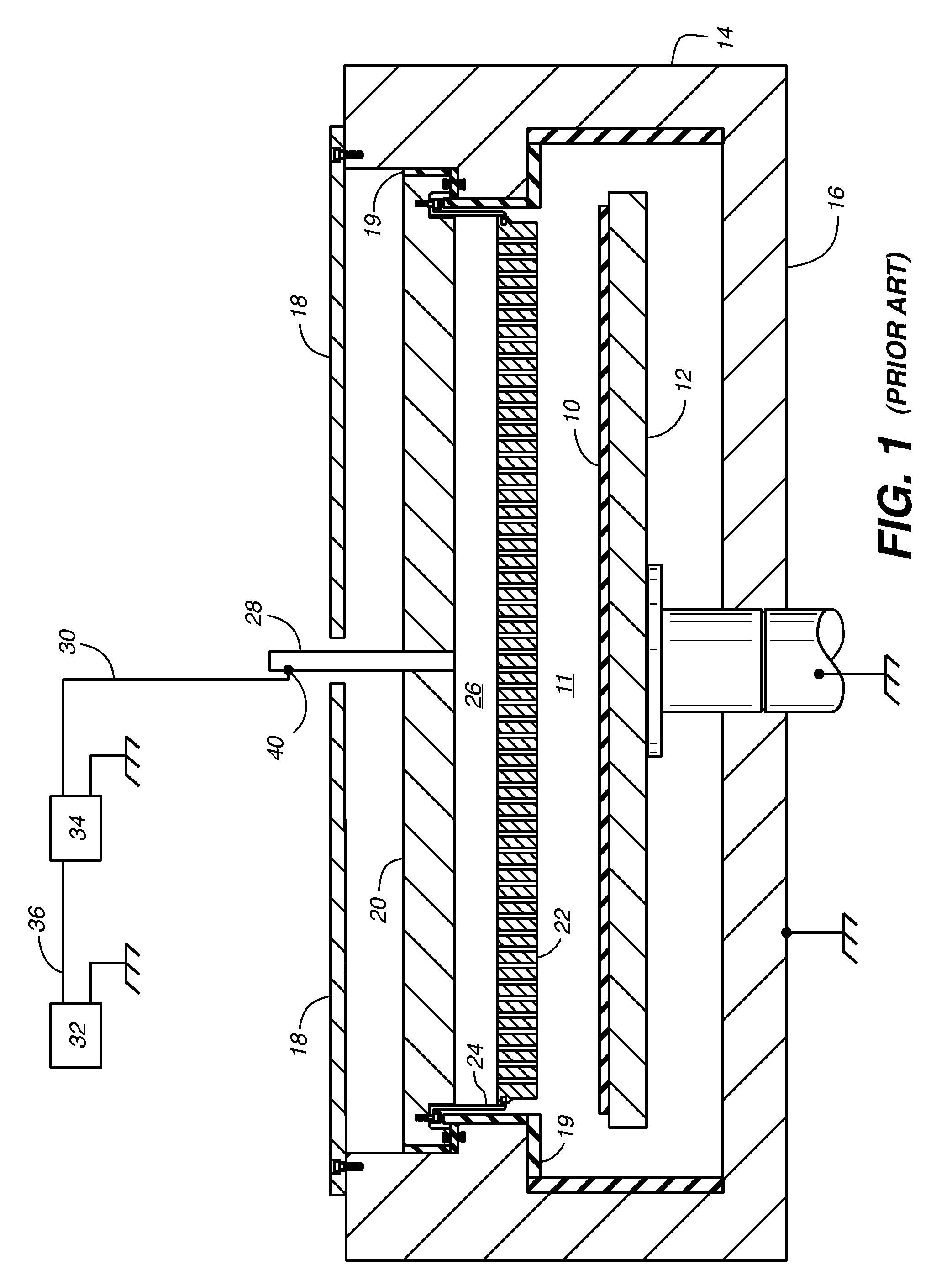

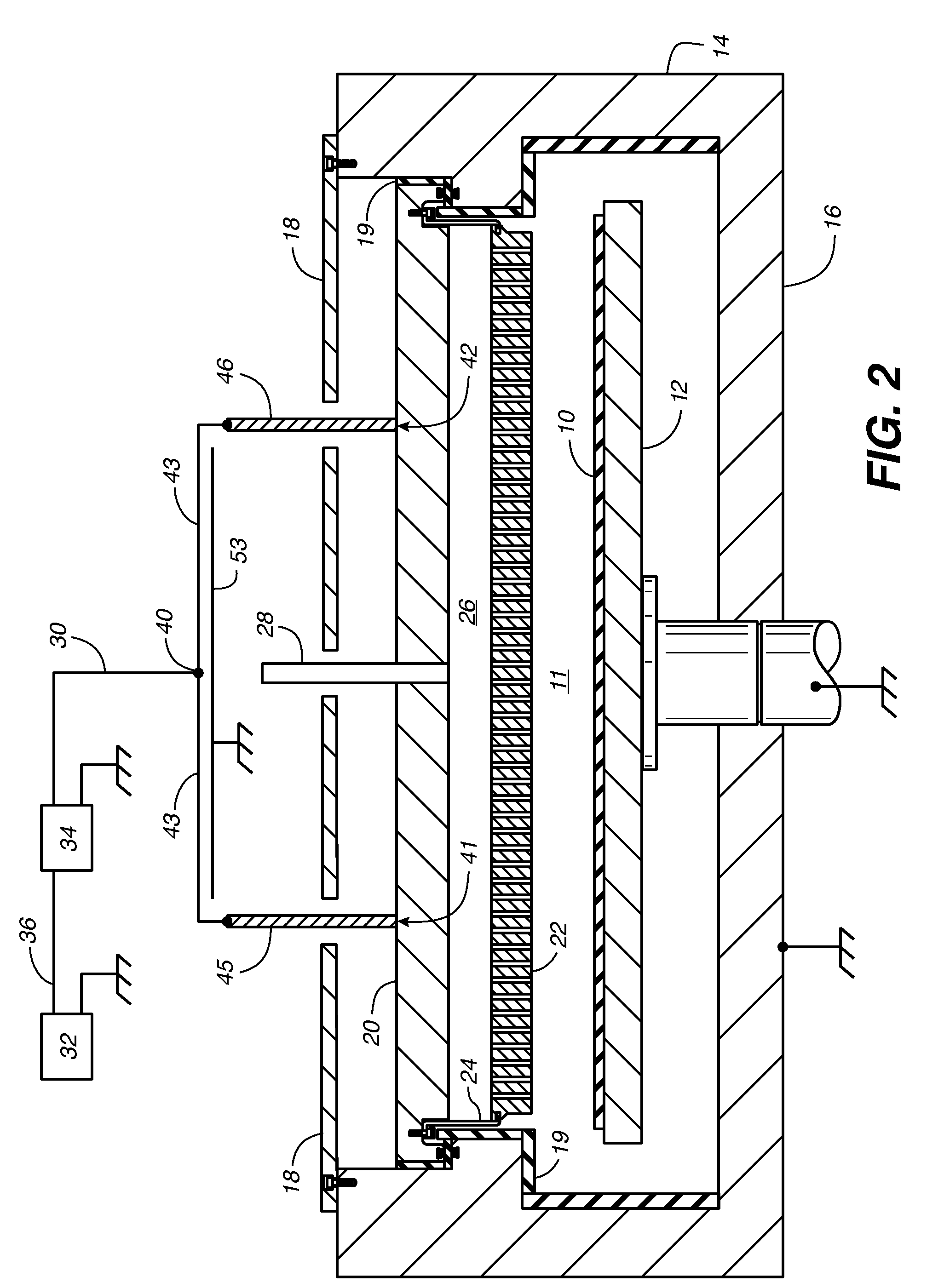

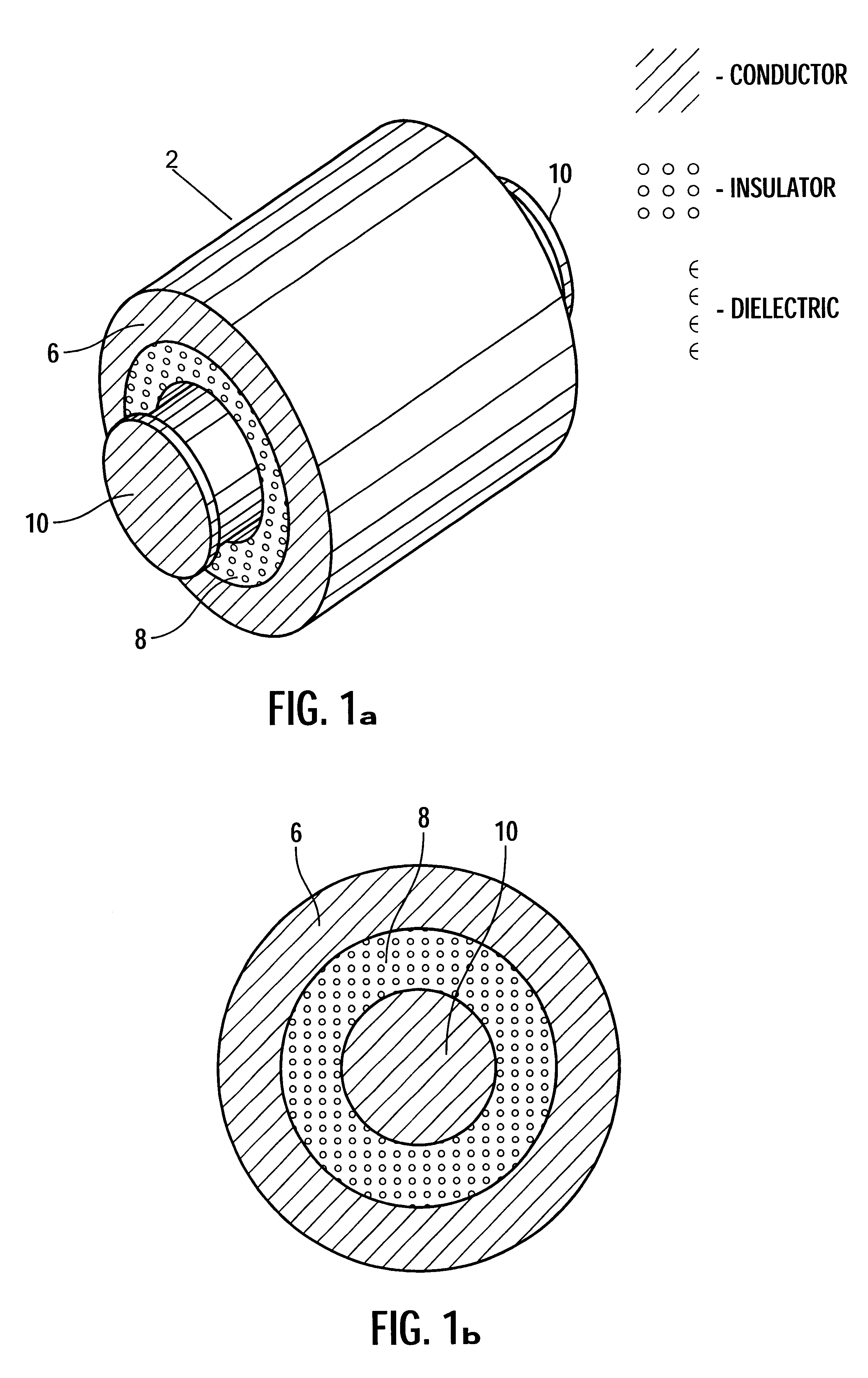

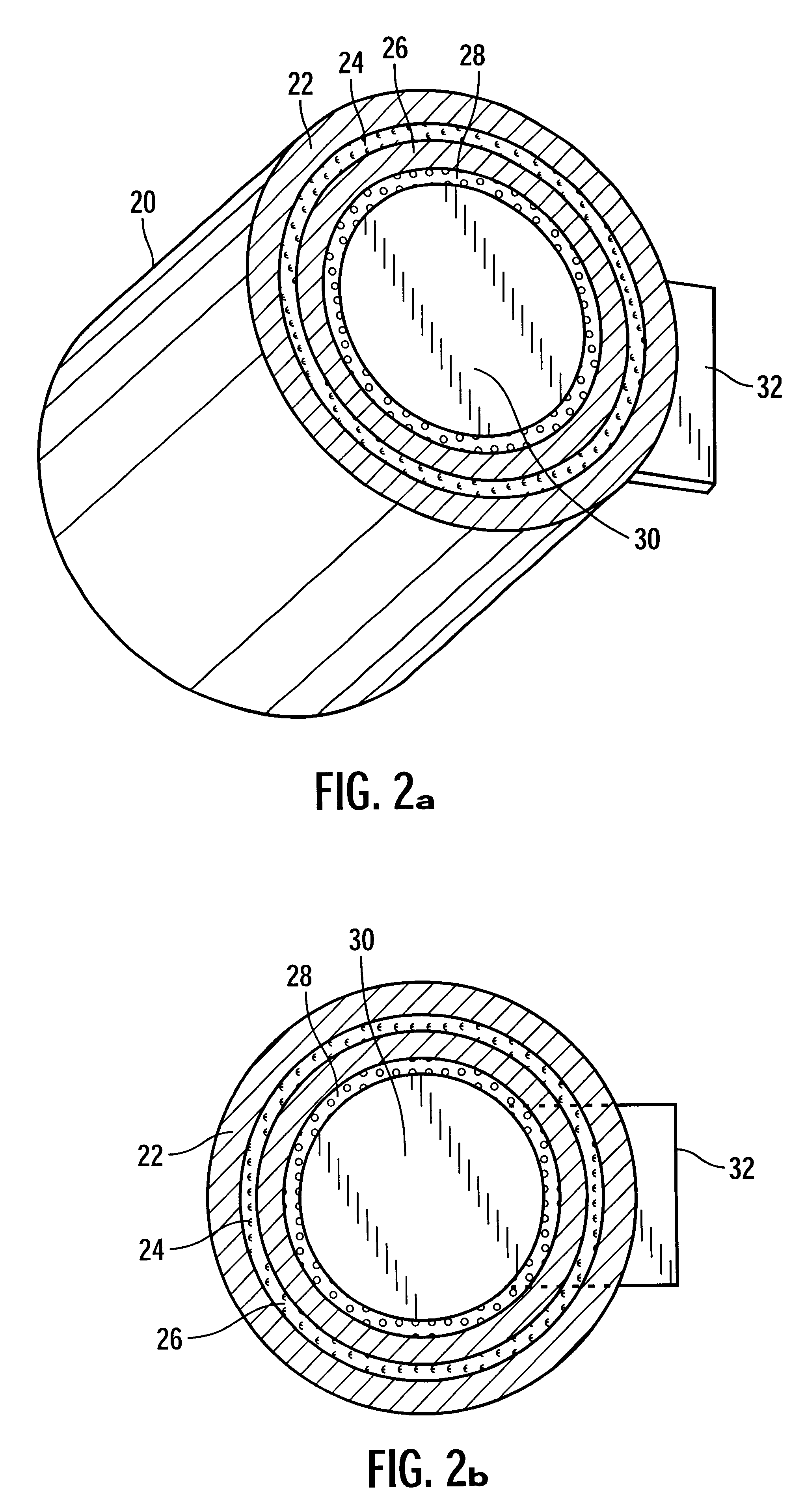

RF bus and RF return bus for plasma chamber electrode

ActiveUS8992723B2Reduce inductanceReduce peak voltageElectric discharge tubesSemiconductor/solid-state device manufacturingElectrical conductorEngineering

For coupling RF power from an RF input of a plasma chamber to the interior of a plasma chamber, an RF bus conductor is connected between the RF input and a plasma chamber electrode. In one embodiment, an RF return bus conductor is connected to an electrically grounded wall of the chamber, and the RF bus conductor and the RF return bus conductor have respective surfaces that are parallel and face each other. In another embodiment, the RF bus conductor has a transverse cross section having a longest dimension oriented perpendicular to the surface of the plasma chamber electrode that is closest to the RF bus conductor.

Owner:APPLIED MATERIALS INC

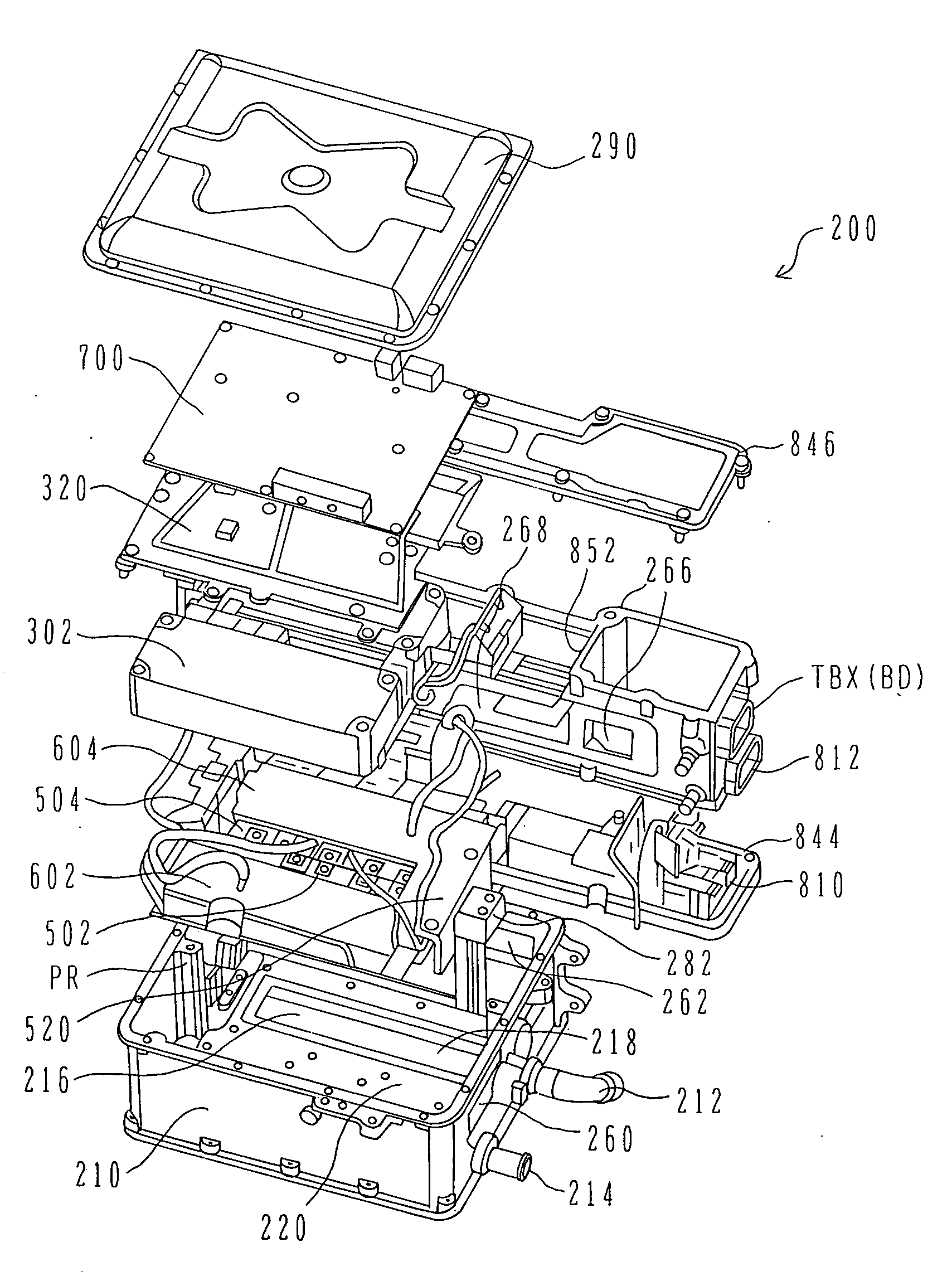

Capacitor module, power converter, vehicle-mounted electrical-mechanical system

ActiveUS20070109715A1Reduce surge voltageSmall sizeElectrolytic capacitorsConversion constructional detailsElectricityElectrical conductor

A capacitor module in which the structure of a connecting portion is highly resistant against vibration and has a low inductance. The capacitor module includes a plurality of capacitors and a laminate made up of a first wide conductor and a second wide conductor joined in a layered form with an insulation sheet interposed between the first and second wide conductors. The laminate comprises a first flat portion including the plurality of capacitors which are supported thereon and electrically connected thereto, a second flat portion continuously extending from the first flat portion while being bent, and connecting portions formed at ends of the first flat portion and the second flat portion and electrically connected to the exterior.

Owner:HITACHI ASTEMO LTD

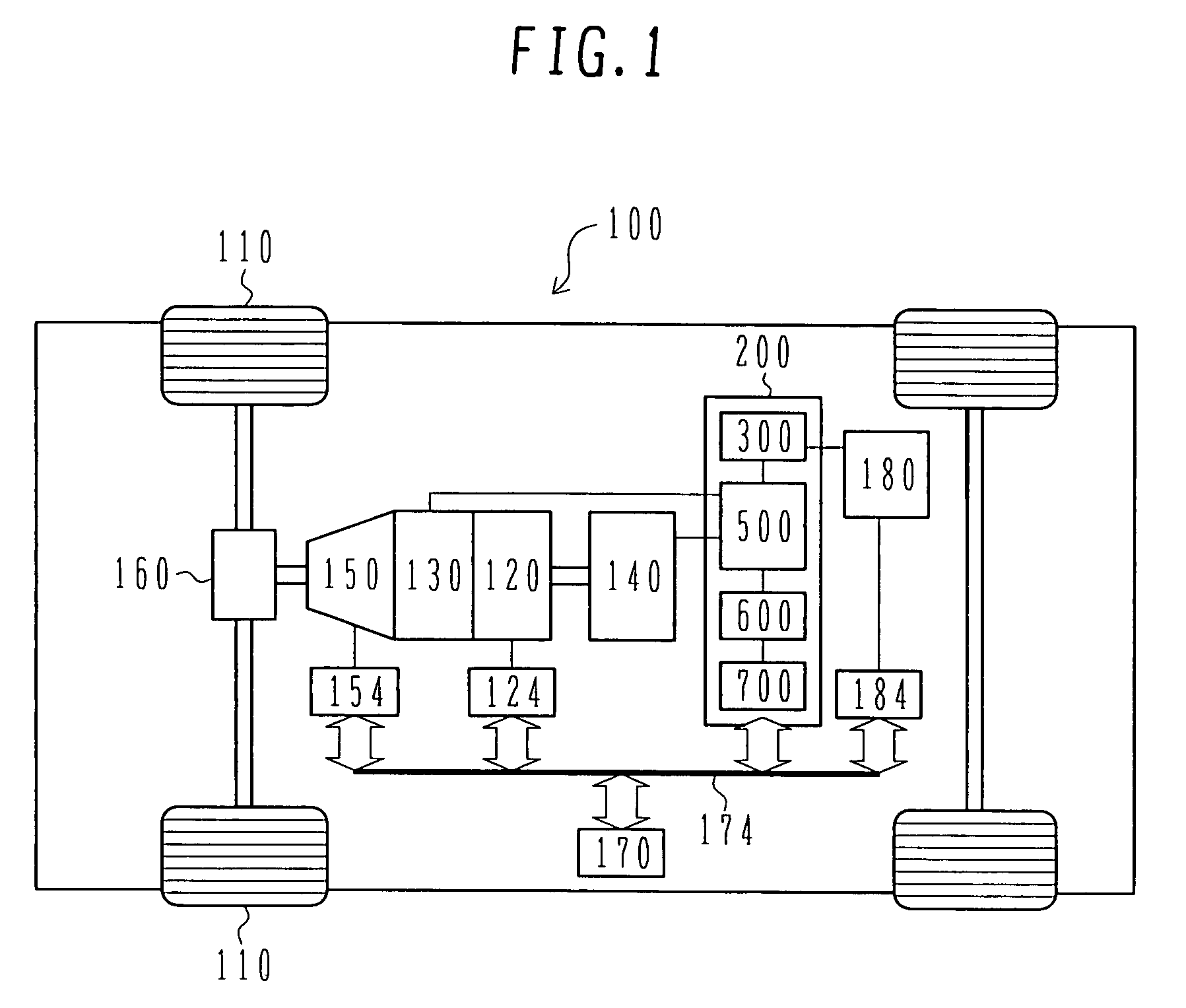

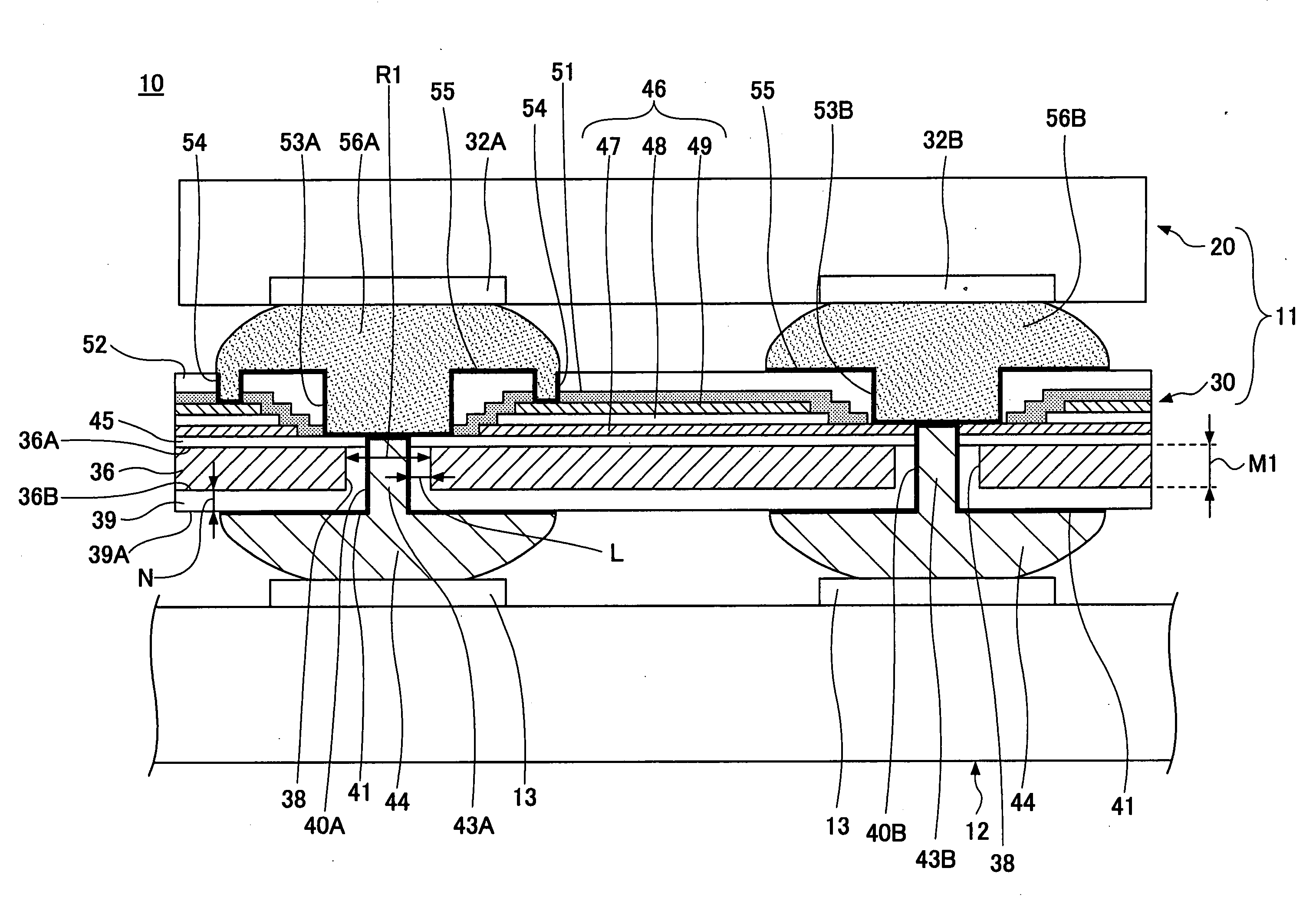

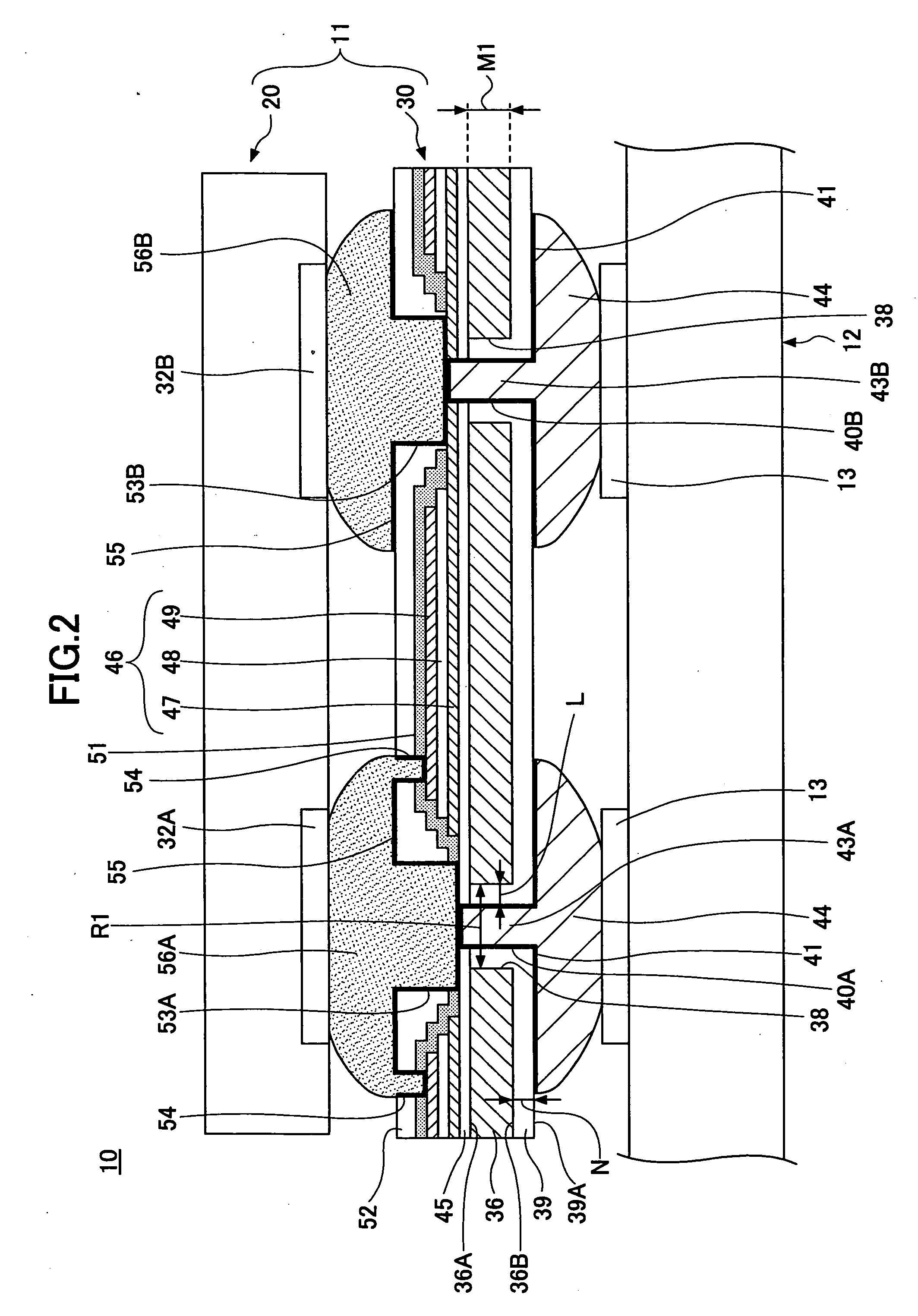

Electric Power Converter

InactiveUS20080049476A1Reduce inductanceReduce heatConversion constructional detailsSolid-state devicesElectrical conductorDielectric substrate

The present invention provides a highly reliable electric power converter reduced in parasitic inductance.An electric power converter that includes a capacitor module which has a DC terminal, an inverter which coverts a direct current into an alternating current, and heat release fins which cool the inverter, is constructed so that: the inverter has a power module including a plurality of power semiconductor elements; the power module further has a metallic base, a dielectric substrate provided on one face of the metallic base, a power semiconductor element fixed to the dielectric substrate, and a DC terminal; the metallic base has the heat release fins on the other face; the DC terminal in the power module and the DC terminal in the capacitor module are each formed by stacking flat plate conductors via an insulator; the two positive and negative DC terminals have respective front ends bent in opposite directions; a plane including the bent sections is used as a surface for connecting the power module and the capacitor module; and the insulators overlap each other at the connection surface.

Owner:HITACHI LTD

Inductor element and method for production thereof, and semiconductor module with inductor element

InactiveUS20070247268A1Reduce inductanceLower quality factorSemiconductor/solid-state device detailsSolid-state devicesAerosol depositionInductor

Owner:SONY CORP

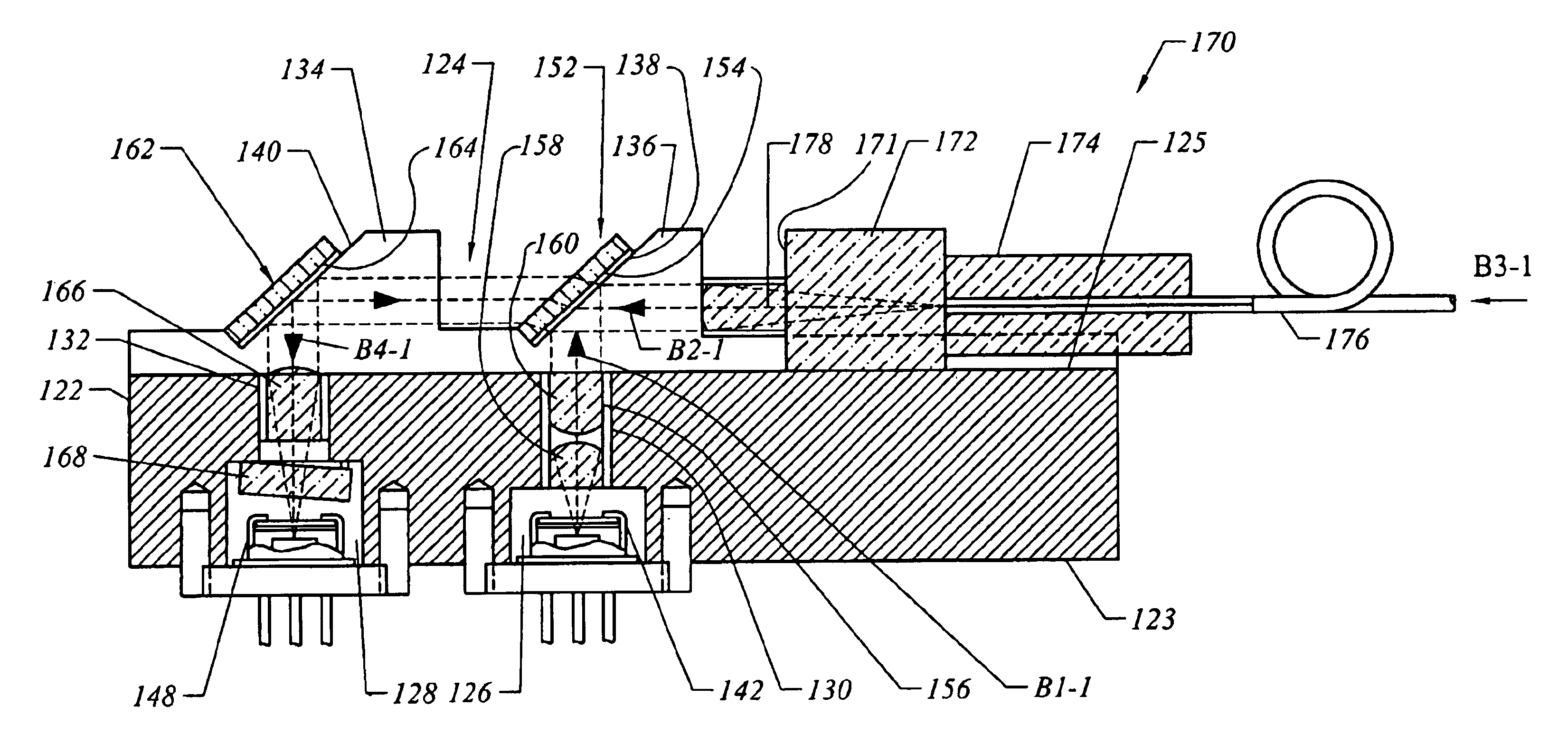

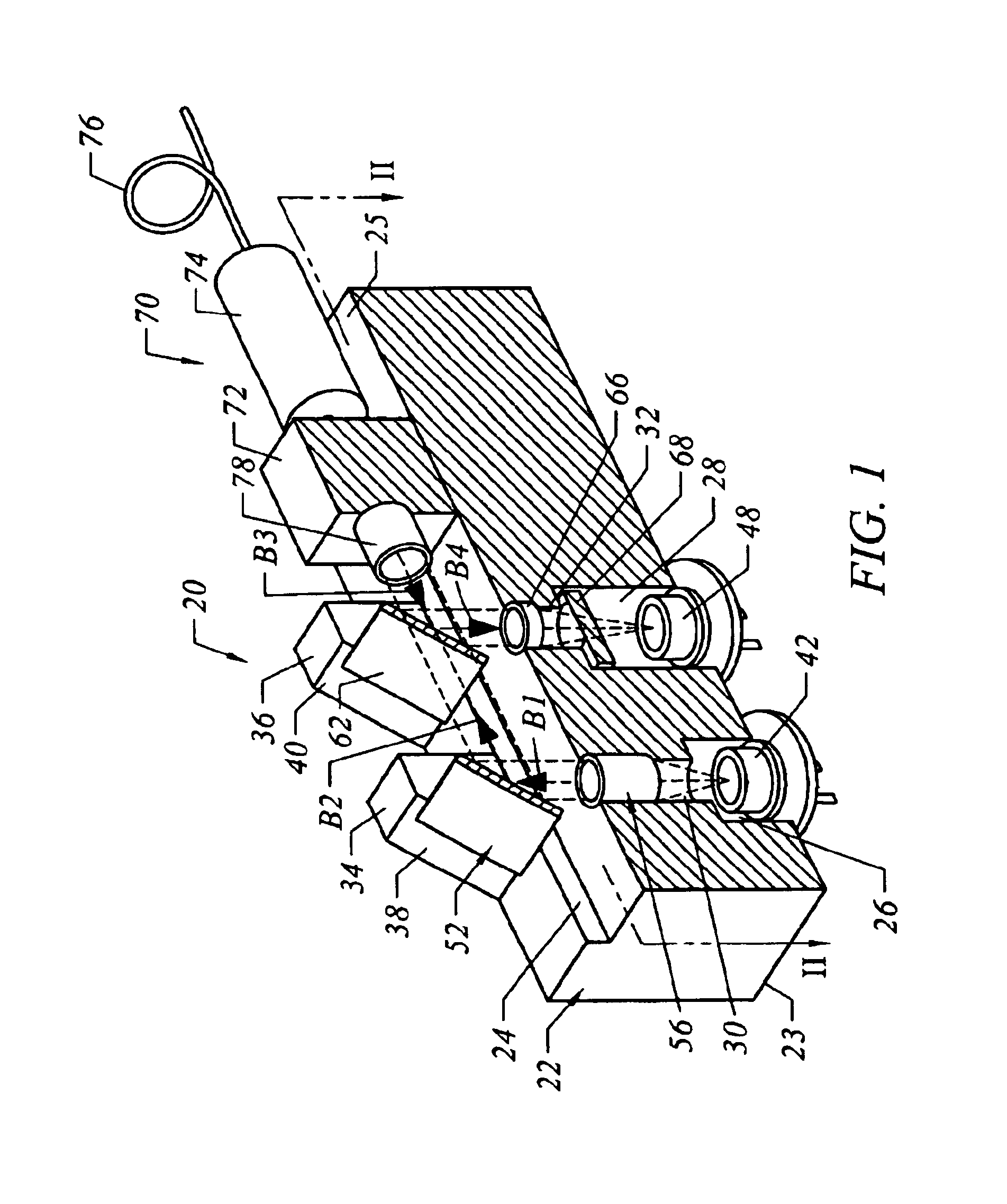

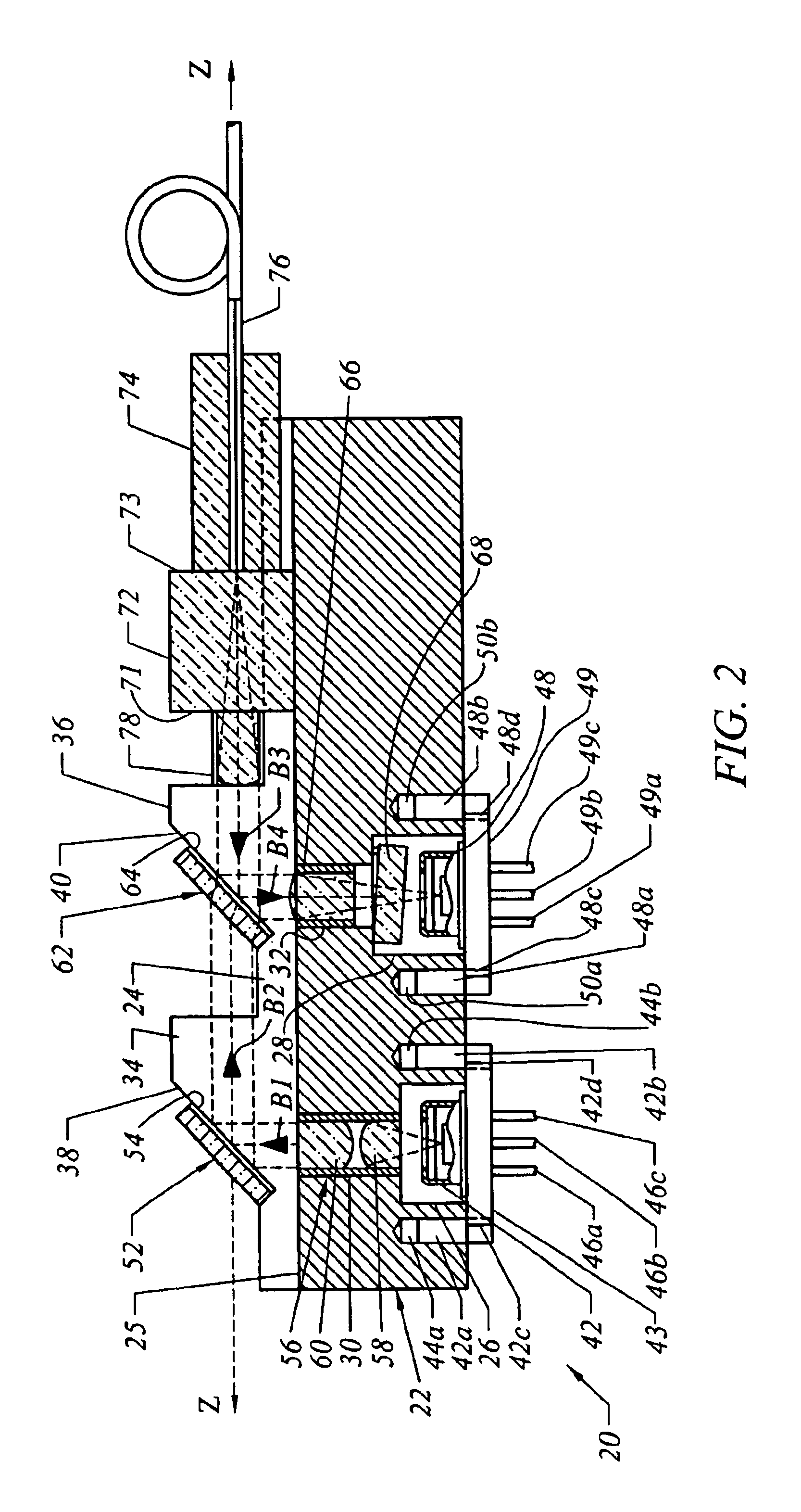

Optical module for high-speed bidirectional transceiver

InactiveUS6939058B2Simplified adjustment procedureEasy constructionCoupling light guidesTransceiverOptical Module

The optical module of the invention for high-speed bidirectional transceiver consists of a signal receiving unit, a signal transmitting unit, a common receiving-transmitting optical fiber, and a fiber coupling unit. The laser diode and the photodiode are arranged parallel to each other in closely located recesses of the module housing. Such an arrangement makes it possible to shorten distances for guiding lead wires from the terminals of the PC board to the respective terminals of the transmitting and receiving diodes. The laser diode emits a first transmitting laser beam that passes through a microobjective that collimates the beam and directs into onto a full-reflection mirror located inside the module housing. The full-reflection mirror reflects the first transmitting beam at an angle of 90° and transmits it to the end face of an optical fiber through an optical fiber collimator that centers the beam with the fiber core. The module is provided with a second mirror, which is fully transparent to the aforementioned first transmitting beam, but is fully reflective to a second transmitting beam that may propagate in a direction opposite to the first transmitting beam on a different wavelength. Alignment of the optical components is facilitated due to the fact that it is carried out with diffractionally limited and collimated beams.

Owner:MICROALIGN TECH +1

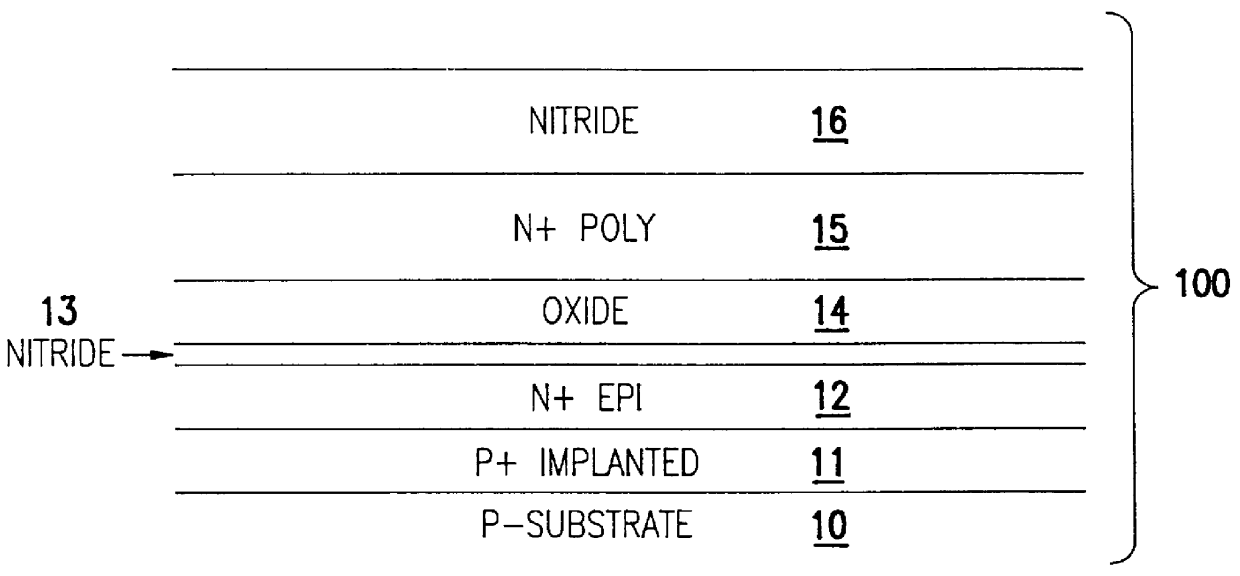

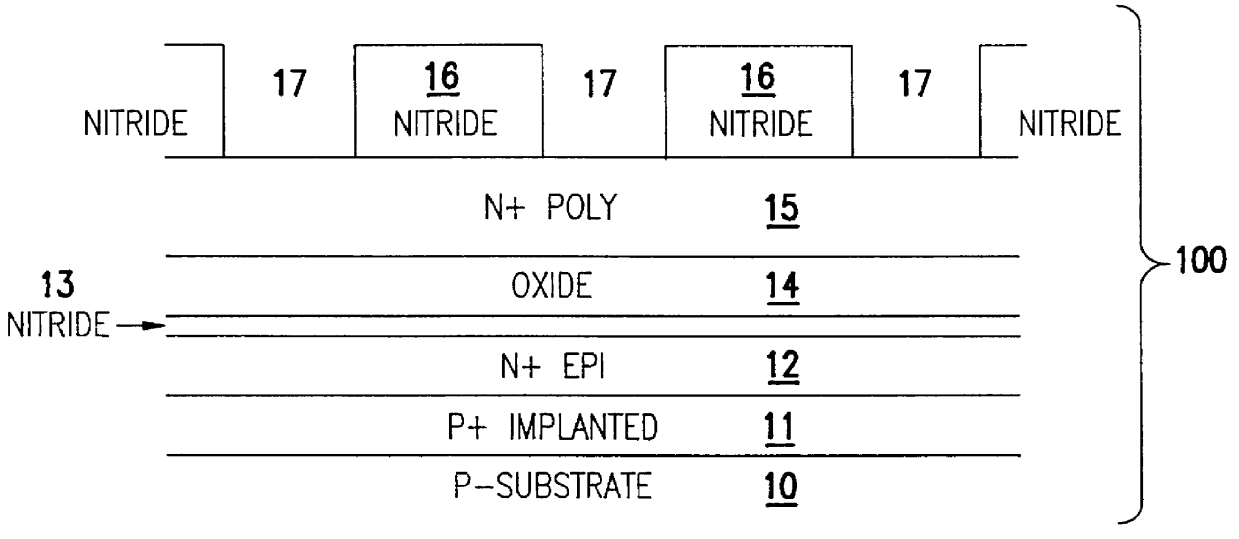

Power transistor having vertical FETs and method for making same

InactiveUS6060746ALower resistanceEasy to controlTransistorSolid-state devicesMOSFETElectrical and Electronics engineering

A power transistor having of a plurality of vertical MOSFET devices combined in parallel to achieve high-performance operation and methods of fabricating this device.

Owner:IBM CORP

Power inverter

ActiveUS20090040724A1Minimized volumeReduce inductanceConversion constructional detailsSolid-state devicesPower inverterCapacitance

In a power inverter, a coolant passage is fixed to a chassis to cool the chassis; the chassis is divided into a first region and a second region by providing the coolant passage in the chassis; a power module is provided in the first region as fixed to the coolant passage; a capacitor module is provided in the second region; and the DC terminal of the capacitor module is directly connected to the DC terminal of the power module.

Owner:HITACHI ASTEMO LTD

RF Bus and RF Return Bus for Plasma Chamber Electrode

ActiveUS20100206483A1Reduce peak voltageReduce riskElectric discharge tubesSemiconductor/solid-state device manufacturingElectrical conductorPlasma chamber

For coupling RF power from an RF input of a plasma chamber to the interior of a plasma chamber, an RF bus conductor is connected between the RF input and a plasma chamber electrode. In one embodiment, an RF return bus conductor is connected to an electrically grounded wall of the chamber, and the RF bus conductor and the RF return bus conductor have respective surfaces that are parallel and face each other. In another embodiment, the RF bus conductor has a transverse cross section having a longest dimension oriented perpendicular to the surface of the plasma chamber electrode that is closest to the RF bus conductor.

Owner:APPLIED MATERIALS INC

Via structure with dual current path

InactiveUS6479764B1Area minimizationReduce inductancePrinted circuit aspectsElectrical connection printed elementsReturn currentPrinted circuit board

Provided is a via for use in a printed circuit board or integrated circuit having first, second, third, and fourth layers. The via includes a first path capable of transmitting a forward current from the first to the second layer and a second path capable of transmitting a return current resulting from the forward current from the third to the fourth layer to return to a source of the forward current.

Owner:IBM CORP

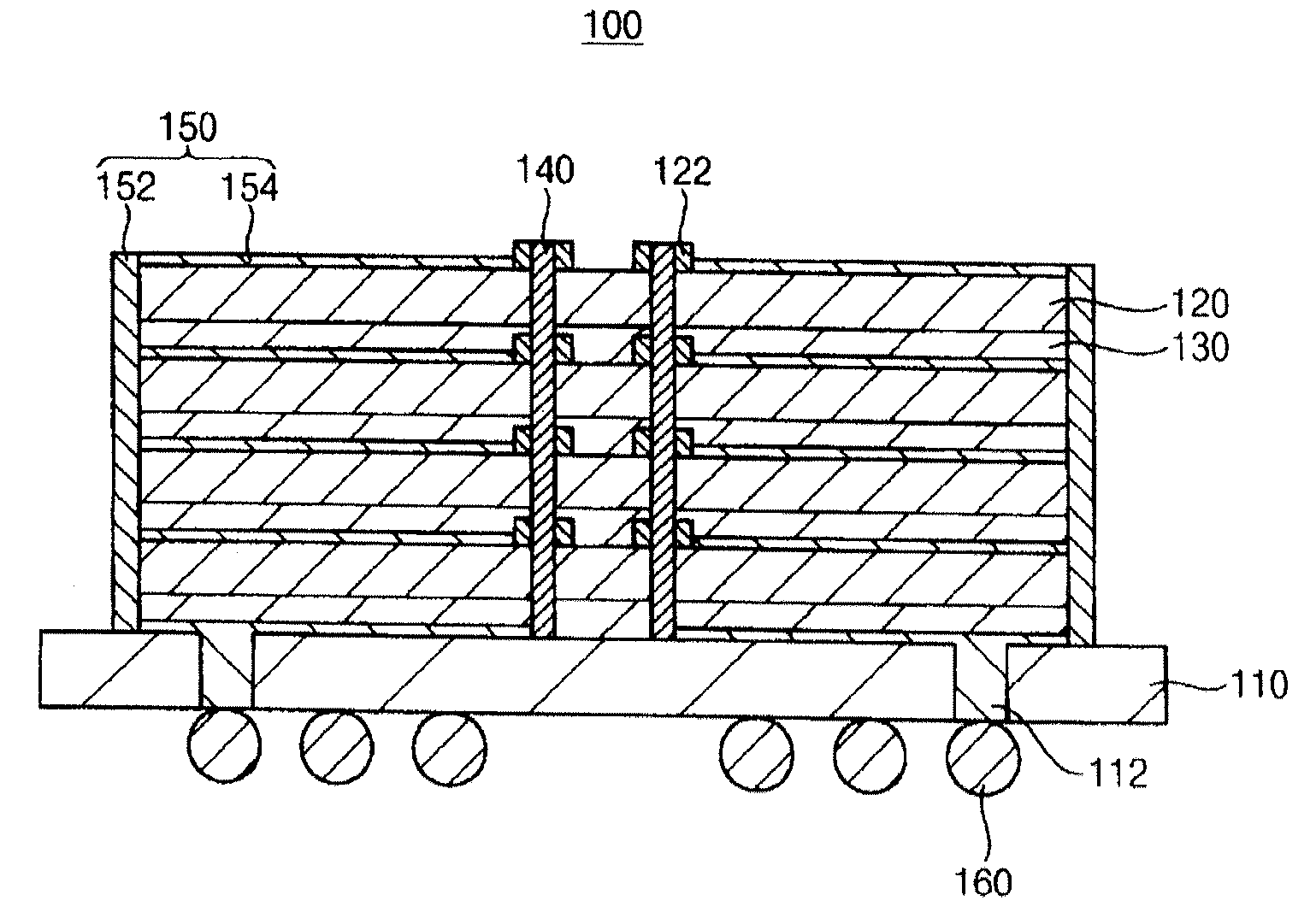

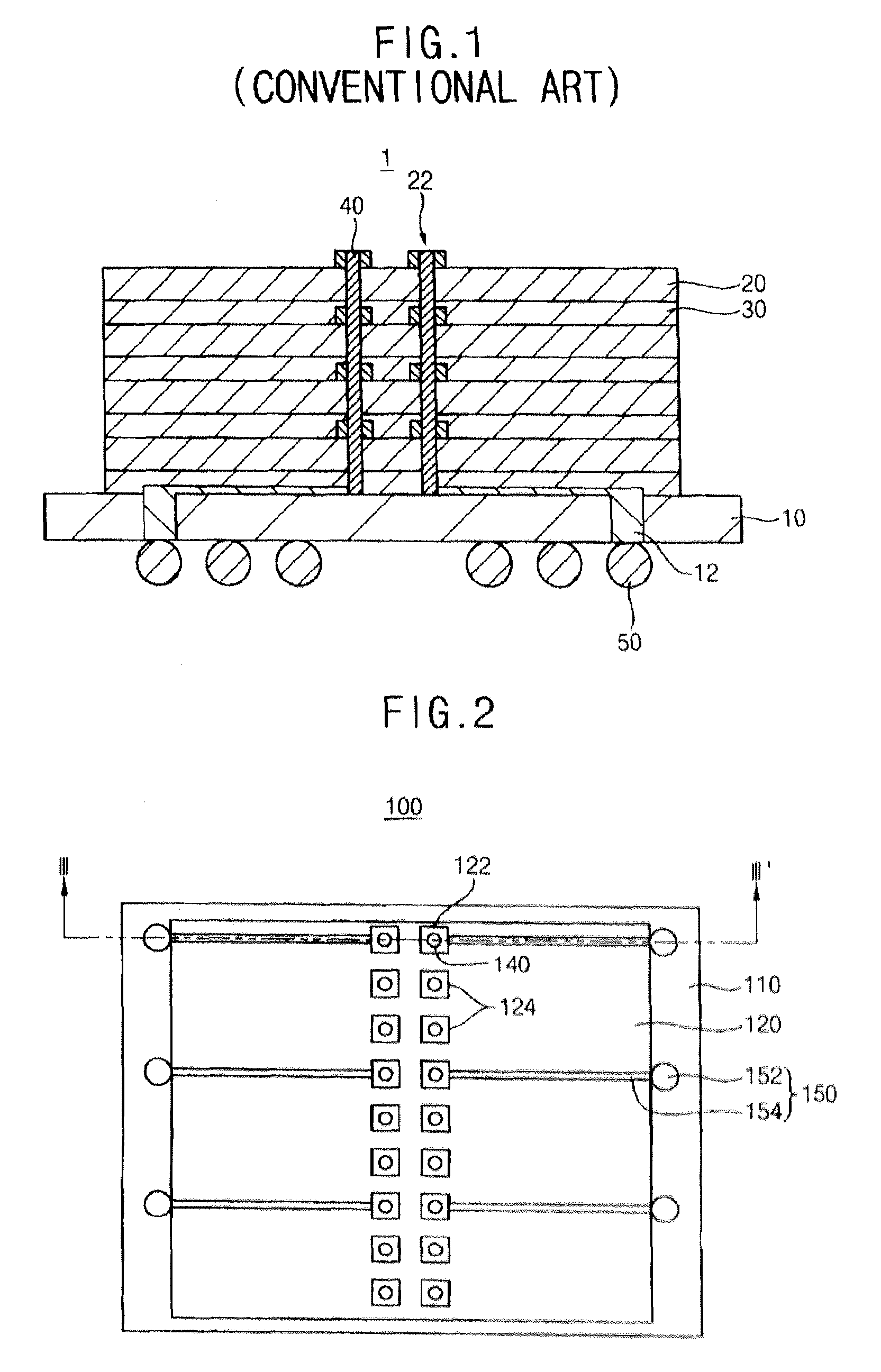

Capacitor-built-in-type printed wiring substrate printed wiring substrate, and capacitor

InactiveUS20050258548A1Reliably eliminate noiseLower resistanceSemiconductor/solid-state device detailsCross-talk/noise/interference reductionEngineeringLow inductance

A capacitor-built-in-type printed wiring substrate which can reliably eliminate noise and attain extremely low resistance and low inductance in connections between an IC chip and the capacitor, and a printed wiring substrate and capacitor for use in the same. A capacitor-built-in-type printed wiring substrate 100 on which an IC chip is mounted includes a capacitor-built-in-type printed wiring substrate 110 and an IC chip 101 mounted on the capacitor-built-in-type printed wiring substrate 110. A printed wiring substrate 120 includes a number of connection-to-IC substrate bumps 152 and a closed-bottomed capacitor accommodation cavity 121 formed therein. A capacitor 130 is disposed in the cavity 121 and includes a pair of electrode groups 133E and 133F and a number of connection-to-IC capacitor bumps 131 connected to either one of the paired electrode groups 133E and 133F. The connection-to-IC capacitor bumps 131 are flip-chip-bonded to corresponding connection-to-capacitor bumps 103 on the IC chip 101. The connection-to-IC substrate bumps 152 are flip-chip-bonded to corresponding connection-to-substrate bumps 104 on the IC chip 101.

Owner:NGK SPARK PLUG CO LTD

Electric power converter

InactiveUS7742303B2Improve power reliabilityOptimize heat dissipation structureConversion constructional detailsSolid-state devicesElectrical conductorDielectric substrate

Owner:HITACHI LTD

Built-in capacitor type wiring board and method for manufacturing the same

InactiveUS20070121273A1Easy to produceAvoid misalignmentSemiconductor/solid-state device detailsCross-talk/noise/interference reductionElectrical conductorEngineering

In order to provide a built-in capacitor type wiring board capable of preventing misalignment of the capacitor, a capacitor built-in type wiring board is provided which includes a core board; a multilayer portion disposed on at least one side of the core board and formed by a plurality of interlayer insulating layers; and a plurality of conductor layers alternately laminated on the core board. The capacitor is of a chip-like shape with first and second main surfaces and includes a dielectric layer; electrode layers laminated on the dielectric layer; and a hole portion opening at least at the second main surface. The capacitor is embedded in the interlayer insulating layers so that the second main surface faces the core board.

Owner:NGK SPARK PLUG CO LTD

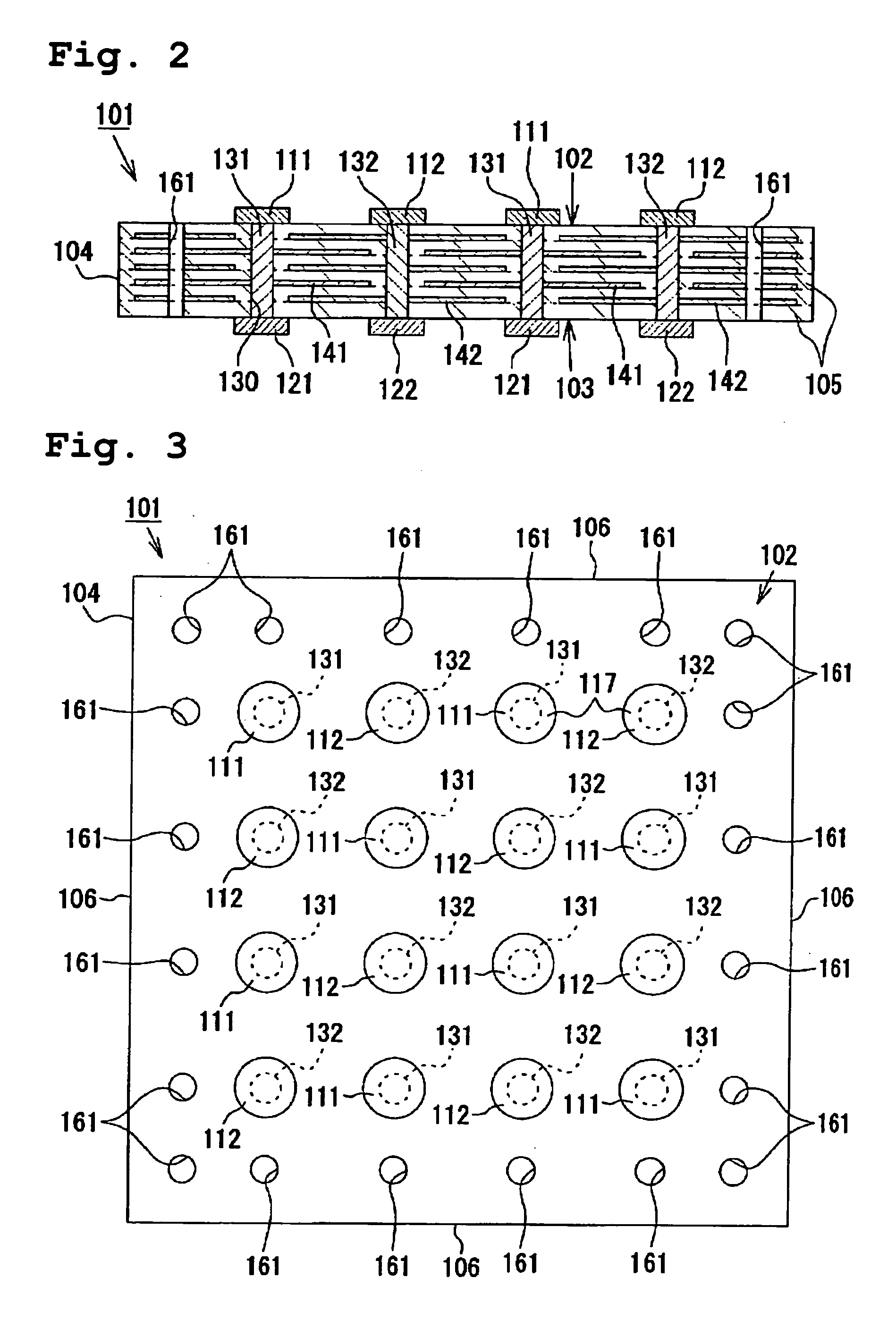

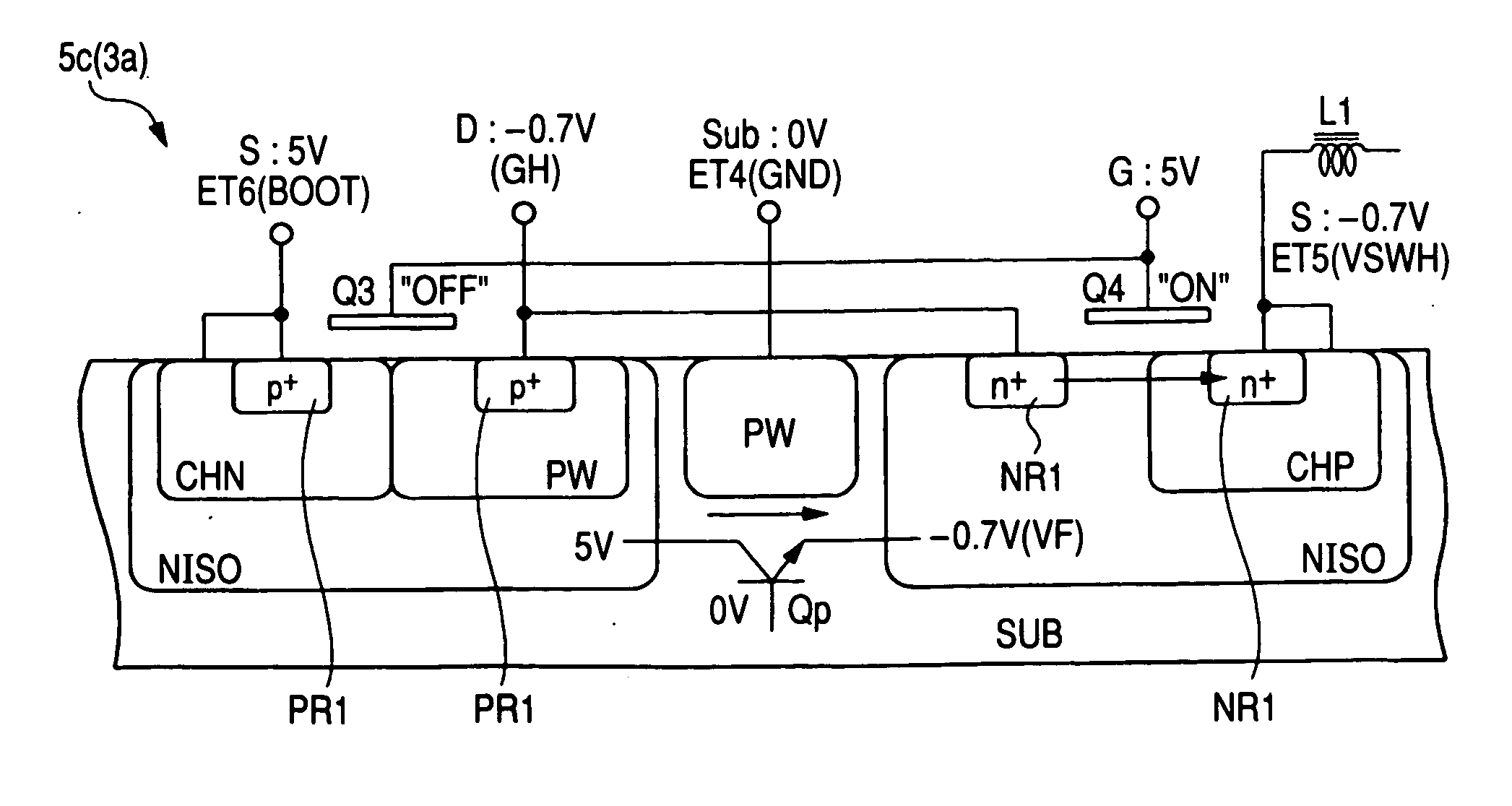

Semiconductor device and a manufacturing method of the same

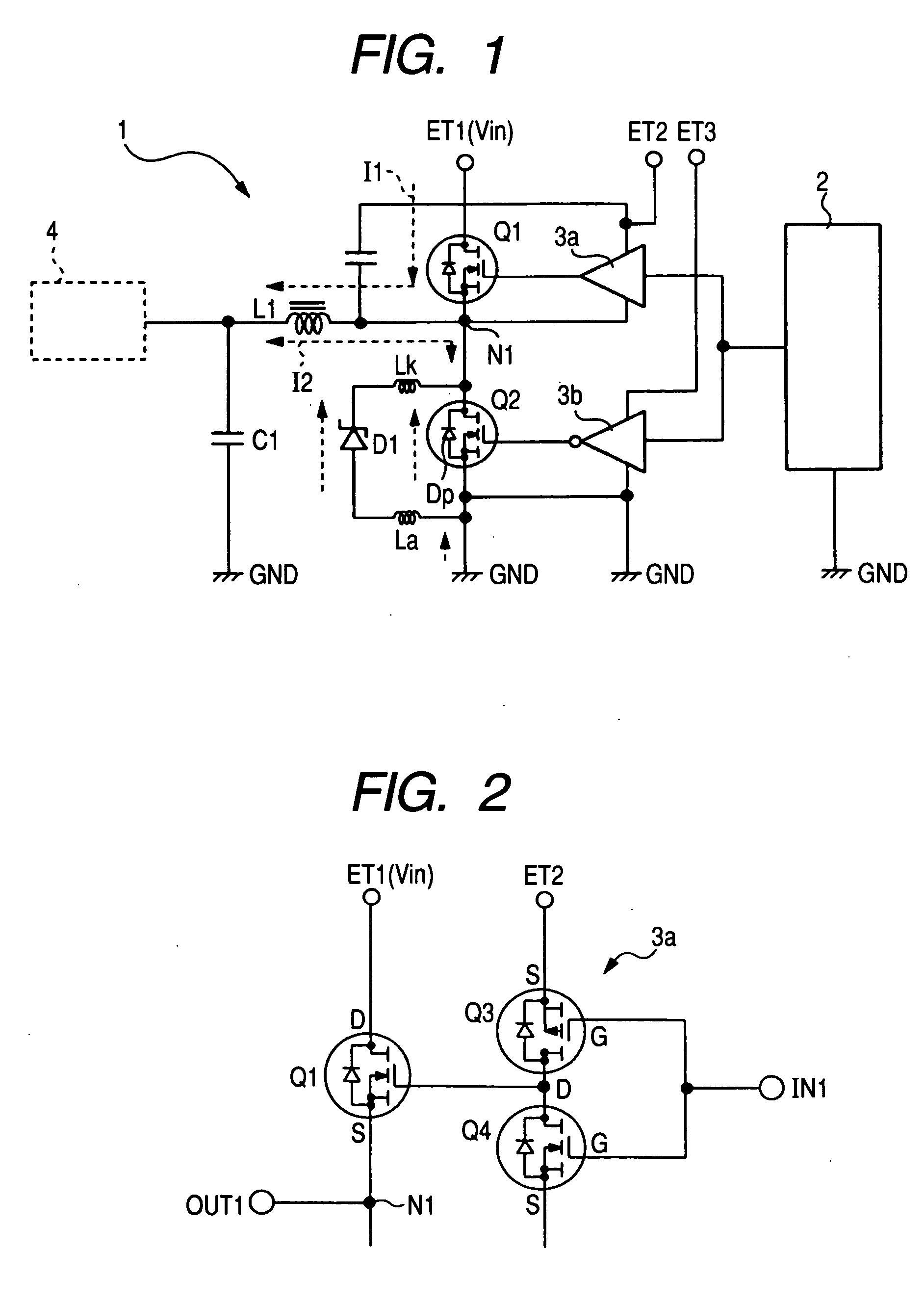

ActiveUS20060022298A1Improve conversion efficiencyReduce inductanceTransistorConversion constructional detailsDc dc converterSchottky barrier

In a non-insulated DC-DC converter having a circuit in which a power MOS•FET high-side switch and a power MOS•FET low-side switch are connected in series, the power MOS•FET low-side switch and a Schottky barrier diode to be connected in parallel with the power MOS•FET GF low-side switch are formed within one semiconductor chip. The formation region SDR of the Schottky barrier diode is disposed in the center in the shorter direction of the semiconductor chips and on both sides thereof, the formation regions of the power MOS•FET low-side switch are disposed. From the gate finger in the vicinity of both long sides on the main surface of the semiconductor chip toward the formation region SDR of the Schottky barrier diode, a plurality of gate fingers are disposed so as to interpose the formation region SDR between them.

Owner:RENESAS ELECTRONICS CORP

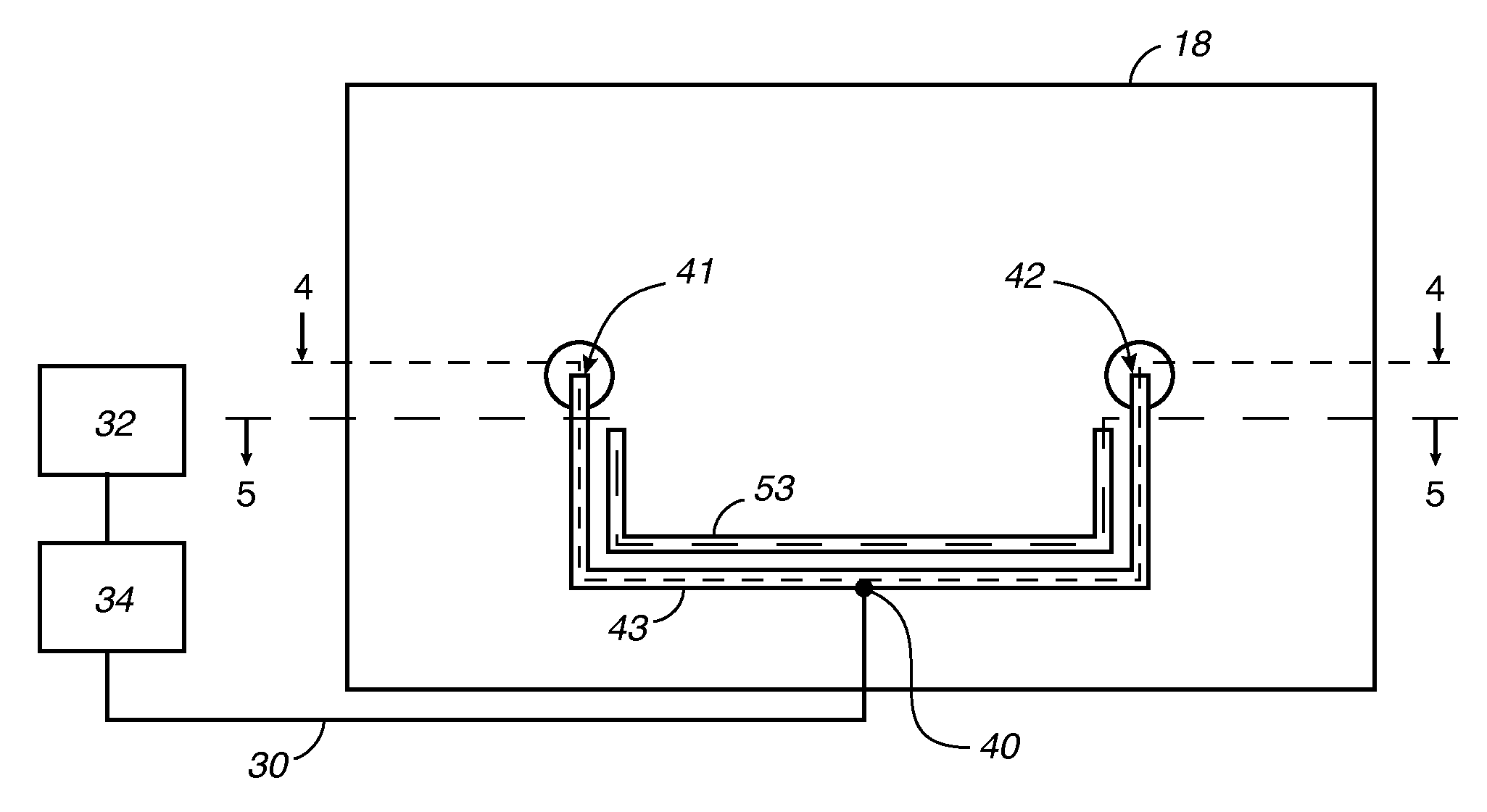

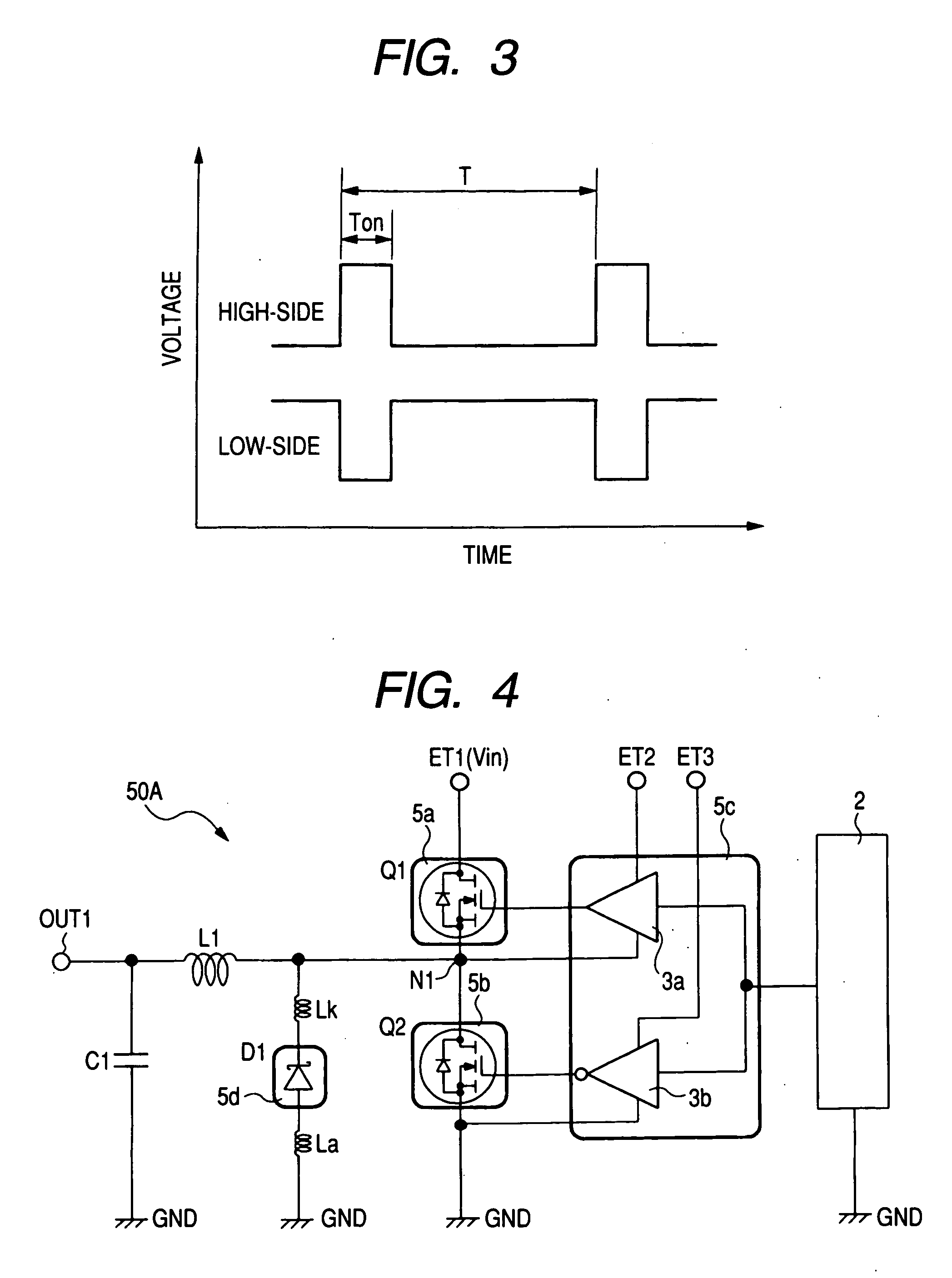

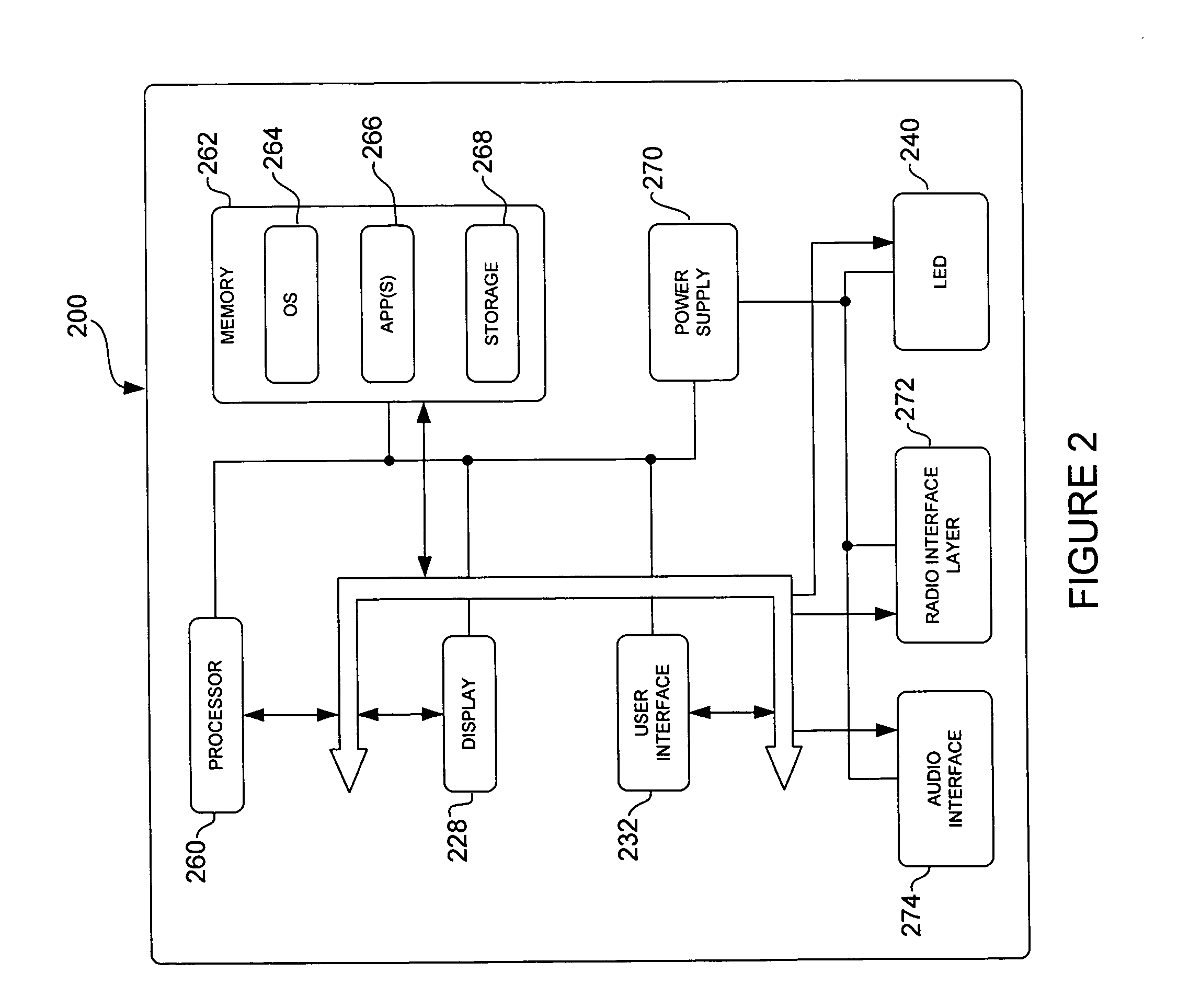

Parallel loop antennas for a mobile electronic device

InactiveUS20060038731A1Reduce inductanceHigh inductance and radiation resistanceLoop antennas with ferromagnetic coreResonant long antennasMobile electronicsInductance

A mobile electronic device, such as a smart personal object includes an antenna system for emitting and receiving signals. The antenna system includes at least two antennas electrically connected in parallel to define an equivalent circuit having a reduced inductance with a substantially unaffected induced voltage for the equivalent circuit.

Owner:MICROSOFT TECH LICENSING LLC

Semiconductor chip and semiconductor device

InactiveUS20080258259A1Reduce in quantitySuppress noiseSemiconductor/solid-state device detailsSolid-state devicesHigh resistanceCapacitance

A semiconductor chip and a semiconductor device mounting the semiconductor chip capable of increasing a capacitance of a capacitor without reducing the number of signal bumps or power bumps of a package and the number of C4 solder balls of the semiconductor chip, and achieving a stable power supply with suppressing fluctuations of power at a resonance frequency without a limitation in a position to mount a capacitor for lowering noise of a signal transceiving interface block. In the semiconductor device, a via hole is provided to the semiconductor chip, a power-supply electrode connected to the via hole is provided to a back surface of the semiconductor chip, and a capacitor is mounted to the electrode on the back surface. And, a high-resistance material is used for a material of a power-supply via hole inside the semiconductor chip, thereby increasing the resistance and lowering the Q factor.

Owner:HITACHI LTD

Semiconductor device, method of manufacturing the same, capacitor structure, and method of manufacturing the same

InactiveUS20060180938A1Lower impedanceReduce inductanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

A semiconductor device is disclosed that includes an interposer and a semiconductor chip. The interposer includes a Si substrate; multiple through vias provided through an insulating material in corresponding through holes passing through the Si substrate; a thin film capacitor provided on a first main surface of the Si substrate so as to be electrically connected to the through vias; and multiple external connection terminals provided on a second main surface of the Si substrate so as to be electrically connected to the through vias. The second main surface faces away from the first main surface. The semiconductor chip is provided on one of the first main surface and the second main surface so as to be electrically connected to the through vias. The Si substrate has a thickness less than the diameter of the through holes.

Owner:FUJITSU LTD

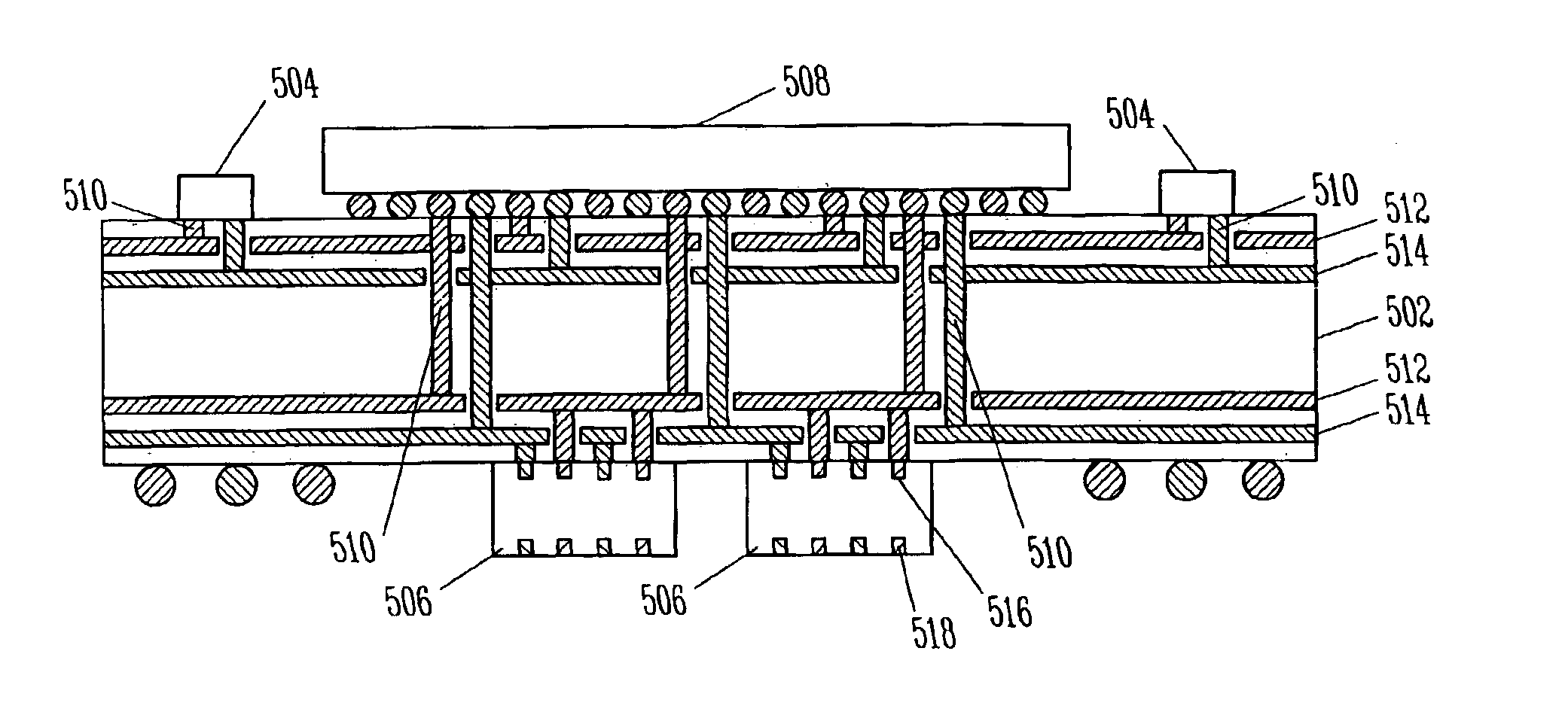

Manufacturing methods for an electronic assembly with vertically connected capacitors

InactiveUS6907658B2High inductance structureShorten the timeSemiconductor/solid-state device detailsSolid-state devicesSurface mountingEngineering

An electronic assembly includes one or more discrete capacitors (506, 804, 1204), which are vertically connected to a housing, such as an integrated circuit package (1704). Surface mounted capacitors (506) are vertically connected to pads (602) on a top or bottom surface of the package. Embedded capacitors (804, 1204) are vertically connected to vias (808, 816, 1210, and / or 1212) or other conductive structures within the package. Vertically connecting a surface mounted or embedded capacitor involves aligning (1604) side segments (416) of some of the capacitor's terminals with the conductive structures (e.g., pads, vias or other structures) so that the side of the capacitor upon which the side segments reside is substantially parallel with the top or bottom surface of the package. Where a capacitor includes extended terminals (1208), the capacitor can be embedded so that the extended terminals provide additional current shunts through the package.

Owner:INTEL CORP

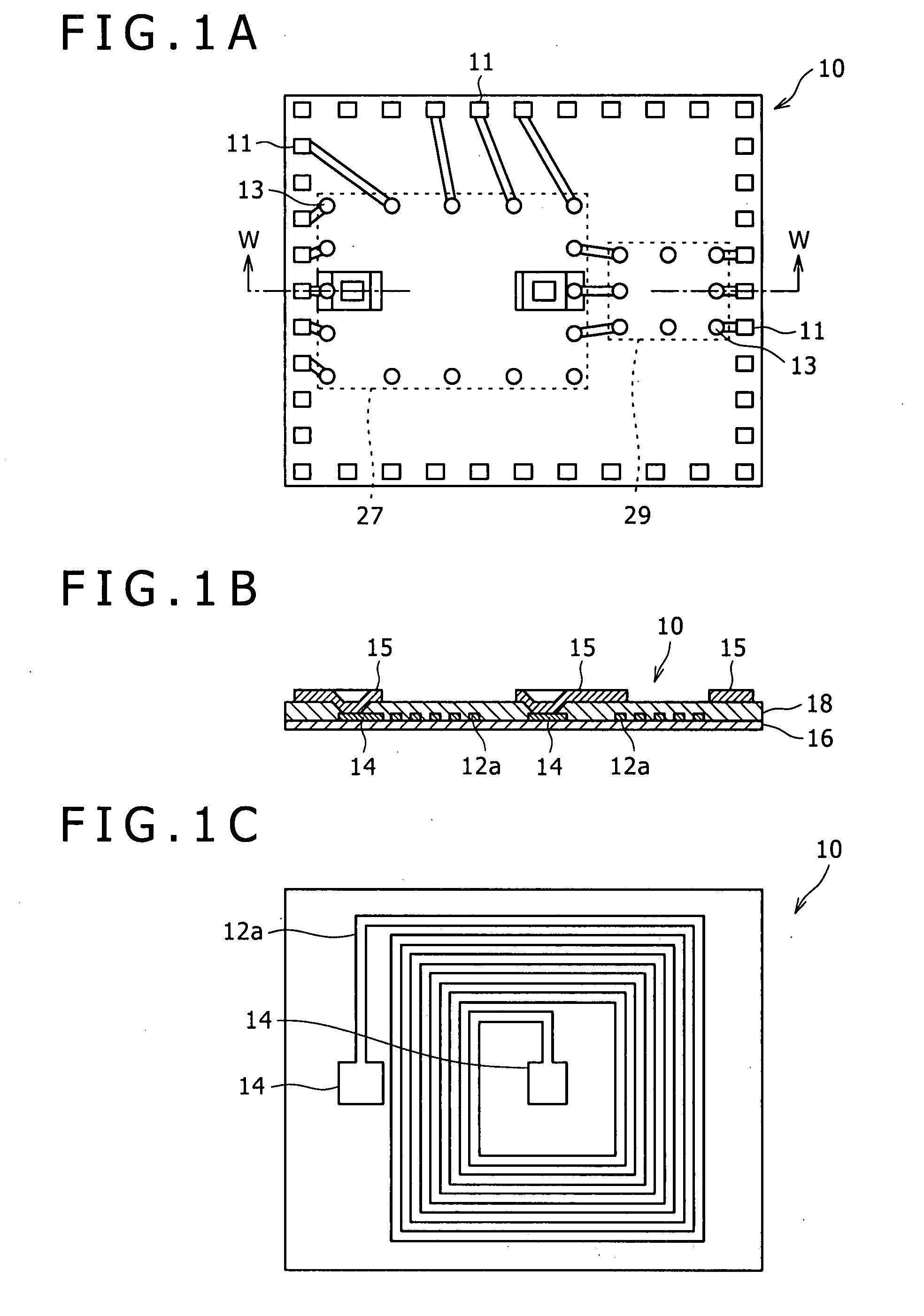

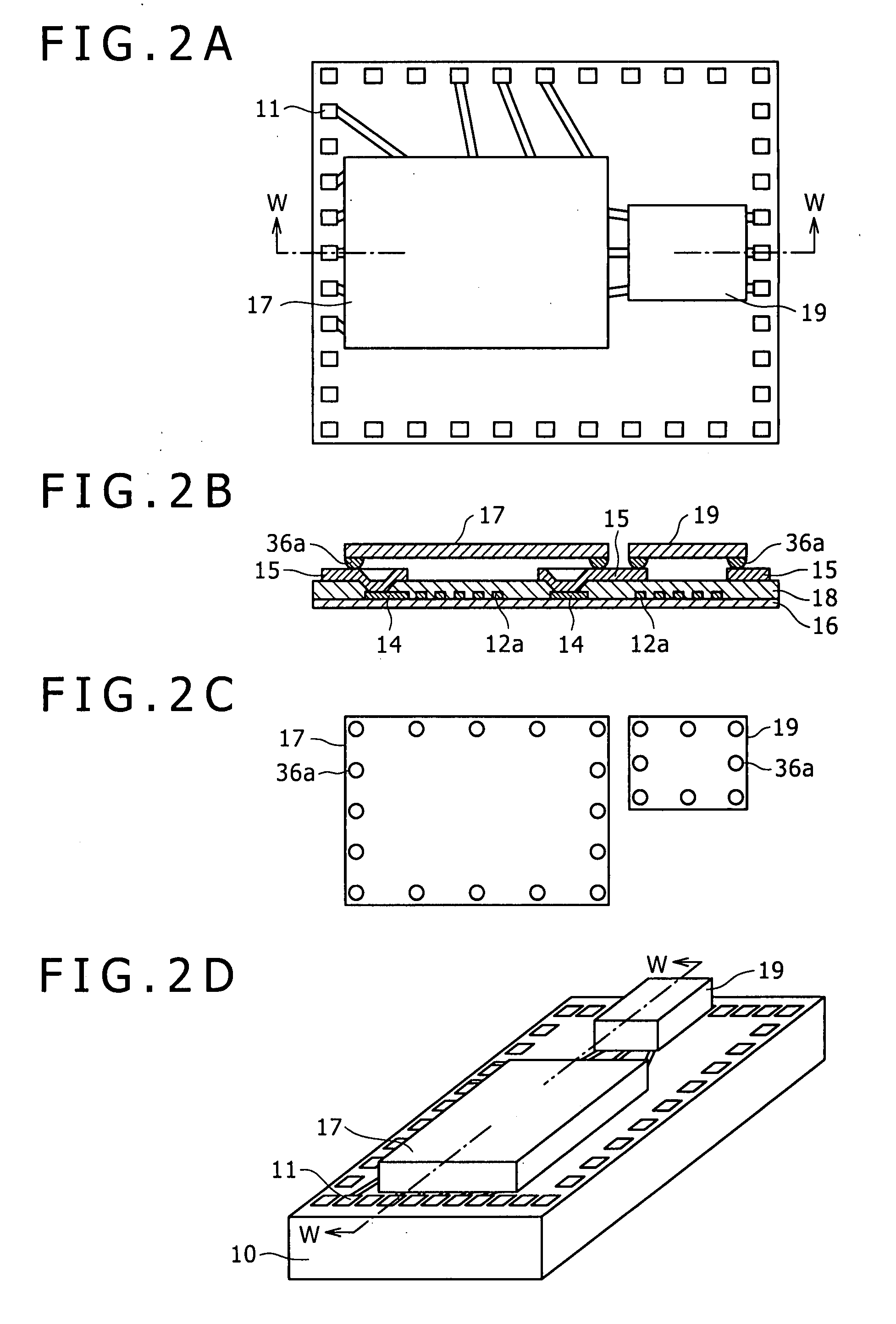

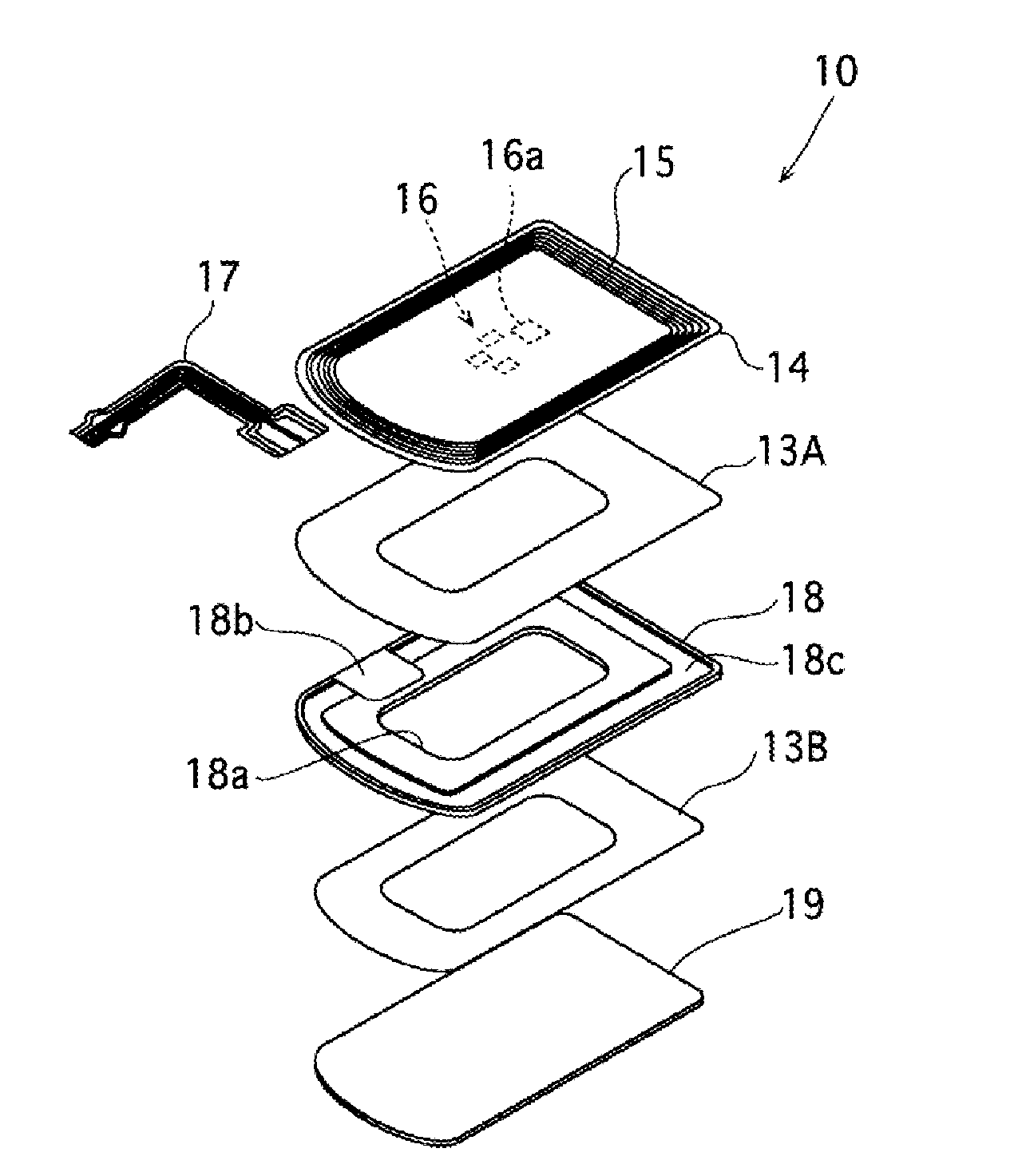

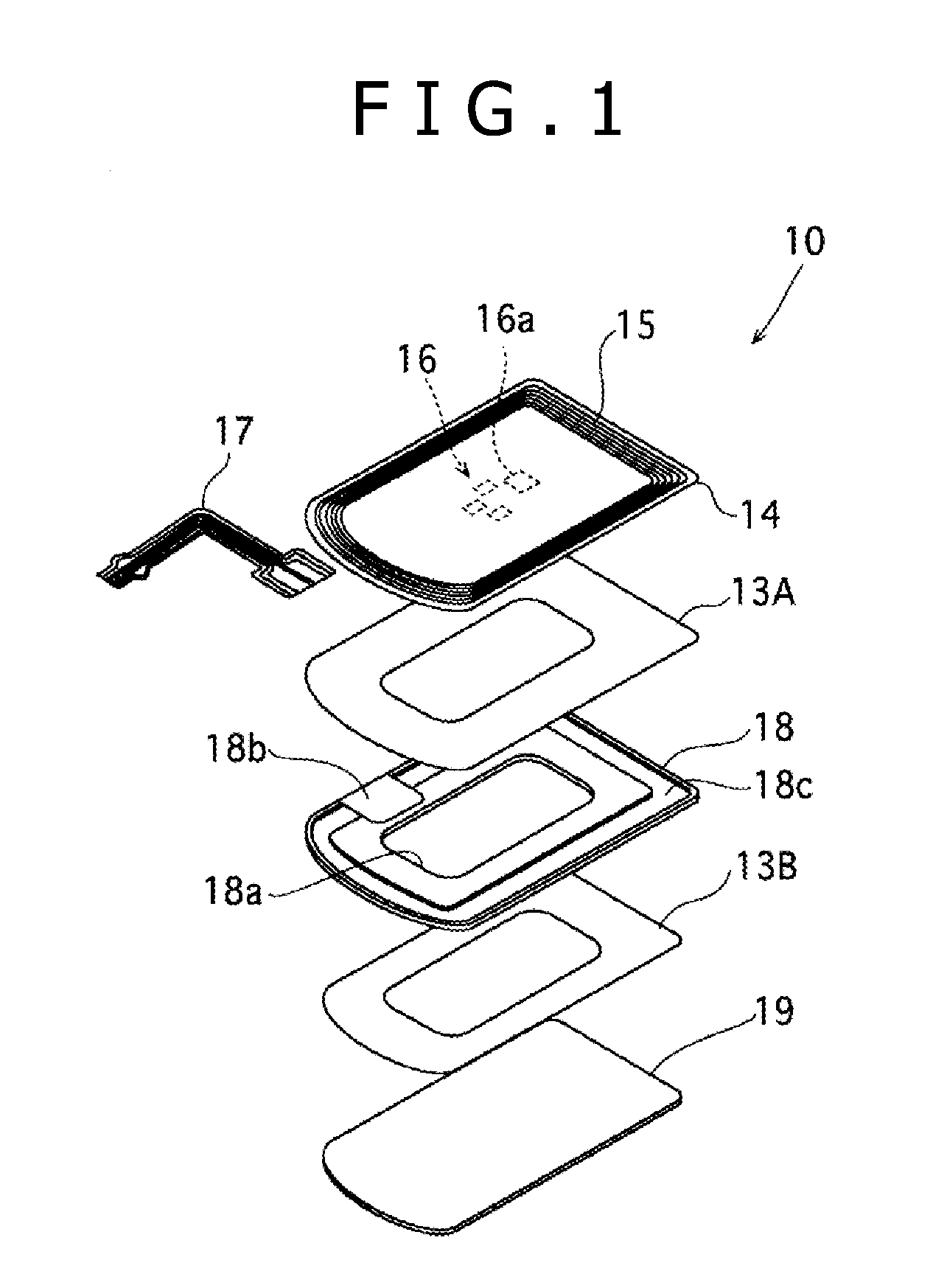

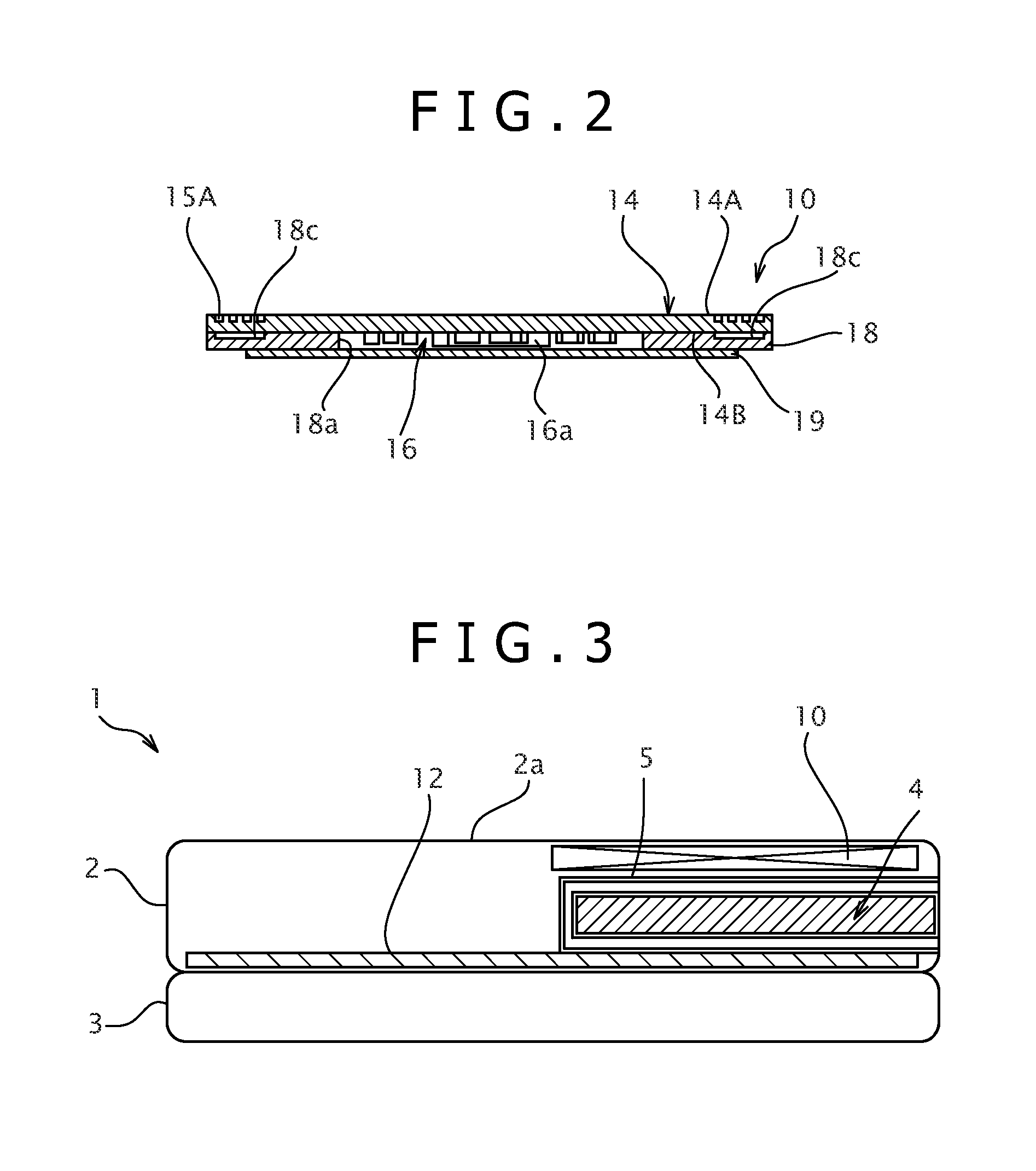

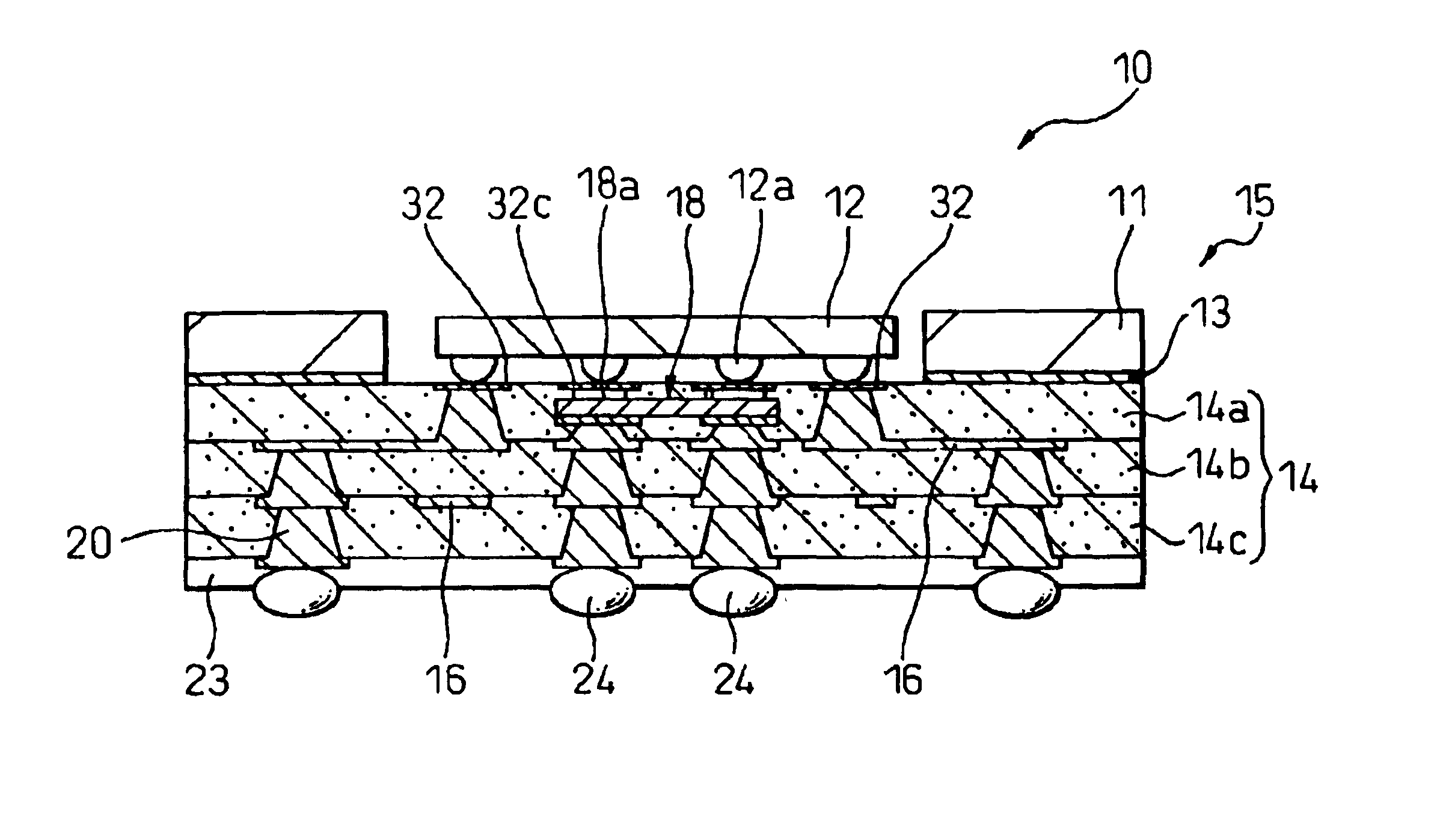

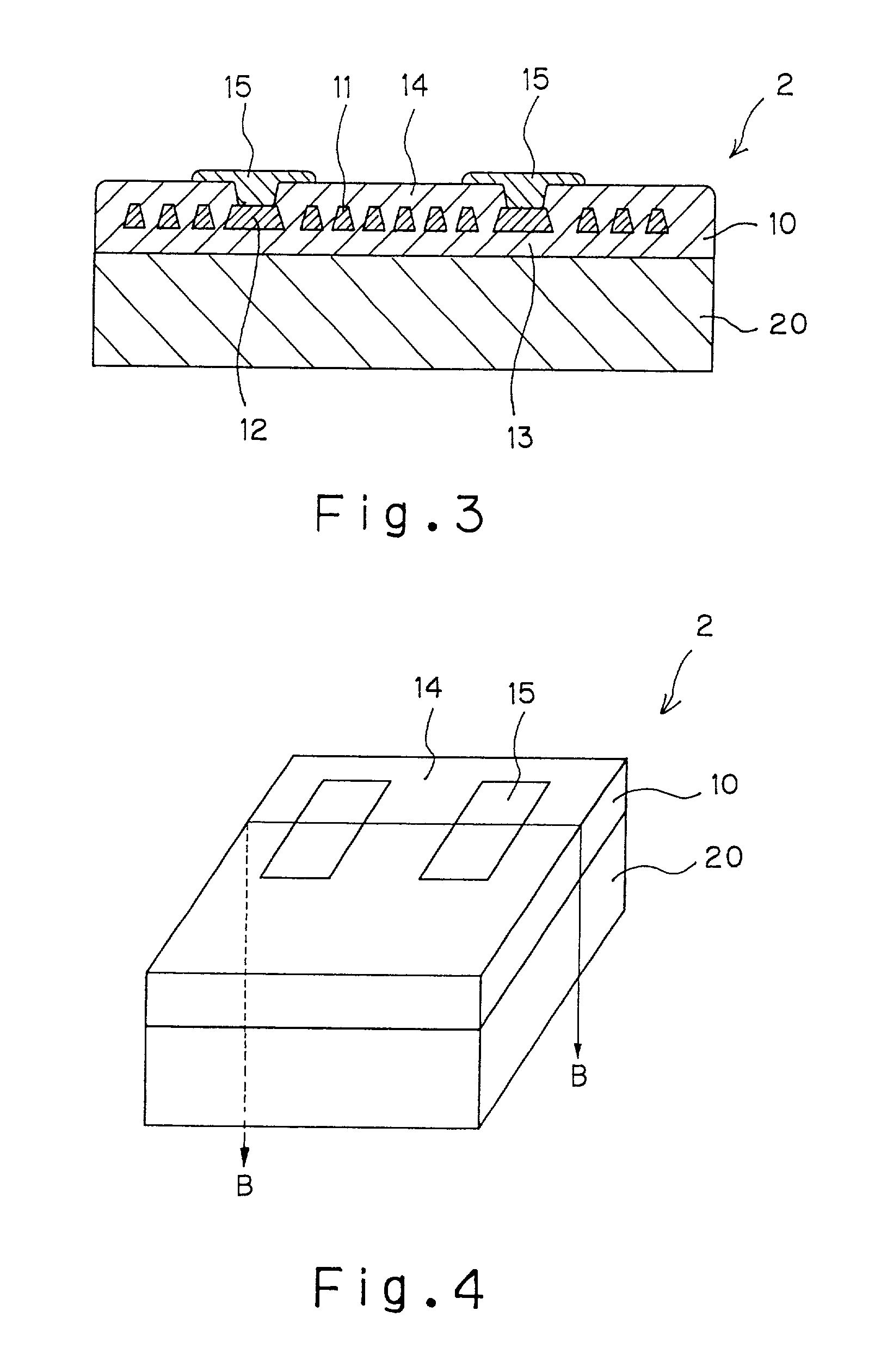

Magnetic core member for antenna module, antenna module and portable information terminal equipped with antenna module

InactiveUS20070069961A1Improve communication distanceImprove permeabilityLoop antennas with ferromagnetic coreAntenna supports/mountingsEddy currentEngineering

There are provided a magnetic core member for an antenna module capable of improving a communication distance without thickening the module, an antenna module, and a portable information terminal equipped with the antenna module. A magnetic core member 18 for an antenna module 10 of the present invention has a ring groove 18c as a recess portion formed on the surface on the side stacking an antenna coil 15 in an area facing a loop portion of the antenna coil 15. An eddy current generated in the magnetic core member 18 in a high frequency magnetic field is concentrated on the surface of the magnetic core member 18 on the side stacking the antenna coil 15 in the area facing the loop portion of the antenna coil 15. According to the present invention, a ring groove 18c is provided in the area to reduce an amount of eddy currents to be generated and improve the communication distance characteristics of the antenna module.

Owner:SONY CORP

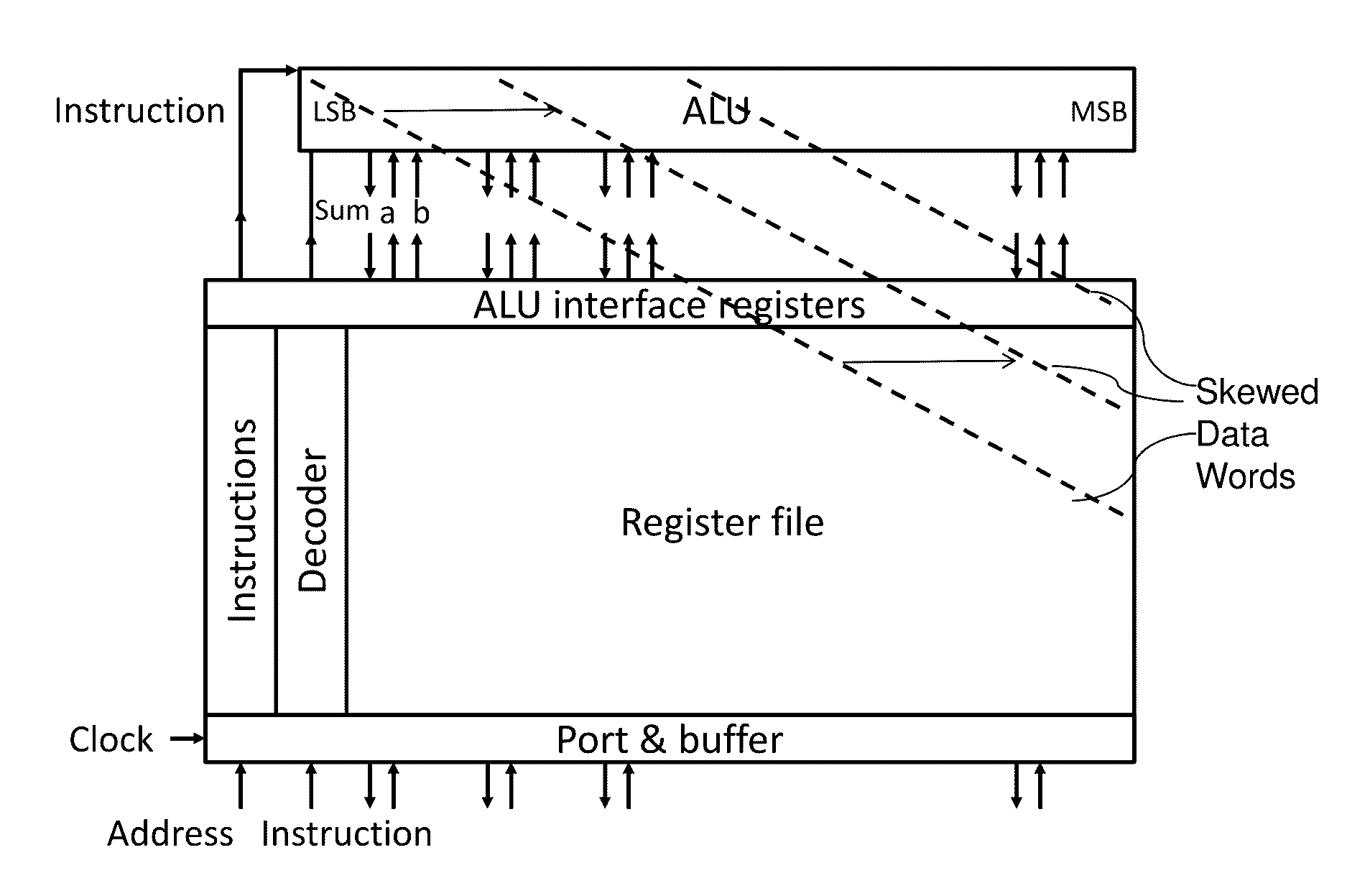

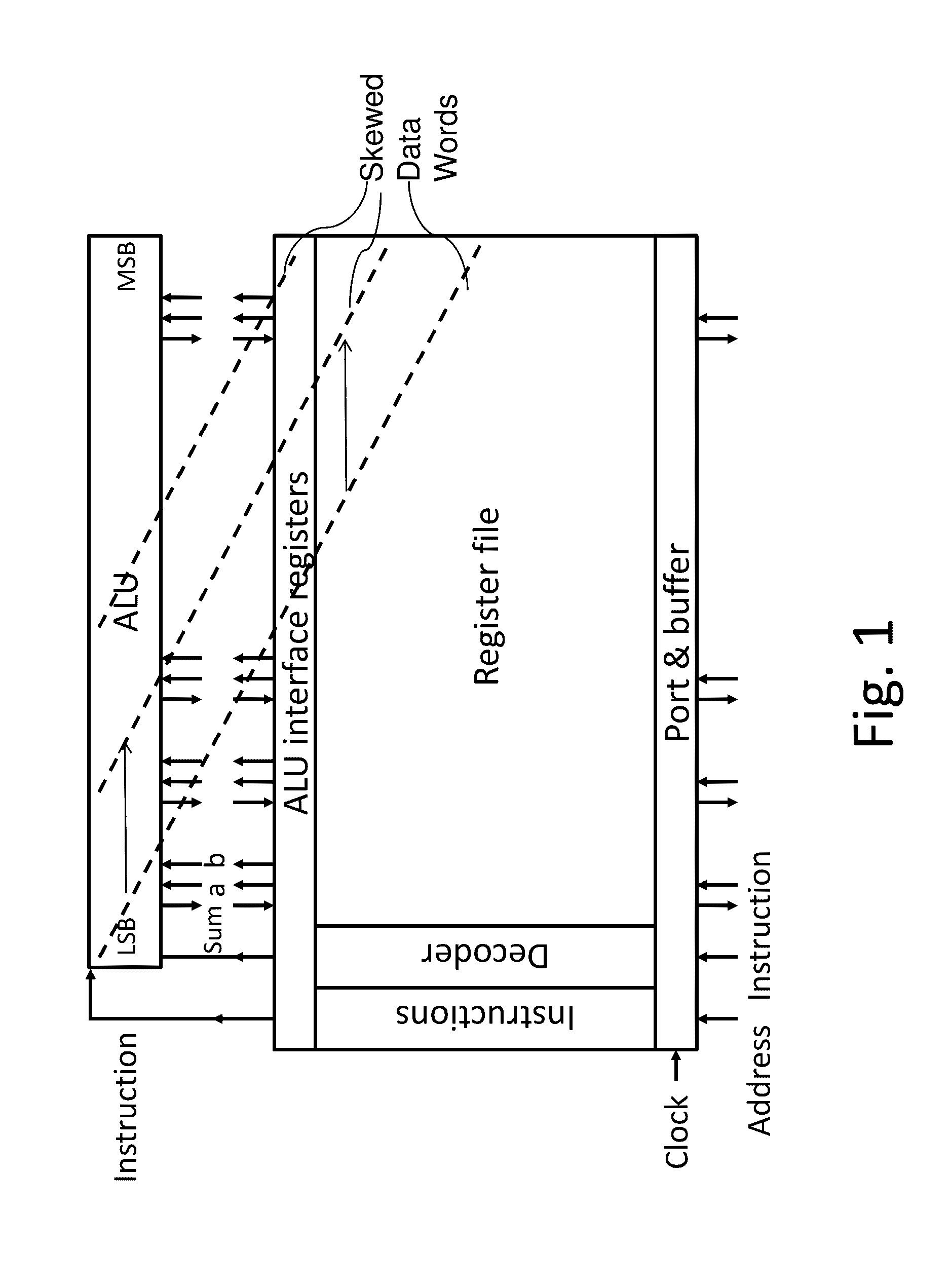

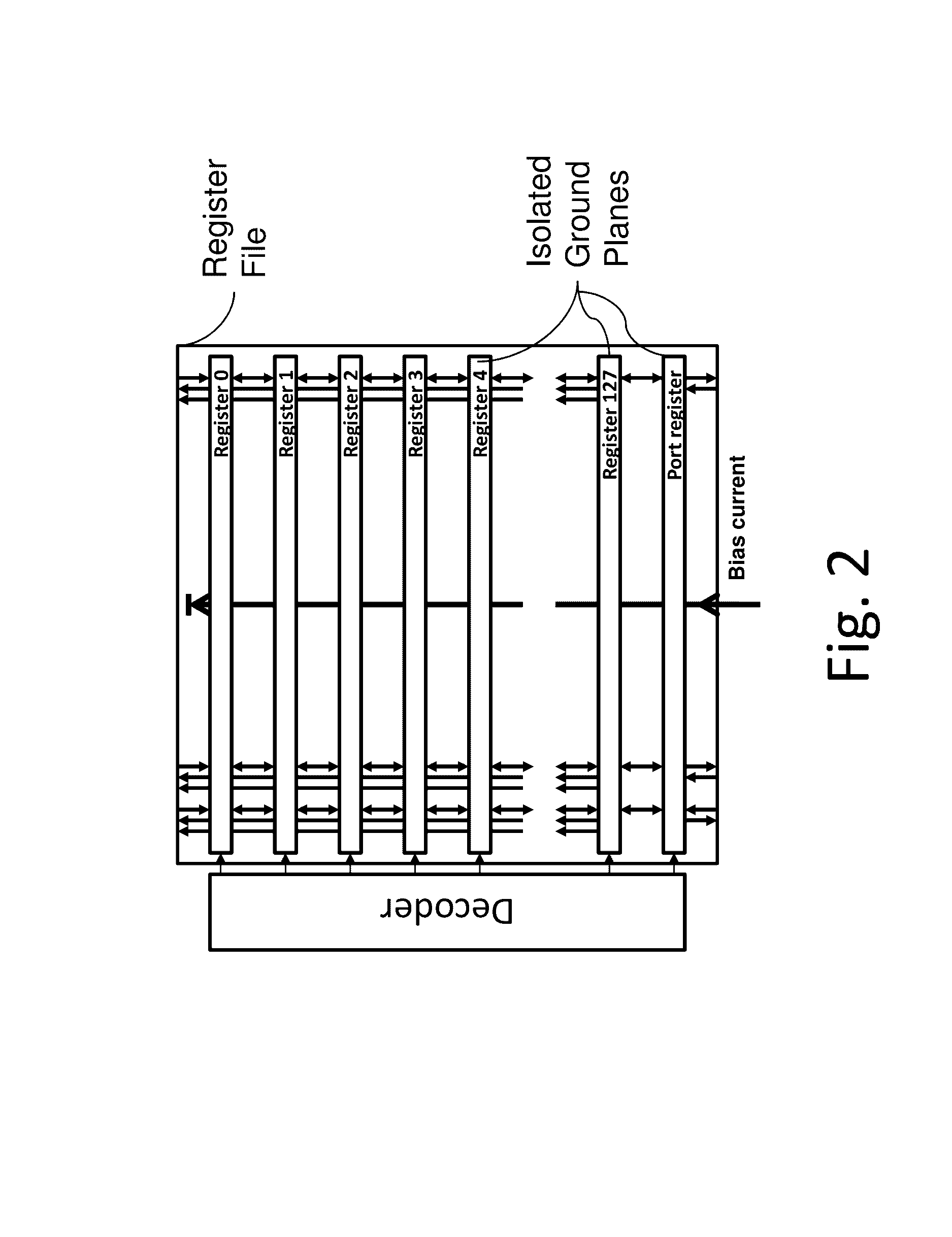

System and method for cryogenic hybrid technology computing and memory

ActiveUS9520180B1Easy to combineTransmission lineCosmetic preparationsQuantum computersLow inductanceDatapath

A system and method for high-speed, low-power cryogenic computing are presented, comprising ultrafast energy-efficient RSFQ superconducting computing circuits, and hybrid magnetic / superconducting memory arrays and interface circuits, operating together in the same cryogenic environment. An arithmetic logic unit and register file with an ultrafast asynchronous wave-pipelined datapath is also provided. The superconducting circuits may comprise inductive elements fabricated using both a high-inductance layer and a low-inductance layer. The memory cells may comprise superconducting tunnel junctions that incorporate magnetic layers. Alternatively, the memory cells may comprise superconducting spin transfer magnetic devices (such as orthogonal spin transfer and spin-Hall effect devices). Together, these technologies may enable the production of an advanced superconducting computer that operates at clock speeds up to 100 GHz.

Owner:SEEQC INC

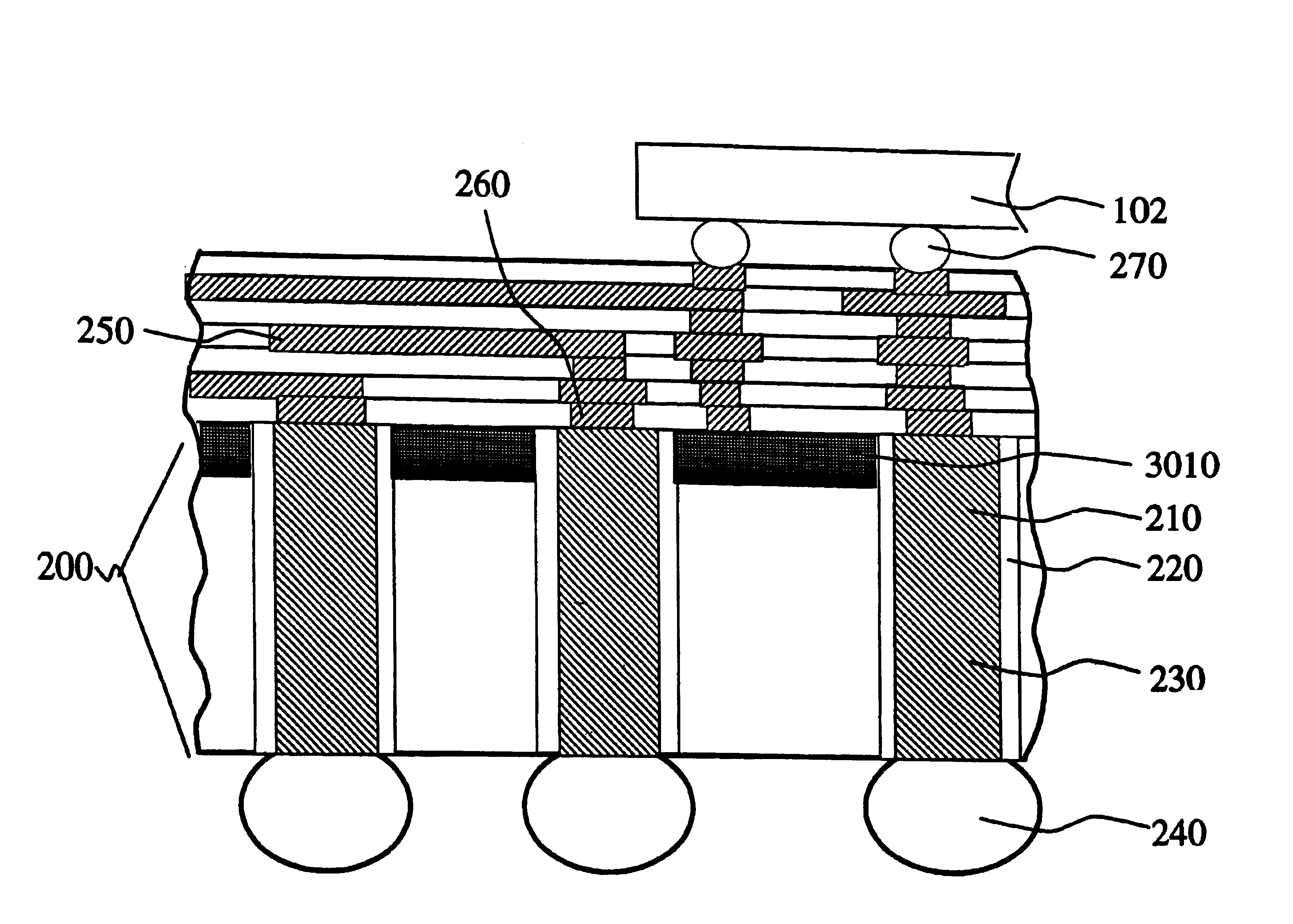

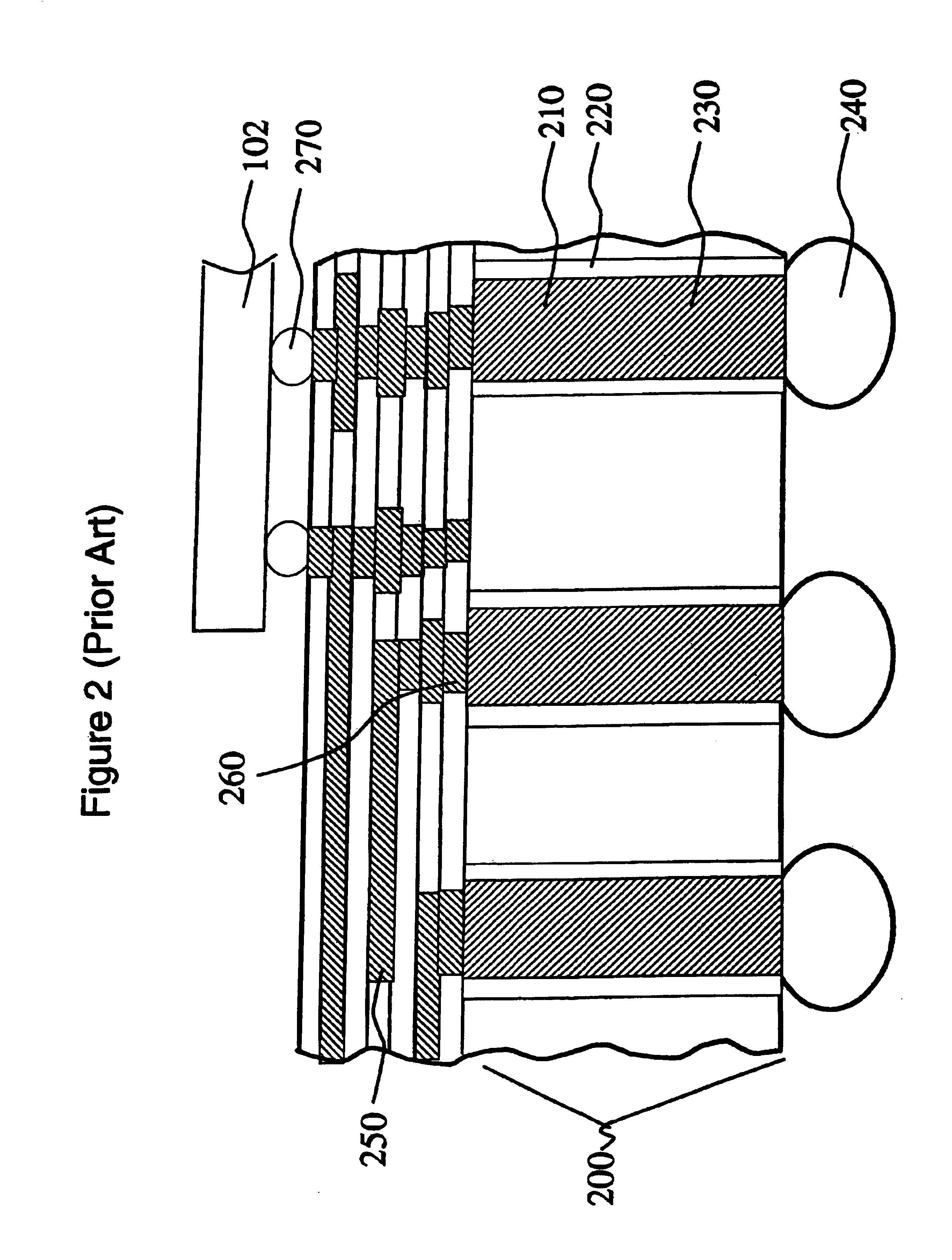

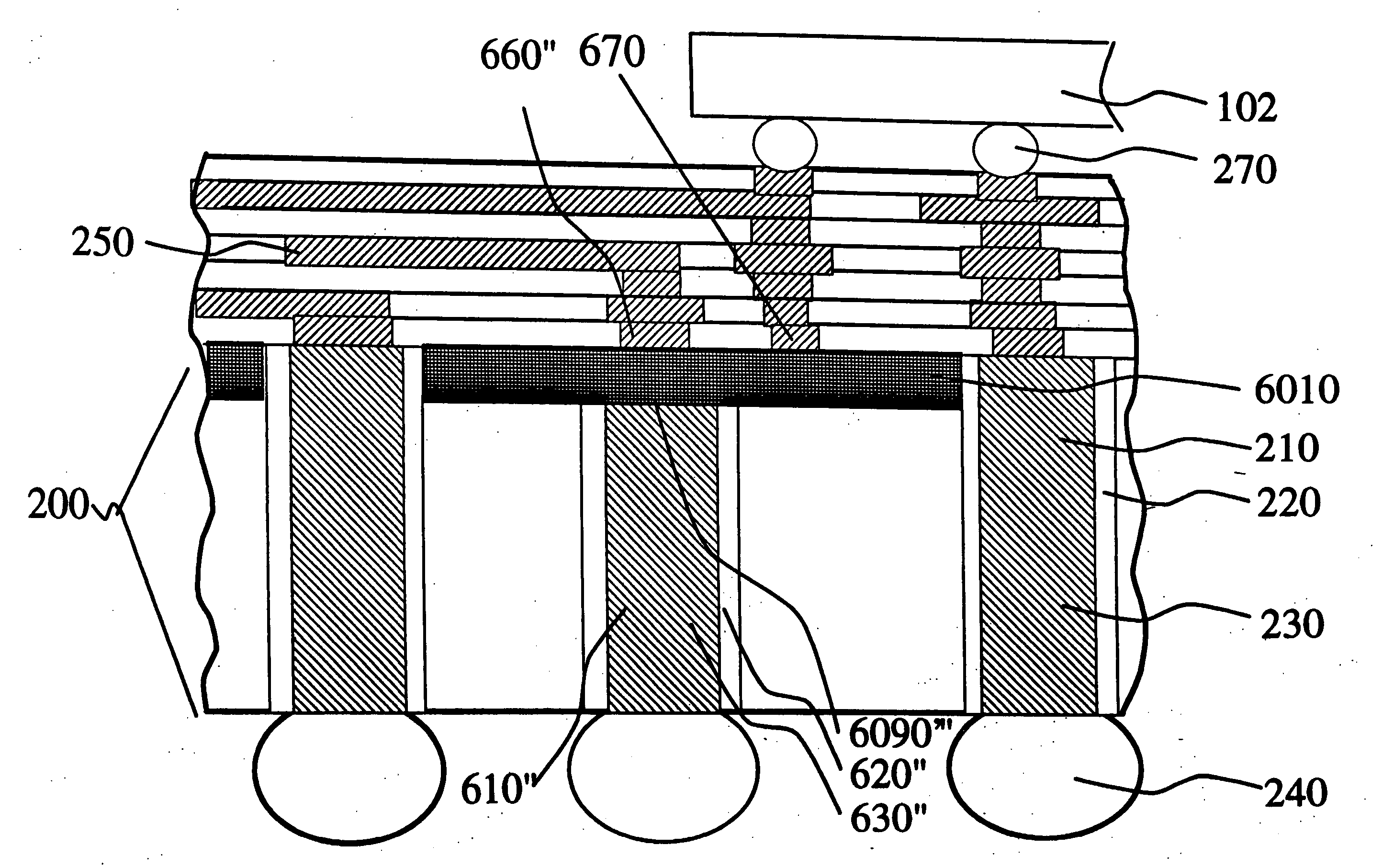

High density chip carrier with integrated passive devices

InactiveUS20050023664A1Fast electrical accessReduce inductanceSemiconductor/solid-state device detailsPrinted circuit aspectsHigh densityChip carrier

A carrier for a semiconductor component is provided having passive components integrated in its substrate. The passive components include decoupling components, such as capacitors and resistors. A set of connections is integrated to provide a close electrical proximity to the supported components.

Owner:GLOBALFOUNDRIES US INC

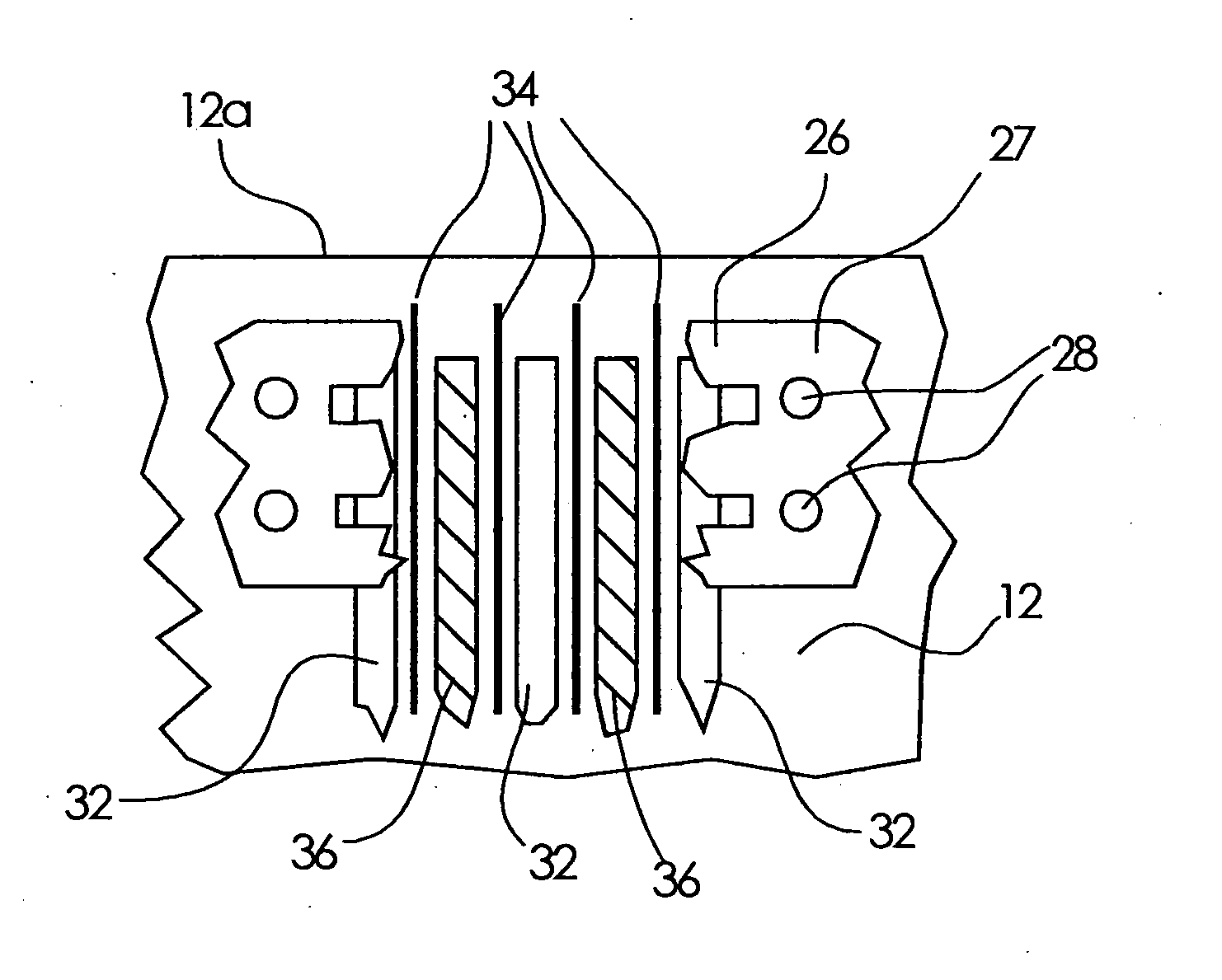

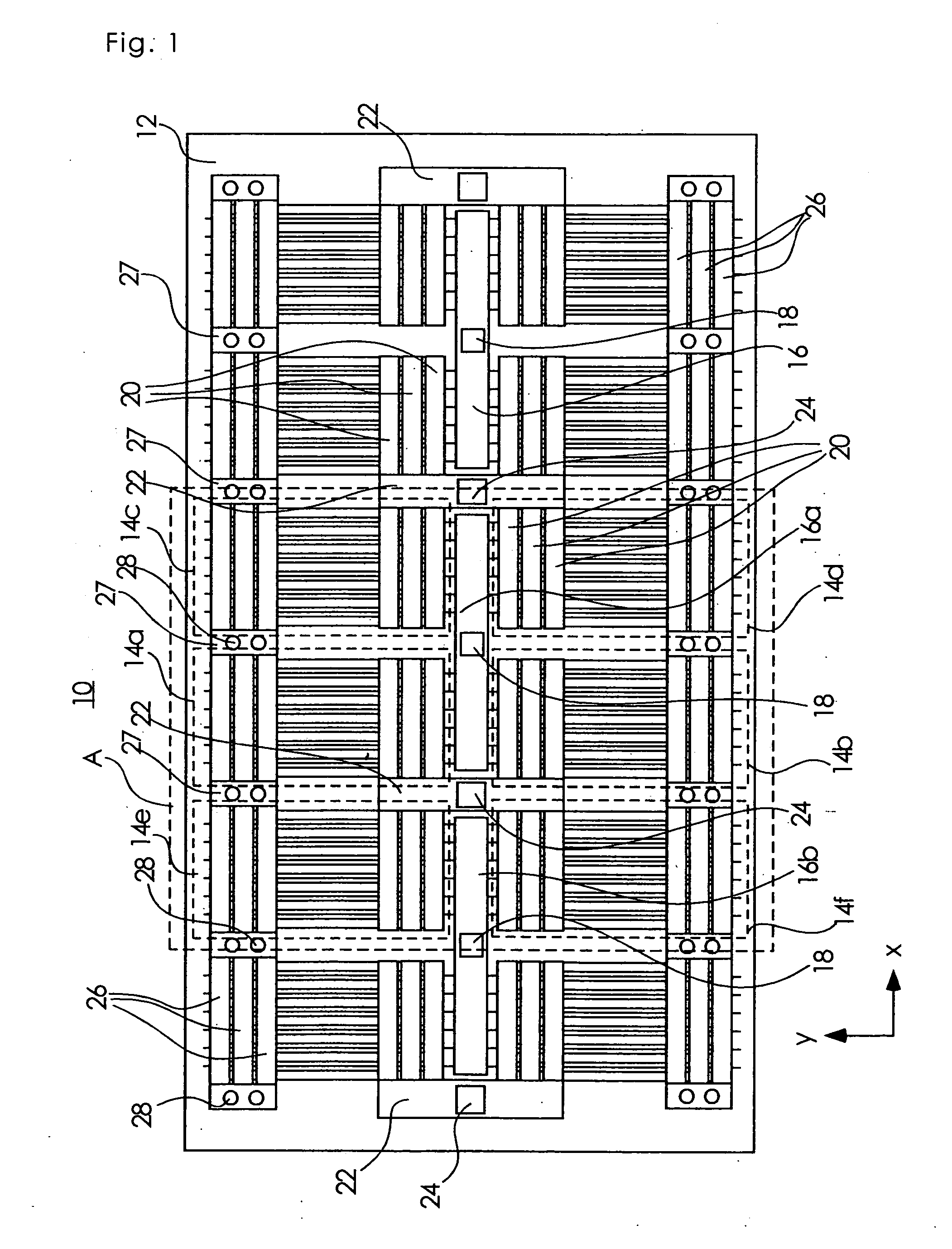

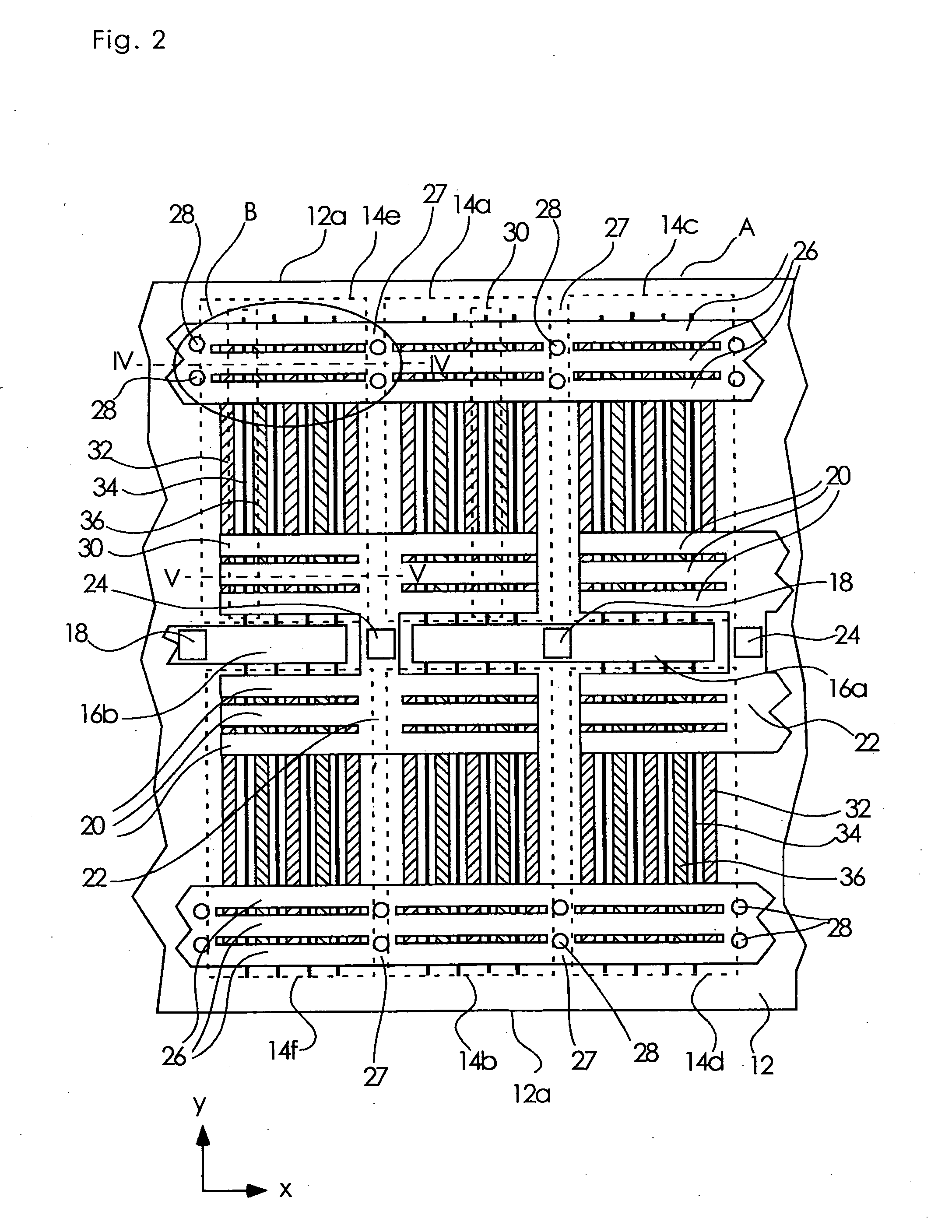

High-frequency semiconductor device

InactiveUS20050133829A1Good high speed performanceHigh power outputTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

A high-frequency semiconductor device includes: a first cell which includes of gate electrodes on a surface of an epitaxial layer of a substrate, drain electrodes and source electrodes alternately located relative to the gate electrodes, a source electrode connection wiring striding over the gate electrodes and the drain electrodes and connecting the source electrodes, and a drain electrode connection wiring striding over the gate electrodes and the source electrodes and connecting the drain electrodes; a second cell which has the same configurations as the first cell, is located in an extended direction of each of the gate electrodes of the first cell, and has the drain electrode connection wiring proximate to the drain electrode connection wiring of the first cell; and a gate electrode bar located between the drain electrode connection wirings of the first and second cells, and to which the gate electrodes of the first and second cells are connected.

Owner:MITSUBISHI ELECTRIC CORP

Wafer-level stack package

InactiveUS20090166840A1Reduce inductanceSemiconductor/solid-state device detailsSolid-state devicesExternal connectionEngineering

A wafer-level stack package includes semiconductor chips, first connection members, a second connection member, a substrate and an external connection terminal. The semiconductor chips have a power / ground pad and a signal pad. The first connection members are electrically connected to the power / ground pad and the signal pad of each of the semiconductor chips. The second connection member is electrically connected to at least one of the power / ground pads of each of the semiconductor chips, the power / ground pads being connected to the first connection members. The substrate supports the stacked semiconductor chips, the substrate including wirings that are electrically connected to the first connection members and the second connection member. The external connection terminal is provided on a surface of the substrate opposite to a surface where the semiconductor chips are stacked, wherein the external connection terminals are electrically connected to the wirings, respectively.

Owner:SAMSUNG ELECTRONICS CO LTD

Capacitor-built-in type printed wiring substrate, printed wiring substrate, and capacitor

InactiveUS7239014B2Reliably eliminate noiseLower resistanceCross-talk/noise/interference reductionSemiconductor/solid-state device detailsLow inductanceLow resistance

A capacitor-built-in-type printed wiring substrate which can reliably eliminate noise and attain extremely low resistance and low inductance in connections between an IC chip and the capacitor, and a printed wiring substrate and capacitor for use in the same. A capacitor-built-in-type printed wiring substrate 100 on which an IC chip is mounted includes a capacitor-built-in-type printed wiring substrate 110 and an IC chip 101 mounted on the capacitor-built-in-type printed wiring substrate 110. A printed wiring substrate 120 includes a number of connection-to-IC substrate bumps 152 and a closed-bottomed capacitor accommodation cavity 121 formed therein. A capacitor 130 is disposed in the cavity 121 and includes a pair of electrode groups 133E and 133F and a number of connection-to-IC capacitor bumps 131 connected to either one of the paired electrode groups 133E and 133F. The connection-to-IC capacitor bumps 131 are flip-chip-bonded to corresponding connection-to-capacitor bumps 103 on the IC chip 101. The connection-to-IC substrate bumps 152 are flip-chip-bonded to corresponding connection-to-substrate bumps 104 on the IC chip 101.

Owner:NGK SPARK PLUG CO LTD

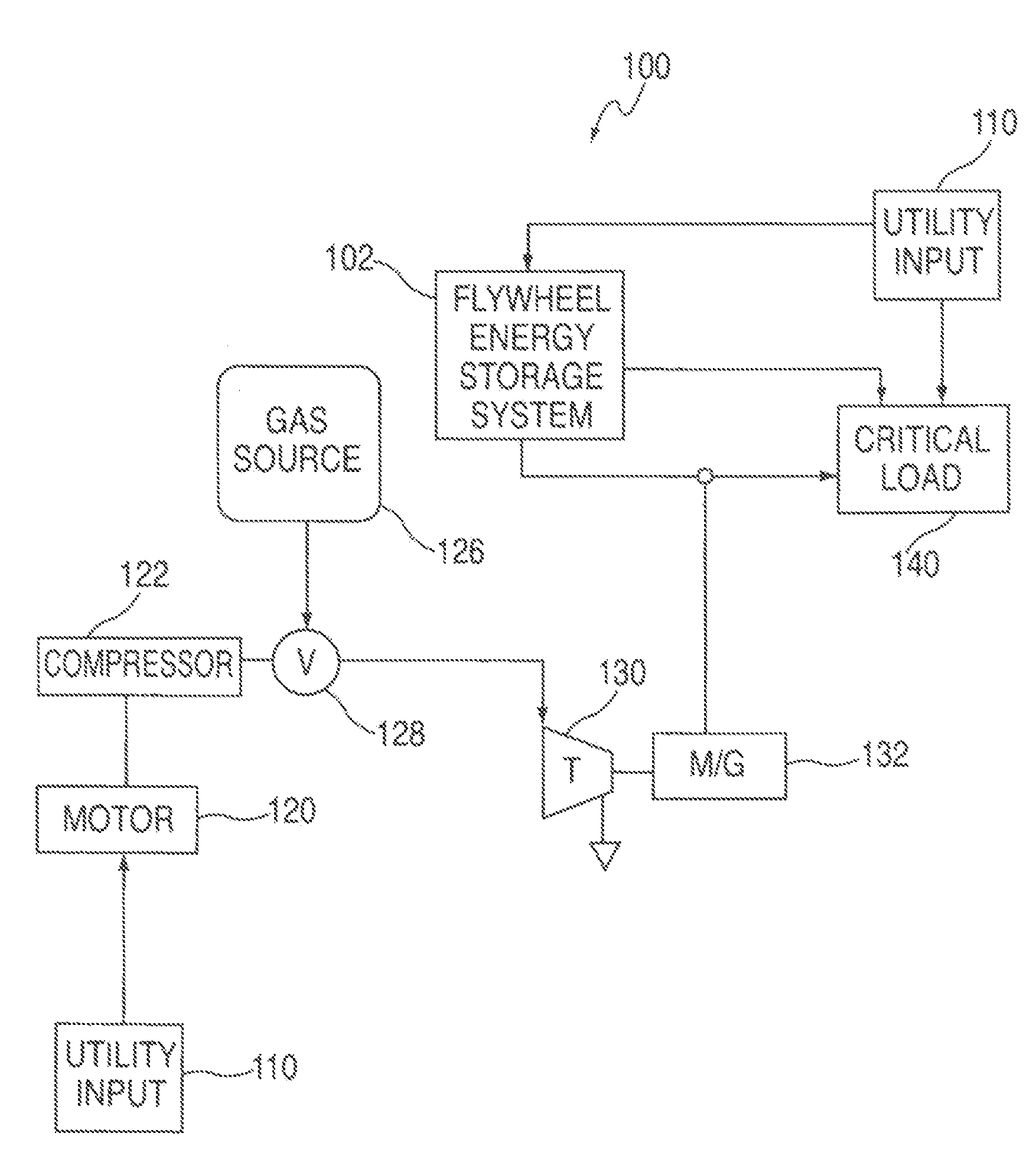

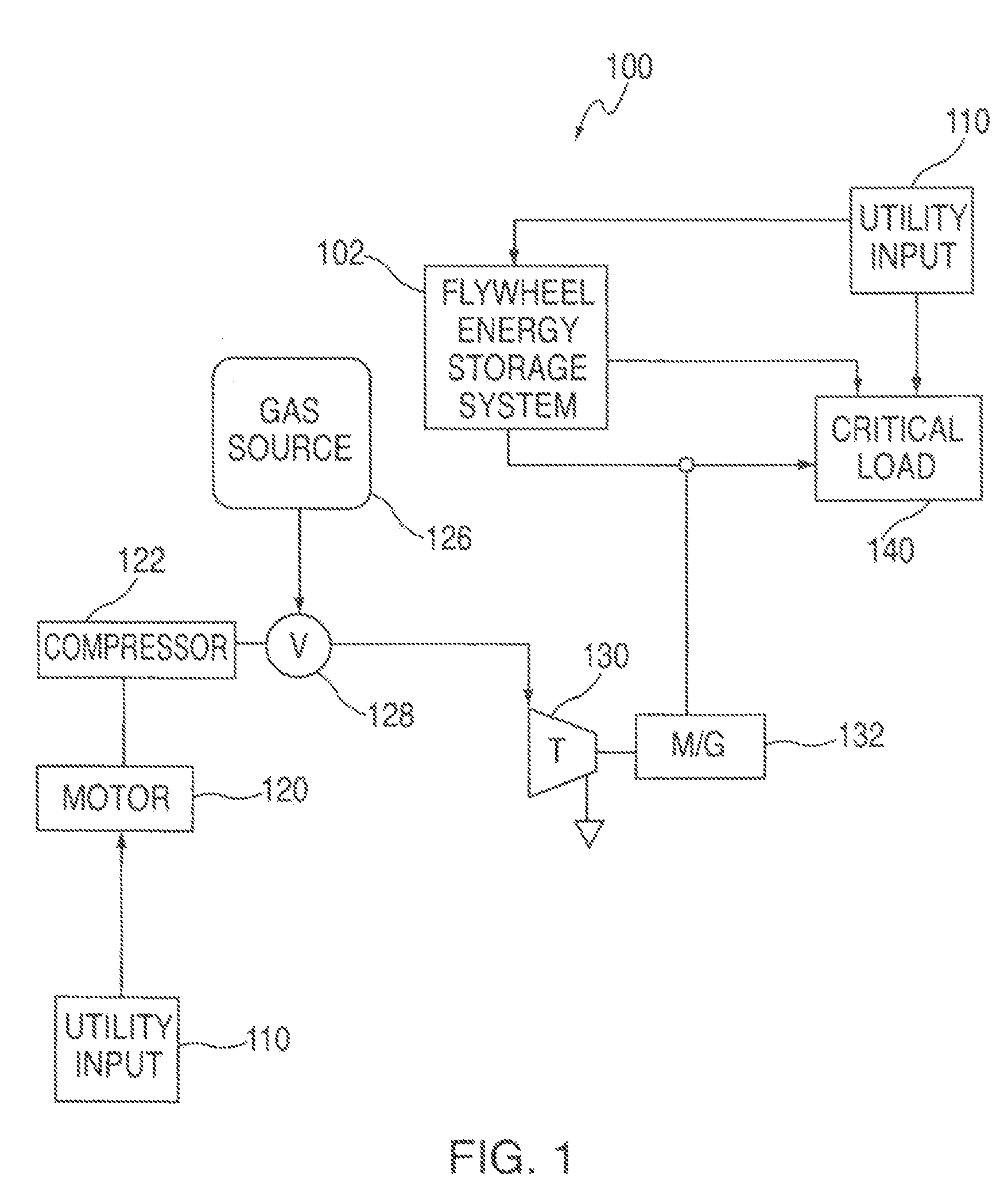

Transient energy systems and methods for use of the same

InactiveUS7400052B1Improve bearing lifeBearing loadElectrical storage systemBatteries circuit arrangementsInduction motorEngineering

This disclosure relates to transient energy systems for supplying power to a load substantially instantaneously on demand. Transient energy systems may include a flywheel coupled the rotor of an induction motor generator. One embodiment of the disclosure refers to systems and methods for reducing loads on a bearing in a transient energy system. In another embodiment, the disclosure refers to an induction motor generator that is optimized for high power transient power generation, yet low power motor operation. Yet another embodiment of the disclosure refers to using a flywheel as a drag pump to cool components of a transient energy system. In yet another embodiment, a slip control scheme is discussed for regulating a DC bus. In yet a further embodiment of the disclosure a method is provided for reducing unnecessary turbine starts by making turbine start a function of the rotational velocity of a flywheel.

Owner:PILLER USA INC

Semiconductor device package and method of production and semiconductor device of same

InactiveUS6914322B2Reduce distanceReduce connectionsThin/thick film capacitorSemiconductor/solid-state device detailsElectrical conductorShortest distance

A semiconductor device including a semiconductor device package providing a capacitor in its circuit board and a semiconductor chip mounted on that package, wherein the capacitor is provided directly under a semiconductor chip mounting surface of the circuit board on which the semiconductor chip is to be mounted and the conductor circuit electrically connecting the semiconductor chip and capacitor is made the shortest distance by having the external connection terminals of the capacitor directly connected to the other surface of the connection pads exposed at one surface at the semiconductor chip mounting surface of the circuit board and to which the electrode terminals of the semiconductor chip are to be directly connected.

Owner:SHINKO ELECTRIC IND CO LTD

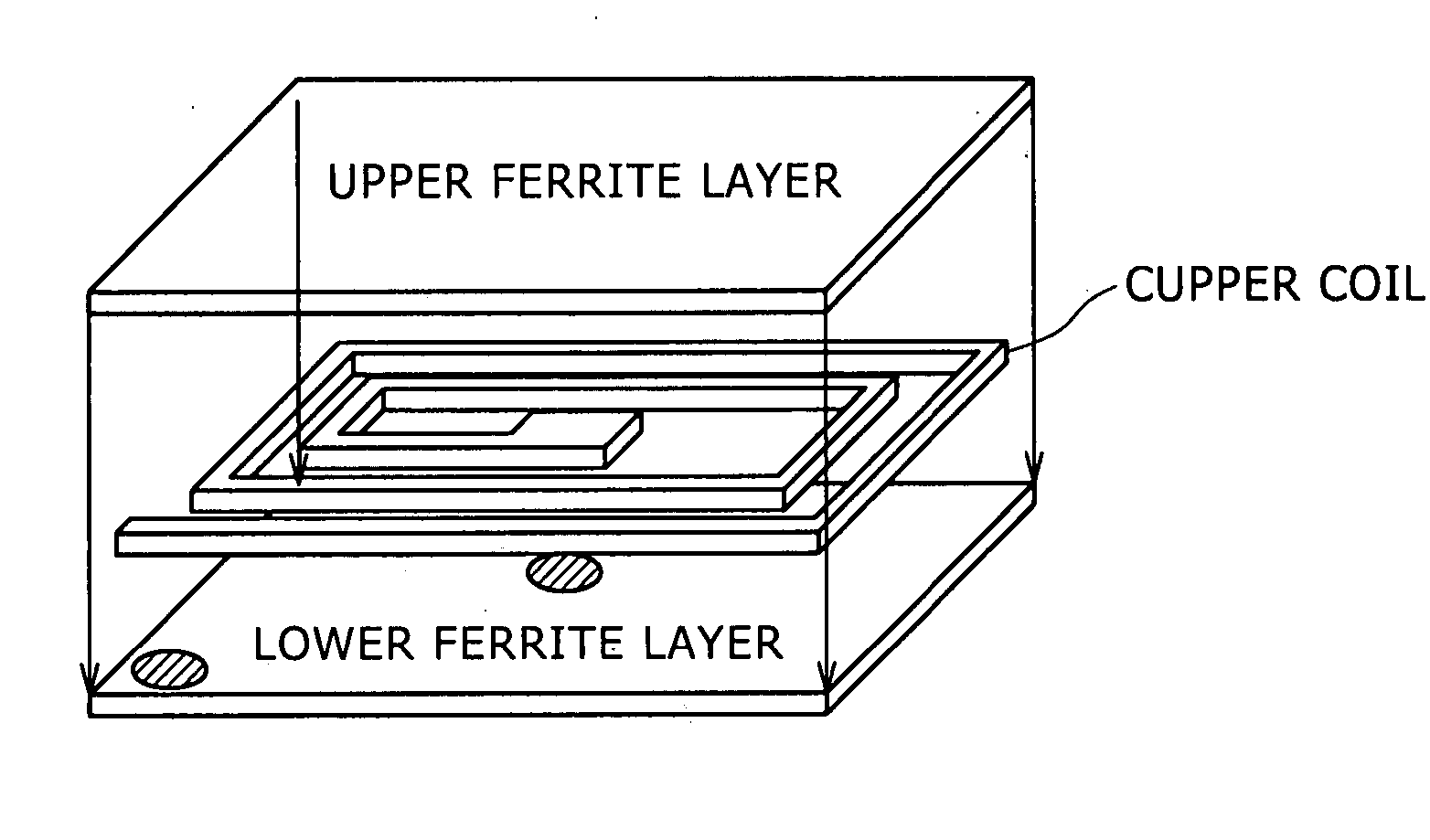

Surface mounting type planar magnetic device and production method thereof

InactiveUS20010024739A1Reduce loss by DC resistance of the coilIncrease the sectionTransformers/inductances coils/windings/connectionsRecord information storageSurface mountingEngineering

This invention provides a surface mounting type planar magnetic device comprised of upper ferrite magnetic film, lower ferrite magnetic film and a planar coil interposed therebetween. For applying surface mount technology, an opening is formed in the upper ferrite magnetic film above a coil terminal portion and then, an external electrode conductive with the coil terminal portion through the opening is formed on the upper ferrite magnetic film. Further, this surface mounting type planar magnetic device is of a thin structure and can be mounted on the surface of a printed board. Its power loss is small, its inductance is large, its frequency characteristic is excellent, the disparity of the characteristic is small and its reliability is excellent.

Owner:KK TOSHIBA +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com