Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2791results about "Thin/thick film capacitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

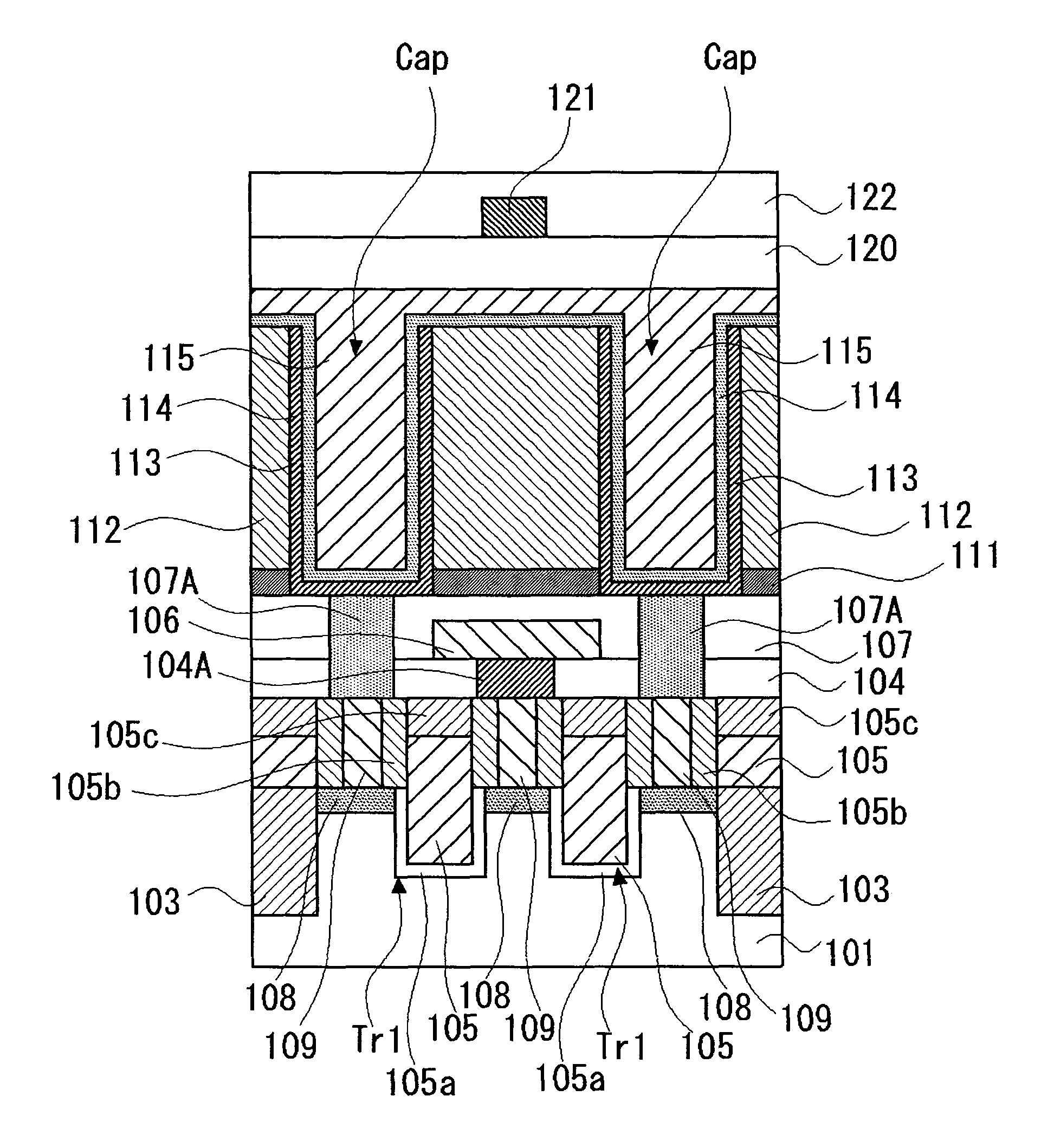

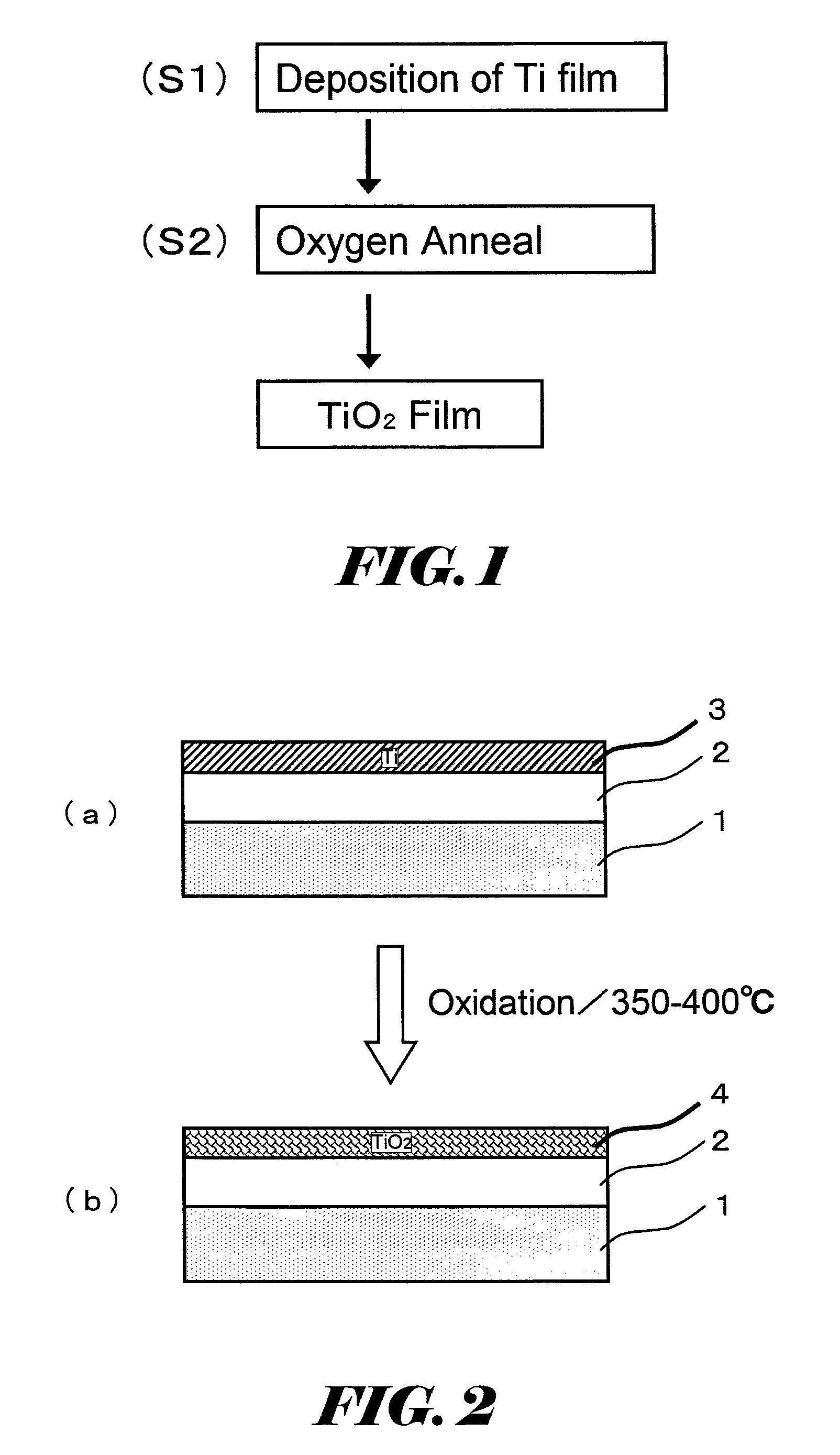

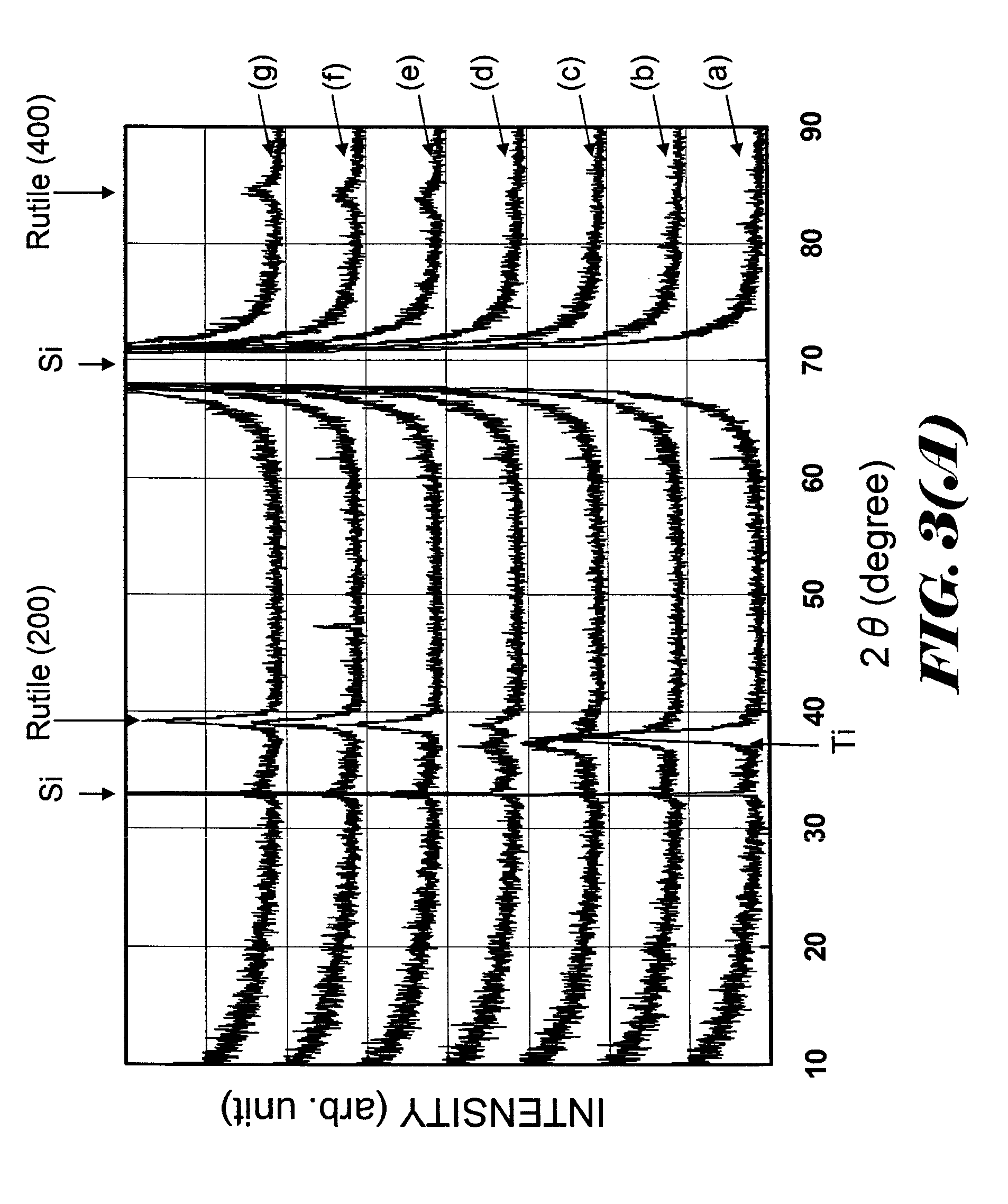

Method of manufacturing capacitive insulating film for capacitor

InactiveUS8198168B2Increase capacitanceReduce adverse effectsThin/thick film capacitorSemiconductor/solid-state device manufacturingCapacitanceCrystal structure

According to the invention, a Ti film is formed on a substrate and is annealed at the temperatures of 350° C.-400° C. under oxidative environment, so that a TiO2 film having a rutile crystal structure is formed. Since the TiO2 film having a rutile crystal structure has a high dielectric constant, it is useful for a capacitive insulating film for a capacitor.

Owner:PS4 LUXCO SARL

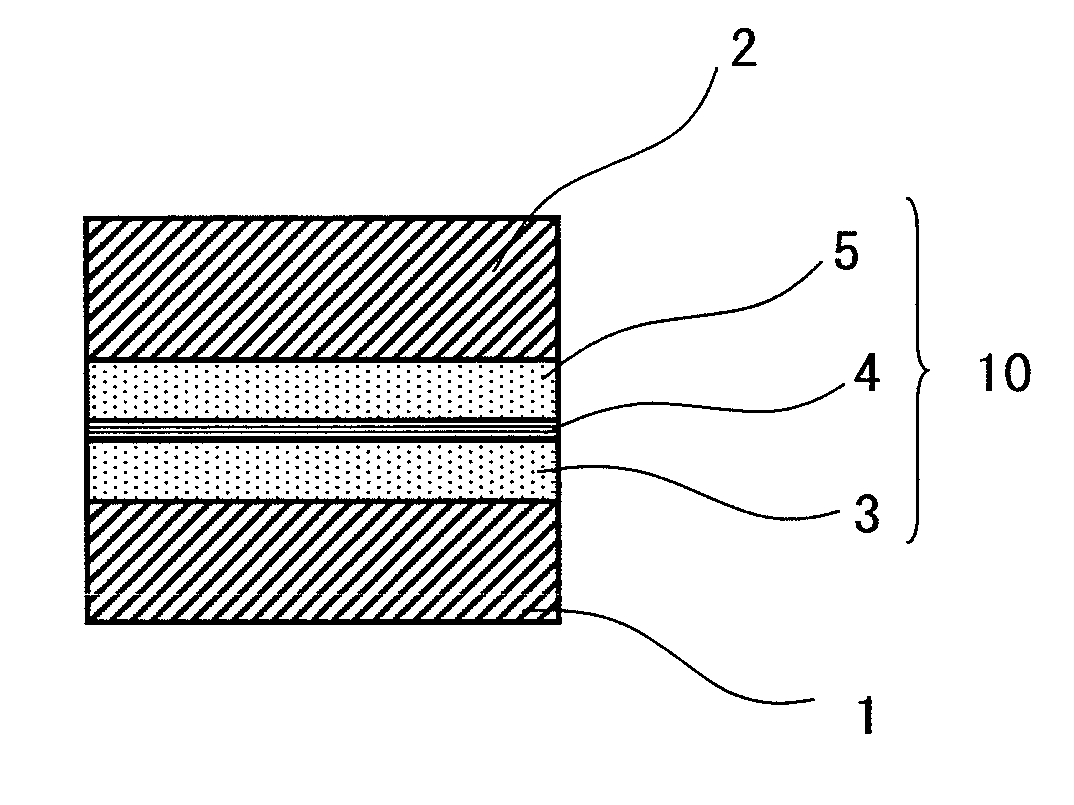

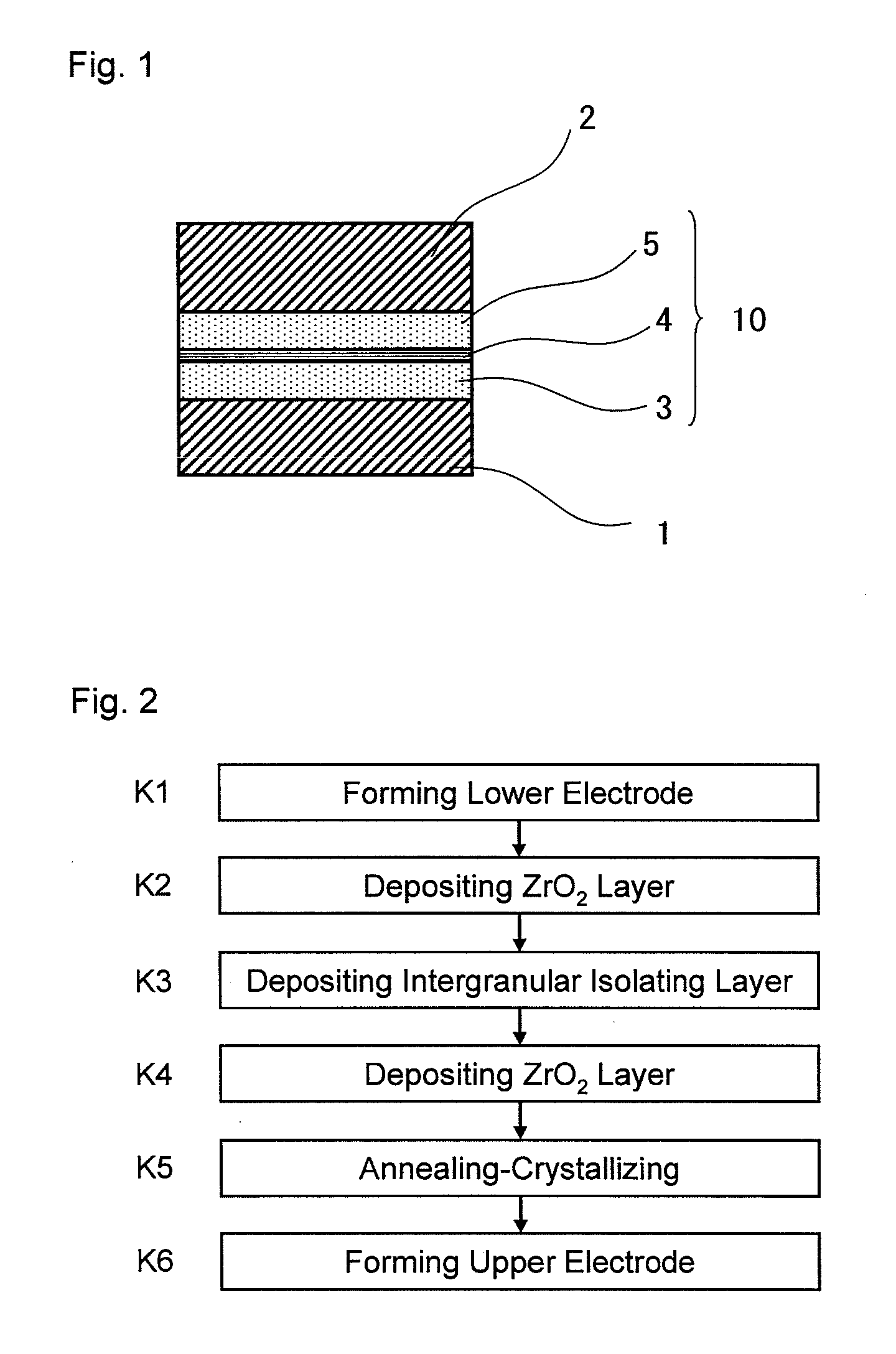

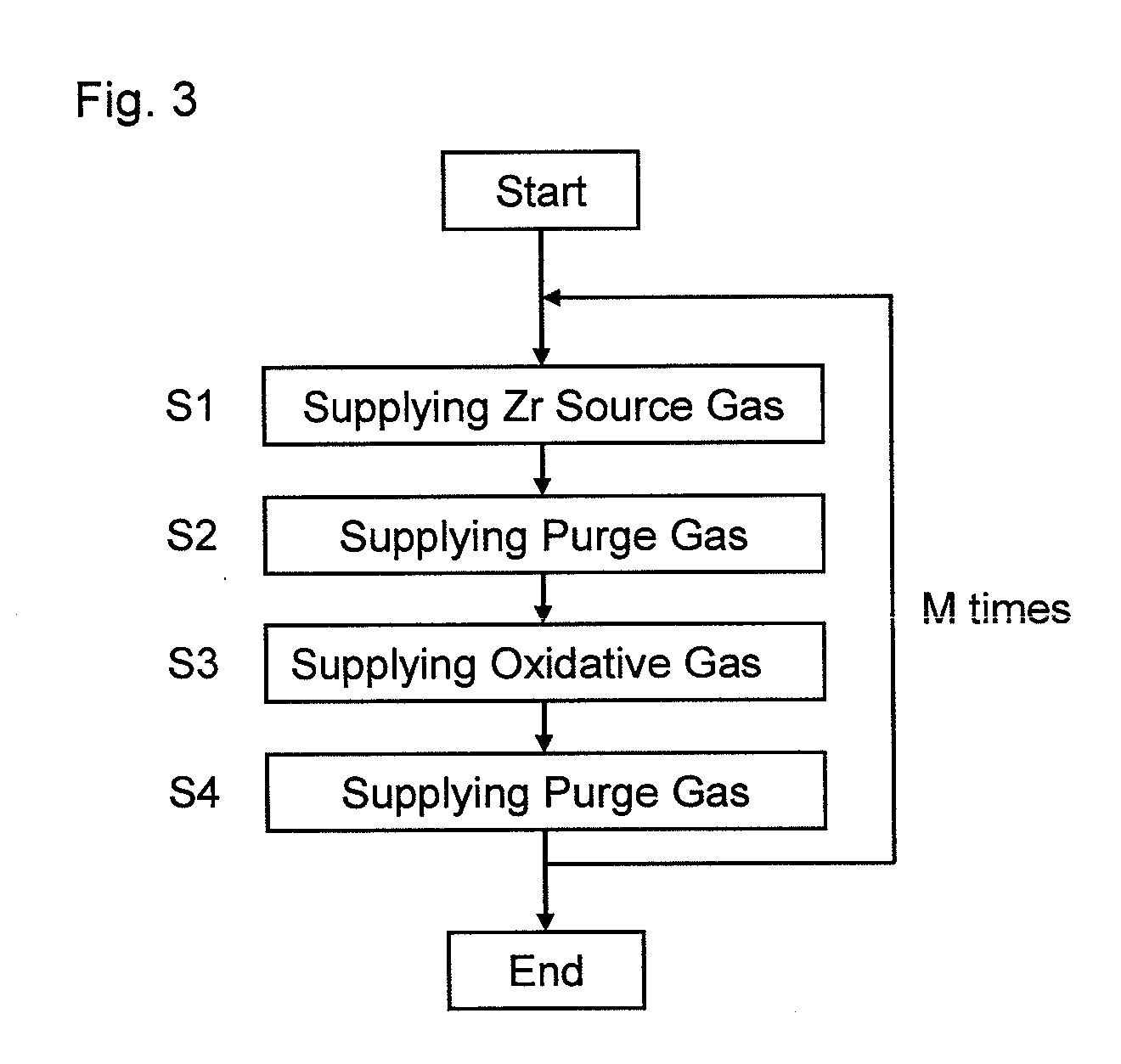

Insulating film, method of manufacturing the same, and semiconductor device

InactiveUS20110048769A1High dielectric constantSmall currentThin/thick film capacitorCeramicsCapacitanceSemiconductor

An exemplary aspect of the invention provides an insulating film which has a high dielectric constant and has small leakage current even when it is sandwiched between electrodes. The insulating film comprises two zirconium oxide layers in crystallized state; and an intergranular isolating layer composed of an amorphous material having a dielectric constant higher than that of zirconium oxide in crystallized state; wherein the intergranular isolating layer is sandwiched between the two zirconium oxide layers. The insulating film is properly used as a capacitive insulating film in a semiconductor device comprising a memory cell including a capacitor element having the capacitive insulating film between an upper electrode and a lower electrode, or as an intergate insulating film in a semiconductor device comprising a nonvolatile memory device having the intergate insulating film between a control gate electrode and a floating gate electrode.

Owner:ELPIDA MEMORY INC

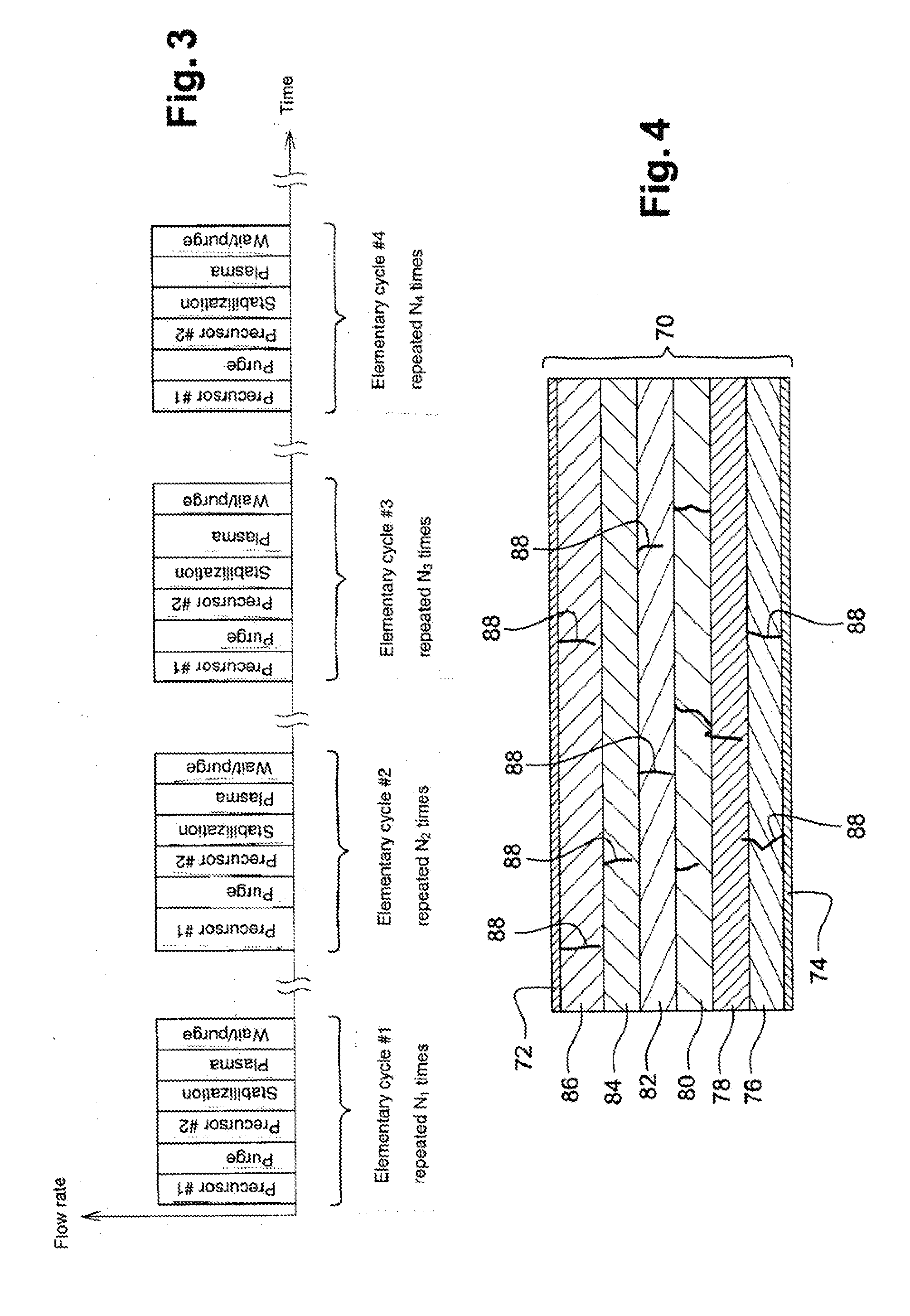

Method for manufacturing a polycrystalline dielectric layer

ActiveUS20120170170A1Format be limitIncrease ratingsThin/thick film capacitorFixed capacitor dielectricDielectric layerCapacitor

A method manufactures a capacitor having polycrystalline dielectric layer between two metallic electrodes. The dielectric layer is formed by a polycrystalline growth of a dielectric metallic oxide on one of the metallic electrodes. At least one polycrystalline growth condition of the dielectric oxide is modified during the formation of the polycrystalline dielectric layer, which results in a variation of the polycrystalline properties of the dielectric oxide within the thickness of said layer.

Owner:STMICROELECTRONICS (CROLLES 2) SAS

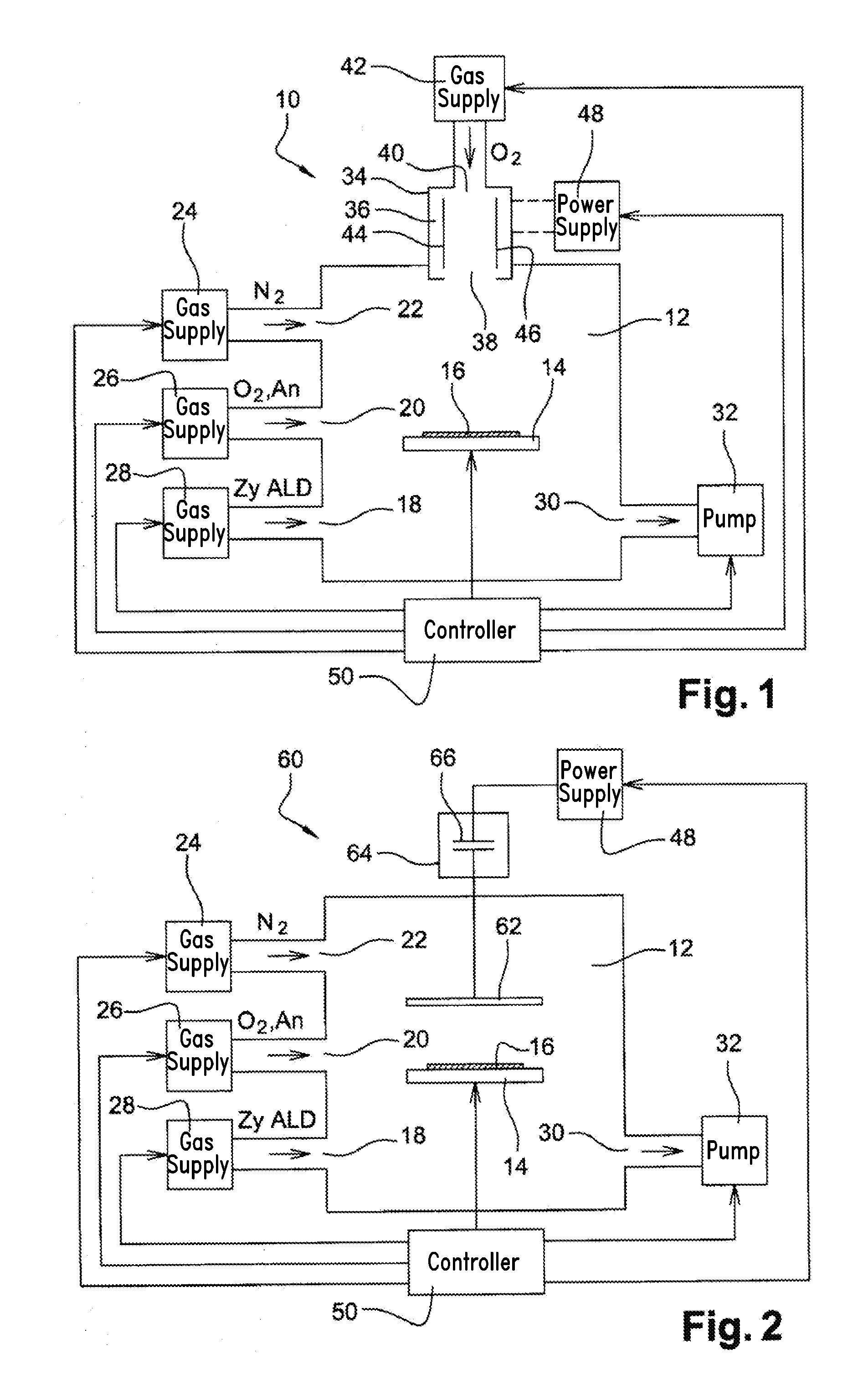

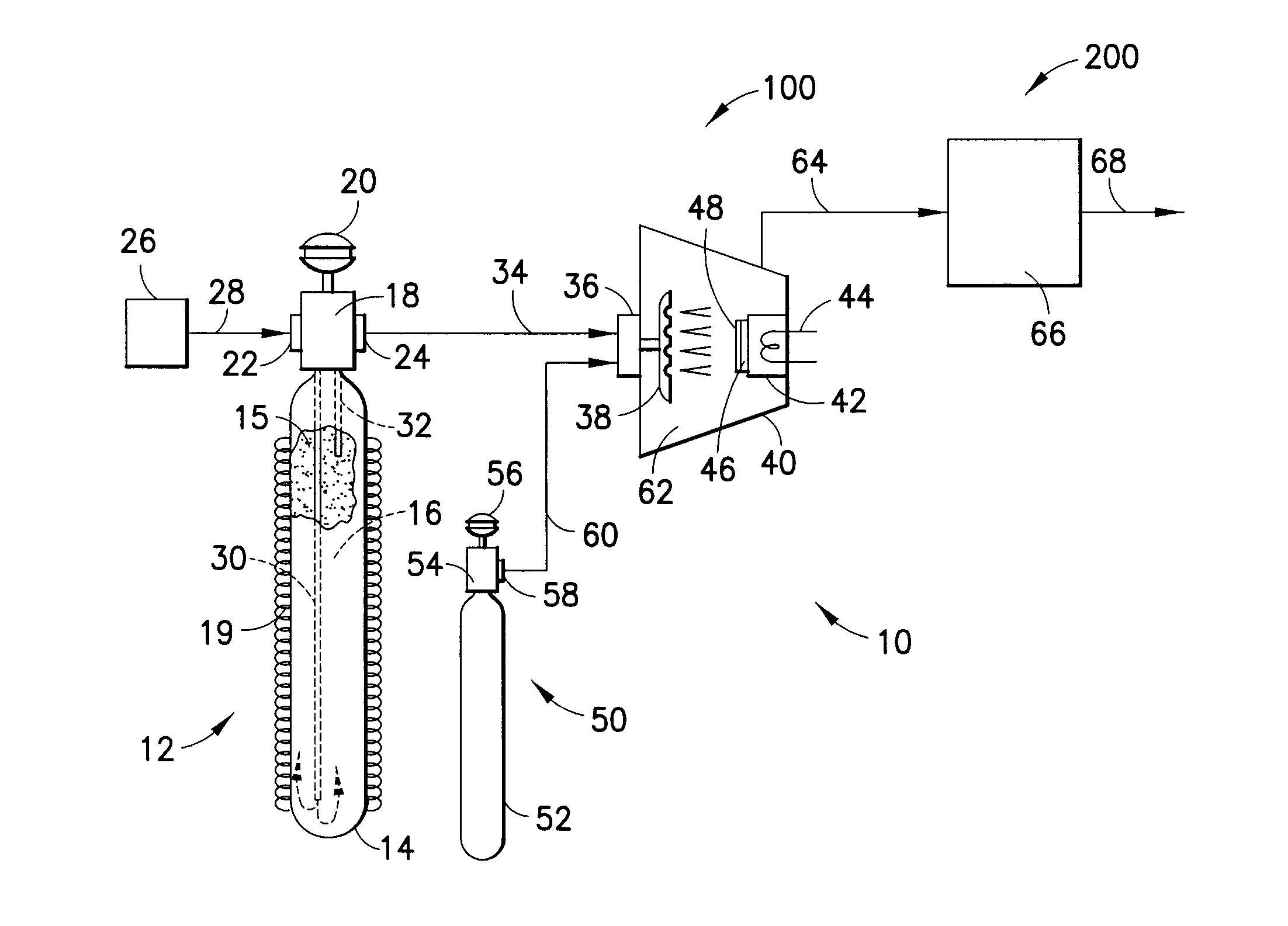

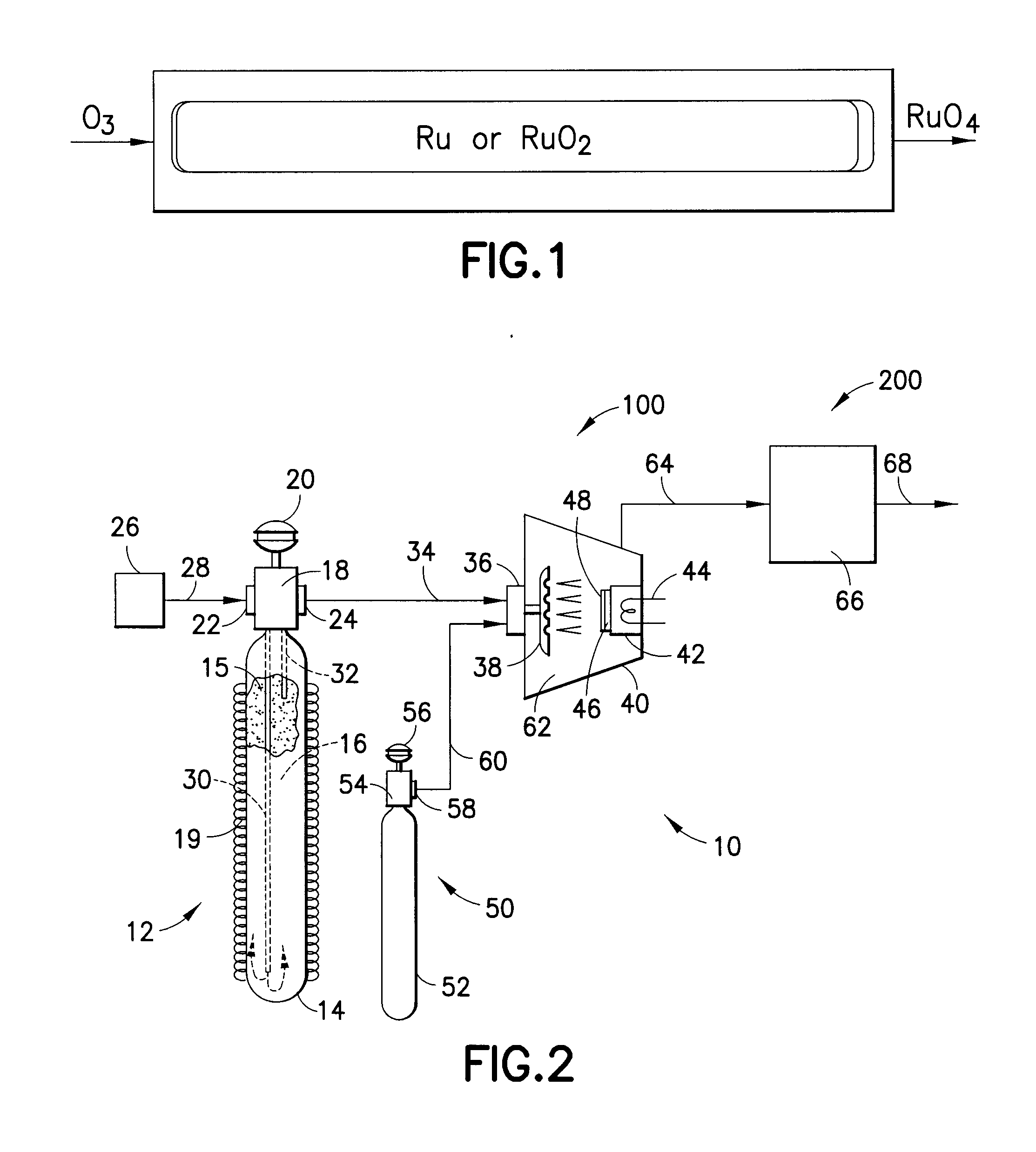

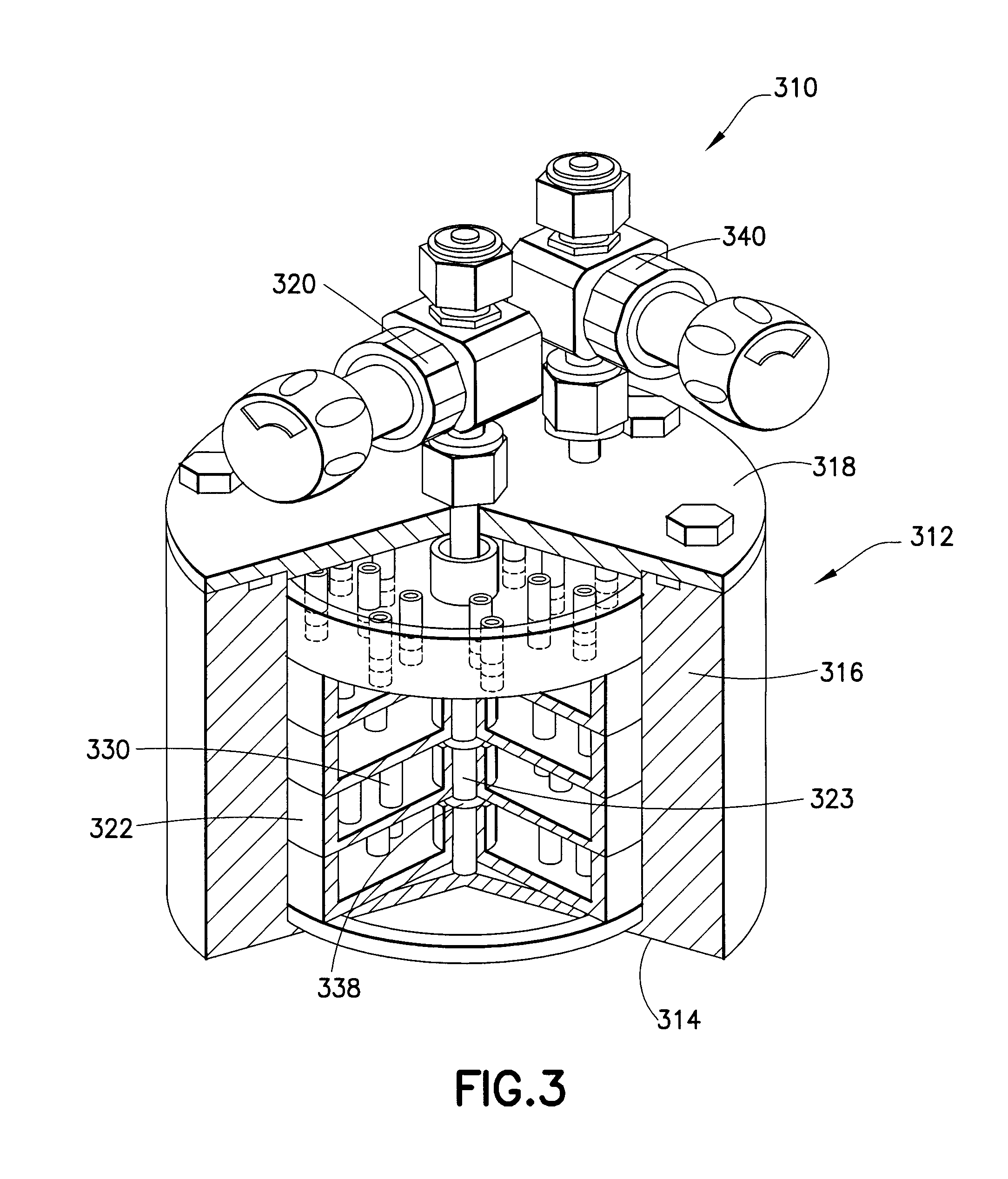

IN SITU GENERATION OF RuO4 FOR ALD OF Ru AND Ru RELATED MATERIALS

Apparatus and method for generating ruthenium tetraoxide in situ for use in vapor deposition, e.g., atomic layer deposition (ALD), of ruthenium-containing films on microelectronic device substrates. The ruthenium tetraoxide can be generated on demand by reaction of ruthenium or ruthenium dioxide with an oxic gas such as oxygen or ozone. In one implementation, ruthenium tetraoxide thus generated is utilized with a strontium organometallic precursor for atomic layer deposition of strontium ruthenate films of extremely high smoothness and purity.

Owner:ENTEGRIS INC

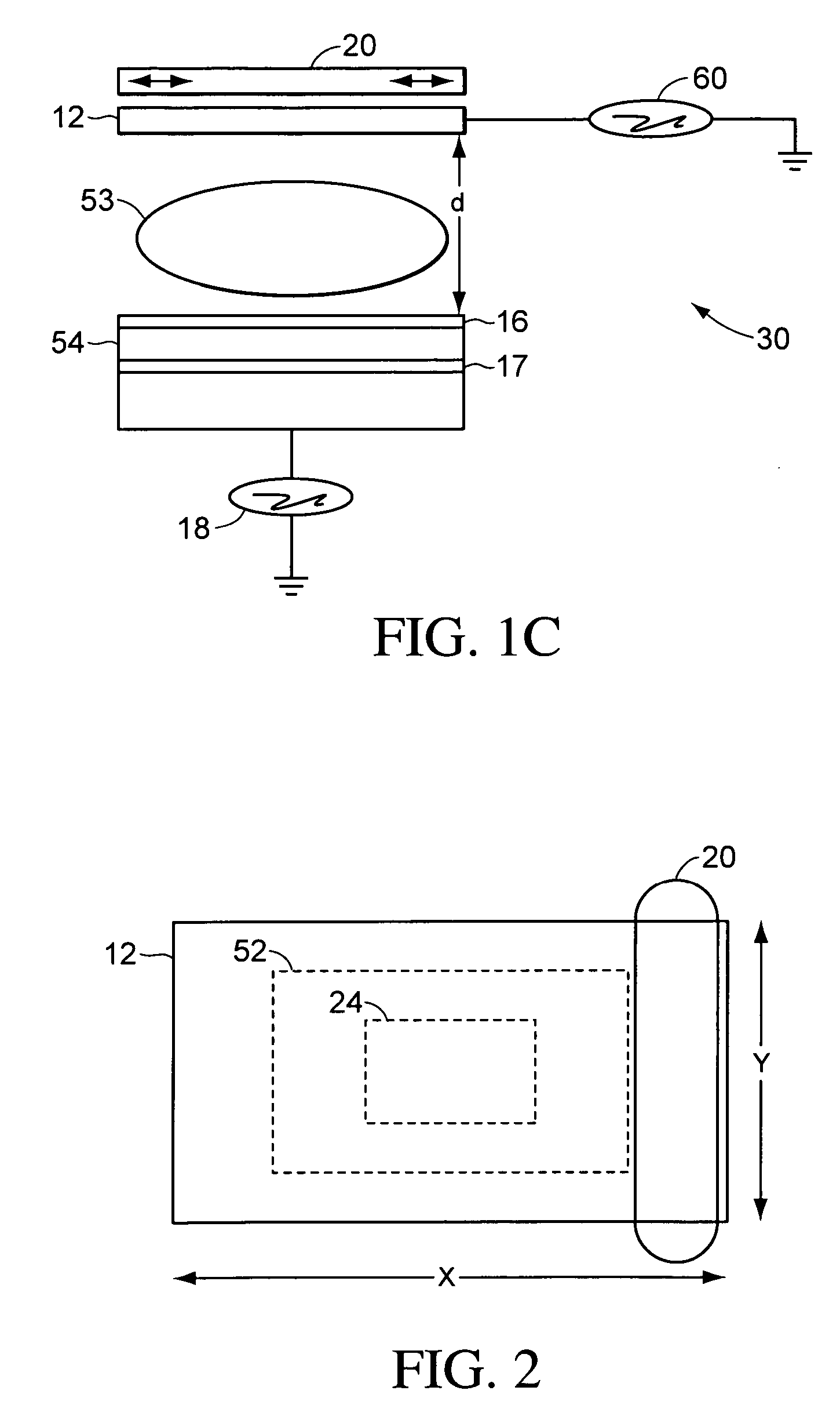

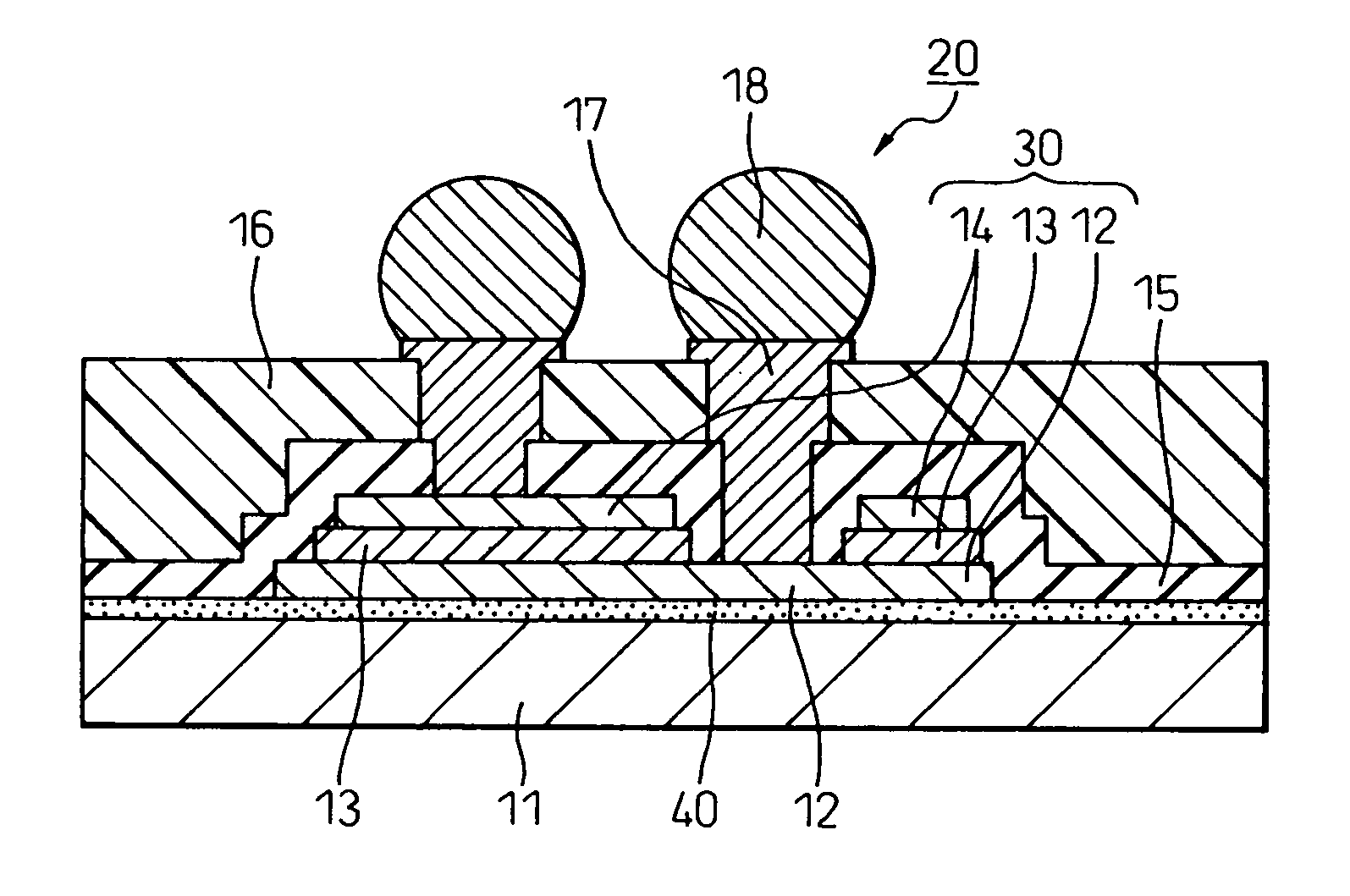

Tunable thin film capacitor

InactiveUS20050082636A1Resistance in the upper electrode layer of the capacitance can be easily loweredElectrode loss can be reducedTransistorThin/thick film capacitorCapacitanceDielectric layer

It is an object of the invention to provide a variable capacitor constituted such that, even when an external control voltage is applied, a stable dielectric constant of the dielectric layer can be obtained. A variable capacitor constituted such that a dielectric layer whose dielectric constant is changed by the application of an external voltage is held between an upper electrode layer and a lower electrode layer, wherein a plurality of capacitance-producing regions a, b are connected to each other.

Owner:KYOCERA CORP

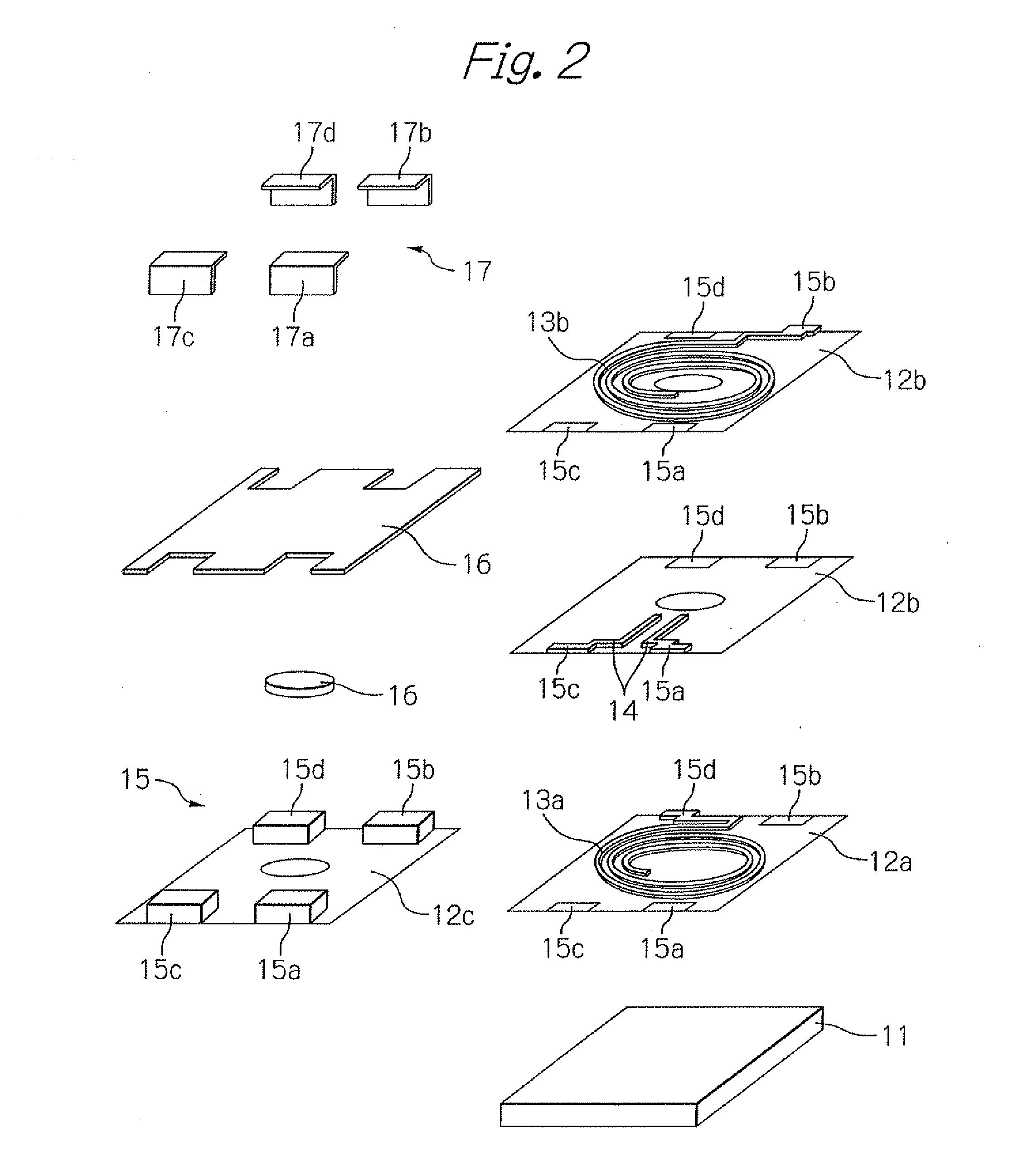

Electronic component and manufacturing method of electronic component

ActiveUS20100157565A1Sufficient soldering strengthIncrease electrode areaSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsInsulation layerElectrical conductor

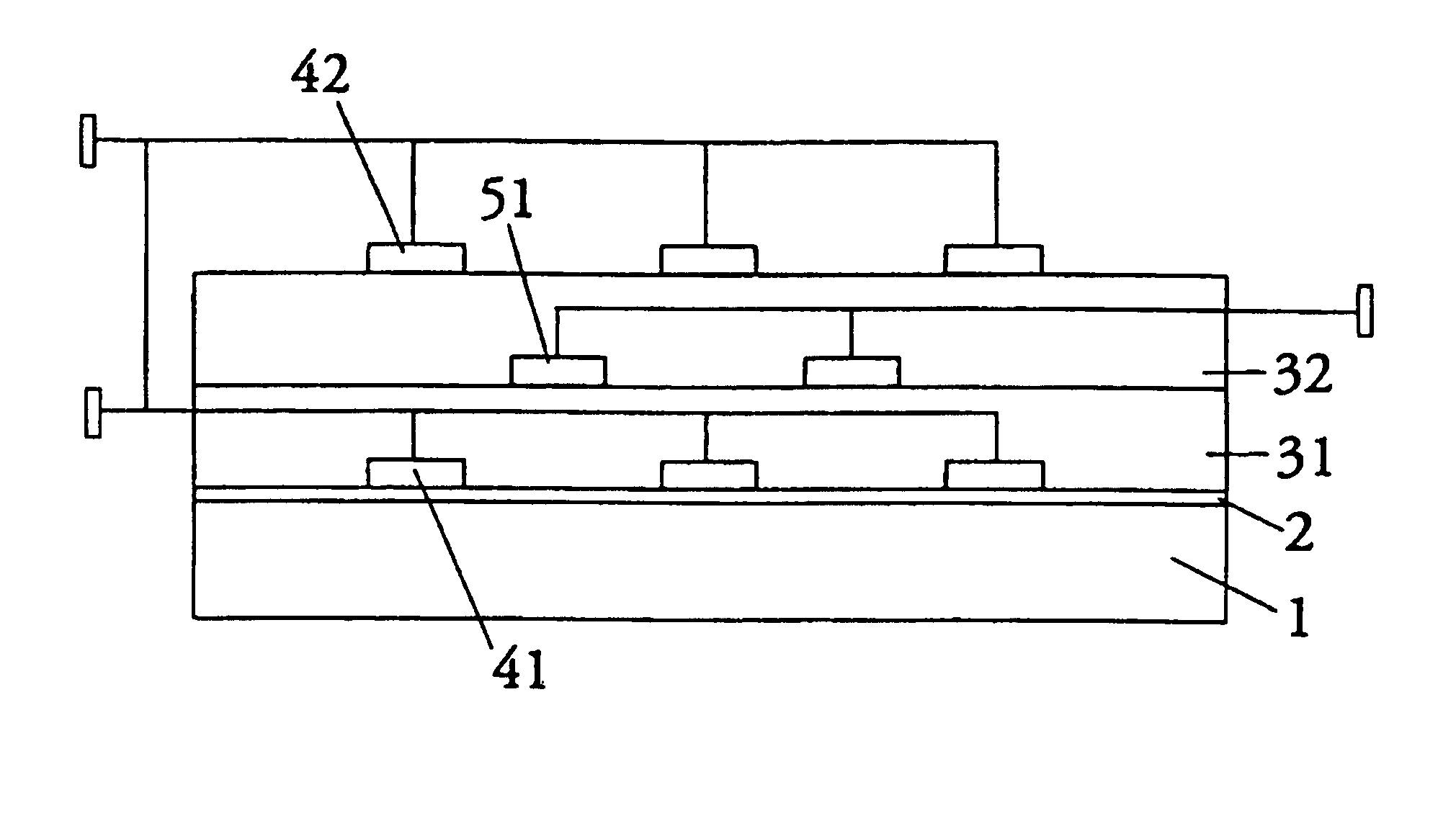

A manufacturing method of electronic components includes forming a first insulation layer on a substrate, forming a plurality of passive elements on the first insulation layer, forming a second insulation layer on the passive elements, forming a plurality of conductor layers electrically connected to the respective passive elements, on the outer side of the second insulation layer to be exposed to an upper surface of each electronic component, and forming grooves between the electronic components including the respective passive elements to expose side surfaces of each electronic component and parts of the conductor layers from the side surfaces of each electronic component. The manufacturing method further including plating a plurality of external electrodes on the respective conductor layers exposed to the upper surface and the side surfaces of each electronic component, and cutting the substrate to completely separate into individual electronic components.

Owner:TDK CORPARATION

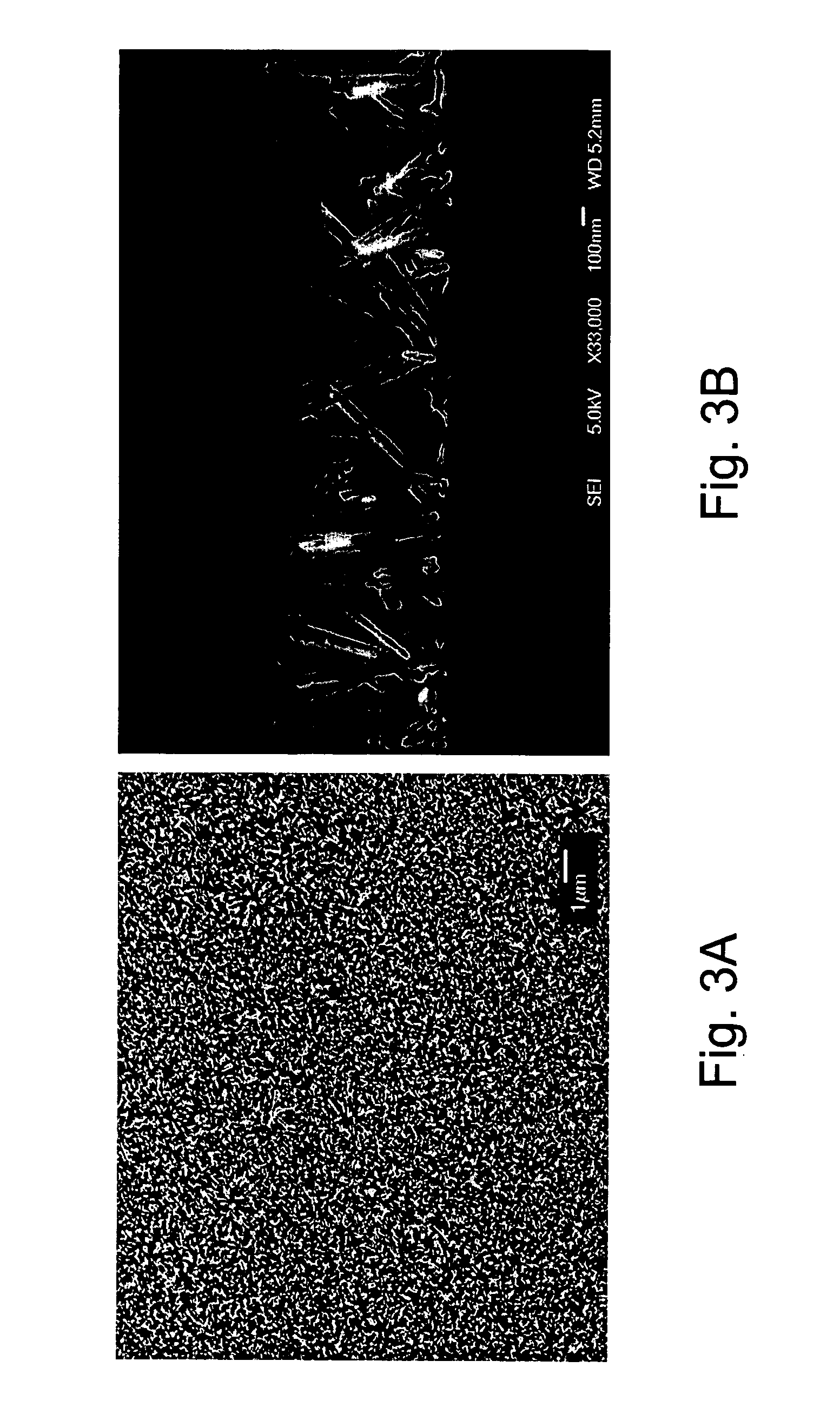

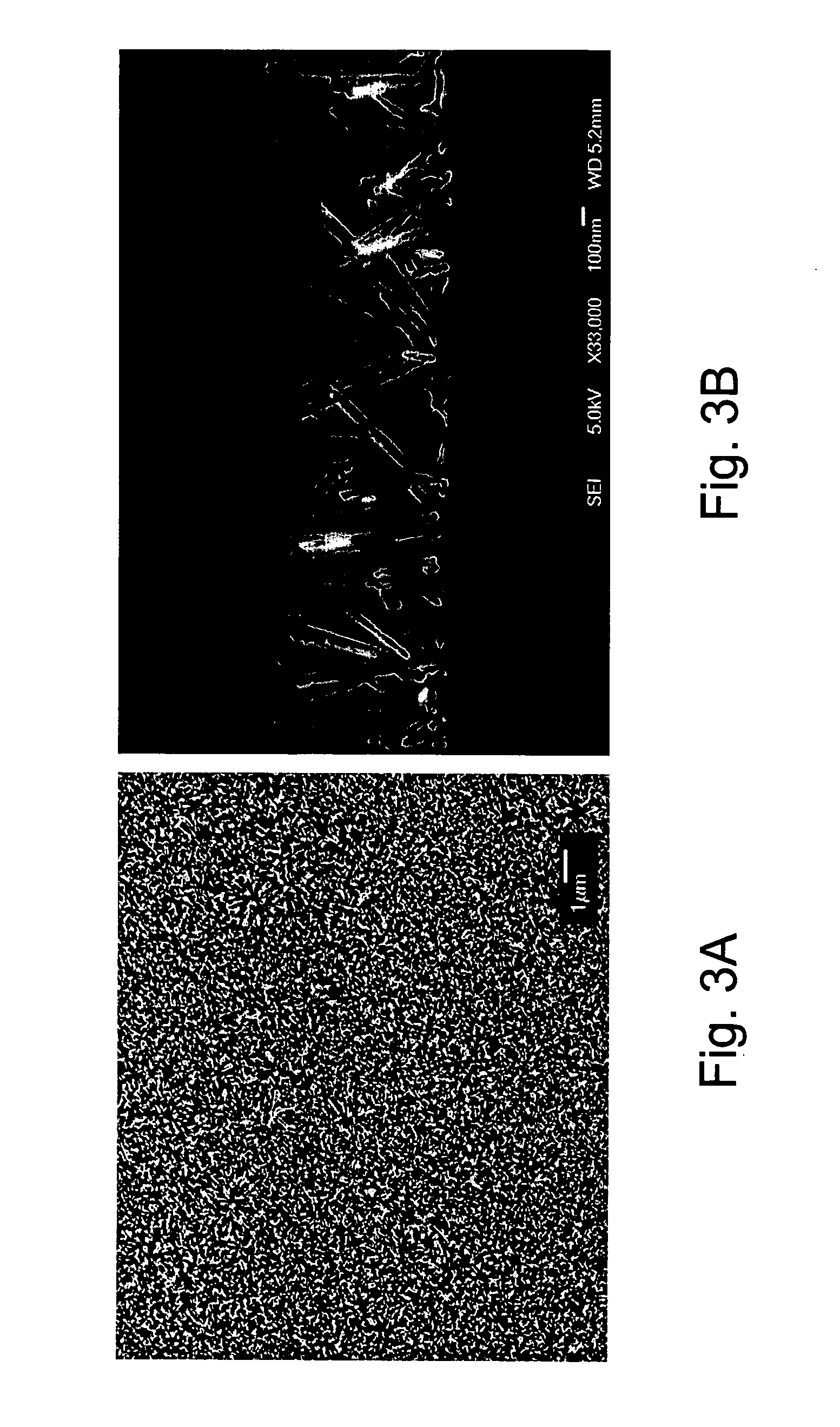

Nanofiber surface based capacitors

ActiveUS7057881B2Increase surface areaFixed capacitor electrodesThin/thick film capacitorNanofiberEngineering

This invention provides novel capacitors comprising nanofiber enhanced surface area substrates and structures comprising such capacitors, as well as methods and uses for such capacitors.

Owner:ONED MATERIAL INC

Nanofiber surface based capacitors

ActiveUS20050219788A1Increase surface areaFixed capacitor electrodesThin/thick film capacitorNanofiberBiomedical engineering

This invention provides novel capacitors comprising nanofiber enhanced surface area substrates and structures comprising such capacitors, as well as methods and uses for such capacitors.

Owner:ONED MATERIAL INC

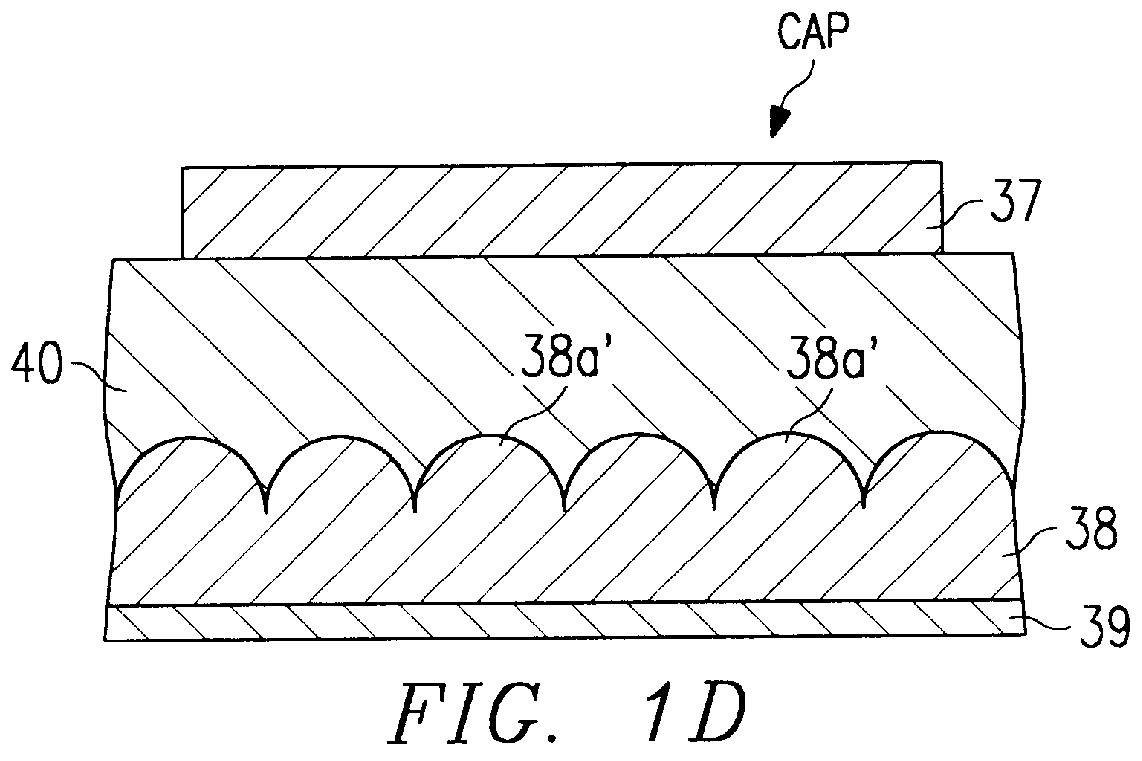

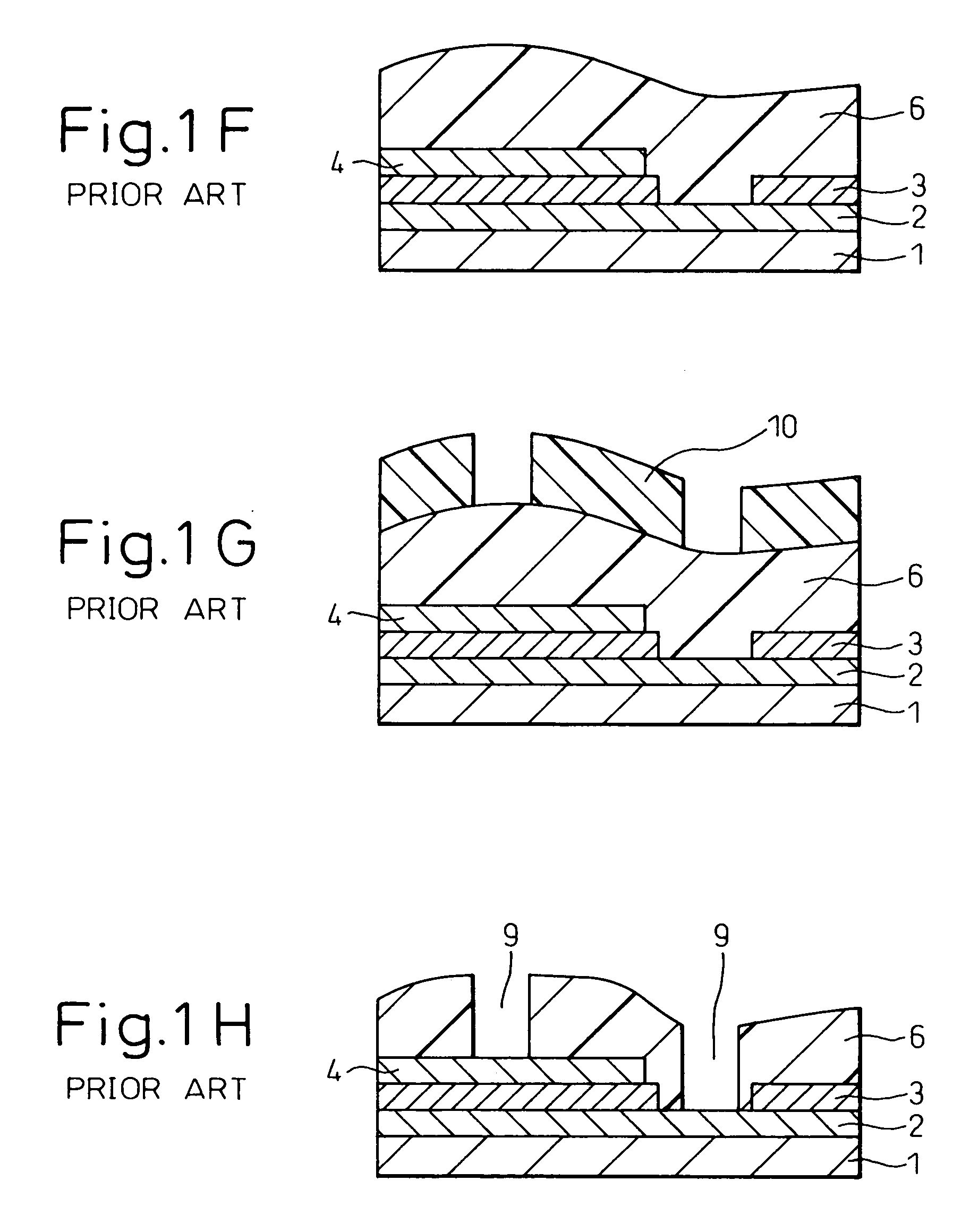

Method for manufacturing dielectric capacitor, dielectric memory device

InactiveUS6033953AReduce leakage currentImprove flatnessTransistorThin/thick film capacitorElectrolysisCapacitor

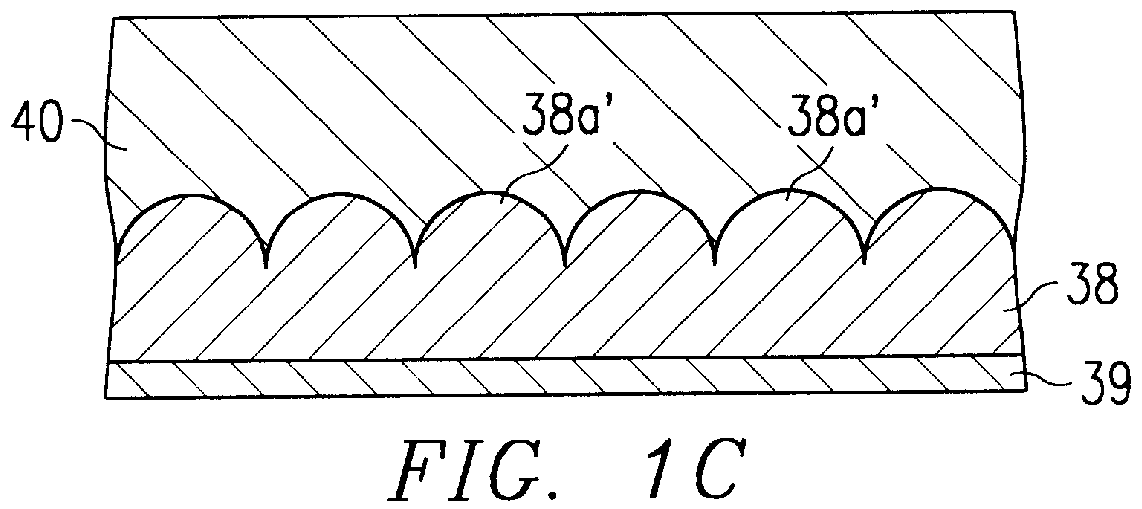

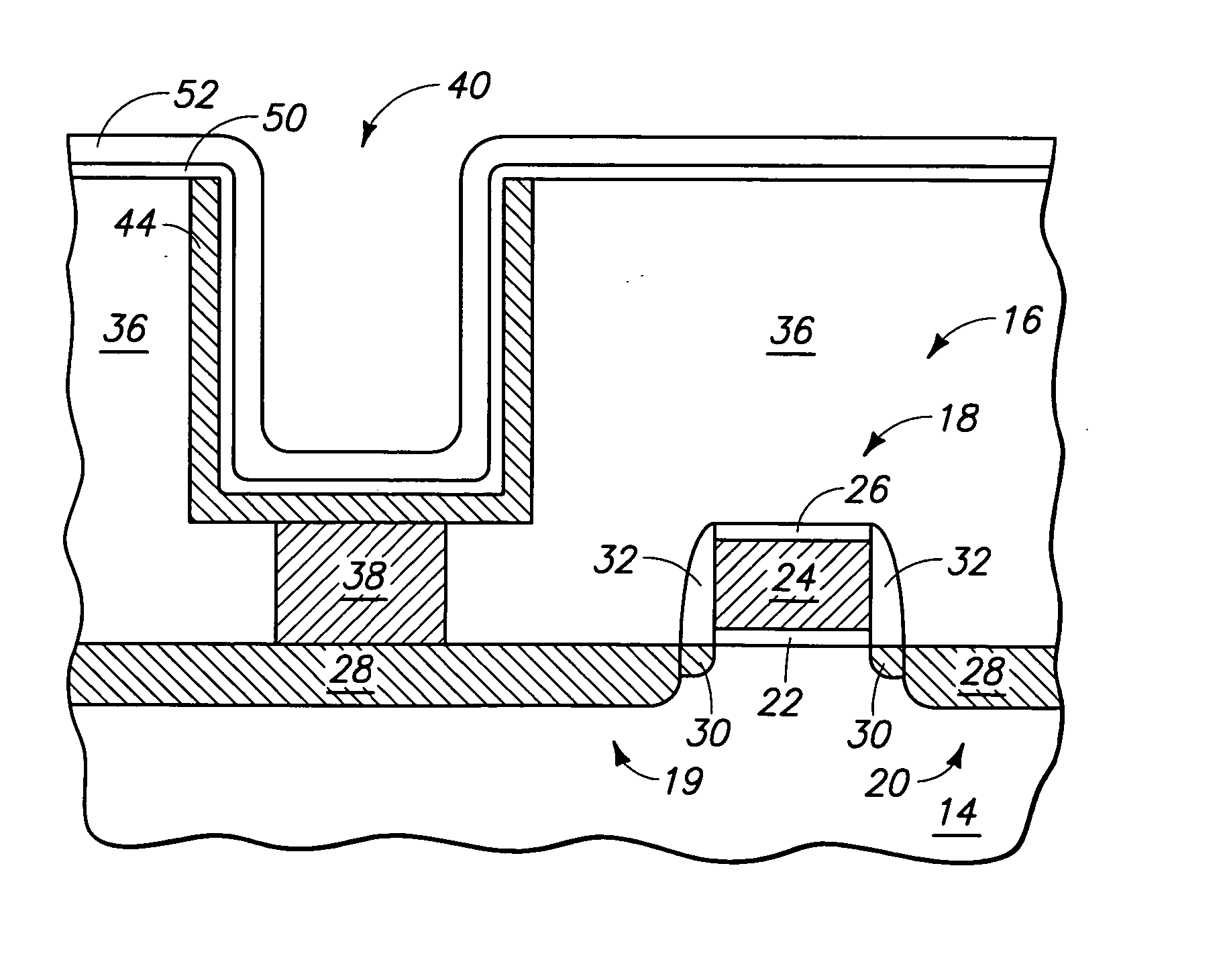

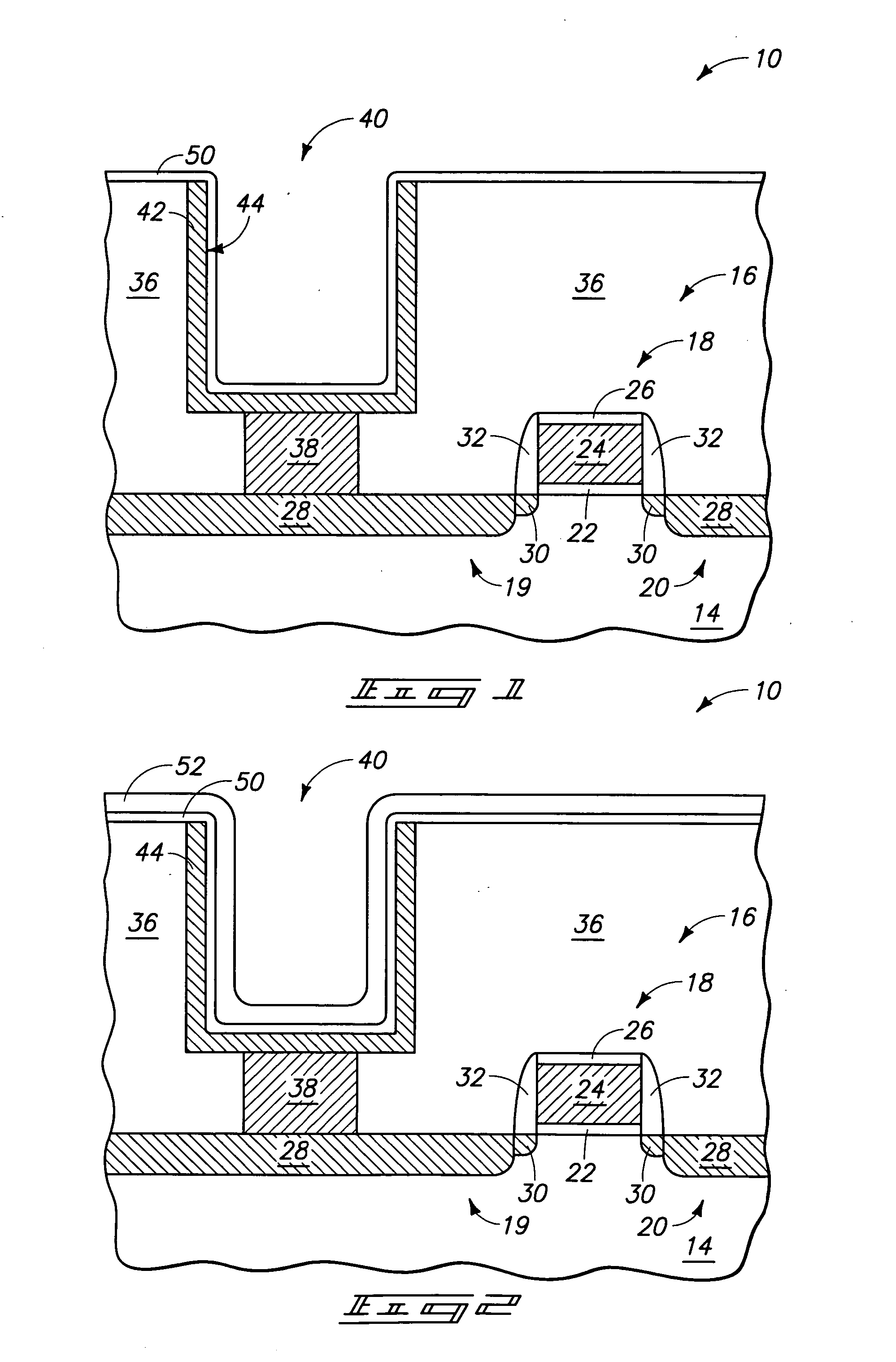

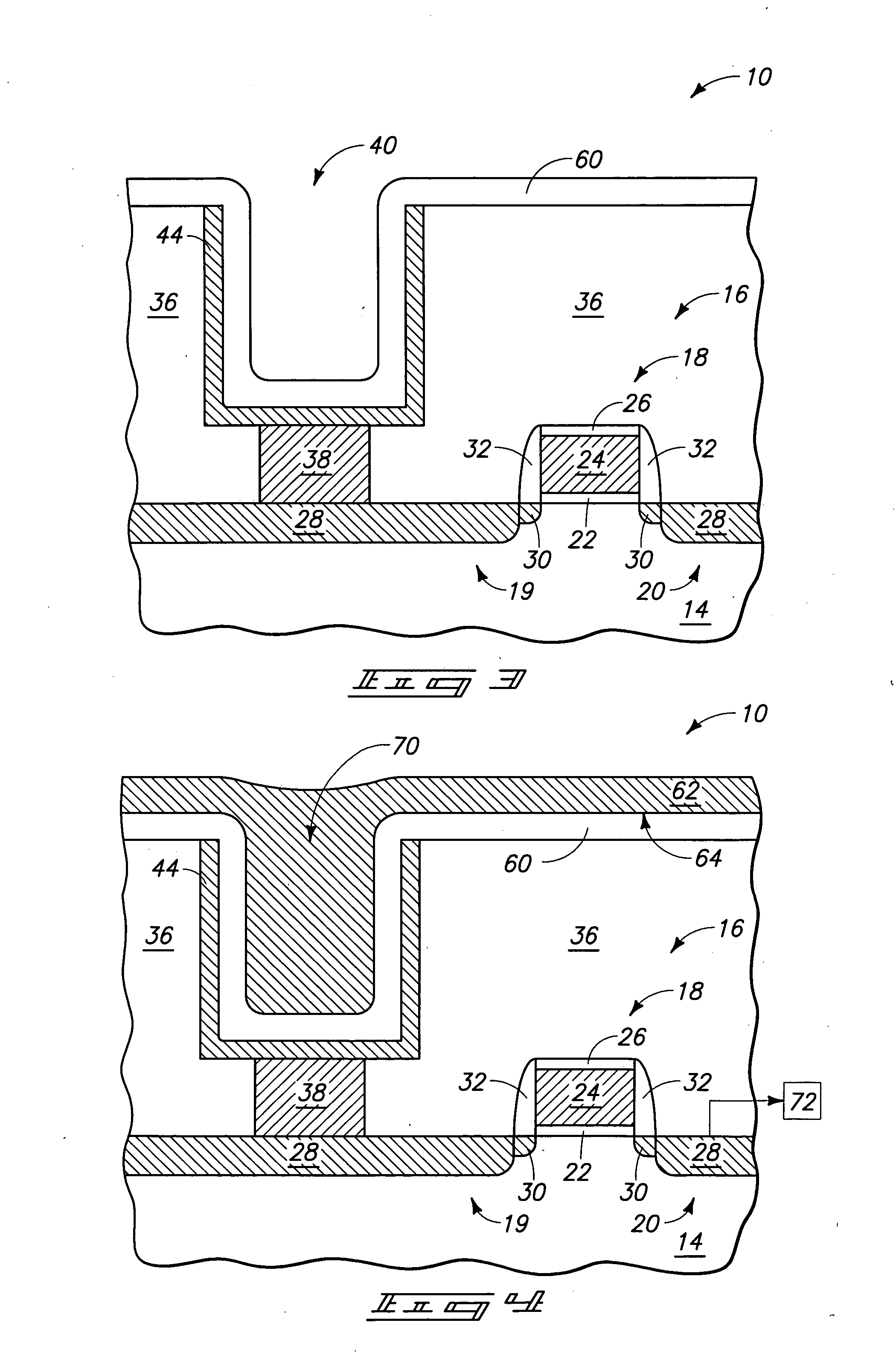

A dielectric capacitor is provided which has a reduced leakage current. The surface of a first electrode (38) of the capacitor is electropolished and a dielectric film (40) and a second electrode (37) are successively laminated on it. The convex parts pointed end (38a) existing on the surface of the first electrode is very finely polished uniformly by dissolving according to electropolishing, a spherical curved surface in which the radius of curvature has been enlarged is formed, and the surface of the first electrode is flattened. Therefore, concentration of electrolysis can be prevented during the operation at the interface of the first electrode and the dielectric film, and the leakage current can be reduced considerably.

Owner:TEXAS INSTR INC

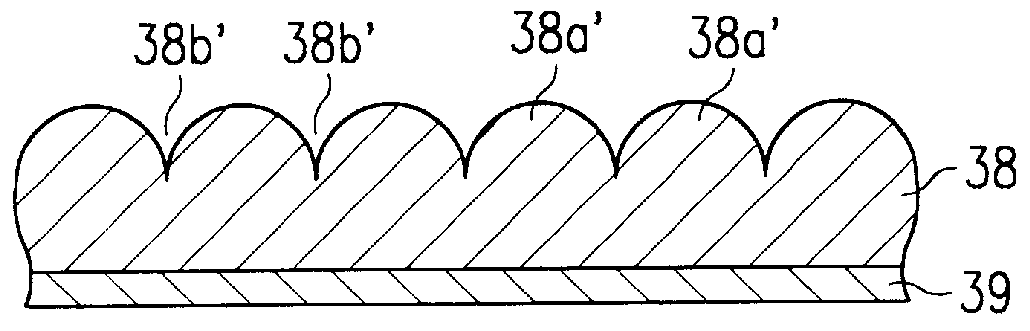

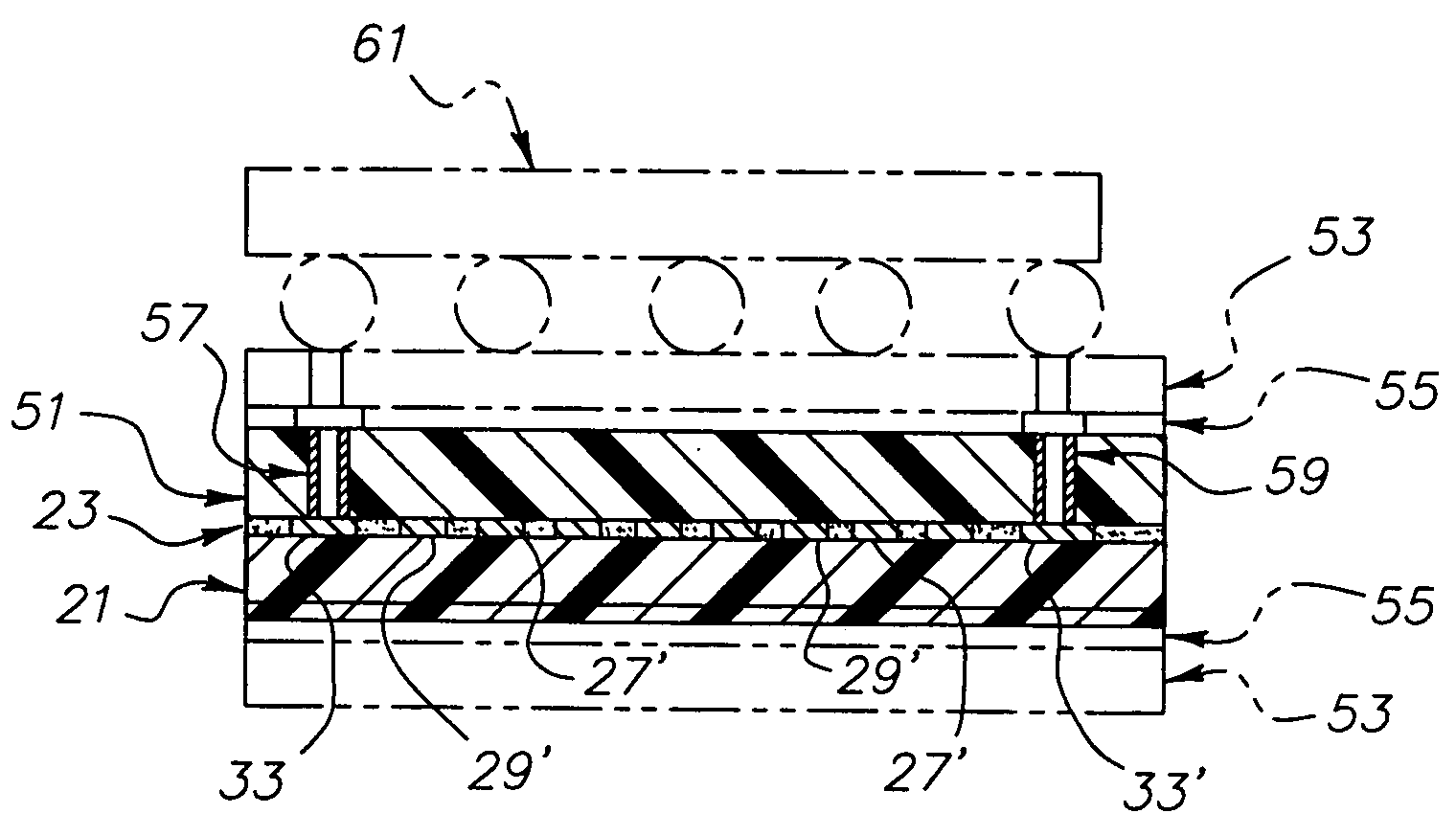

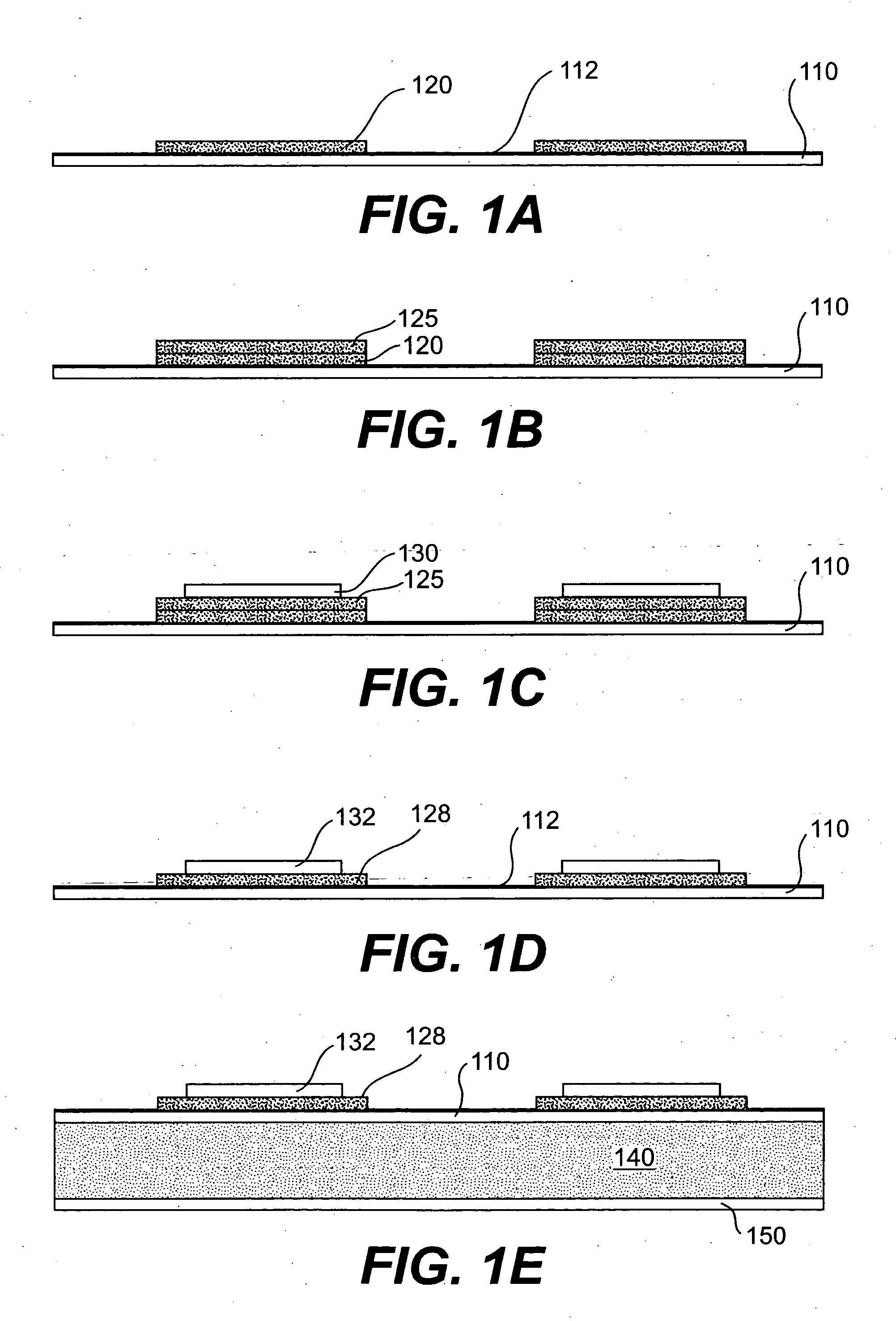

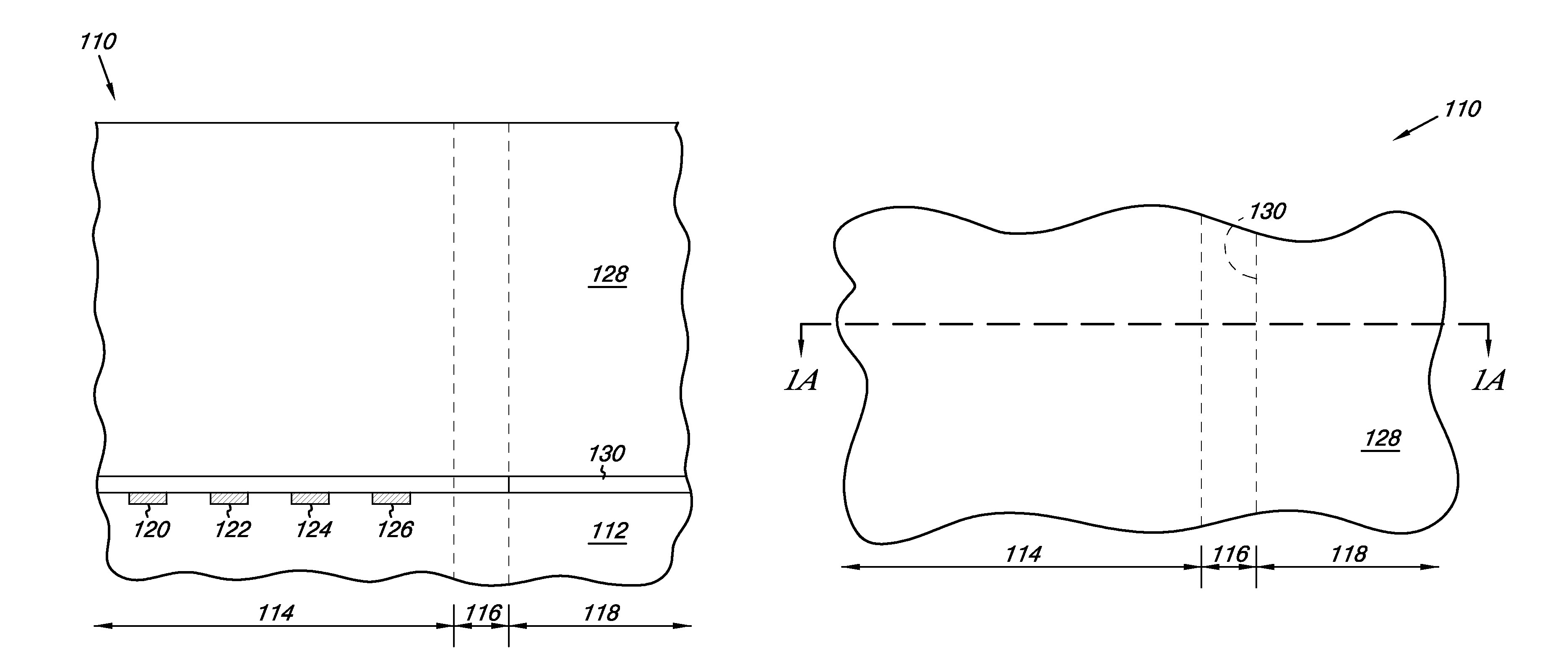

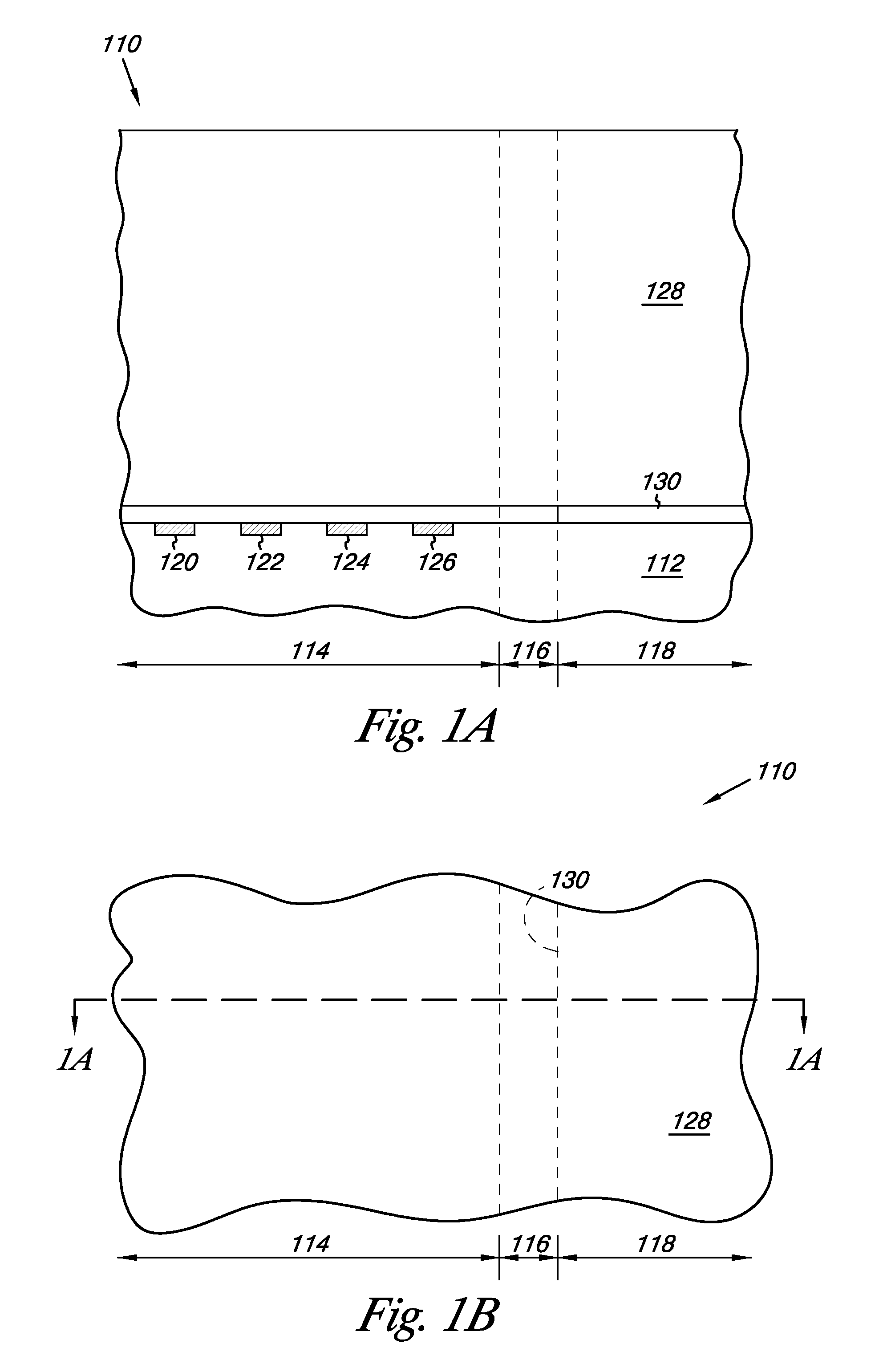

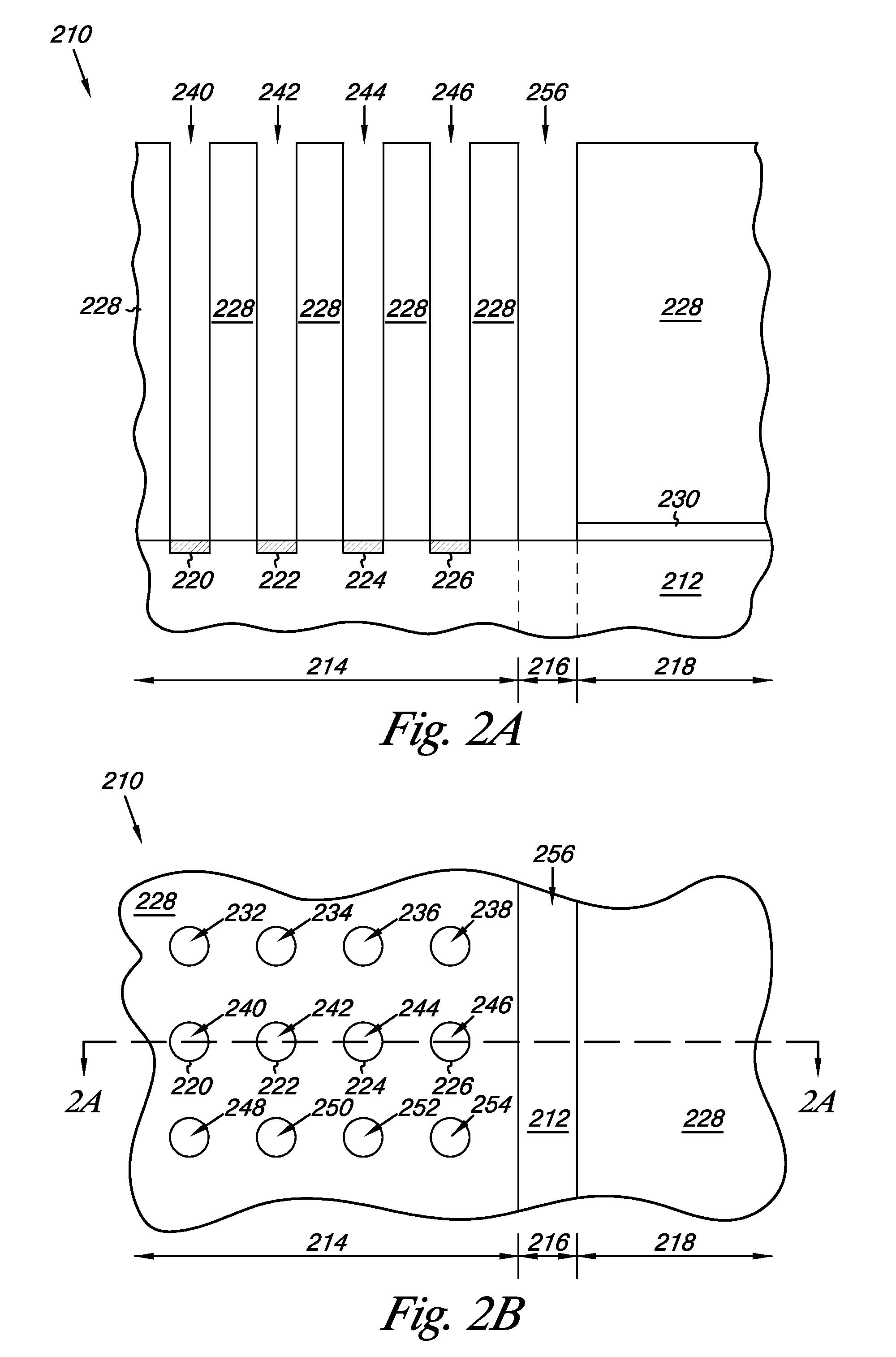

Method of making a circuitized substrate having at least one capacitor therein

InactiveUS20080248596A1Enhance circuitized substrate artEnhance the circuitized substrate artThin/thick film capacitorPrinted circuit aspectsCapacitanceConductive materials

A method of making a circuitized substrate which includes at least one and possibly several capacitors as part thereof. In one embodiment, the substrate is produced by forming a layer of capacitive dielectric material on a dielectric layer and thereafter forming channels with the capacitive material, e.g., using a laser. The channels are then filled with conductive material, e.g., copper, using selected deposition techniques, e.g., sputtering, electro-less plating and electroplating. A second dielectric layer is then formed atop the capacitor and a capacitor “core” results. This “core” may then be combined with other dielectric and conductive layers to form a larger, multilayered PCB or chip carrier. In an alternative approach, the capacitive dielectric material may be photo-imageable, with the channels being formed using conventional exposure and development processing known in the art. In still another embodiment, at least two spaced-apart conductors may be formed within a metal layer deposited on a dielectric layer, these conductors defining a channel there-between. The capacitive dielectric material may then be deposited (e.g., using lamination) within the channels.

Owner:ENDICOTT INTERCONNECT TECH

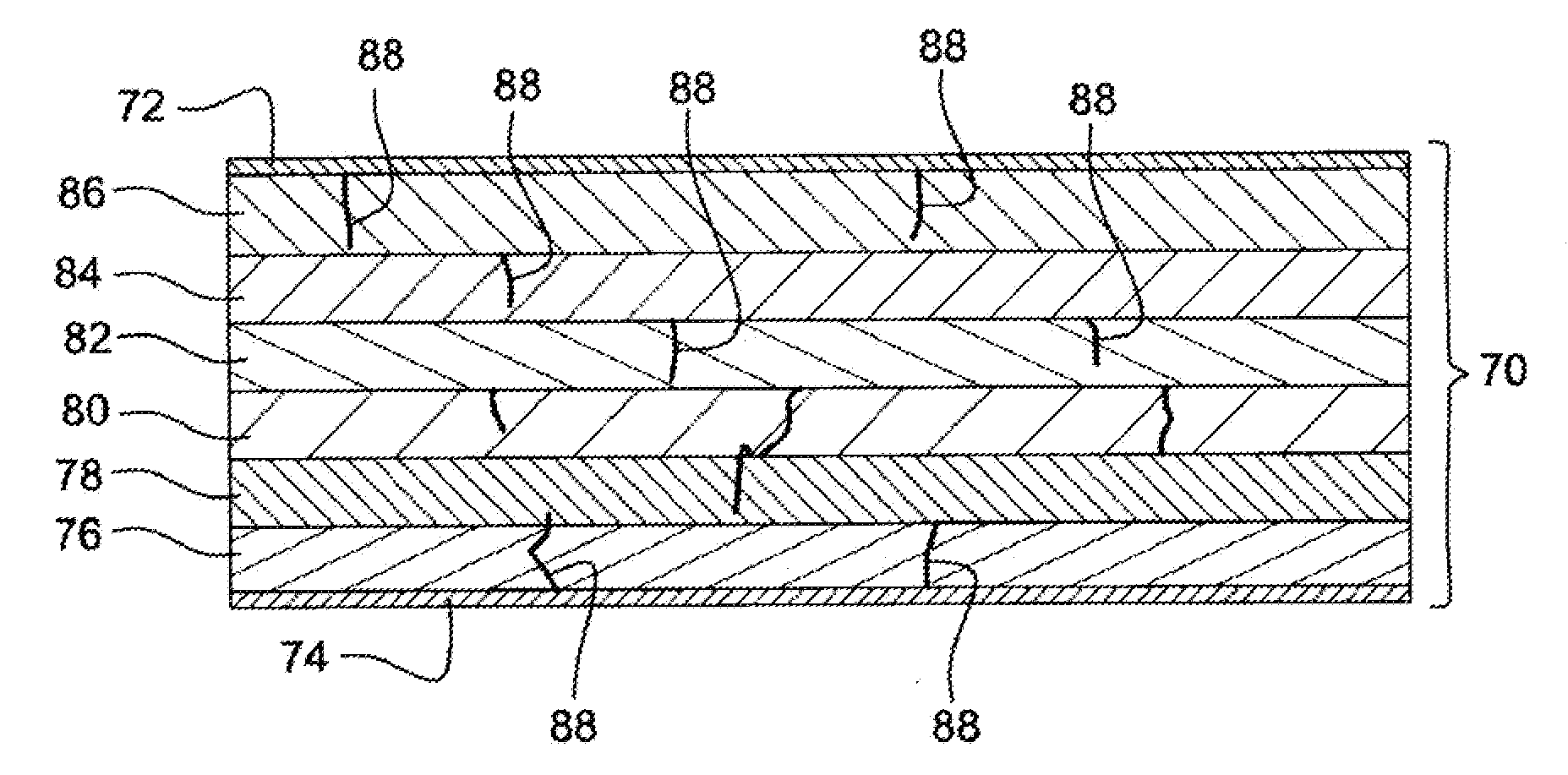

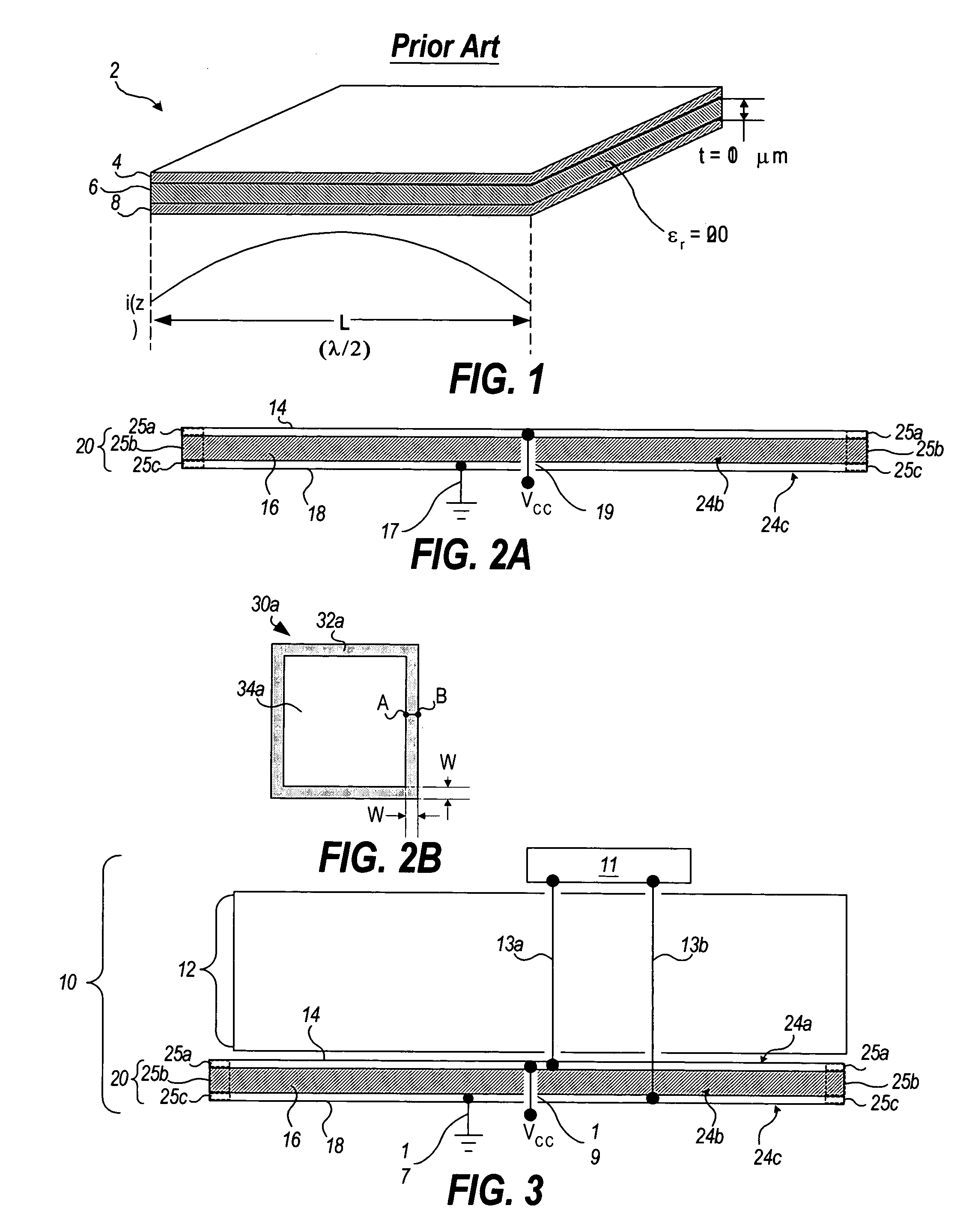

Structure for a thin film multilayer capacitor

An electronic component structure is proposed, wherein an interposer thin film capacitor structure is employed between an active electronic component and a multilayer circuit card. A method for making the interposer thin film capacitor is also proposed. In order to eliminate fatal electrical shorts in the overlying thin film regions that arise from pits, voids, or undulations on the substrate surface, a thick first metal layer, on the order of 0.5-10 mu m thick, is deposited on the substrate upon which the remaining thin films, including a dielectric film and second metal layer, are then applied. The first metal layer includes of Pt or other electrode metal, or a combination of Pt, Cr, and Cu metals, and a diffusion barrier layer. Additional Ti layers may be employed for adhesion enhancement. The thickness of the first metal layers are approximately: 200 A for the Cr layer; 0.5-10 mu m for the Cu layer; 1000 A-5000 A for the diffusion barrier; and 100 A-2500 A for a Pt layer.

Owner:IBM CORP

Methods of forming hafnium-containing materials, methods of forming hafnium oxide, and constructions comprising hafnium oxide

The invention includes methods of forming hafnium-containing materials, such as, for example, hafnium oxide. In one aspect, a semiconductor substrate is provided, and first reaction conditions are utilized to form hafnium-containing seed material in a desired crystalline phase and orientation over the substrate. Subsequently, second reaction conditions are utilized to grow second hafnium-containing material over the seed material. The second hafnium-containing material is in a crystalline phase and / or orientation different from the crystalline phase and orientation of the hafnium-containing seed material. The second hafnium-containing material can be, for example, in an amorphous phase. The seed material is then utilized to induce a desired crystalline phase and orientation in the second hafnium-containing material. The invention also includes capacitor constructions utilizing hafnium-containing materials, and circuit assemblies comprising the capacitor constructions.

Owner:MICRON TECH INC

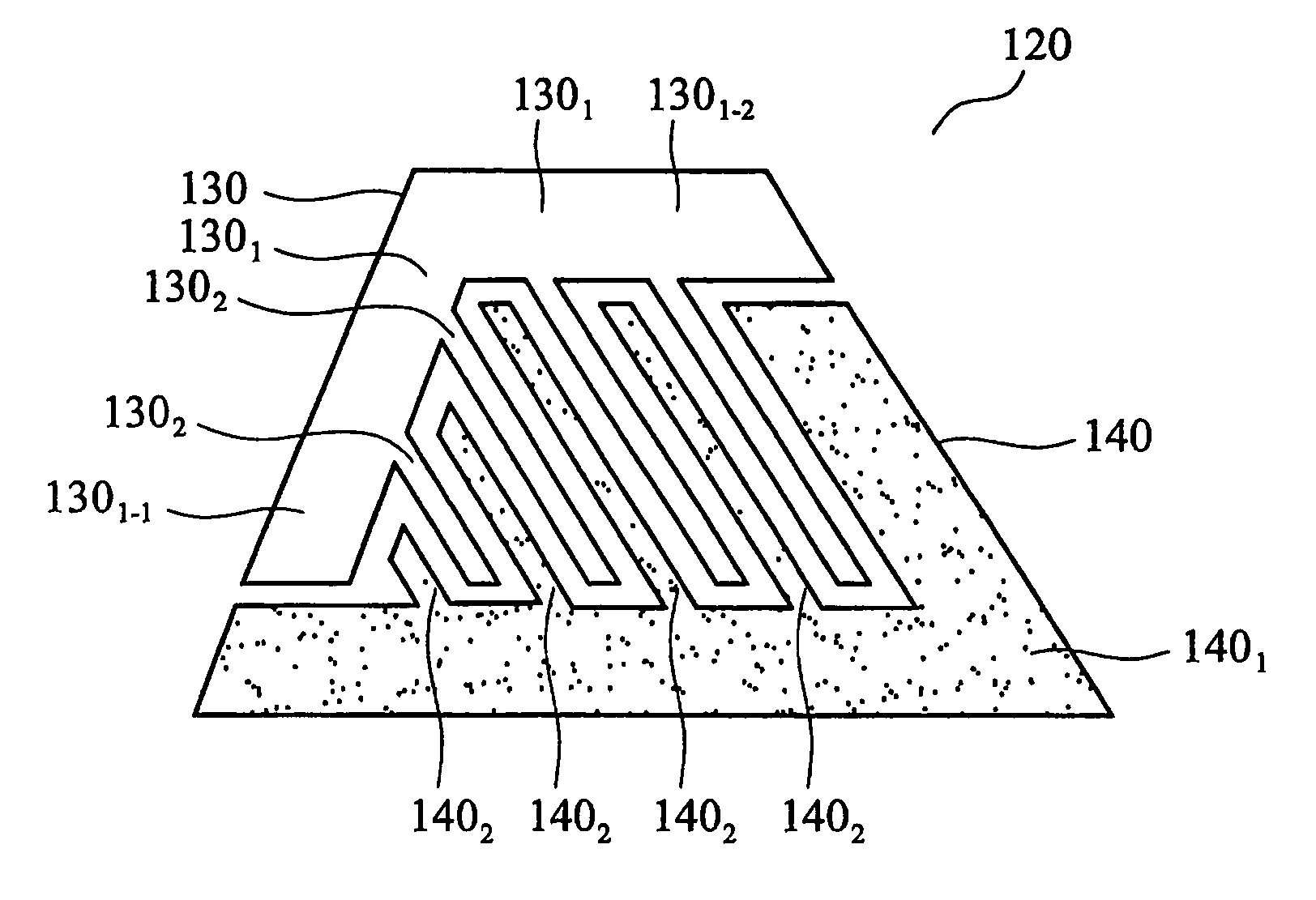

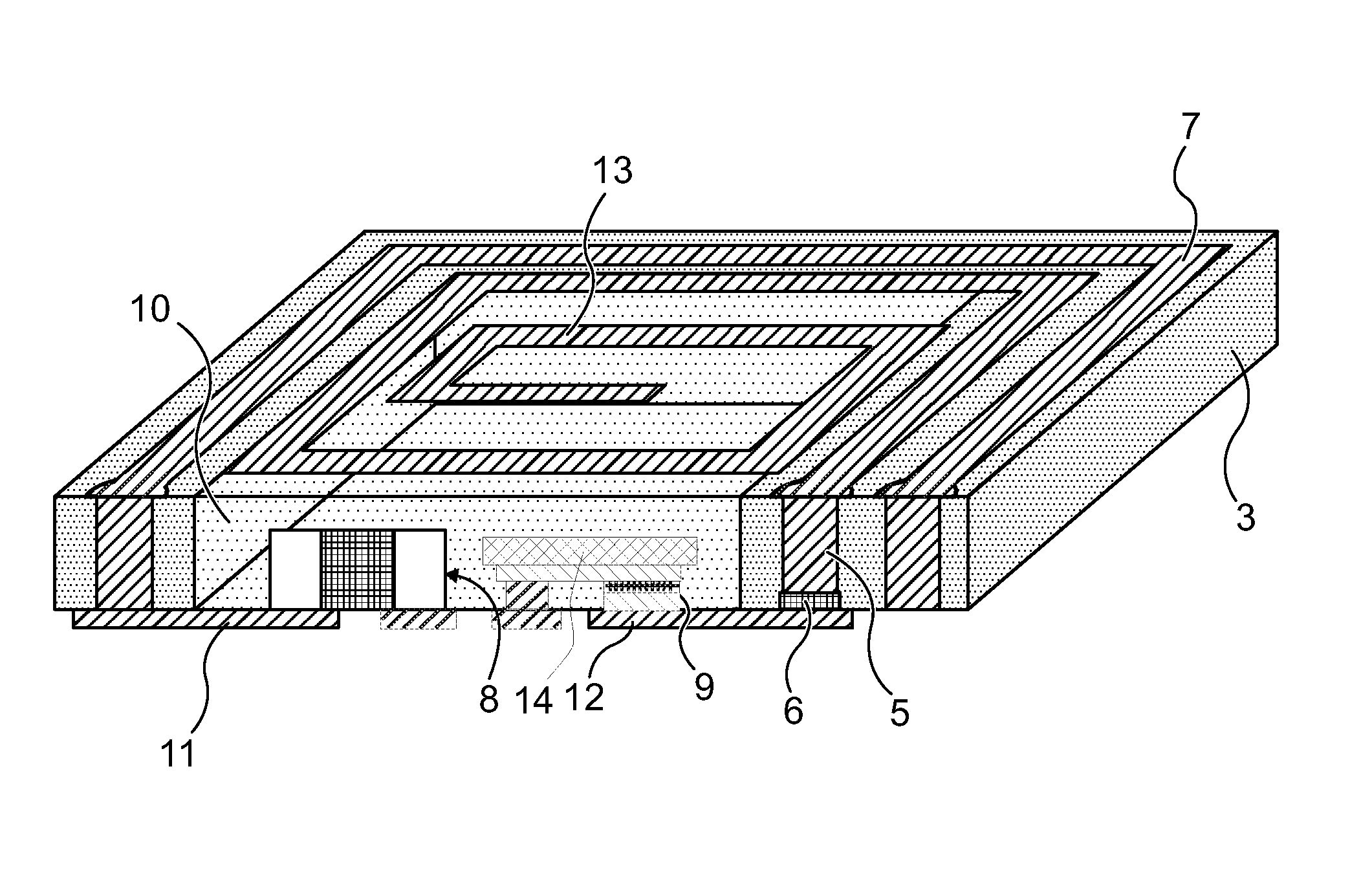

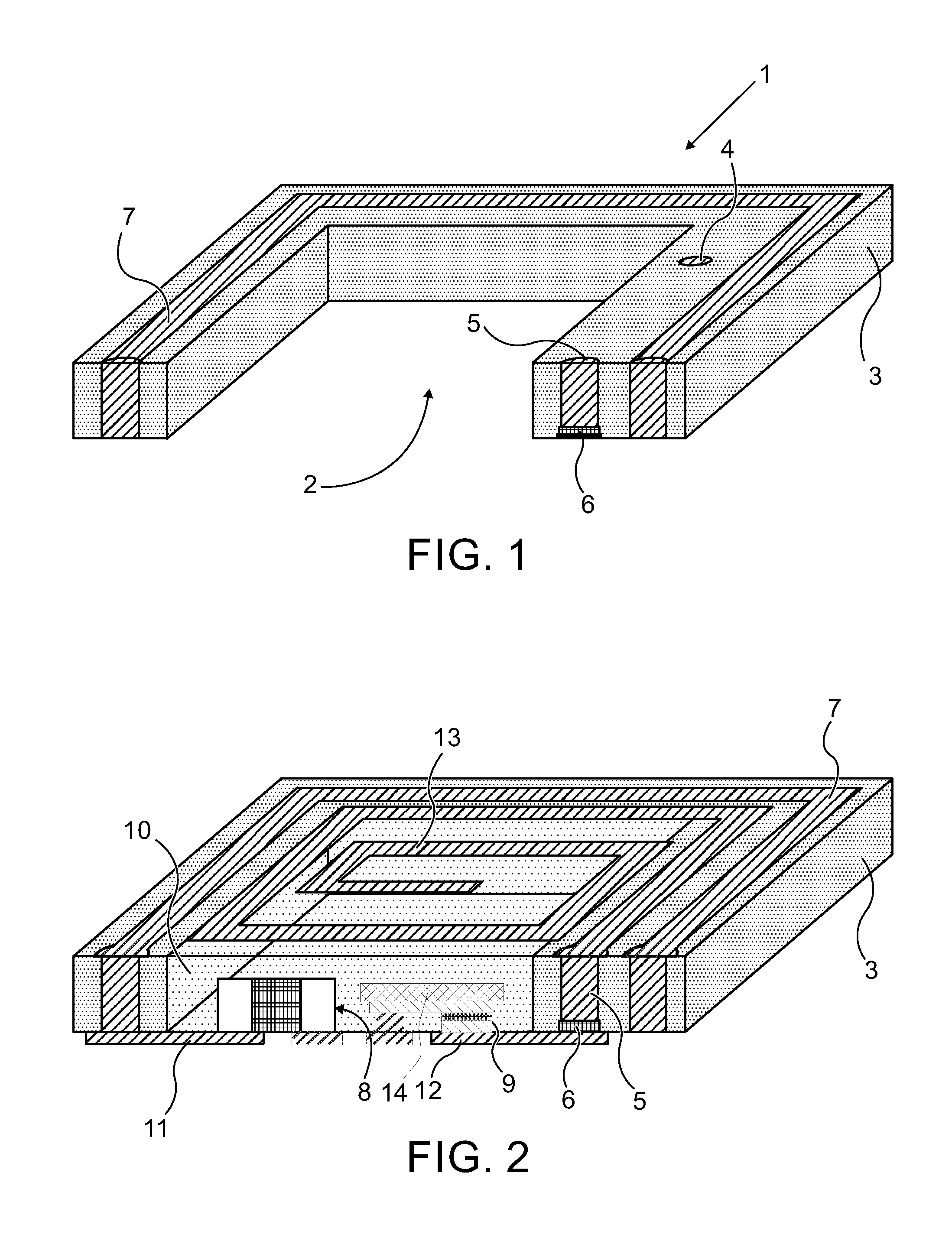

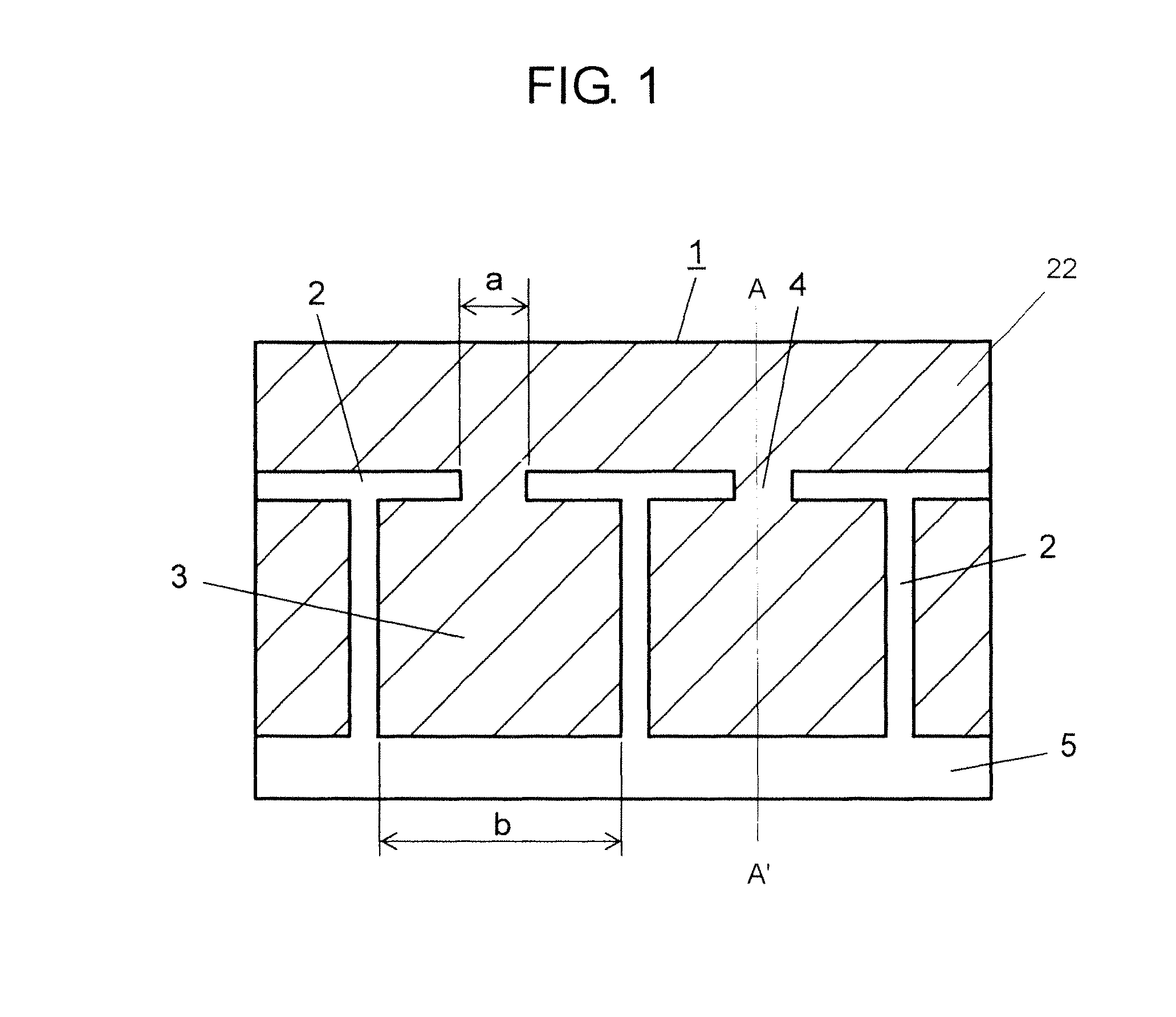

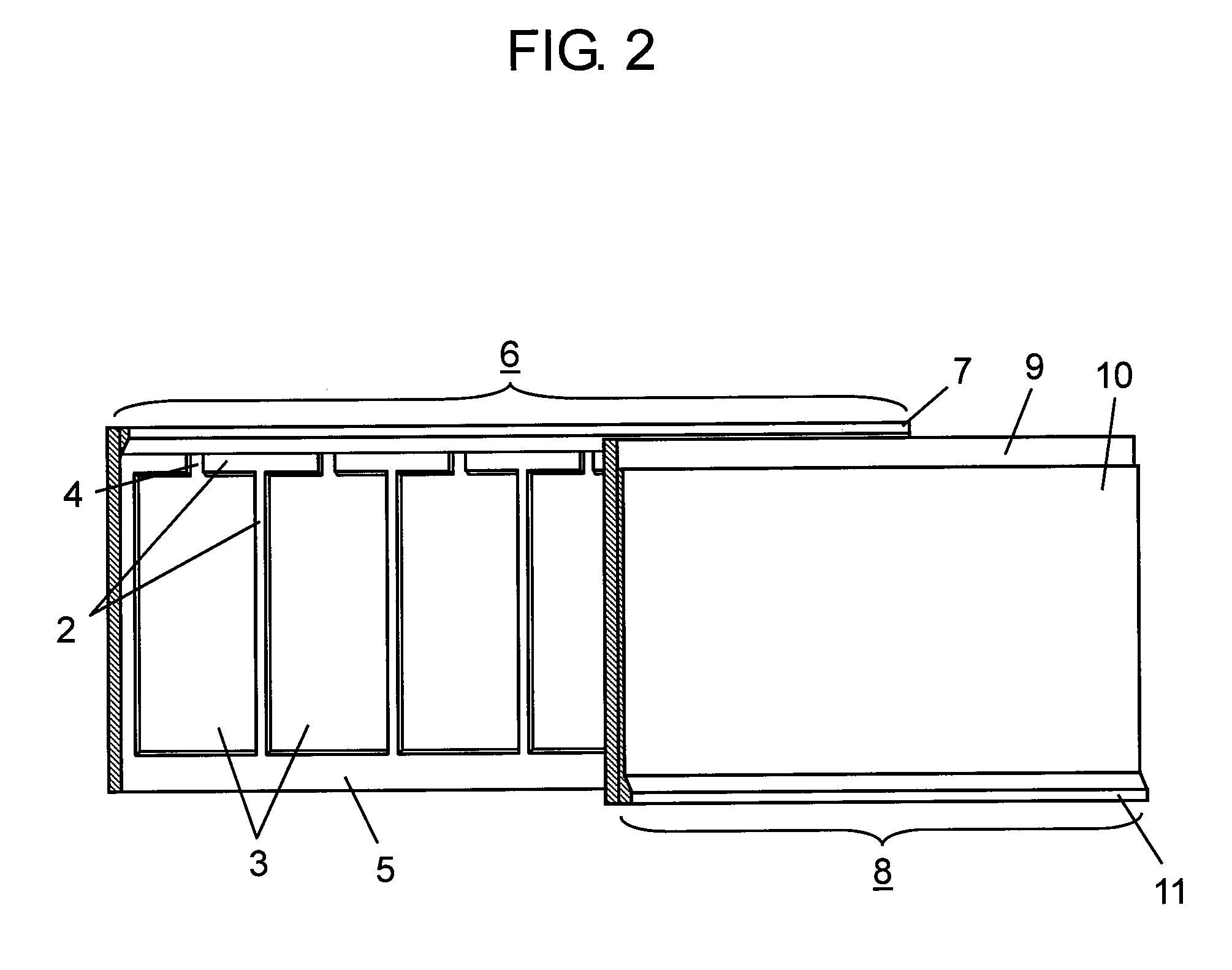

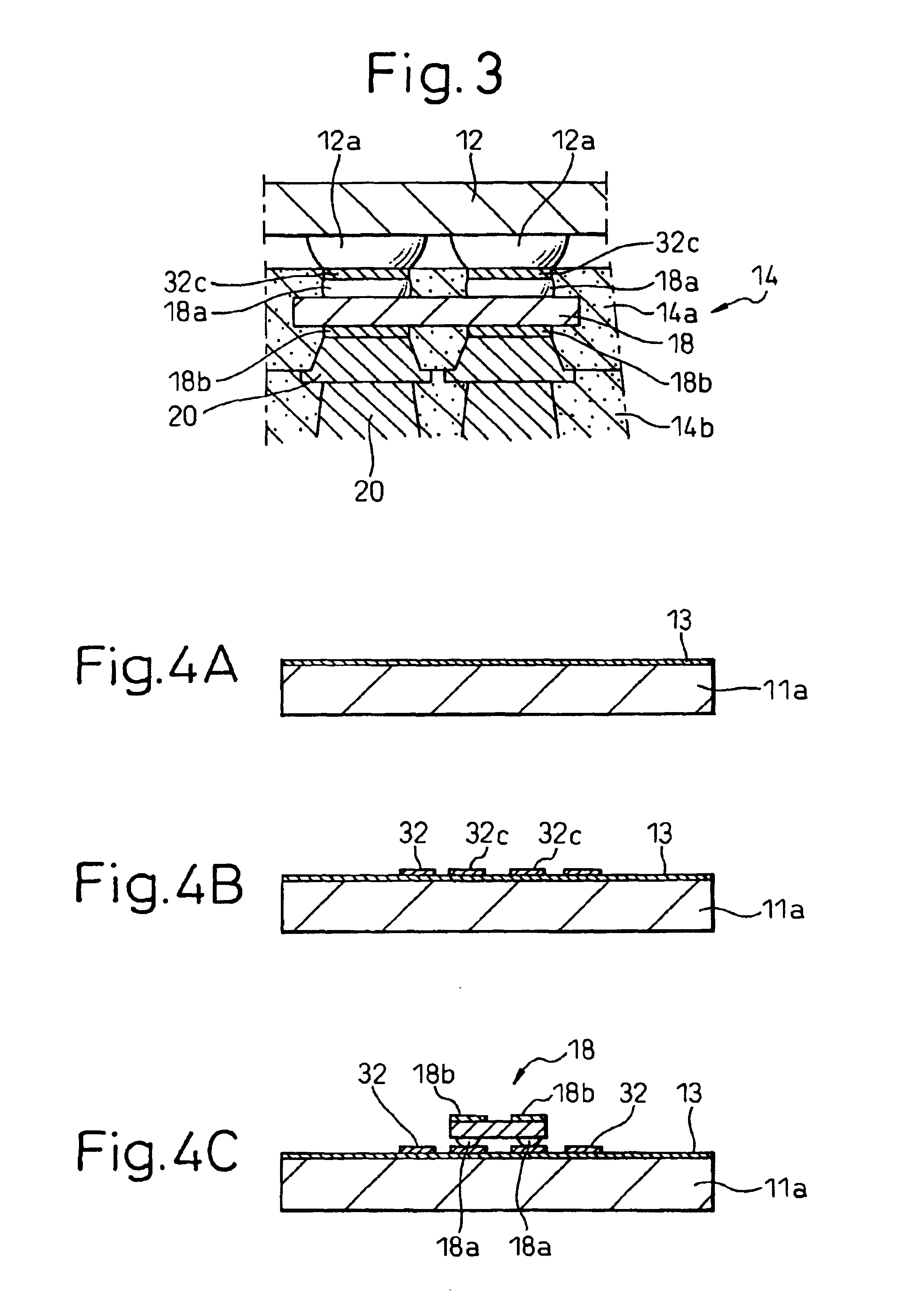

Breakdown-resistant thin film capacitor with interdigitated structure

InactiveUS6999297B1High breakdown resistanceIncrease capacitanceThin/thick film capacitorFixed capacitor electrodesDielectricEngineering

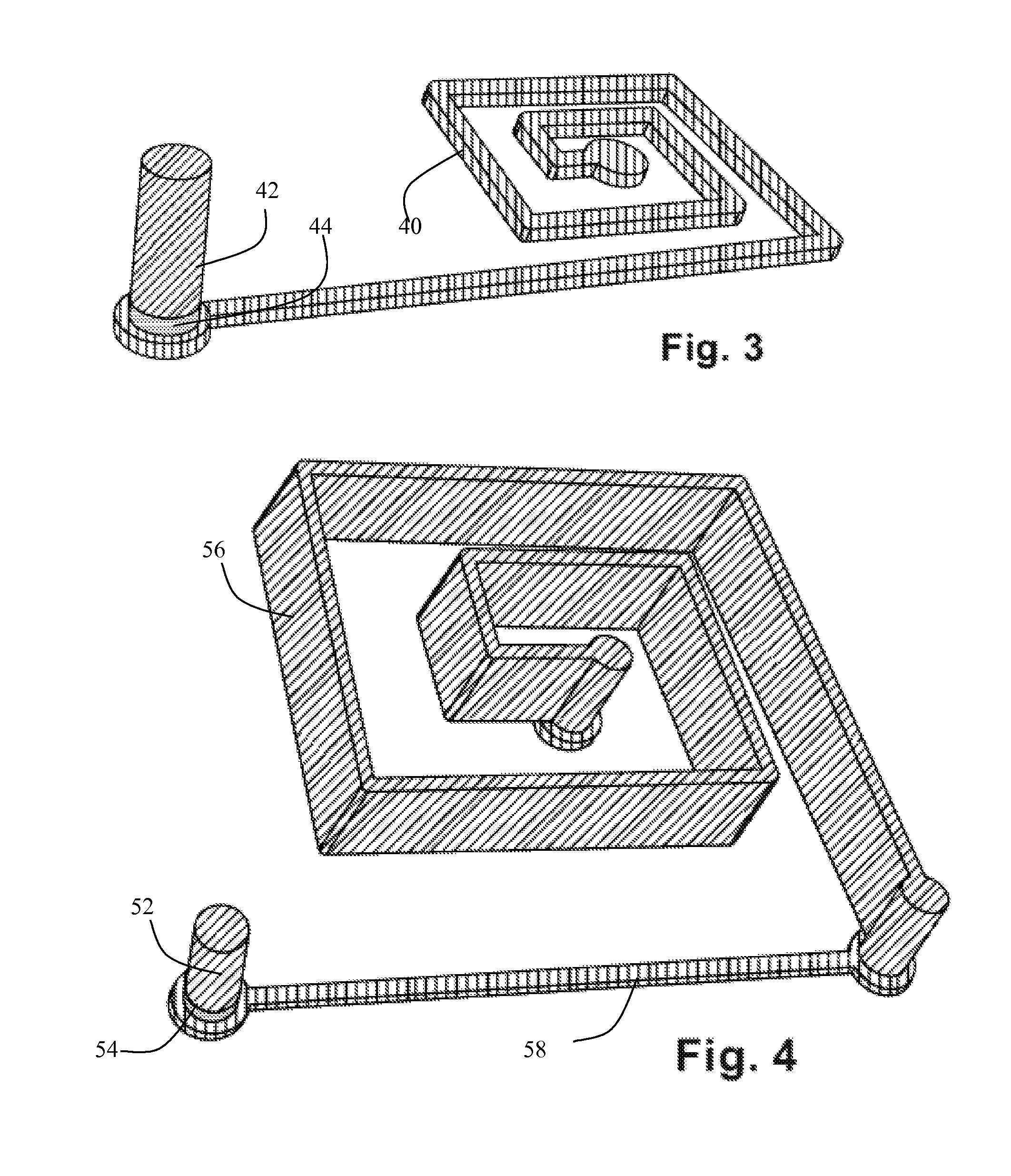

The invention relates to a thin film capacitor with a carrier substrate, at least two interdigitated electrodes, and a dielectric. A staggered arrangement of at least one interdigitated electrode below the dielectric with respect to an interdigitated electrode above the dielectric results in a breakdown-resistant thin film capacitor which can be manufactured in the same production process as a standard monolayer capacitor.

Owner:NXP BV

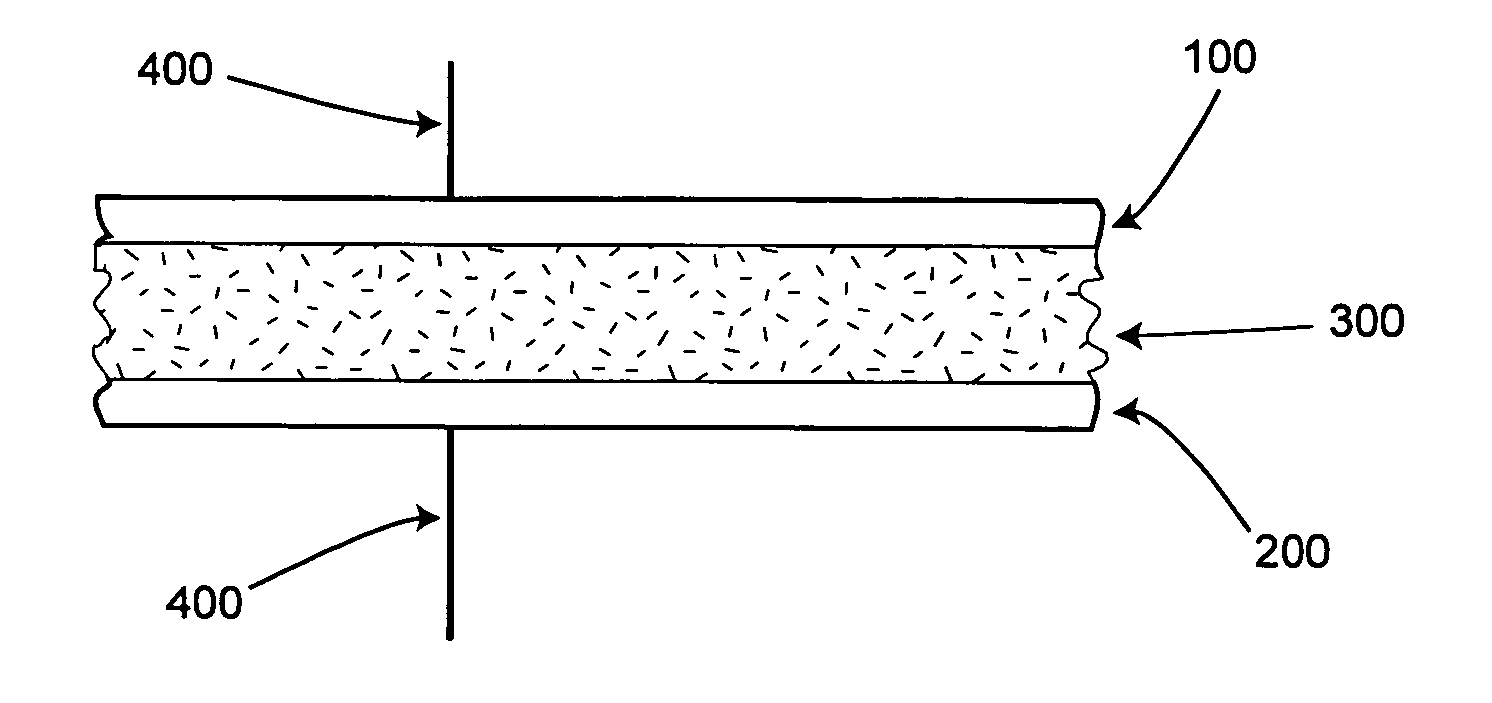

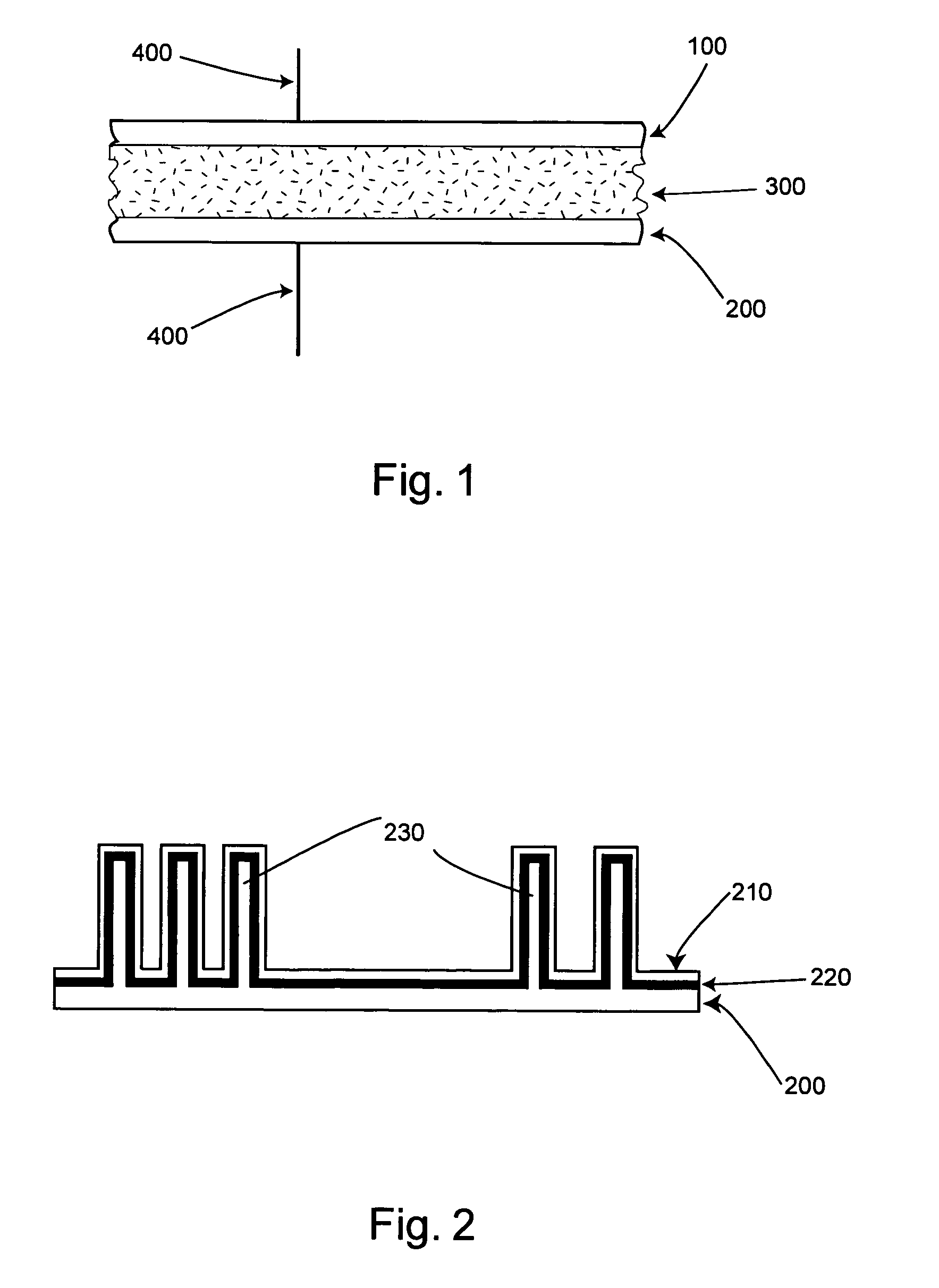

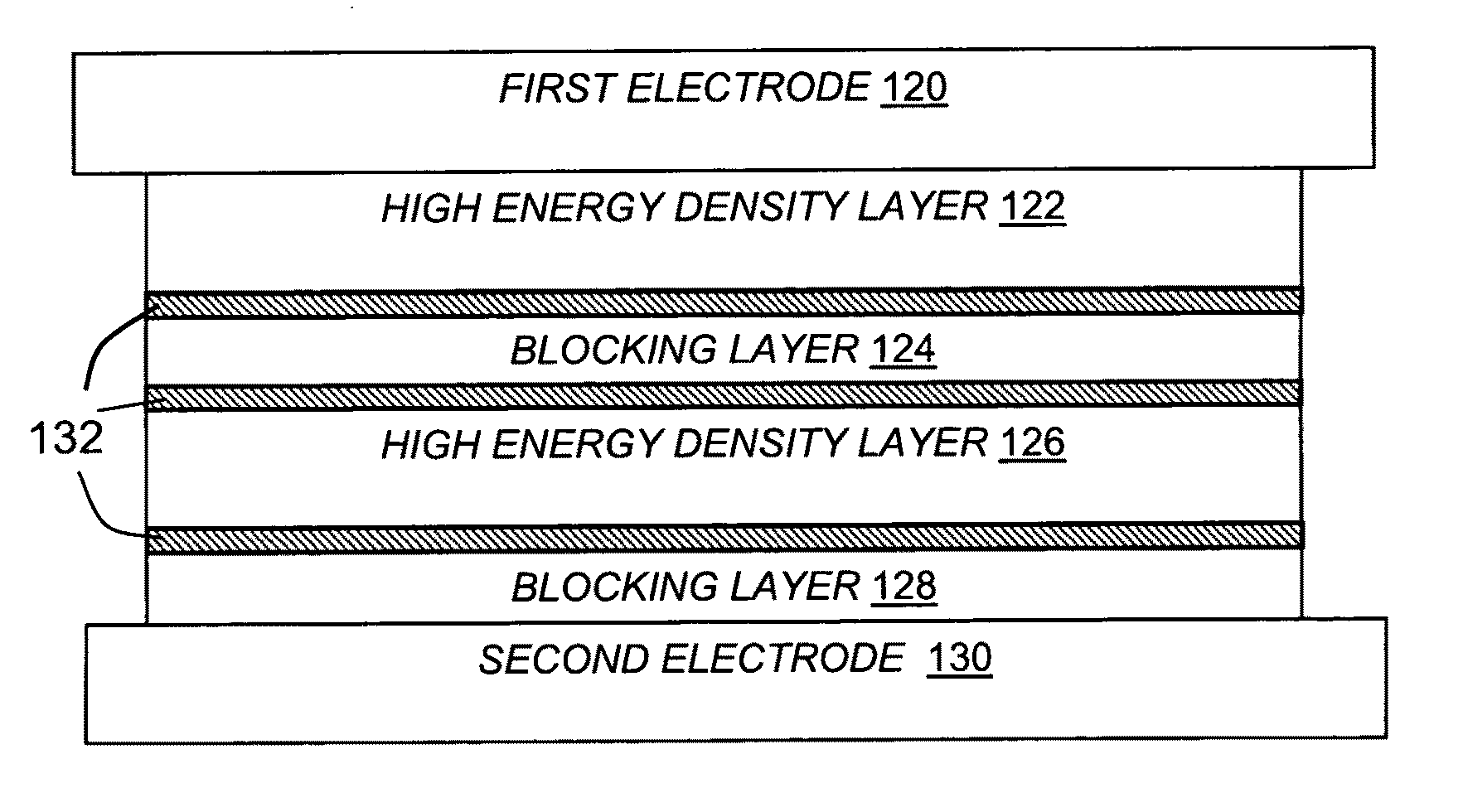

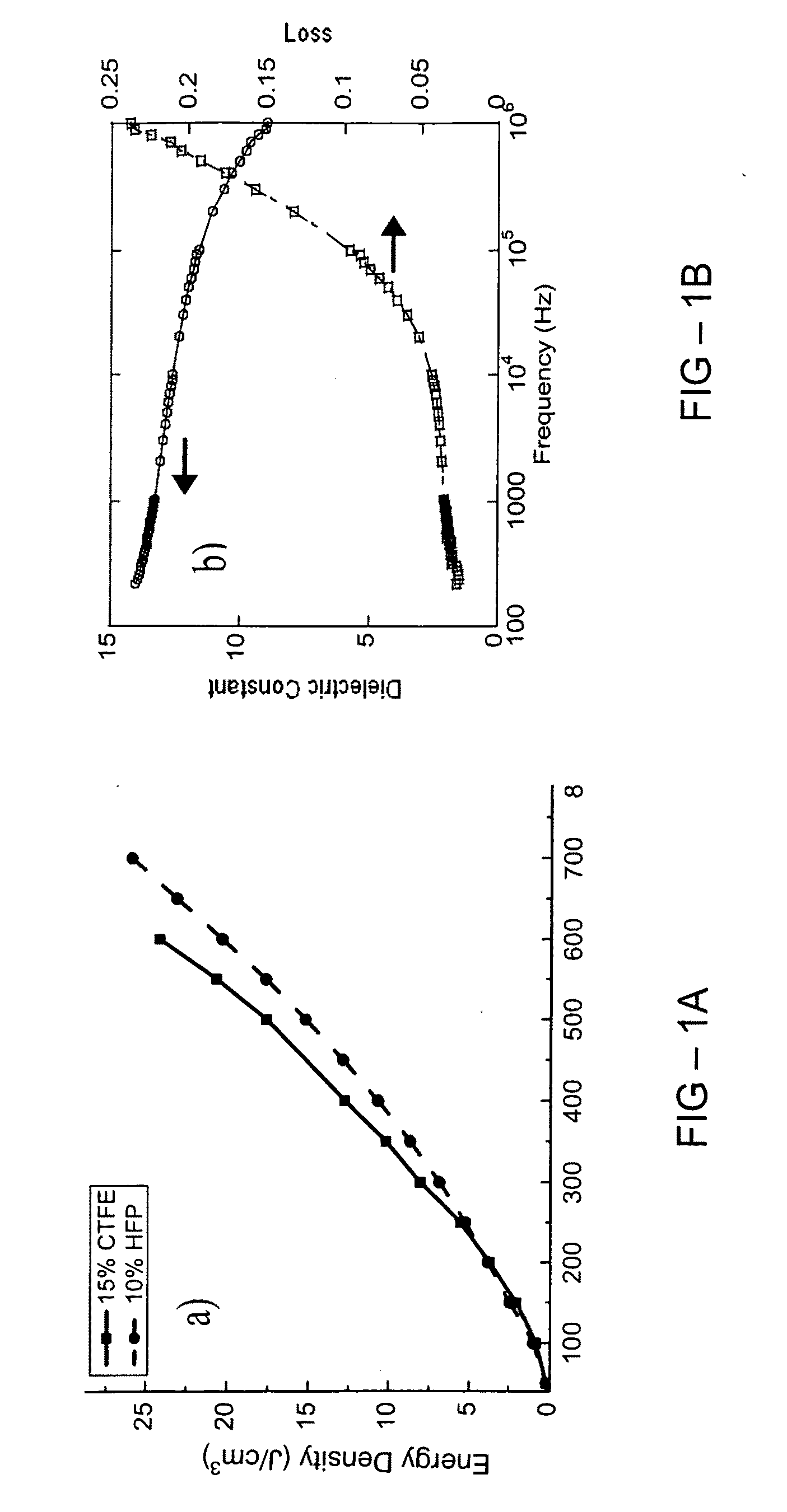

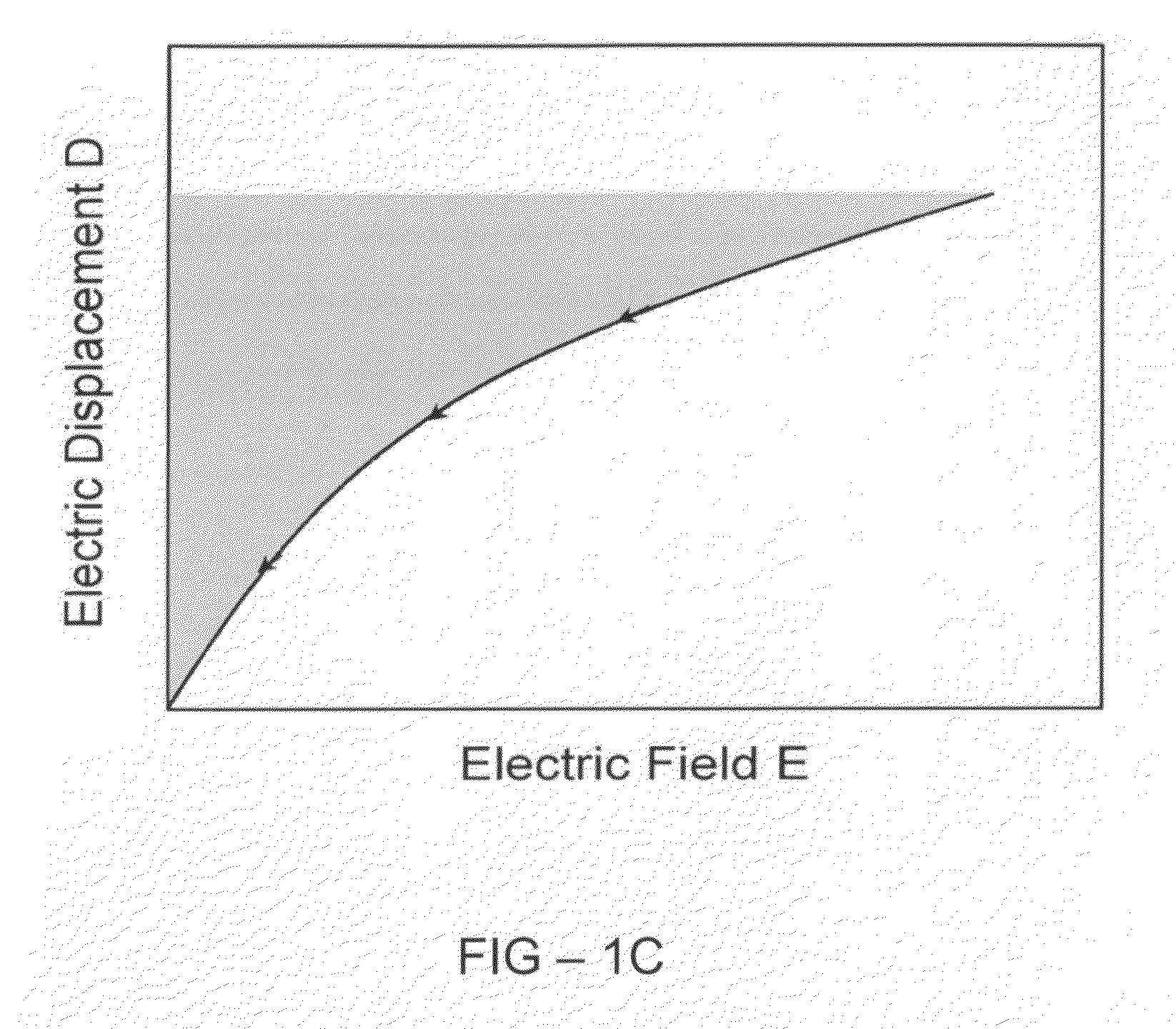

Methods to improve the efficiency and reduce the energy losses in high energy density capacitor films and articles comprising the same

InactiveUS20110110015A1Reduce conduction lossHigh breakdown strengthThin/thick film capacitorFixed capacitor dielectricCapacitanceDielectric loss

A multilayer film useful for capacitive applications comprises a high energy density layer and a dielectric blocking layer. In some embodiments, a conducting film is located between the high energy density layer and the blocking layer. The high energy density layer may be a fluoropolymer, such as a polymer or copolymer of poly-1,1-difluoroethene or a derivative thereof. The multilayer film may have high energy density (for example,. >8 J / cm3) and low dielectric loss, for example less than 2%, and preferably less than 1%.

Owner:PENN STATE RES FOUND

Flexible metal-oxide-metal capacitor design

ActiveUS7485912B2Increase the areaEasy to useTransistorFixed capacitor electrodesAcute angleEngineering

Owner:TAIWAN SEMICON MFG CO LTD

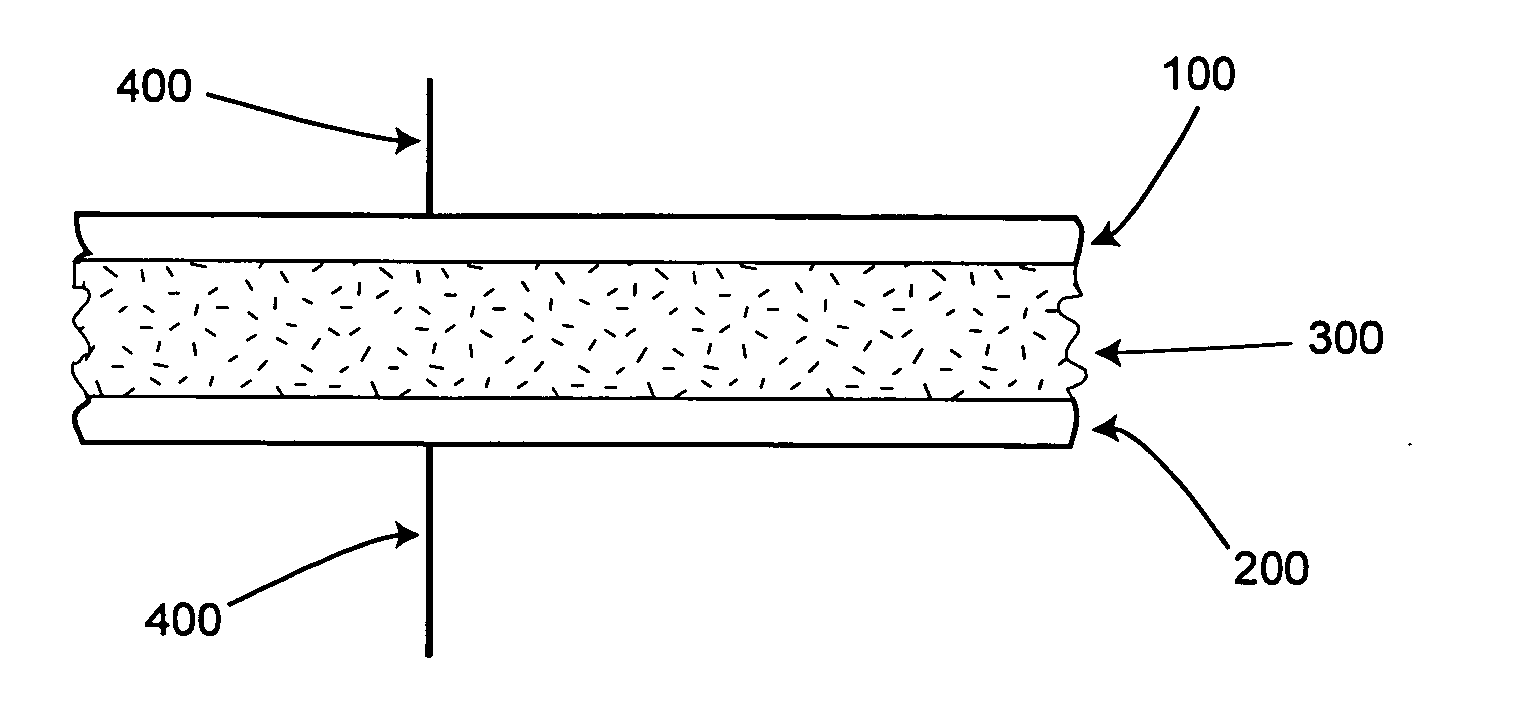

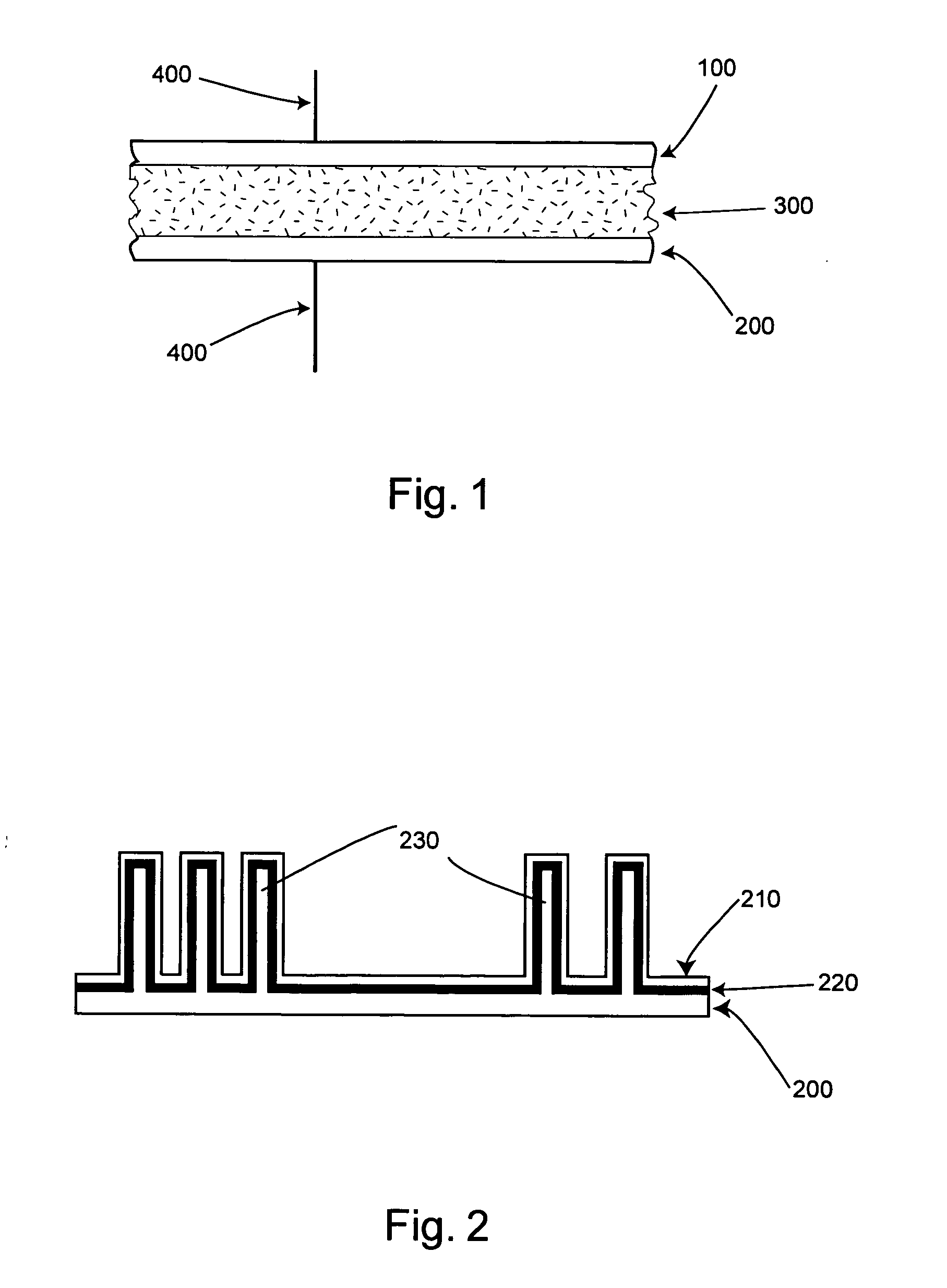

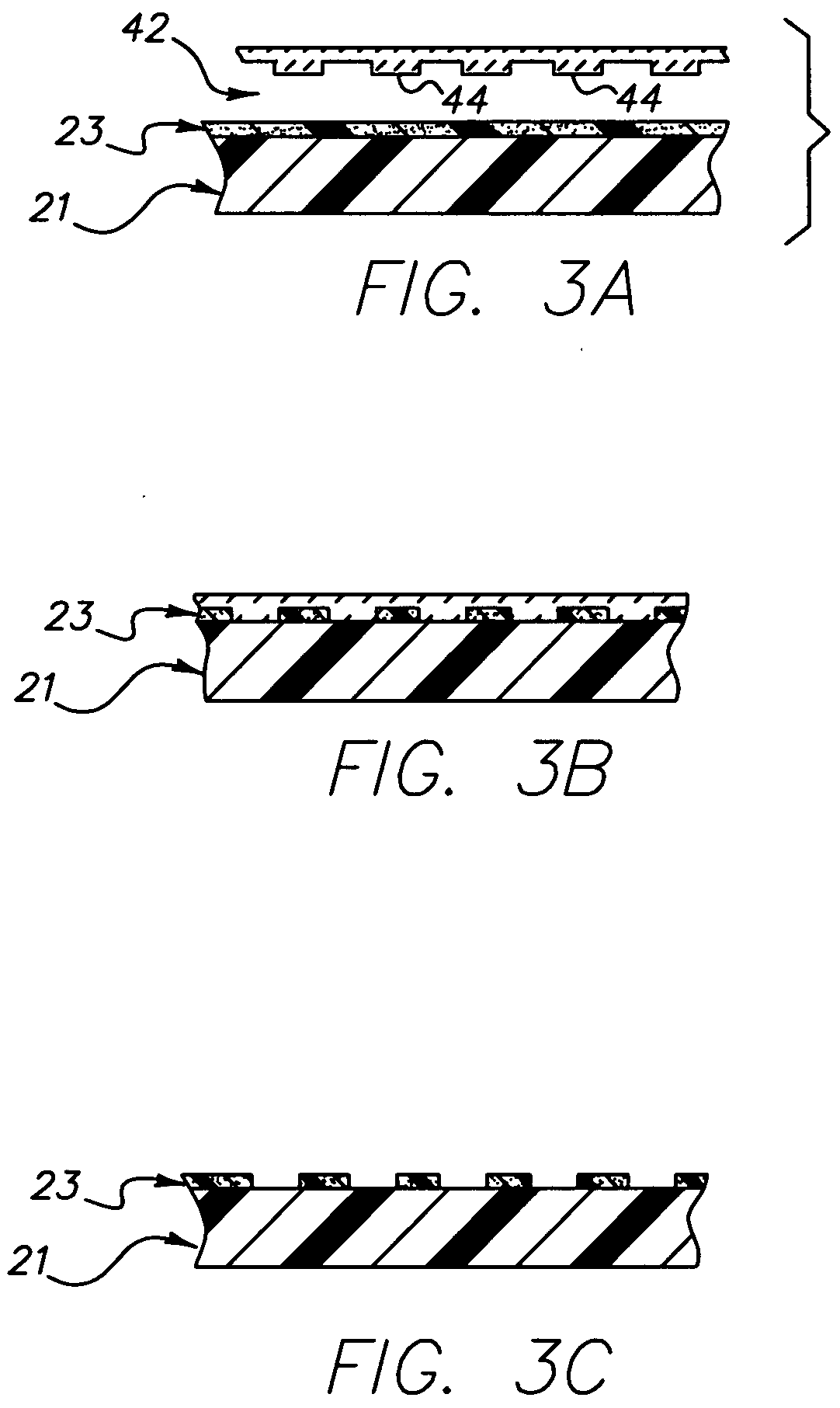

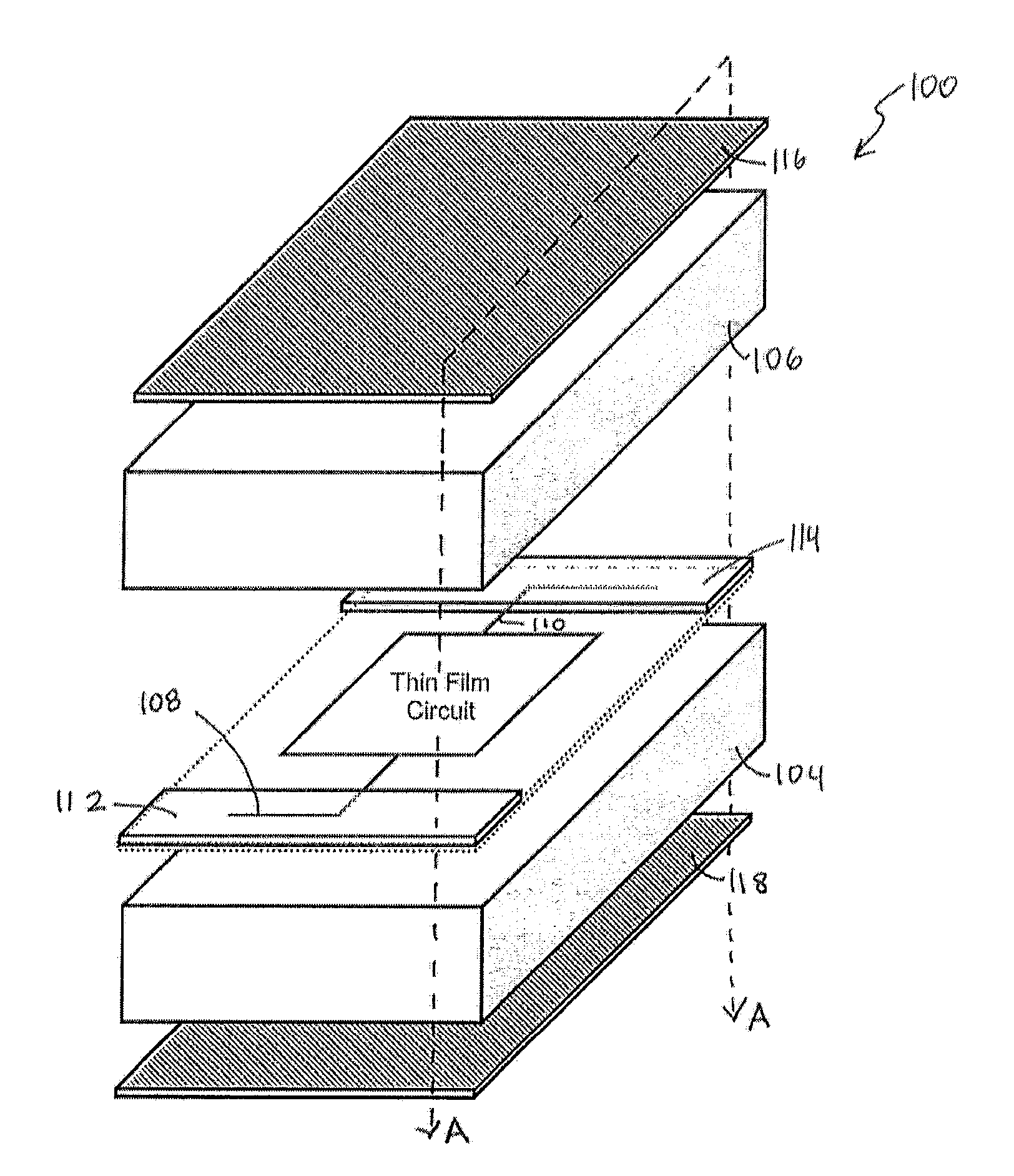

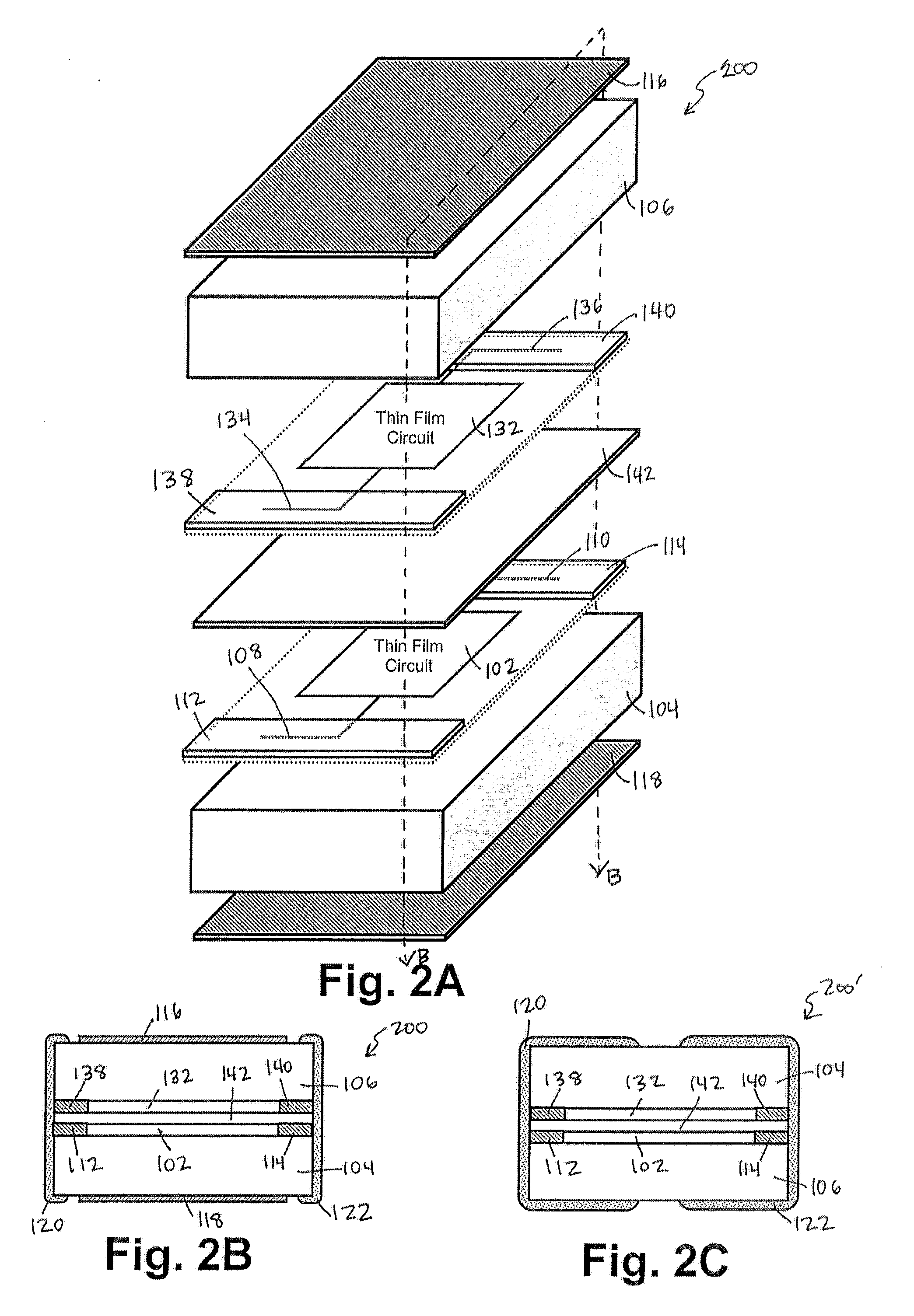

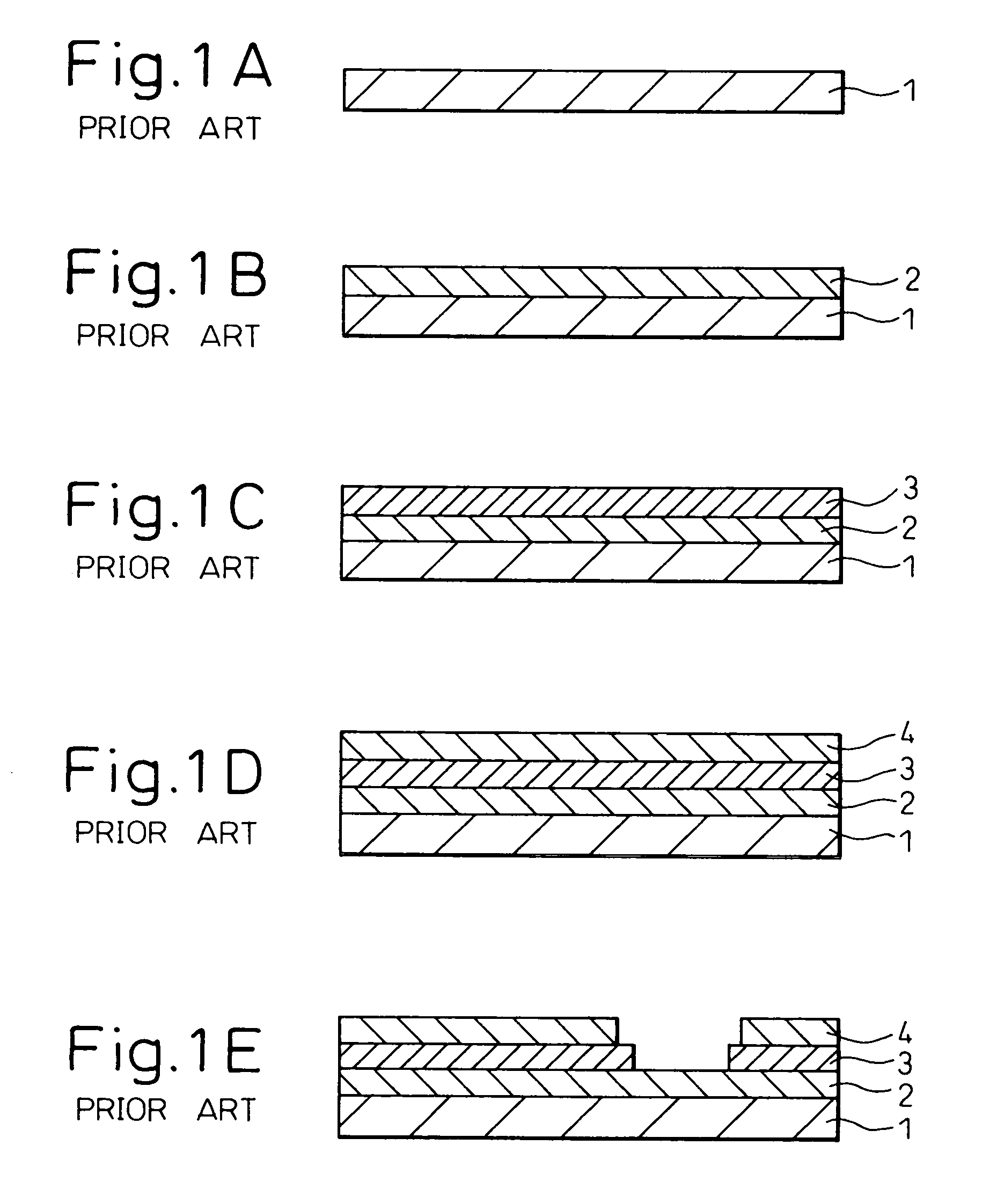

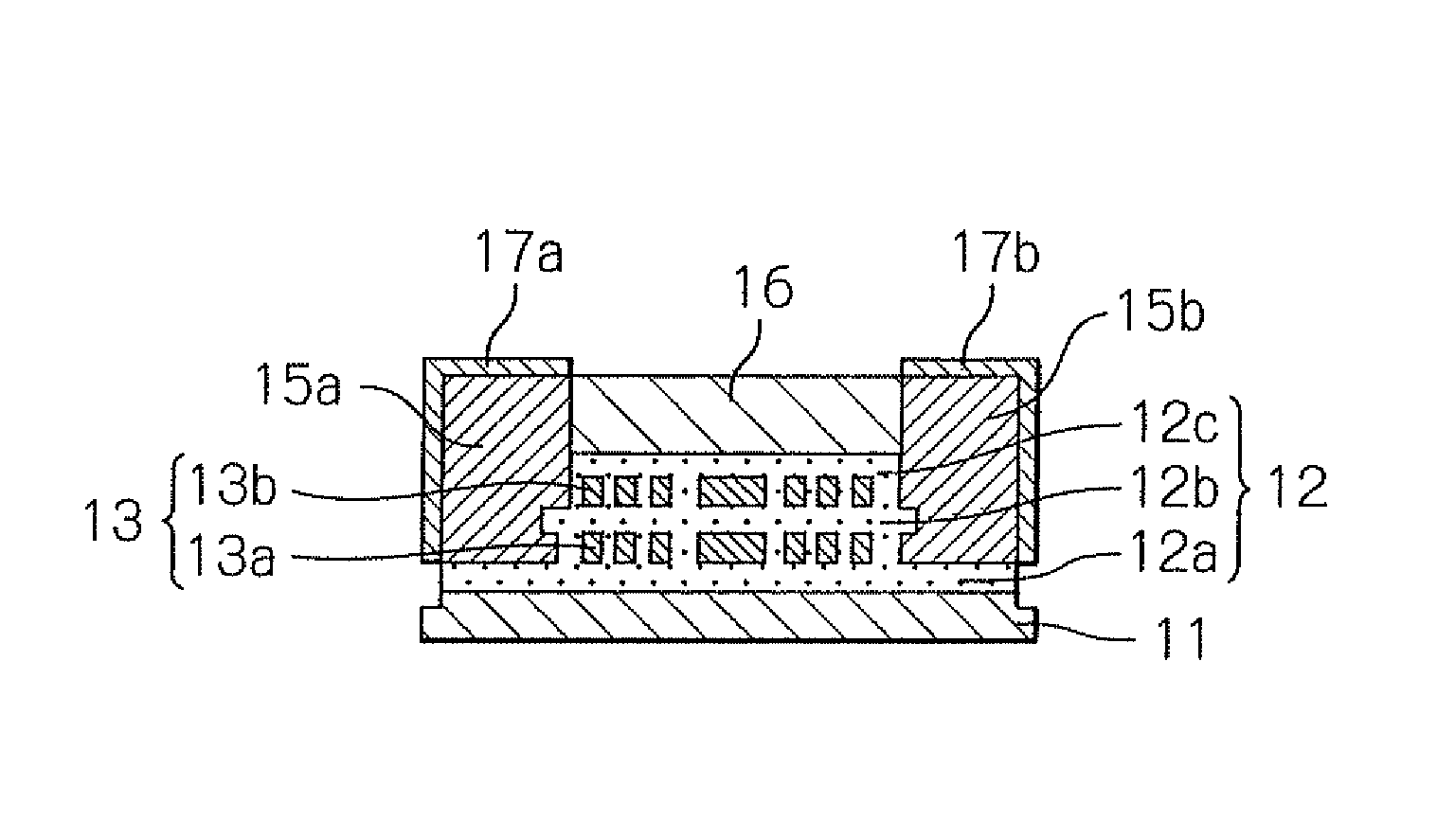

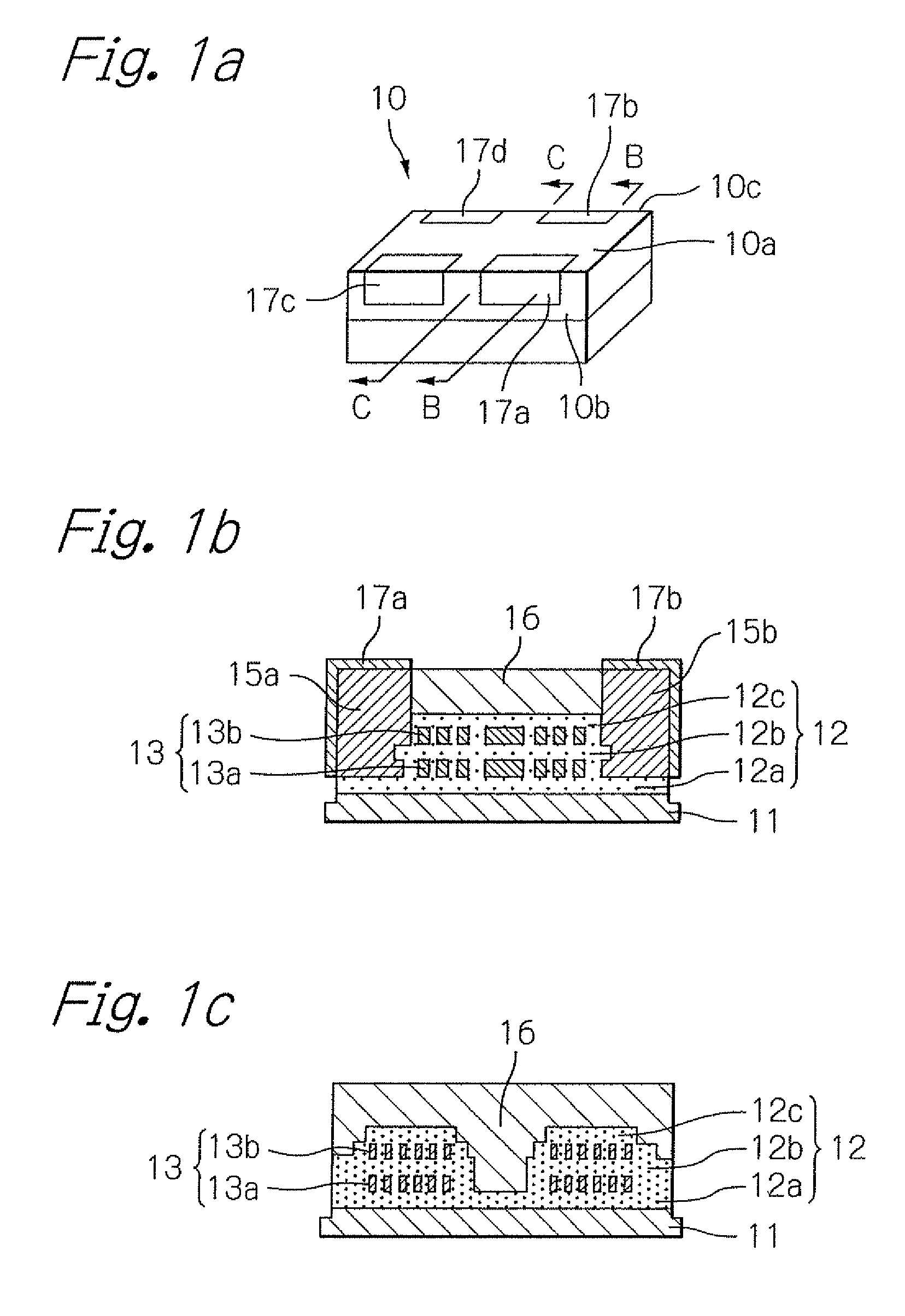

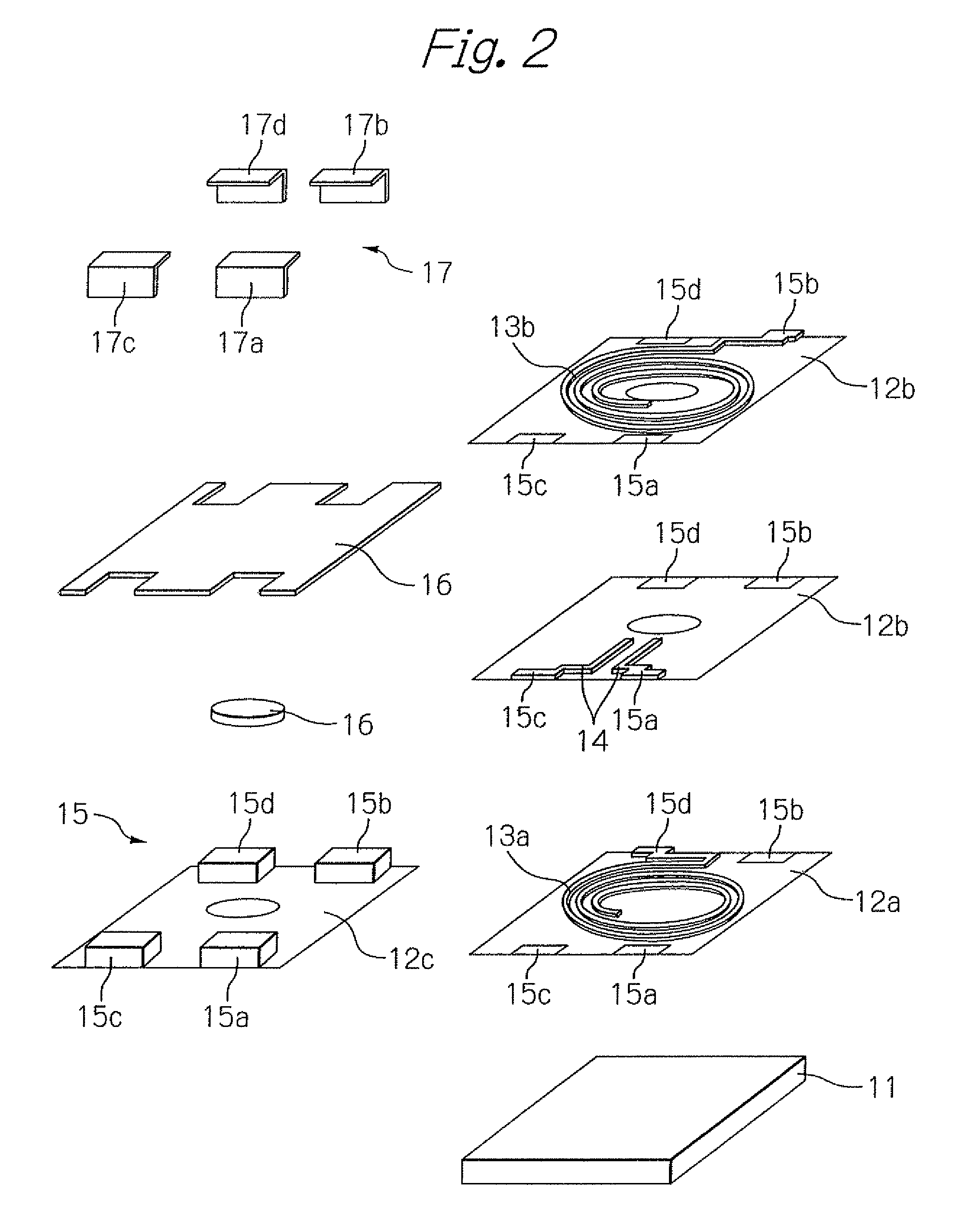

Thin film surface mount components

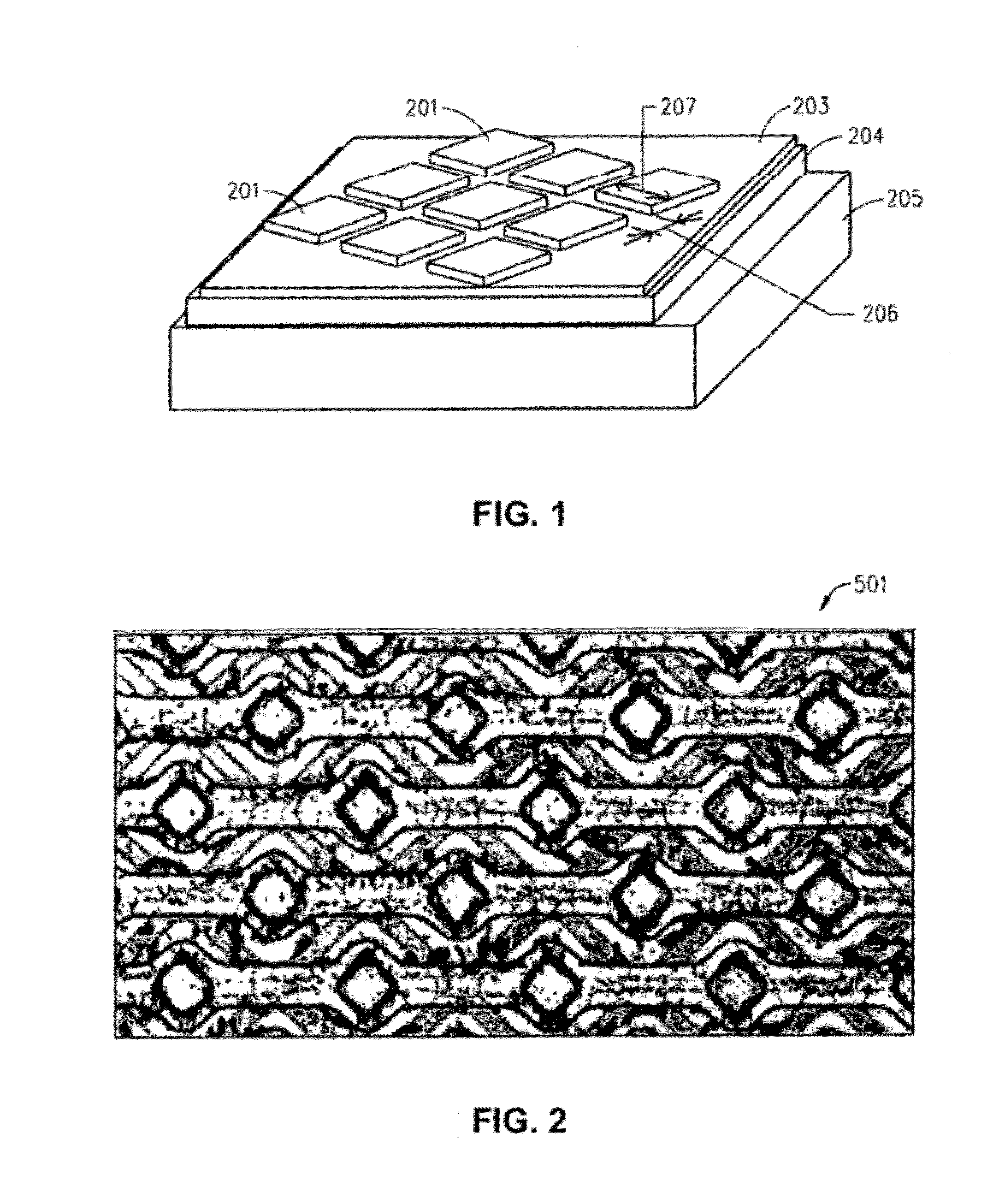

ActiveUS20110090665A1Lowering termination costImprove functionalityMultiple-port networksDigital data processing detailsSurface mountingConductive polymer

Surface mount components and related methods of manufacture involve one or more thin film circuits provided between first and second insulating substrates. The thin film circuits may include one or more passive components, including resistors, capacitors, inductors, arrays of one or more passive components, networks or filters of multiple passive components. Such thin film circuit(s) can be sandwiched between first and second insulating substrates with internal conductive pads being exposed between the substrates on end and / or side surfaces of the surface mount component. The exposed conductive pads are then electrically connected to external terminations. The external terminations may include a variety of different materials, including at least one layer of conductive polymer and may be formed as termination stripes, end caps or the like. Optional shield layers may also be provided on top and / or bottom device surfaces to protect the surface mount components from signal interference. For embodiments where one or more thin film circuits are provided between insulating base and cover substrates, such thin film circuit(s) can be formed with conductive pads that extend to and are initially exposed along one or more surfaces of the resultant component. The cover substrate is formed with a plurality of conductive elements (e.g., internal active electrodes, internal anchor electrodes and / or external anchor electrodes) that are designed to generally align with the conductive pads formed on the base substrate such that conductive element portions are exposed in groups along one or more peripheral surfaces of a device. External plated terminations are then formed directly to the exposed portions of the conductive elements.

Owner:KYOCERA AVX COMPONENTS CORP

Polymer Frame for a Chip, Such That the Frame Comprises at Least One Via in Series with a Capacitor

ActiveUS20150228416A1Interference minimizationMiniaturizationMultiple-port networksSemiconductor/solid-state device detailsEngineeringDielectric layer

A chip socket defined by an organic matrix framework, wherein the organic matrix framework comprises at least one via post layer where at least one via through the framework around the socket includes at least one capacitor comprising a lower electrode, a dielectric layer and an upper electrode in contact with the via post.

Owner:ZHUHAI ADVANCED CHIP CARRIERS & ELECTRONICS SUBSTRATE SOLUTIONS TECH

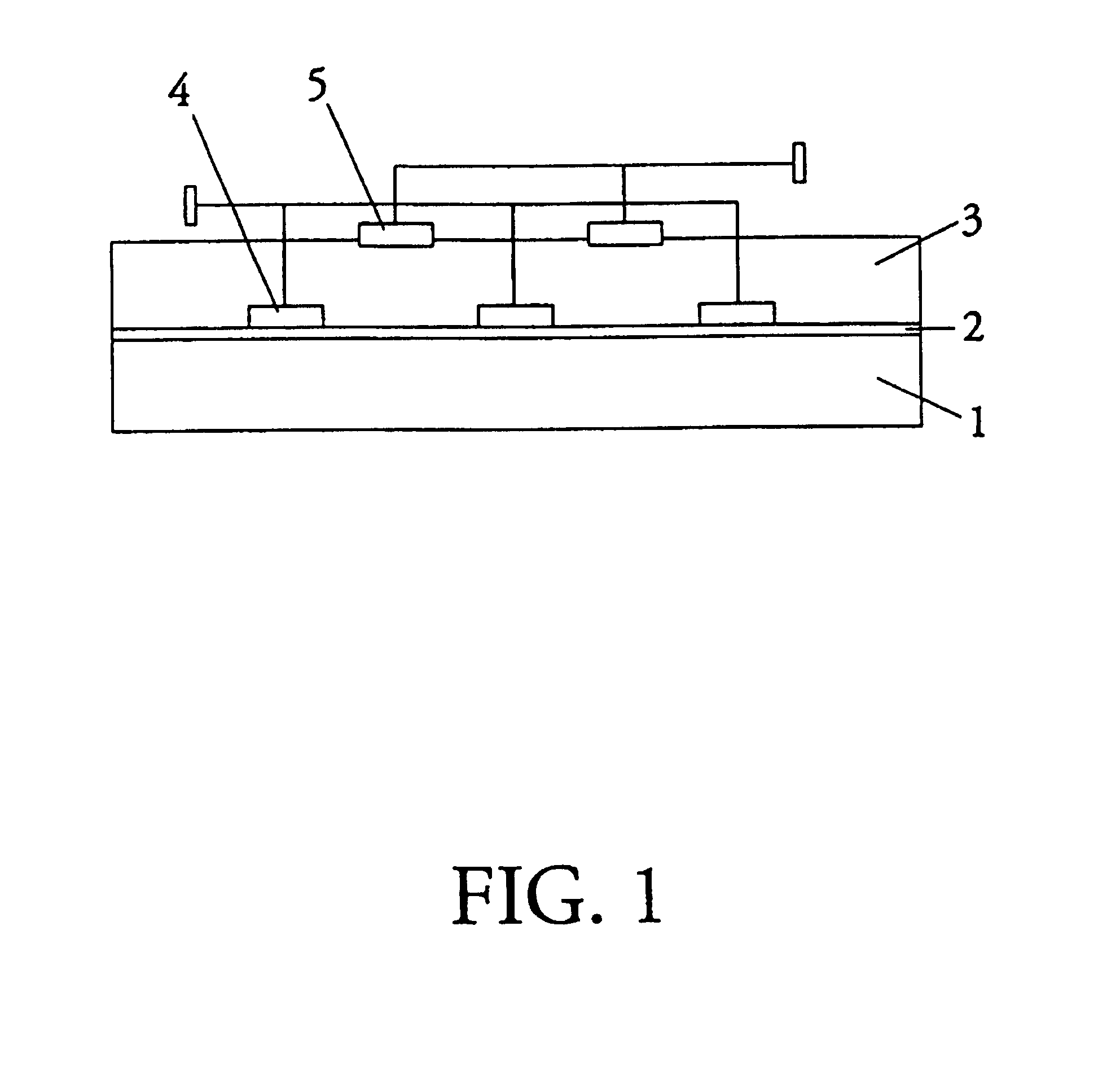

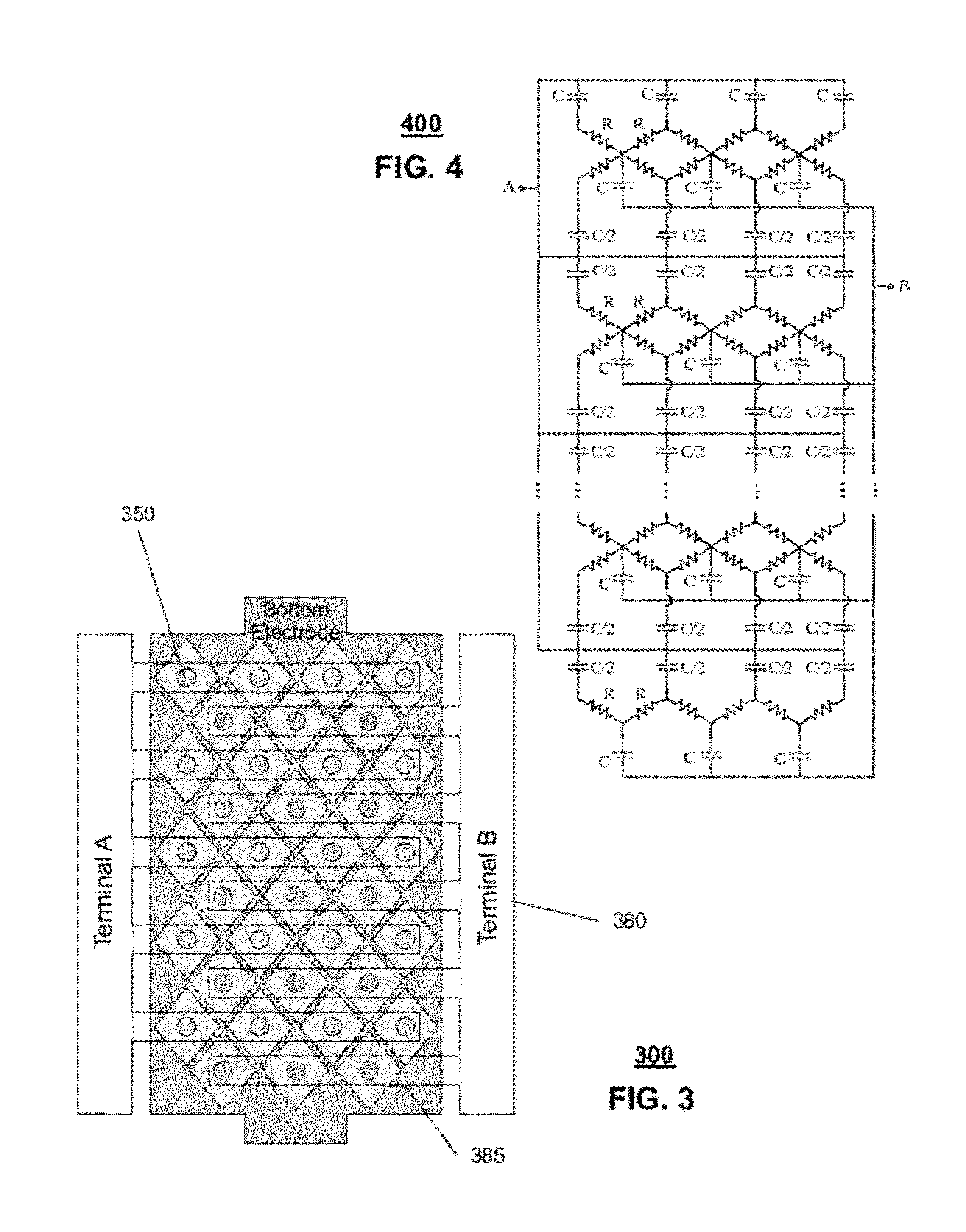

Thin film capacitors

A system that incorporates teachings of the present disclosure may include, for example, a first solid electrode, a second electrode separated into subsections, and a dielectric medium separating the subsections from the first solid electrode, where the subsections of the second electrode include a first group of subsections and a second group of subsections, where the first group of subsections are connectable with a first terminal for receiving an input signal, and where the second group of subsections is connectable with a second terminal for providing an output signal. Other embodiments are disclosed.

Owner:NXP USA INC

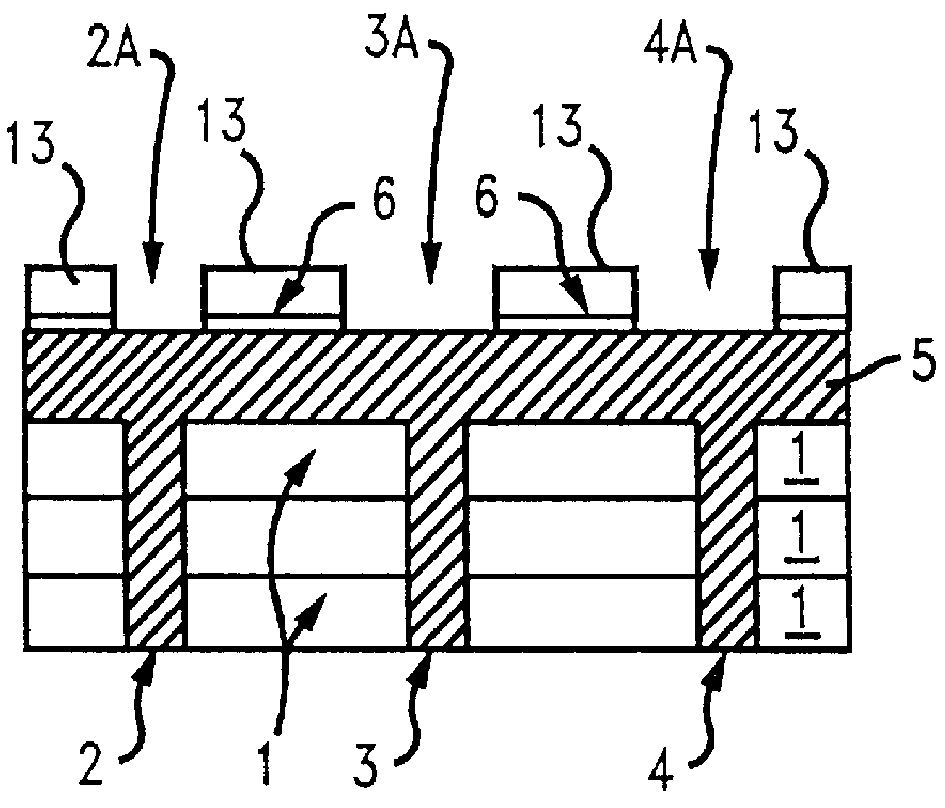

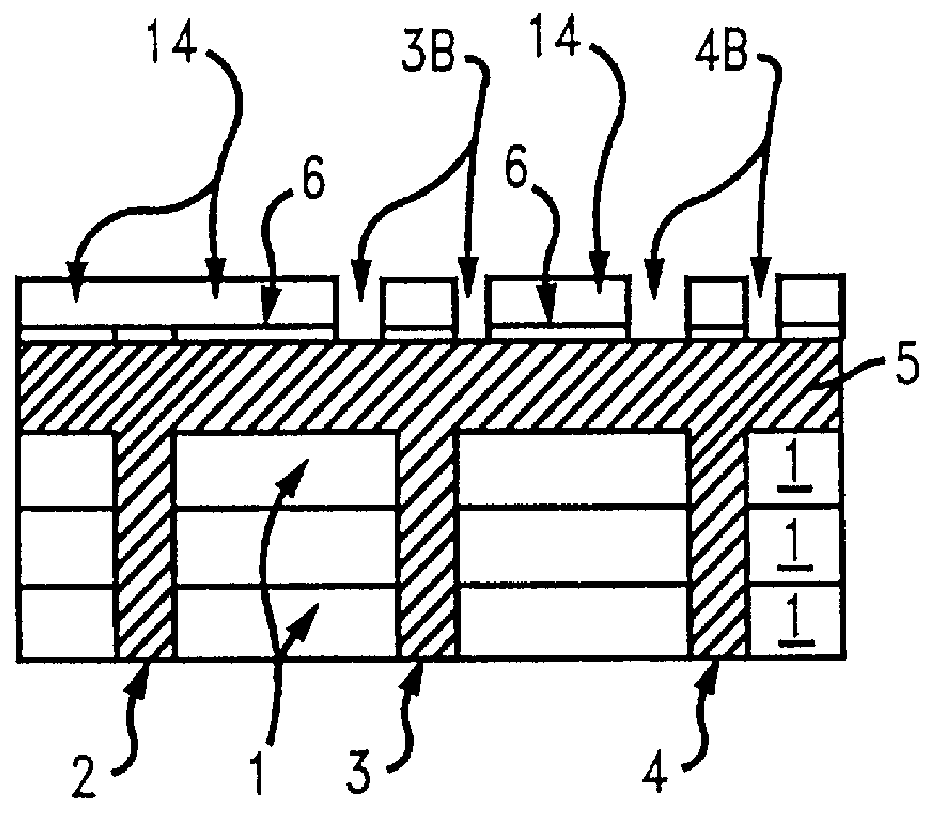

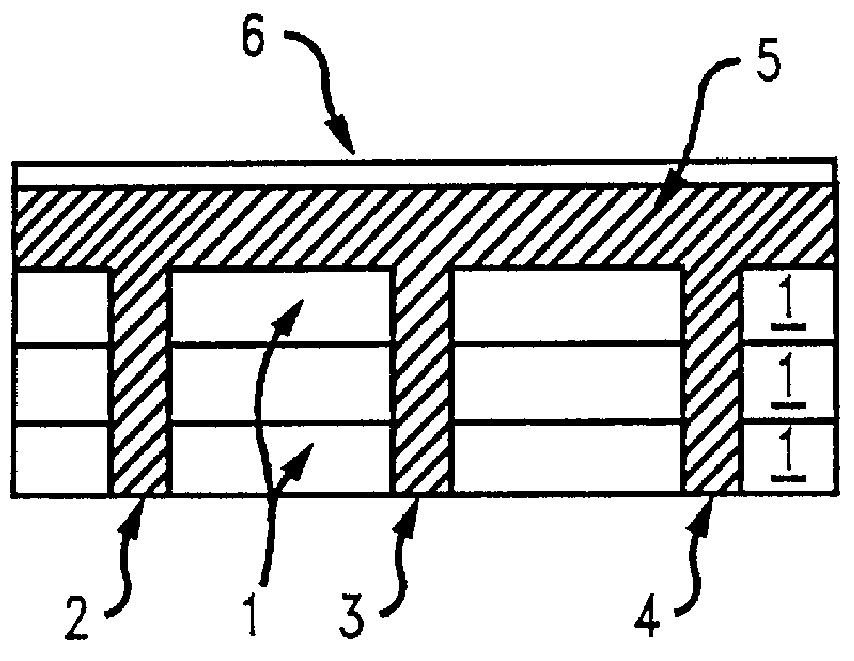

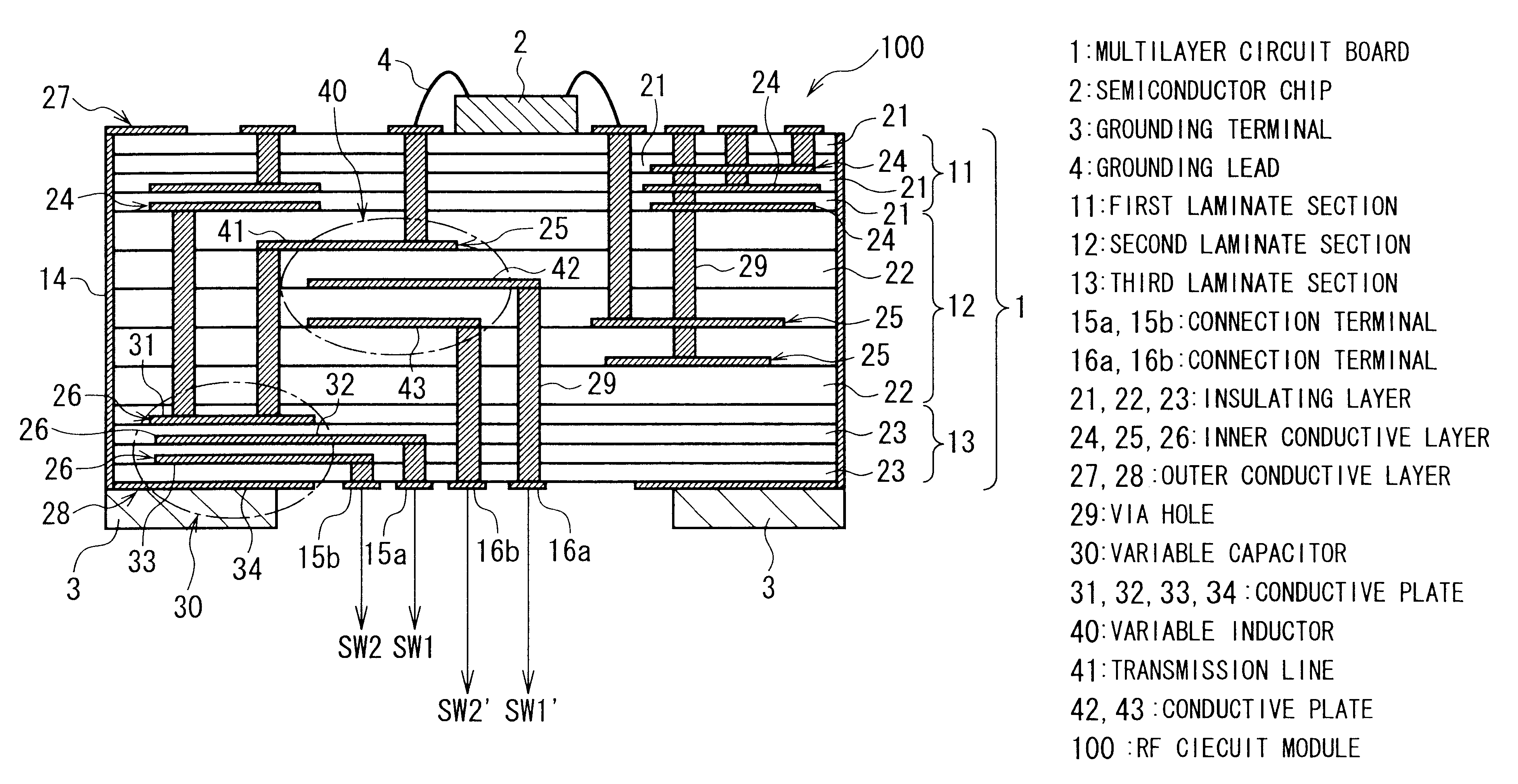

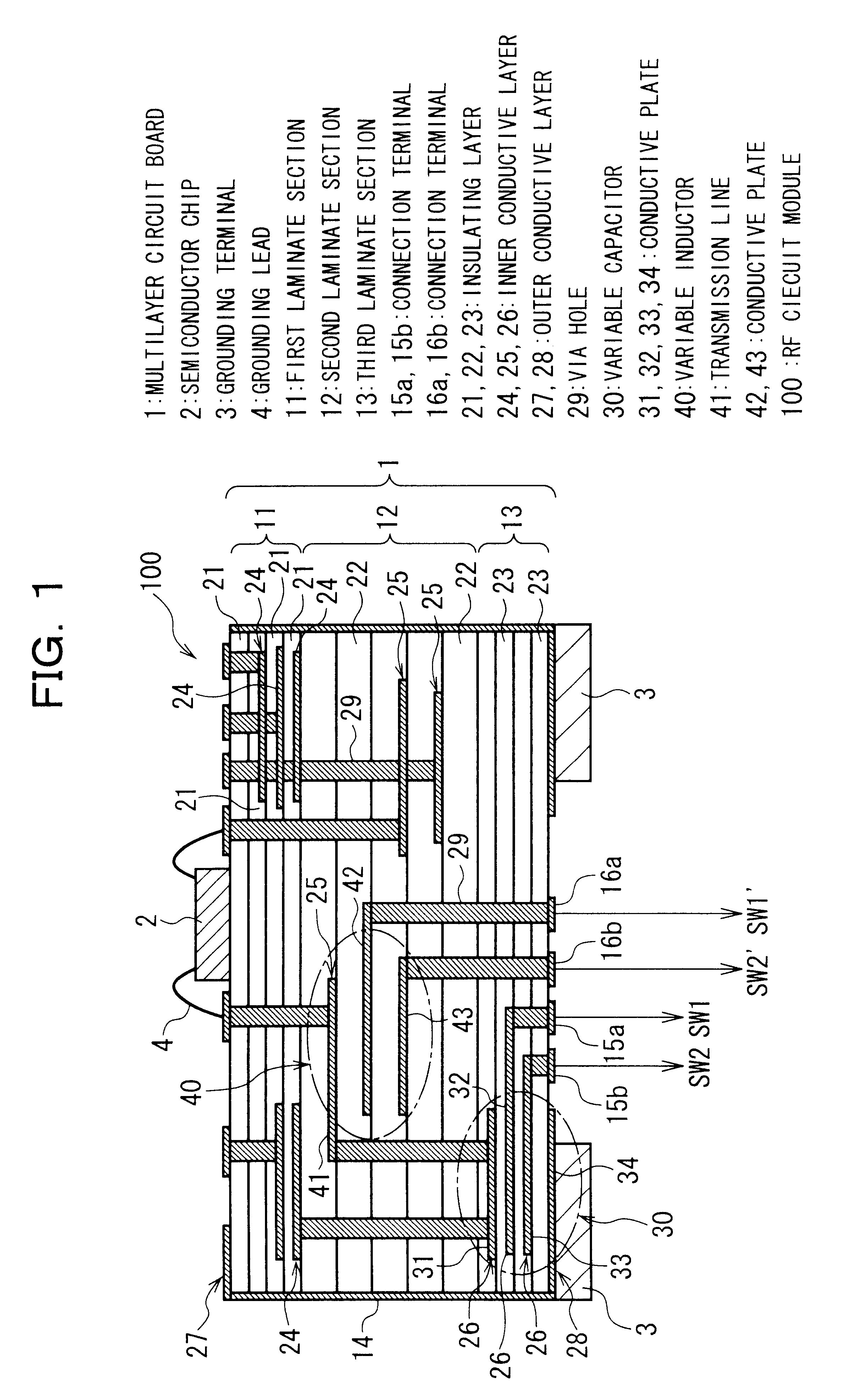

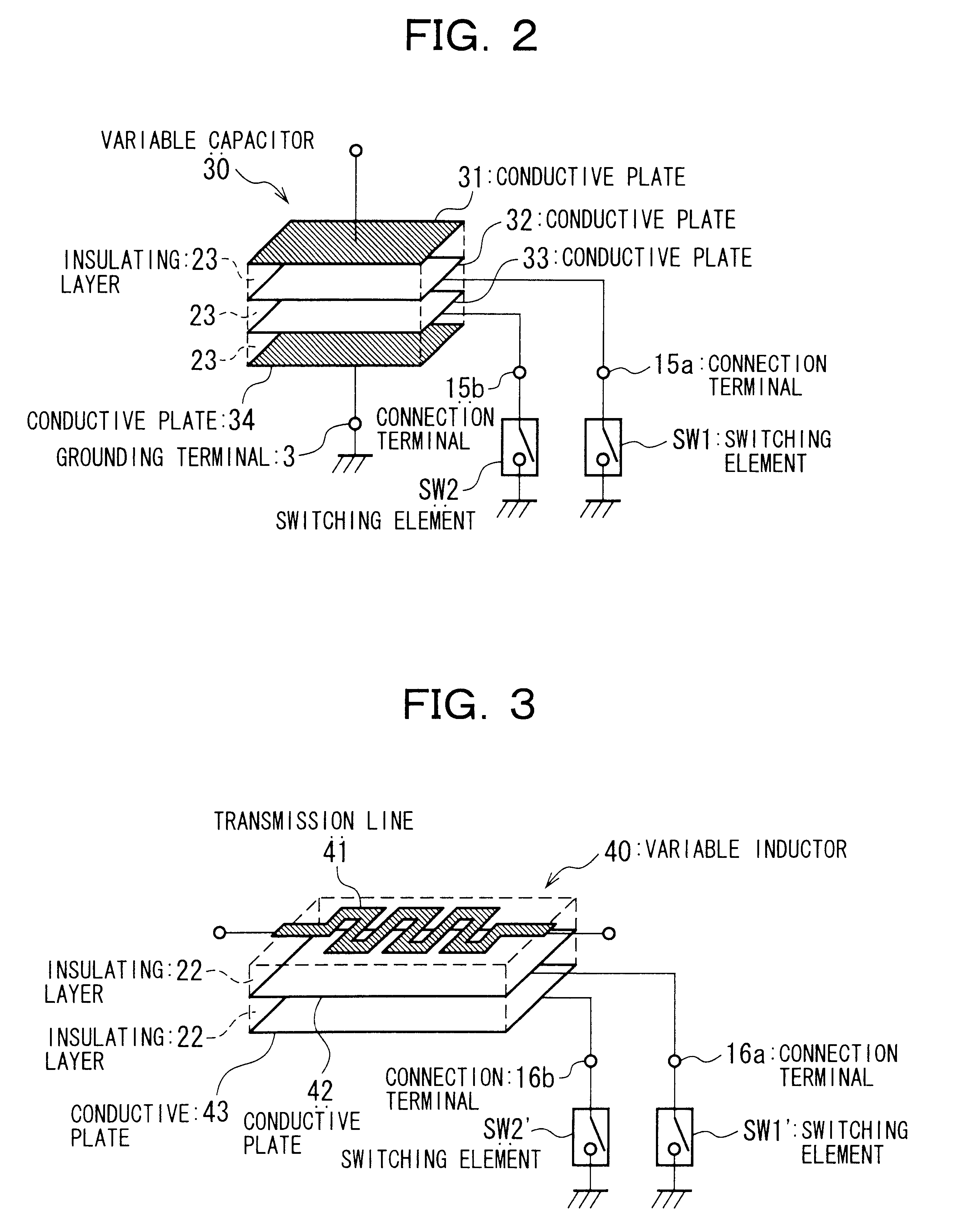

Variable capacitor and a variable inductor

InactiveUS6556416B2Compact implementationEasy to adjustMultiple-port networksHigh frequency amplifiersEngineeringInductor

A variable capacitor is formed by a multilayer circuit board having a plurality of dielectric layers; a first conductive plate, provided within the multilayer circuit board, for serving as one electrode of the variable capacitor; a second conductive plate, provided within the multilayer circuit board, for serving as the other electrode of the variable capacitor; a plurality of third conductive plates provided between the first conductive plate and the second conductive plate; and a plurality of switching means provided for grounding the third conductive plates selectively.

Owner:NEC CORP

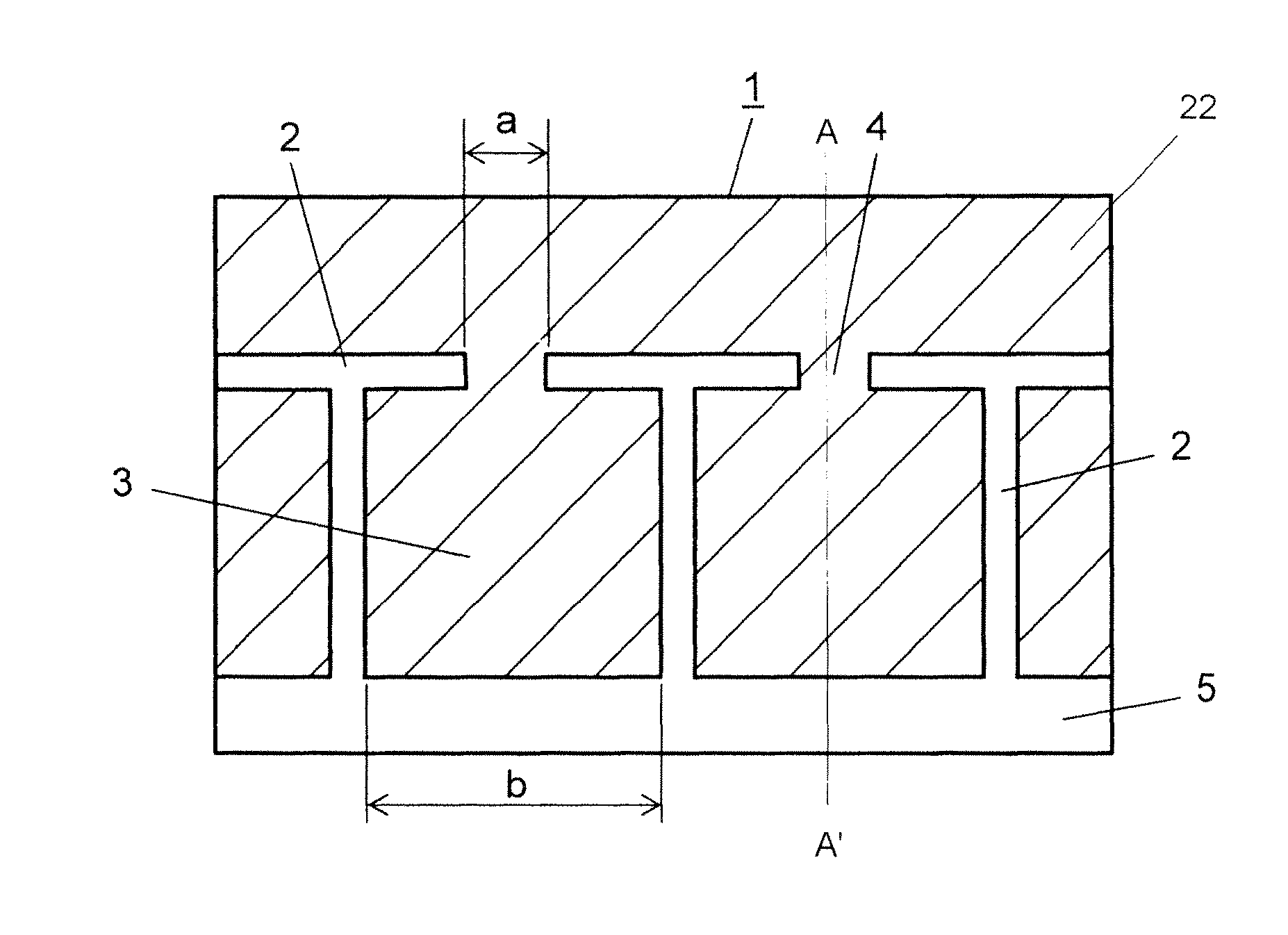

Metallization film capacitor having divided electrode with fuse

InactiveUS8310802B2Improve heat resistanceImprove pressure resistanceFixed capacitor electrodesThin/thick film capacitorHeat resistancePass rate

A metallization film capacitor that achieves both high heat resistance and high withstand voltage at the same time. A metal-deposited electrode is formed on a PEN film in each of a pair of metalized films. These metalized films are wound such that the metal-deposited electrodes face each other via the dielectric film in between. A metalized contact electrode is formed on both end faces of these wound metalized films to configure the metallization film capacitor. A divisional electrode is provided on the metal-deposited electrode. In addition, a fuse is coupled to this divisional electrode for providing a self-maintaining function. Pass rate a / b of a deposition pattern is set to 4.0 or smaller, where ‘a’ is the fuse width, and ‘b’ is the length of the divisional electrode in a lengthwise direction of the metalized films.

Owner:PANASONIC CORP

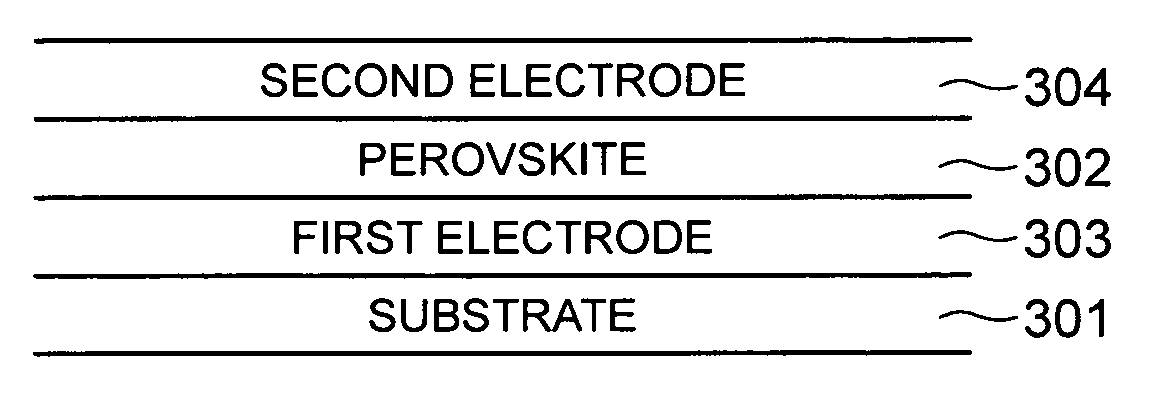

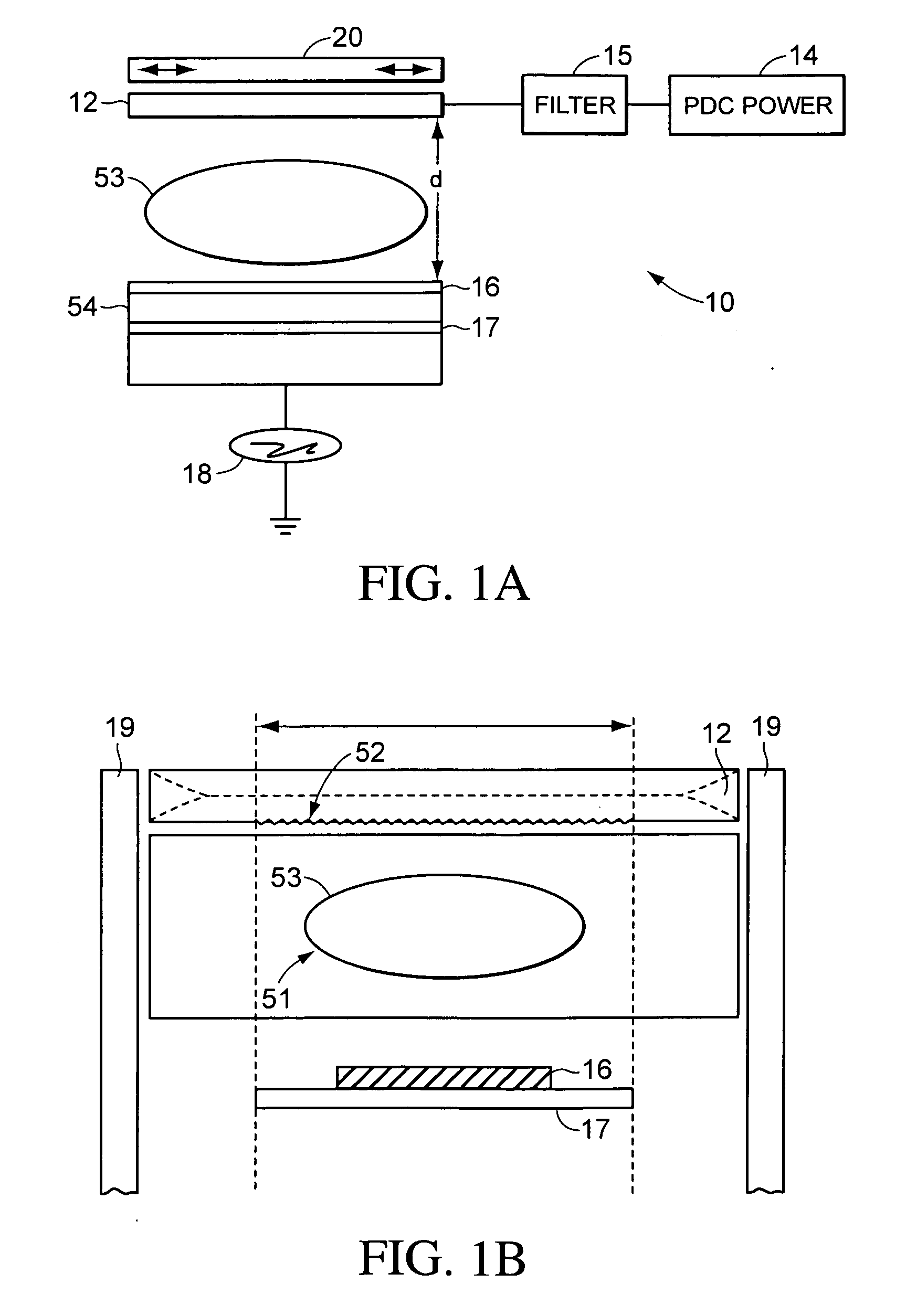

Deposition of perovskite and other compound ceramic films for dielectric applications

InactiveUS20070053139A1Increase capacitanceReduce the temperatureThin/thick film capacitorFixed capacitor dielectricHigh ratePulsed DC

In accordance with the present invention, deposition of perovskite material, for example barium strontium titanite (BST) film, by a pulsed-dc physical vapor deposition process or by an RF sputtering process is presented. Such a deposition can provide a high deposition rate deposition of a layer of perovskite. Some embodiments of the deposition address the need for high rate deposition of perovskite films, which can be utilized as a dielectric layer in capacitors, other energy storing devices and micro-electronic applications. Embodiments of the process according to the present invention can eliminate the high temperature (>700° C.) anneal step that is conventionally needed to crystallize the BST layer.

Owner:DEMARAY

Layer capacitor element and production process as well as electronic device

InactiveUS7161793B2Excellent high-frequency tracking performanceReduce deteriorationTransistorFixed capacitor electrodesThin layerInorganic materials

Owner:FUJITSU LTD

Very thin film capacitor for dynamic random access memory (DRAM)

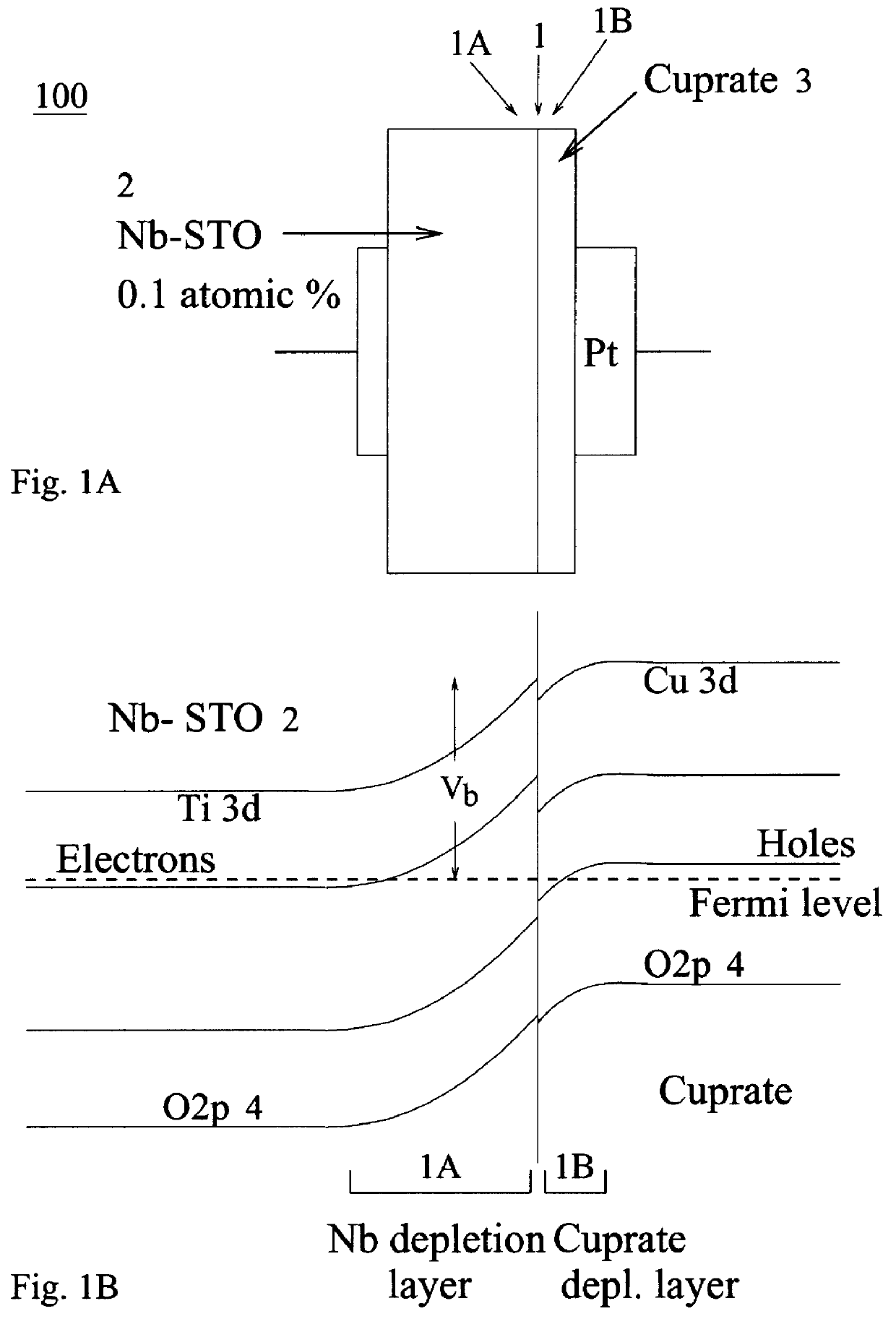

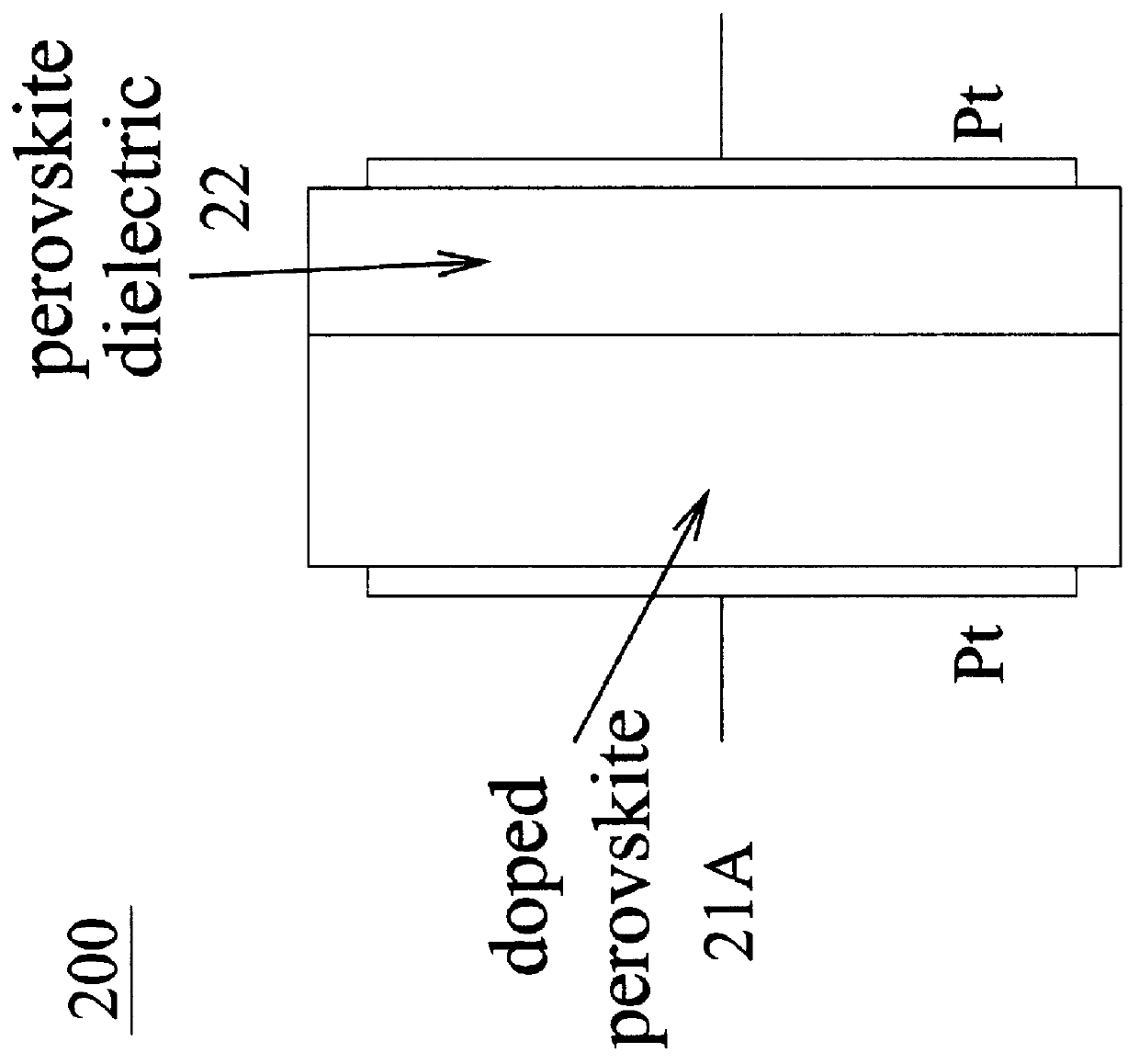

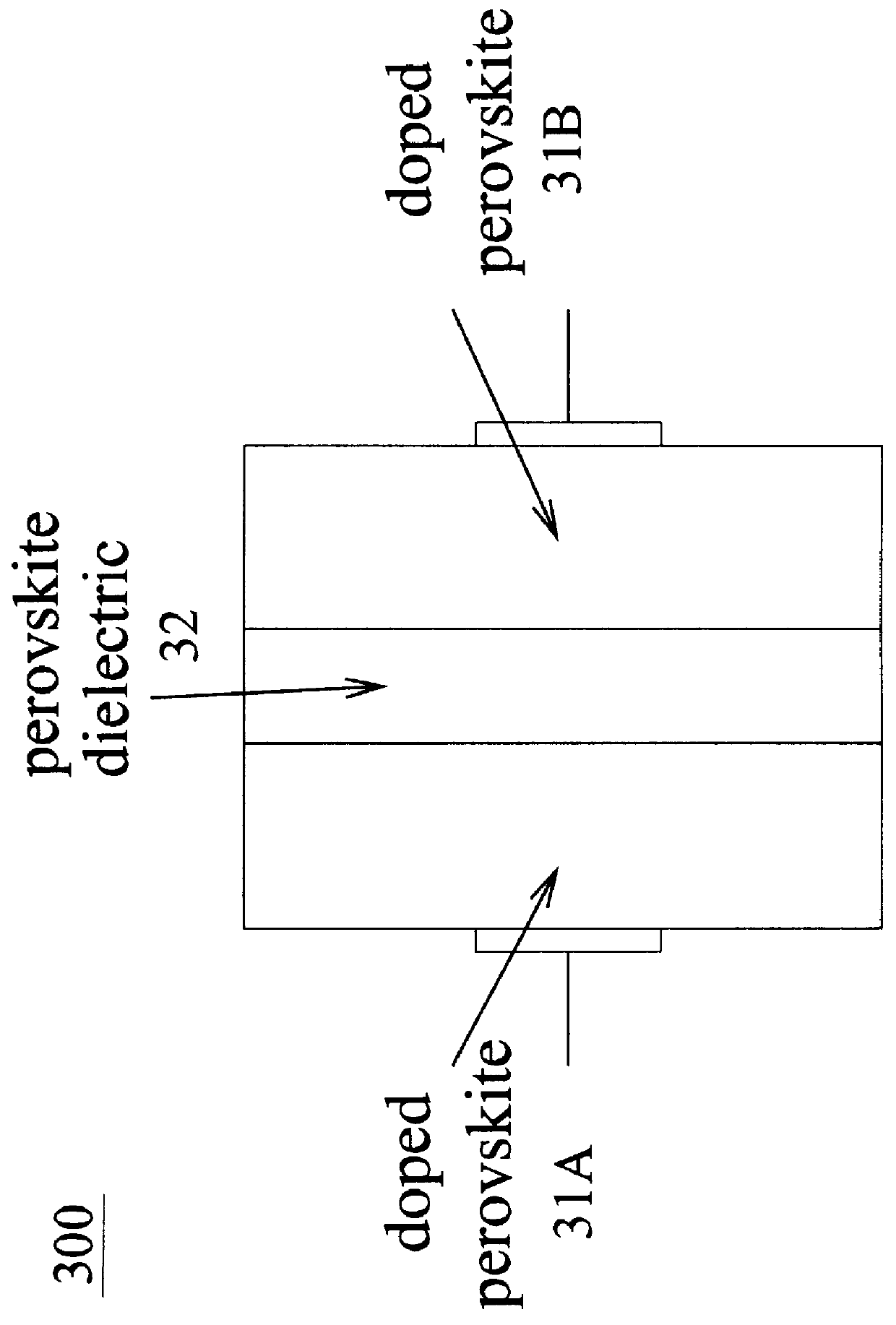

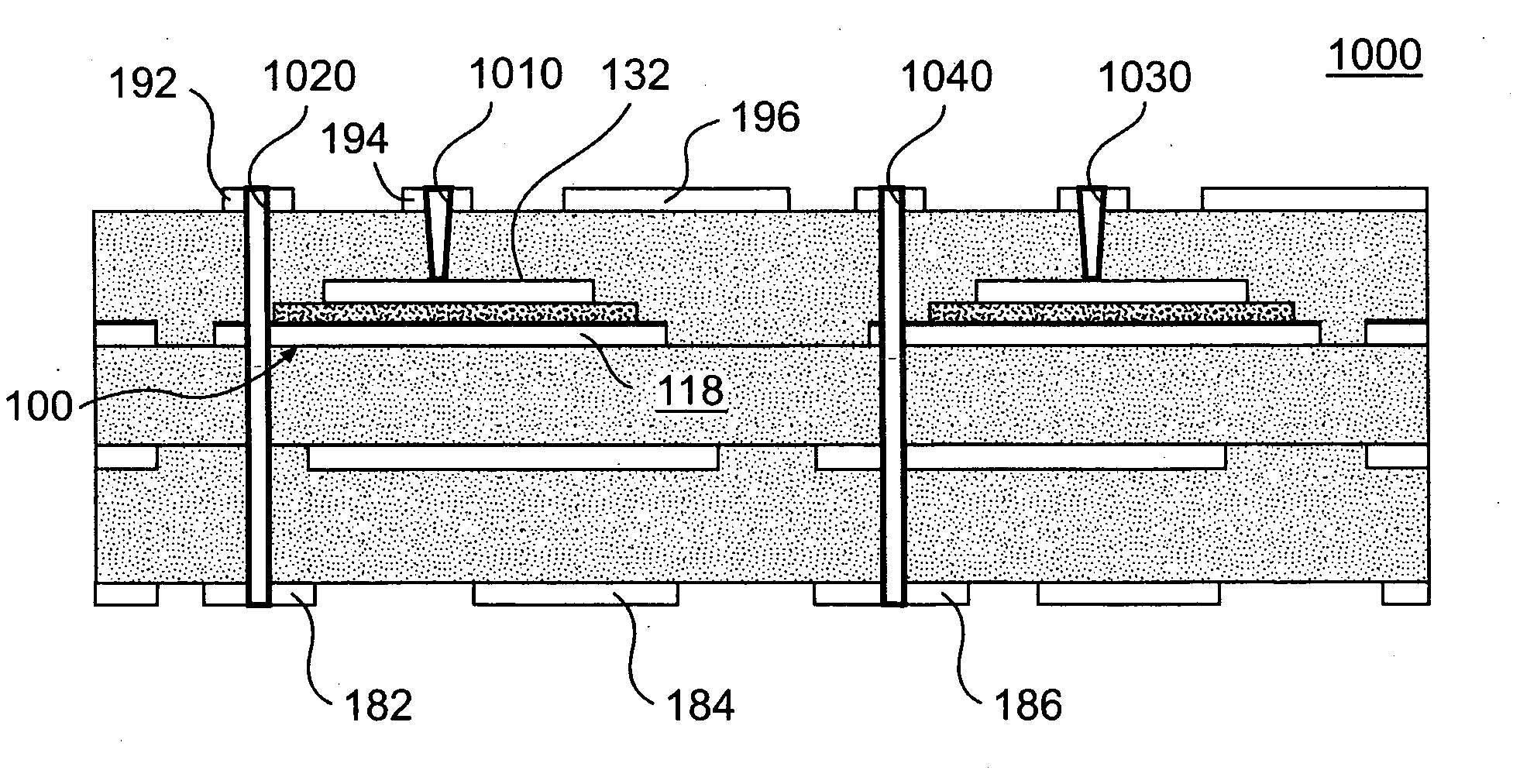

A capacitor and a dynamic random access memory (DRAM) incorporating such a capacitor, includes a first layer of conducting, doped perovskite material, a second layer of another conducting, doped perovskite of opposite polarity in contact with the first layer, and a depletion layer formed at an interface between the first and second layers of conducting perovskite materials, the depletion layer being an insulating layer of the capacitor. Another capacitor and DRAM incorporating such a capacitor, includes a first electrode, a second electrode opposing the first electrode, and a thin-film of high dielectric constant perovskite material sandwiched between the first and second electrodes. At least one of the first and second electrodes is formed from substantially the same perovskite material, as the thin-film, in conducting, doped form.

Owner:IBM CORP

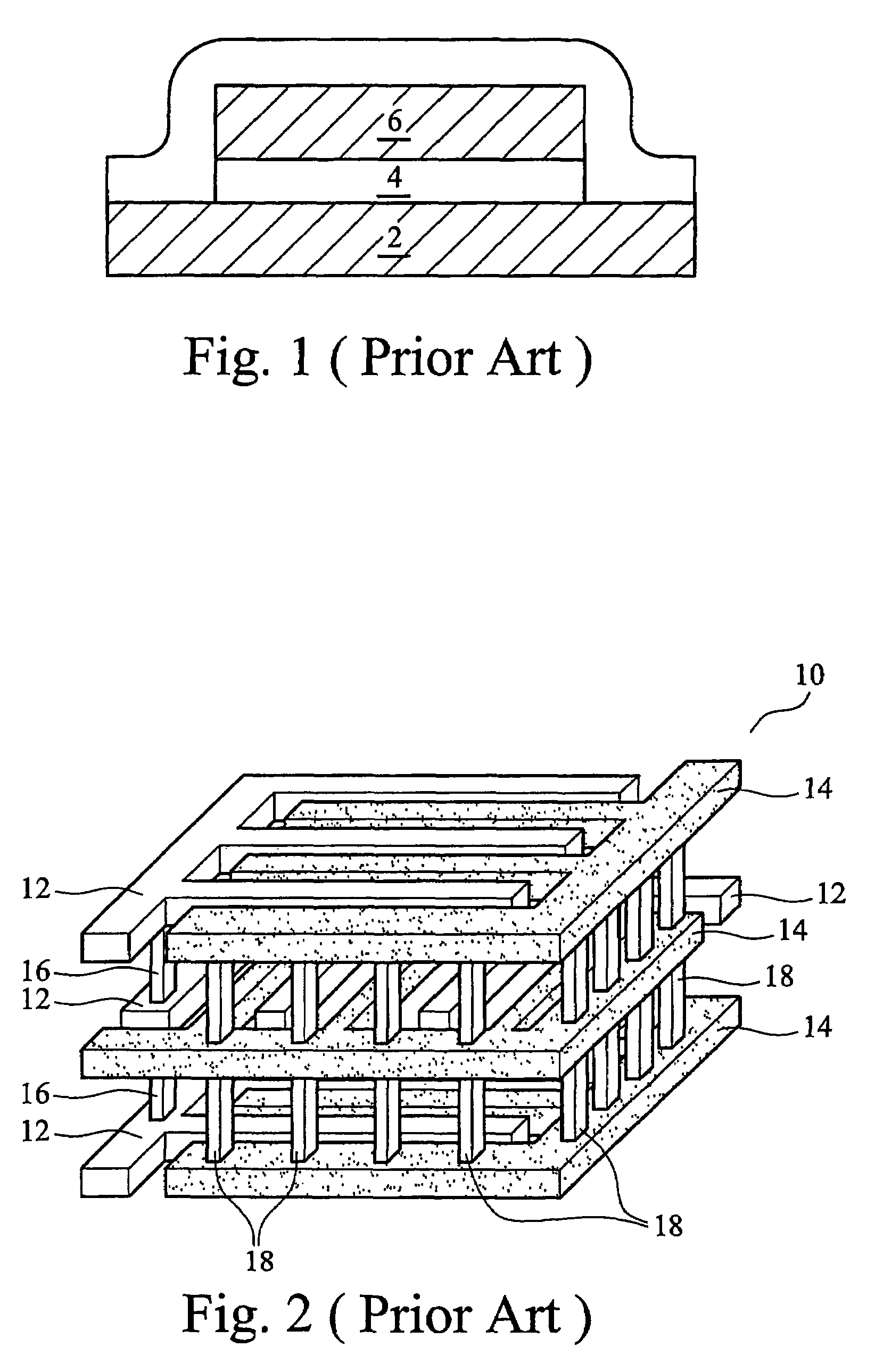

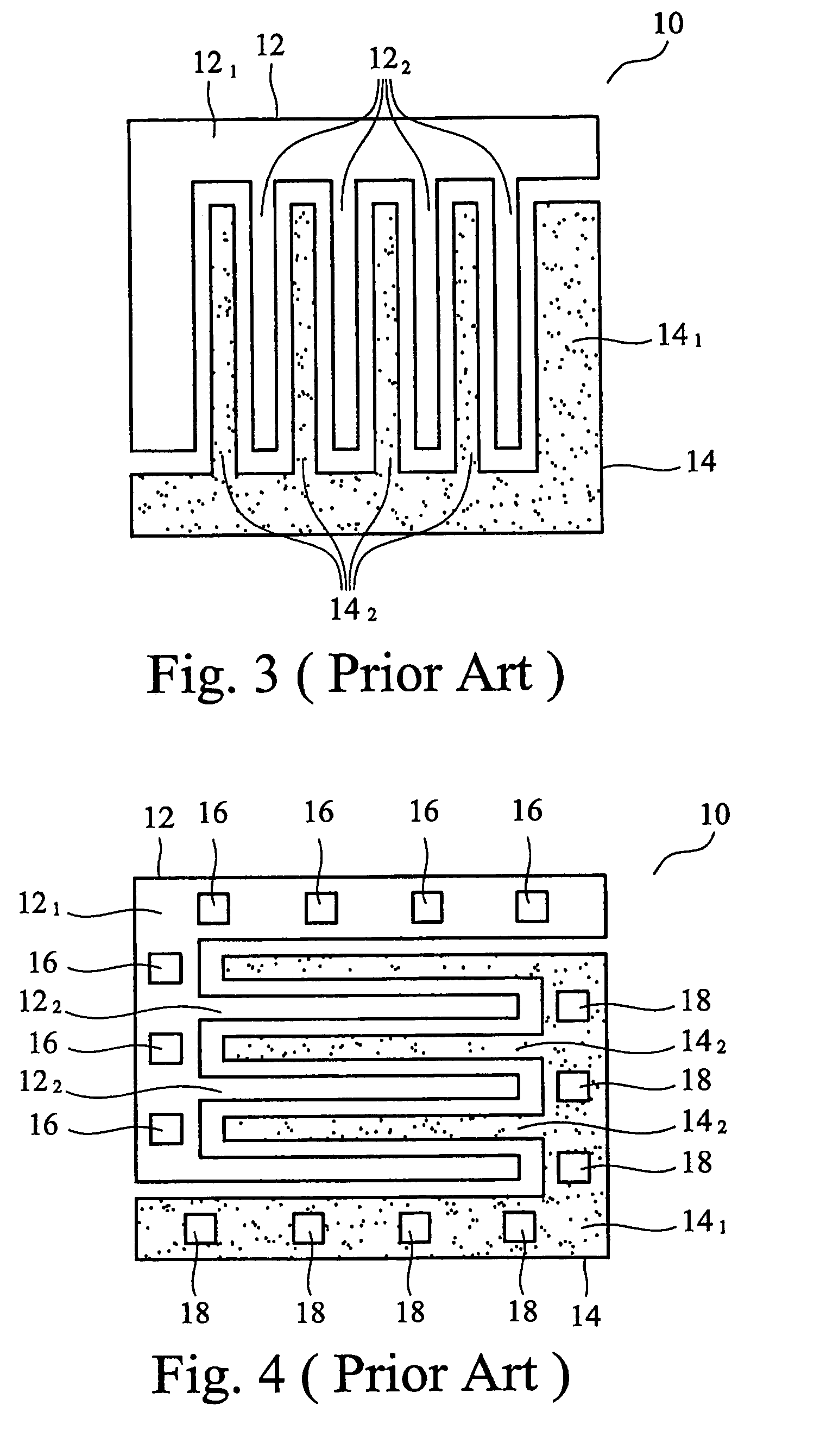

Thick film capacitors, embedding thick-film capacitors inside printed circuit boards, and methods of forming such capacitors and printed circuit boards

ActiveUS20060002097A1Reduce resultant dielectric constantImprove performancePrinted circuit assemblingLine/current collector detailsFilm capacitorElectrical and Electronics engineering

Owner:CHEMTRON RES

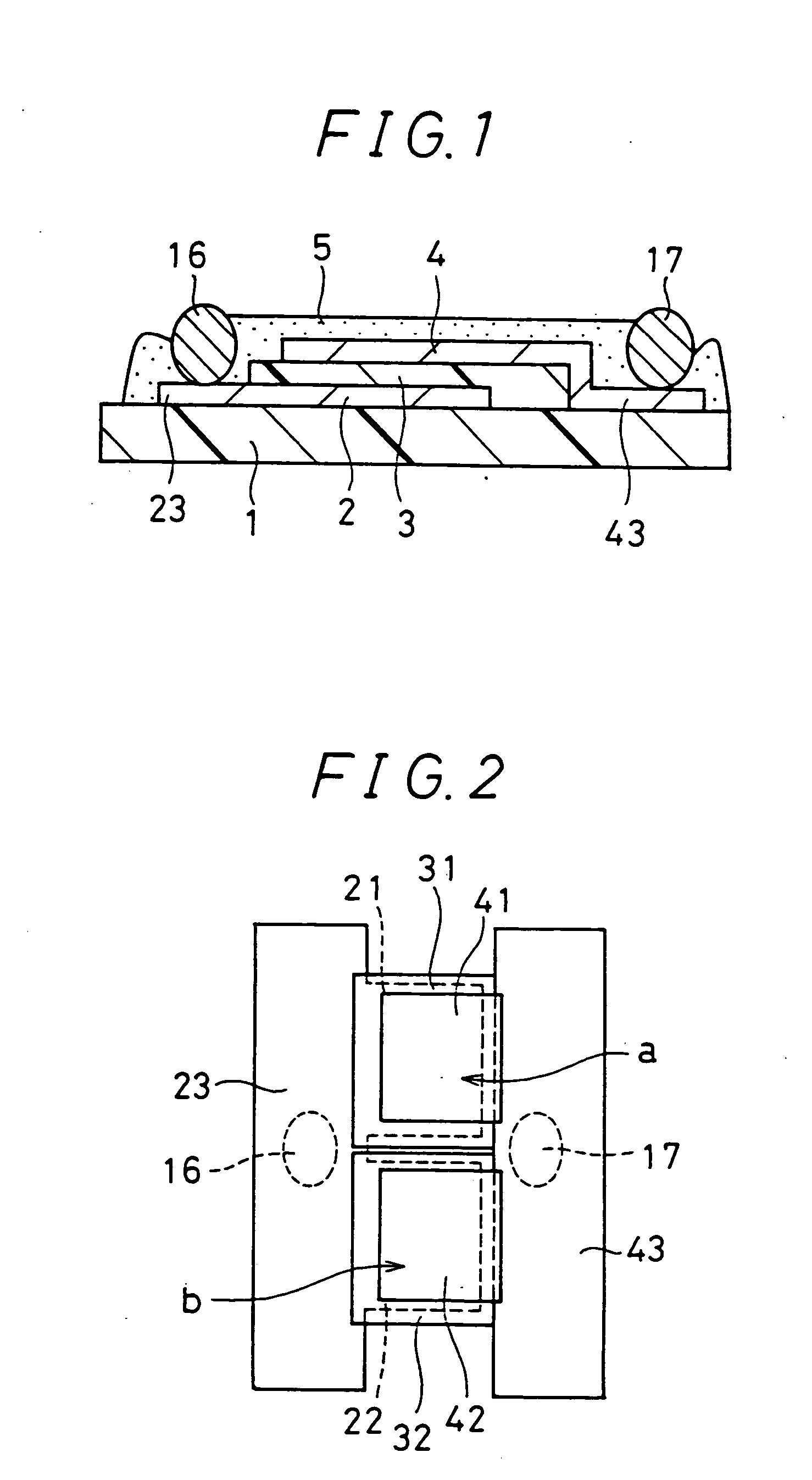

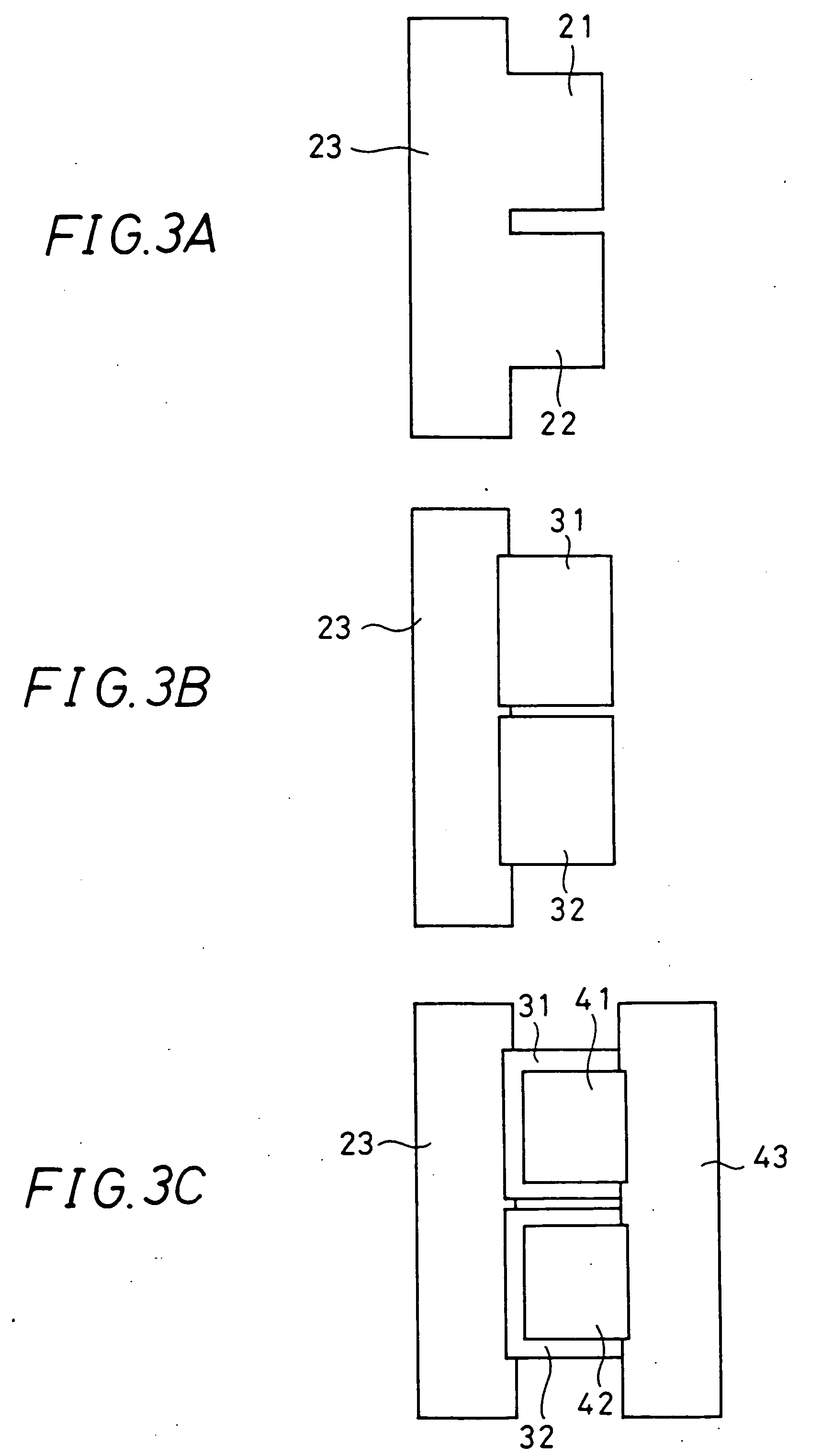

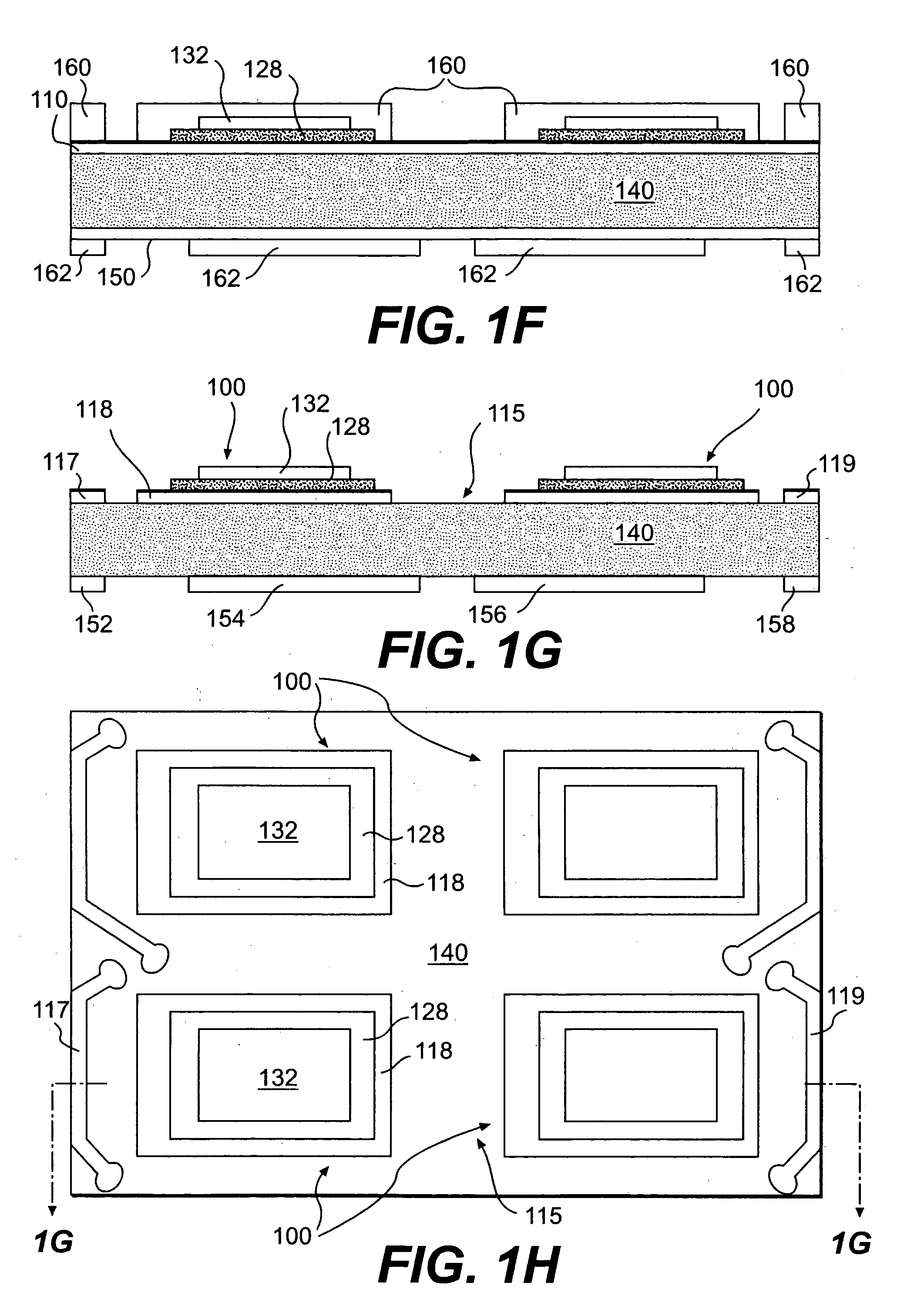

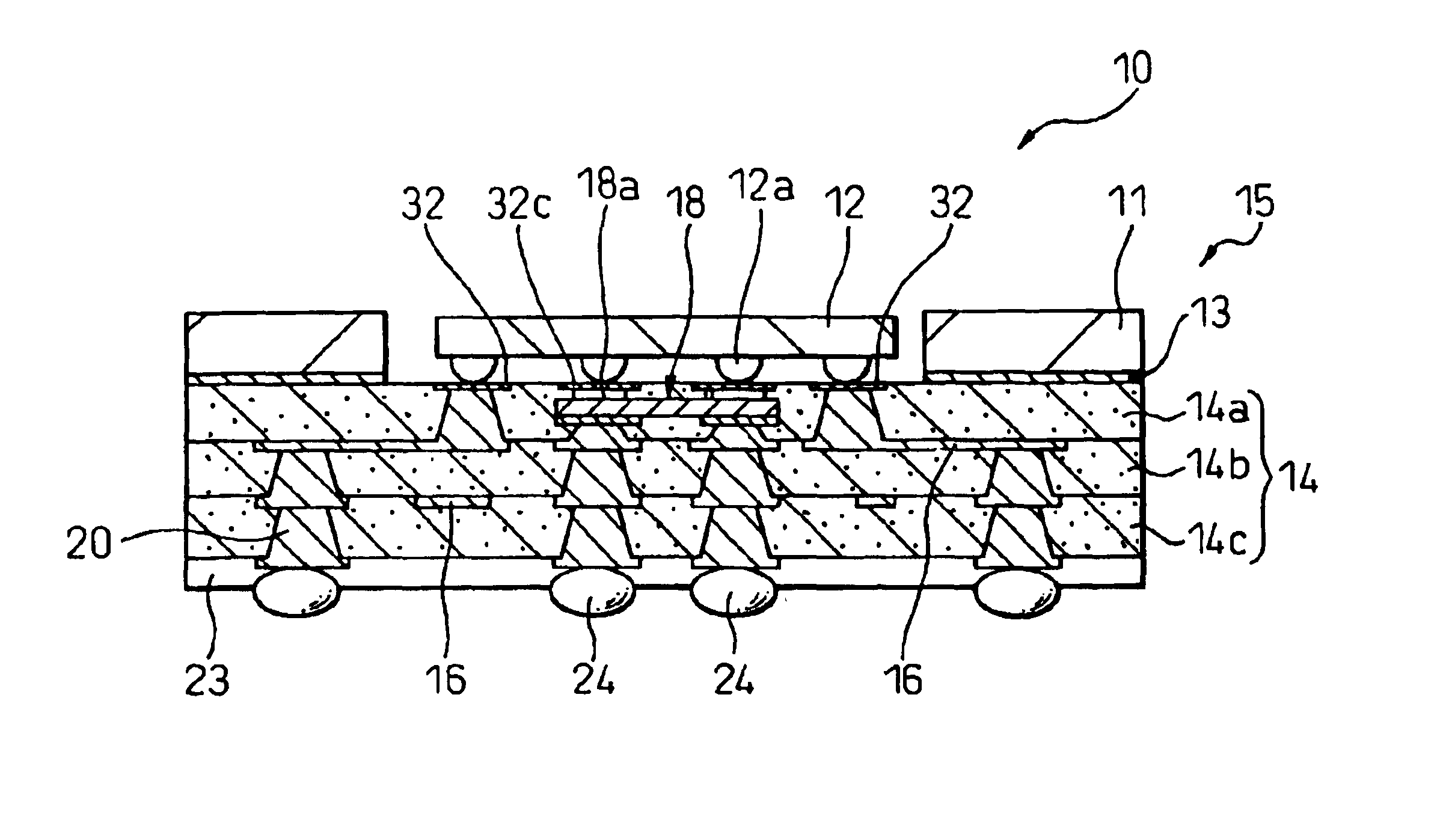

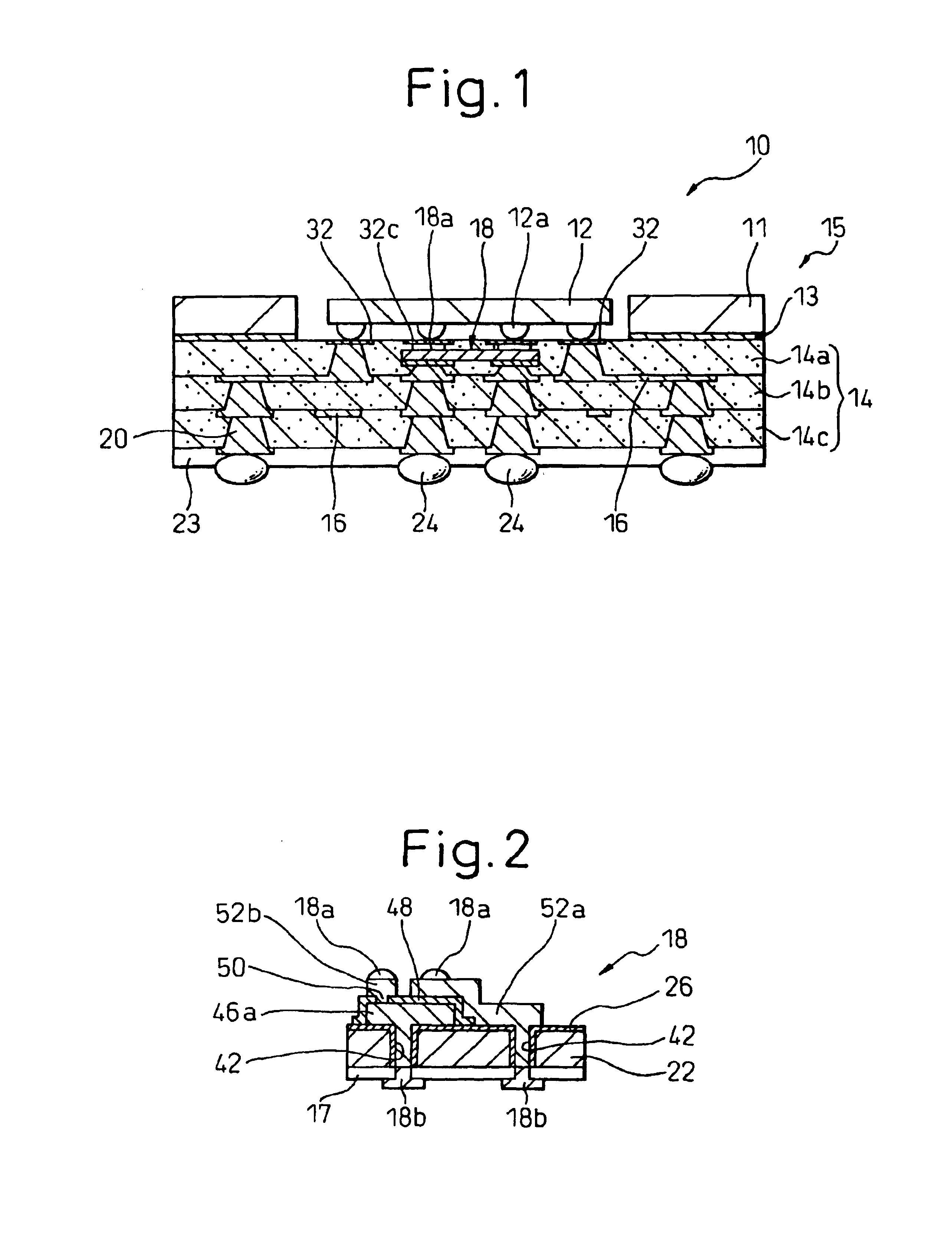

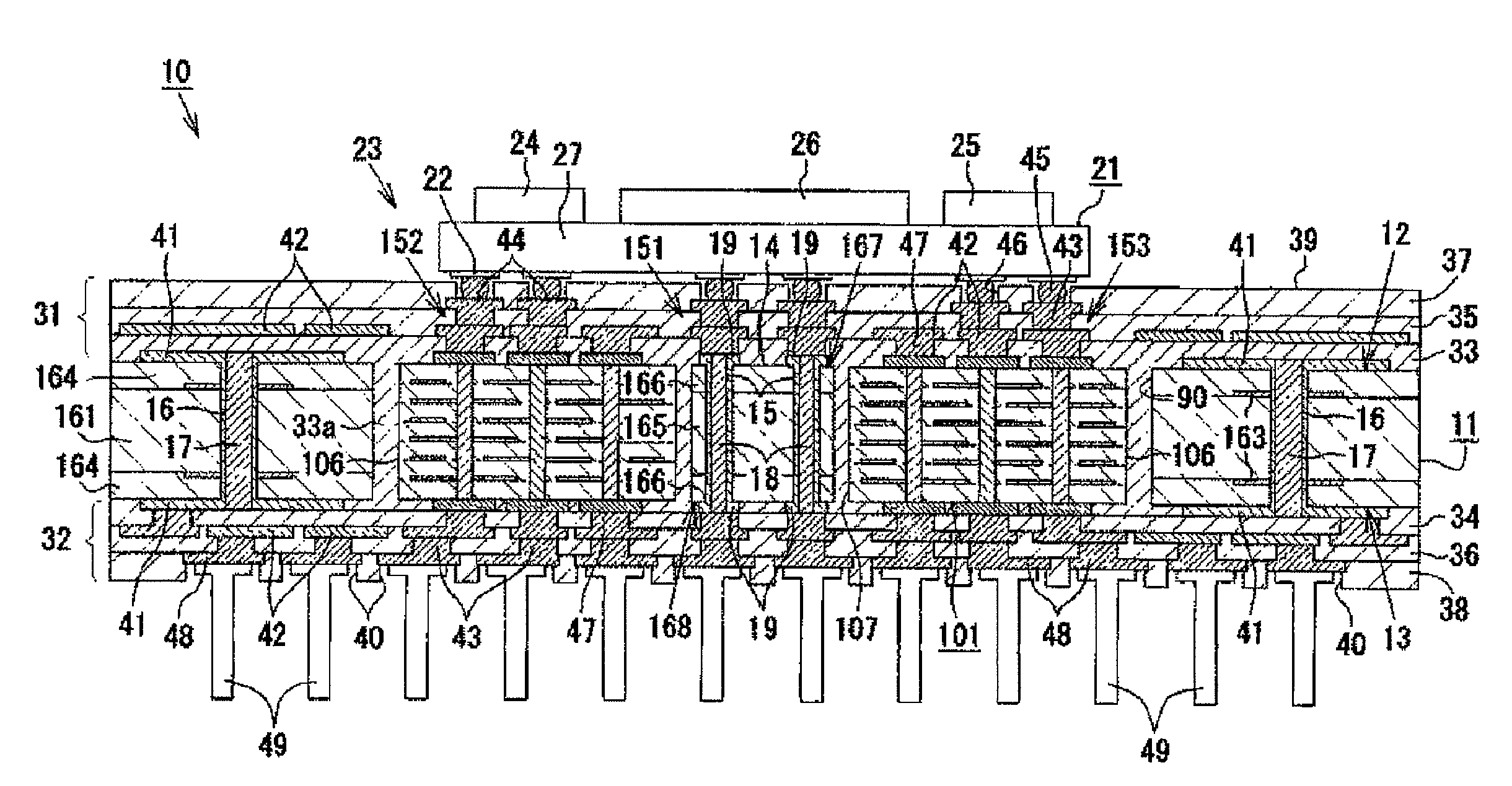

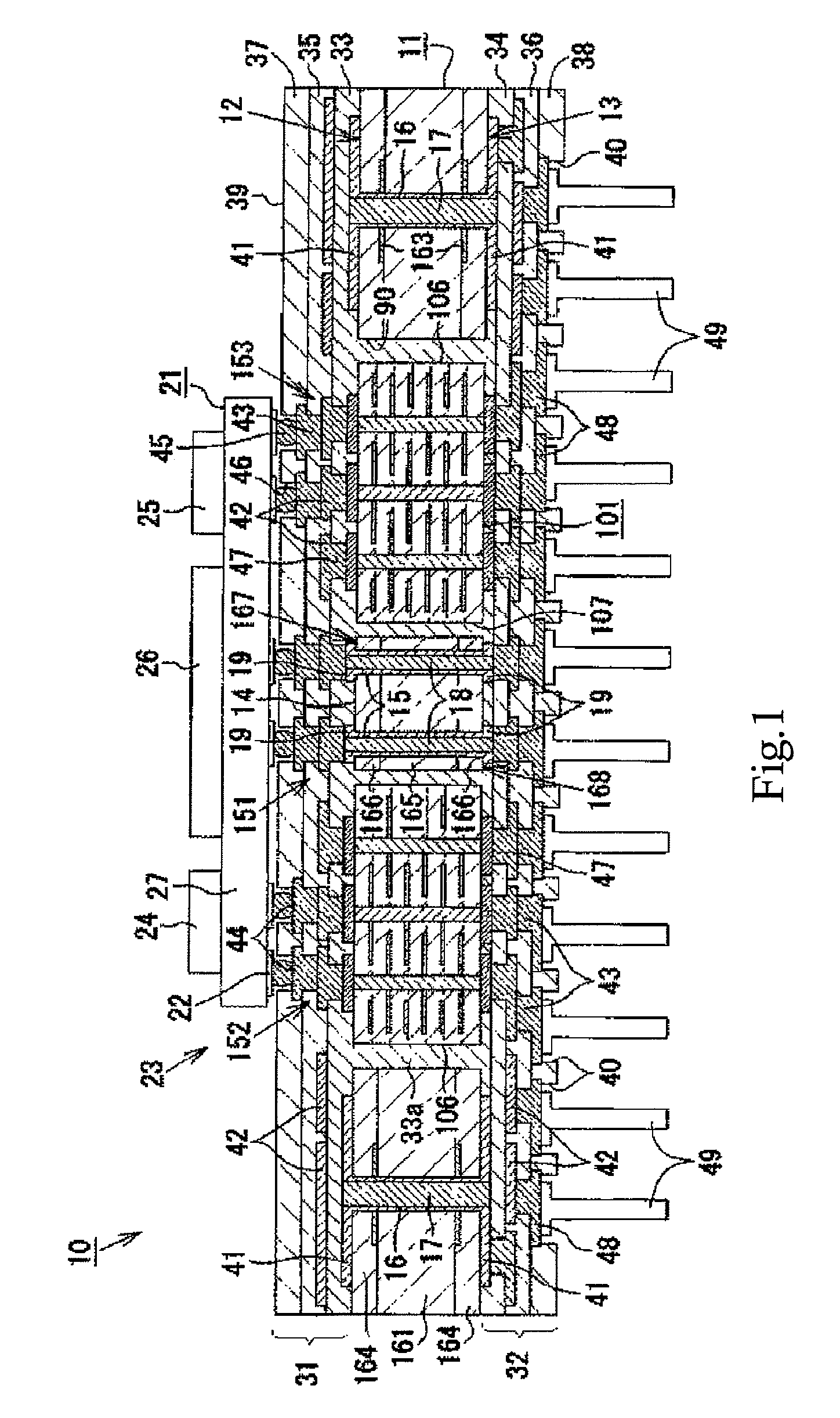

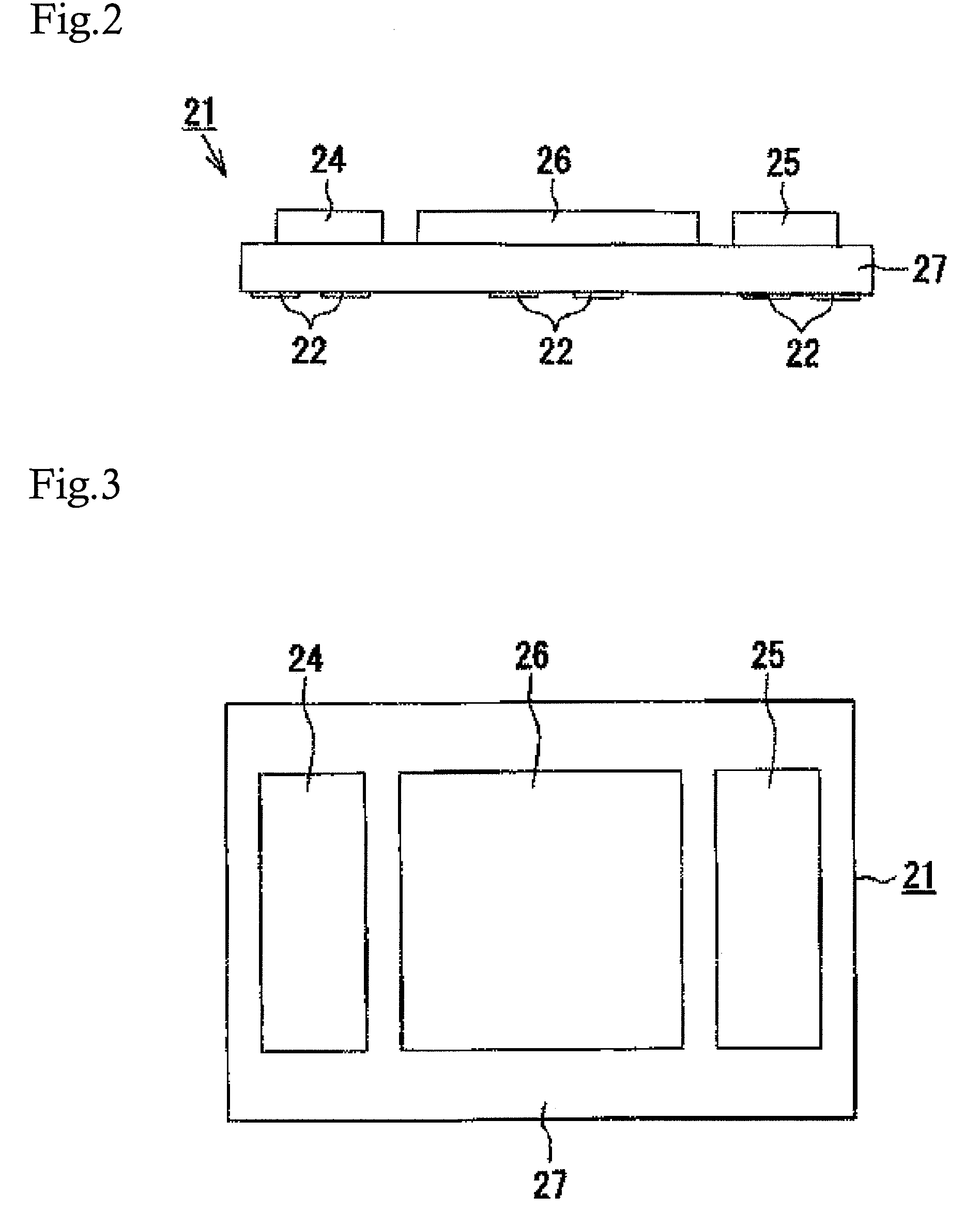

Semiconductor device package and method of production and semiconductor device of same

InactiveUS6914322B2Reduce distanceReduce connectionsThin/thick film capacitorSemiconductor/solid-state device detailsElectrical conductorShortest distance

A semiconductor device including a semiconductor device package providing a capacitor in its circuit board and a semiconductor chip mounted on that package, wherein the capacitor is provided directly under a semiconductor chip mounting surface of the circuit board on which the semiconductor chip is to be mounted and the conductor circuit electrically connecting the semiconductor chip and capacitor is made the shortest distance by having the external connection terminals of the capacitor directly connected to the other surface of the connection pads exposed at one surface at the semiconductor chip mounting surface of the circuit board and to which the electrode terminals of the semiconductor chip are to be directly connected.

Owner:SHINKO ELECTRIC IND CO LTD

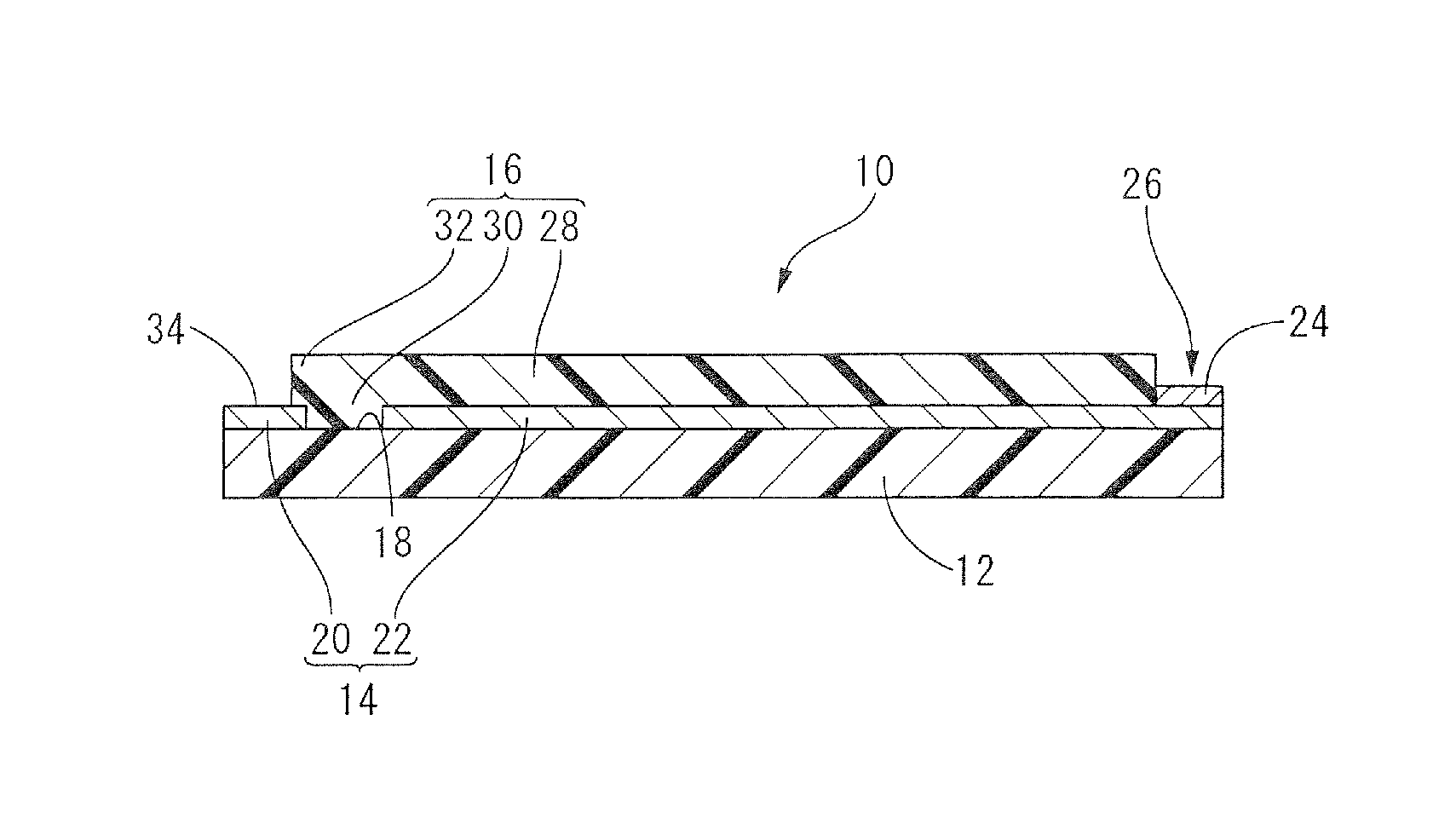

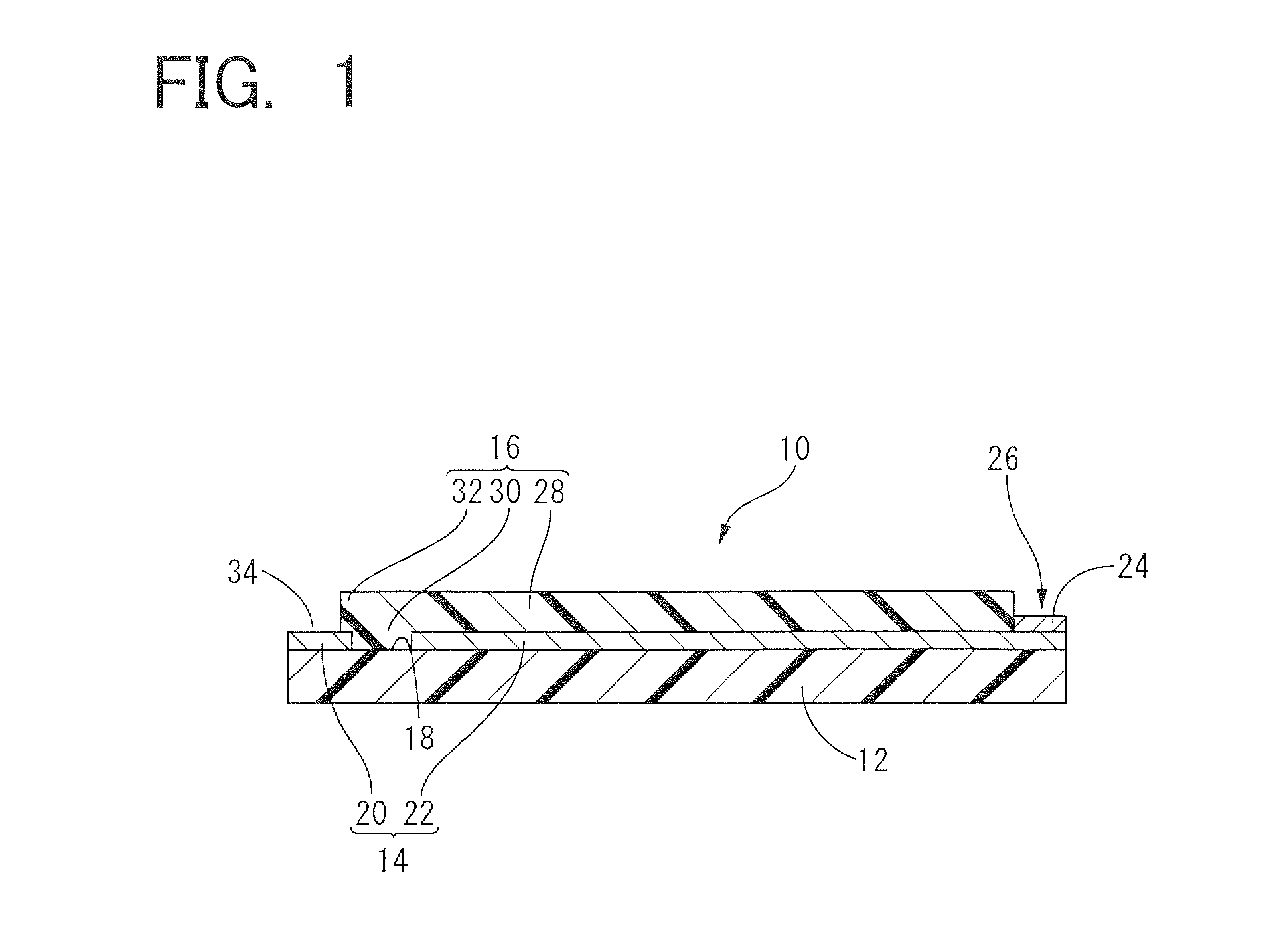

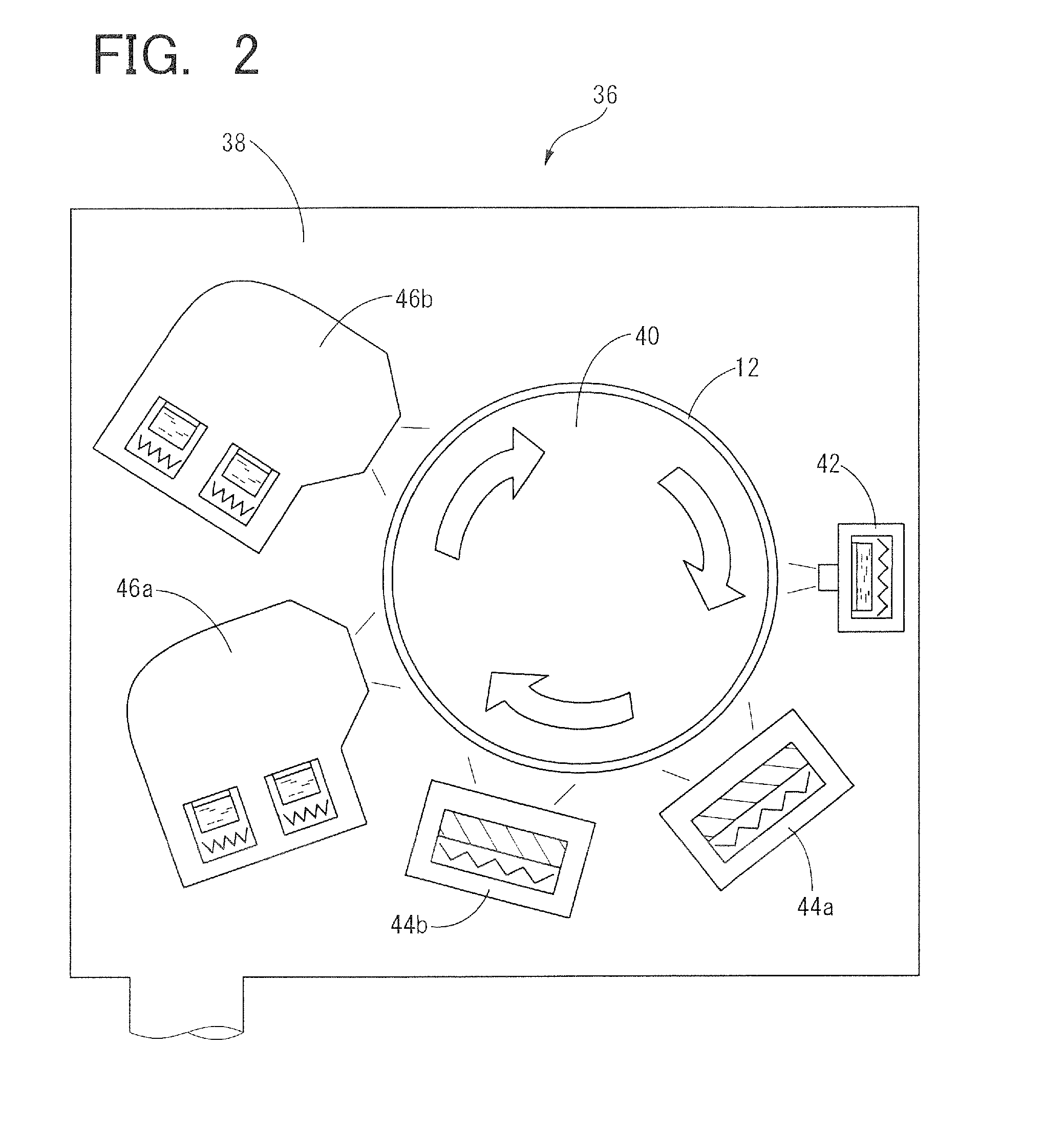

Film capacitor element, film capacitor, and method of producing the film capacitor element

InactiveUS8861178B2Effectively increased degree of adhesivenessSuitably producedFixed capacitor electrodesThin/thick film capacitorDielectricVapor deposition polymerization

A film capacitor element including a base dielectric film layer 12, a vapor-deposition metal film layer 14 formed on the base dielectric film layer 12 and consisting of a first film portion 20 and a second film portion 22 that are spaced apart from each other by a margin portion 18, and a dielectric covering film layer 16 which is formed integrally on the second film portion 22 by vapor-deposition polymerization or coating and which has a covering portion 30 which fills the margin portion 18 and covers an entire area of an end face of the second film portion 22 on the side of the margin portion 18. The first film portion 20 including a non-covered portion 34 which is not covered by the dielectric covering film layer 16.

Owner:KOJIMA PRESS IND CO LTD

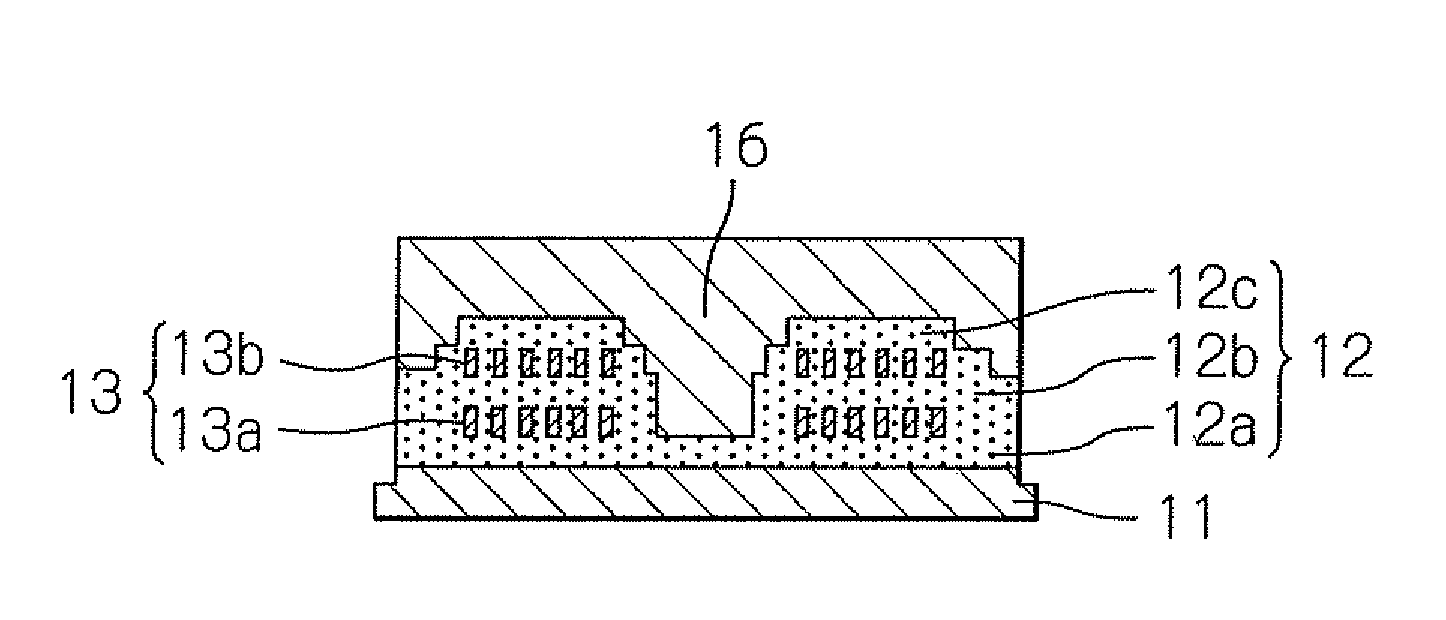

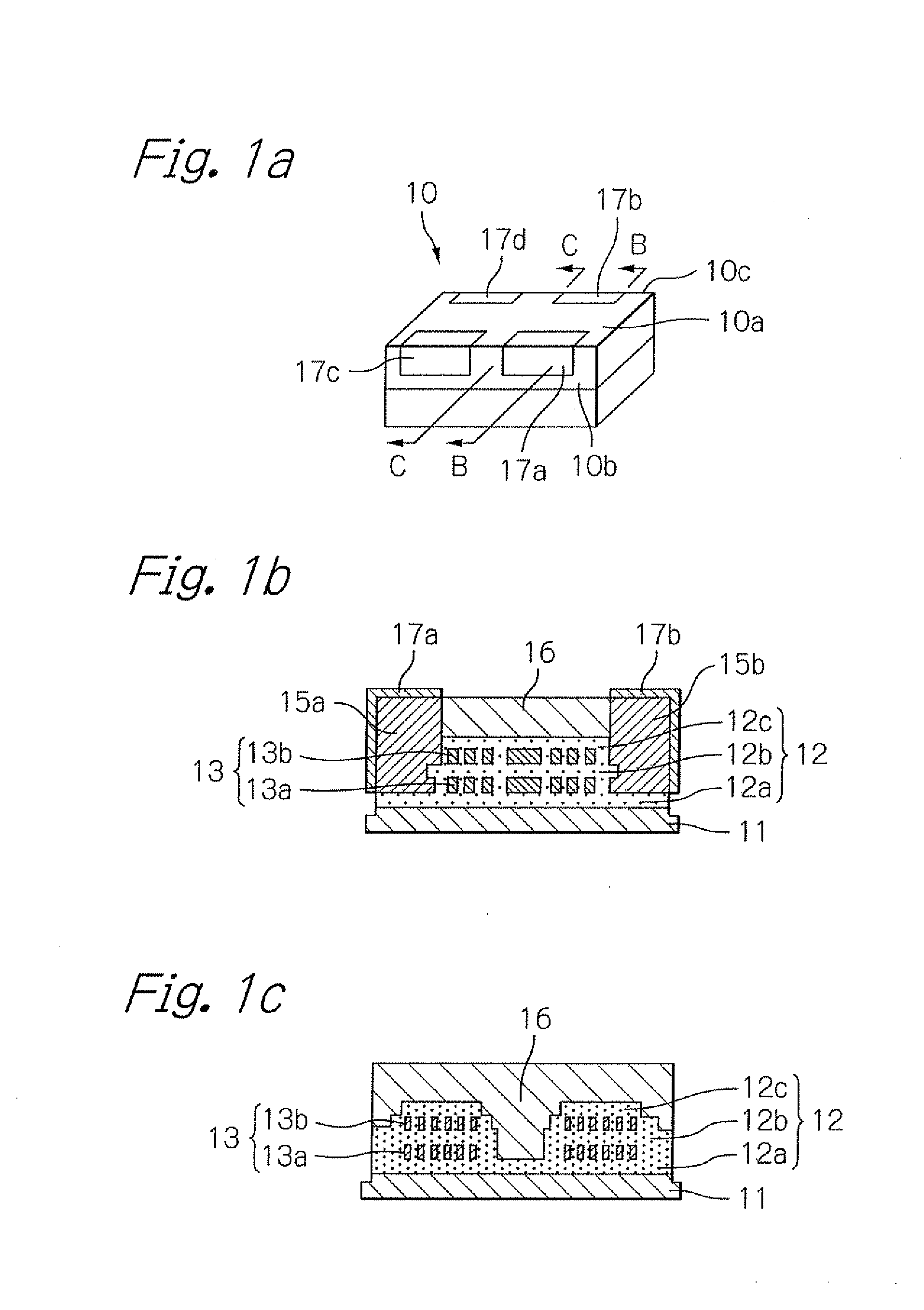

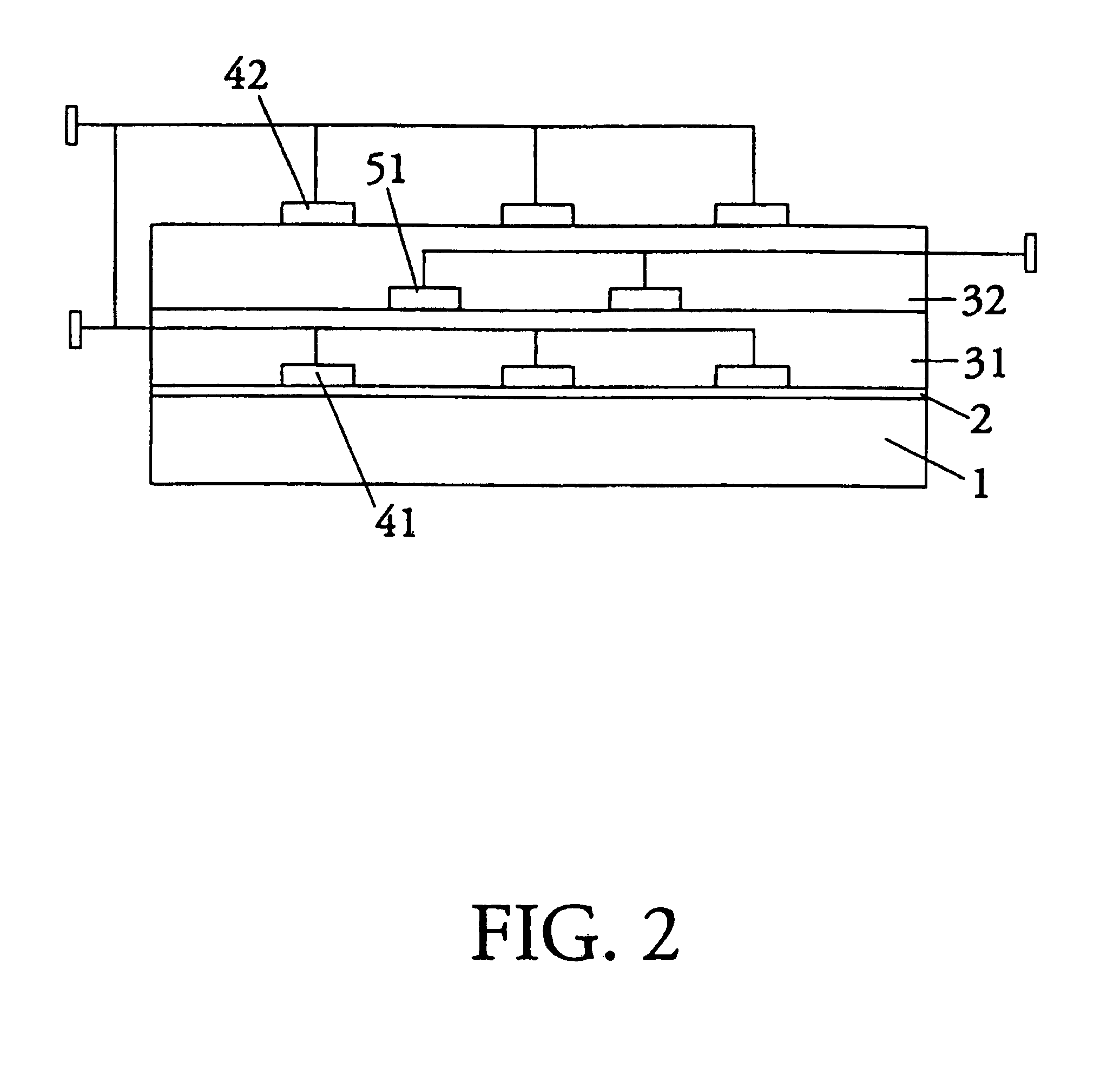

Electronic component and manufacturing method of electronic component

ActiveUS8174349B2High strengthIncrease the areaSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical conductorInsulation layer

A manufacturing method of electronic components includes forming a first insulation layer on a substrate, forming a plurality of passive elements on the first insulation layer, forming a second insulation layer on the passive elements, forming a plurality of conductor layers electrically connected to the respective passive elements, on the outer side of the second insulation layer to be exposed to an upper surface of each electronic component, and forming grooves between the electronic components including the respective passive elements to expose side surfaces of each electronic component and parts of the conductor layers from the side surfaces of each electronic component. The manufacturing method further including plating a plurality of external electrodes on the respective conductor layers exposed to the upper surface and the side surfaces of each electronic component, and cutting the substrate to completely separate into individual electronic components.

Owner:TDK CORPARATION

Capacitor built-in wiring board

InactiveUS20080239685A1Increase capacityImprove wiring reliabilityThin/thick film capacitorSemiconductor/solid-state device detailsCapacitanceElectrical conductor

A wiring board is comprised of a core board, a capacitor, a conductor containing portion and a laminated wiring portion. The core board has an accommodation hole. The capacitor has a through hole therein and is accommodated in the accommodation hole. The conductor containing portion has a current supplying conductor and is disposed in the through hole so as to be surrounded by the capacitor. The laminated wiring portion includes a component mounting region in which a first connection terminal electrically connected to the current supplying conductor is provided. Further, second connection terminals are disposed so as to sandwich the first connection terminal therebetween.

Owner:NGK SPARK PLUG CO LTD

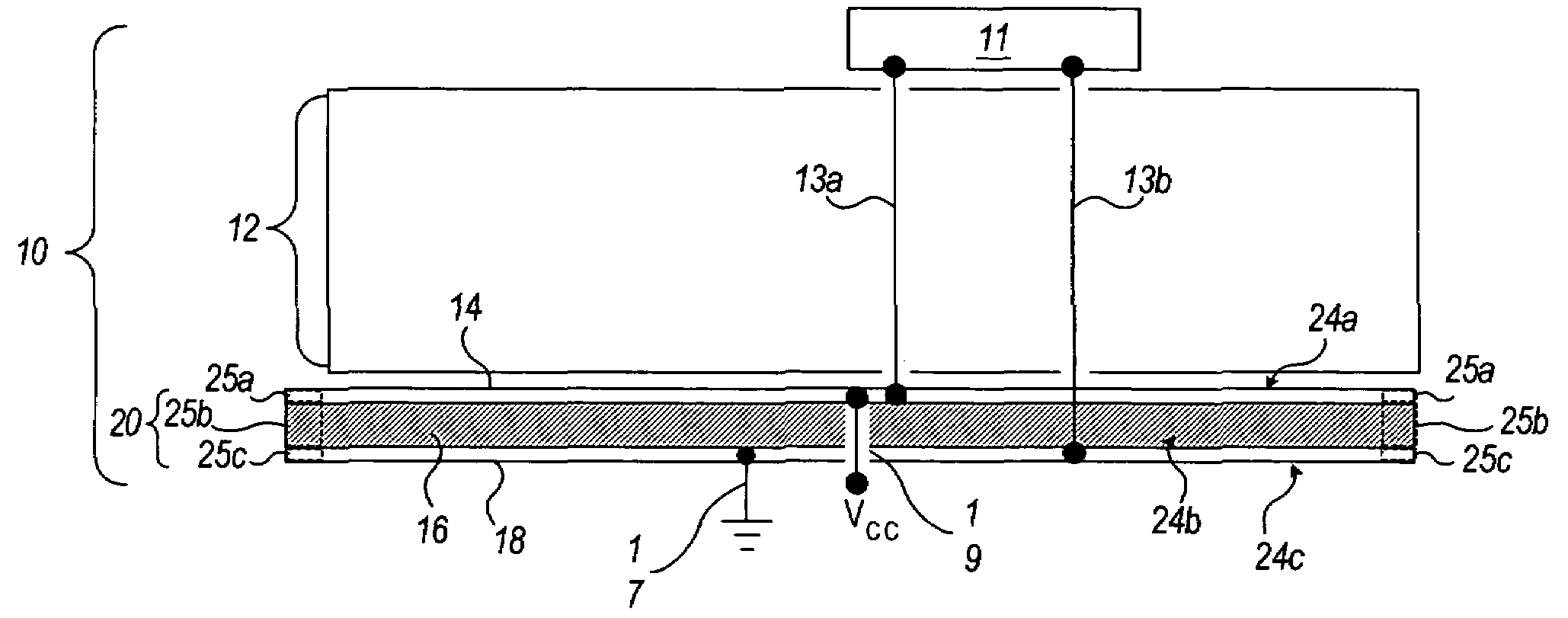

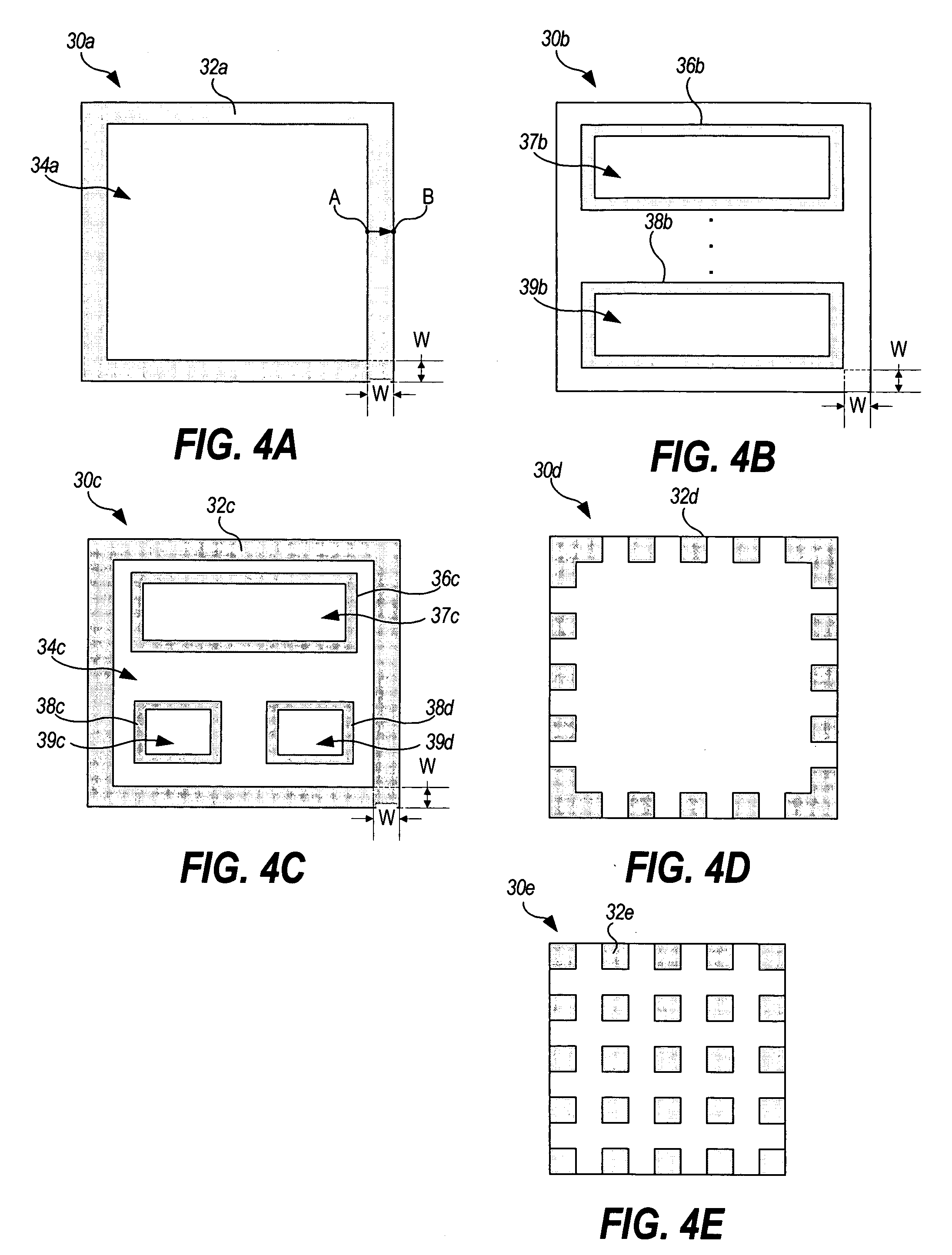

Integral charge storage basement and wideband embedded decoupling structure for integrated circuit

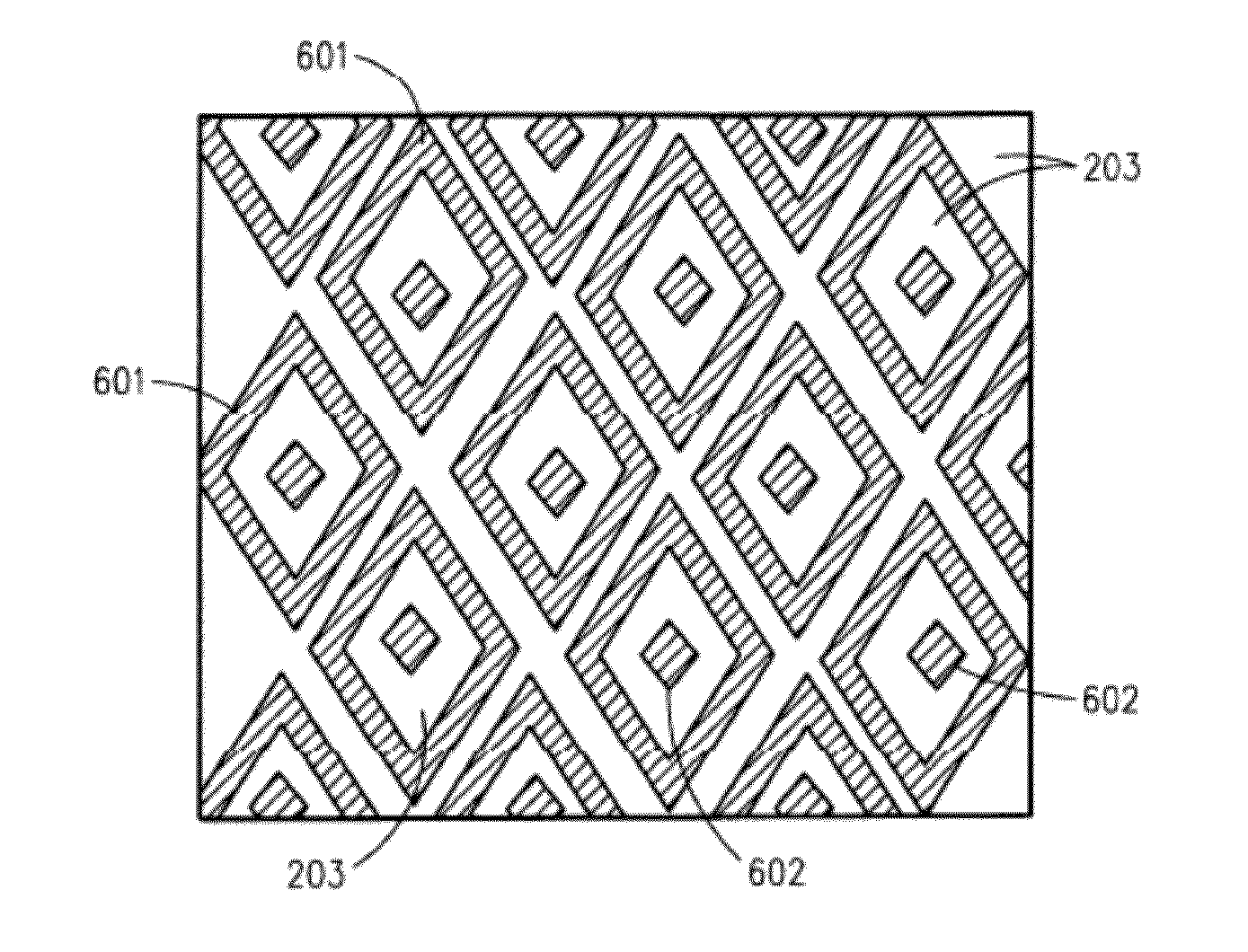

InactiveUS7428136B2Limit upper frequency usefulnessMinimizing restrictionThin/thick film capacitorFixed capacitor dielectricRadiation lossCapacitance

A capacitive structure and technique for allowing near-instantaneous charge transport and reliable, wide-band RF ground paths in integrated circuit devices such as integrated circuit dies, integrated circuit packages, printed circuit boards, and electronic circuit substrates is presented. Methods for introducing resistive loss, dielectric loss, magnetic loss, and / or radiation loss in a signal absorption ring implemented around a non-absorptive area of one or more conductive layers of an integrated circuit structure to dampen laterally flowing Electro-Magnetic (EM) waves between electrically adjacent conductive layers of the device are also presented.

Owner:GEOMAT INSIGHTS

High aspect ratio openings

A capacitor forming method includes forming an electrically conductive support material over a substrate, with the support material containing at least 25 at % carbon. The method includes forming an opening through at least the support material where the opening has an aspect ratio of at least 20:1 within a thickness of the support material. After forming the opening, the method includes processing the support material to effect a reduction in conductivity, and forming a capacitor structure in the opening.

Owner:MICRON TECH INC

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com