Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

15593results about "Individual semiconductor device testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

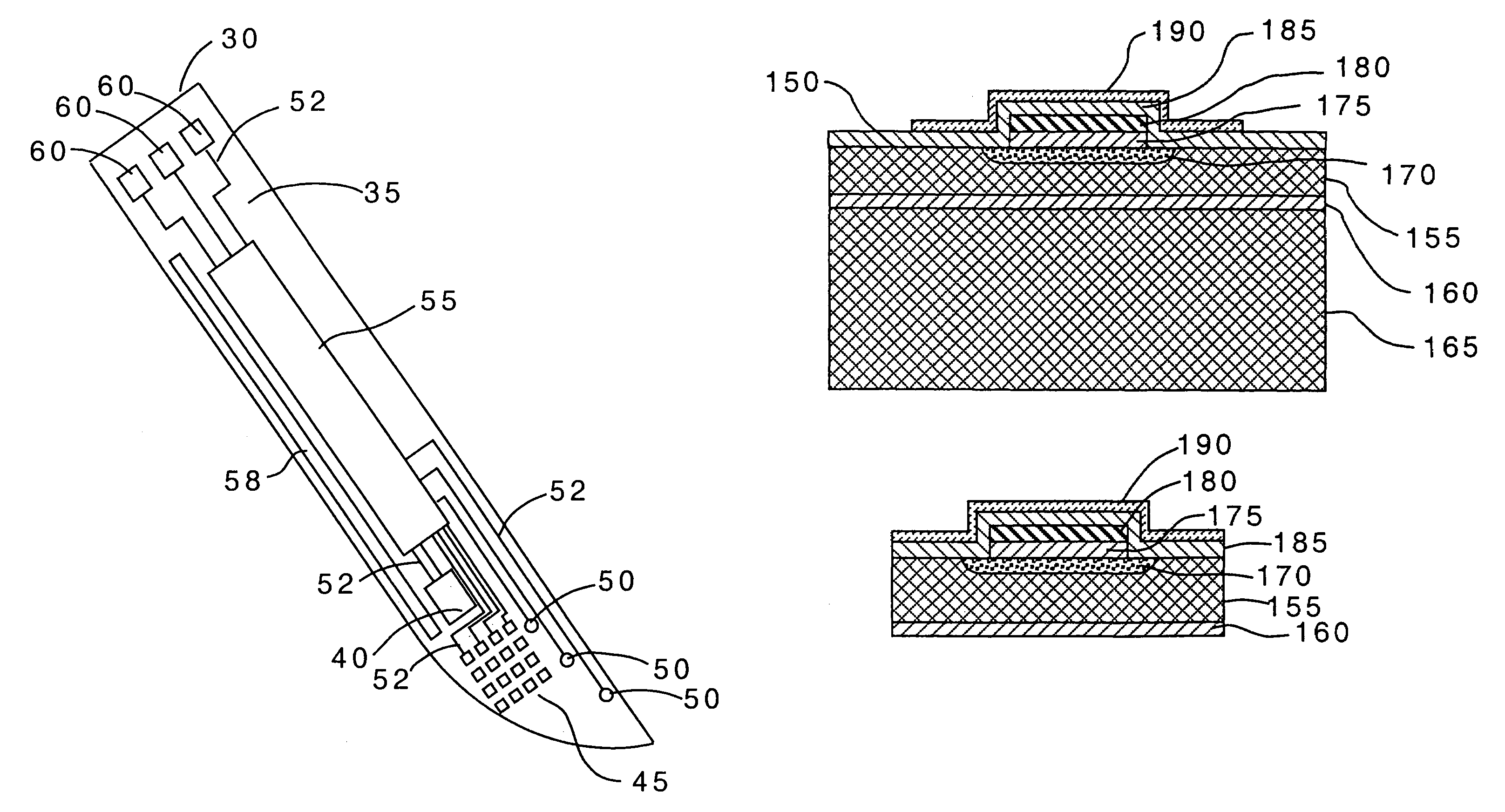

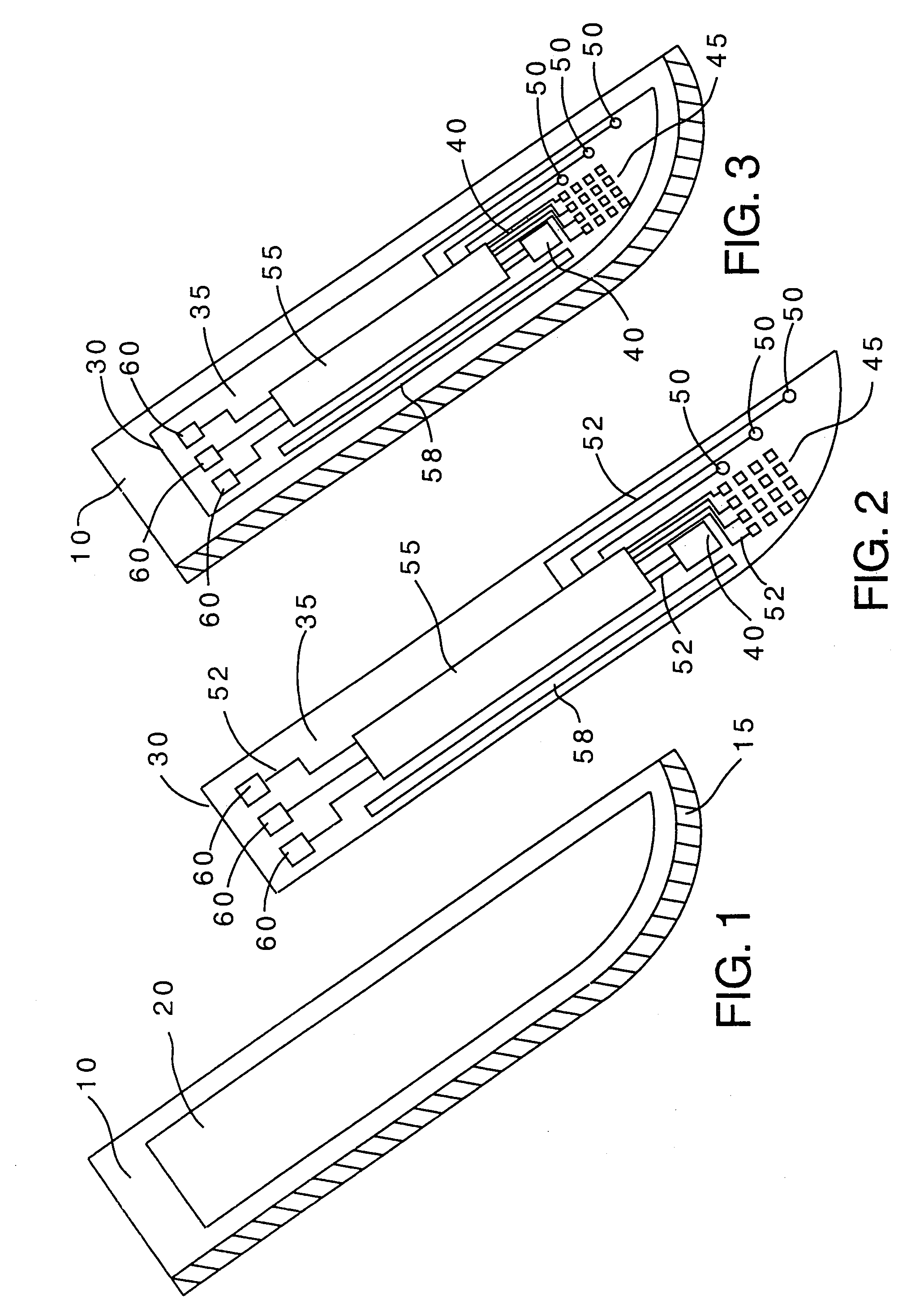

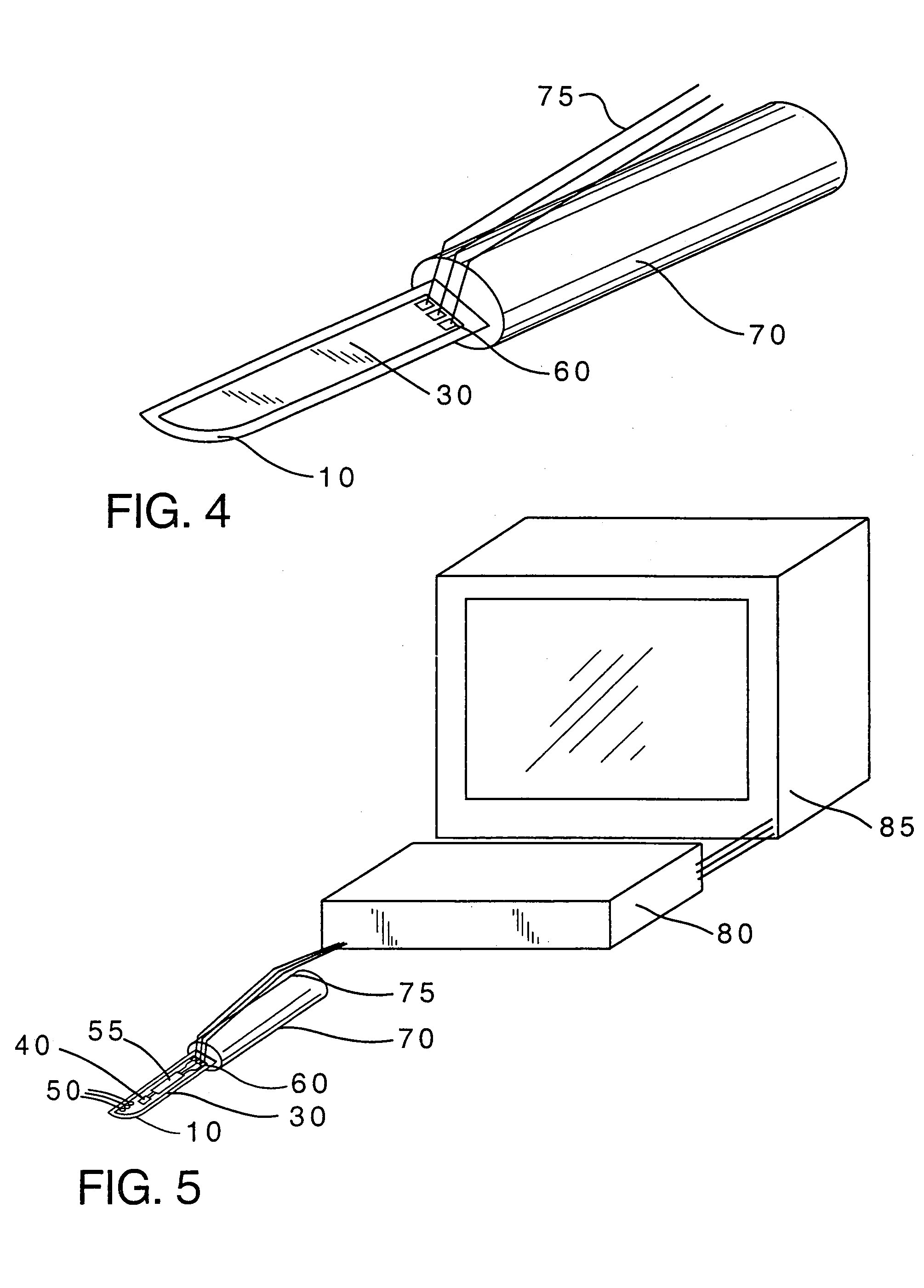

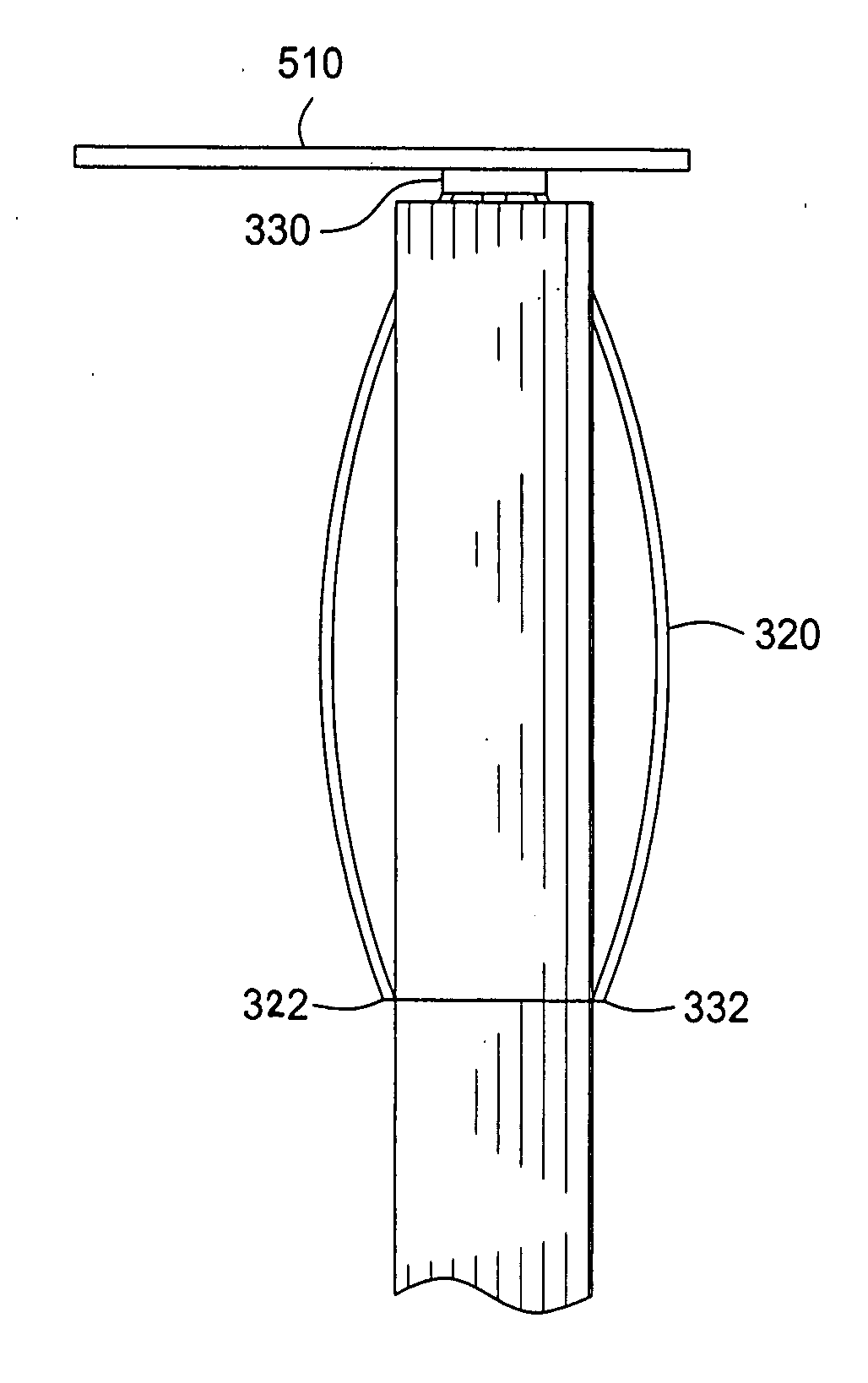

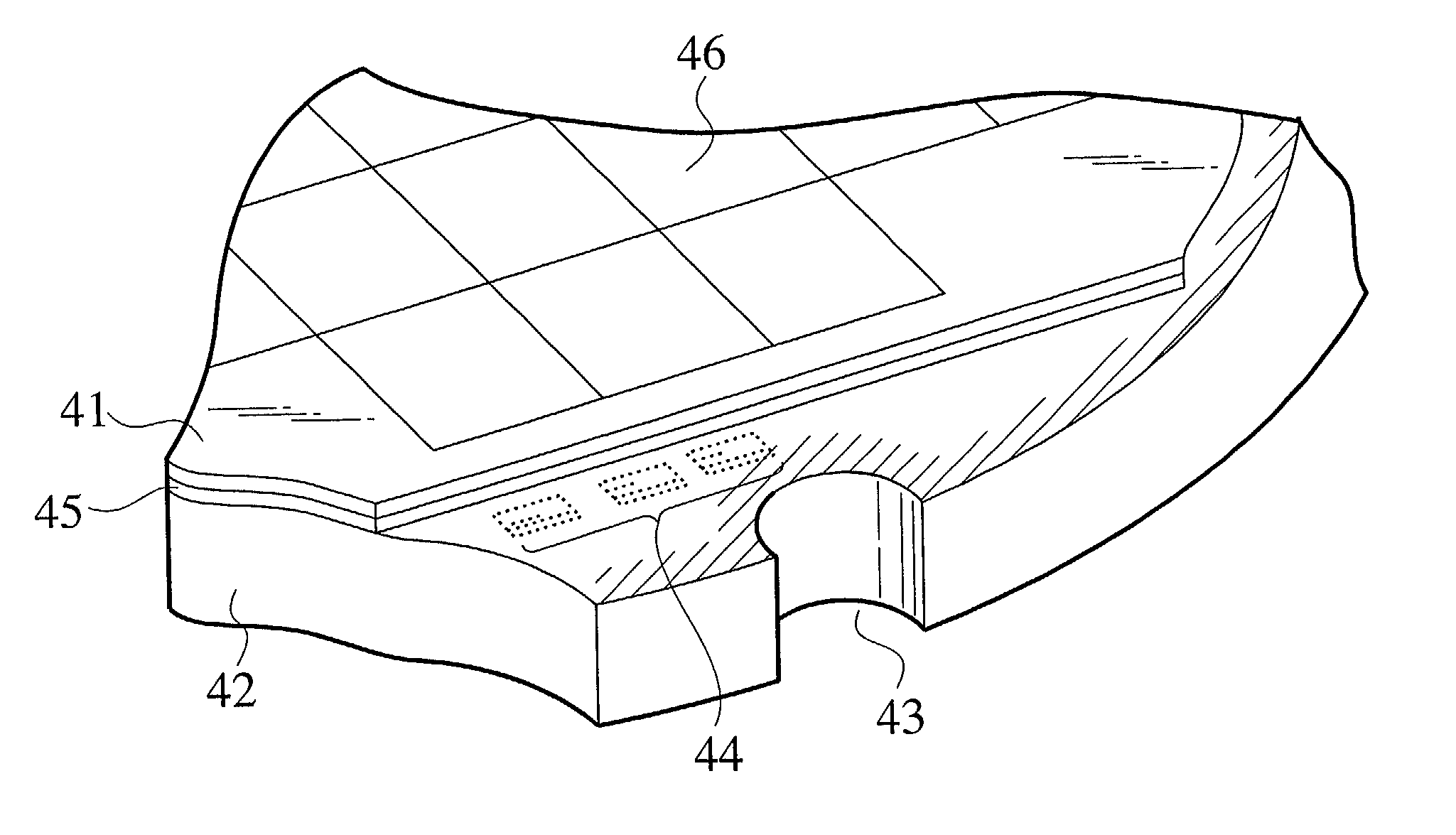

Method of making a cutting instrument having integrated sensors

A cutting instrument including a metal blade has a recess formed therein and a semiconductor substrate affixed to the blade in the recess. The semiconductor substrate includes at least one sensor formed thereon. The sensor formed on the semiconductor substrate may comprise at least one or an array of a strain sensors, pressure sensors, nerve sensors, temperature sensors, density sensors, accelerometers, and gyroscopes. The cutting instrument may also further include a handle wherein the blade is affixed to the handle and the semiconductor substrate is electrically coupled to the handle. The handle may then be coupled, either physically or by wireless transmission, to a computer that is adapted to display information to a person using the cutting instrument based on signals generated by one or more of the sensors formed on the semiconductor substrate. The computer or handle may also be adapted to store data based on the signals generated by one or more of the sensors. A method of making said cutting instrument includes the steps of at least one sensor being formed on a semiconductor wafer and a layer of photoresist being applied on a top side of the semiconductor wafer according to a pattern that matches the defined shape of the semiconductor substrate. The portion of the semiconductor wafer not covered by the photoresist is removed and thereafter the photoresist is removed from the semiconductor wafer, thereby leaving the semiconductor substrate having a defined shape and at least one sensor formed thereon. The semiconductor substrate having a defined shape and at least one sensor formed thereon is then affixed to a metal blade in a recess formed in said blade.

Owner:VERIMETRA

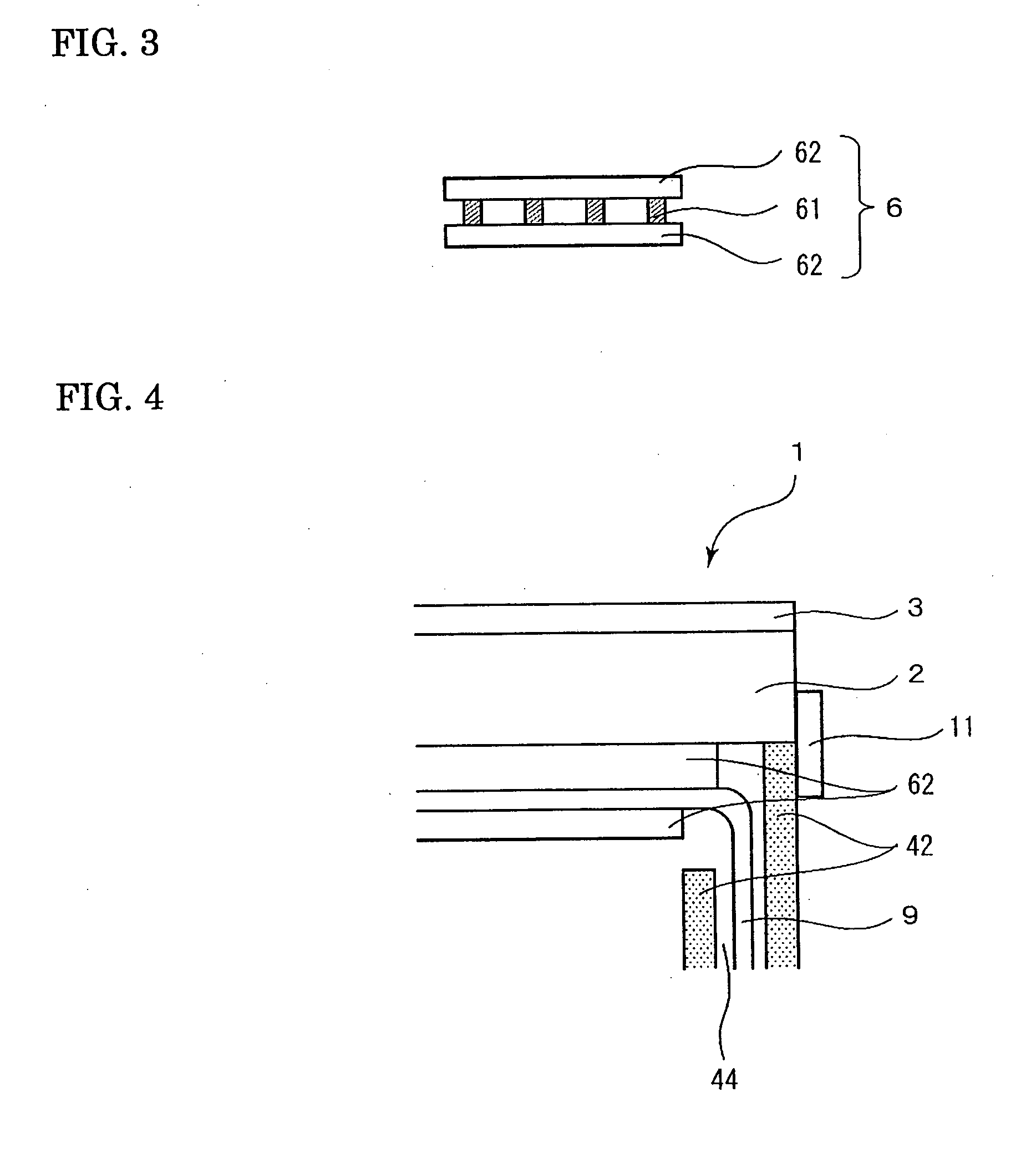

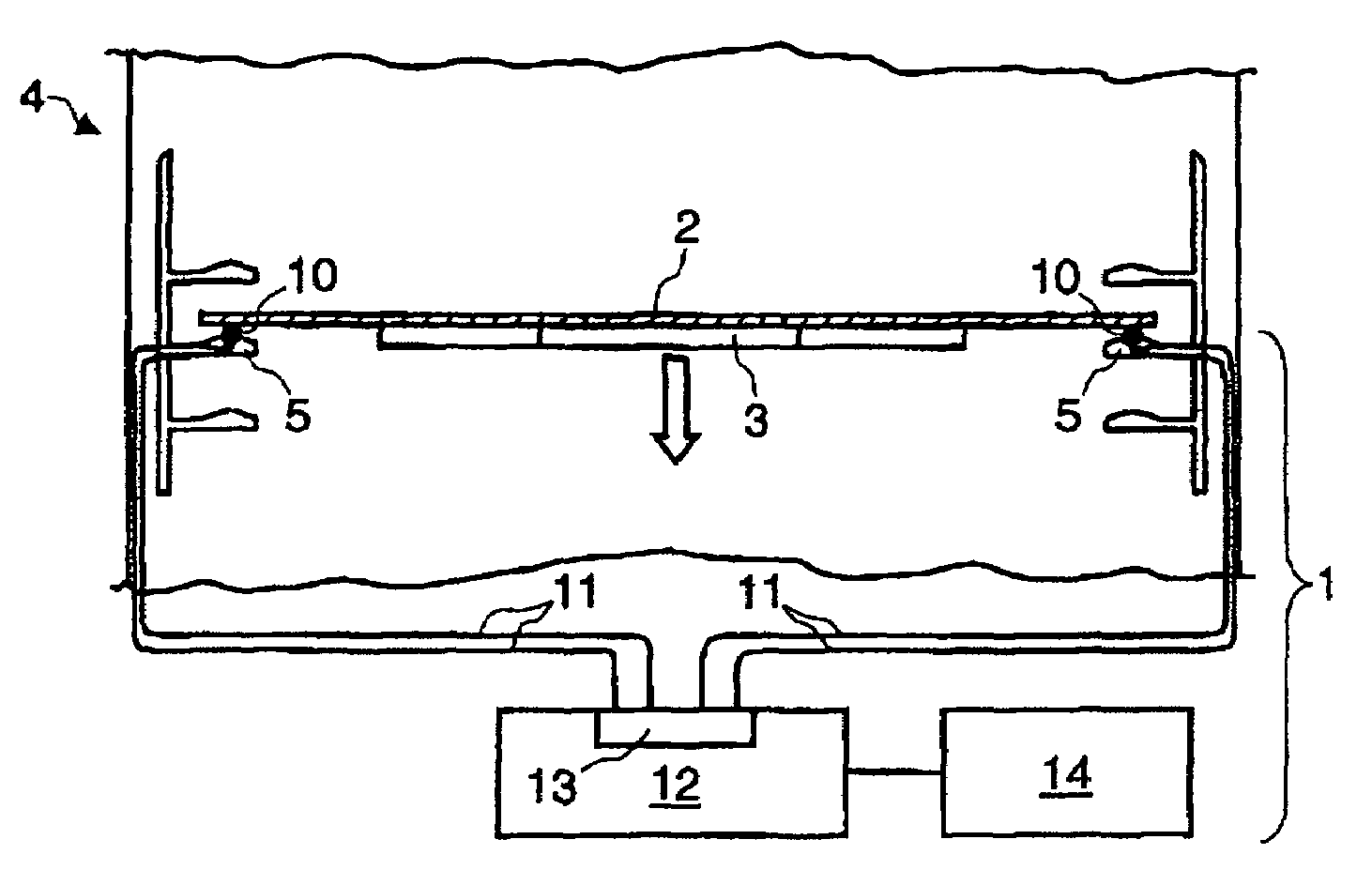

Unit for varying a temperature of a test piece and testing instrument incorporating same

ActiveUS7115838B2Easy to control temperatureUniform temperature distributionDrying solid materials with heatDomestic cooling apparatusInstrumentationCoolant

Owner:ESPEC CORP

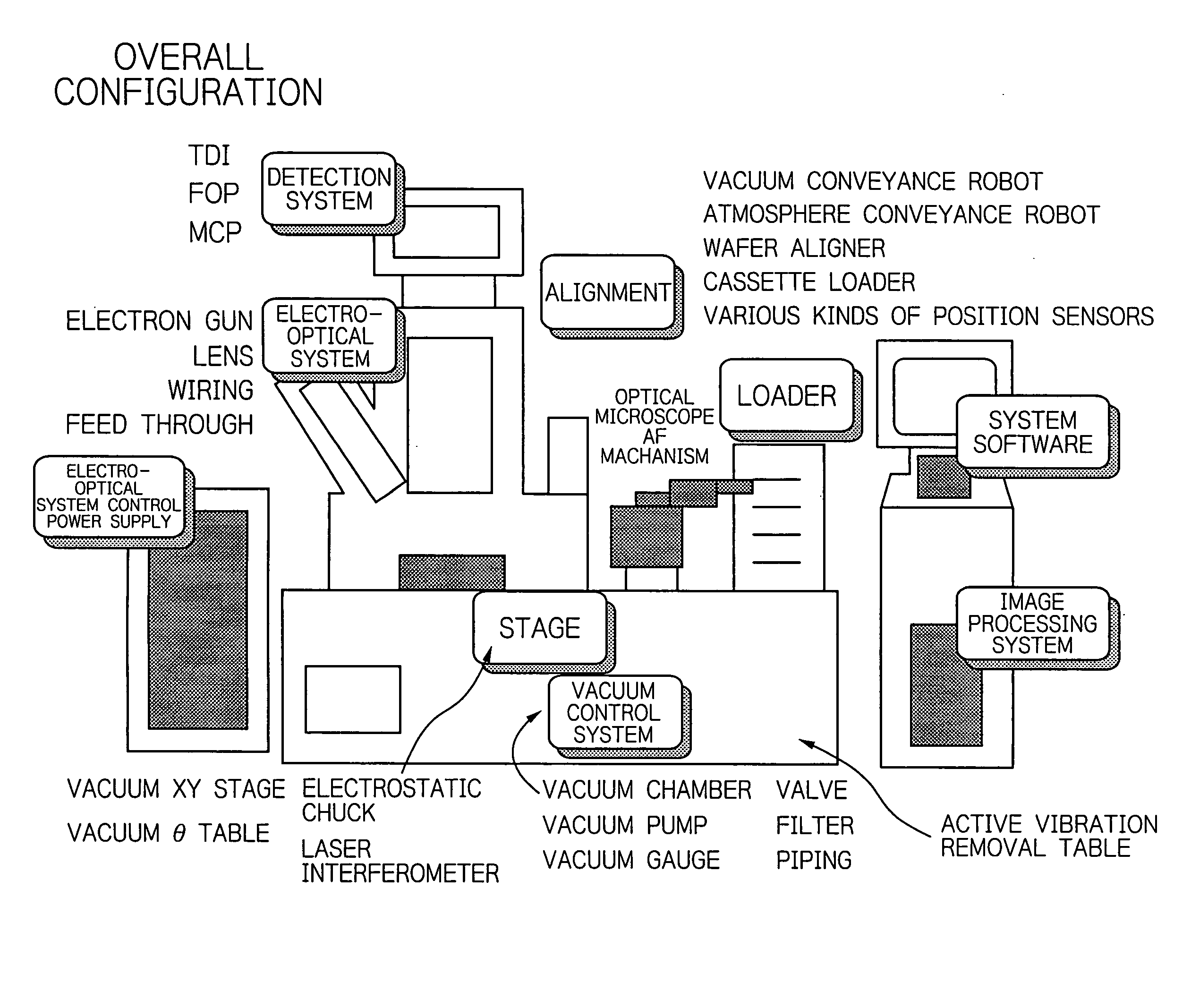

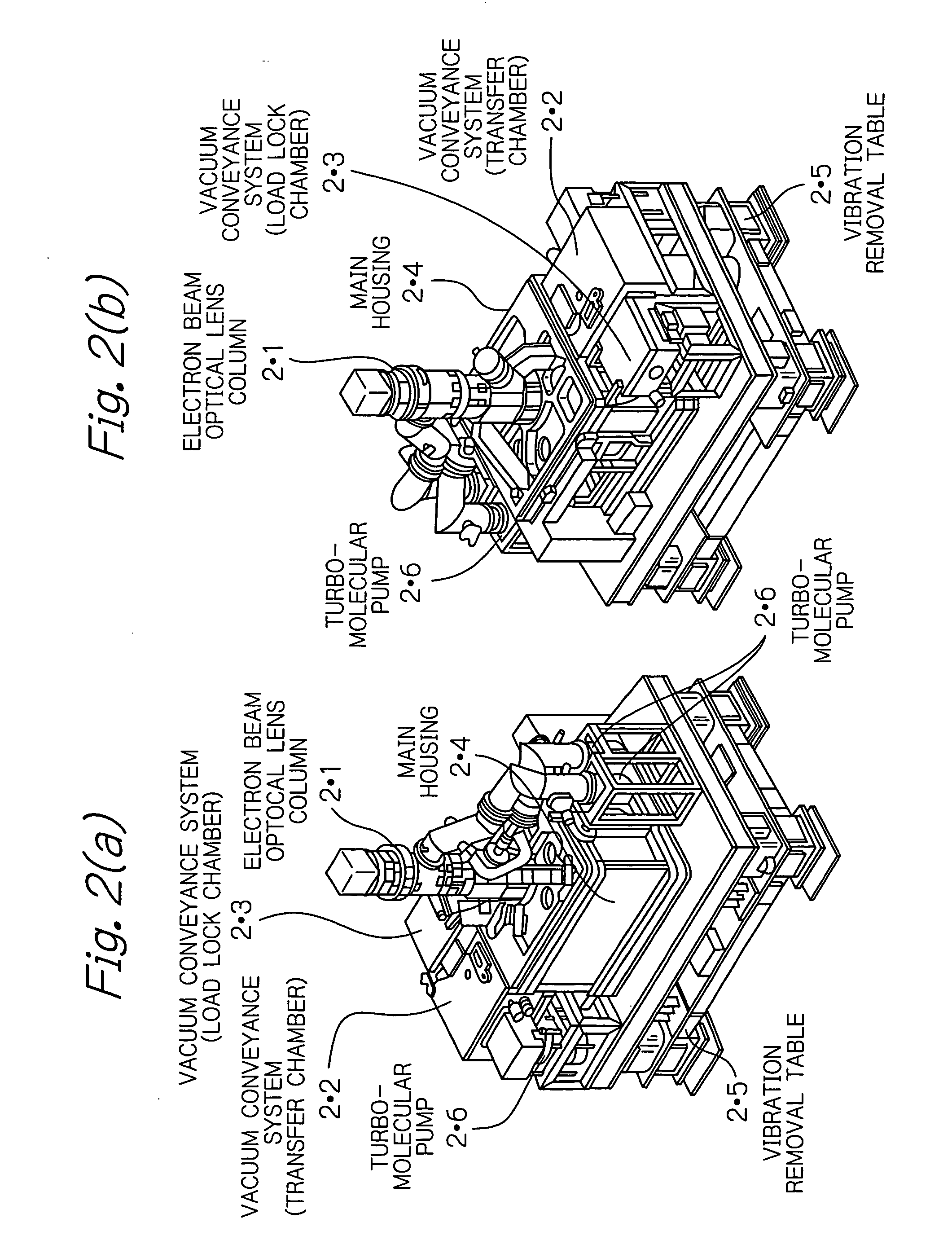

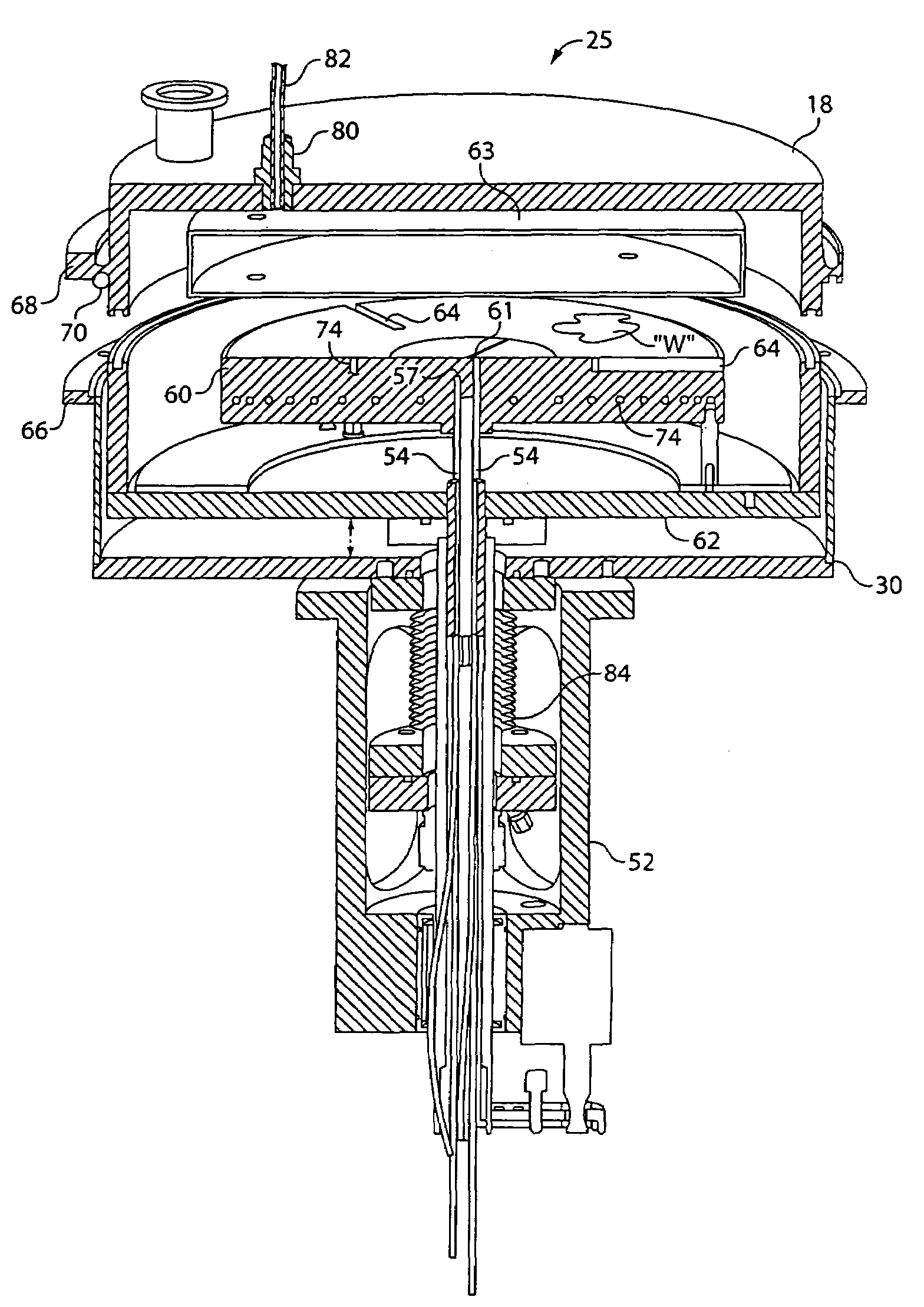

Testing apparatus using charged particles and device manufacturing method using the testing apparatus

ActiveUS20050045821A1Material analysis using wave/particle radiationElectric discharge tubesAtomic physicsPhysics

A system for further enhancing speed, i.e. improving throughput in a SEM-type inspection apparatus is provided. An inspection apparatus for inspecting a surface of a substrate produces a crossover from electrons emitted from an electron beam source 25••1, then forms an image under a desired magnification in the direction of a sample W to produce a crossover. When the crossover is passed, electrons as noises are removed from the crossover with an aperture, an adjustment is made so that the crossover becomes a parallel electron beam to irradiate the substrate in a desired sectional form. The electron beam is produced such that the unevenness of illuminance is 10% or less. Electrons emitted from the sample W are detected by a detector 25•11.

Owner:EBARA CORP

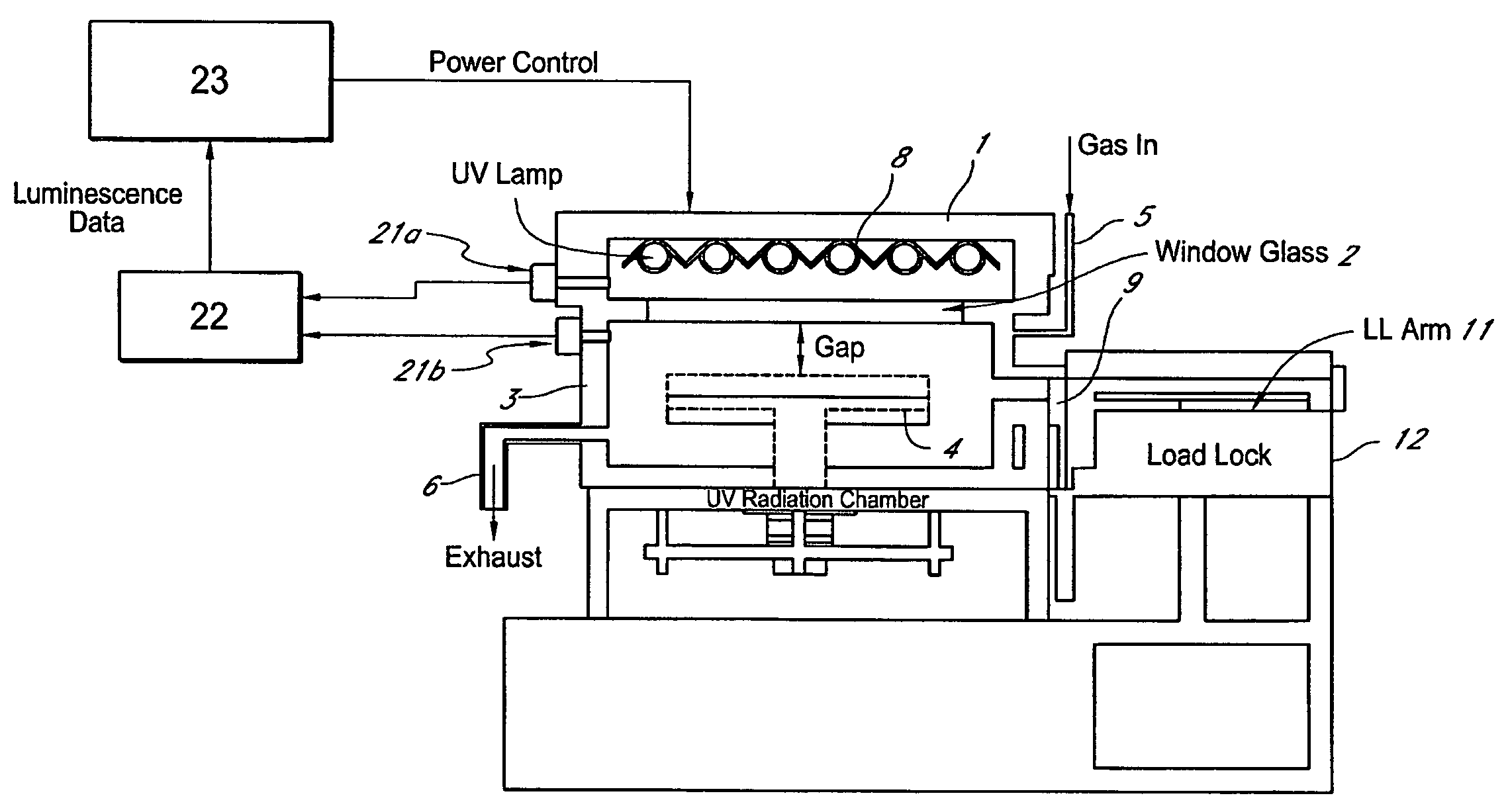

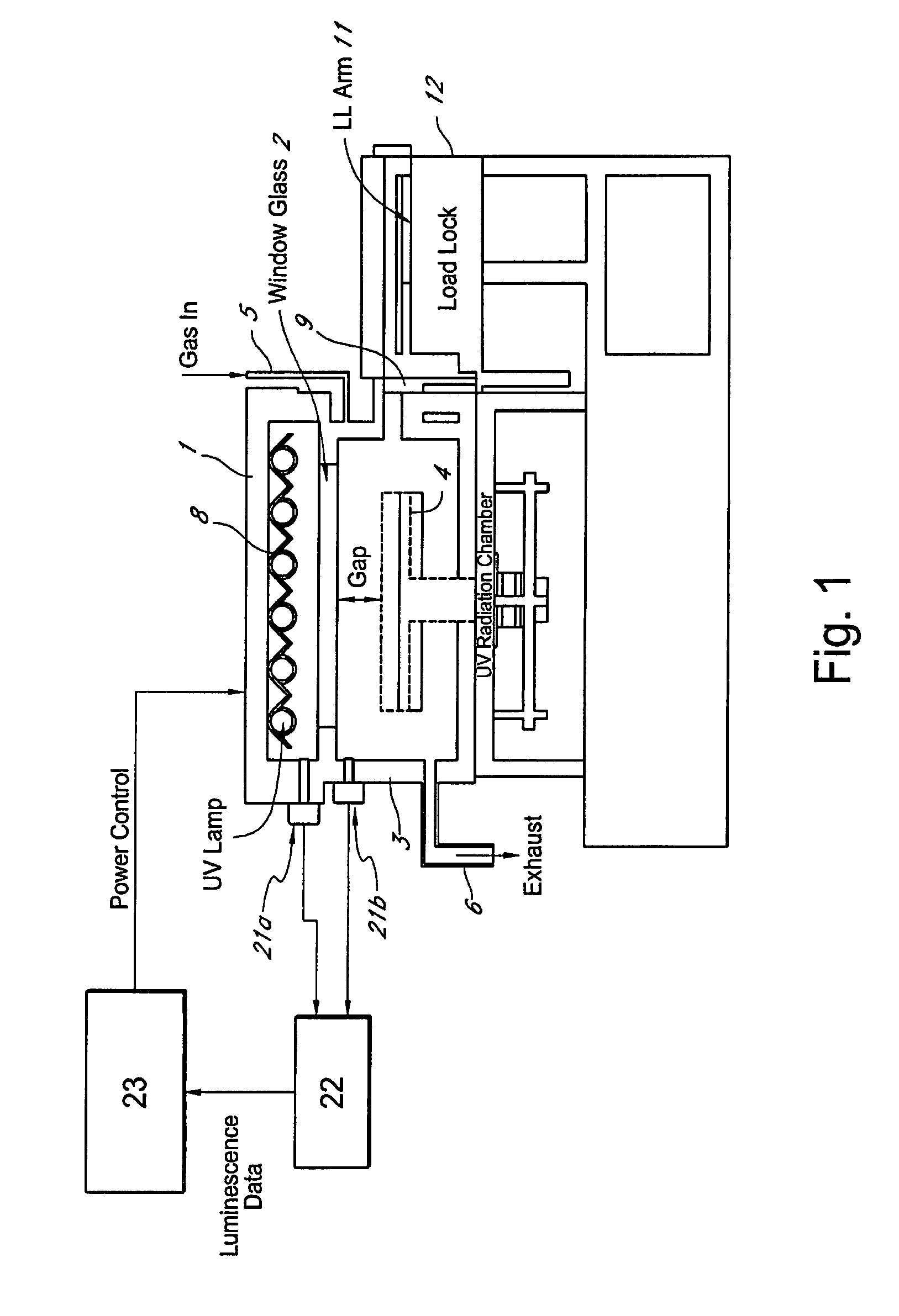

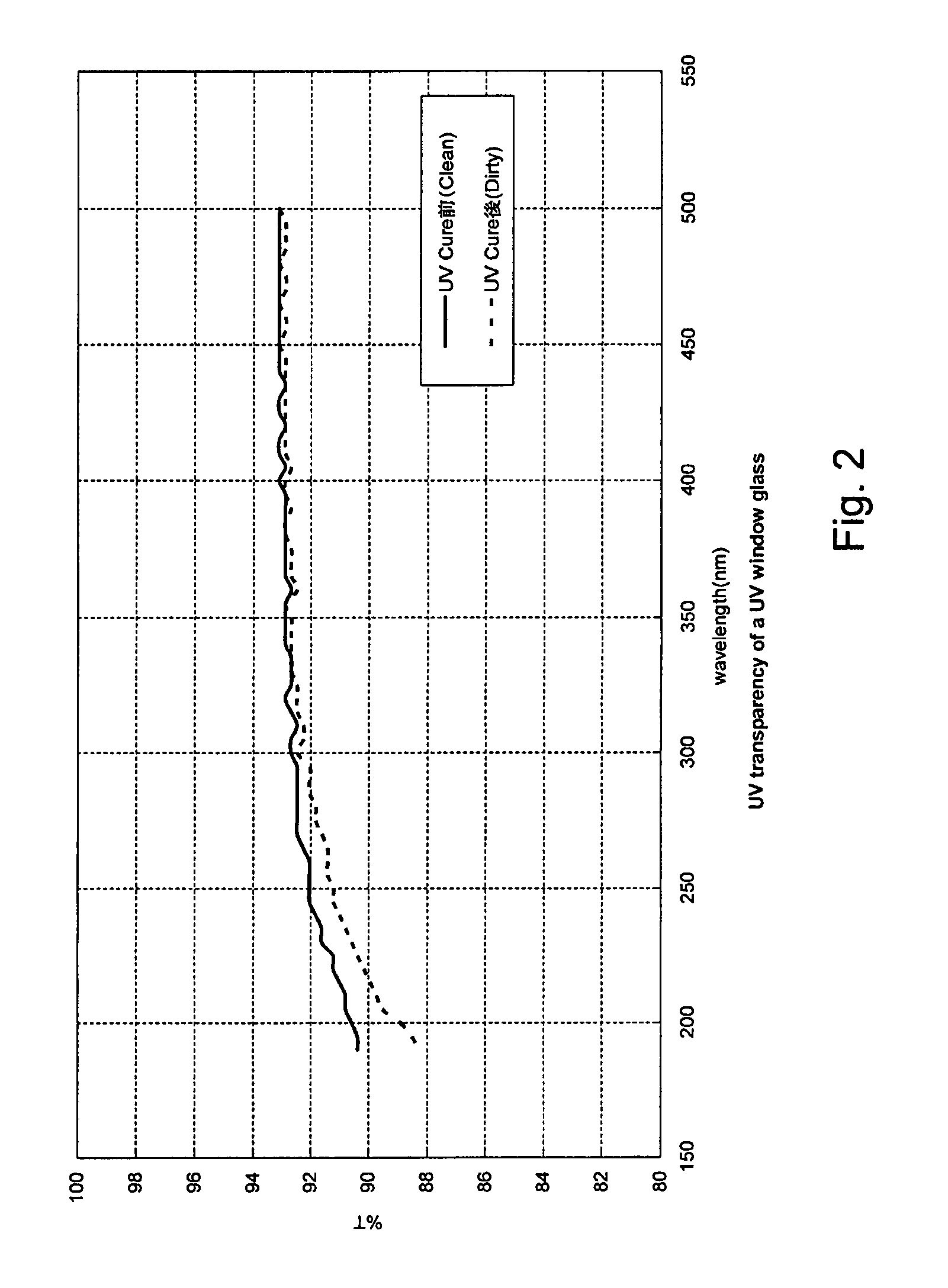

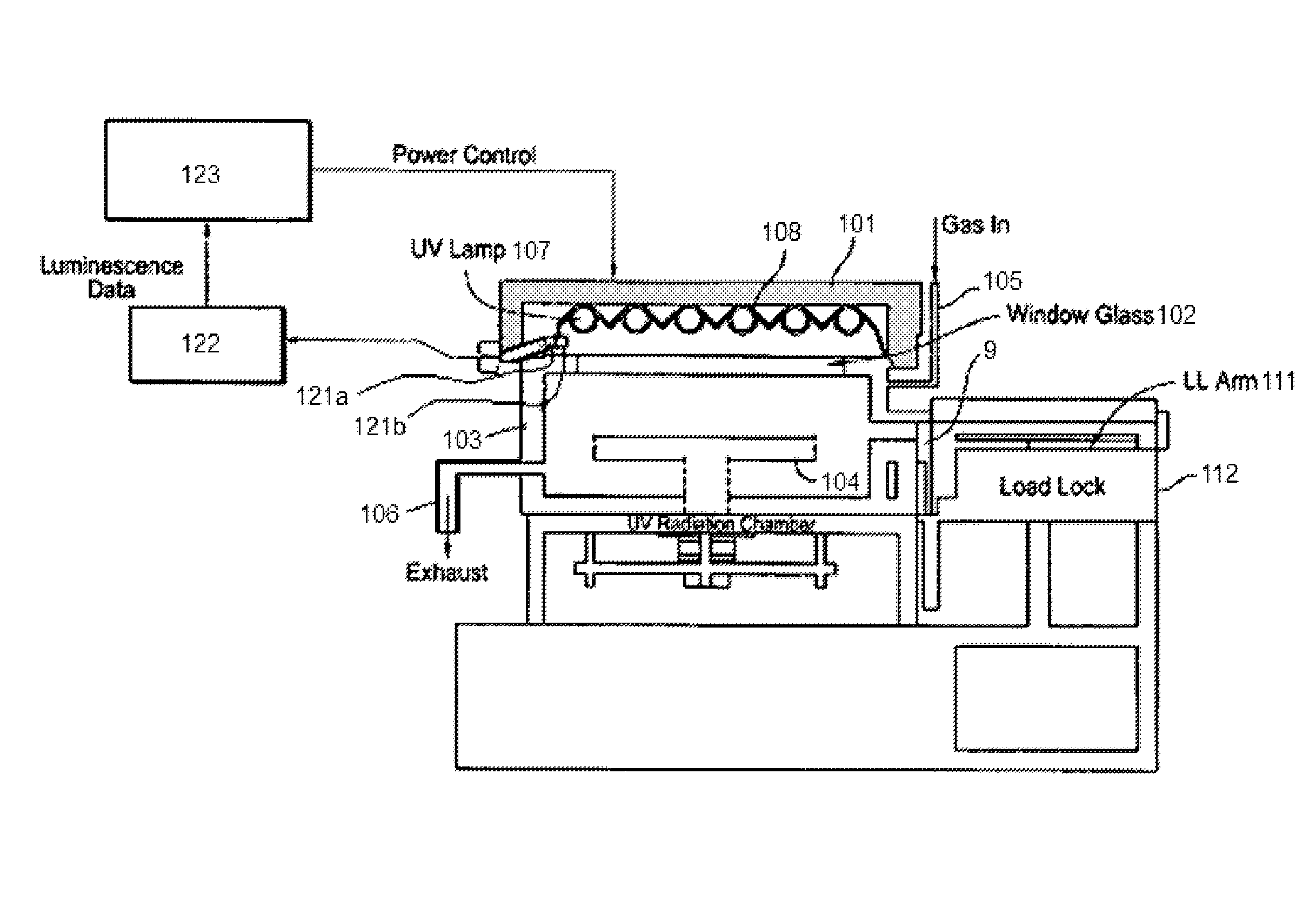

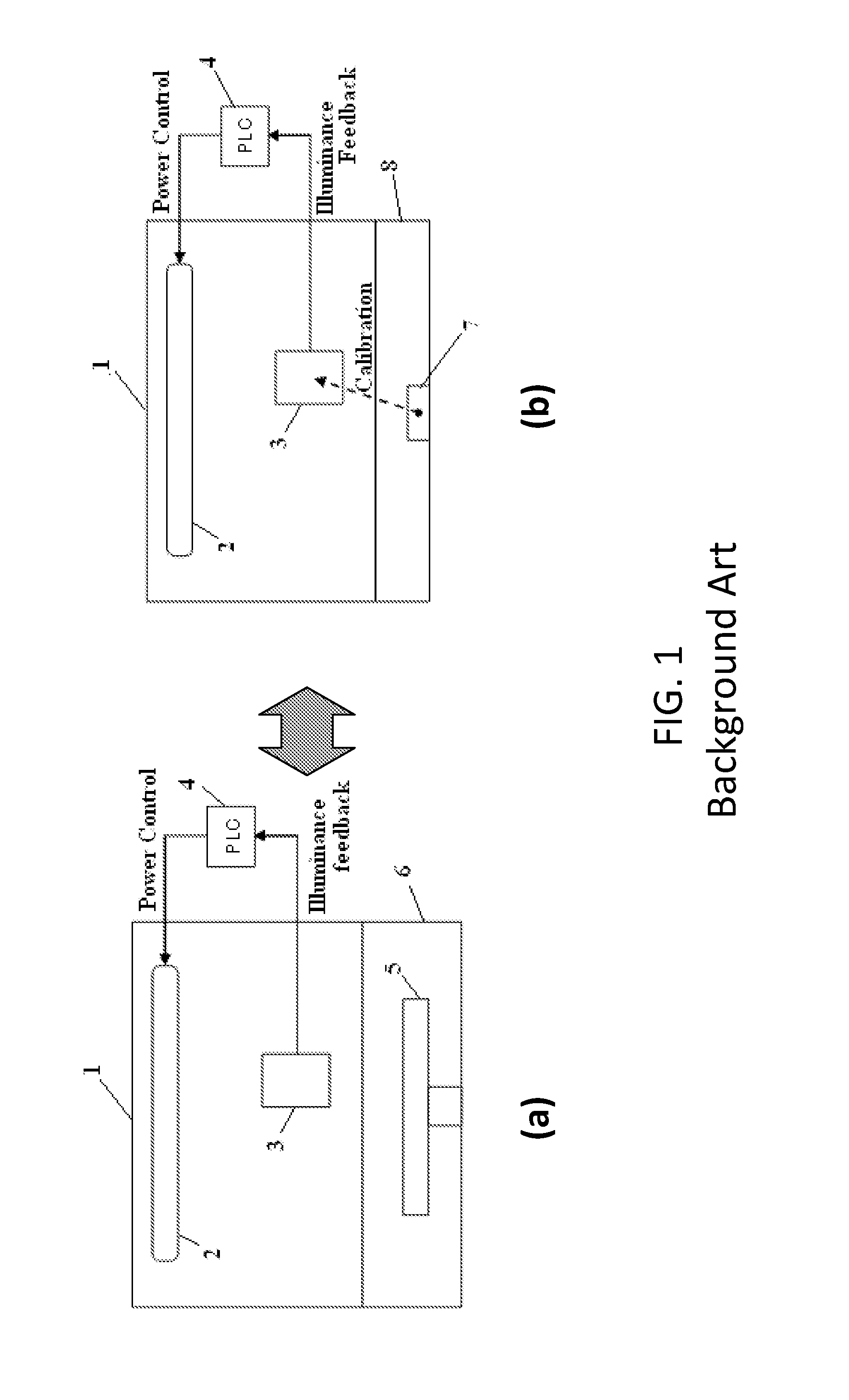

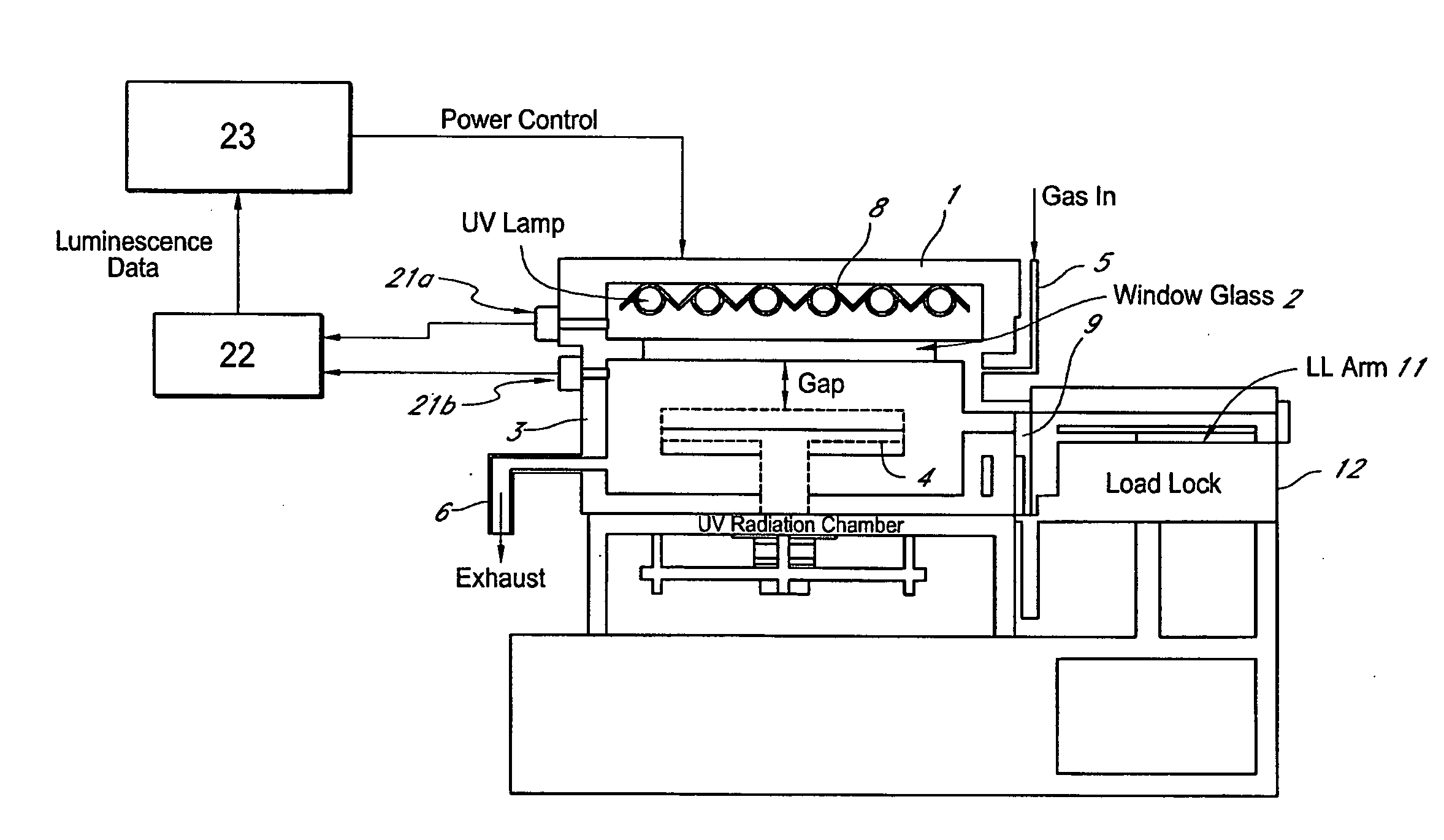

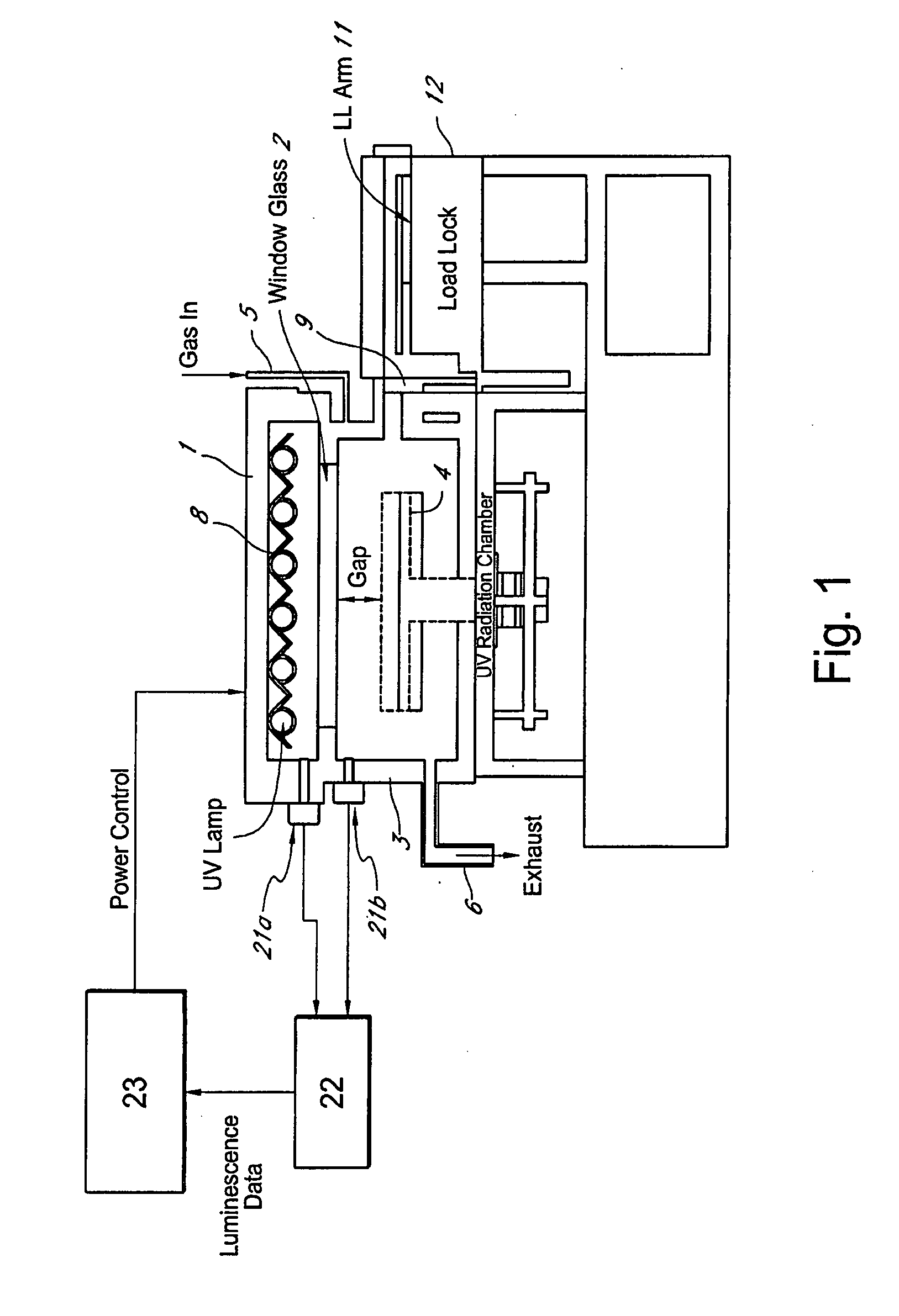

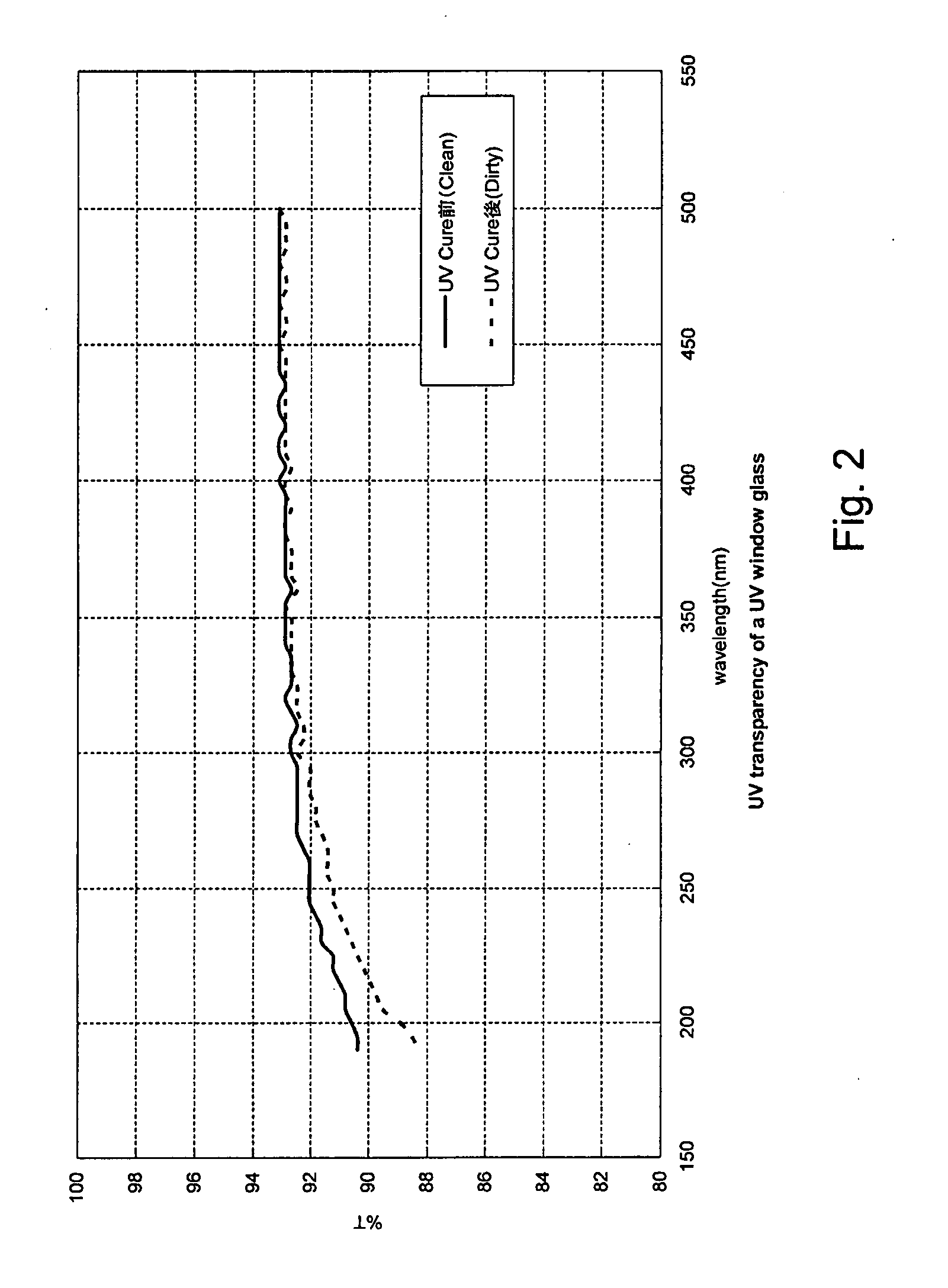

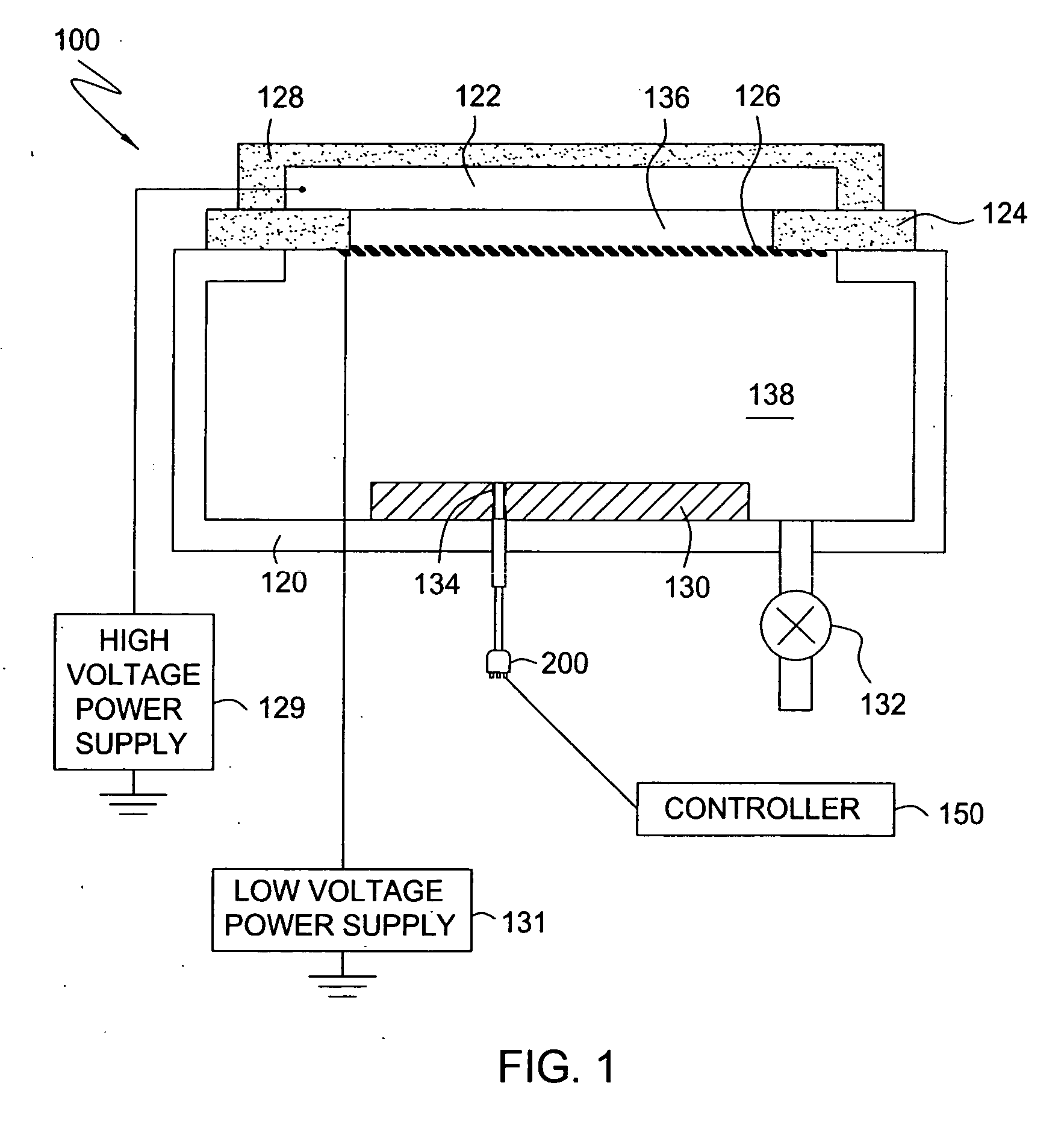

Method for managing UV irradiation for curing semiconductor substrate

ActiveUS7501292B2Maintain levelAutomatic controlSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingIlluminanceEngineering

A method for managing UV irradiation for curing a semiconductor substrate, includes: passing UV light through a transmission glass window provided in a chamber for curing a semiconductor substrate placed in the chamber; monitoring an illuminance upstream of the transmission glass window and an illuminance downstream of the transmission glass window; determining a timing and / or duration of cleaning of the transmission glass window, a timing of replacing the transmission glass window, a timing of replacing a UV lamp, and / or an output of the UV light based on the monitored illuminances.

Owner:ASM JAPAN

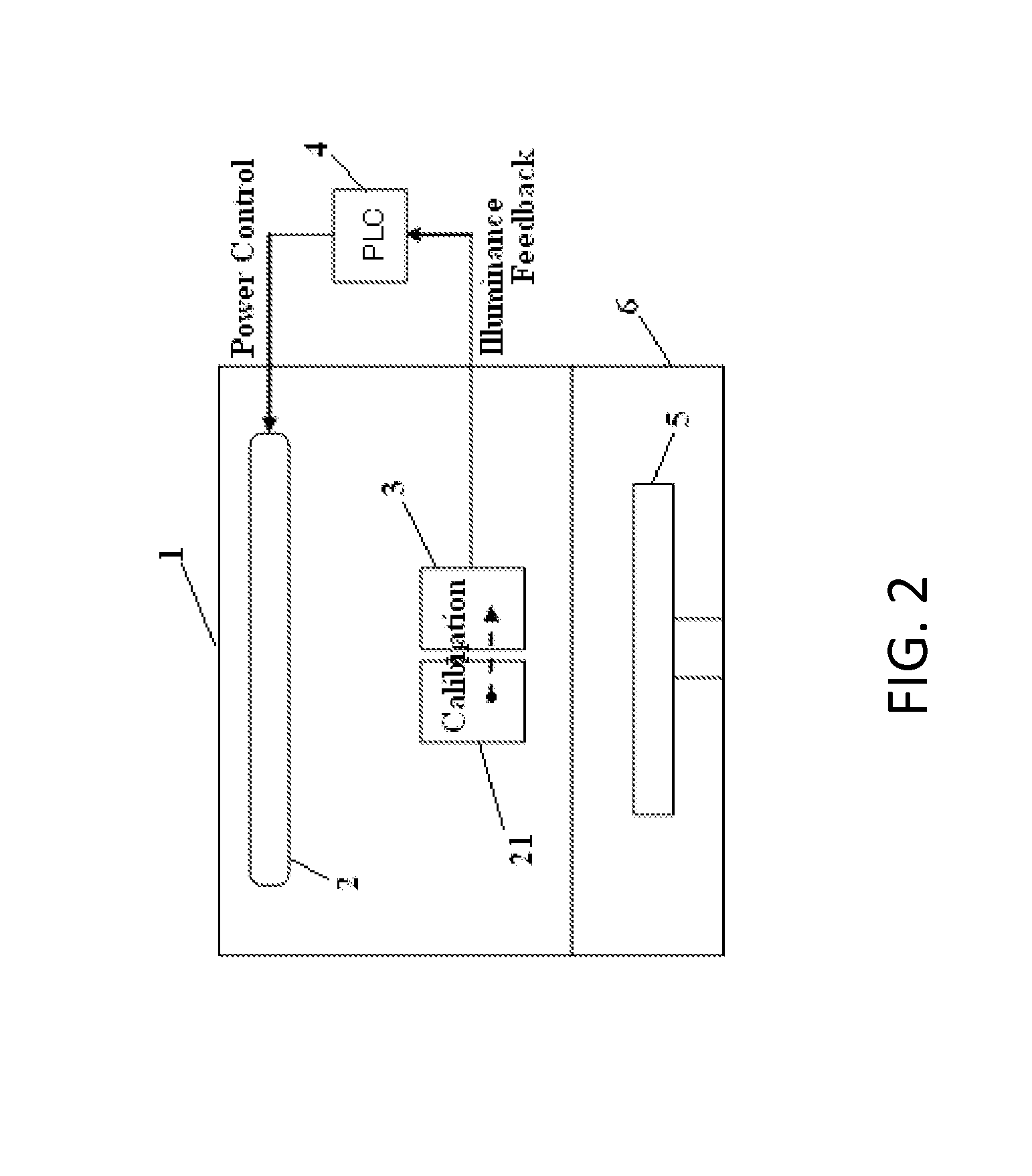

Calibration method of UV sensor for UV curing

ActiveUS8466411B2Reduce exposureEliminate errorsSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingUV curingUltraviolet

A method for managing UV irradiation for treating substrates in the course of treating multiple substrates consecutively with UV light, includes: exposing a first UV sensor to the UV light at first intervals to measure illumination intensity of the UV light so as to adjust the illumination intensity to a desired level based on the measured illumination intensity; and exposing a second UV sensor to the UV light at second intervals to measure illumination intensity of the UV light so as to calibrate the first UV sensor by equalizing the illumination intensity measured by the first UV sensor substantially with the illumination intensity measured by the second UV sensor, wherein each second interval is longer than each first interval.

Owner:ASM JAPAN

Method for managing UV irradiation for curing semiconductor substrate

ActiveUS20090023229A1Automatic controlMaintain levelSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingIlluminanceEngineering

A method for managing UV irradiation for curing a semiconductor substrate, includes: passing UV light through a transmission glass window provided in a chamber for curing a semiconductor substrate placed in the chamber; monitoring an illuminance upstream of the transmission glass window and an illuminance downstream of the transmission glass window; determining a timing and / or duration of cleaning of the transmission glass window, a timing of replacing the transmission glass window, a timing of replacing a UV lamp, and / or an output of the UV light based on the monitored illuminances.

Owner:ASM JAPAN

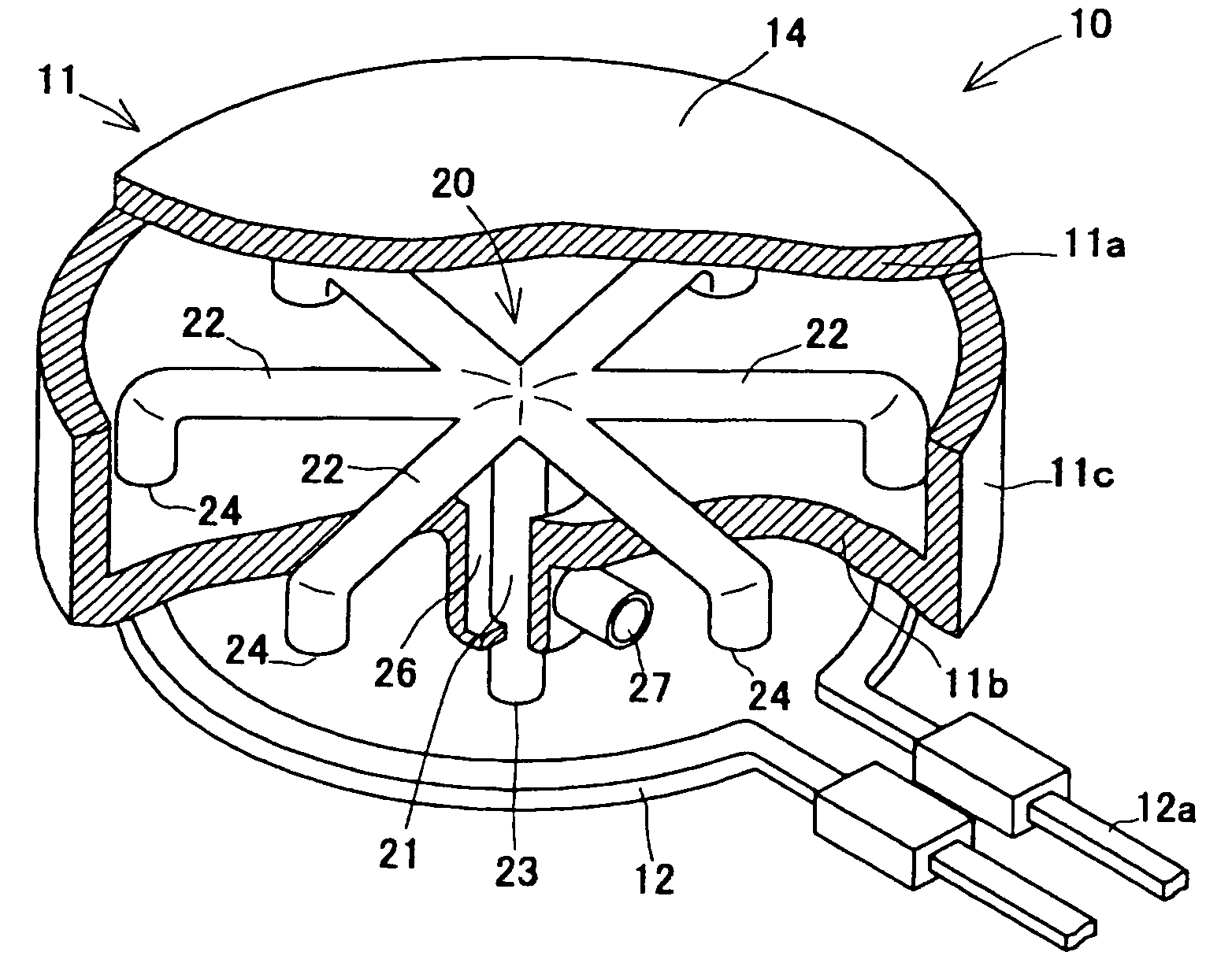

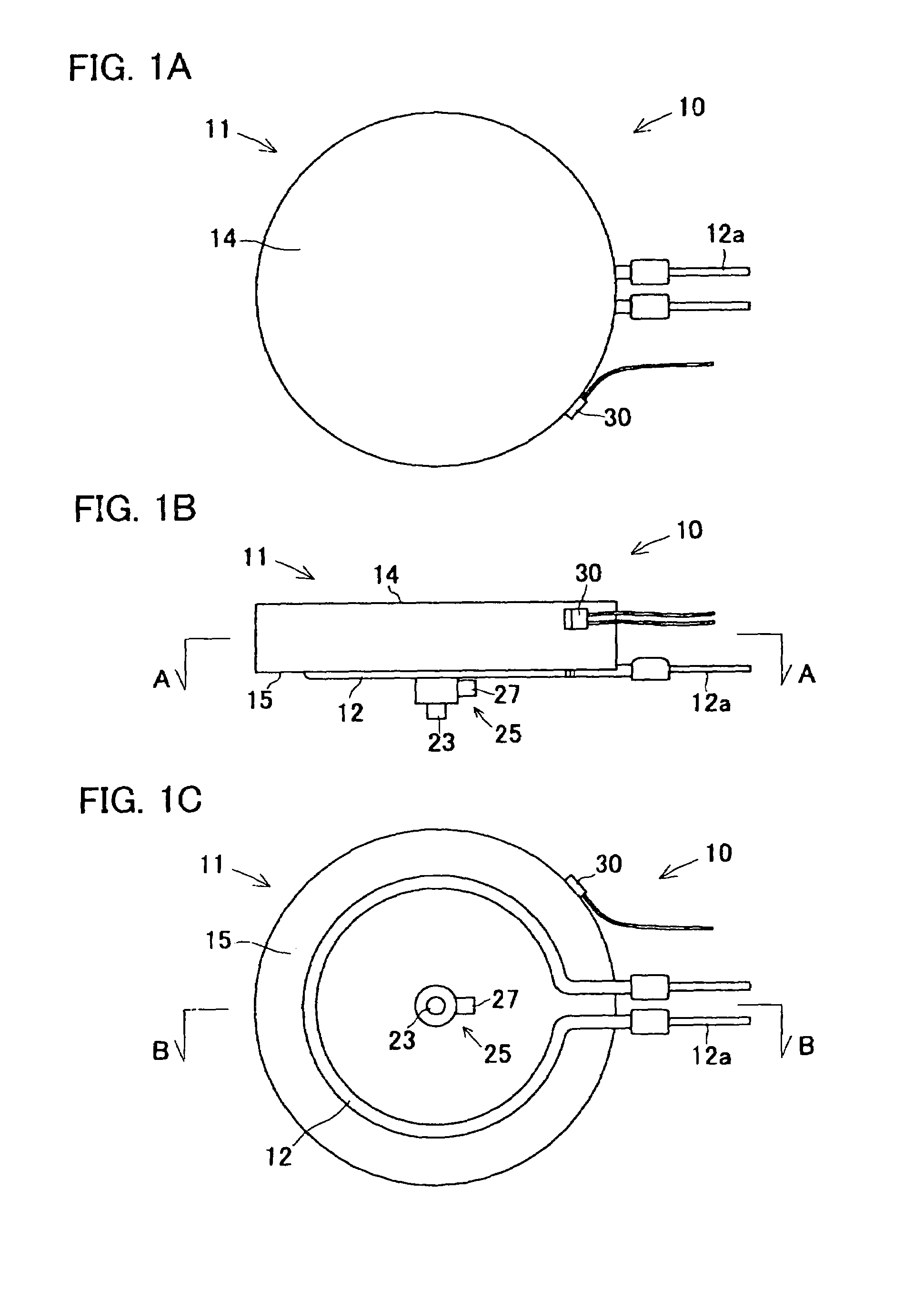

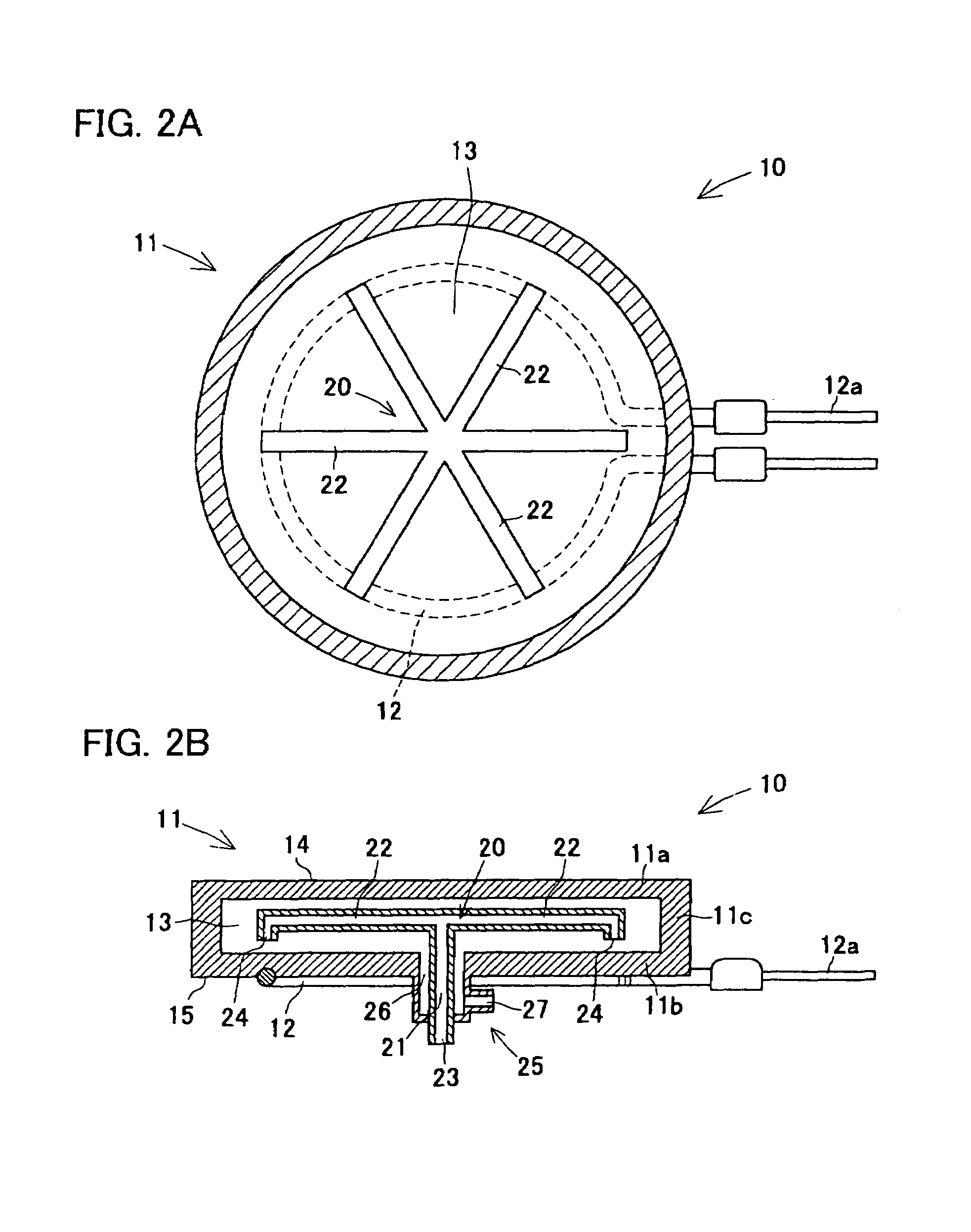

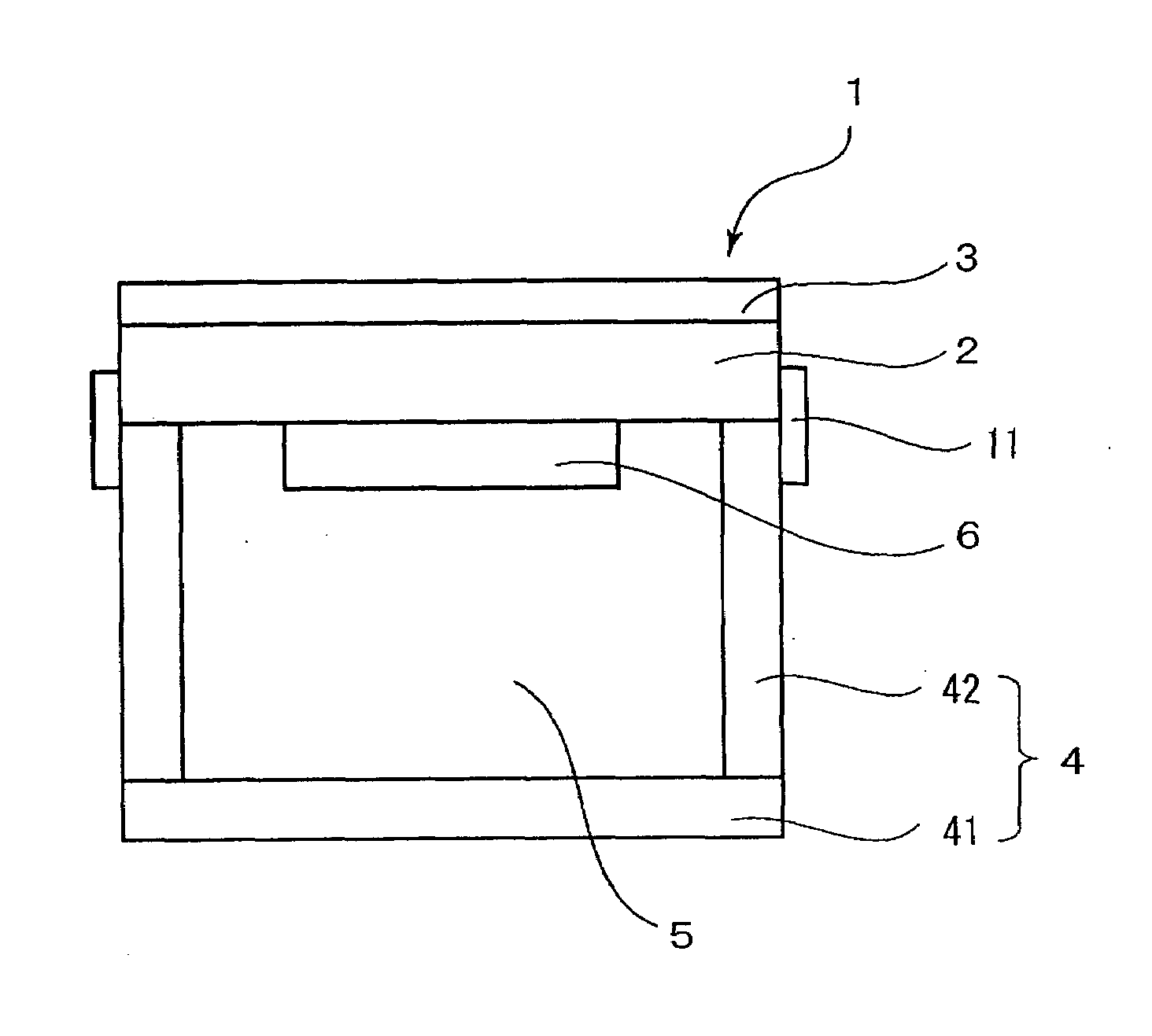

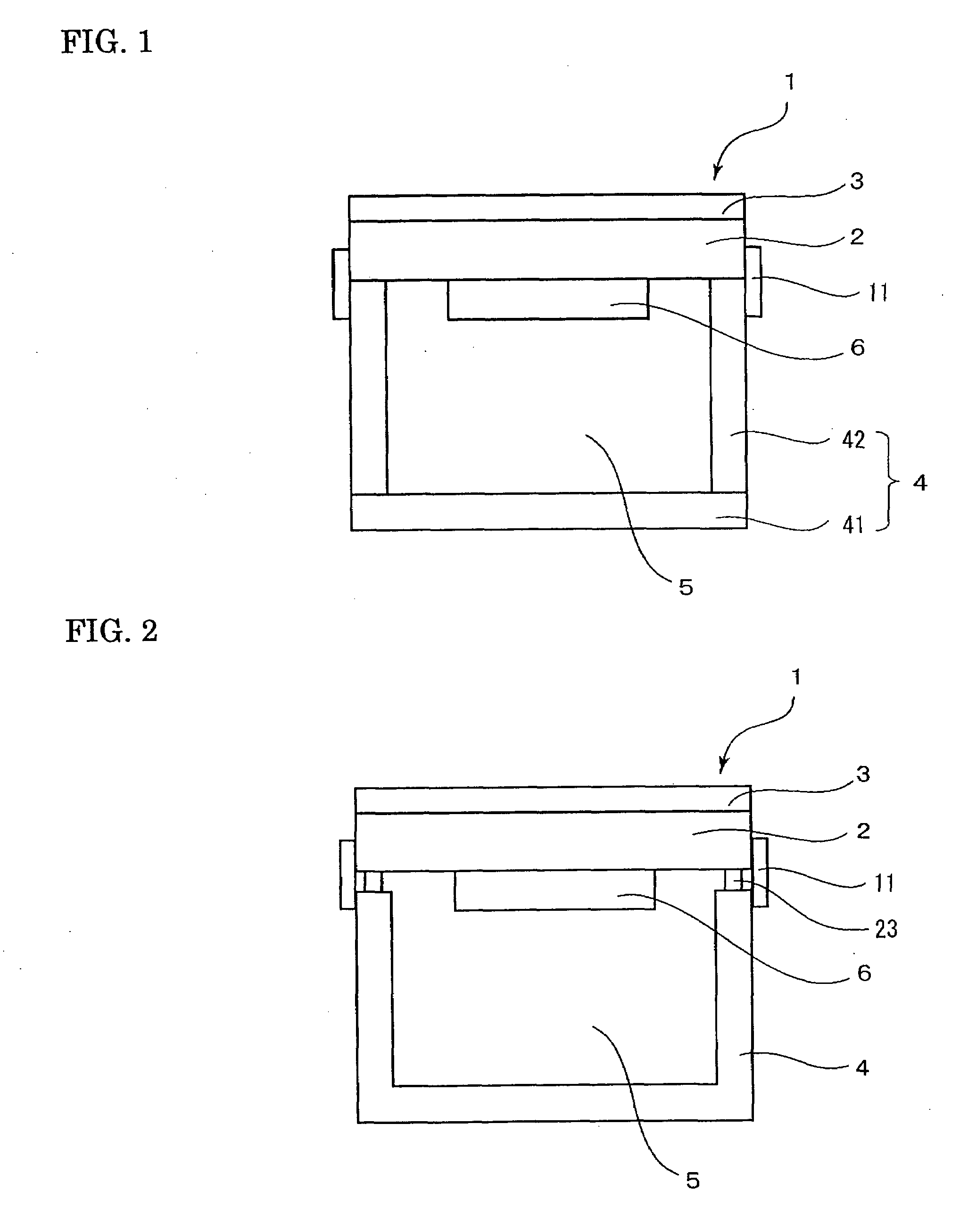

Wafer holder for wafer prober and wafer prober equipped with same

InactiveUS20090045829A1Improve rigidityGood effectHot plates heating arrangementsIndividual semiconductor device testingRoom temperatureEngineering

It is an object of the present invention to provide a wafer prober wafer holder that is highly rigid and increases the heat insulating effect, thereby improving positional accuracy, thermal uniformity, and chip temperature ramp-up and cooling rates, as well as a wafer prober device equipped therewith.A wafer holder of the present invention includes a chuck top that mounts a wafer, and a support member that supports the chuck top, wherein, a restricting member is provided that covers an interface between the chuck top and the support member. By covering the gap between the chuck top and the support member with the restricting member, the heat insulating effect can be increased by preventing the flow of outside air through the gap into the support member, and the cooling rate can be particularly improved if cooling to a temperature below room temperature.

Owner:SUMITOMO ELECTRIC IND LTD

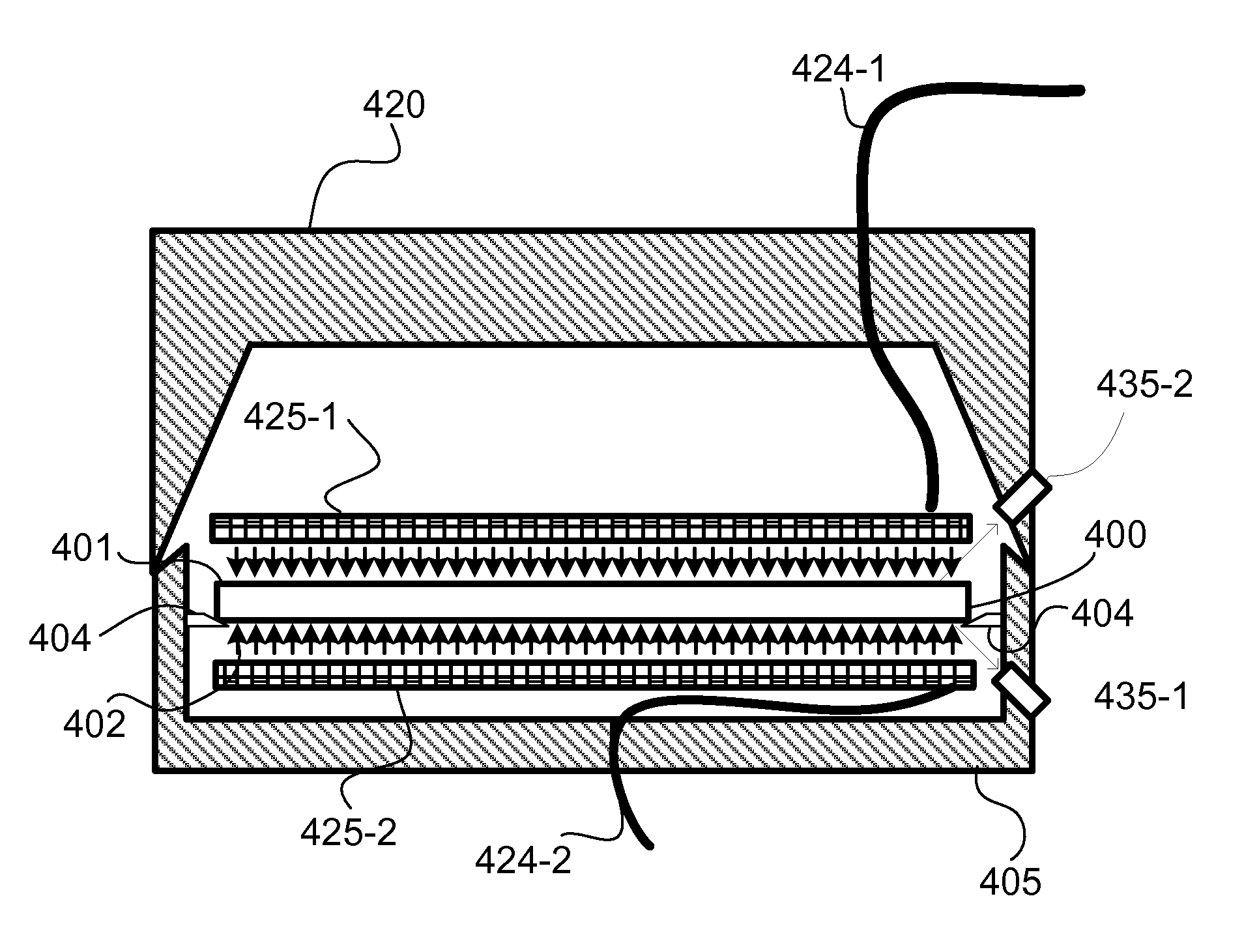

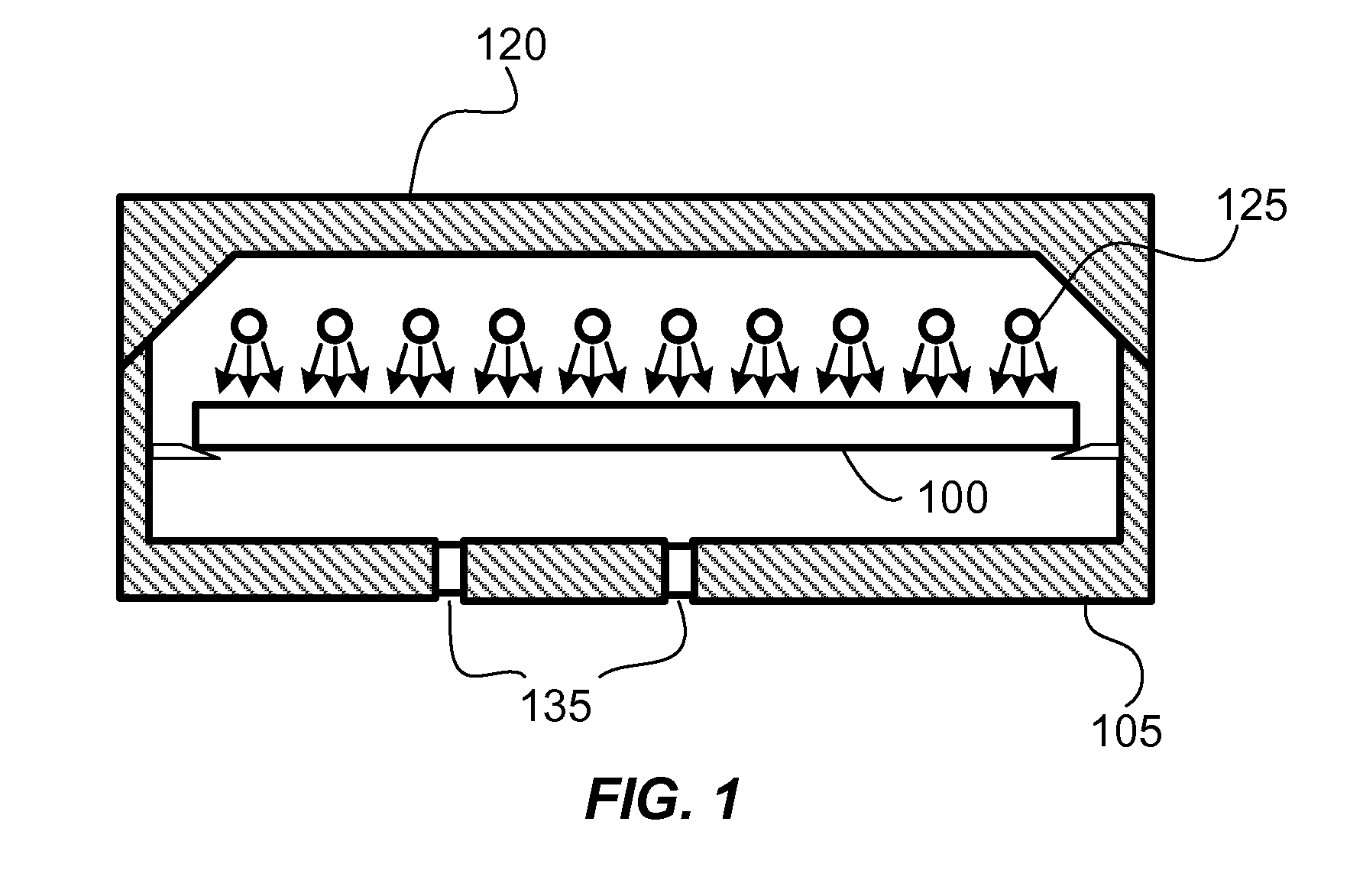

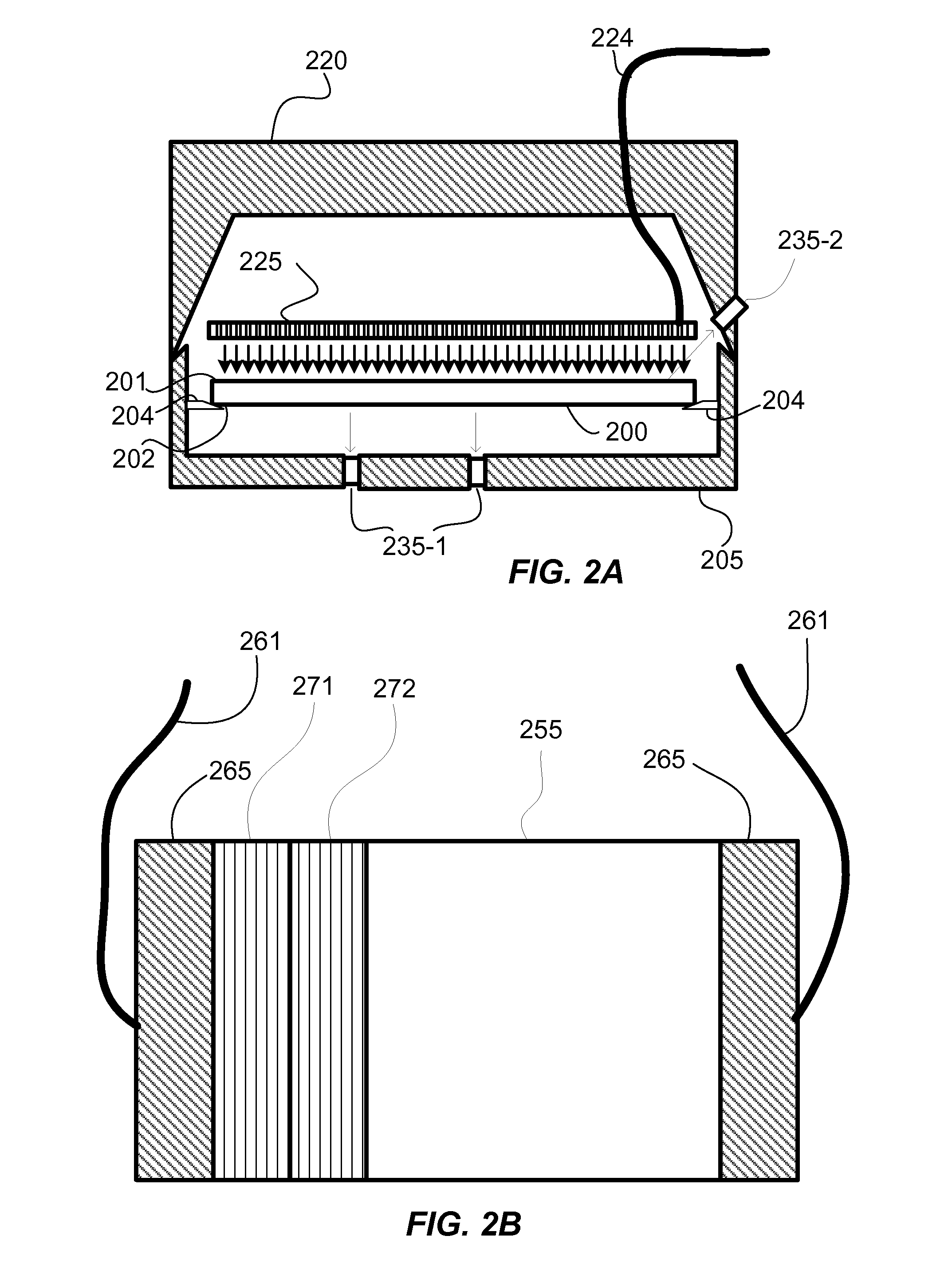

LED substrate processing

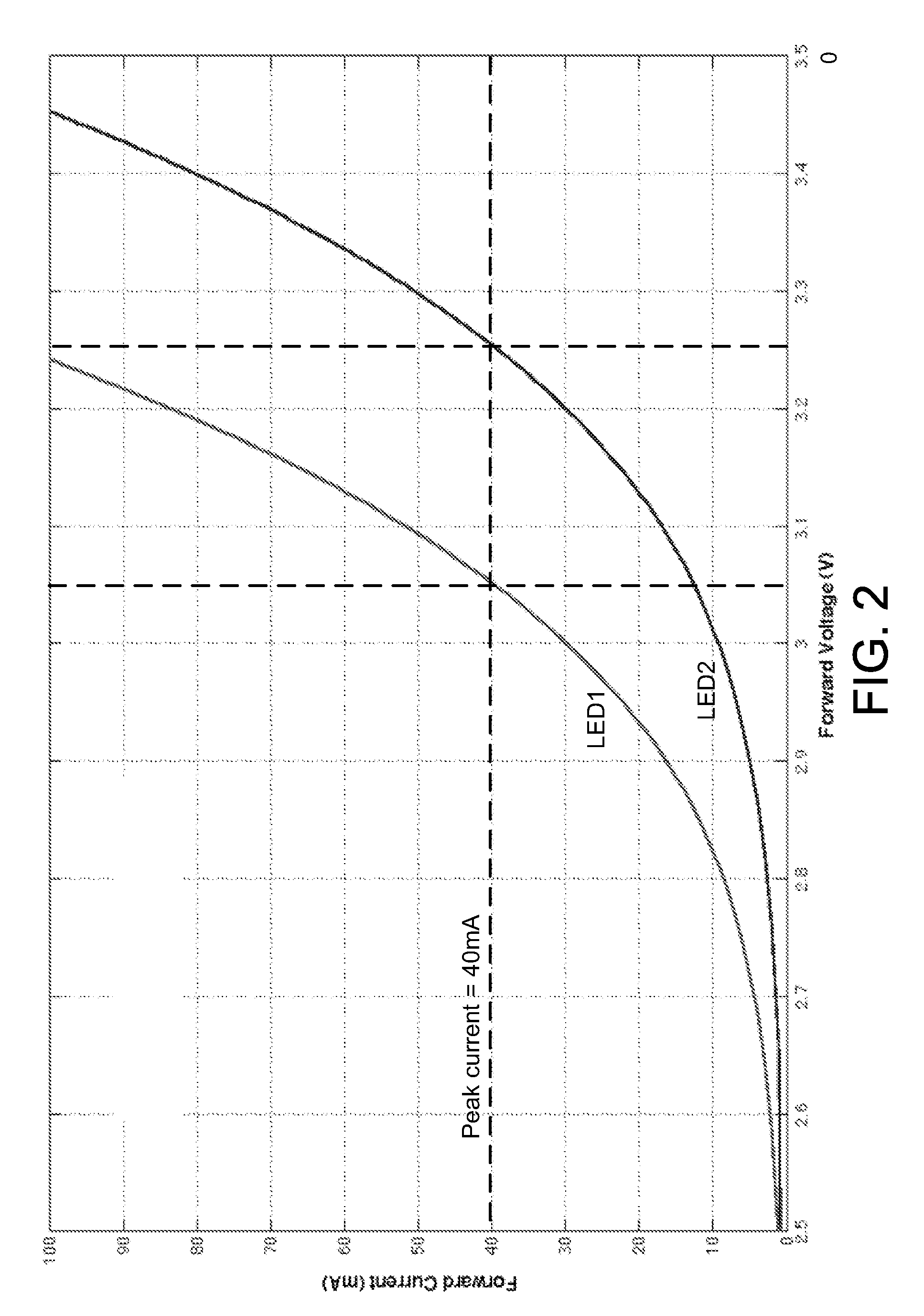

ActiveUS8404499B2Improve efficiencyFast response timeSemiconductor/solid-state device testing/measurementMuffle furnacesLong pulseLight-emitting diode

Embodiments of the present invention pertain to substrate processing equipment and methods incorporating light emitting diodes (LEDs) for thermally processing substrates. Such light sources offer a variety of advantages including higher efficiency and more rapid response times. Pulse widths are selectable down to under a millisecond but can be for long pulses up to and exceeding a second. LEDs are preferable to tungsten-halogen lamps even in circumstances that allow longer processing times, since LEDs produce light with greater than 50% efficiency and tungsten-halogen lamps operate with less than 5% efficiency.

Owner:APPLIED MATERIALS INC

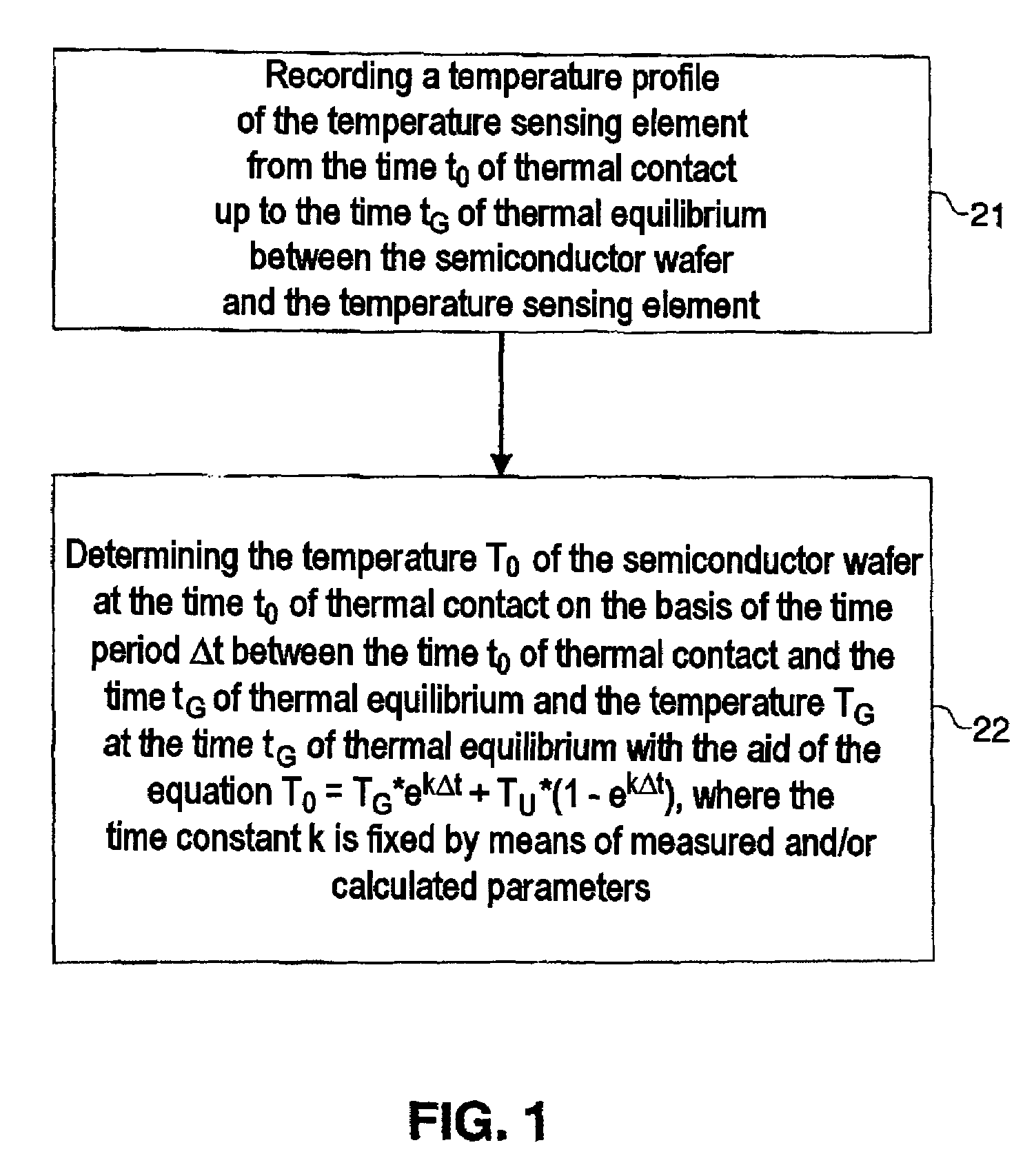

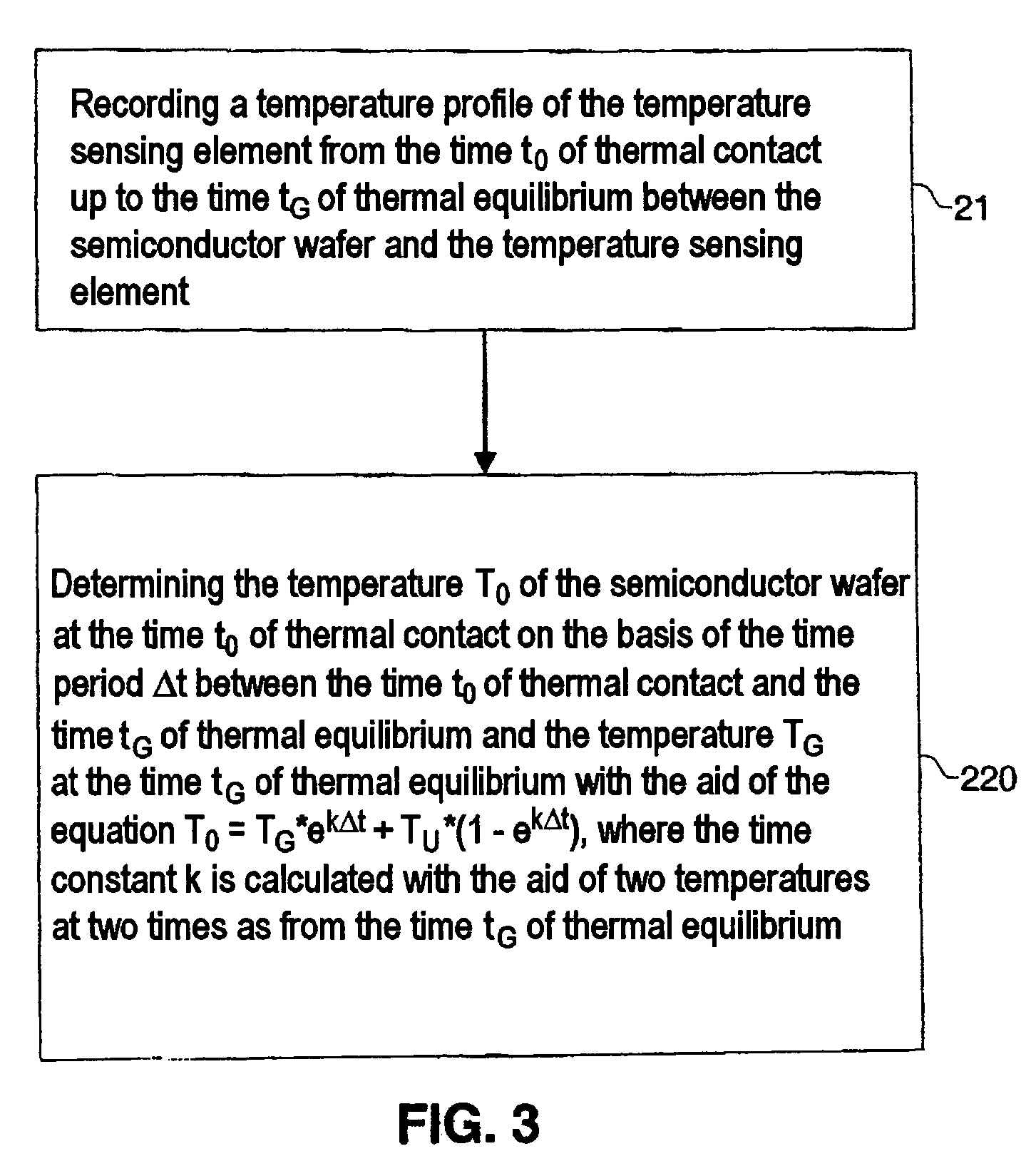

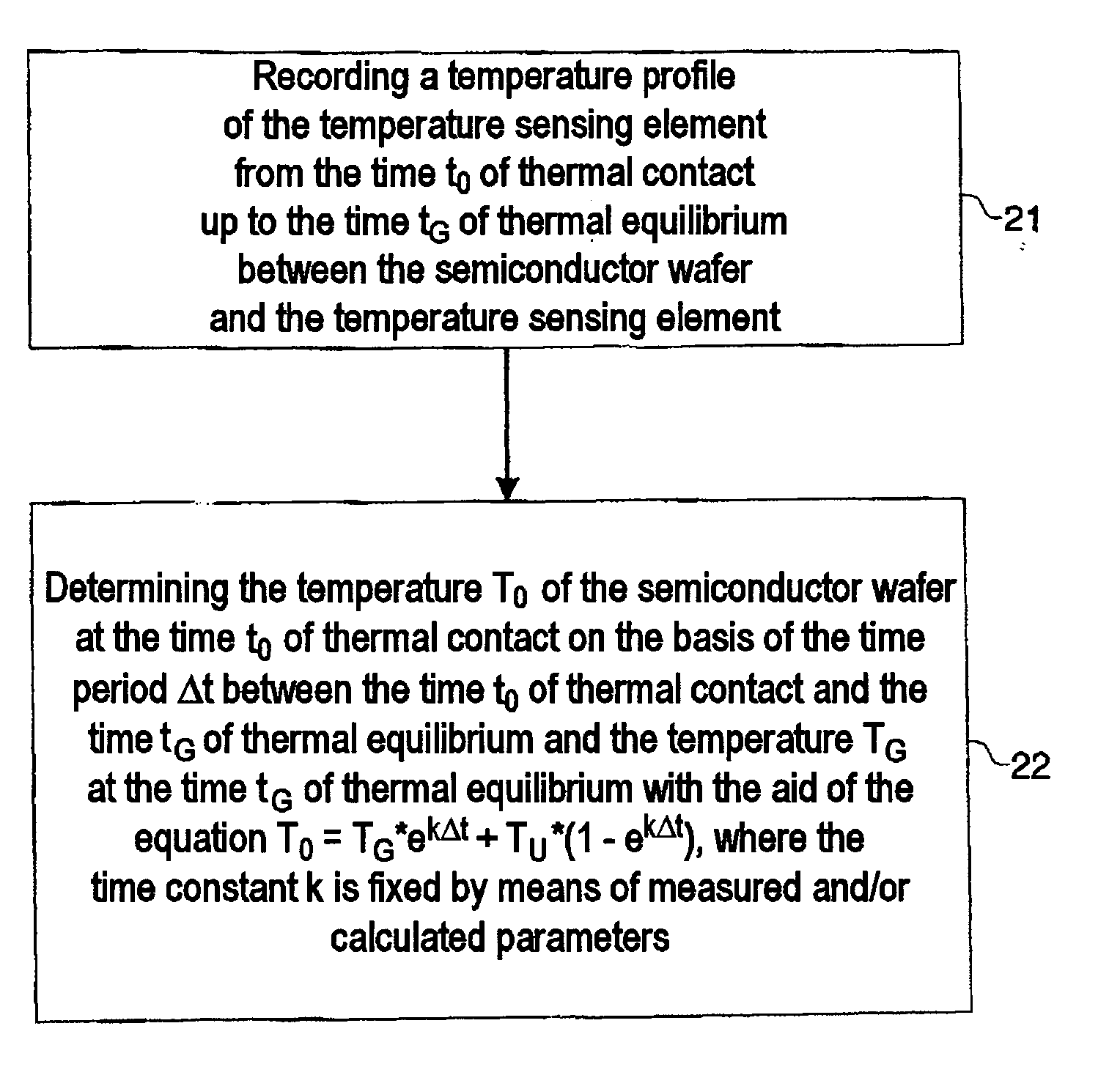

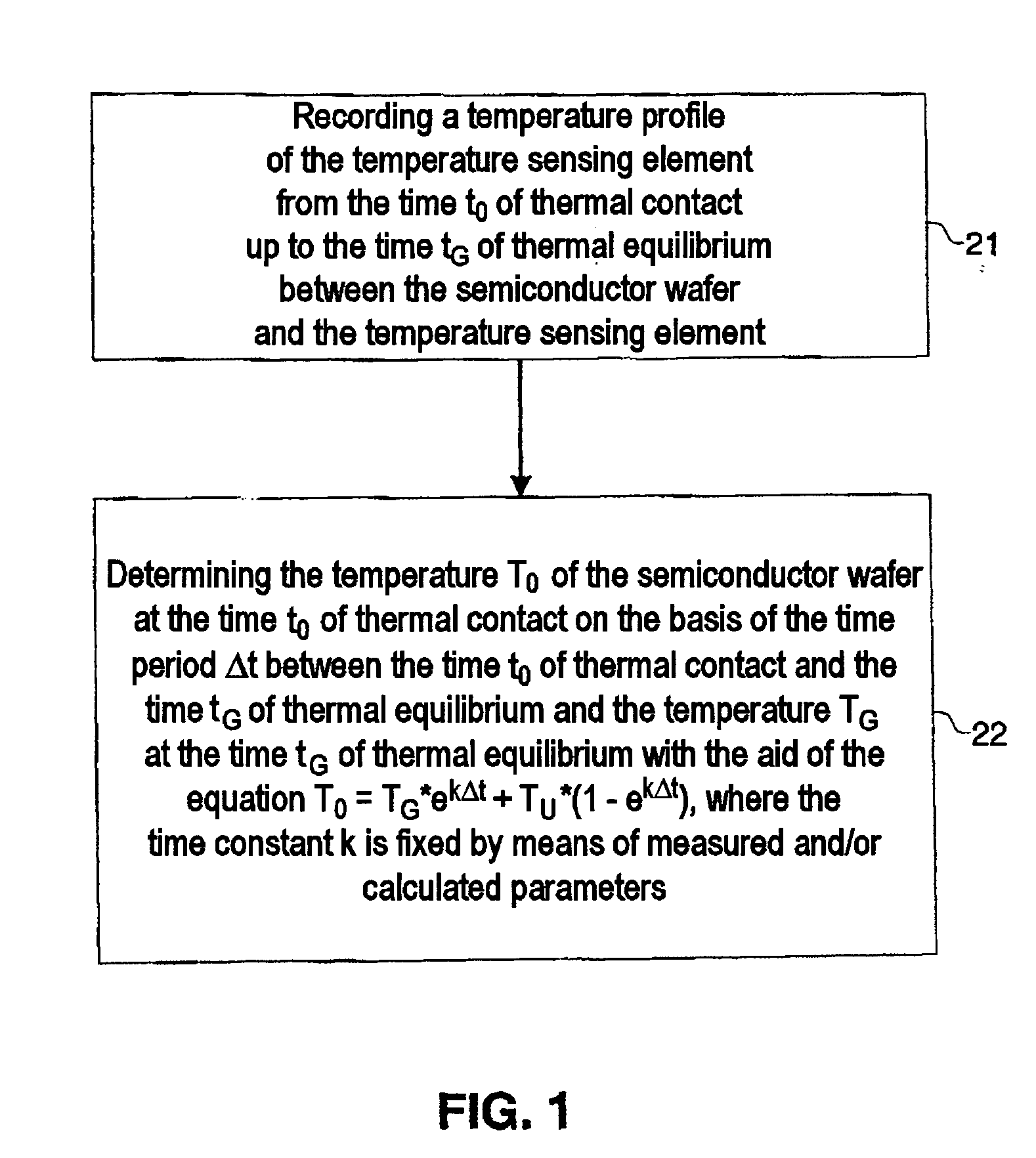

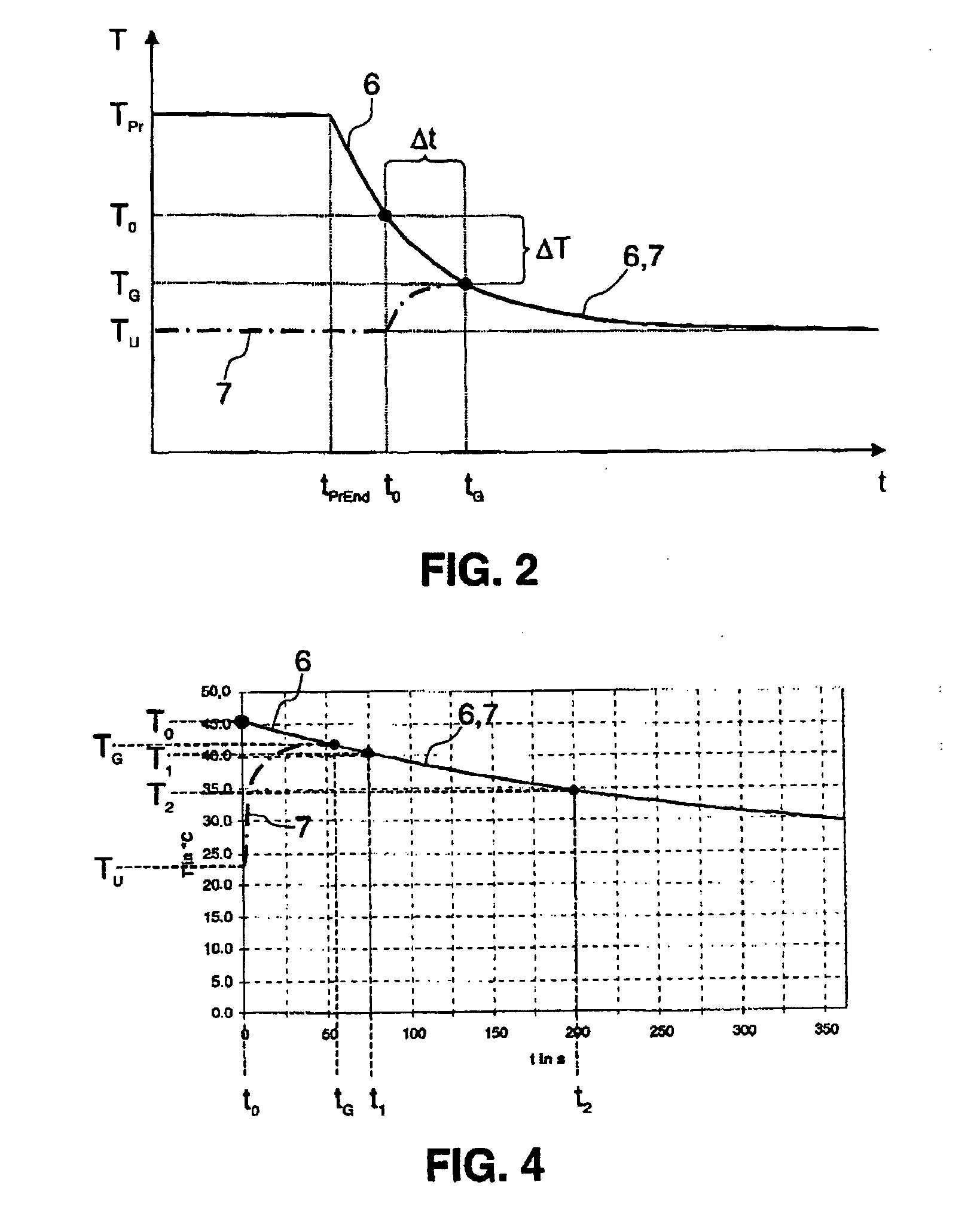

System and method for determining the temperature of a semiconductor wafer

InactiveUS7274867B2High precisionImprove convenienceDrying solid materials with heatSemiconductor/solid-state device testing/measurementTime segmentBack calculation

A system and method for determining the temperature of a semiconductor wafer at the time of thermal contact of the semiconductor wafer with a temperature sensing element. According to the invention, a temperature profile of the temperature sensing element is recorded from the time of thermal contact up to the time of thermal equilibrium between the semiconductor wafer and the temperature sensing element and the temperature of the semiconductor wafer at the time of thermal contact is determined on the basis of a time period between the time of thermal contact and the time of thermal equilibrium and the temperature TG of the semiconductor wafer reached at the time tG of thermal equilibrium is determined by back calculation with the aid of an equation derived from Newton's law of cooling.

Owner:POLARIS INNOVATIONS LTD

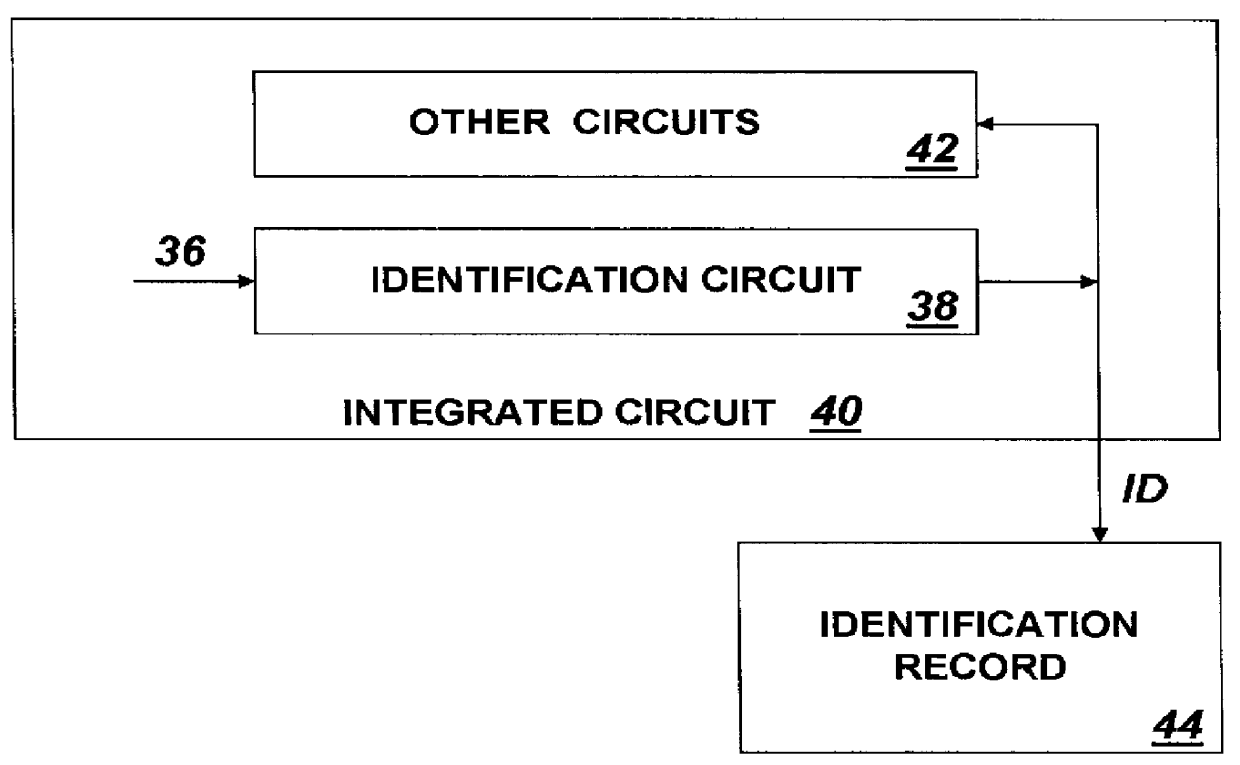

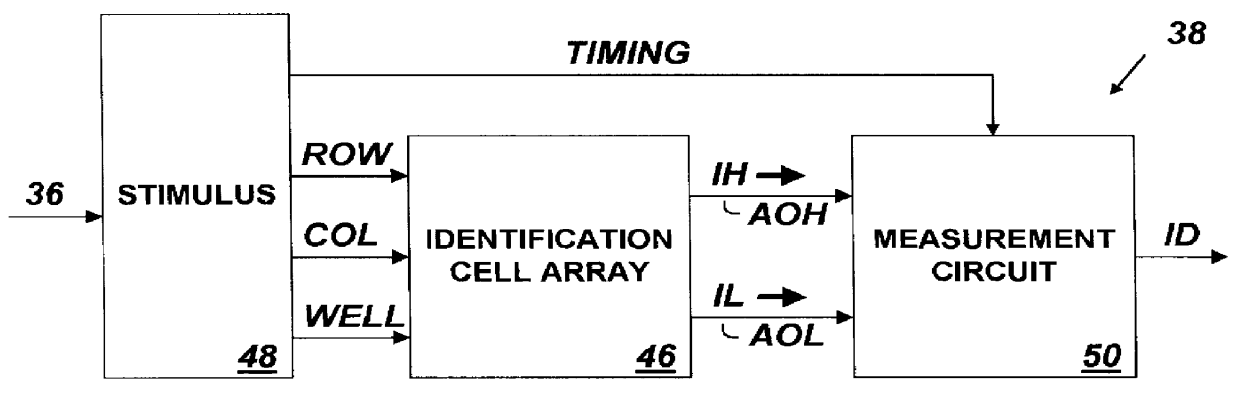

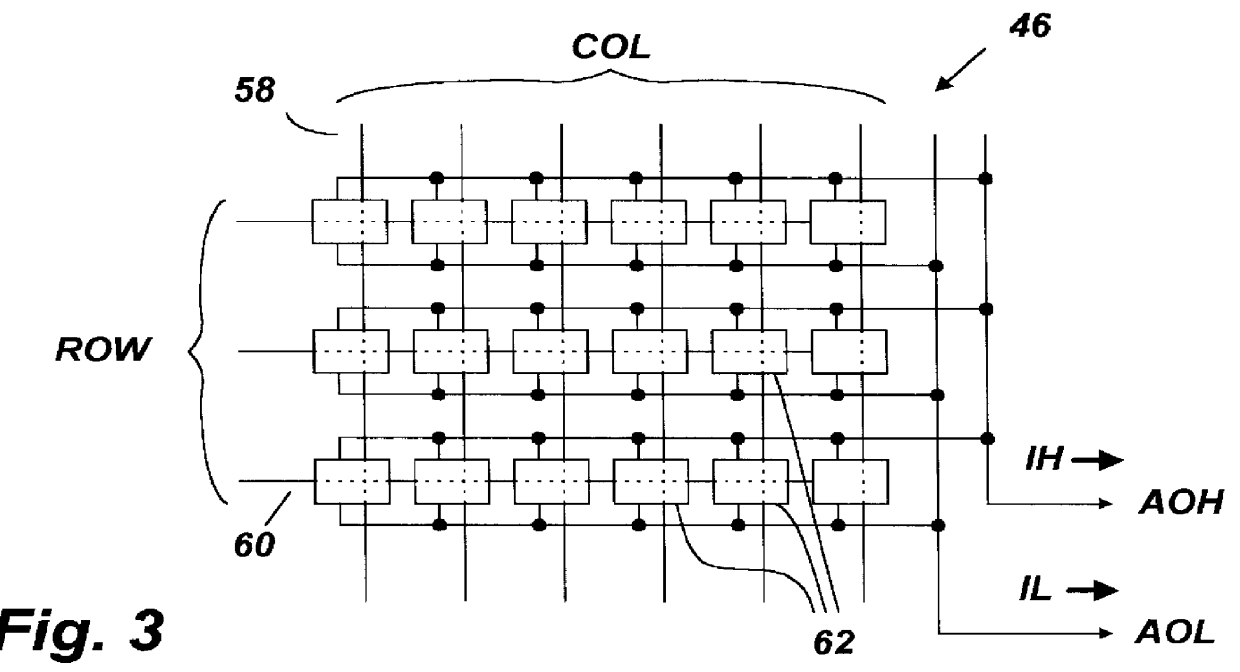

System for providing an integrated circuit with a unique identification

InactiveUS6161213ANoise figure or signal-to-noise ratio measurementSemiconductor/solid-state device detailsIdentification deviceIntegrated circuit

An integrated circuit identification device (ICID) to be incorporated into an integrated circuit (IC) includes an array of electronic cells in which the magnitude of an output signal of each cell is a function of randomly occurring parametric variations which vary from cell-to-cell. The ICID also includes a circuit for measuring the output of each cell and for producing output data having a value reflecting the particular combination of measured characteristics of all of the elements of the array. When we make the number of elements in the array large enough, we insure that to a high degree of probability, the pattern of measured array cell characteristics for an ICID embedded in any one IC will be unique and distinguishable from such patterns measured by ICIDs embedded in millions of other ICs. Thus the value of the output data produced by an ICID circuit acts as a unique "fingerprint" for the IC in which it is installed, and can be used as a unique identification (ID) for that IC.

Owner:ICID

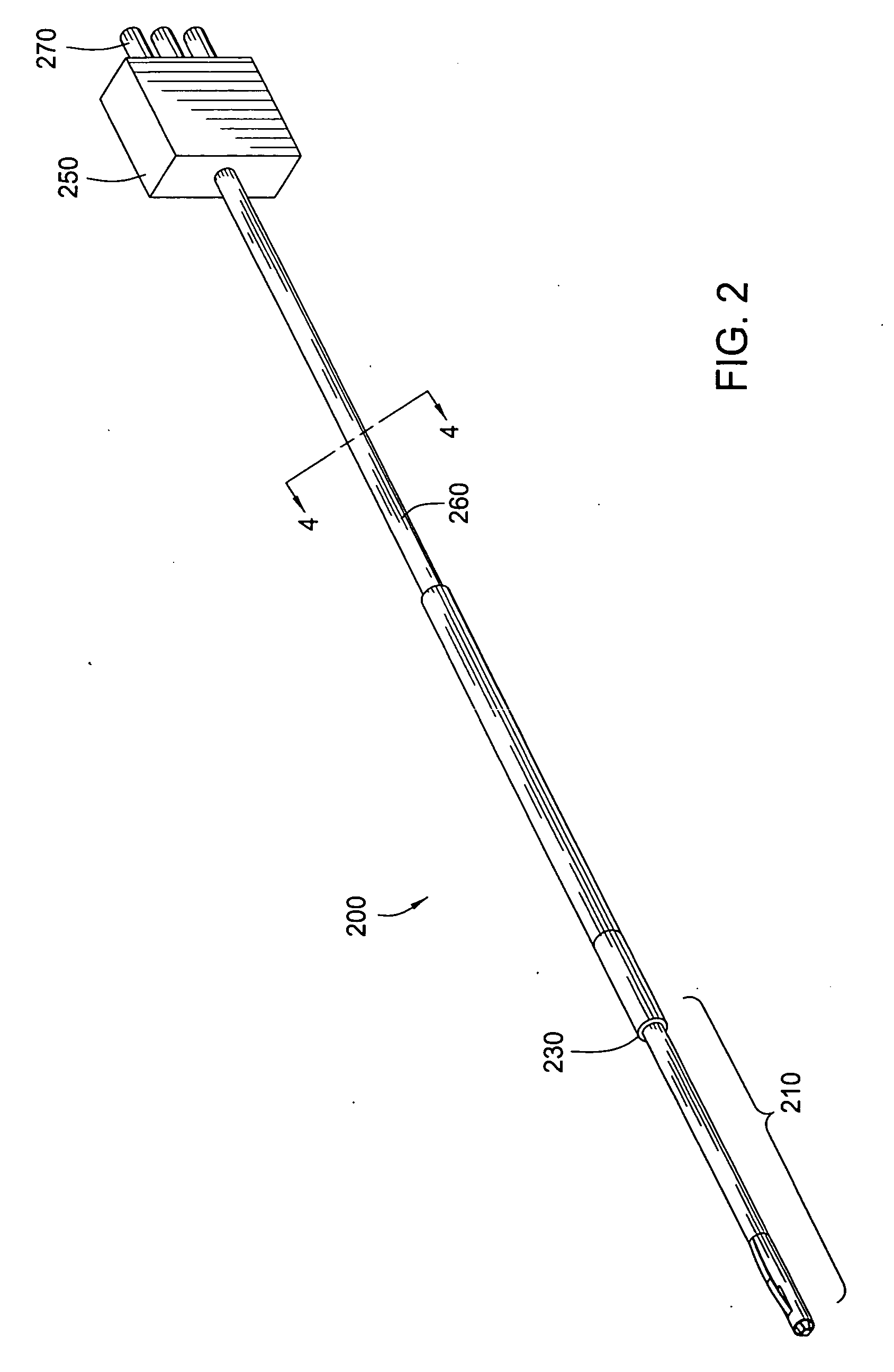

Thermally conductive ceramic tipped contact thermocouple

InactiveUS20060275933A1Thermometer detailsSemiconductor/solid-state device testing/measurementThermocoupleMaterials science

An apparatus for processing a substrate. The apparatus comprising a tubular member with a first end and a second end. The first end comprising an opening; and a temperature sensor disposed in the opening. The temperature sensor comprising a resilient member. The resilient member comprising a surface made of a ceramic material wherein the surface made of a ceramic material extends through the opening to provide a substrate contact surface.

Owner:APPLIED MATERIALS INC

System and method for determining the temperature of a semiconductor wafer

InactiveUS20050042778A1High precisionImprove convenienceDrying solid materials with heatSemiconductor/solid-state device testing/measurementBack calculationThermal contact

A system and method for determining the temperature of a semiconductor wafer at the time of thermal contact of the semiconductor wafer with a temperature sensing element. According to the invention, a temperature profile of the temperature sensing element is recorded from the time of thermal contact up to the time of thermal equilibrium between the semiconductor wafer and the temperature sensing element and the temperature of the semiconductor wafer at the time of thermal contact is determined on the basis of a time period between the time of thermal contact and the time of thermal equilibrium and the temperature TG of the semiconductor wafer reached at the time tG of thermal equilibrium is determined by back calculation with the aid of an equation derived from Newton's law of cooling.

Owner:POLARIS INNOVATIONS LTD

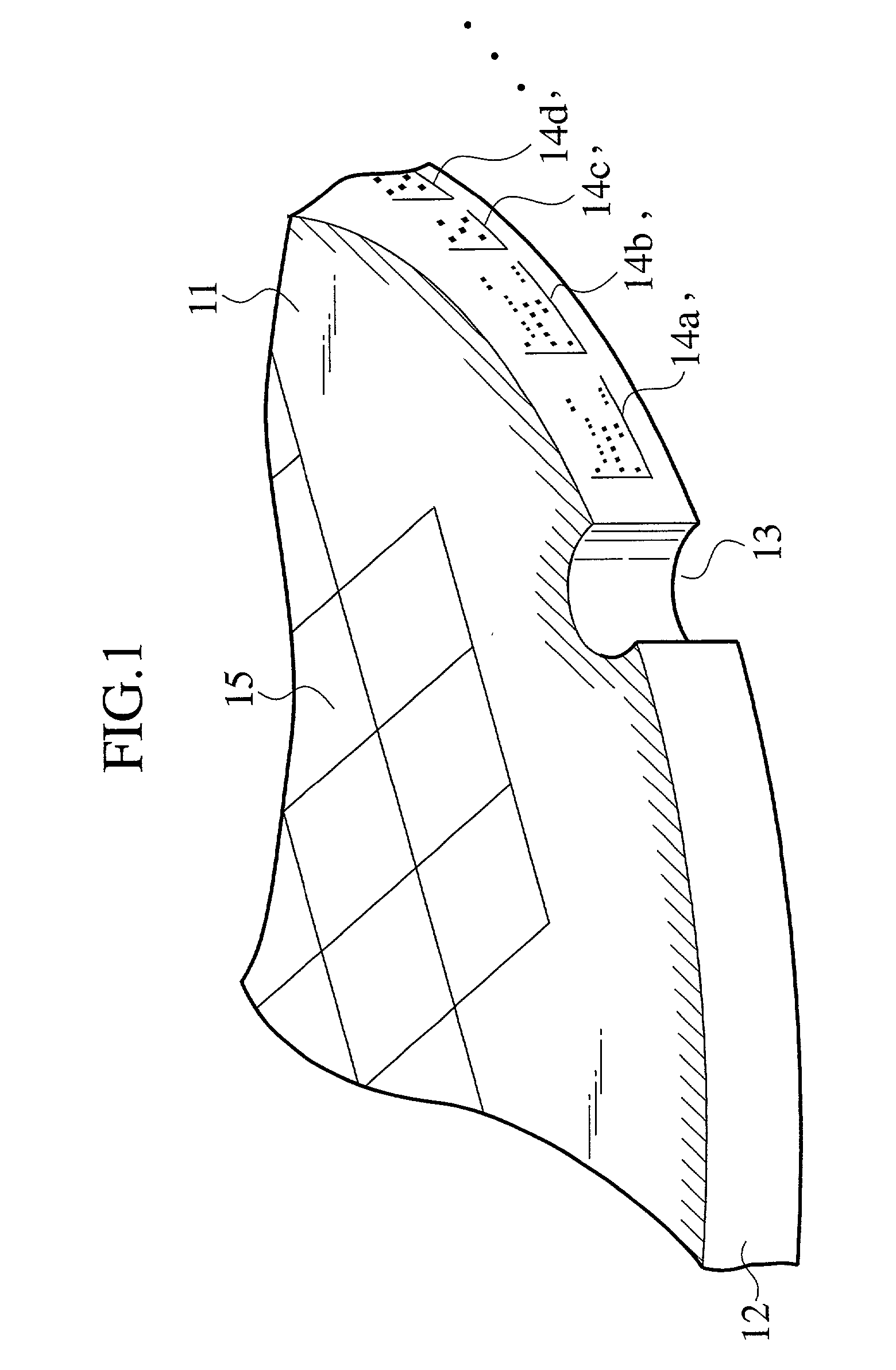

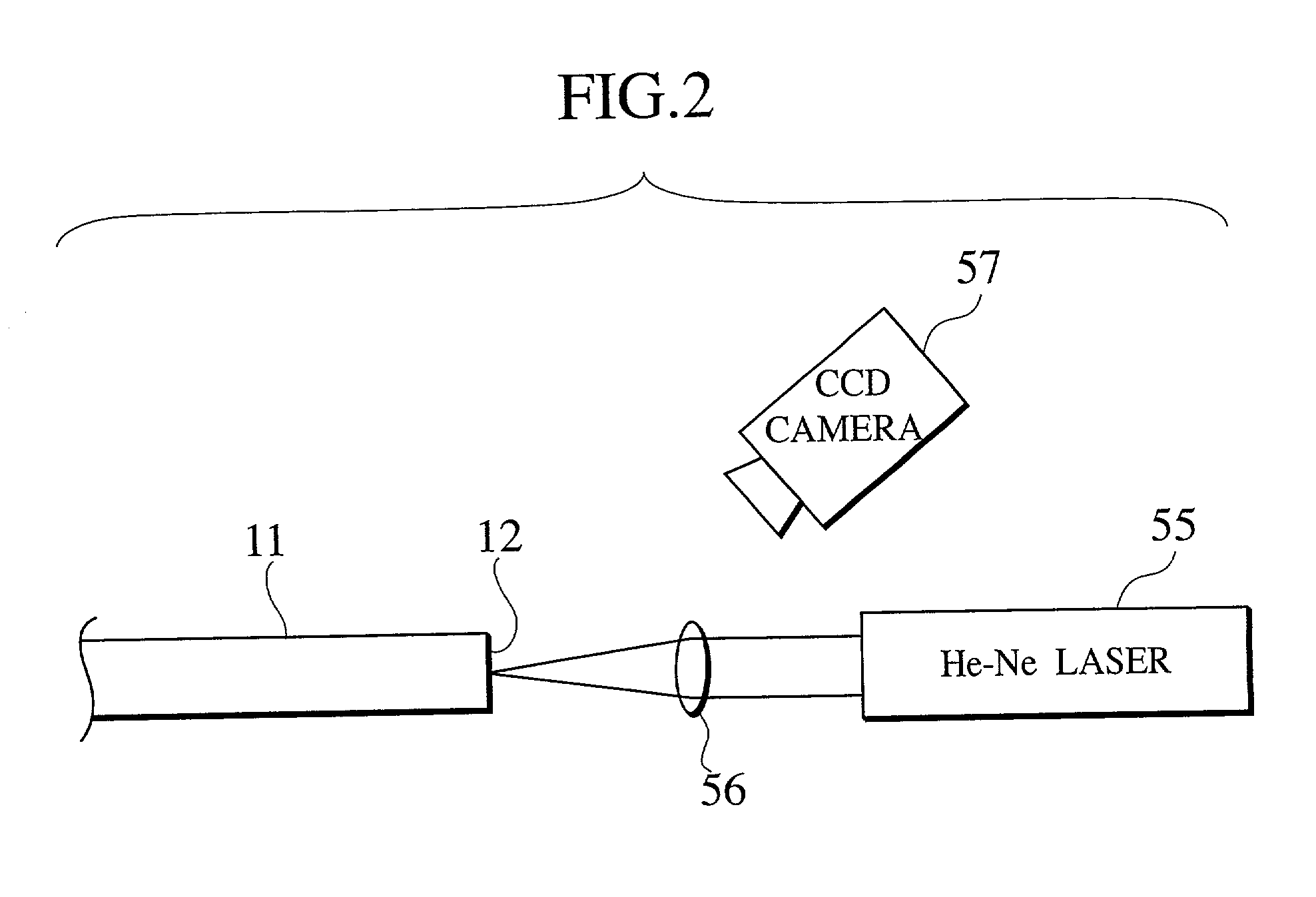

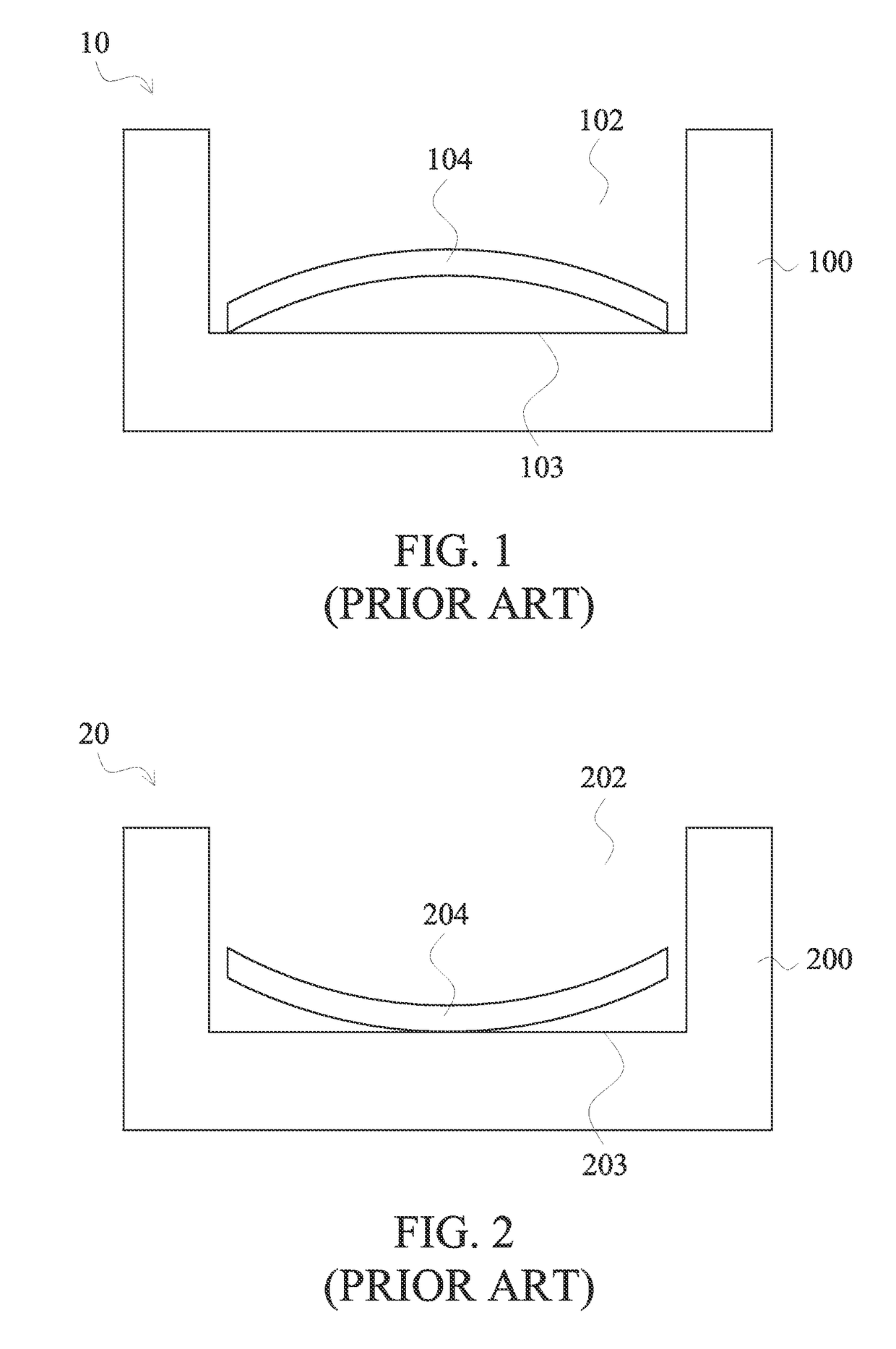

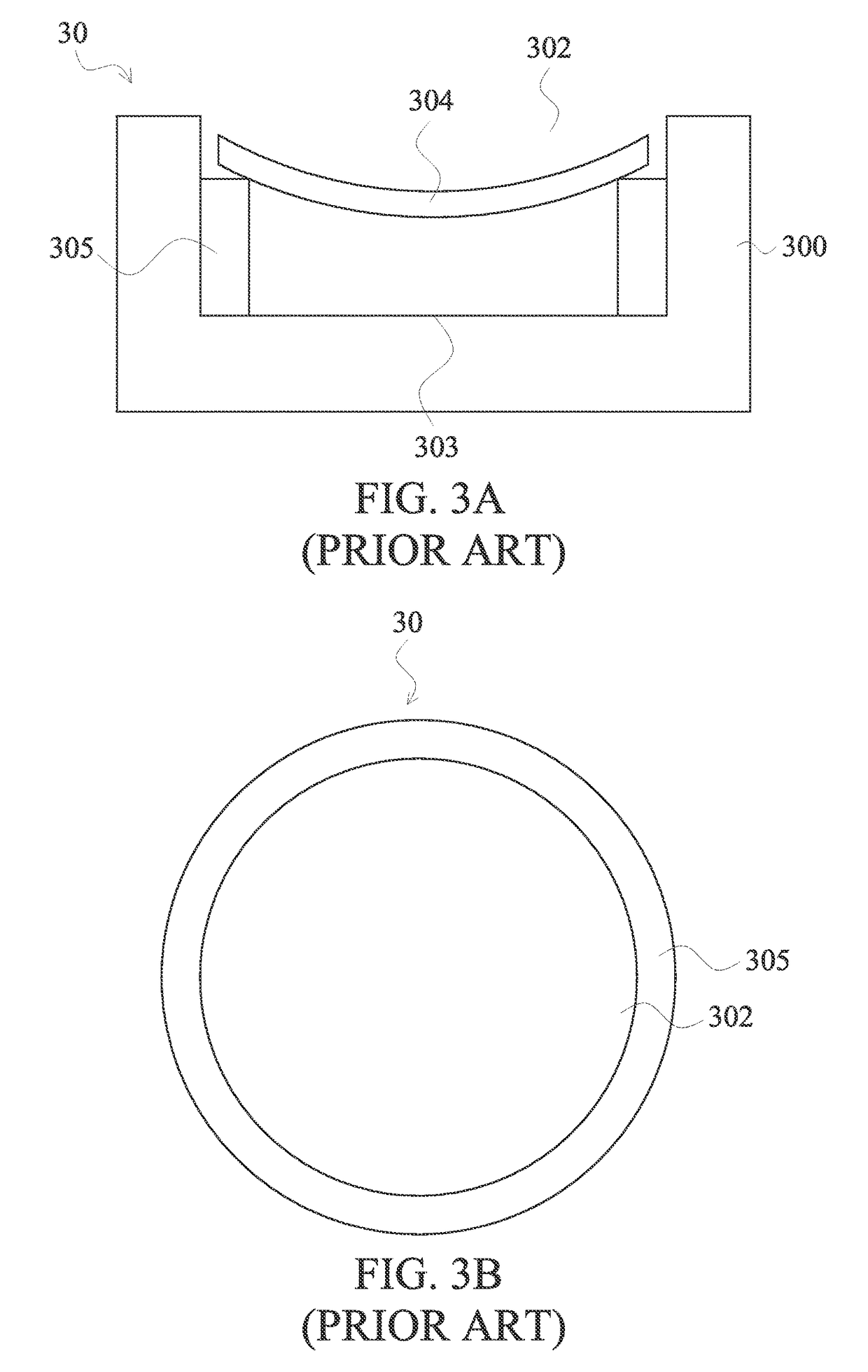

Semiconductor wafer with ID mark, equipment for and method of manufacturing semiconductor device from them

InactiveUS20030003608A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsContour formEngineering

A semiconductor wafer has a bevel contour formed along the periphery thereof, products formed on the wafer, and an ID mark formed on the bevel contour. The ID mark shows at least the properties, manufacturing conditions, and test results of the products.

Owner:KK TOSHIBA

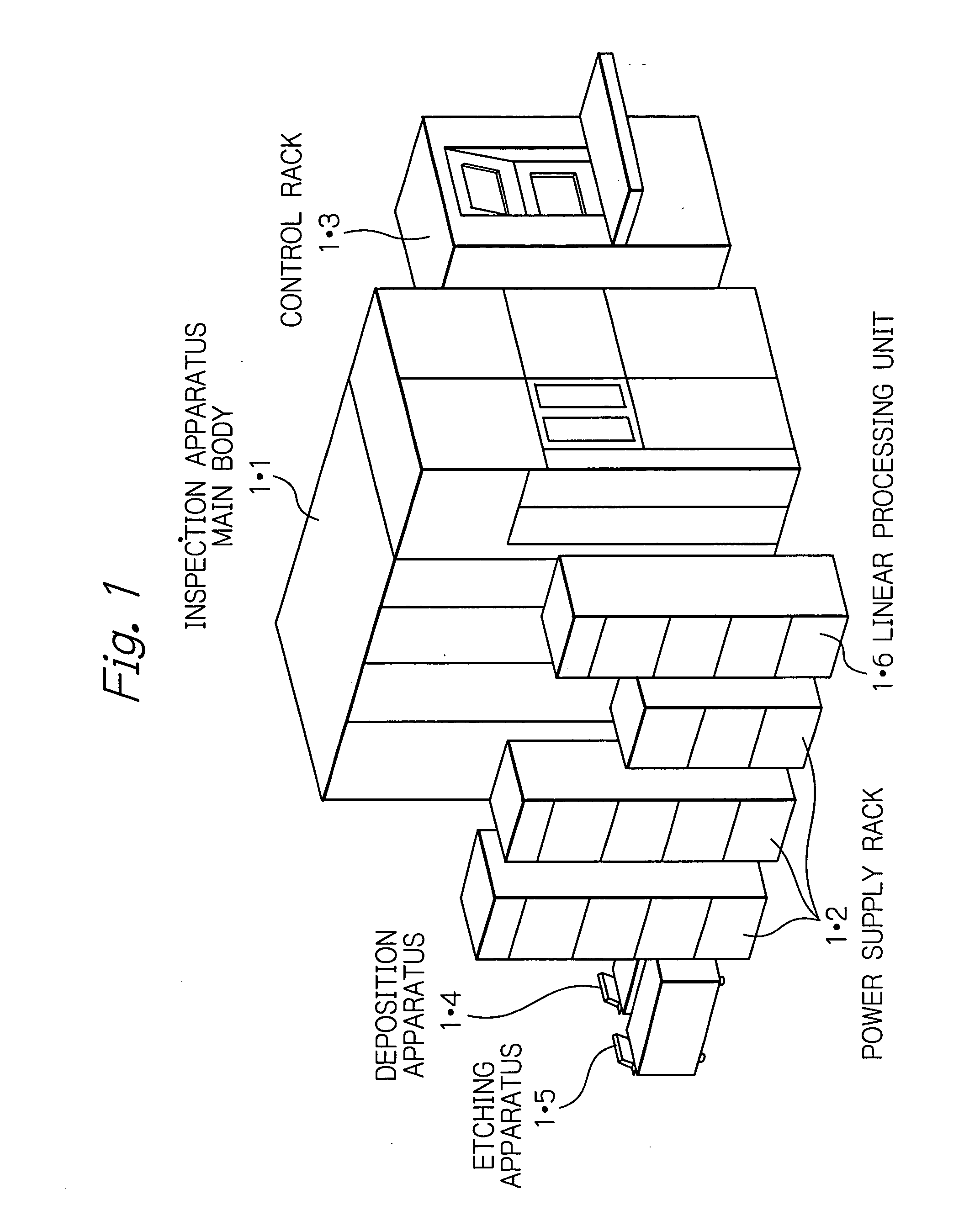

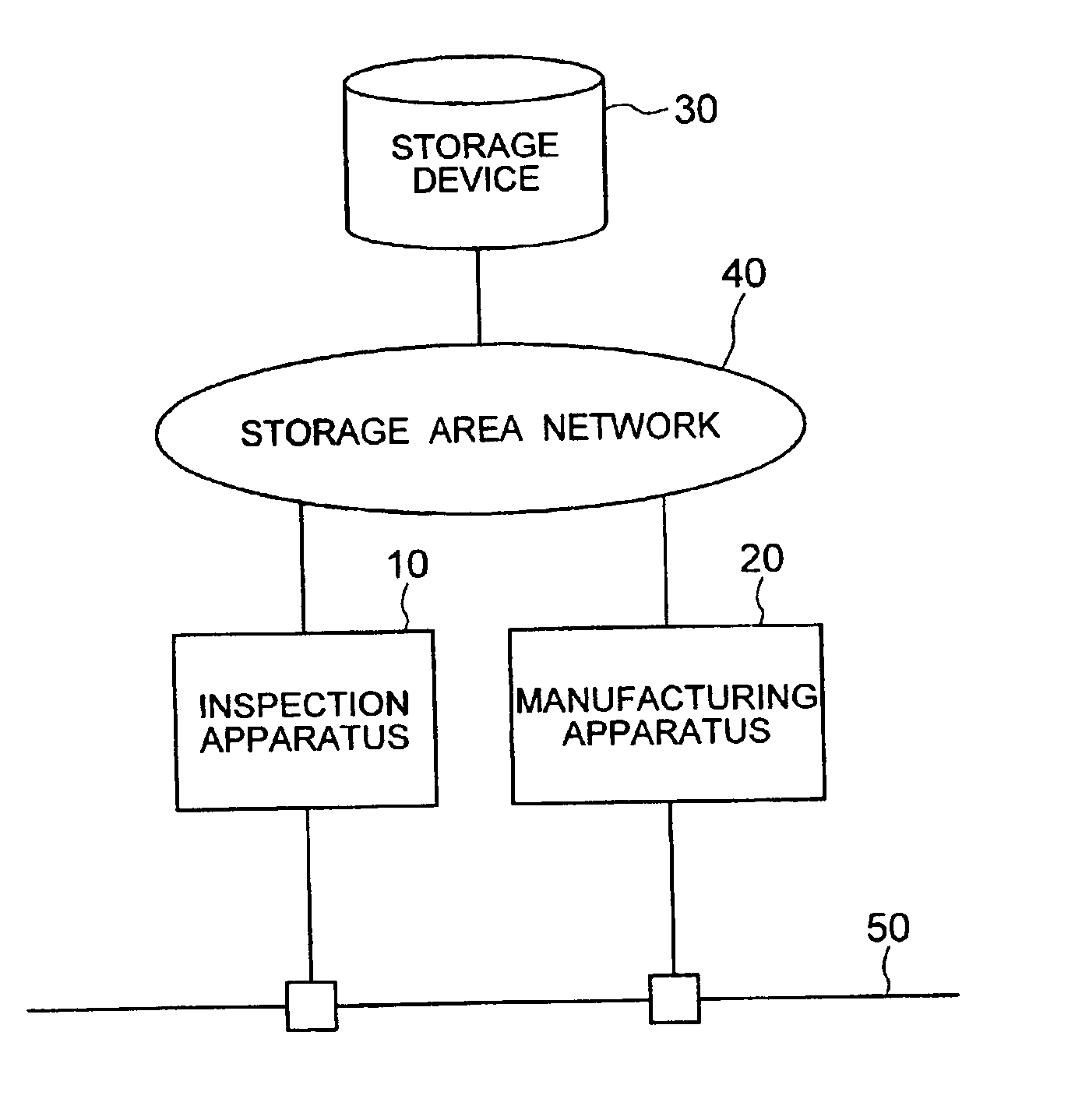

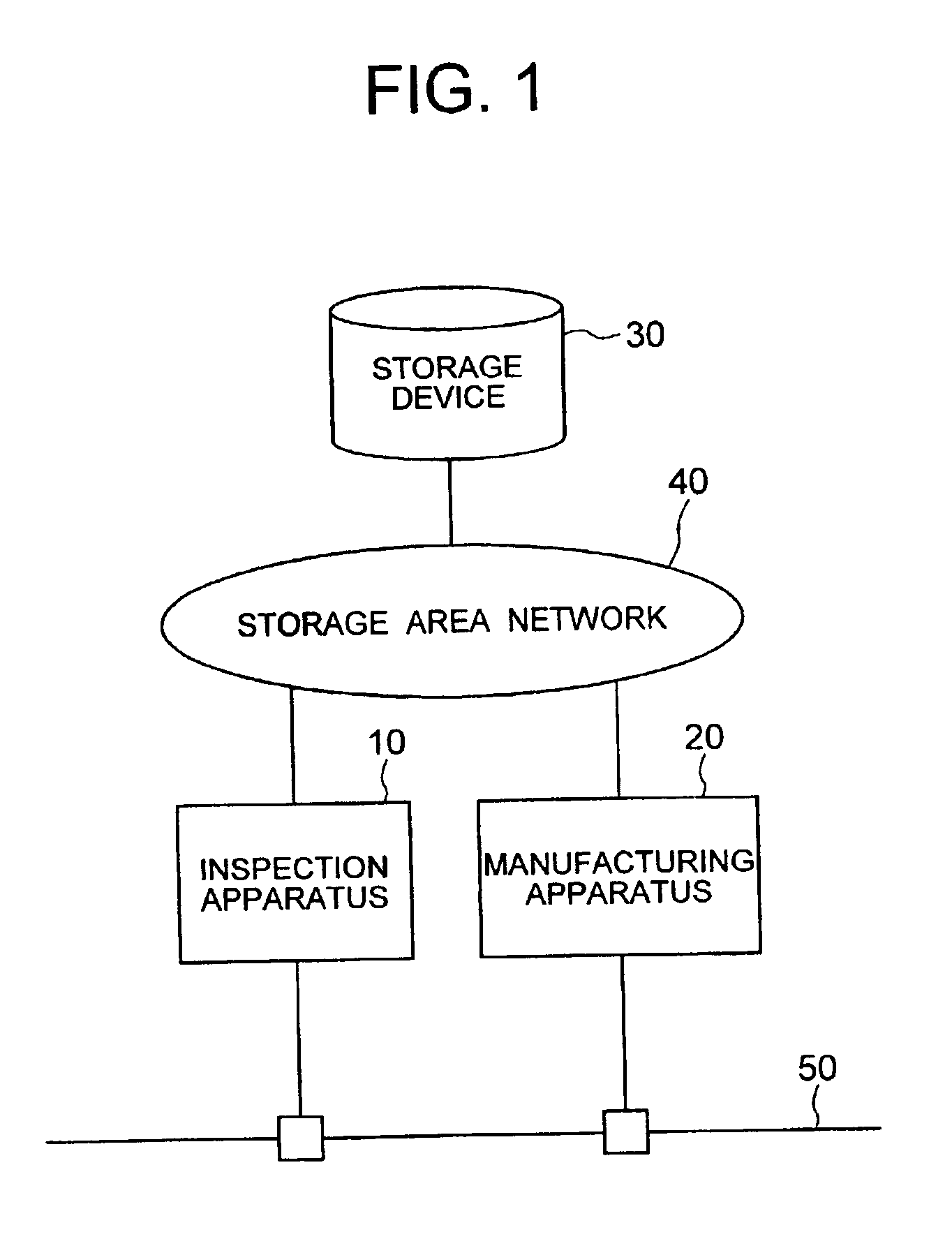

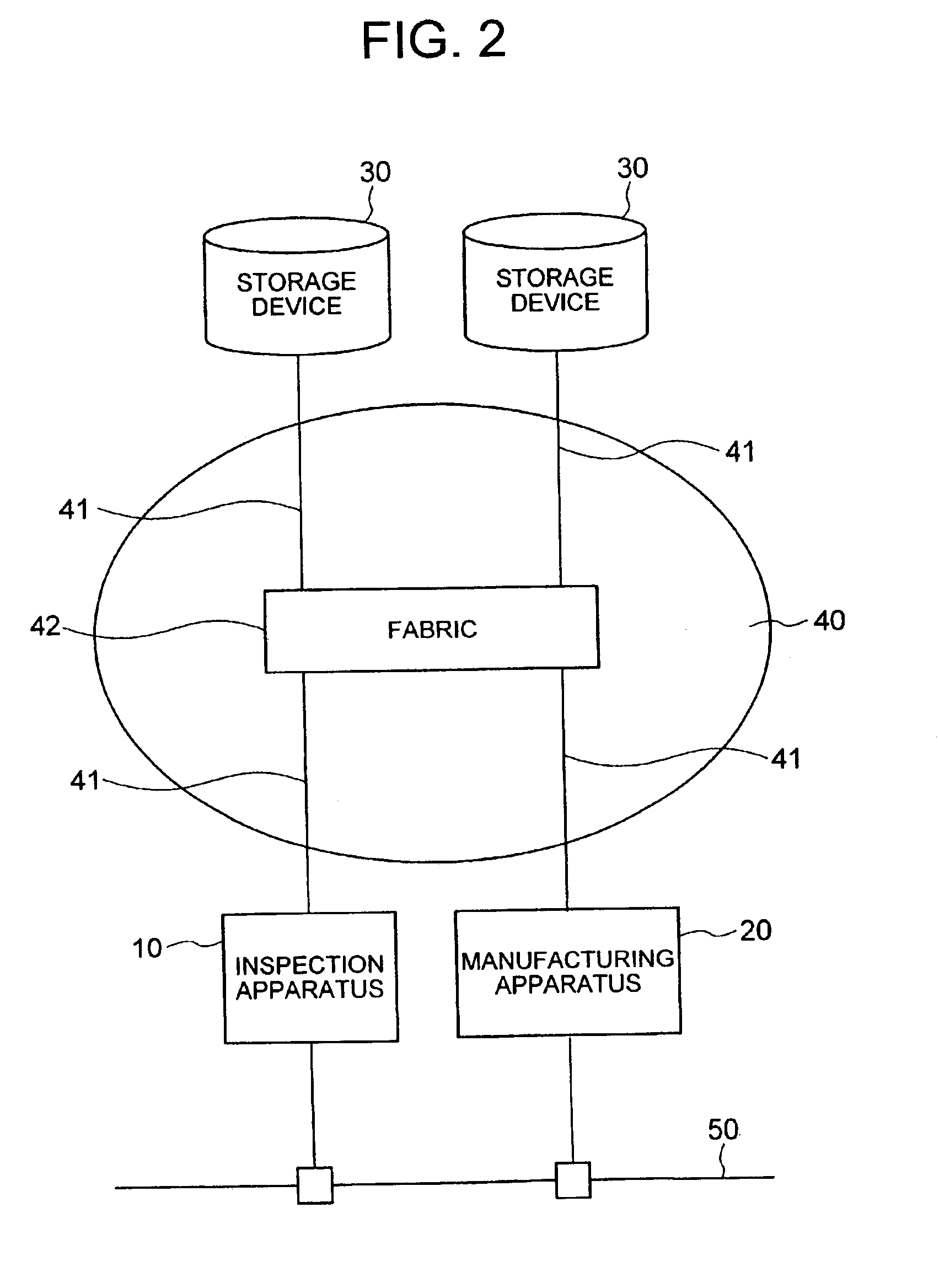

Semiconductor production system

InactiveUS6850854B2Improve system throughputIncrease in sizeSemiconductor/solid-state device testing/measurementElectronic circuit testingStorage area networkObservation unit

A semiconductor production system has a semiconductor manufacturing apparatus having an exposure unit, a control unit for controlling the exposure unit and a storage device; a semiconductor inspection apparatus having an observation unit, a control unit for controlling the observation unit and a storage device; and a storage device commonly used by the semiconductor manufacturing apparatus and the semiconductor inspection apparatus. The manufacturing apparatus, the inspection apparatus and the commonly used storage device are interconnected via a storage area network. With the semiconductor manufacturing apparatus and the storage device linked together via the storage area network, a large volume of image data or design data can be communicated at high speed, thus improving the system throughput.

Owner:HITACHI LTD

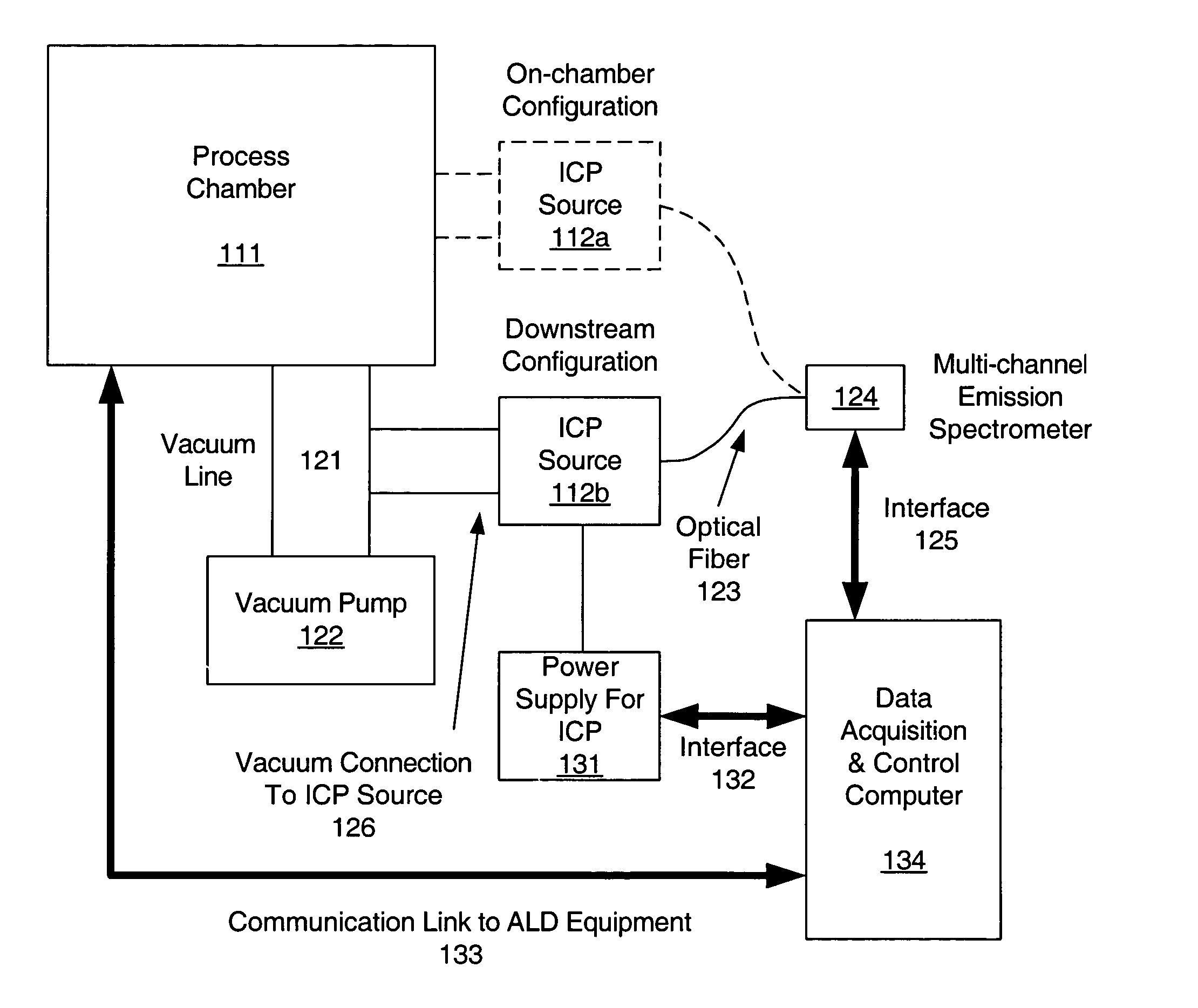

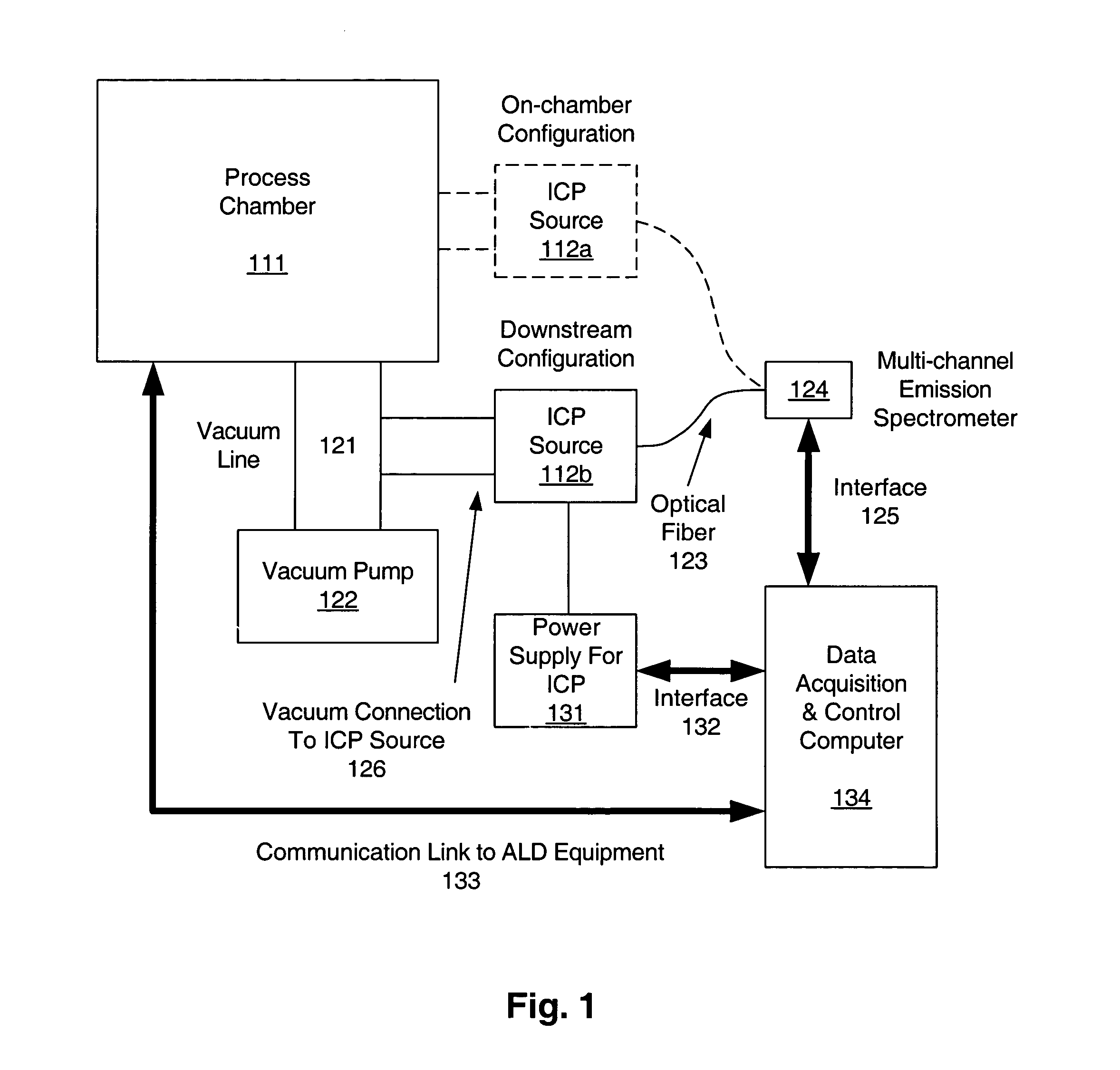

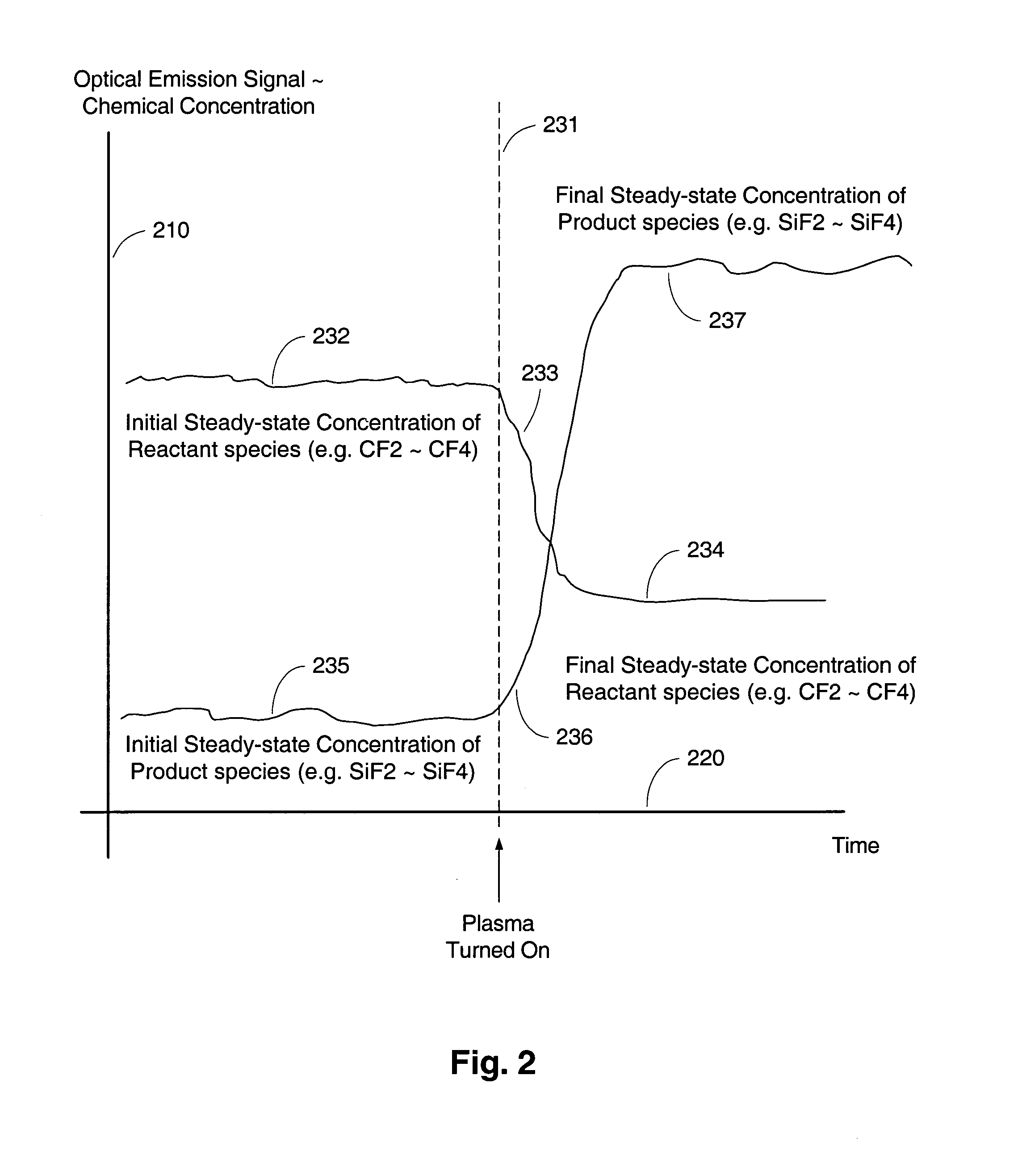

Method and apparatus for chemical monitoring

The present invention relates to monitoring chemicals in a process chamber using a spectrometer having a plasma generator, based on patterns over time of chemical consumption. The relevant patterns may include a change in consumption, reaching a consumption plateau, absence of consumption, or presence of consumption. In some embodiments, advancing to a next step in forming structures on the workpiece depends on the pattern of consumption meeting a process criteria. In other embodiments, a processing time standard is established, based on analysis of the relevant patterns. Yet other embodiments relate to controlling work on a workpiece, based on analysis of the relevant patterns. The invention may be either a process or a device including logic and resources to carry out a process.

Owner:LIGHTWIND CORP

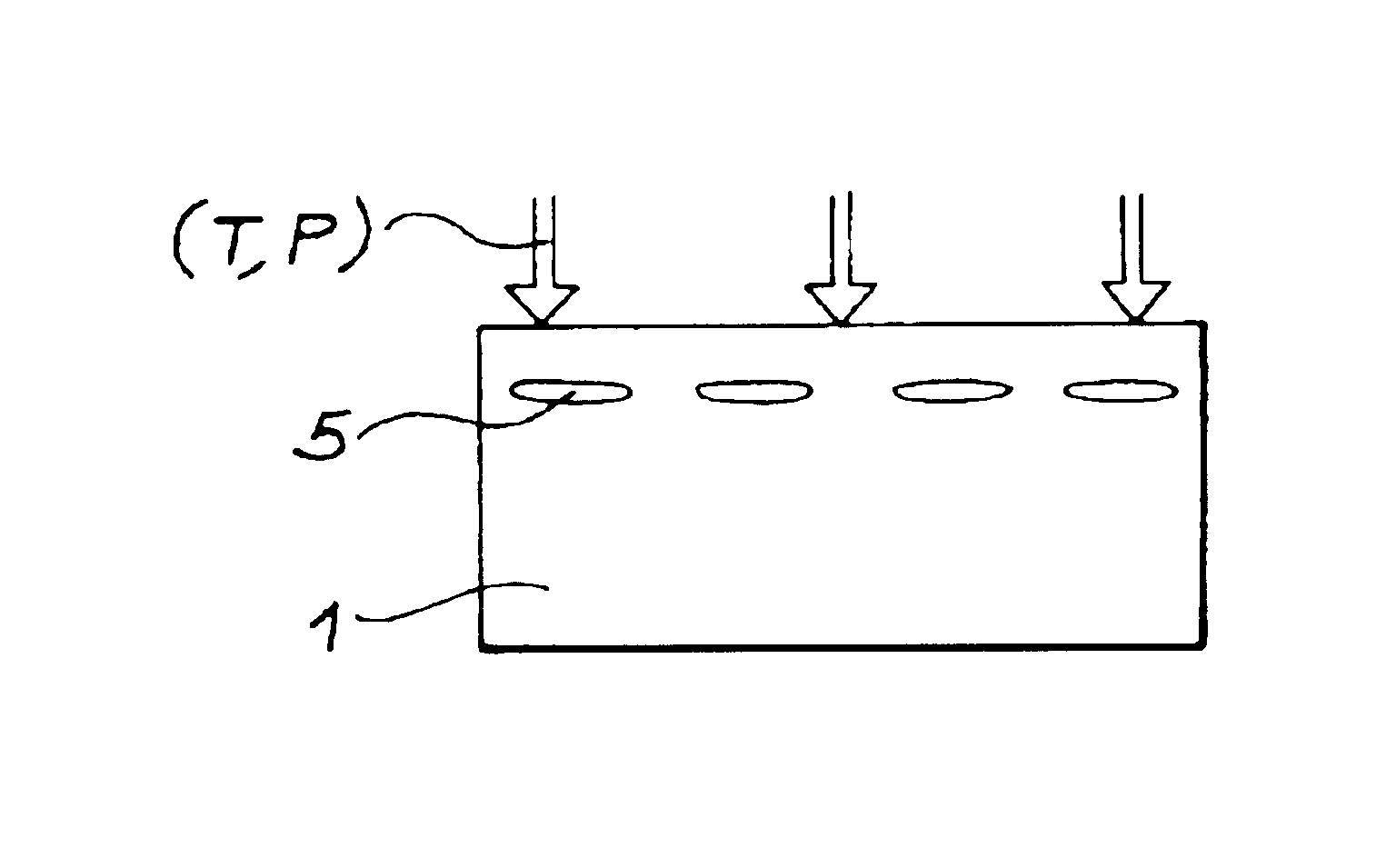

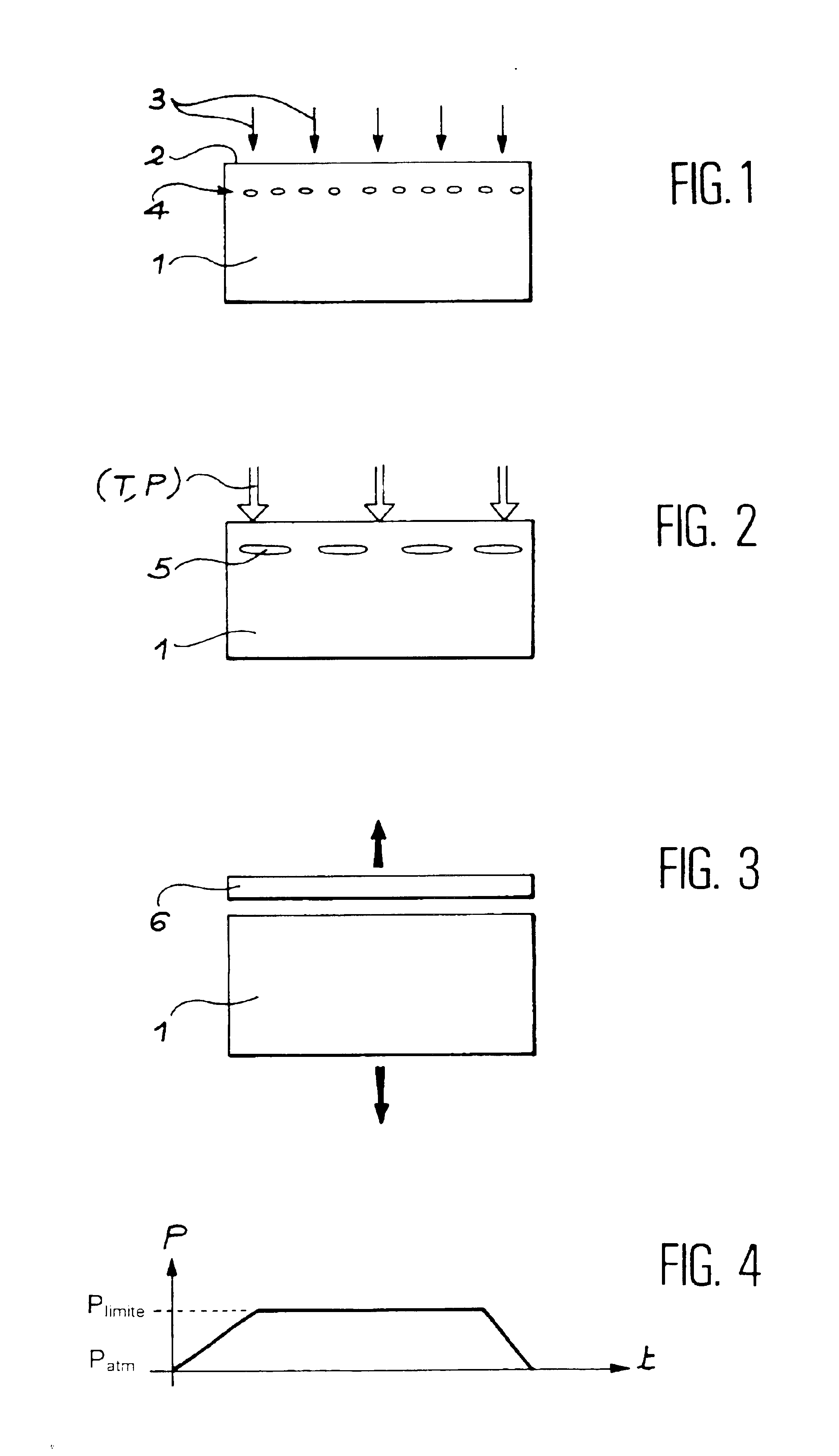

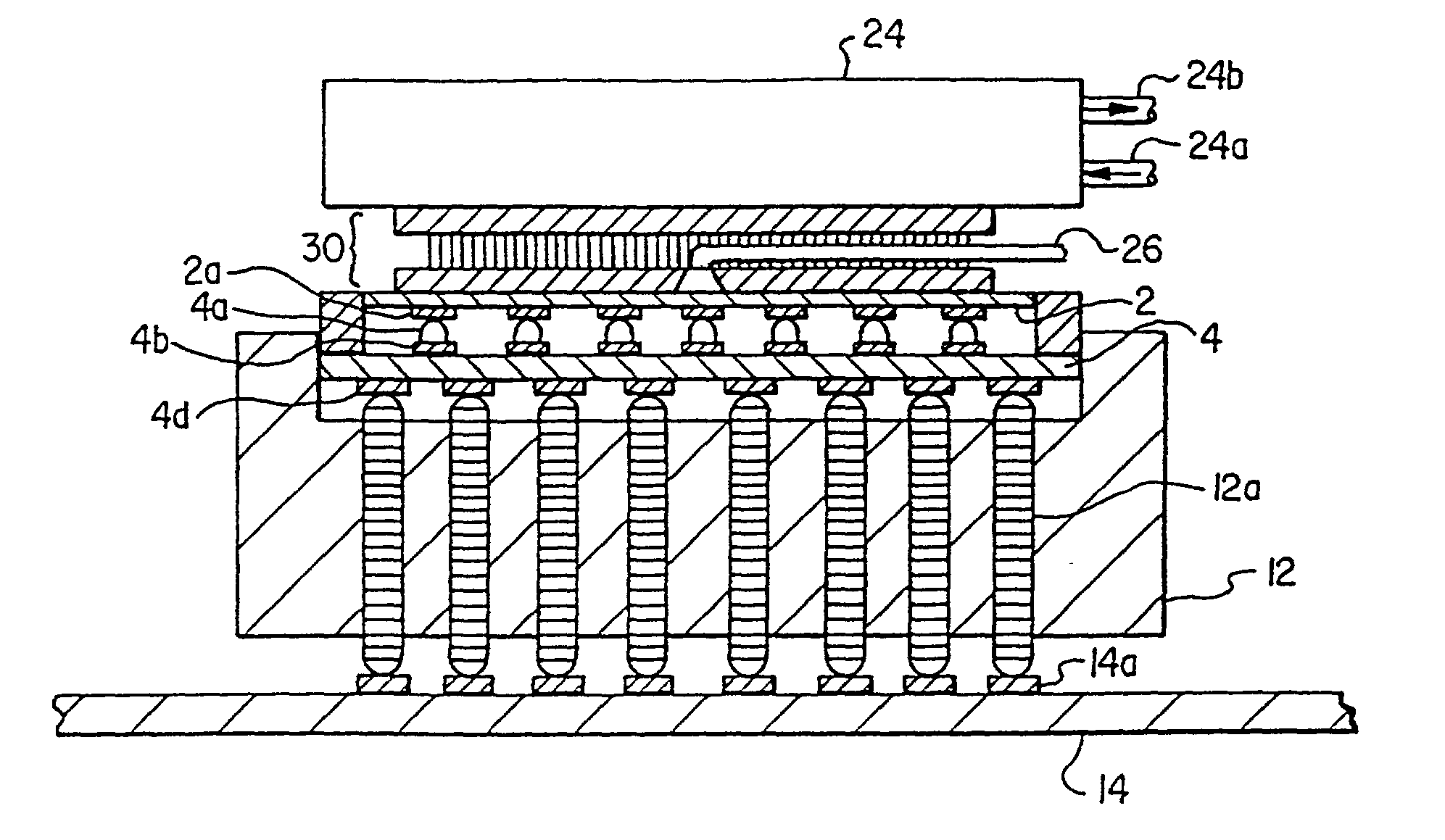

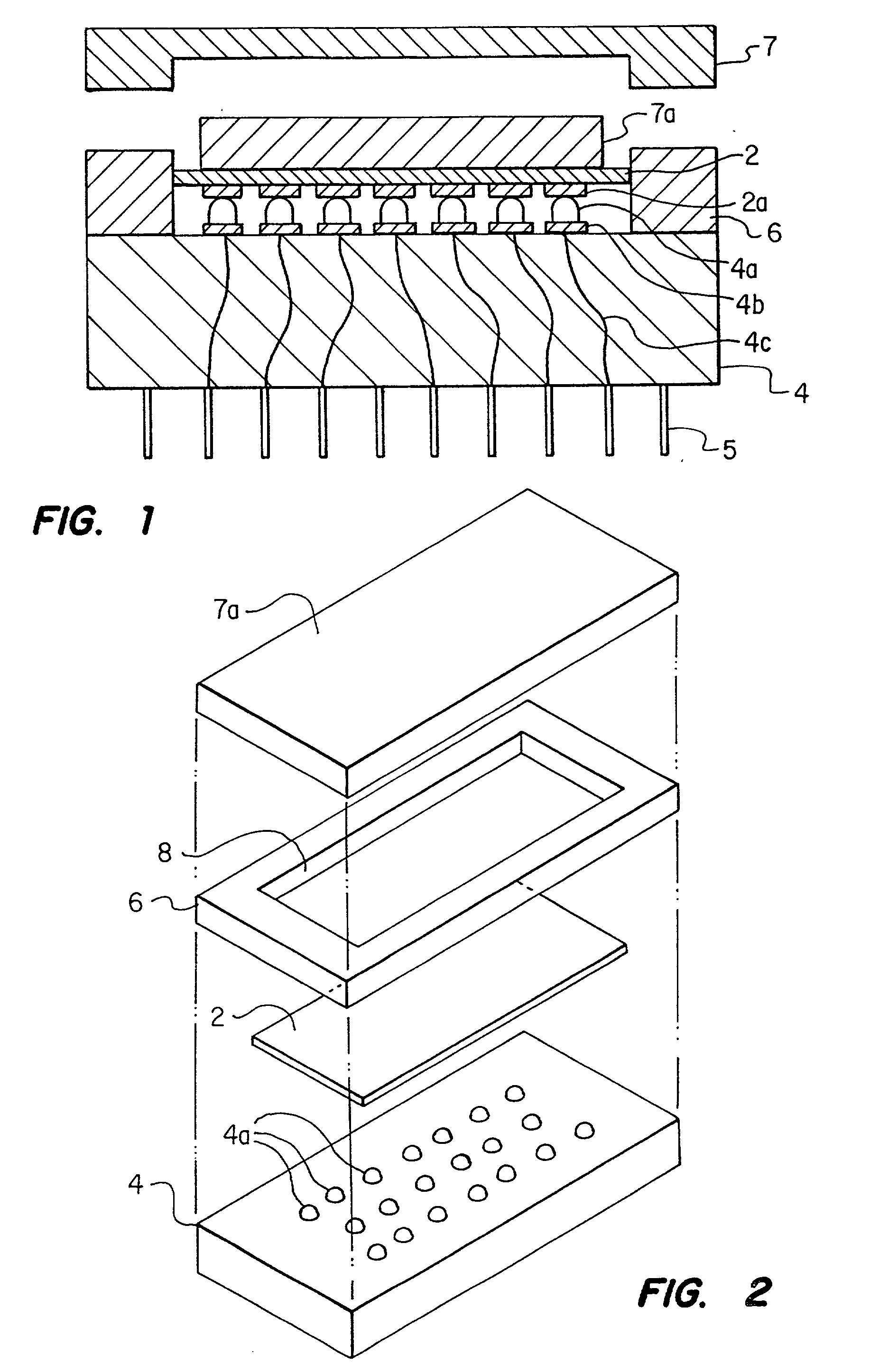

Method for making a thin film using pressurization

InactiveUS6809044B1Inhibition formationEncouraging coalescenceSemiconductor/solid-state device testing/measurementSolid-state devicesThermal energyChemistry

The invention relates to a process for making a thin film starting from a substrate (1) of a solid material with a plane face (2) comprising:the implantation of gaseous compounds in the substrate (1) to make a layer of micro-cavities (4) at a depth from the said plane face (2) corresponding to the thickness of the required thin film, the gaseous compounds being implanted under conditions that could weaken the substrate at the layer of micro-cavities,partial or total separation of the thin film from the rest of the substrate (1), this separation comprising a step in which thermal energy is added and pressure is applied to the said plane face (2).

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

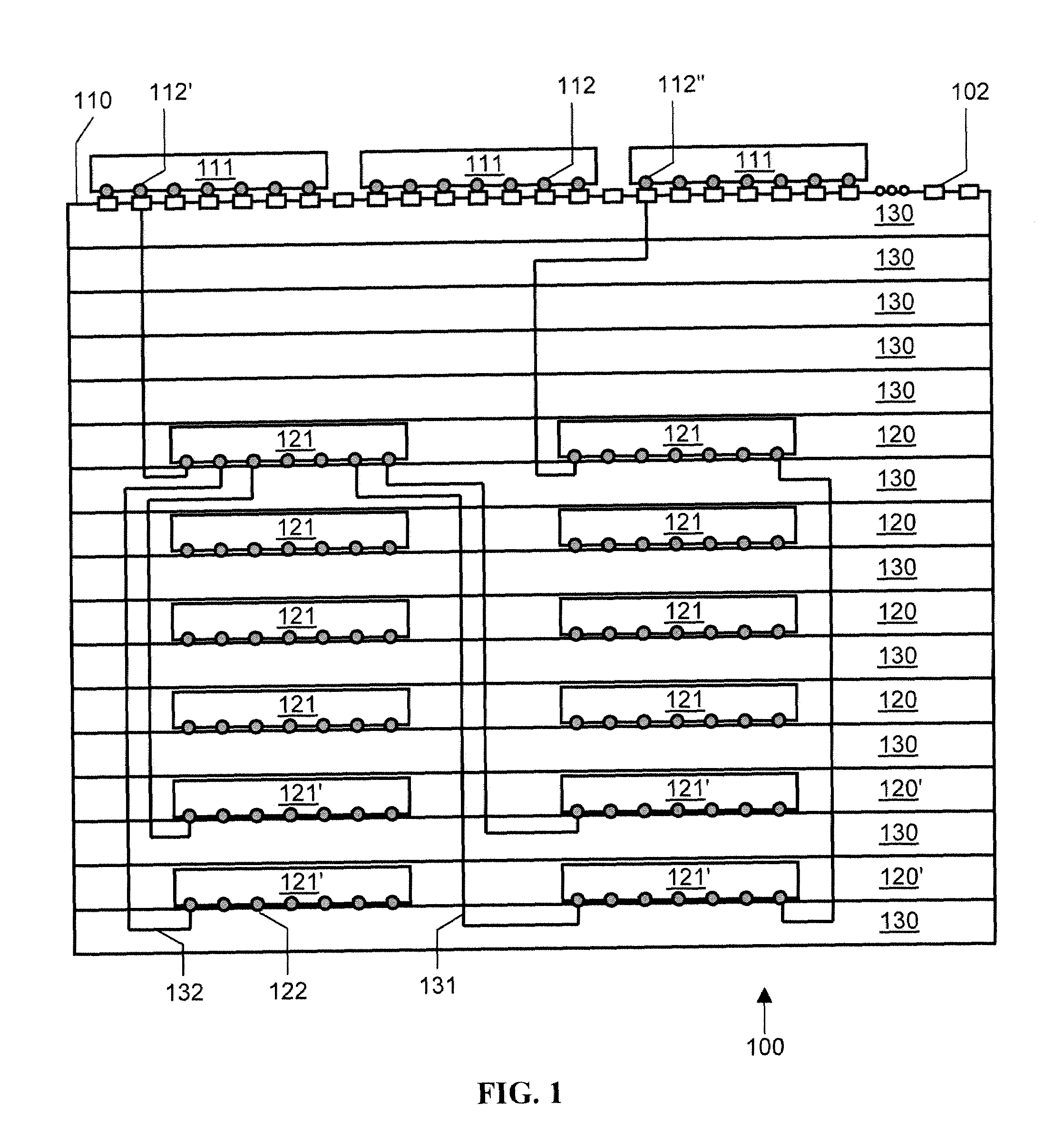

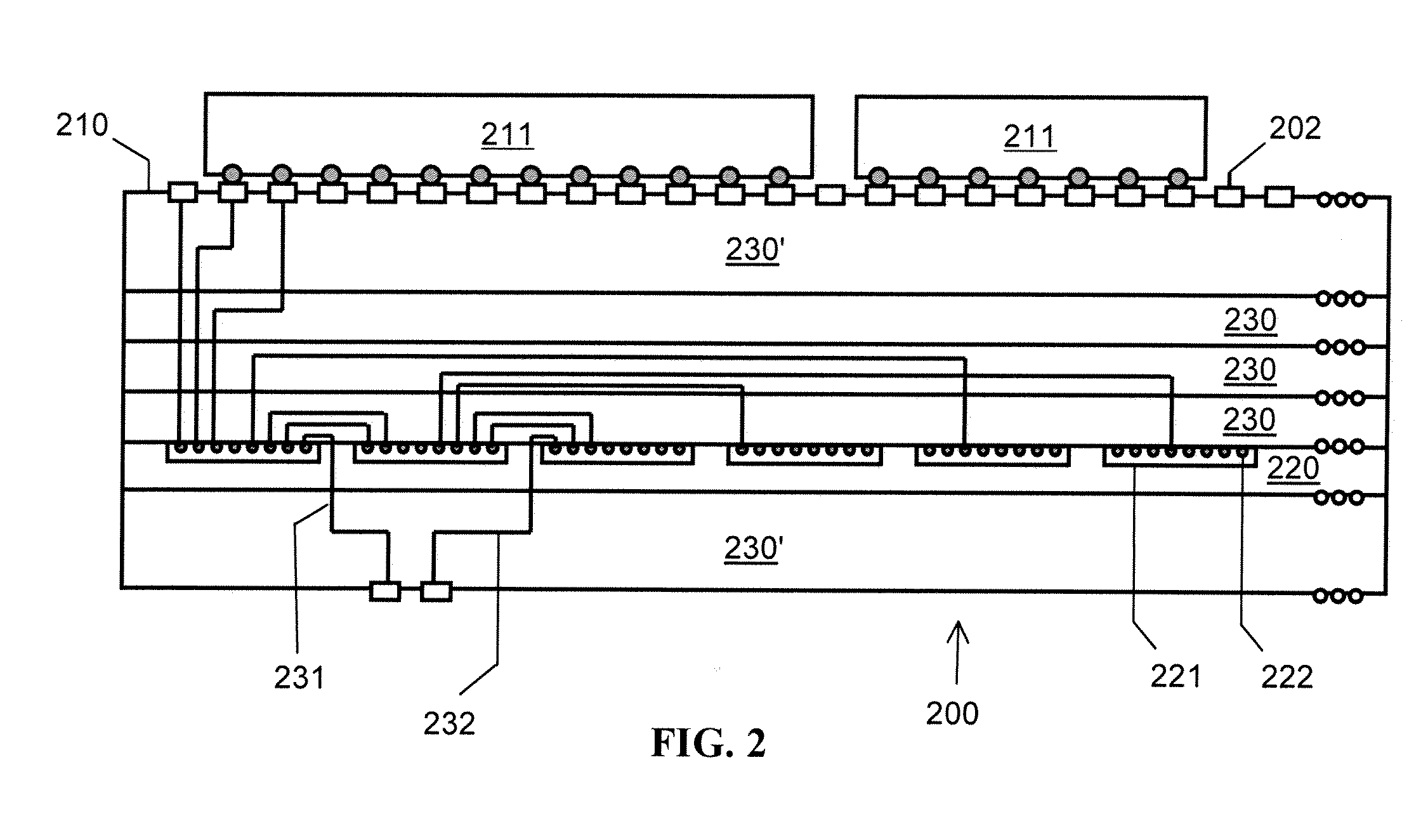

Reprogrammable circuit board with alignment-insensitive support for multiple component contact types

InactiveUS20080143379A1Semiconductor/solid-state device testing/measurementWave amplification devicesSignal conditioningContact type

The present invention is directed to a system that programmably interconnects integrated circuit chips and other components at near-intra-chip density. The system's contact structure allows it to adapt to components with a wide variety of contact spacings and interconnection requirements, the use of releasable attachment means allows component placement to be modified as needed, the system identifies the contacts and the components to facilitate specifying the inter-component connections, and the system provides signal conditioning and retiming to minimize issues with signal integrity and signal skew.

Owner:NORMAN RICHARD

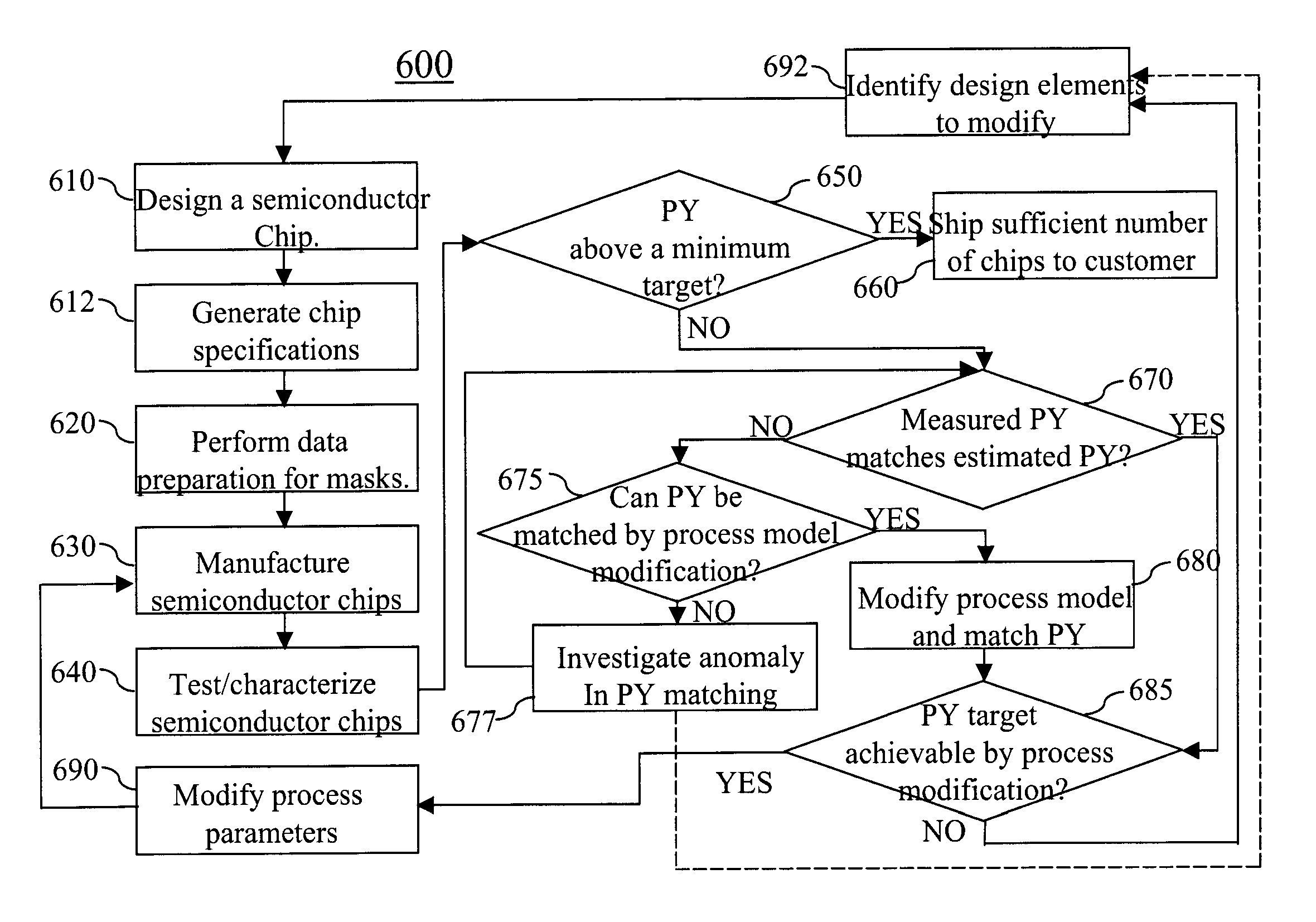

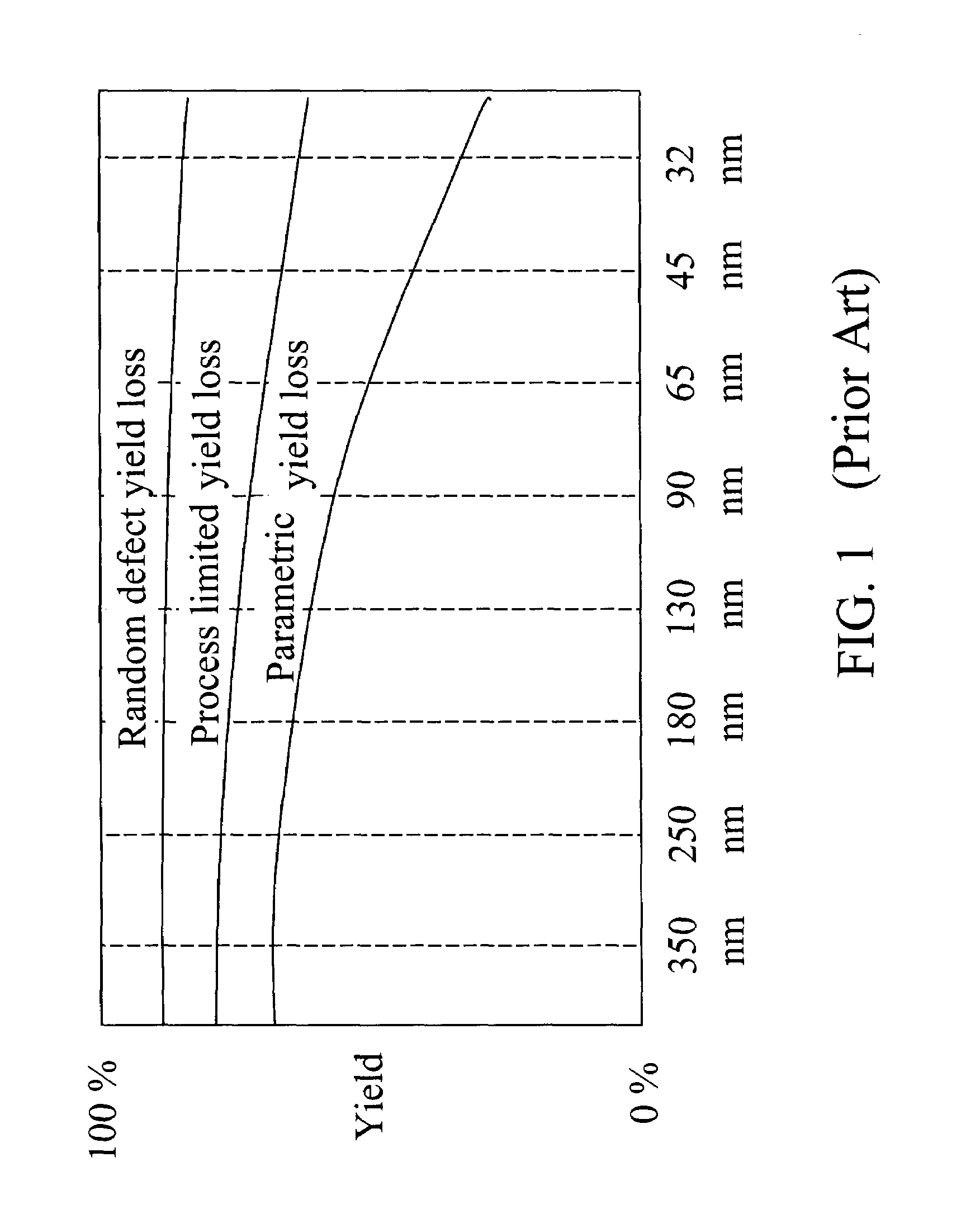

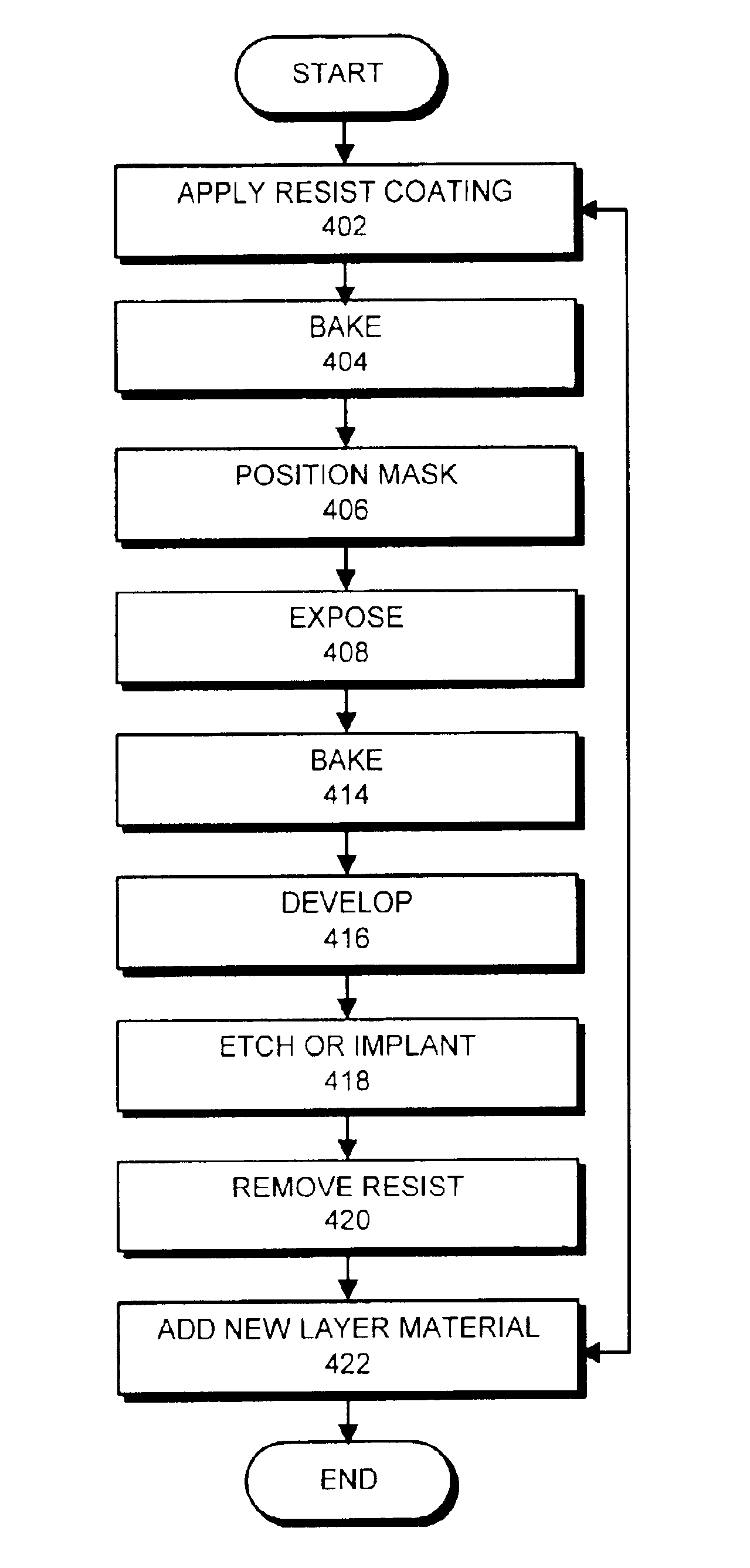

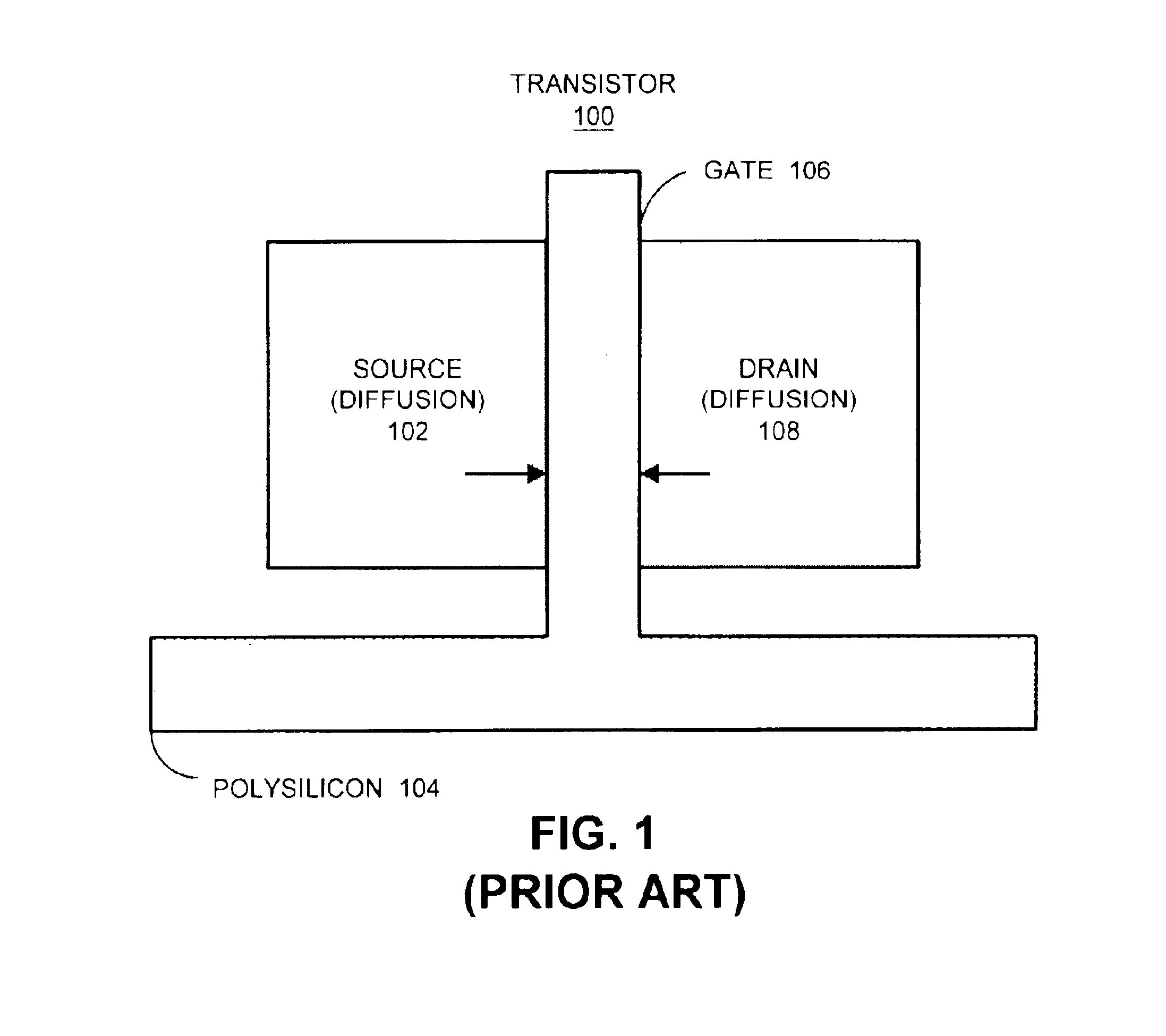

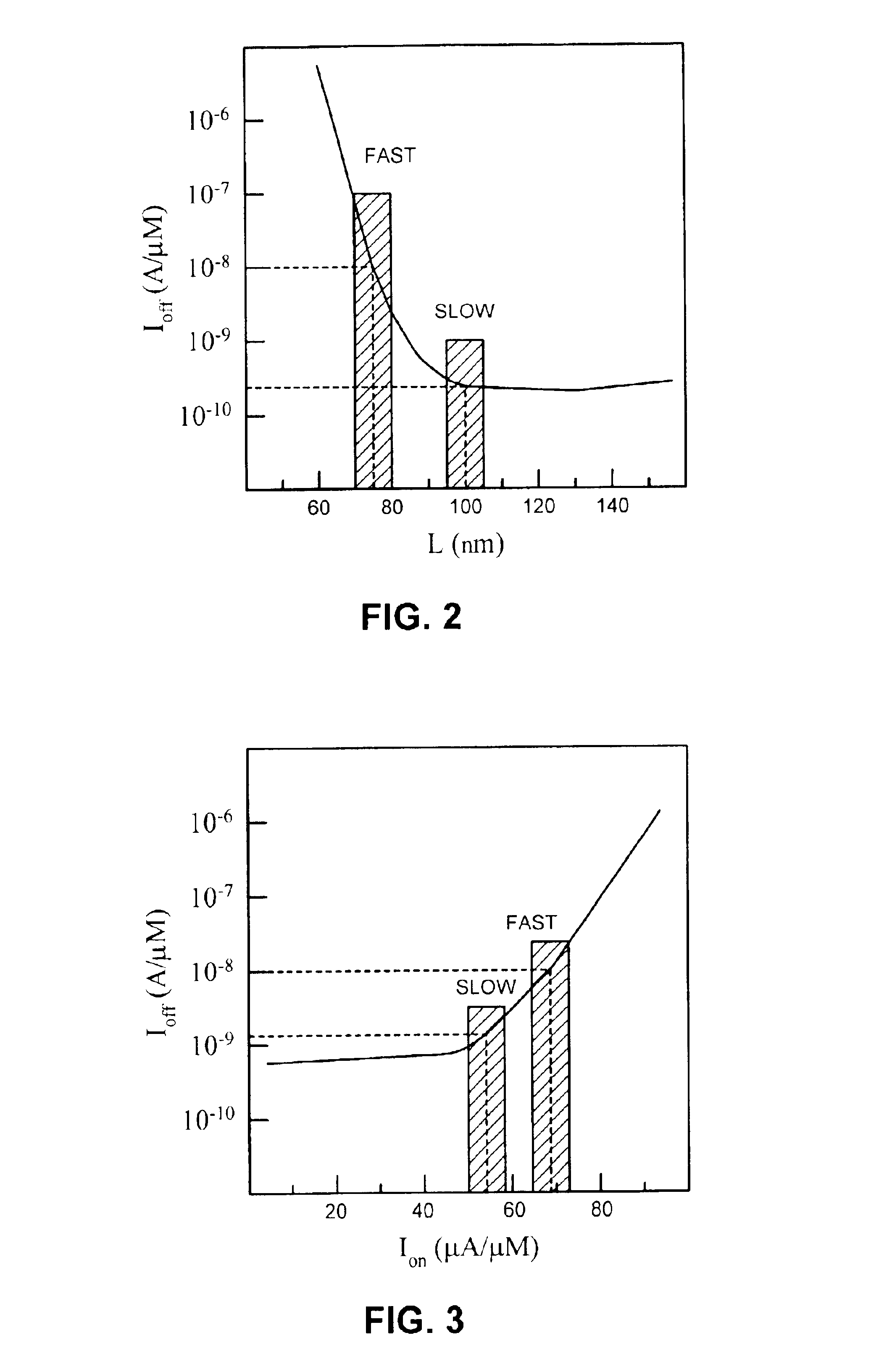

Methods and system for analysis and management of parametric yield

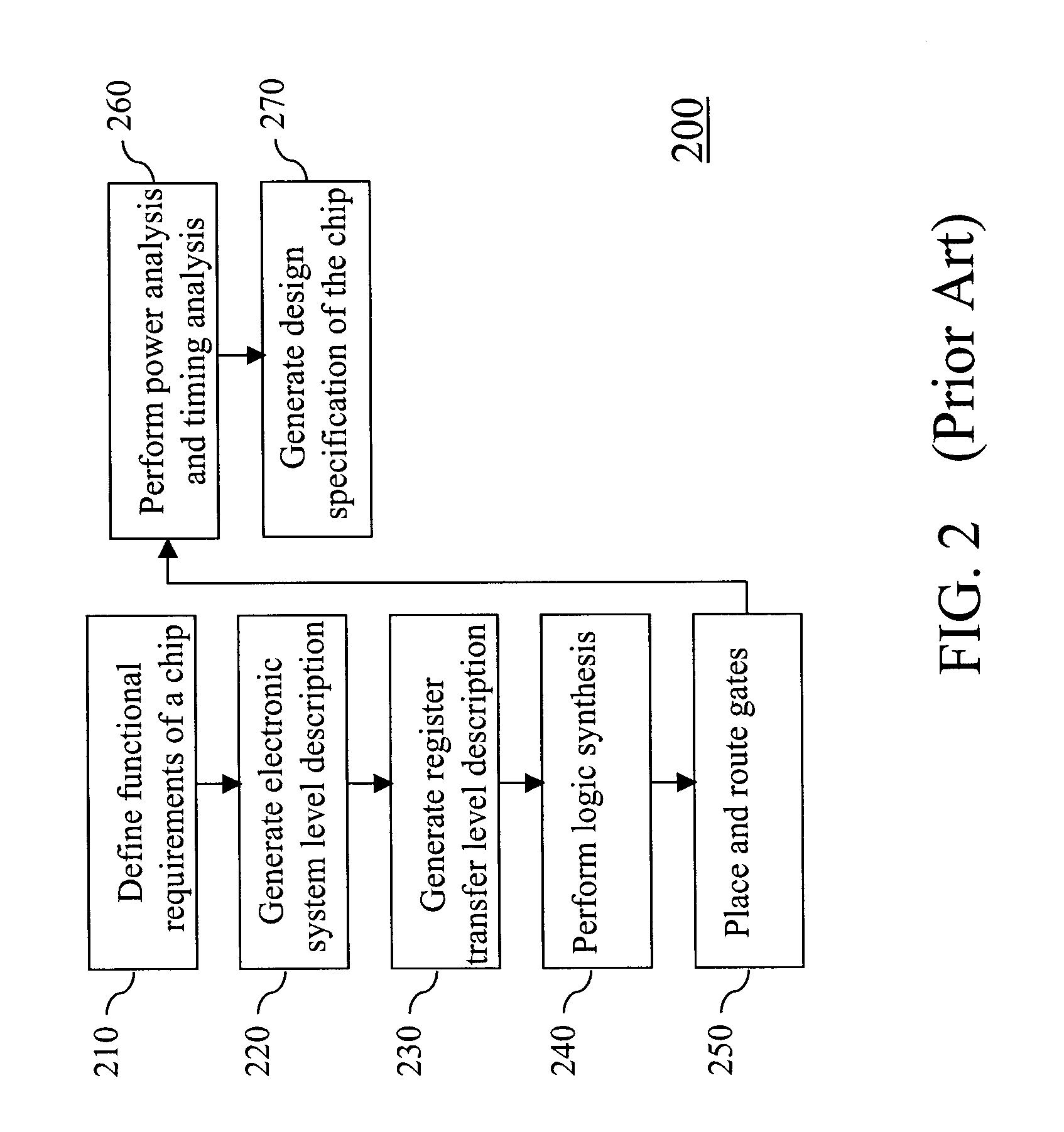

InactiveUS20090106714A1Improve accuracyCAD circuit designSoftware simulation/interpretation/emulationDesign phaseThermionic emission

Impact on parametric performance of physical design choices for transistors is scored for on-current and off-current of the transistors. The impact of the design parameters are incorporated into parameters that measure predicted shift in mean on-current and mean off-current and parameters that measure predicted increase in deviations in the distribution of on-current and the off-current. Statistics may be taken at a cell level, a block level, or a chip level to optimize a chip design in a design phase, or to predict changes in parametric yield during manufacturing or after a depressed parametric yield is observed. Further, parametric yield and current level may be predicted region by region and compared with observed thermal emission to pinpoint any anomaly region in a chip to facilitate detection and correction in any mistakes in chip design.

Owner:MENTOR GRAPHICS CORP

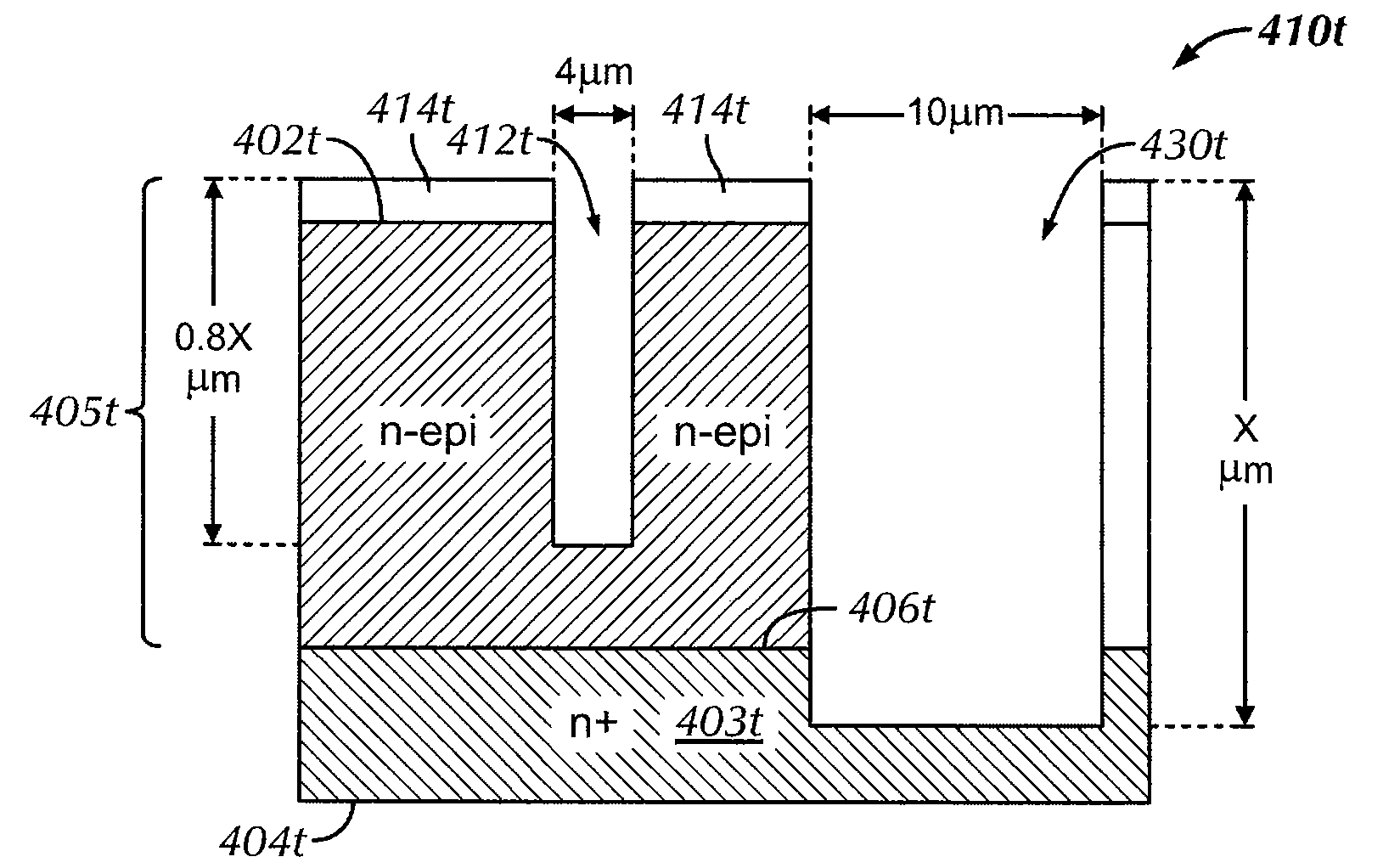

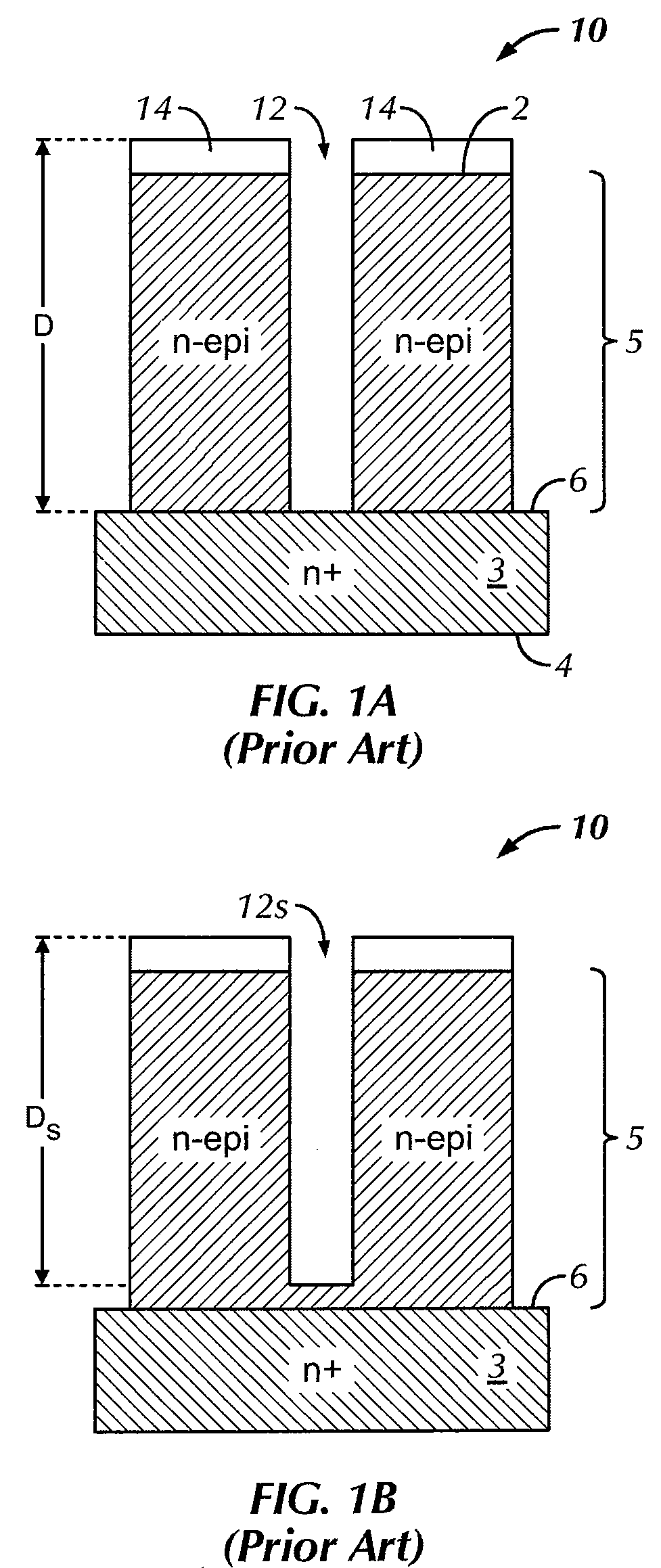

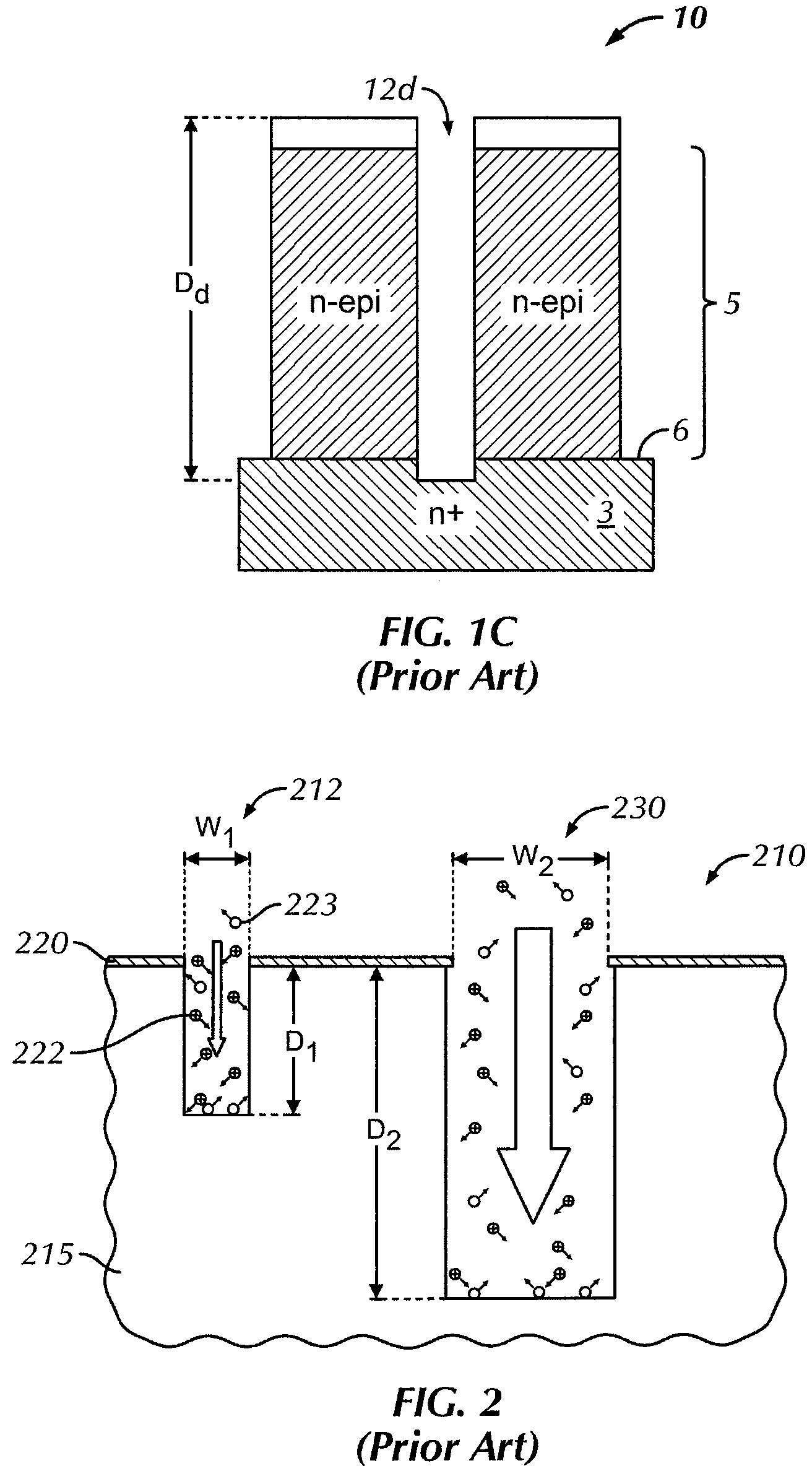

Trench depth monitor for semiconductor manufacturing

ActiveUS20090200547A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor materialsEngineering

A method of manufacturing a semiconductor wafer having at least one device trench extending to a first depth position includes providing a semiconductor substrate having first and second main surfaces and a semiconductor material layer having first and second main surfaces disposed on the first main surface of the semiconductor substrate and determining an etch ratio. The least one device trench and at least one monitor trench are simultaneously formed in the first main surface of the semiconductor material layer. The at least one monitor trench is monitored to detect when it extends to a second depth position. A ratio of the first depth position to the second depth position is generally equal to the etch ratio.

Owner:ICEMOS TECH

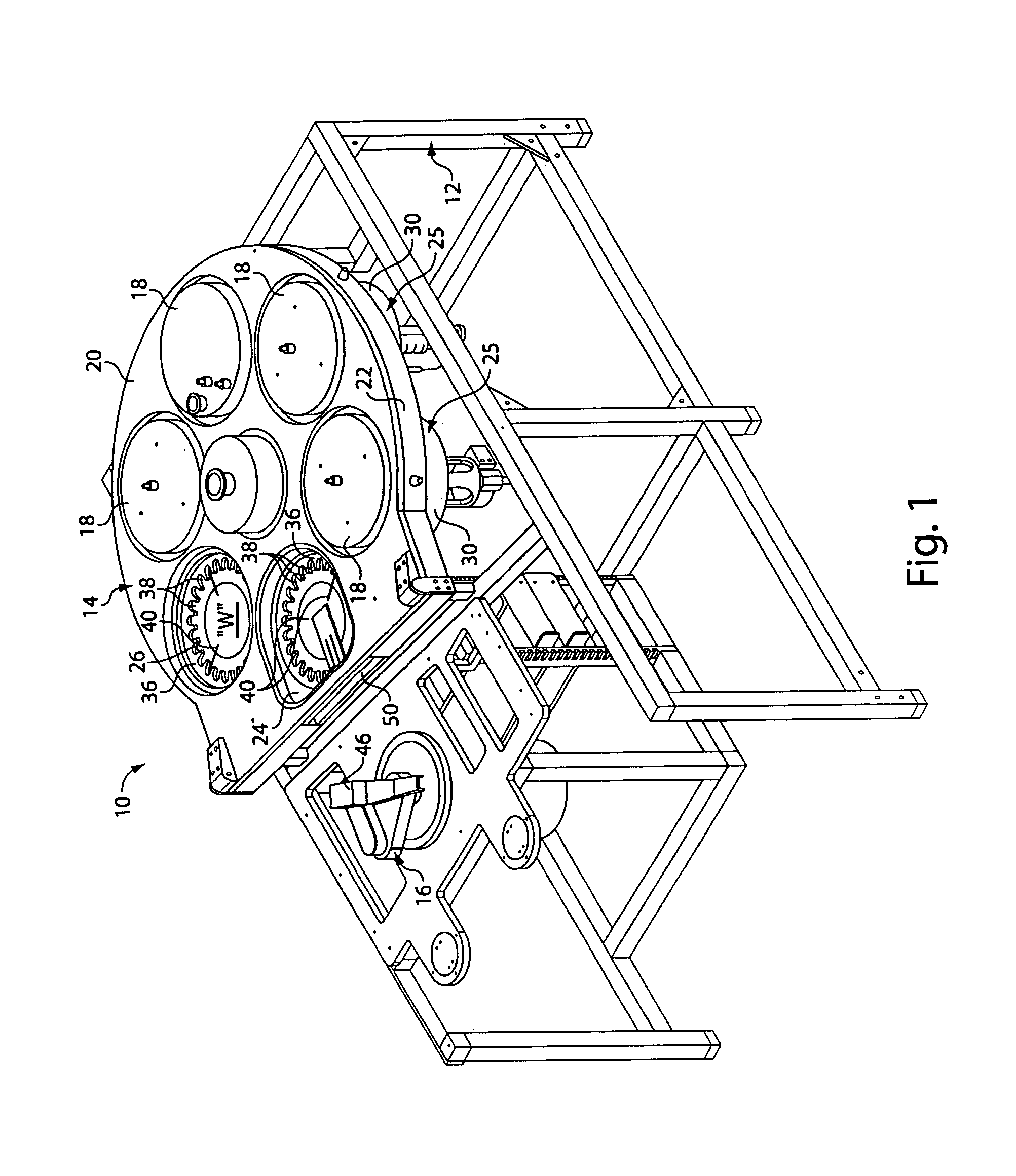

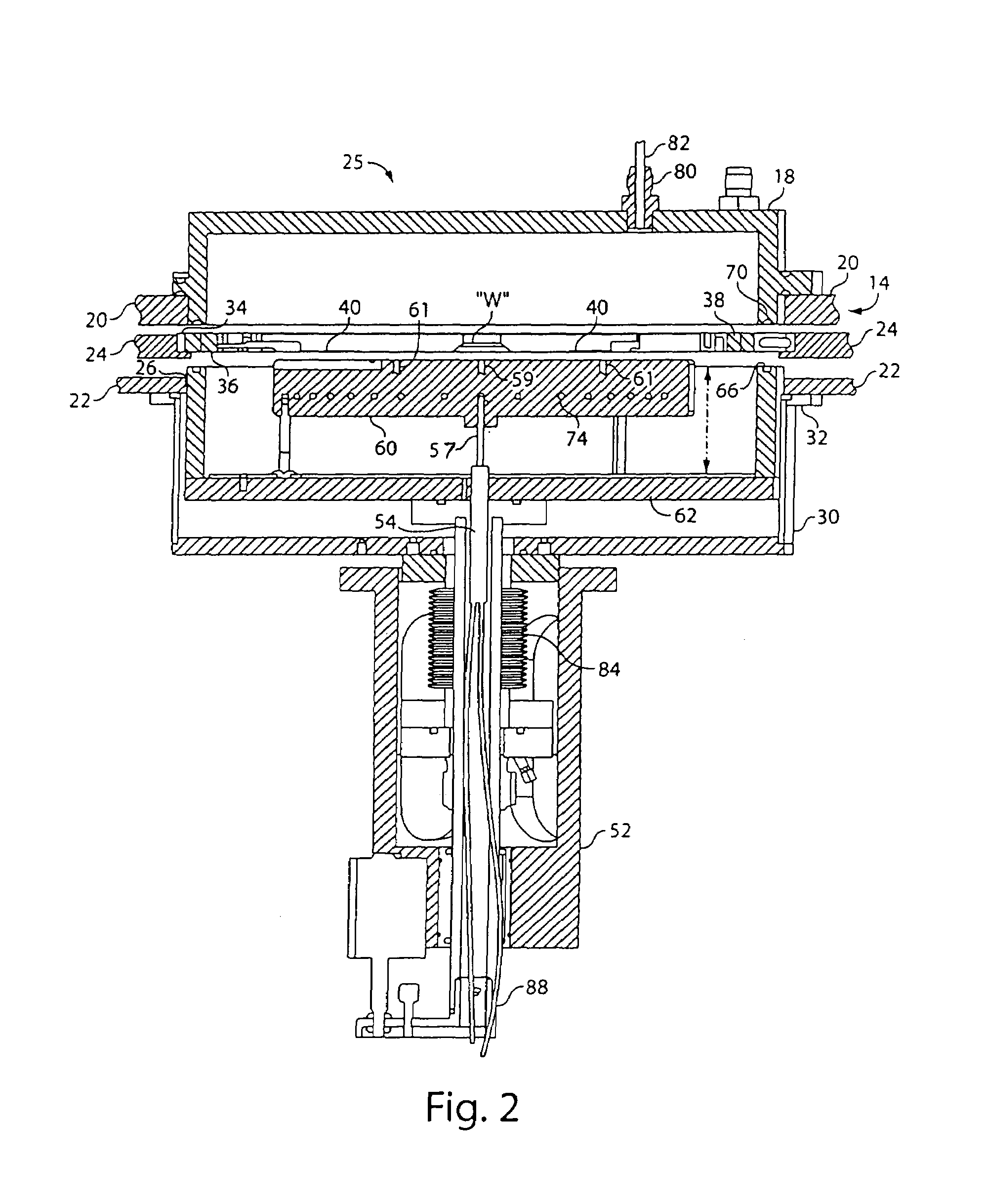

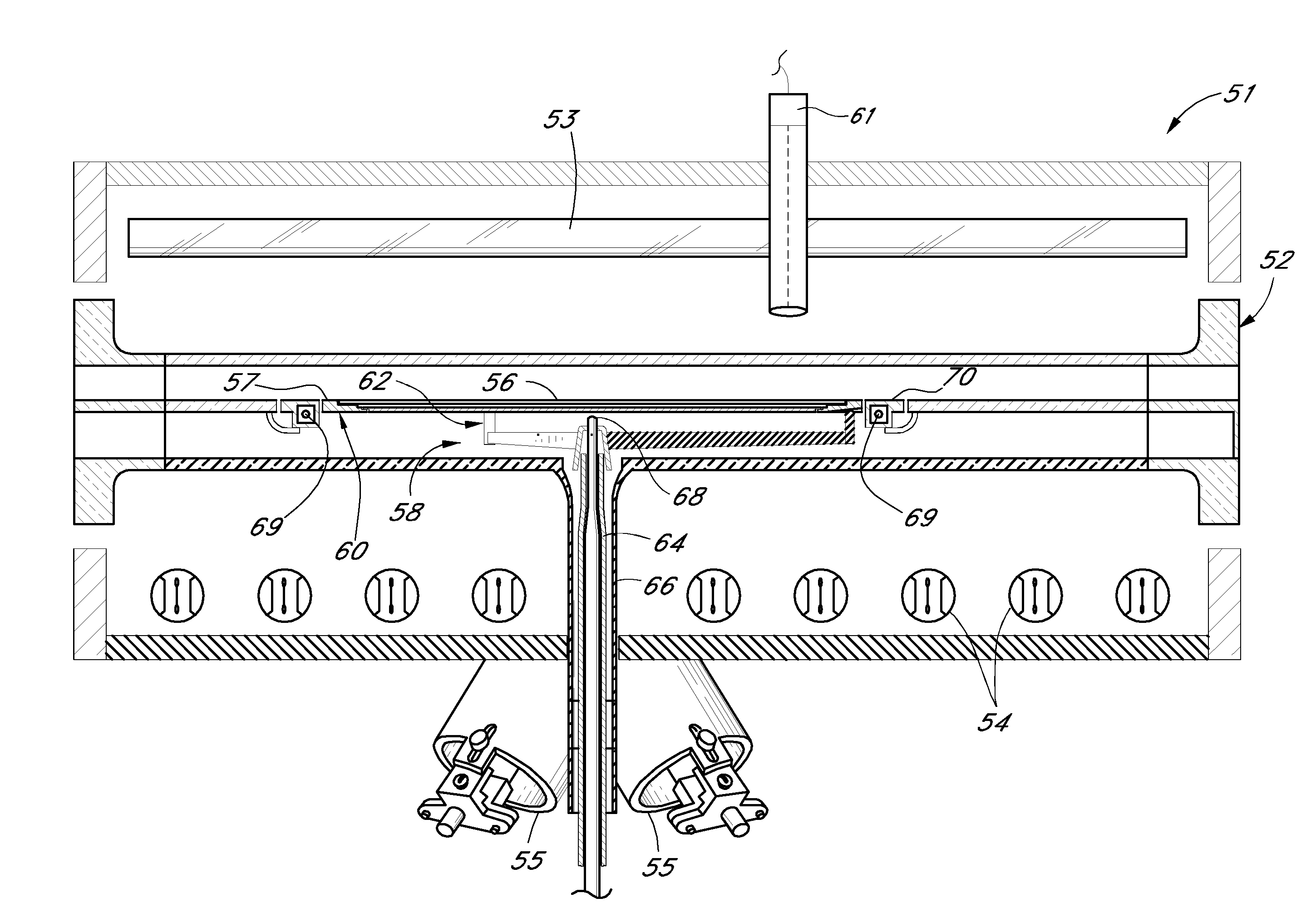

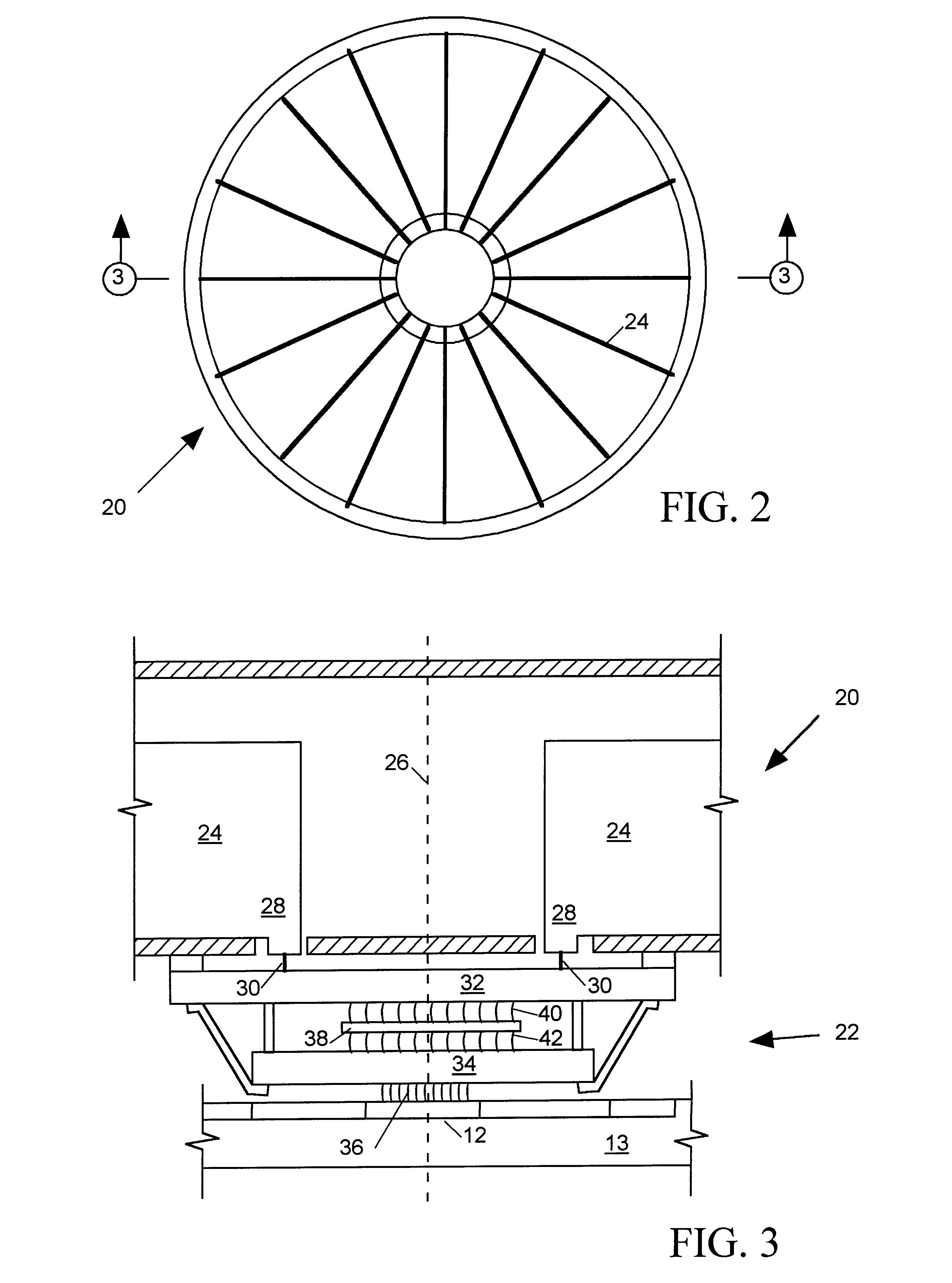

Isolation chamber arrangement for serial processing of semiconductor wafers for the electronic industry

InactiveUS7008879B2Simplifies loading and unloadingOptimization mechanismSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingBiochemical engineeringComputer module

An apparatus for the treatment of semiconductor wafers, comprising a supportive frame and a process table arranged on the supportive frame. The process table comprises a stationary upper platen and a stationary lower plate. An intermediate indexing plate is rotatively arranged between the upper platen and the lower plate. At least one wafer support pin is attached to the indexing plate for the support of a wafer by the indexing plate. An upper housing is arranged on the upper platen and an outer lower housing is arranged on the lower plate. A displacable lower isolation chamber is disposed within the outer lower housing, being displacable against the indexing plate to define a treatment module between the upper housing and the lower isolation chamber in which the wafer is treated. A wafer supporting treatment plate is arranged within the lower isolation chamber, for controlled rapid treatment of a wafer within the treatment module.

Owner:SEMLGEAR INC

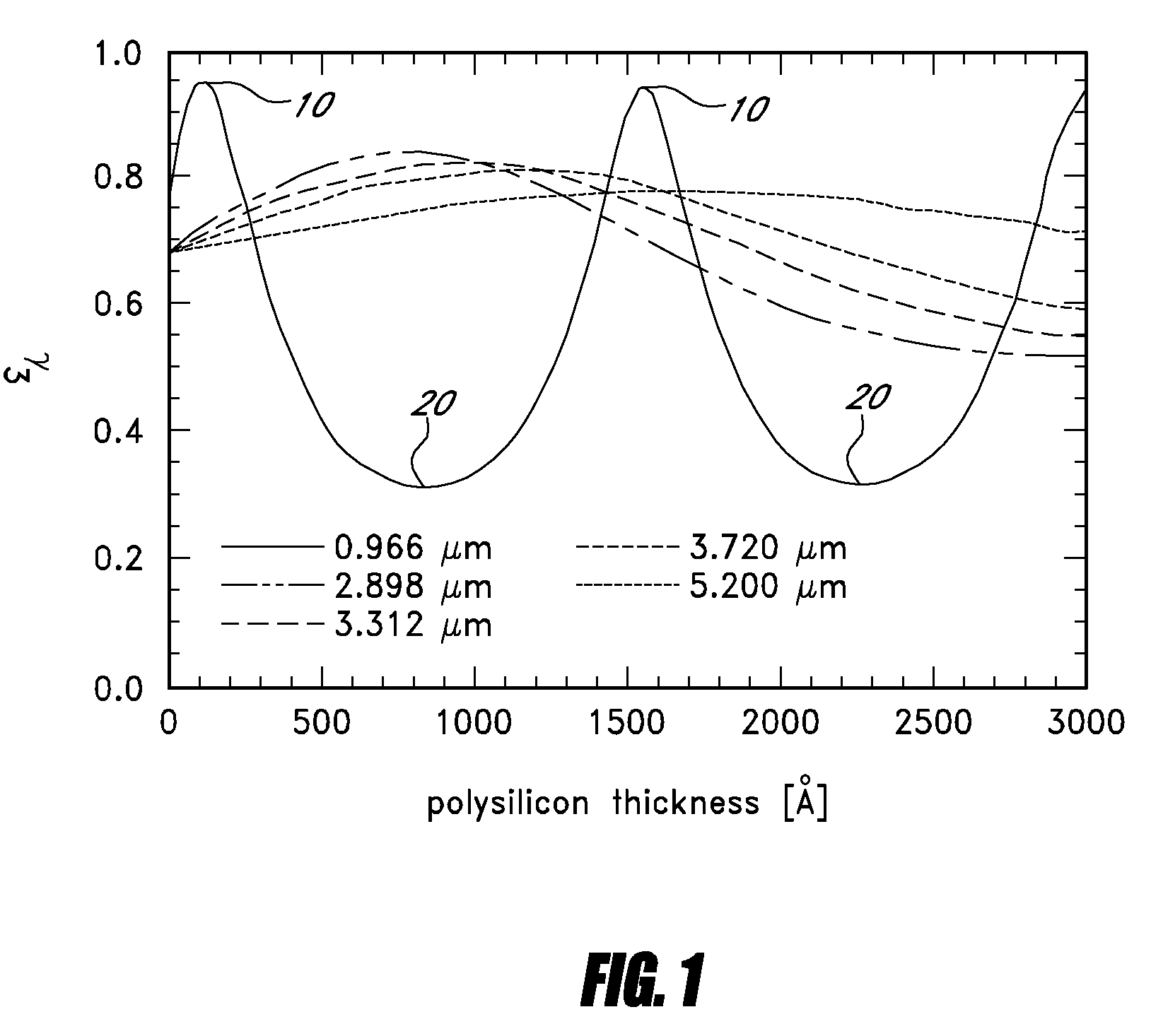

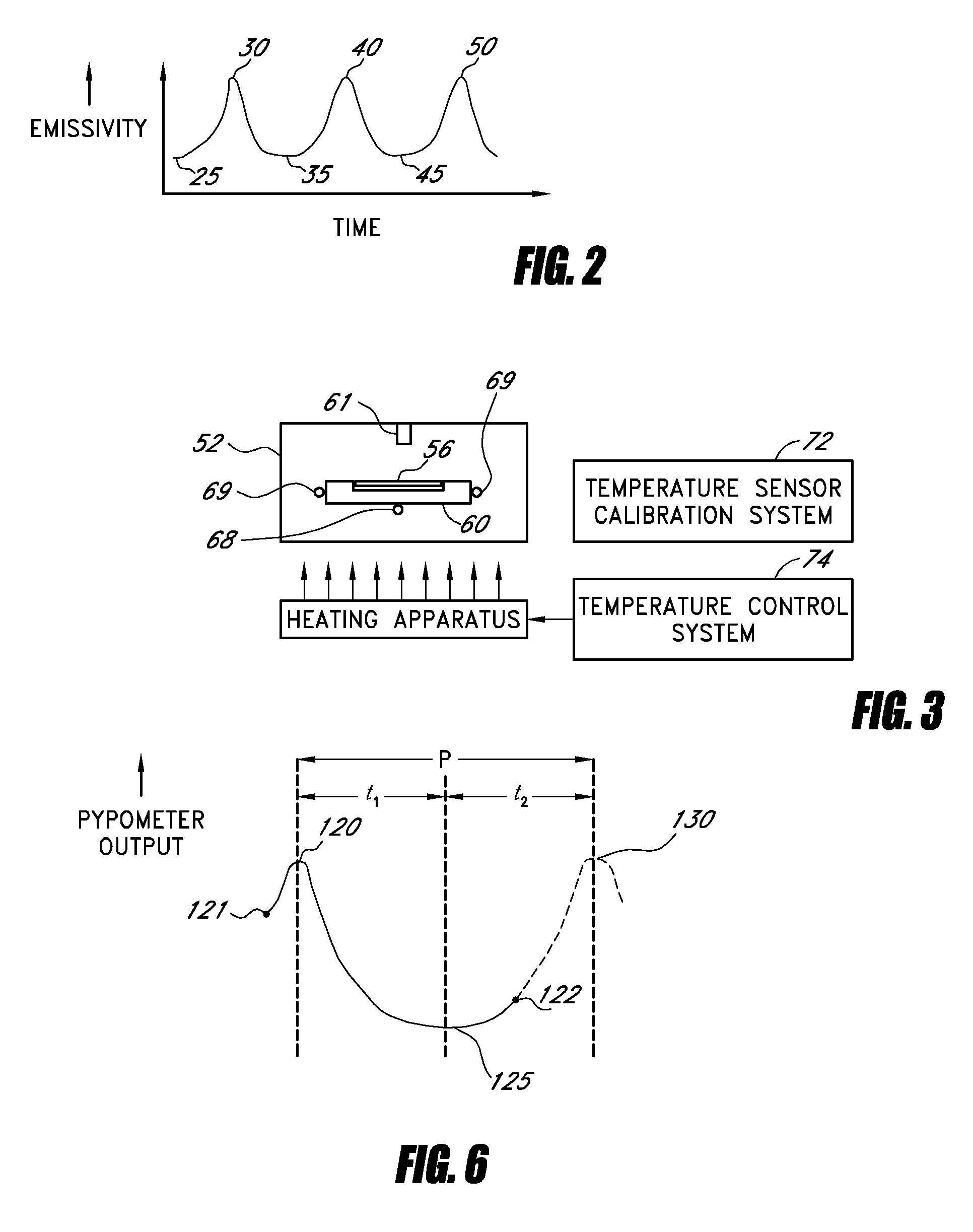

Calibration of temperature control system for semiconductor processing chamber

ActiveUS20090147819A1Readily apparentSemiconductor/solid-state device testing/measurementThermometers using electric/magnetic elementsTemperature controlControl system

Methods and systems for calibrating a temperature control system in a vapor deposition chamber. A temperature sensor senses temperature within a semiconductor processing chamber and generates an output signal. A temperature control system controls a chamber temperature by controlling a heating apparatus based on the output signal. A method includes instructing the control system to target a setpoint temperature, and depositing a layer of material onto a surface in the chamber by a vapor deposition process. A variation of a property of the layer is measured while depositing the layer, the property known to vary cyclically as a thickness of the layer increases. The measured property is allowed to vary cyclically for one or more cycles. If there is a difference between a time period of one or more of the cycles and an expected time period associated with the setpoint temperature, the temperature control system is adjusted based on the difference.

Owner:ASM IP HLDG BV

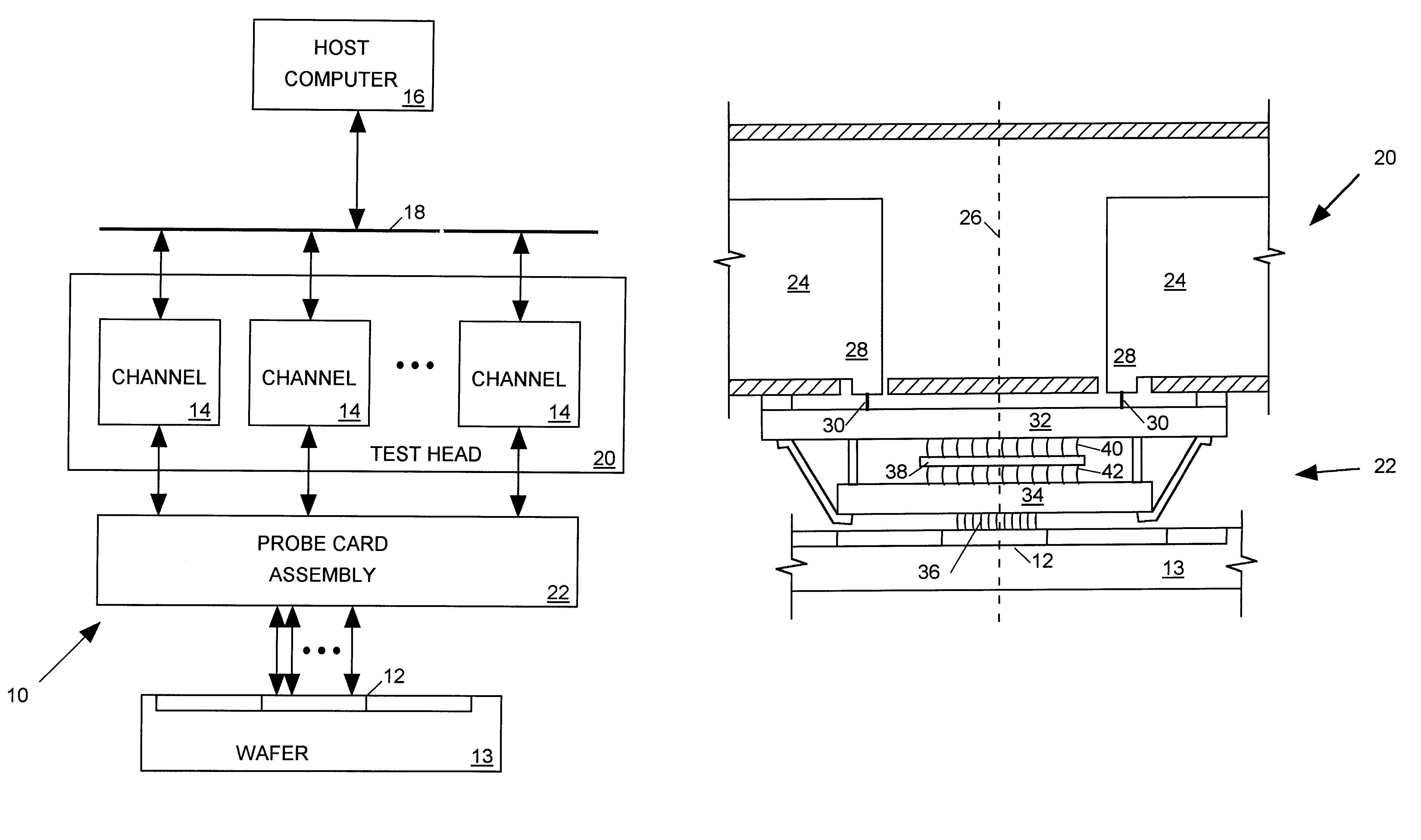

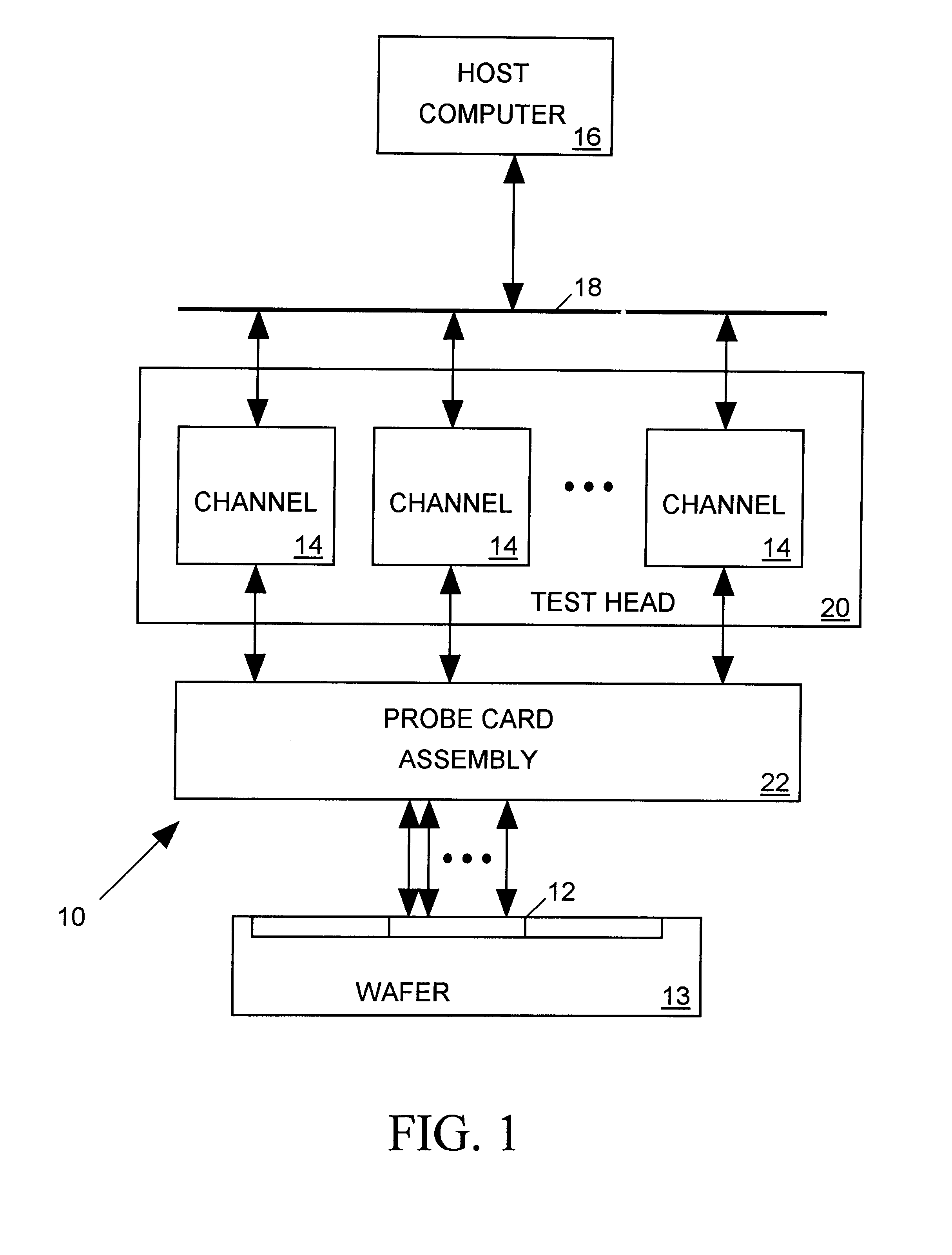

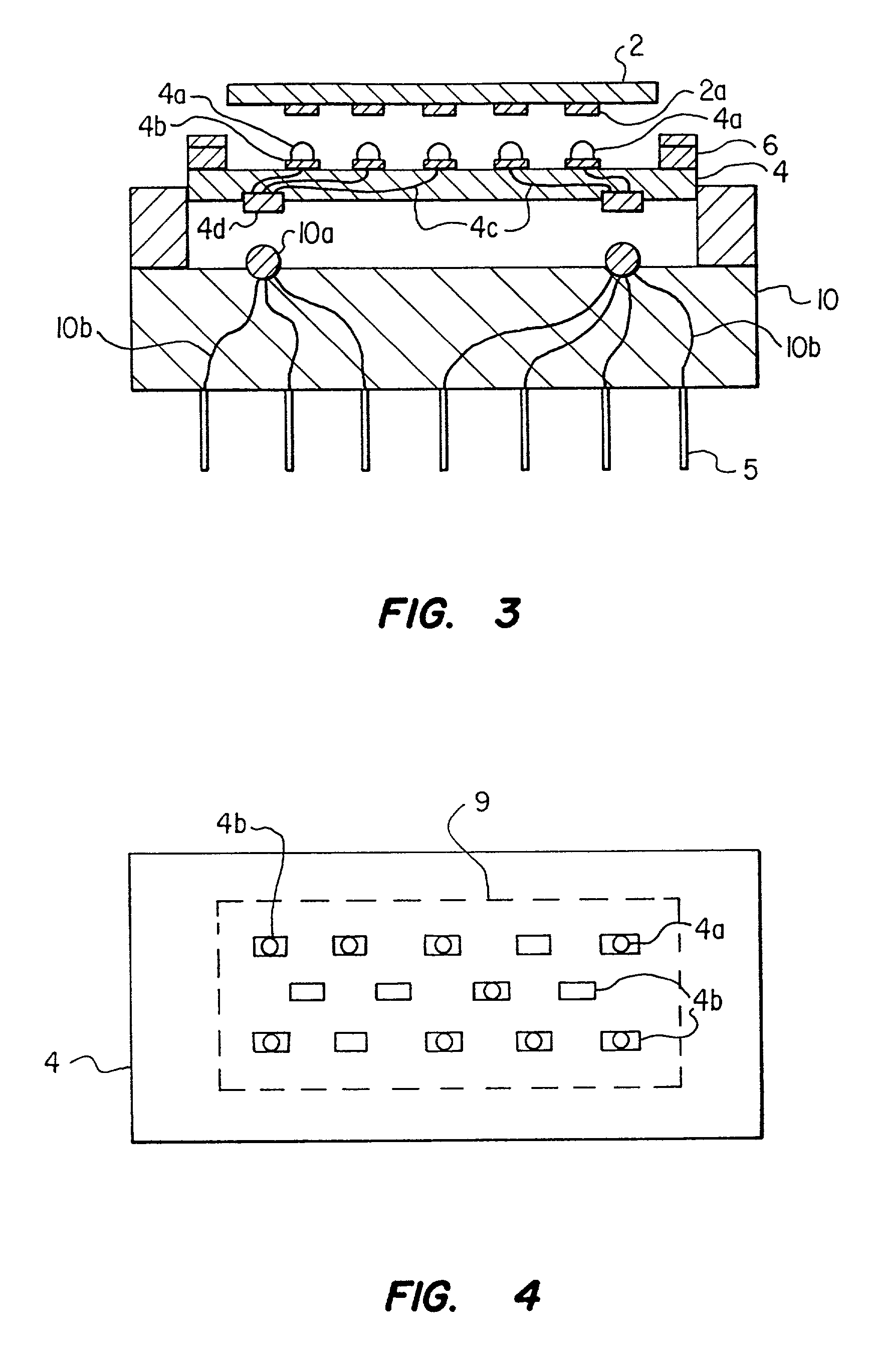

High bandwidth passive integrated circuit tester probe card assembly

InactiveUS6218910B1Multiple-port networksElectrical measurement instrument detailsCapacitanceProbe card

Described herein is a probe card assembly providing signal paths for conveying high frequency signals between bond pads of an integrated circuit (IC) and an IC tester. The frequency response of the probe card assembly is optimized by appropriately distributing, adjusting and impedance matching resistive, capacitive and inductive impedance values along the signal paths so that the interconnect system behaves as an appropriately tuned Butterworth or Chebyshev filter.

Owner:FORMFACTOR INC

Selectively applying resolution enhancement techniques to improve performance and manufacturing cost of integrated circuits

InactiveUS6928635B2Reduce delaysReduction of gate lengthSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingResolution enhancement technologiesImage resolution

One embodiment of the present invention provides a system that applies resolution enhancement techniques (RETs) selectively to a layout of an integrated circuit. Upon receiving the layout of the integrated circuit, the system identifies a plurality of critical regions within the layout based on an analysis of one or more of, timing, dynamic power, and off-state leakage current. The system then performs a first set of aggressive RET operations on the plurality of critical regions. The system also performs a second set of less aggressive RET operations on other non-critical regions of the layout.

Owner:SYNOPSYS INC

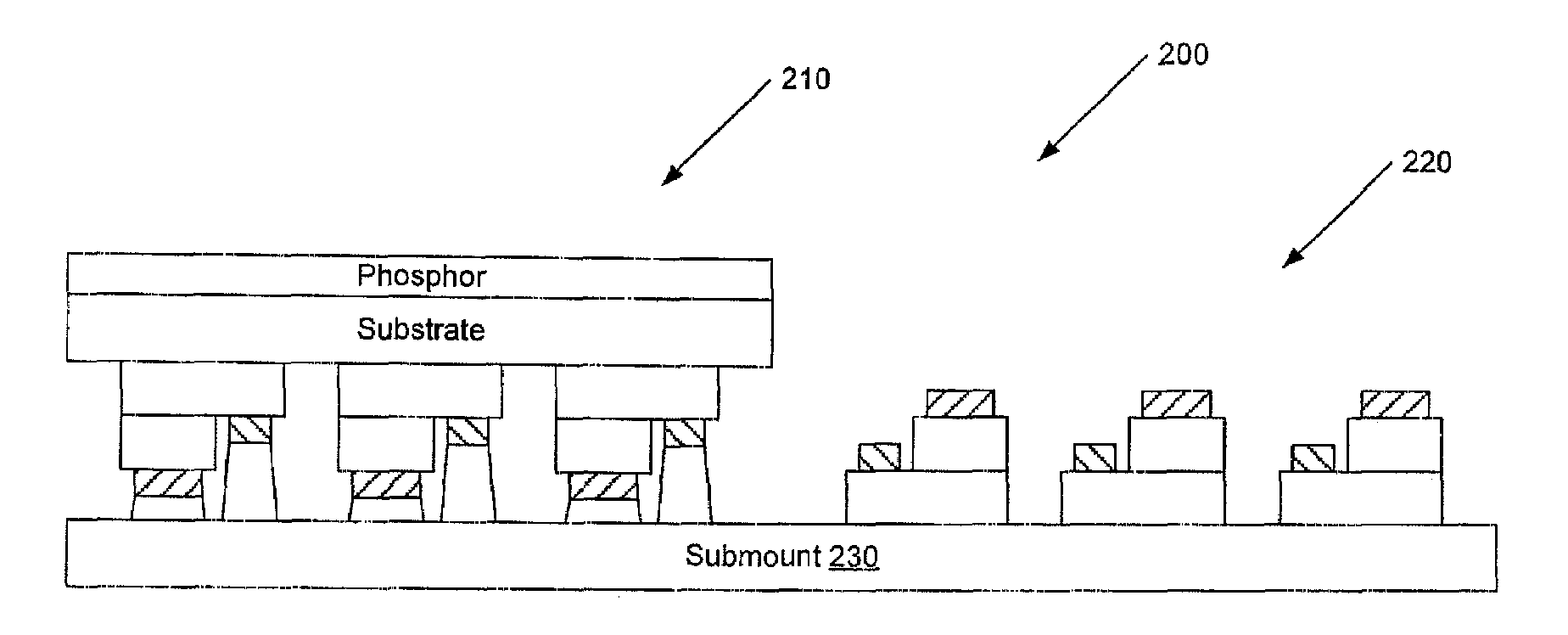

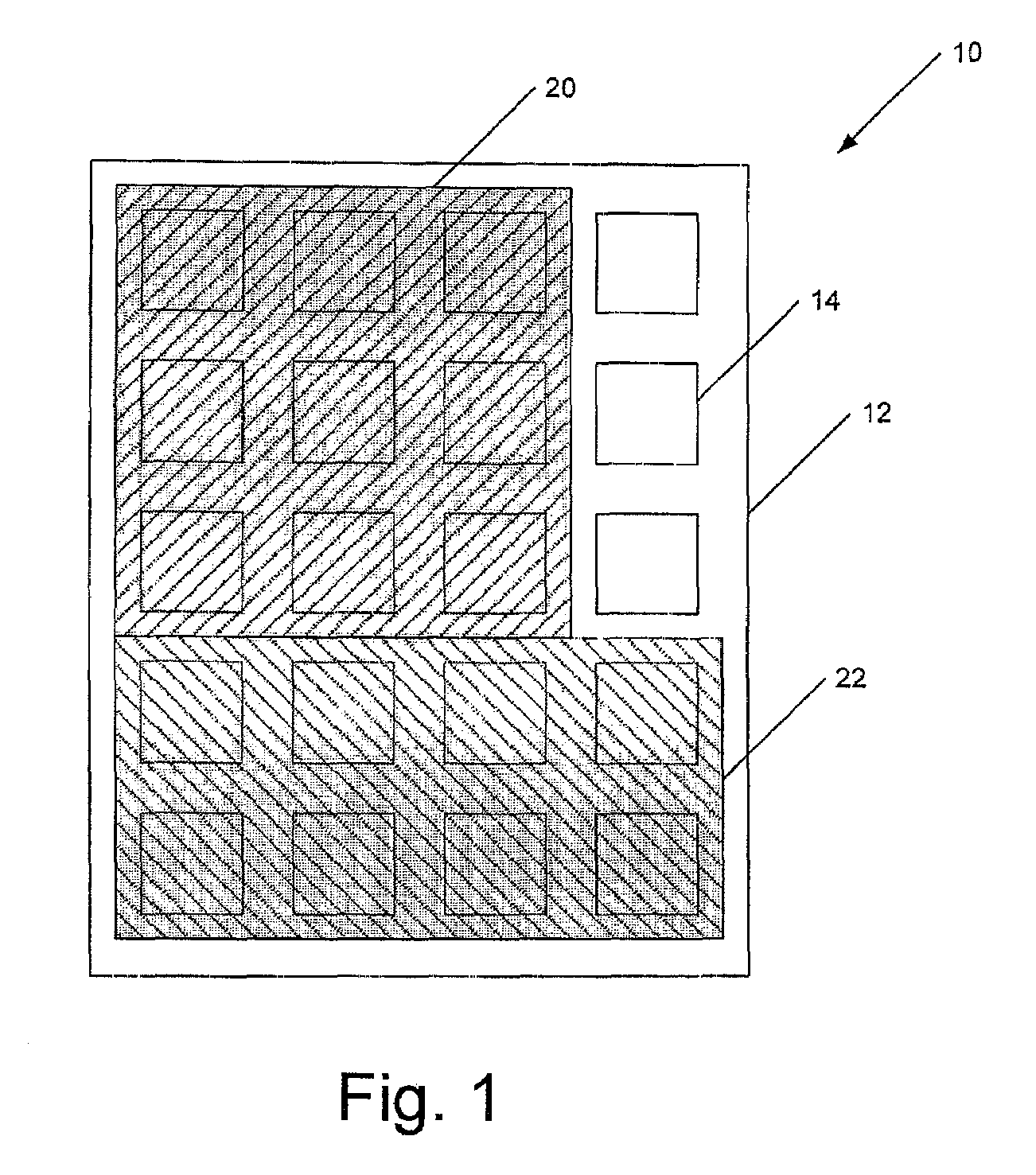

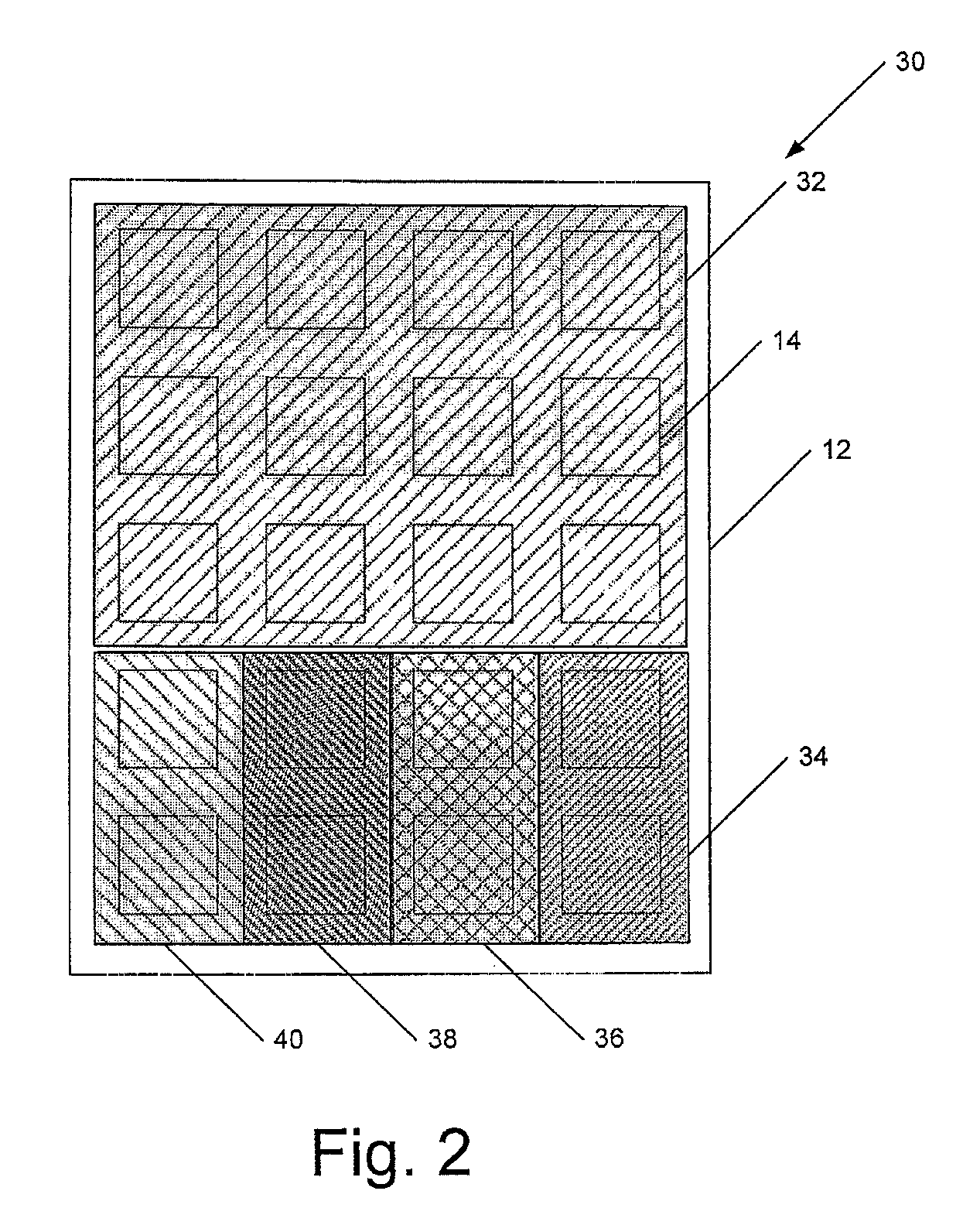

Illumination device having one or more lumiphors, and methods of fabricating same

InactiveUS20090108269A1Semiconductor/solid-state device testing/measurementSolid-state devicesInterconnectionLight emission

A light emitter comprising a monolithic die comprising at least one solid state light emitting device and at least a first lumiphor covering part of a light emission region of the die. In some embodiments, at least a second lumiphor is provided on the die. The first lumiphor can be part of a first pattern of lumiphors, and / or the second lumiphor can be part of a second pattern of lumiphors. The first and second lumiphors can differ in luminescent material, size, shape and / or concentration of luminescent material. The lumiphors can overlap completely, partially, or not at all. Some embodiments comprise an electrical interconnection to electrically connect respective solid state light emitting devices. Also, a light emitter comprising unit cells each comprising a group of light emitting devices and at least one lumiphor. Methods of fabricating light emitters comprise selectively applying at least one lumiphor to a monolithic die.

Owner:CREE INC

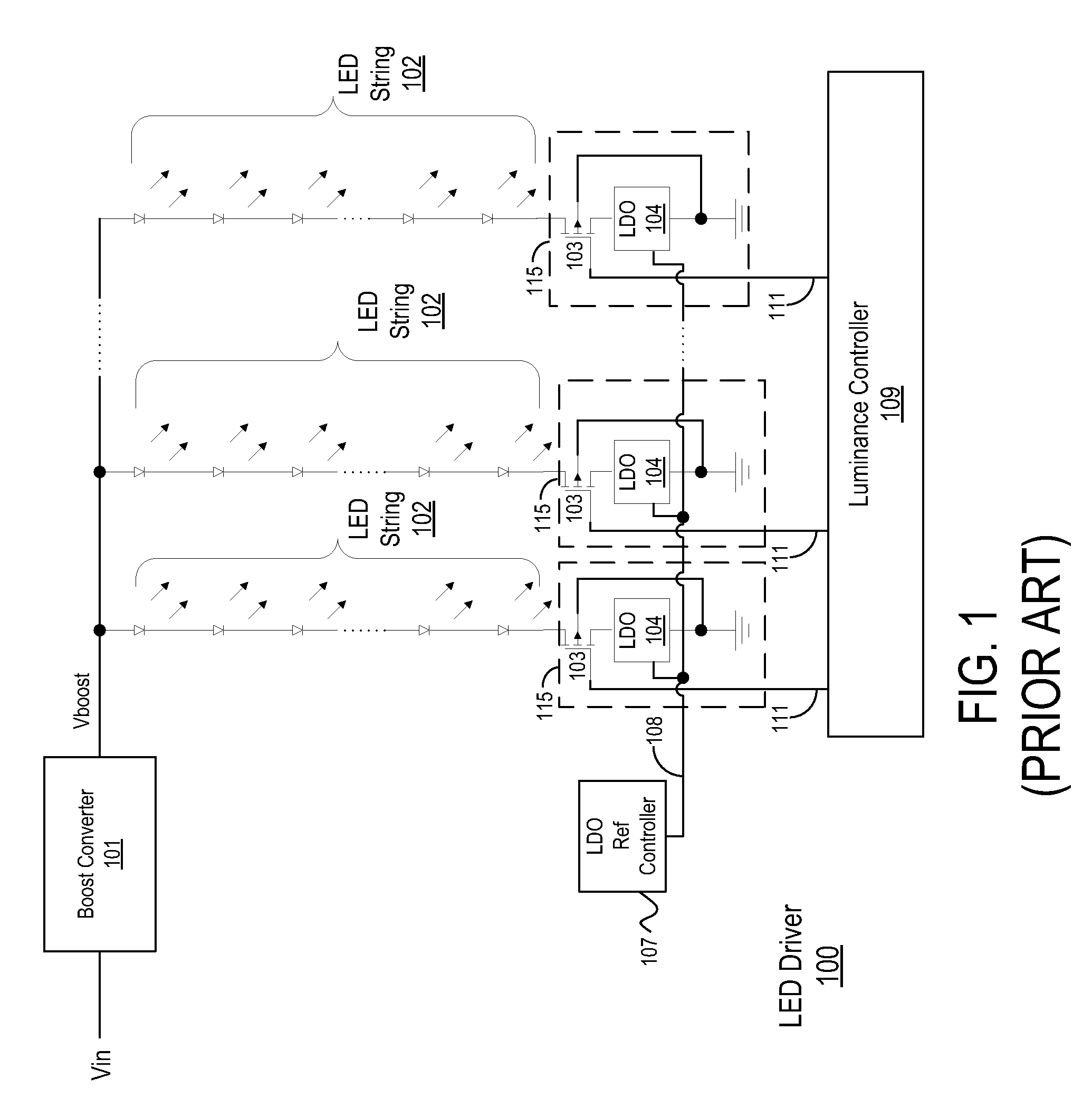

Adaptive Switch Mode LED Driver

ActiveUS20110062872A1Exact matchFast dynamic responseSemiconductor/solid-state device testing/measurementElectroluminescent light sourcesPower flowEngineering

An adaptive switch mode LED driver provides an intelligent approach to driving multiple strings of LEDs. The LED driver determines an optimal current level for each LED channel from a limited set of allowed currents. The LDO driver then determines a PWM duty cycle for driving the LEDs in each LED channel to provide precise brightness control over the LED channels. Beneficially, the LED driver minimizes the power dissipation in the LDO circuits driving each LED string, while also ensuring that the currents in each LED string are maintained within a limited range. A sample and hold LDO allows PWM control over extreme duty cycles with very fast dynamic response. Furthermore, fault protection circuitry ensures fault-free startup and operation of the LED driver.

Owner:DIALOG SEMICONDUCTOR INC

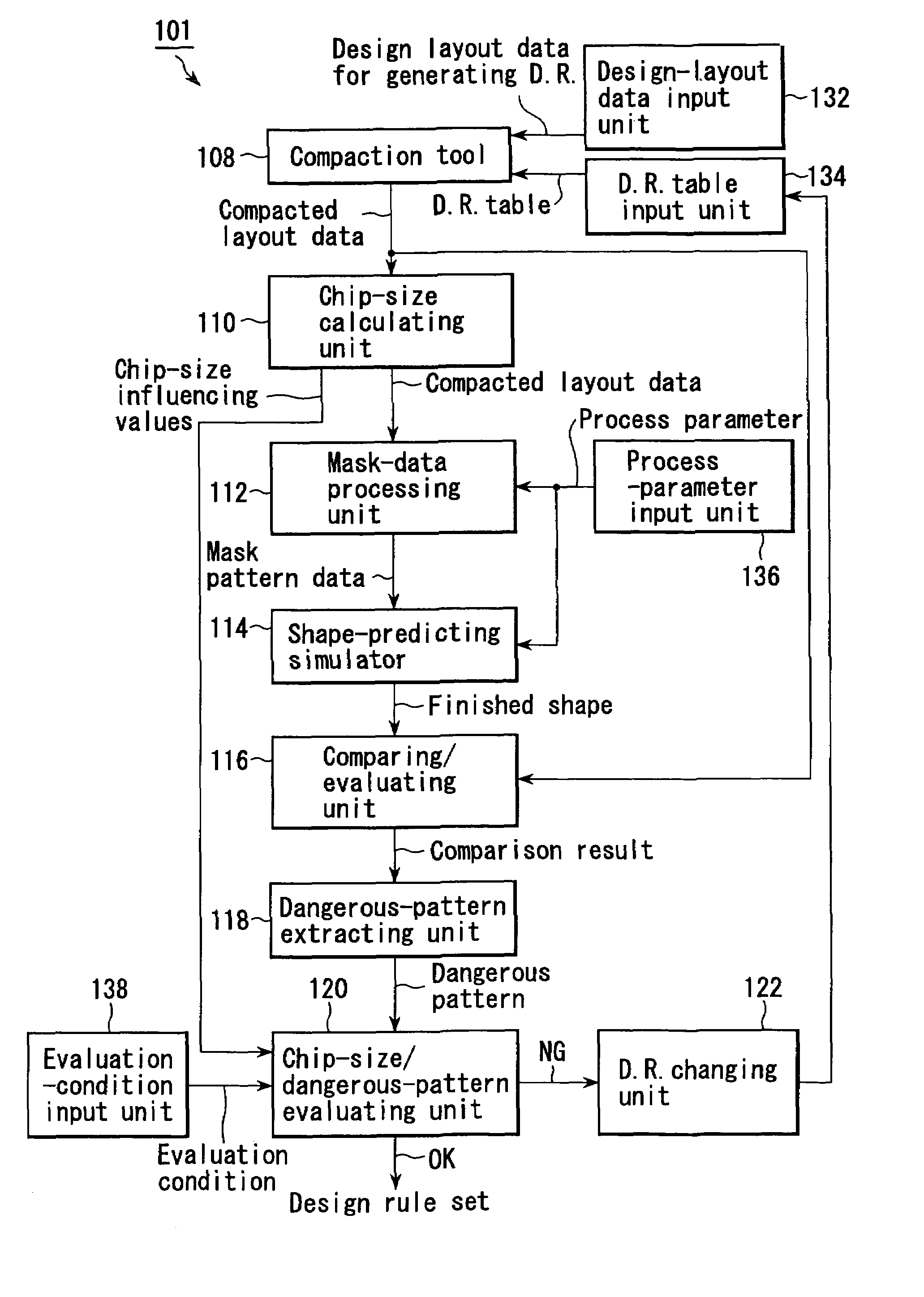

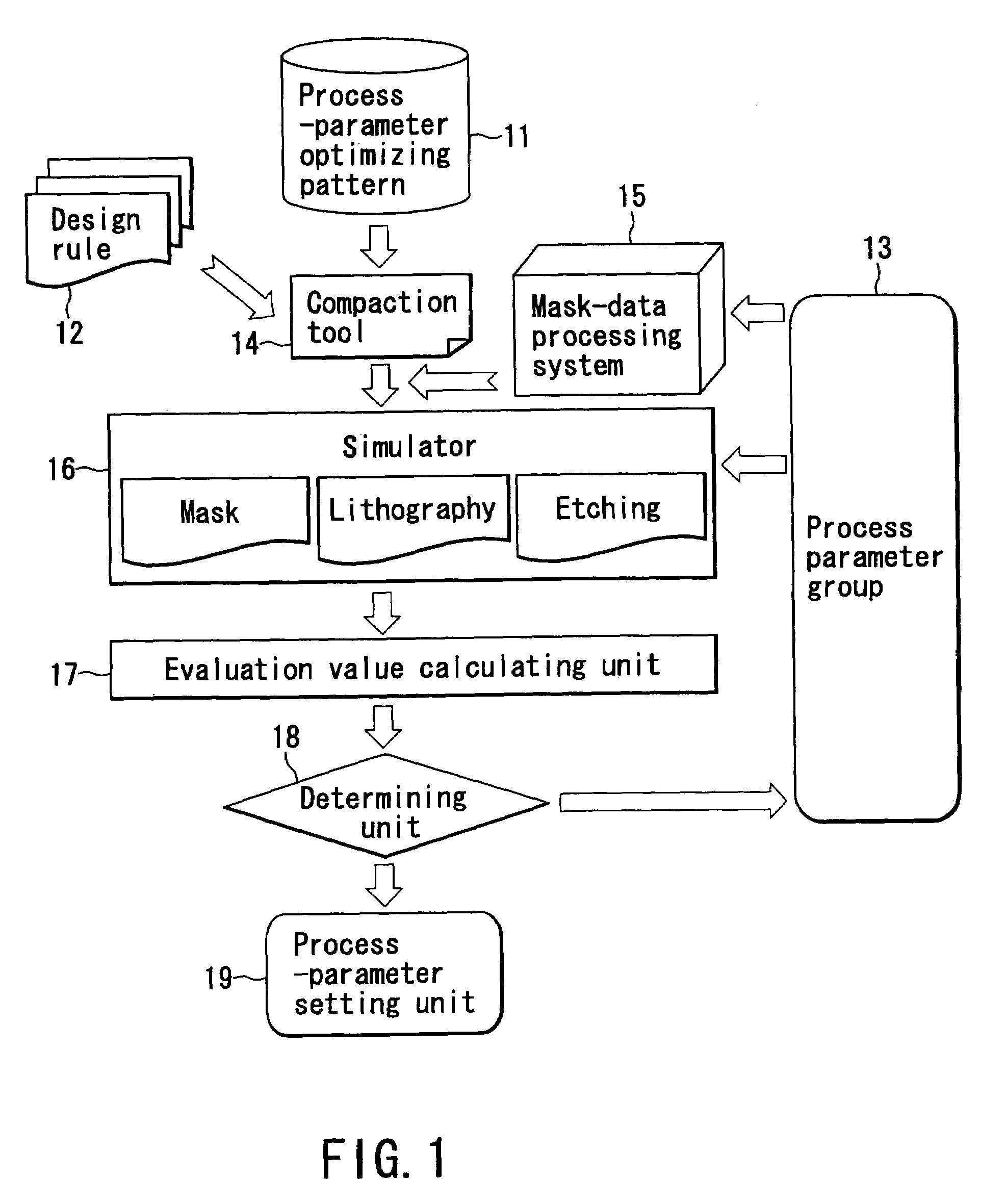

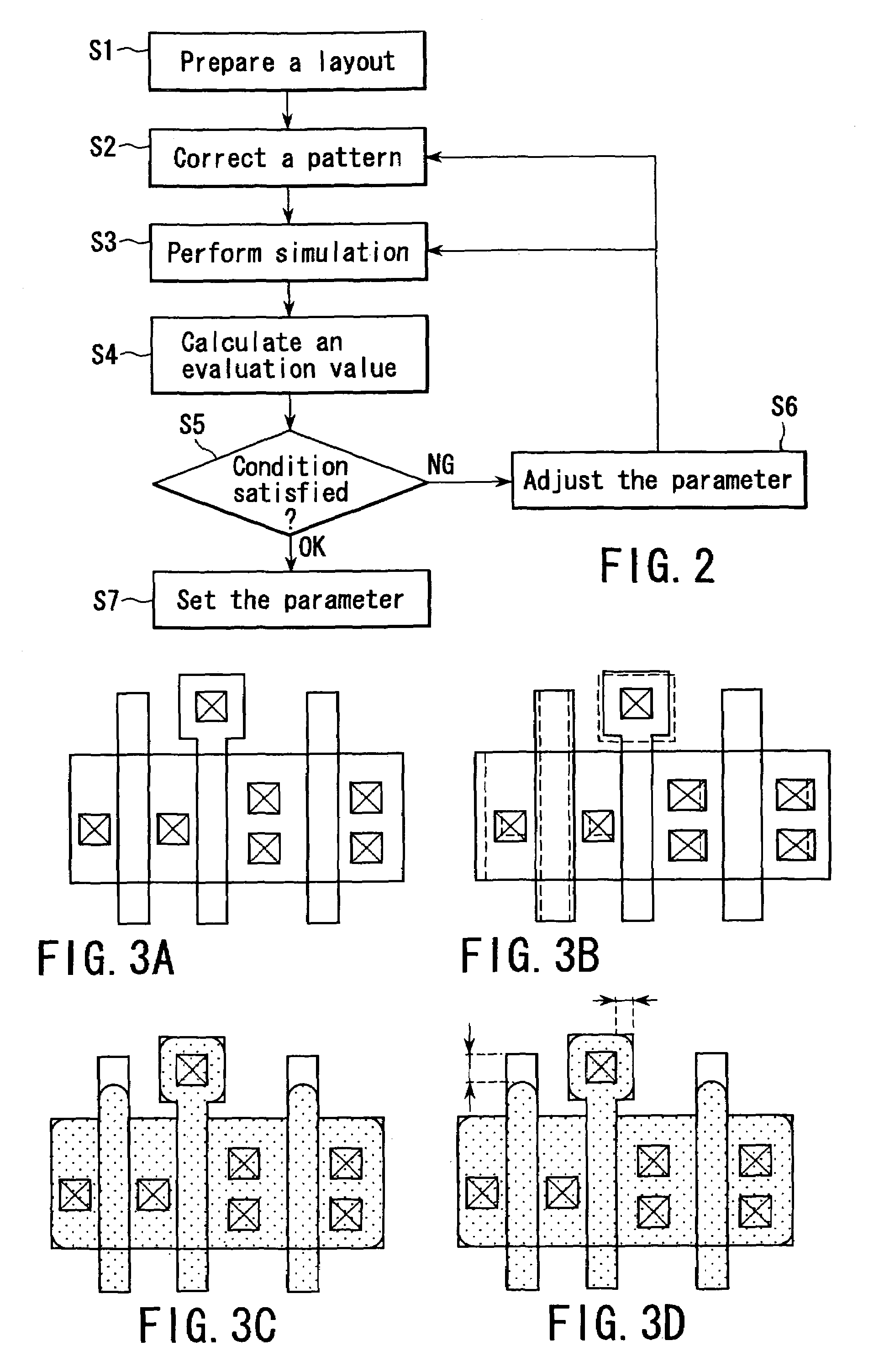

Method of setting process parameter and method of setting process parameter and/or design rule

Disclosed is a method of setting a process parameter for use in manufacturing a semiconductor integrated circuit, comprising correcting a first pattern by using process parameter information to obtain a second pattern, the first pattern being one which corresponds to a design layout of the semiconductor integrated circuit, predicting a third pattern by using the process parameter information, the third pattern being one which corresponds to the second pattern and which is to be formed on a semiconductor wafer in an etching process, obtaining an evaluation value by comparing the third pattern with the first pattern, determining whether the evaluation value satisfies a preset condition, and changing the process parameter information when the evaluation value is found not to satisfy the preset condition.

Owner:KIOXIA CORP

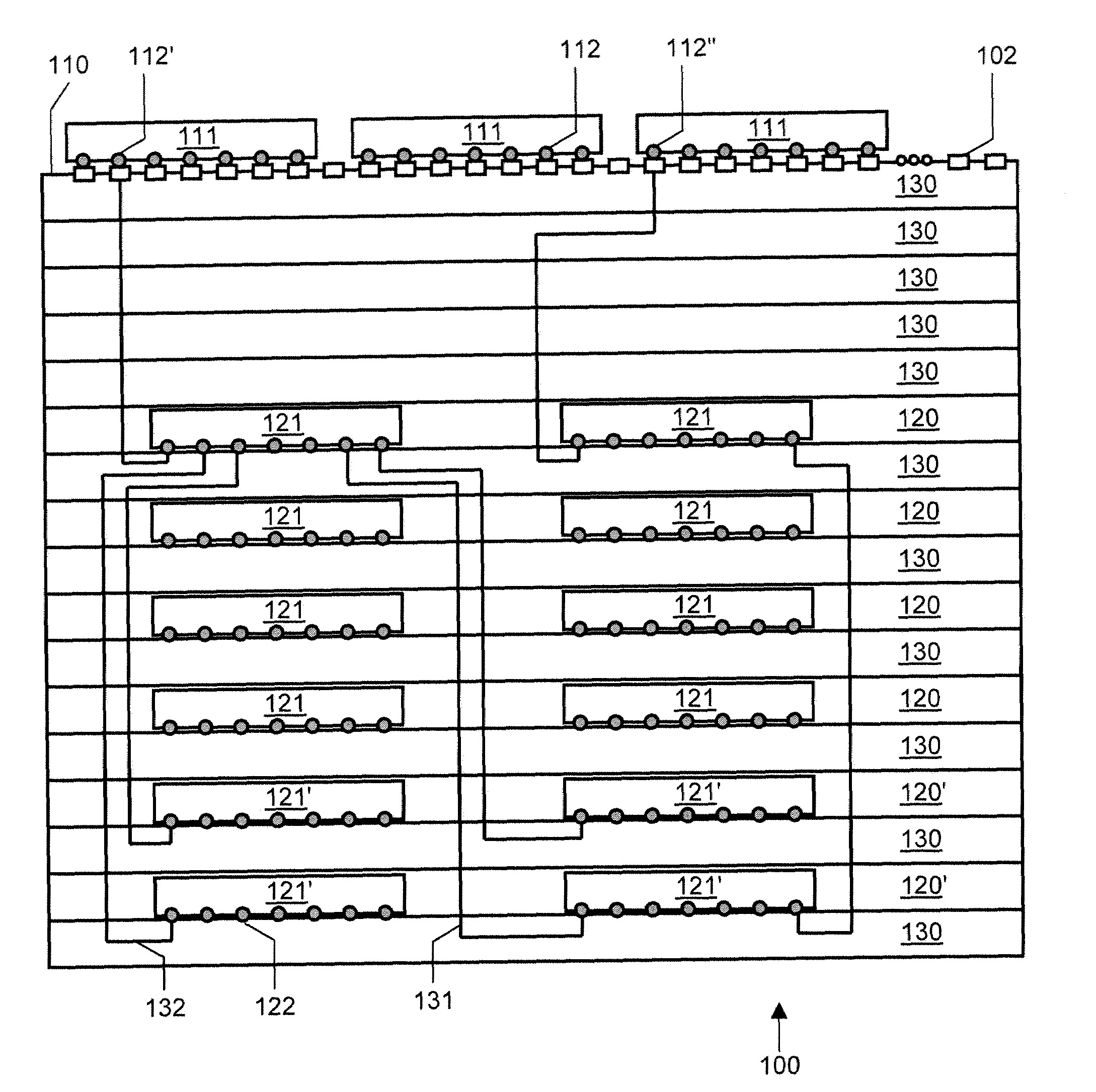

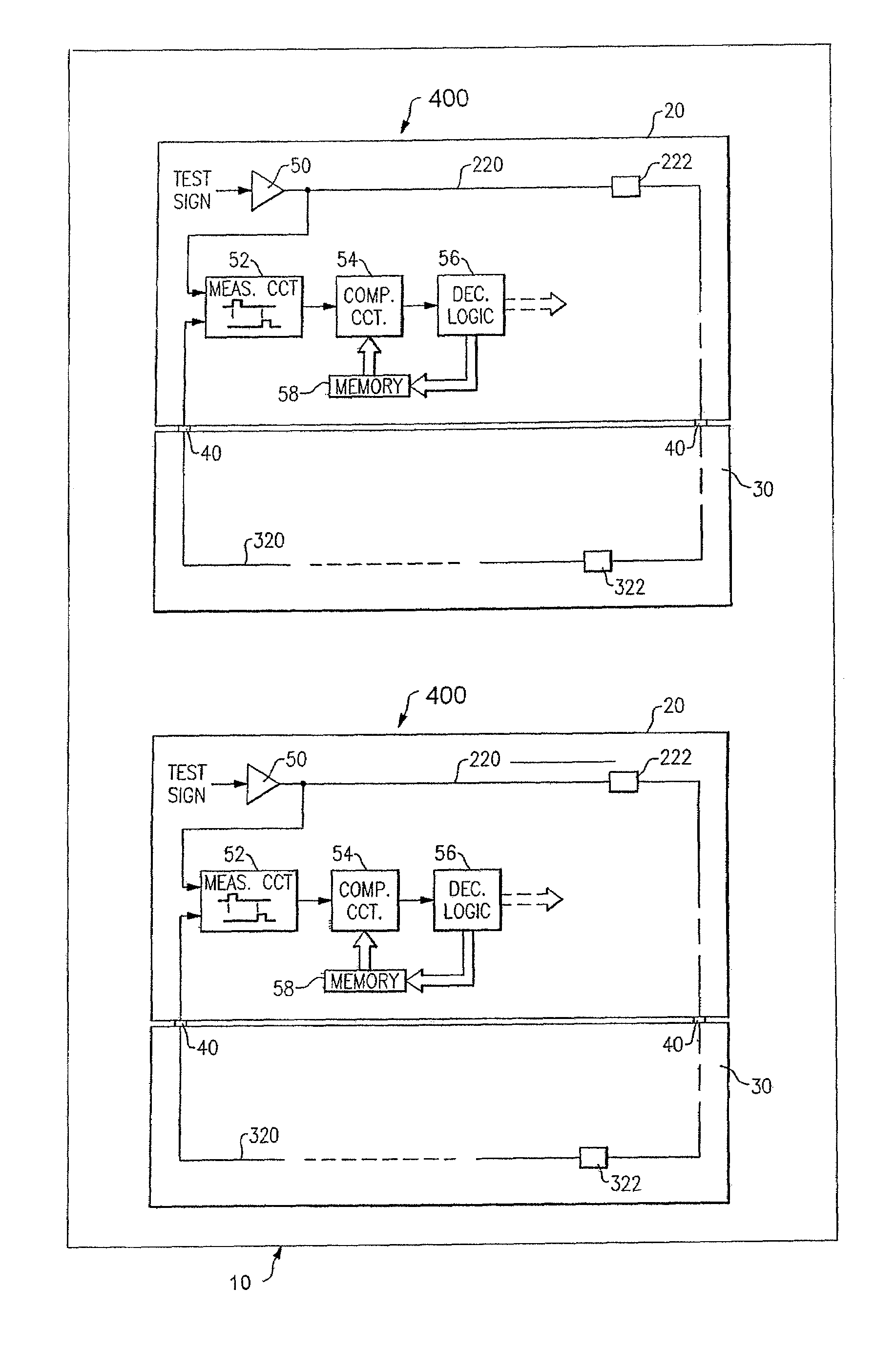

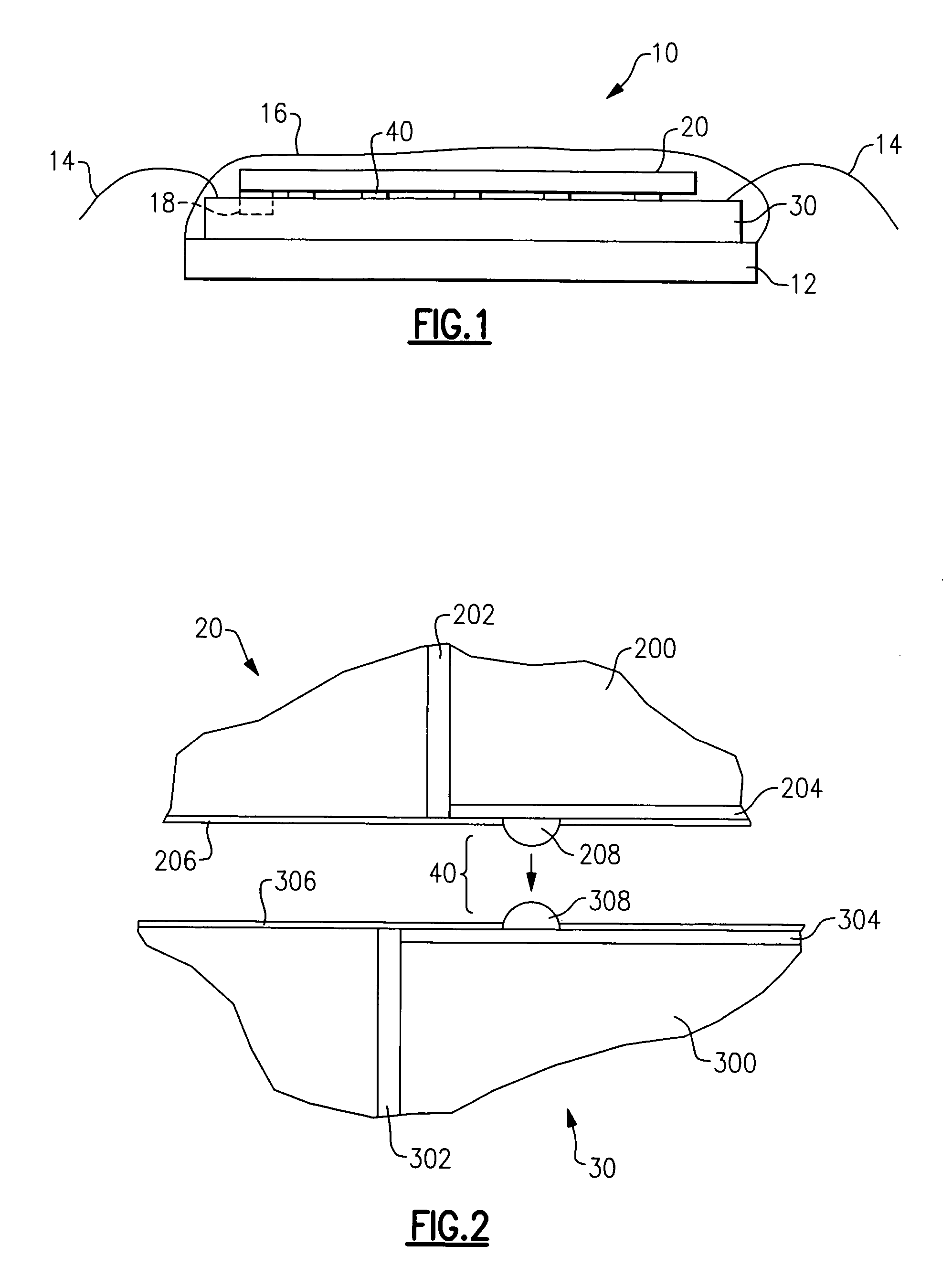

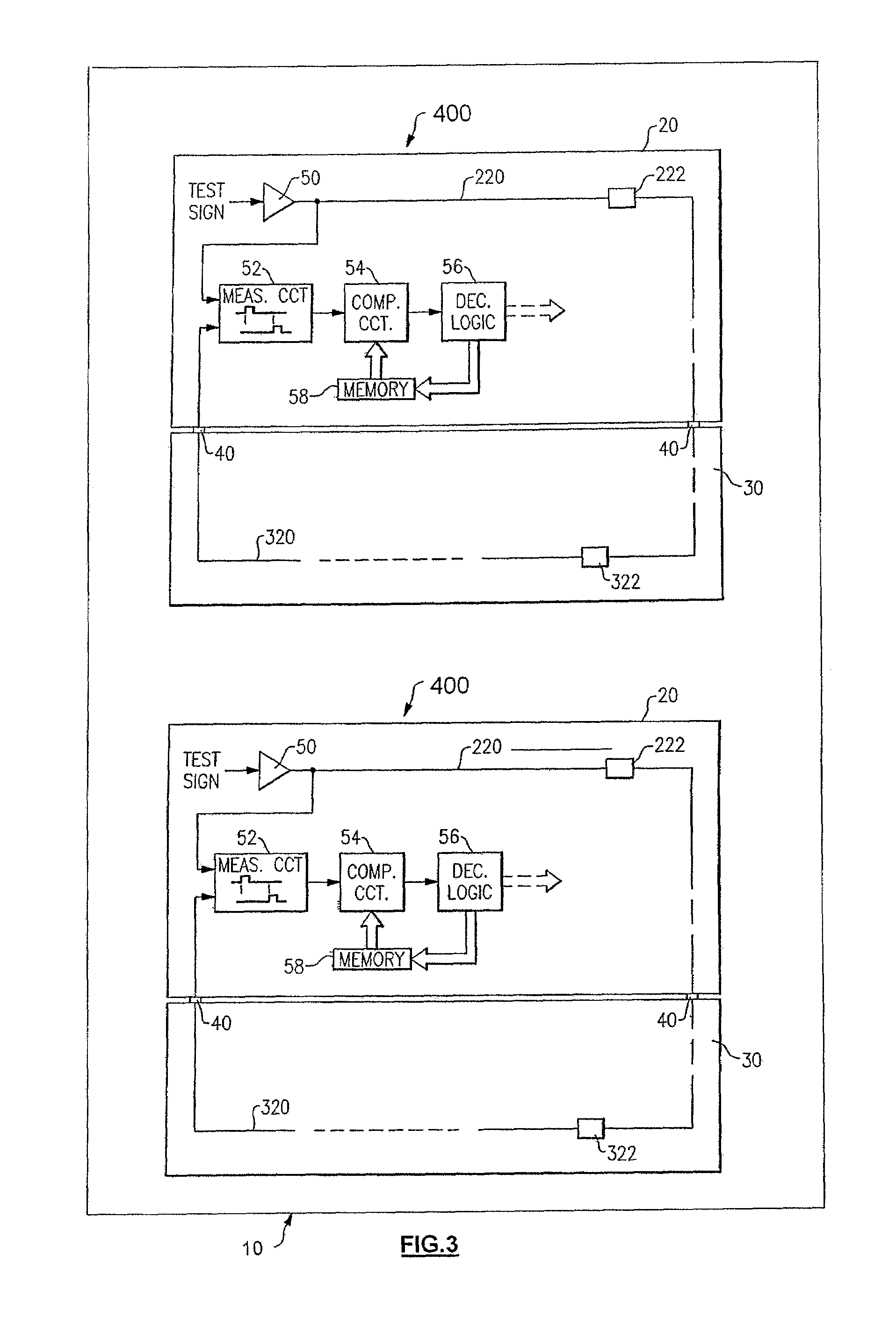

Stacked chip security

InactiveUS7557597B2Semiconductor/solid-state device testing/measurementElectronic circuit testingSemiconductor chipInterconnection

The present invention is directed to an integrated circuit module device. The device includes a first semiconductor chip having a first circuit layer and at least one first interconnection element disposed on a first chip surface. The at least one first interconnection element is electrically coupled to the first circuit layer. A second semiconductor chip includes a second circuit layer and at least one second interconnection element disposed on a second chip surface. The at least one second interconnection element is electrically coupled to the second circuit layer. The at least one first interconnection element is connected to the at least one second interconnection element to establish electrical continuity between the first circuit layer and the second circuit layer. The first surface is adjoined to the second surface. At least one ring delay circuit includes a first ring delay path partially disposed on the first circuit layer and a second ring delay path partially disposed on the second circuit layer. The first ring delay path and the second ring delay path form a signal path having a predetermined measurement signature. The ring delay circuit compares the predetermined measurement signature to a test measurement signature.

Owner:INT BUSINESS MASCH CORP

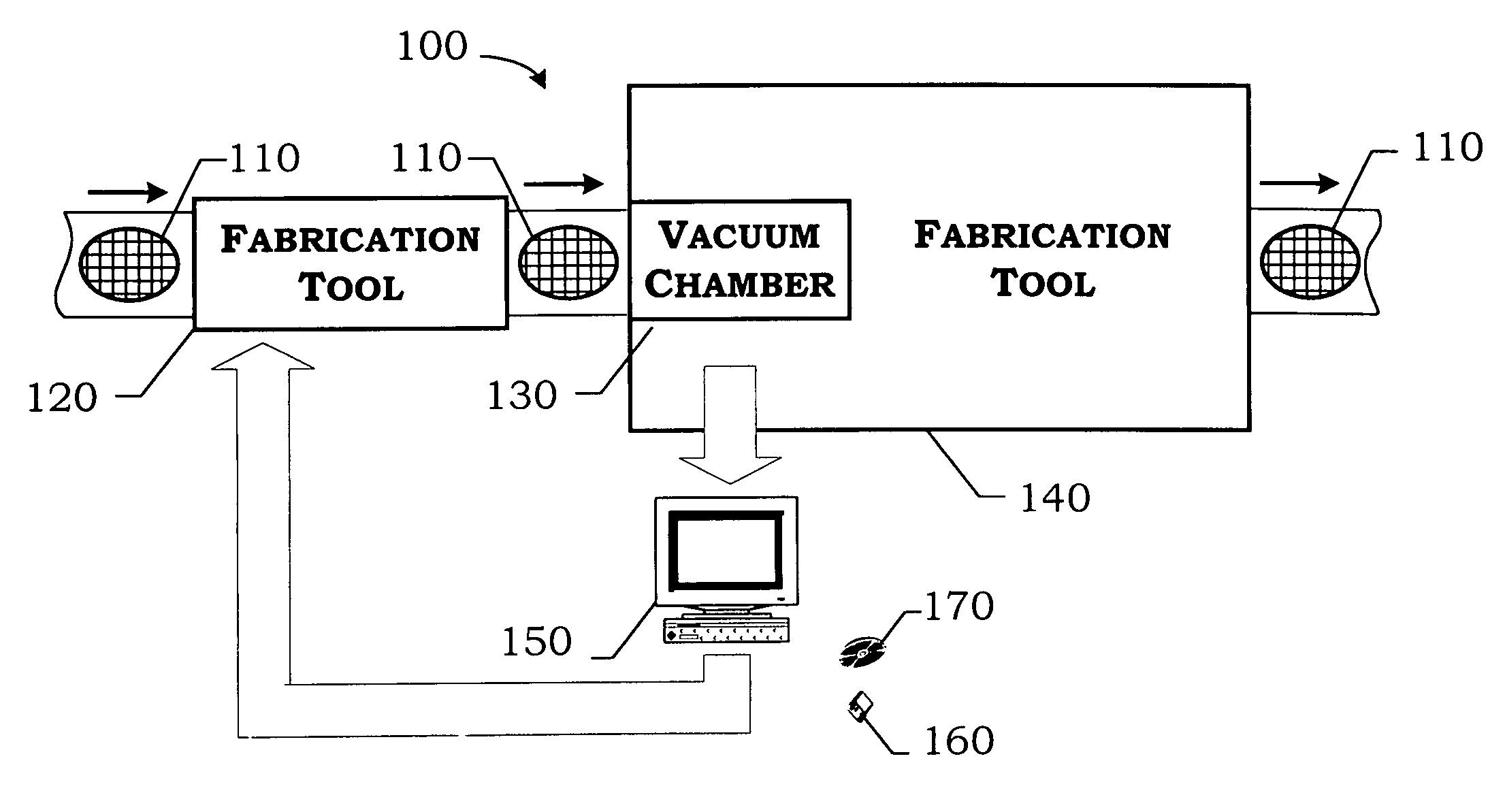

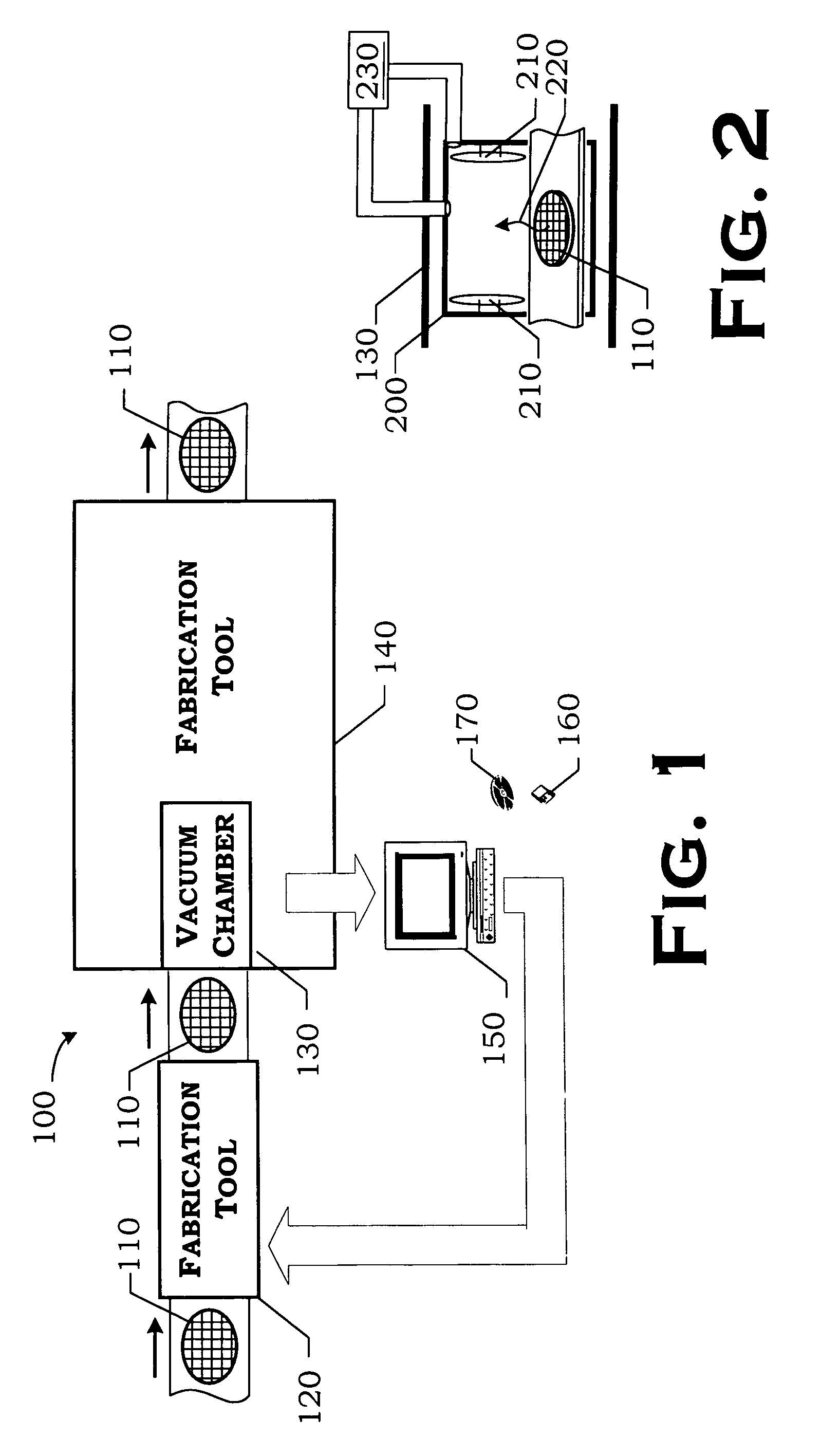

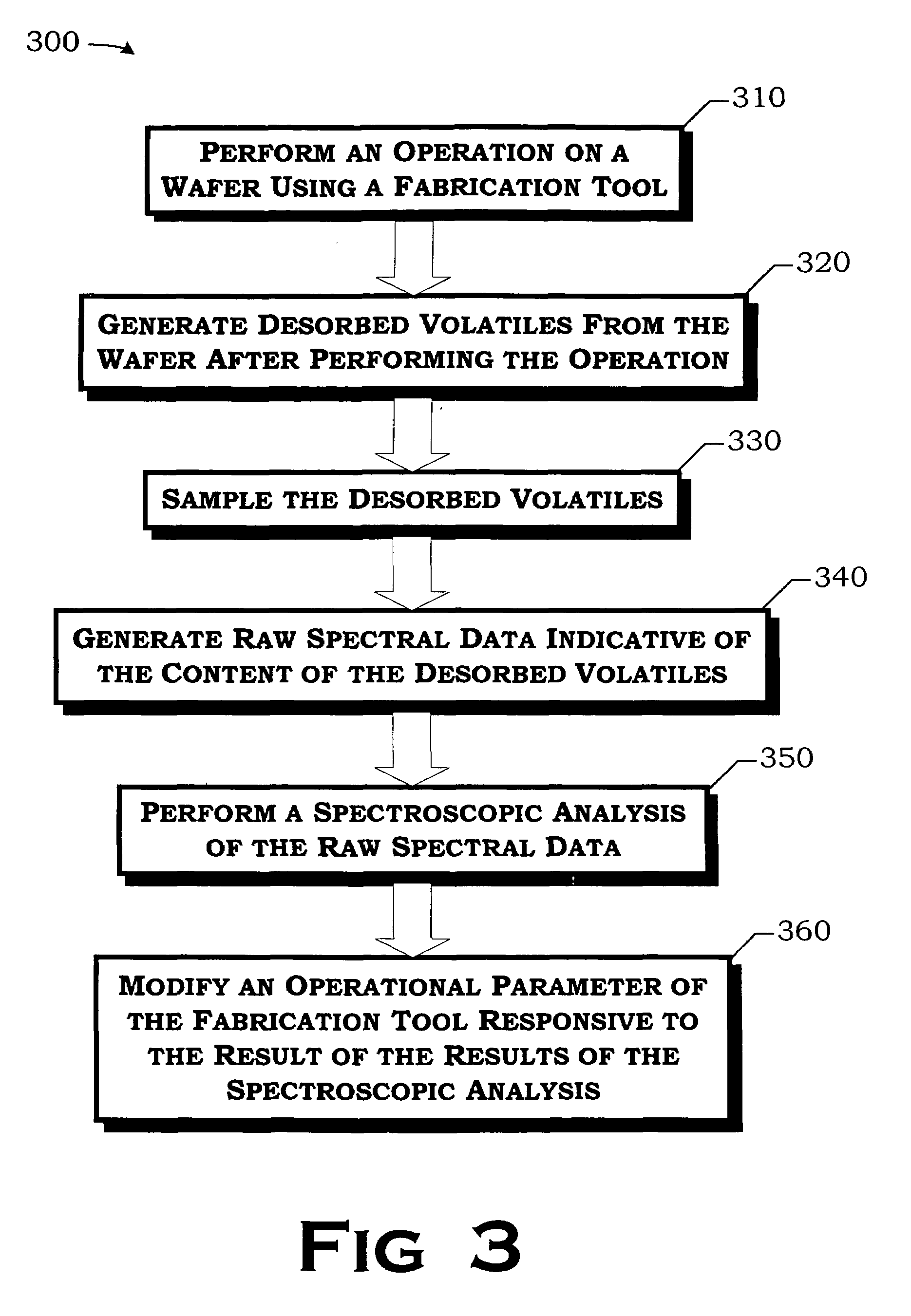

Closed loop residual gas analyzer process control technique

InactiveUS6955928B1Reduce the amount requiredSemiconductor/solid-state device testing/measurementSolid-state devicesResidual gas analyzerClosed loop

A technique for use in fabricating an integrated circuit are disclosed. The method generally begins by performing an operation on a wafer using a fabrication tool. Next, volatiles are desorbed from the wafer. The desorbed volatiles are sampled and raw spectral data indicating the content of the desorbed volatiles is generated. The raw spectral data is subjected to a spectroscopic analysis. An operational parameter of the fabrication tool is then modified responsive to the result of the results of the spectroscopic analysis. In one particular aspect of the invention, a controller receives the raw spectral data and processes the raw spectral data to determine the presence of a residual material on the wafer. The controller then controls the process flow operation to reduce the amount of the residual material on the wafer responsive to the results of processing the raw spectral data. Other aspects of the invention include the apparatus implementing the process flow and the controller itself.

Owner:TAIWAN SEMICON MFG CO LTD

Method for forming conductive bumps for the purpose of contrructing a fine pitch test device

InactiveUS20020011859A1Semiconductor/solid-state device testing/measurementElectrical measurement instrument detailsElectricityEngineering

A system is described for using with fine pitch devices including singulated bare die, semiconductor wafers, chip sized packages, printed circuit boards, and the like to determine that the fine pitch device is not faulty. The system is also usable for transfer of data, energy, for collecting data measurements or measurement-related data between two pieces, and for effecting at least part of an identification process. The disclosed embodiment includes a substrate having a circuit pad pattern in the mirror image of the pattern of contact points, usually bond pads of the fine pitch device to be connected. A conductive elastomeric probe is permanently formed on the circuit pads of the substrate such that the probe is malleable and allows repetitive electrical contact. The system may also contain an alignment template for orienting the fine pitch device onto the elastomeric probes of the contact point pattern of the substrate.

Owner:EPITECH +1

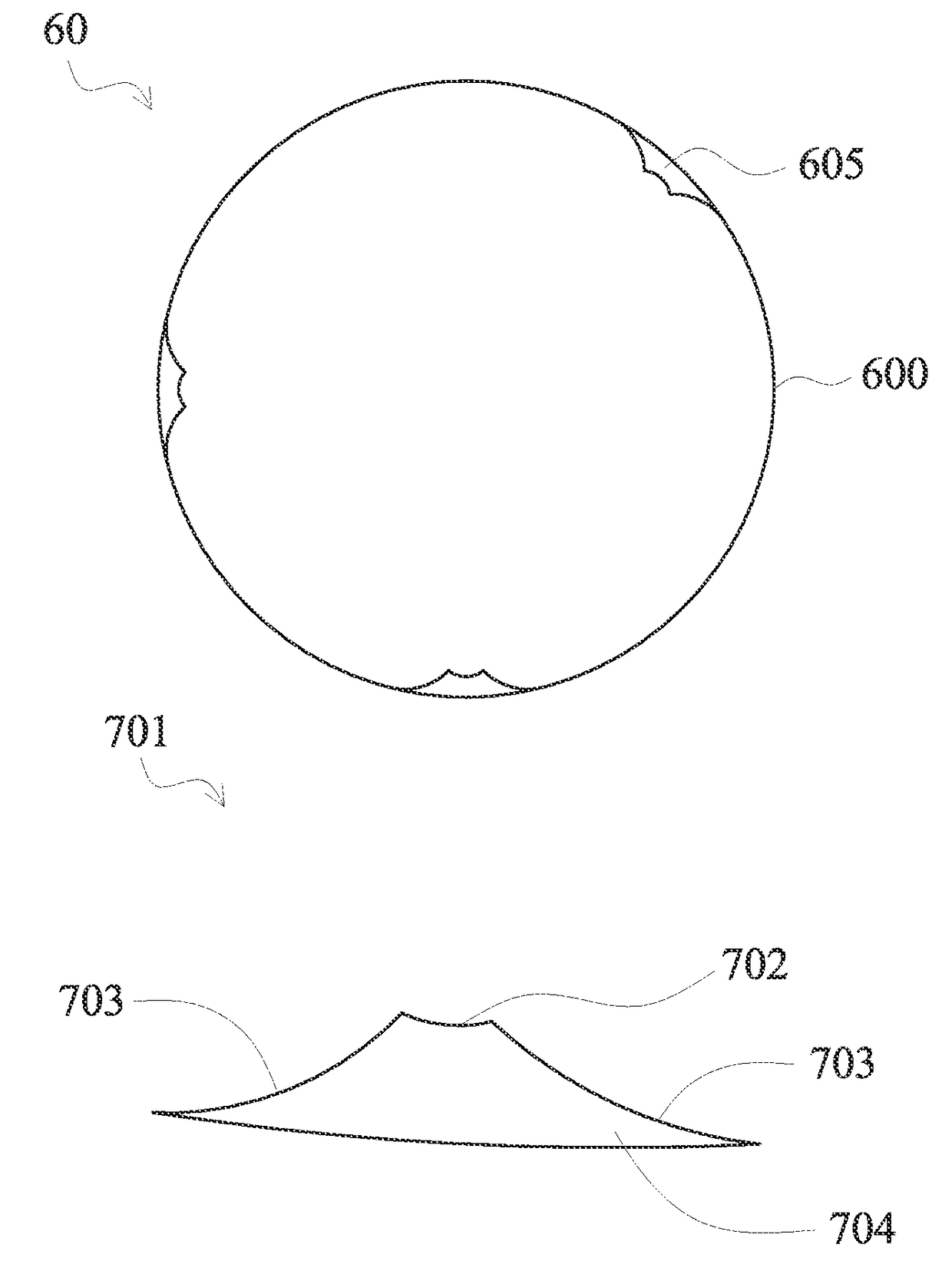

Wafer carrier

ActiveUS9691668B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringMechanical engineering

A wafer carrier comprises a supporting body having an opening therein, wherein said opening in said supporting body has a concave sidewall and a bottom surface in said supporting body which is curved in cross section; a plurality of vertical supporting rods configured to support and contact a wafer received in said opening and to displace said wafer from the bottom surface of the opening in said supporting body; wherein one of said supporting rods has an end for contacting and supporting said wafer; and wherein when viewing from a top view of the wafer carrier, one of said supporting rods has a base lining on the concave sidewall of said opening in said supporting body, a first concave side opposite to the base and two second concave sides connecting the base and the first concave side.

Owner:EPISTAR CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com