Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

9149 results about "Interface circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

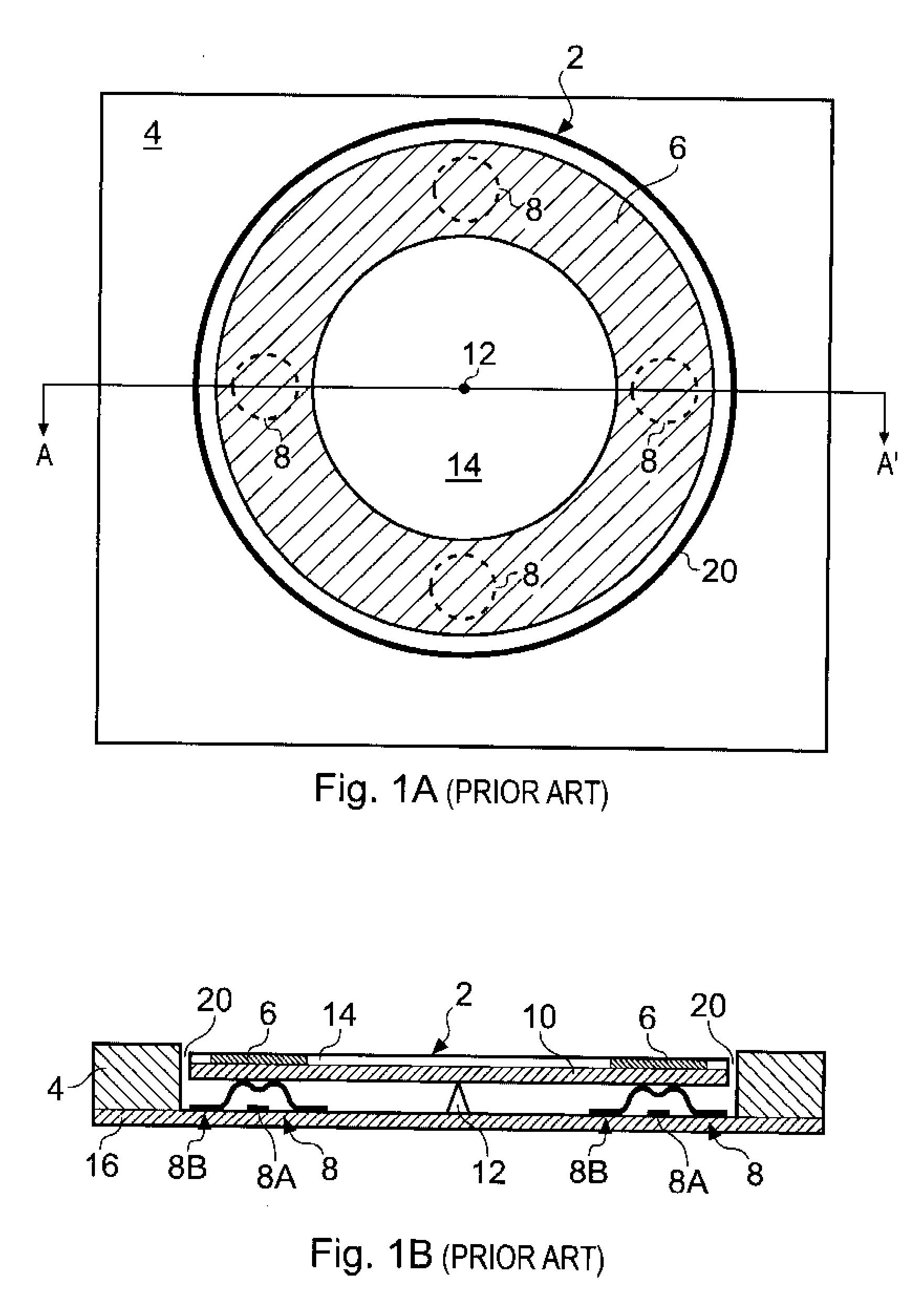

Method and apparatus for providing leak detection in data monitoring and management systems

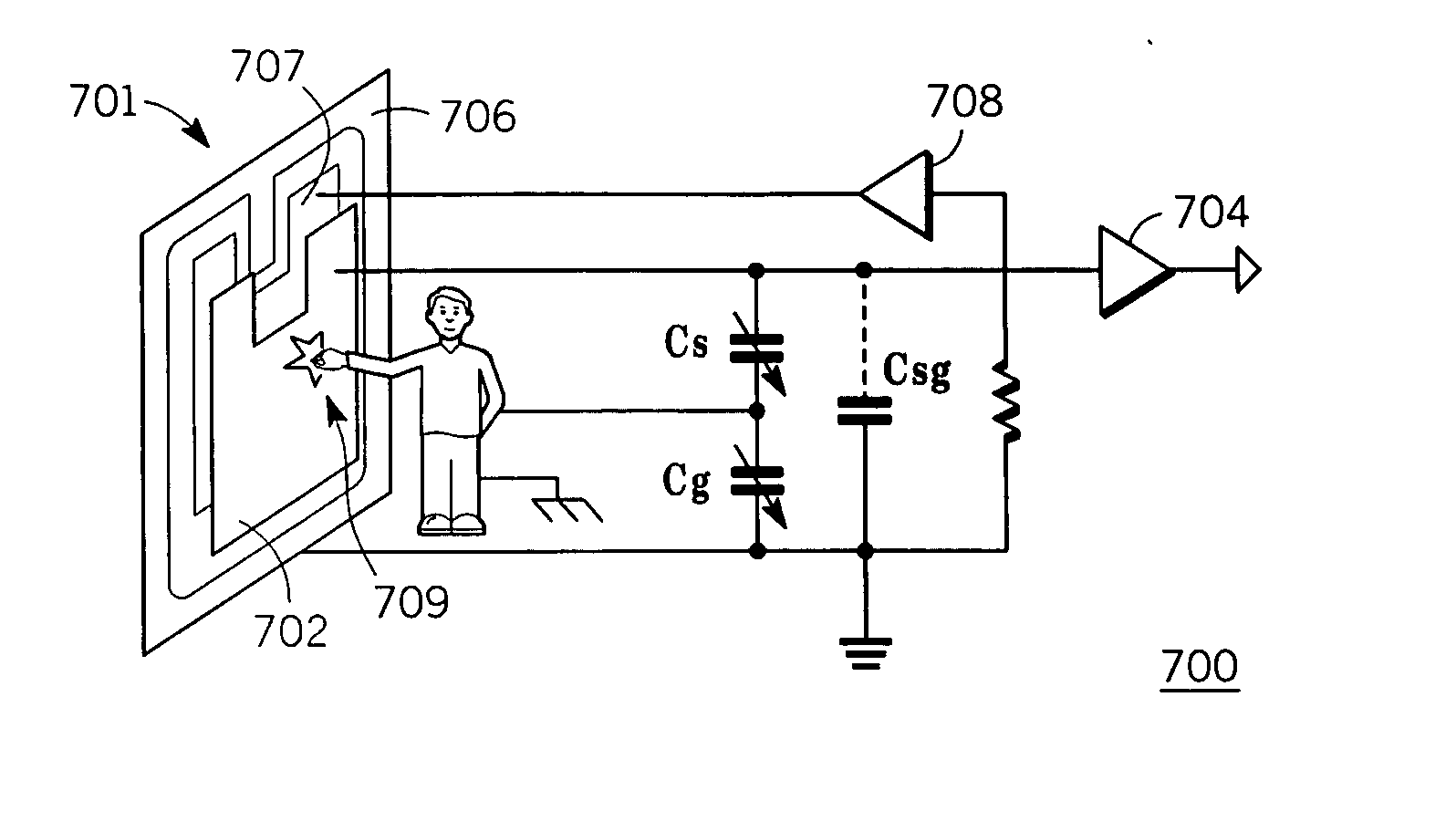

InactiveUS20060247508A1Resistance/reactance/impedenceFlow propertiesGlucose sensorsMonitoring system

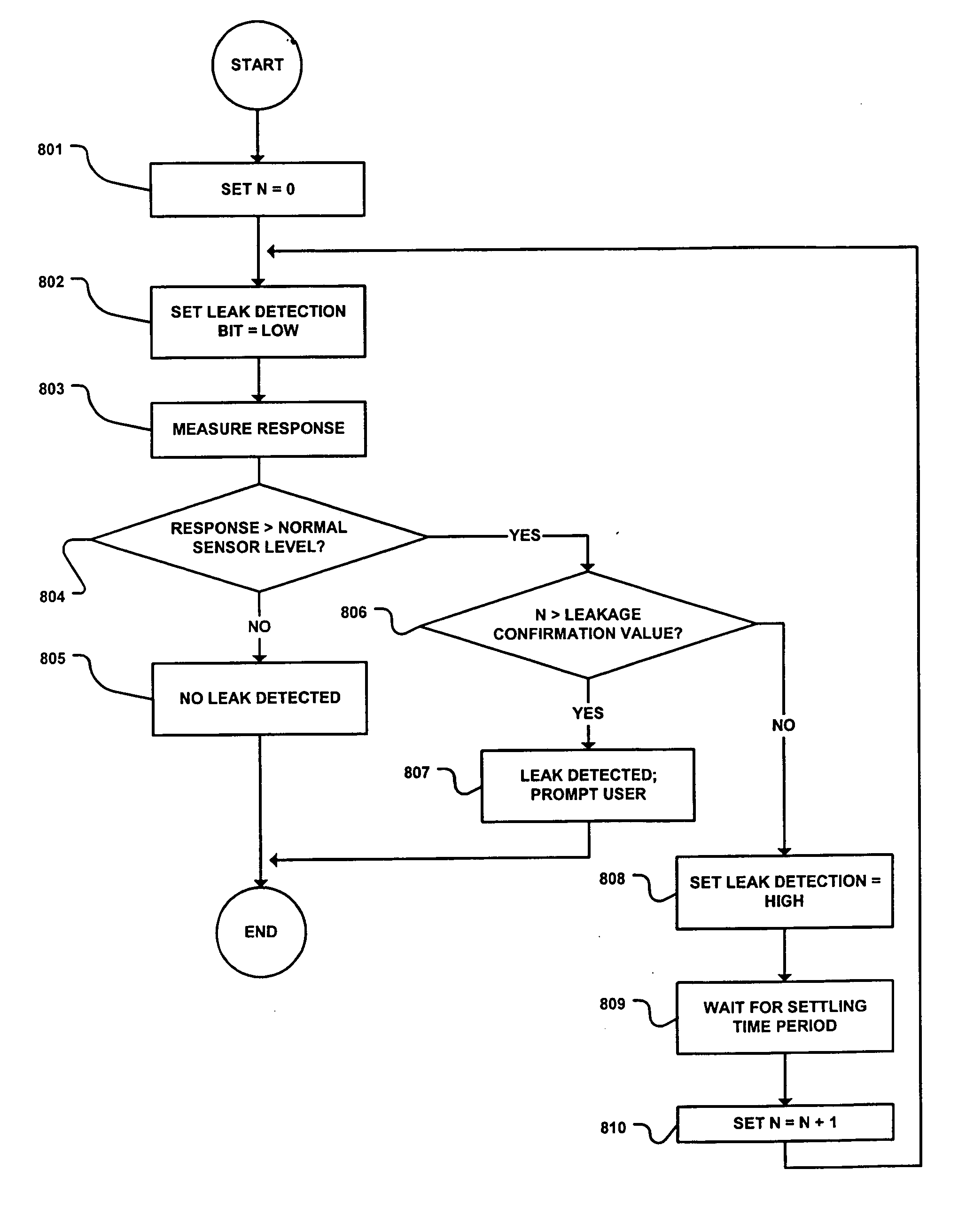

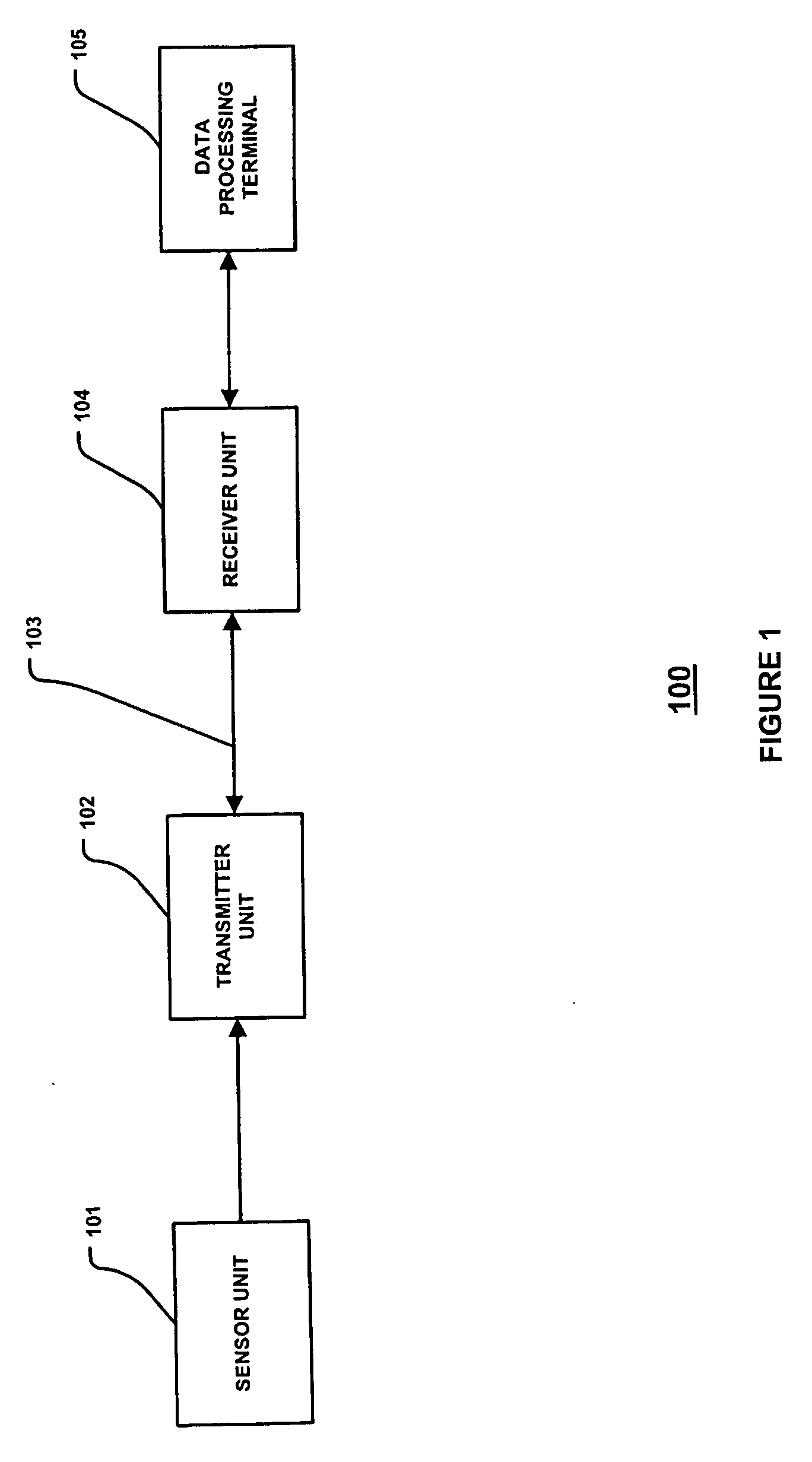

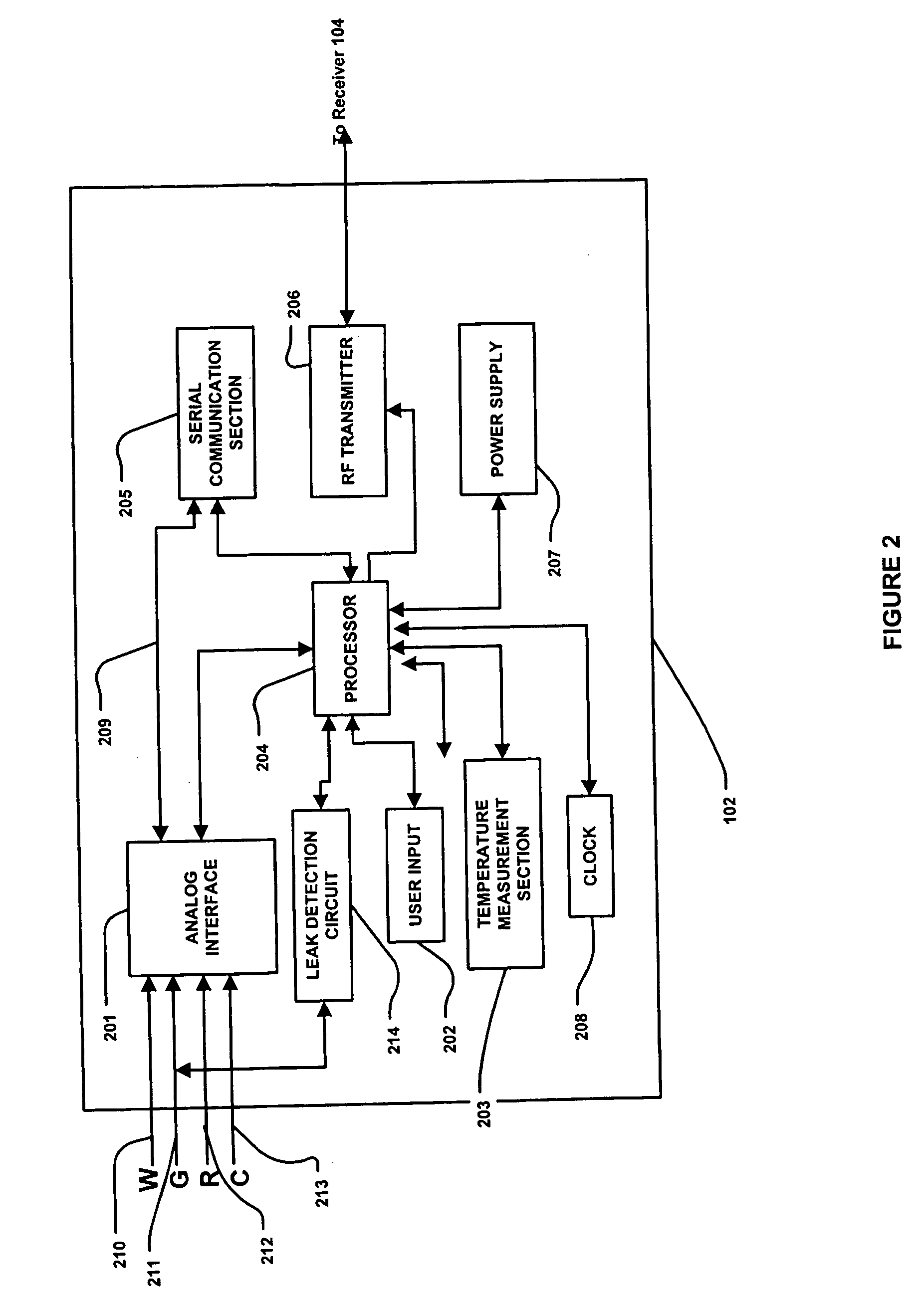

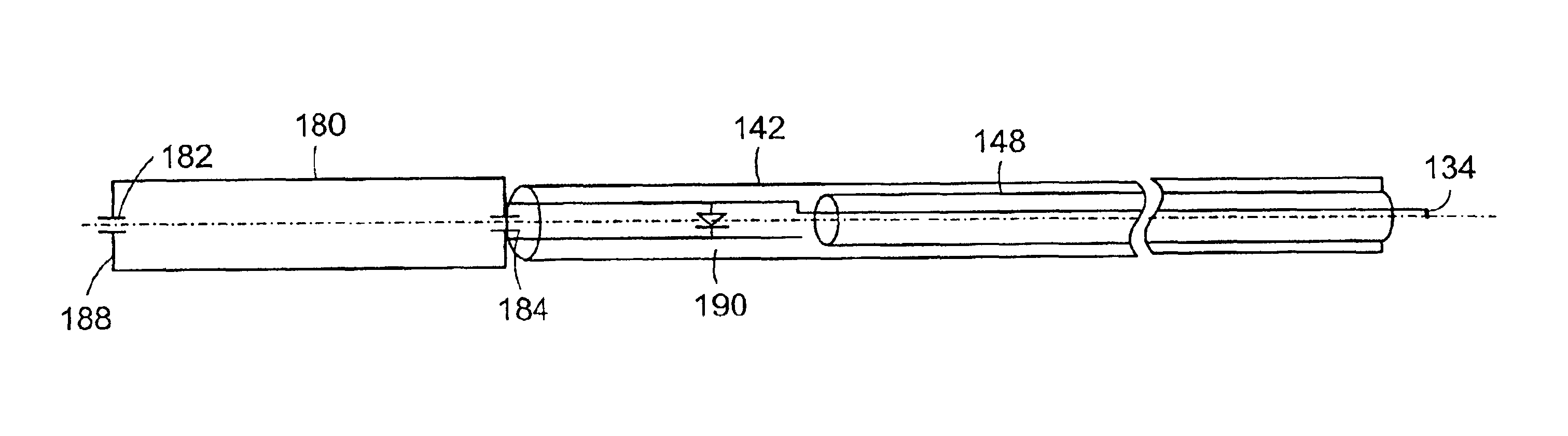

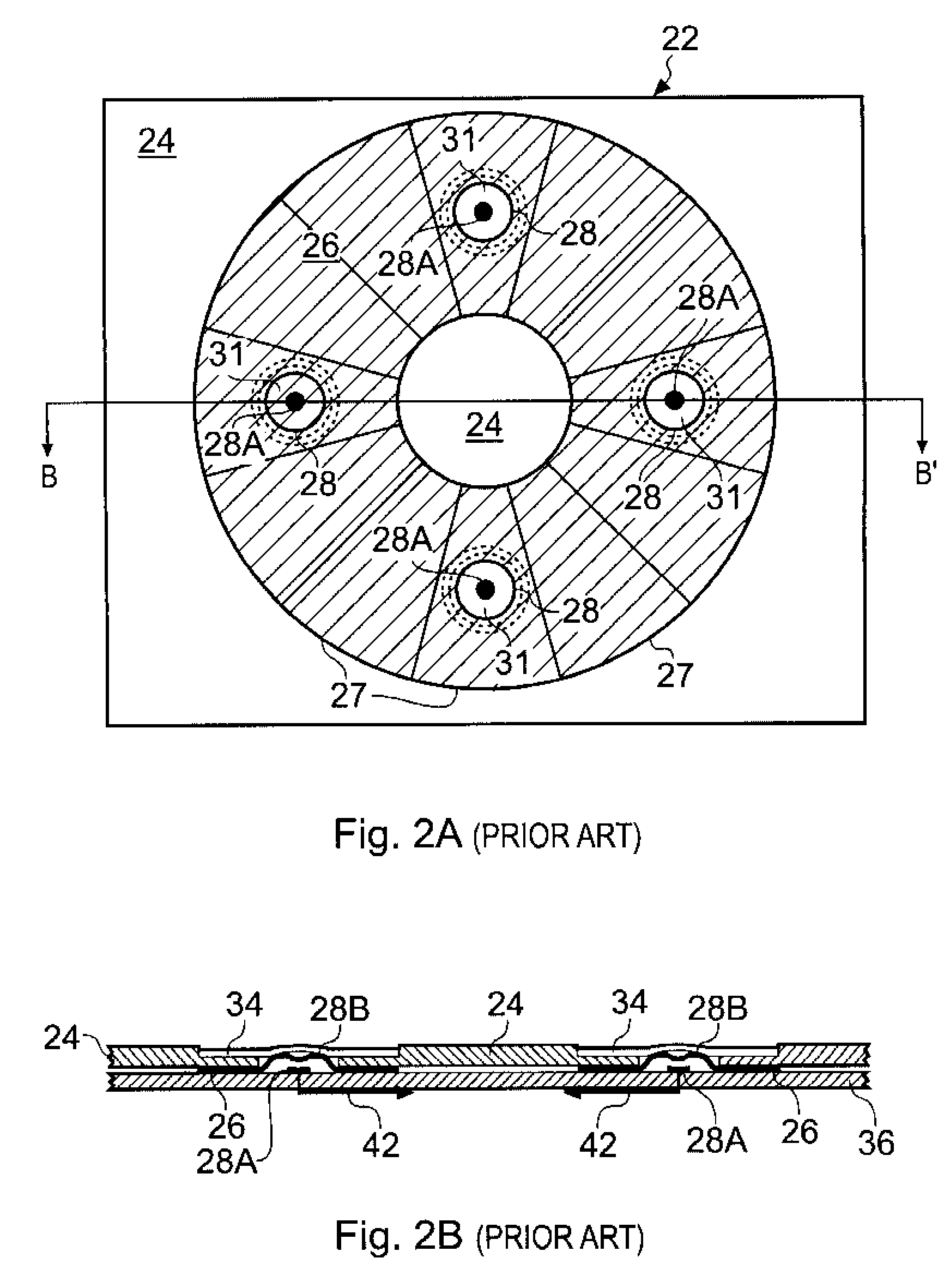

Method and apparatus for providing a leak detection circuit for data monitoring and management system using the guard trace of a glucose sensor by applying a leak detection test signal to determine whether a leakage current is present is provided. The leak detection circuit may includes an interface circuit such as a capacitor coupled to the guard trace to detect the leakage current when the leak detection test signal is applied to the guard trace, such that the user or patient using the data monitoring and management system such as glucose monitoring systems may be promptly and accurately notified of a failed sensor, and to alert the user to replace the sensor.

Owner:ABBOTT DIABETES CARE INC

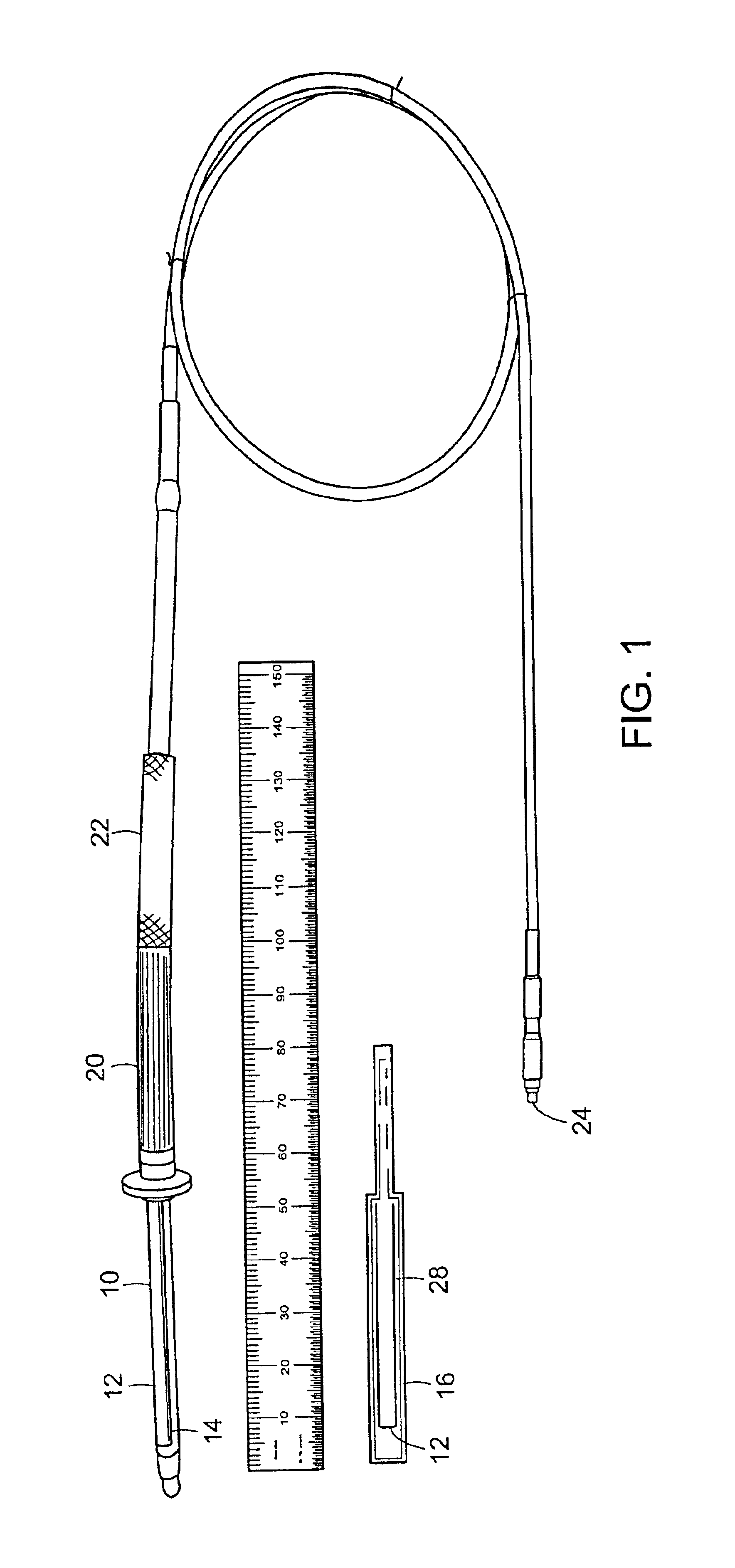

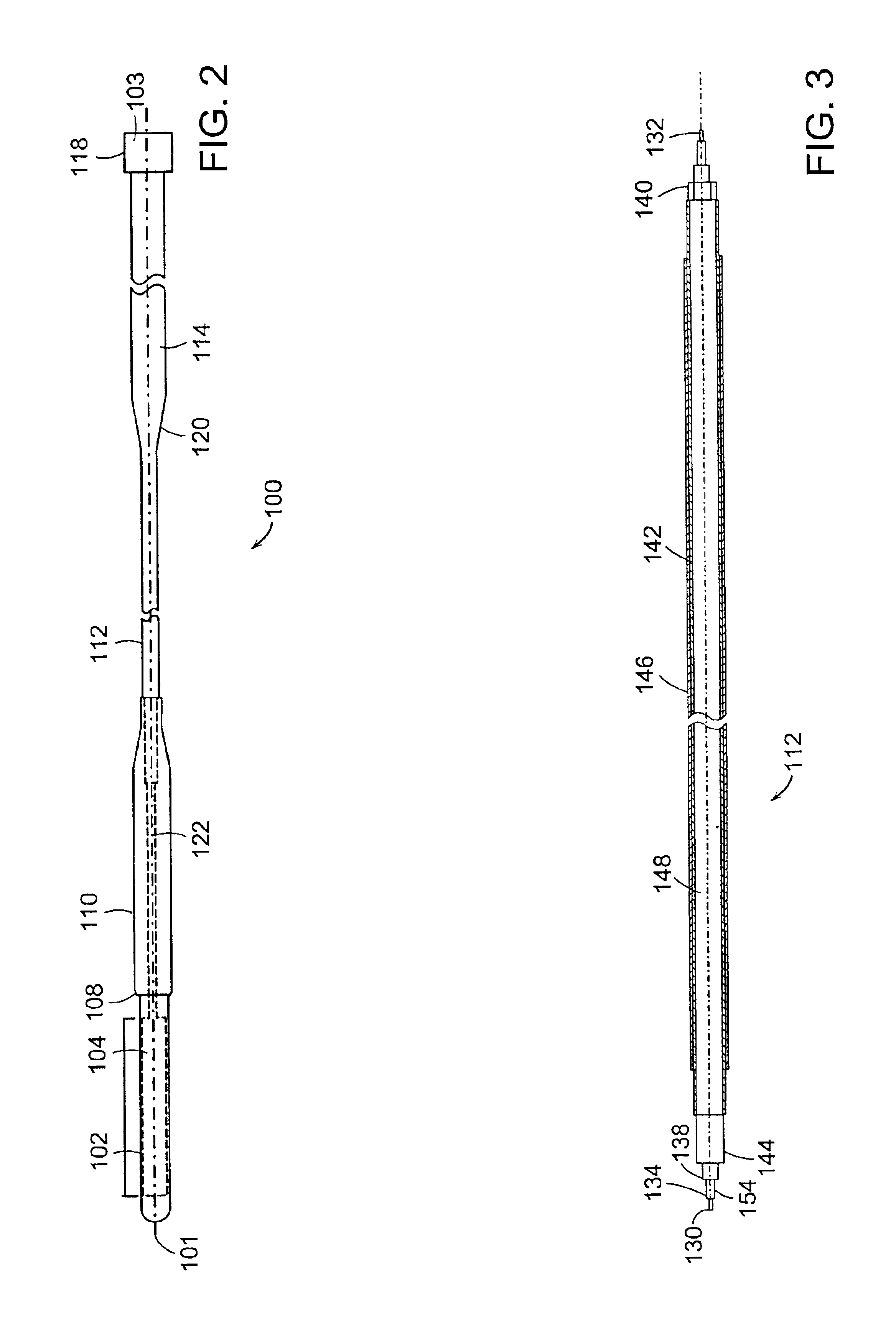

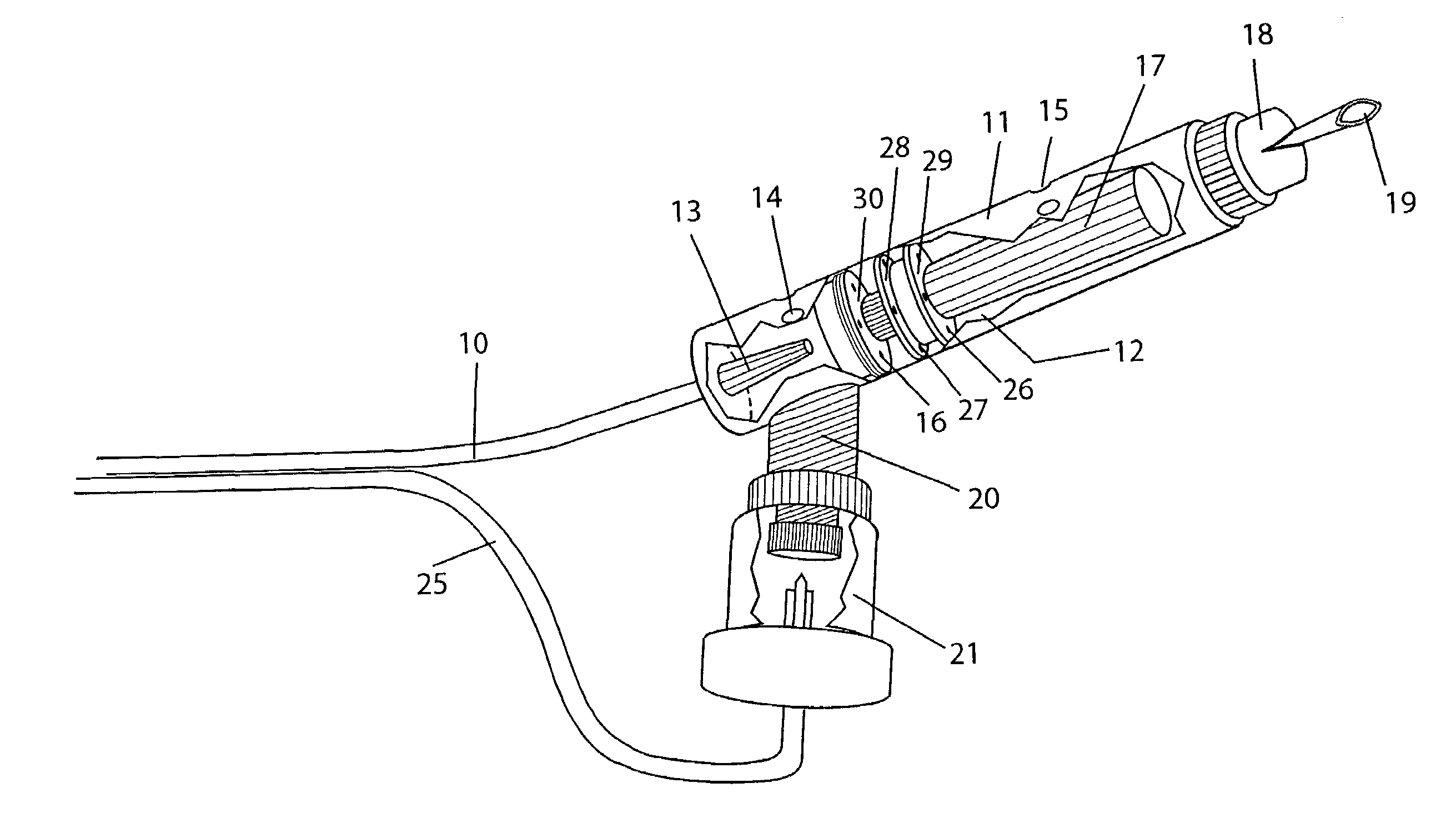

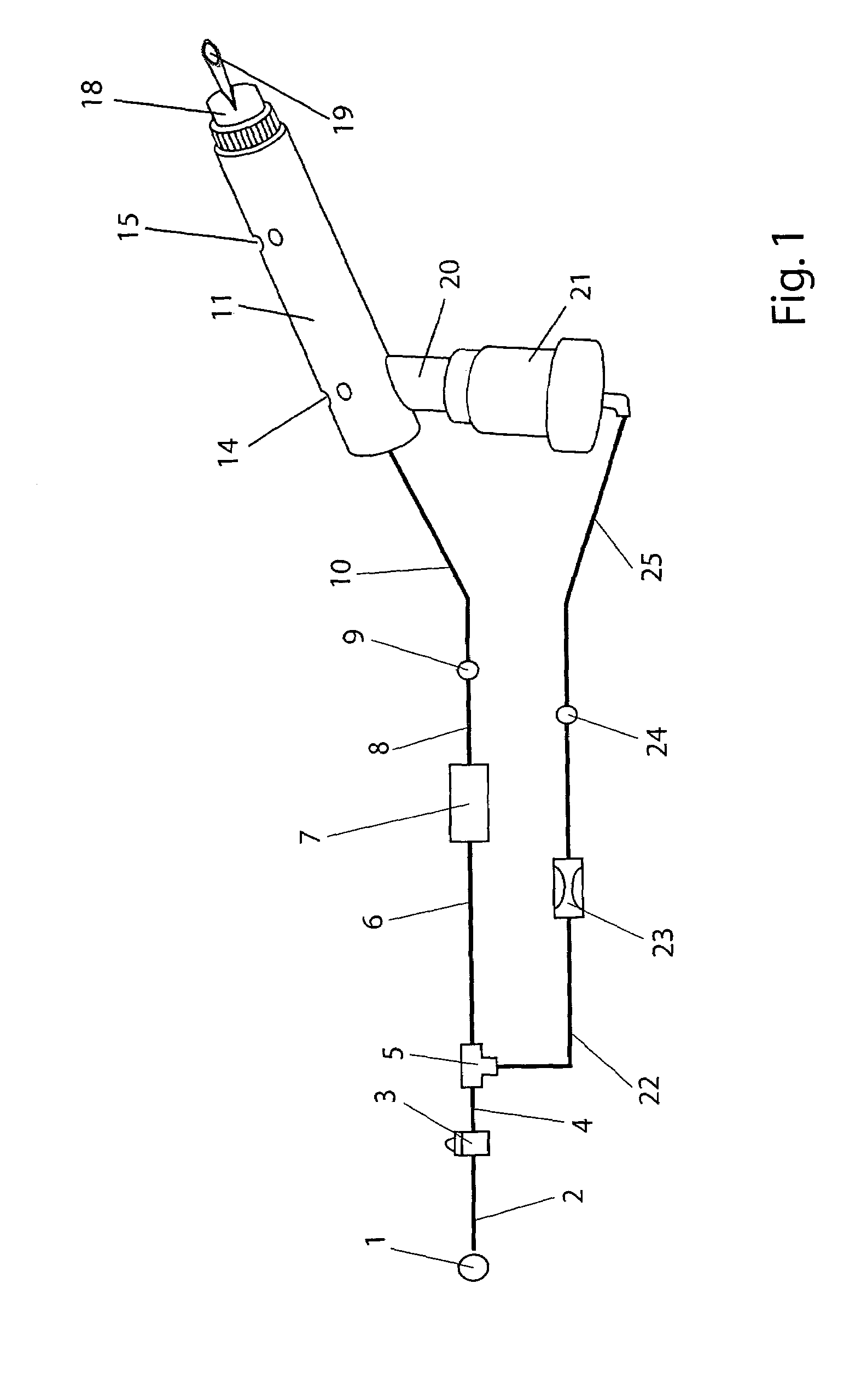

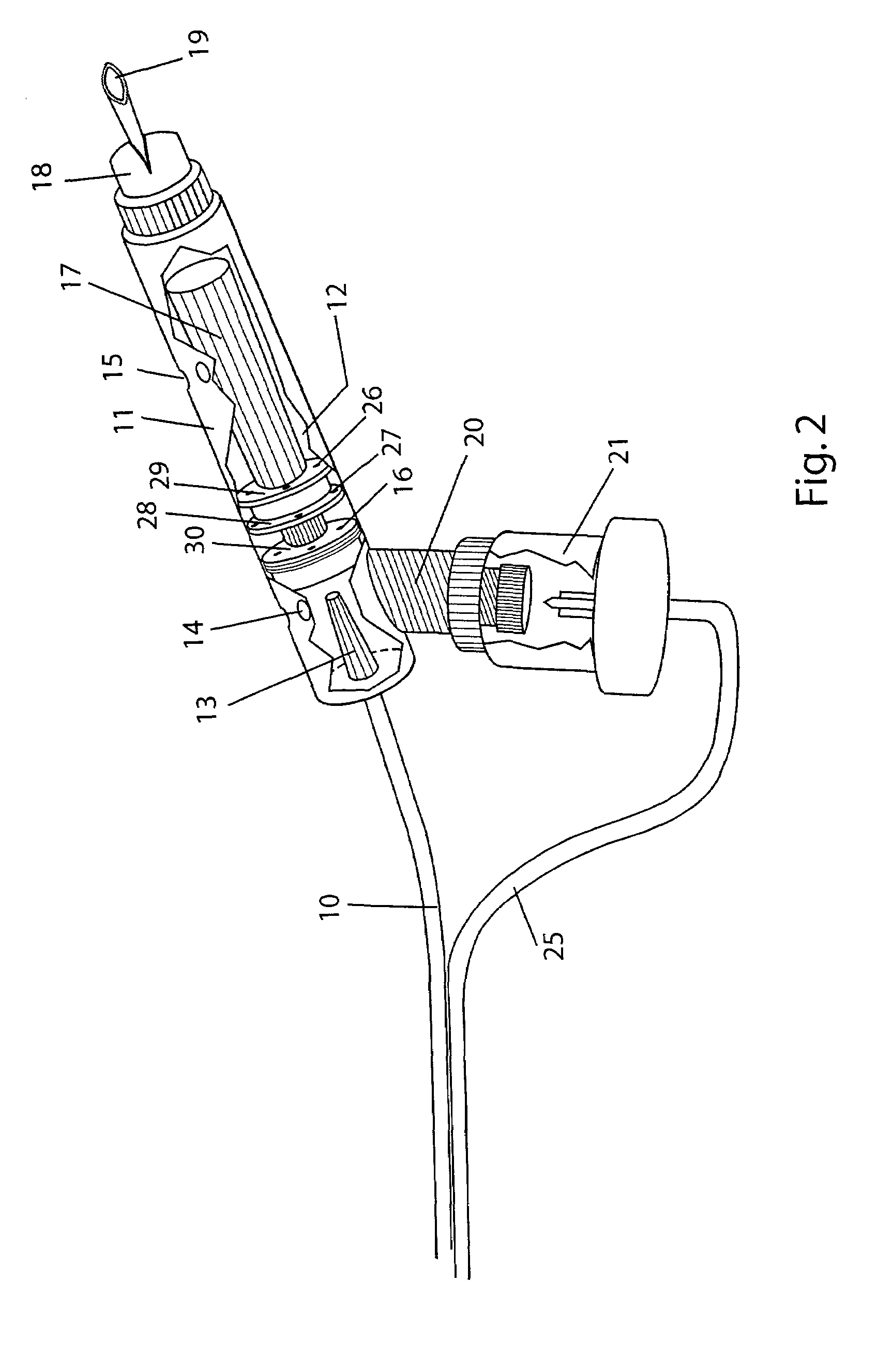

Systems and methods for evaluating the urethra and the periurethral tissues

InactiveUS6898454B2Reduce thermal effectsImprove performanceGastroscopesOesophagoscopesDiseaseUrethra

The present invention provides systems and methods for the evaluation of the urethra and periurethral tissues using an MRI coil adapted for insertion into the male, female or pediatric urethra. The MRI coil may be in electrical communication with an interface circuit made up of a tuning-matching circuit, a decoupling circuit and a balun circuit. The interface circuit may also be in electrical communication with a MRI machine. In certain practices, the present invention provides methods for the diagnosis and treatment of conditions involving the urethra and periurethral tissues, including disorders of the female pelvic floor, conditions of the prostate and anomalies of the pediatric pelvis.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE +1

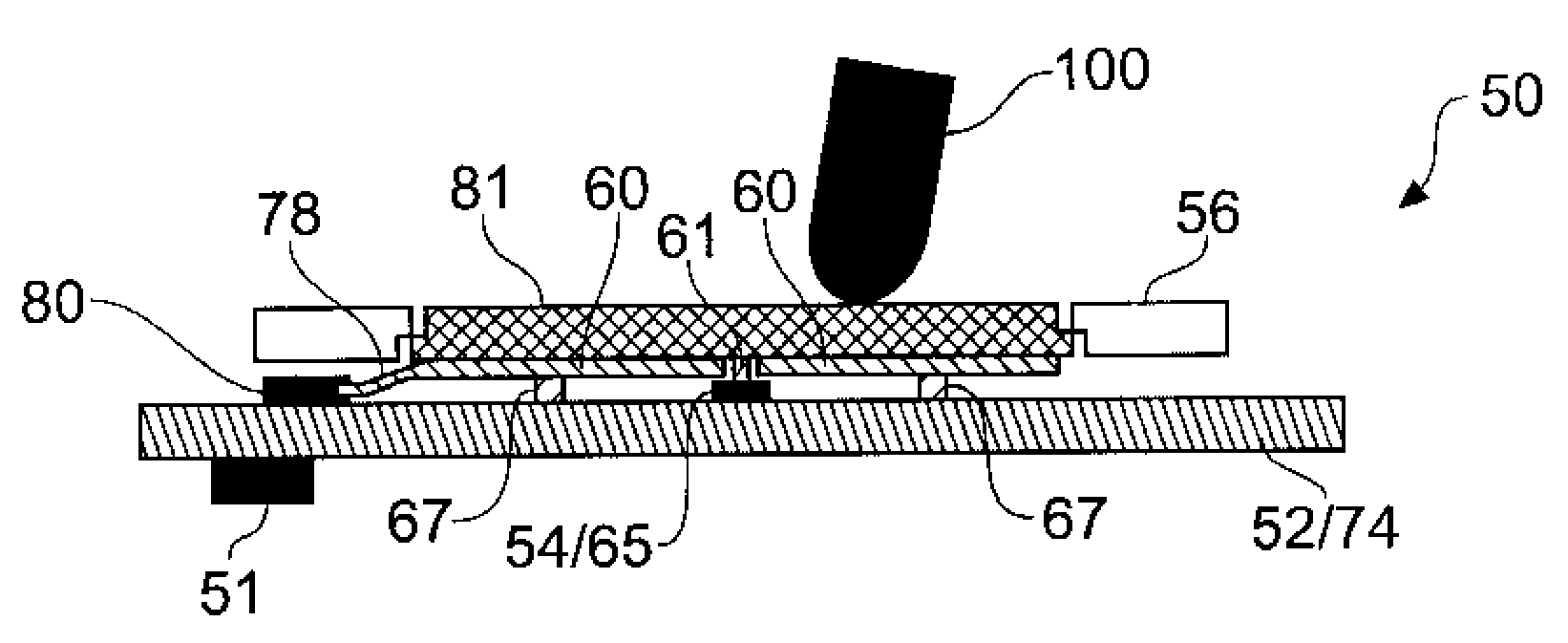

Tilting Touch Control Panel

InactiveUS20080202824A1Displacement is detectedExtend your lifeInput/output for user-computer interactionTransmission systemsPressure senseEngineering

A control panel for controlling a device in response to user indications, the control panel comprising, a position sensing element (60) having a sensing surface, and a position interface circuit (76). The position interface circuit (76) is operable to determine a position of an object (100) on the sensing surface, when the object (100) is applied to the sensing surface of the position sensing element (60). At least one pressure sensing device (54, 66) and the sensing surface of the position sensing element (60) are arranged with the effect that a displacement of the sensing surface with respect to the pressure sensing device in response to the pressure applied by the object is detectable by the pressure sensing device. As such, in one example, the position interface circuit (76) is operable to identify one or more of a plurality of user indicated signals by correlating the position of the object on the sensing surface with a pressure detected by the pressure sensing device. The sensing surface may include pre-designated and pre-determined locations representing virtual buttons so that by determining whether the object is at one of a plurality of pre-determined locations on the sensing surface of the position sensing element, the position interface circuit (76) can identify the user indicated signal by correlating the position of the object at one of the predetermined locations with the detected pressure, each of the pre-determined location corresponding to one of the plurality of user indicated signals.

Owner:ATMEL CORP

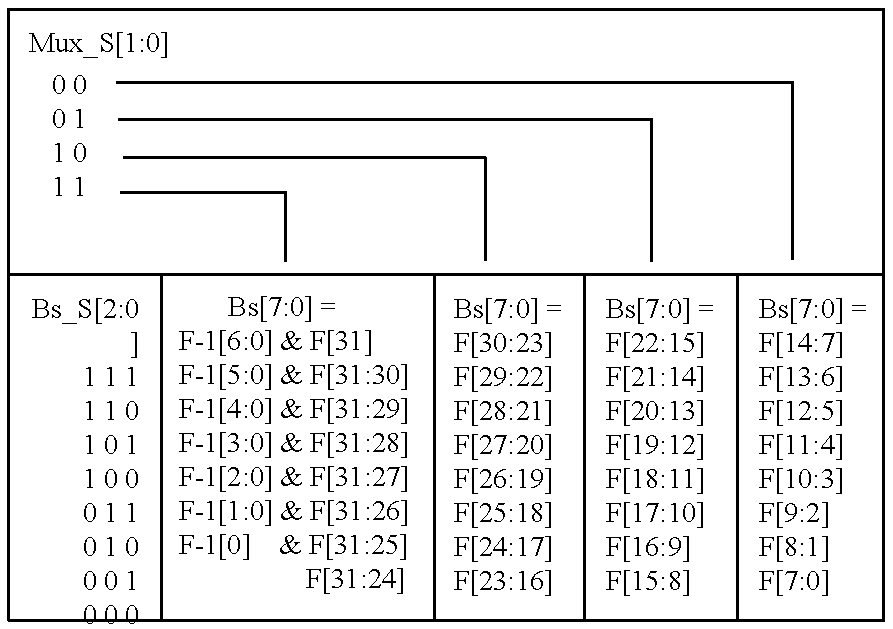

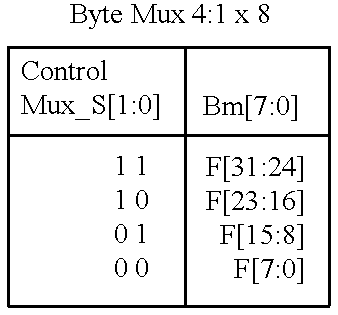

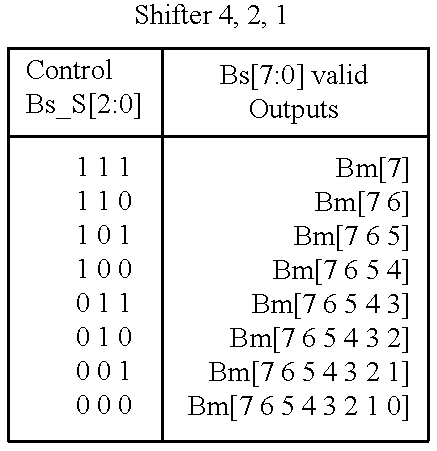

Audio and video decoder circuit and system

InactiveUS6369855B1Accelerates memory block moveAvoid confictTelevision system detailsPulse modulation television signal transmissionCoprocessorNetwork packet

An improved audio-visual circuit is provided that includes a transport packet parsing circuit for receiving a transport data packet stream, a CPU circuit for initializing said integrated circuit and for processing portions of said data packet stream, a ROM circuit for storing data, a RAM circuit for storing data, an audio decoder circuit for decoding audio portions of said data packet stream, a video decoder circuit for decoding video portions of said data packet stream, an NTSC / PAL encoding circuit for encoding video portions of said data packet stream, an OSD coprocessor circuit for processing OSD portions of said data packets, a traffic controller circuit moving portions of said data packet stream between portions of said integrated circuit, an extension bus interface circuit, a P1394 interface circuit, a communication coprocessors circuit, an address bus connected to said circuits, and a data bus connected to said circuits.

Owner:TEXAS INSTR INC

Managing bad blocks in various flash memory cells for electronic data flash card

InactiveUS20080082736A1Small sizeLow costMemory architecture accessing/allocationMemory systemsComputer accessFlash memory controller

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT ELECTRONICS

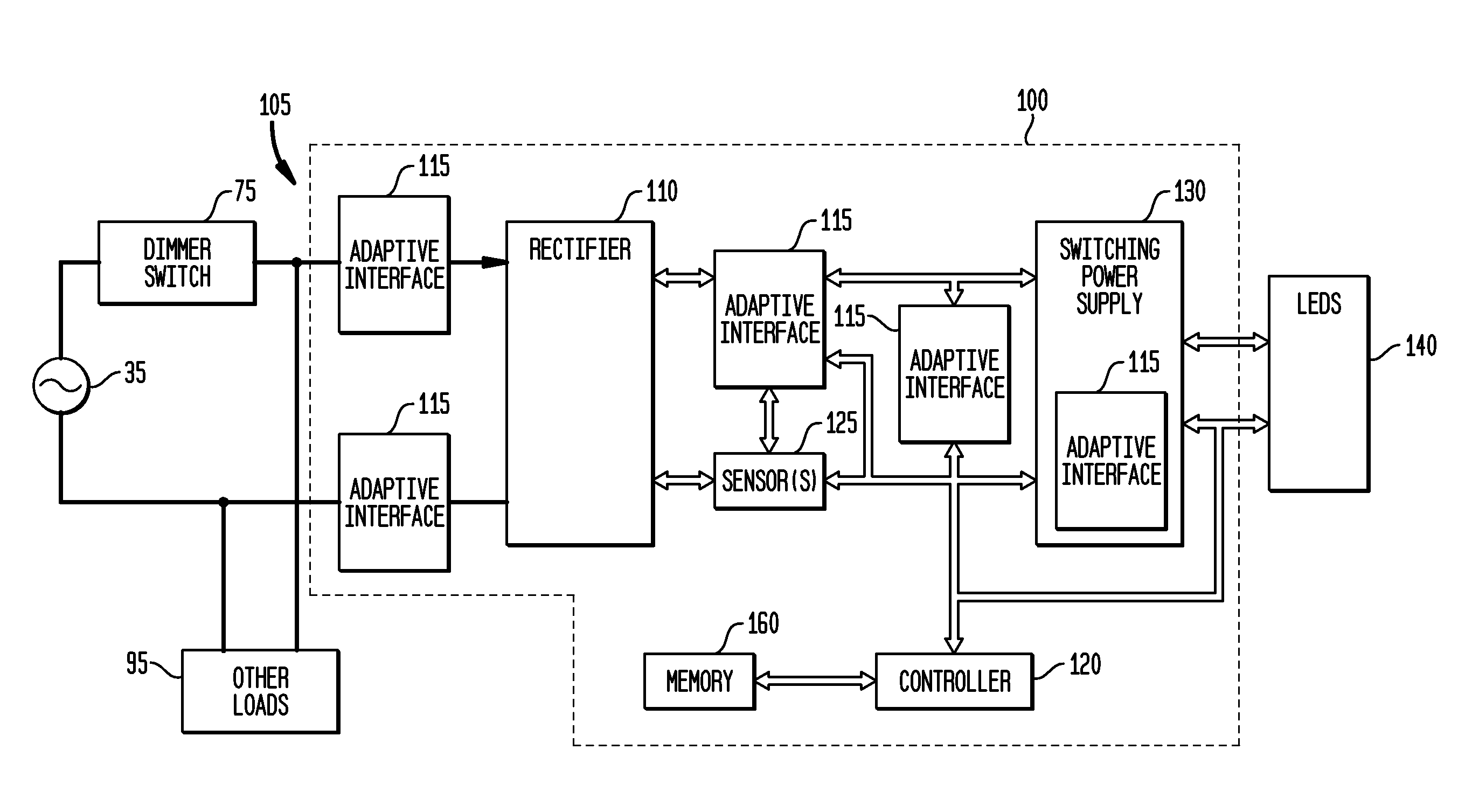

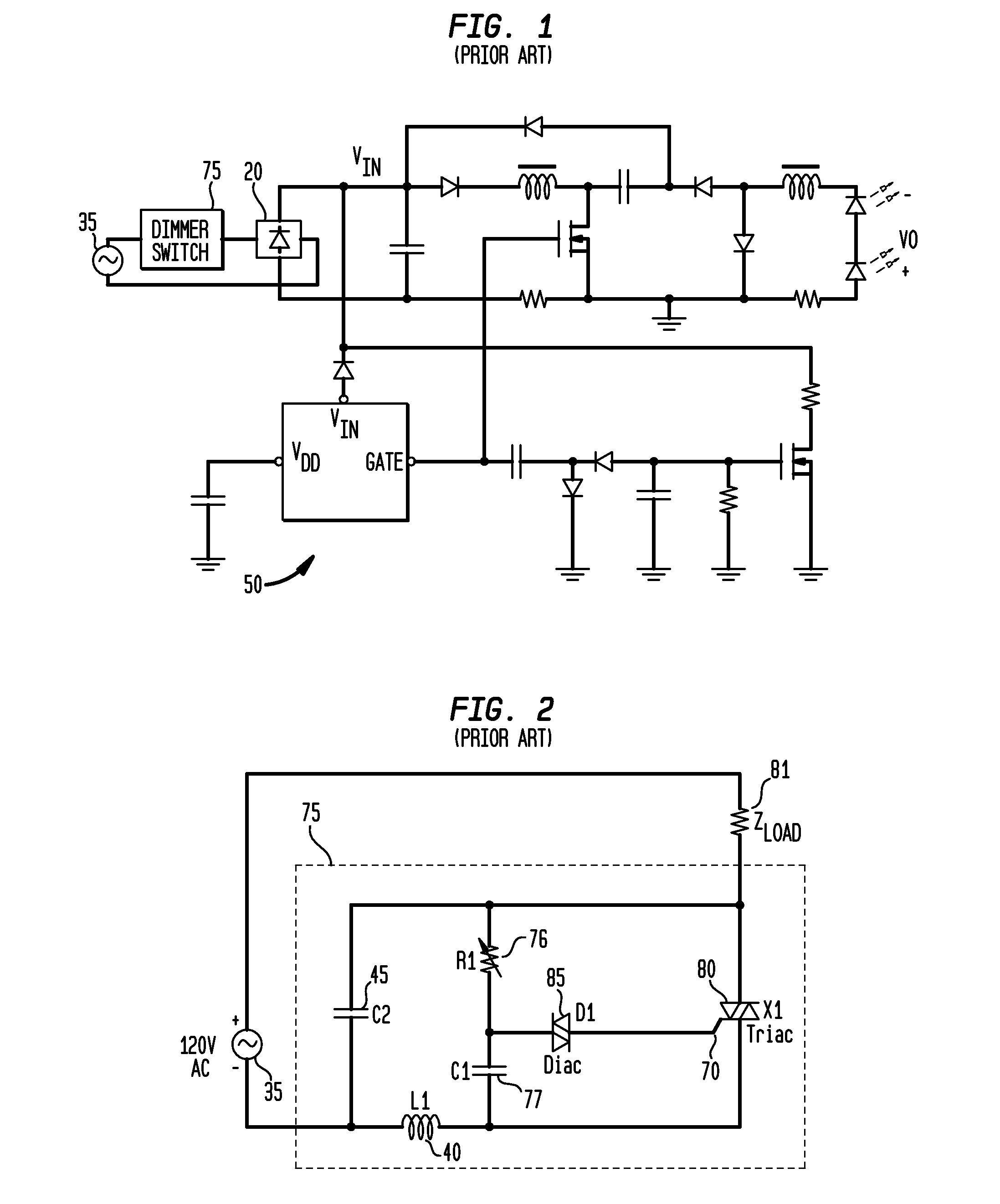

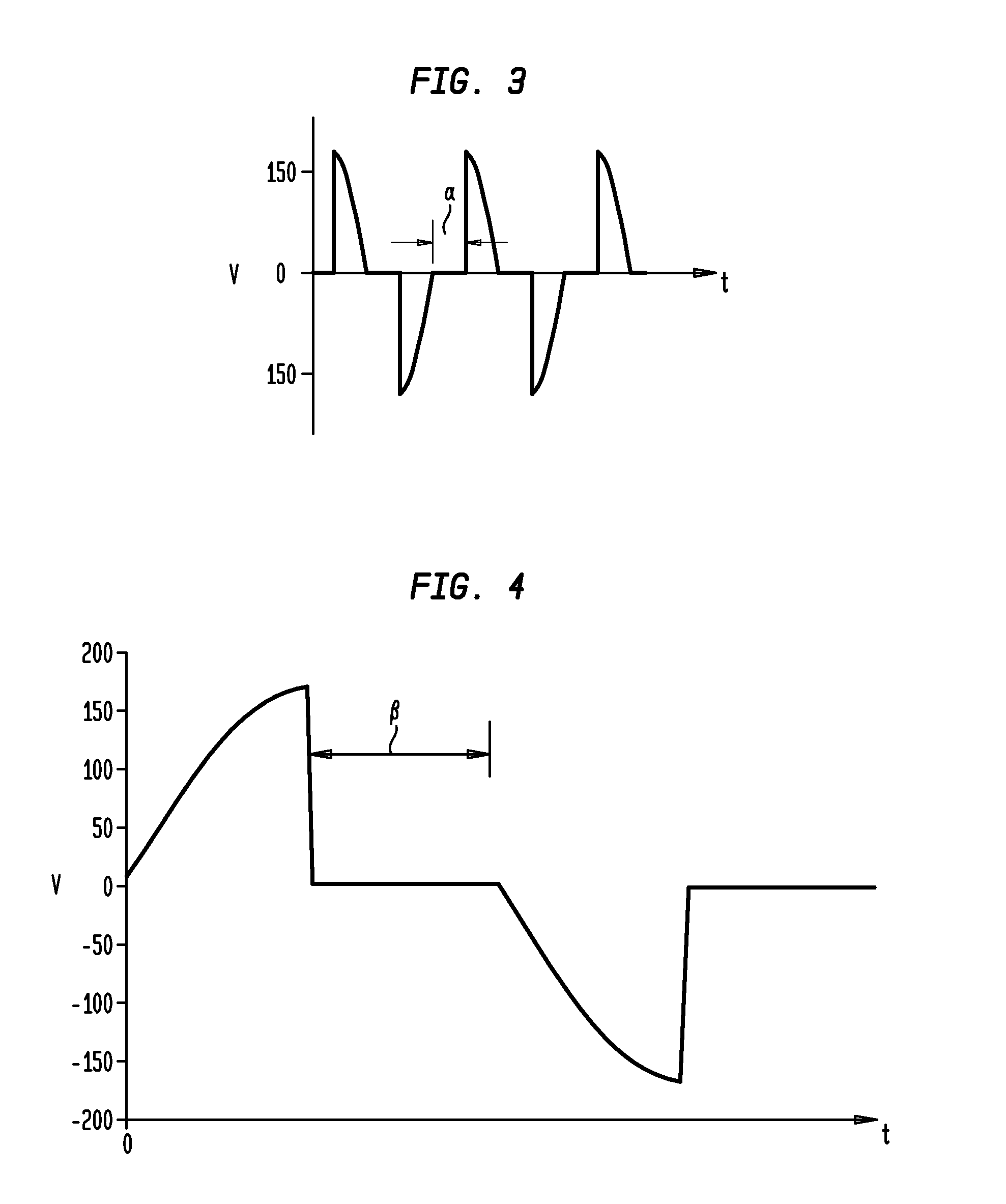

Adaptive Current Regulation for Solid State Lighting

ActiveUS20100213859A1Low component requirementsSeamless and stable operationElectrical apparatusElectroluminescent light sourcesDimmerEngineering

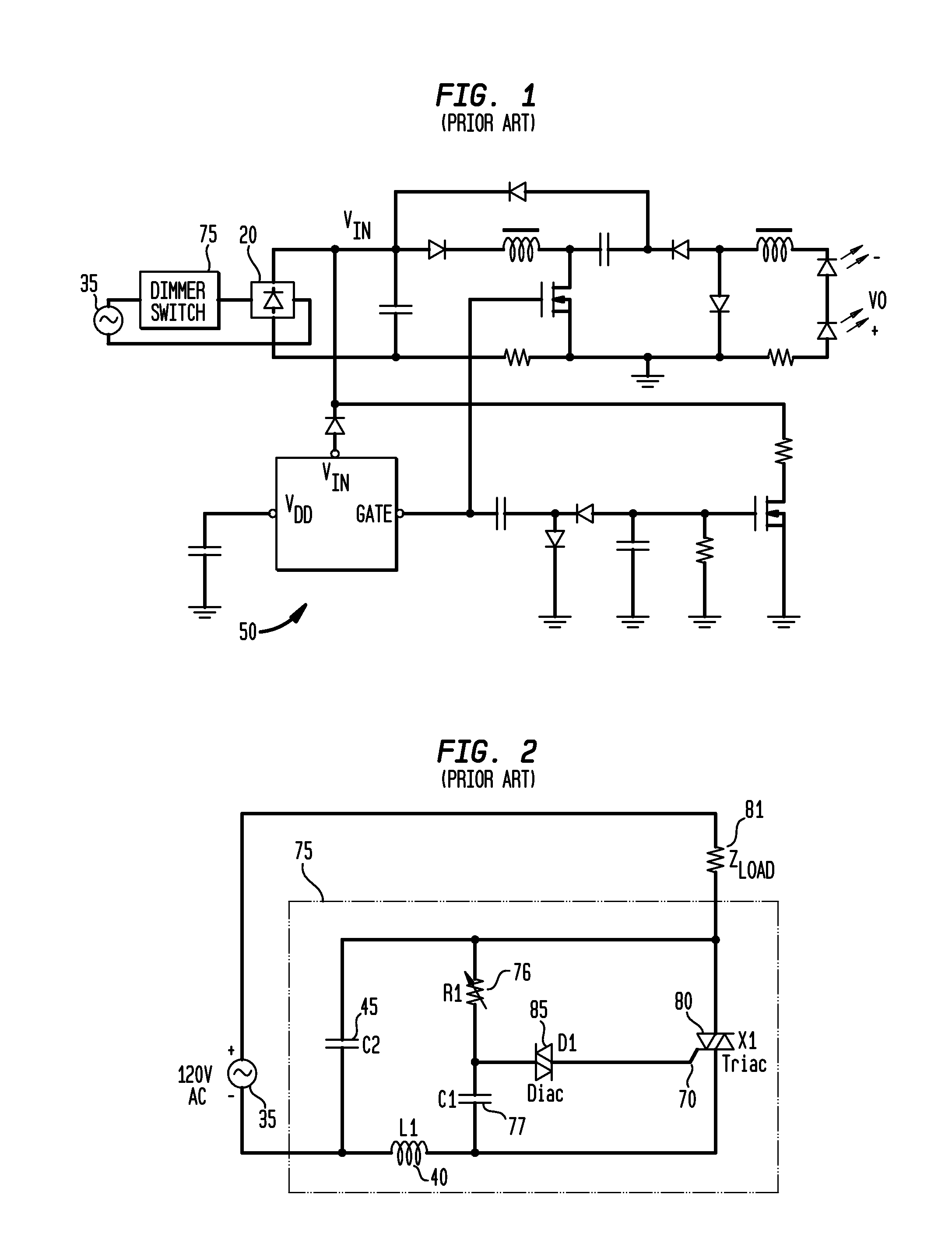

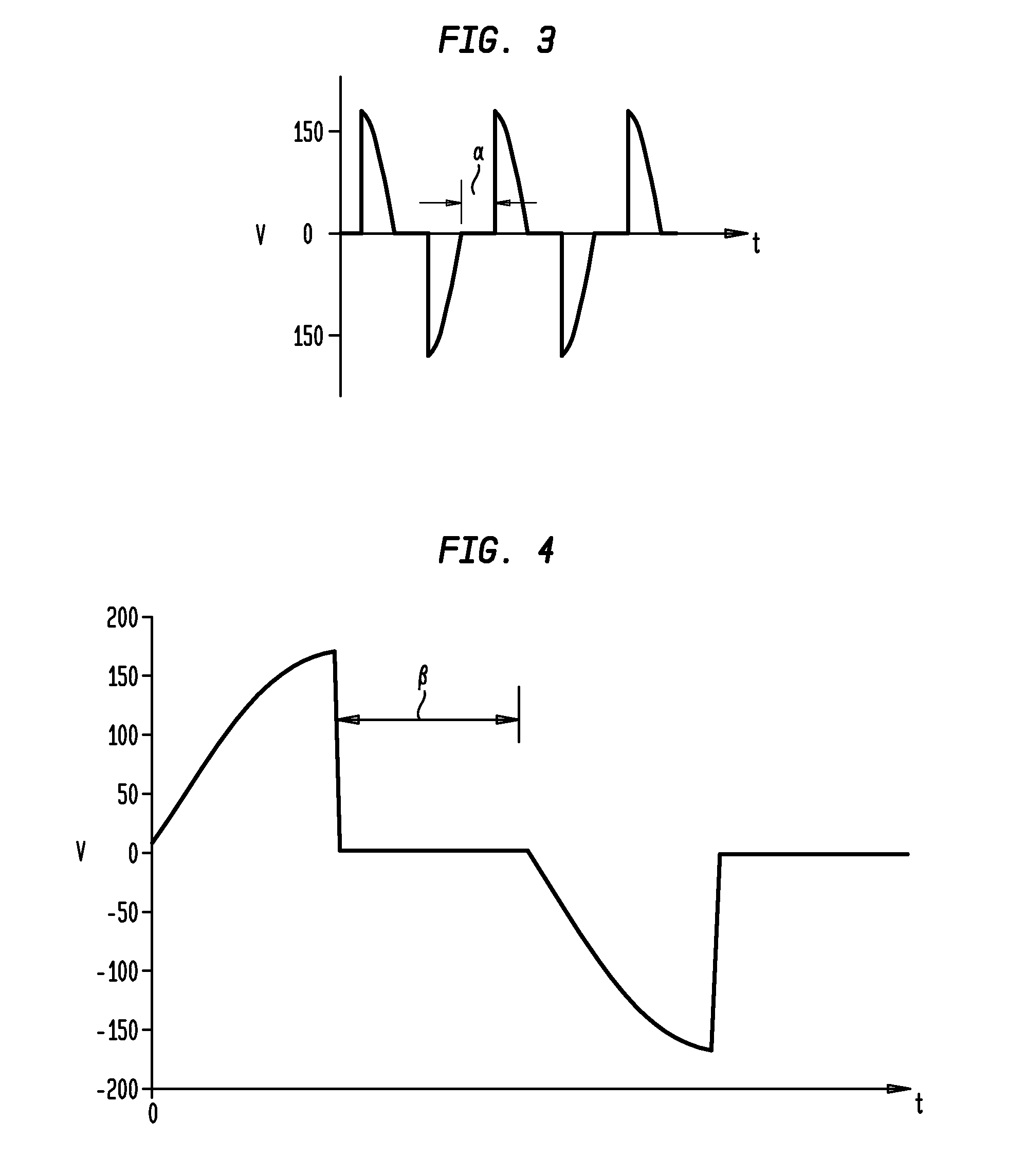

Exemplary embodiments provide an apparatus, system and method for power conversion to provide power to solid state lighting, and which may be coupled to a first switch, such as a dimmer switch. An exemplary system for power conversion comprises: a switching power supply comprising a second, power switch; solid state lighting coupled to the switching power supply; a voltage sensor; a current sensor; a memory; a first adaptive interface circuit to provide a resistive impedance to the first switch and conduct current from the first switch in a default mode; a second adaptive interface circuit to create a resonant process when the first switch turns on; and a controller to modulate the second adaptive interface circuit when the first switch turns on to provide a current path during the resonant process of the switching power supply.

Owner:CHEMTRON RES

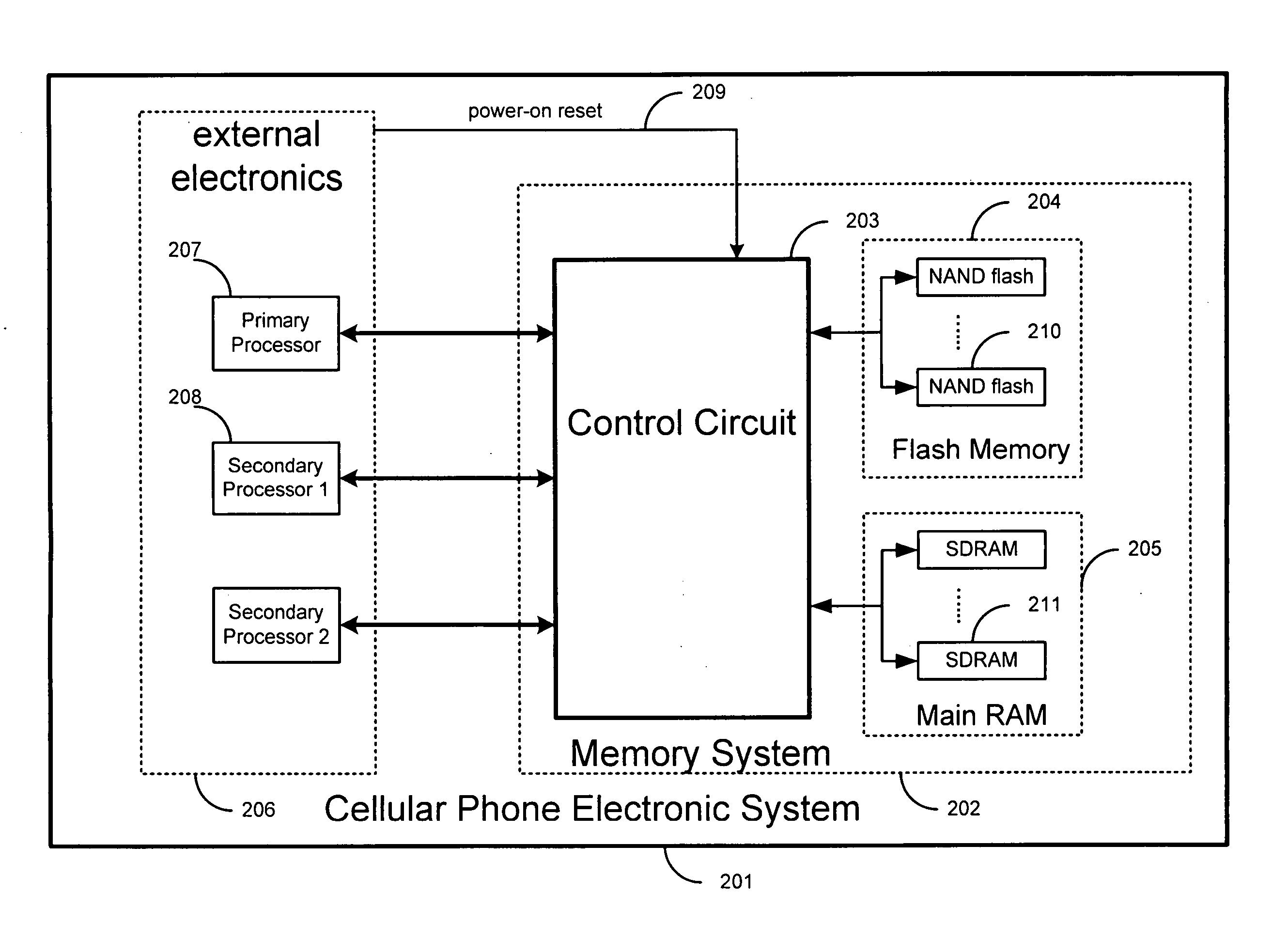

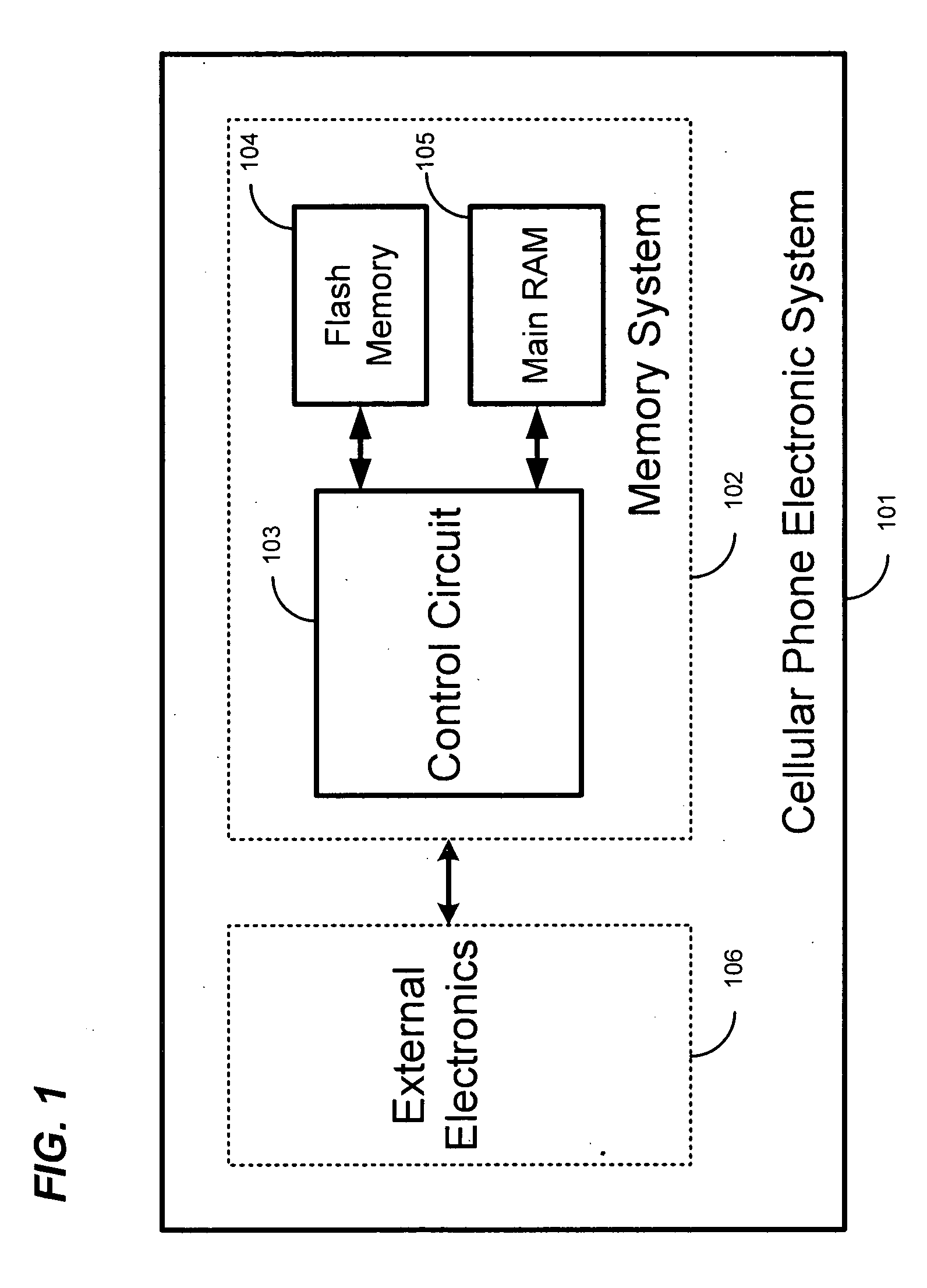

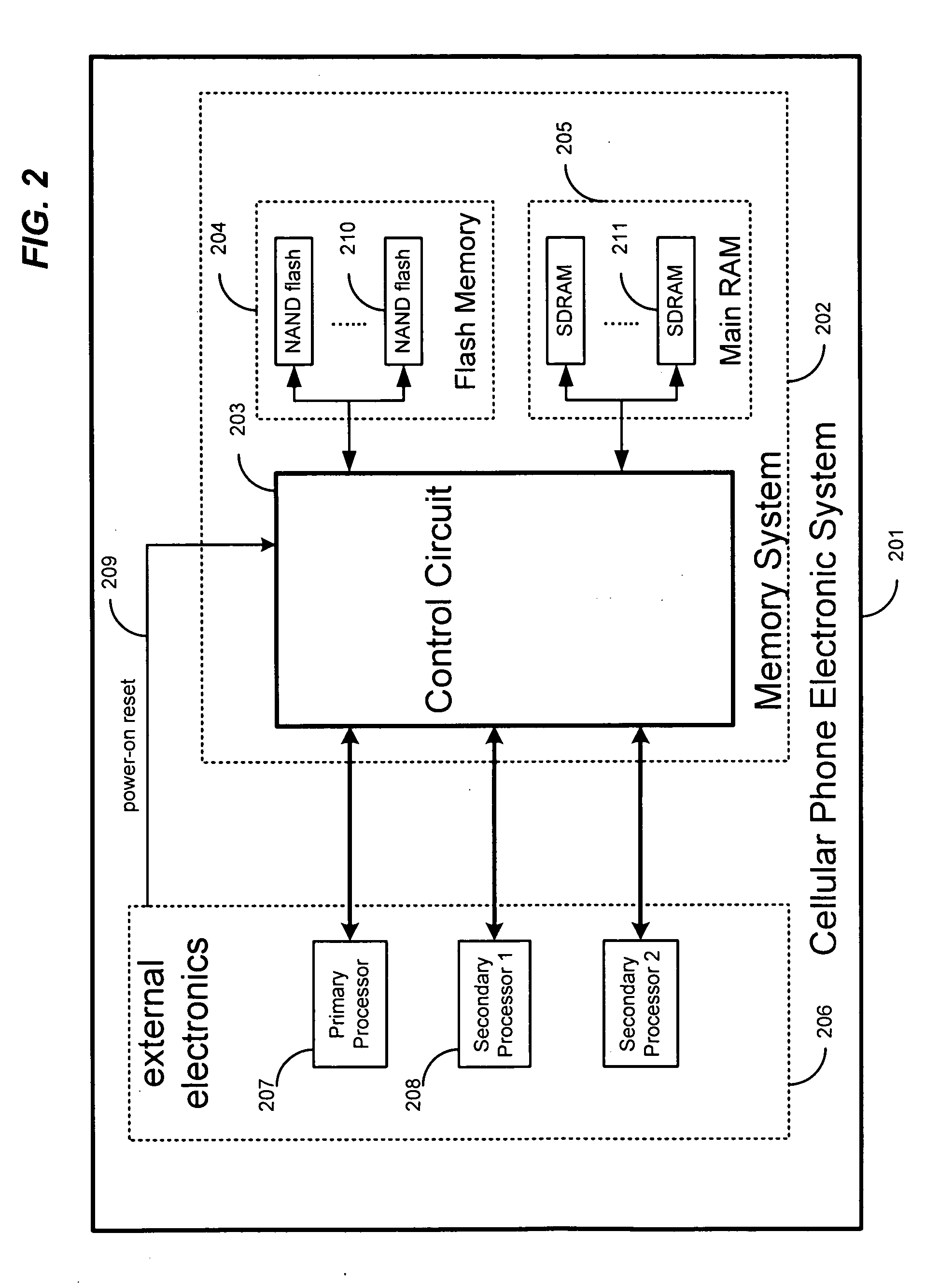

Systems and methods for providing nonvolatile memory management in wireless phones

ActiveUS20060053246A1Low costSmall sizeUnauthorized memory use protectionDigital storageMemory controllerInterface circuits

The present invention is related to memory management, and in particular, to methods and systems for accessing and managing nonvolatile, such as in a wireless phone. A wireless phone memory controller is disclosed that, comprises a first interface circuit configured to be coupled to wireless phone nonvolatile memory, a second interface circuit configured to be coupled to wireless phone volatile memory, a first processor interface configured to be coupled to a first wireless phone processor, wherein the first processor interface is configured to provide the first processor with access to the wireless phone volatile memory, a second processor interface configured to be coupled to a second wireless phone processor, and a controller circuit configured to copy at least a portion of wireless phone nonvolatile memory data to the wireless phone volatile memory.

Owner:GOOGLE LLC

Adaptive Current Regulation for Solid State Lighting

ActiveUS20110309759A1Low component requirementsSeamless and stable operationElectrical apparatusElectroluminescent light sourcesElectrical resistance and conductanceDimmer

Exemplary embodiments provide an apparatus, system and method for power conversion to provide power to solid state lighting, and which may be coupled to a first switch, such as a dimmer switch. An exemplary system comprises: a switching power supply; solid state lighting; a first adaptive interface circuit to provide a resistive impedance to the first switch and conduct current from the first switch in a default mode; and a second adaptive interface circuit to create a resonant process. An exemplary apparatus comprises: a switching power supply; and an adaptive interface circuit comprising a resistive impedance coupled in series to a reactive impedance to conduct current from the first switch in a first current path in a default mode, and further comprising a second switch coupled to the reactive impedance to conduct current from the first switch in a second current path, with the adaptive interface circuit further damping oscillation when the first switch turns on.

Owner:CHEMTRON RES

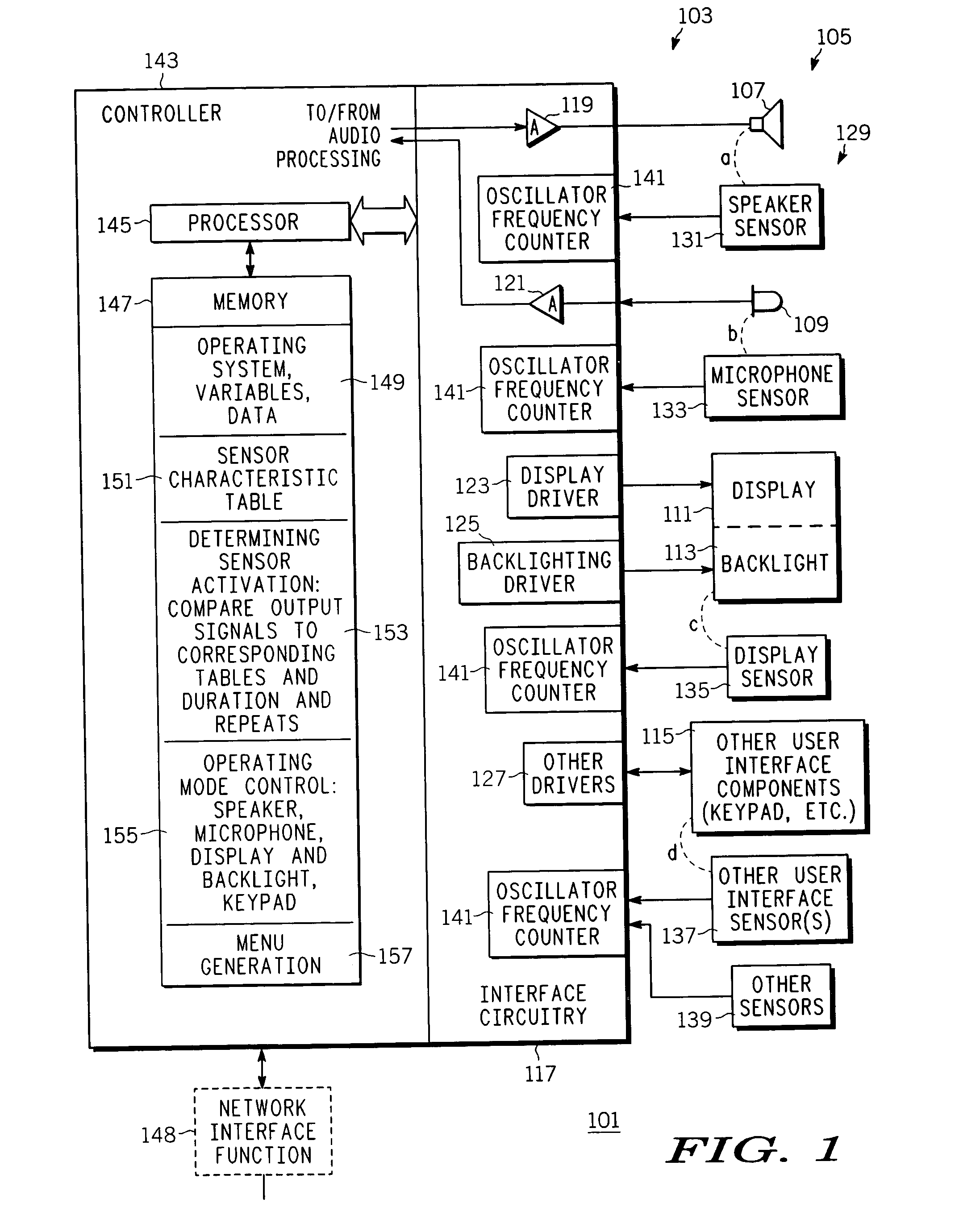

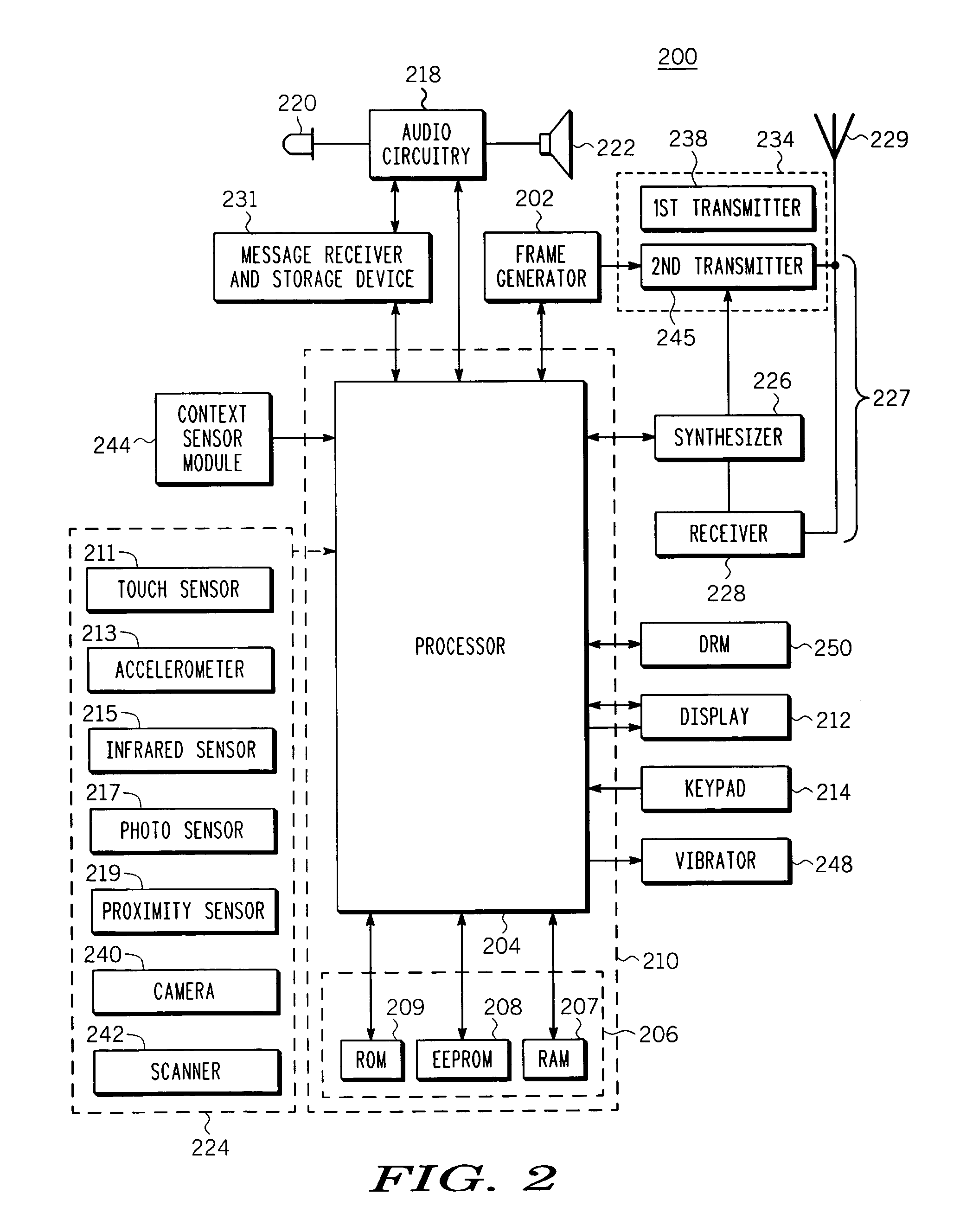

Intuitive user interface and method

InactiveUS20050219228A1Input/output for user-computer interactionDigital data processing detailsDisplay deviceOperation mode

A user interface 103 for an electronic device 101 (and corresponding method) is arranged and constructed for intuitive control of interface functionality. The user interface includes: a user interface component, e.g. speaker, microphone, display backlighting, etc., that is one of a plurality of user interface components 105; interface circuitry 117 coupled to the user interface components 105; and a sensor 129 located in a position that is logically associated with, e.g. proximate to or co-located with, the user interface component and configured to provide an output signal when the sensor 129 is triggered, e.g. by proximity to a user, where the output signal facilitates, via for example a controller 143, a change in an operating mode of one or more of the user interface components 105.

Owner:MOTOROLA INC

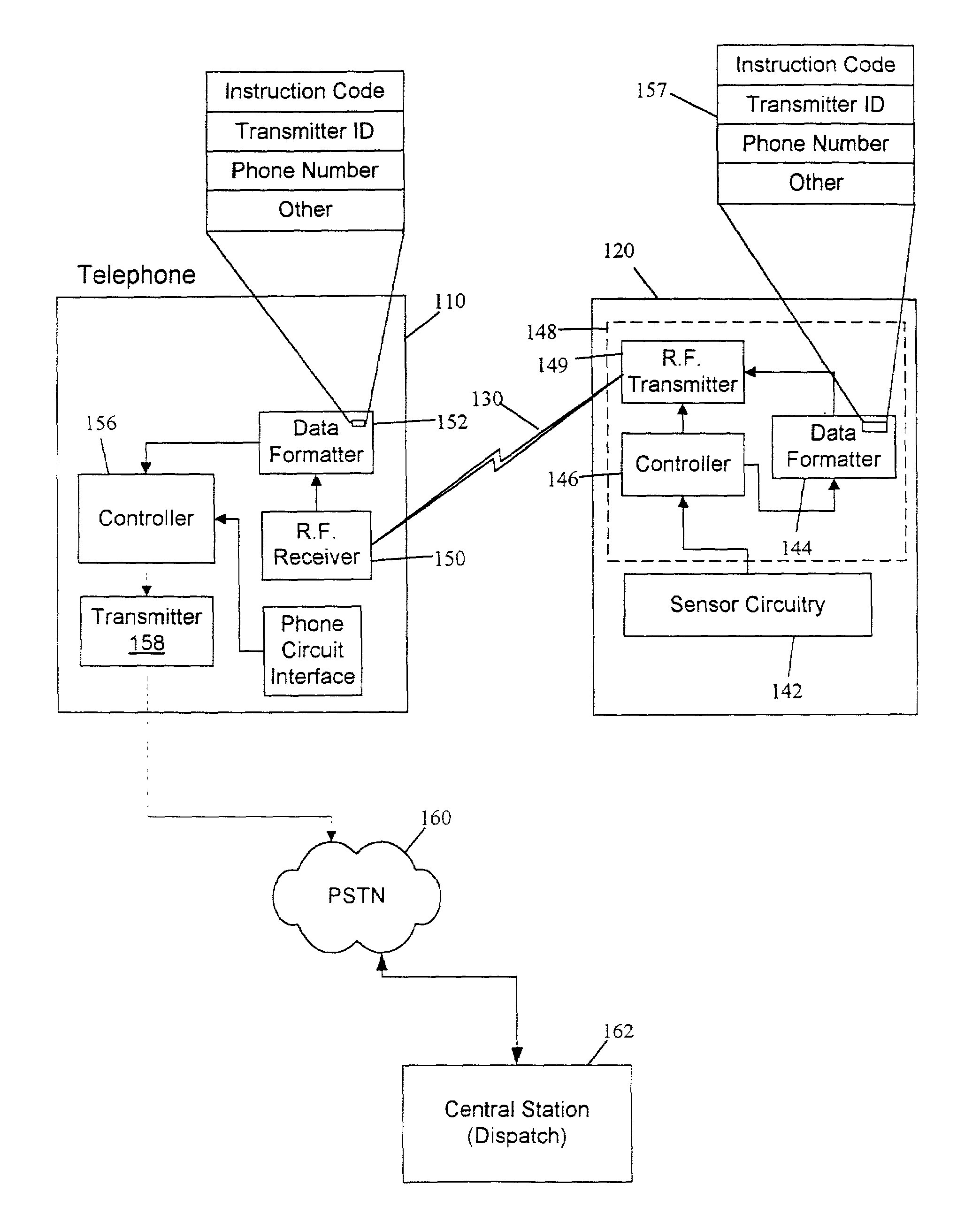

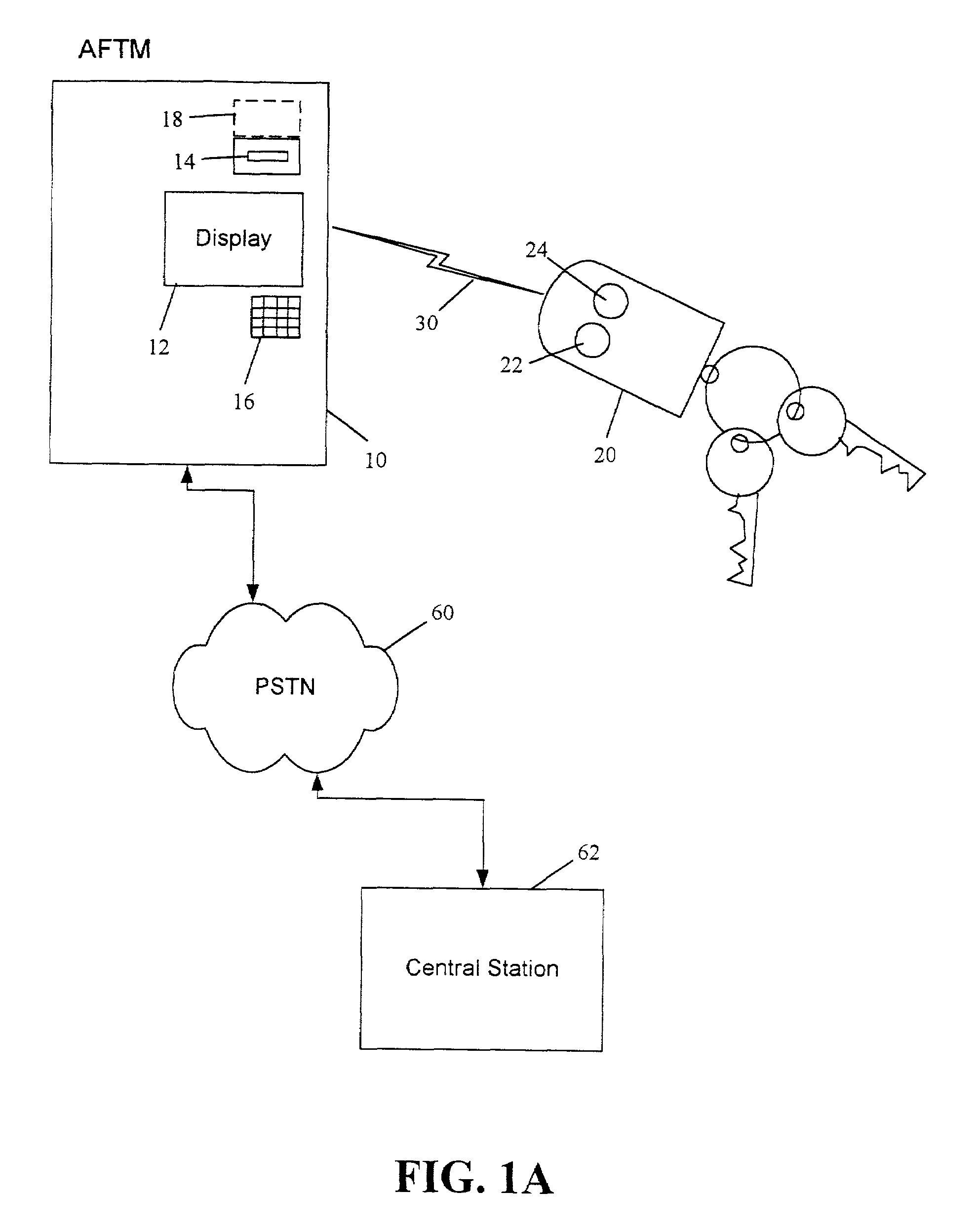

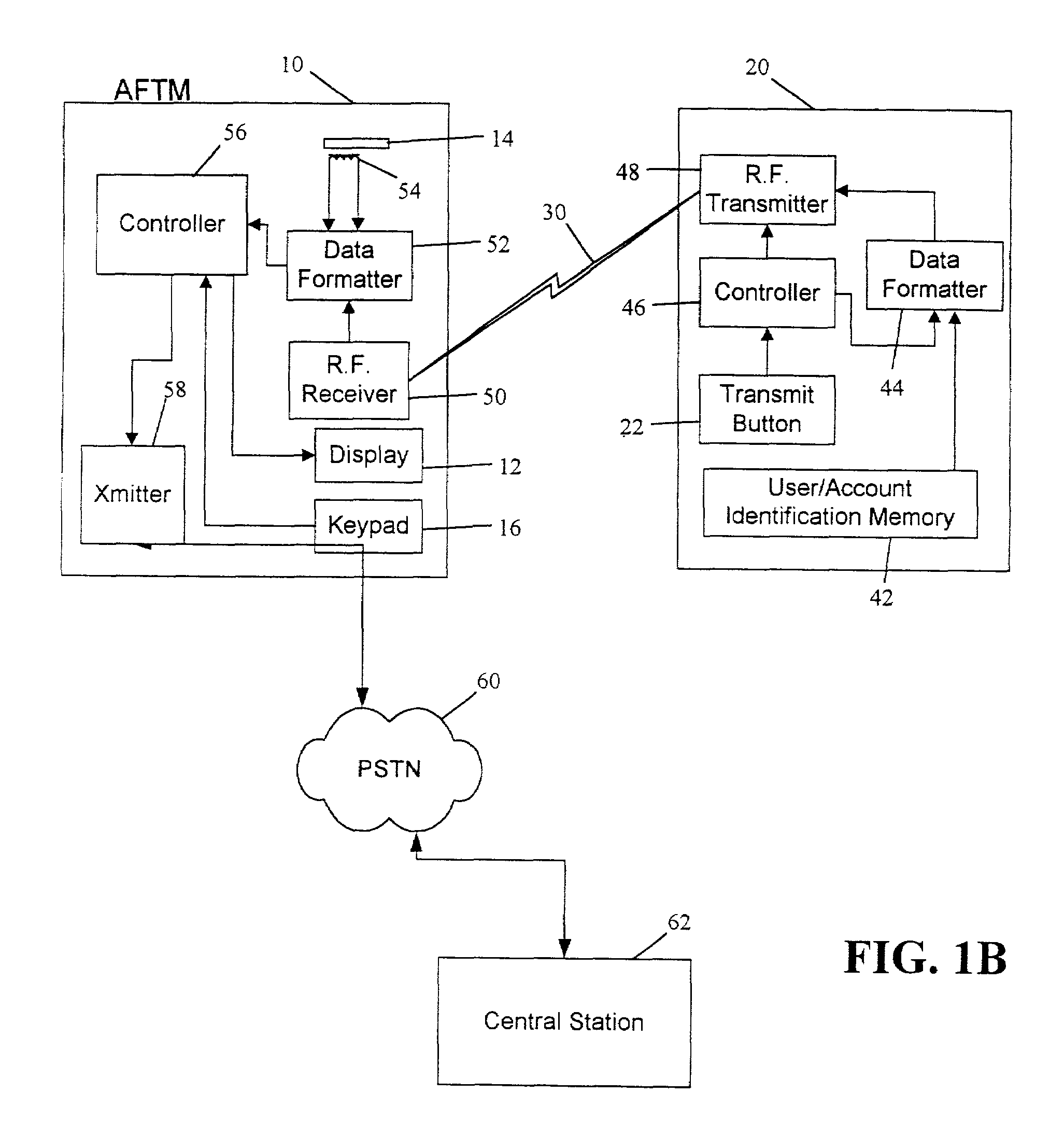

Multi-function general purpose transceiver

InactiveUS7397907B2Controlling coin-freed apparatusUnauthorised/fraudulent call preventionGeneral purposeTransceiver

The present invention is generally directed to a system and associated method for communicating information to a predetermined location. The system includes a transmitter disposed at a first location and configured to transmit a signal containing an instruction code that uniquely identifies an instruction to be carried out. The system further includes a transceiver disposed remotely from the transmitter and configured to receive the transmitted signal. The transceiver circuit includes a line interface circuit configured to interface with a telephone line that is part of the public switched telephone network (PSTN) and initiate a phone call over the telephone line. Finally, the system includes a central station remotely located from said transceiver but being in communication with said transceiver via the PSTN The central station further include a decoder configured to decode the instruction code. In accordance with a broader aspect, the invention is directed to a general purpose transceiver having a receiver for receiving an information signal and a transmitter configured to transmit an outgoing signal over a phone line to a central station A portion of the information signal includes an instruction code, which may be decoded by the central station and acted upon accordingly Consistent with the general purpose nature of the transceiver, the phone number of the central station may be transmitted to the transceiver as part of the information signal.

Owner:STATSIGNAL IPC

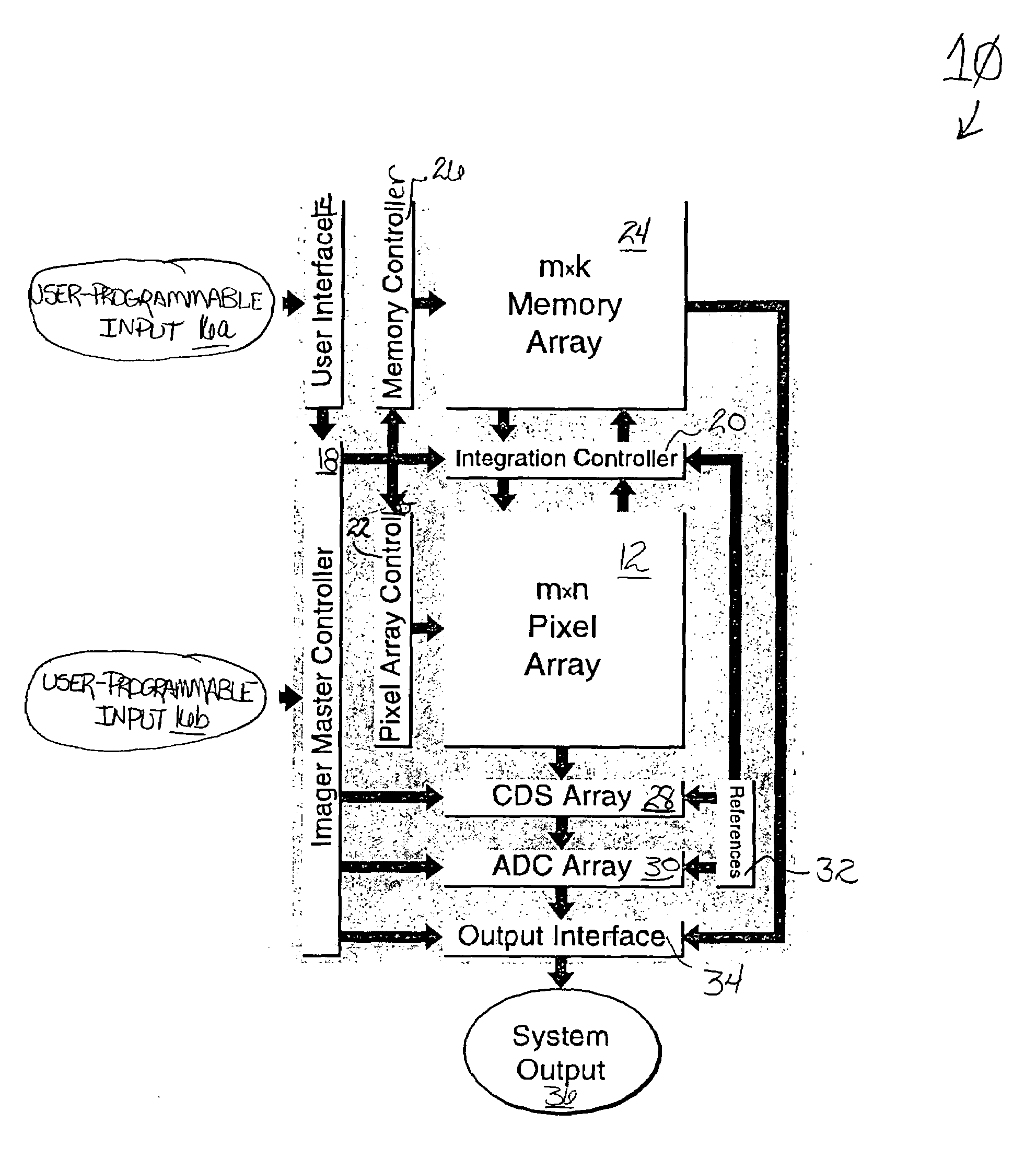

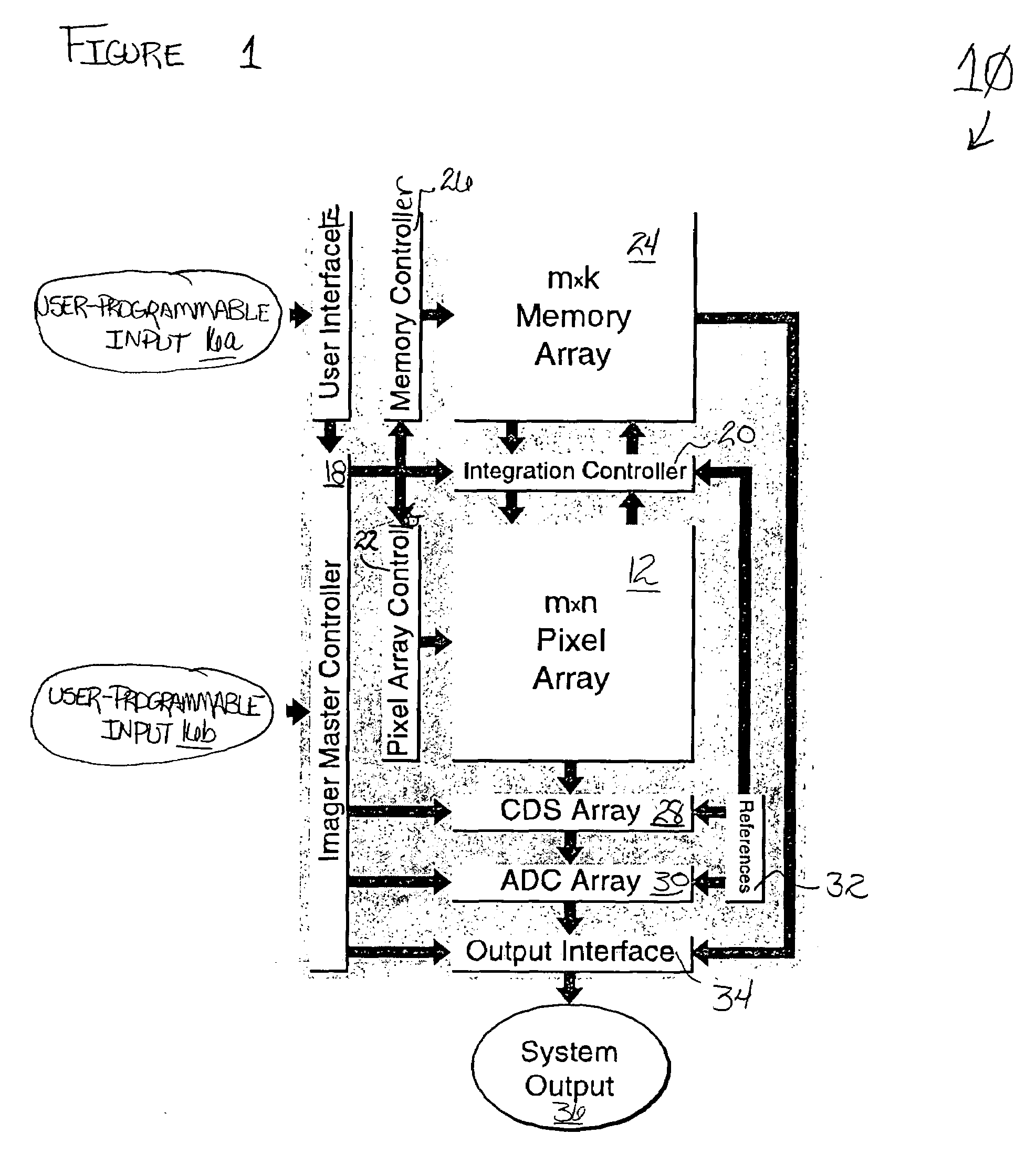

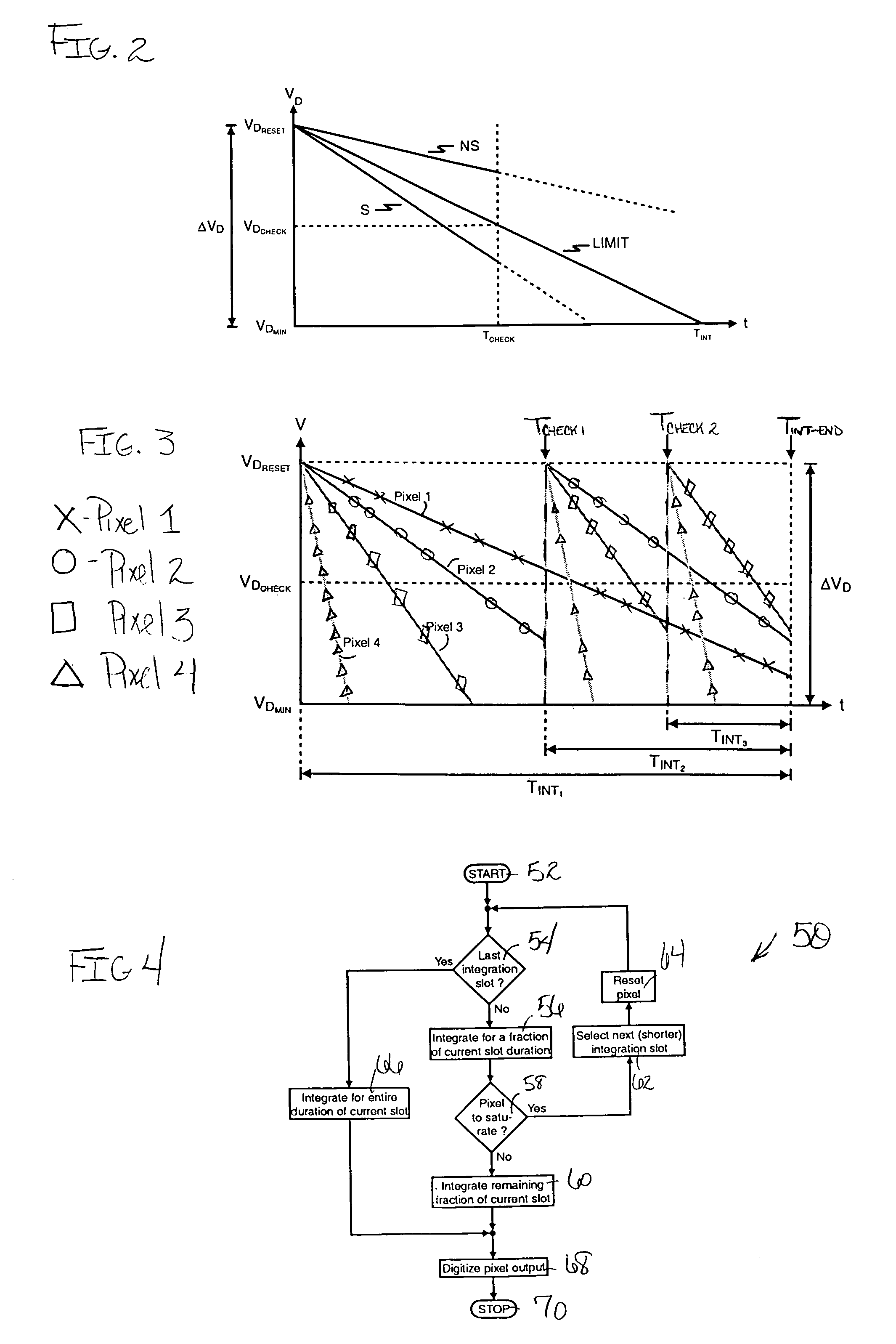

Single-chip imager system with programmable dynamic range

InactiveUS6977685B1Elegantly simple input/output connectionProduced cost-effectivelyTelevision system detailsTelevision system scanning detailsControl signalEngineering

The imager system of the invention, provided in a semiconductor substrate, includes a plurality of photosensitive, charge integrating pixels that are arranged in rows and columns of a pixel array for capturing illumination of a scene to be imaged. Each pixel includes a photogenerated charge accumulation region of the semiconductor substrate and a sense node at which an electrical signal, indicative of pixel charge accumulation, can be measured without discharging the accumulation region. Pixel access control circuitry is connected to pixel array rows and columns to deliver pixel access signals generated by the access control circuitry for independently accessing a selected pixel in the array. An input interface circuit is connected to accept a dynamic range specification input for the array pixels. Integration control circuitry is connected to access a selected pixel of the array to read the sense node electrical signal of the selected pixel, and configured to generate pixel-specific integration control signals delivered to the selected pixel, independent of other pixels, based on dynamic range specification input provided by the input interface circuit. An output interface circuit is connected to the pixel array to produce output image data based on sense node electrical signals from the pixel array.

Owner:MASSACHUSETTS INST OF TECH

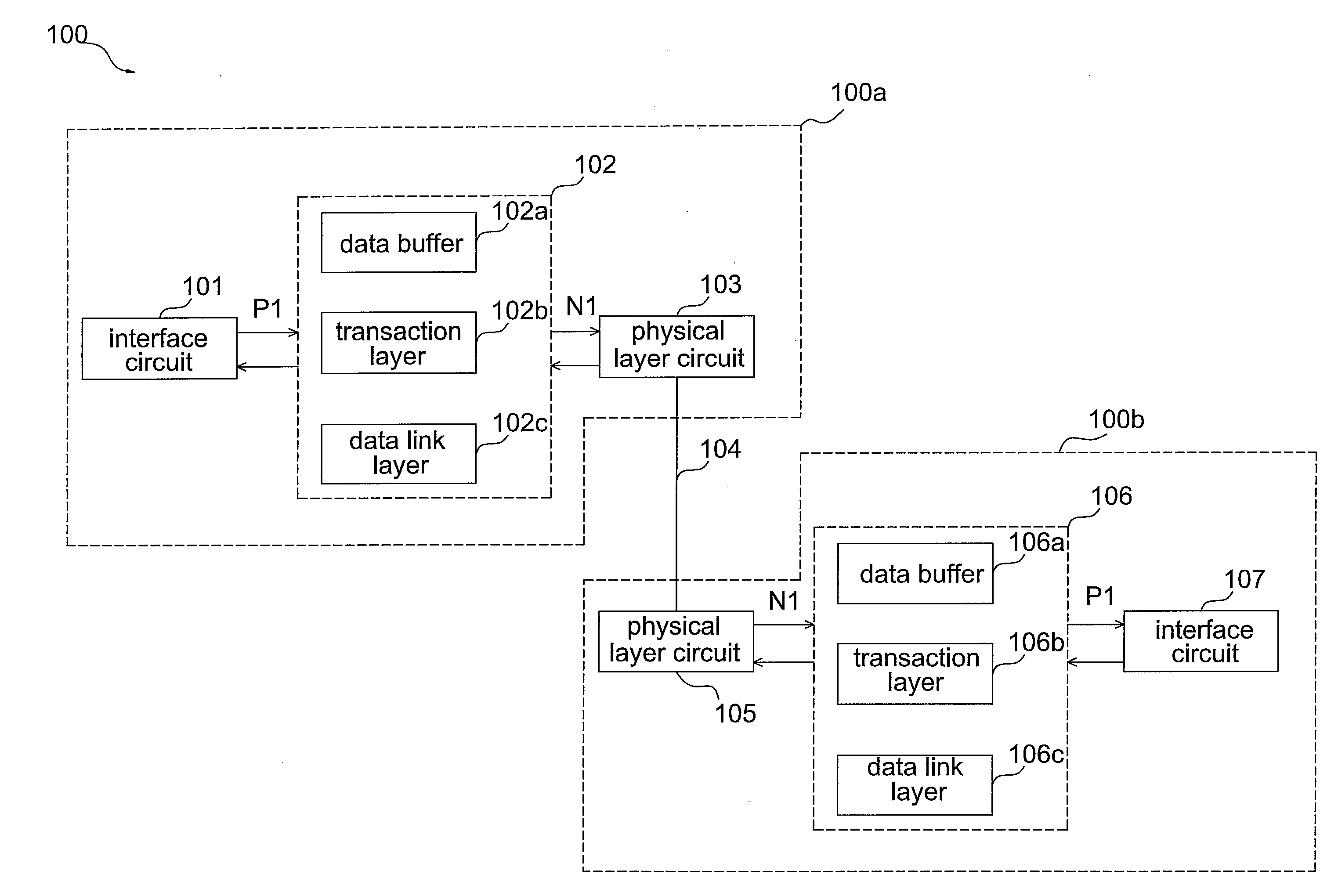

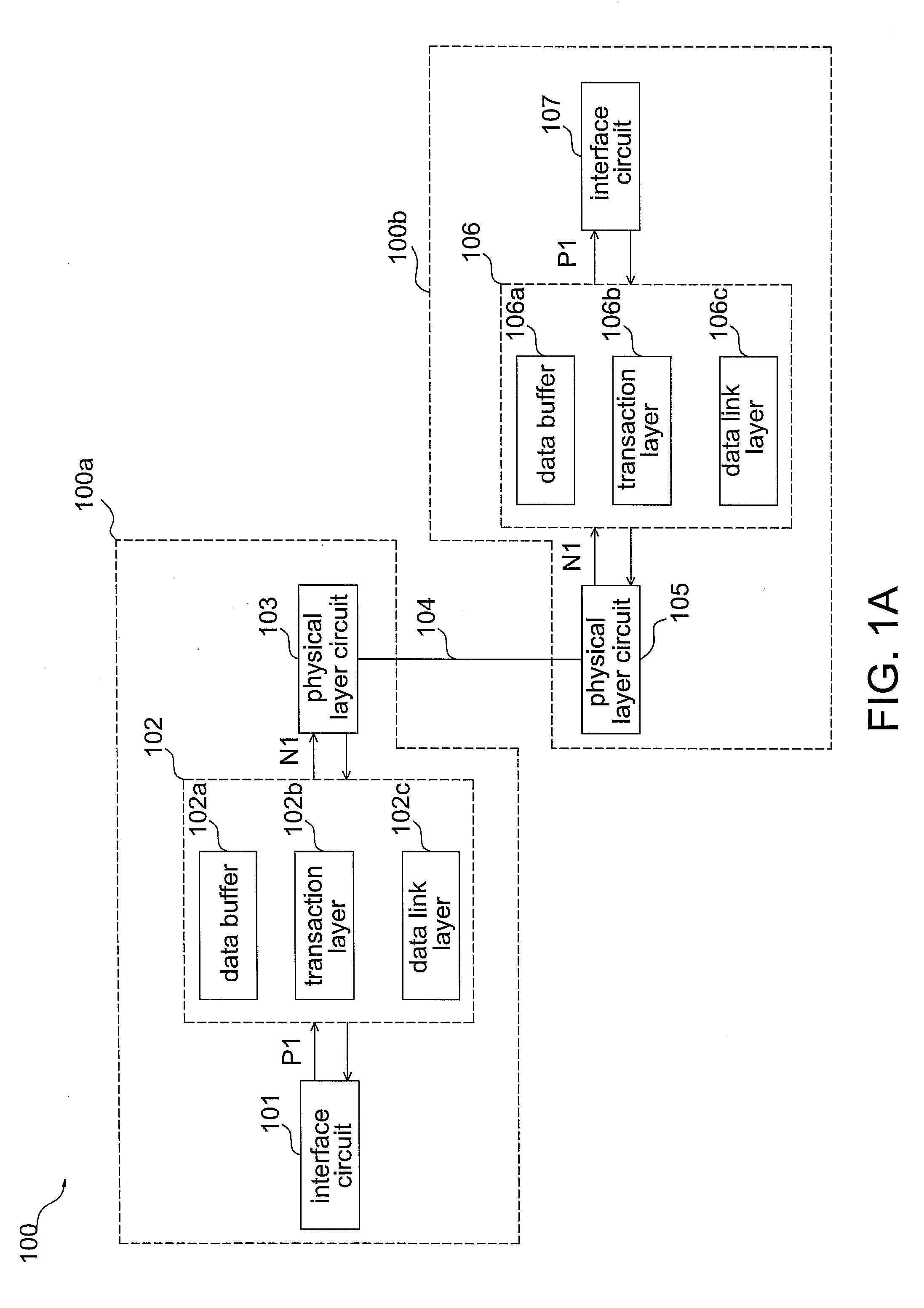

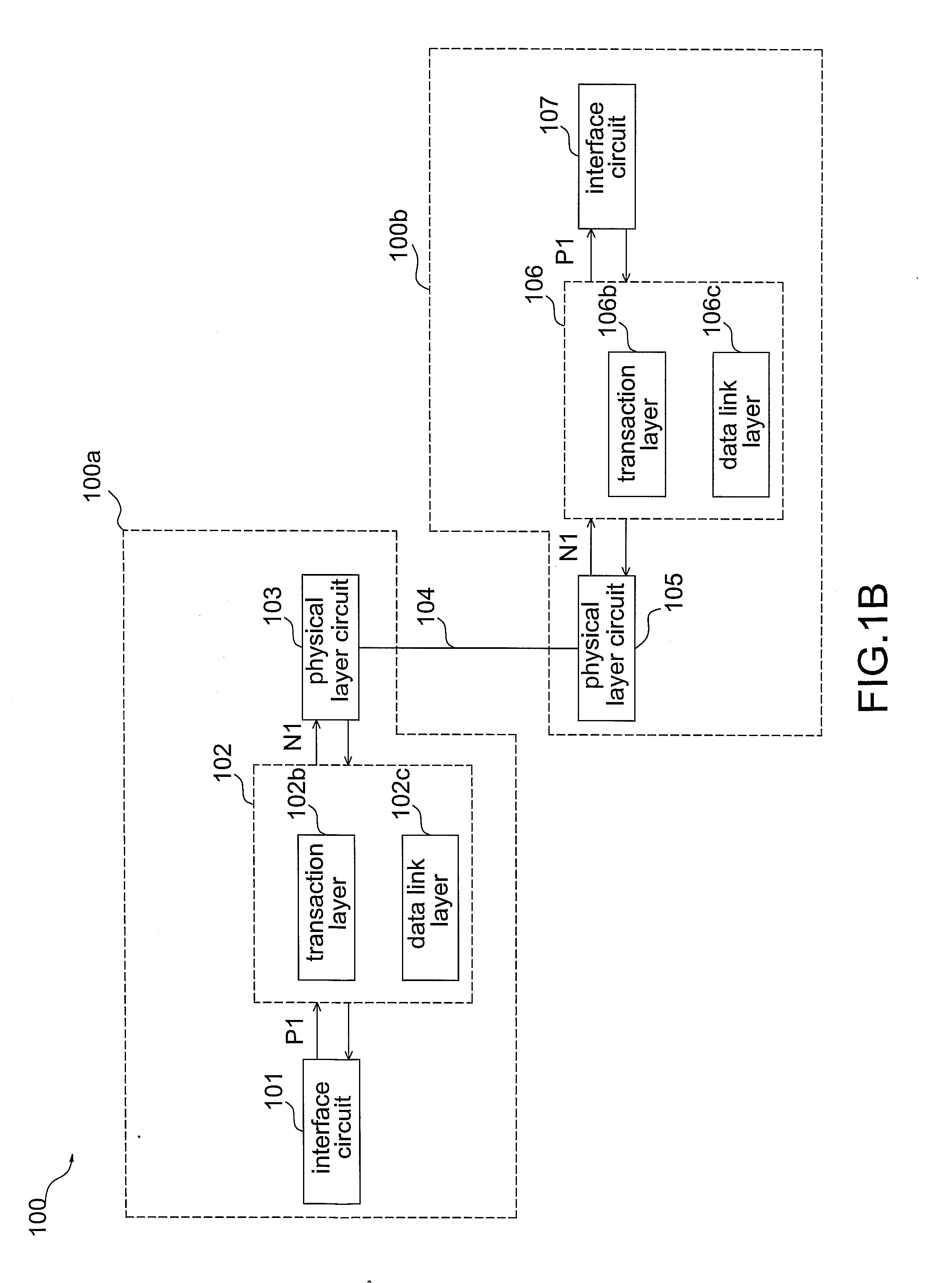

Transmission device and data extended transmission method

InactiveUS20100027559A1Reduce design expenseLow production costNetwork connectionsElectric digital data processingPhysical layerInterface circuits

The invention discloses a transmission device. The transmission device includes an interface circuit, a data converting circuit, at least a physical layer and a transmission medium. The interface circuit is used to receive a PCIe signal or a PCI signal. The data converting circuit is coupled to the interface circuit and used to convert the PCIe signal or the PCI signal into at least a data packet. The physical layer is coupled to the data converting circuit and used to process and transfer the data packet. The transmission medium receives and transfers the data packet.

Owner:ASPEED TECH

Imager array interfaces

ActiveUS20110279721A1Provide informationTelevision system detailsTelevision system scanning detailsComputer visionSampling circuits

Owner:FOTONATION LTD

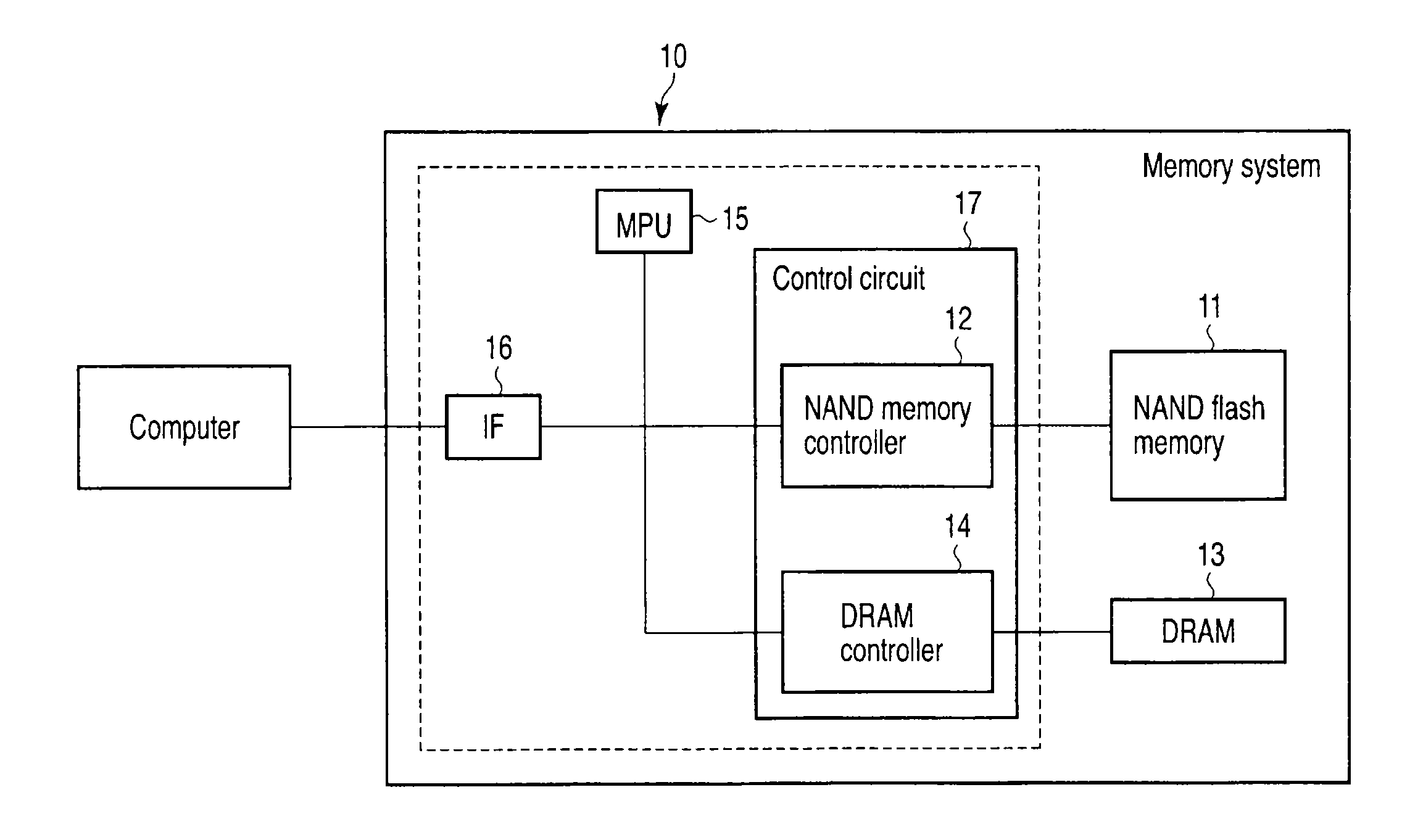

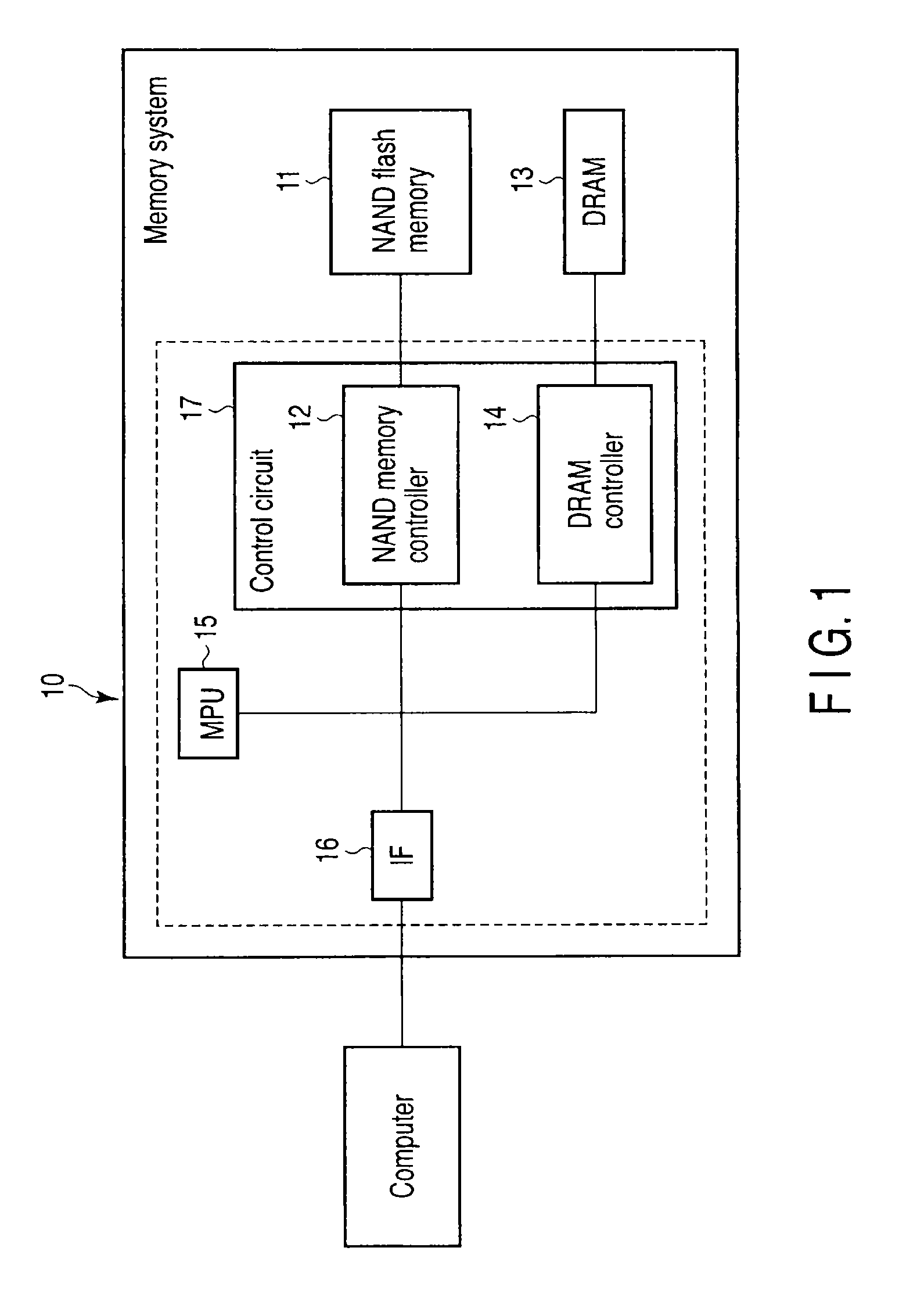

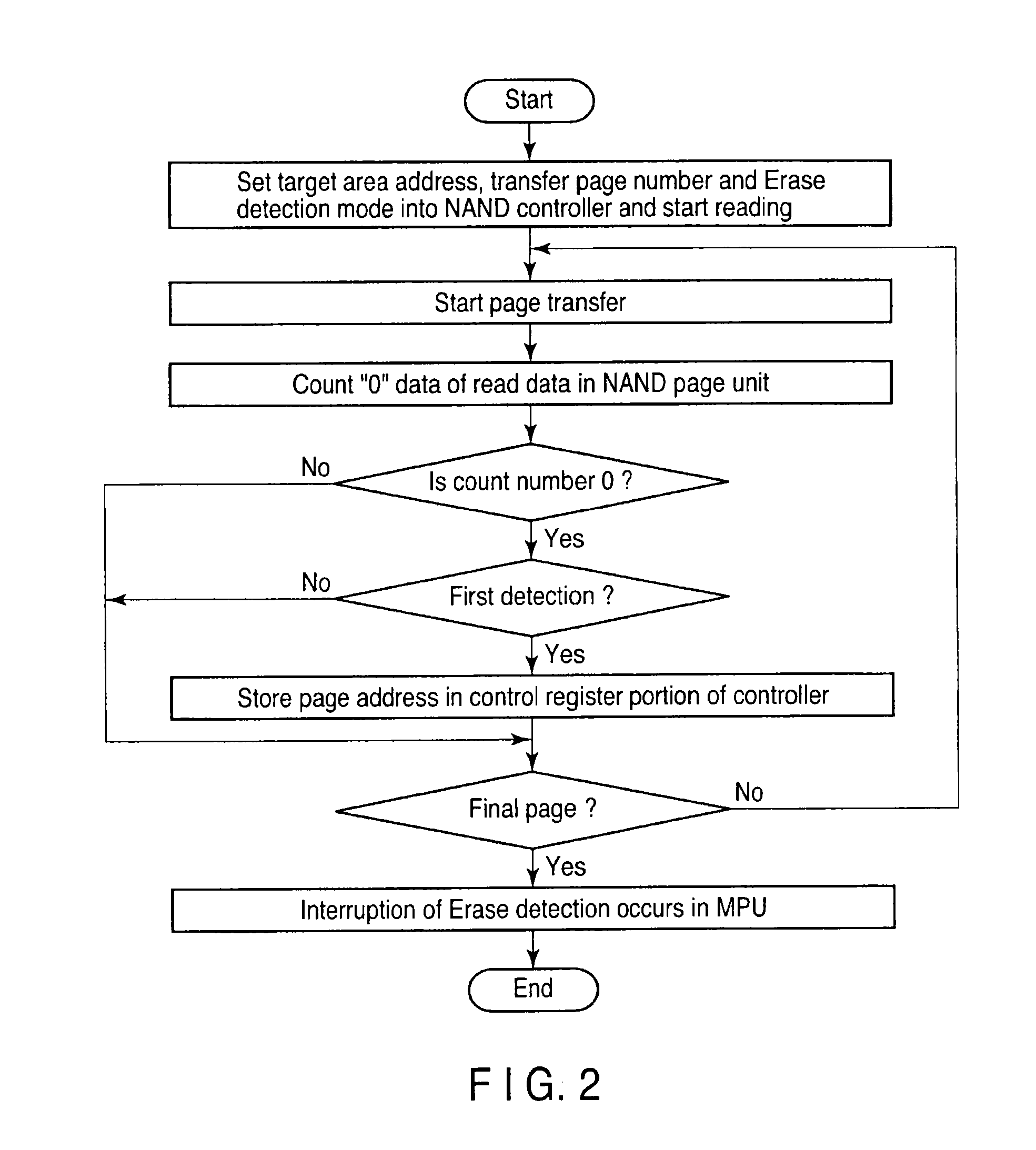

Memory system

ActiveUS20140289588A1Memory architecture accessing/allocationMemory adressing/allocation/relocationCounting NumberParallel computing

A memory system (10) is disclosed, which comprises a flash-EEPROM nonvolatile memory (11) having a plurality of memory cells that have floating gates and in which data items are electrically erasable and writable, a cache memory (13) that temporarily stores data of the flash-EEPROM nonvolatile memory (11), a control circuit (12, 14) that controls the flash-EEPROM nonvolatile memory (11) and the cache memory (13), and an interface circuit (16) that communicates with a host, in which the control circuit functions to read data from a desired target area to-be-determined of the flash-EEPROM nonvolatile memory and detect an erased area to determine a written area / unwritten area by using as a determination condition whether or not a count number of data “0” of the read data has reached a preset criterion count number.

Owner:KIOXIA CORP

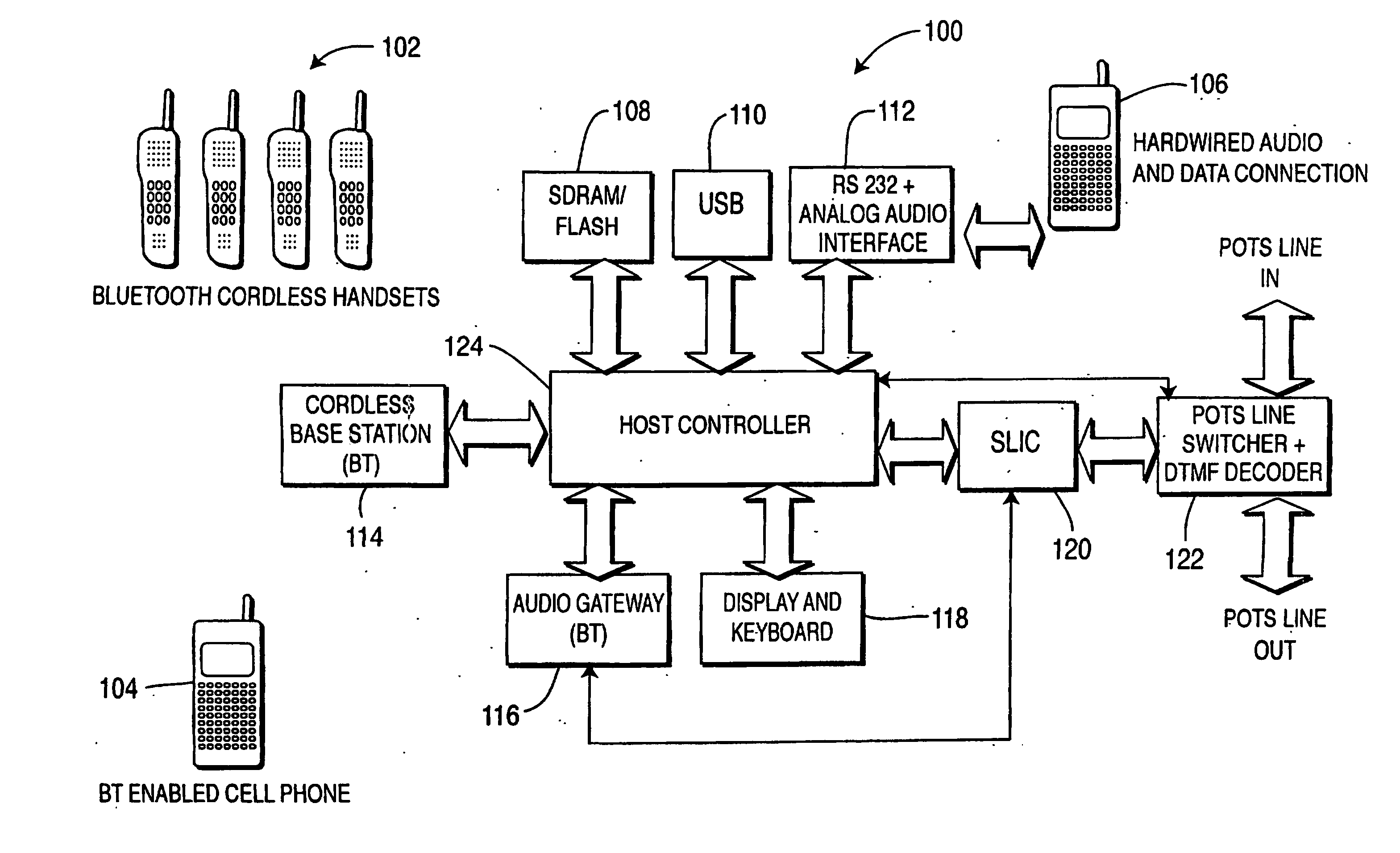

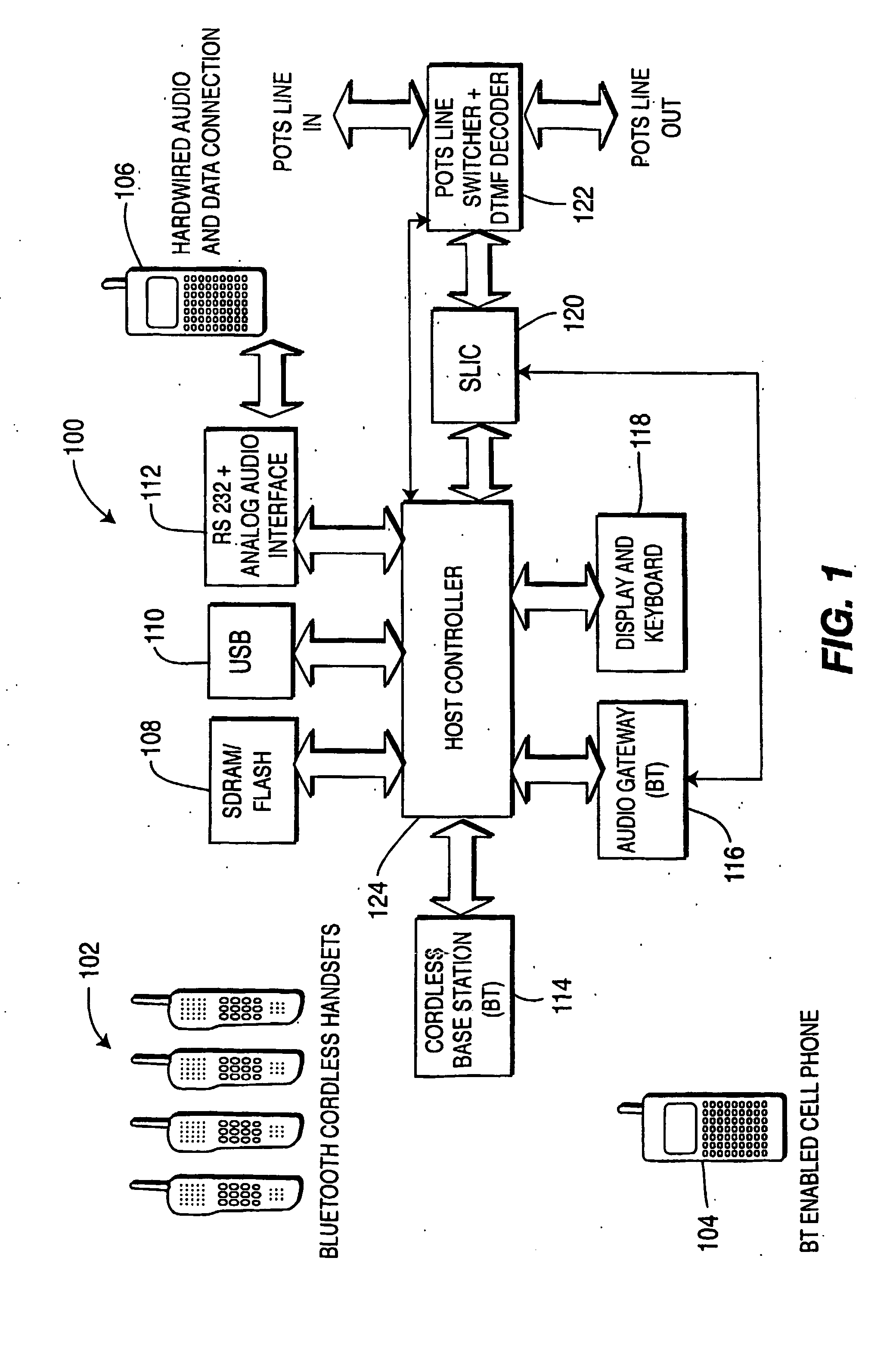

Integrated cellular/pcs-pots communication system

ActiveUS20070105548A1Network topologiesDevices with bluetooth interfacesInterface circuitsTelephone network

There is provided a system for integrating at least one residential Plain Old Telephone System (POTS) phone to a cellular phone network. A Subscriber Line Interface Circuit (SLIC 120 ) interfaces audio from the cellular phone network to the at least one residential POTS phone. A line switcher ( 122 ), connected to the SLIC, connects the at least one residential POTS phone to any one of a POTS line or a cellular line. An audio gateway ( 116 ), connected to the SLIC, wirelessly receives the audio from a cellular phone connected to the cellular phone network for subsequent transmission to the at least one residential phone and wirelessly transmits the audio from the POTS line to the cellular phone.

Owner:THOMSON LICENSING SA

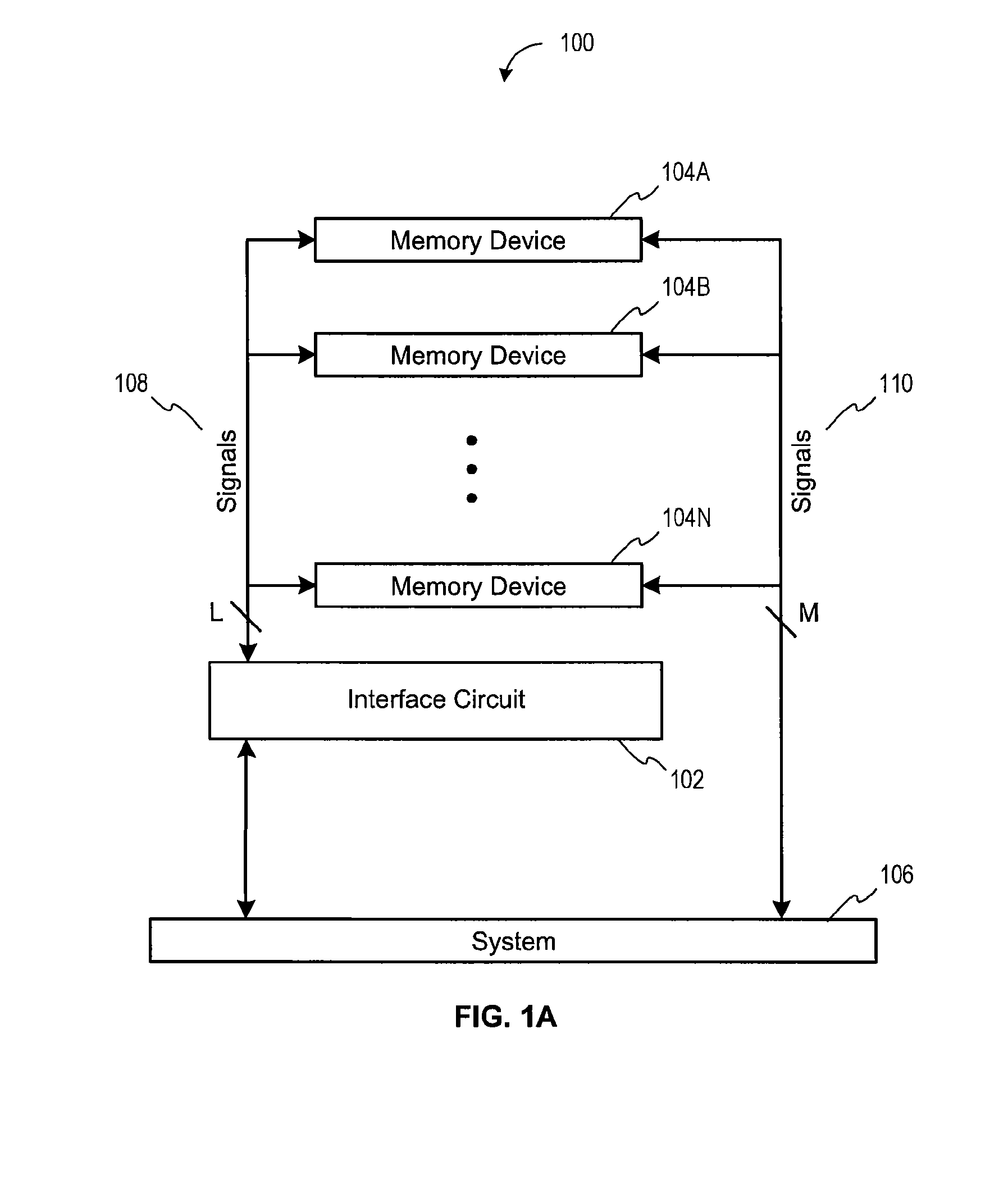

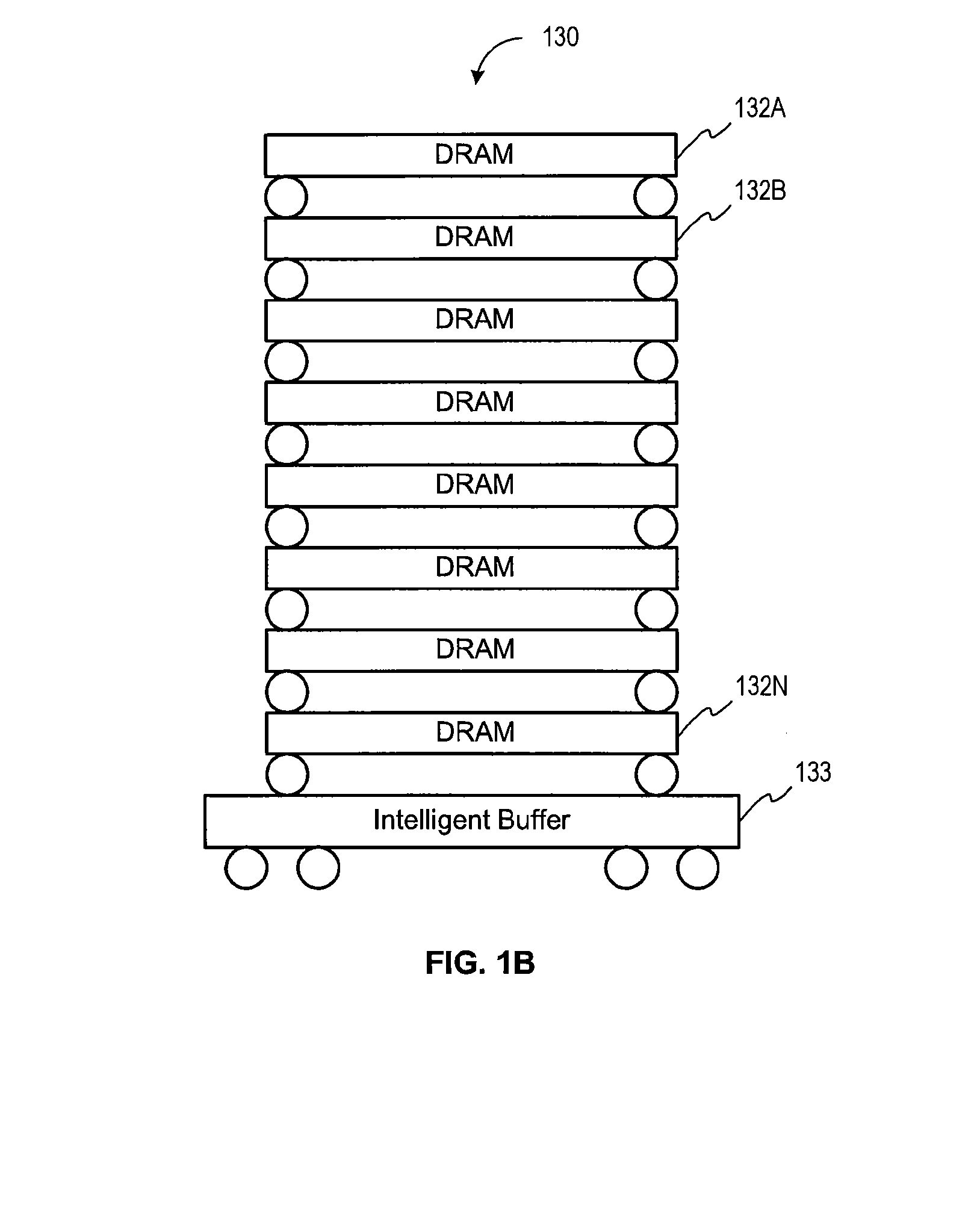

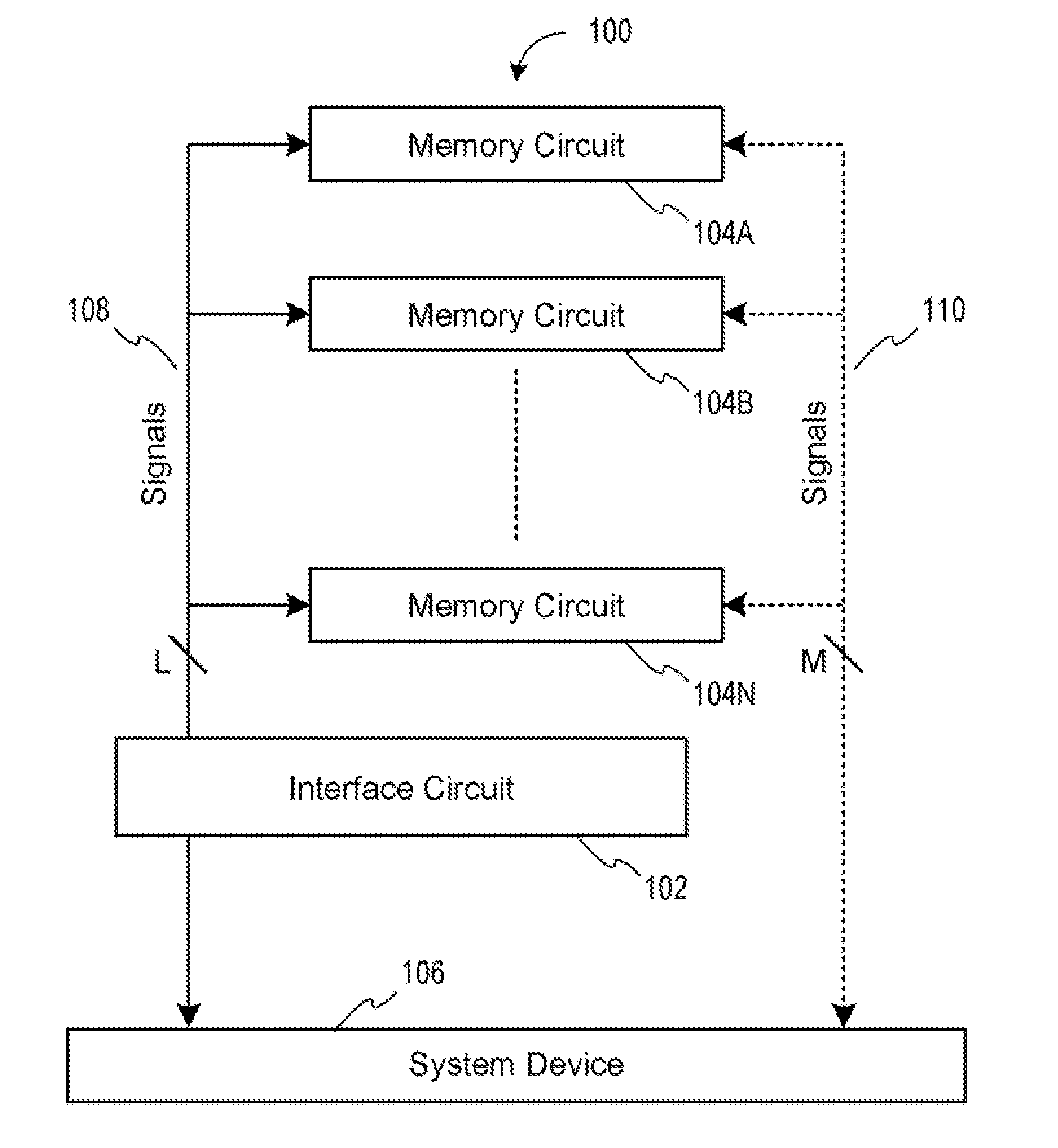

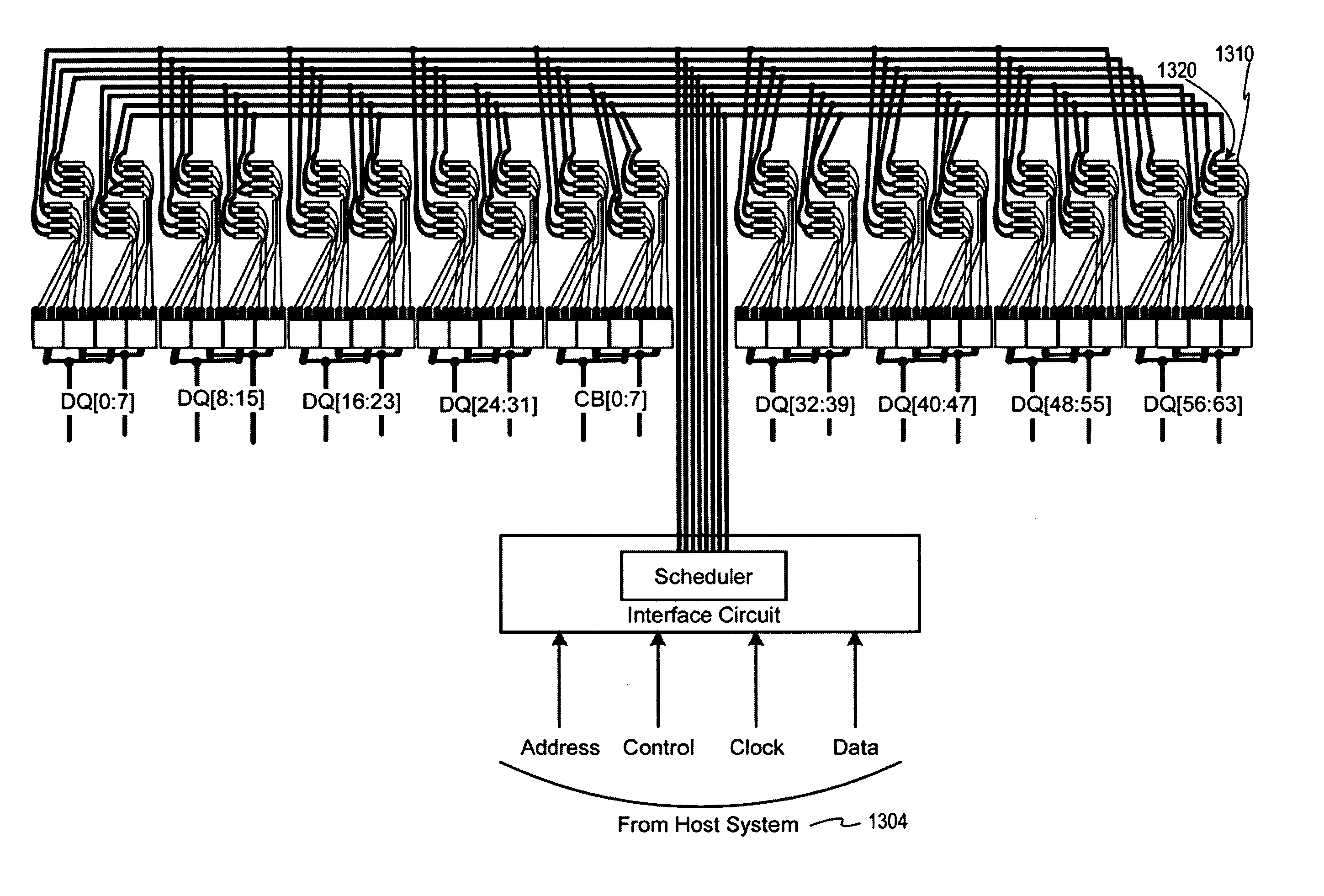

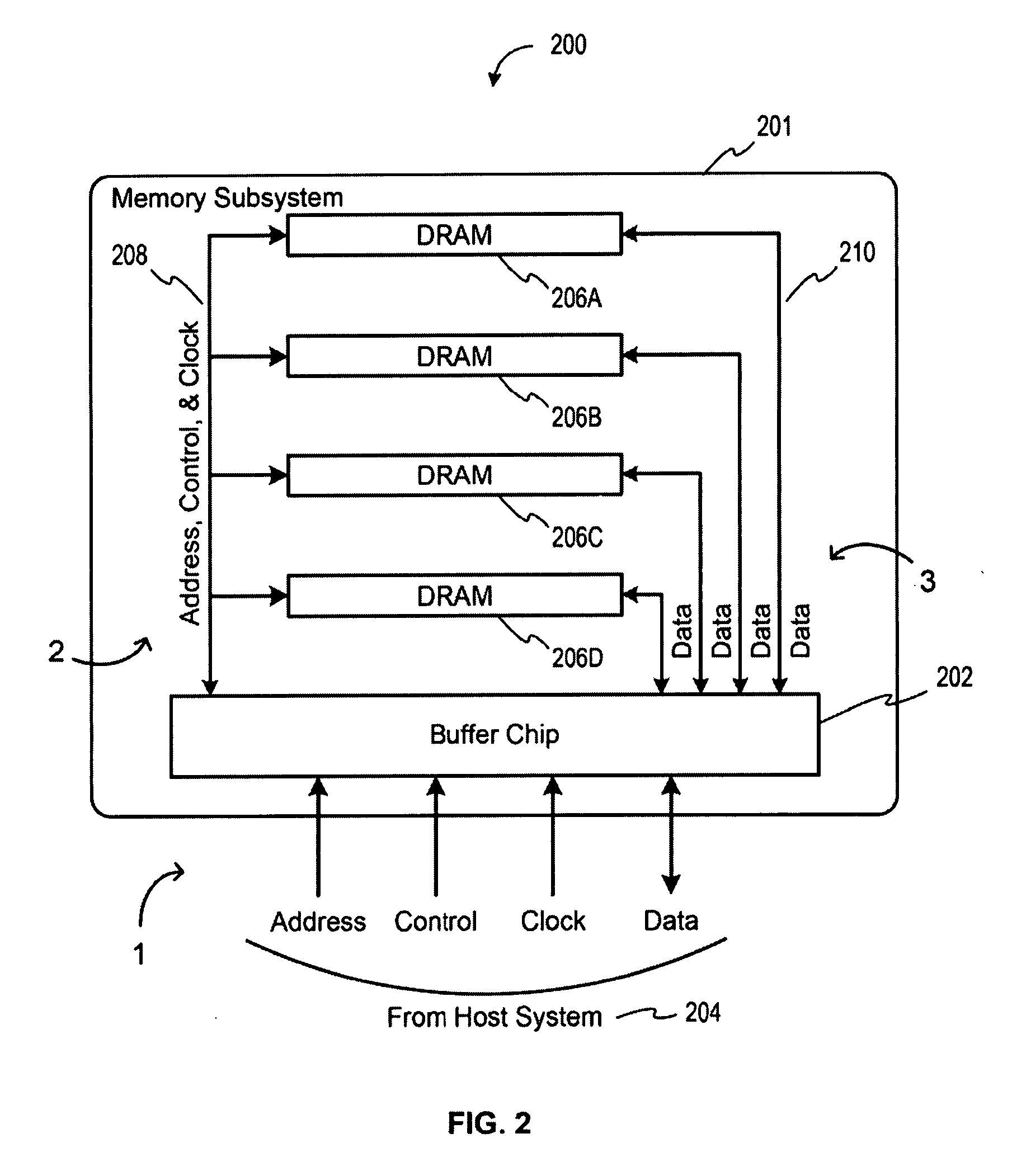

Method and Apparatus For Refresh Management of Memory Modules

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, clock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller, and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

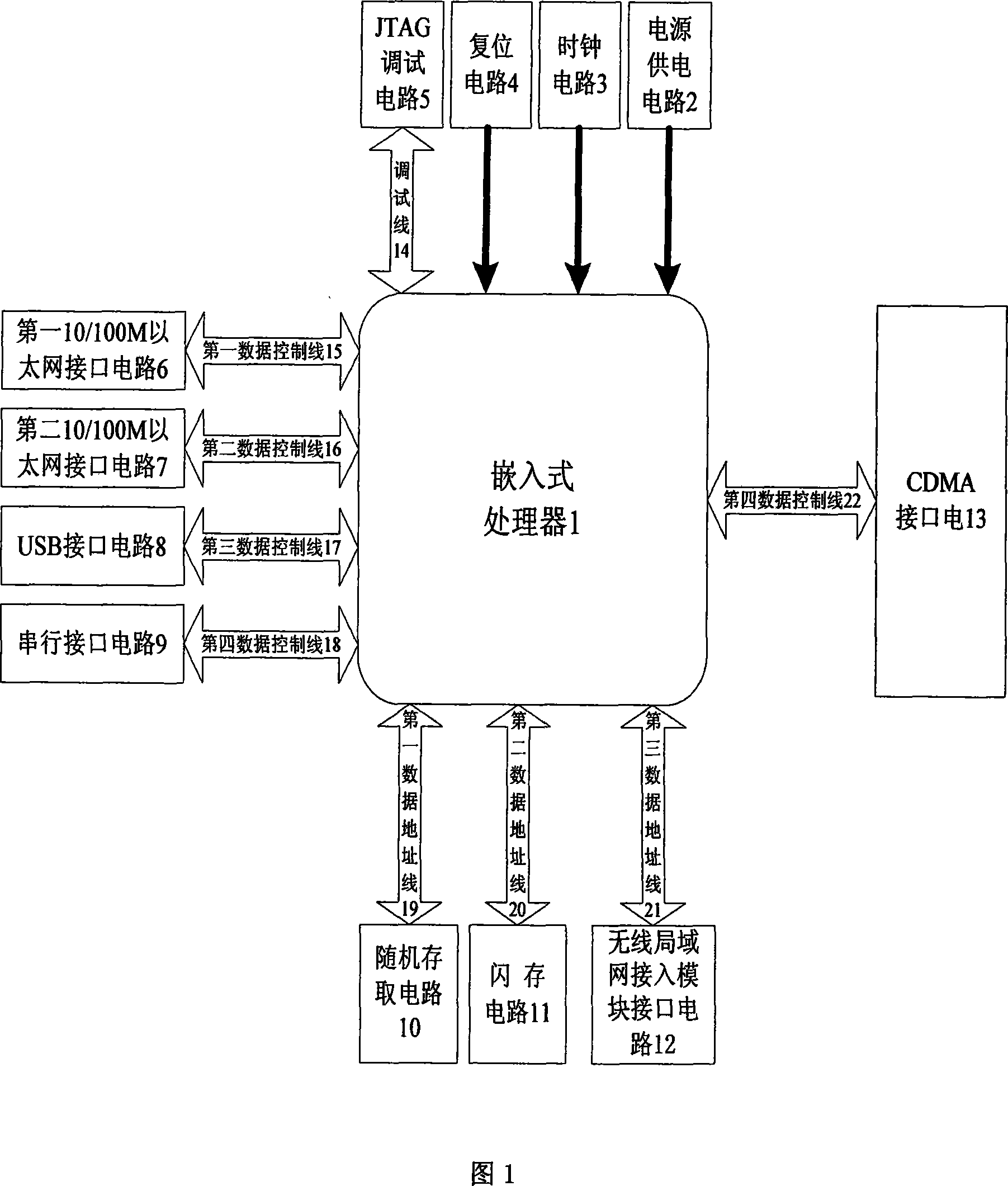

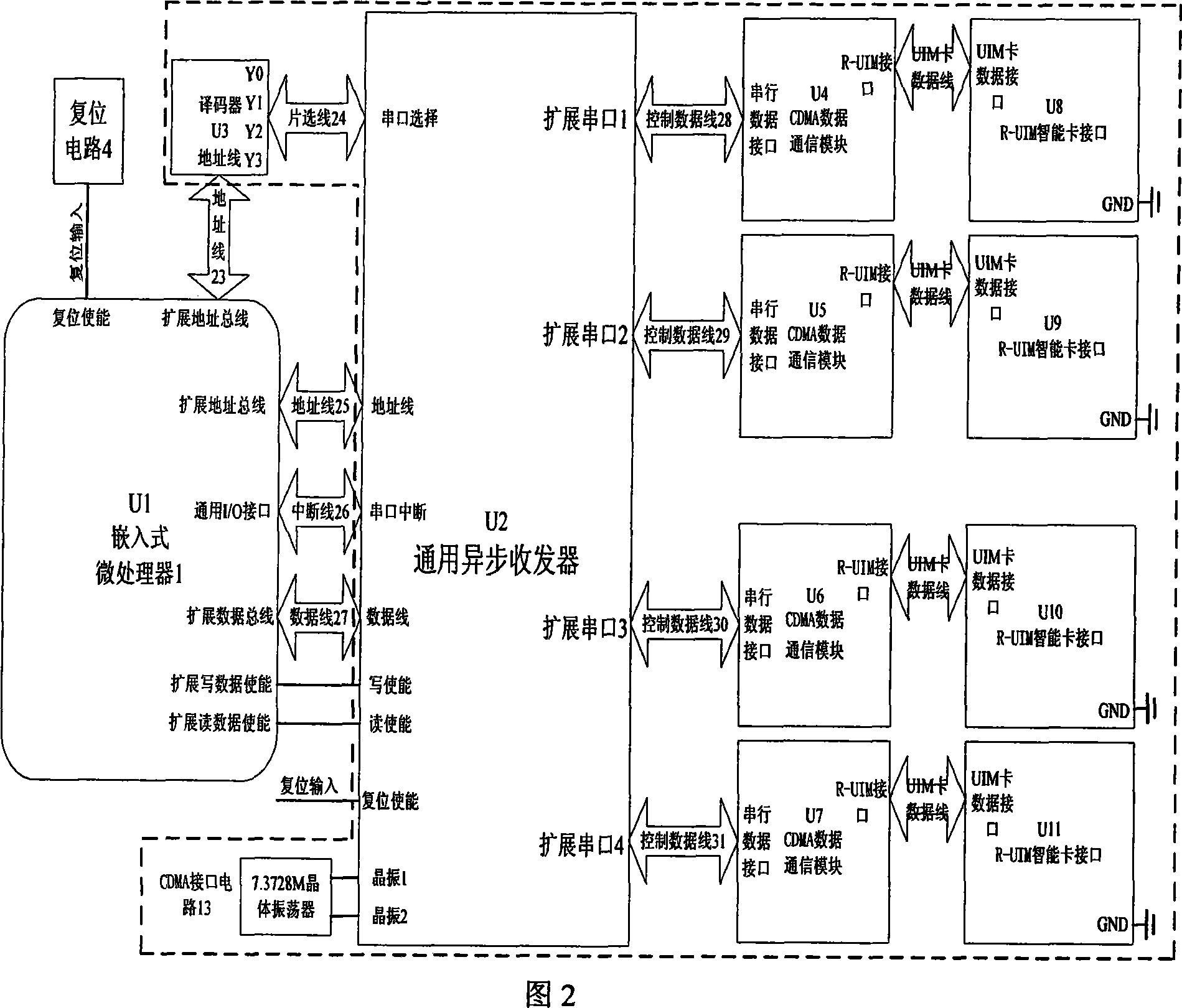

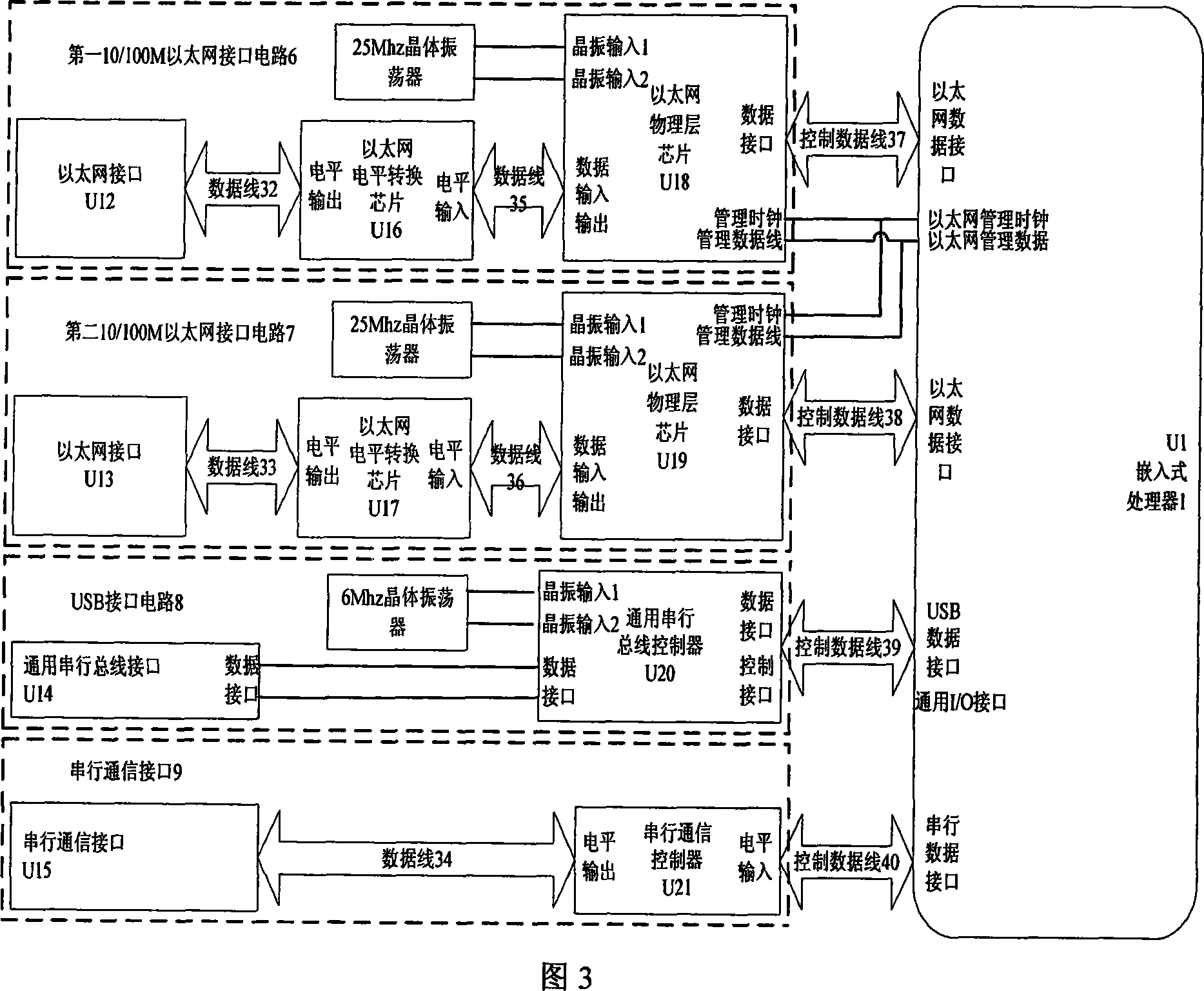

Mobile wireless local network access device and method based on code division multi-address technology

InactiveCN101123553AEasy to set upBig spaceNetwork topologiesData switching by path configurationInterface circuitsMulti access

A method and a mobile wireless local area network access device based on Code Division Multiple Access technology relate to a method and a local area network access device, in particular to a method and a mobile wireless local area network access device based on Code Division Multiple Access (CDMA) technology, wherein the device comprises an embedded hardware platform, a multi-access CDMA interface module circuit and a wireless local area network access module circuit. The embedded hardware platform comprises an embedded microprocessor, a power supply module circuit, a clock module circuit, a reset module circuit, a JTAG debug port, an Ethernet interface, a USB interface module circuit, a serial interface module circuit, a random access module circuit and a flash memory circuit. The multi-access CDMA interface module circuit comprises a serial interface extensive module circuit and one to four CDMA 2000 1X data links, each of which comprises a CDMA communication module circuit and a R-UIM intelligent card module circuit. The wireless local area network access module circuit comprises a MiniPCI interface circuit and a local area network wireless access module.

Owner:SOUTHEAST UNIV

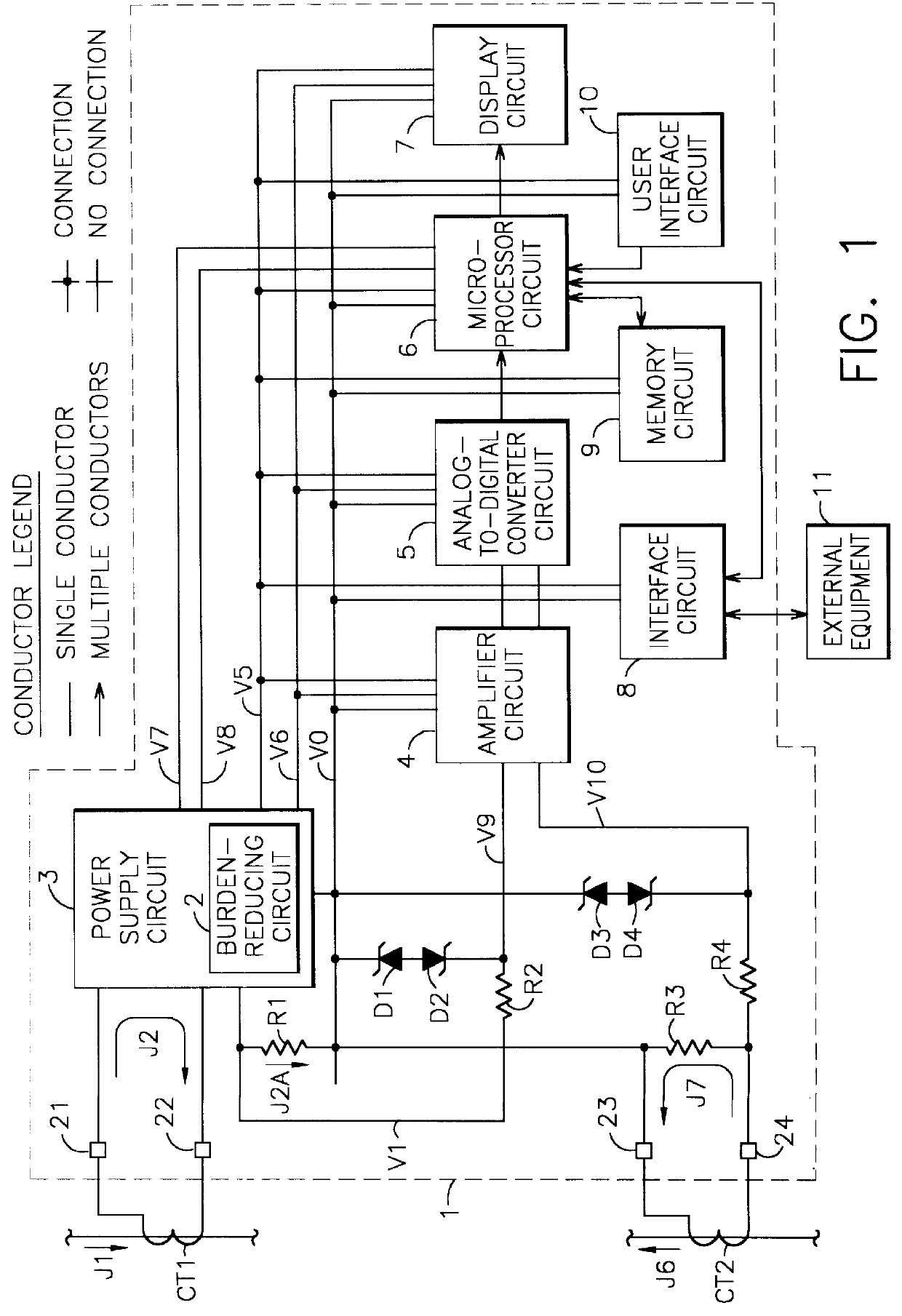

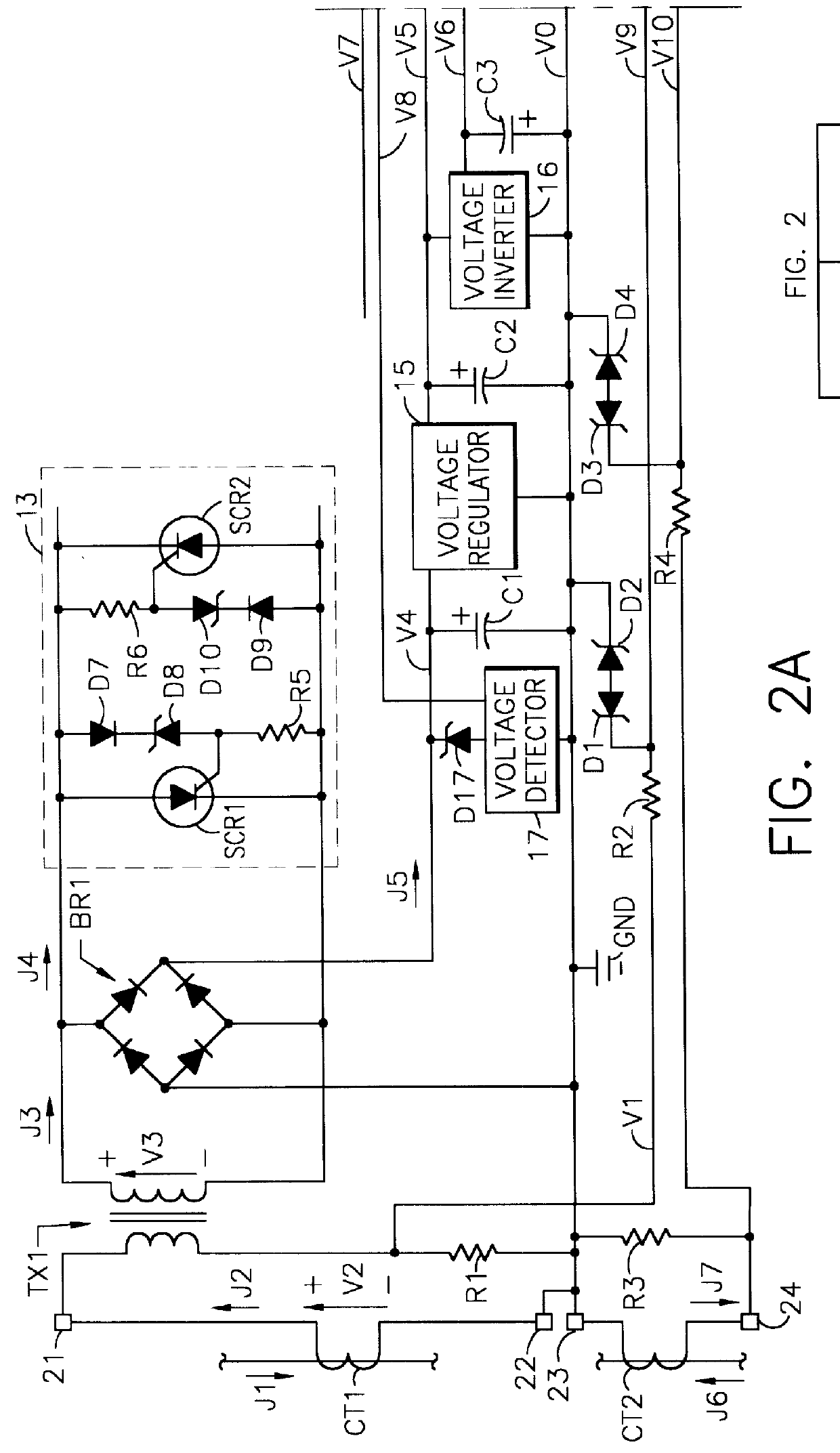

Self-powered current monitor

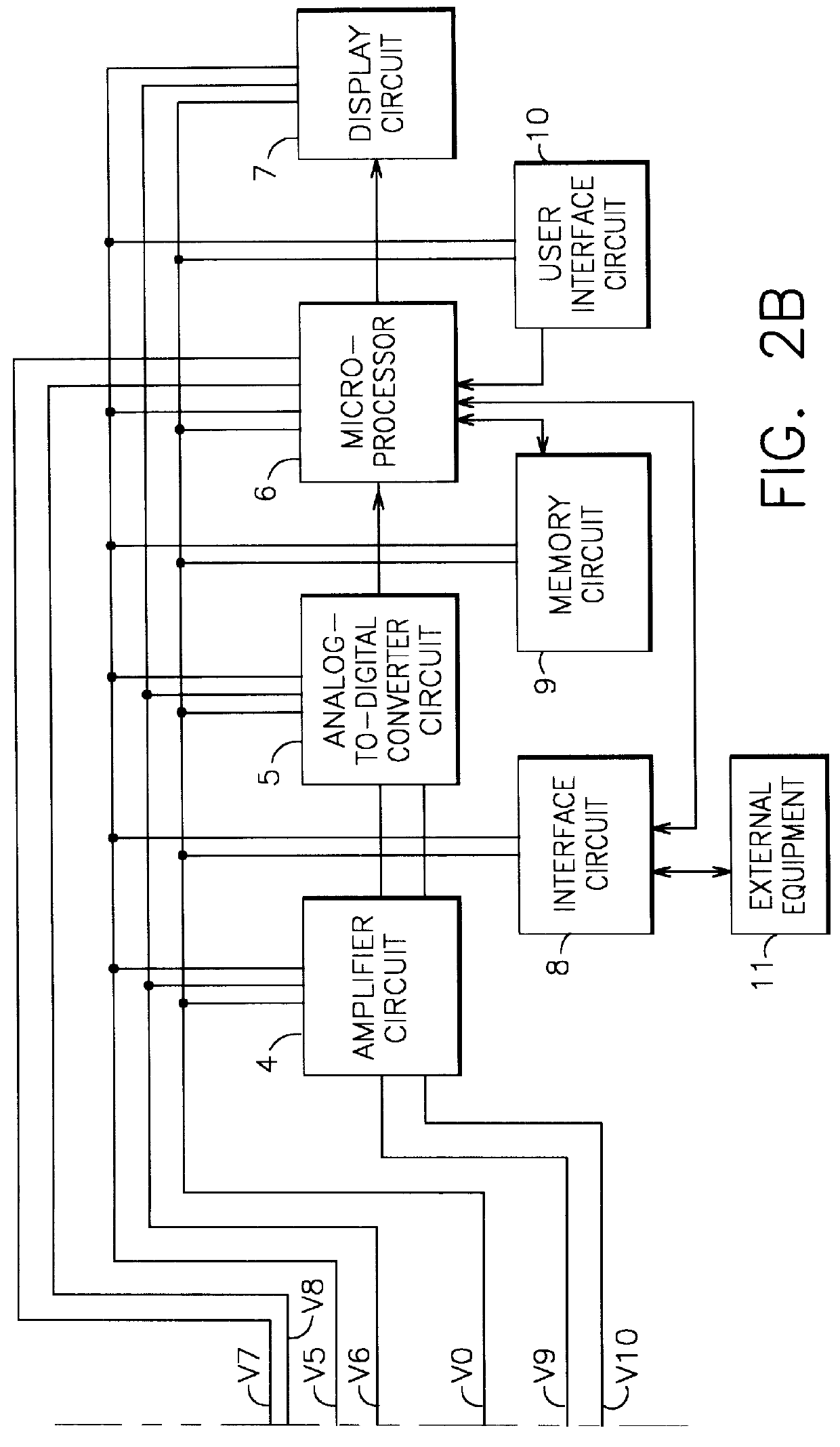

A self-powered current monitor for monitoring current in electric power systems. Various data relating to input currents may be displayed, such as current magnitude, current demand, and harmonics levels. Operating power is derived from one or more of the input currents. The power supply configuration may include a burden-reducing means to reduce the burden on input current sources during sampling of the input currents. The self-powered current monitor (1) includes a power supply section (3), input resistors (R1 and R3), an analog-to-digital converter circuit (5), a microprocessor circuit (6), a memory circuit (9), and a display circuit (7). Optional features include a burden-reducing circuit (2), input circuit protective elements (D1, D2, D3, D4, R2, and R4), an amplifier circuit (4), a user interface circuit (10), and an interface circuit (8) for communication to other equipment.

Owner:EDEL THOMAS G

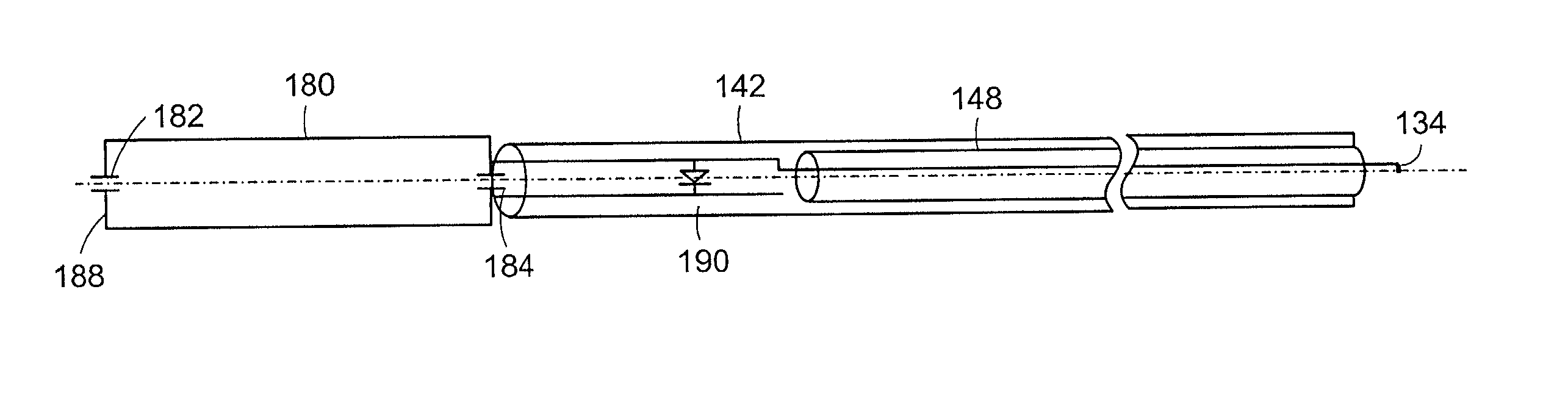

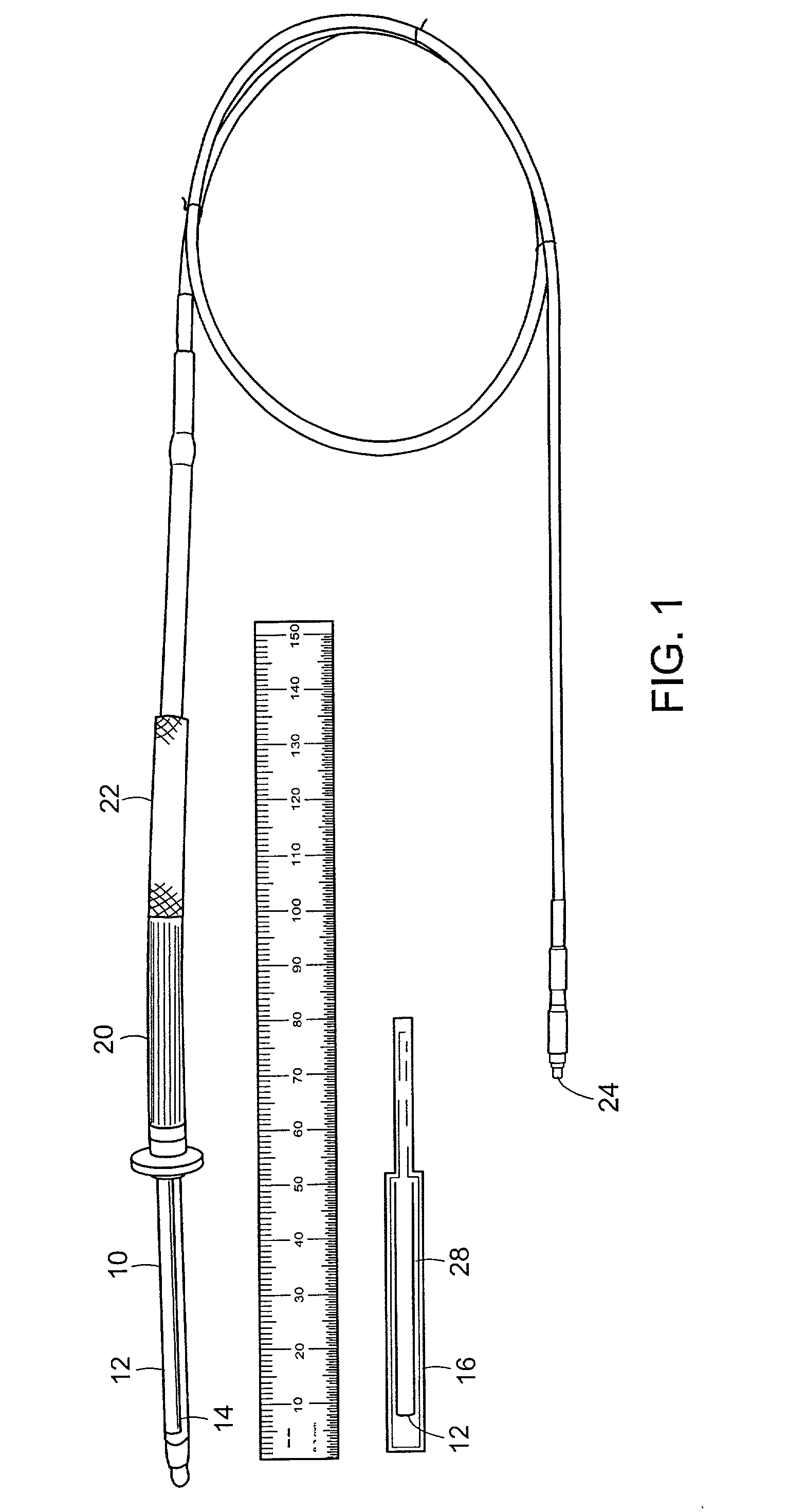

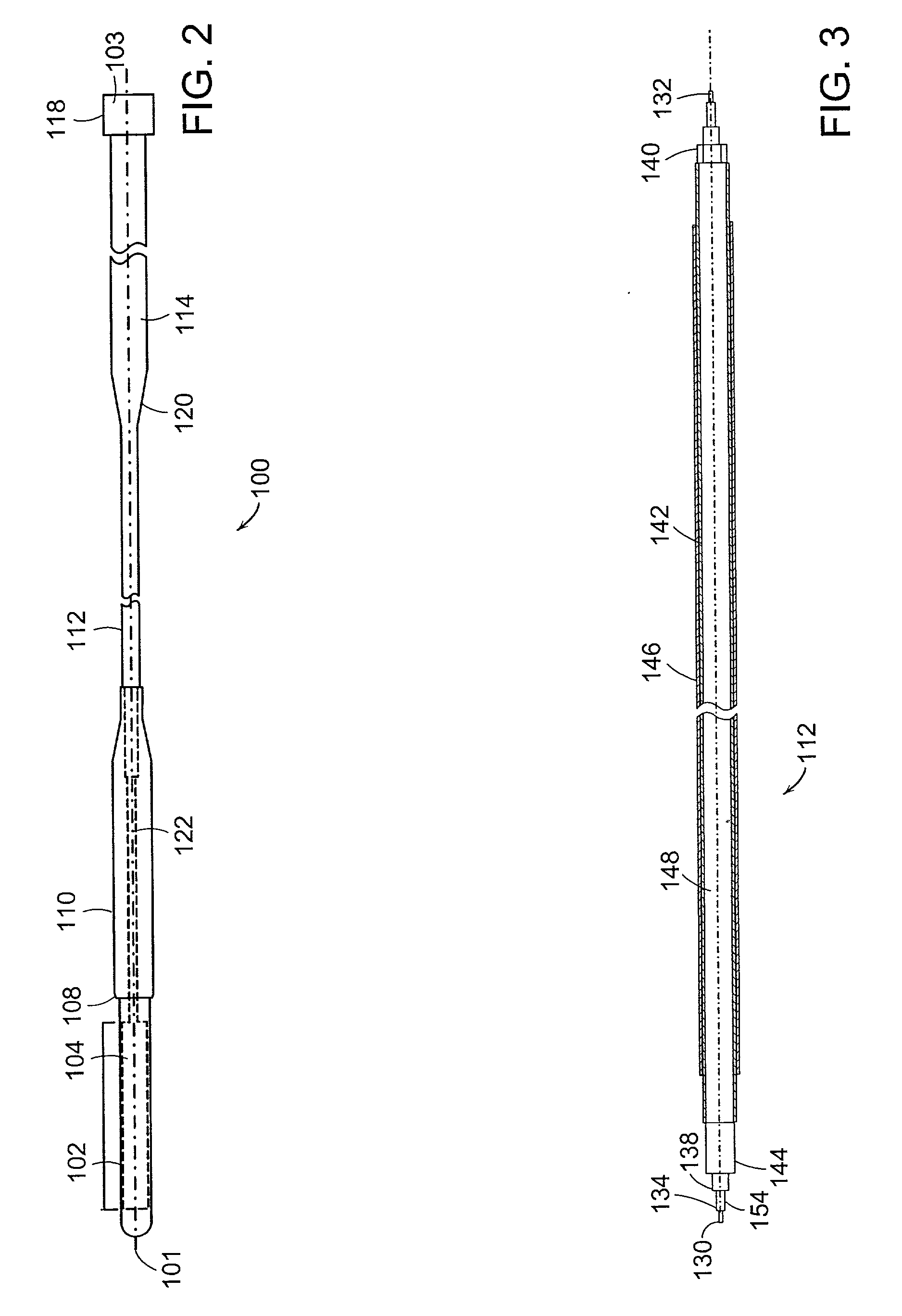

Systems and methods for evaluating the urethra and the periurethral tissues

InactiveUS20020040185A1Accurate diagnosisImprove clinical outcomesGastroscopesOesophagoscopesDiseaseUrethra

The present invention provides systems and methods for the evaluation of the urethra and periurethral tissues using an MRI coil adapted for insertion into the male, female or pediatric urethra. The MRI coil may be in electrical communication with an interface circuit made up of a tuning-matching circuit, a decoupling circuit and a balun circuit. The interface circuit may also be in electrical communication with a MRI machine. In certain practices, the present invention provides methods for the diagnosis and treatment of conditions involving the urethra and periurethral tissues, including disorders of the female pelvic floor, conditions of the prostate and anomalies of the pediatric pelvis.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE +1

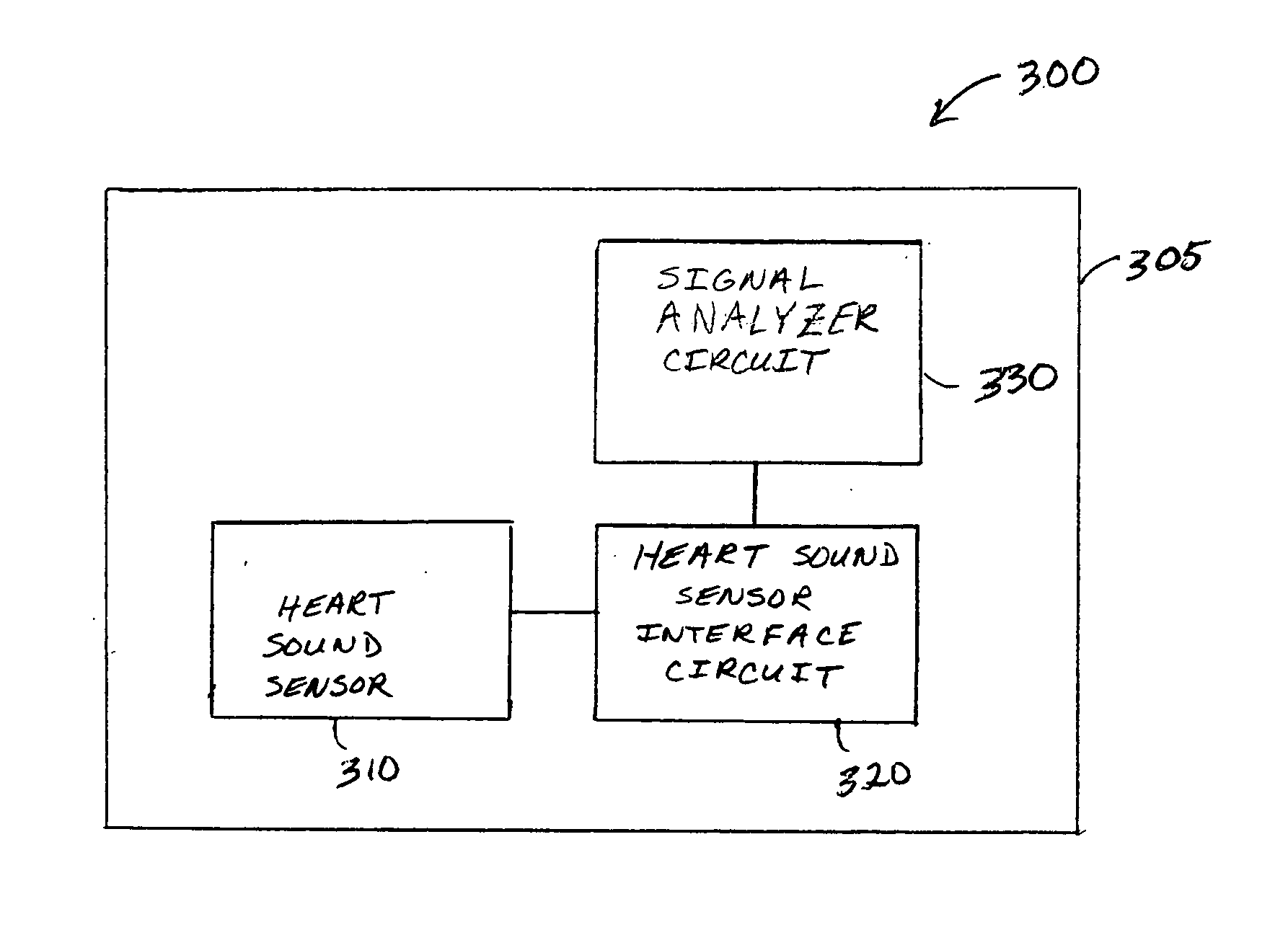

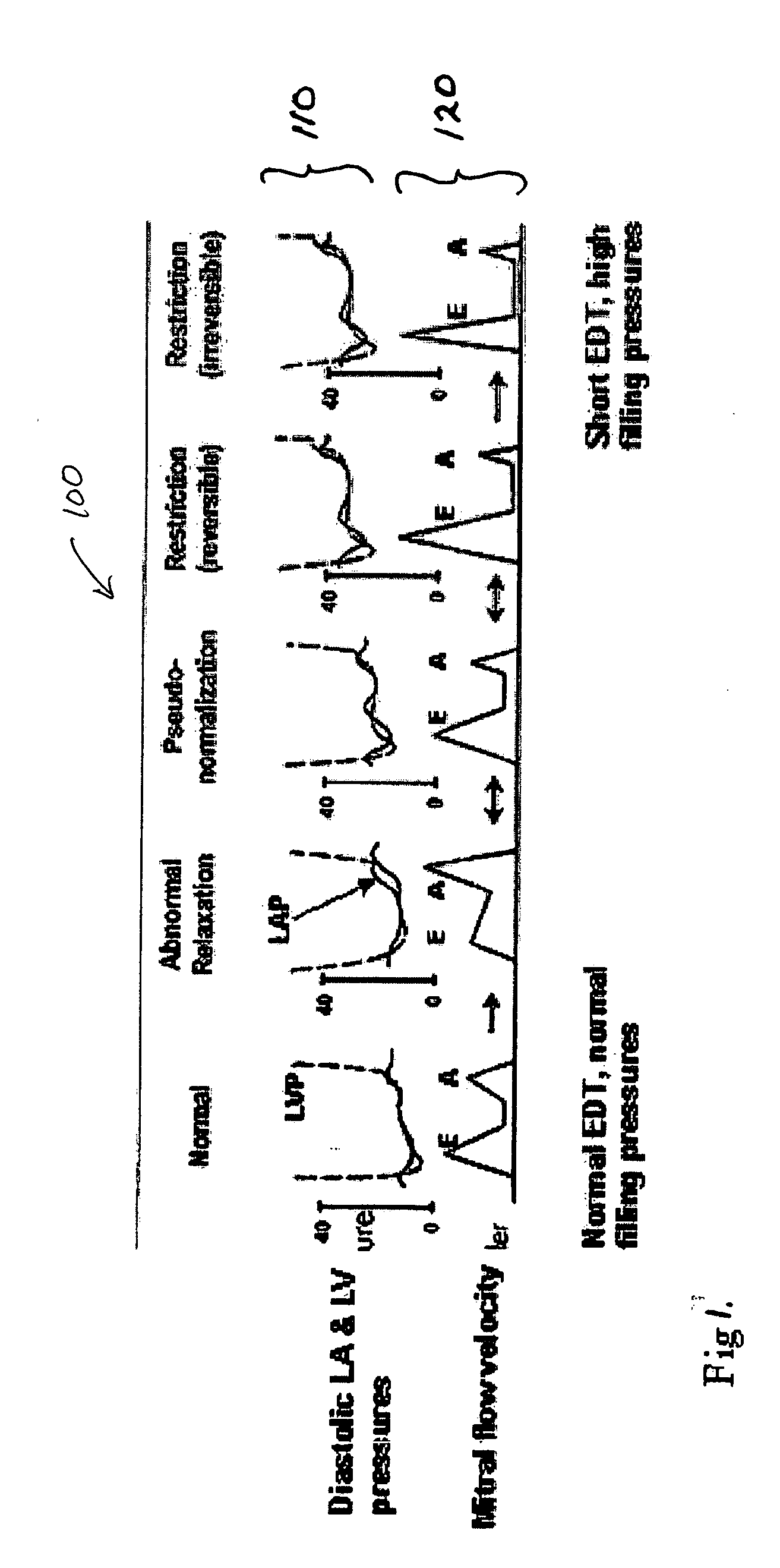

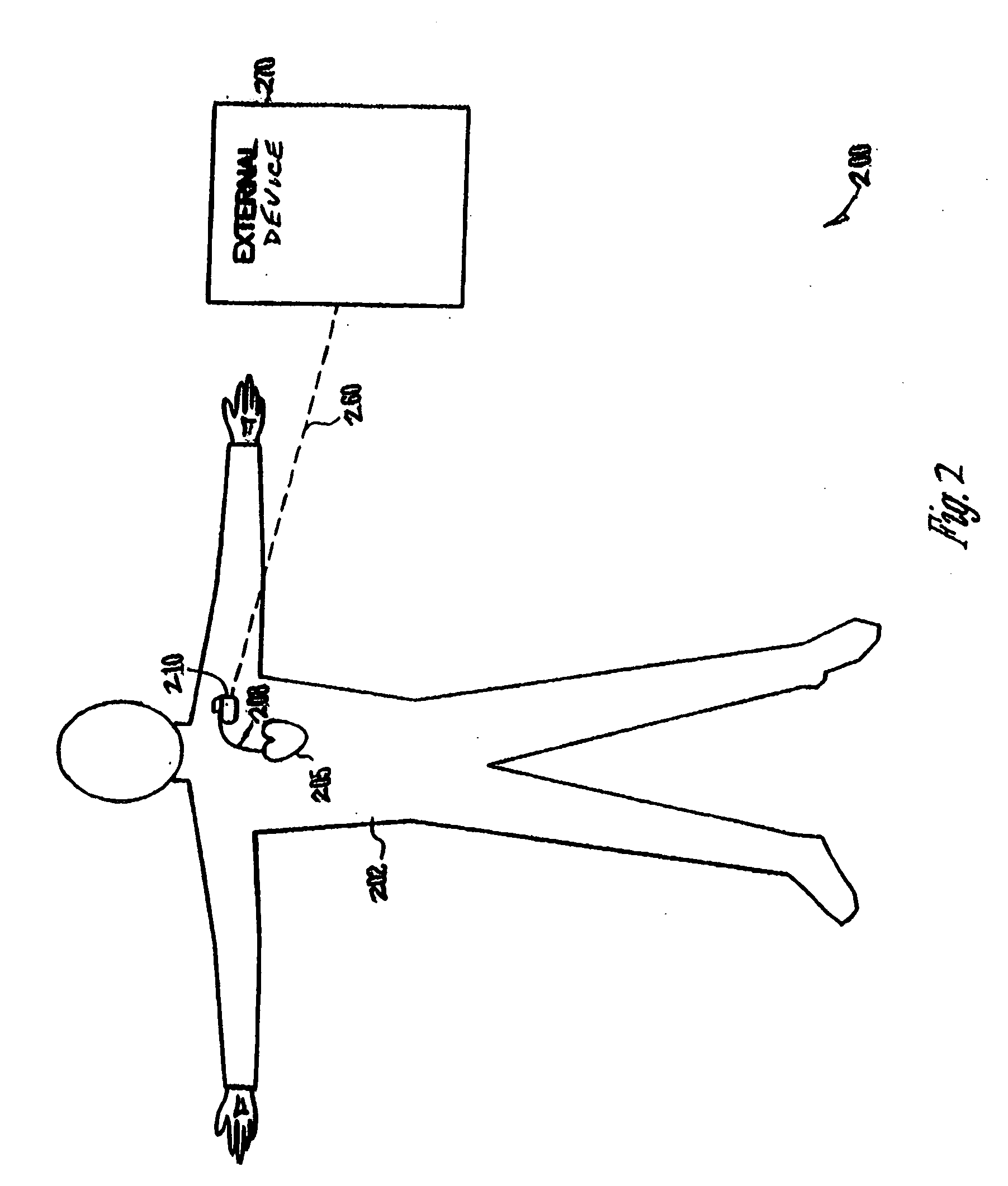

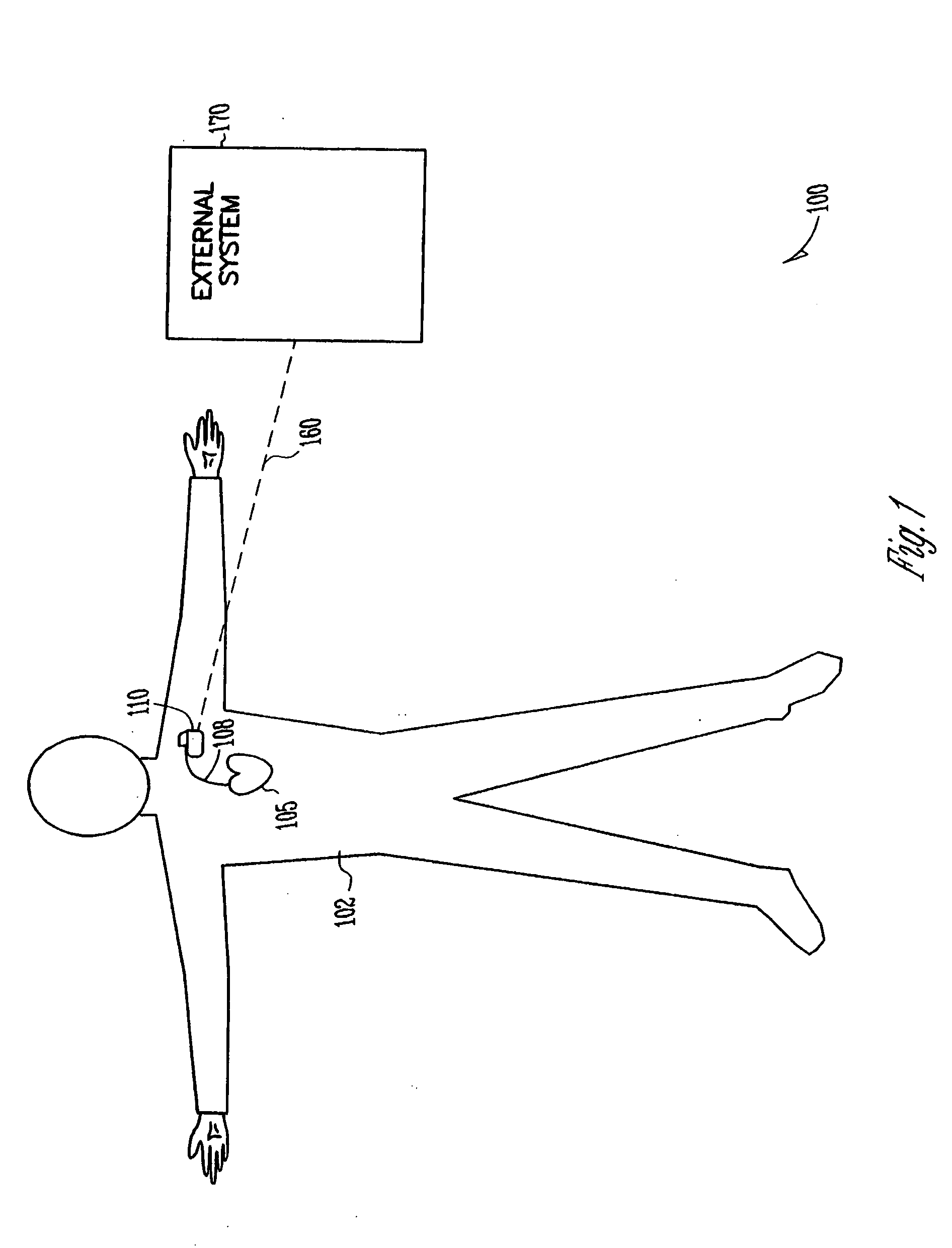

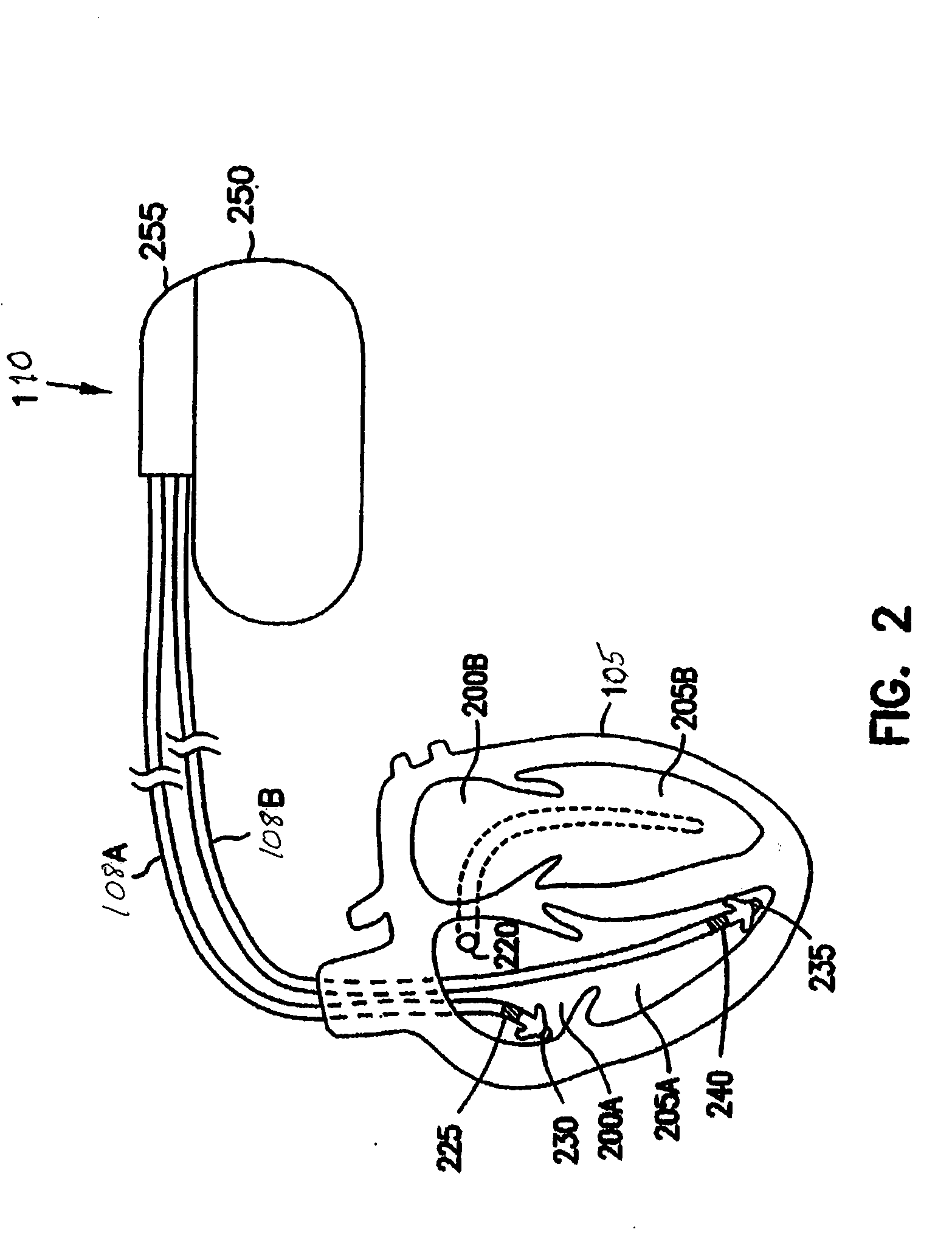

Ischemia detection using a heart sound sensor

A system comprising an implantable medical device (IMD) includes an implantable heart sound sensor to produce an electrical signal representative of at least one heart sound. The heart sound is associated with mechanical activity of a patient's heart. Additionally, the IMD includes a heart sound sensor interface circuit coupled to the heart sound sensor to produce a heart sound signal, and a signal analyzer circuit coupled to the heart sound sensor interface circuit. The signal analyzer circuit measures a baseline heart sound signal, and deems that an ischemic event has occurred using, among other things, a measured subsequent change in the heart sound signal from the established baseline heart sound signal.

Owner:CARDIAC PACEMAKERS INC

Method and apparatus for refresh management of memory modules

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, clock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller, and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

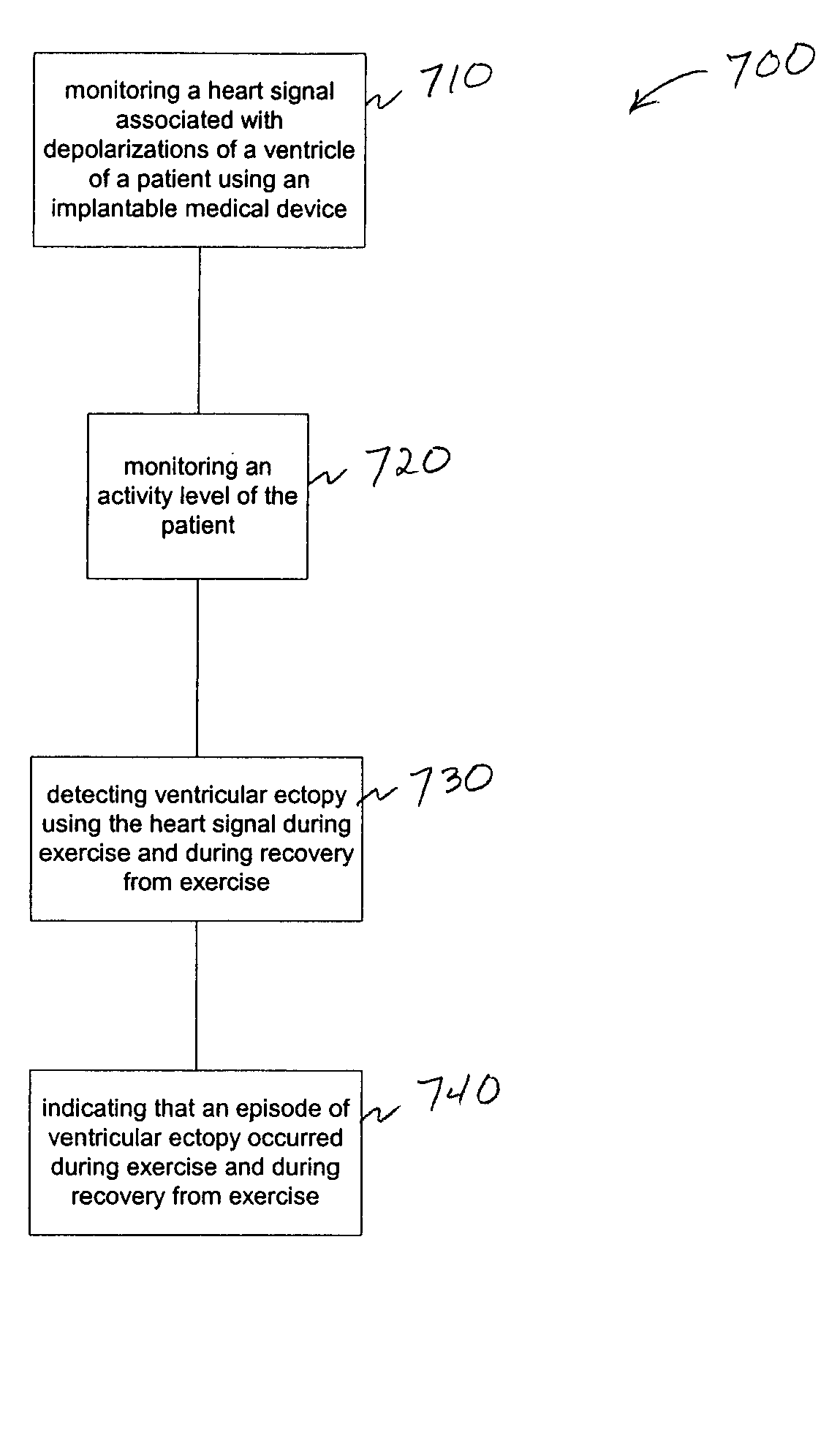

Risk of death indicator

A system comprising an implantable medical device (IMD). The IMD comprises a ventricular heart signal sensing circuit to provide a ventricular heart signal, at least one sensor operable to provide an electrical signal representative of patient activity, a sensor interface circuit coupled to the at least one sensor to provide an activity signal, and a controller circuit coupled to the heart signal sensing circuit and the sensor interface circuit. The controller circuit is operable to determine whether ventricular ectopy occurs during recovery from exercise using the heart signal, and to set at least one warning indicator if ventricular ectopy occurs during the recovery from exercise.

Owner:CARDIAC PACEMAKERS INC

Continuous high-frequency oscillation breathing treatment apparatus

ActiveUS7191780B2Assist in mucus secretionSimply and inexpensively manufacturingRespiratorsOperating means/releasing devices for valvesInhalationBreathing treatments

Owner:COMEDICA INC

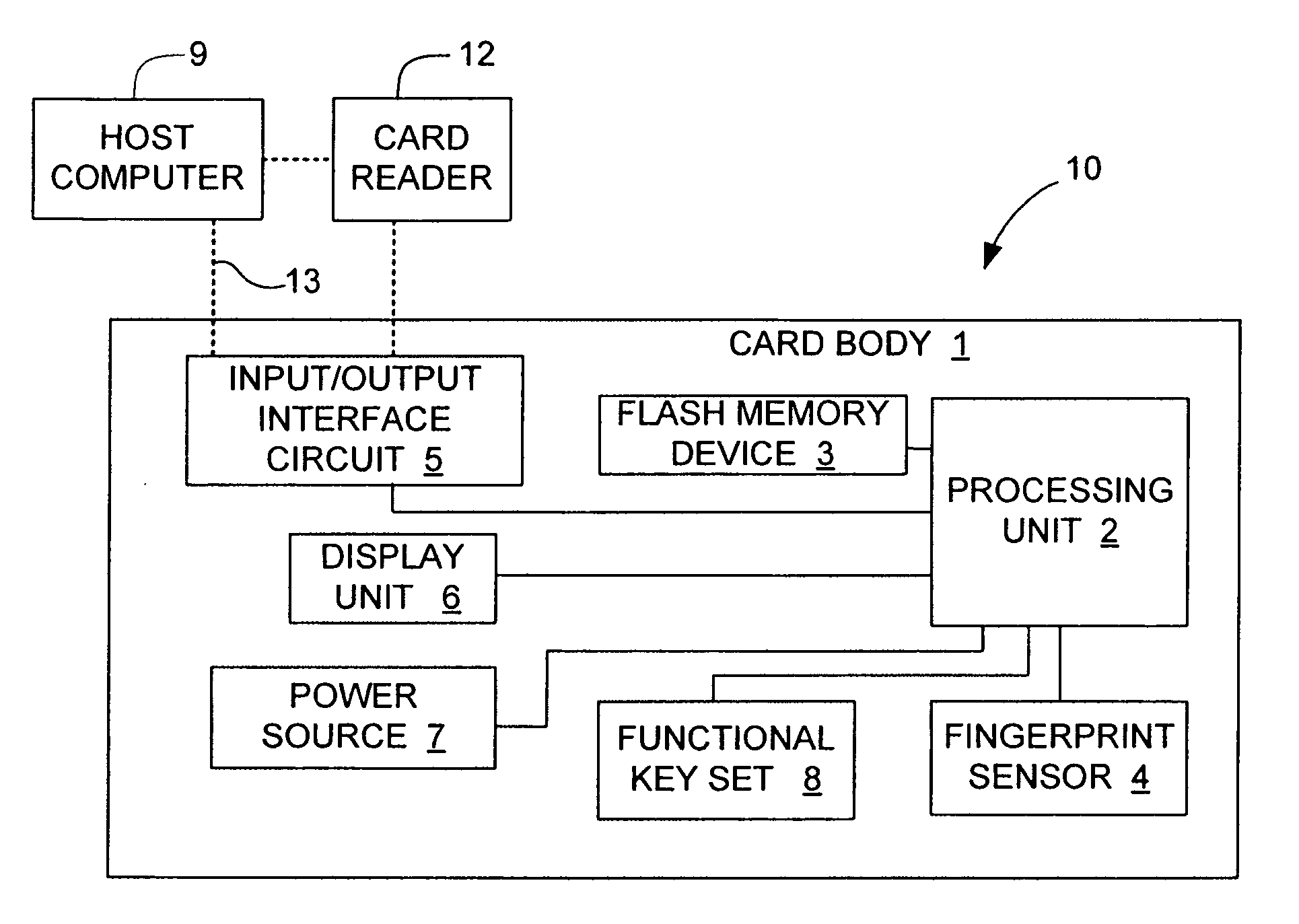

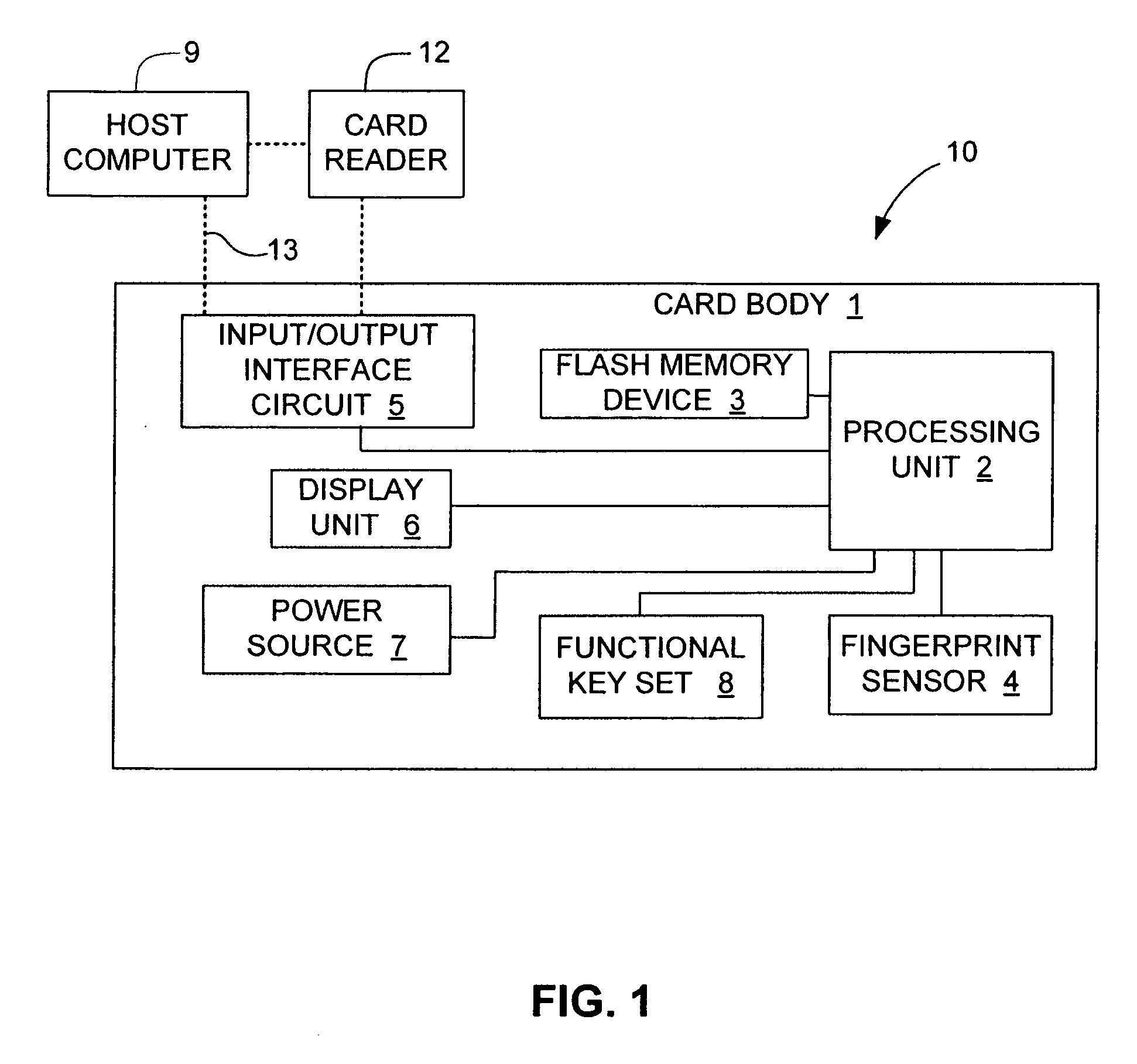

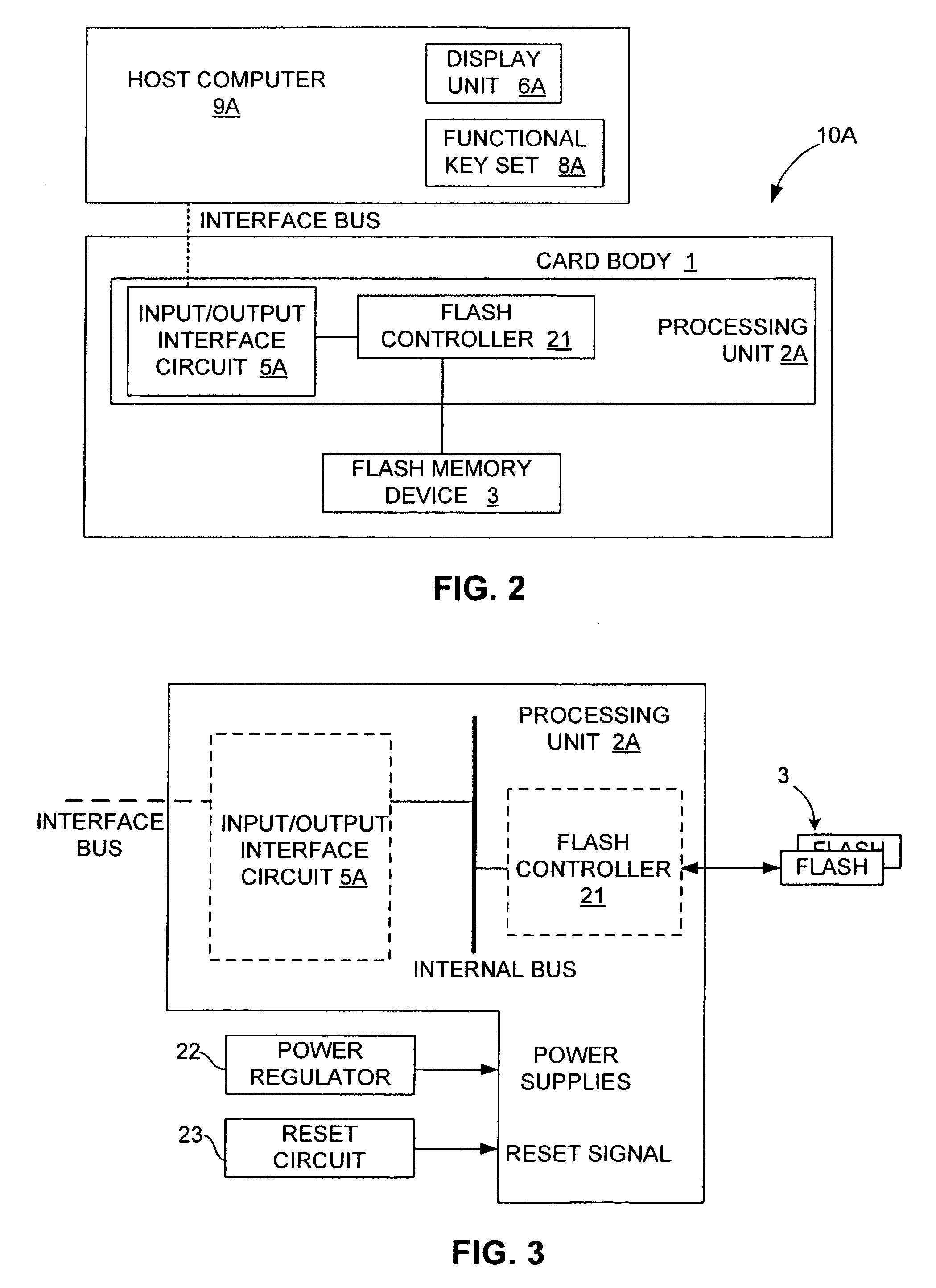

Managing Bad Blocks In Flash Memory For Electronic Data Flash Card

InactiveUS20070283428A1Reduce search timeAvoid congestionDigital data processing detailsUser identity/authority verificationLogical block addressingComputer access

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT TECH CORP

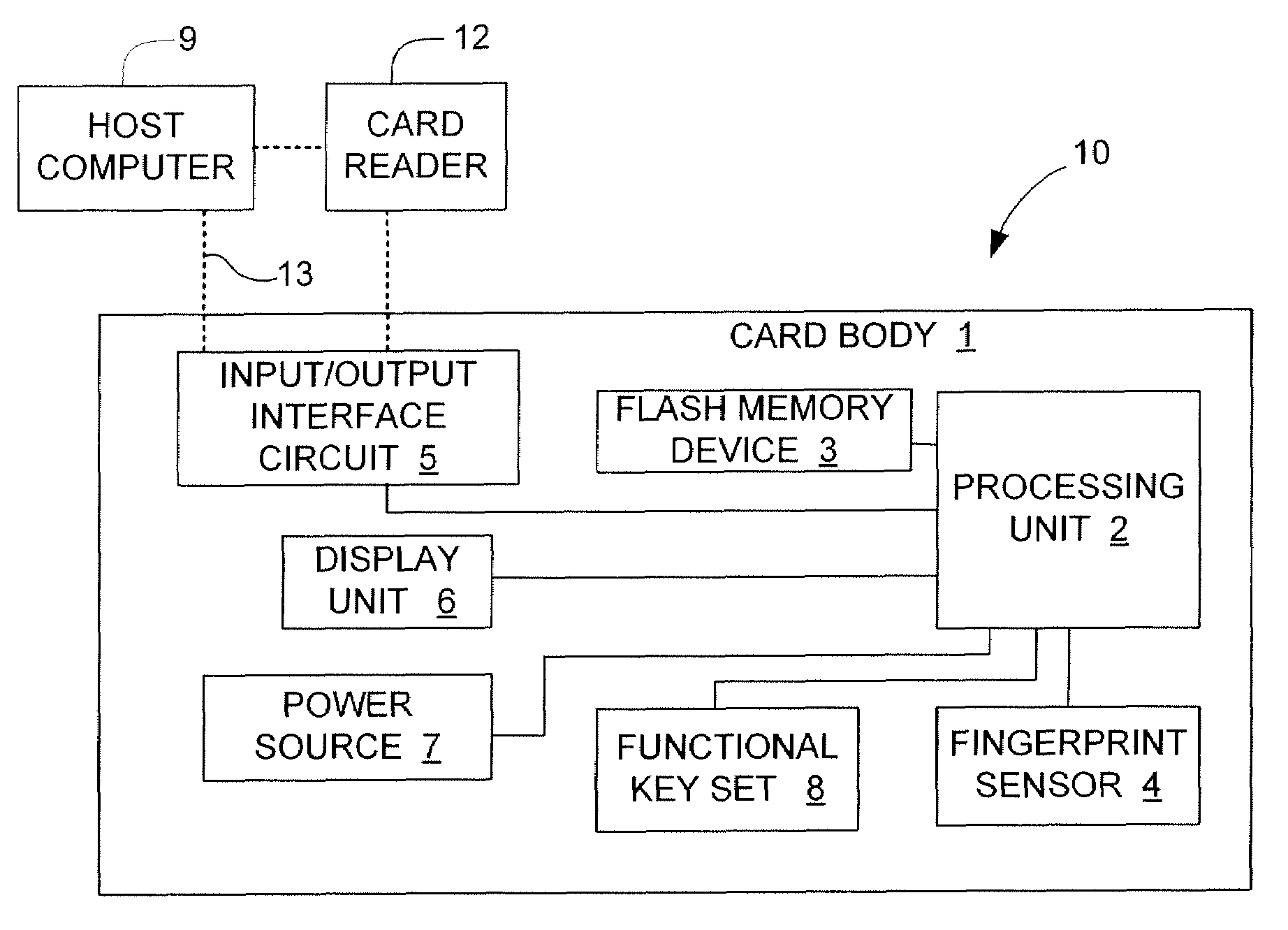

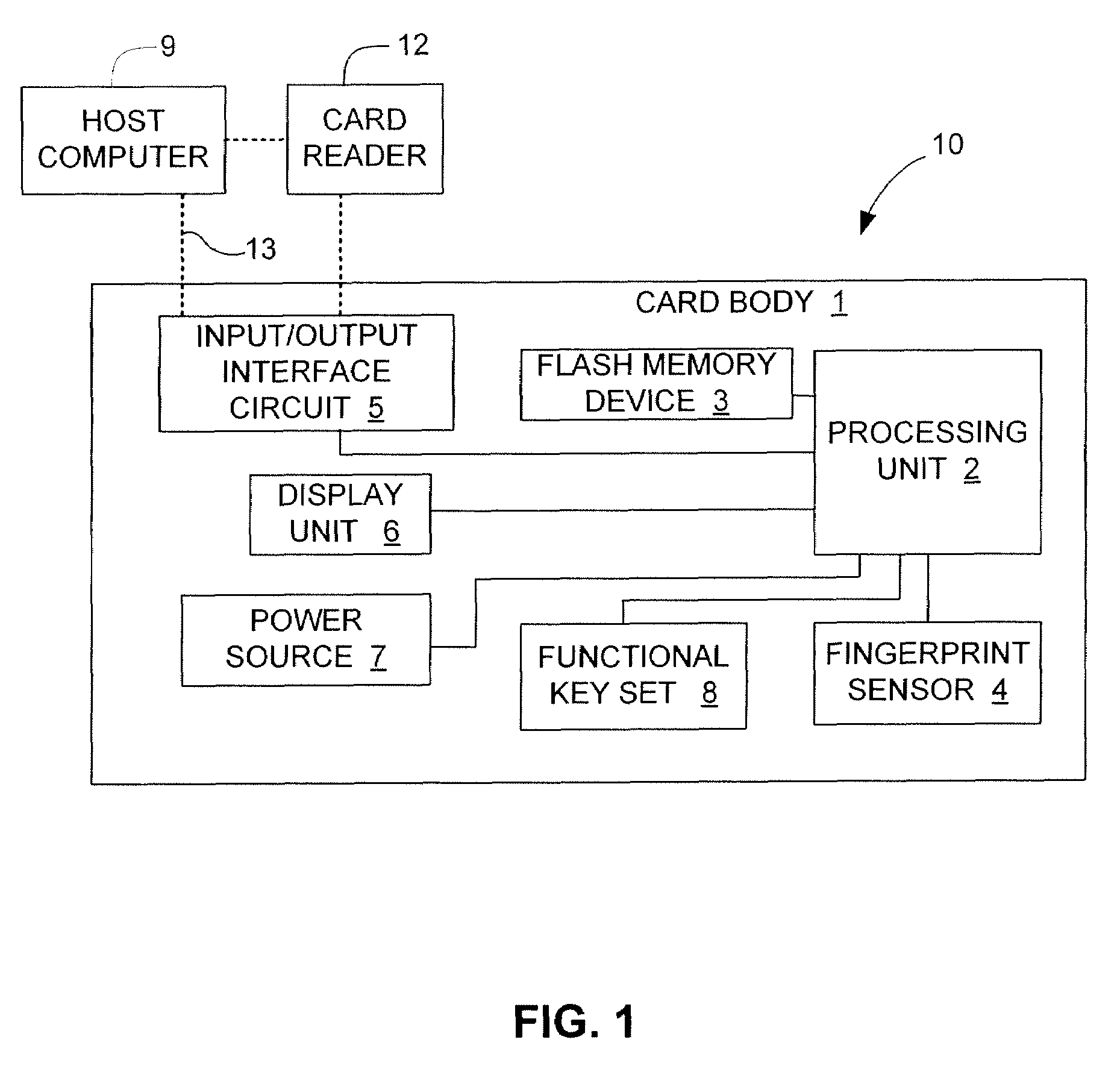

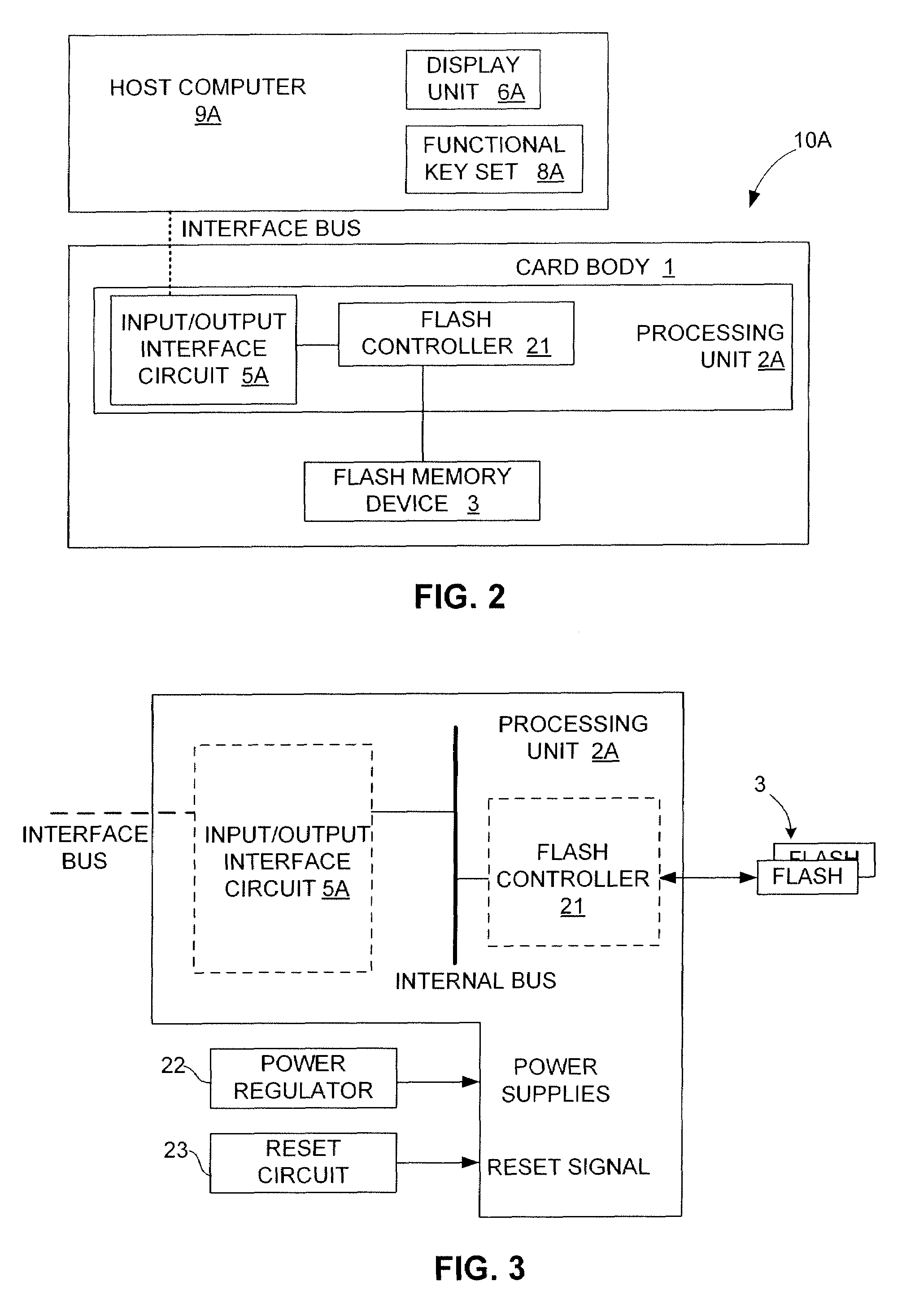

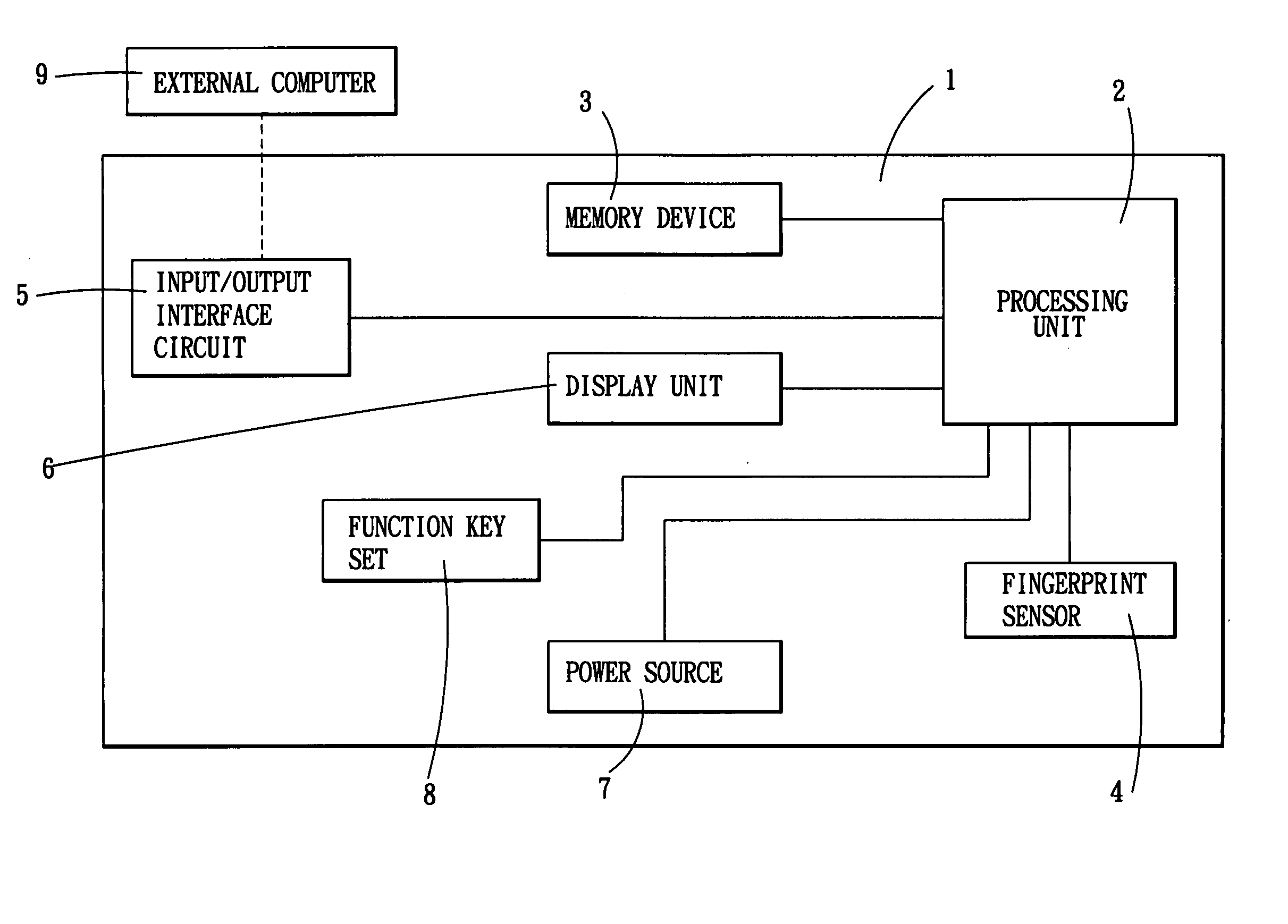

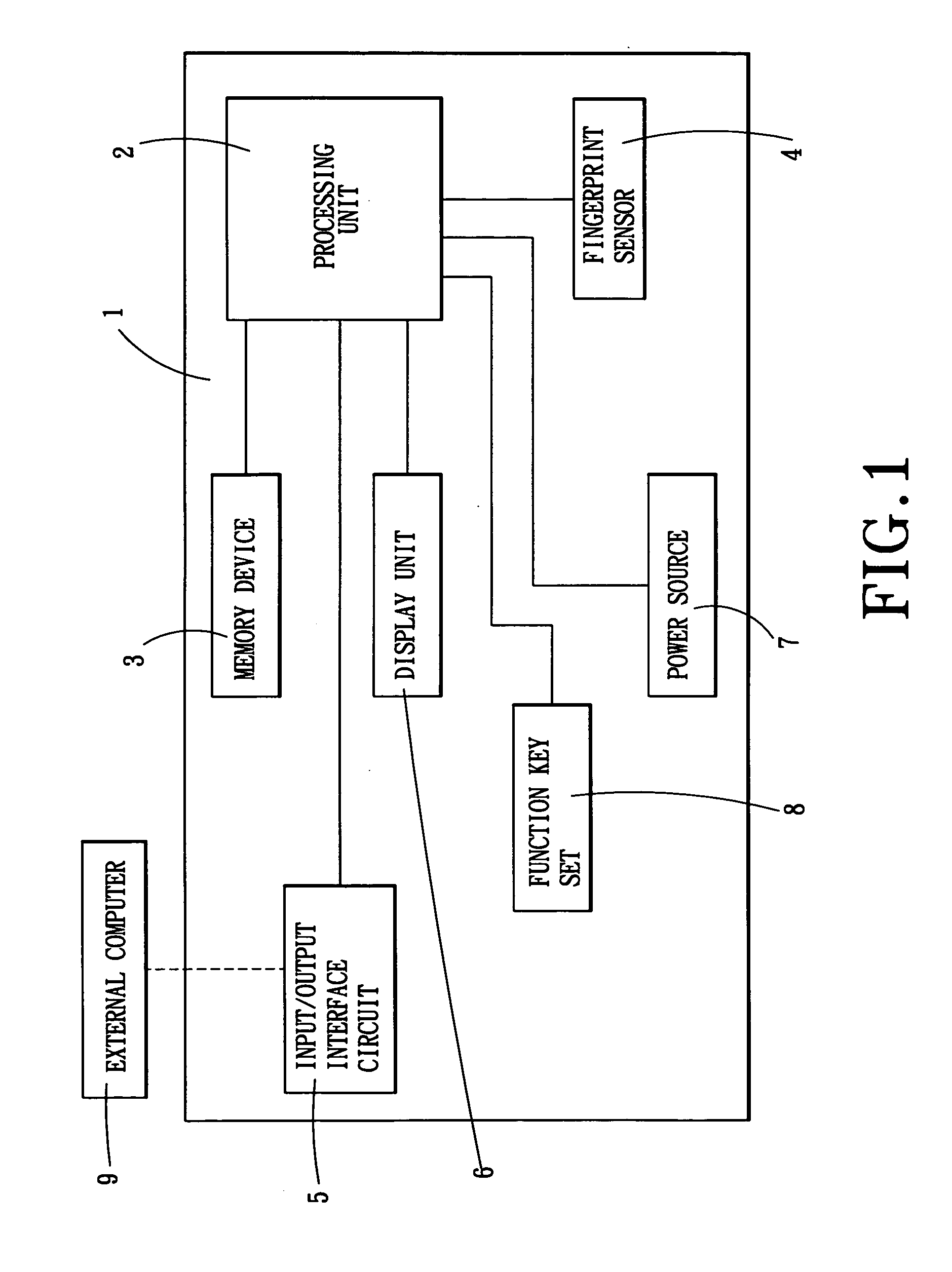

Electronic data storage medium with fingerprint verification capability

Owner:SUPER TALENT TECH CORP

Method and apparatus for refresh management of memory modules

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, dock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller. and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

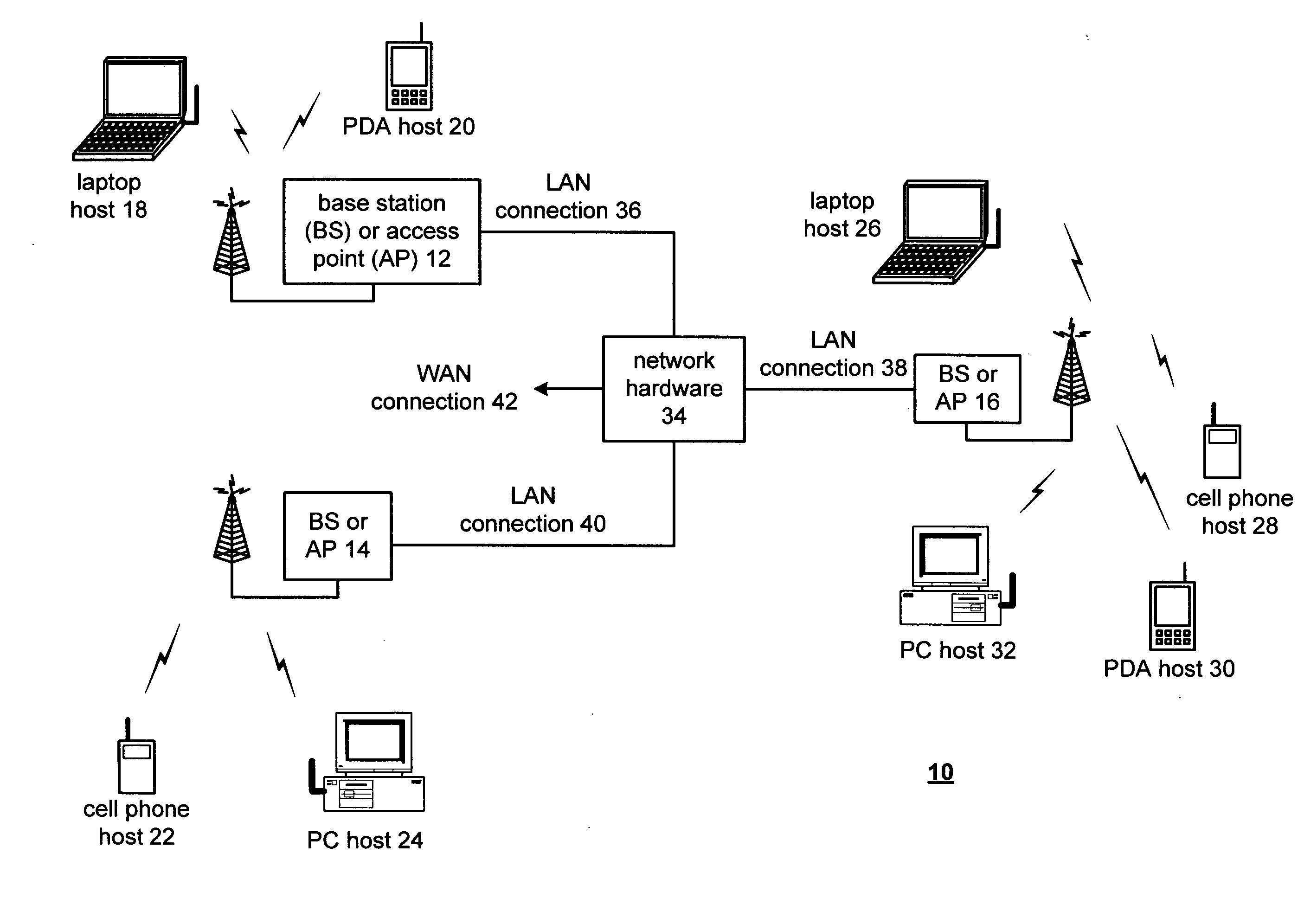

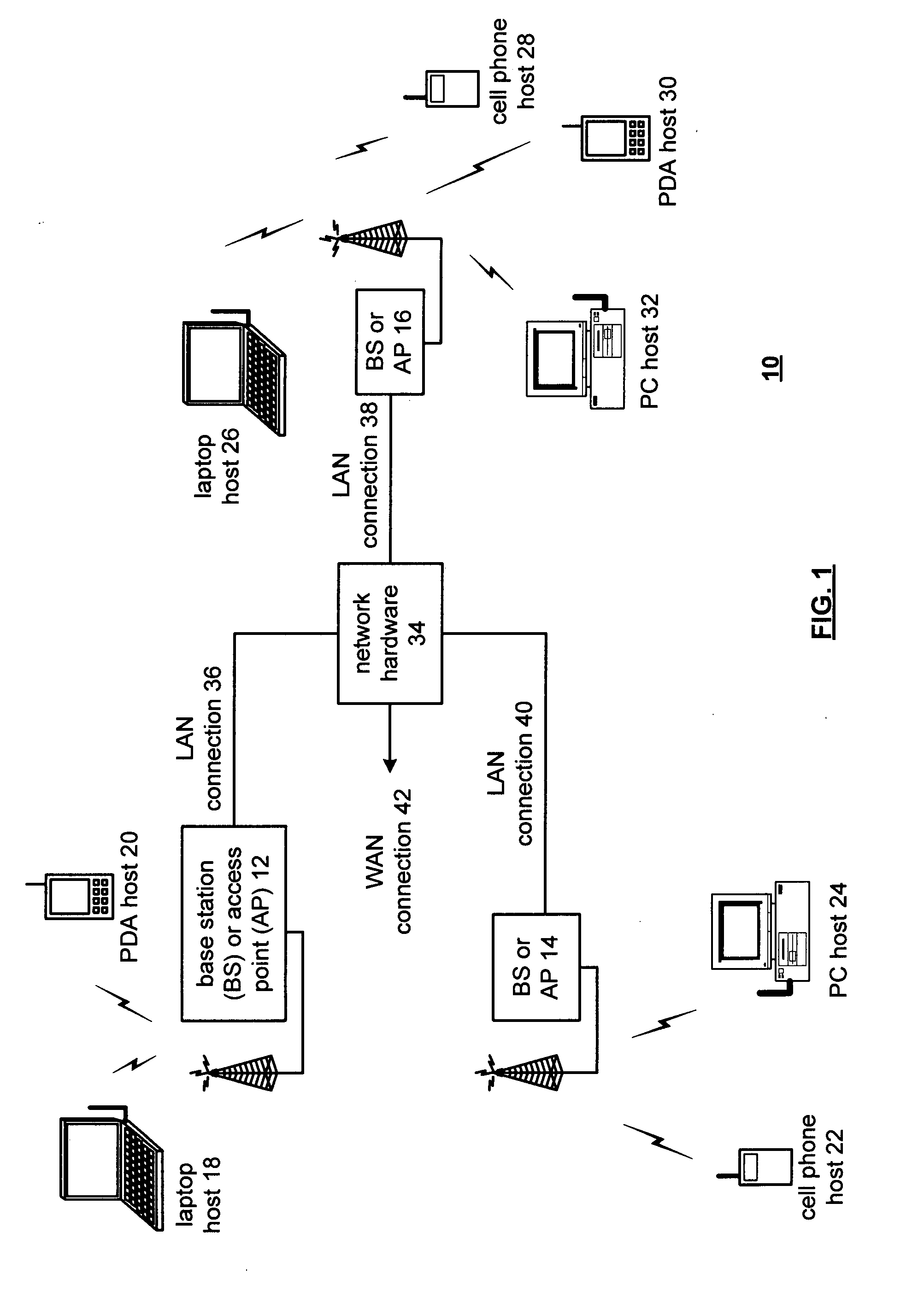

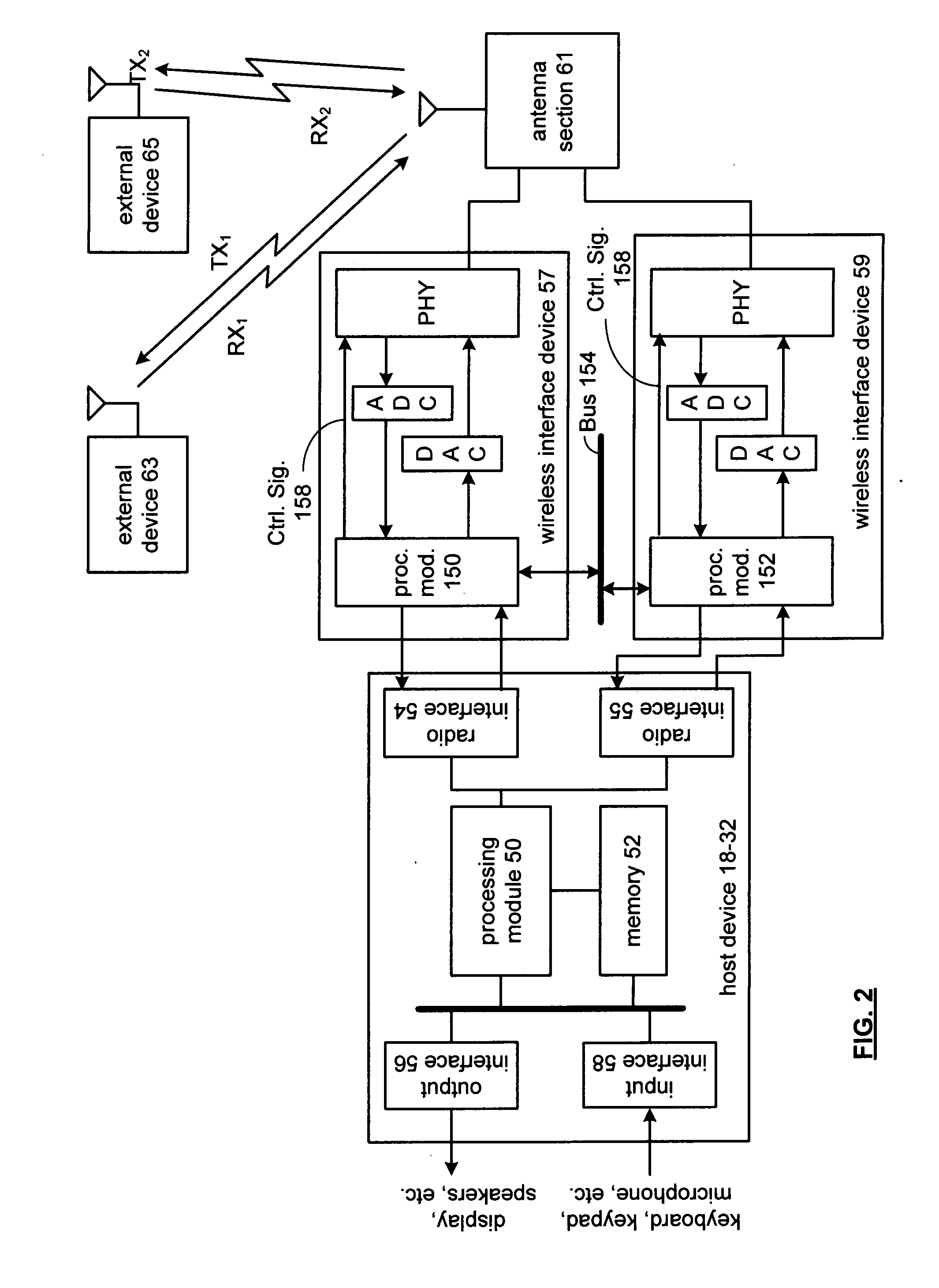

Cooperative transceiving between wireless interface devices of a host device

ActiveUS20080259846A1Network traffic/resource managementTime-division multiplexWireless communication protocolFrequency spectrum

A circuit includes a first wireless interface circuit that transceives packetized data with a first external device in accordance with a first wireless communication protocol. A second wireless interface circuit transceives packetized data with a second external device in accordance with a second wireless communication protocol and wherein the operation of the second wireless interface circuit interferes with the operation of the first wireless interface circuit. A processing module selectively preempts use of the second frequency spectrum by the second external device using a plurality of preemption modes including a first preemption mode and a second preemption mode.

Owner:AVAGO TECH INT SALES PTE LTD

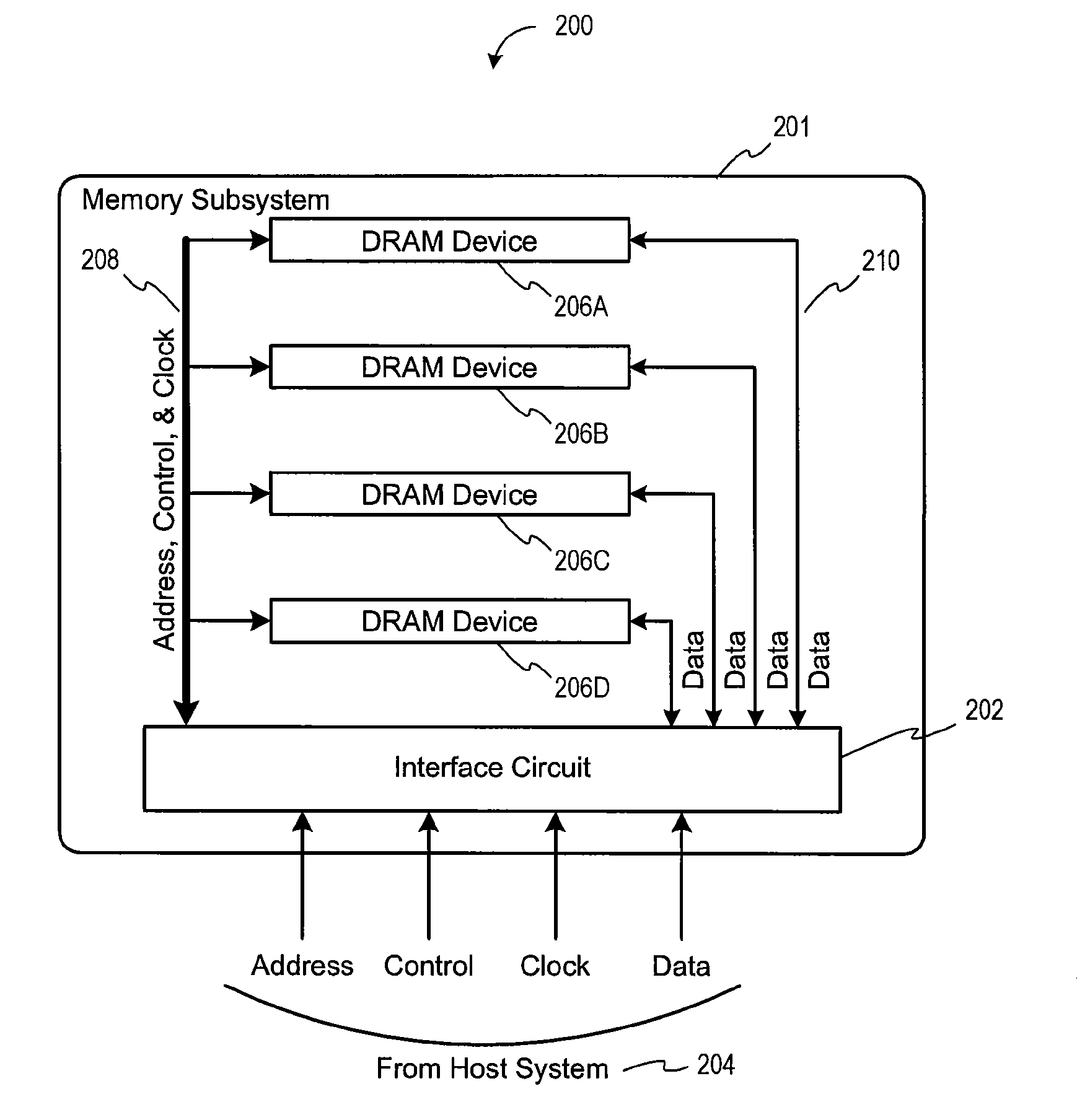

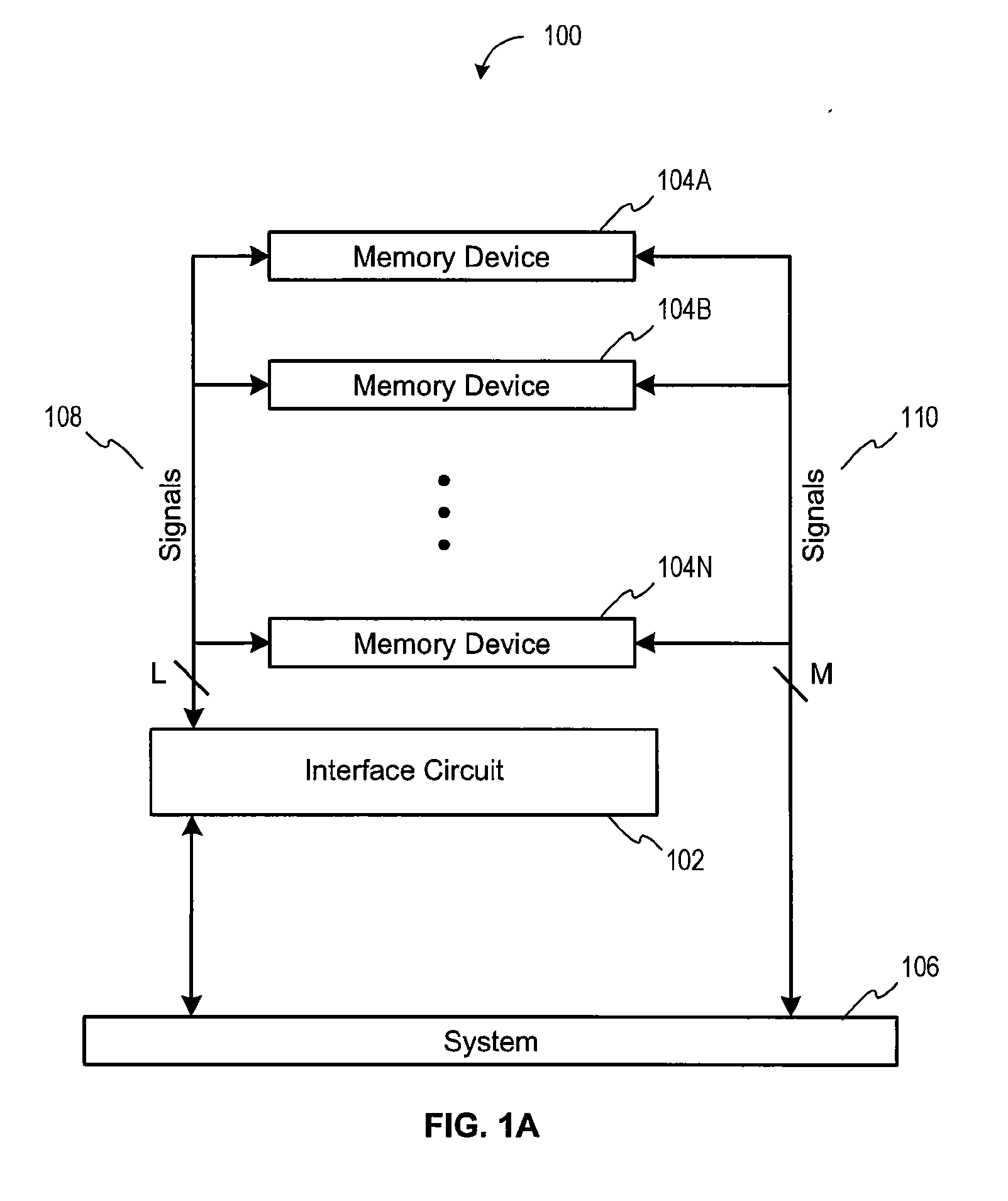

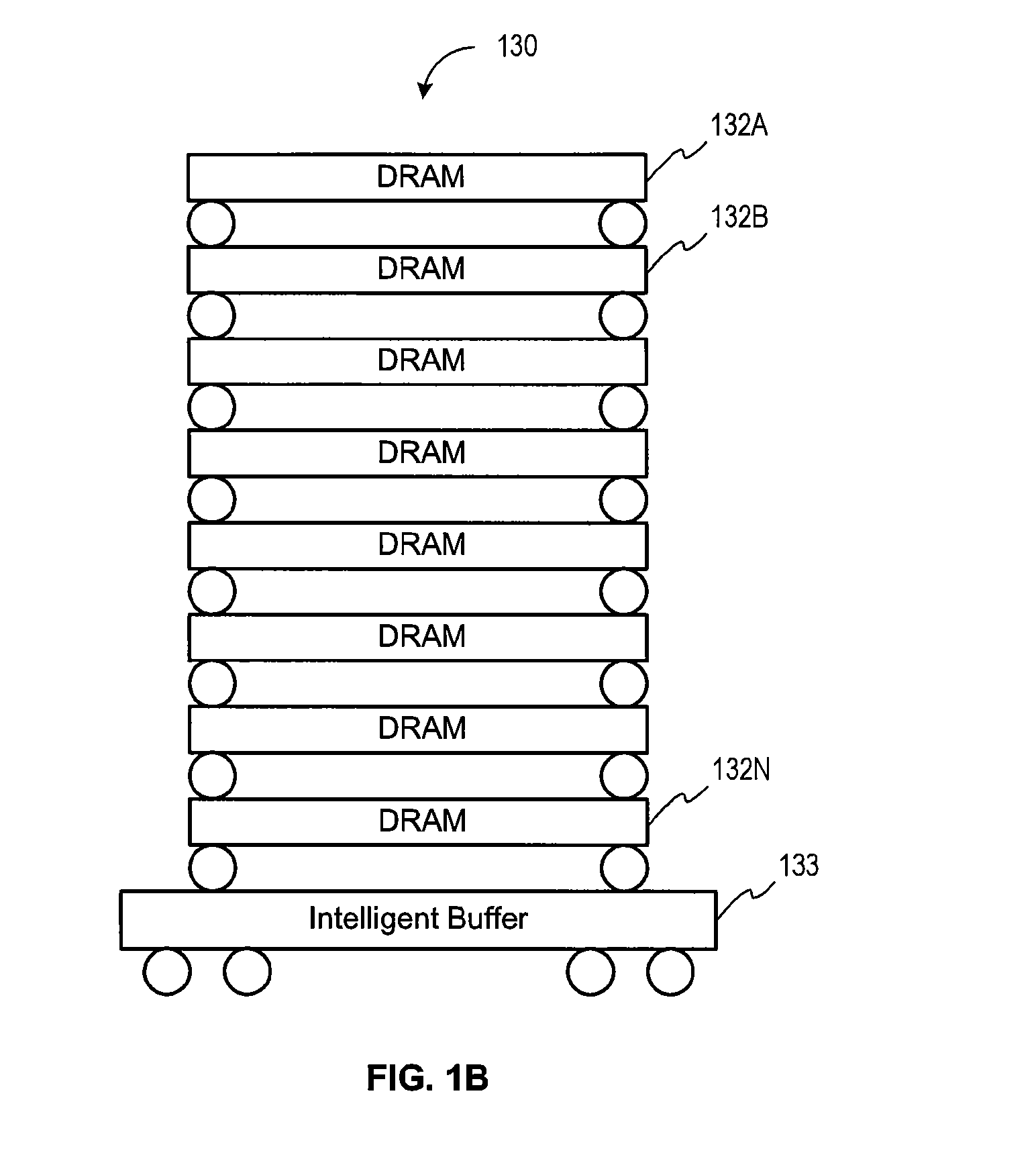

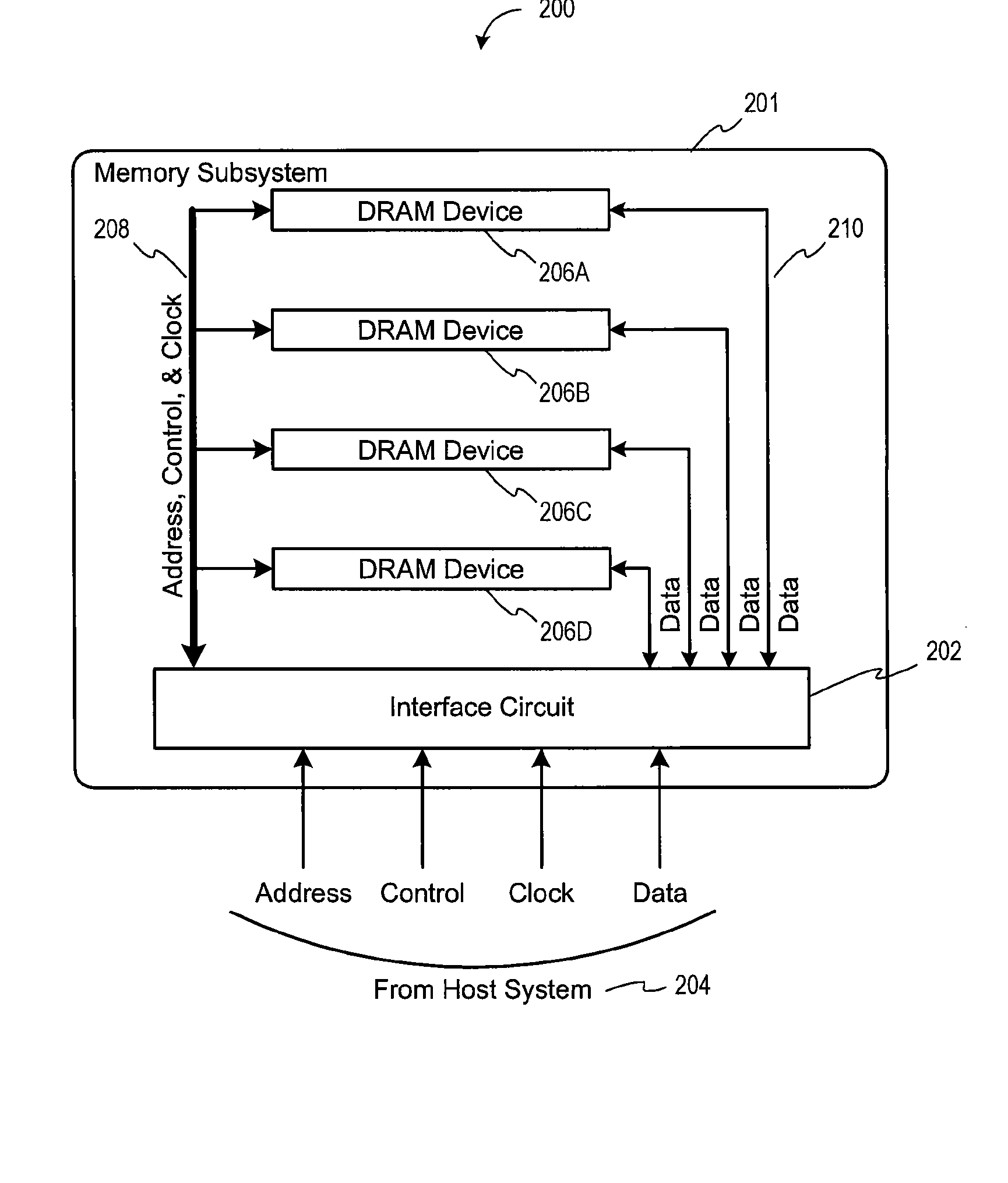

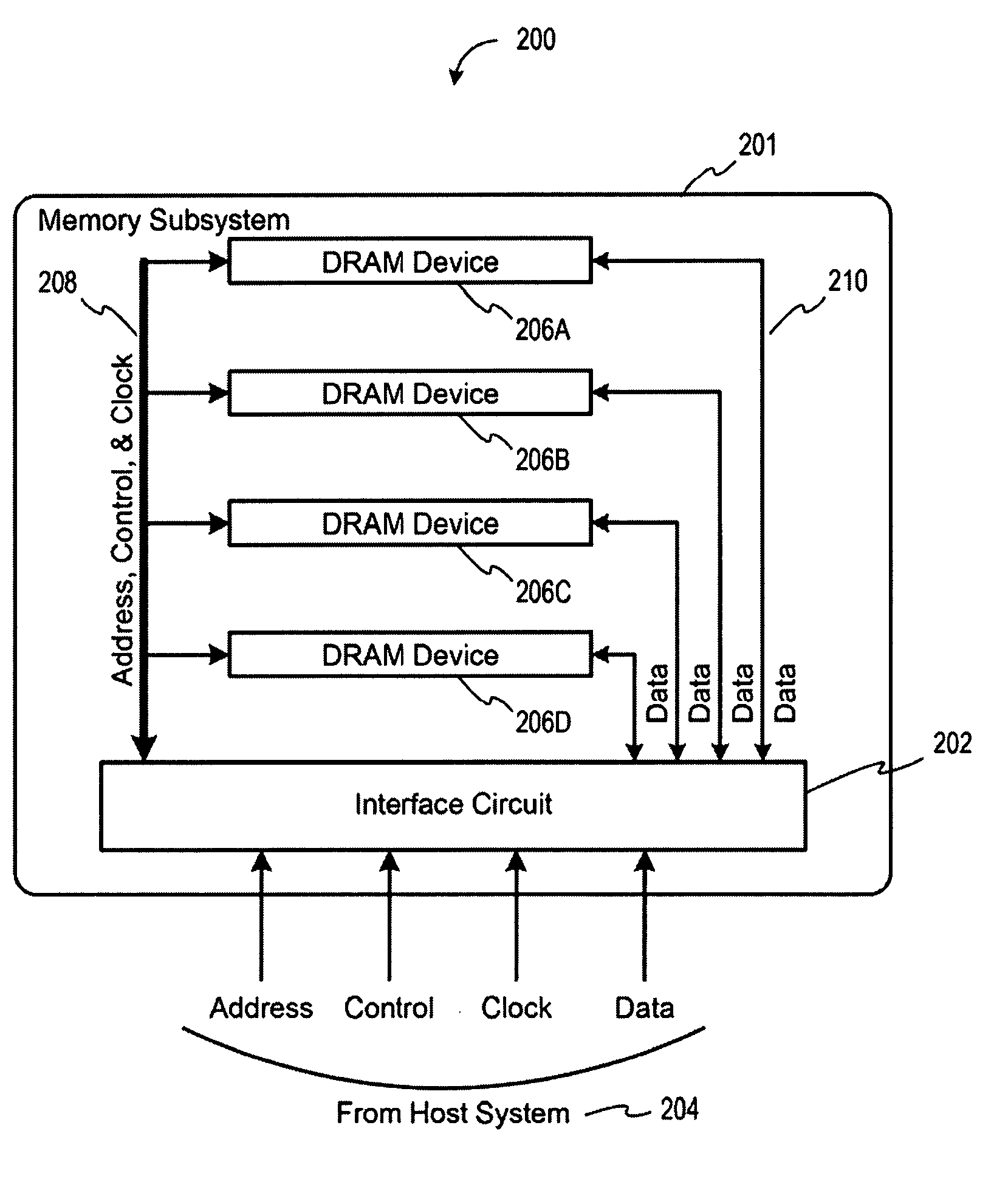

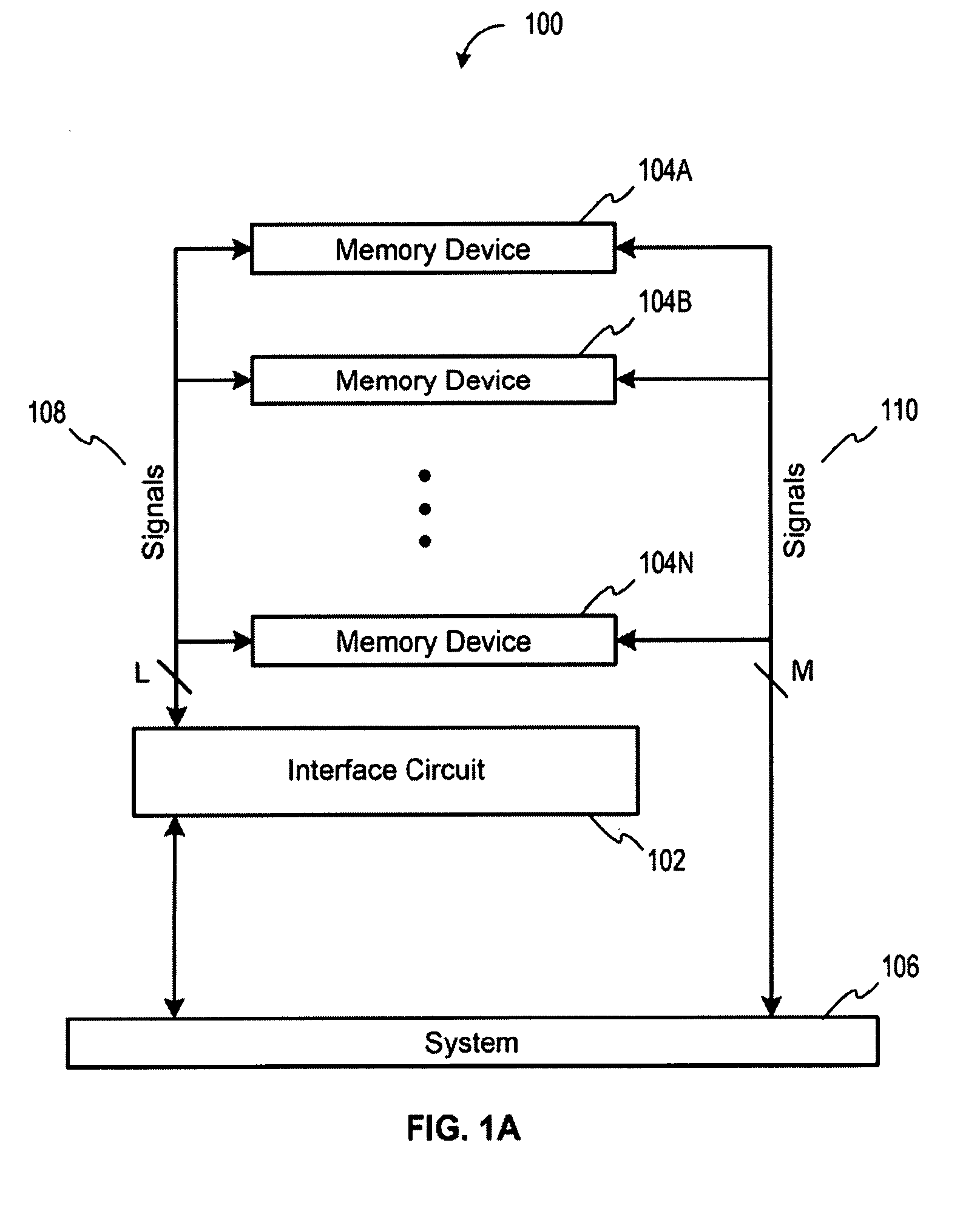

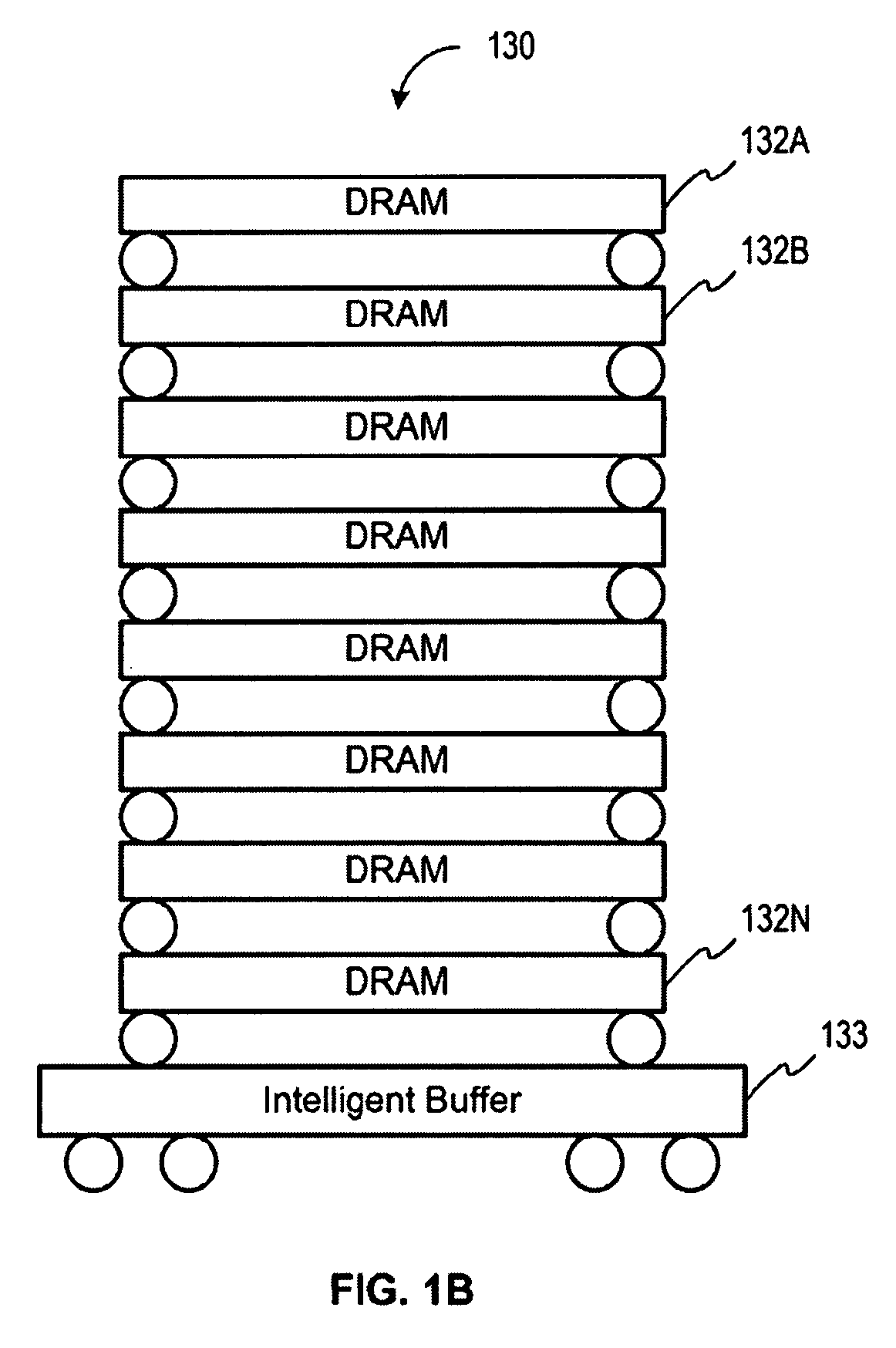

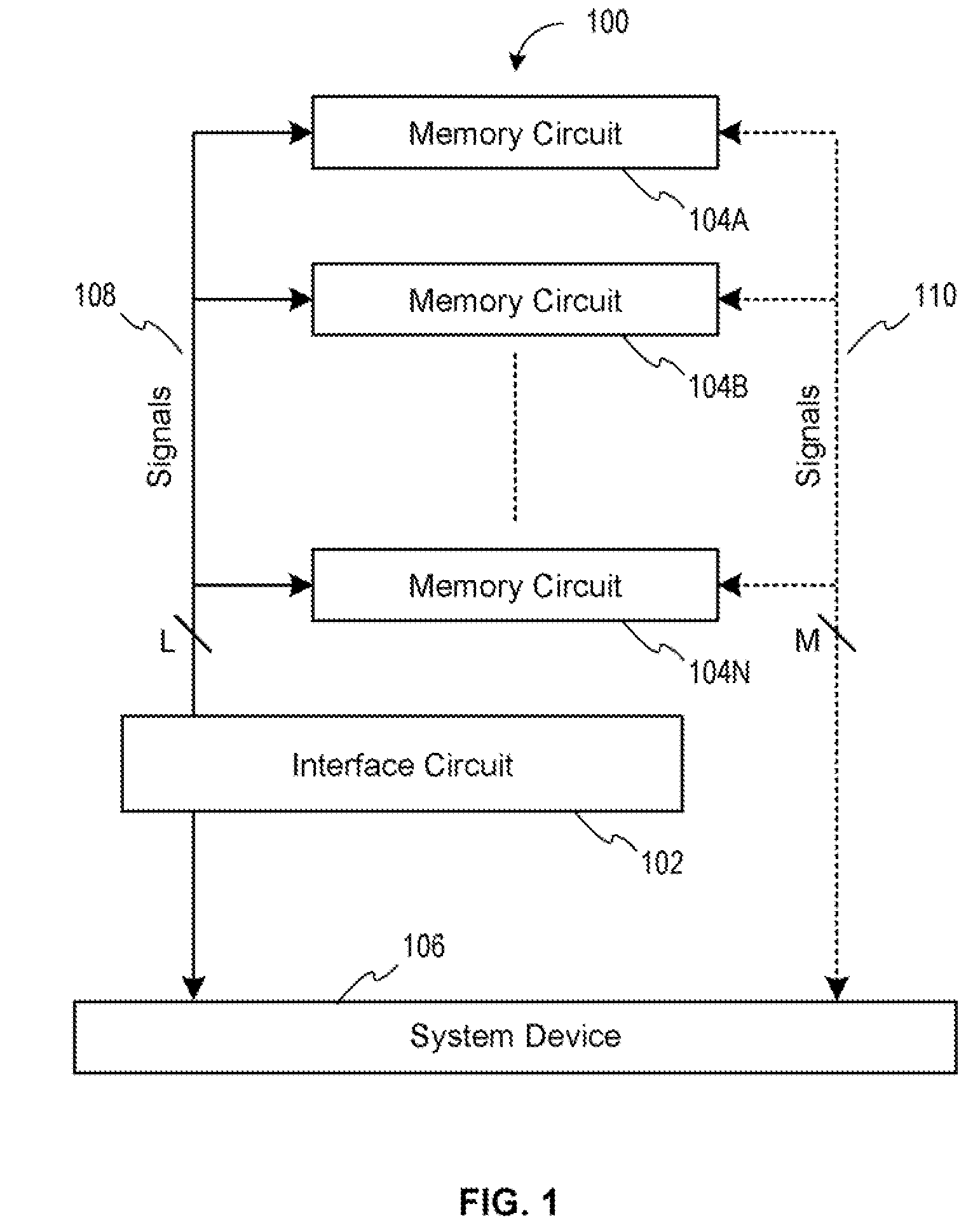

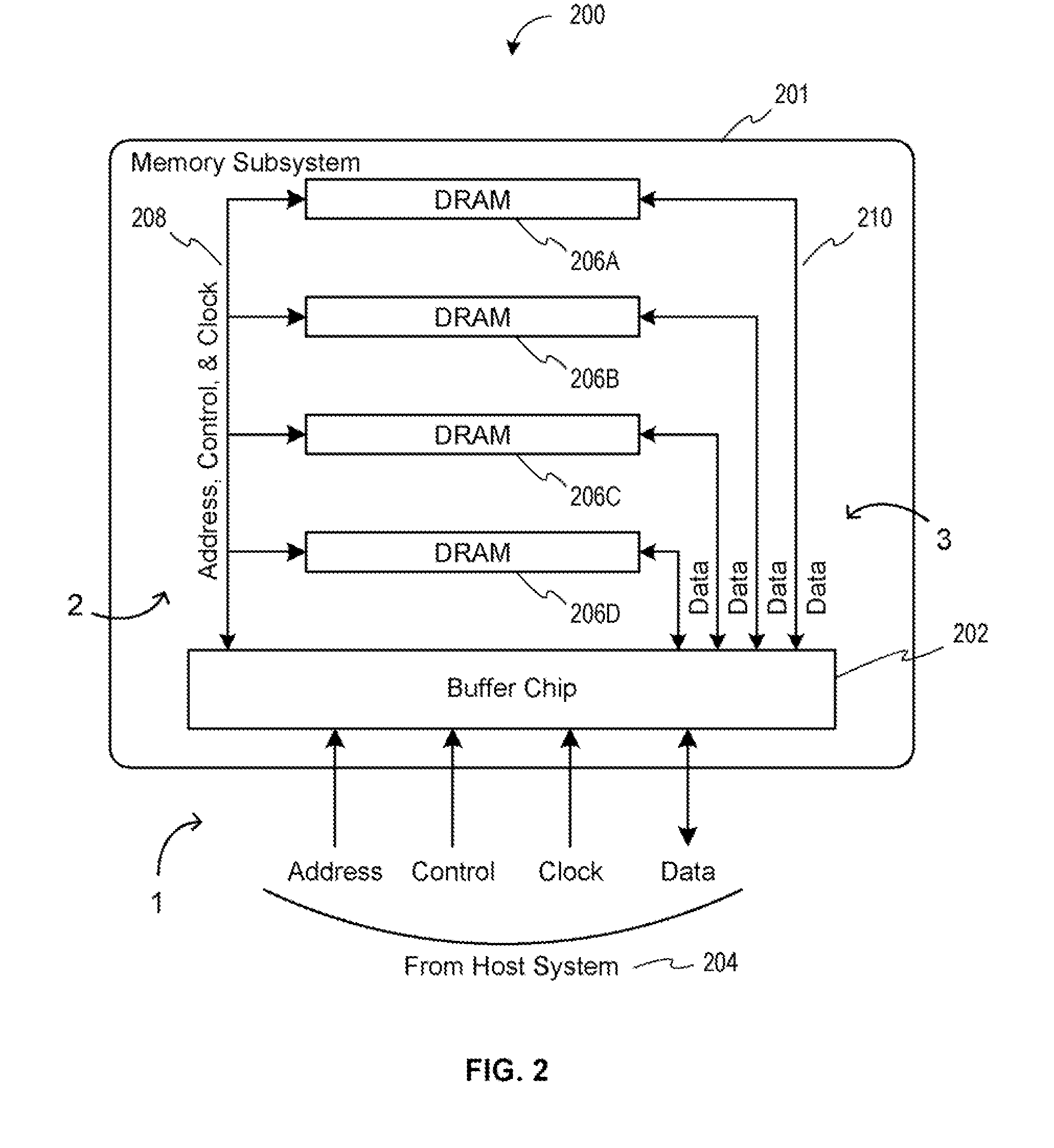

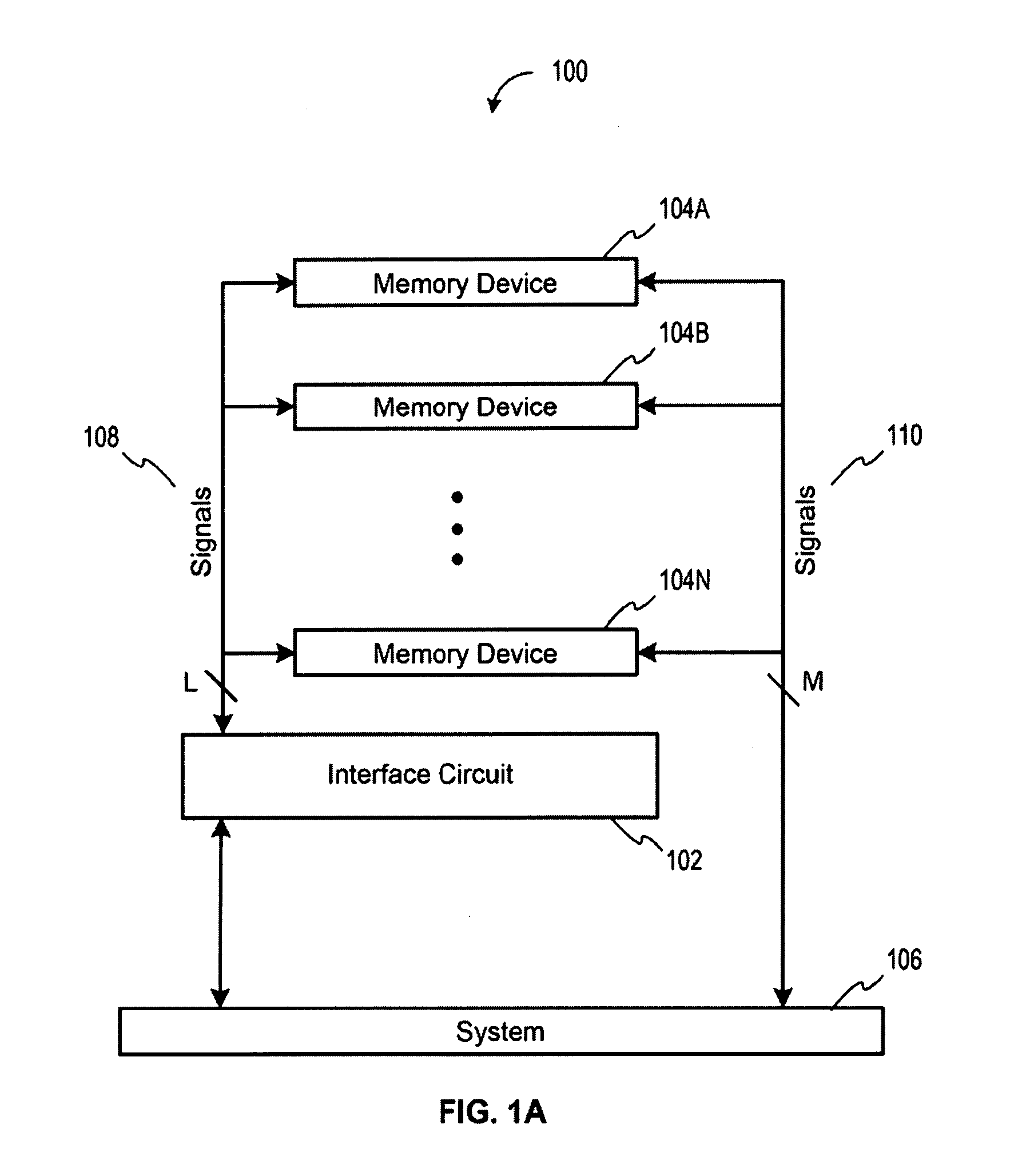

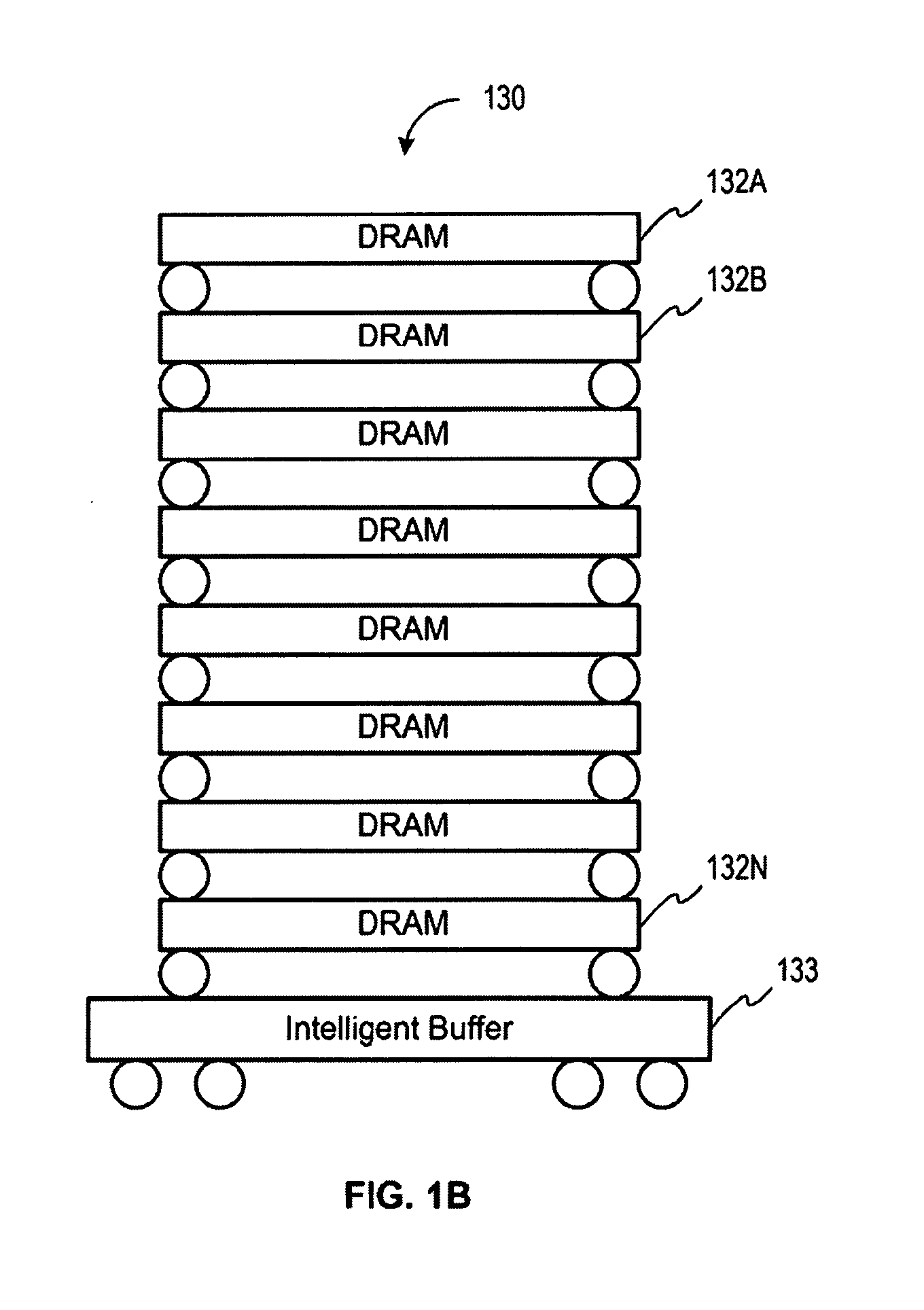

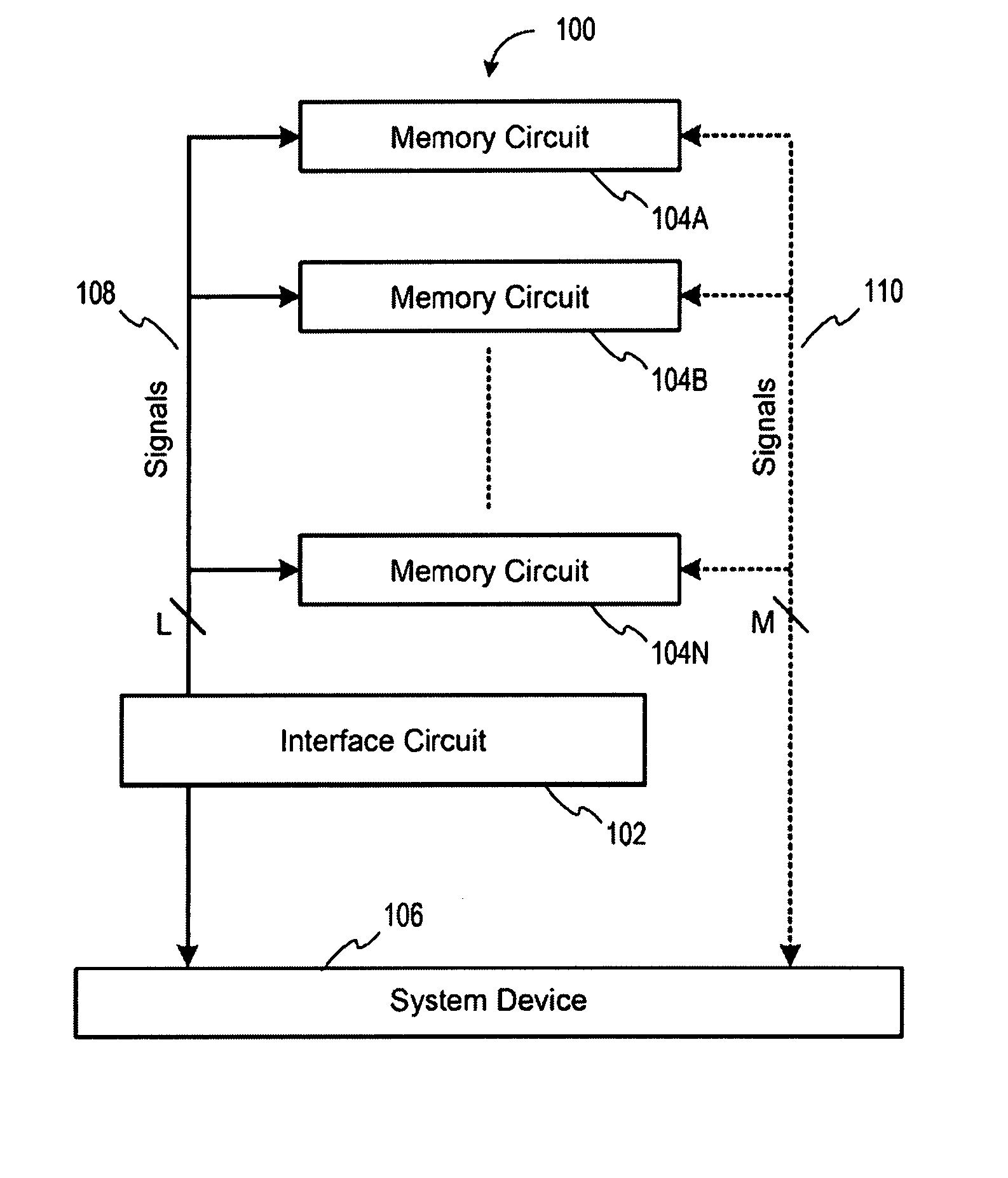

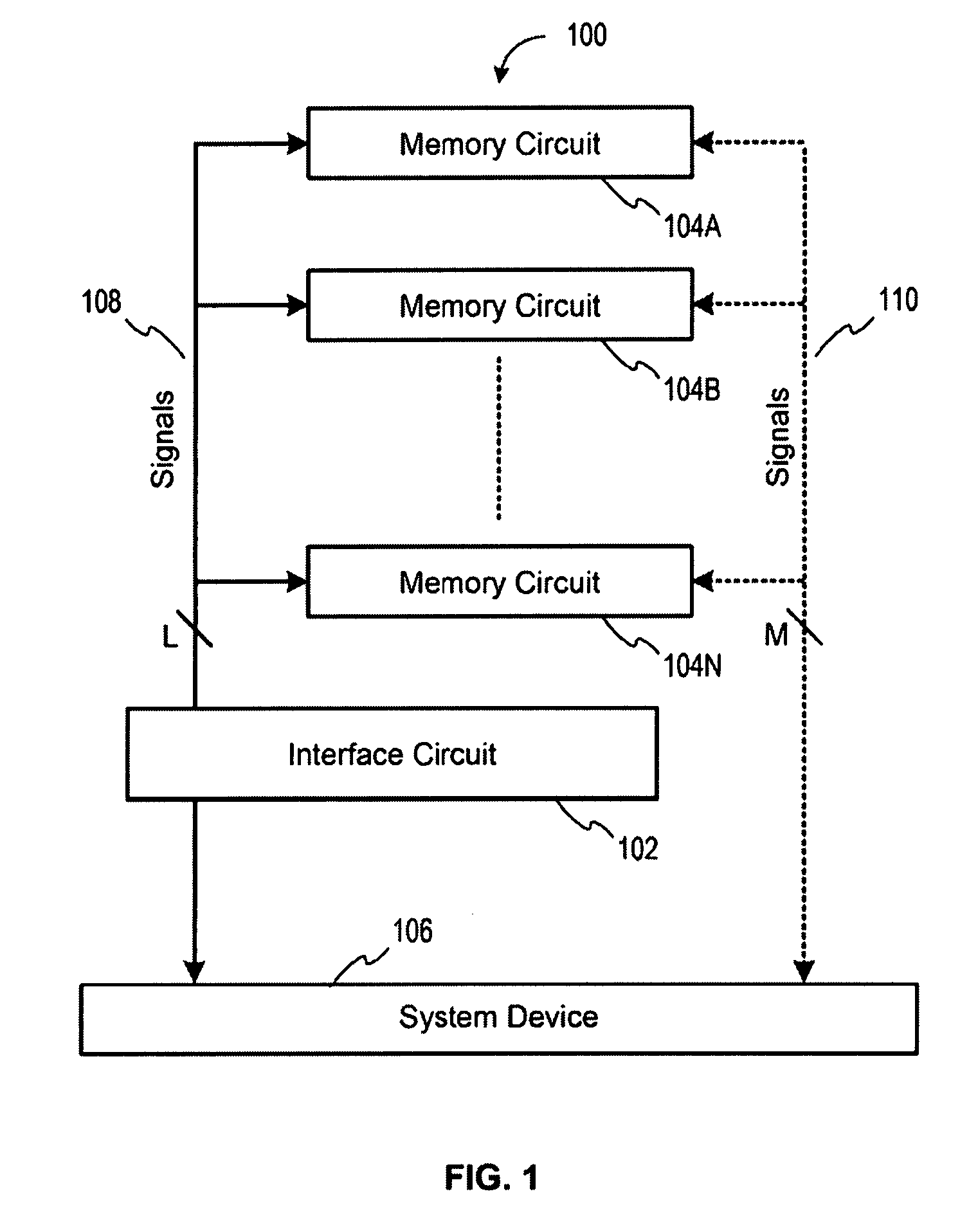

Memory device with emulated characteristics

A memory subsystem is provided including an interface circuit adapted for communication with a system and a majority of address or control signals of a first number of memory circuits. The interface circuit includes emulation logic for emulating at least one memory circuit of a second number.

Owner:GOOGLE LLC

Method and apparatus for refresh management of memory modules

One embodiment sets forth an interface circuit configured to manage refresh command sequences that includes a system interface adapted to receive a refresh command from a memory controller, clock frequency detection circuitry configured to determine the timing for issuing staggered refresh commands to two or more memory devices coupled to the interface circuit based on the refresh command received from the memory controller, and at least two refresh command sequence outputs configured to generate the staggered refresh commands for the two or more memory devices

Owner:GOOGLE LLC

Memory device with emulated characteristics

A memory subsystem is provided including an interface circuit adapted for communication with a system and a majority of address or control signals of a first number of memory circuits. The interface circuit includes emulation logic for emulating at least one memory circuit of a second number.

Owner:GOOGLE LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com