Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

10815results about "Building locks" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

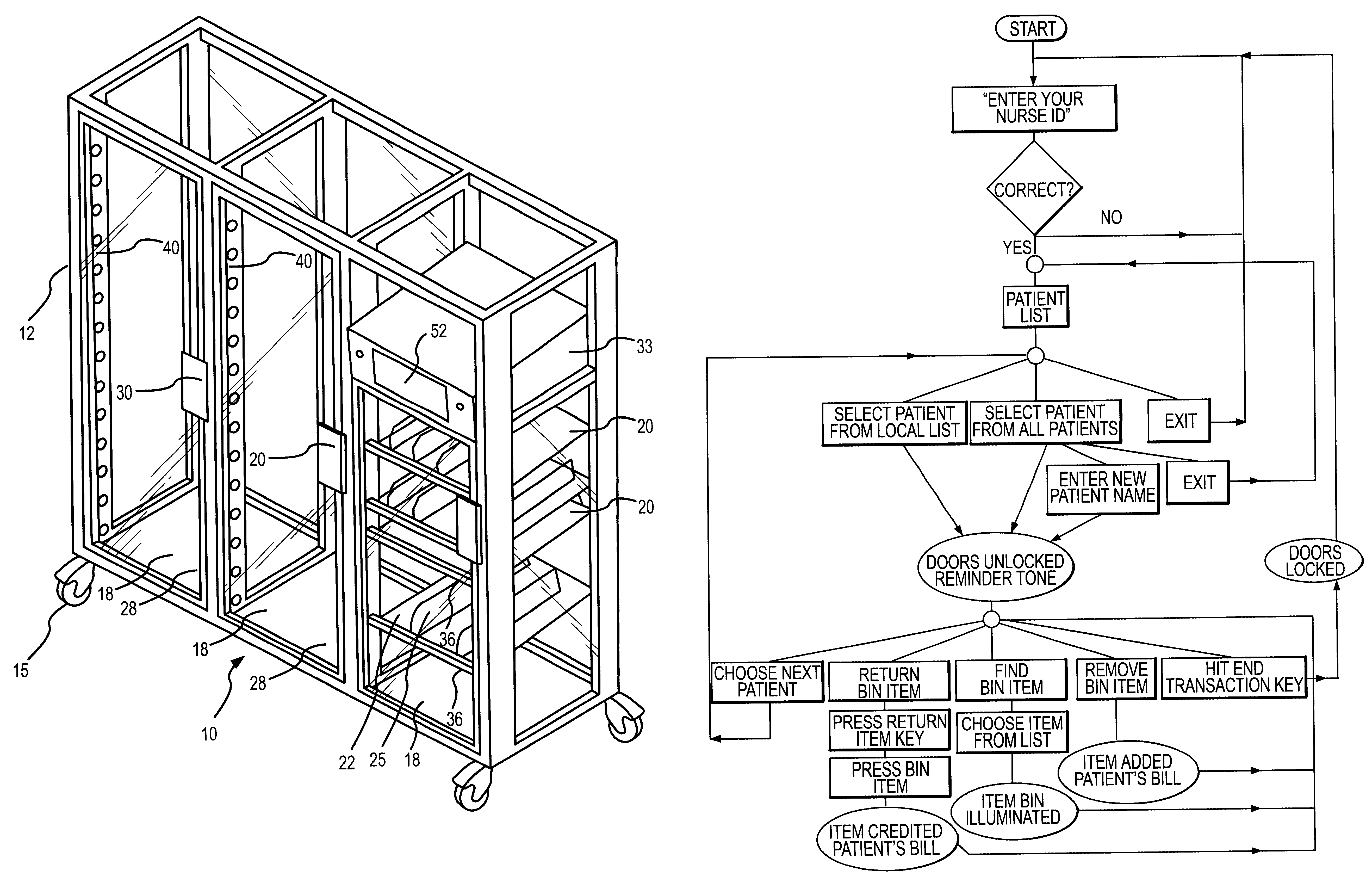

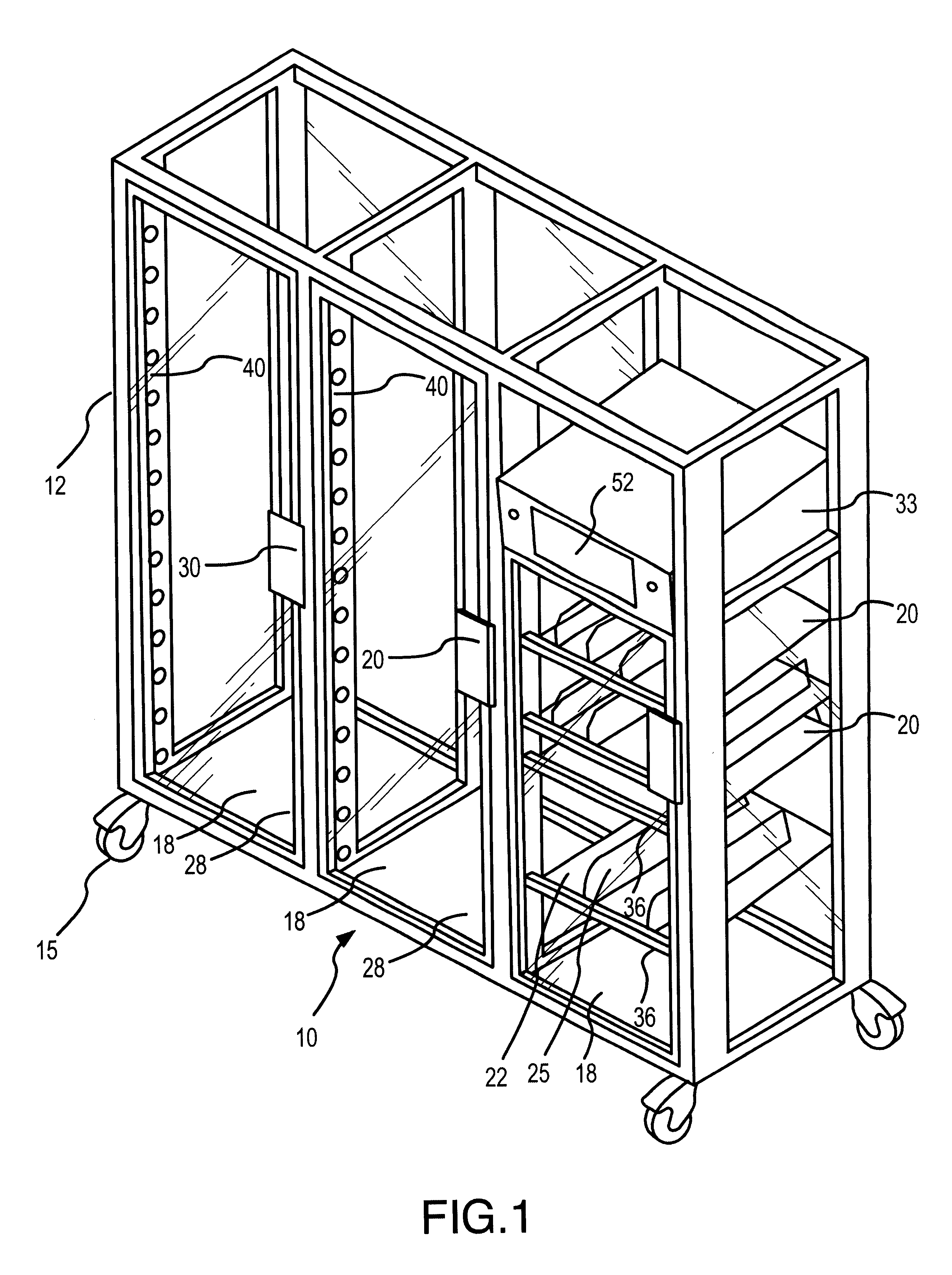

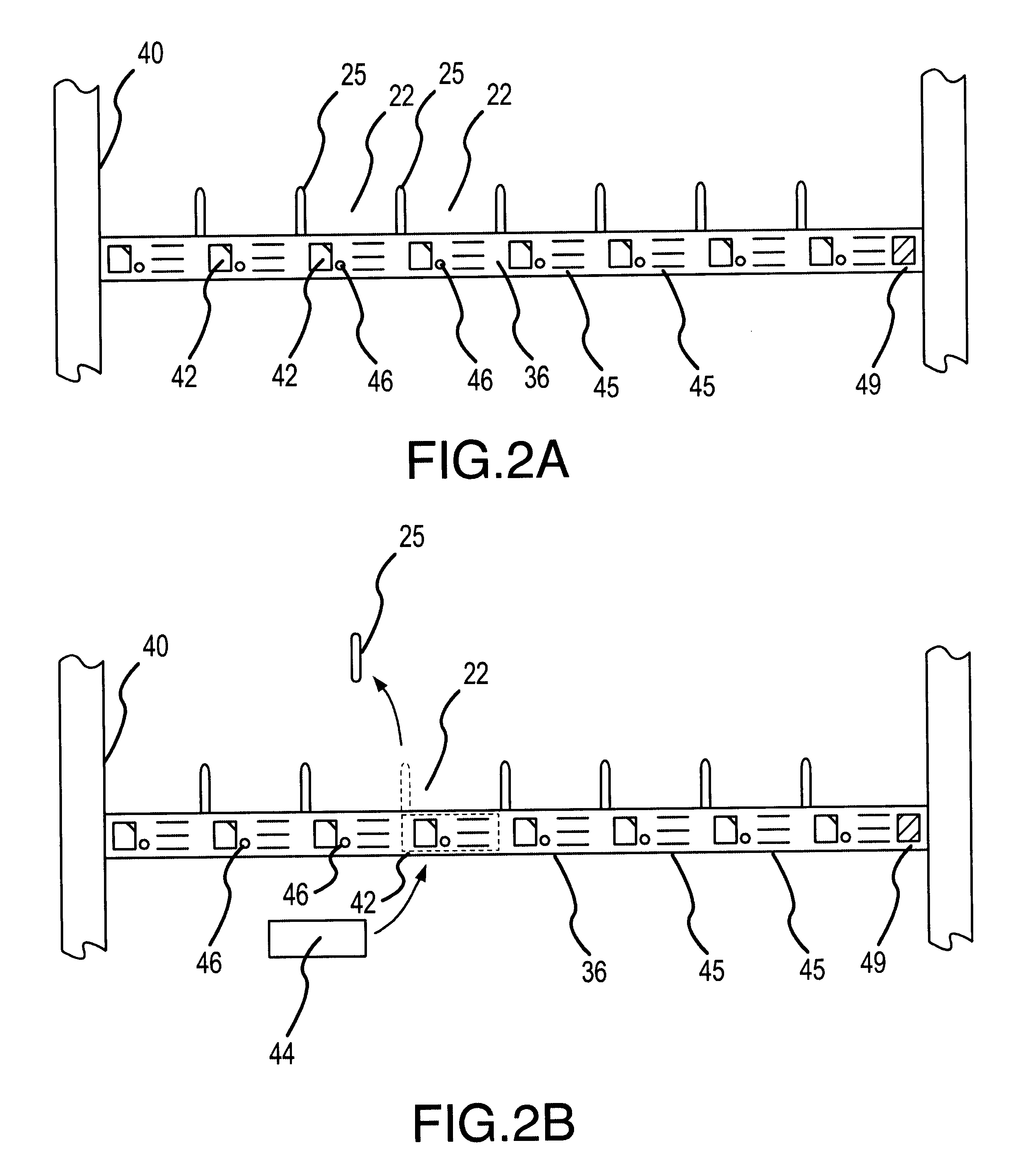

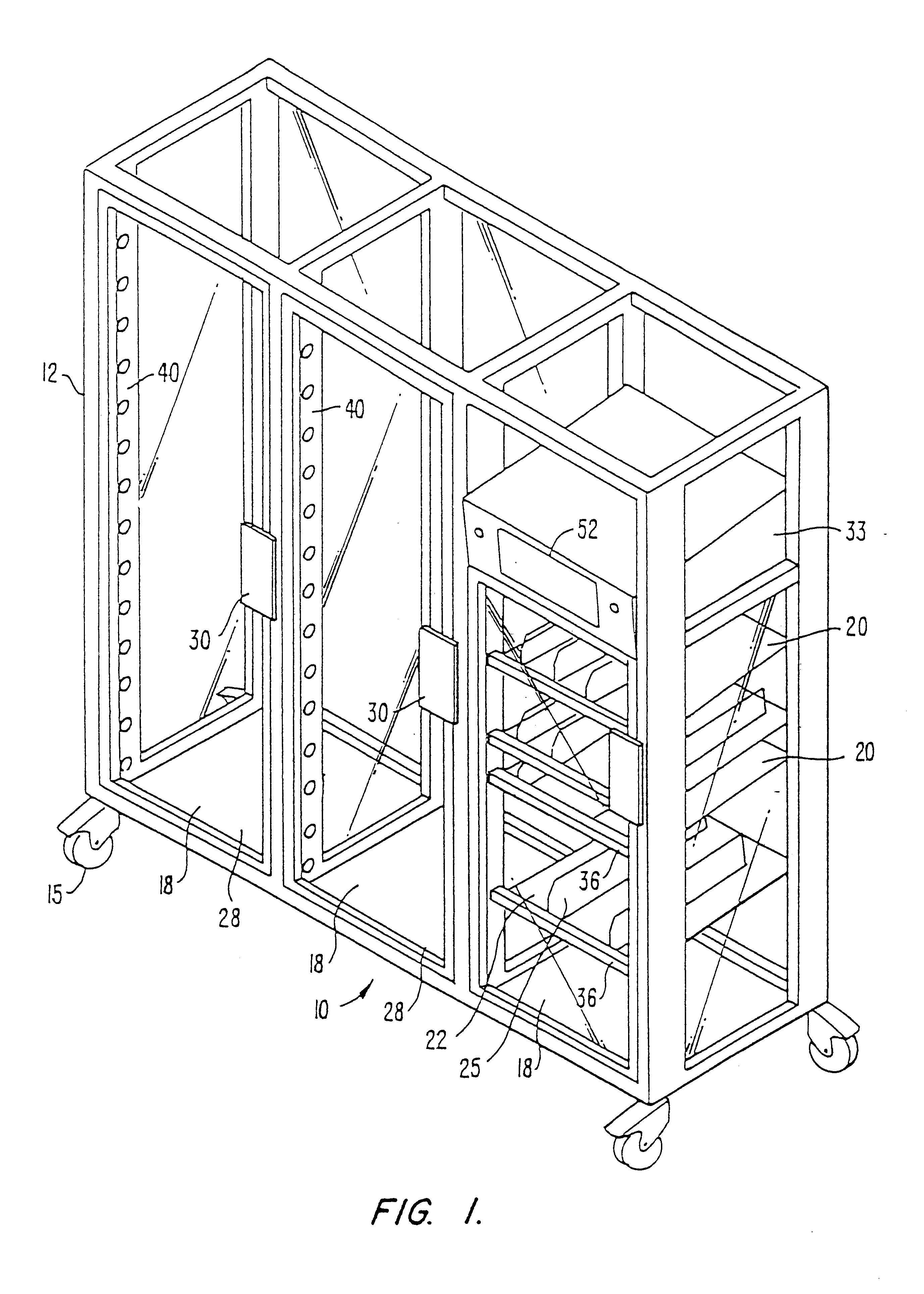

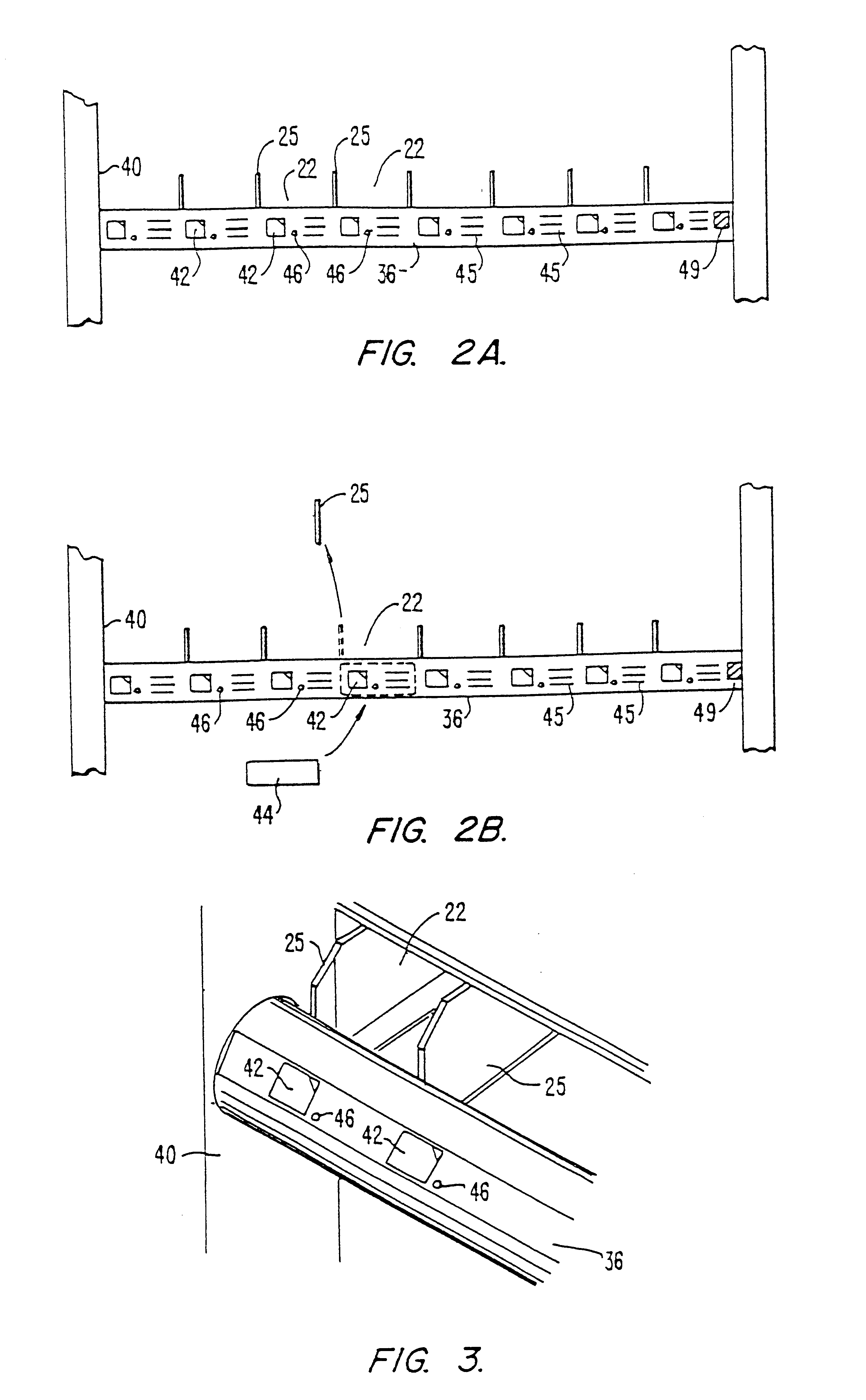

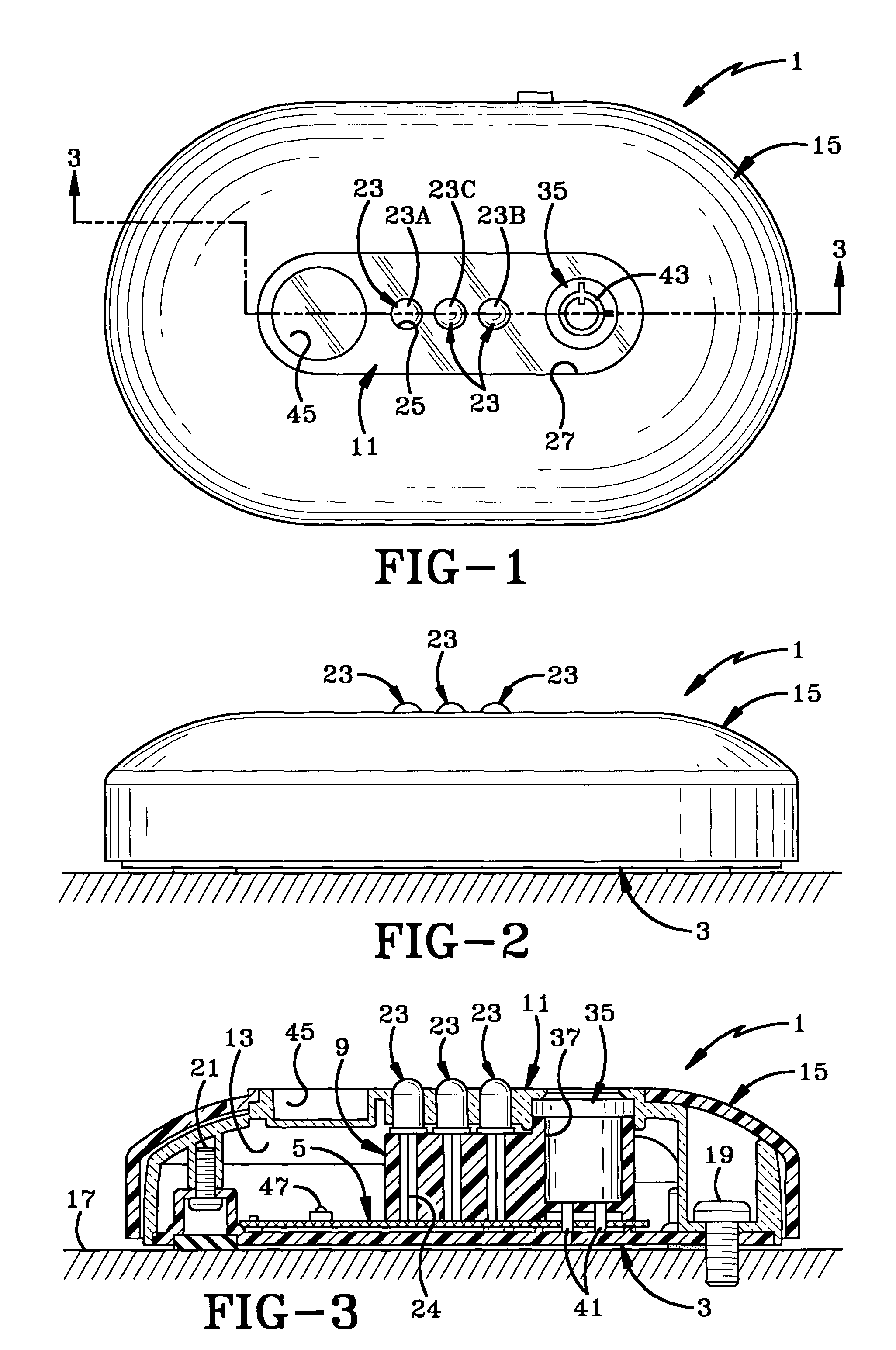

Methods and apparatus for dispensing items

InactiveUS6609047B1Credit registering devices actuationDiagnosticsLight-emitting diodeComputer science

The invention provides methods and apparatus for dispensing items from a dispensing unit. According to the invention, the dispensing unit comprises a plurality of locations in which the items are held, a processor in which records corresponding to the items on the unit are stored, and a plurality of item switches corresponding to the locations in which the items are held. The item switches are connected to the processor so that a user of the dispensing unit can input records of items removed from the unit into the processor. The apparatus described is particularly suited for dispensing medical supplies although the apparatus will be usable for other types of items as well. Preferred embodiments will include a plurality of visual indicators, typically in the form of light emitting diodes, corresponding to the locations in which the items are held. Upon selection of a desired item from a list of items held by the unit, the visual indicator corresponding to the item is actuated so that the user can locate the desired item quickly and conveniently with the help of the visual indicator.

Owner:OMNICELL

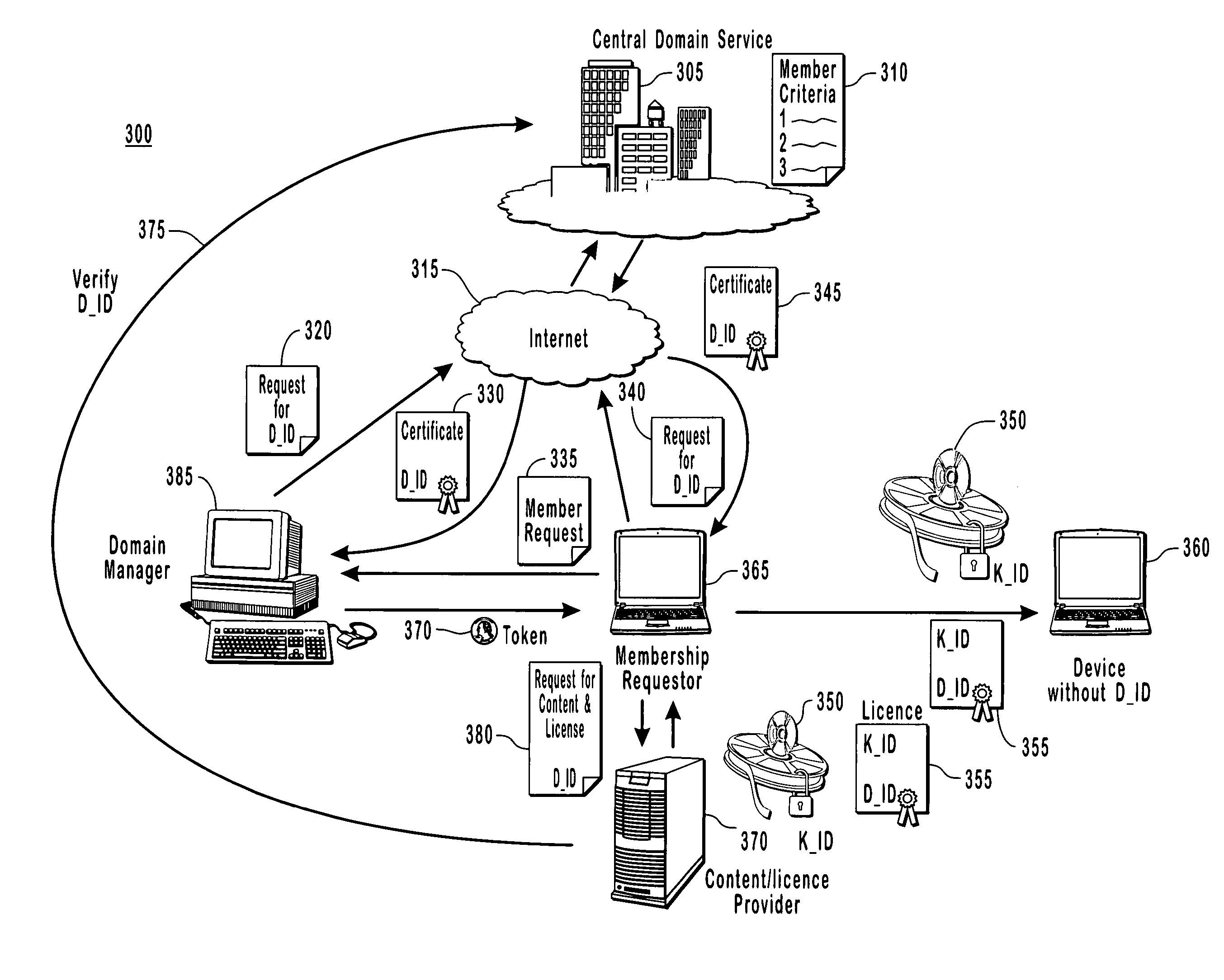

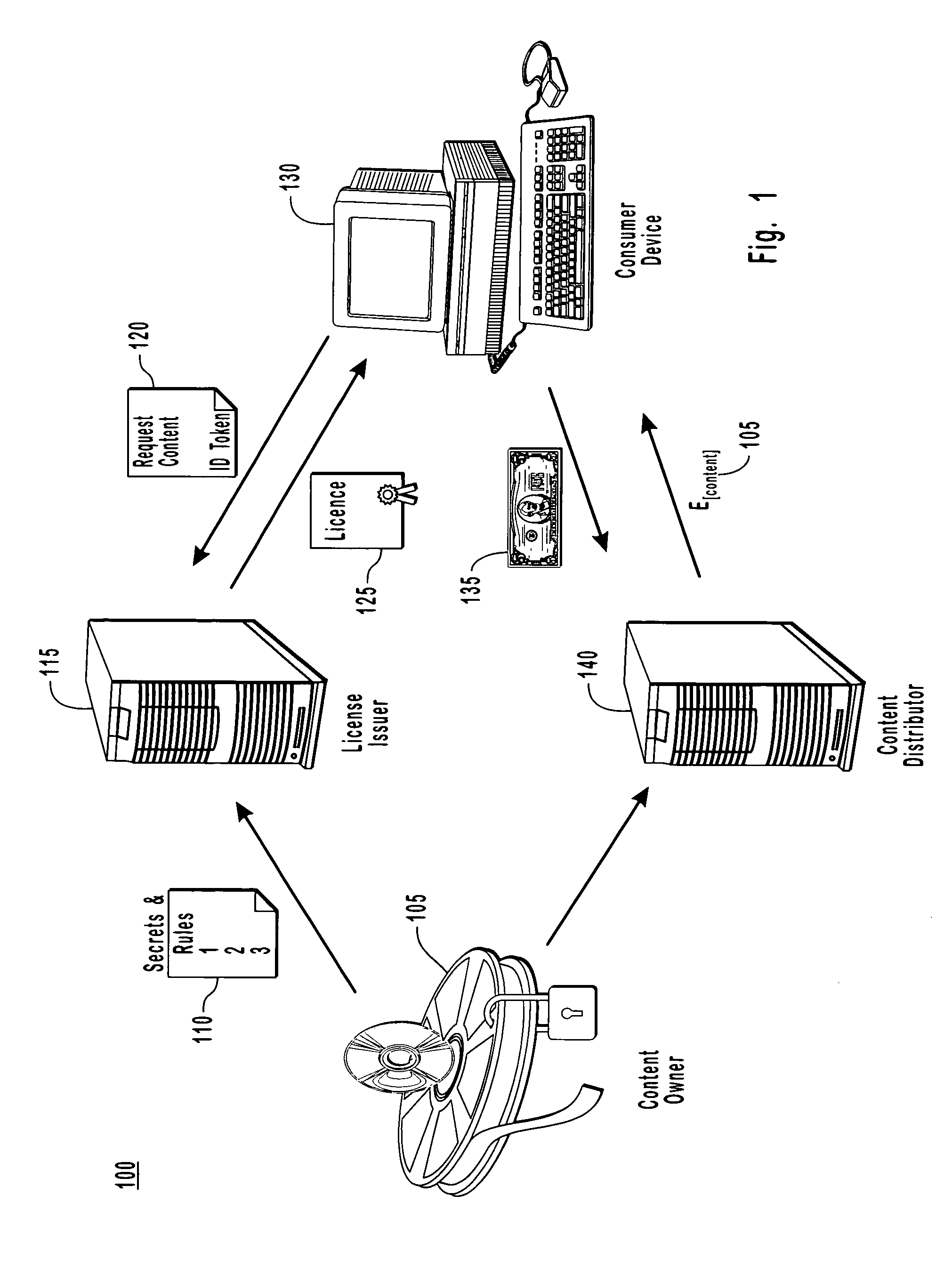

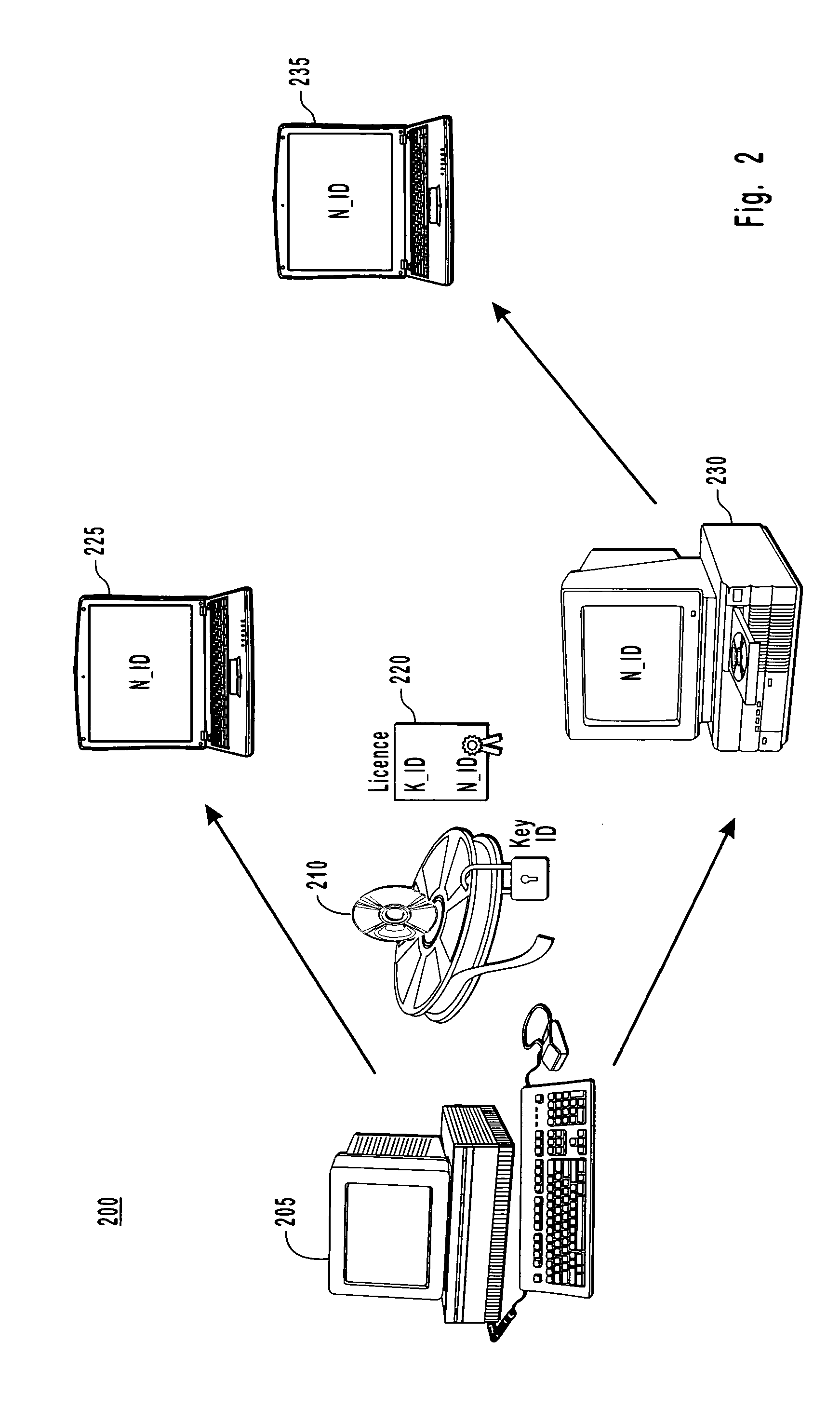

Binding content to a domain

The present invention provides for a digital rights management system with a centralized domain service capable of creating and managing membership criteria for joining a domain in accordance with business rules defined by ac content owner. A domain identification is created that allows a content provider to uniquely bind content licenses to a domain. The content licenses include usage rights that define how content associated with the licenses may be consumed by one or more members of the domain. The centralized domain service can enforce digital rights by validating membership criteria including at least one of a domain proximity check for validating that a requestor is in close proximity to the domain, a total number of requestors, or the frequency that the requests have been made by various requesters to join the domain and unjoin from the domain.

Owner:ZHIGU HLDG

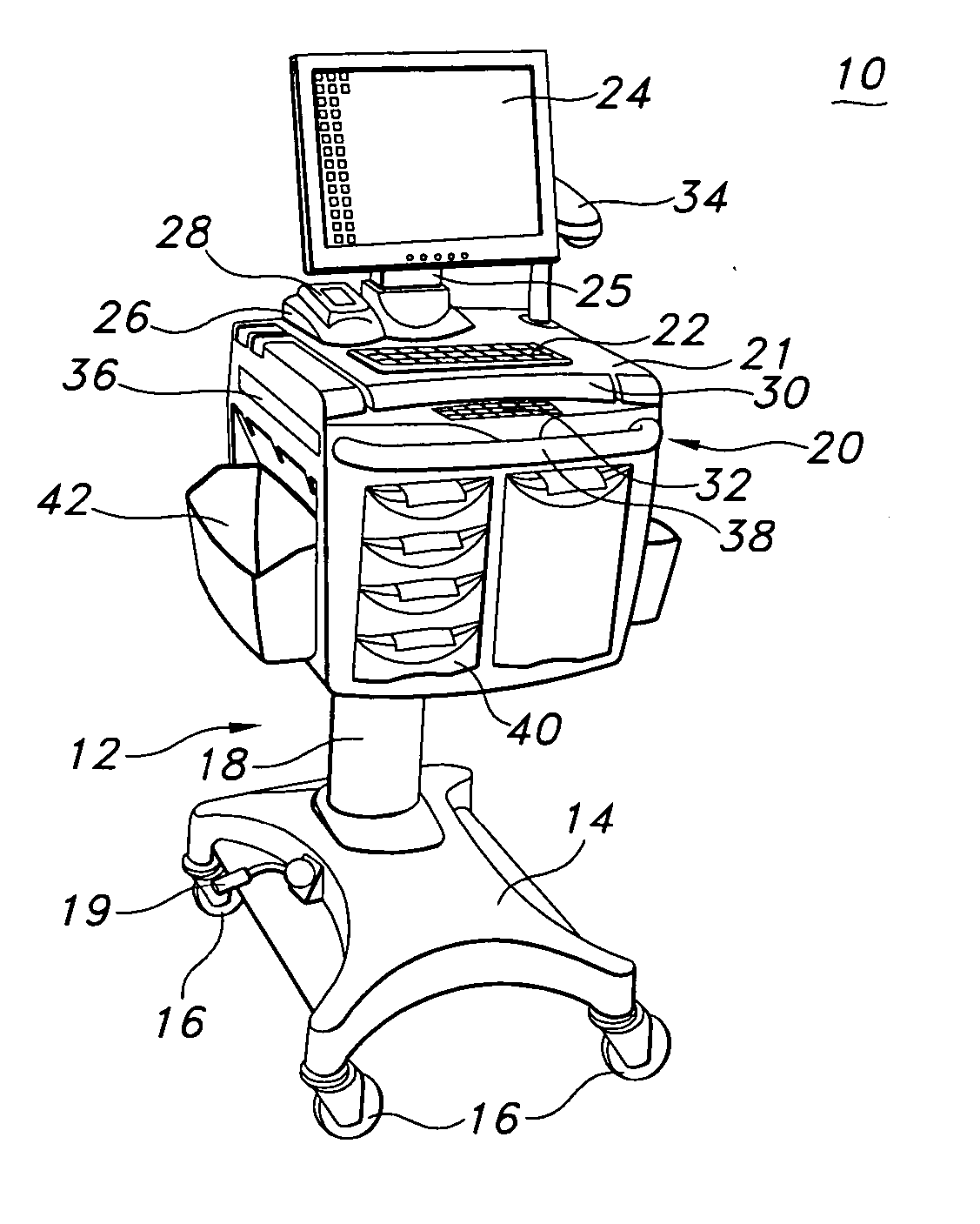

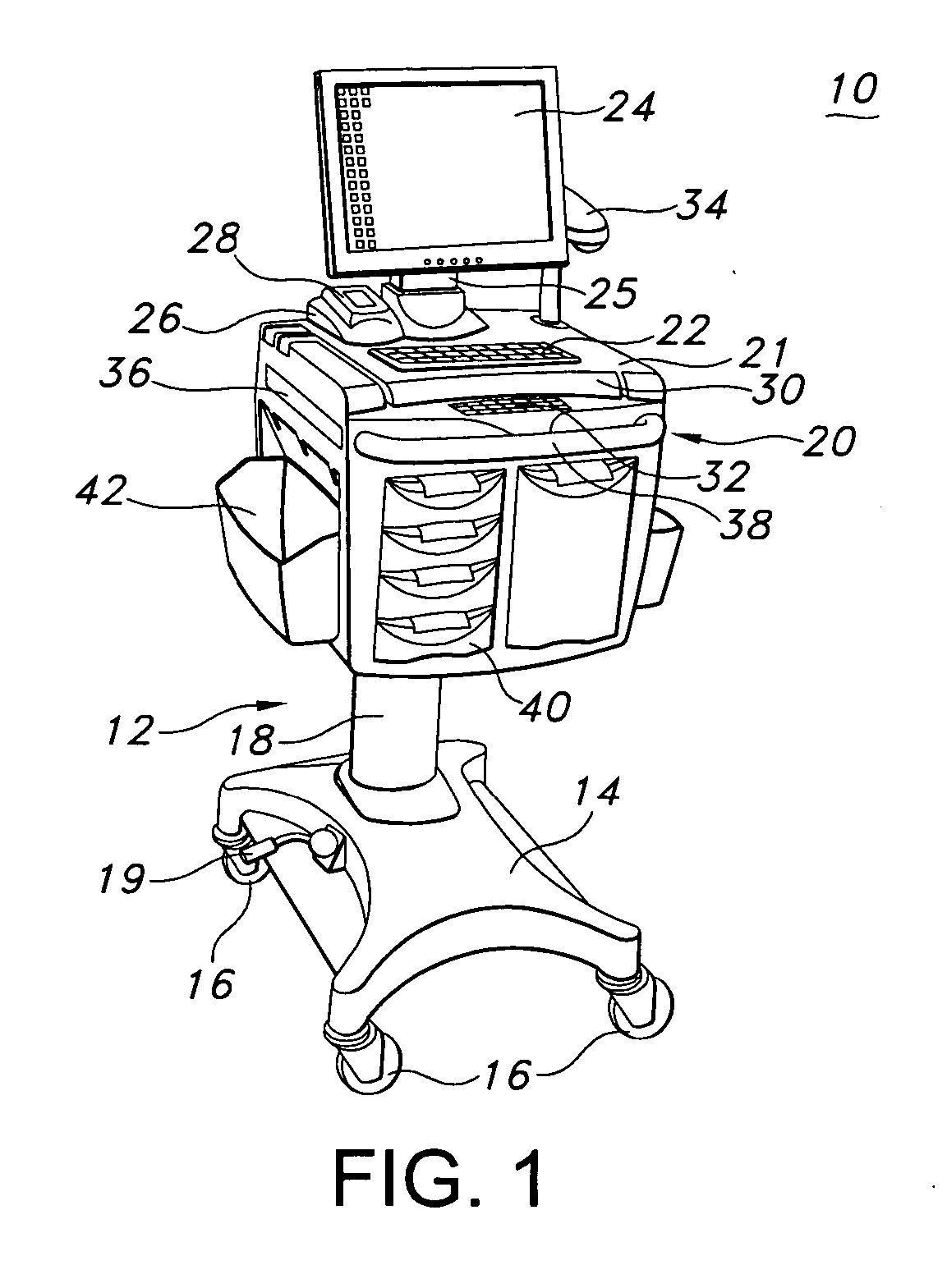

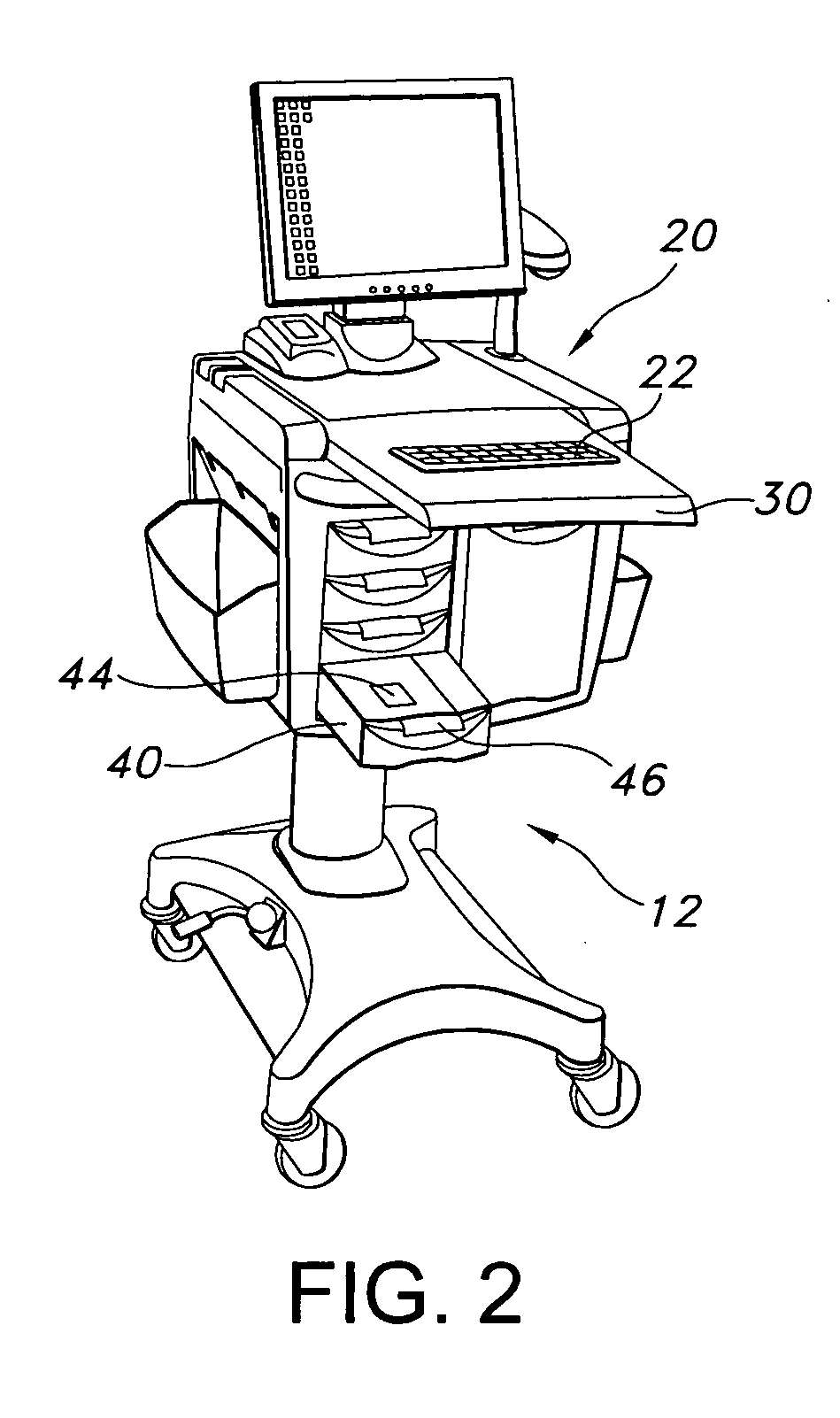

Mobile point of care system and associated method and computer program product

A wireless, mobile point-of-care system is provided including a plurality of mobile point-of-care carts, each capable of transporting a plurality of patient-specific medication or supply drawers or containers. The mobile point-of-care carts provide for both auto-identification of patient containers carried by the cart, as well as real-time tracking of the carts themselves. Using the combination of these two features, each patient-specific drawer can be located throughout the hospital at any given time. A method is further provided for utilizing this location information to generate a medication delivery / removal plan or route, which can be used by delivery personnel to alleviate the burden caused by making medication carts mobile.

Owner:OMNICELL

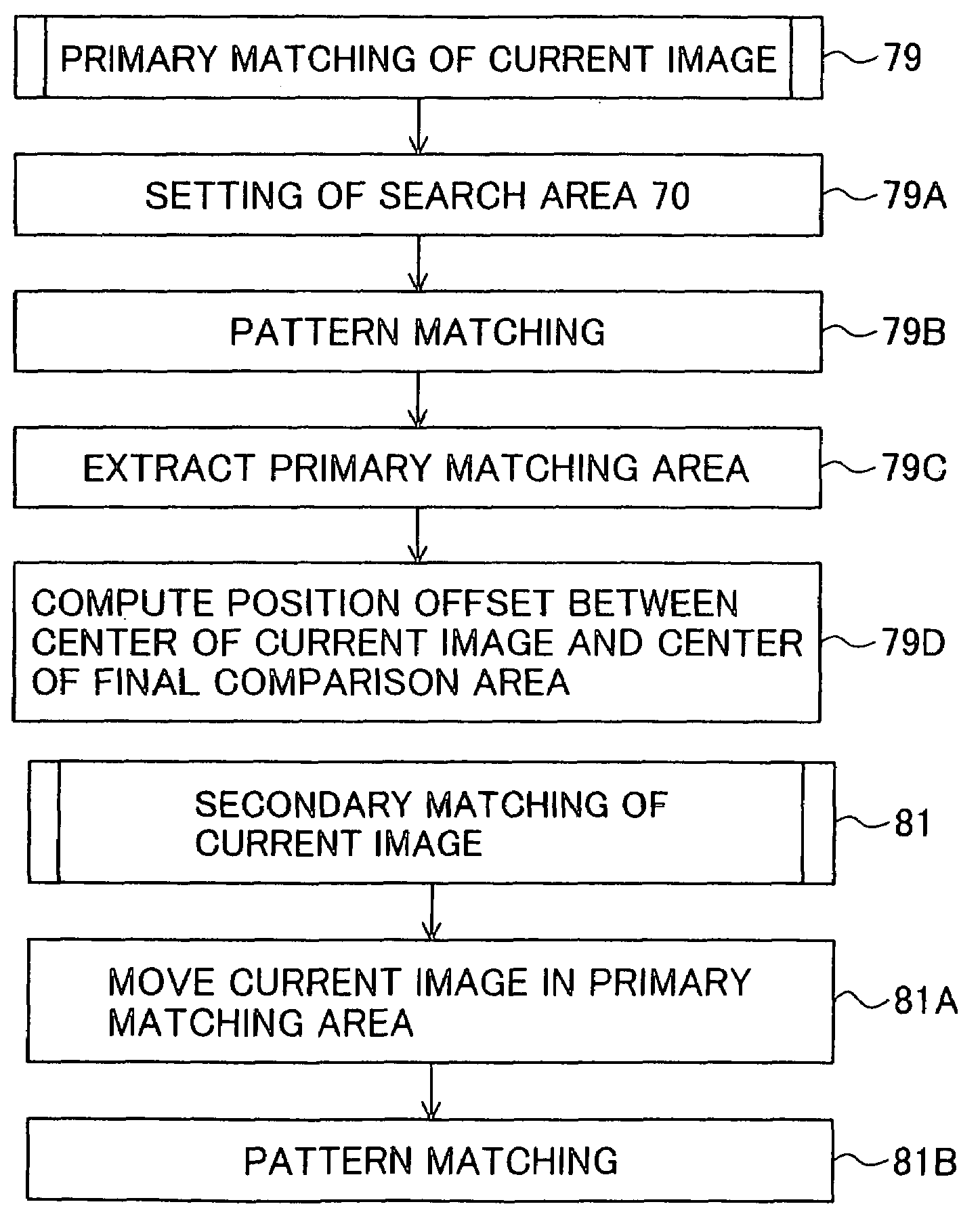

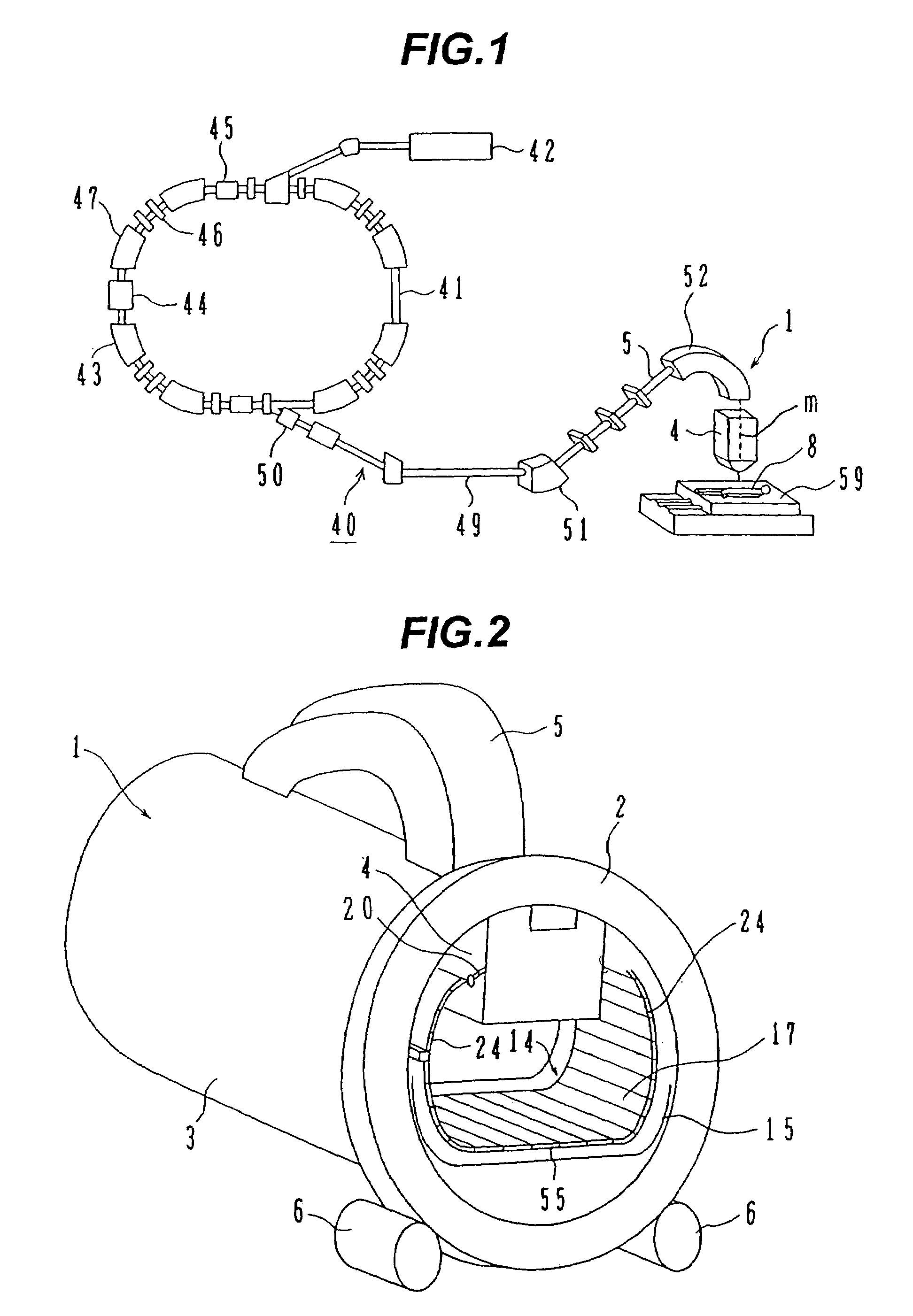

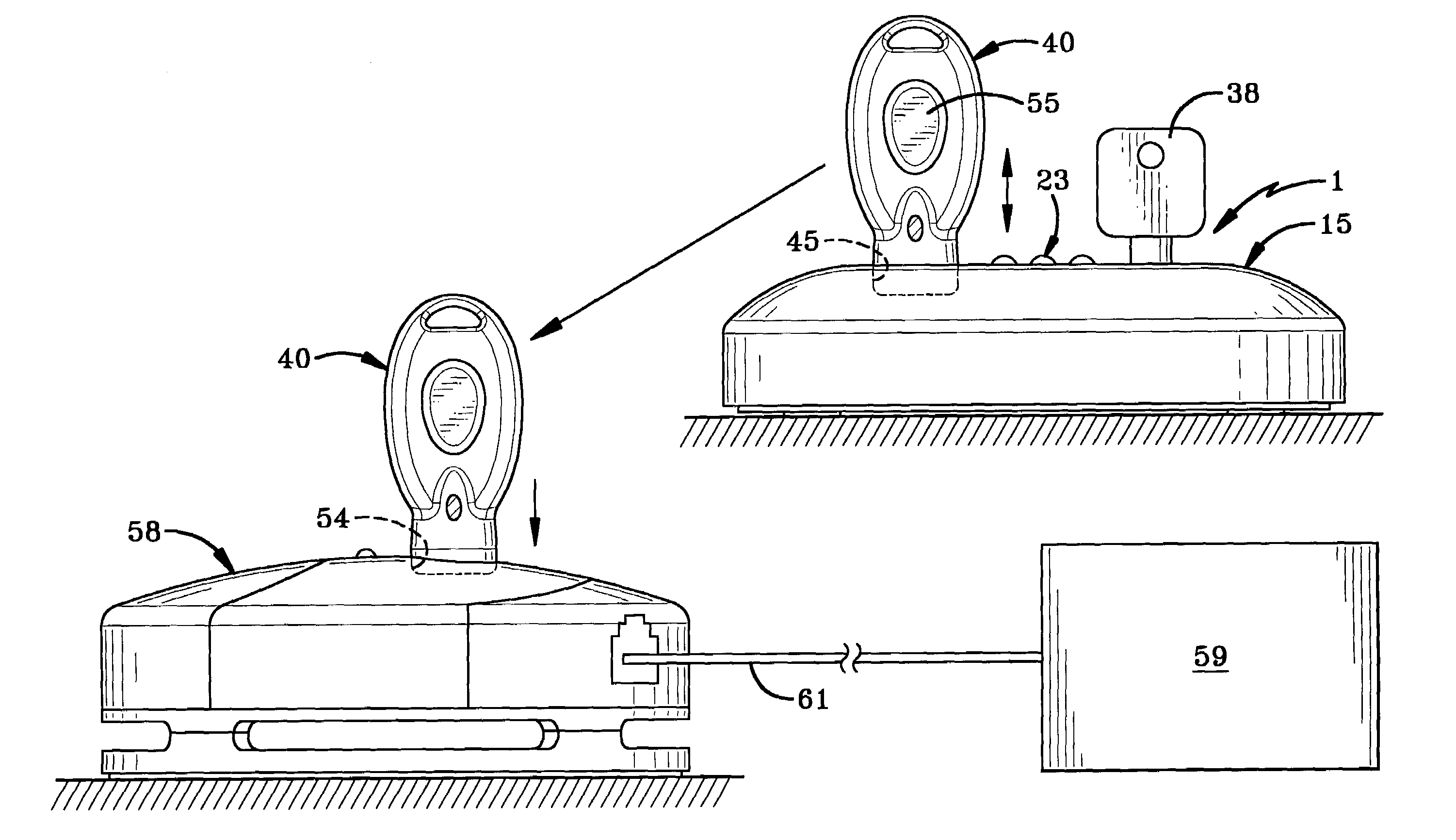

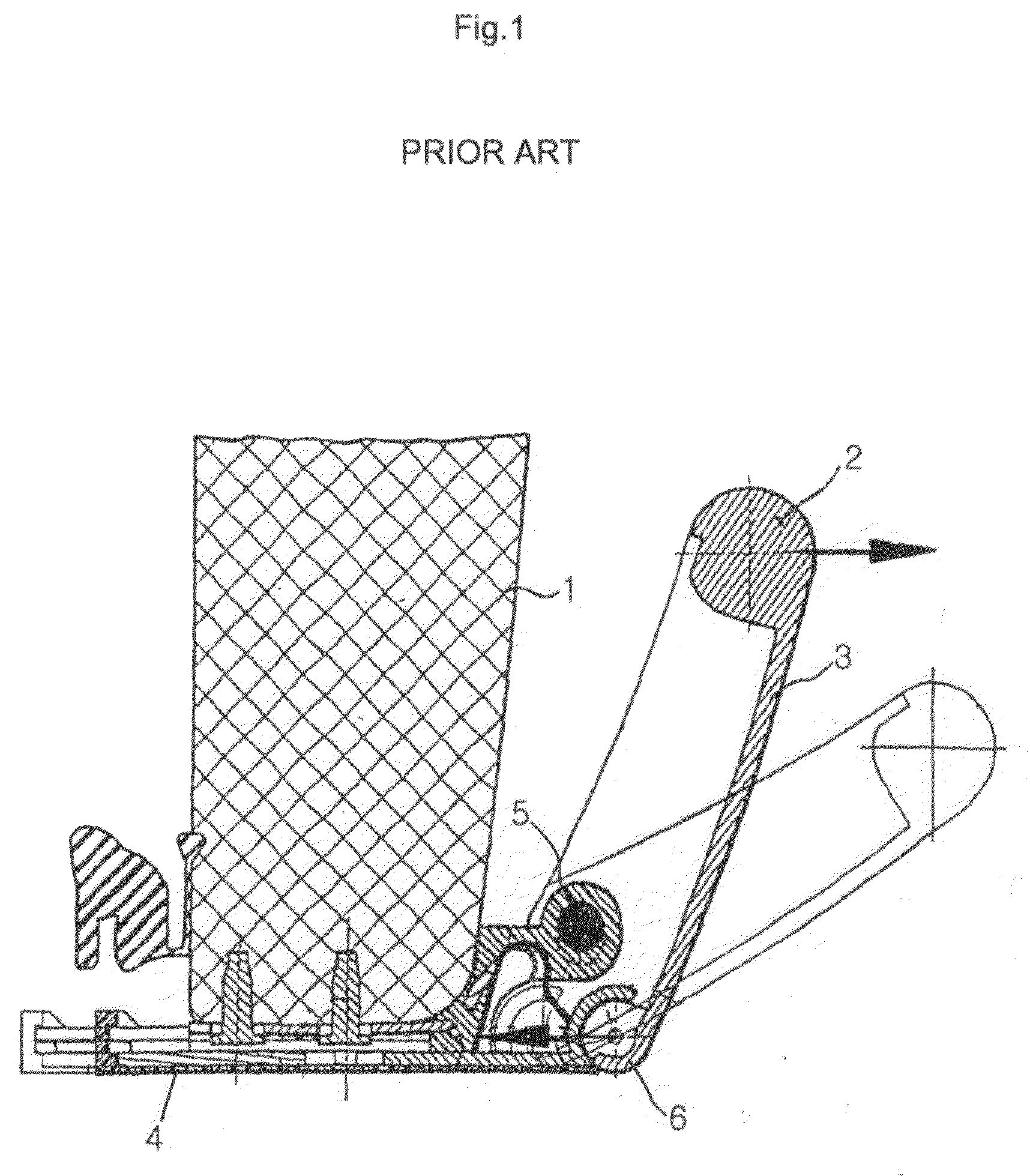

Patient positioning device and patient positioning method

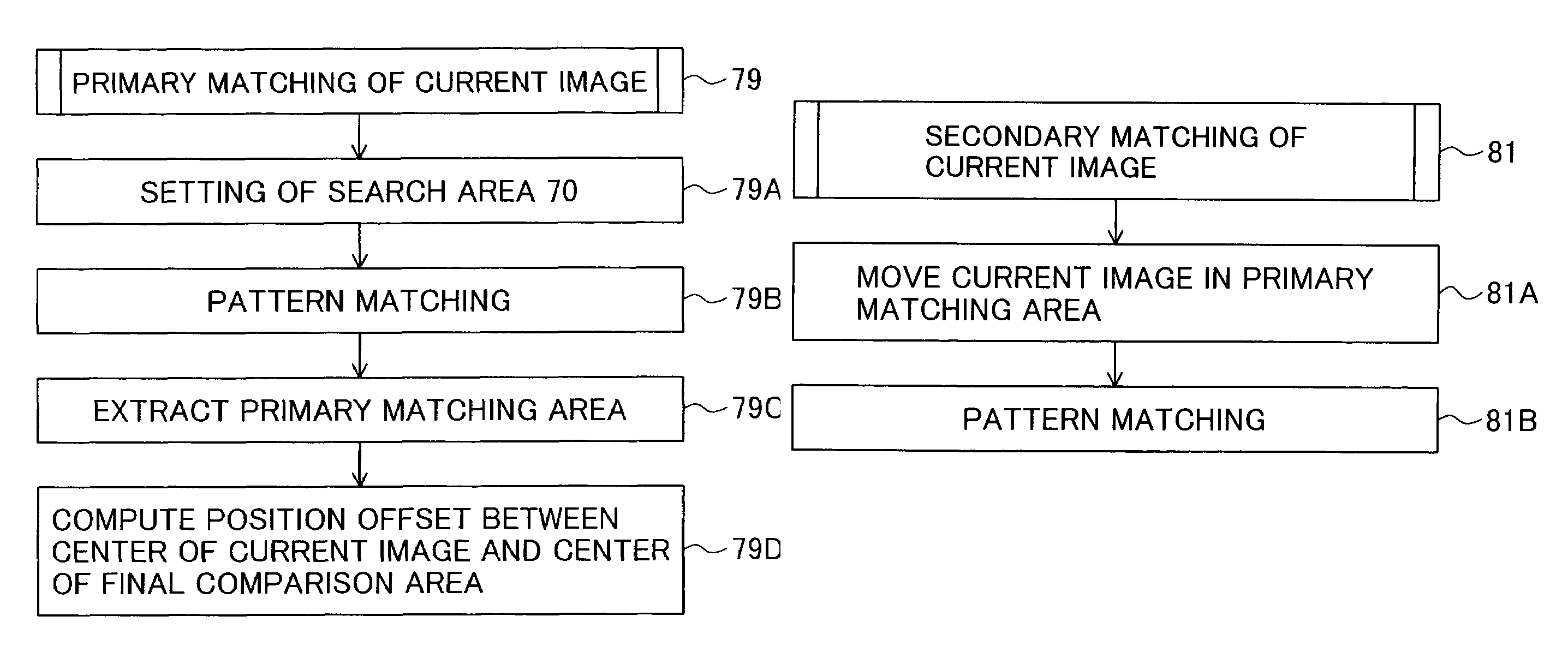

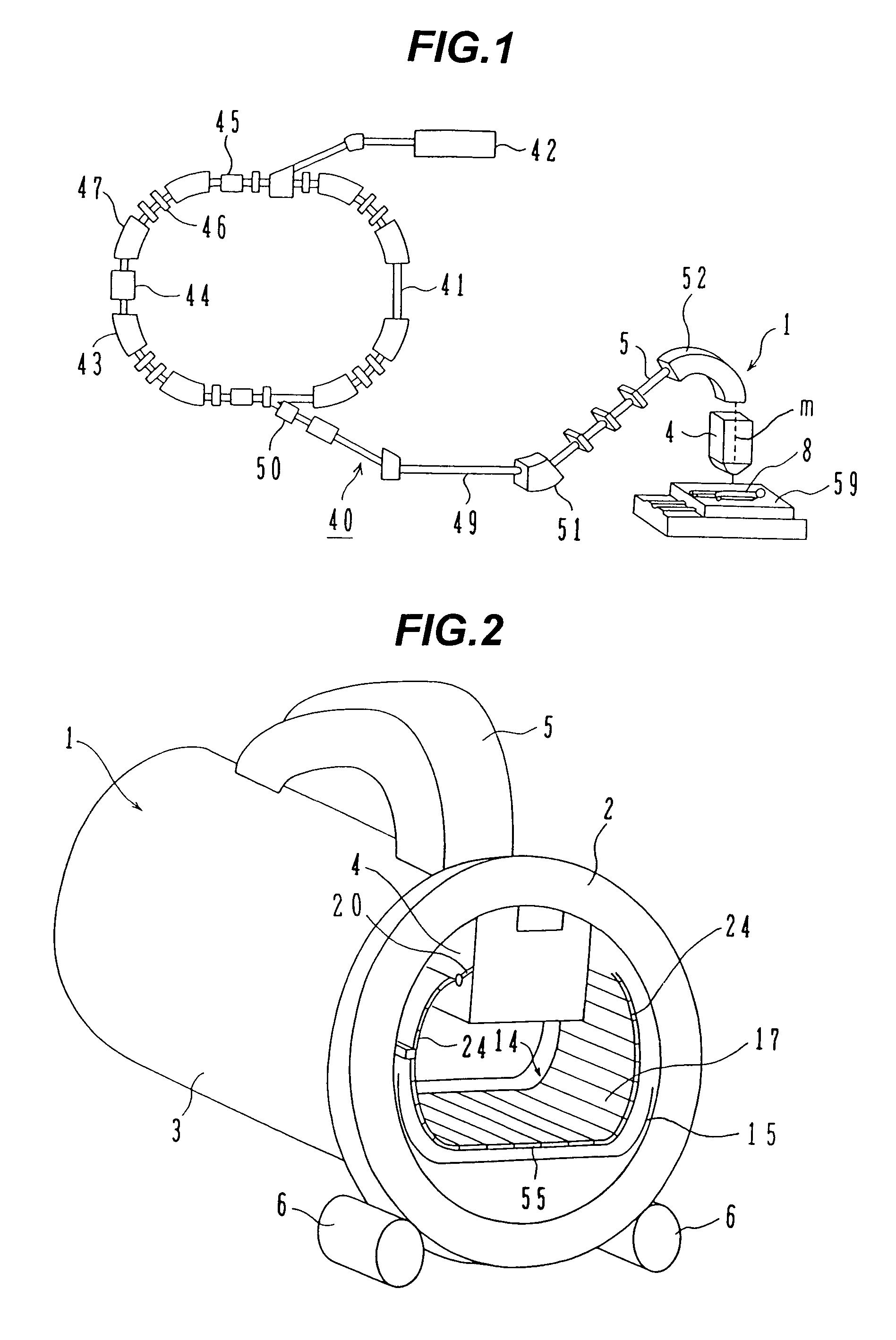

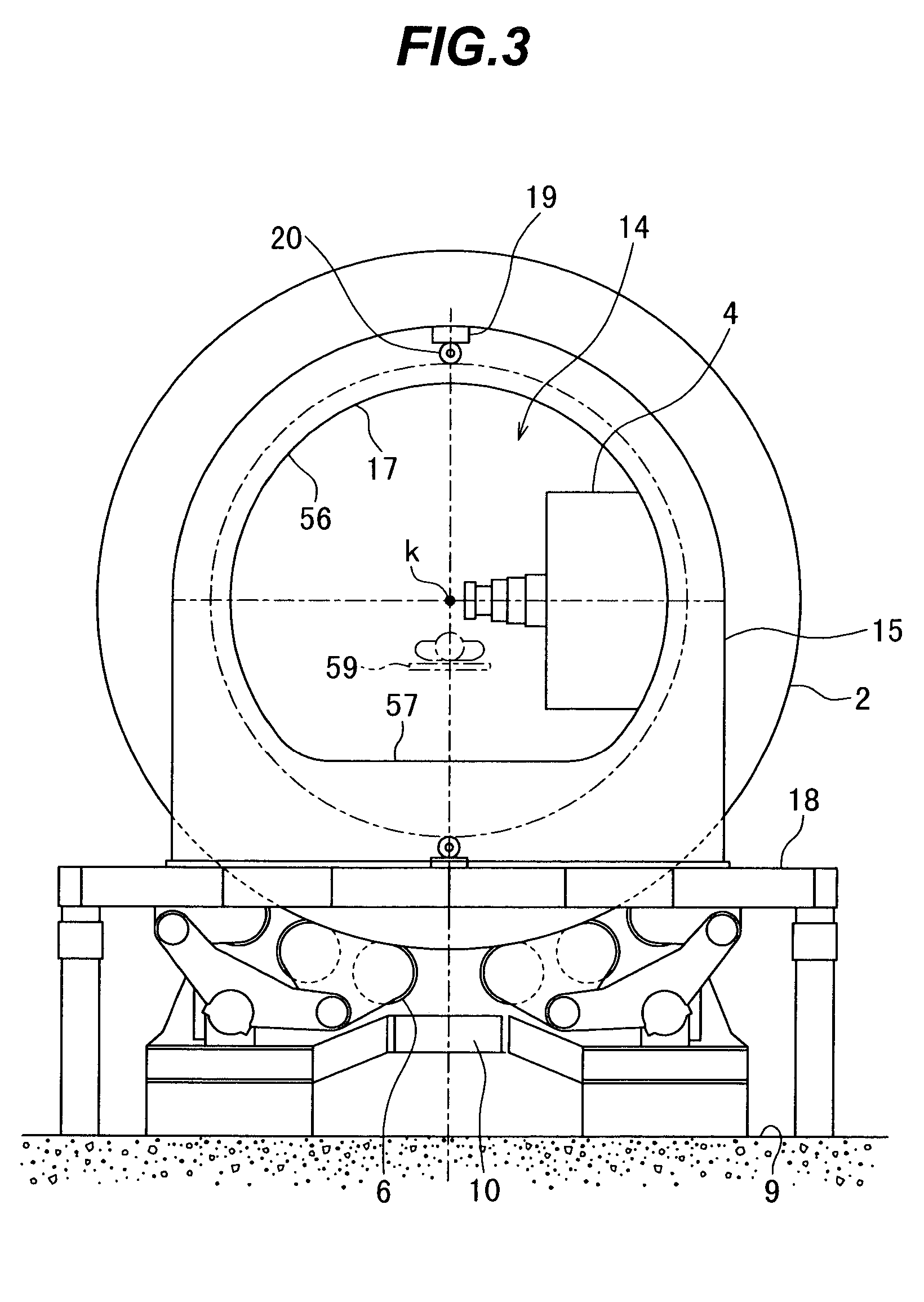

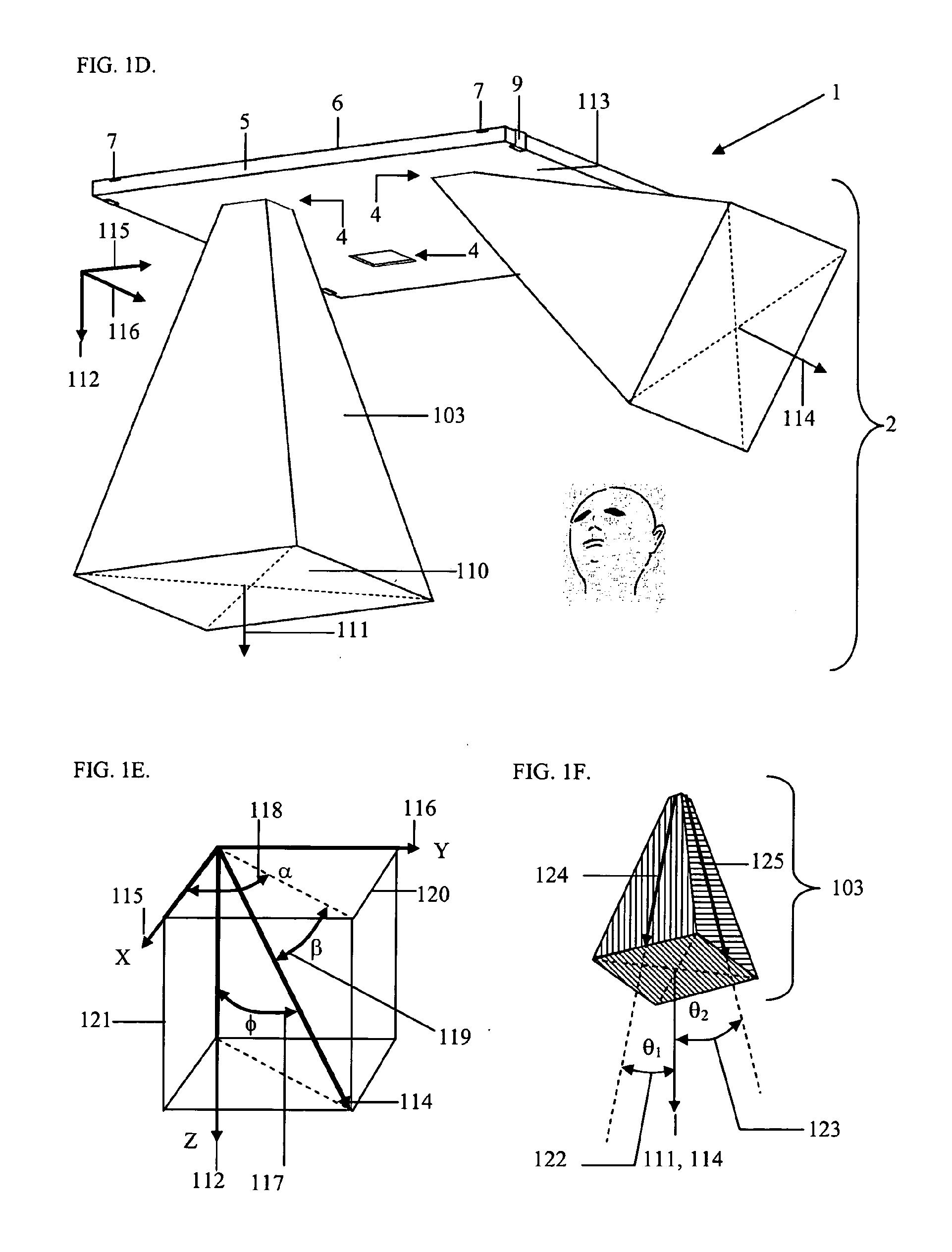

InactiveUS7212608B2Improve accuracyAvoid accuracyBuilding locksPatient positioning for diagnosticsPattern matchingX-ray

The invention is intended to always ensure a sufficient level of patient positioning accuracy regardless of the skills of individual operators. In a patient positioning device for positioning a patient couch 59 and irradiating an ion beam toward a tumor in the body of a patient 8 from a particle beam irradiation section 4, the patient positioning device comprises an X-ray emission device 26 for emitting an X-ray along a beam line m from the particle beam irradiation section 4, an X-ray image capturing device 29 for receiving the X-ray and processing an X-ray image, a display unit 39B for displaying a current image of the tumor in accordance with a processed image signal, a display unit 39A for displaying a reference X-ray image of the tumor which is prepared in advance, and a positioning data generator 37 for executing pattern matching between a comparison area A being a part of the reference X-ray image and including an isocenter and a comparison area B or a final comparison area B in the current image, thereby producing data used for positioning of the patient couch 59 during irradiation.

Owner:HITACHI LTD

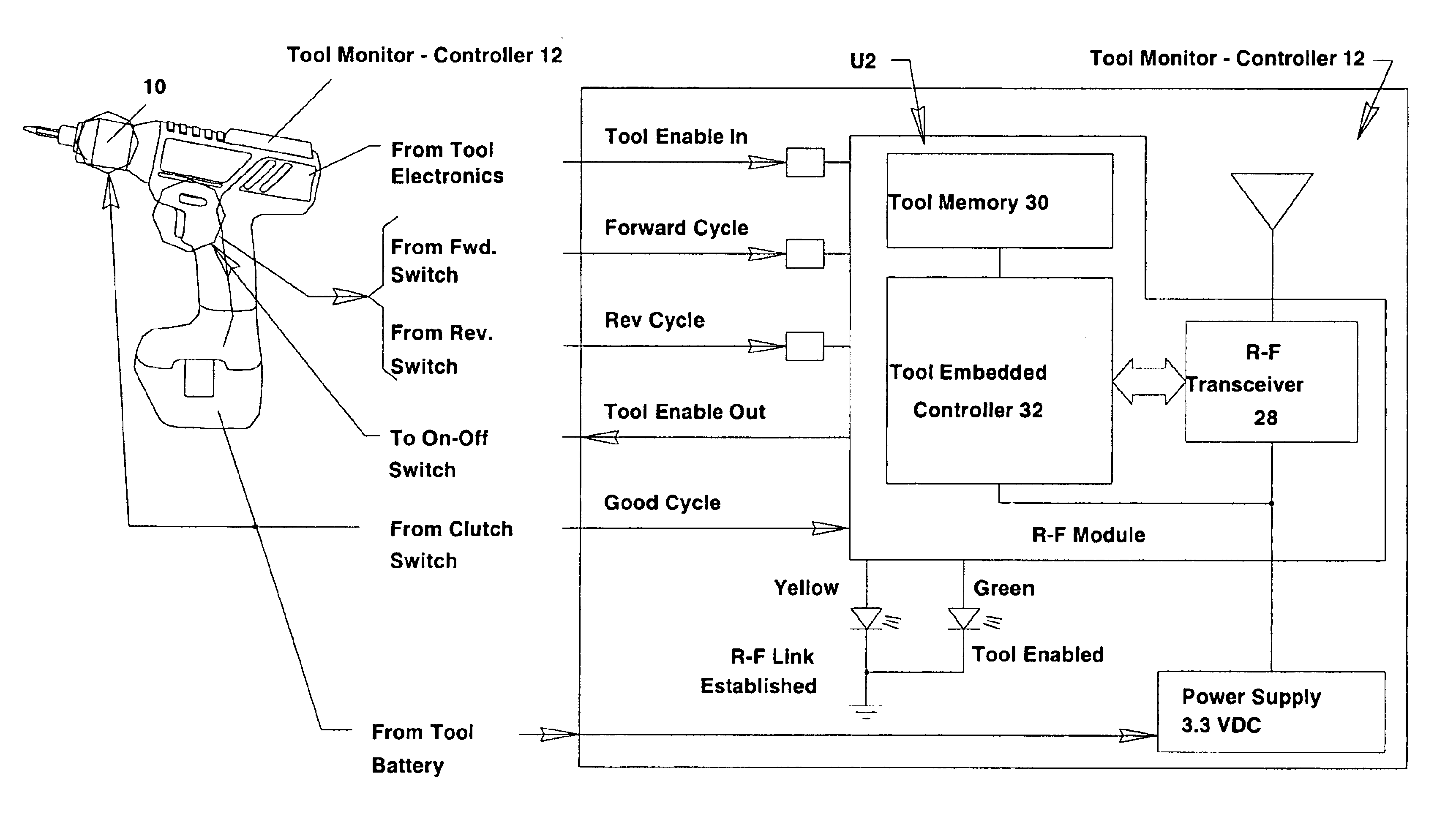

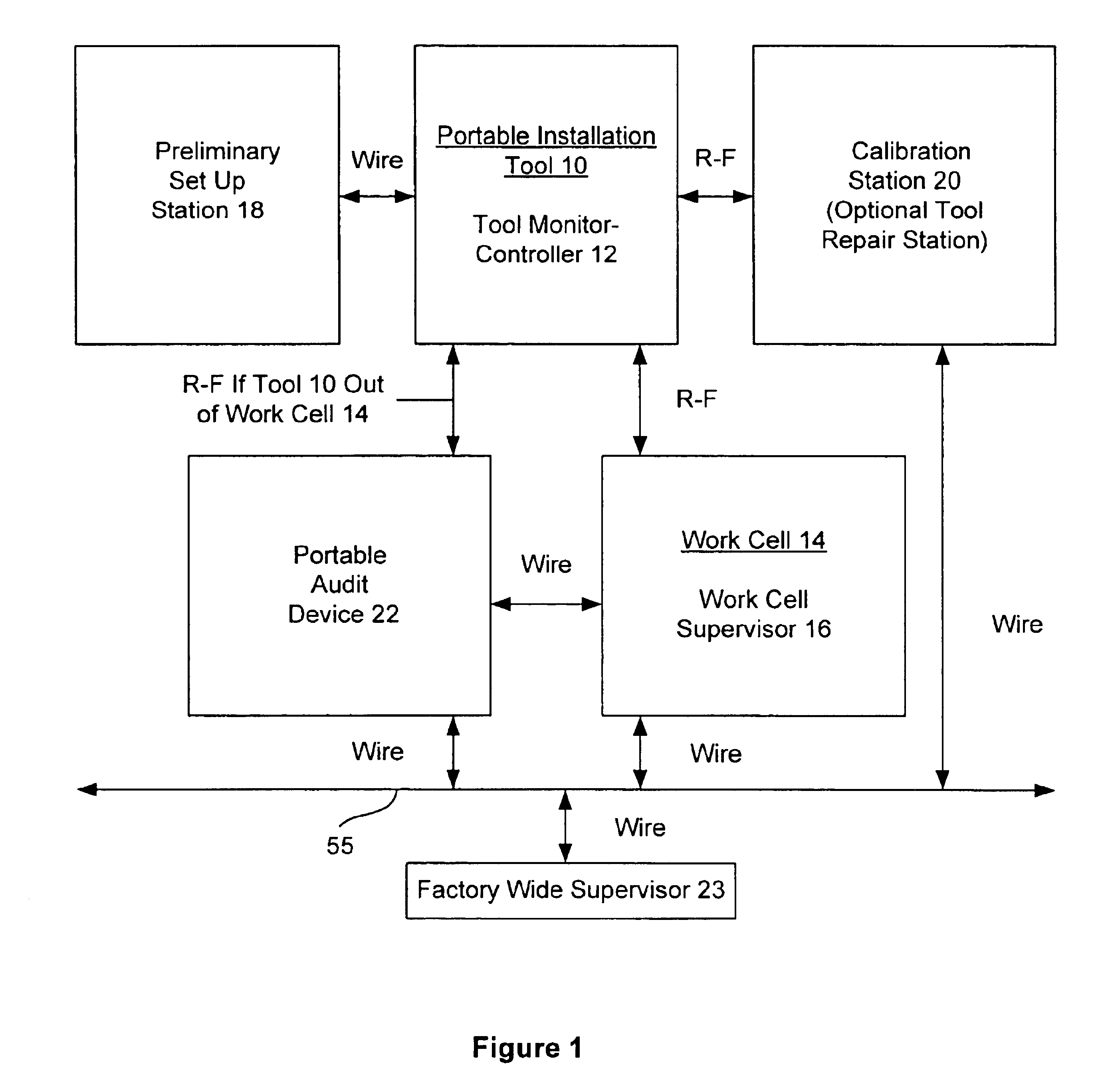

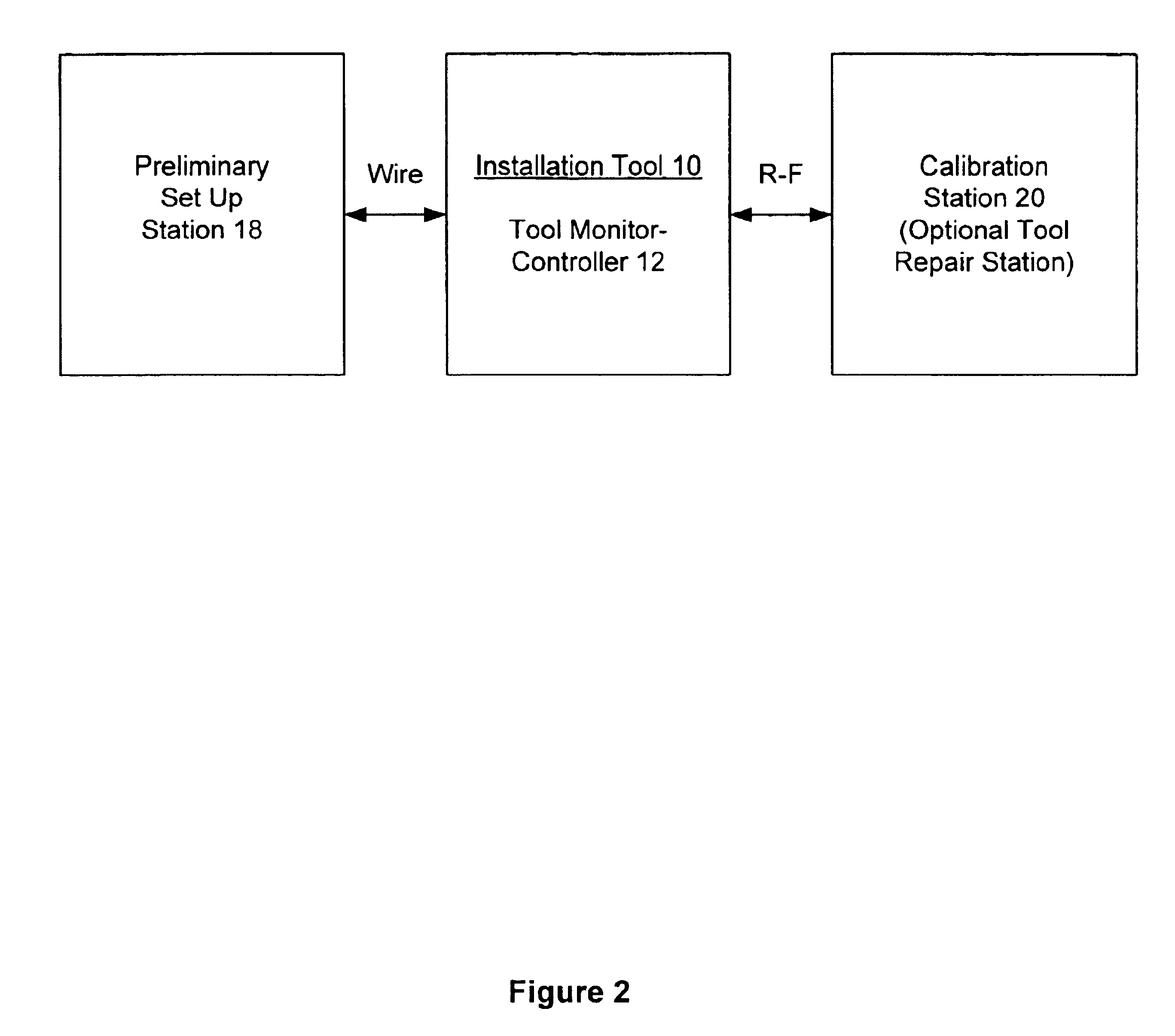

Error proofing system for portable tools

ActiveUS6845279B1Easy to useEasy to monitorProgramme controlComputer controlWork cellElectrical and Electronics engineering

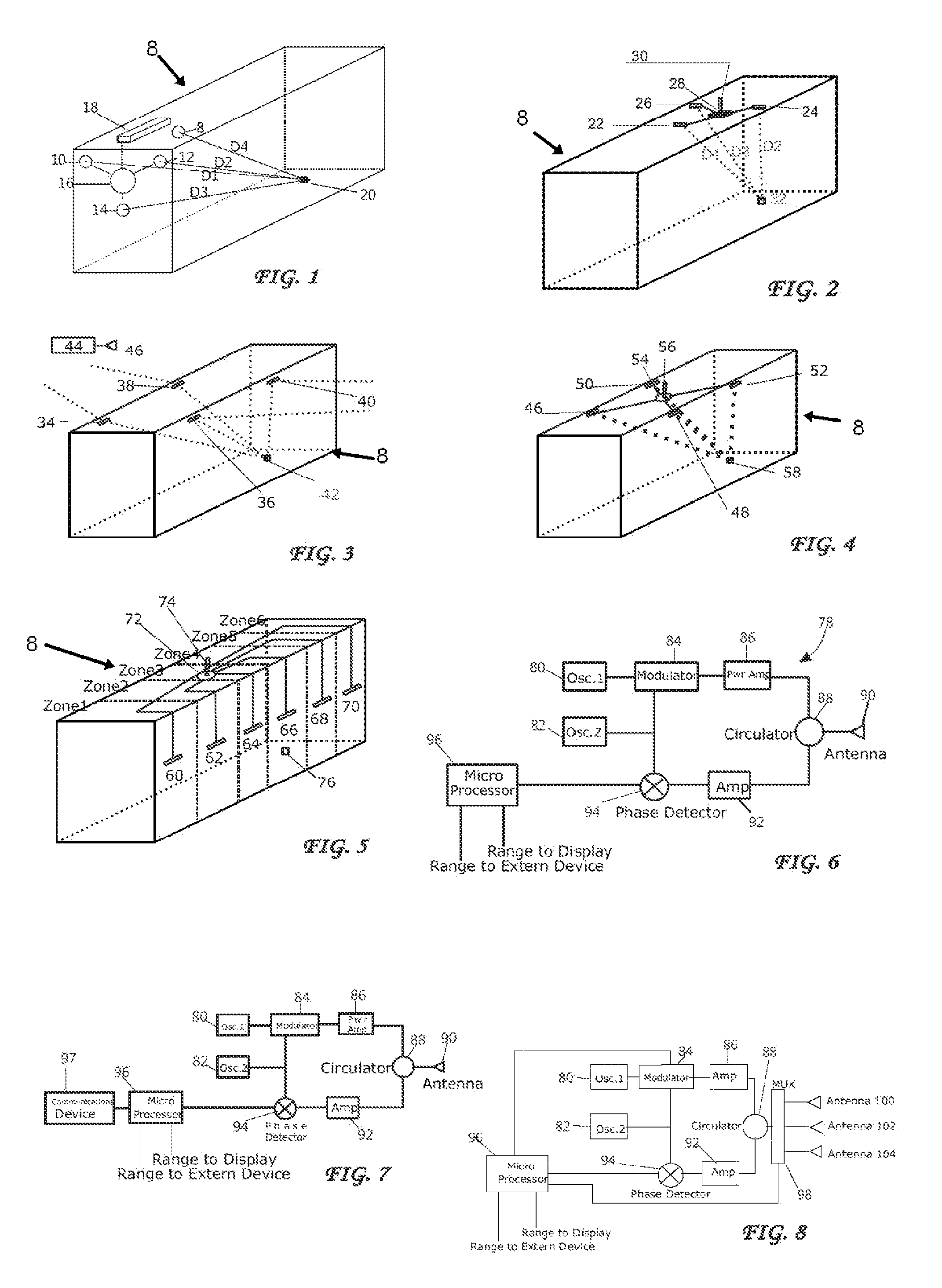

A system for controlling and monitoring portable tools at a particular work cell remotely by R-F communication to provide error proofing of various parameters including that the correct tool is to be used at a work cell, the tool is properly calibrated for the operation to be performed, that it is being used a proper number of times per part being assembled or inspected, and that the tool has been calibrated within a selected service interval. The tools will be made actuable only by R-F communication with specific factory apparatus whereby theft of such portable tools will be inhibited.

Owner:ATLAS COPCO INDAL TECHN AB

Patient positioning device and patient positioning method

InactiveUS7212609B2Improve accuracyAvoid accuracyMaterial analysis using wave/particle radiationRadiation/particle handlingPattern matchingX-ray

The invention is intended to always ensure a sufficient level of patient positioning accuracy regardless of the skills of individual operators. In a patient positioning device for positioning a patient couch 59 and irradiating an ion beam toward a tumor in the body of a patient 8 from a particle beam irradiation section 4, the patient positioning device comprises an X-ray emission device 26 for emitting an X-ray along a beam line m from the particle beam irradiation section 4, an X-ray image capturing device 29 for receiving the X-ray and processing an X-ray image, a display unit 39B for displaying a current image of the tumor in accordance with a processed image signal, a display unit 39A for displaying a reference X-ray image of the tumor which is prepared in advance, and a positioning data generator 37 for executing pattern matching between a comparison area A being a part of the reference X-ray image and including an isocenter and a comparison area B or a final comparison area B in the current image, thereby producing data used for positioning of the patient couch 59 during irradiation.

Owner:HITACHI LTD

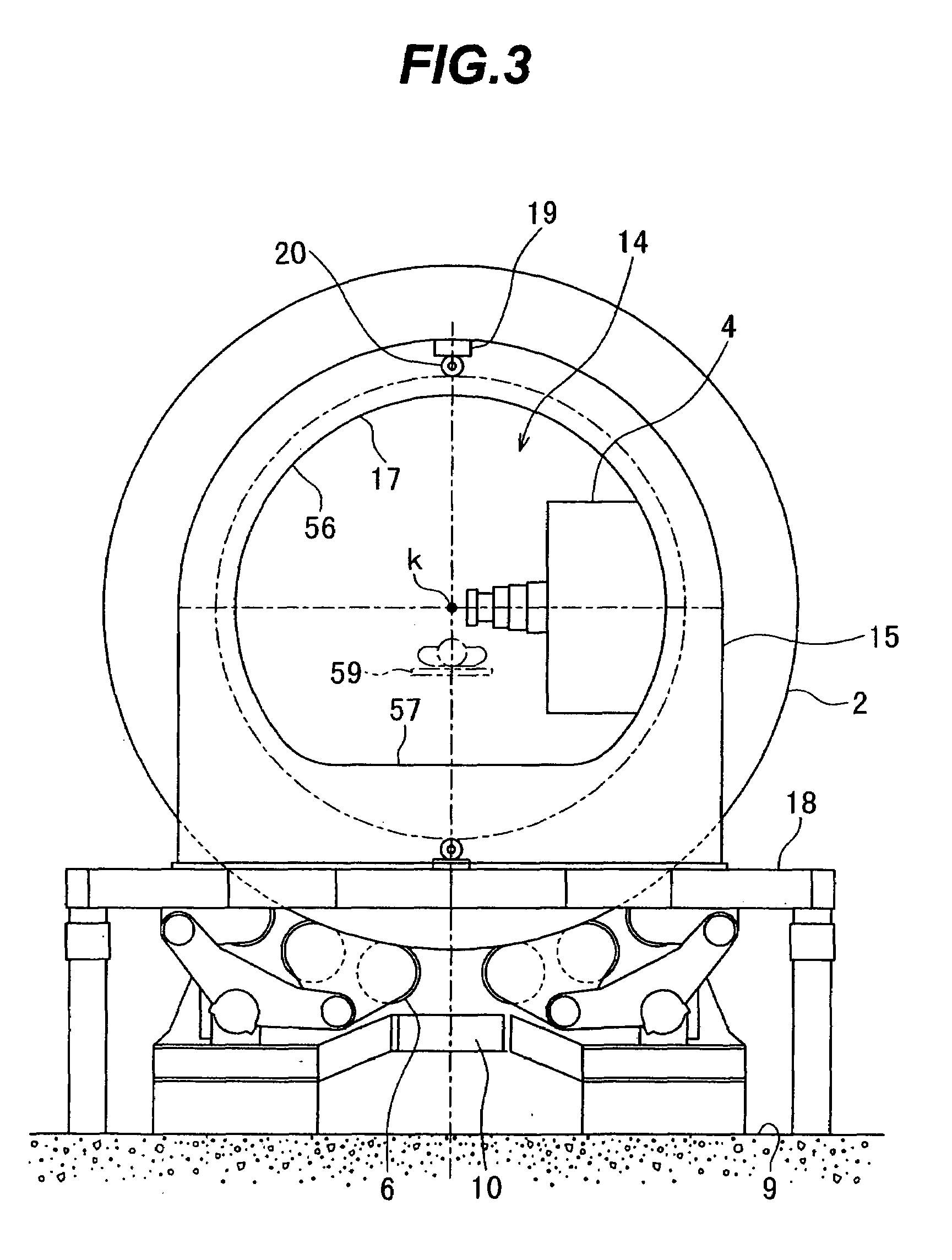

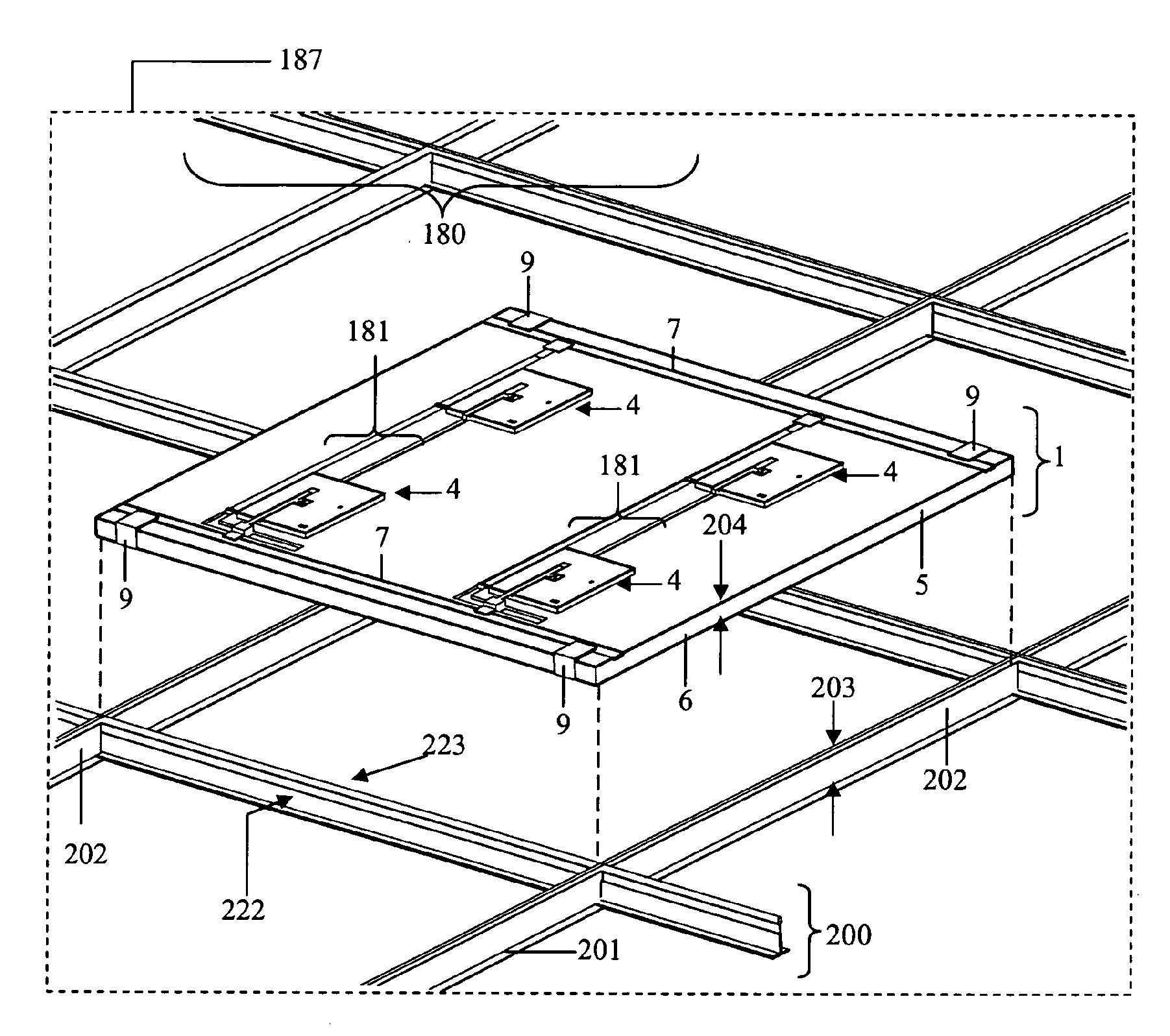

Distributed illumination system

ActiveUS20110175533A1Increase rangeImprove aesthetic qualityCeilingsLight source combinationsSmart lightingControl system

The present invention introduces a new class of lightweight tile-based illumination systems for uses wherein thin directionally-illuminating light distributing engines are embedded into the body of otherwise standard building materials like conventional ceiling tiles along with associated means of electrical control and electrical power interconnection. As a new class of composite light emitting ceiling materials, the present invention enables a lighter weight more flexibly distributed overhead lighting system alternatives for commercial office buildings and residential housing without changing the existing materials. One or more spot lighting, task lighting, flood lighting and wall washing elements having cross-sectional thickness matched to that of the building material or tile into which they are embedded, are contained and interconnected within the material body's cross-section. Embedded power control devices interconnected to each lighting element in the distributed system communicate with a central switching center that thereby controls each light-emitting element in the system.

Owner:SNAPTRACK

Methods and apparatus for dispensing items

InactiveUS6272394B1Credit registering devices actuationDiagnosticsLight-emitting diodeMedical treatment

The invention provides methods and apparatus for dispensing items from a dispensing unit. According to the invention, the dispensing unit comprises a plurality of locations in which the items are held, a processor in which records corresponding to the items on the unit are stored, and a plurality of item switches corresponding to the locations in which the items are held. The item switches are connected to the processor so that a user of the dispensing unit can input records of items removed from the unit into the processor. The apparatus described is particularly suited for dispensing medical supplies although the apparatus will be usable for other types of items as well. Preferred embodiments will include a plurality of visual indicators, typically in the form of light emitting diodes, corresponding to the locations in which the items are held. Upon selection of a desired item from a list of items held by the unit, the visual indicator corresponding to the item is actuated so that the user can locate the desired item quickly and conveniently with the help of the visual indicator.

Owner:COMDISCO

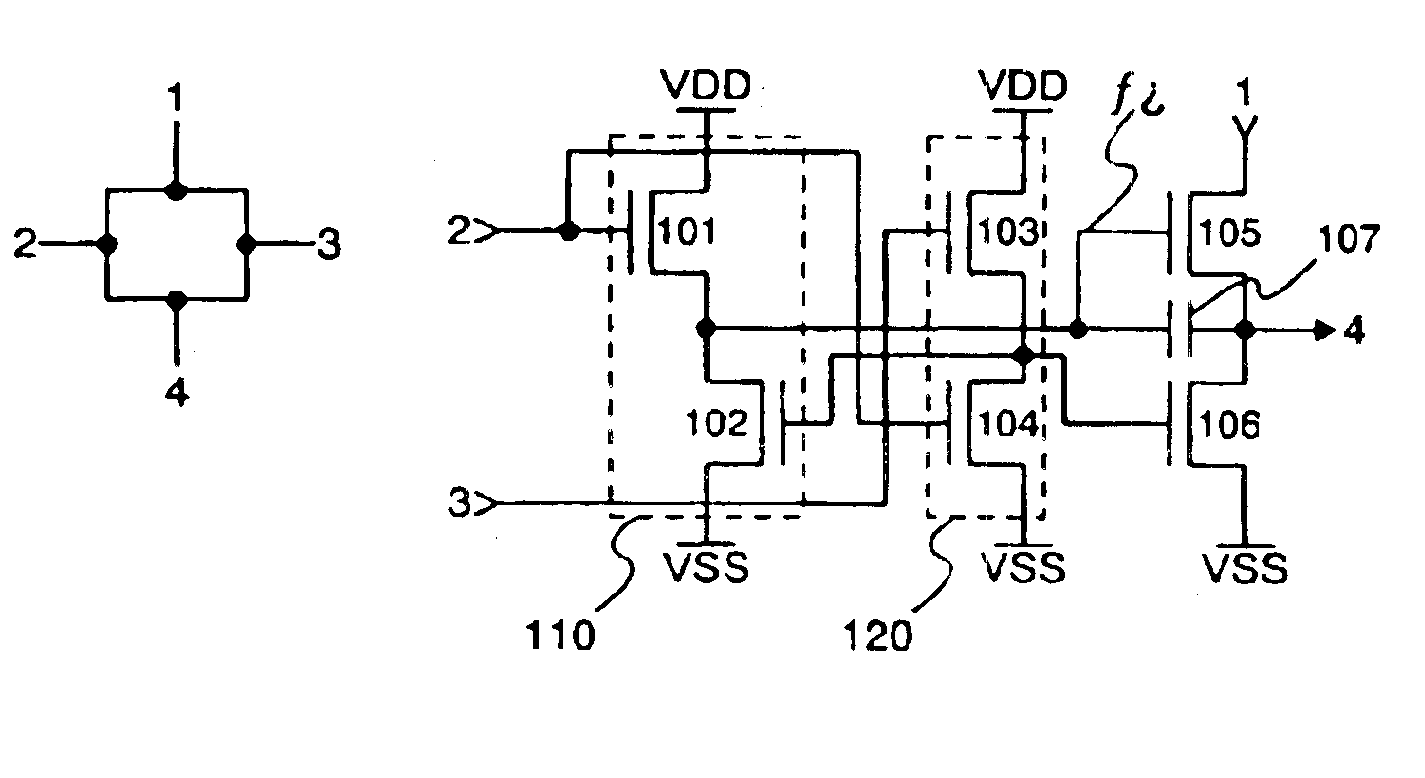

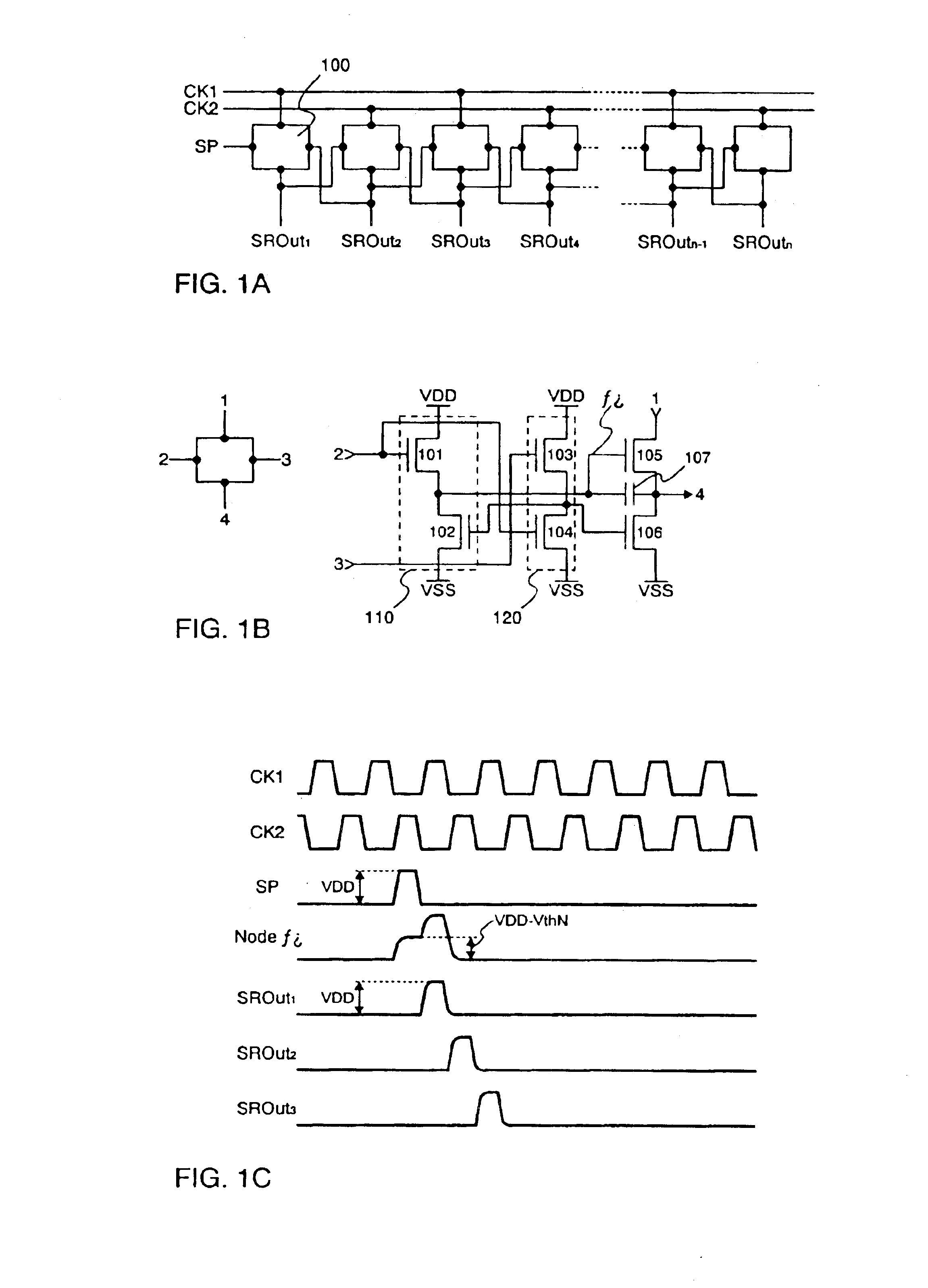

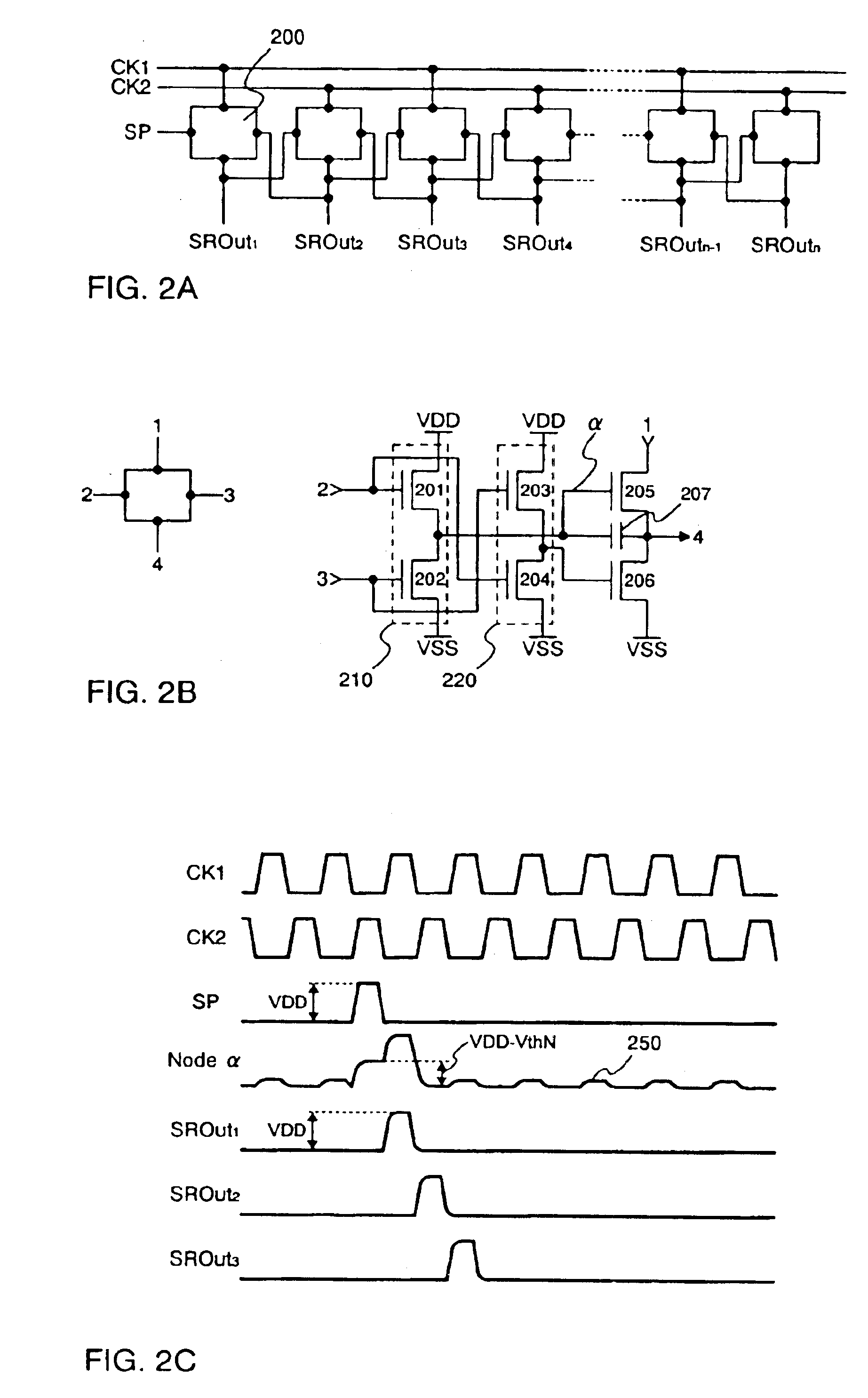

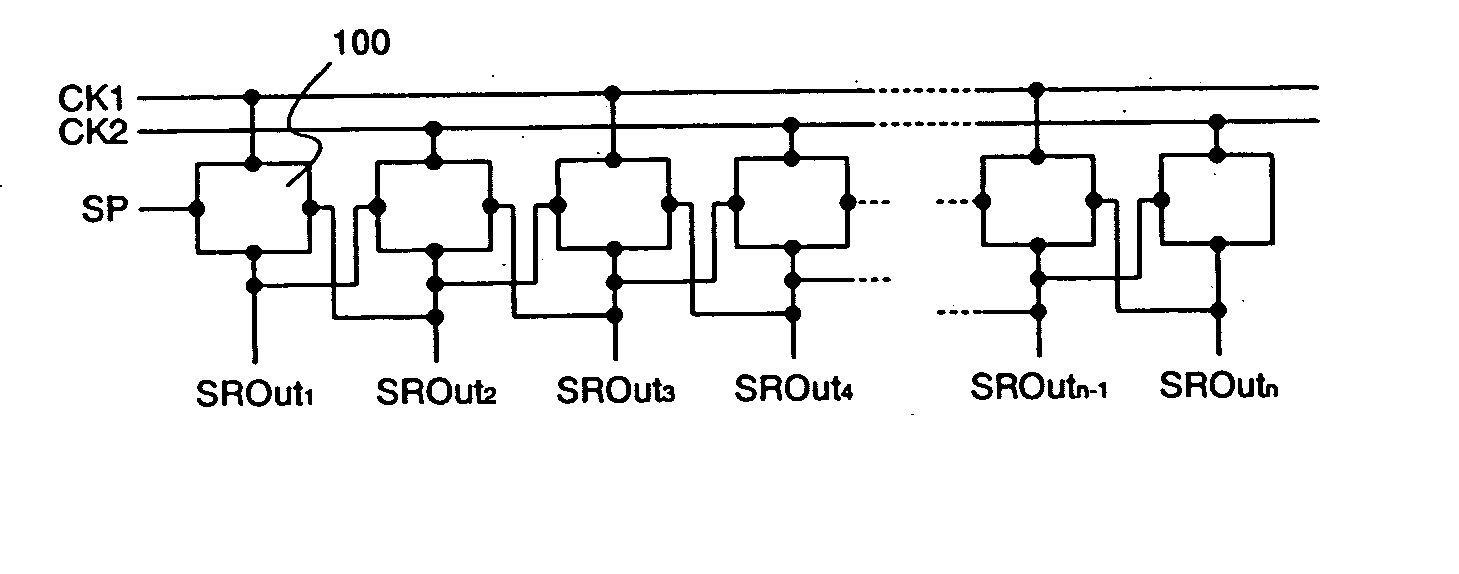

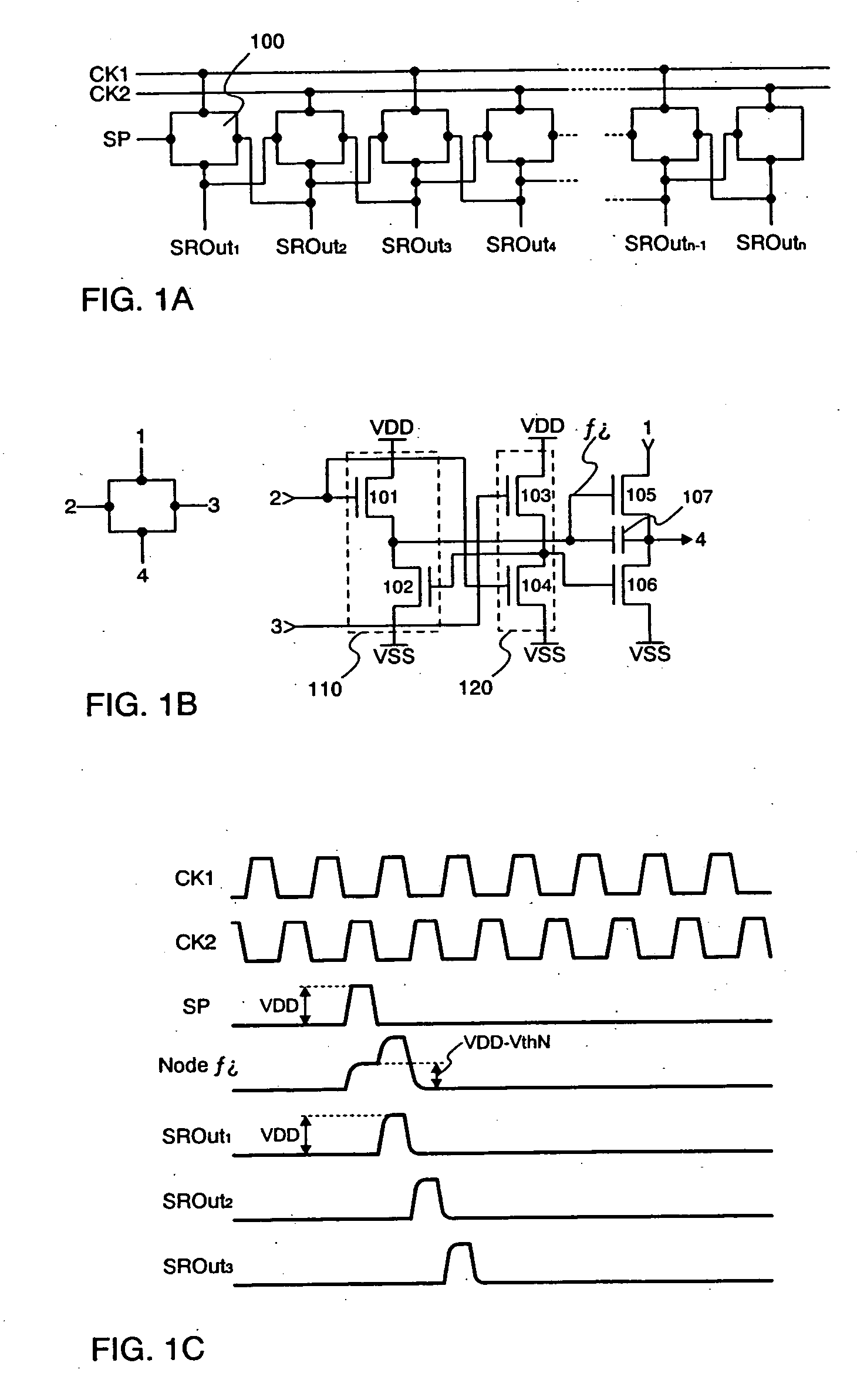

Pulse output circuit, shift register and electronic equipment

A driver circuit of a display device, which includes TFTs of a single conductivity type and outputs an output signal with normal amplitude. A pulse is inputted to TFTs 101 and 104 to turn ON the TFTs and a potential of a node alpha is raised. When the potential of the node alpha reaches (VDD-VthN), the node alpha becomes in a floating state. Accordingly, a TFT 105 is turned ON and a potential of an output node is raised as a clock signal becomes High level. On the other hand, a potential of a gate electrode of the TFT 105 is further raised due to an operation of a capacitance means 107 as the potential of the output node is raised, so that the potential of the gate electrode of the TFT 105 becomes higher than (VDD+VthN). Thus, the potential of the output node is raised to VDD without causing a voltage drop due to a threshold voltage of the TFT 105. An output at the subsequent stage is then inputted to a TFT 103 to turn the TFT 103 On, while the potential of the node alpha of TFTs 102 and 106 is dropped to turn the TFT 105 OFF. As a result, the potential of the output node becomes Low level.

Owner:SEMICON ENERGY LAB CO LTD

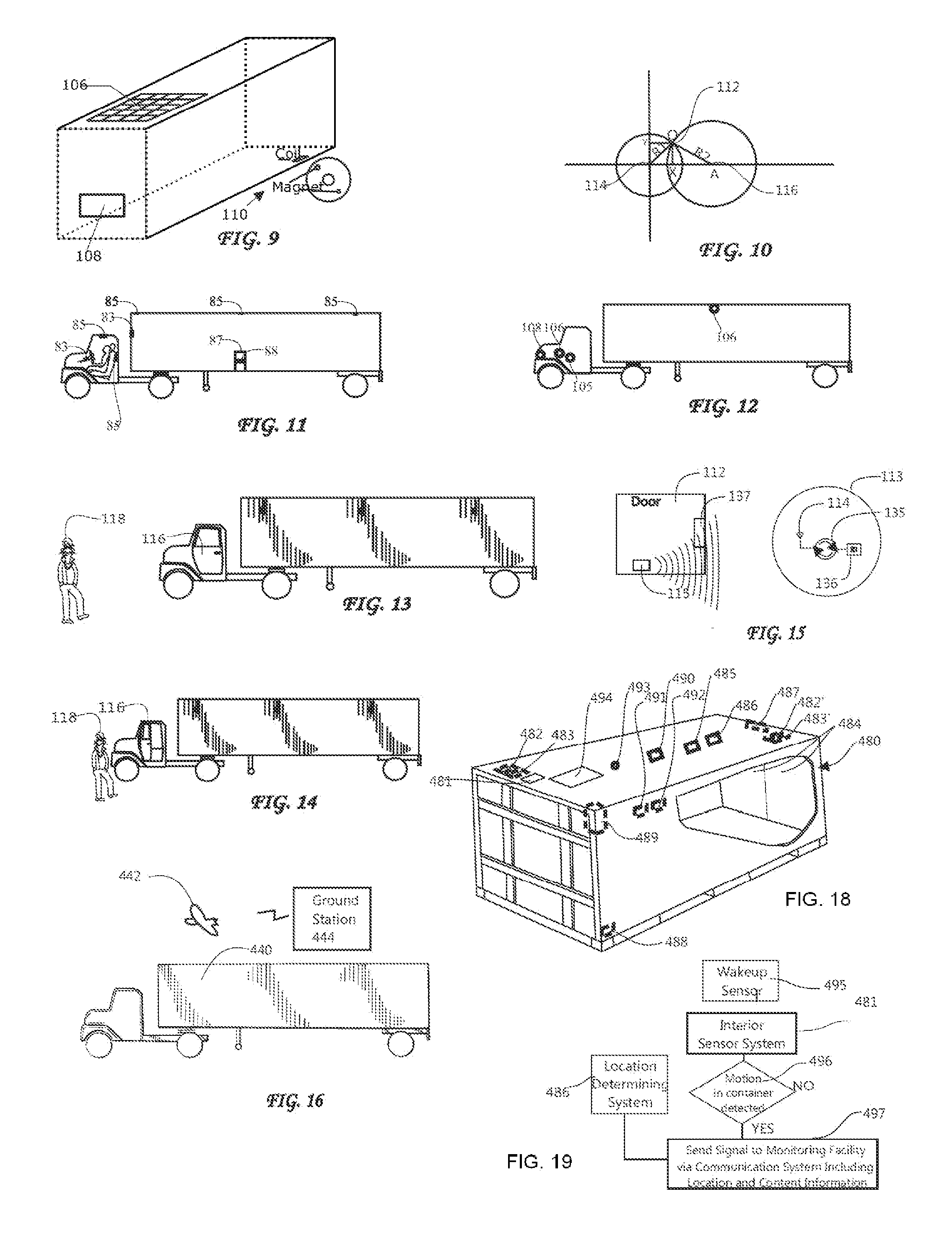

Cargo theft prevention using text messaging

InactiveUS20130033381A1Reducing and eliminating theftEfficient powerBraking element arrangementsBuilding locksDriver/operatorCargo container

Method for monitoring a cargo container in which a transmitter is arranged on the container and periodically transmits messages to a remote site or location according to a schedule of messages. When a message is not received according to the schedule, which may be the result of tampering with the transmitter or another nefarious action involving the container, it may be considered that the container has been stolen. A rate of transmission of the messages may be modified based on a condition of the vehicle, such as the presence of a driver inside the vehicle, a distance between a driver inside the vehicle and the vehicle, the vehicle being at rest after motion of the vehicle stops, a location of the vehicle, biometric identification of a driver of the vehicle and deviation of the vehicle from an expected route, and / or based on current time and weather around the vehicle.

Owner:INTELLIGENT TECH INT

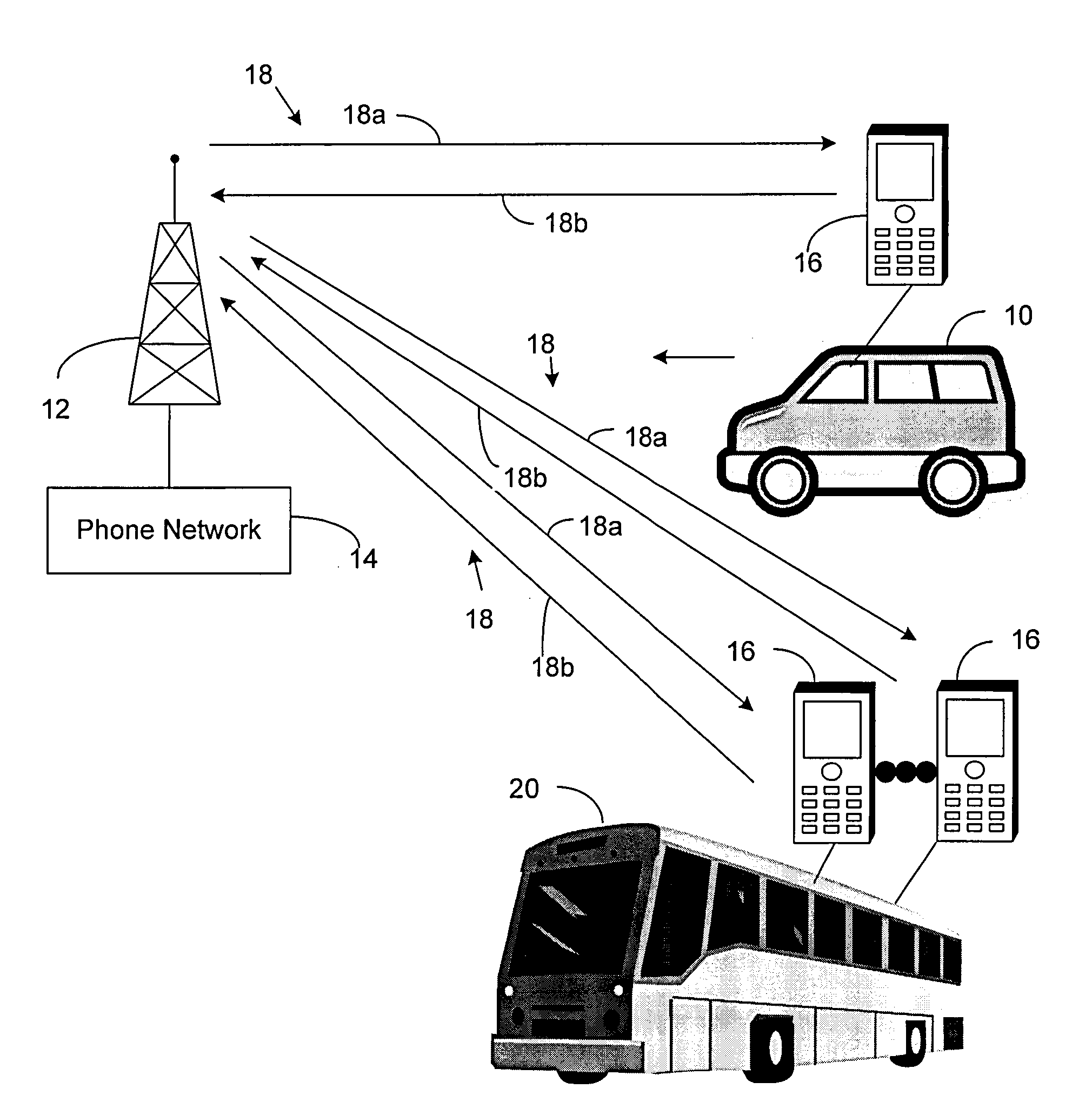

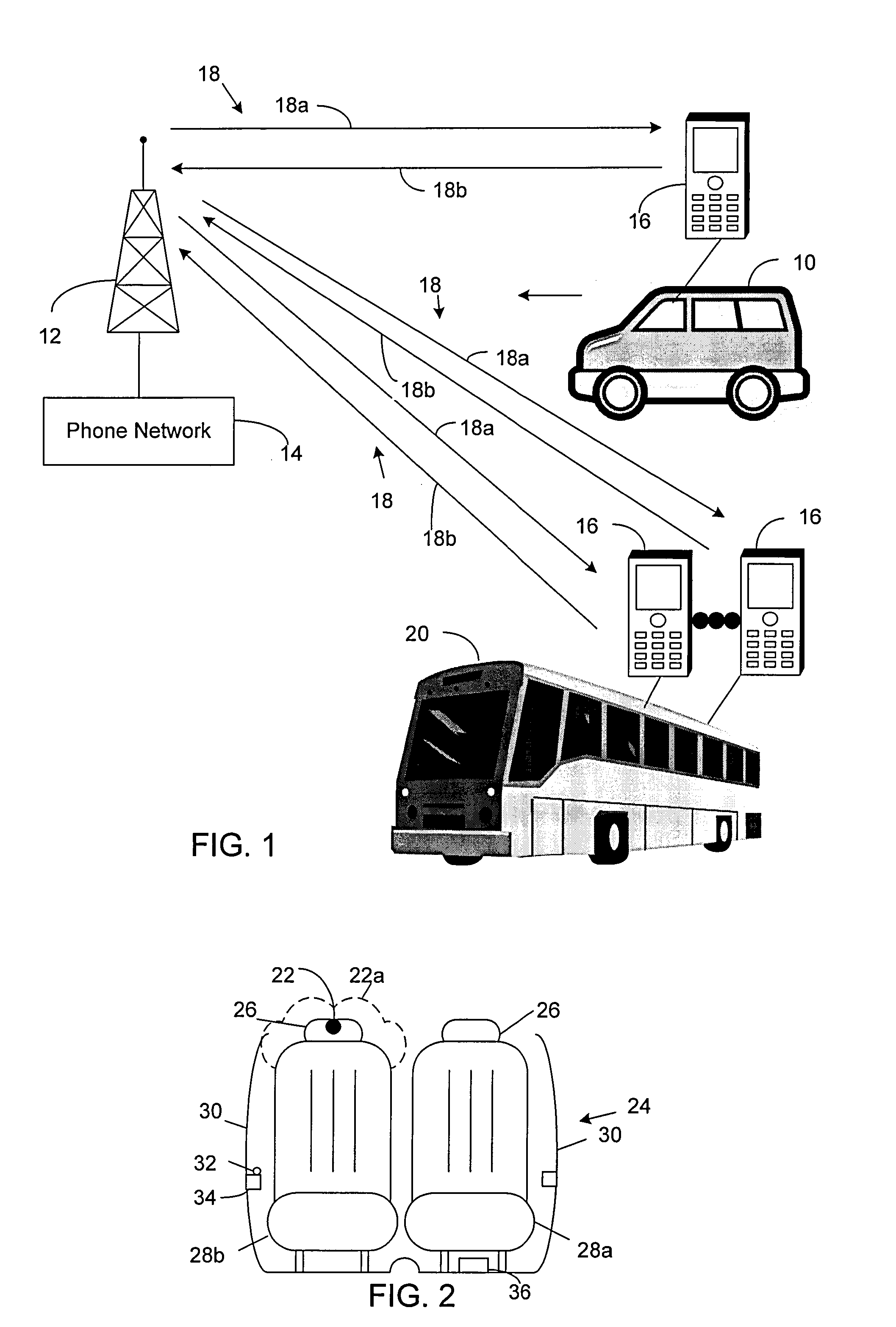

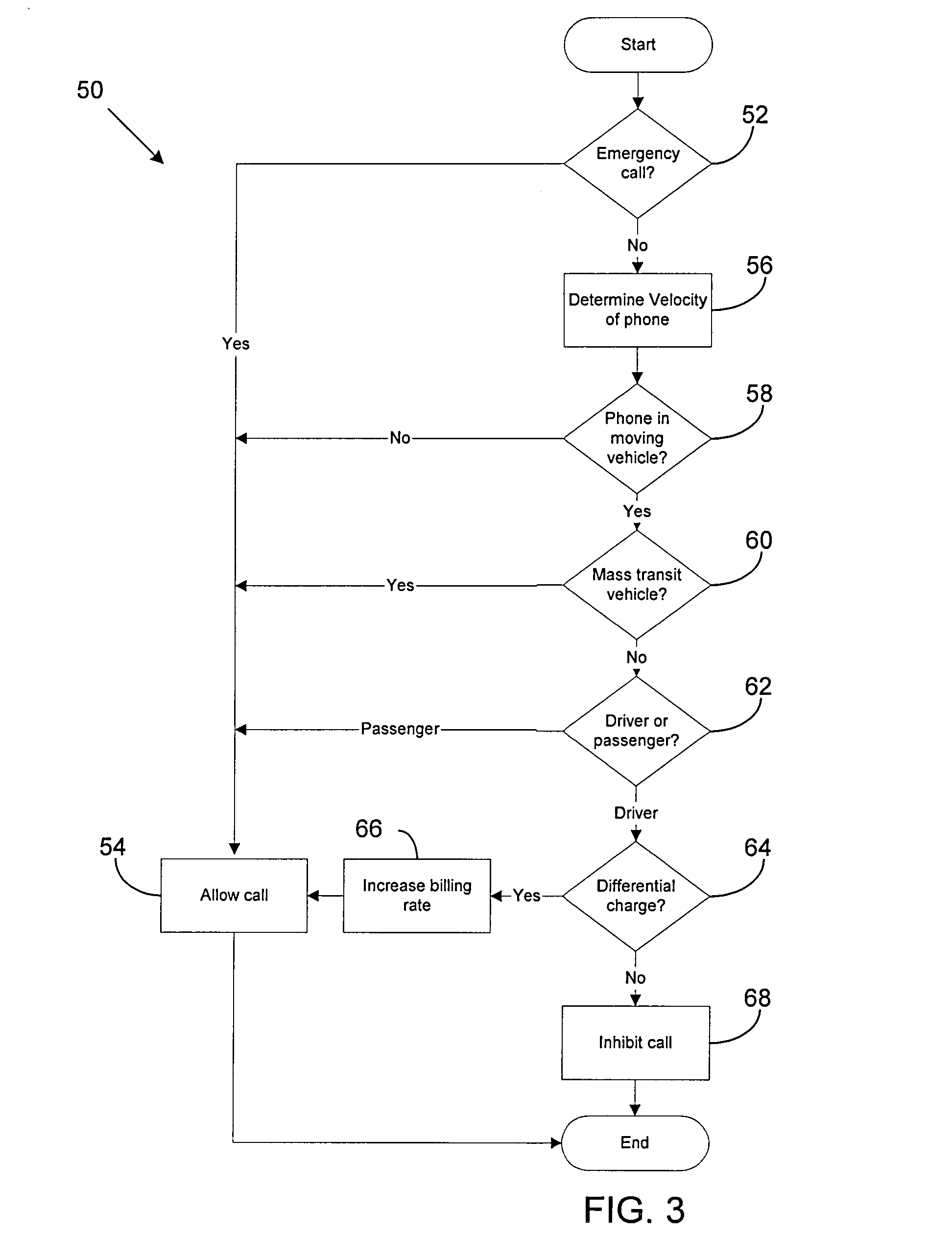

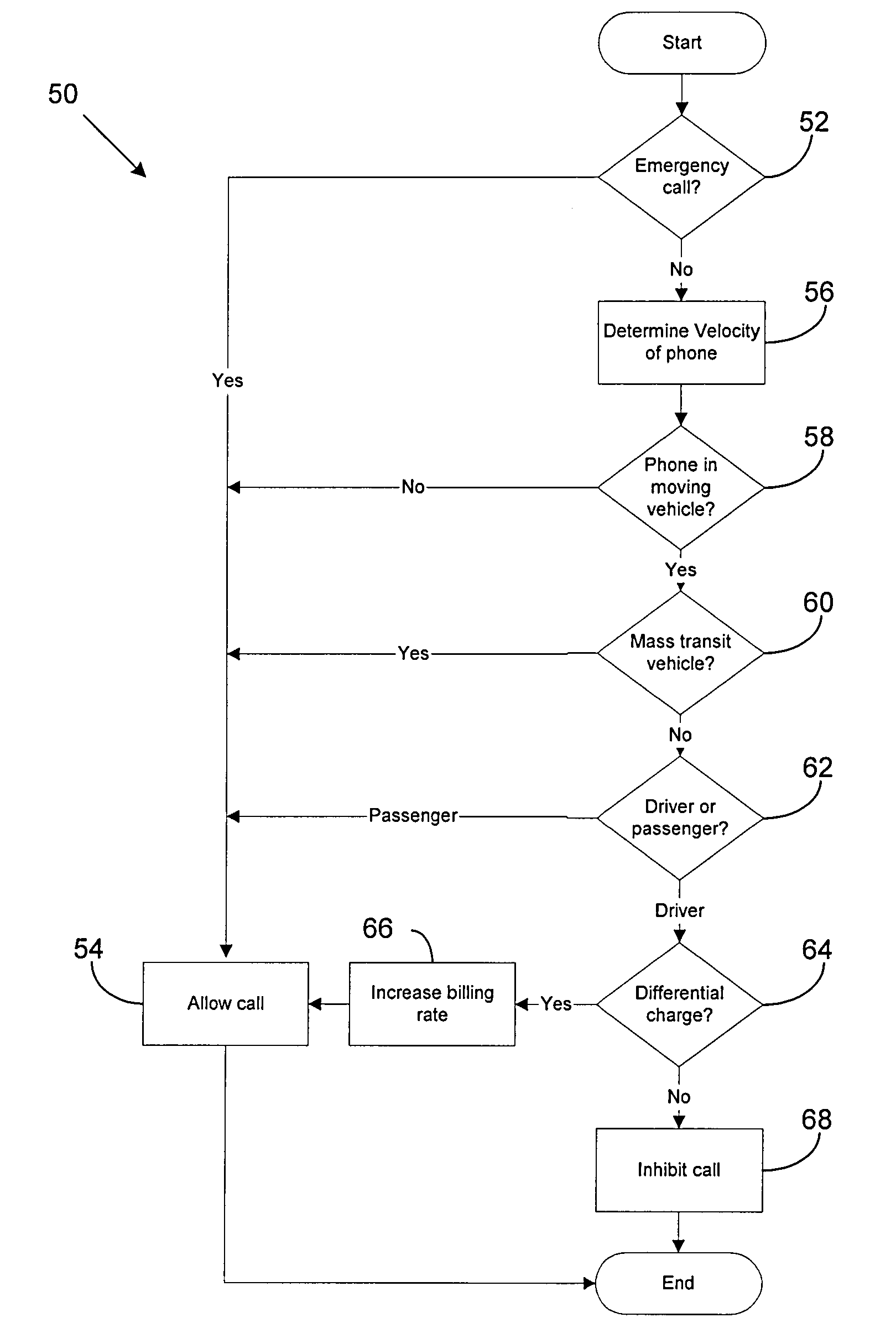

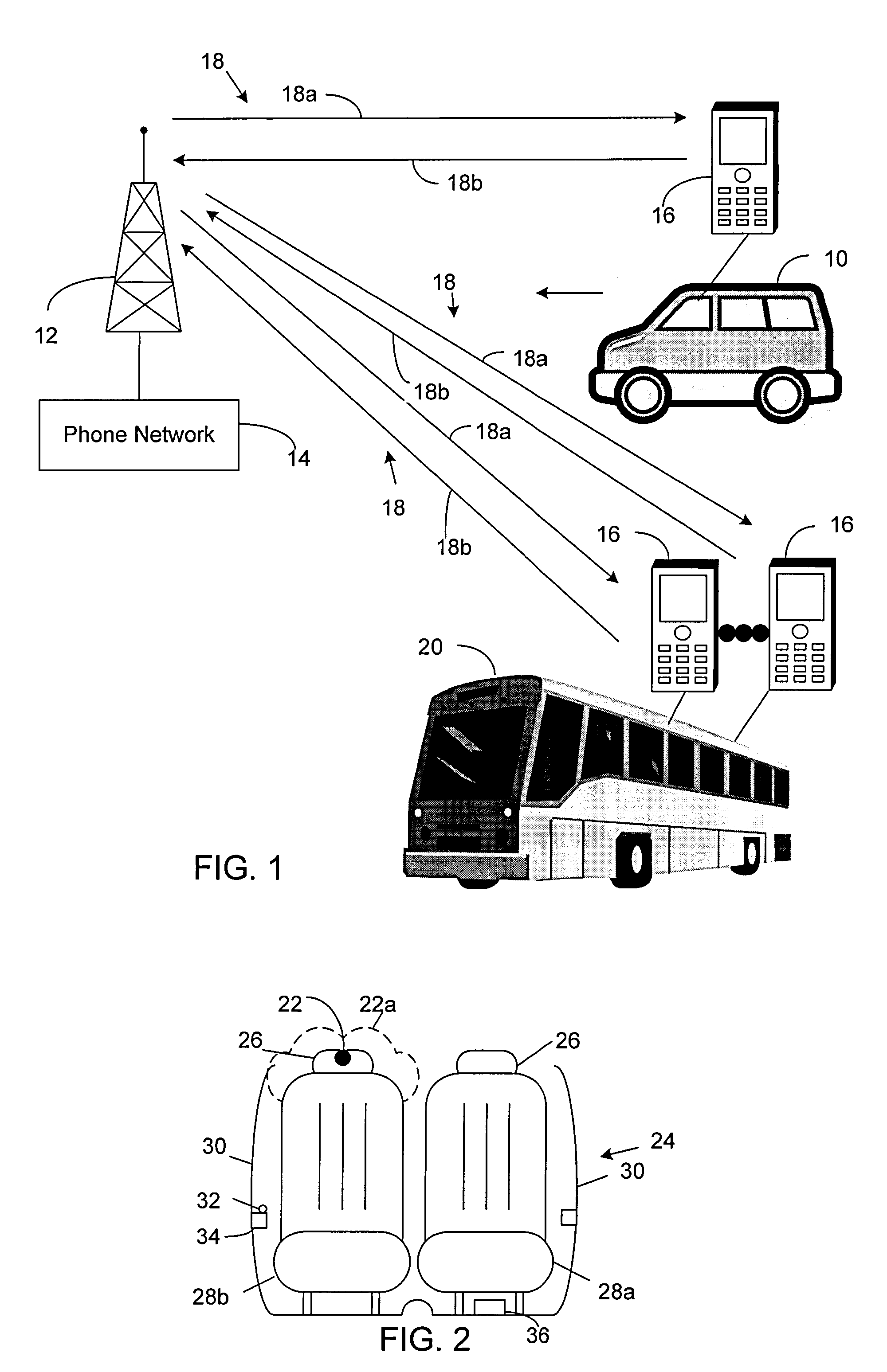

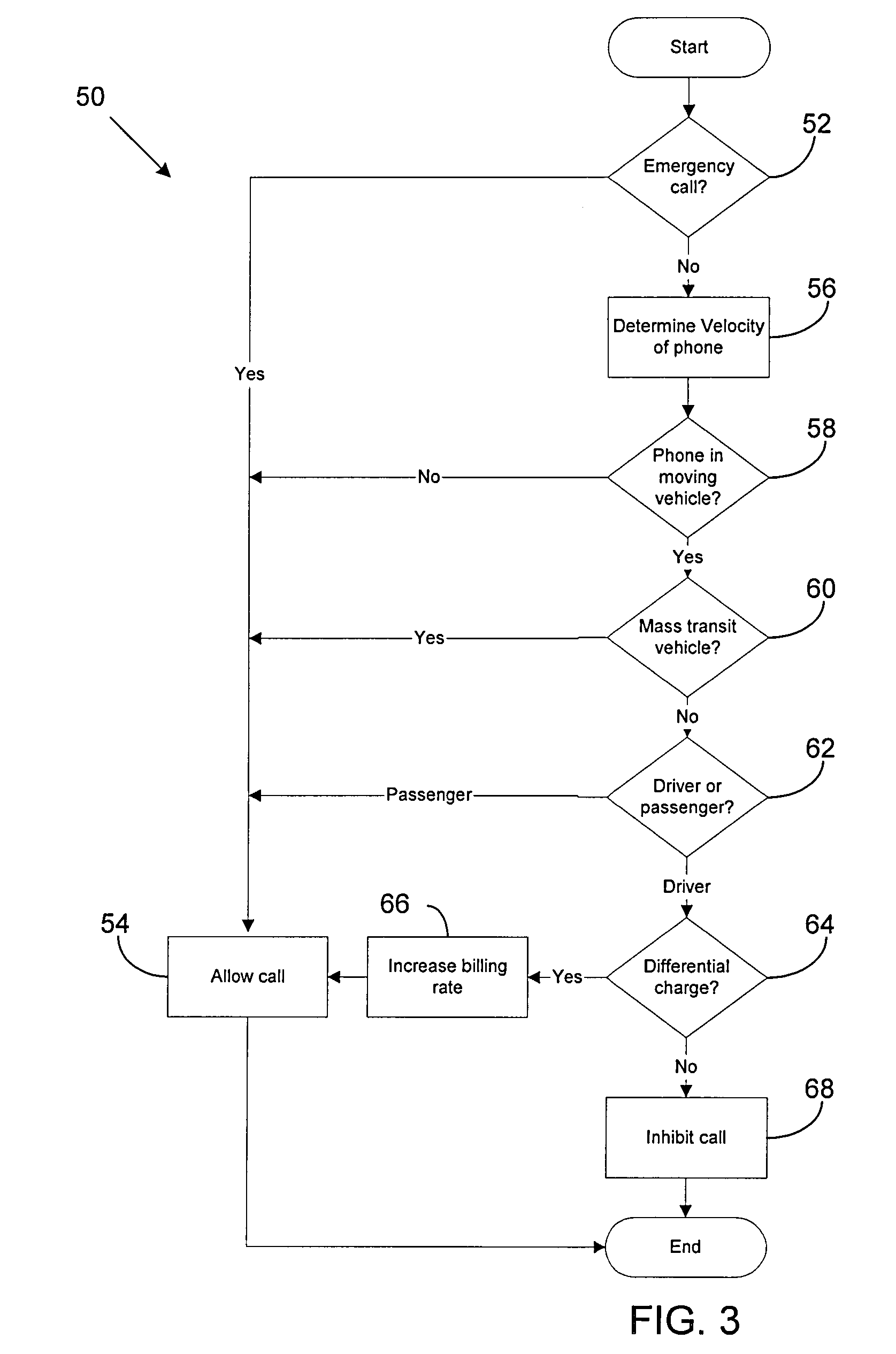

Method for safe operation of mobile phone in a car environment

InactiveUS20080064446A1Unauthorised/fraudulent call preventionBuilding locksMobile vehicleSafe operation

A method of operating electronic equipment, wherein said electronic equipment utilizes a wireless signal to communicate, includes determining if the electronic equipment is operated within a moving vehicle based on a characteristic of the wireless signal and inhibiting operation of the electronic equipment if the electronic equipment is in a moving vehicle.

Owner:SONY ERICSSON MOBILE COMM AB

Method for safe operation of mobile phone in a car environment

InactiveUS7697917B2Unauthorised/fraudulent call preventionDigital data processing detailsMobile vehicleSafe operation

Owner:SONY ERICSSON MOBILE COMM AB

Pulse output circuit, shift register and electronic equipment

A driver circuit of a display device, which includes TFTs of a single conductivity type and outputs an output signal with normal amplitude. A pulse is inputted to TFTs 101 and 104 to turn ON the TFTs and a potential of a node alpha is raised. When the potential of the node alpha reaches (VDD-VthN), the node alpha becomes in a floating state. Accordingly, a TFT 105 is turned ON and a potential of an output node is raised as a clock signal becomes High level. On the other hand, a potential of a gate electrode of the TFT 105 is further raised due to an operation of a capacitance means 107 as the potential of the output node is raised, so that the potential of the gate electrode of the TFT 105 becomes higher than (VDD+VthN). Thus, the potential of the output node is raised to VDD without causing a voltage drop due to a threshold voltage of the TFT 105. An output at the subsequent stage is then inputted to a TFT 103 to turn the TFT 103 ON, while the potential of the node alpha of TFTs 102 and 106 is dropped to turn the TFT 105 OFF. As a result, the potential of the output node becomes Low level.

Owner:SEMICON ENERGY LAB CO LTD

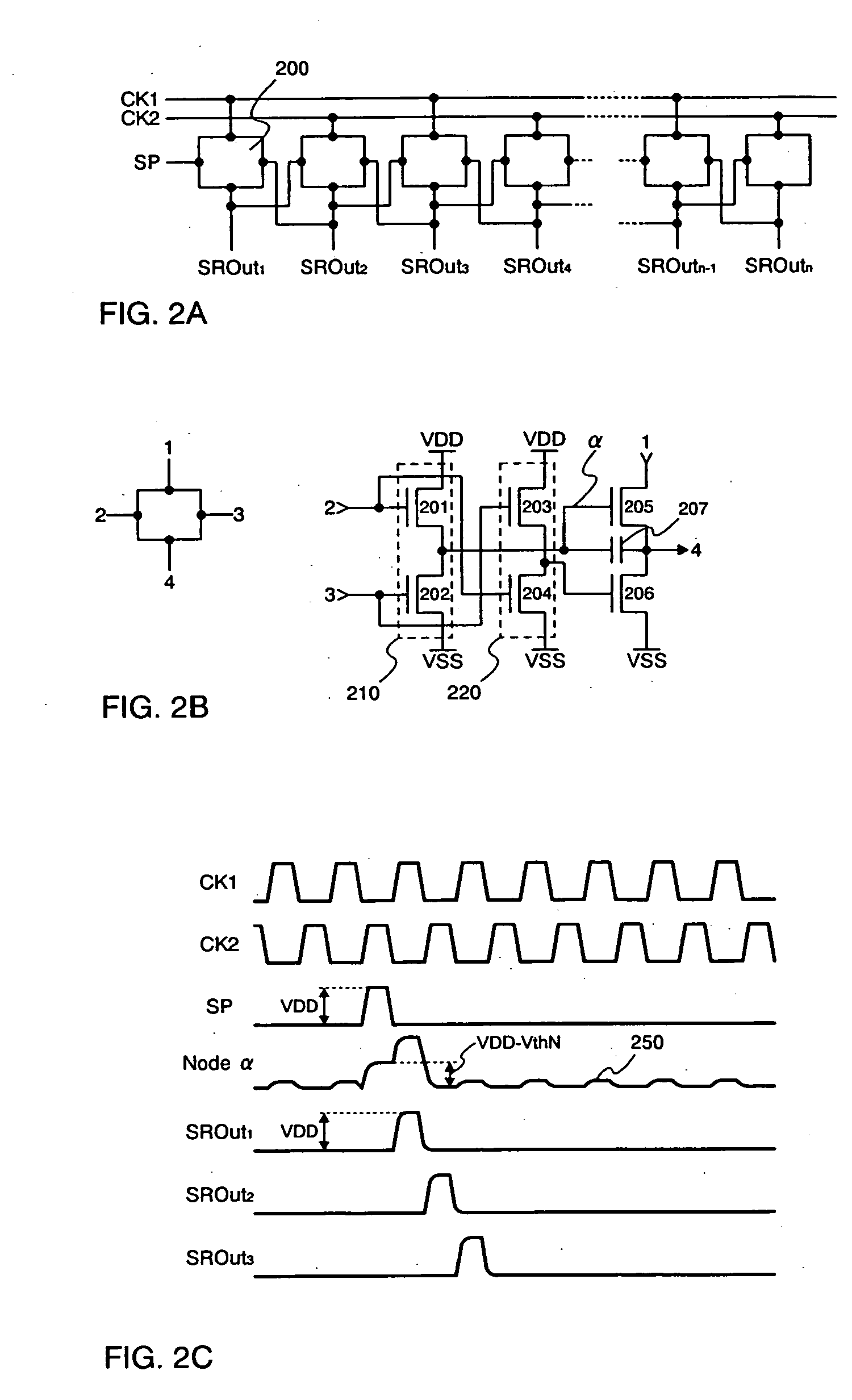

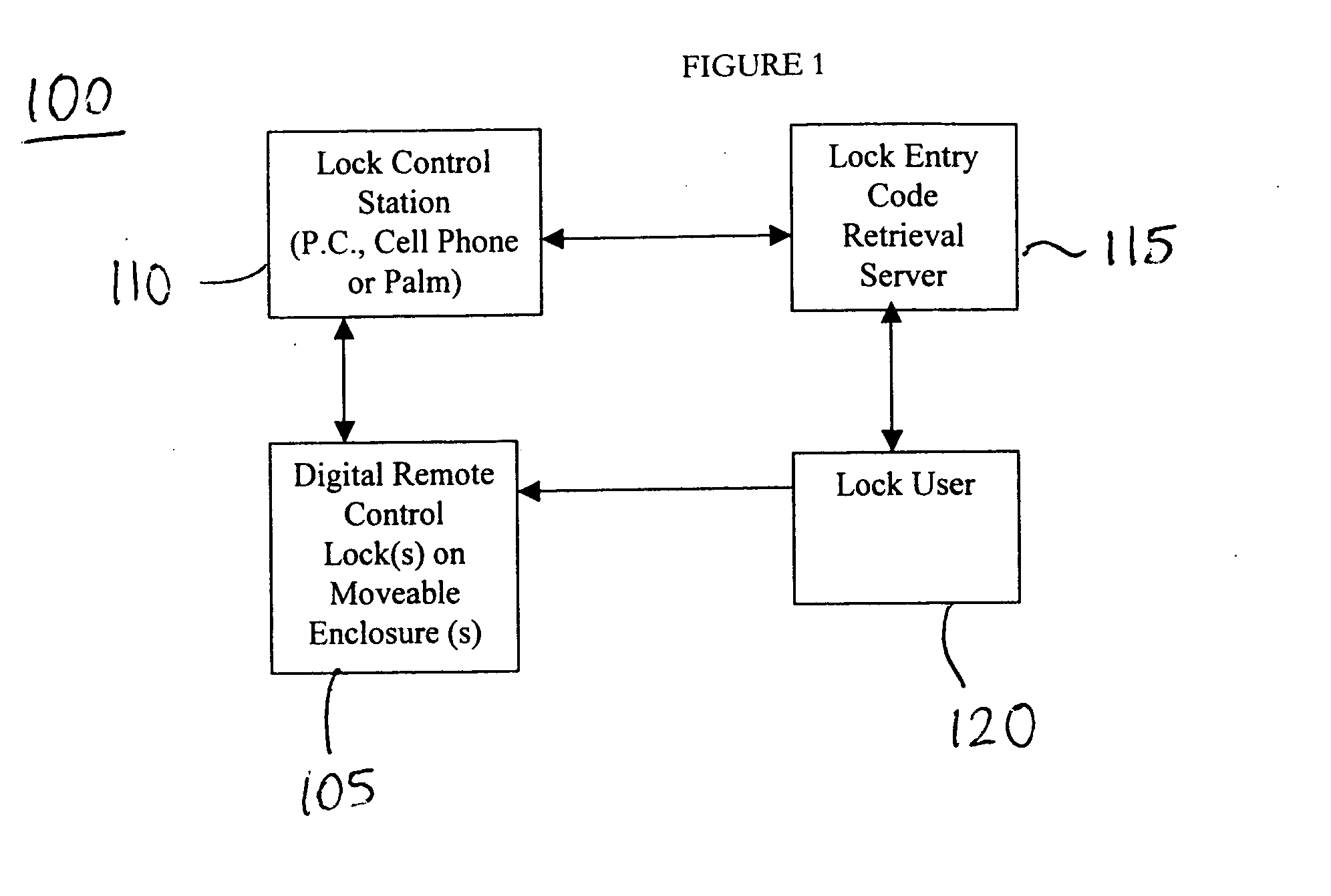

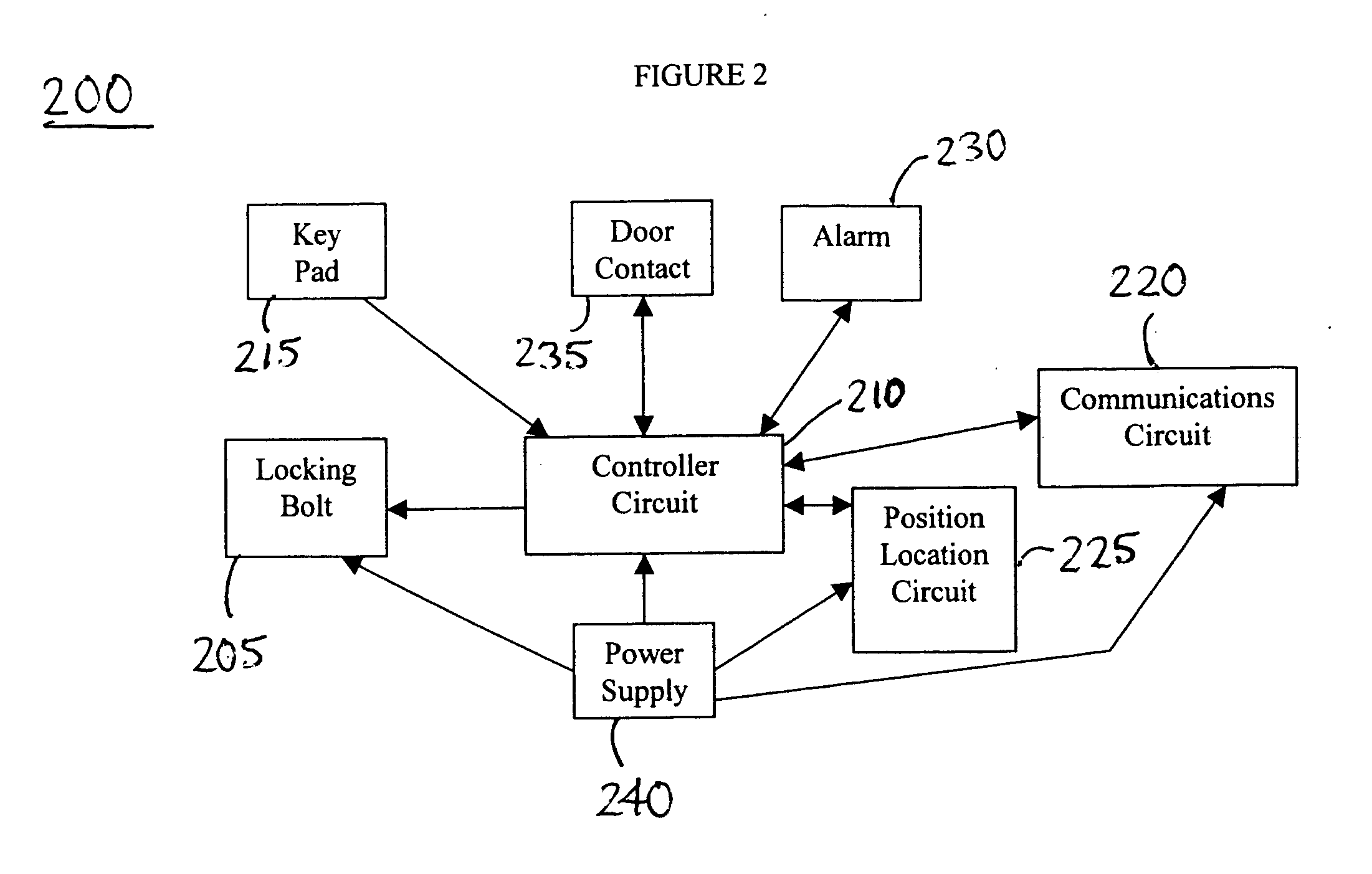

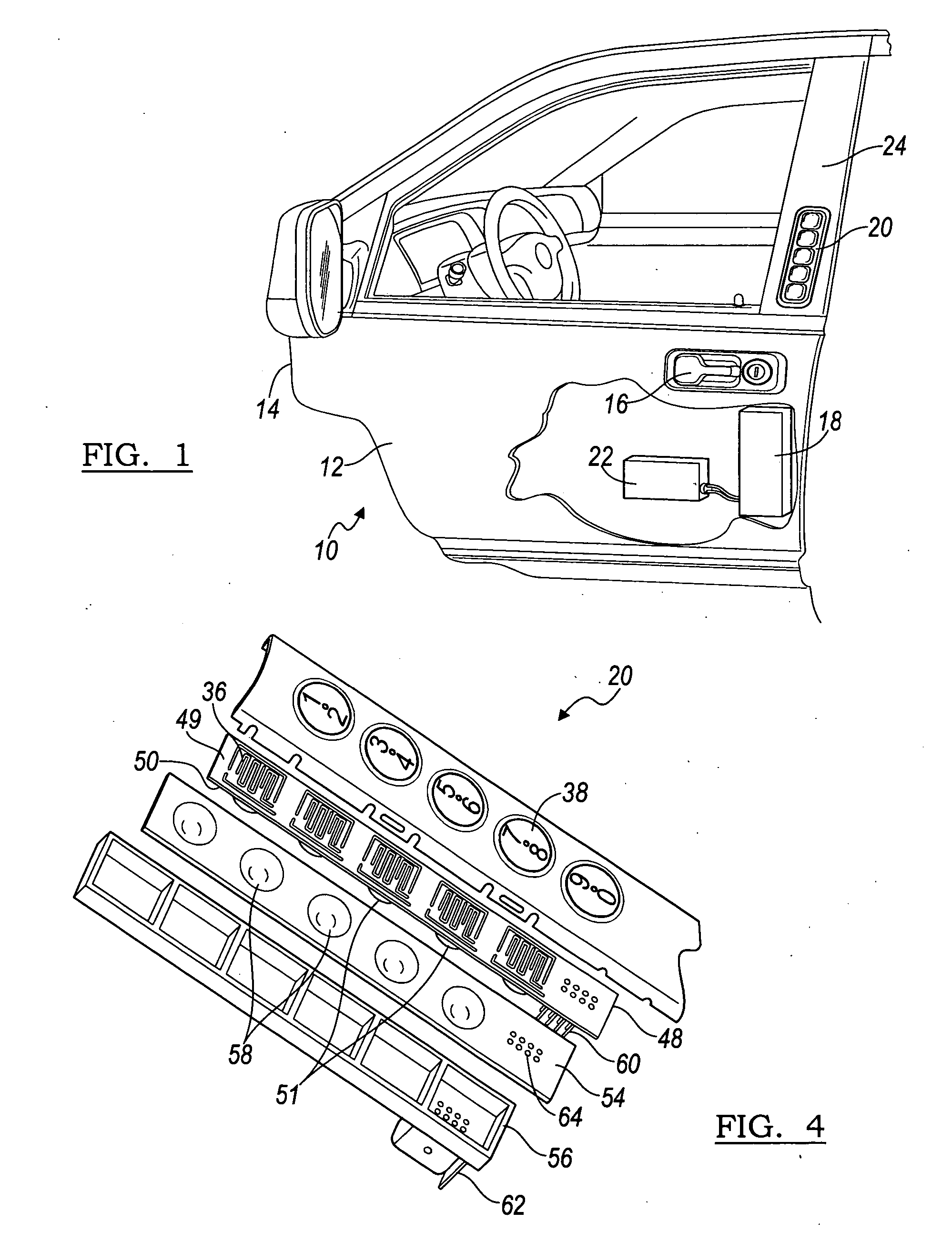

Method and system for setting entry codes via a communications network for access to moveable enclosures

InactiveUS20050044906A1Electric signal transmission systemsDigital data processing detailsMeasurement deviceSecret code

A system and method for controlling access to a moveable enclosure are provided. The system includes a lock on the moveable enclosure, a control circuit coupled to the lock and configured to i) receive an entry code and ii) open the lock in response to receipt of the entry code, a time measurement device and / or Global Positioning System device coupled to the control circuit and configured to generate time and position data, such as latitude and longitude data, relating to the moveable enclosure; and a personal computing device wirelessly coupleable to the control circuit and configured to generate the entry code using the latitude and longitude data. The entry code may be erased after a single use. The validity of entry code may depend upon the time of its entry and the physical location of the moveable enclosure.

Owner:SPIELMAN TIMOTHY G

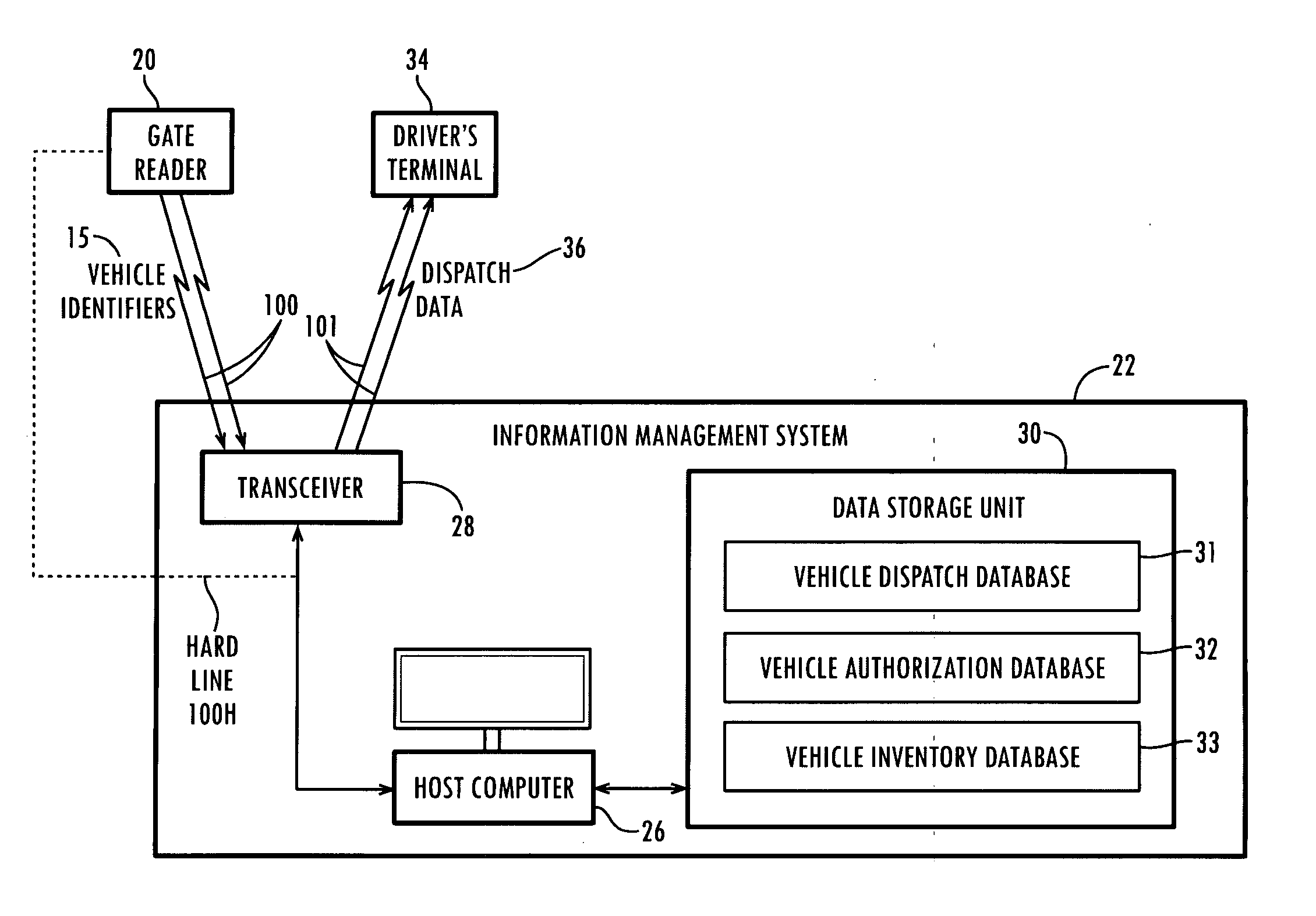

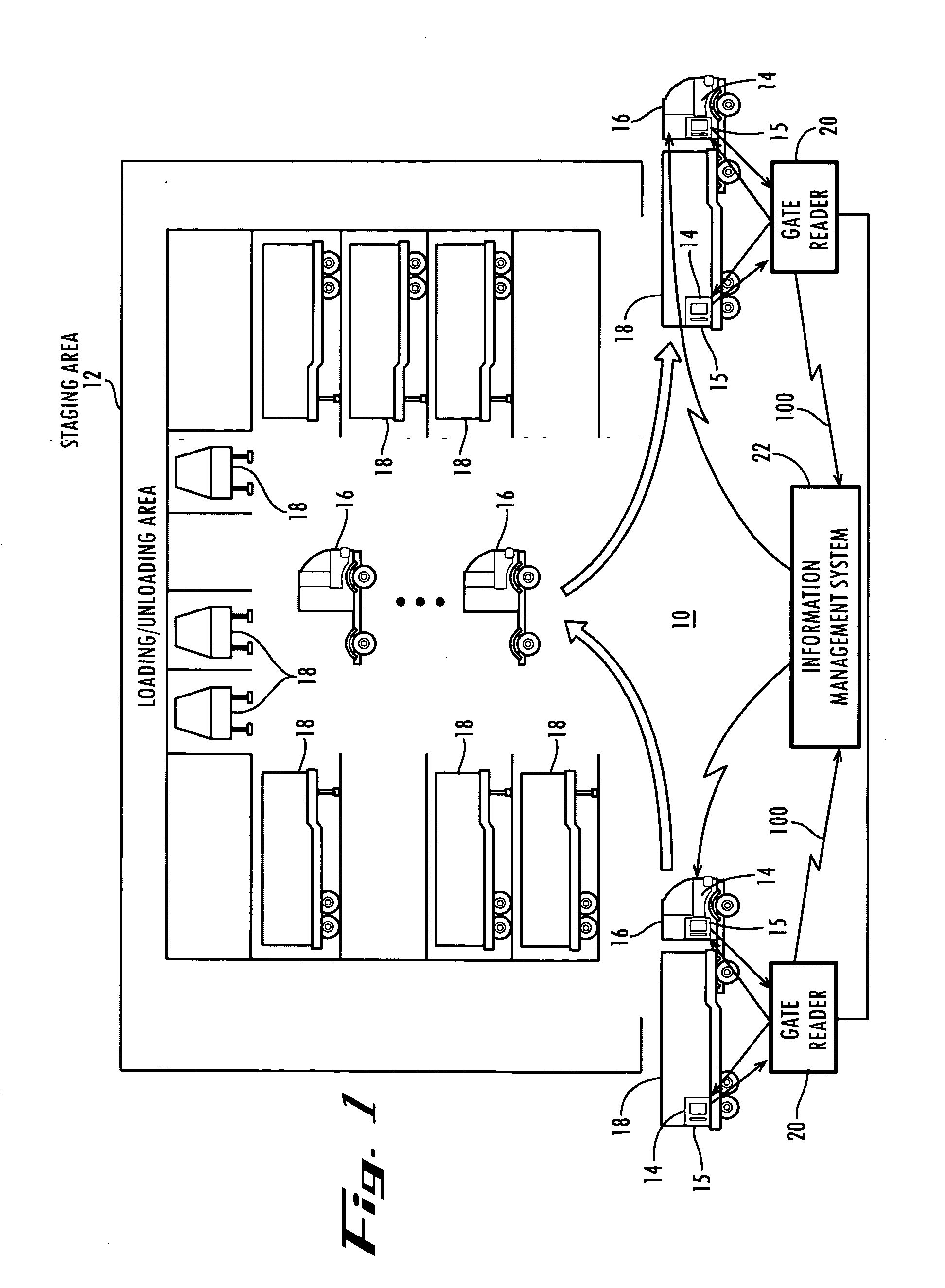

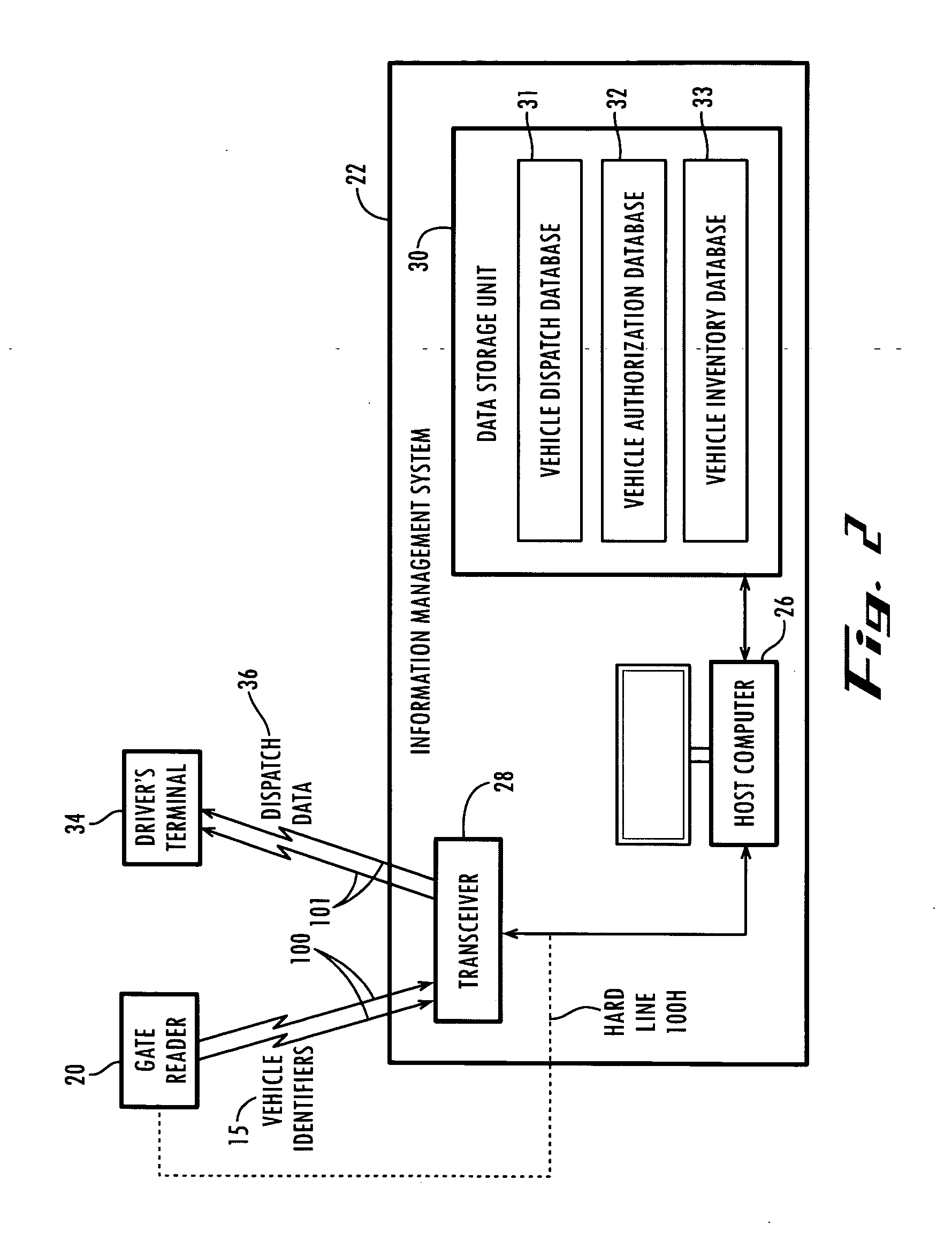

Wirelessly enabled trailer locking/unlocking

A method and system for providing improved handling of tractors and trailers )pr any powered vehicle and storage devices towed thereby) with a staging area. One invention relates to the provision of automatic locking or unlocking of a trailer door when the trailer leaves or enters the hub, respectively. A RFID signal strength evaluation scheme is also provided, which monitors successful RFID-to-antennae communications under various weather conditions, in order to determine an optimum read process. Under another embodiment, Geofencing and / or Wi-Fi can be used to trigger various events.

Owner:UNITED PARCEL SERVICE OF AMERICAN INC

Location-based intelligent remote vehicle function control

ActiveUS7346439B2Increase costWide deploymentDigital data processing detailsRoad vehicles traffic controlTime segmentIn vehicle

An in-vehicle monitor detects the occurrence of a meta-event related to the operation of a vehicle, such as the vehicle's operation over a maximum allowable speed, operation in a prohibited geographic area, operation during a specific time frame, or combinations thereof. The monitor signals a server via a wireless data link, and the server determines an appropriate deferred action to be taken by an in-vehicle controller, such as disabling the engine, limiting vehicle speed, and locking vehicle doors, upon occurrence of a second meta-event including conditions such as time delays, vehicle speed and direction, and vehicle location. The system can thereby allow orderly and safe control of vehicle functions for purposes such as terminating a pursuit, enforcing legal sentences and operator restrictions, and controlling fleet vehicle operations.

Owner:GOOGLE LLC

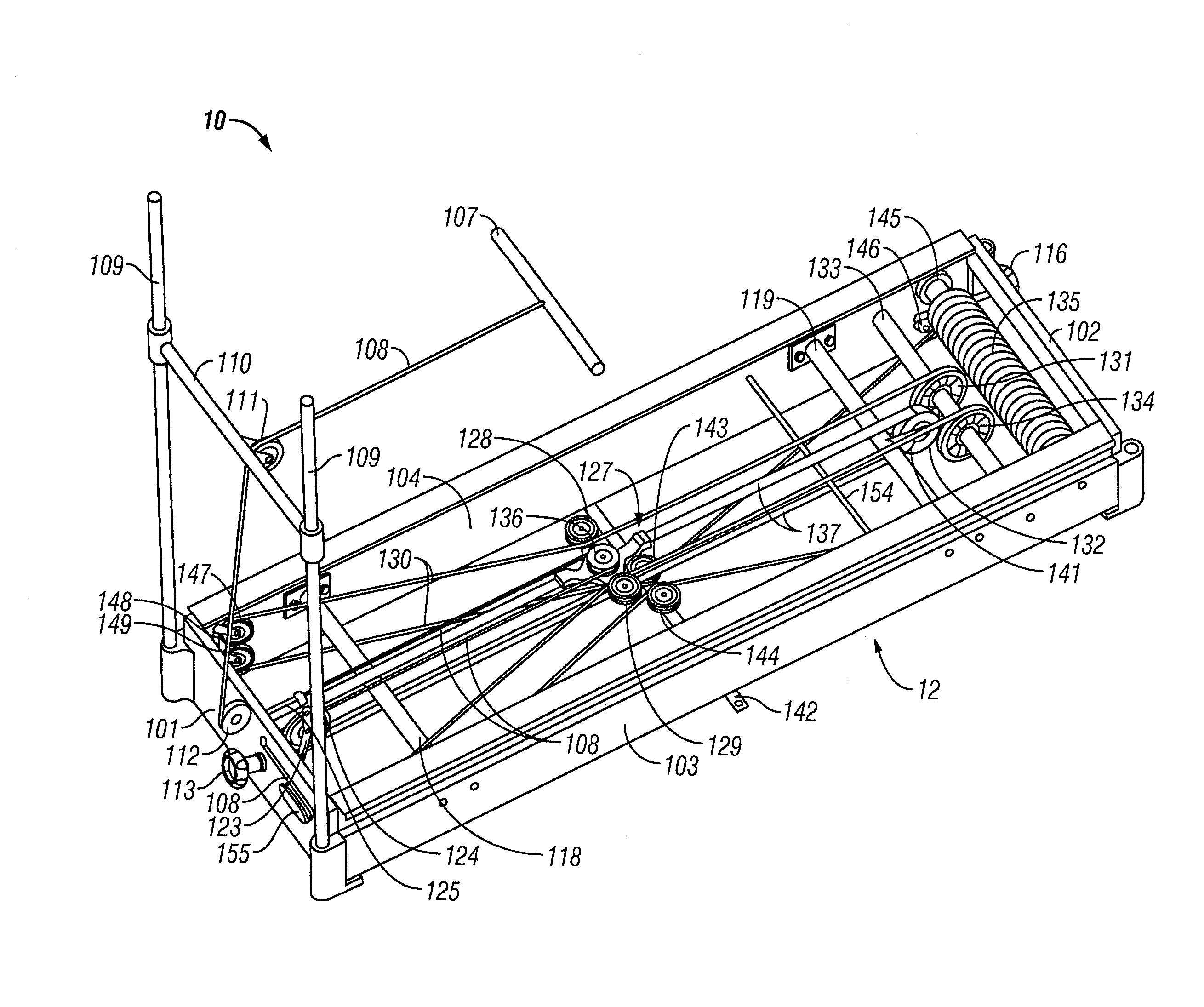

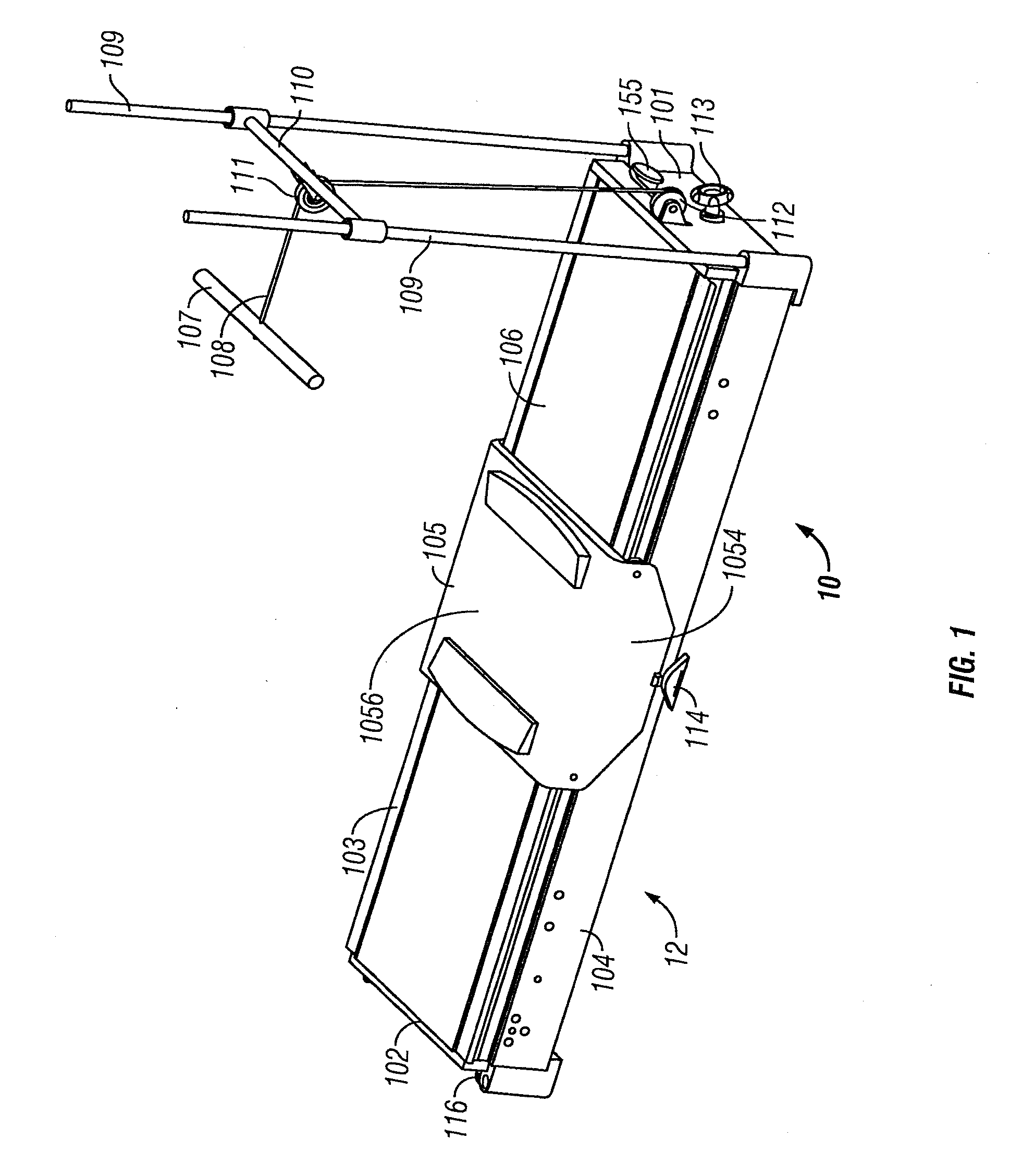

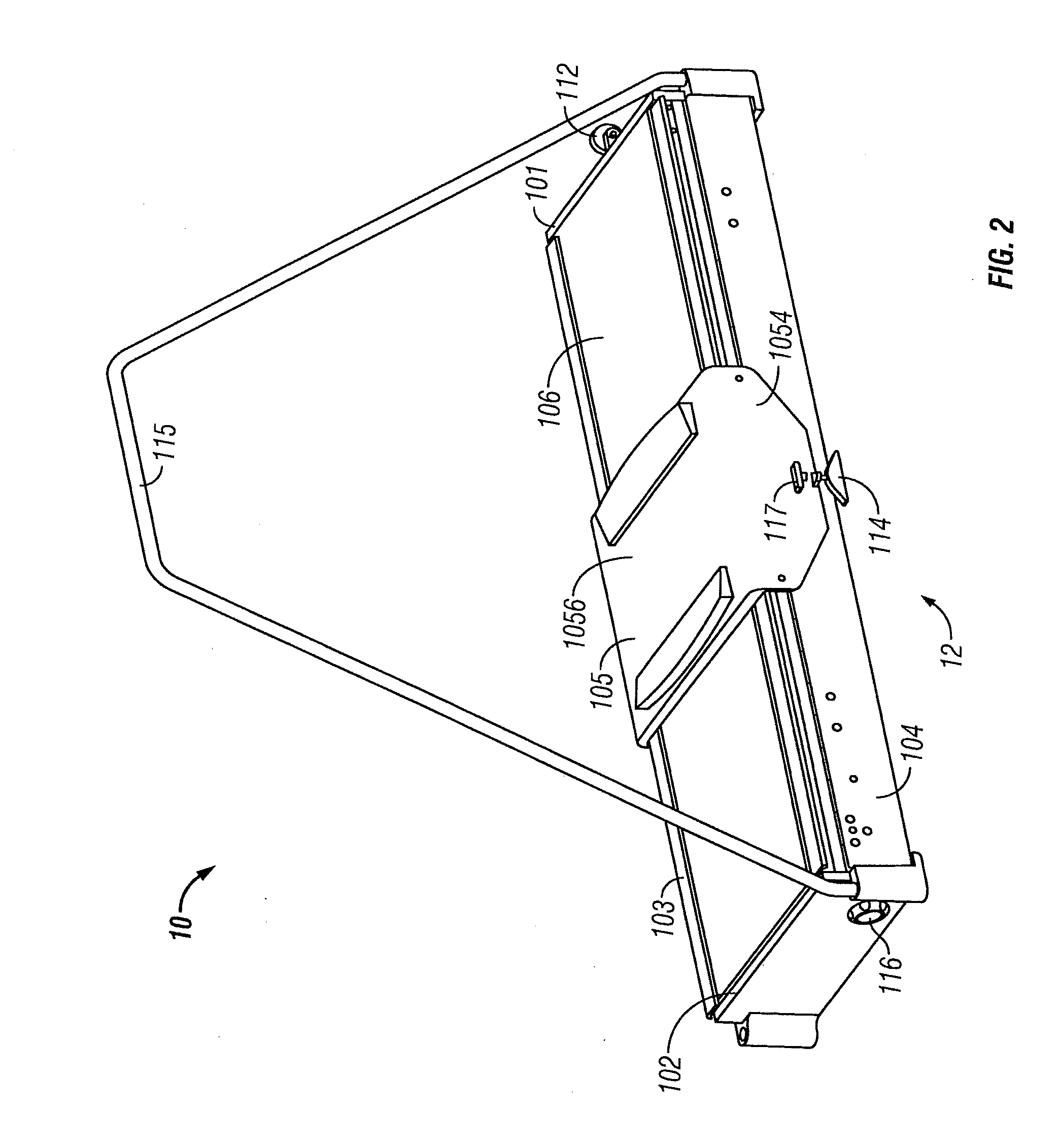

Multipurpose exercise system

An exercise system is provided in which multiple exercise routines may be conducted with a single system. The exercise system may be used for skiing exercises, rowing exercises, and for weight training / resistance exercises. The exercise system may also be stored in a compact position and may by integrated with articles of furniture for space saving benefits. In one embodiment, resistance to motion is provided by one or more tension transmission members and may be selectively adjusted by controlling the configuration of the tension transmission member relative to a torsion spring. Use of intermediate devices between the spring and the tension transmission member are described that provide a non-linear relationship between force and displacement. In another embodiment, the tension transmission member may be configured in different positions by adjusting the position of movable pulleys, thereby allowing the device to be used for a number of different exercise routines.

Owner:STUDIO MODERNA SA

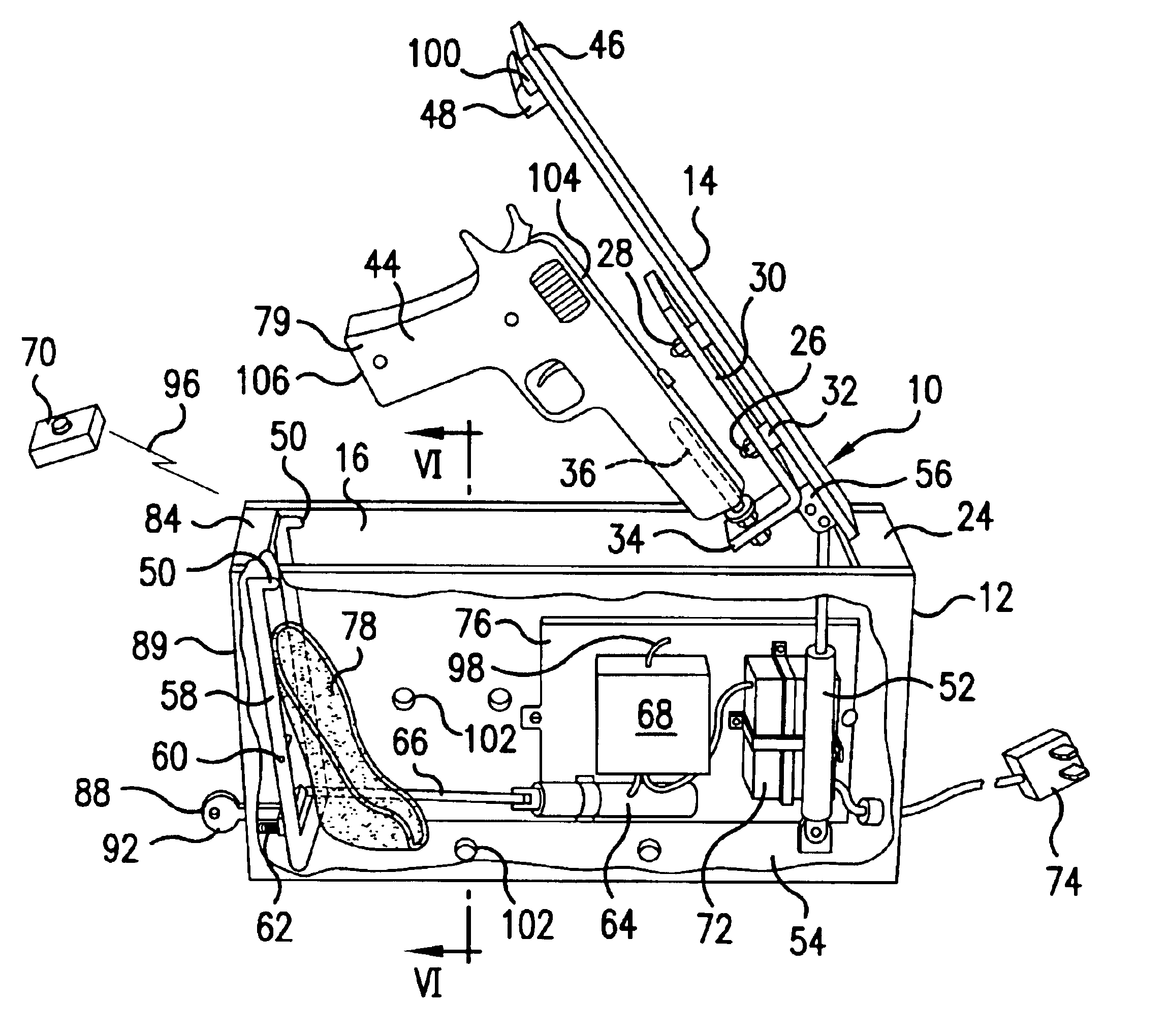

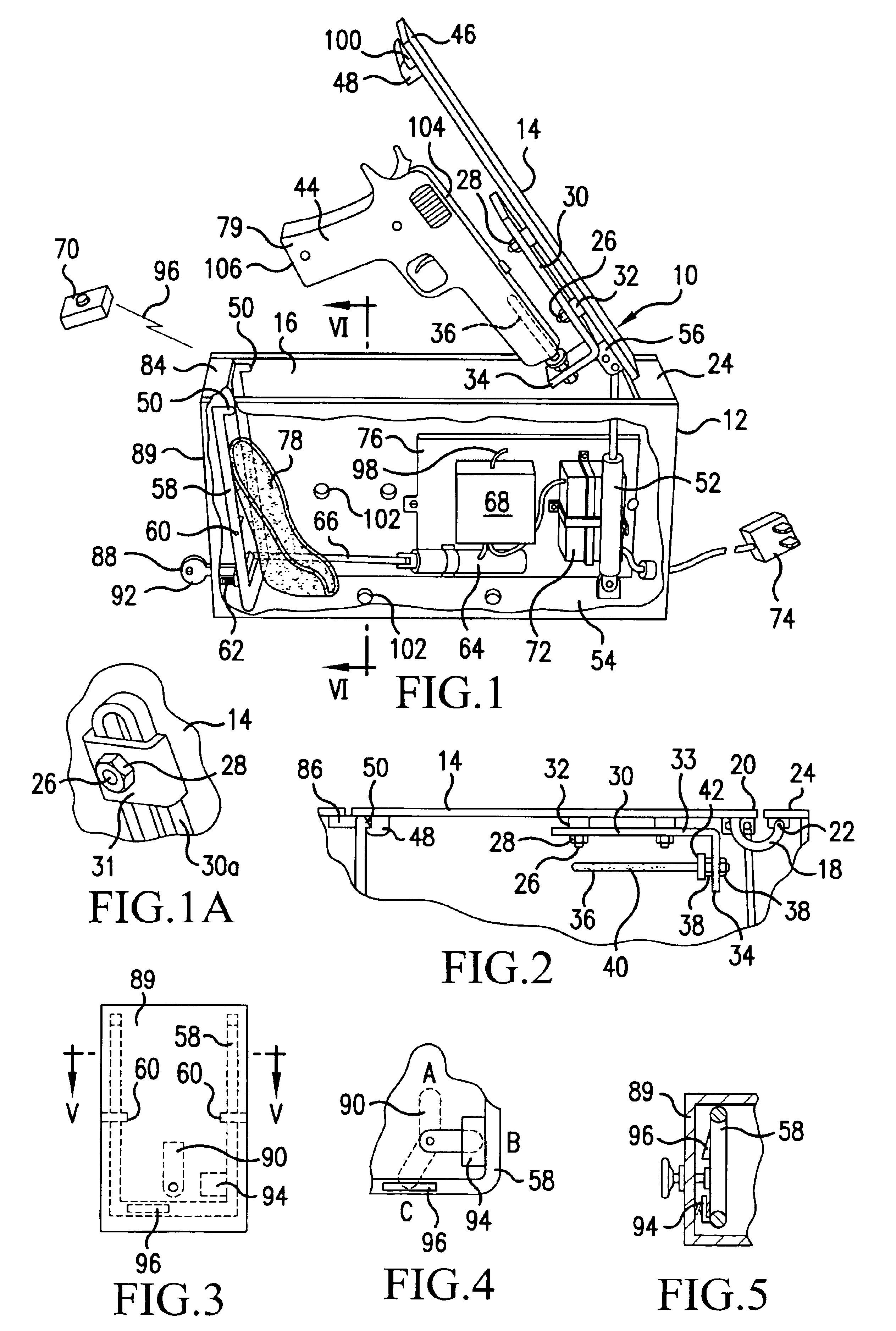

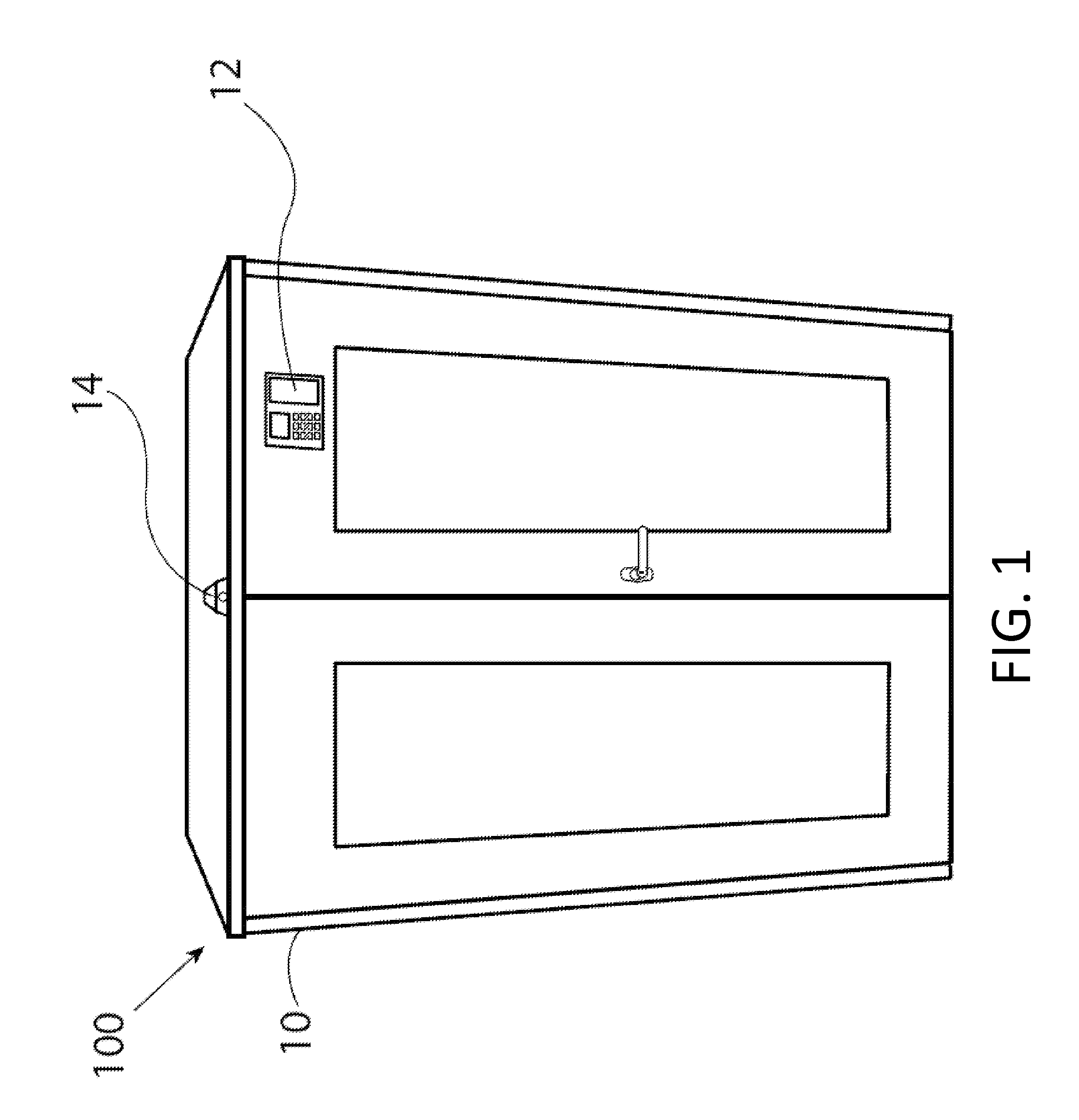

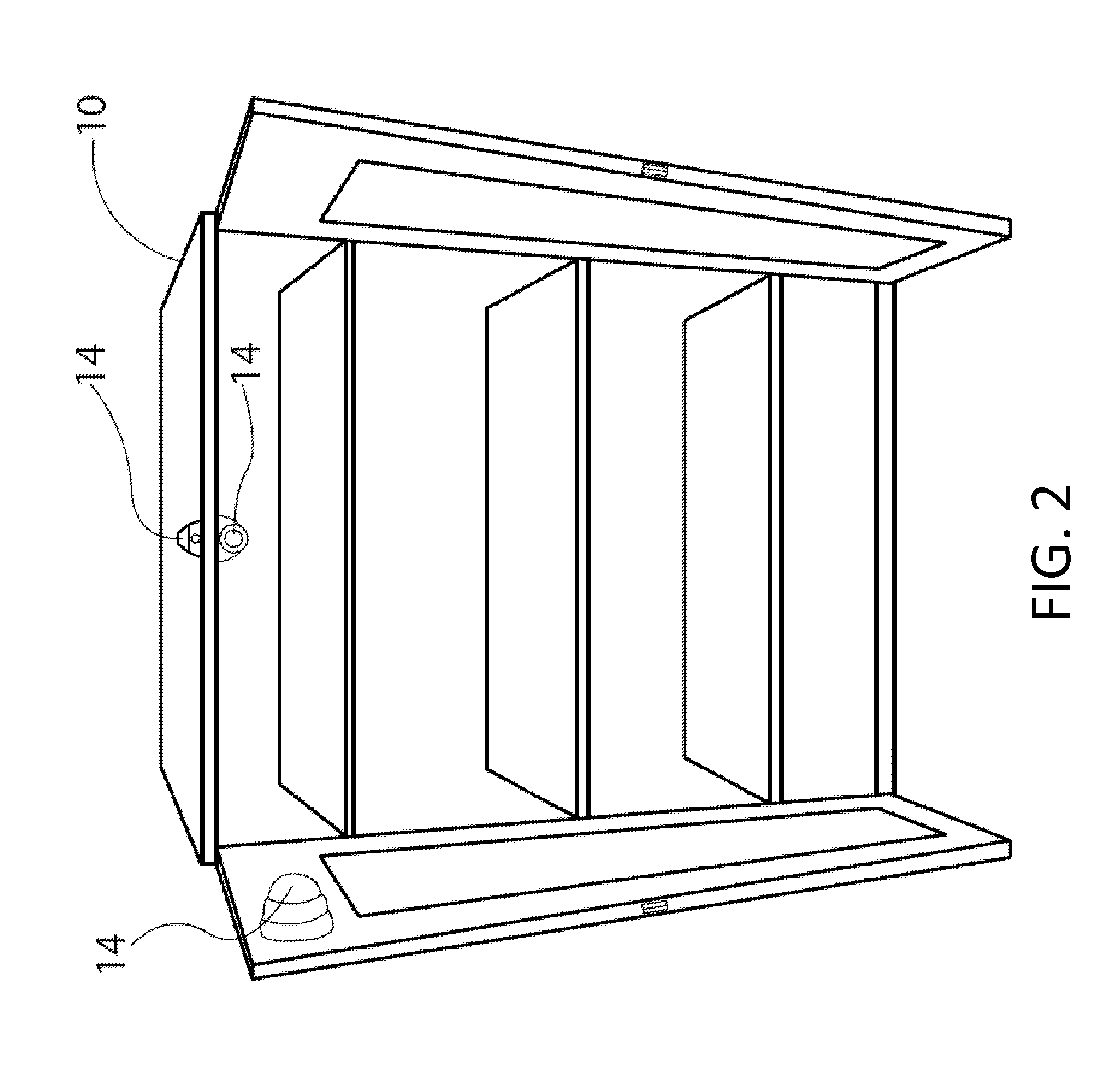

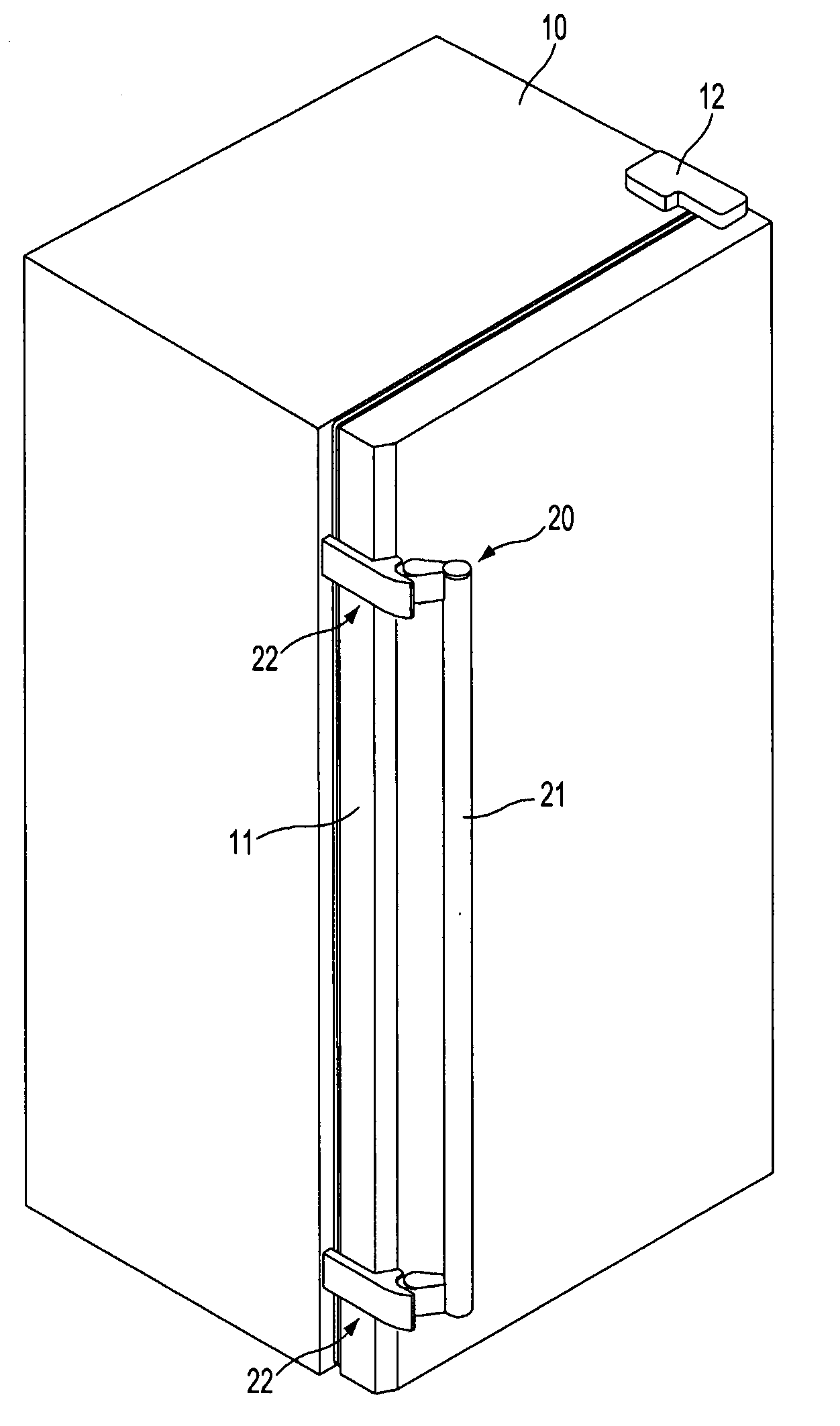

Secure firearm holder

InactiveUS6843081B1Easy to removeQuickly and easily removedSafety arrangementBuilding locksLocking mechanismEngineering

A secure firearm holder (10) includes an outwardly swinging hinged plate (14) that is hinged to a holder base (12) with a gun (44) mounted at a side of the plate in a ready-to-use orientation when the plate swings outwardly. In a preferred embodiment, a bore shaft (36) is mounted on the hinged plate, the bore shaft extending into the firearm. When the plate is in a first, closed, position, the holder base prevents the gun from being removed from the bore shaft, but when a motivating member (52) rotates the plate to a second position, the gun can be easily and quickly removed from the bore shaft from a ready-to-use orientation. The motivating member biases the lid toward the second position but is held closed in the first position by a latch (50), which latch is remotely releasable. A locking mechanism has three positions: a totally-locked position (B) for locking the latch (50) against remote release of the lid; an active position (A) for allowing remote release of the lid; and a manual-release position (C) for releasing the lid manually.

Owner:PAINTER TERRY M

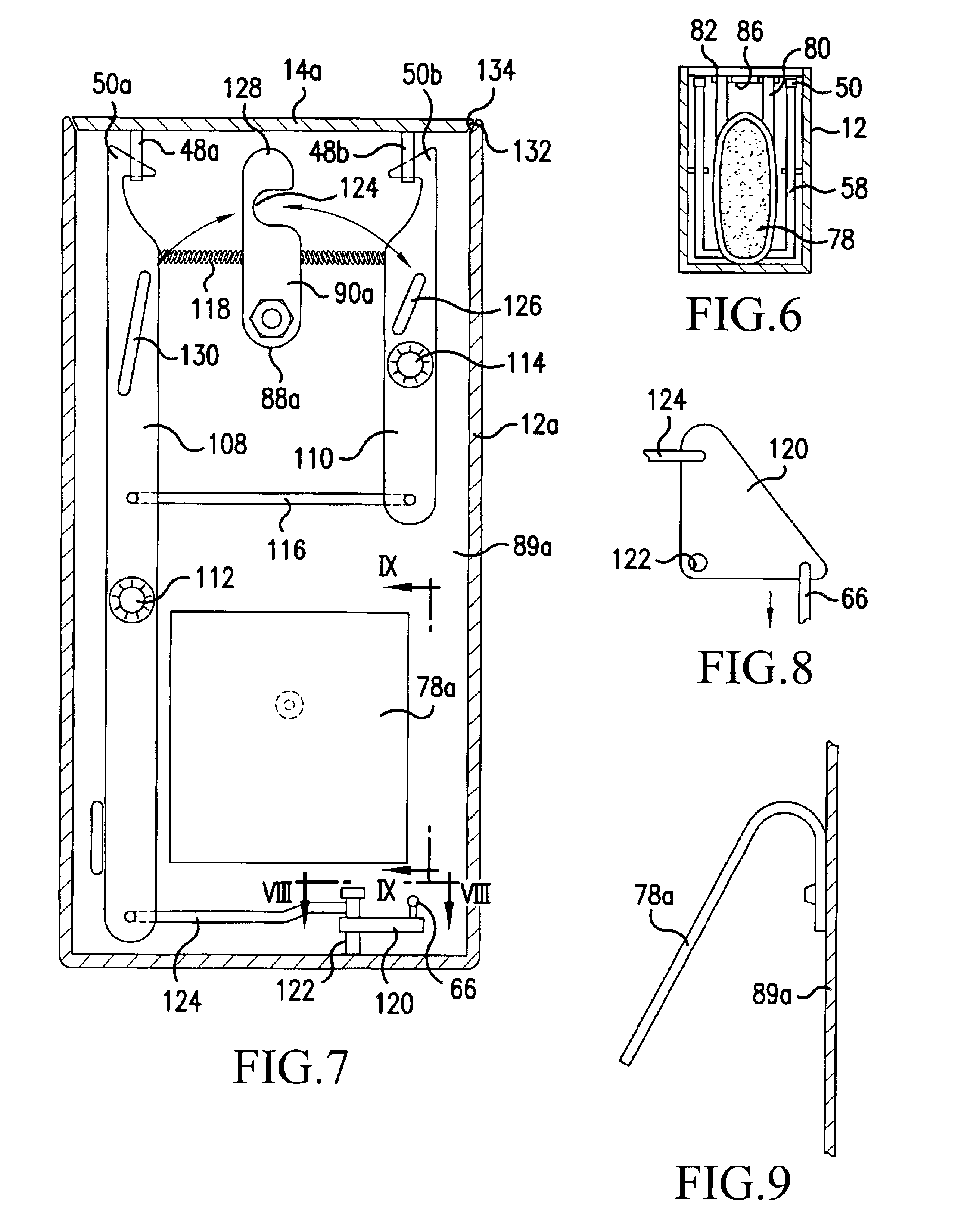

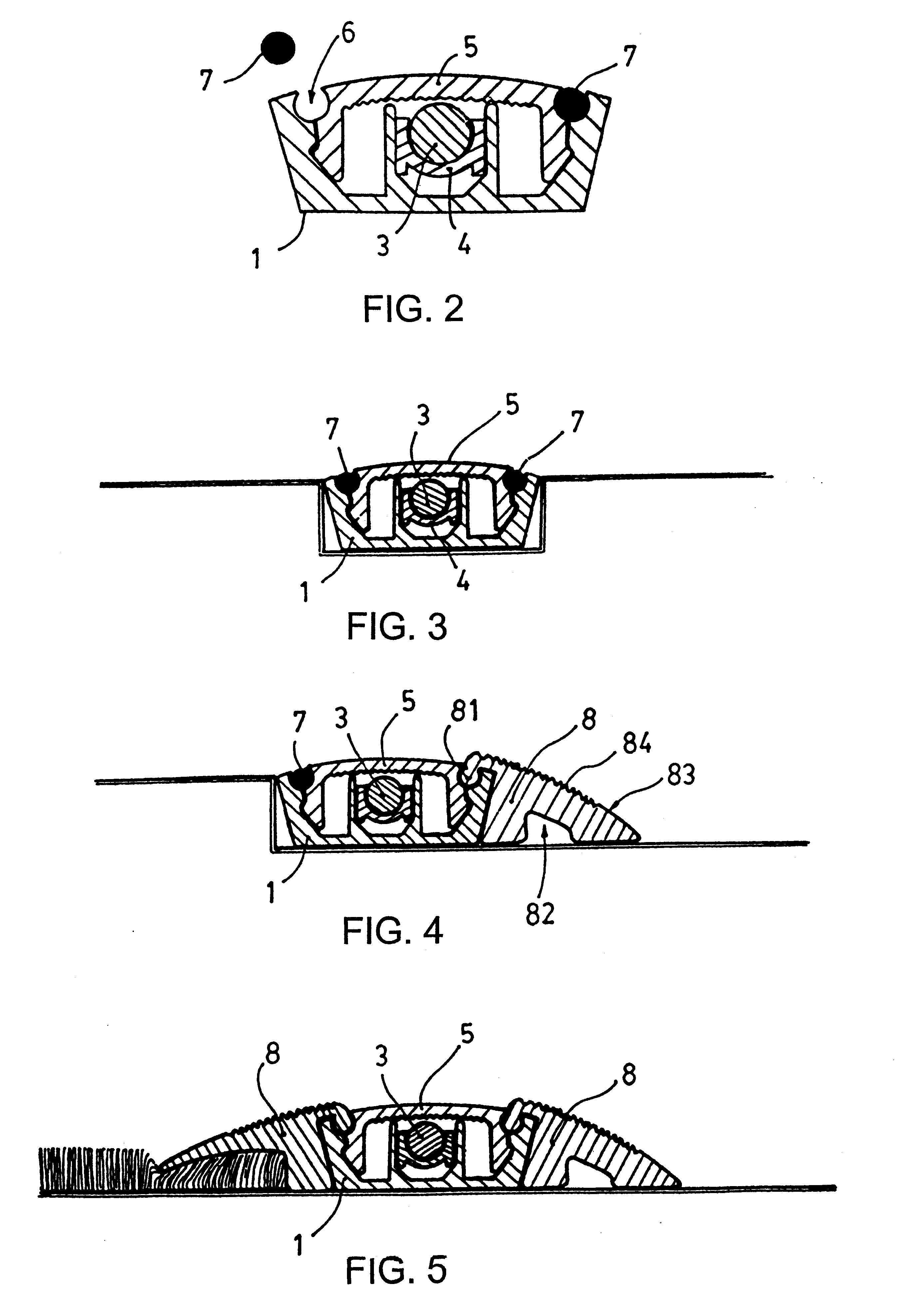

Light signaling device for floors

A lit-up marking device for floors includes a section with a generally U-shaped layout defined by a flat base and by two end wings. Intermediate inlets for the pressure-fitting of a translucent protector are at the flat base. Lighting is positioned on a longitudinal support housed in the section and a translucent protector has a central portion and two side feet forming an arrow-head for fitting into the section. The wings of the section have, on their interior end, respective concavities which face concavities formed on the exterior in the initial zone of the side legs of the translucent protector. The cavities form one cavity with an opening for inserting optional elements for fixing the translucent protector onto the section.

Owner:HOFFMANN FRIEDEMAN

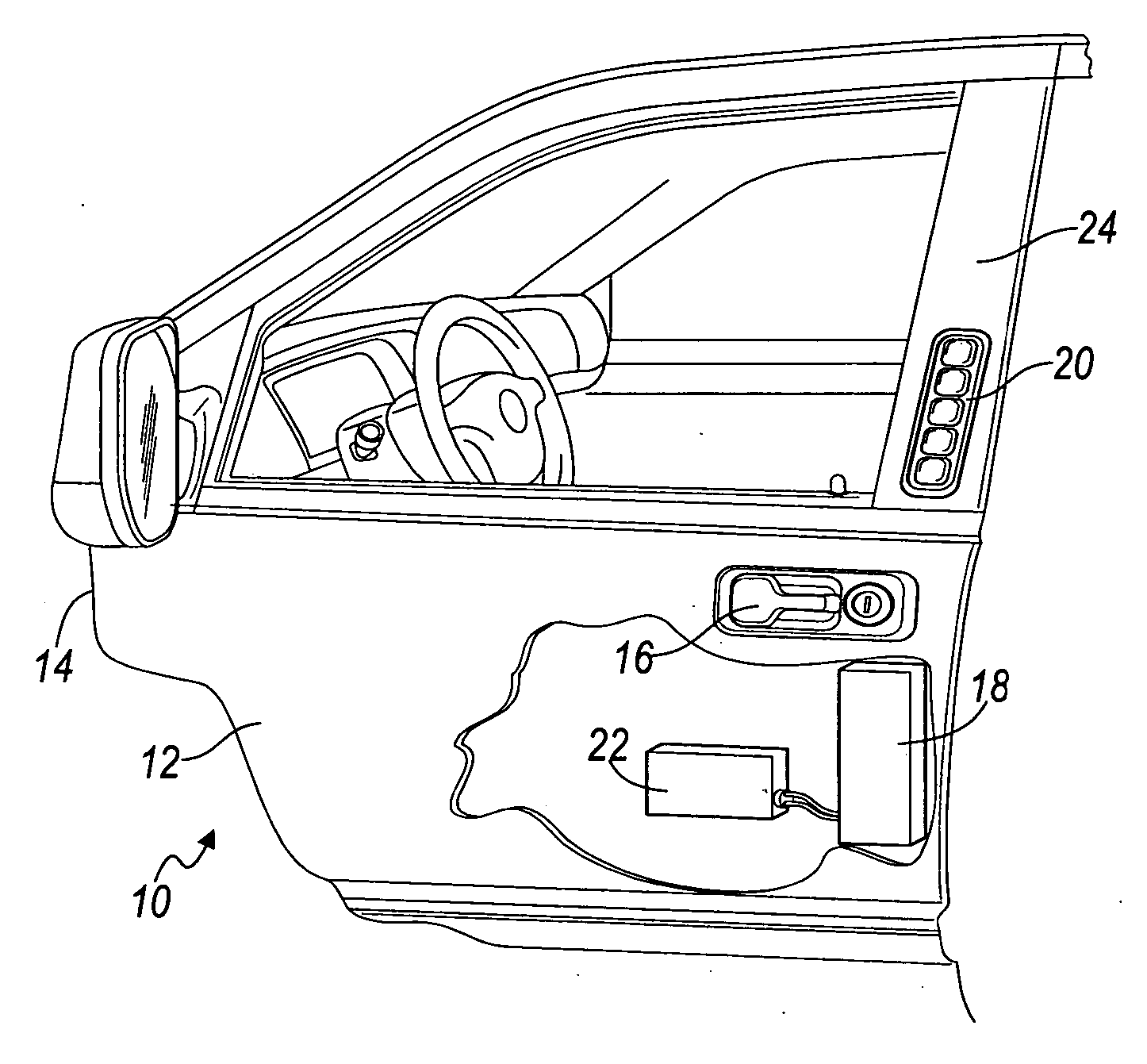

Illuminated keyless entry control device

A vehicular control device includes a trim member having a plurality of graphics for identifying a plurality of manual activation regions and a printed circuit board having a plurality of proximity sensors. Each of the plurality of proximity sensors generates a respective electromagnetic field within a respective manual activation region and is responsive to an object disposed in the respective manual activation region. The printed circuit board is semi-translucent and includes a plurality of illumination elements for illuminating light away from the printed circuit board. A back cover member is adaptable to the trim member for encasing the printed circuit board therebetween. A sealing member is disposed between the trim member and the back cover member. The illuminating light from the plurality of illumination elements is reflected toward the printed circuit board. The printed circuit board receives the illuminating light and diffuses the illuminating light therethrough for backlighting the plurality of graphics.

Owner:LEAR CORP

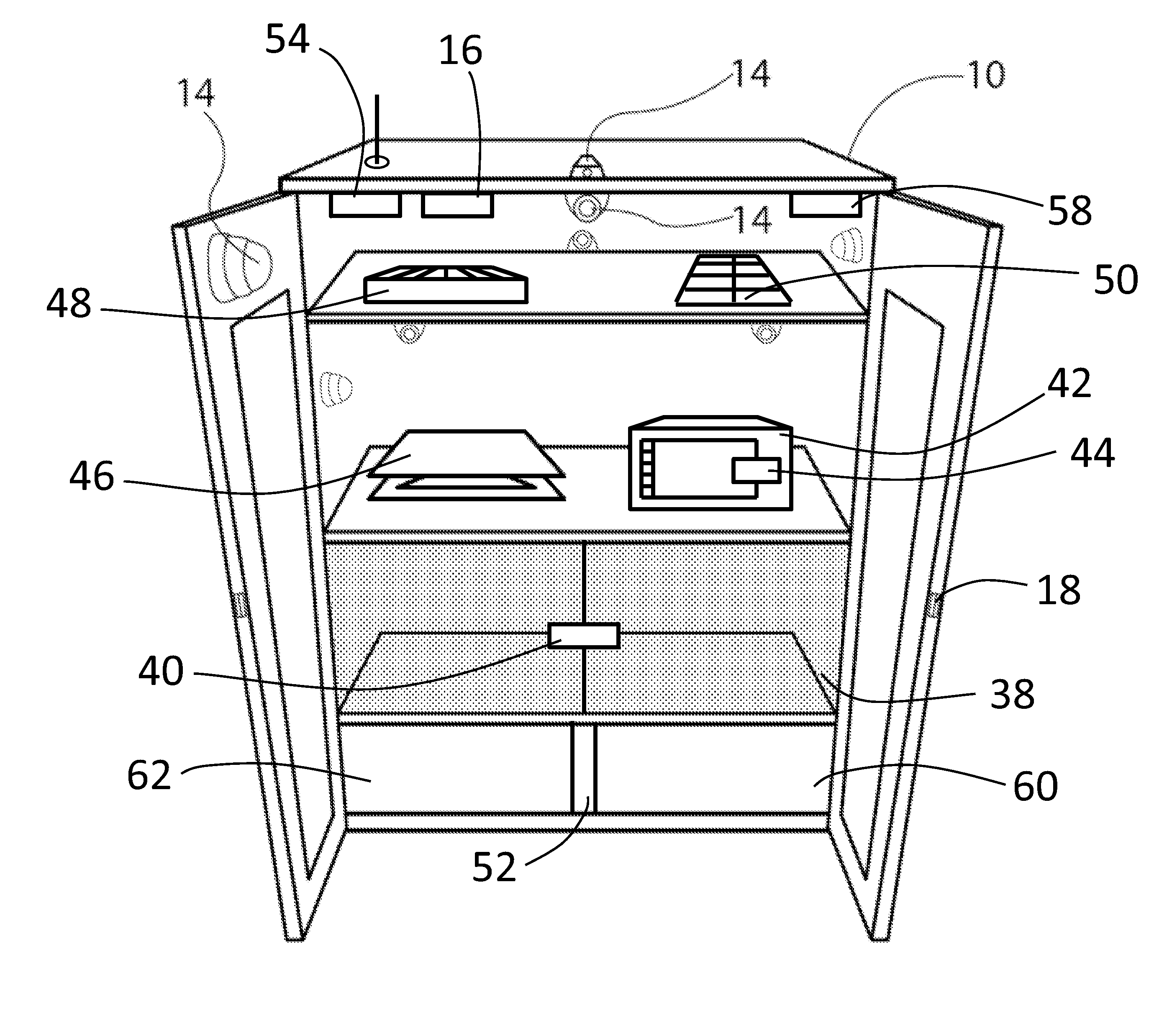

Storage container with inventory control

ActiveUS20140297487A1Undesired vibrations/sounds insulation/absorptionBuilding locksWorld Wide WebImage capture

Systems and methods of the invention relate to managing an inventory of items within a storage container. A storage container can house one or more items for distribution among one or more users such as, for instance, employees. The storage container discussed herein provides authentication of a user, tracking of the inventory each user removes or returns, video / image capture of user during access of the storage container, wireless tracking of items housed within the storage container, among others.

Owner:3 STRIKE

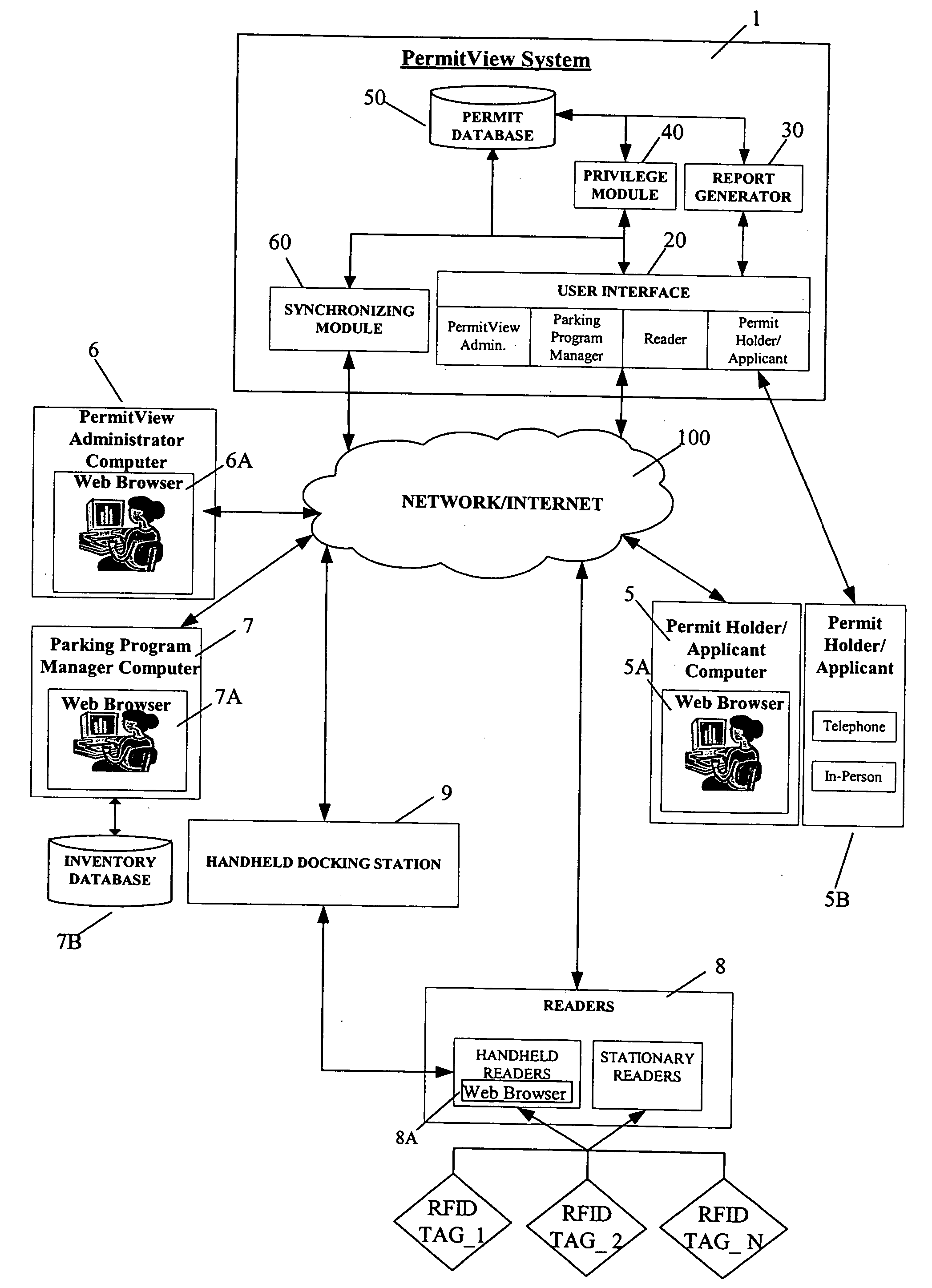

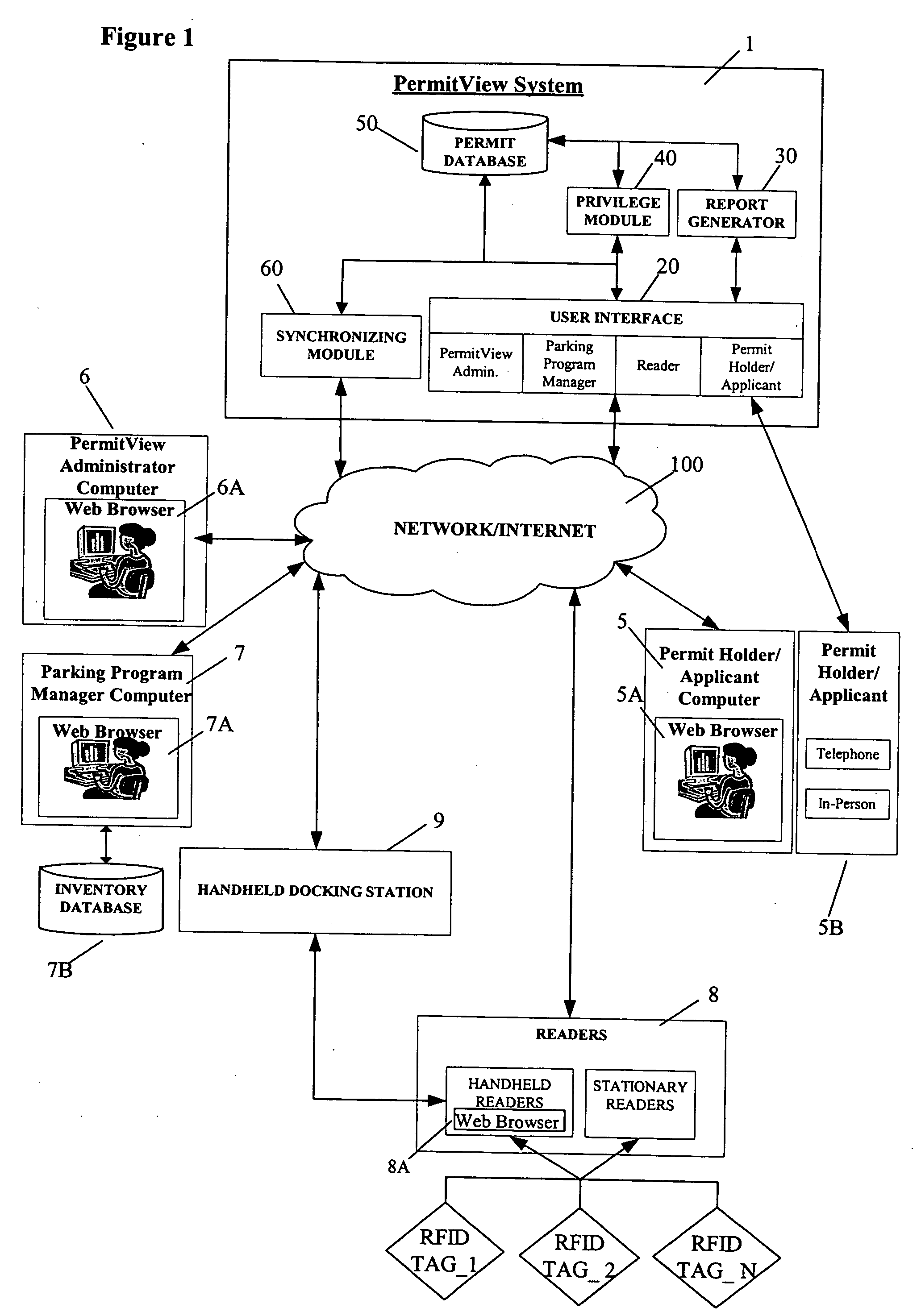

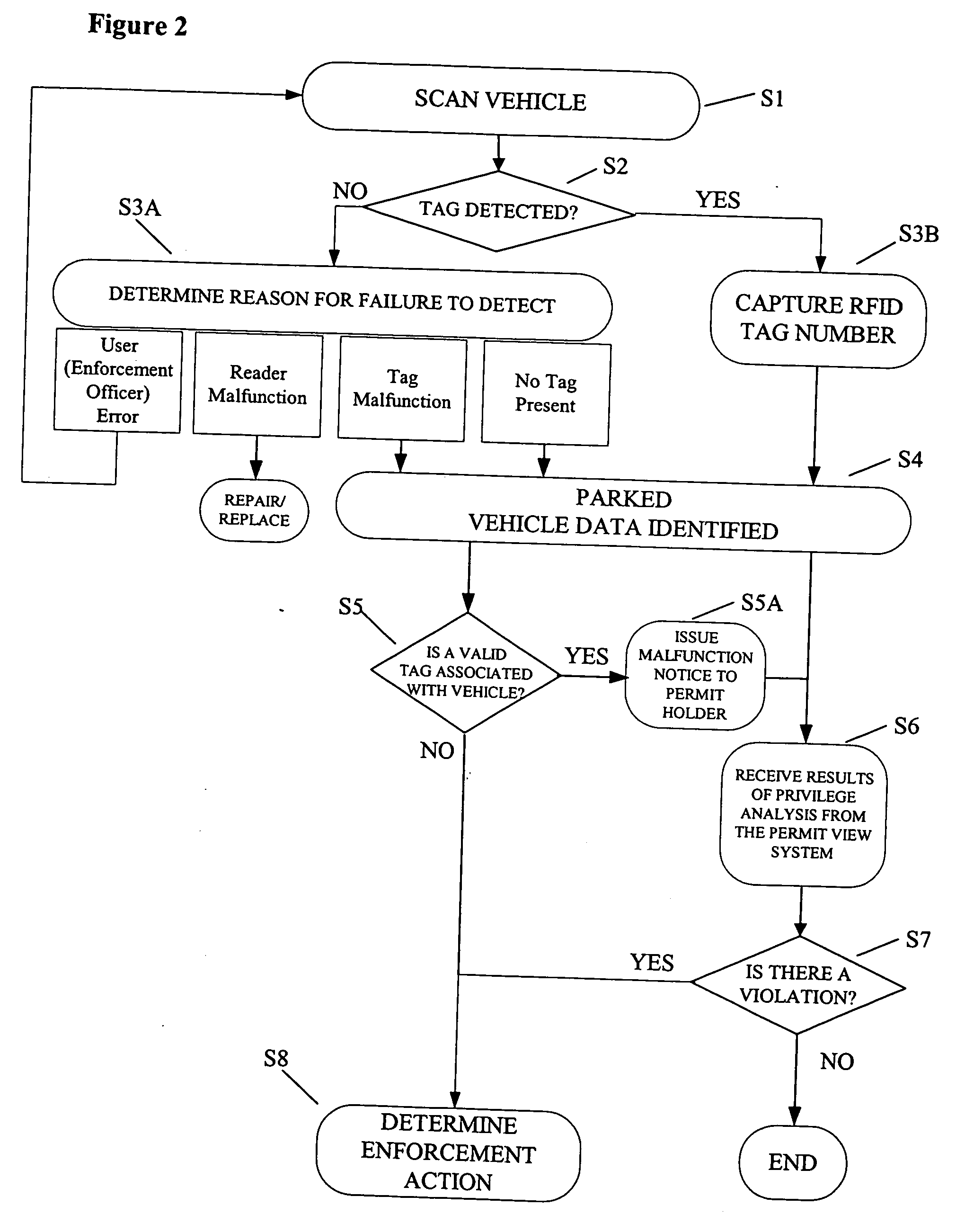

Parking environment management system and method

ActiveUS20060255119A1Realized benefitsGood release performanceAnti-theft cycle devicesBuilding locksProgram managementManagement system

A system and method for managing a permit-based parking environment governed by a parking program. The permit-based parking environment includes a number of parking permits each including a unique RFID tag and tag number. One or more RFID readers are used to scan the vehicles parked in the parking environment to determine if a RFID tag is associated with the parked vehicle. The results of the scan along with information related to the parked vehicle are provided to a permit management system to determine if the vehicle is parked within the scope of privileges pre-defined for that vehicle, pursuant to the parking program governing the parking environment. The permit management system stores, manages, and monitors data related to the permits controlled under the parking program.

Owner:IPT

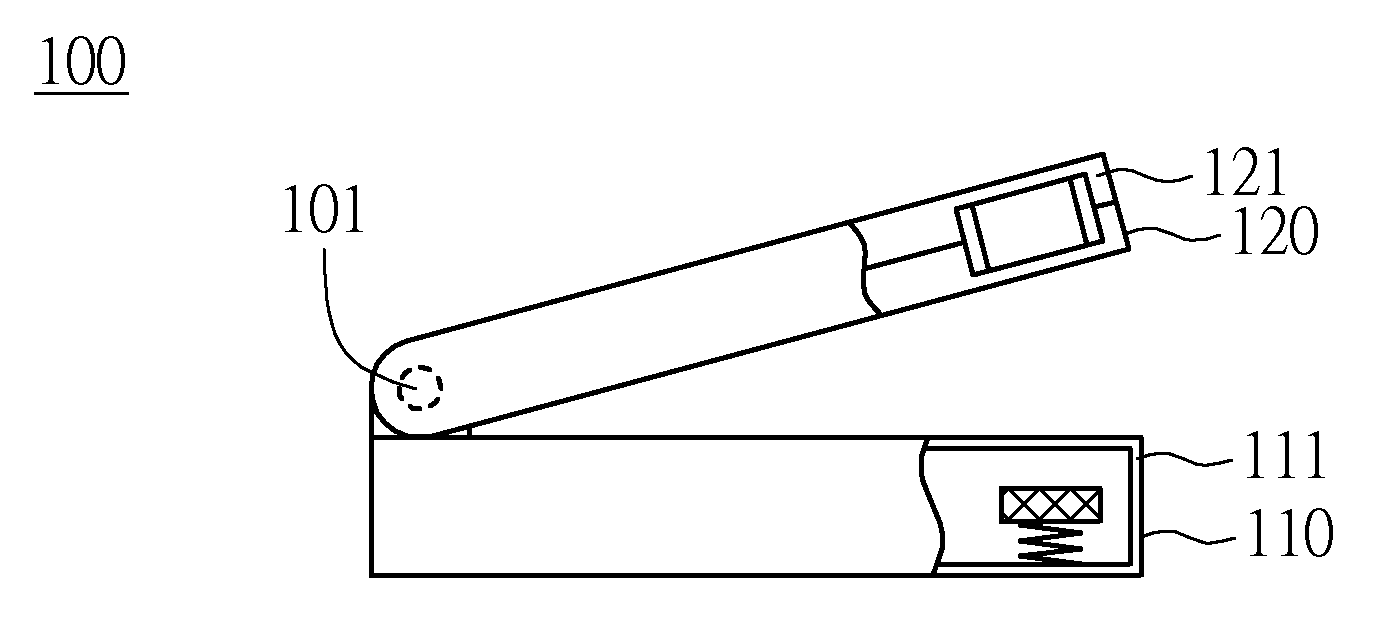

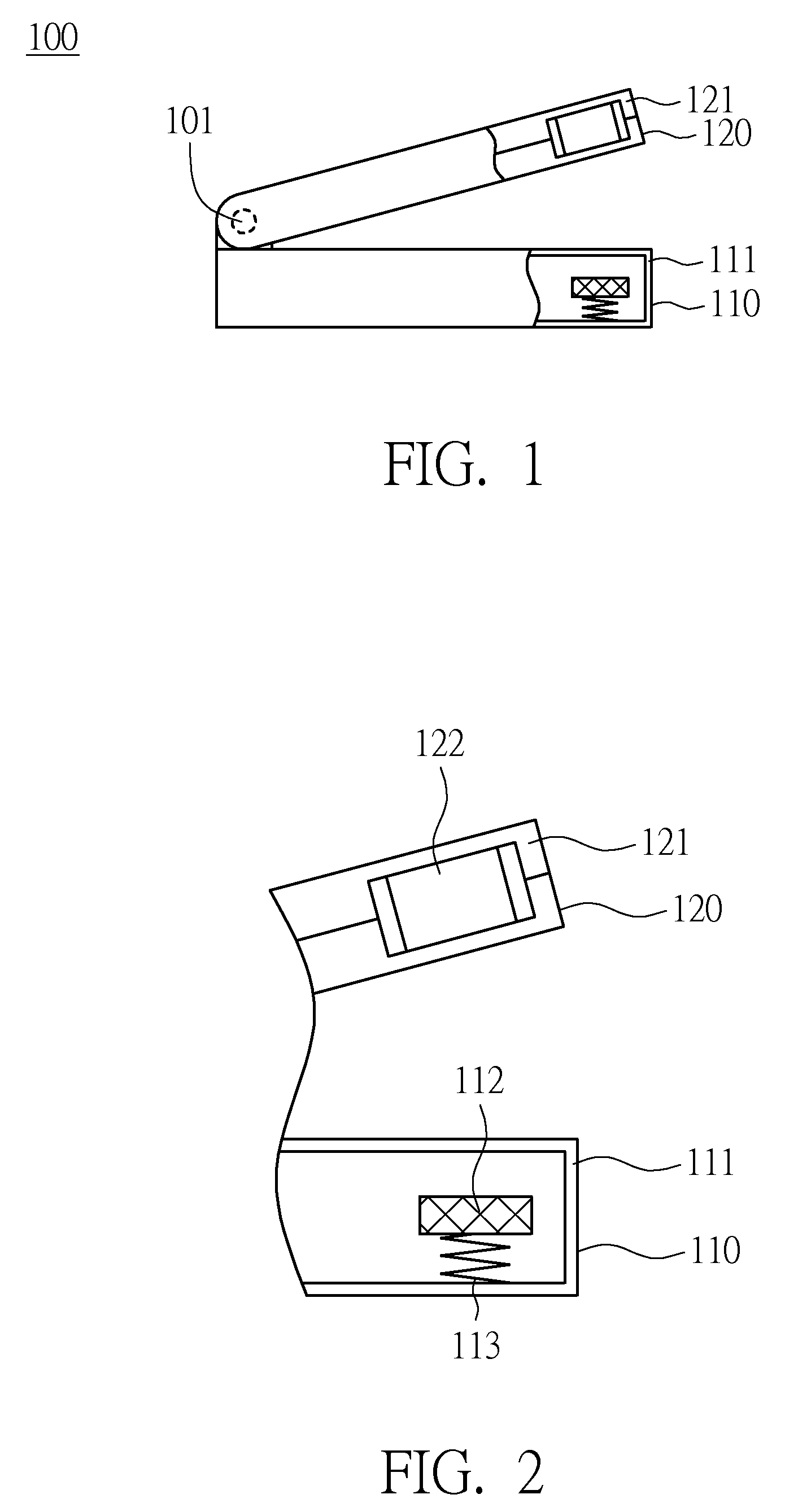

Electronic device

InactiveUS20090103261A1Enhanced magnetic forceBuilding locksWing fastenersEngineeringElectrical and Electronics engineering

Owner:HTC CORP

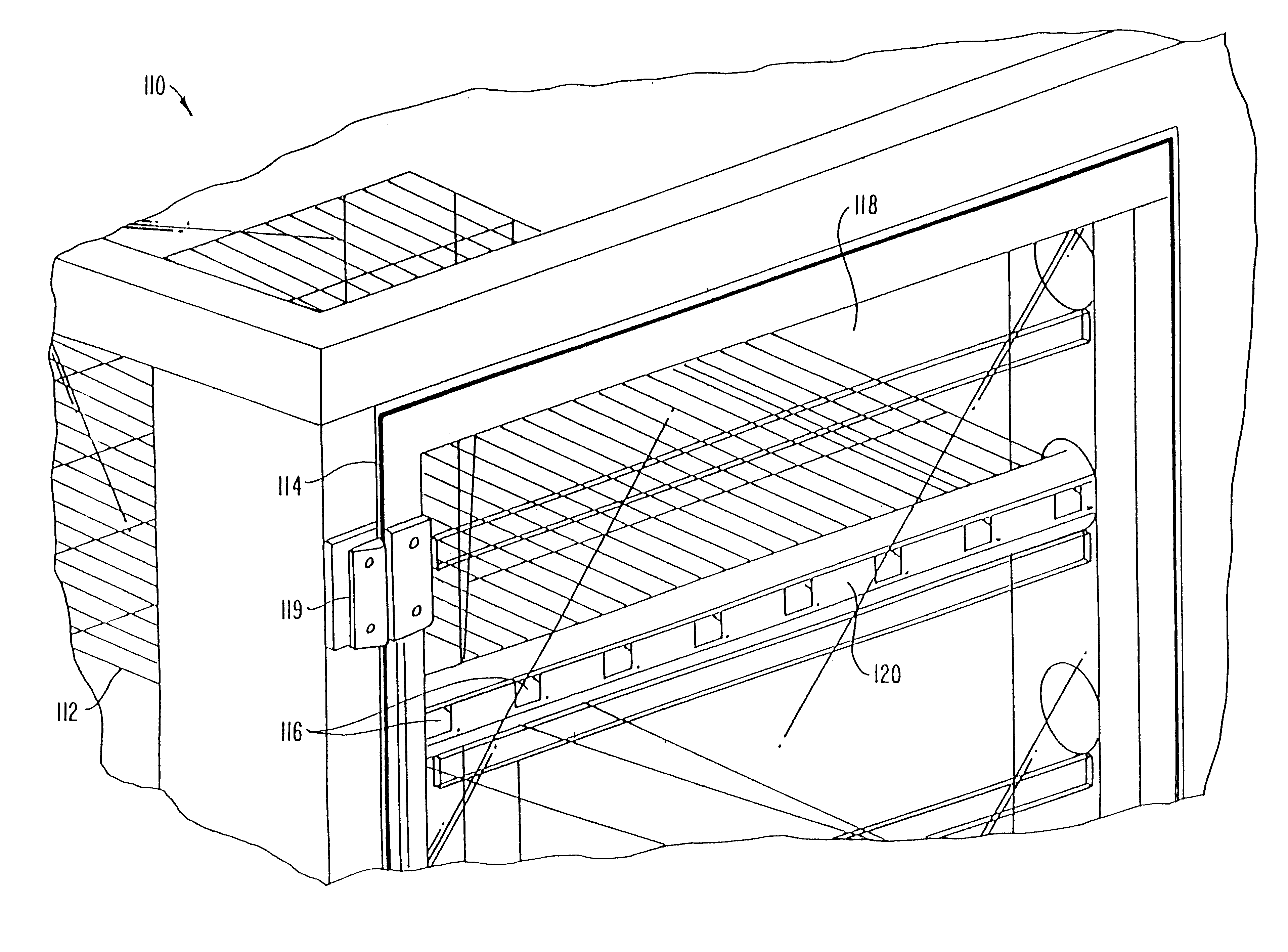

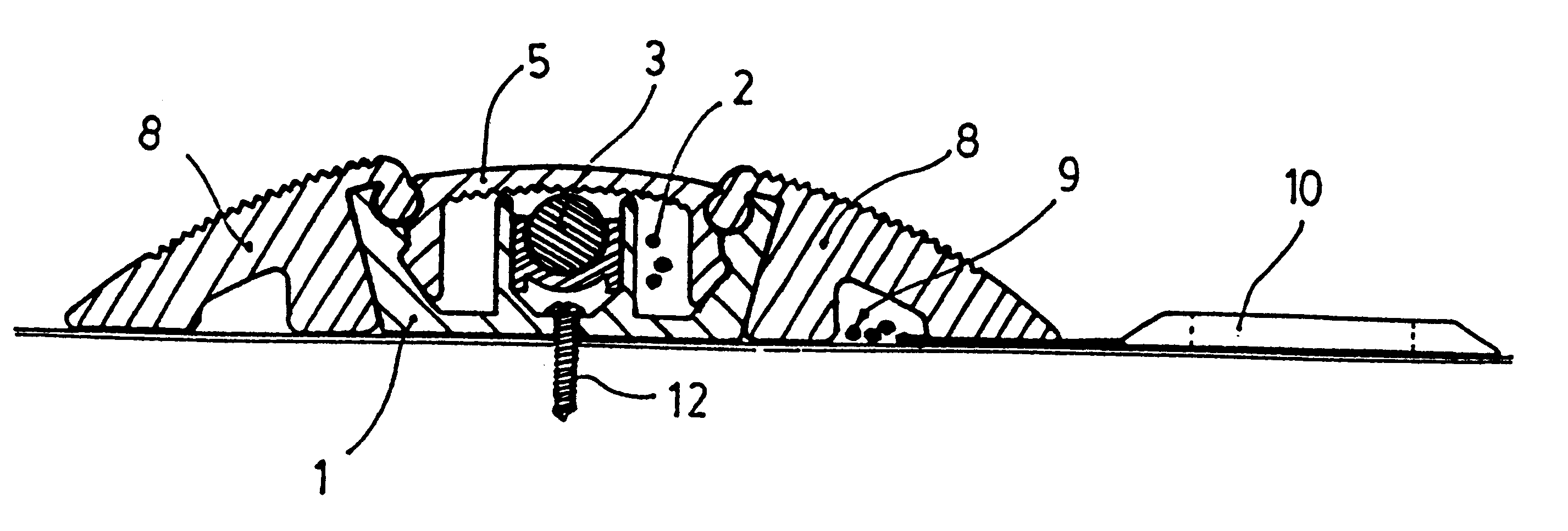

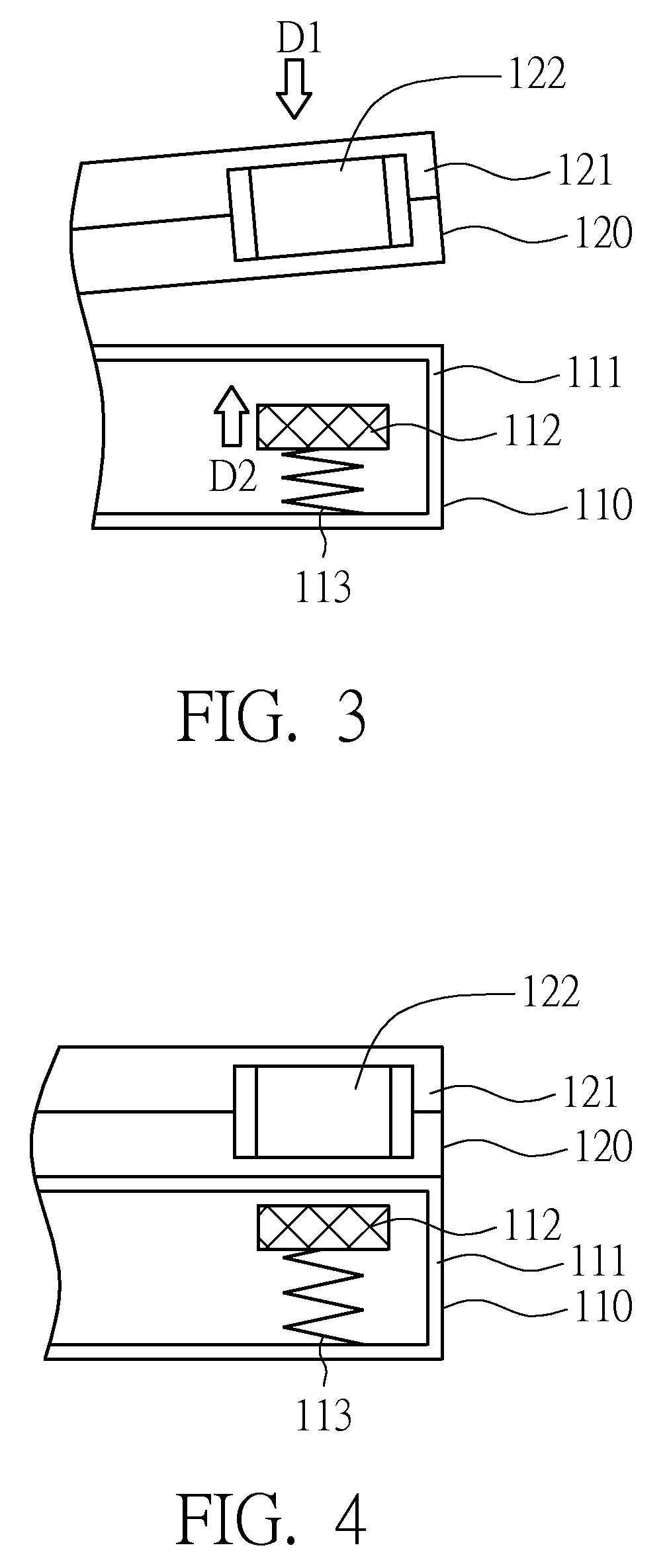

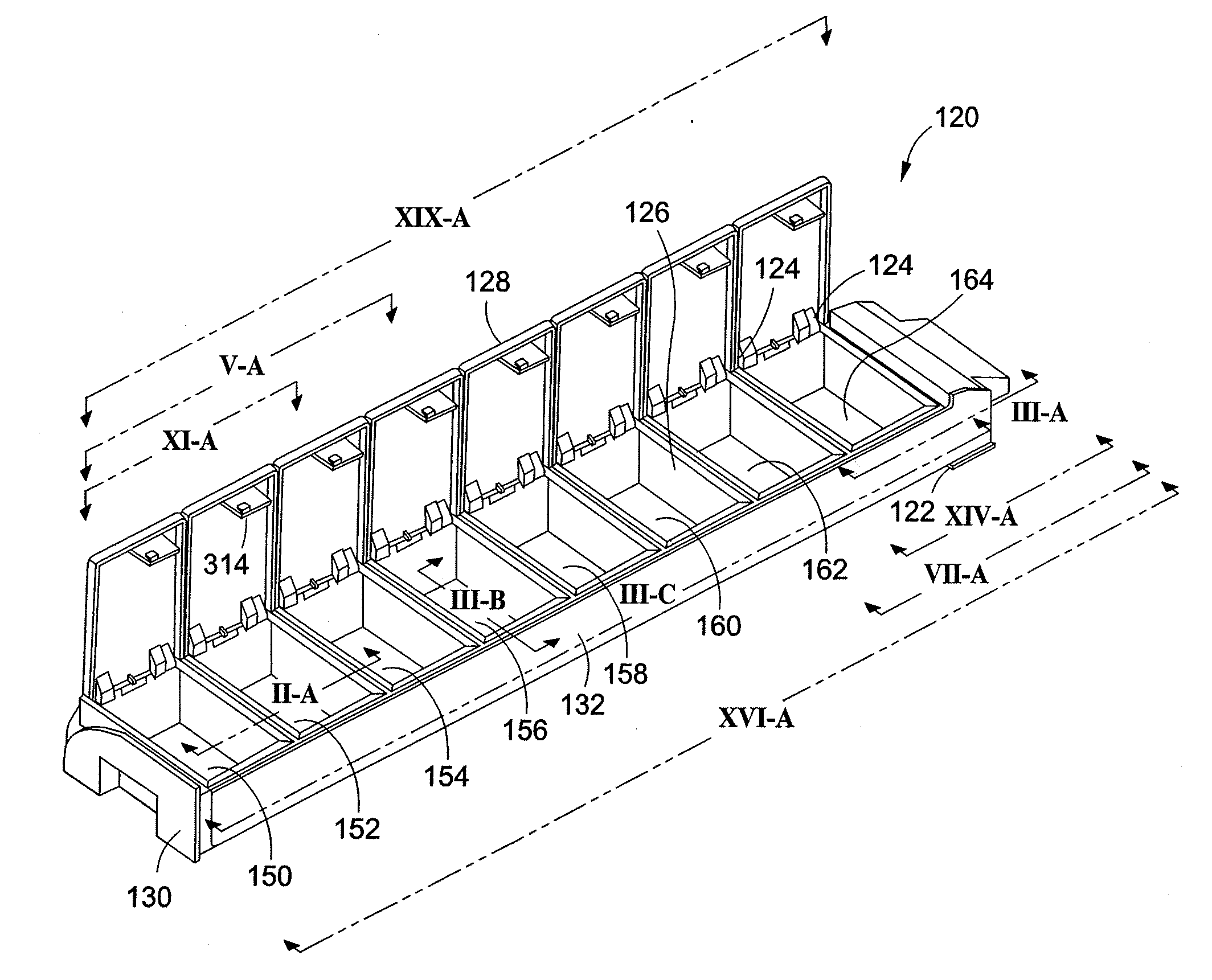

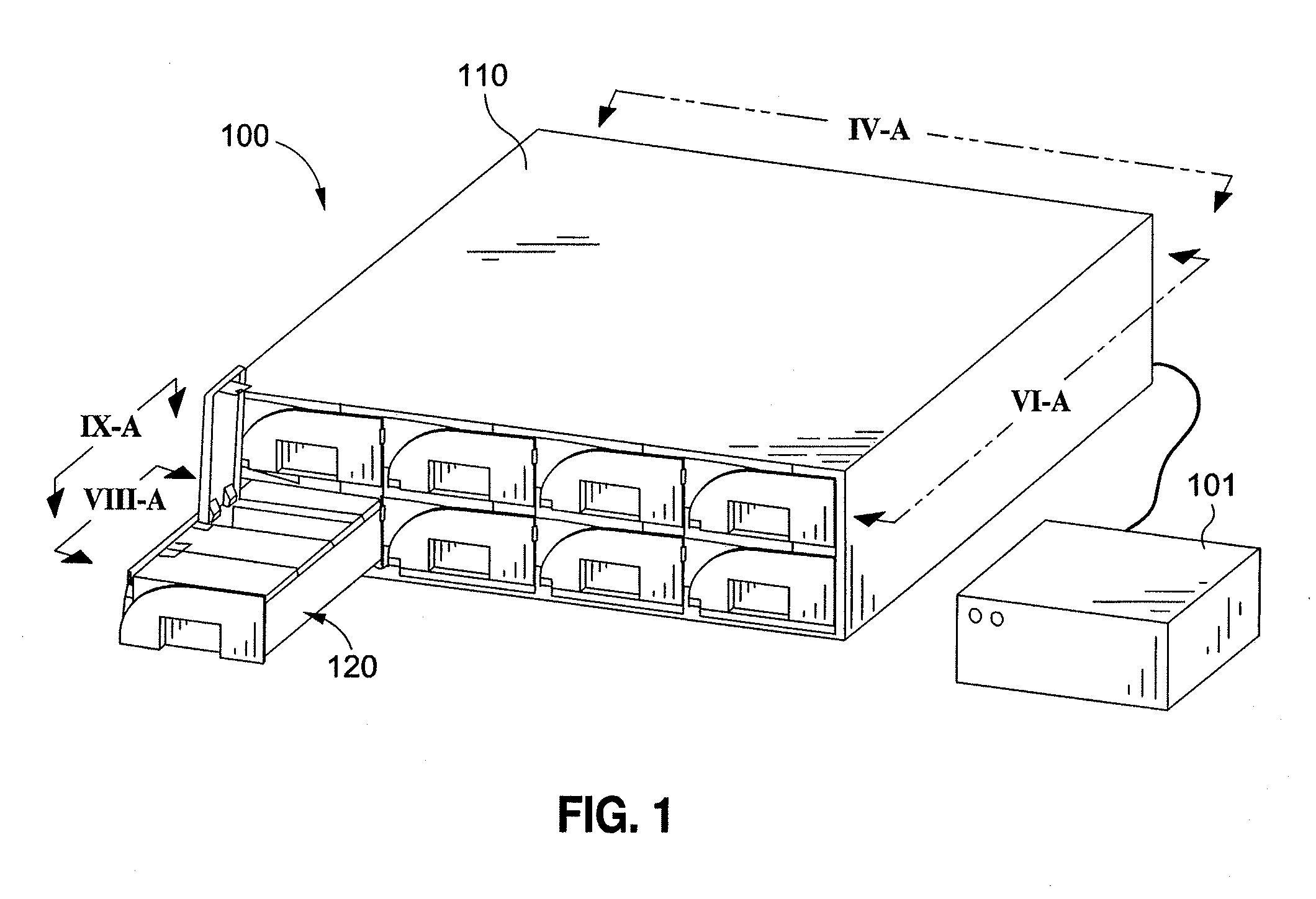

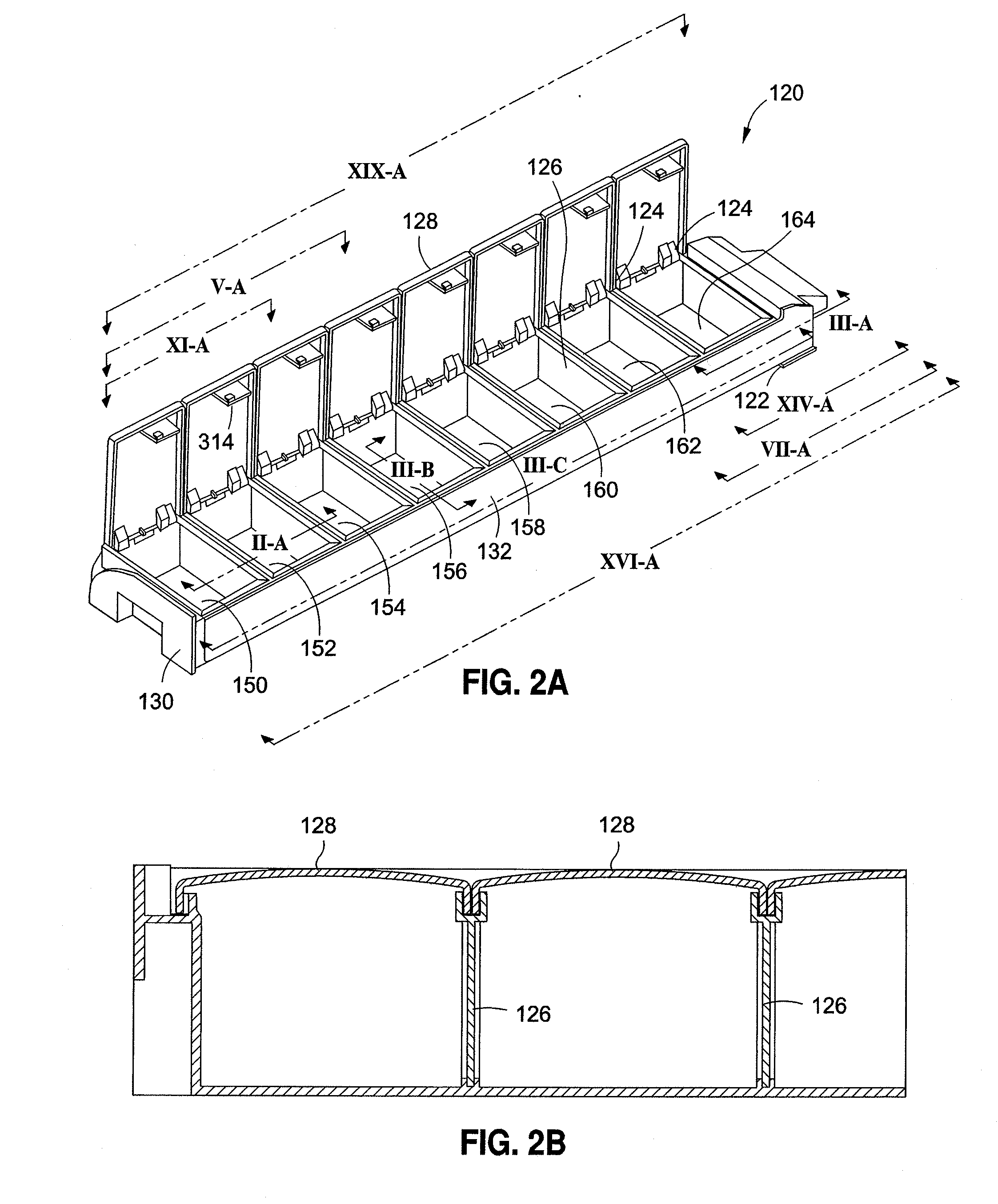

Lidded drawer for single line item dispensing

ActiveUS20090224638A1Efficient dispensingEfficient storageDiagnosticsBuilding locksElectrical connectionEngineering

A medication cabinet that includes at least one drawer, a drive mechanism, and a drawer latching mechanism, is disclosed. The drawer includes a slider, and a container that includes a receptacle and a lid that moves between an open position and a closed position. The container also includes a fastener to fasten the lid to the receptacle. The slider maintains the lid in the closed position when at least a portion of the wall is coupled with the fastener, and actuates the lid from the closed position to the open position when the fastener passes through an opening in the wall. The drive mechanism controls longitudinal movement of the slider, and is mounted to the chassis, allowing the drawer to be free of electrical connections with the chassis. When the drive mechanism is not used to move the lid into the open position, longitudinal movement of the slider is inhibited.

Owner:CAREFUSION 303 INC

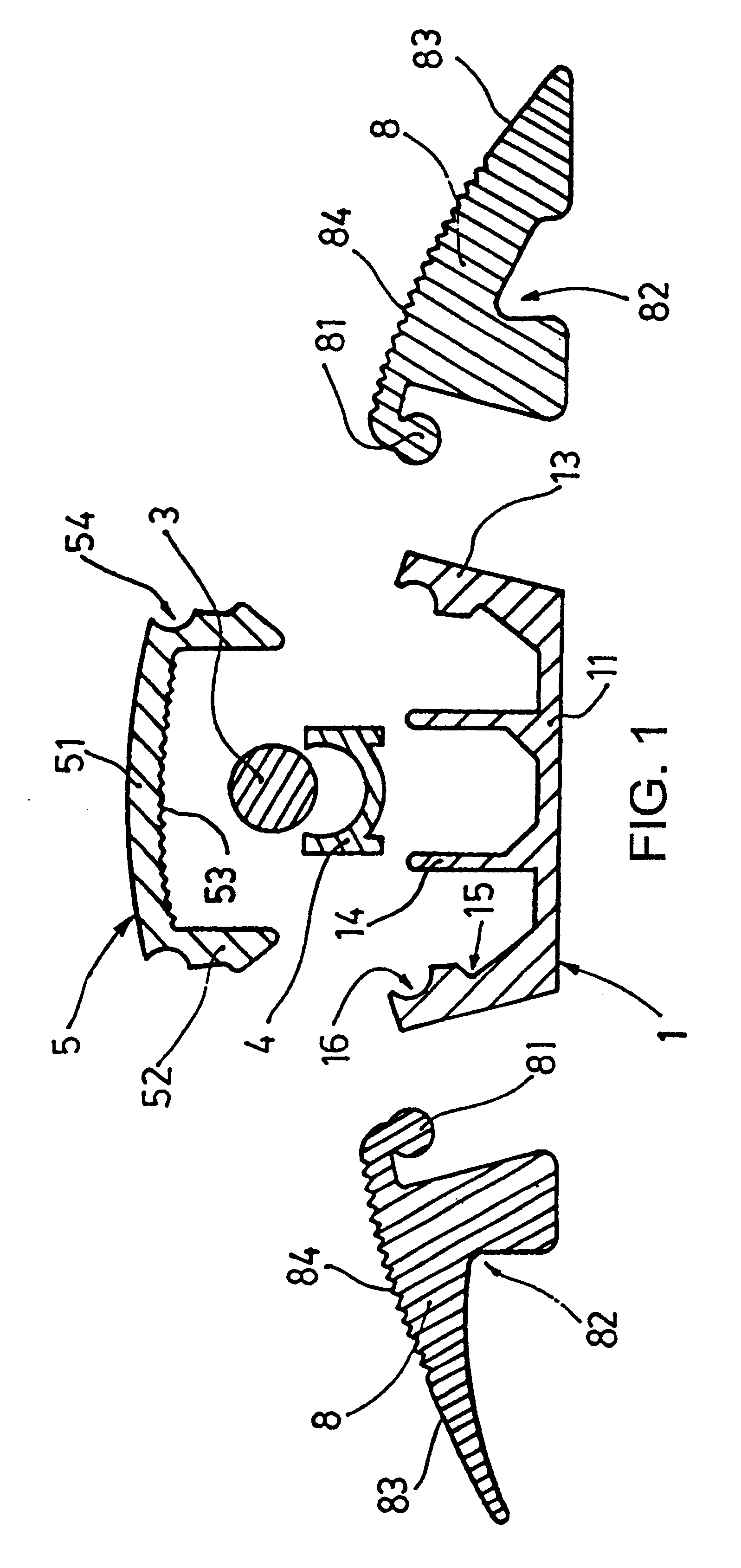

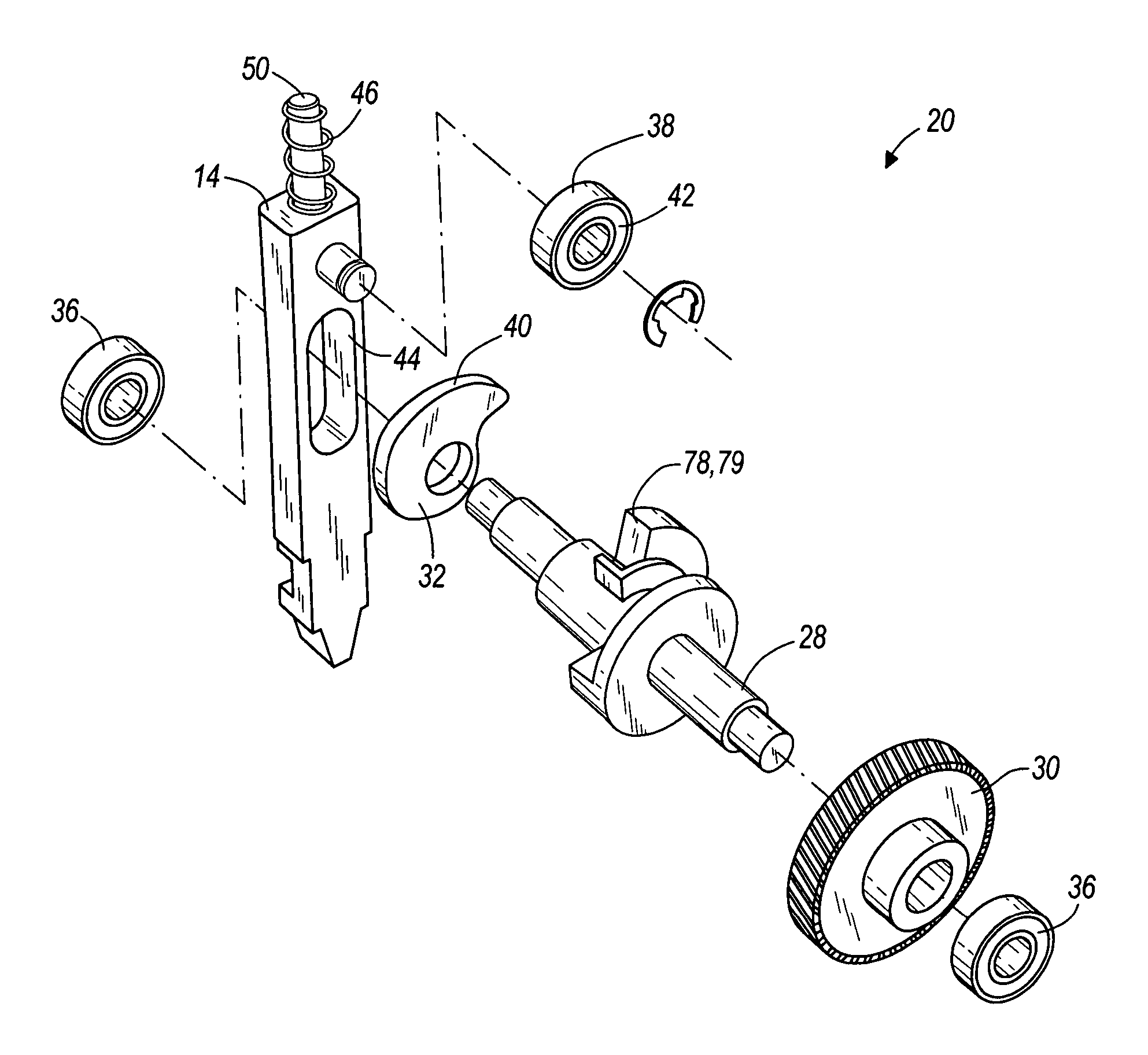

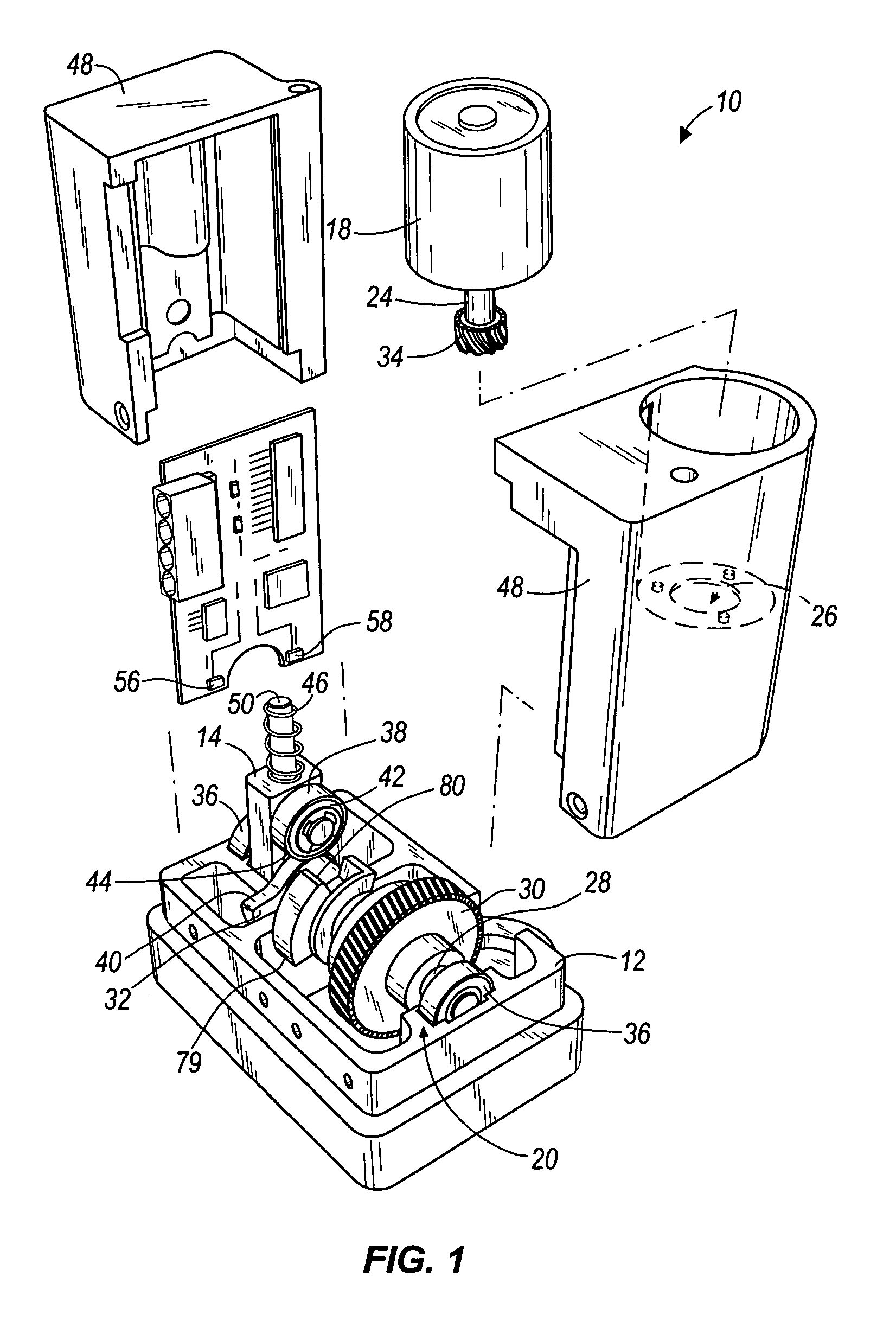

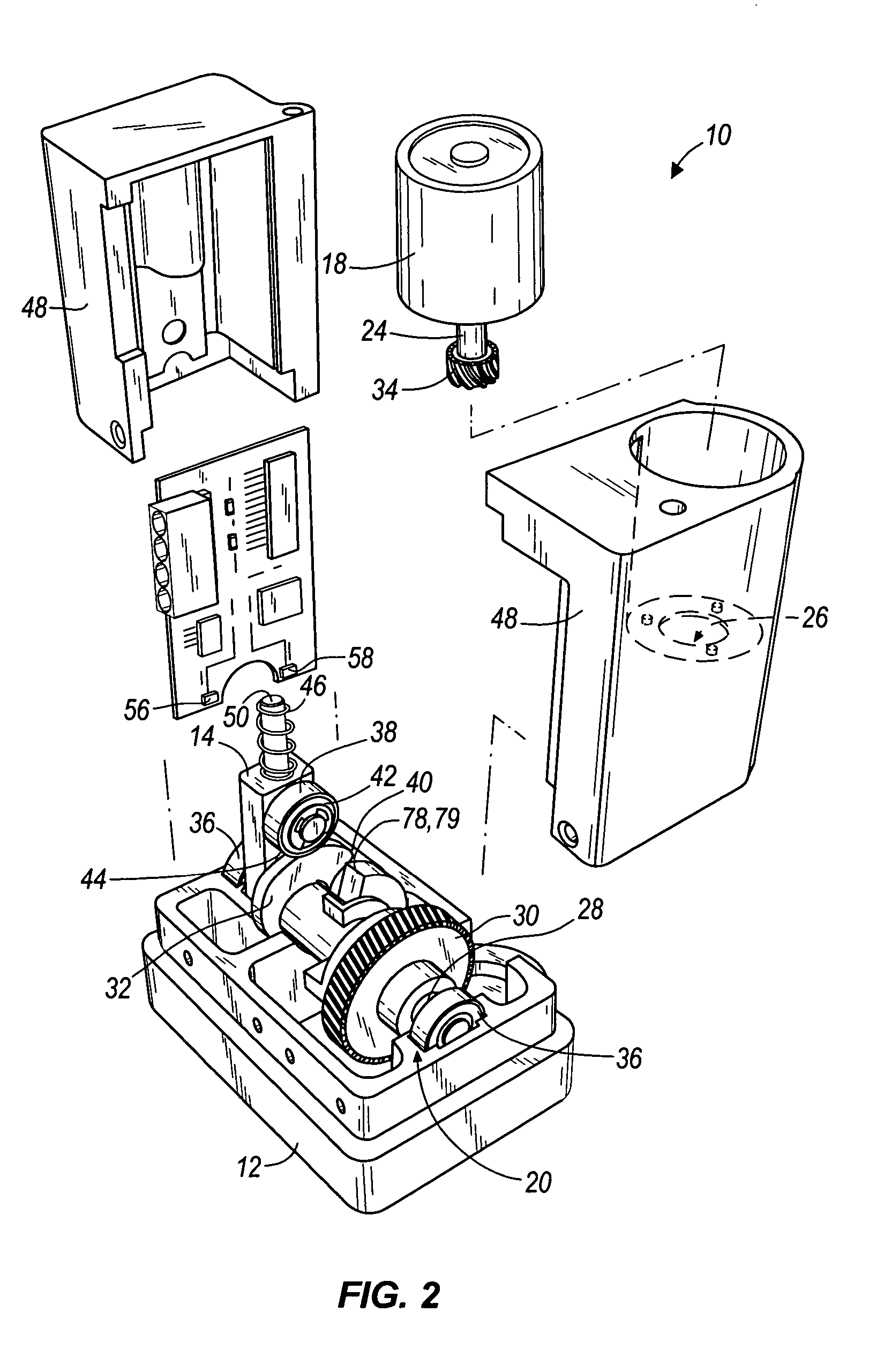

Steering column lock apparatus and method

A lock bolt extendible and retractable by movement of a power transmission assembly driven by an actuator and having a cam thereon which cams against the lock bolt to retract the lock bolt and unlock the steering column. In some embodiments, the cam has a curved surface with varying distance from the axis of rotation of the cam or pivot to improved lock bolt motion. The cam can have a gradual ramp surface to extract a lock bolt even in binding conditions of the lock bolt.

Owner:STRATTEC SECURITY

Programming station for a security system for protecting merchandise

ActiveUS7737844B2Reduce usageEnhance transmission and receptionElectric signal transmission systemsMultiple keys/algorithms usageComputer hardwareCommunications system

A programming apparatus for generating and retaining a security disarm code (SDC) for use in a security system for protecting items of merchandise has a housing and a logic control circuit located within the housing. The control circuit includes a controller for generating the SDC, a memory for storing the generated SDC and a wireless communication system for interfacing with a programmable key used for operating a security device attached to an item of merchandise. A visual display includes a plurality of LEDs which indicate the status of the logic control circuit. The SDC is generated initially as a random SDC by the programming apparatus, which SDC is retained in the controller of the apparatus for the life of the programming apparatus.

Owner:INVUE SECURITY PROD INC

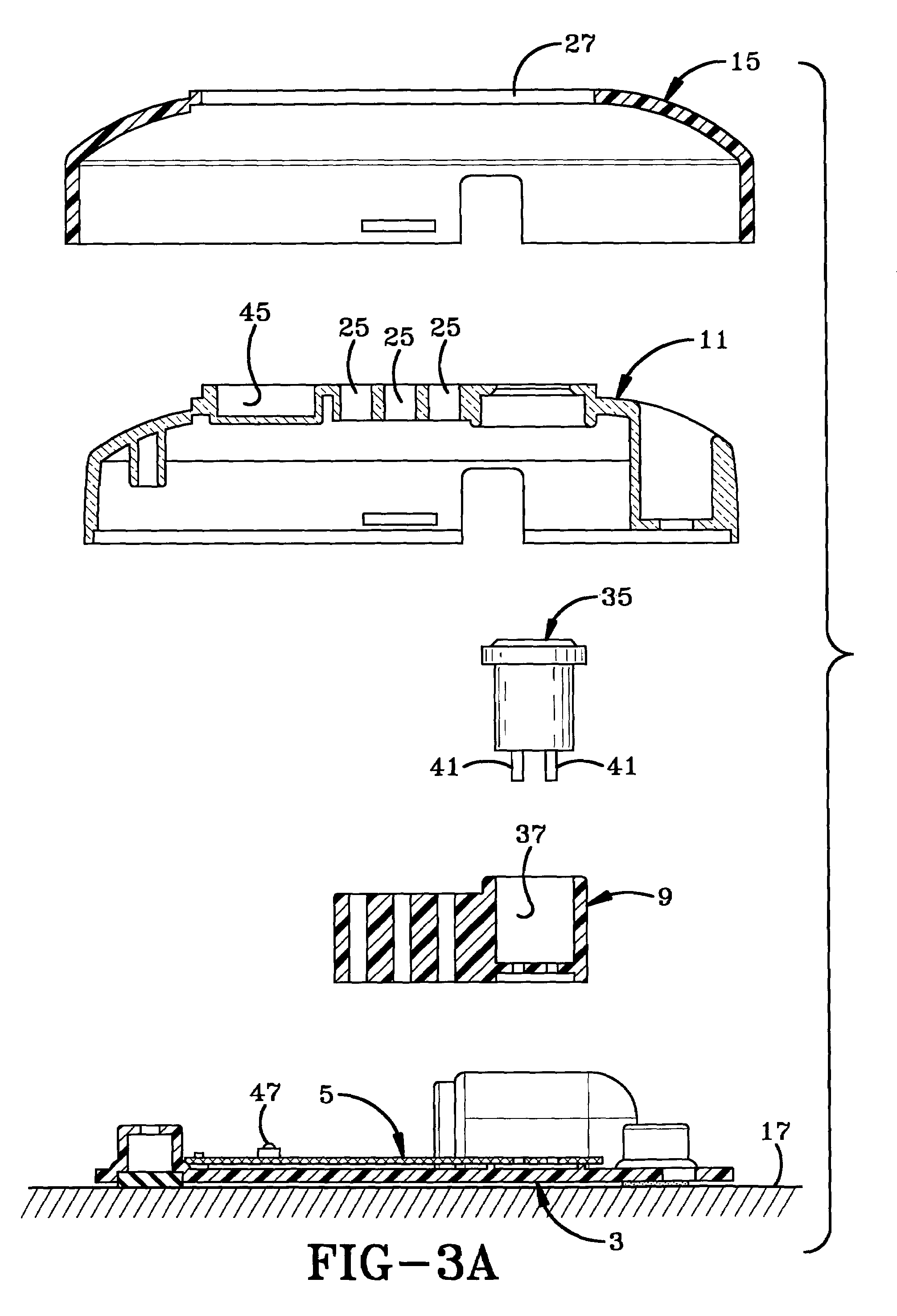

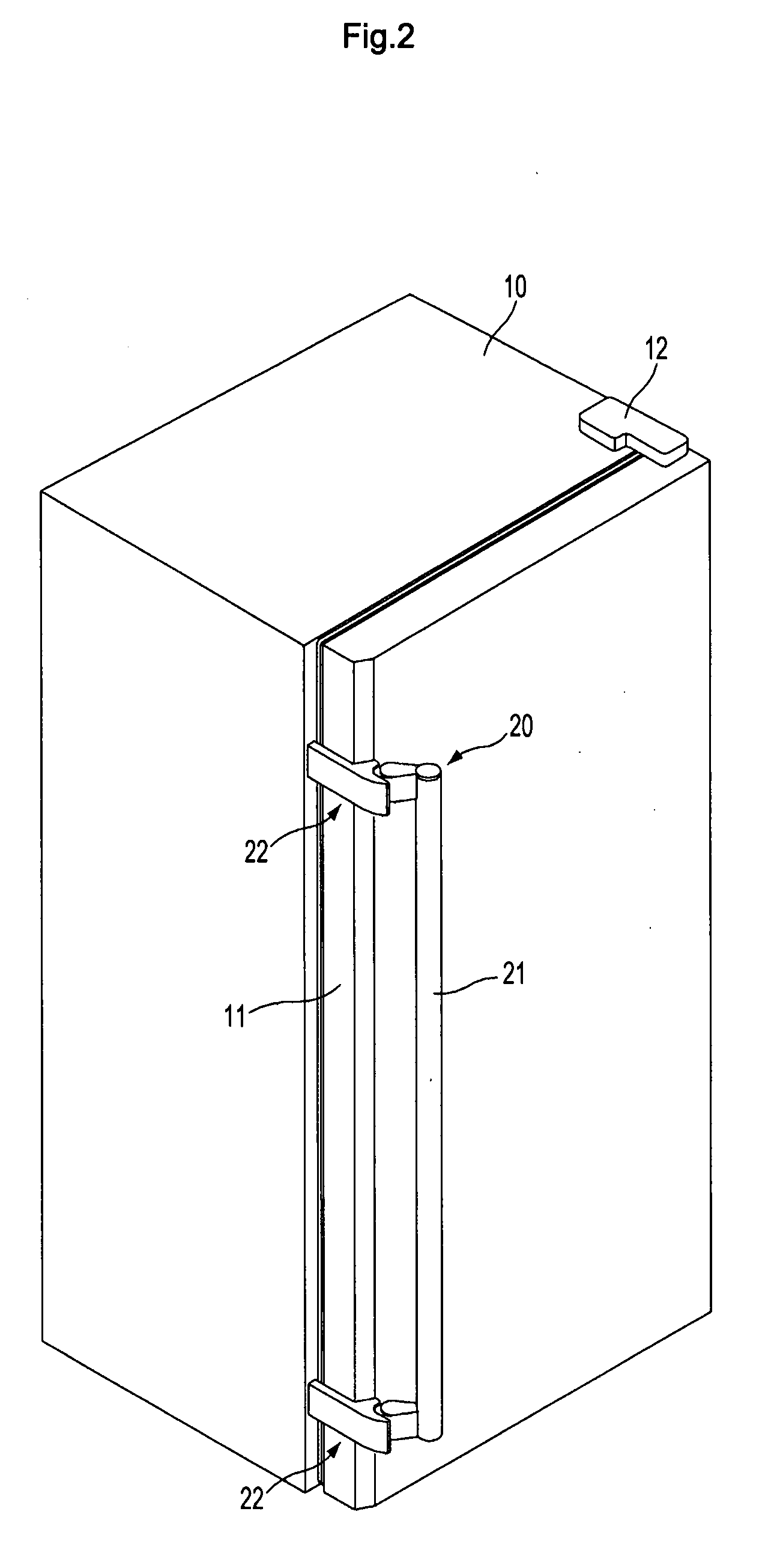

Refrigerator

InactiveUS20080000052A1Avoid damage to the appearanceEasy to openDomestic cooling apparatusLighting and heating apparatusEngineeringCompression member

A refrigerator includes a door handle, which can prevent damage of an appearance of the refrigerator or noise by an operation of the door handle, and which can permit easy opening of a door with a small force being required by a user. The refrigerator includes a door installed to a main body of the refrigerator, and the door handle installed on the door. The door handle includes a rotational member rotatably coupled with the door, a compressive member installed on the door, to linearly move in order to compress the main body, a gear connection part to convert a rotational movement of the rotational member to a linear movement of the compressive member, and a returning member to return the rotational member to an original position.

Owner:SAMSUNG ELECTRONICS CO LTD

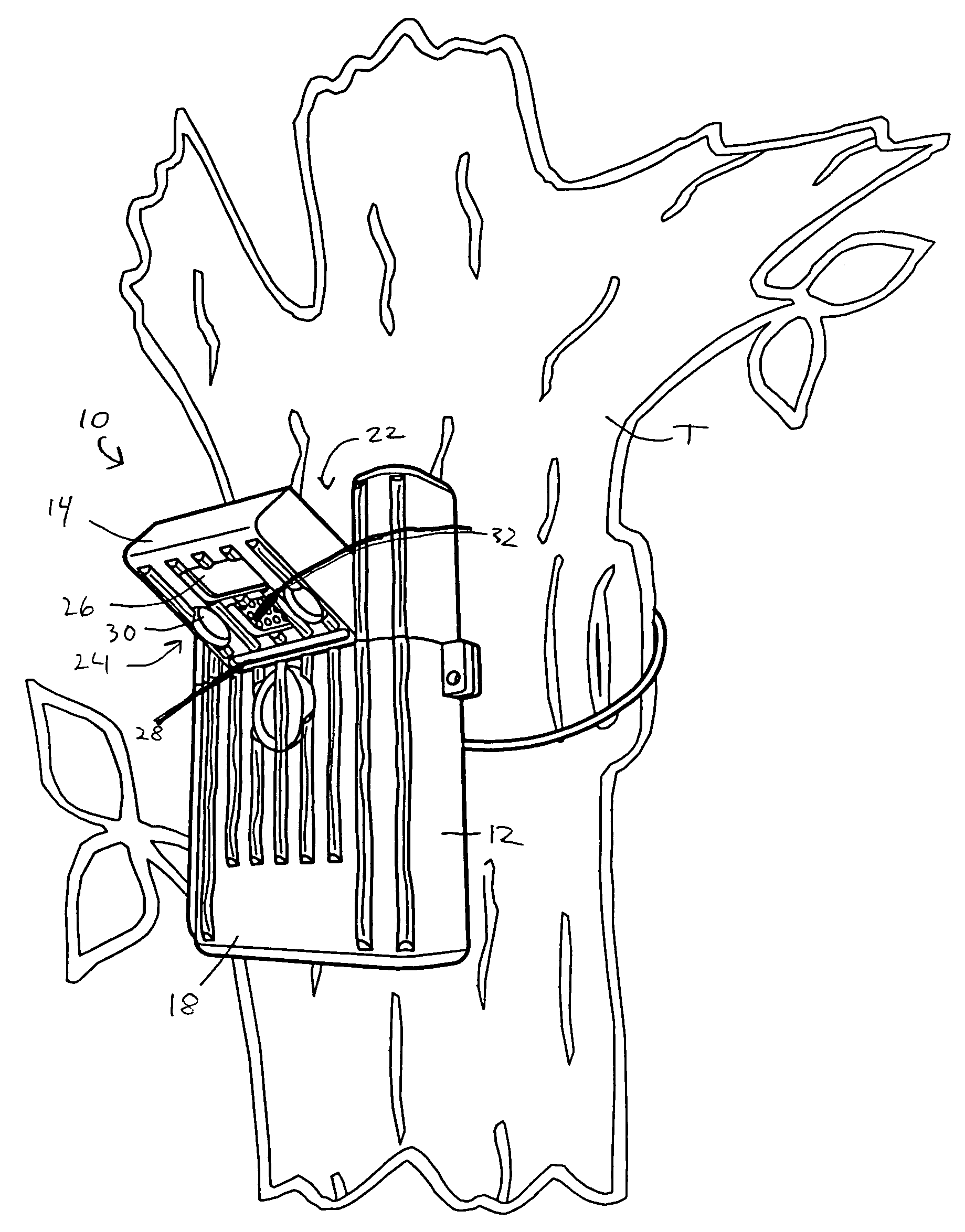

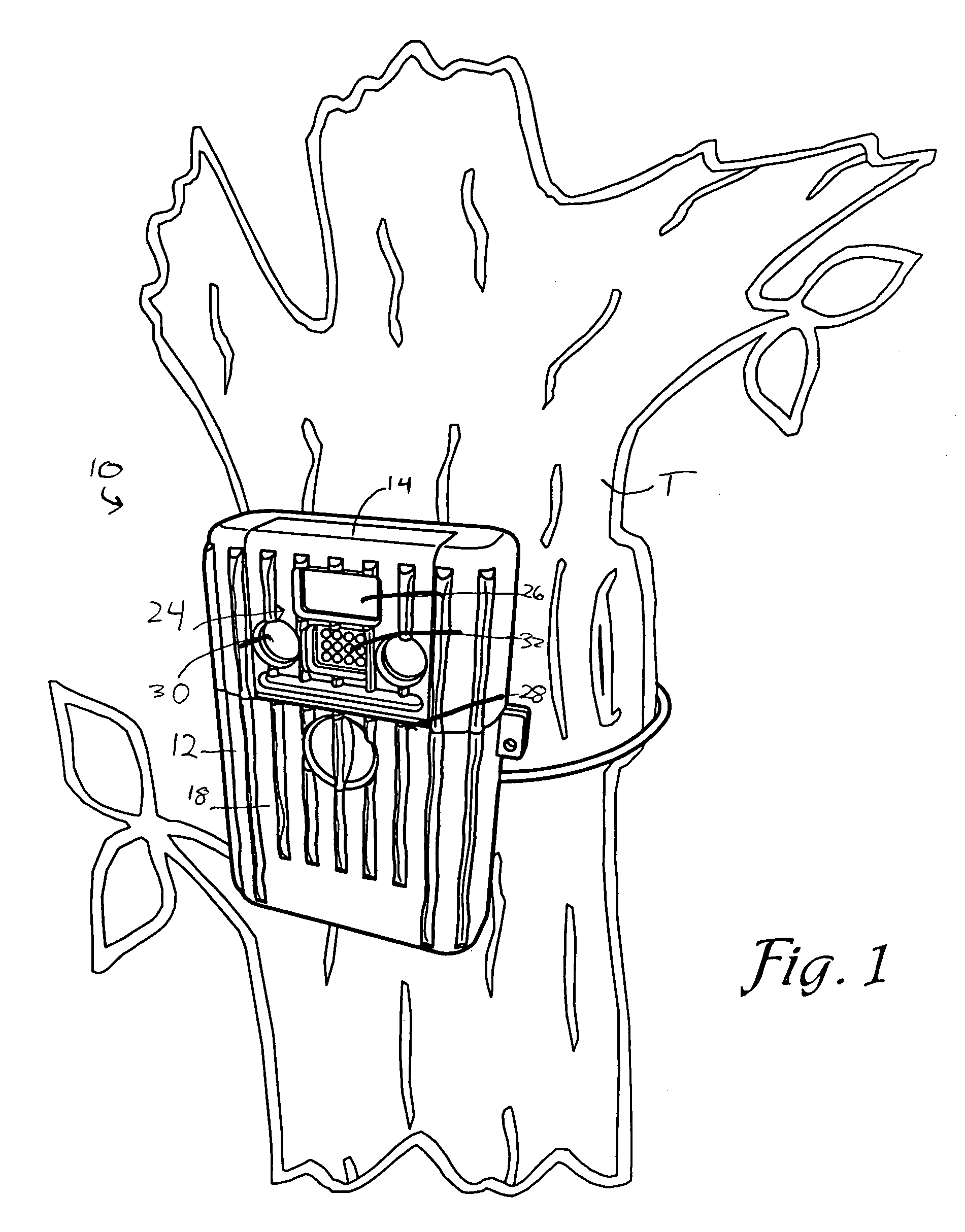

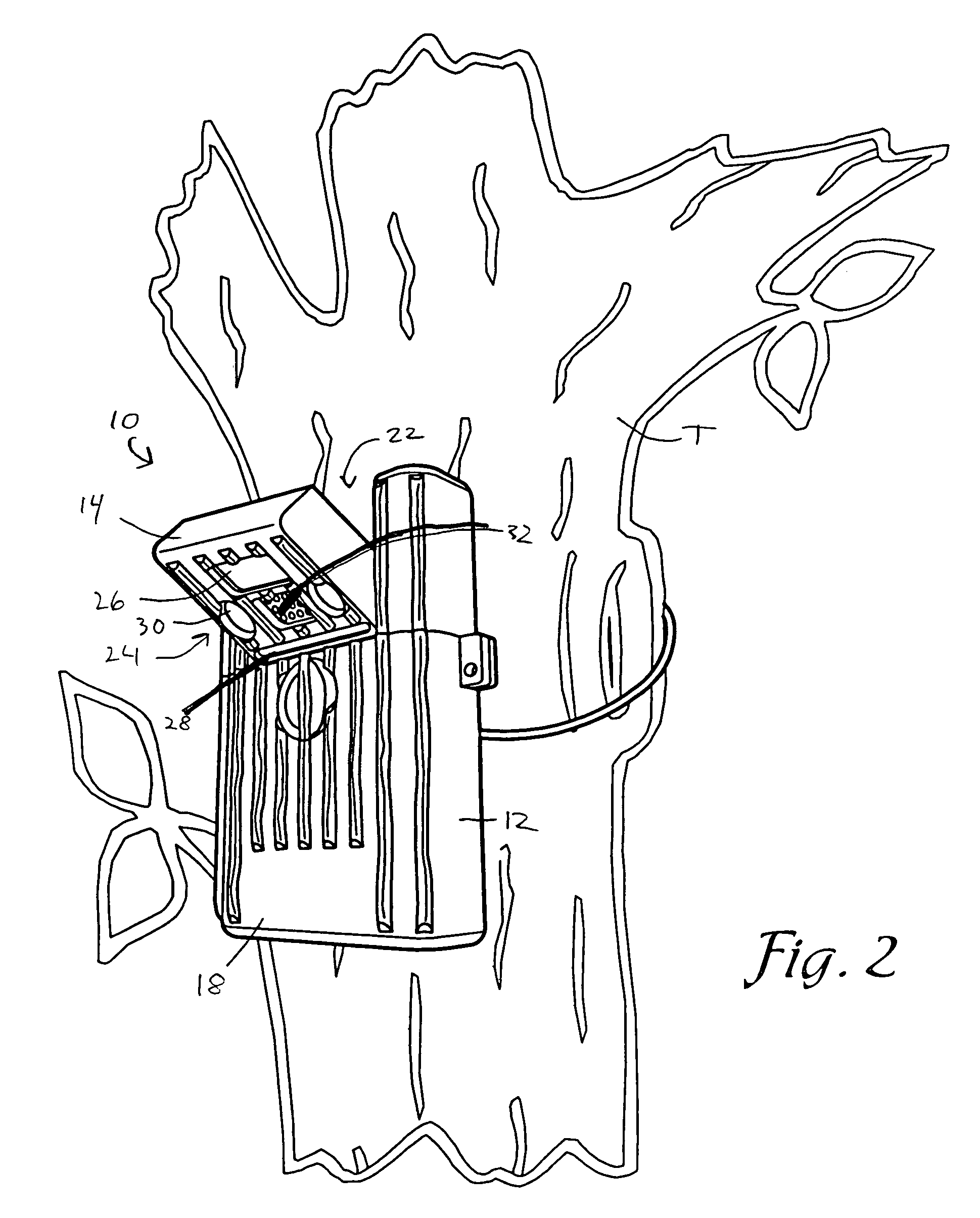

Trail camera

Owner:BUSHNELL

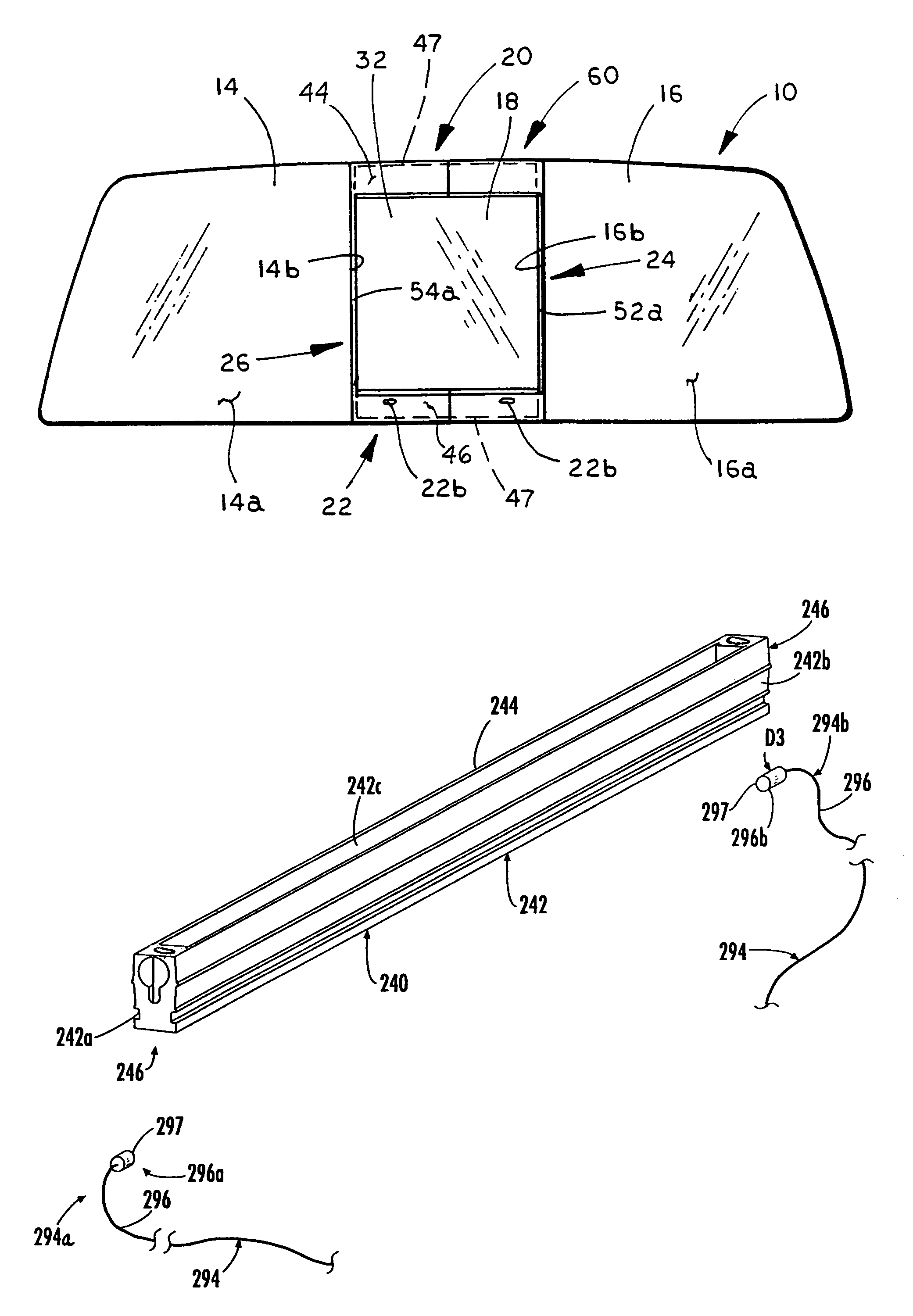

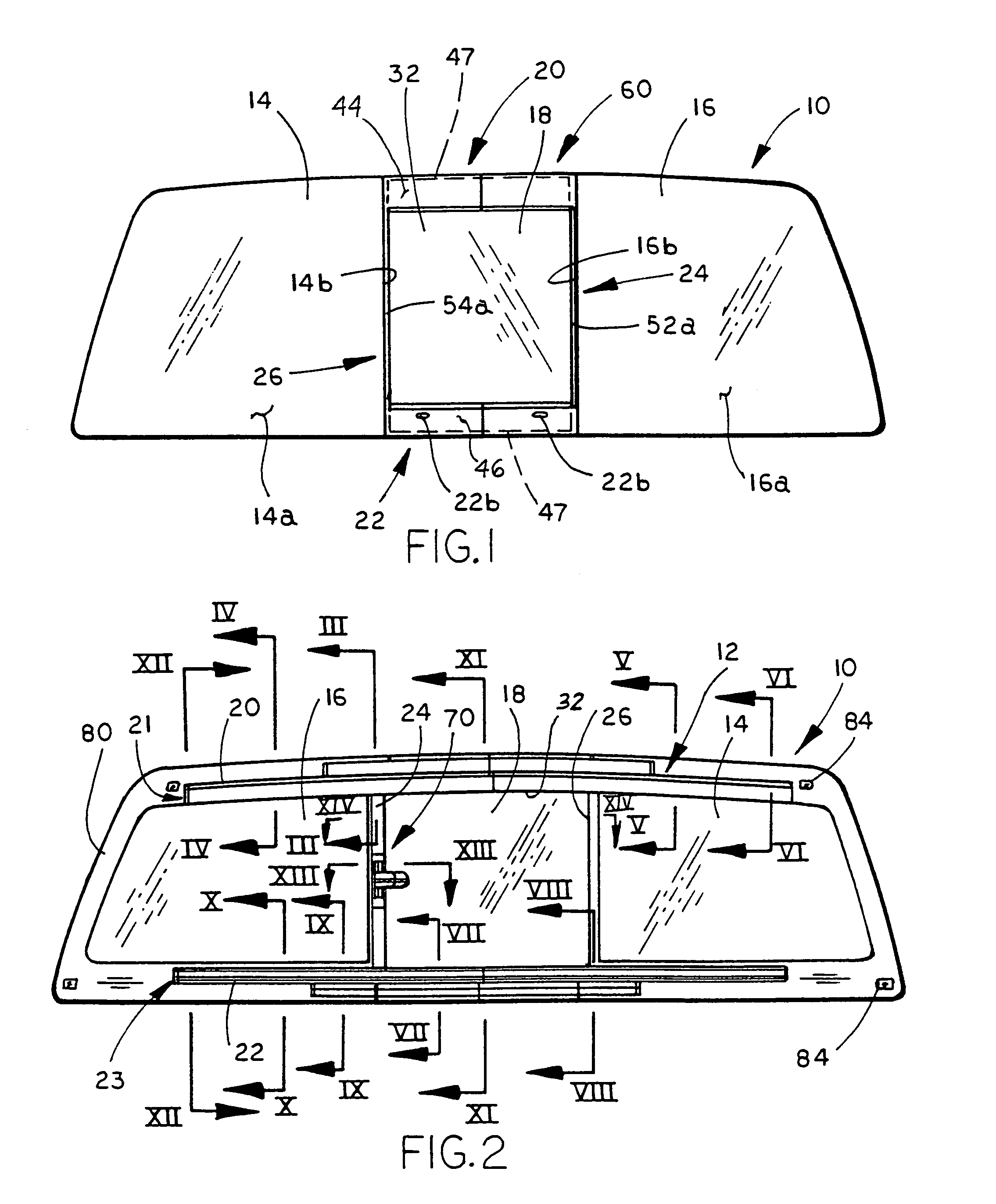

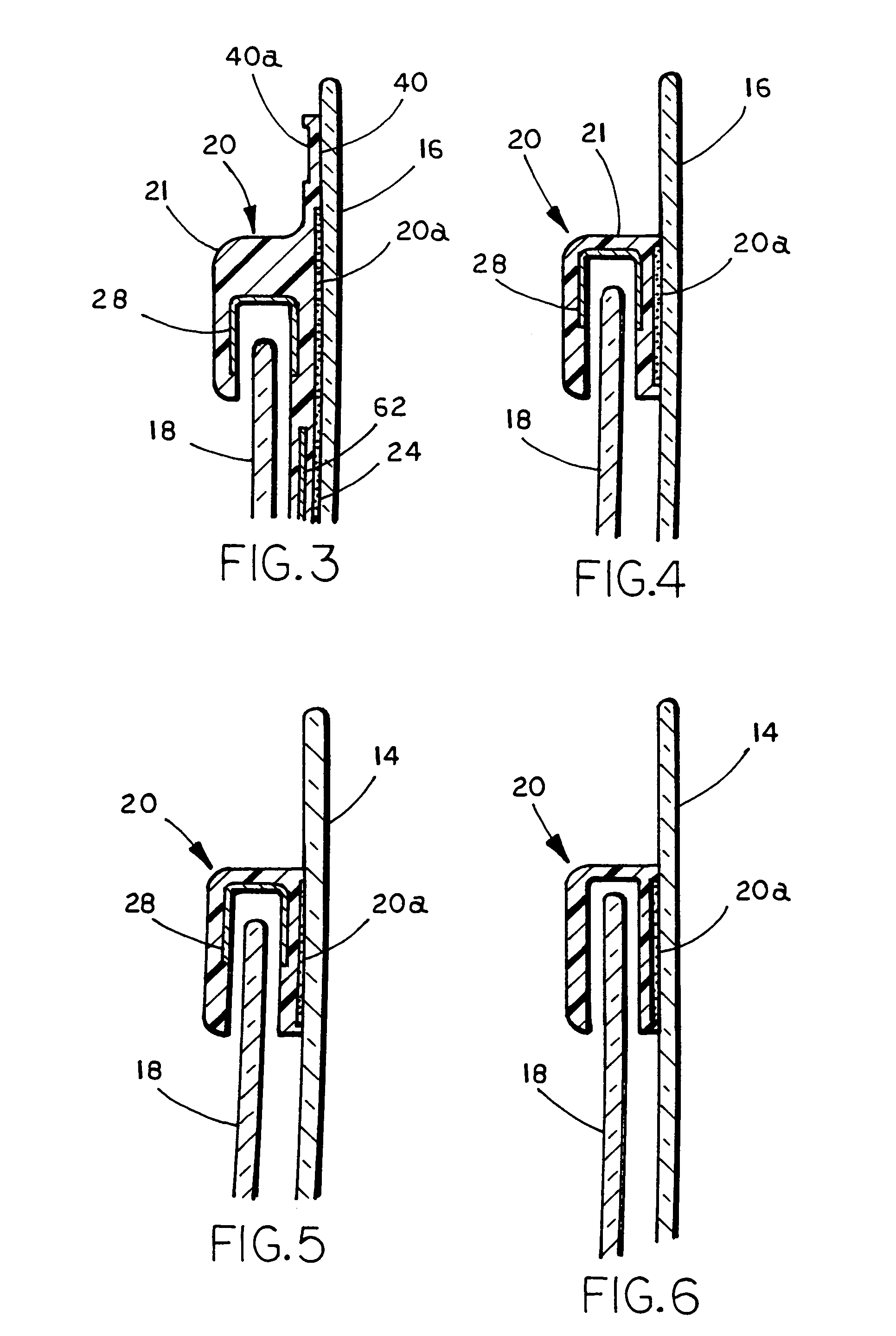

Horizontal slider window assembly

ActiveUS7073293B2Increased durabilityIncrease resistanceWindowsWindscreensSupporting systemEngineering

A vehicular rear window assembly for a vehicle comprises a first fixed pane, a second fixed pane, a sliding pane, which is supported for horizontal movement between open and closed positions, and a drive assembly. The slider window assembly includes a support system that supports the fixed panes in a manner to define a central opening. The support system further includes a carrier that supports the sliding pane for horizontal movement and, further, provides an enhanced engagement between the sliding pane and the drive assembly.

Owner:DONNELLY CORP

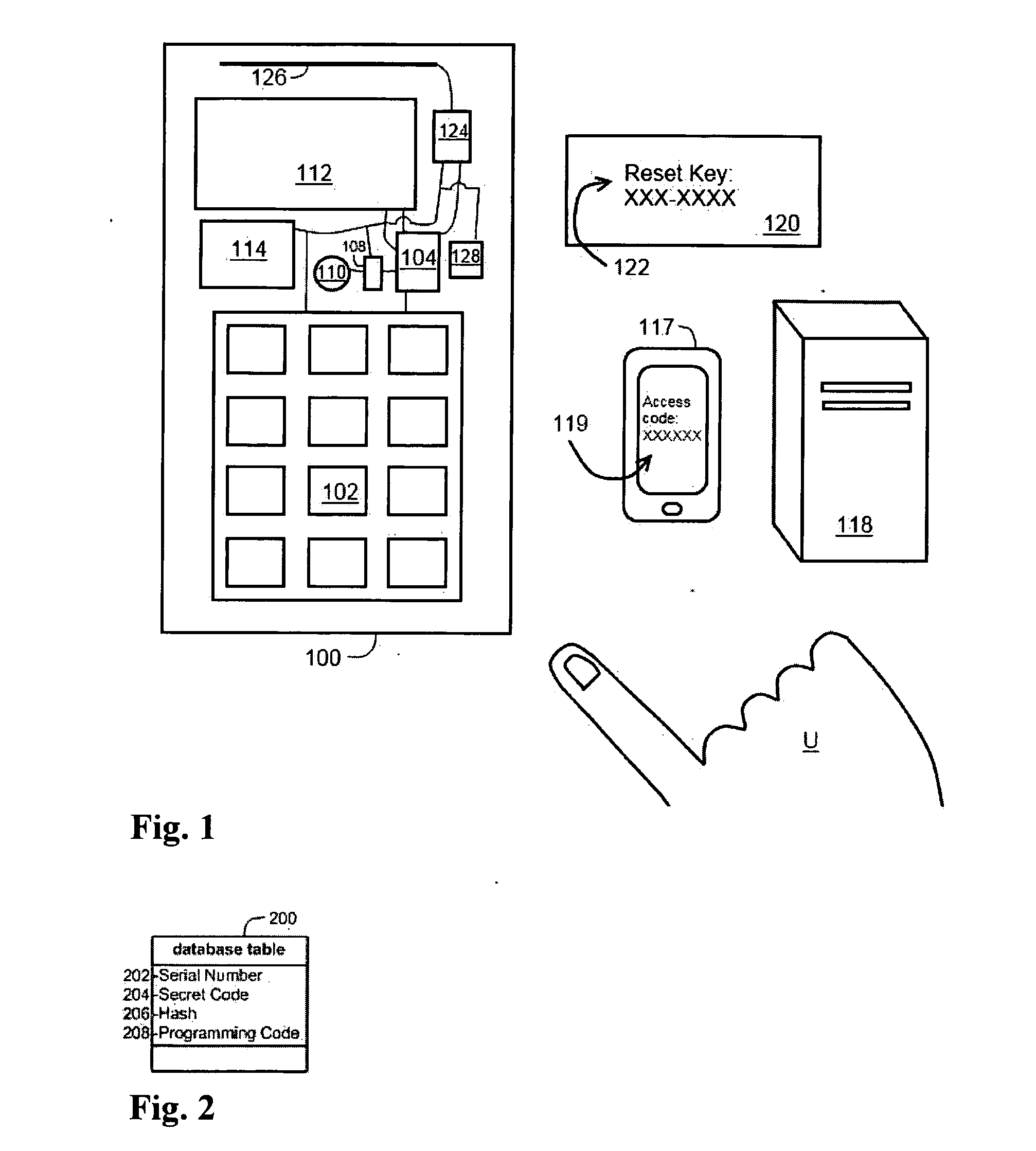

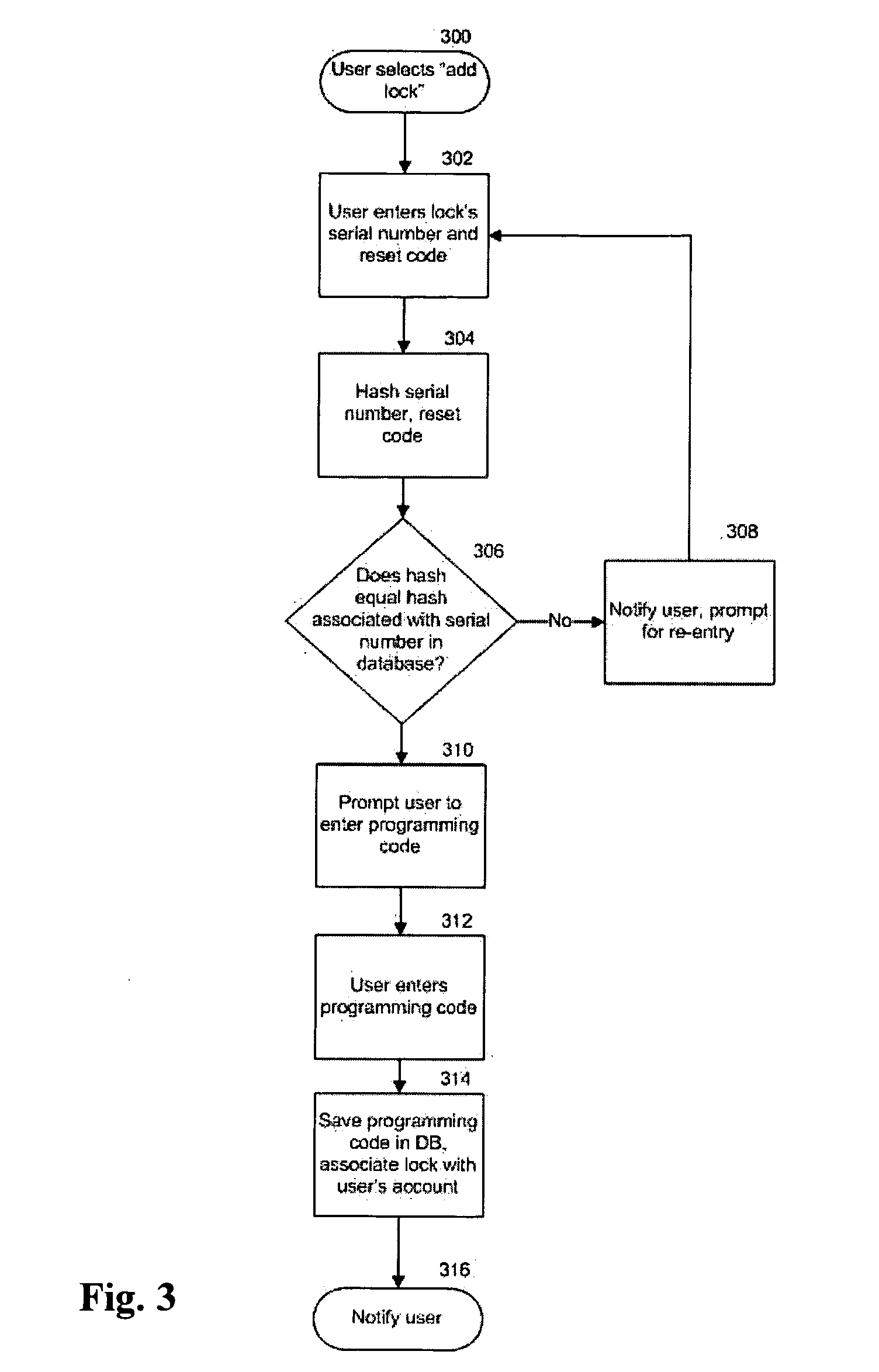

Electronic lock and method

InactiveUS20130043973A1Avoids wasting battery power performing hashesImprove securityProgramme controlElectric signal transmission systemsMicrocontrollerHash function

An electronic lock, system and method for dynamic controlled access, without the lock communicating with or connected to a code server, are provided. The lock includes a locking mechanism, a clock, a microprocessor, and a memory storing a hash function and programmed instructions for the microprocessor to perform certain operations. The microprocessor and memory may be comprised in a microcontroller. When an access code is entered into the lock, the lock microcontroller hashes currently valid access start date / duration combinations with lock identifying data to return valid access codes. If the entered access code equals any of the valid access codes, the locking mechanism is opened. The lock identifying data may include data stored by a lock manufacturer and / or data created by a lock owner. Static access codes may also be programmed into the lock if desired. Caching of valid access codes may be used to reduce processing time.

Owner:GREISEN ENTERPRISES

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com