Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4878 results about "Drain current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Current drain occurs under two separate circumstances. If you are a radio operator the current drain is a rating on how well, or efficiently, the Field Effect Transistor (FET) circuit works for transmitting a radio signal. Current drain, under the second circumstance, relates to our cars not starting in the morning.

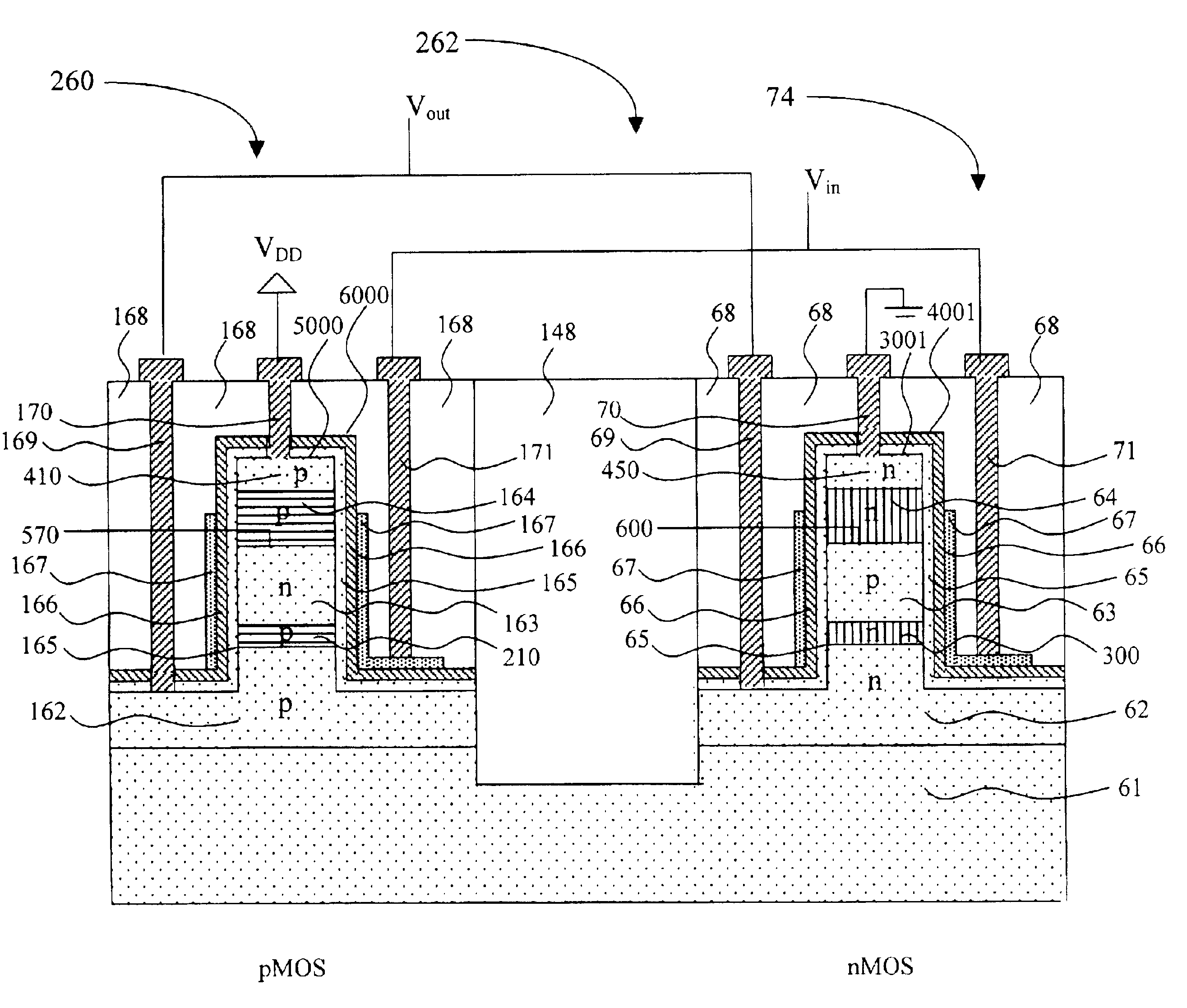

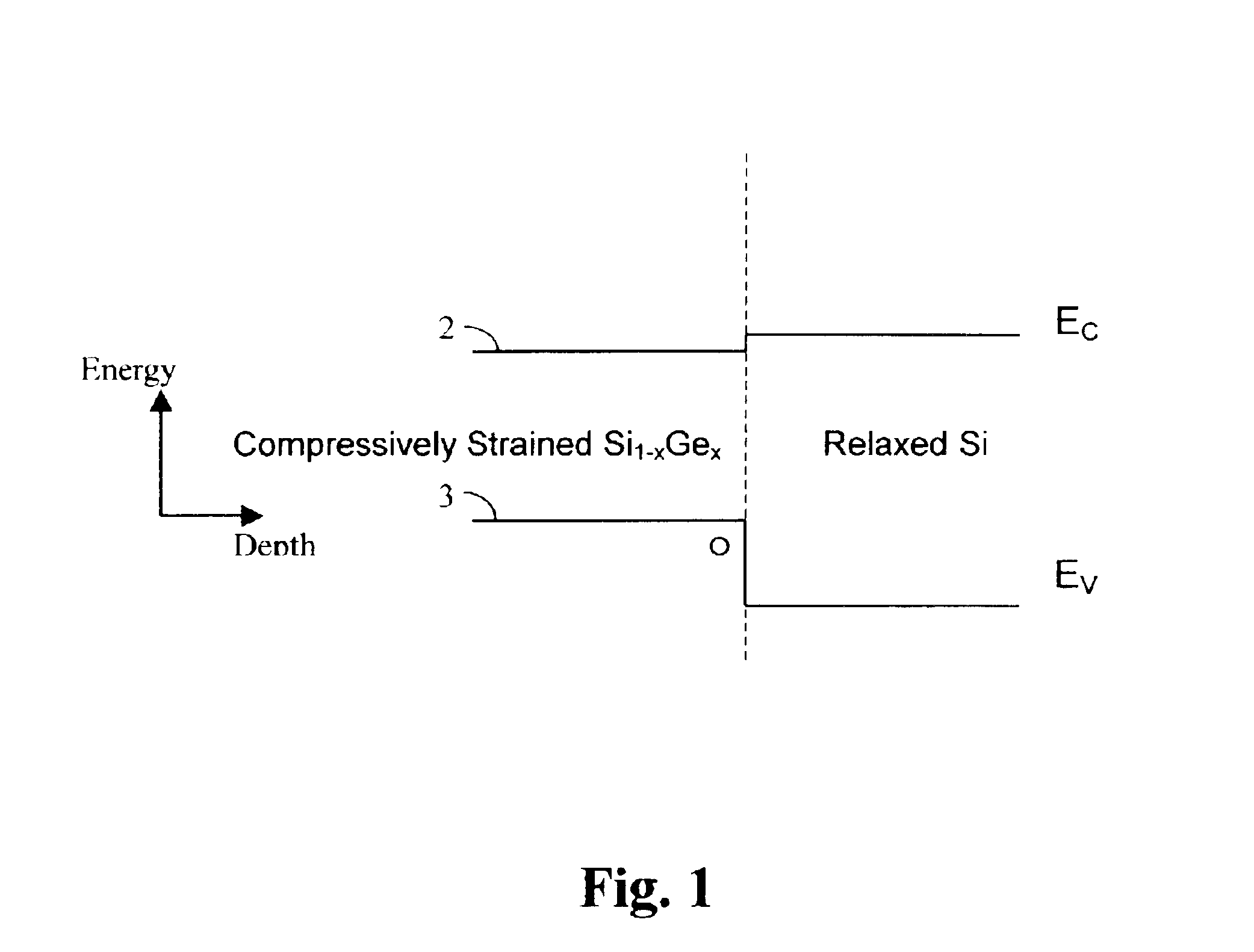

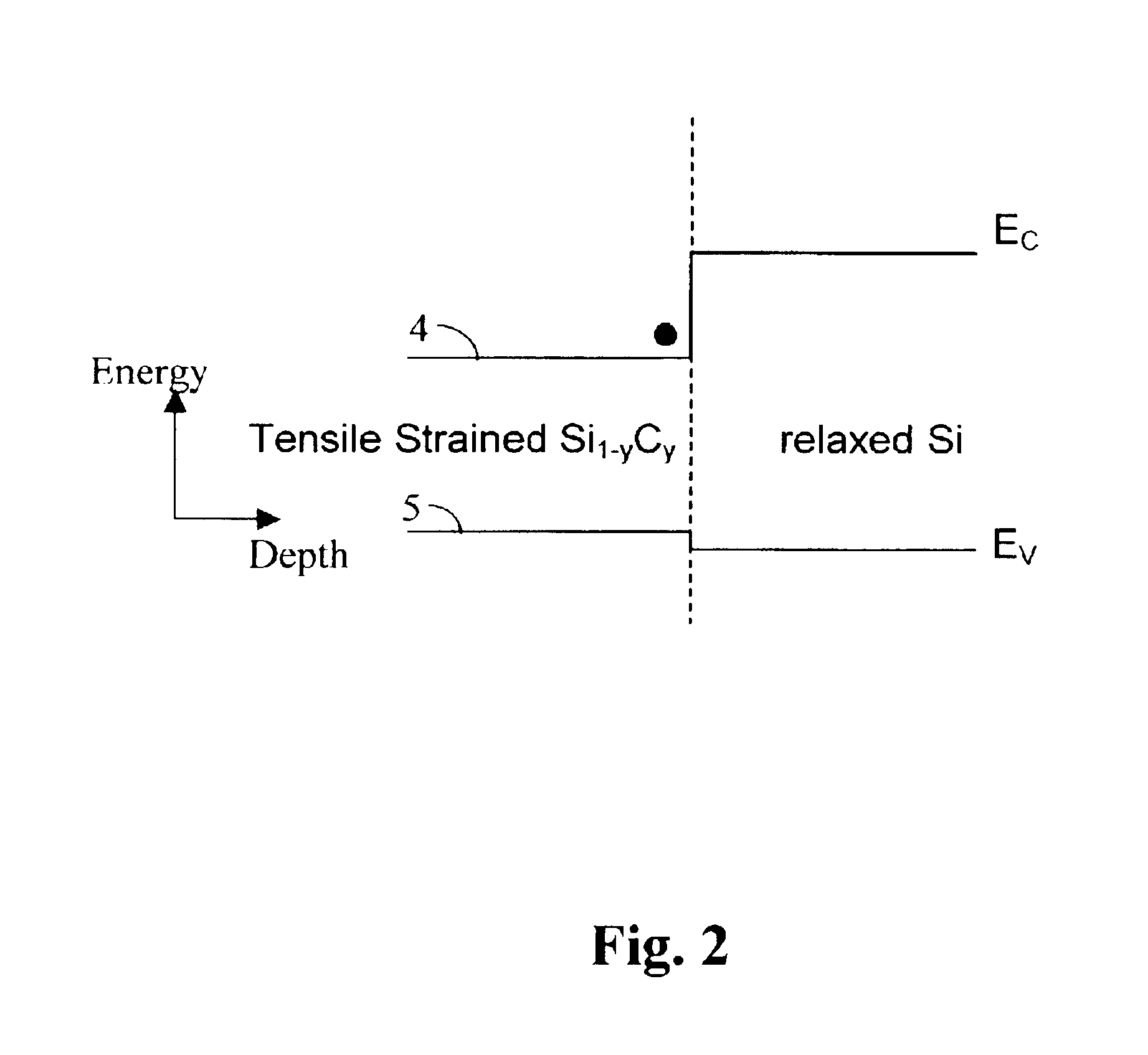

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

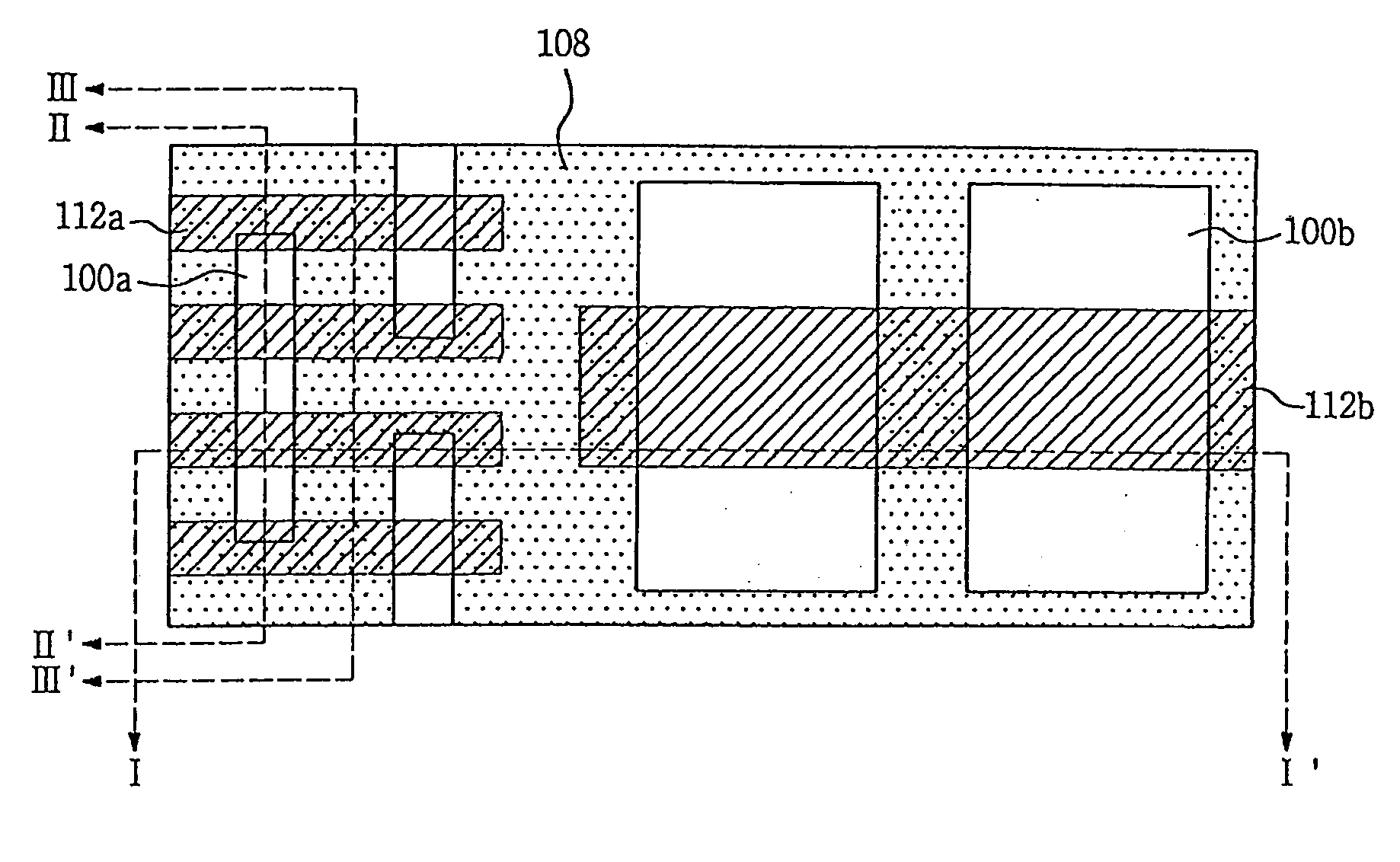

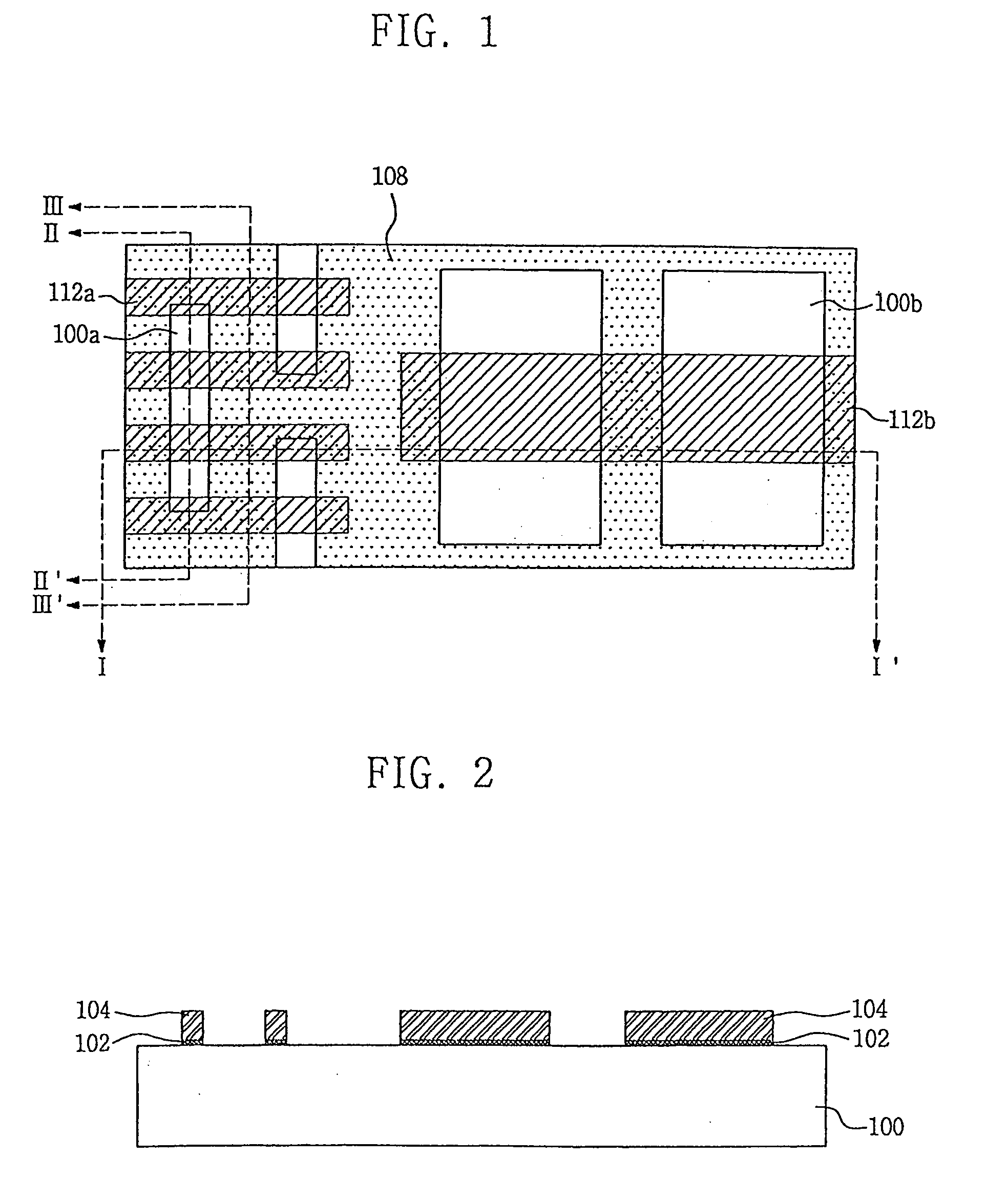

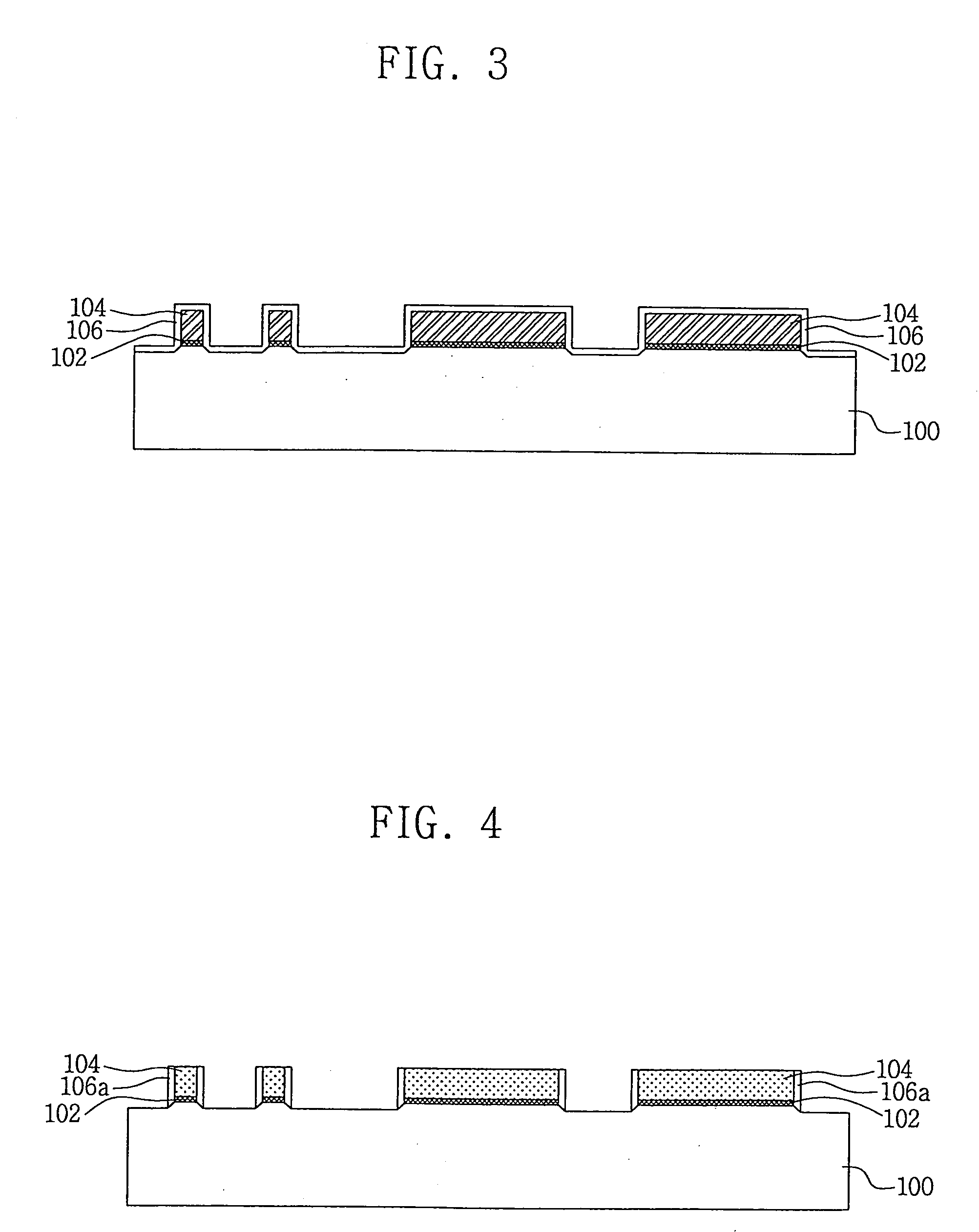

Method of forming fin field effect transistor

ActiveUS20050153490A1Prevent and substantially reduce leakage currentElectrode can be separatedTransistorSolid-state devicesInsulation layerDrain current

According to some embodiments, a fin type active region is formed under an exposure state of sidewalls on a semiconductor substrate. A gate insulation layer is formed on an upper part of the active region and on the sidewalls, and a device isolation film surrounds the active region to an upper height of the active region. The sidewalls are partially exposed by an opening part formed on the device isolation film. The opening part is filled with a conductive layer that partially covers the upper part of the active region, forming a gate electrode. Source and drain regions are on a portion of the active region where the gate electrode is not. The gate electrode may be easily separated and problems causable by etch by-product can be substantially reduced, and a leakage current of channel region and an electric field concentration onto an edge portion can be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

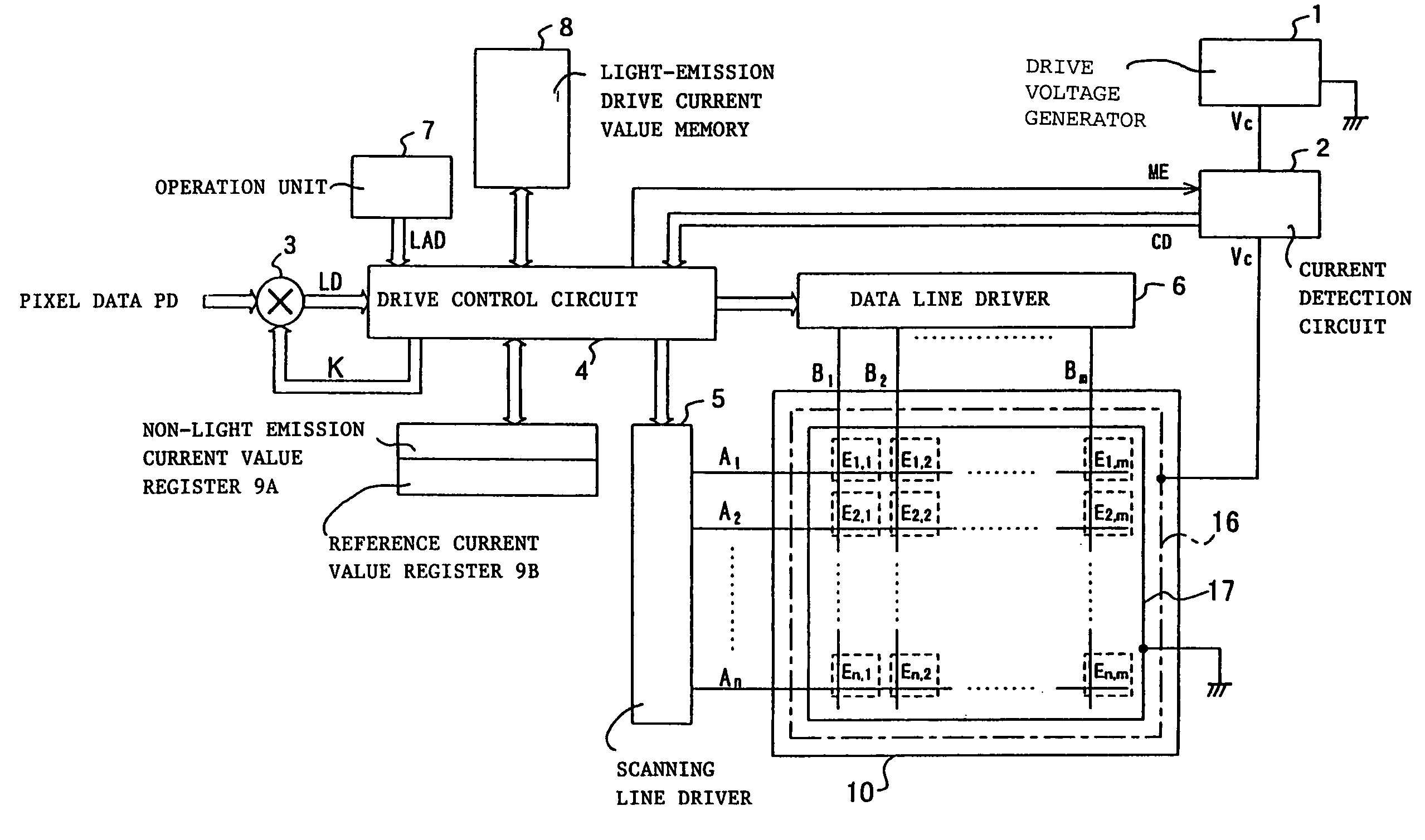

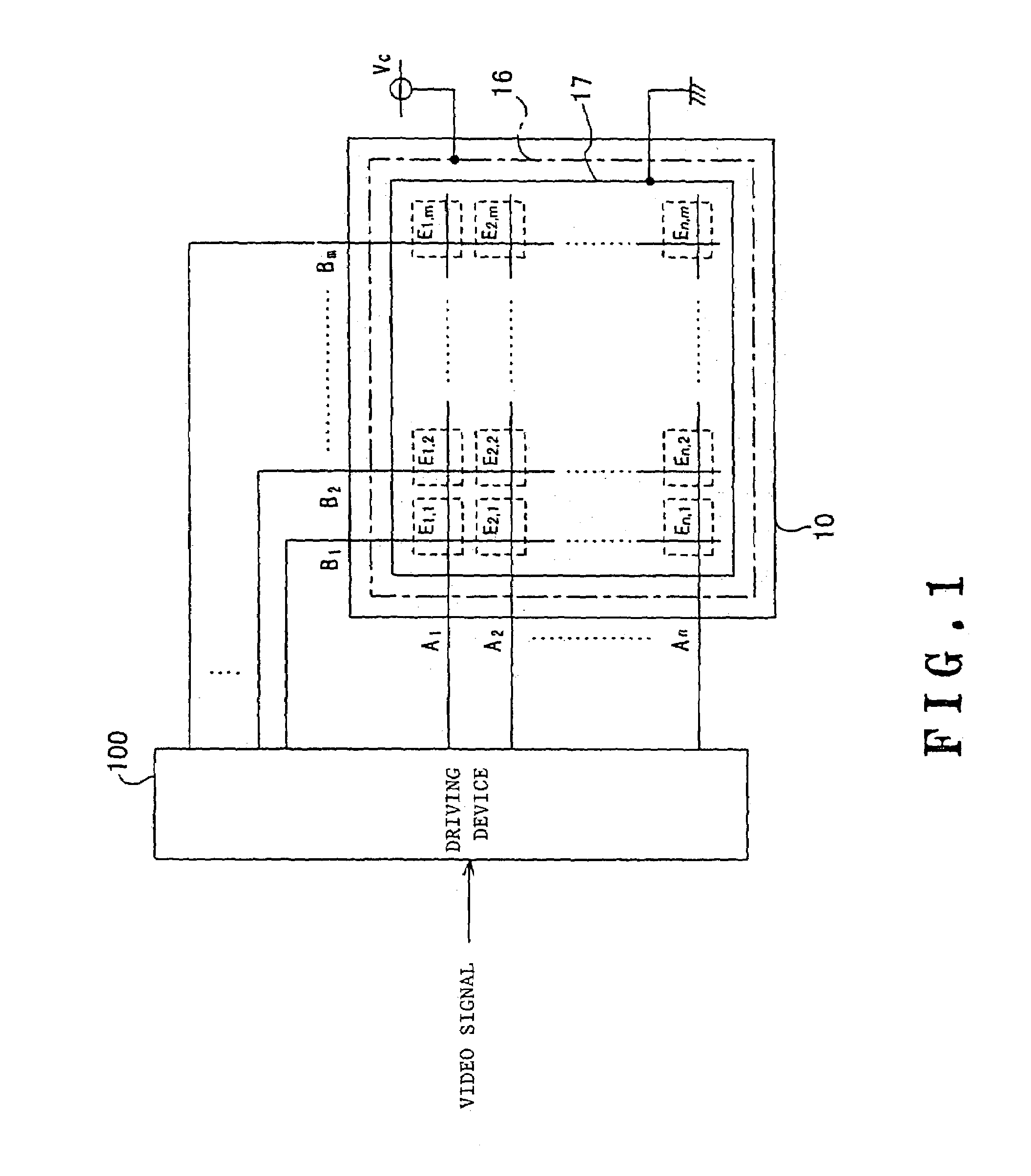

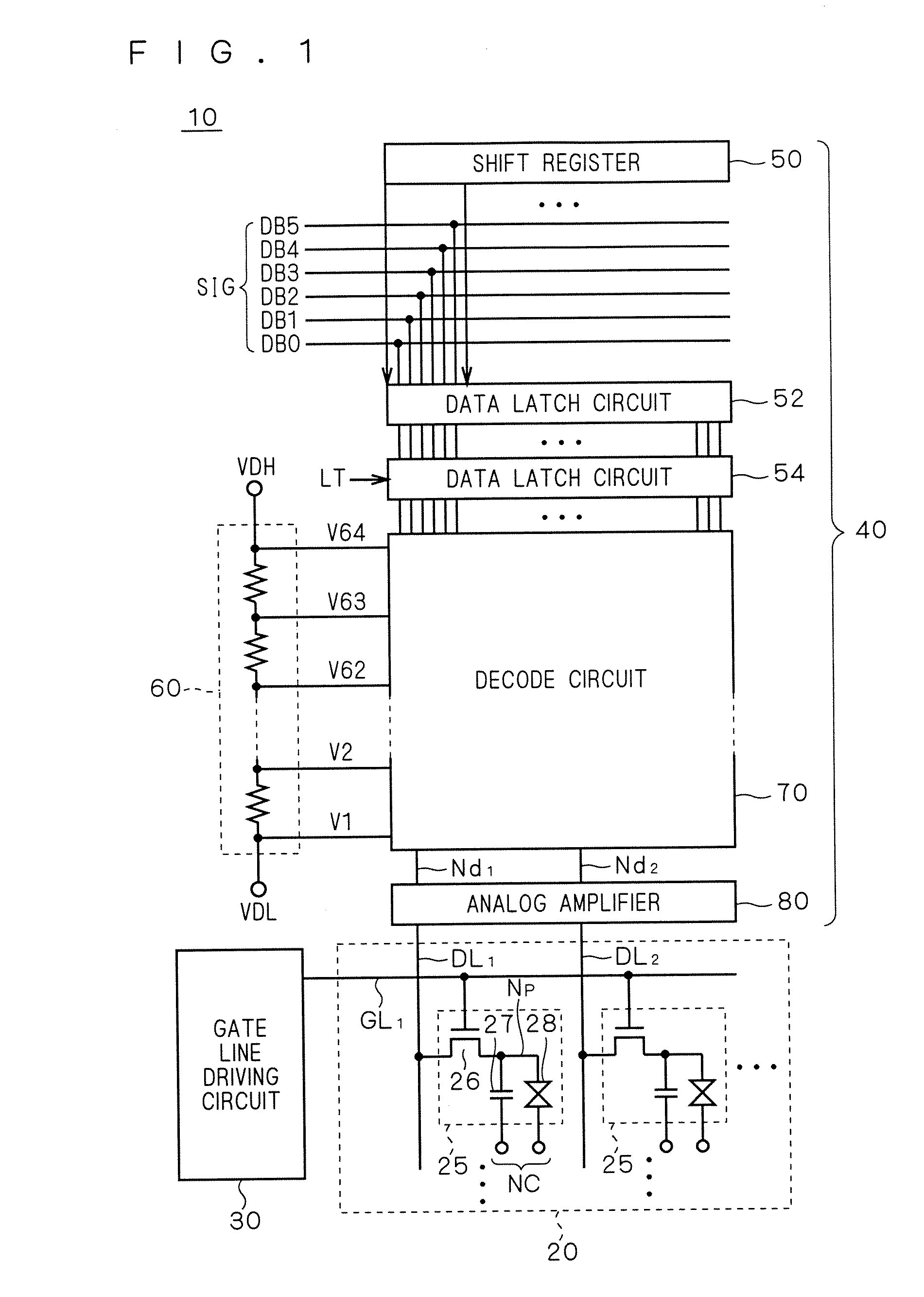

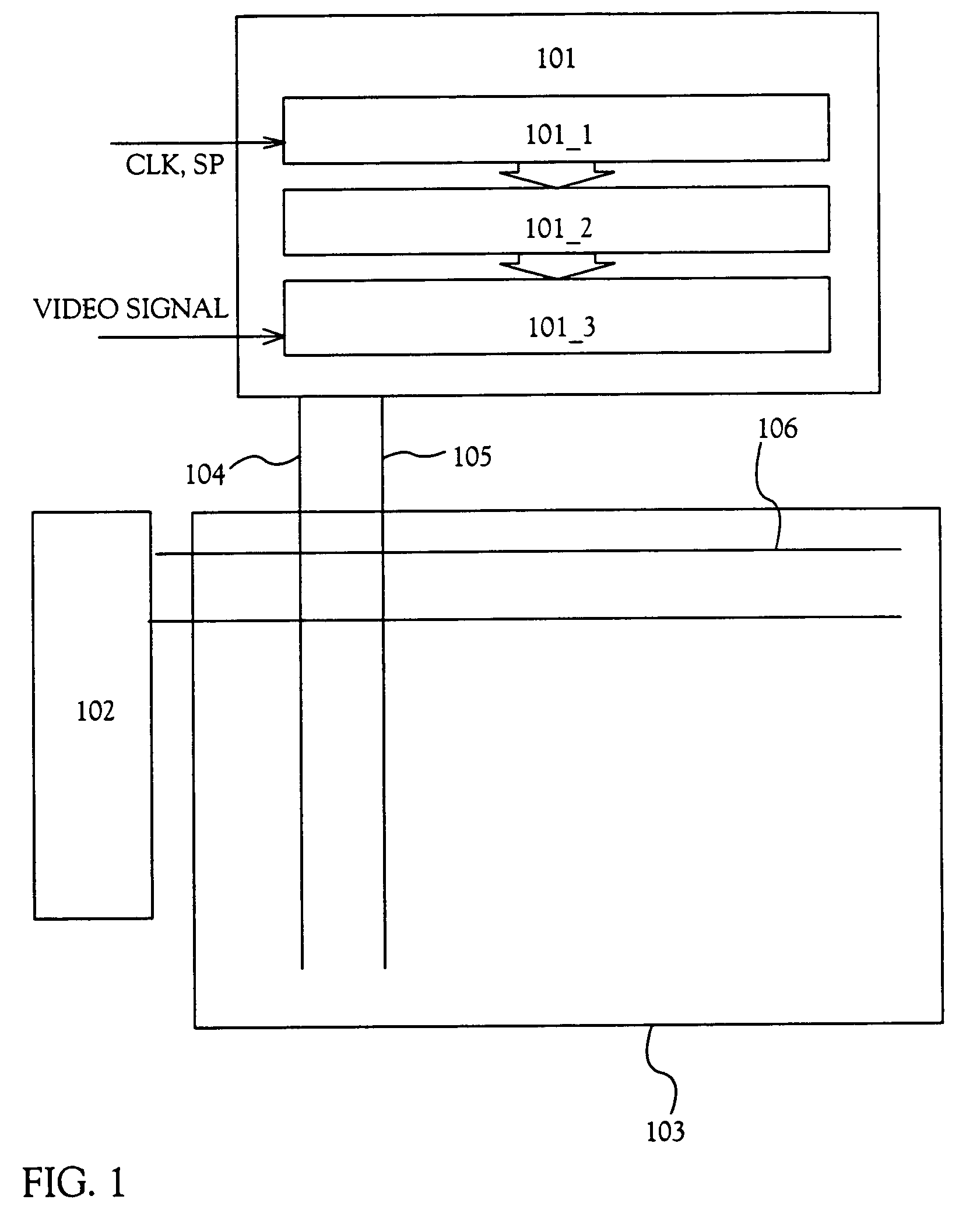

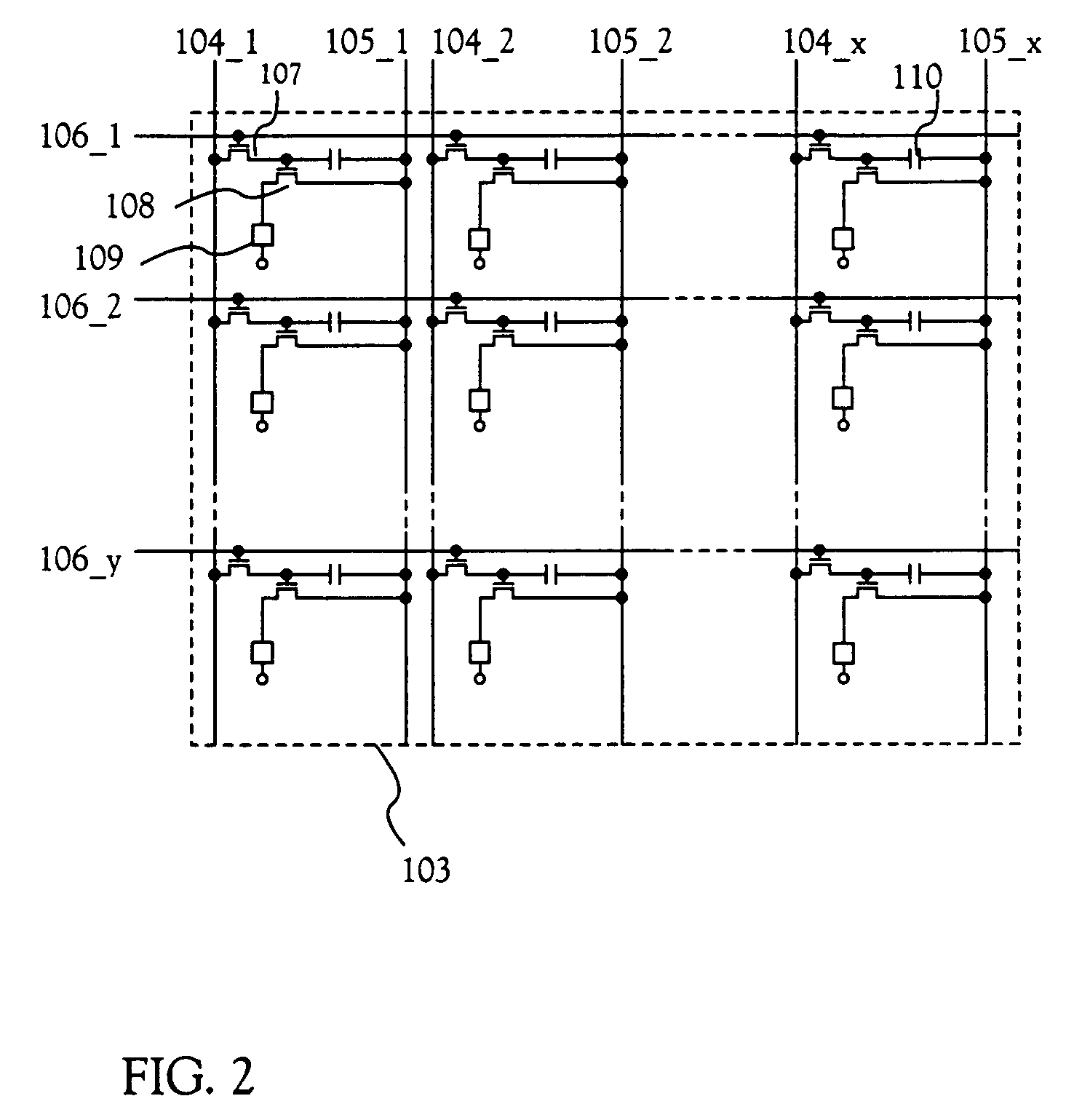

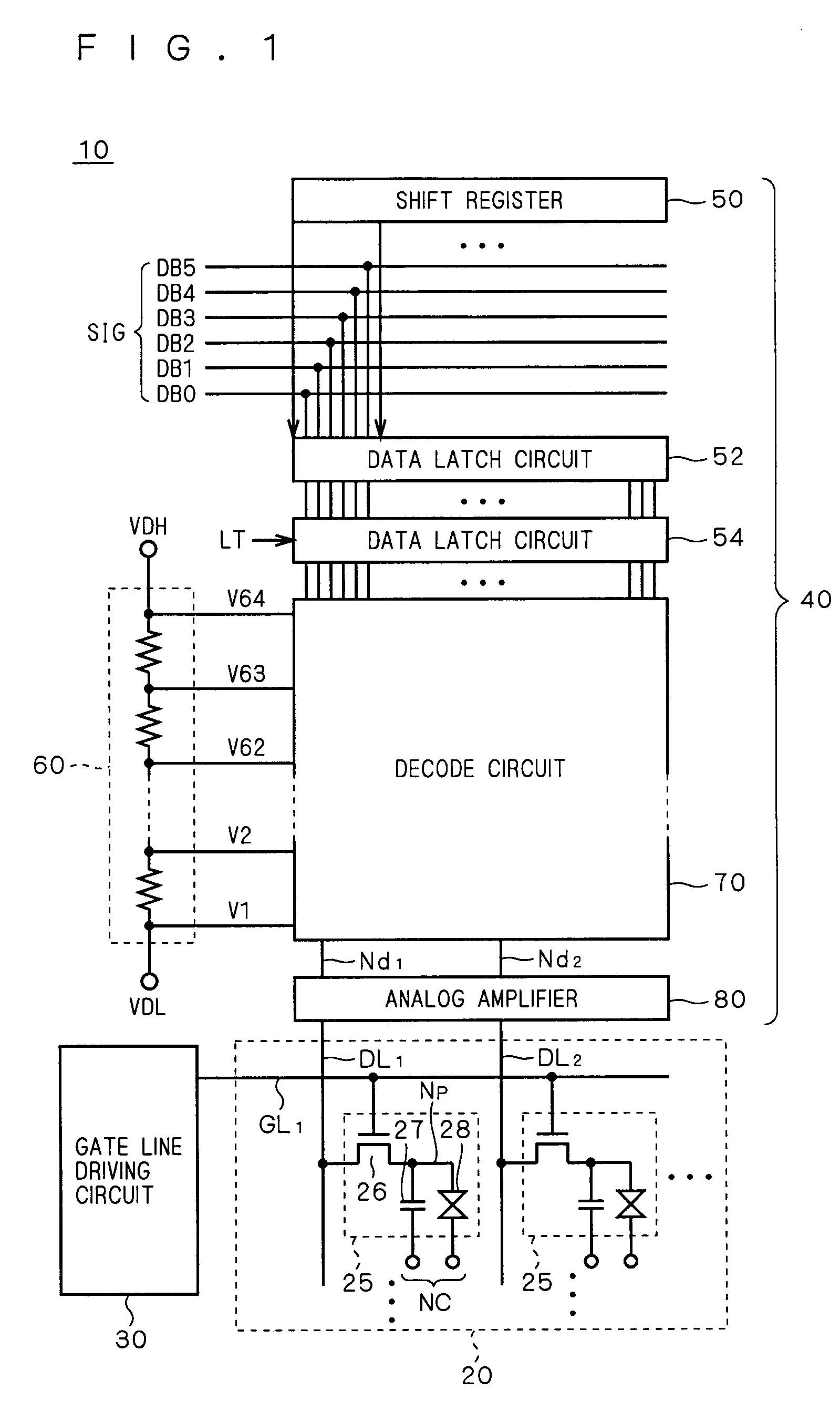

Panel display driving device and driving method

ActiveUS7274363B2Cathode-ray tube indicatorsInput/output processes for data processingDriving currentVoltage generator

A display panel driving device and driving method for providing high quality images without irregular luminance even after long-time use. The value of the light-emission drive current flowing when causing each light-emission elements bearing each pixel to independently emit light in succession is measured, then the luminance is corrected for each input pixel data based on the above light-emission drive current values, associated with the pixels corresponding to the input pixel data. According to another aspect, the voltage value of the drive voltage is adjusted in such a manner that one value among each measured light-emission drive current value becomes equal to a predetermined reference current value. According to a further aspect, the current value is measured while an off-set current component corresponding to a leak current of the display panel is added to the current outputted from the drive voltage generator circuit and the resultant current is supplied to each of the pixel portions.

Owner:PIONEER CORP

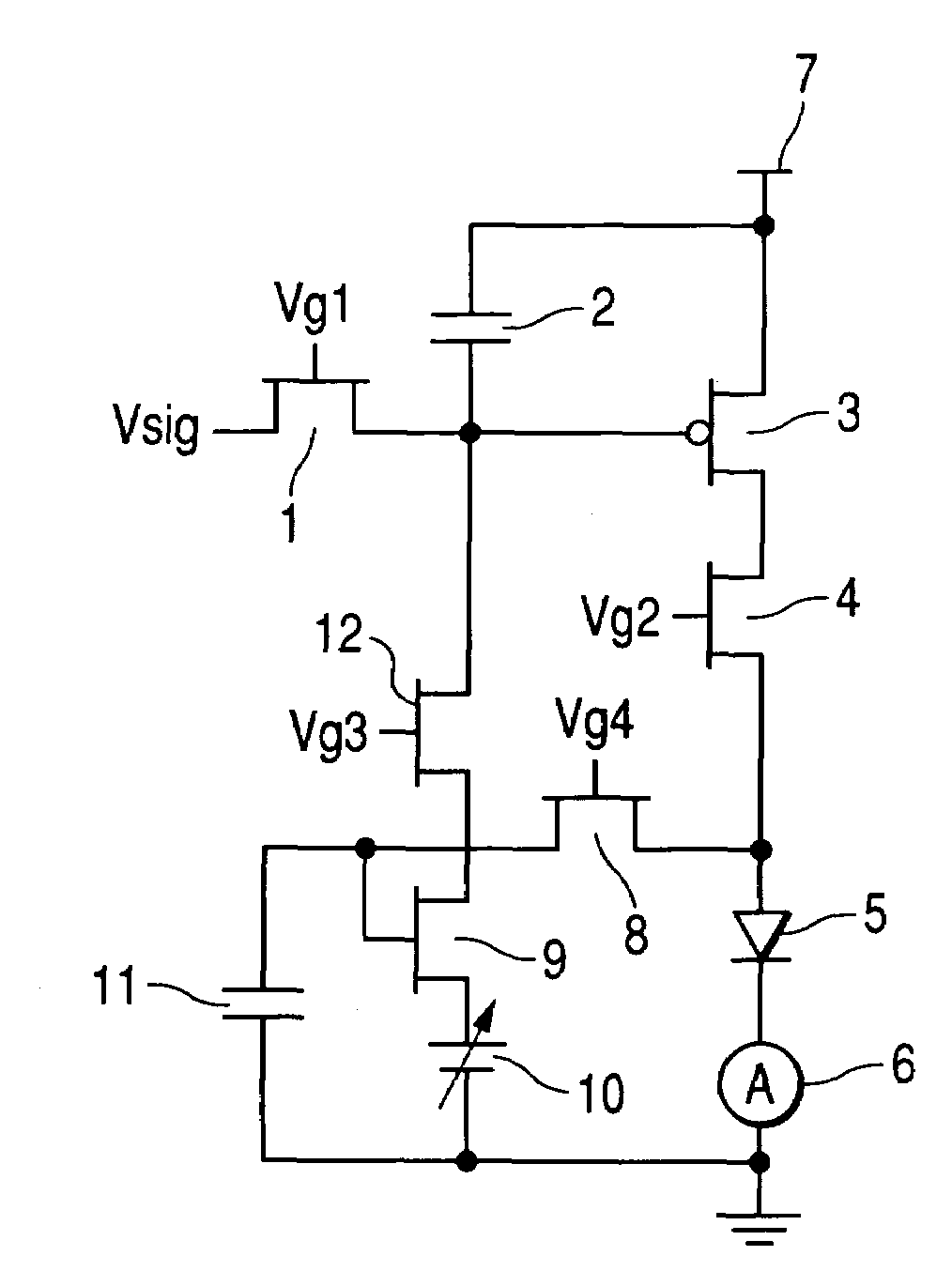

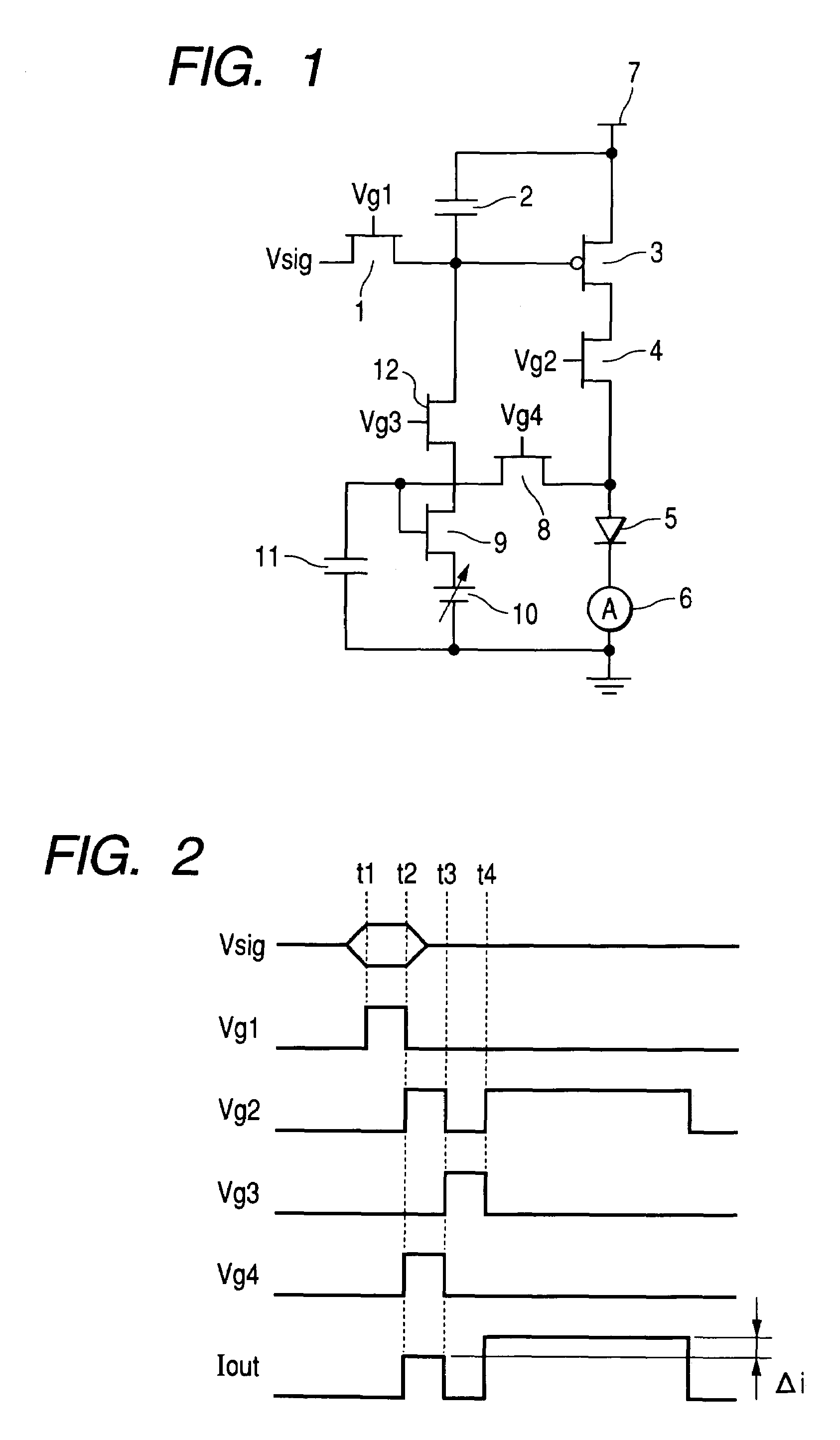

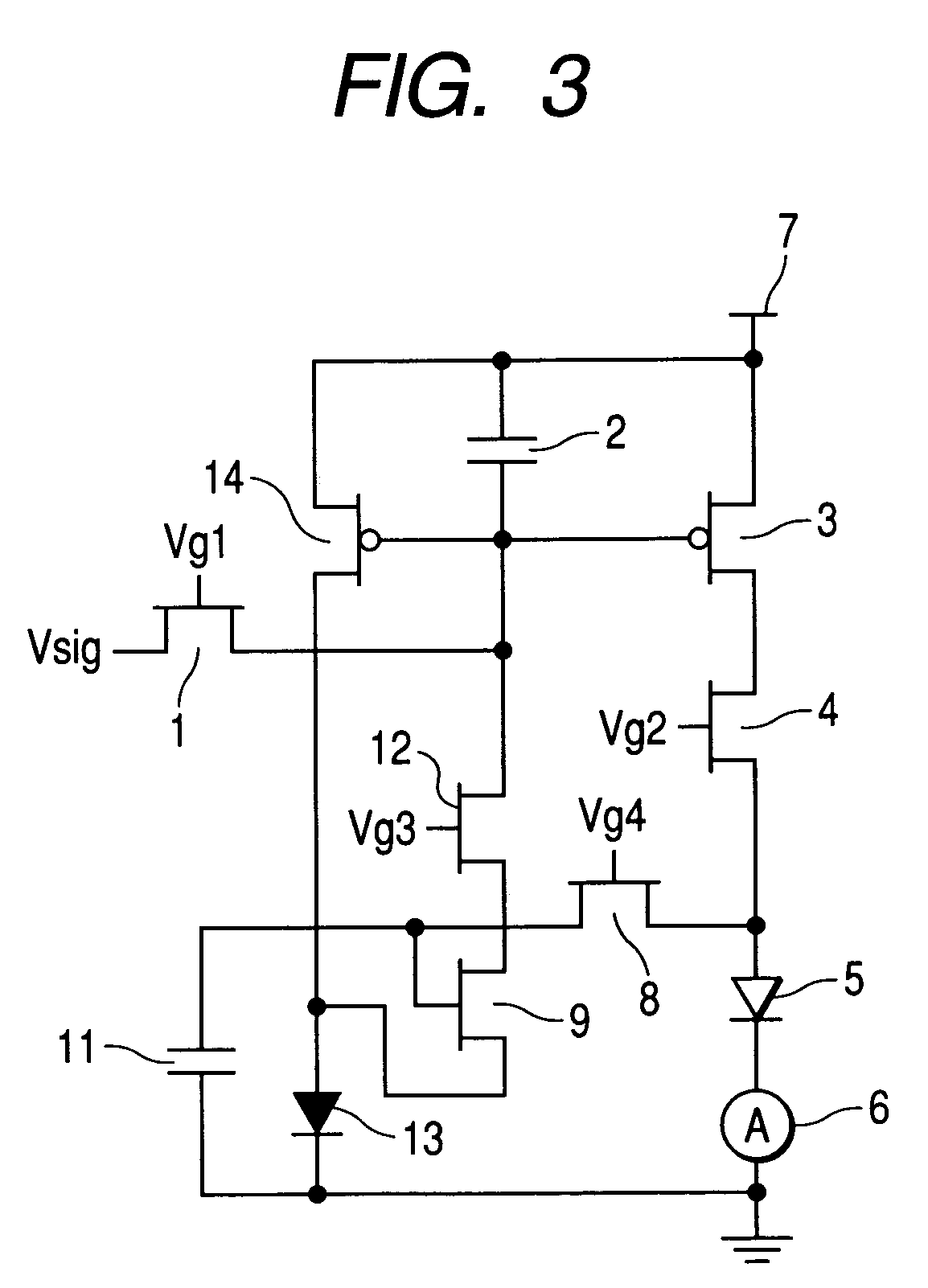

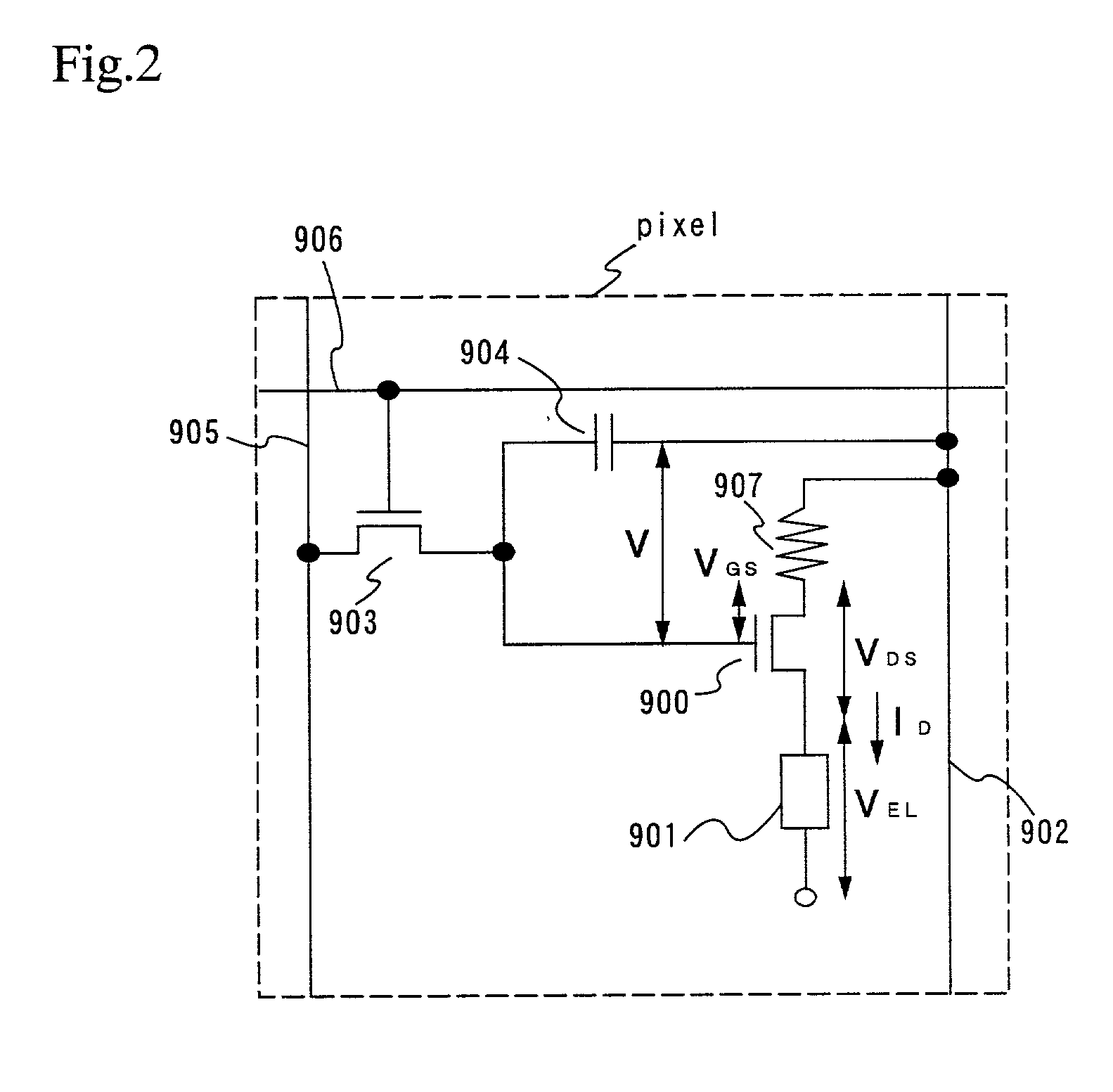

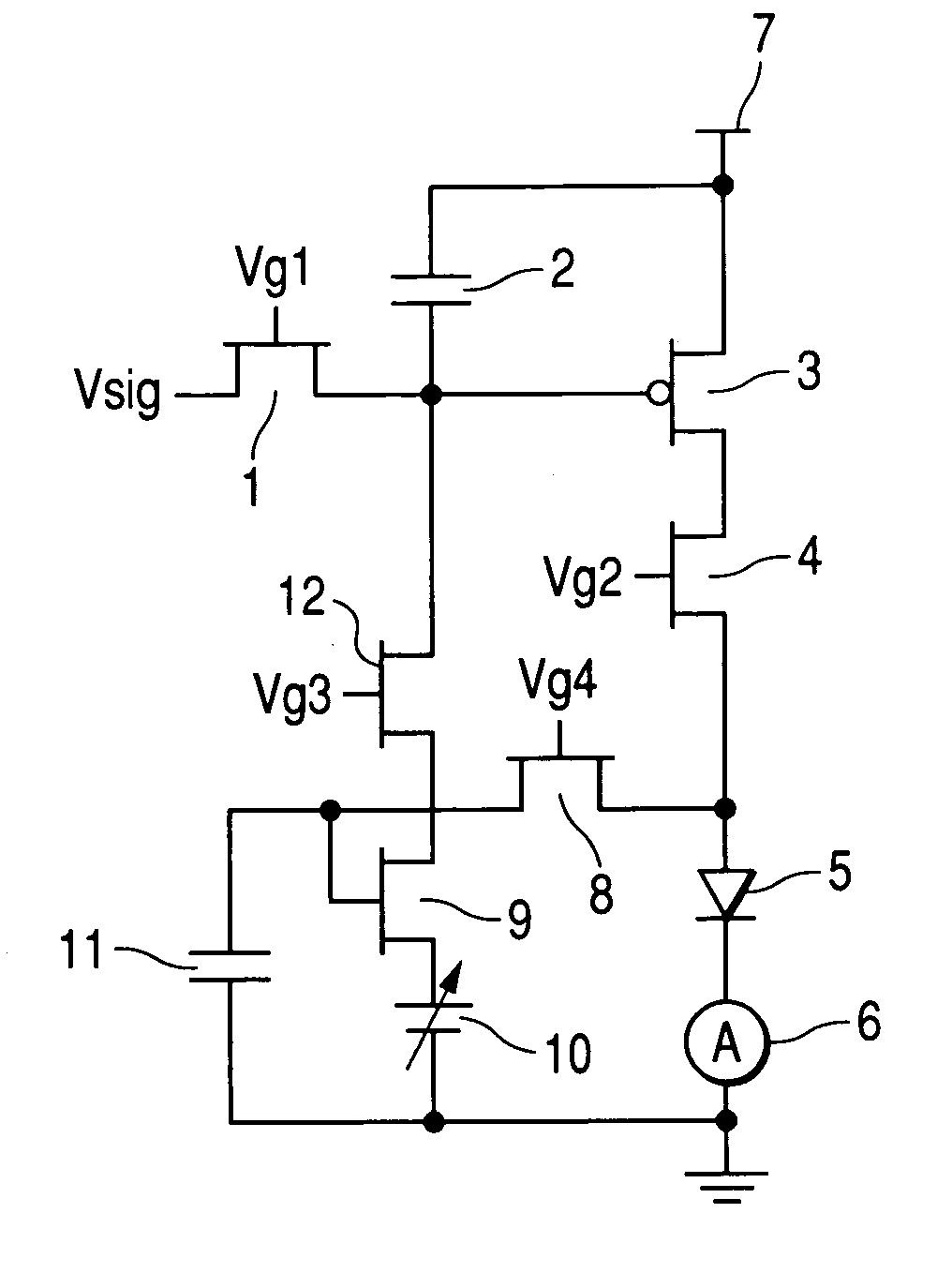

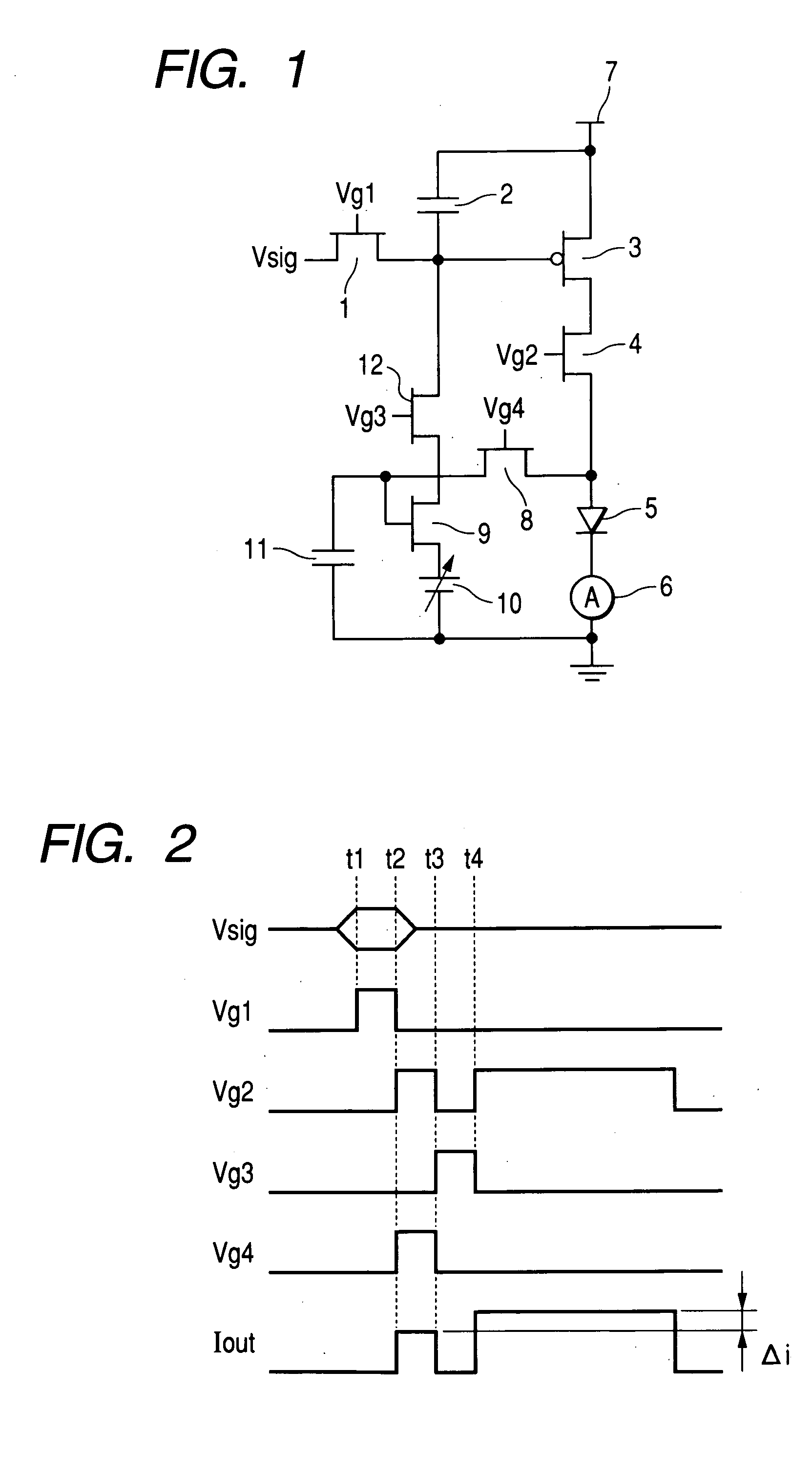

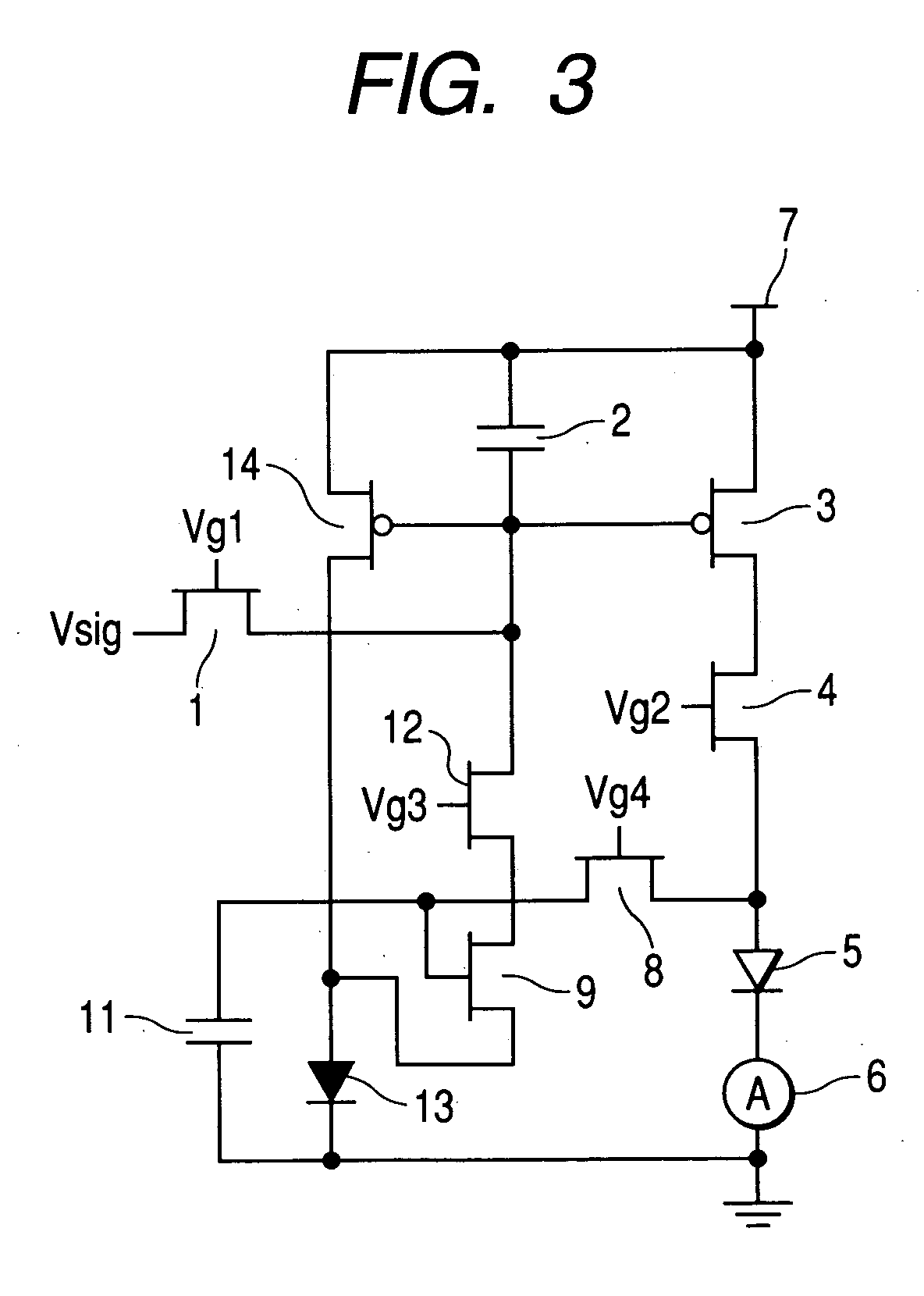

Drive circuit and image forming apparatus using the same

InactiveUS7502000B2Image stabilizationCathode-ray tube indicatorsInput/output processes for data processingDriver circuitDriving current

A drive circuit including a drive transistor for feeding to a load a drive current corresponding to an input signal. The drive circuit has a correction circuit that supplies a correction signal corresponding to an impedance of the load to a gate of the drive transistor to correct the drive current to be fed to the load by the drive transistor, and in which the load is a light-emitting element. One terminal of the light-emitting element is connected to a gate of a transistor for correction, and when a predetermined potential Ps is set to a value calculated by deducting a threshold voltage Vth of the transistor for correction from a terminal potential Pi of the light-emitting element with respect to a drive current, the drive circuit sets a source potential of the transistor for correction to the predetermined potential Ps to thereby generate a voltage corresponding to an impedance of the light-emitting element as a source-to-drain current of the transistor for correction.

Owner:CANON KK

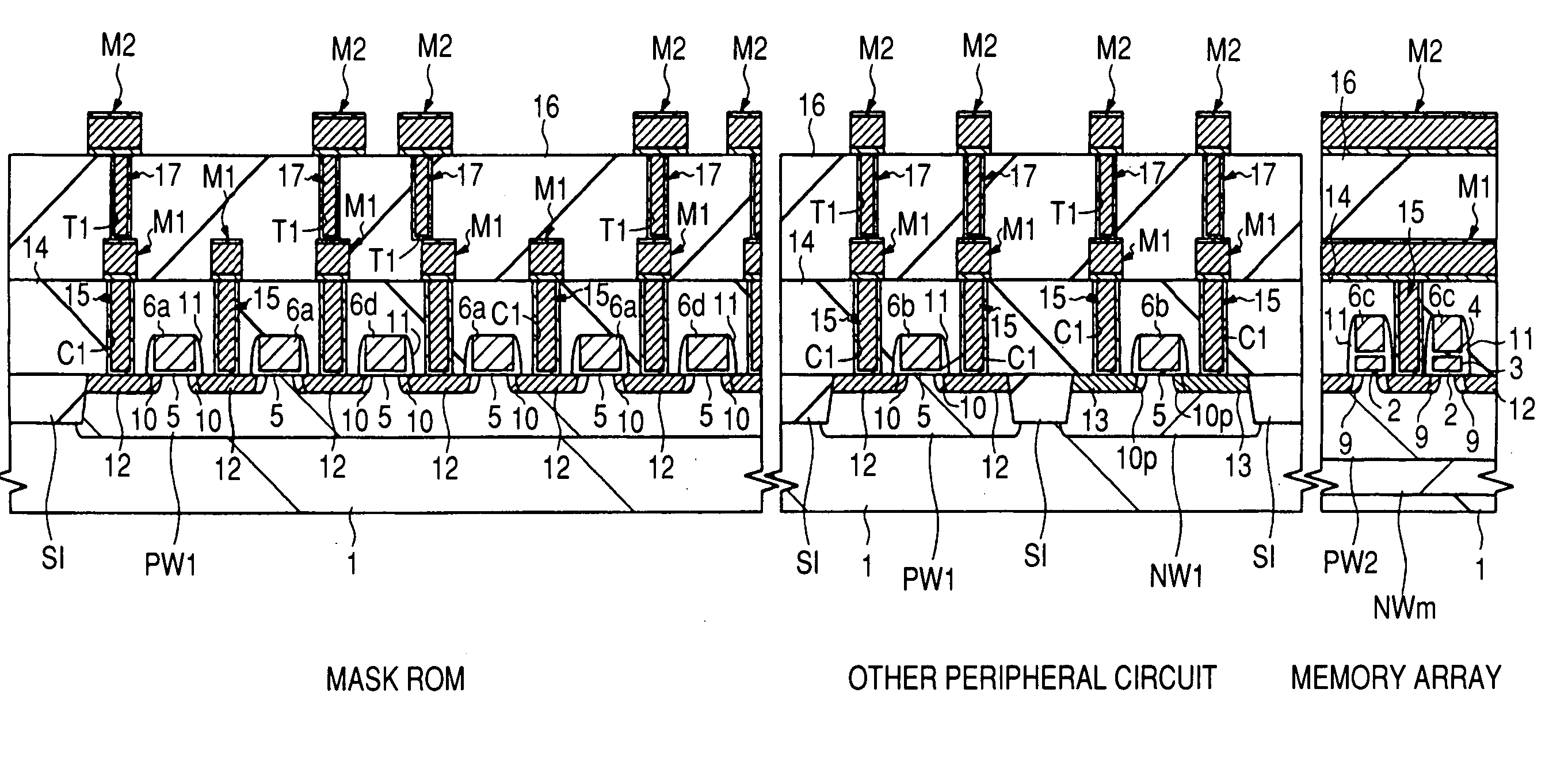

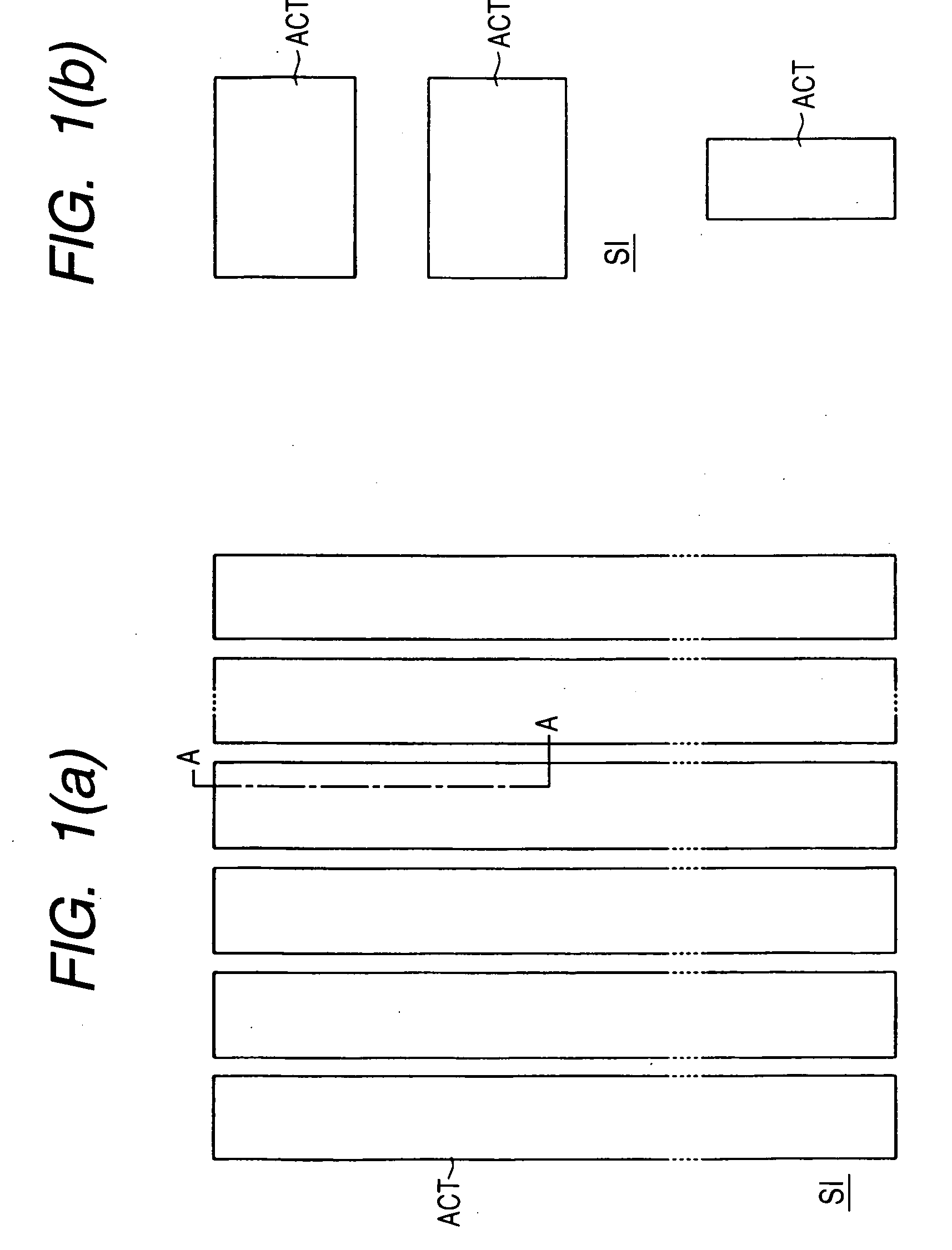

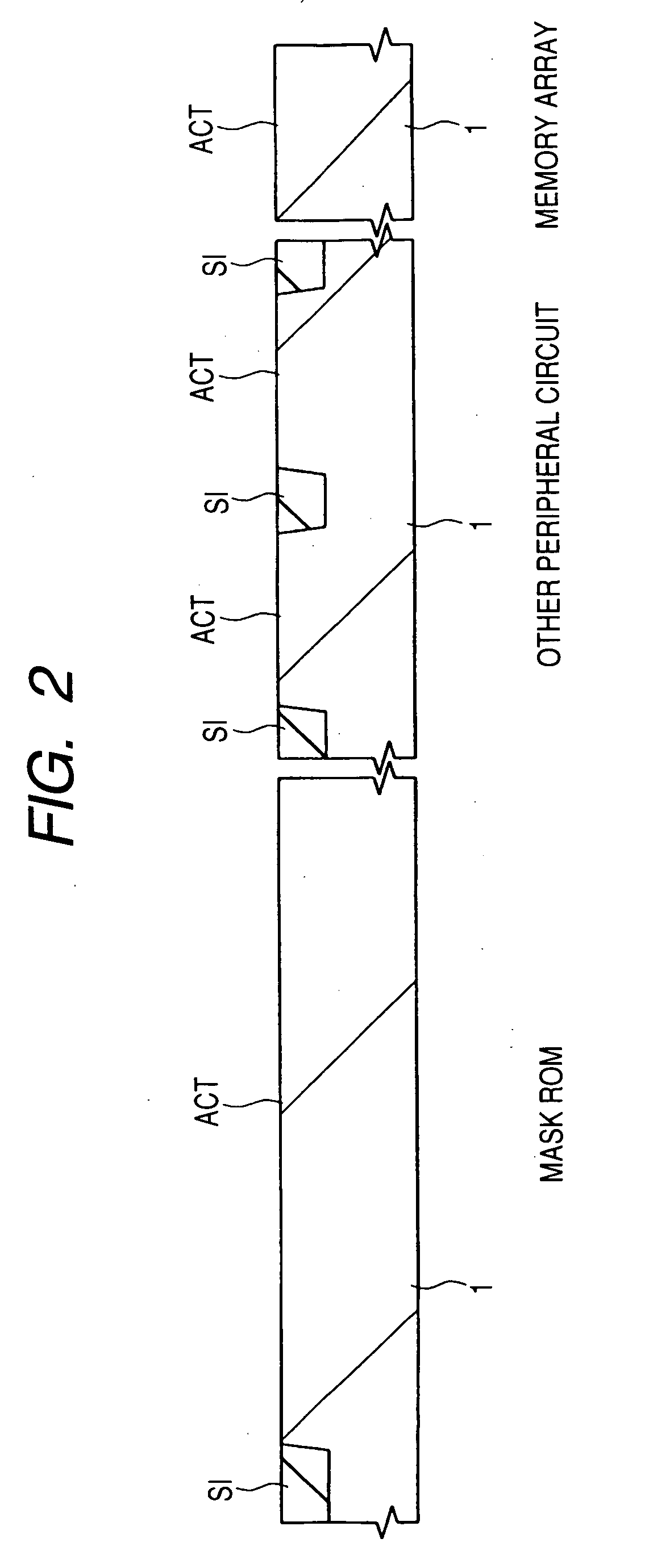

Semiconductor device and a method of manufacturing the same

InactiveUS20060125024A1Improve reliabilityGood effectSolid-state devicesSemiconductor/solid-state device manufacturingMask ROMDevice material

To improve reliability of FETs having element isolation regions for electrically isolating field effect transistors adjacent to each other in the gate length direction in a mask ROM region, the isolation regions are each constructed by field plate isolation formed simultaneously with gate electrodes of the field effect transistors. This relatively lessens a stress generated in an active region ACT sandwiched by the element isolation regions even if the isolation width of each element isolation region is made relatively small, specifically, less than 0.3 μm. It is therefore possible to relax or prevent the generation of crystal defects resulting from the stress, thereby reducing occurrence of an undesired leak current between the source and drain of each field effect transistor.

Owner:RENESAS TECH CORP

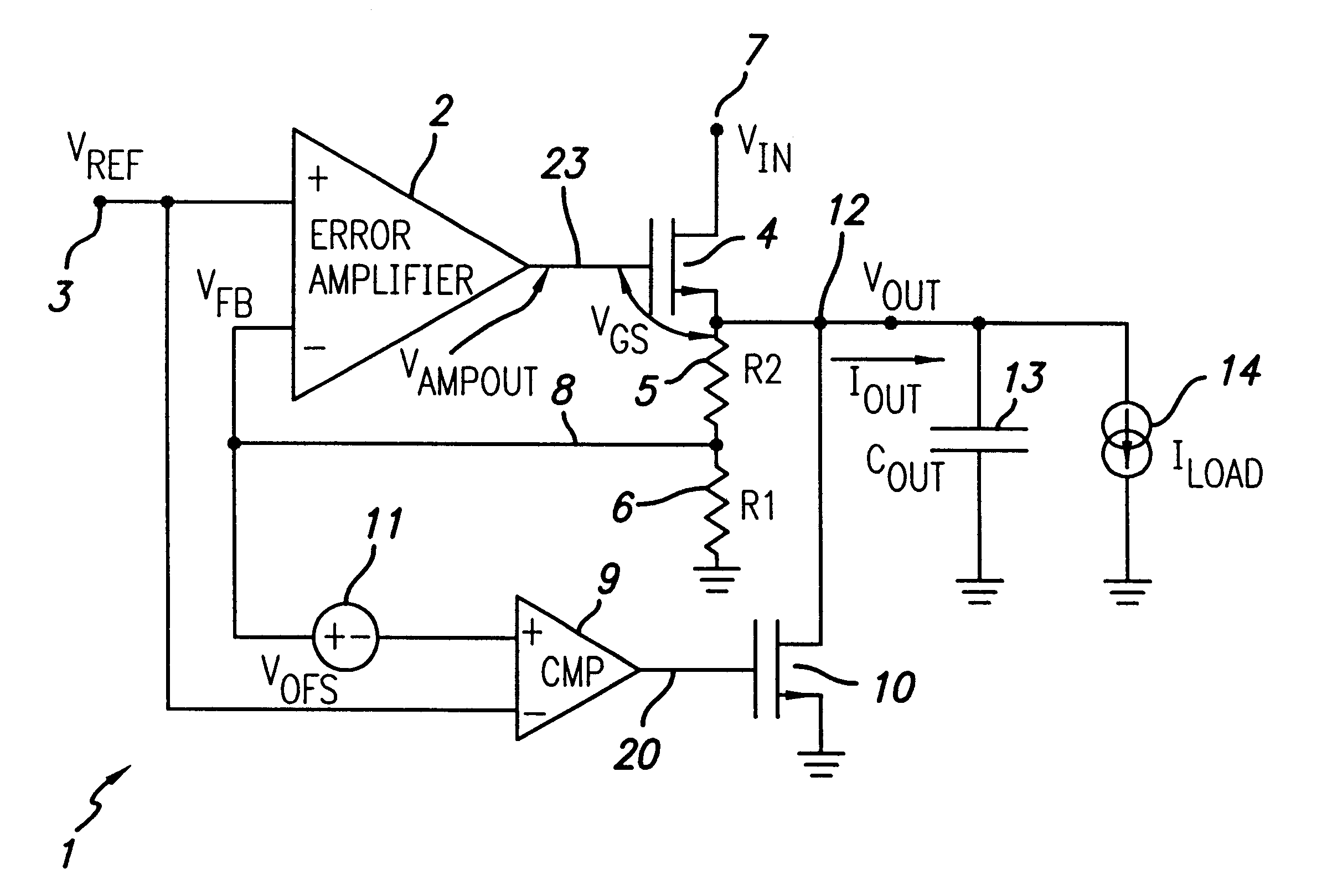

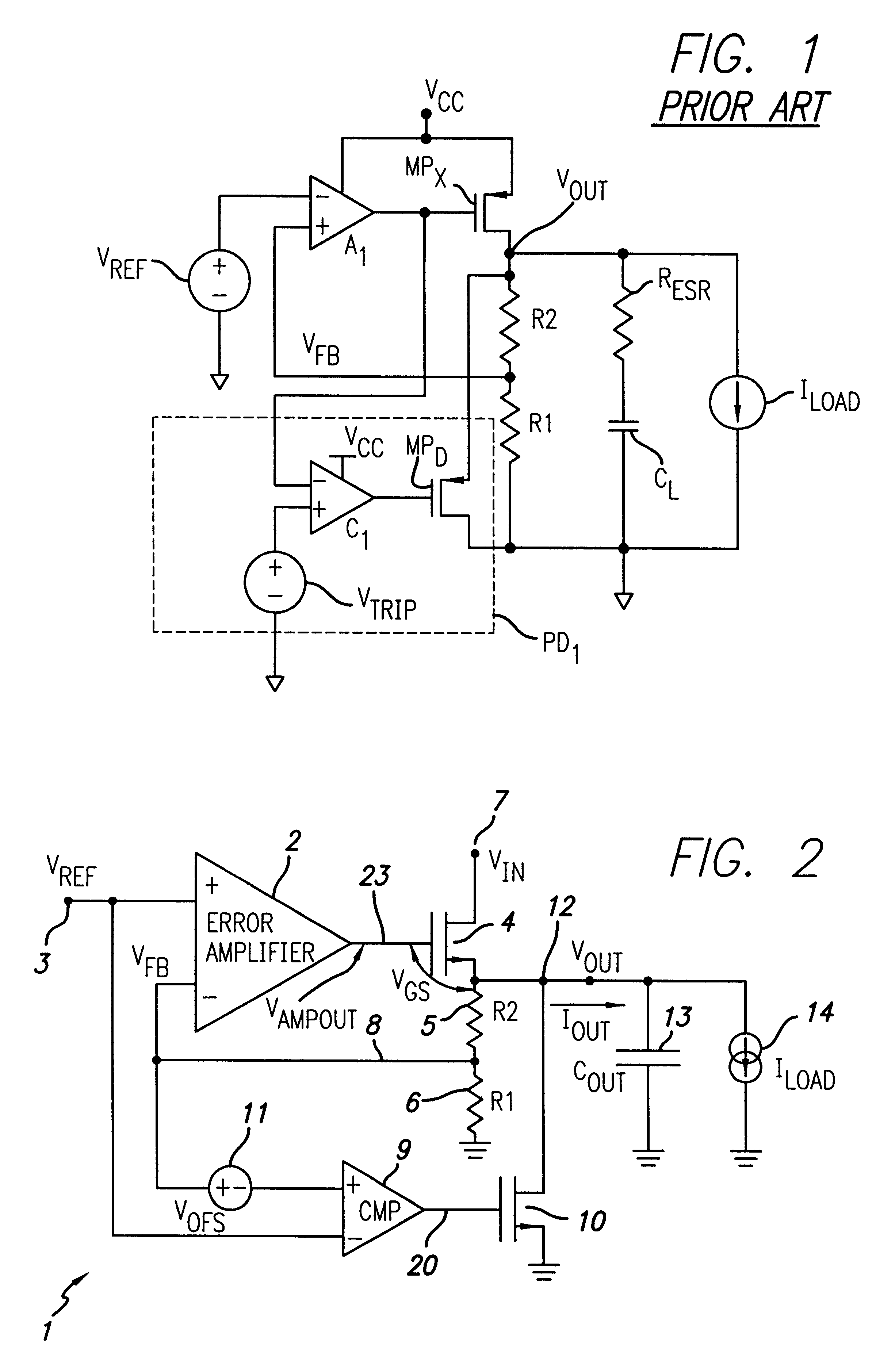

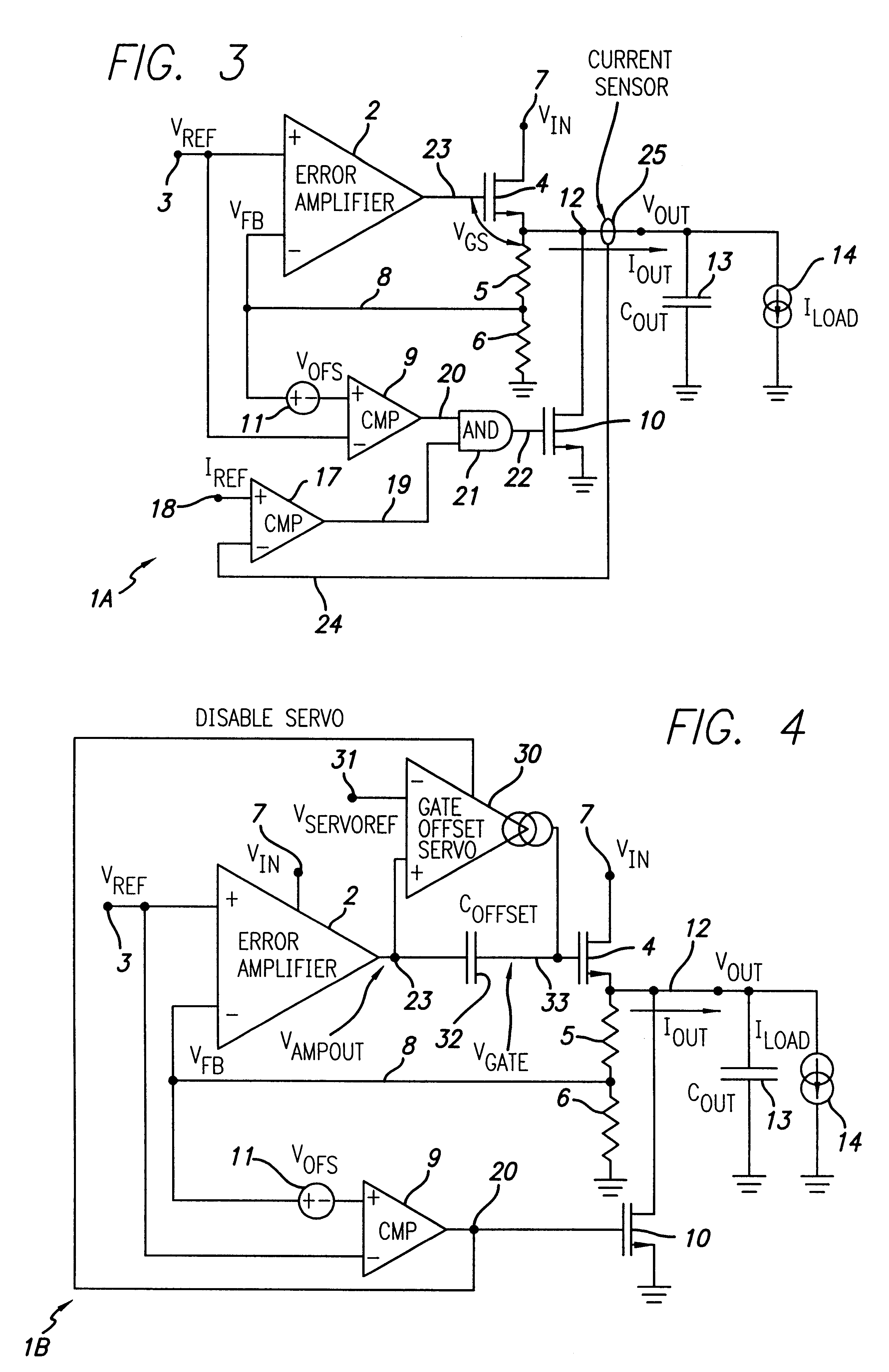

Overvoltage sensing and correction circuitry and method for low dropout voltage regulator

InactiveUS6201375B1Reduce severityEmergency protective arrangements for limiting excess voltage/currentArrangements responsive to excess voltageOvervoltageElectrical conductor

Owner:BURR-BROWN CORPORATION

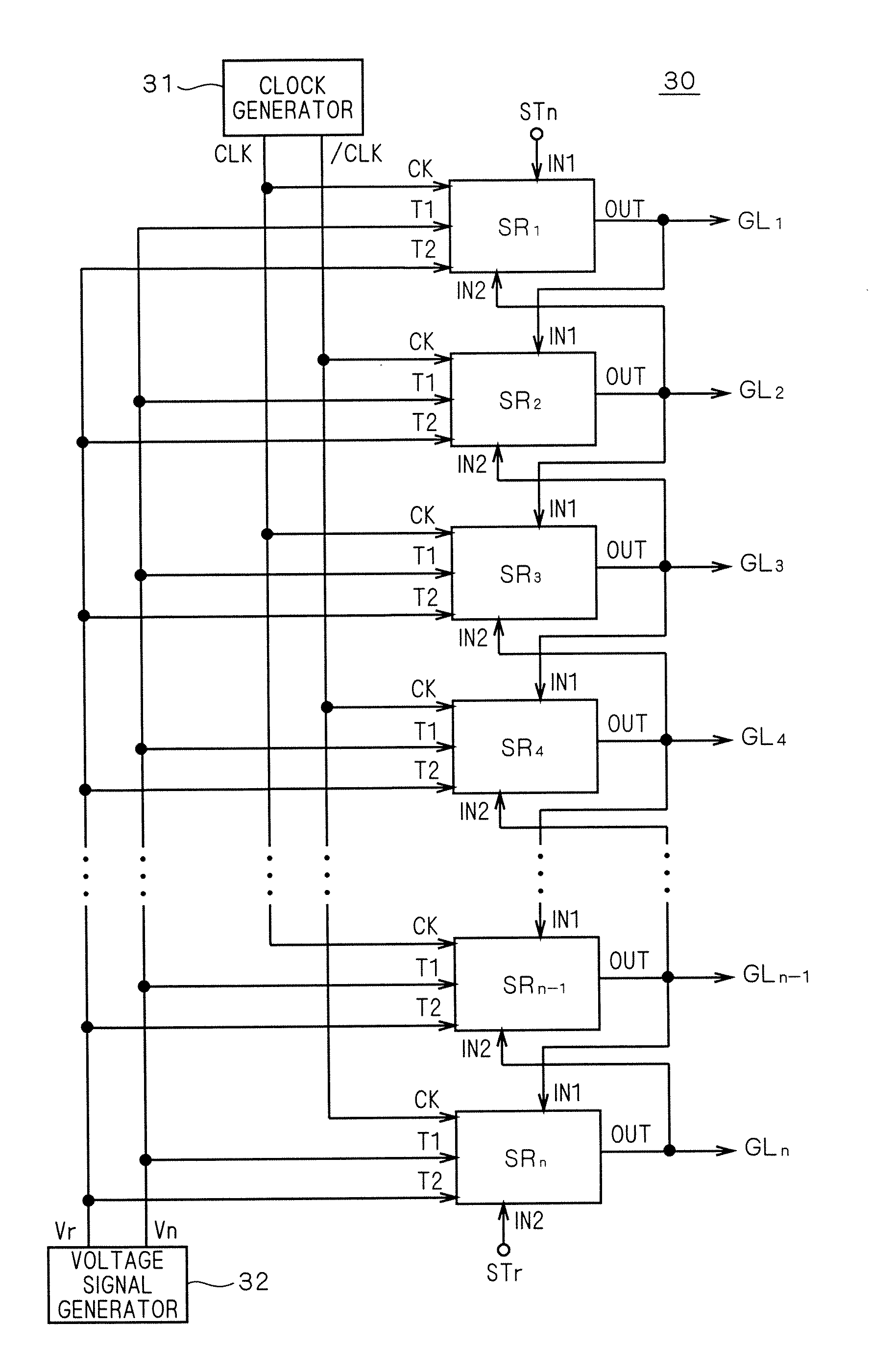

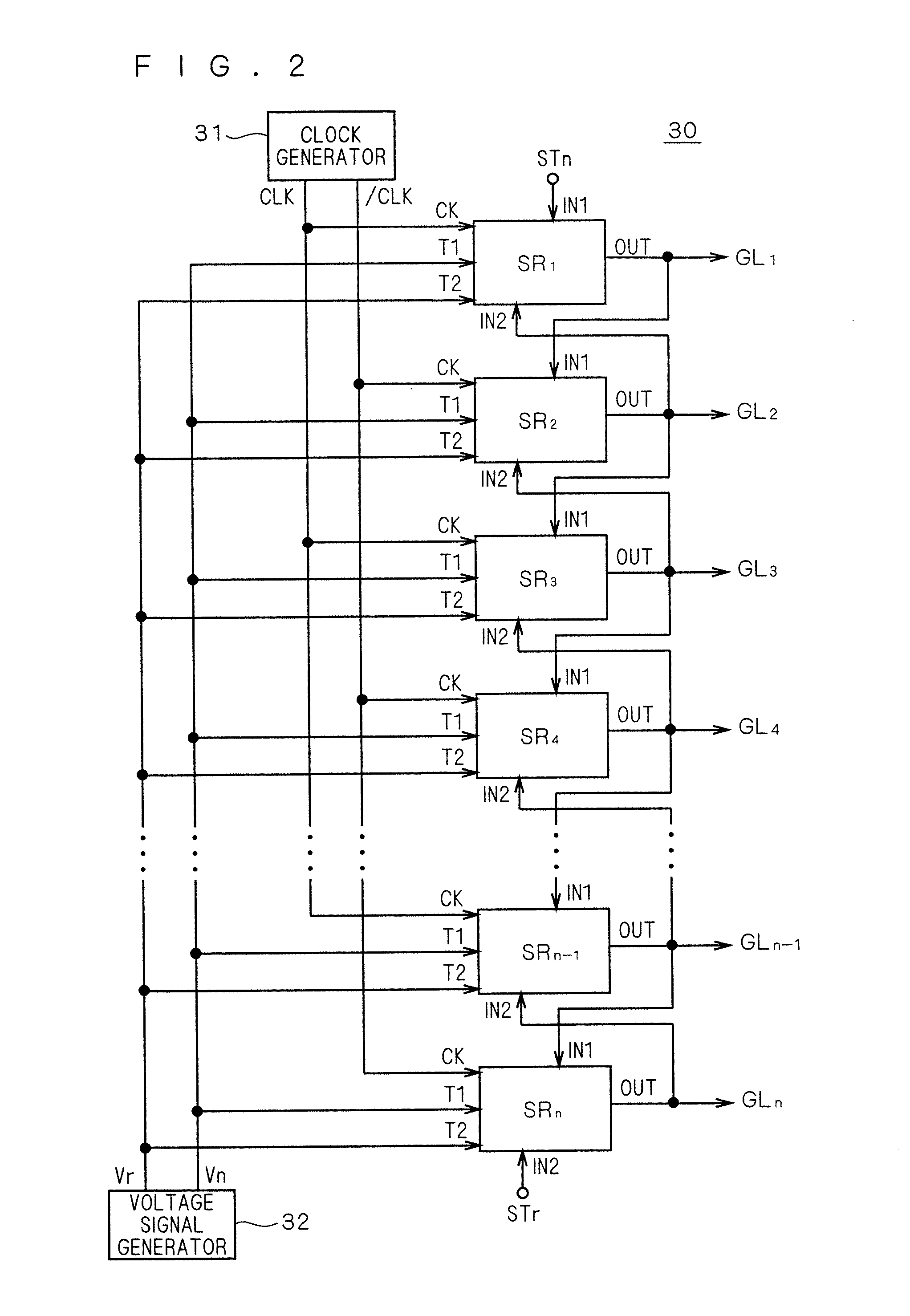

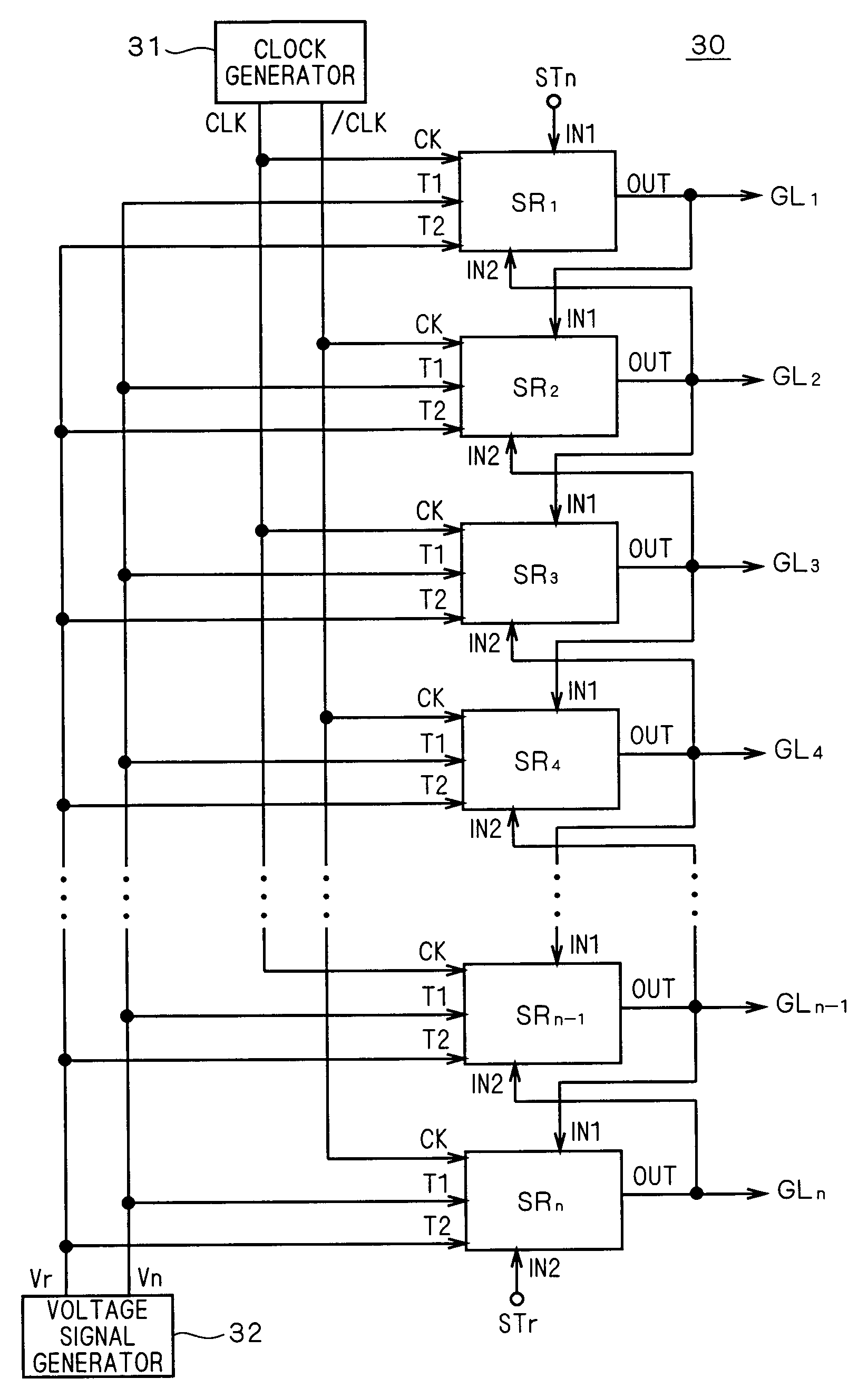

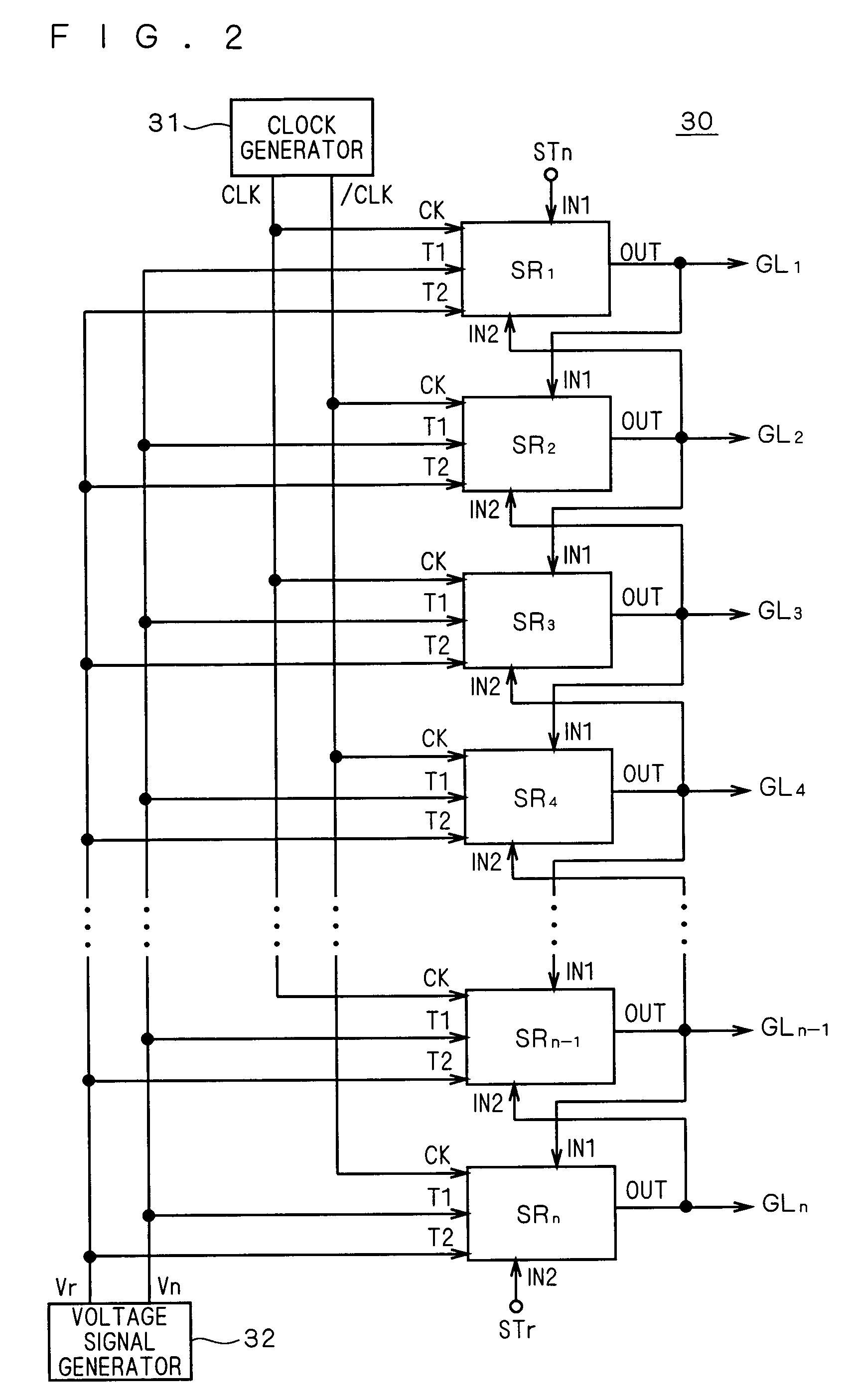

Shift register circuit and image display apparatus equipped with the same

InactiveUS20070274433A1Suppress failureIncrease computing speedStatic indicating devicesDigital storageShift registerElectricity

Malfunction caused by leakage current of the transistor and shift in threshold voltage is prevented in the shift register in which the signal can be shifted bi-directionally. The bi-directional unit shift register includes a first transistor Q1 for providing a first clock signal CLK to an output terminal OUT, a second transistor Q2 for discharging the output terminal OUT based on a second clock signal, third and fourth transistors Q3, Q4 for providing first and second voltage signals Vn, Vr complementary to each other to a first node, which is a gate node of the first transistor Q1, and a fifth transistor Q5 connected between the first node and the output terminal OUT. The fifth transistor Q5 is in an electrically conducted state based on the first clock signal CLK when the gate of the transistor Q1 is at L (Low) level.

Owner:MITSUBISHI ELECTRIC CORP

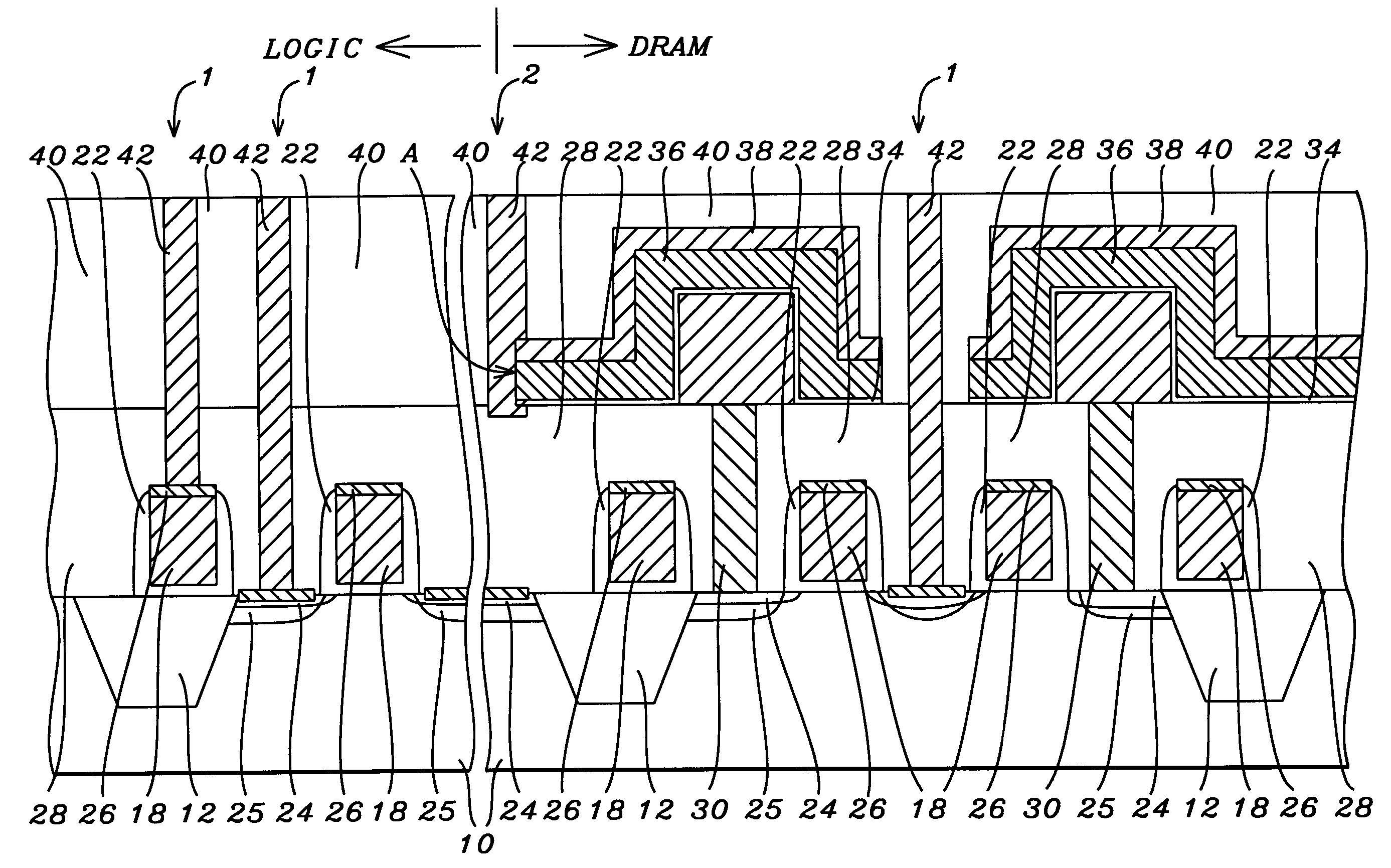

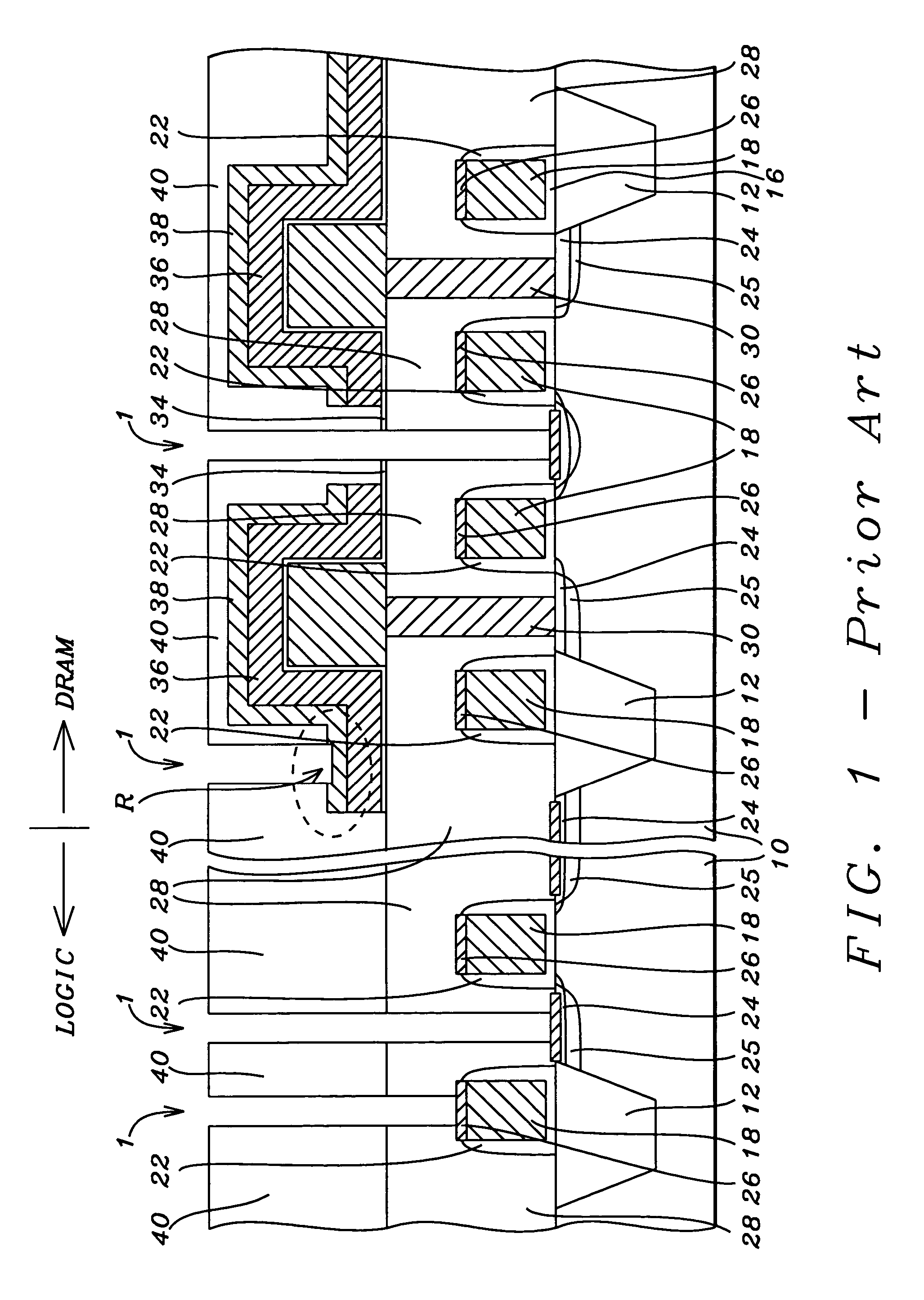

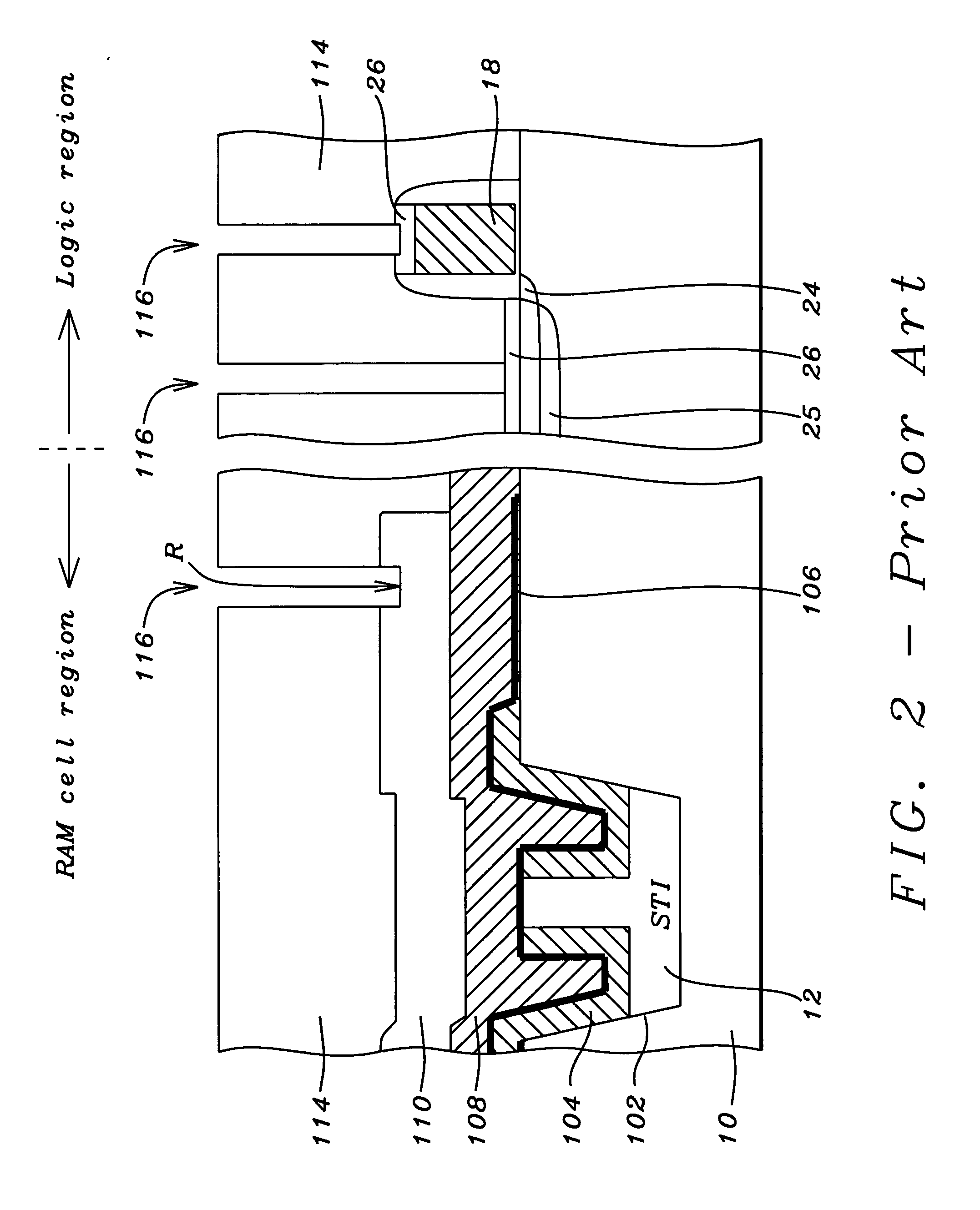

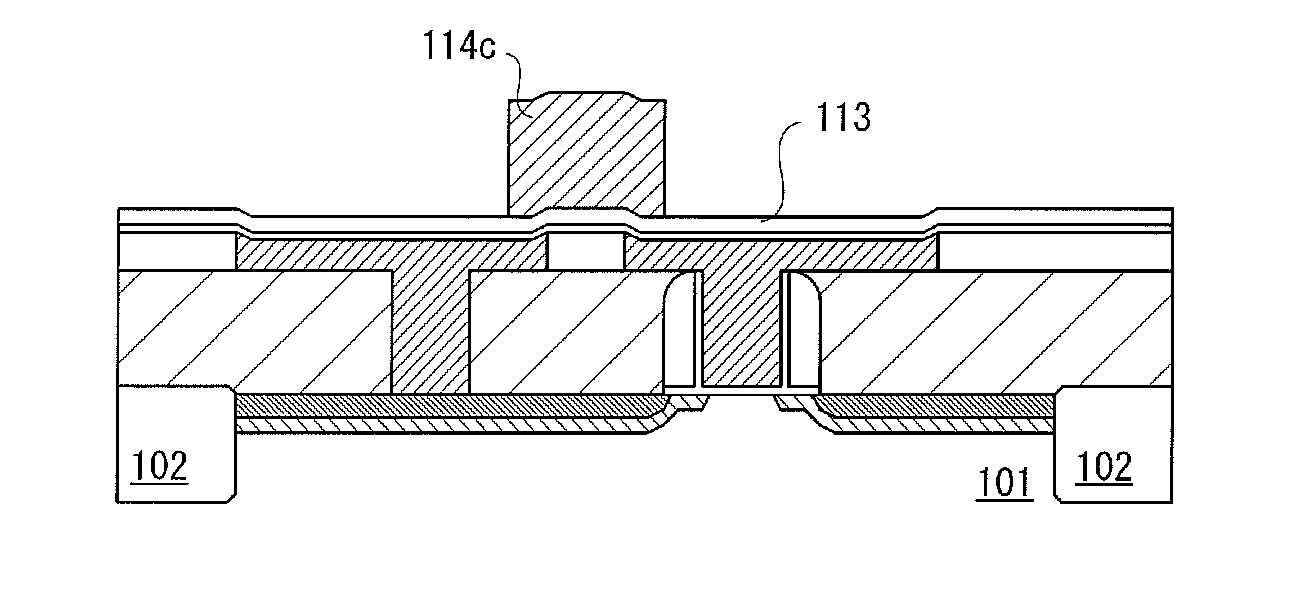

Structure for reducing leakage currents and high contact resistance for embedded memory and method for making same

ActiveUS20050093147A1More alignment toleranceReduce manufacturing costTransistorSemiconductor/solid-state device detailsDrain currentCapacitor

A method for fabricating an insulating layer having contact openings of varying depths for logic / DRAM circuits is achieved using a single mask and etch step. After forming stacked or trench capacitors, a planar insulating layer is formed. Contact openings are etched in the planar insulating layer to the substrate, and contact openings that extend over the edge of the stacked or trench capacitor top electrode, having an ARC, are etched using a novel mask design and a single etching step. This allows one to make contacts to the substrate without overetching while making low-resistance contacts to the sidewall of the capacitor top electrode. In the trench capacitor open areas are formed to facilitate making contact openings that extend over the top electrode. A series of contact openings that are skewed or elongated also improve the latitude in alignment tolerance.

Owner:TAIWAN SEMICON MFG CO LTD

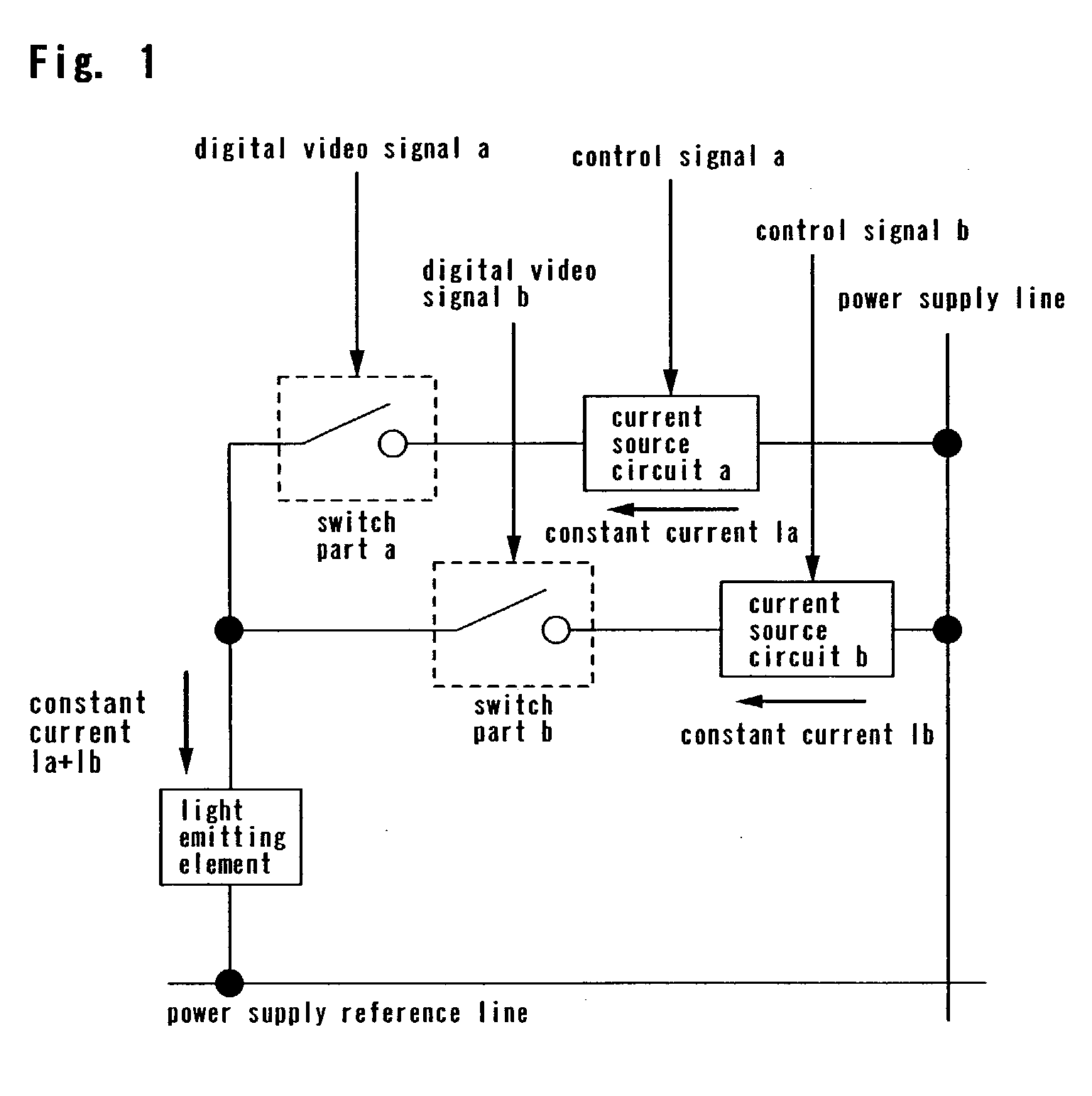

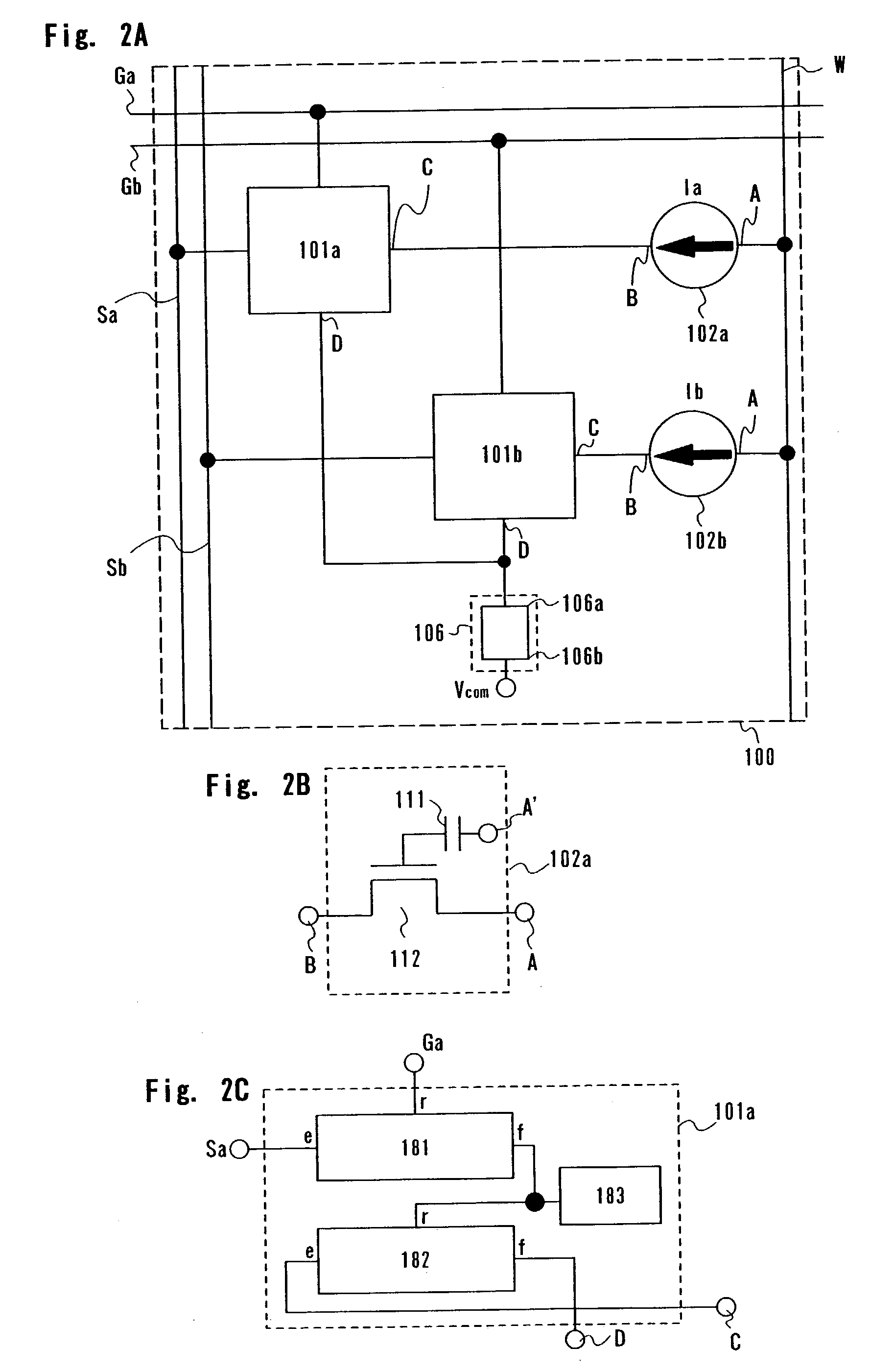

Display apparatus and driving method thereof

InactiveUS7474285B2Suppress mutationReduce variationStatic indicating devicesDigital videoEngineering

This invention provides a display apparatus in which it is possible to have a light emitting element emitted light with constant luminance without coming under the influence of deterioration over time, and it is possible to realize accurate gray scale express, and yet, it is possible to speed up writing of a signal current to each pixel, and influence of noise of a leak current etc. is suppressed, and a driving method thereof. A plurality of pairs of switch parts and current source circuits are disposed in each pixel. Switching of each of a plurality of the switch parts is controlled by a digital video signal. When the switch part is turned on, by a current supplied from the current source circuit making a pair with the switch part, the light emitting element emits light. A current which is supplied from one current source circuit to the light emitting element is constant. A value of a current flowing through the light emitting element is comparable to a value of added currents which are supplied to the light emitting element from respective all current source circuits making pairs with the switch parts which are in the conductive states.

Owner:SEMICON ENERGY LAB CO LTD

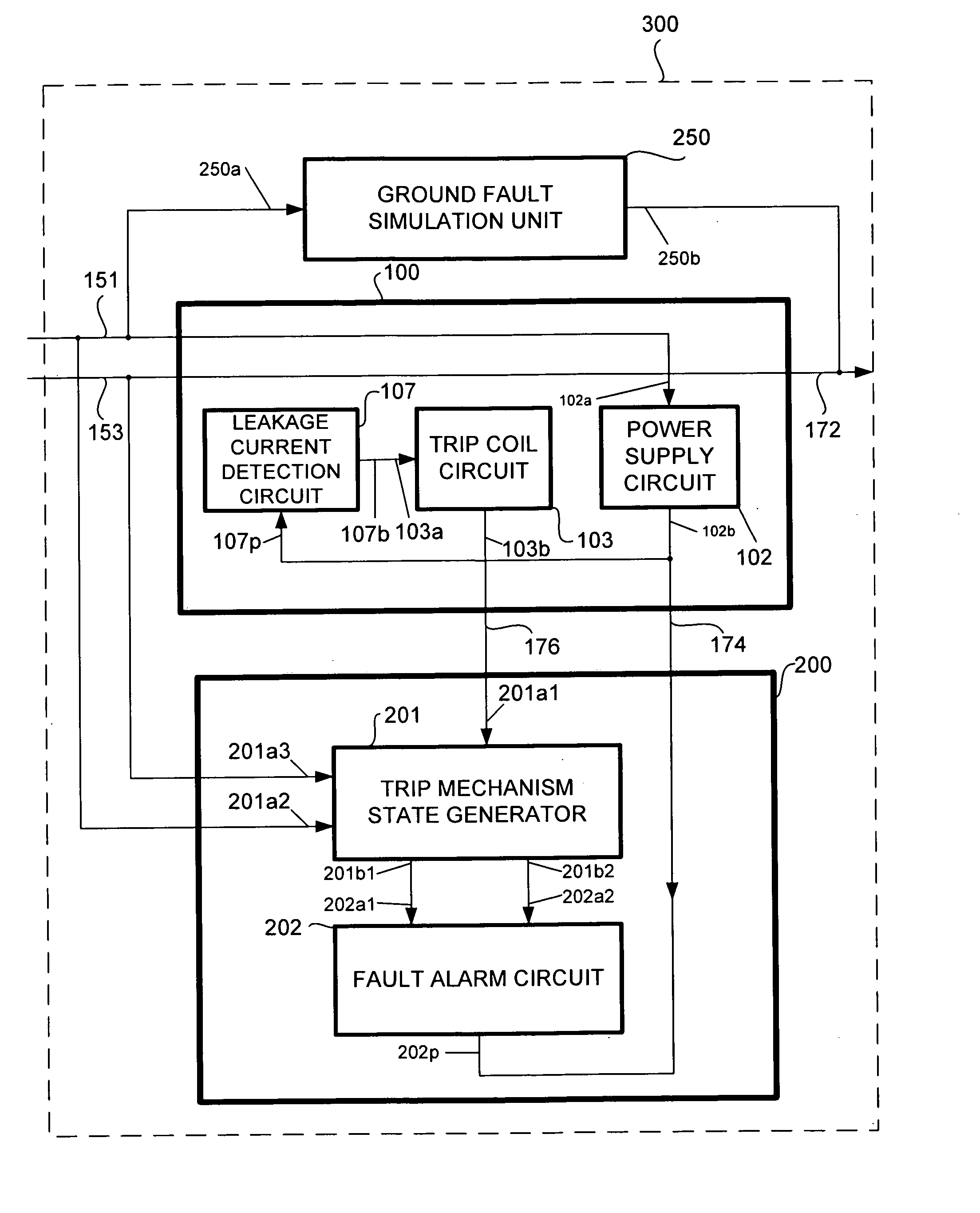

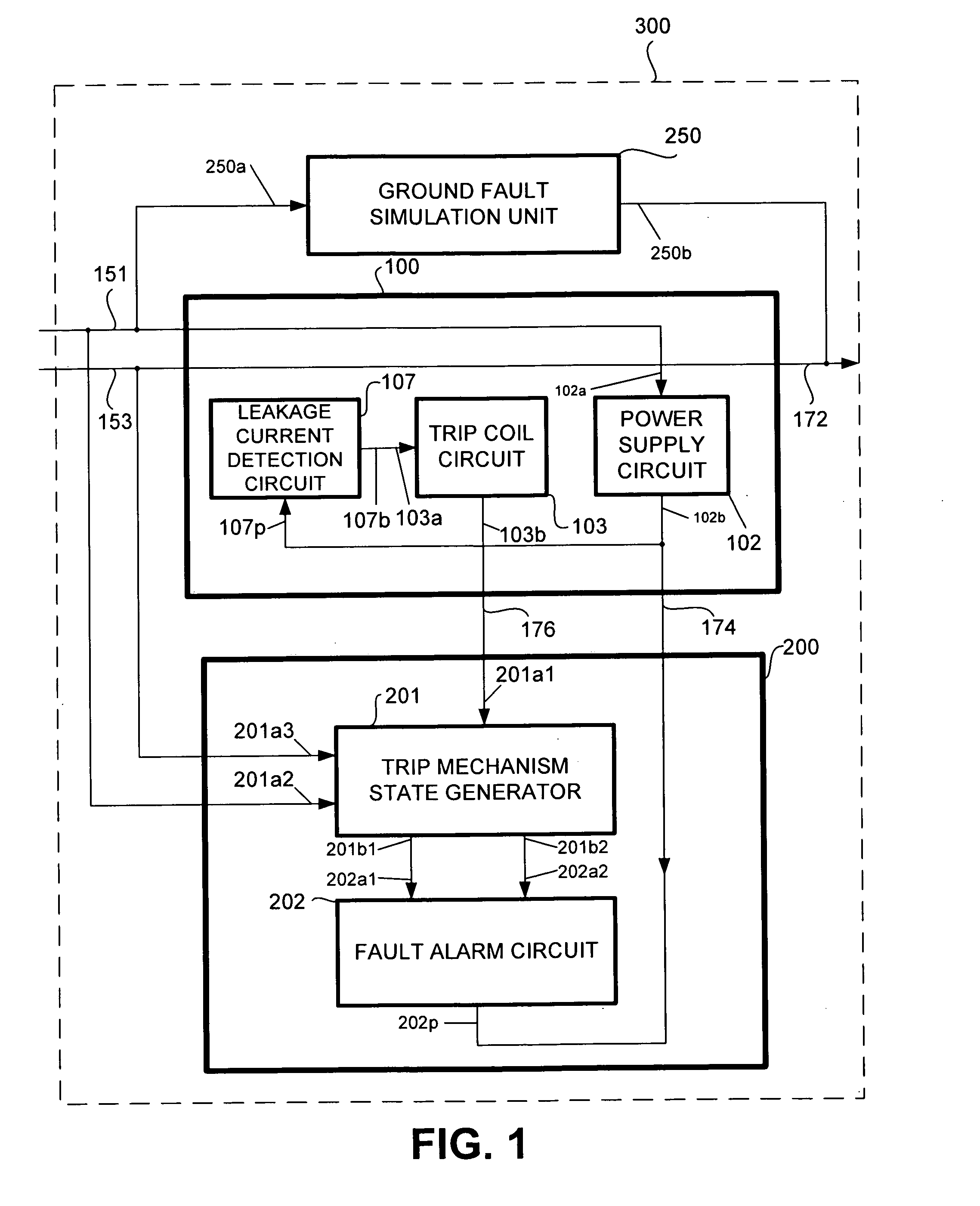

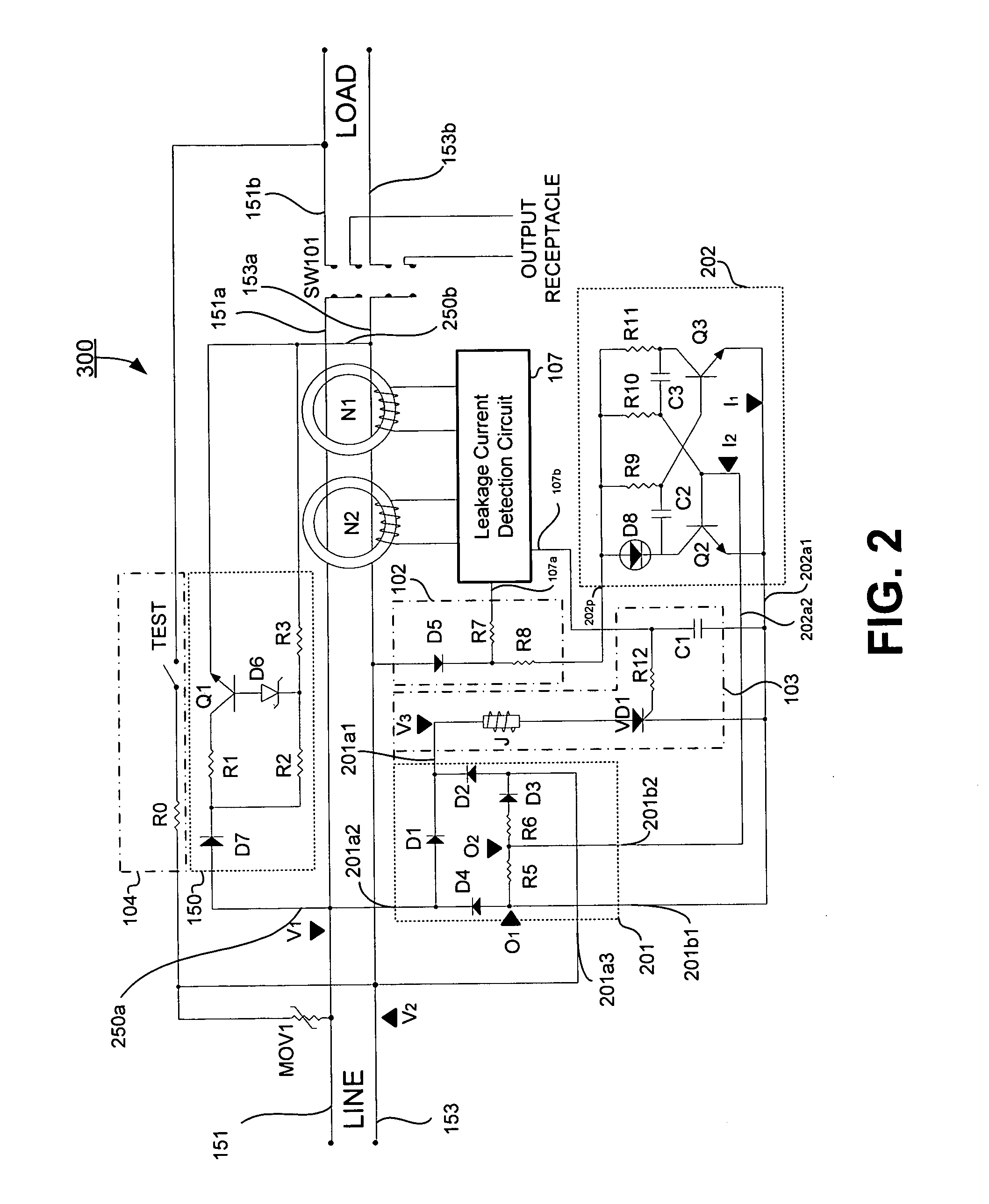

Intelligent life testing methods and apparatus for leakage current protection

ActiveUS20070164750A1Short-circuit testingEmergency protective arrangements for automatic disconnectionEngineeringLife testing

An apparatus for testing the life of a leakage current protection device having a leakage current detection circuit. In one embodiment, the apparatus a trip mechanism state generator, a fault alarm generator, a ground fault simulation unit. In operation, the ground fault simulation unit generates a simulated ground fault signal during every positive half-wave of an AC power, the simulated ground fault signal is detected by the leakage current detection circuit, the leakage current detection circuit responsively generates a signal to turn a switching device into its conductive state so as to allow a current to pass therethrough, the passed current is converted into a DC voltage in accordance with a trip mechanism state generated by the trip mechanism state generator, the fault alarm circuit receives and analyzes the DC voltage and indicates whether a fault exists in the leakage current protection device.

Owner:CHEN HENG

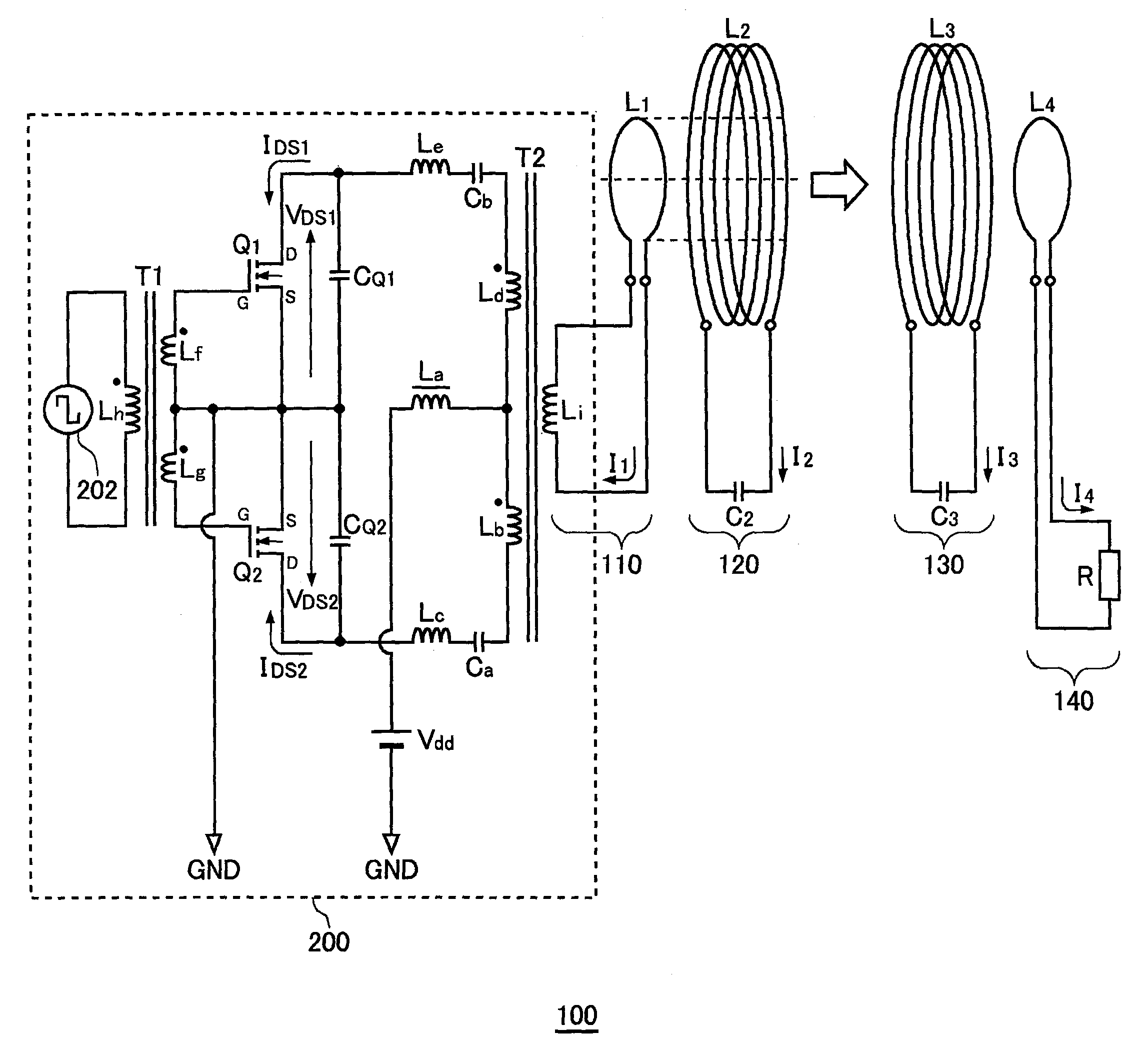

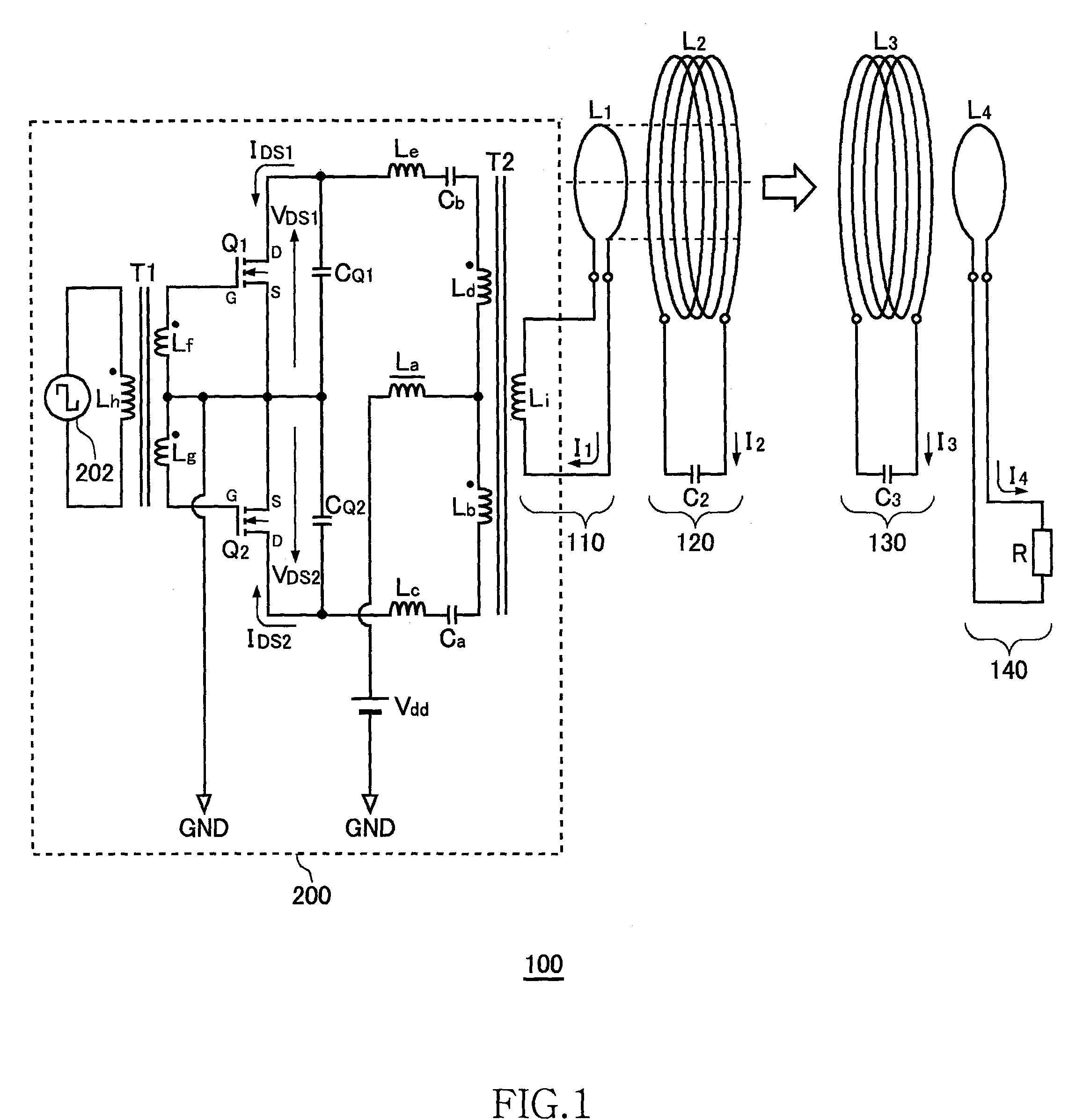

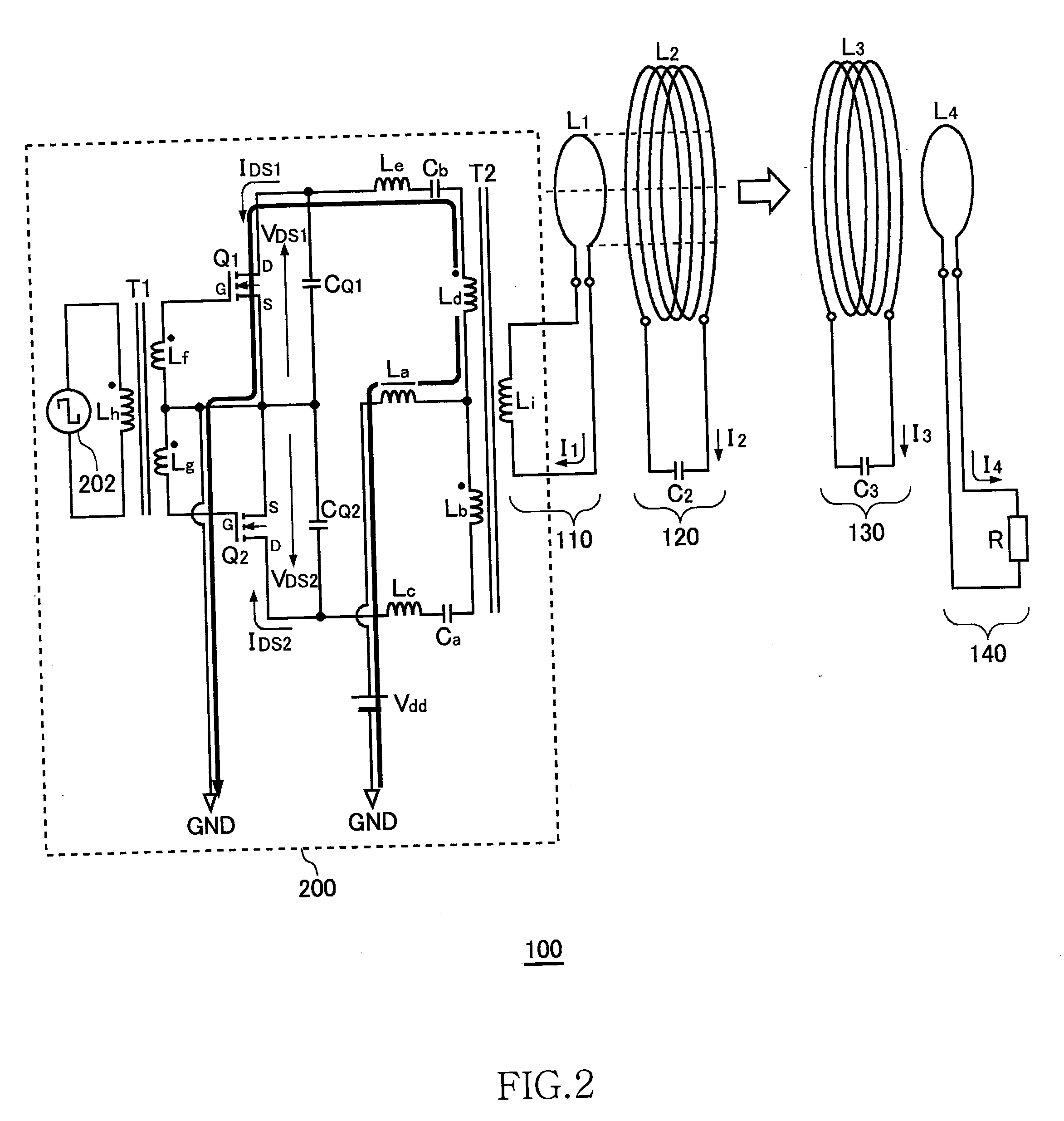

Wireless power feeder and wireless power transmission system

InactiveUS20110049997A1Improve efficiencySuppressing influence on the resonance characteristics of the feeding coilElectromagnetic wave systemTransformersPhase differenceResonance

Power is transmitted from a feeding coil L2 to a receiving coil L2 by magnetic resonance. A power circuit 200 turns ON / OFF switching transistors Q1 and Q2 to feed AC current to an exciting circuit 110, whereby the AC power is fed from an exciting coil L1 to a feeding coil L2. A phase detection circuit 150 sets the switching transistor Q2 of the power circuit 200 as a measurement target and detects the phase difference between source-drain current IDS2 and source-drain voltage VDS2 from the current phase and voltage phase thereof.

Owner:TDK CORPARATION

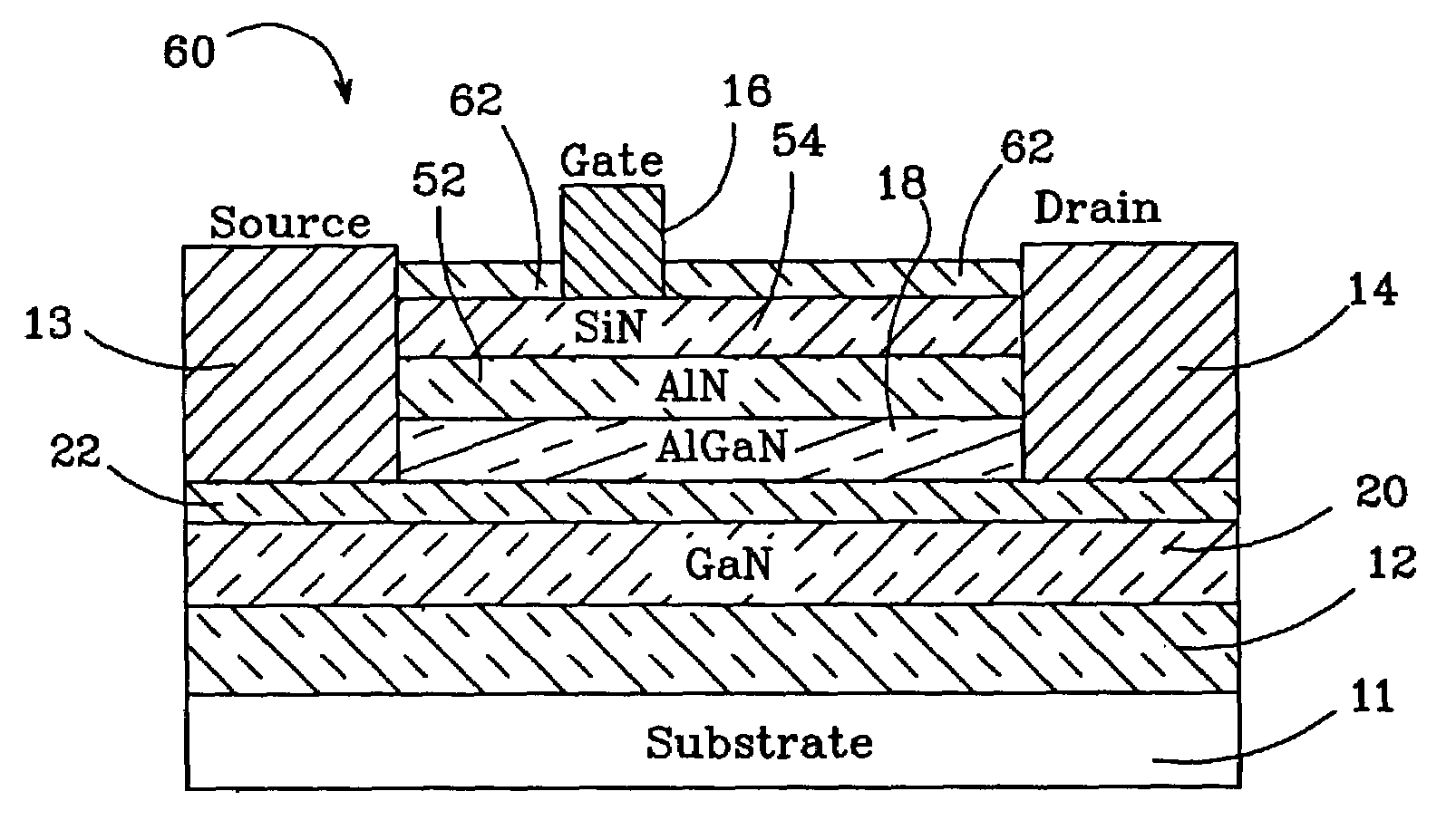

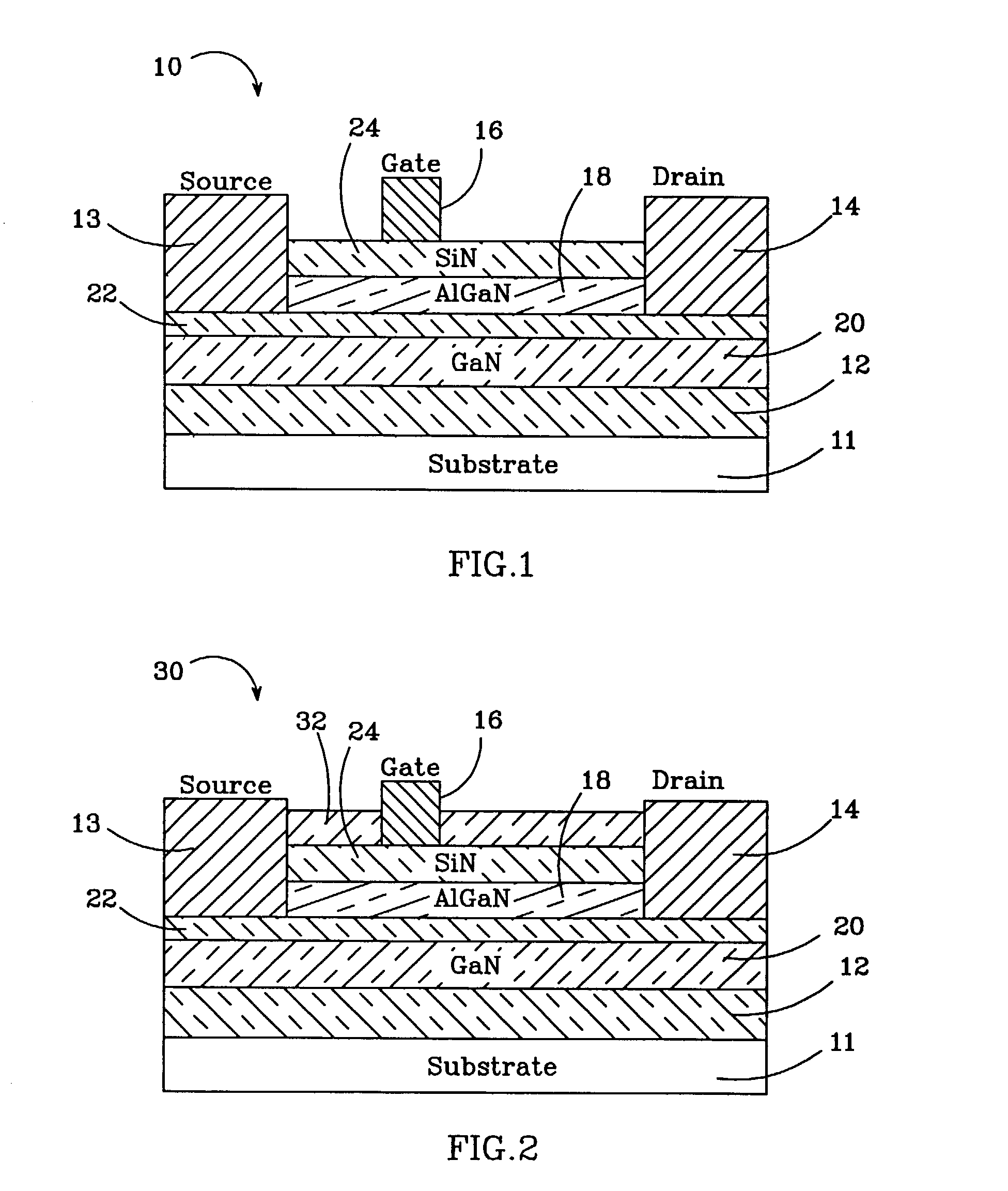

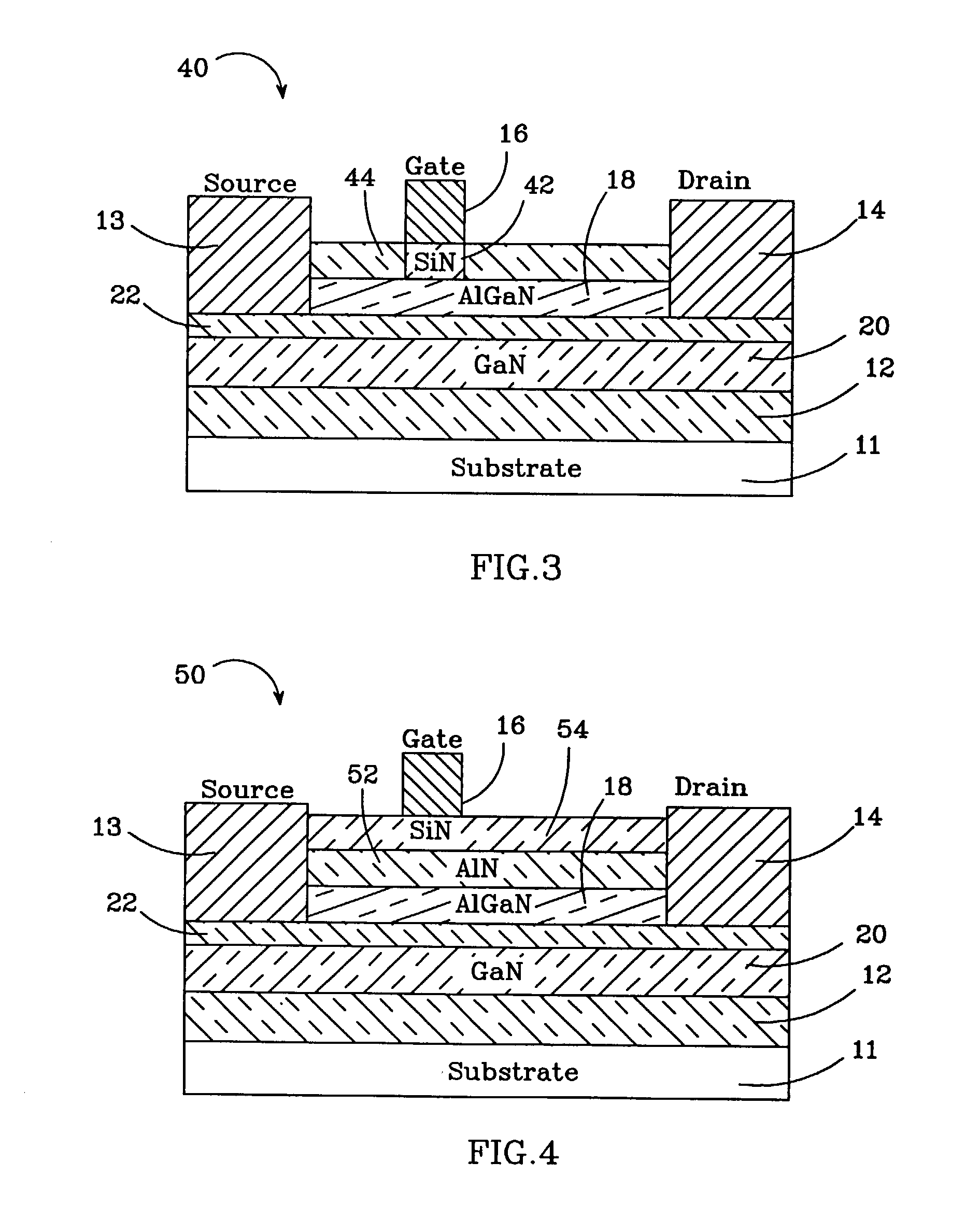

Insulating gate AlGaN/GaN HEMT

InactiveUS7230284B2Reduce trappingReduce gate leakageSemiconductor/solid-state device detailsSolid-state devicesGate leakage currentDriving current

AlGaN / GaN HEMTs are disclosed having a thin AlGaN layer to reduce trapping and also having additional layers to reduce gate leakage and increase the maximum drive current. One HEMT according to the present invention comprises a high resistivity semiconductor layer with a barrier semiconductor layer on it. The barrier layer has a wider bandgap than the high resistivity layer and a 2DEG forms between the layers. Source and drain contacts contact the barrier layer, with part of the surface of the barrier layer uncovered by the contacts. An insulating layer is included on the uncovered surface of the barrier layer and a gate contact is included on the insulating layer. The insulating layer forms a barrier to gate leakage current and also helps to increase the HEMT's maximum current drive. The invention also includes methods for fabricating HEMTs according to the present invention. In one method, the HEMT and its insulating layer are fabricated using metal-organic chemical vapor deposition (MOCVD). In another method the insulating layer is sputtered onto the top surface of the HEMT in a sputtering chamber.

Owner:CREE INC

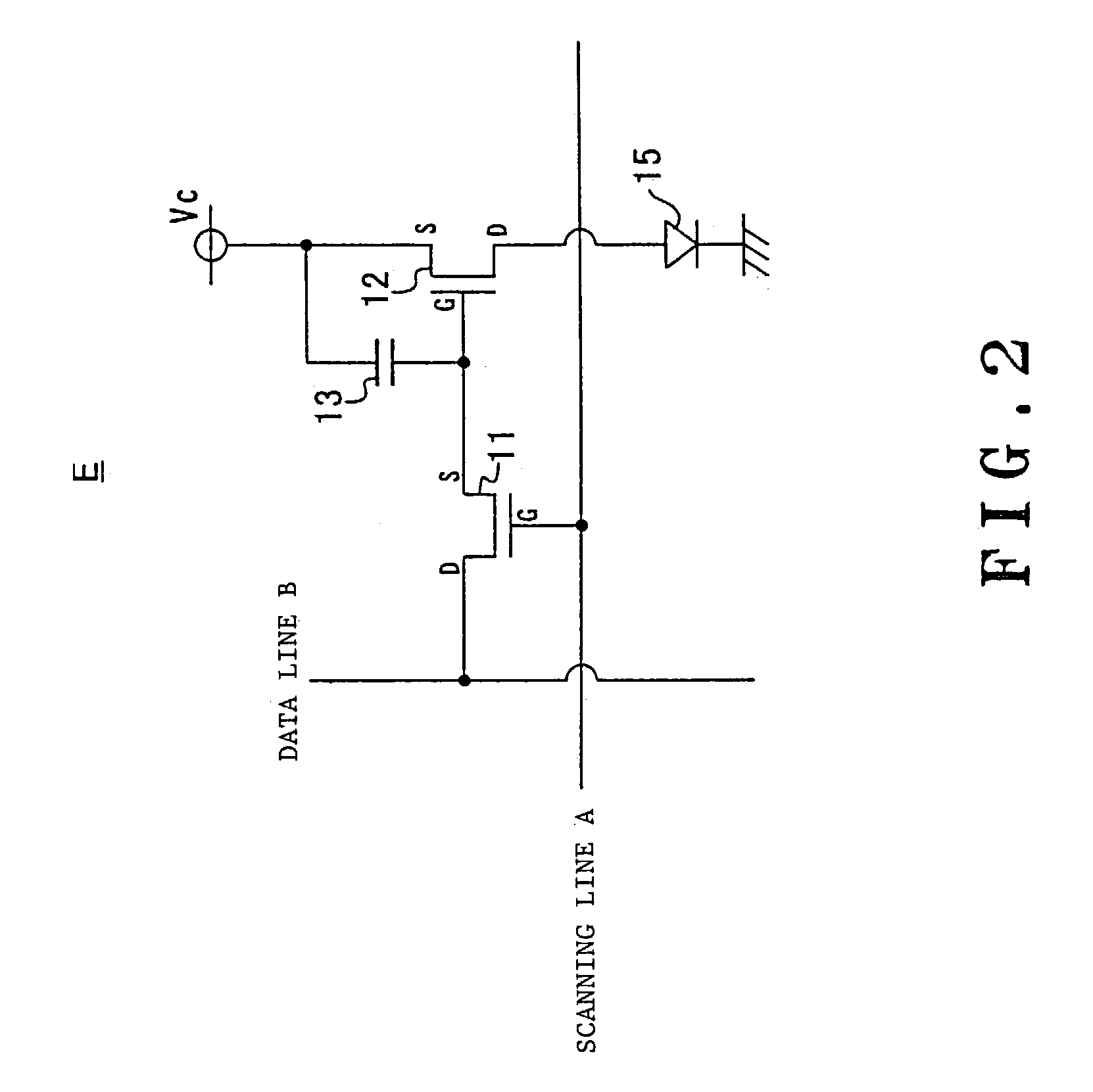

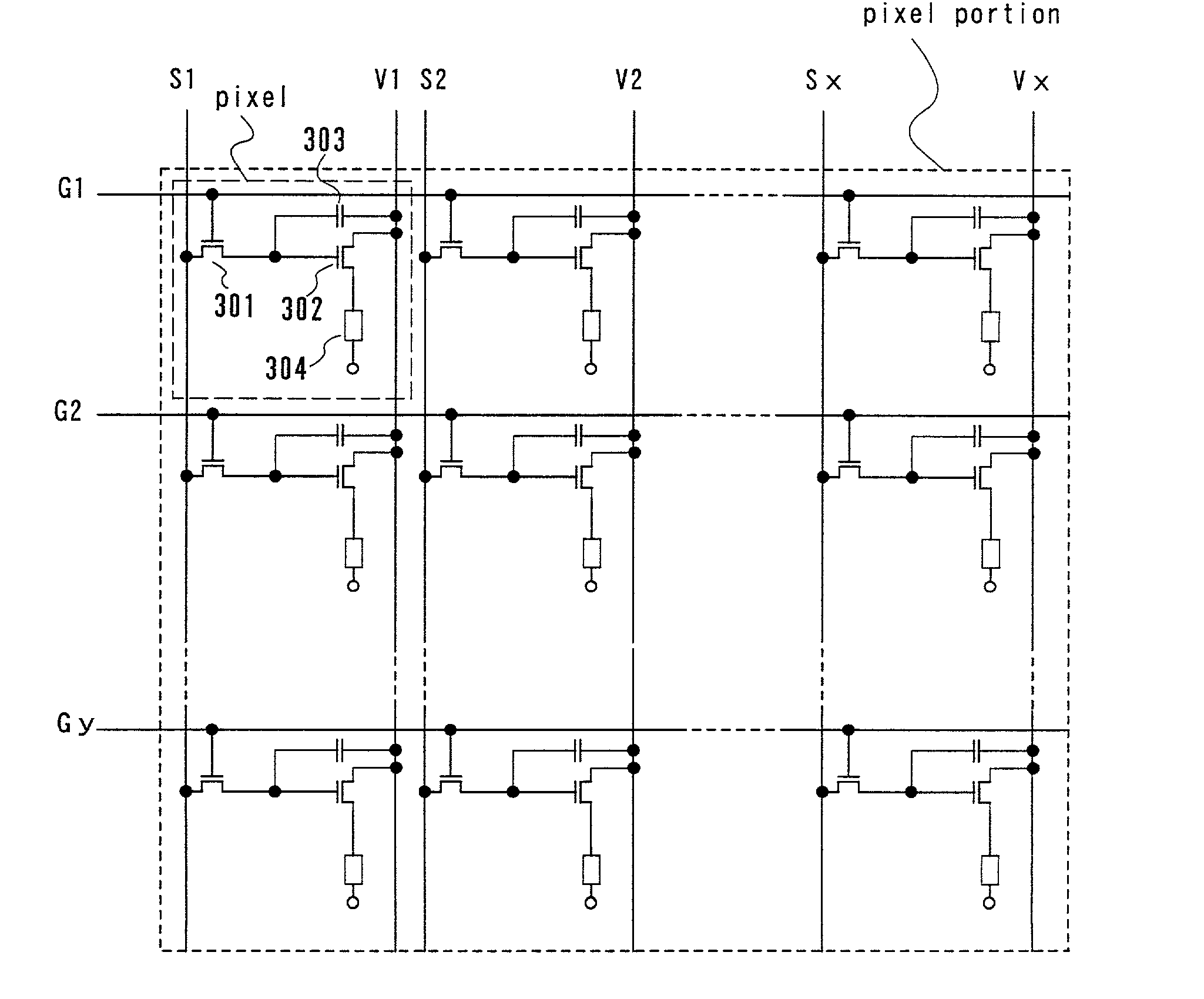

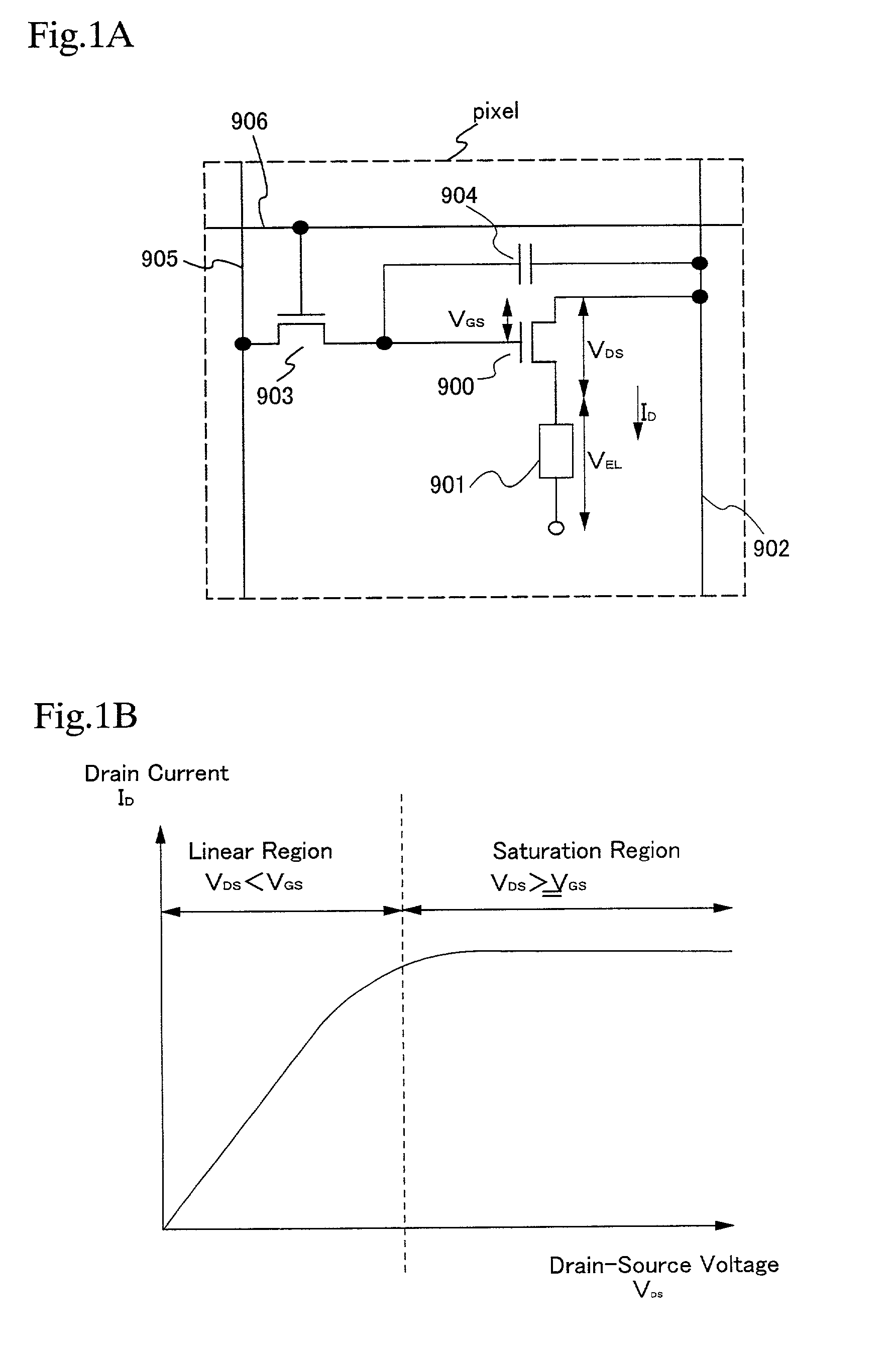

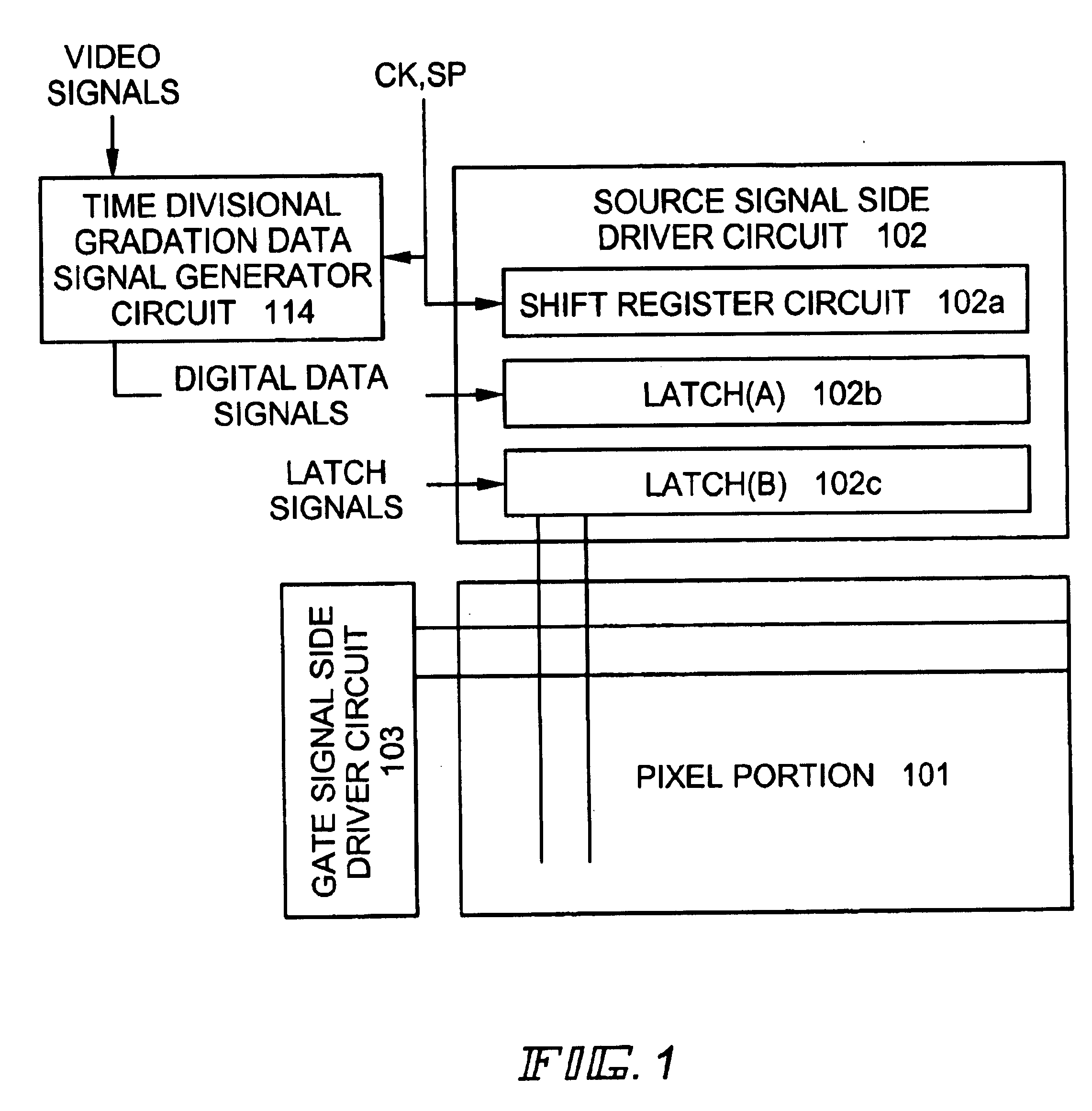

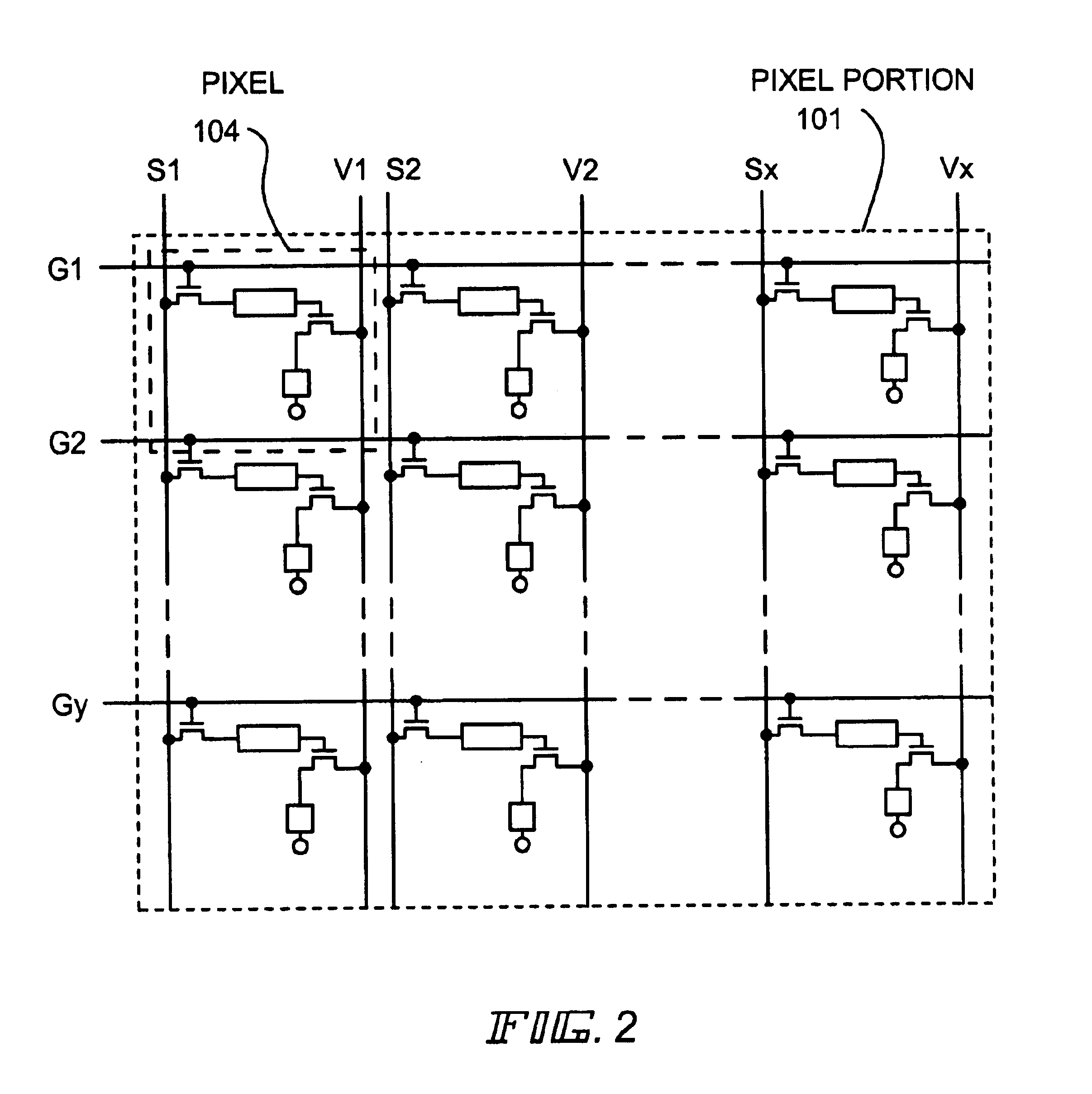

Method of driving display device

An active matrix type EL display device is provided, which is capable of suppressing the unevenness of luminance display due to the unevenness of the characteristics of TFTs which constitute pixels, or due to variations in the environmental temperature at which the display device is used. The active matrix type EL display is driven by a time gray scale method, and is capable of keeping the drain current of each of its EL driving TFTs constant by operating each of the EL driving TFTs in a saturation region in an ON state. Accordingly, constant current can be made to flow in each of the EL elements, whereby it is possible to provide an active matrix type EL display device with accurate gray scale display and high image quality.

Owner:SEMICON ENERGY LAB CO LTD

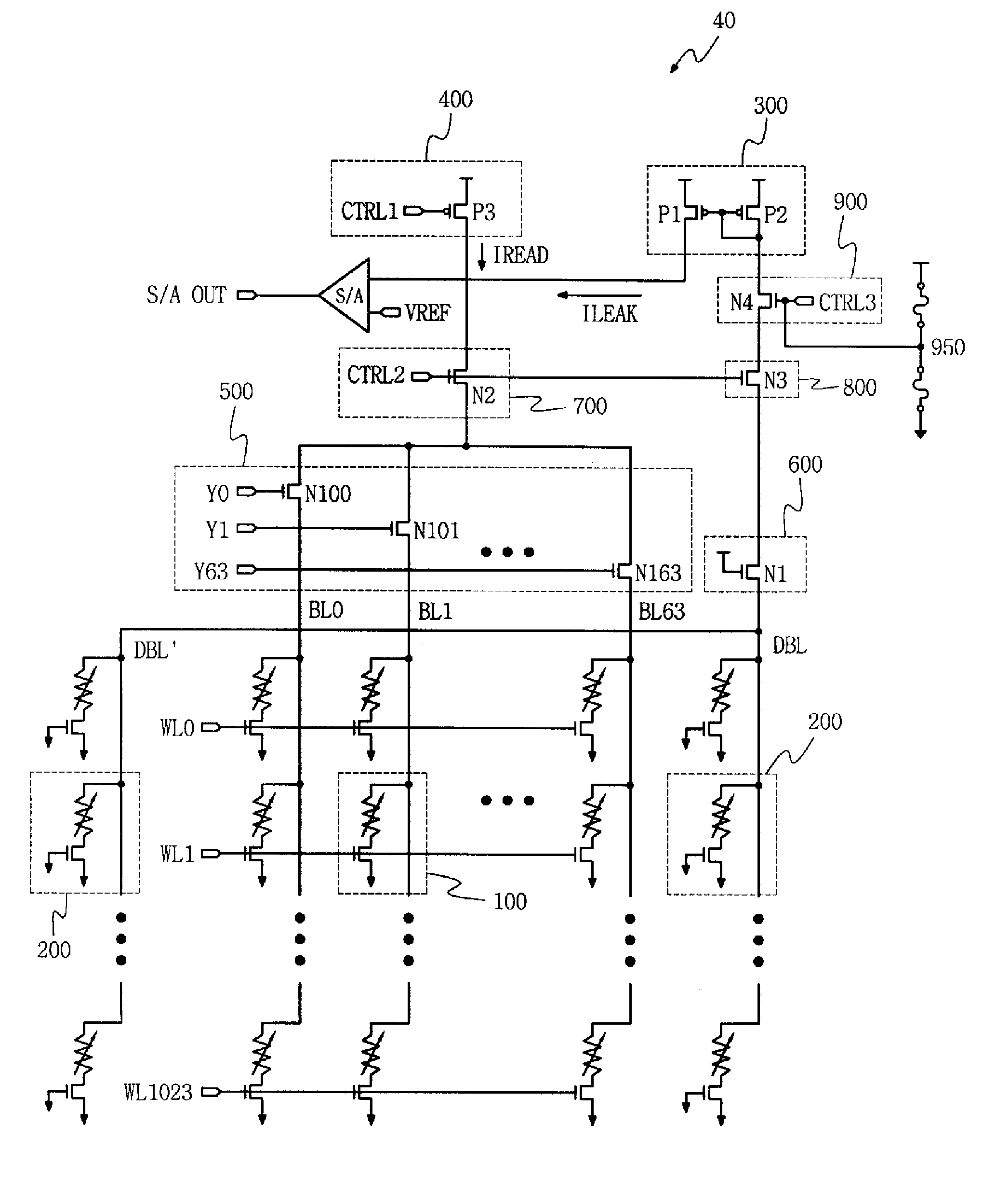

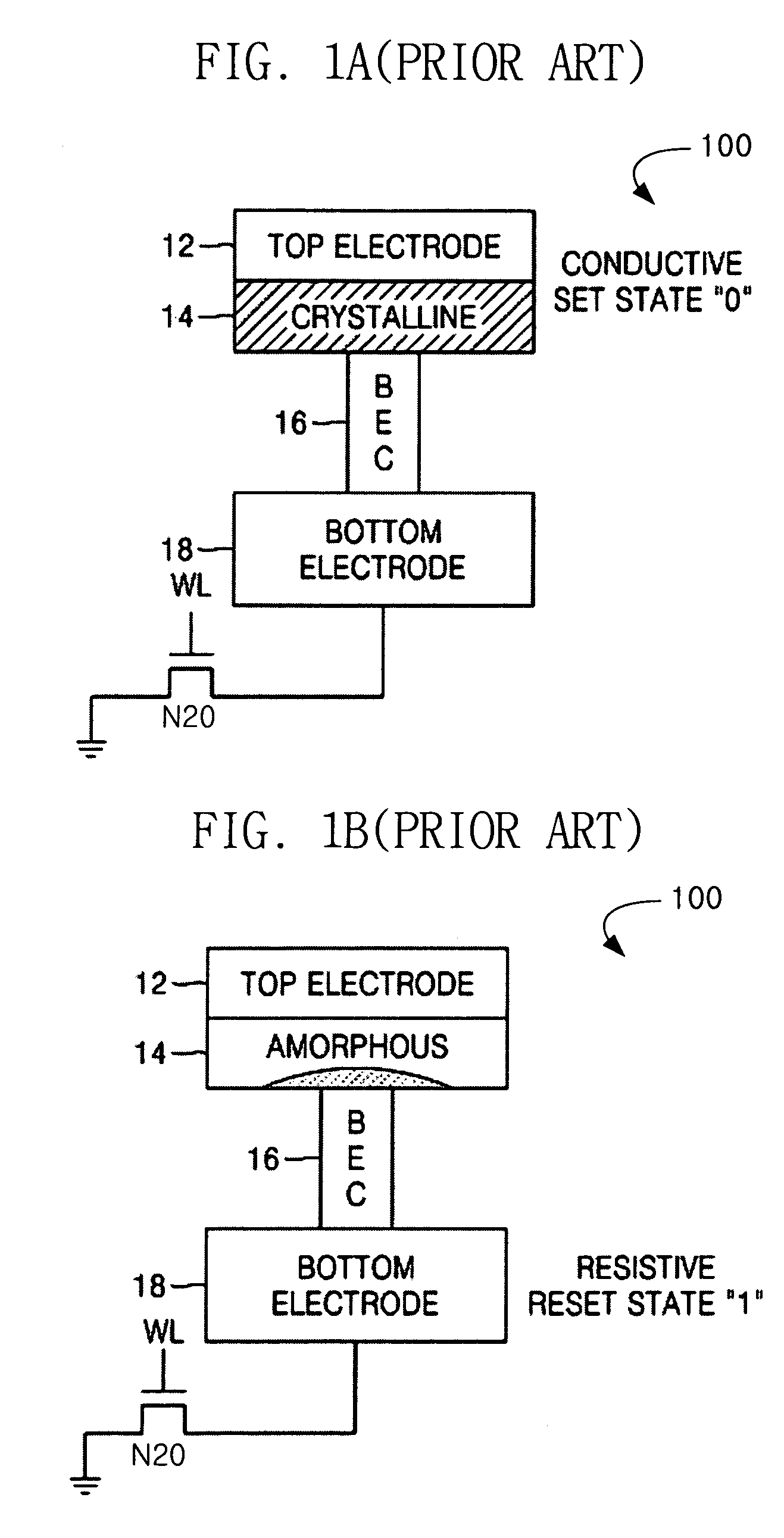

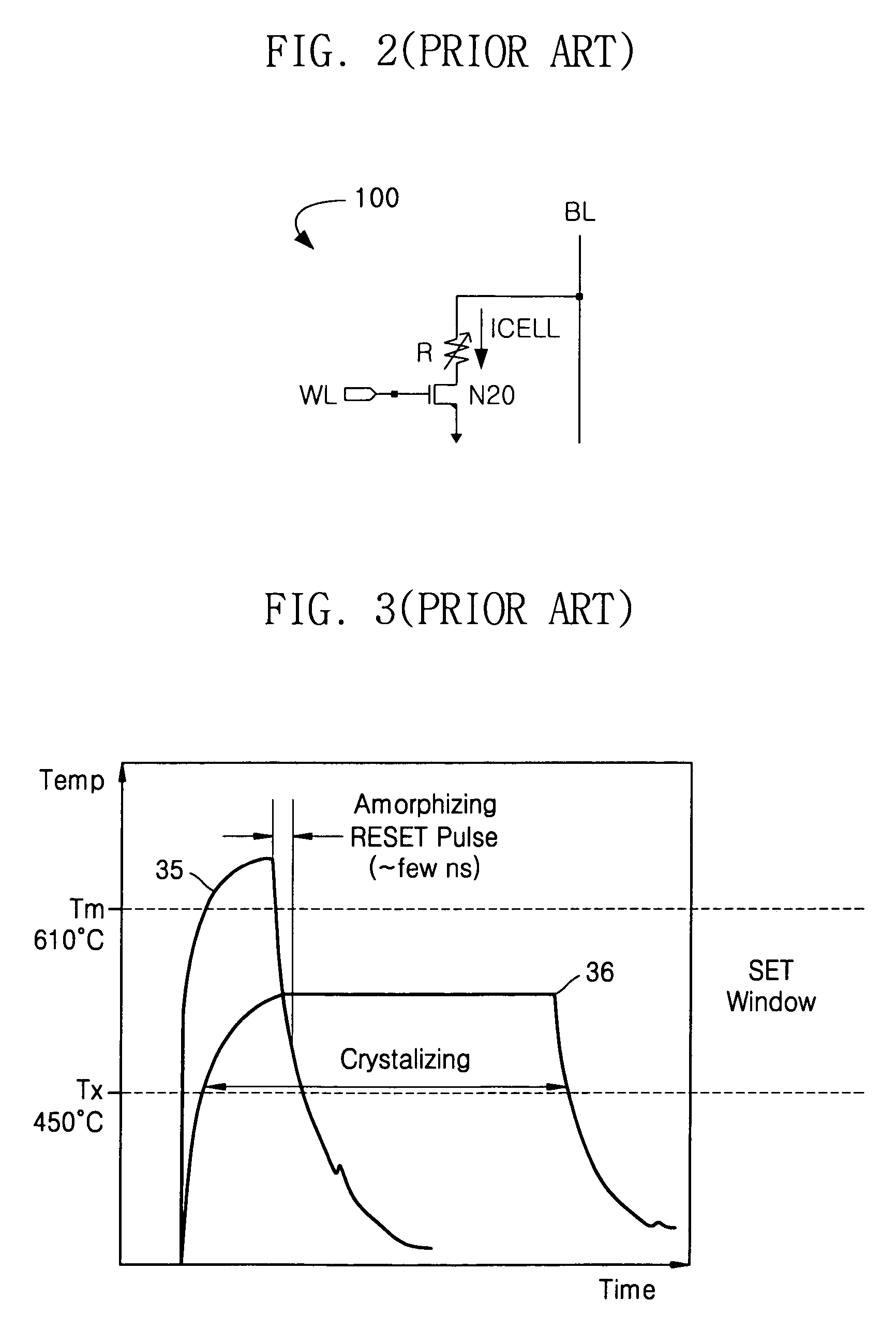

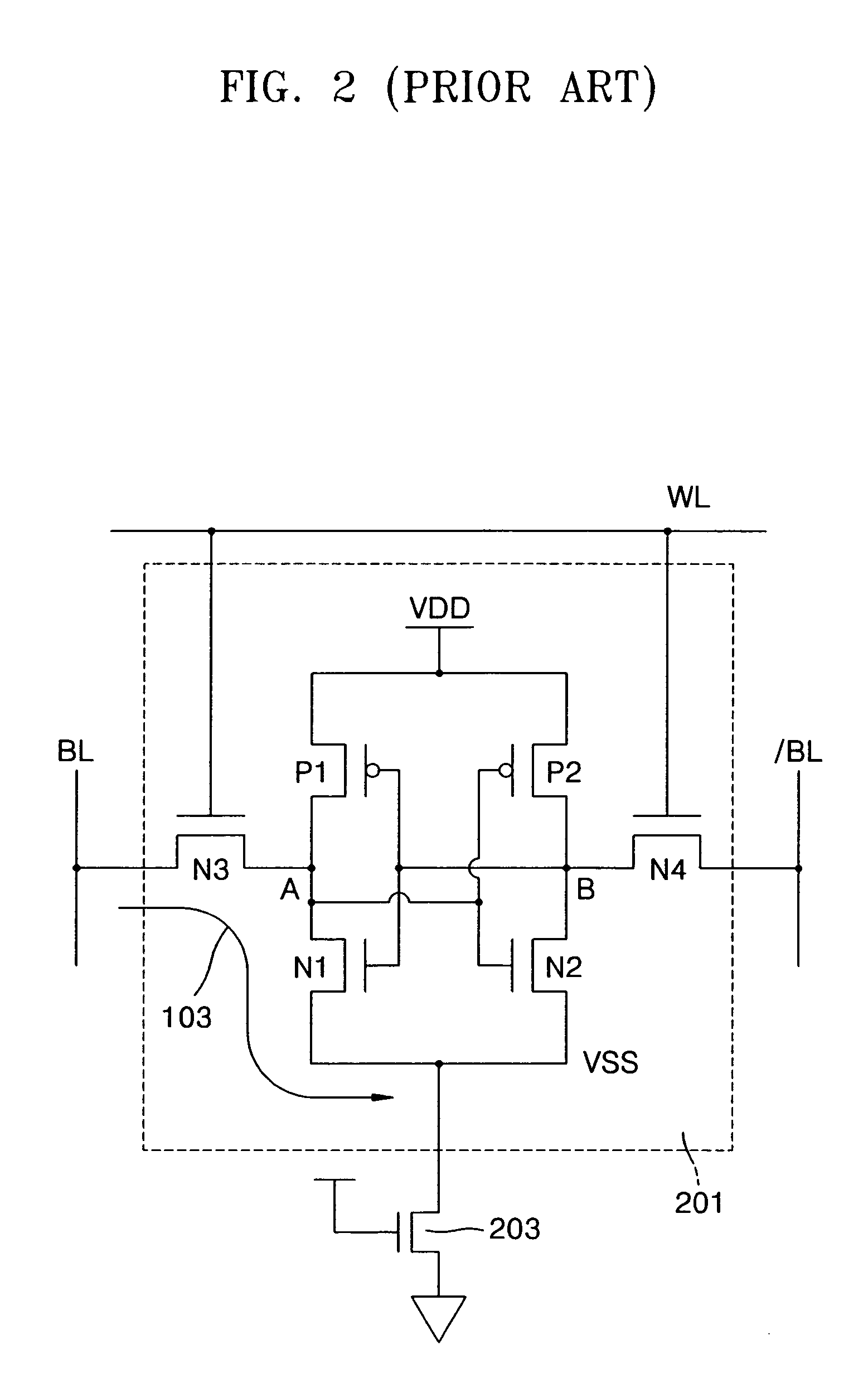

Semiconductor memory device capable of compensating for leakage current

ActiveUS7248494B2Convenient and highly integratedReduce power consumptionDigital storageBit linePhase-change memory

A semiconductor memory device compensates leakage current. A plurality of memory cells is disposed at intersections of word lines and bit lines. A plurality of dummy cells is connected to at least one dummy bit line. A leakage compensation circuit is connected to the at least one dummy bit line that outputs a leakage compensation current to at least one of the bit lines. A read current supply circuit outputs a read current necessary for a read operation to at least one of the bit lines in response to a first control signal. The memory device is a phase-change memory device containing phase-change material. The semiconductor memory device compensates leakage current in a read operation and supplies the leakage compensation current to a selected bit line, thereby suppressing error operation occurrence caused by leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

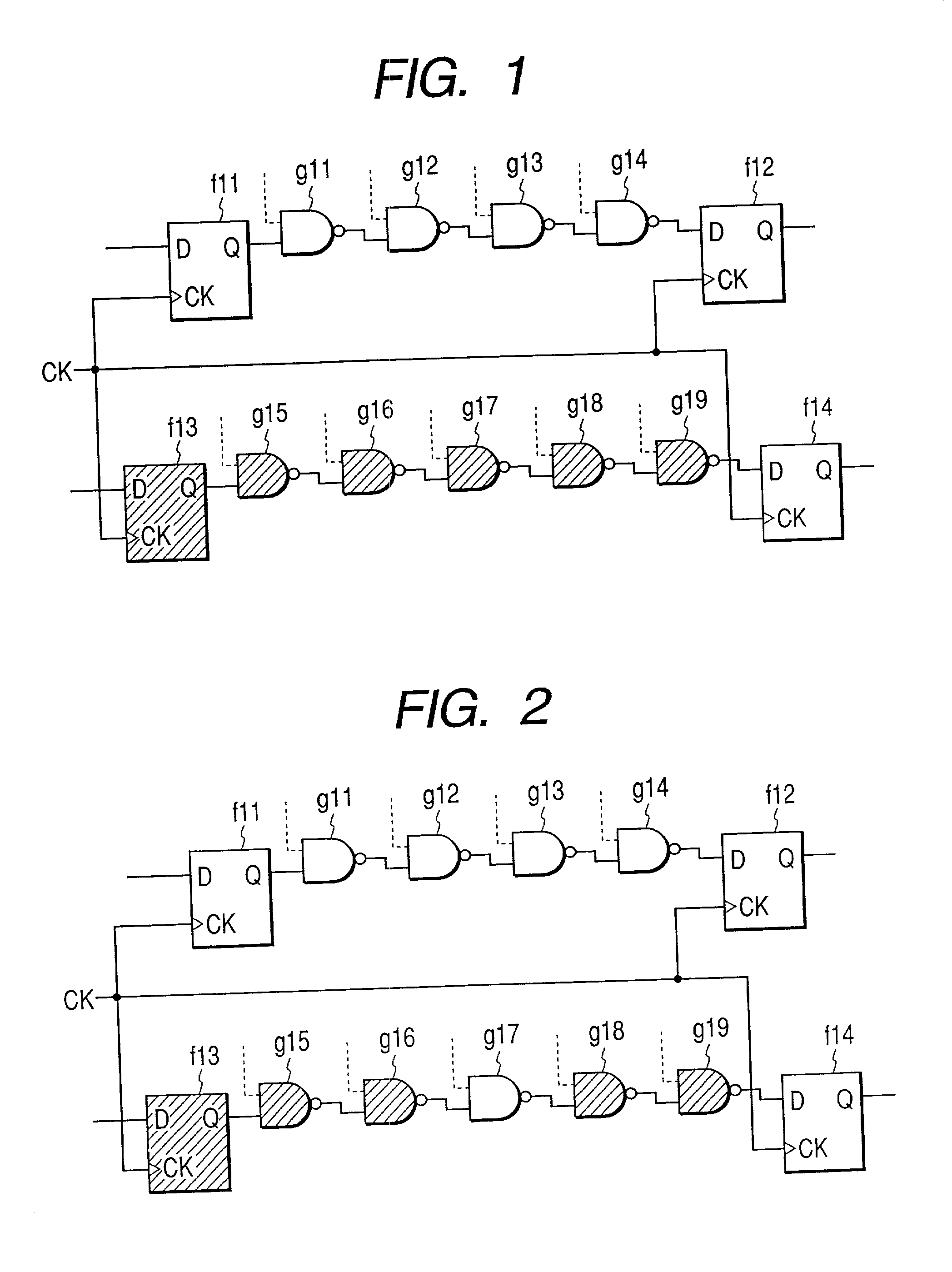

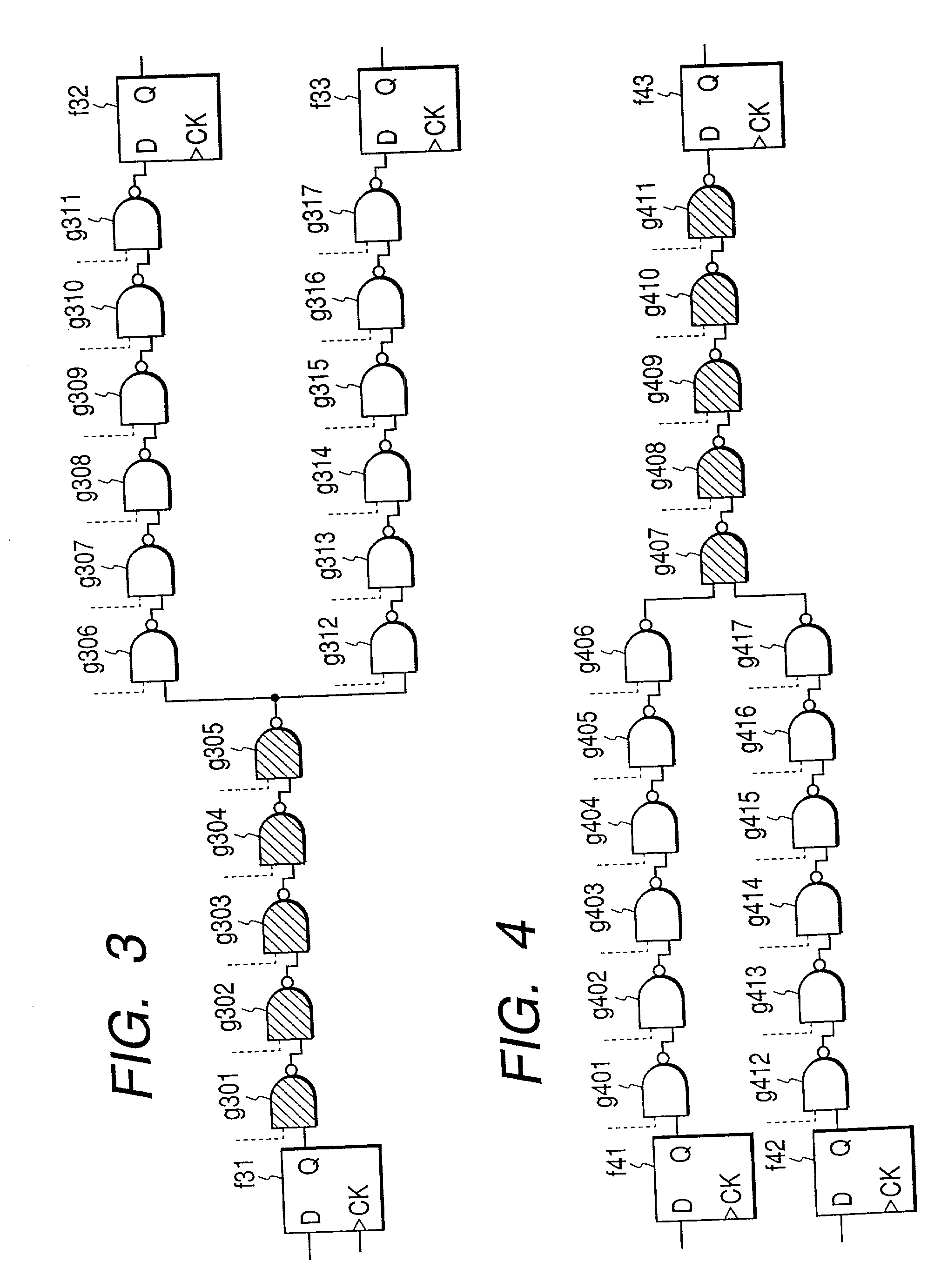

Semiconductor integrated circuit device, storage medium on which cell library is stored and designing method for semiconductor integrated circuit

InactiveUS20020079927A1Power reduction in field effect transistorsSolid-state devicesMOSFETDrain current

Owner:RENESAS ELECTRONICS CORP

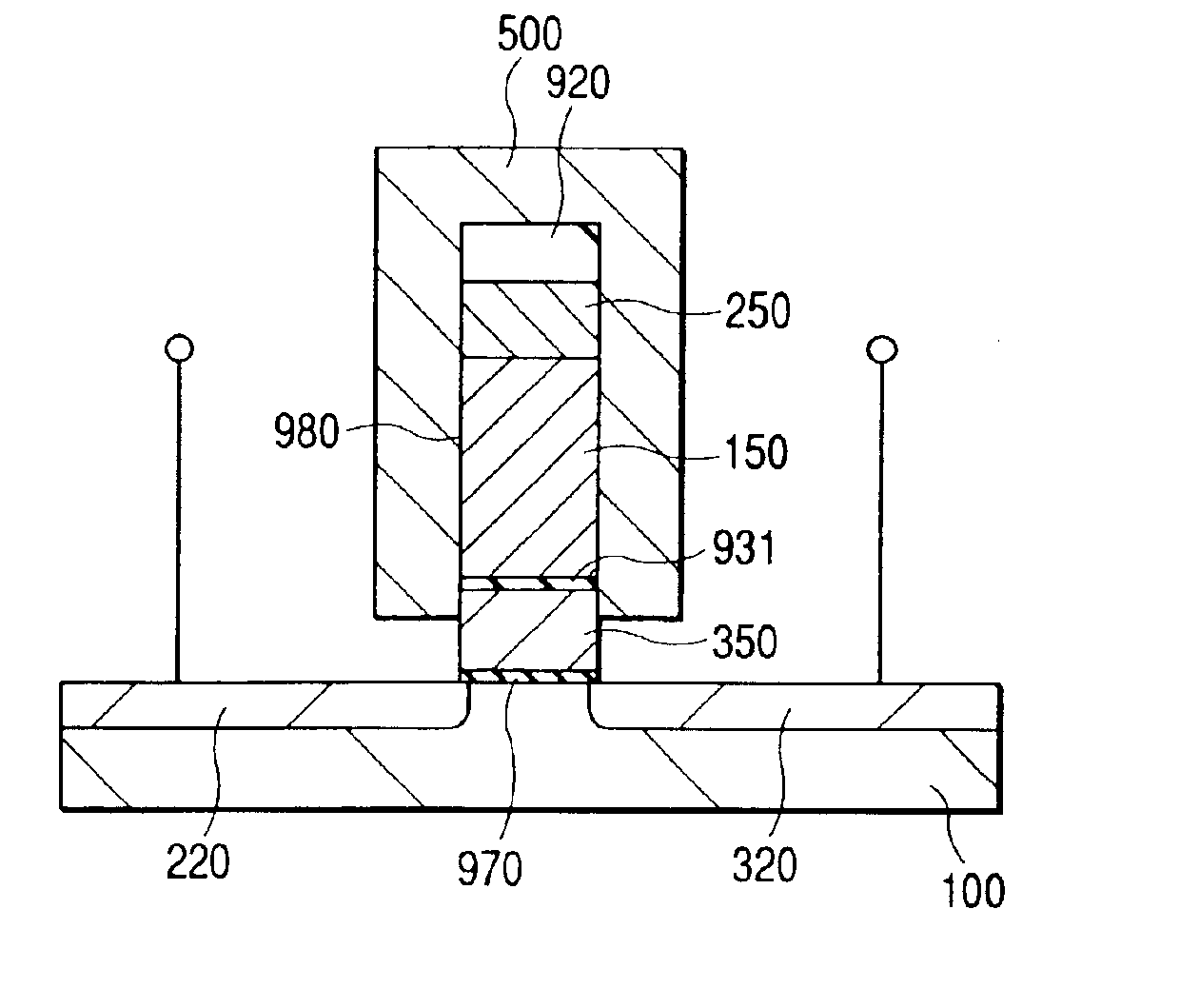

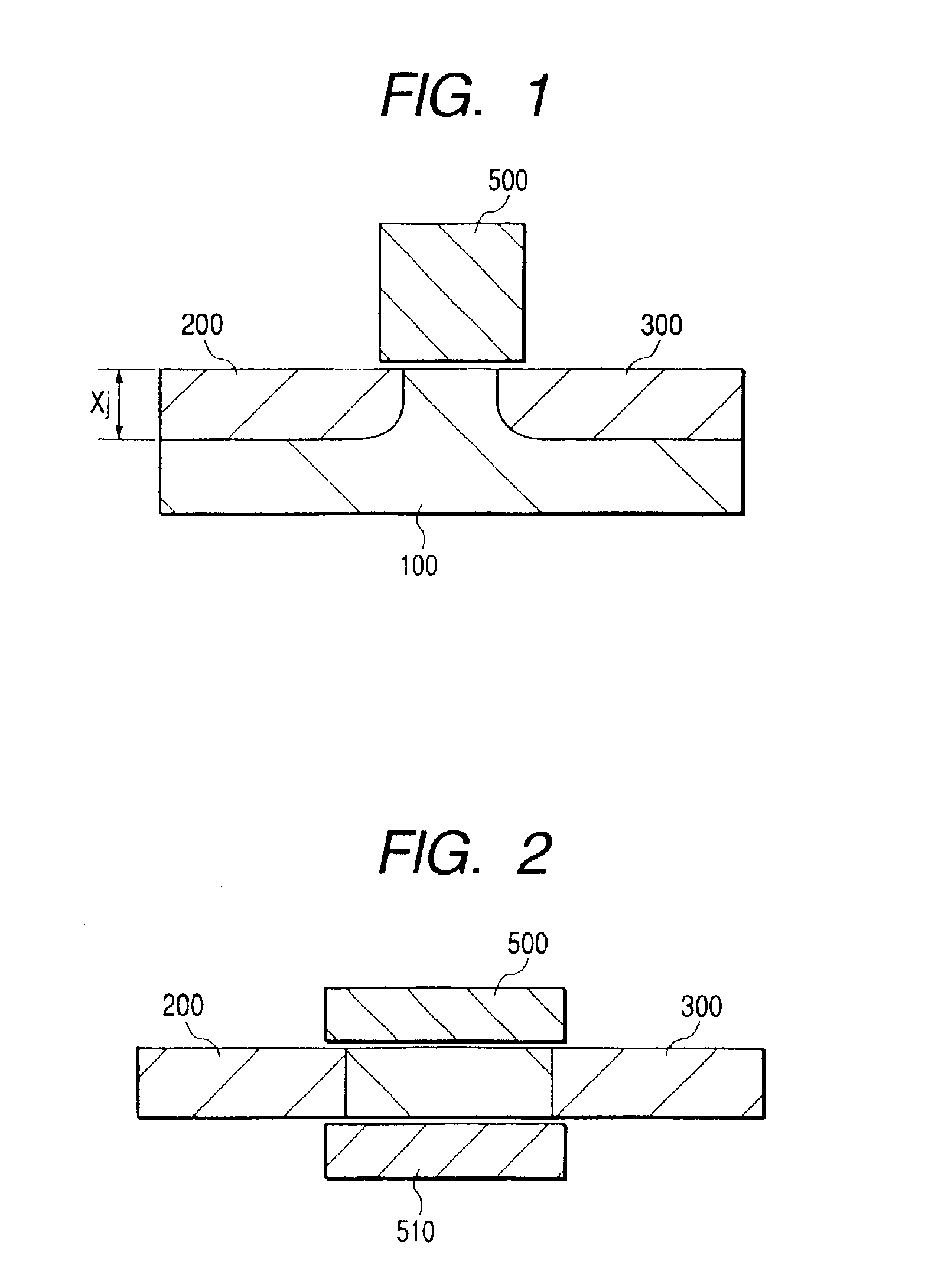

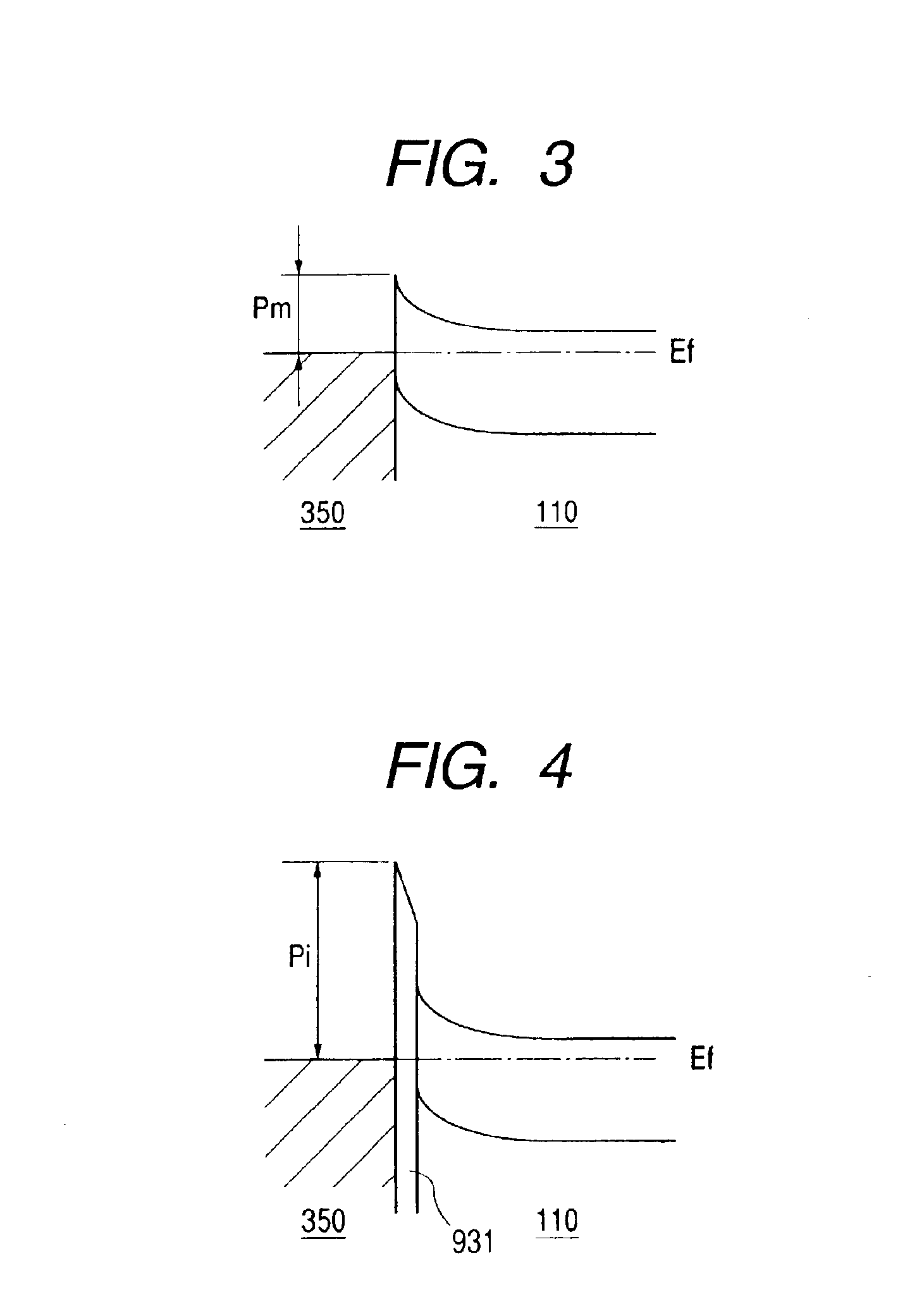

Vertical semiconductor device with tunnel insulator in current path controlled by gate electrode

InactiveUS6873009B2Suppress lowering of driving forceLower average currentTransistorSolid-state devicesGate leakage currentJunction leakage

It is an object of the present invention to provides a field effect transistor with extremely low leakage current. It is another object of the invention to provide a semiconductor memory device having an excellent information holding characteristic. It is a further object of the invention to provide a method for manufacturing in a simple manner a novel field effect transistor or semiconductor memory device with extremely low leakage current. According to a typical basic configuration of the present invention, a thin insulating film is inserted in a vertically disposed Schottky junction to form source and drain electrodes and a tunnel of the insulating film in the junction is controlled by a gate electrode. The gate electrode is disposed on each of both sides of a vertical channel, permitting a field effect to be exerted effectively on the junction, whereby a junction leakage in an OFF state can be made extremely low.

Owner:HITACHI LTD

Active matrix display with pixel memory

InactiveUS6765549B1Improve visibilityStatic indicating devicesSolid-state devicesDigital dataActive matrix

A display device capable of preventing a reduction of an electric charge stored in a gate electrode of an EL driver TFT, reduction due to a leak current of a switching TFT, and capable of preventing a reduction of the brightness of light emitted by an EL element is provided. One region of a source region and a drain region of a switching TFT is connected to an input side of an SRAM, and an output side of the SRAM and a gate electrode of the EL driver TFT are connected. The SRAM stores an input digital data signal until the next digital data signal is input.

Owner:SEMICON ENERGY LAB CO LTD

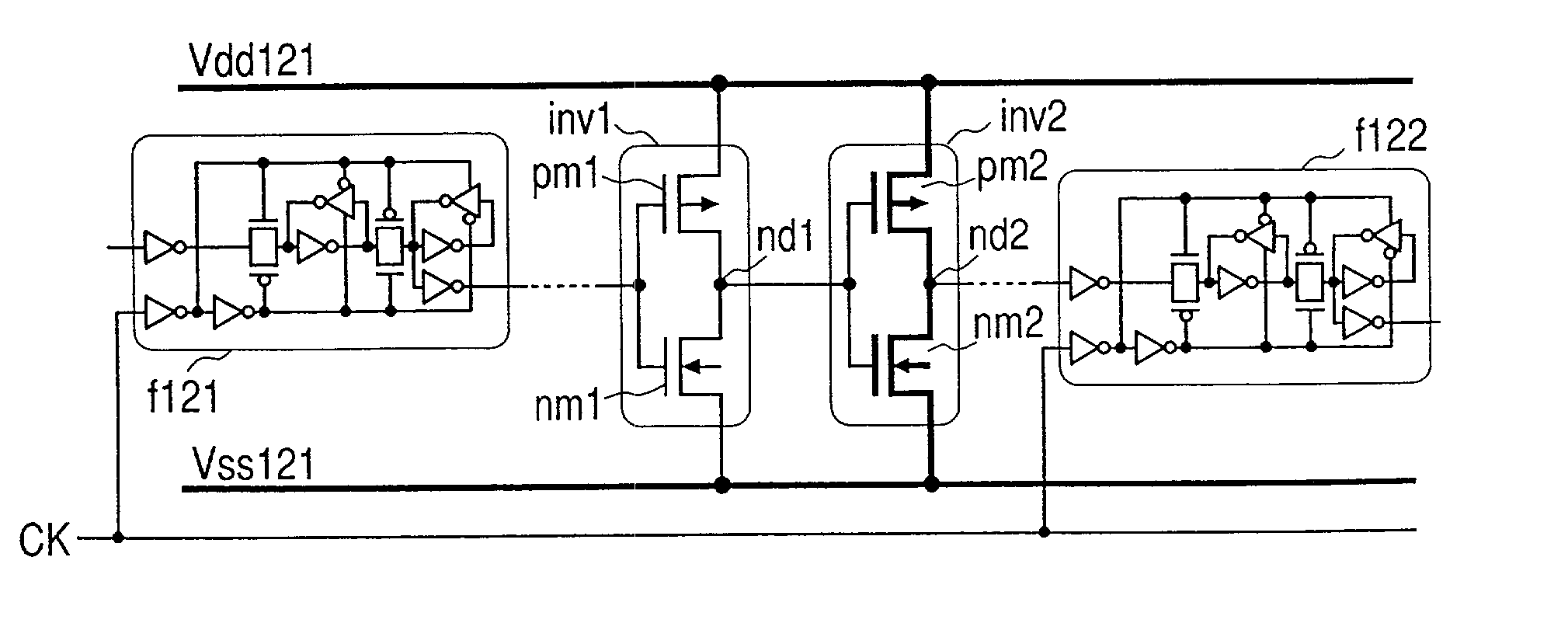

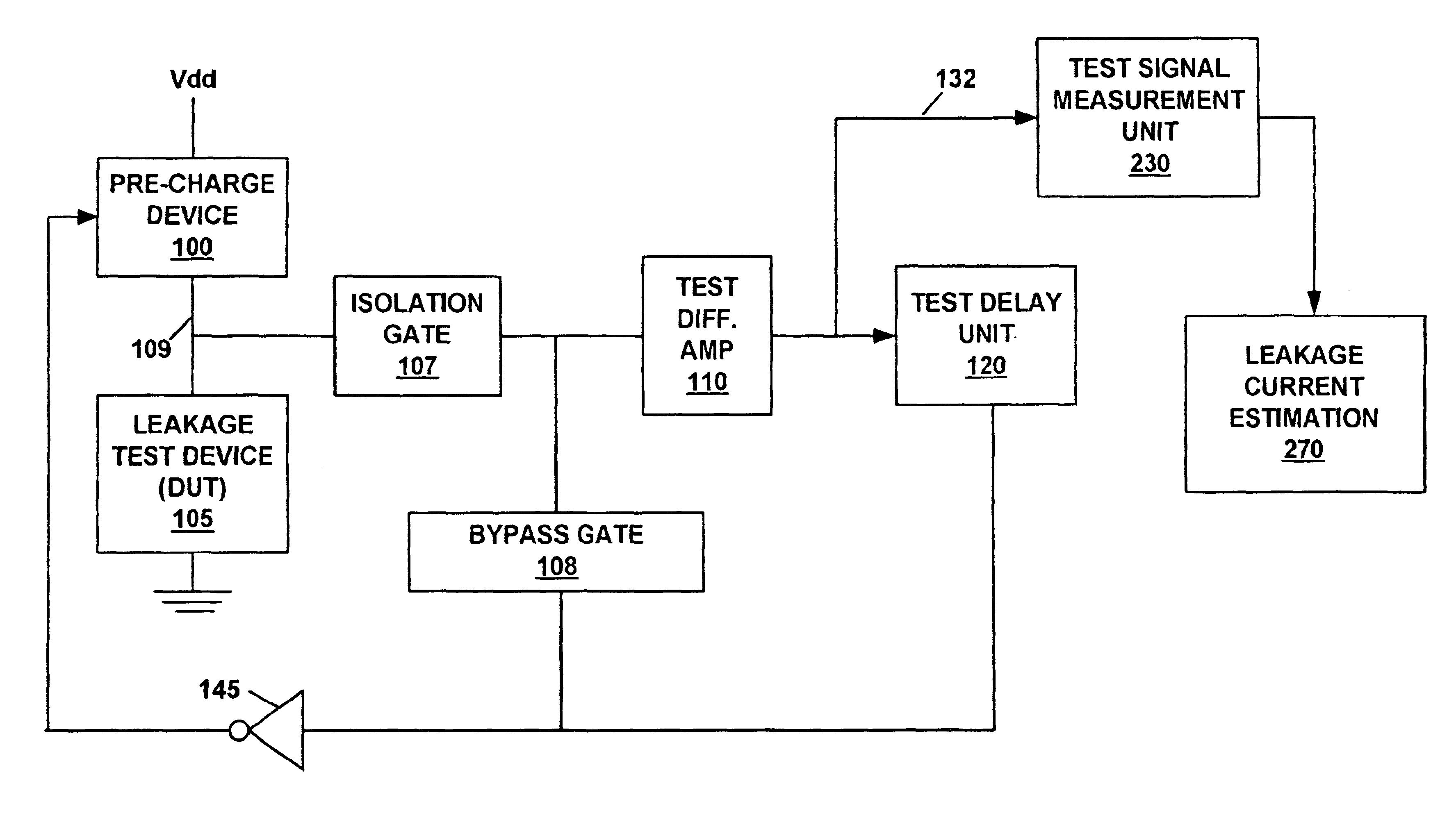

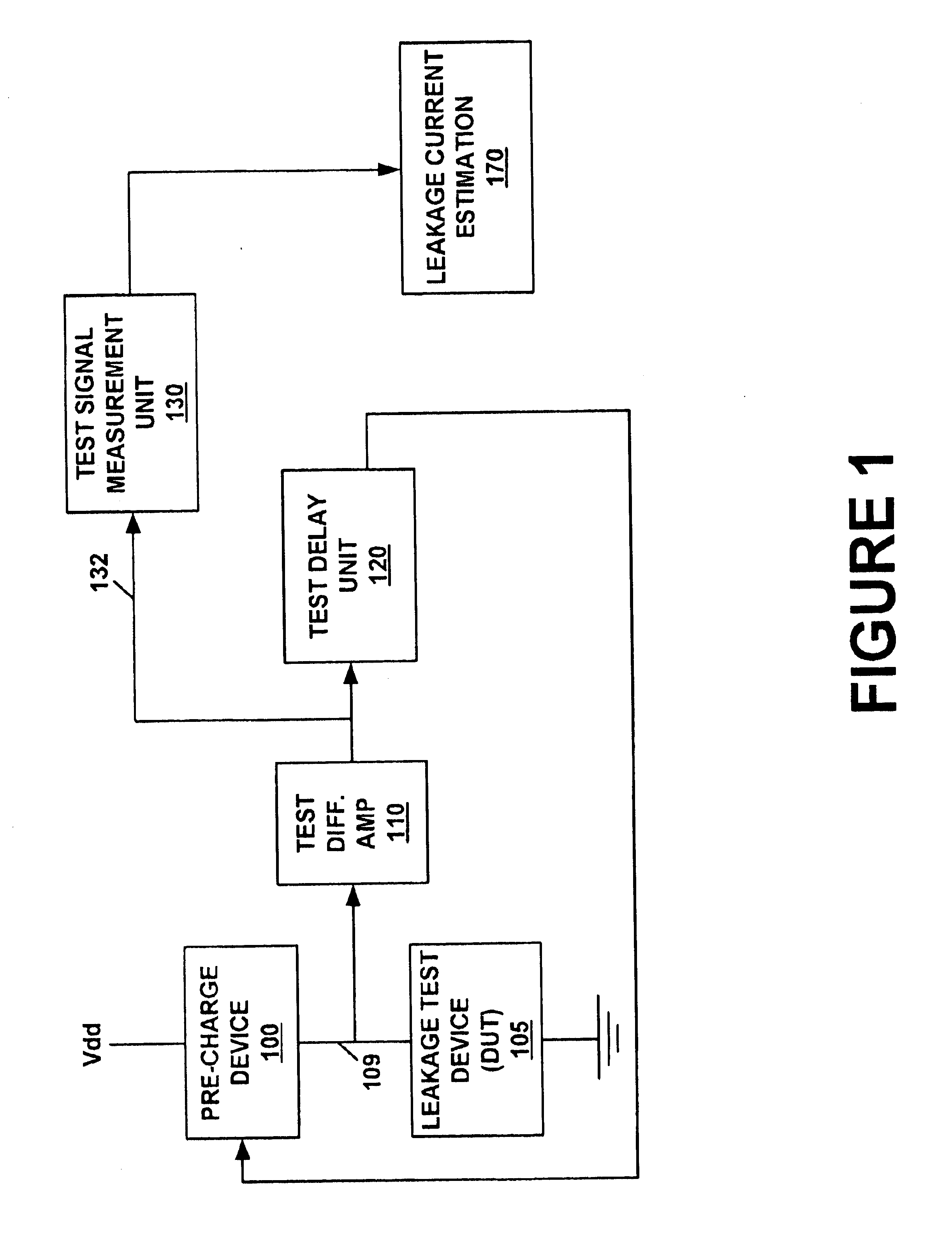

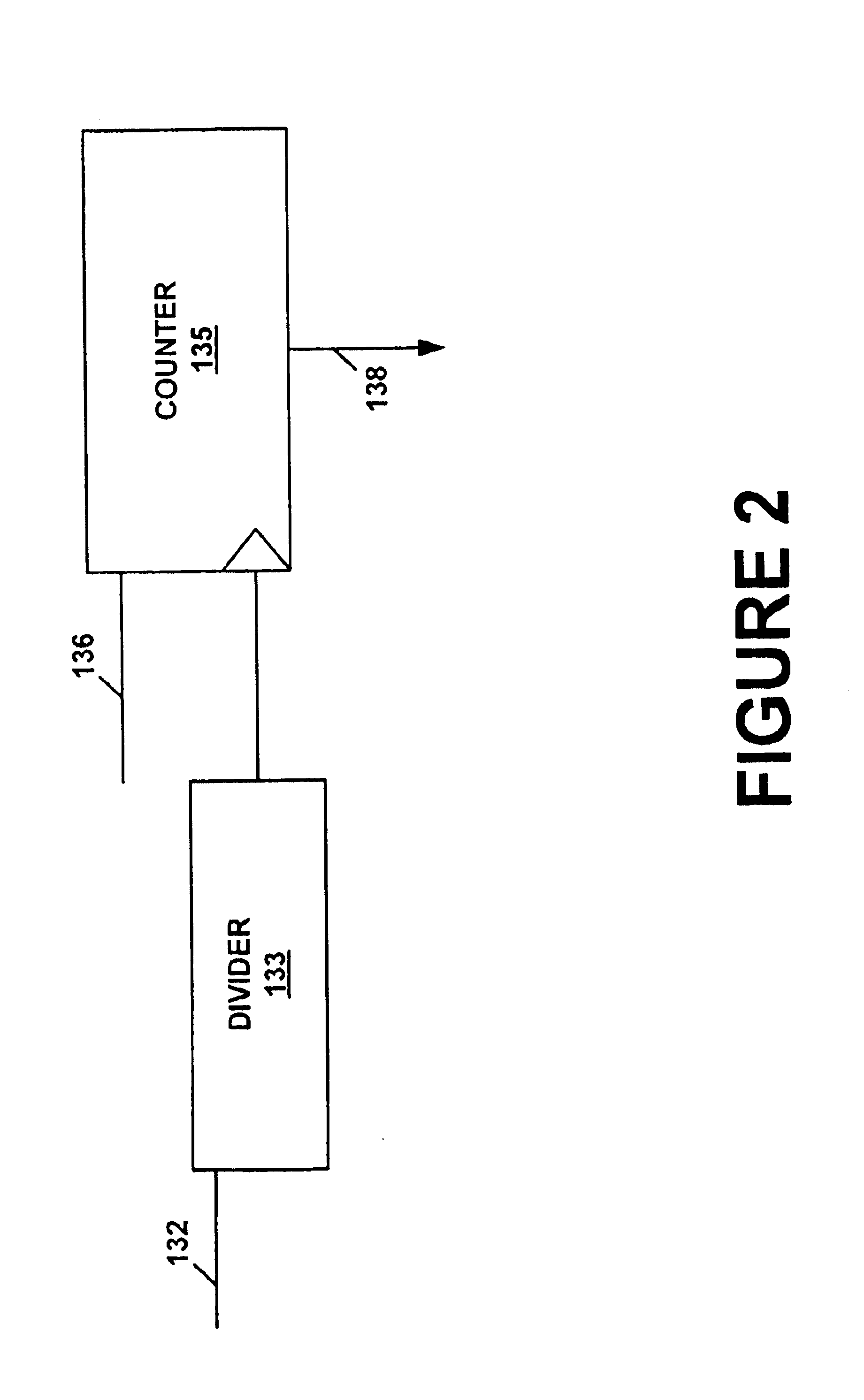

System and method for measuring transistor leakage current with a ring oscillator

InactiveUS6882172B1Accurate measurementAccurately leakage currentElectronic circuit testingShort-circuit testingLeakage testDrain current

A method of measuring the transistor leakage current. In one embodiment, the method involves driving a ring oscillator with a dynamic node driver having a leakage test device biased to an off state to produce a test signal. The test signal is extracted and the frequency is measured. The leakage current is estimated from the measured frequency.

Owner:META PLATFORMS INC

Drive circuit and image forming apparatus using the same

InactiveUS20050179626A1Keep for a long timeImage stabilizationCathode-ray tube indicatorsInput/output processes for data processingImage formationHemt circuits

Owner:CANON KK

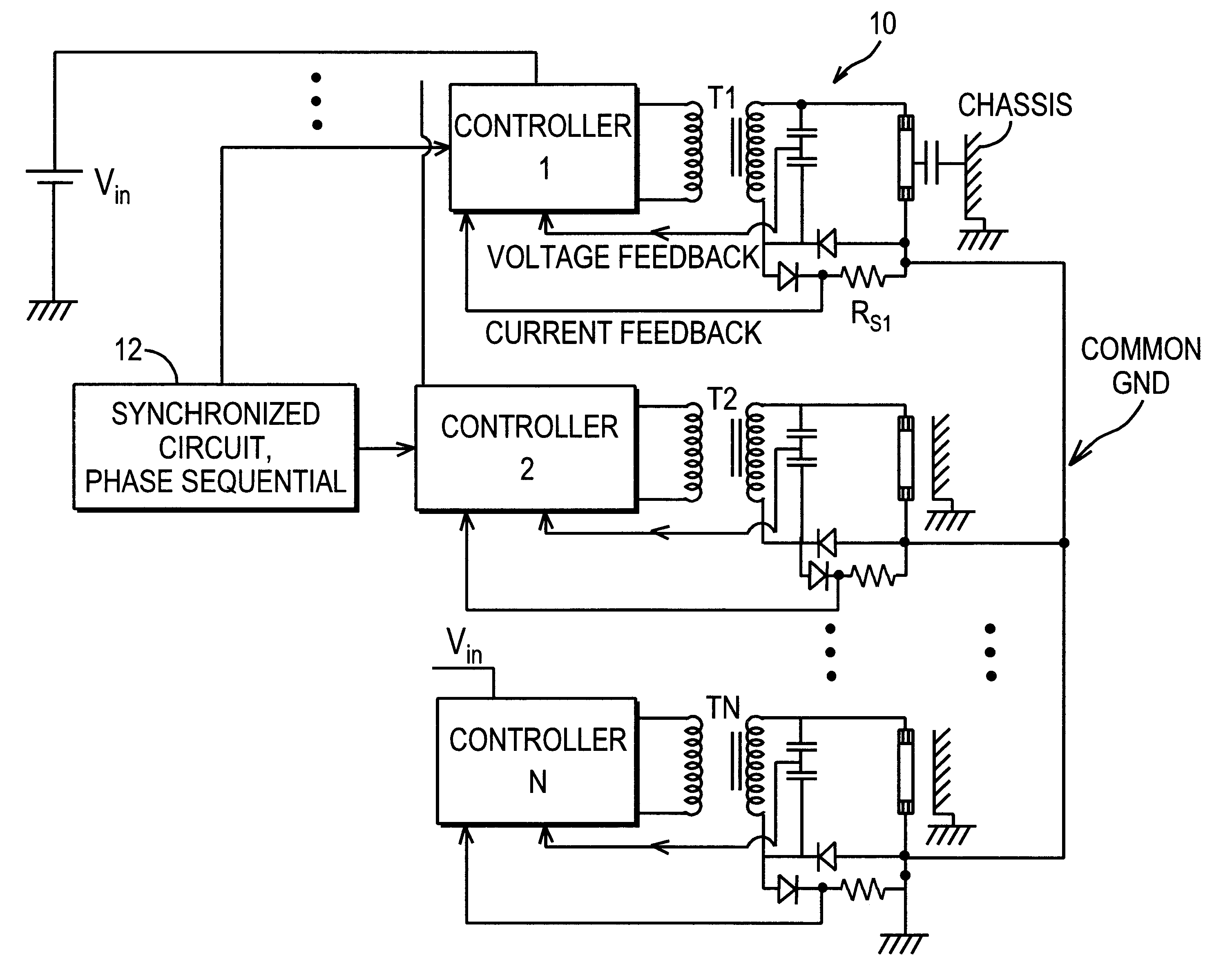

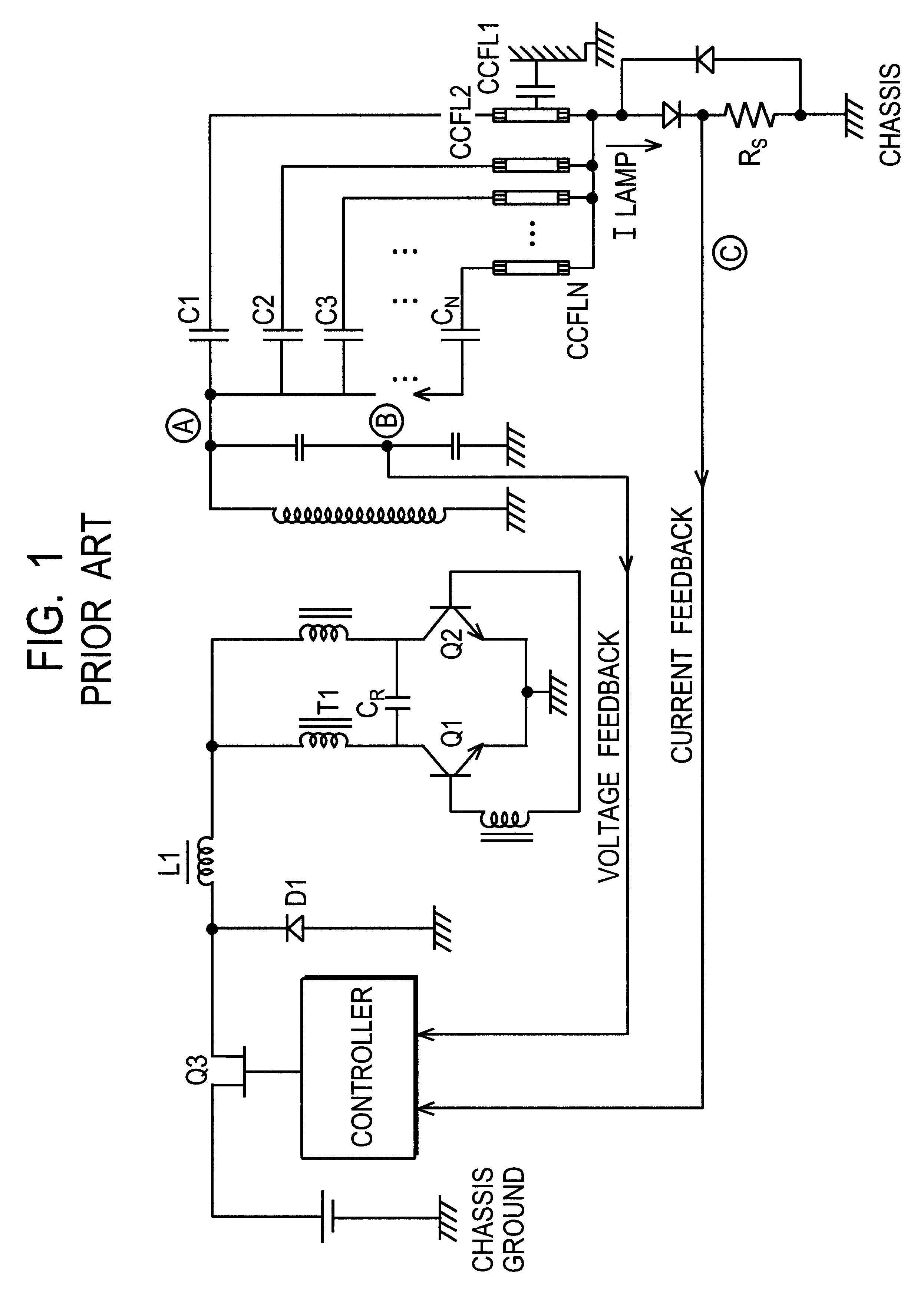

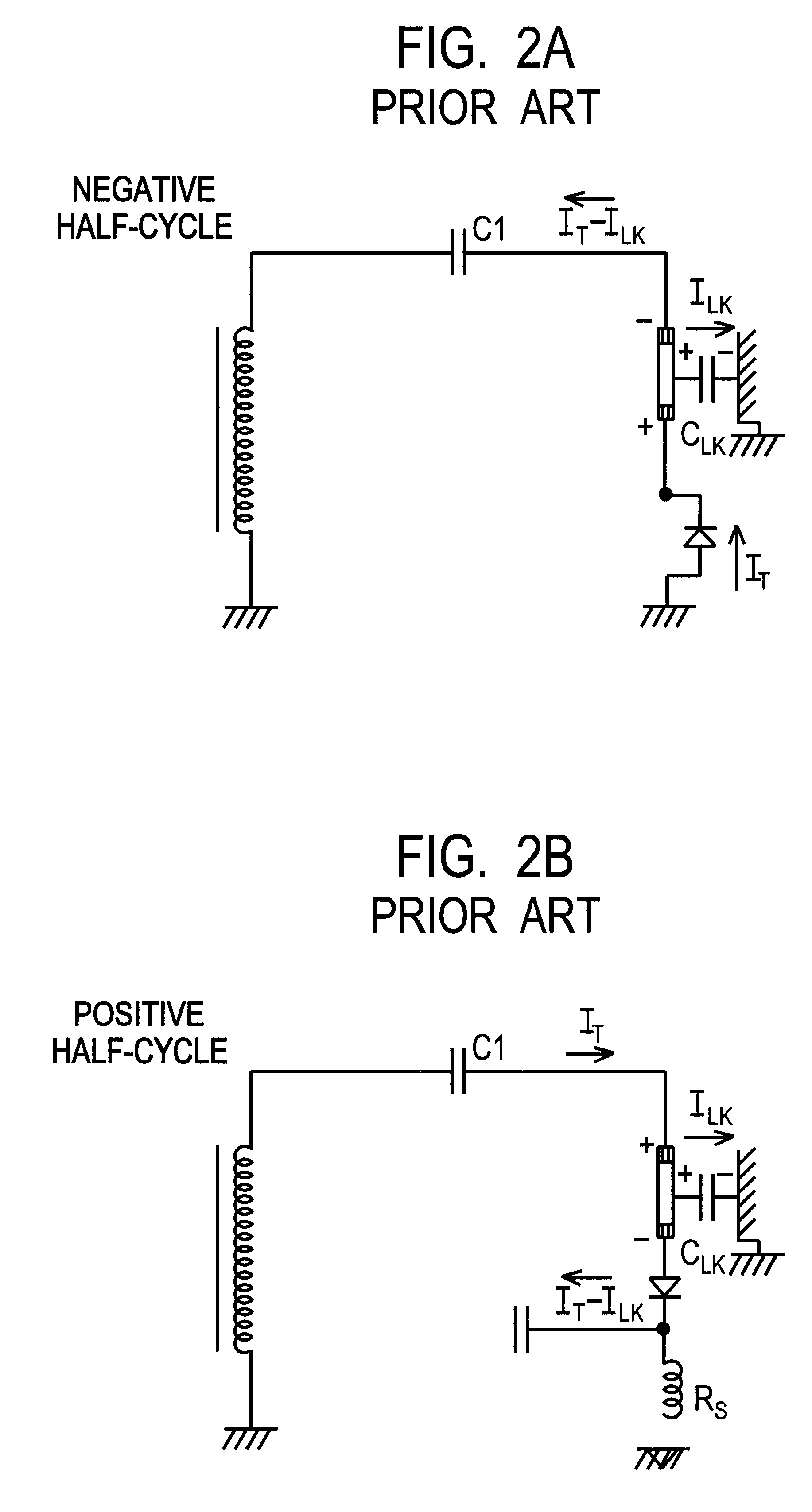

Lamp grounding and leakage current detection system

InactiveUS6570344B2Conversion with intermediate conversion to dcDc-dc conversionGround systemEngineering

A common ground system and methodology for one or more loads. In exemplary embodiments, a lamp load is regulated by providing a common ground on the secondary side of the transformer and the load. Lamp regulation is provided, in part, via a current feedback loop provided on the secondary side that is commonly grounded between the bottom of the transformer and the bottom of the lamp through the current feedback loop. In this manner, a feedback signal is developed that includes the leakage current of the lamp.

Owner:O2 MICRO INT LTD

Light-emitting device

InactiveUS7129917B2Drop in opening ratioSuppression of uneven brightnessTransistorDischarge tube luminescnet screensDisplay deviceEngineering

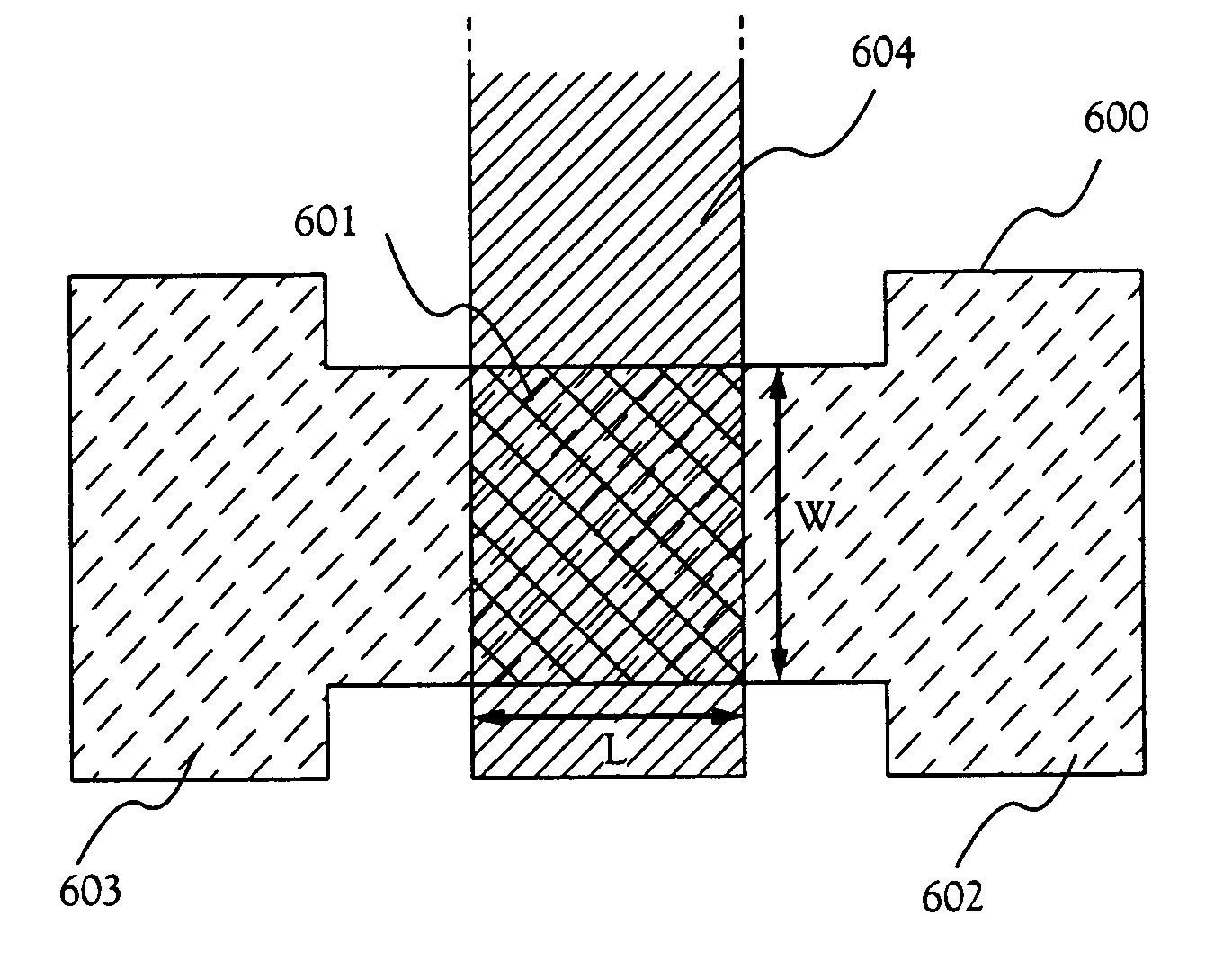

There is provided an EL light-emitting device with less uneven brightness. When a drain current of a plurality of current controlling TFTs is Id, a mobility is μ, a gate capacitance per unit area is Co, a maximum gate voltage is Vgs(max), a channel width is W, a channel length is L, an average value of a threshold voltage is Vth, a deviation from the average value of the threshold voltage is ΔVth, and a difference in emission brightness of a plurality of EL elements is within a range of ±n %, a semiconductor display device is characterized in thatA=2Idμ*C0A(Vgs(max)-Vth)2≦WL≦(1+n100-1)2*AΔVth2ΔVth≦(1+n100-1)*A*L / W

Owner:SEMICON ENERGY LAB CO LTD

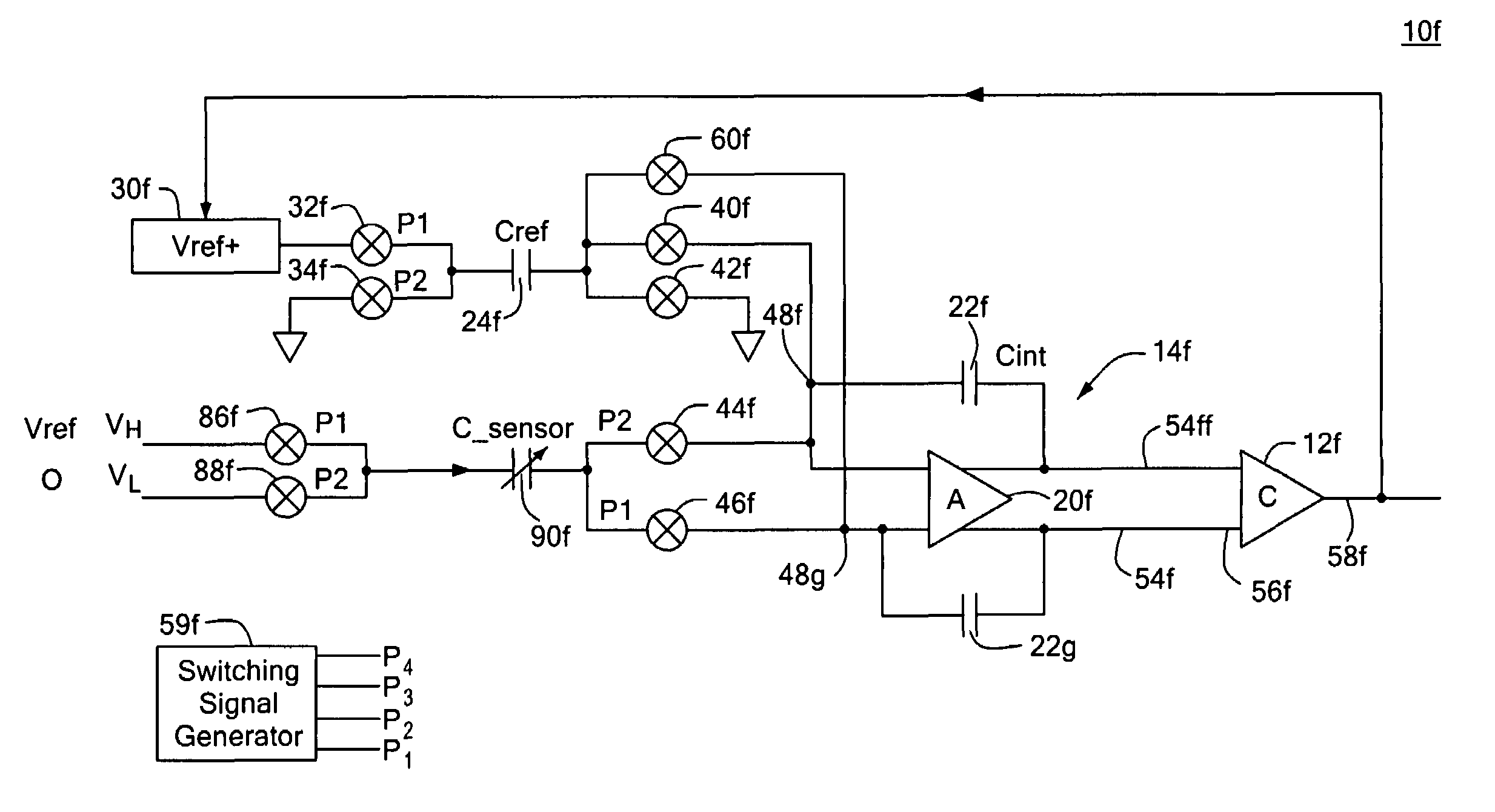

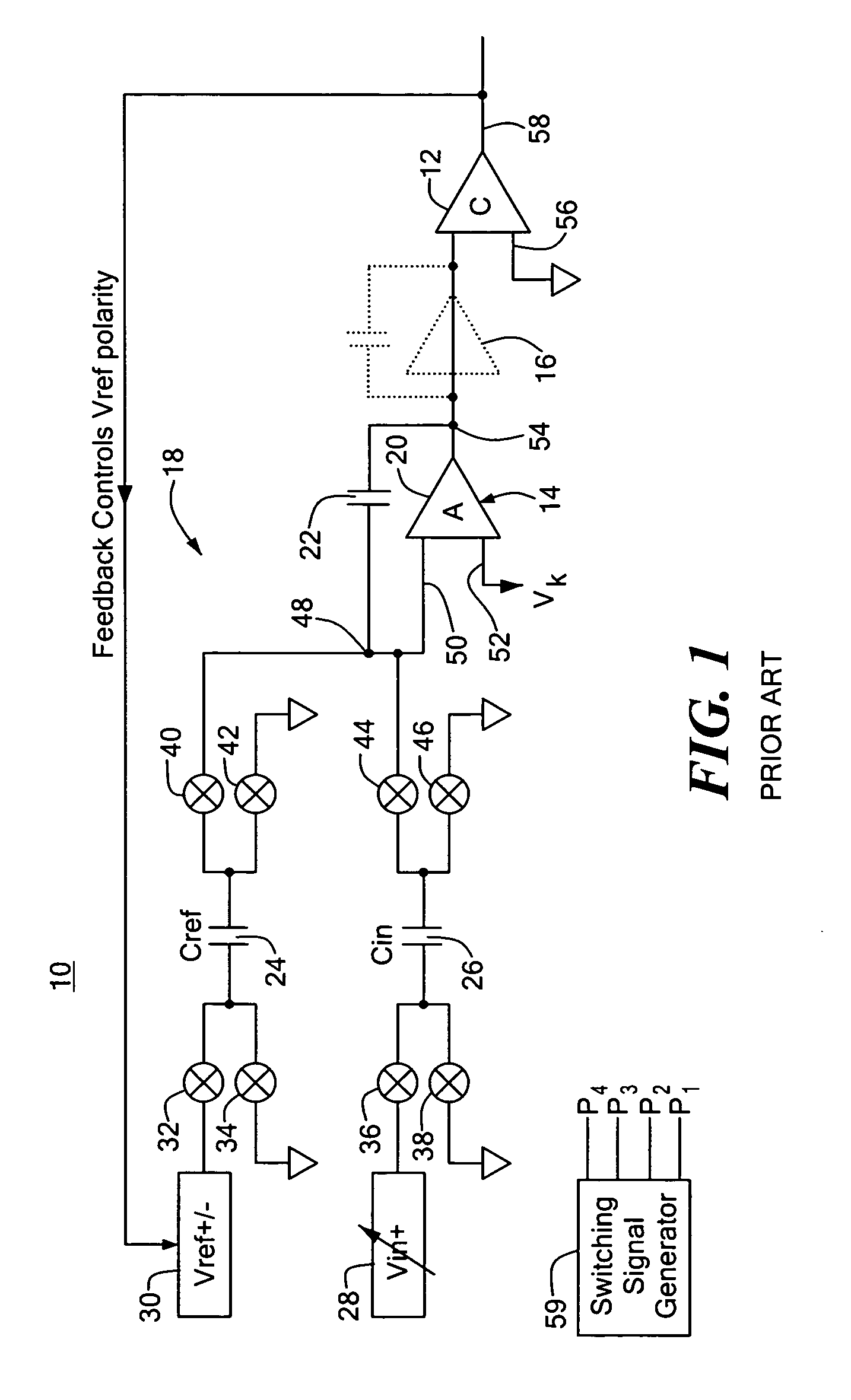

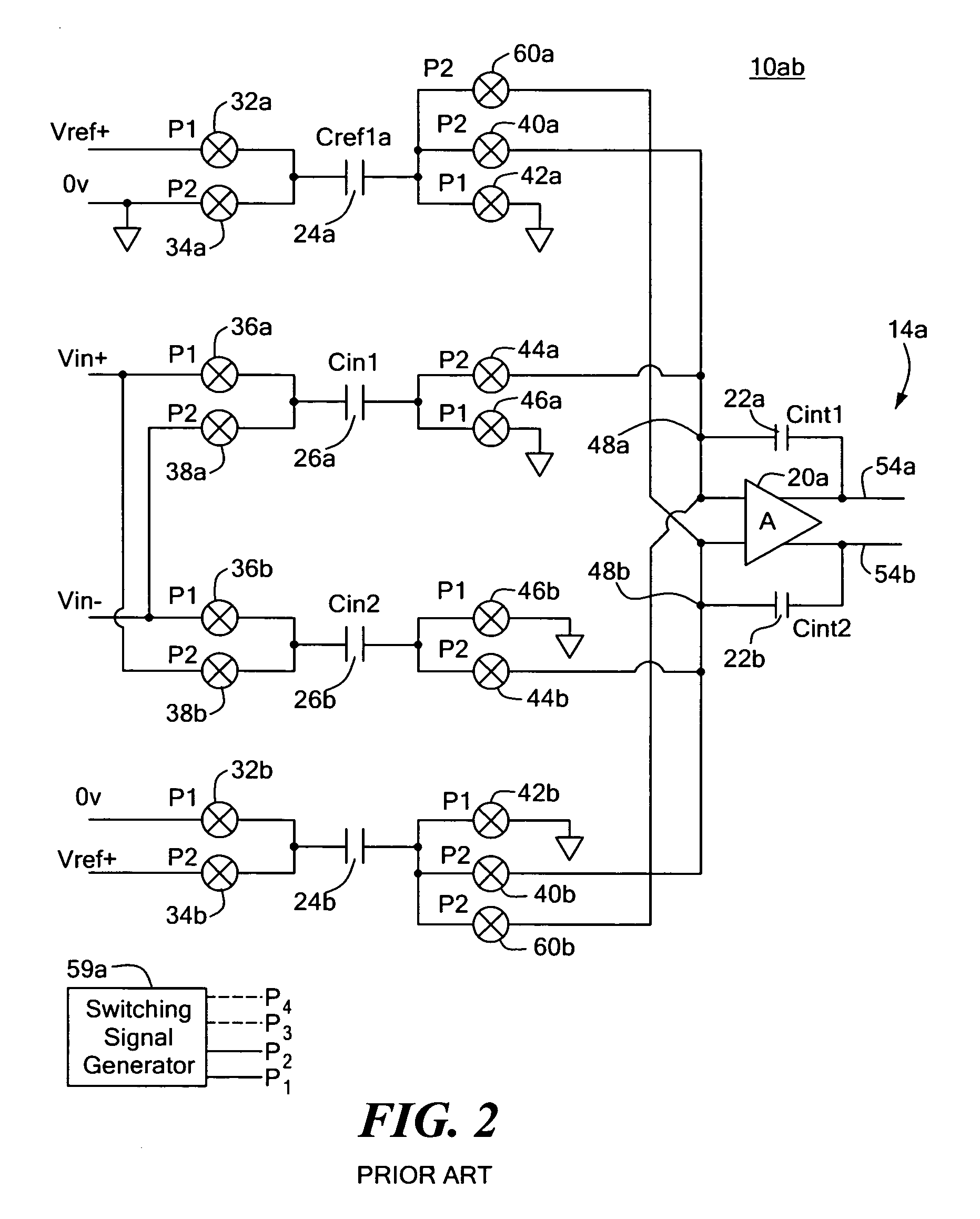

Variable capacitance switched capacitor input system and method

ActiveUS6970126B1Current errorElectric signal transmission systemsDelta modulationCapacitanceIntegrator

A variable capacitance switched capacitor input system and method includes a differential integrator circuit having first and second input summing nodes and a variable sensing capacitor; one terminal of the variable sensing capacitor is connected to one of the nodes in the first phase and to the other of the nodes in the second phase; an input terminal connected to a second terminal of the variable sensing capacitor receives a first voltage level in the first phase and a second voltage level in the second phase for delivering the charge on the variable sensing capacitor to the first summing node in the first phase and to the second summing node in the second phase and canceling errors in a differential integrator circuit output caused by leakage current.

Owner:ANALOG DEVICES INC

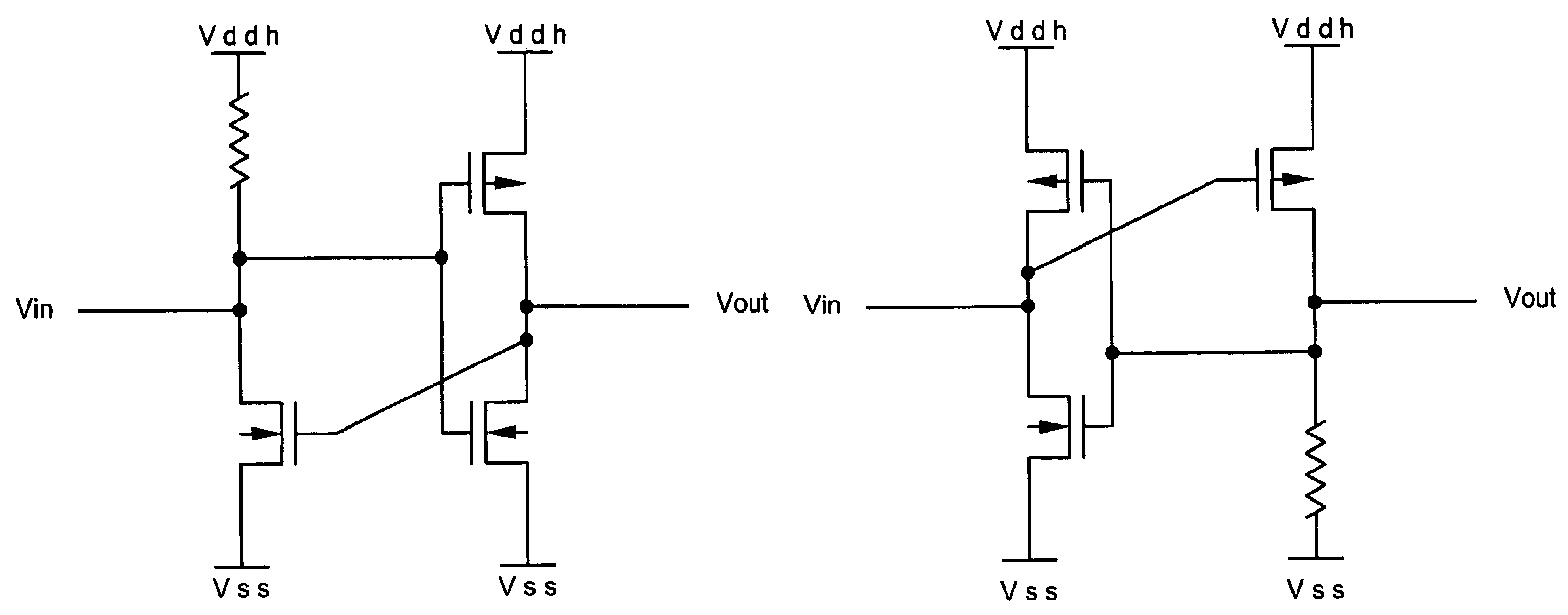

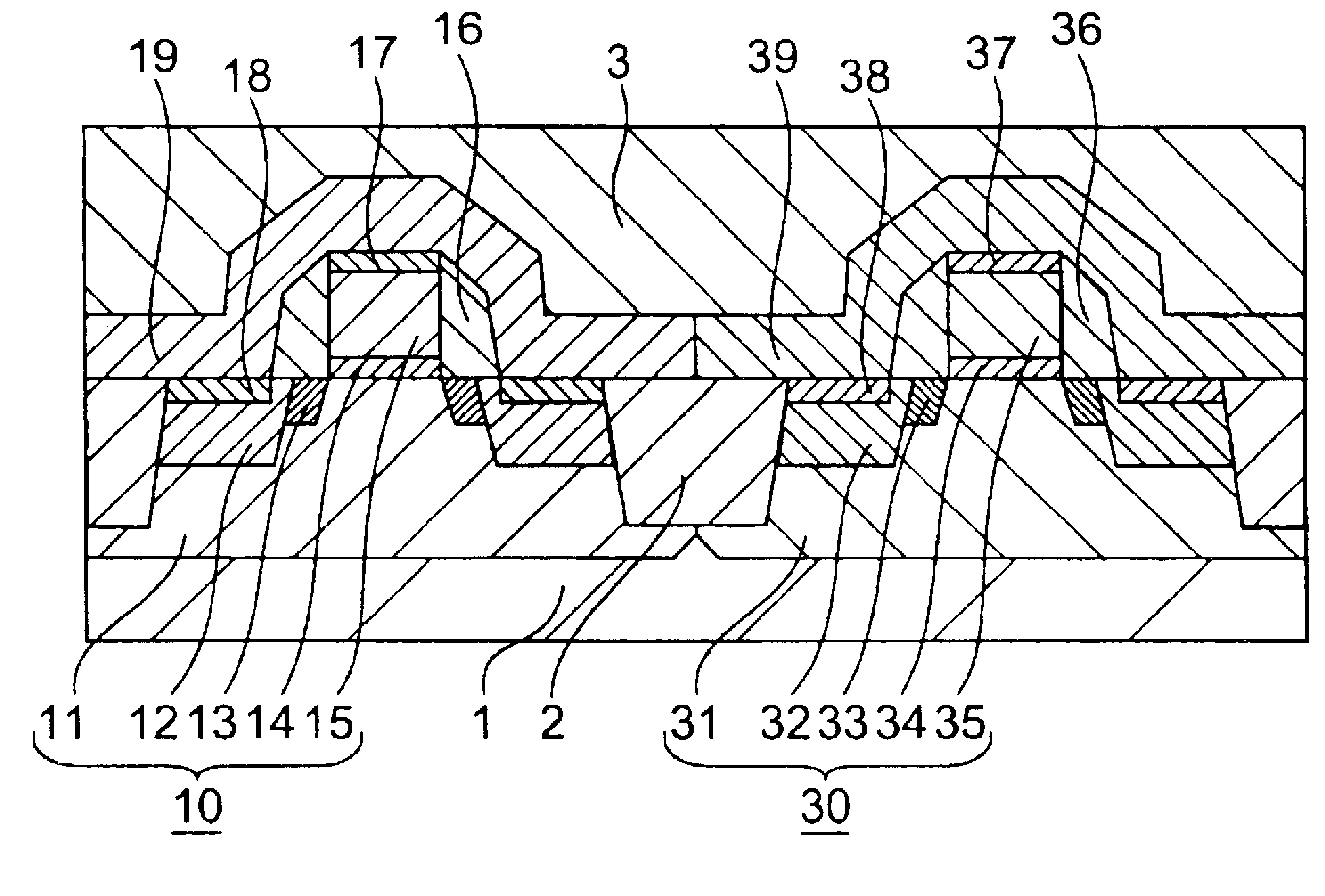

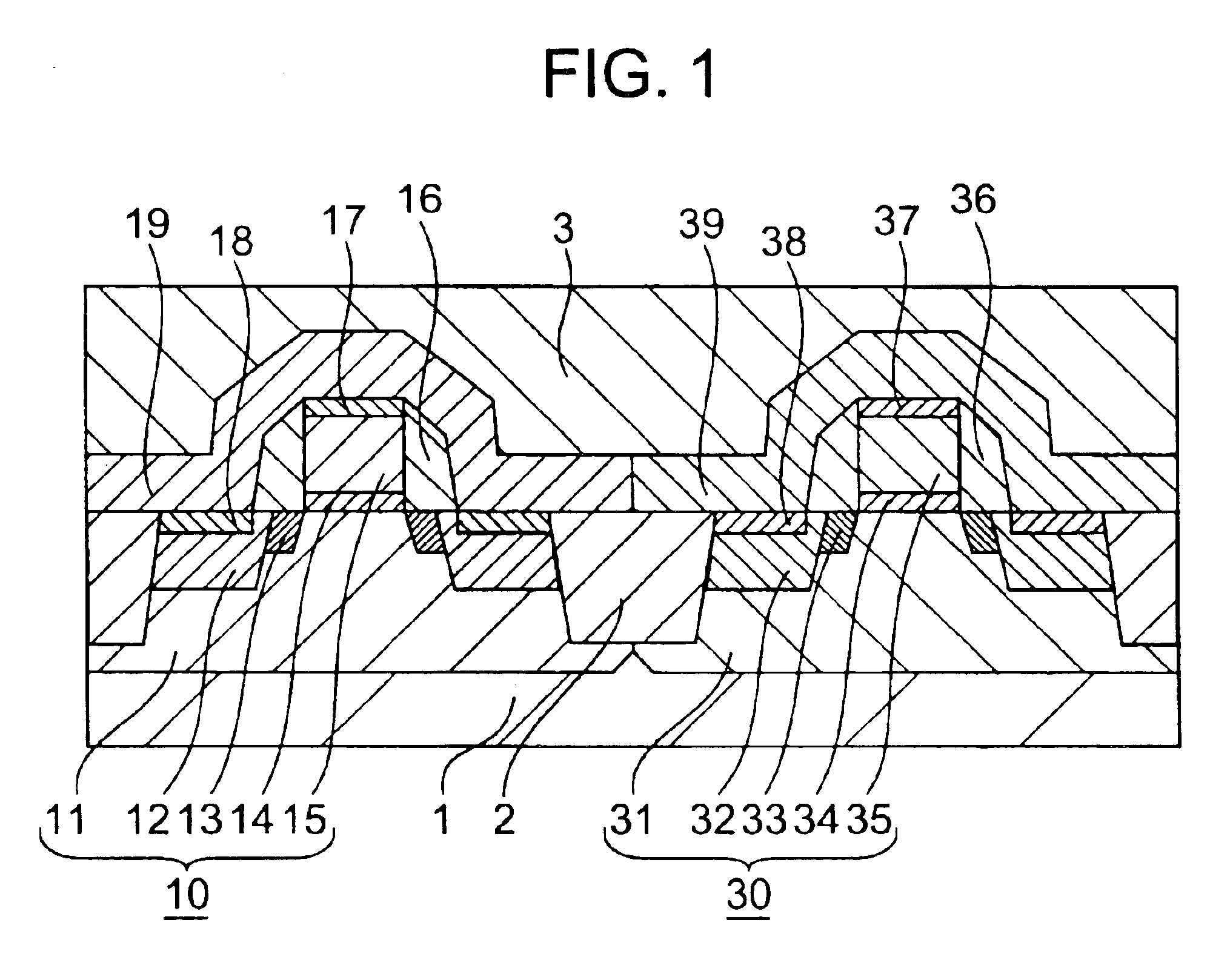

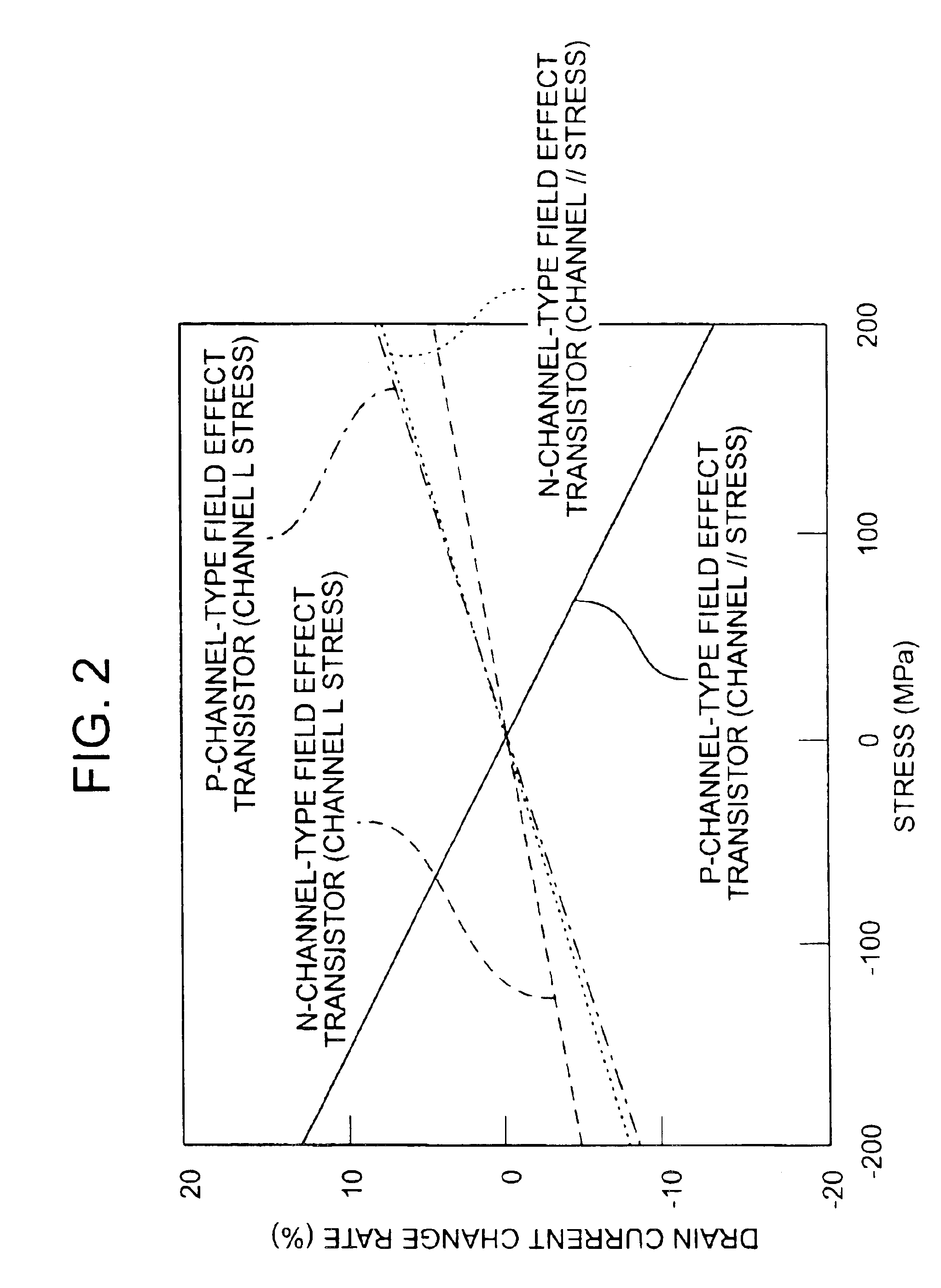

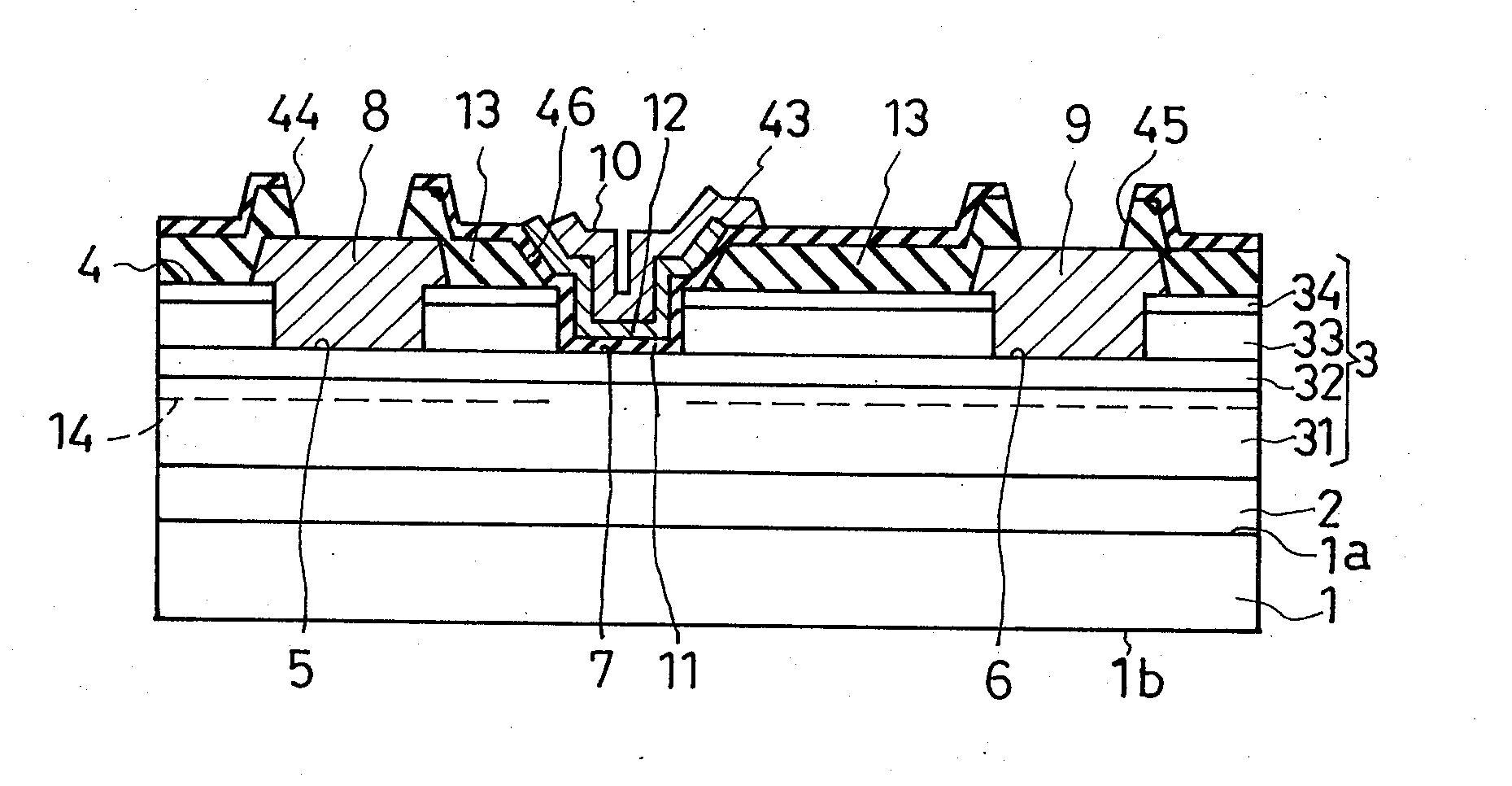

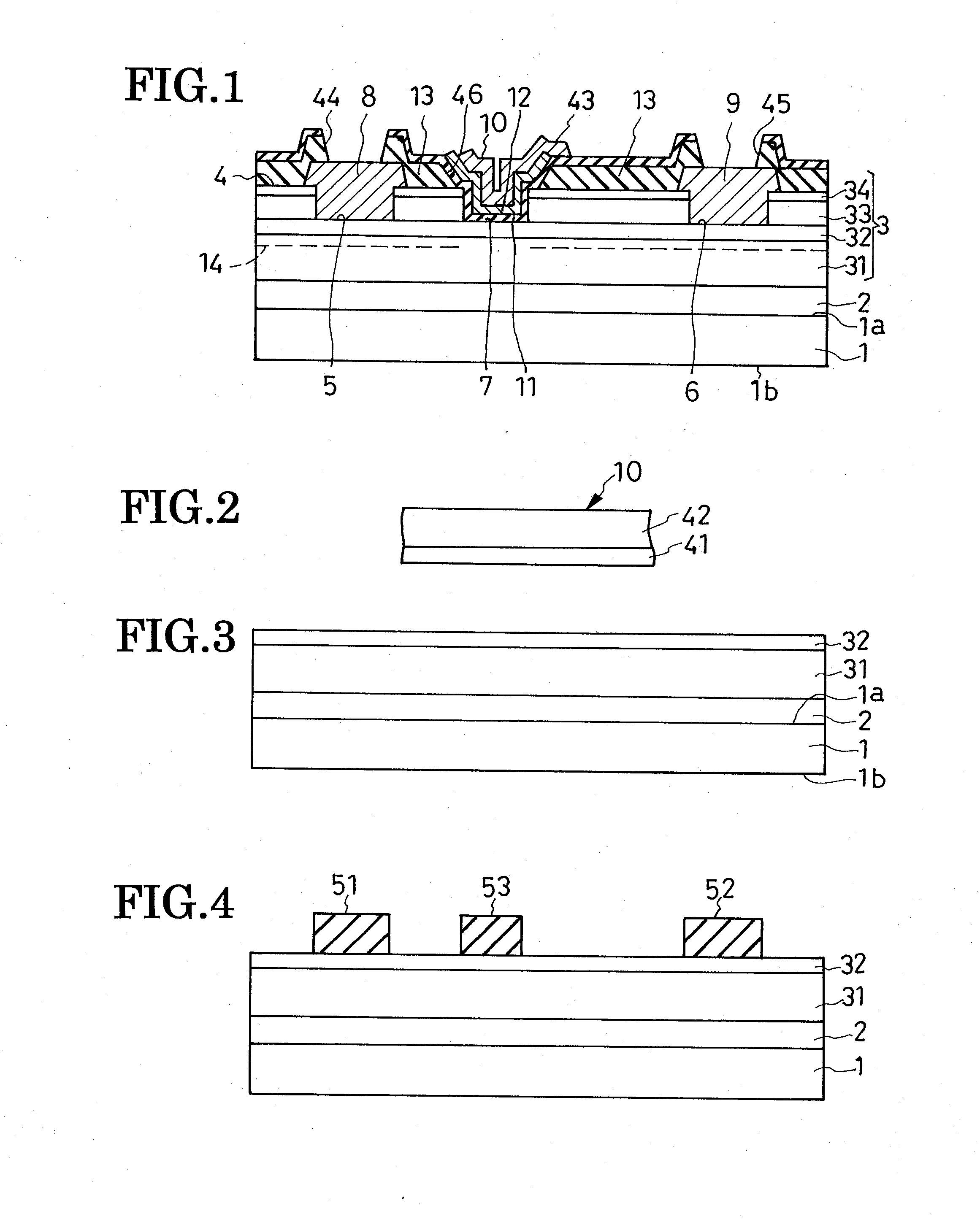

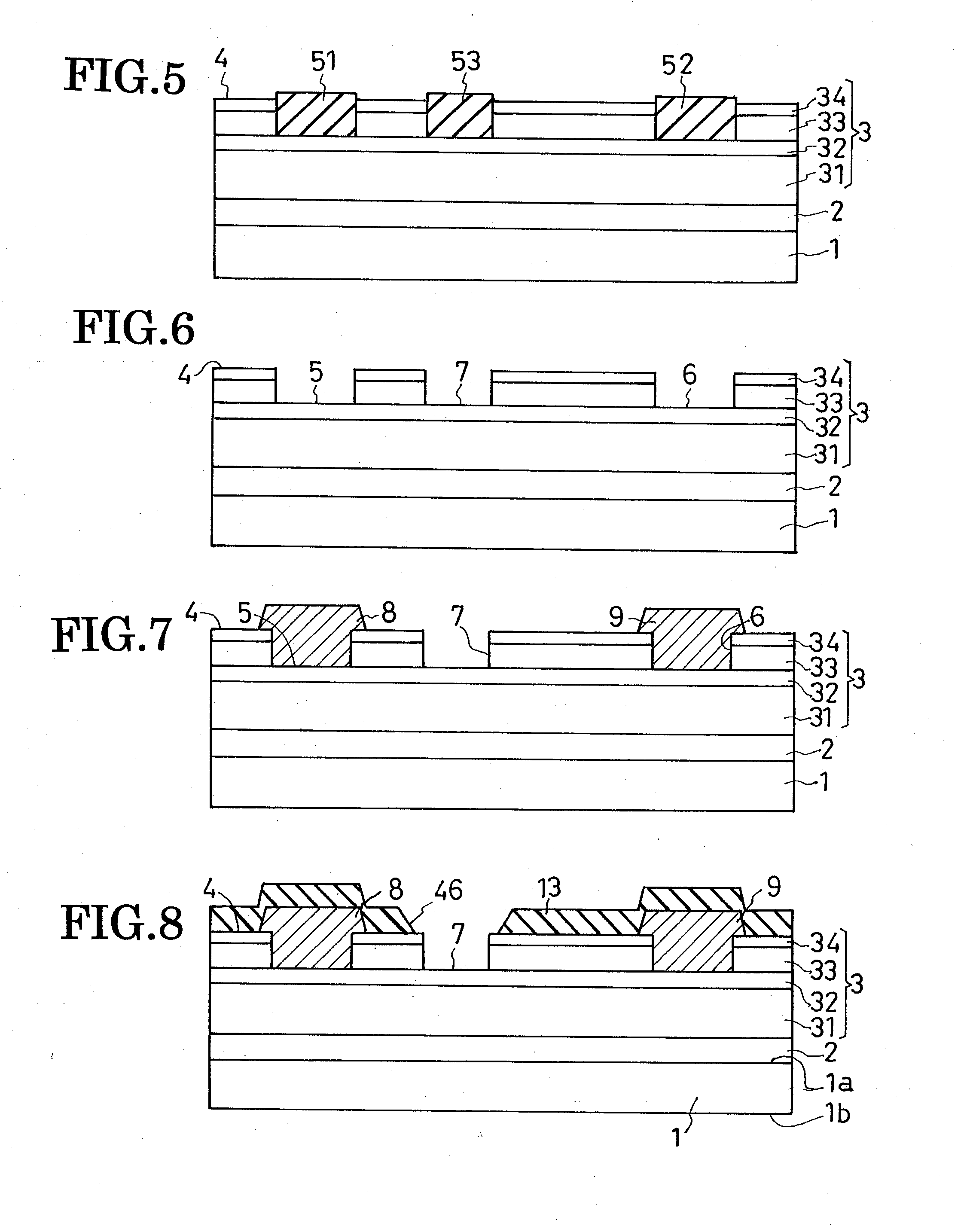

Semiconductor device with CMOS-field-effect transistors having improved drain current characteristics

InactiveUS6982465B2High speedImprove mobilityTransistorSemiconductor/solid-state device detailsCMOSField-effect transistor

The present invention provides a semiconductor device including n-channel field effect transistors and p-channel field effect transistors all of which have excellent drain current characteristics.In a semiconductor device including an n-channel field effect transistor 10 and a p-channel field effect transistor 30, a stress control film 19 covering a gate electrode 15 of the n-channel field effect transistor 10 undergoes film stress mainly composed of tensile stress. A stress control film 39 covering a gate electrode 15 of the p-channel field effect transistor 30 undergoes film stress mainly caused by compression stress compared to the film 19 of the n-channel field effect transistor 10. Accordingly, drain current is expected to be improved in both the n-channel field effect transistor and the p-channel field effect transistor. Consequently, the characteristics can be generally improved.

Owner:RENESAS ELECTRONICS CORP

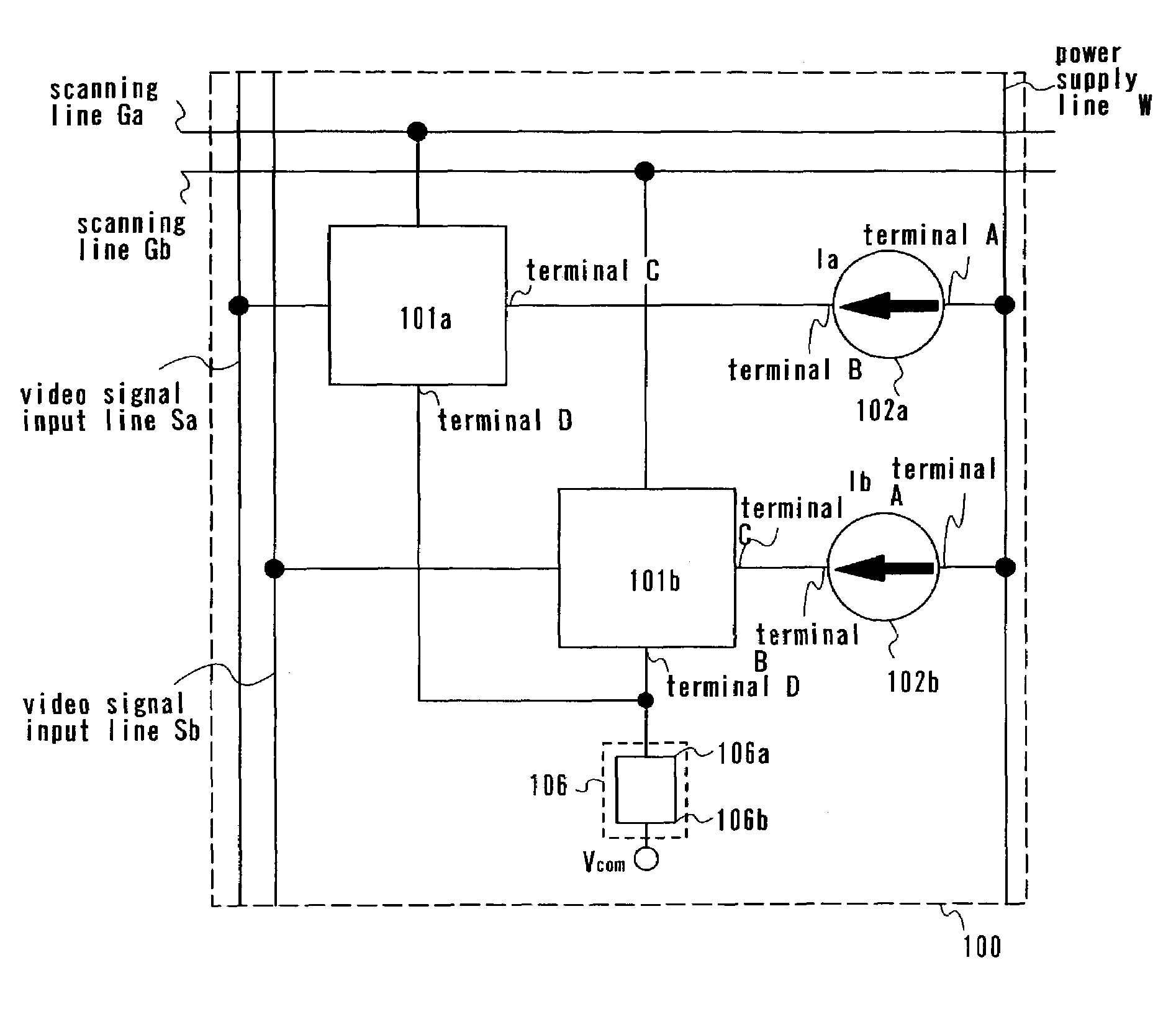

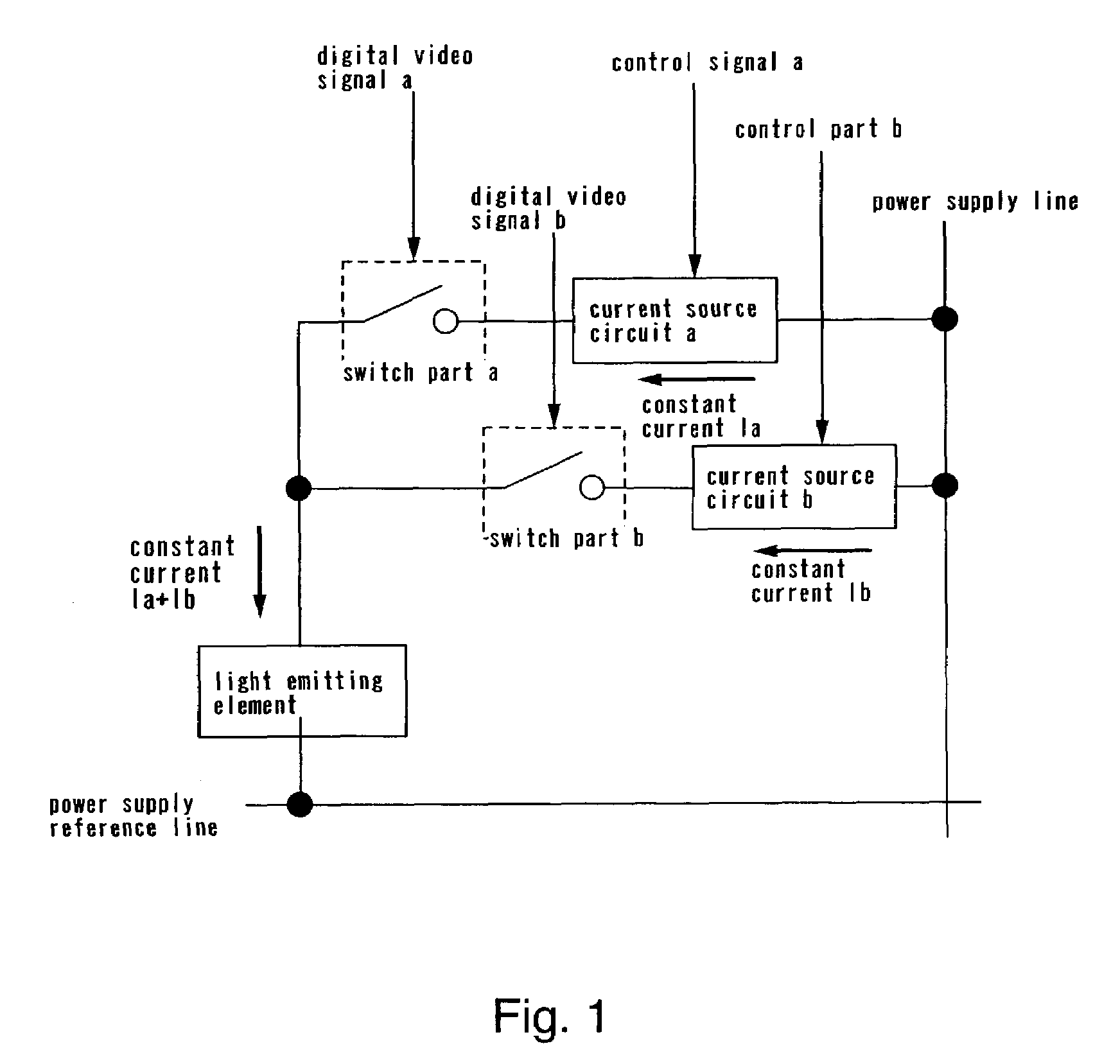

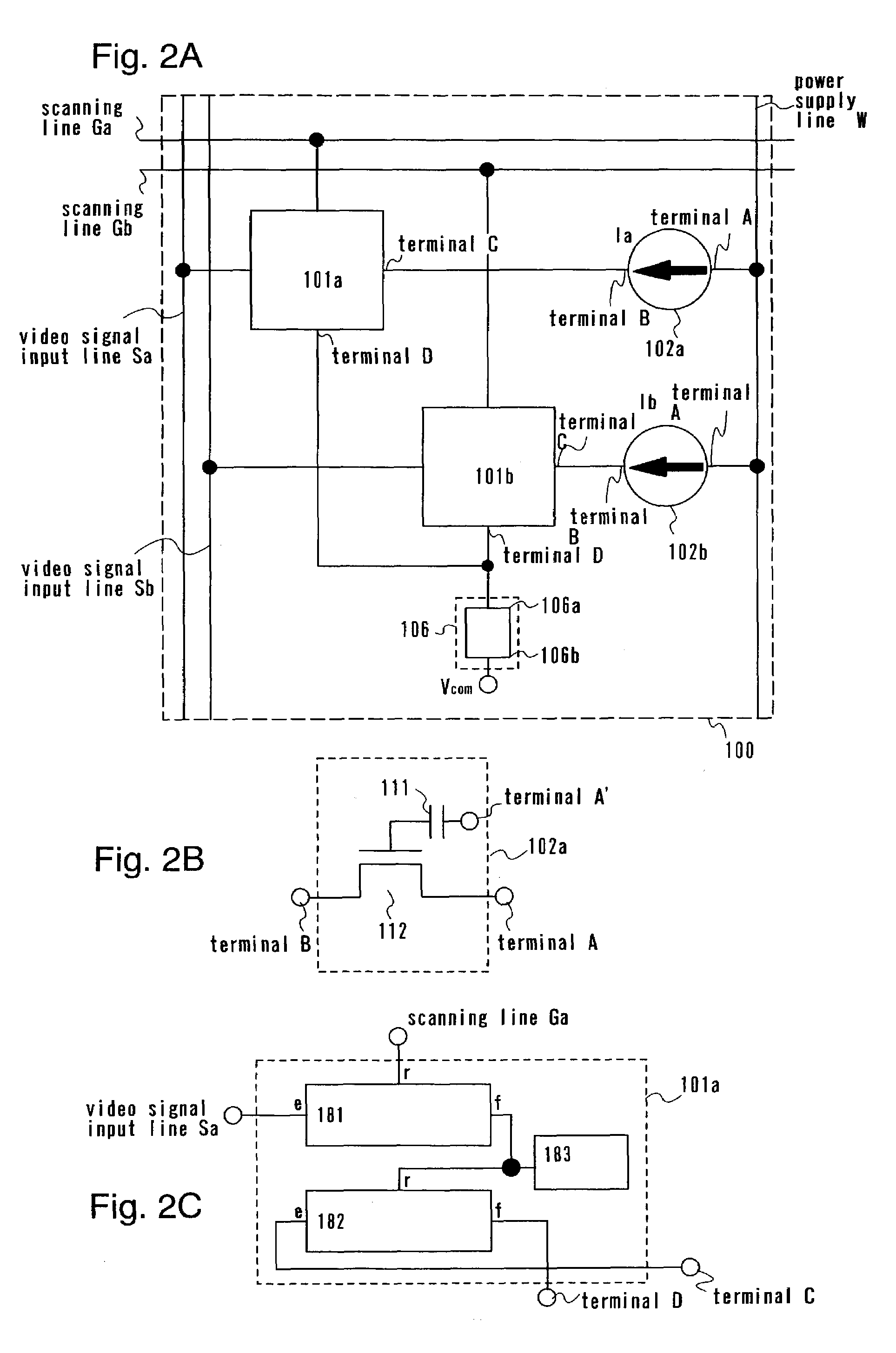

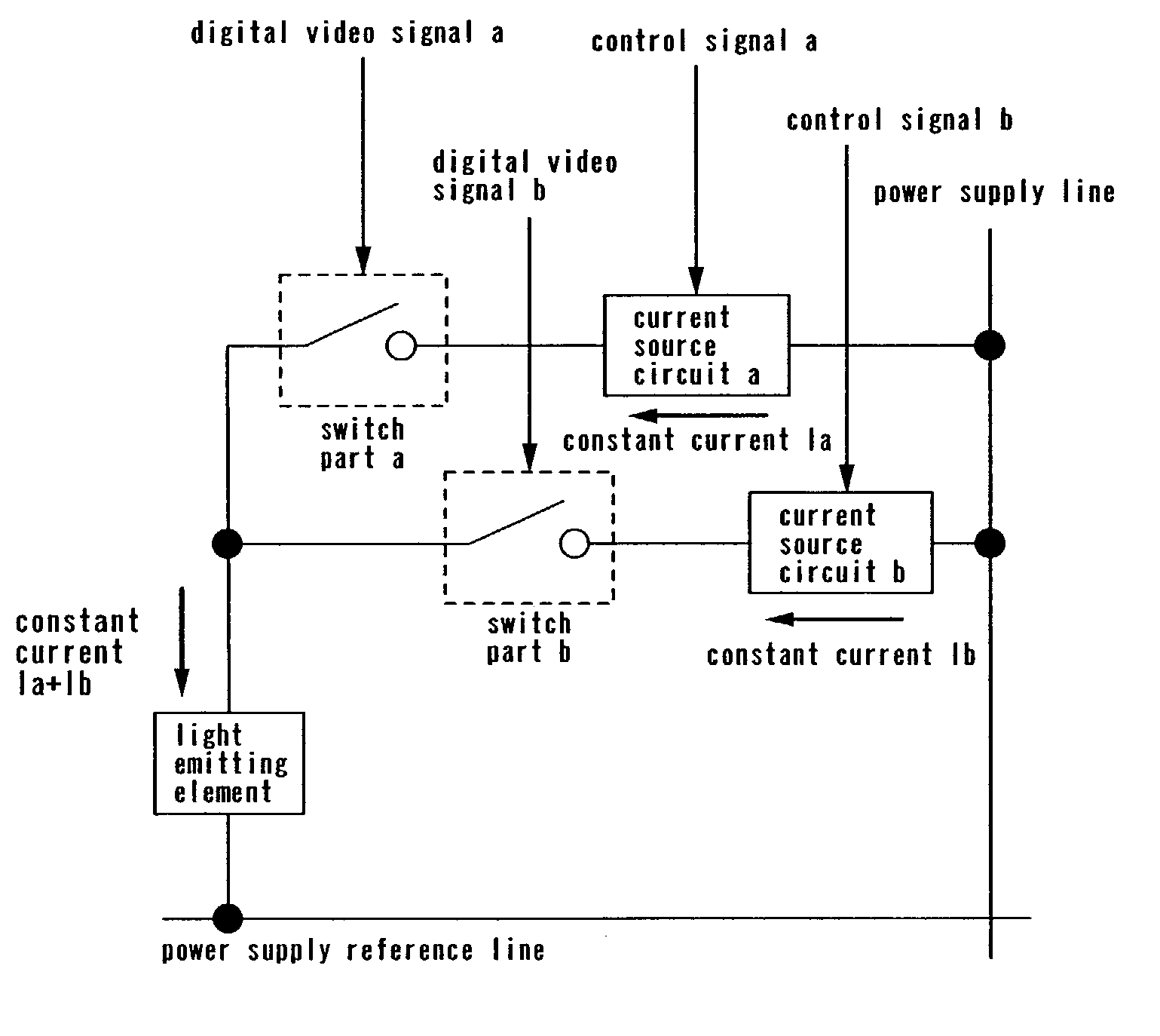

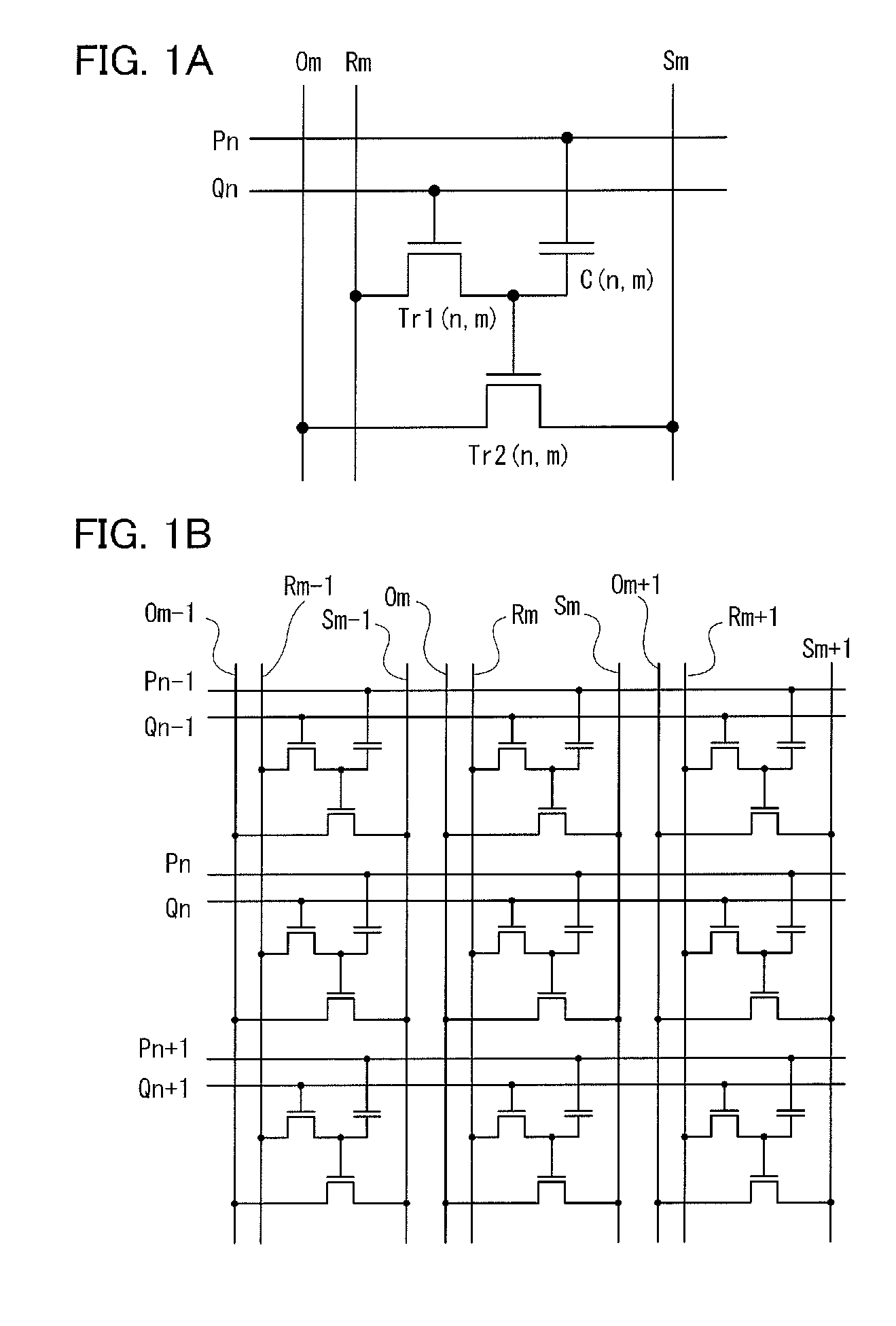

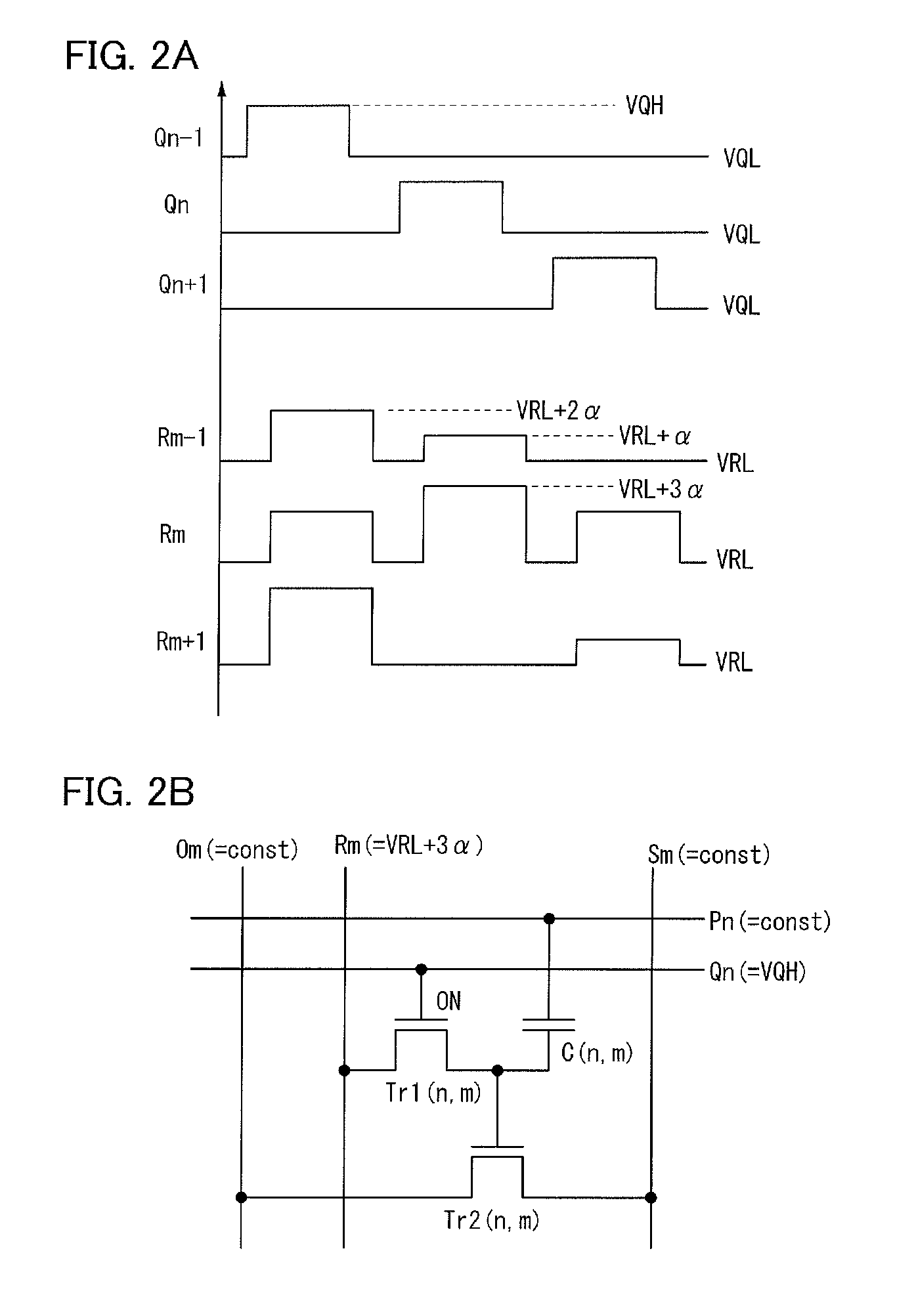

Display apparatus and driving method thereof

InactiveUS20030214465A1Quicken writingReduce impactCathode-ray tube indicatorsInput/output processes for data processingDigital videoDisplay device

This invention provides a display device in which it is possible to have a light emitting element emitted light with constant luminance without coming under the influence of deterioration over time, and it is possible to realize accurate gray scale express, and yet, it is possible to speed up writing of a signal current to each pixel, and influence of noise of a leak current etc. is suppressed, and a driving method thereof. A plurality of pairs of switch parts and current source circuits are disposed in each pixel. Switching of each of a plurality of the switch parts is controlled by a digital video signal. When the switch part is turned ON, by a current supplied from the current source circuit making a pair with the switch part, the light emitting element emits light. A current which is supplied from one current source circuit to the light emitting element is constant. A value of a current flowing through the light emitting element is comparable to a value of added currents which are supplied to the light emitting element from respective all current source circuits making pairs with the switch parts which are in the conductive states.

Owner:SEMICON ENERGY LAB CO LTD

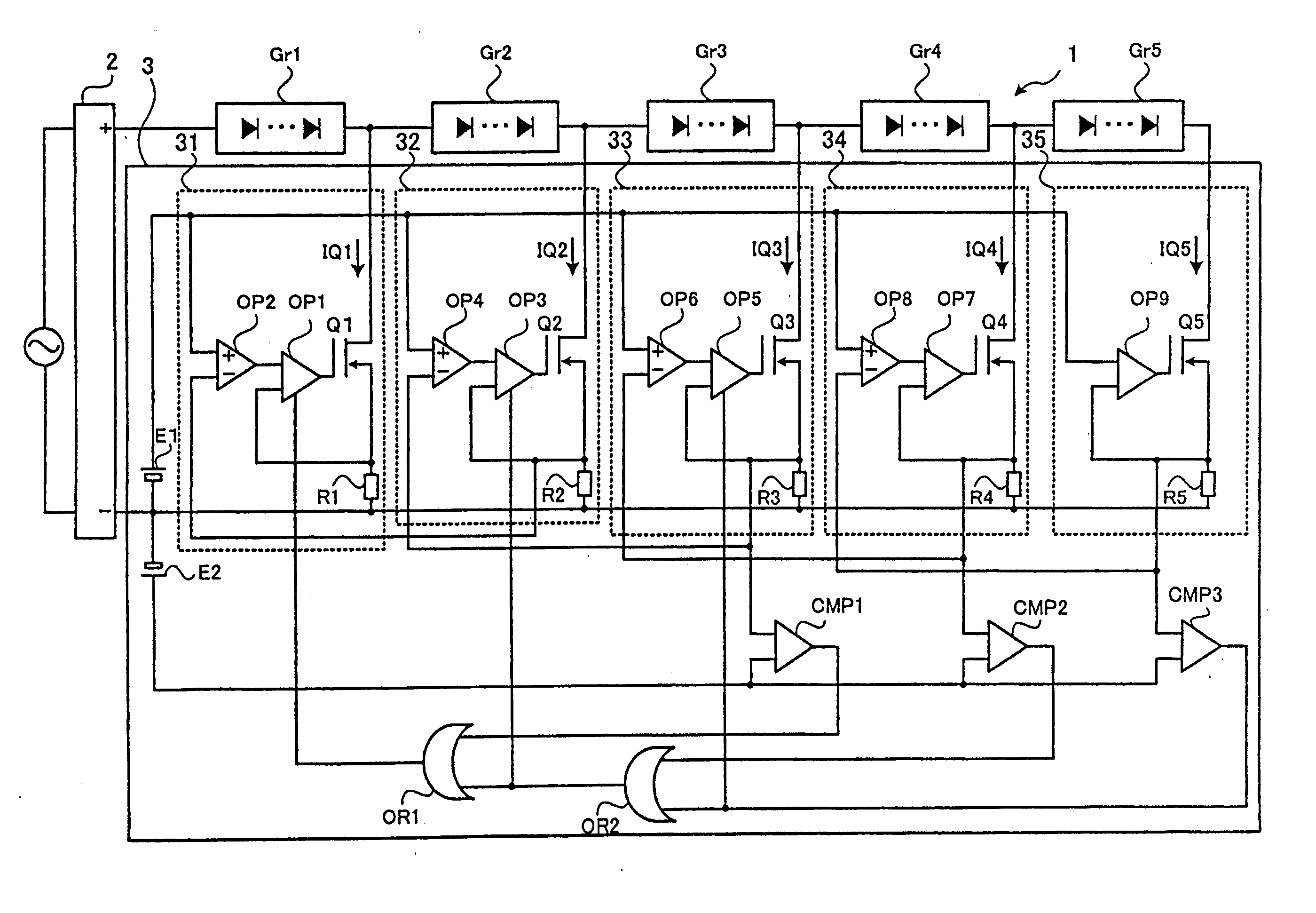

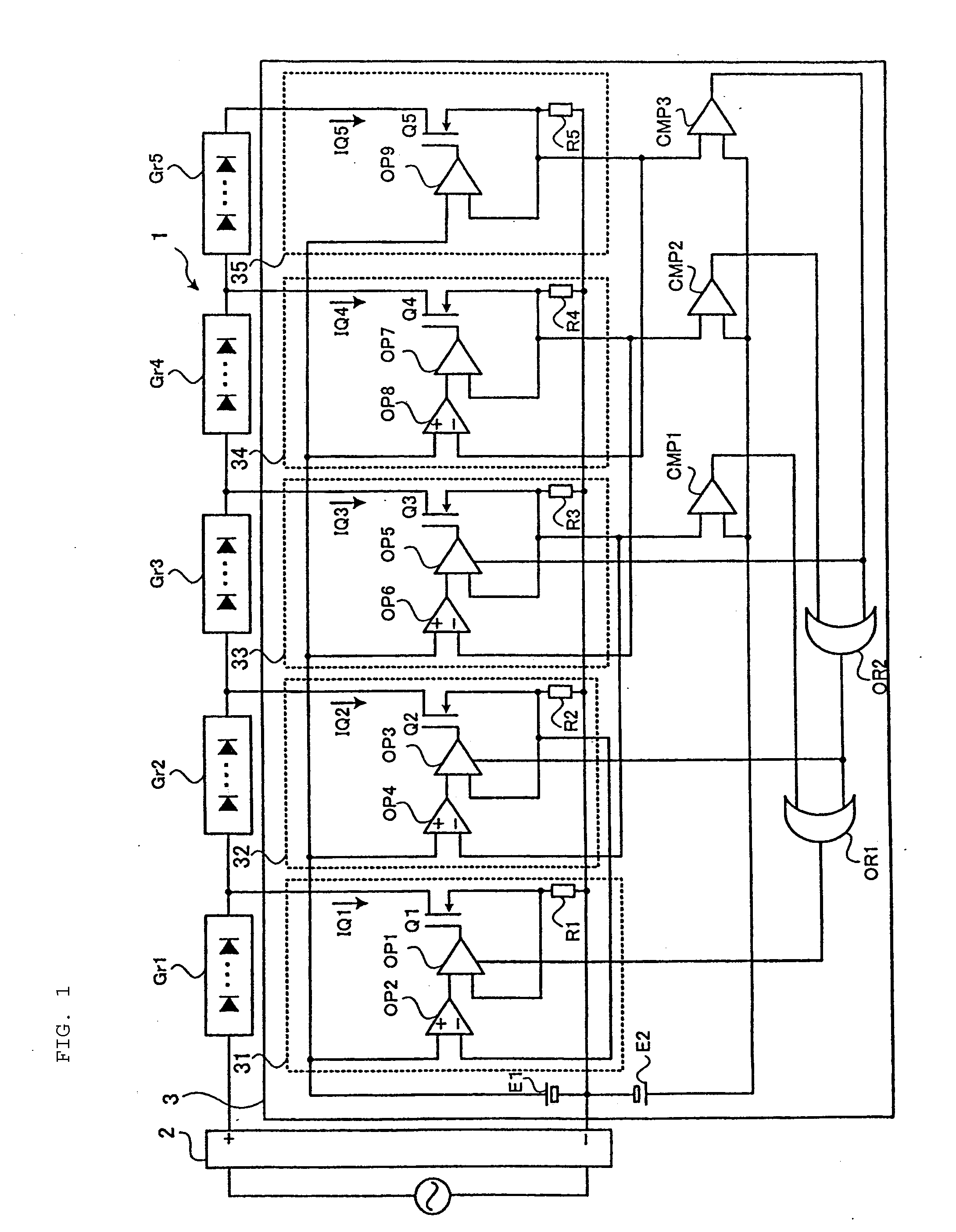

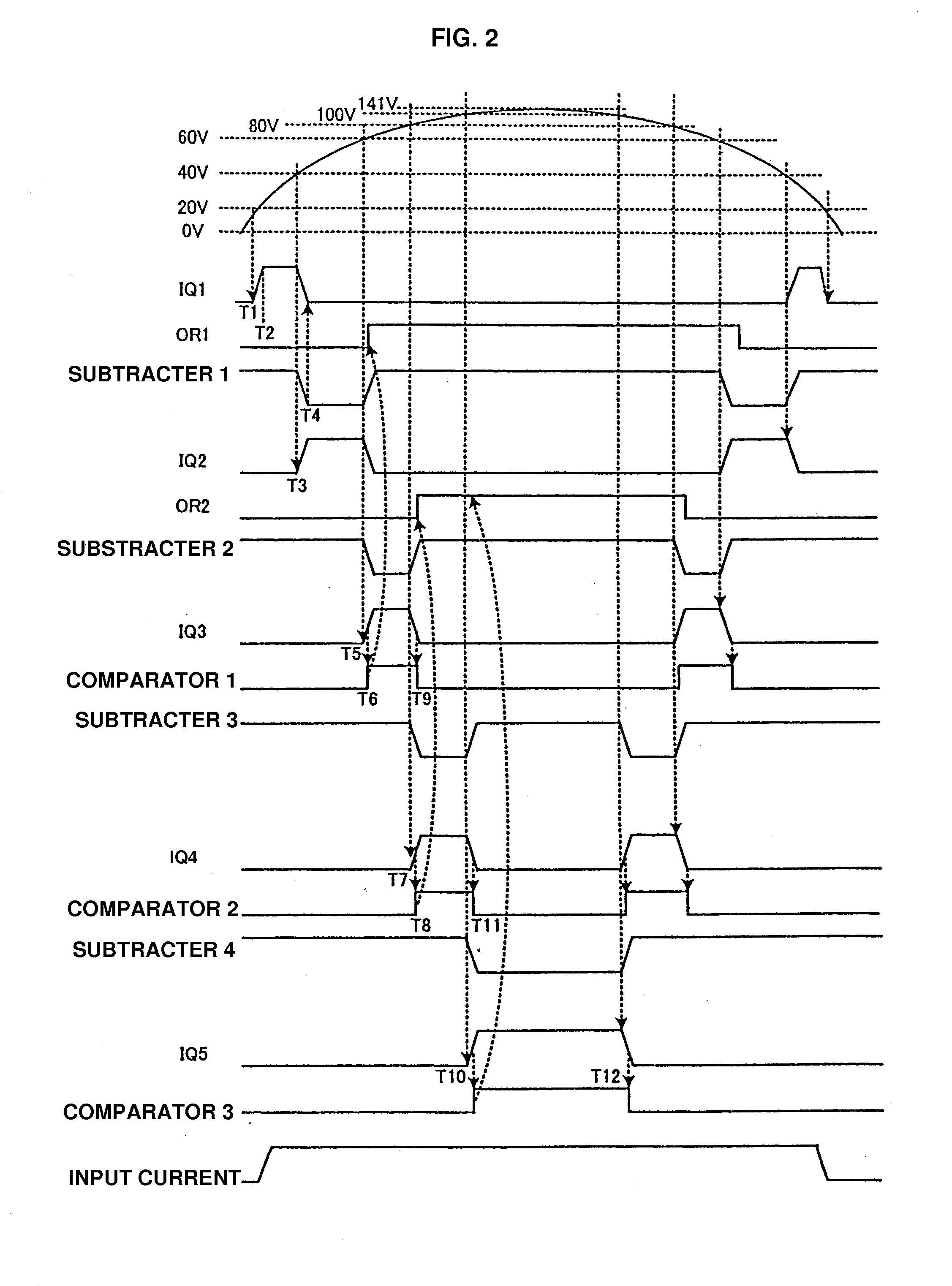

LED drive device, LED drive method and lighting system

InactiveUS20100194298A1Efficient switchingSmooth switchingElectrical apparatusElectroluminescent light sourcesDriver circuitEngineering

Owner:FUJI ELECTRIC CO LTD

Field-effect semiconductor device, and method of fabrication

ActiveUS20100155720A1Leakage currentLittle and no physical impairmentSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionField effect

A heterojunction field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on a major surface of the main semiconductor region and electrically coupled to the 2DEG layer. Between these electrodes, a gate electrode is received in a recess in the major surface of the main semiconductor region via a p-type metal oxide semiconductor film and insulating film, whereby a depletion zone is normally created in the 2DEG layer, making the device normally off. The p-type metal oxide semiconductor film of high hole concentration serves for the normally-off performance of the device with low gate leak current, and the insulating film for further reduction of gate leak current.

Owner:SANKEN ELECTRIC CO LTD

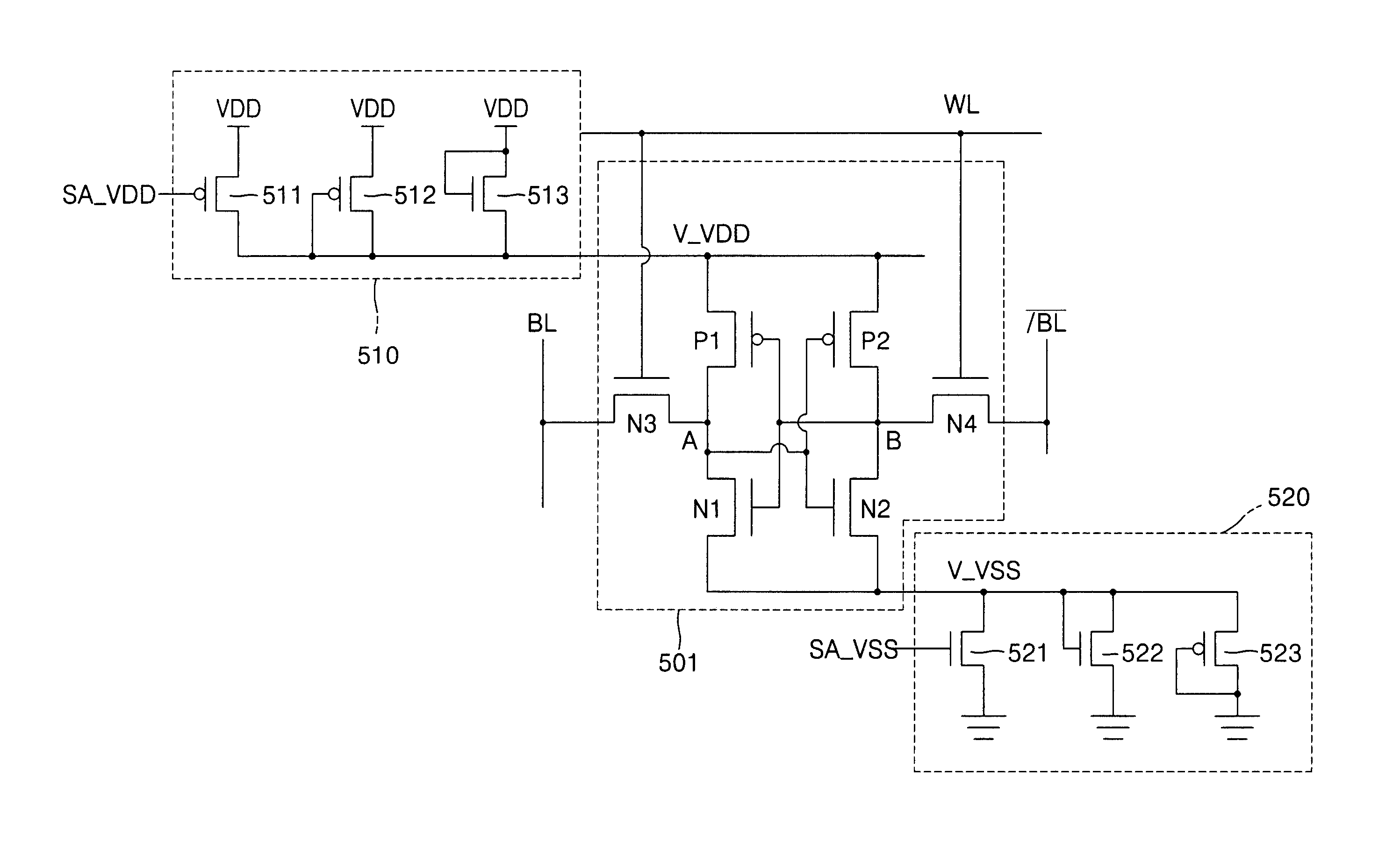

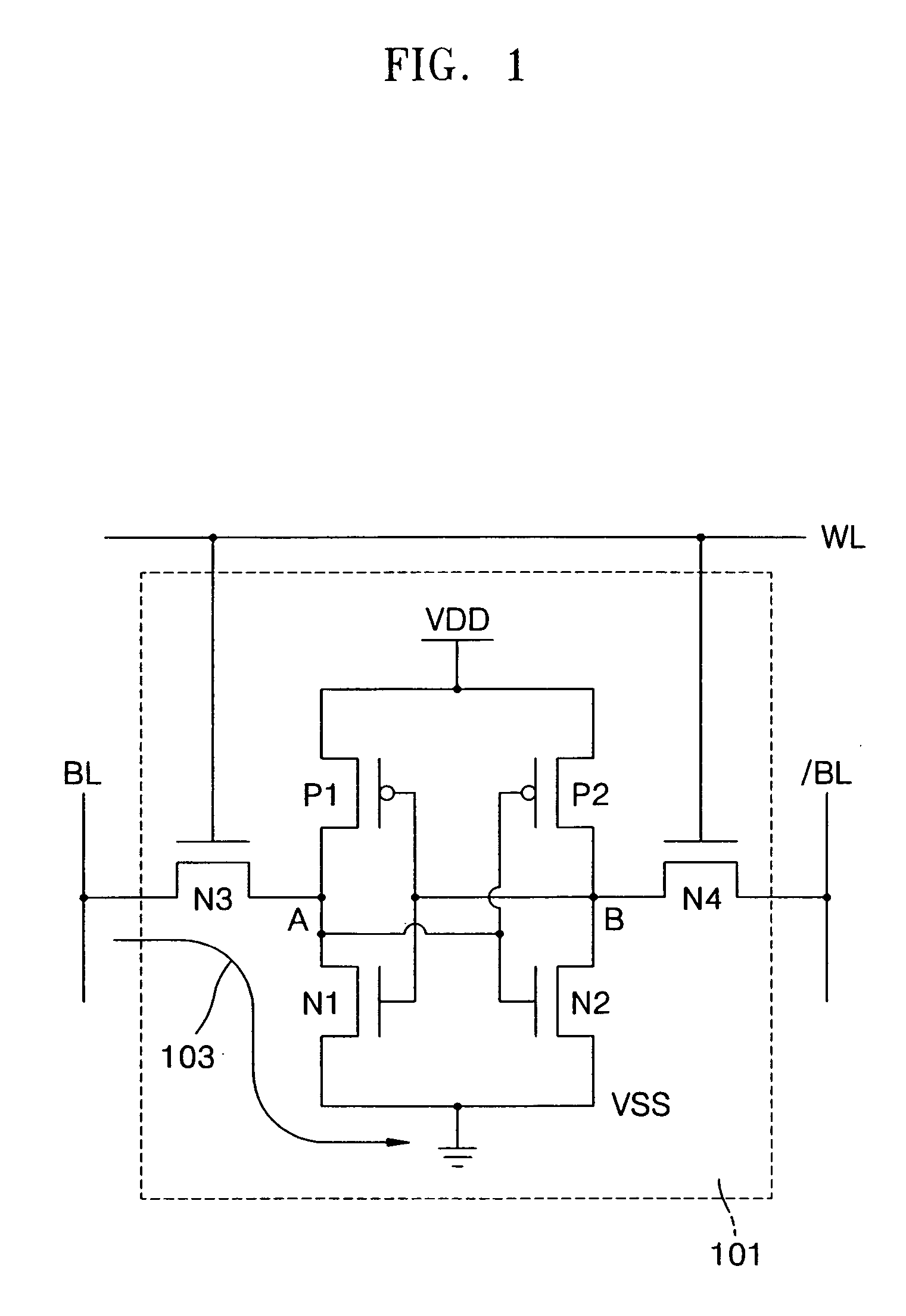

SRAM employing virtual rail scheme stable against various process-voltage-temperature variations

An SRAM employs a virtual rail configuration that is stable against process-voltage-temperature (PVT) variation. The SRAM provides a virtual power supply voltage to an SRAM cell that is obtained by lowering a power supply voltage by a threshold voltage of a transistor and a virtual ground voltage obtained by raising a ground voltage by a threshold voltage of a transistor. Due to the use of PMOS and NMOS transistors of diode types connected between the power supply voltage and the virtual power supply voltage and the use of NMOS and PMOS transistors of diode types connected between the ground voltage and the virtual ground voltage, a virtual power supply voltage level and a virtual ground voltage level that are stable even against various PVT variations are provided, so that low-leakage current characteristics are stable.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device and driving method thereof

ActiveUS20110182110A1Reduce power consumptionNovel structureSolid-state devicesRead-only memoriesWrite bitEngineering

A semiconductor device which stores data by using a transistor whose leakage current between source and drain in an off state is small as a writing transistor. In a matrix including a plurality of memory cells in which a drain of the writing transistor is connected to a gate of a reading transistor and the drain of the writing transistor is connected to one electrode of a capacitor, a gate of the writing transistor is connected to a writing word line; a source of the writing transistor is connected to a writing bit line; and a source and a drain of the reading transistor are connected to a reading bit line and a bias line. In order to reduce the number of wirings, the writing bit line or the bias line is substituted for the reading bit line in another column.

Owner:SEMICON ENERGY LAB CO LTD

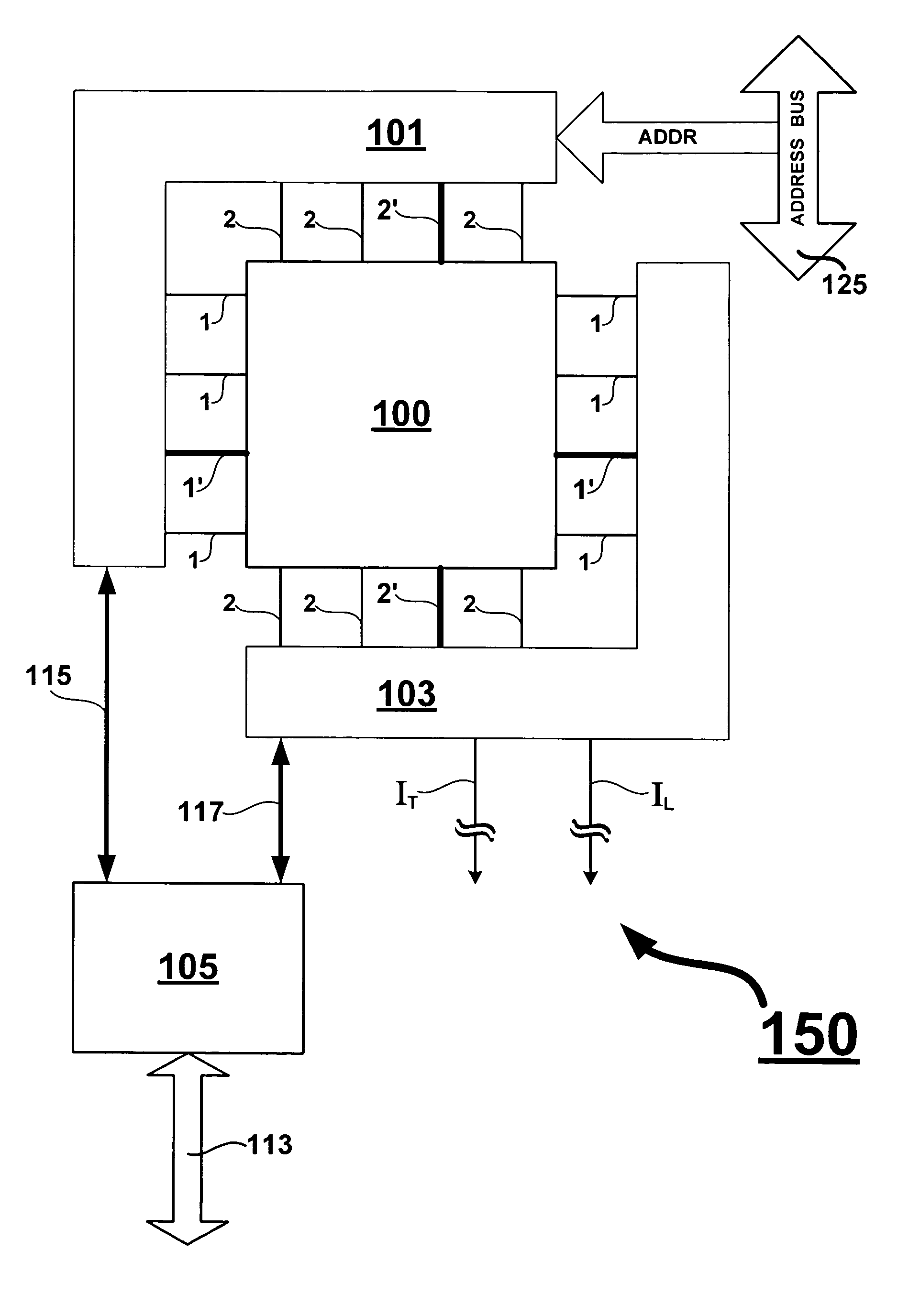

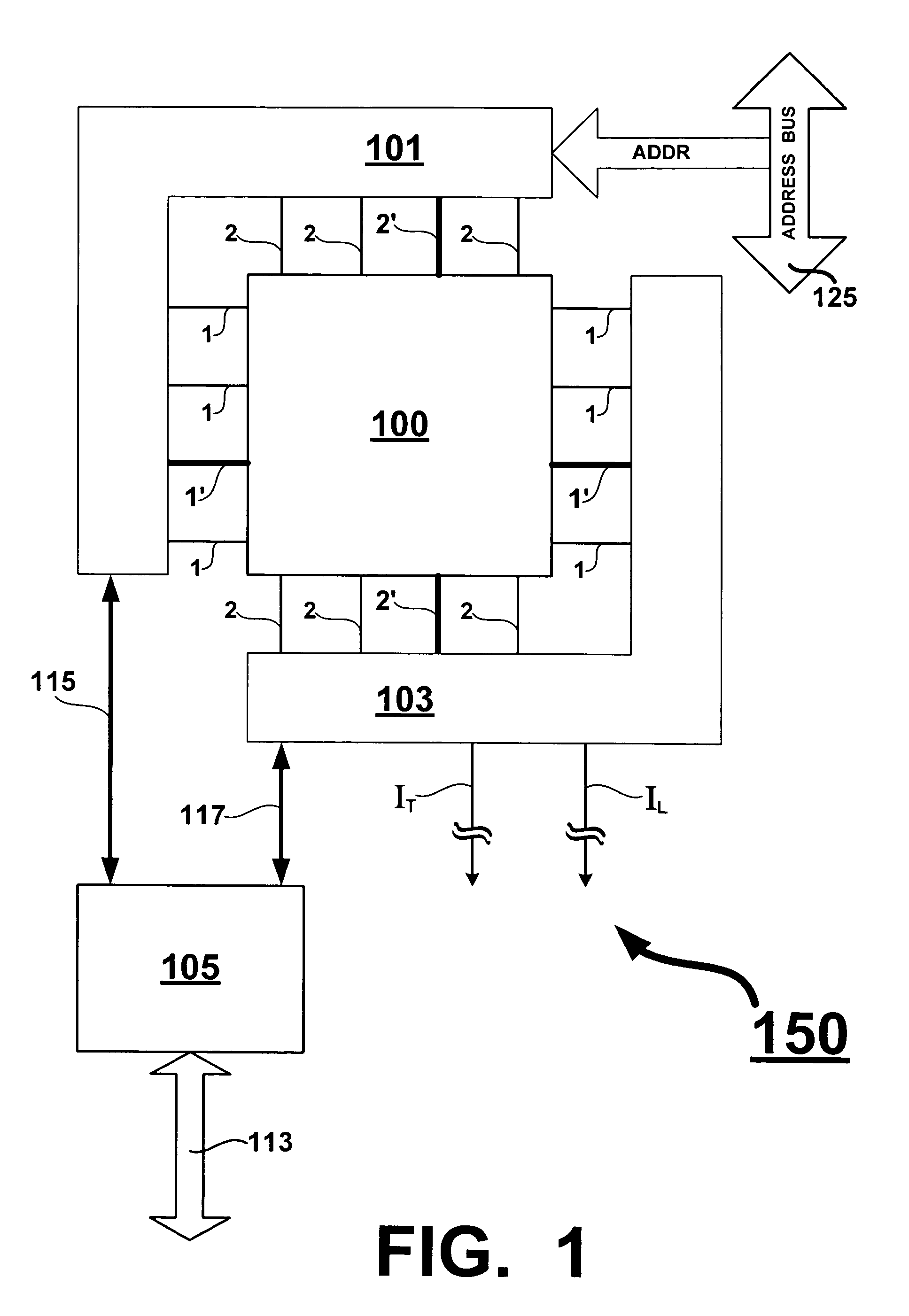

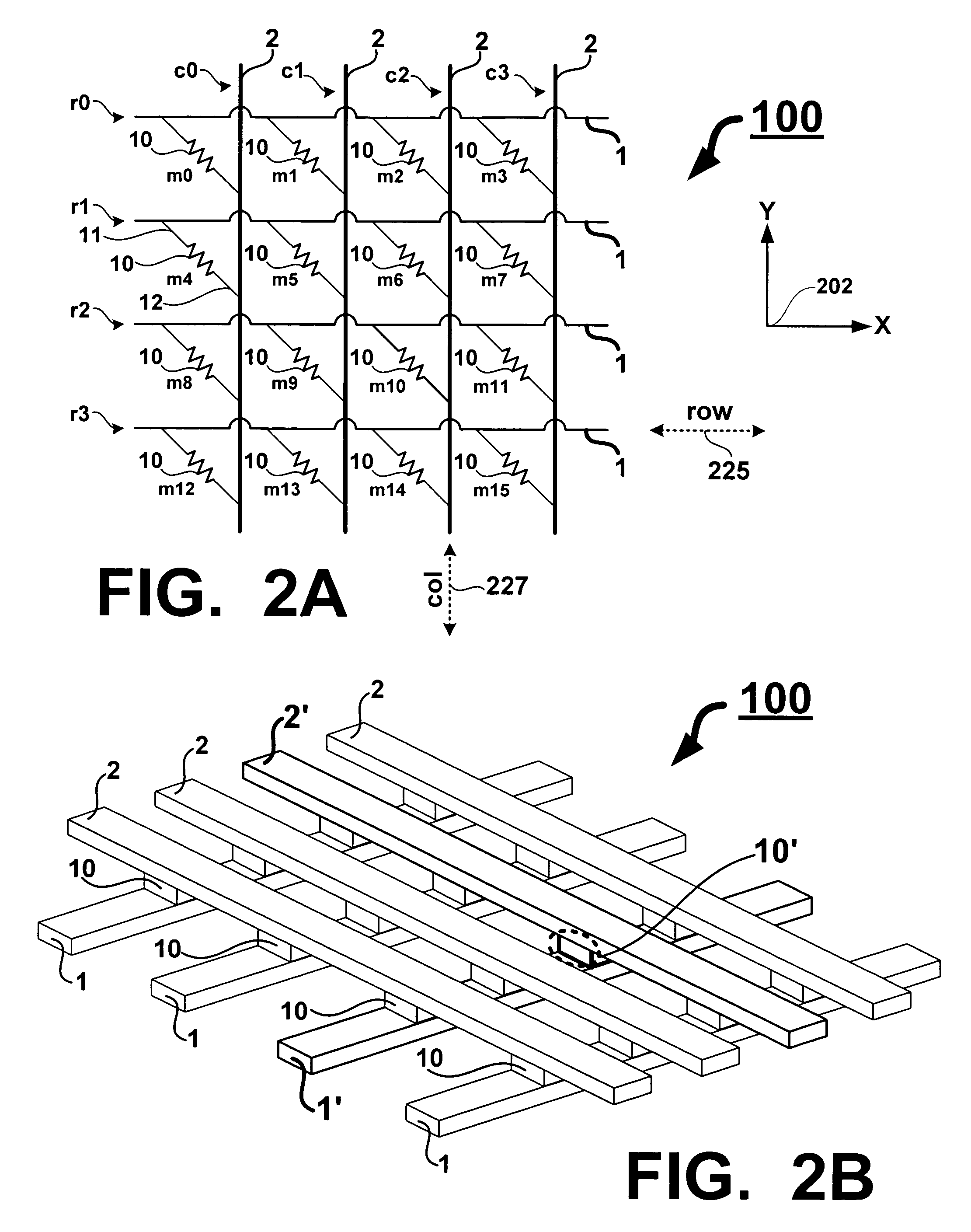

Two-cycle sensing in a two-terminal memory array having leakage current

A two-terminal memory array includes a plurality of first and second conductive traces. An address unit operatively applies a select voltage across a selected pair of the first and second conductive traces and applies a non-select voltage potential to unselected traces. A total current flowing in the selected first conductive trace and a leakage current flowing through unselected second conductive traces are sensed by a sense unit in a one cycle or a two cycle pre-read operation. The total and leakage currents can be combined with a reference signal to derive a data signal indicative of one of a plurality of conductivity profiles that represent stored data. The conductivity profiles can be stored in a resistive state memory element that is electrically in series with the selected first and second conductive traces.

Owner:III HLDG 1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com