Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

236results about "Logic circuits using semiconductor devices" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

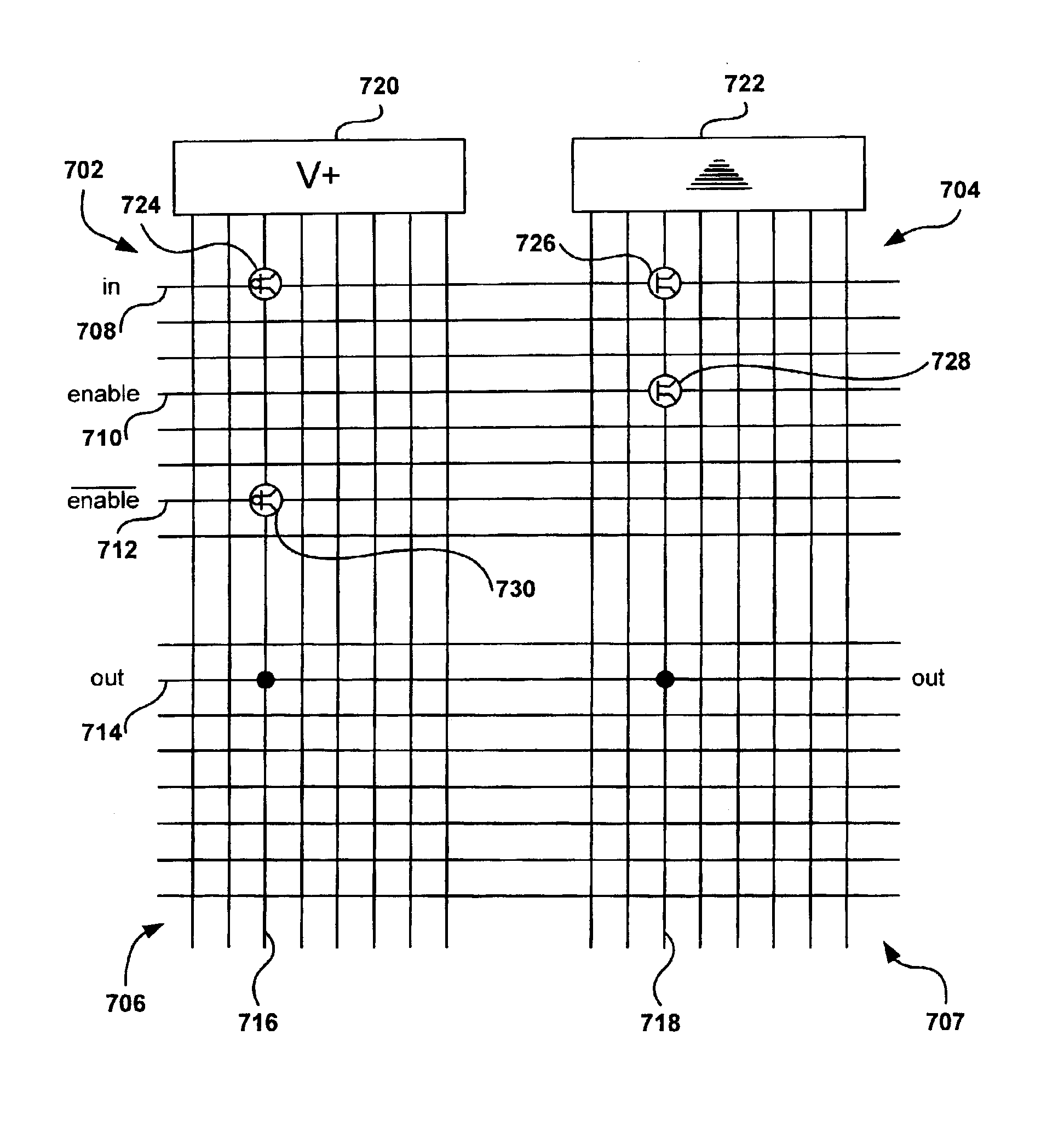

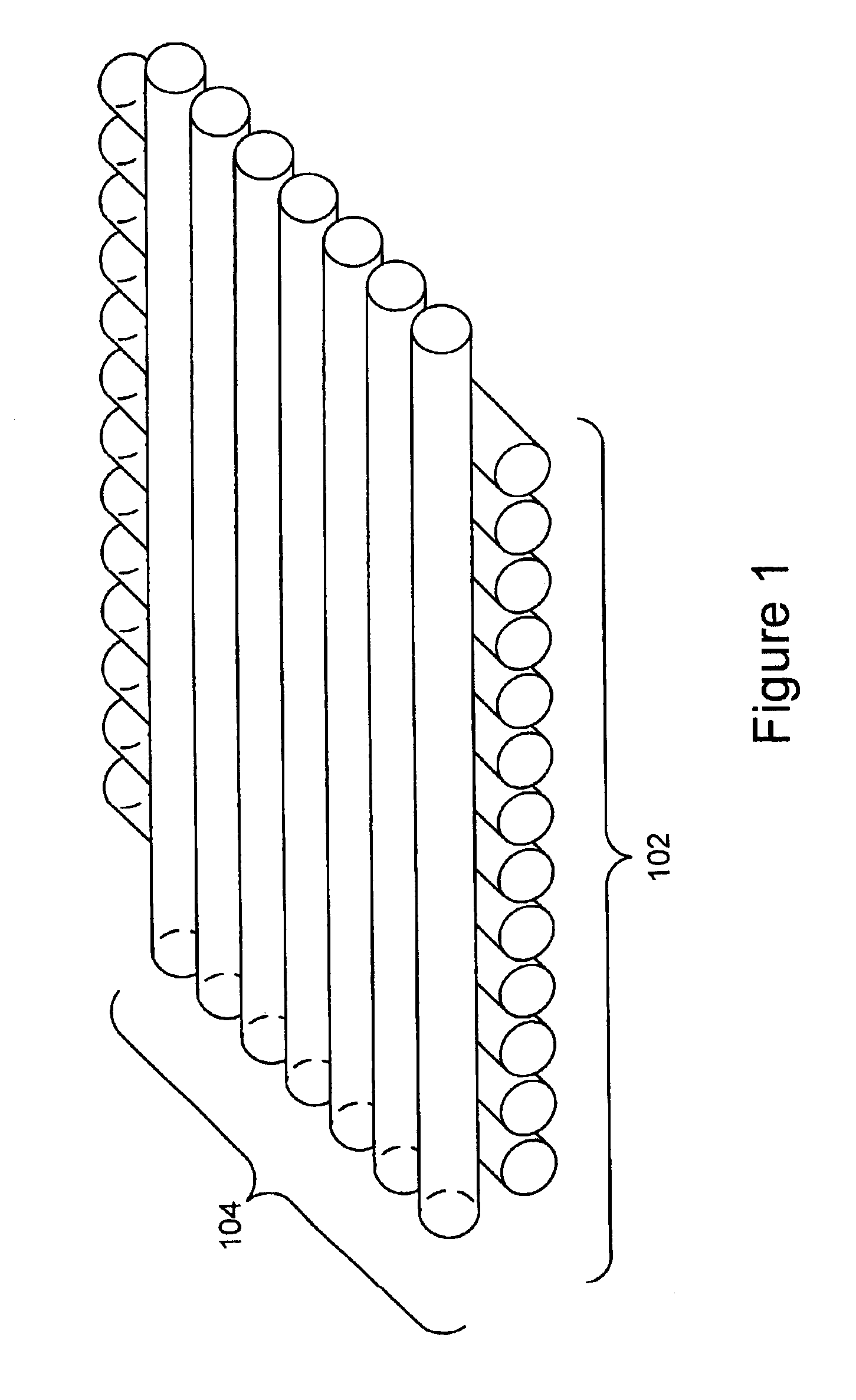

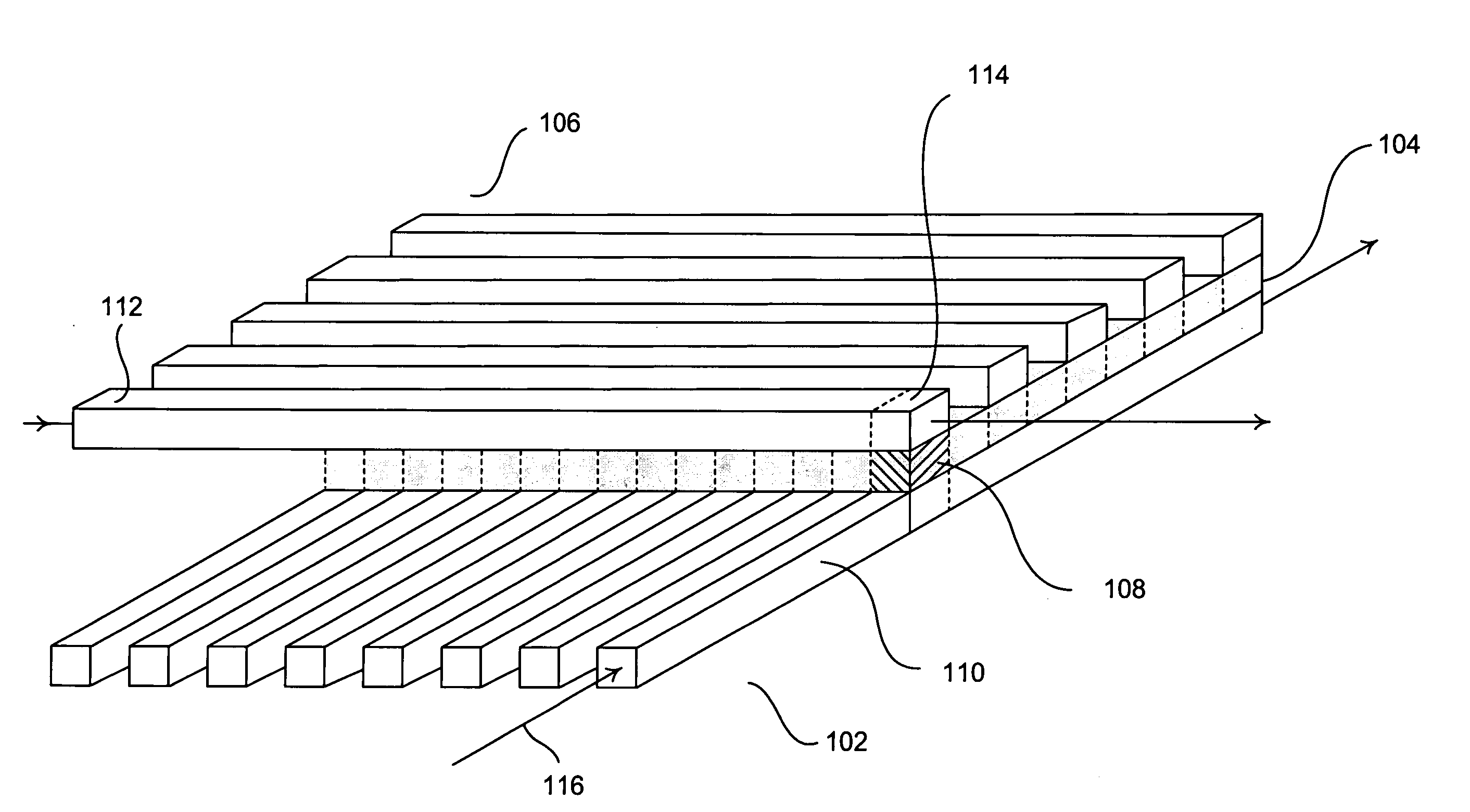

Molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits, and more complex circuits composed, in part, from molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits

InactiveUS6919740B2High densityLittle powerLogic circuits characterised by logic functionNanoinformaticsCrossbar switchNanowire

Methods for implementing familiar electronic circuits at nanoscale sizes using molecular-junction-nanowire crossbars, and nanoscale electronic circuits produced by the methods. In one embodiment of the present invention, a 3-state inverter is implemented. In a second embodiment of the present invention, two 3-state inverter circuits are combined to produce a transparent latch. The 3-state inverter circuit and transparent-latch circuit can then be used as a basis for constructing additional circuitry, including master / slave flip-flops, a transparent latch with asynchronous preset, a transparent latch with asynchronous clear, and a master / slave flip-flop with asynchronous preset. 3-state inverters can thus be used to compose latches and flip-flops, and latches and flip-flops can be used, along with additional Boolean circuitry, to compose a wide variety of useful, state-maintaining circuits, all implementable within molecular-junction-nanowire crossbars by selectively configuring junctions within the molecular-junction-nanowire crossbars.

Owner:HEWLETT PACKARD DEV CO LP

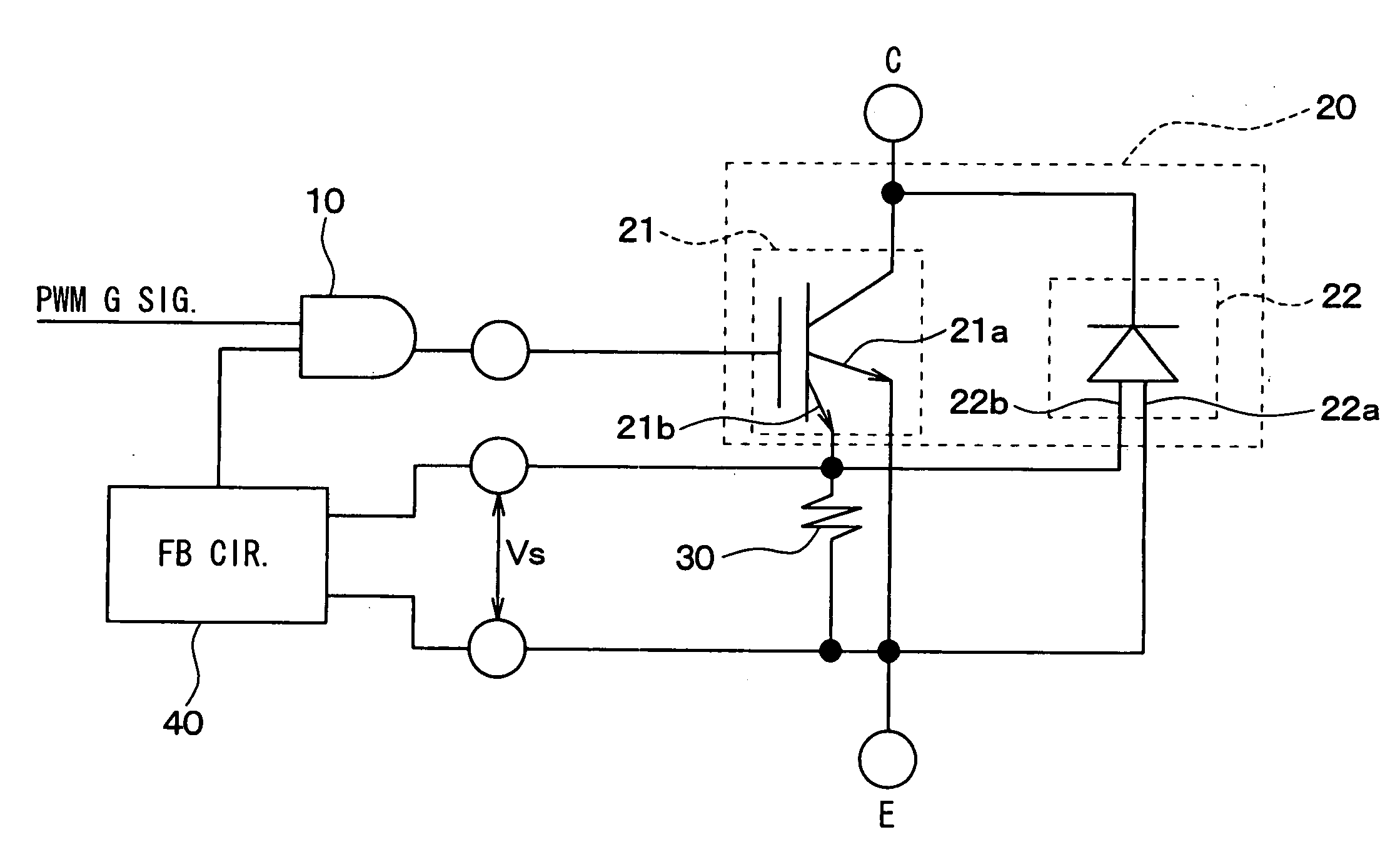

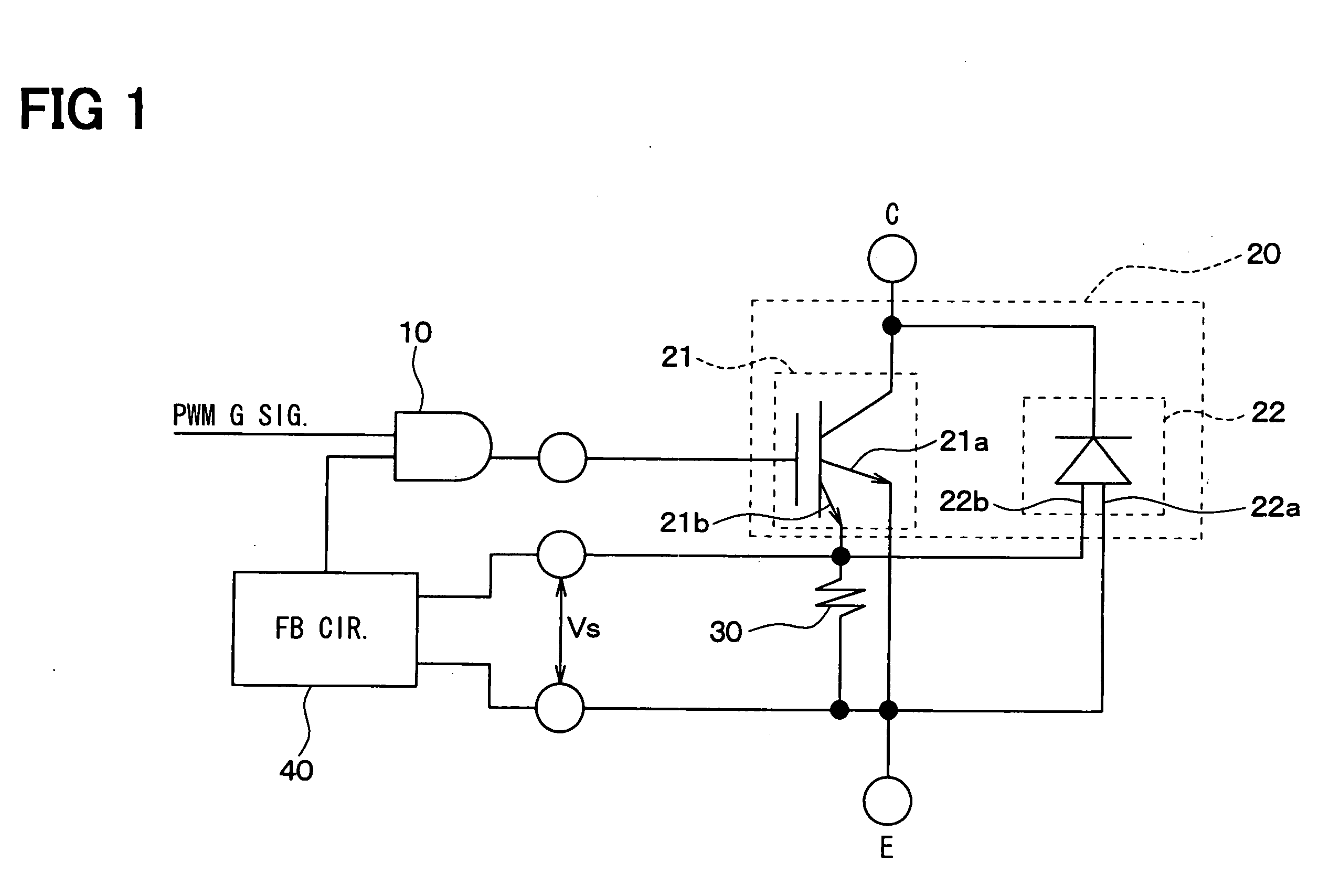

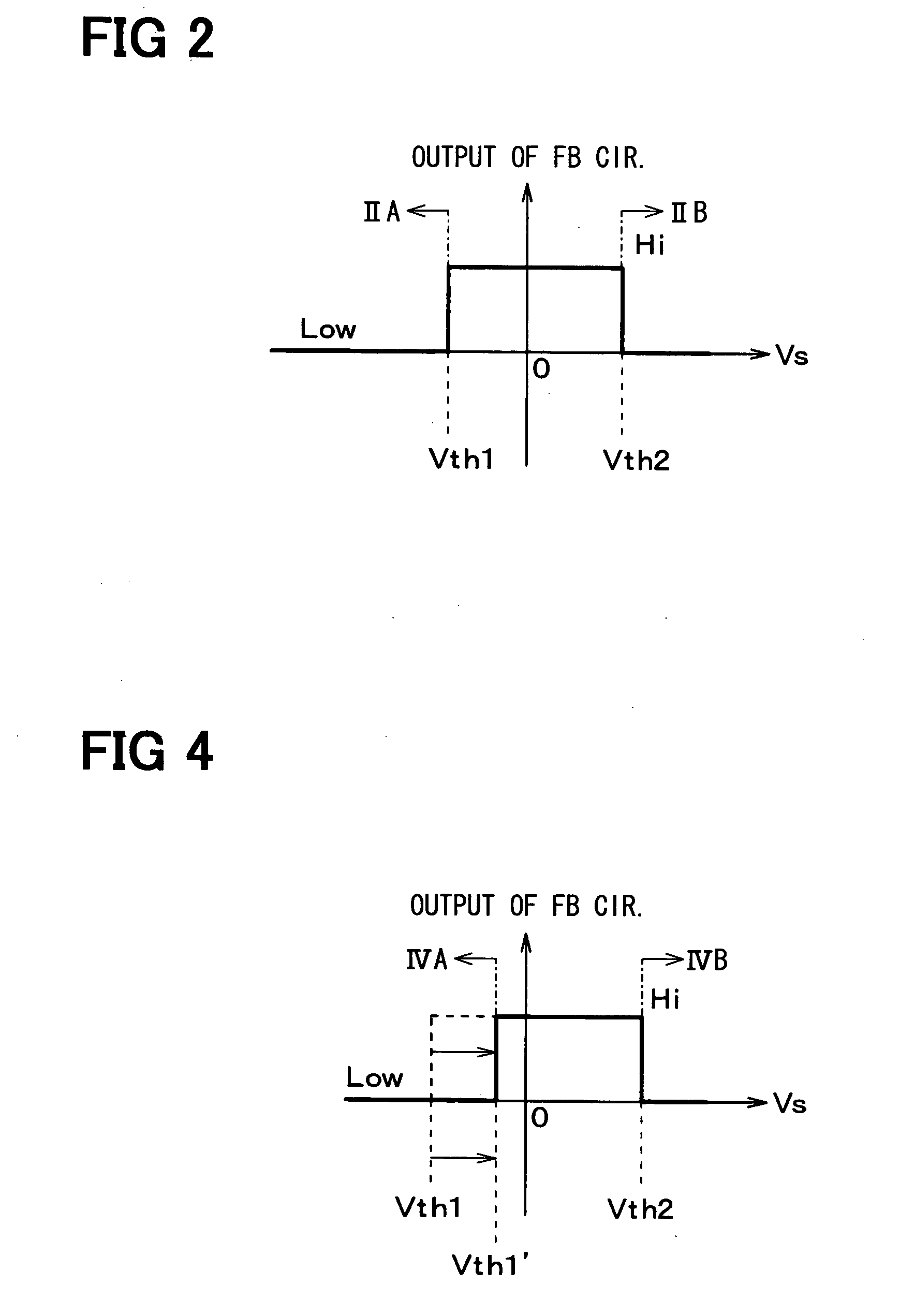

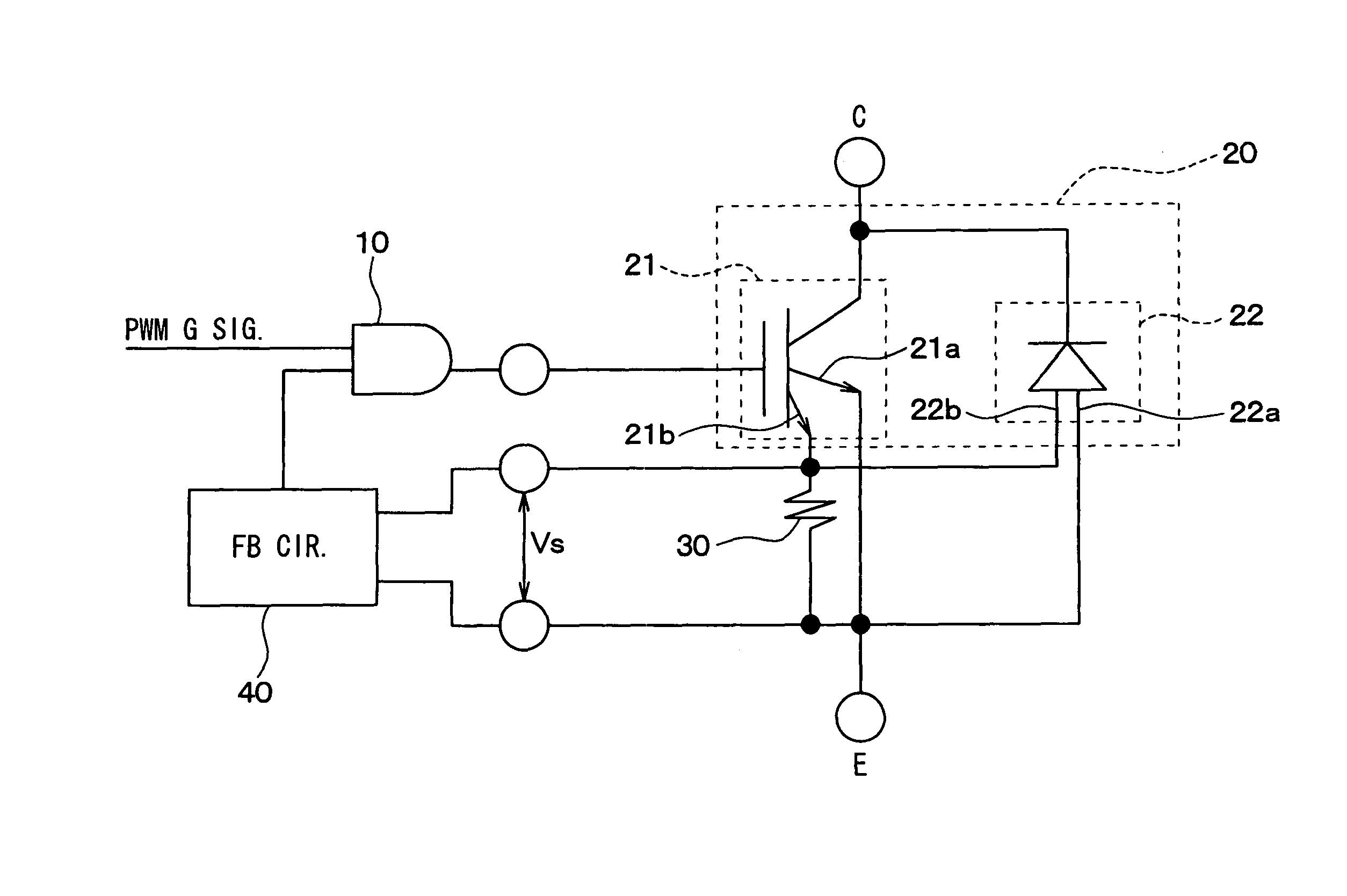

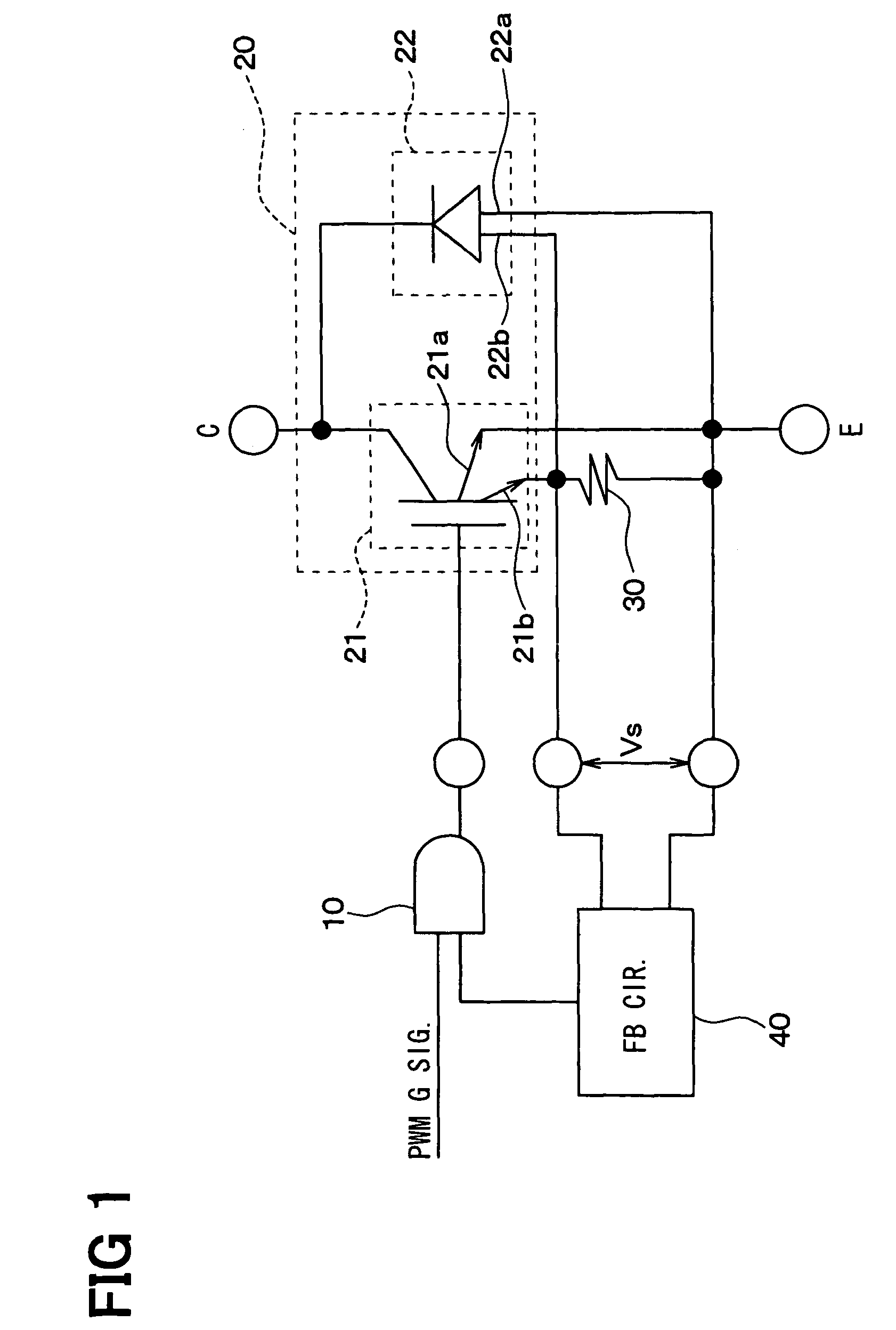

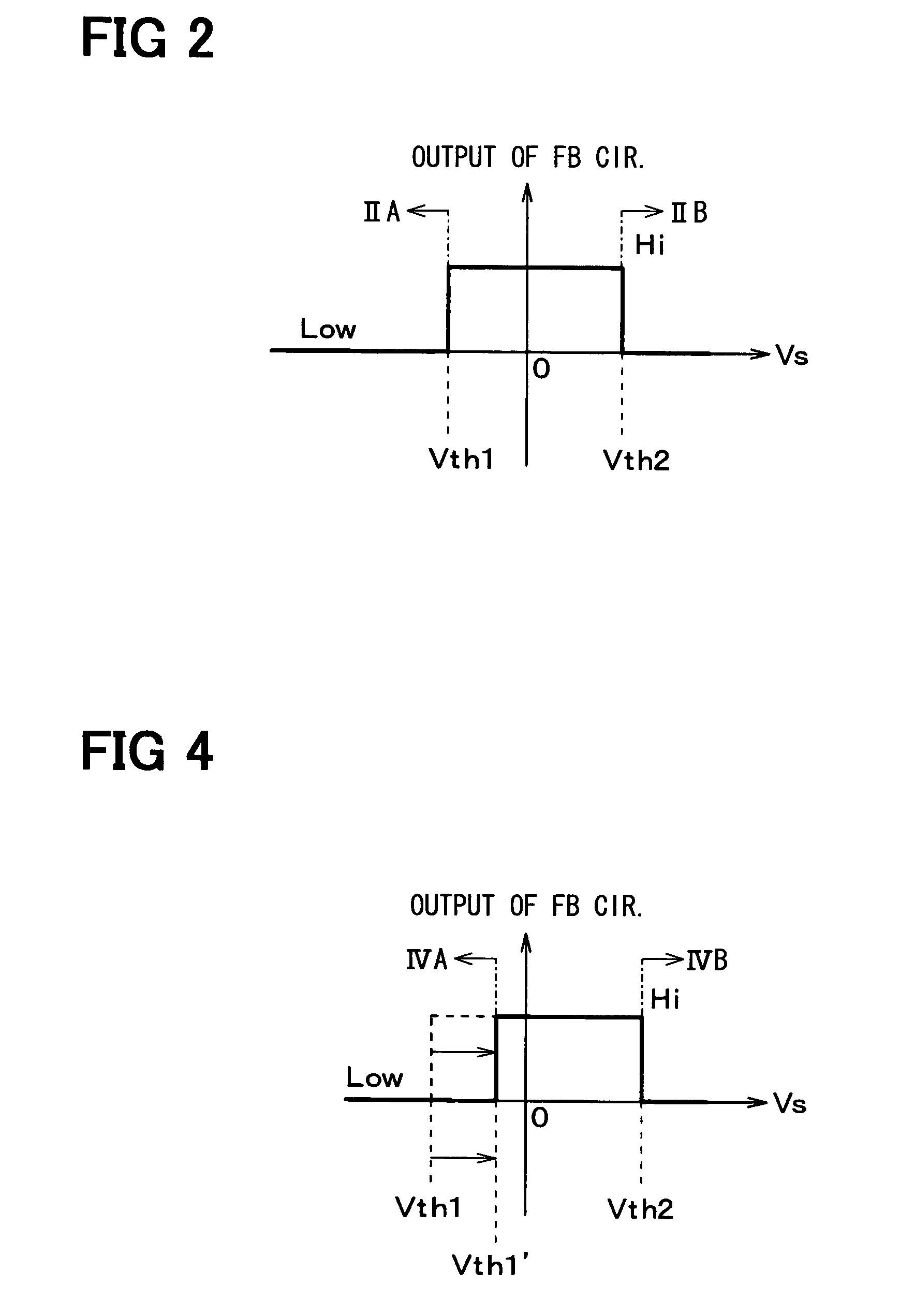

Semiconductor device having diode-built-in IGBT and semiconductor device having diode-built-in DMOS

ActiveUS20090057832A1Increase lossTransistorLogic circuits characterised by logic functionSemiconductorSemiconductor device

A semiconductor device includes: a semiconductor substrate; a diode-built-in insulated-gate bipolar transistor having an insulated-gate bipolar transistor and a diode, which are disposed in the substrate, wherein the insulated-gate bipolar transistor includes a gate, and is driven with a driving signal input into the gate; and a feedback unit for detecting current passing through the diode. The driving signal is input from an external unit into the feedback unit. The feedback unit passes the driving signal to the gate of the insulated-gate bipolar transistor when the feedback unit detects no current through the diode, and the feedback unit stops passing the driving signal to the gate of the insulated-gate bipolar transistor when the feedback unit detects the current through the diode.

Owner:DENSO CORP

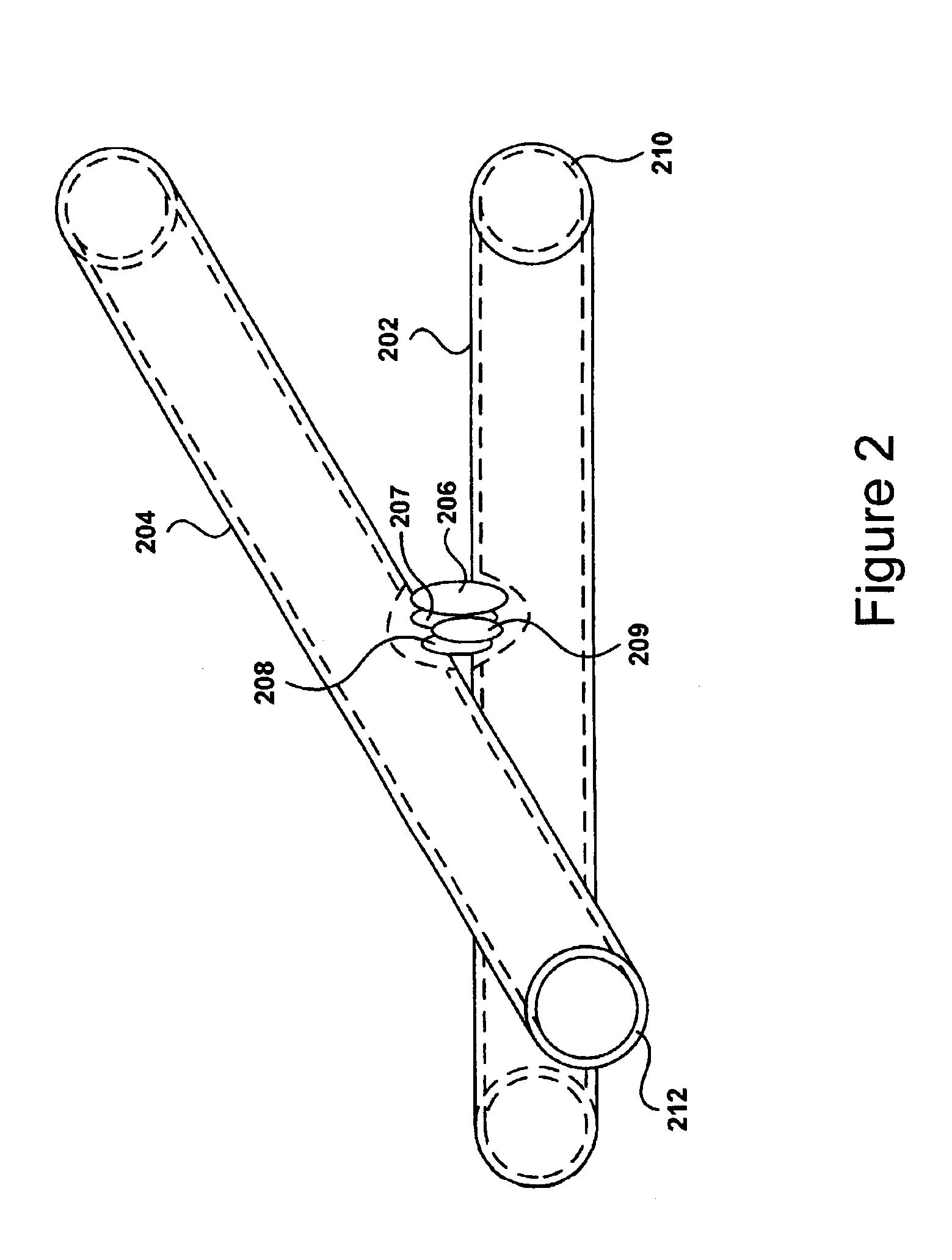

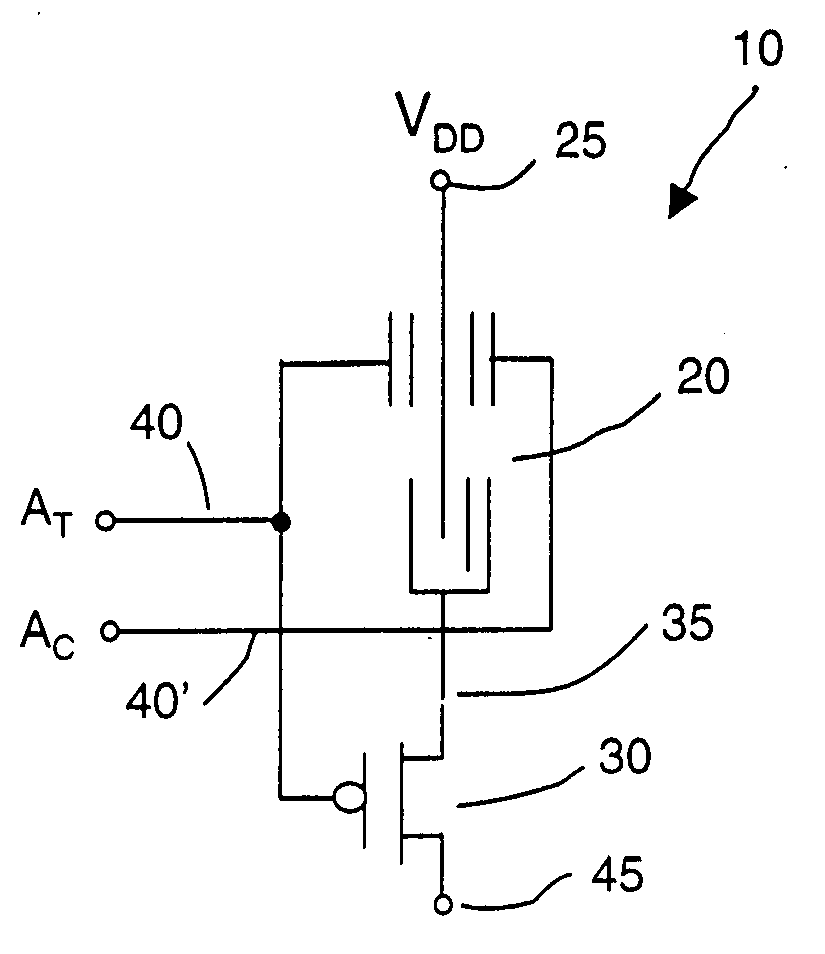

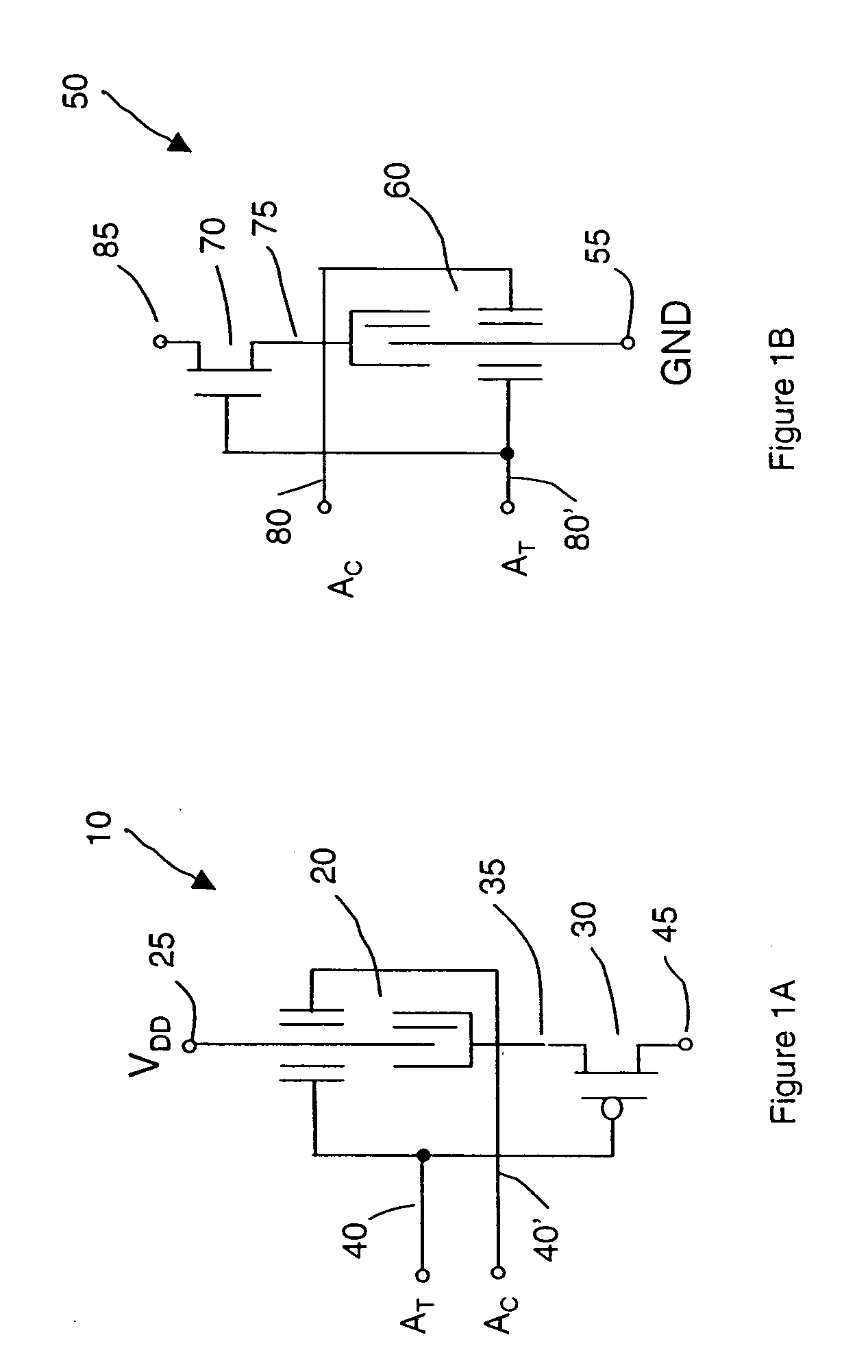

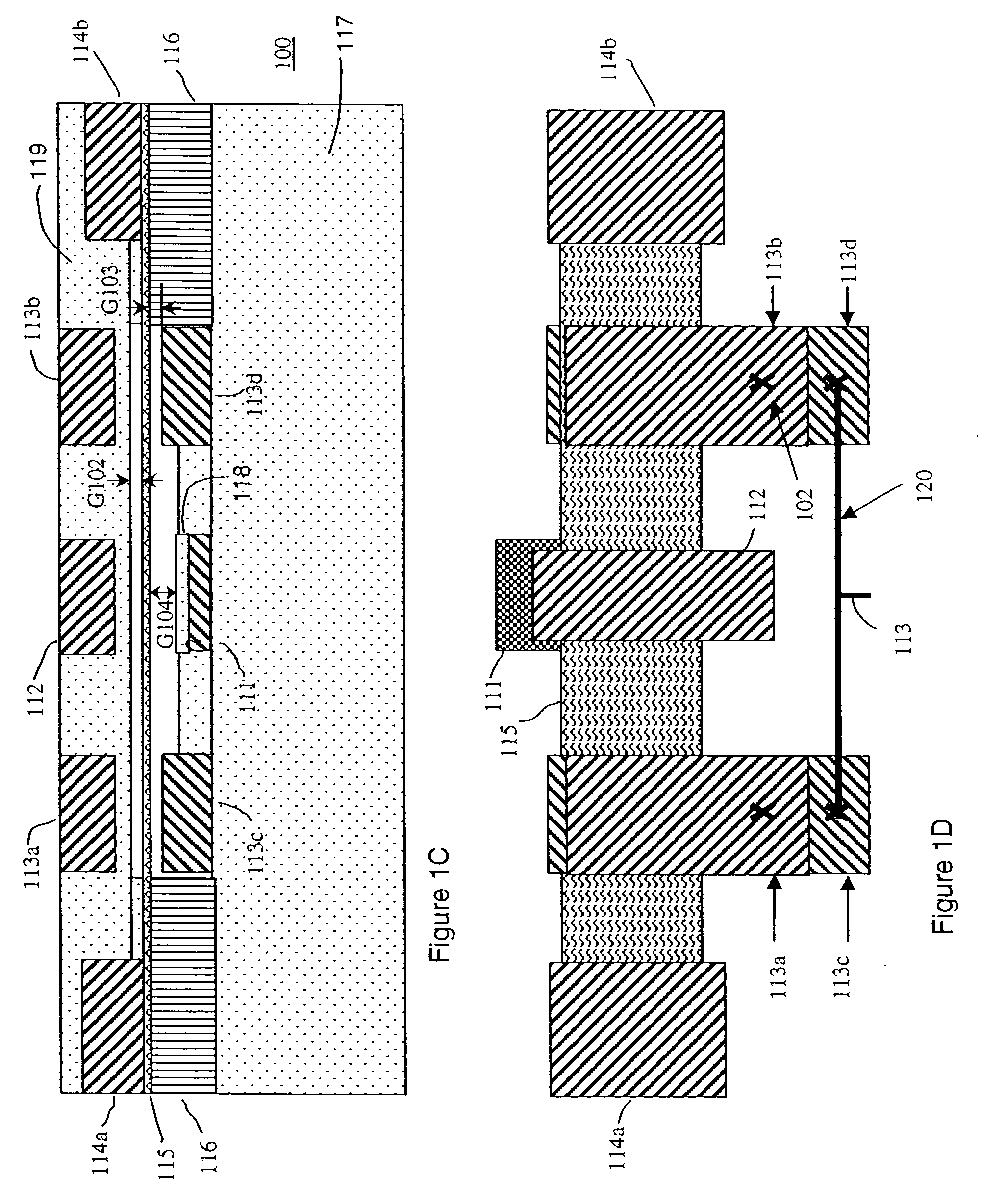

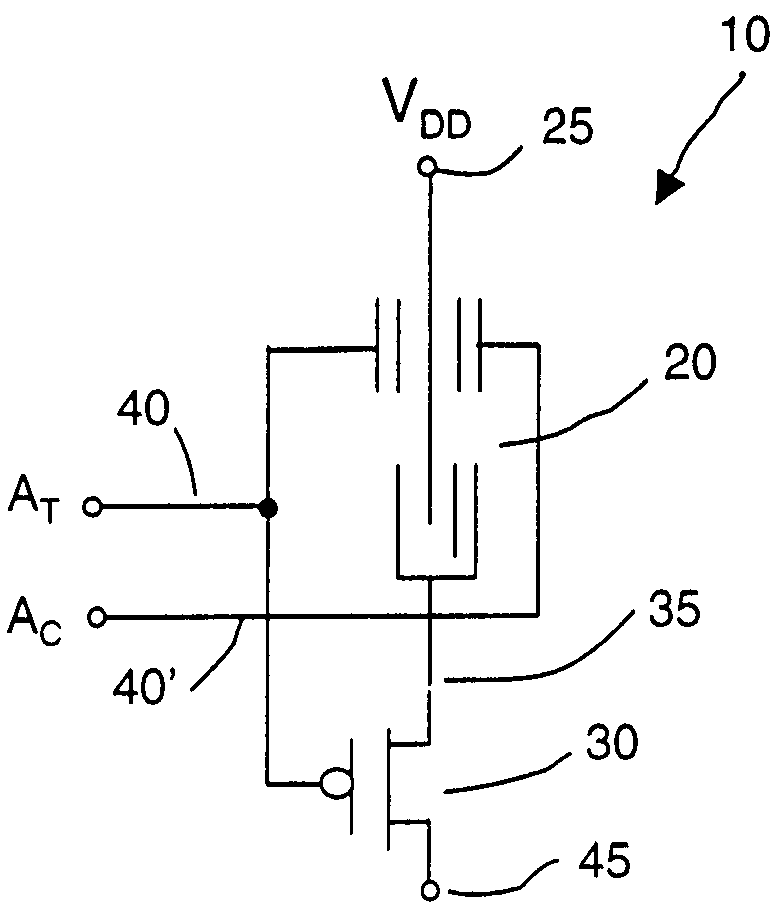

Integrated nanotube and field effect switching device

ActiveUS20060061389A1Logic circuits characterised by logic functionNanoelectromechanical switchesElectricityDevice form

Hybrid switching devices integrate nanotube switching elements with field effect devices, such as NFETs and PFETs. A switching device forms and unforms a conductive channel from the signal input to the output subject to the relative state of the control input. In embodiments of the invention, the conductive channel includes a nanotube channel element and a field modulatable semiconductor channel element. The switching device may include a nanotube switching element and a field effect device electrically disposed in series. According to one aspect of the invention, an integrated switching device is a four-terminal device with a signal input terminal, a control input terminal, a second input terminal, and an output terminal. The devices may be non-volatile. The devices can form the basis for a hybrid NT-FET logic family and can be used to implement any Boolean logic circuit.

Owner:NANTERO

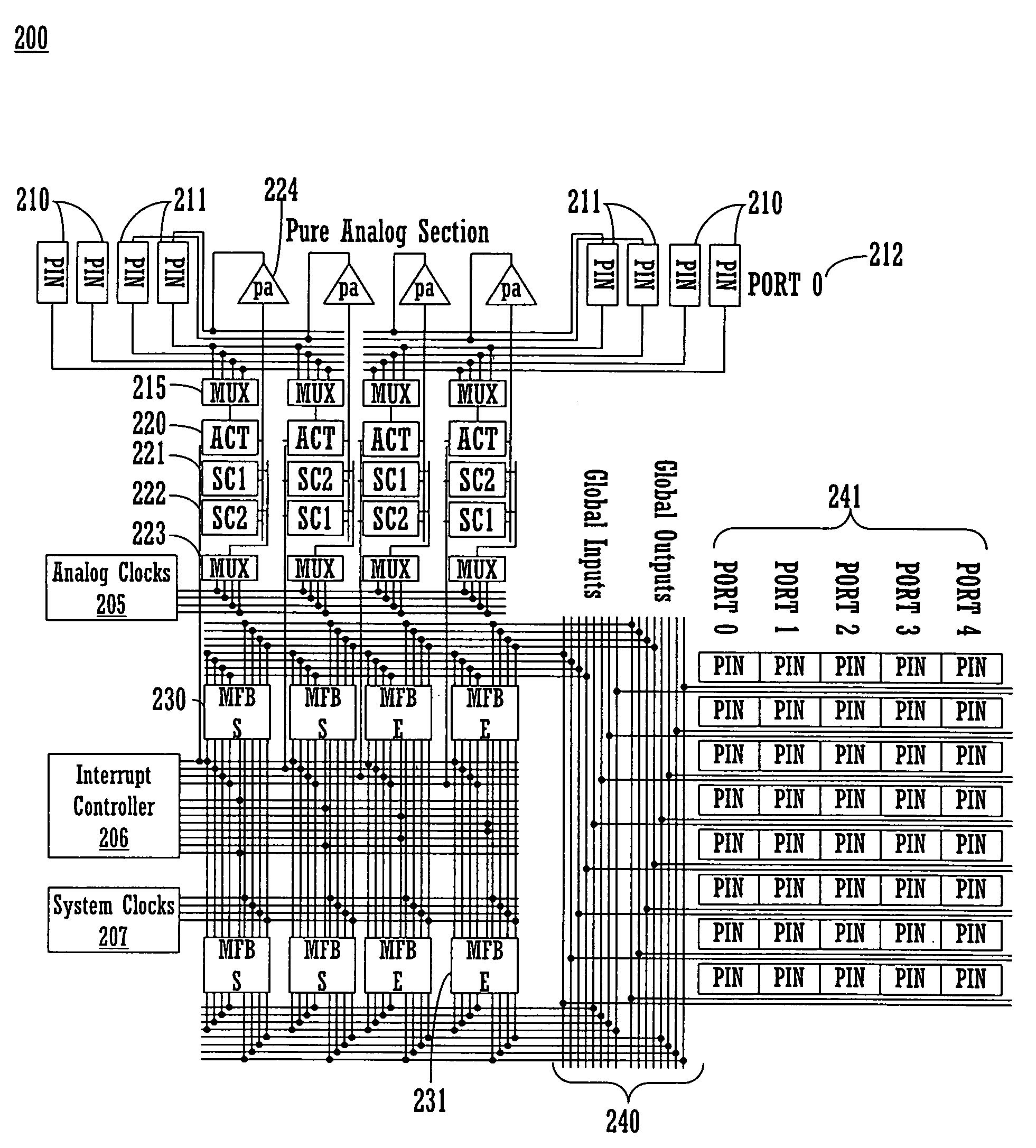

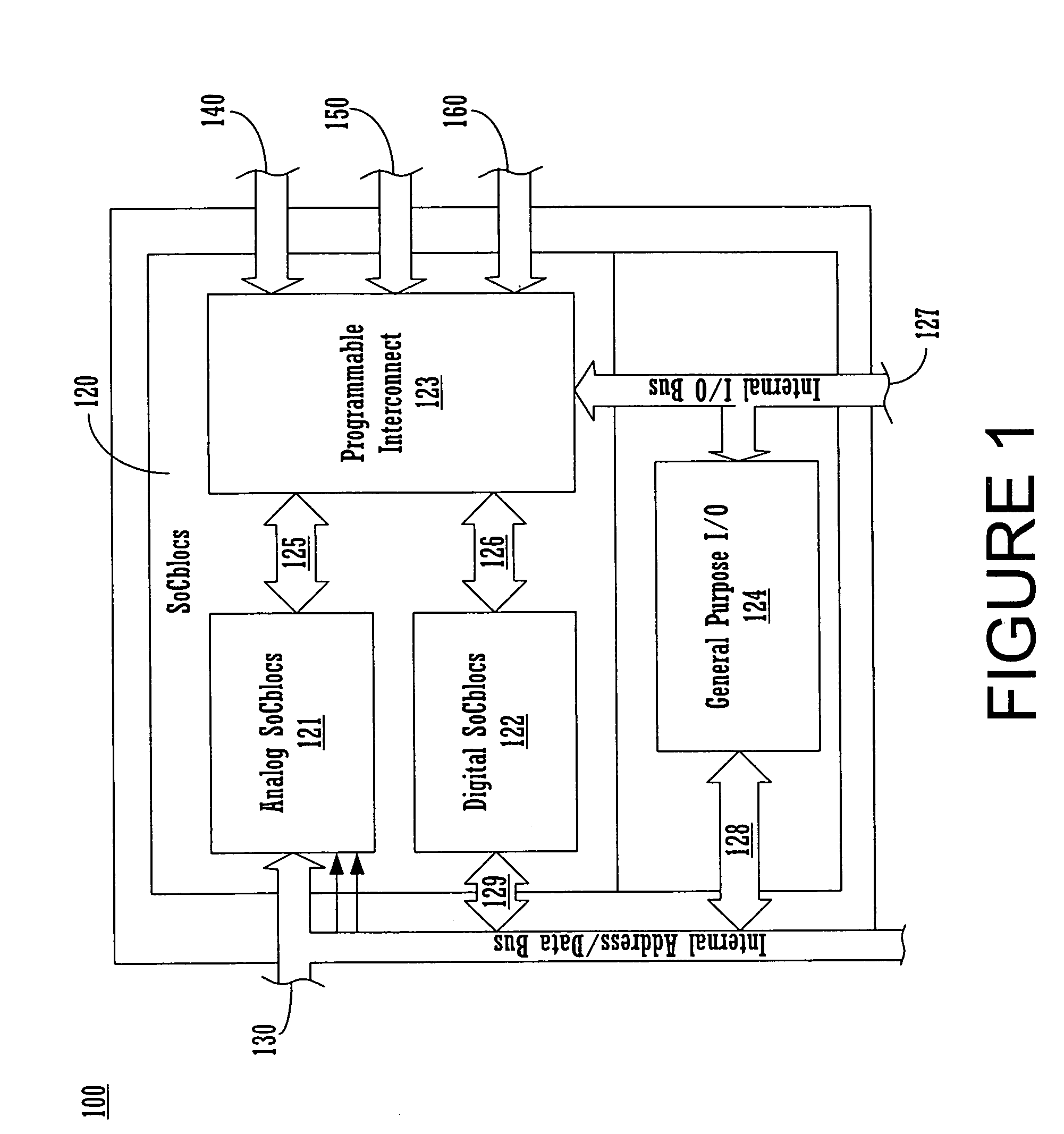

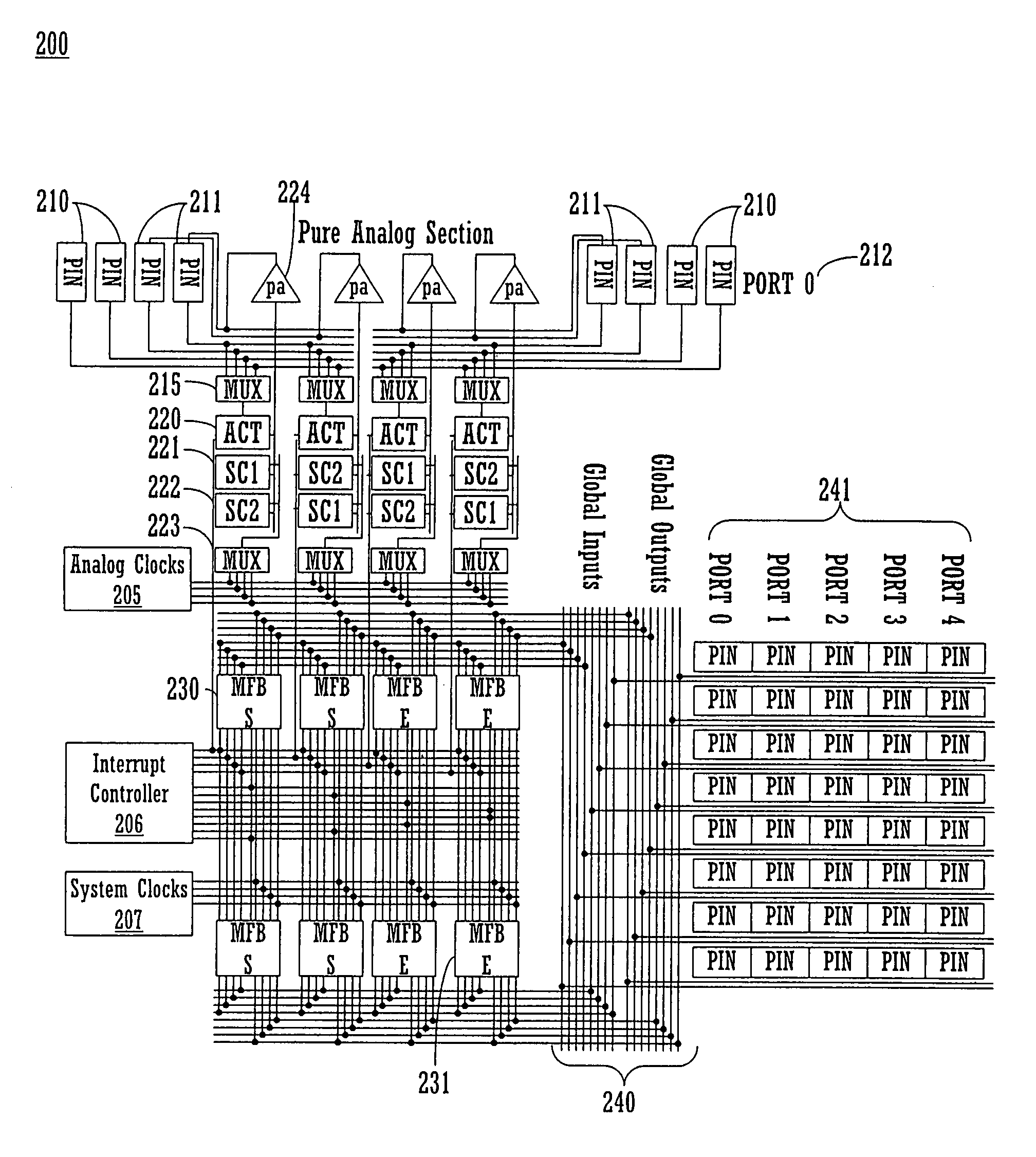

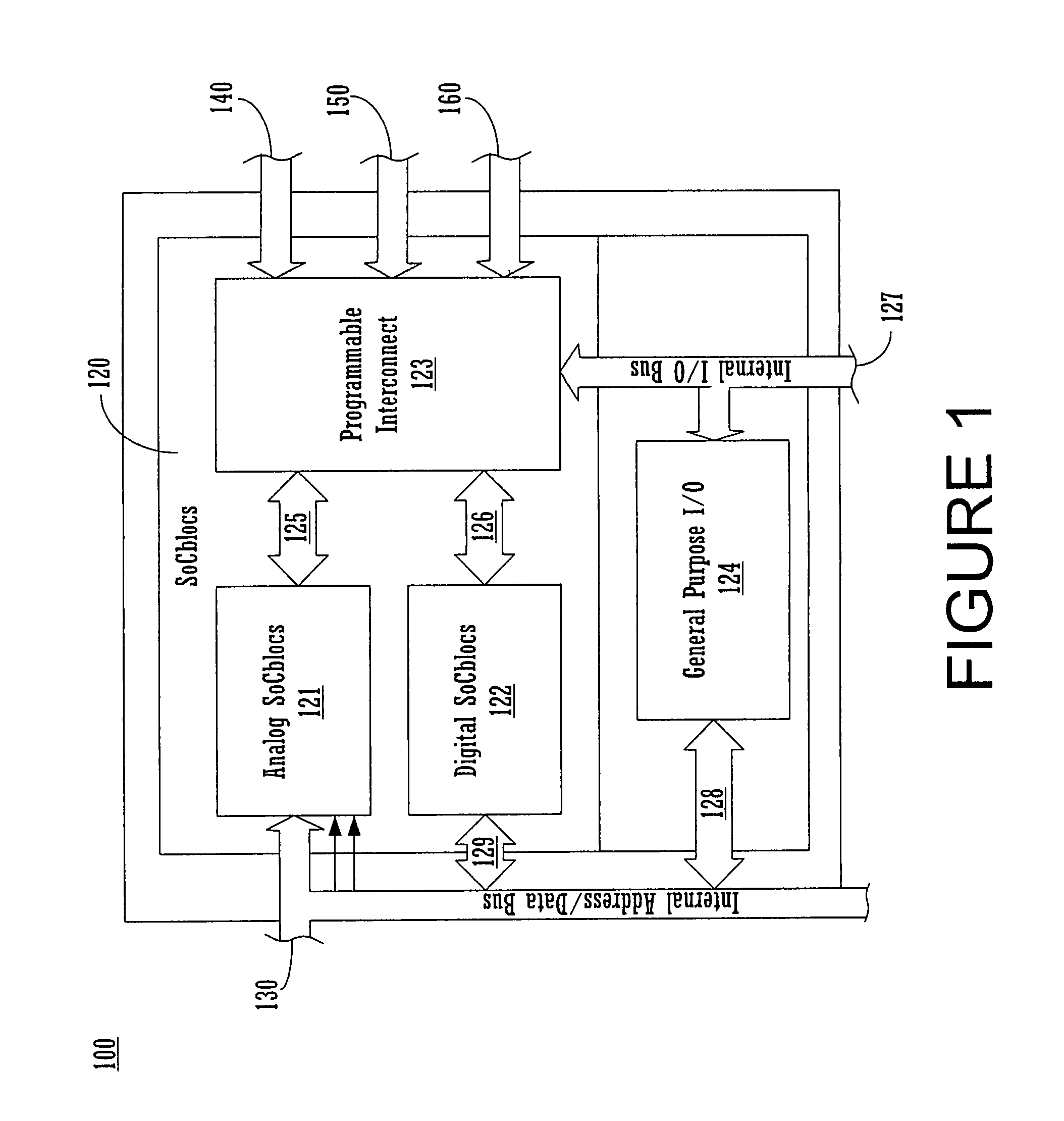

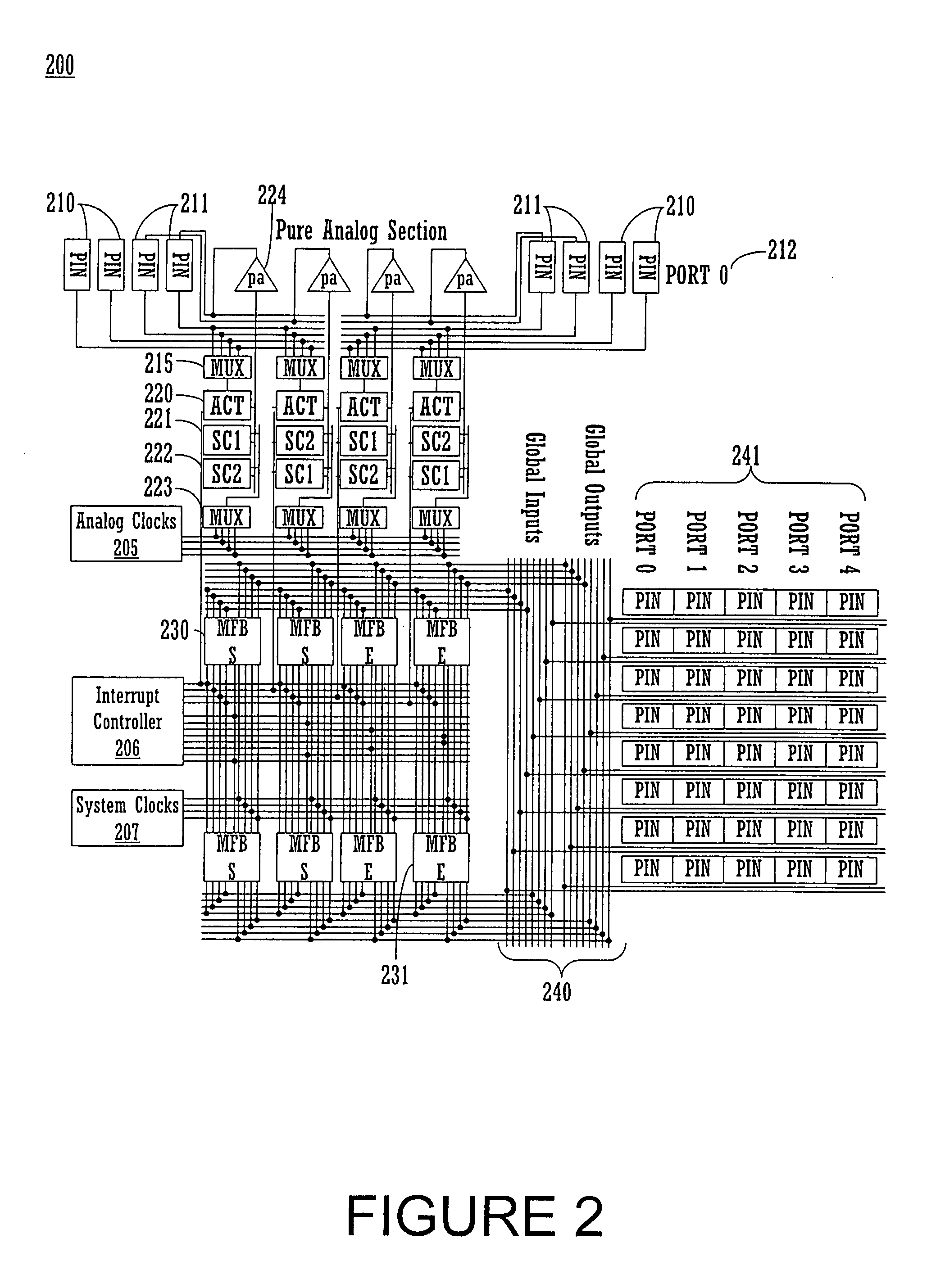

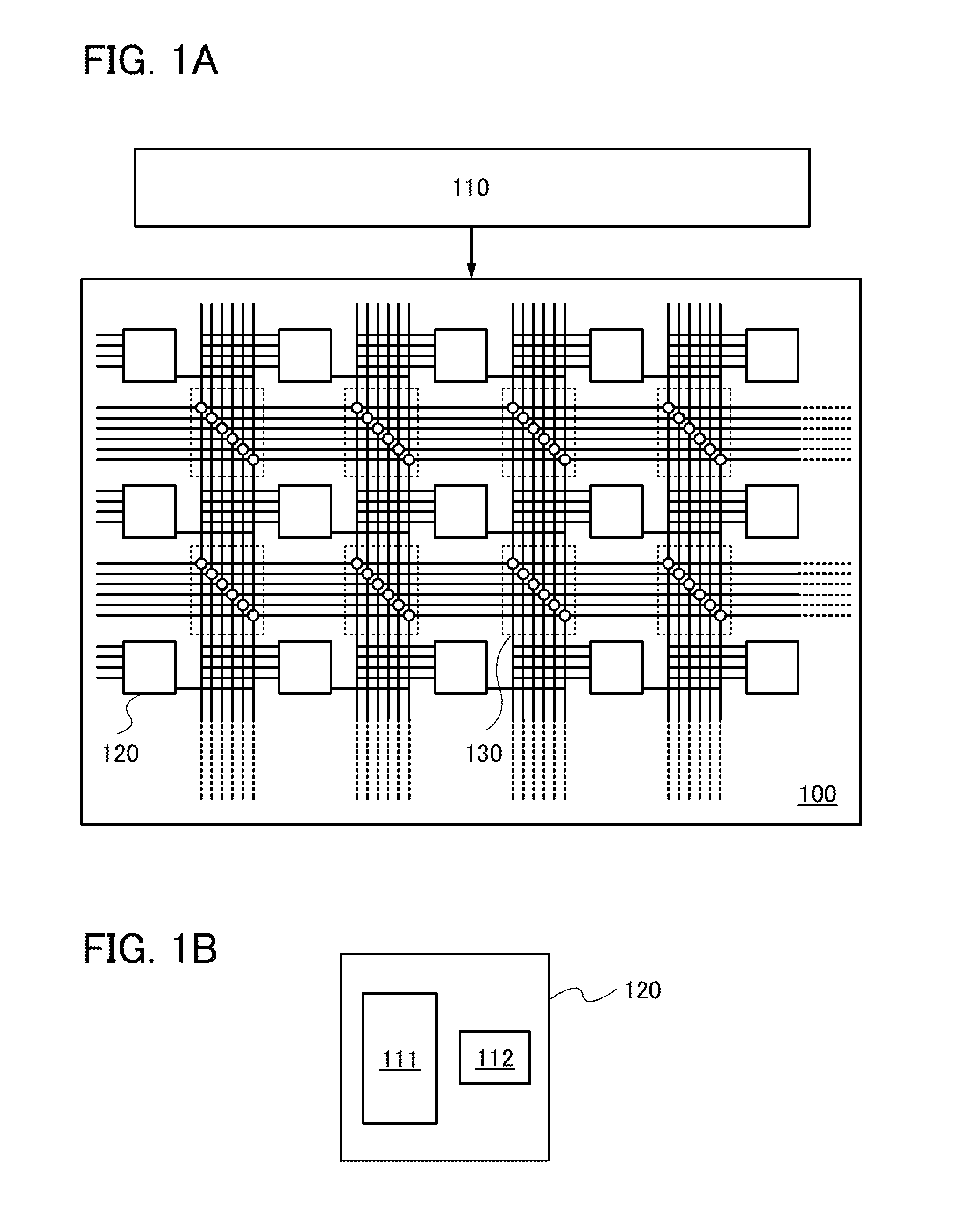

Programmable microcontroller architecture (mixed analog/digital)

InactiveUS7221187B1Excellent interfaceNeed be solveDigital technique networkSolid-state devicesCapacitanceDigital circuitry

A microcontroller with a mixed analog / digital architecture including multiple digital programmable blocks and multiple analog programmable blocks in a communication array having a programmable interconnect structure. The single chip design is implemented by integration of programmable digital and analog circuit blocks that are able to communicate with each other. Robust analog and digital blocks that are flash memory programmable can be utilized to realize complex design applications that otherwise would require multiple chips and / or separate applications. The programmable chip architecture includes a novel array having programmable digital blocks that can communicate with programmable analog blocks using a programmable interconnect structure. The programmable analog array contains a complement of Continuous Time (CT) blocks and a complement of Switched Capacitor (SC) blocks that can communicate together. The analog blocks consist of multi-function circuits programmable for one or more different analog functions, and fixed function circuits programmable for a fixed function with variable parameters. The digital blocks include standard multi-function circuits and enhanced circuits having functions not included in the standard digital circuits. The programmable array is programmed by flash memory and programming allows dynamic reconfiguration. That is, “on-the-fly” reconfiguration of the programmable blocks is allowed. The programmable analog array with both Continuous Time analog blocks and Switched Capacitor analog blocks are offered on a single chip along with programmable digital blocks. The programmable interconnect structure provides for communication of input / output data between all analog and digital blocks.

Owner:MONTEREY RES LLC

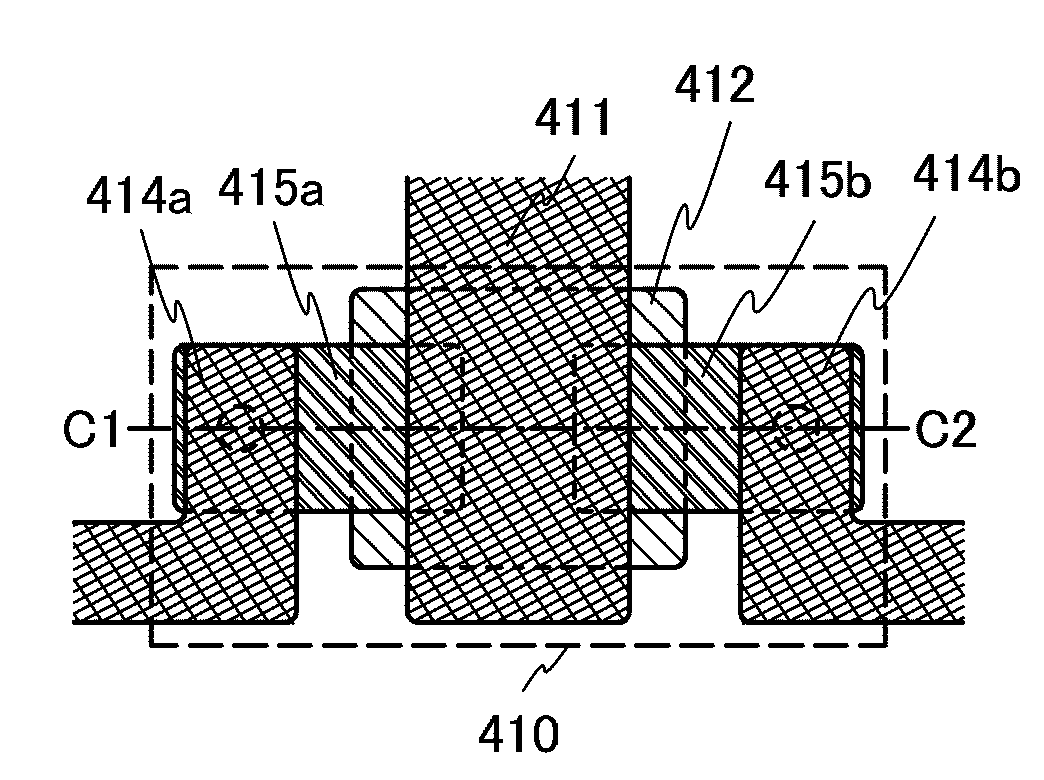

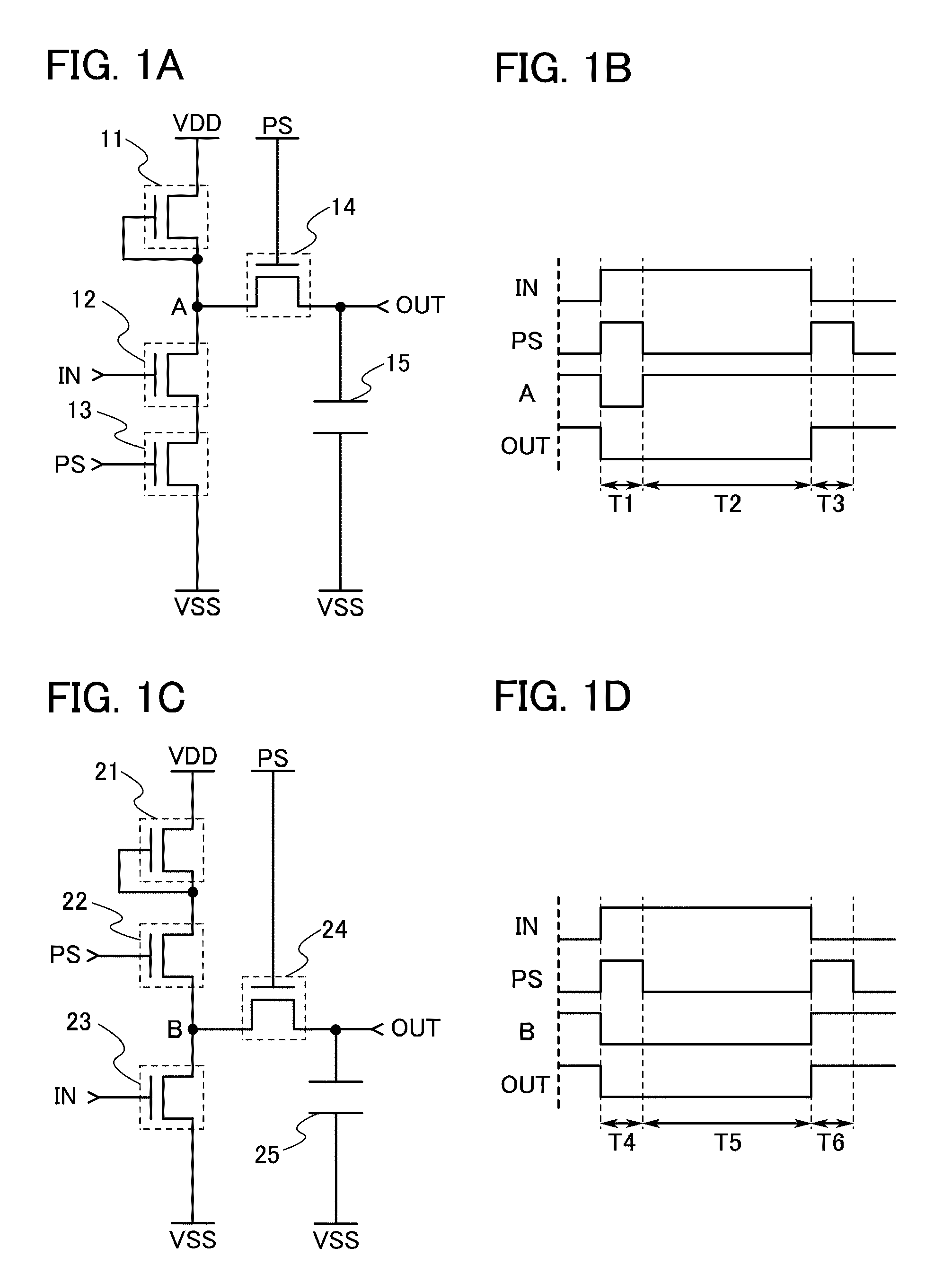

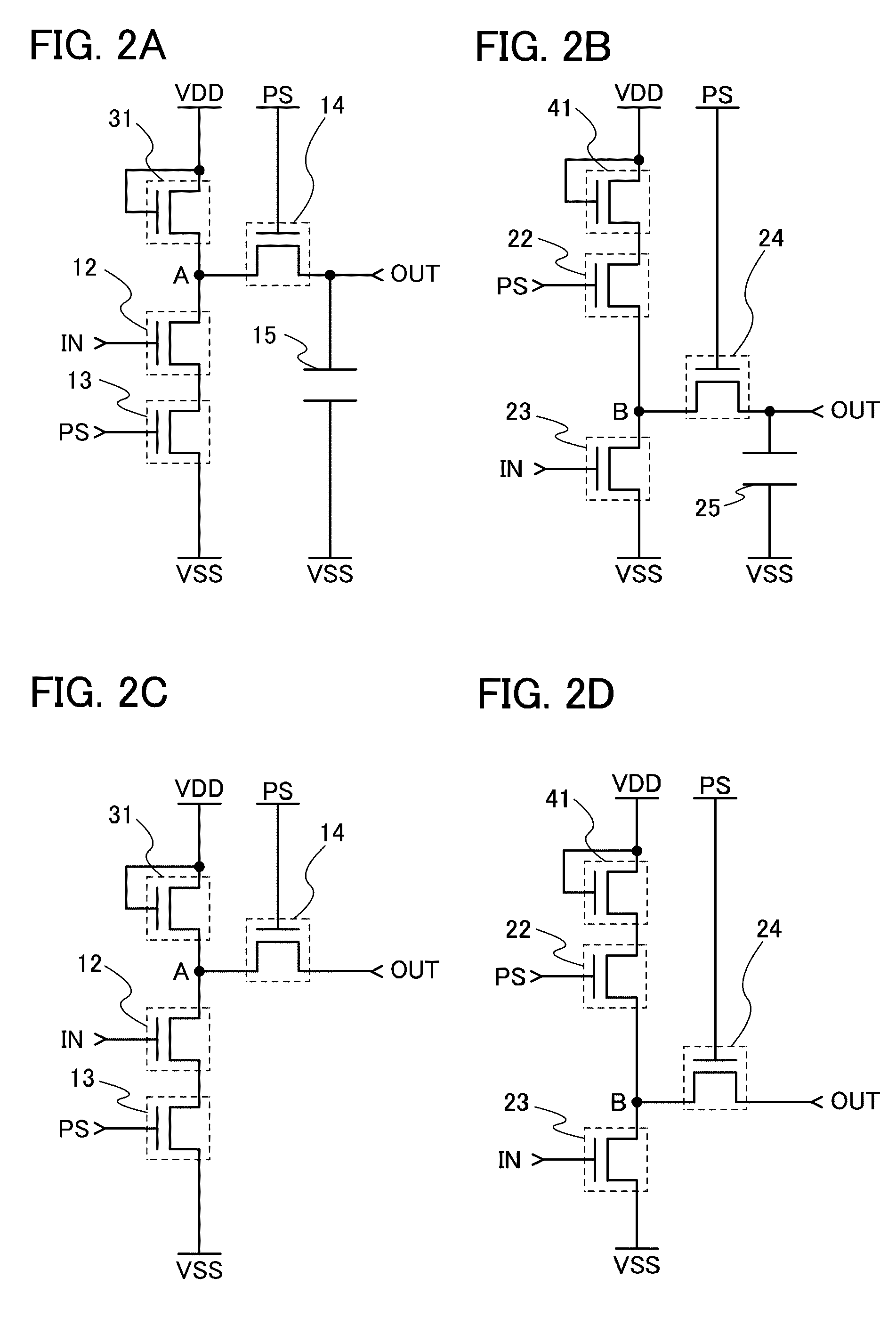

Logic circuit and semiconductor device

ActiveUS20110089975A1Reduce hydrogen concentrationTotal current dropSemiconductor/solid-state device testing/measurementSolid-state devicesEngineeringElectric field

A logic circuit includes a thin film transistor having a channel formation region formed using an oxide semiconductor, and a capacitor having terminals one of which is brought into a floating state by turning off the thin film transistor. The oxide semiconductor has a hydrogen concentration of 5×1019 (atoms / cm3) or less and thus substantially serves as an insulator in a state where an electric field is not generated. Therefore, off-state current of a thin film transistor can be reduced, leading to suppressing the leakage of electric charge stored in a capacitor, through the thin film transistor. Accordingly, a malfunction of the logic circuit can be prevented. Further, the excessive amount of current which flows in the logic circuit can be reduced through the reduction of off-state current of the thin film transistor, resulting in low power consumption of the logic circuit.

Owner:SEMICON ENERGY LAB CO LTD

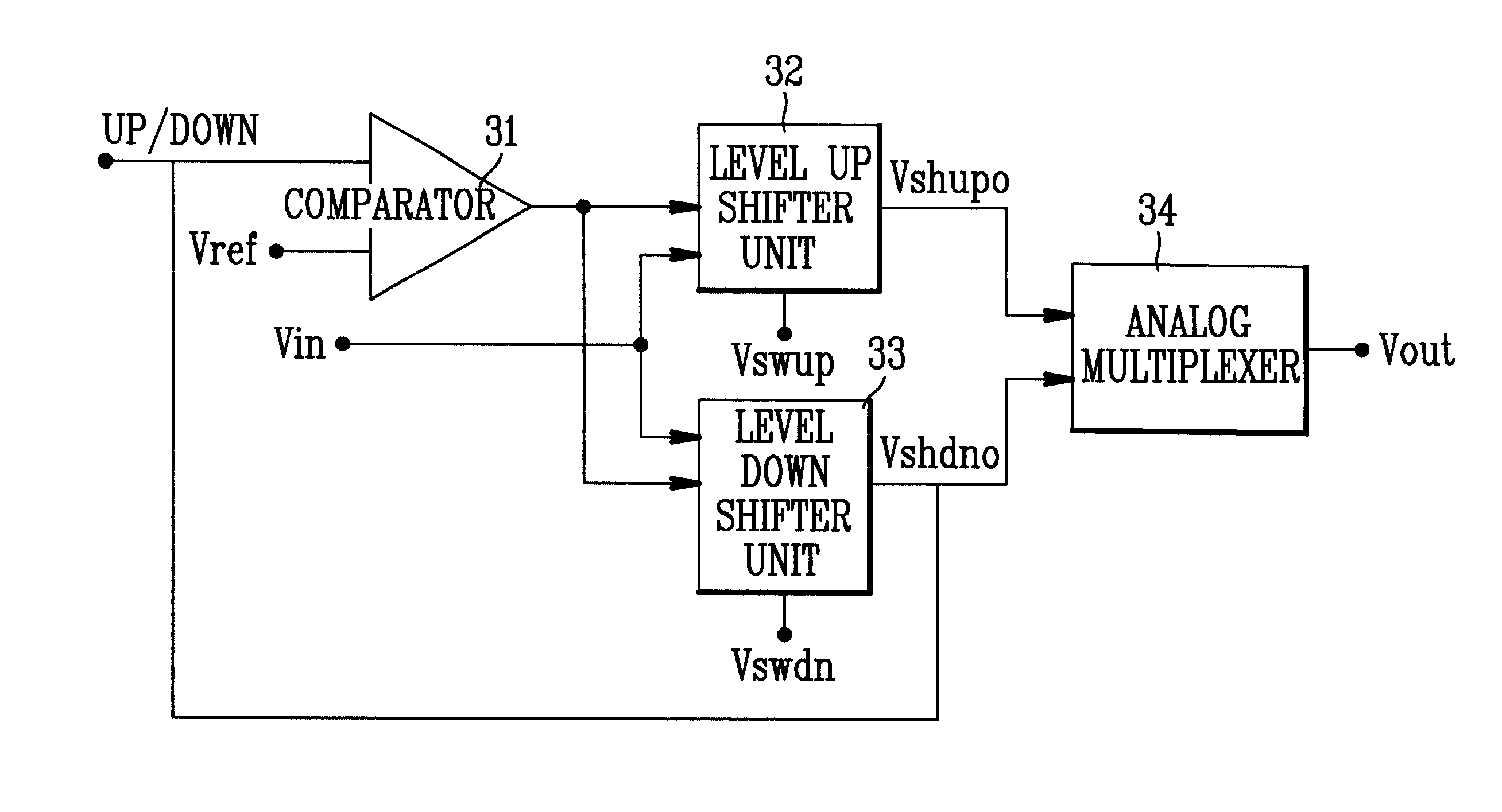

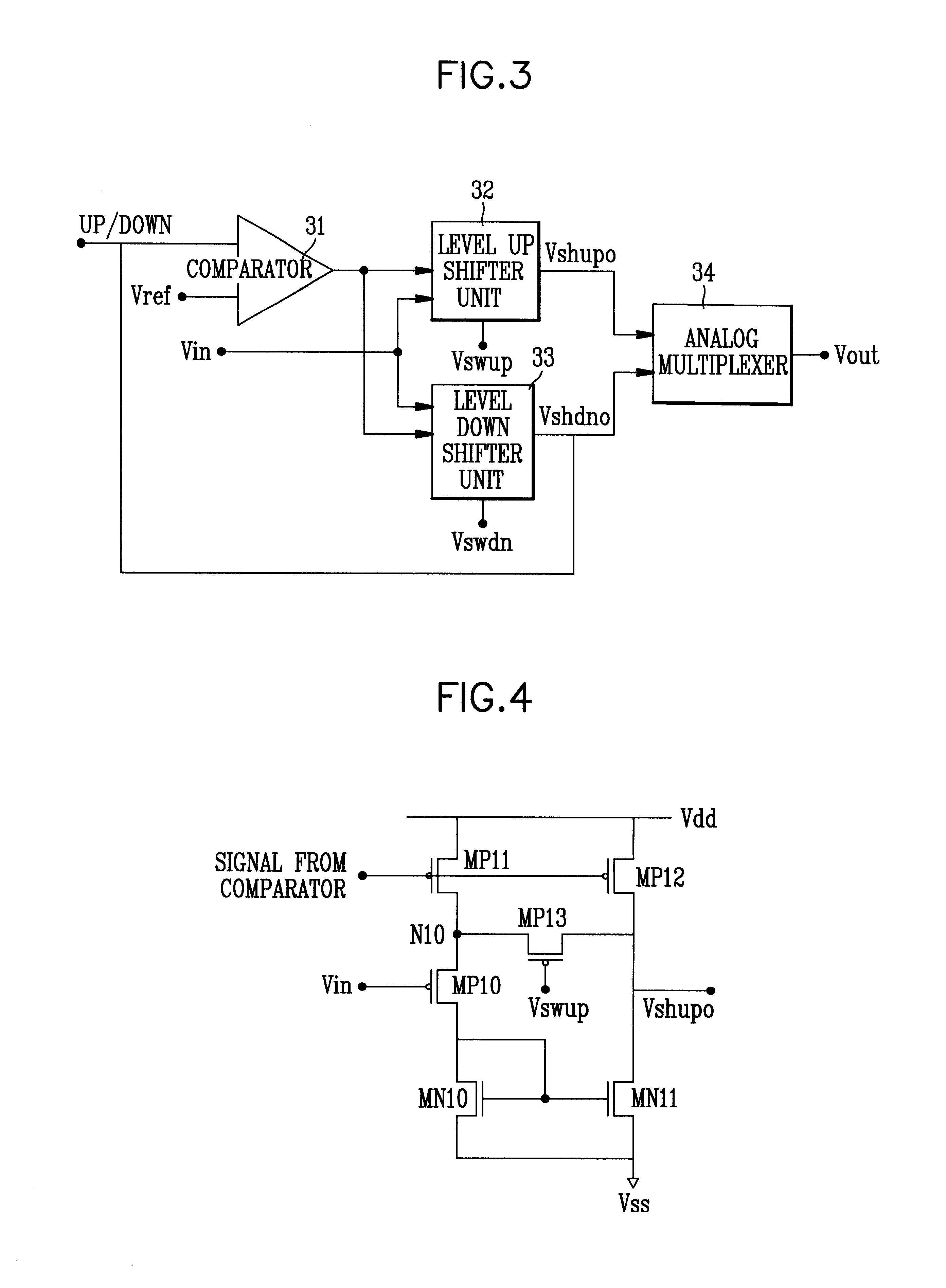

Level shifter circuit

InactiveUS6222385B1Efficient level shift operationGuaranteed uptimeLogic circuits coupling/interface using field-effect transistorsLogic circuits using semiconductor devicesControl signalMultiplexer

Level shifter circuit which can make an efficient level shift to level up or level down according to a change of a digital logic characteristic, including a comparator for comparing an up / down control signal to a reference signal in disabling either one of the level up shifter or the level down shifter according to the up / down control signal, a level up shifter unit for leveling up of an input voltage in response to a level up shifter / level down shifter disable signal from the comparator, a level down shifter unit for leveling down of an input voltage in response to a level up shifter / level down shifter disable signal from the comparator; and an analog multiplexer for selectively providing a leveled up signal or a leveled down signal from the level up shifter unit or the level down shifter unit.

Owner:CHIAO TUNG HLDG LLC

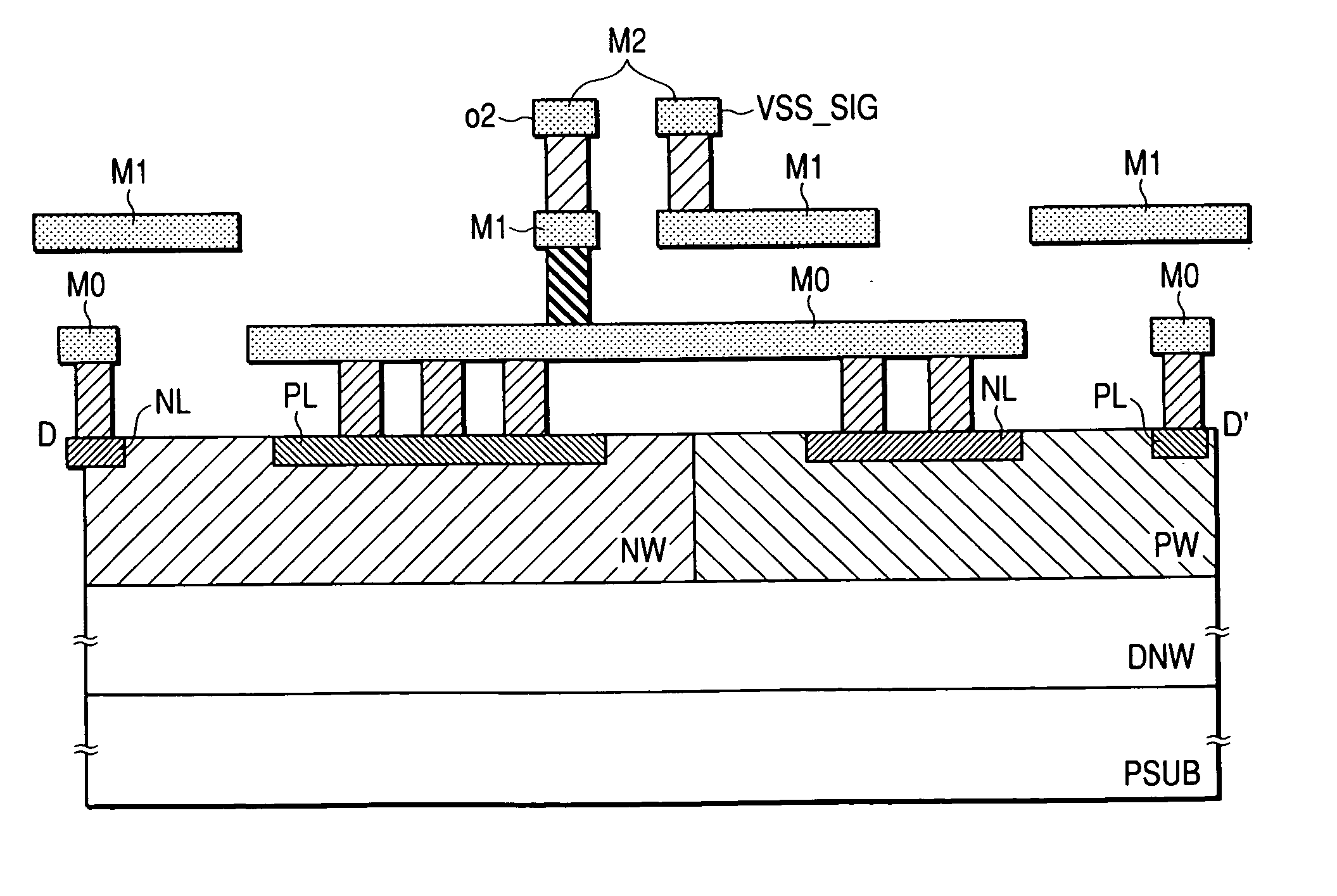

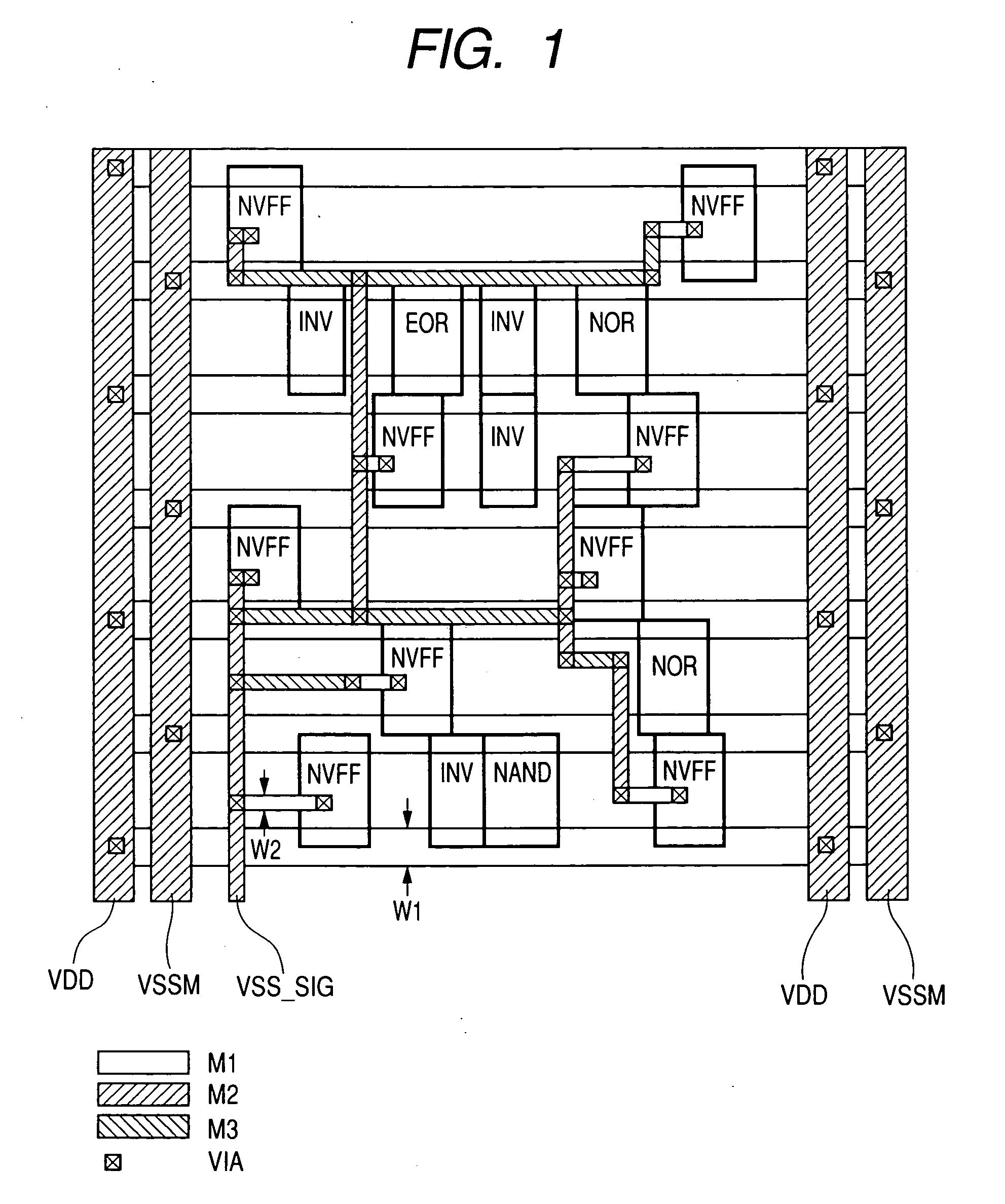

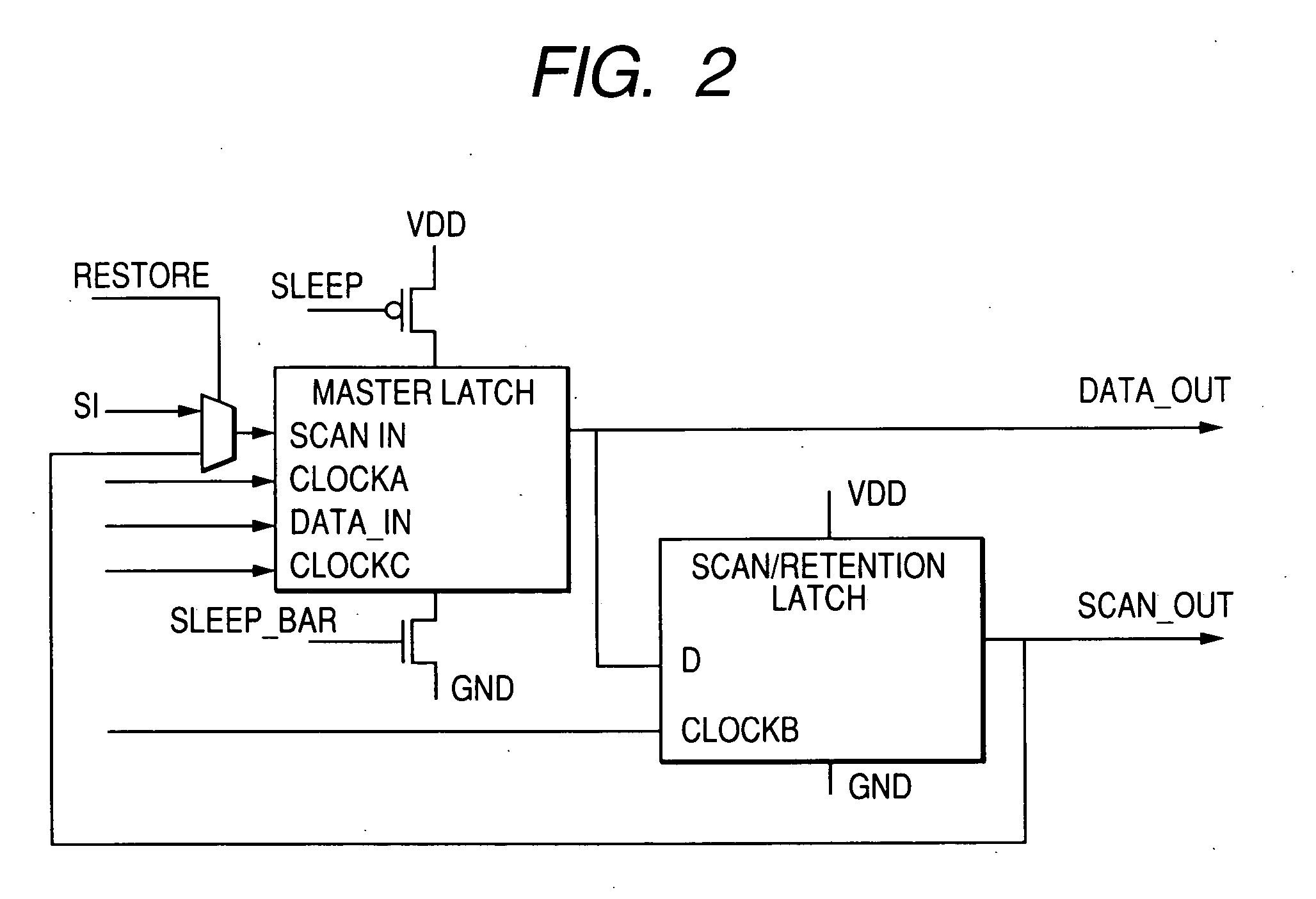

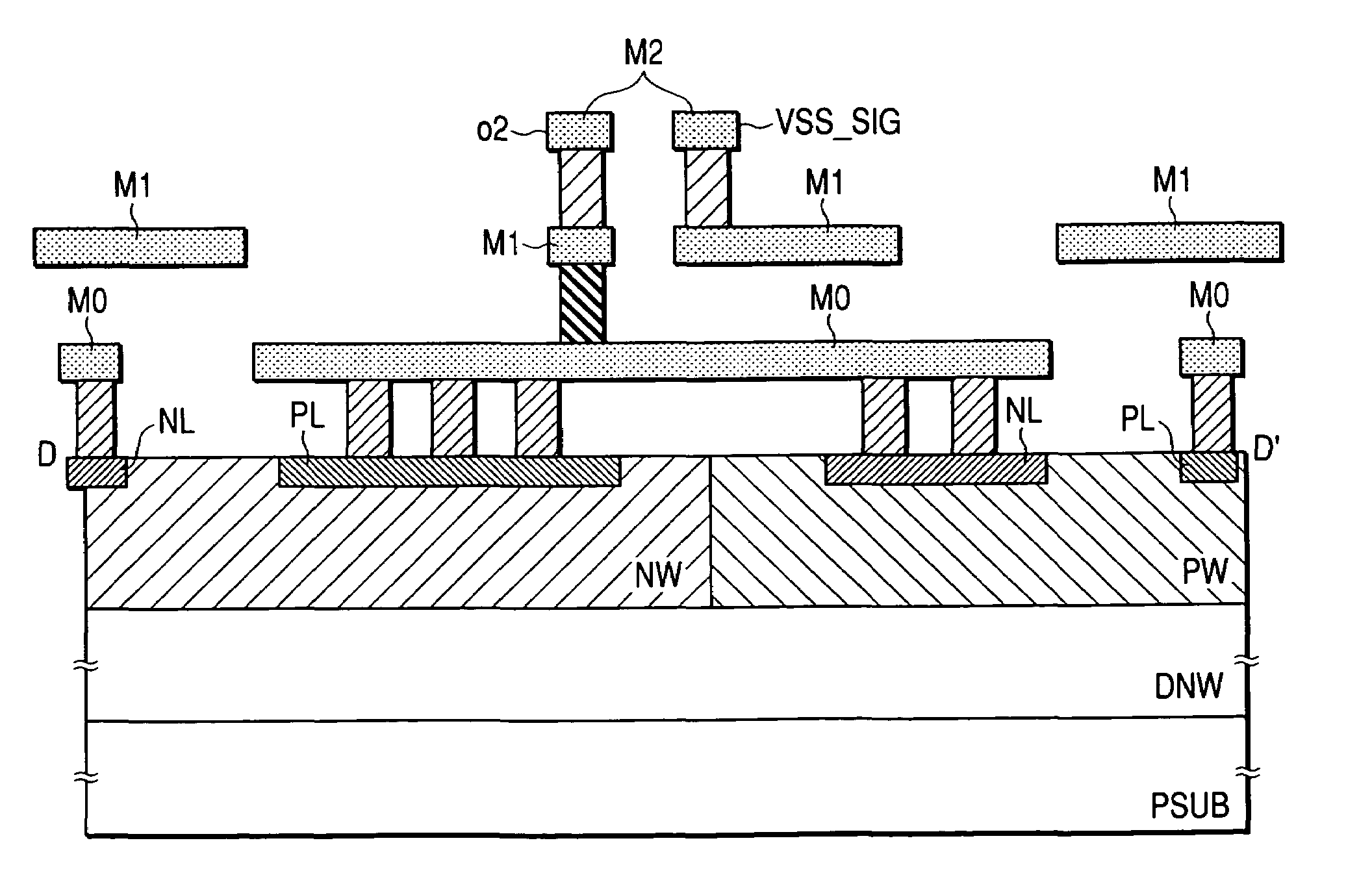

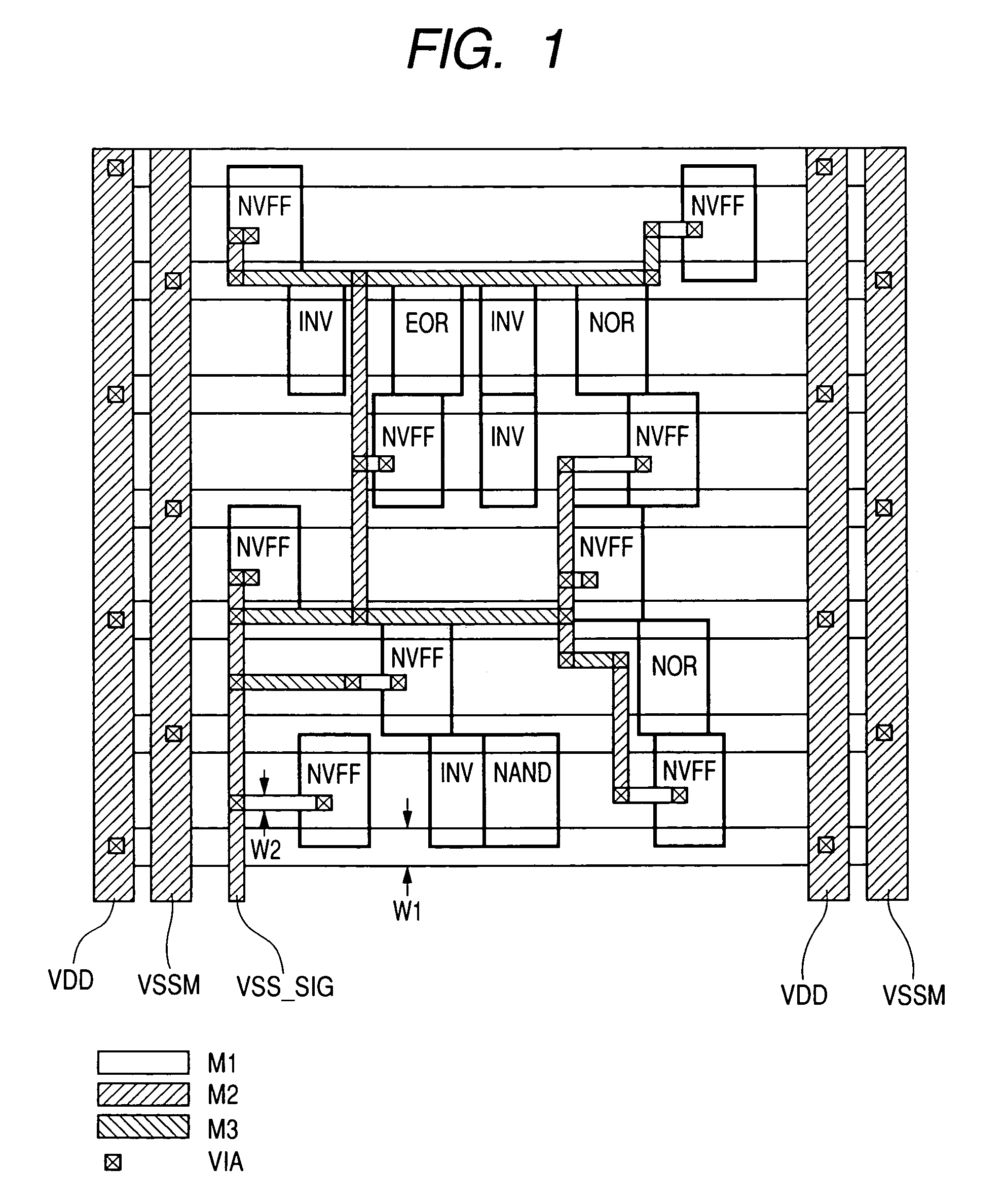

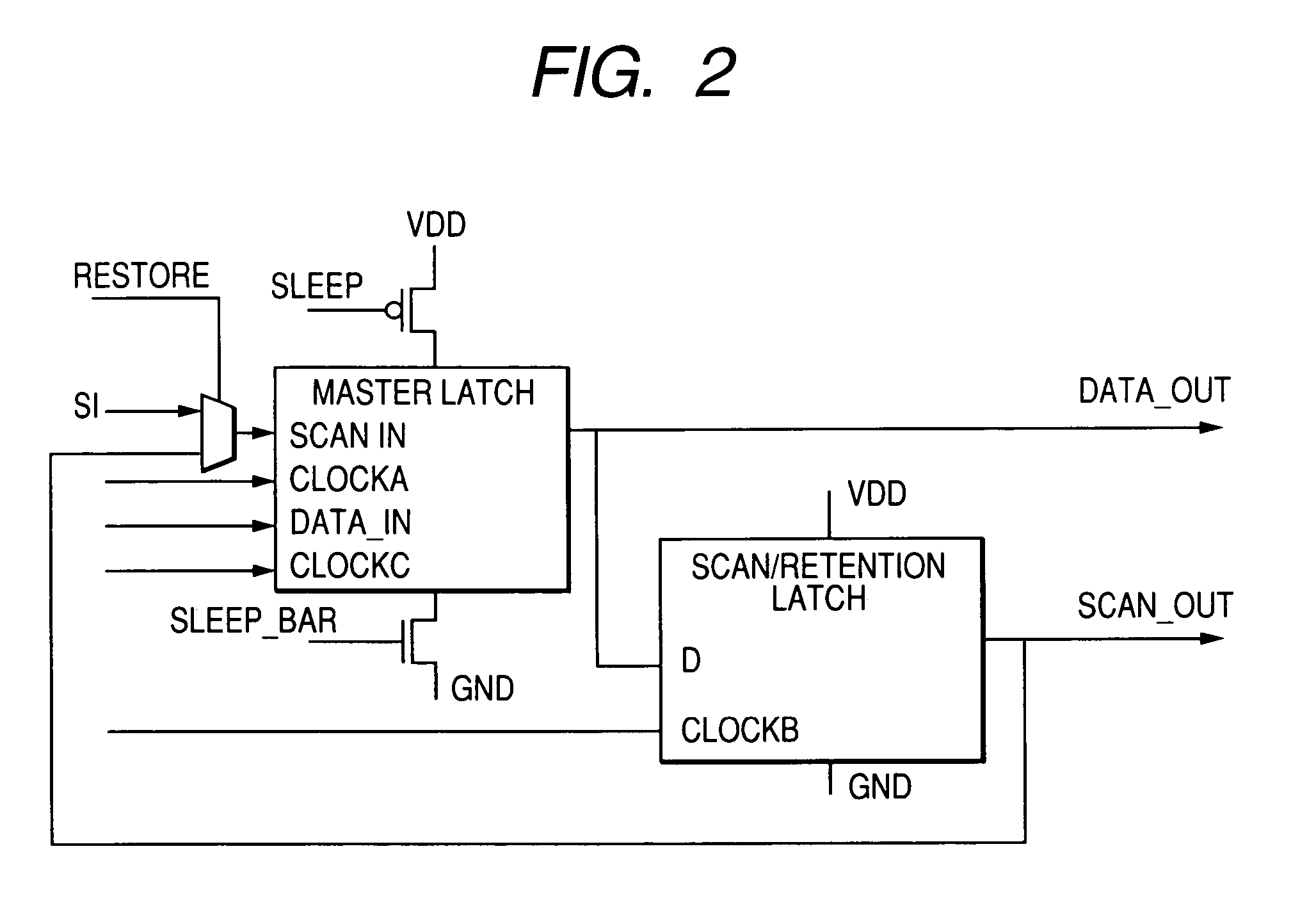

Semiconductor integrated circuit device

InactiveUS20050104133A1Cell height can be increasedRestricted degrees of freedomTransistorPower reduction by control/clock signalEngineeringSemiconductor

In a low power consumption mode in which prior data is retained upon power shutdown, the return speed thereof is increased. While use of an existent data retaining flip-flop may be considered, this is not preferred since it increases area overhead such as enlargement of the size of a cell. A power line for data retention for power shutdown is formed with wirings finer than a usual main power line. Preferably, power lines for a data retention circuit are considered as signal lines and wired by automatic placing and mounting. For this purpose, terminals for the power line for data retention are previously designed by providing the terminals therefor for the cell in the same manner as in the existent signal lines. Additional layout for power lines is no longer necessary for the cell, which enables a decrease in the area and design by an existent placing and routing tool.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device having diode-built-in IGBT and semiconductor device having diode-built-in DMOS

ActiveUS8072241B2Increase lossTransistorLogic circuits characterised by logic functionSemiconductorSemiconductor device

A semiconductor device includes: a semiconductor substrate; a diode-built-in insulated-gate bipolar transistor having an insulated-gate bipolar transistor and a diode, which are disposed in the substrate, wherein the insulated-gate bipolar transistor includes a gate, and is driven with a driving signal input into the gate; and a feedback unit for detecting current passing through the diode. The driving signal is input from an external unit into the feedback unit. The feedback unit passes the driving signal to the gate of the insulated-gate bipolar transistor when the feedback unit detects no current through the diode, and the feedback unit stops passing the driving signal to the gate of the insulated-gate bipolar transistor when the feedback unit detects the current through the diode.

Owner:DENSO CORP

Programmable microcontroller architecture(mixed analog/digital)

InactiveUS7825688B1Simple interfaceDigital technique networkSolid-state devicesController architectureCapacitance

Owner:MONTEREY RES LLC

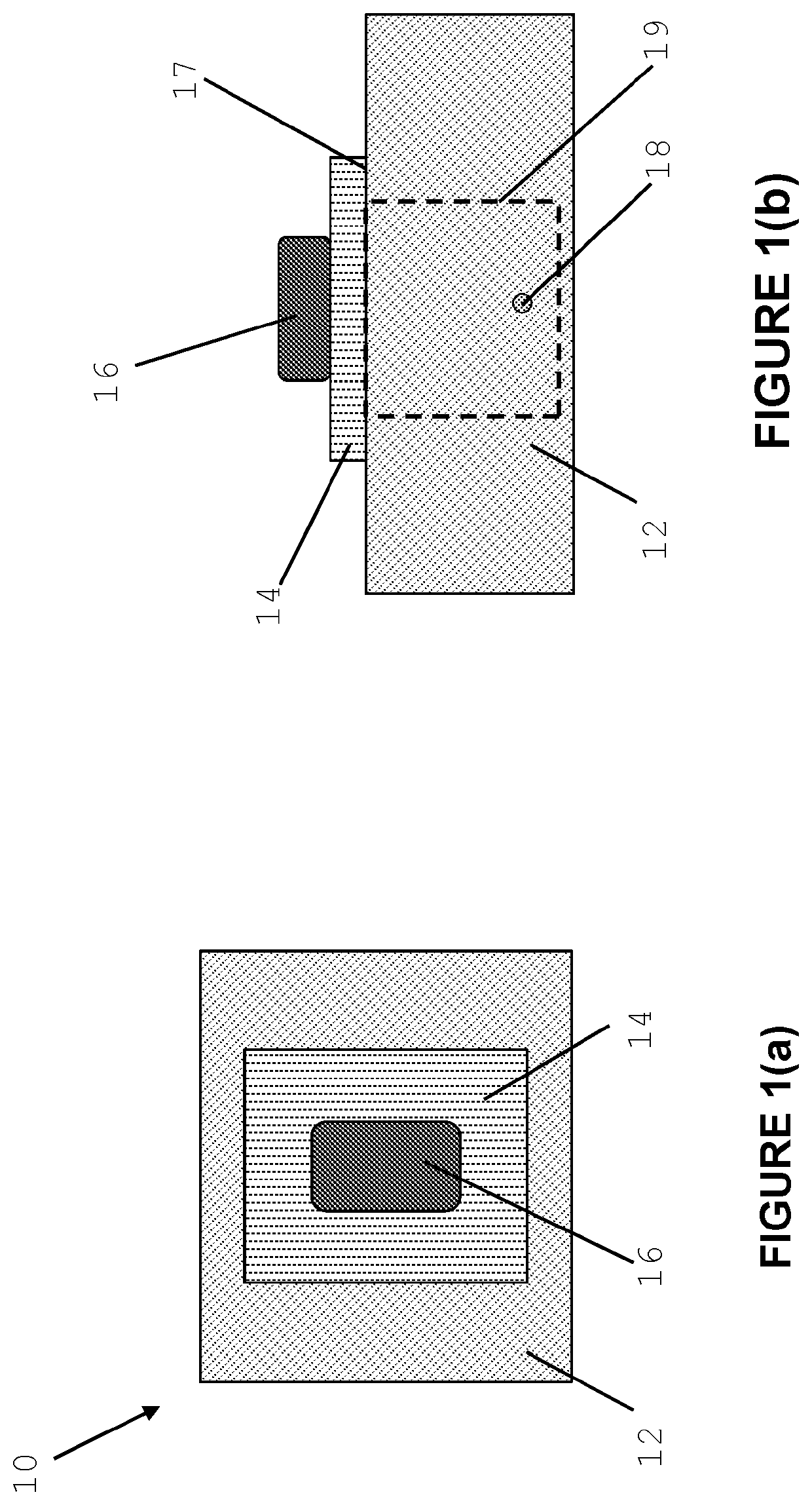

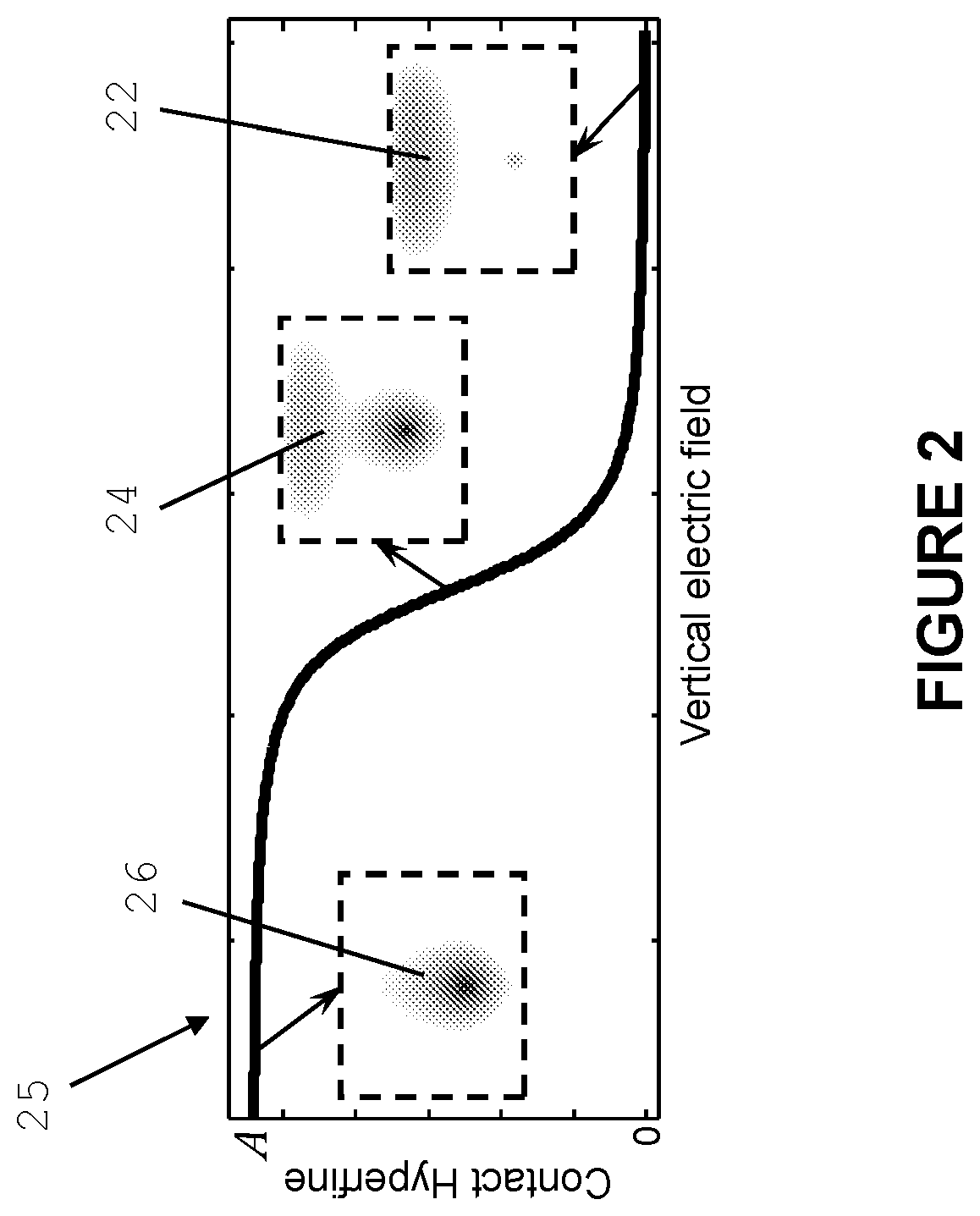

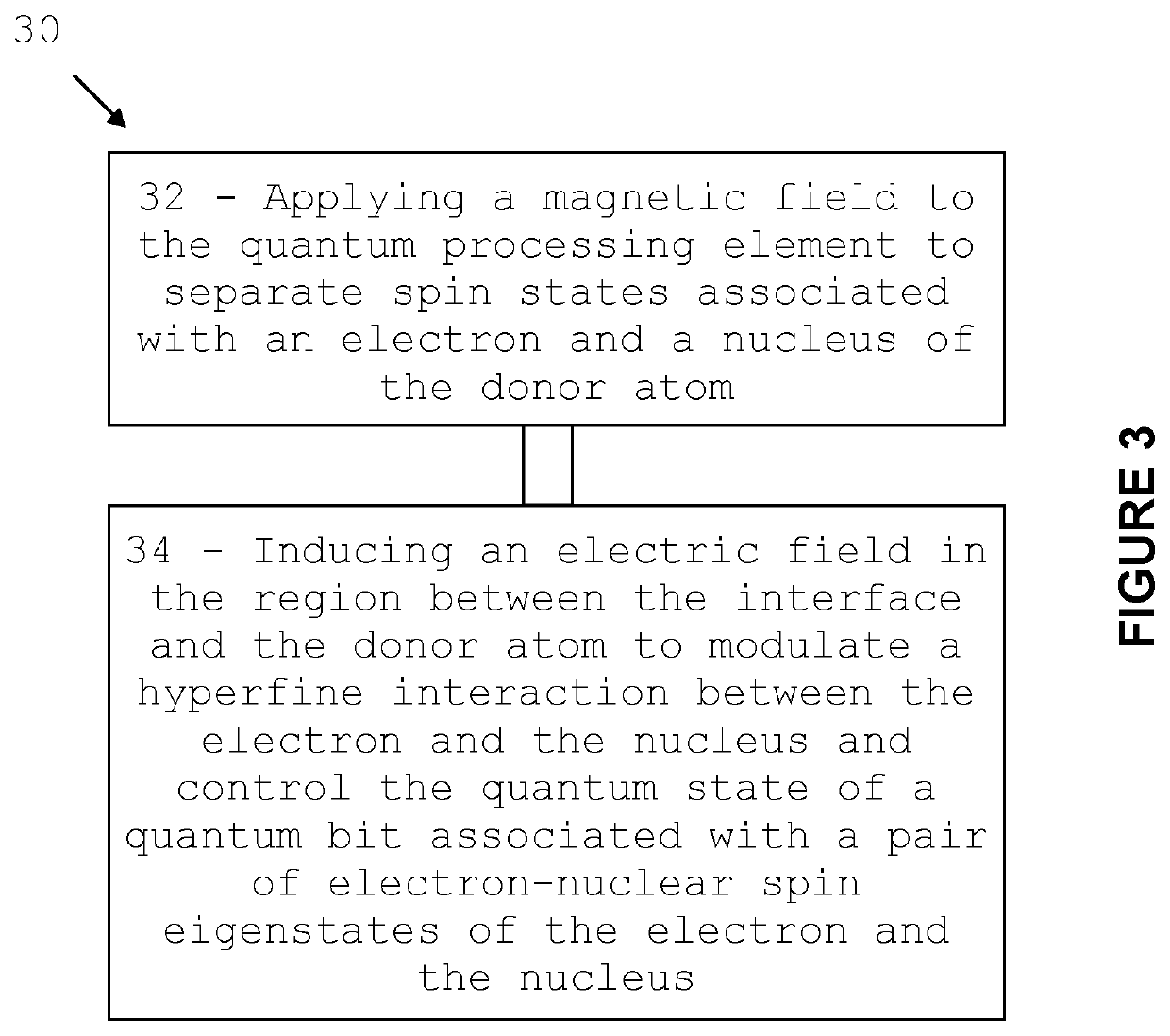

Quantum processing apparatus and a method of operating a quantum processing apparatus

ActiveUS10528884B2Made preciselyAccuracy in donor placementQuantum computersNanoinformaticsQuantum propertyParticle physics

The present disclosure provides a method of operation of a quantum processing element and an advanced processing apparatus comprising a plurality of quantum processing elements operated in accordance with the method. Embodiments of the methods disclosed allow using the quantum properties of an MOS structure and a donor atom embedded in the semiconductor to implement electron and nuclear spin qubits and provide multi-qubit coupling, including coupling at longer distances facilitated by a resonator.

Owner:NEWSOUTH INNOVATIONS PTY LTD

Semiconductor integrated circuit device

InactiveUS7023058B2Curb overheadShorten return timeTransistorPower reduction by control/clock signalSemiconductorElectric power

In a low power consumption mode in which prior data is retained upon power shutdown, the return speed thereof is increased. While use of an existent data retaining flip-flop may be considered, this is not preferred since it increases area overhead such as enlargement of the size of a cell. A power line for data retention for power shutdown is formed with wirings finer than a usual main power line. Preferably, power lines for a data retention circuit are considered as signal lines and wired by automatic placing and mounting. For this purpose, terminals for the power line for data retention are previously designed by providing the terminals therefor for the cell in the same manner as in the existent signal lines. Additional layout for power lines is no longer necessary for the cell, which enables a decrease in the area and design by an existent placing and routing tool.

Owner:RENESAS ELECTRONICS CORP

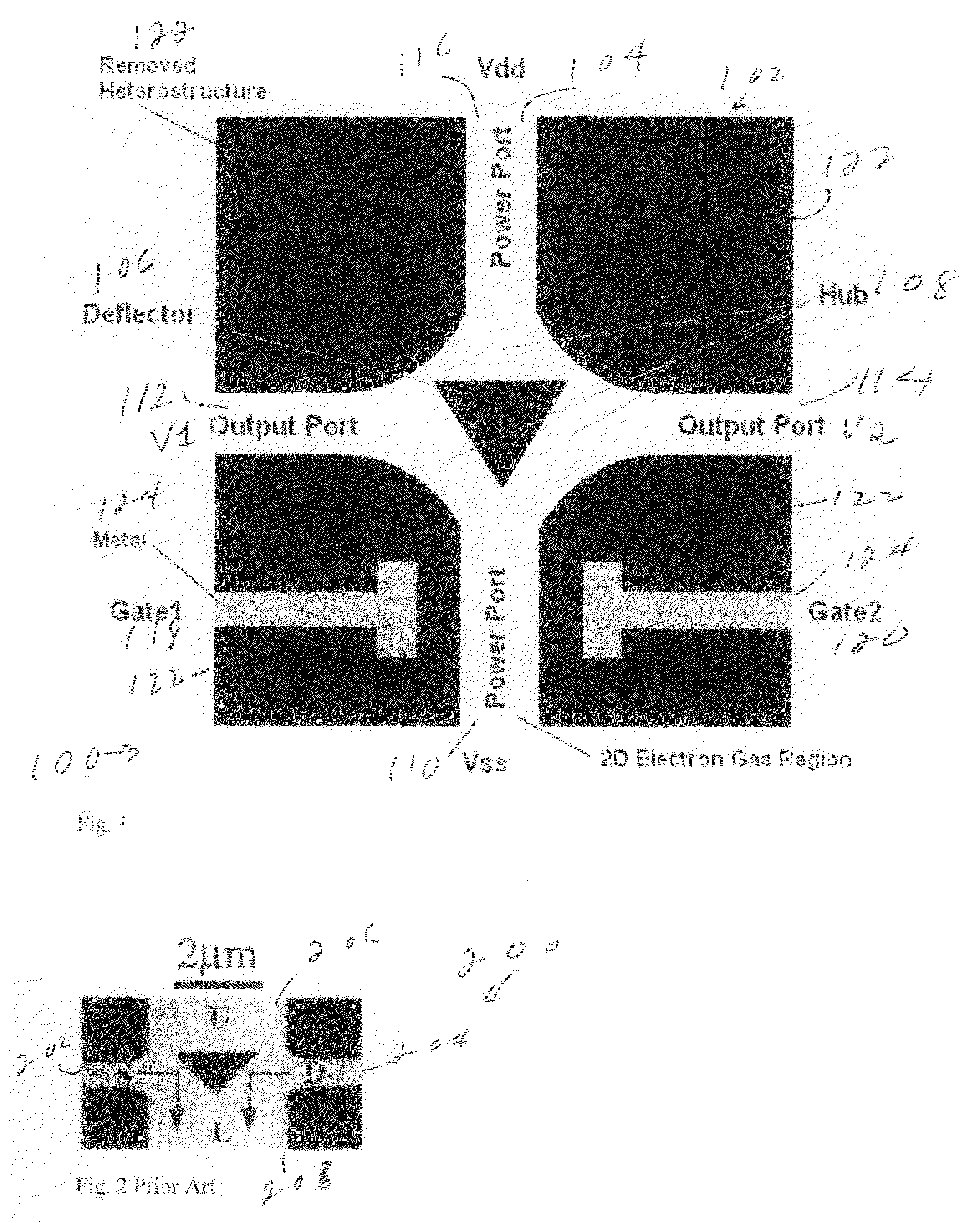

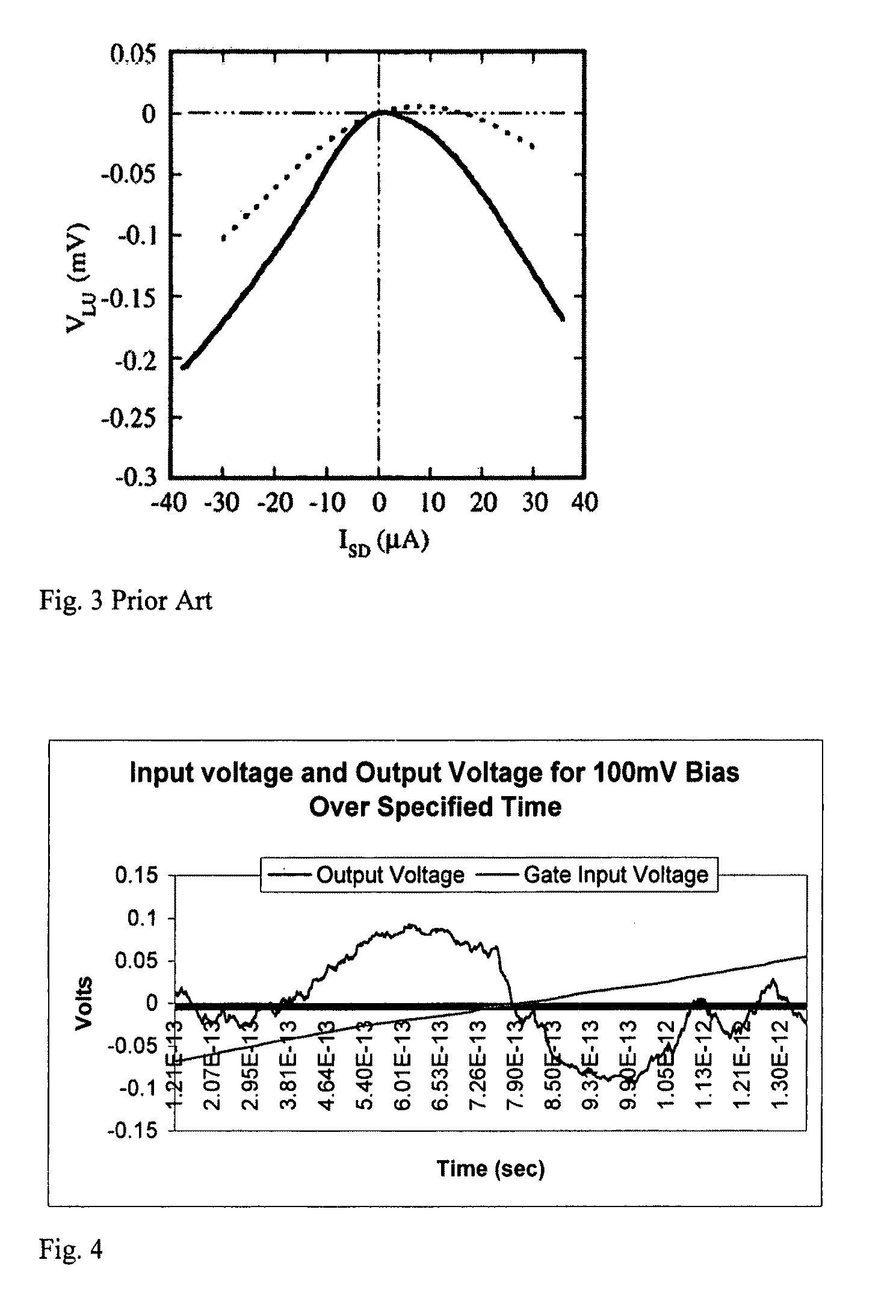

Ballistic deflection transistor and logic circuits based on same

InactiveUS7576353B2Reduce noiseReduce power consumptionNanoinformaticsSolid-state devicesQuantum wellEngineering

A quantum well is formed in a substrate to define a hub, ports extending from the hub, and a deflective structure in the hub. Electrons move through the hub and ports according to the ballistic electron effect. Gates control the movement of the electrons, causing them to be incident on the deflective structure on one side or the other, thus controlling the direction in which they are deflected and the port through which they pass.

Owner:UNIVERSITY OF ROCHESTER

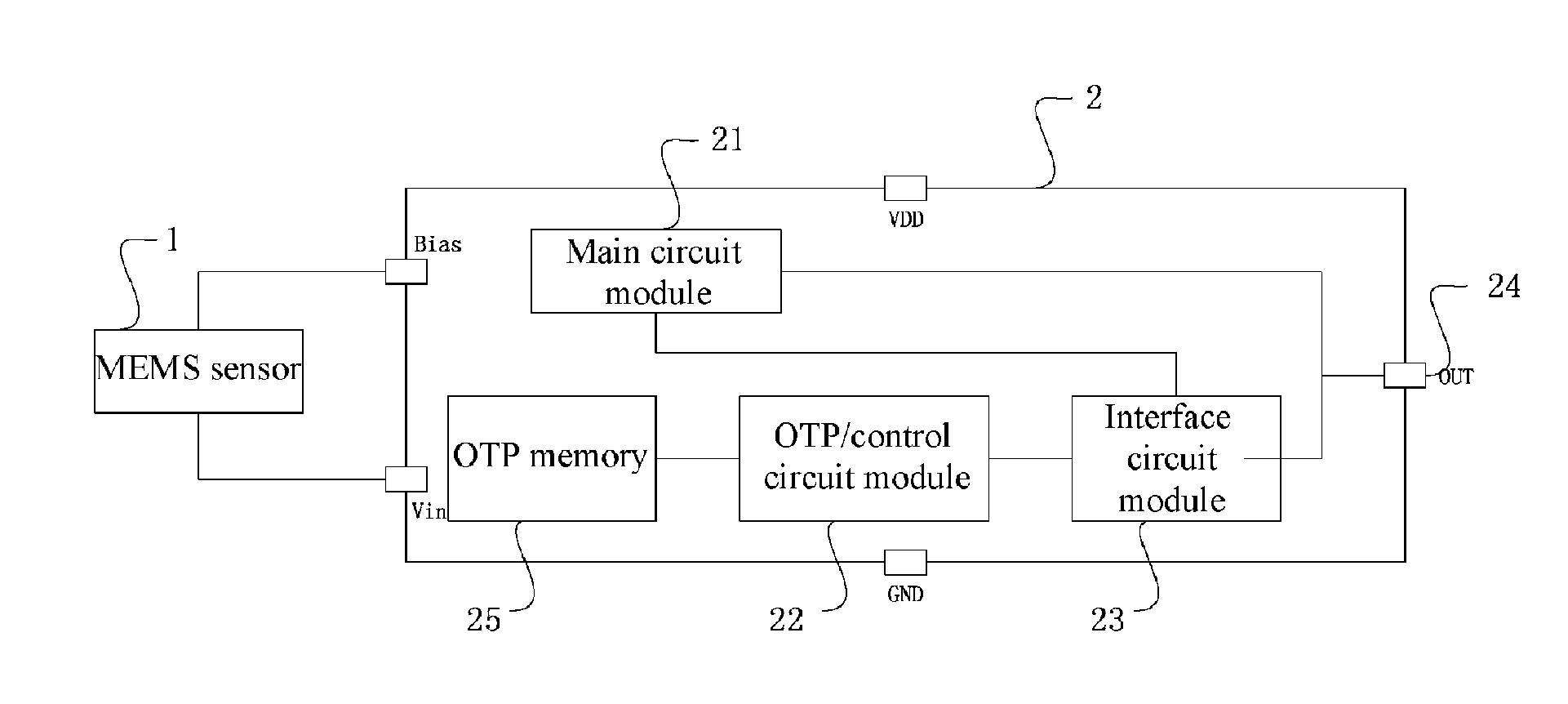

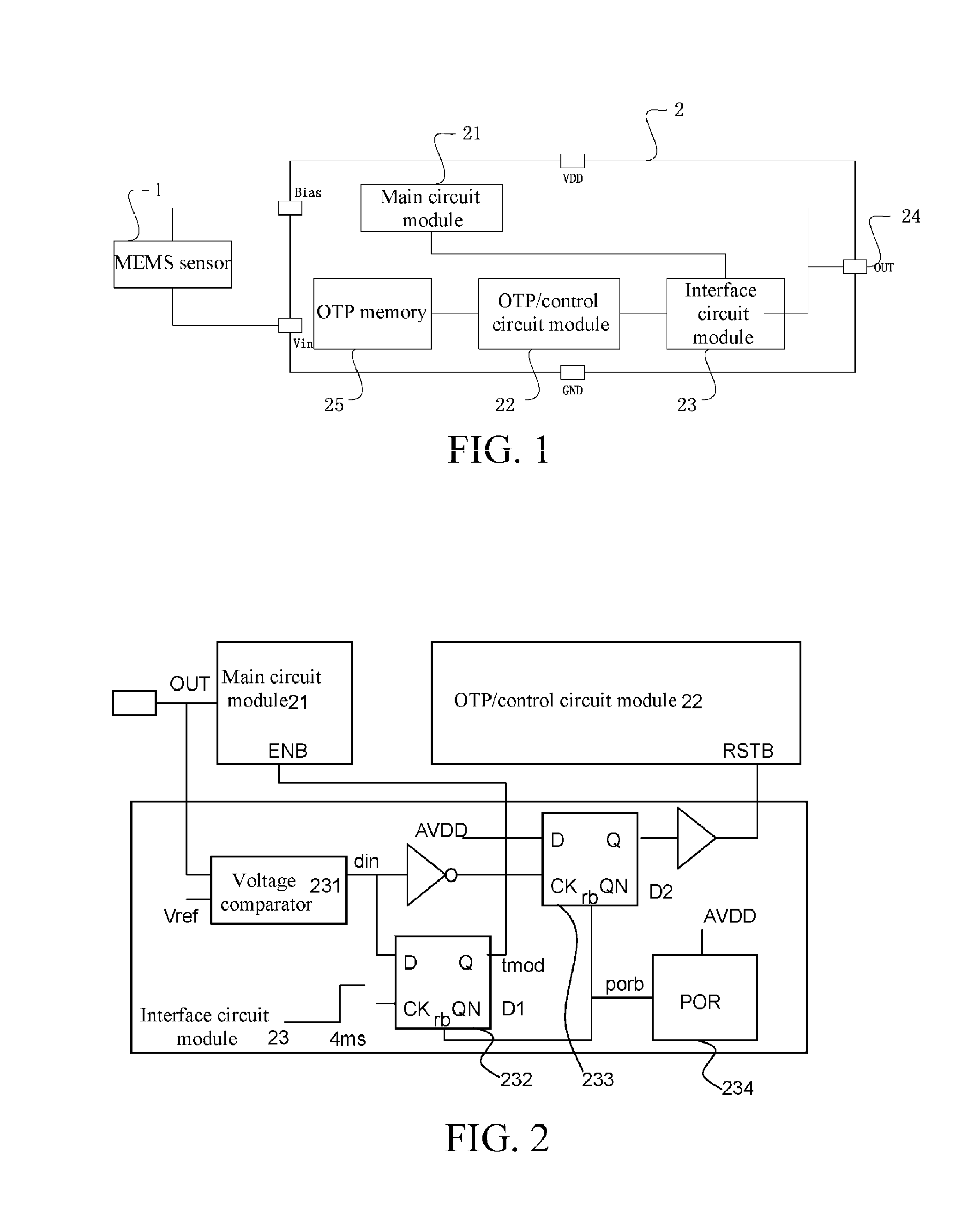

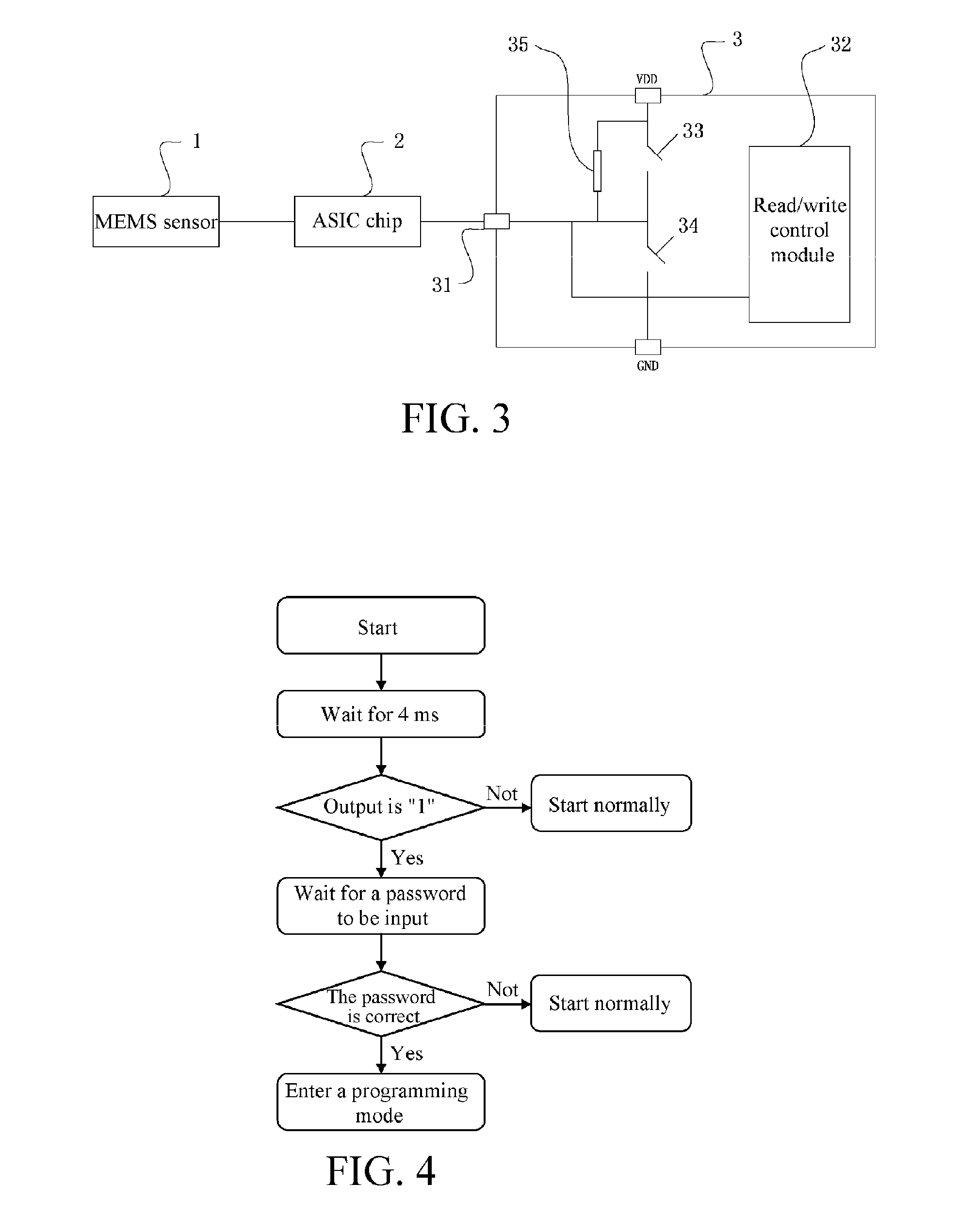

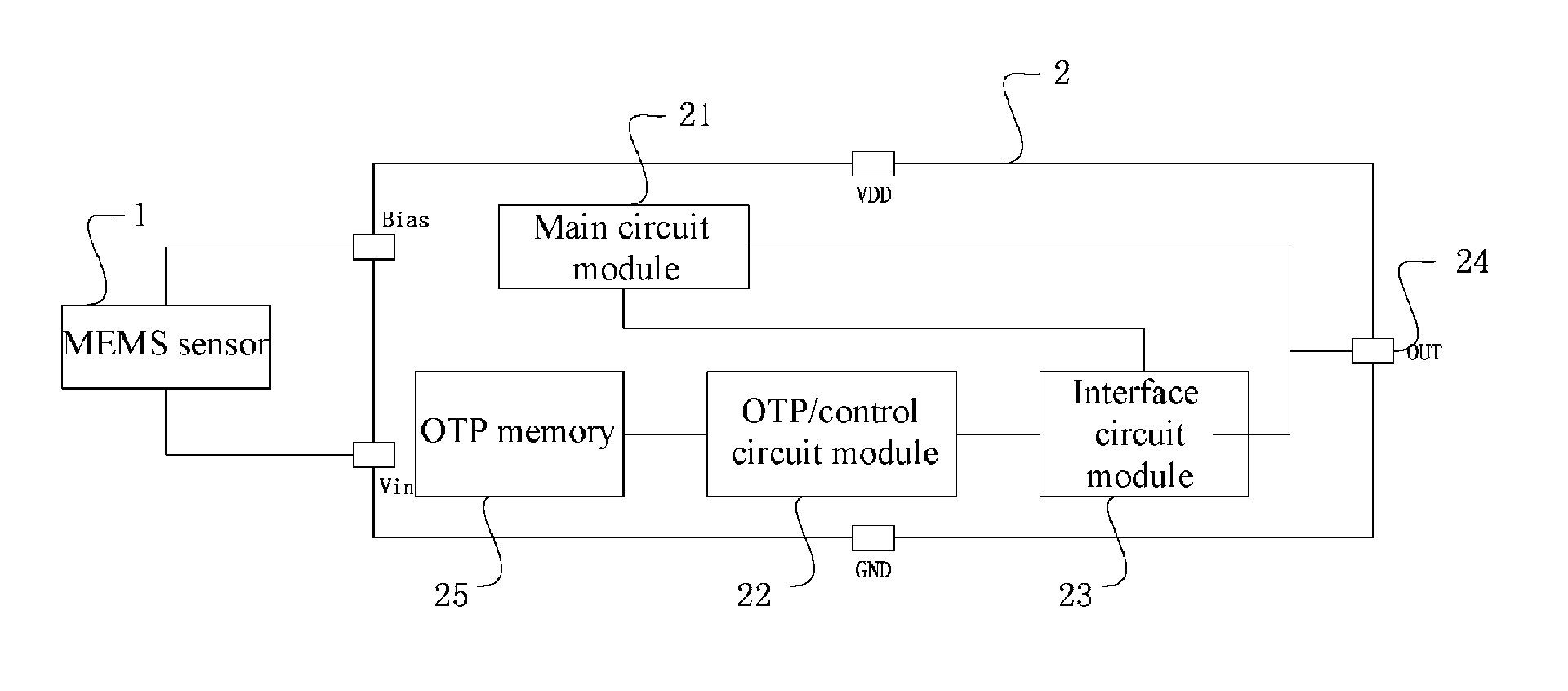

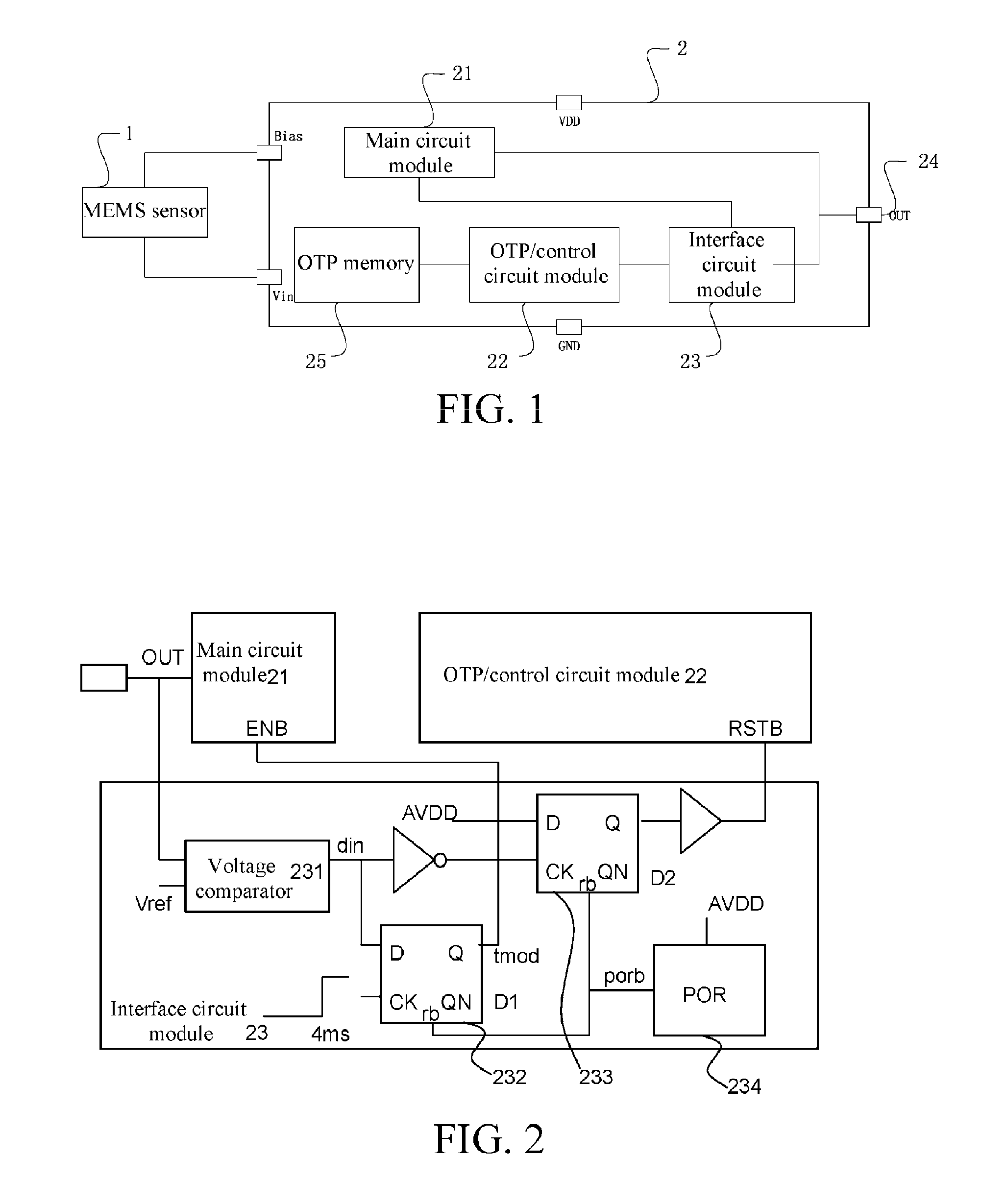

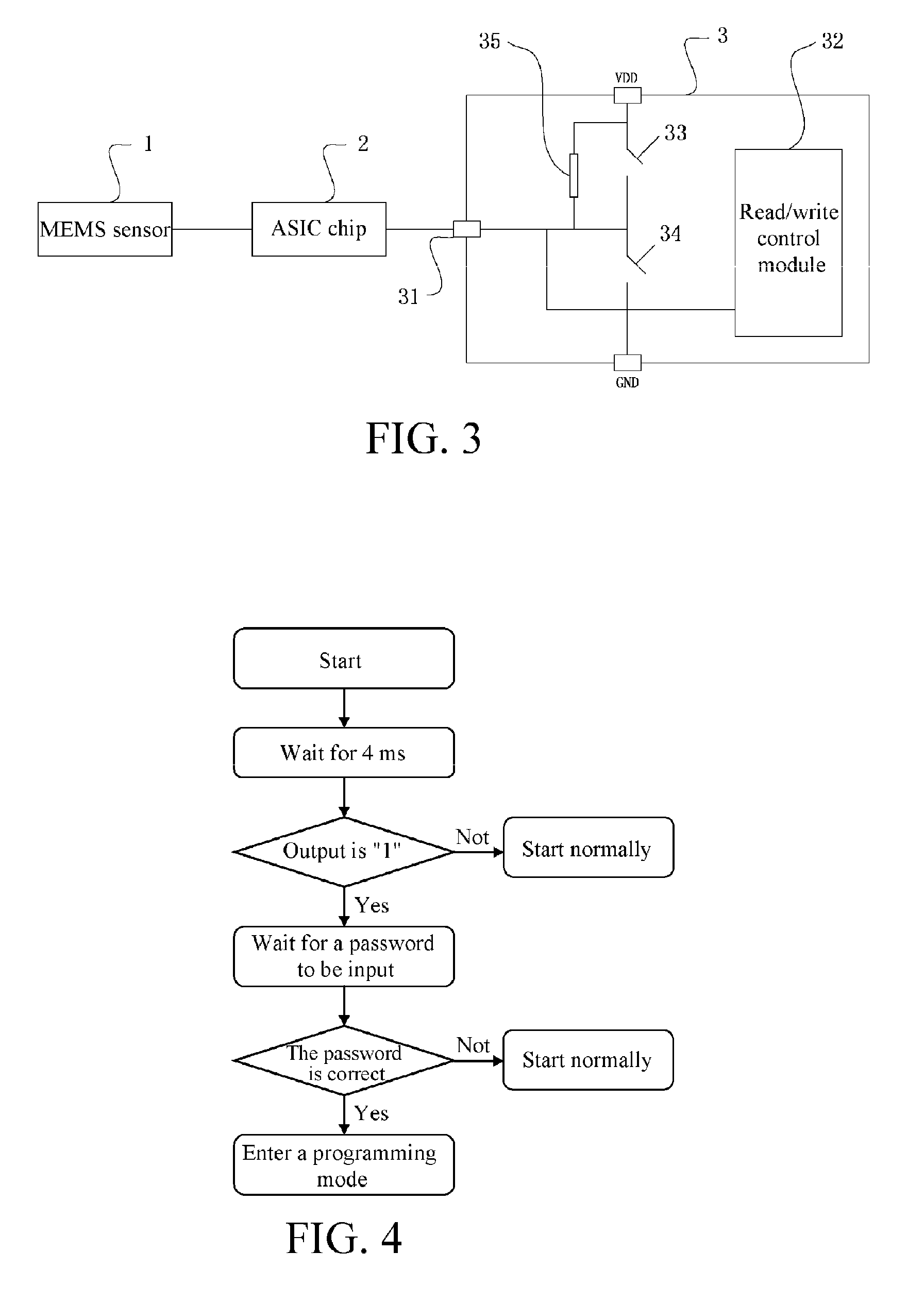

Single-Wire Programmable MEMS Microphone, Programming Method and System Thereof

ActiveUS20130195288A1Calibration of gainOptimizationSemiconductor electrostatic transducersElectrostatic transducer microphonesMultiplexingMems sensors

The present invention provides a single wire programmable Micro Electromechanical System (MEMS) microphone and a programming method and system thereof. The single wire programmable MEMS microphone includes an MEMS sensor and an Application Specific Integrated Circuit (ASIC) chip connected to each other; the MEMS sensor is used for implementing acoustic-electric conversion; the ASIC chip includes an OUT interface, so that an upper computer judges, according to an output signal of the OUT interface, whether the ASIC chip is in a normal start mode or a programming mode, where if the output signal of the OUT interface is at a high level, the ASIC chip is in the normal start mode, and otherwise, the ASIC chip enters the programming mode. Through the present invention, multiplexing of the OUT interface of the MEMS microphone is implemented, and gain configuration for the OTP memory in the ASIC chip is implemented by multiplexing the OUT interface, thereby achieving calibration of the gain of the MEMS microphone product after package.

Owner:ZILLTEK TECH SHANGHAI +1

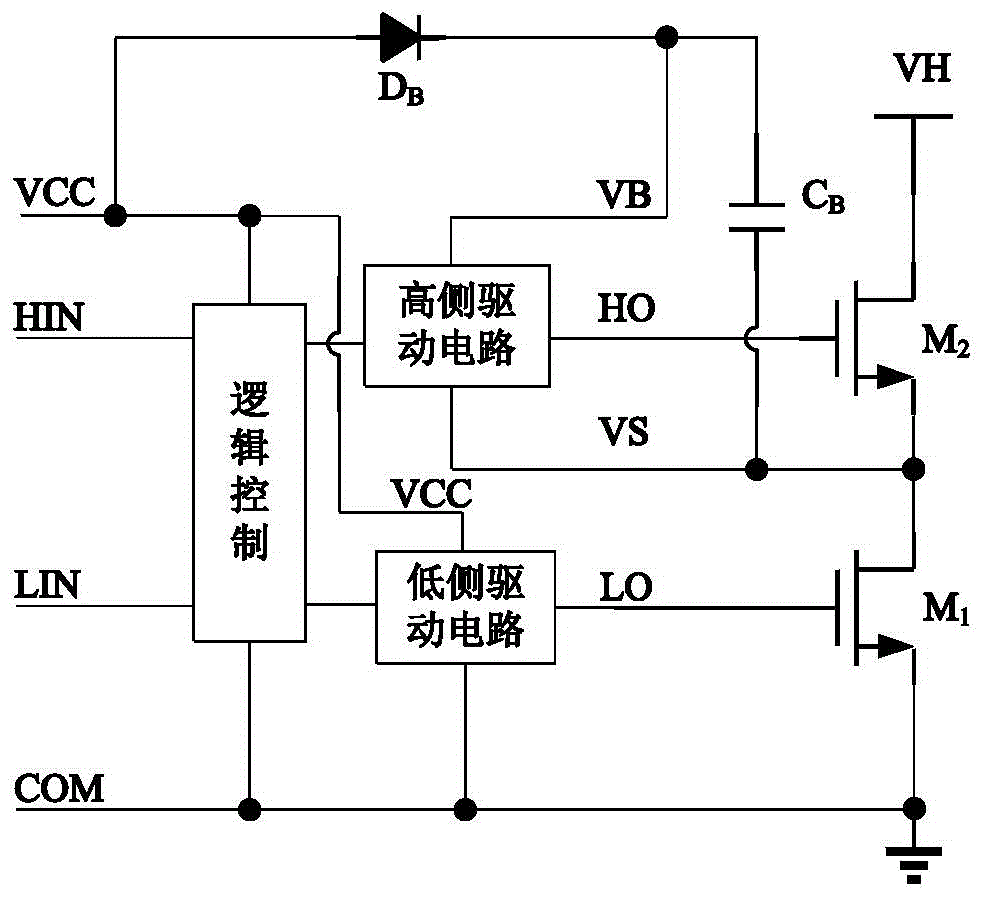

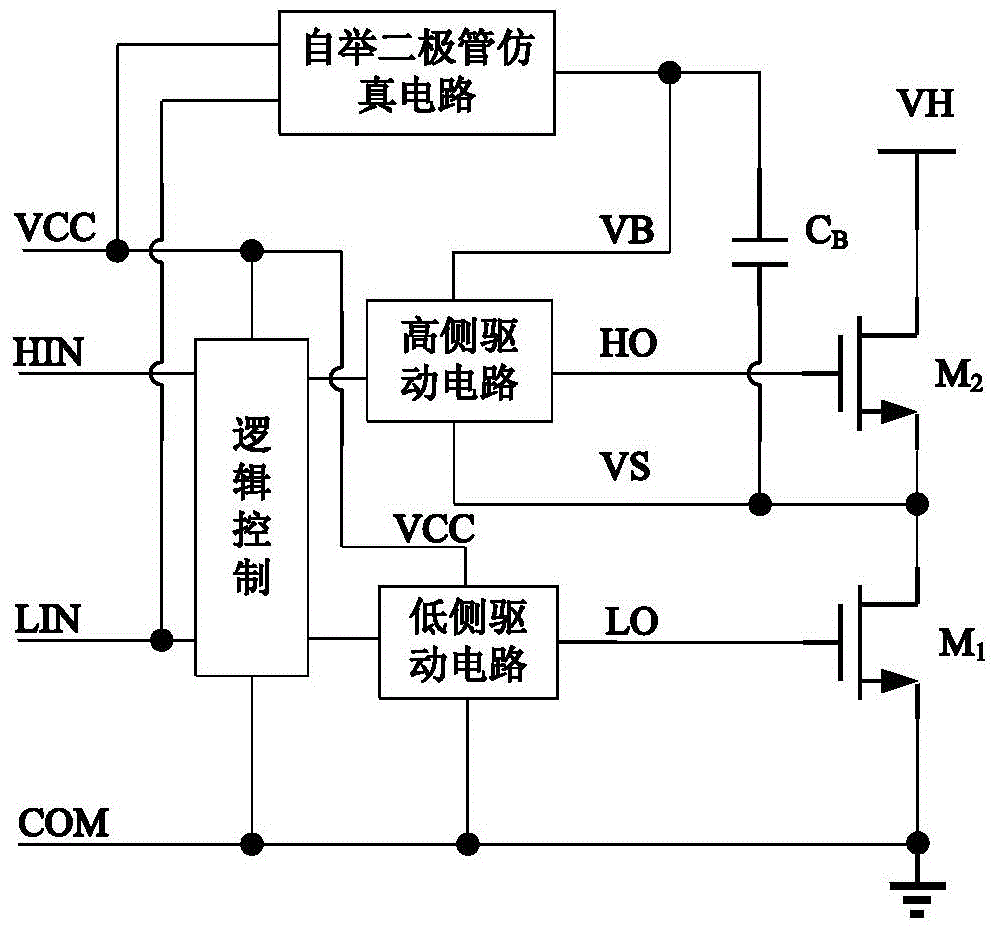

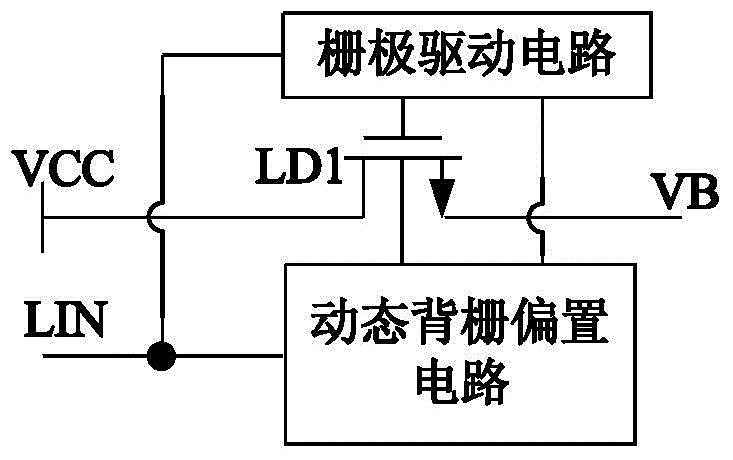

Bootstrapping diode artificial circuit in half-bridge driving circuit

ActiveCN104022776ARaise the gate voltageIncrease charging currentLogic circuits using semiconductor devicesCapacitanceEngineering

The invention provides a bootstrapping diode artificial circuit in a half-bridge driving circuit. An electrical level displacement and a simple charge pump are added into a grid driving circuit structure in an existing bootstrapping diode artificial circuit; when a grid driving input signal is a low electrical level, grid voltage output to an N-channel LDMOS (Lateral Diffusion Metal Oxide Semiconductor) transistor LD1 by a grid driving circuit is a low electrical level; the N-channel LDMOS transistor LD1 is turned off. When the grid driving input signal is a high electrical level, the grid voltage output to the N-channel LDMOS transistor LD1 by the grid driving circuit is a high electrical level so that the grid voltage of the N-channel LDMOS transistor LD1 is improved, the conduction resistance of the LD1 is reduced and the charging current to a bootstrapping capacitor is improved.

Owner:SOUTHEAST UNIV

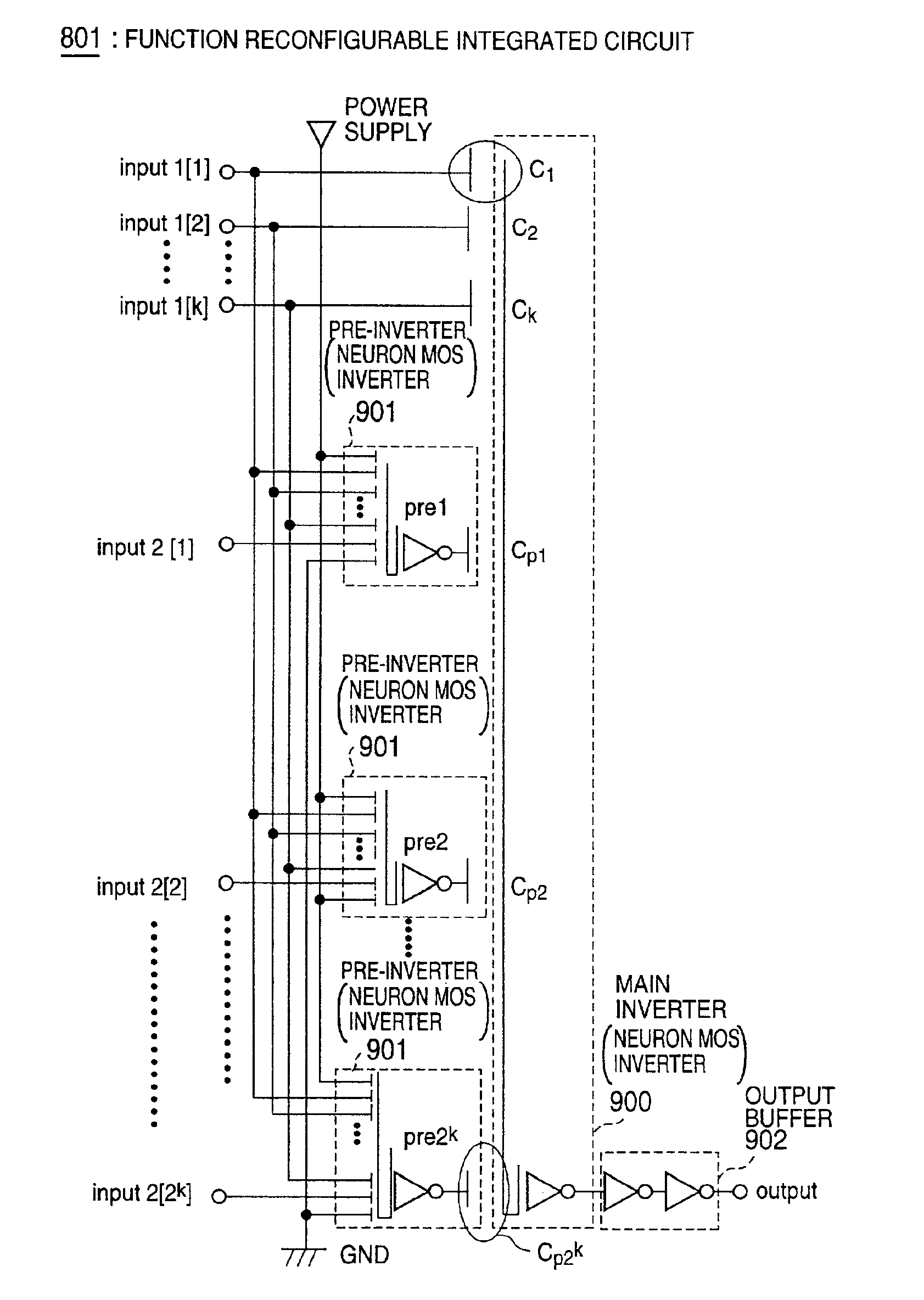

Function reconfigurable semiconductor device and integrated circuit configuring the semiconductor device

InactiveUS7075827B2Improve performanceReduce areaTransistorElectric analogue storesDevice materialEngineering

A function reconfigurable semiconductor device is provided. The function reconfigurable semiconductor device includes a plurality of function cells, each of the function cells being a basic unit which realizes a function; each of the function cells including a plurality of threshold elements; each of the threshold elements including means which stores a threshold value; and wherein a function which is realized by the function cell is determined by determining the threshold value in each of the threshold elements. In addition, the semiconductor device includes a nonvolatile memory which stores data for realizing the function in the function cells.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

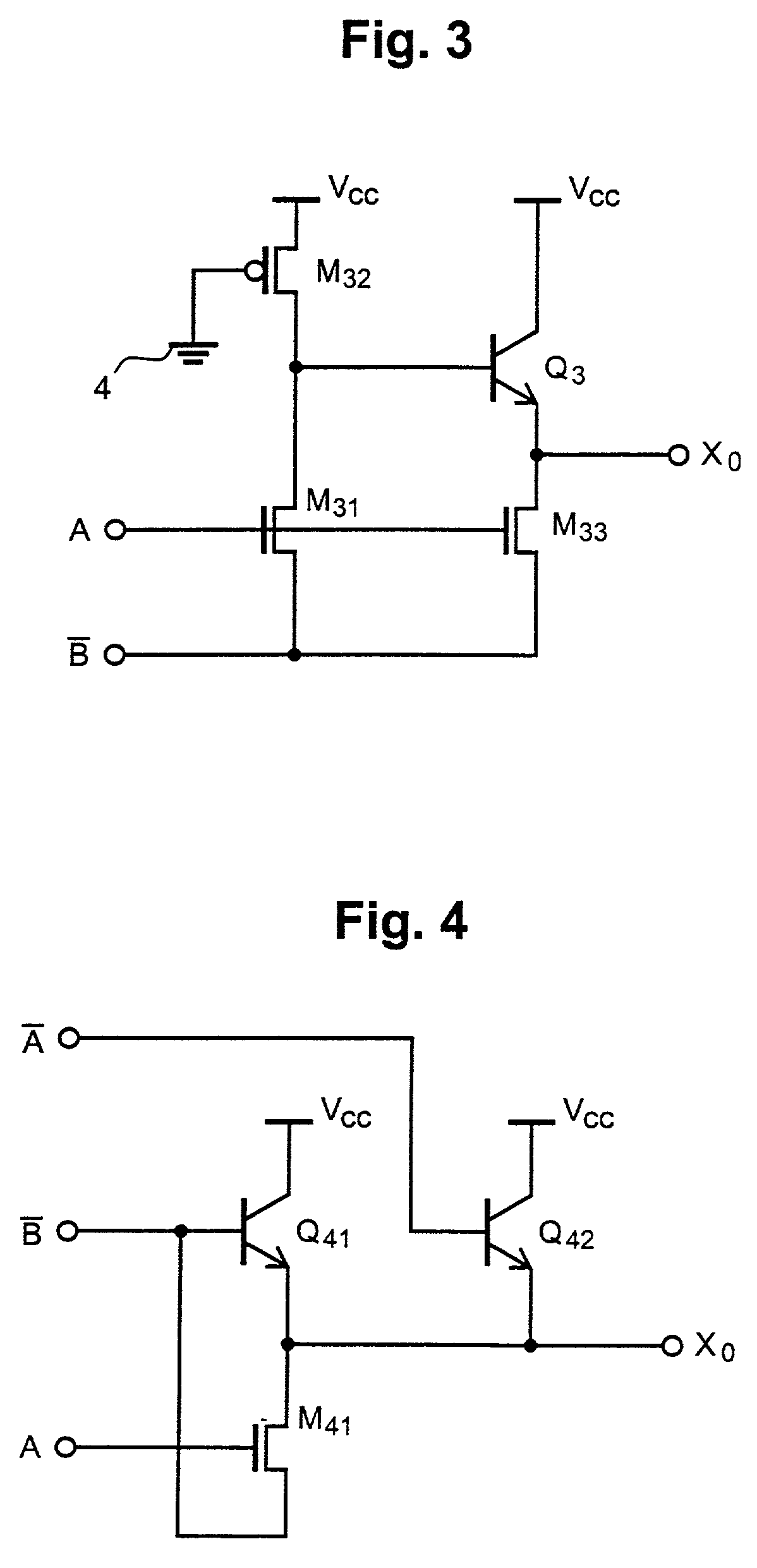

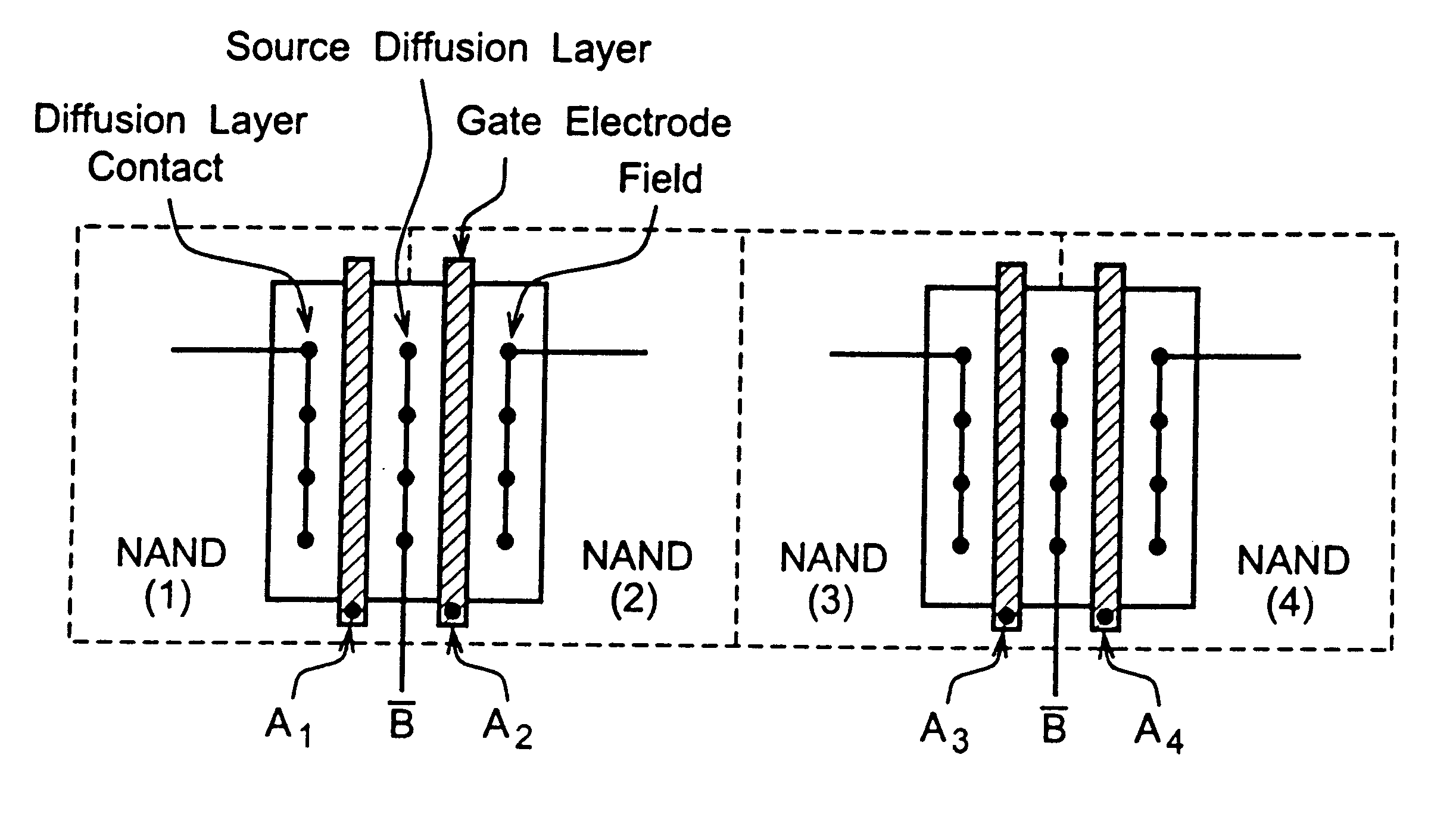

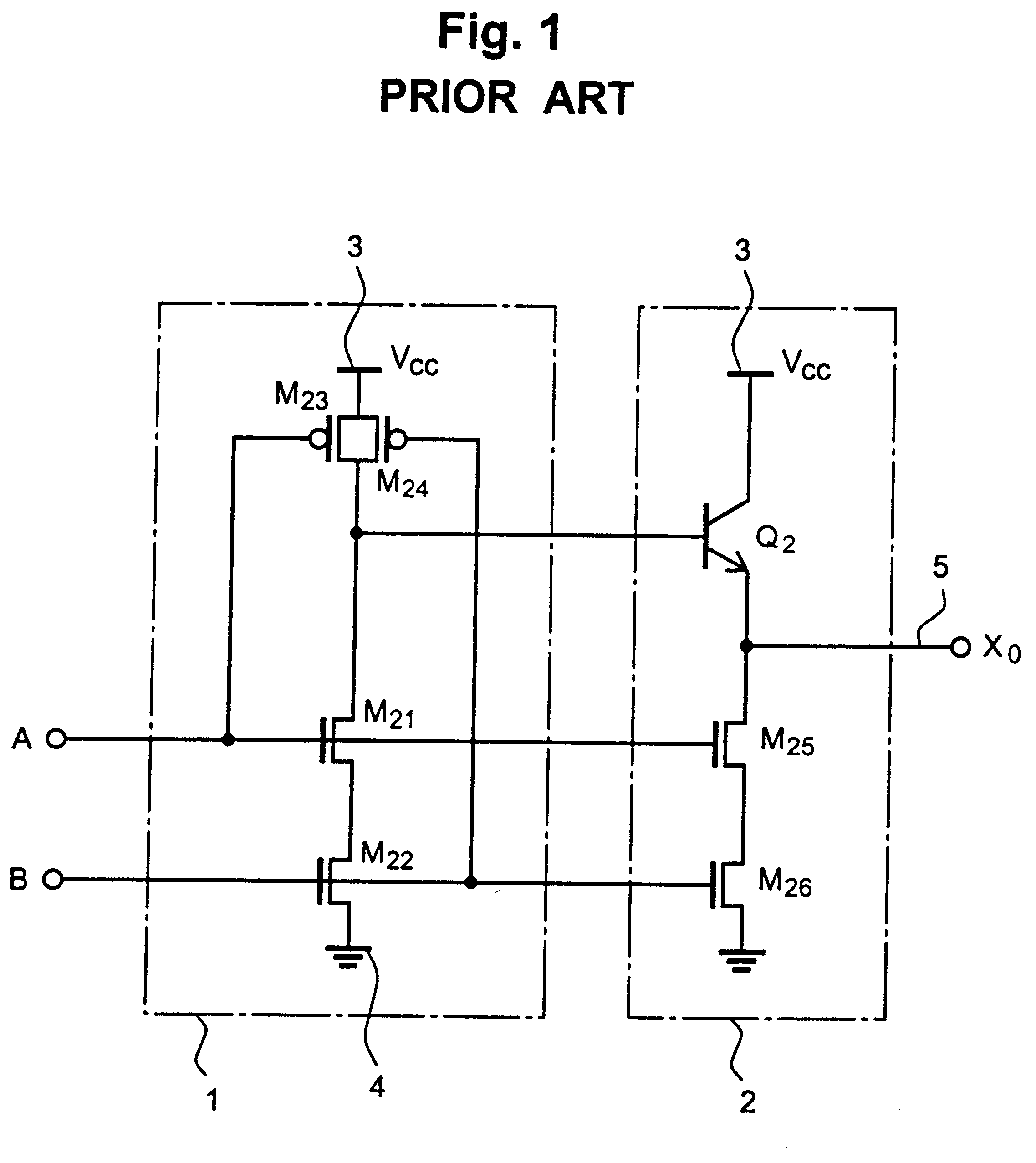

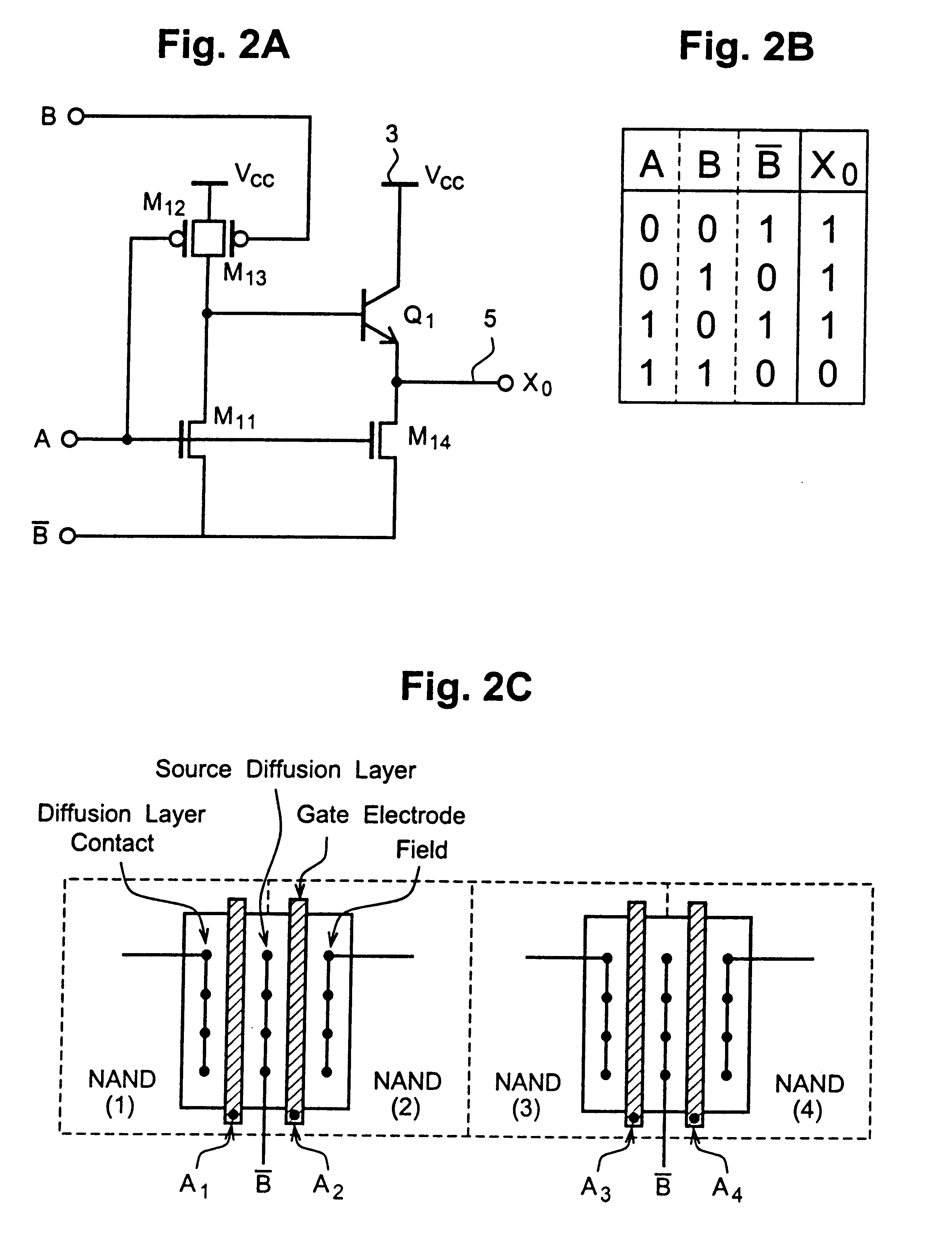

Logic circuit with single charge pulling out transistor and semiconductor integrated circuit using the same

InactiveUS20010040469A1Logic circuits characterised by logic functionLogic circuits using semiconductor devicesCapacitanceEngineering

A logic circuit performs a predetermined logic operation by supplying charge to an external load or putting out charge therefrom according to a combination of the states of a plurality of externally inputted binary signals. The logic circuit includes a first transistor for supplying charge through an output terminal to the external load and a second transistor for pulling out the charge from the load through the output terminal. One of the first and second transistors is constituted by a MOS field-effect transistor having a drain connected to the output terminal. The MOS field-effect transistor has a source receiving an inverse signal inverse to a signal combined for logic operation with an input signal inputted to a gate of the MOS field-effect transistor. The number of the series transistors is reduced, resulting in an increase of the current capacity and in a reduction of the layout area. Adjacent ones of the logic circuits have a common source diffusion layer so that the load capacitance with respect to the inverse signal can be significantly reduced, thus enabling the high speed operation.

Owner:NEC ELECTRONICS CORP

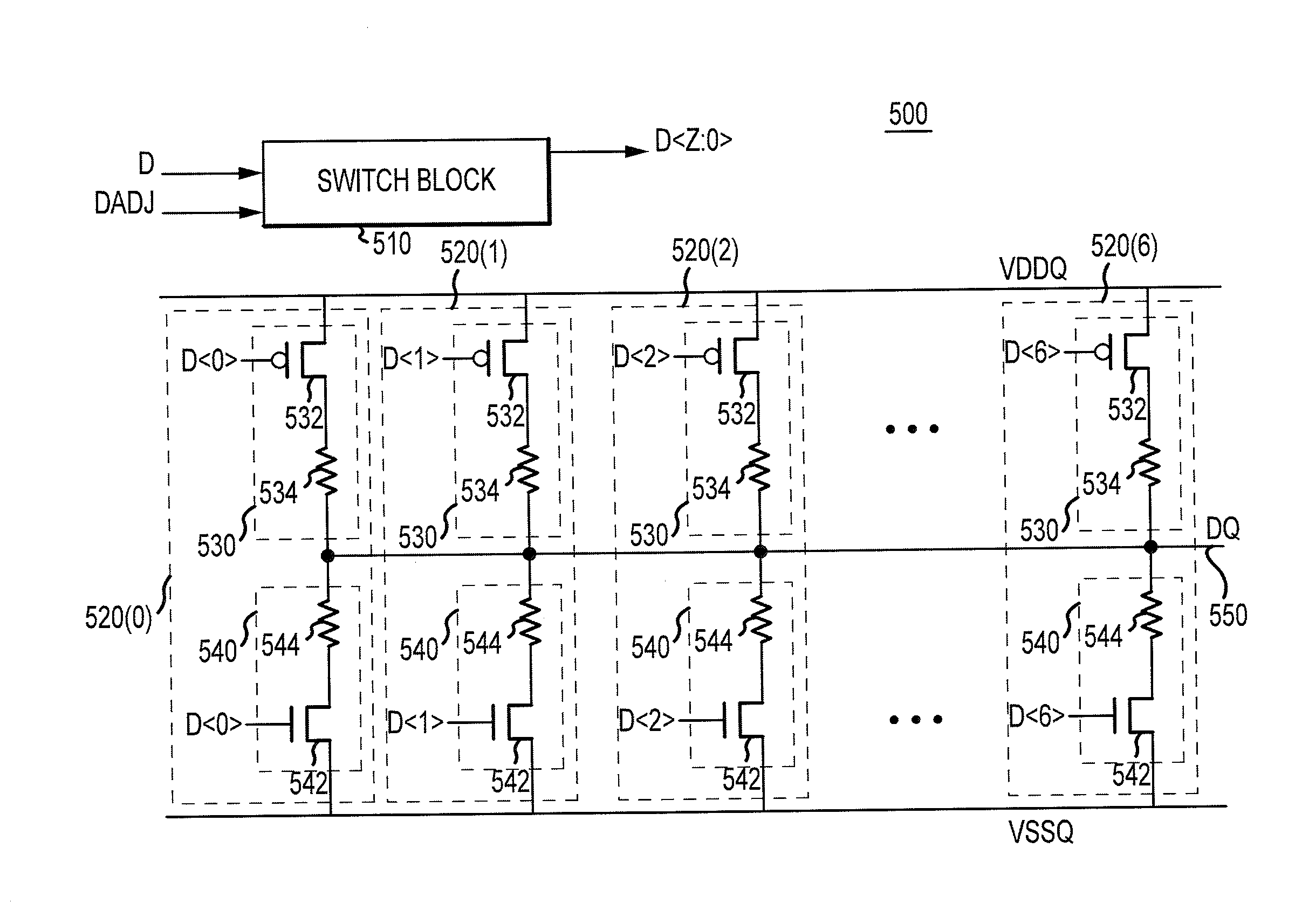

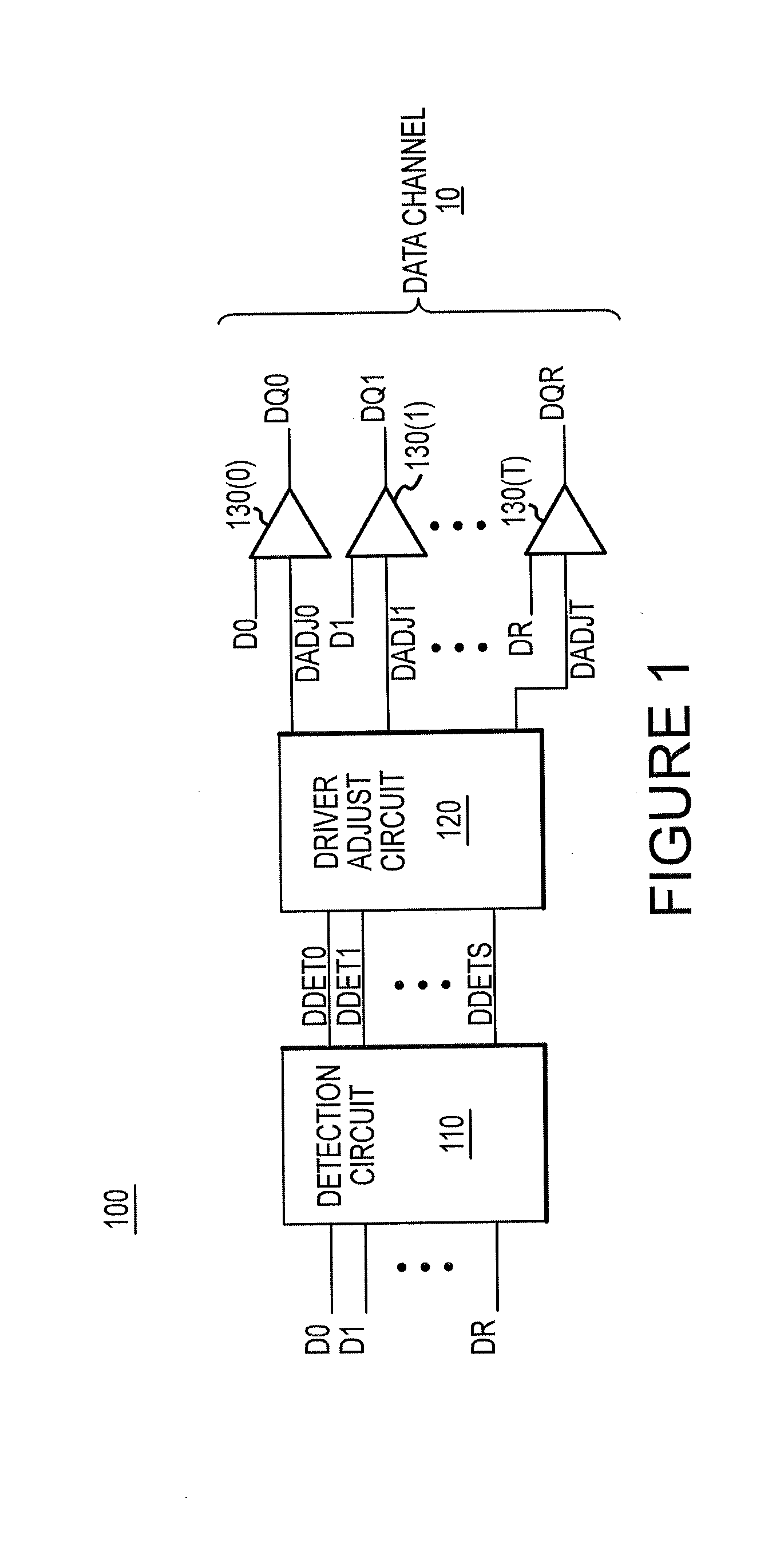

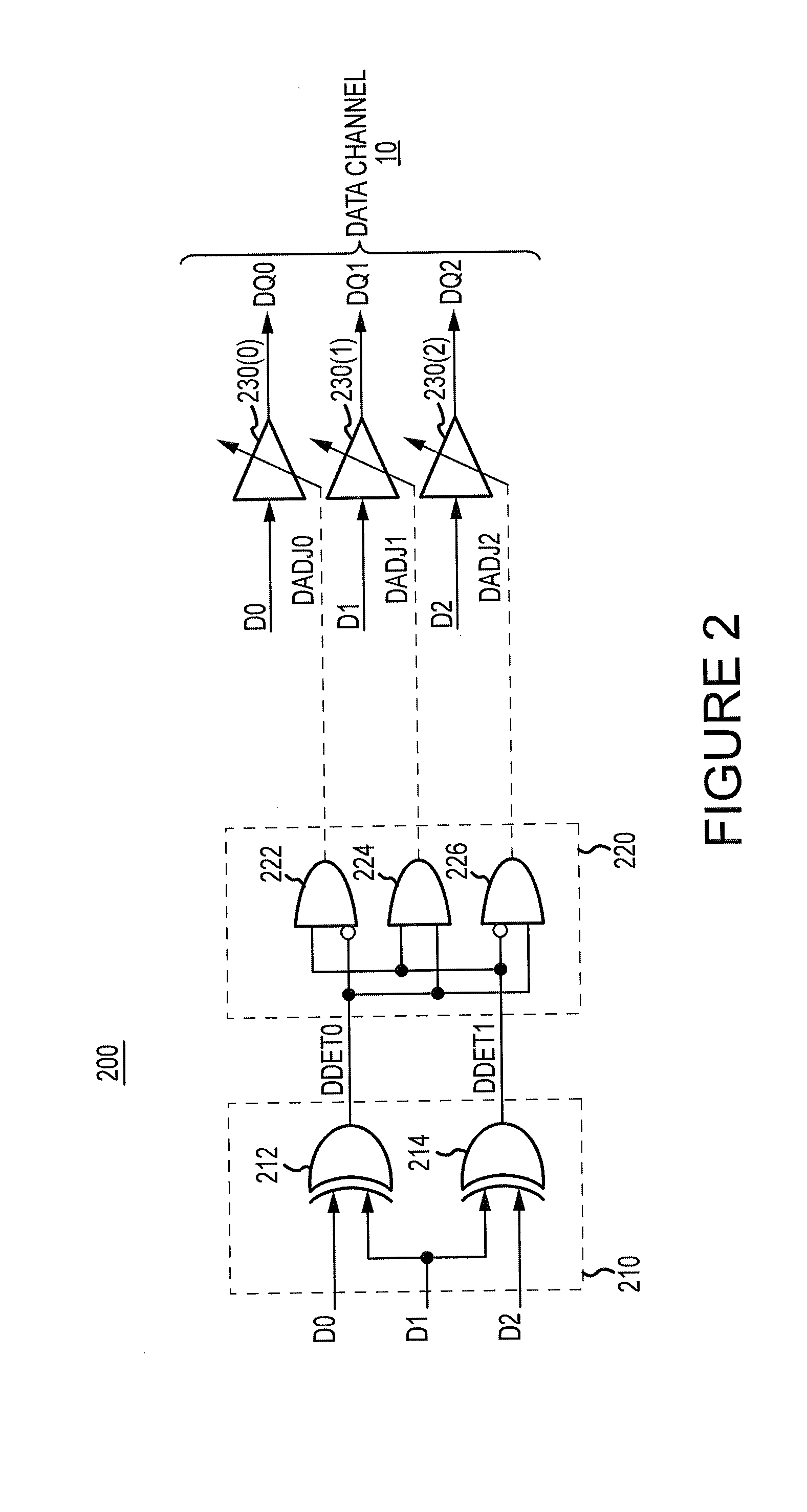

Adjustable data drivers and methods for driving data signals

ActiveUS20130043900A1Input/output impedence modificationReliability increasing modificationsData signalEngineering

Apparatuses and methods for driving input data signals onto signal lines as output data signals are disclosed. An example apparatus includes a detection circuit, a driver adjust circuit, and a data driver. The detection circuit is configured to detect a characteristic(s) of a group of input data signals to be driven onto adjacent signal lines. A characteristic could be, for example, a particular combination of logic levels and / or transitions for, the group of input data signals. The driver adjust circuit is configured to provide a driver adjustment signal based at least in part on a detection signal, that is provided by the detection circuit. A data driver is configured to drive a respective one of the group of input data signals as a respective one of the output data signals, wherein the data driver is adjusted based at least in part on the driver adjustment signal.

Owner:MICRON TECH INC

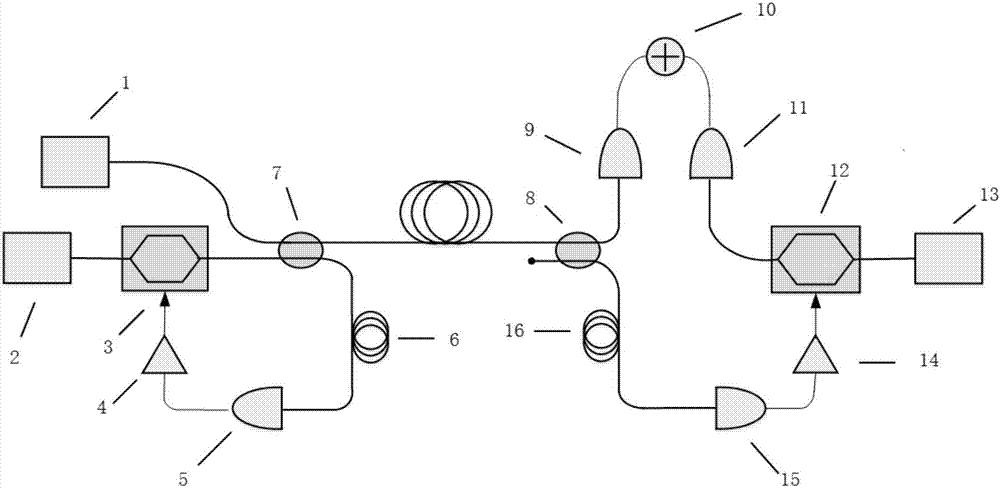

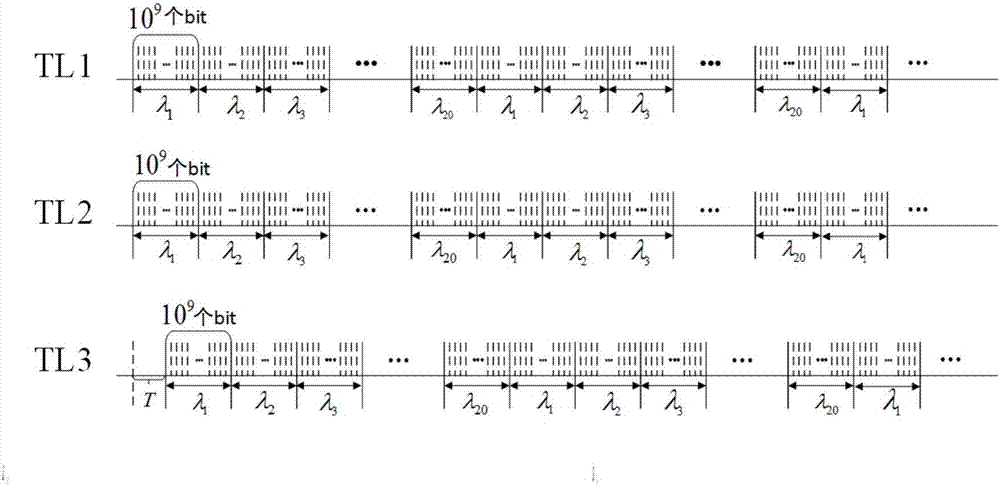

High-dimension chaotic laser secrecy communication system

ActiveCN107508665AIncrease the difficultyImprove securityLogic circuits using semiconductor devicesSecuring communication by chaotic signalsThird partyPhotovoltaic detectors

A high-dimension chaotic laser secrecy communication system disclosed by the present invention comprises an emission terminal and a reception terminal, the emission terminal comprises a first tunable laser, a second tunable laser, a first Mach-Zehnder modulator, a first radio frequency amplifier, a first photoelectric detector, a first optical delay line and a first optical fiber coupler, and the reception terminal comprises a third tunable laser, a second Mach-Zehnder modulator, a second optical fiber coupler, a second optical delay line, a second radio frequency amplifier, a second photoelectric detector, a third photoelectric detector, a fourth photoelectric detector and a summator. The high-dimension chaotic laser secrecy communication system of the present invention uses the tunable lasers to generate the chaotic carriers and the load information, by controlling the switching and matching of the wavelengths of the lasers, and on the condition that a third party does not know the wavelengths, enables the information decoding difficulty to be improved substantially, and has the important significance for the enterprises and departments having the secrecy demands, and especially for the national defense information security field.

Owner:NANJING UNIV

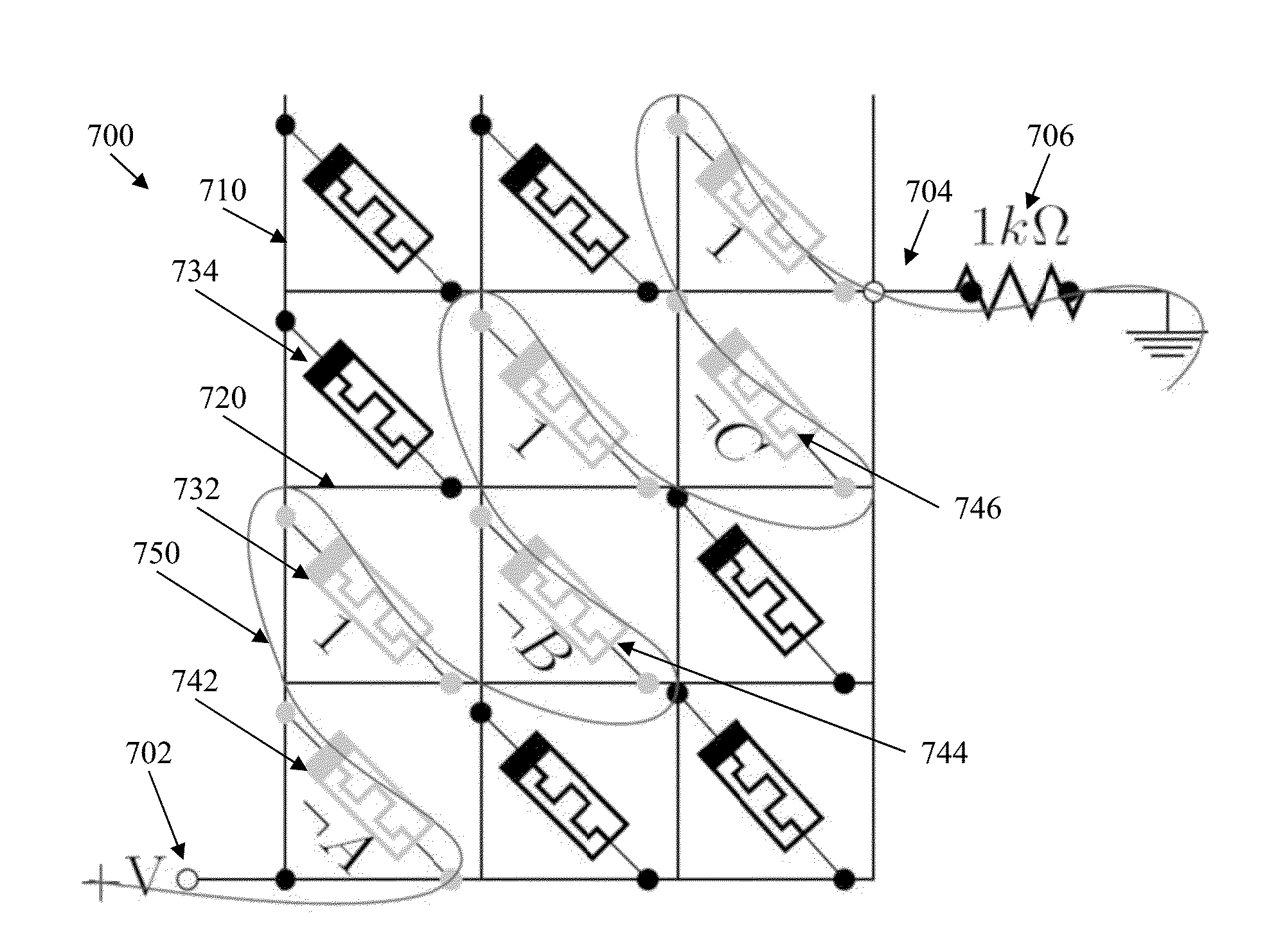

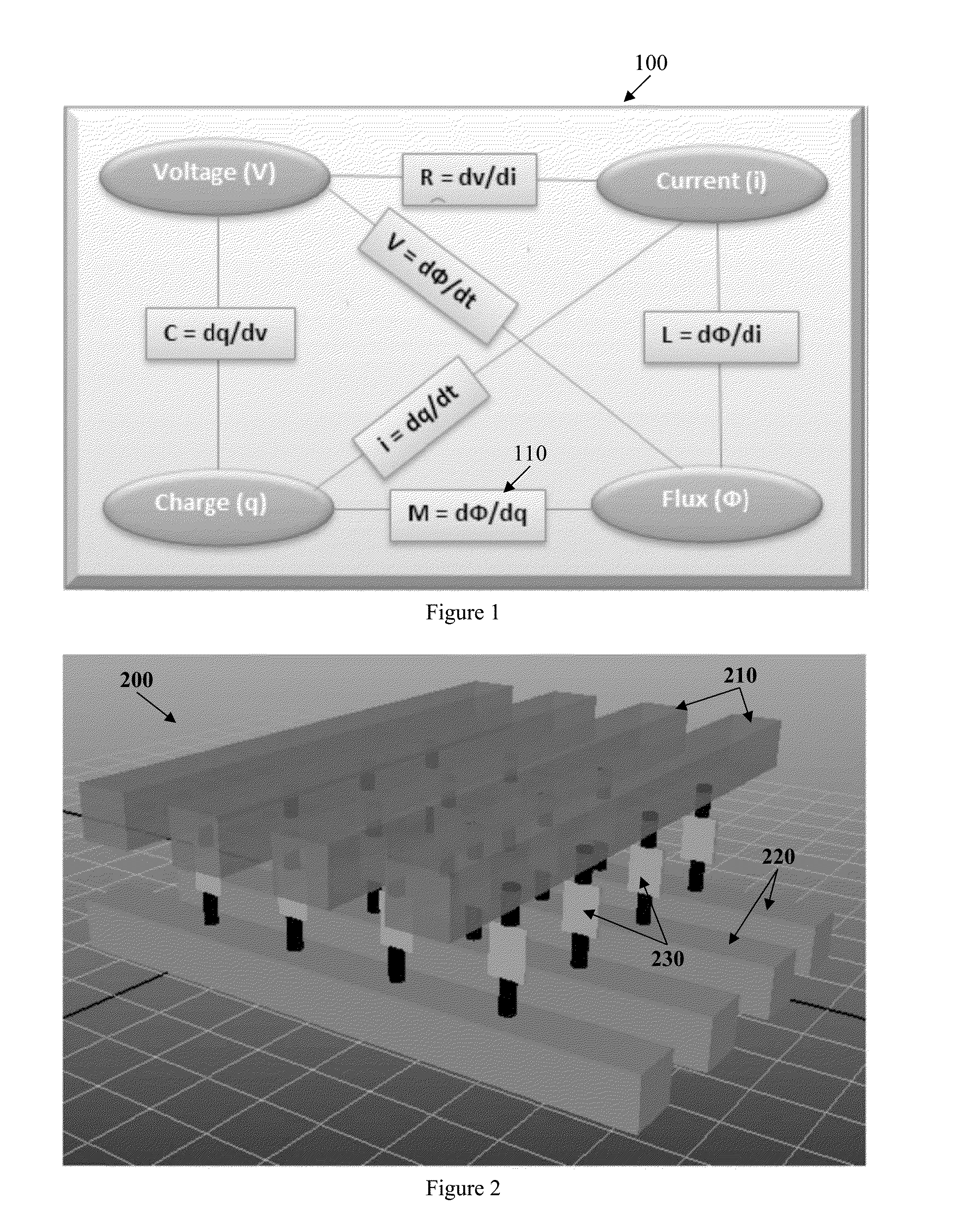

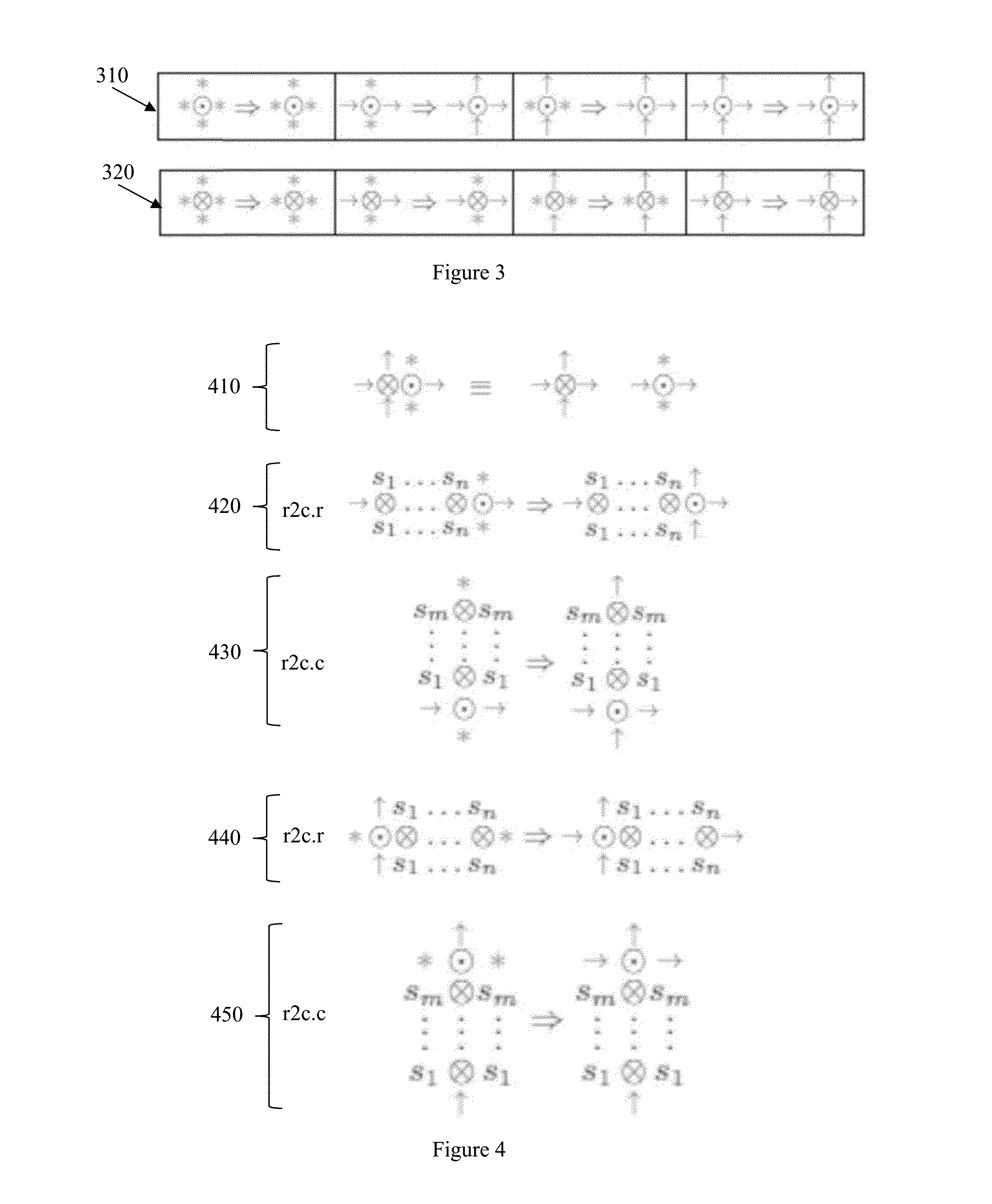

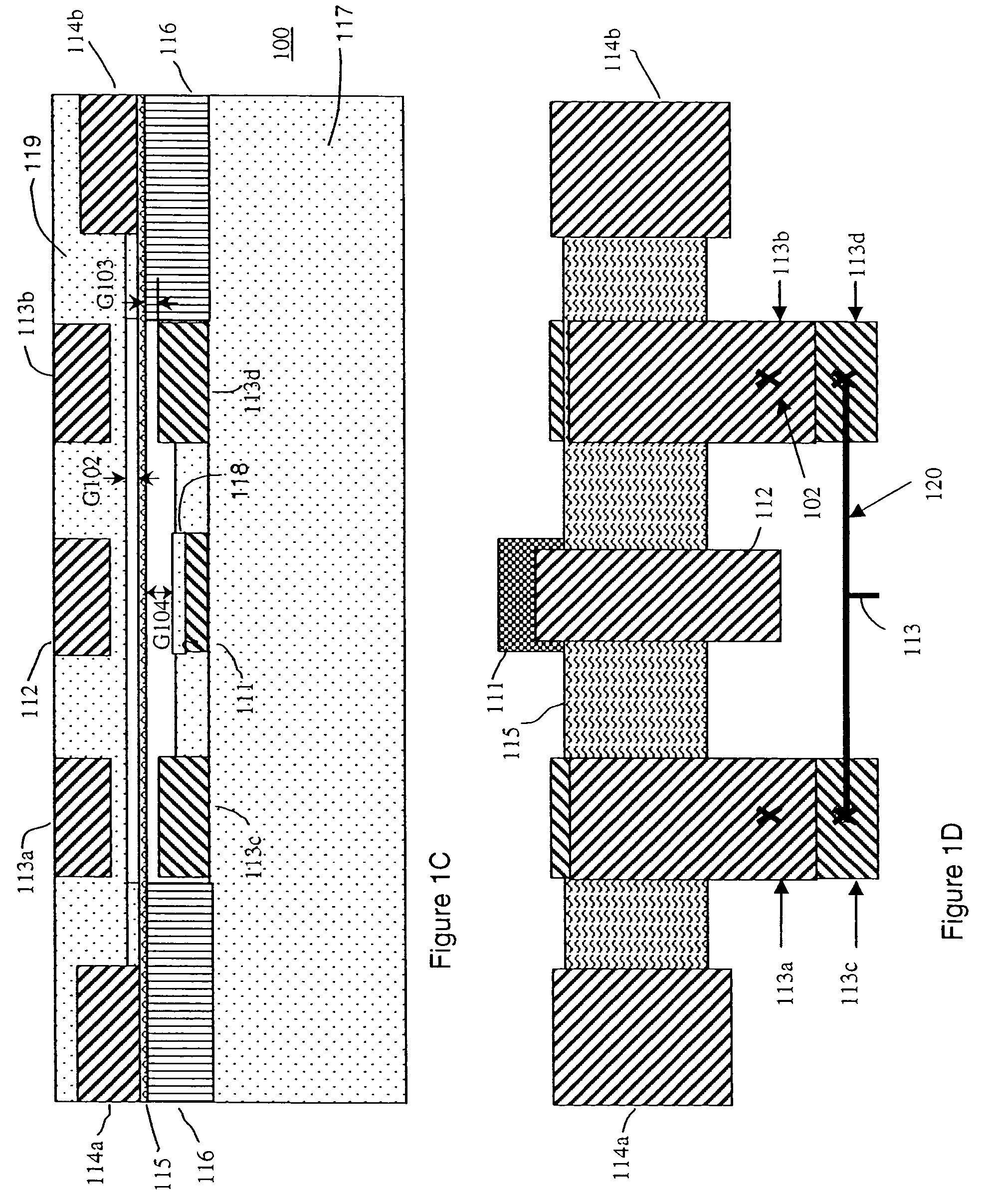

Computation of boolean formulas using sneak paths in crossbar computing

ActiveUS20150171868A1Programmable logic circuit arrangementsLogic circuits using semiconductor devicesGeneral purposeTheoretical computer science

Memristor-based nano-crossbar computing is a revolutionary computing paradigm that does away with the traditional Von Neumann architectural separation of memory and computation units. The computation of Boolean formulas using memristor circuits has been a subject of several recent investigations. Crossbar computing, in general, has also been a topic of active interest, but sneak paths have posed a hurdle in the design of pervasive general-purpose crossbar computing paradigms. Various embodiments are disclosed which demonstrate that sneak paths in nano-crossbar computing can be exploited to design a Boolean-formula evaluation strategy. Such nano-crossbar designs are also an effective approach for synthesizing high performance customized arithmetic and logic circuits.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE +1

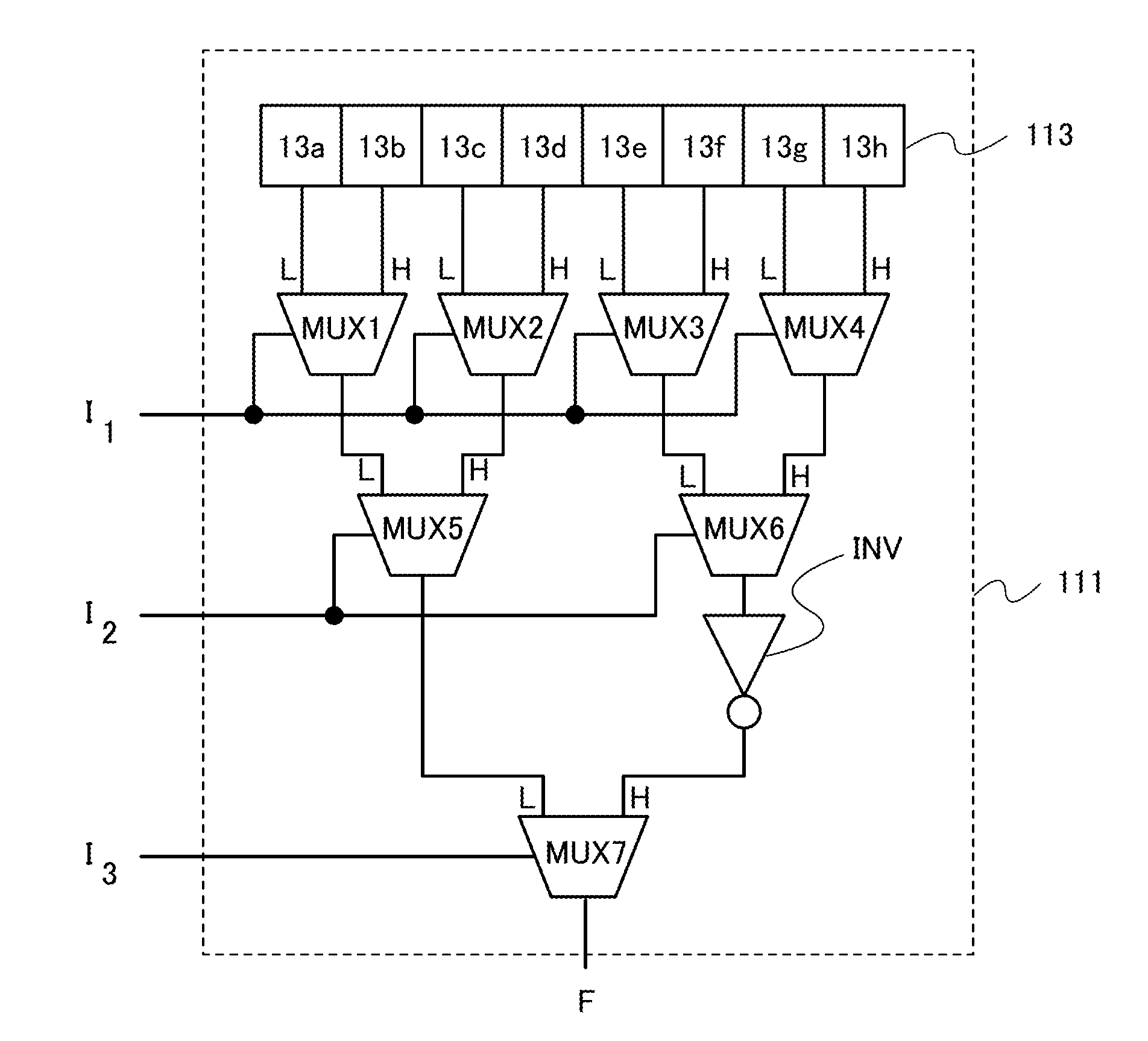

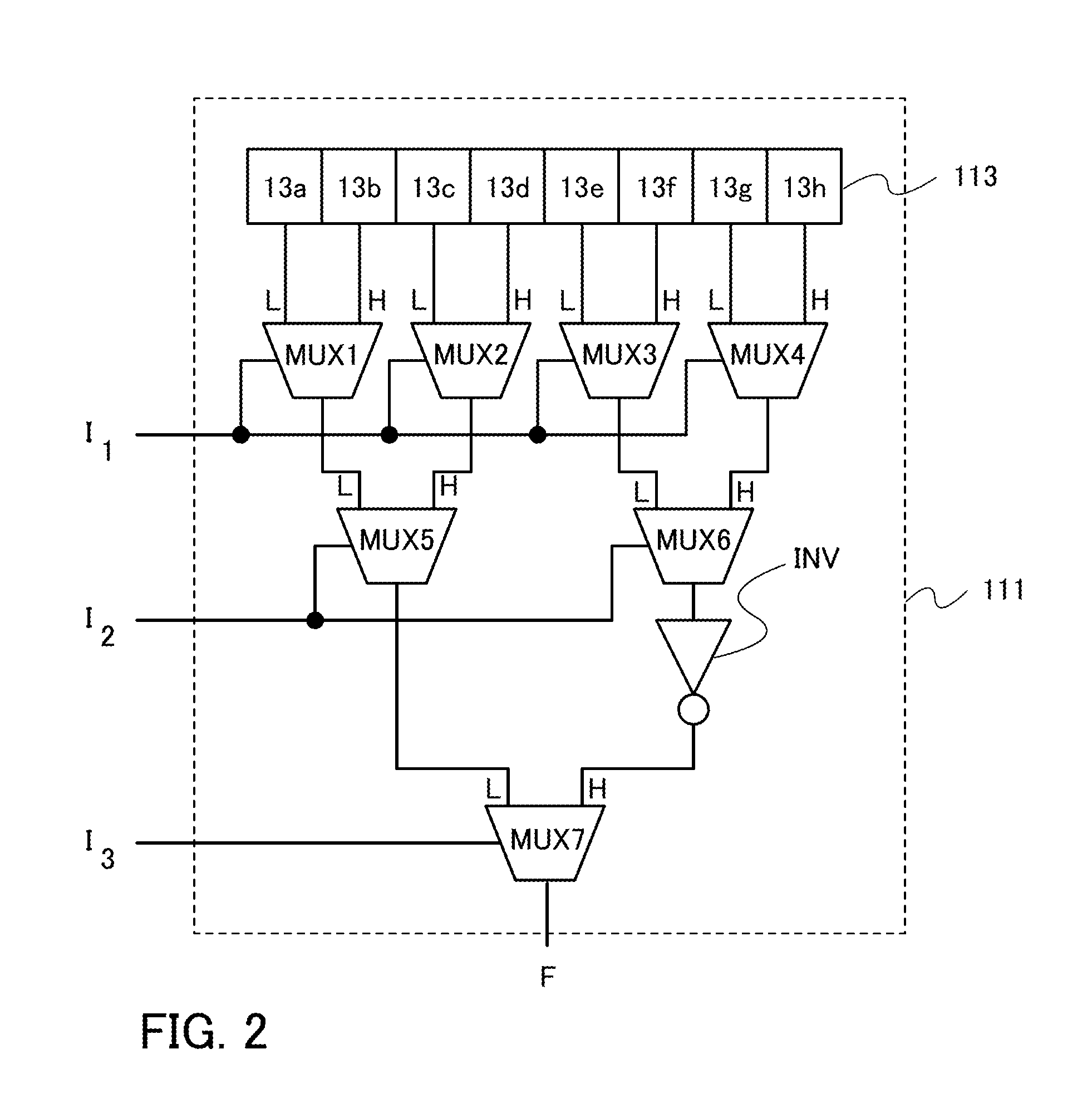

Lookup table and programmable logic device including lookup table

InactiveUS20130293262A1Reduce in quantityConvenient ArrangementLogic circuits using semiconductor devicesDigital storageMultiplexerProgrammable logic device

To optimize the arrangement of configuration data stored in a configuration memory. A lookup table includes a memory configured to store configuration data, a plurality of multiplexers each configured to select one signal from a plurality of input signals in accordance with the configuration data supplied from the memory and output the one signal, and an inverter. The plurality of multiplexers are connected in a binary tree with multiple levels. The inverter is provided between one of input terminals of a multiplexer in an uppermost level and an output terminal of a multiplexer in one level lower than the uppermost level. Signal selection is performed in each of the multiplexers so that the multiplexer in the uppermost level outputs, as an output signal, one signal of all input signals of the multiplexers in a lowermost level.

Owner:SEMICON ENERGY LAB CO LTD

Integrated nanotube and field effect switching device

ActiveUS7288970B2Logic circuits characterised by logic functionNanoelectromechanical switchesElectricityDevice form

Owner:NANTERO

Logic circuit with single charge pulling out transistor and semiconductor integrated circuit using the same

InactiveUS6445215B1Logic circuits characterised by logic functionLogic circuits using semiconductor devicesCapacitanceEngineering

A logic circuit performs a predetermined logic operation by supplying charge to an external load or pulling out charge therefrom according to a combination of the states of a plurality of externally inputted binary signals. The logic circuit includes a first transistor for supplying charge through an output terminal to the external load and a second transistor for pulling out the charge from the load through the output terminal. One of the first and second transistors is constituted by a MOS field-effect transistor having a drain connected to the output terminal. The MOS field-effect transistor has a source receiving an inverse signal inverse to a signal combined for logic operation with an input signal inputted to a gate of the MOS field-effect transistor. The number of the series transistors is reduced, resulting in an increase of the current capacity and in a reduction of the layout area. Adjacent ones of the logic circuits have a common source diffusion layer so that the load capacitance with respect to the inverse signal can be significantly reduced, thus enabling the high speed operation.

Owner:RENESAS ELECTRONICS CORP

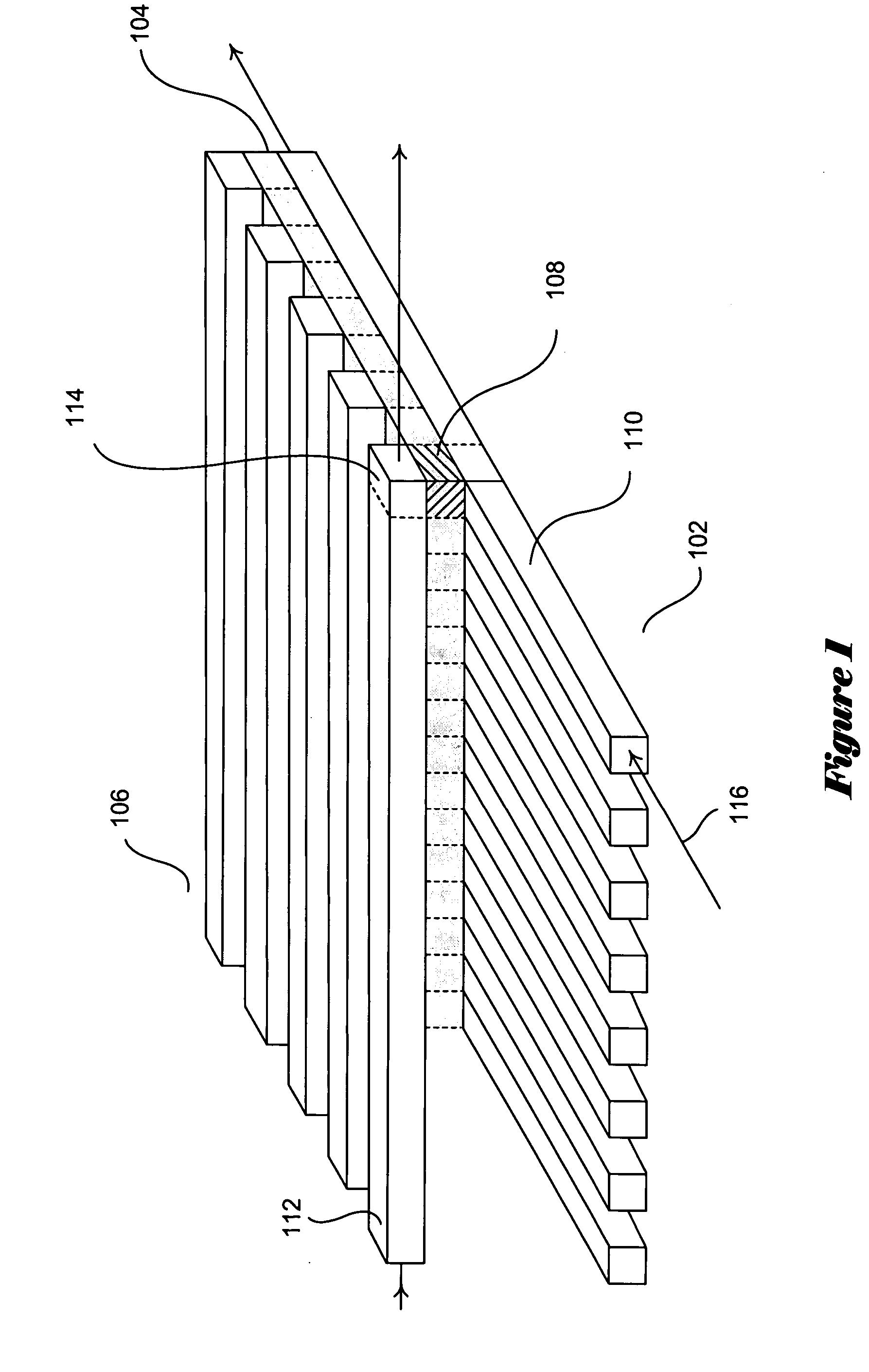

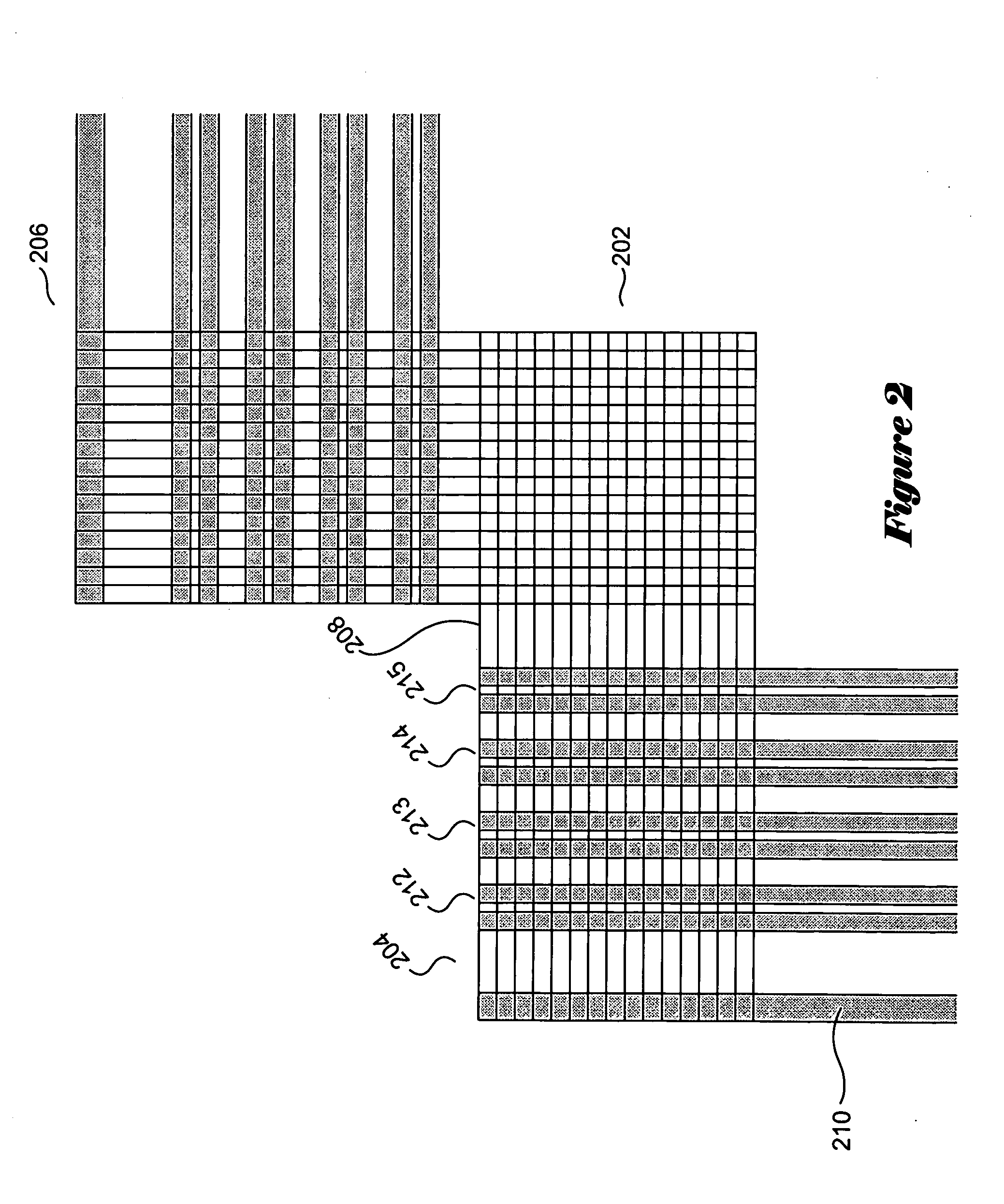

Multiplexer interface to a nanoscale-crossbar

ActiveUS20060238223A1Logic circuits characterised by logic functionNanoinformaticsNanowireNanoscale crossbar

Various embodiments of the present invention are directed to electronic means for reading the content of a nanowire-crossbar memory. In one embodiment of the present invention, a microscale or sub-microscale signal line is interconnected with one set of parallel nanowires emanating from a nanowire-crossbar memory by configurable, nanowire-junction switches. The microscale or sub-microscale signal line serves as a single-wire multiplexer, allowing the contents of any particular single-bit storage element within the nanowire-crossbar memory to be read in a three-cycle READ operation.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

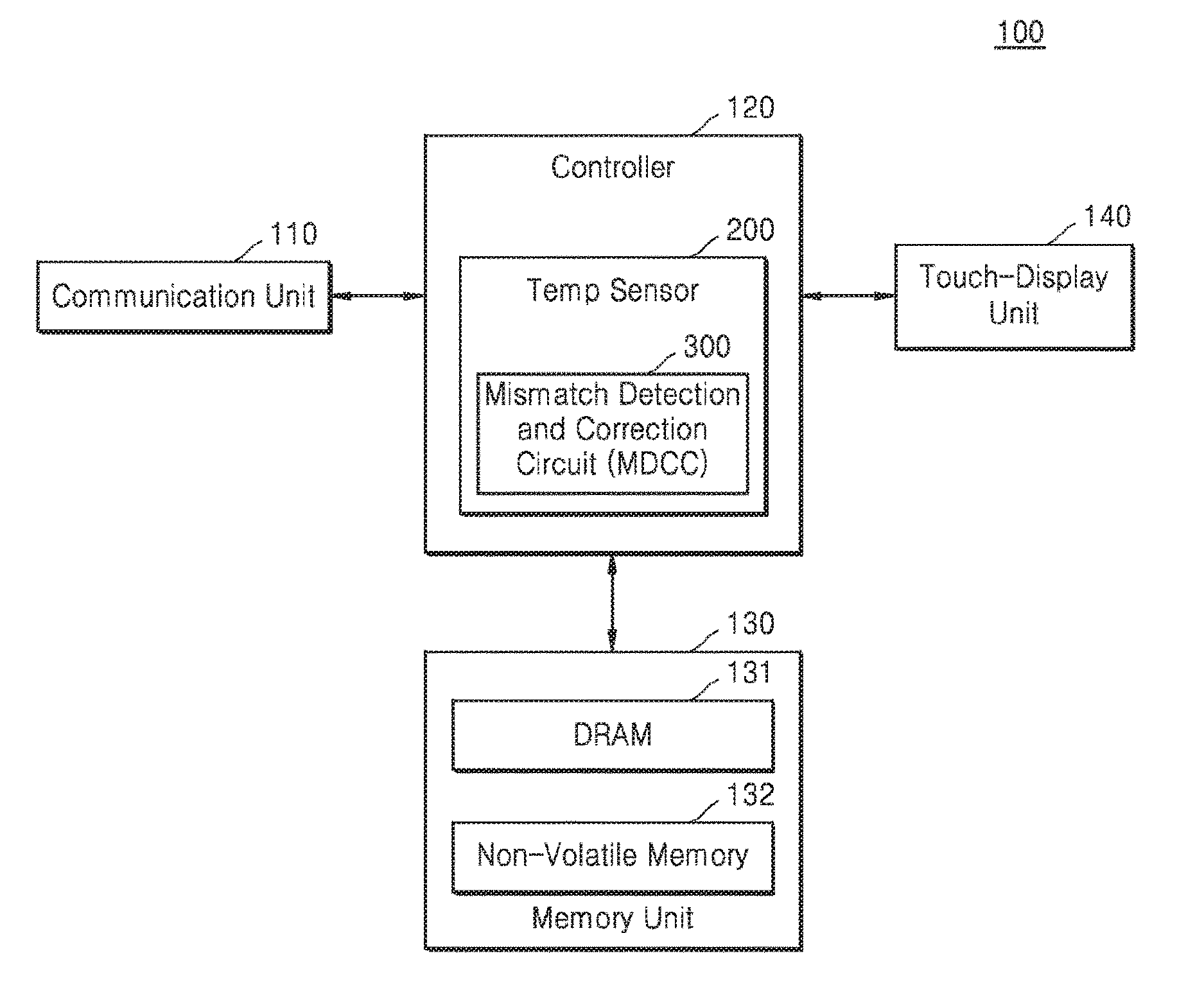

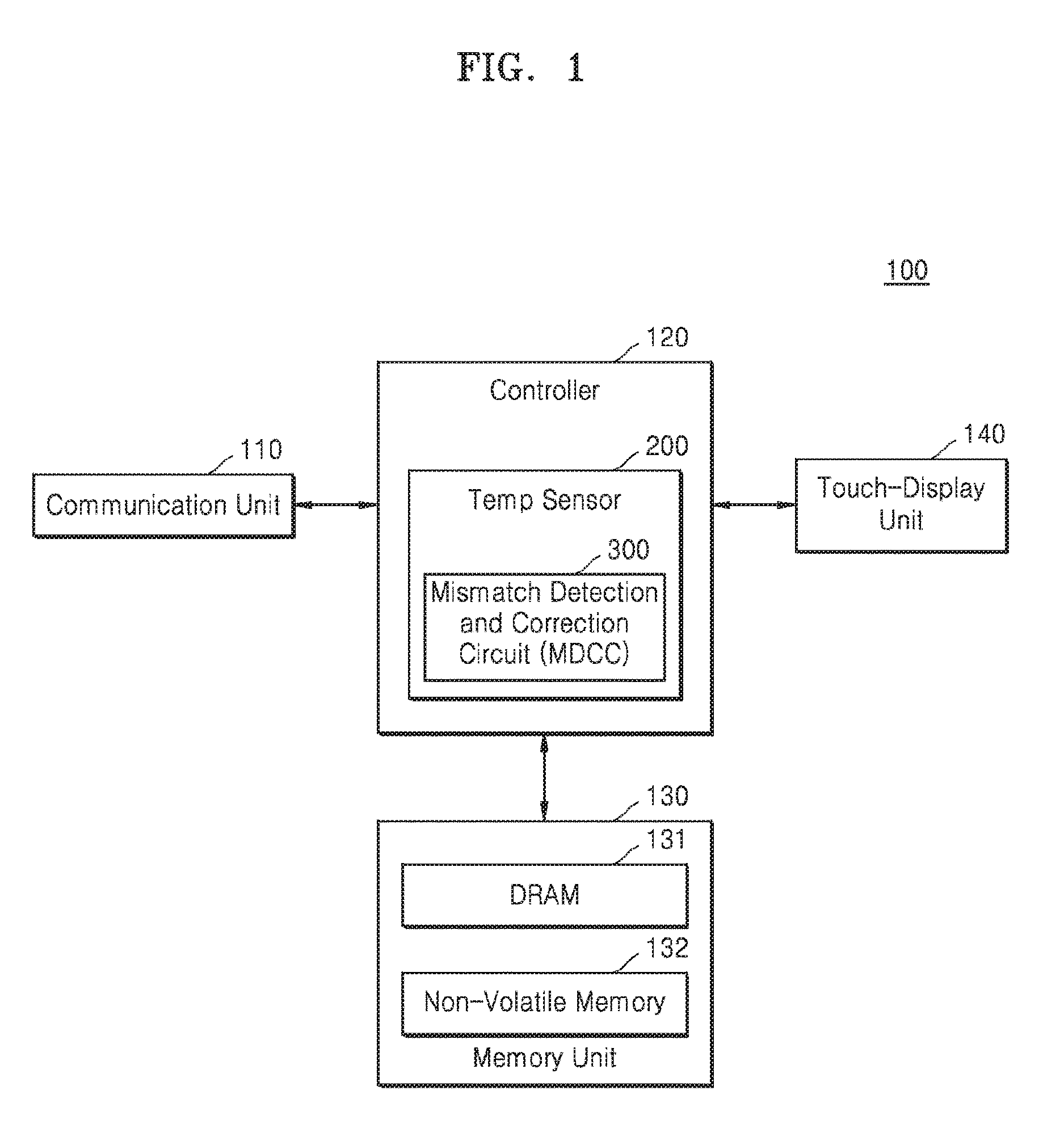

Semiconductor device having a mismatch detection and correction circuit

ActiveUS20170023966A1Correction errorThermometer detailsElectronic circuit testingDevice materialEngineering

A semiconductor device includes: an integrated circuit (IC) including an internal circuit; and a mismatch detection and correction circuit connected to the internal circuit of the IC, the mismatch detection and correction circuit configured to detect a process mismatch and correct an error in the internal circuit caused by the process mismatch using a current difference between a first current and a second current based on a charged voltage of a capacitor.

Owner:SAMSUNG ELECTRONICS CO LTD

A four-redundancy simulation signal hardware voting circuit

ActiveCN103516351ASimple designImplement cross-redundancy votingLogic circuits using semiconductor devicesAudio power amplifierControl system

The invention belongs to the technical field of telex flight control systems, and especially relates to a four-redundancy simulation signal hardware voting circuit. The four-redundancy simulation signal hardware voting circuit of the invention mainly comprises a quad operational amplifier chip with a high gain, eight diodes and several resistors. The circuit of the invention is simple and practical. The production cost is low. The circuit is reliable. Lagging of signal selection voting will not occur. The design and the debugging are convenient. A synthesis problem of four-redundancy driving signals of a control system can be easily solved, and intersecting redundancy voting from a controller to execution parts is realized. The design of the controller is enabled to be simplified so as to raise the reliability of the system.

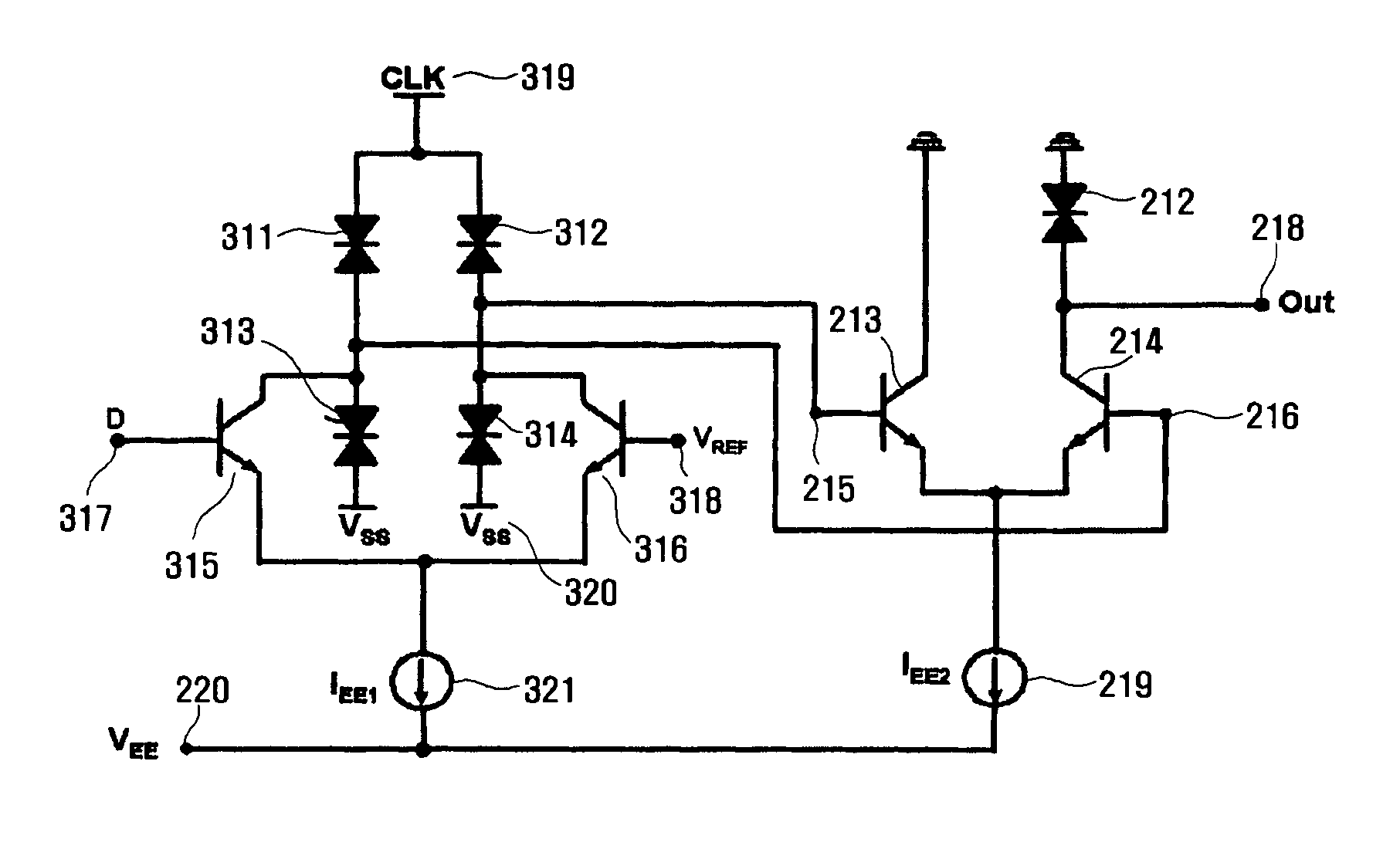

SET/RESET latch circuit, Schmitt trigger circuit, and MOBILE based D-type flip flop circuit and frequency divider circuit thereof

InactiveUS7573310B2Easy to useHigh speedLogic circuits characterised by logic functionDiodeSchmitt triggerEngineering

The present invention relates to a SET / RESET latch circuit a Schmitt trigger circuit, and a MOBILE based D-type flip flop circuit and frequency divider circuit using the SET / RESET latch circuit and Schmitt trigger circuit. The SET / RESET latch circuit is configured with CML-type transistors and negative differential resistance diodes. The SET / RESET latch circuit can be applied to very high speed digital circuits.

Owner:KOREA ADVANCED INST OF SCI & TECH

Single-wire programmable MEMS microphone, programming method and system thereof

ActiveUS9161112B2Calibration of gainOptimizationGain controlSemiconductor electrostatic transducersMultiplexingElectricity

The present invention provides a single wire programmable Micro Electromechanical System (MEMS) microphone and a programming method and system thereof. The single wire programmable MEMS microphone includes an MEMS sensor and an Application Specific Integrated Circuit (ASIC) chip connected to each other; the MEMS sensor is used for implementing acoustic-electric conversion; the ASIC chip includes an OUT interface, so that an upper computer judges, according to an output signal of the OUT interface, whether the ASIC chip is in a normal start mode or a programming mode, where if the output signal of the OUT interface is at a high level, the ASIC chip is in the normal start mode, and otherwise, the ASIC chip enters the programming mode. Through the present invention, multiplexing of the OUT interface of the MEMS microphone is implemented, and gain configuration for the OTP memory in the ASIC chip is implemented by multiplexing the OUT interface, thereby achieving calibration of the gain of the MEMS microphone product after package.

Owner:ZILLTEK TECH SHANGHAI +1

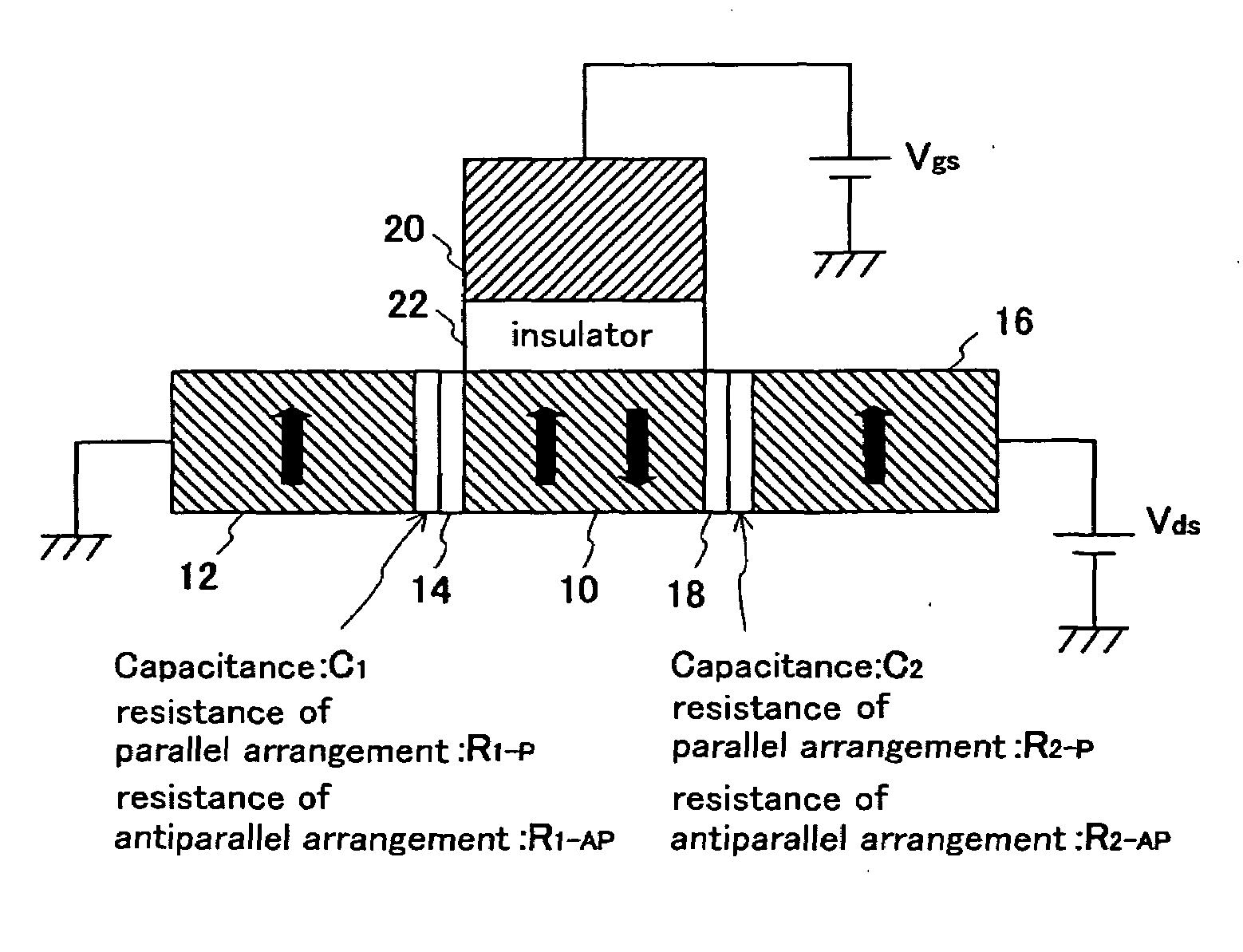

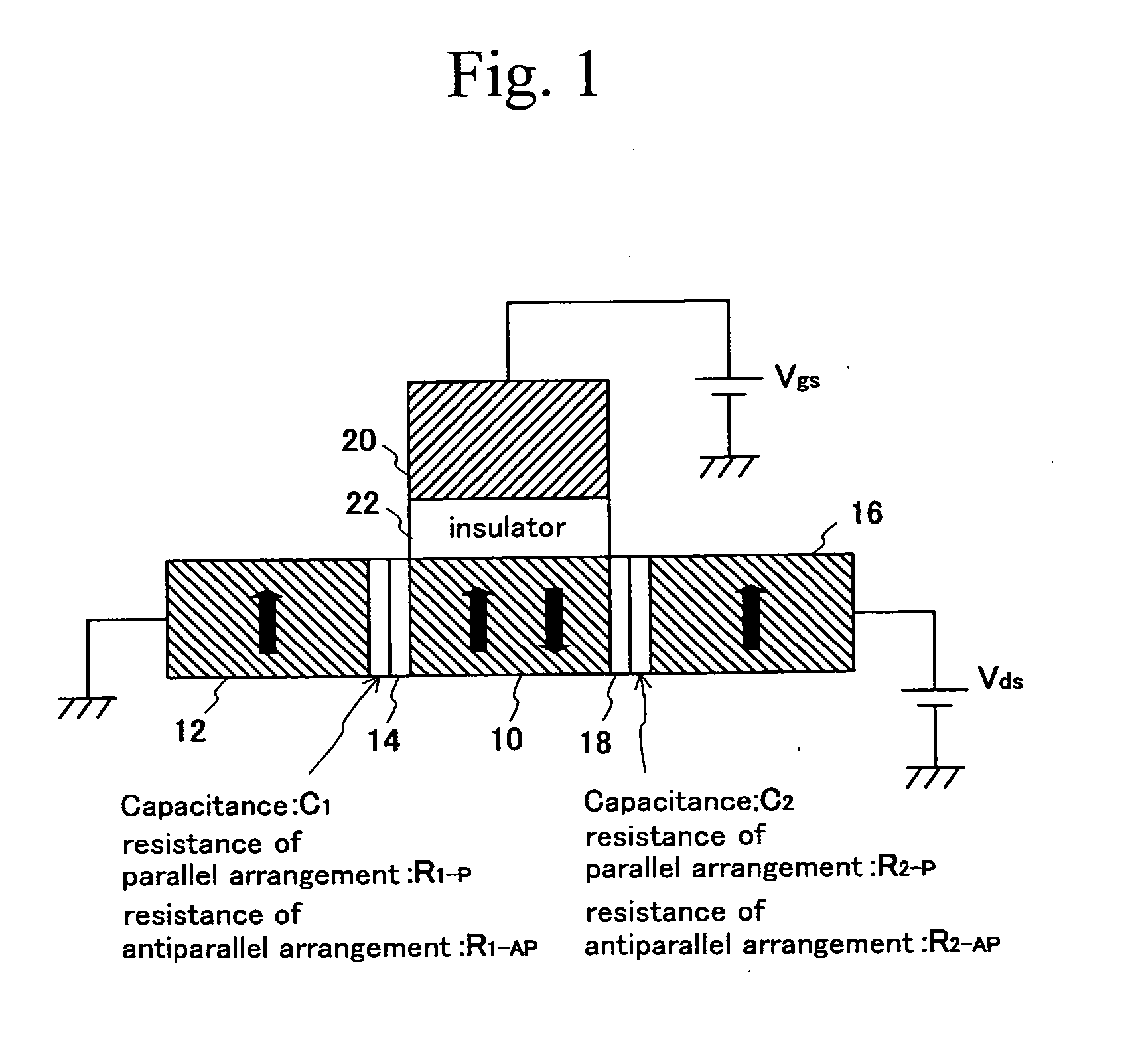

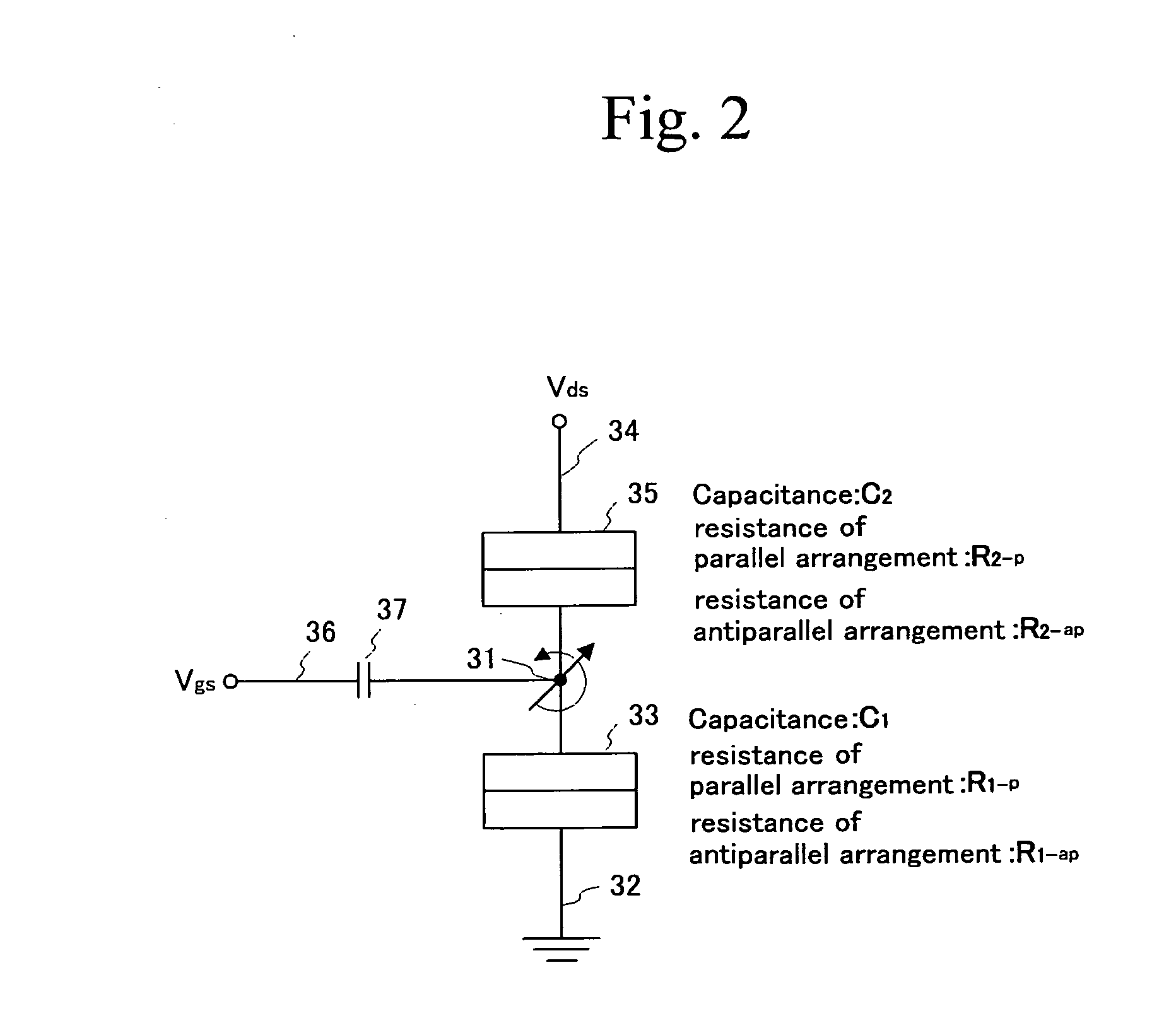

Logic Circuit and Single-Electron Spin Transistor

InactiveUS20090039401A1Reduce areaSolve the large power consumptionNanoinformaticsSemiconductor/solid-state device manufacturingSingle electronCapacitance

A logic circuit that can reconfigure its functions in a nonvolatile manner and a single-electron transistor to be used in the logic circuits are provided. The logic circuit has a single-electron spin transistor that includes: a source; a drain; an island that is provided between the source and the drain, and has tunnel junctions between the island and the source and drain; and a gate that is capacitively coupled to the island. In this logic circuit, at least one of the source, the drain, and the island includes a ferromagnetic material having a variable magnetization direction.

Owner:JAPAN SCI & TECH CORP

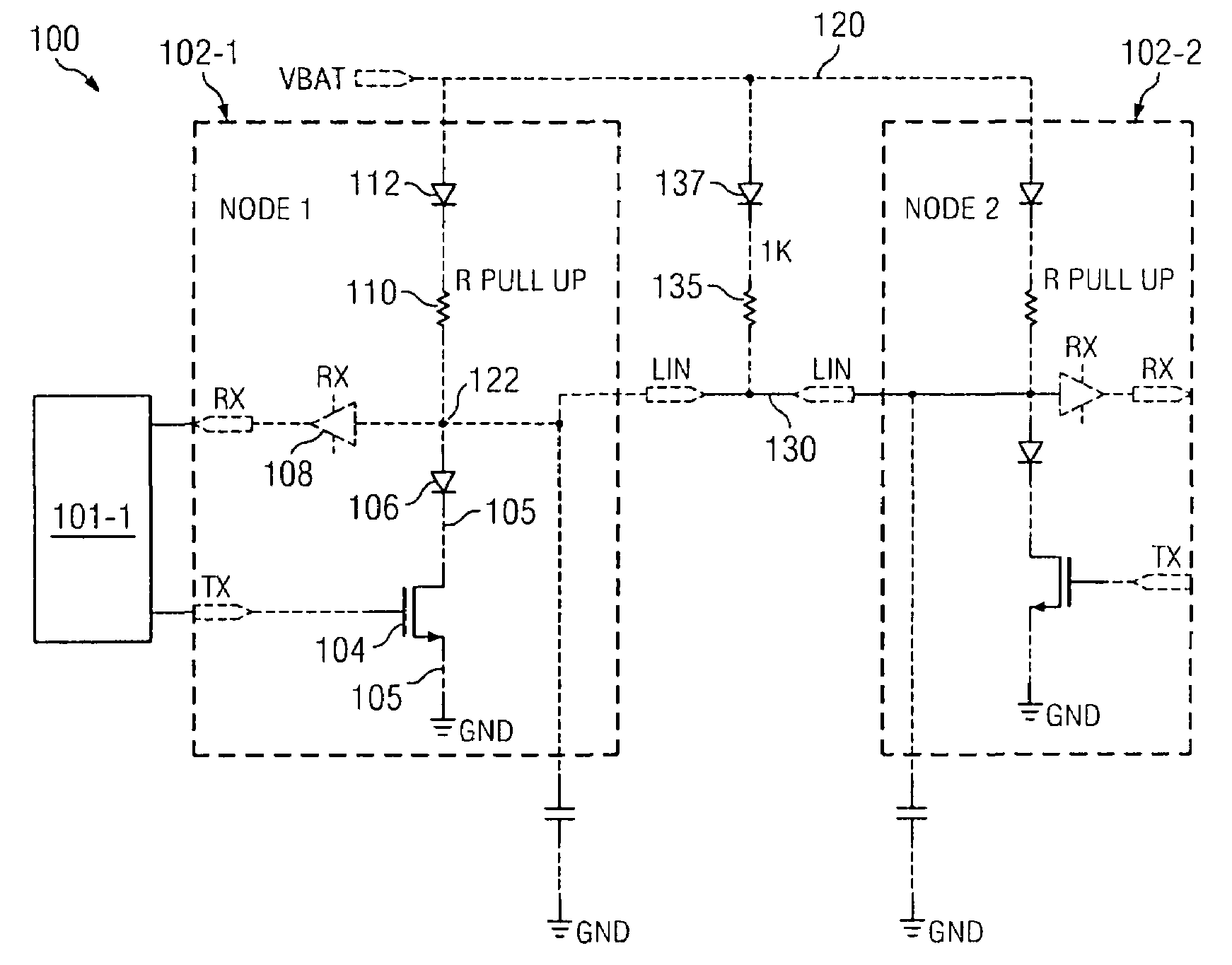

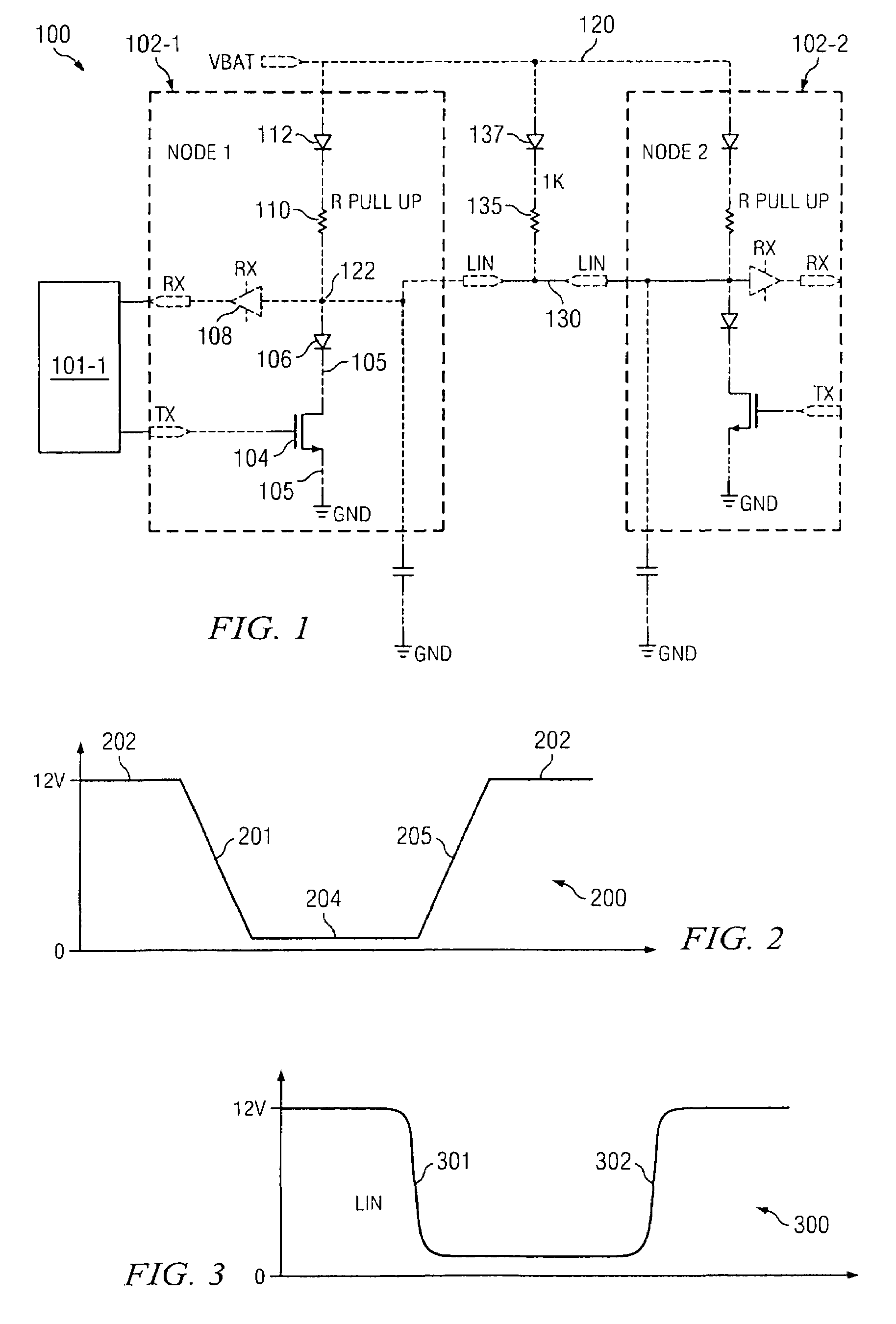

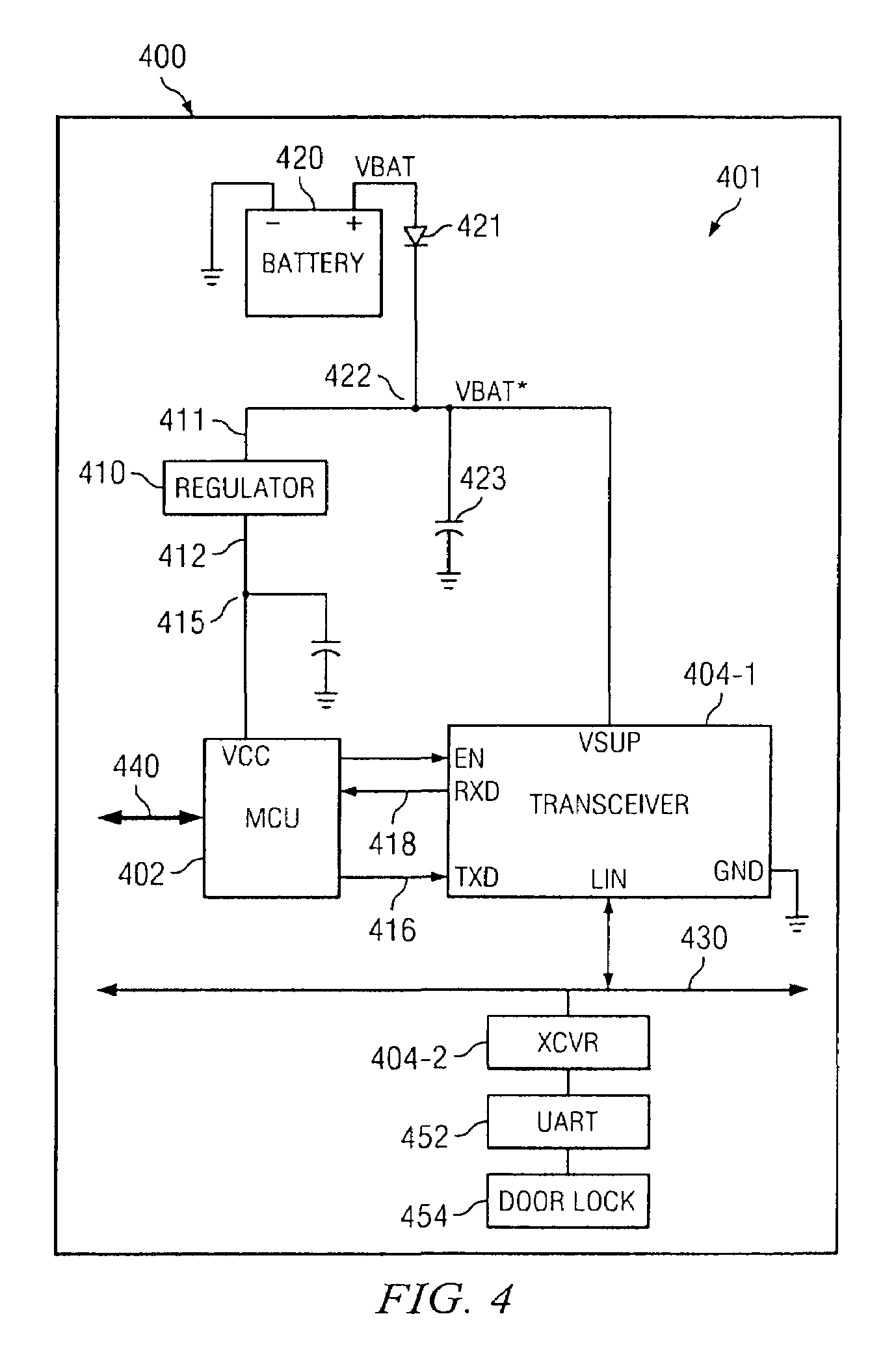

Current driver suitable for use in a shared bus environment

InactiveUS7688113B2Logic circuits using semiconductor devicesElectric pulse generatorMobile vehicleTransceiver

A transceiver suitable for interfacing a logic device to a shared bus includes a transmit node that receives an input signal from the logic device and an I / O node, that is coupled to the shared bus. The transceiver may be designed for use with a shared-bus, single master, multiple slave architecture, e.g., a Local Interconnect Network (LIN). In a LIN compliant implementation, the transceiver may be suitable for use in at least some types of automobiles and other motorized vehicles. Control logic coupled to the transmit node may assert a current driver enable signal in response to detecting an assertion of the input signal. A current driver of the transceiver is configured to draw a time varying driver current from the shared bus node after detecting an assertion of the current driver enable signal. The driver current may cause a sinusoidal transition of the shared bus voltage.

Owner:NORTH STAR INNOVATIONS

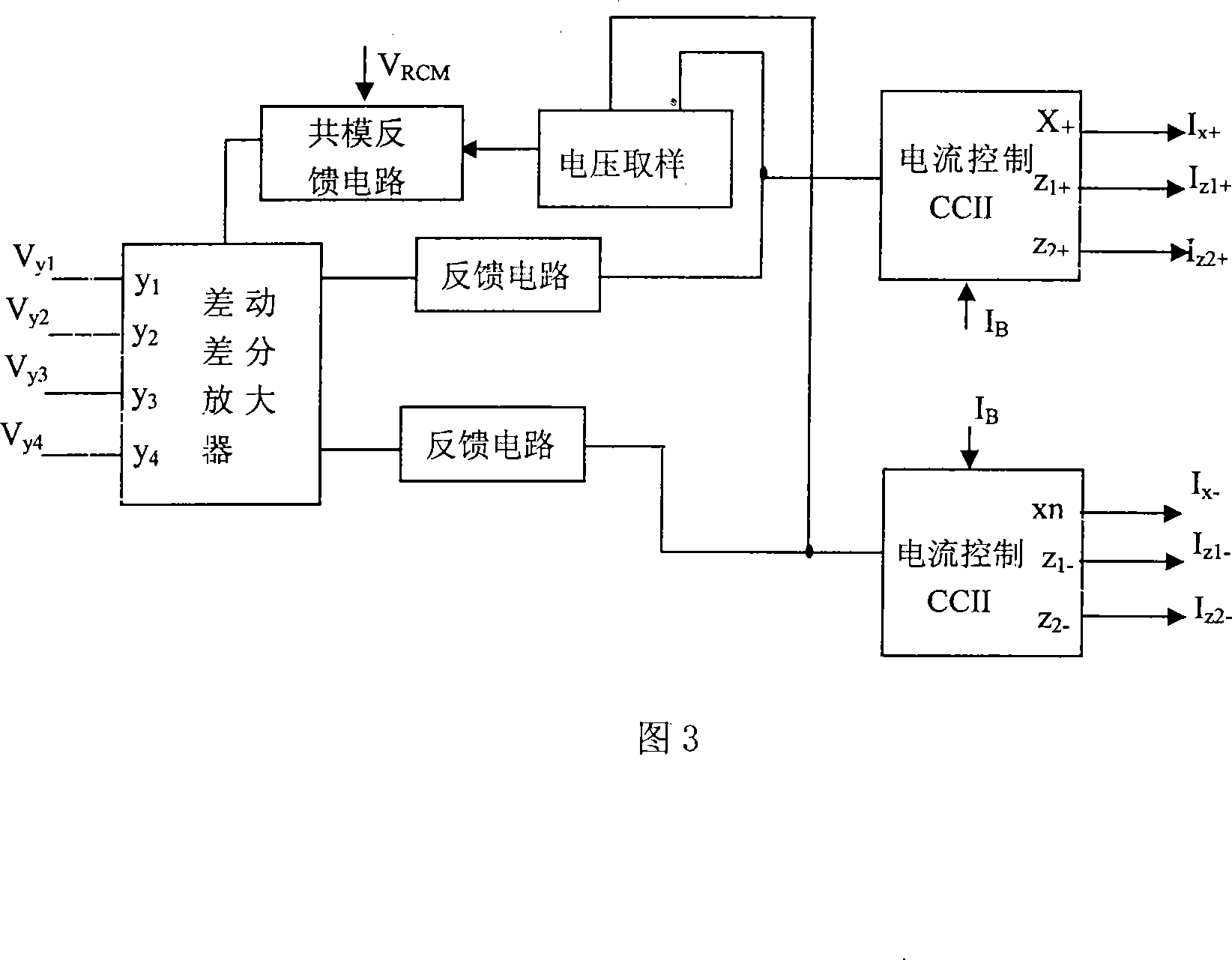

Current controlled full-balance differential current transmitter

InactiveCN101047383AWith electronic tuningSuppress noiseLogic circuits using semiconductor devicesInput impedanceEngineering

A current transmission unit of current control in all-balance differential mode consists of a pair of voltage differential input ends, high input impedance, a pair of differential voltage tracking ends, a pair of current output ends with the same phase and a pair of current output ends with opposite phase. It is featured as enabling to control relation of voltage at a pair of differential voltage tracking ends to differential voltage at a pair of voltage differential input ends by regulating bias current of the circuit.

Owner:HUNAN UNIV

Popular searches

Bulk negative resistance effect devices Special data processing applications Logic circuit coupling/interface arrangements Semiconductor devices Electronic switching Power conversion systems Power supply for data processing Generating/distributing signals Oscillations generators Architecture with single central processing unit

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com