Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

137 results about "Lateral diffusion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Lateral diffusion is the process whereby information can be spread from one node in a social network to another, often in a selective way, and can rapidly traverse an entire population, but preferentially to those nodes likely to be interested, or needing to know. In this way it has been shown that typically no more than 6 intermediaries are likely to link the most extreme chain of lateral diffusion—see six degrees of separation even worldwide. Messages or information are also subject to query and modification en route. This is in contrast to central media where one message or perspective is broadcast to a large number of people simultaneously. Thus lateral diffusion can be said to occur in lateral media. This is similar to how rumours, gossip and jokes rapidly spread. But note that each sender can be selective: a sender wouldn't necessarily tell a superior a joke he might not approve of. Senders also tend to pass on information to those who they know from personal experience would be interested or need to know.

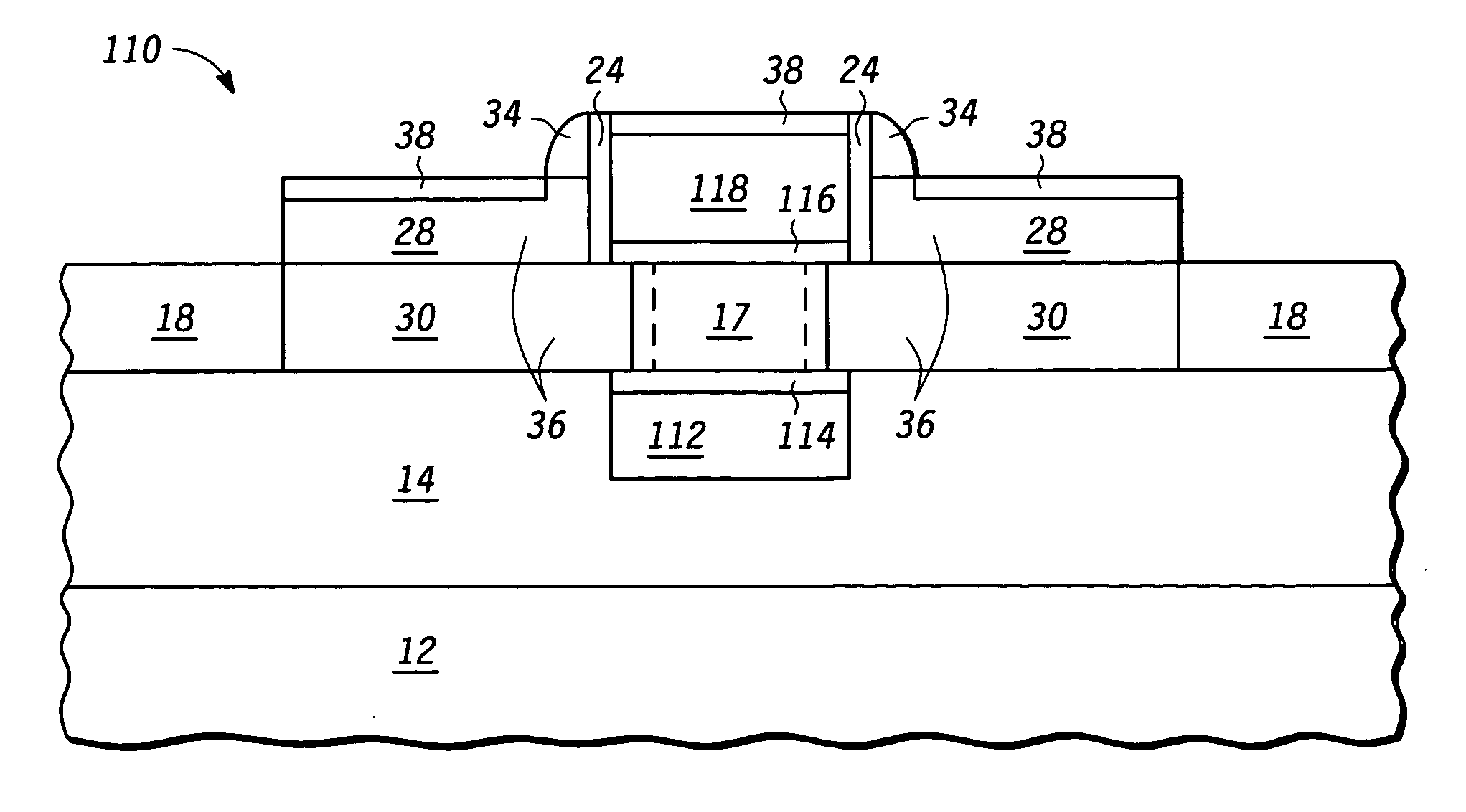

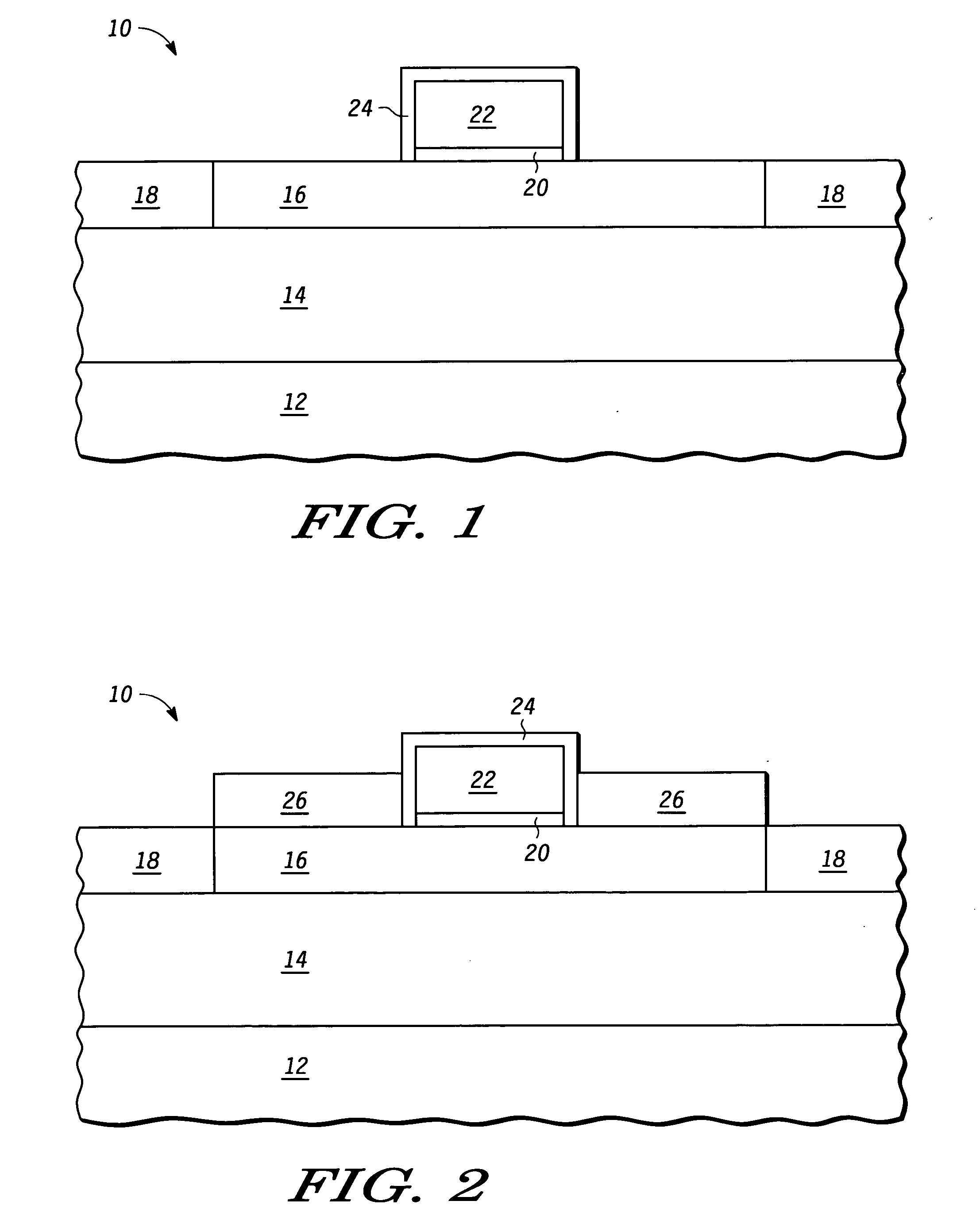

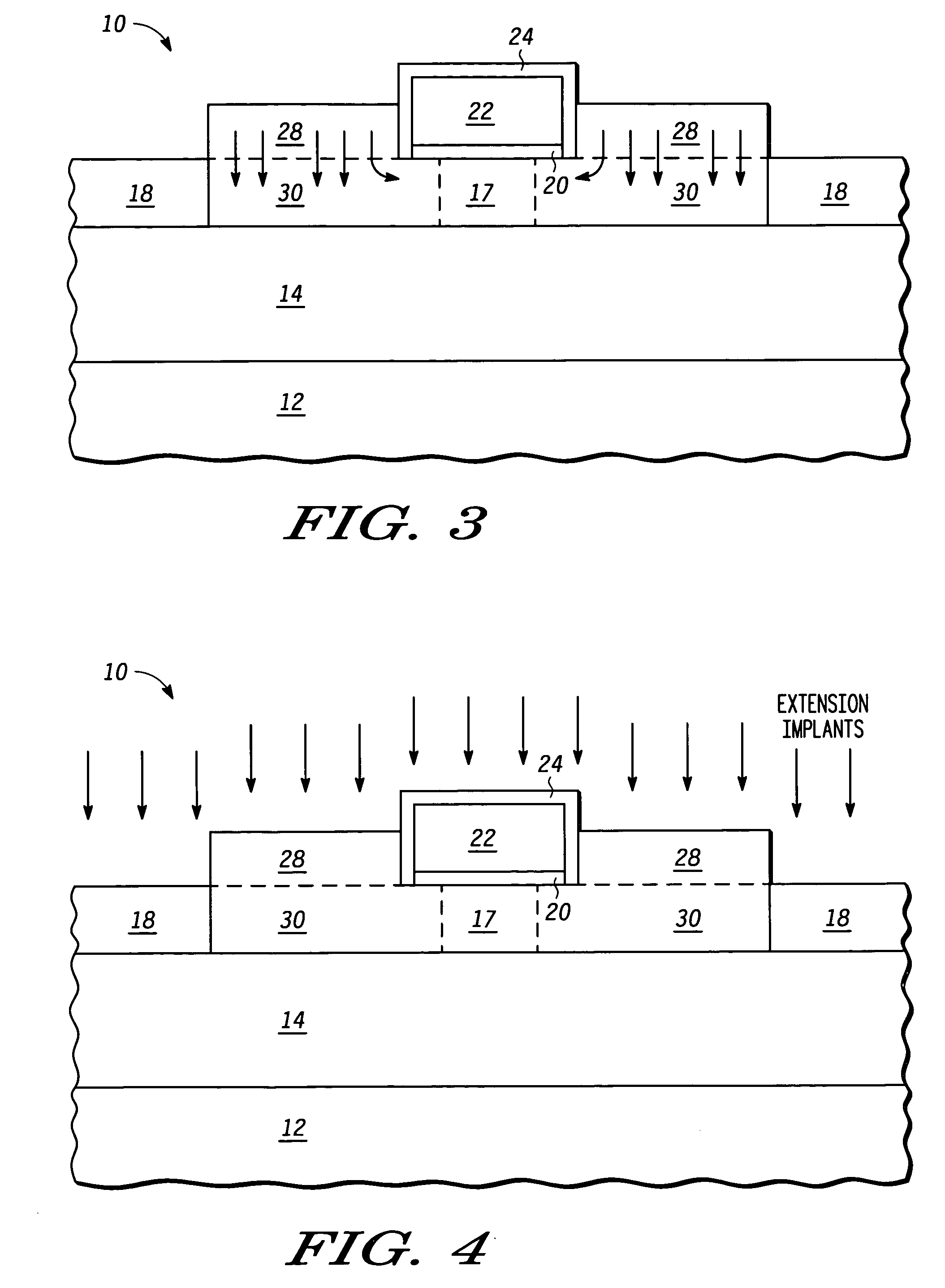

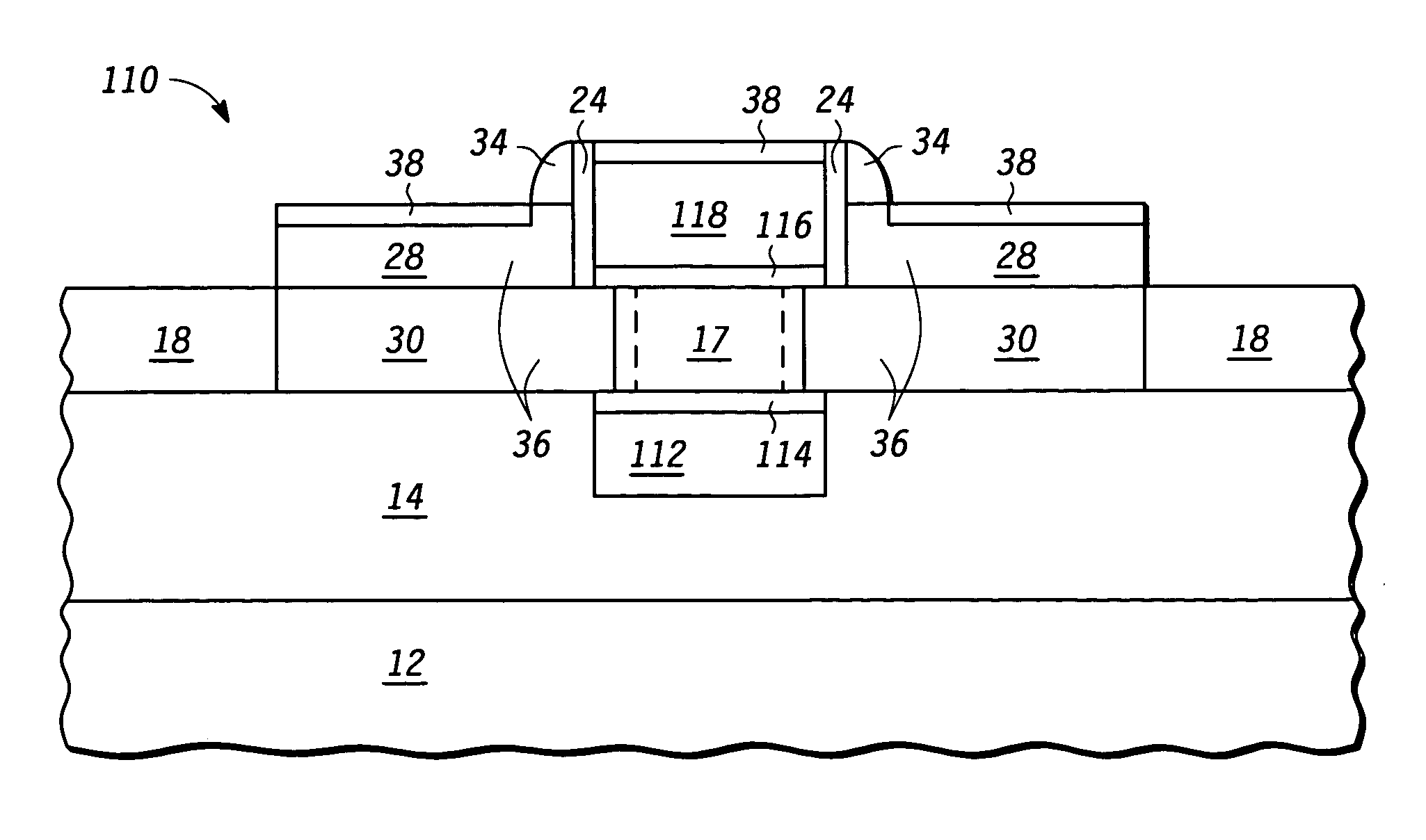

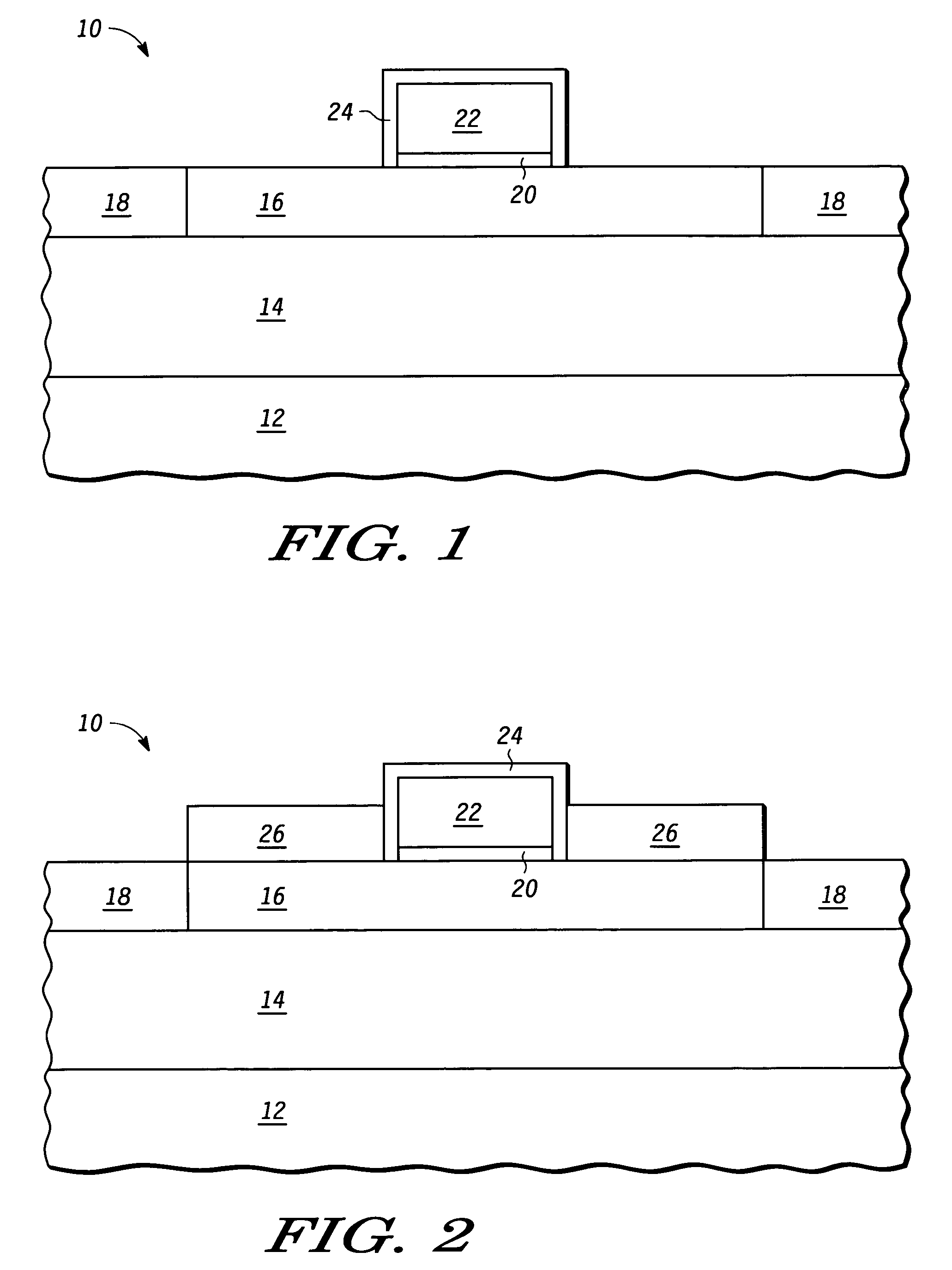

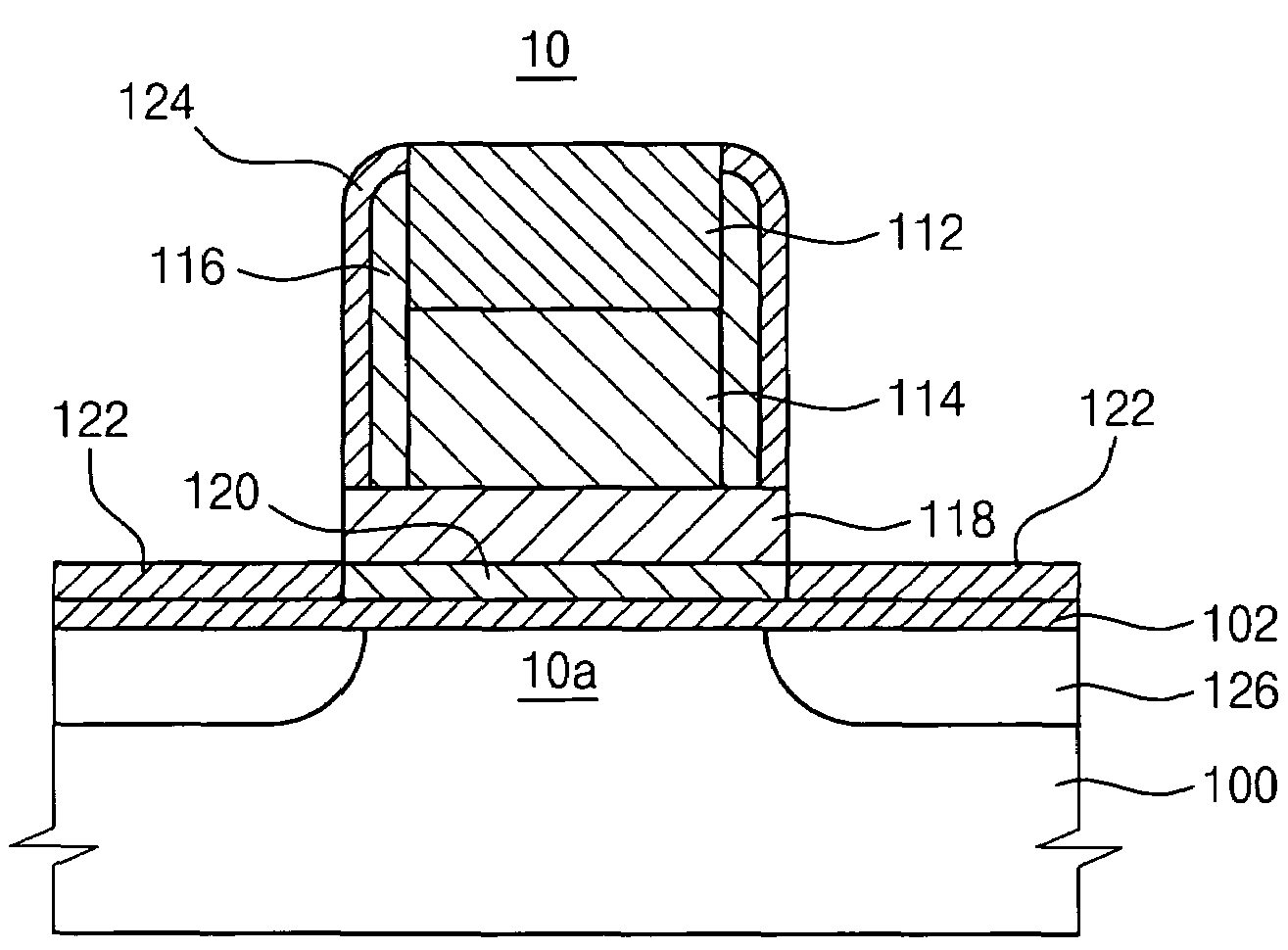

Method for forming a semiconductor device having a strained channel and a heterojunction source/drain

InactiveUS20060068553A1Semiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSemiconductor materials

Owner:NORTH STAR INNOVATIONS

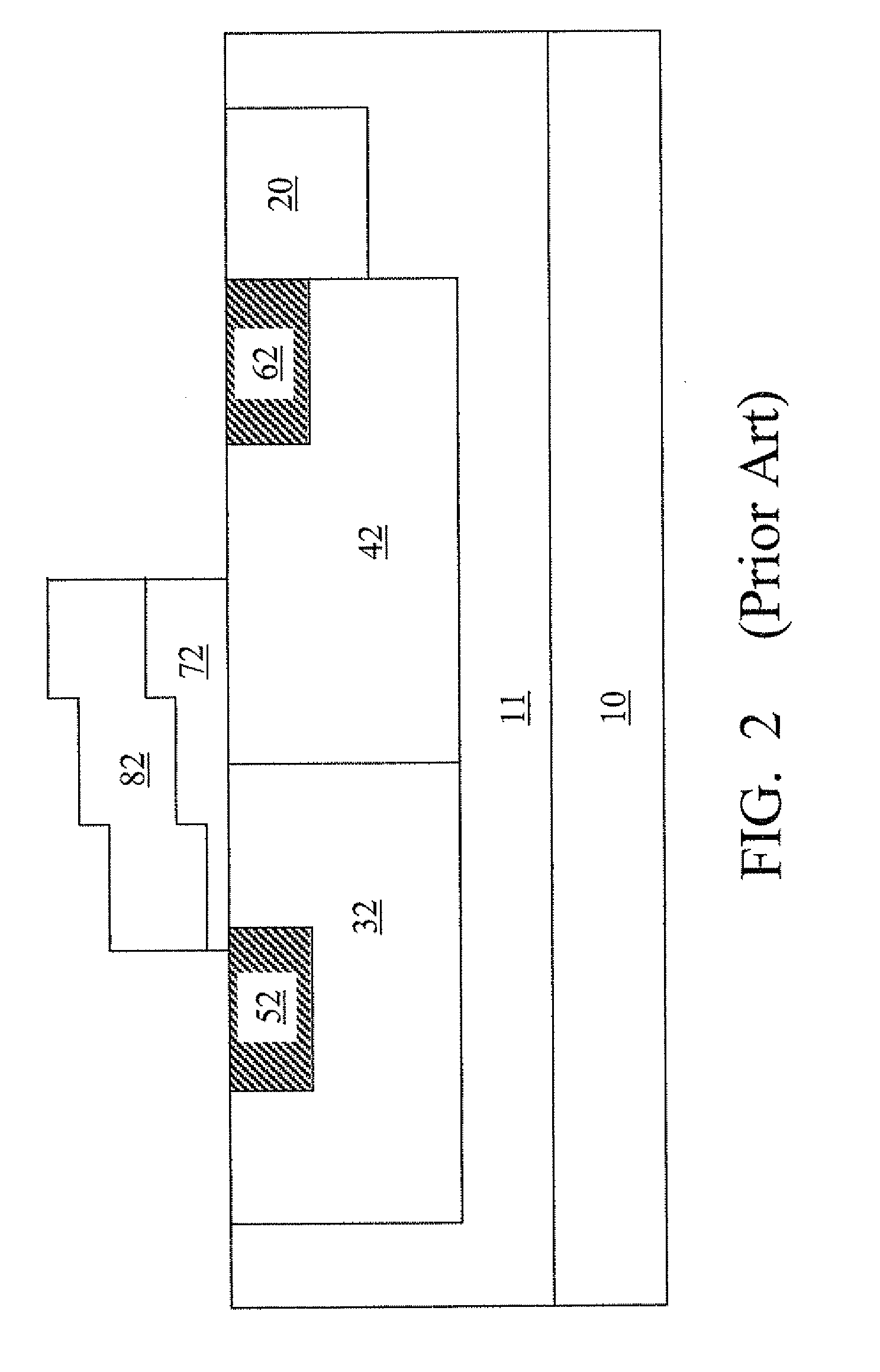

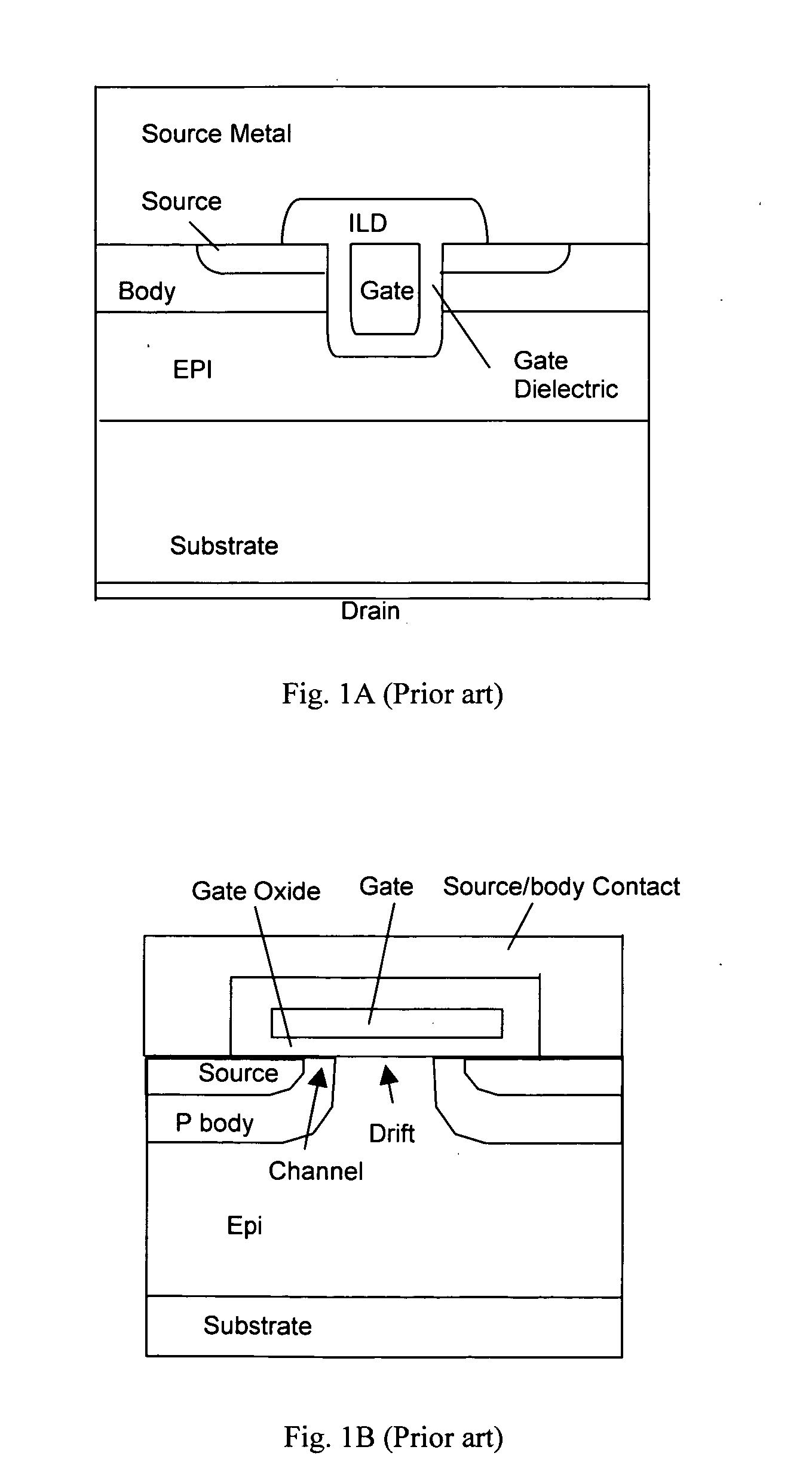

Bottom source LDMOSFET structure and method

ActiveUS20080023785A1Reduce manufacturing costReduce cell pitchTransistorSemiconductor/solid-state device detailsCapacitanceLDMOS

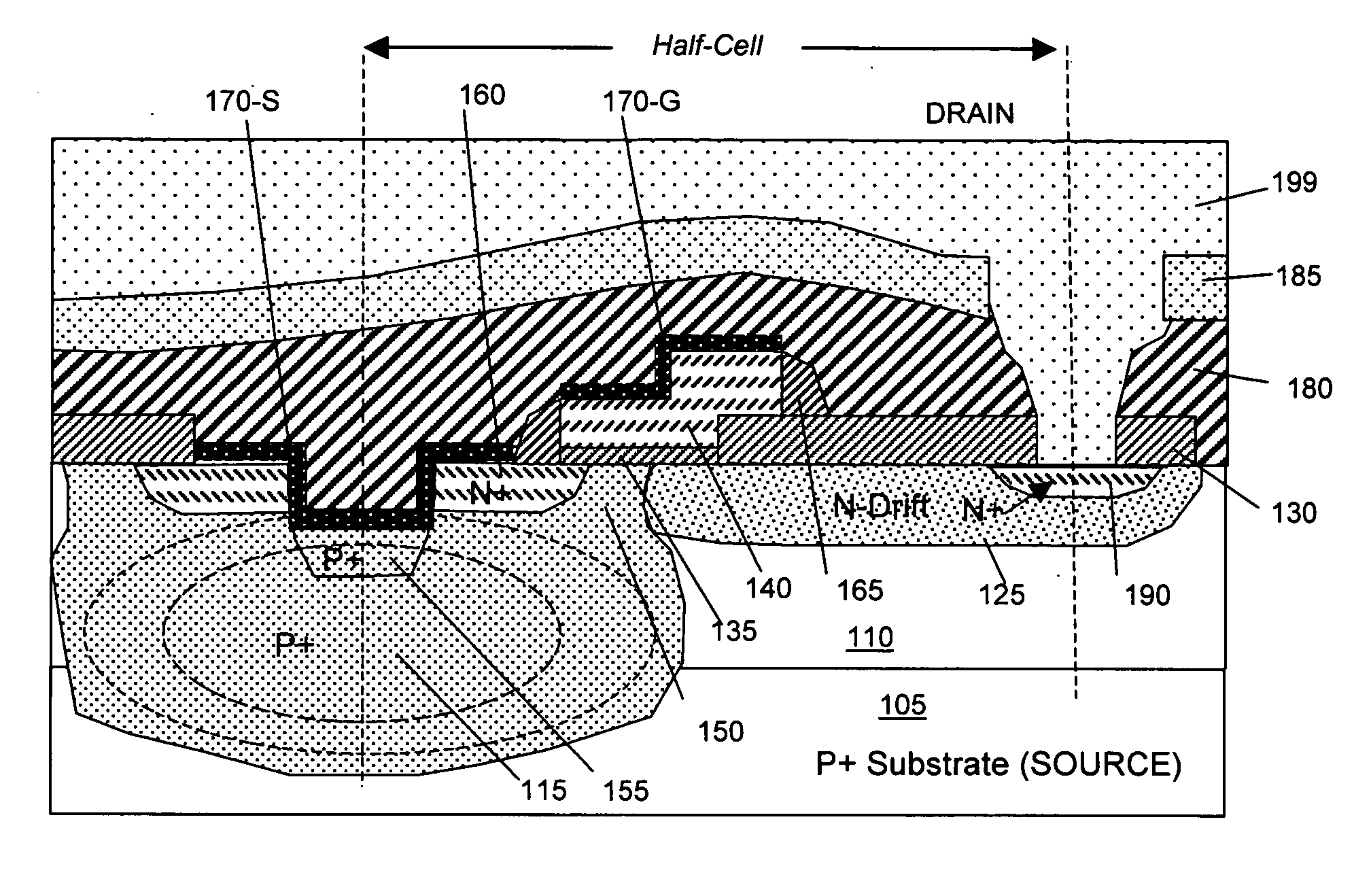

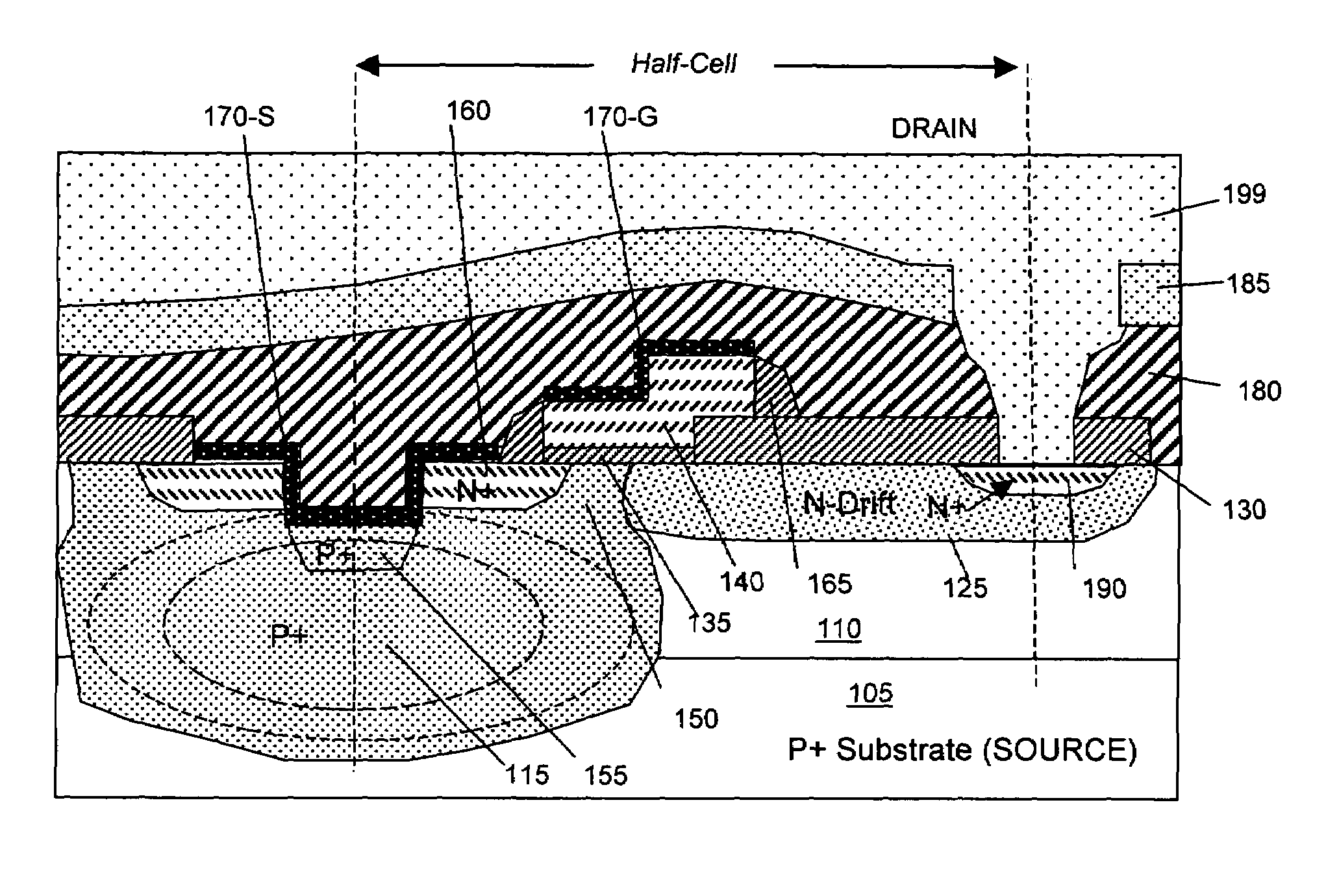

This invention discloses bottom-source lateral diffusion MOS (BS-LDMOS) device. The device has a source region disposed laterally opposite a drain region near a top surface of a semiconductor substrate supporting a gate thereon between the source region and a drain region. The BS-LDMOS device further has a combined sinker-channel region disposed at a depth in the semiconductor substrate entirely below a body region disposed adjacent to the source region near the top surface wherein the combined sinker-channel region functioning as a buried source-body contact for electrically connecting the body region and the source region to a bottom of the substrate functioning as a source electrode. A drift region is disposed near the top surface under the gate and at a distance away from the source region and extending to and encompassing the drain region. The combined sinker-channel region extending below the drift region and the combined sinker-channel region that has a dopant-conductivity opposite to and compensating the drift region for reducing the source-drain capacitance.

Owner:ALPHA & OMEGA SEMICON LTD

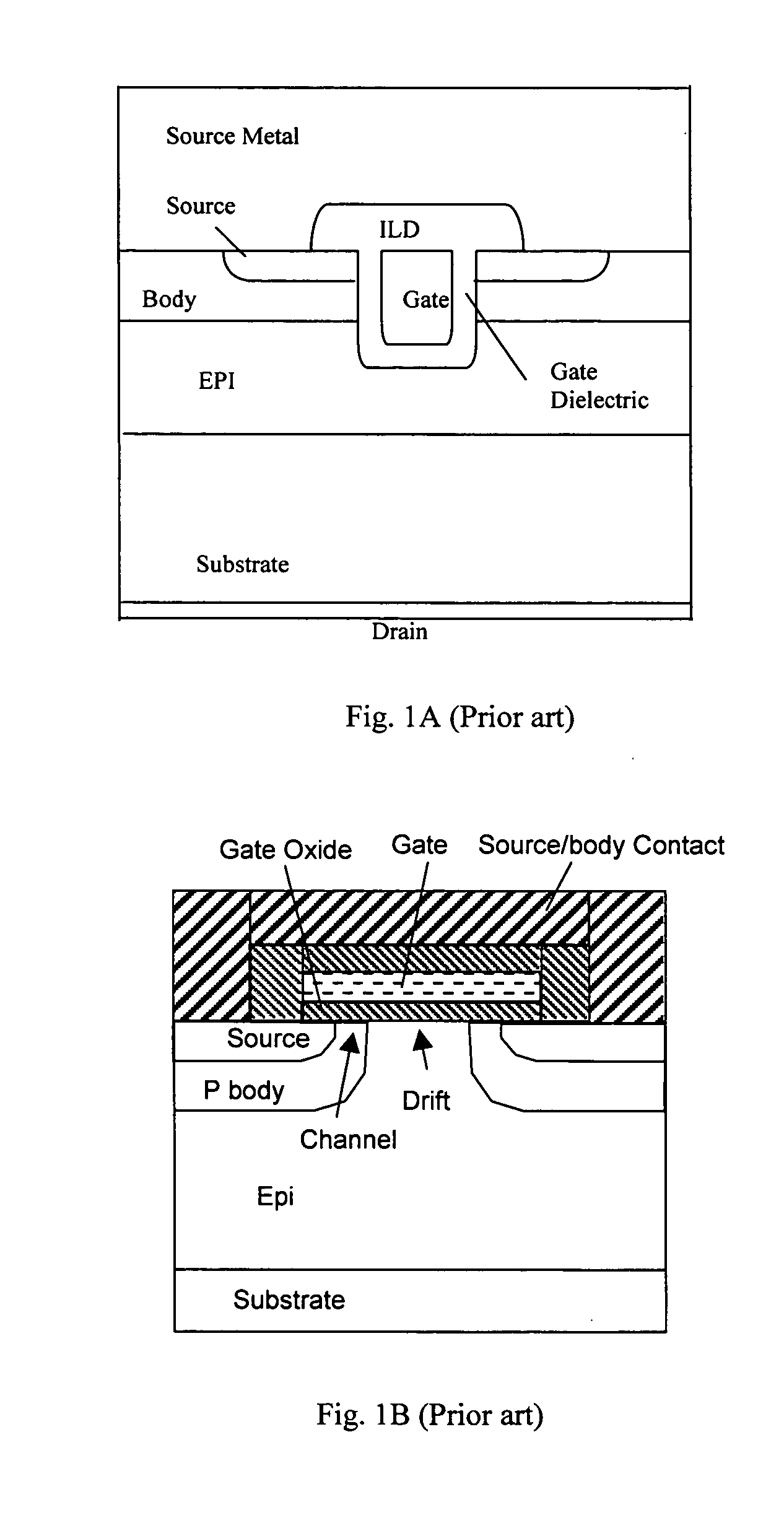

Lateral diffusion field effect transistor with a trench field plate

InactiveUS20090140343A1High conductanceImprove the immunityTransistorSolid-state devicesGate dielectricElectrical conductor

A dielectric material layer is formed on a bottom surface and sidewalls of a trench in a semiconductor substrate. The silicon oxide layer forms a drift region dielectric on which a field plate is formed. Shallow trench isolation may be formed prior to formation of the drift region dielectric, or may be formed utilizing the same processing steps as the formation of the drift region dielectric. A gate dielectric layer is formed on exposed semiconductor surfaces and a gate conductor layer is formed on the gate dielectric layer and the drift region dielectric. The field plate may be electrically tied to the gate electrode, may be an independent electrode having an external bias, or may be a floating electrode. The field plate biases the drift region to enhance performance and extend allowable operating voltage of a lateral diffusion field effect transistor during operation.

Owner:GLOBALFOUNDRIES INC

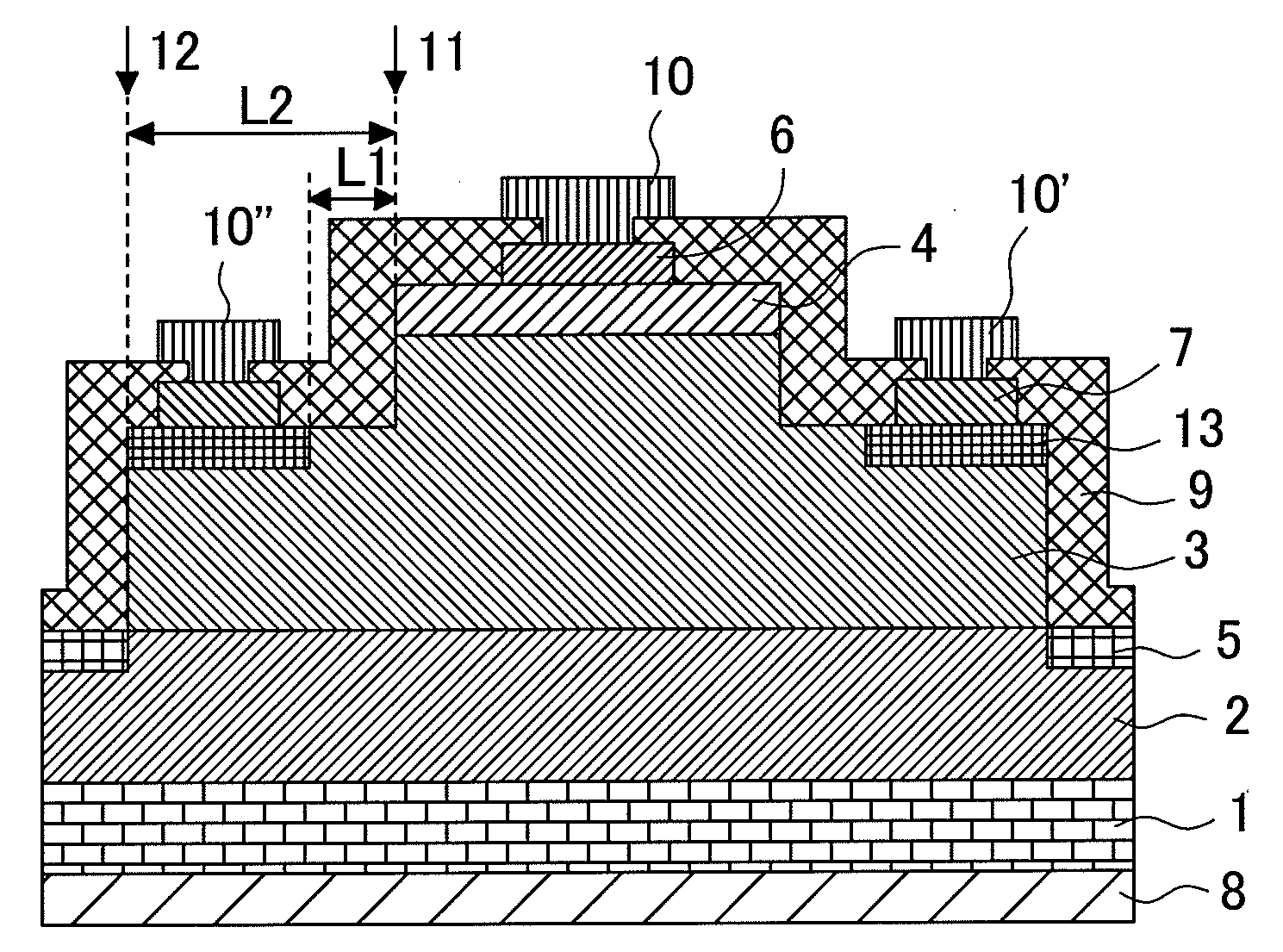

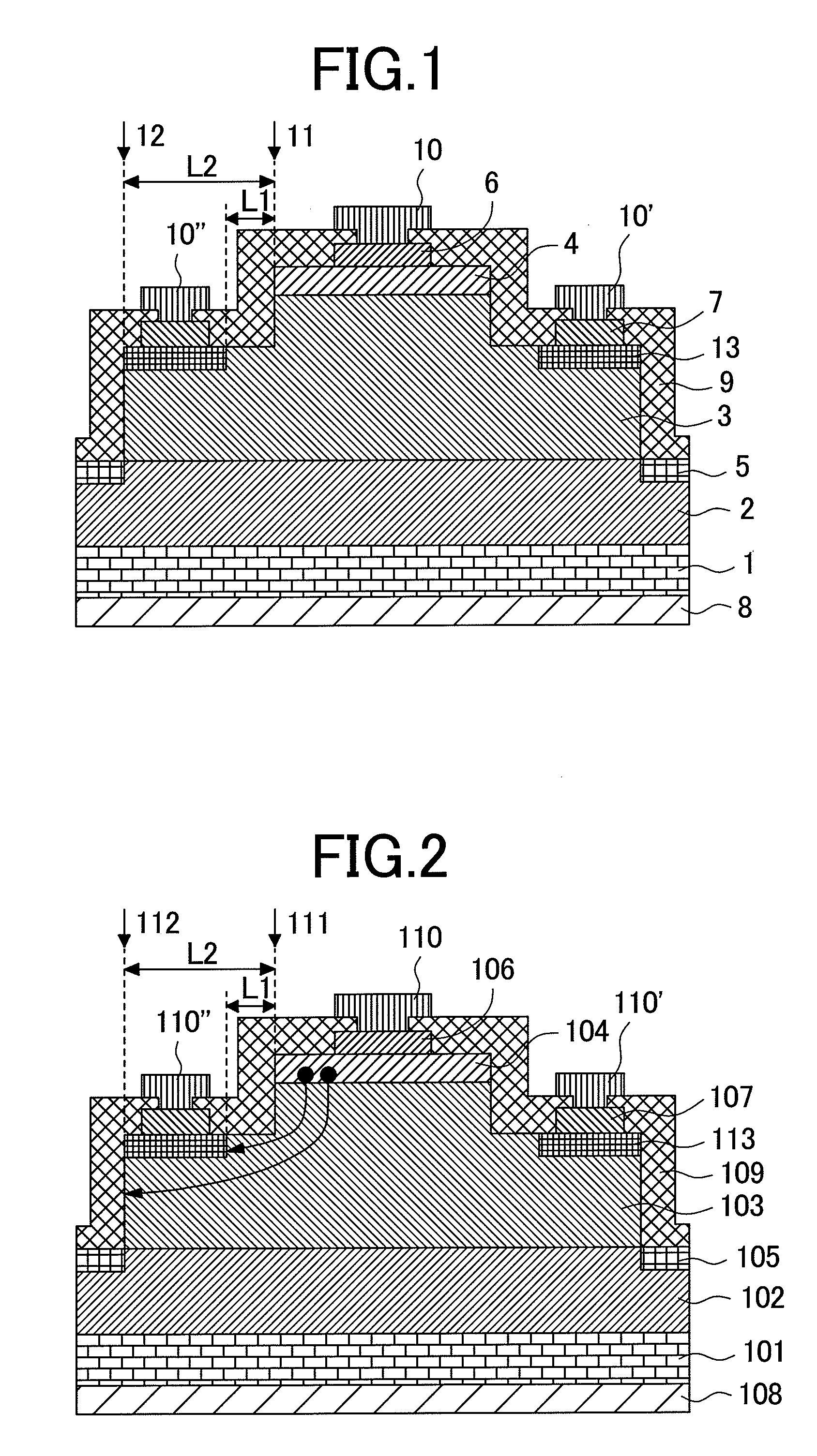

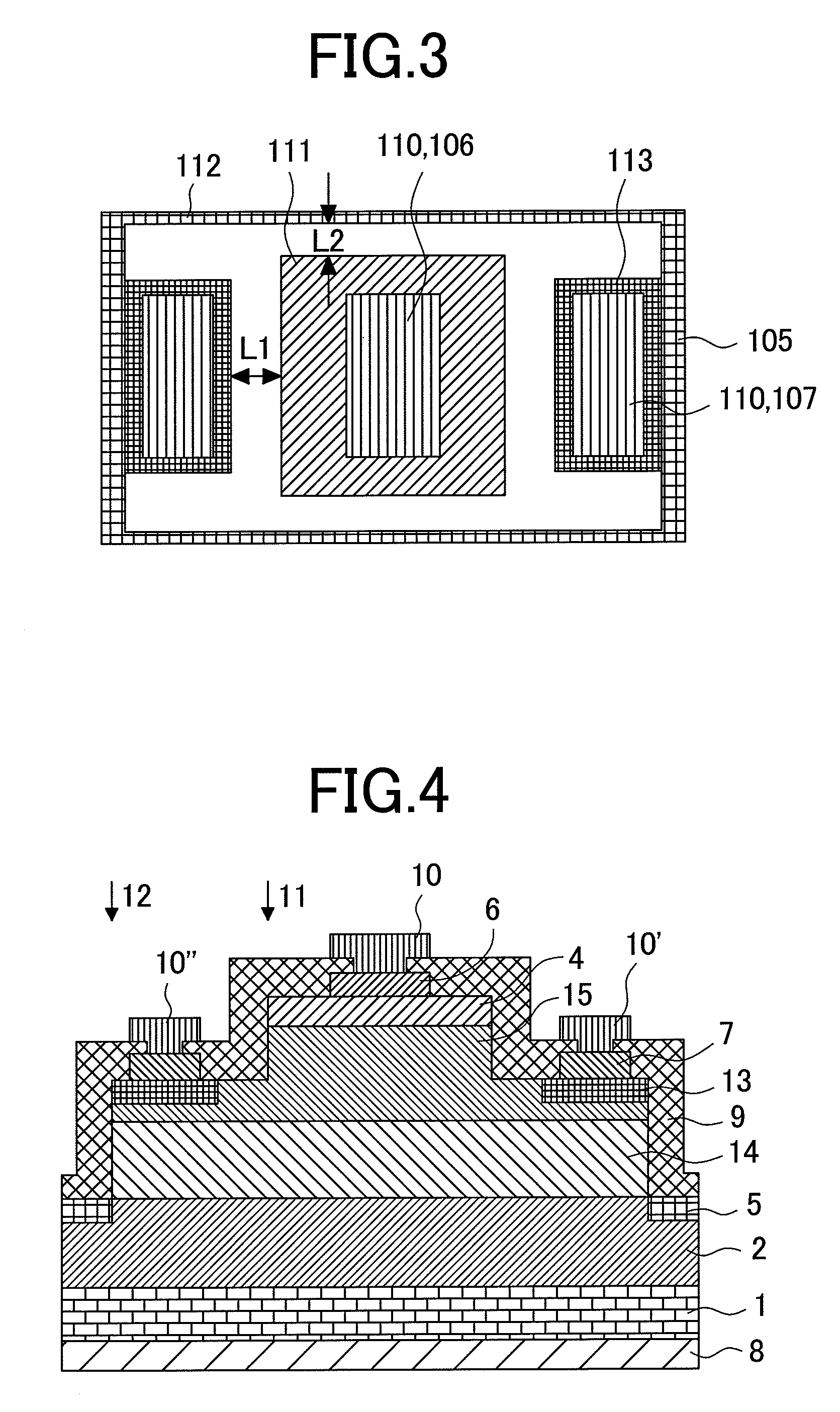

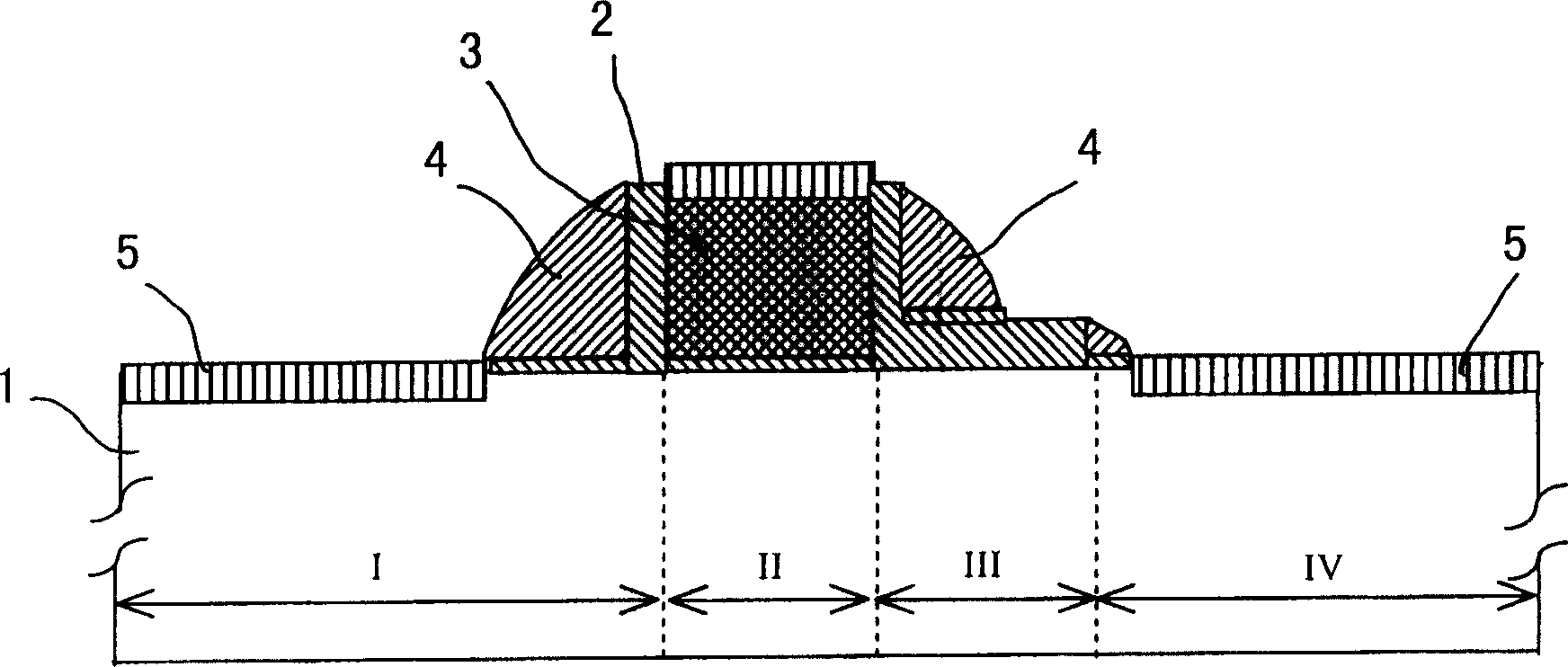

Mesa-type bipolar transistor

InactiveUS20070241427A1Good repeatabilityImprove controllabilityTransistorSolid-state devicesHigh densityPower switching

In conventional mesa-type npn bipolar transistors, the improvement of a current gain and the miniaturization of the transistor have been unachievable simultaneously as a result of a trade-off being present between lateral diffusion and recombination of the electrons which have been injected from an emitter layer into a base layer, and a high-density base contact region—emitter mesa distance. In contrast to the above, the present invention is provided as follows:The gradient of acceptor density in the depth direction of a base layer is greater at the edge of an emitter layer than at the edge of a collector layer. Also, the distance between a first mesa structure including the emitter layer and the base layer, and a second mesa structure including the base layer and the collector layer, is controlled to range from 3 μm to 9 μm. In addition, in order for the above to be implemented with high controllability, the base layer is formed of a first p-type base layer having an acceptor of uniform density, and a second p-type base layer whose density is greater than the uniform acceptor density of the first base layer while having a gradient in the depth direction of the second base layer. These features produce the advantageous effect that it is possible to provide a high-temperature adaptable, power-switching bipolar transistor that ensures a current gain high enough for practical use and is suitable for miniaturization.

Owner:HITACHI LTD

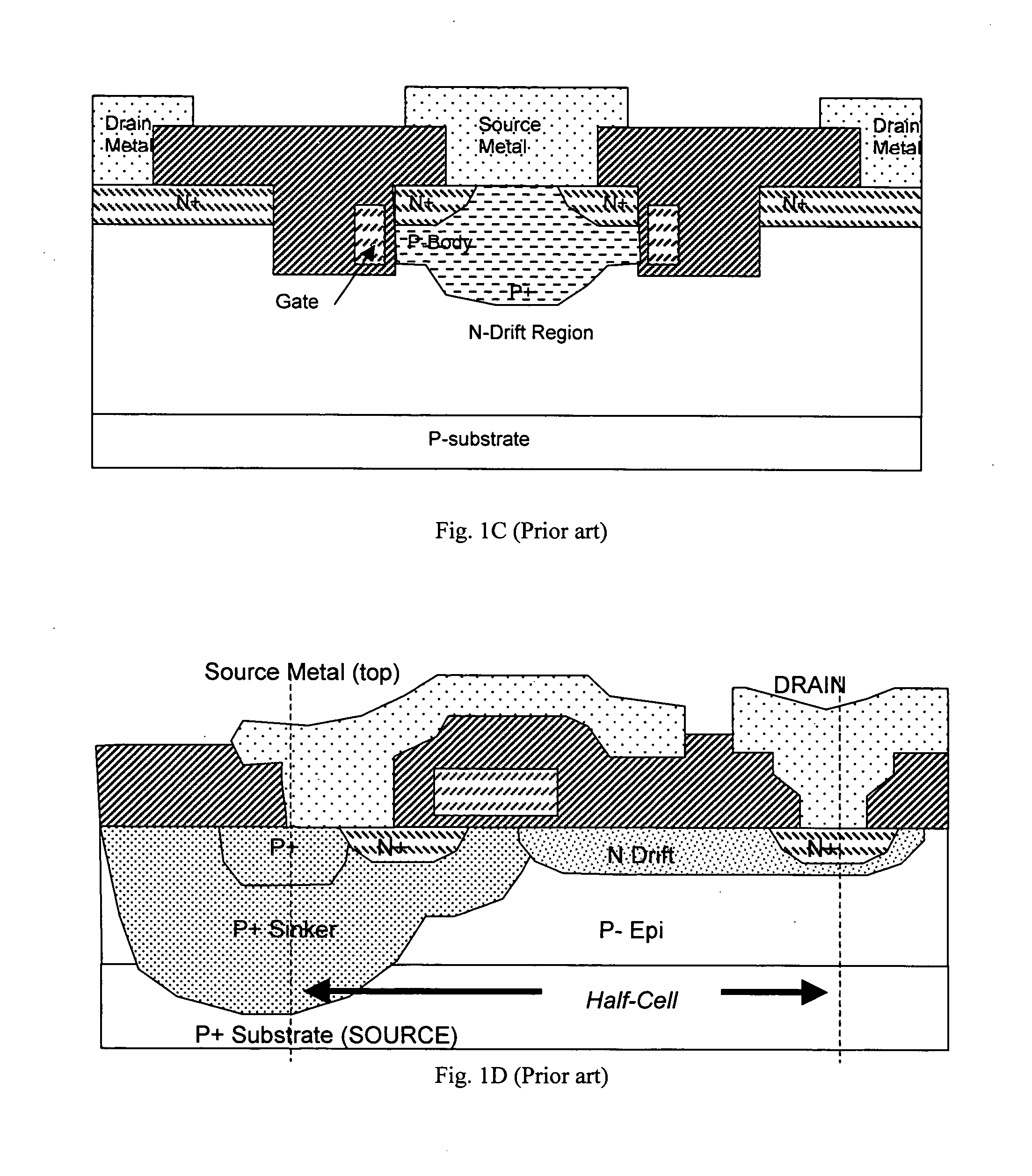

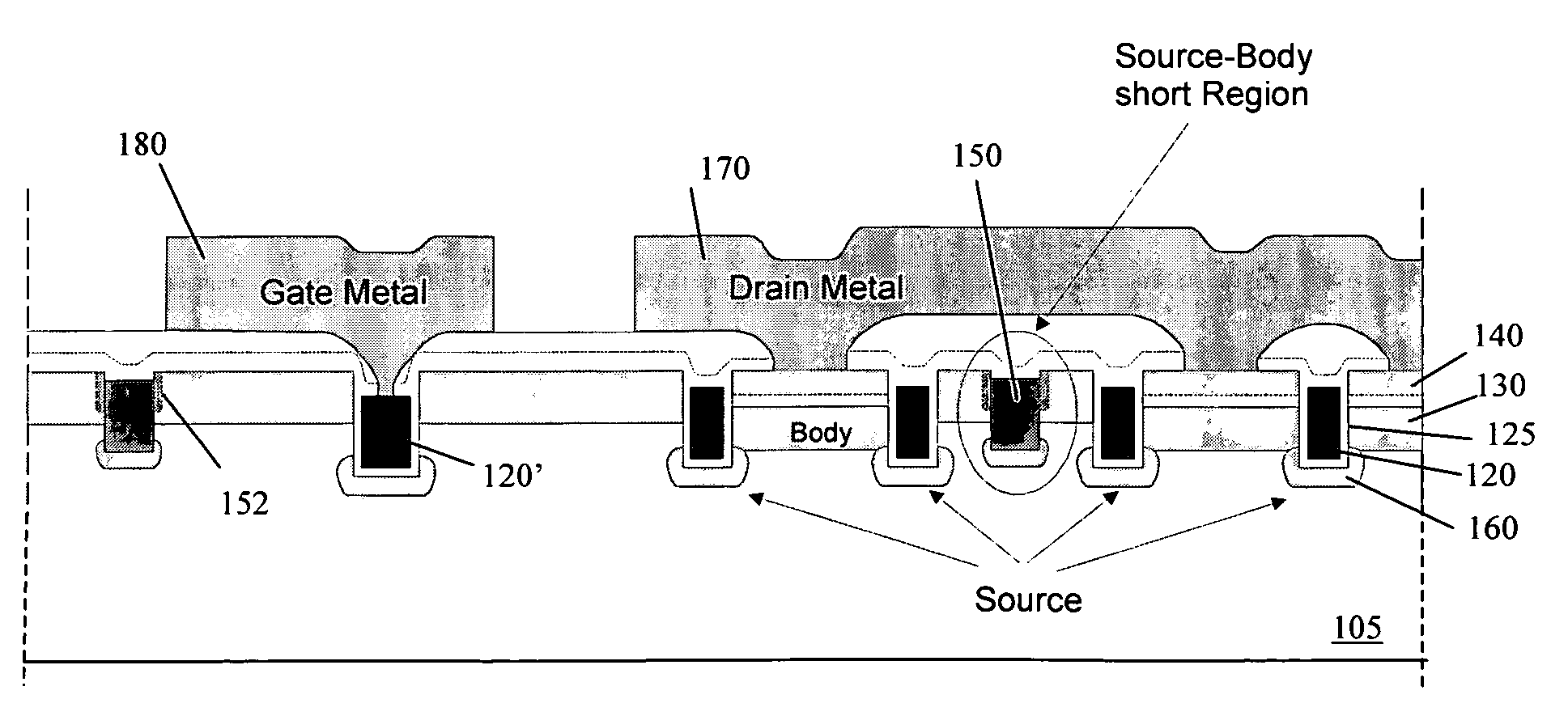

Inverted-trench grounded-source FET structure with trenched source body short electrode

ActiveUS20080067584A1Reduce manufacturing costReduced cell pitchTransistorSolid-state devicesCapacitanceLDMOS

This invention discloses bottom-source lateral diffusion MOS (BS-LDMOS) device. The device has a source region disposed laterally opposite a drain region near a top surface of a semiconductor substrate supporting a gate thereon between the source region and a drain region. The BS-LDMOS device further has a combined sinker-channel region disposed at a depth in the semiconductor substrate entirely below a body region disposed adjacent to the source region near the top surface wherein the combined sinker-channel region functioning as a buried source-body contact for electrically connecting the body region and the source region to a bottom of the substrate functioning as a source electrode. A drift region is disposed near the top surface under the gate and at a distance away from the source region and extending to and encompassing the drain region. The combined sinker-channel region extending below the drift region and the combined sinker-channel region that has a dopant-conductivity opposite to and compensating the drift region for reducing the source-drain capacitance.

Owner:ALPHA & OMEGA SEMICON LTD

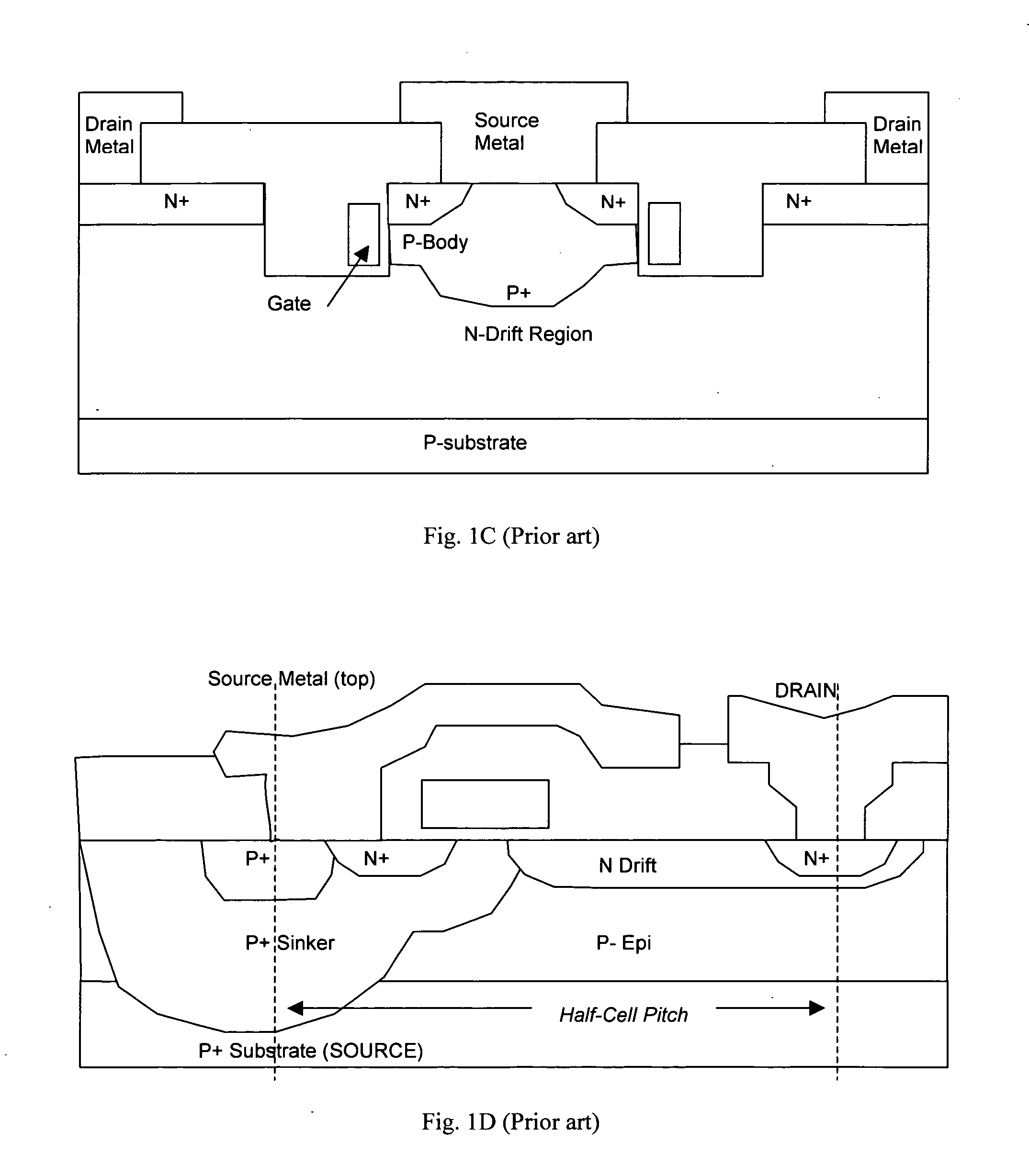

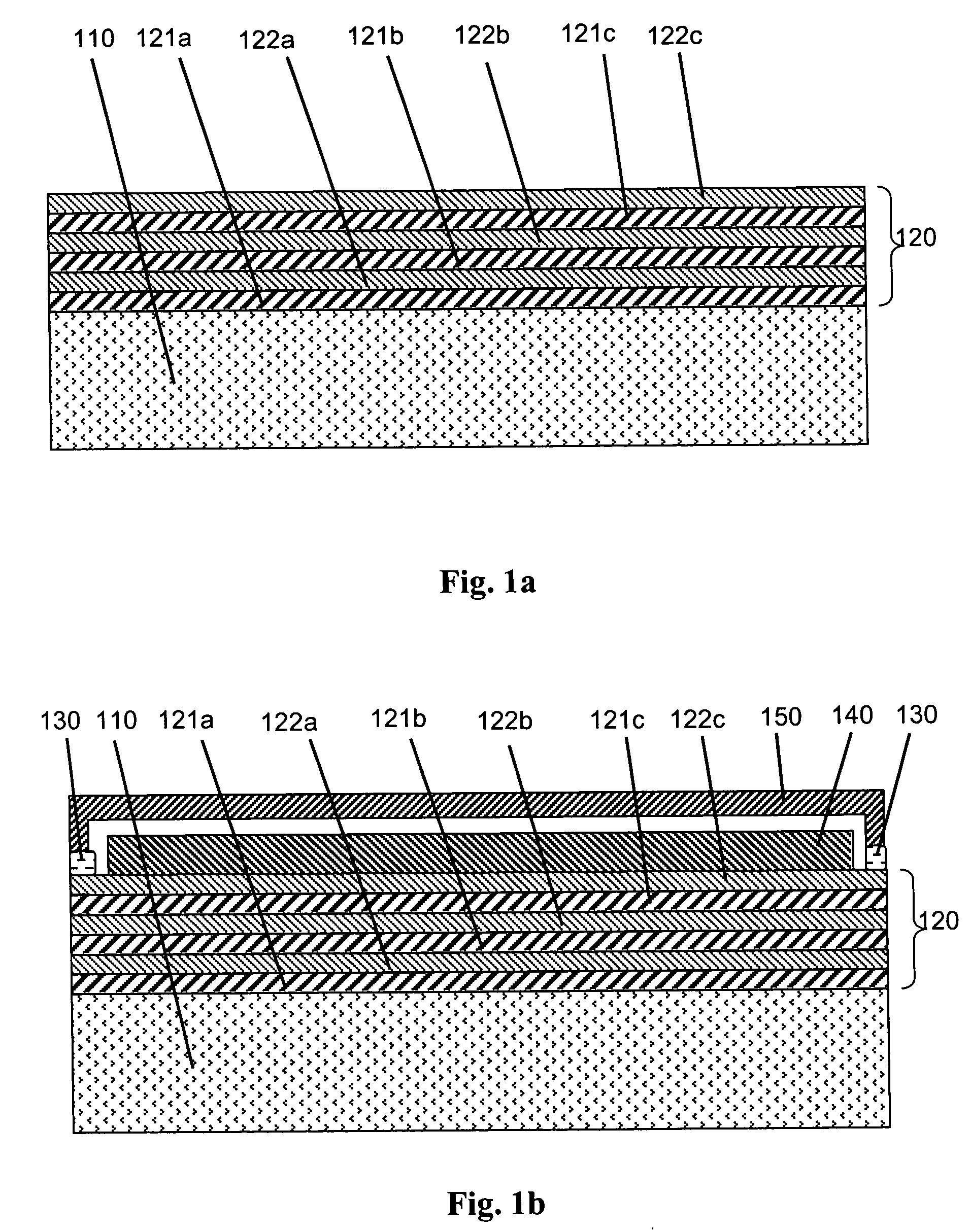

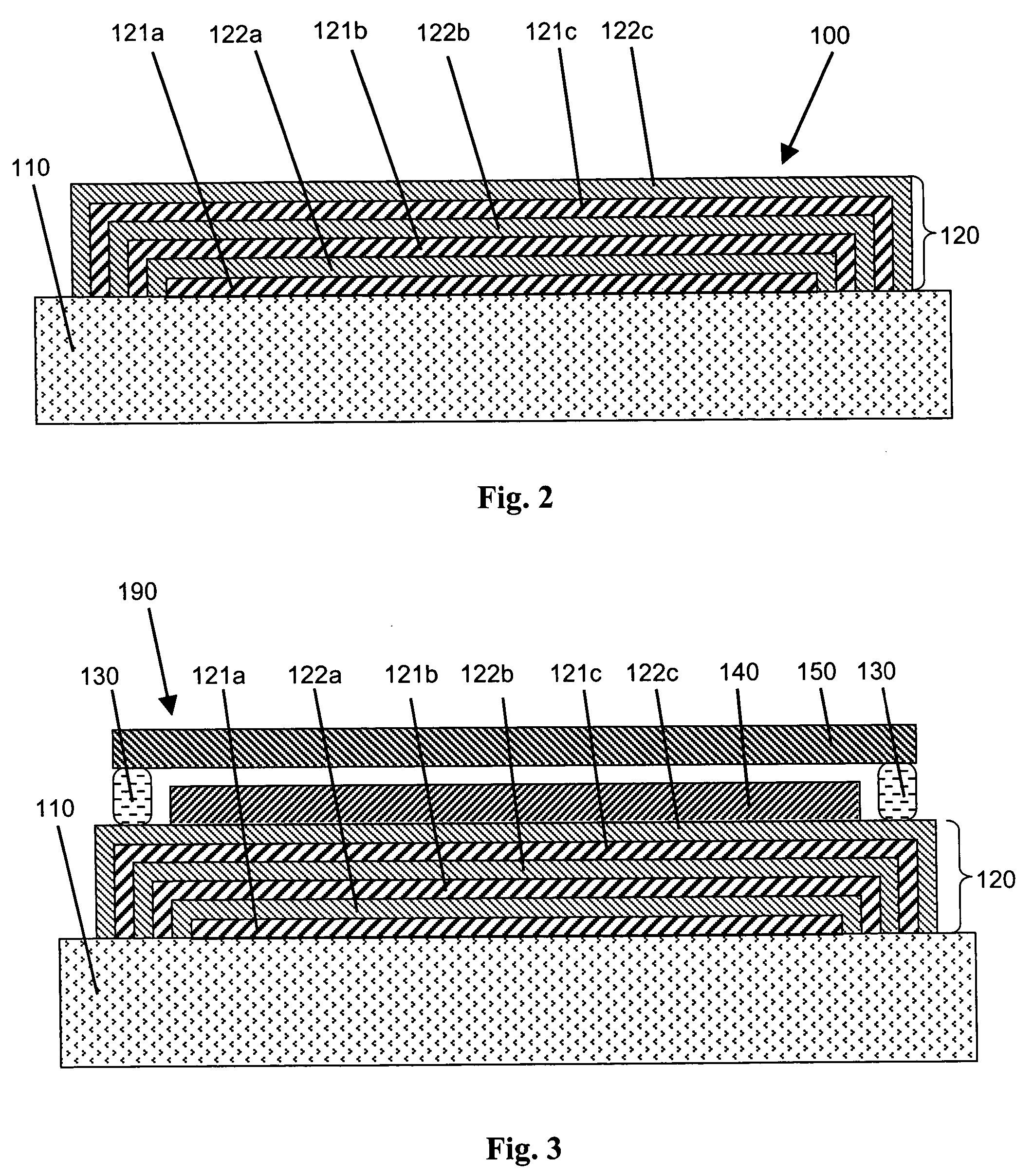

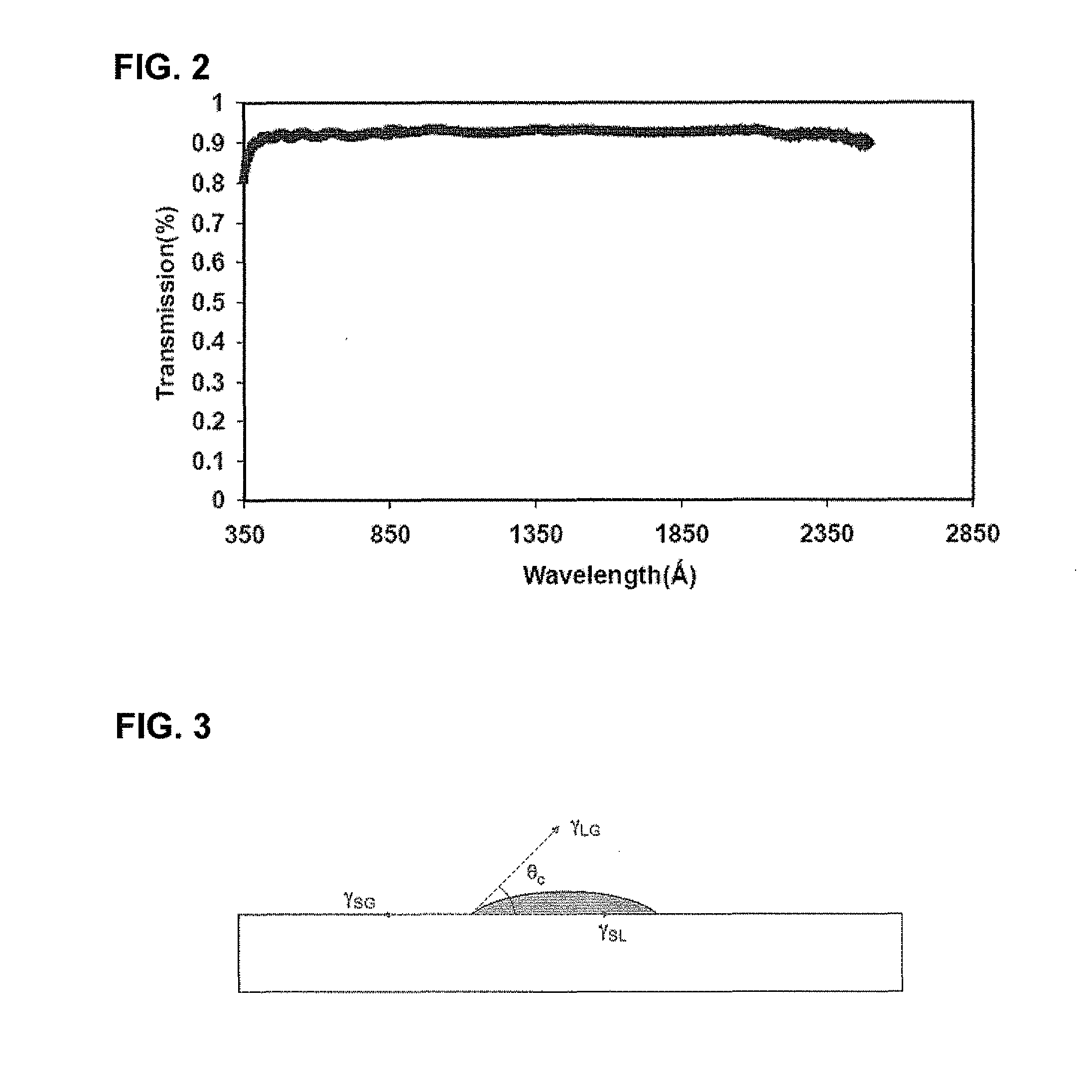

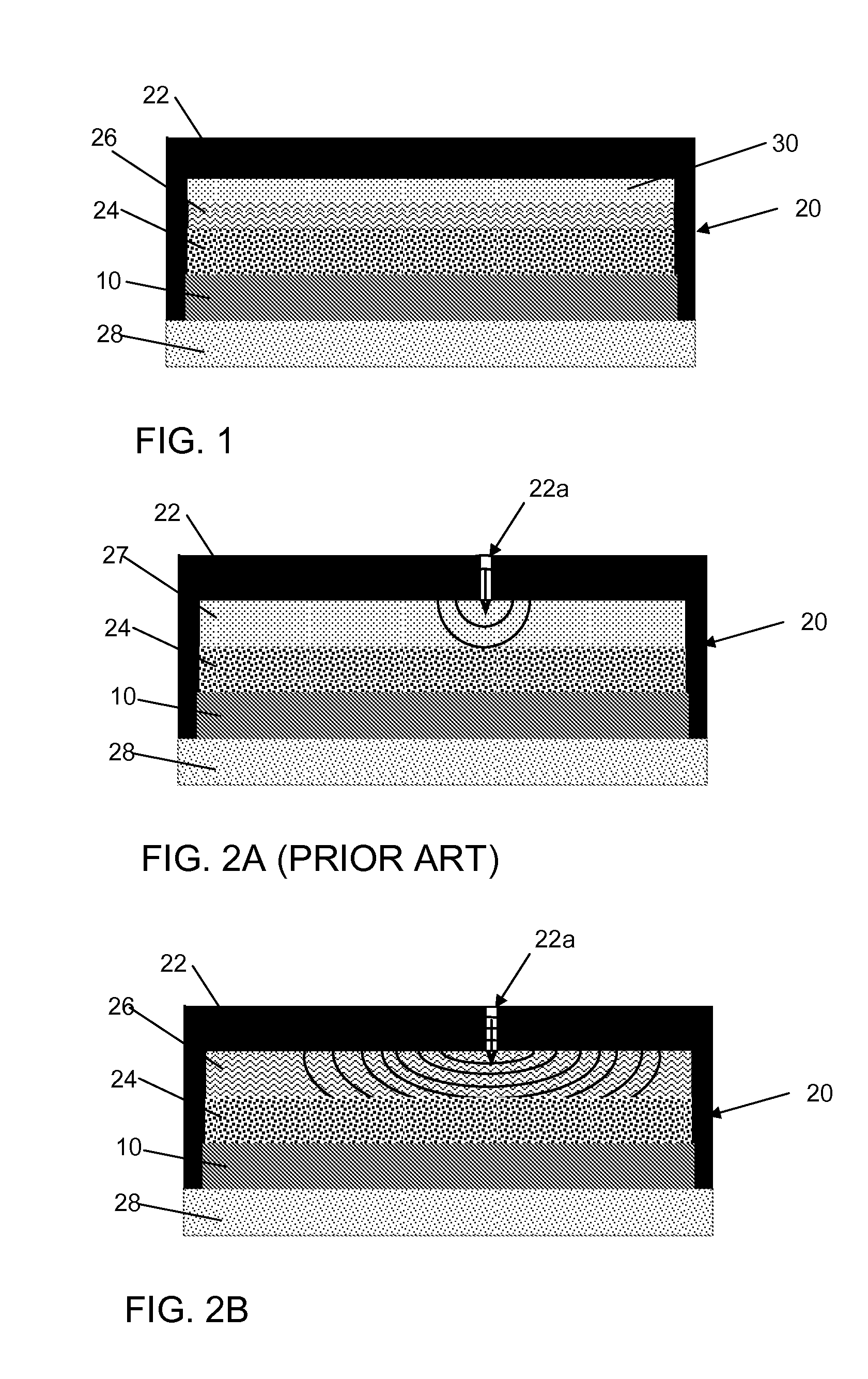

Methods and structures for reducing lateral diffusion through cooperative barrier layers

InactiveUS7187119B2Reduce adverse effectsReadily apparentDischarge tube luminescnet screensElectroluminescent light sourcesHigh densityDisplay device

A covered substrate is described, which comprises: (a) a flexible substrate layer; and (b) a plurality of cooperative barrier layers disposed on the substrate layer. The plurality of cooperative barrier layers further comprise one or more planarizing layers and one or more high-density layers. Moreover, at least one high-density layer is disposed over at least one planarizing layer in a manner such that the at least one high-density layer extends to the substrate layer and cooperates with the substrate layer to completely surround the at least one planarizing layer. When combined with an additional barrier region, such covered substrates are effective for enclosing organic optoelectronic devices, such organic light emitting diodes, organic electrochromic displays, organic photovoltaic devices and organic thin film transistors. Preferred organic optoelectronic devices are organic light emitting diodes.

Owner:UNIVERSAL DISPLAY

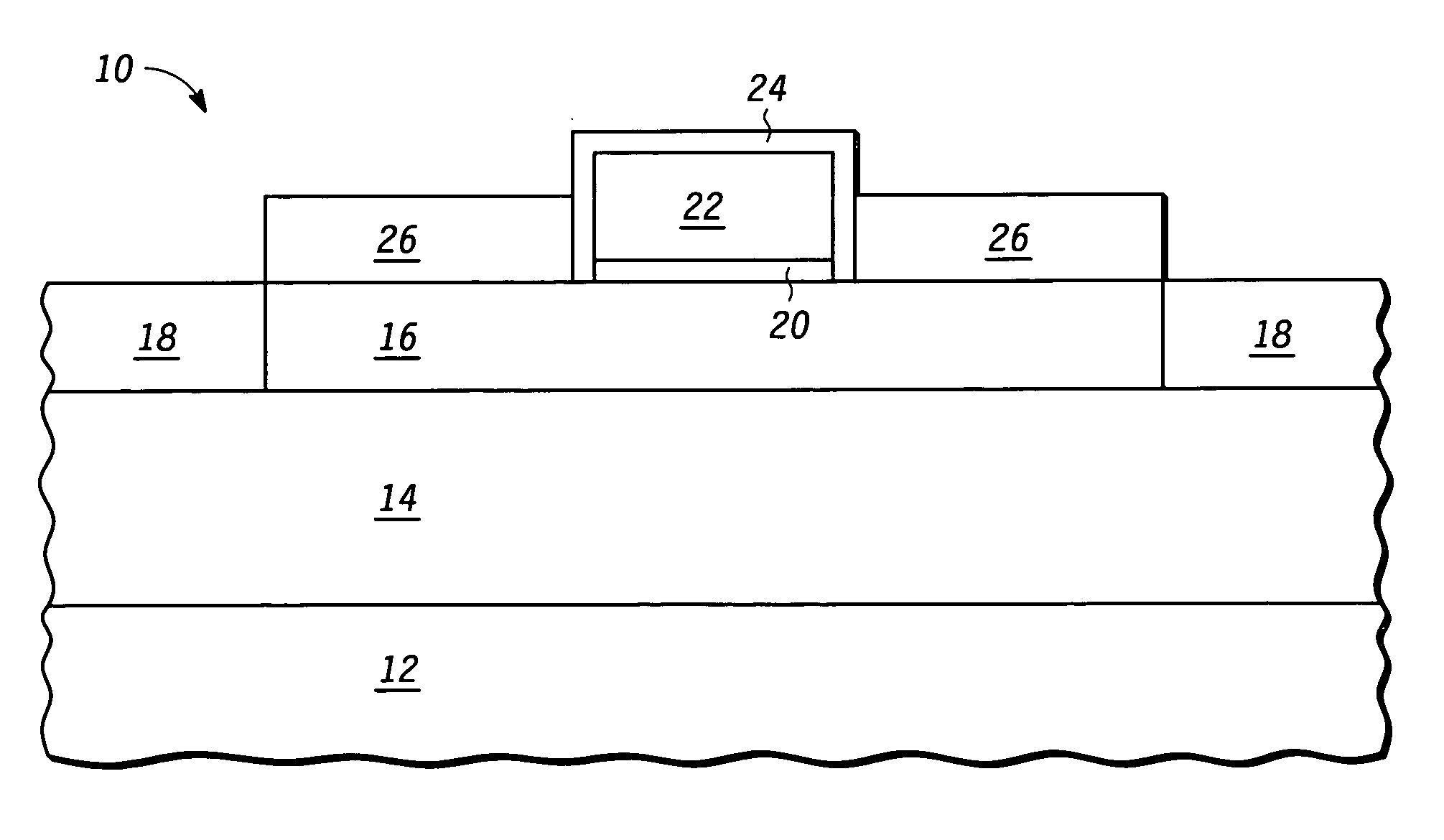

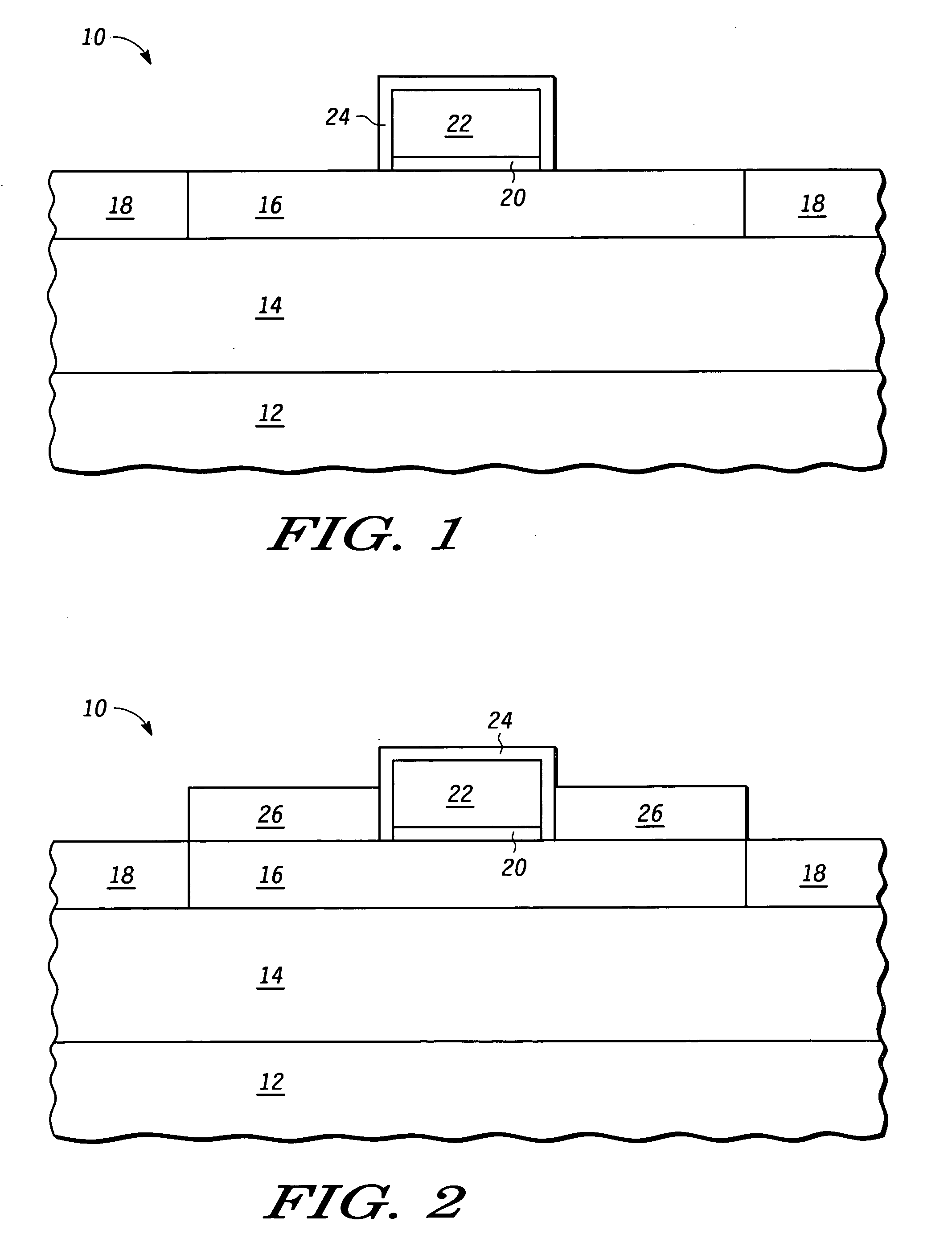

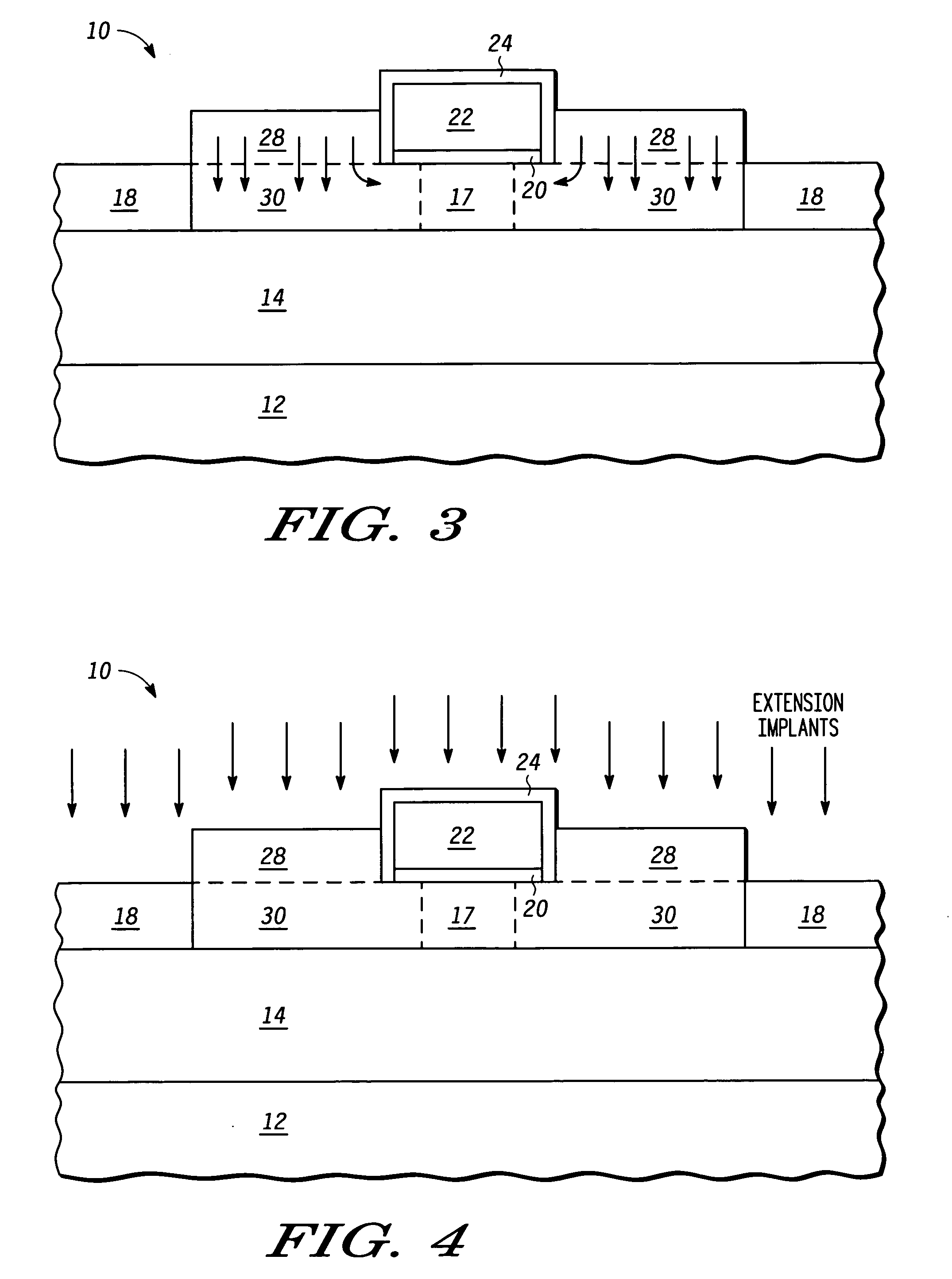

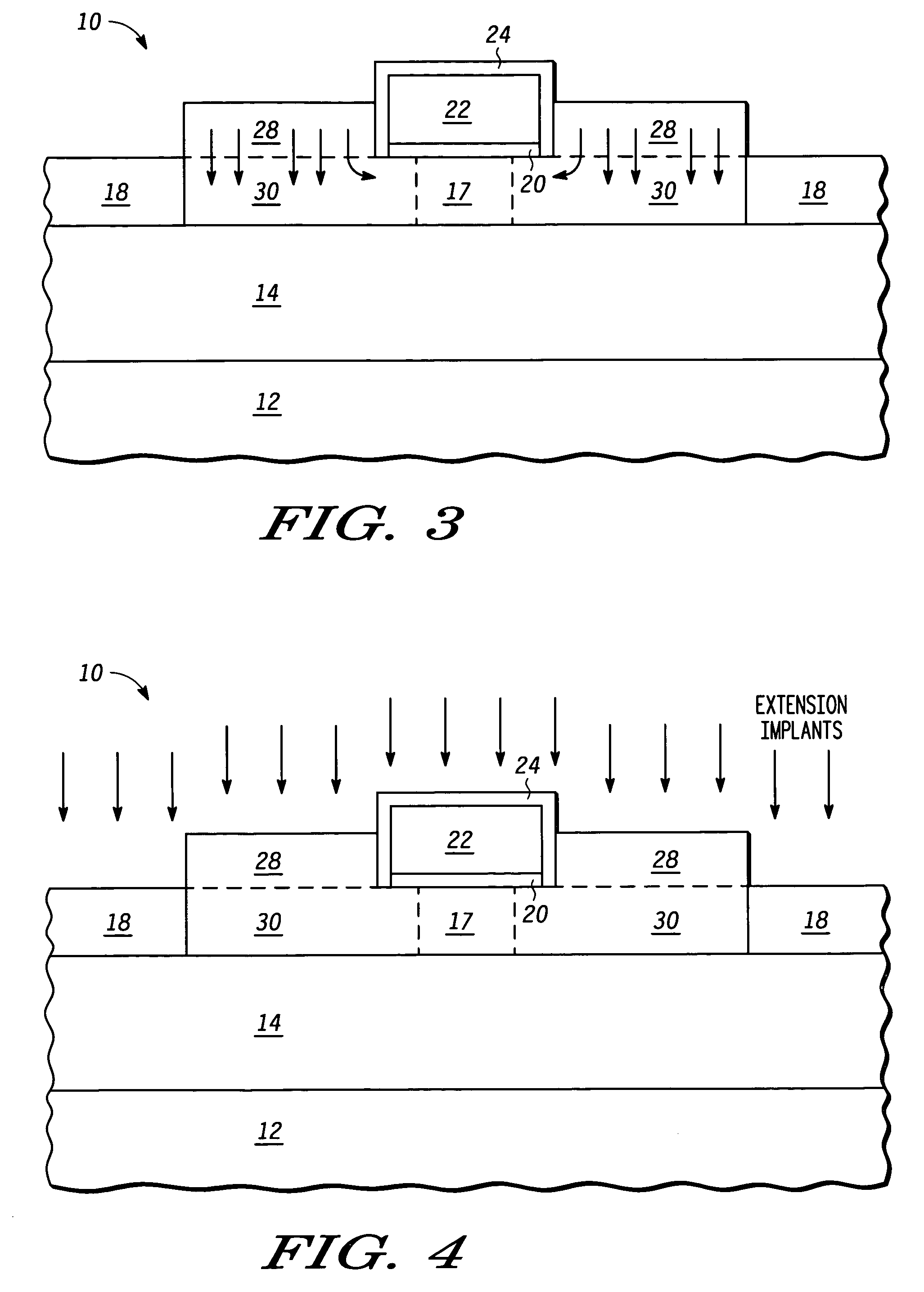

Double gate device having a heterojunction source/drain and strained channel

A semiconductor device (10) is formed by positioning a gate (22) overlying a semiconductor layer (16) of preferably silicon. A semiconductor material (26) of, for example only, SiGe or Ge, is formed adjacent the gate over the semiconductor layer and over source / drain regions. A thermal process diffuses the stressor material into the semiconductor layer. Lateral diffusion occurs to cause the formation of a strained channel (17) in which a stressor material layer (30) is immediately adjacent the strained channel. Extension implants create source and drain implants from a first portion of the stressor material layer. A second portion of the stressor material layer remains in the channel between the strained channel and the source and drain implants. A heterojunction is therefore formed in the strained channel. In another form, oxidation of the stressor material occurs rather than extension implants to form the strained channel.

Owner:NXP USA INC

Hybrid layers for use in coatings on electronic devices or other articles

ActiveUS20110114994A1Solid-state devicesSemiconductor/solid-state device manufacturingGas phaseChemical vapor deposition

A method for protecting an electronic device comprising an organic device body. The method involves the use of a hybrid layer deposited by chemical vapor deposition. The hybrid layer comprises a mixture of a polymeric material and a non-polymeric material, wherein the weight ratio of polymeric to non-polymeric material is in the range of 95:5 to 5:95, and wherein the polymeric material and the non-polymeric material are created from the same source of precursor material. Also disclosed are techniques for impeding the lateral diffusion of environmental contaminants.

Owner:UNIVERSAL DISPLAY +1

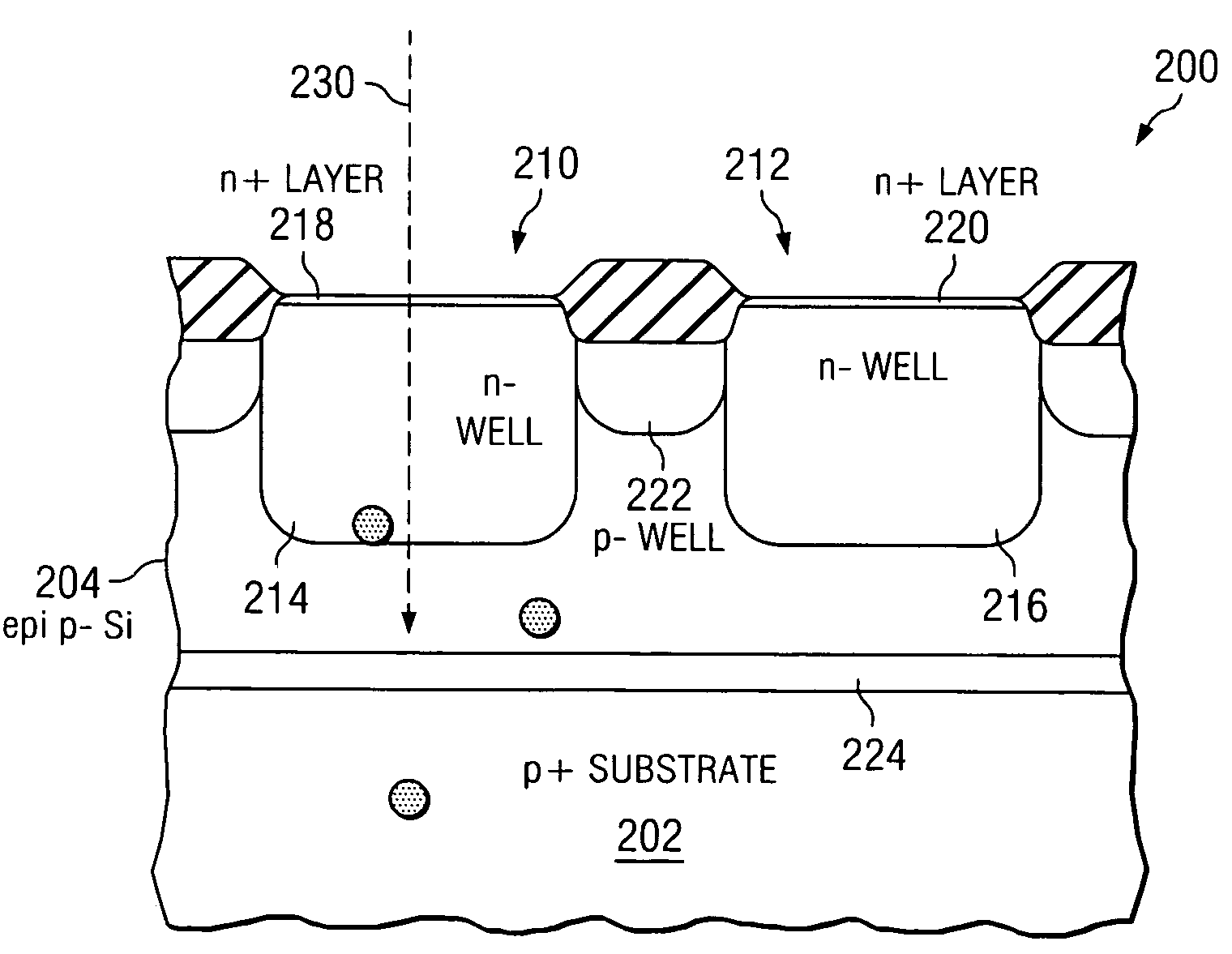

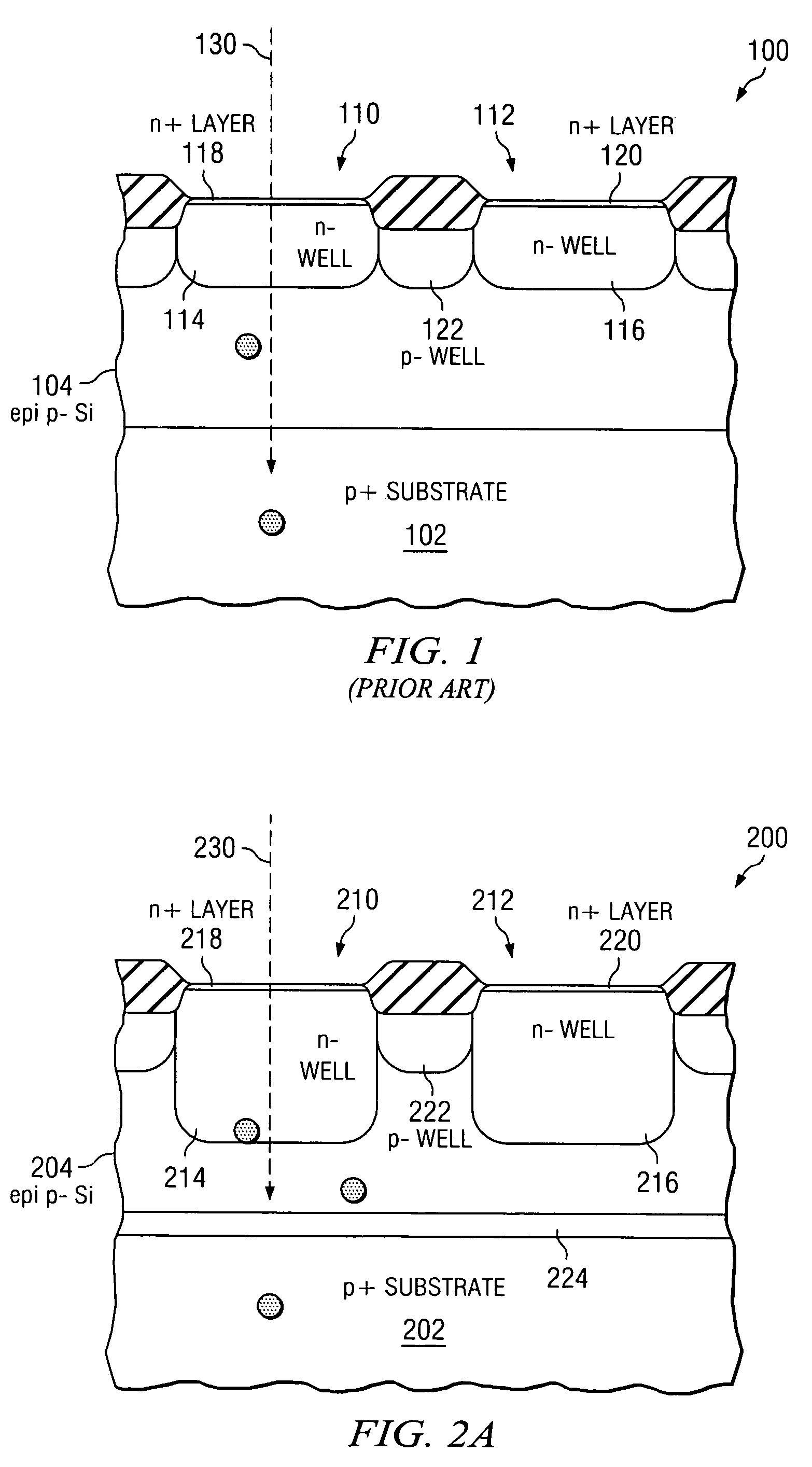

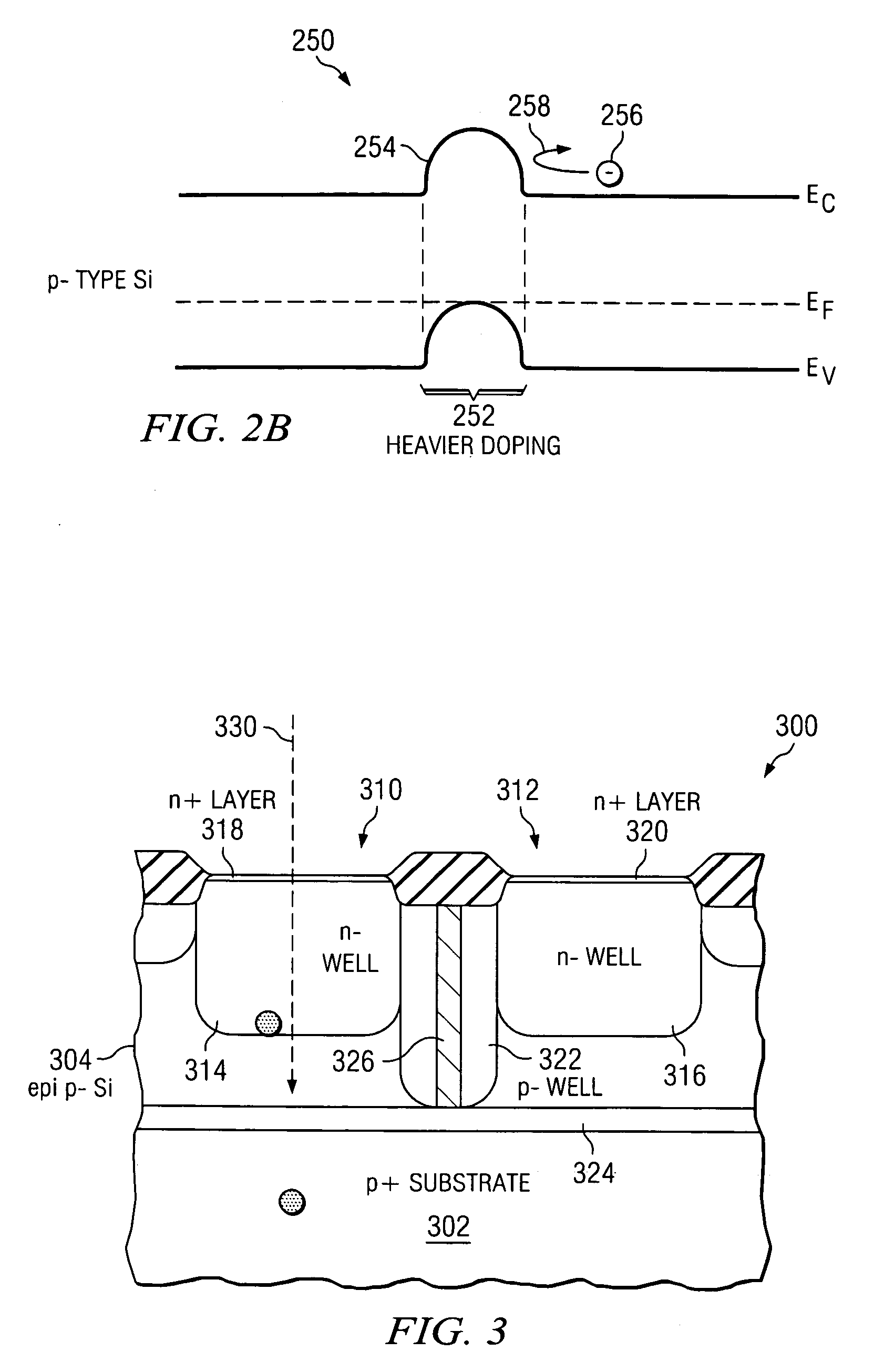

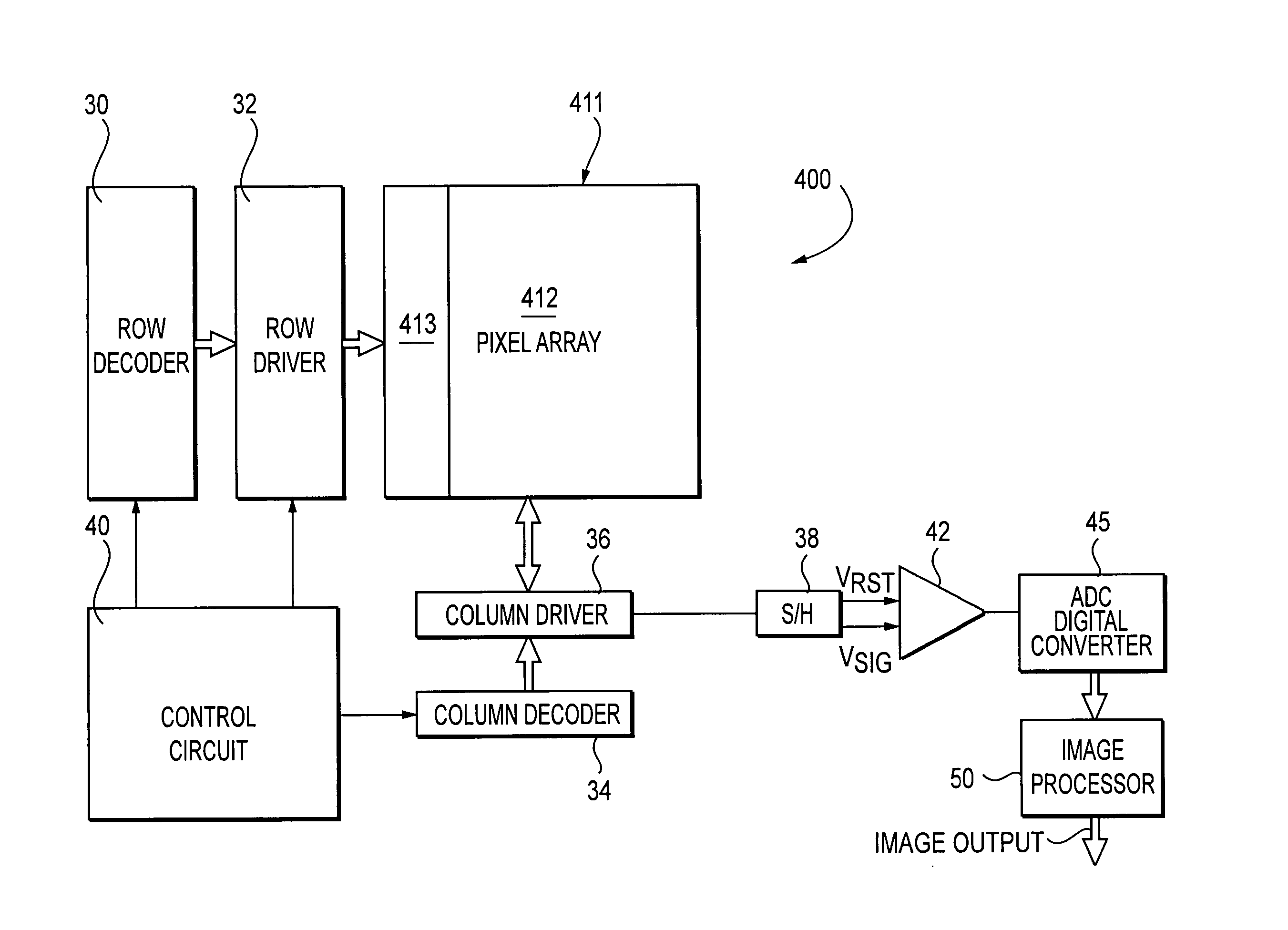

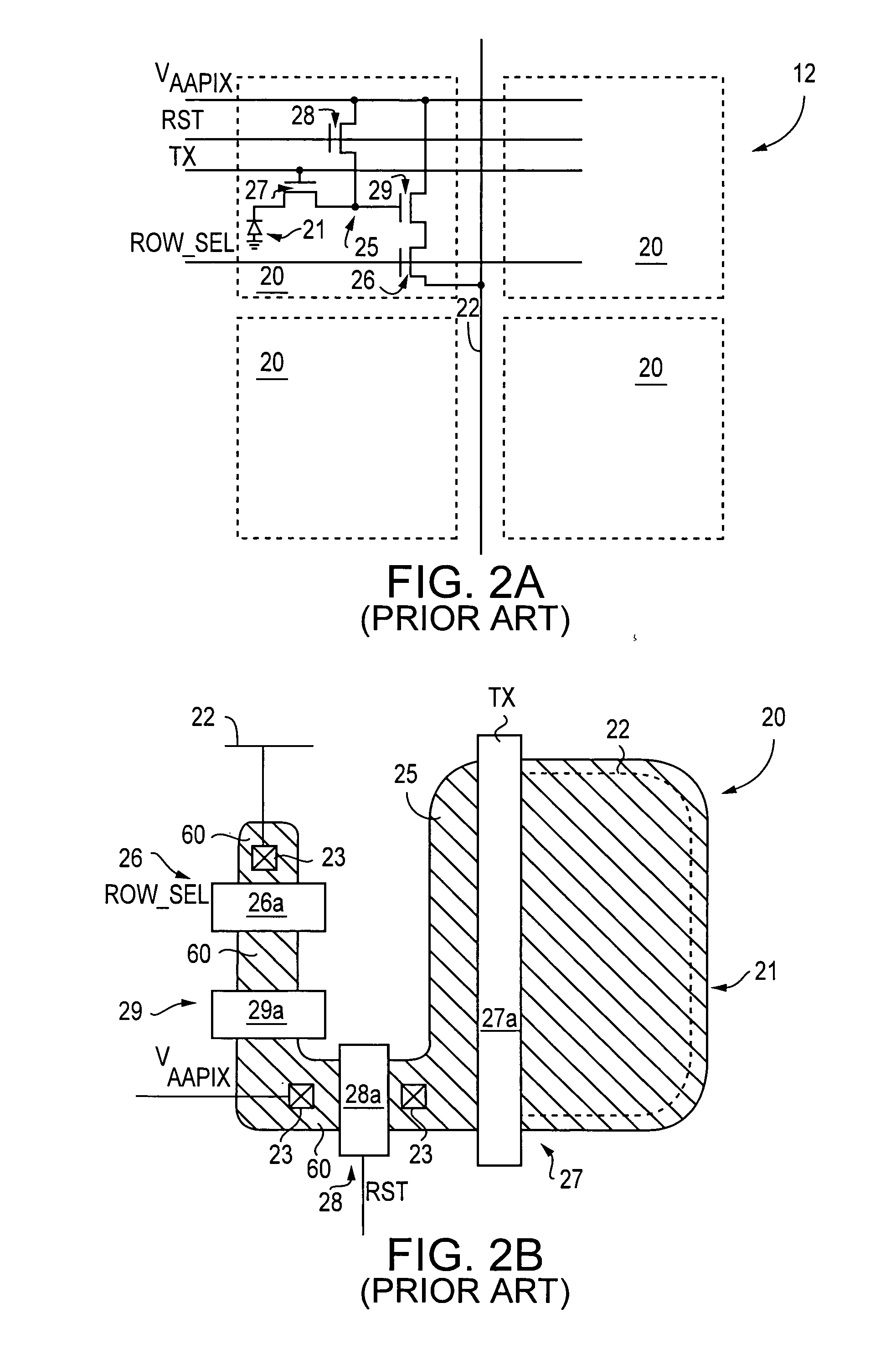

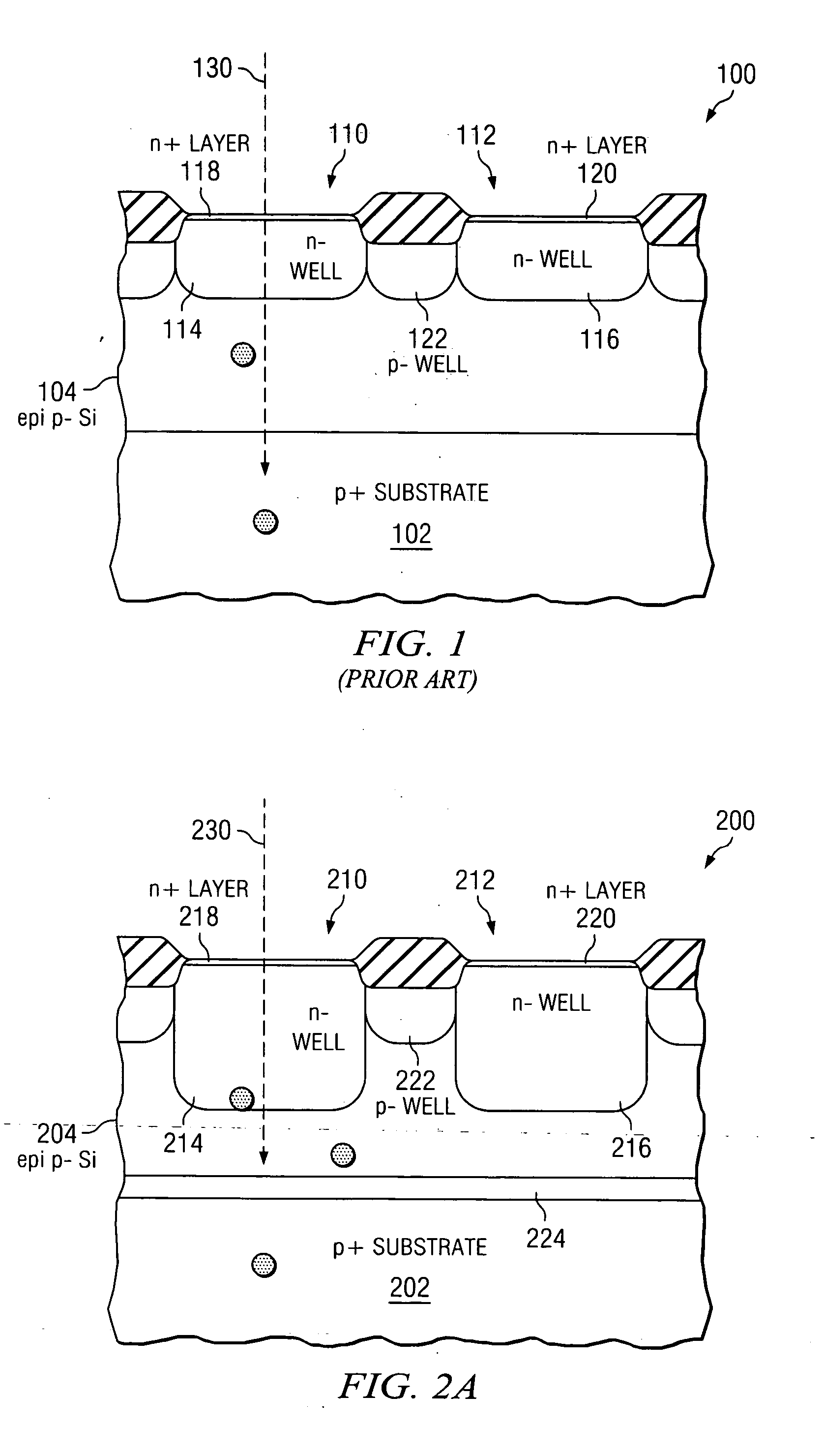

Reduced crosstalk CMOS image sensors

ActiveUS7307327B2High sensitivityReduce crosstalkSolid-state devicesRadiation controlled devicesCMOSCharge carrier

CMOS image sensor having high sensitivity and low crosstalk, particularly at far-red to infrared wavelengths, and a method for fabricating a CMOS image sensor. A CMOS image sensor has a substrate, an epitaxial layer above the substrate, and a plurality of pixels extending into the epitaxial layer for receiving light. The image sensor also includes at least one of a horizontal barrier layer between the substrate and the epitaxial layer for preventing carriers generated in the substrate from moving to the epitaxial layer, and a plurality of lateral barrier layers between adjacent ones of the plurality of pixels for preventing lateral diffusion of electrons in the epitaxial layer.

Owner:APTINA IMAGING CORP

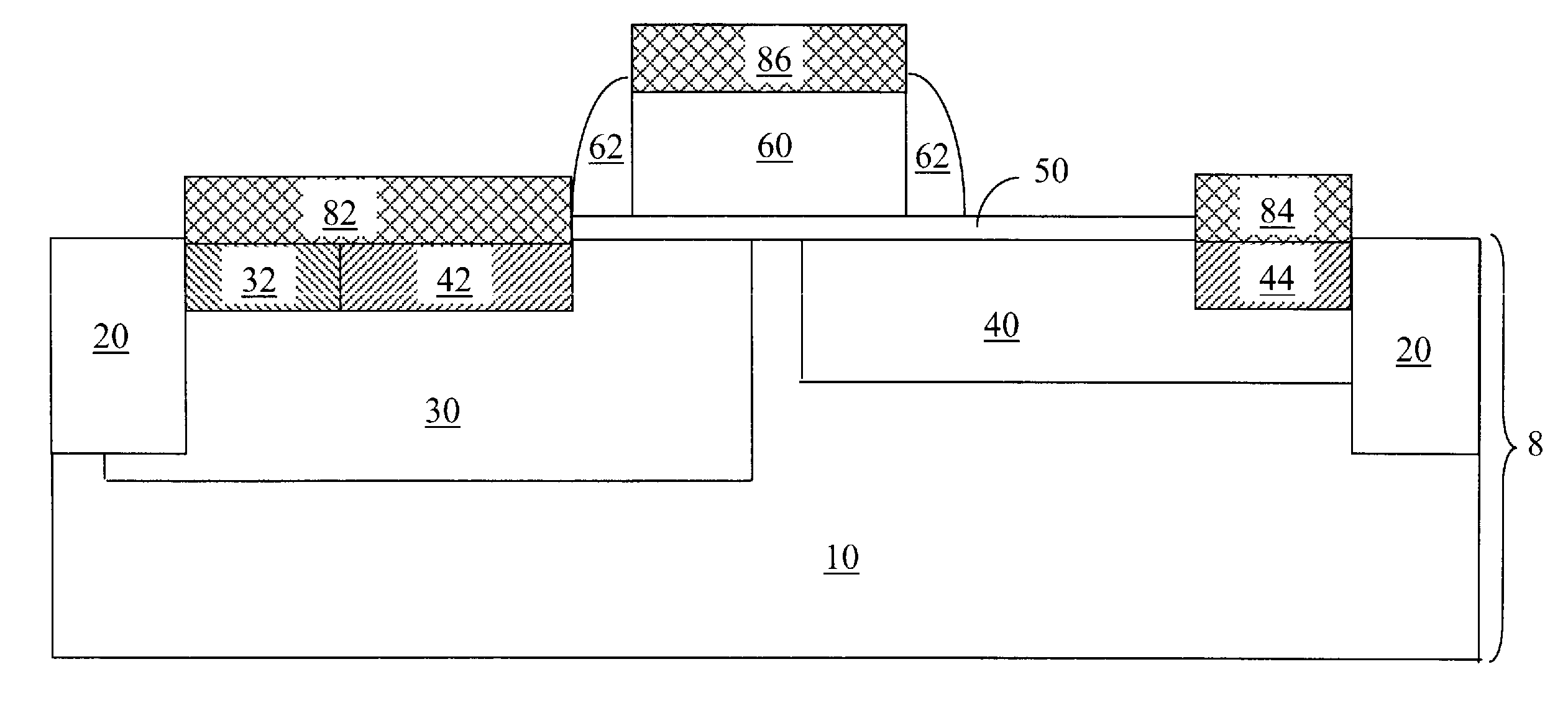

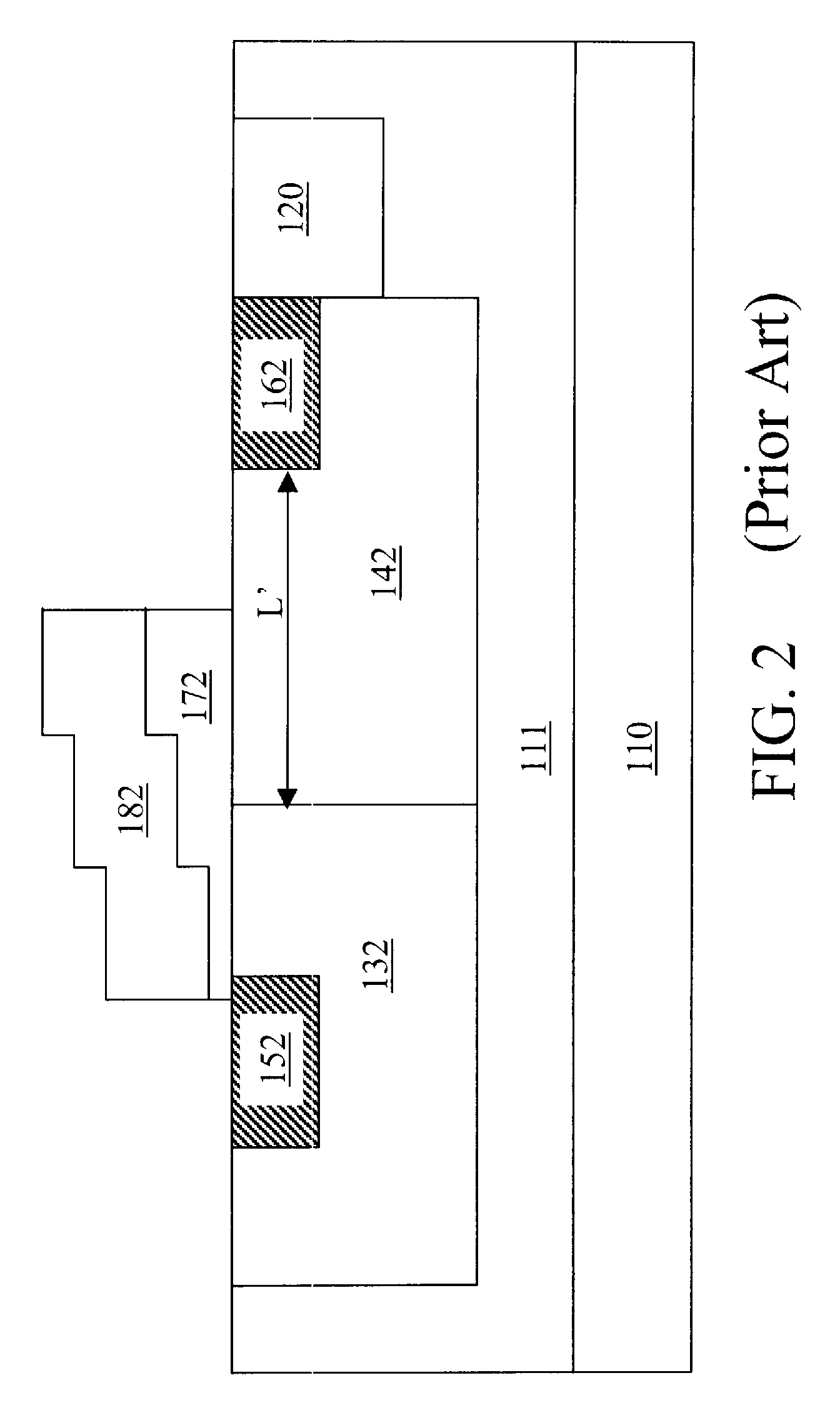

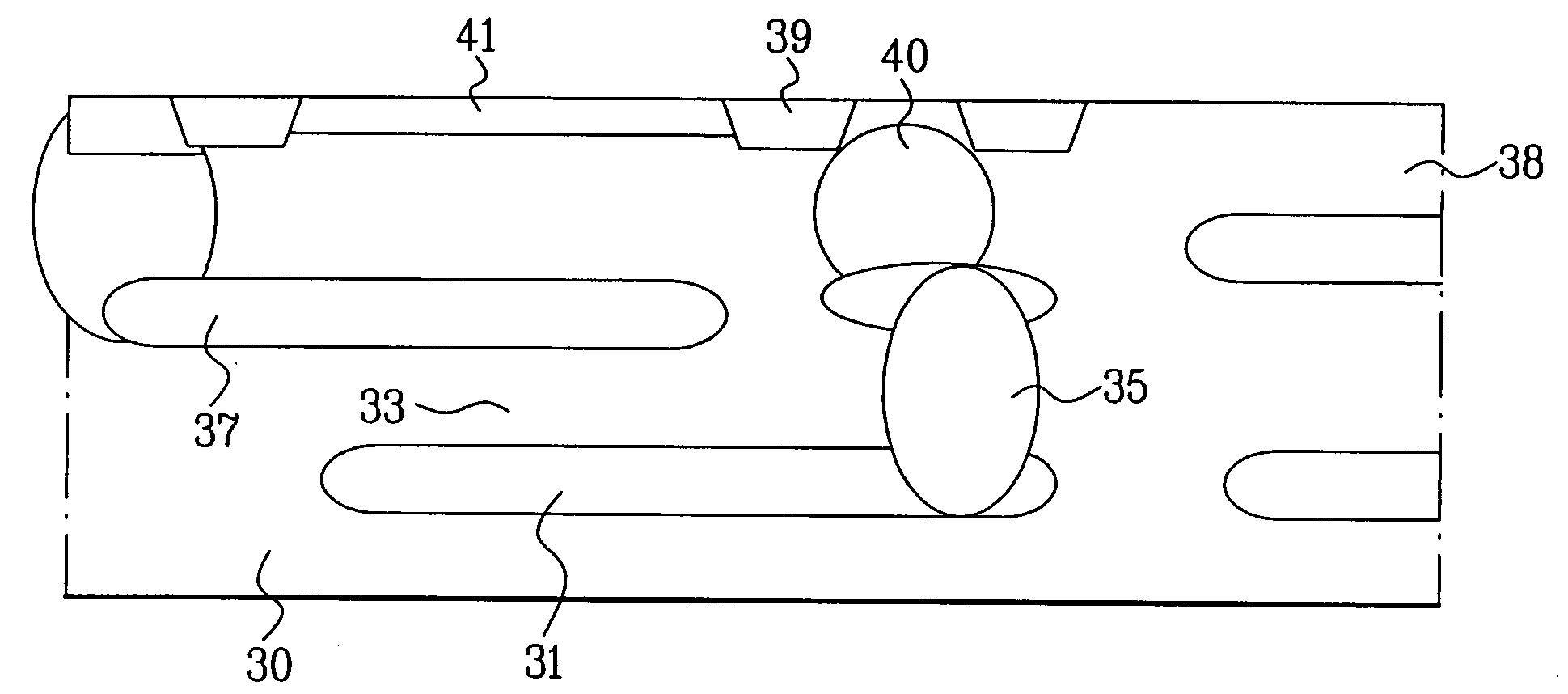

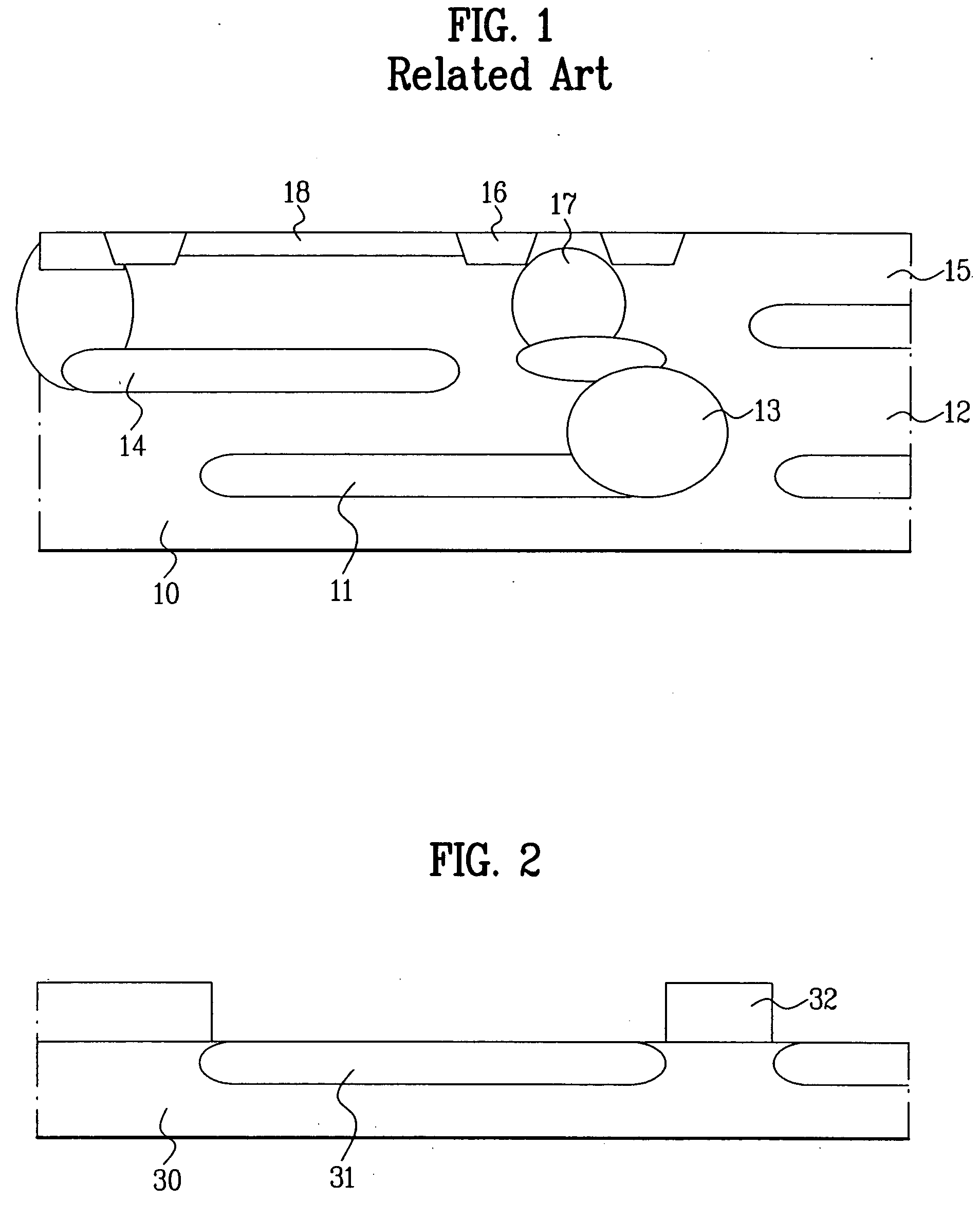

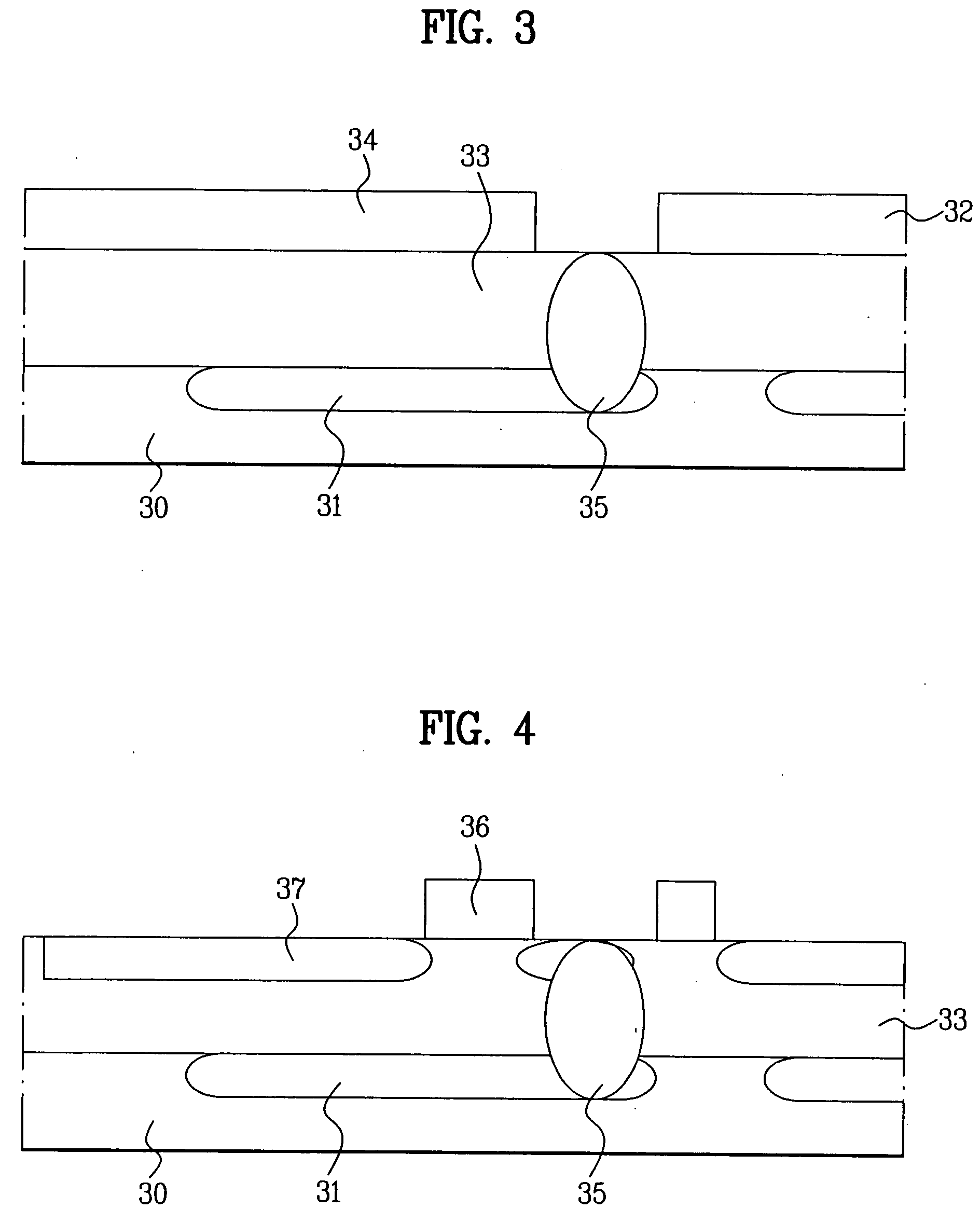

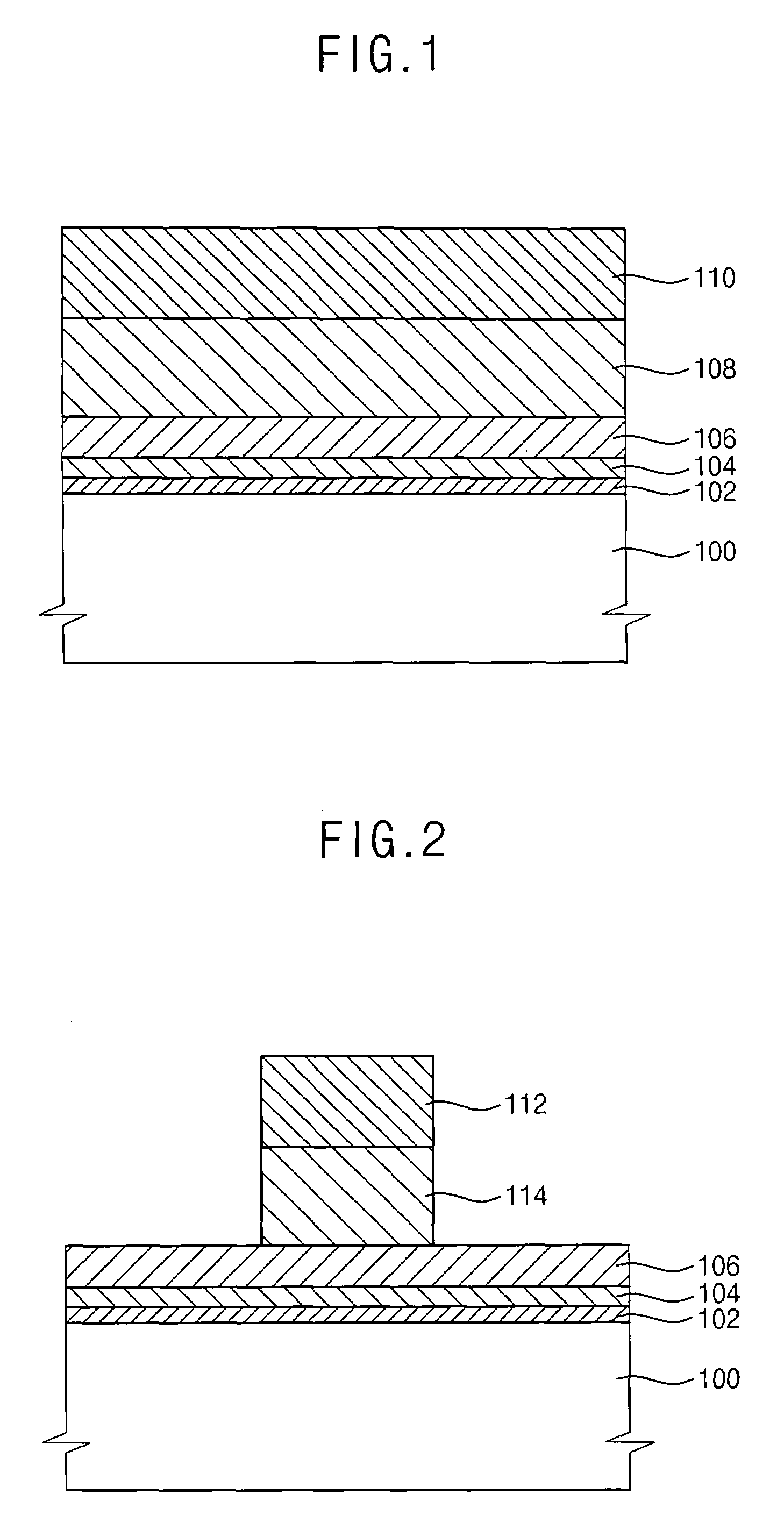

Lateral diffusion field effect transistor with drain region self-aligned to gate electrode

InactiveUS20090261426A1Constant drift distanceSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorLateral diffusion

A disposable structure displaced from an edge of a gate electrode and a drain region aligned to the disposable structure is formed. Thus, the drain region is self-aligned to the edge of the gate electrode. The disposable structure may be a disposable spacer, or alternately, the disposable structure may be formed simultaneously with, and comprise the same material as, a gate electrode. After formation of the drain regions, the disposable structure is removed. The self-alignment of the drain region to the edge of the gate electrode provides a substantially constant drift distance that is independent of any overlay variation of lithographic processes.

Owner:GLOBALFOUNDRIES INC

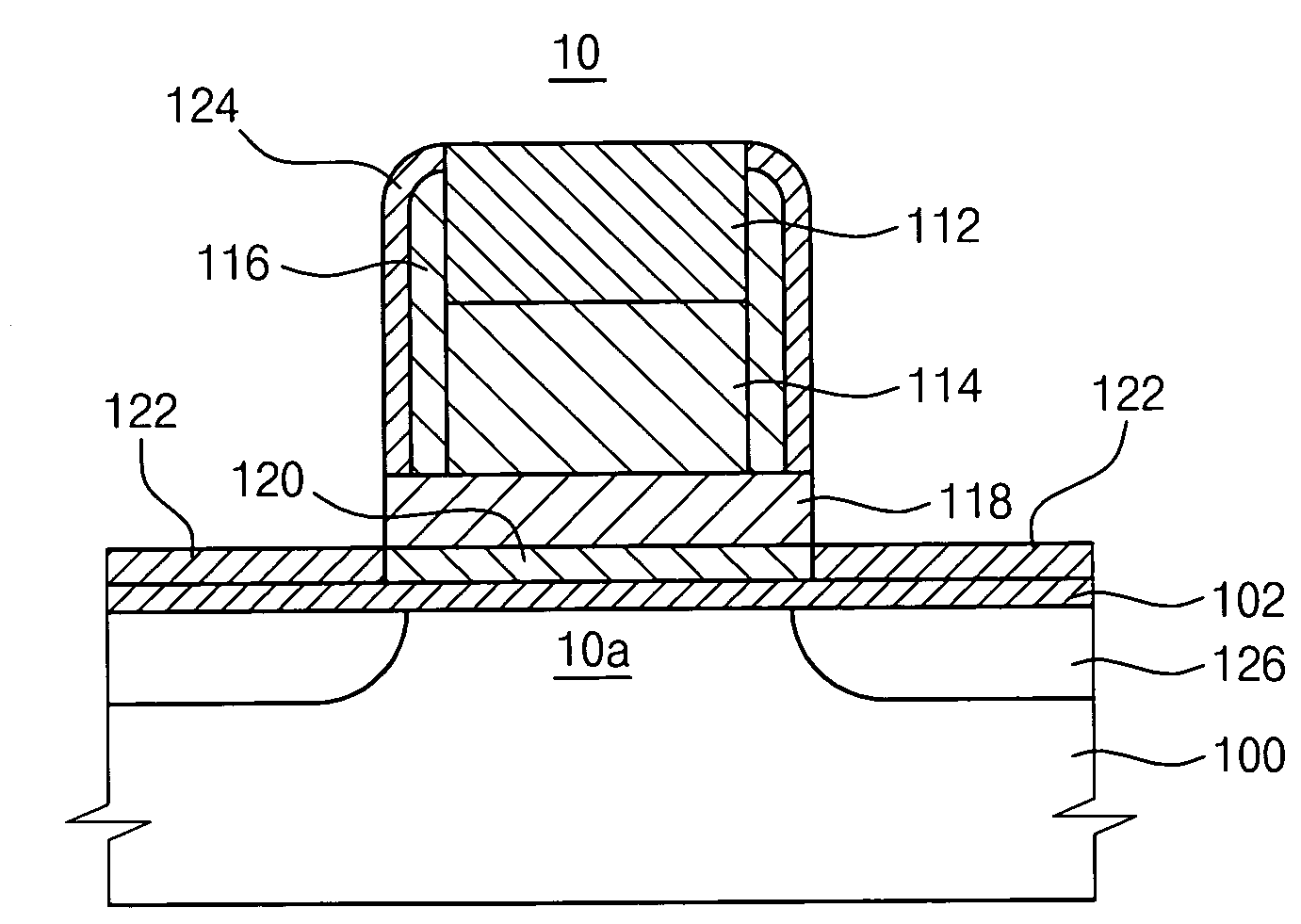

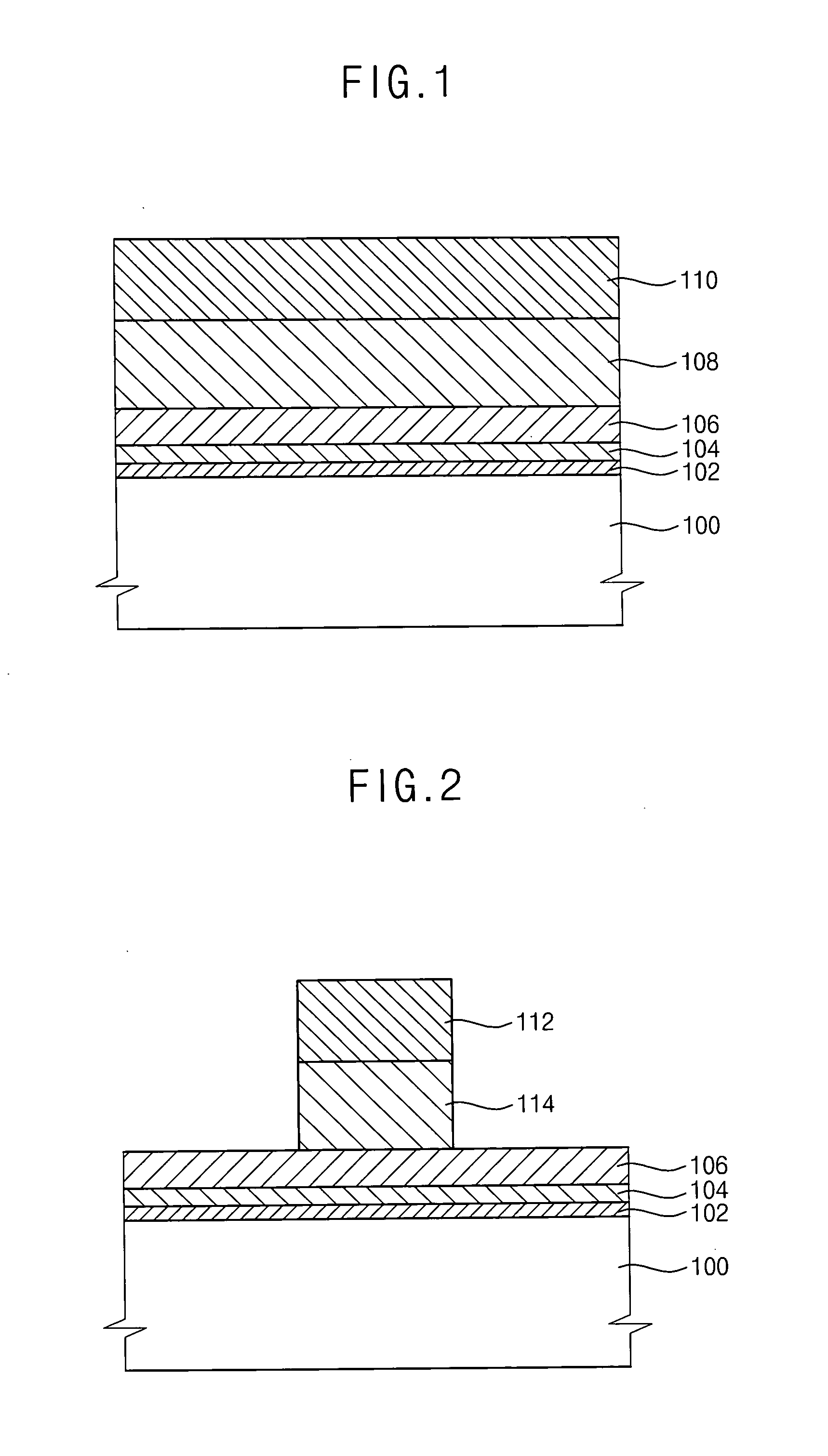

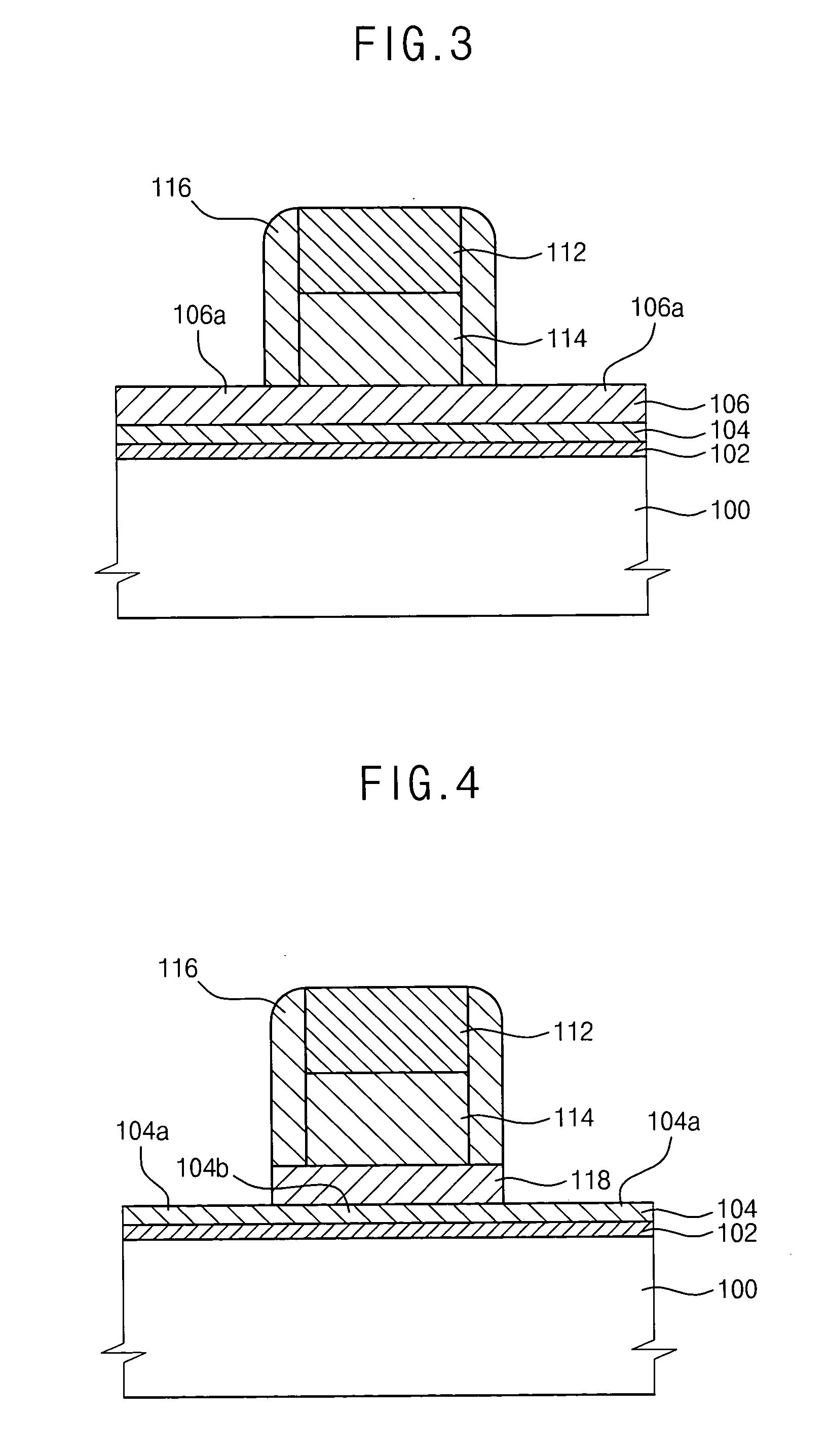

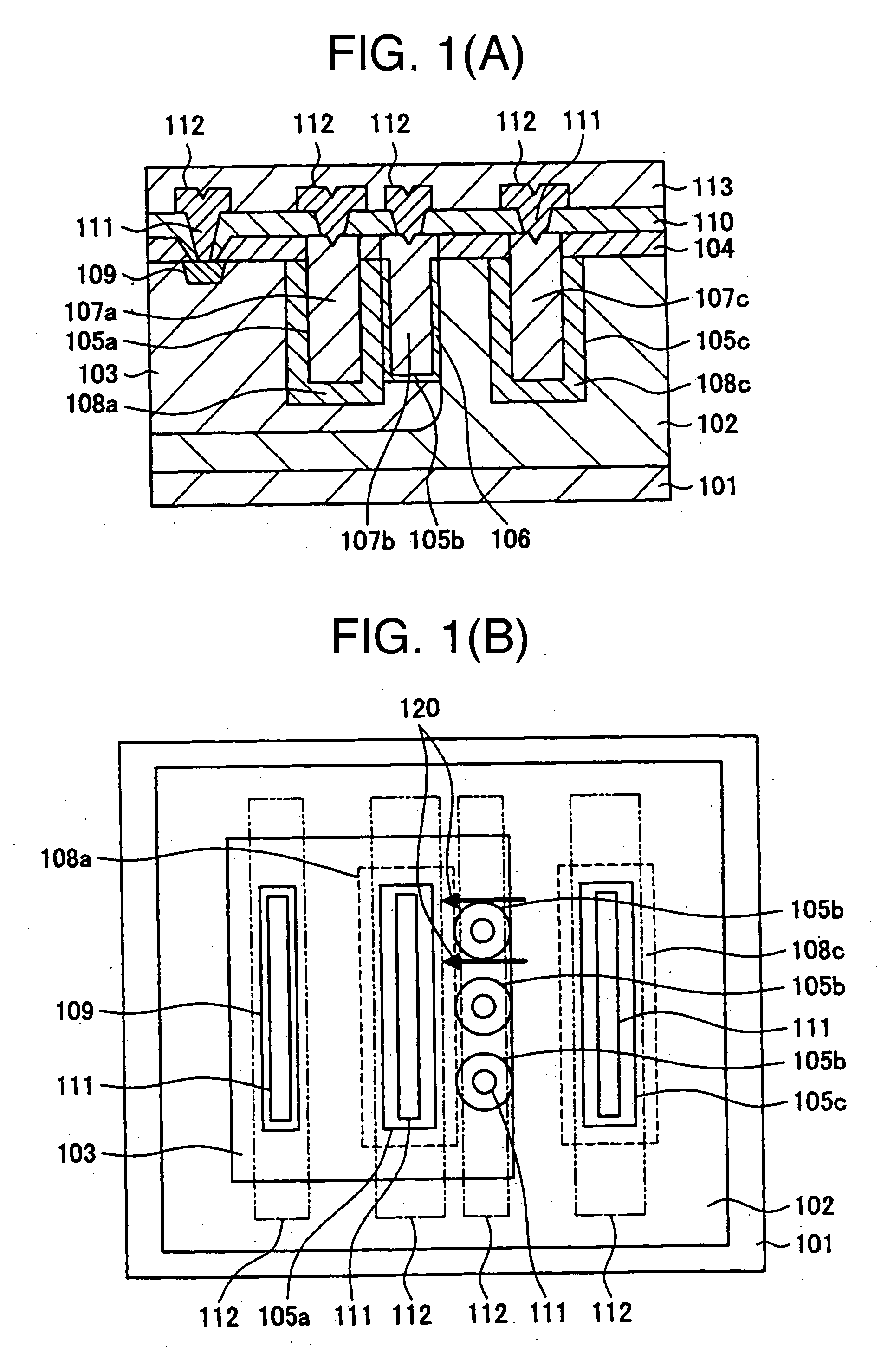

Non-volatile memory devices and methods of manufacturing the same

ActiveUS20080150008A1Lateral diffusion can be restrictedAvoid lateral spreadNanoinformaticsSemiconductor/solid-state device manufacturingTrappingLateral diffusion

Non-volatile memory devices include a tunnel insulating layer on a channel region of a substrate, a charge-trapping layer pattern on the tunnel insulating layer and a first blocking layer pattern on the charge-trapping layer pattern. Second blocking layer patterns are on the tunnel insulating layer proximate sidewalls of the charge-trapping layer pattern. The second blocking layer patterns are configured to limit lateral diffusion of electrons trapped in the charge-trapping layer pattern. A gate electrode is on the first blocking layer pattern. The second blocking layer patterns may prevent lateral diffusion of the electrons trapped in the charge-trapping layer pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

Bottom source LDMOSFET structure and method

ActiveUS7554154B2Reduce cell pitchReduce manufacturing costTransistorSolid-state devicesLDMOSCapacitance

This invention discloses bottom-source lateral diffusion MOS (BS-LDMOS) device. The device has a source region disposed laterally opposite a drain region near a top surface of a semiconductor substrate supporting a gate thereon between the source region and a drain region. The BS-LDMOS device further has a combined sinker-channel region disposed at a depth in the semiconductor substrate entirely below a body region disposed adjacent to the source region near the top surface wherein the combined sinker-channel region functioning as a buried source-body contact for electrically connecting the body region and the source region to a bottom of the substrate functioning as a source electrode. A drift region is disposed near the top surface under the gate and at a distance away from the source region and extending to and encompassing the drain region. The combined sinker-channel region extending below the drift region and the combined sinker-channel region that has a dopant-conductivity opposite to and compensating the drift region for reducing the source-drain capacitance.

Owner:ALPHA & OMEGA SEMICON LTD

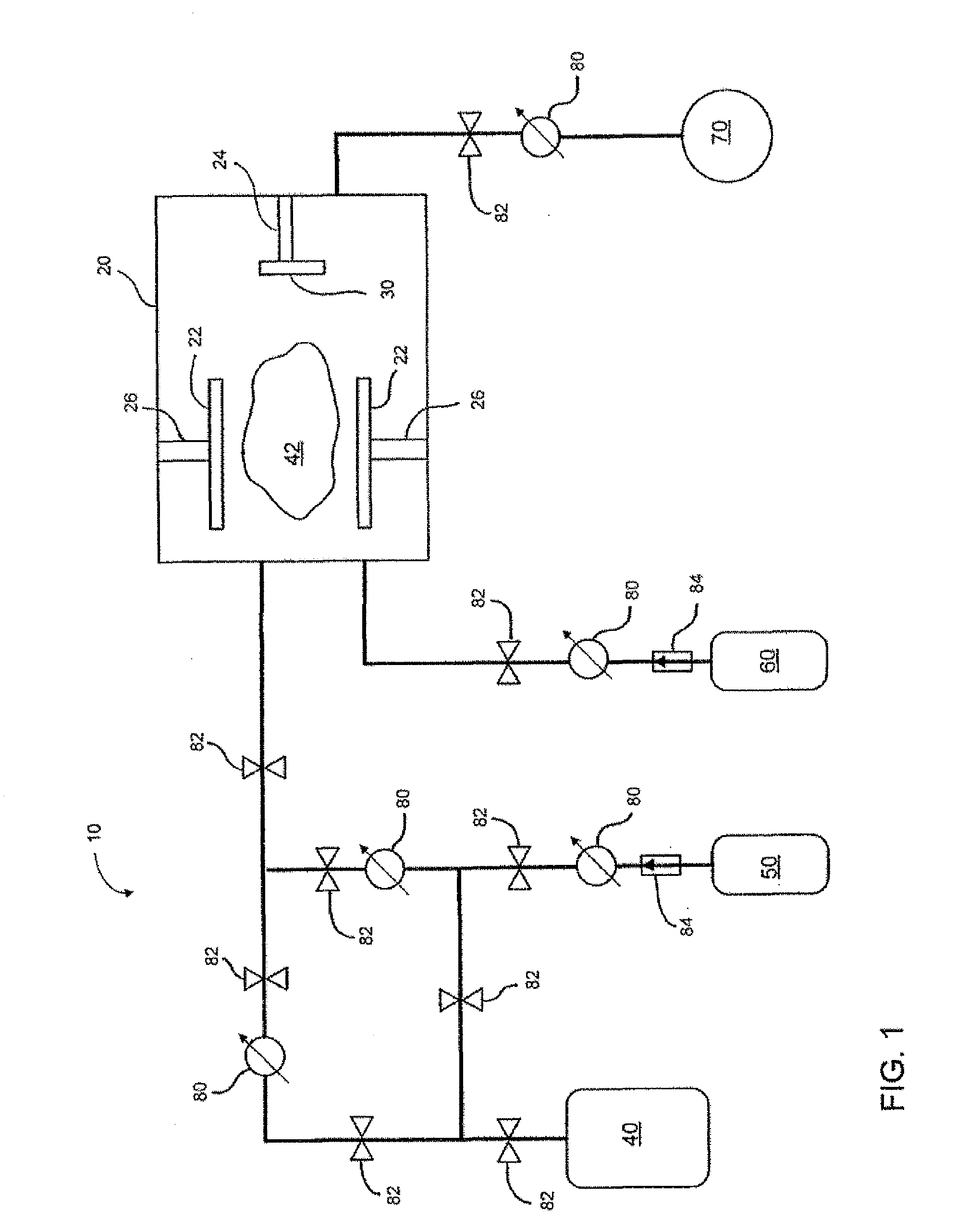

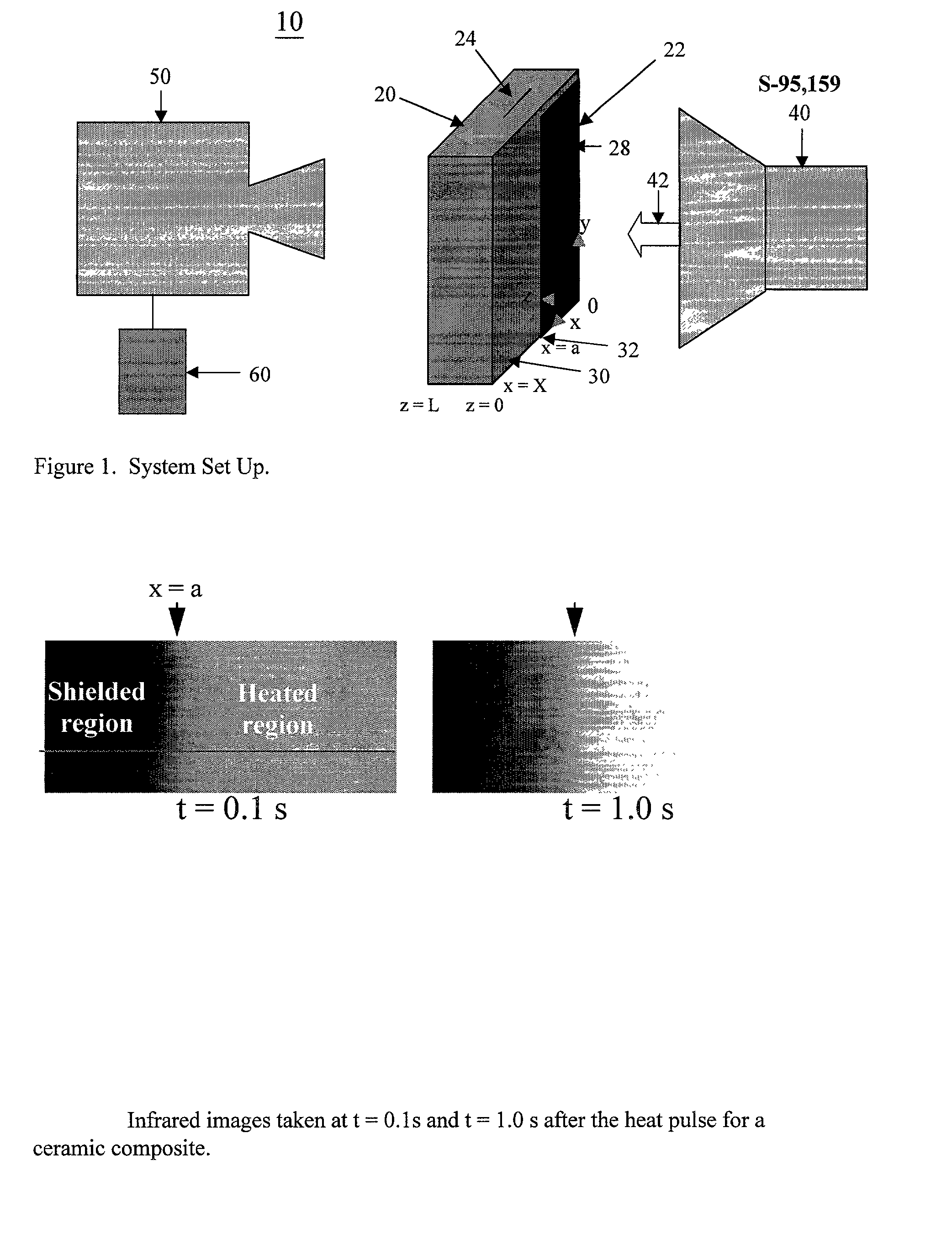

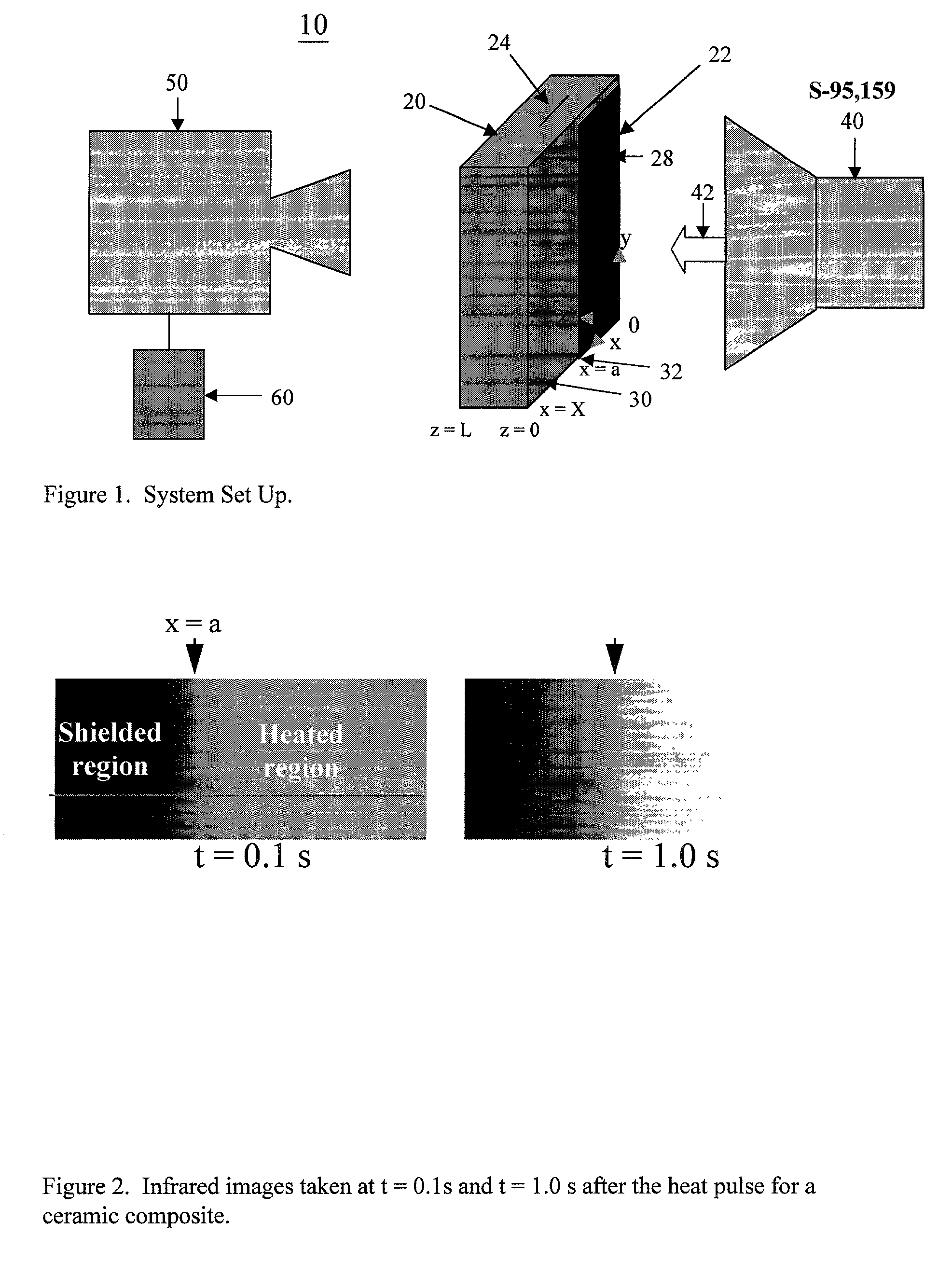

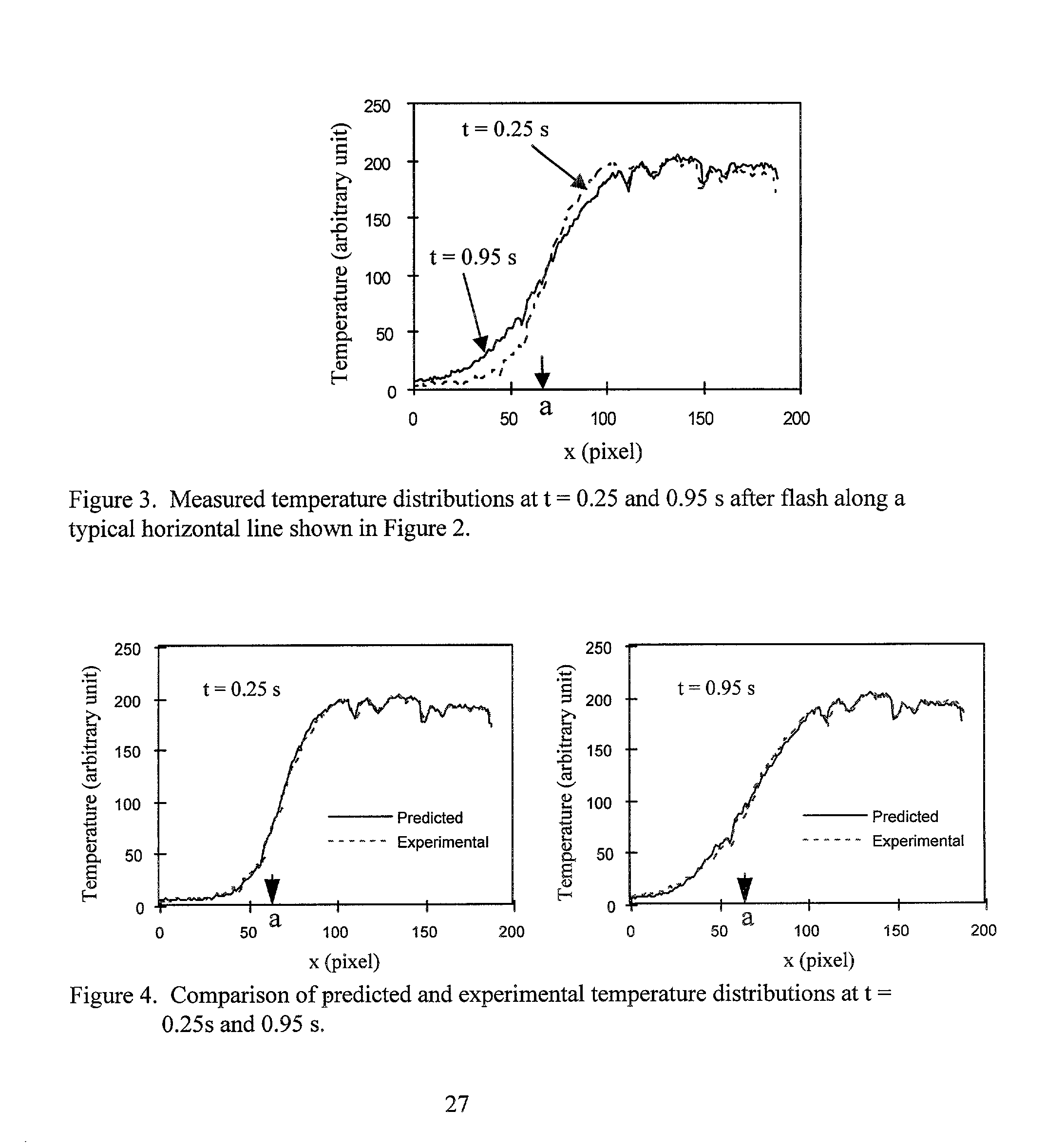

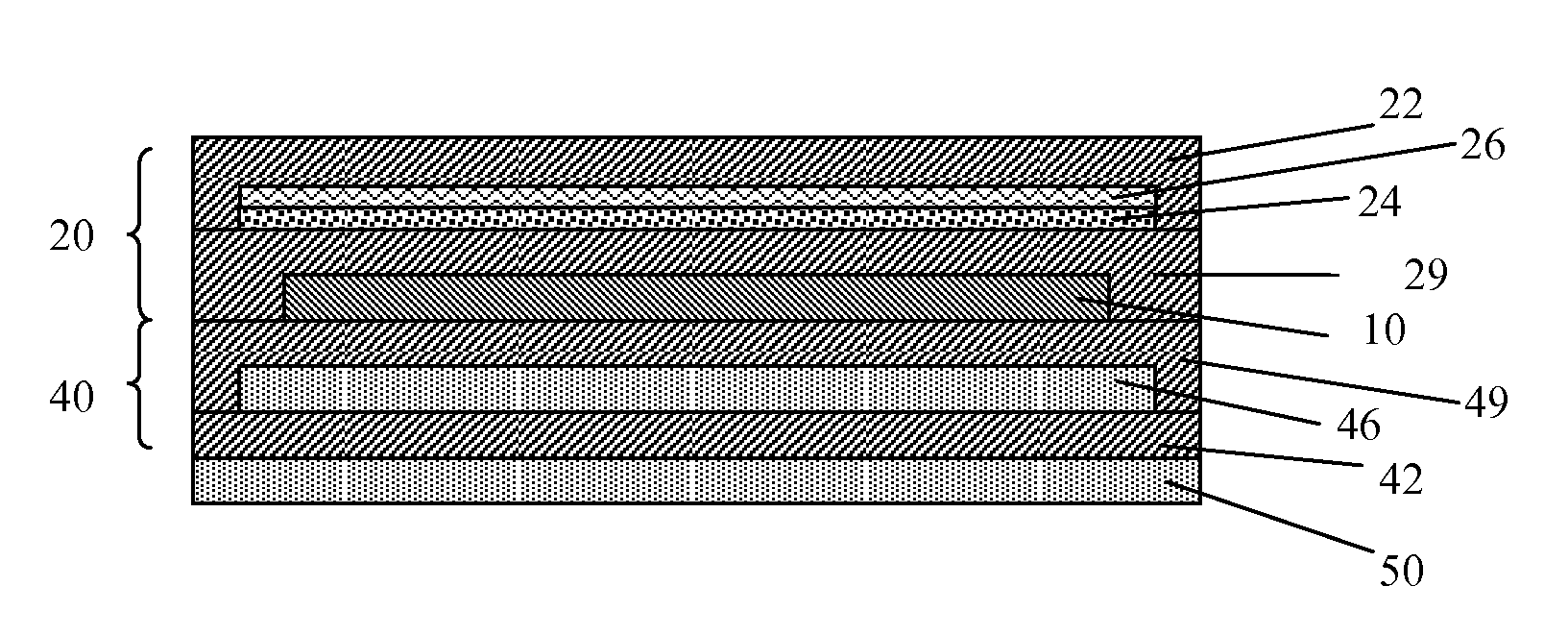

Thermal imaging measurement of lateral diffusivity and non-invasive material defect detection

InactiveUS20020126730A1Accurate methodRadiation pyrometryMaterial heat developmentMaterial defectOrthogonal coordinates

A system and method for determining lateral thermal diffusivity of a material sample using a heat pulse; a sample oriented within an orthogonal coordinate system; an infrared camera; and a computer that has a digital frame grabber, and data acquisition and processing software. The mathematical model used within the data processing software is capable of determining the lateral thermal diffusivity of a sample of finite boundaries. The system and method may also be used as a nondestructive method for detecting and locating cracks within the material sample.

Owner:THE UNITED STATES AS REPRESENTED BY THE DEPARTMENT OF ENERGY

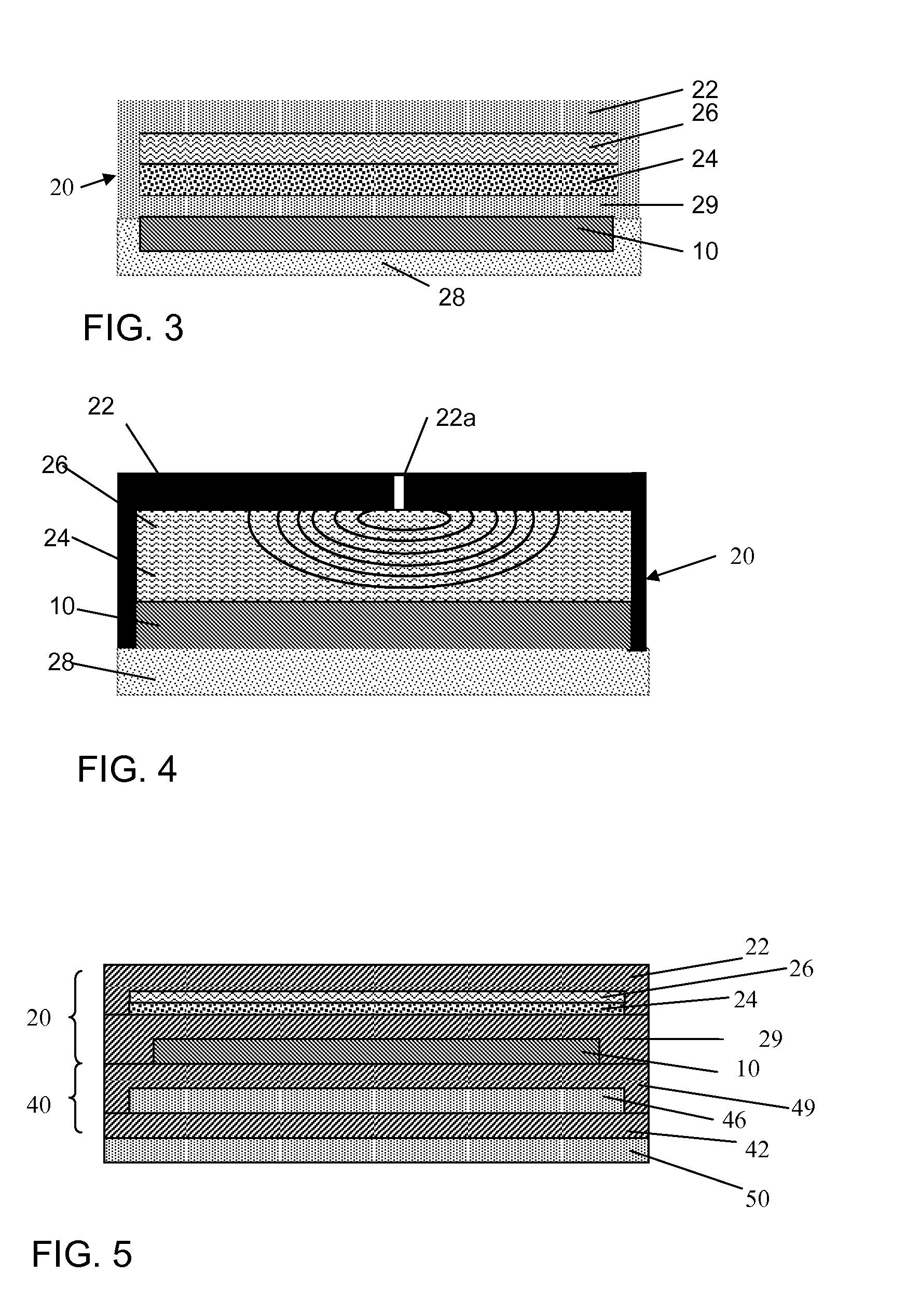

Opto-Electric Device and Method of Manufacturing an Opto-Electric Device

An opto-electric device is presented that comprises an opto-electric element (10) enclosed by a barrier structure (20) for inhibiting a transmission of moisture from an environment towards the opto-electric element. The barrier structure includes a stack of layers comprising at least an inorganic layer (22) and a moisture getter material in a layer arranged between the inorganic layer and the opto-electric element. The stack includes a lateral diffusion layer (26), wherein the getter material is present in a separate getter layer (24) arranged between the opto-electric element (10) and the lateral diffusion layer (26) and / or the getter material is present in the lateral diffusion layer (26).

Owner:NEDERLANDSE ORG VOOR TOEGEPAST-NATUURWETENSCHAPPELIJK ONDERZOEK (TNO) +2

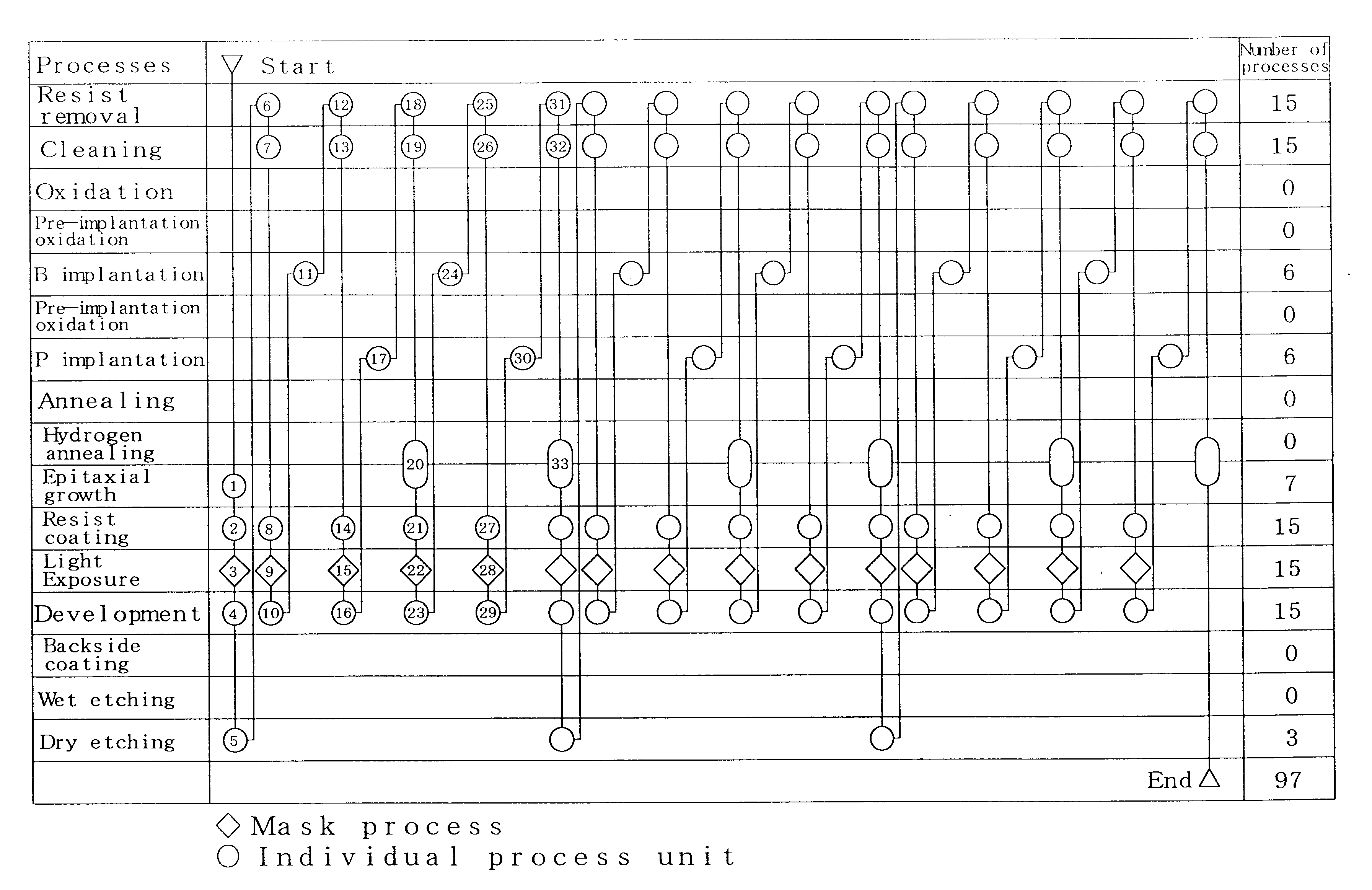

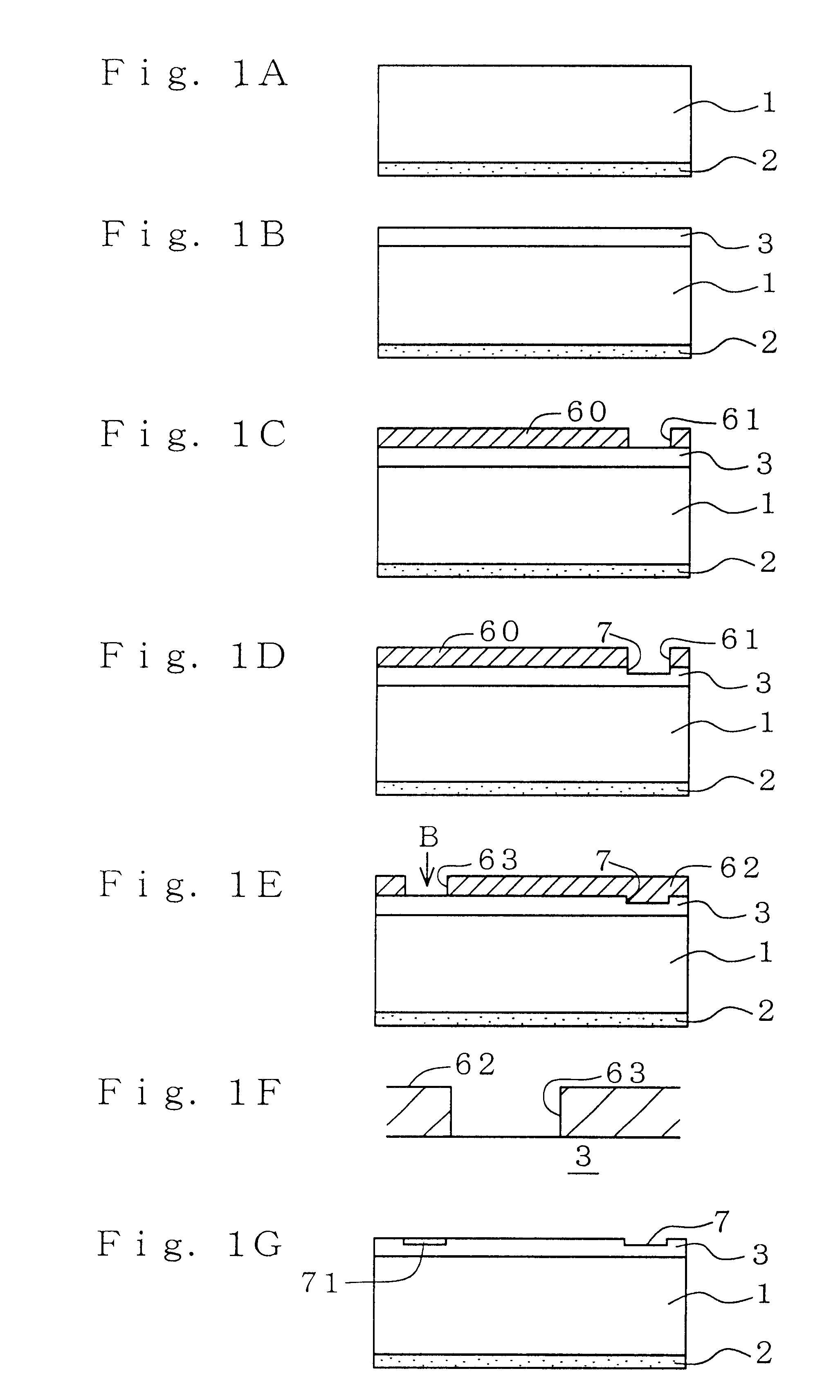

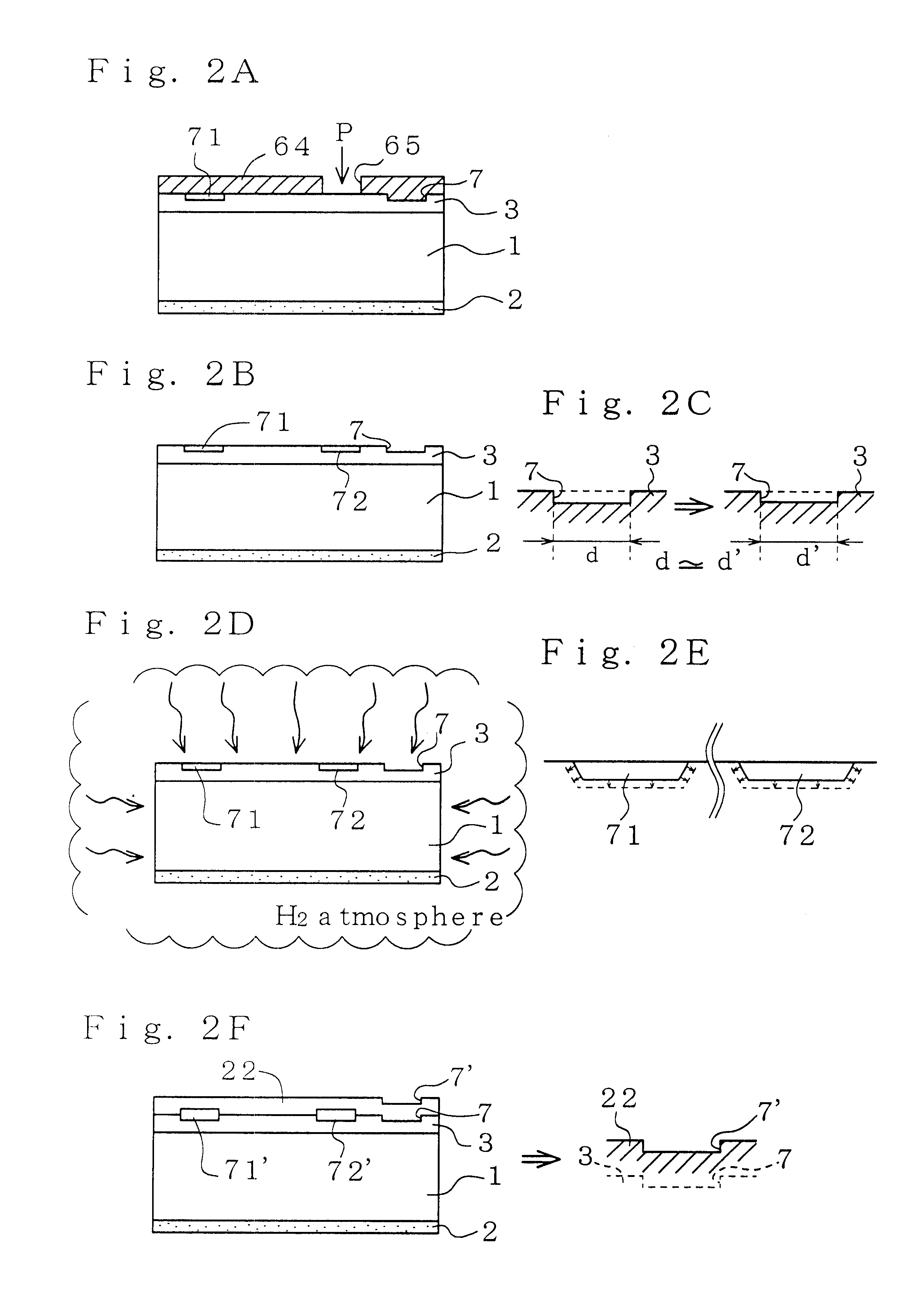

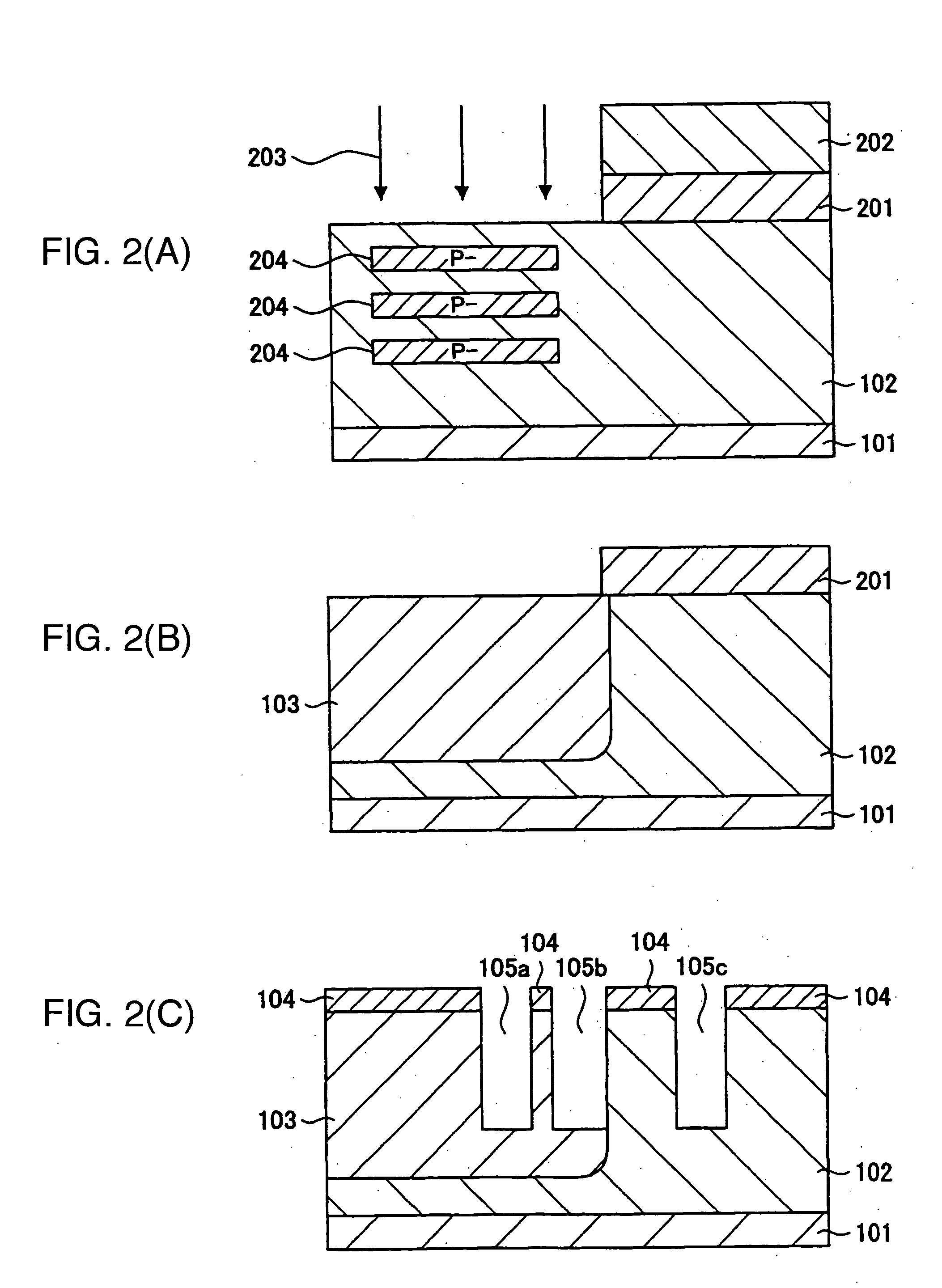

Production method for silicon epitaxial wafer and silicon epitaxial wafer

InactiveUS6589336B1Polycrystalline material growthSemiconductor/solid-state device manufacturingResistWafering

Performing the post-implantation annealing for recovering crystallinity in a hydrogen atmosphere can successfully suppress the surface roughening on the ion-implanted layers without pre-implantation oxidation. This allows omission of the pre-implantation oxidation and allows ion implantation using only a photoresist film as a mask in a method for producing an epitaxial wafer having buried ion-implanted layers. Since an intentional formation of an oxide film, including such pre-implantation oxidation, on an epitaxial layer is omitted, the number of repetition of the thermal history exerted to the buried ion-implanted layers can be reduced, which effectively suppresses lateral diffusion of implanted ions. Since the formation and removal of the oxide film is thus no more necessary, the number of process steps in the production of the epitaxial wafer can dramatically be reduced.

Owner:SHIN-ETSU HANDOTAI CO LTD

Method for fabricating vertical CMOS image sensor

ActiveUS20060138531A1Highly integratedSmall sizeSolid-state devicesSemiconductor/solid-state device manufacturingCMOSPhotodiode

A method of fabricating a vertical CMOS image sensor is disclosed, to improve the integration with the decrease in size of pixel by minimizing the lateral diffusion, in which phosphorous and arsenic ions are implanted while controlling the dose and energy, the method including forming a first photodiode in a semiconductor substrate; forming a first epitaxial layer on the semiconductor substrate; forming a first plug by sequentially implanting first and second ions in the first epitaxial layer; forming a second photodiode in the first epitaxial layer; forming a second epitaxial layer in the first epitaxial layer; forming an isolation area in the second epitaxial layer; and forming a third photodiode and a second plug in the second epitaxial layer.

Owner:DONGBU HITEK CO LTD

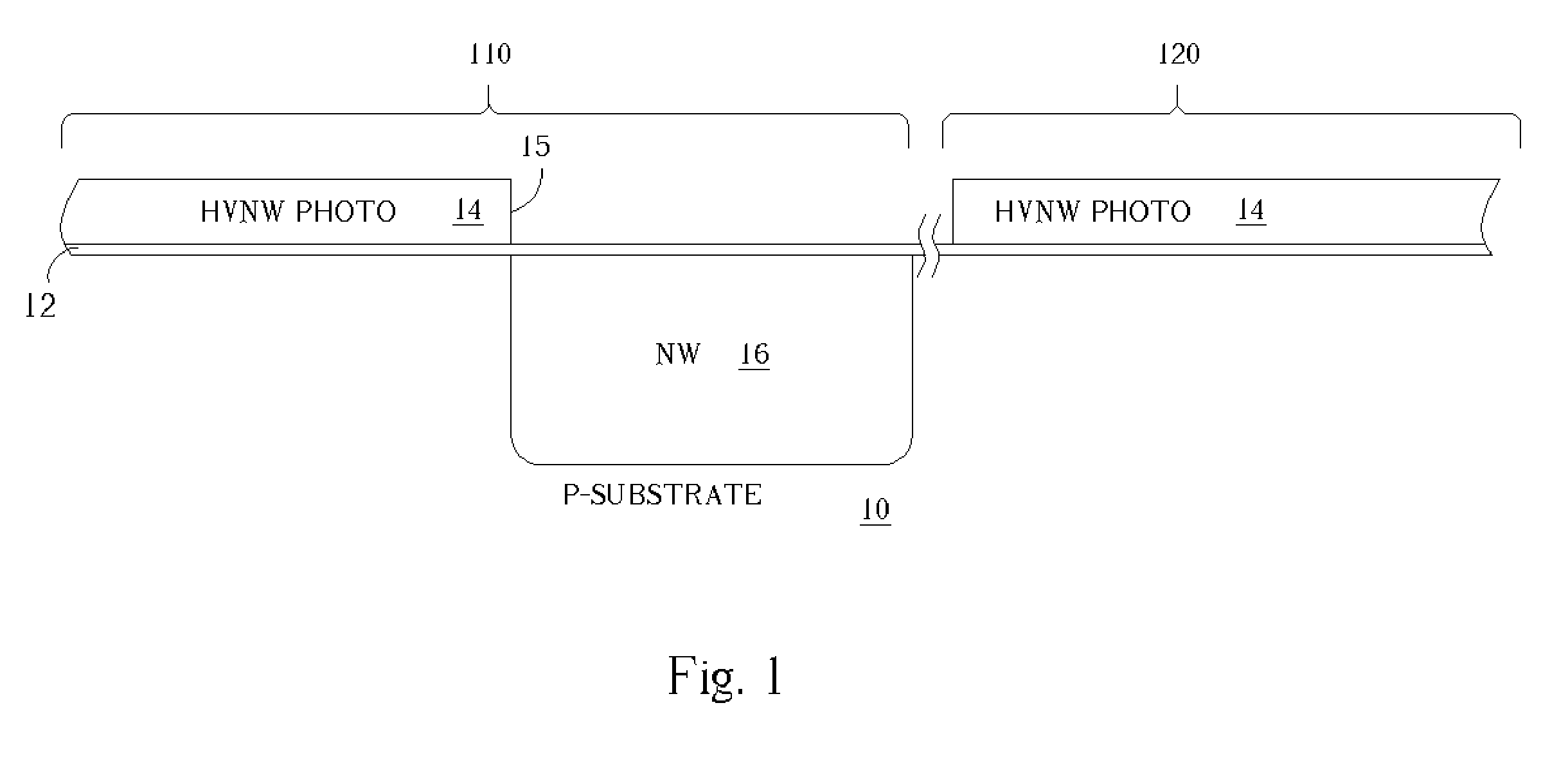

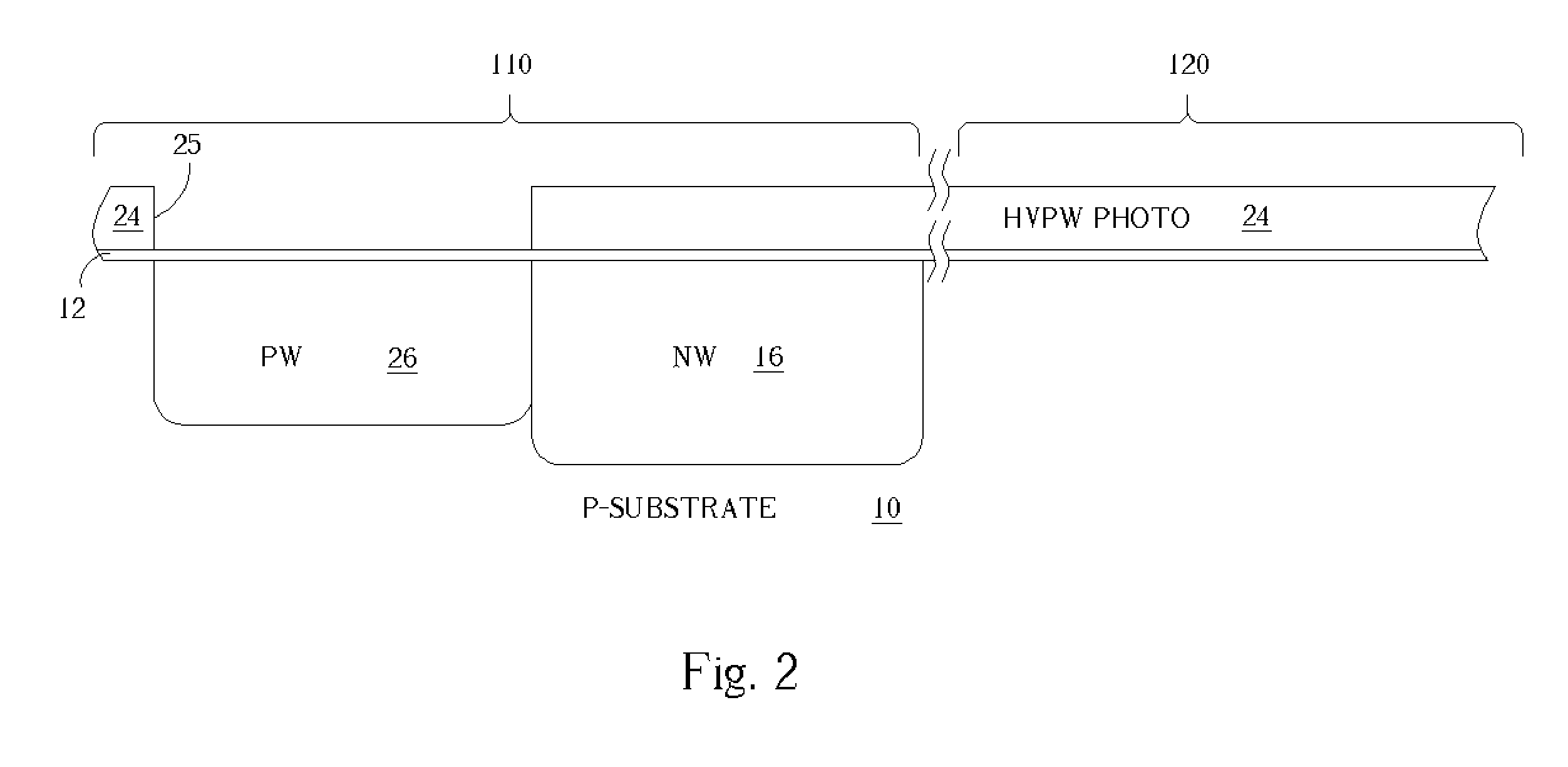

Method for fabricating integrated circuits having both high voltage and low voltage devices

A high-voltage semiconductor MOS process that is fully compatible with low-voltage MOS process is provided. The high-voltage N / P well are implanted into the substrate prior to the definition of active areas. The channel stop doping regions are formed after the formation of field oxide layers, thus avoiding lateral diffusion of the channel stop doping regions. In addition, the grade drive-in process used to activate the grade doping regions in the high-voltage device area and the gate oxide growth of the high-voltage devices are performed simultaneously.

Owner:UNITED MICROELECTRONICS CORP

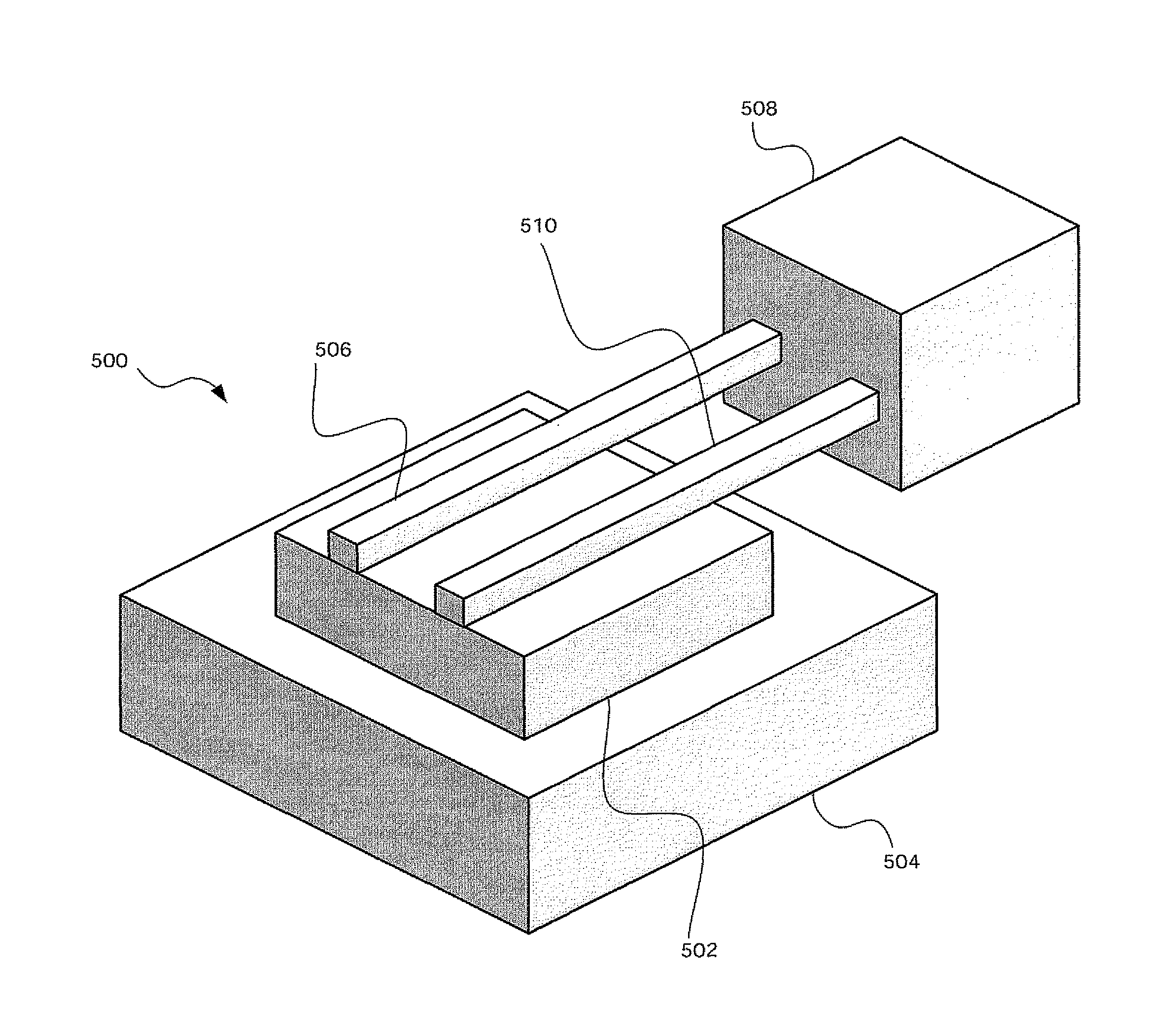

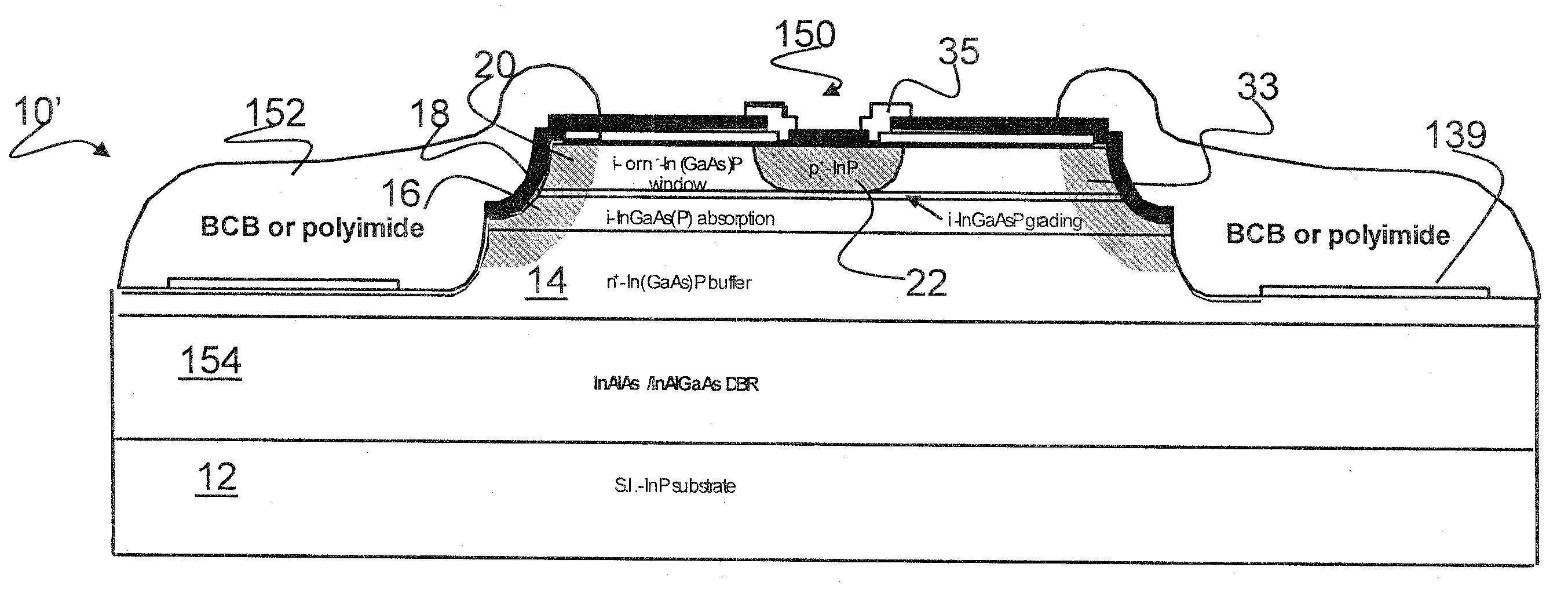

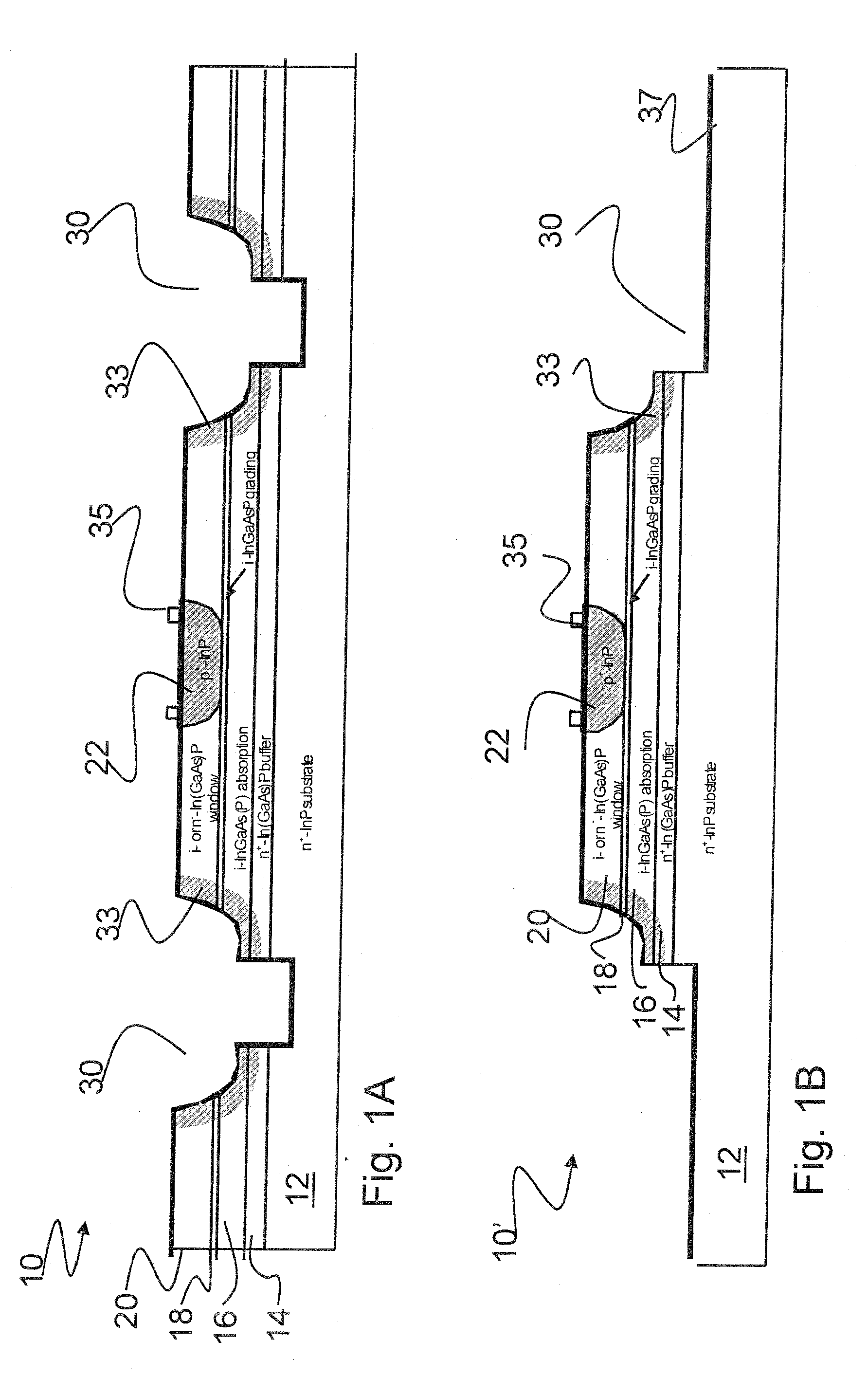

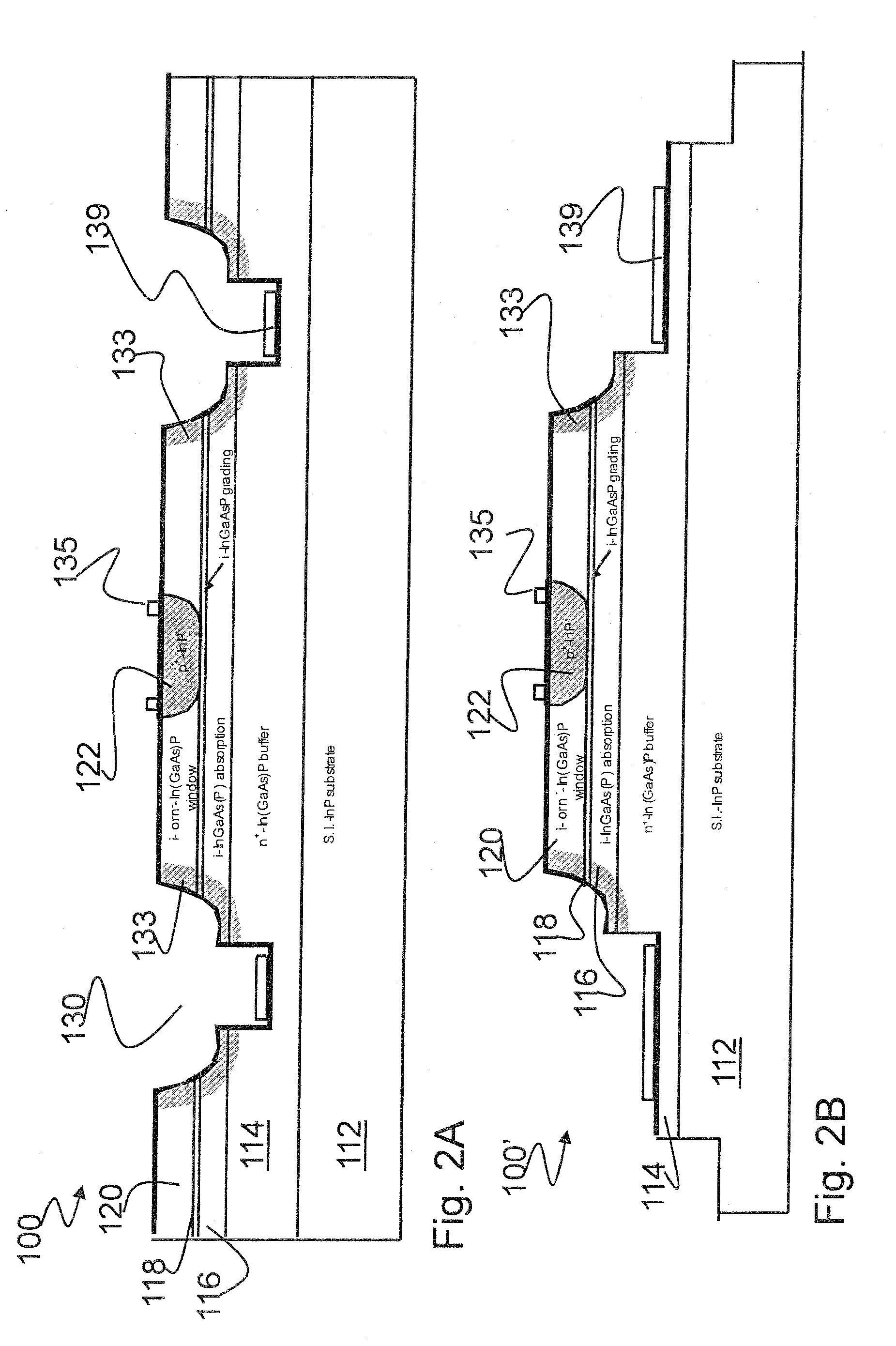

Mesa-Type Photodetectors With Lateral Diffusion Junctions

ActiveUS20090020841A1Improve reliabilityQuality improvementSemiconductor/solid-state device manufacturingPhotovoltaic energy generationDopantImpurity diffusion

The present invention relates to a stable mesa-type photodetector with lateral diffusion junctions. The invention has found that without resorting to the complicated regrowth approach, a simple Zn diffusion process can be used to create high-quality semiconductor junction interfaces at the exposed critical surface or to terminate the narrow-bandgap photon absorption layers. The invention converts the epi material layers near or at the vicinity of the etched mesa trench or etched mesa steps into a different dopant type through impurity diffusion process. Preferably the diffused surfaces are treated with a subsequent surface passivation. This invention can be applied to both top-illuminating and bottom-illuminating configurations.

Owner:LUMENTUM OPERATIONS LLC

Self-aligning silicide method for RF lateral diffusion field-effect transistor

InactiveCN1691295AImprove RF performanceReduce source-drain series resistanceSemiconductor/solid-state device manufacturingHigh resistanceResist

A method for radio frequency lateral diffusing self-alignment silicides of the field-effect-transistor, comprising the steps of: on the silicon chips, injecting the etched multiple crystal grids to the drifting zone without mask; depositing a thin silicon dioxide layer with tetraethylorthosilicate heat decomposition method; protecting drifting zone with photo resist and resisting silicon dioxide, forming a silicon dioxide sidewall on the gate side nearby the source; source-drain self-aligning injection and striping; quick heat annealing to eliminate injection damage and activate impurity; separately depositing a thin pad silicon dioxide with tetraethylorthosilicate heat decomposition method and depositing a silicon nitride with low pressure chemical vapour deposition method; sequentially resisting silicon nitride and silicon dioxide, forming a silicon nitride secondary sidewall on the silicon dioxide primary sidewall; sputtering a thin titanium layer; quick heat annealing to form the titanium silicides from the silicon and titanium; etching and removing the rest titanium; quick heat annealing to forming low resistance titanium silicides from high resistance ones.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

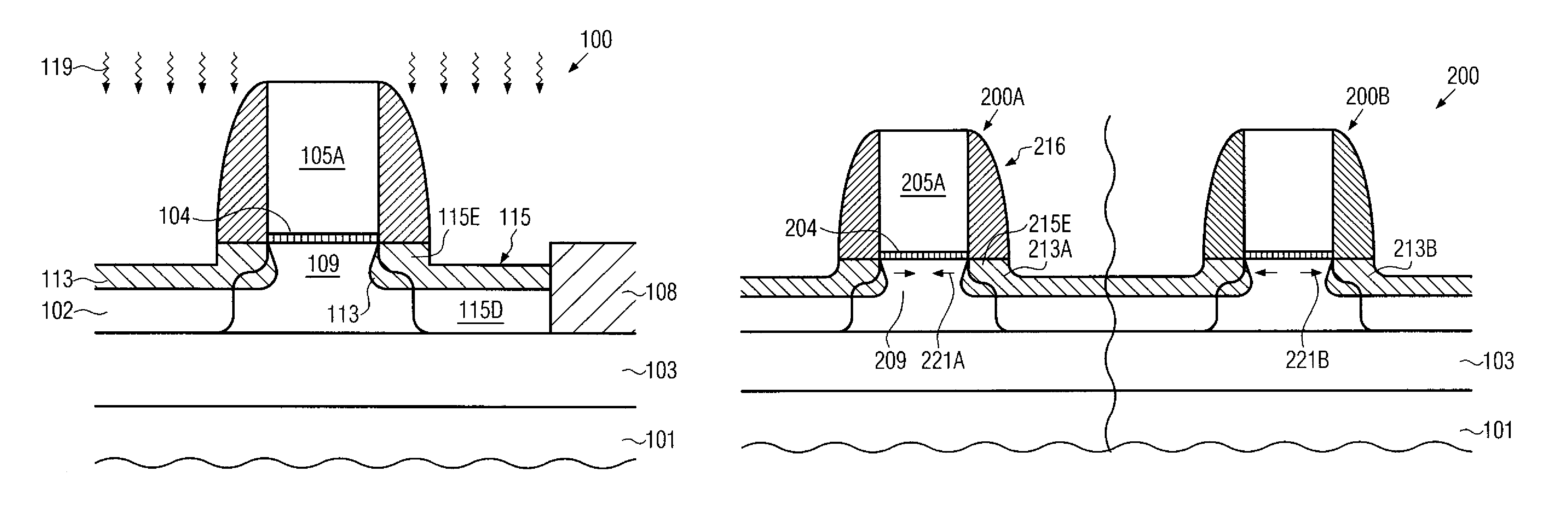

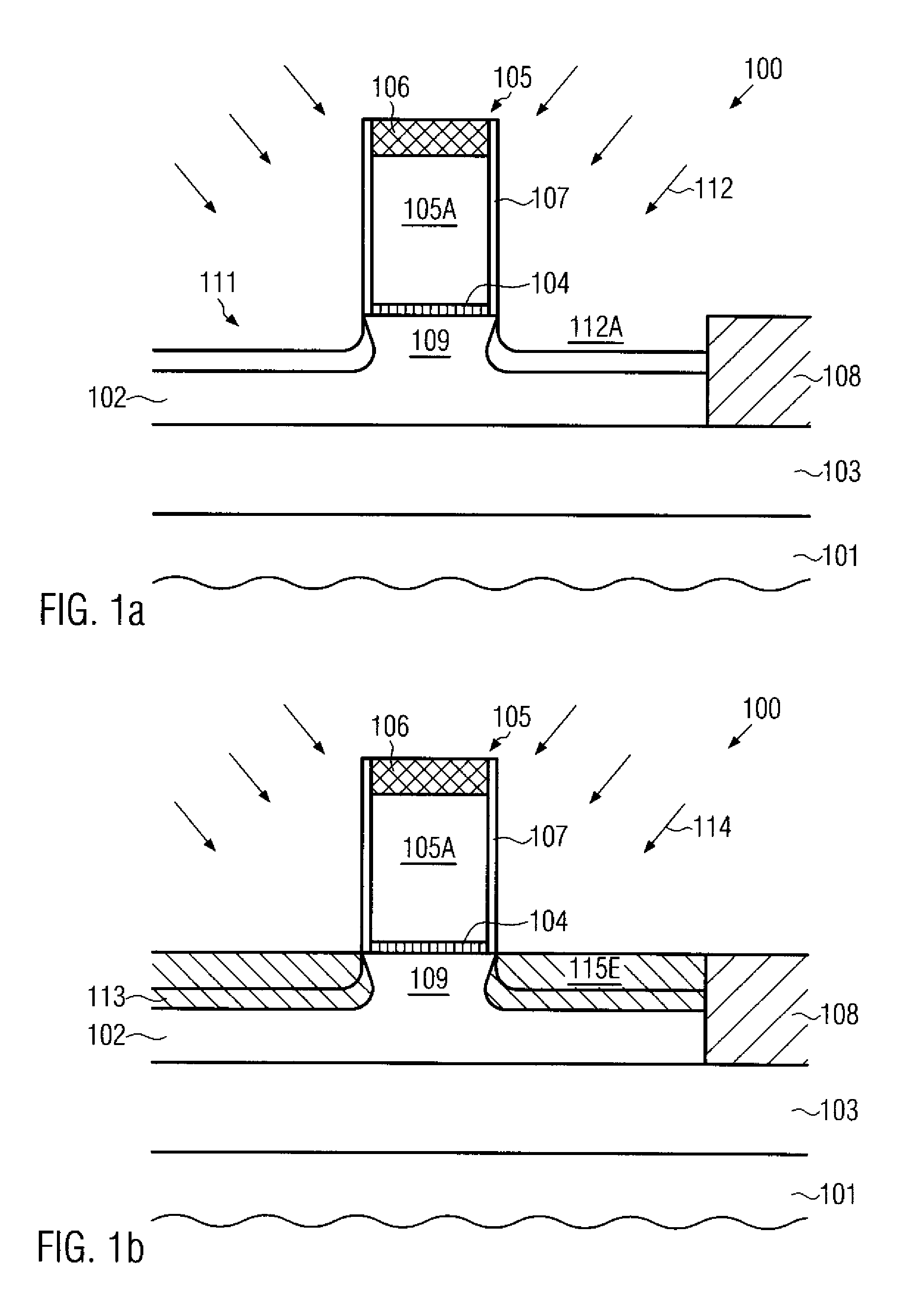

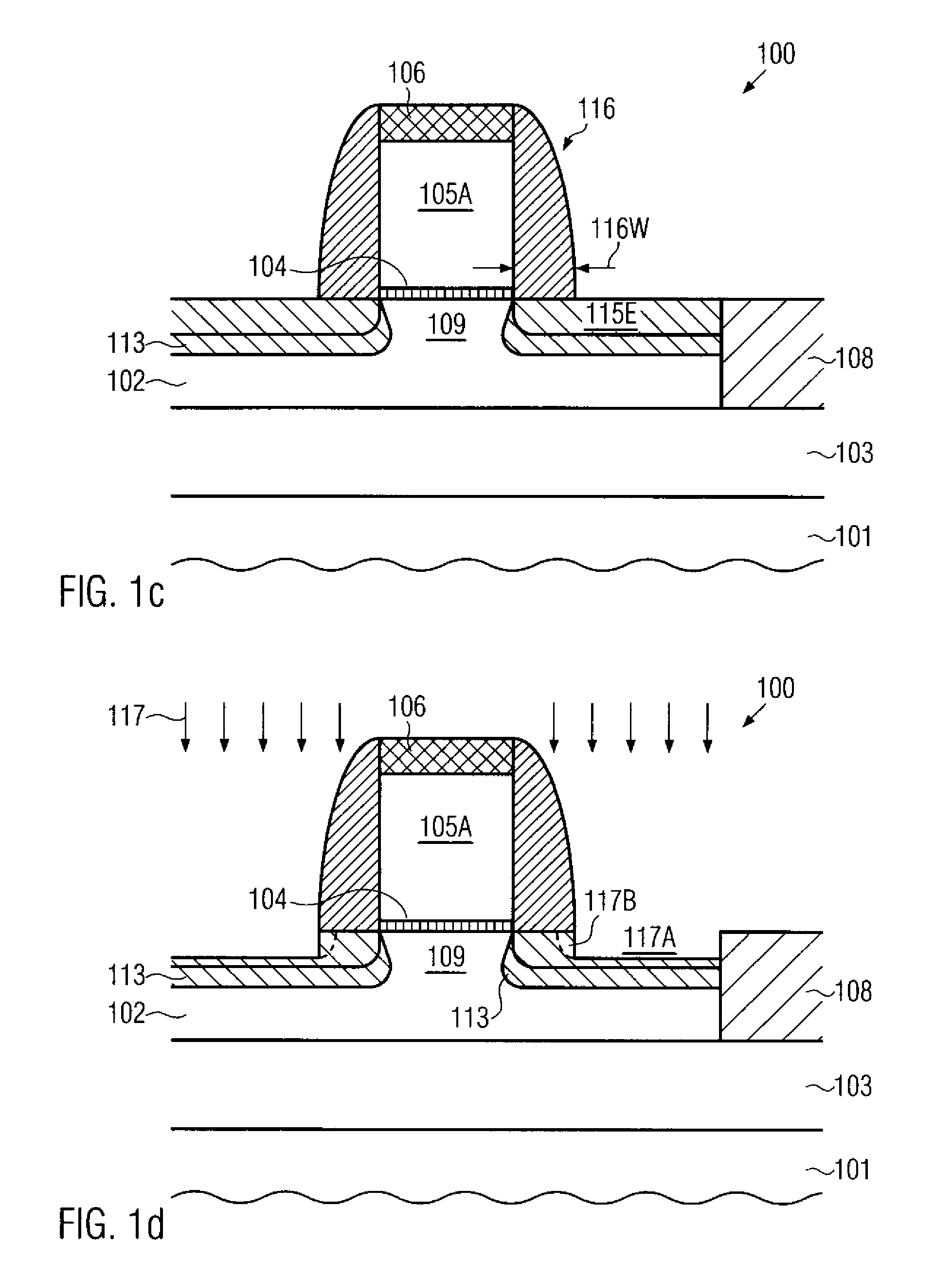

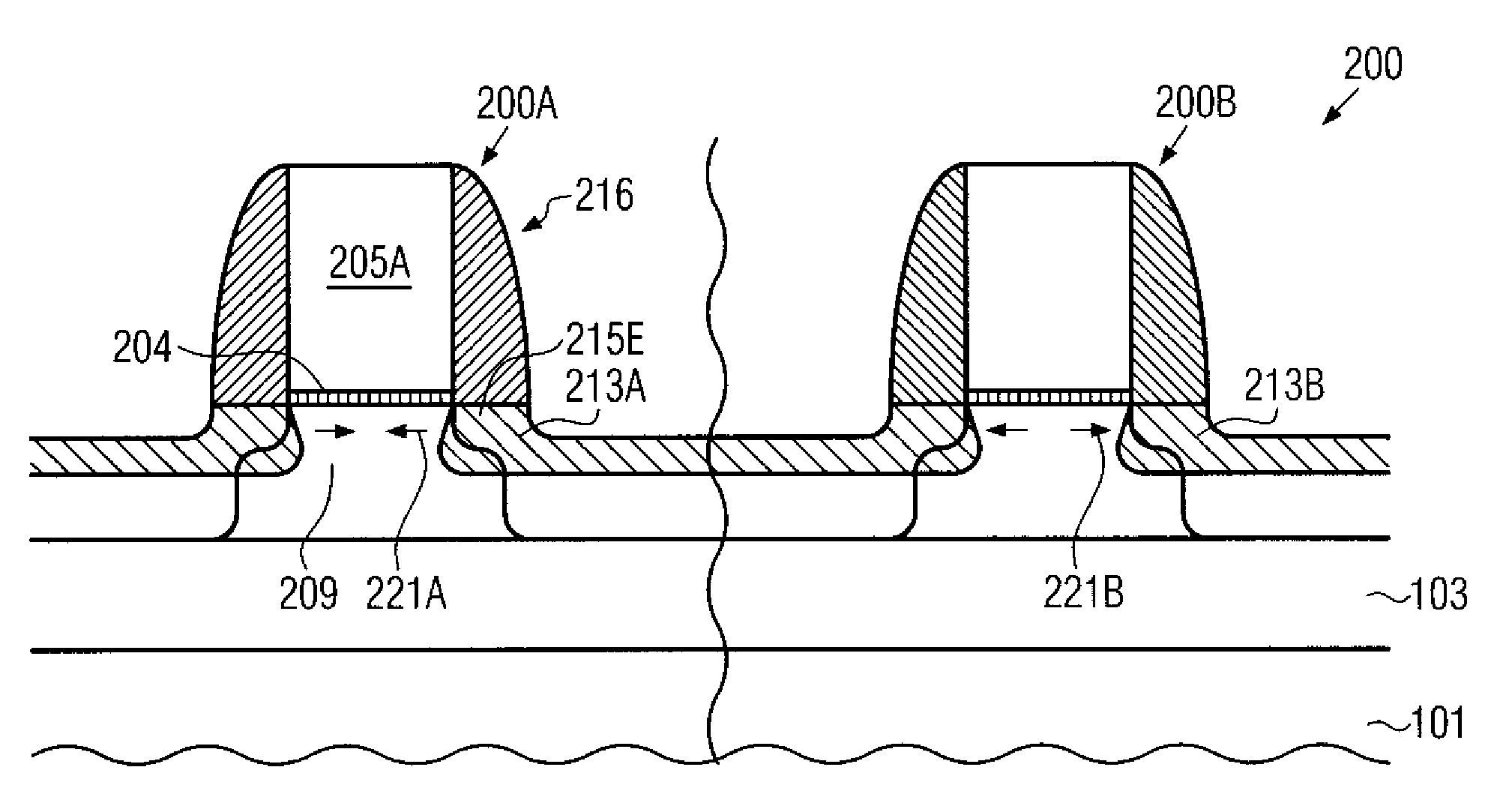

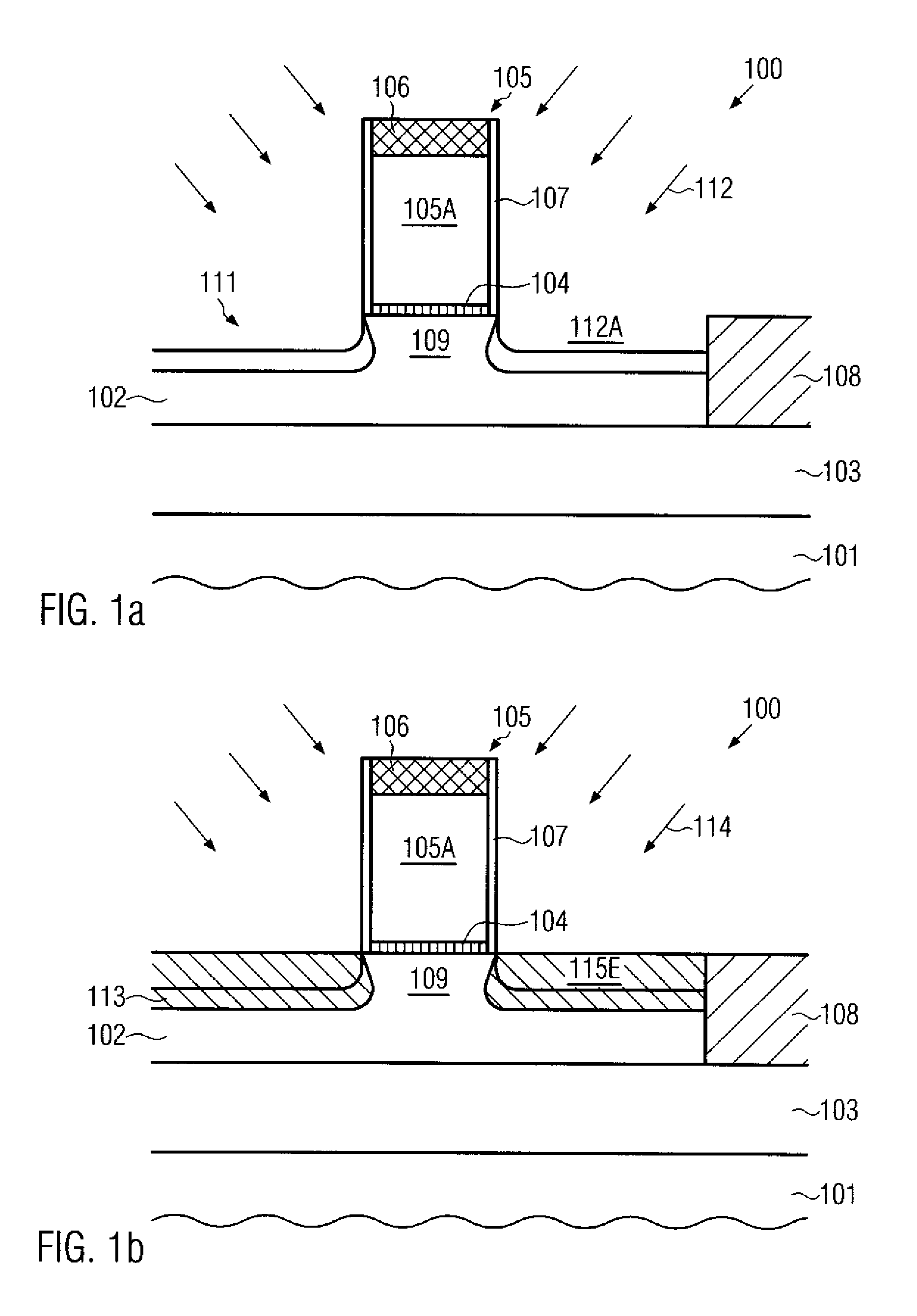

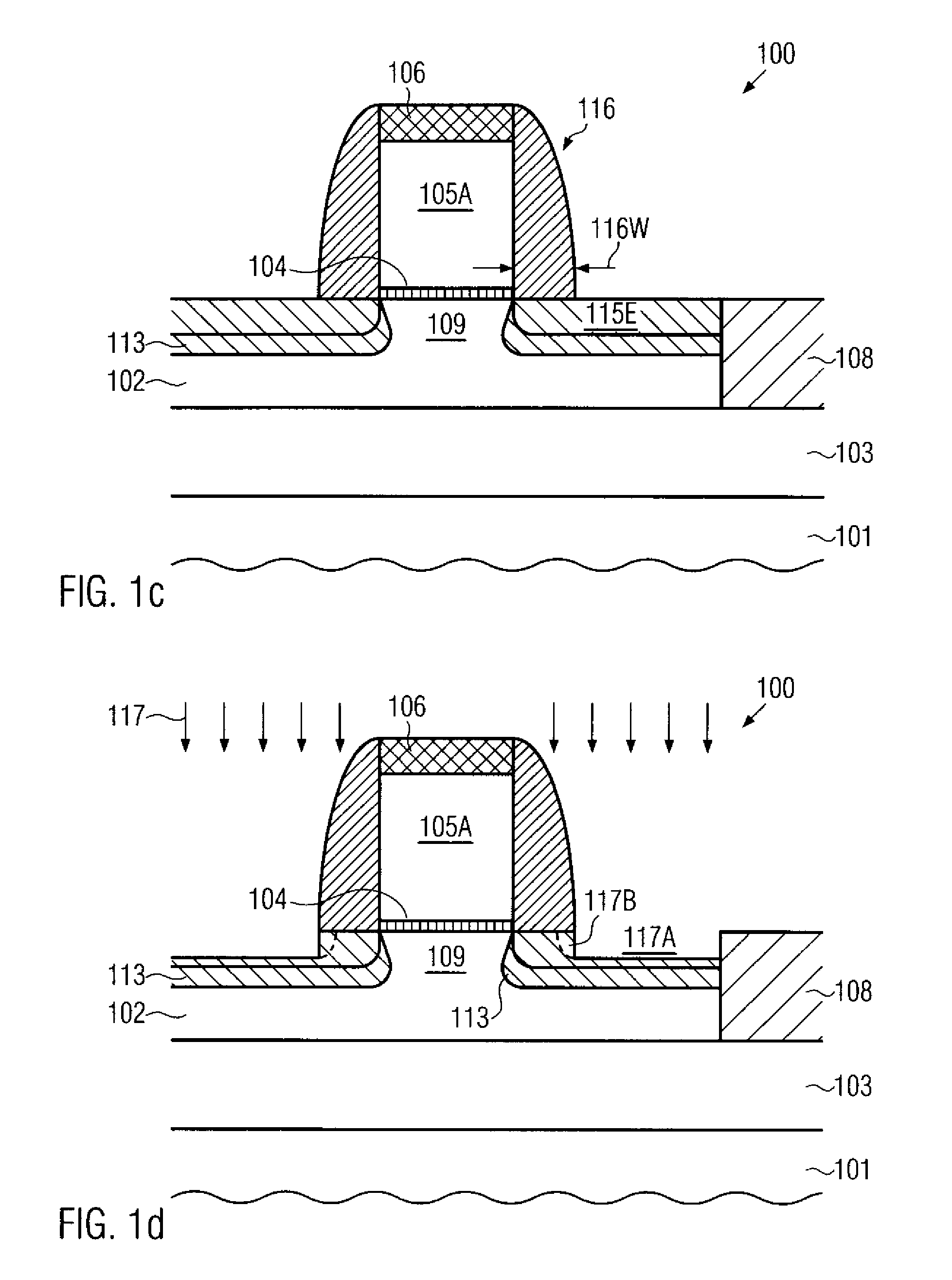

Reducing transistor junction capacitance by recessing drain and source regions

By recessing portions of the drain and source areas on the basis of a spacer structure, the subsequent implantation process for forming the deep drain and source regions may result in a moderately high dopant concentration extending down to the buried insulating layer of an SOI transistor. Furthermore, the spacer structure maintains a significant amount of a strained semiconductor alloy with its original thickness, thereby providing an efficient strain-inducing mechanism. By using sophisticated anneal techniques, undue lateral diffusion may be avoided, thereby allowing a reduction of the lateral width of the respective spacers and thus a reduction of the length of the transistor devices. Hence, enhanced charge carrier mobility in combination with reduced junction capacitance may be accomplished on the basis of reduced lateral dimensions.

Owner:CONVERSANT INTPROP MANAGEMENT INC

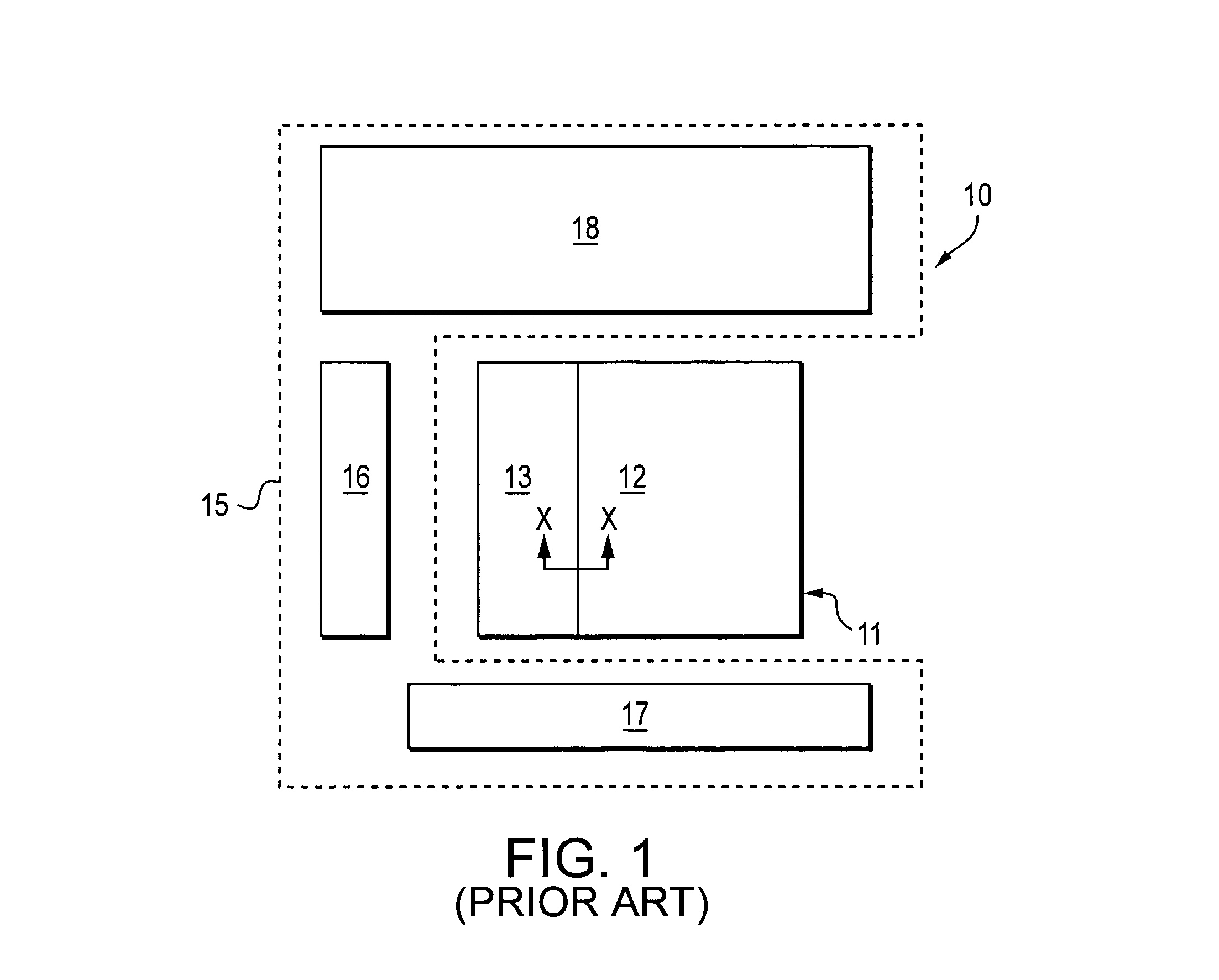

Method and apparatus for shielding correction pixels from spurious charges in an imager

ActiveUS20070041062A1Avoid absorptionSemiconductor/solid-state device detailsSolid-state devicesImage correctionVoltage source

A barrier for isolating the dark correction pixels from spurious charges within an image sensor. The barrier comprises a charge absorbing region in a substrate electrically connected to a voltage source terminal. The charge absorbing region completely surrounds the dark correction region of a pixel array. The charge absorbing region absorbs carriers generated by lateral diffusion, near-infrared and infrared light reflected from the bottom of the silicon substrate, and other sources. This absorbing region prevents carriers from being absorbed into the dark correction pixel cells and causing image correction distorting effects.

Owner:APTINA IMAGING CORP

Reduced crosstalk CMOS image sensors

ActiveUS20070029589A1High sensitivityReduce crosstalkSolid-state devicesRadiation controlled devicesCMOSLateral diffusion

CMOS image sensor having high sensitivity and low crosstalk, particularly at far-red to infrared wavelengths, and a method for fabricating a CMOS image sensor. A CMOS image sensor has a substrate, an epitaxial layer above the substrate, and a plurality of pixels extending into the epitaxial layer for receiving light. The image sensor also includes at least one of a horizontal barrier layer between the substrate and the epitaxial layer for preventing carriers generated in the substrate from moving to the epitaxial layer, and a plurality of lateral barrier layers between adjacent ones of the plurality of pixels for preventing lateral diffusion of electrons in the epitaxial layer.

Owner:APTINA IMAGING CORP

Reducing transistor junction capacitance by recessing drain and source regions

By recessing portions of the drain and source areas on the basis of a spacer structure, the subsequent implantation process for forming the deep drain and source regions may result in a moderately high dopant concentration extending down to the buried insulating layer of an SOI transistor. Furthermore, the spacer structure maintains a significant amount of a strained semiconductor alloy with its original thickness, thereby providing an efficient strain-inducing mechanism. By using sophisticated anneal techniques, undue lateral diffusion may be avoided, thereby allowing a reduction of the lateral width of the respective spacers and thus a reduction of the length of the transistor devices. Hence, enhanced charge carrier mobility in combination with reduced junction capacitance may be accomplished on the basis of reduced lateral dimensions.

Owner:CONVERSANT INTPROP MANAGEMENT INC

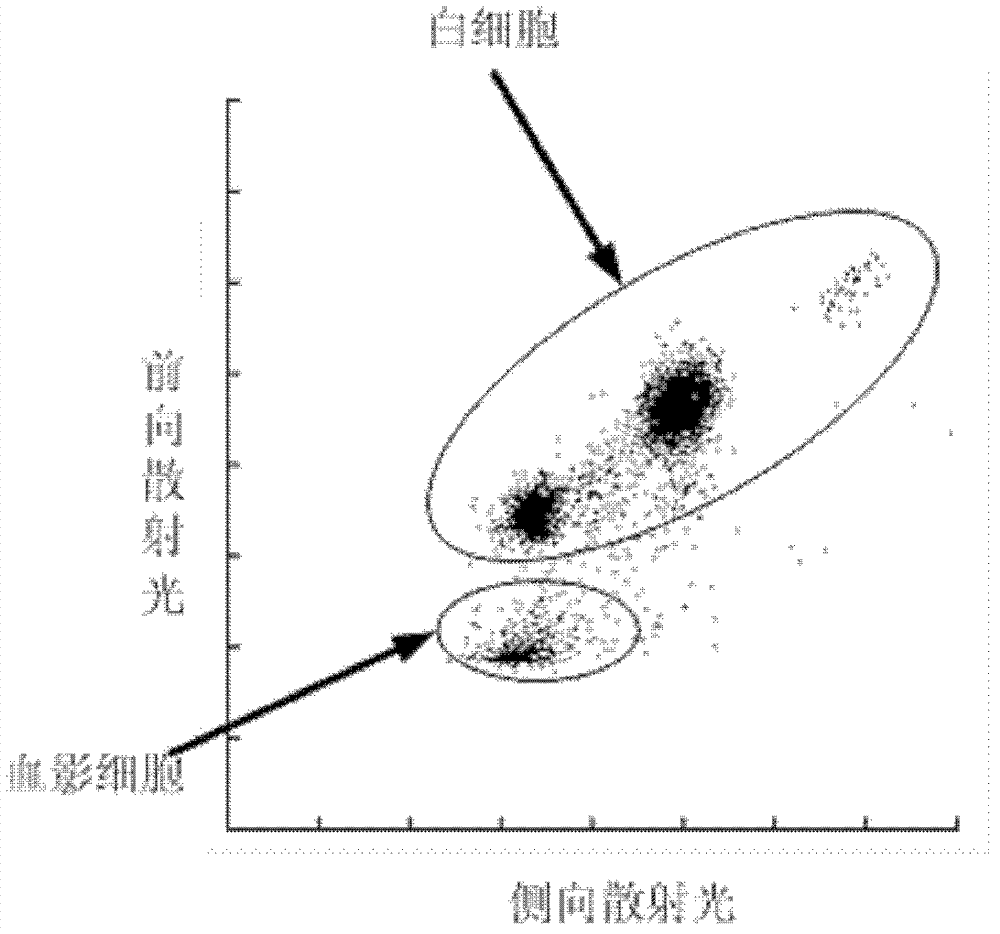

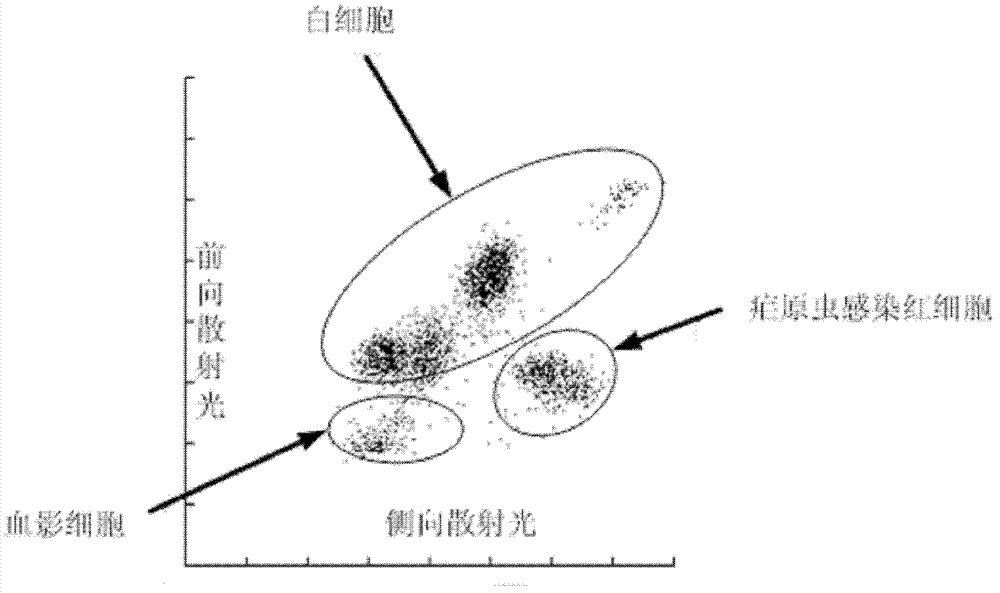

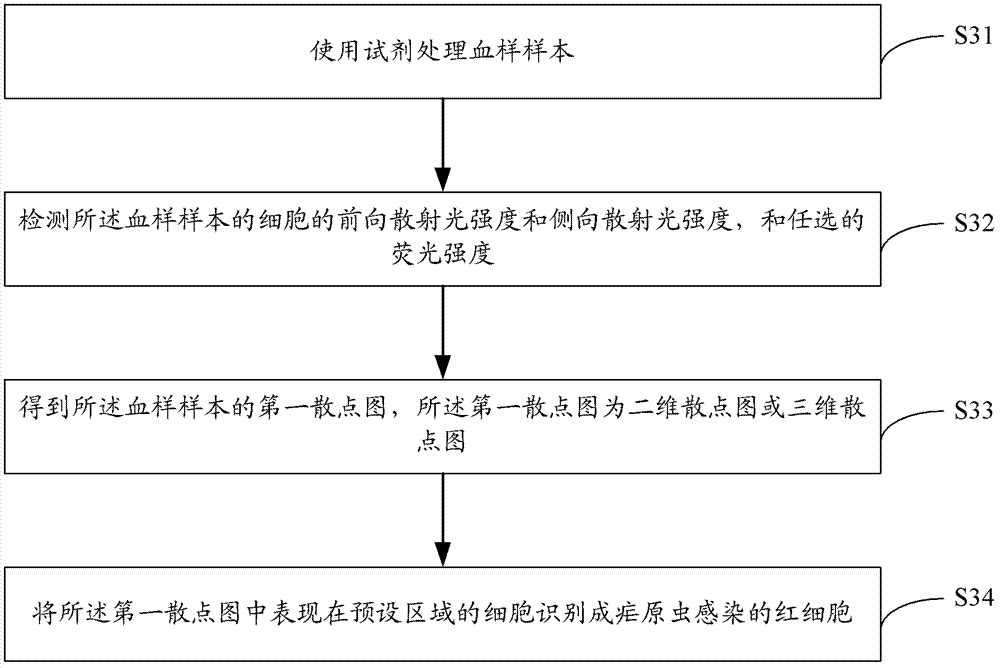

Plasmodium infected erythrocyte identification method and device thereof

ActiveCN103091286AA large amountReduce the impact of recognition accuracyBiological material analysisScattering properties measurementsDiffusionInfected erythrocyte

The invention is suitable for the medical field, and provides a plasmodium infected erythrocyte identification method and a device thereof. The method comprises the following steps: acquiring the forward diffusion light signal and the lateral diffusion light signal of cells in a sample, and an optional fluorescence signal; obtaining a first two-dimensional point diagram according to the forward diffusion light signal and the lateral diffusion light signal, or obtaining a three-dimensional point diagram based on the forward diffusion light signal, the lateral diffusion light signal and the fluorescence signal; and identifying cells appearing in the preset area of the first two-dimensional point diagram or the three-dimensional point diagram as plasmodium infected erythrocytes. The method has a high identification precision.

Owner:SHENZHEN MINDRAY BIO MEDICAL ELECTRONICS CO LTD +1

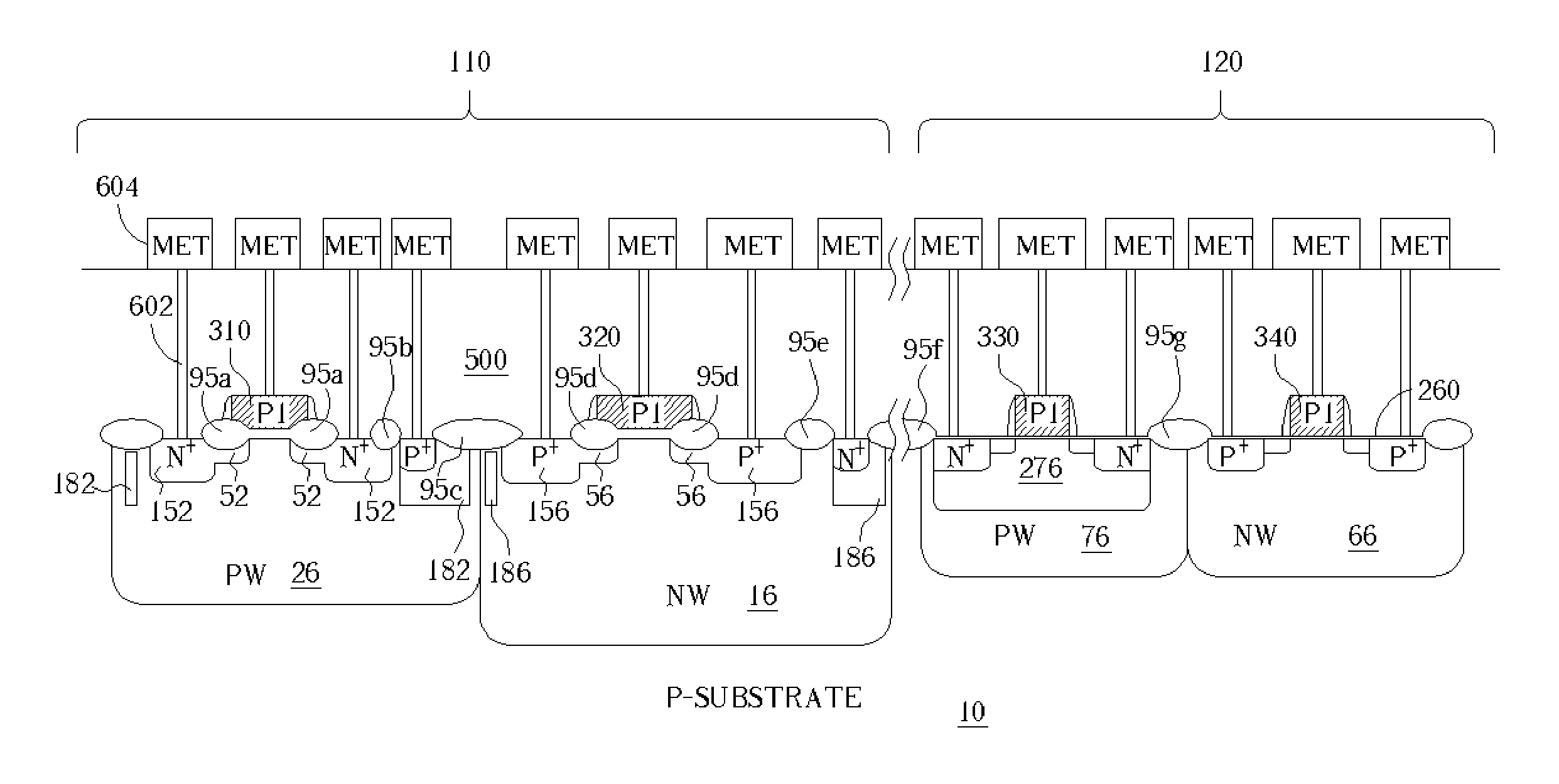

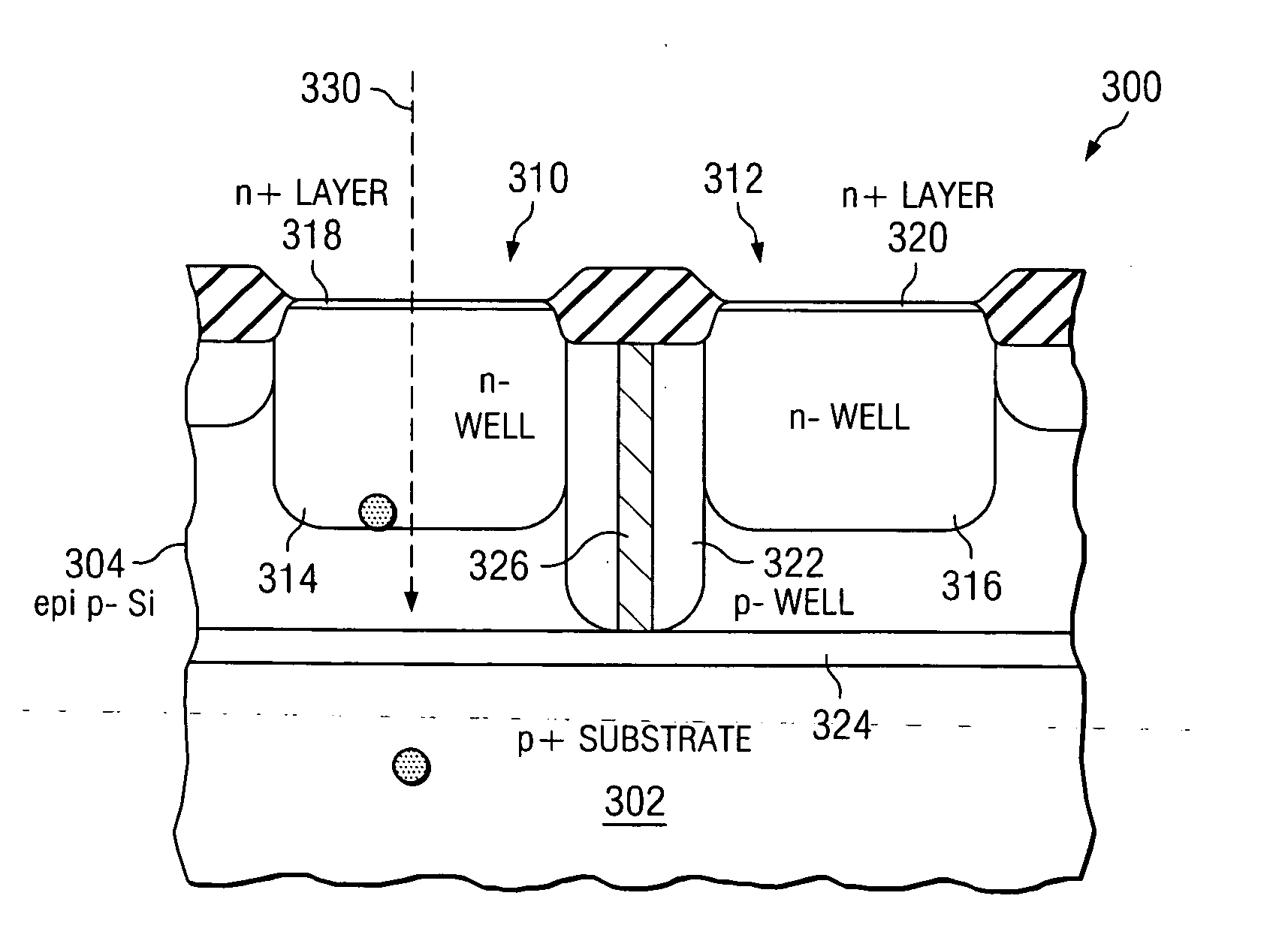

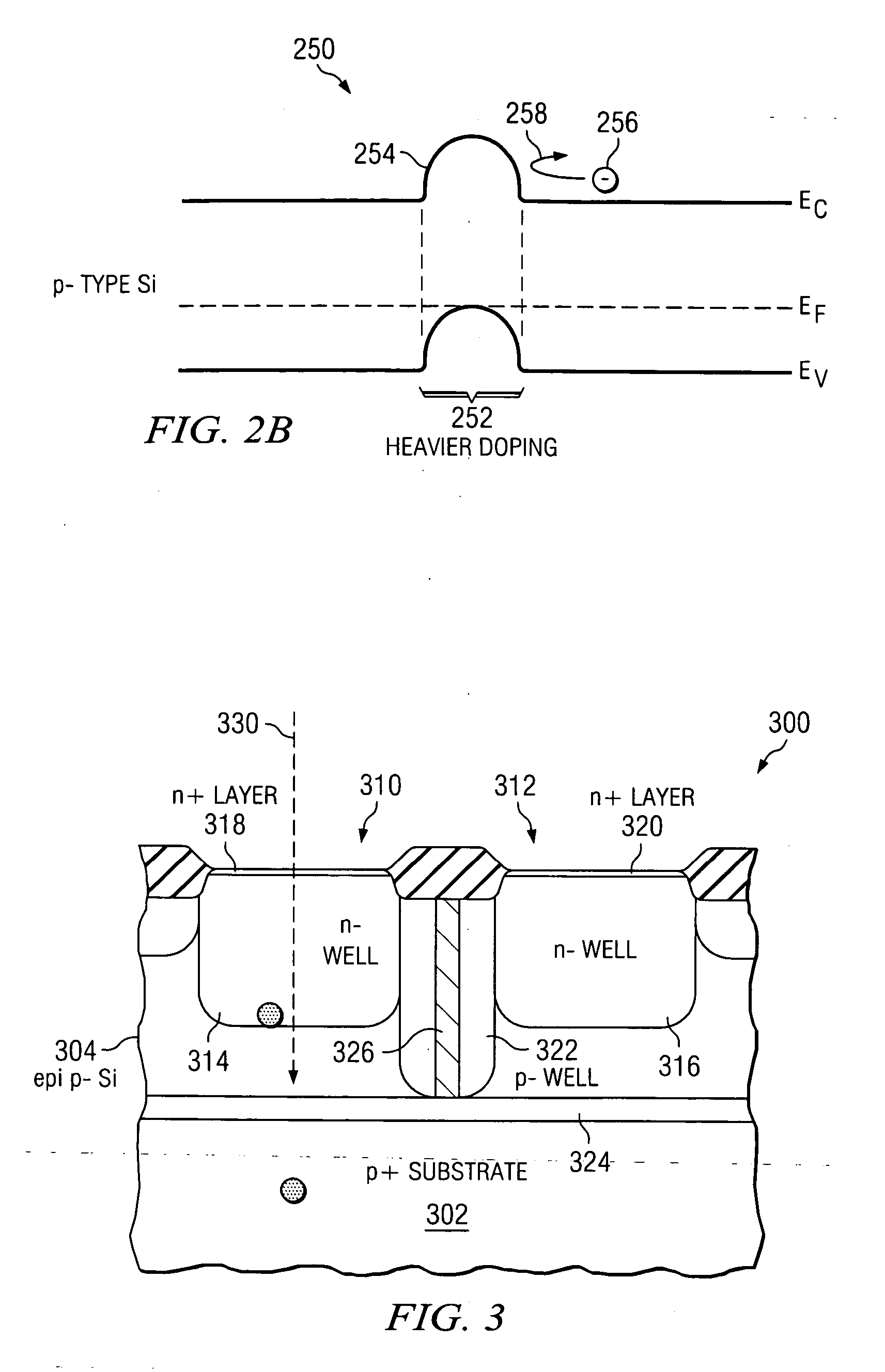

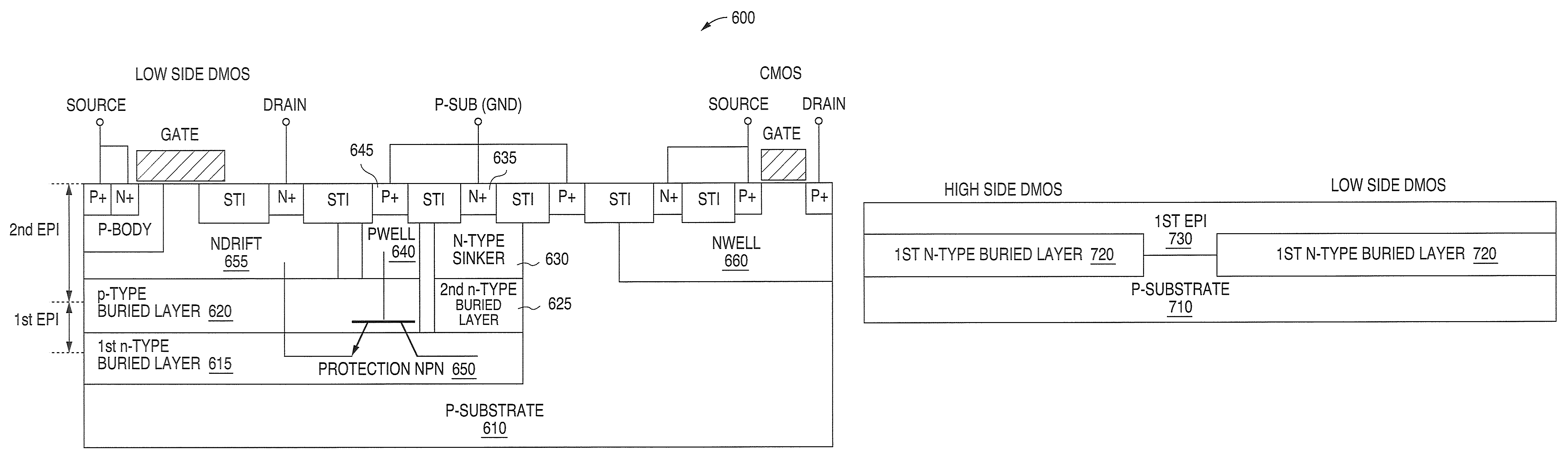

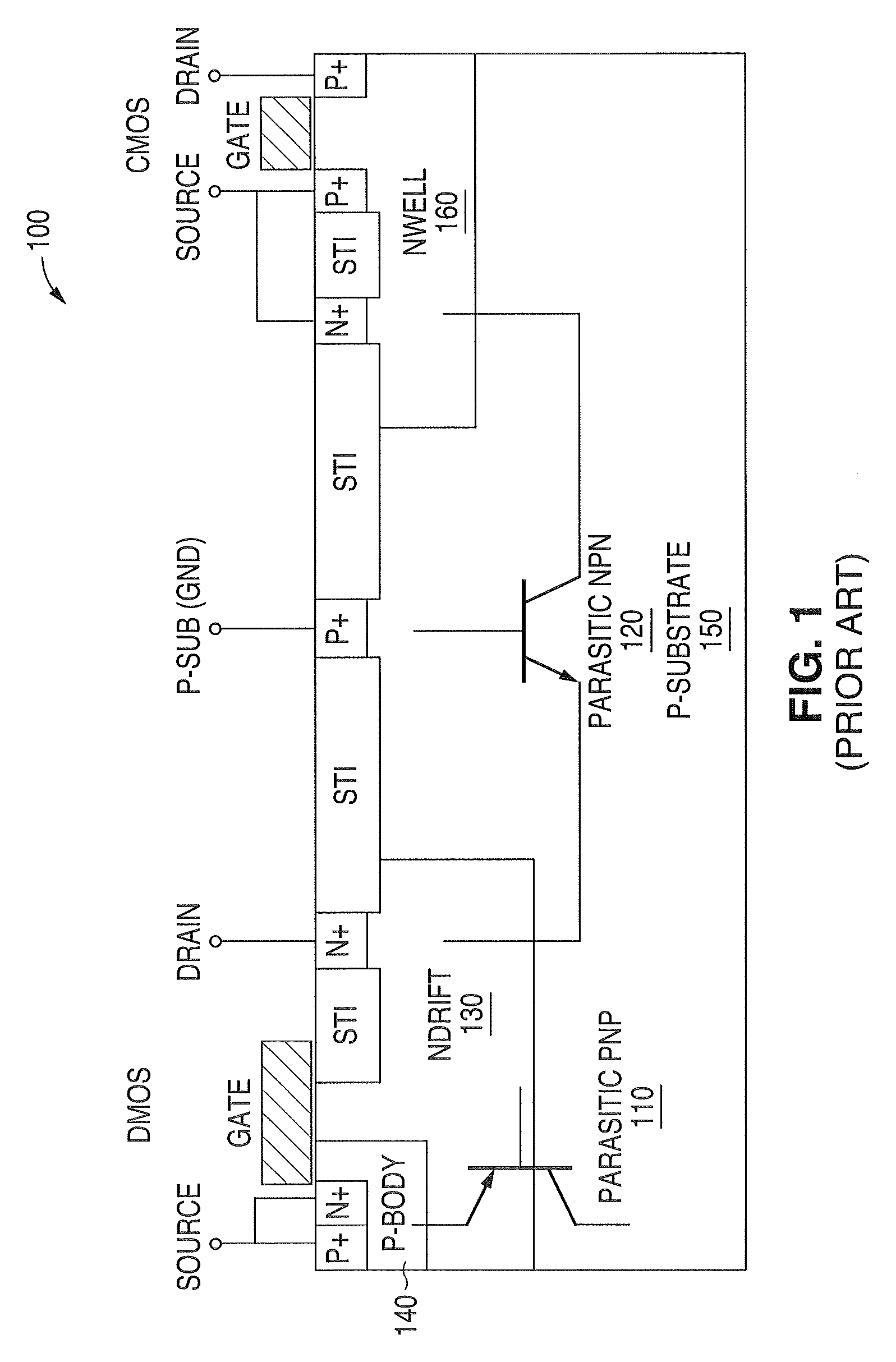

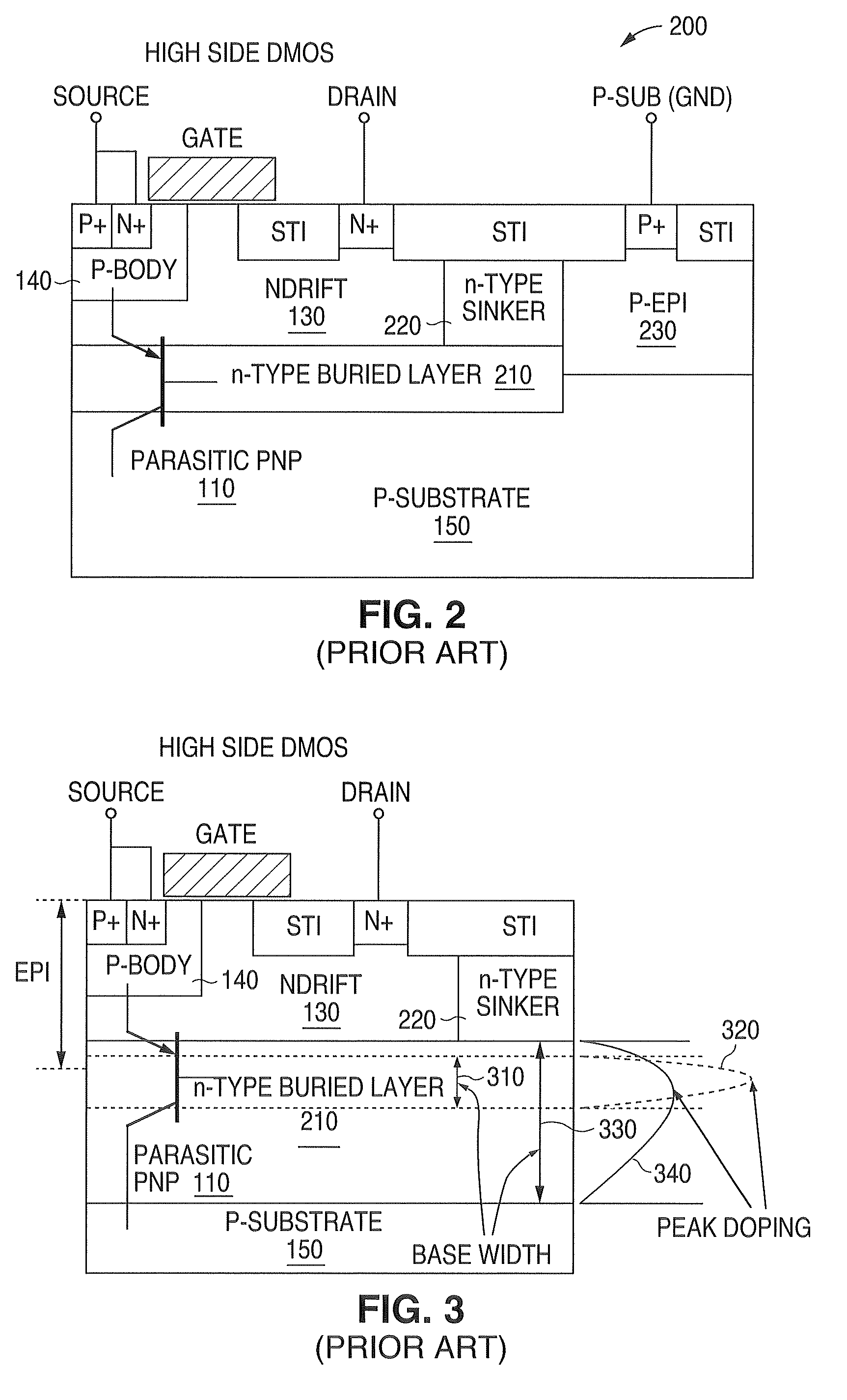

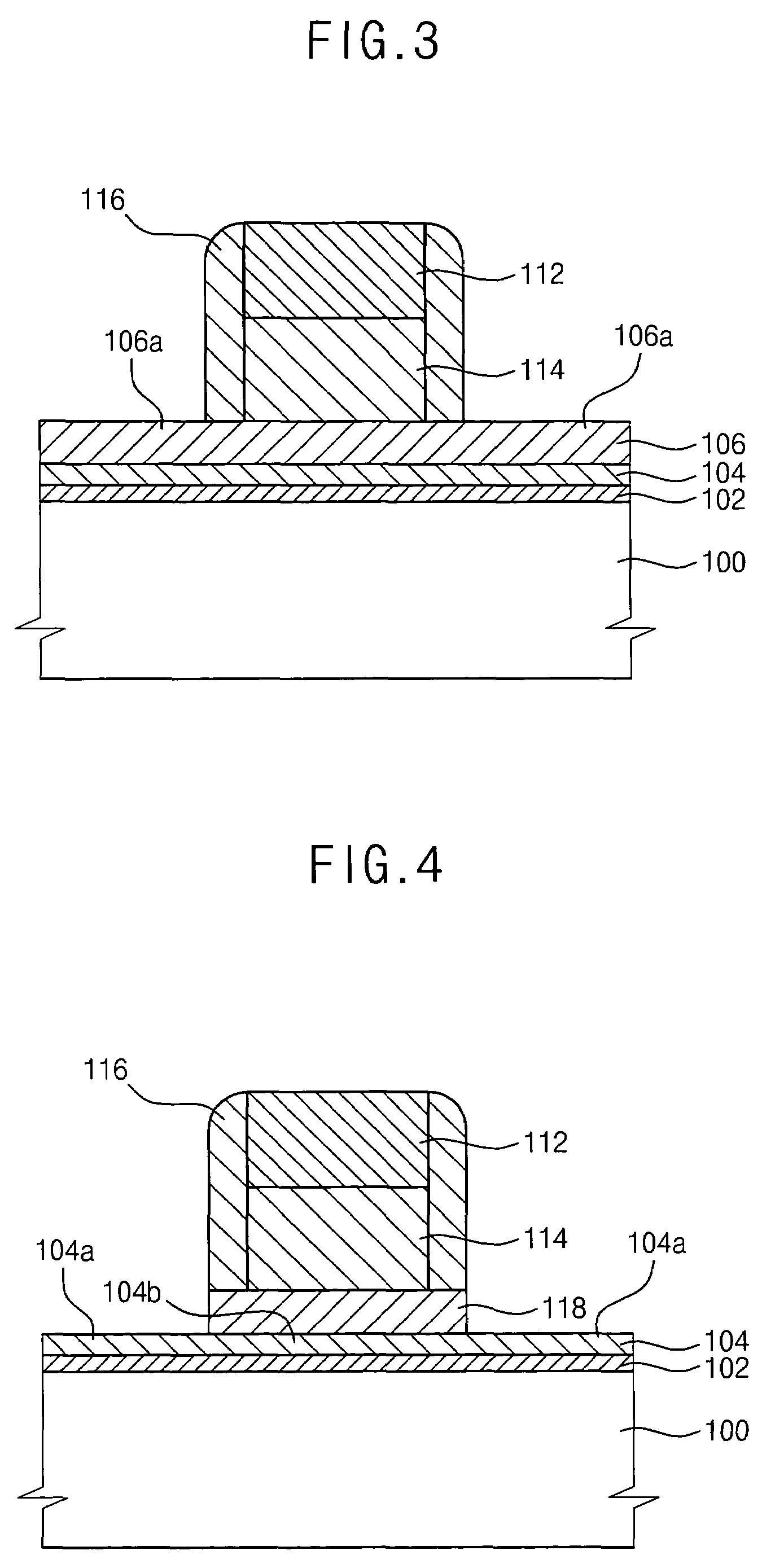

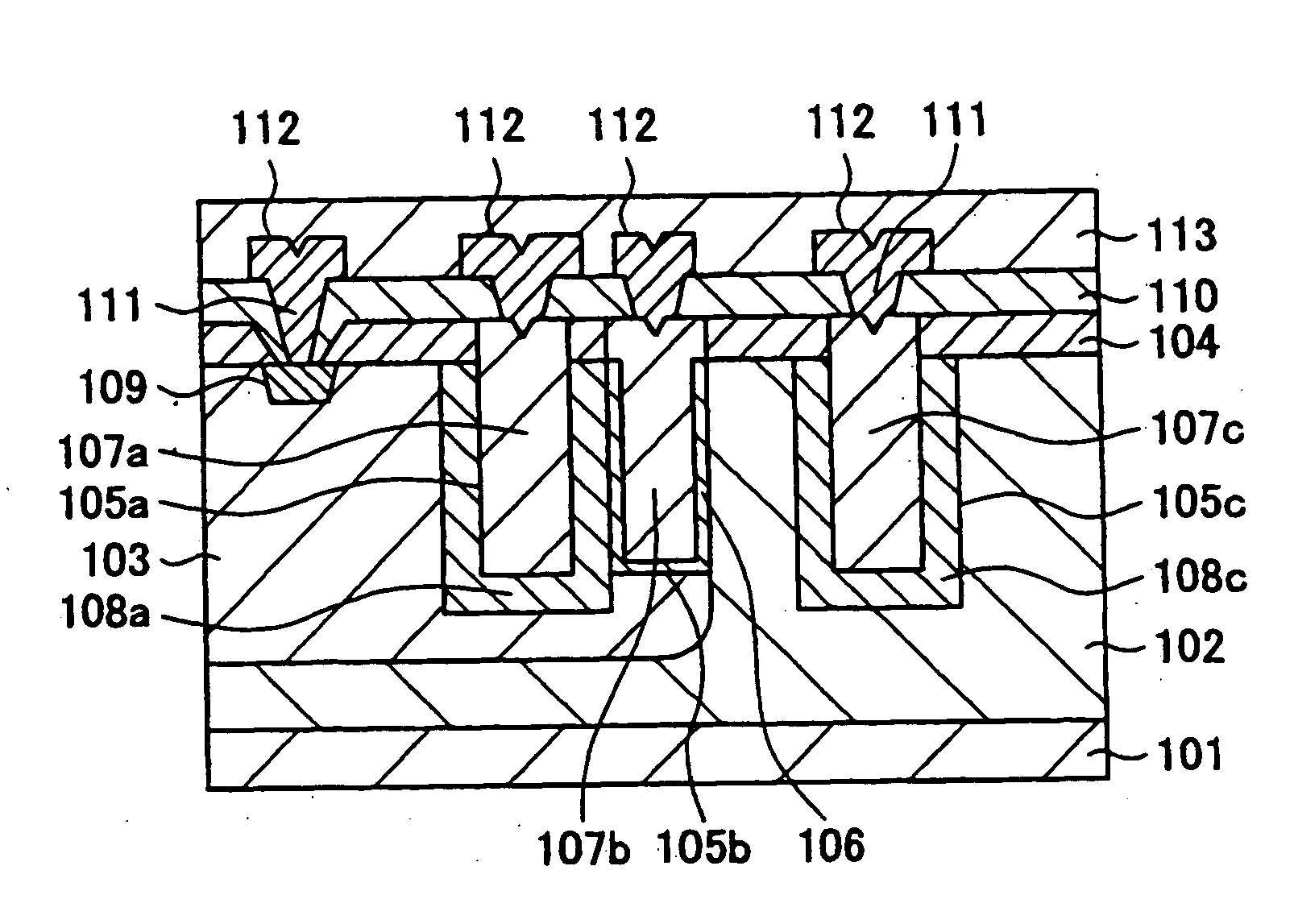

System and method for manufacturing double EPI N-type lateral diffusion metal oxide semiconductor transistors

ActiveUS7960222B1Reduces and minimizes effectMinimizes effect of parasiticSolid-state devicesSemiconductor/solid-state device manufacturingParasitic bipolar transistorPeak value

A system and a method are disclosed for manufacturing double epitaxial layer N-type lateral diffusion metal oxide semiconductor transistors. In one embodiment two N-type buried layers are used to minimize the operation of a parasitic PNP bipolar transistor. The use of two N-type buried layers increases the base width of the parasitic PNP bipolar transistor without significantly decreasing the peak doping profiles in the two N-type buried layers. In one embodiment two N-type buried layers and one P-type buried layer are used to form a protection NPN bipolar transistor that minimizes the operation of parasitic NPN bipolar transistor. The N-type lateral diffusion metal oxide semiconductor transistors of the invention are useful in inductive full load or half bridge converter circuits that drive very high current.

Owner:NAT SEMICON CORP

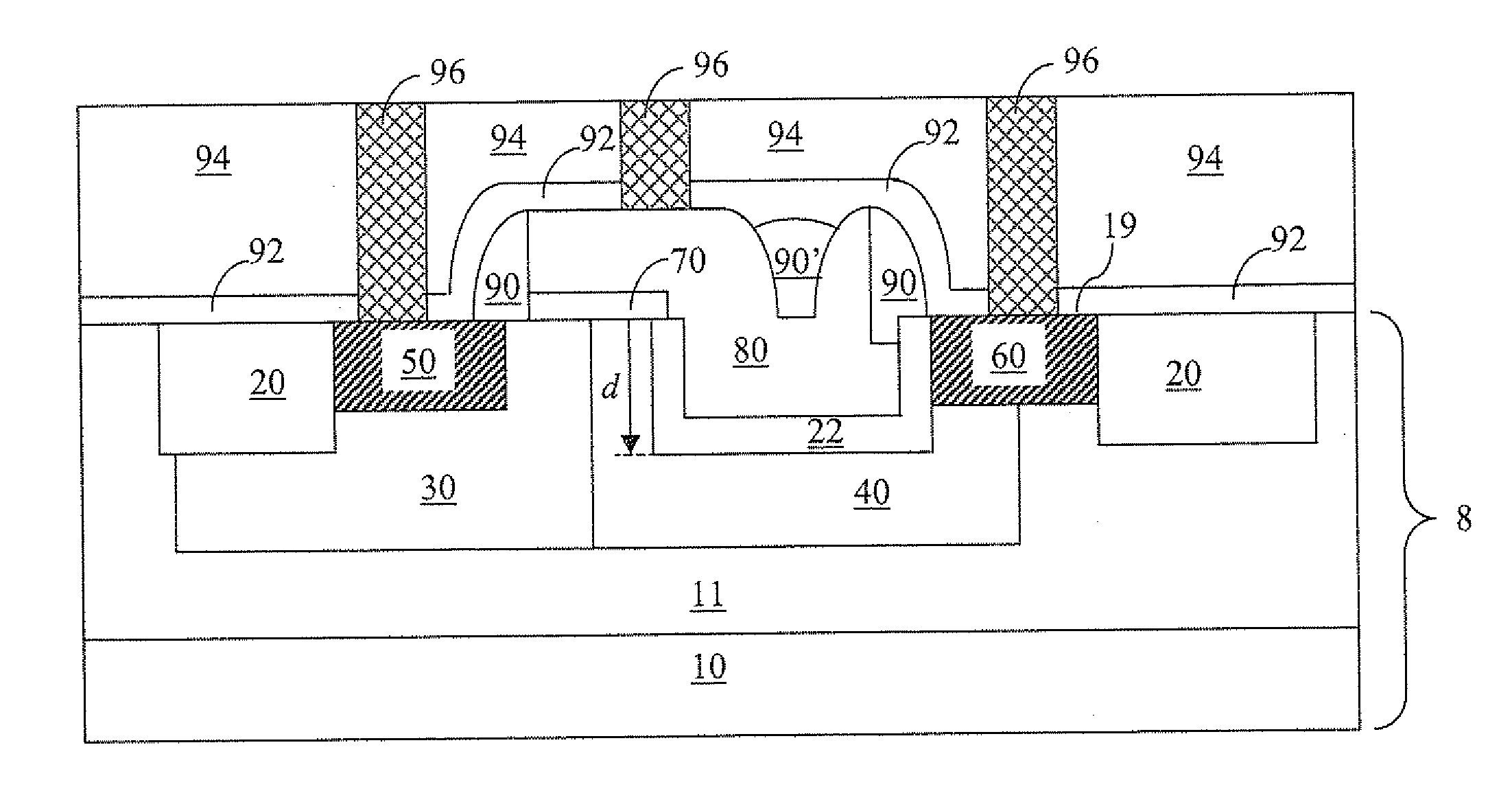

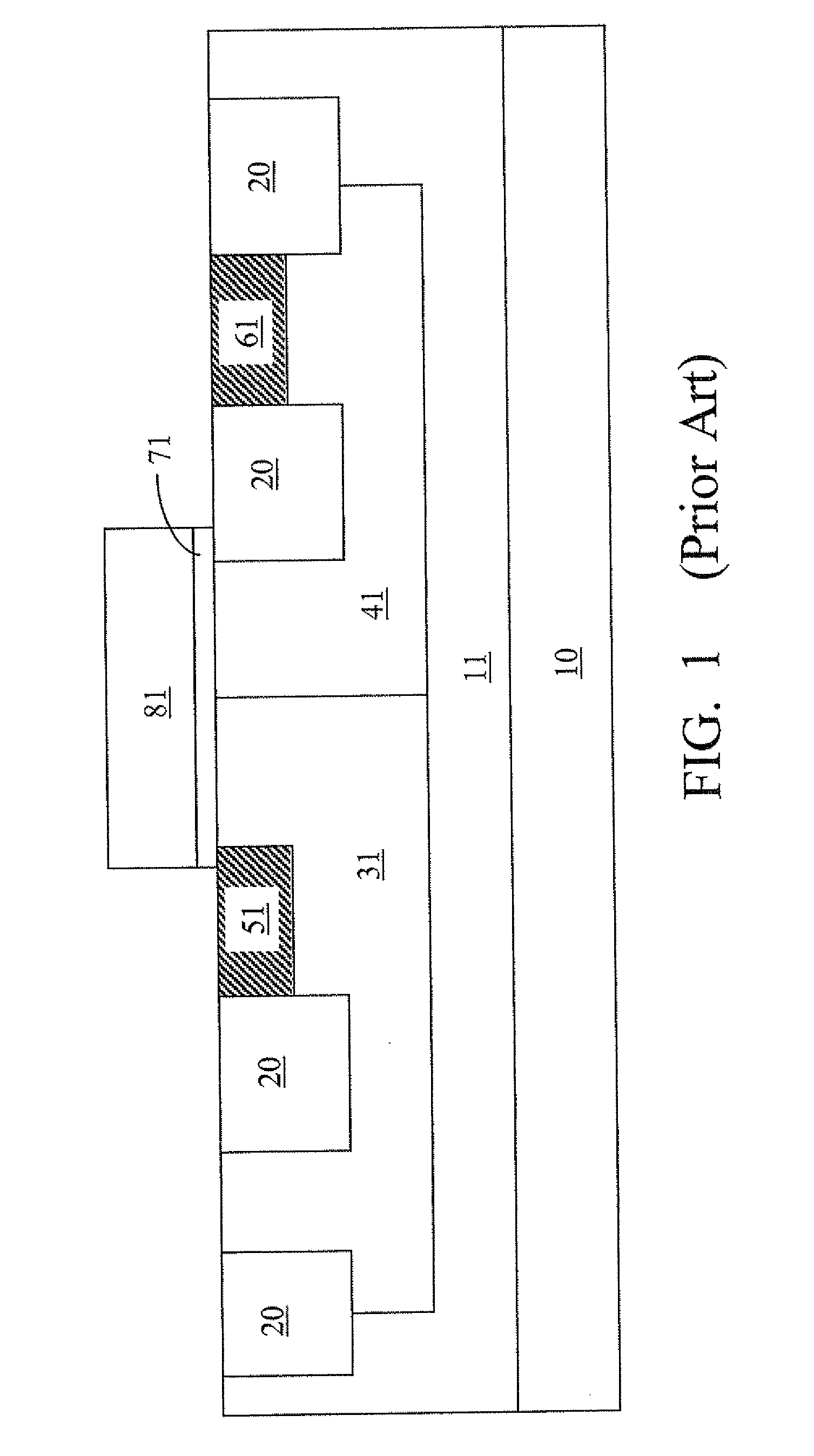

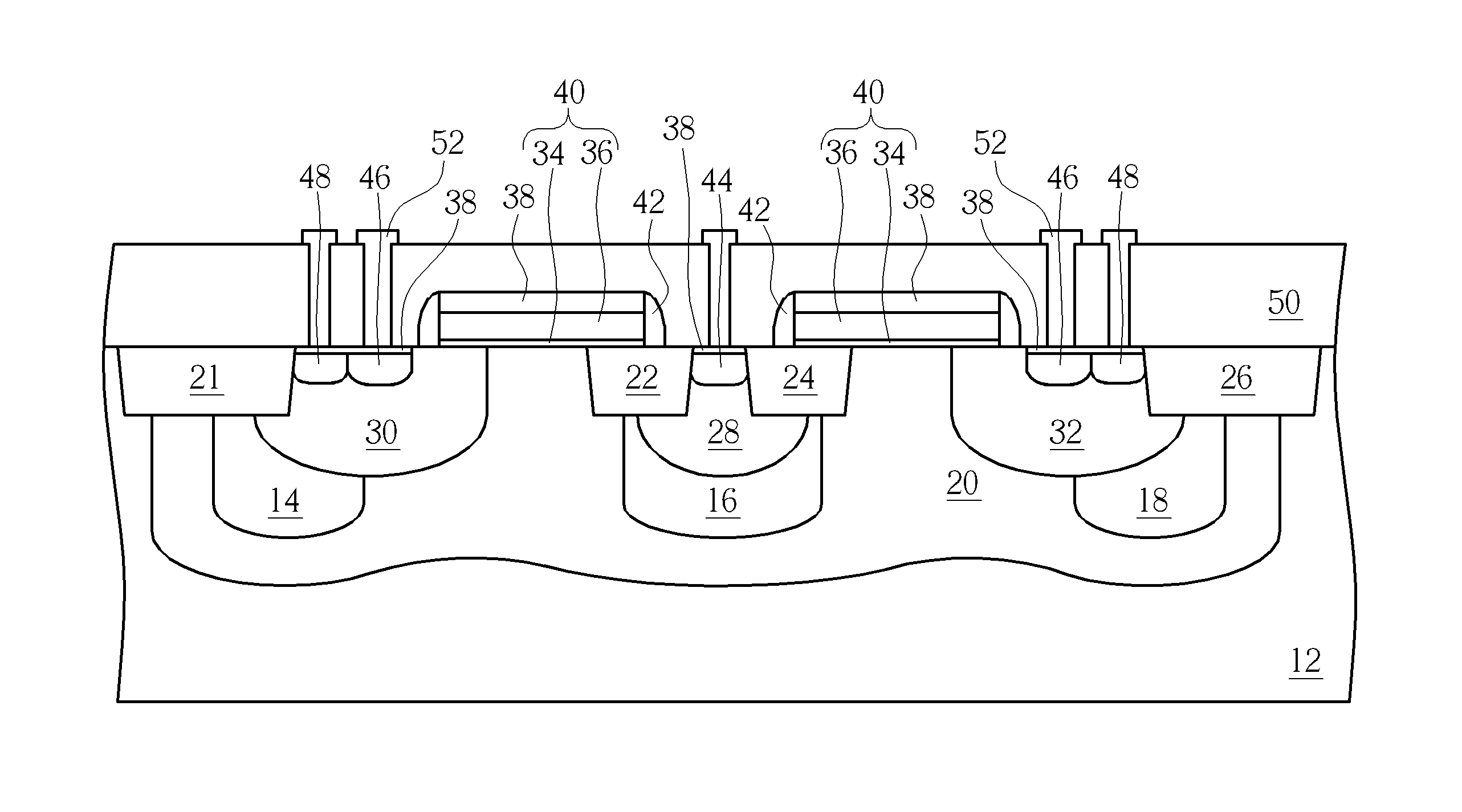

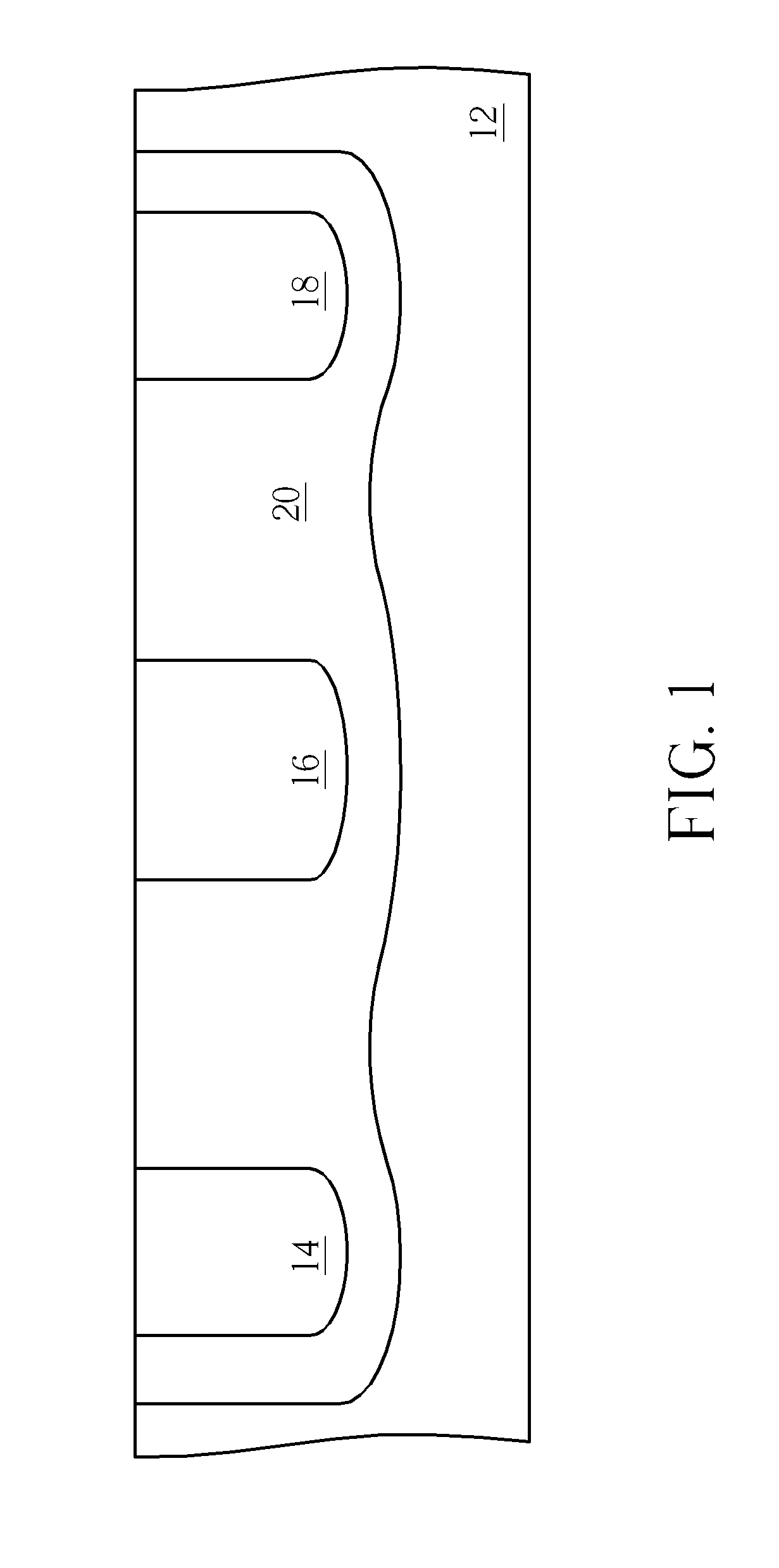

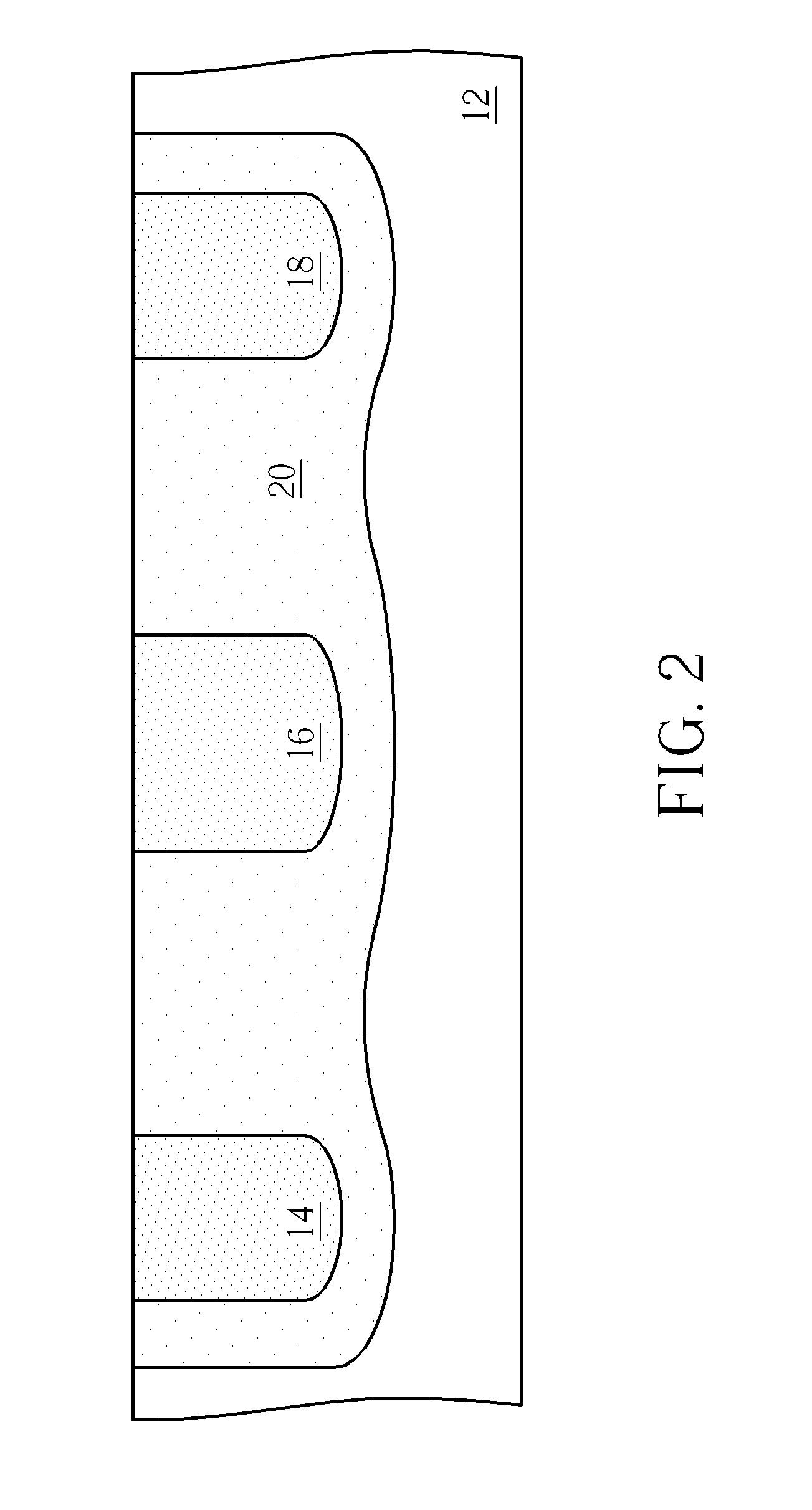

Lateral-diffusion metal-oxide semiconductor device and method for fabricating the same

ActiveUS20110233673A1Improve breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesDopantLDMOS

A method for fabricating a lateral-diffusion metal-oxide semiconductor (LDMOS) device is disclosed. The method includes the steps of: providing a semiconductor substrate; forming a first region and a second region both having a first conductive type in the semiconductor substrate, wherein the first region not contacting the second region; and performing a thermal process to diffuse the dopants within the first region and the second region into the semiconductor substrate to form a deep well, wherein the doping concentration of the deep well is less than the doping concentration of the first region and the second region.

Owner:UNITED MICROELECTRONICS CORP

Non-volatile memory devices and methods of manufacturing the same

ActiveUS7564094B2Controlled diffusionAvoid lateral spreadNanoinformaticsSemiconductor/solid-state device manufacturingTrappingLateral diffusion

Non-volatile memory devices include a tunnel insulating layer on a channel region of a substrate, a charge-trapping layer pattern on the tunnel insulating layer and a first blocking layer pattern on the charge-trapping layer pattern. Second blocking layer patterns are on the tunnel insulating layer proximate sidewalls of the charge-trapping layer pattern. The second blocking layer patterns are configured to limit lateral diffusion of electrons trapped in the charge-trapping layer pattern. A gate electrode is on the first blocking layer pattern. The second blocking layer patterns may prevent lateral diffusion of the electrons trapped in the charge-trapping layer pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

A structure of a lateral diffusion mos transistor in widespread use as a power control device

InactiveUS20050093060A1High currentShort pathTransistorSolid-state devicesDevice materialHigh pressure

There is provided a semiconductor device structured so as to be mounted jointly with other devices on one chip, and capable of controlling a large current in spite of a small device area while having small on-resistance, thereby enabling a high voltage resistance to be obtained. In the case of NLDMOS, the semiconductor device comprises an N well layer, formed on a p-type semiconductor substrate, a P well layer formed in the N well layer, a source electrode formed in a source trench cavity within the P well layer, a gate electrode formed in at least one of gate trench cavities within the P well layer, through the intermediary of an oxide film, and a drain electrode formed in a drain trench cavity within the N well layer, and further, N+ diffused layers are formed around the source trench cavity, the drain trench cavity, respectively.

Owner:LAPIS SEMICON CO LTD

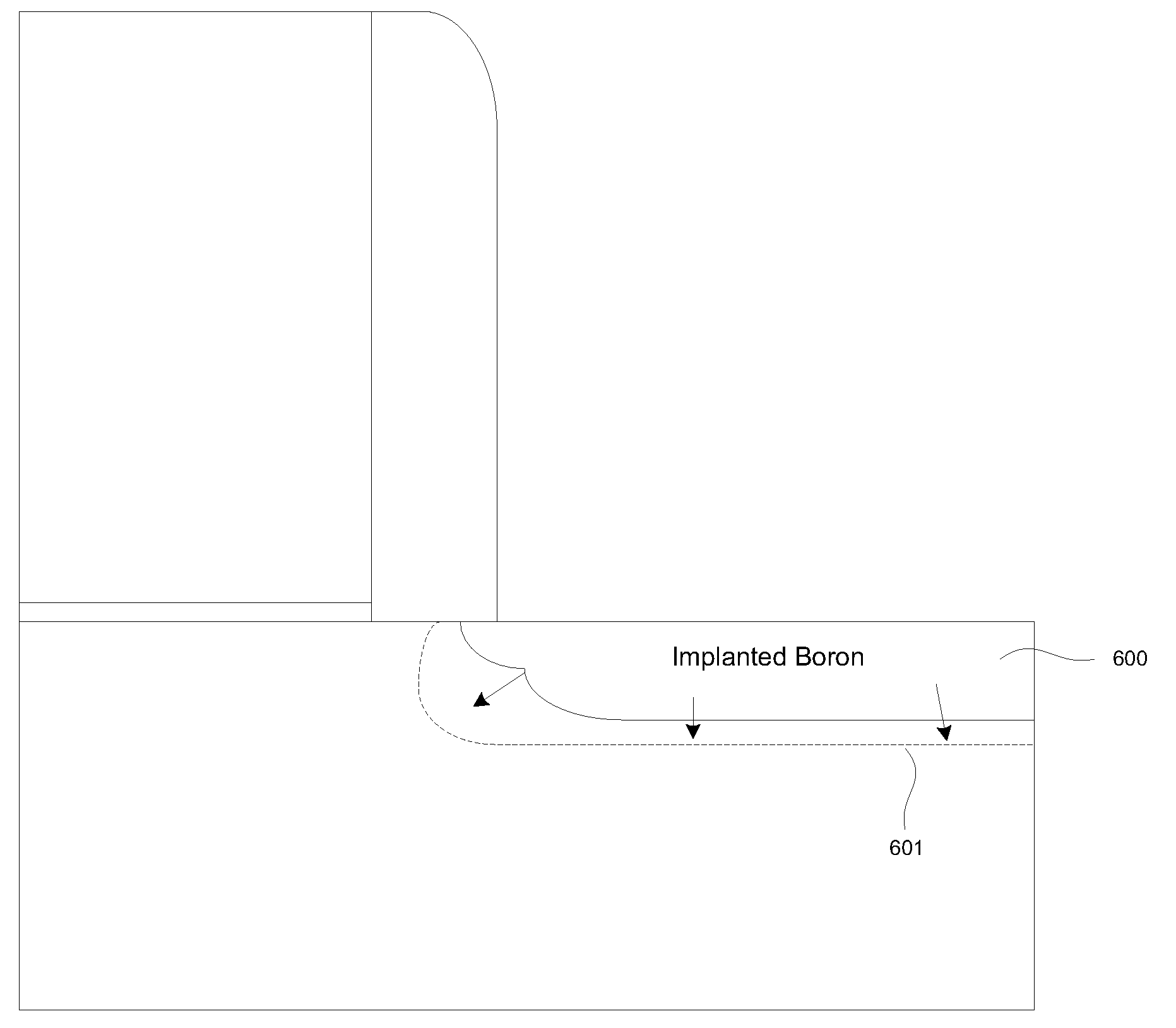

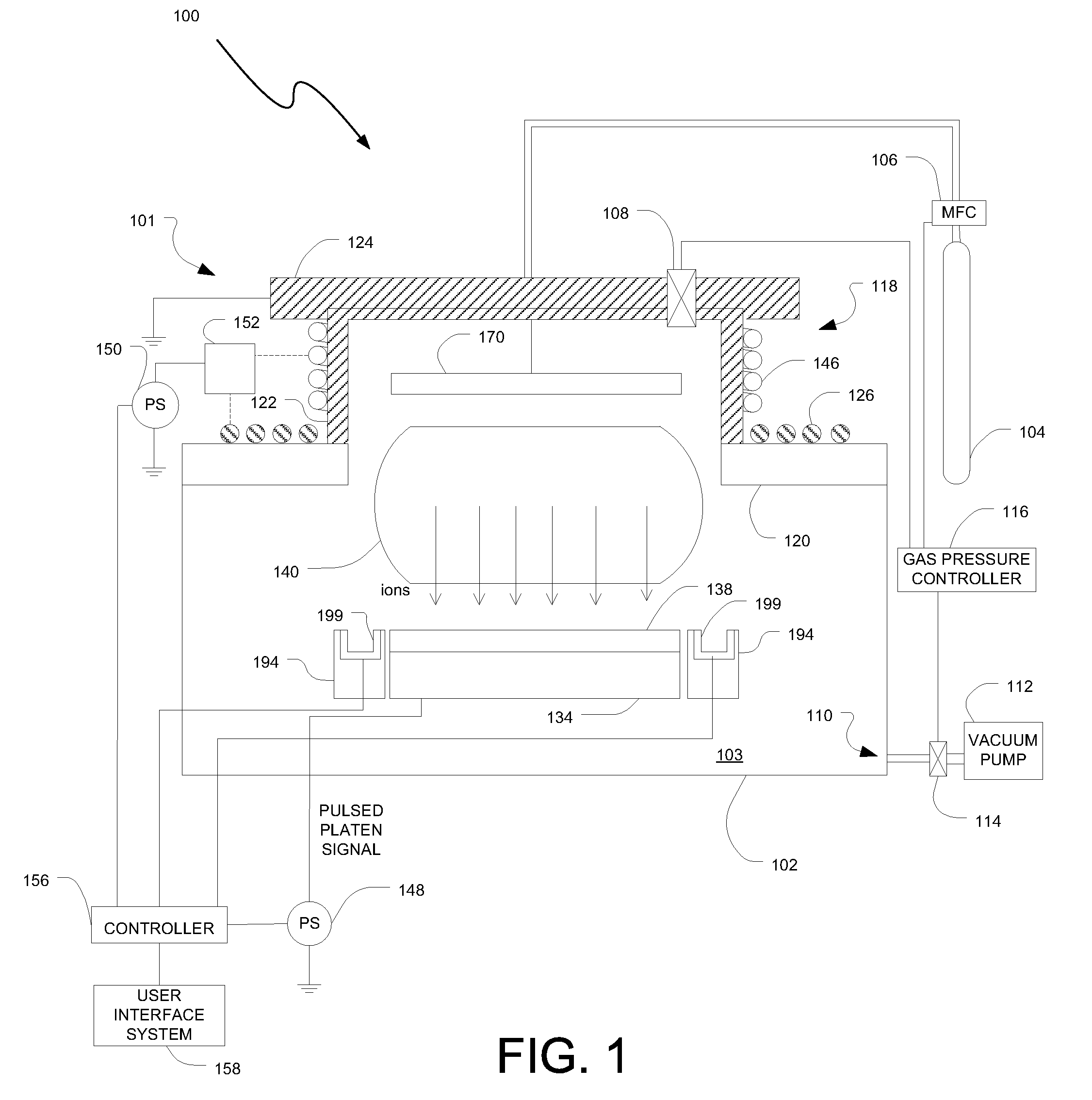

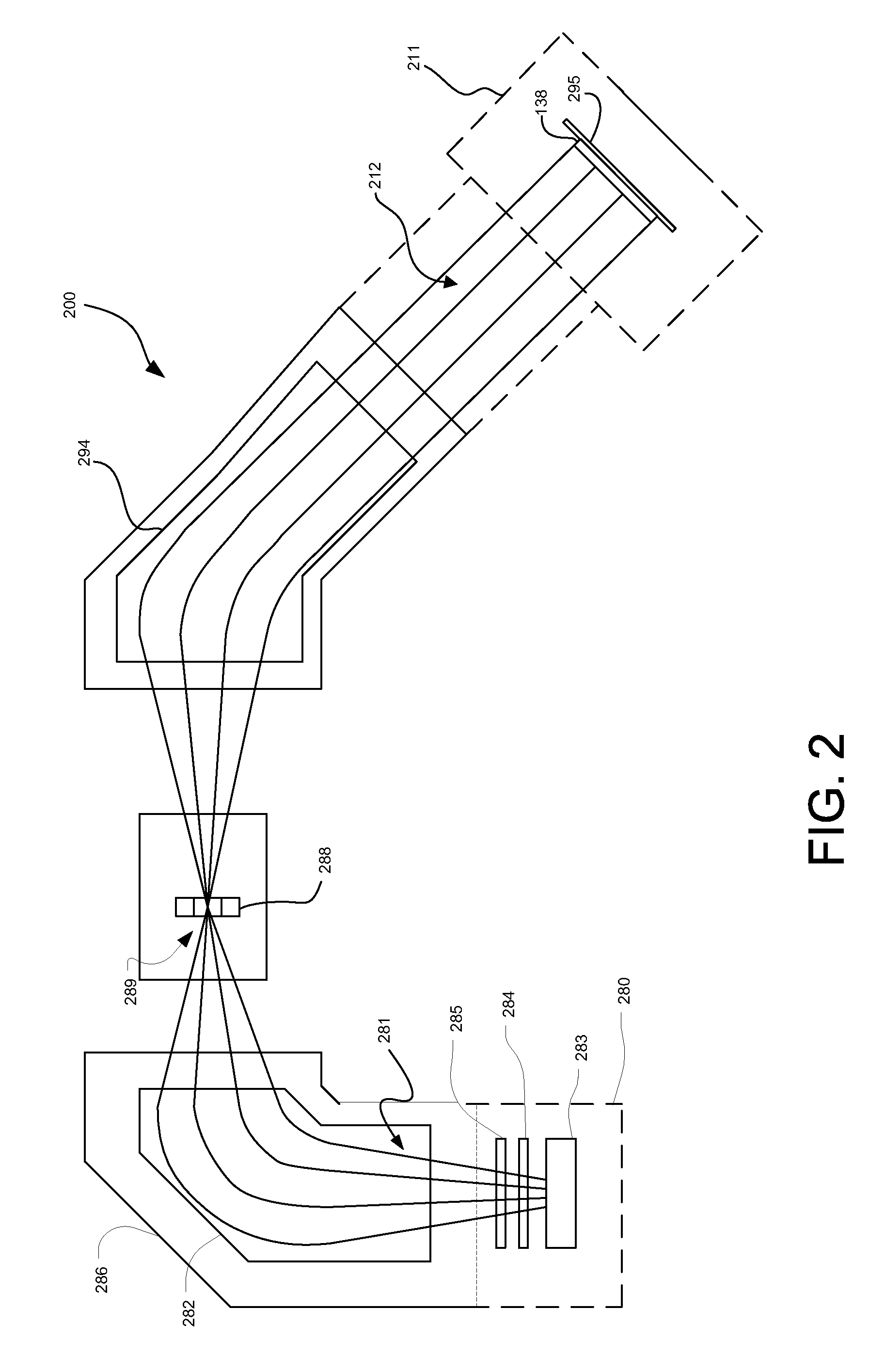

Usj techniques with helium-treated substrates

ActiveUS20100041218A1Increased activationLowering substrate resistanceAntibacterial agentsTransistorDopantDose rate

A method of using helium to create ultra shallow junctions is disclosed. A pre-implantation amorphization using helium has significant advantages. For example, it has been shown that dopants will penetrate the substrate only to the amorphous-crystalline interface, and no further. Therefore, by properly determining the implant energy of helium, it is possible to exactly determine the junction depth. Increased doses of dopant simply reduce the substrate resistance with no effect on junction depth. Furthermore, the lateral straggle of helium is related to the implant energy and the dose rate of the helium PAI, therefore lateral diffusion can also be determined based on the implant energy and dose rate of the helium PAI. Thus, dopant may be precisely implanted beneath a sidewall spacer, or other obstruction.

Owner:VARIAN SEMICON EQUIP ASSOC INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com