Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3549results about "Pulse duration/width modulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

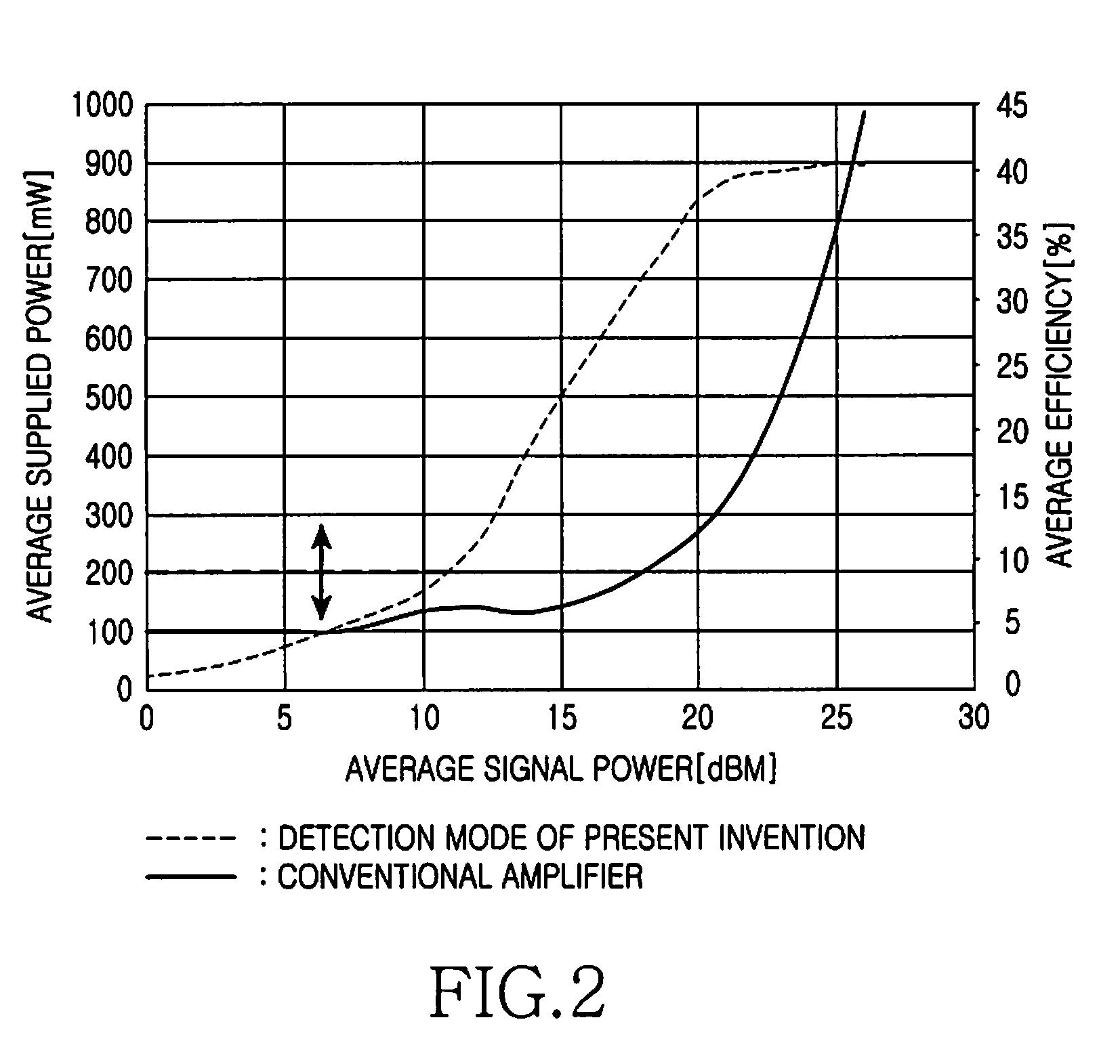

Method for software driven generation of multiple simultaneous high speed pulse width modulated signals

InactiveUS7113541B1Electroluminescent light sourcesVoltage-current phase angleTime segmentControl signal

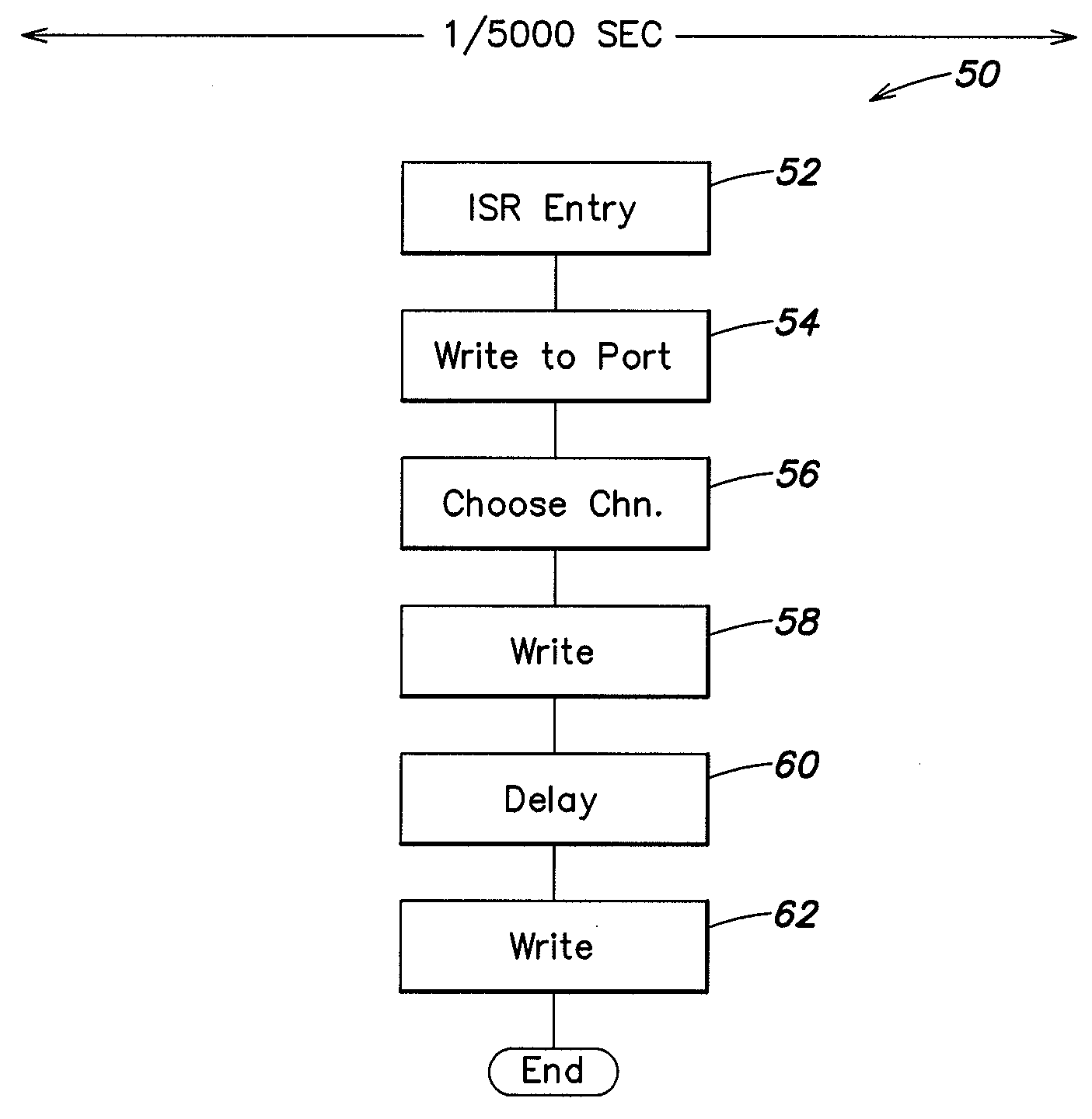

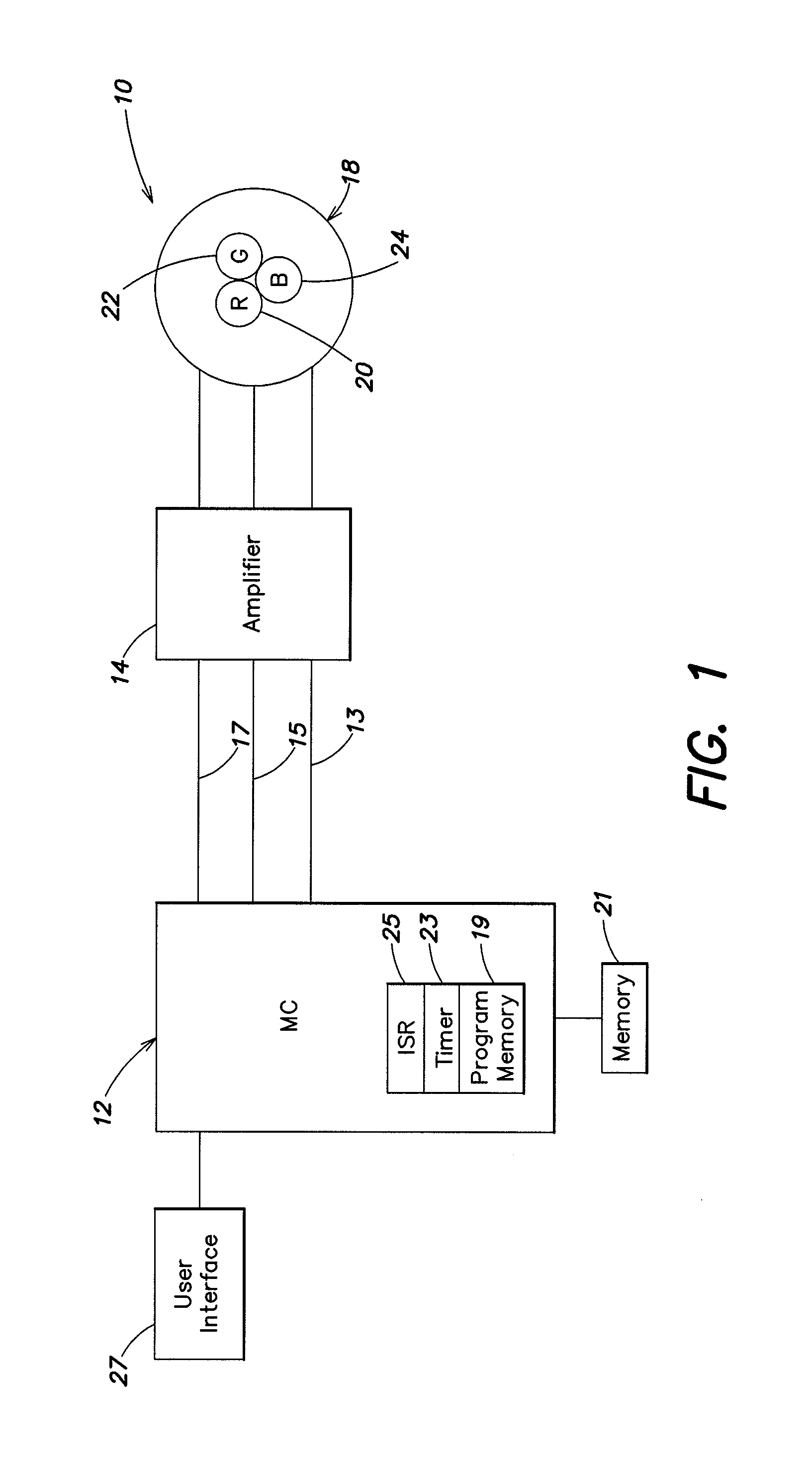

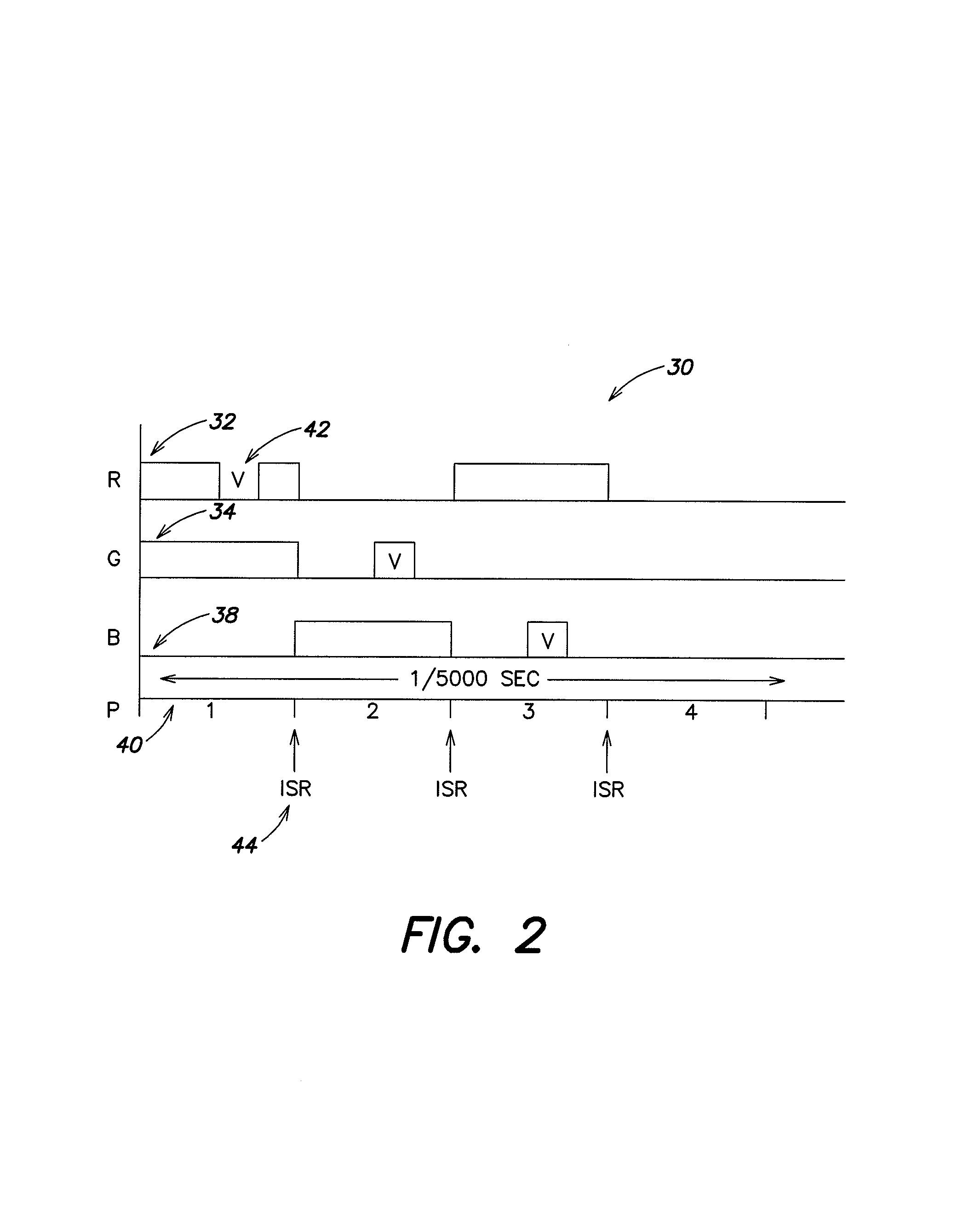

Systems and methods can provide, in one aspect, a method for modulating the pulse width of control signals generated on a plurality of separate channels. In one practice, the methods described herein are suitable for execution on a microprocessor or micro controller platform that includes a timer interrupt mechanism which will generate an interrupt in response to a timer counting down a selected time interval or time period. In one practice, the timer is set to count down a period of time that is representative of a portion, or sub period, of the PWM cycle. Upon expiration of that time period, the timer executes an interrupt that causes the micro controller to enter an interrupt service routine (ISR) that can further modulate the PWM cycle of one or more signals.

Owner:PHILIPS SOLID STATE LIGHTING SOLUTIONS

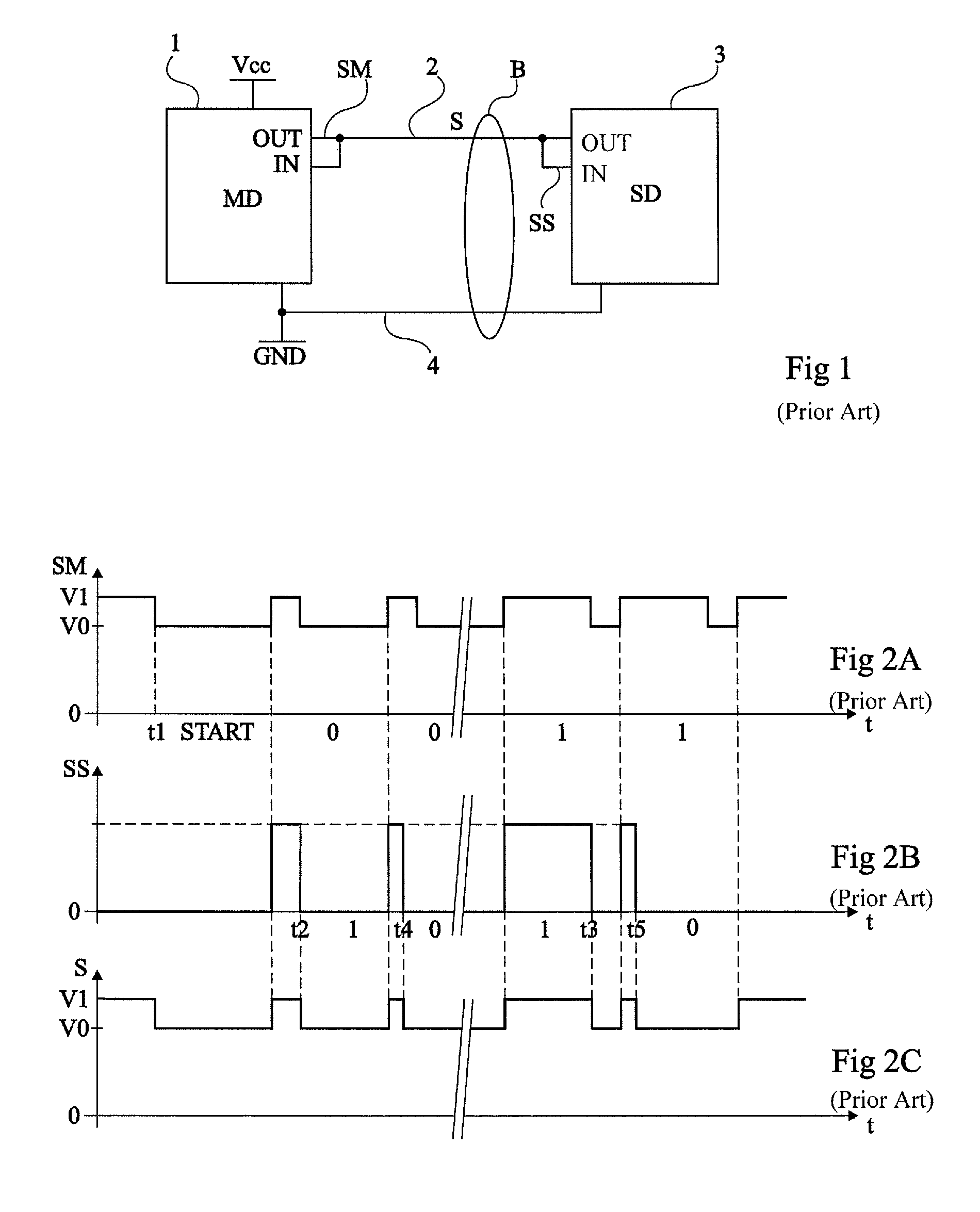

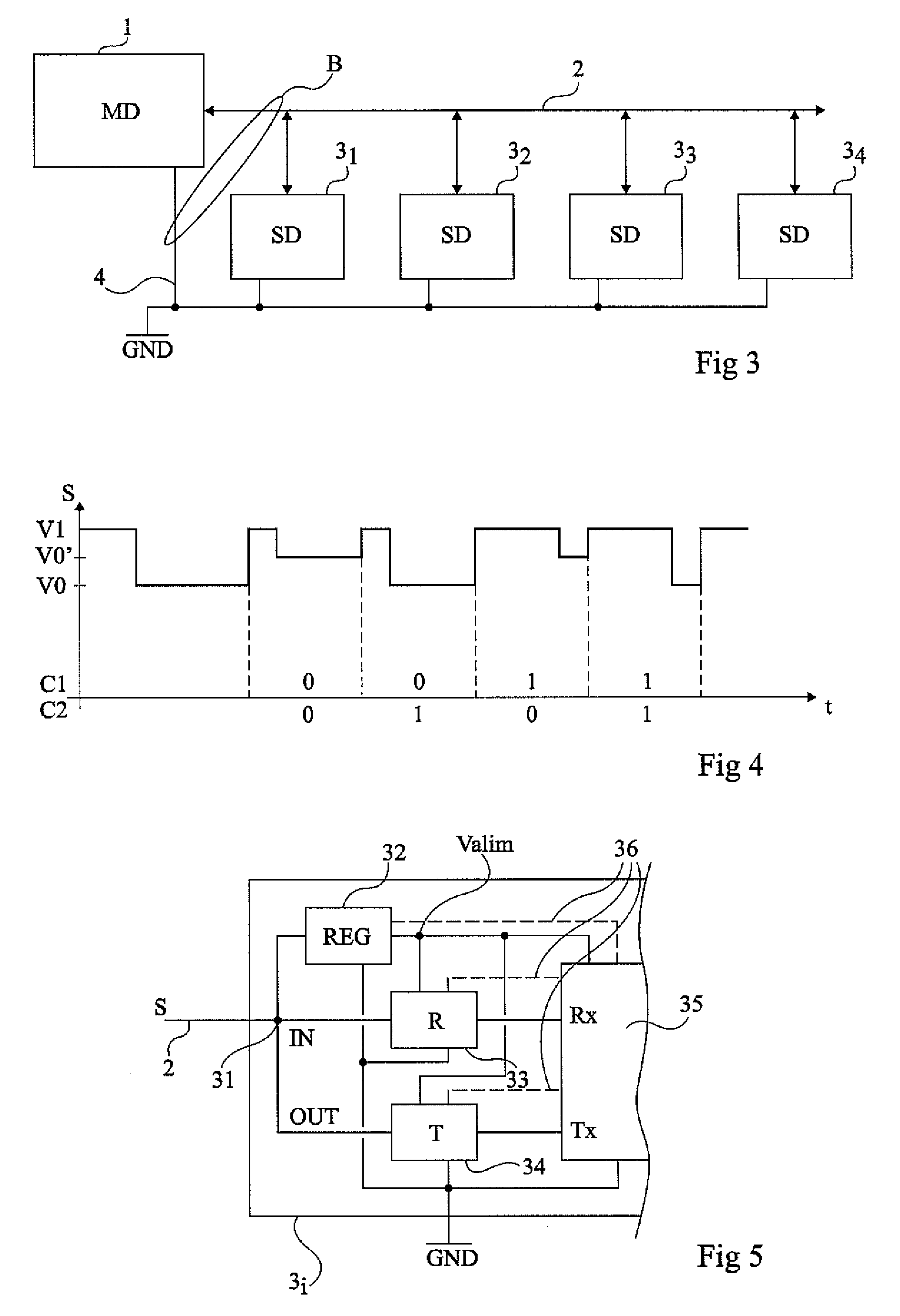

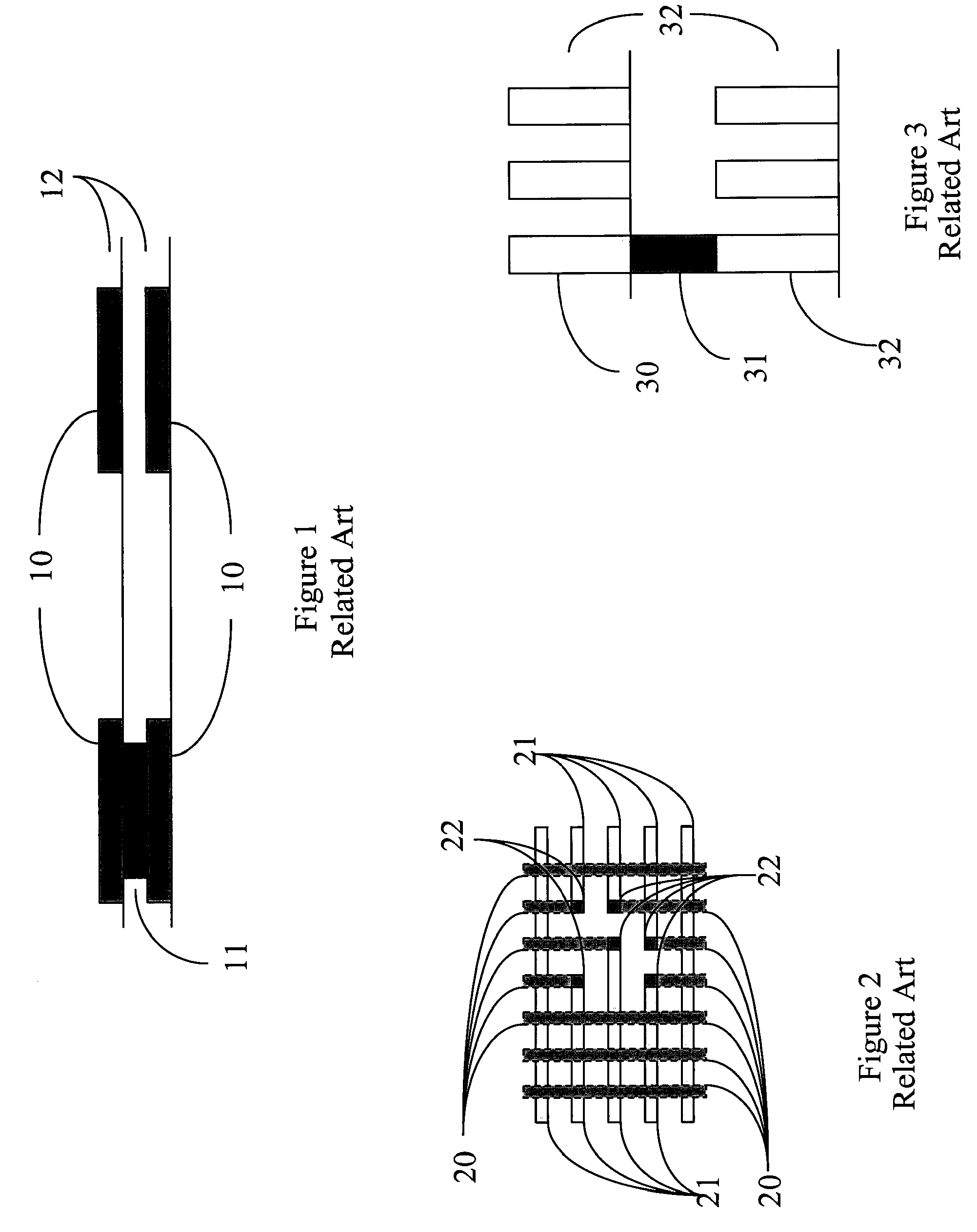

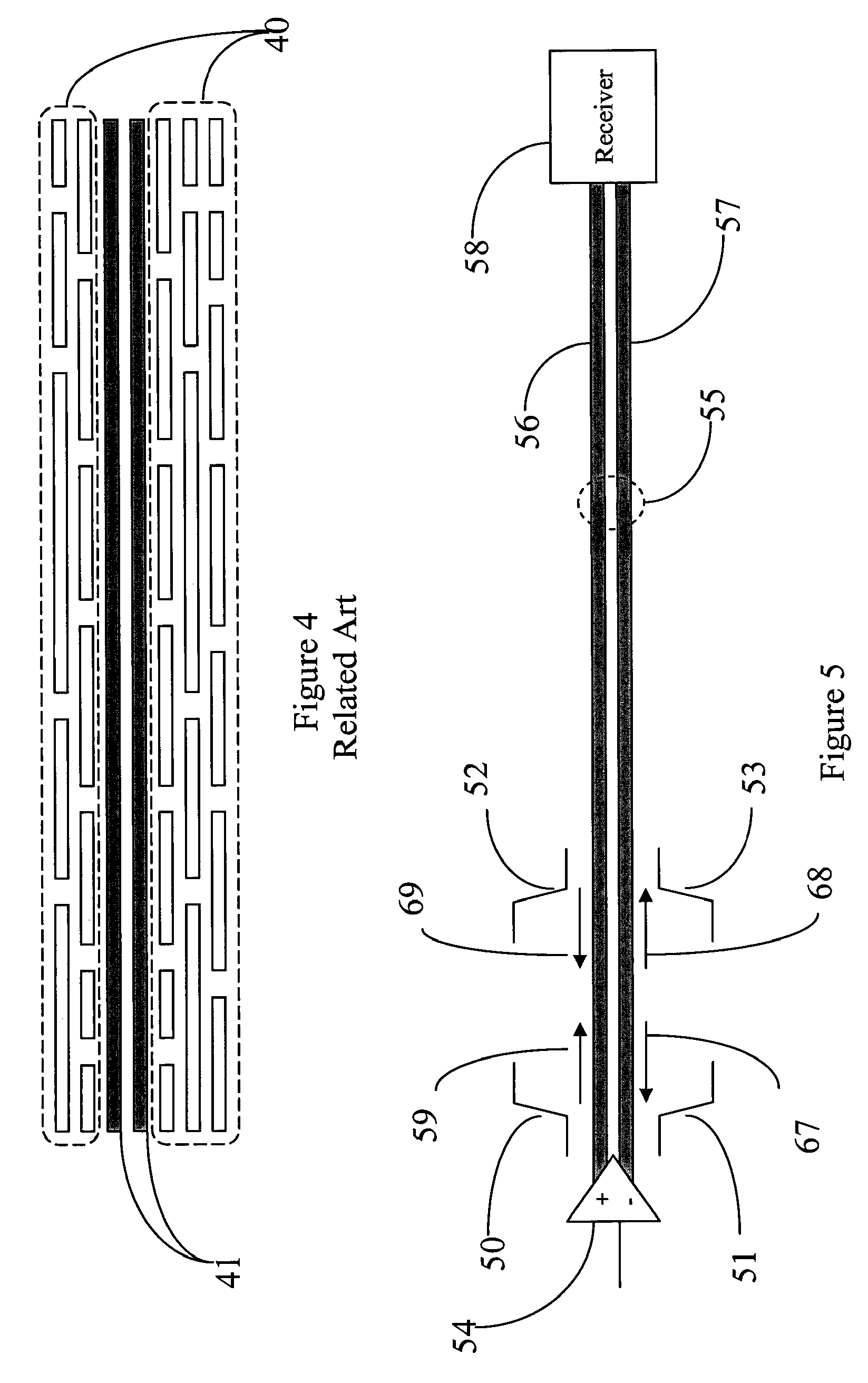

Multiple-channel transmission over a single-wire bus

ActiveUS8509318B2Batteries circuit arrangementsTransmission/receiving by adding signal to waveTransmission channelPower over

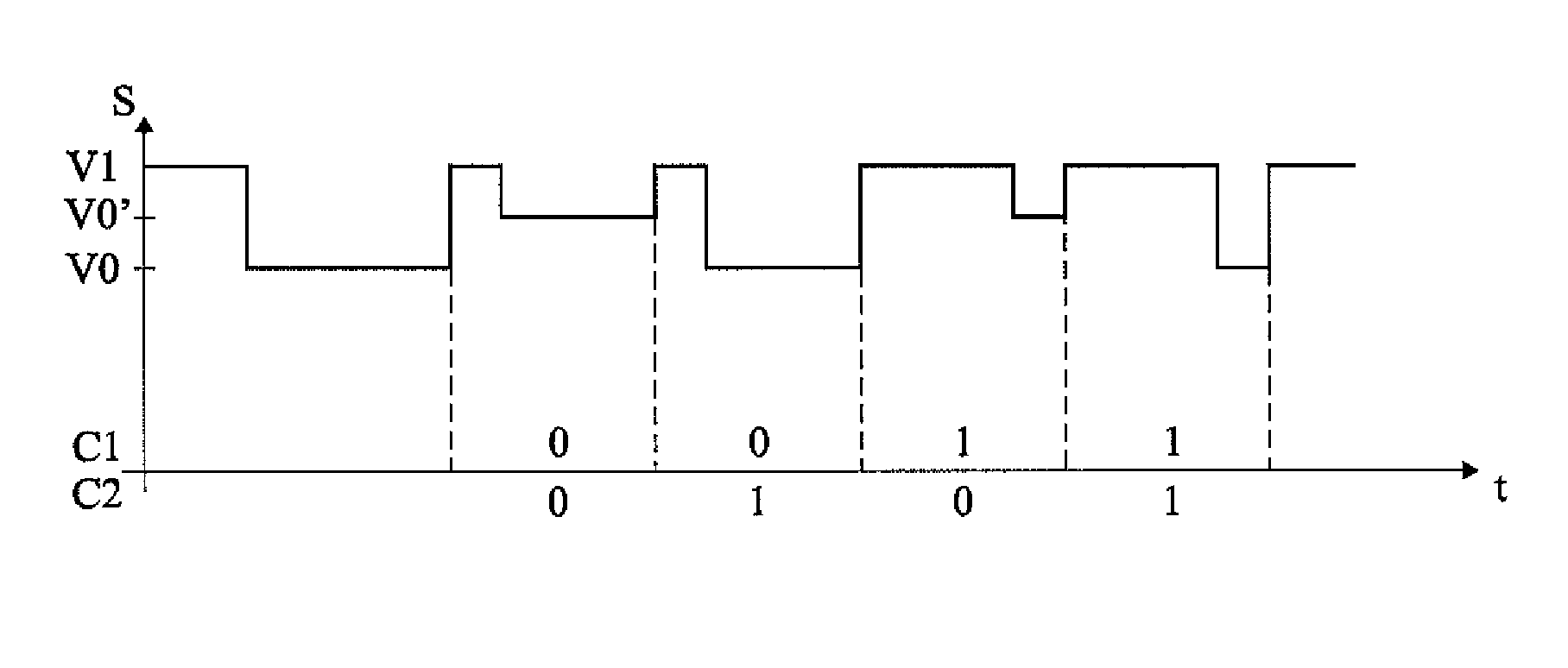

Apparatus and methods are described that enable concurrent transmission of multiple data signals including clock, synchronization, and power over a single-wire bus between a master device and one or more slave devices. A first transmission channel from the master device to the slave device may modulate the width of periodic pulses between a first voltage level and a second voltage level with respect to a reference potential. A second transmission channel may modulate the amplitude of at least one of the first and second voltage levels to at least one third voltage level. Concurrent communications between a master device and one or more slave devices over a single-wire bus can be achieved.

Owner:STMICROELECTRONICS (ROUSSET) SAS

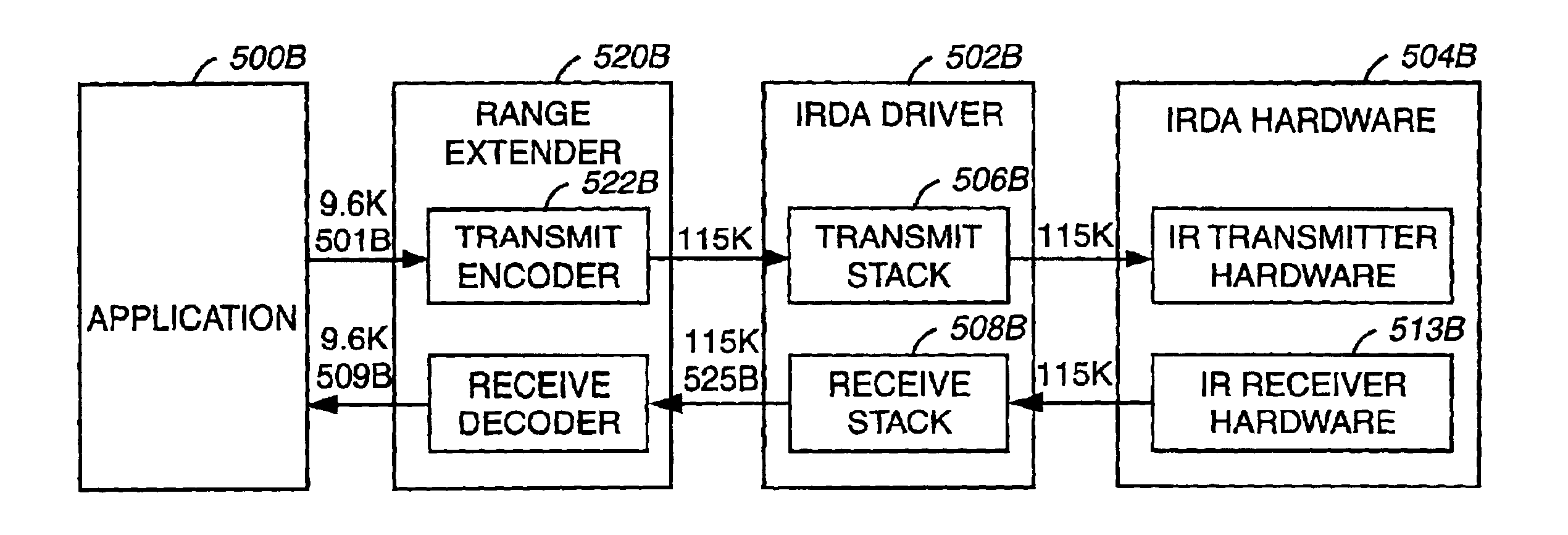

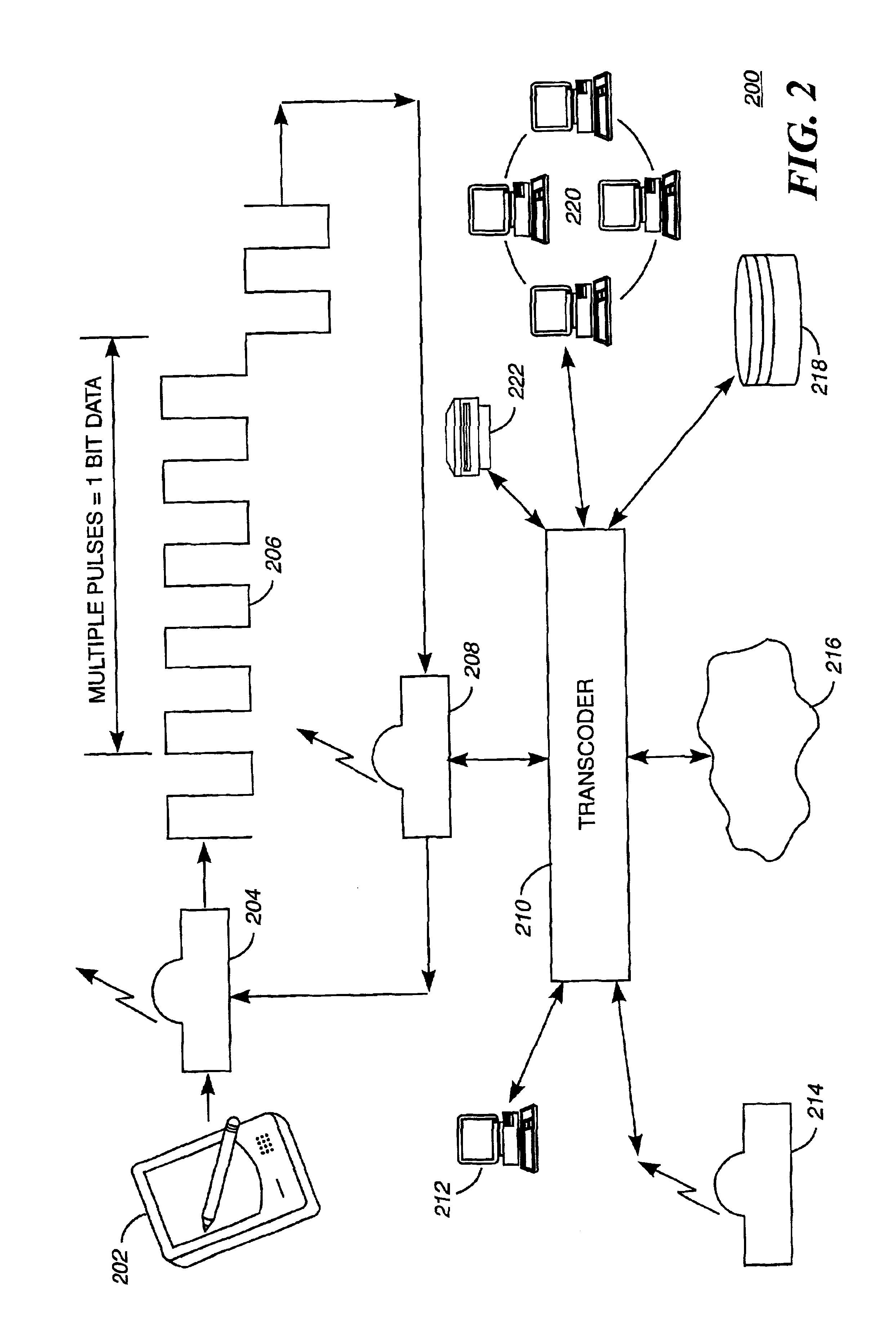

System and method for remote optical digital networking of computing devices

InactiveUS6920289B2Widely distributedIncrease rangeElectric signal transmission systemsFrequency/rate-modulated pulse demodulationData transmissionMobile device

This invention extends the range of optical data of mobile device by trading speed for distance as well as integrating a plurality of pulses over time to define a single bit of information. The present invention uses a number of integrated pulses to represent a single bit instead of utilizing a one to one correspondence between pulses and bits. The present invention executes a range extender application which executes on the mobile device without any hardware modification to the mobile device. The range extender application causes the optical transmitter to “stutter” or repetitively emanate the identical pulse representing a bit of information. Sufficient photons are thereby gathered at a receiver to reach a predetermined threshold. A tradeoff of the data transmission frequency in this invention is that a signal intensity drops by a factor of 100 when distance increases by a factor of 10 yielding a distance / intensity ratio of {fraction (1 / 10)}.

Owner:GLOBALFOUNDRIES US INC

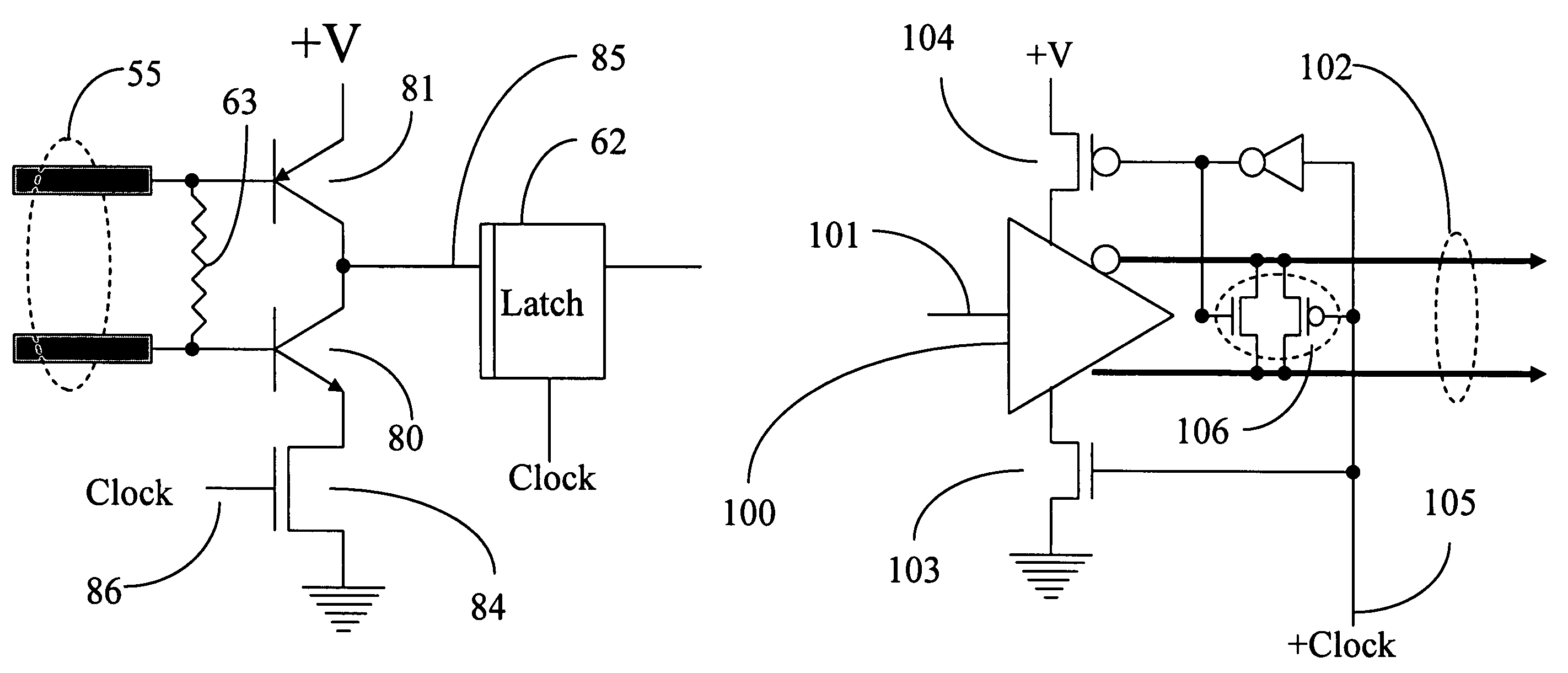

Integrated circuit communication techniques

ActiveUS7439773B2Reduce the required powerReduce power consumptionReliability increasing modificationsPower reduction by control/clock signalEngineeringSemiconductor

Owner:TAHOE RES LTD

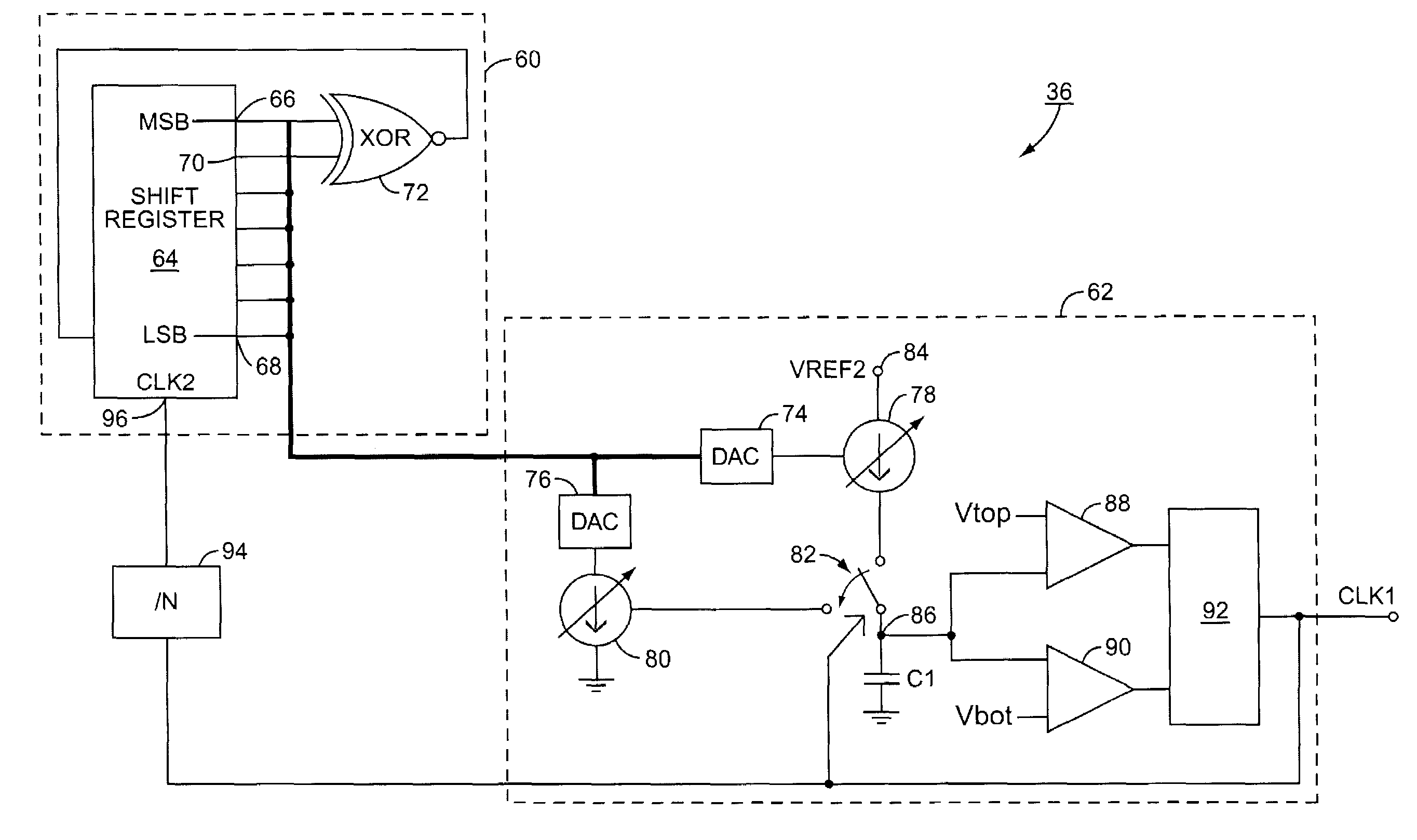

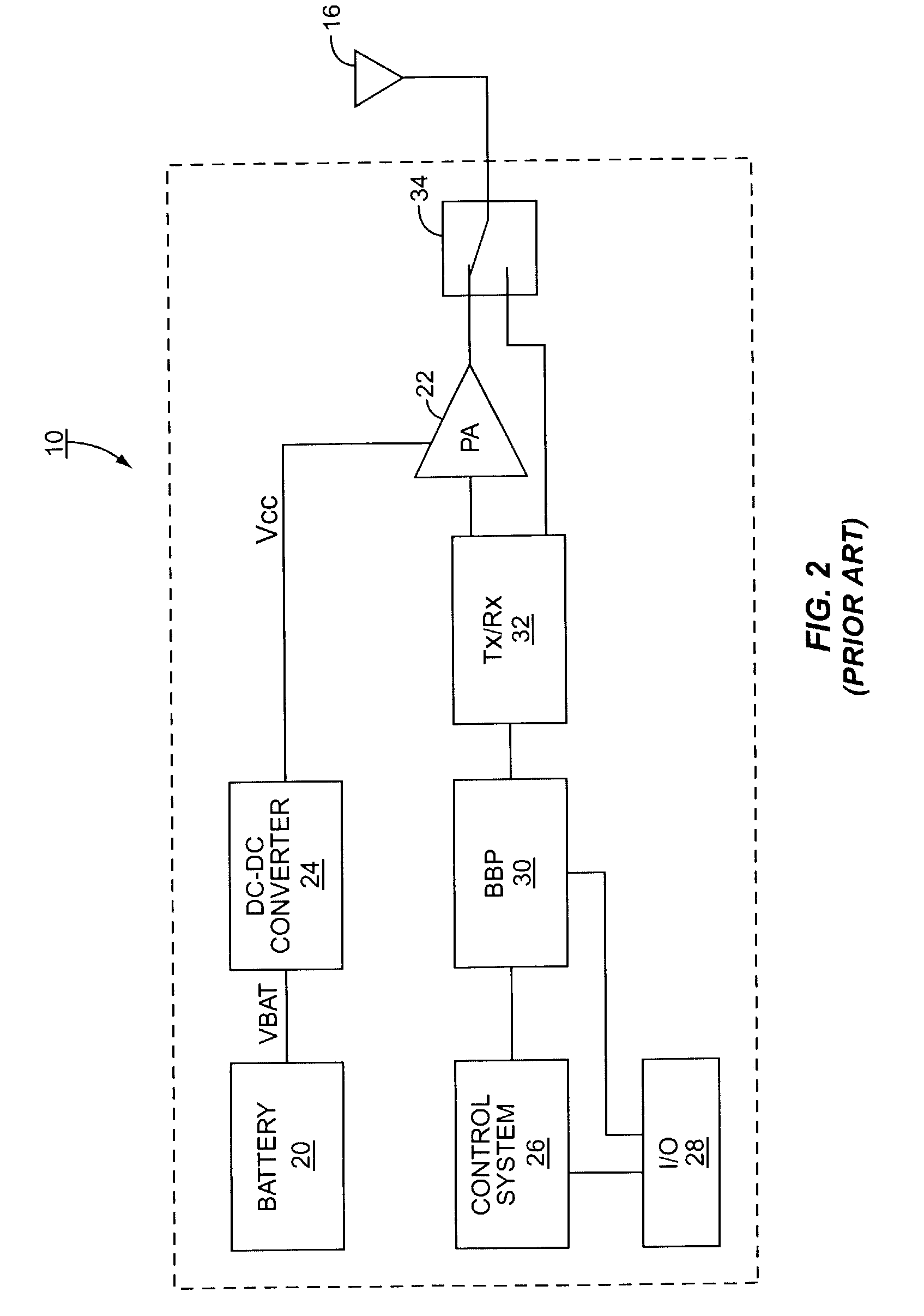

DC-DC converter with reduced electromagnetic interference

InactiveUS6969978B2Emission reductionLess spaceDc-dc conversionPulse duration/width modulationDc dc converterControl system

A DC-DC converter includes a variable frequency oscillator, a control system and a power train. The DC-DC converter is well suited for use in a cell phone. The control system uses the output of the oscillator to control the power train. The oscillator varies its frequency as a function of a pseudo random number generator, thereby reducing electromagnetic interference caused by ripple in the output of the DC-DC converter.

Owner:QORVO US INC

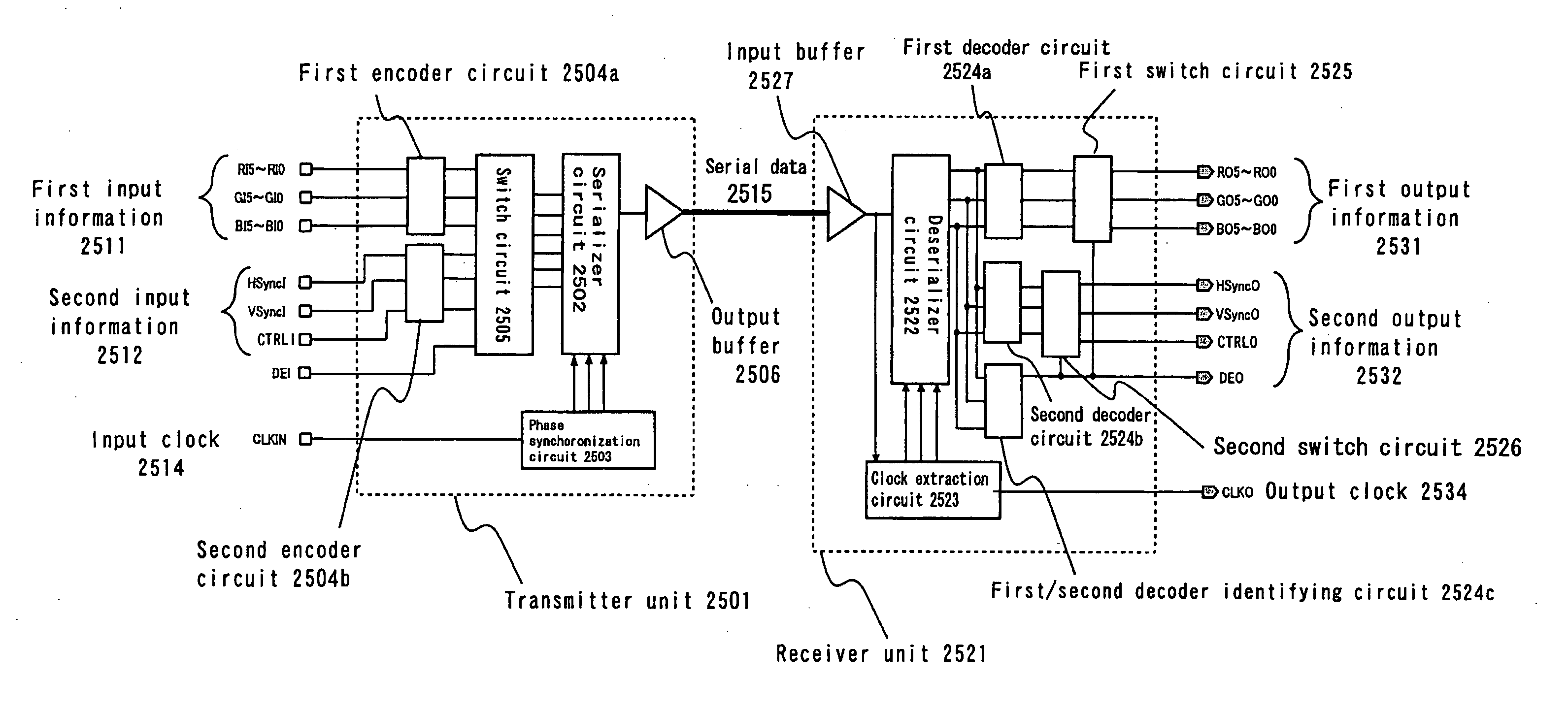

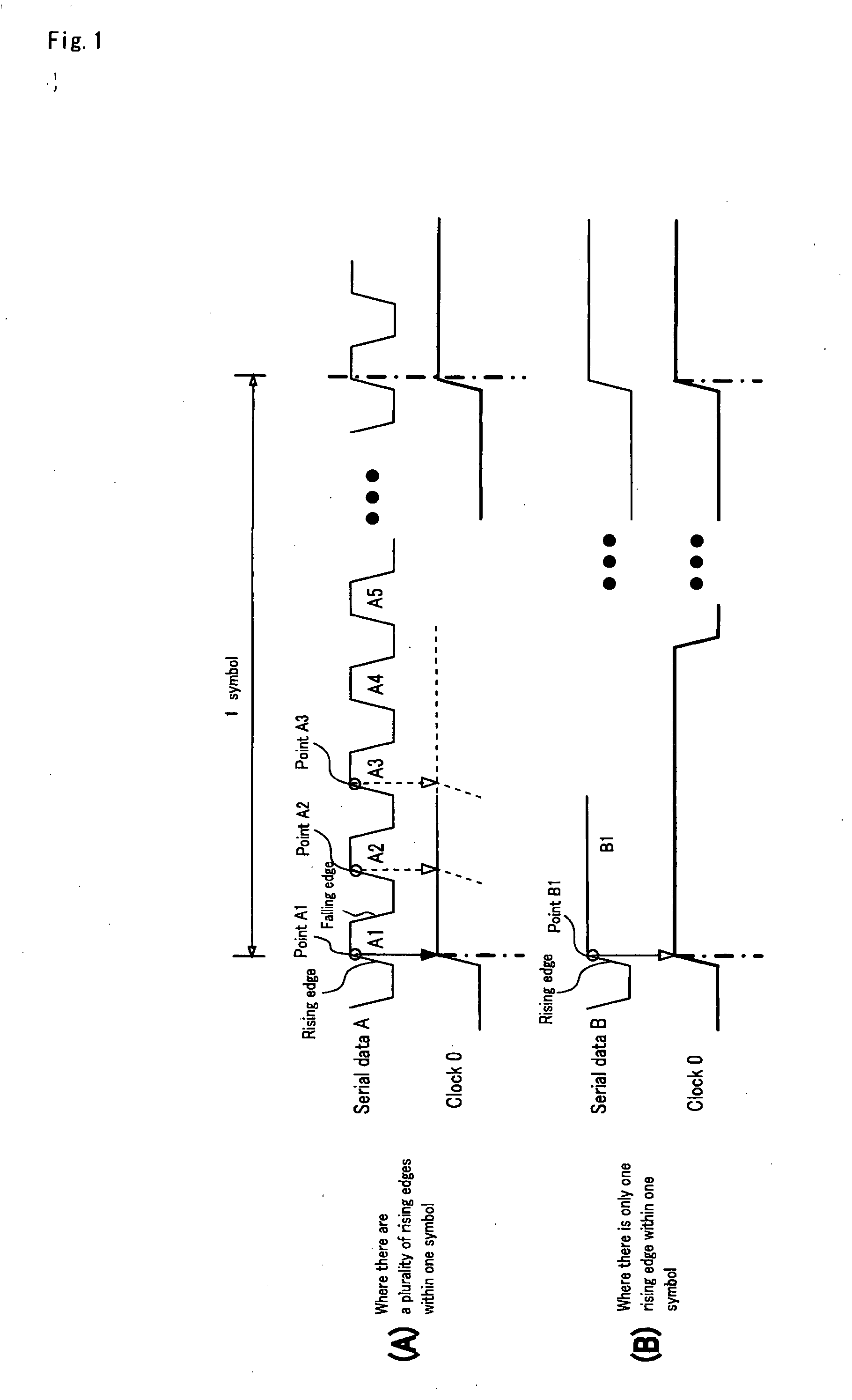

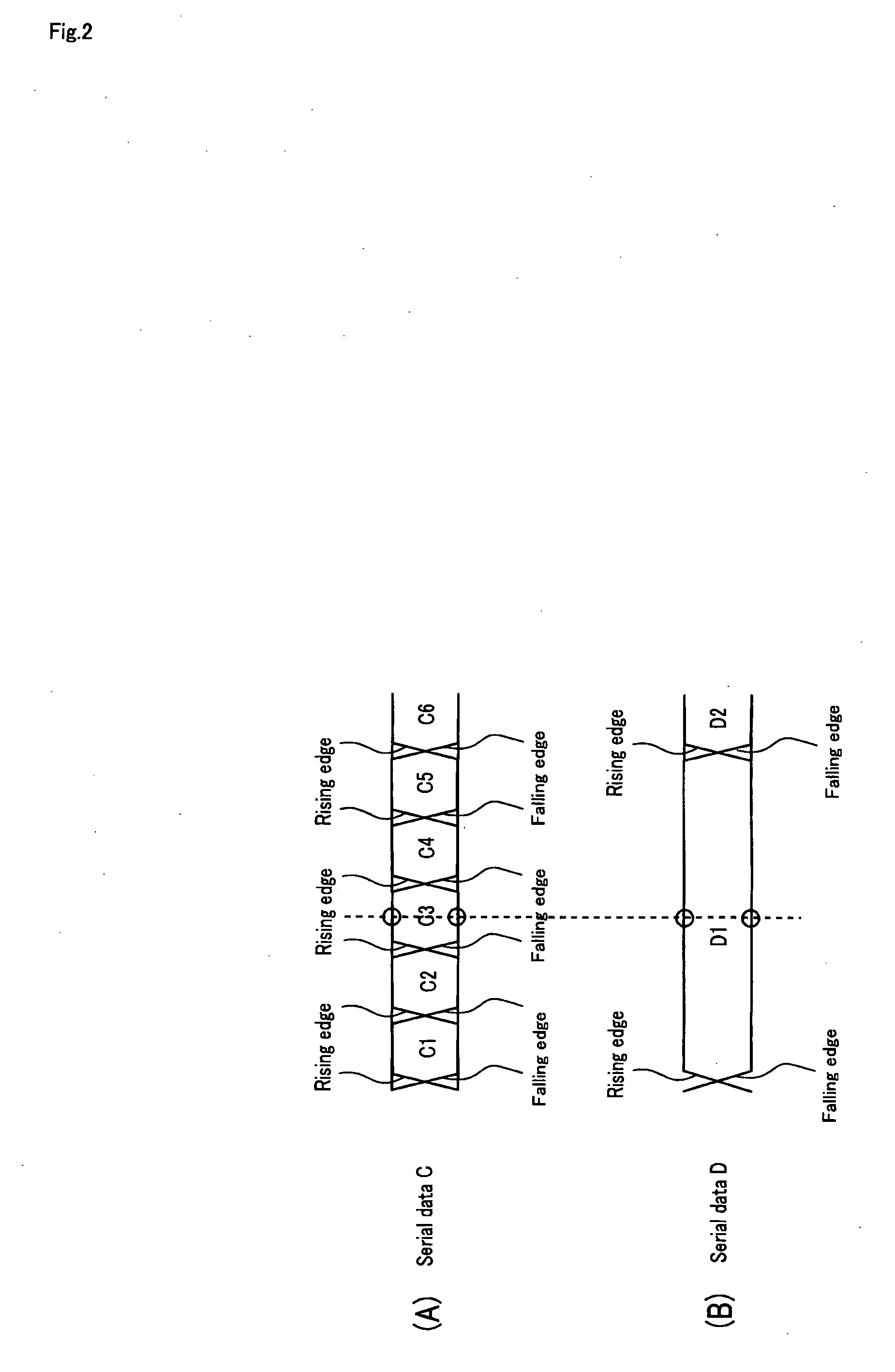

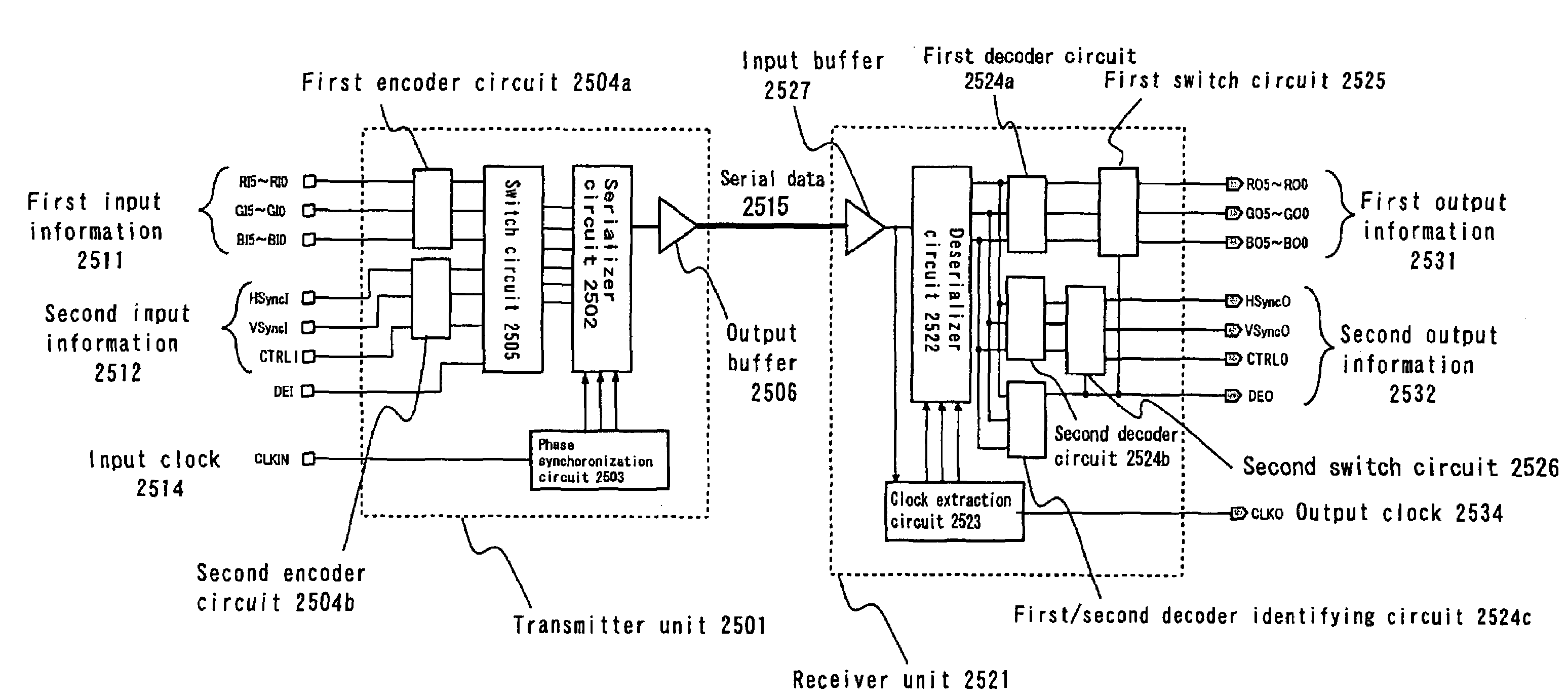

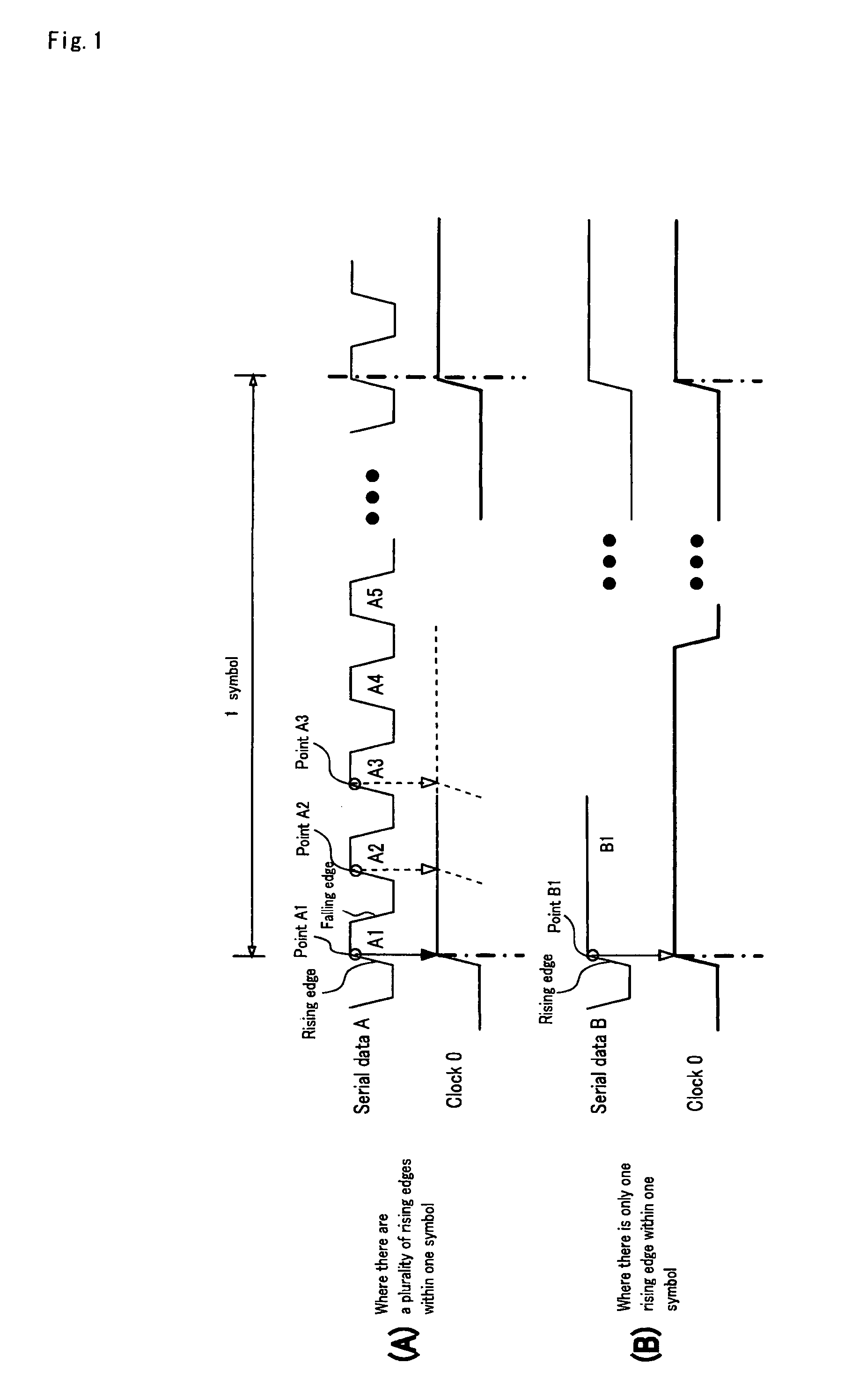

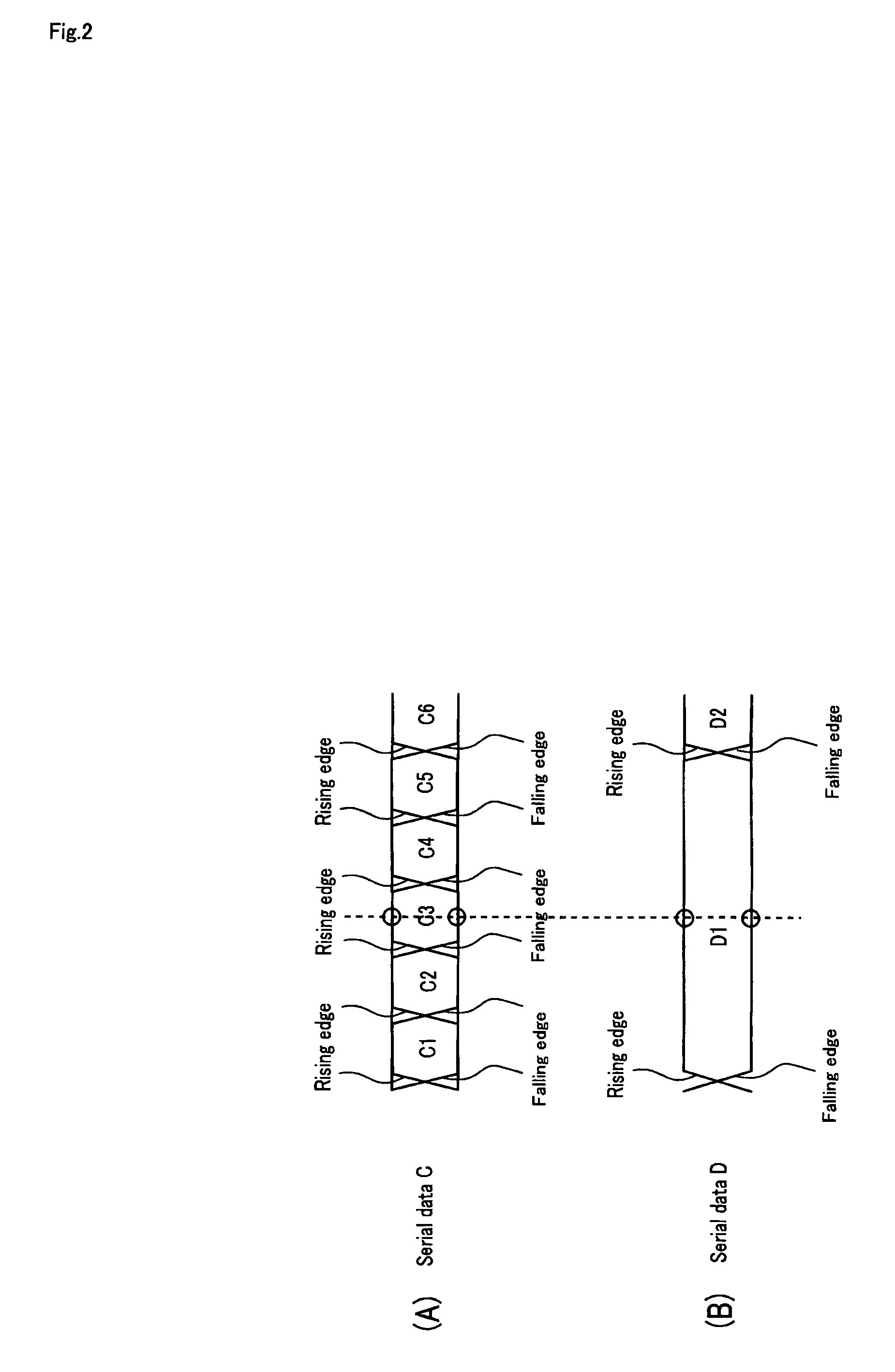

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS20050286643A1Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation. [Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

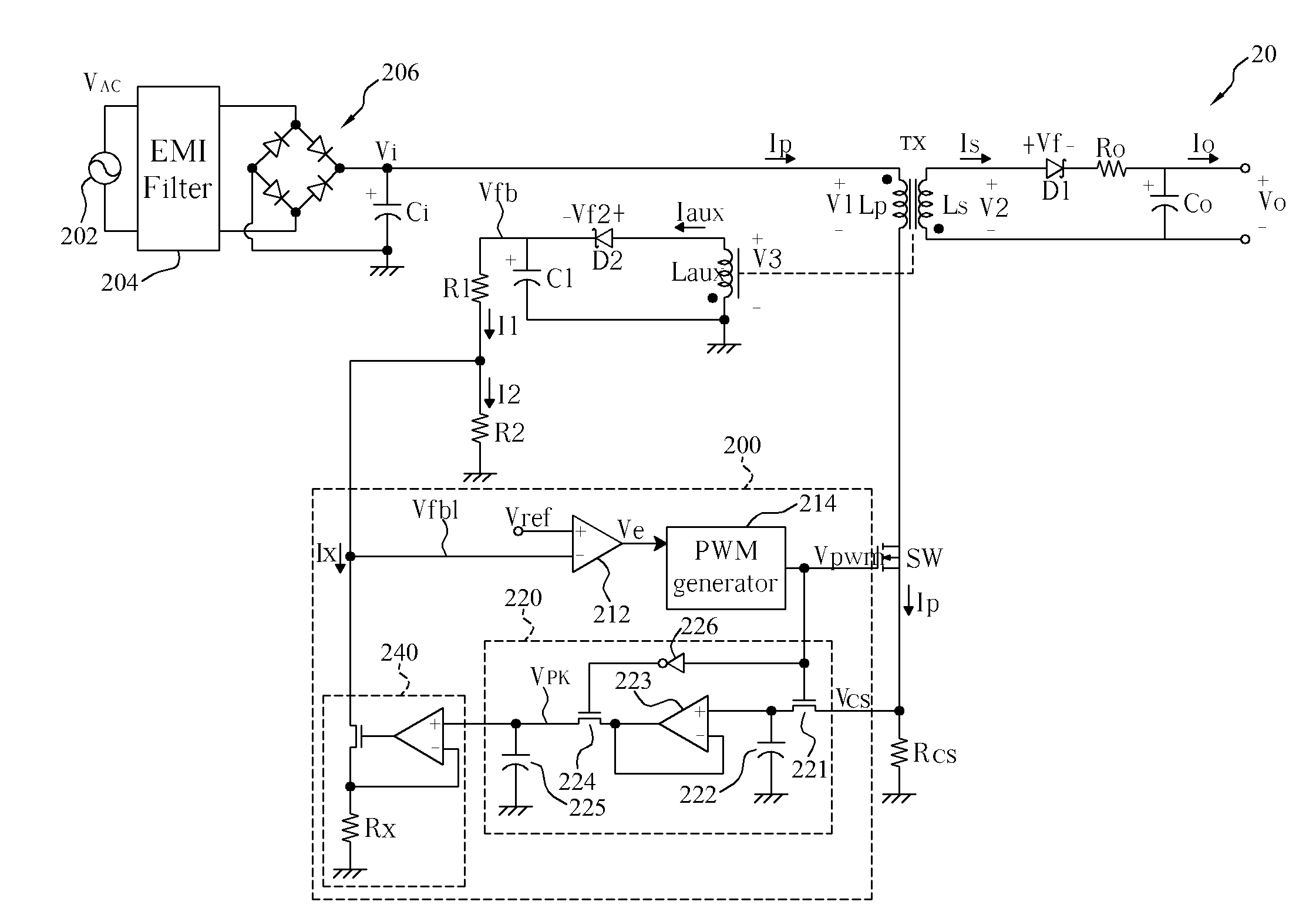

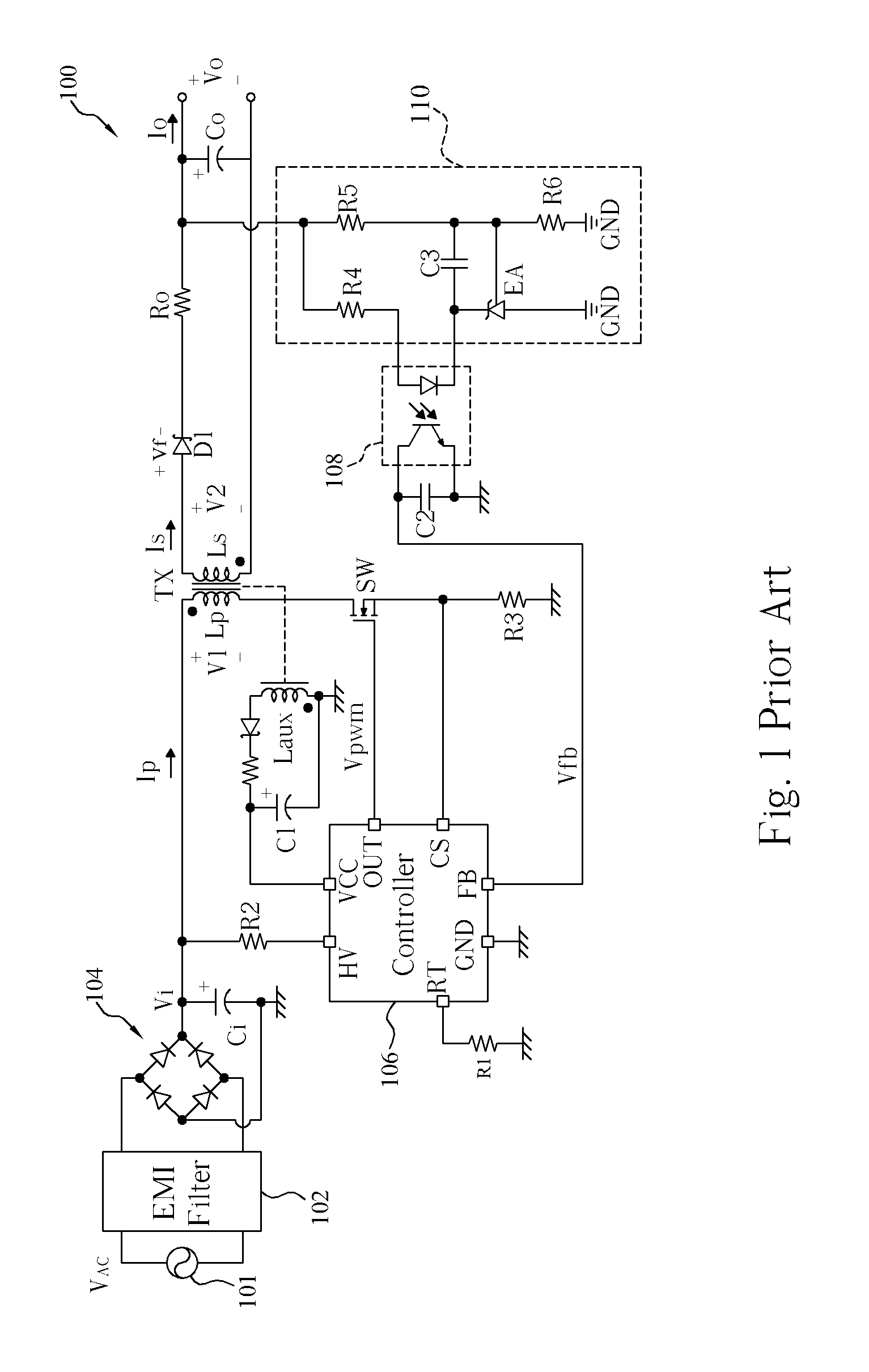

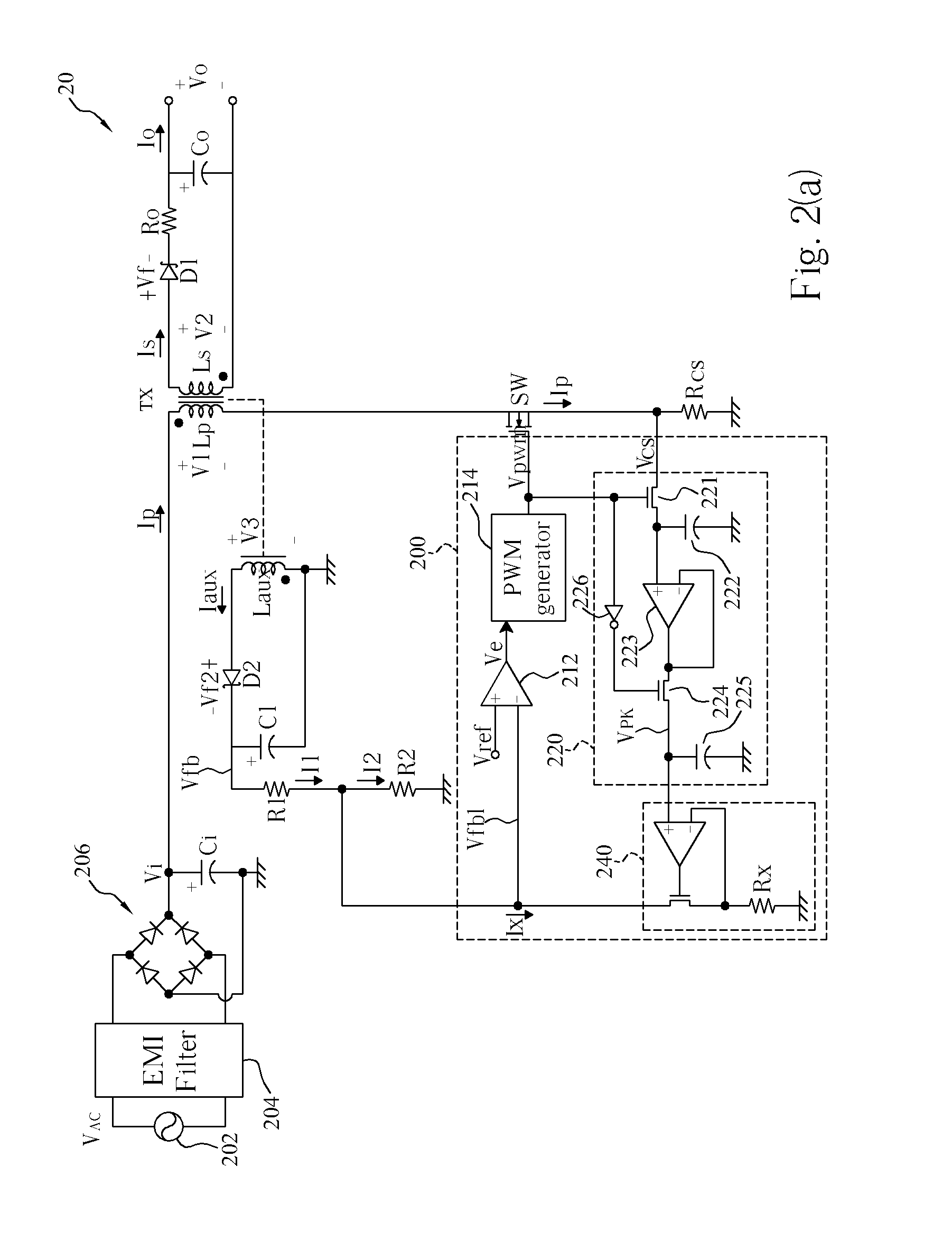

Switching-mode power converter and pulse-width-modulation control circuit with primary-side feedback control

A pulse-width-modulation control circuit of a switching-mode power converter with a primary-side feedback control is disclosed. The switching-mode power converter includes a transformer, a power switch, a current sensing resistor and the pulse-width-modulation control circuit. The transformer includes a primary-side winding, a secondary-side winding and an auxiliary winding. The pulse-width-modulation control circuit includes a sample and hold circuit, a transconductor circuit, an error amplifier and a pulse-width-modulation generator.

Owner:LEADTREND TECH

Time domain symbols

ActiveUS8848808B2Modulated-carrier systemsDuration/width modulated pulse demodulationTime domainElectrical and Electronics engineering

Methods and apparatus are described for time domain signals. A method includes creating a bipolar pulse whose high (up) and low (down) periods are separately and precisely controllable.

Owner:LIGHTFLEET CORP

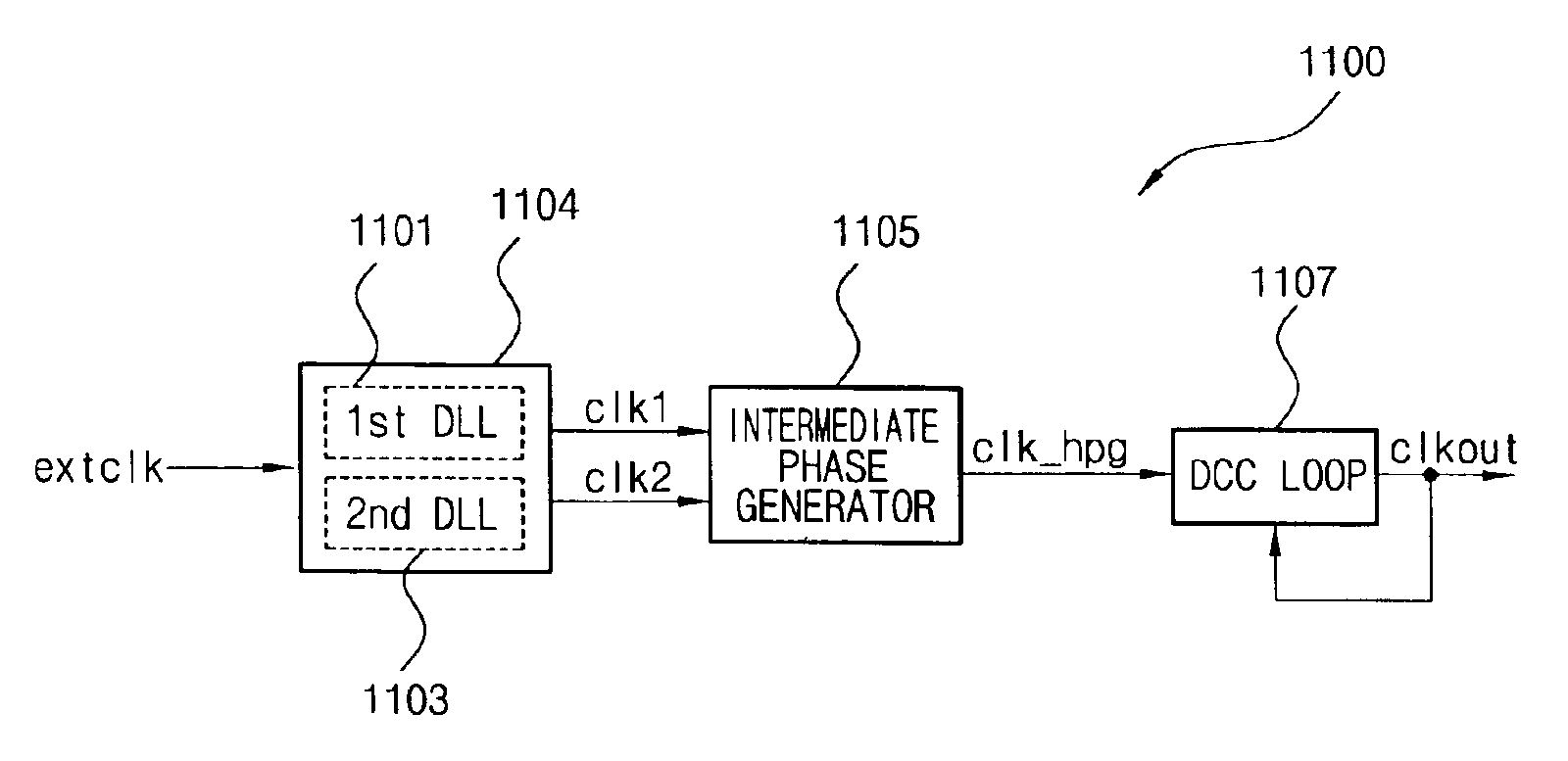

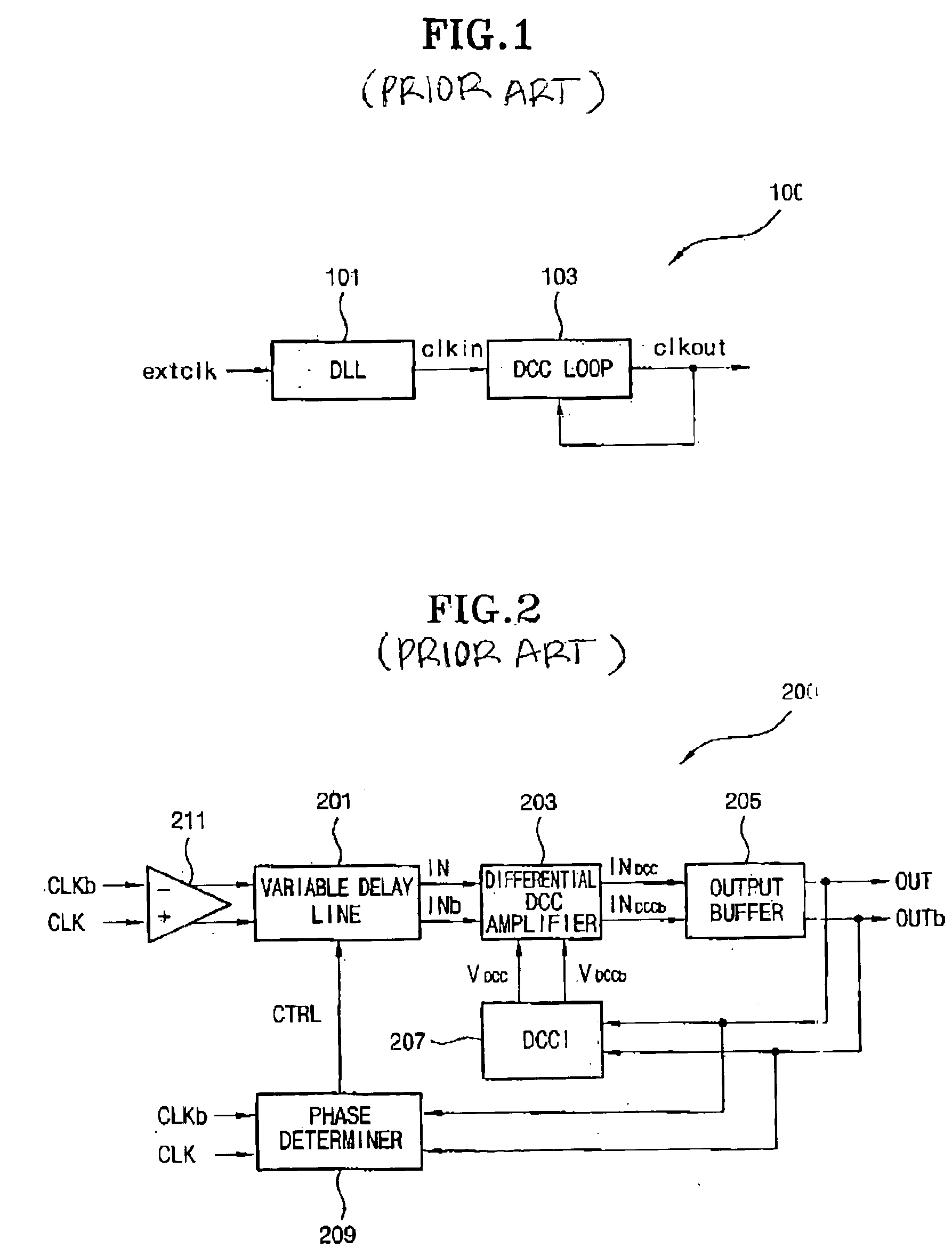

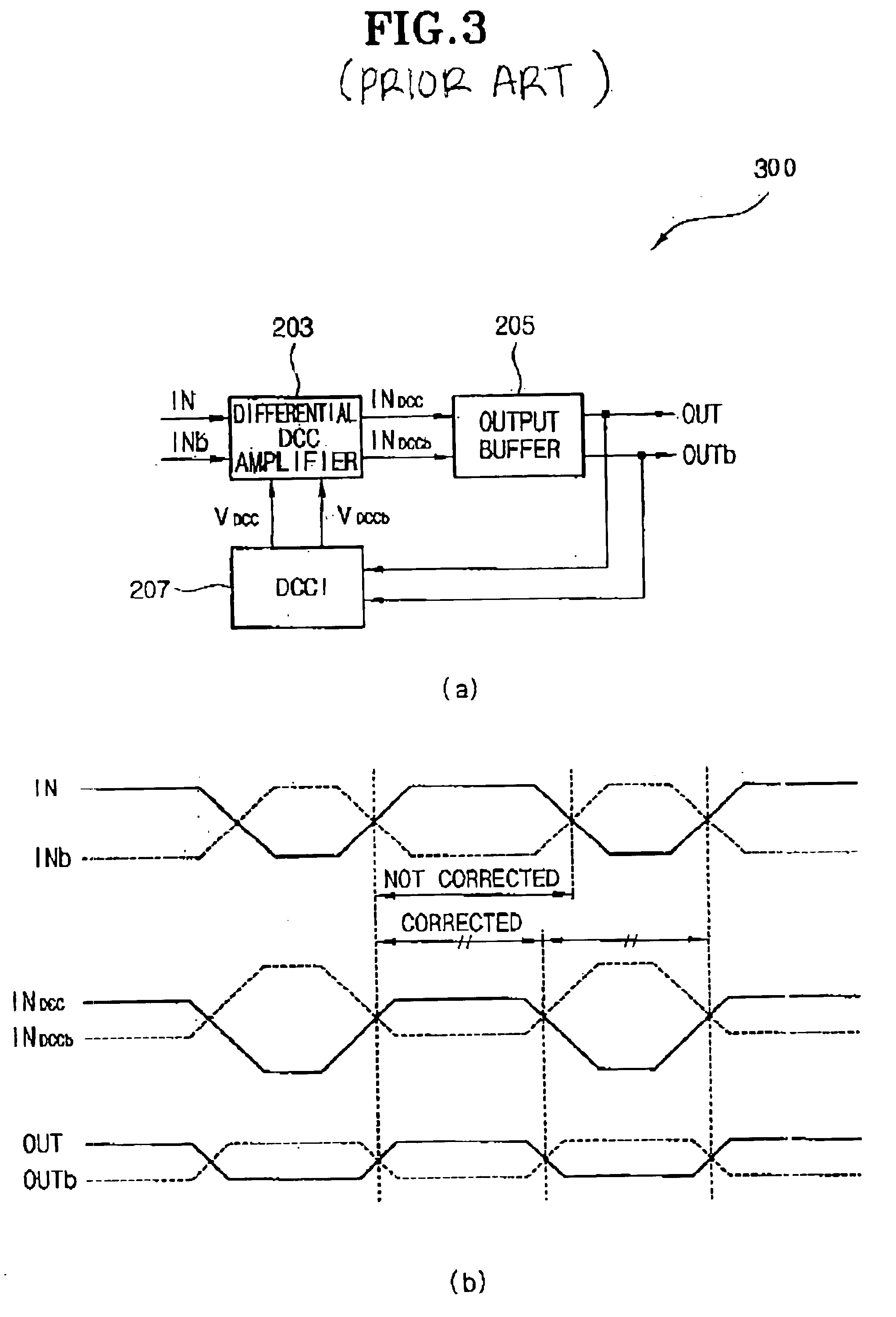

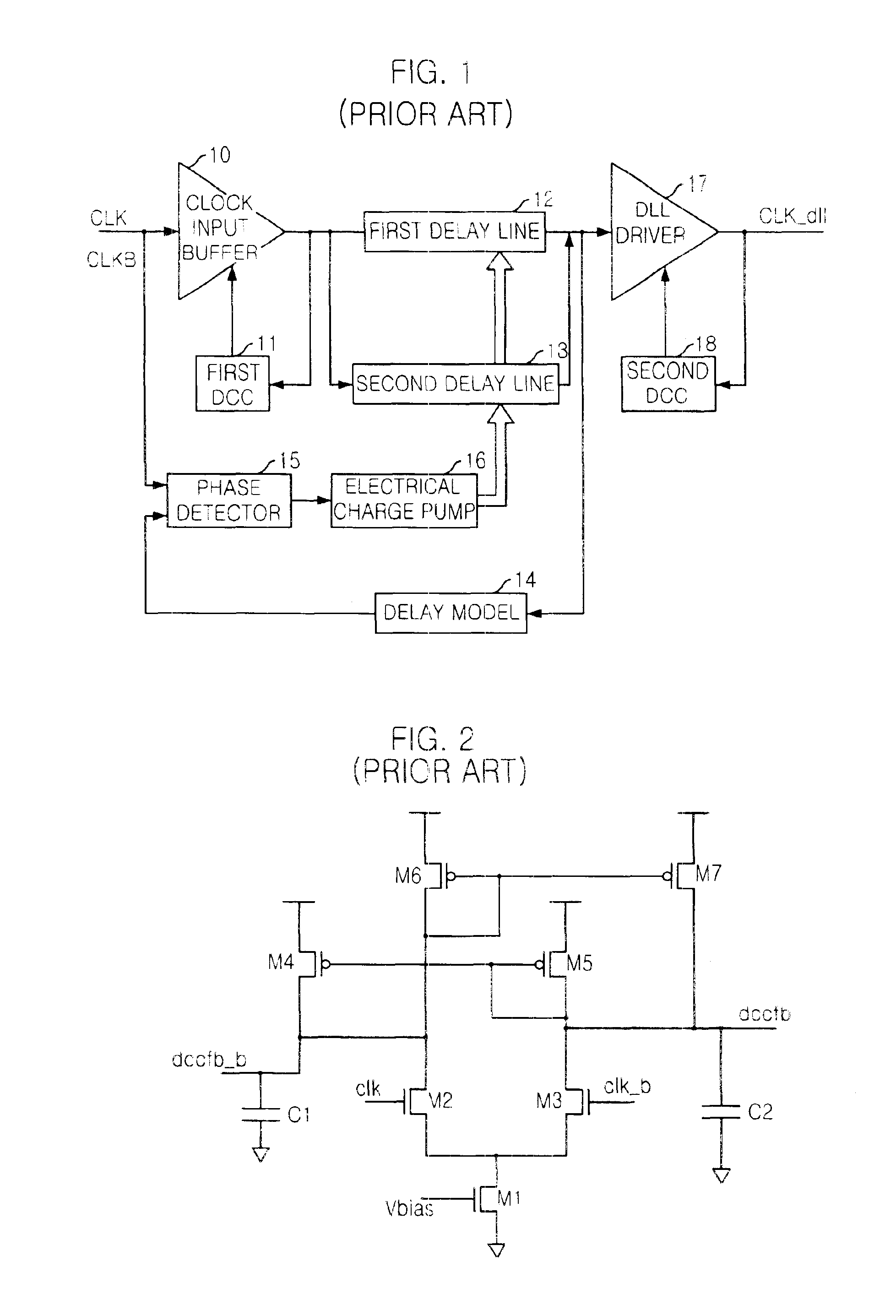

Delay locked loop circuit with duty cycle correction function

InactiveUS6853225B2Improve accuracyShort lock timePulse automatic controlContinuous to patterned pulse manipulationNegative feedbackDelay-locked loop

A delay locked loop (DLL) circuit having a structure in which a method of performing duty cycle correction (DCC) using two DLLs and an intermediate phase composer and a method of performing DCC by forming a closed loop using a negative feedback are combined with each other is provided. The DLL circuit includes a first DLL for receiving an external clock signal and generating a first clock signal and a second DLL for receiving an external clock signal and generating a second clock signal. The first clock signal and the second clock signal are synchronized with an external clock signal. The DLL circuit further includes an intermediate phase generation circuit for receiving the first and second clock signals and generating an intermediate phase clock signal and a DCC loop for receiving the intermediate phase clock signal and generating an output clock signal. The intermediate phase clock signal has an intermediate phase between the phases of the first and second clock signals. The output clock signal is generated through correction of the duty cycle of the intermediate phase clock signal using a value obtained by integrating the output clock signal.

Owner:SK HYNIX INC

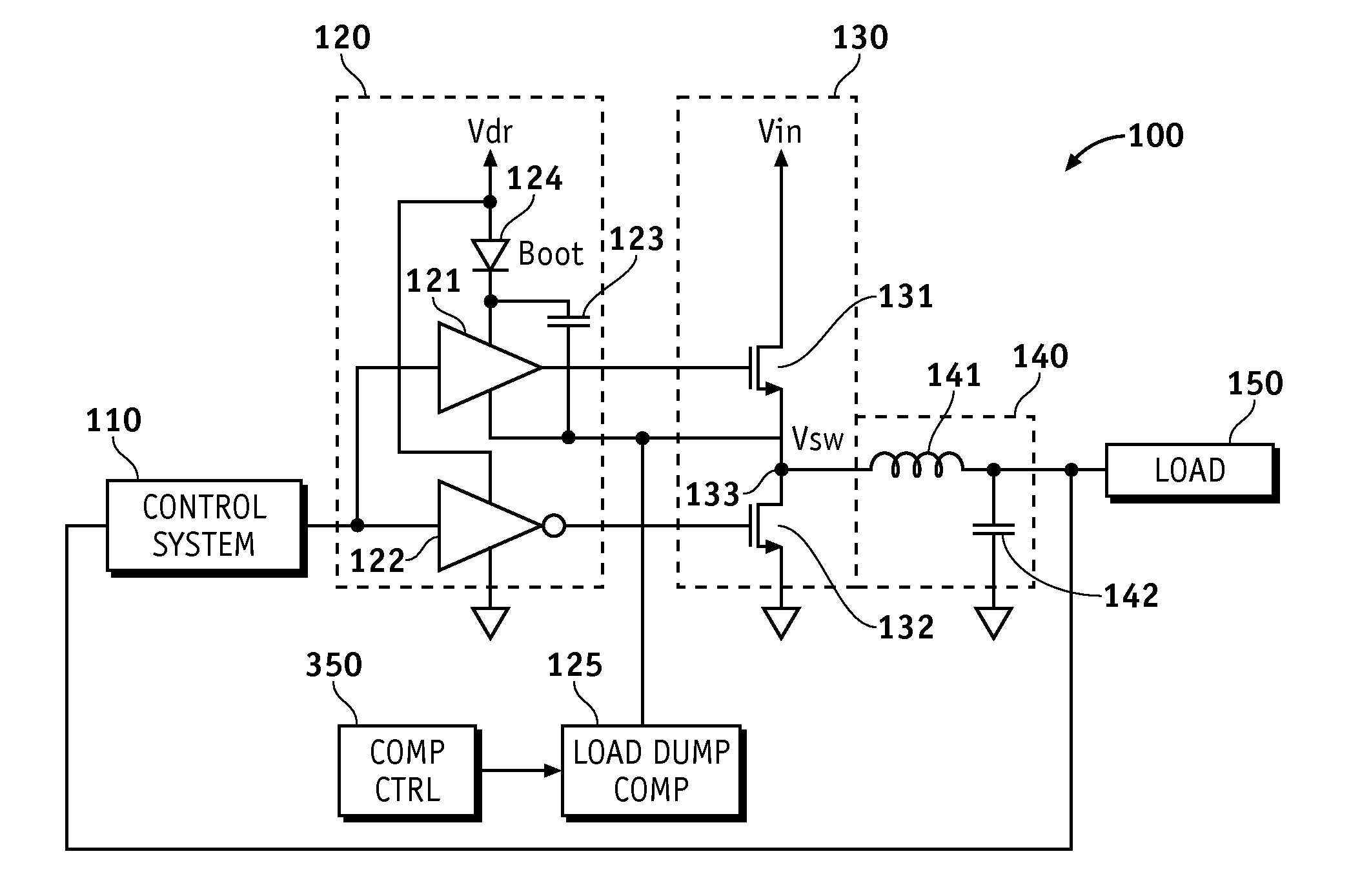

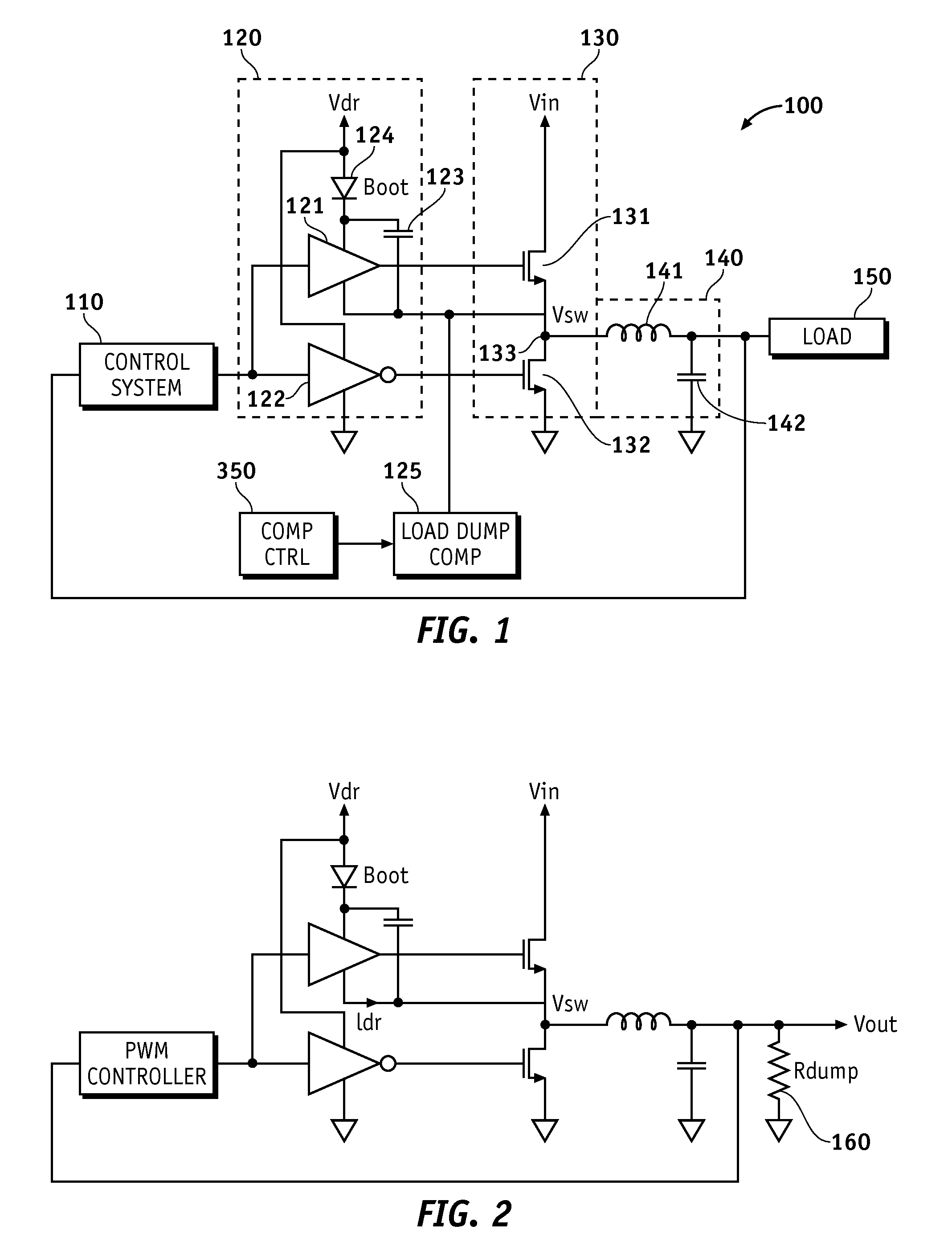

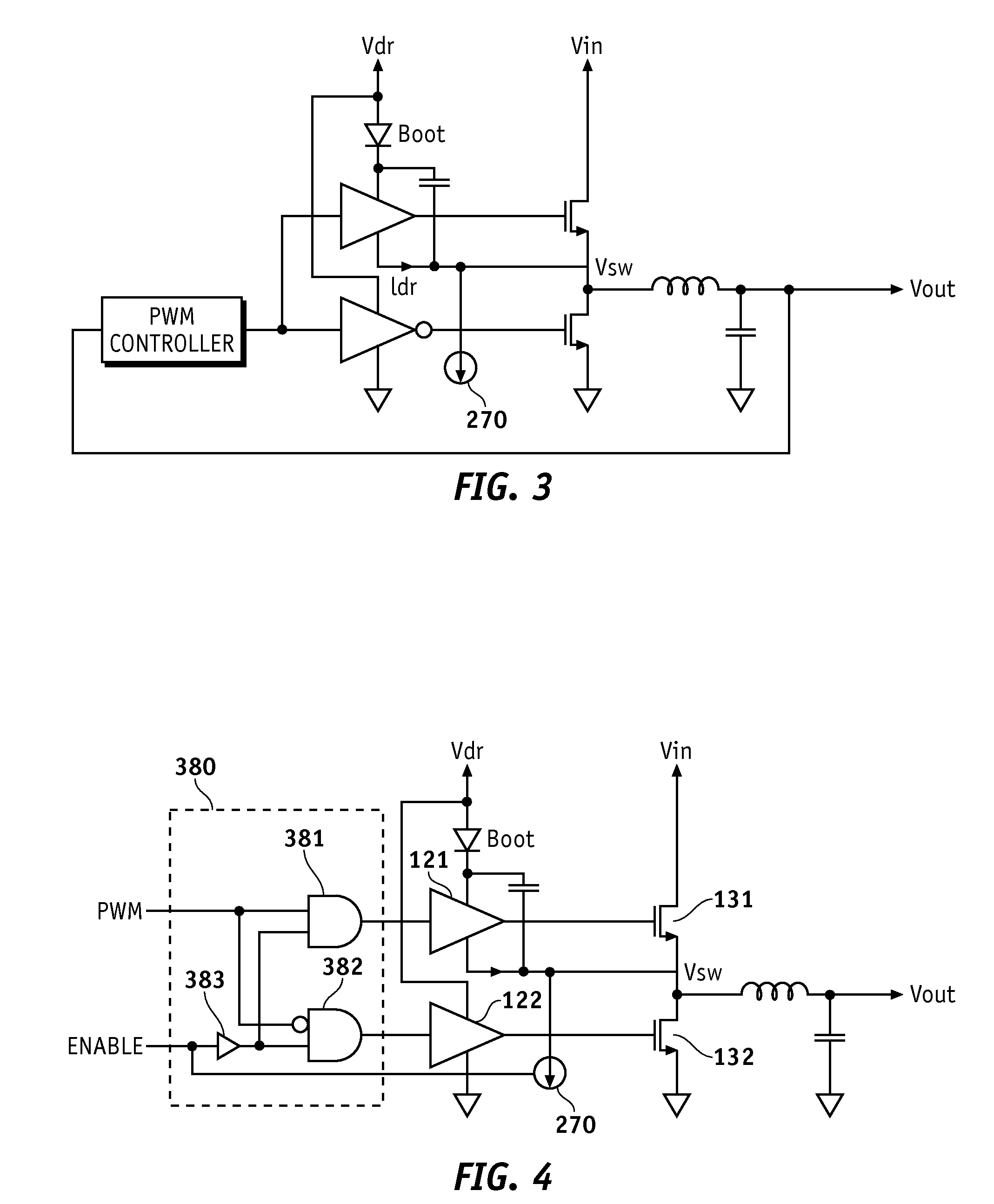

Methods and apparatus for power supply load dump compensation

Methods and apparatus for power supply load dump compensation according to various aspects of the present invention may operate in conjunction with a power stage system, such as a power stage system comprising a bootstrapped driver circuit and a power stage responsive to the driver circuit. The power stage system may further include a load dump compensation circuit connected to the driver circuit, wherein the load dump compensation circuit is configured to remove a bias current generated by the bootstrapped driver circuit. Various aspects of the present invention may be implemented in conjunction with any appropriate power supply, such as a switching regulator, for example a buck converter.

Owner:INFINEON TECH AUSTRIA AG

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS7535957B2Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation.[Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

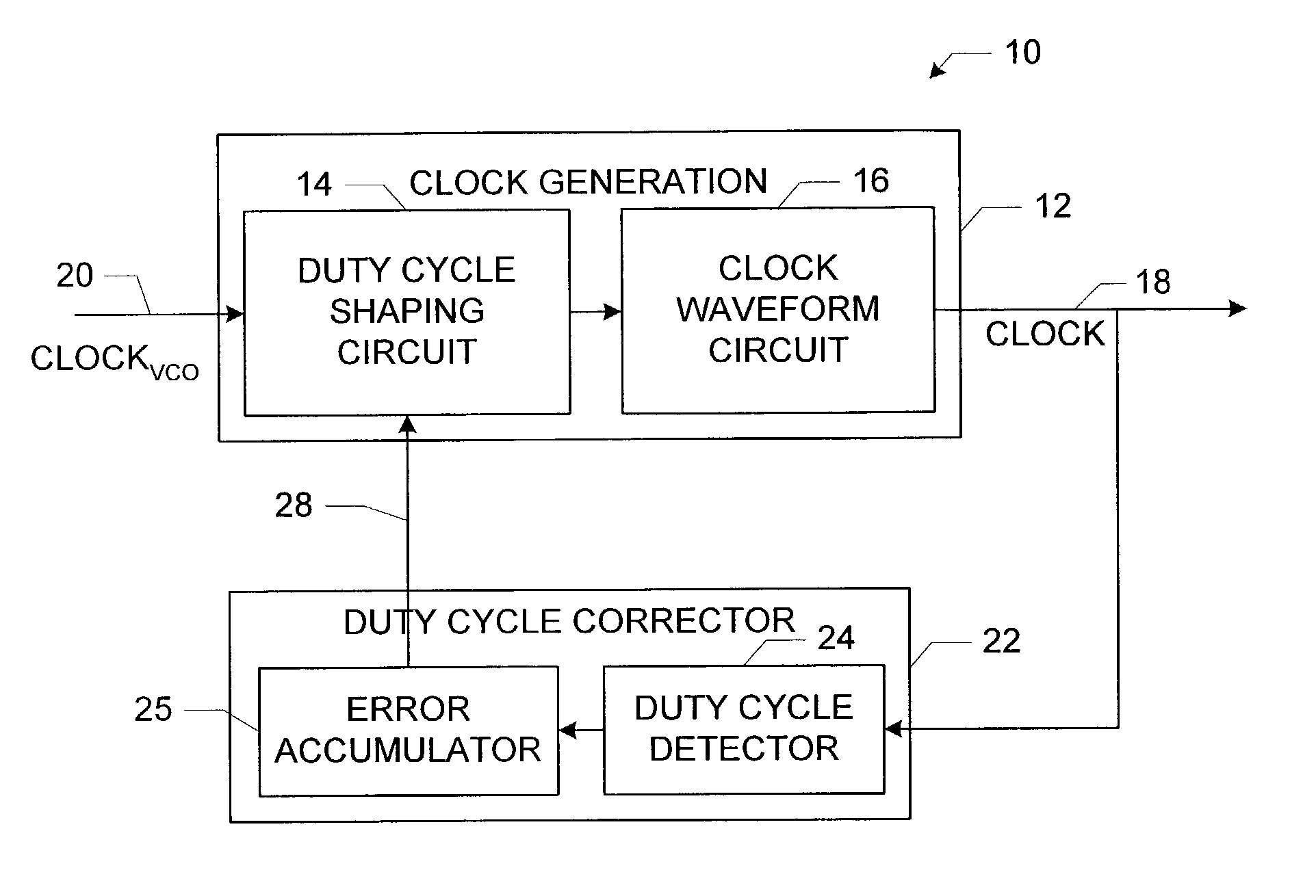

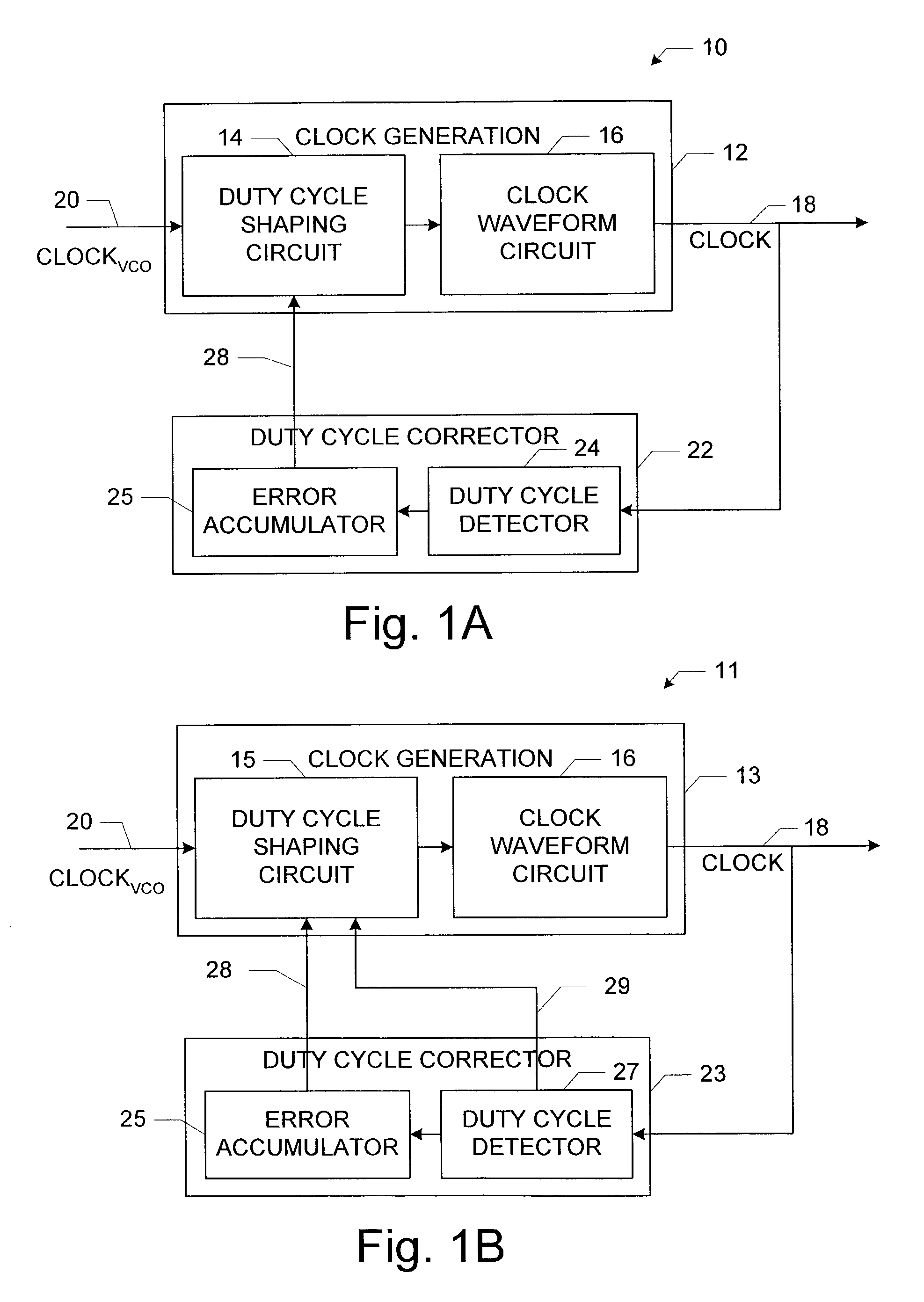

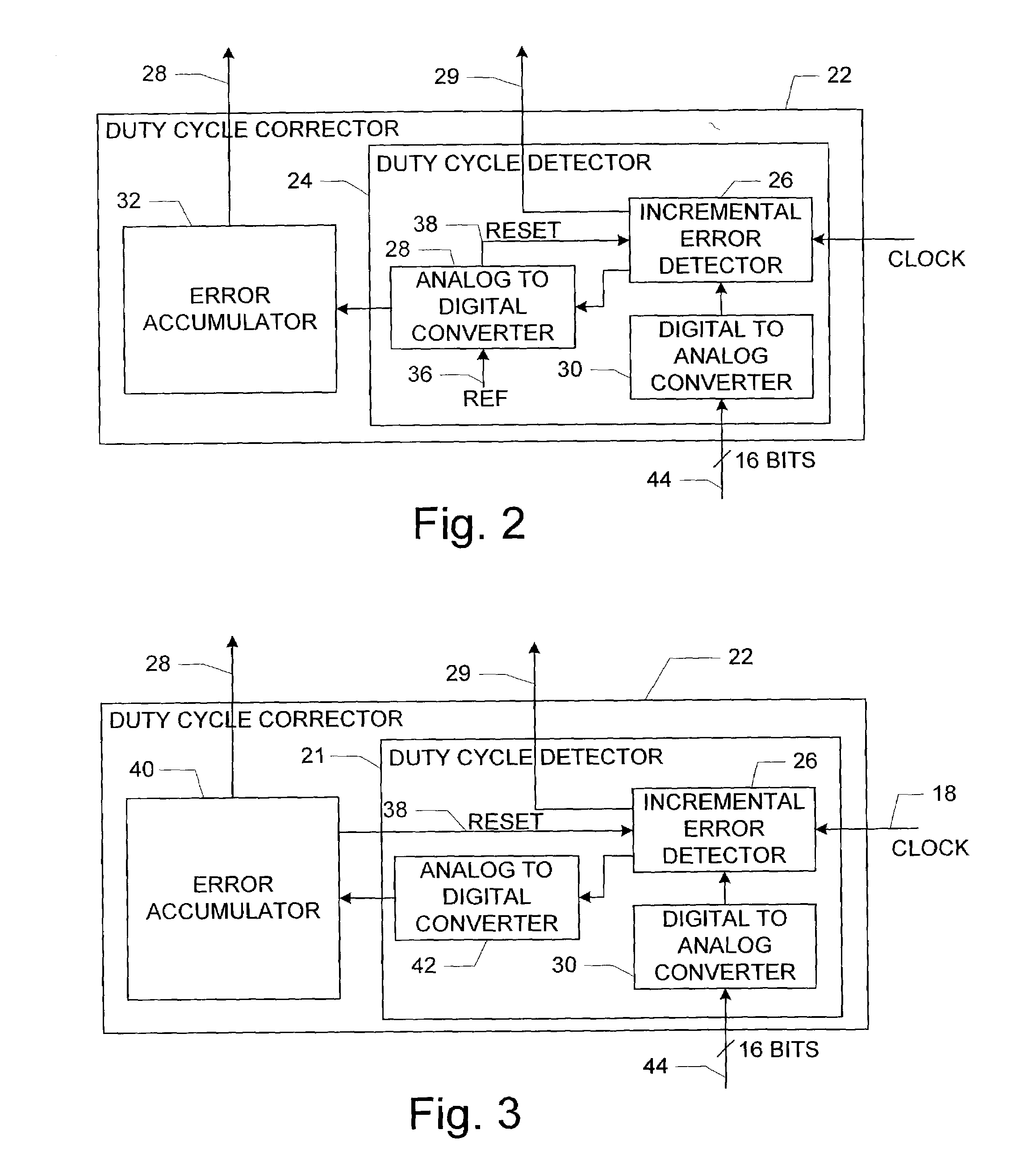

Method and apparatus for digital duty cycle adjustment

InactiveUS6967514B2Reliability increasing modificationsContinuous to patterned pulse manipulationError signalClock signal

Adjusting a clock duty cycle. An incremental error signal is generated in response to the clock signal. A cumulative error signal is generated in response to the incremental error signal. The incremental error signal is reset and the duty cycle of the clock signal is adjusted in response to the cumulative error signal.

Owner:RAMBUS INC

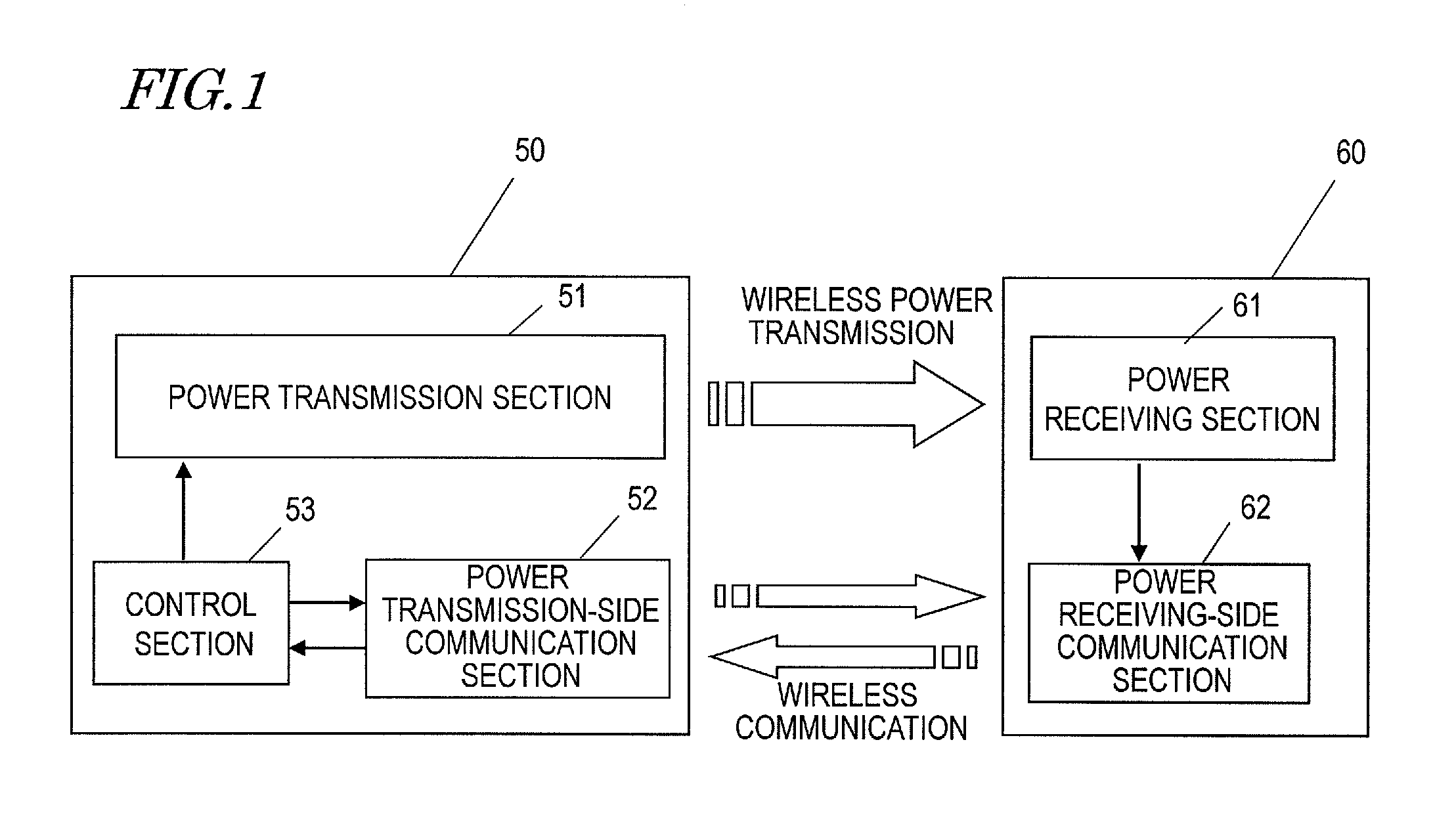

Power transmitter and wireless power transmission system

ActiveUS20120063505A1Stable wireless power transmissionStable power deliveryMicrophonesElectrical transducersElectric power transmissionTransmitted power

A power transmitter 50 is usable in a wireless power transmission system for transmitting power wirelessly. The power transmitter 50 includes a power transmitting section 51 for transmitting power; a communication section 52 for communicating information, for controlling the transmission of the power, with the power receiver 60; and a control section 53 for controlling the power transmitting section 51 such that the power to be sent out by the power transmitting section 51 is higher while the communication section 52 is performing the communication.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

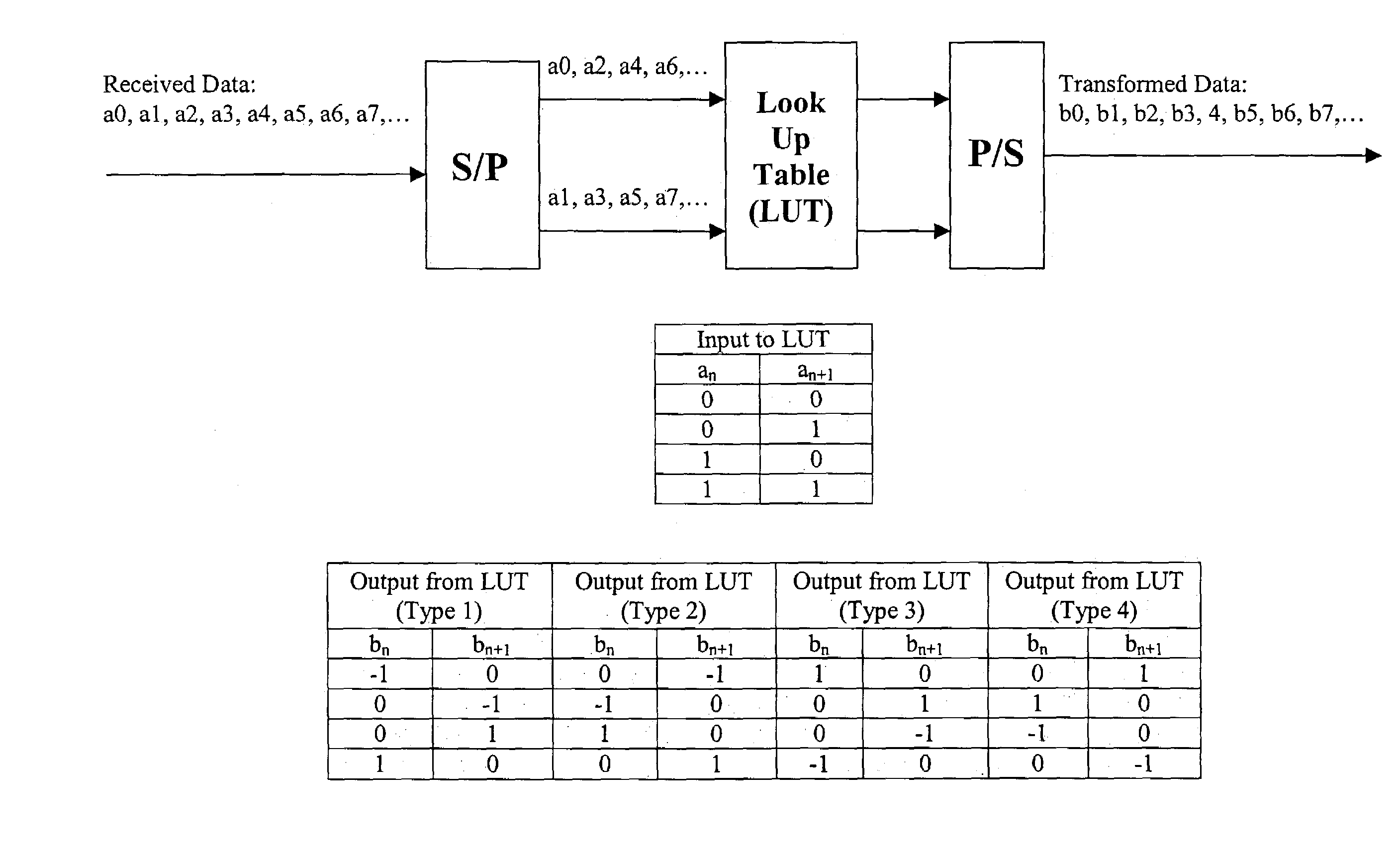

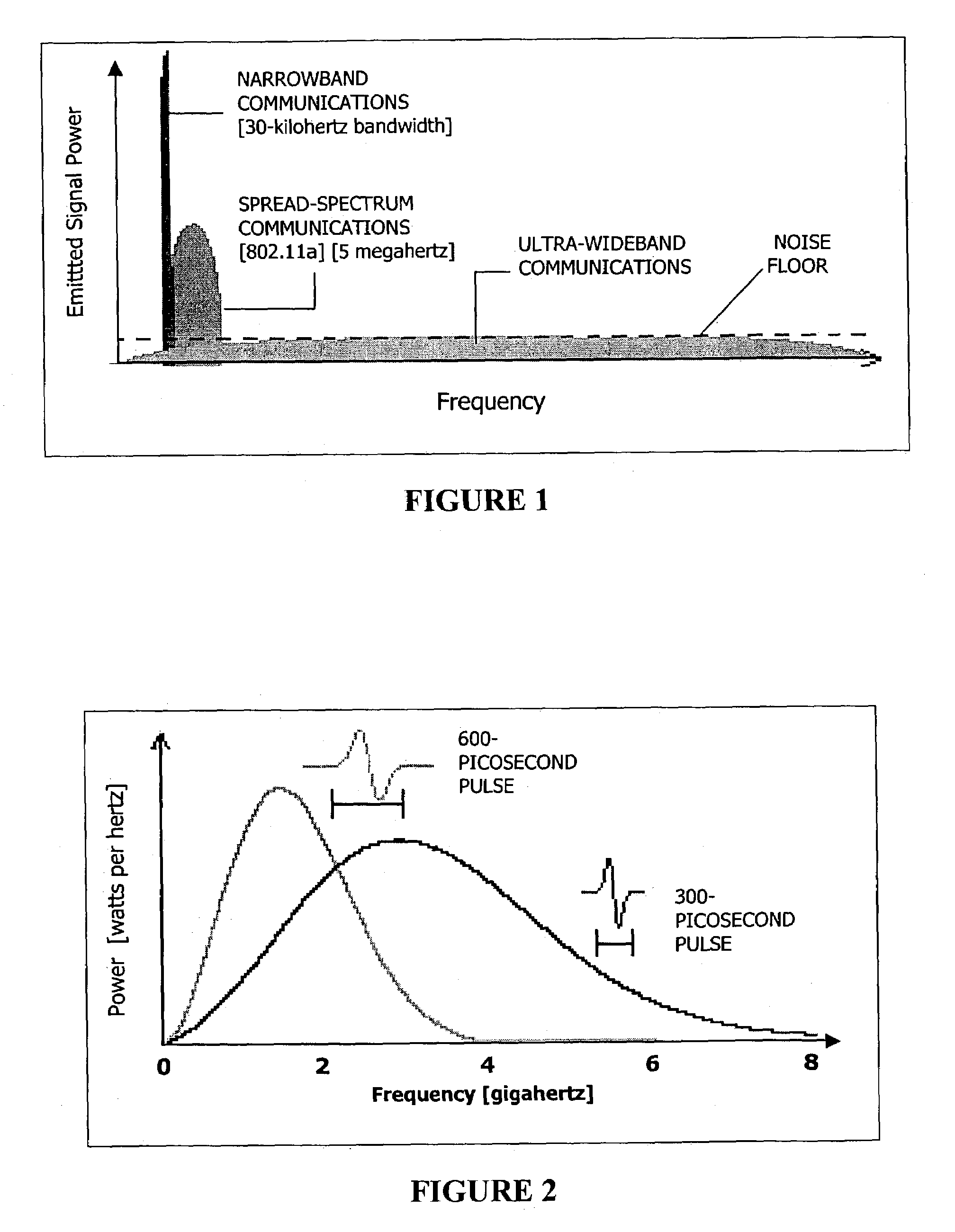

Ultra-wideband pulse modulation system and method

InactiveUS7190722B2Available bandwidth of communicationIncrease powerFrequency/rate-modulated pulse demodulationIndividual digits conversionUltra-widebandFiber

An ultra-wideband pulse modulation system and method is provided. One method of the present invention includes transforming data into a ternary data set with data being represented with states of zero, positive one and negative one. The modulation and pulse transmission method of the present invention enables the simultaneous coexistence of the ultra-wideband pulses with conventional carrier-wave signals. The present invention may be used in wireless and wired communication networks such as hybrid fiber-coax networks. This Abstract is provided for the sole purpose of complying with the Abstract requirement rules that allow a reader to quickly ascertain the subject matter of the disclosure contained herein. This Abstract is submitted with the explicit understanding that it will not be used to interpret or to limit the scope or the meaning of the claims.

Owner:INTELLECTUAL VENTURES HLDG 73

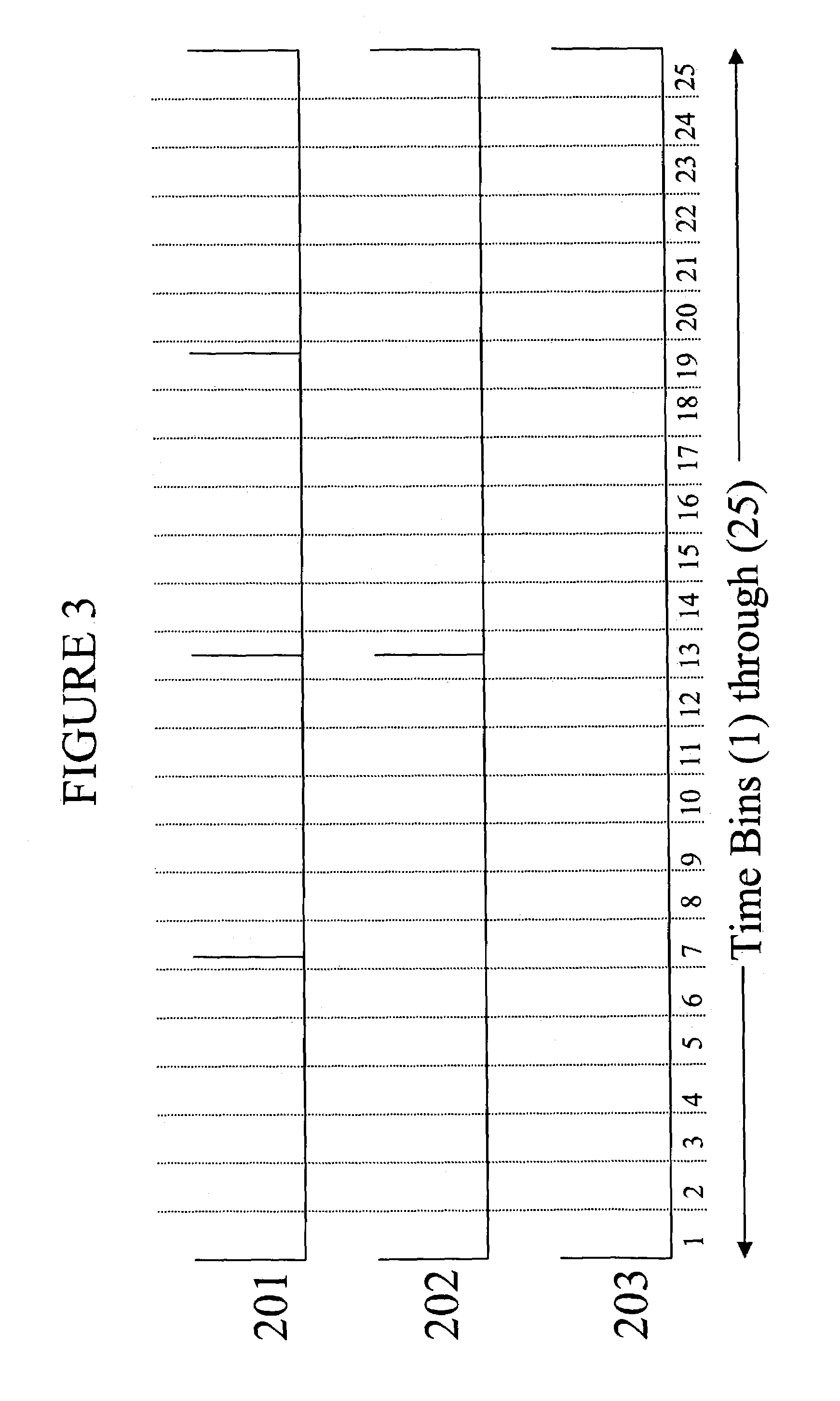

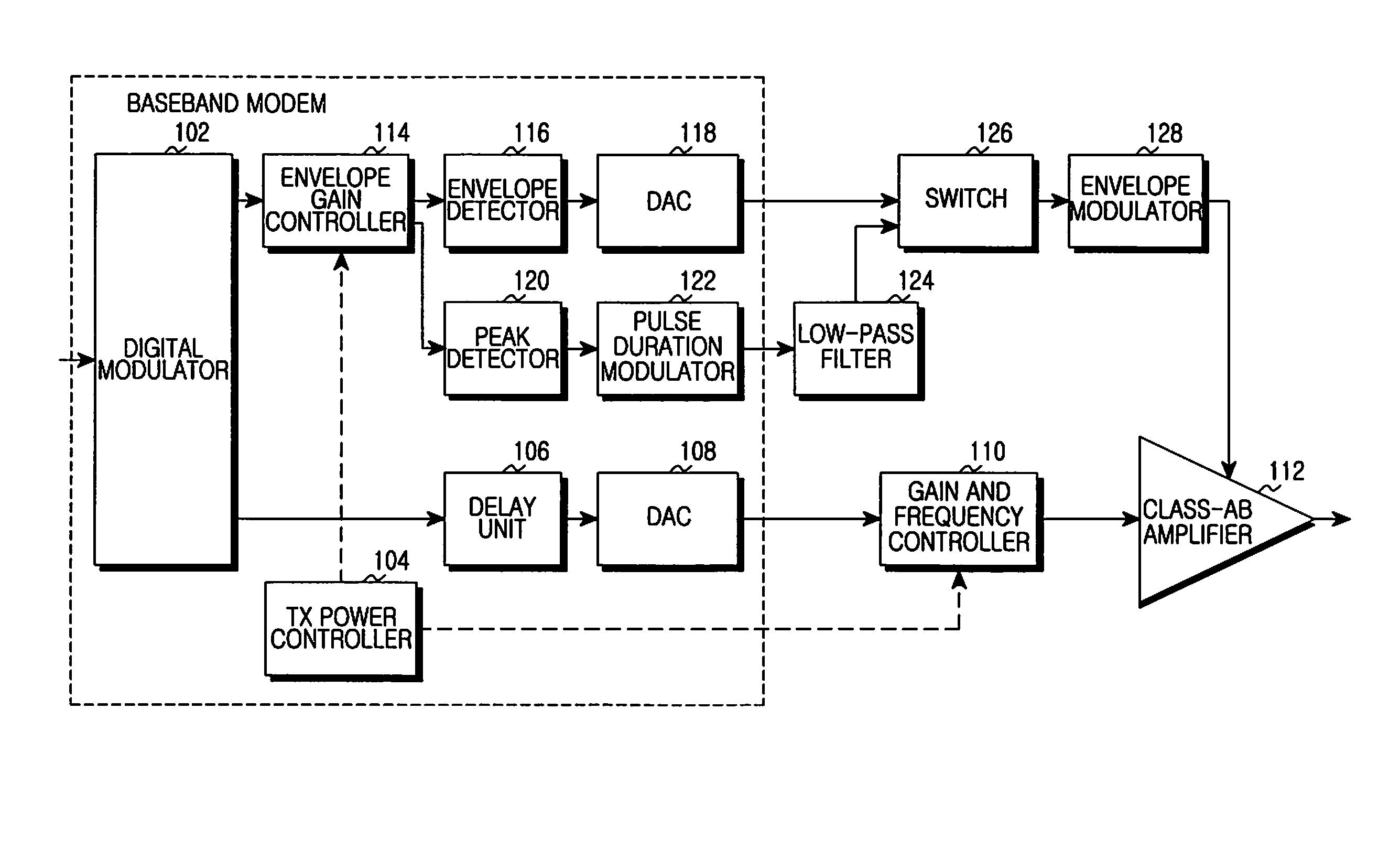

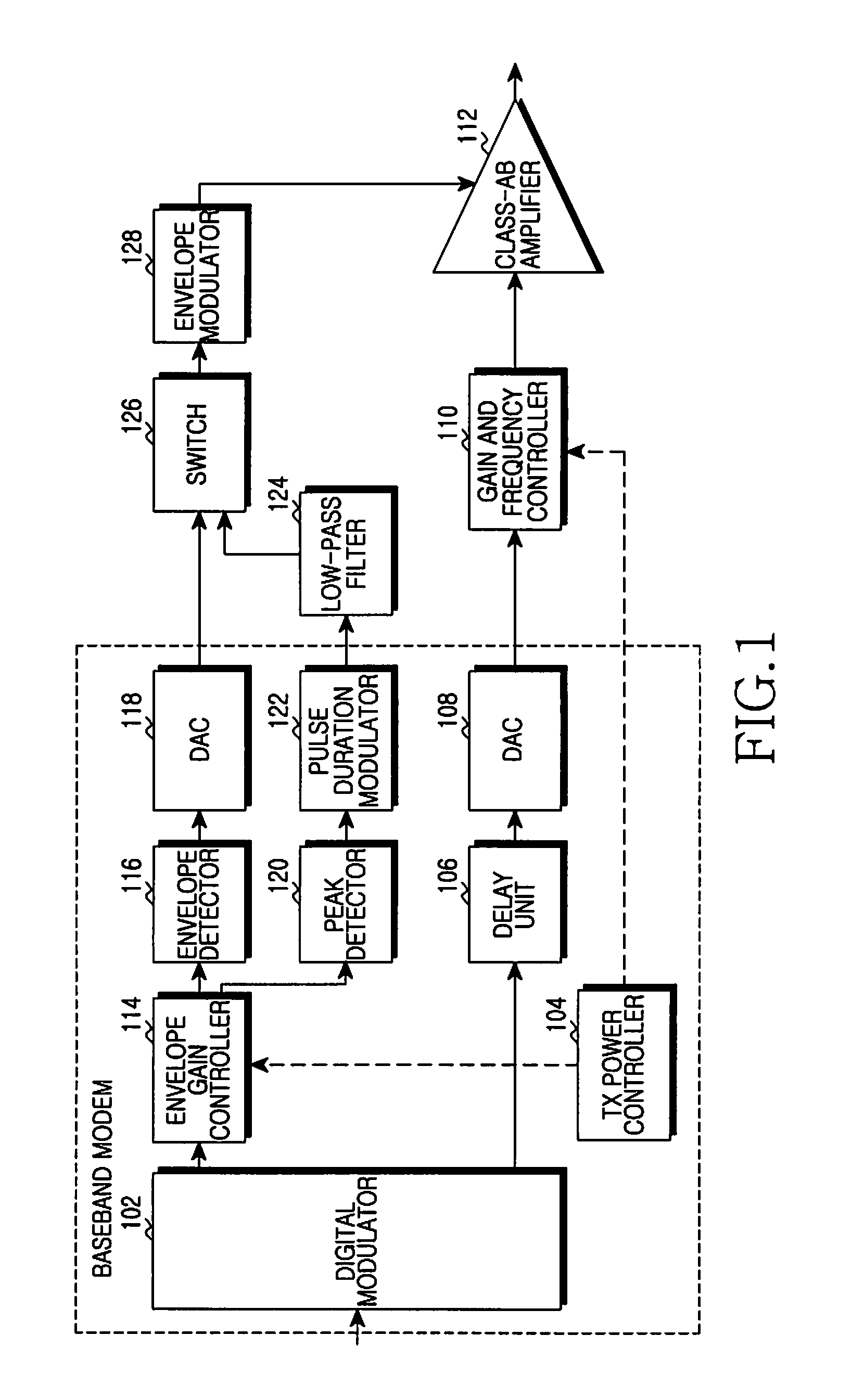

Apparatus and method for envelope tracking power amplifier in wireless communication system

ActiveUS20110058601A1Enhanced signalPulse automatic controlModulated-carrier systemsCommunications systemAudio power amplifier

An apparatus and method for amplifying a Transmit (Tx) signal according to an Envelope Tacking (ET) scheme in a wireless communication system are provided. A transmitting end apparatus includes an envelope gain controller for controlling a gain of a digital baseband Tx signal in accordance with power control, a detector for detecting an envelope signal from the digital baseband Tx signal whose gain is controlled, and for shaping on the envelope signal, a first Digital to Analog Converter (DAC) for converting the shaped envelope signal into an analog signal, and an envelope modulator for generating a drain bias of a power amplifier that amplifies a Radio Frequency (RF) Tx signal by using the analog envelope signal. Accordingly, a digital-based ET scheme is implemented, and by using a plurality of shaping tables, efficiency of the ET scheme can be maximized in a transmitting end that uses power control.

Owner:SAMSUNG ELECTRONICS CO LTD

PWM controller with dual-edge modulation using dual ramps

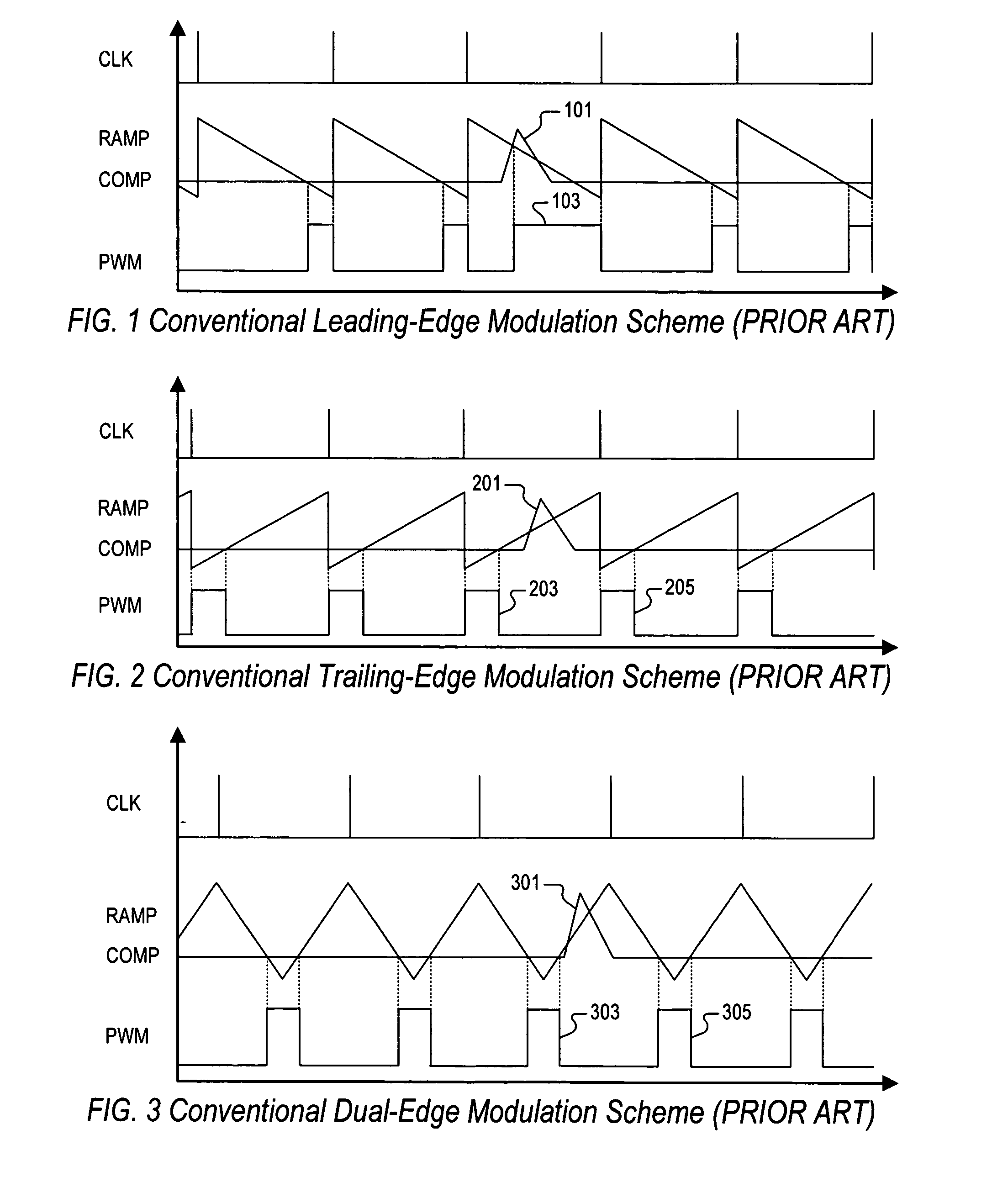

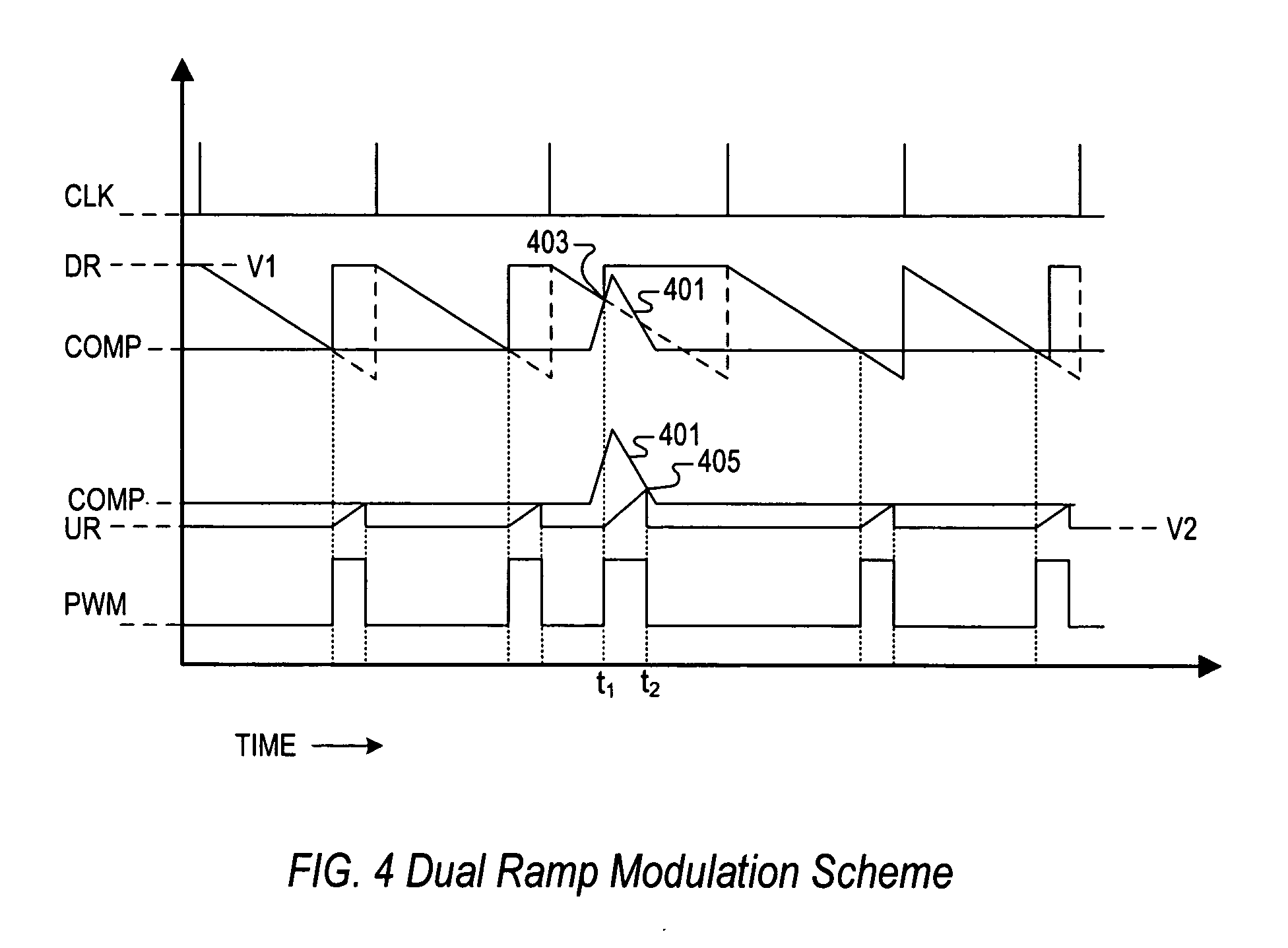

ActiveUS20070013356A1Efficient power electronics conversionDc-dc conversionLeading edgePulse control

A dual-edge modulation controller including first and second ramp circuits, first and second comparators, an error amplifier and pulse control logic. The first ramp circuit provides a leading-edge ramp synchronous with a clock. The error amplifier compares a feedback signal with a reference and provides a compensation signal. The first comparator compares the leading-edge ramp with the compensation signal and asserts a set signal. The second ramp circuit provides a trailing-edge ramp that begins ramping when the set signal is asserted. The second comparator compares the trailing-edge ramp with the compensation signal and asserts a reset signal. The pulse control logic asserts a PWM signal when the set signal is asserted and de-asserts the PWM signal when the reset signal is asserted. The controller may control multiple phases with current balancing. The slew rate of the ramps may be adjusted based on the number of PWM signal asserted.

Owner:INTERSIL INC

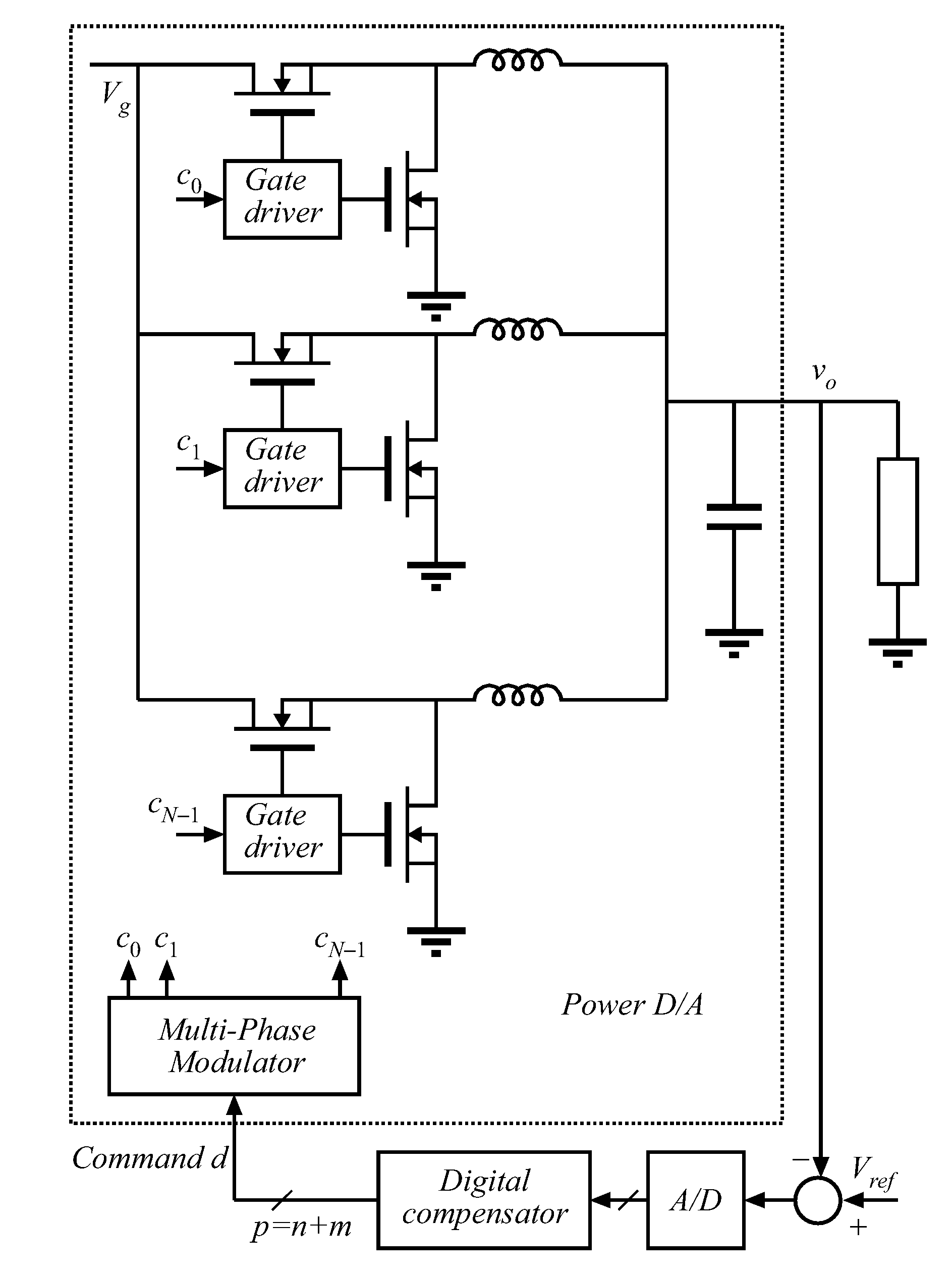

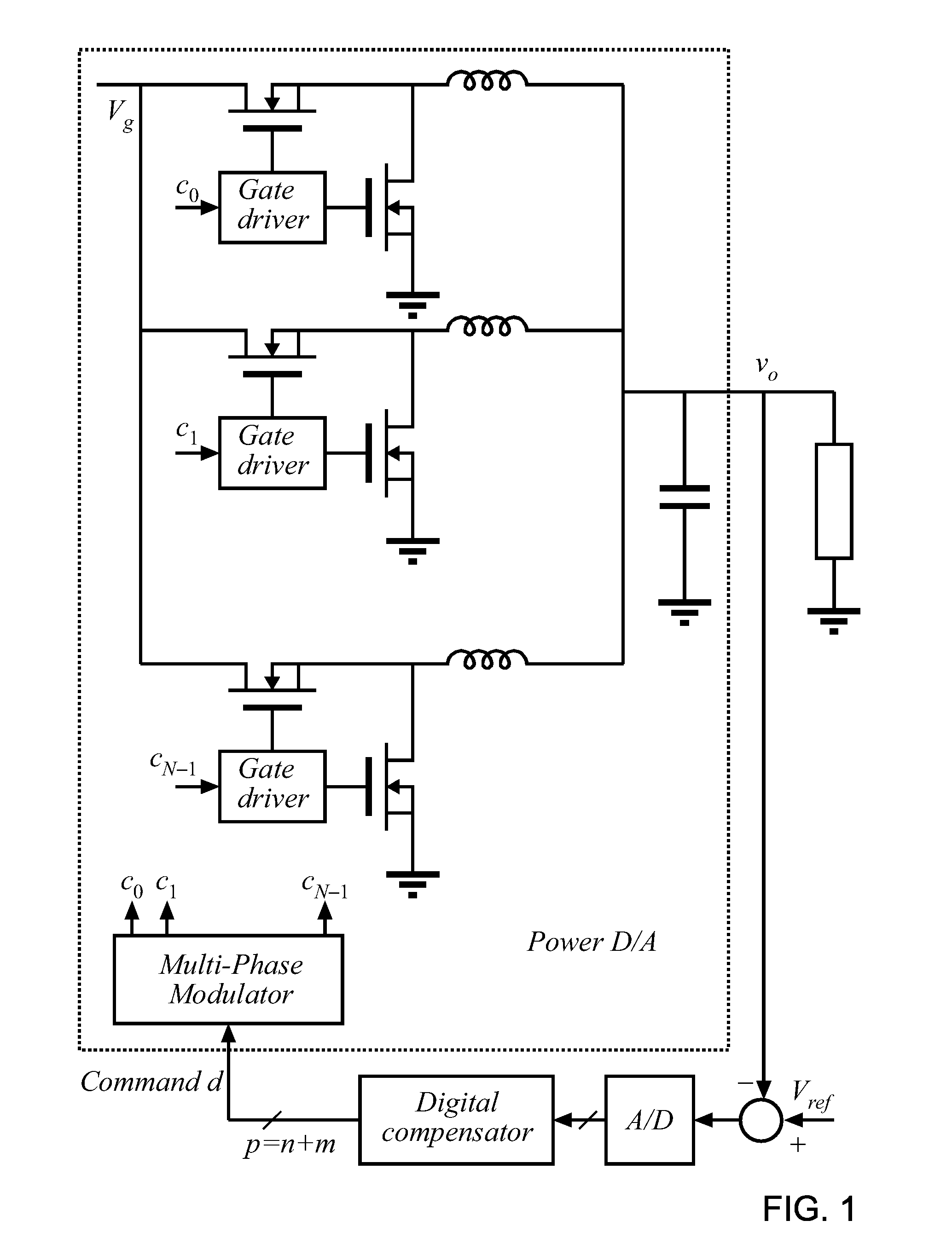

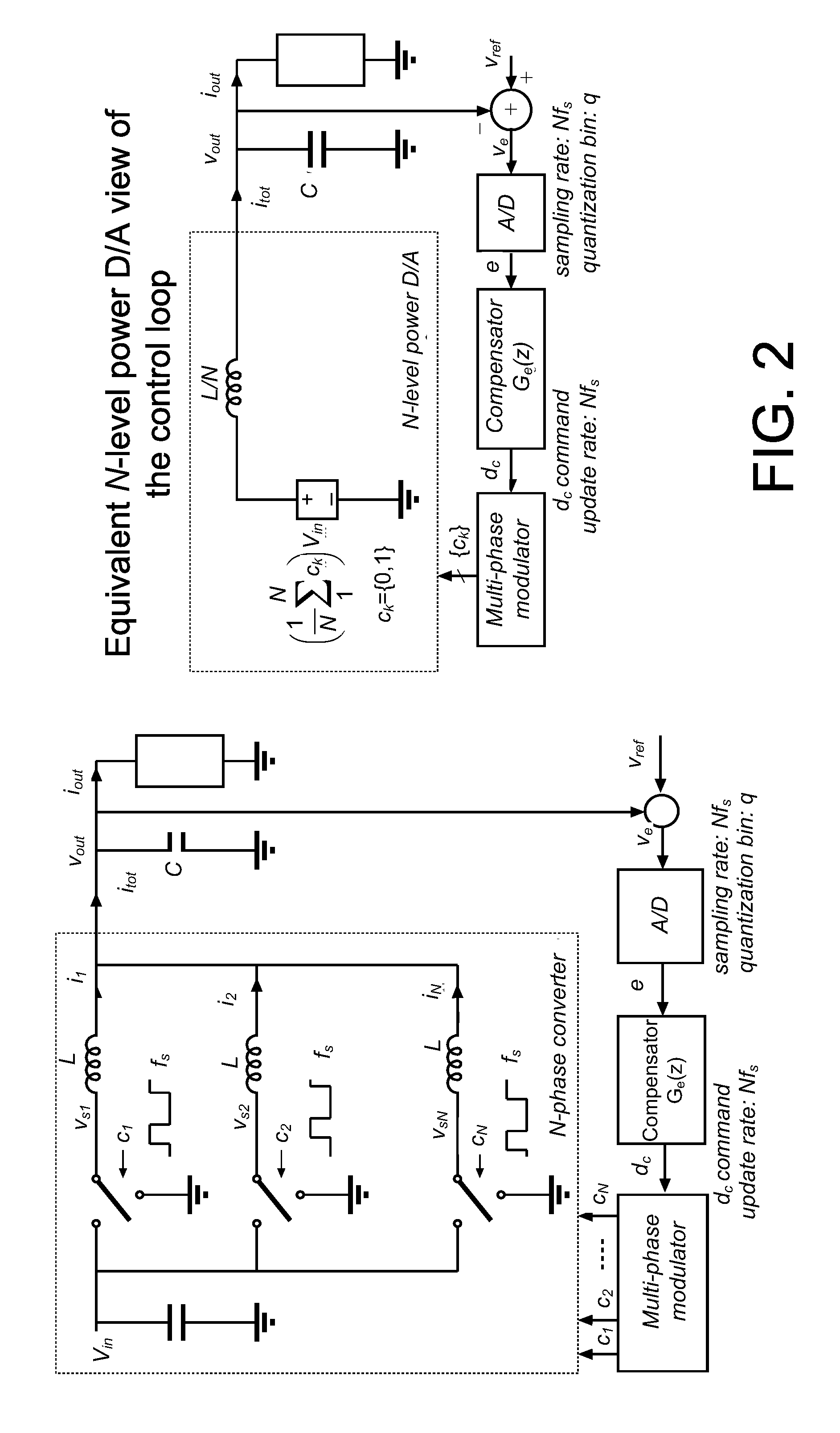

Multi-phase modulator

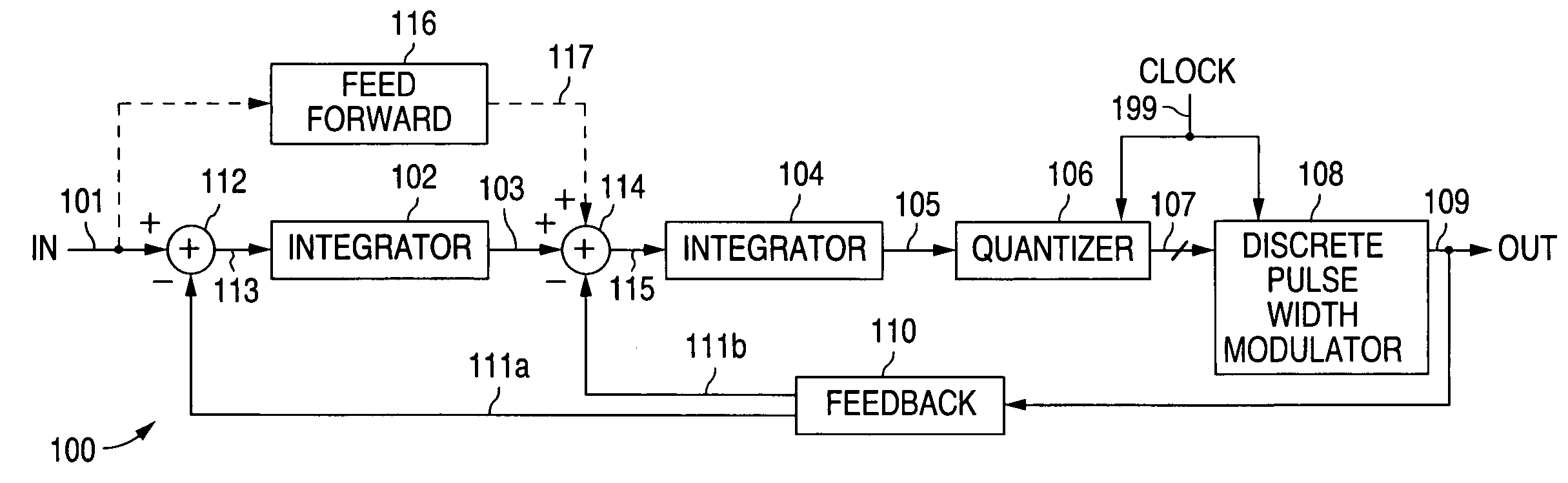

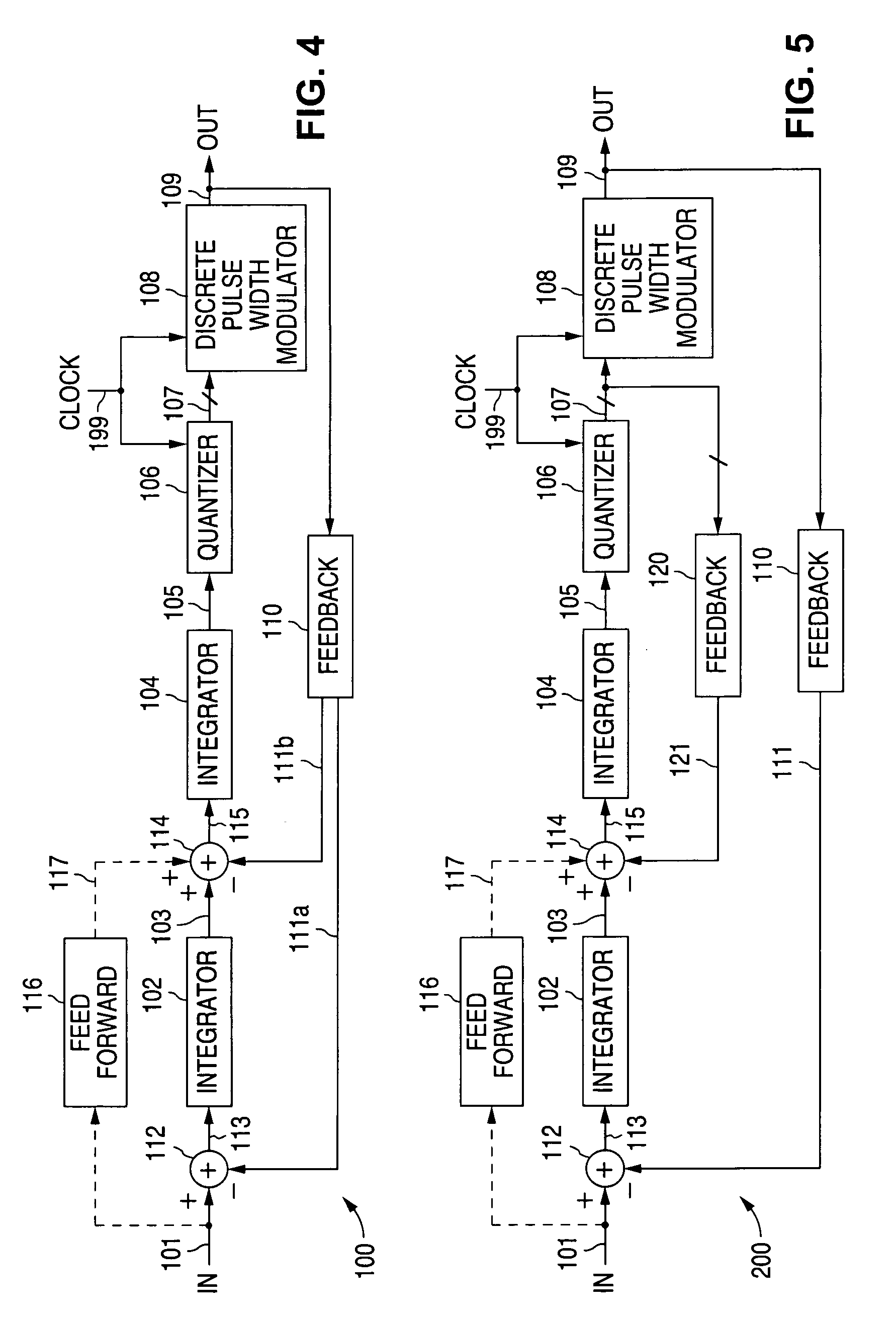

ActiveUS20080310200A1Dc-dc conversionDc source parallel operationResolution enhancement technologiesImage resolution

An architecture is described for digital multi-phase modulators (MPM) that leads to an efficient, high performance hardware realization. The combined modulator, switching phases and output filter can be viewed as a multi-level digital to analog converter with high power output, or a power D / A, and concepts used in D / A converters are leveraged to achieve high performance and hardware efficiency. The modulator can be split into three functional blocks including a decoder that determines how many phases are on at any time, a selector that determines which phases are on at any time, and a single high resolution module that is time shared among all phases. The resulting architecture scales favorably with a large number of phases, fs, facilitates fast update rates of the input command well above the single phase switching frequency and is compatible with a wide range of known DPWM techniques for the LSB module and resolution-enhancement techniques such as dithering or Σ-Δ modulation.

Owner:UNIV OF COLORADO THE REGENTS OF

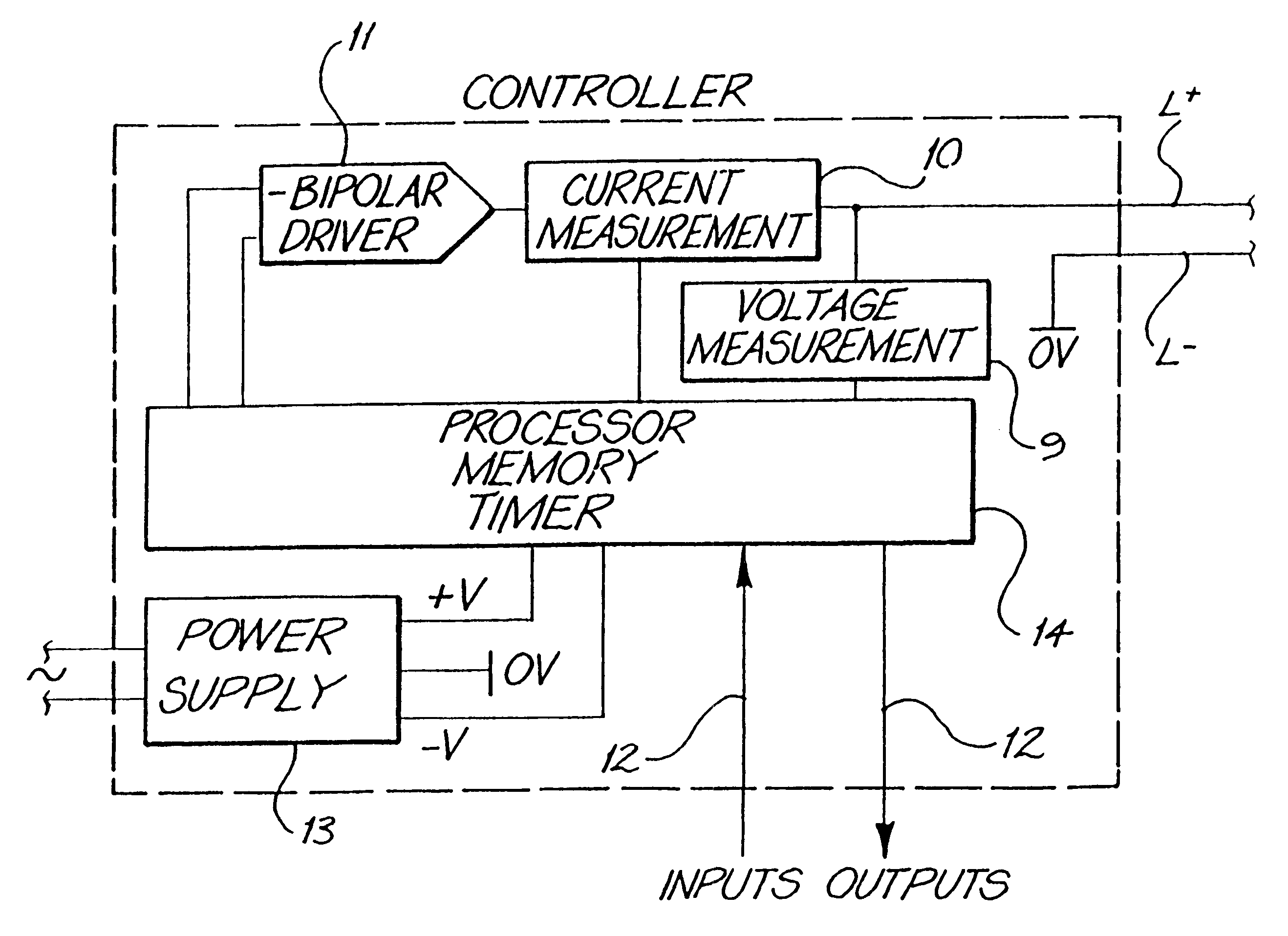

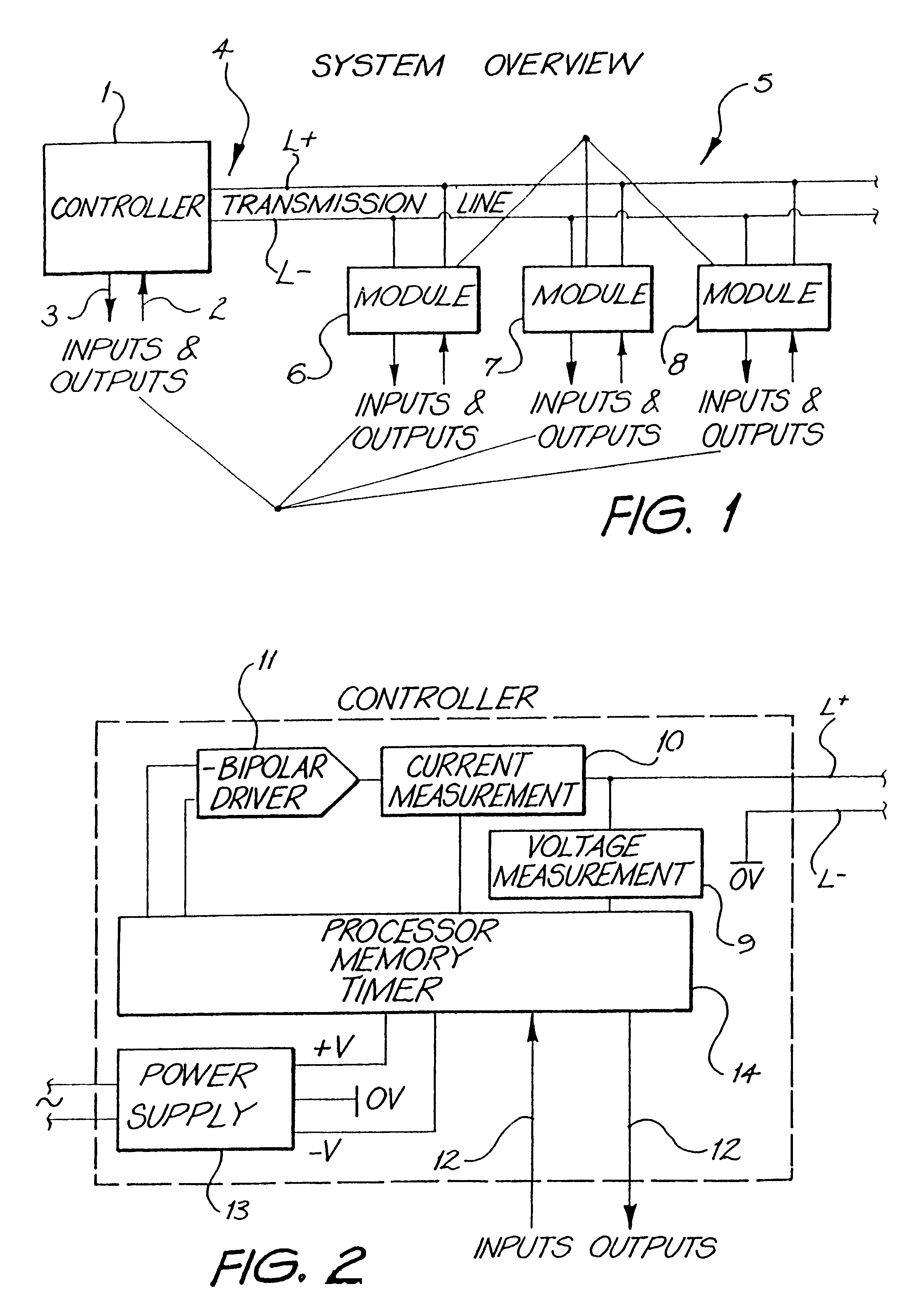

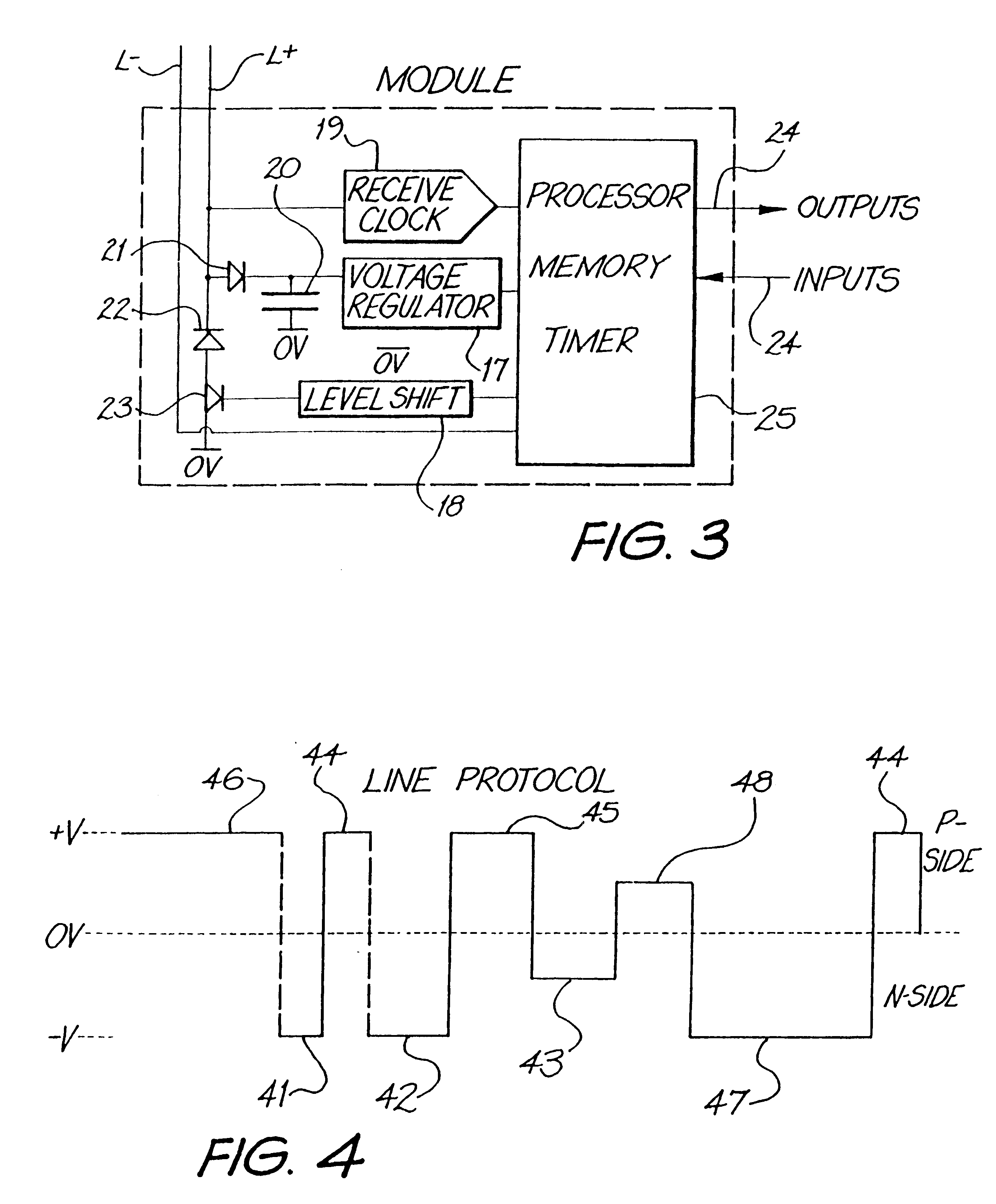

Two wire communication system

InactiveUS6459363B1Without loss of data transmission timeElectric signal transmission systemsTransmission/receiving by adding signal to waveElectric power transmissionElectrical conductor

A two wire communication system capable of transmitting data and transferring power by the used of an electrical bi-polar waveform across a two wire conductor from a controller in communication with the two-wire conductor to at least one module in communication with the controller and capable of transmitting data from the module to the controller; and a remote electrical device in communication with the controller. Usable data may be continuously transmitted across the two wire conductor independent of and during power transmission between the controller and the at least one module without loss of data transmission time and without affecting the transfer of power to the at least one module. The data is transmitted across the two wire conductor to the modules by pulse duration signals at the same time power is transmitted to the modules. The system is capable of using up to 100% of transmission time to transmit data without affecting transfer of power to the at least one module.

Owner:AMPCONTROL PTY LTD

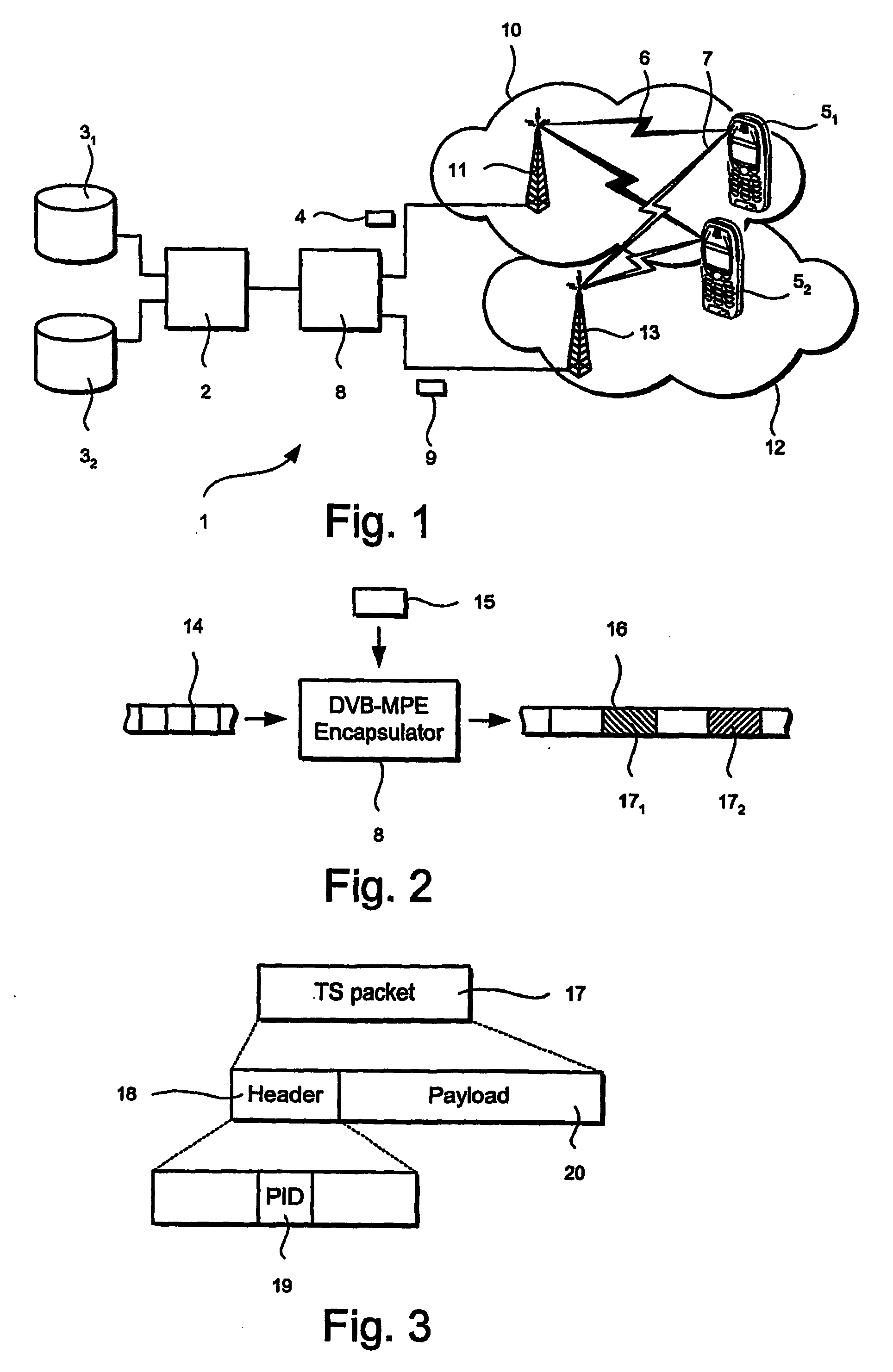

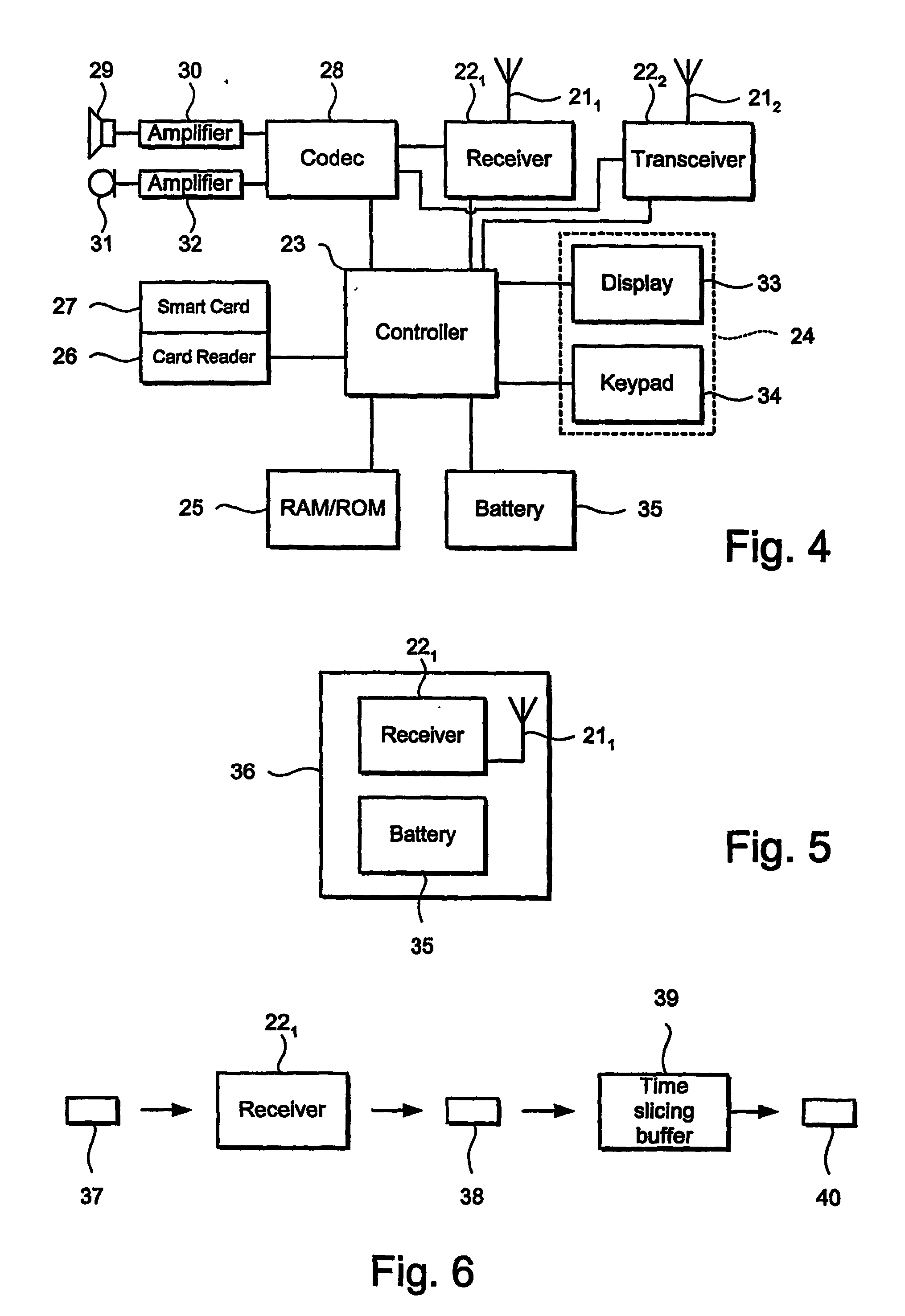

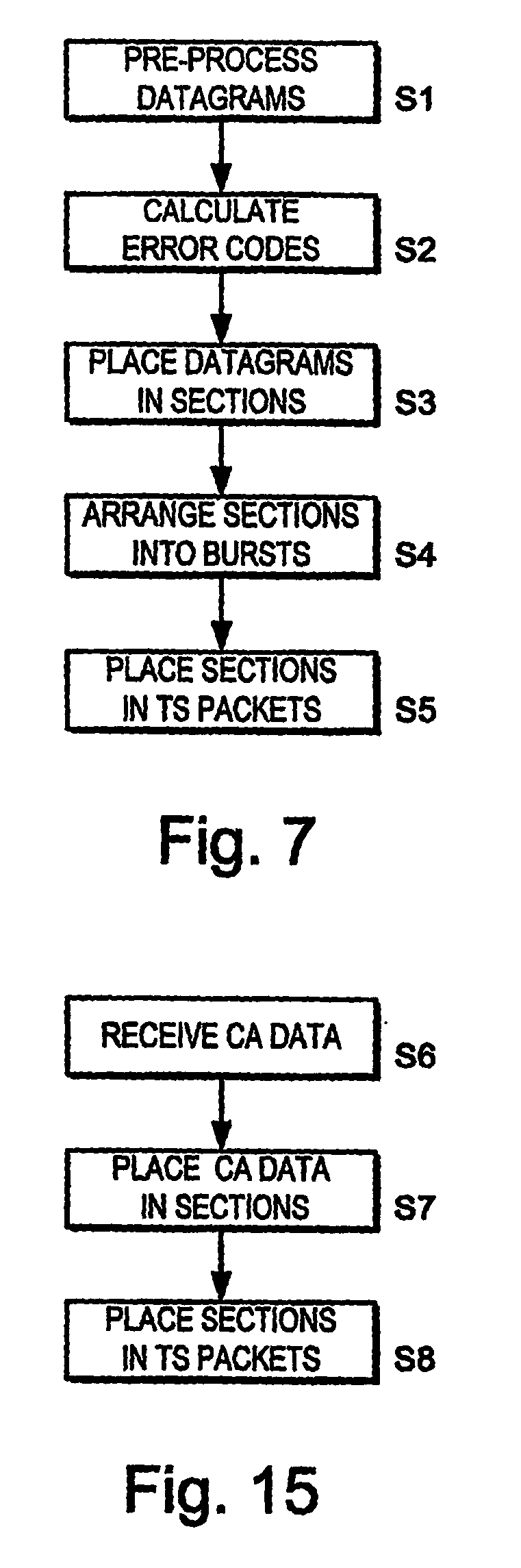

Burst transmission

ActiveUS20060245488A1Pulse modulation television signal transmissionError preventionBurst transmissionMultiprotocol Encapsulation

A terrestrial digital video broadcasting (DVB-T) network is used to transmit IP datagrams to receiving devices using multiprotocol encapsulation (MPE). MPE datagram section and, if forward error correction (FEC) is used, MPE-FEC datagram sections may include time-slicing parameters, such as a “delta-t” parameter for specifying a time until the next burst is transmitted and a flag for indicating the end of a burst. Thus, MPE and MPE-FEC datagram sections can be transmitted in bursts. Other types of sections, however, do not include such time-slicing parameters and thus cannot usually be transmitted in bursts. Nevertheless, by assembling a burst including at least one MPE or MPE-FEC datagram section which specifies delta-t and MPE or MPE-FEC datagram section at the end of a burst which indicates its position, other types of sections can benefit from being transmitted in bursts.

Owner:HTC CORP

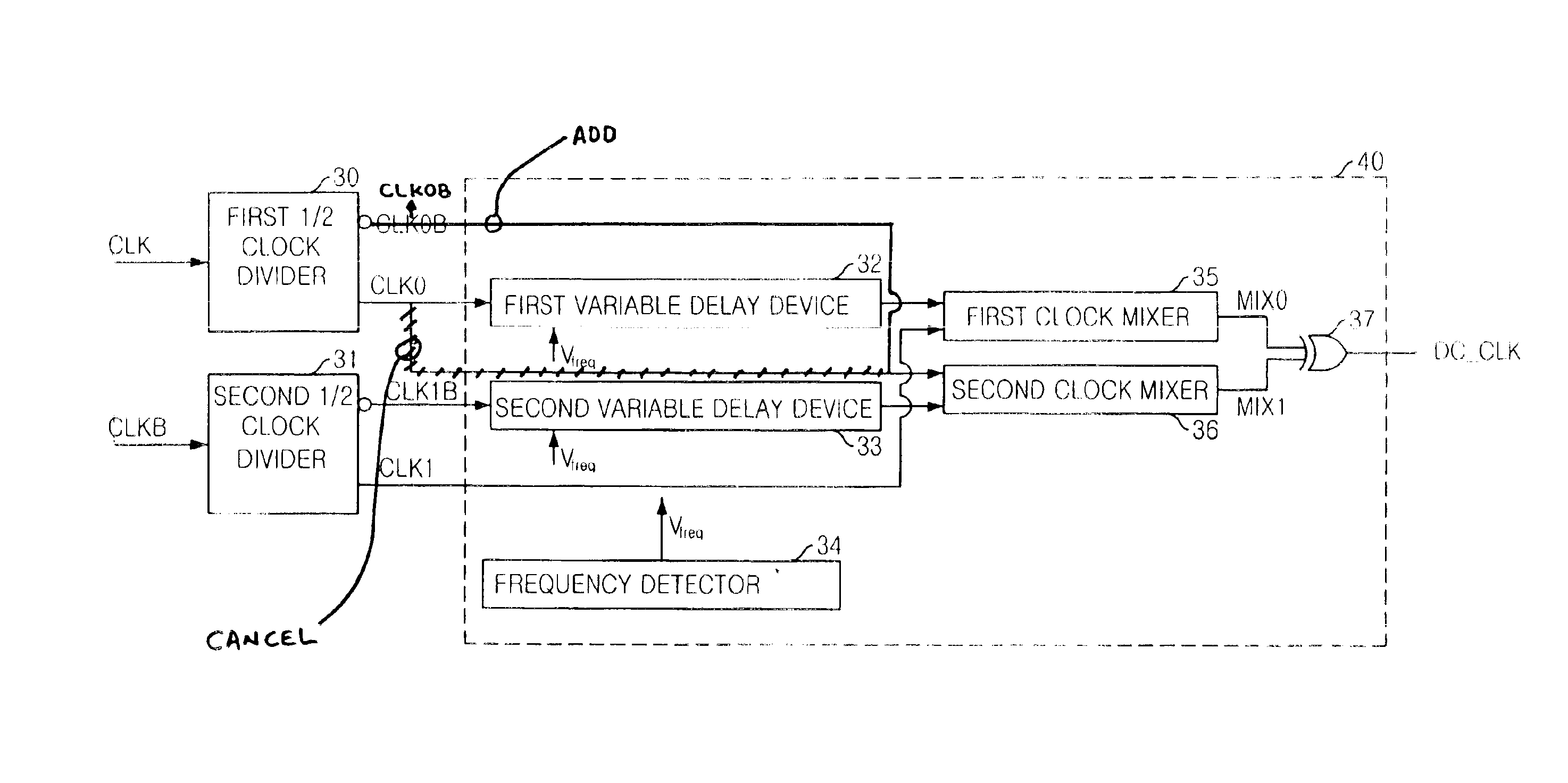

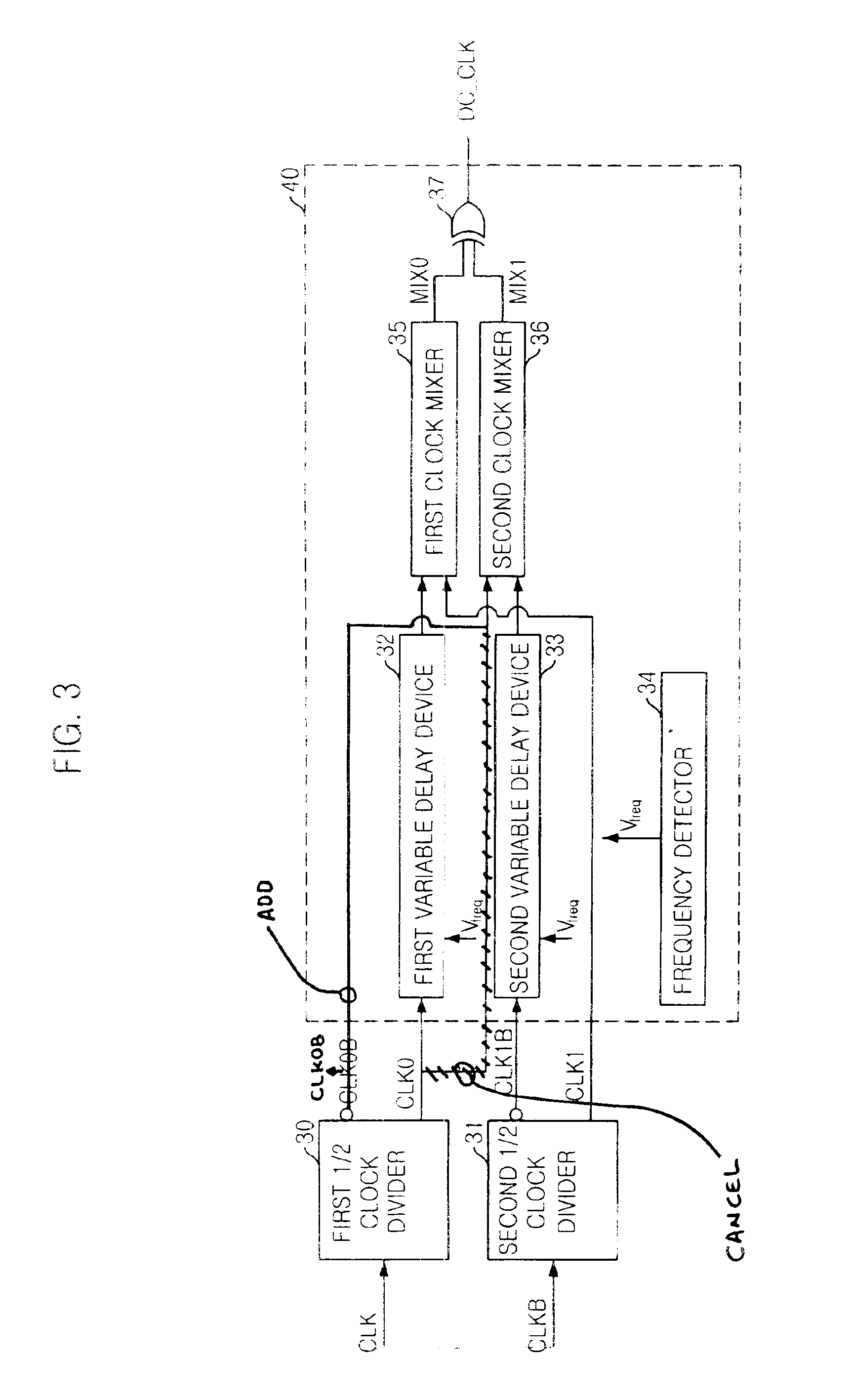

Duty cycle correction circuit and delay locked loop having the same

InactiveUS6859081B2Reduce power consumptionPulse automatic controlContinuous to patterned pulse manipulationClock rateFrequency mixer

A duty cycle correction (DCC) circuit including first and second clock dividers for dividing ordinary and sub-input clocks. Optional first and second variable delay devices delay the divided clocks. First and second mixers mix an optionally delayed ordinary divided clock and sub-ordinary divided clock, or an ordinary divided clock and an optionally delayed sub-ordinary divided clock. A logic combination device is included to produce a clock at the same frequency as the ordinary and sub-input clocks, with a corrected duty cycle.

Owner:CONVERSANT INTPROP MANAGEMENT INC

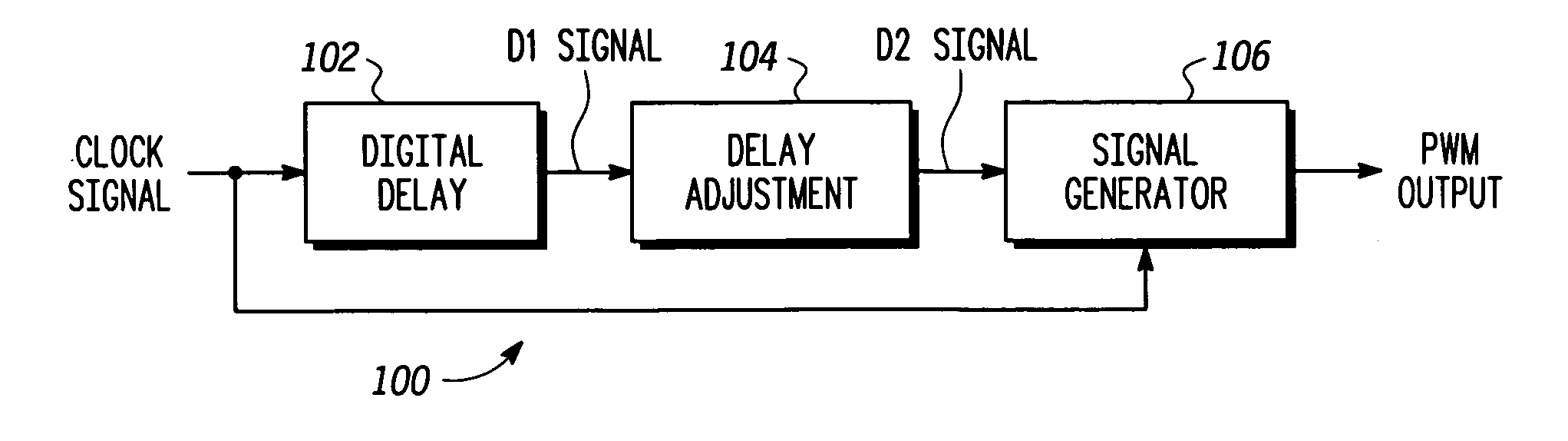

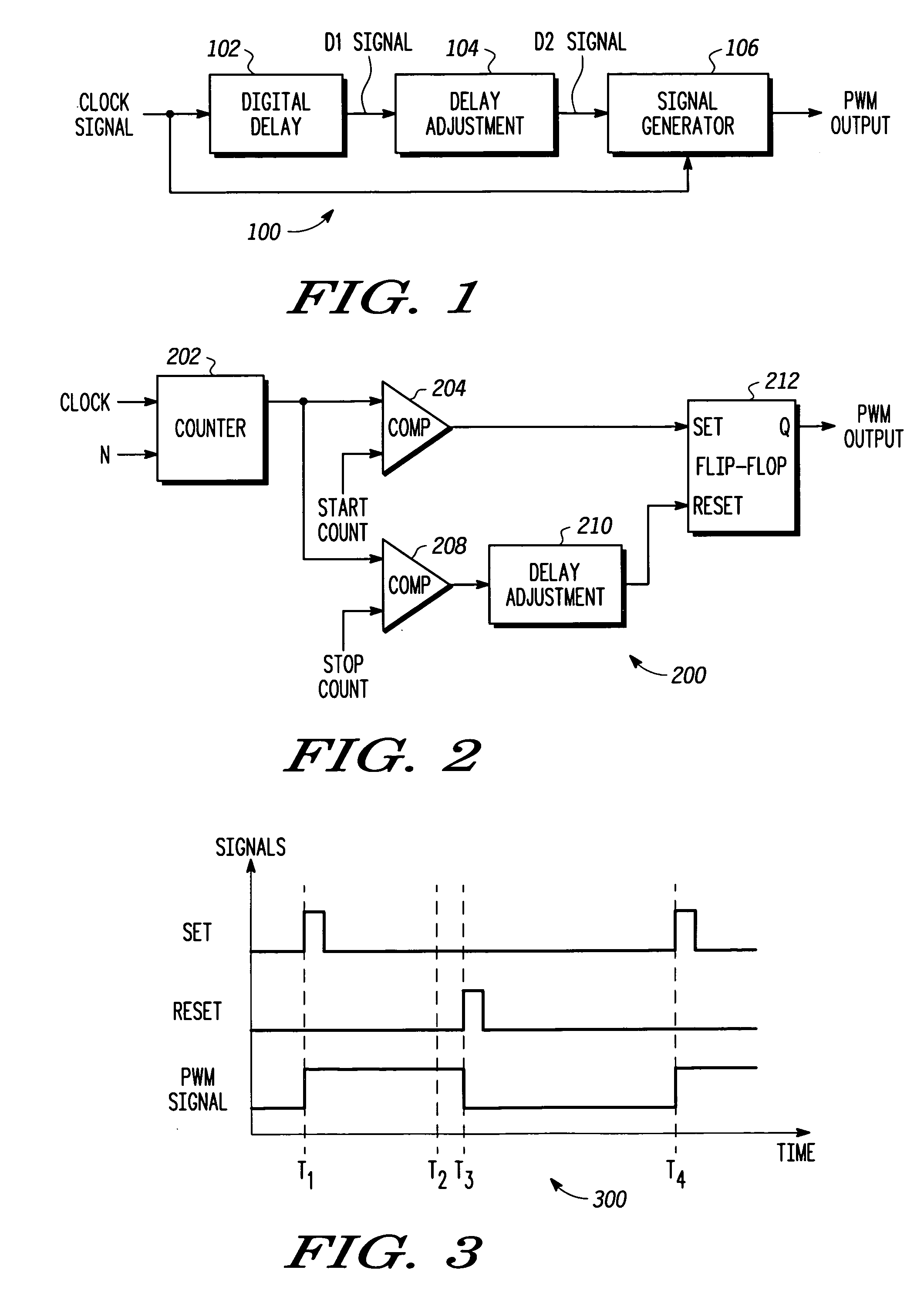

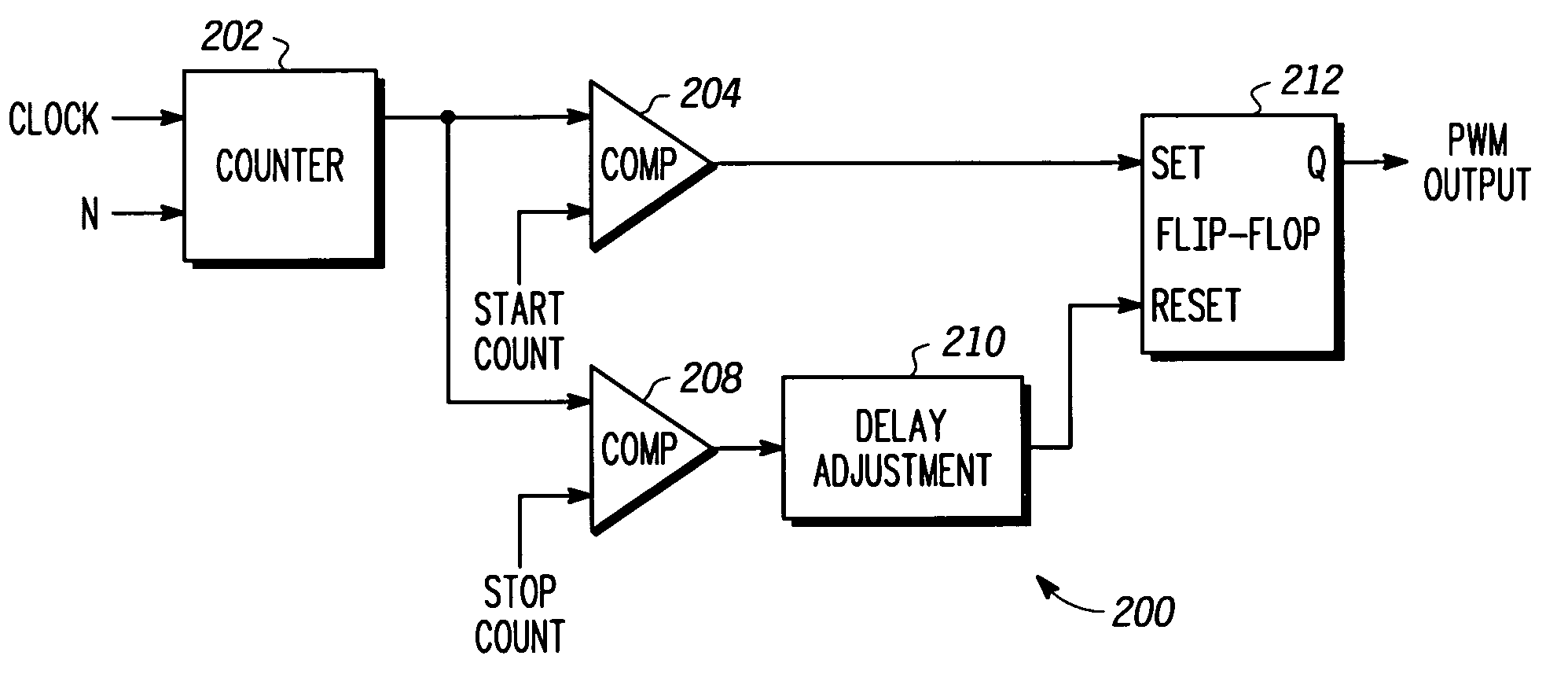

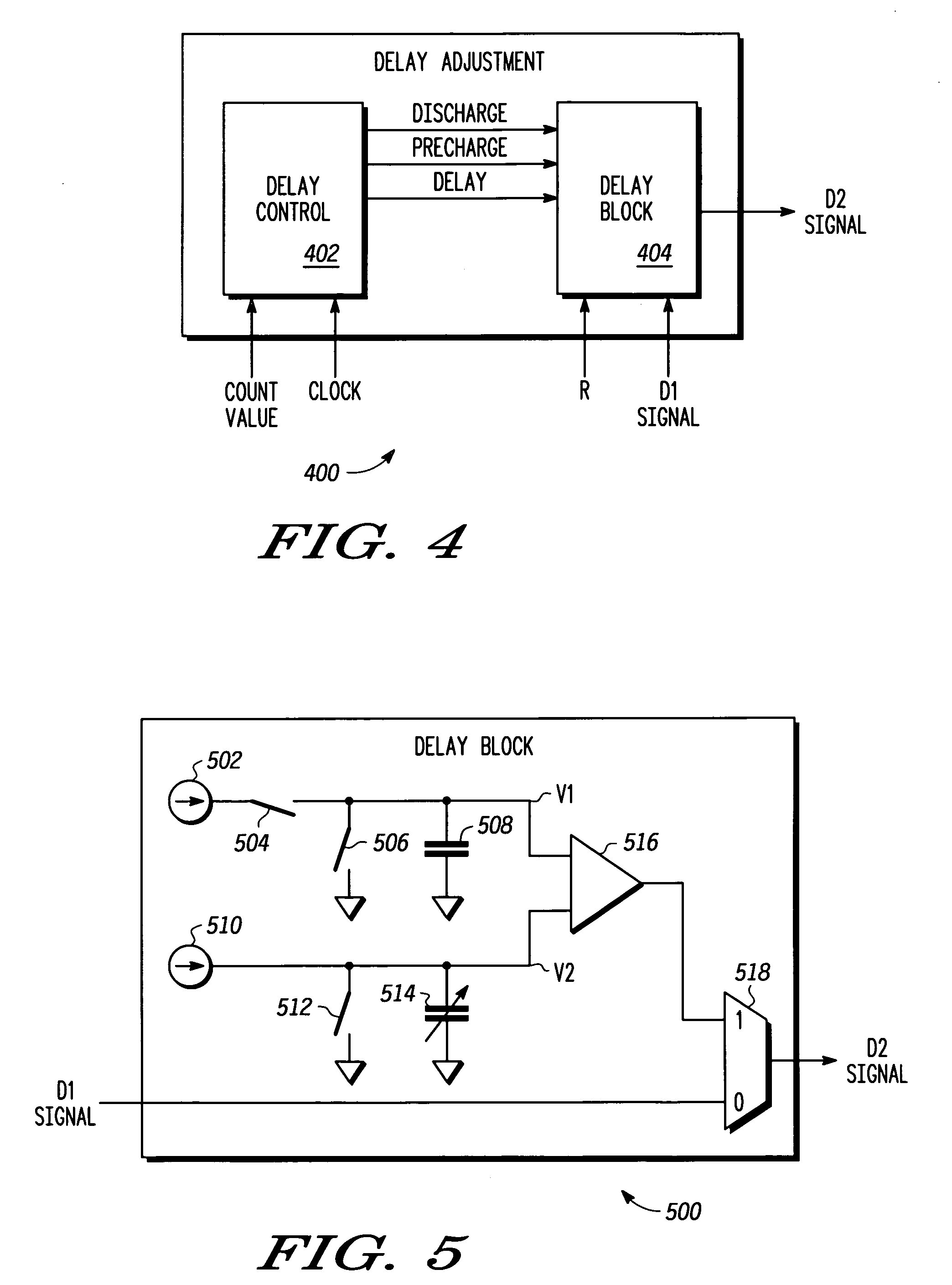

High resolution pulse width modulator

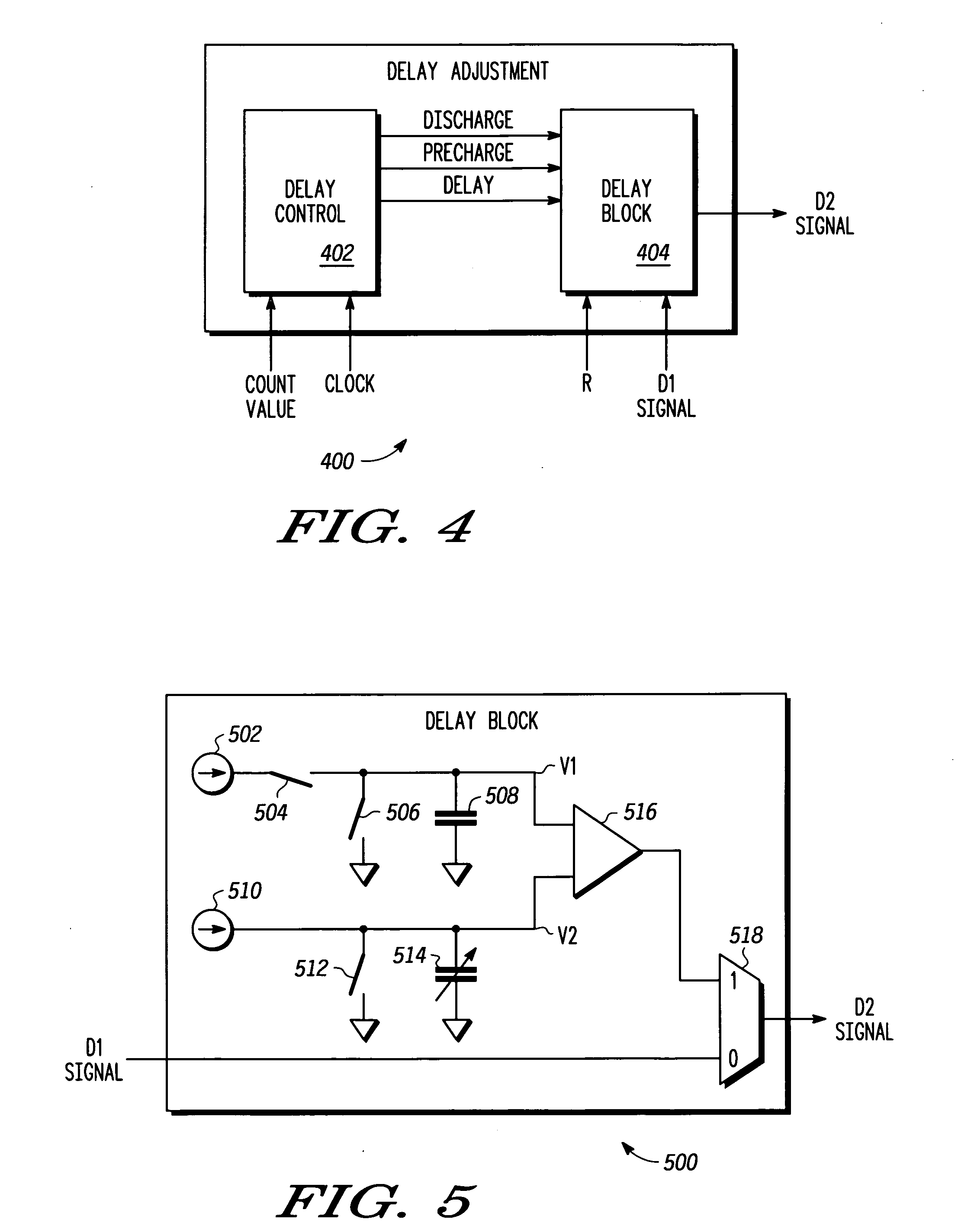

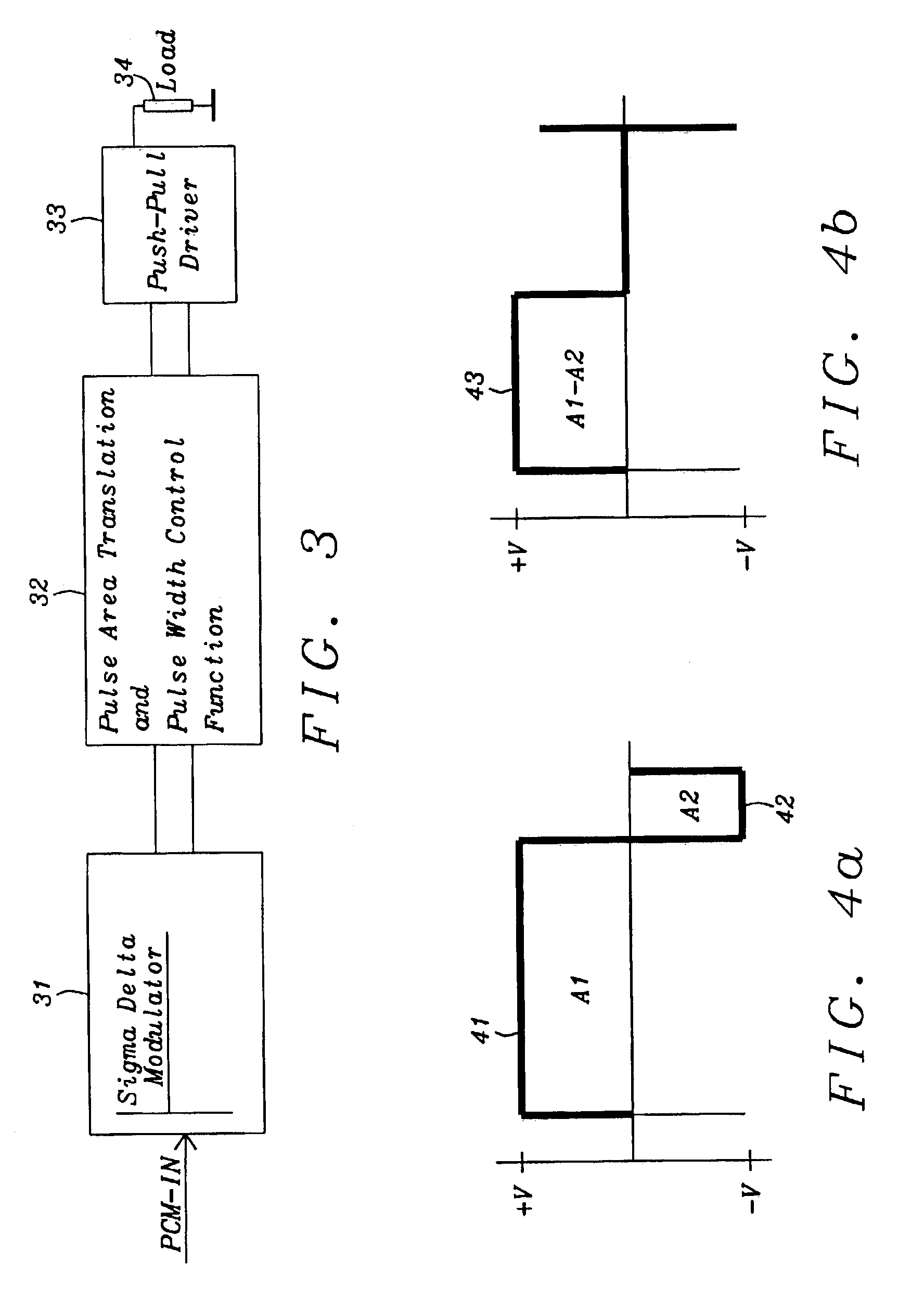

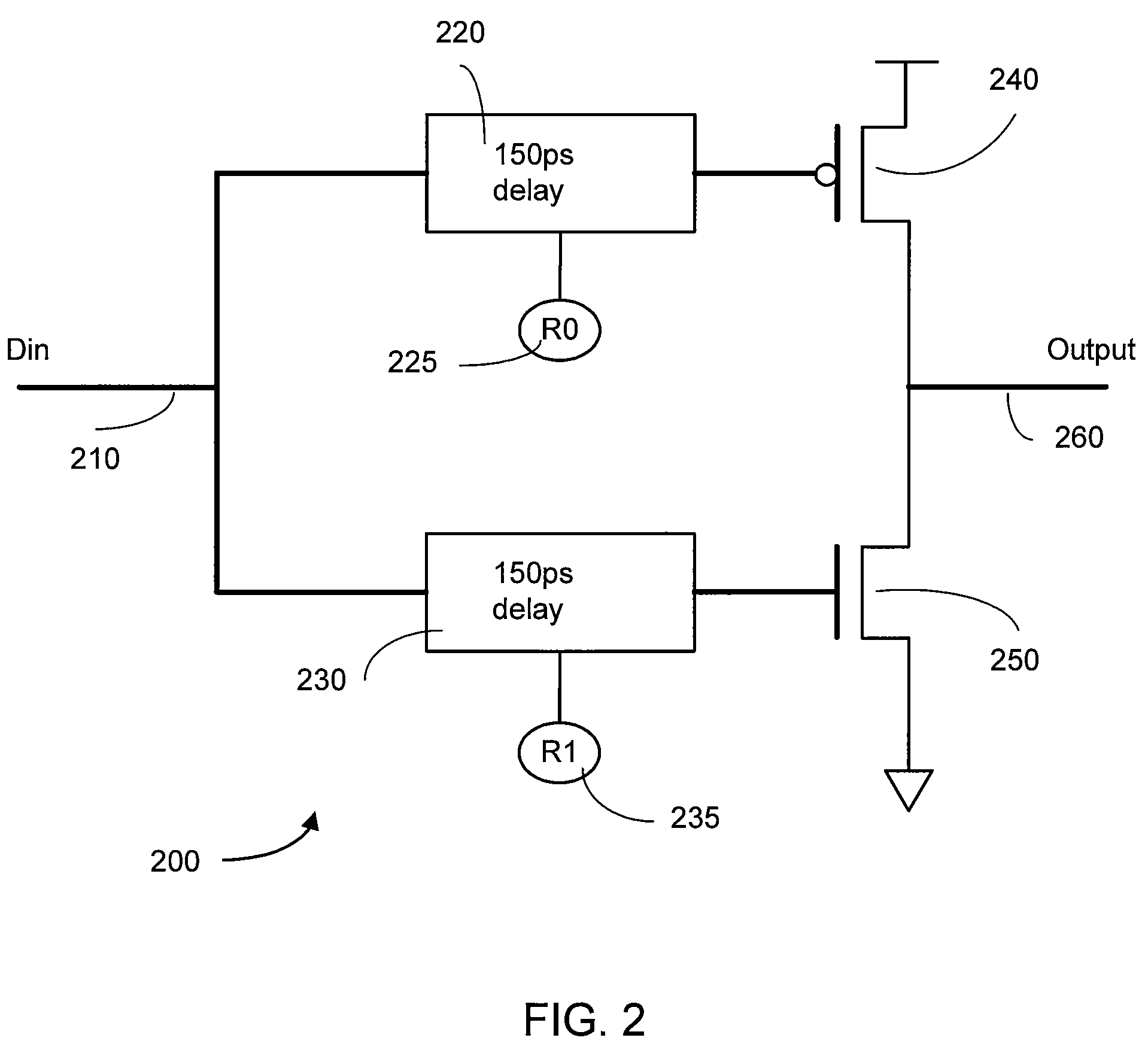

A pulse width modulator (100) and method that facilitates high resolution pulse width modulation is provided. The pulse width modulator (100) creates a pulse width modulated signal having a duty cycle that is proportional to a controllable delay in the modulator. The pulse width modulator combines a first digitally controllable delay (102) with a delay adjustment (104) to provide the controllable delay. In one embodiment, a digital counter (202) is used to provide coarse delay, with the delay adjustment device (210) coupled to the digital counter (202) to provide the fine, high resolution, delay control. Together the digital counter (202) and delay adjustment device (210) provide high resolution pulse width modulation. In one particular implementation, the analog delay adjustment device (100) comprises a delay block (500) designed to provide delay adjustment that is selectively controllable by changing a capacitance in the device.

Owner:APPLE INC

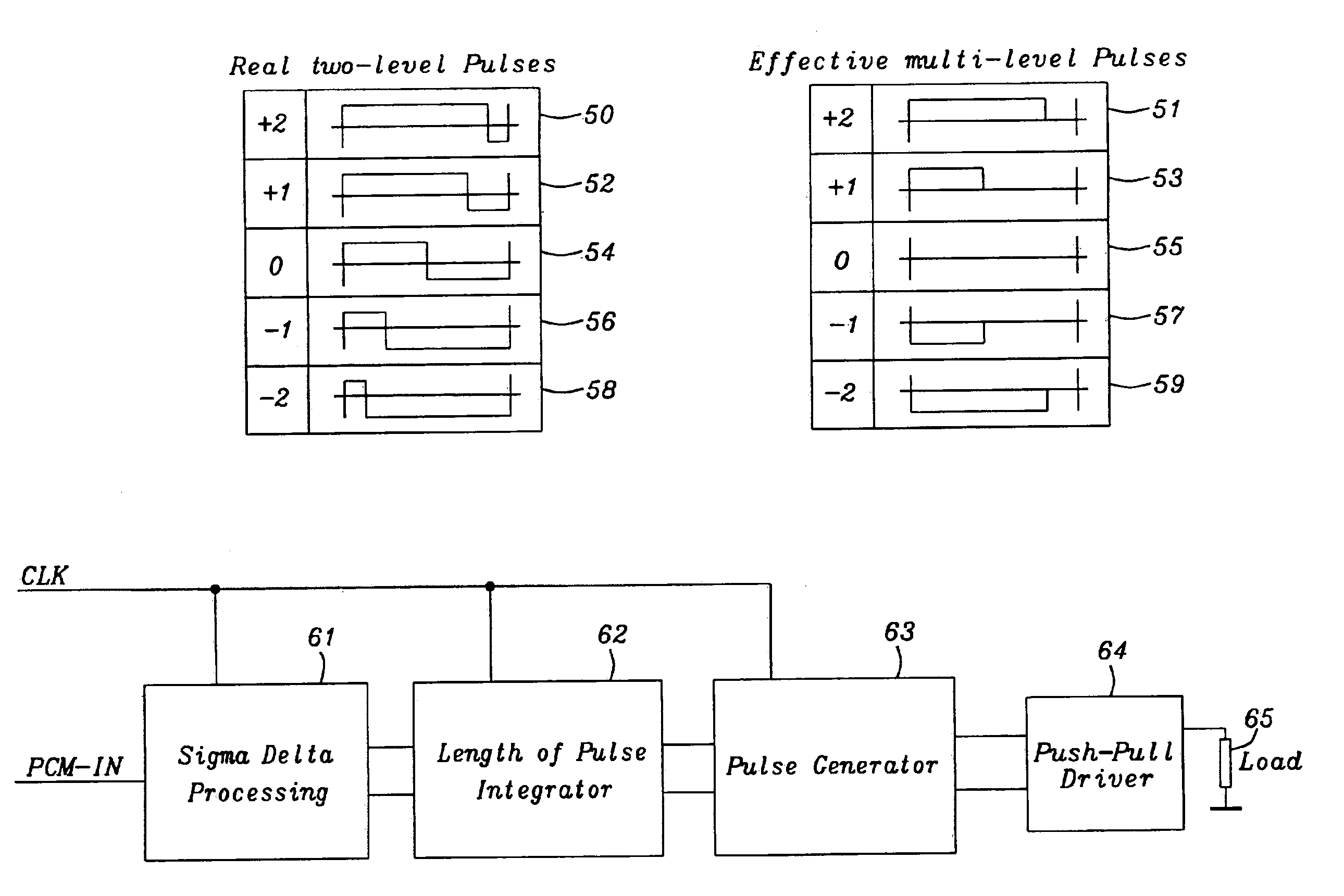

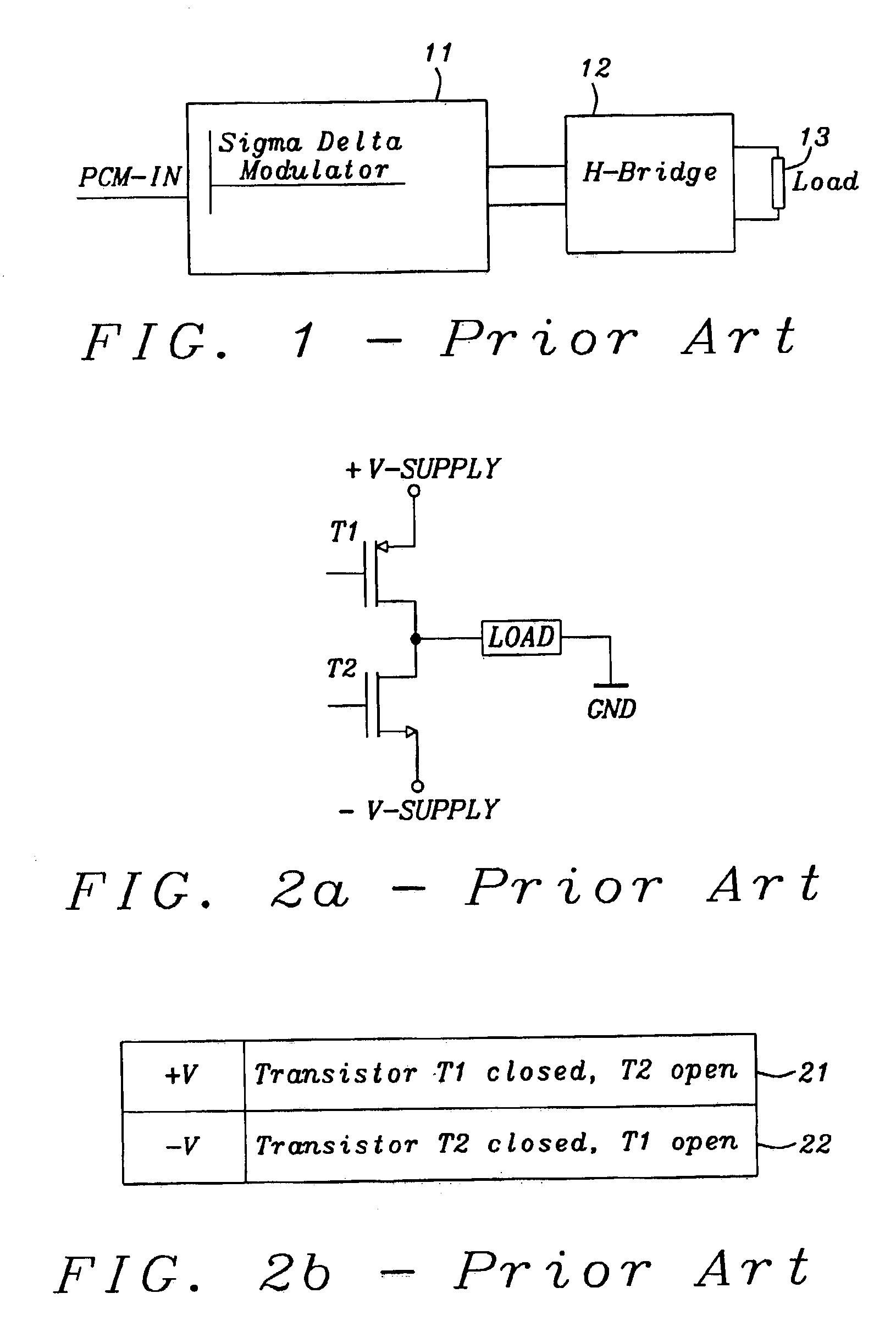

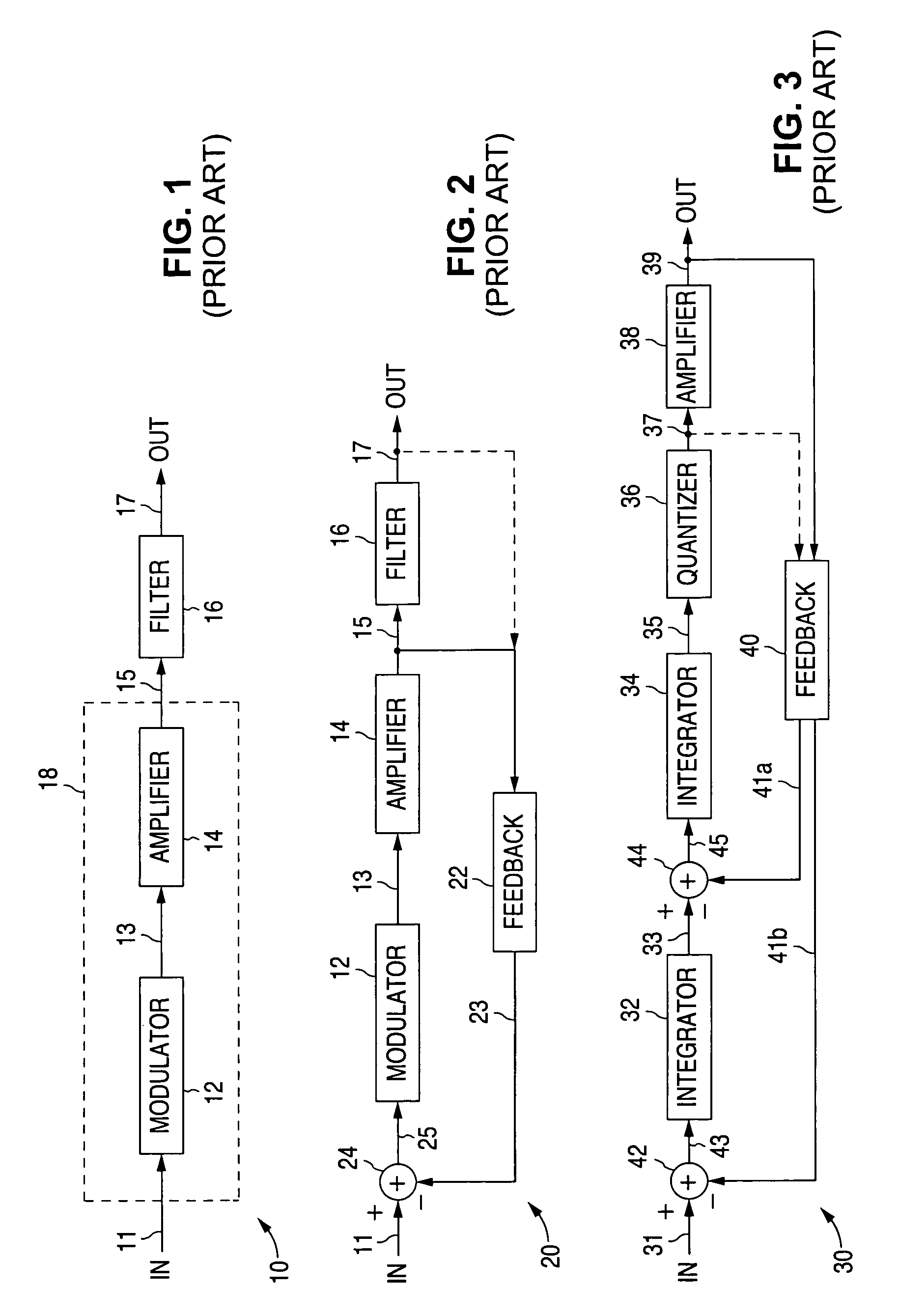

Multi-level Class-D amplifier by means of 2 physical layers

InactiveUS6842070B2Good quality output signalReduce electromagnetic interferencePush-pull amplifiersPhase-splittersSignal qualityClass-D amplifier

Introduce a pulse length control mechanism to generate virtual multi-level output pulses for a Class-D Amplifier, which has only 2 physical output levels. Typically a Sigma-Delta-Modulator converts the input signal into high frequency low bit rate. The disclosed invention adds functions to transform the SDM signal into pulses with equivalent multi-level time-voltage areas and adds a pulse-length-control mechanism to produce various output pulse patterns, where the summations of the positive and negative pulses, within one sampling period, result in time-voltage area values, corresponding to 3 or more digital levels. Thus the invention produces higher signal quality at lower sampling rates.

Owner:DIALOG SEMICONDUCTOR GMBH

High resolution pulse width modulator

A pulse width modulator (100) and method that facilitates high resolution pulse width modulation is provided. The pulse width modulator (100) creates a pulse width modulated signal having a duty cycle that is proportional to a controllable delay in the modulator. The pulse width modulator combines a first digitally controllable delay (102) with a delay adjustment (104) to provide the controllable delay. In one embodiment, a digital counter (202) is used to provide coarse delay, with the delay adjustment device (210) coupled to the digital counter (202) to provide the fine, high resolution, delay control. Together the digital counter (202) and delay adjustment device (210) provide high resolution pulse width modulation. In one particular implementation, the analog delay adjustment device (100) comprises a delay block (500) designed to provide delay adjustment that is selectively controllable by changing a capacitance in the device.

Owner:APPLE INC

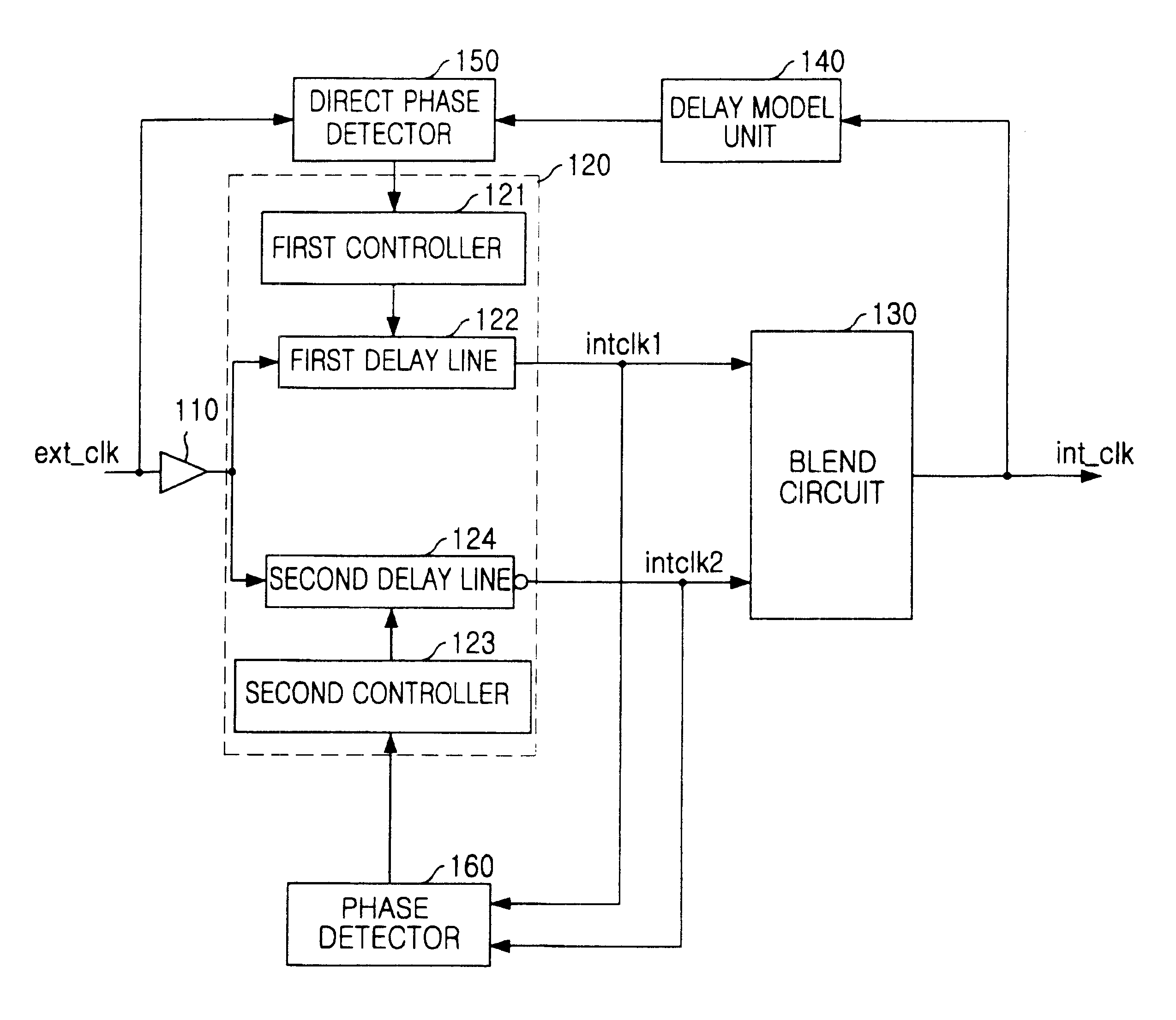

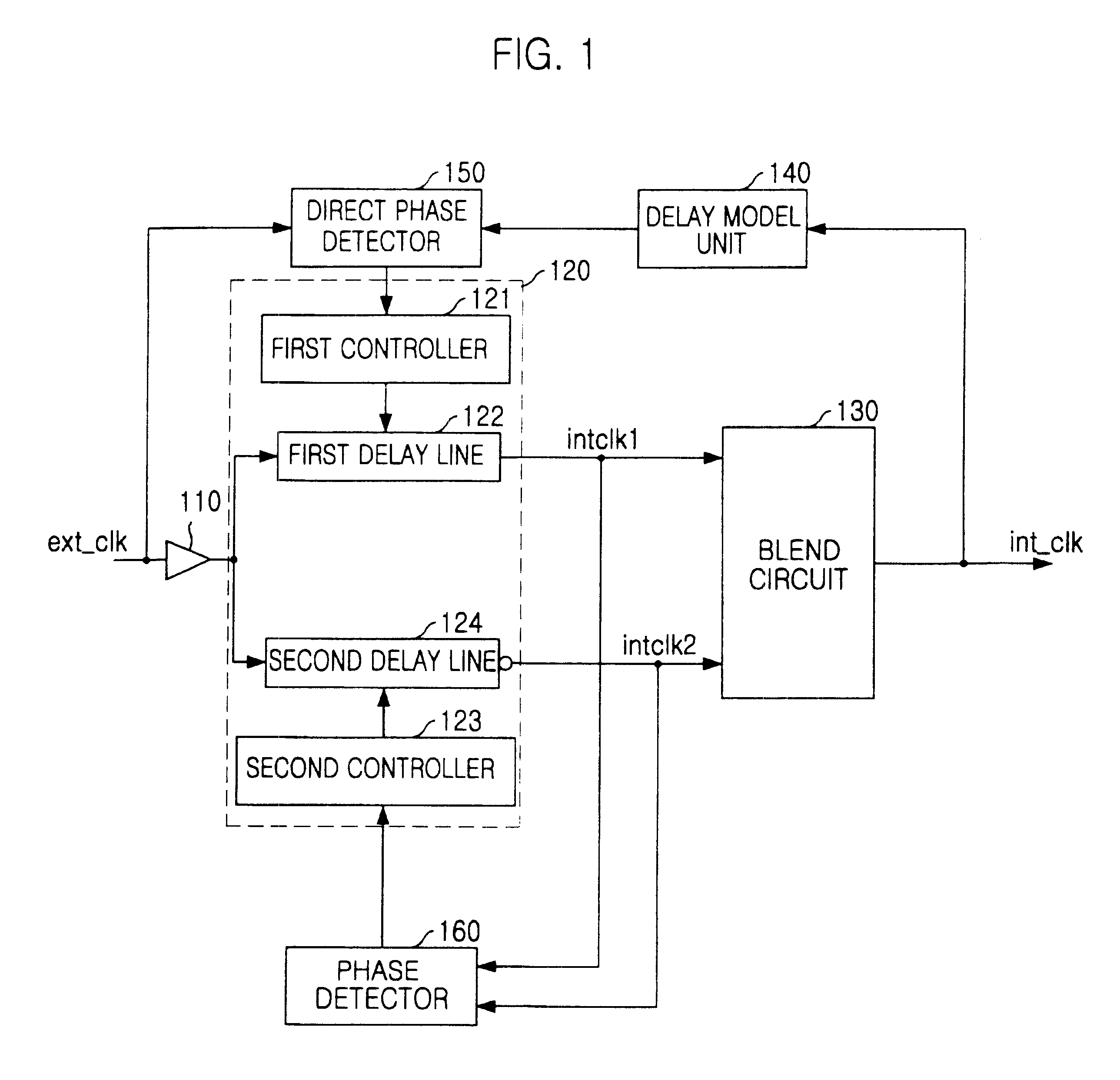

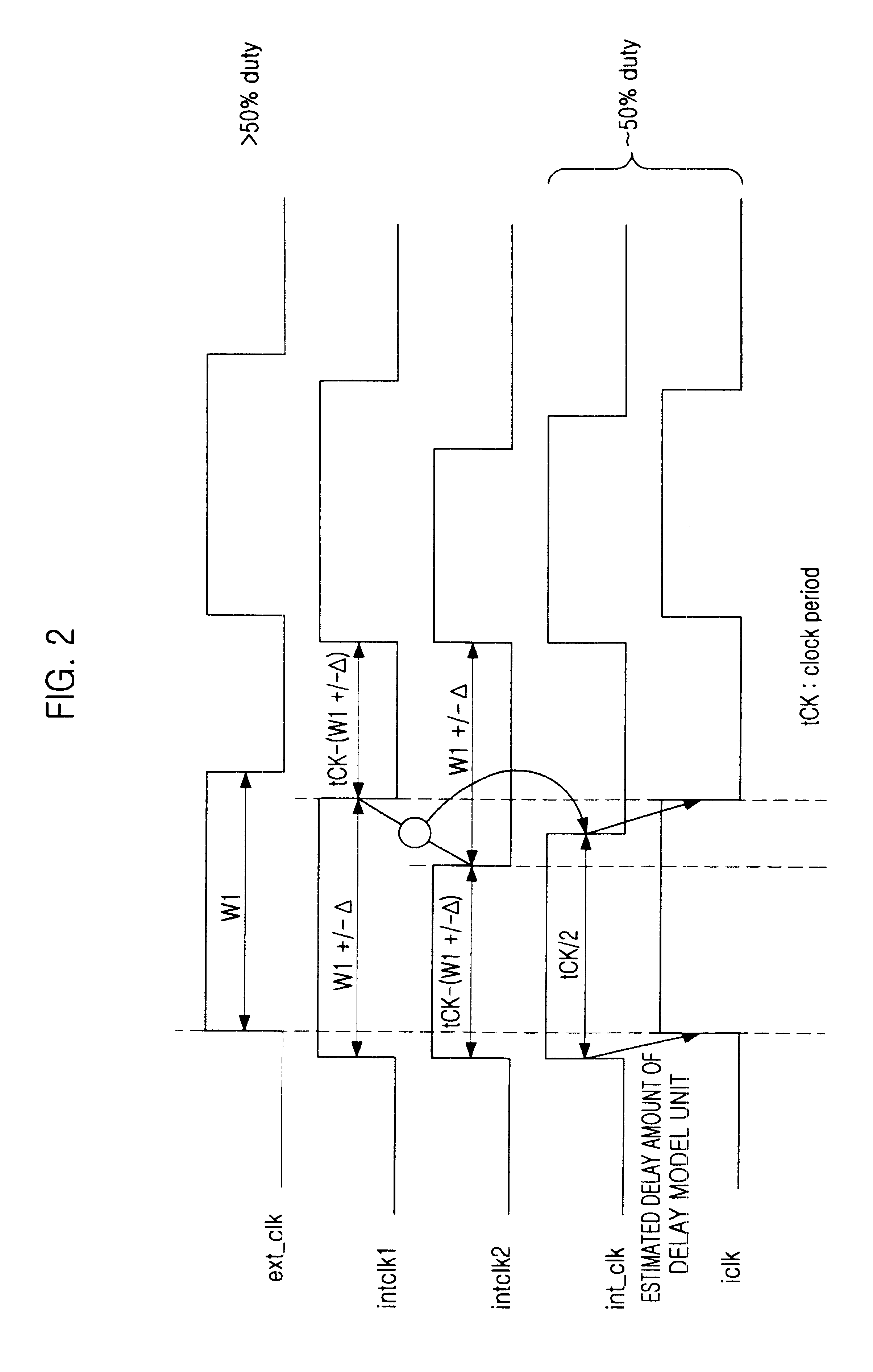

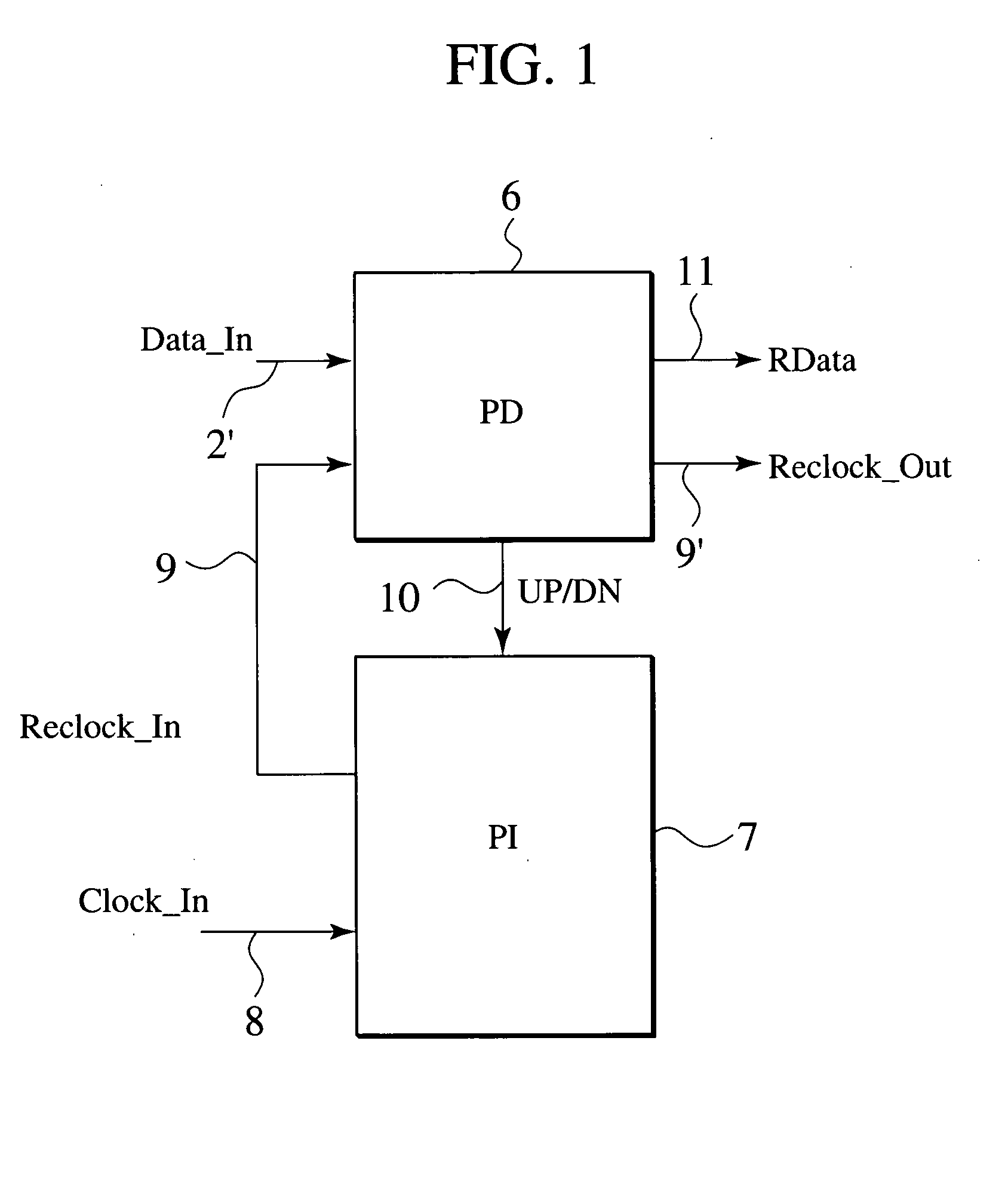

Digital DLL apparatus for correcting duty cycle and method thereof

InactiveUS6677792B2Pulse automatic controlContinuous to patterned pulse manipulationPhase detectorEngineering

A digital DLL apparatus and a method for correcting a duty cycle are disclosed. The digital DLL apparatus for correcting a duty cycle, includes: a buffer for producing a clock input signal; a delay line unit for receiving / delaying the clock input signal and outputting the clock input signal; a blend circuit for bypassing the first clock signal or producing a blended clock signal; a delay model unit for compensating a time difference of an external clock and an internal clock and generating a compensate clock signal; a direct phase detector for generating a first comparison signal; and a phase detector for generating a second comparison signal. The disclosed apparatus can correct the duty error by using the blend circuit and generate an internal clock signal having 50% of duty cycle.

Owner:SK HYNIX INC

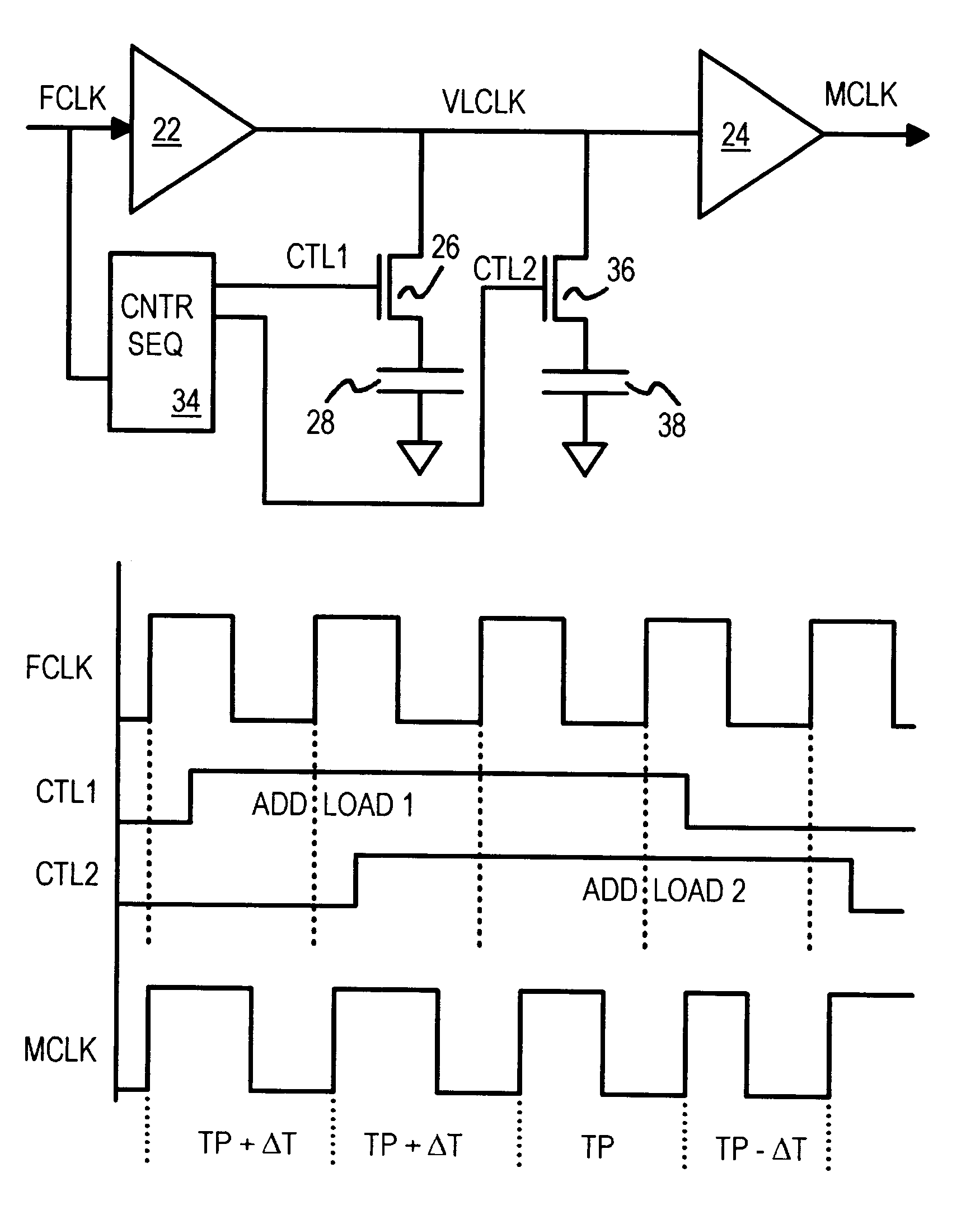

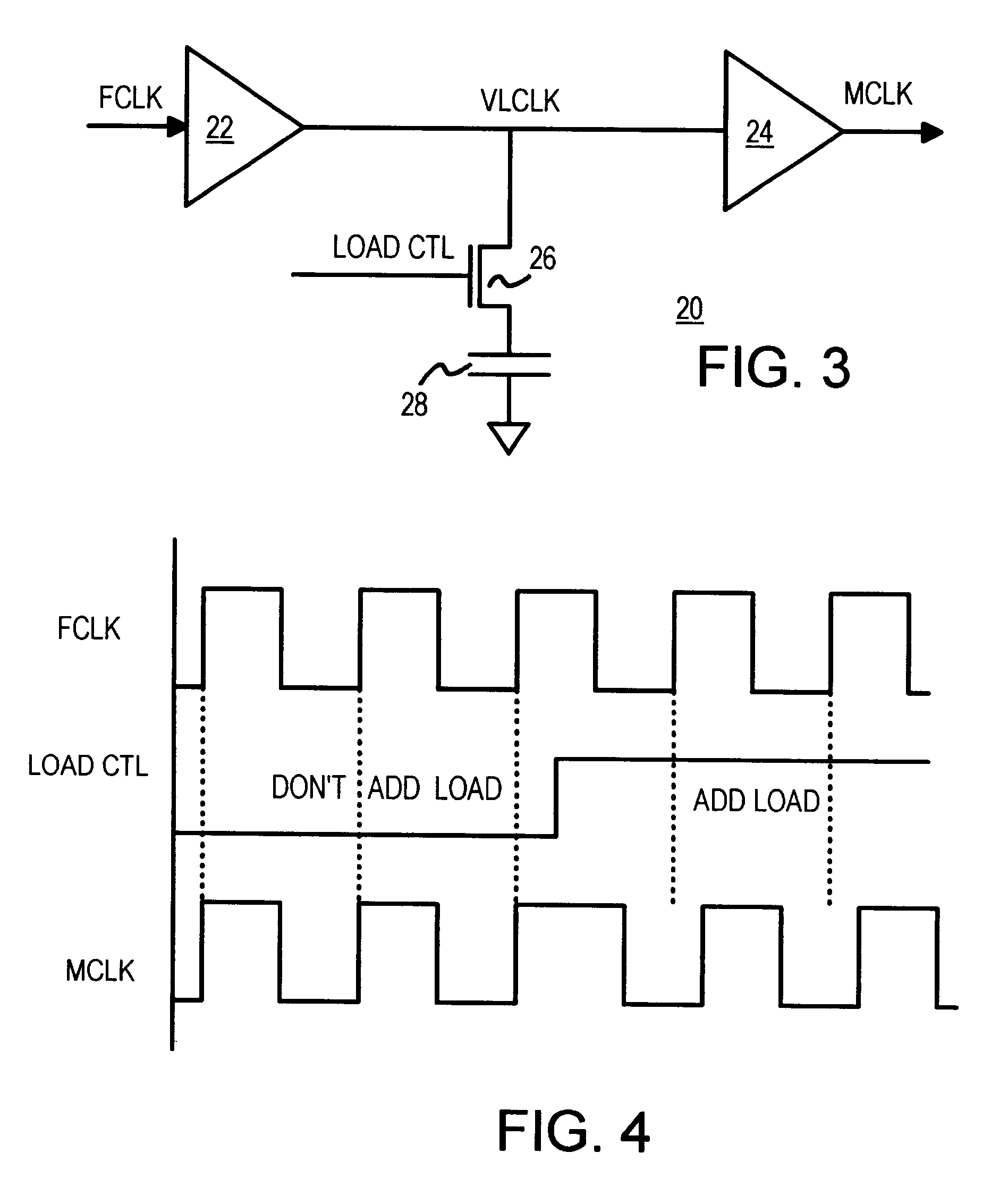

Spread-spectrum clock buffer/driver that modulates clock period by switching loads

A clock modulator spreads the frequency spectrum of an input clock to generate an output clock. A capacitor is connected to an intermediate clock node by a load-switching transistor. When the transistor is turned on, the capacitor increases the loading on the intermediate clock node, increasing delay. When the transistor is turned off, the delay is reduced. Output clock cycle periods are extended when delay is added, and reduced when the transistor turns off. A counter or sequencer is clocked by the input clock and drives the load-switching transistor. The transistor is turned on and off for alternate cycles when the counter is a toggle flip-flop, spreading the frequency over two frequencies every two clock cycles. Two capacitors of different sizes, connected to the intermediate clock node by two transistors, can be switched by a 2-bit sequencer, spreading the output clock over 7 frequencies every 7 clock cycles.

Owner:DIODES INC

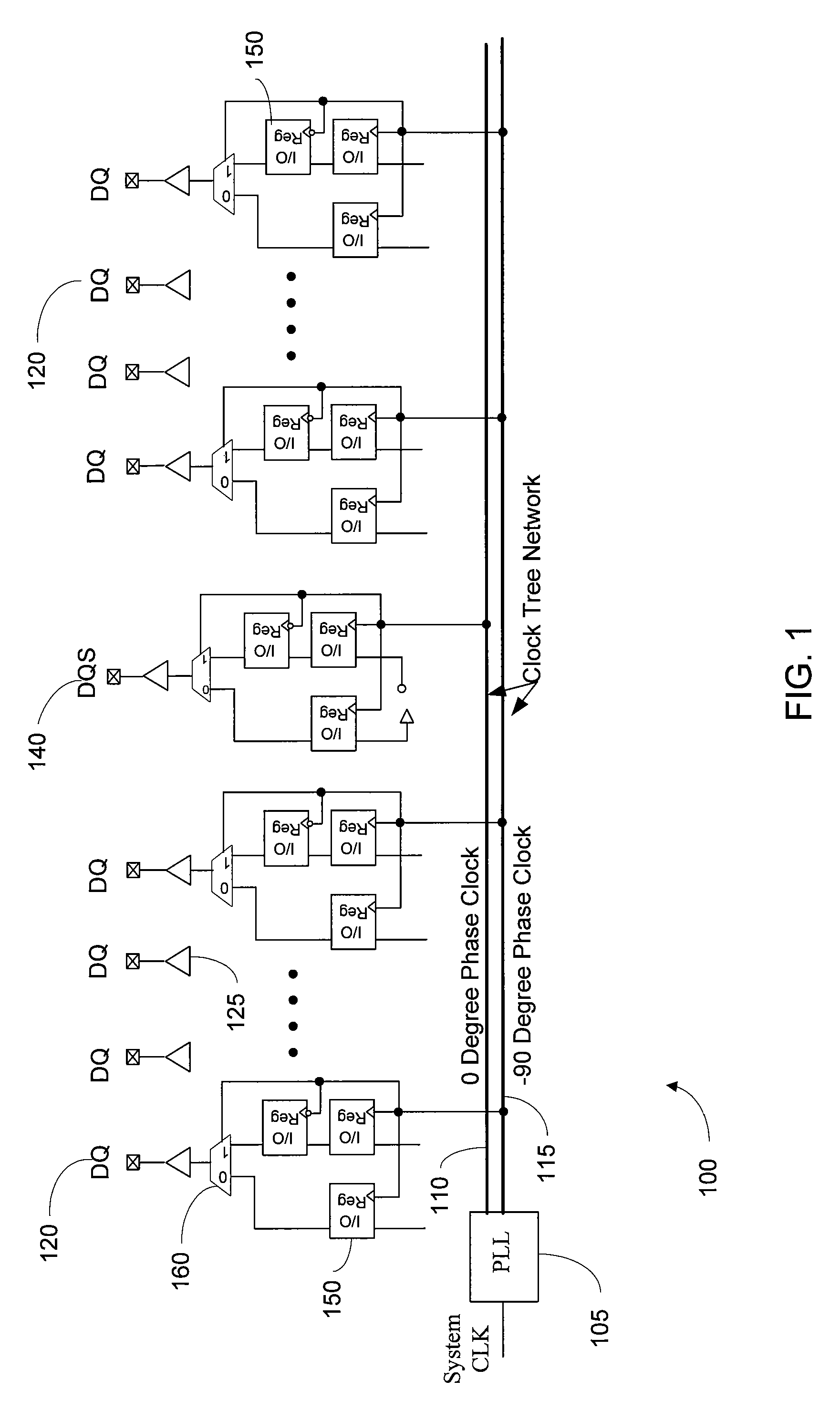

I/O duty cycle and skew control

Circuits, methods and apparatus are provided to control the duty cycle of a signal. The rising and falling edges of a signal can be delayed independently to provide the selection or tuning of the duty cycle of the signal. Additionally, the delays can be used to reduce skew among both edges of signals being provided or transmitted by a data interface. The delays can be made to not cause a high-Z during a transition of the signal.

Owner:ALTERA CORP

Apparatus and method for converting analog signal to pulse-width-modulated signal

InactiveUS6970503B1Analogue/digital conversionElectric signal transmission systemsAudio power amplifierEngineering

Owner:NAT SEMICON CORP

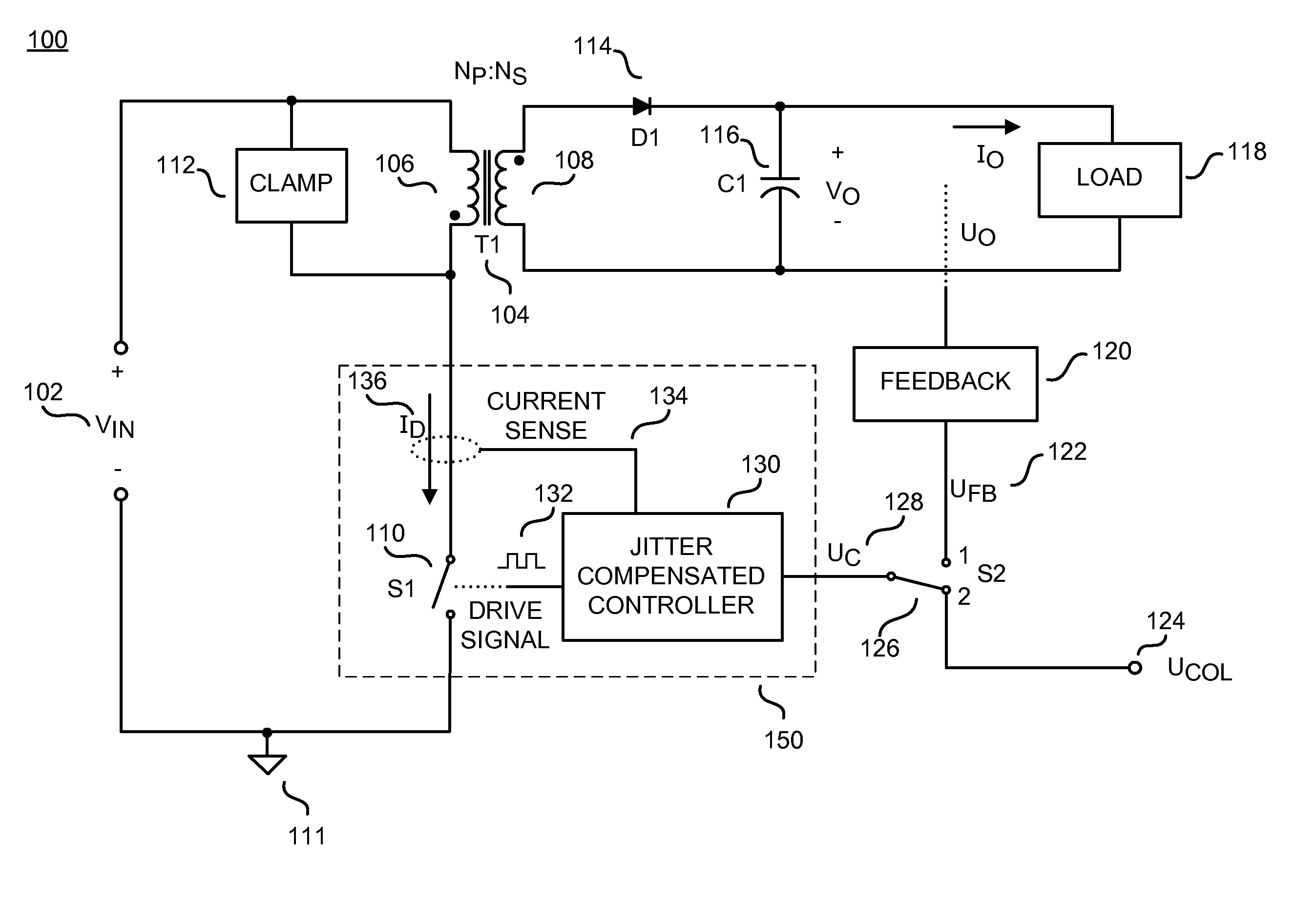

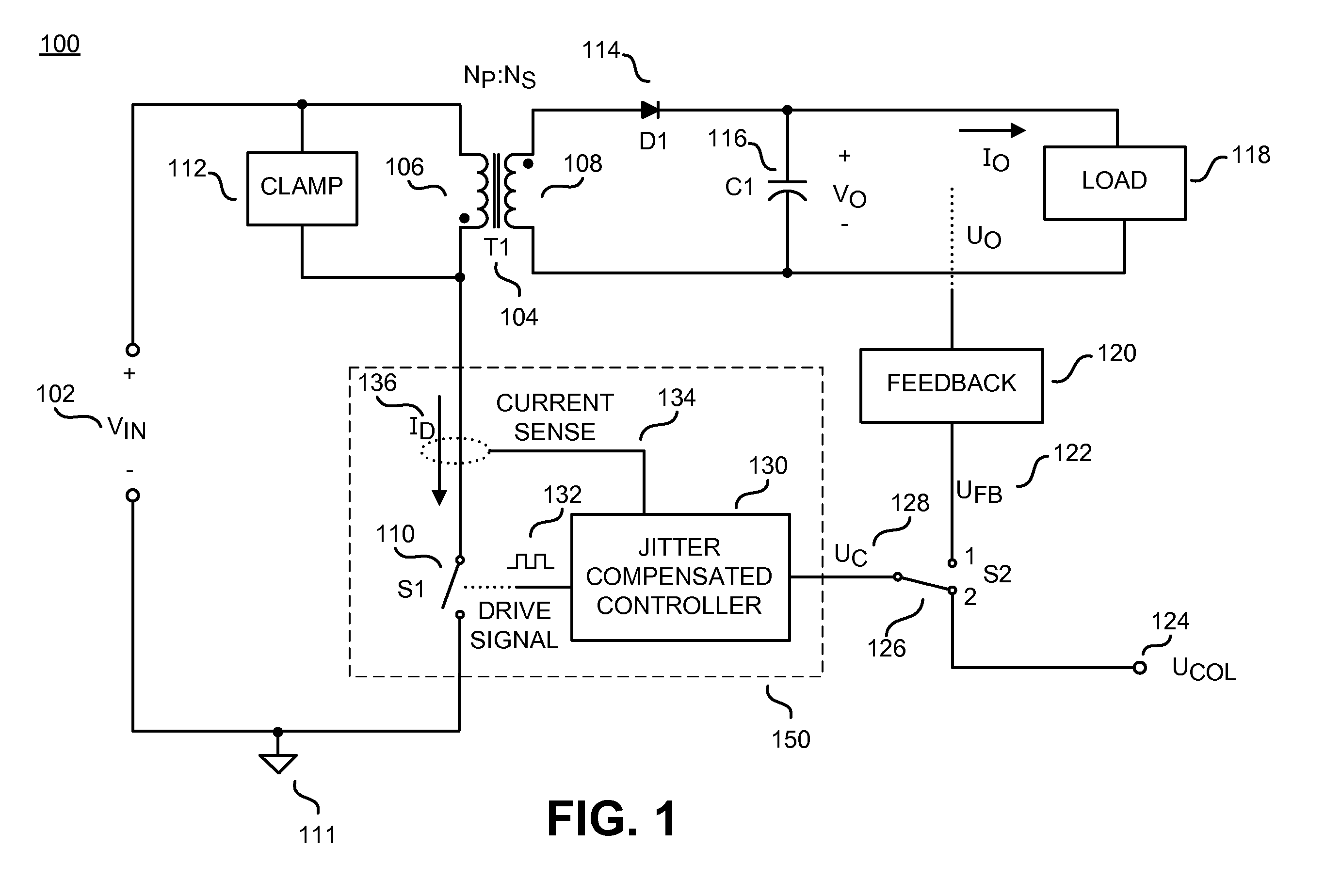

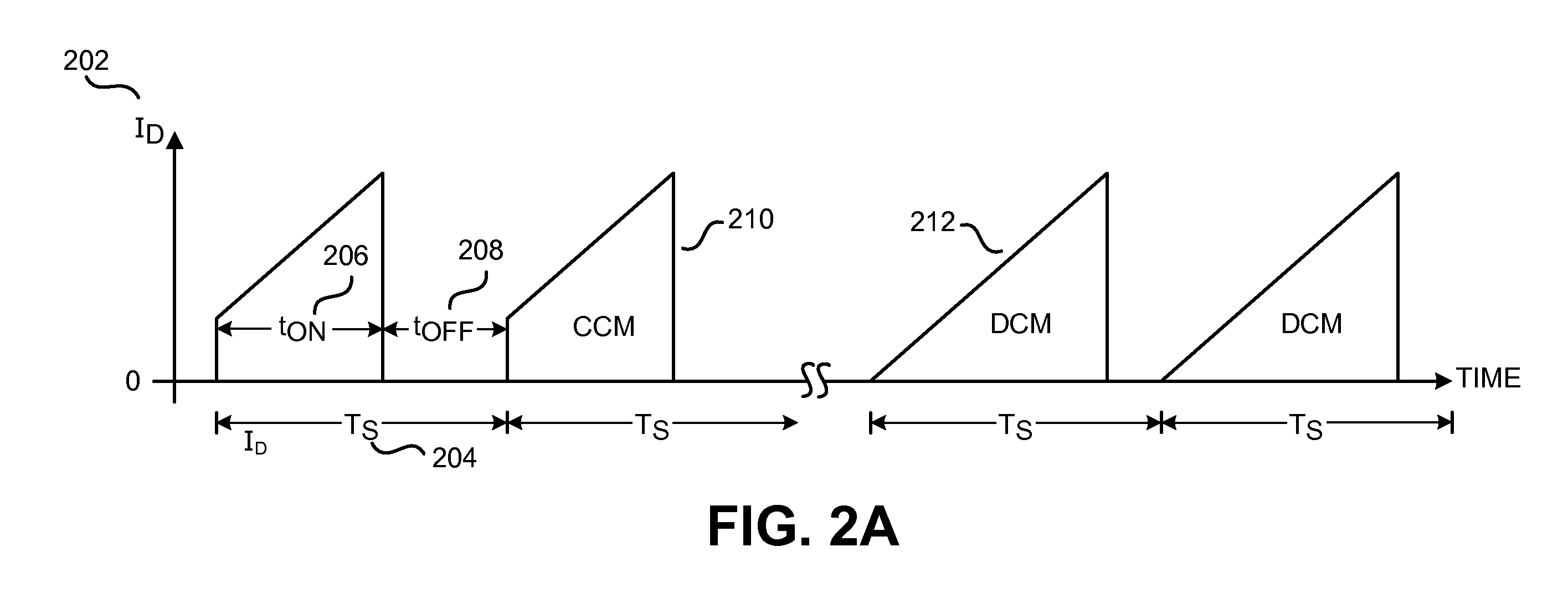

Controller compensation for frequency jitter

An example controller for use in a power supply in accordance with the present teachings includes a drive signal generator, a jitter signal generator and a compensator signal generator. The drive signal generator is coupled to output a drive signal having a switching period and a duty ratio to control switching of a switch that is to be coupled to the controller. The jitter signal generator is coupled to provide a jitter signal, where the switching period of the drive signal varies in response to the jitter signal. The compensator signal generator is coupled to provide a compensator signal responsive to the jitter signal, where the duty ratio of the drive signal is varied in response to the compensator signal.

Owner:POWER INTEGRATIONS INC

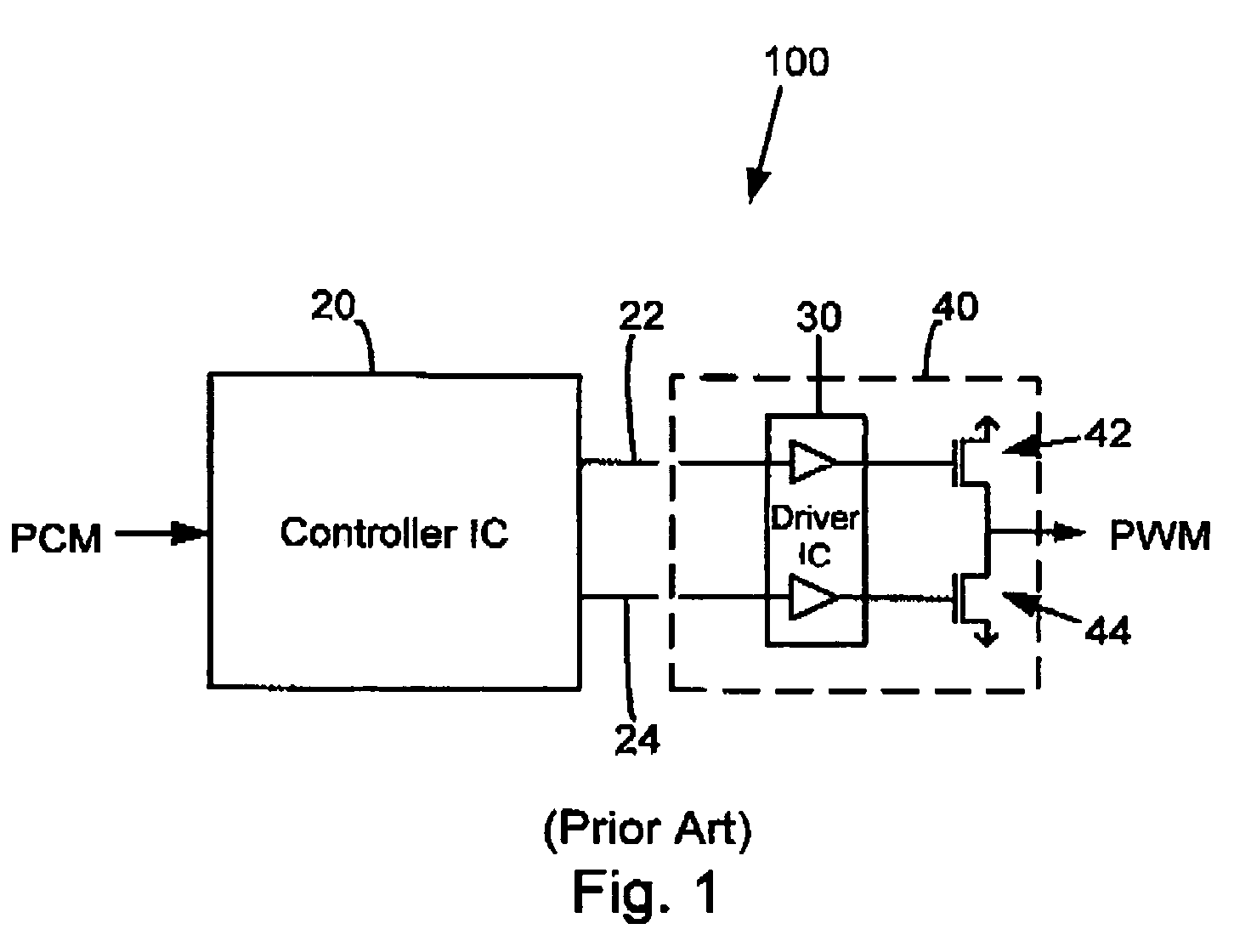

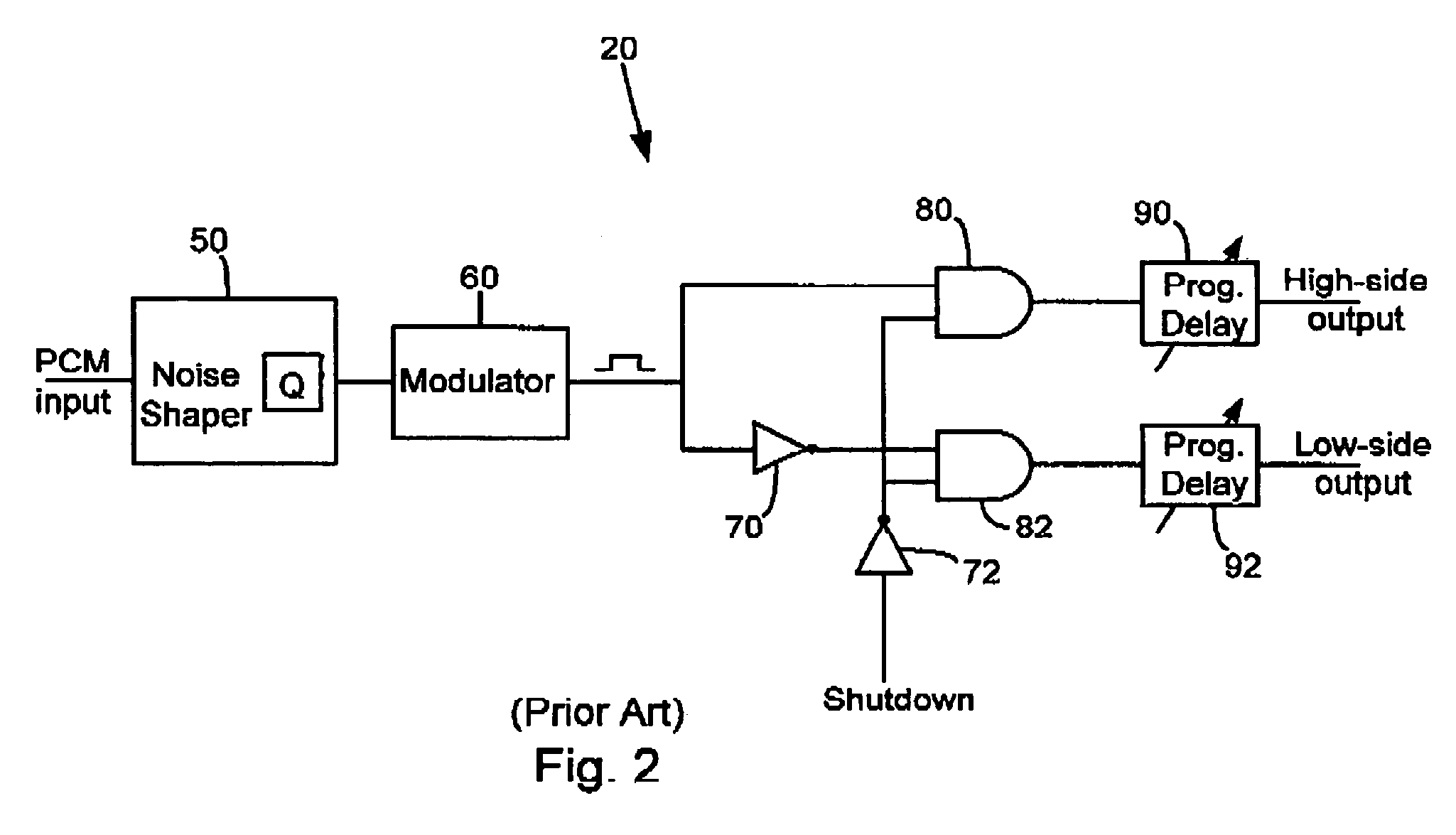

Integrated PULSHI mode with shutdown

InactiveUS7078963B1Enabling usePulse duration/width modulationDc amplifiers with modulator-demodulatorAudio power amplifierPulse-code modulation

Systems and methods for controlling amplification of a pair of pulse width modulated signals. In one embodiment, a system comprises an audio amplifier which is configured to receive a pulse code modulated (PCM) input signal, convert this signal to a pulse width modulated (PWM) signal in a controller, and amplify the PWM signal in an output stage. The controller separates the PWM signal into a high-side signal and a low-side signal. The controller incorporates digitally programmable delays into the processing paths for each of the high-side and low-side signals. The high-side and low-side signals are separately provided to the output stage. The separate high-side and low-side signals can be used to individually control (e.g., turn off) the high-side and low-side transistors. Circuitry is included to generate a short low-side pulse when both transistors are turned off in order to drain the gate charge from the high-side transistor.

Owner:INTERSIL INC

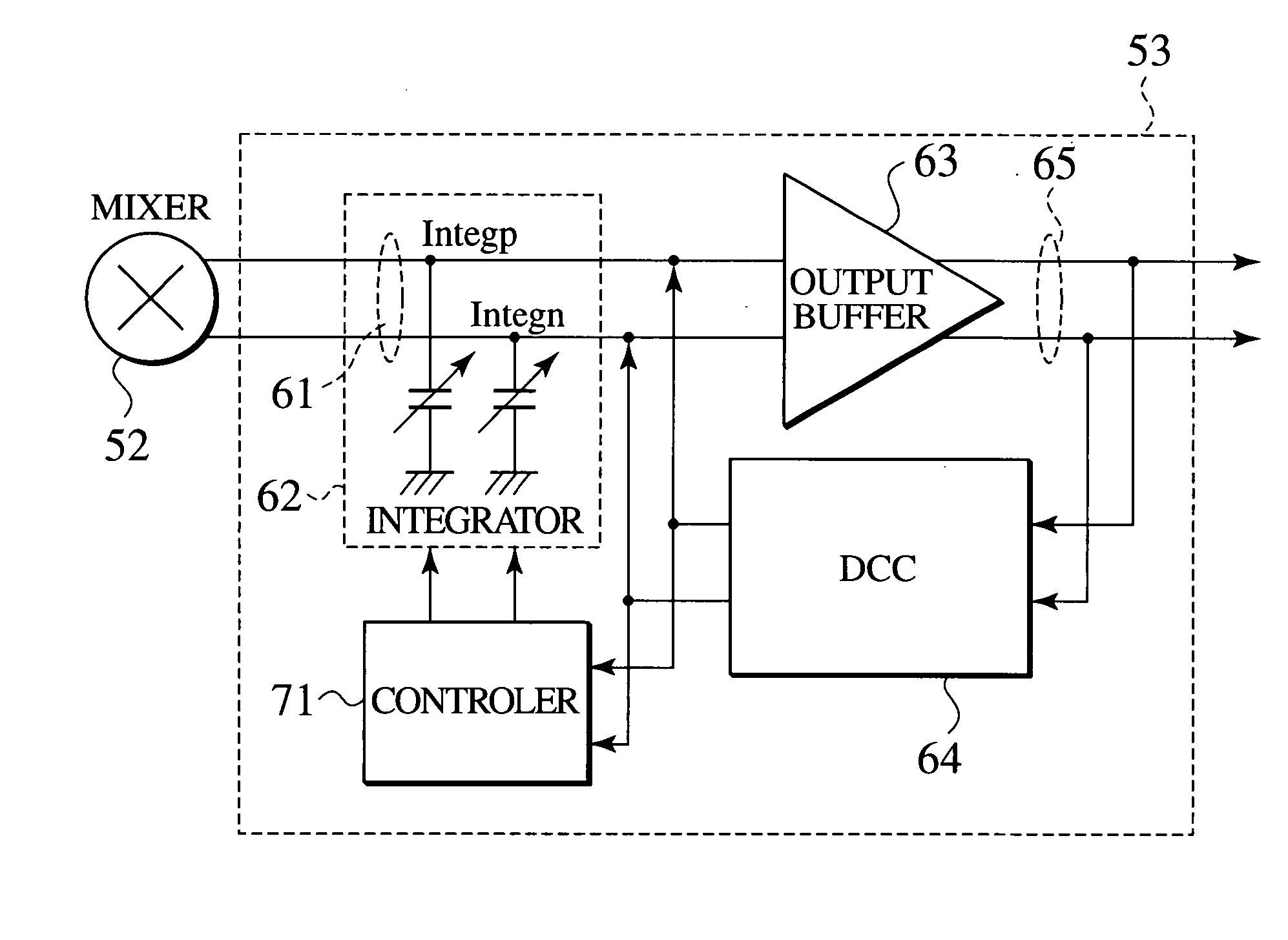

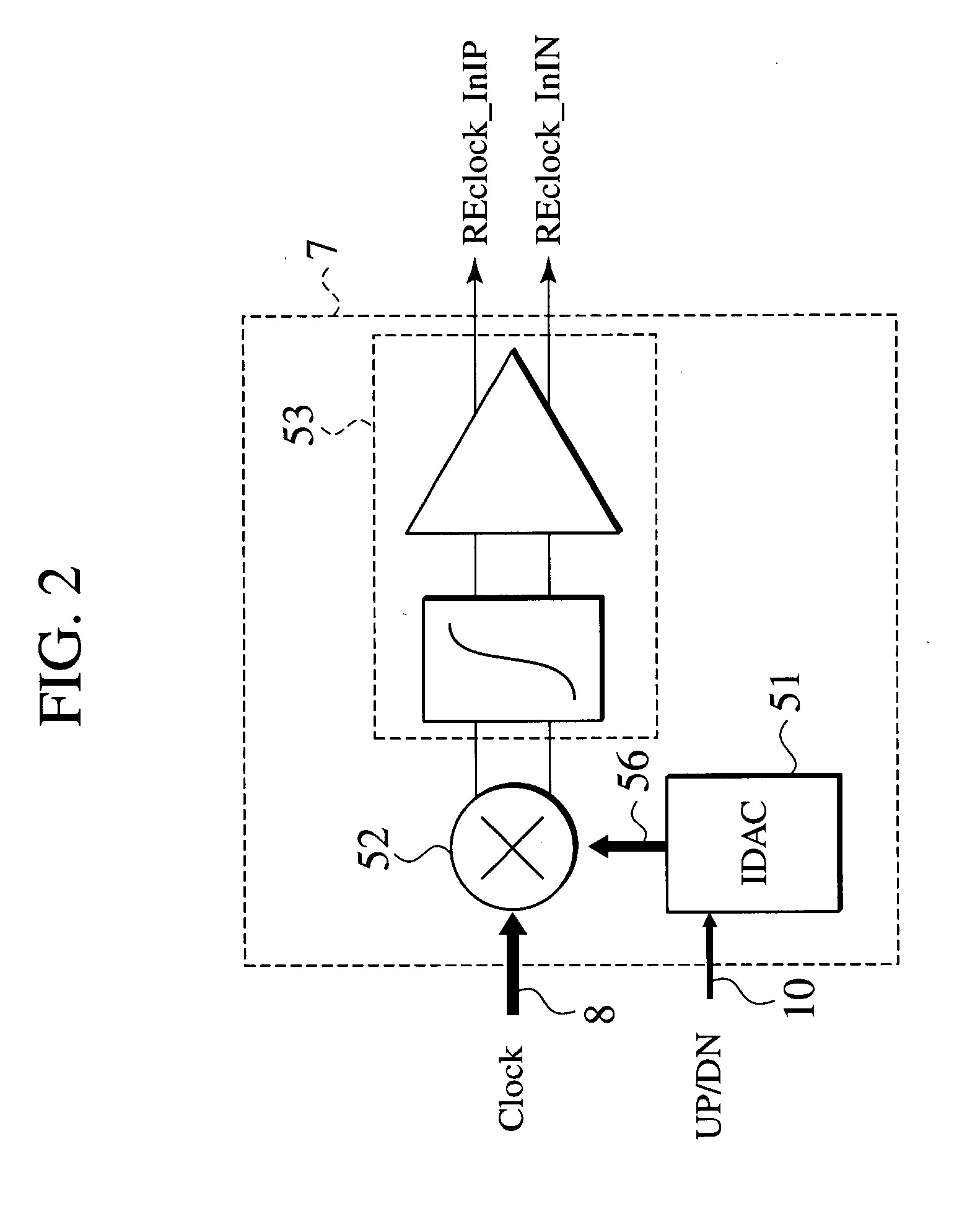

Phase interpolator and receiver

InactiveUS20040189363A1Pulse automatic controlContinuous to patterned pulse manipulationIntegratorEngineering

An aspect of the present invention provides a phase interpolator for adjusting a phase of differential clock signals of a receiver to a phase of a data from a transmitter that includes, an integrator configured to slew edges of differential clock signals adjusted to the phase of the data from the transmitter, a output buffer configured to amplify an output of the integrator, a duty cycle correction circuit configured to feed duty correction signals back to the adjusted differential clock signals, and a controller configured to ensure operations of an amplitude of the output buffer and a data read circuit to adjust the swings and duties of the adjusted differential clock signals.

Owner:KK TOSHIBA

Popular searches

Semiconductor lamp usage Electric light circuit arrangement Pulse characteristics measurements Special data processing applications Synchronising arrangement Amplitude-modulated pulse demodulation Baseband systems Selection arrangements Pulse amplitude modulation Multiple input and output pulse circuits

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com