Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

36results about How to "Improve jitter characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

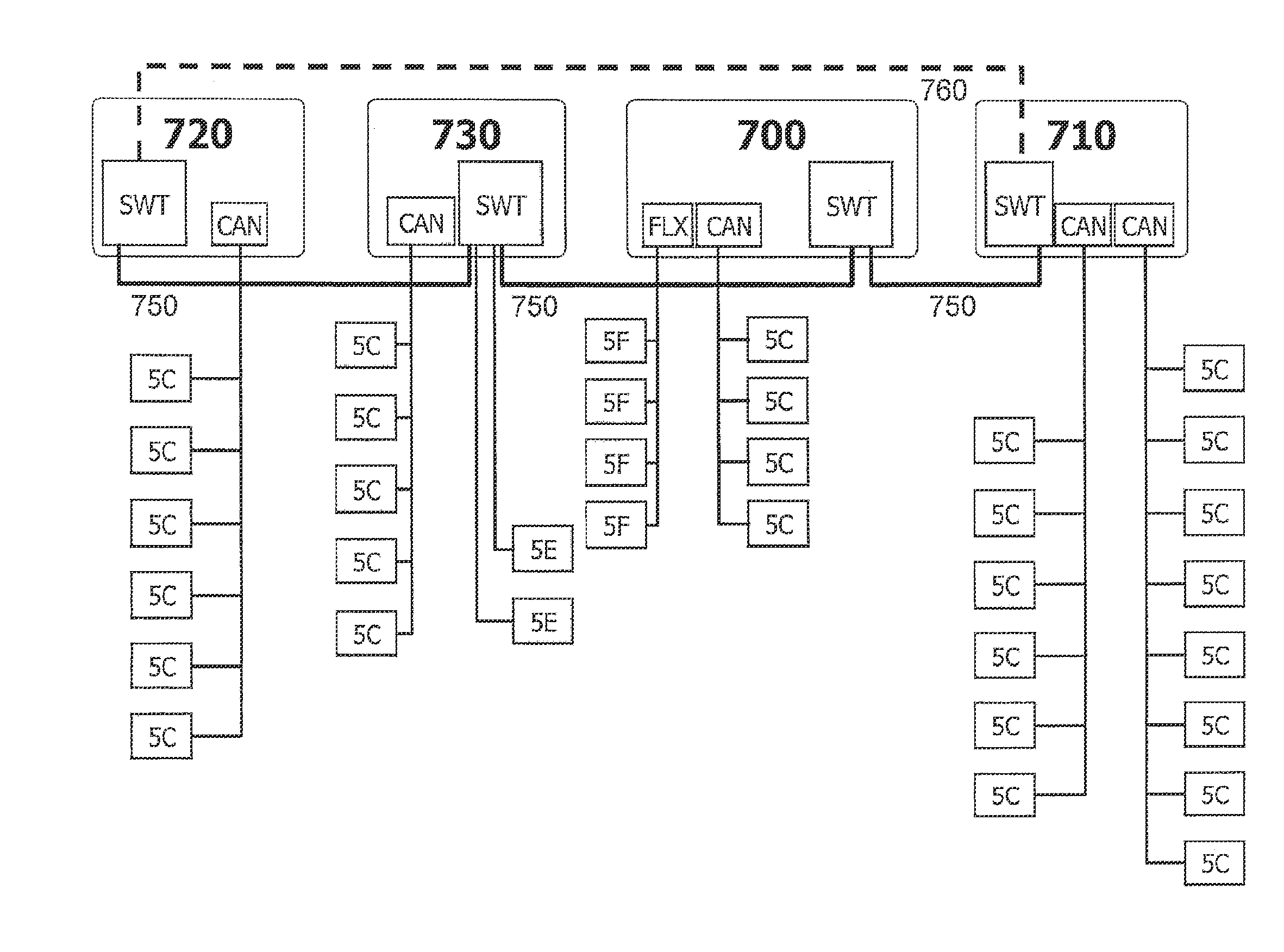

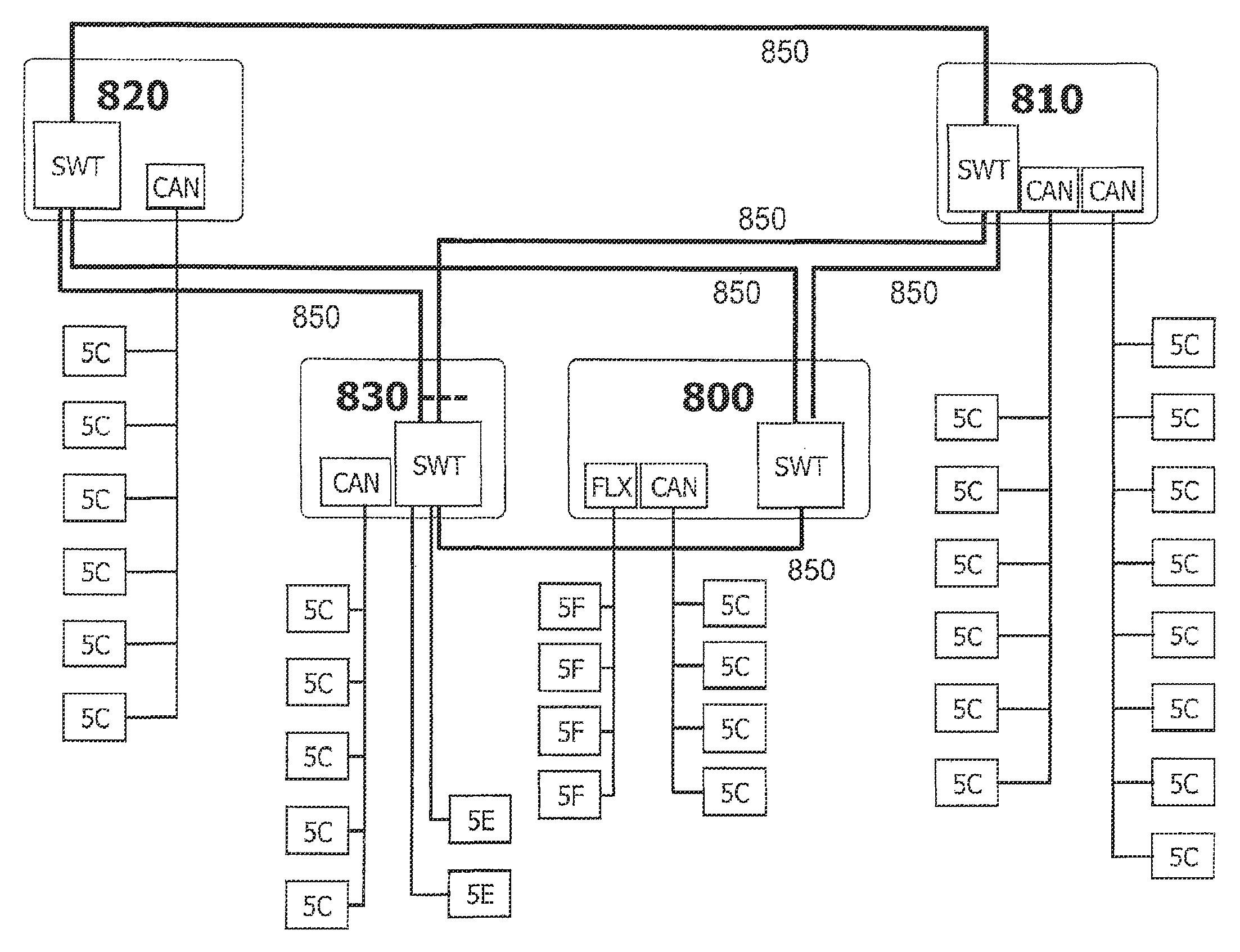

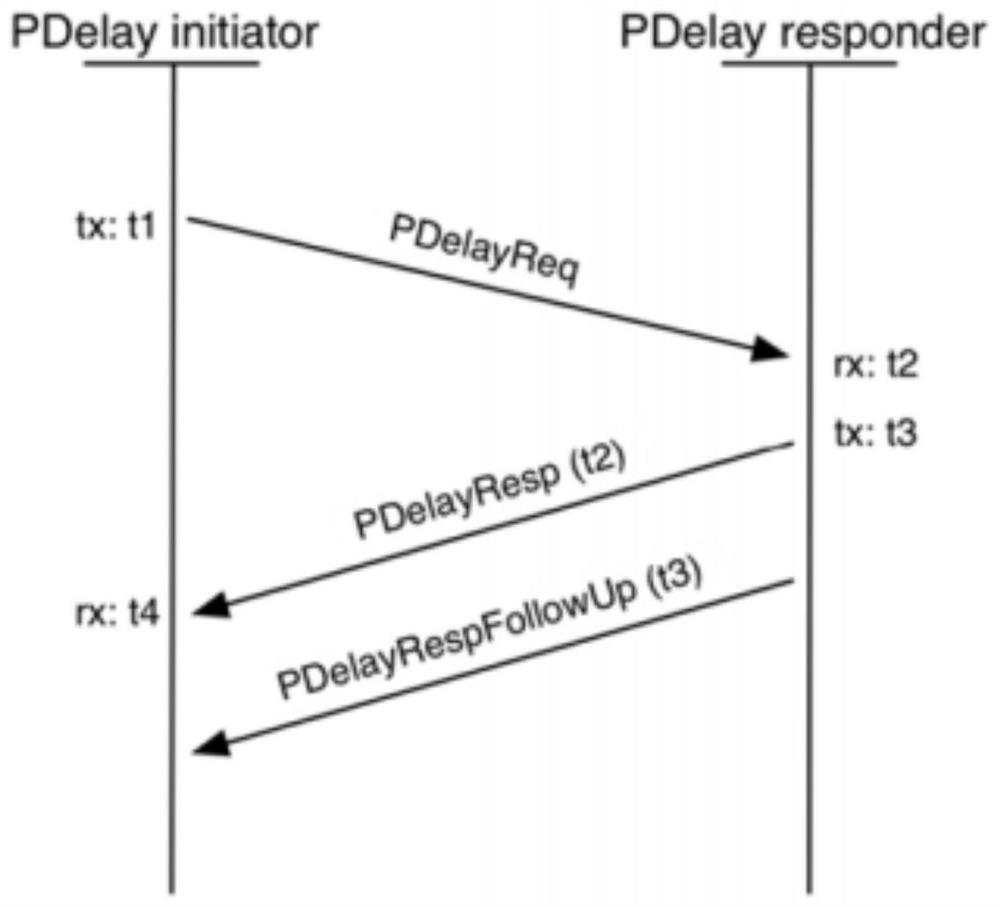

Gateway module for a communications system, communications system, and method for transmitting data between users of a communications system

ActiveUS20140133350A1Save powerShorten the timeData switching by path configurationEnergy efficient computingCommunications systemNetwork Communication Protocols

A gateway module for connection of at least two sub-networks is described. A first sub-network of the at least two sub-networks supports a data transmission in accordance with a first communications protocol, especially CAN, FlexRay, LIN, MOST or Ethernet, and a second sub-network of the at least two sub-networks supports a data transmission in accordance with a second communications protocol, especially CAN, FlexRay, LIN, MOST or Ethernet. The gateway module has a configurable hardware circuit which is adapted to manipulate and forward data from the first sub-network and to the second sub-network taking into consideration the first communications protocol and the second communications protocol.

Owner:ROBERT BOSCH GMBH

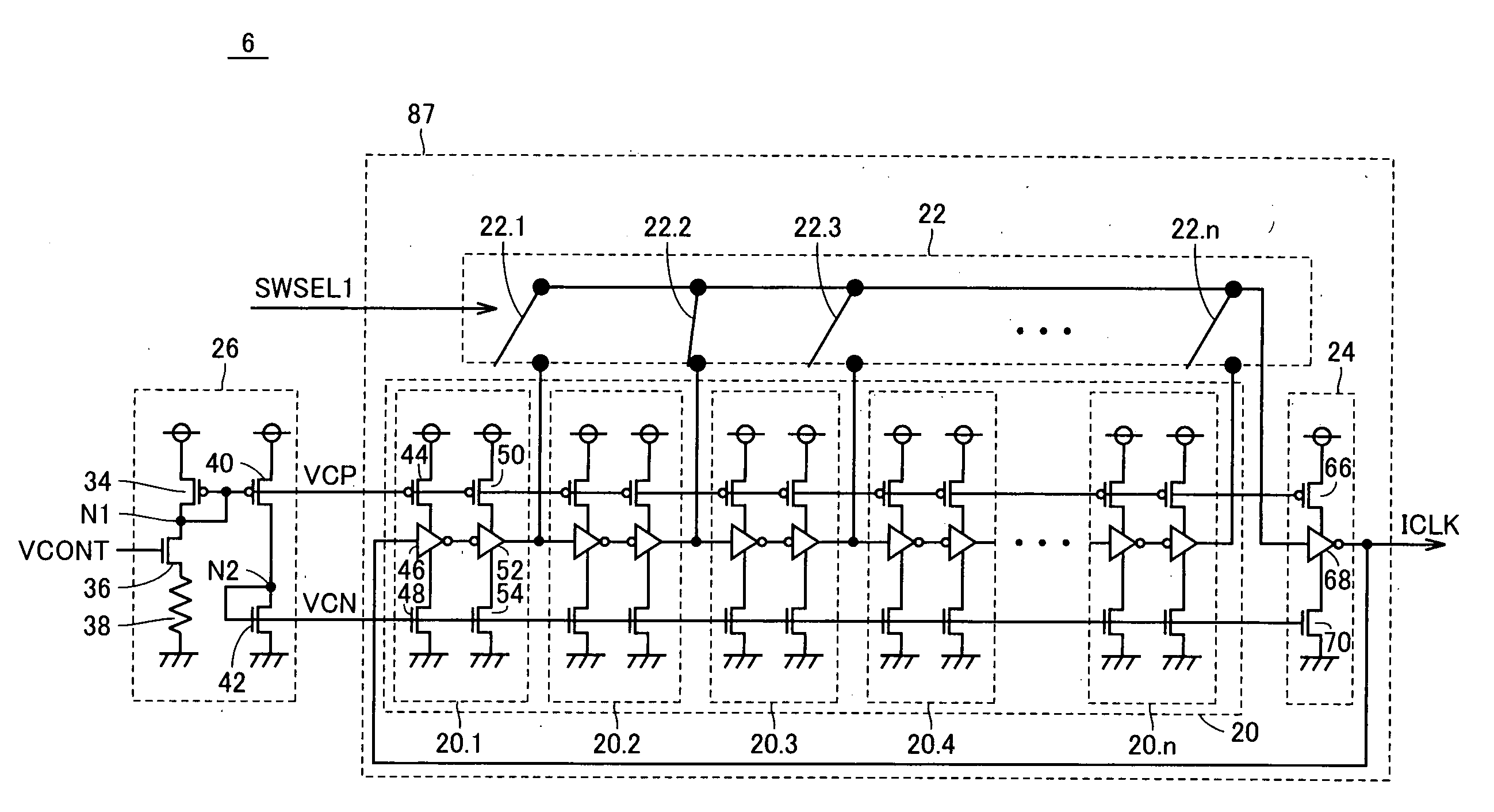

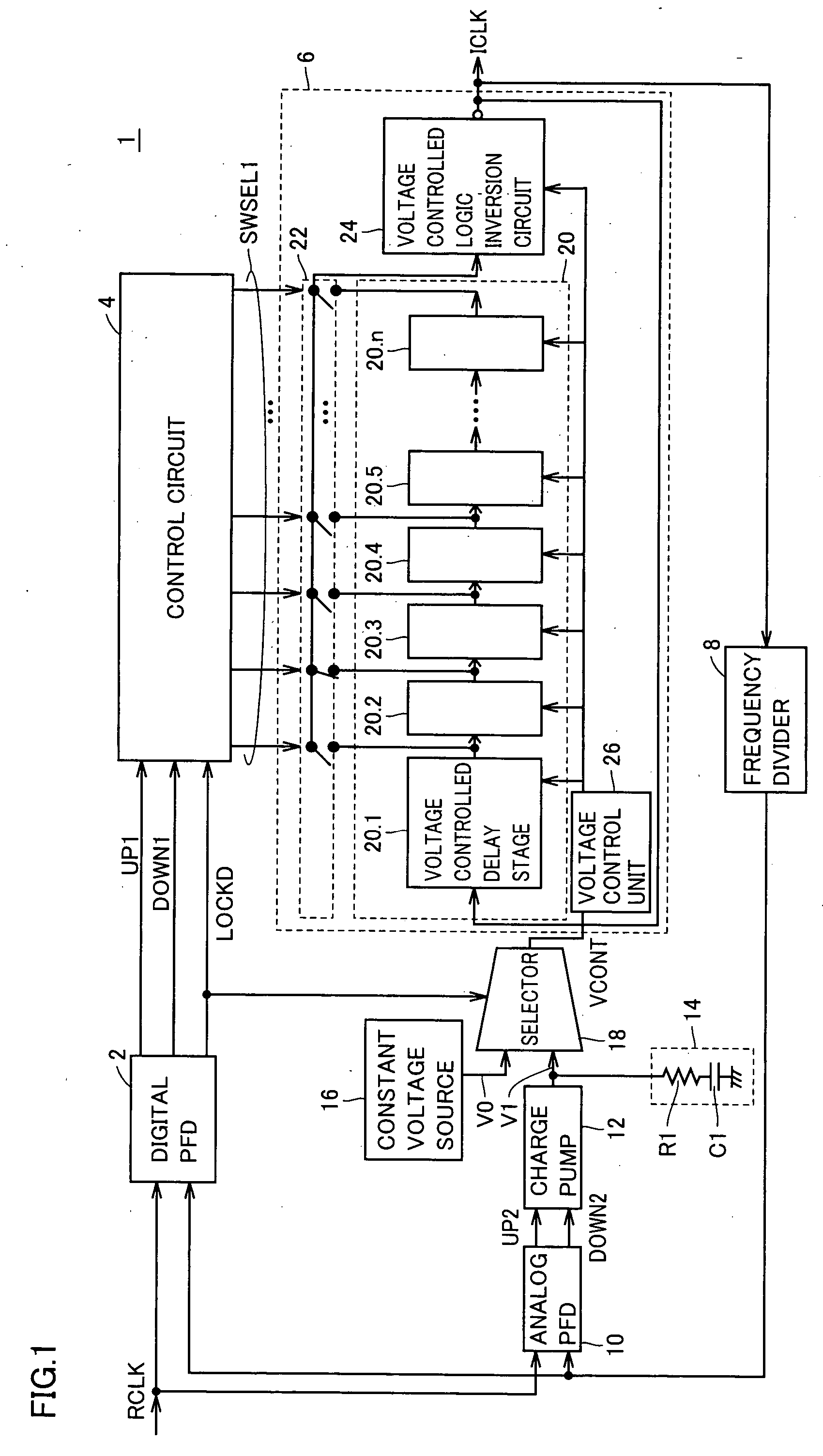

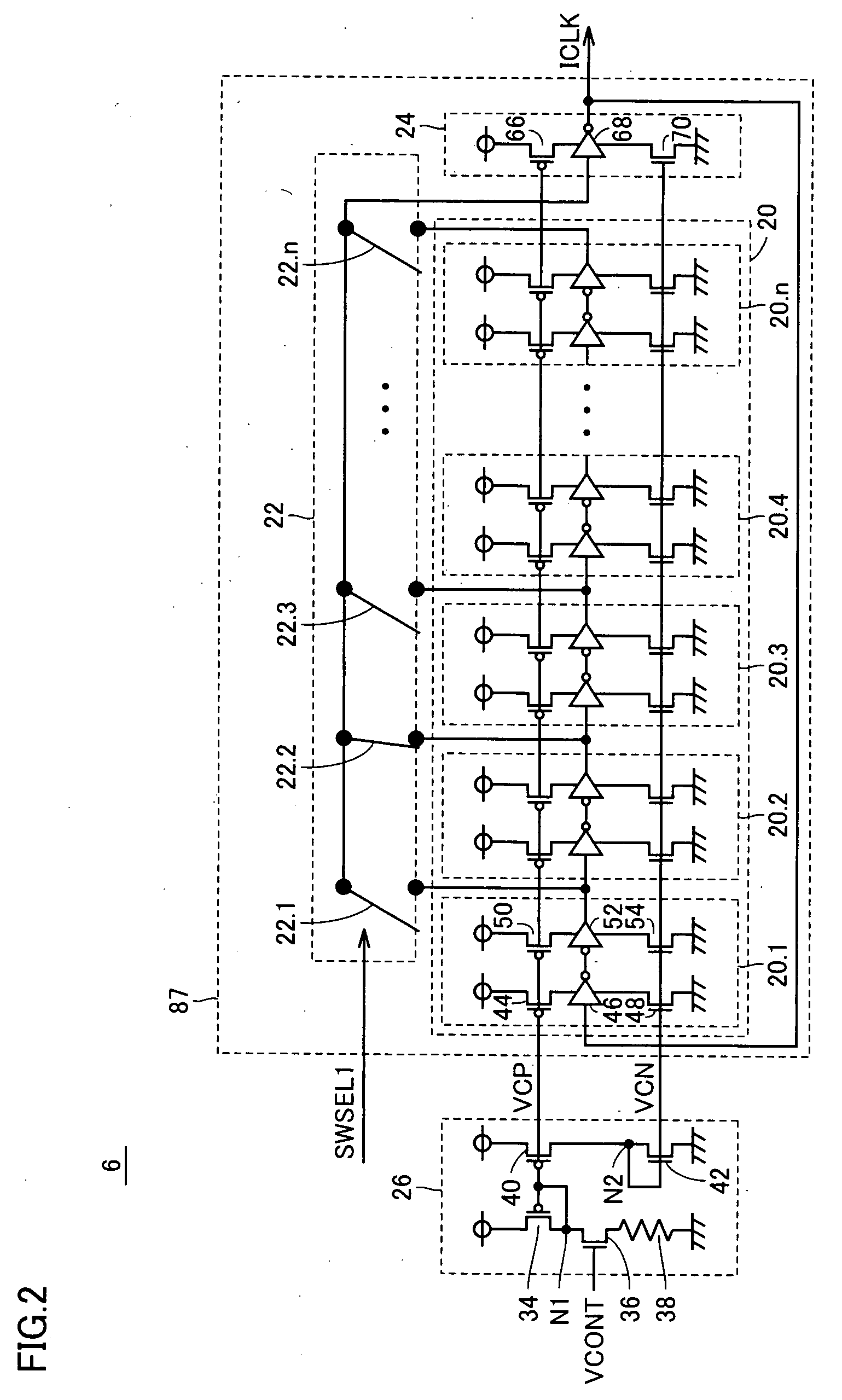

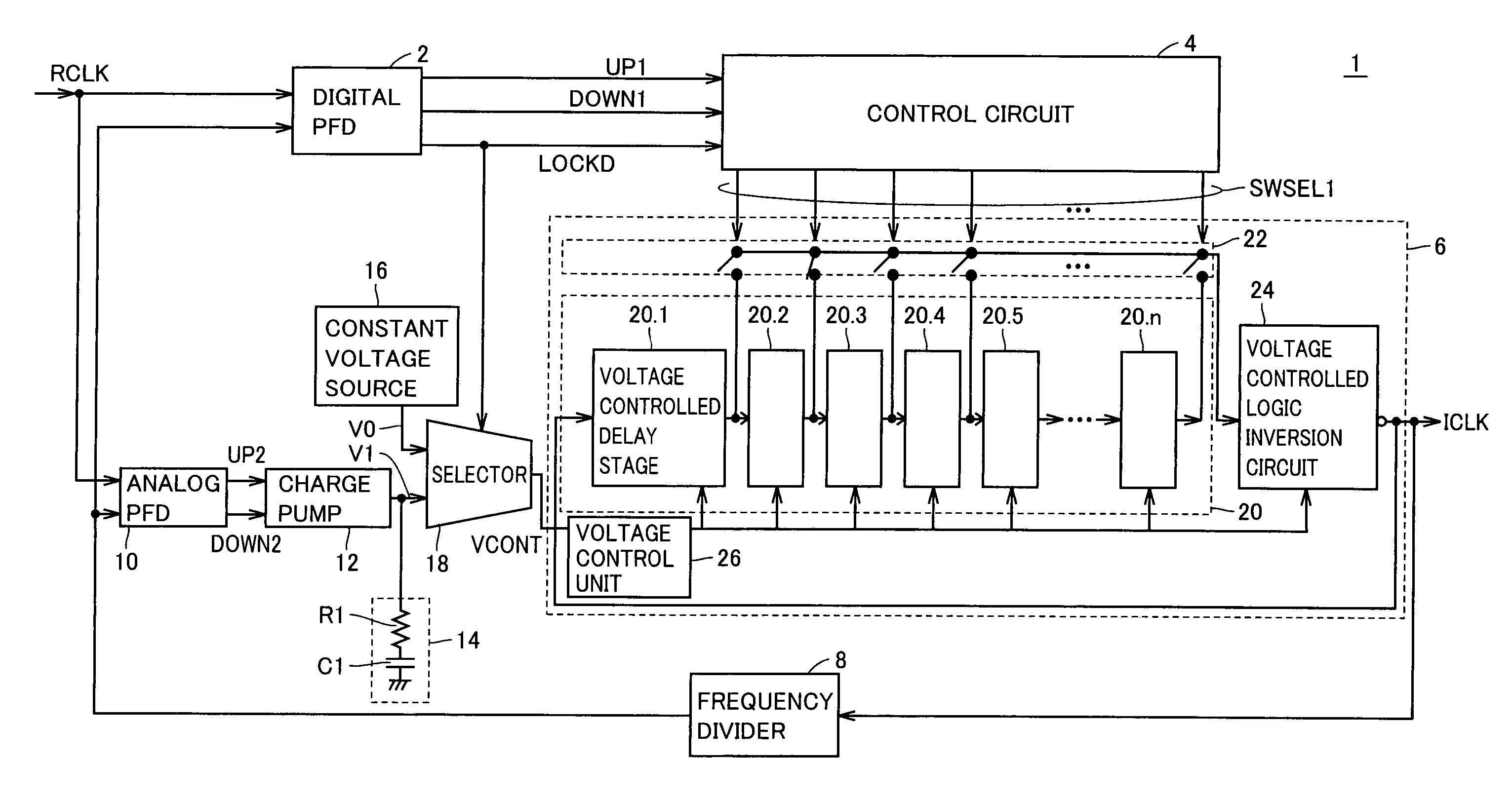

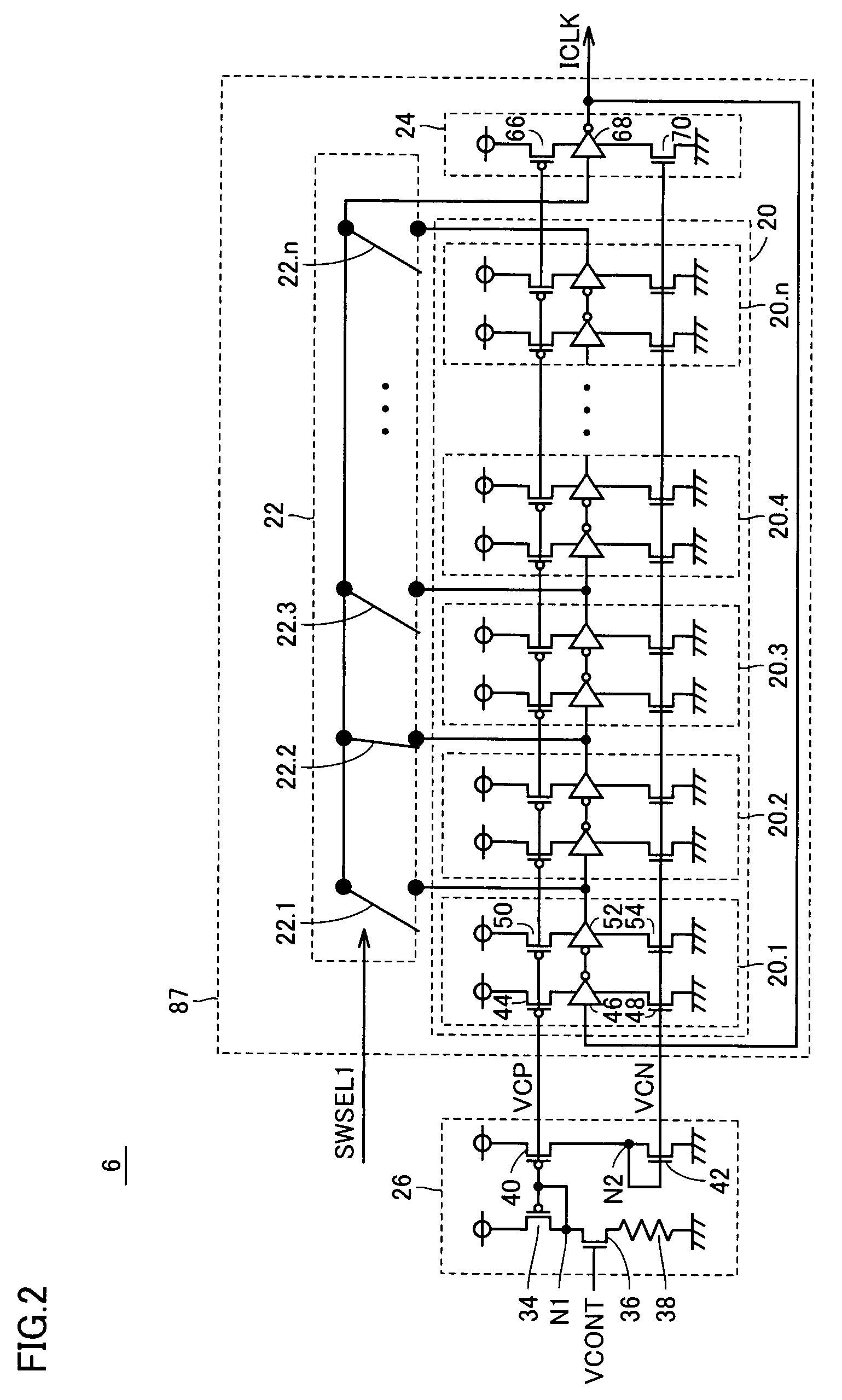

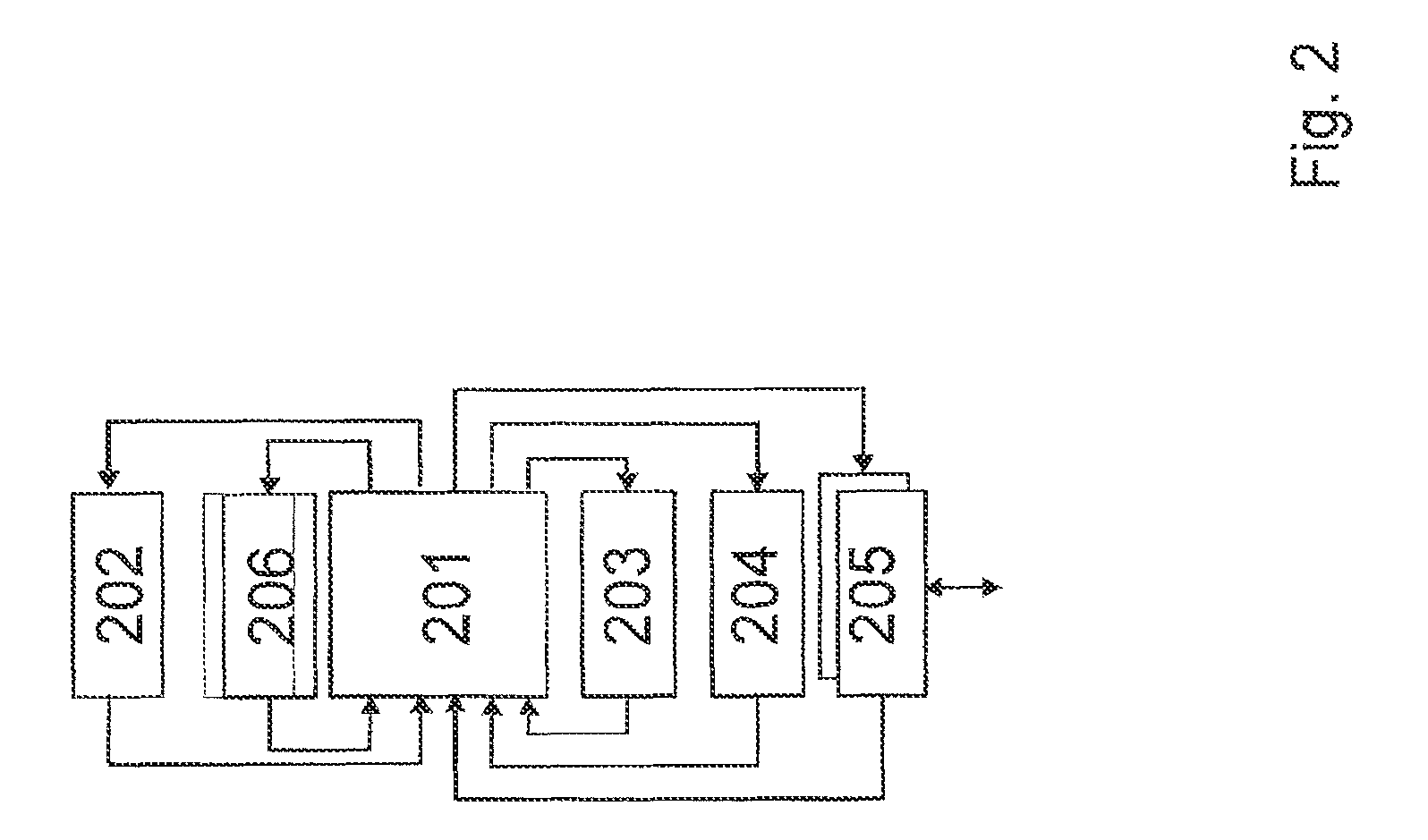

Synchronous clock generation circuit capable of ensuring wide lock-in range and attaining lower jitter

InactiveUS20050046497A1Wide lock-in rangeImprove jitter characteristicsPulse automatic controlPulse generation by logic circuitsLow jitterEngineering

At a first step, in a synchronous clock generation circuit, the number of delay stages serving as a digital PLL circuit is increased / decreased, and an oscillation circuit performs an oscillation operation when an optimal number of delay stages is set. Thereafter, in an operation at a second step, a control voltage is controlled with the optimal number of delay stages being set for serving as an analog PLL circuit, thereby attaining a lock-in state. As the lock-in state is finally maintained under analog control, an excellent jitter characteristic can be obtained. Thus, ensuring a lock-in range that has been a problem in the analog PLL circuit is solved by varying the number of delay stages in the operation at the first step, and a high jitter characteristic that has been a problem in a digital PLL circuit can be solved by analog control in the operation at the second step.

Owner:RENESAS TECH CORP

Synchronous clock generation circuit capable of ensuring wide lock-in range and attaining lower jitter

InactiveUS7064621B2Improve jitter characteristicsPulse automatic controlPulse generation by logic circuitsLow jitterEngineering

Owner:RENESAS TECH CORP

Gateway module for a communications system, communications system, and method for transmitting data between users of a communications system

ActiveUS9191467B2Improve jitter characteristicsImprove throughputData switching by path configurationNetwork connectionsCommunications systemNetwork Communication Protocols

A gateway module for connection of at least two sub-networks is described. A first sub-network of the at least two sub-networks supports a data transmission in accordance with a first communications protocol, especially CAN, FlexRay, LIN, MOST or Ethernet, and a second sub-network of the at least two sub-networks supports a data transmission in accordance with a second communications protocol, especially CAN, FlexRay, LIN, MOST or Ethernet. The gateway module has a configurable hardware circuit which is adapted to manipulate and forward data from the first sub-network and to the second sub-network taking into consideration the first communications protocol and the second communications protocol.

Owner:ROBERT BOSCH GMBH

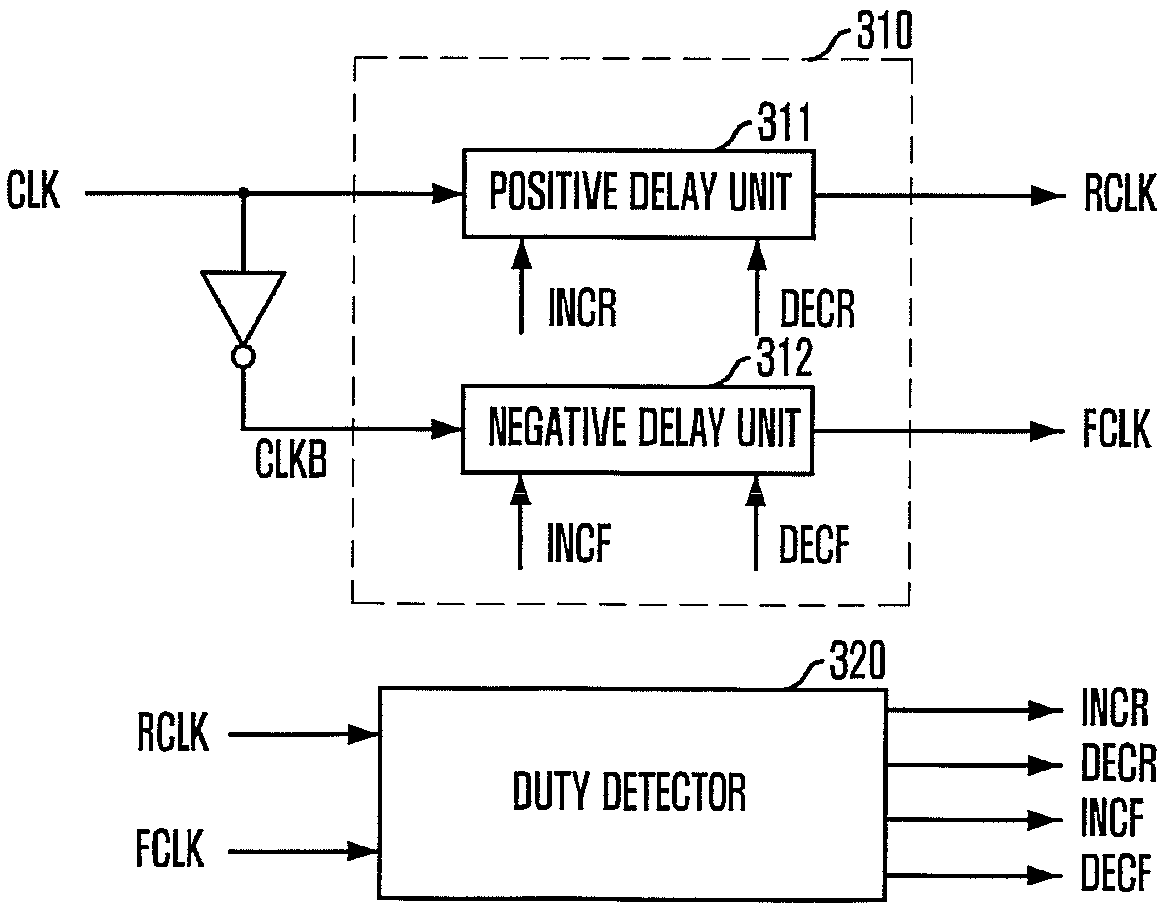

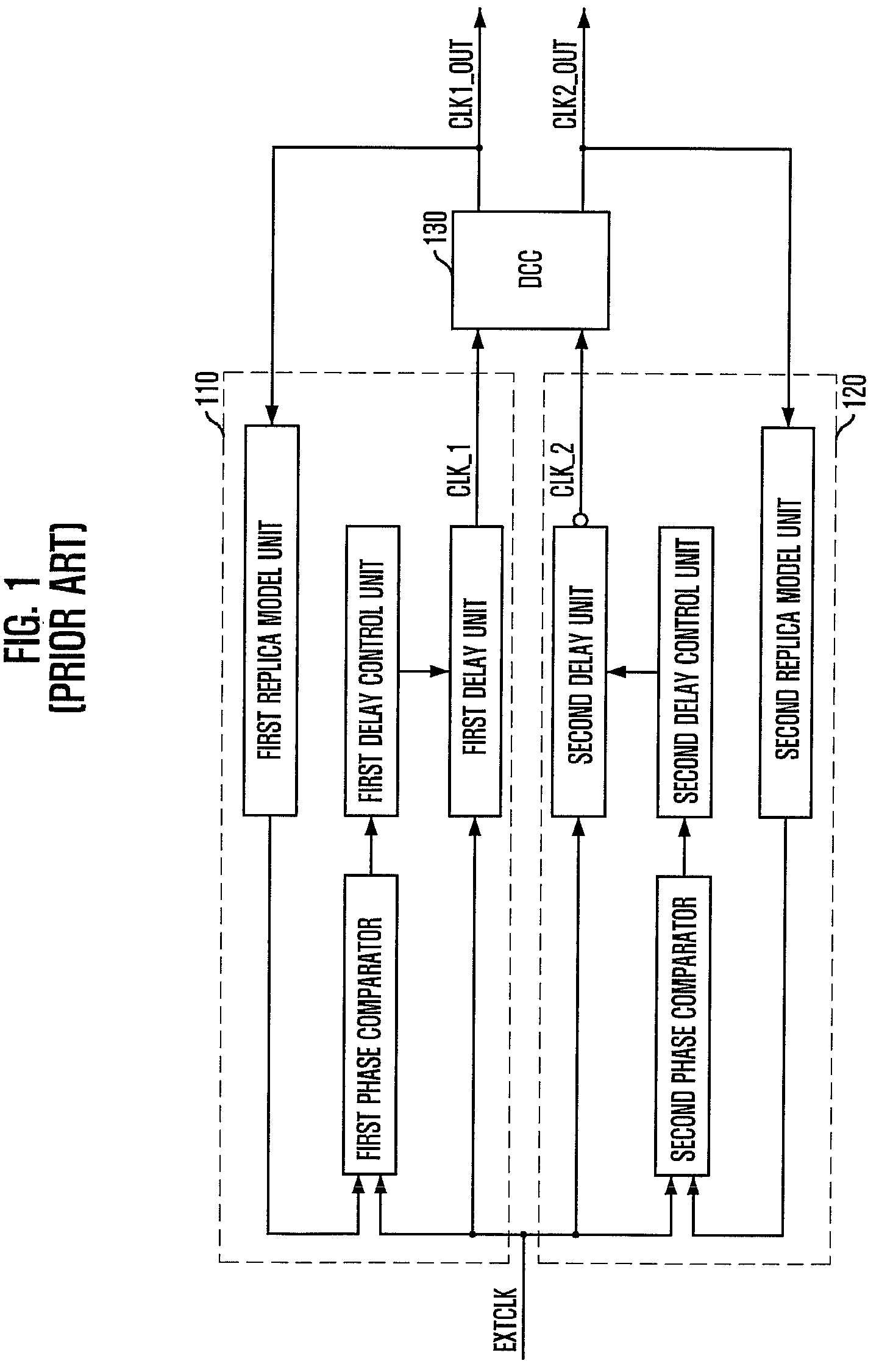

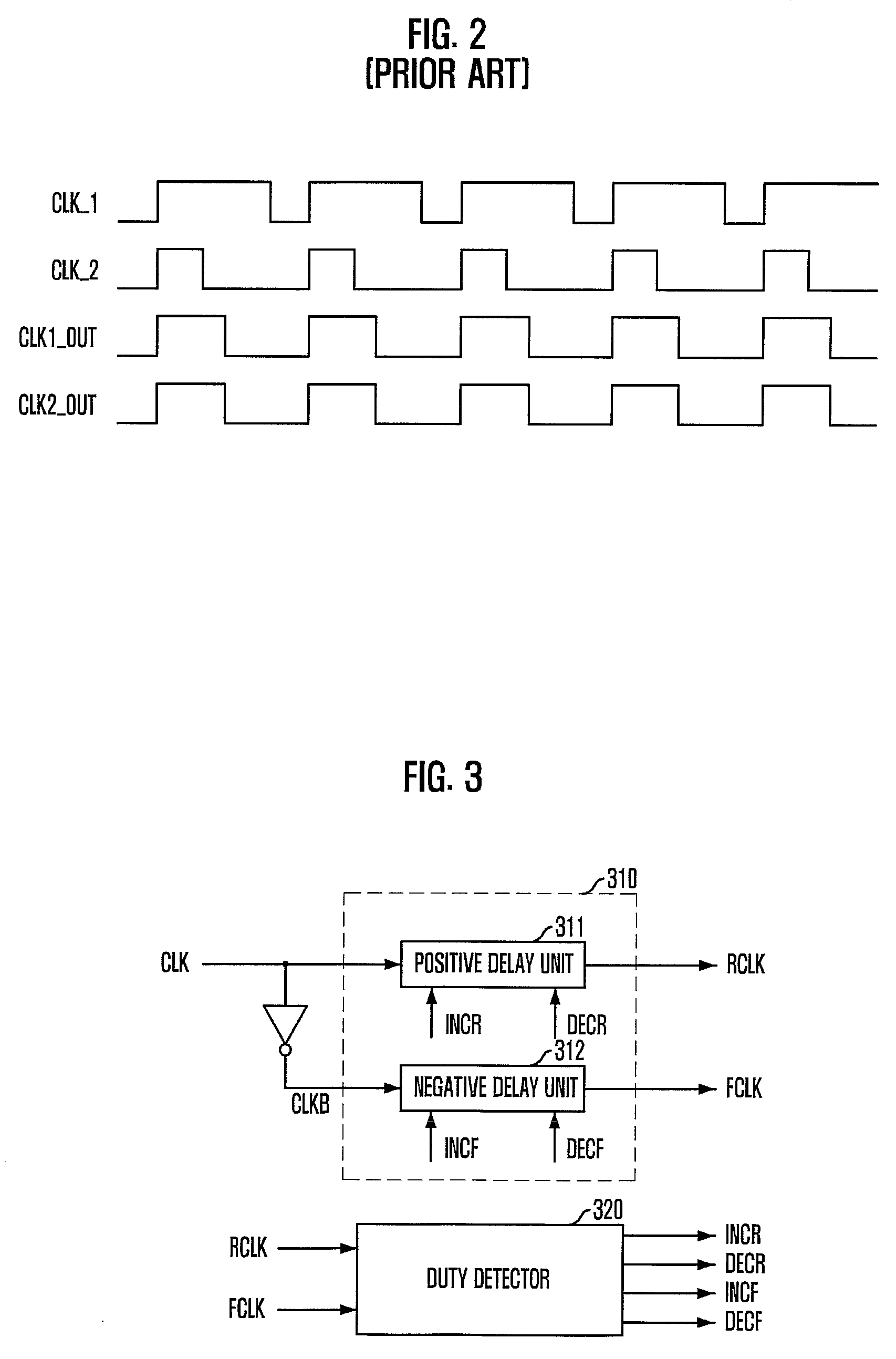

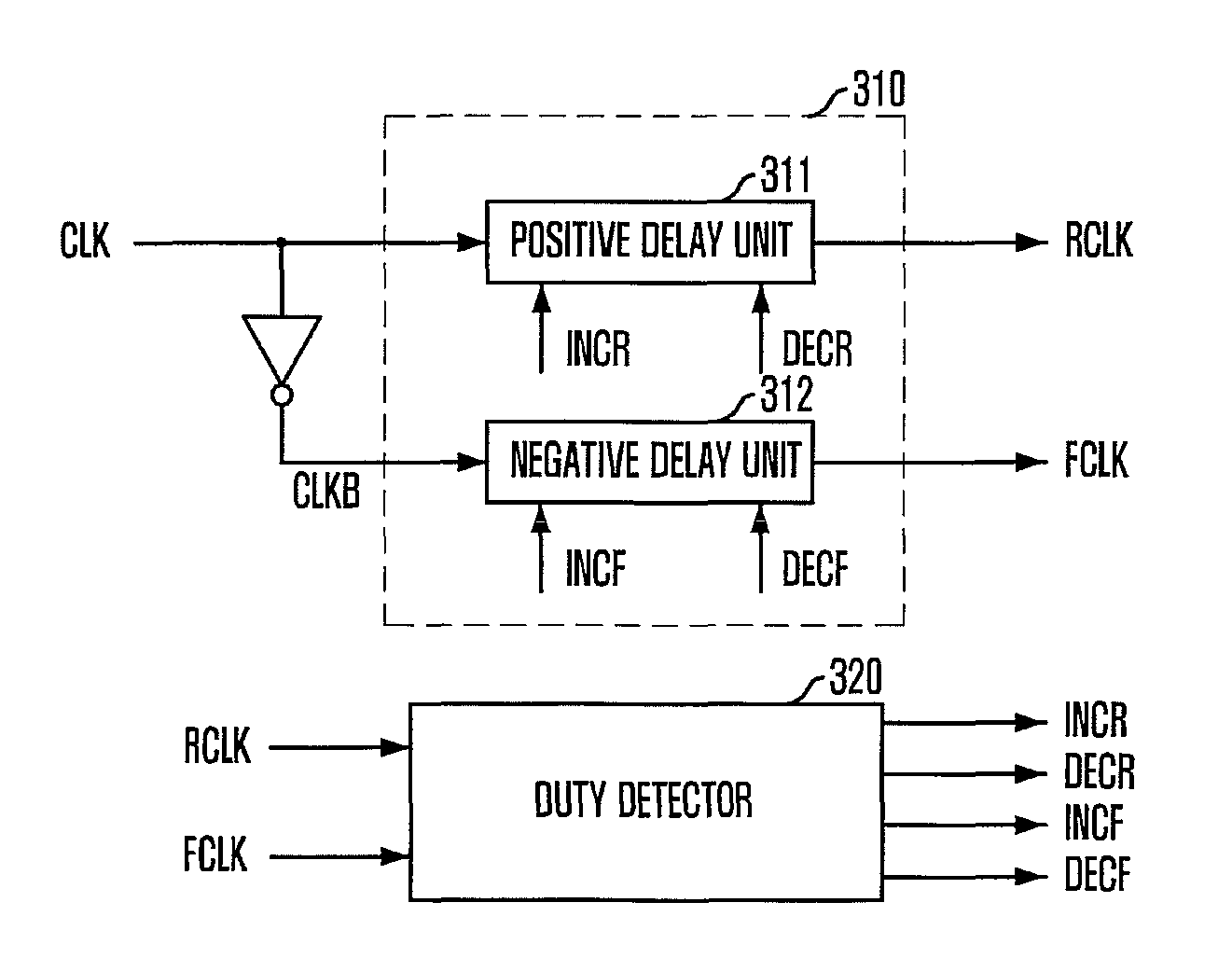

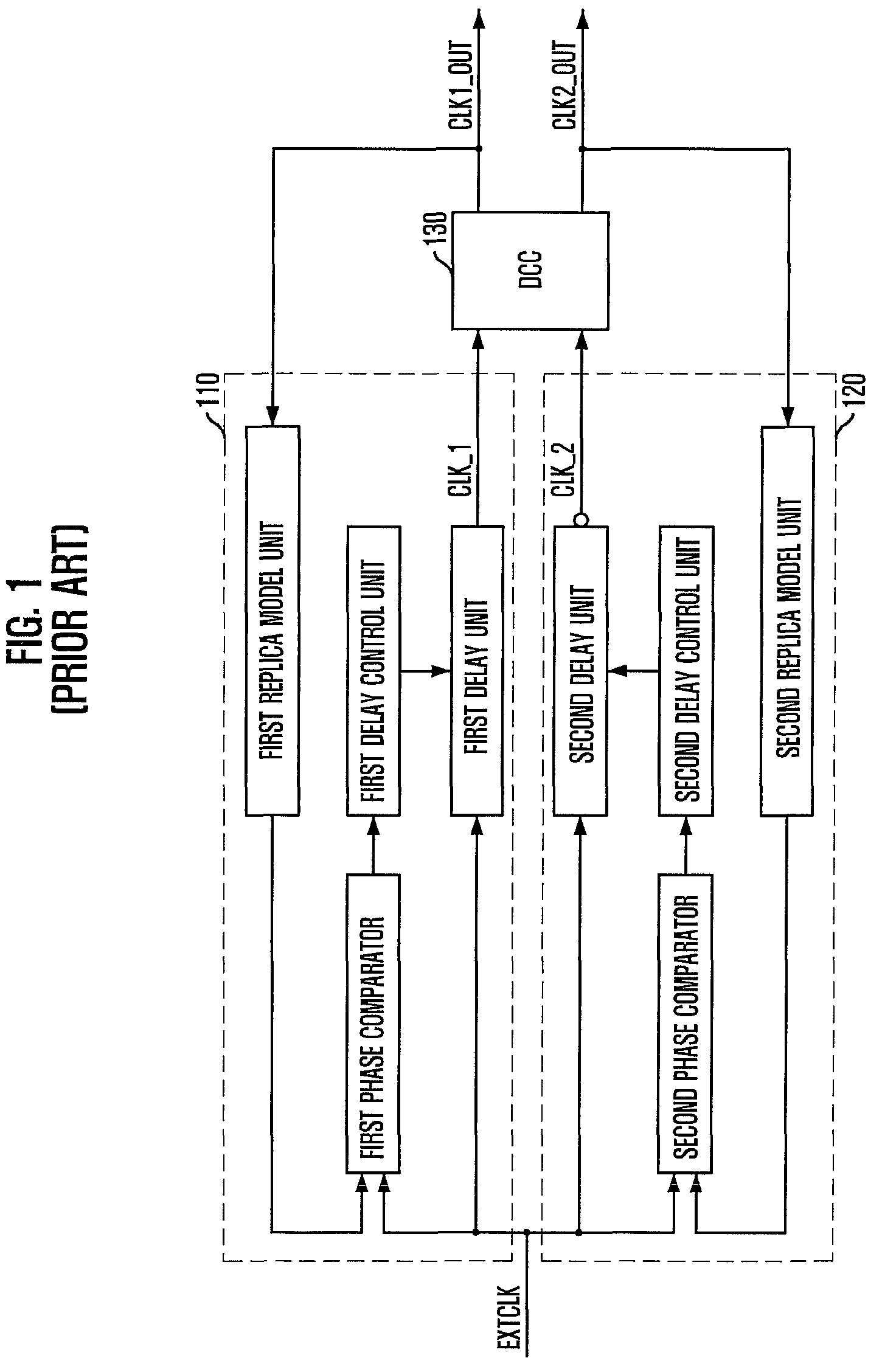

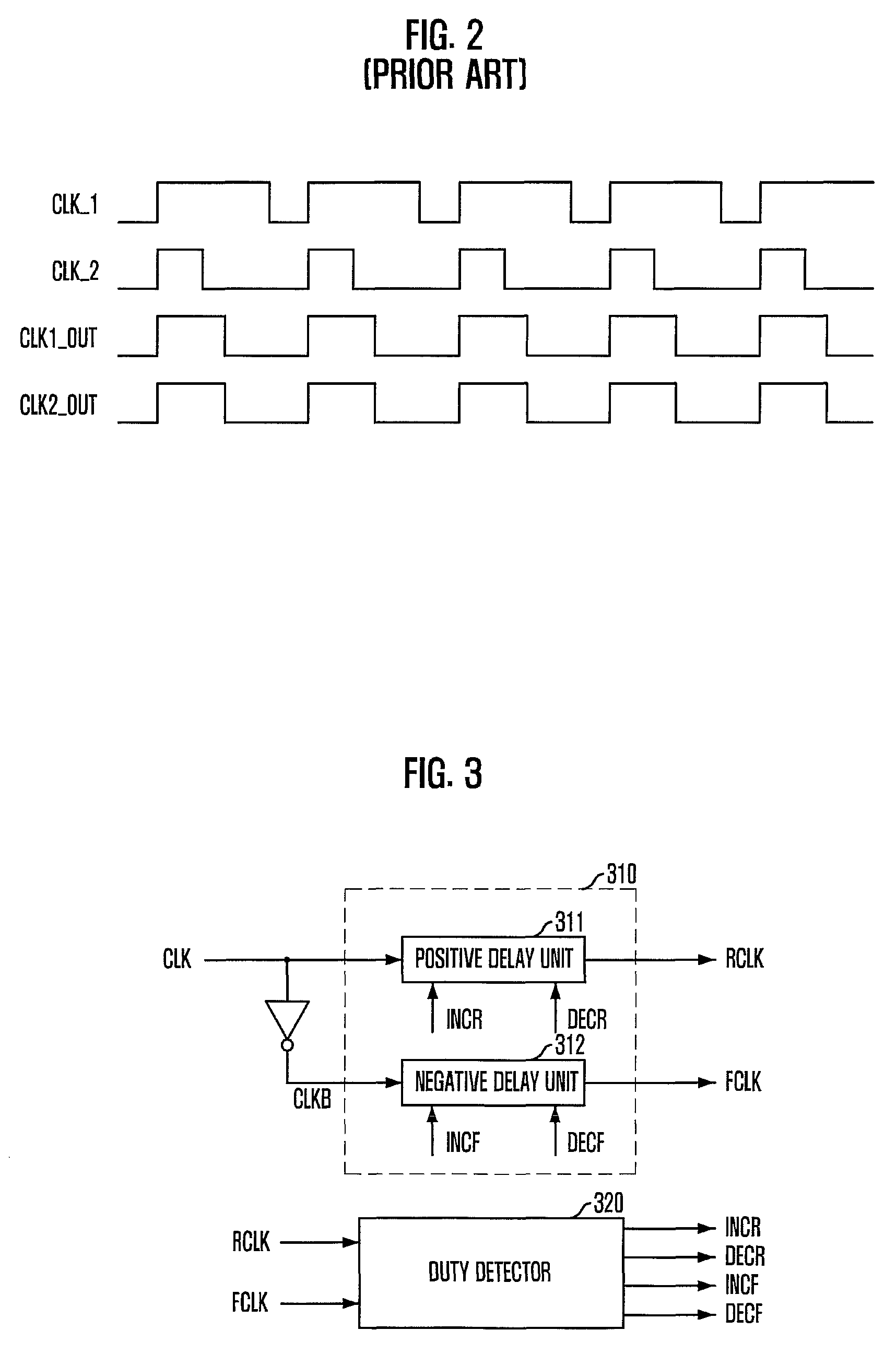

Duty cycle corrector and clock generator having the same

InactiveUS20100073057A1Improve jitter characteristicsPulse automatic controlSingle output arrangementsControl signalEngineering

A duty cycle corrector includes a delay unit configured to adjust an input clock and an inverted input clock with a delay value controlled in response to one or more control signals and to generate a positive clock and a negative clock, and a duty detector configured to receive the positive clock and the negative clock, to detect duty ratios of the positive clock and the negative clock and to generate the one or more control signals.

Owner:SK HYNIX INC

Duty cycle corrector and clock generator having the same

InactiveUS7994834B2Improve jitter characteristicsPulse automatic controlSingle output arrangementsControl signalClock generator

A duty cycle corrector includes a delay unit configured to adjust an input clock and an inverted input clock with a delay value controlled in response to one or more control signals and to generate a positive clock and a negative clock, and a duty detector configured to receive the positive clock and the negative clock, to detect duty ratios of the positive clock and the negative clock and to generate the one or more control signals.

Owner:SK HYNIX INC

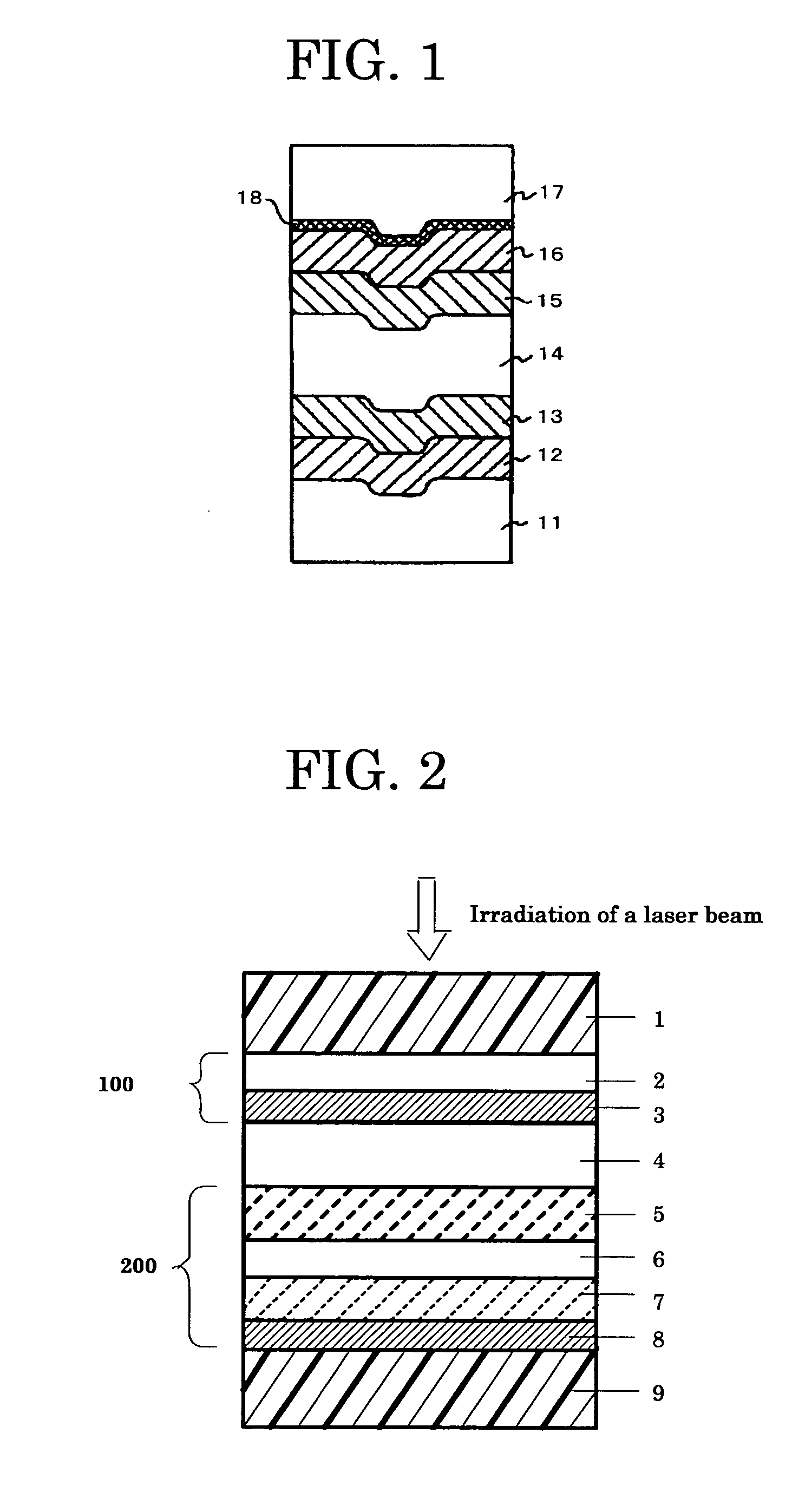

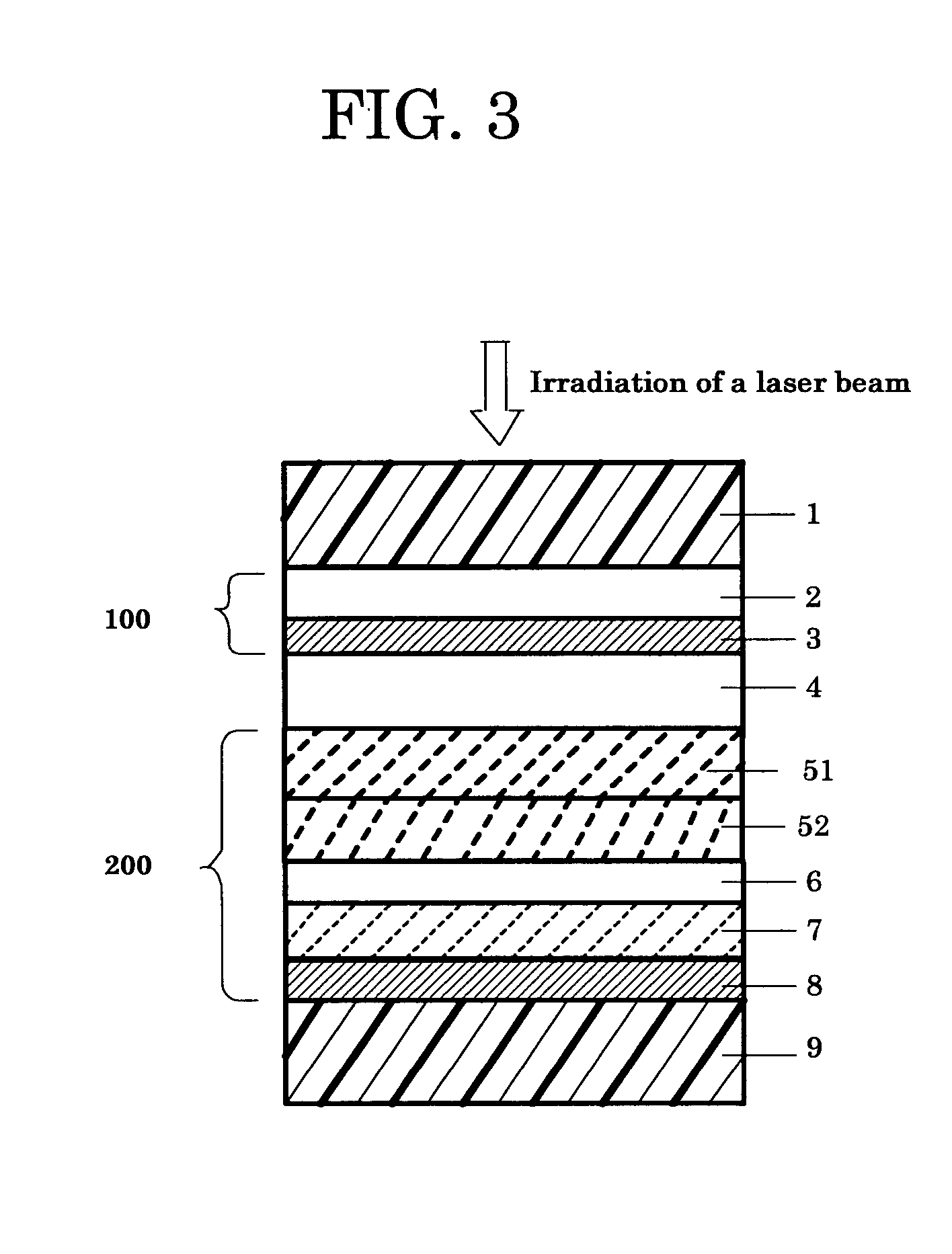

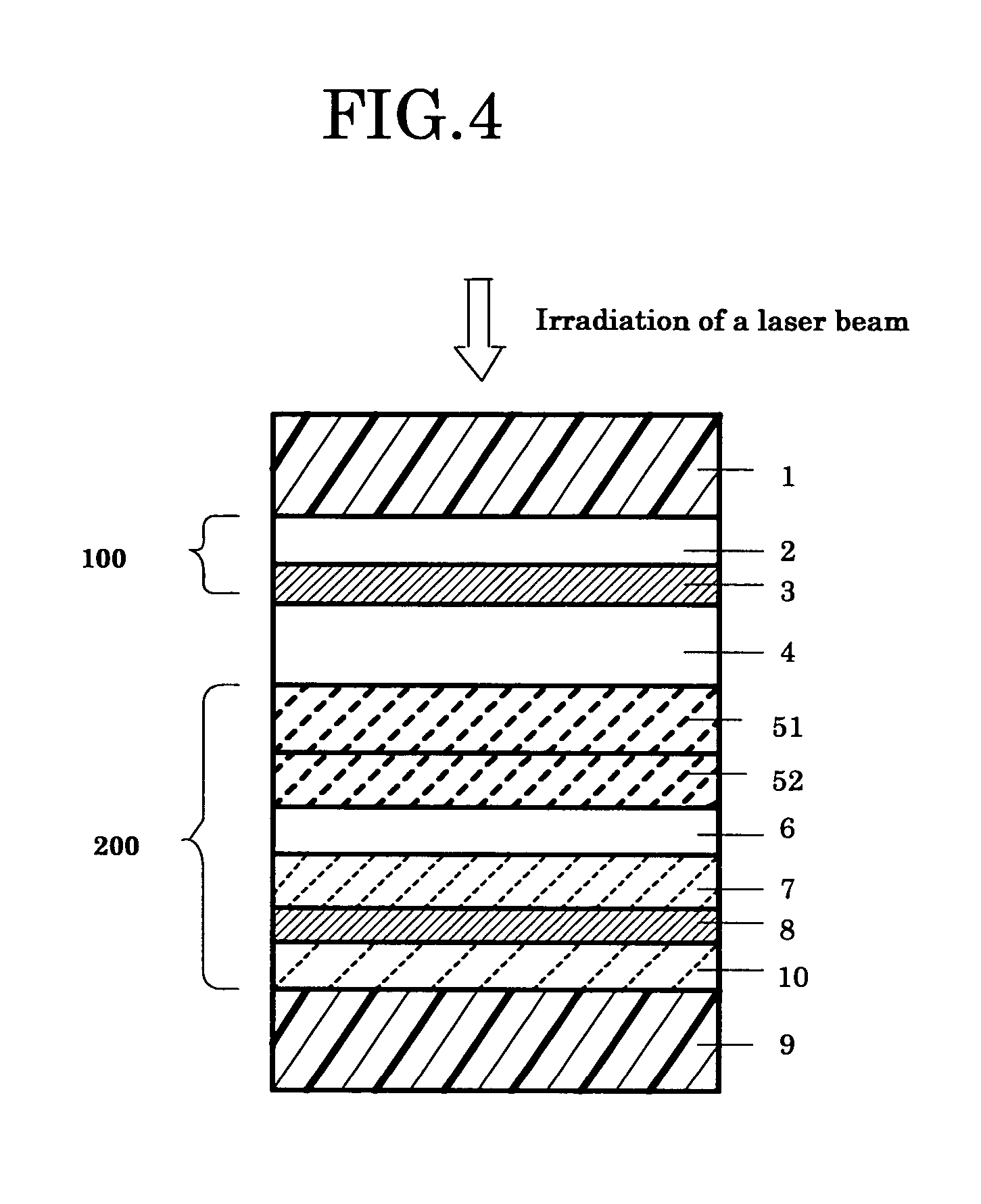

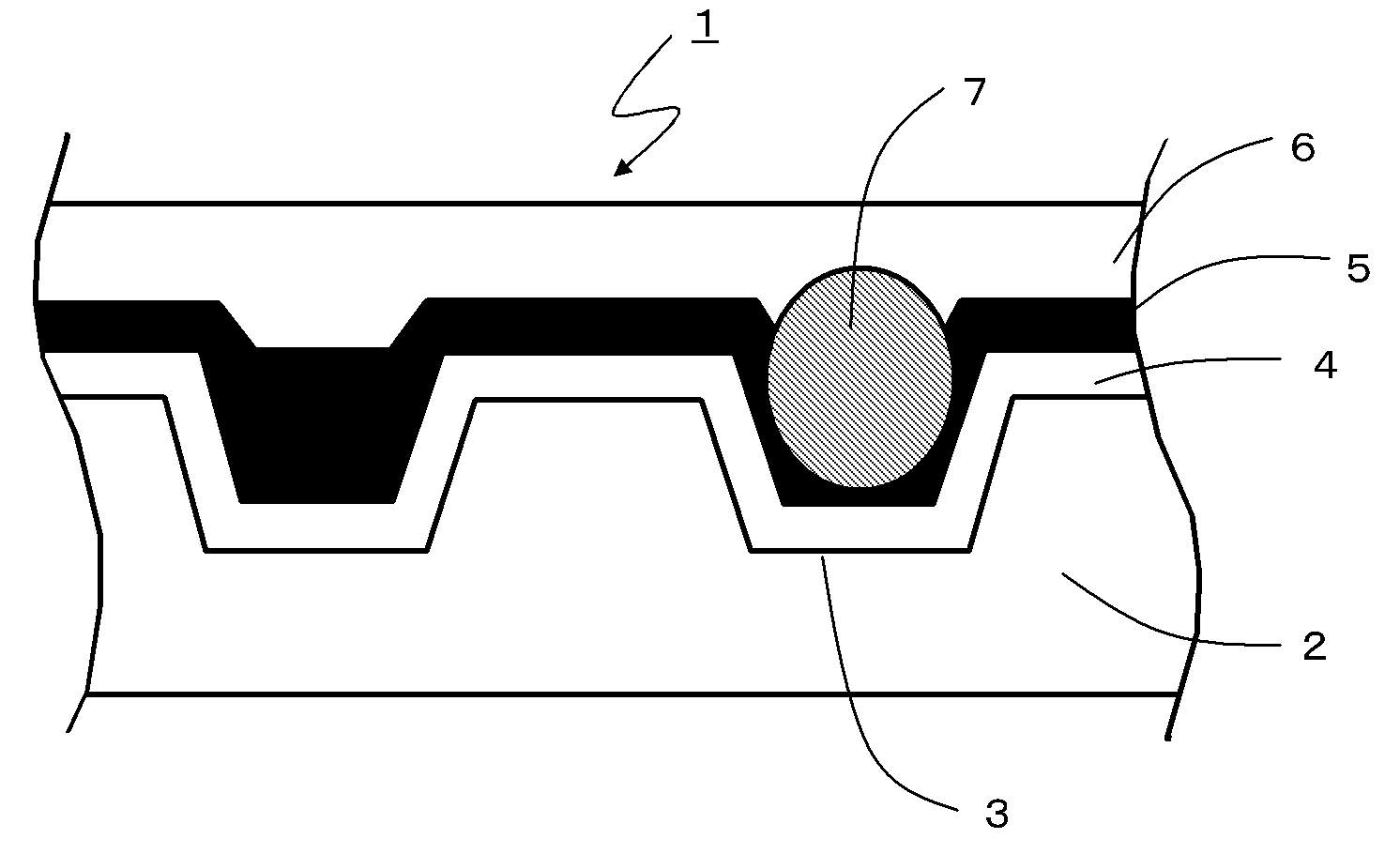

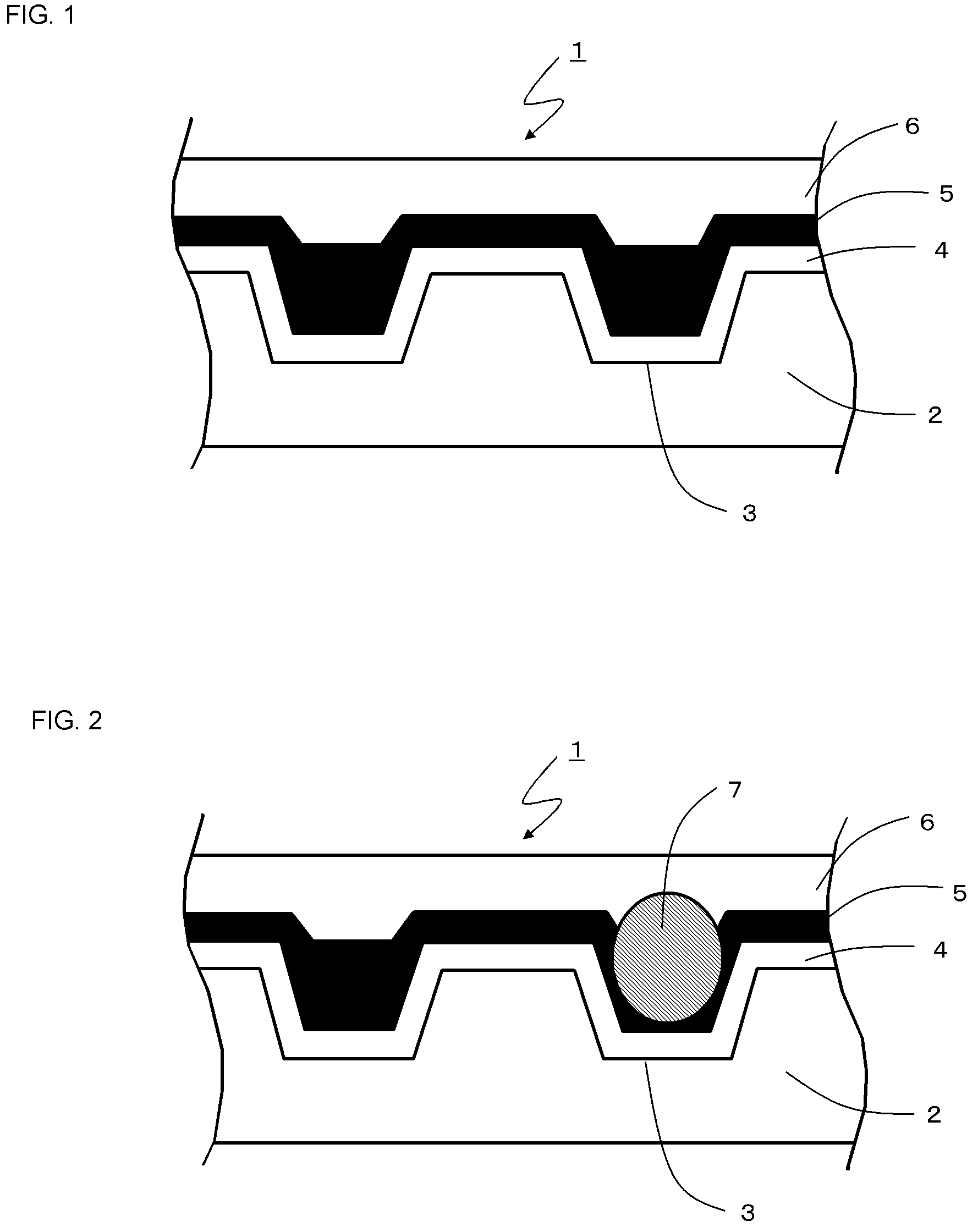

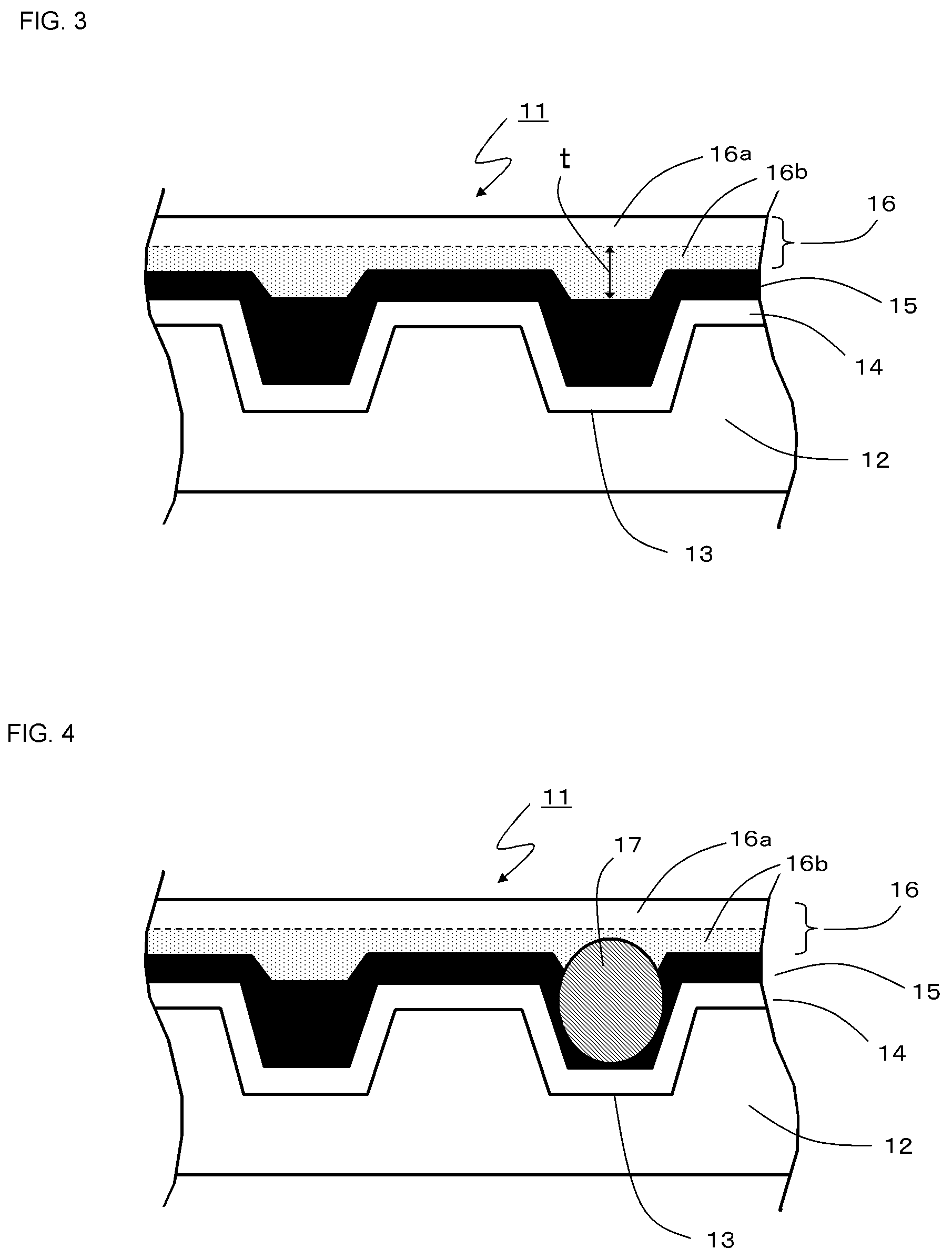

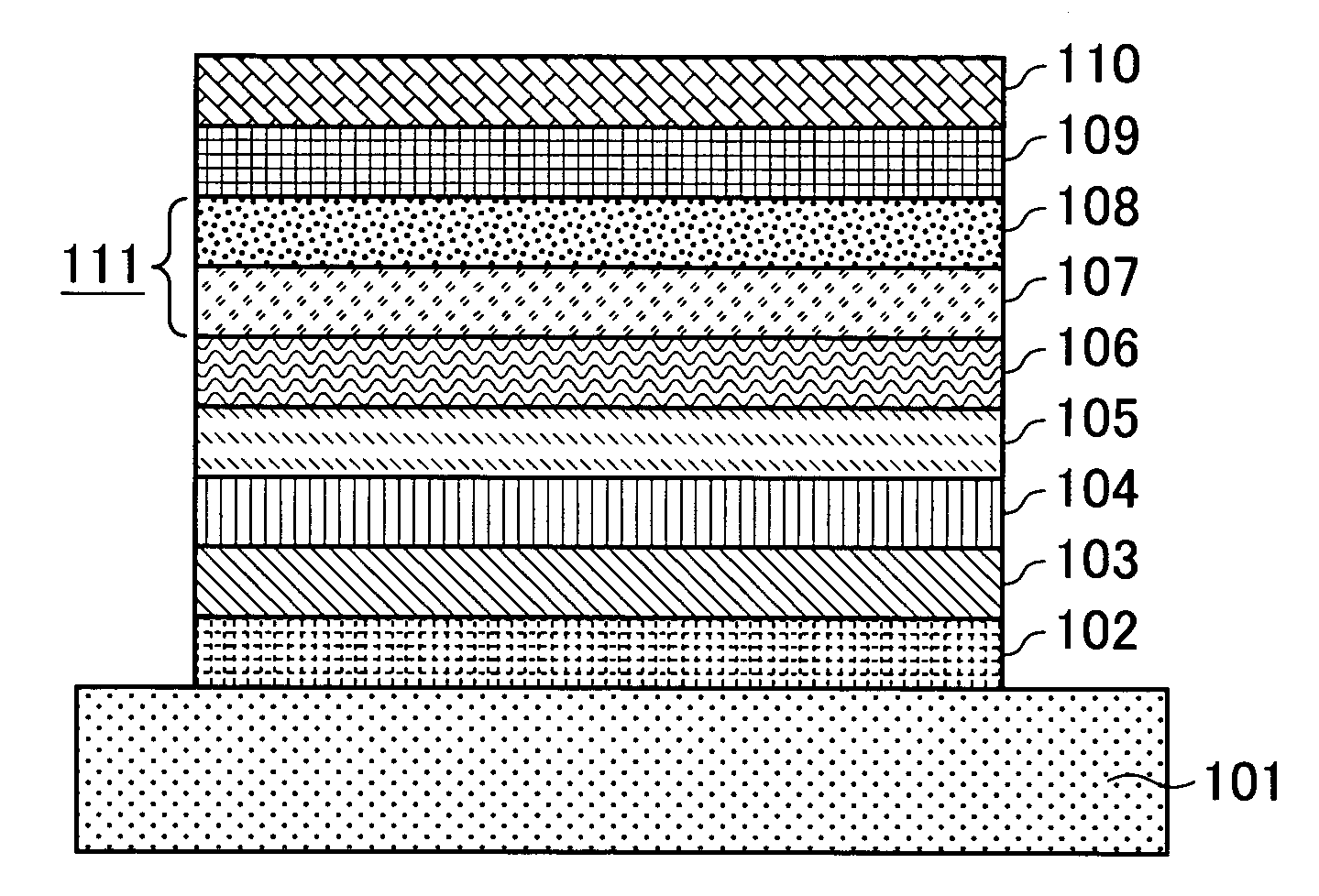

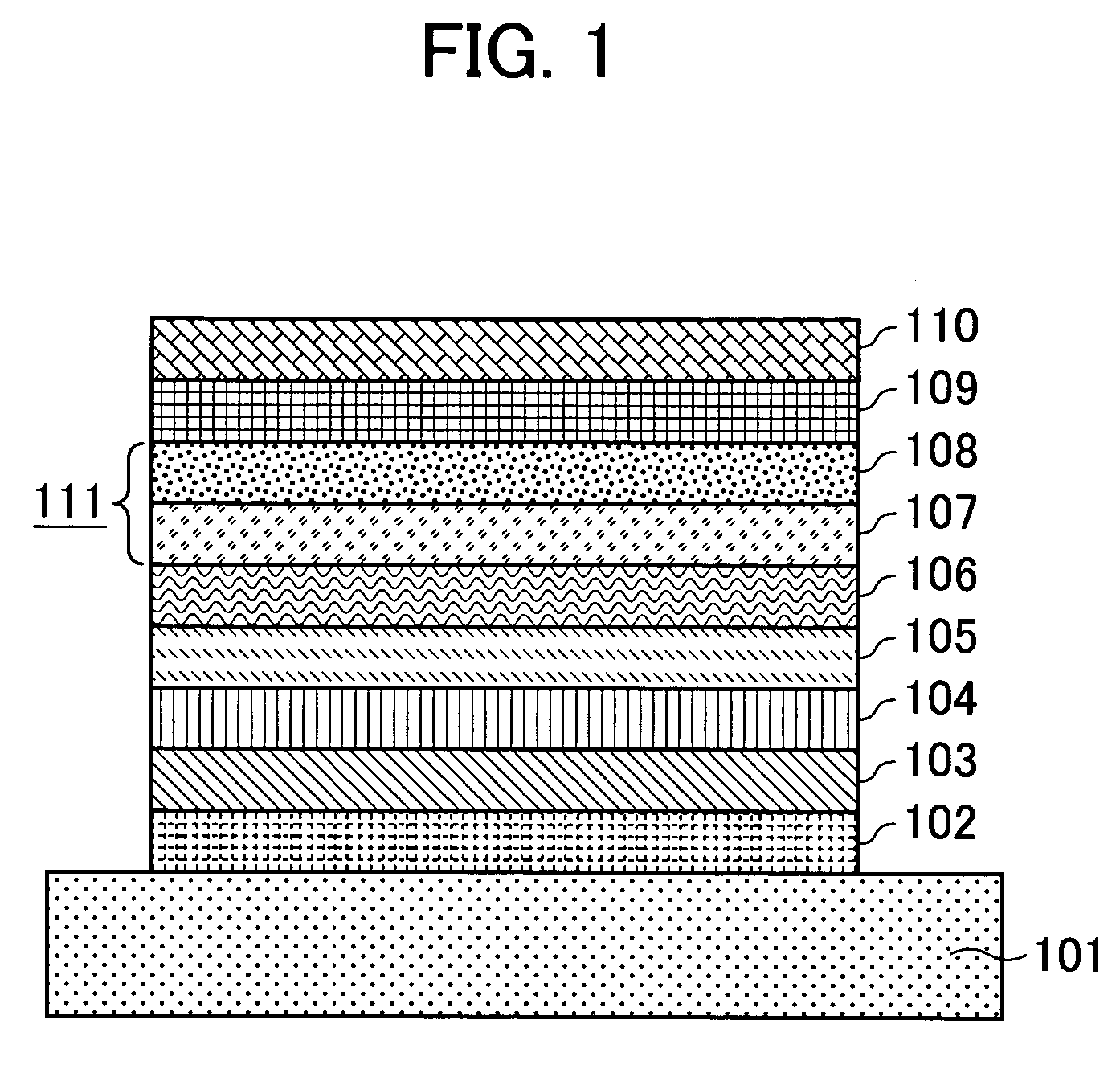

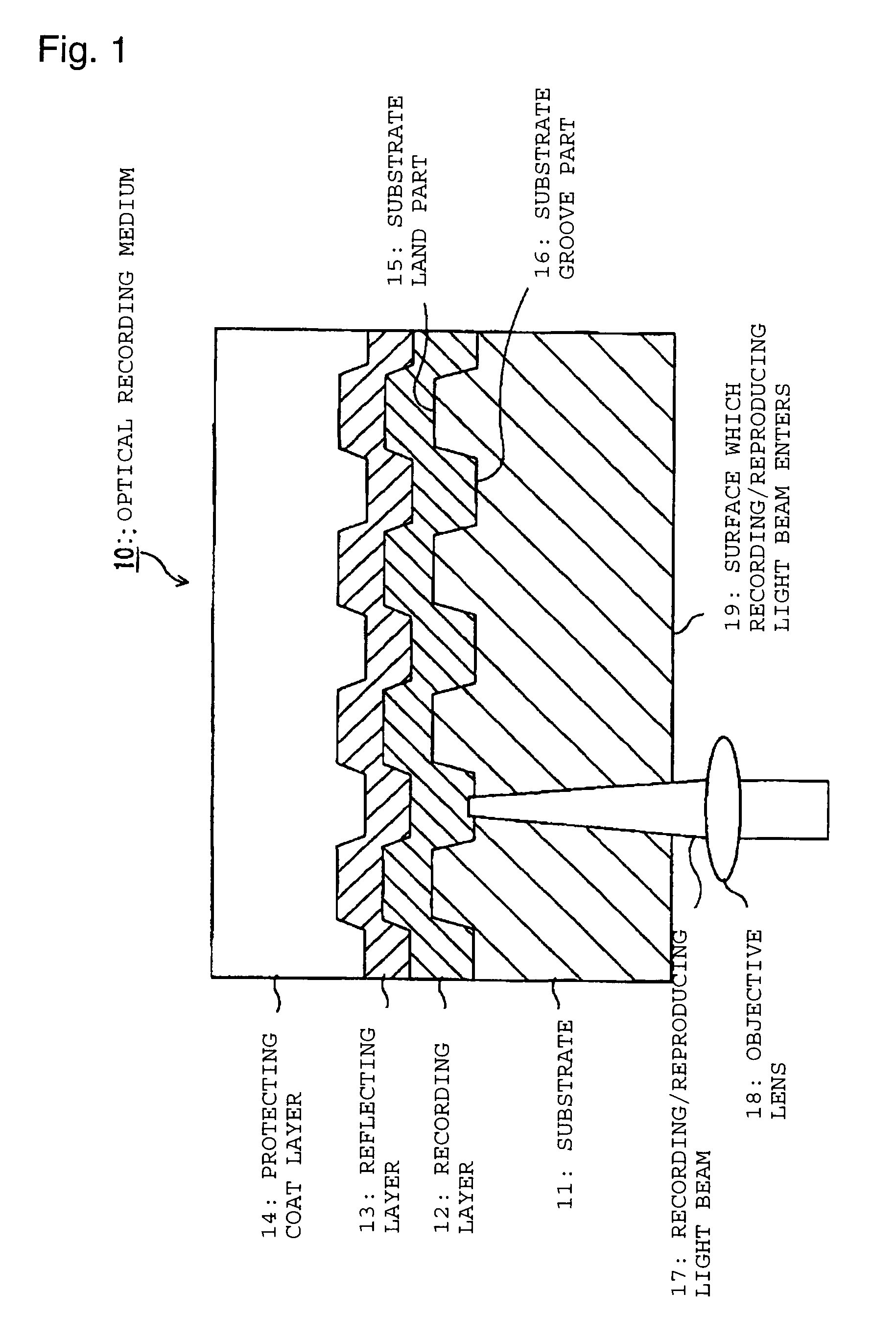

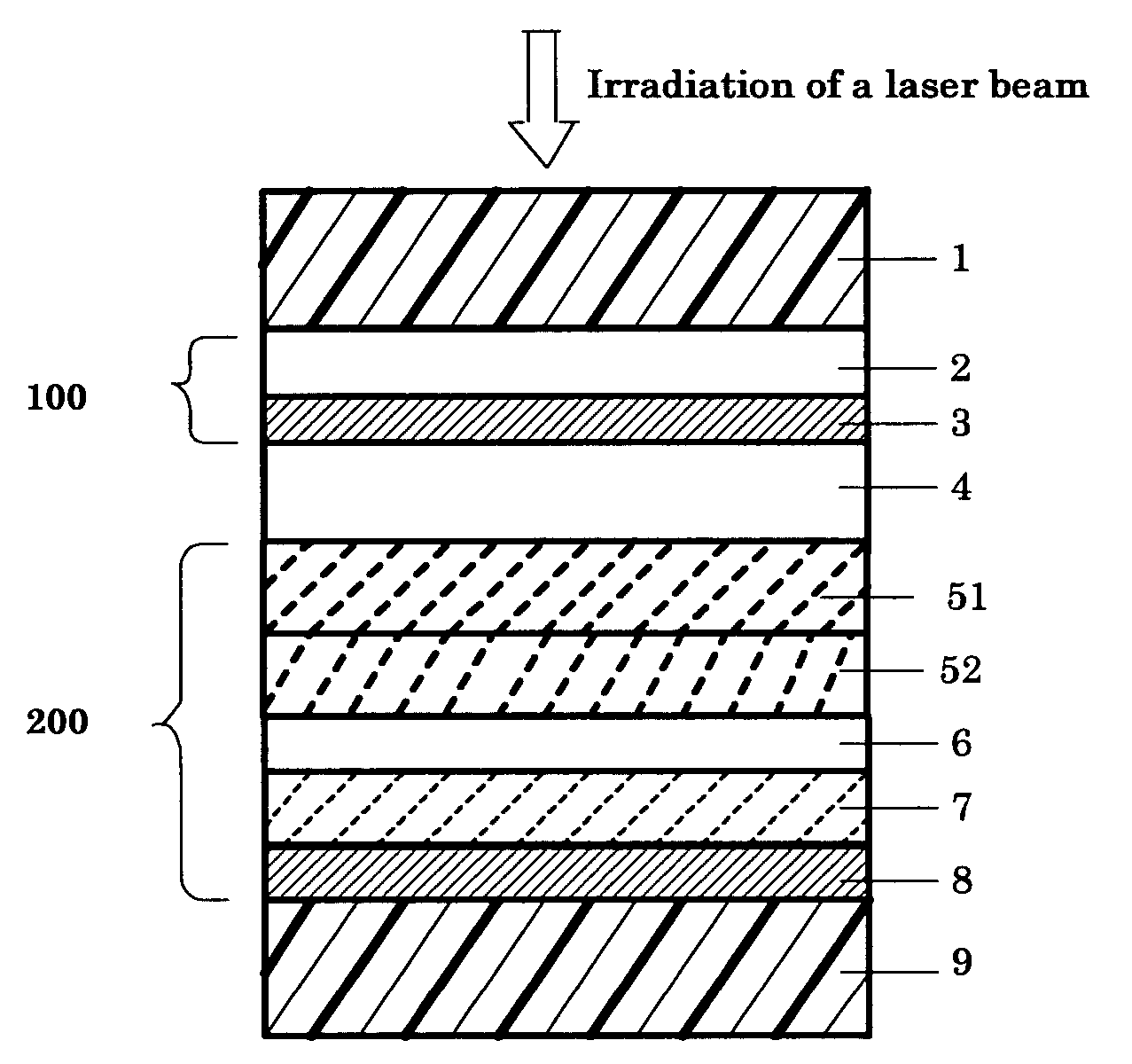

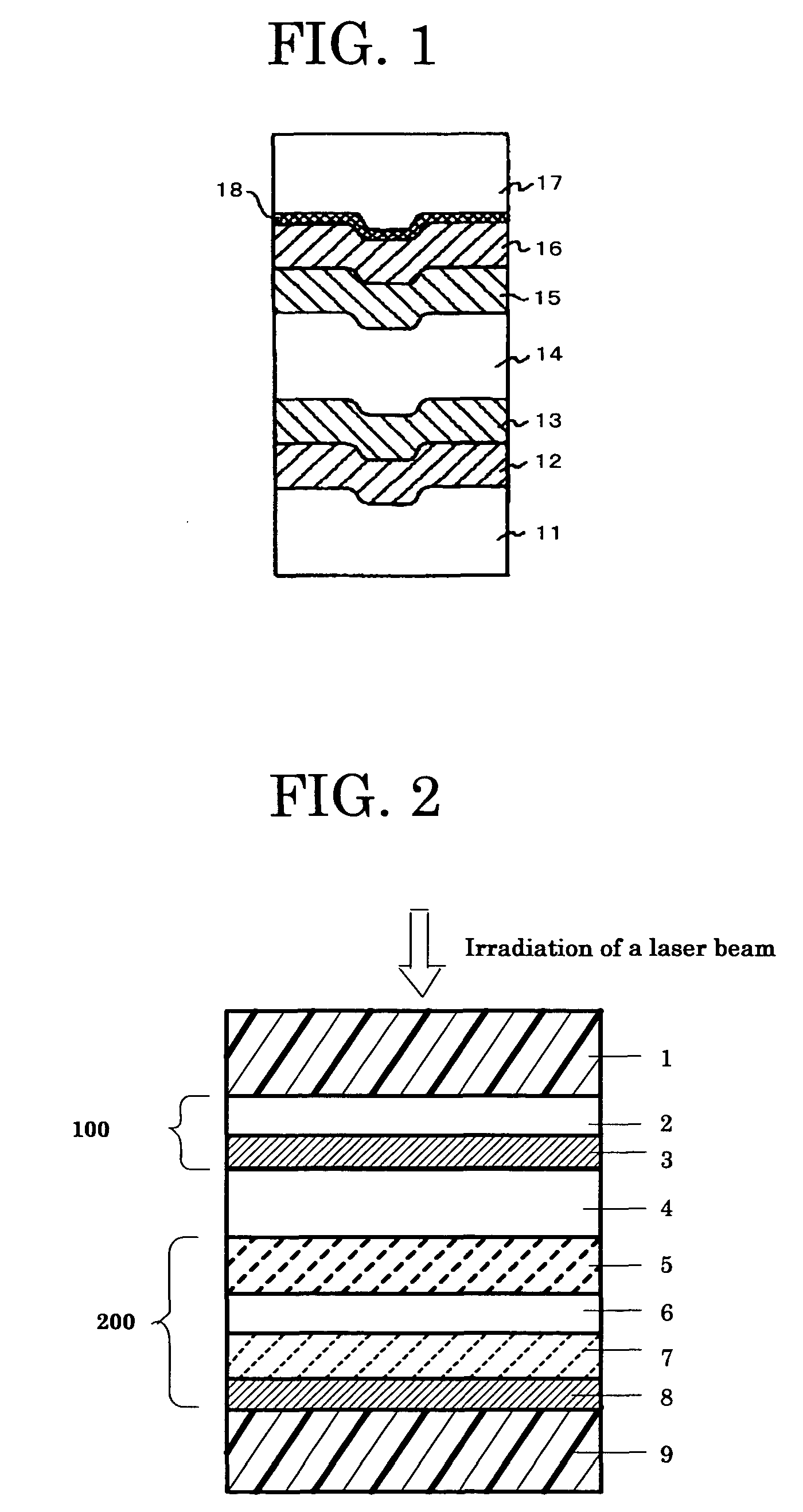

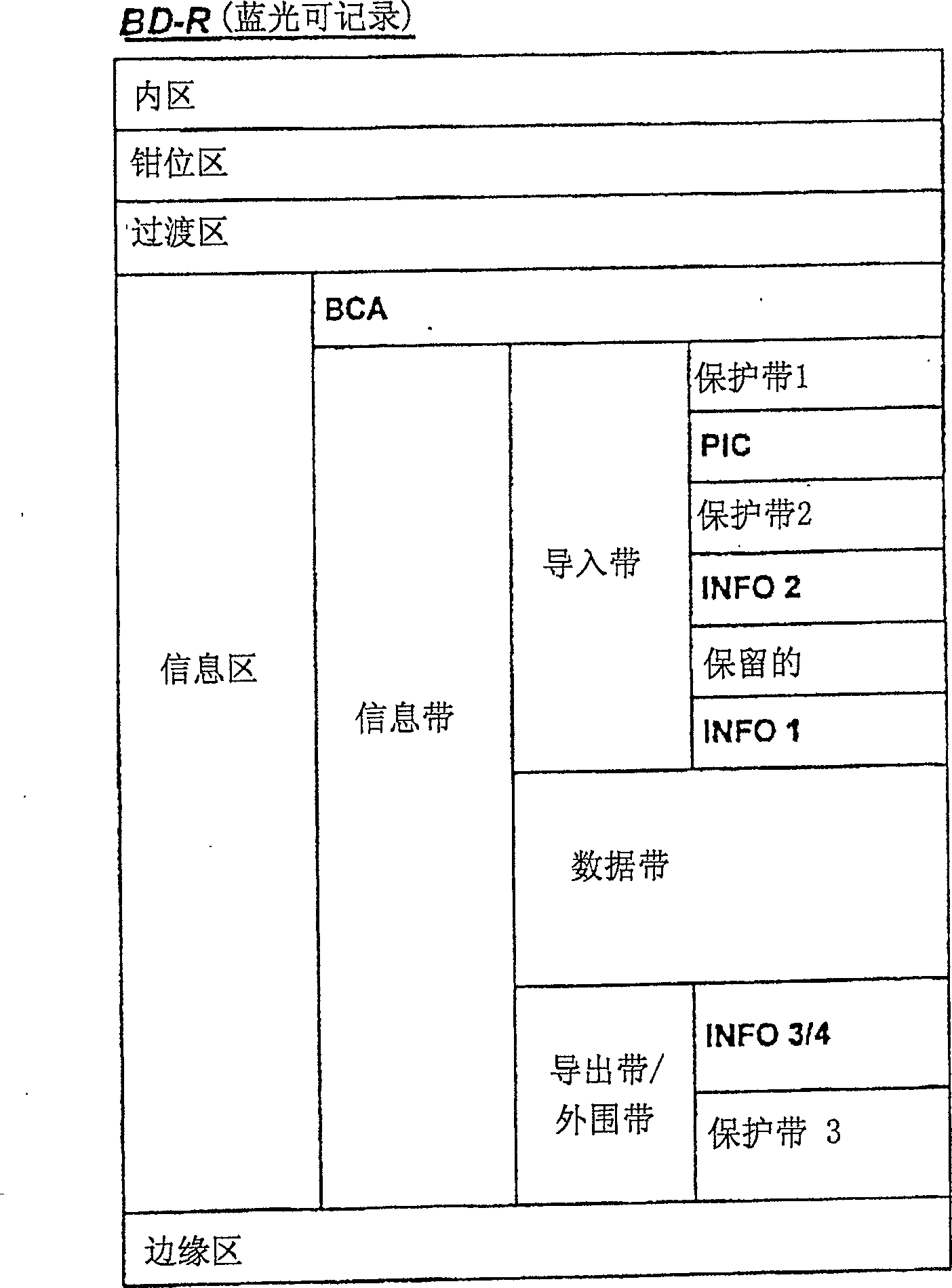

Optical recording medium, and, method for manufacturing the same, and method and apparatus for optical recording and reproduction thereof

InactiveUS20050255281A1High-density recordingWet propertyRecord carriersSynthetic resin layered productsInformation layerOrganic dye

The object of the present invention is to provide an optical recording medium which comprises a substrate, and a first information layer and a second information layer disposed on the substrate, and an intermediate layer disposed between the first information layer and the second information layer, wherein any one of recording and reproducing is performed in the first information layer and the second information layer by irradiating a laser beam from the first information layer side, the second information layer comprises a protective layer, a second dye layer which comprises an organic dye, an oxidized layer, and a reflective layer in this order from the laser beam irradiation side, and the oxidized layer comprises an oxide which is a material constituting the reflective layer.

Owner:RICOH KK

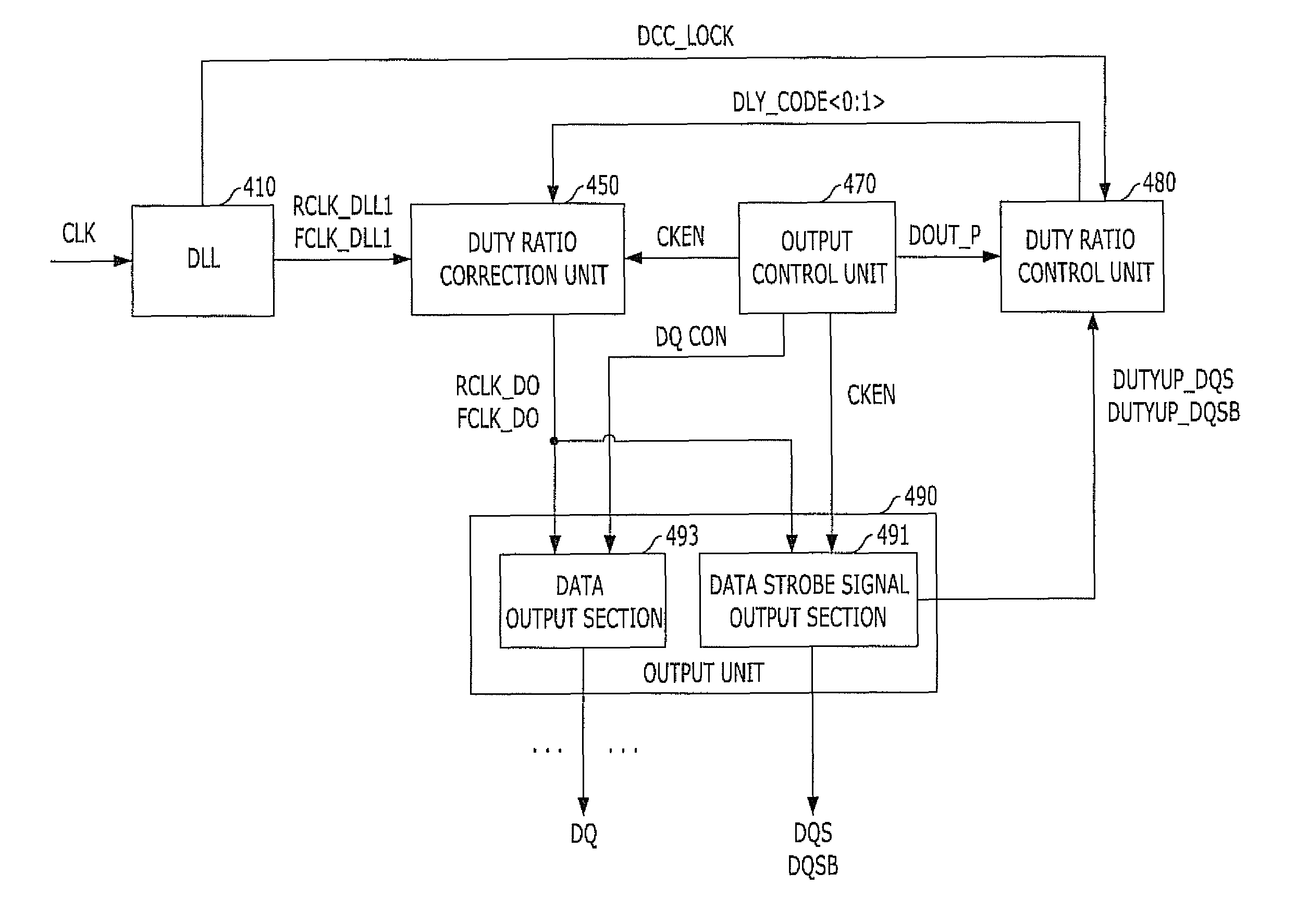

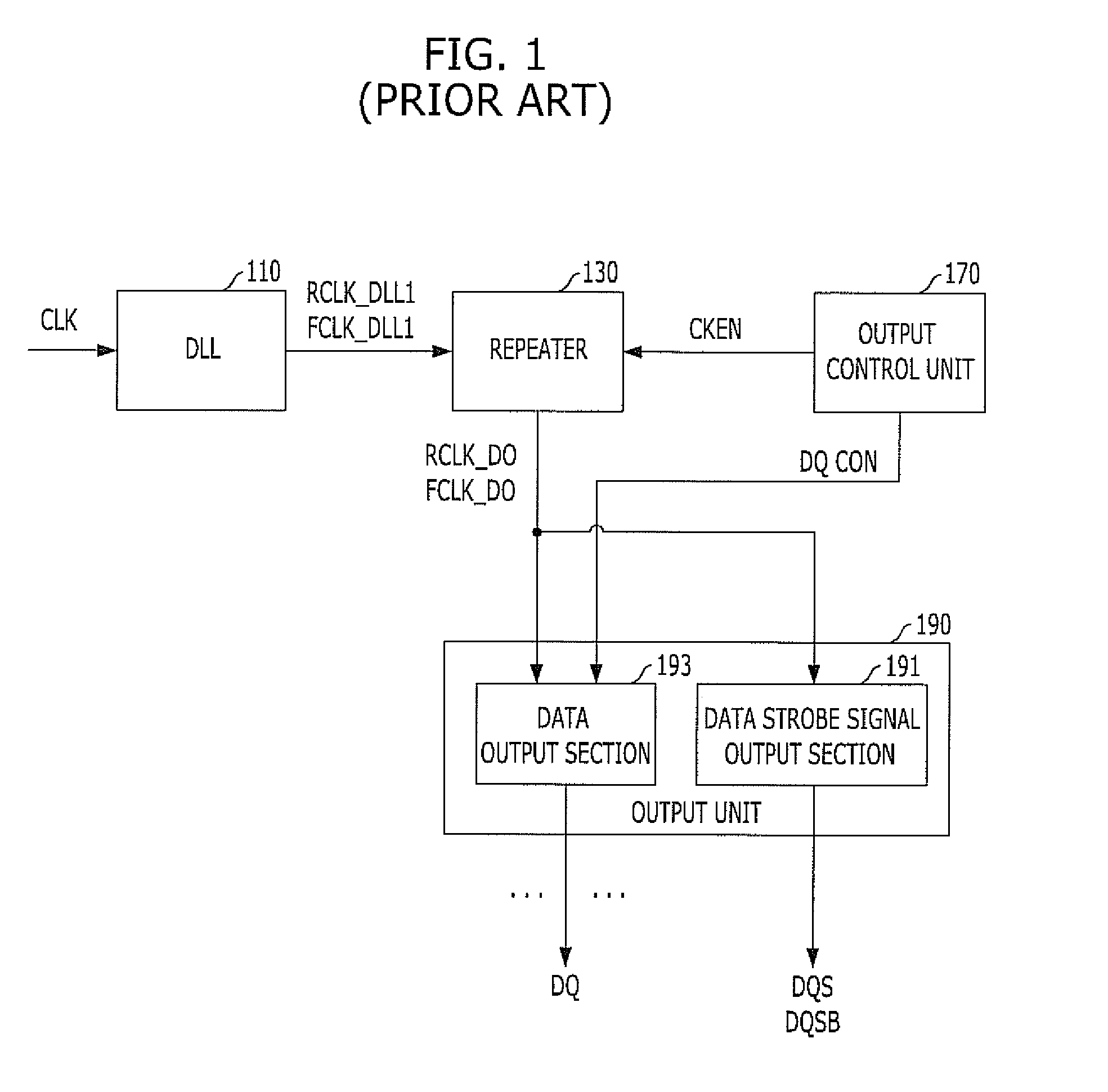

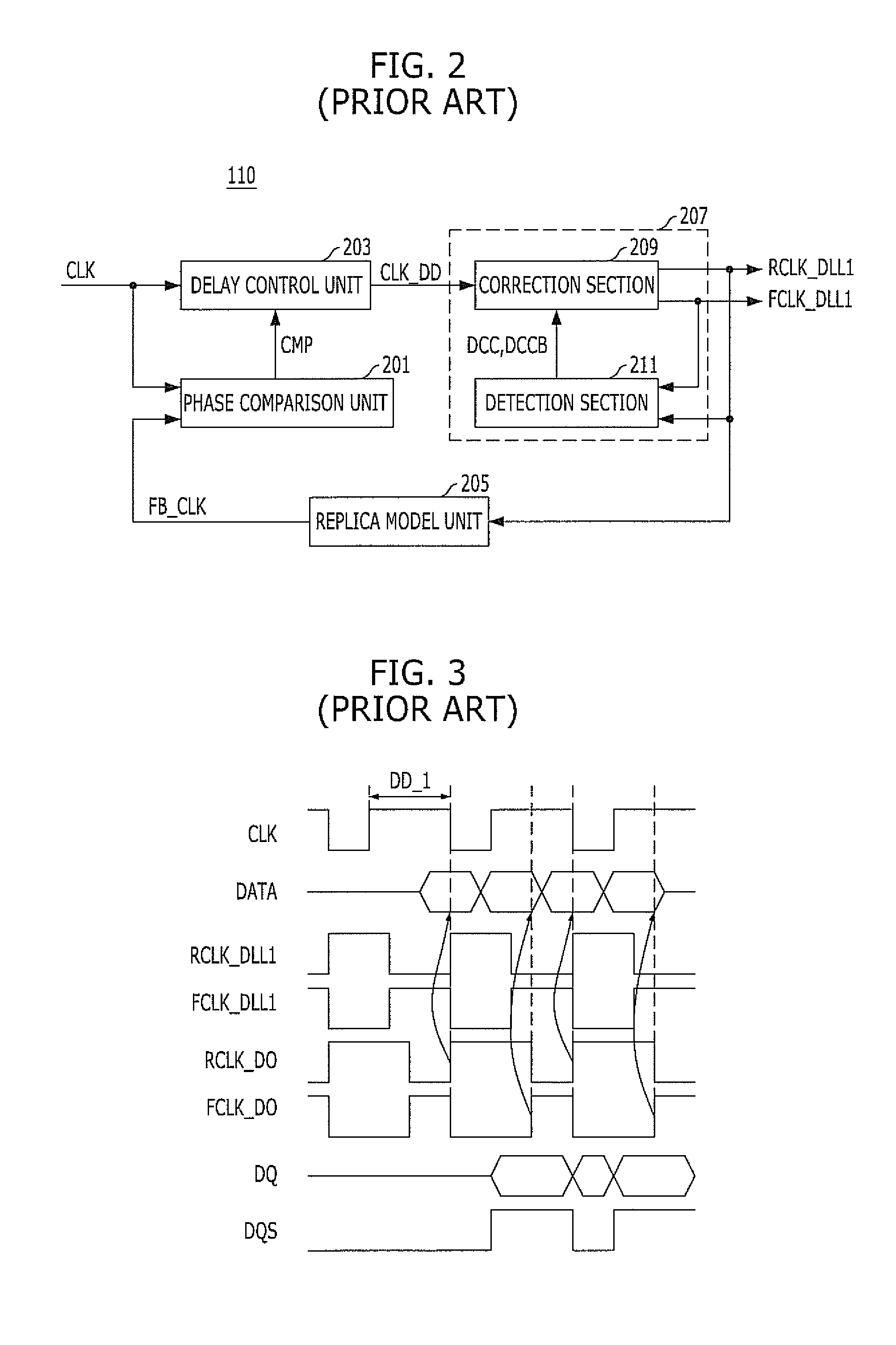

Data output circuit and data output method thereof

InactiveUS8508272B2Improve featuresEnsuring data marginPulse automatic controlElectric pulse generatorDelay-locked loopEngineering

A data output circuit and a data output method thereof are provided. The data output circuit includes a delay locked loop, a duty ratio correction block, and an output unit. The delay locked loop corrects a duty ratio of a first internal clock. The delay locked loop includes a correction enable signal output unit configured to output a correction enable signal when the operation of correcting the duty ratio of the first internal clock is completed. The duty ratio correction block corrects the duty ratio of the first internal clock by using a duty ratio detection signal in response to the correction enable signal, and outputs the corrected first internal clock as an output clock. The output unit detects a duty ratio of the output clock, generates the duty ratio detection signal to the duty ratio correction block, and outputs a data strobe signal in response to the output clock.

Owner:SK HYNIX INC

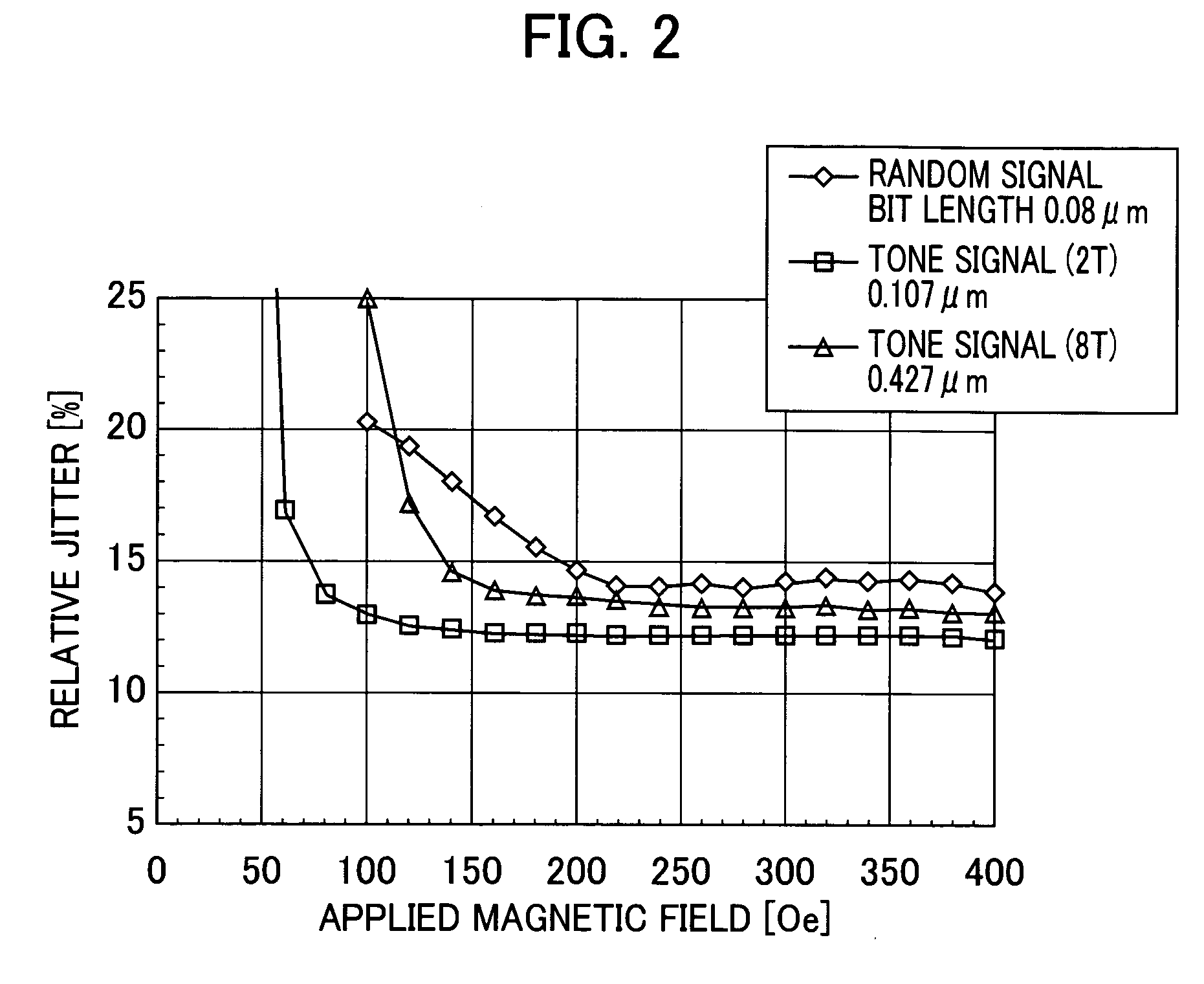

Optical information recording medium

InactiveUS7867595B2Improve jitter characteristicsExcellent degree of modulationLayered productsPhotomechanical apparatusEngineeringRecording layer

An optical information recording medium is provided having a superior jitter property even when an organic substance is used for a recording layer. The optical information recording medium has a substrate having a penetrating hole in a central portion thereof and a spiral pre-groove provided in one surface of the substrate, a reflection layer provided on the surface of the substrate in which the pre-groove is provided, a recording layer which is provided on the reflection layer and which is composed of an organic substance including a dye, and a light transmissive cover layer provided on the recording layer. In the optical information recording medium, the cover layer has an elastic modulus of 40 MPa or less at 25° C. in an interface region facing the recording layer.

Owner:TAIYO YUDEN KK

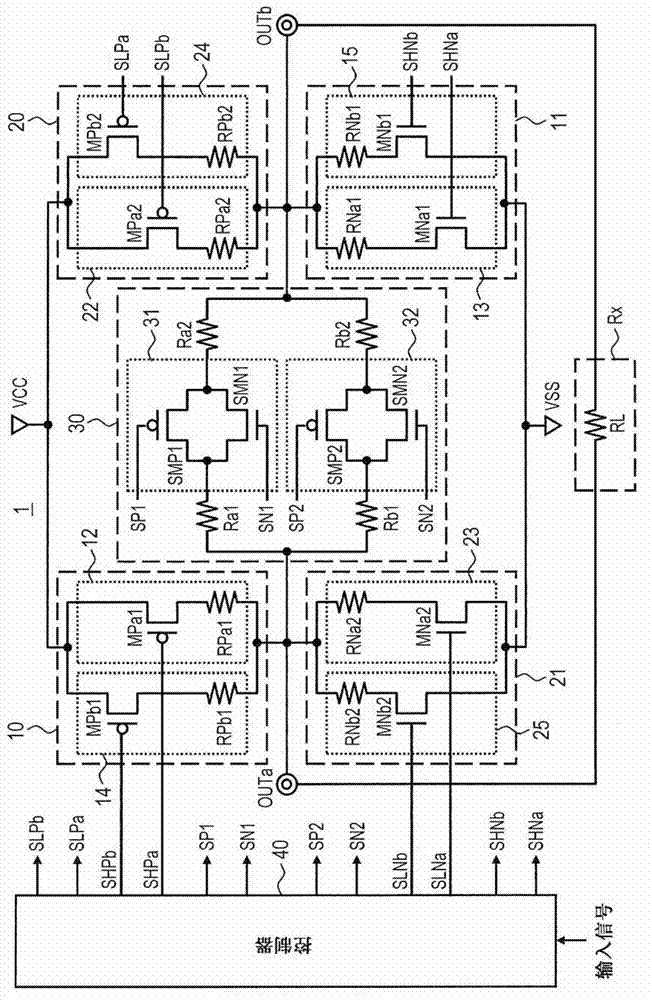

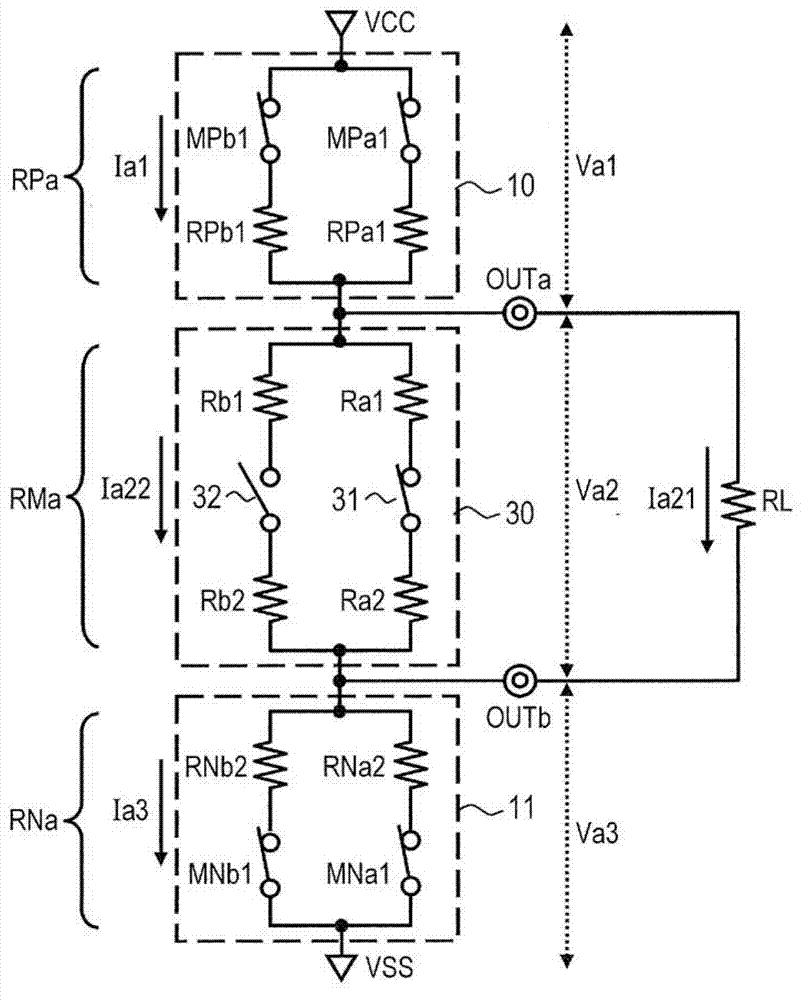

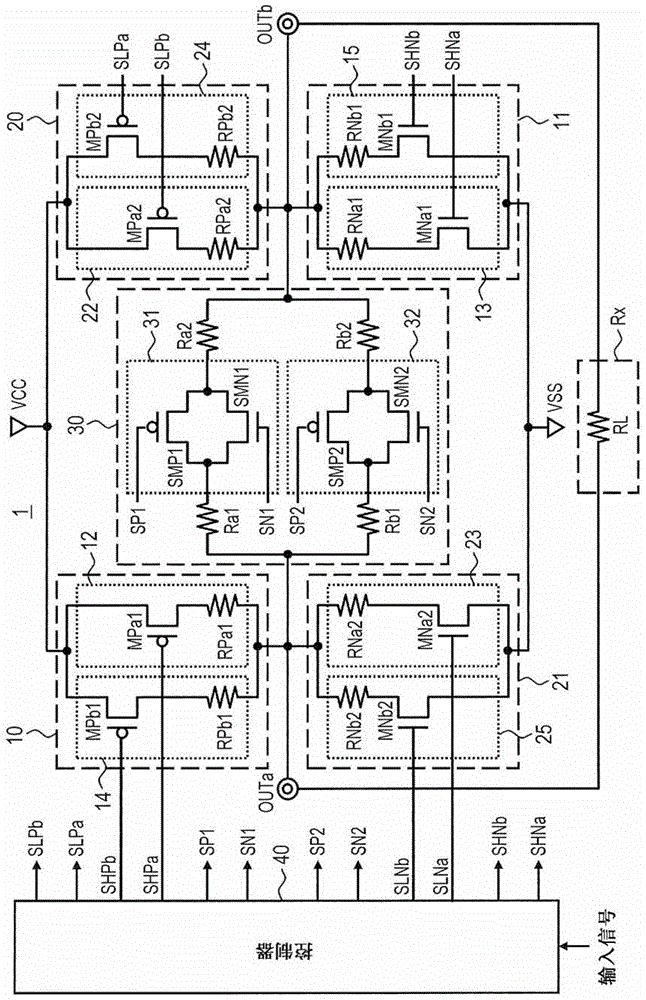

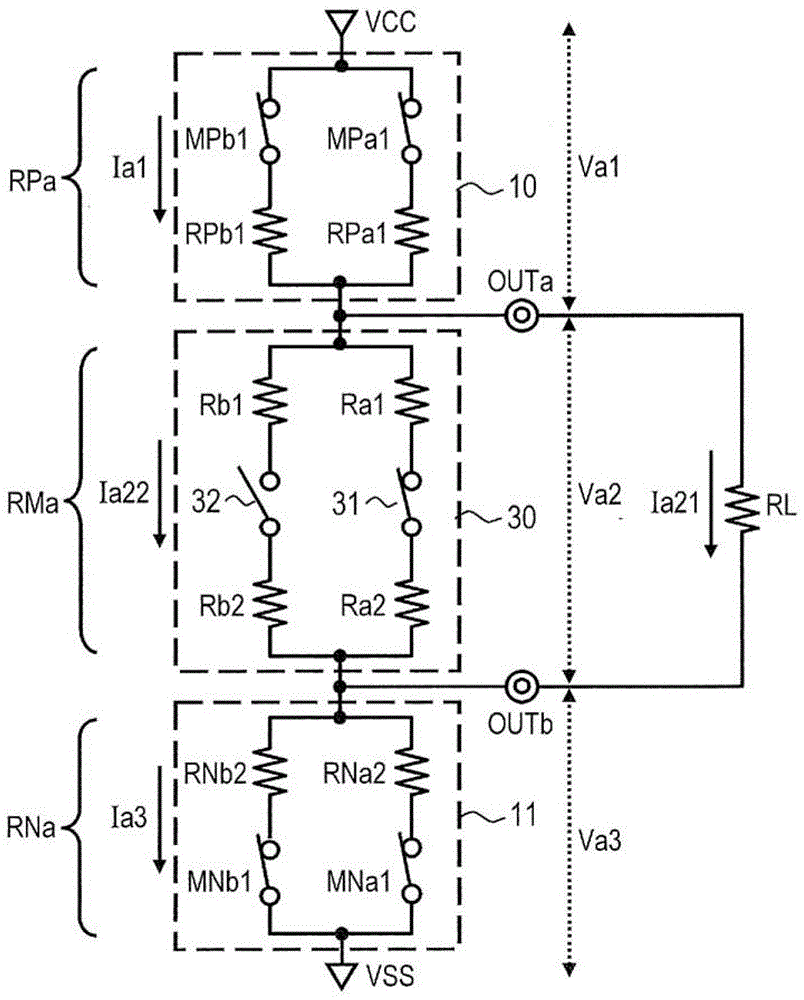

Semiconductor device

InactiveCN102957420AImprove jitter characteristicsLogic circuits using semiconductor devicesElectric pulse generatorEngineeringSemiconductor

A semiconductor device includes a variable resistor that sets a resistance value as a first resistance value in an emphasis mode, and as a second resistance value smaller than the first resistance value in a de-emphasis mode, a first driver that sets an output impedance as a third resistance value in the emphasis mode, and as a fourth resistance value larger than the third resistance value in the de-emphasis mode, a second driver that sets the output impedance as a fifth resistance value in the emphasis mode, and as a sixth resistance value larger than the fifth resistance value in the de-emphasis mode, and a controller that controls conductive states of the first and second drivers according to an input signal, and switches the output impedances of the first and second drivers and the resistance value of the variable resistor between the emphasis mode and the de-emphasis mode.

Owner:RENESAS ELECTRONICS CORP

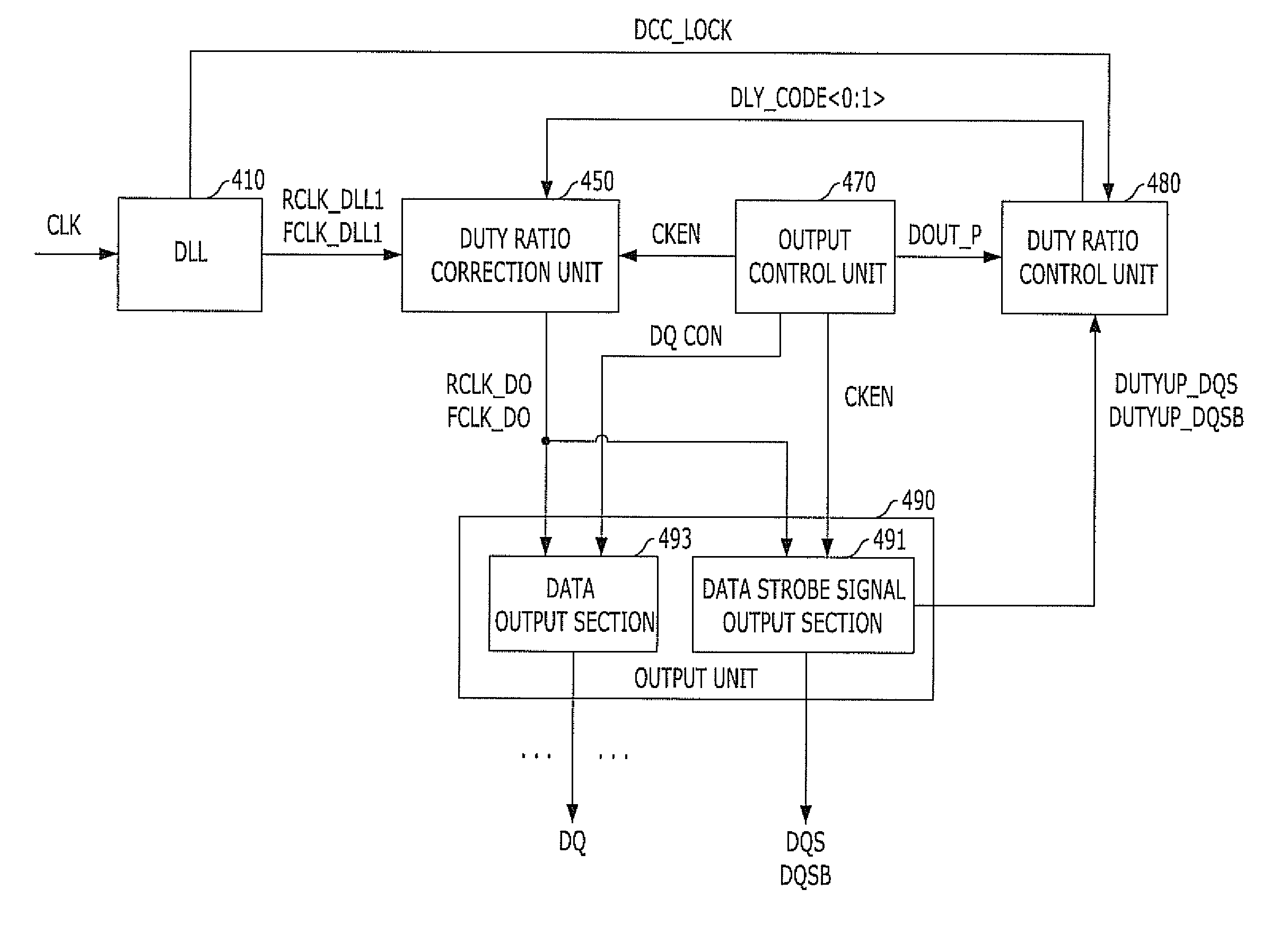

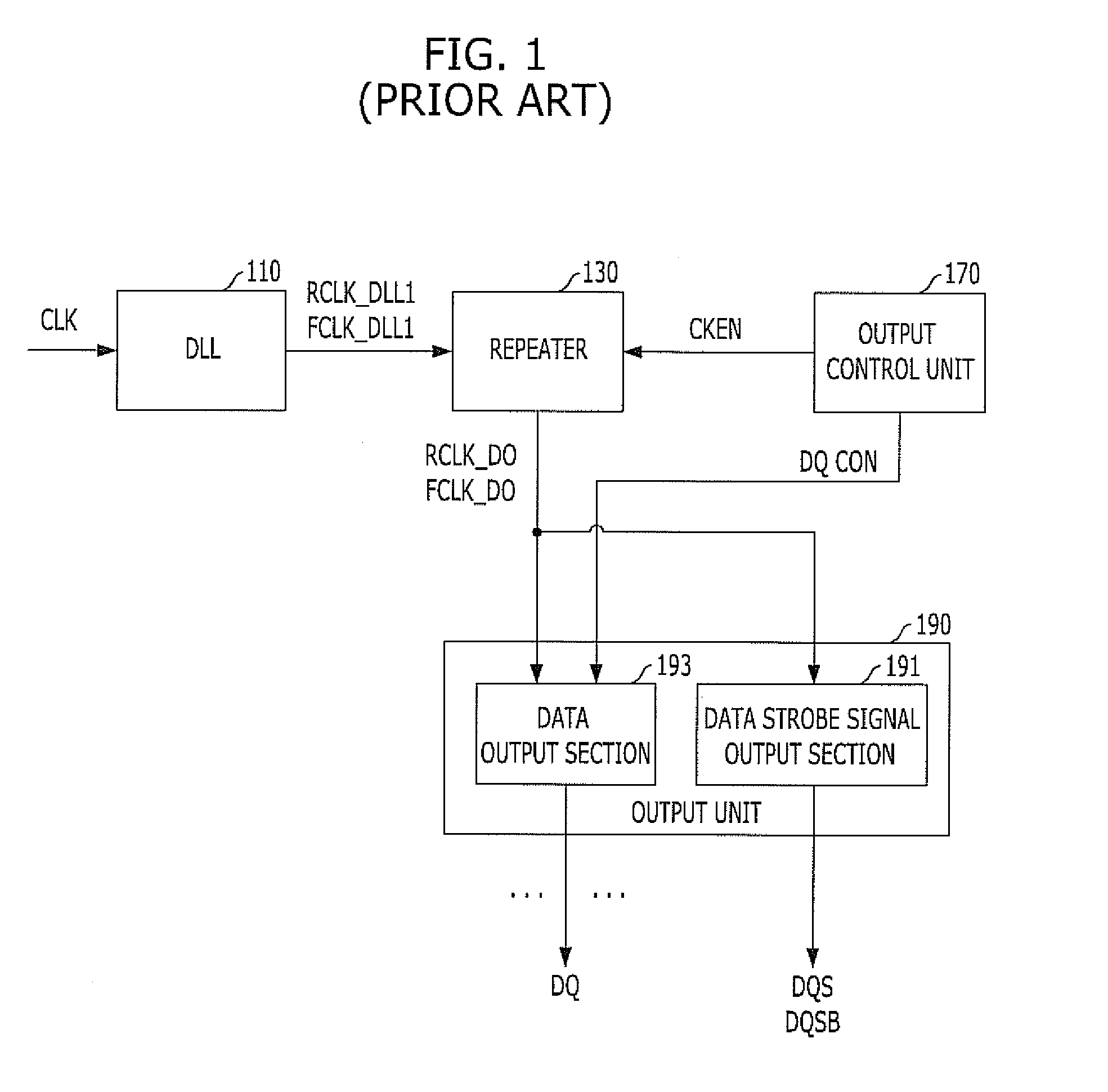

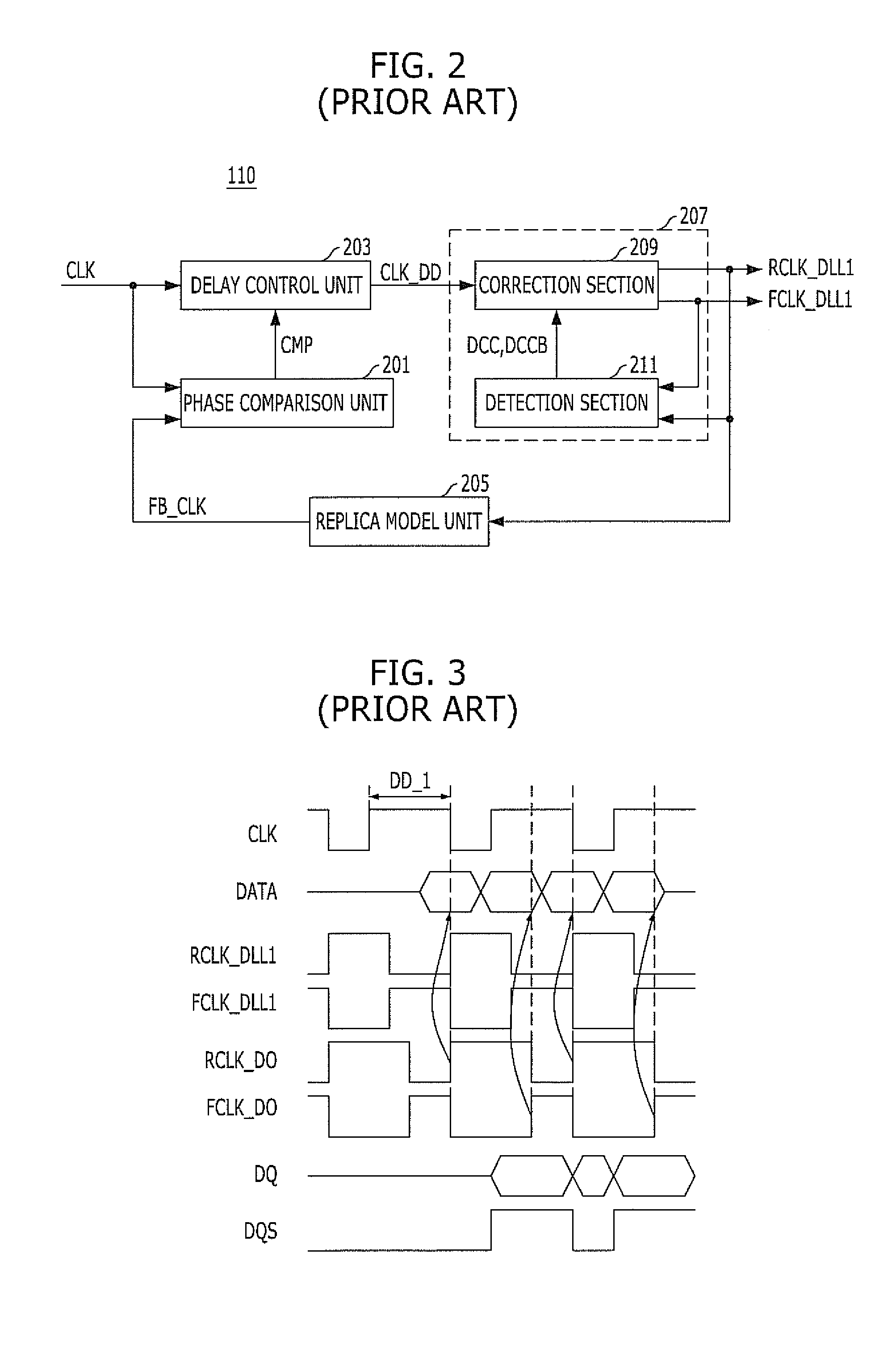

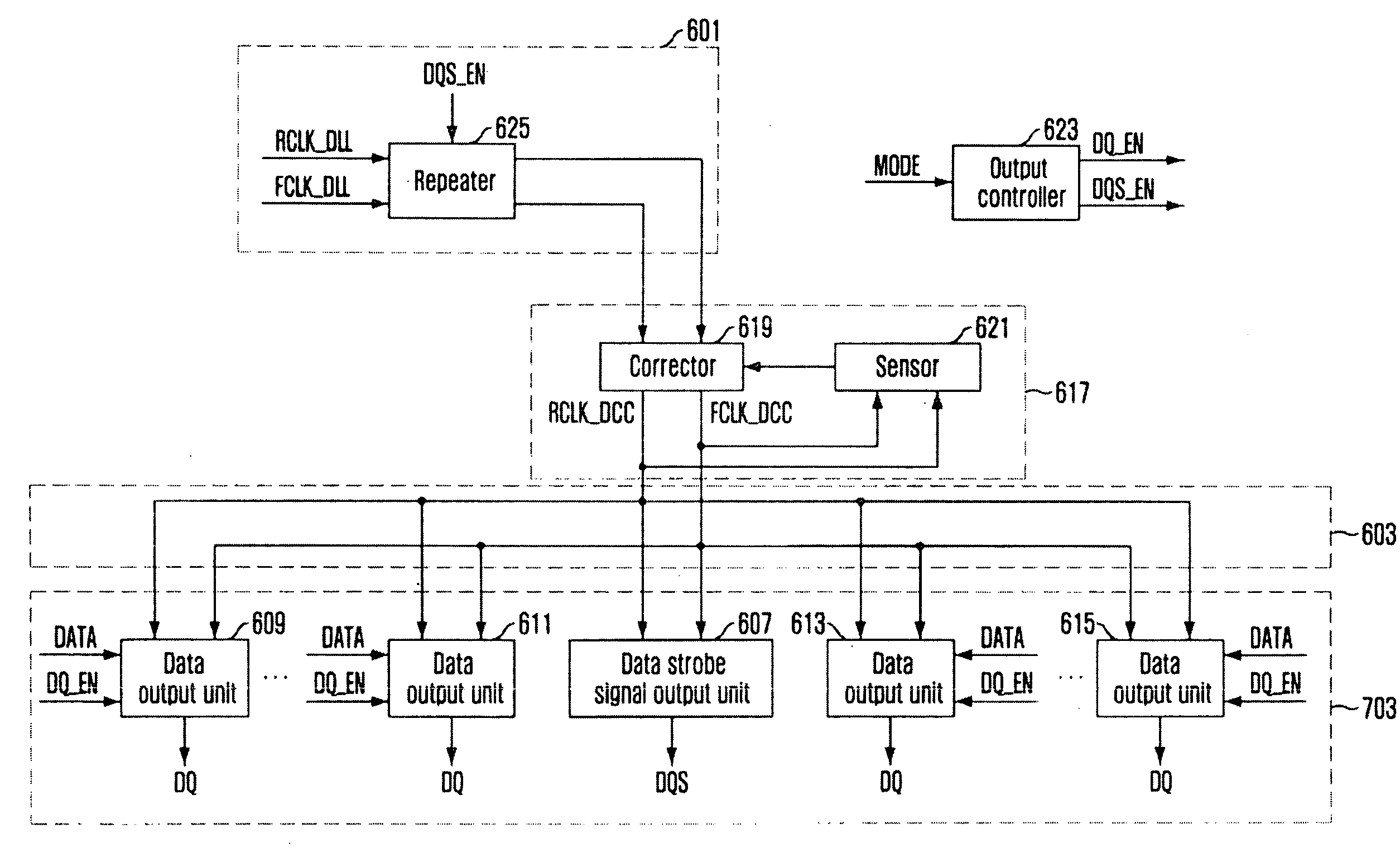

Data output circuit and data output method thereof

InactiveUS20110210773A1Improve jitter characteristicsEnsuring data marginPulse automatic controlElectric pulse generatorDelay-locked loopElectrical and Electronics engineering

A data output circuit and a data output method thereof are provided. The data output circuit includes a delay locked loop, a duty ratio correction block, and an output unit. The delay locked loop corrects a duty ratio of a first internal clock. The delay locked loop includes a correction enable signal output unit configured to output a correction enable signal when the operation of correcting the duty ratio of the first internal clock is completed. The duty ratio correction block corrects the duty ratio of the first internal clock by using a duty ratio detection signal in response to the correction enable signal, and outputs the corrected first internal clock as an output clock. The output unit detects a duty ratio of the output clock, generates the duty ratio detection signal to the duty ratio correction block, and outputs a data strobe signal in response to the output clock.

Owner:SK HYNIX INC

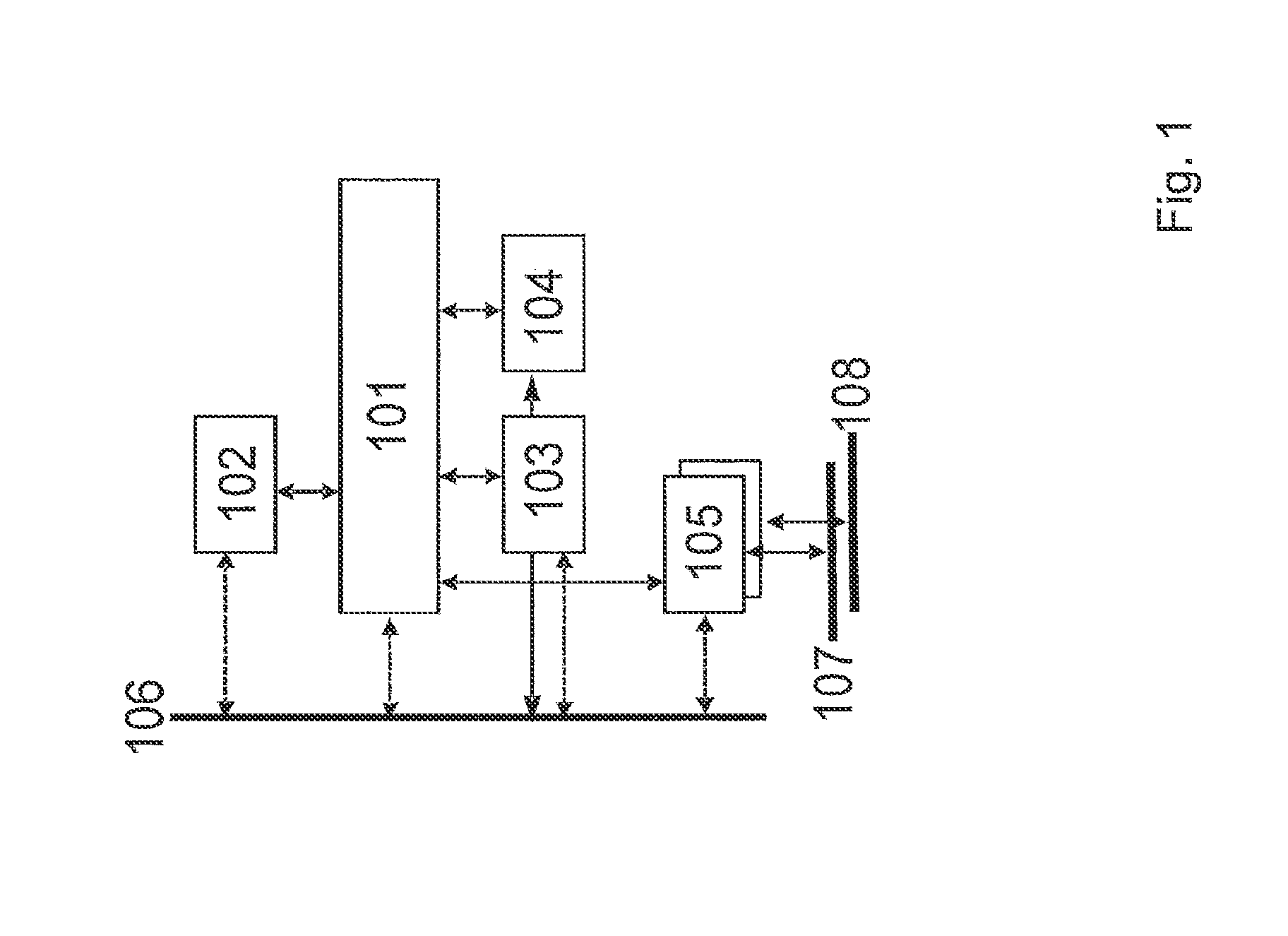

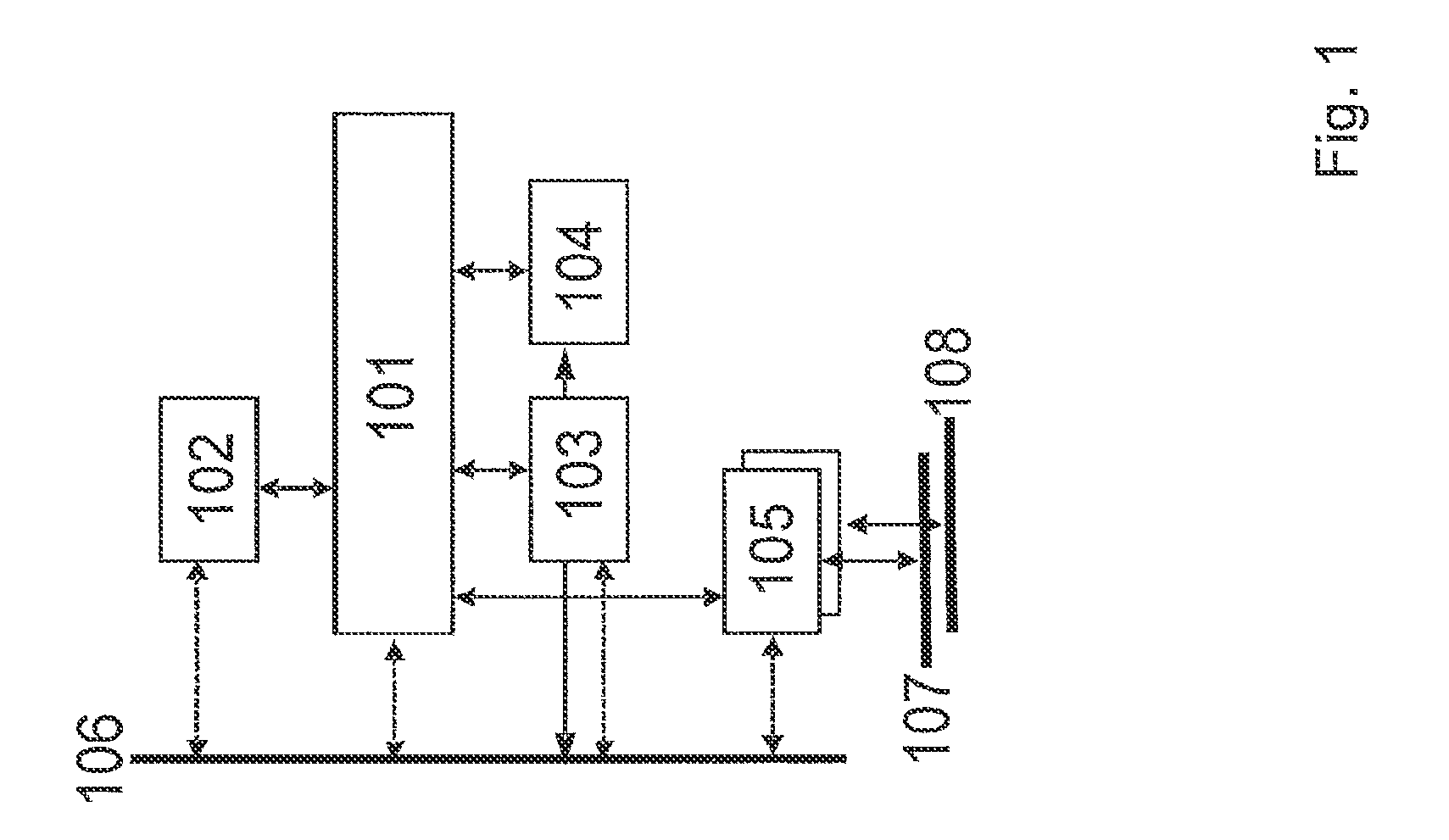

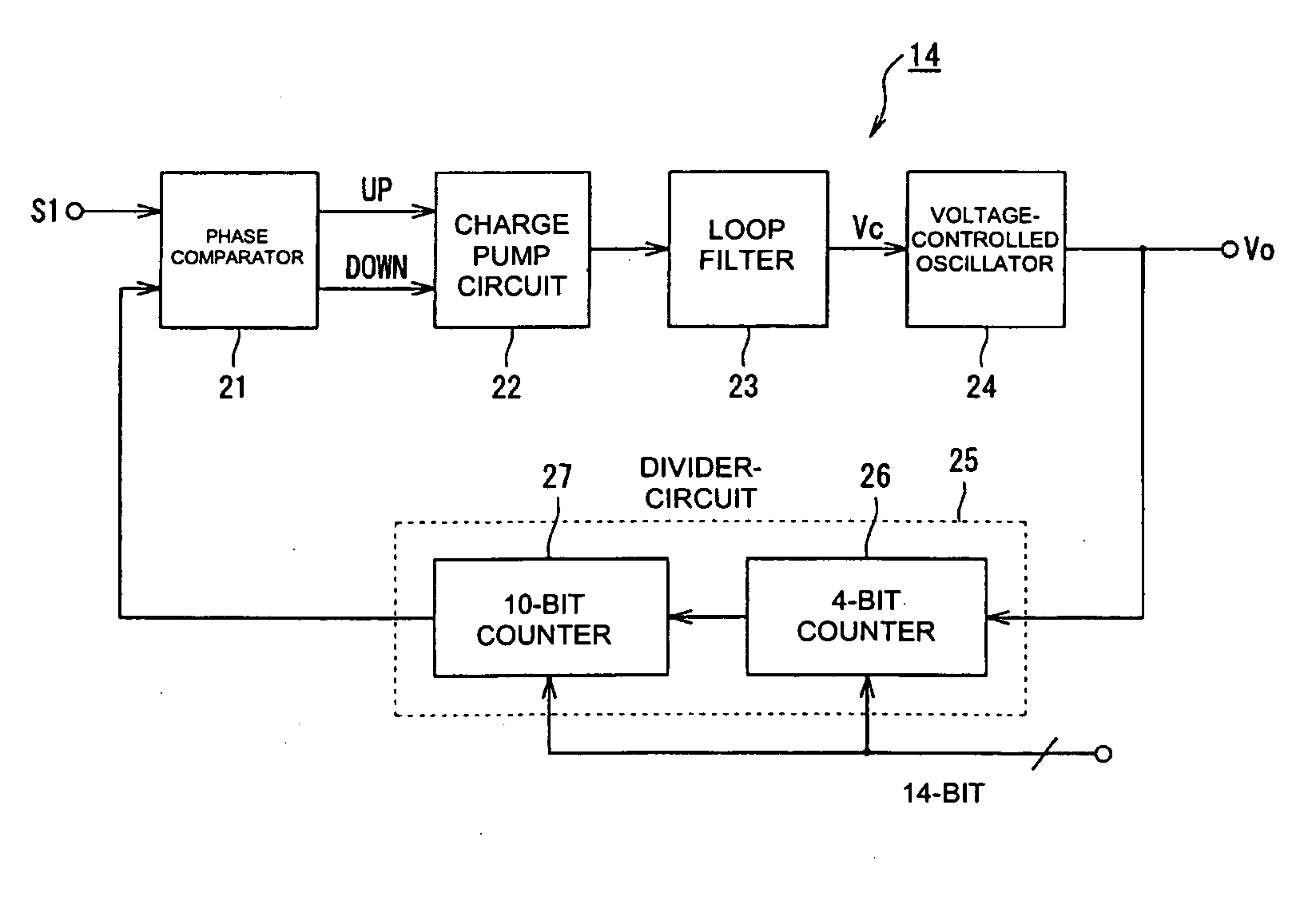

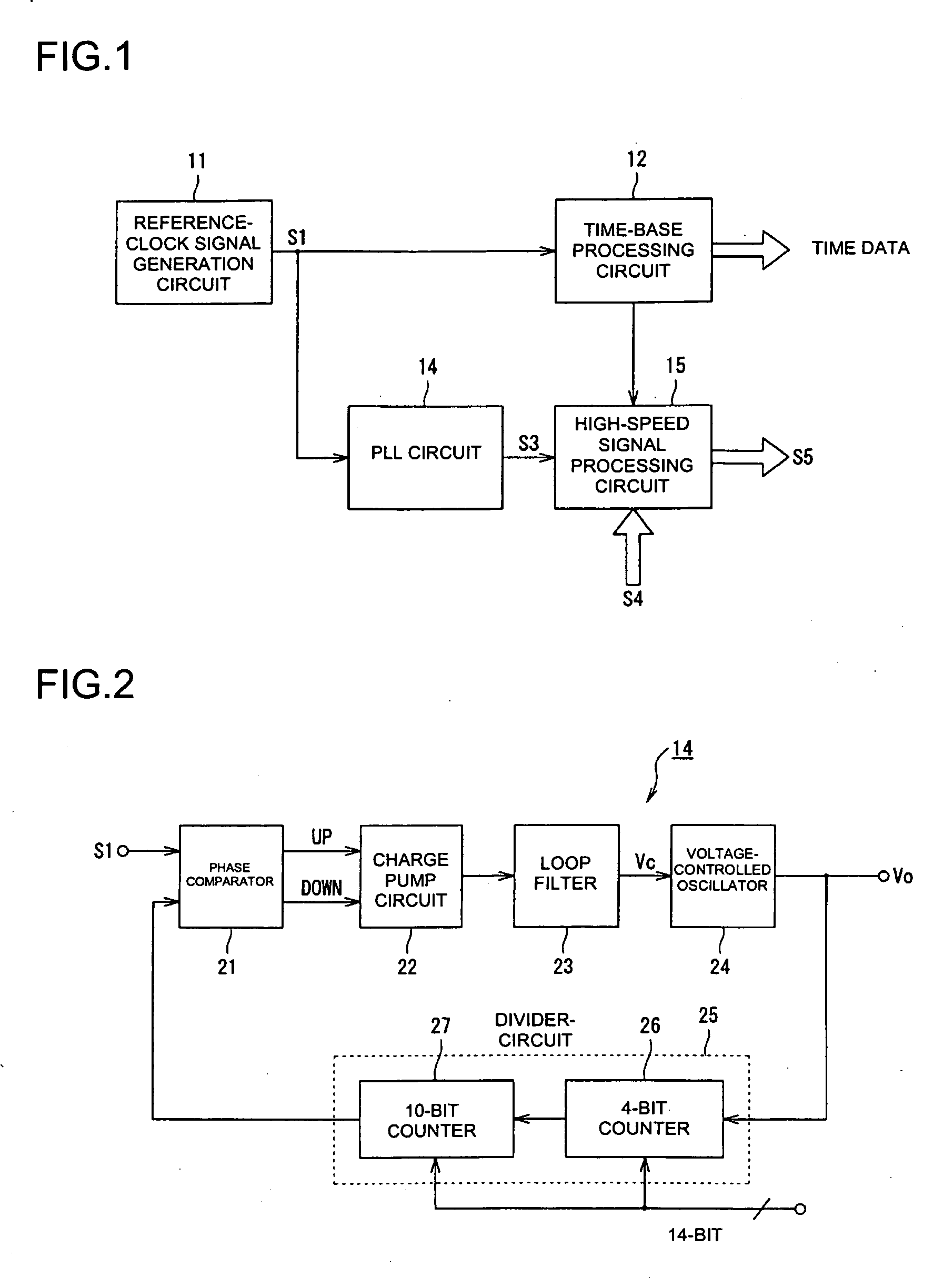

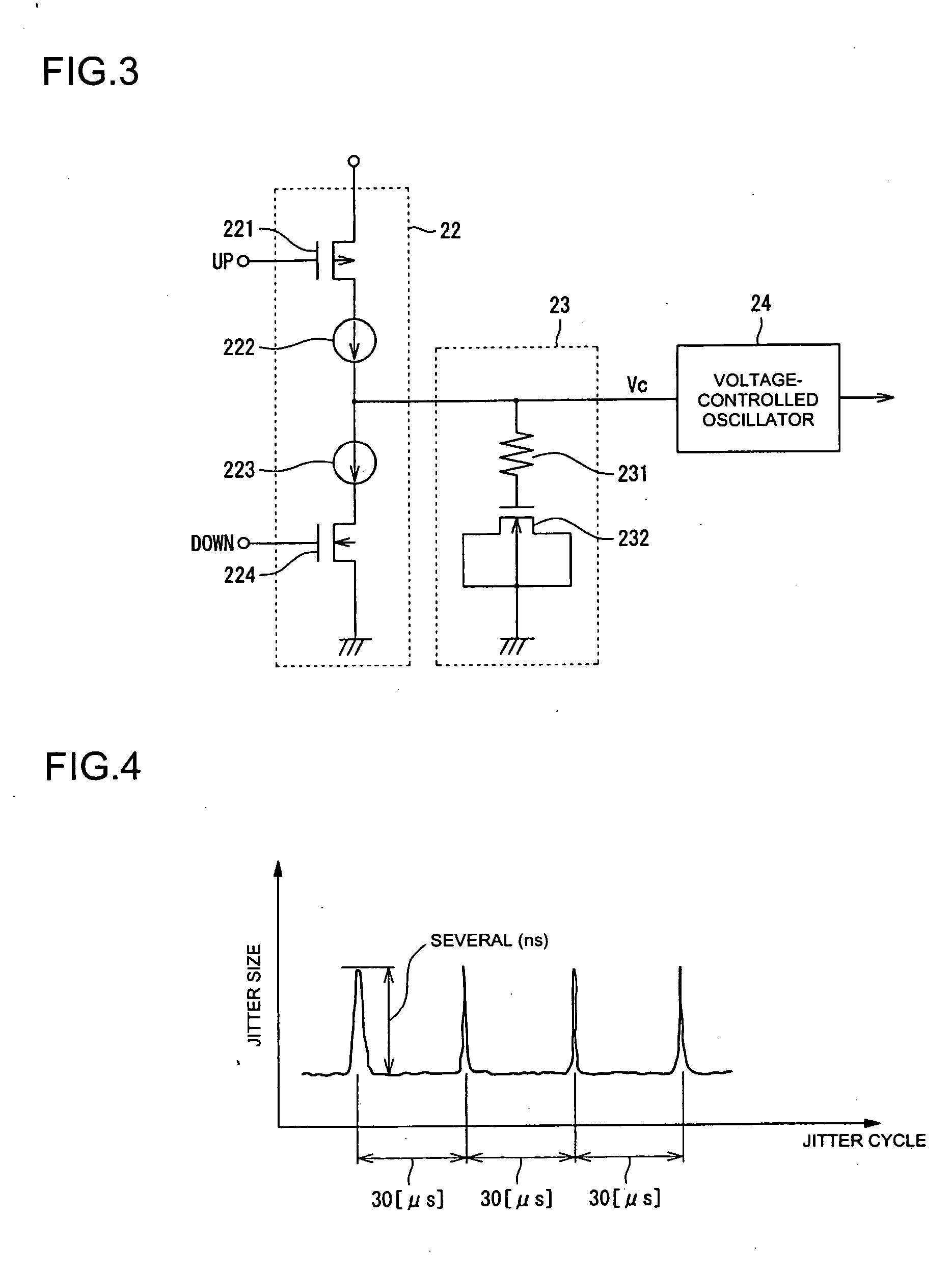

Semiconductor integrated device

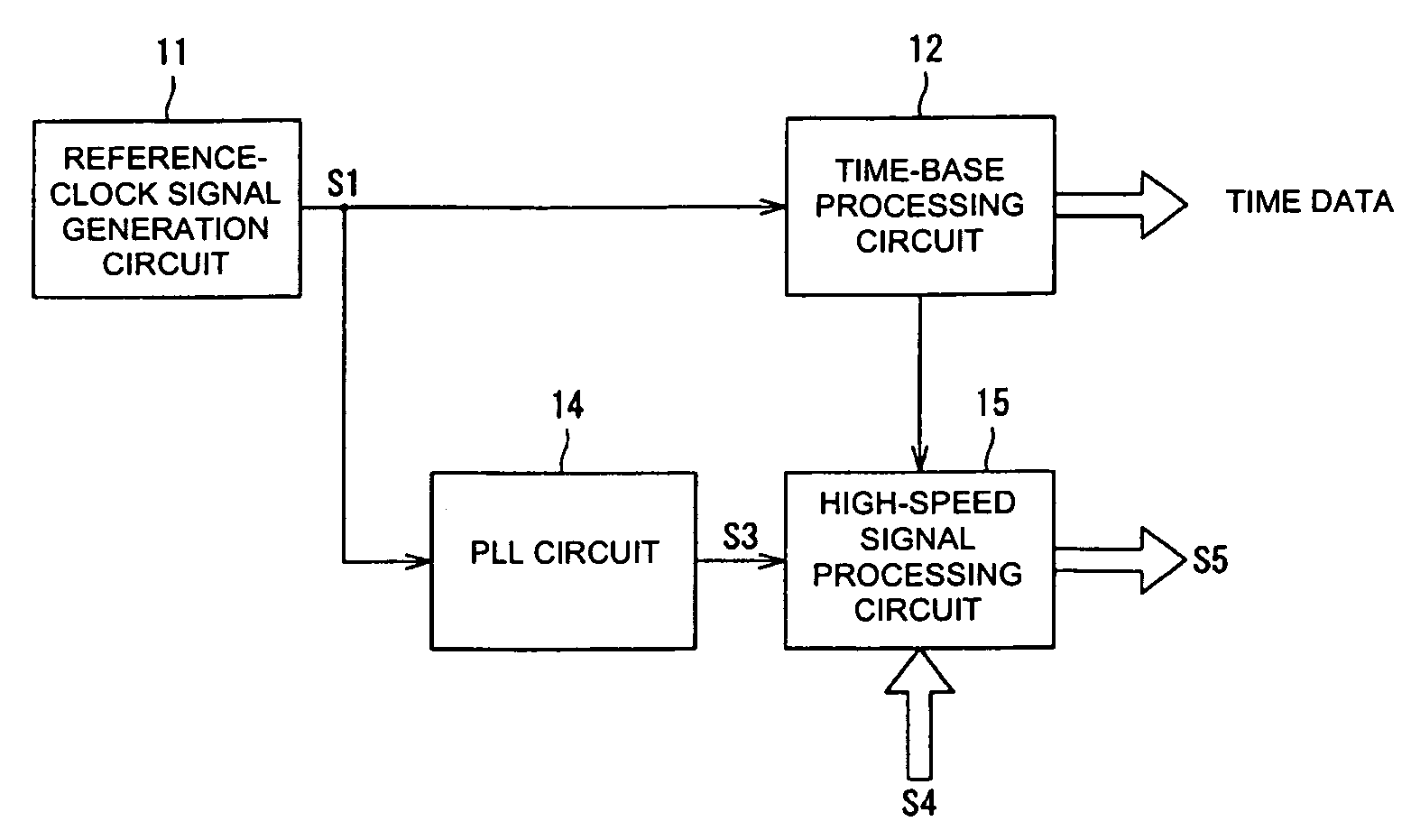

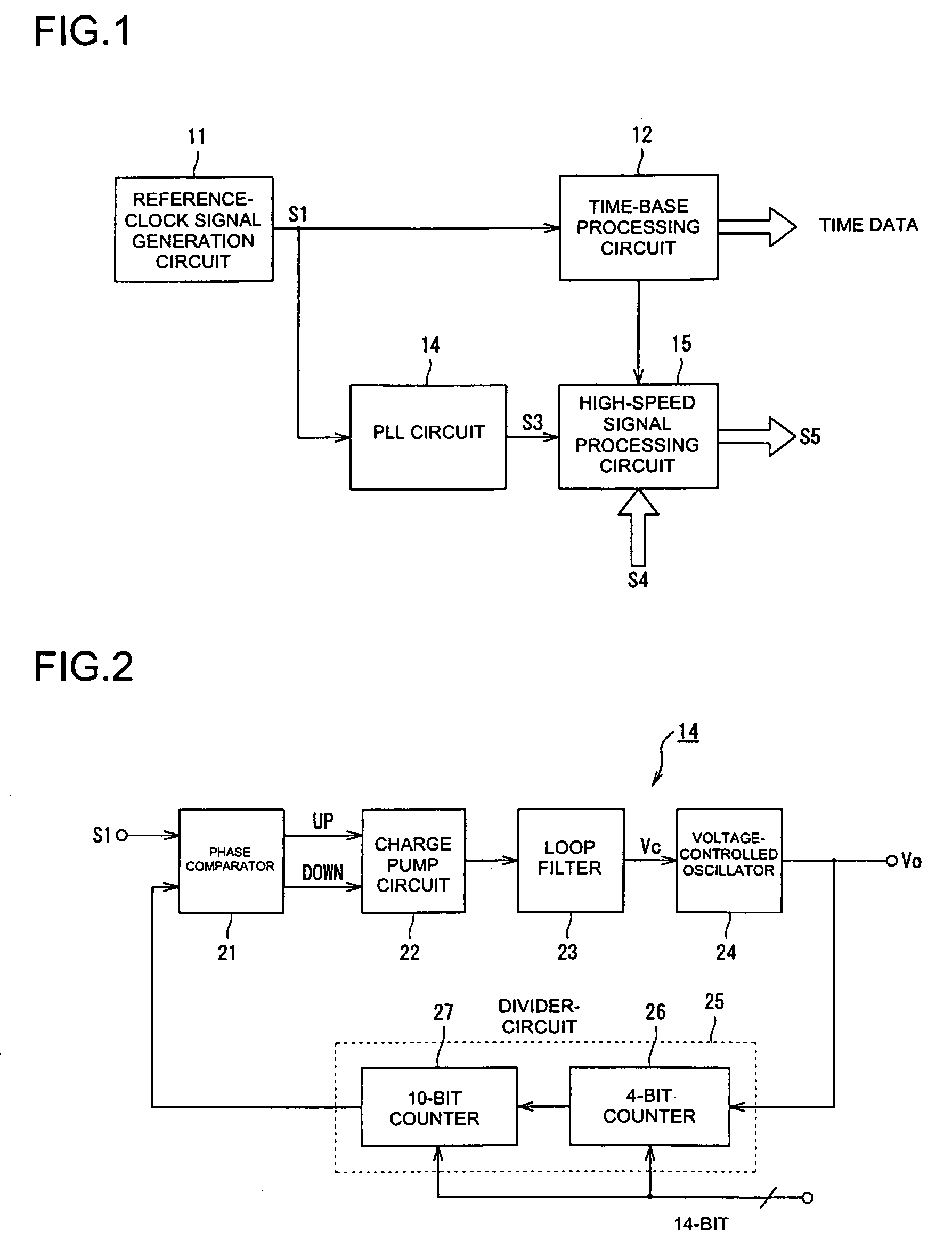

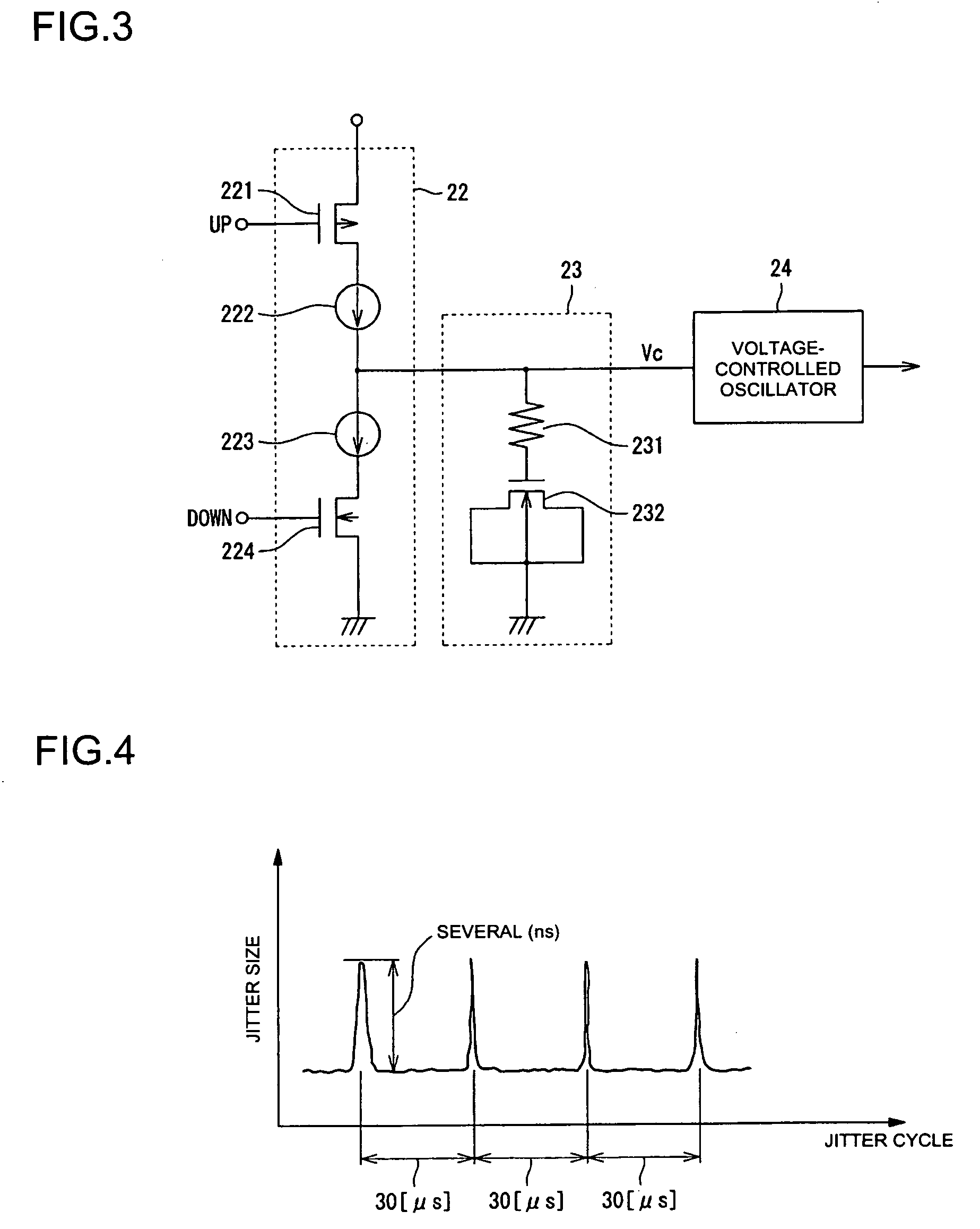

ActiveUS20050127962A1Reduce the amount requiredImprove jitter characteristicsPulse automatic controlGenerating/distributing signalsDamping factorSignal processing circuits

A structure is provided for significantly reducing the current excessively consumed for generating a high-speed clock signal necessary for signal processing, and significantly improve the jitter characteristics of the high-speed clock signal. The structure includes a reference-clock signal generation circuit, a time-base processing circuit, a PLL circuit, and a high-speed signal processing circuit. A low-speed reference-clock signal generated by the reference-clock signal generation circuit is provided to the PLL circuit. The PLL circuit generates a high-speed clock signal by multiplying the reference-clock signal by a factor of N. The factor N is at least 100. To reduce a jitter of the high-speed clock signal generated by the PLL circuit, a natural angular frequency ωn and a damping factor ζ that relate to the response characteristics of the system of the PLL circuit are set to range from 3 kHz to 10 kHz, and 0.01 or less, respectively.

Owner:SEIKO EPSON CORP

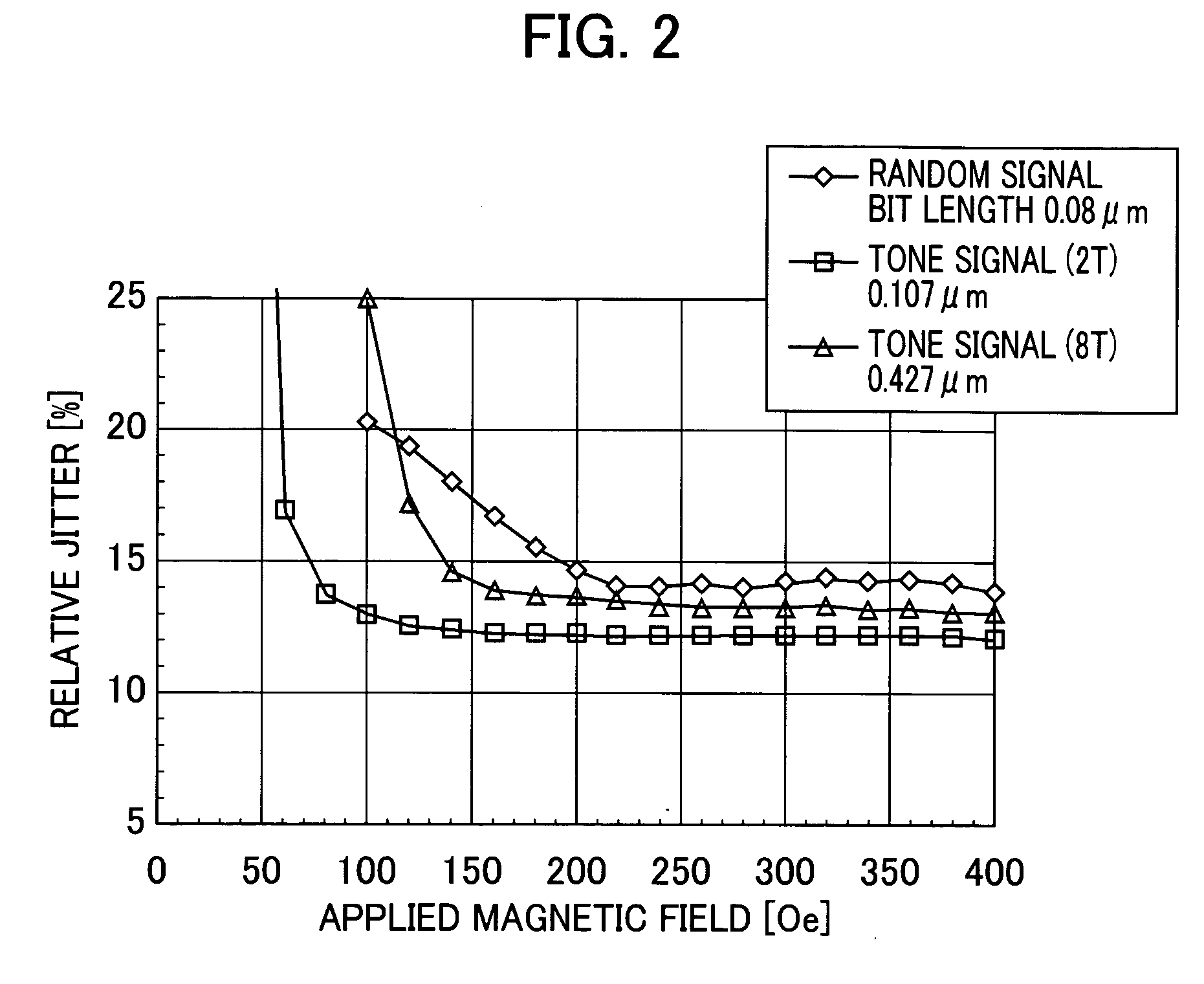

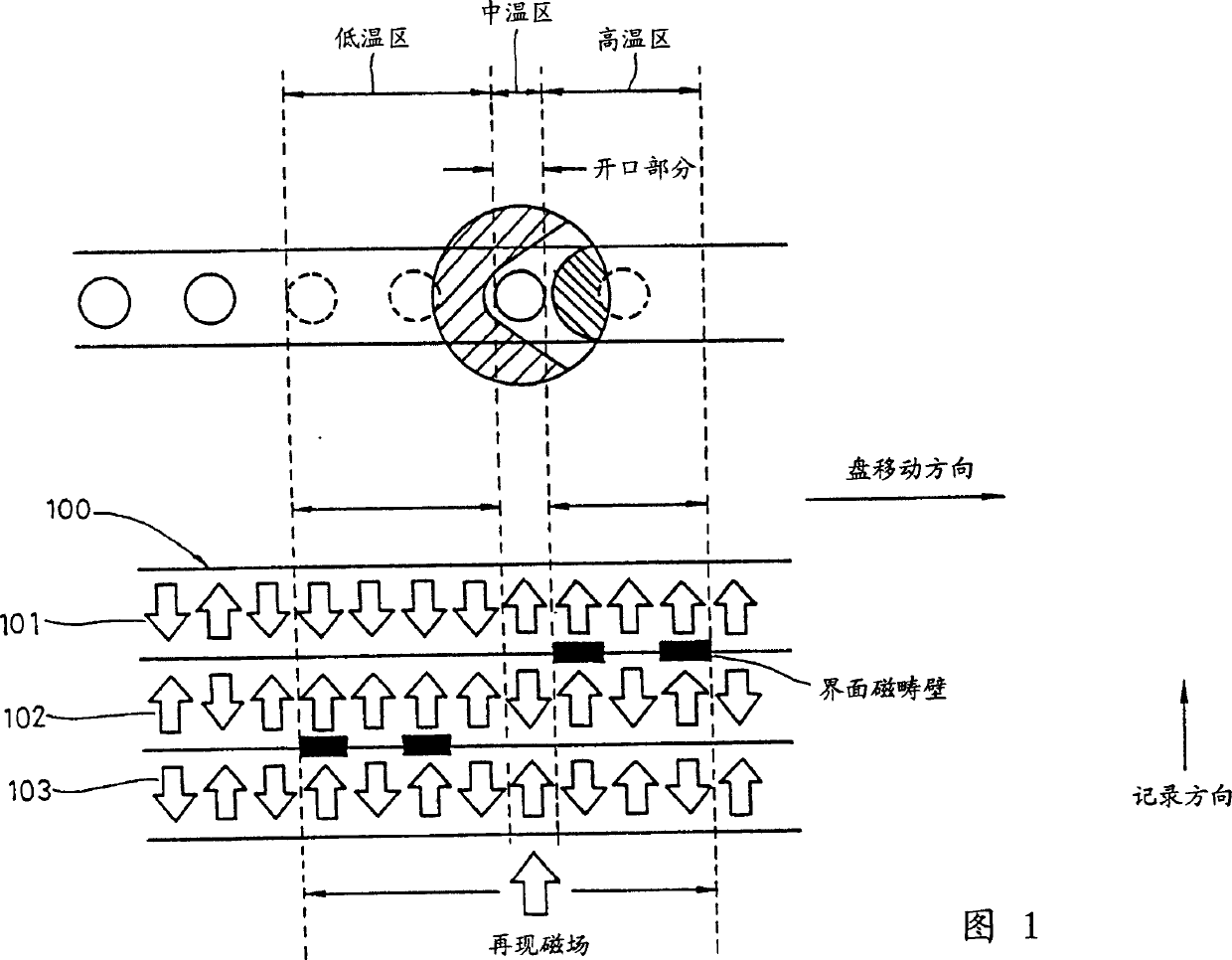

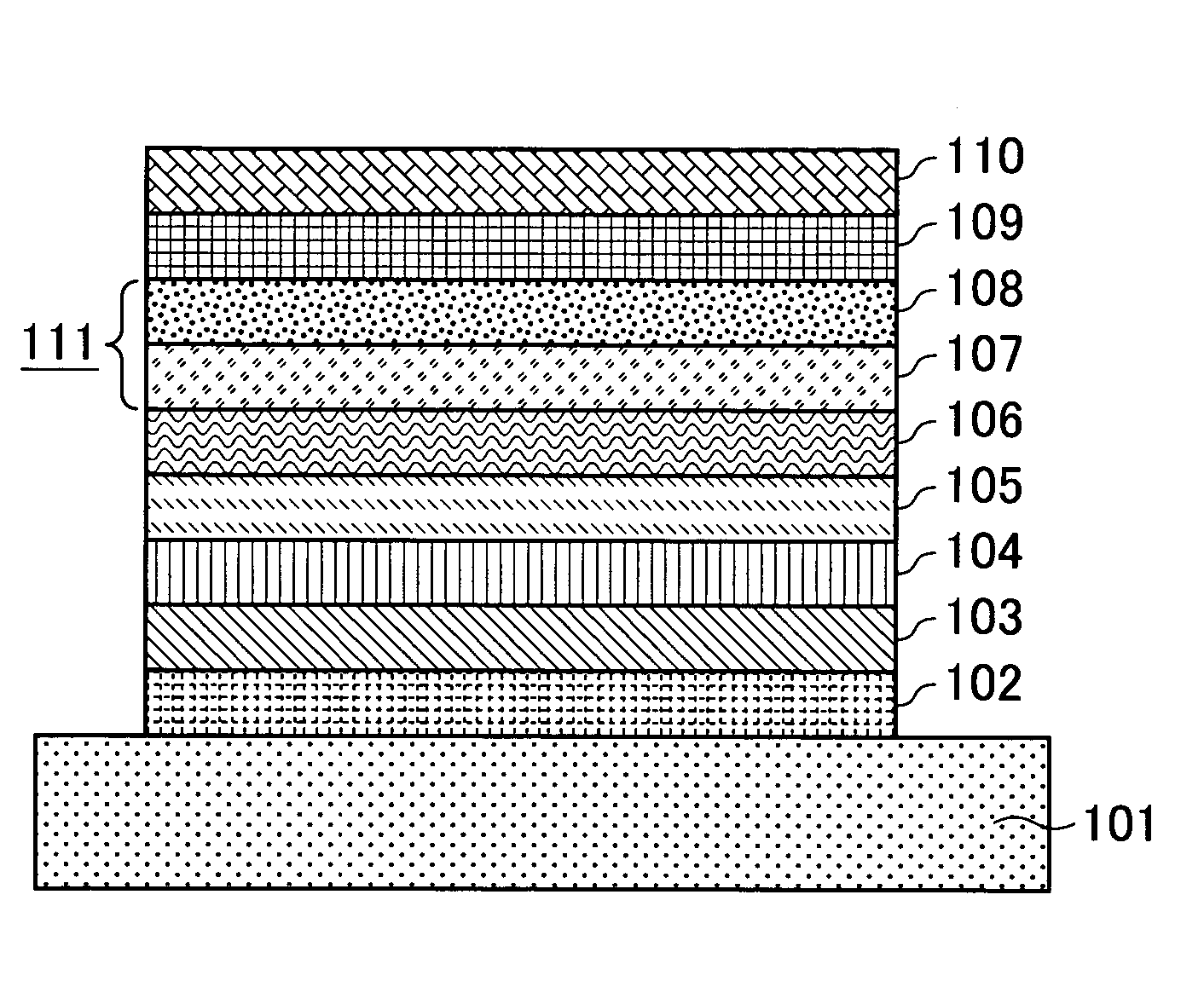

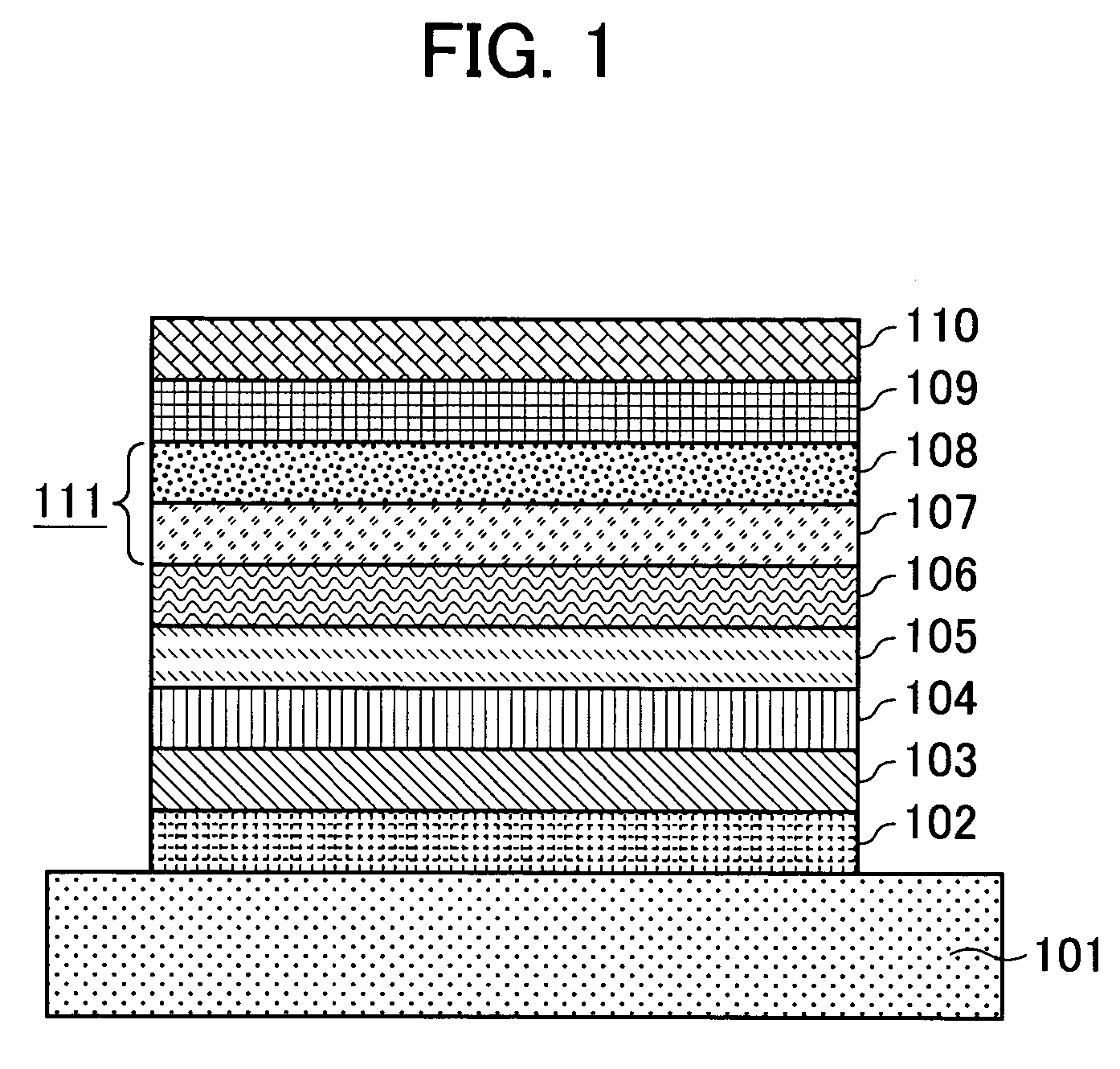

Magneto-optical recording medium having in-plane magnetizing layer

InactiveUS20050028183A1High sensitivityImprove jitter characteristicsRecord information storageFlat record carrier containersIn planeHigh density

A high-density magneto-optical recording medium having excellent jitter properties is provided. A pattern-dependent shift of the length of a recorded mark does not occur even when a minute mark has increased sensitivity to a recording magnetic field. A magneto-optical recording medium has at least a displacement layer, a memory layer, and an auxiliary memory layer. A mark with a length up to the diffraction-limit of the optical system is recorded and read out. The magneto-optical recording medium includes an in-plane magnetization-inducing layer principally made of cobalt on the auxiliary memory layer.

Owner:CANON KK

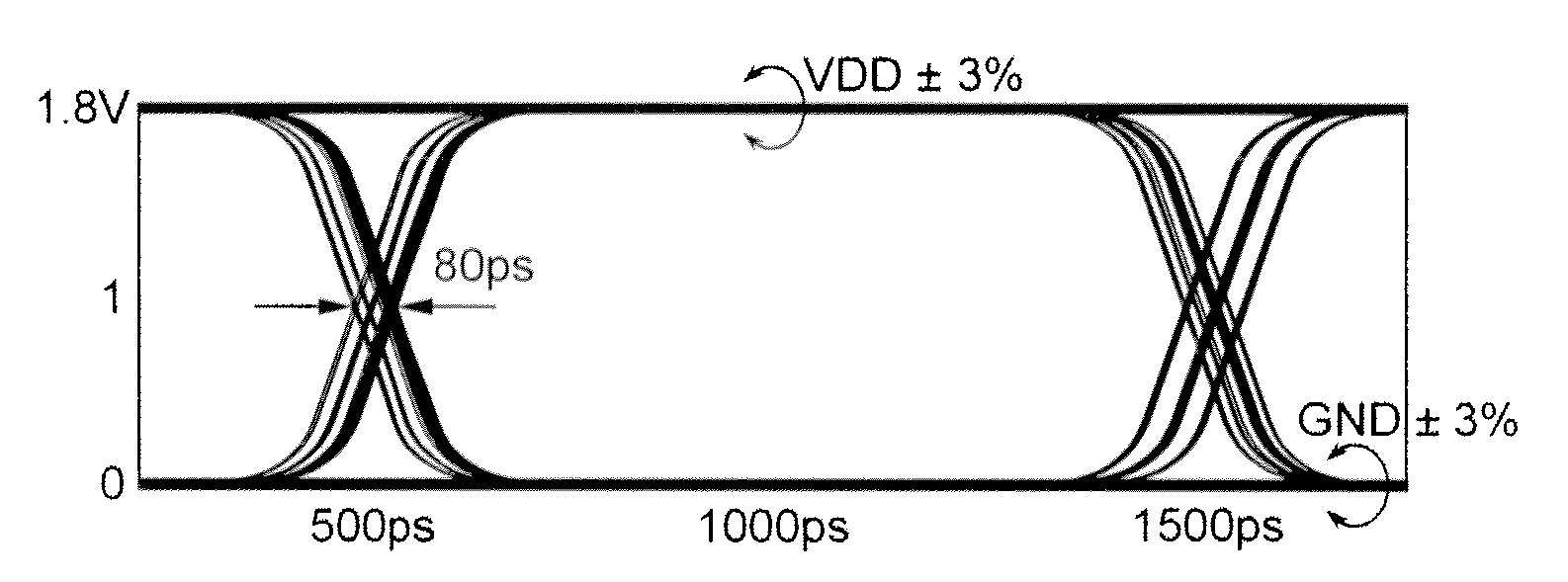

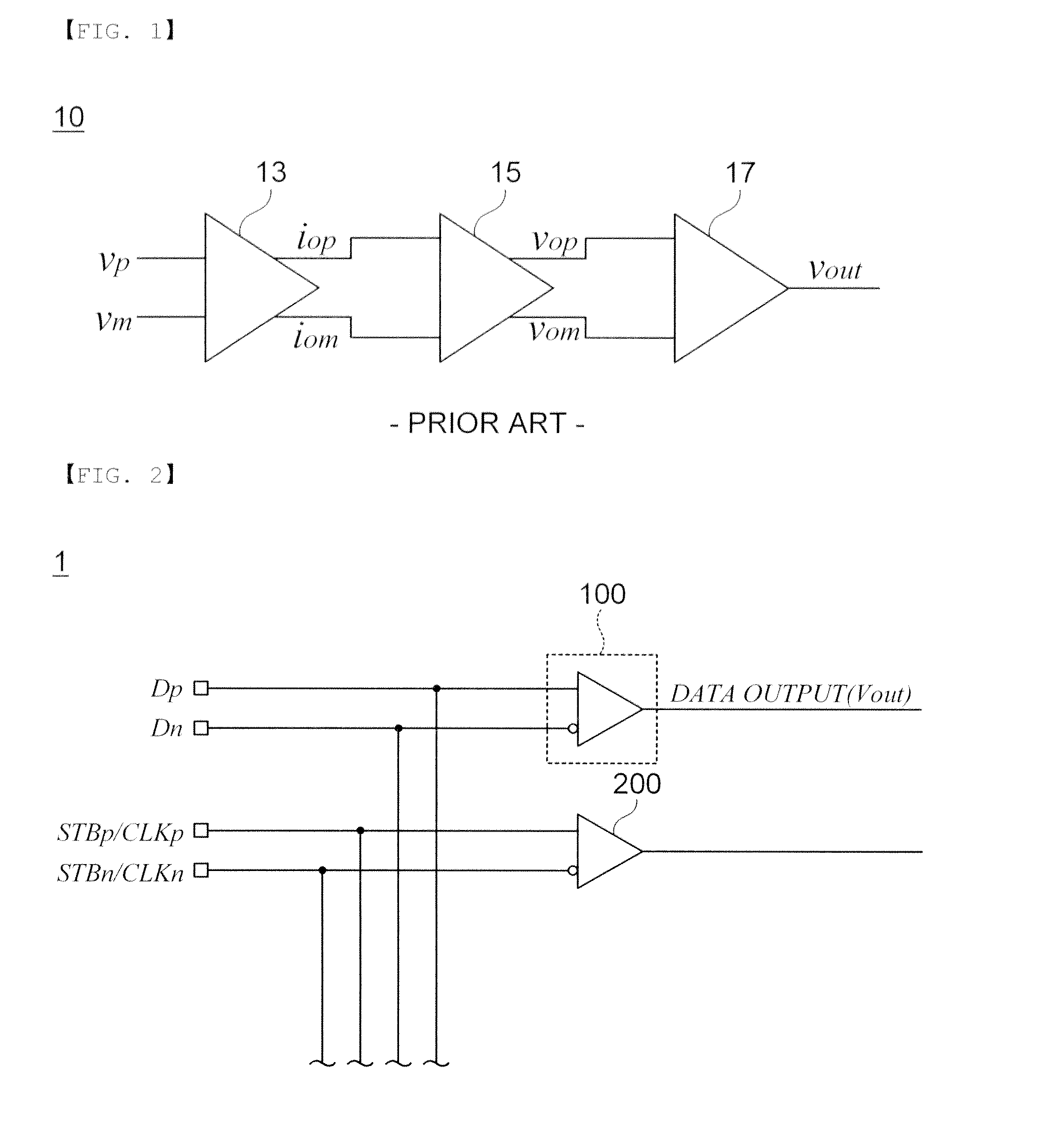

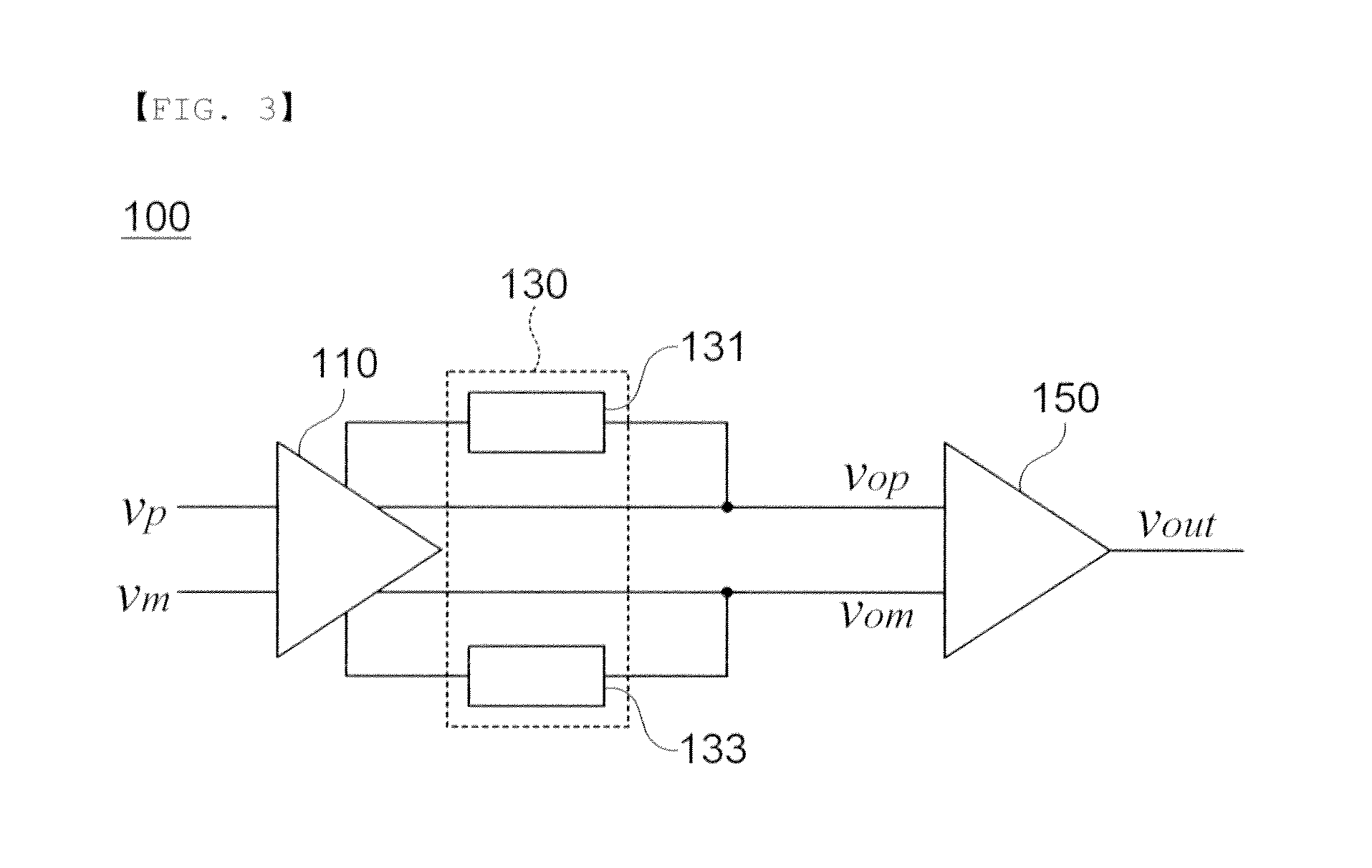

Low jitter 2-stage interface receiver for low power application

InactiveUS20130136217A1Improve jitter characteristicsImprove featuresError preventionAmplifier with semiconductor-devices/discharge-tubesTiming marginNegative feedback

Disclosed herein is an interface receiver including: an input terminal receiving first and second data signals; a negative feedback unit negatively feeding back the first and second data signals input to the input terminal to generate first and second feedback signals; and an output terminal outputting logic level signals by using the first and second feedback signals generated by the negative feedback unit, whereby a timing margin can be secured.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

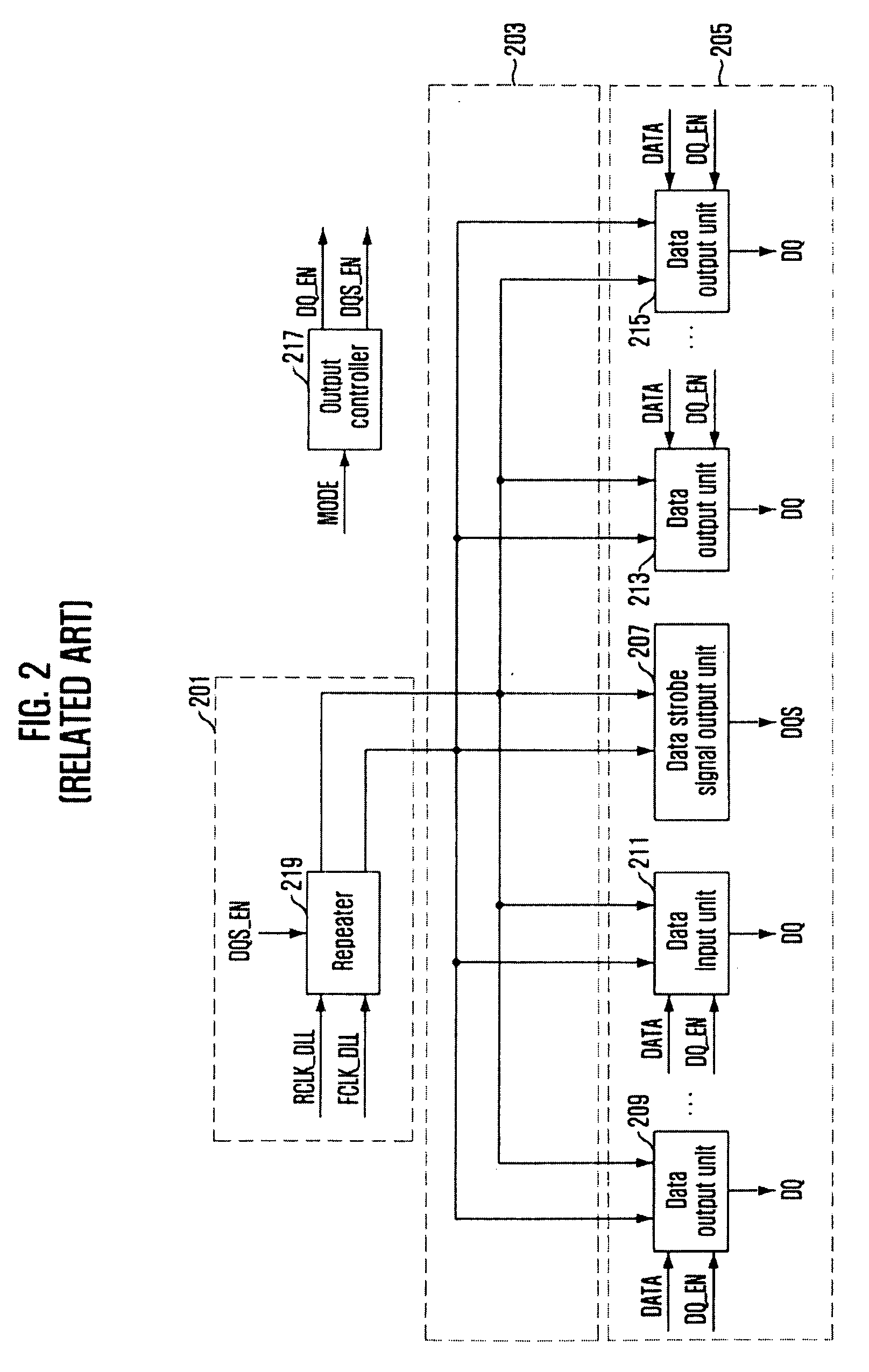

Data input/output circuit

InactiveUS20100054055A1Improve jitter characteristicsEnough data marginDigital storageTransmission lineInput/output

A data input / output circuit includes an output unit for outputting a first data strobe signal and first data in response to an internal clock generated in a delay locked loop, a first transmission line unit having a clock tree structure for transmitting the internal clock to the output unit, a second transmission line unit for transmitting the internal clock from the delay locked loop to the first transmission line unit, a duty cycle ratio correcting unit interconnected between the first transmission line unit and the second transmission line unit for correcting a duty cycle ratio of the internal clock, a data strobe signal input unit for receiving a second data strobe signal from an outside of a semiconductor memory device and generating an internal data strobe signal, and a plurality of data input units for outputting a second data in response to the internal data strobe signal.

Owner:SK HYNIX INC

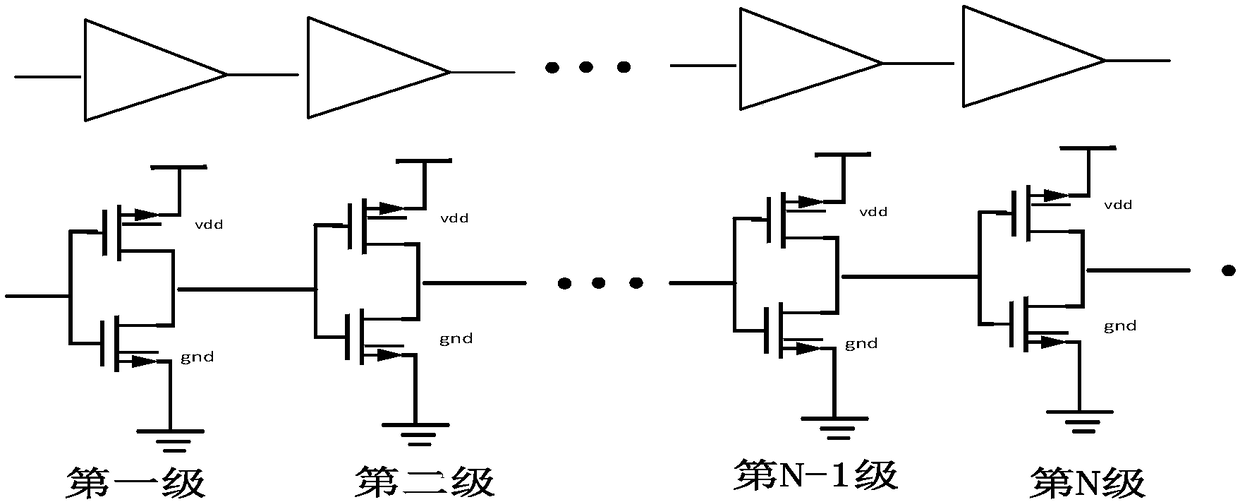

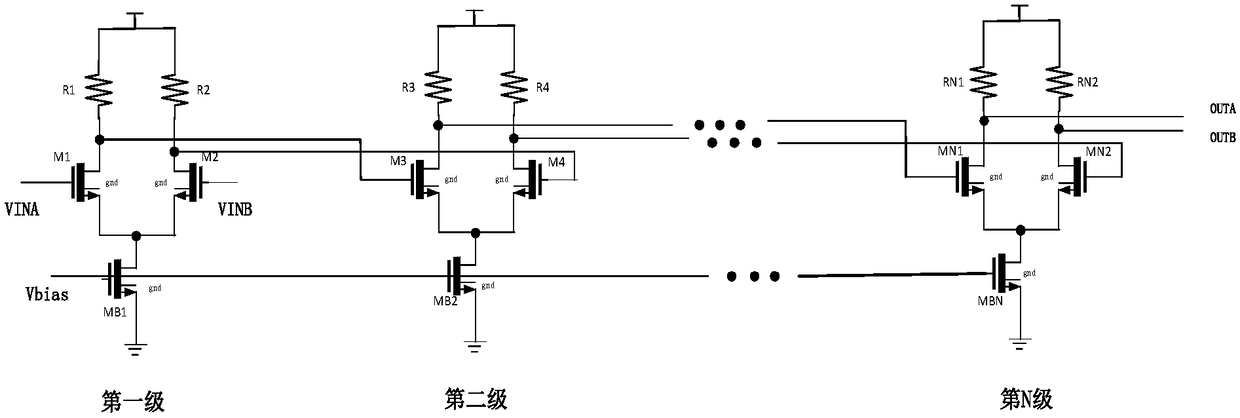

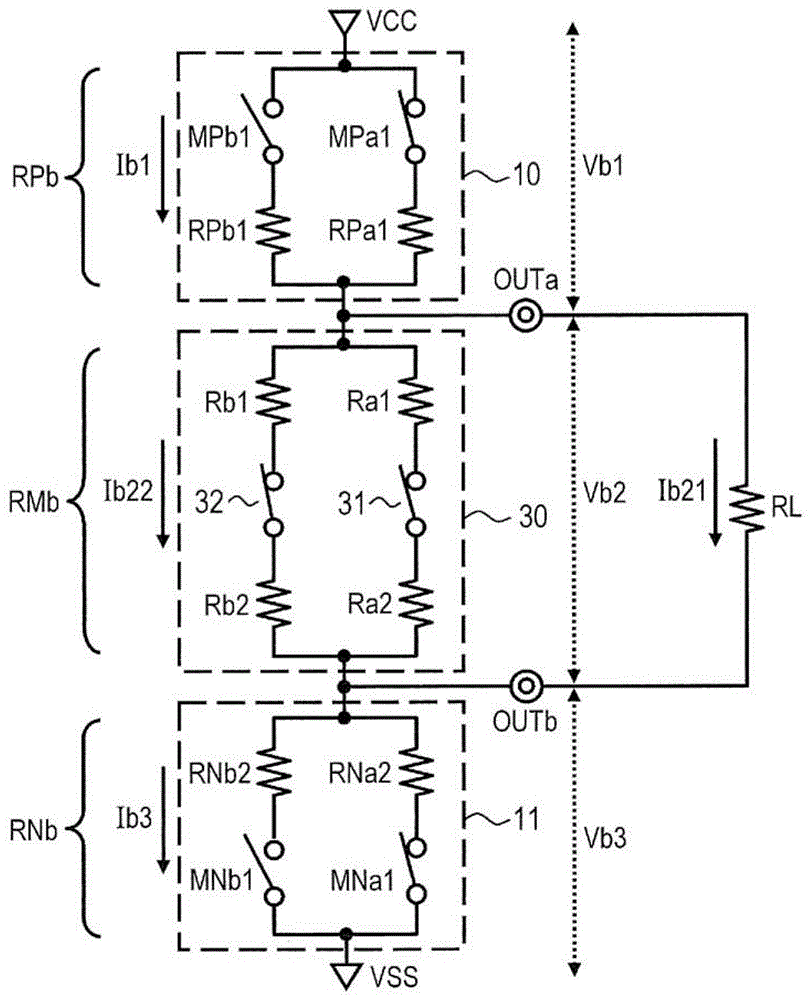

Differential clock tree circuit for high-speed multi-channel interface bus

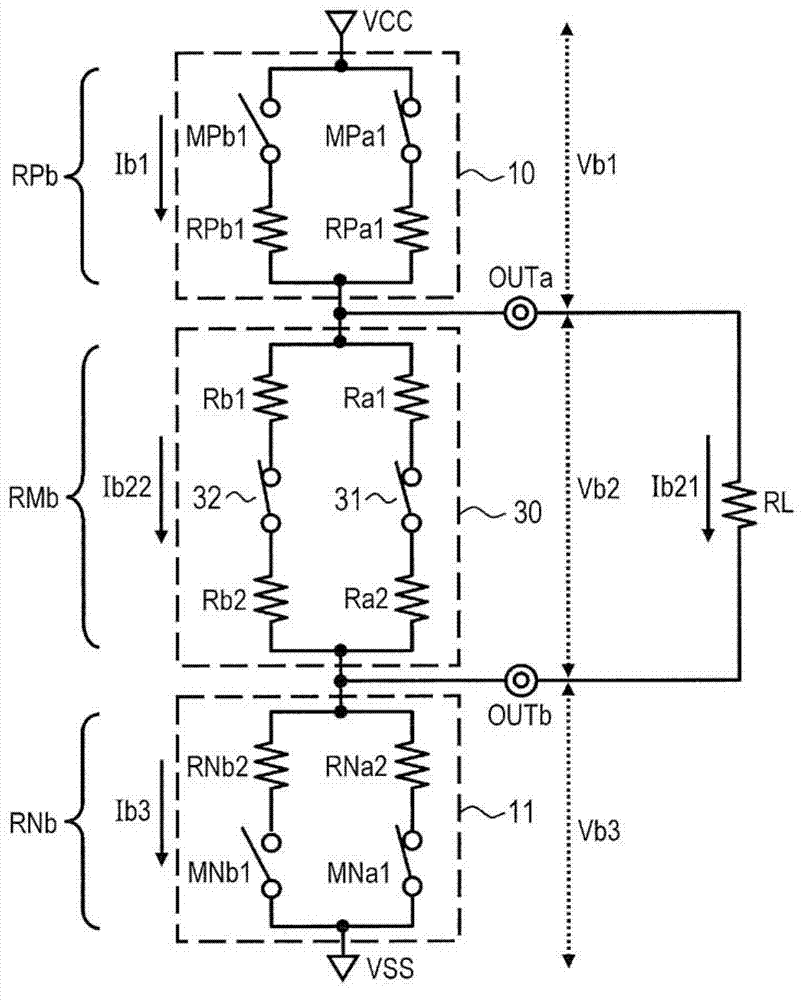

PendingCN108233918AReduce jitterSimple structureLogic circuits coupling/interface using field-effect transistorsLogic circuit interface arrangementsElectrical resistance and conductanceDifferential signaling

The invention discloses a differential clock tree circuit for a high-speed multi-channel interface bus. The differential clock tree circuit for the high-speed multi-channel interface bus has the characteristics of being low in jitter, simple in structure, capable of being cascaded and high in anti-noise capability, and long-distance transmission of a high-speed clock can be achieved. The highly symmetric full analog differential clock tree circuit of the invention has the characteristics of being low in jitter, simple in structure, capable of being cascaded and high in anti-noise capability, and long-distance transmission of the high-speed clock can be achieved. A cascade circuit formed on the basis of the differential clock tree circuit is of a full differential structure, the differential structure appears in pairs and has strong ability to suppress noises; secondly, the structure adopted by the differential clock tree circuit is a differential input / output structure form, which canrealize cascading; thirdly, a field-effect transistor is used for bias power supply, thus noises on the power supply and ground can be shielded, and the low-jitter characteristics can be realized; andfinally, a collector series resistor of a transistor is adopted to reduce the swing amplitude of a differential signal, the driving capability is high, and long-distance transmission can be realized.

Owner:高科创芯(北京)科技有限公司

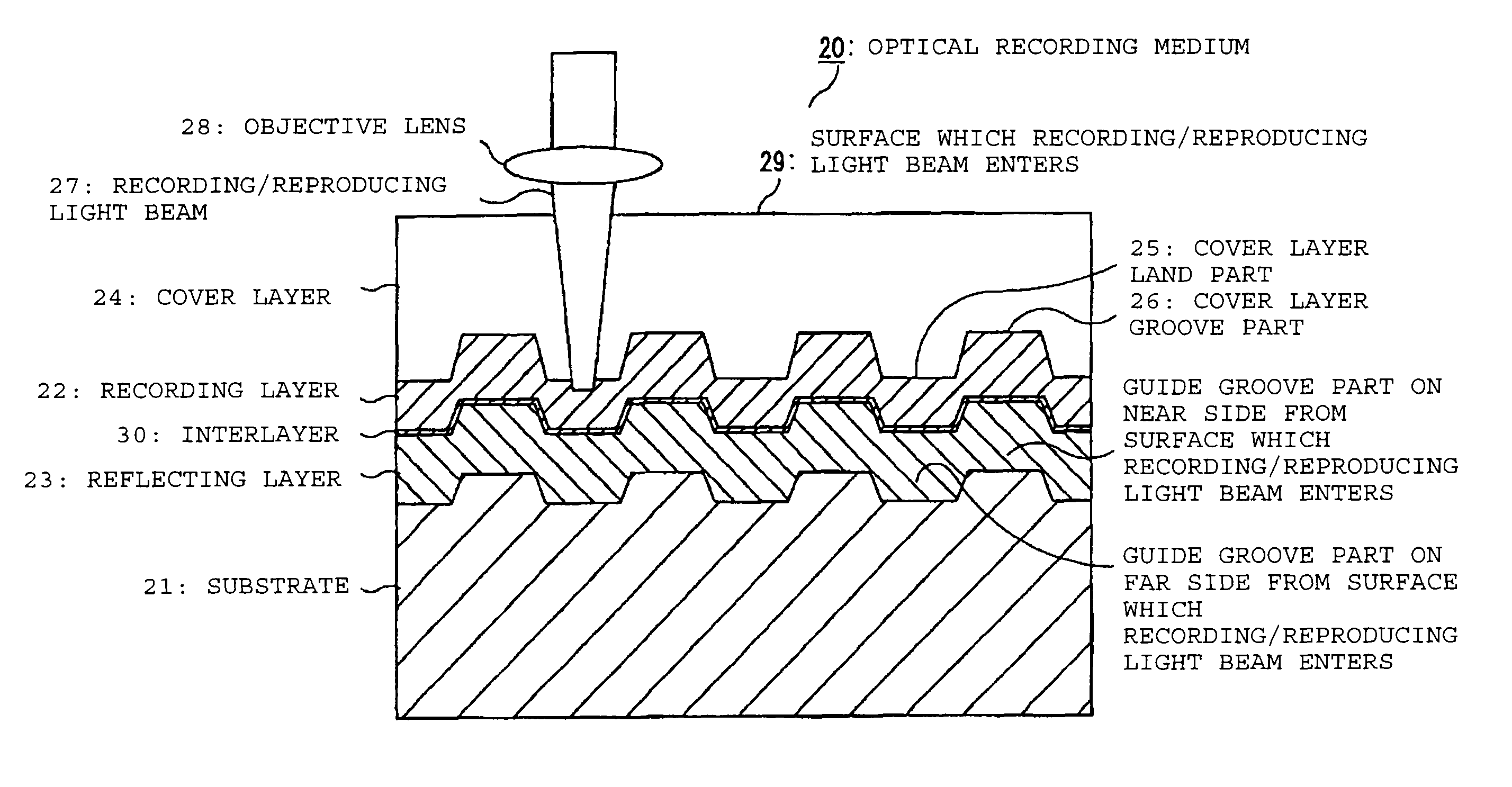

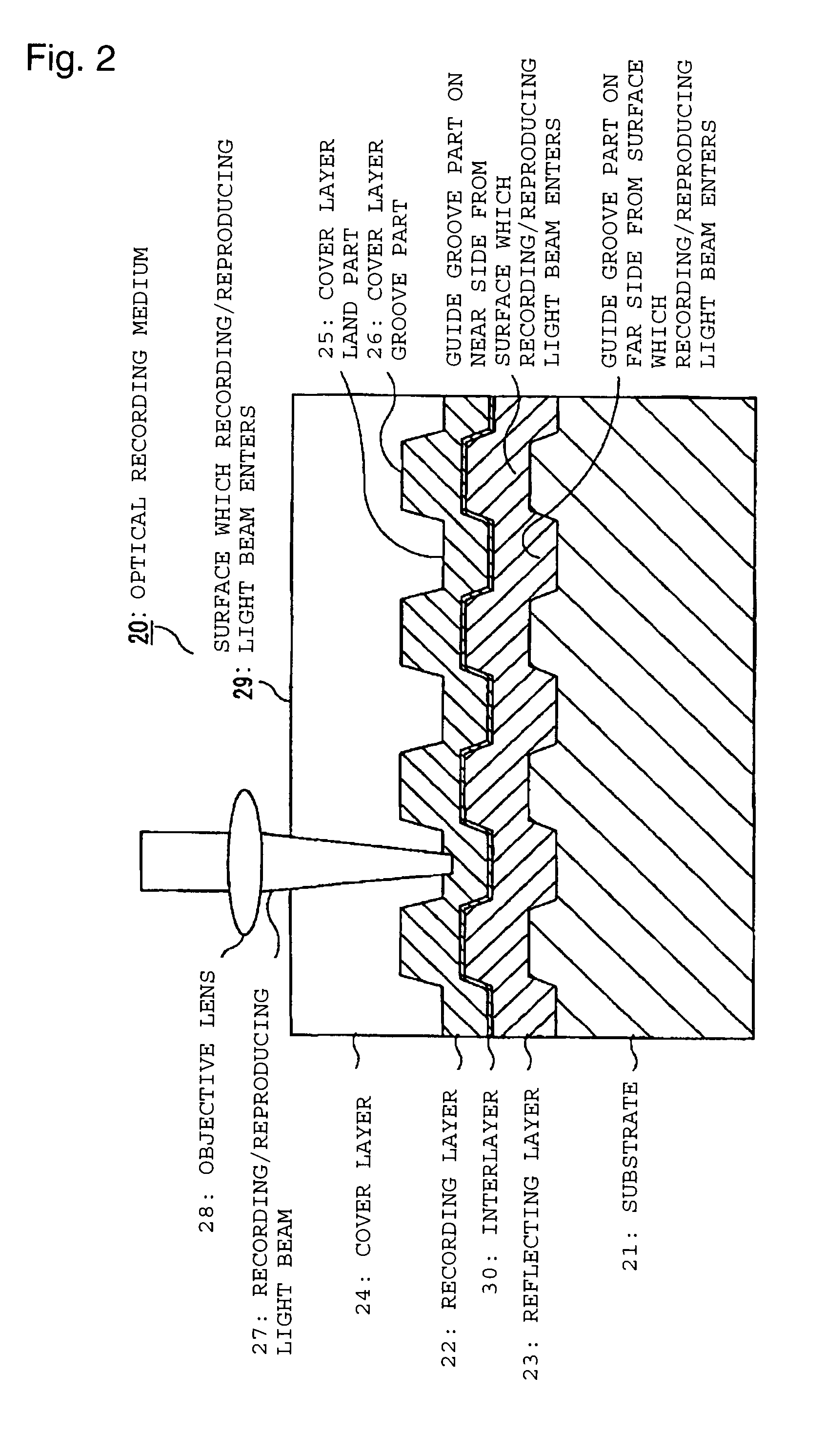

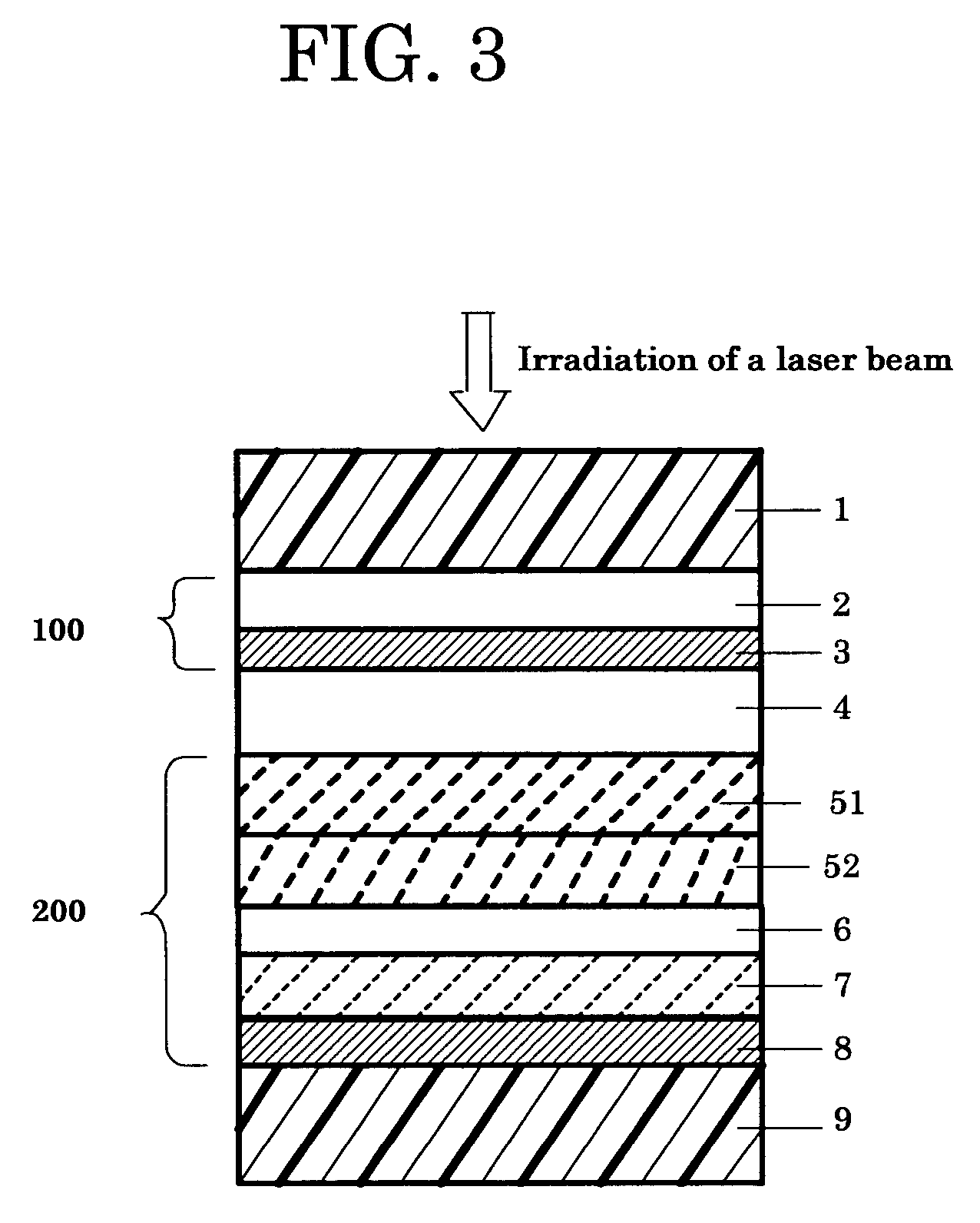

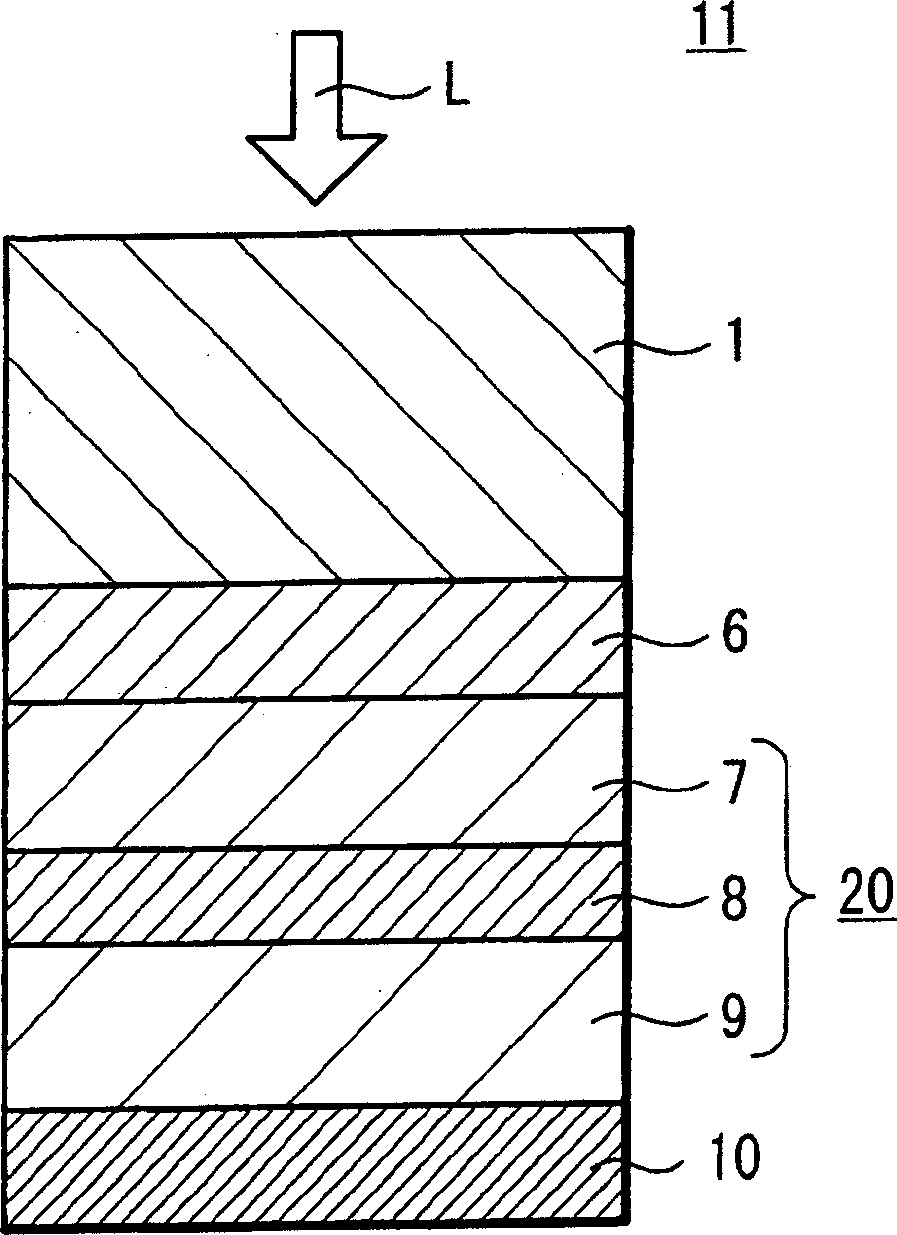

Optical recording medium

ActiveUS8114496B2Improve jitter characteristicsHigh-density optical recordingLayered productsPhotomechanical apparatusHigh densityInter layer

Provided is an extremely high-density optical recording medium with excellent jitter characteristics and good recording / reproducing characteristics.An optical recording medium 20 comprises a substrate 21 with a guide groove formed therein, a layer 23 with a light reflection function, a recording layer 22 comprising a dye as a main component with a light absorption function for a wavelength of recording / reproducing light in an unrecorded state, and a cover layer 24 capable of transmitting the recording / reproducing light incident to the recording layer 22, in the order mentioned; an interlayer 30 containing at least one element selected from the group consisting of Ta, Nb, V, W, Mo, Cr and Ti, is provided between the layer 23 with the light reflection function and the recording layer 22.

Owner:CMC MAGNETICS CORPORATION

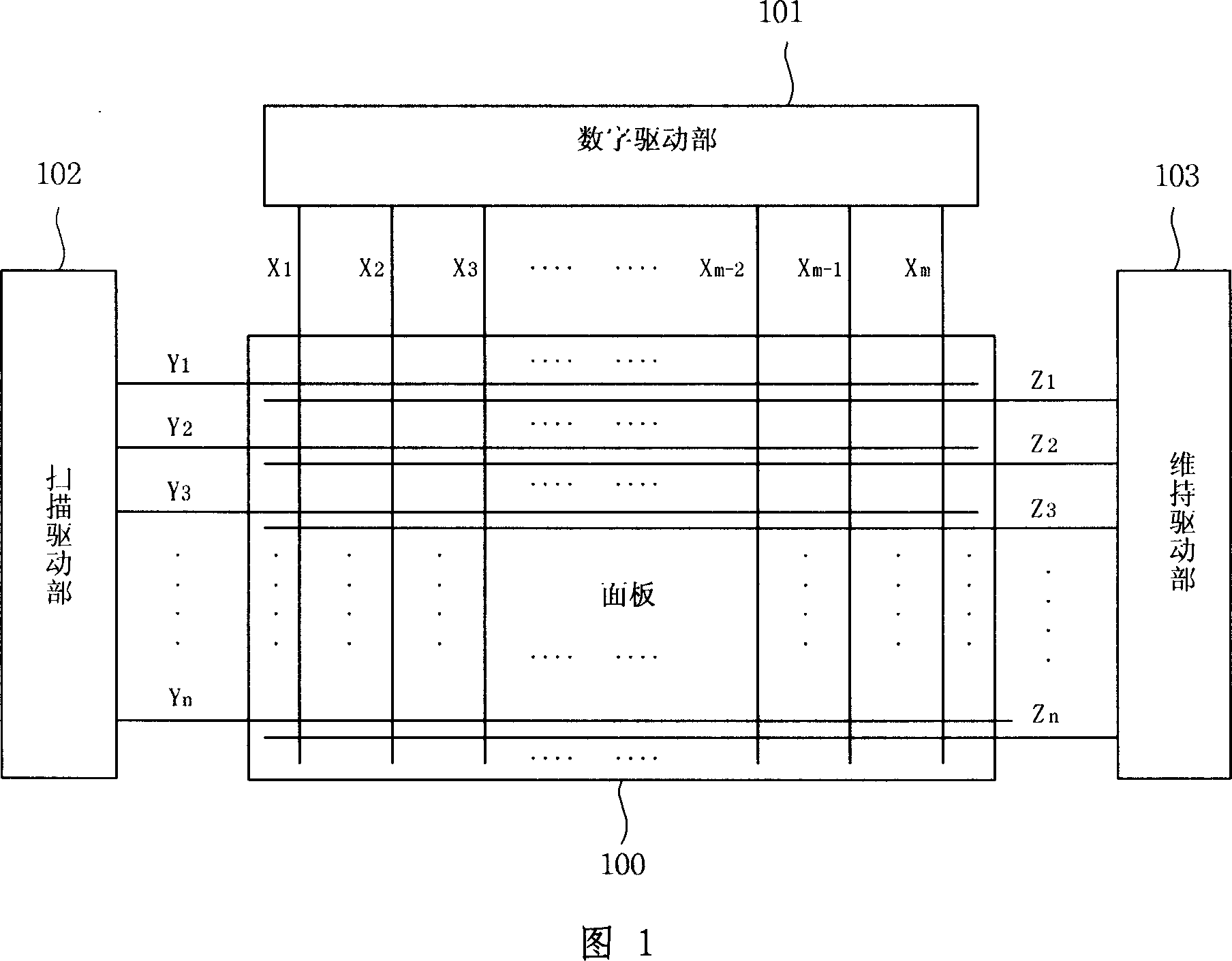

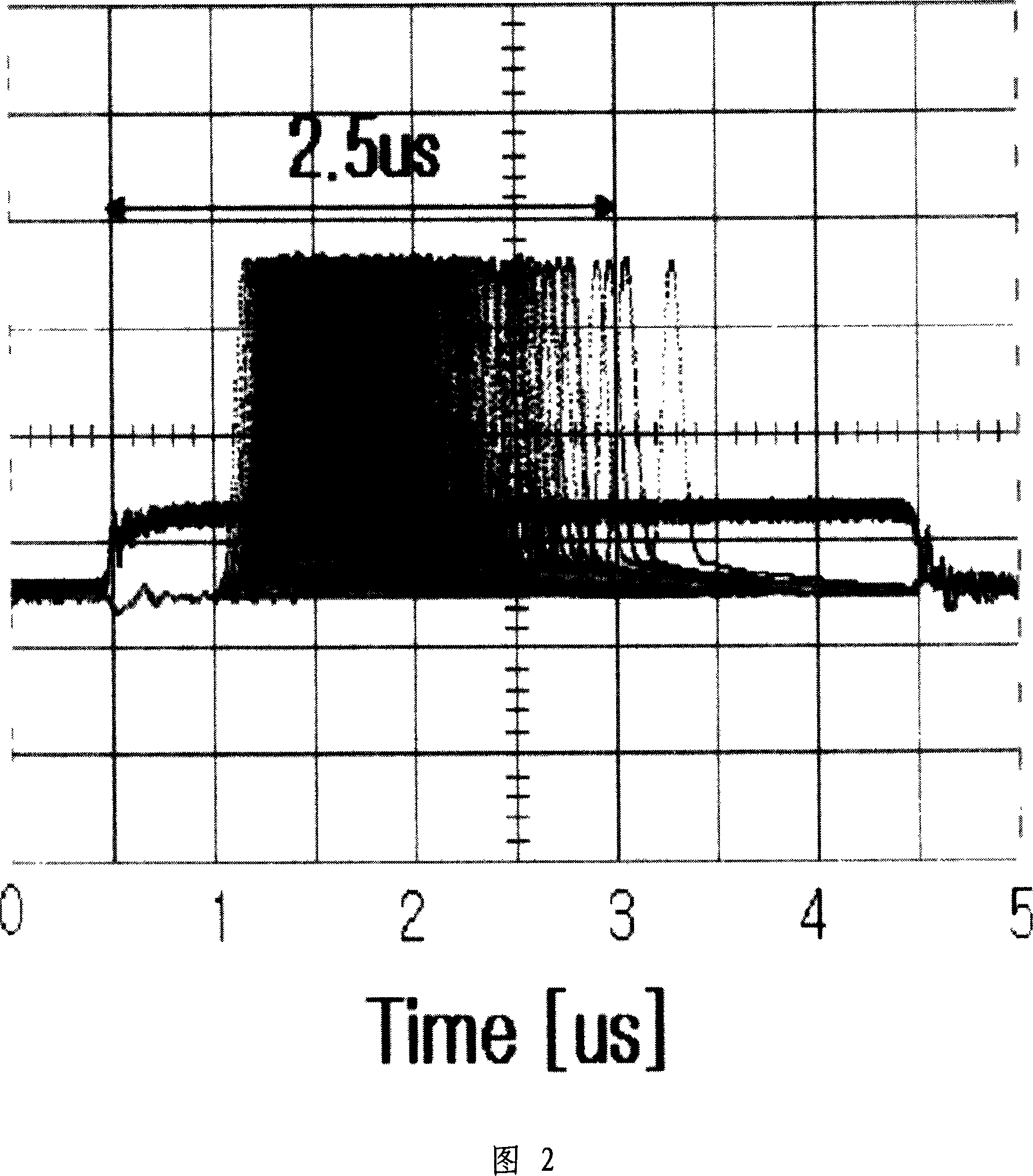

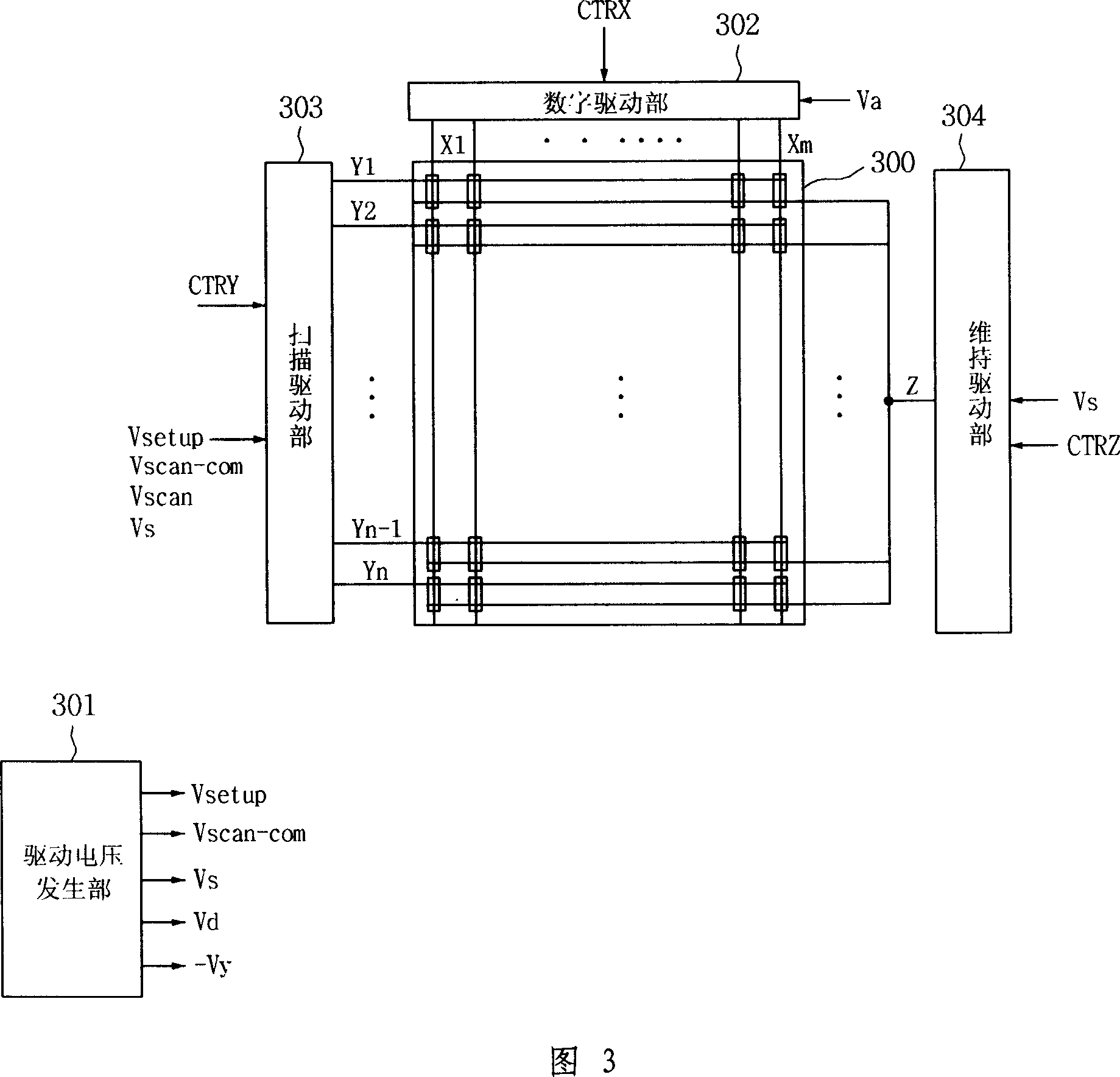

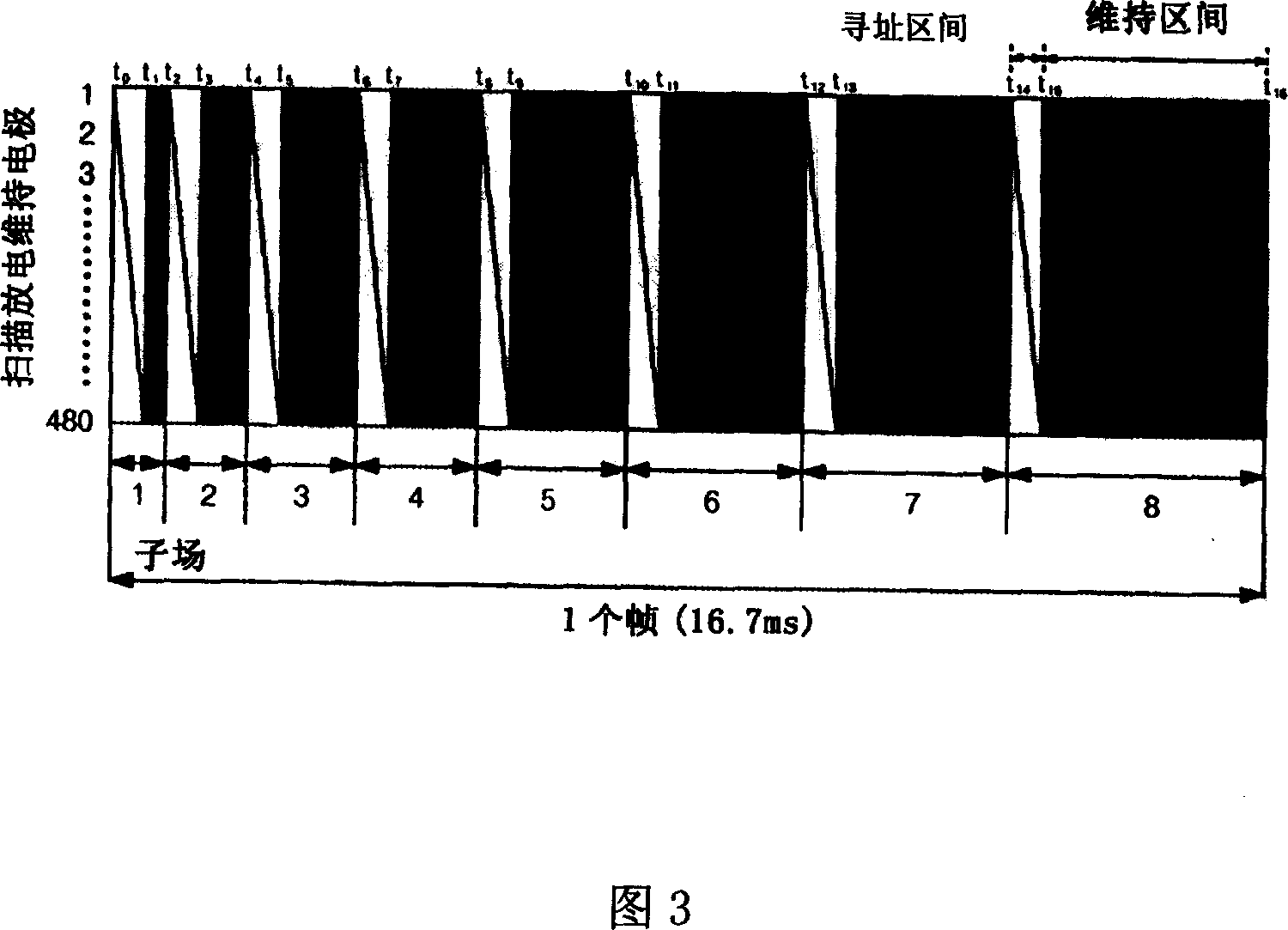

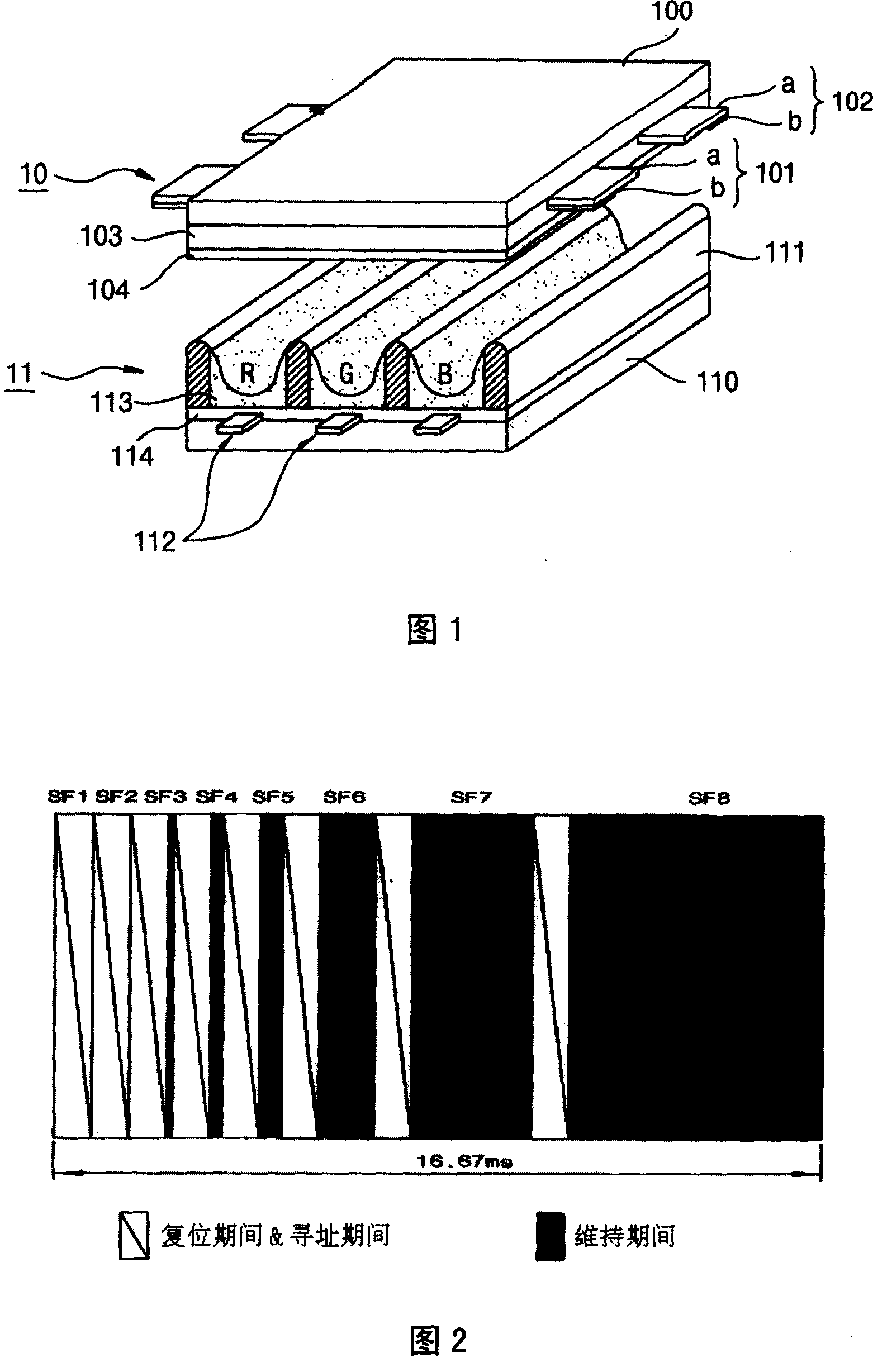

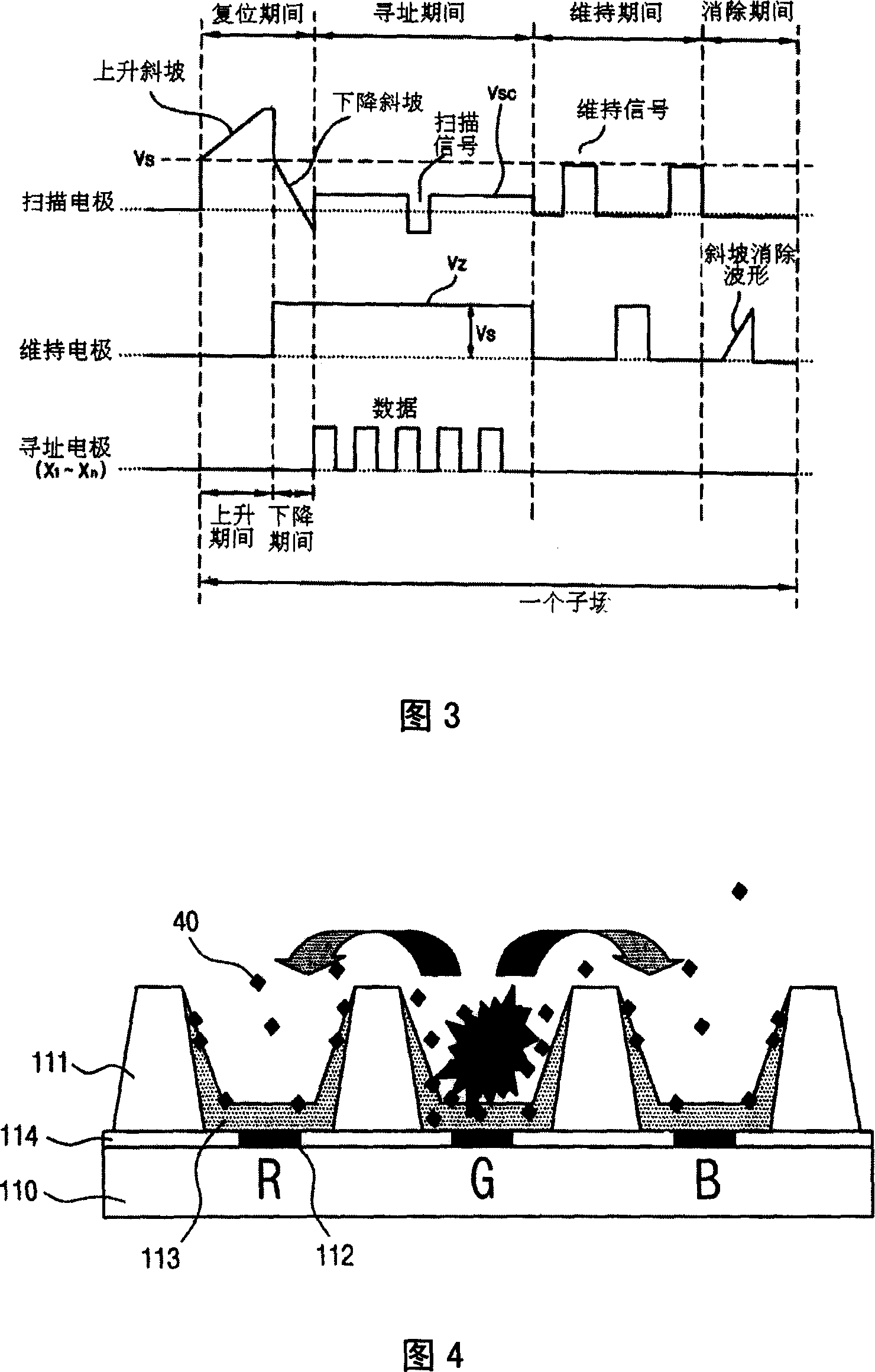

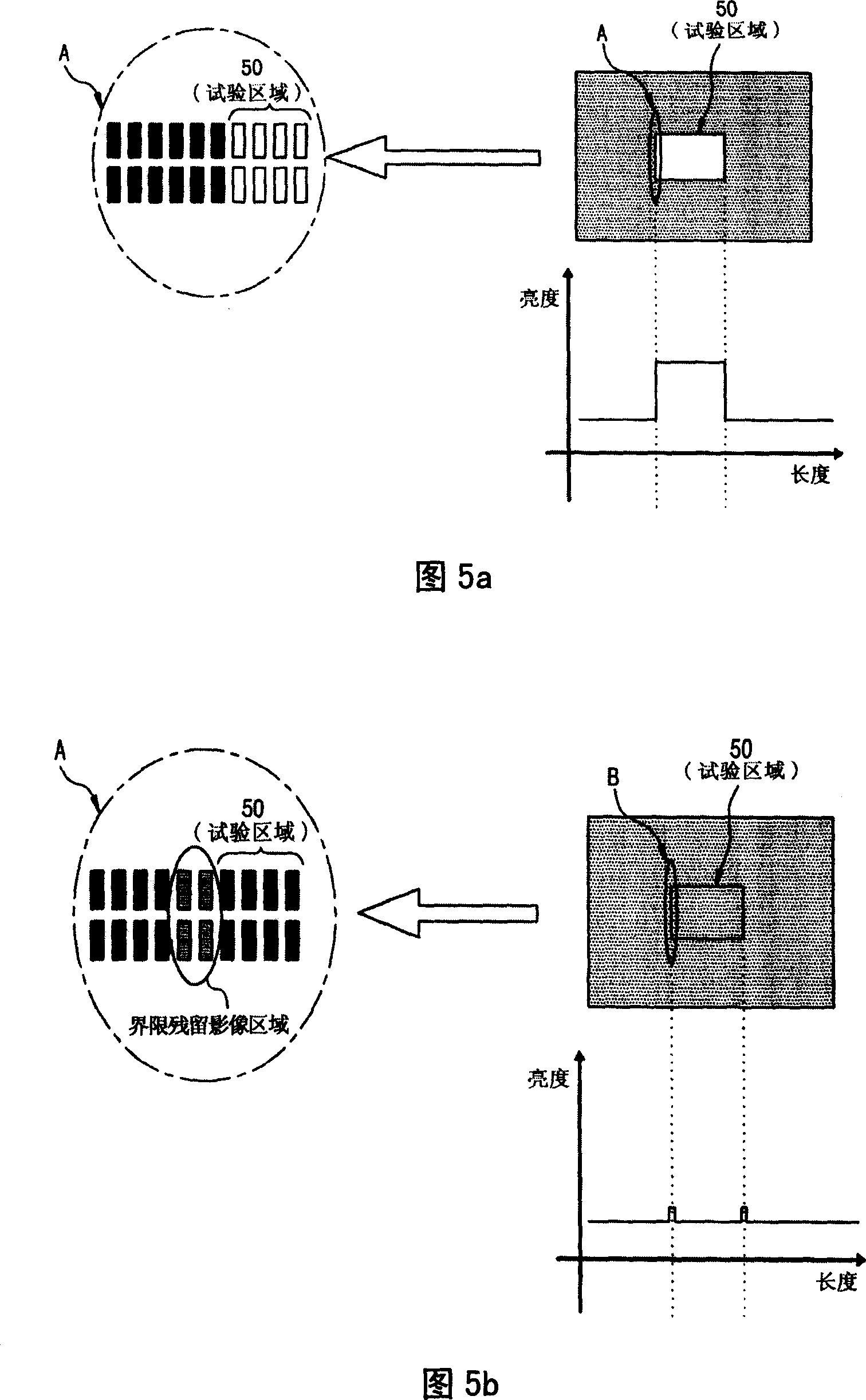

Plasma display device and its driving method

InactiveCN1975839AEnsure wall chargePrevent misdischargeStatic indicating devicesCold-cathode tubesPulse controlDisplay device

The present invention relates to a plasma display device, and more specifically, relates to a plasma display device and a driving method thereof for adjusting a positive waveform voltage negatively applied to a sustain electrode, improving discharge accuracy, and improving jitter characteristics . As described above, the plasma display device in the present invention includes: a plasma display panel including sustain electrodes; a sustain drive unit that drives the sustain electrodes; and controls the sustain drive unit so that subfields (frame) During the falling edge period of sub-field) and the positioning period or during any one of the positioning periods, the positive polarity waveform voltage applied to the above-mentioned sustain electrode is changed from the first voltage level to the second voltage level with a certain gradient. The drive pulse control unit.

Owner:LG ELECTRONICS(NANJING) PLASMA CO LTD

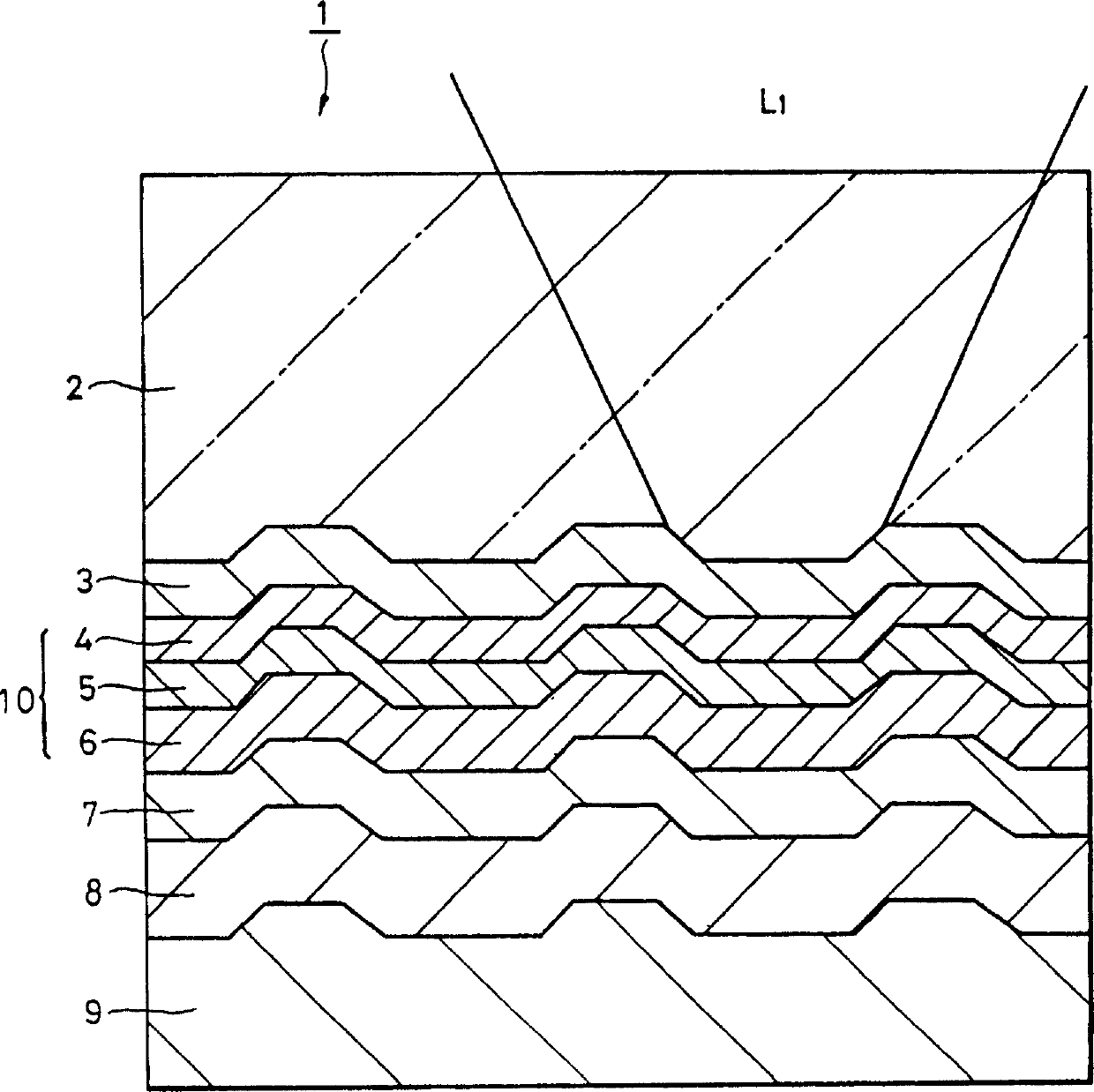

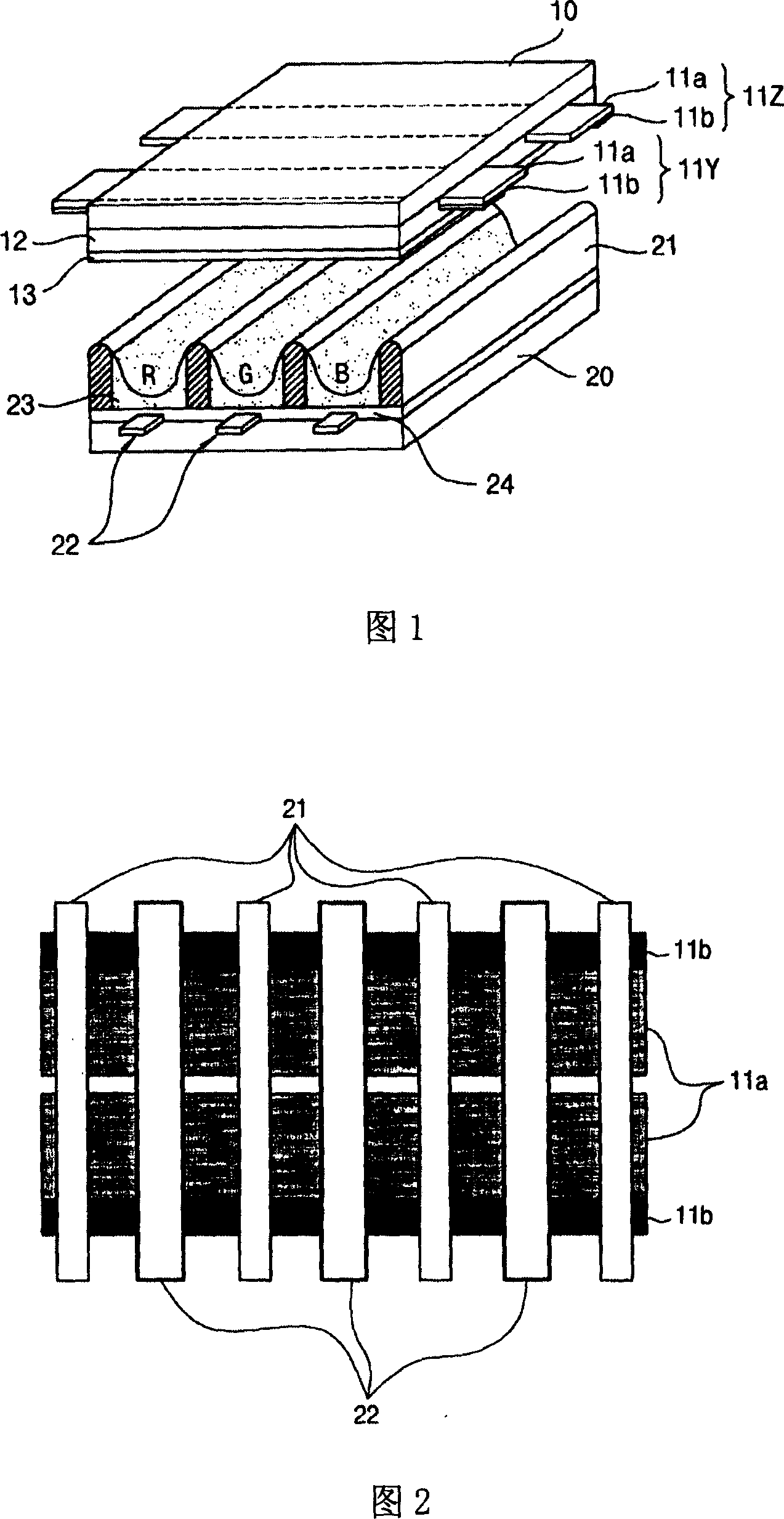

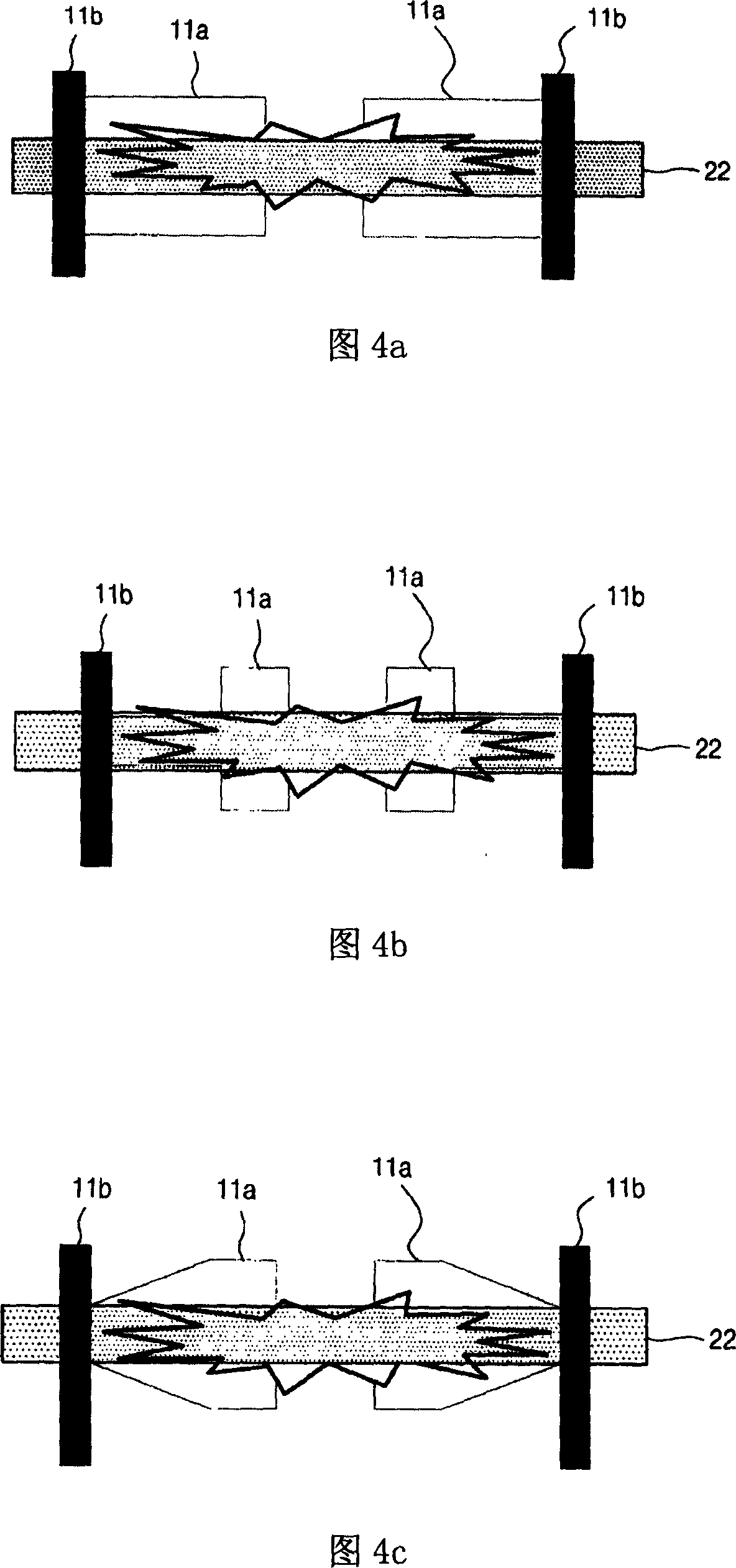

Sagneto-optical recording medium and its production method

InactiveCN1543645AGuaranteed powerImprove jitter characteristicsRecord information storageLight beam reproducingMagneto opticalGas pressure

A magneto-optical disk (1) comprises a disk substrate (2) having lands and grooves on and in a major surface thereof, a first dielectric layer (3), a multilayer magnetic film (10) including a first magnetic layer (4) having a vertical magnetic isotropy at room temperature, a second magnetic layer (5) having a plane magnetic isotropy at room temperature, and a third magnetic layer (6) having a vertical magnetic isotropy at room temperature, a second dielectric layer (7), a reflective layer (8), and a protective layer (9) all the layers and film being formed on the disk substrate (2) in order. The saturation magnetization of the second magnetic layer (5) is 8.80*10-2 to 1.76*10-1 Wb / m2. The gas pressure under which the second magnetic layer (5) is formed is 0.6 to 3.0 Pa. The third magnetic layer (6) contains 15 to 17 atom% of Co.

Owner:SONY CORP

Optical recording medium, and, method for manufacturing the same, and method and apparatus for optical recording and reproducing thereof

InactiveUS7767284B2Improving wet properties of dye coating to materialsImprove jitter characteristicsRecord carriersSynthetic resin layered productsInformation layerOrganic dye

The object of the present invention is to provide an optical recording medium which comprises a substrate, and a first information layer and a second information layer disposed on the substrate, and an intermediate layer disposed between the first information layer and the second information layer, wherein any one of recording and reproducing is performed in the first information layer and the second information layer by irradiating a laser beam from the first information layer side, the second information layer comprises a protective layer, a second dye layer which comprises an organic dye, an oxidized layer, and a reflective layer in this order from the laser beam irradiation side, and the oxidized layer comprises an oxide which is a material constituting the reflective layer.

Owner:RICOH KK

Plasma display device

InactiveCN101083195AImprove discharge efficiencyImprove jitter characteristicsSolid cathode detailsCold-cathode tubesDischarge efficiencyCell region

The invention relates to a PDP (plasma display panel), especially a PDP able to raise discharging efficiency and improve dither characteristic as discharging by forming addressing electrodes matching with transparent electrode structure. And the PDP comprises: a front substrate equipped with scan electrodes and sustain electrodes; a rear substrate equipped with addressing electrodes staggered with the scan electrodes and the sustain electrodes; barriers for partitioning discharging cell regions on the rear substrate, where the scan electrodes and the sustain electrodes are respectively composed of transparent electrodes and bus electrodes, and in a discharging cell, the area of the addressing electrode is more than the maximum area of the transparent electrode.

Owner:LG ELECTRONICS(NANJING) PLASMA CO LTD

Magneto-optical recording medium having in-plane magnetizing layer

InactiveUS7210155B2High sensitivityImprove jitter characteristicsRecord information storageFlat record carrier containersIn planeHigh density

A high-density magneto-optical recording medium having excellent jitter properties is provided. A pattern-dependent shift of the length of a recorded mark does not occur even when a minute mark has increased sensitivity to a recording magnetic field. A magneto-optical recording medium has at least a displacement layer, a memory layer, and an auxiliary memory layer. A mark with a length up to the diffraction-limit of the optical system is recorded and read out. The magneto-optical recording medium includes an in-plane magnetization-inducing layer principally made of cobalt on the auxiliary memory layer.

Owner:CANON KK

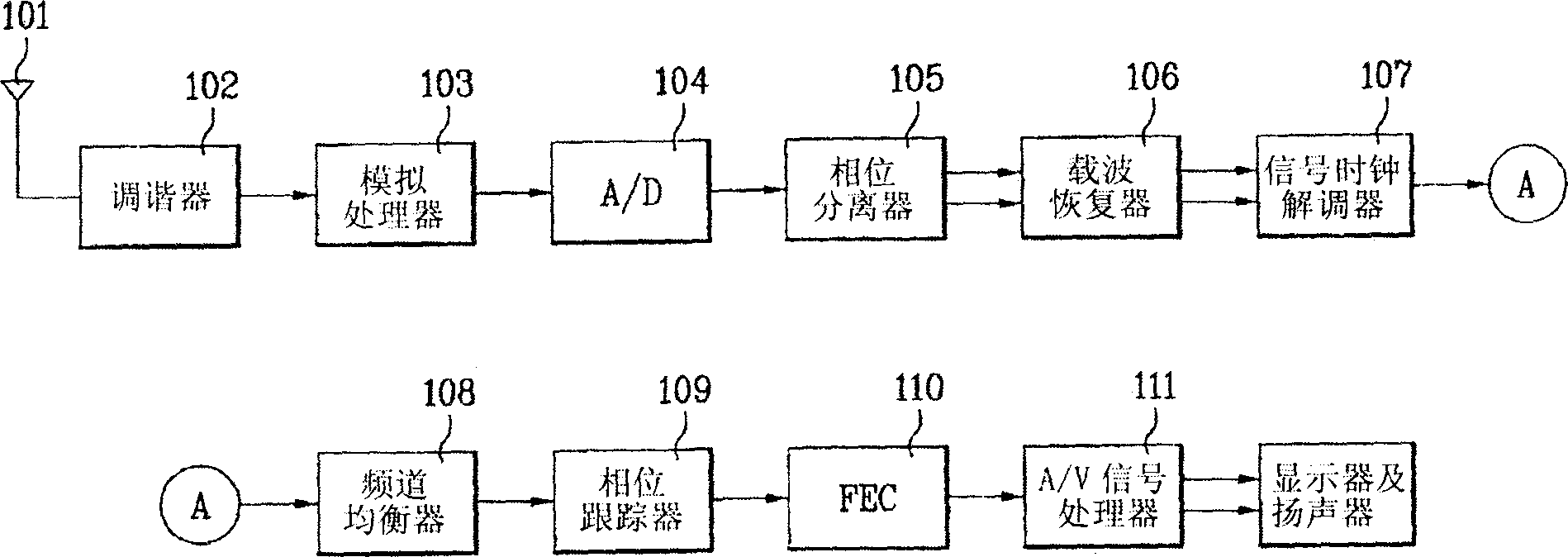

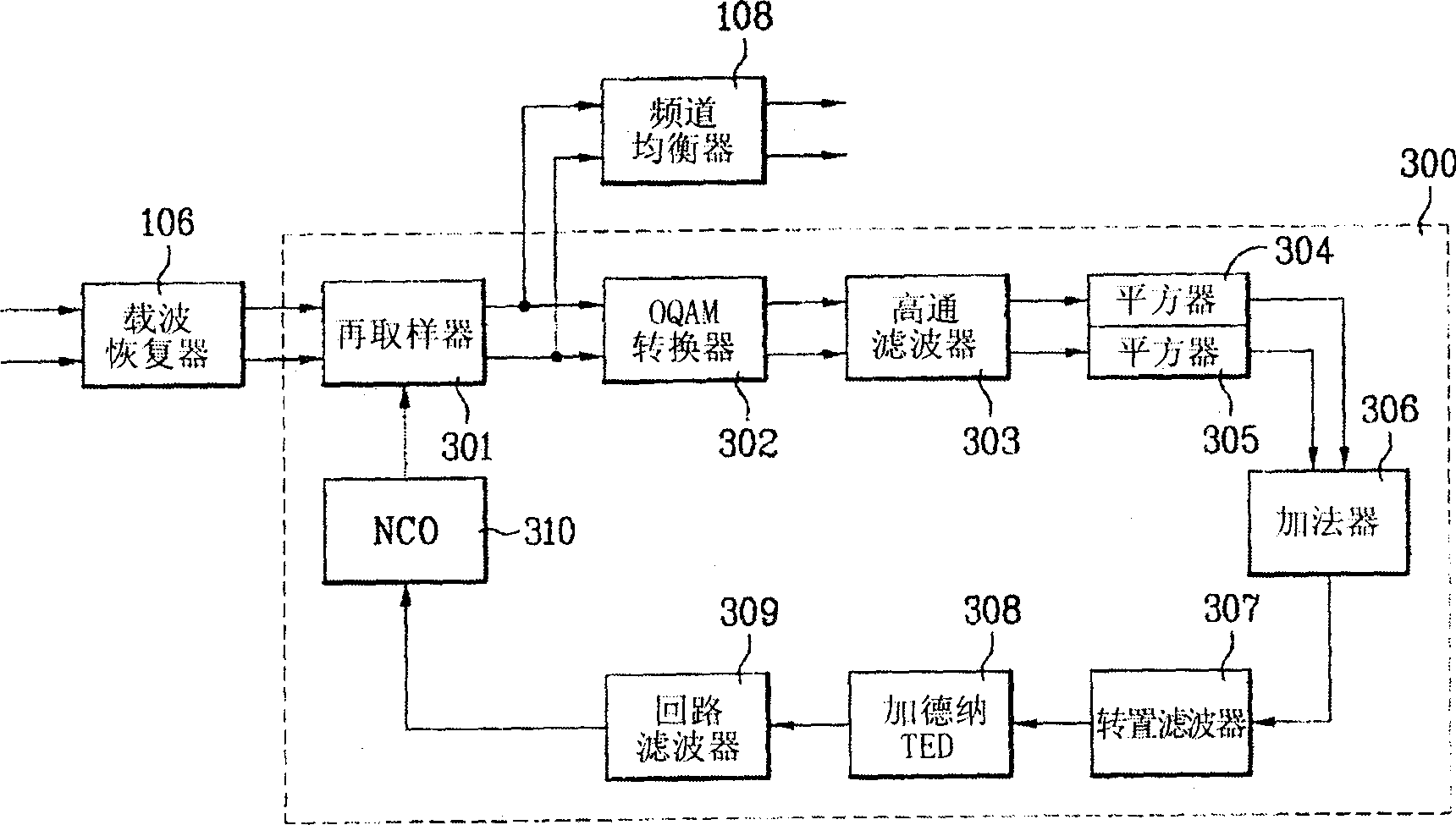

Signal clock demodulating device

InactiveCN1735153ADemodulation stabilityImprove jitter characteristicsTelevision system detailsColor television detailsTime errorFrequency spectrum

The invention relates to signal clock demodulating device for digital TV receiver. Wherein, using time error detector with nonlinear unit to detect the time error for demodulating signal clock; the front end of the said detector is arranged with an OQAM converter, a high-pass filter, a squarer and an adder. It can eliminate the unnecessary compositions and improves jitter performance. This invention can also use gain regulator and DC calculator to adjust the tone for signal clock and improve demodulating device performance on the disturbance from multi-way.

Owner:LEJIN GUANGDIAN ELECTRONIC CO LTD SHANGHAI

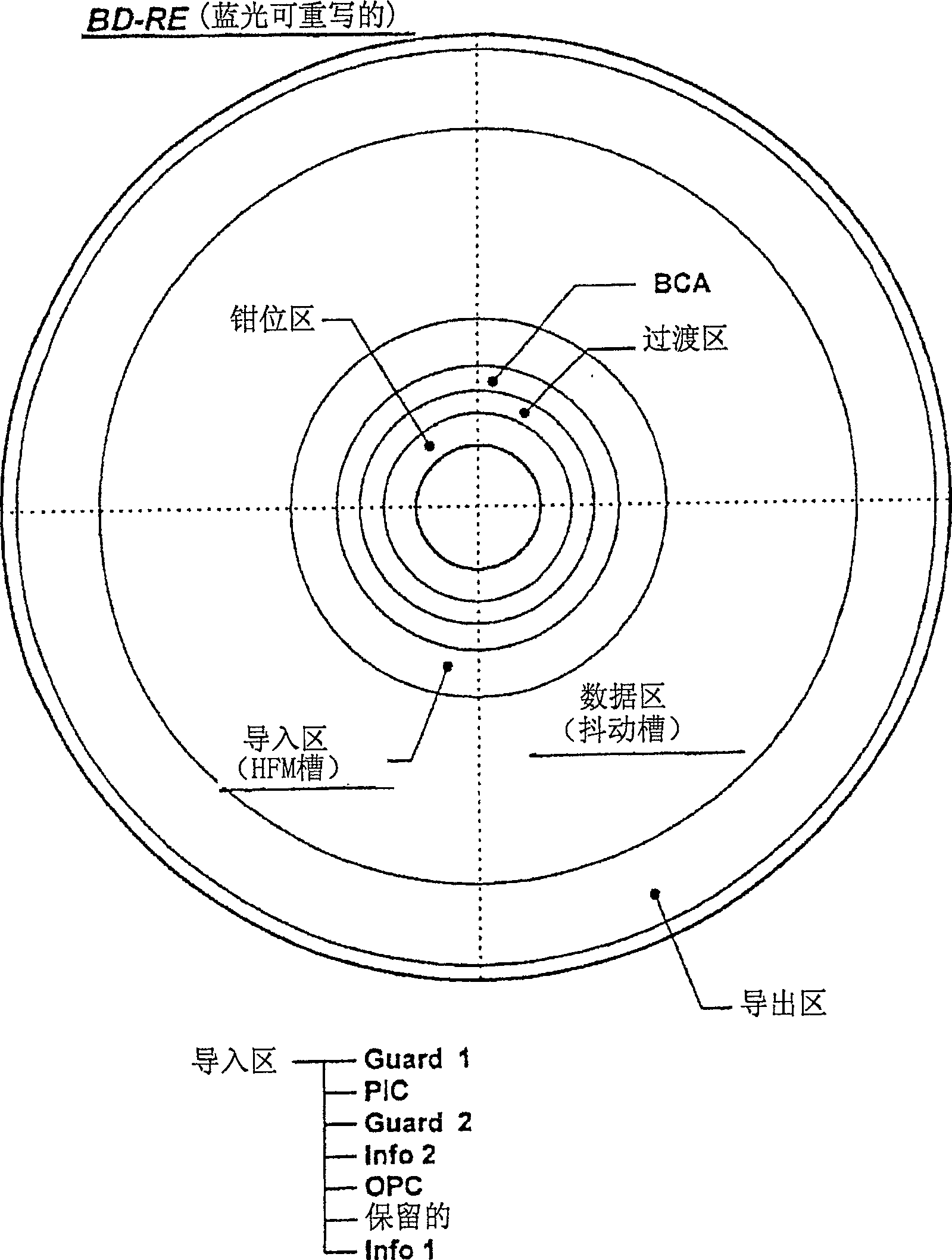

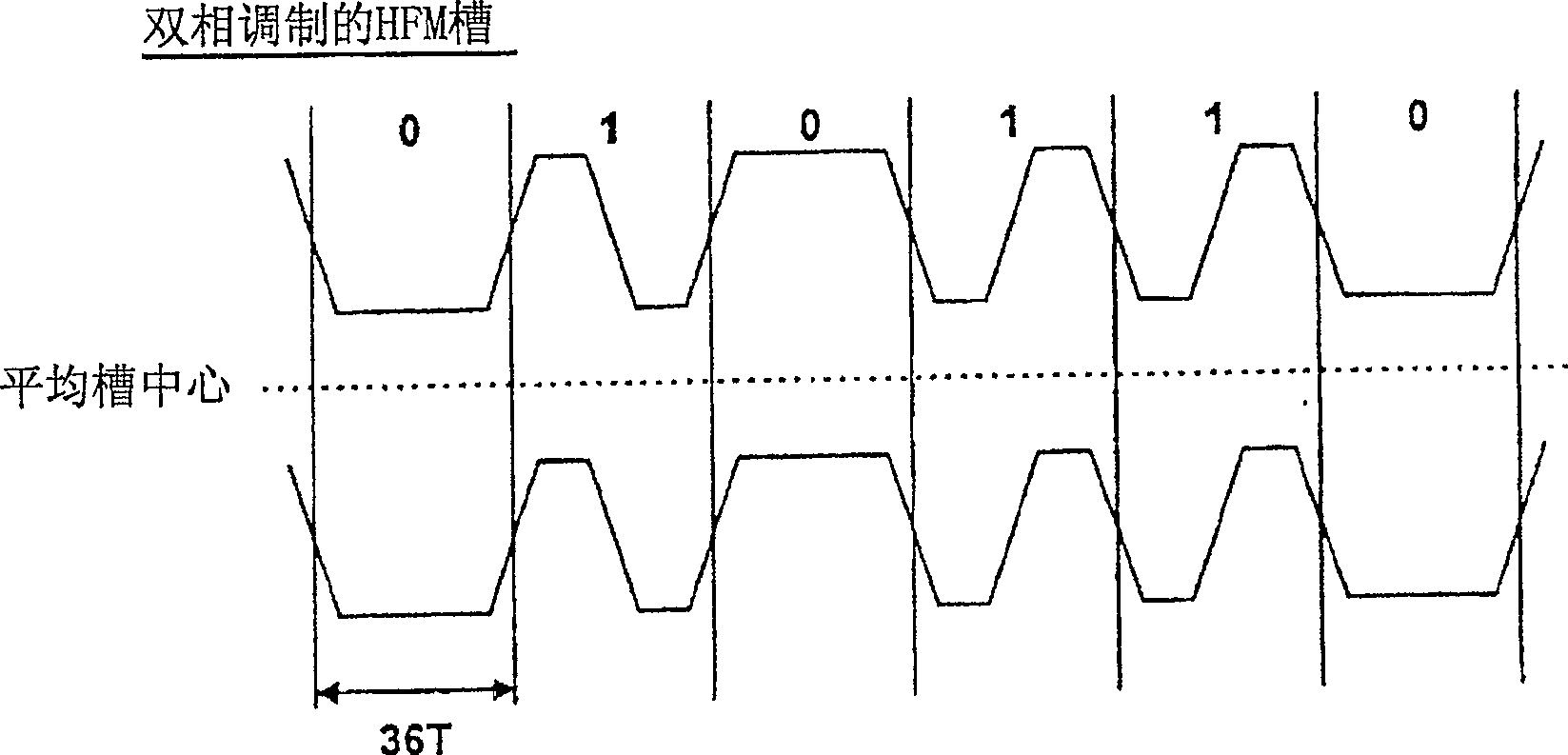

Recording medium and method for recording and reproducing data on and from the same

InactiveCN100485790CImprove jitter characteristicsRecord information storageDigital signal formattingControl dataRecording media

Owner:LG ELECTRONICS INC

Drive method of plasma display device

InactiveCN101083040AEvenly distributedReduce the differenceStatic indicating devicesCold-cathode tubesDisplay deviceEngineering

The invention discloses a driving method of plasma display to modify reset waveshape during rising period of reset stage, which is characterized by the following: reducing residual image; modifying shake property; utilizing at least one subfield combination to display image of address-searching electrode, scanning electrode and extra voltage of maintaining electrode during reset period, address-searching period and maintaining period; driving the reset period into rising period and falling period; proceeding at least one surface discharge between scanning electrode and maintaining electrode and at least one opposite direction discharge between scanning electrode and address-searching electrode during rising period.

Owner:LG ELECTRONICS(NANJING) PLASMA CO LTD

Semiconductor integrated device having reduced jitter and reduced current consumption

ActiveUS7126392B2Reduce the amount requiredImprove jitter characteristicsPulse automatic controlGenerating/distributing signalsDamping factorLow speed

A structure is provided for significantly reducing the current excessively consumed for generating a high-speed clock signal necessary for signal processing, and significantly improve the jitter characteristics of the high-speed clock signal. The structure includes a reference-clock signal generation circuit, a time-base processing circuit, a PLL circuit, and a high-speed signal processing circuit. A low-speed reference-clock signal generated by the reference-clock signal generation circuit is provided to the PLL circuit. The PLL circuit generates a high-speed clock signal by multiplying the reference-clock signal by a factor of N. The factor N is at least 100. To reduce a jitter of the high-speed clock signal generated by the PLL circuit, a natural angular frequency ωn and a damping factor ζ that relate to the response characteristics of the system of the PLL circuit are set to range from 3 kHz to 10 kHz, and 0.01 or less, respectively.

Owner:SEIKO EPSON CORP

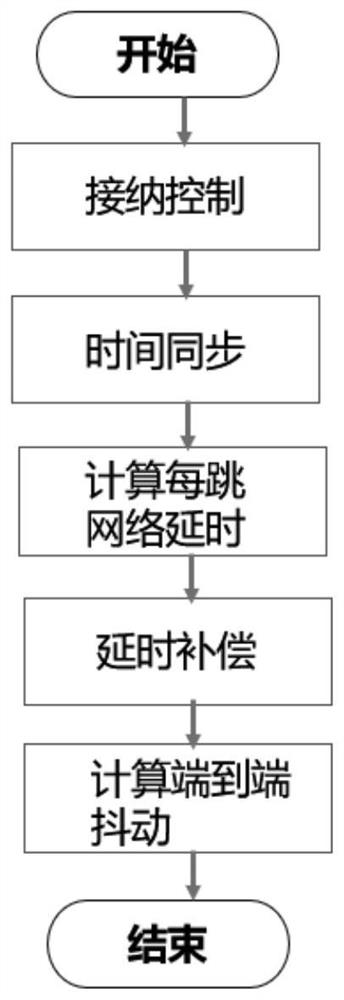

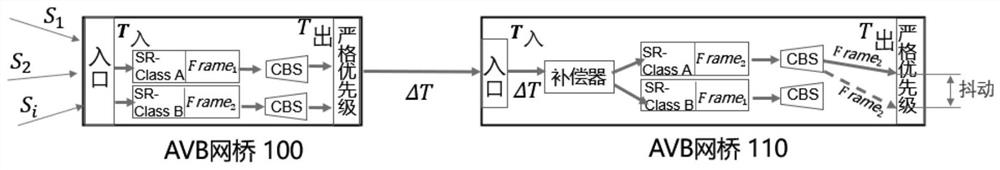

A vehicle Ethernet AVB jitter optimization method, system and storage medium

ActiveCN112600739BImprove jitter characteristicsMeet the delayNetworks interconnectionVideo transmissionIn vehicle

Owner:PURPLE MOUNTAIN LAB

Semiconductor device

InactiveCN102957420BImprove jitter characteristicsLogic circuits using semiconductor devicesBaseband systemsDevice materialControl theory

The present invention relates to semiconductor devices. A semiconductor device, including: a variable resistor whose resistance value is set to a first resistance value in an emphasis mode and whose resistance value is set to a second resistance value smaller than the first resistance value in a de-emphasis mode. ; The first driver sets its output impedance to a third resistance value in the emphasis mode and sets its output impedance to a fourth resistance value greater than the third resistance value in the de-emphasis mode; the second driver sets its output impedance to a third resistance value in the emphasis mode; In the de-emphasis mode, its output impedance is set to a fifth resistance value and in the de-emphasis mode, its output impedance is set to a sixth resistance value greater than the fifth resistance value; and a controller that controls the first and second resistance values according to the input signal. the on-state of the driver, and switches the output impedances of the first and second drivers and the resistance value of the variable resistor between emphasis mode and de-emphasis mode.

Owner:RENESAS ELECTRONICS CORP

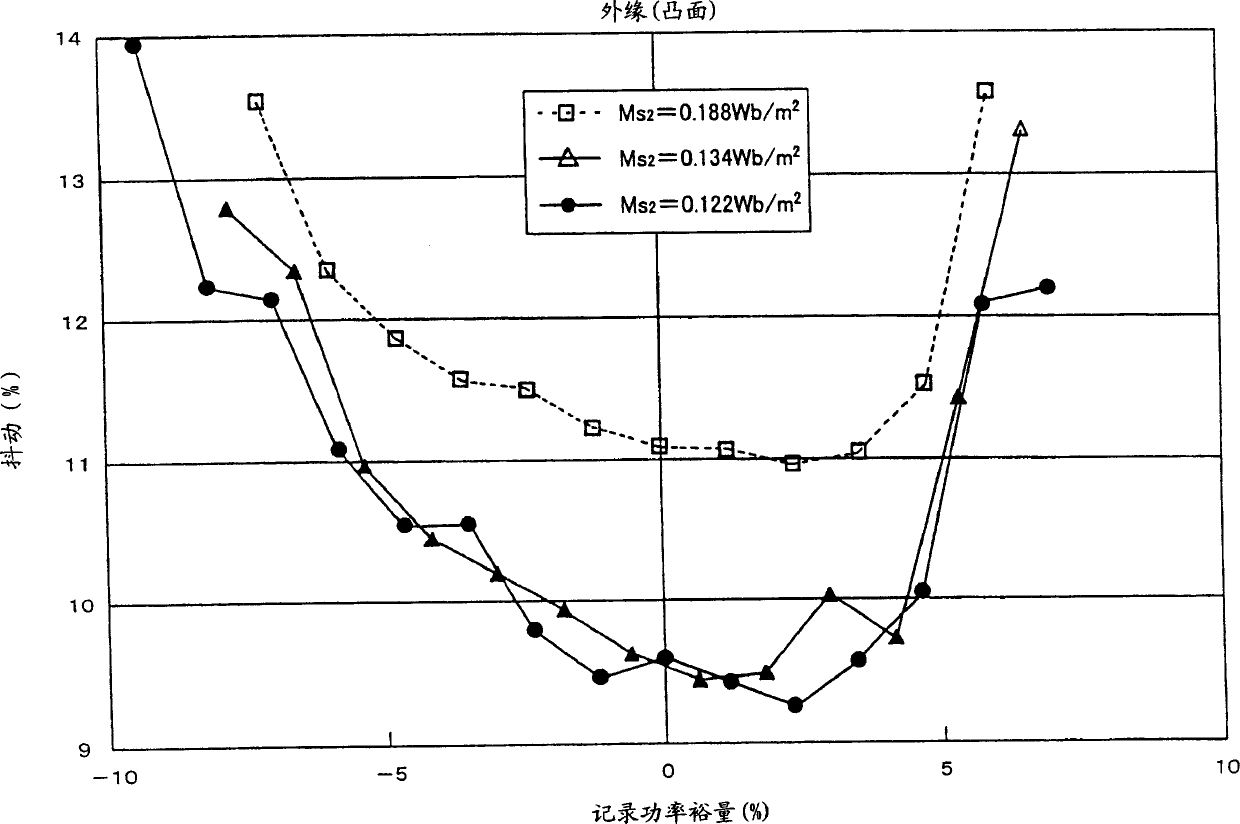

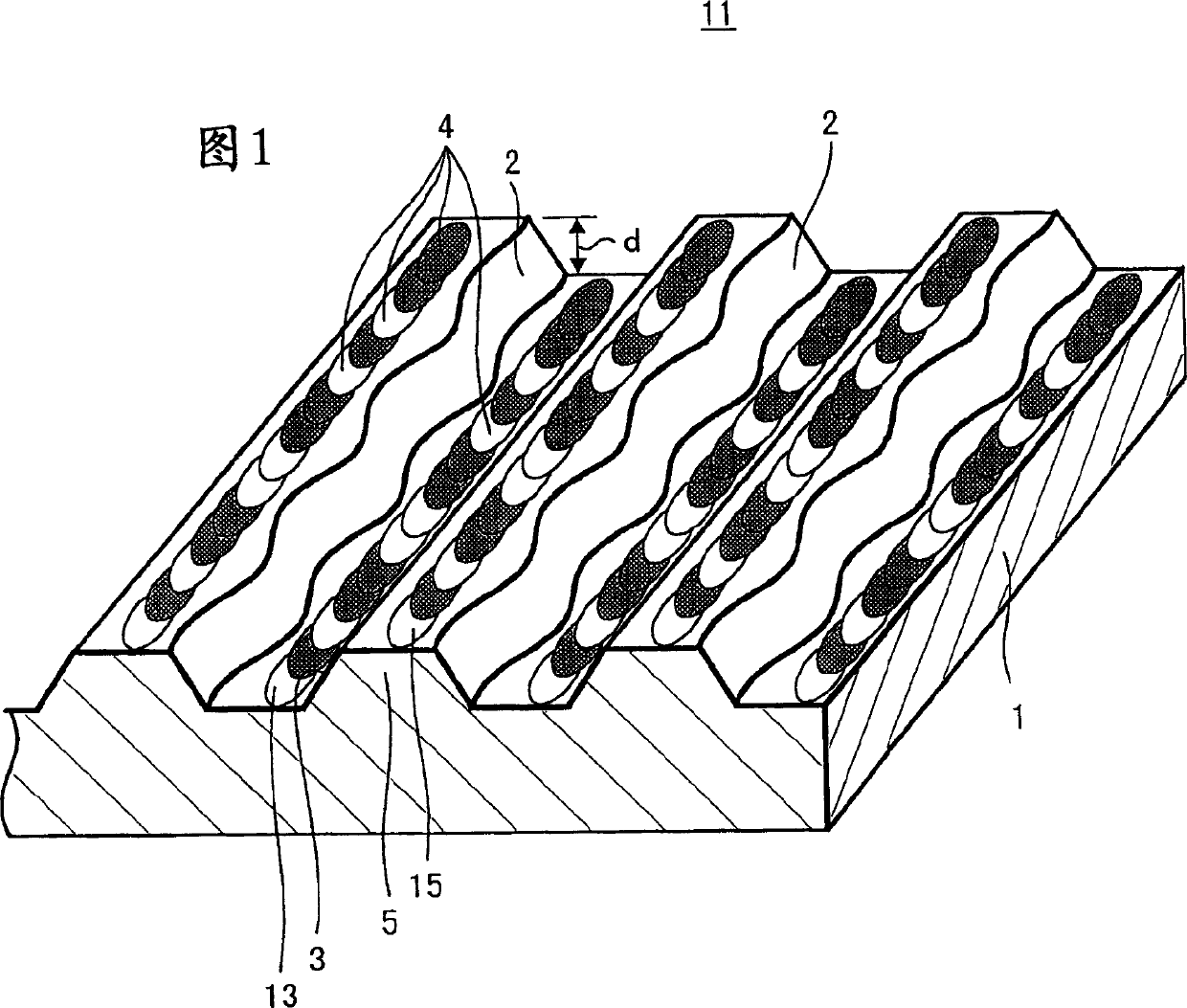

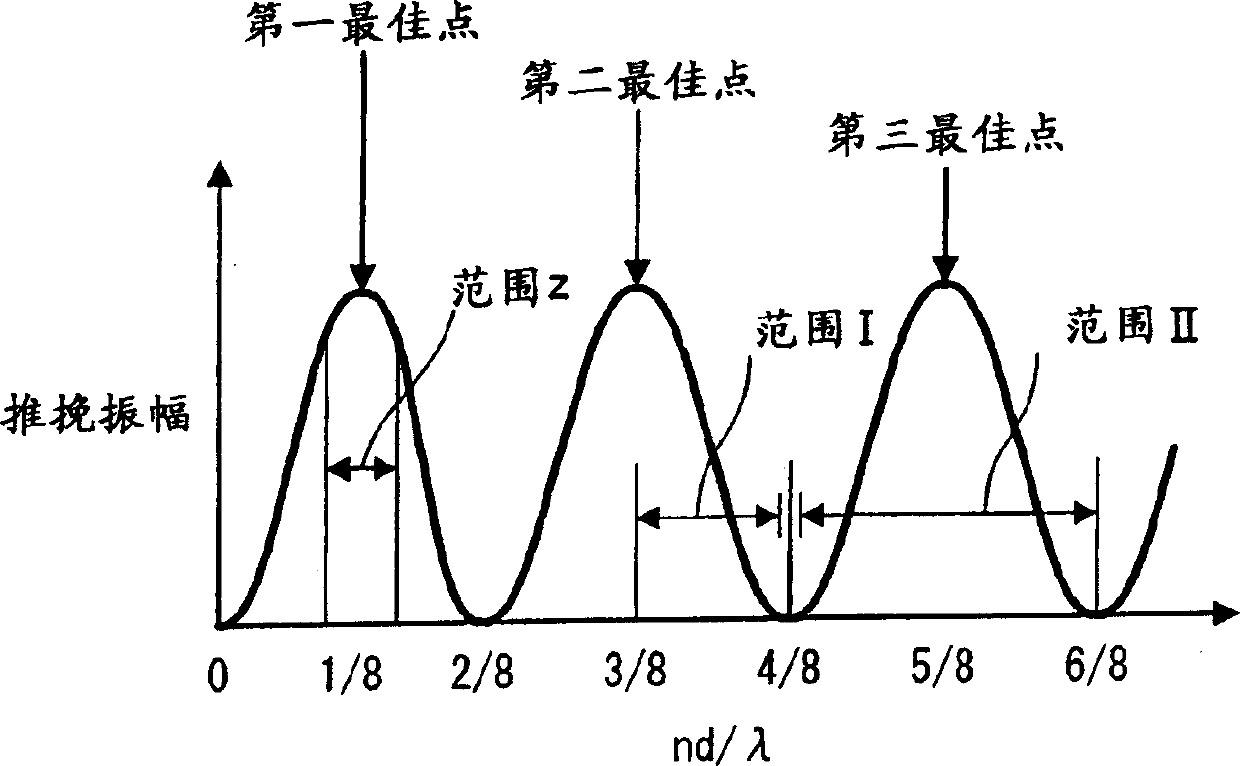

Optical recording medium, production method of optical recording medium, optical recording method and optical reproducing method for optical recording medium

InactiveCN1526134AImprove jitter characteristicsImproved recording power toleranceRecord information storageLight beam reproducingEngineeringOptical recording

In a DWDD (Domain Wall Displacement Detection) optical recording medium of a land and groove recording system, characteristics of a land and a groove can be well equilibrated by selecting a depth d (nm) of a groove 3 of an optical recording medium so as to satisfy the following equation: 3lambda / 8n G11B 11 / 105 14 19 0 2002 / 4 / 23 1526134 2004 / 9 / 1 000000000 Sony Corp. Japan Fujita Goro Sakamoto Tetsuhiro feng gengxuan 11038 The Patent Agency of the Chinese Council for the Promotion of International Trade (CCPIT) No.1 Waidajie, Fuxingmen, Beijing 100086 Japan 2001 / 4 / 24 126158 / 2001 2003 / 11 / 14 PCT / JP2002 / 004027 2002 / 4 / 23 WO2002 / 089129 2002 / 11 / 7 Japanese

Owner:SONY CORP

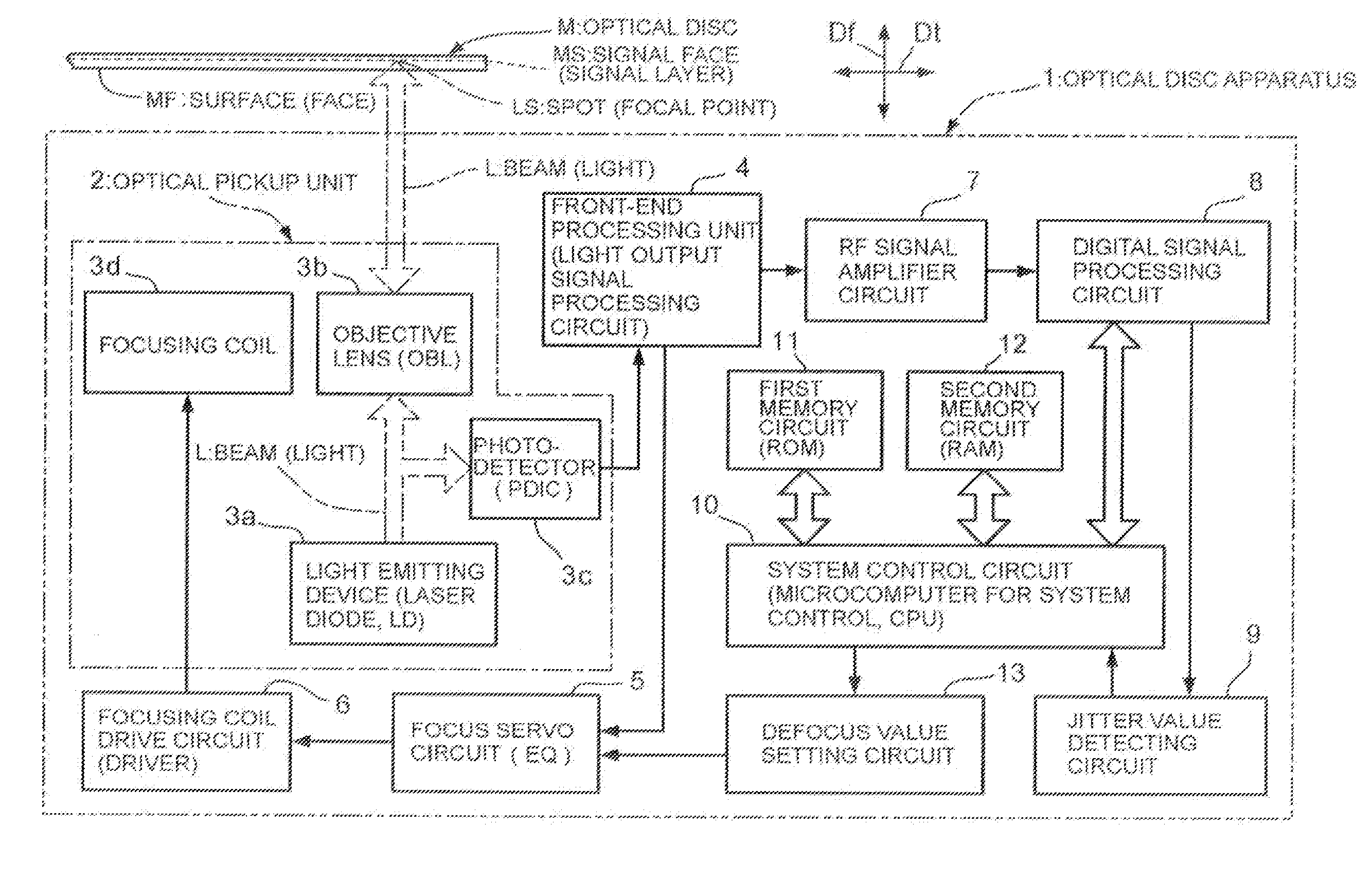

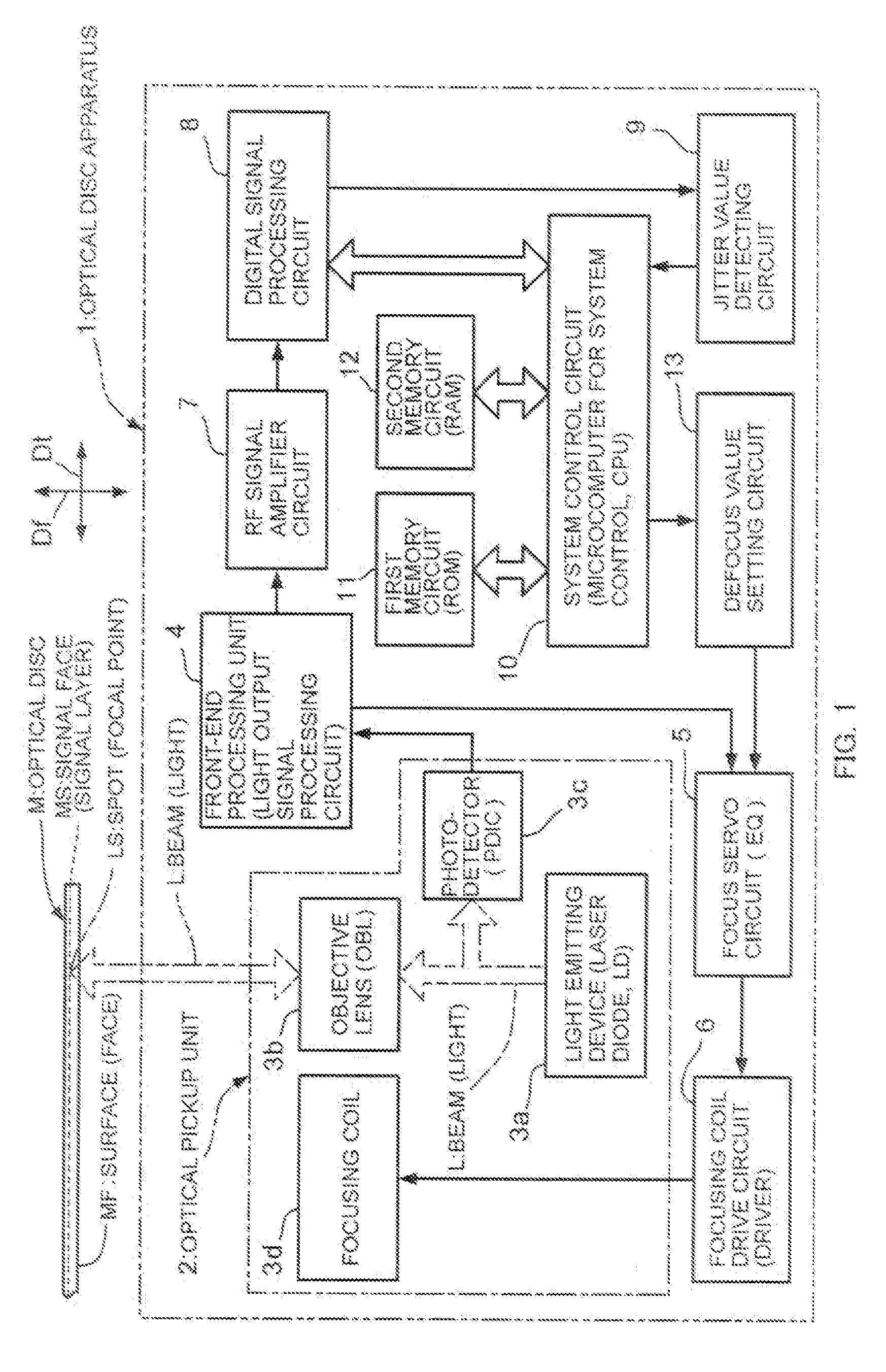

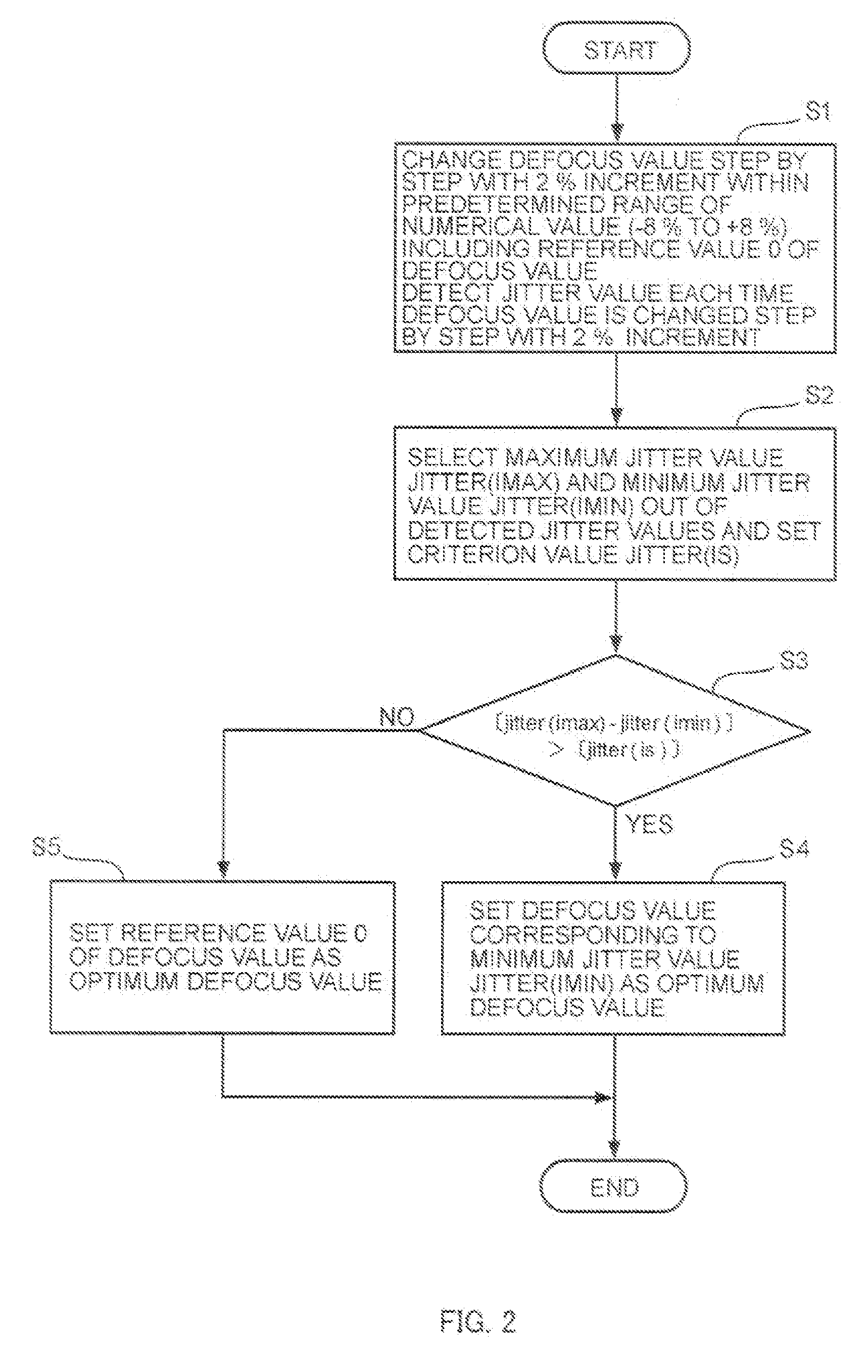

Optical disc apparatus and method of setting defocus value thereof

InactiveUS20080037123A1Improve jitter characteristicsImprove featuresRecord information storageOptical recording/reproducingOptical axisComputer science

An optical disc apparatus is disclosed that comprises a jitter value detecting circuit that detects a jitter value based on the signal read out from an optical disc; and a defocus value setting circuit that adjusts a defocus value used for moving an objective lens along the direction of a light axis when focusing of the objective lens to the optical disc is performed, based on the signal that has gone through the jitter value detecting circuit, and causes a defocus adjustment to be made based on the defocus value.

Owner:SANYO ELECTRIC CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com