Clock pulse width modulation circuit and clock pulse width modulation method

A technology of width modulation and clock pulse, applied in the field of clock pulse width modulation, which can solve the problems of long clock signal modulation time and large output clock signal jitter, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0096] In the present invention, by tracking a transition edge of the clock signal to be modulated, one transition edge of the output clock signal is obtained, and only the other transition edge within one clock cycle is modulated, effectively reducing the modulation time, and using The charge pump loop and the delay trigger circuit modulate the second jump edge in one clock cycle, so that an output clock signal with higher precision and less jitter can be obtained.

[0097] The specific implementation of the present invention will be described in detail below in conjunction with the accompanying drawings.

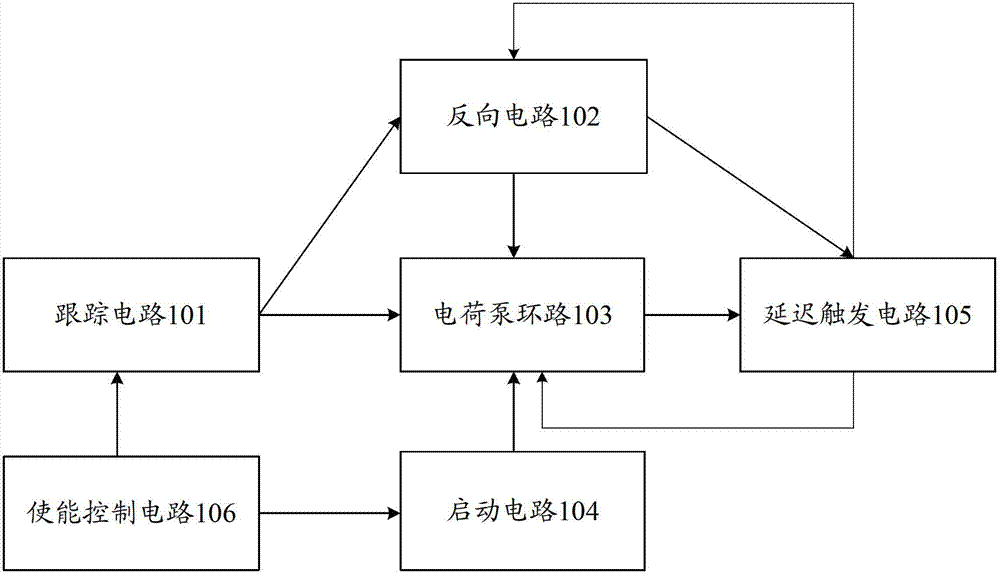

[0098] see figure 1 , figure 1 It is a structural schematic diagram of the clock pulse width modulation circuit of the present invention. figure 1 Among them, the clock pulse width modulation circuit includes: tracking circuit 101, reverse circuit 102, charge pump loop 103, startup circuit 104, delay trigger circuit 105 and enable control circuit 106;

[0099] The tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com