Phase locked loop fast lock method

A phase-locked loop and phase technology, applied in the field of phase-locked loops, can solve the problems of reducing frequency offset accuracy and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In general, the method disclosed in this patent to reduce settling time and improve output clock quality during settling includes the following steps: estimating a new frequency offset, ramping an integrator to the new frequency offset, phase compensation or phase pulling , the decay time interval, and switching to higher bandwidth and / or lower damping to allow PLL tuning.

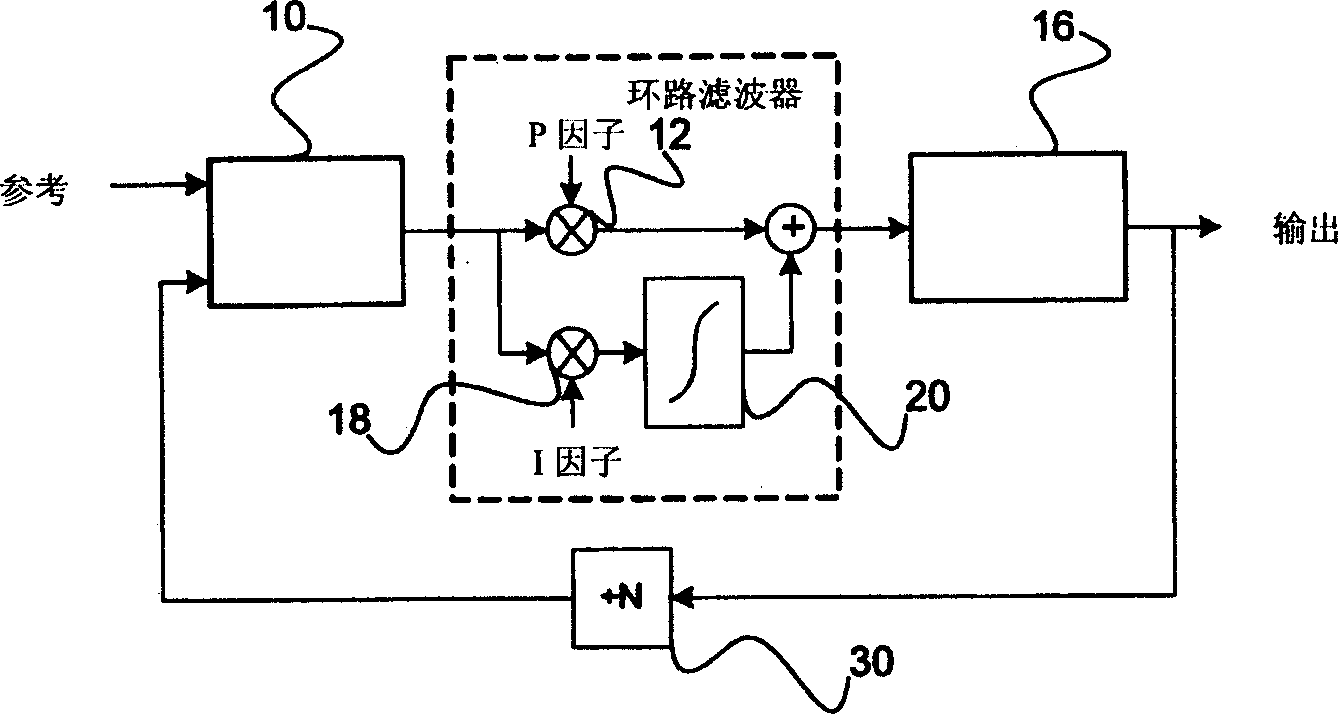

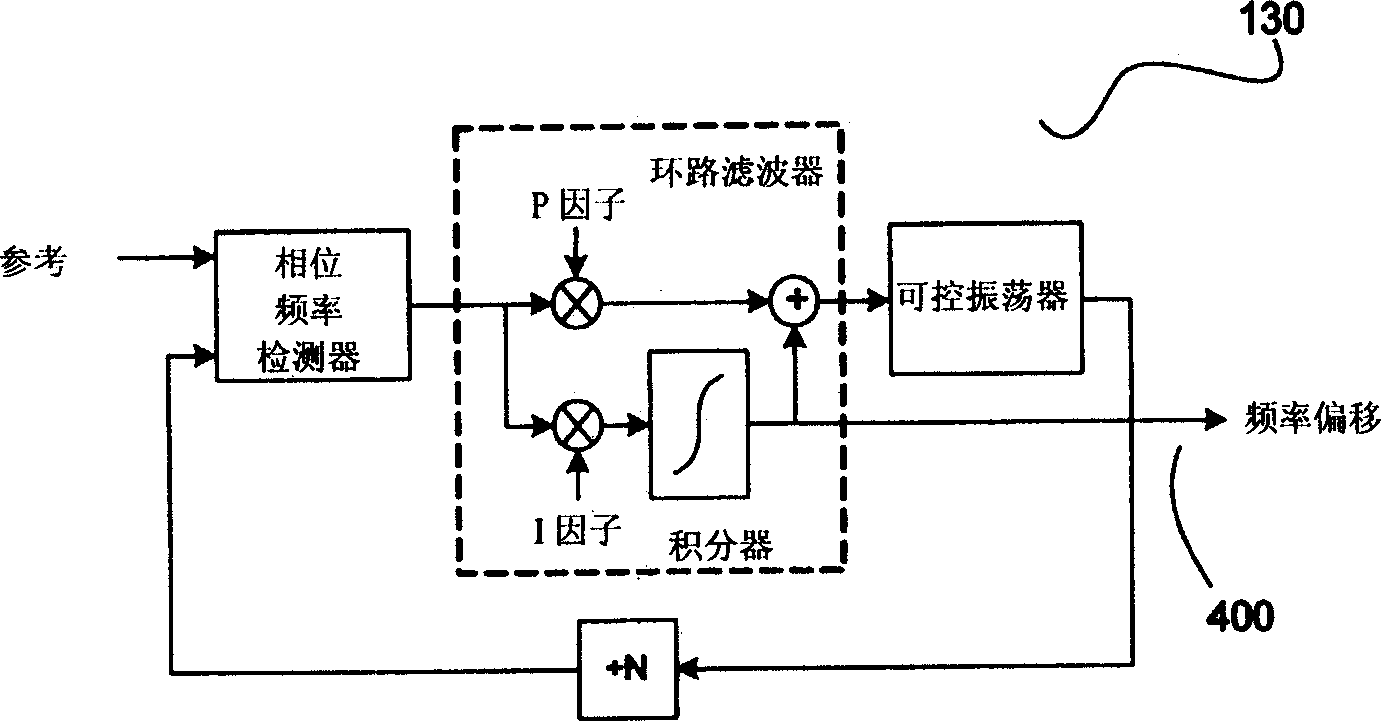

[0044] Figure 4 A PLL according to the teachings of the present invention is illustrated. The phase and frequency detector 100 outputs to an adder 110 and a register 112 which is controlled by a control unit 114 . The output of the register 112 is connected to the adder 110 . Register 112 is a preferred embodiment of the phase compensation circuit described in detail below. The output of the adder 110 is connected to a comparator 118 . The output of adder 110 is also connected to a pair of multipliers 120, 180 which introduce P and I factors, respectively. The multiplier 120 is connected to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com