Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2806 results about "Delay unit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A time delay unit is a structure that provides a specific time delay, or programmable time delay, using a multi-path structure. It is similar to a phase shifter, but different. A phase shifter usually provides a fixed insertion phase difference between two states (flat phase over frequency).

Memory command delay balancing in a daisy-chained memory topology

InactiveUS20060041730A1Effective predictionAccurately ascertainedEnergy efficient ICTDigital storageDIMMControl power

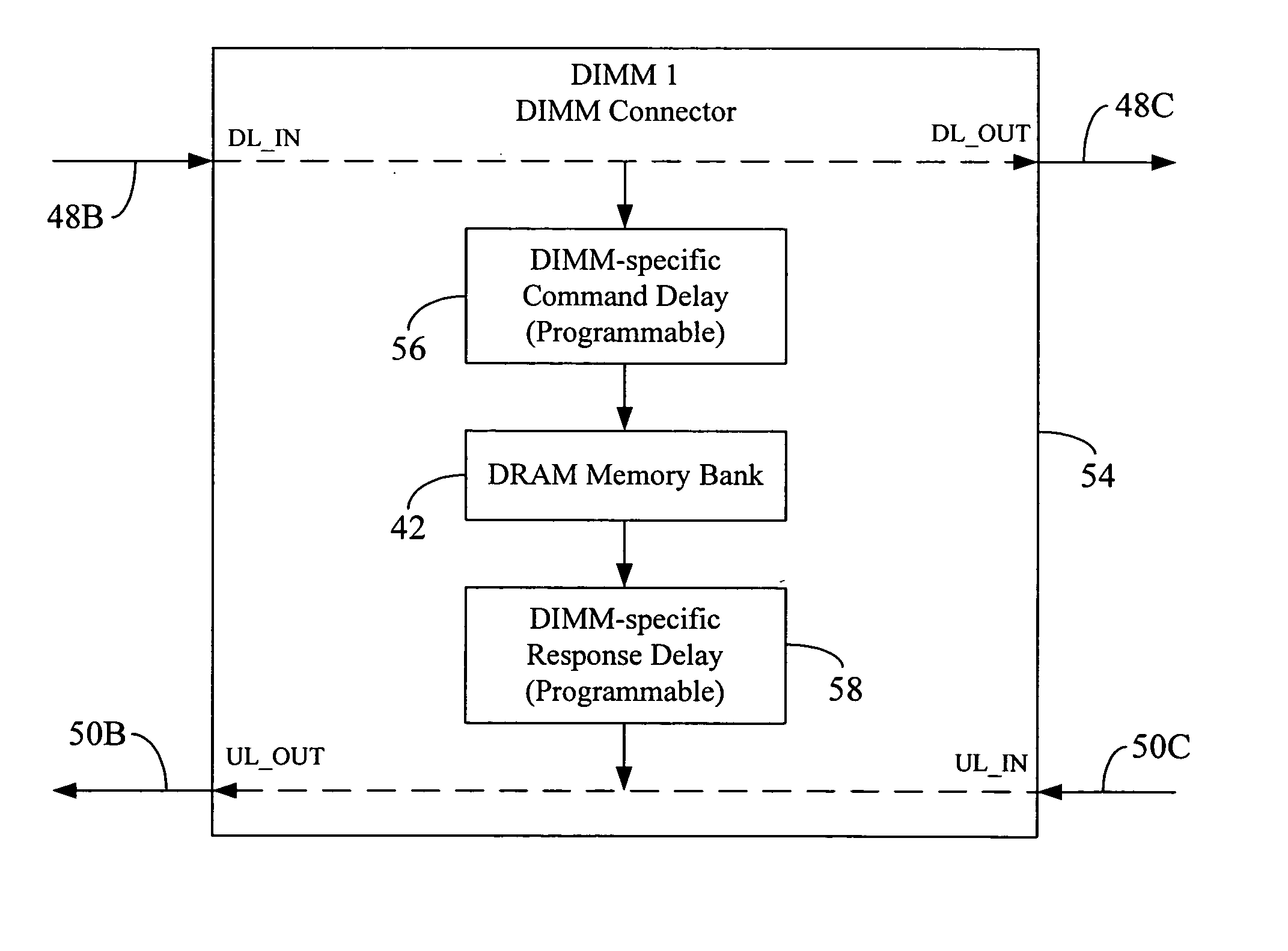

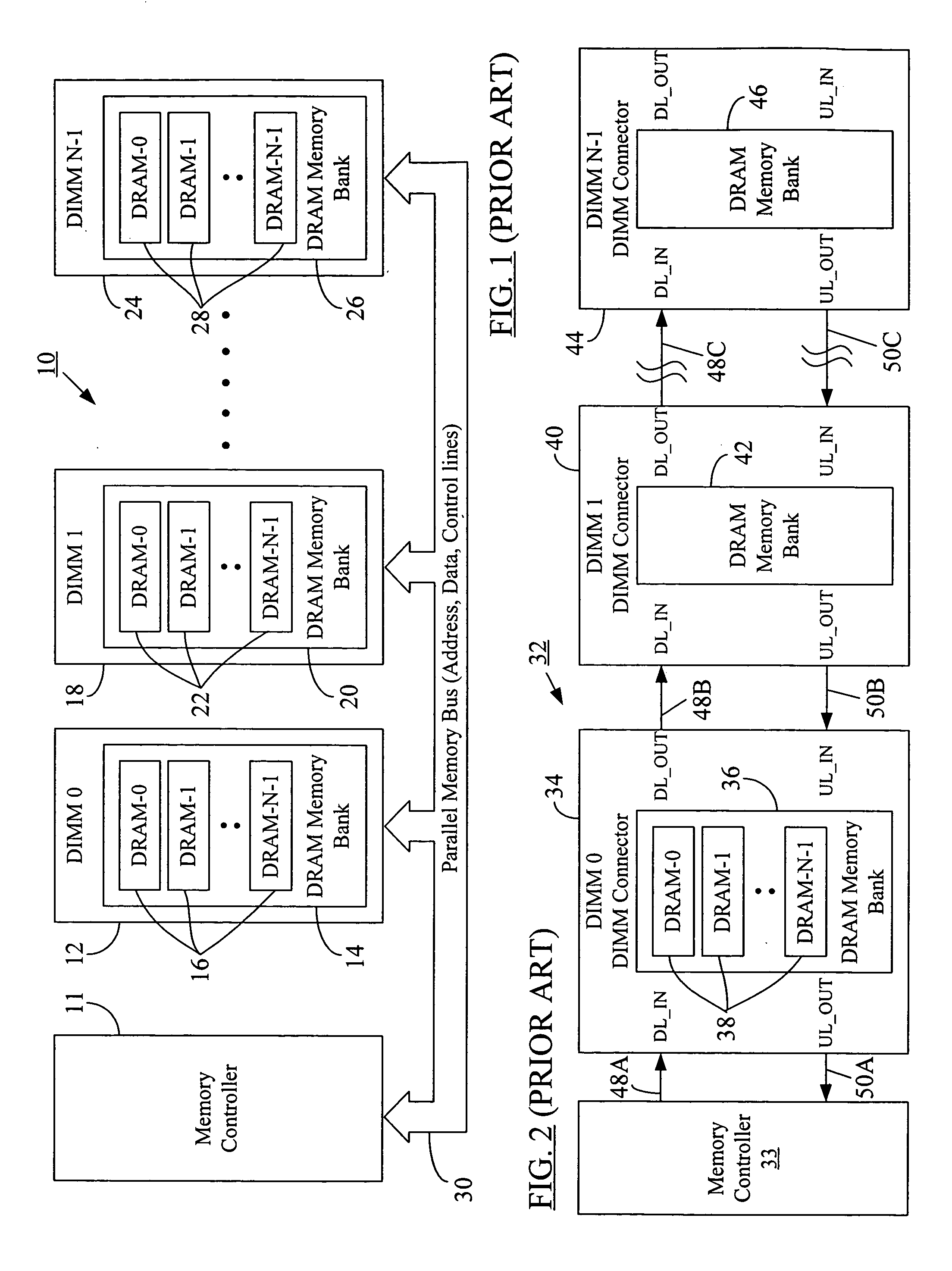

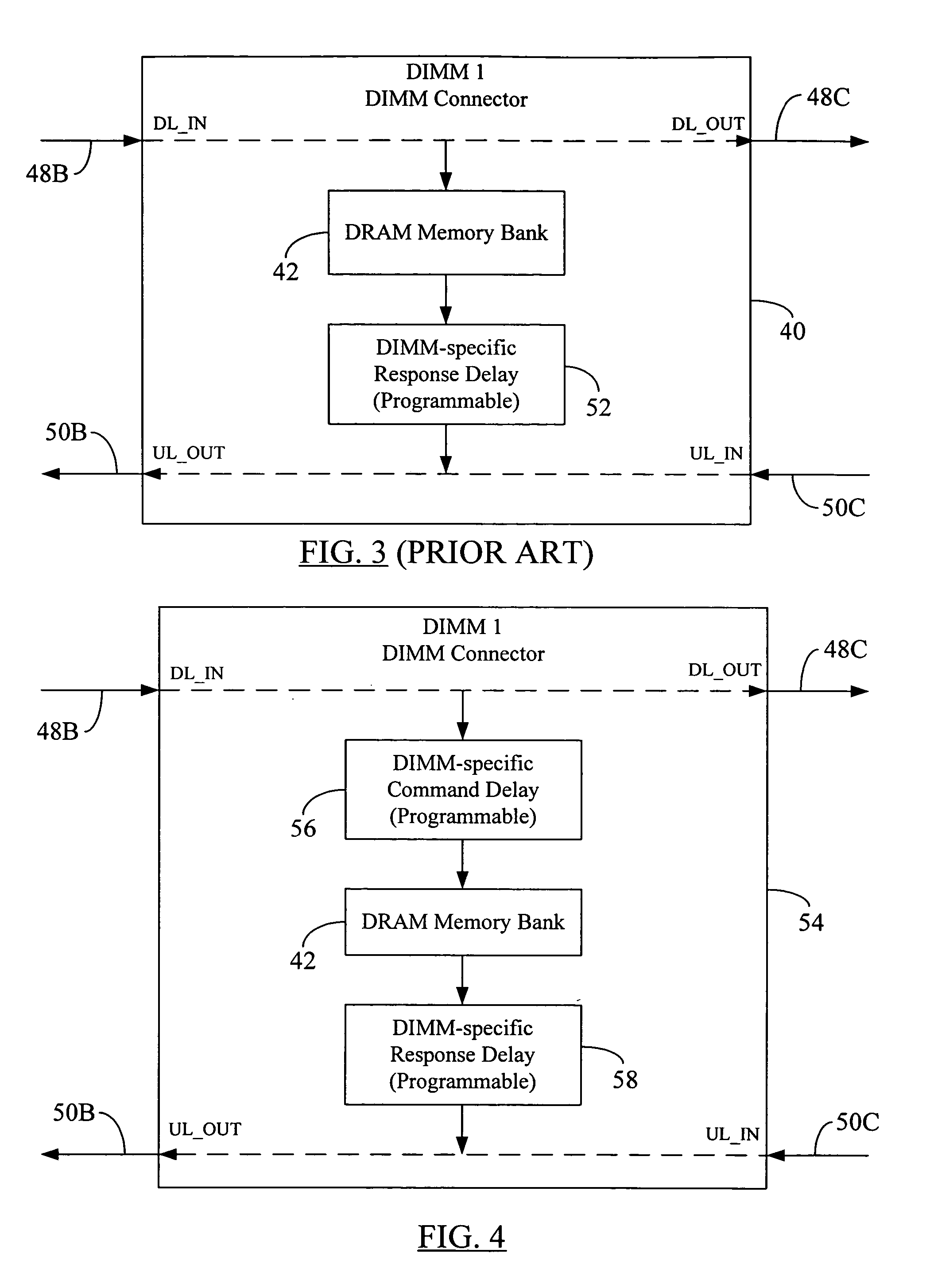

A methodology for a daisy-chained memory topology wherein, in addition to the prediction of the timing of receipt of a response from a memory module (DIMM), the memory controller can effectively predict when a command sent by it will be executed by the addressee DIMM. By programming DIMM-specific command delay in the DIMM's command delay unit, the command delay balancing methodology according to the present disclosure “normalizes” or “synchronizes” the execution of the command signal across all DIMMs in the memory channel. With such ability to predict command execution timing, the memory controller can efficiently control power profile of all the DRAM devices (or memory modules) on a daisy-chained memory channel. A separate DIMM-specific response delay unit in the DIMM may also be programmed to provide DIMM-specific delay compensation in the response path, further allowing the memory controller to accurately ascertain the timing of receipt of a response thereat, and, hence, to better manage further processing of the response.

Owner:ROUND ROCK RES LLC

Blind adaptive filter for narrowband interference cancellation

ActiveUS20110305306A1Wide applicationError preventionDigital adaptive filtersSelf adaptiveSweep rate

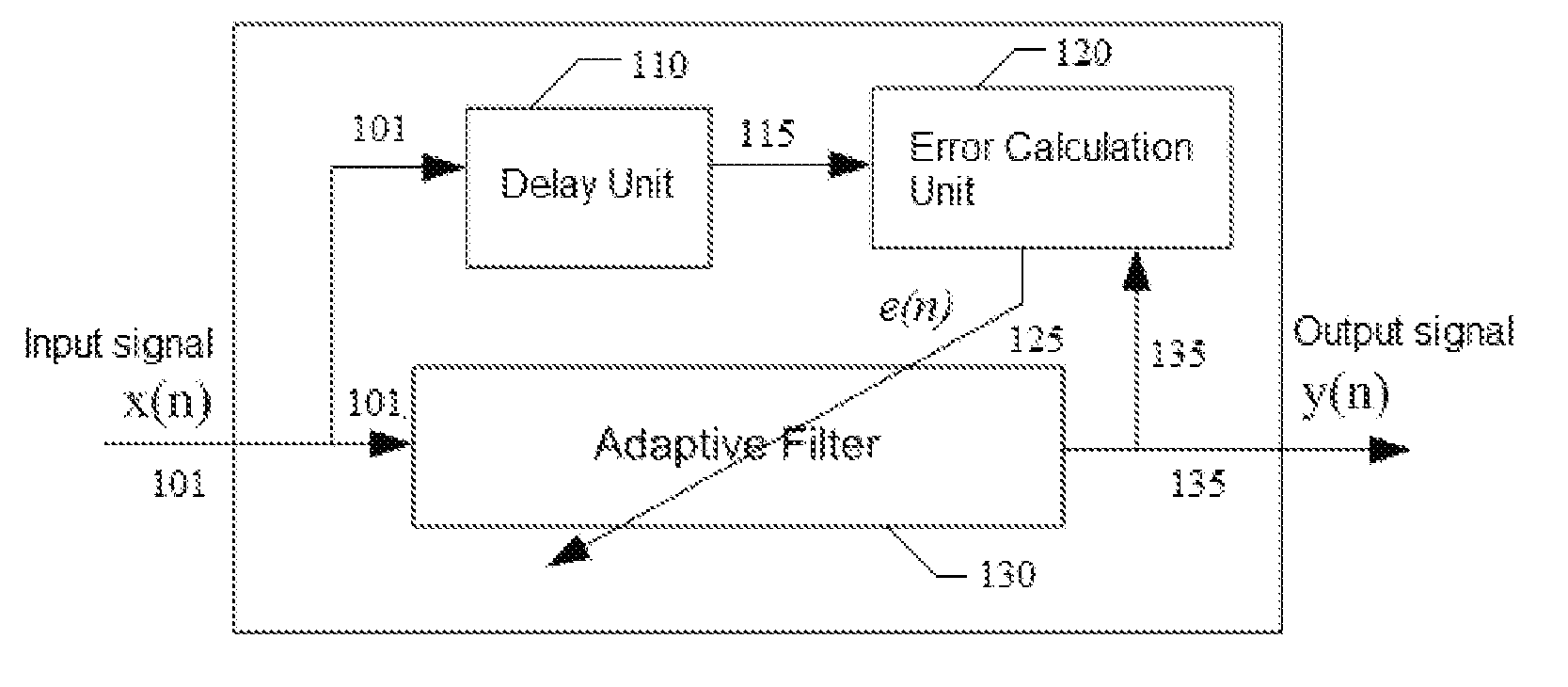

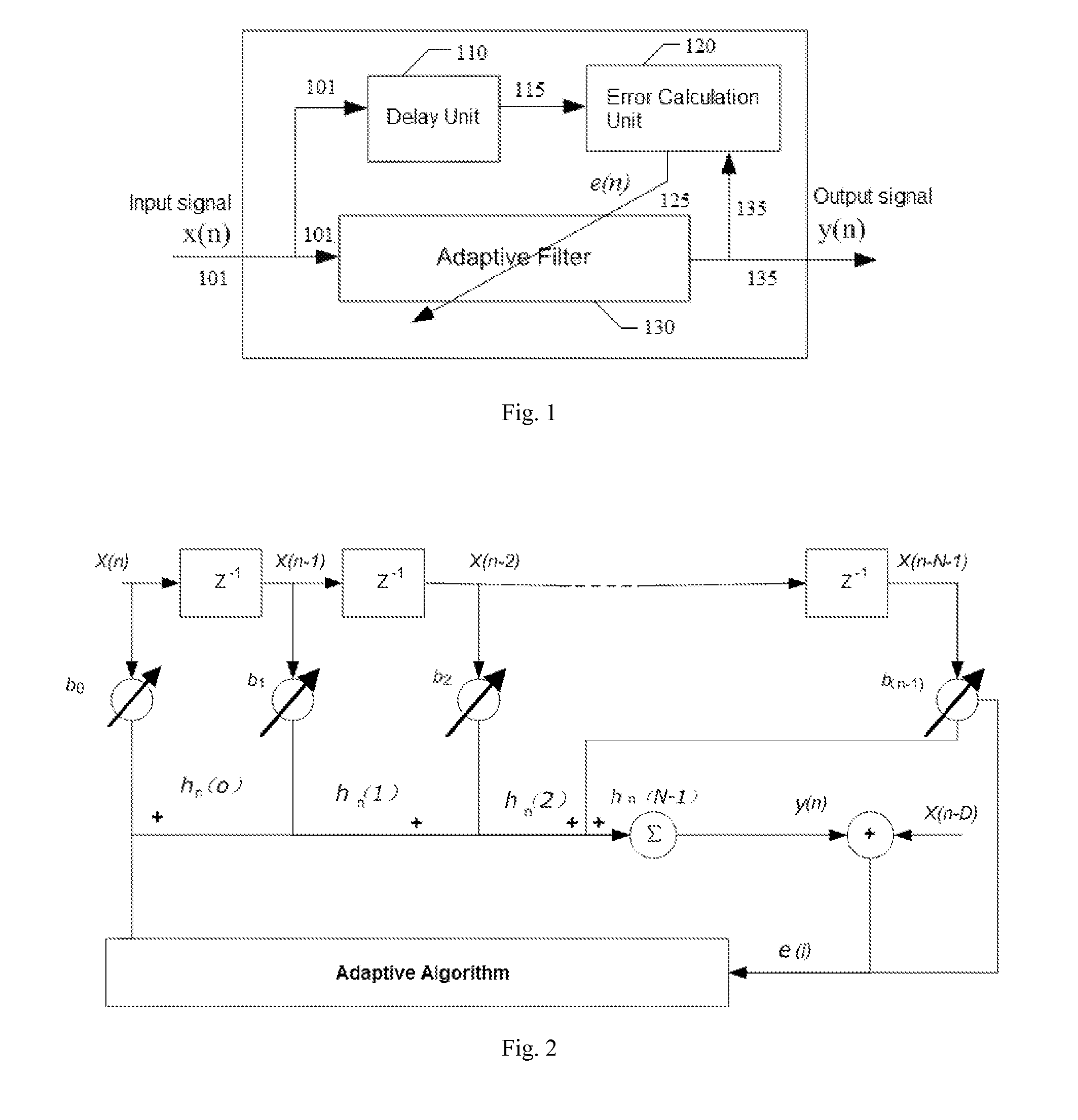

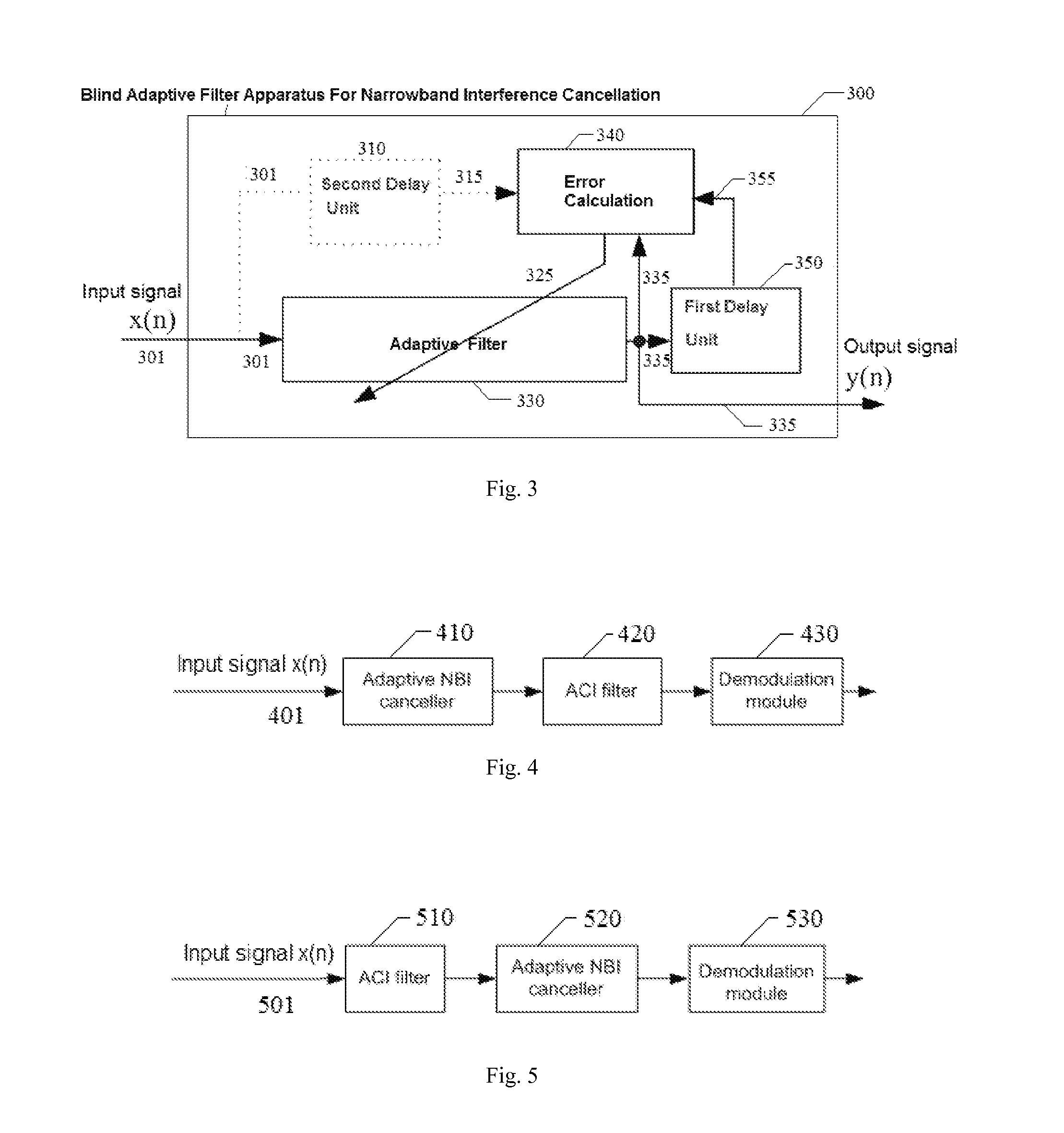

The present invention relates to a blind adaptive filter for narrowband interference cancellation, which includes an adaptive filter, a delay unit coupled to the adaptive filter for generating a delayed signal with a predetermined delay length from the output signal of the adaptive filter, and an error calculation unit coupled to the adaptive filter and the delay unit. The error calculation unit compares the output signal from the adaptive filter and the delayed signal from the delay unit to extract error information, and feedback the first error information to the adaptive filter. The first error information is formed of a transfer function including a number of coefficients, and used to adjust the adaptive filter and remove interference in the next input signal. The disclosed technique is also applicable in wideband receivers, as well as resisting multiple strong narrowband interferences having a frequency sweep rate of tens of milliseconds.

Owner:MONTAGE TECHNOLOGY CO LTD

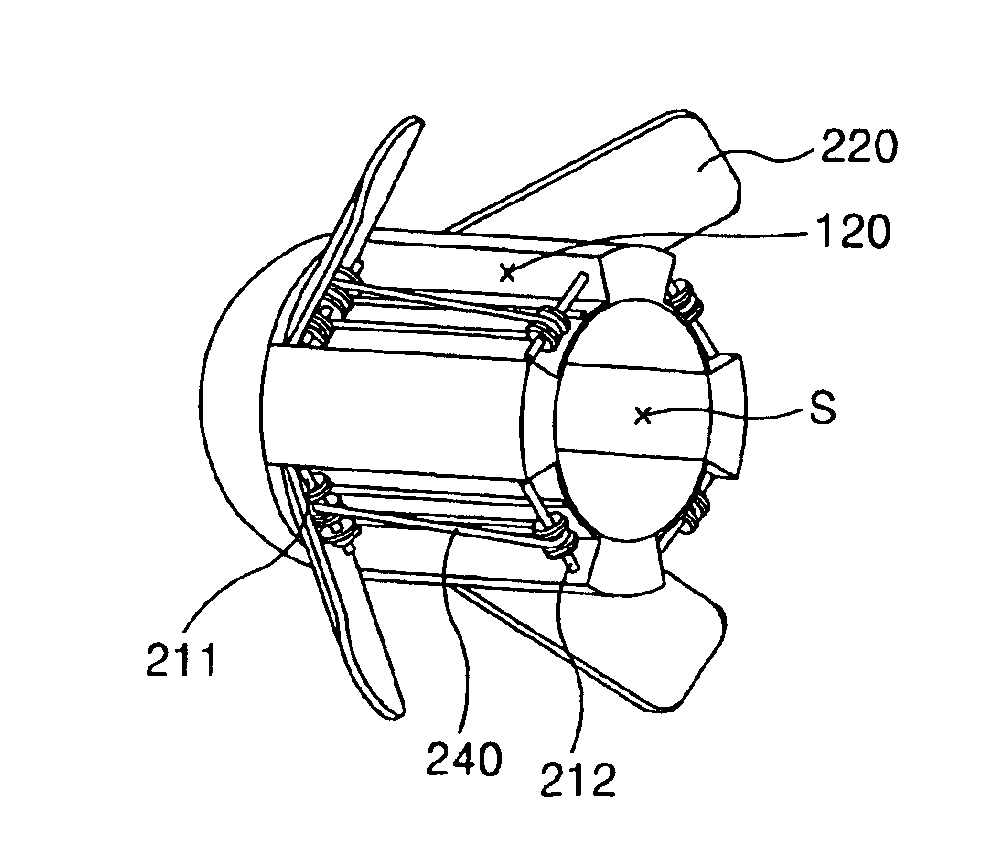

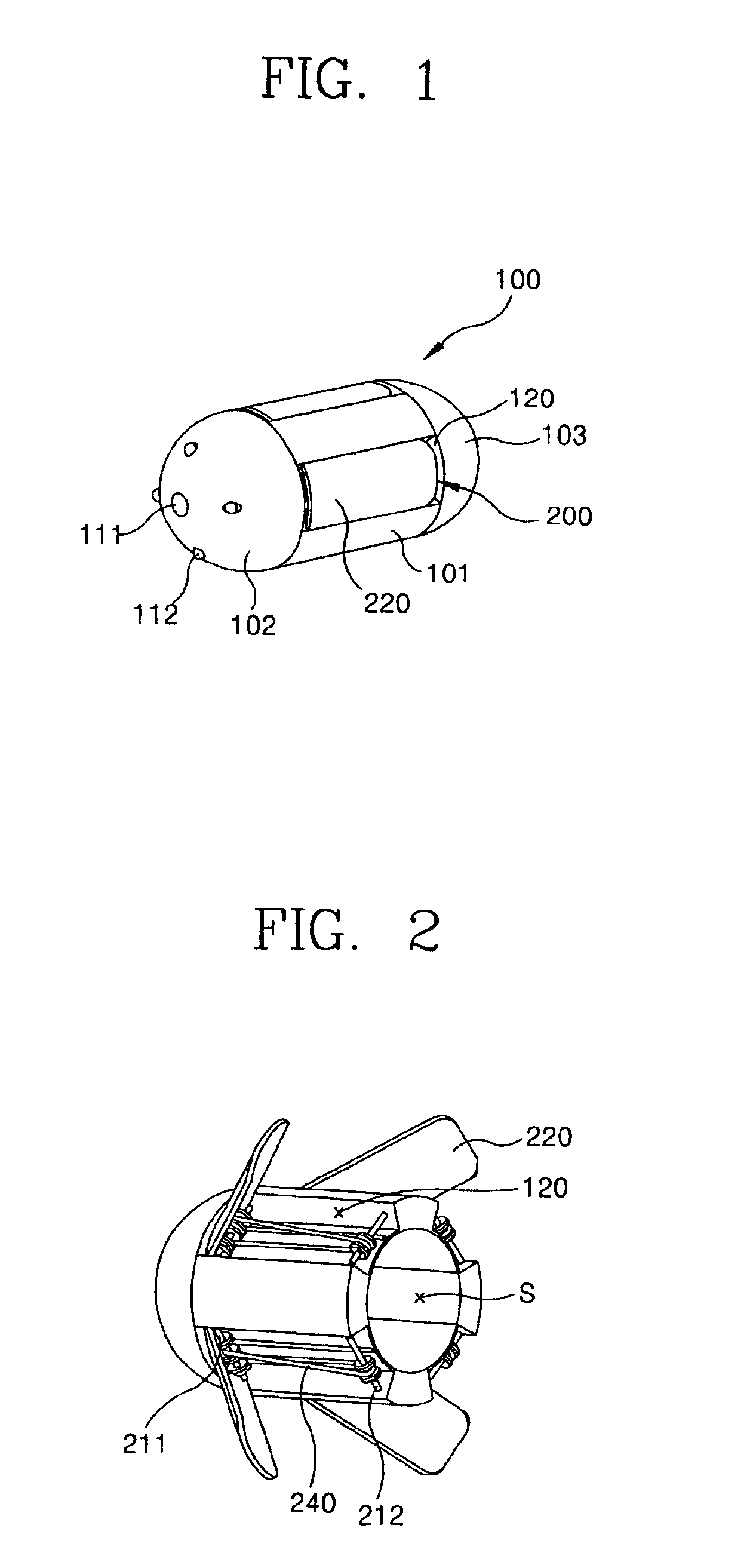

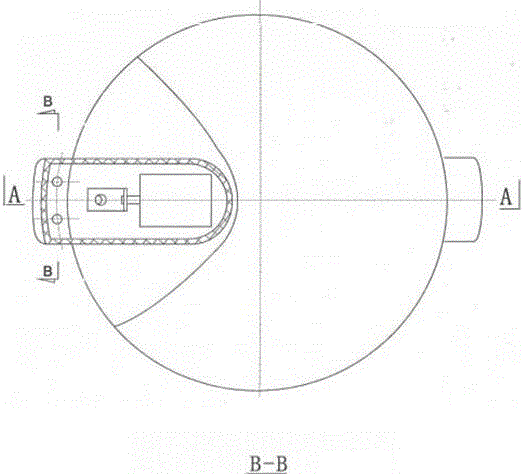

Micro capsule robot

A micro capsule robot comprises a body unit; a body movement control unit, which is installed on an outer circumferential surface of the body unit, including a linear driving device, and wings which are unfolded from the outer circumferential surface of the body unit by operation of the linear driving device for delaying or stopping the movement of the body unit; and a controlling unit installed in the body unit for controlling the body movement delay unit.

Owner:KOREA INST OF SCI & TECH

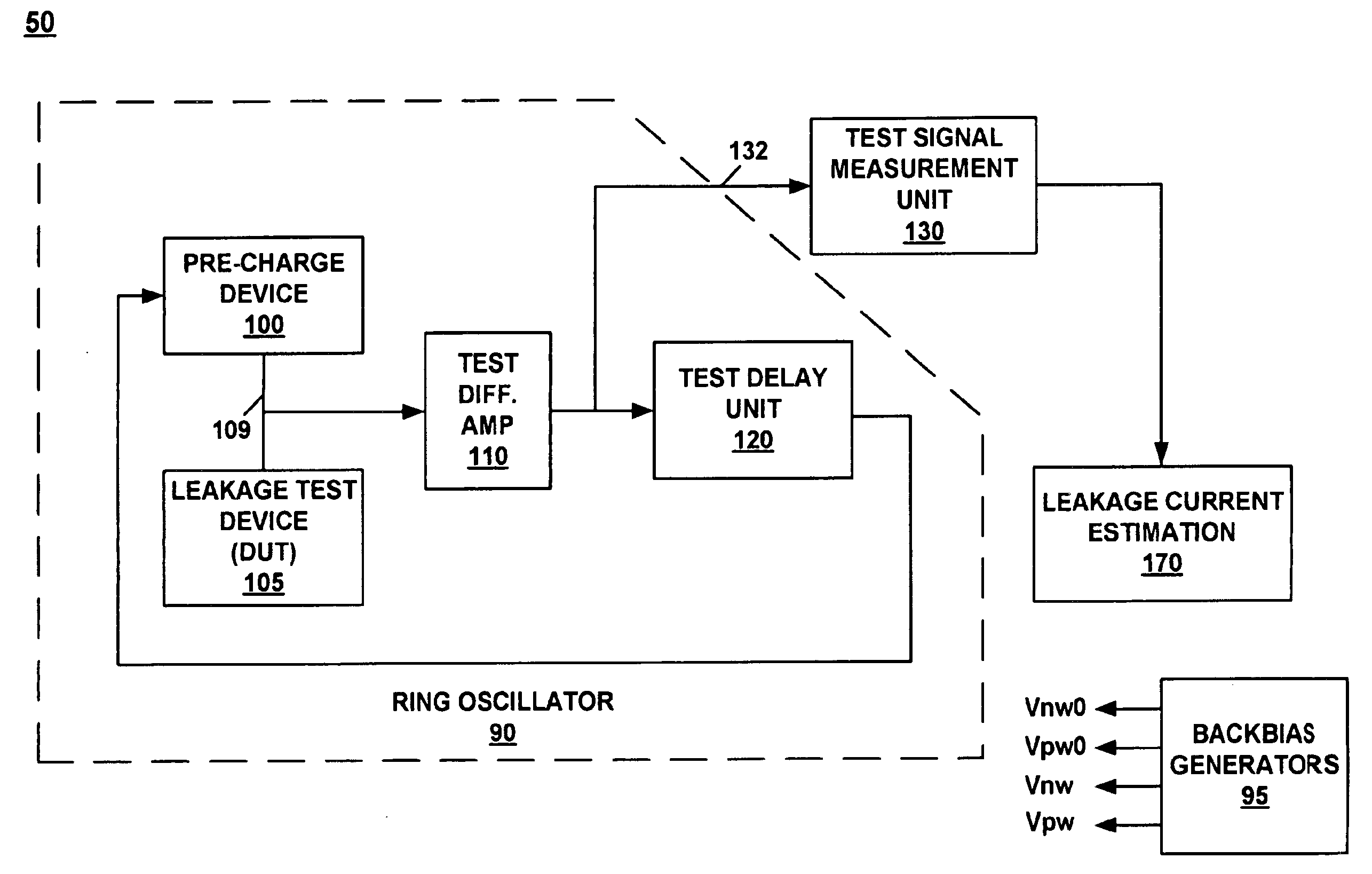

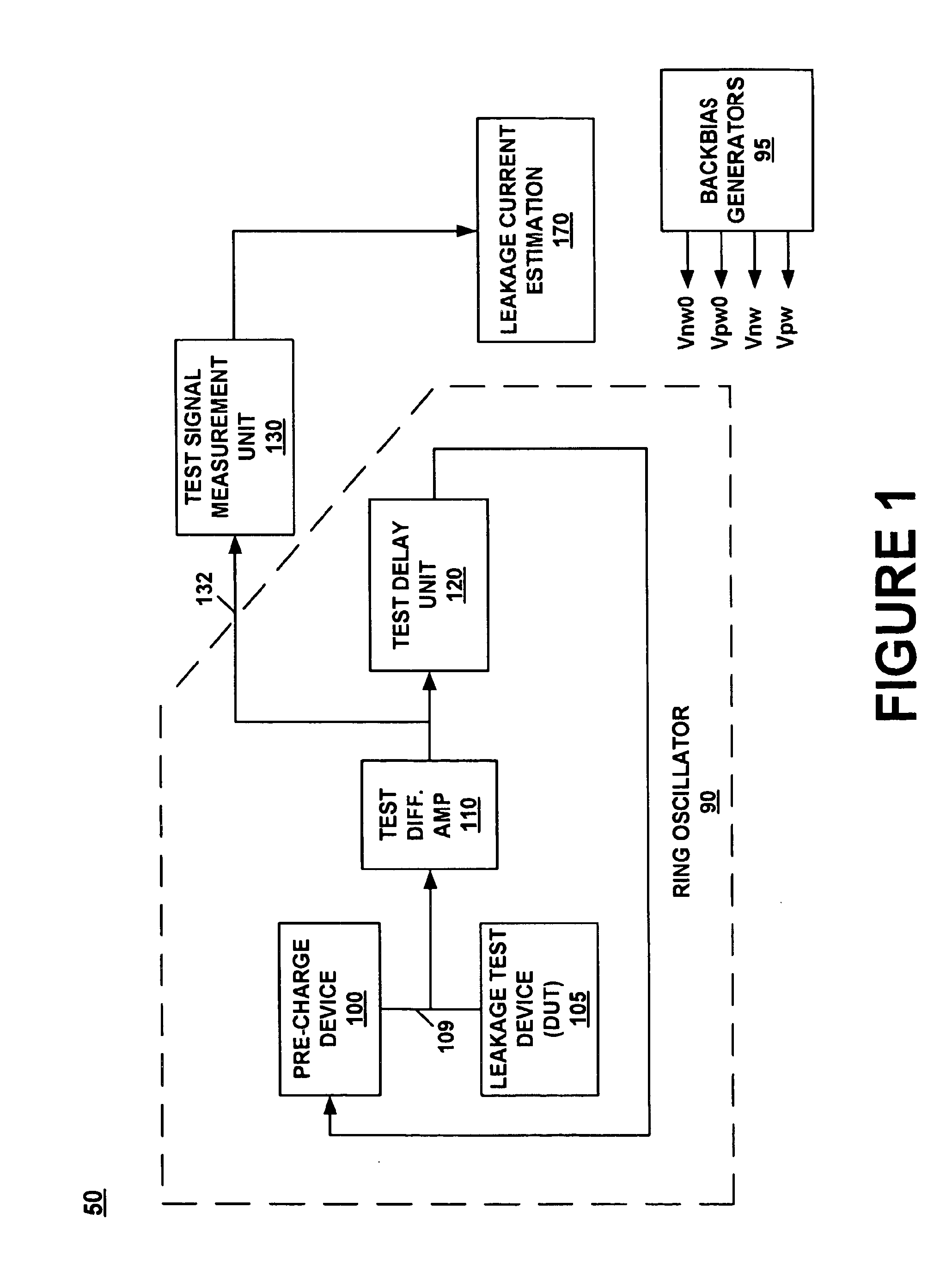

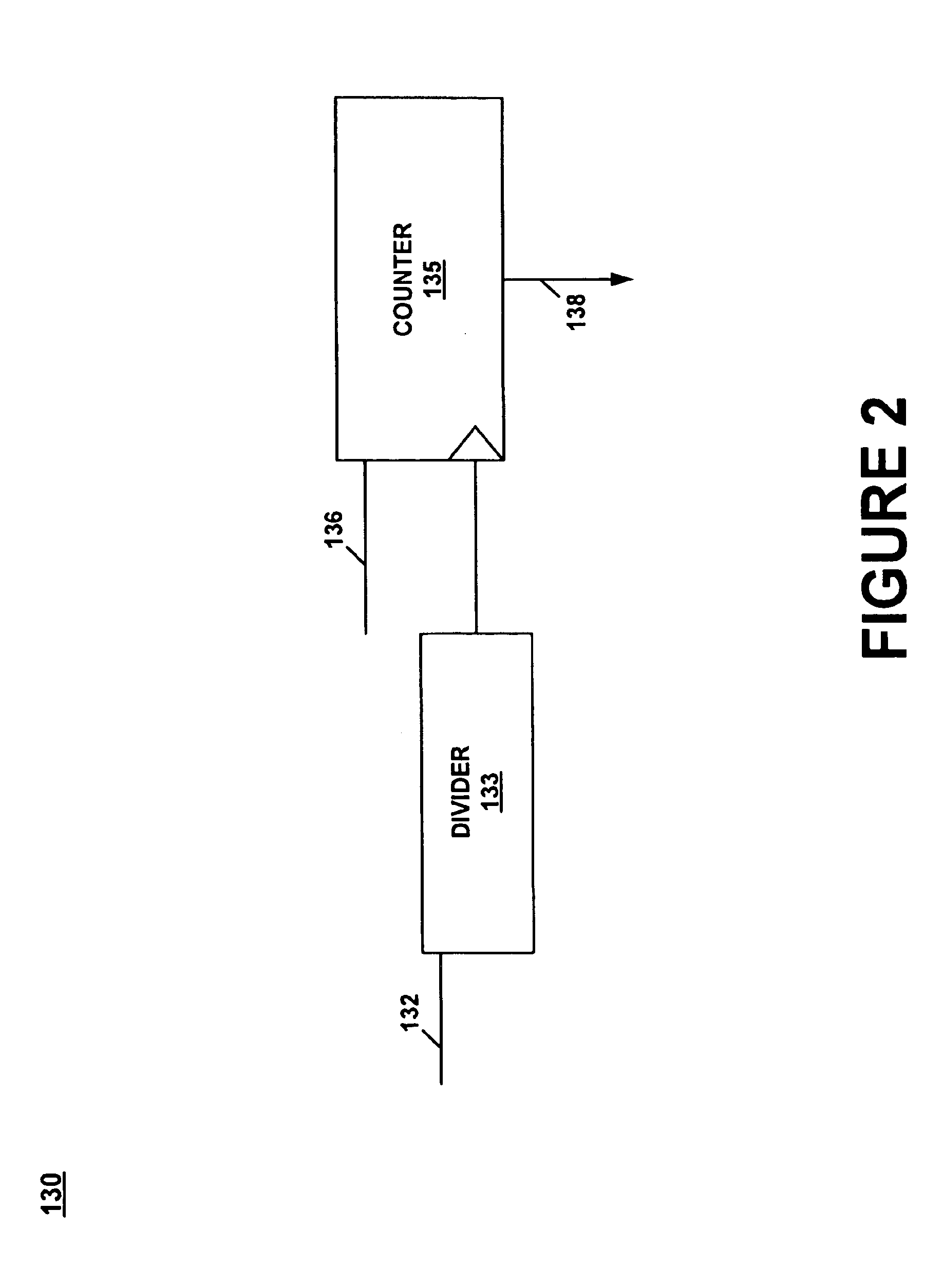

System and method for measuring transistor leakage current with a ring oscillator with backbias controls

A circuit and method thereof for measuring leakage current are described. The circuit includes a pre-charge device subject to a first backbias voltage and a leakage test device subject to a second backbias voltage. The leakage test device is coupled to the pre-charge device. The leakage test device is biased to an off state. A differential amplifier is coupled to the pre-charge device and the leakage test device. A delay unit is coupled to the differential amplifier and to an input of the pre-charge device. The pre-charge device is turned on and off at a frequency that corresponds to said leakage current.

Owner:META PLATFORMS INC

Non-linear dynamic predictive device

InactiveUS6453308B1Improve accuracyFast computerSimulator controlElectric testing/monitoringHorizonDead time

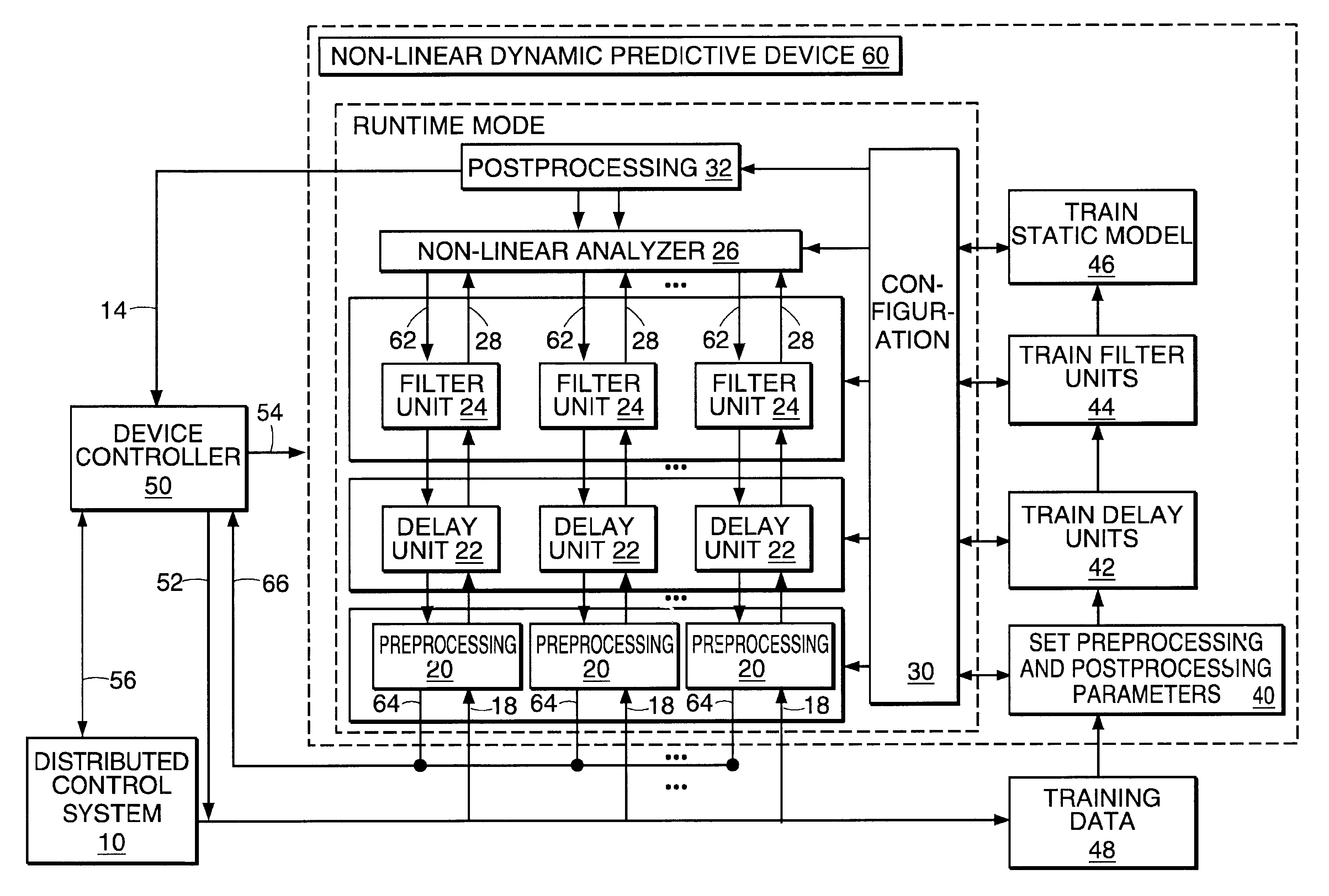

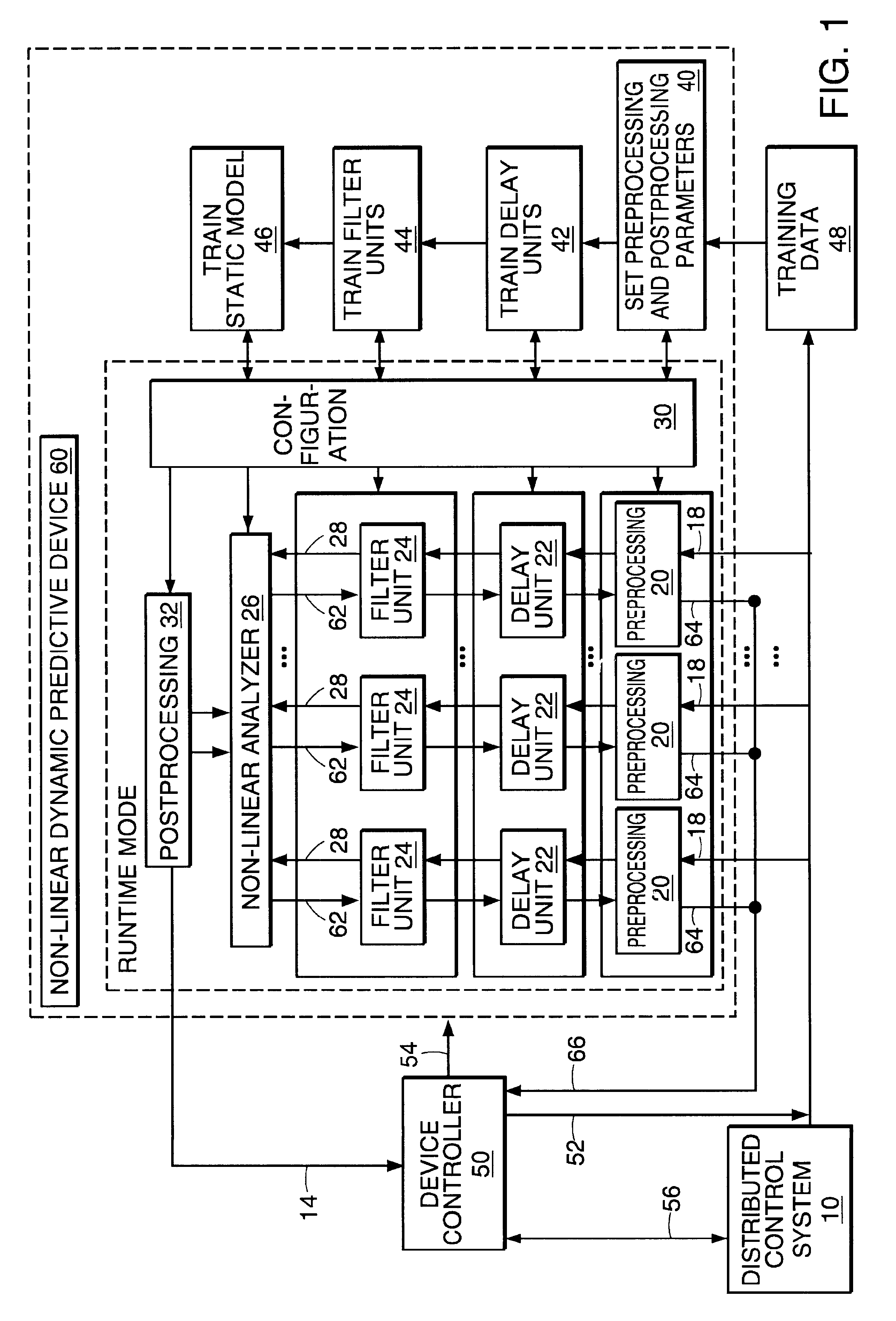

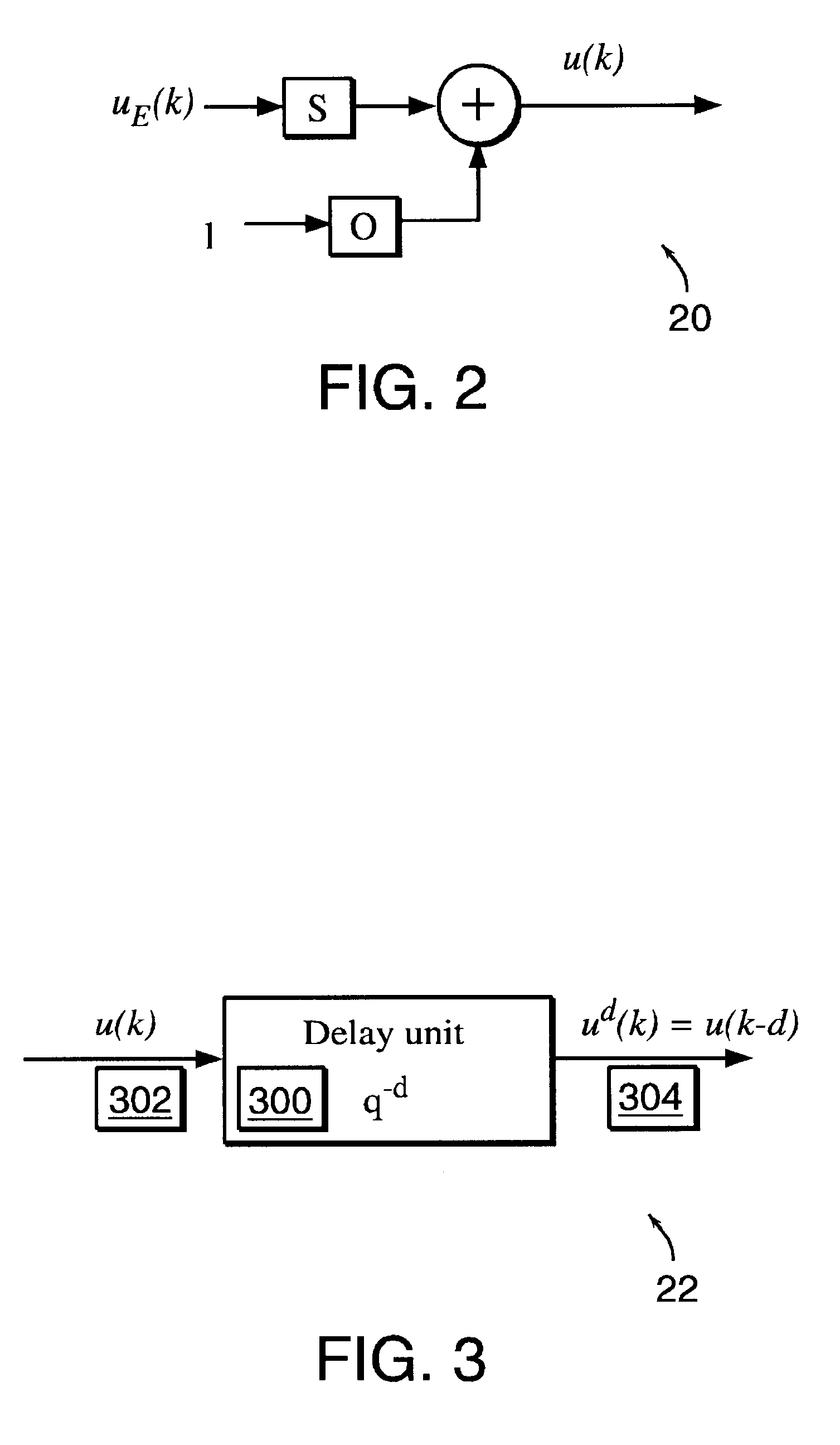

A non-linear dynamic predictive device (60) is disclosed which operates either in a configuration mode or in one of three runtime modes: prediction mode, horizon mode, or reverse horizon mode. An external device controller (50) sets the mode and determines the data source and the frequency of data. In prediction mode, the input data are such as might be received from a distributed control system (DCS) (10) as found in a manufacturing process; the device controller ensures that a contiguous stream of data from the DCS is provided to the predictive device at a synchronous discrete base sample time. In prediction mode, the device controller operates the predictive device once per base sample time and receives the output from the predictive device through path (14). In horizon mode and reverse horizon mode, the device controller operates the predictive device additionally many times during base sample time interval. In horizon mode, additional data is provided through path (52). In reverse horizon mode data is passed in a reverse direction through the device, utilizing information stored during horizon mode, and returned to the device controller through path (66). In the forward modes, the data are passed to a series of preprocessing units (20) which convert each input variable (18) from engineering units to normalized units. Each preprocessing unit feeds a delay unit (22) that time-aligns the input to take into account dead time effects such as pipeline transport delay. The output of each delay unit is passed to a dynamic filter unit (24). Each dynamic filter unit internally utilizes one or more feedback paths that are essential for representing the dynamic information in the process. The filter units themselves are configured into loosely coupled subfilters which are automatically set up during the configuration mode and allow the capability of practical operator override of the automatic configuration settings. The outputs (28) of the dynamic filter units are passed to a non-linear analyzer (26) which outputs a value in normalized units. The output of the analyzer is passed to a post-processing unit (32) that converts the output to engineering units. This output represents a prediction of the output of the modeled process. In reverse horizon mode, a value of 1 is presented at the output of the predictive device and data is passed through the device in a reverse flow to produce a set of outputs (64) at the input of the predictive device. These are returned to the device controller through path (66). The purpose of the reverse horizon mode is to provide essential information for process control and optimization. The precise operation of the predictive device is configured by a set of parameters. that are determined during the configuration mode and stored in a storage device (30). The configuration mode makes use of one or more files of training data (48) collected from the DCS during standard operation of the process, or through structured plant testing. The predictive device is trained in four phases (40, 42, 44, and 46) correspo

Owner:ASPENTECH CORP

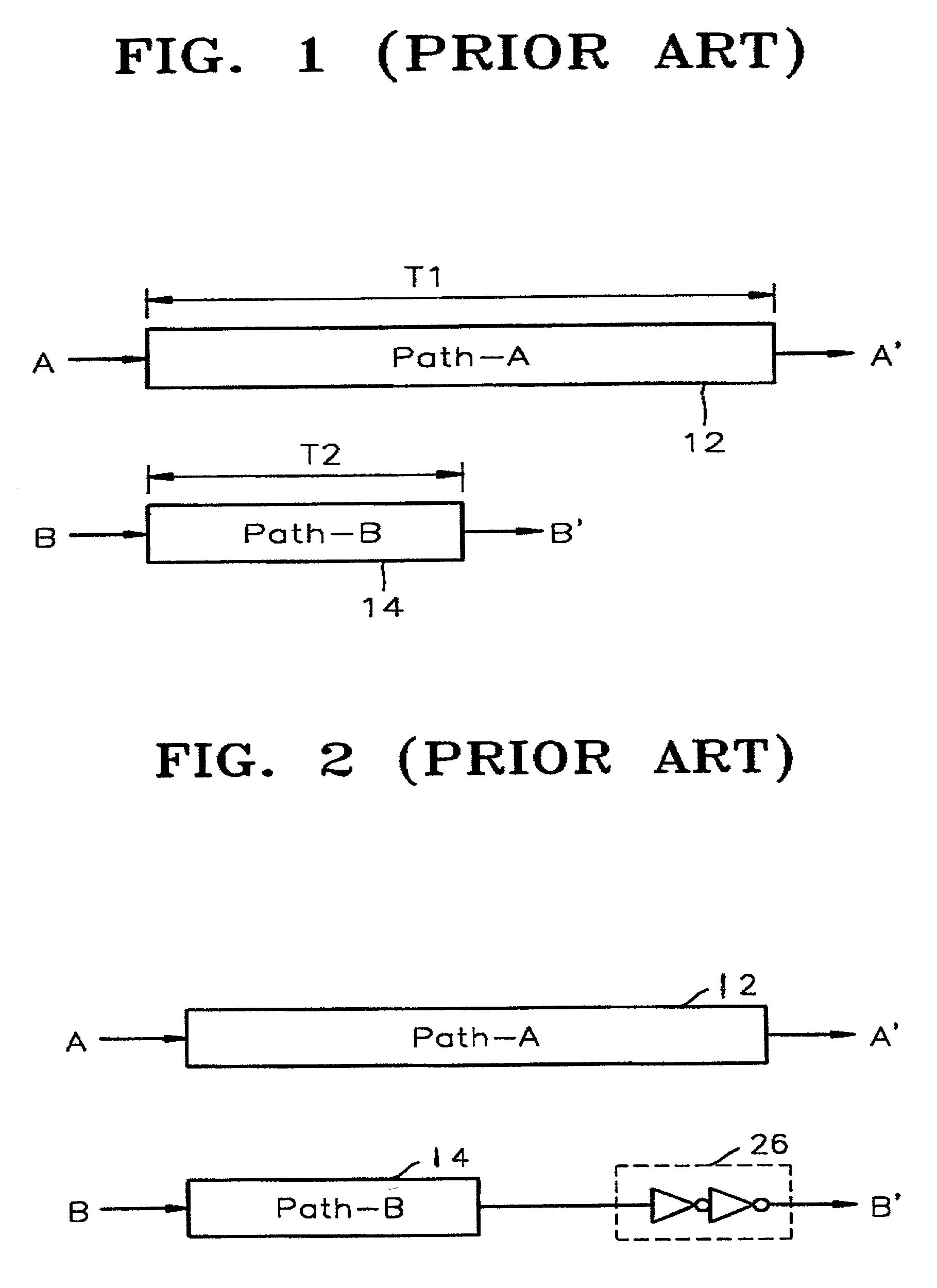

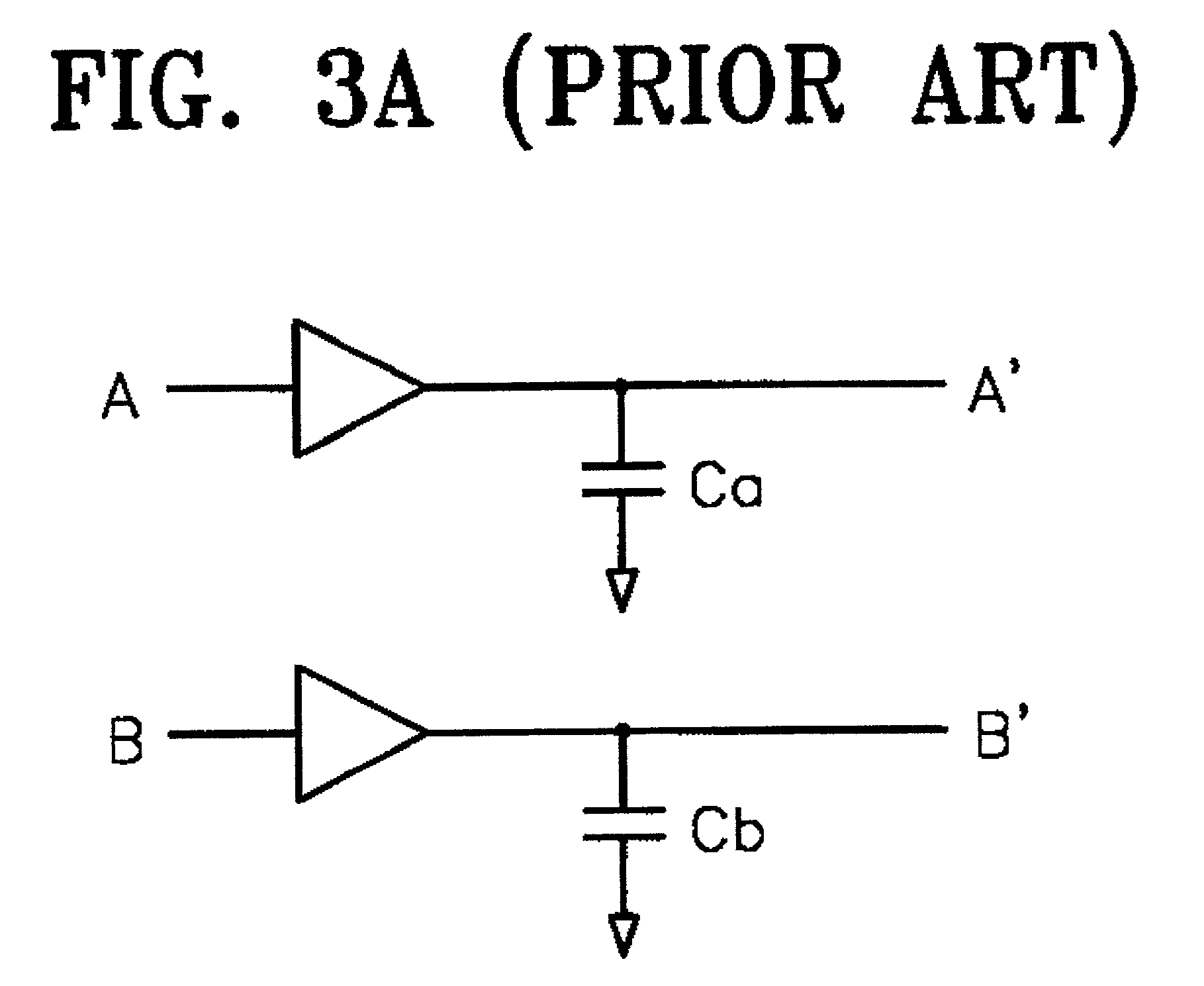

Signal transmission circuit and method for equalizing disparate delay times dynamically, and data latch circuit of semiconductor device implementing the same

InactiveUS7085336B2Accurate compensationKeep in syncChannel dividing arrangementsError preventionDelayed timeDatapath

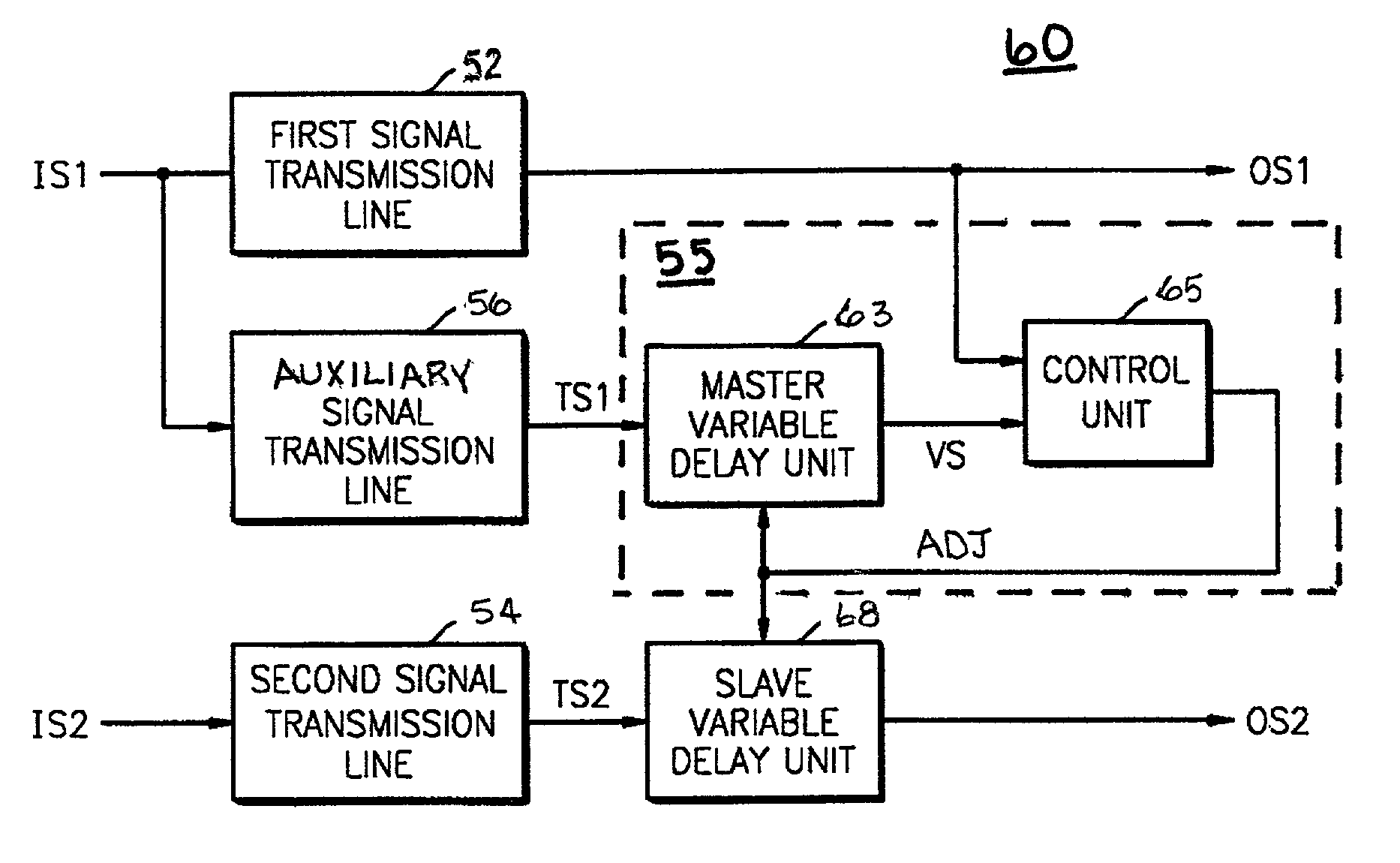

A signal transmission circuit and a method equalize differential delay characteristics of two signal transmission lines. A controllable delay unit is connected serially to the second line, so as to compensate by adding its internal delay. An auxiliary signal transmission line replicates the second transmission line, while it processes the input signal of the first. A controlling unit compares the output signal of the first transmission line and the of the auxiliary signal transmission line, and adjusts dynamically the internal delay of the controllable delay unit, to attain continuous synchronization. A data latch circuit synchronizes the delays of data paths by having one controllable delay units in each of the data paths.

Owner:SAMSUNG ELECTRONICS CO LTD

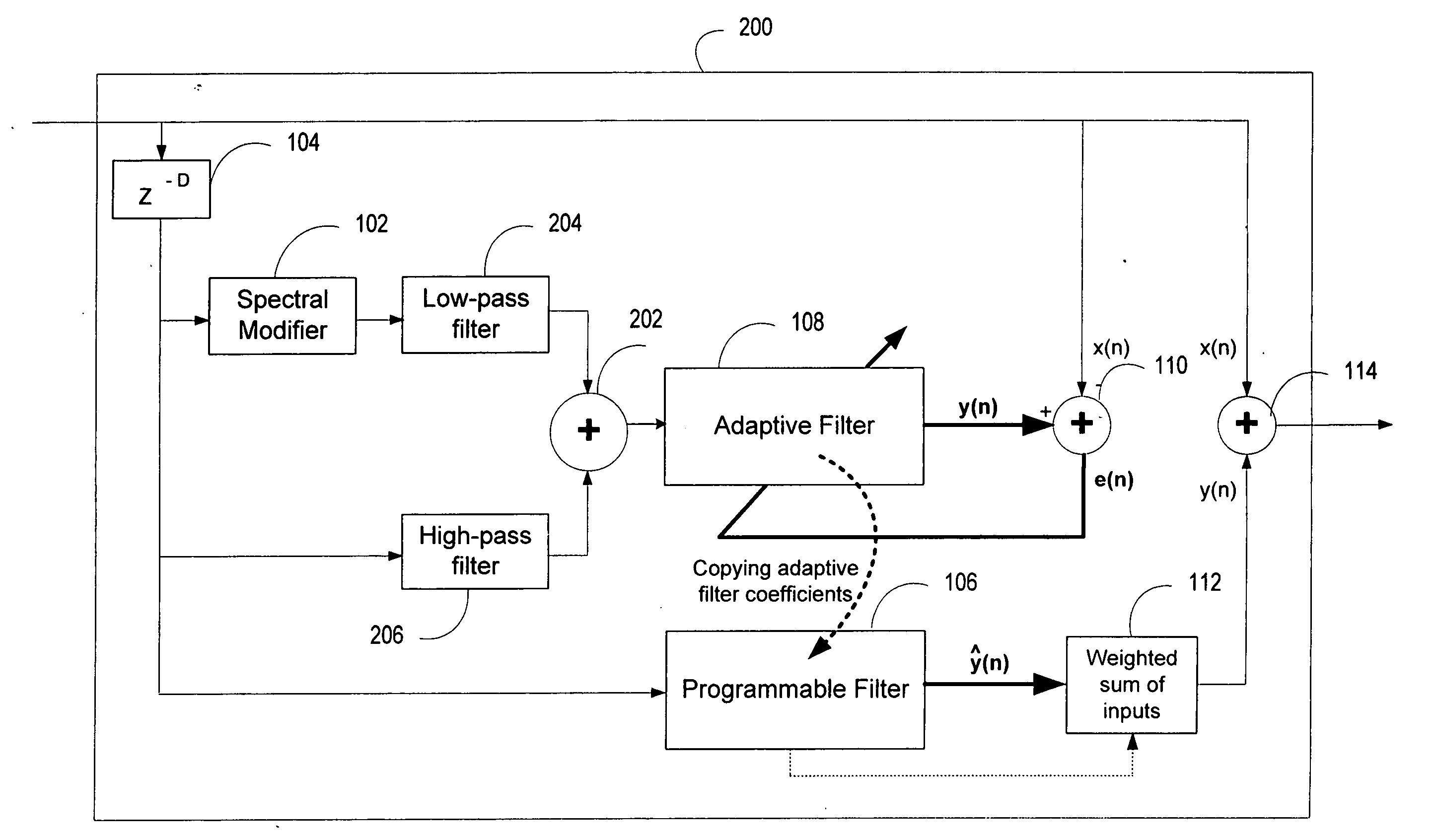

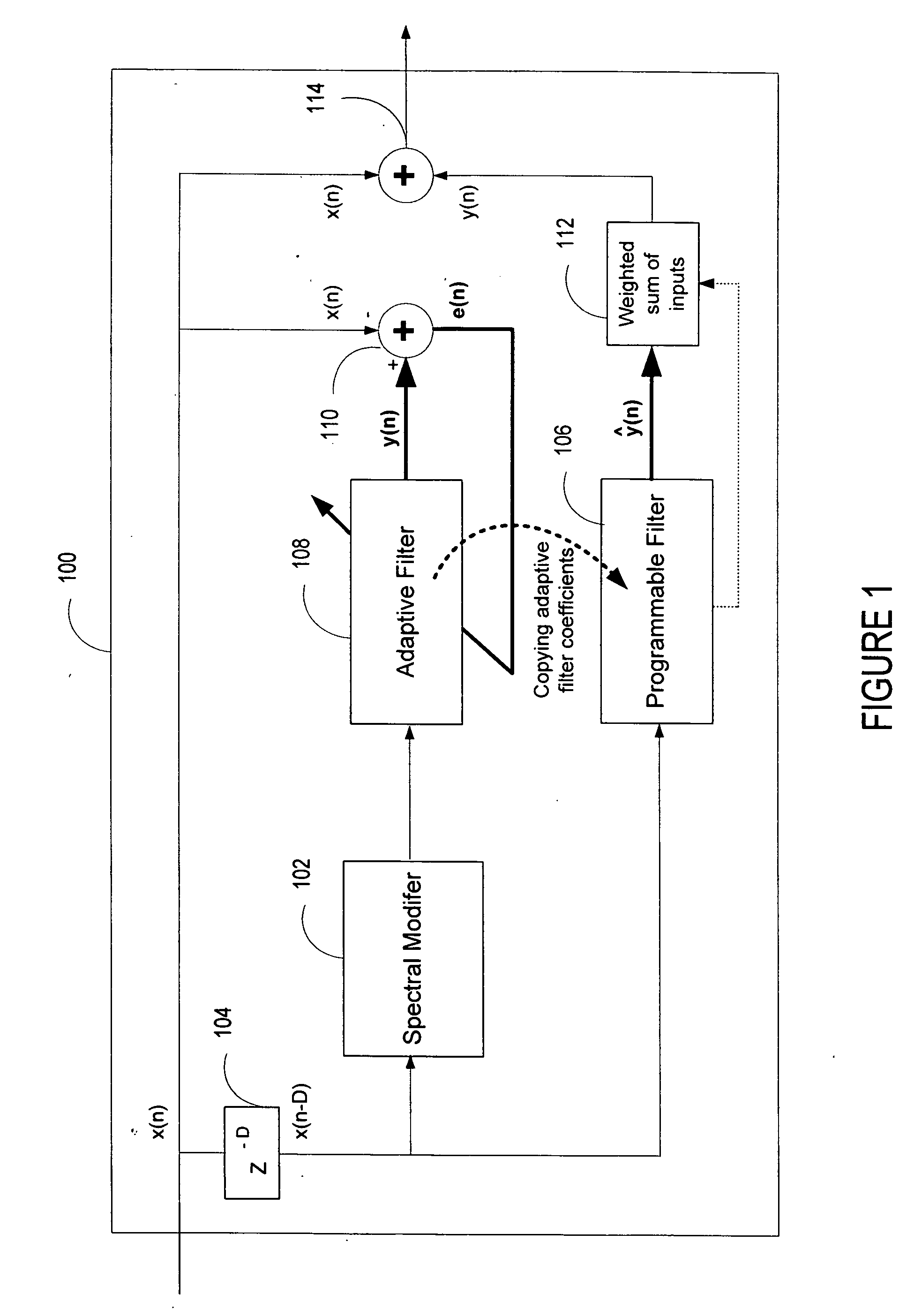

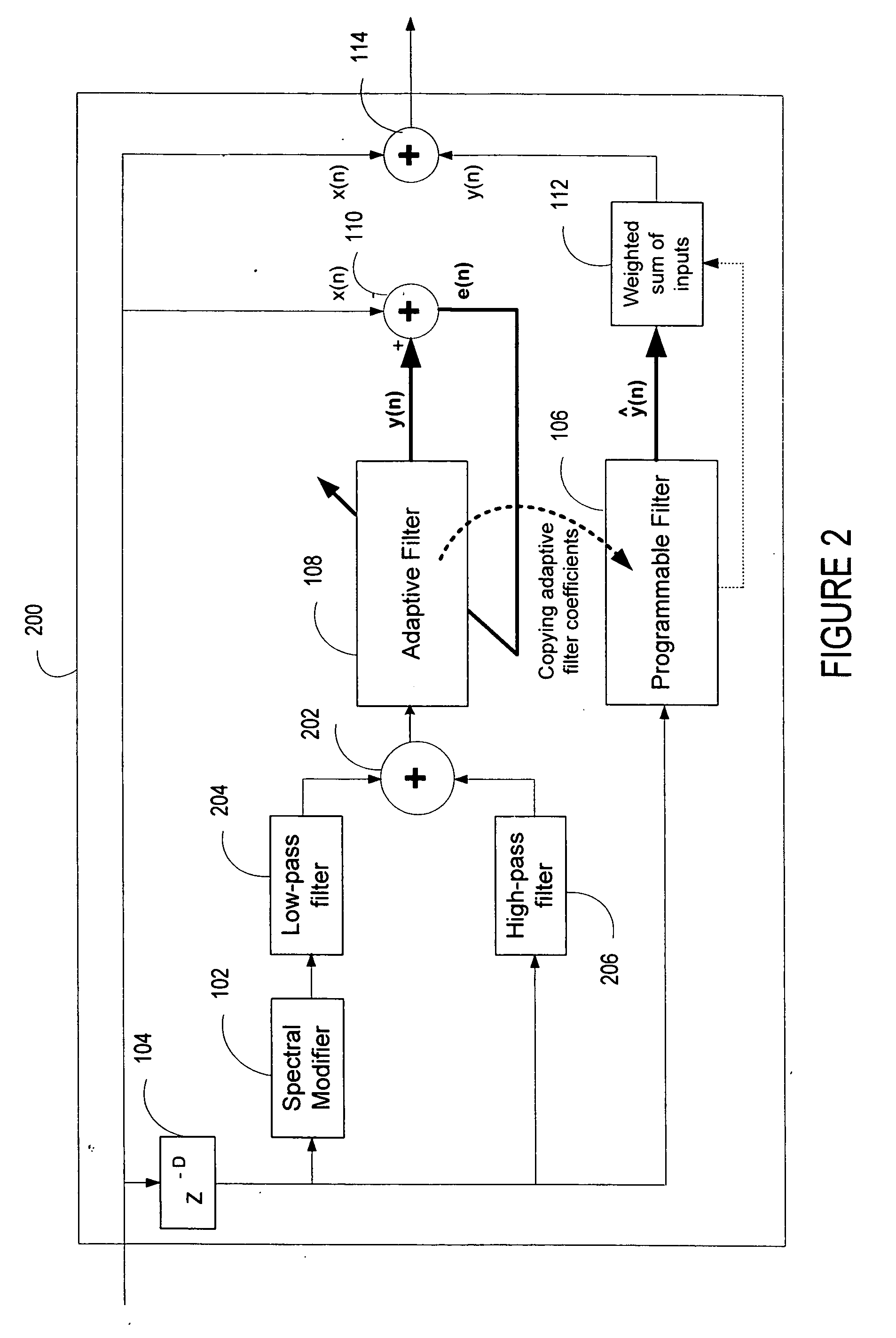

Advanced periodic signal enhancement

ActiveUS20060136199A1Improve processing qualityFlatten spectral character of background noiseAdaptive networkSpeech analysisFrequency spectrumProgrammable filters

An enhancement system improves the perceptual quality of a processed speech. The system includes a delay unit that delays a signal received through a discrete input. A spectral modifier linked to the delay unit is programmed to substantially flatten the spectral character of a background noise. An adaptive filter linked to the spectral modifier adapts filter characteristics to match a response of a non-delayed signal. A programmable filter is linked to the delay unit. The programmable filter has a transfer function functionally related to a transfer function of the adaptive filter.

Owner:BLACKBERRY LTD

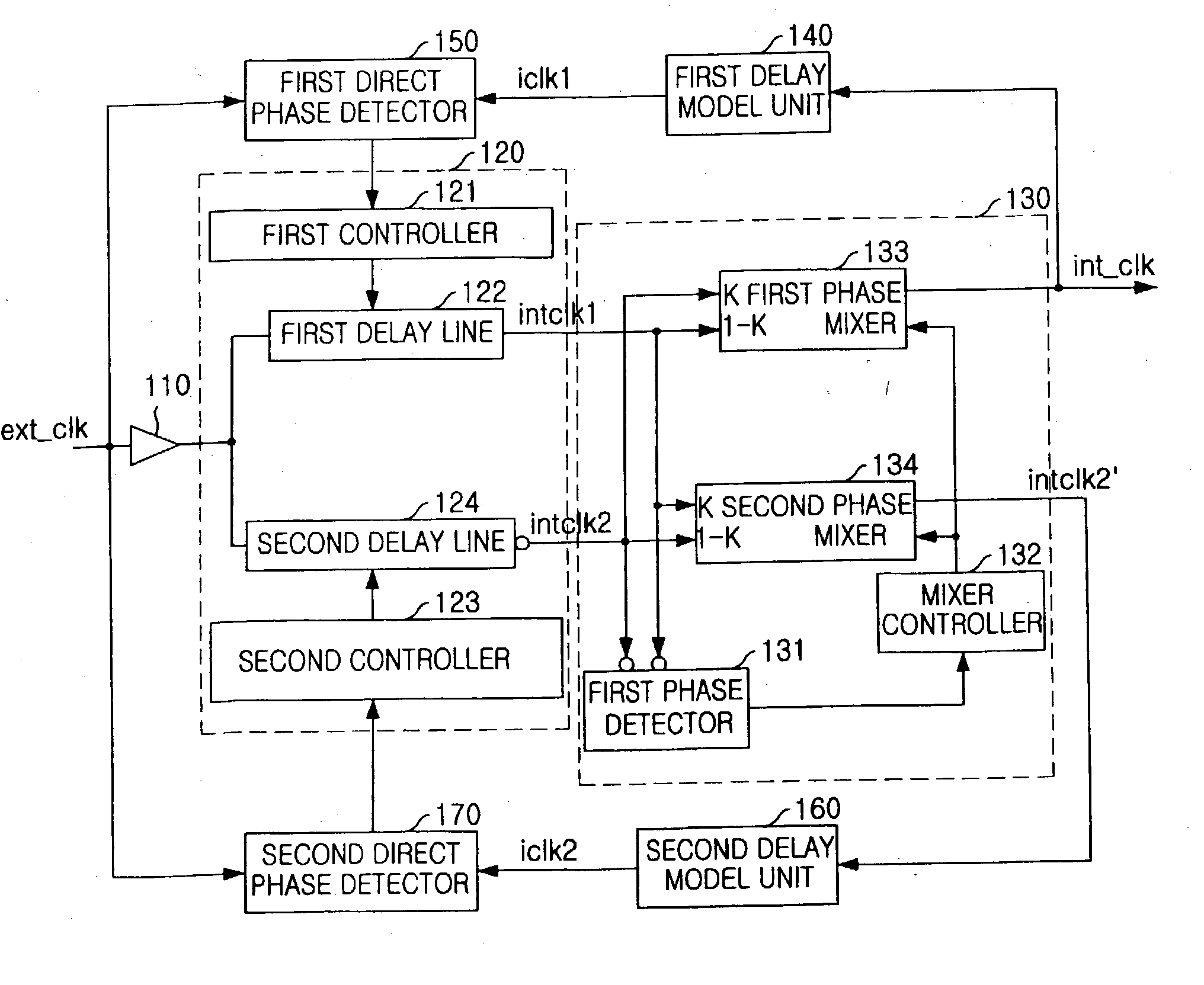

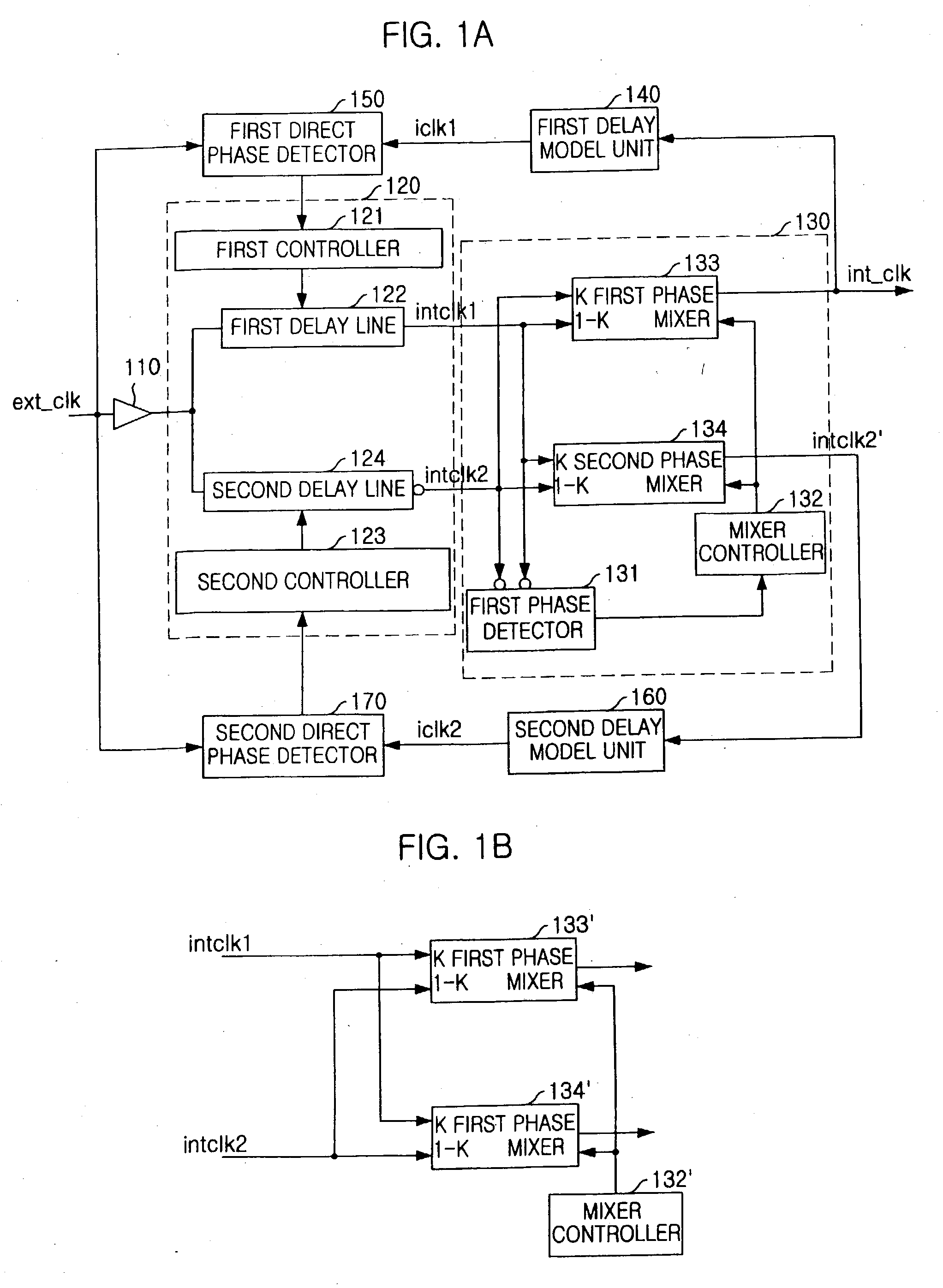

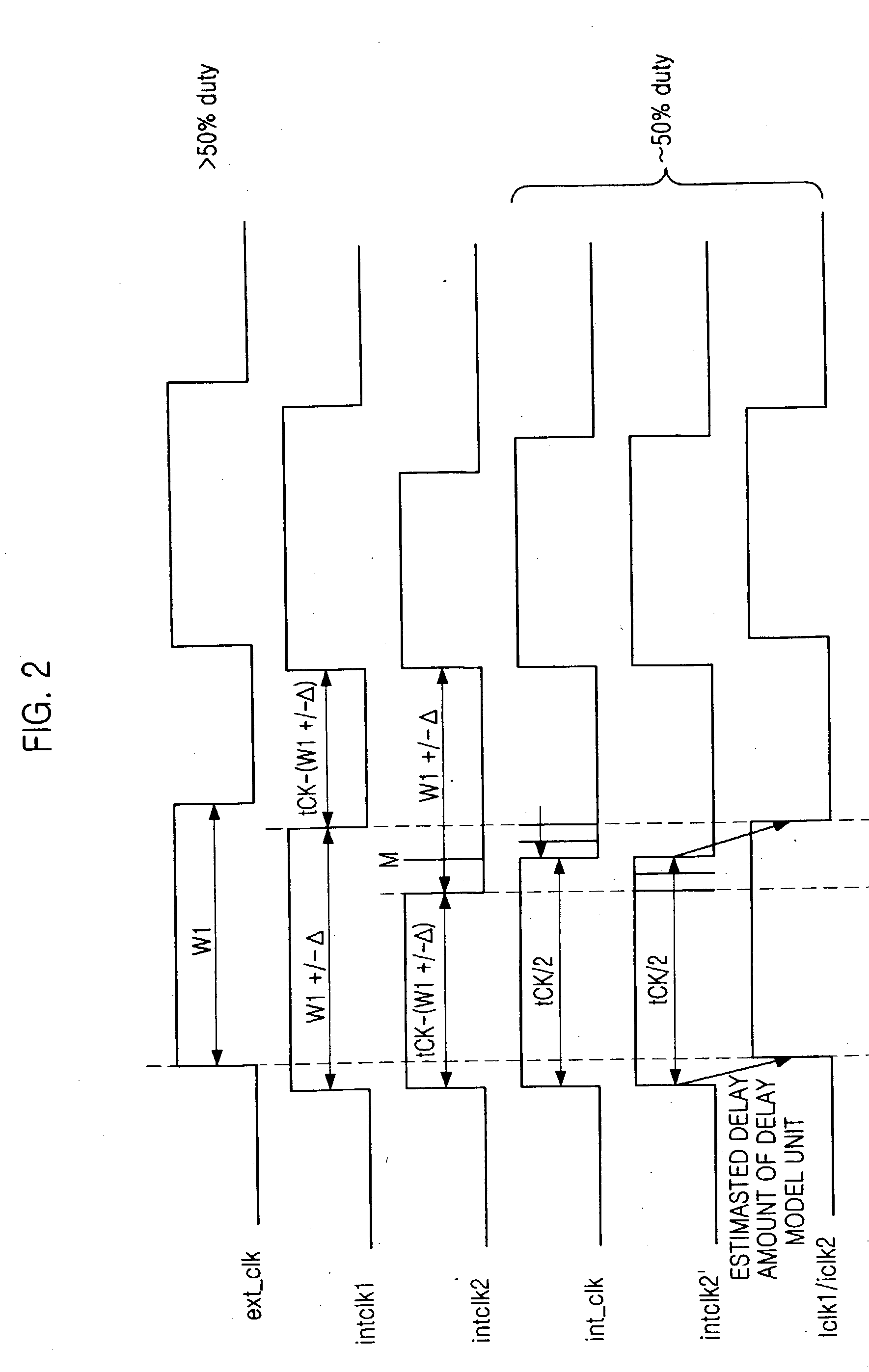

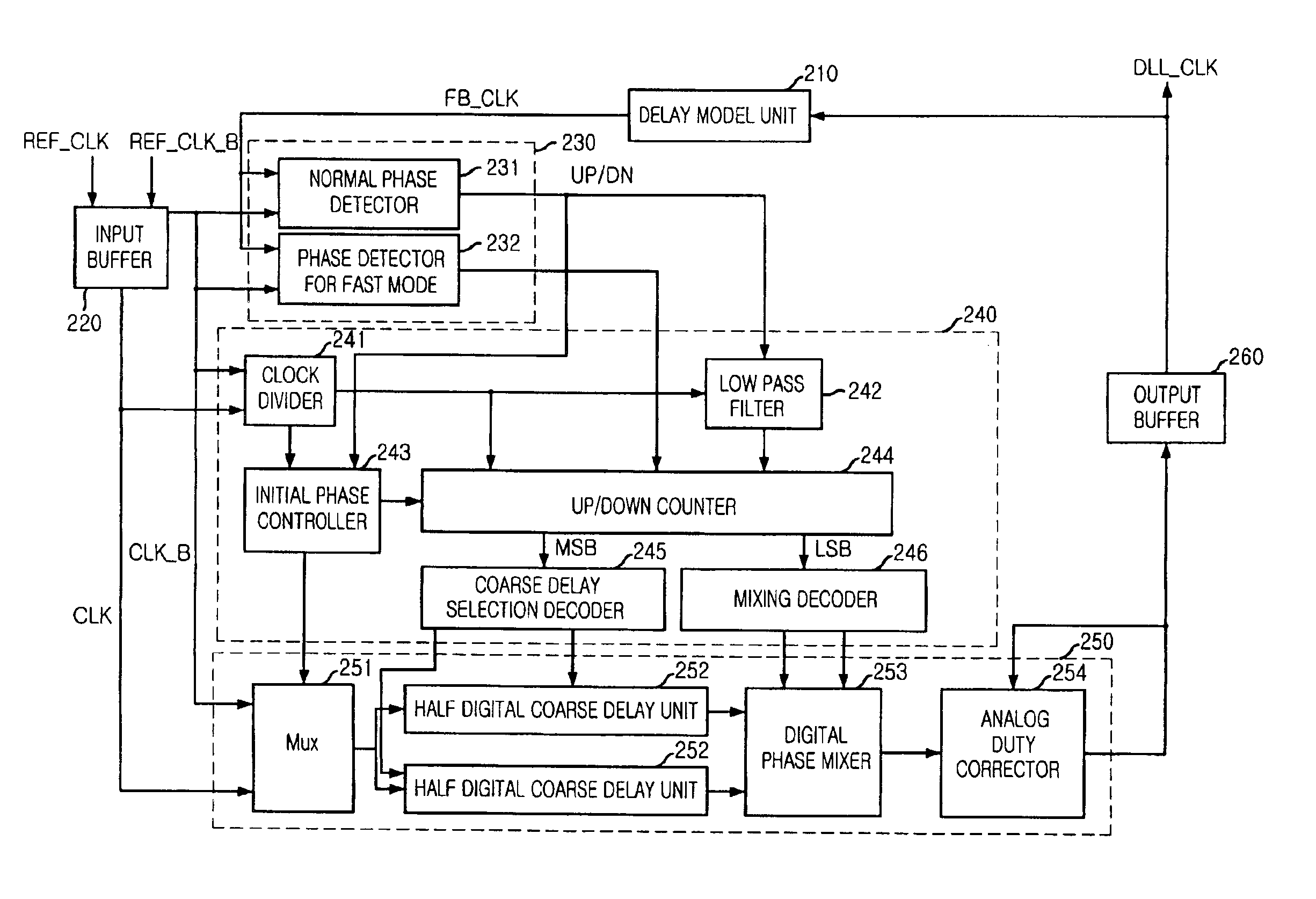

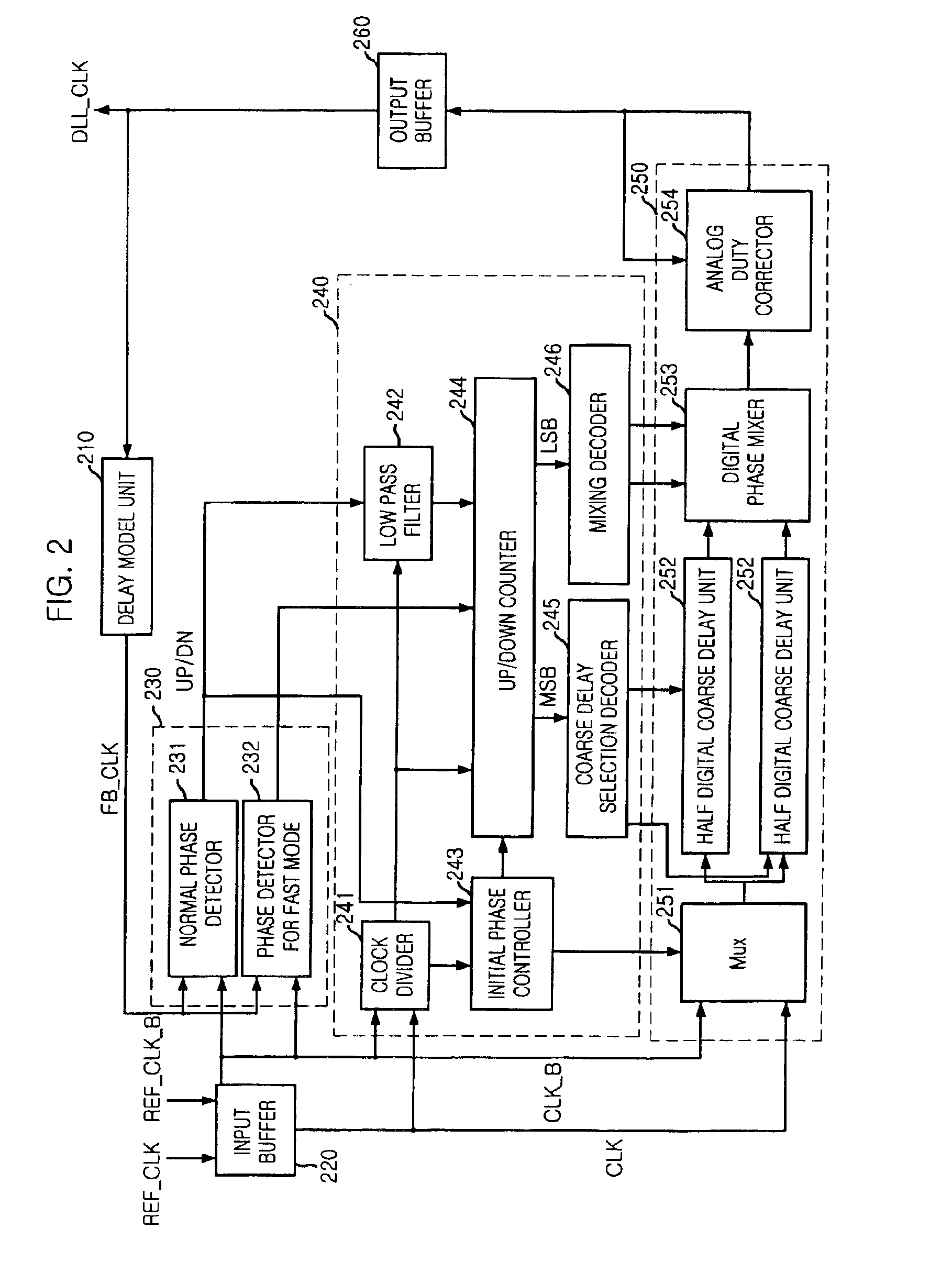

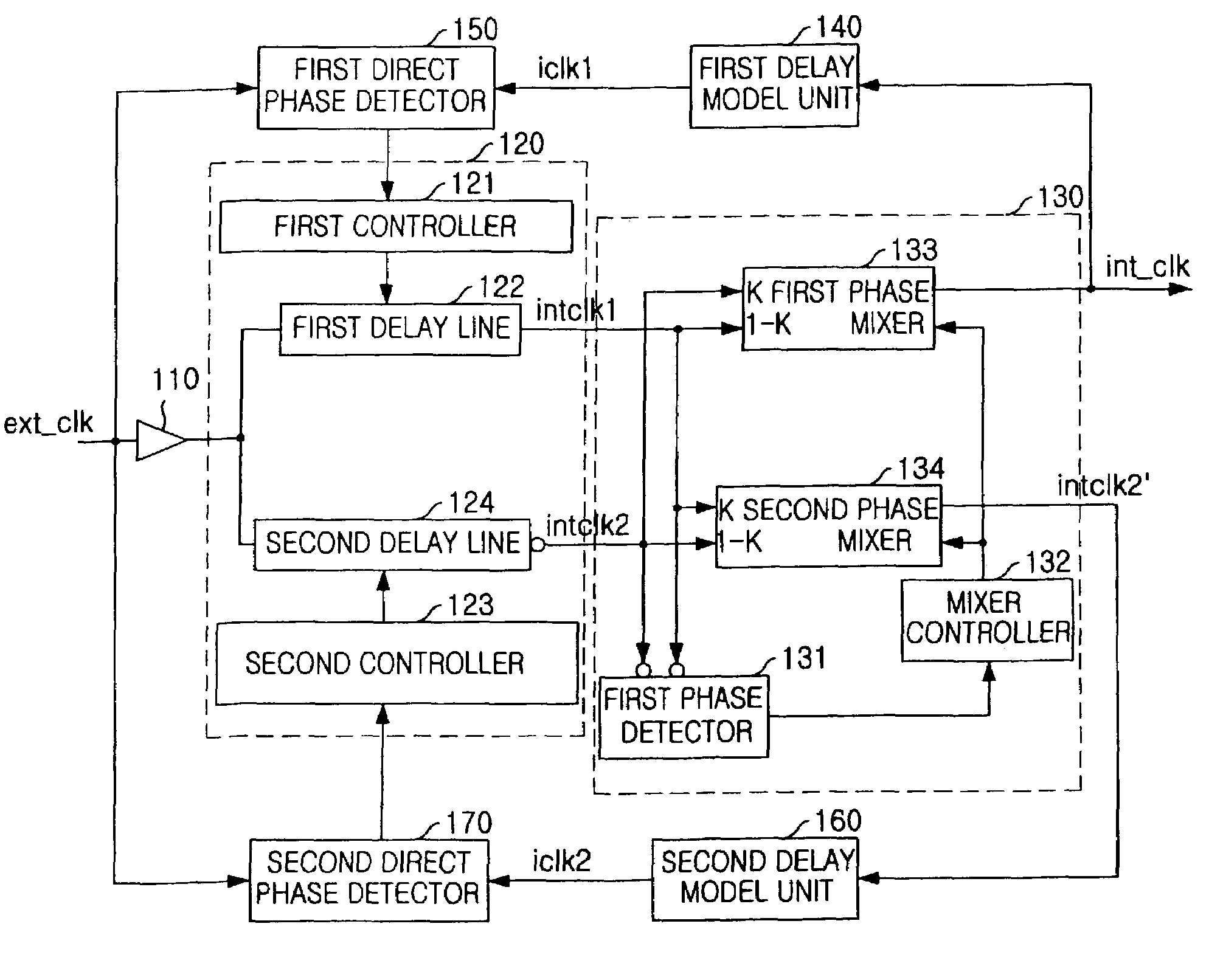

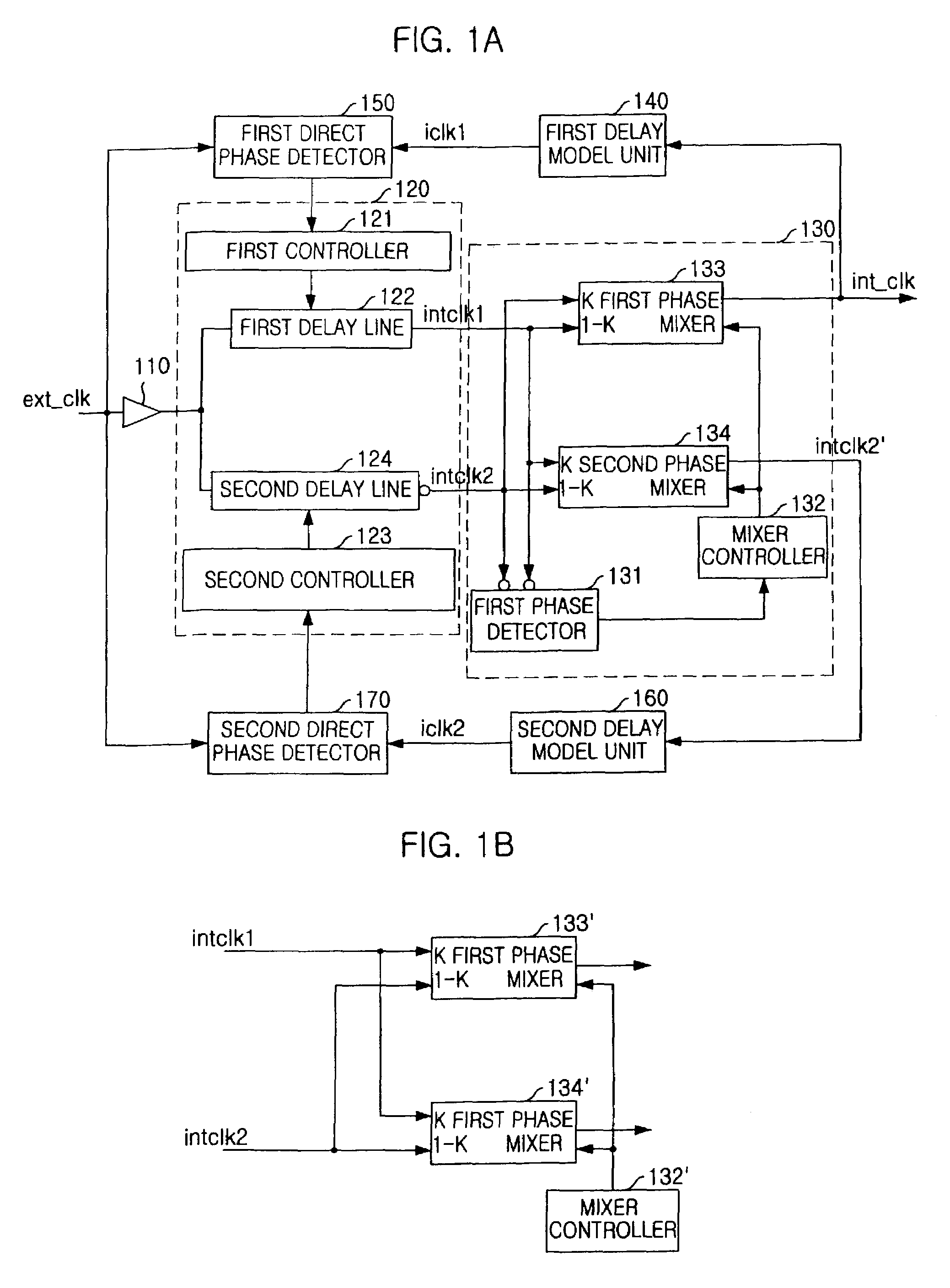

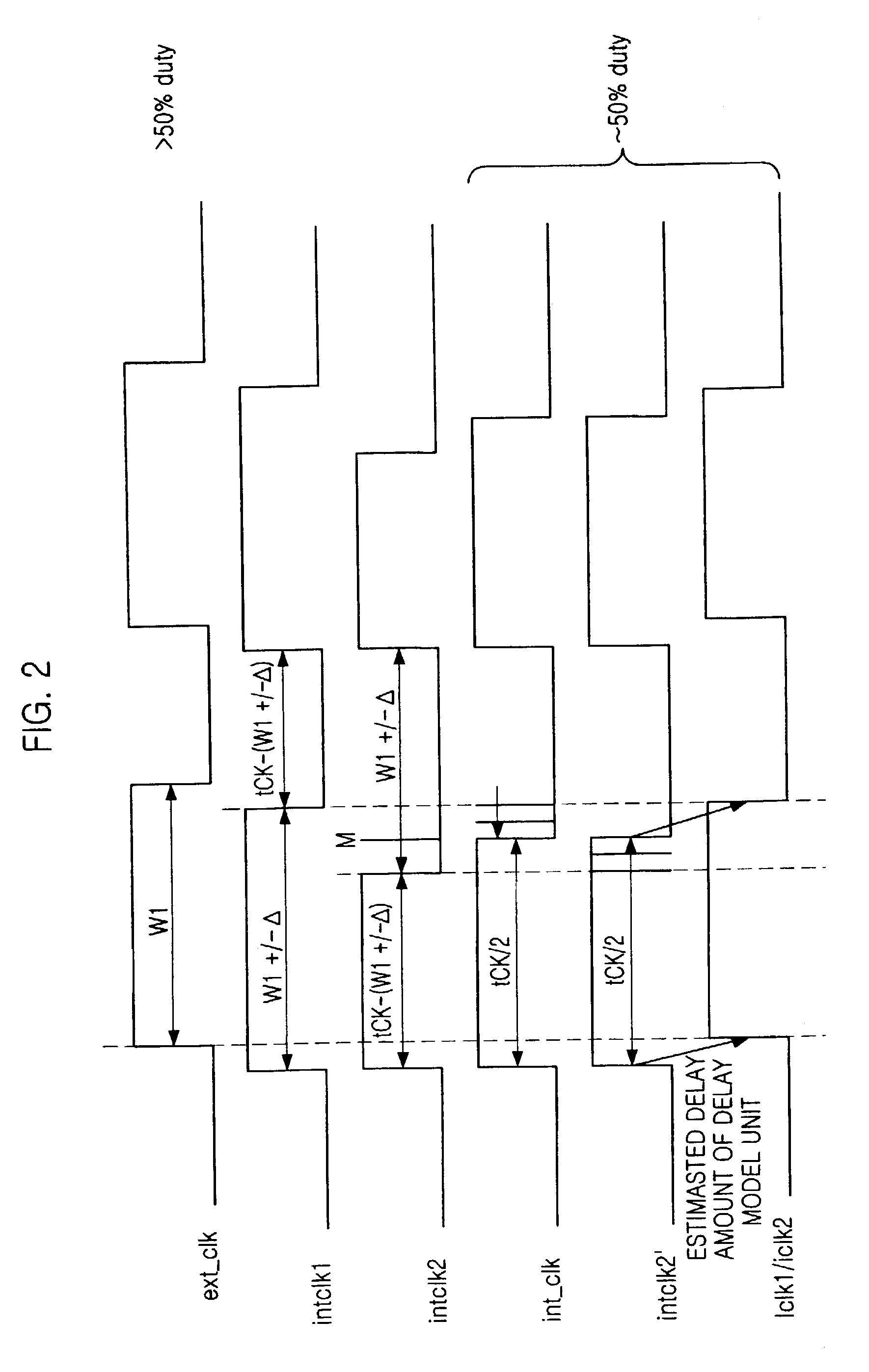

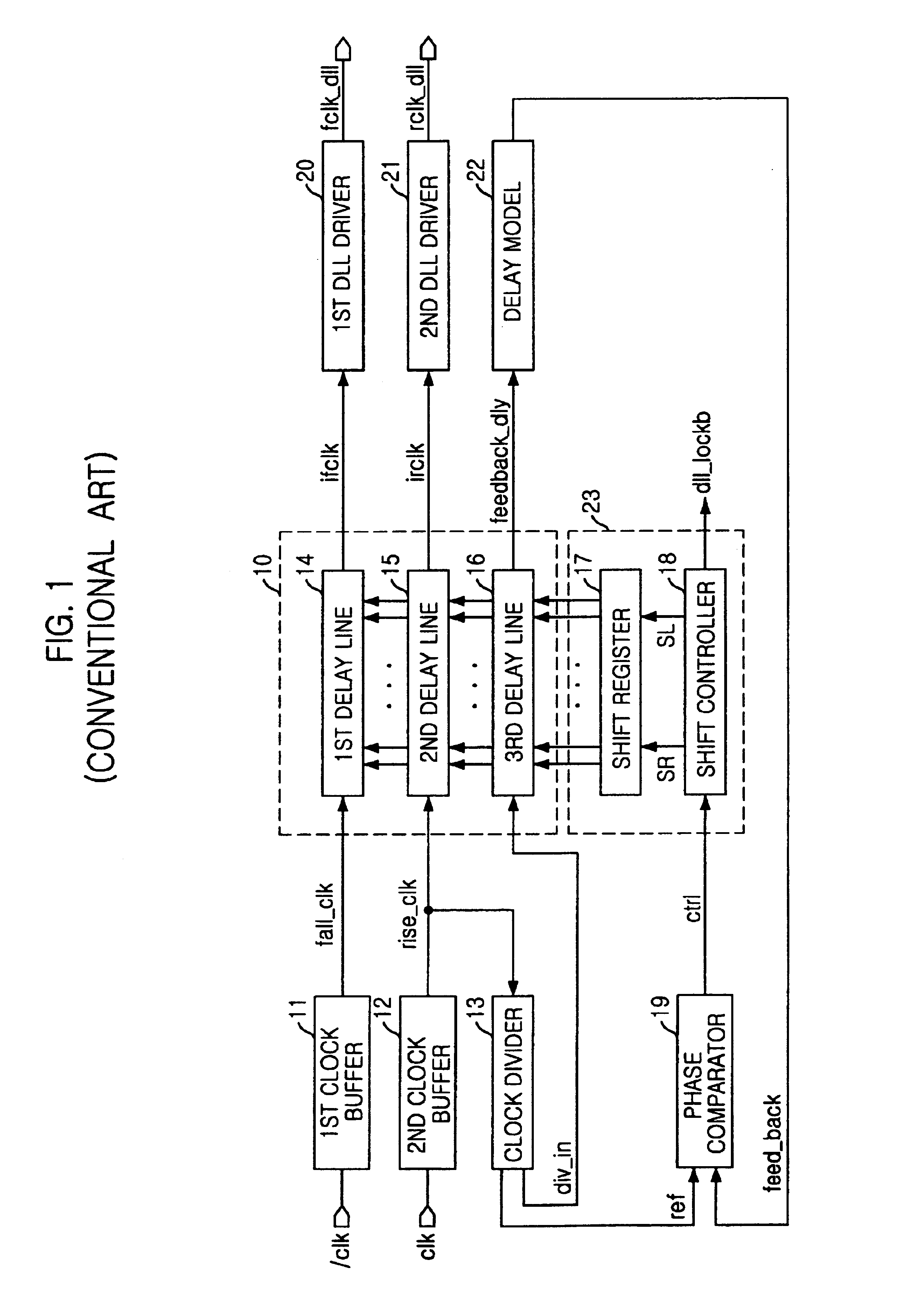

Digital DLL apparatus for correcting duty cycle and method thereof

A digital DLL apparatus and a method for correcting a duty cycle are disclosed. The apparatus includes: a delay line unit for receiving external clock signal and generating first and second delayed internal clock signals by delaying the external clock signal; a duty error controller for receiving the first and second delayed clock signals and outputting a first duty controlled clock signal and second duty controlled clock signal by shifting edges of the first and second delayed internal clock signals; and a delay model unit for compensating a delay of the duty controlled clock signal by estimating a delay amount of system. The present invention can correct the duty error by using the phase mixer and generate an internal clock signal having 50% of duty cycle.

Owner:SK HYNIX INC

Image sensor and control method of the image sensor

ActiveUS20060243885A1Increase speedImprove accuracyTelevision system detailsElectric signal transmission systemsLight signalComputer science

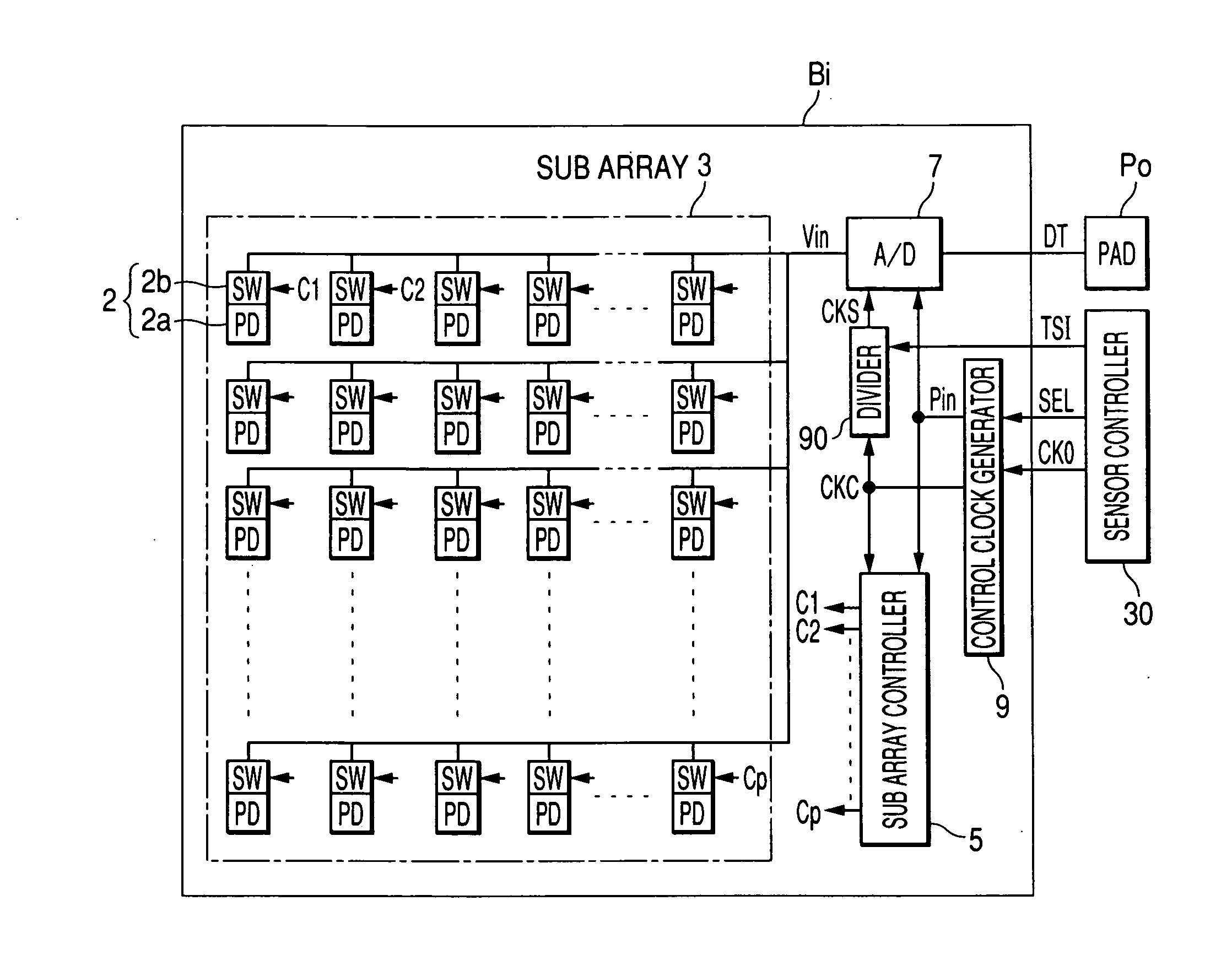

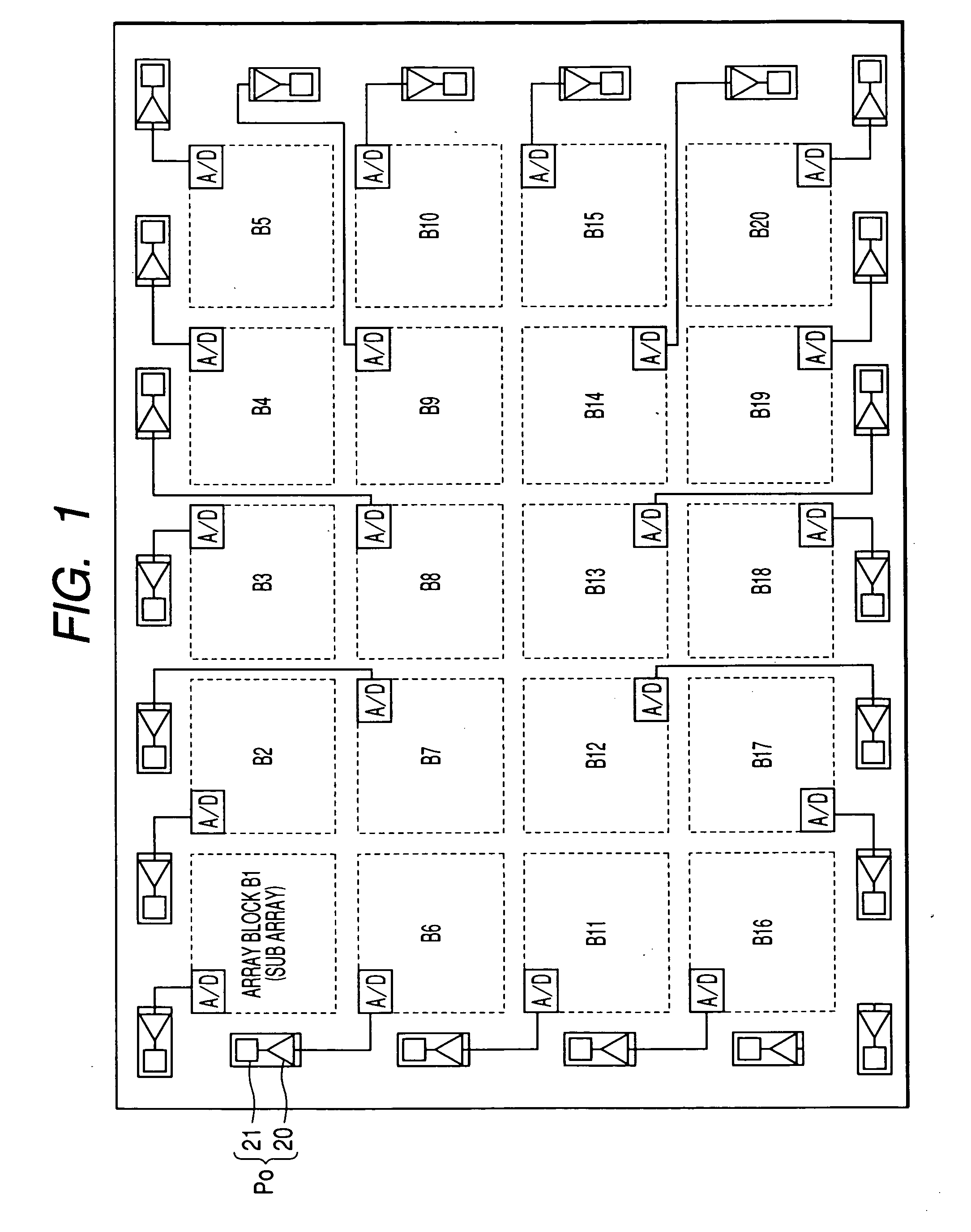

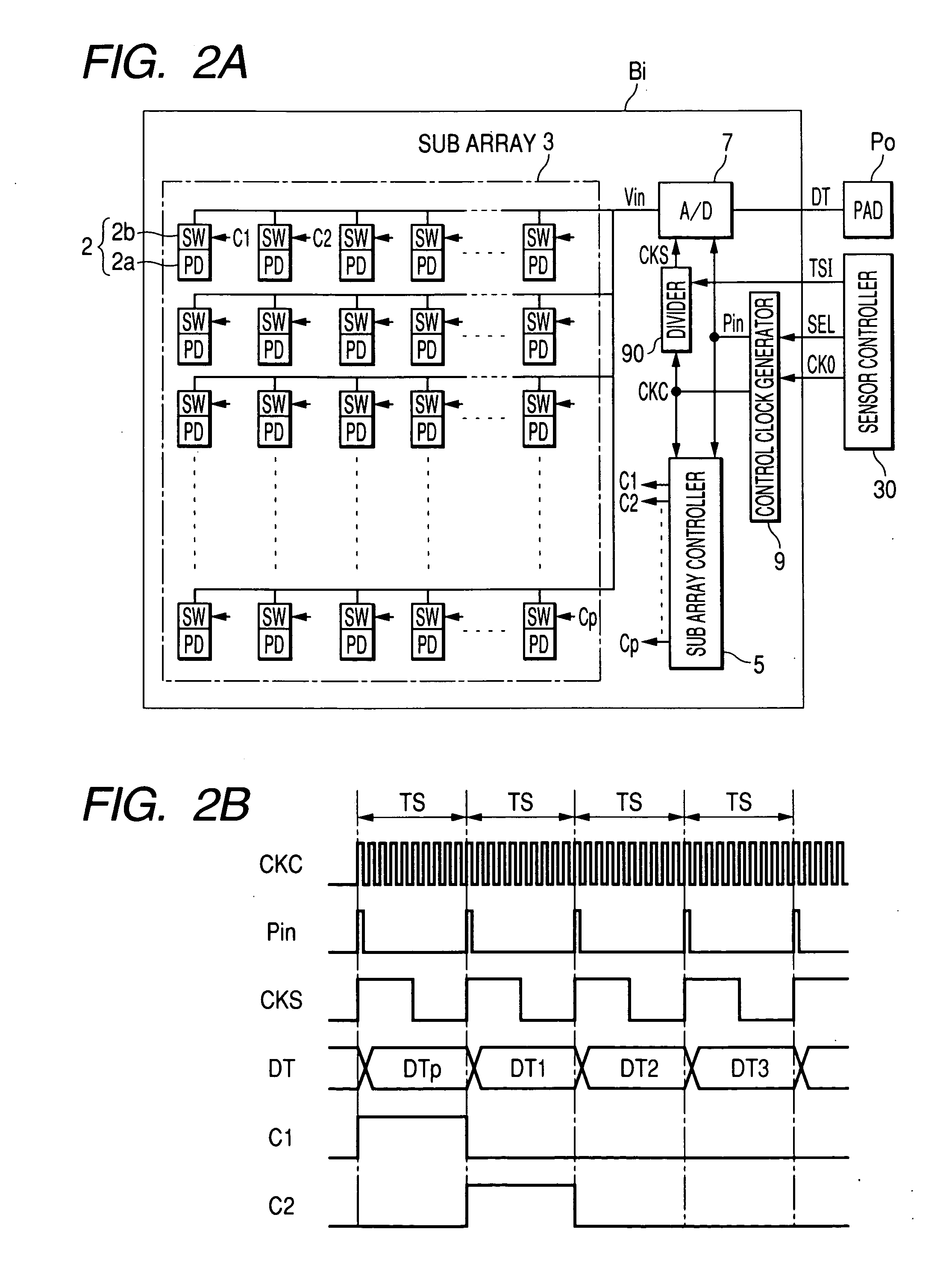

An image sensor has plural array blocks B1 to B20 arranged in a two dimensional (2D) arrangement. Each array block has a sub array and a corresponding analogue to digital (A / D) converter for performing an A / D conversion of light signals (or detection signals) output from the sub array. The sub array has plural picture element cells arranged in a 2D arrangement. Each A / D converter has a pulse delay circuit having delay units of plural stages connected in series. Each delay unit delays an input pulse by a delay time corresponding to a level of the light signals received from the sub array. A pulse delay type A / D converter is used as the A / D converter, which outputs the number of the delay units as an A / D conversion data item through which the input pulse passes for a measurement time period.

Owner:DENSO CORP

Delay compensation circuit

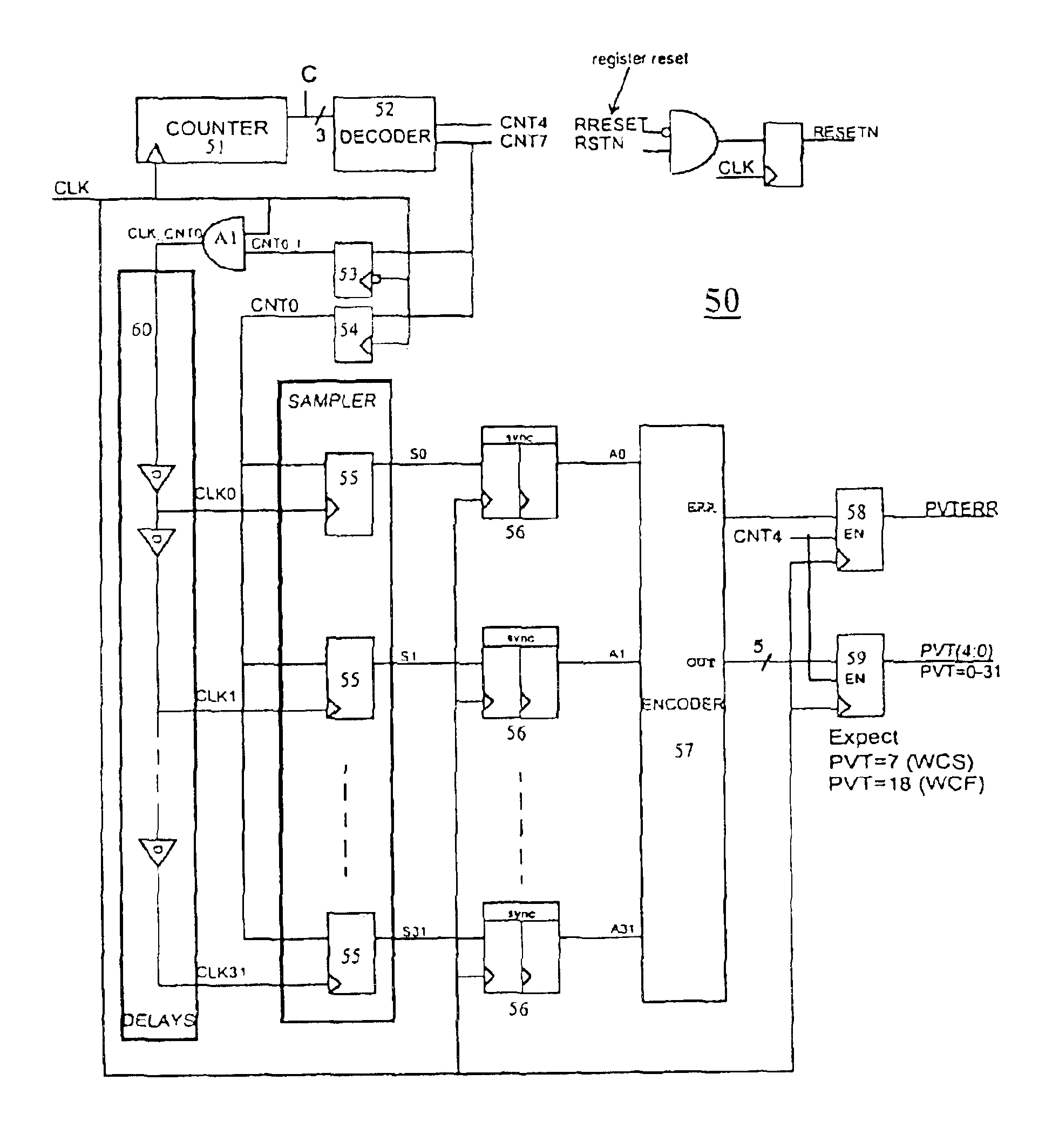

A delay compensation circuit that determines the effects of process, voltage, and temperature (PVT) conditions of a chip by measuring the effective delay time of delay components inside the chip. The delay compensation circuit includes a plurality of sampler modules, each of which receives a delayed clock signal from one of a series of delay cells within a tapped delay circuit. The delay compensation circuit generates an output value based on the total number of sampling modules that lock into a fixed input signal using the delayed clock signals. Since the delay time of each delay cell changes based on variations of PVT conditions, the output values generated by the delay compensation circuit are determinate of PVT conditions in the chip. These output values can be used to design components to compensate for variances in PVT conditions or to control a variable delay component based on detected PVT conditions.

Owner:ALCATEL-LUCENT USA INC +1

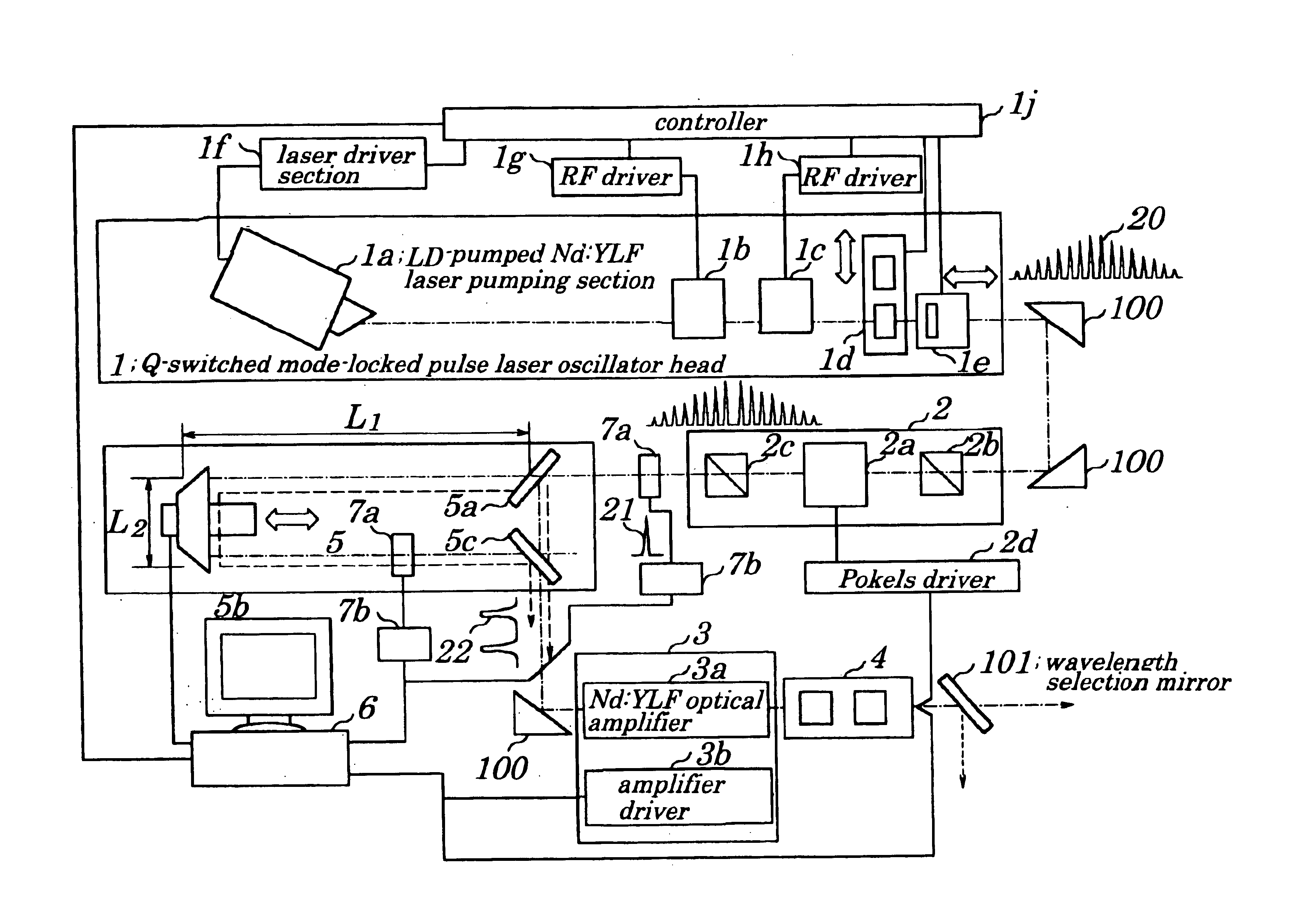

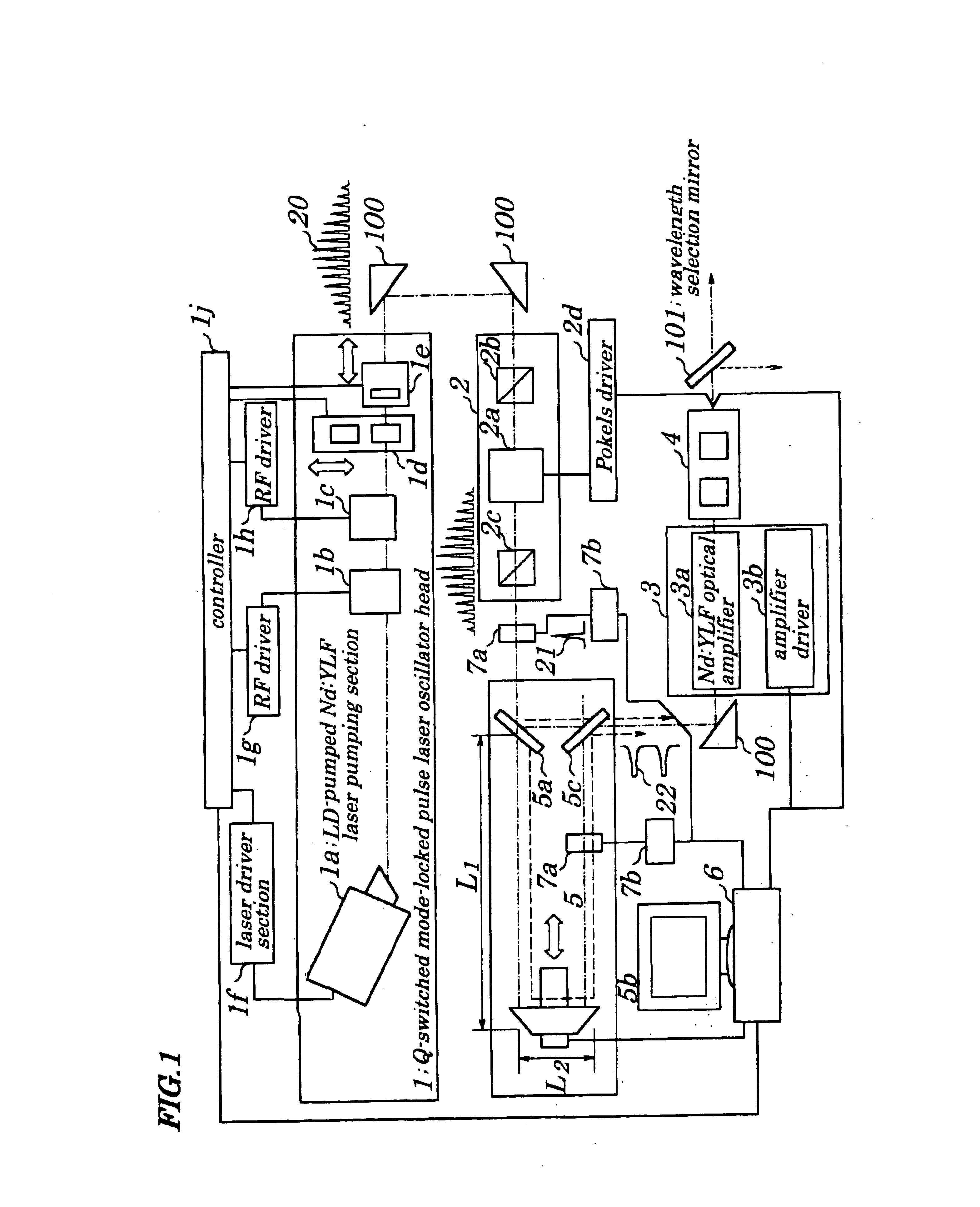

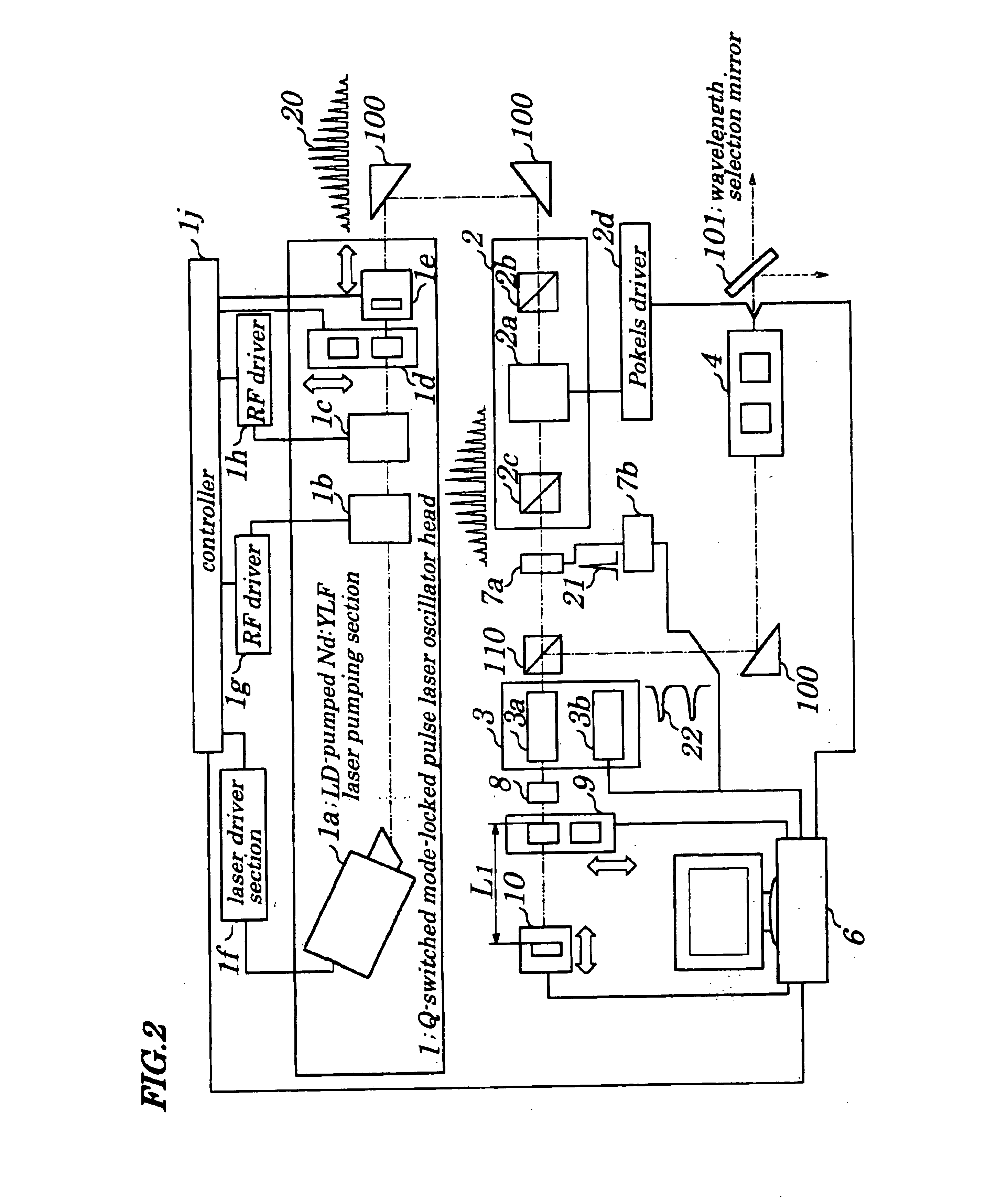

Method and apparatus for performing pattern defect repair using Q-switched mode-locked pulse laser

InactiveUS6879605B2Less heatPromote repairLaser detailsSemiconductor/solid-state device detailsThin metalOptoelectronics

A method for repairing a pattern by using a laser and a laser-based pattern repair apparatus are provided which are capable of reducing splashes, rolling-up, and damage to a glass substrate to a minimum in pattern defects repairing processing by removing a thin metal layer such as a chromium layer. A part of a string of pulses obtained by slicing, using an optical shutter, pulses from laser light having a pulse width of 10 ps to 300 ps emitted from a Q-switched mode-locked pulse laser is used to produce multi-pulses which are divided into two portions in terms of time base correction using an optical delaying unit.

Owner:NEC CORP

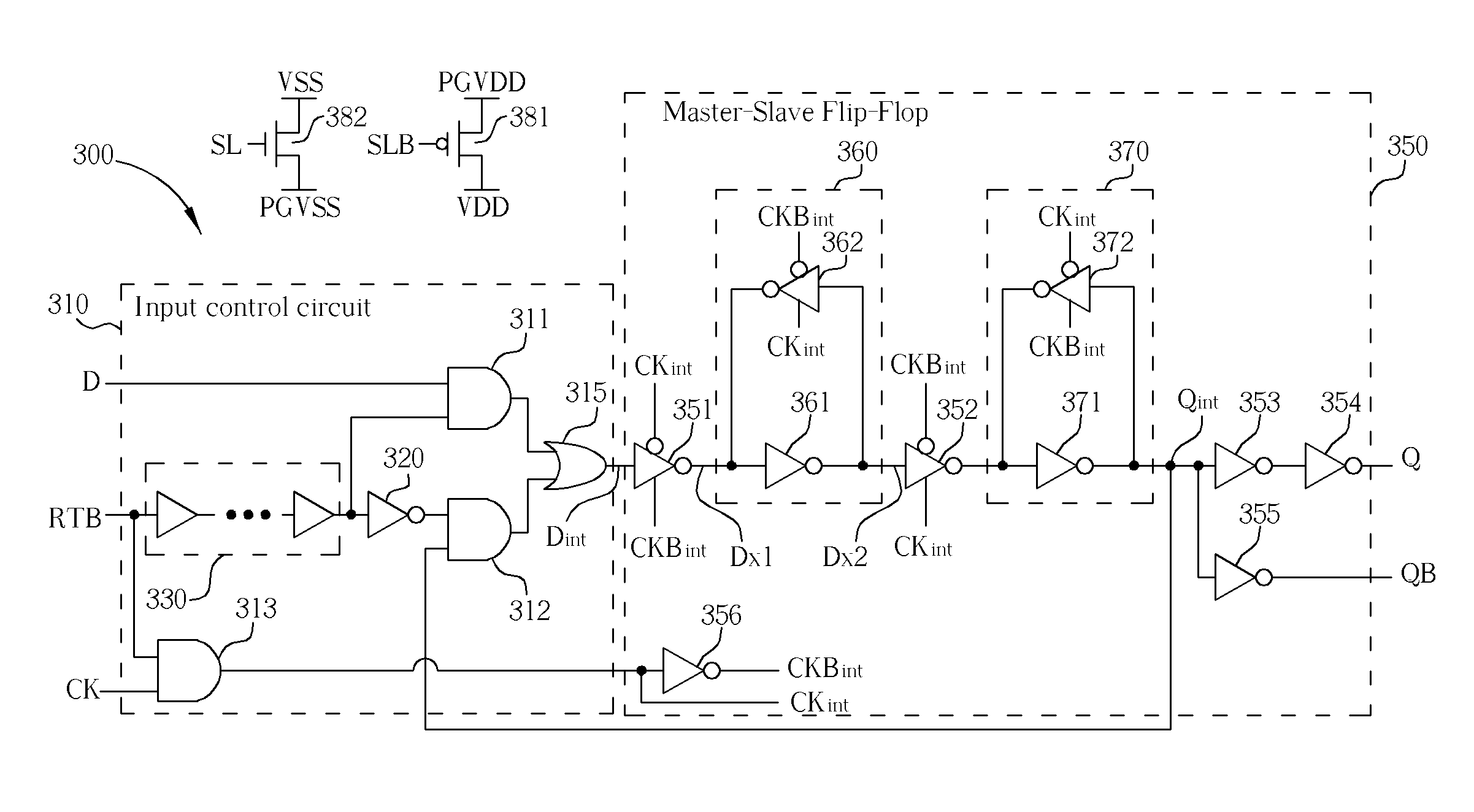

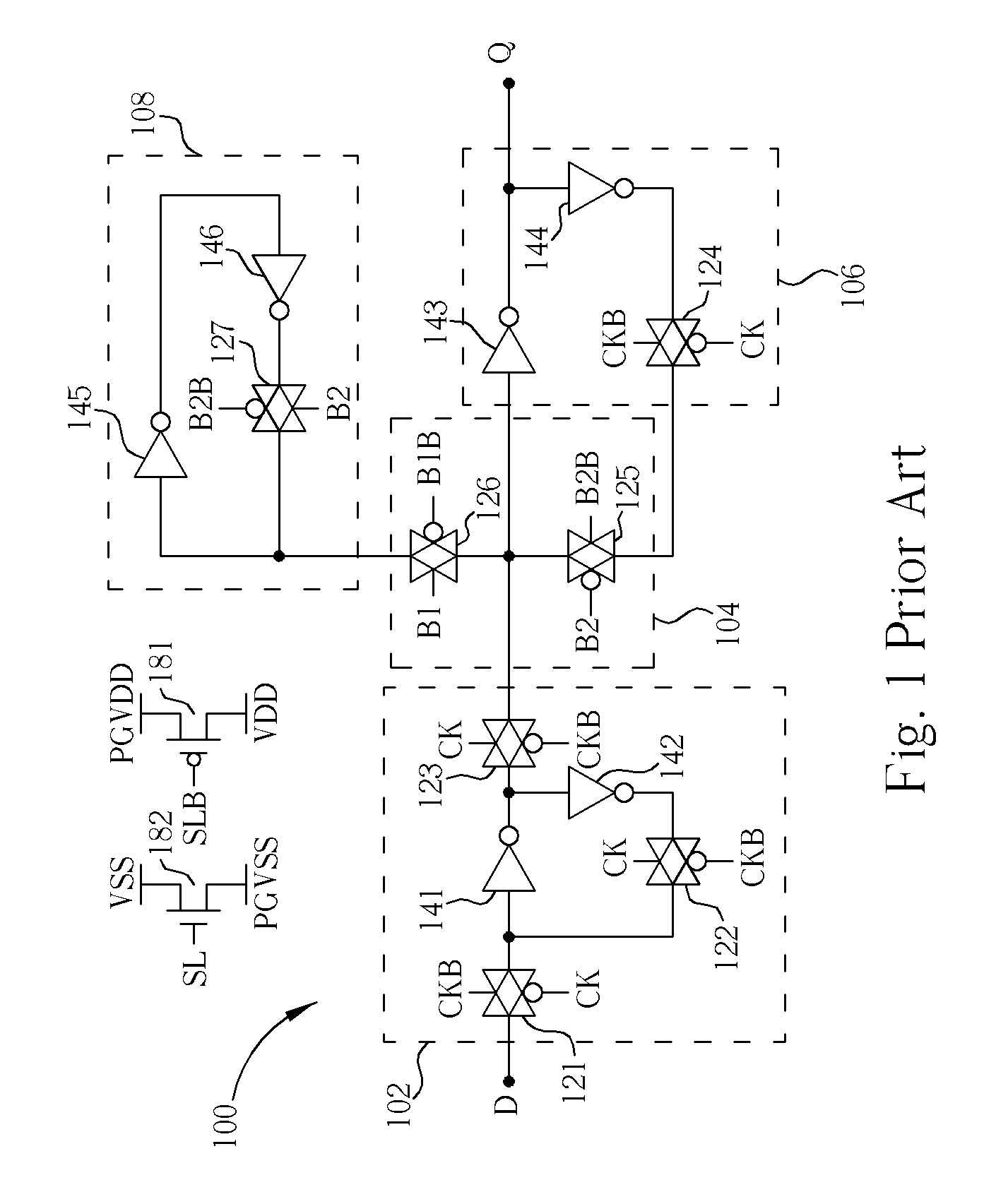

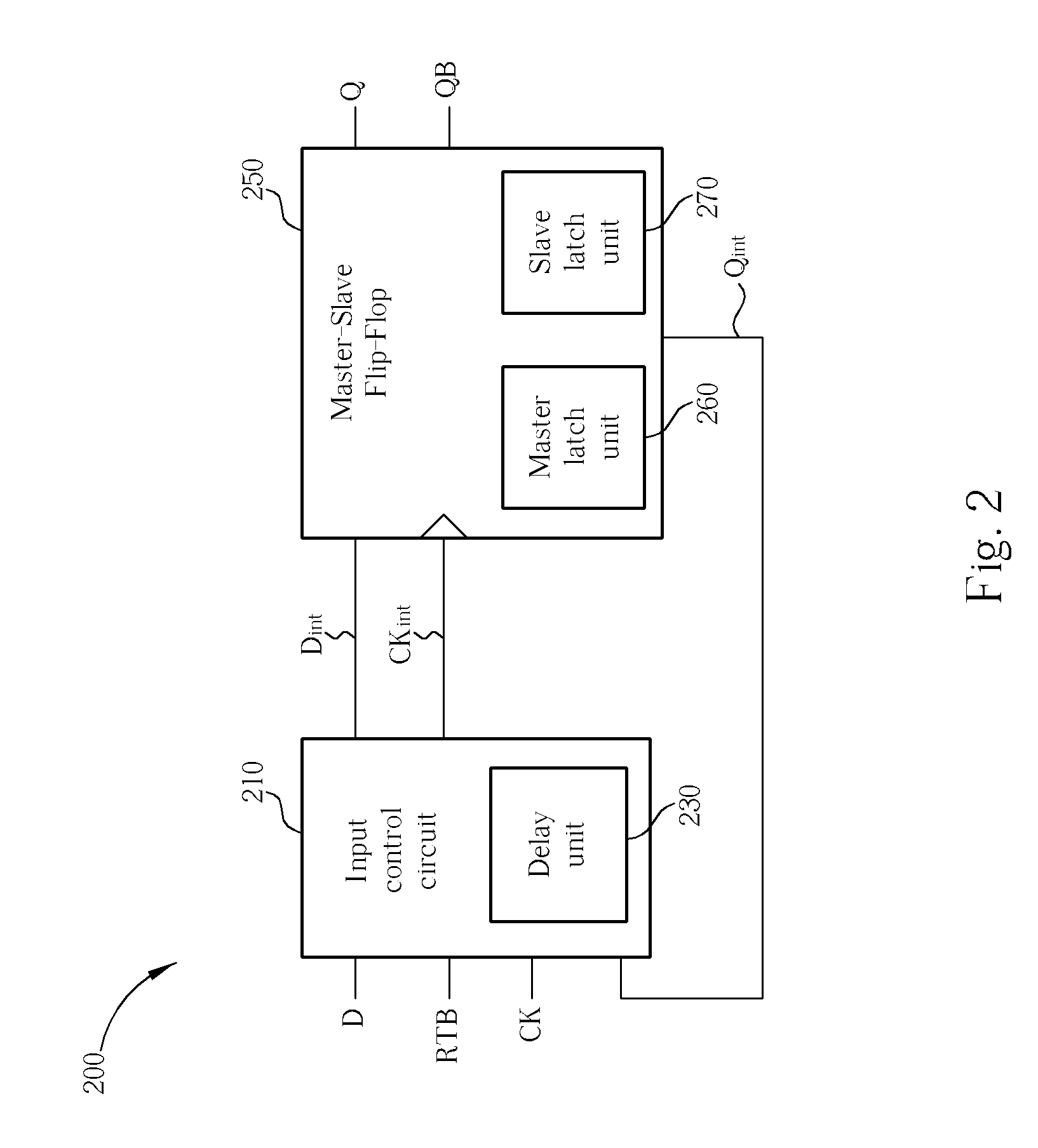

Data retention cell and data retention method based on clock-gating and feedback mechanism

ActiveUS7391250B1Logic circuits characterised by logic functionDigital storageInput controlData signal

For retaining an output data signal of a data retention cell in a power-saving mode, a slave latch unit of the data retention cell is powered with a real power for preserving the output data signal. The output data signal is furnished backward to an input control circuit of the data retention cell. The data signal furnished to a master latch unit of the data retention cell is controlled to switch between an input data signal and the output data signal by the input control circuit in response to a retention signal. The switching of the data signal for refreshing the master latch unit is delayed by a delay unit of the input control circuit, which functions to make sure that the data-preserving process is properly operated on any transition from the power-saving mode to a power-active mode.

Owner:MARLIN SEMICON LTD

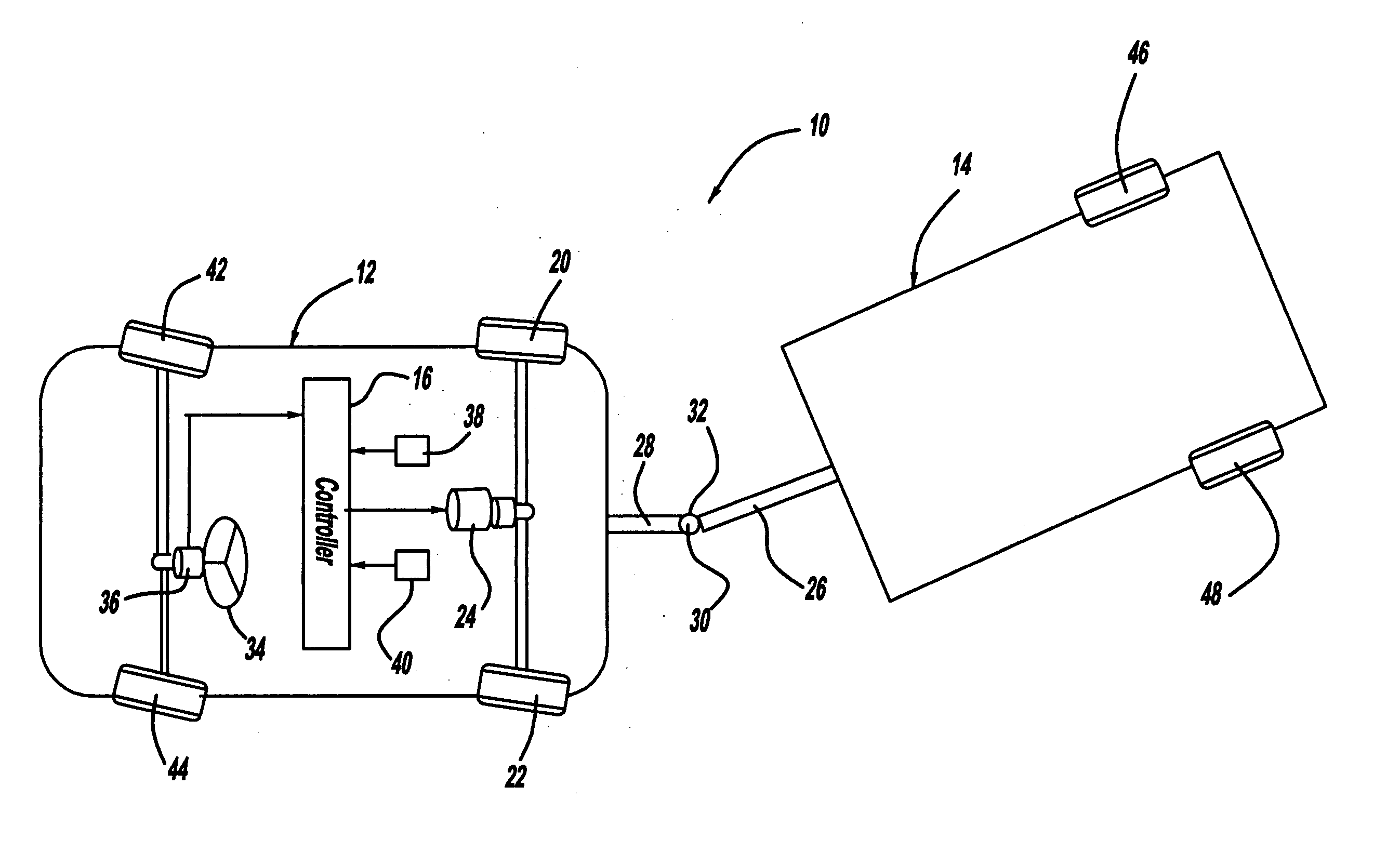

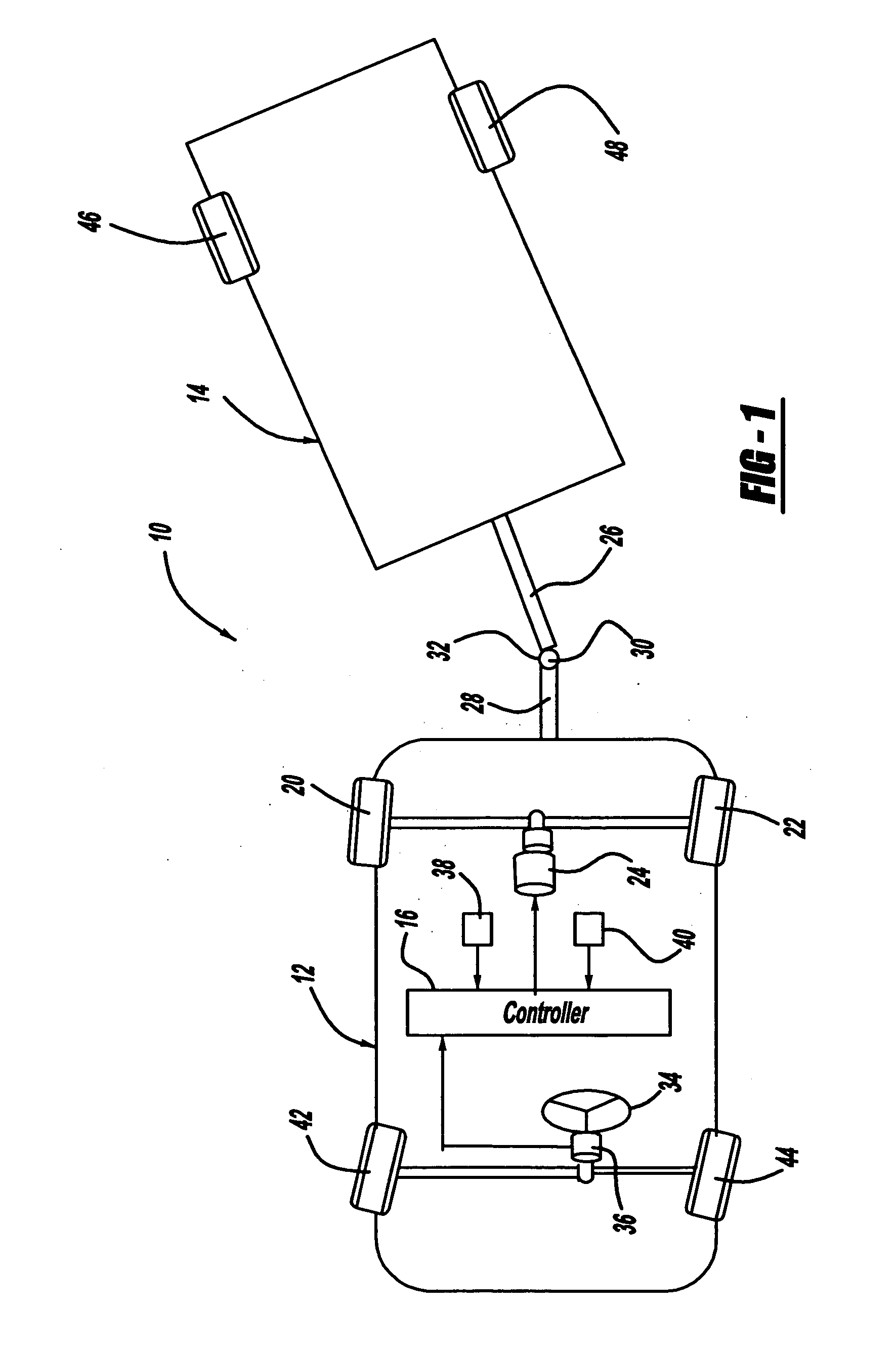

Vehicle-trailer low-speed offtracking control

InactiveUS20070152424A1Steering precisionSteering linkagesAutomatic initiationsLow speedControl system

An offtracking control system for a vehicle / trailer combination that properly steers the rear wheels of the vehicle to control the hitch angle between the vehicle and the trailer to prevent trailer offtracking. The control system generates a desired hitch angle and a time delay between the front wheels of the vehicle and the rear wheels of the trailer. A delay unit generates a hitch angle command from the desired hitch angle and the time delay. The hitch angle command is subtracted from a measured hitch angle to generate a hitch angle error signal. The hitch angle error signal is sent to a feedback controller that generates a closed-loop rear-wheel steering signal. The closed-loop rear-wheel steering signal is added to an open-loop rear-wheel steering signal to generate a rear-wheel steering command signal that prevents trailer offtracking.

Owner:GM GLOBAL TECH OPERATIONS LLC

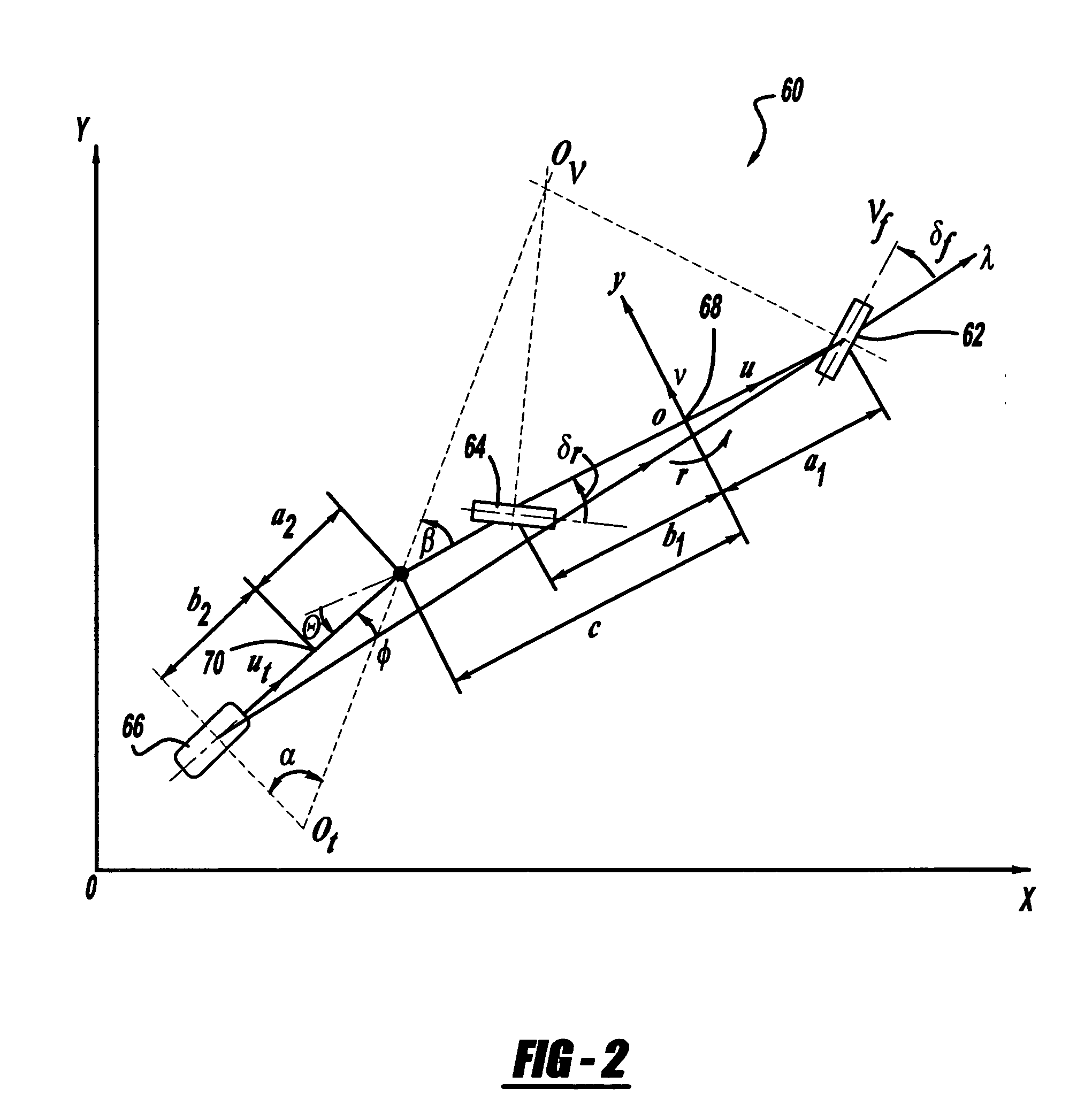

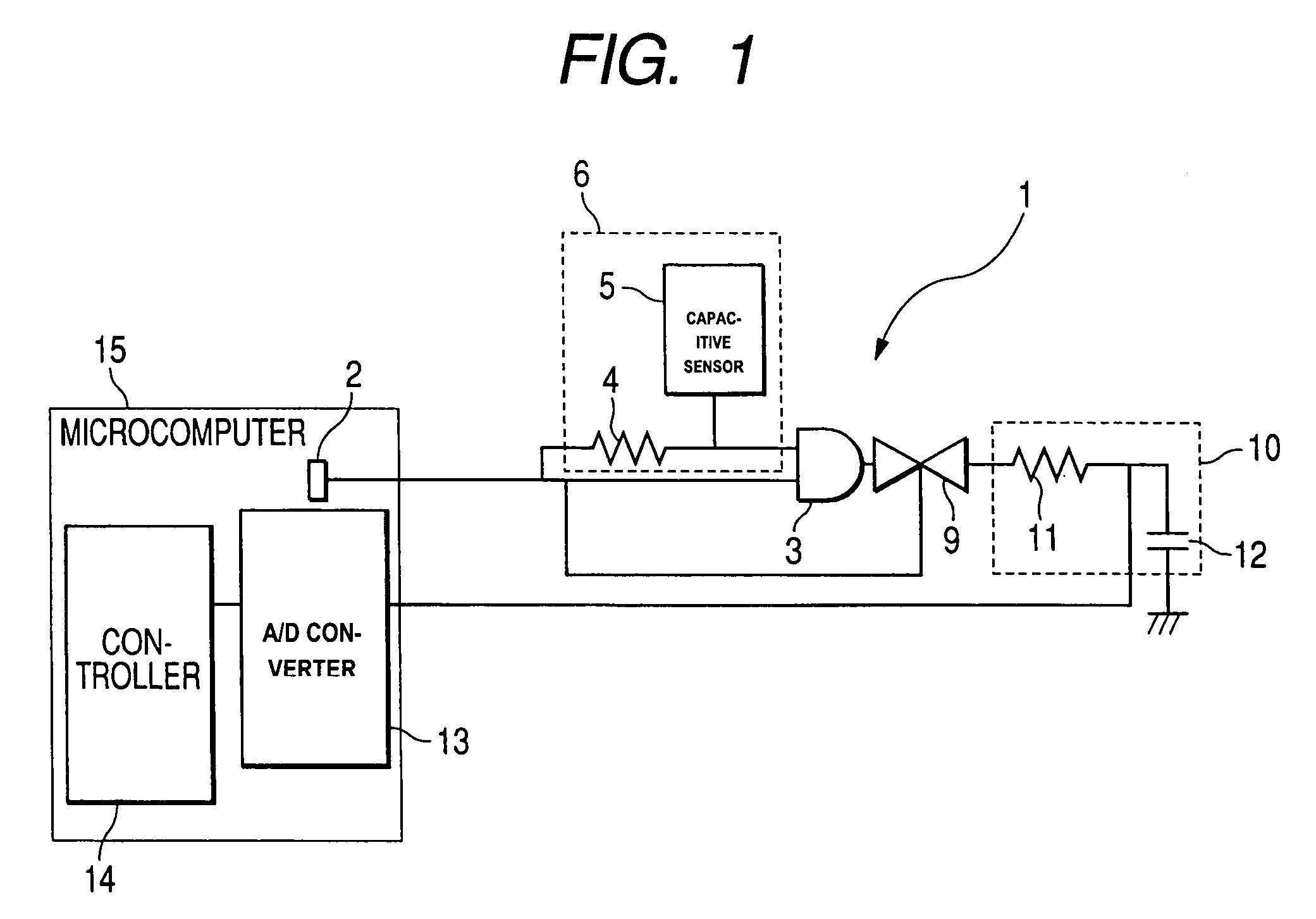

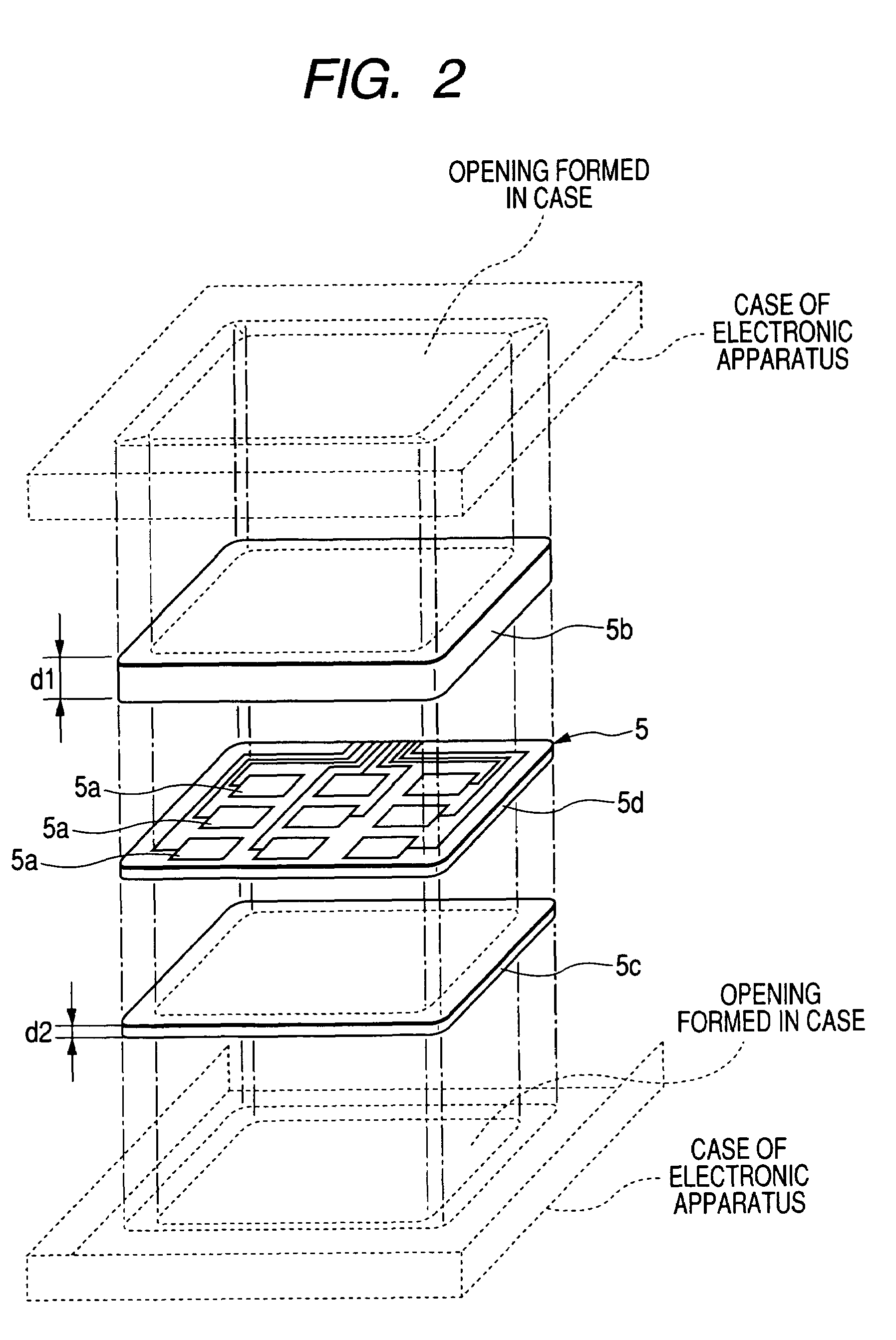

Capacitive input device

ActiveUS7348898B2Easy to operateSmall sizeTransmission systemsElectronic switchingDielectricSignal on

A input device is provided which includes a clock signal generator that generates a clock signal; a delay unit that has a capacitive sensor where an electrode is formed on a substrate; protective sheets each of which is formed of a dielectric and which are disposed on front and rear surfaces of the capacitive sensor; a logical product unit that transmits an output signal on the basis of a clock signal obtained from the clock signal generator and a delay signal obtained from the delay unit; and a controller that makes a predetermined program executed in accordance with an output signal obtained on the basis of the logical product unit.

Owner:ALPS ALPINE CO LTD

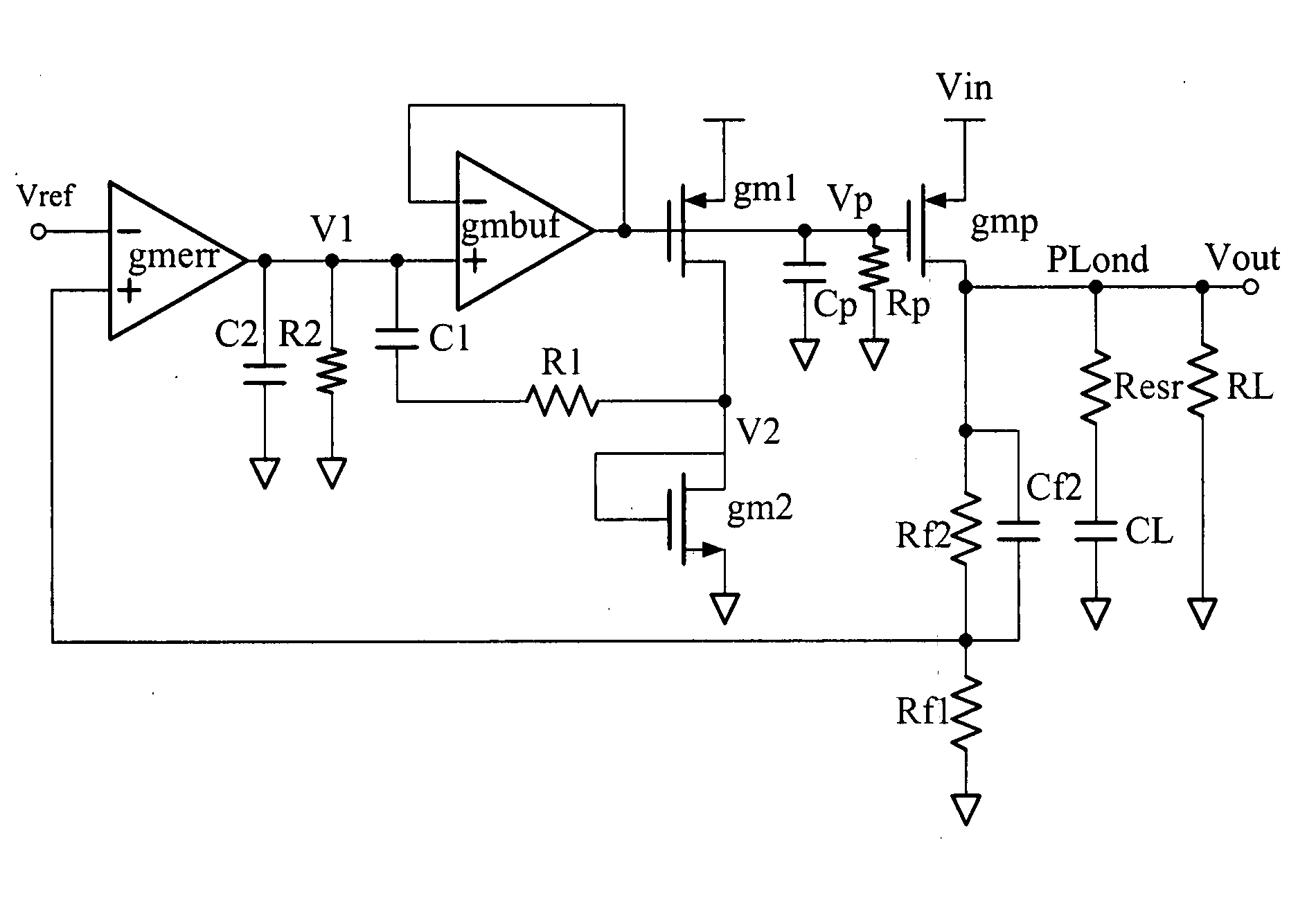

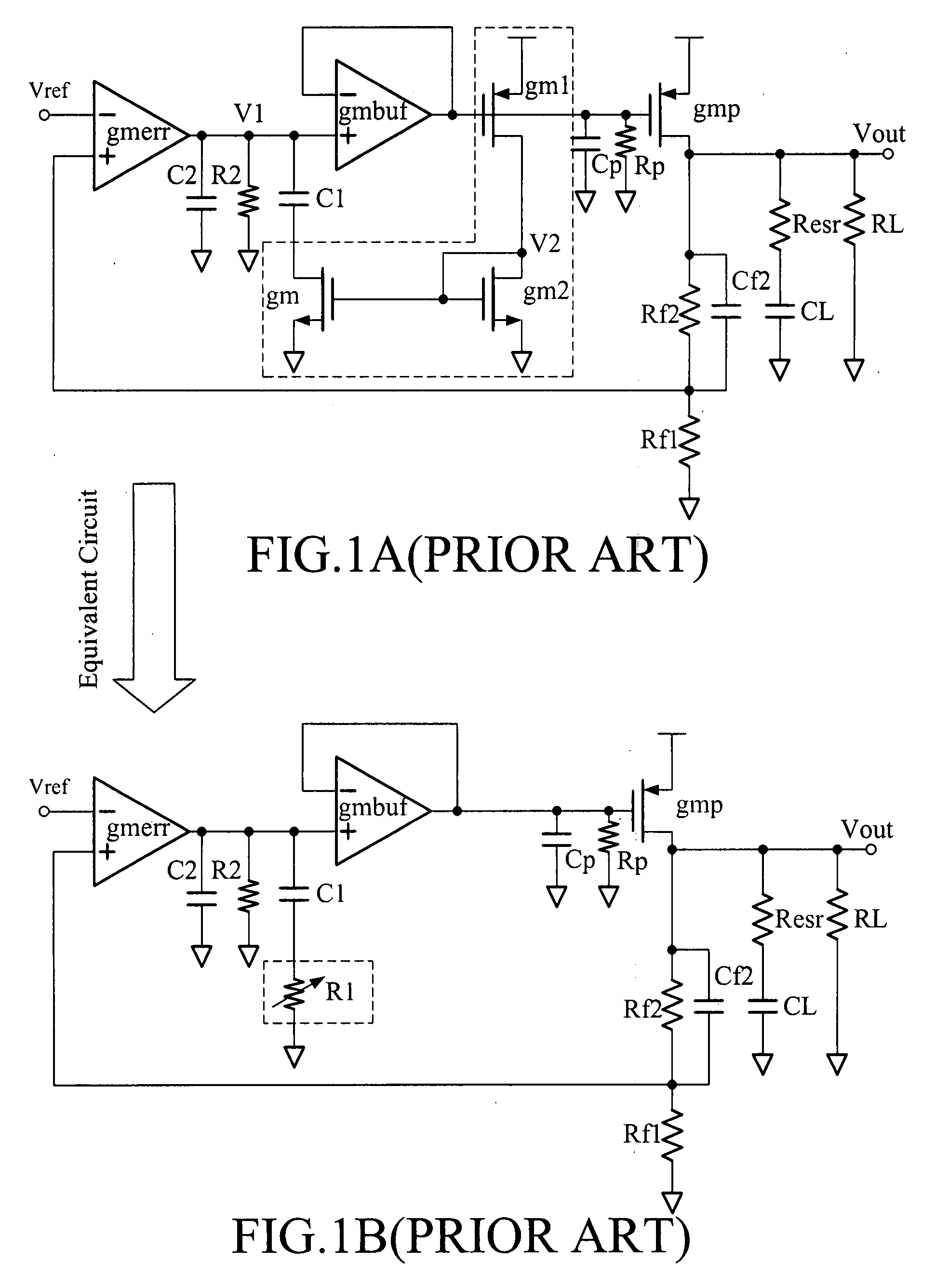

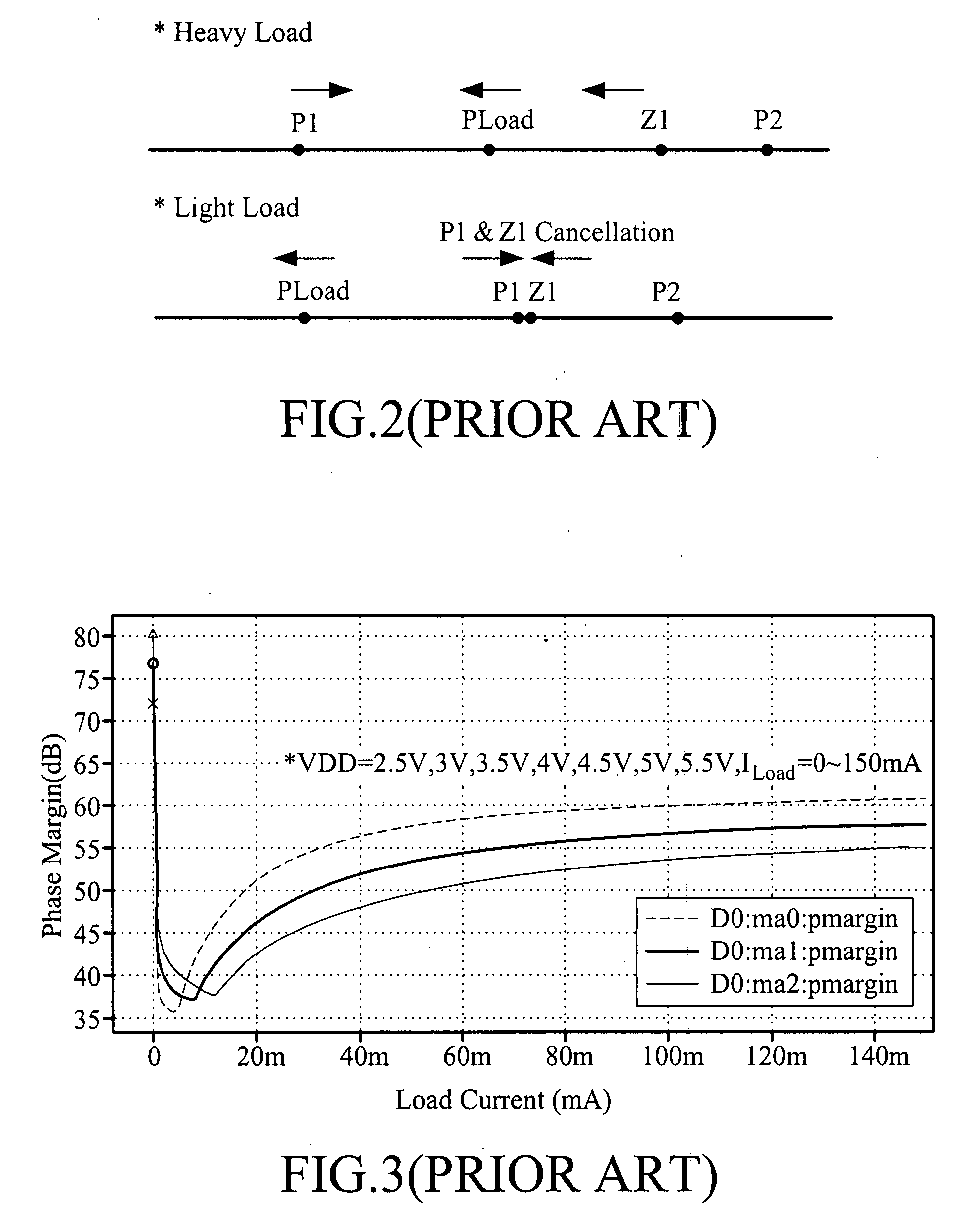

Adaptive pole and zero and pole zero cancellation control low drop-out voltage regulator

InactiveUS20080157735A1Good phase marginBandwidth of loop will become largeElectric variable regulationEngineeringControl theory

Owner:IND TECH RES INST

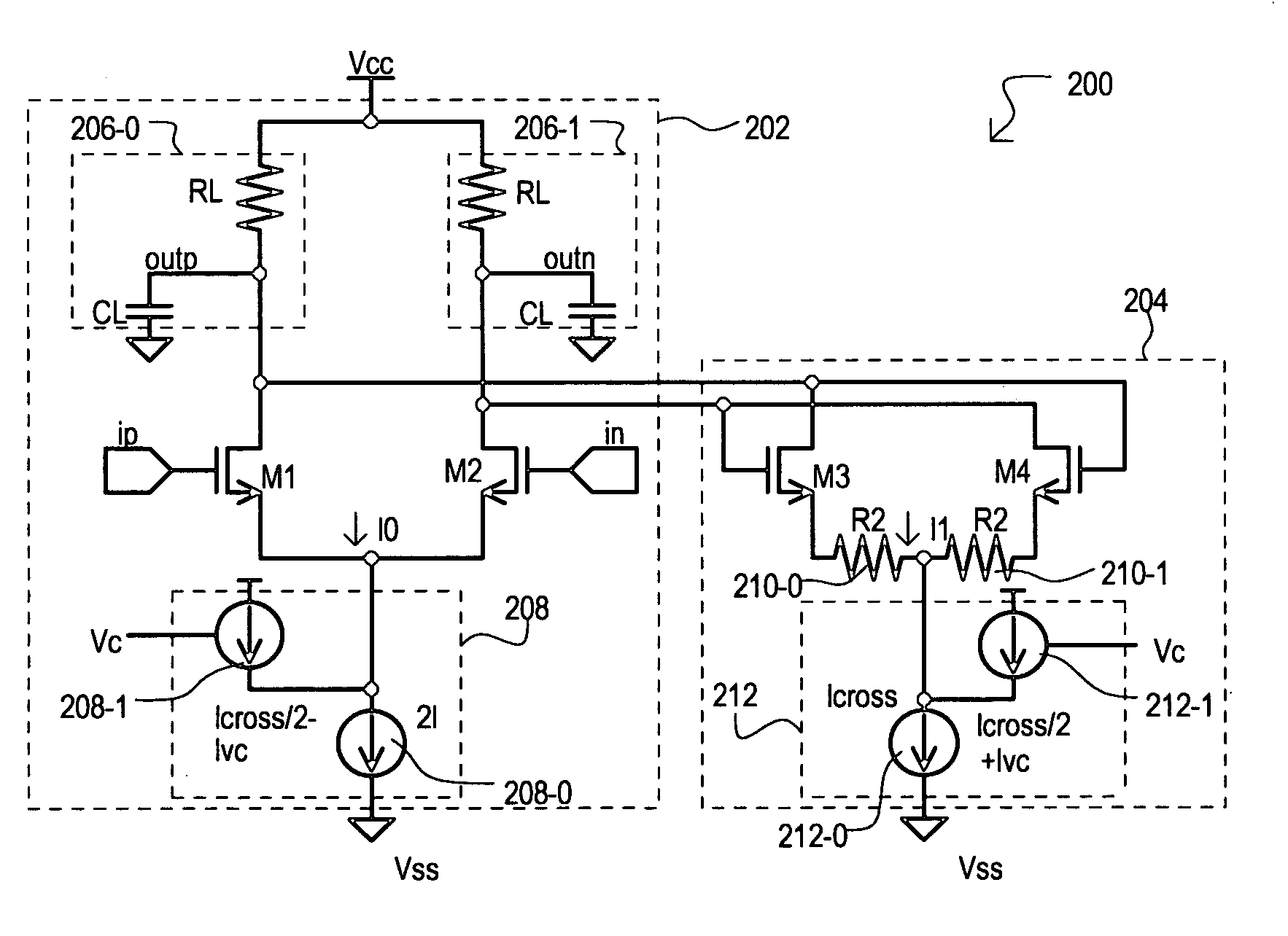

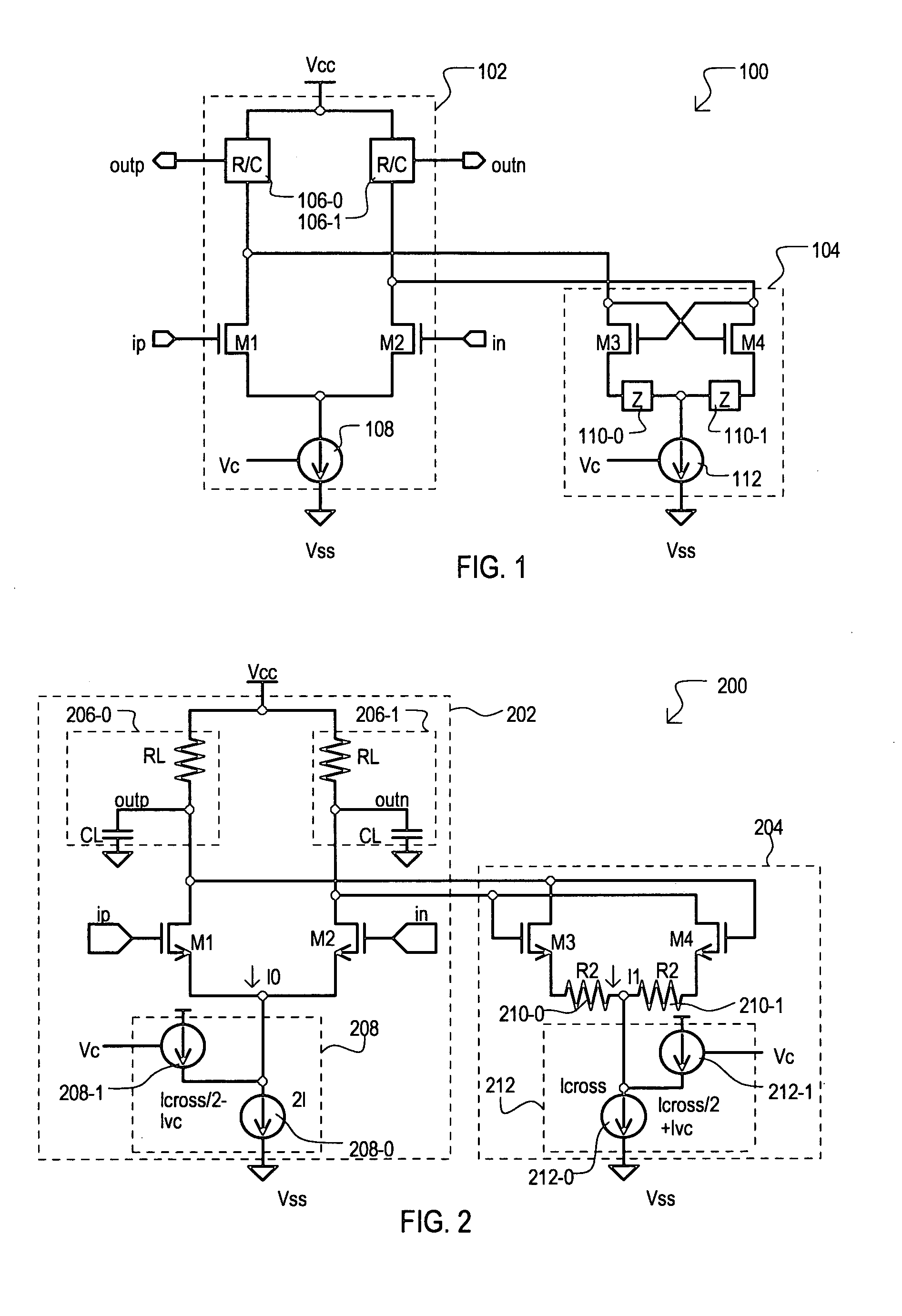

Voltage controlled oscillator delay cell and method

A delay cell circuit (200) is disclosed. The delay cell circuit may include a differential stage (202) and a cross-coupled stage (204). The cross-coupled stage can include resistors (210-0 and 210-1) the function to reduce a gain. The differential stage (202) and cross-coupled stage (204) can include variable currents sources (208 and 212), respectively. As frequency of operation increases, variable current source (208) provides a larger current to the differential stage (202) and variable current source (212) provides a smaller current to cross-coupled stage (204). Delay cell circuit (200) may be used in a voltage controlled oscillator (VCO). By including gain attenuating devices such as resistors (210-0 and 210-1), a frequency tuning range of the VCO may be increased.

Owner:MONTEREY RES LLC

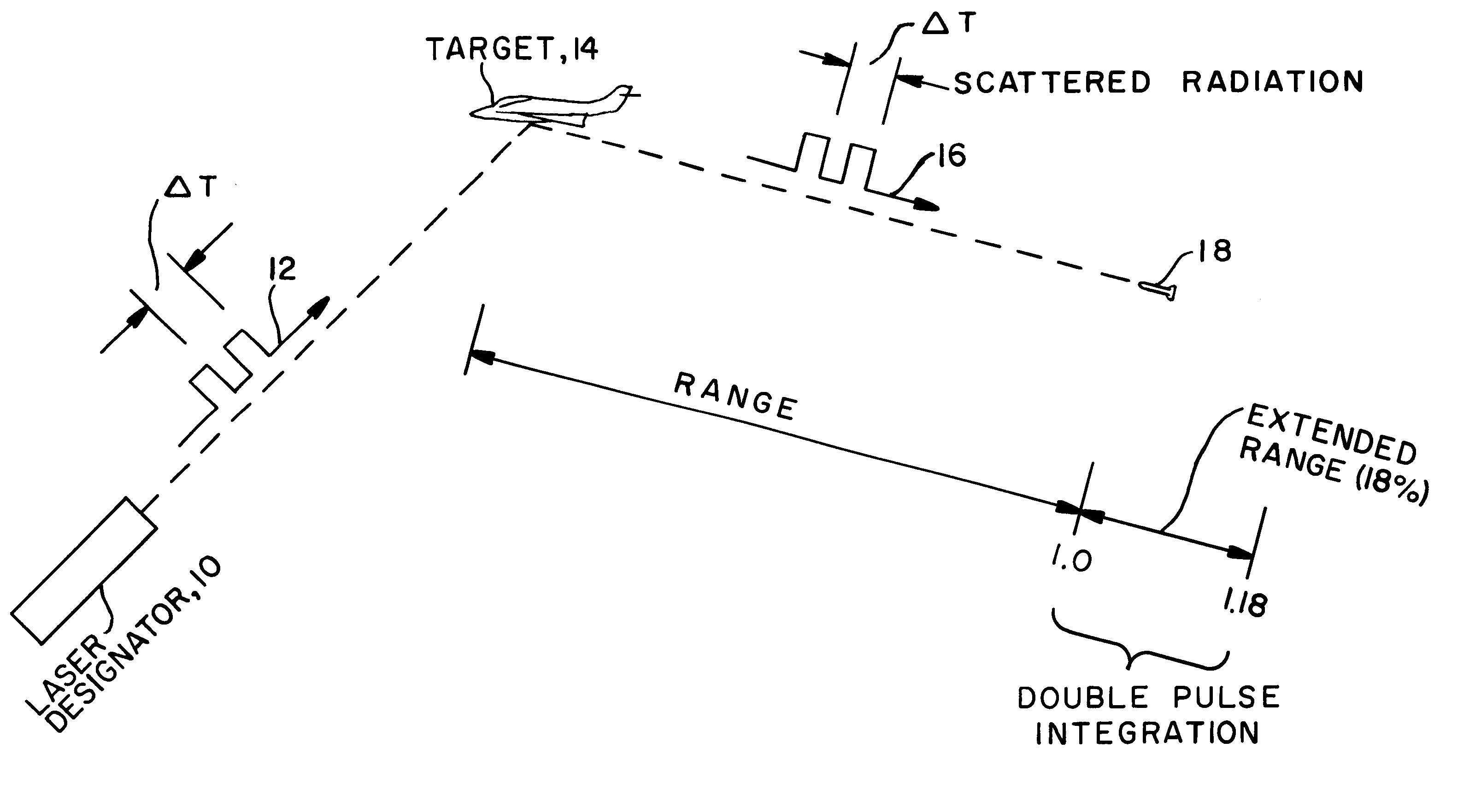

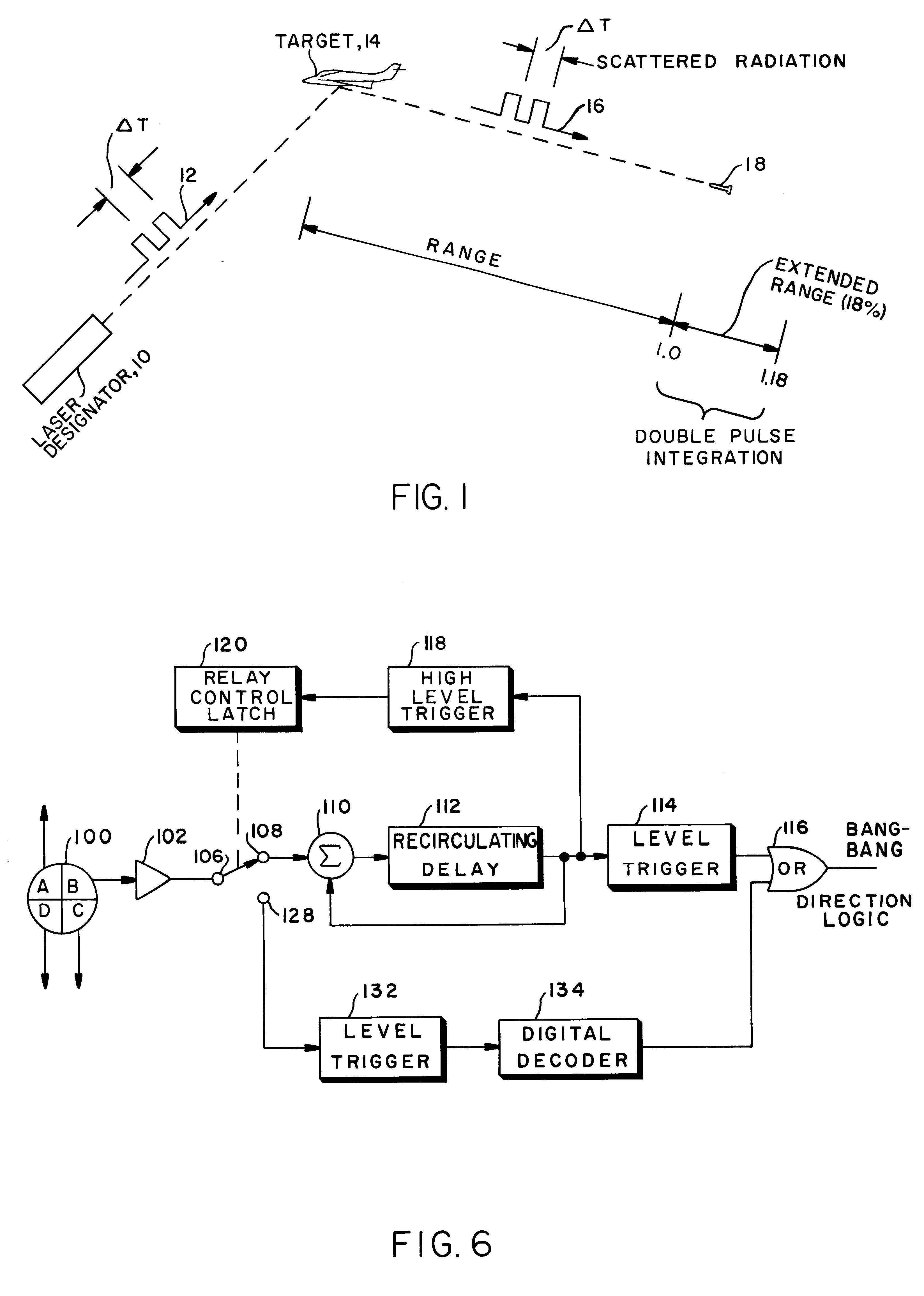

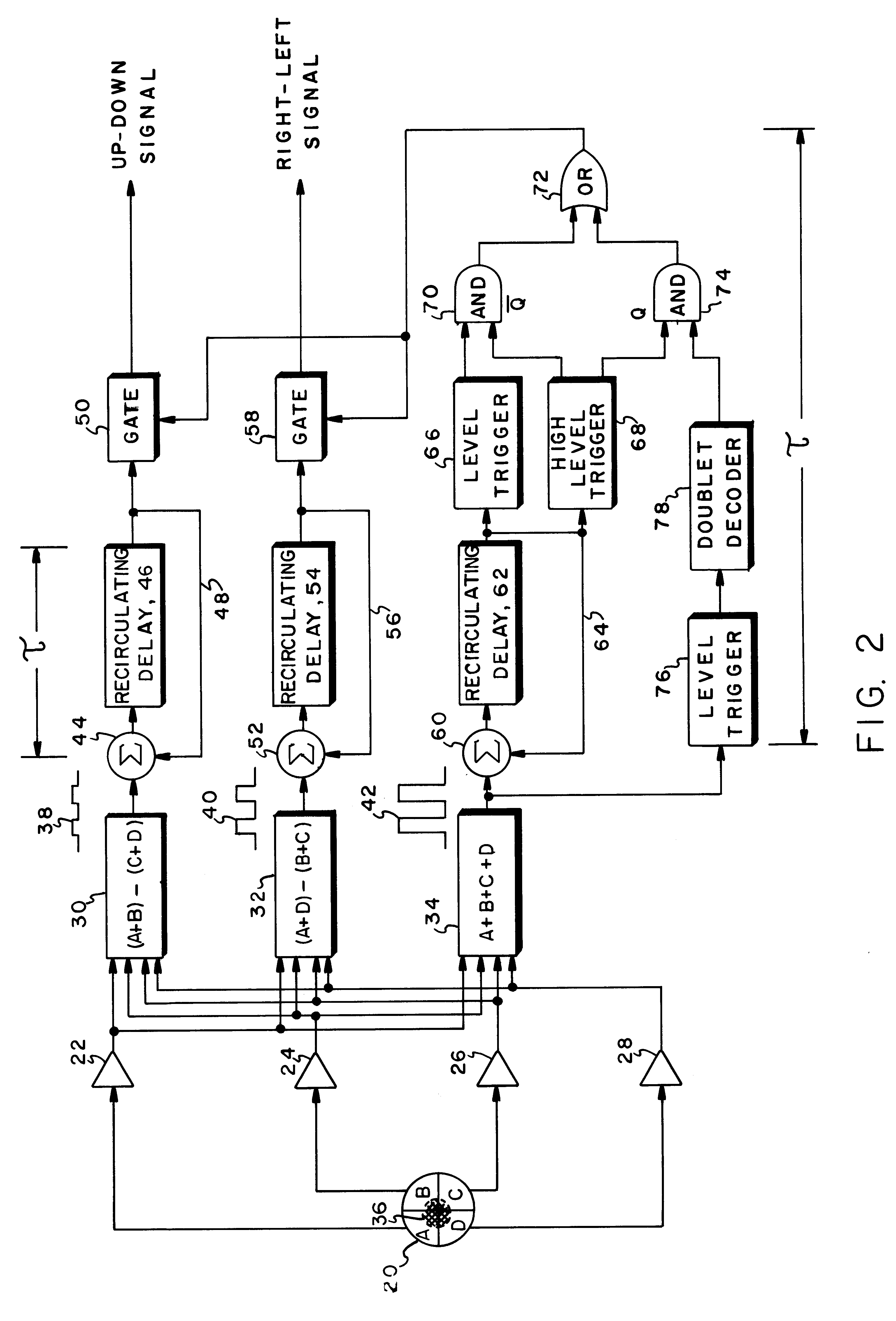

Extended range, light weight laser target designator

InactiveUS6926227B1Improve signal-to-noise ratioReduce false alarm rateDirection controllersPosition fixationLaser targetCountermeasure

Pulse integration is utilized on board an optically guided missile or other ordinance device used as a part of a target designation system for extending the lock-on range of the missile by approximately 18%, when a double pulse laser is utilized to illuminate and designate the target. Pulse integration is accomplished with a recirculating delay unit which superimposes the first pulse on the second pulse, such that while the pulses add coherently, noise does not add in phase. The pulse integration technique therefore enhances the signal-to-noise ratio when the missile is at the outer limits of its operating range. When the missile is sufficiently close to the target, doublet decoding is actuated to offer countermeasure resistance. At this point, pulse integration may proceed in lieu of doublet decoding or may be dispensed with in view of the increased signal-to-noise ratio due to the close range of the missile to the target.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC +1

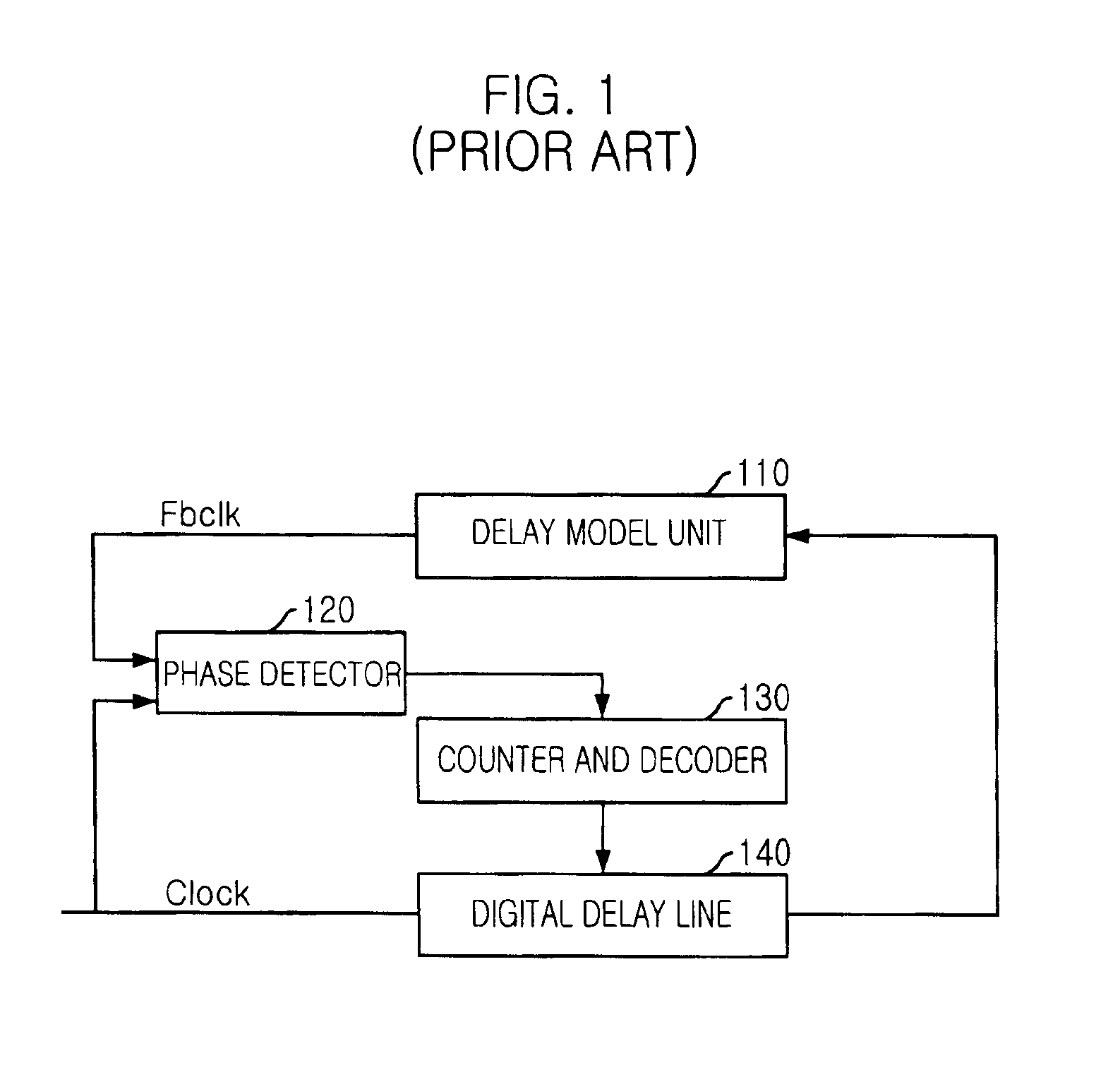

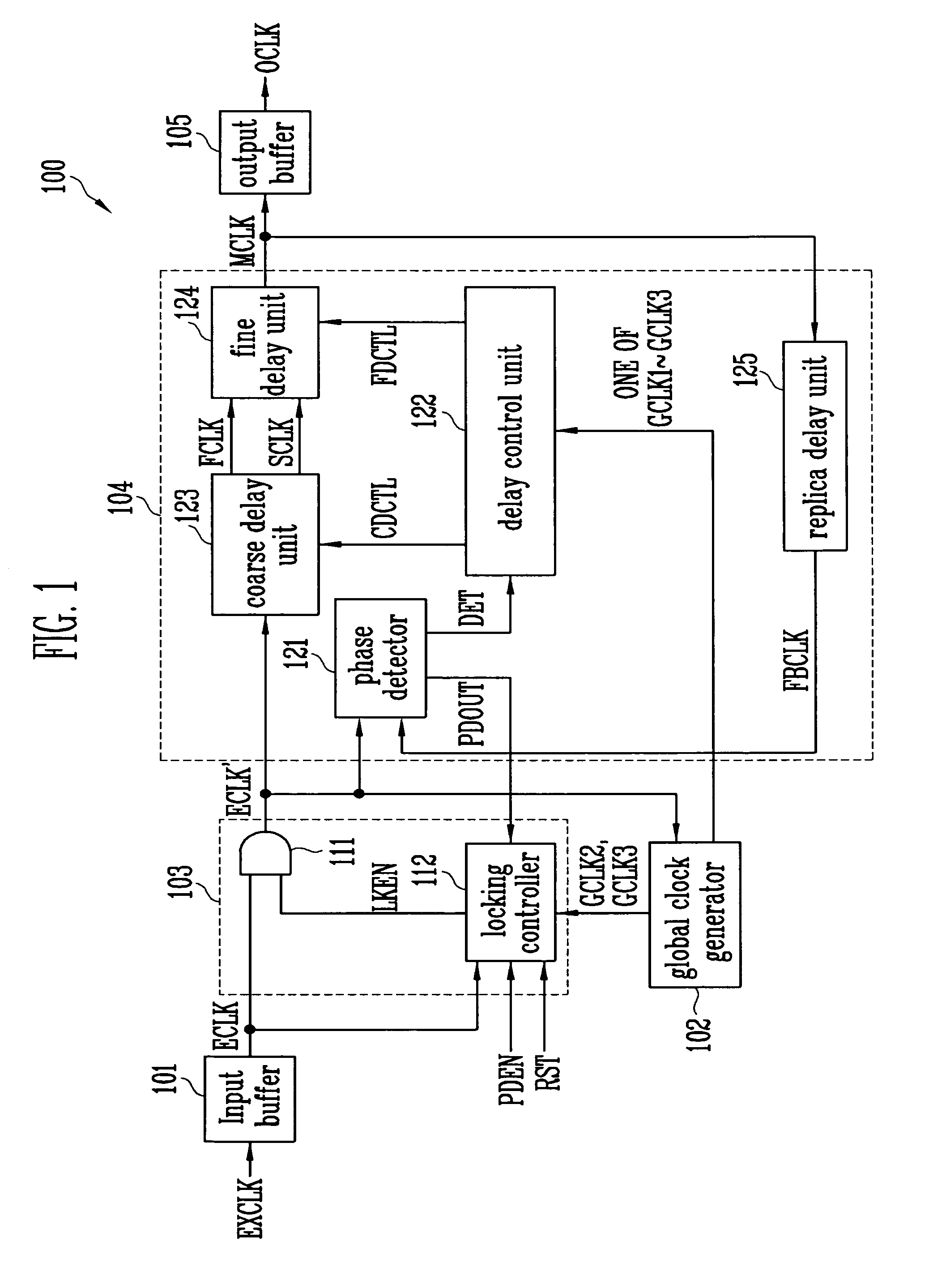

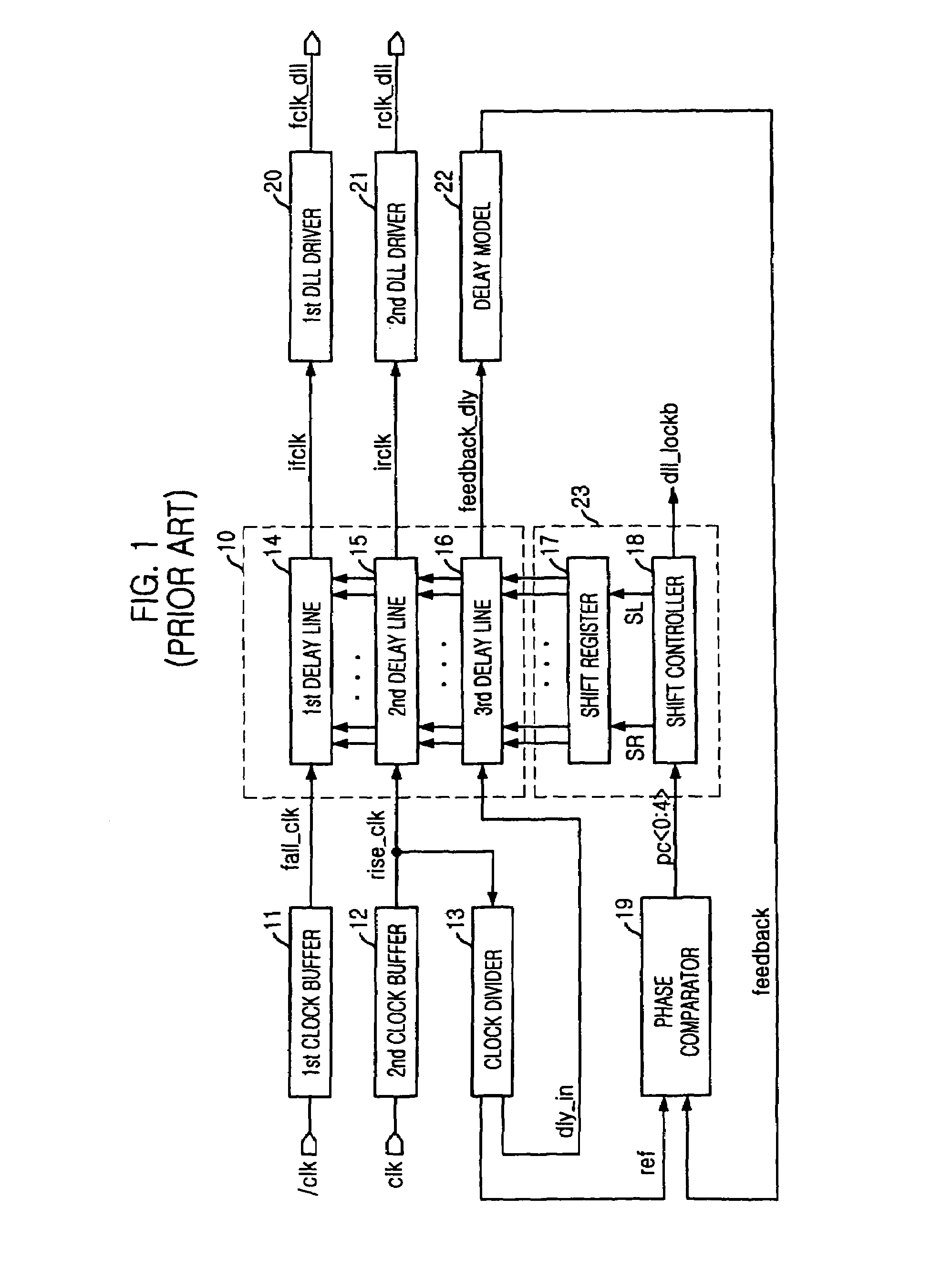

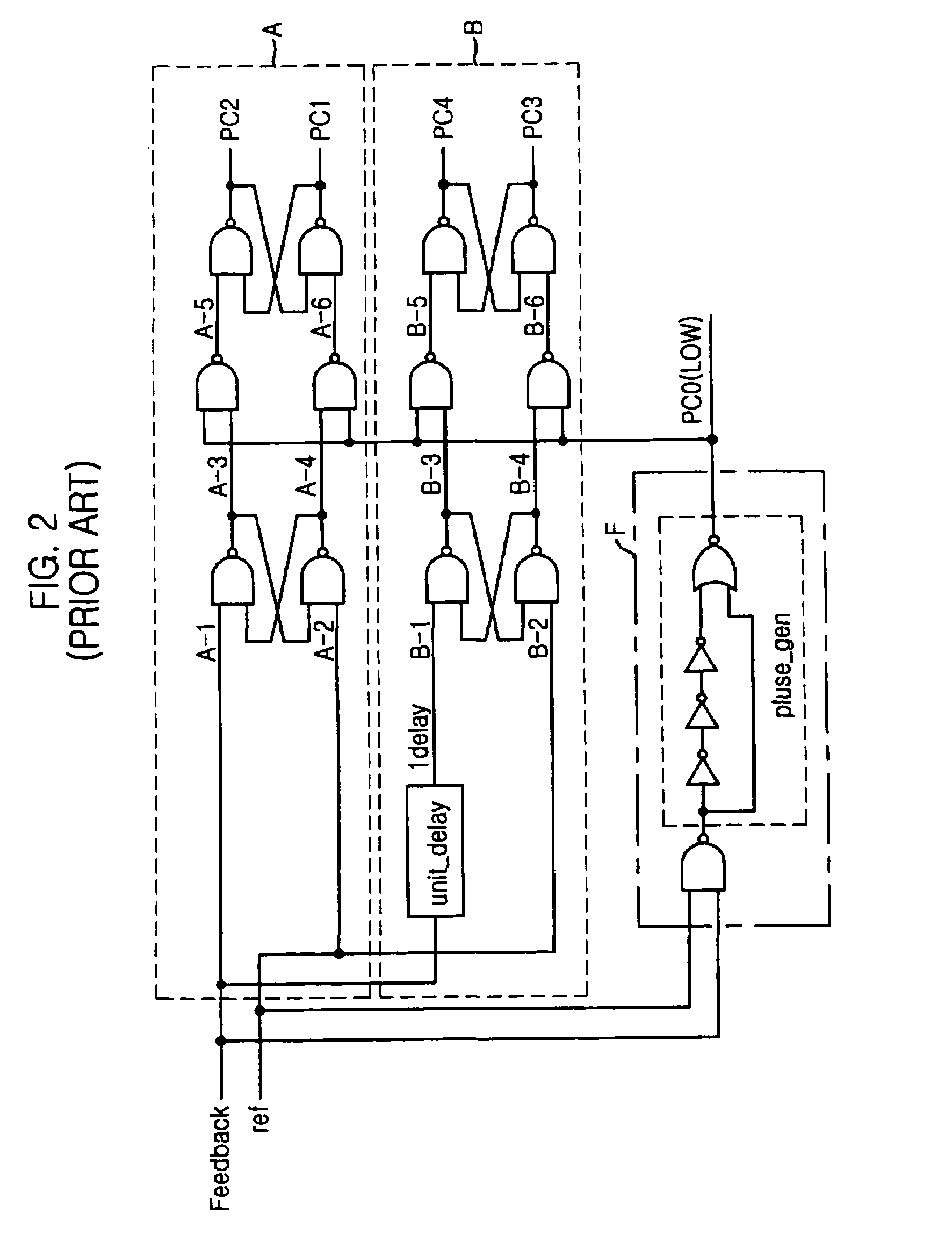

Delay locked loop having low jitter in semiconductor device

InactiveUS6917229B2Reduce jitterPulse automatic controlAngle demodulation by phase difference detectionControl signalDelay-locked loop

A DLL circuit having a low jitter in a semiconductor device, includes a delay model unit for compensating a time difference between an external clock signal and an internal clock signals and generating a compensation signal; an input buffer for receiving a reference clock signal and an inverted clock signal, and for outputting a clock signal and an inverted clock signal activated at each edges of the reference clock signal and the inverted clock signal; a phase detection unit for generating a comparison signal by comparing the compensation signal with the inverted clock signal, and for outputting the comparison signal with a normal mode or a fast mode; a control unit for generating a plurality of control signals by receiving the comparison signal, the inverted clock signal and the clock signal; a delay unit for delaying in response to the plurality of control signals; and an output buffer for outputting a delayed clock signal by receiving an output signal of the duty corrector.

Owner:SK HYNIX INC

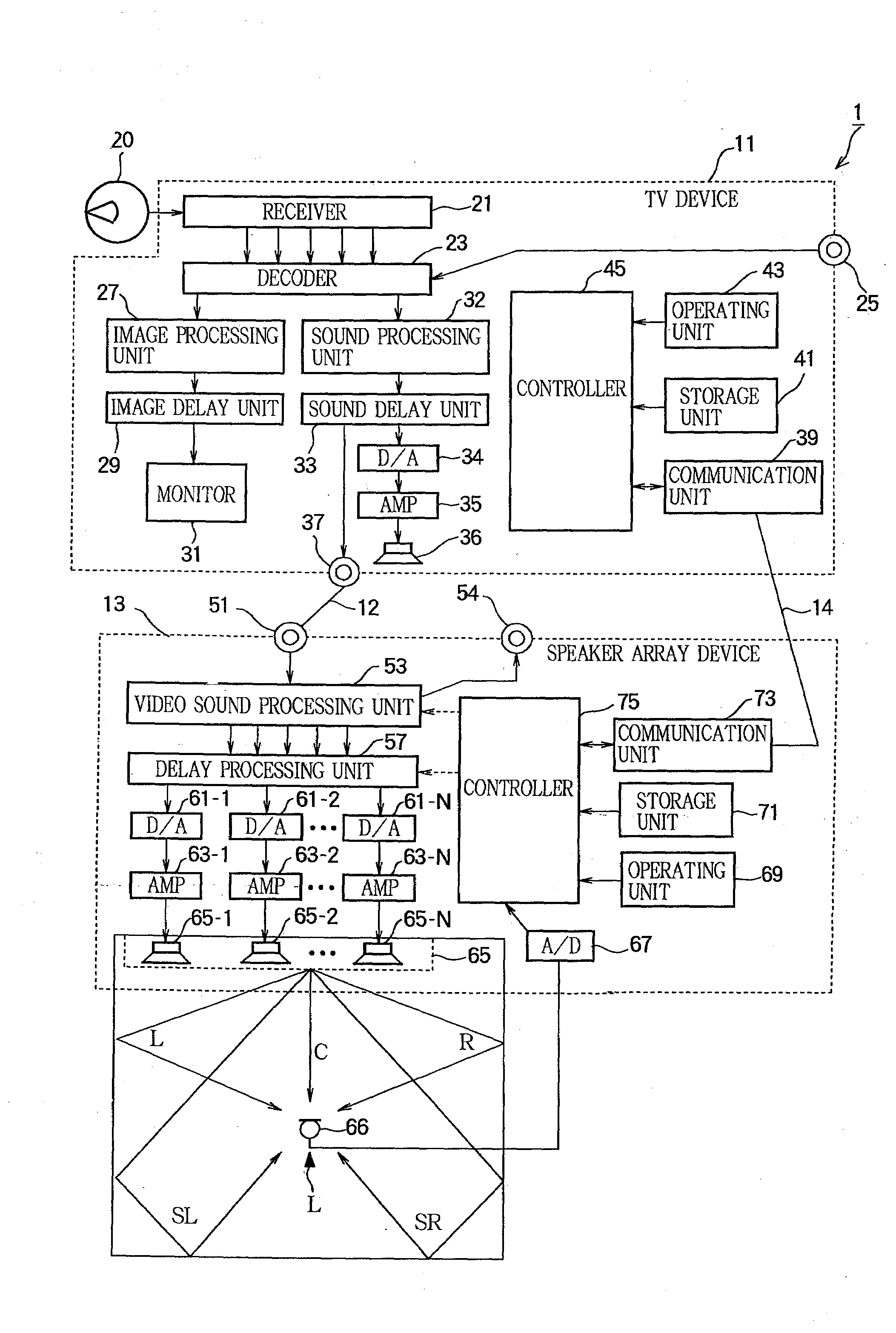

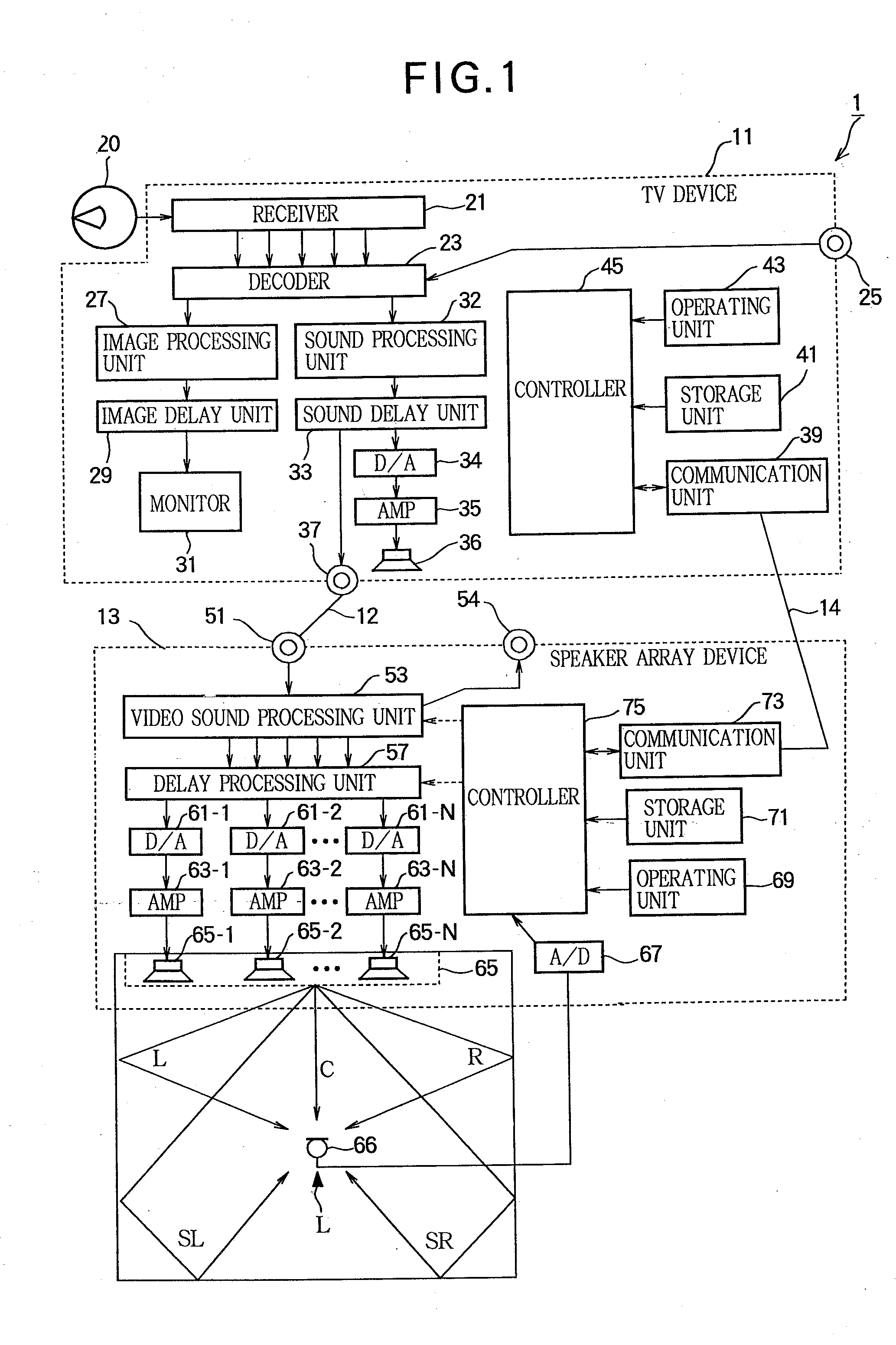

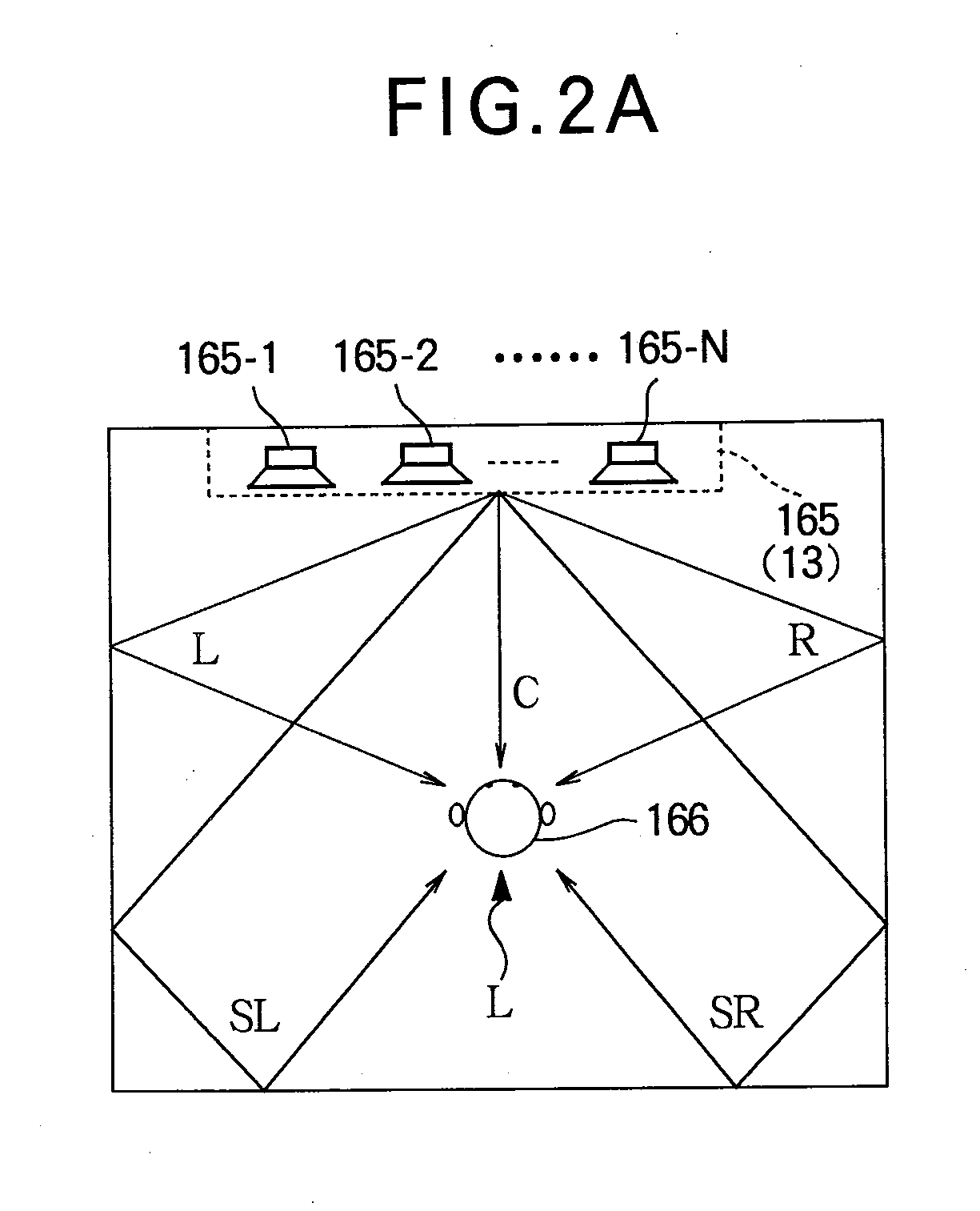

AV System

InactiveUS20090290064A1Enabling synchronizationEliminate lack of synchronizationTelevision system detailsMicrophonesTime informationCommunication unit

AV content is input and output in an AV system. In the AV system, a plurality of AV devices process a signal of the content to reproduce the content. A source device broadcasts the content to each of the AV devices. In each of the AV devices, a reproduction unit receives the content broadcast by the source device and performs reproduction processing on the received content. A communication unit communicates reproduction processing time information with another AV device, the reproduction processing time information indicating a time required for the reproduction processing of the content. A delay unit delays a time to reproduce the content, such that the delay unit delays reproduction of the content in accordance with an AV device having a latest reproduction timing based on the reproduction processing time information.

Owner:YAMAHA CORP

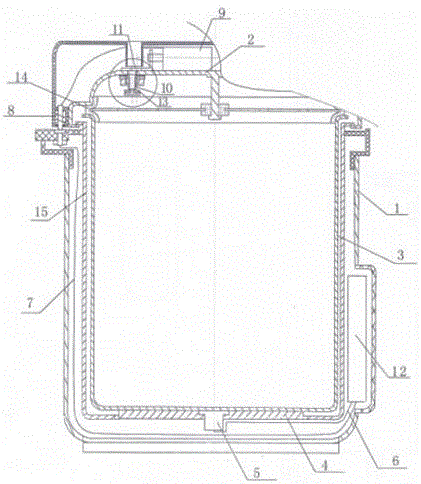

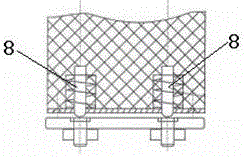

Electromagnetic control delay booster electric pressure cooker

InactiveCN106691171ASolve the problem of poor cooking effectEasy to solvePressure-cookersAtmospheric airControl delay

Disclosed is an electromagnetic control delay booster electric pressure cooker. A floater limited block is connected with an electromagnet, and the electromagnet drives the floater limited block to the position of the limiting floater or the releasing floater. At the position of the limited floater, the floater limited block blocks the floater, and limits the rising of the float, keeping expelling the steam in the cooker to the atmosphere through the vent hole of the floater; At the position of the releasing floater, the floater rises and falls freely; the line control institutions are provided with a delay control unit to control the electromagnet, and start the delay unit to control the work of the electromagnet in the specified delay time when the temperature of the temperature detector rises to the set delay startup time. The cooker has the advantages that: when the electric pressure cooker is cooking rice, the cooker releases partial steam insides after the rice boiling, and grain of rice in the cooker continues boiling in the condition of half a high-pressure, forcing the grain of rice absorb moisture quickly; close the outlet after reaching the set time, making the pressure in the cooker rises; shut off the power and keep heat to cook the rice. In this way, the rice grain is through core, chewiness and smooth when entering the mouth.

Owner:陆一铭

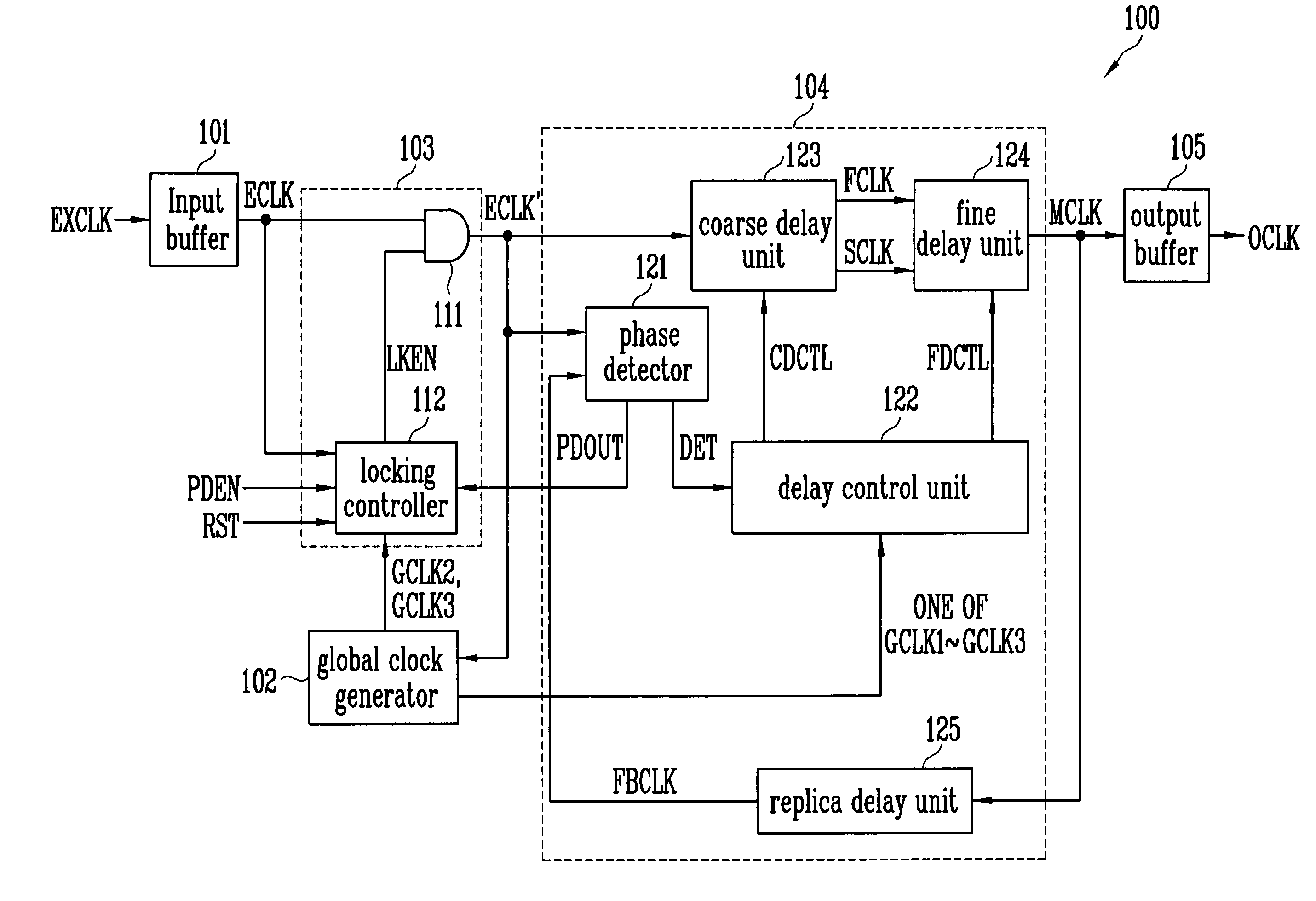

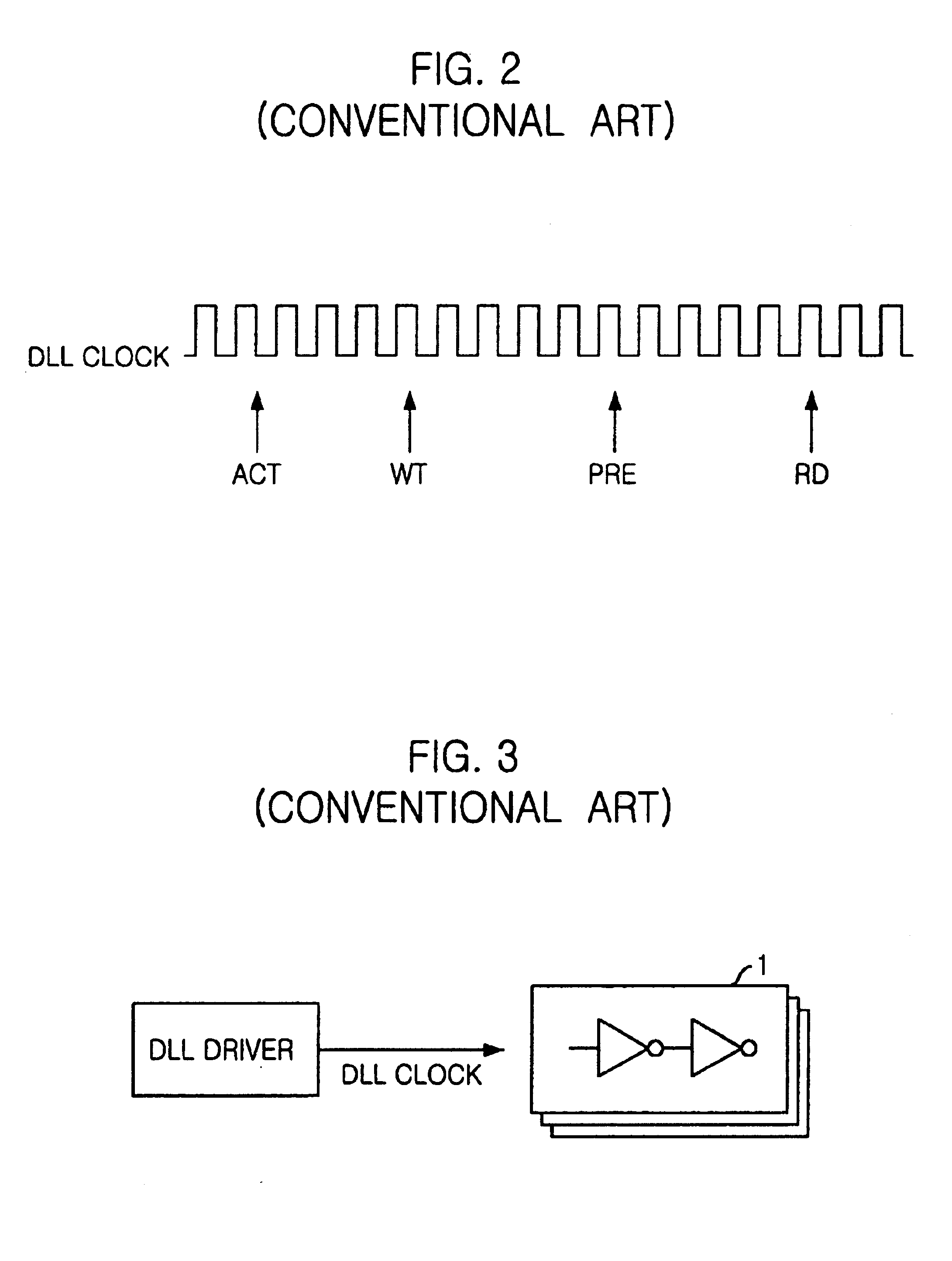

Delay locked loop with a function for implementing locking operation periodically during power down mode and locking operation method of the same

ActiveUS7388415B2Reduce power consumptionHigh speedPulse automatic controlElectricityPhase difference

A Delay Locked Loop (DLL) having a function of periodically executing a locking operation during a power down mode and a locking operation method of the same, which includes a global clock generator, a clock delay unit, and a power down control unit. The power down control unit, in response to some of a plurality of global clock signals, a phase detection signal, and a power down signal, outputs an input clock signal to each of the global clock generator and the clock delay unit. During the power down mode, the clock delay unit is enabled to periodically carry out the locking operation whenever it receives the input clock signal. Therefore, a consumed power of the DLL can be decreased during the power down mode, and a phase difference between an external clock signal and an internal clock signal during the power down mode can be decreased by the periodical locking operation of the clock delay unit, so that the DLL can operate at a fast speed after the power down mode.

Owner:SK HYNIX INC

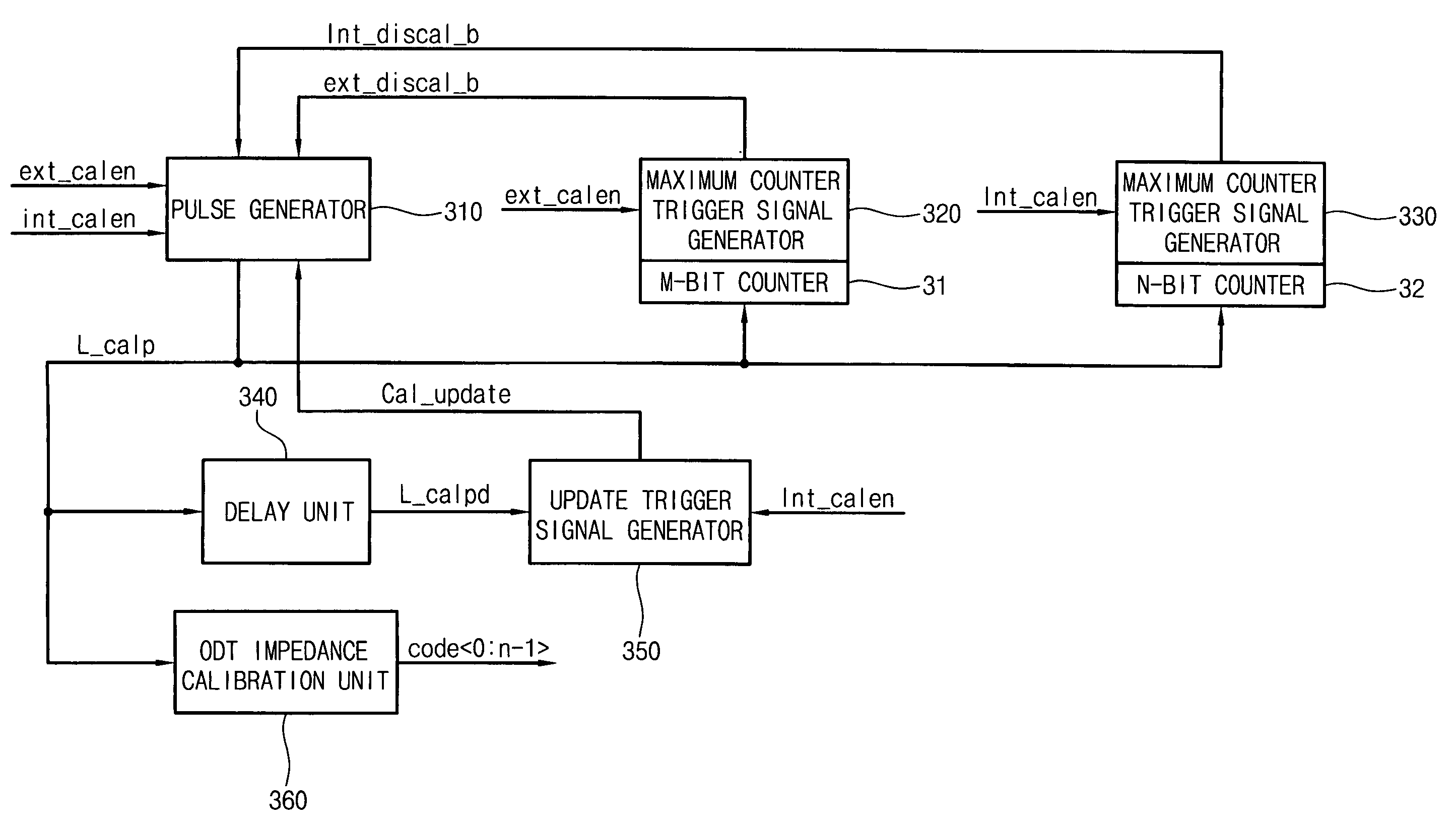

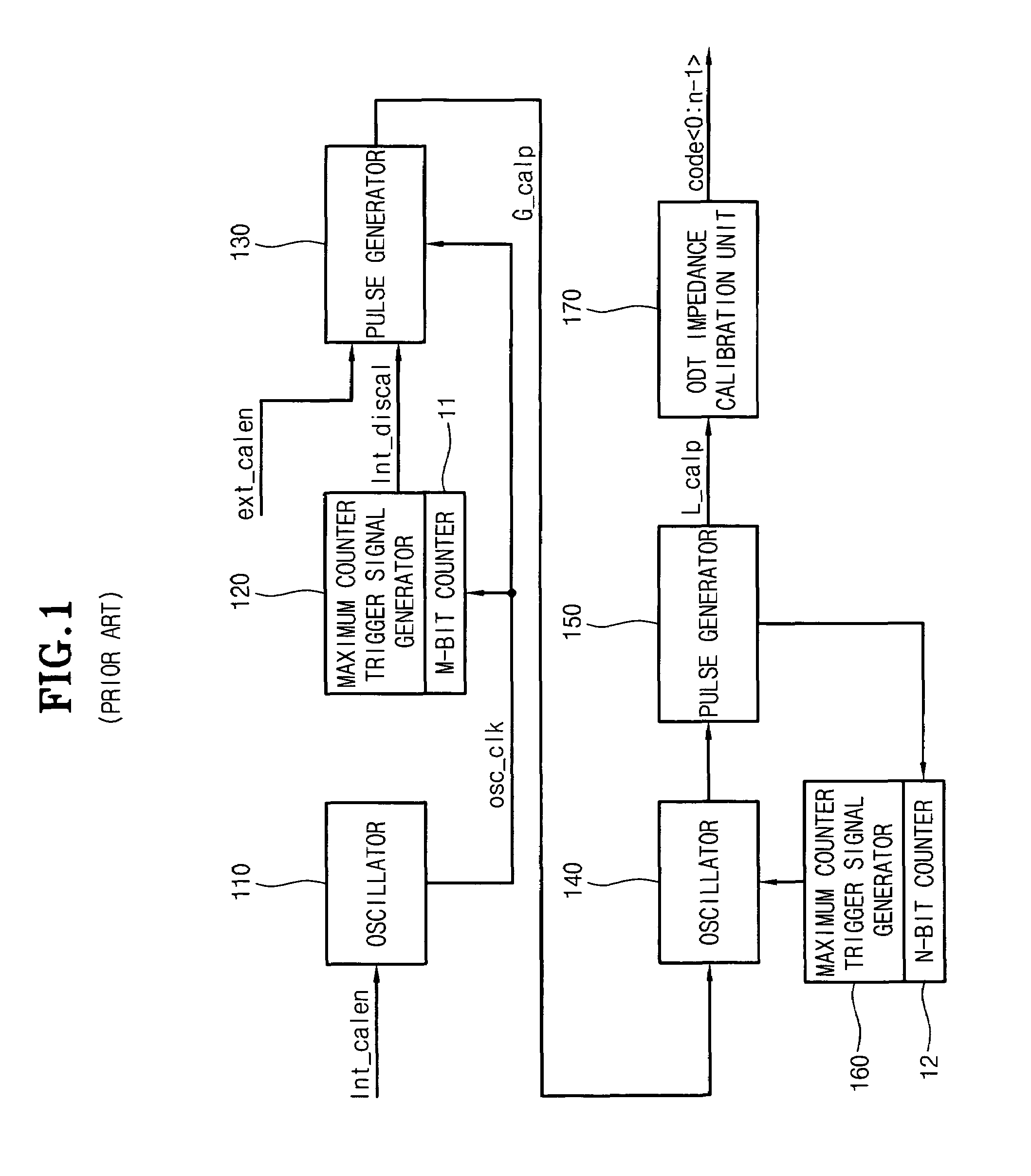

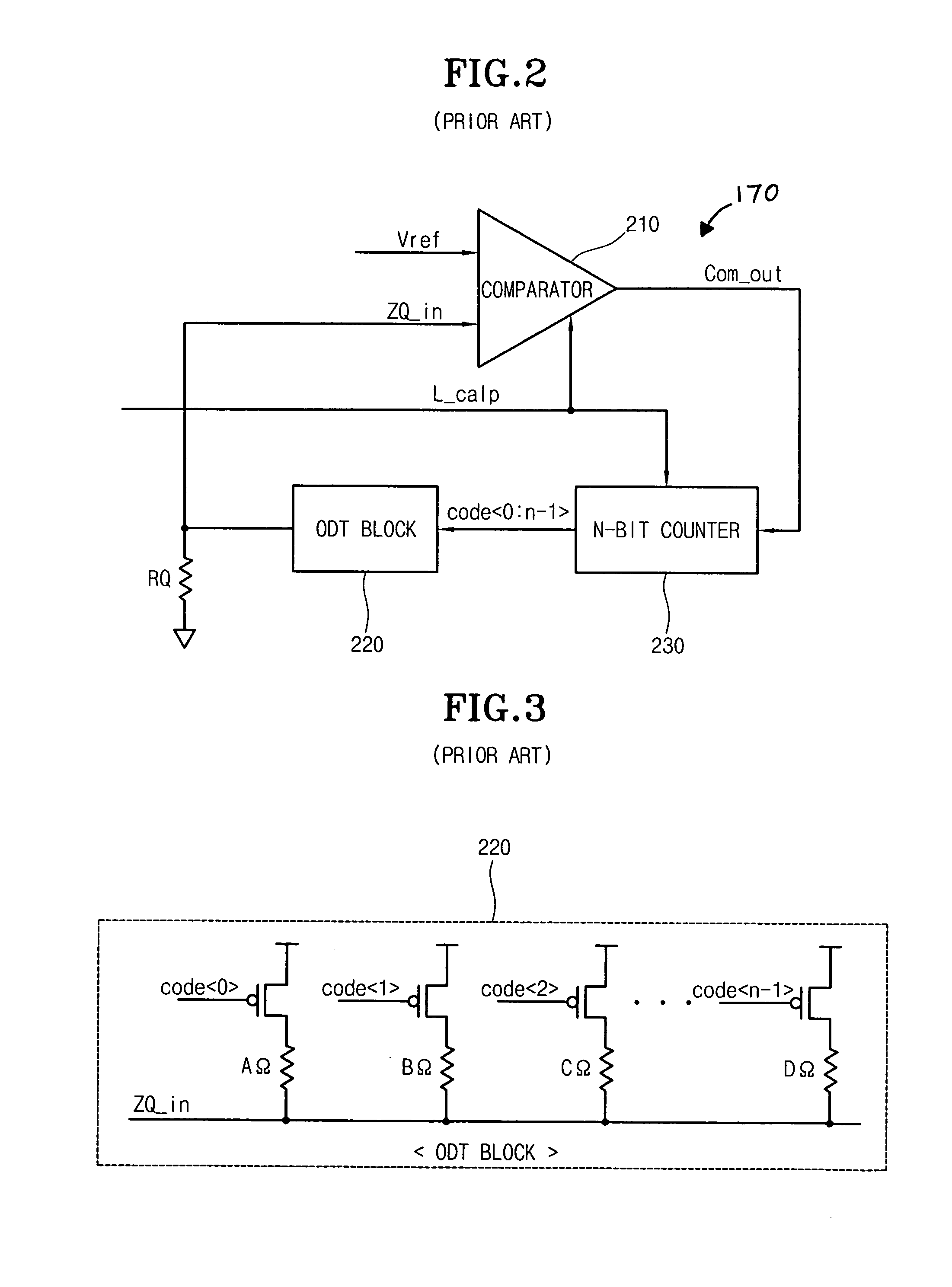

On-die termination impedance calibration device

InactiveUS7176711B2Multiple-port networksReliability increasing modificationsControl signalSignal generator

Disclosed is an on-die termination (‘ODT’) impedance calibration device. The ODT impedance calibration device comprises: a pulse generator for outputting a calibration signal of a pulse type for calibrating an ODT impedance; an M-bit counter for counting the number of pulses of the calibration signal; a first maximum counter trigger signal generator controlled by the M-bit counter; an N-bit counter for counting the number of pulses of the calibration signal; a second maximum counter trigger signal generator controlled by the N-bit counter; a delay unit for receiving a delay signal and outputting the delay signal after a predetermined period of time; an update trigger signal generator for outputting a pulse signal which is toggled according to an output signal of the delay unit; and an ODT impedance calibration unit for receiving the calibration signal and outputting a control signal for calibrating an ODT impedance.

Owner:SK HYNIX INC

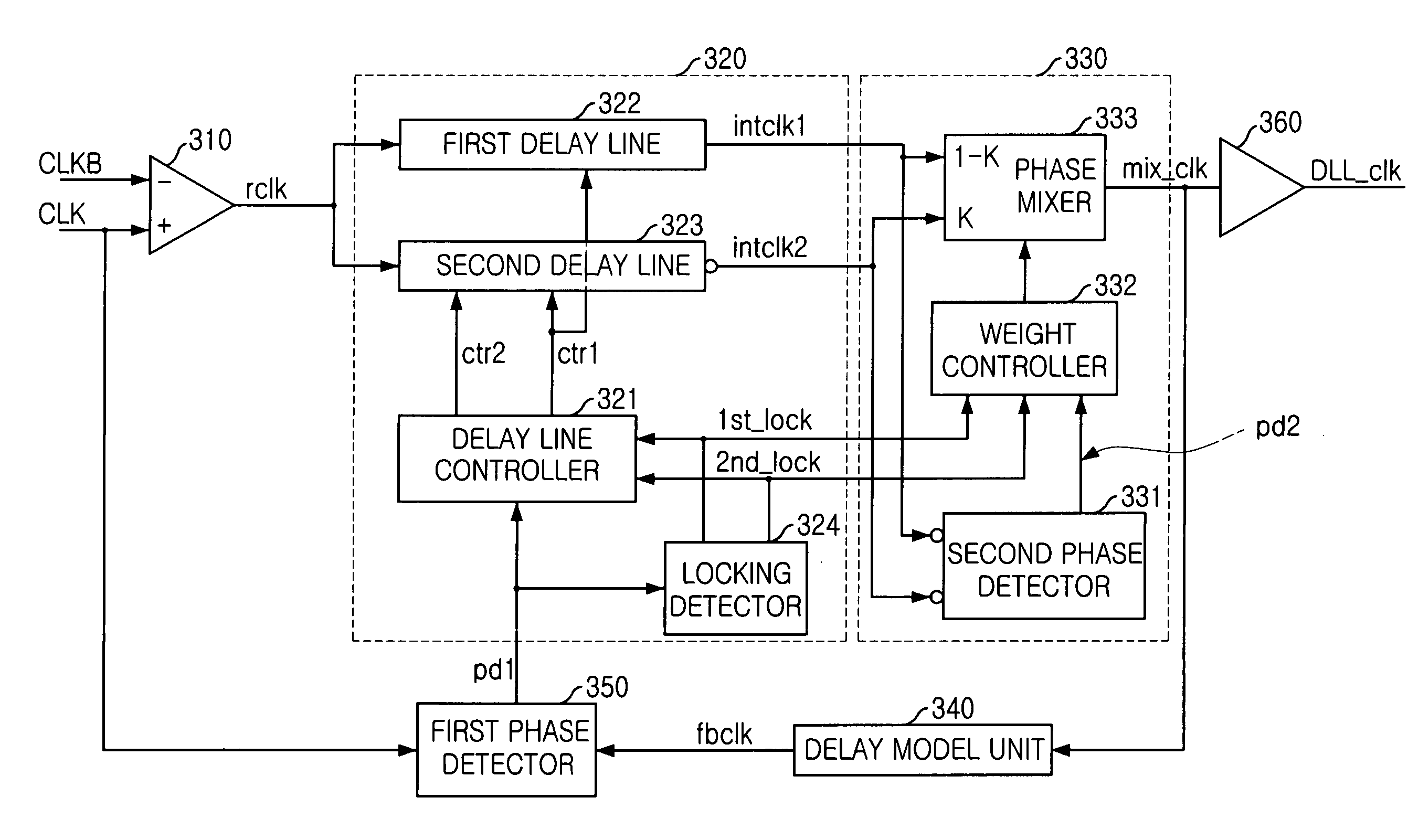

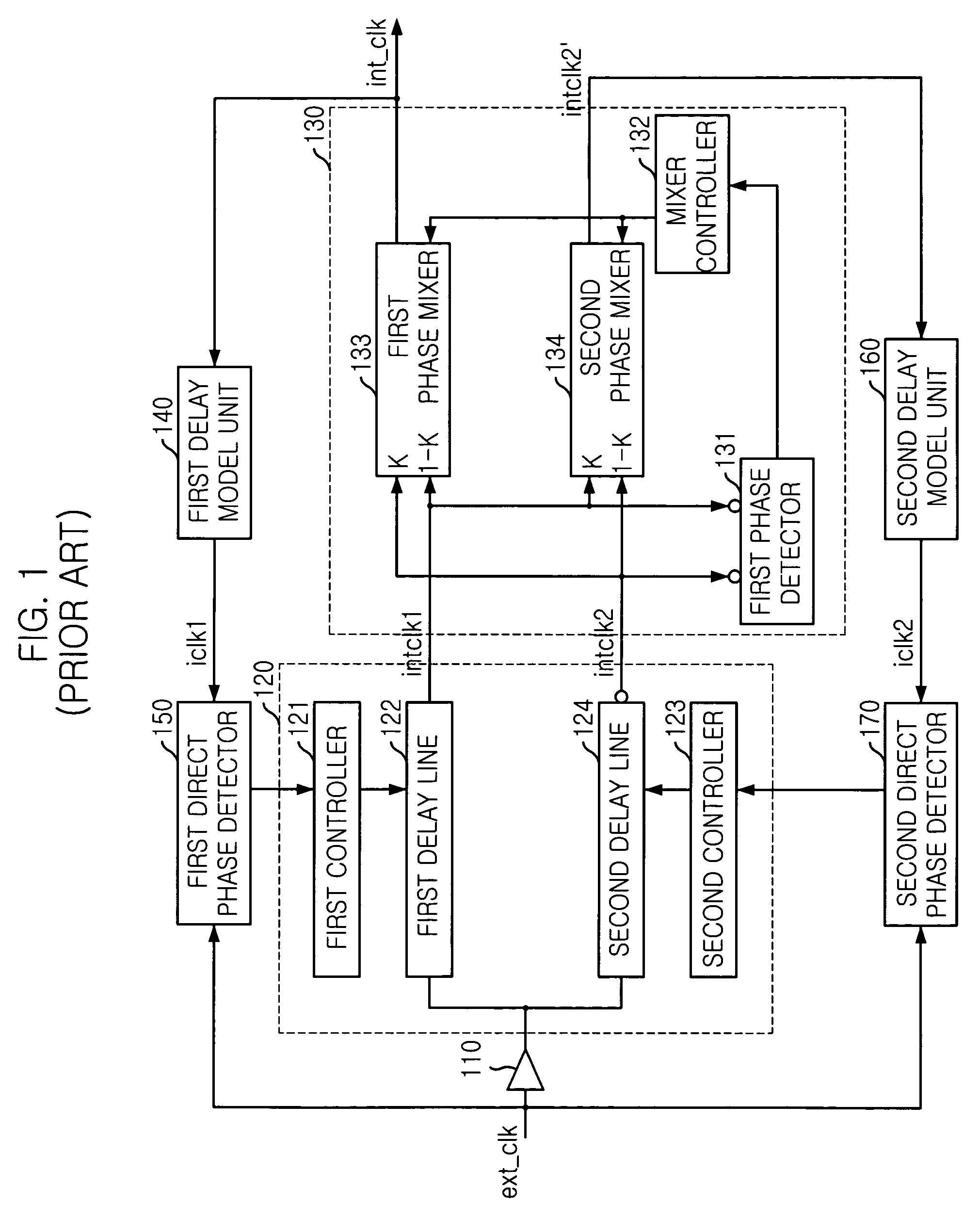

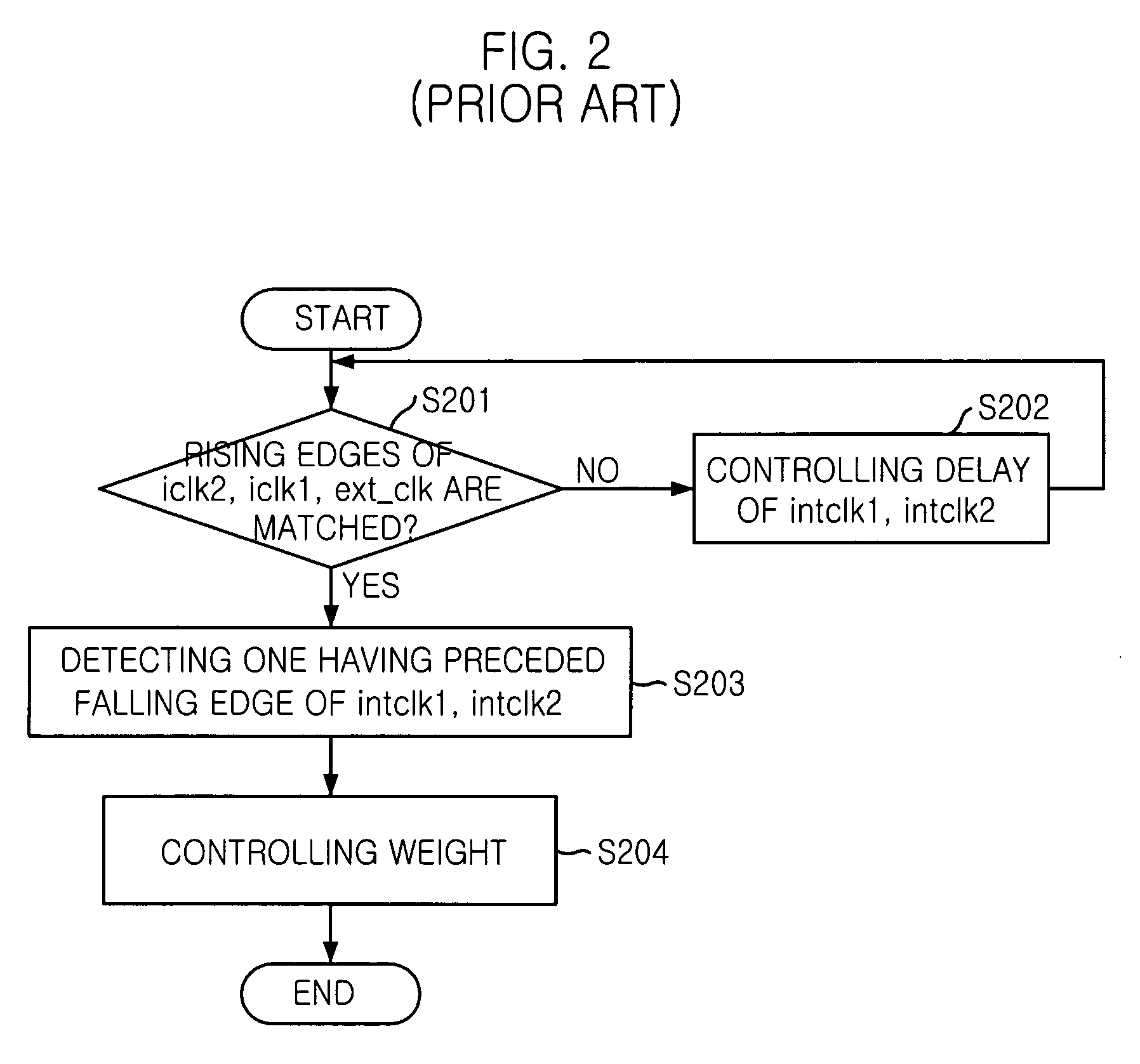

Digital DLL apparatus for correcting duty cycle and method thereof

A digital DLL apparatus and a method for correcting a duty cycle are disclosed. The apparatus includes: a delay line unit for receiving external clock signal and generating first and second delayed internal clock signals by delaying the external clock signal; a duty error controller for receiving the first and second delayed clock signals and outputting a first duty controlled clock signal and second duty controlled clock signal by shifting edges of the first and second delayed internal clock signals; and a delay model unit for compensating a delay of the duty controlled clock signal by estimating a delay amount of system. The present invention can correct the duty error by using the phase mixer and generate an internal clock signal having 50% of duty cycle.

Owner:SK HYNIX INC

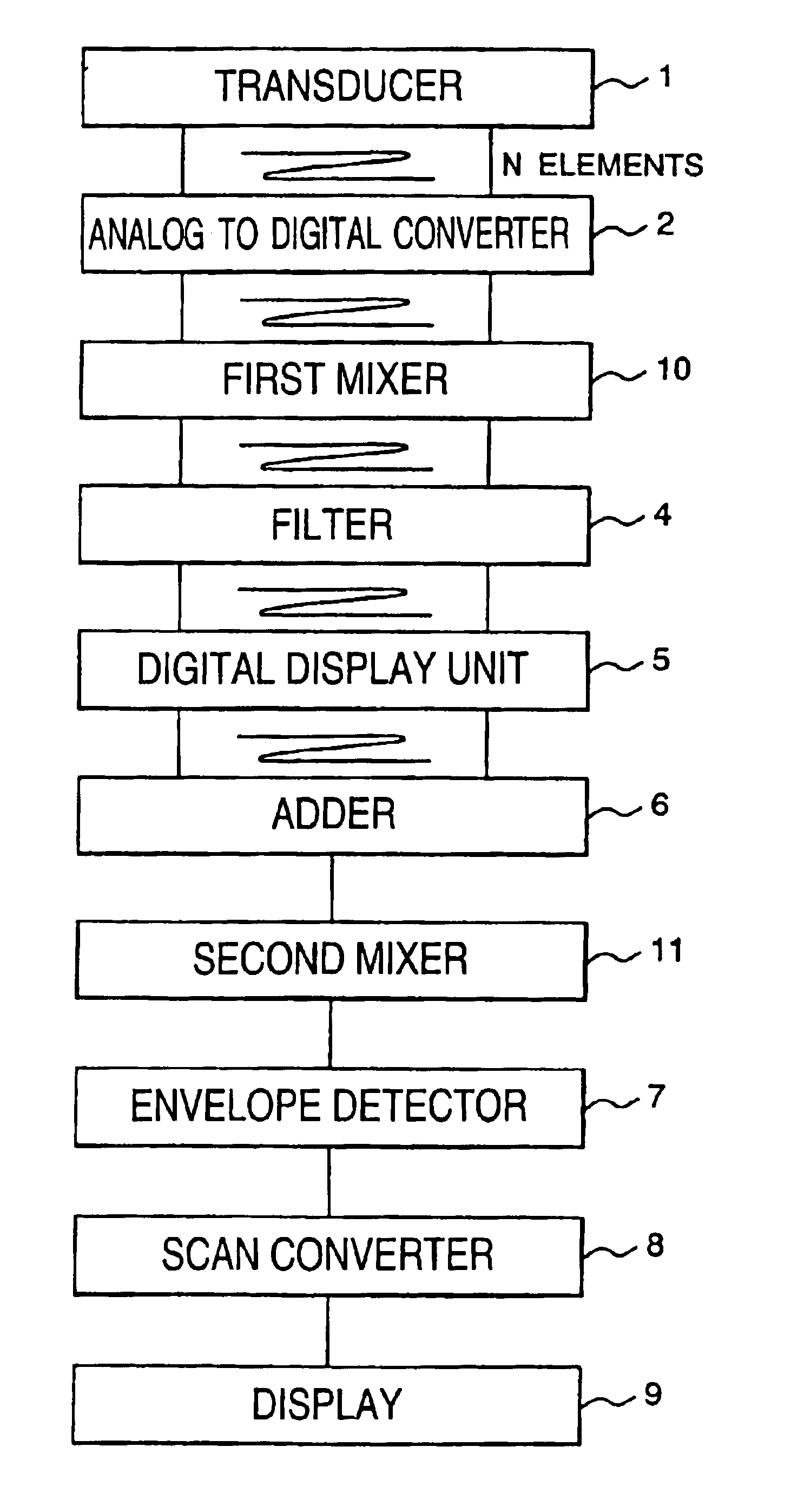

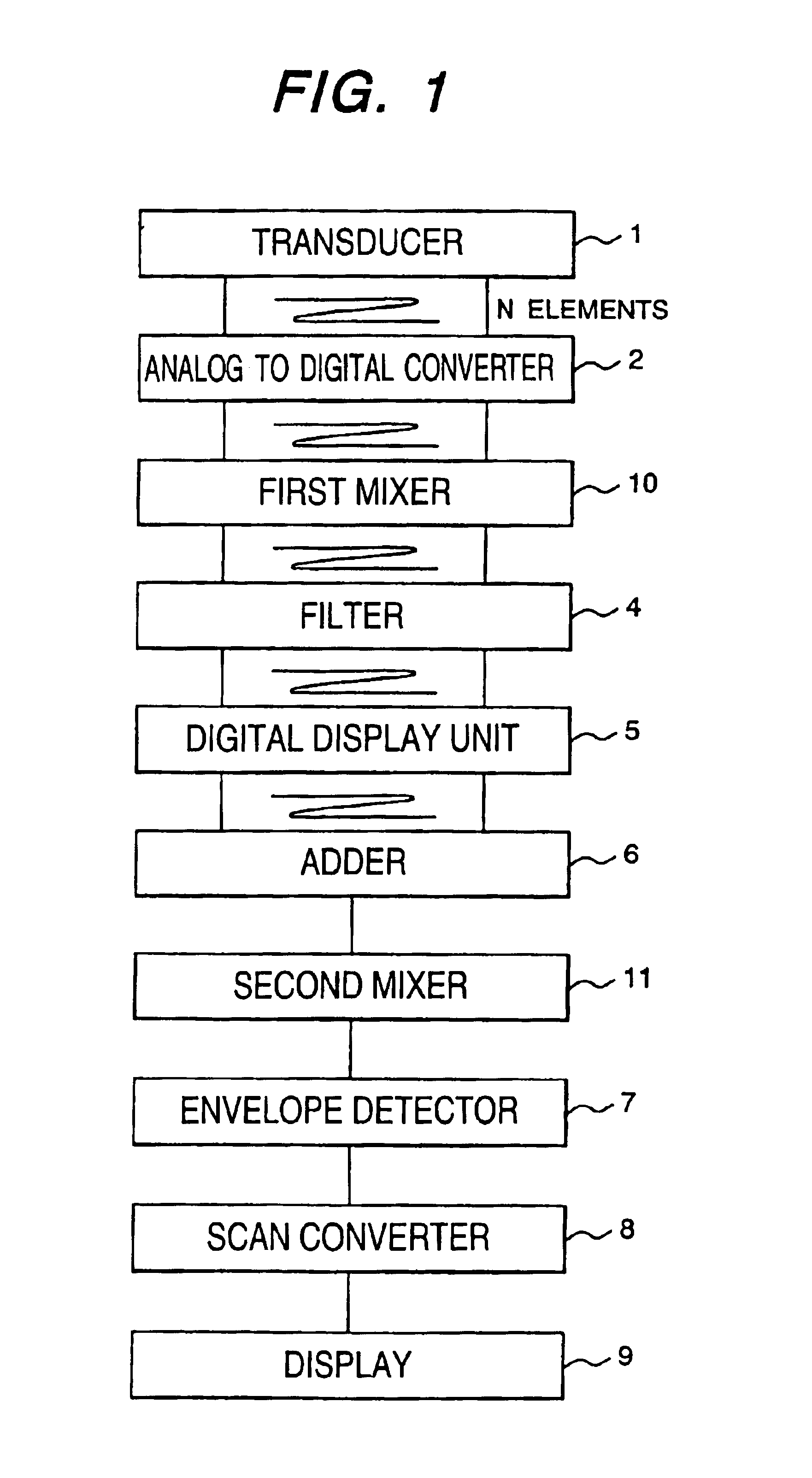

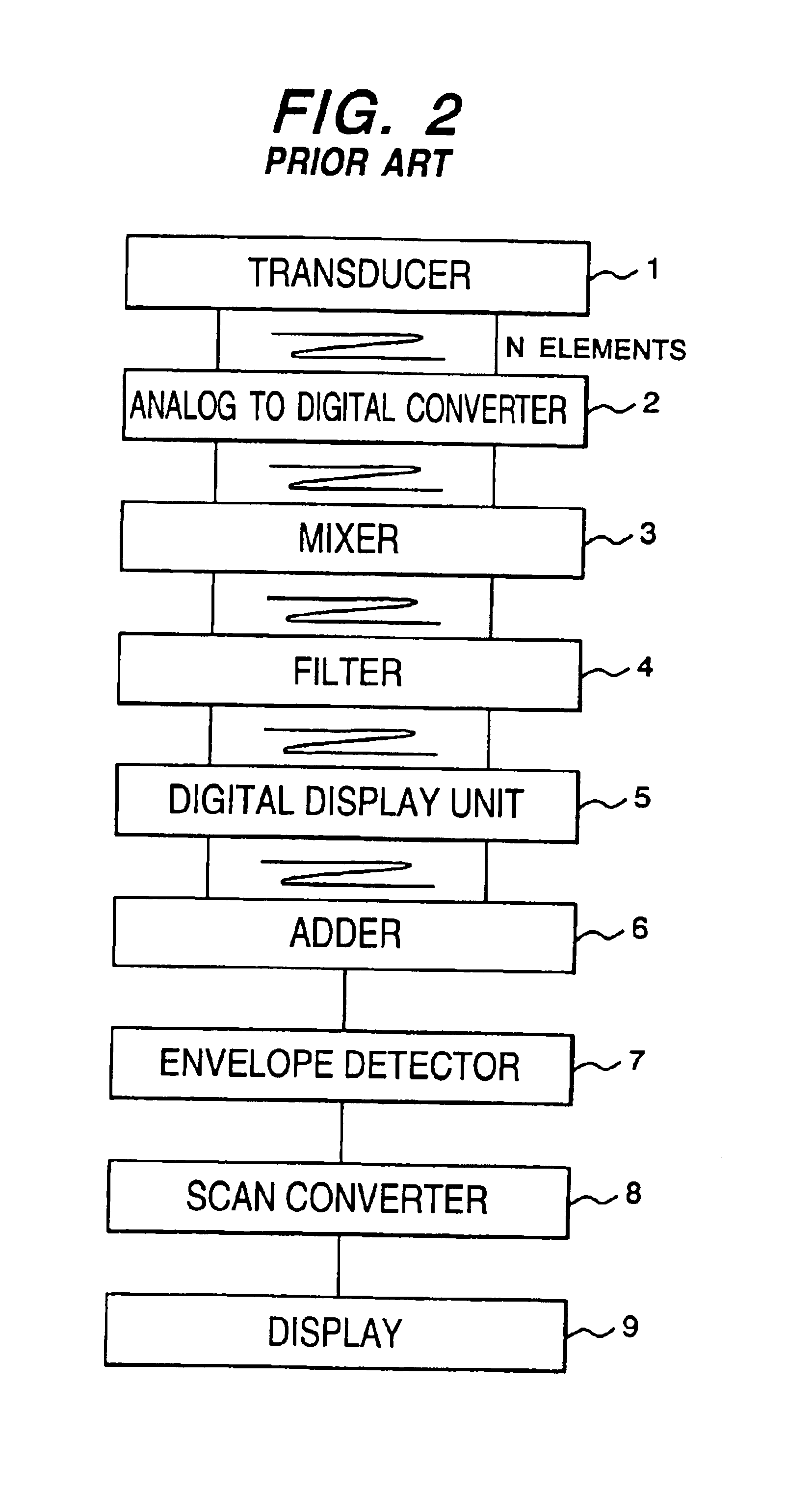

Ultrasonic diagnostic apparatus and method for processing ultrasonic signal

InactiveUS6878113B2Ultrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsSonificationAnalog-to-digital converter

An ultrasonic diagnostic apparatus acquires images different in a frequency. The invention is composed of a transducer including plural elements for sending an ultrasonic wave and receiving the reflected ultrasonic wave, analog to digital converters that digitize plural received signals, first mixers that respectively multiply a signal from the converter and a first digital reference signal, first filters that respectively extract a signal having a predetermined center frequency from a signal from each first mixer, digital delay units that respectively delay a signal from each first filter, an adder that adds plural signals from the digital delay units, and a second mixer that multiplies a signal from the adder and a second digital reference signal. An envelope detector detects a signal from the second mixer, and a scan converter converts a signal from the detector to a picture signal for display, so the pass band of the filter is not required to be changed.

Owner:HITACHI LTD

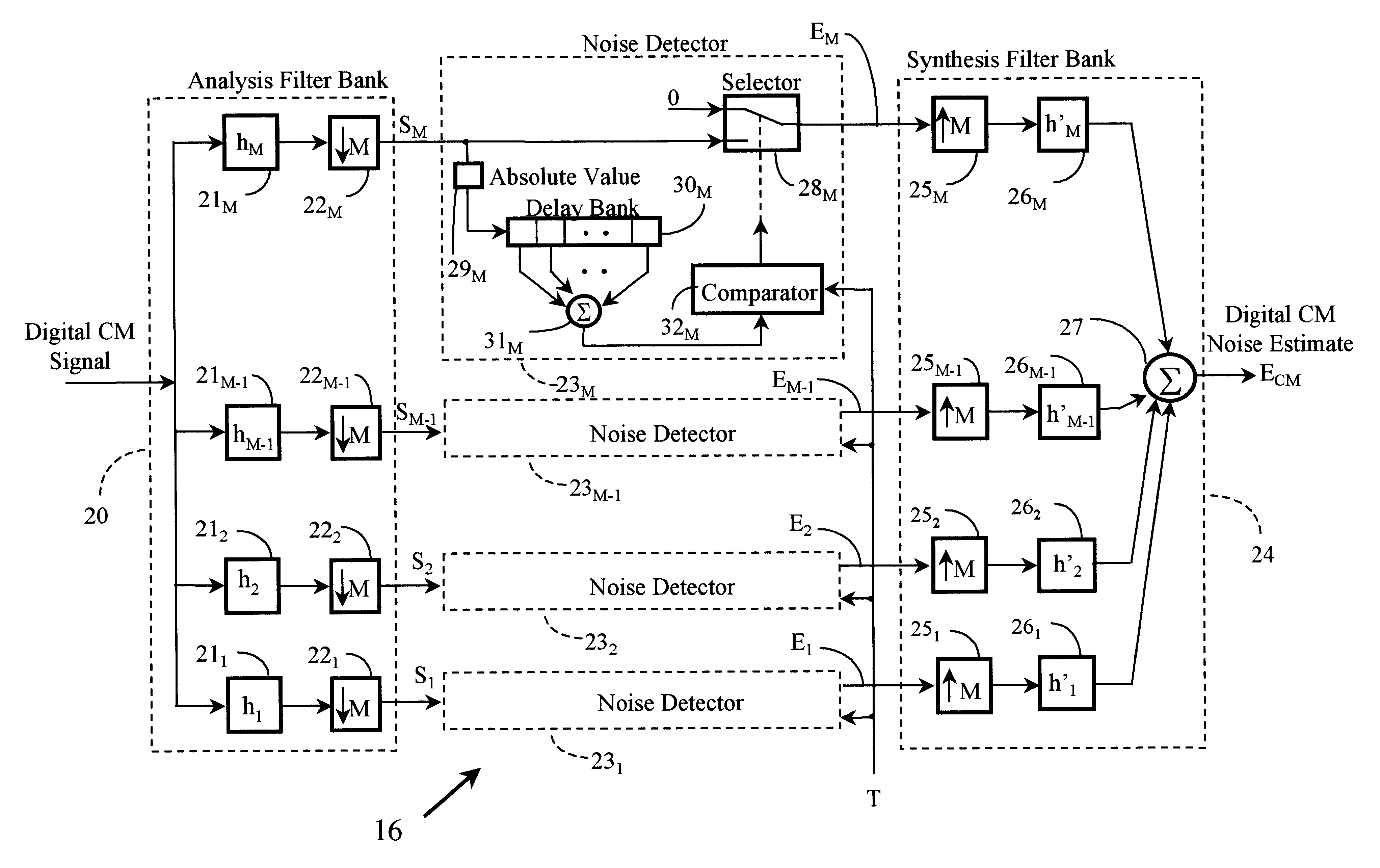

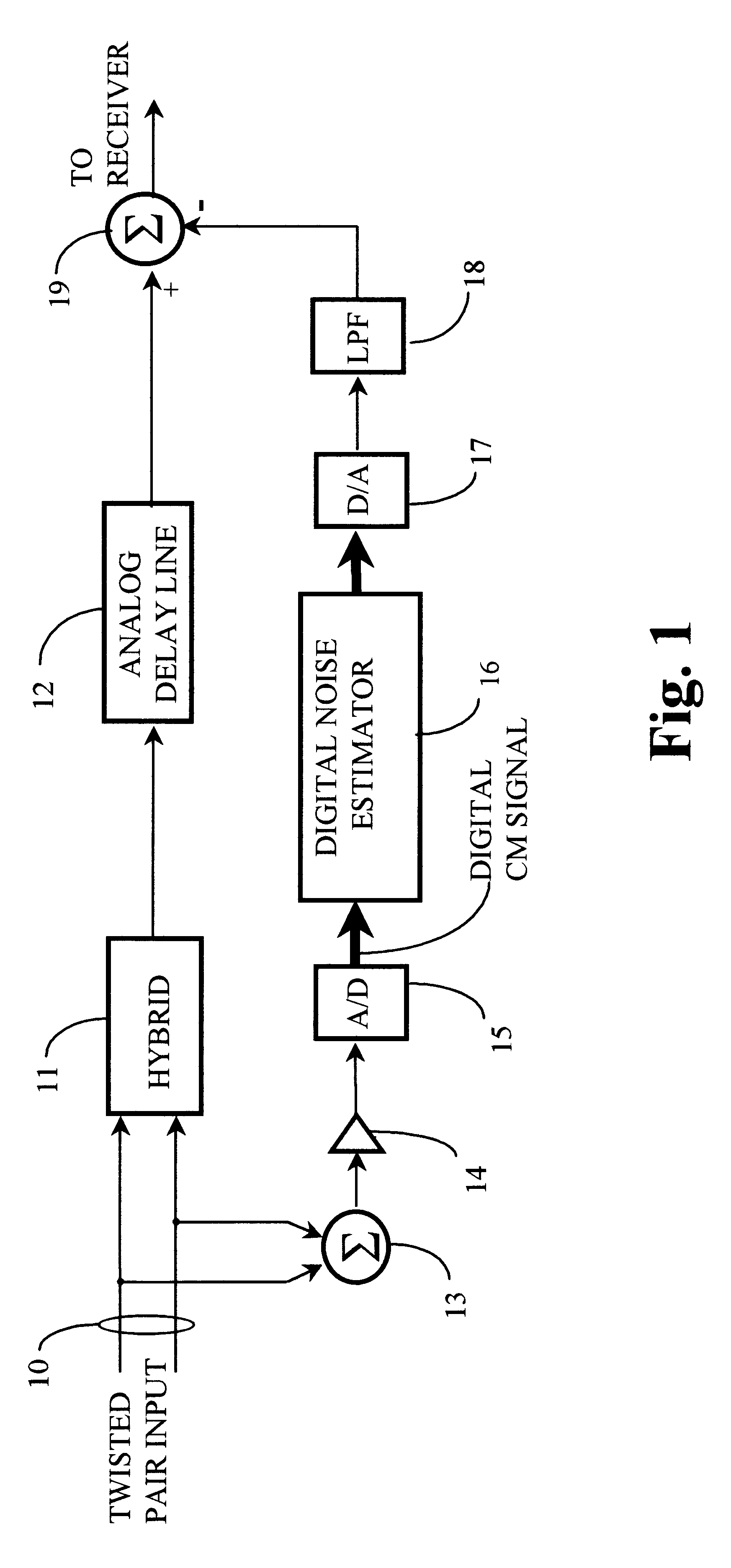

Suppression of radio frequency interference and impulse noise in communications channels

InactiveUS6546057B1Error preventionUnbalanced current interference reductionDifferential signalingEngineering

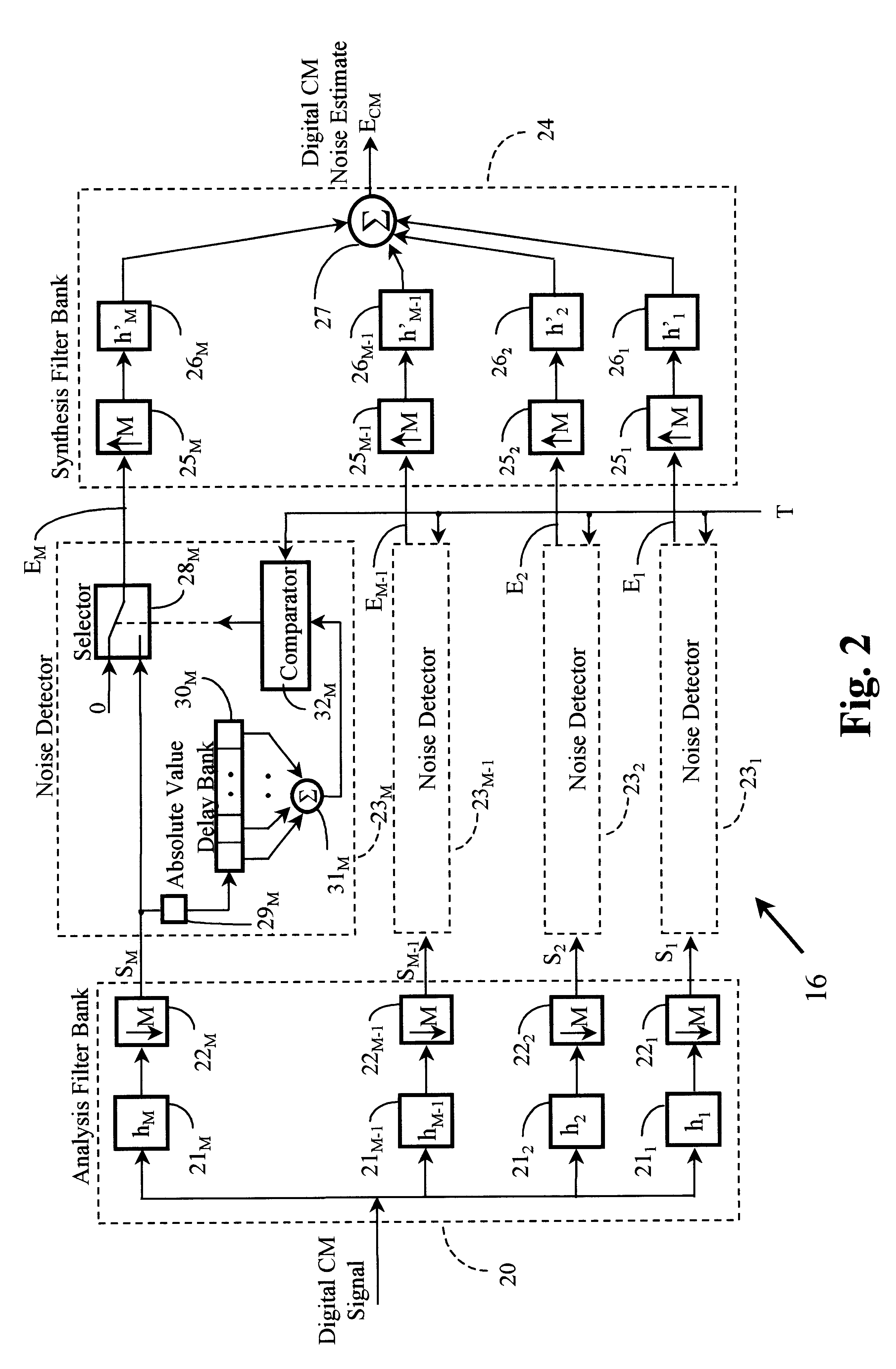

A noise suppression circuit for a communications channel (10) comprises a hybrid device (11) coupled to the channel for providing a differential output signal corresponding to a received signal. A delay unit (12) delays the differential signal by a suitable amount to allow for the generation and subtraction of a noise estimate. A summing device (13) extracts a digital common mode signal from the channel, and a noise estimation unit (16) provides a common mode noise estimate signal in dependence upon a history of the common mode signal over a predetermined period of time and over a plurality of frequency bands. The common mode noise estimate signal is combined subtractively (19) with the delayed differential signal to cancel common mode noise elements of the delayed differential signal. The noise estimation unit may comprise an analysis filter bank (20) for producing a plurality of subband signals (S1-SM), each at a different one of a plurality of different frequencies, a plurality of noise detection circuits (231-23M), each for processing a respective one of the plurality of subband signals to provide a component of the common mode noise estimate signal, and a synthesis filter bank (24) for processing the common mode noise signal components to provide the noise estimate signal.

Owner:BELL CANADA

Delay locked loop and its control method

InactiveUS7046059B2Small sizeLow powerPulse automatic controlDigital storageDelay-locked loopEngineering

A delay locked loop (DLL) capable of correcting a duty ratio of a clock signal including: a clock buffer which receives an external clock signal for outputting a rising edge clock signal; a delay unit for delaying the rising edge clock signal based on a first comparison signal in order to generate a first internal clock signal, a second internal clock signal, a first delay locking signal and a second delay locking signal; a duty correction unit for receiving the first and the second internal clock signals and the first and the second delay locking signals and generating a delay locked clock signal by correcting a duty cycle of the external clock signal; and a clock feed-back unit for receiving the delay locked clock signal and the external clock signal in order to generate the first comparison signal.

Owner:SK HYNIX INC

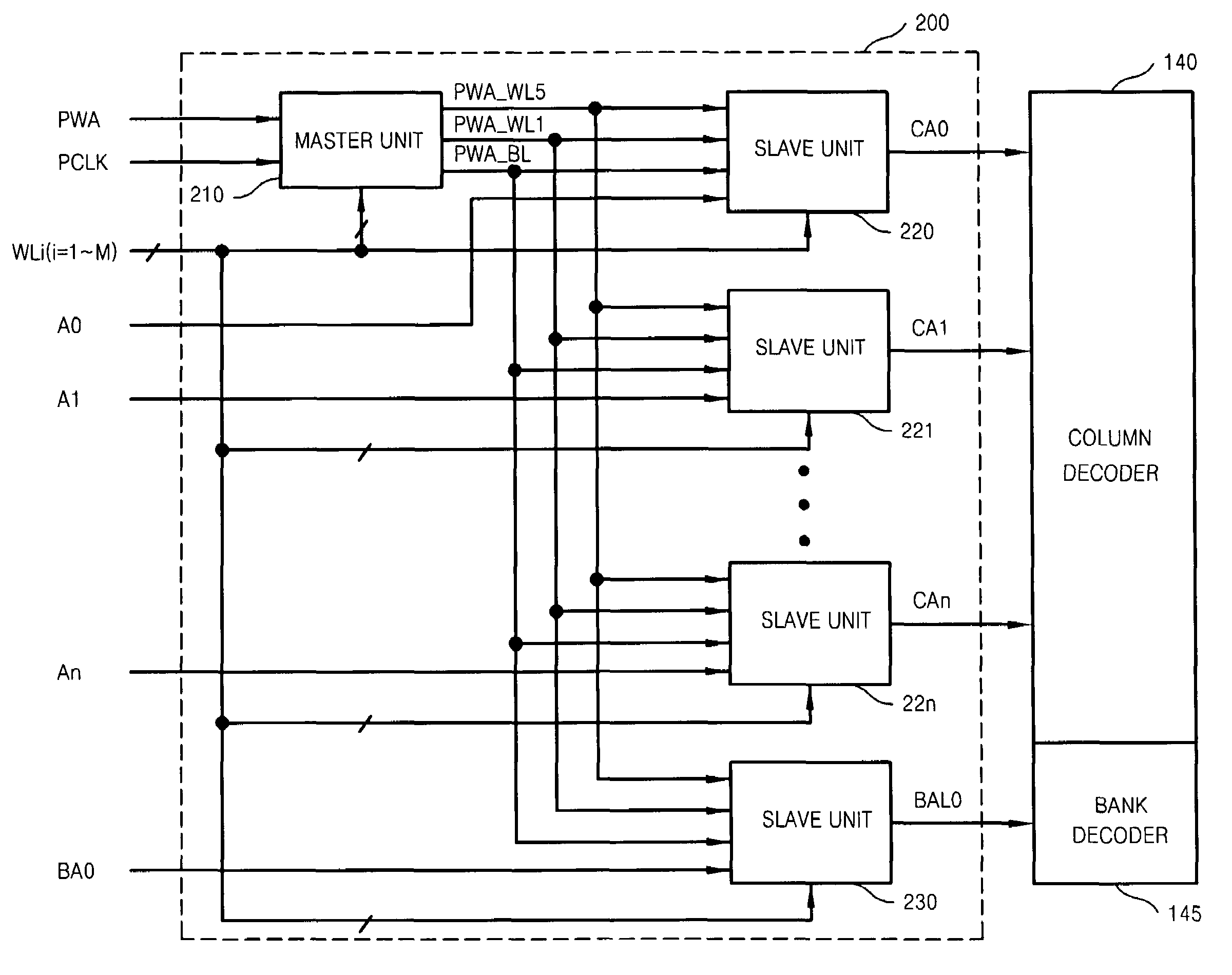

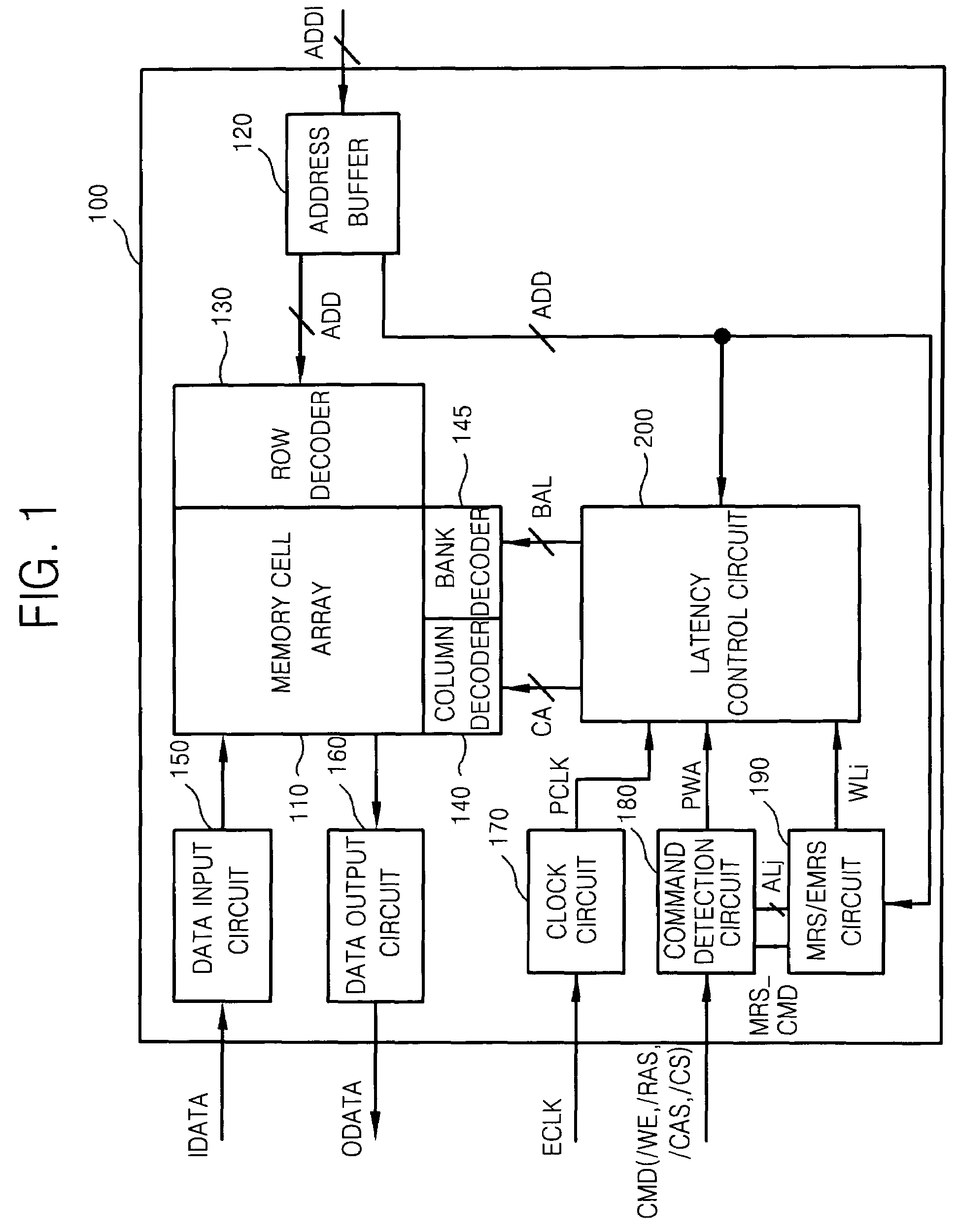

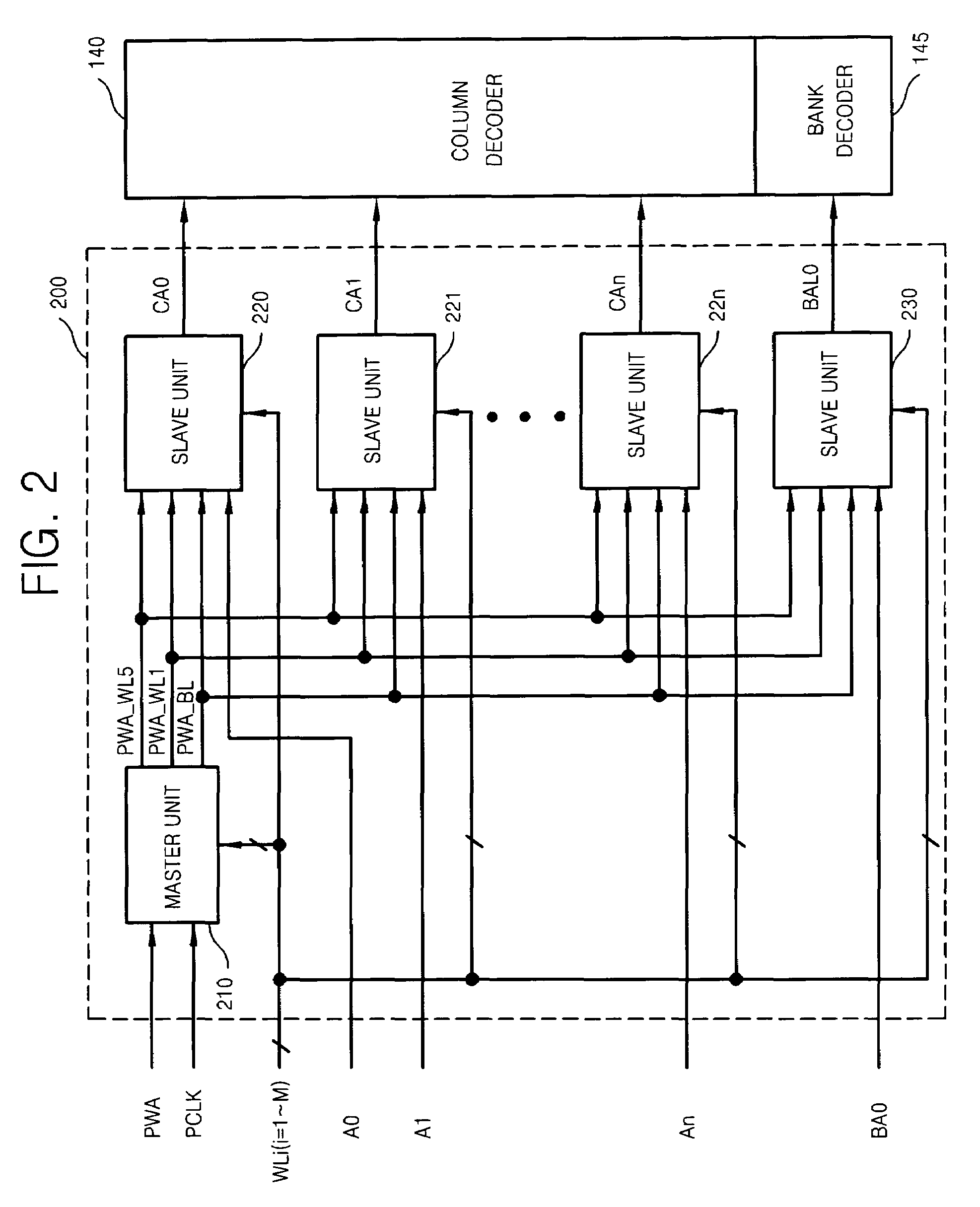

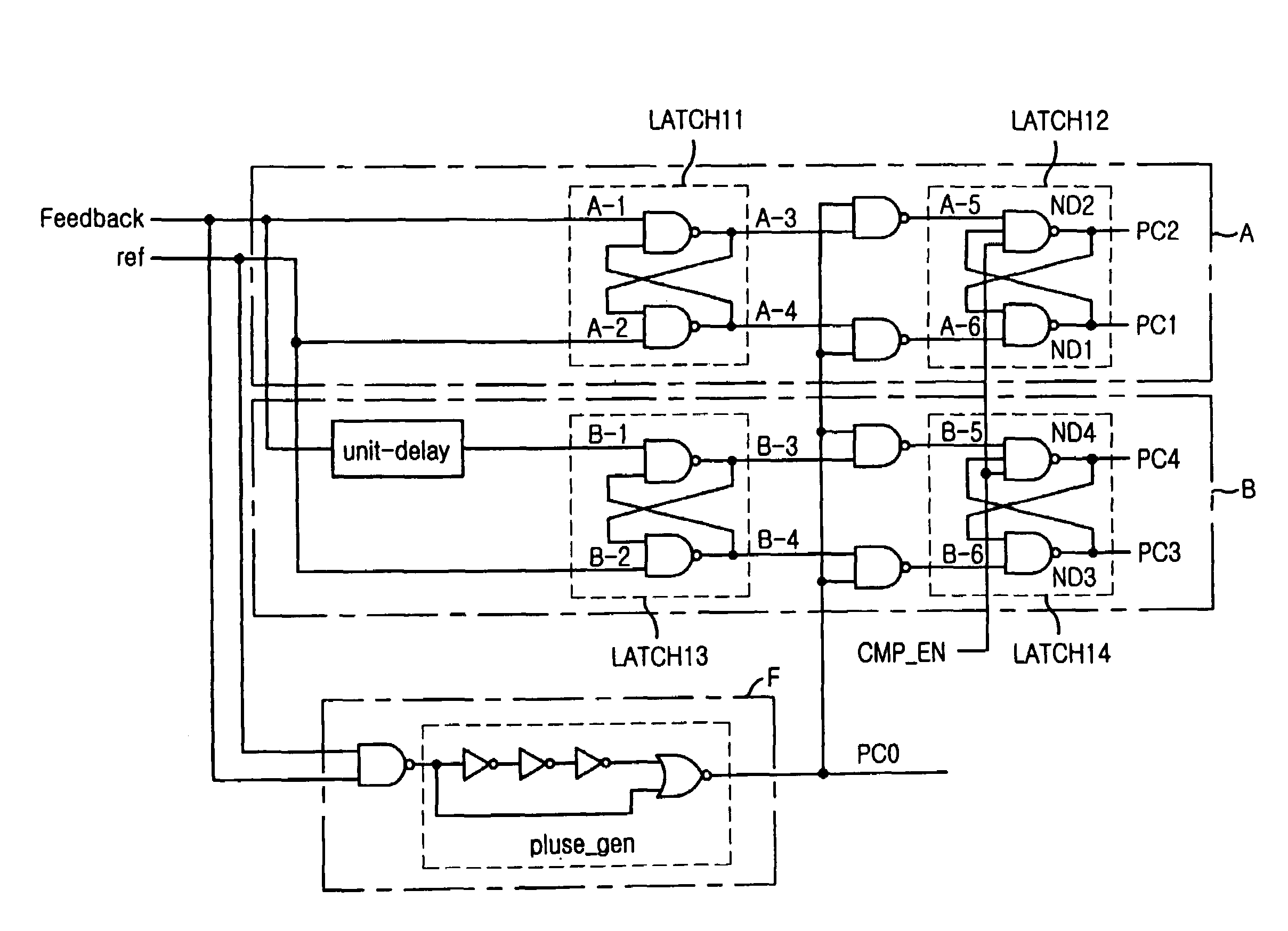

Latency control circuit and method thereof and an auto-precharge control circuit and method thereof

InactiveUS7609584B2Decreasing routing complexity and circuit area and delayReduced footprintDigital storageMinimum timeMemory bank

A latency control circuit and method thereof and auto-precharge control circuit and method thereof are provided. The example latency control circuit may include a master unit activating at least one master signal based on a reference signal and an internal clock signal and a plurality of slave units receiving the at least one master signal, each of the plurality of slave units receiving a plurality of signals and outputting an output signal based at least in part upon one of the received plurality of signals. The example method of latency control may include receiving at least one master signal, the received at least one master signal activated based on a reference signal and an internal clock signal and receiving a plurality of signals and outputting an output signal based at least in part upon one of the received plurality of signals and latency information. The example auto-precharge control circuit may include a precharge command delay unit generating a plurality of first precharge command delay signals in response to an internal clock signal and a write auto-precharge command signal, at least one bank address delay unit outputting a delayed bank address signal and a precharge main signal generator outputting a precharge main signal to banks based on the delayed bank address signal. The method of performing a precharging operation with the auto-precharge control circuit may include delaying a bank address signal based on a minimum time interval between executed memory commands and outputting a precharge main signal to one or more memory banks based on the delayed bank address signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Register controlled delay locked loop circuit

A register controlled delay locked loop (DLL) includes a clock divider, a shift controller, a delay unit and a delay model to synchronize an external clock signal with an internal clock. The register controlled DLL further includes a reset signal generator to generate a reset signal used to initialize the delay locked loop (DLL), a phase comparator to initialize a phase comparison signal in which the phase of a feedback clock signal delayed by a reference clock signal and the delay model is compared and outputted into a predetermined signal by using a comparison enable signal having an inverse phase to that of the reset signal, and a shift register to block an electric current running on a first latch of a plurality of latches with the reset signal during the initialization.

Owner:SK HYNIX INC

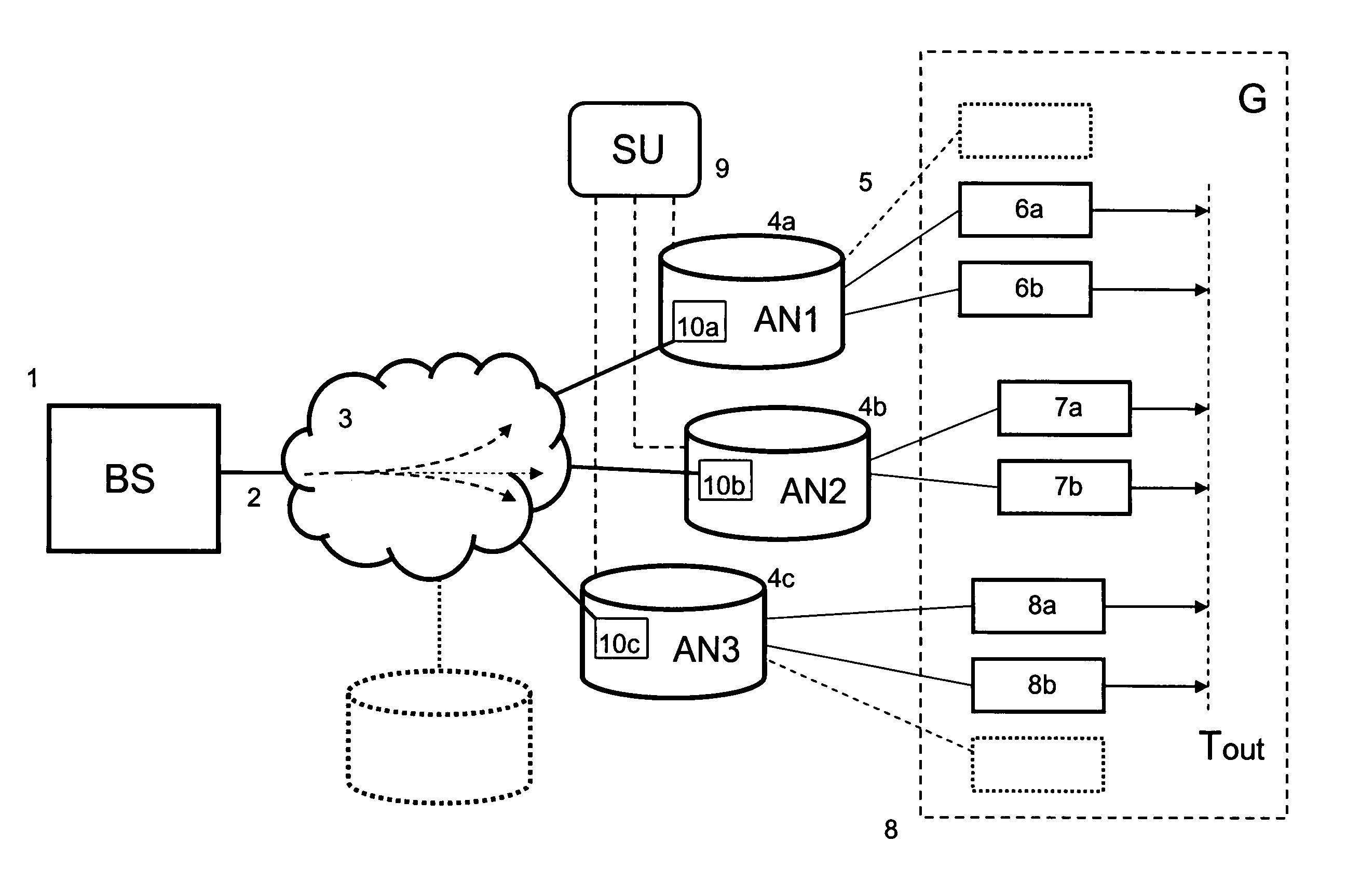

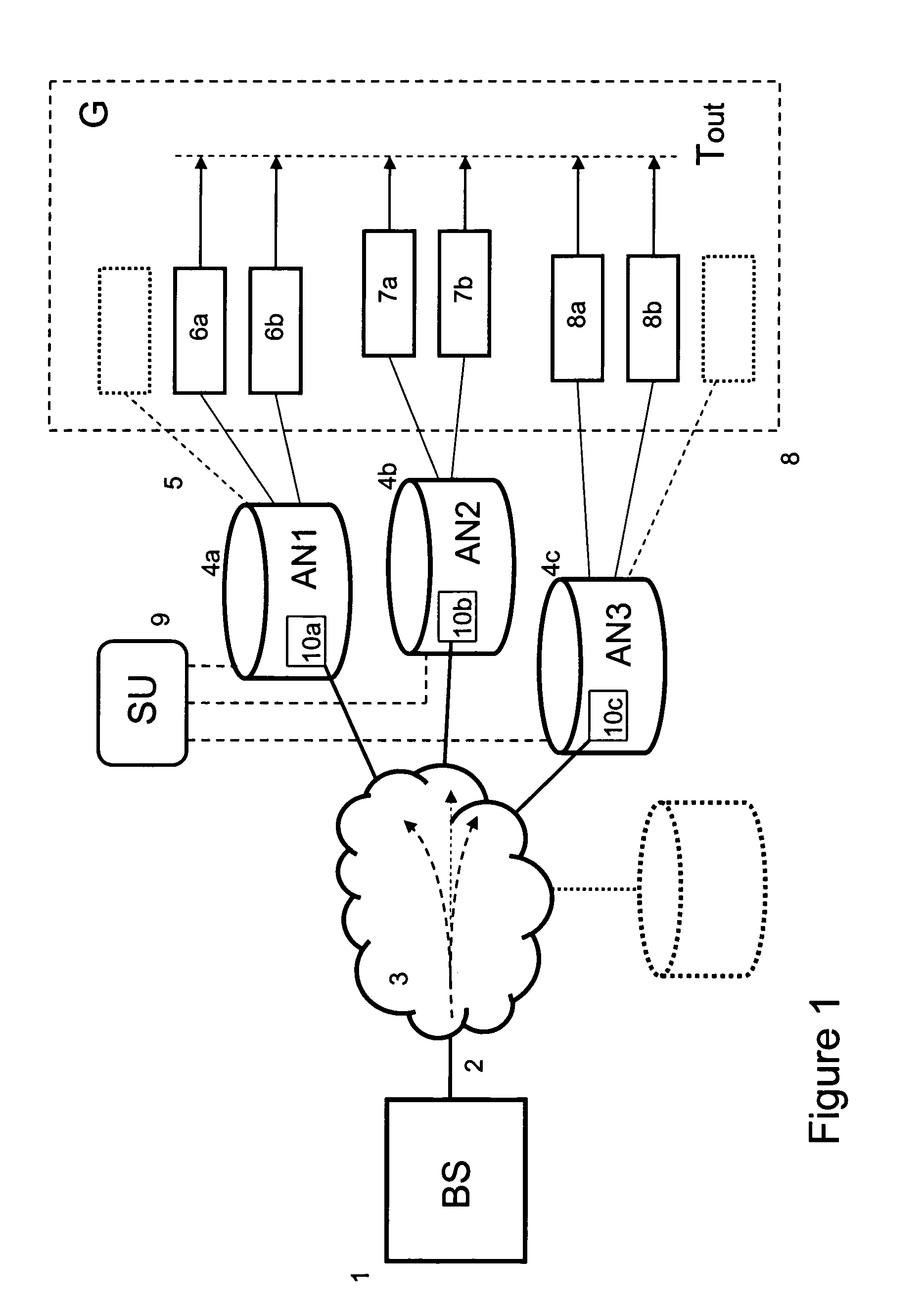

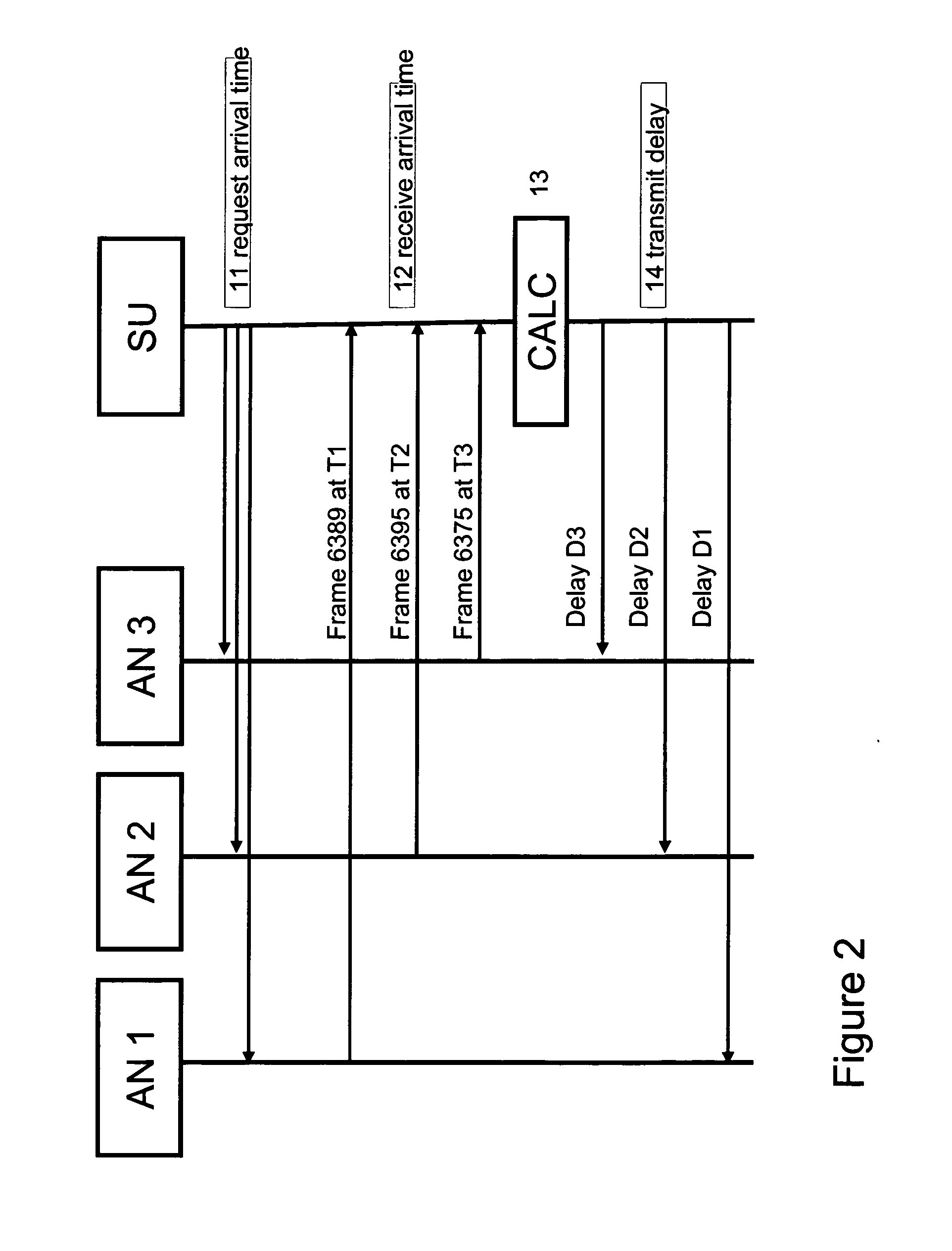

Method and System for Synchronizing a Group of End-Terminals

ActiveUS20100303100A1Error preventionFrequency-division multiplex detailsComputer networkTelecommunications

A method is described for synchronizing the transmission of a stream to a group of end-terminals. The method is used in a system comprising a station transmitting a packetized stream over a network to at least a first and second network node. Each network node comprises a variable delay unit and each network node is connected to one or more end-terminals. In the method the synchronization unit receives arrival time information of a packet in the broadcast stream at the first and second network node. Delay information is calculated for the first and second network node on the basis of the arrival time information of the packet. Further, the delay information is transmitted to the first and second network node so that the variable delay unit in the first and second network node is able to transmit the broadcast stream to the first and second end-terminal in a substantially synchronized way.

Owner:KONINK KPN NV +1

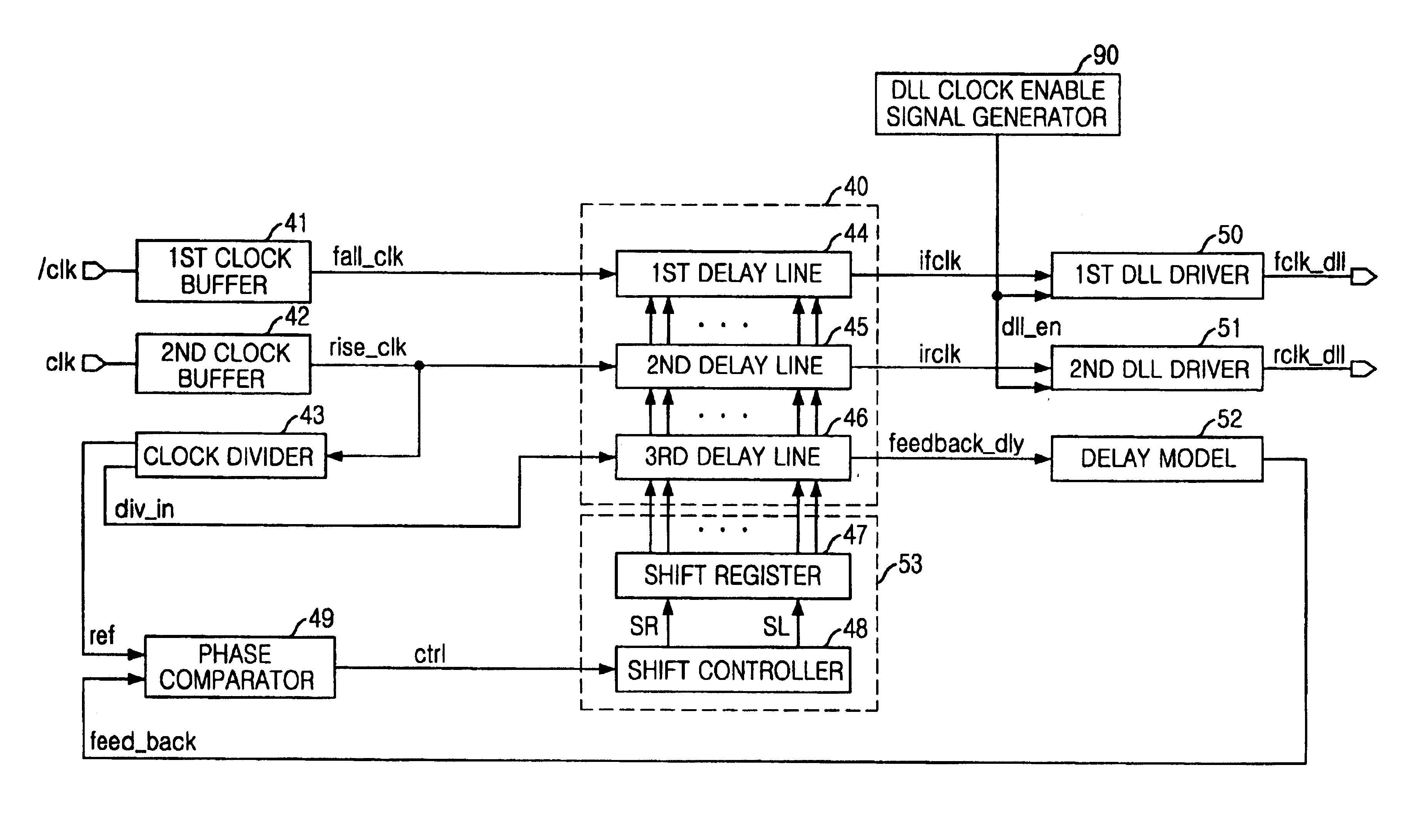

Register controlled DLL for reducing current consumption

InactiveUS6914798B2Reduce current consumptionTotal current dropPulse automatic controlSingle output arrangementsDelay-locked loopEngineering

A register controlled delay locked loop (DLL) usable in a semiconductor device is provided. The register controlled delay locked loop includes an internal clock generating unit generating a delayed clock signal and a reference clock signal, a first delay unit compensating for an amount of delay caused by a signal transmission path of the delayed clock signal, a phase comparator detecting a difference between the reference clock signal and the delayed clock signal and thereby generating a detection signal, a controller having a plurality of second delay units for controlling an amount of delay of the delayed clock signal in response to the detection signal, a driver driving a DLL clock signal, and an enable signal generator enabling the driver in response to an activation or non-activation signal of the semiconductor device.

Owner:SK HYNIX INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com