Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

6034 results about "Delay time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

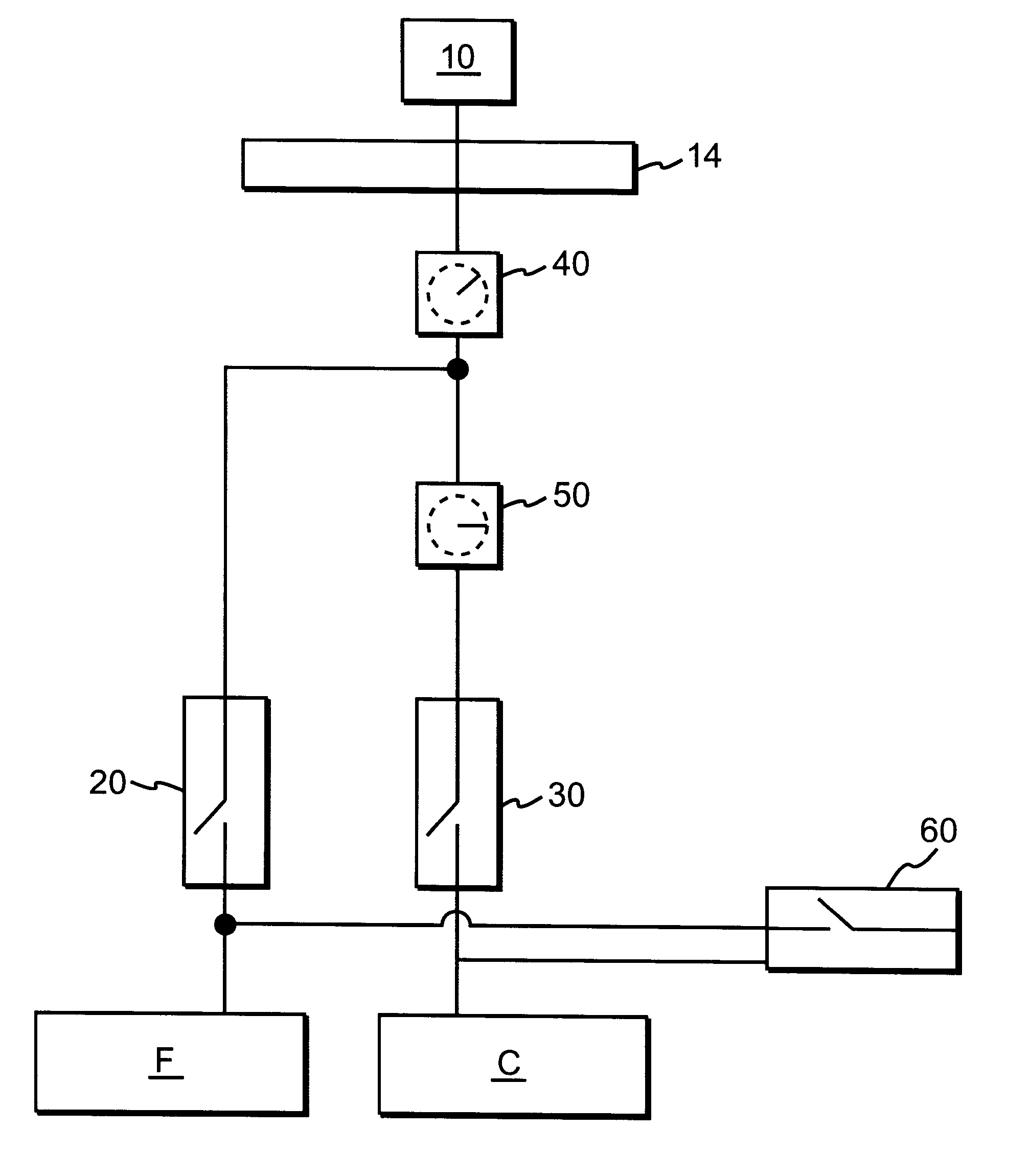

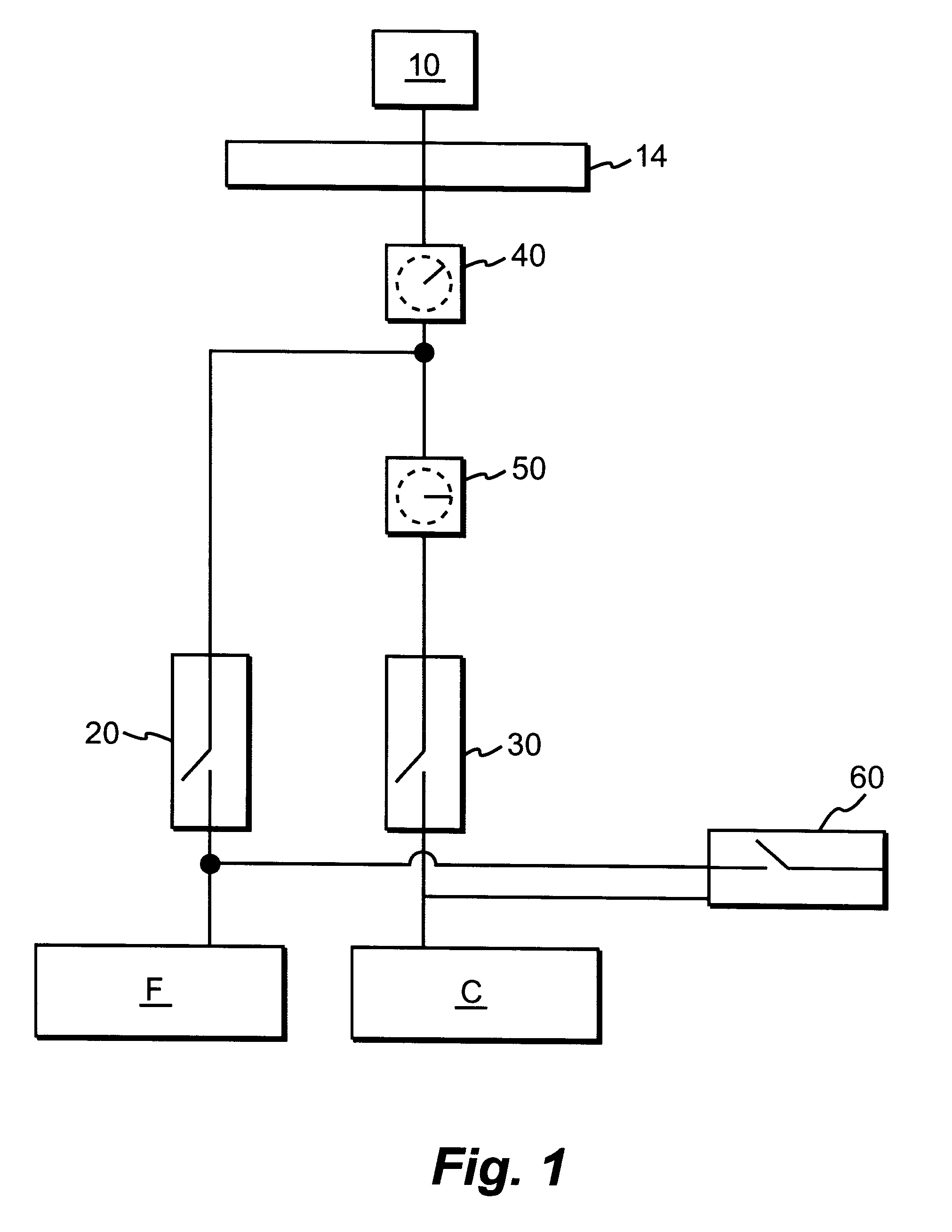

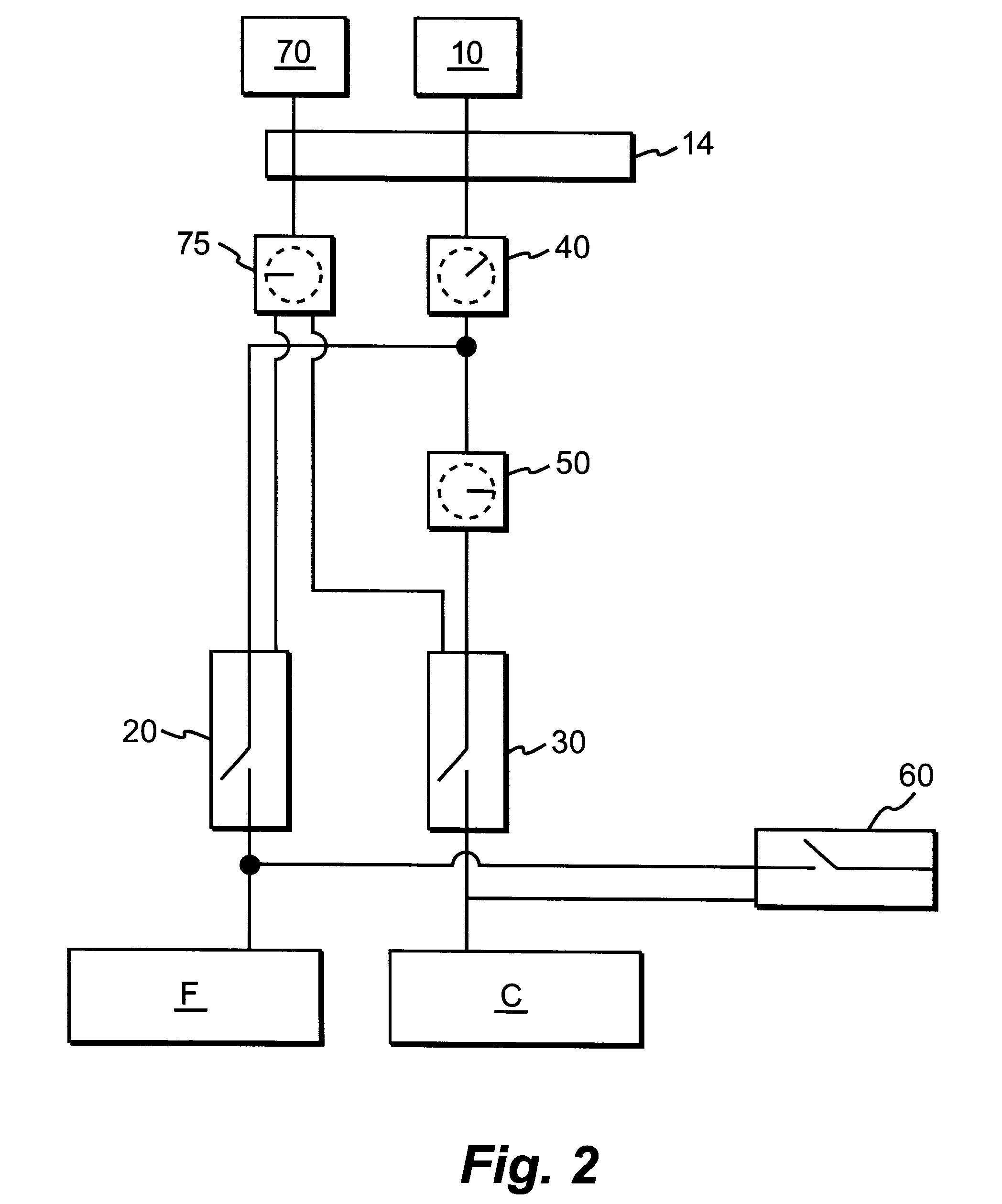

Method and apparatus for detecting respiratory disturbances

ActiveUS7160252B2Easy to identifyRespiratorsOperating means/releasing devices for valvesAnesthesiaMedical device

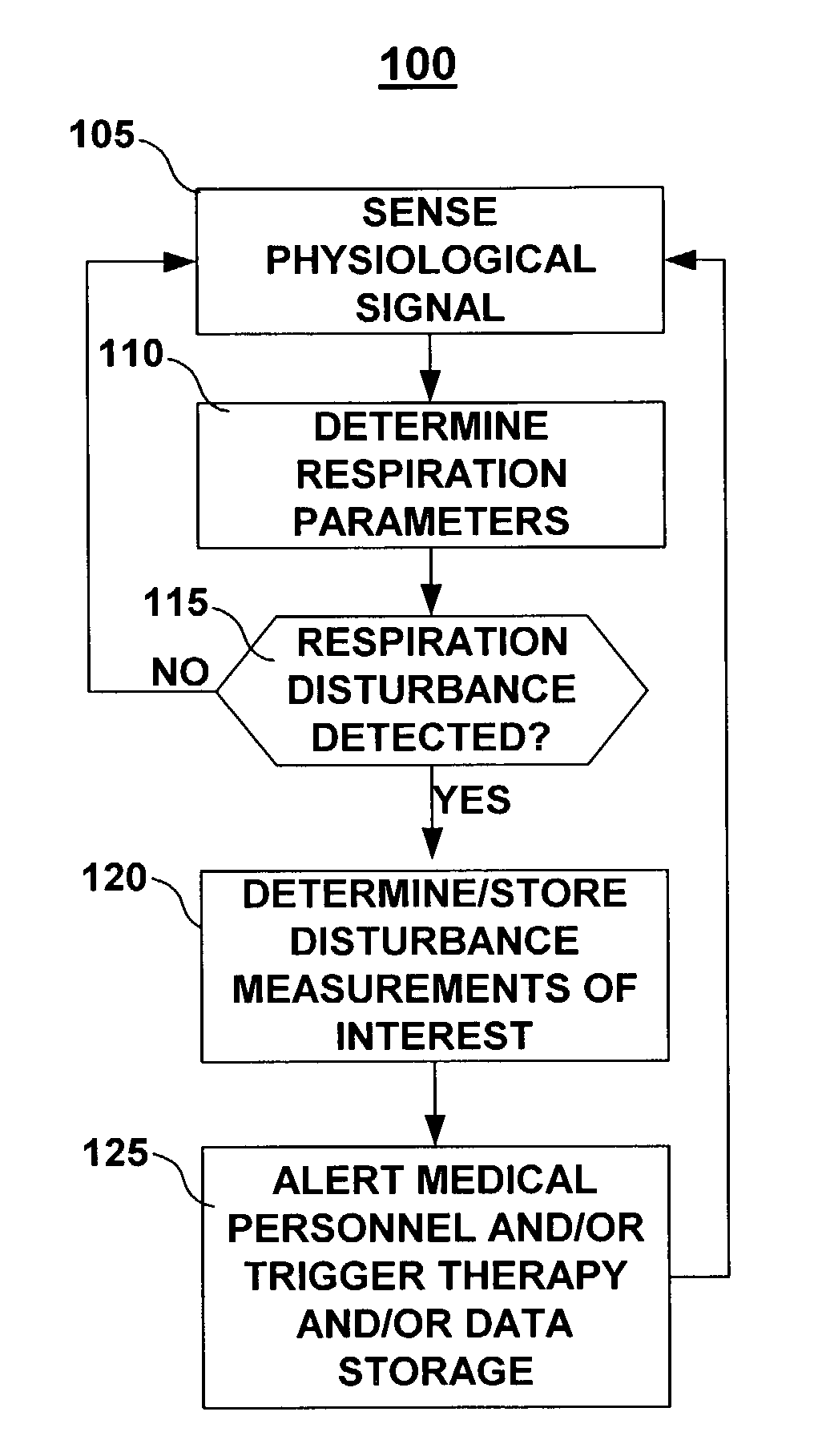

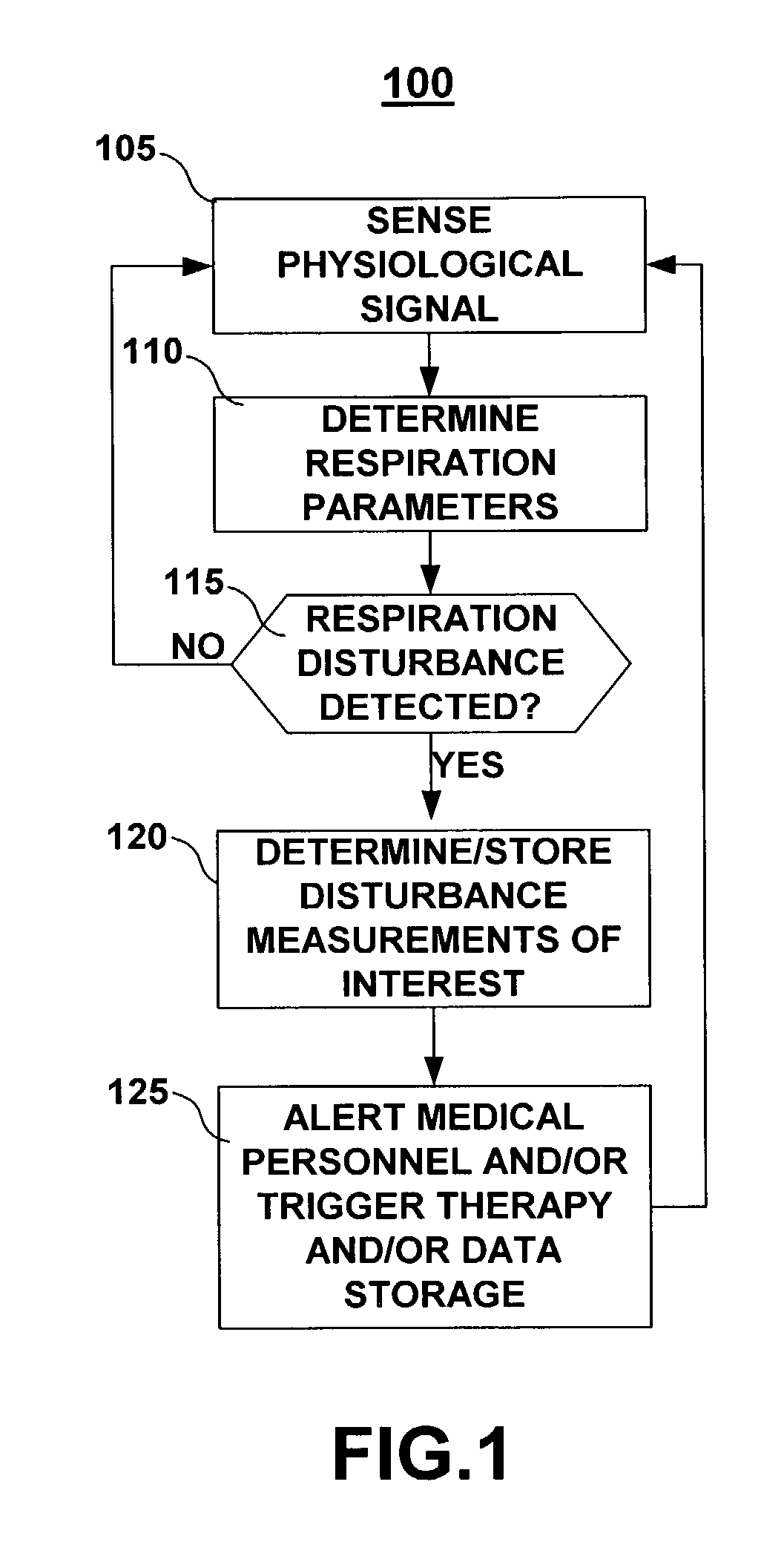

A system and method for monitoring respiration including sensing a signal that varies with respiration, deriving a respiration parameter, applying criteria for detecting a respiration disturbance and determining one or more respiratory disturbance metrics. The system preferably includes an implantable sensor with an associated implantable medical device such that chronic respiration monitoring is possible. The implantable medical device may execute methods for detecting and measuring respiratory disturbances or may store data to be transferred to an external device for detecting and measuring respiratory disturbances. Respiratory disturbance detection may trigger a responsive action such as physiological data storage, a change in therapy delivery, or a clinician warning. Assessment of cardiac function may be made based on metrics of respiratory disturbances or a measure of circulatory delay time following detection of a respiratory disturbance.

Owner:MEDTRONIC INC

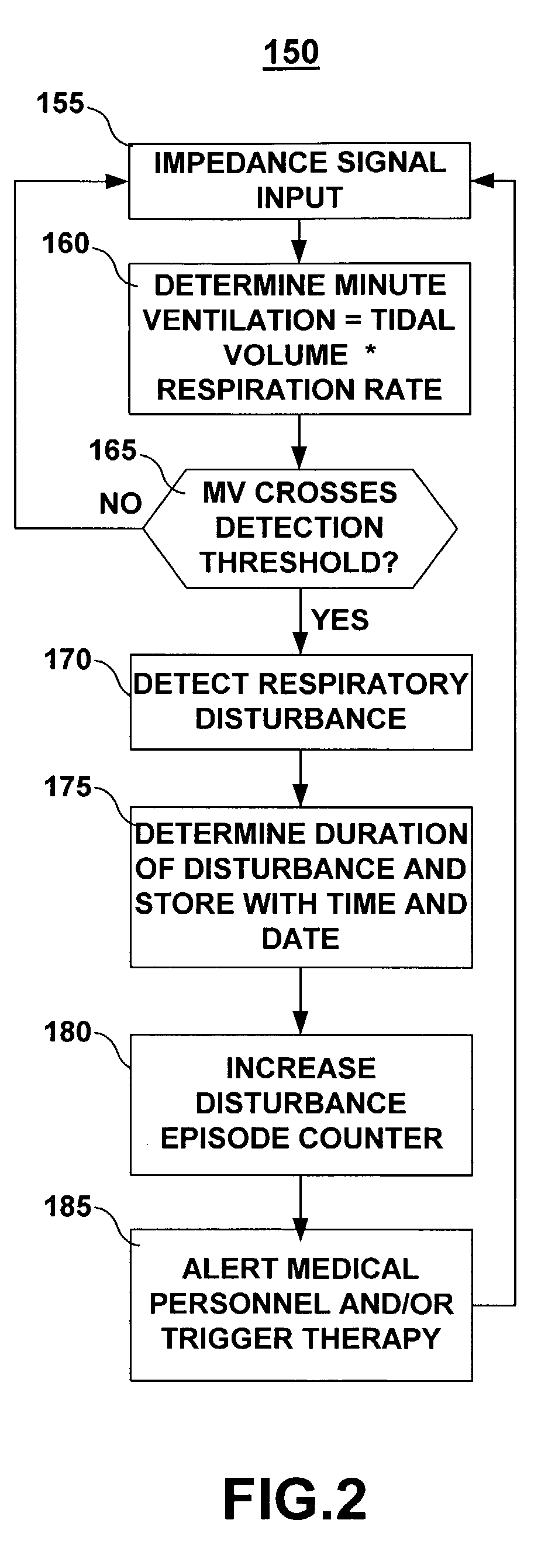

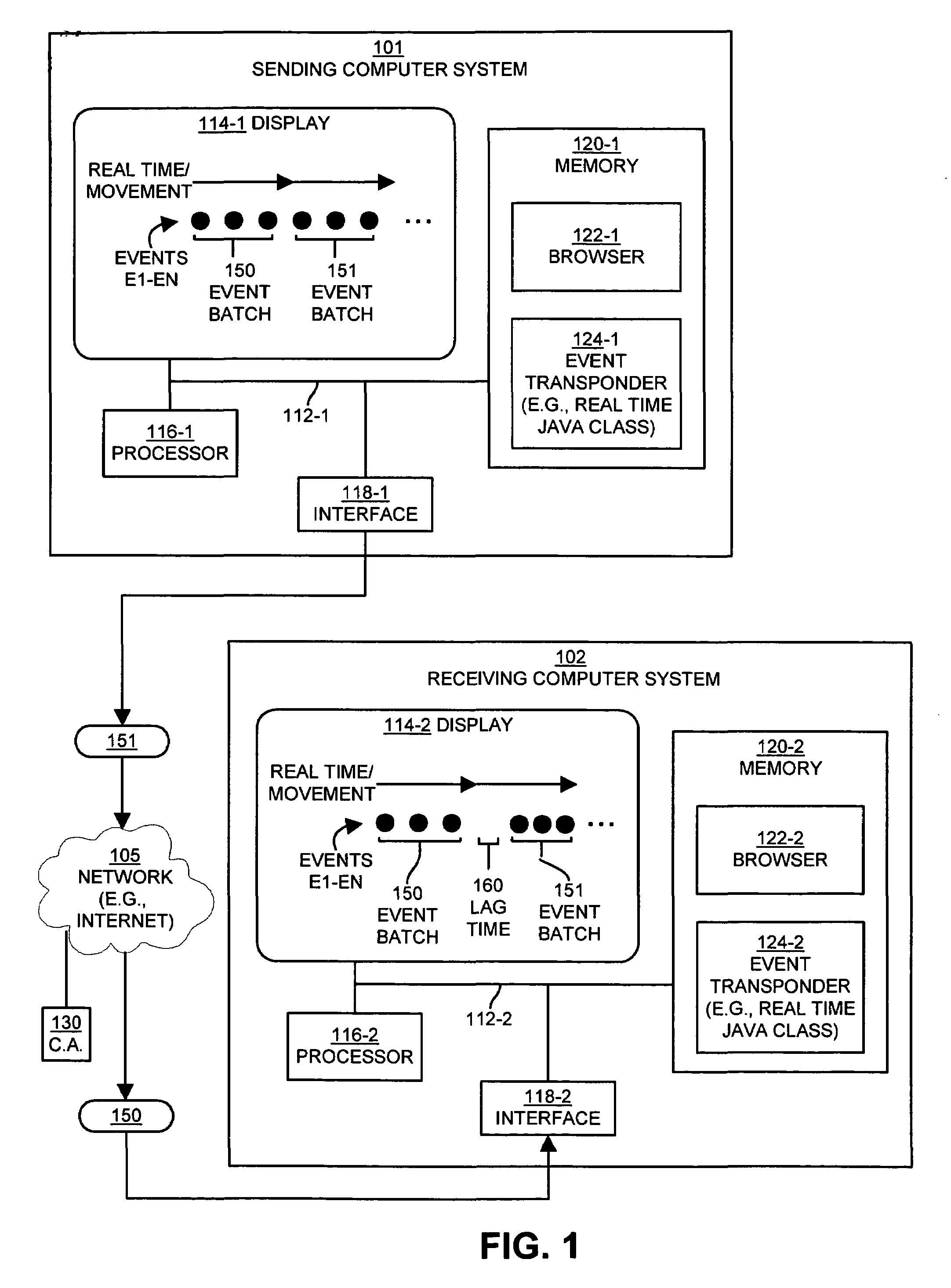

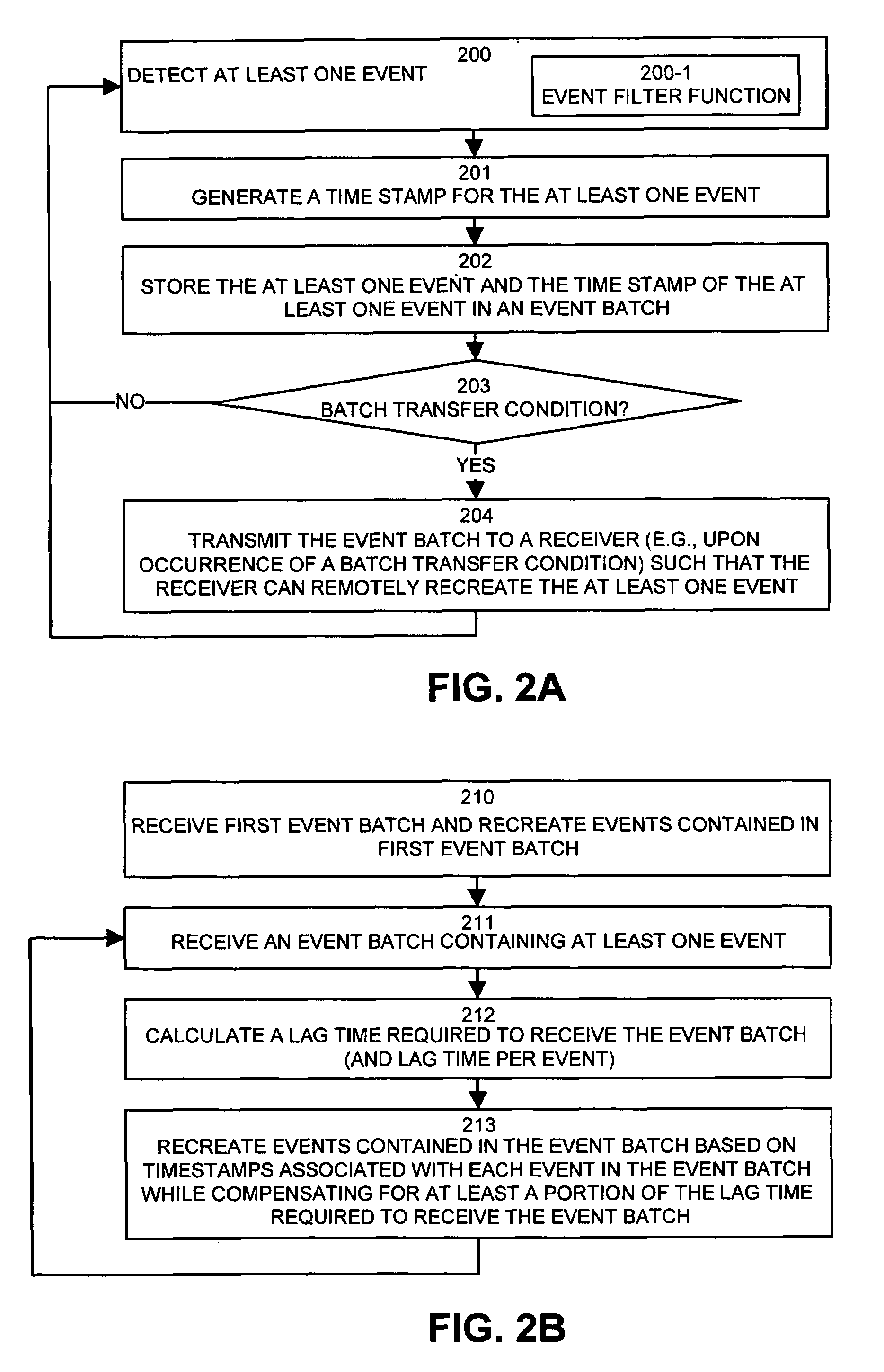

Method and apparatus for exchanging event information between computer systems that reduce perceived lag times by subtracting actual lag times from event playback time

InactiveUS6934766B1Shorten the time intervalMinimize amount of timeRecording carrier detailsRecord information storageTimestampComputerized system

Owner:CISCO TECH INC

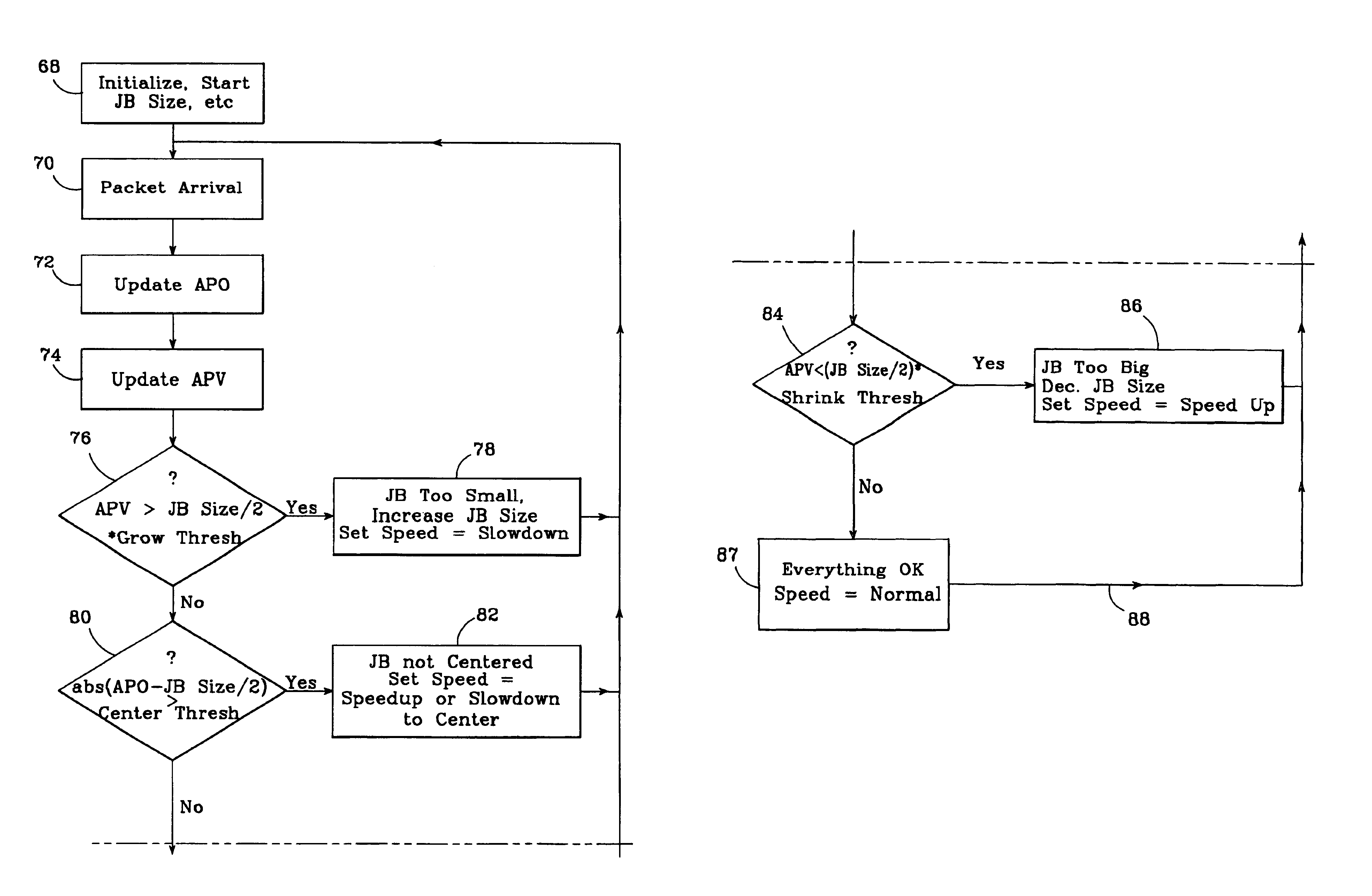

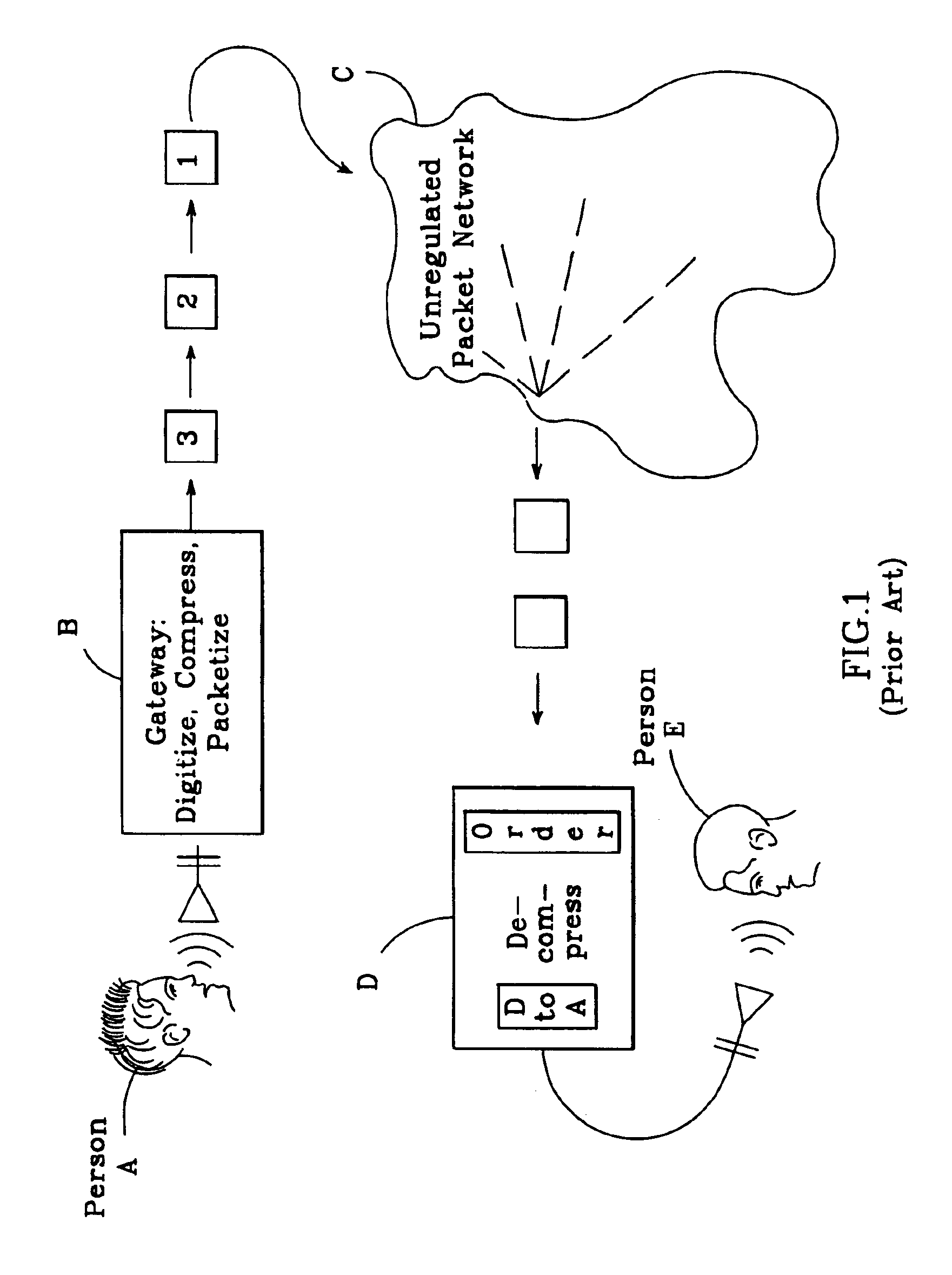

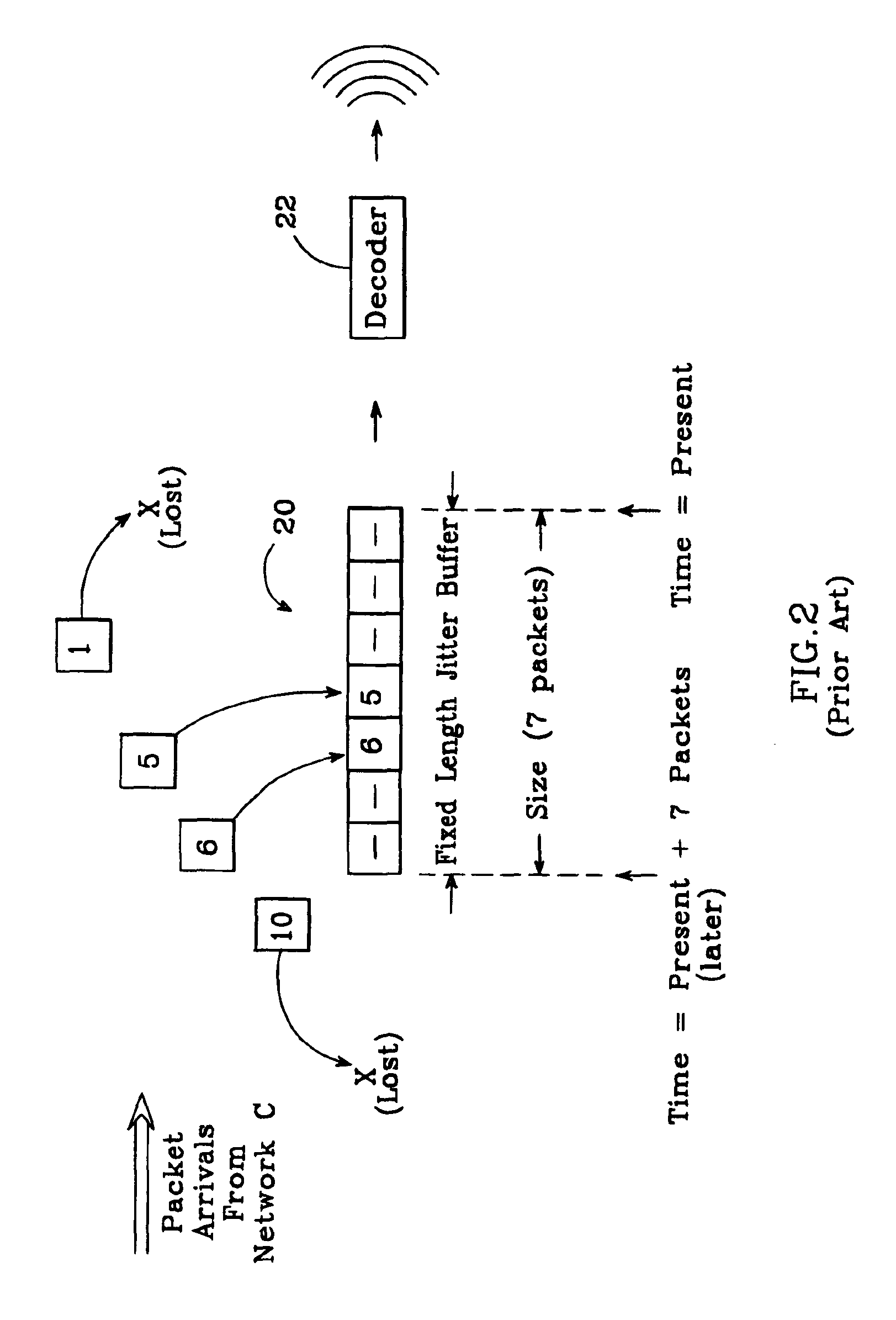

Adaptive jitter buffer for internet telephony

InactiveUS6862298B1Improve audio qualityTo overcome the large delayError preventionFrequency-division multiplex detailsPacket arrivalControl signal

In an improved system for receiving digital voice signals from a data network, a jitter buffer manager monitors packet arrival times, determines a time varying transit delay variation parameter and adaptively controls jitter buffer size in response to the variation parameter. A speed control module responds to a control signal from the jitter buffer manager by modifying the rate of data consumption from the jitter buffer, to compensate for changes in buffer size, preferably in a manner which maintains audio output with acceptable, natural human speech characteristics. Preferably, the manager also calculates average packet delay and controls the speed control module to adaptively align the jitter buffer's center with the average packet delay time.

Owner:GOOGLE LLC

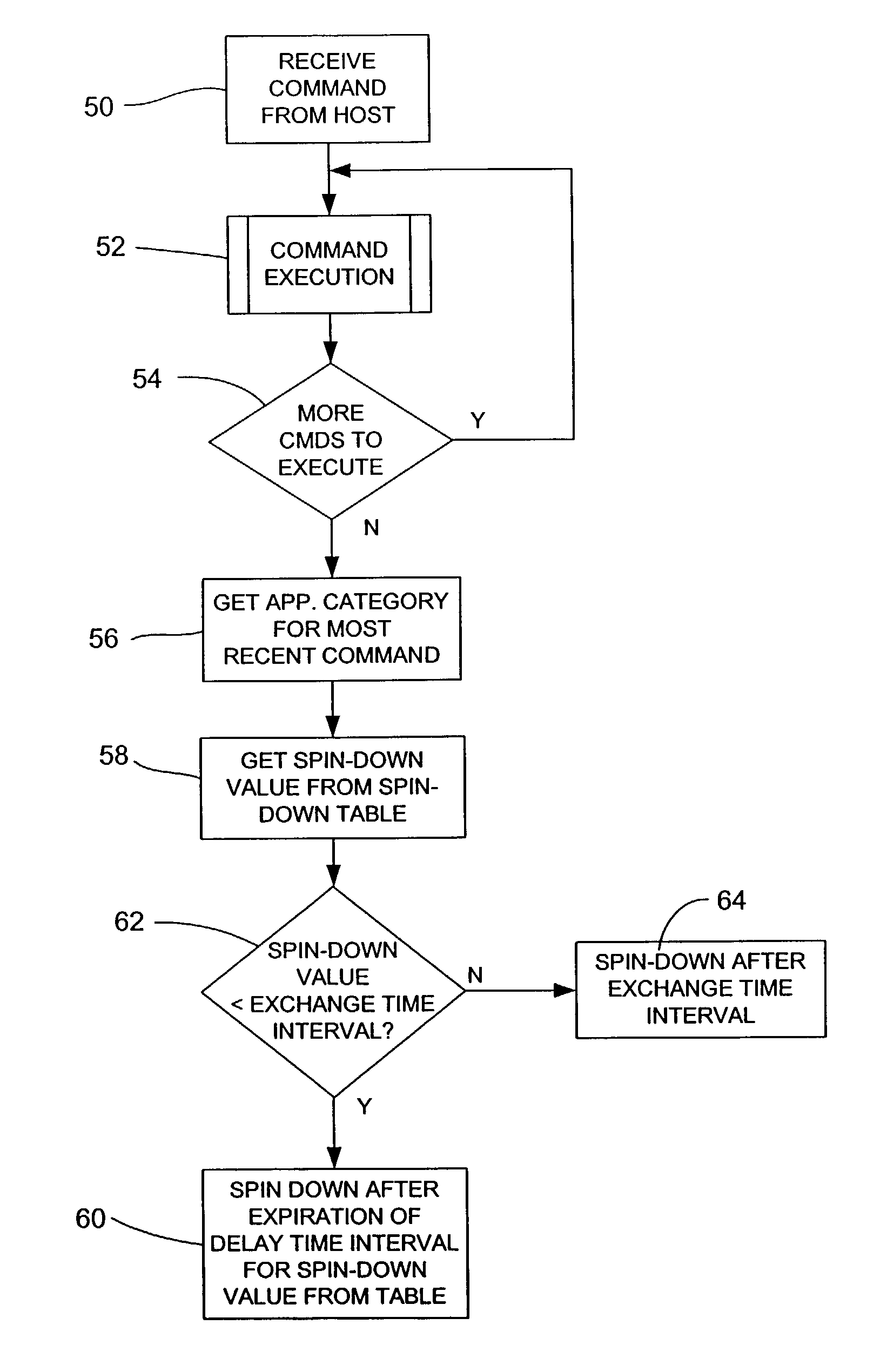

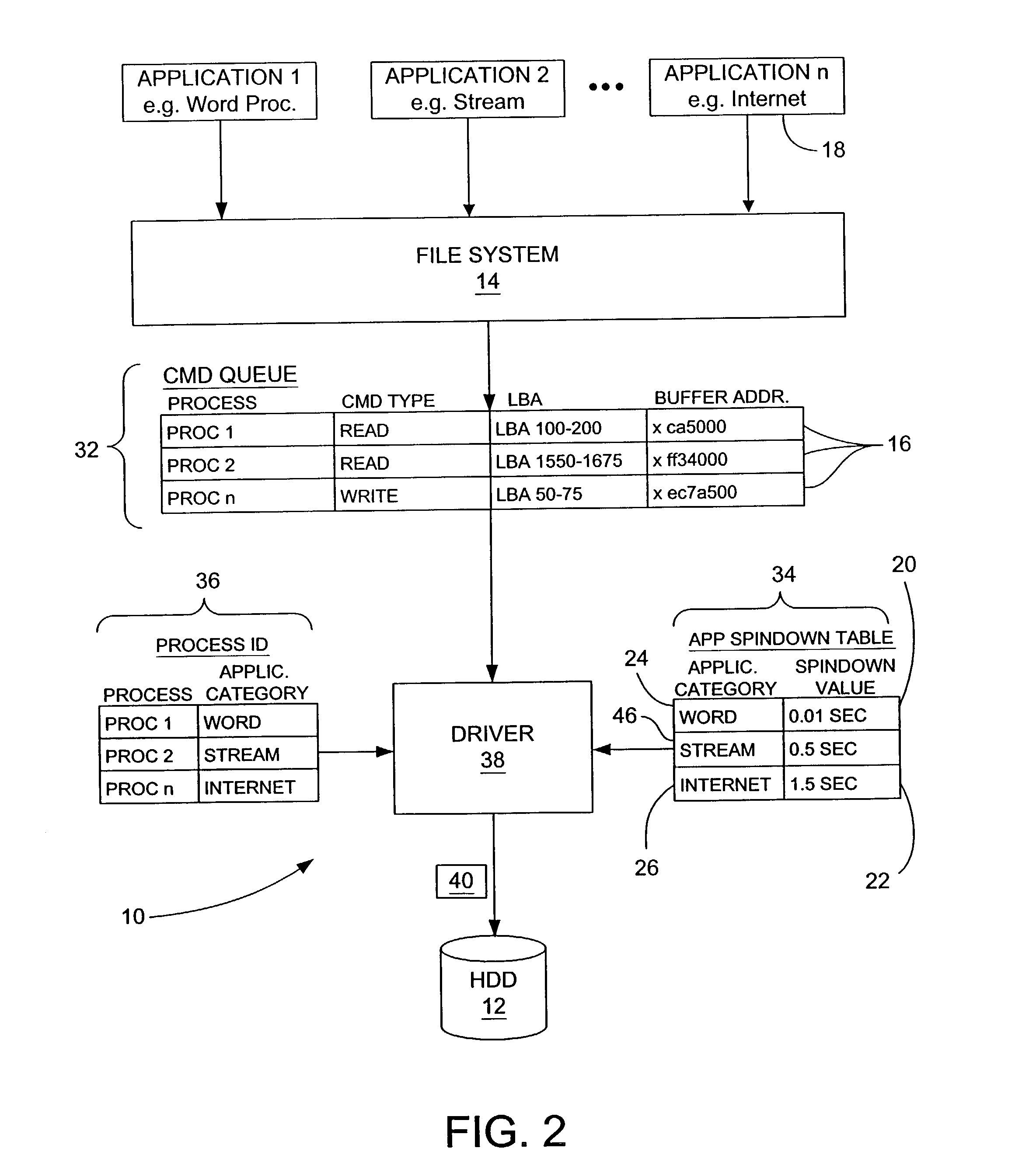

Method for setting a power operating mode transition interval of a disk drive in a mobile device based on application category

InactiveUS7120806B1Optimizing power usageIncrease power levelEnergy efficient ICTVolume/mass flow measurementHand heldPower usage

The invention may be embodied in a method for operating a disk drive in a mobile device to optimize power usage based on an application category. The mobile device may be a hand held computing device such as a personal digital assistant (PDA) or a mobile terminal such as a cellular telephone. A technique of the invention may spin down the disk drive after an adjustable delay time interval that is set based on an application category associated with a most recent data transfer command.

Owner:WESTERN DIGITAL TECH INC

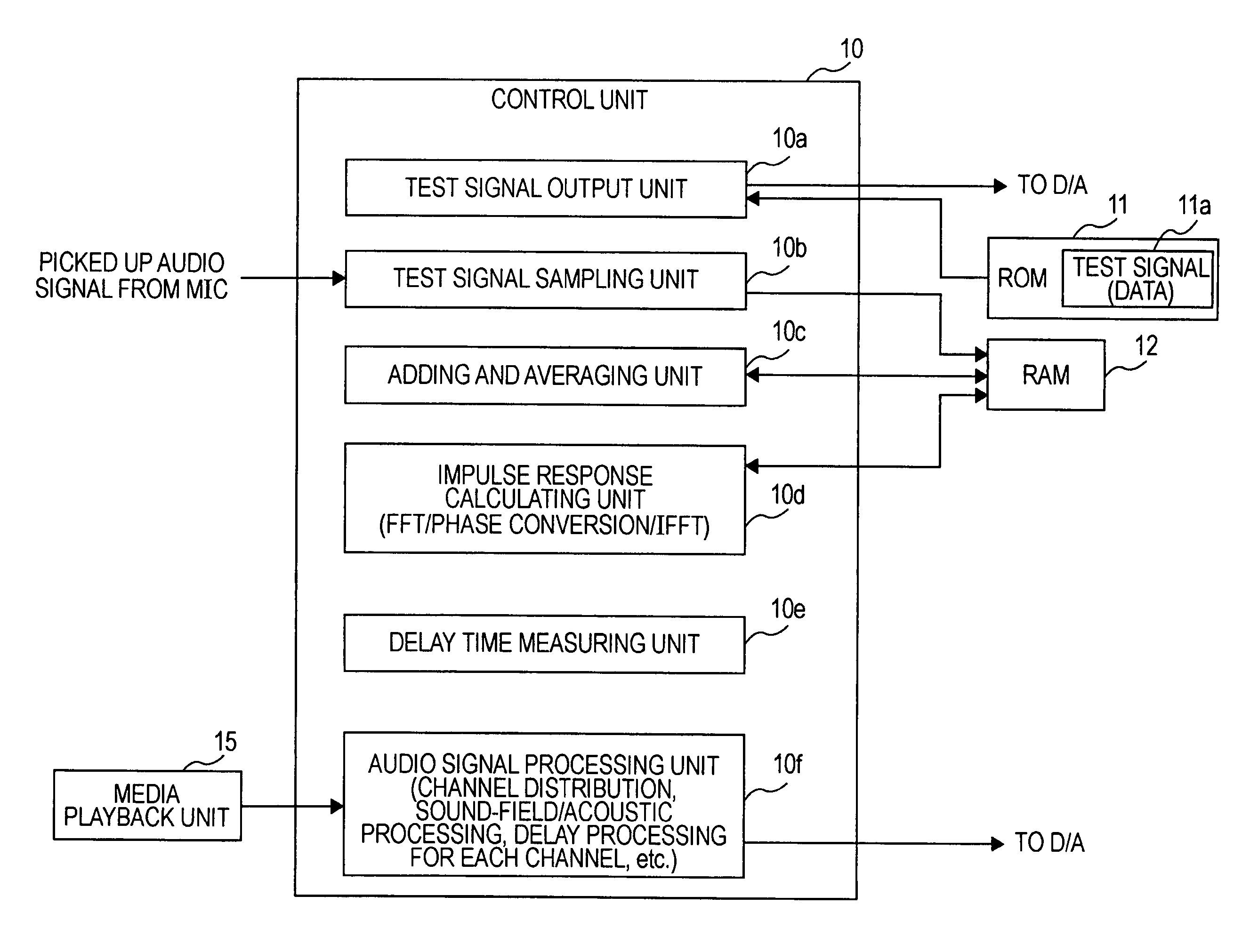

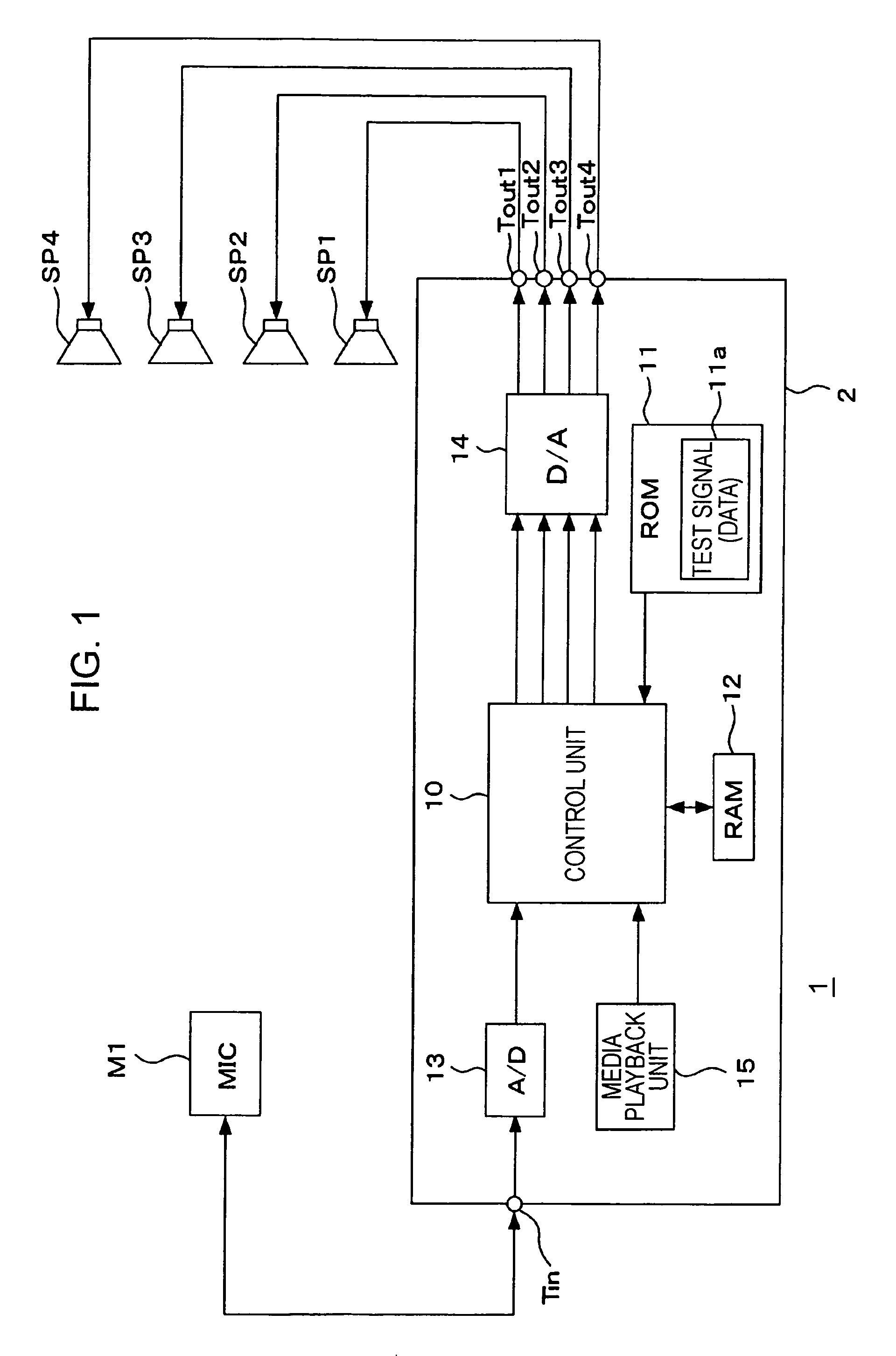

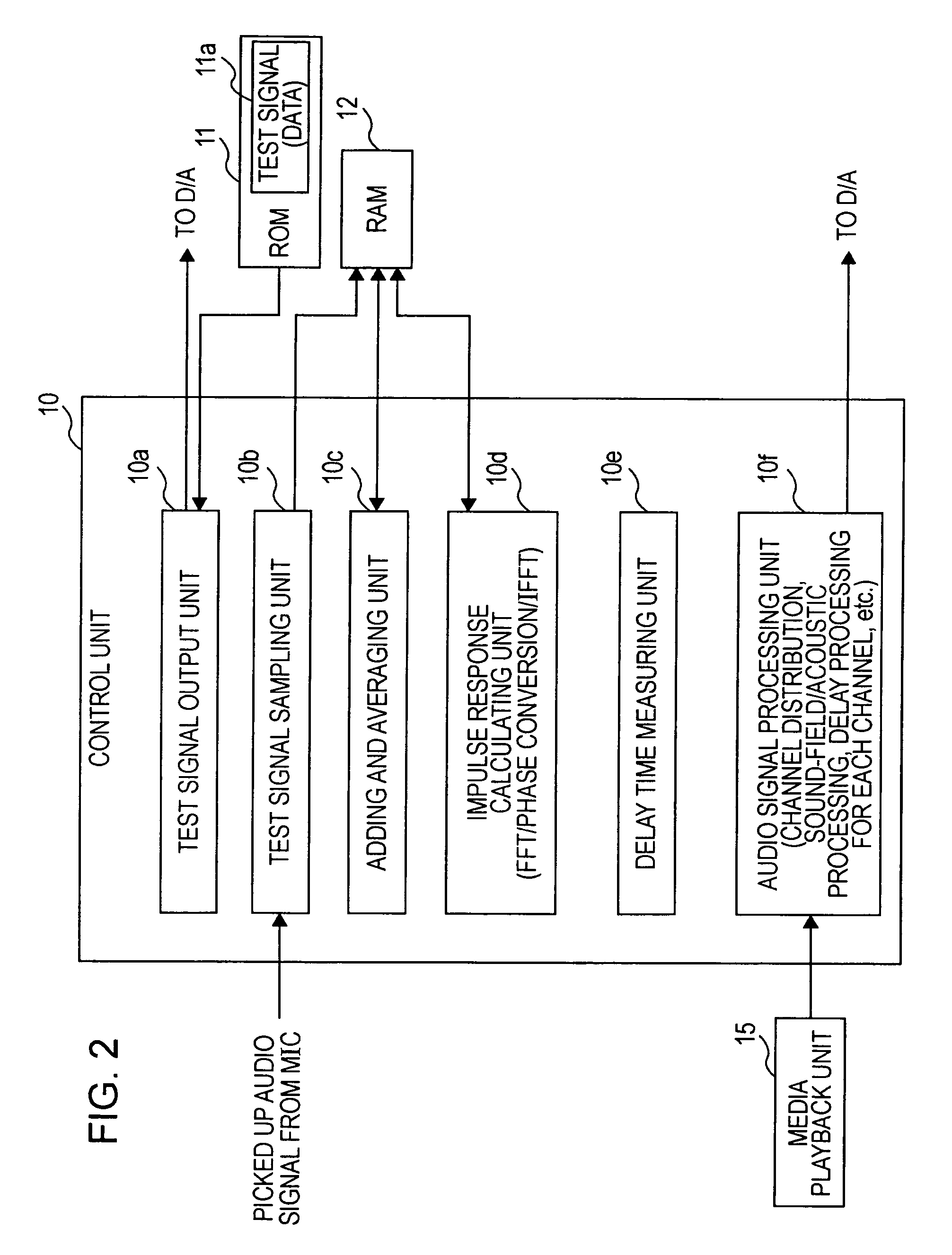

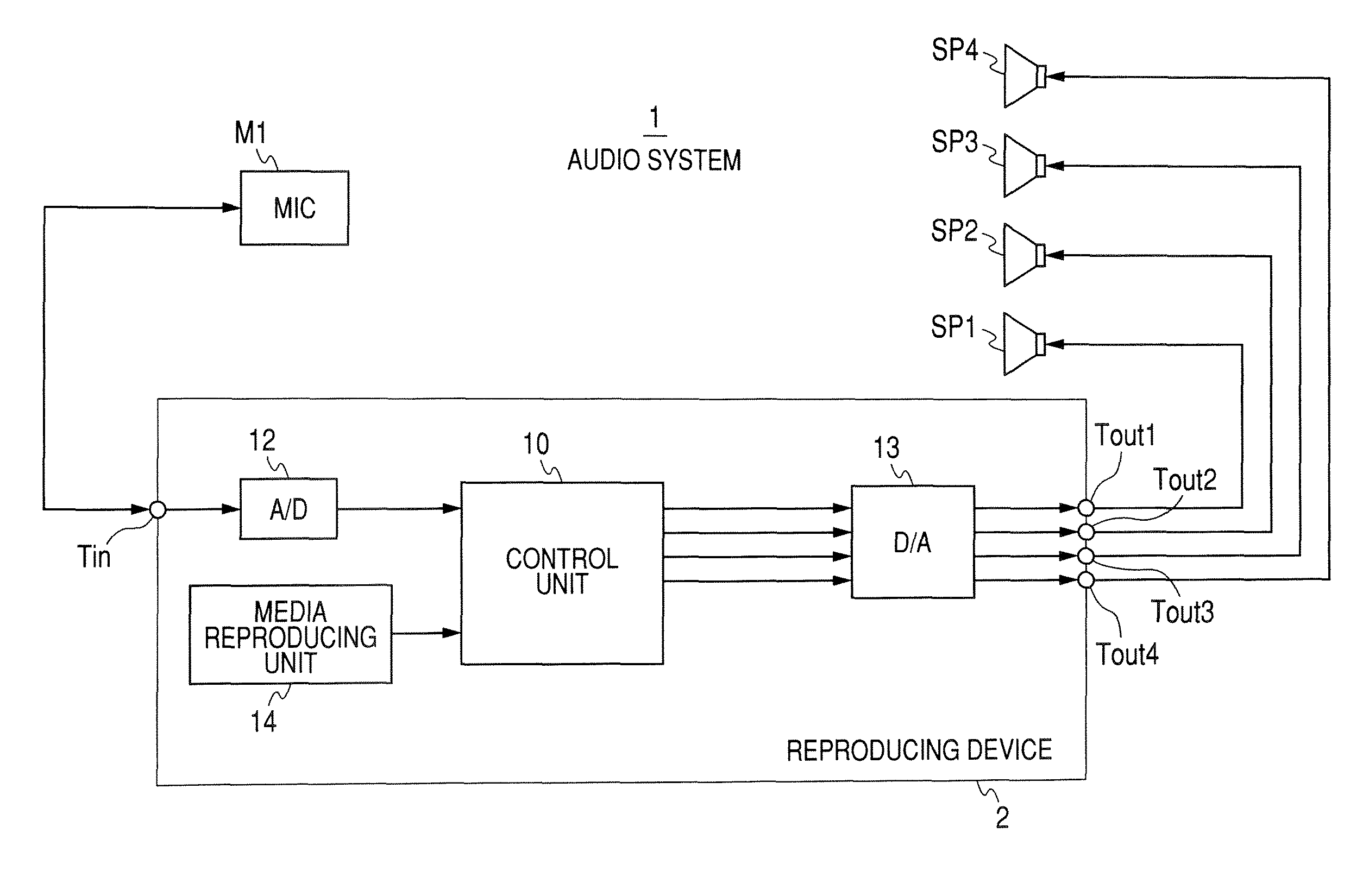

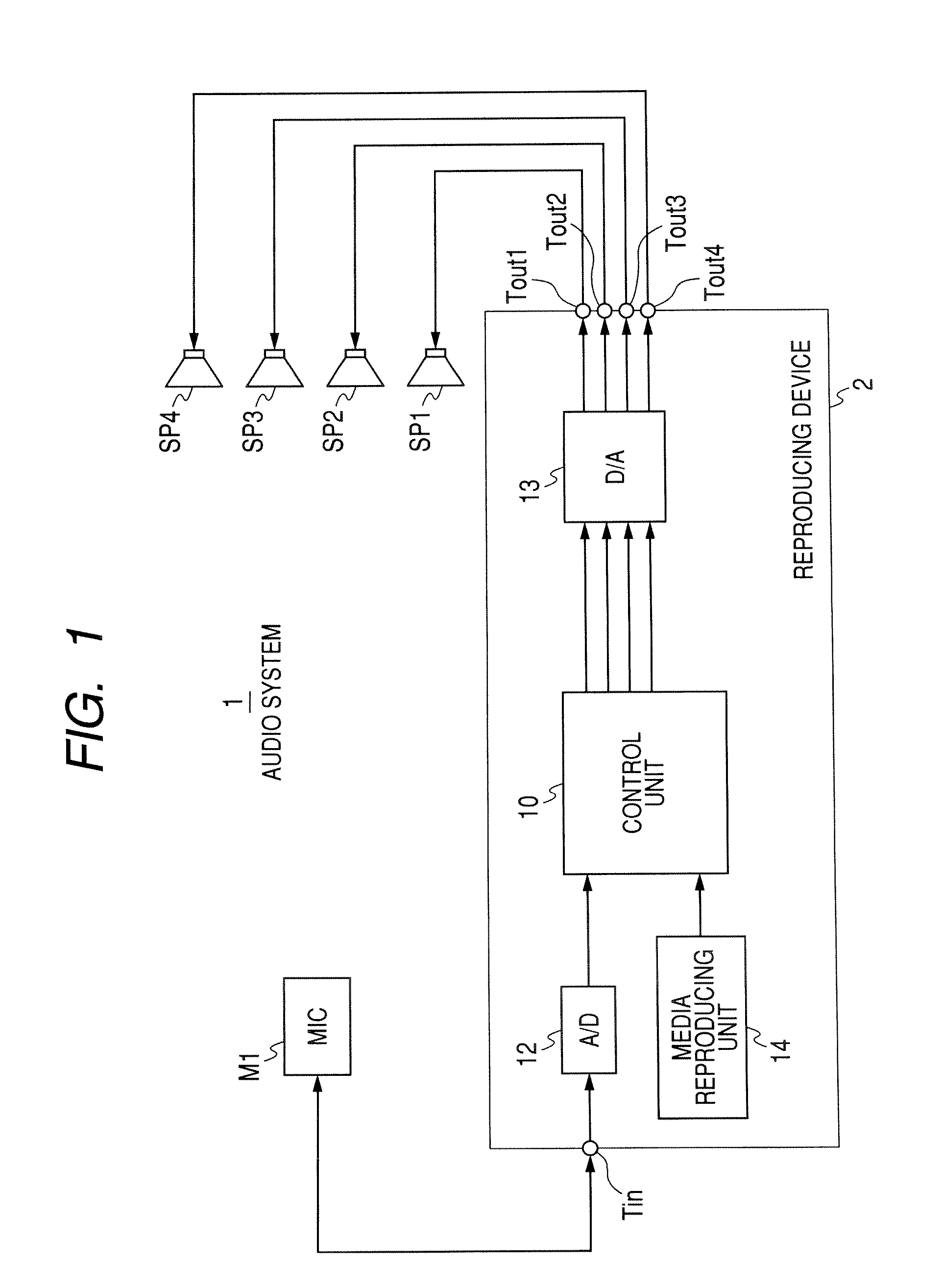

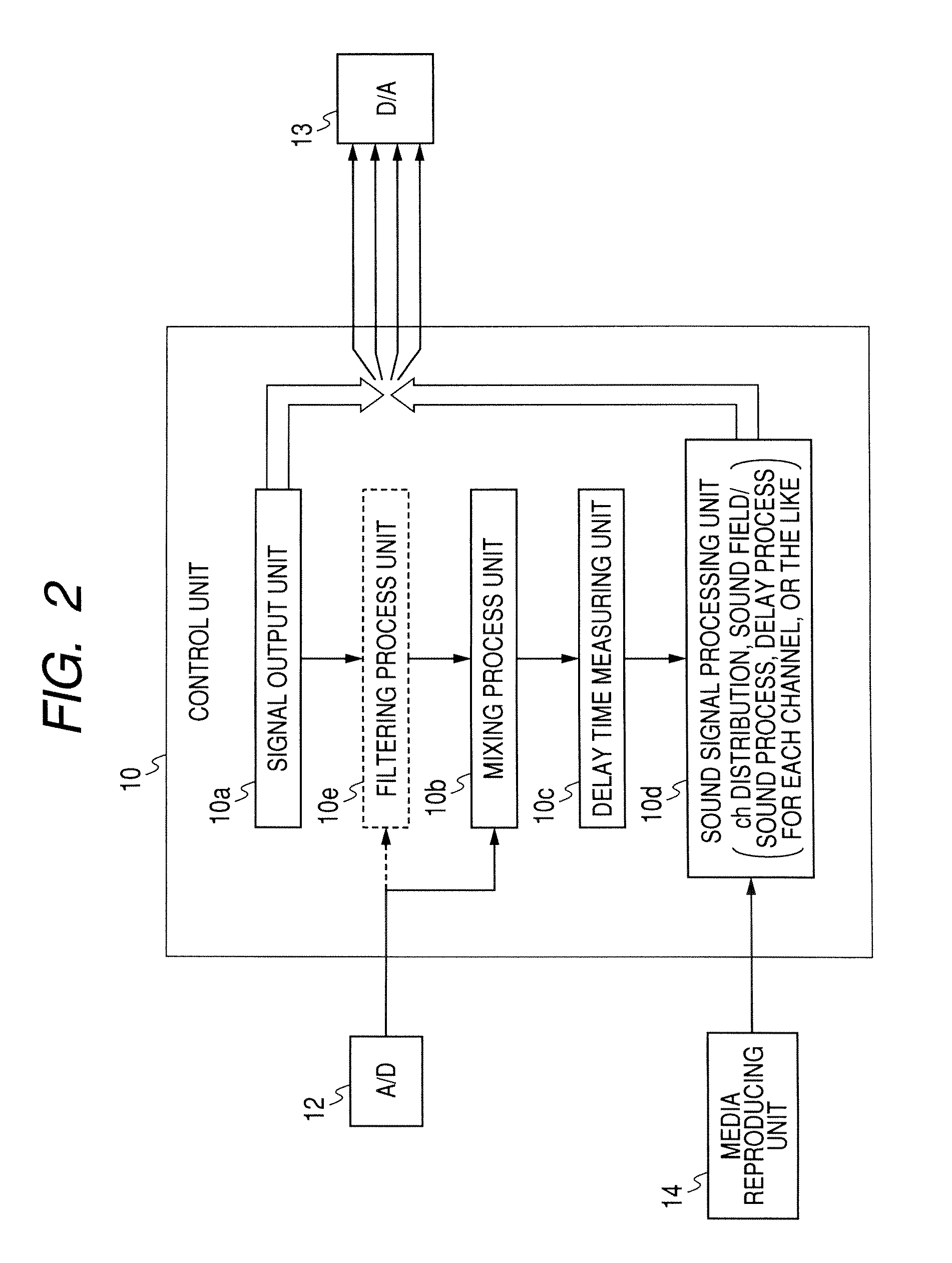

Sound measuring apparatus and method, and audio signal processing apparatus

InactiveUS7949140B2Increase sample sizeLong delay timeTwo-channel systemsSpecial data processing applicationsEngineeringLoudspeaker

A sound measuring apparatus for measuring a sound-arrival delay time from a speaker to a microphone on the basis of a result obtained by outputting a test signal from the speaker and picking up the test signal using the microphone includes the following elements. A control unit performs control so that the test signal is expanded in a time axis and is then output from the speaker. A delay time measuring unit measures an expansion-based measured delay time on the basis of a delay time that is measured on the basis of a time difference between the test signal expanded in the time axis and output from the speaker and a signal obtained from the microphone by picking up the output expanded test signal, and obtains the sound-arrival delay time as the expansion-based measured delay time.

Owner:SONY CORP

Measuring apparatus, measuring method, and sound signal processing apparatus

InactiveUS7961893B2Long delay timeEasy to operateLoudspeaker spatial/constructional arrangementsStereophonic systemsMeasurement deviceLoudspeaker

Owner:SONY CORP

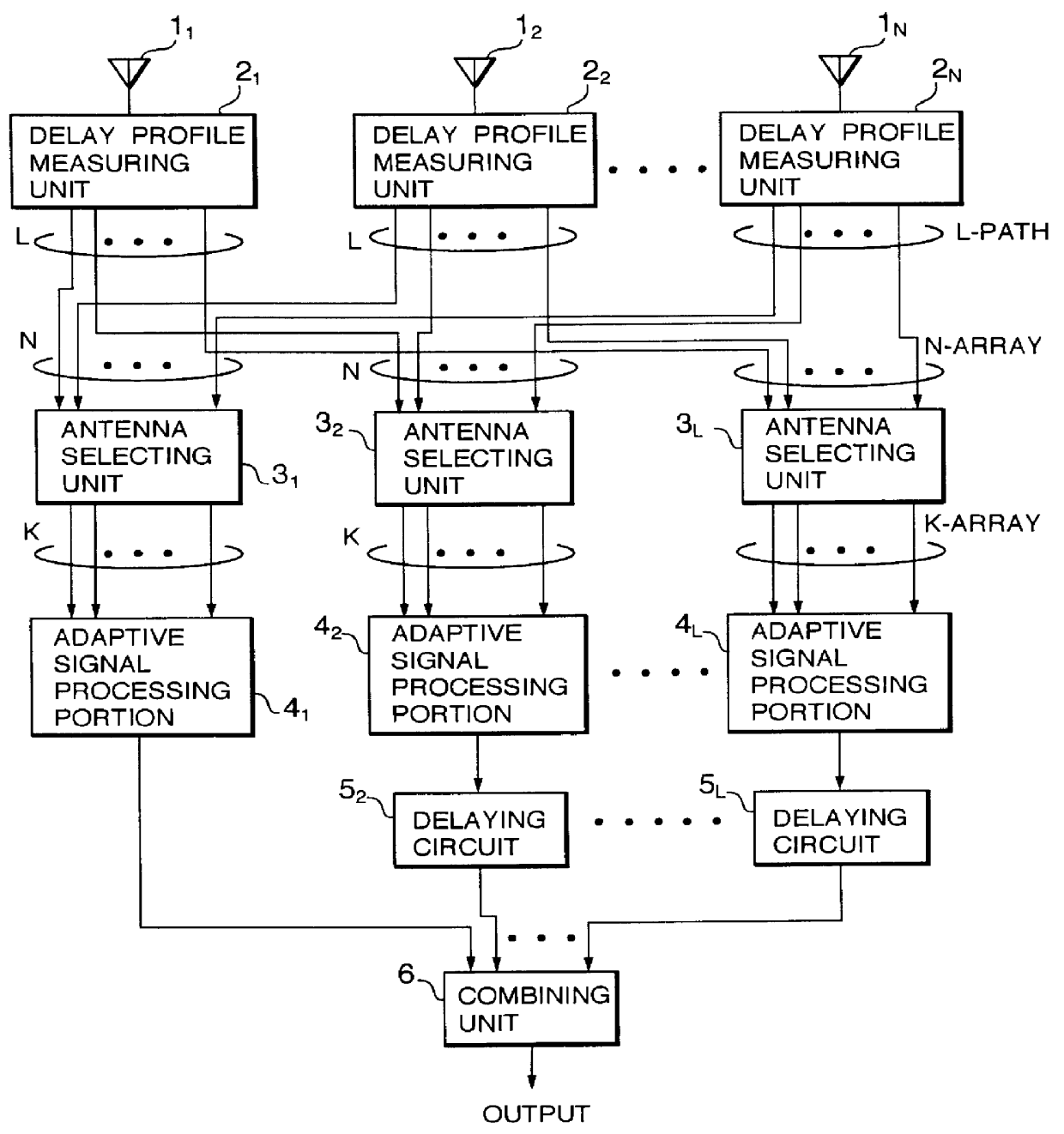

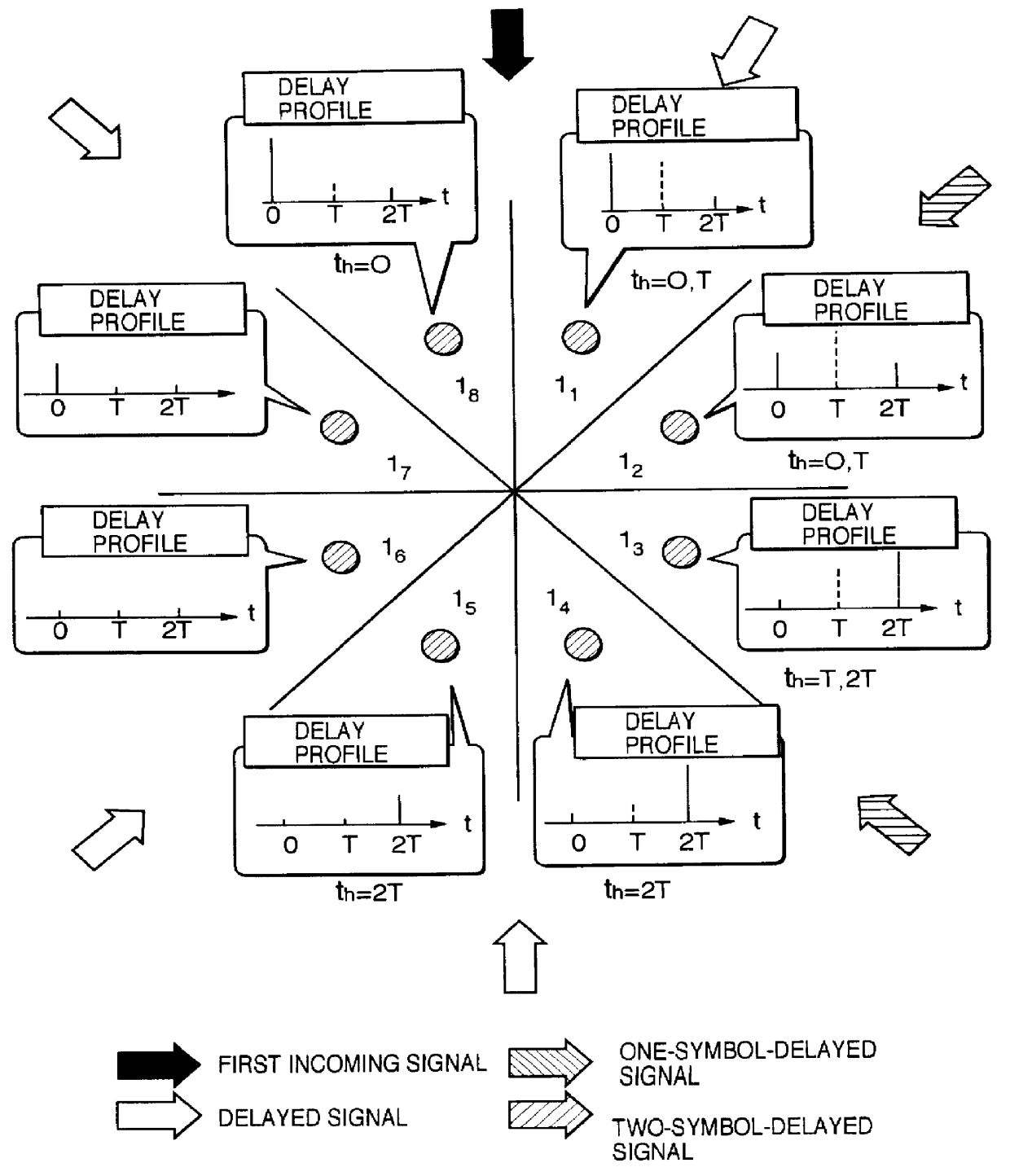

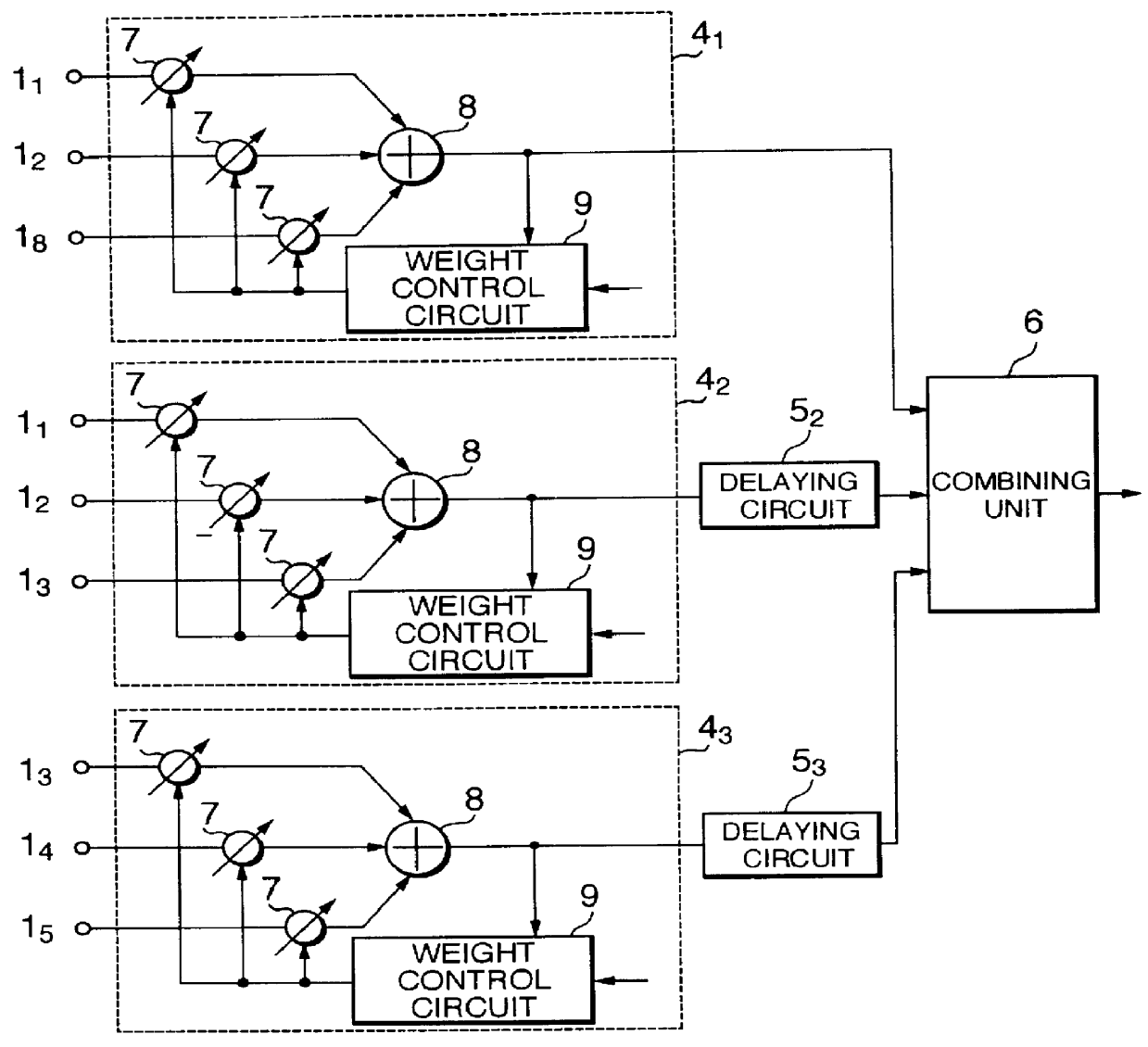

Adaptive antenna

An adaptive antenna is disclosed, that comprises a plurality of antenna elements 11, 12, . . . , and 1N with different directivity, delay profile measuring units 21, 22, . . . , and 2N for estimating states of received signals of the antenna elements for each of delay times that have been designated, antenna selecting units 31, 32, . . . , and 3L for selecting a part of the antenna elements for each of the delay times corresponding to the estimated result, adaptive signal processing portions 41, 42, . . . , and 4L for determining the received signals of the part of the antenna elements that have been selected and multiplying the received signals to which relevant weights have been determined for each of the delay time and summing the weighted signals, delaying circuits 52 and 53 for compensating the time lag, or delay of each of the received signals for each of the delay times, and a combining unit 6 for combining the weighted signals that have been compensated for the delay times.

Owner:KK TOSHIBA

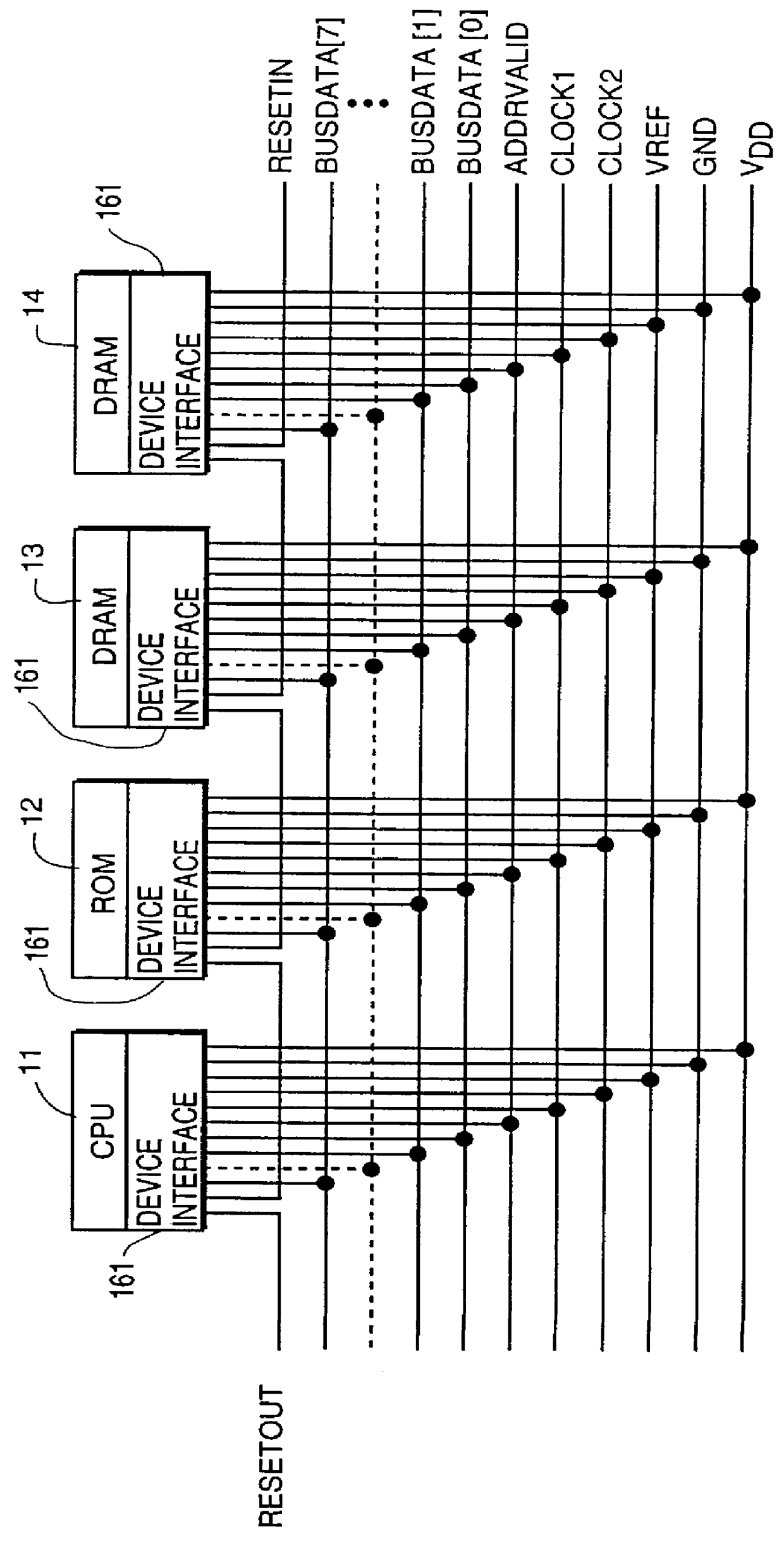

Single-chip microcomputer using adjustable timing to fetch data from an external memory

InactiveUS6125431AIncrease costEasy to operateMemory adressing/allocation/relocationProgram controlMicrocontrollerInternal memory

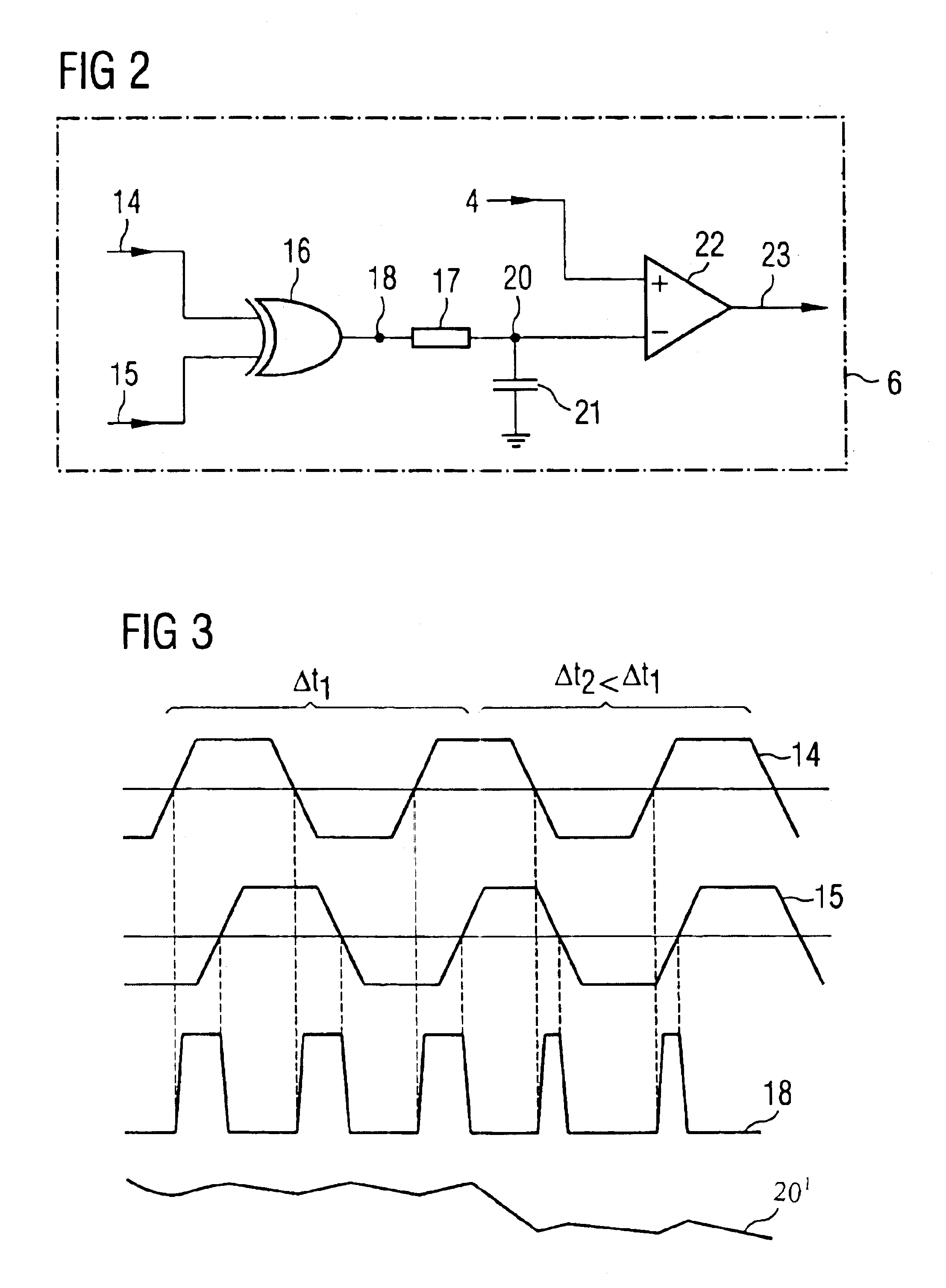

It is an object of the present invention to provide a one-chip microcomputer which permits the access time for an external memory to be equal to that for an internal memory. The one-chip microcomputer 10 includes an internal ROM 11, control circuit 12, output terminals 13, input terminals 14, control circuit 15, selector 16, instruction register 17, delay circuit 18, and fetch control signal select gate 19. For selection of the external ROM 30, a control arrangement 20 and a delay circuit 18 are employed in one embodiment to adjust the time at which ROM data is fetched by the instruction register 17, based on the delay time for accessing the external ROM 30.

Owner:LAPIS SEMICON CO LTD

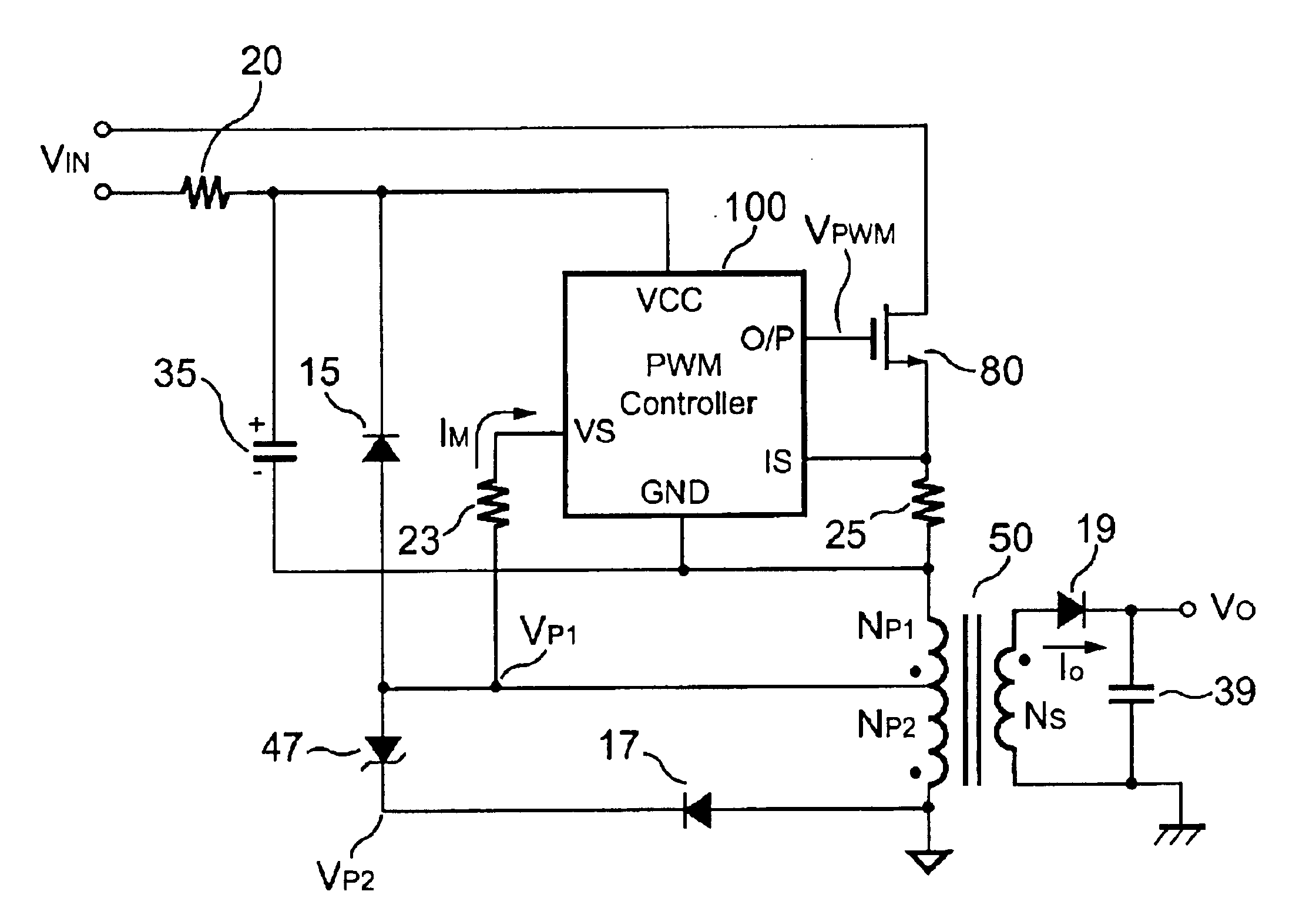

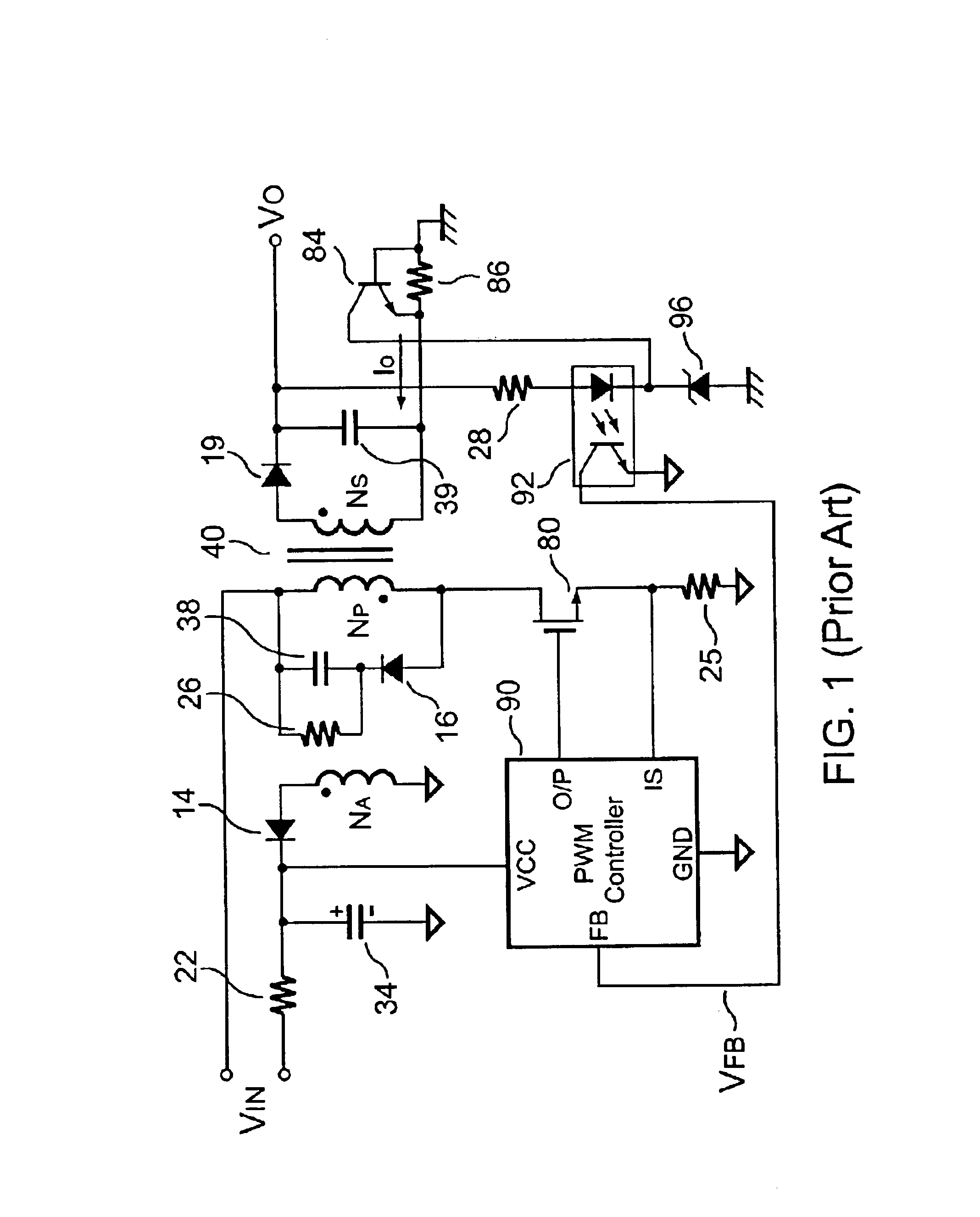

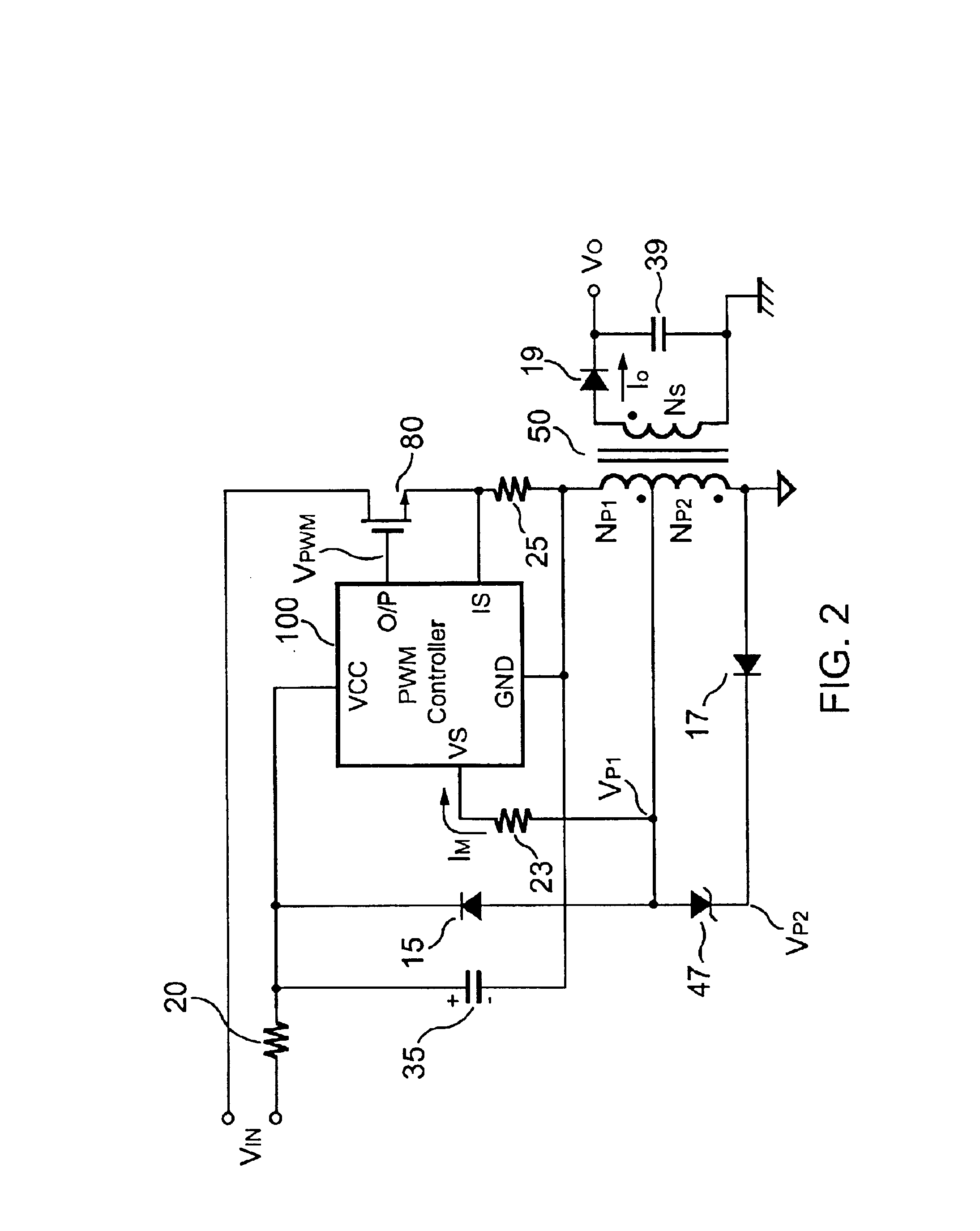

Flyback power converter having a constant voltage and a constant current output under primary-side PWM control

InactiveUS6862194B2Accurate supervisionSmall sizeAc-dc conversion without reversalEmergency protective circuit arrangementsConductor CoilPwm signals

A primary-side flyback power converter supplies a constant voltage and a constant current output. To generate a well-regulated output voltage under varying load conditions, the power converter includes a PWM controller. The PWM controller generates a PWM signal to control a switching transistor in response to a flyback voltage detected from the first primary winding of the power supply transformer. To reduce power consumption, the flyback energy of the first primary winding is used as a DC power source for the PWM controller. The flyback voltage is sampled following a delay time to reduce interference from the inductance leakage of the transformer. To generate a more accurate DC output voltage, a bias current is pulled from the detection input to form a voltage drop across a detection resistor for compensating for the voltage drop of the output rectifying diode.

Owner:FAIRCHILD TAIWAN

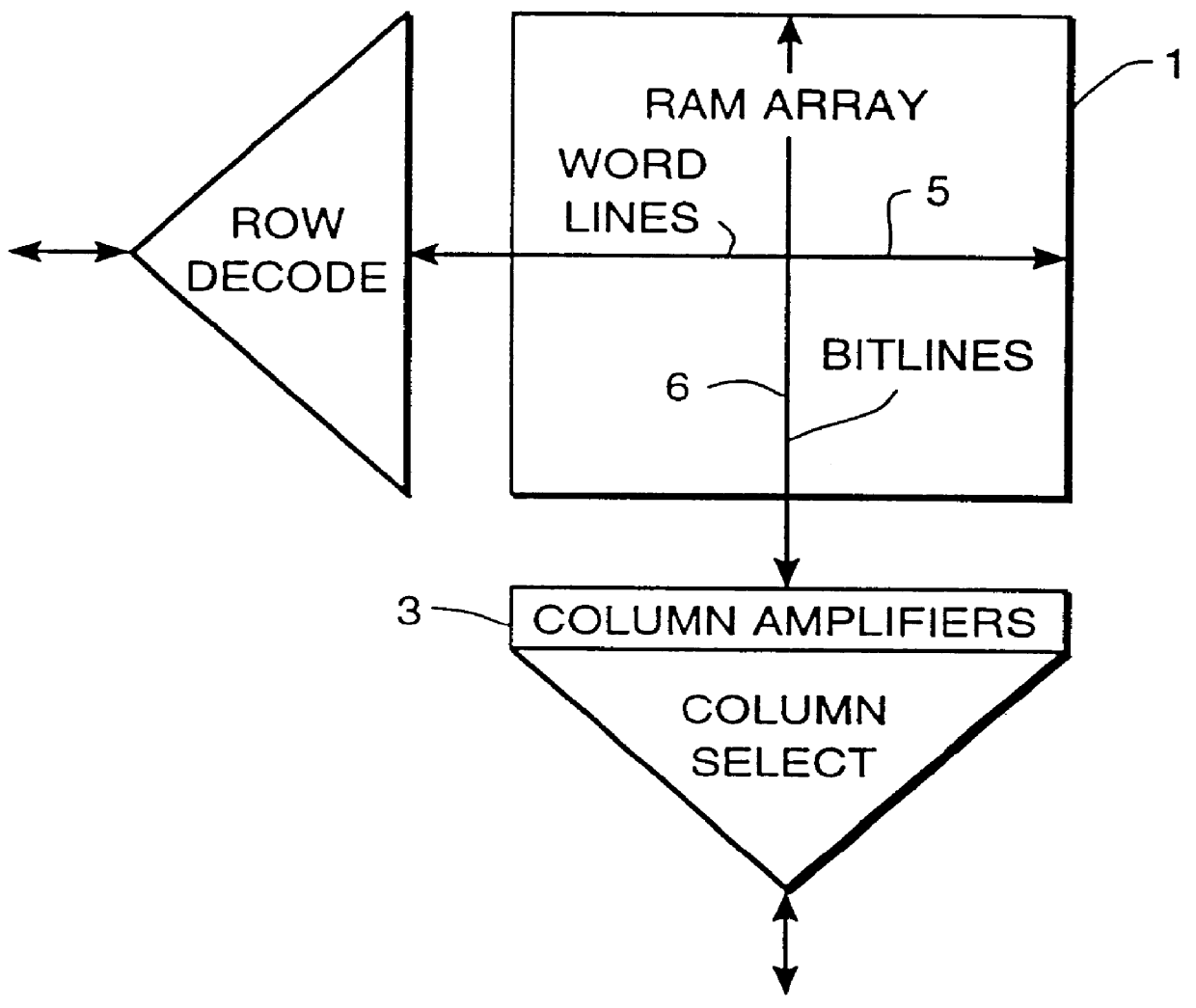

Dual clocked synchronous memory device having a delay time register and method of operating same

InactiveUS6035365AFast readWrite quicklyEnergy efficient ICTMemory adressing/allocation/relocationProcessor registerDelay-locked loop

A synchronous memory device having at least one memory section which includes a plurality of memory cells. The memory device comprises a register to store a value which is representative of a delay time after which the memory device responds to a read request and clock receiver circuitry to receive first and second external clock signals. The memory device also includes an output driver(s) to output data on a bus, in response to a read request and in accordance with the delay time, wherein a first portion of the data is output synchronously with respect to the first external clock signal and a second portion of the data is output synchronously with respect to the second external clock signal. The memory device may include a delay locked loop to generate internal clock signal(s) using the external clock signal(s). The output drivers output data on the bus in response to the internal clock signal(s). The memory device may include input receiver circuitry, coupled to the bus, the receive the read request, wherein the read request is sampled from the bus synchronously with respect to the first external clock signal.

Owner:RAMBUS INC

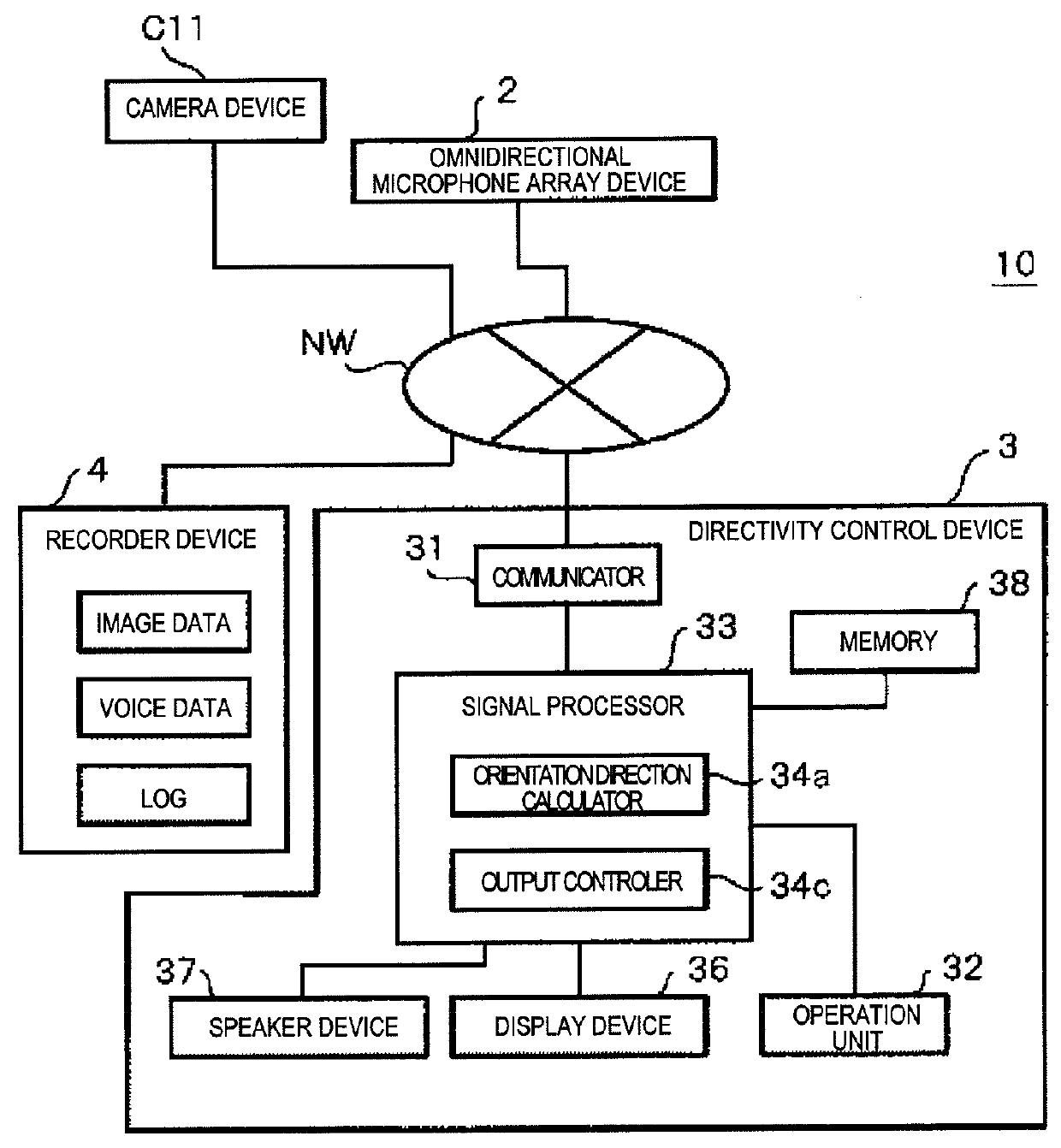

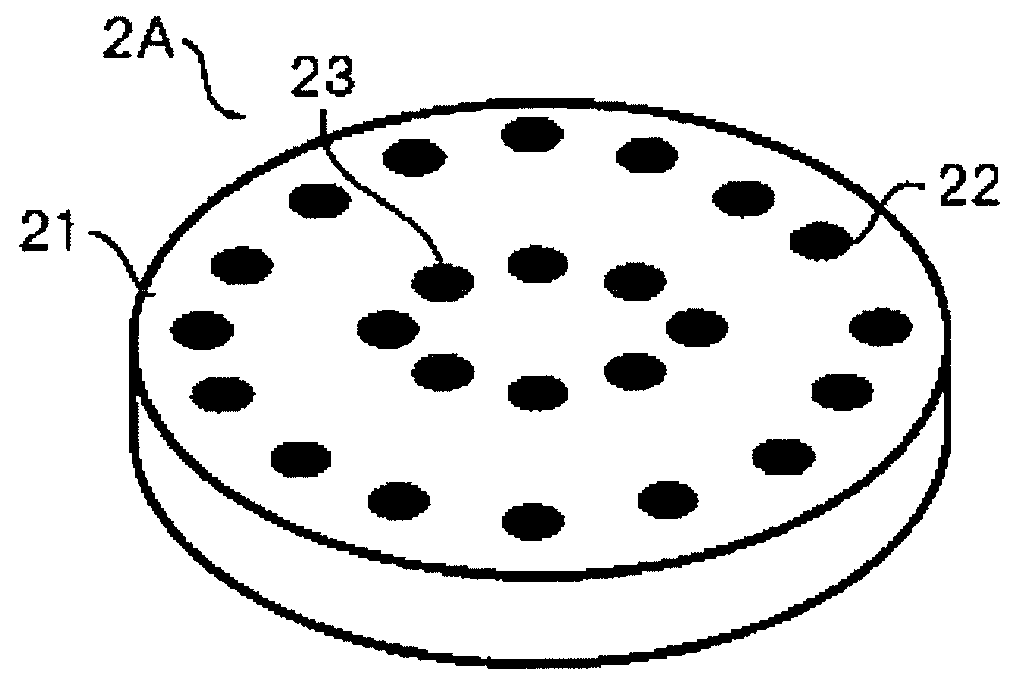

Failure detection system and failure detection method

A failure detection system includes an omnidirectional microphone array device having a plurality of microphone elements and a directivity control device that calculates a delay time of a voice propagated from a sound source to each microphone element and forms a directivity of the voice using the delay time and the voice collected by the omnidirectional microphone array device, and detects a failure of the microphone element. A smoothing unit calculates an average power of one microphone element. An average calculator calculates a total average power of a plurality of usable microphone elements included in the omnidirectional microphone array device. A comparison unit compares whether or not a difference between the average power and the total average power exceeds a range of ±6 dB, and determines whether the microphone element is in failure based on the comparison result.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

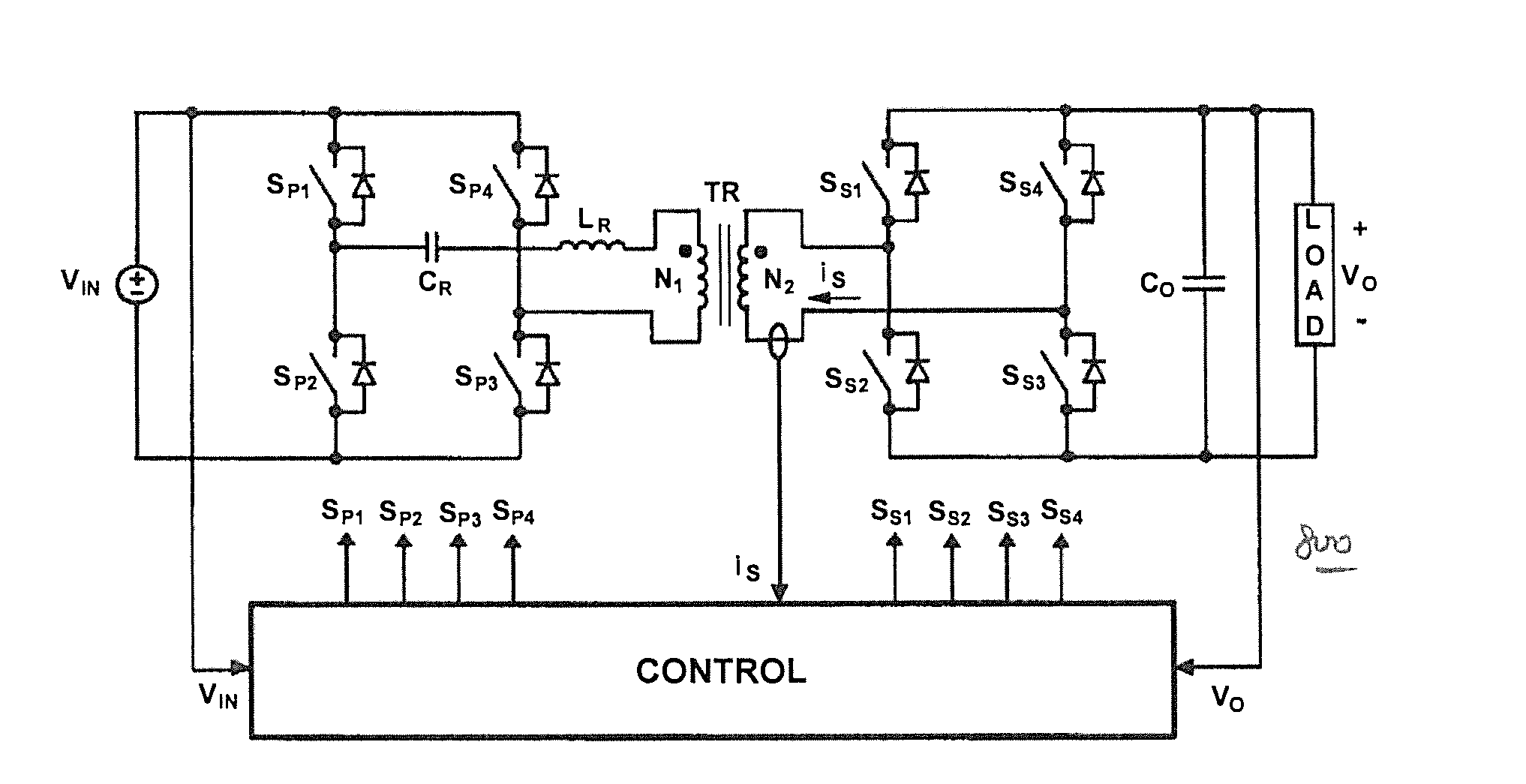

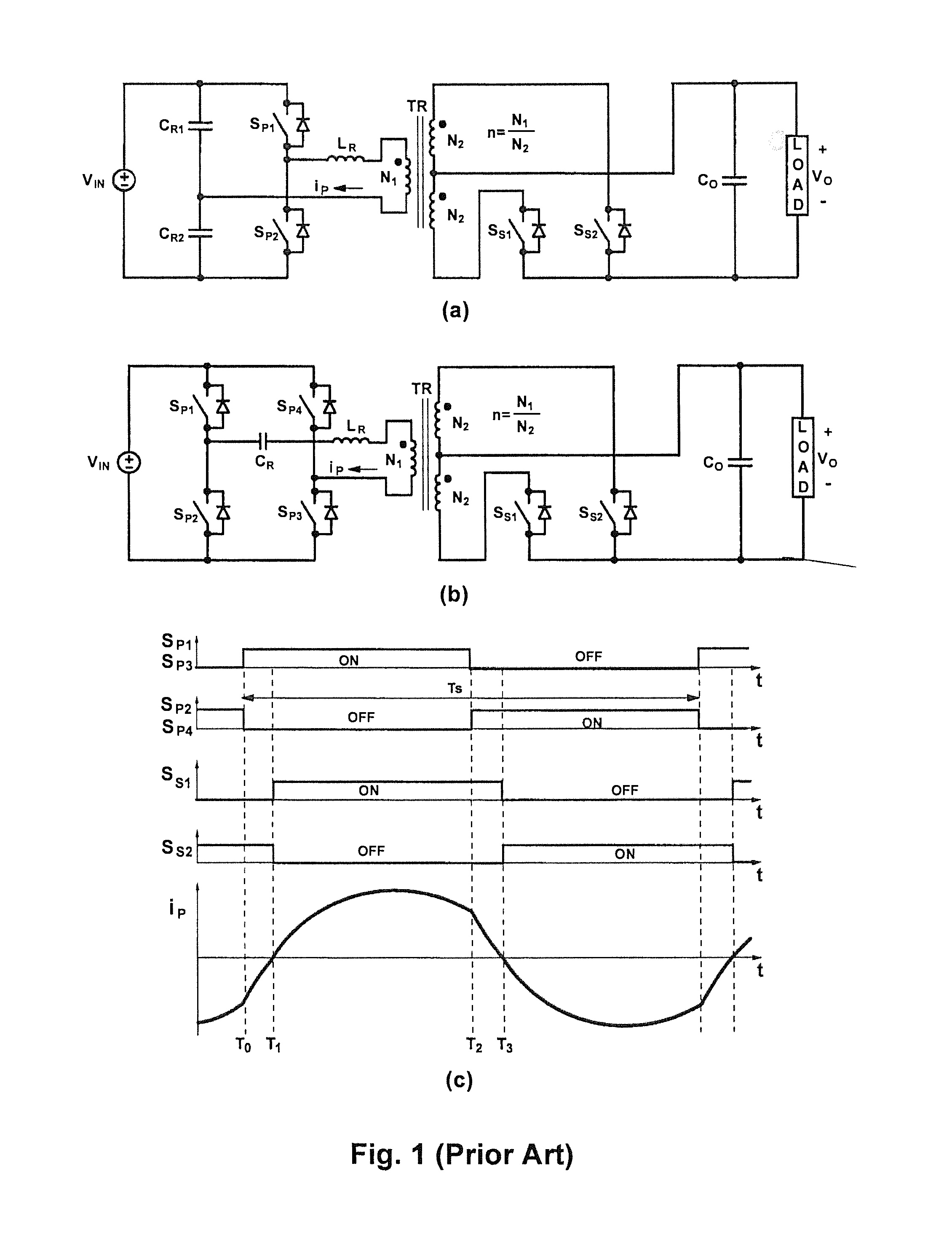

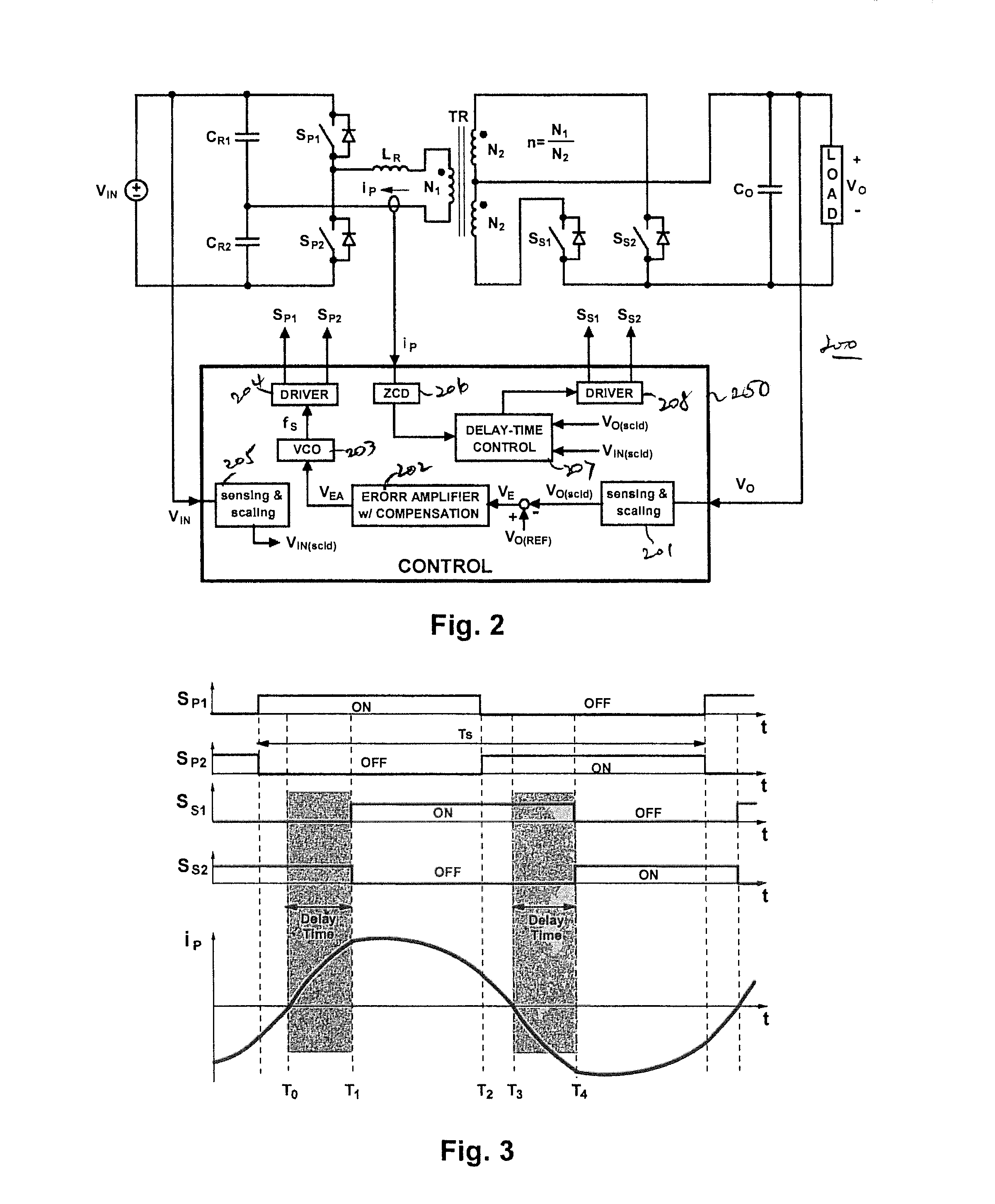

Resonant converters and control methods thereof

ActiveUS20150229225A1Improve performanceReducing switching-frequency rangeEfficient power electronics conversionDc-dc conversionTime delaysEngineering

Control methods for resonant converters offer improved performance in resonant converters that operate with a wide input-voltage range or a wide output-voltage range (or both) by substantially reducing the switching-frequency range. Reduction in the switching frequency range is achieved by controlling the output voltage with a combination of variable-frequency control and time-delay control. Variable-frequency control may be used to control the primary switches of an isolated resonant converter, while delay-time control may be used to control secondary-side rectifier switches provided in place of diode rectifiers. The secondary-side control may be implemented by sensing the secondary current or the primary current (or both) and by delaying the turning-off of the corresponding secondary switch with respect to the zero crossings in the secondary current or the primary current.

Owner:DELTA ELECTRONICS INC

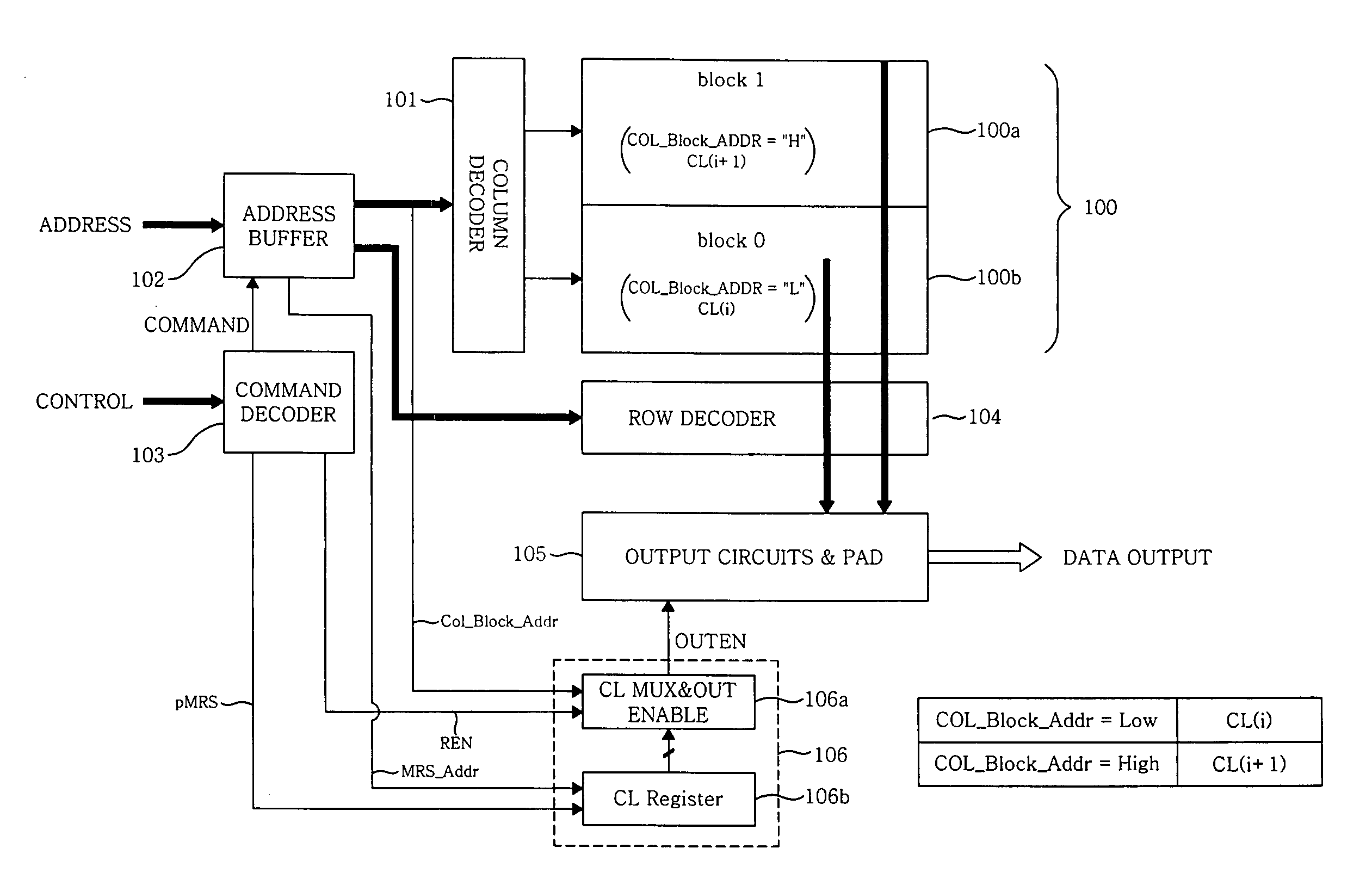

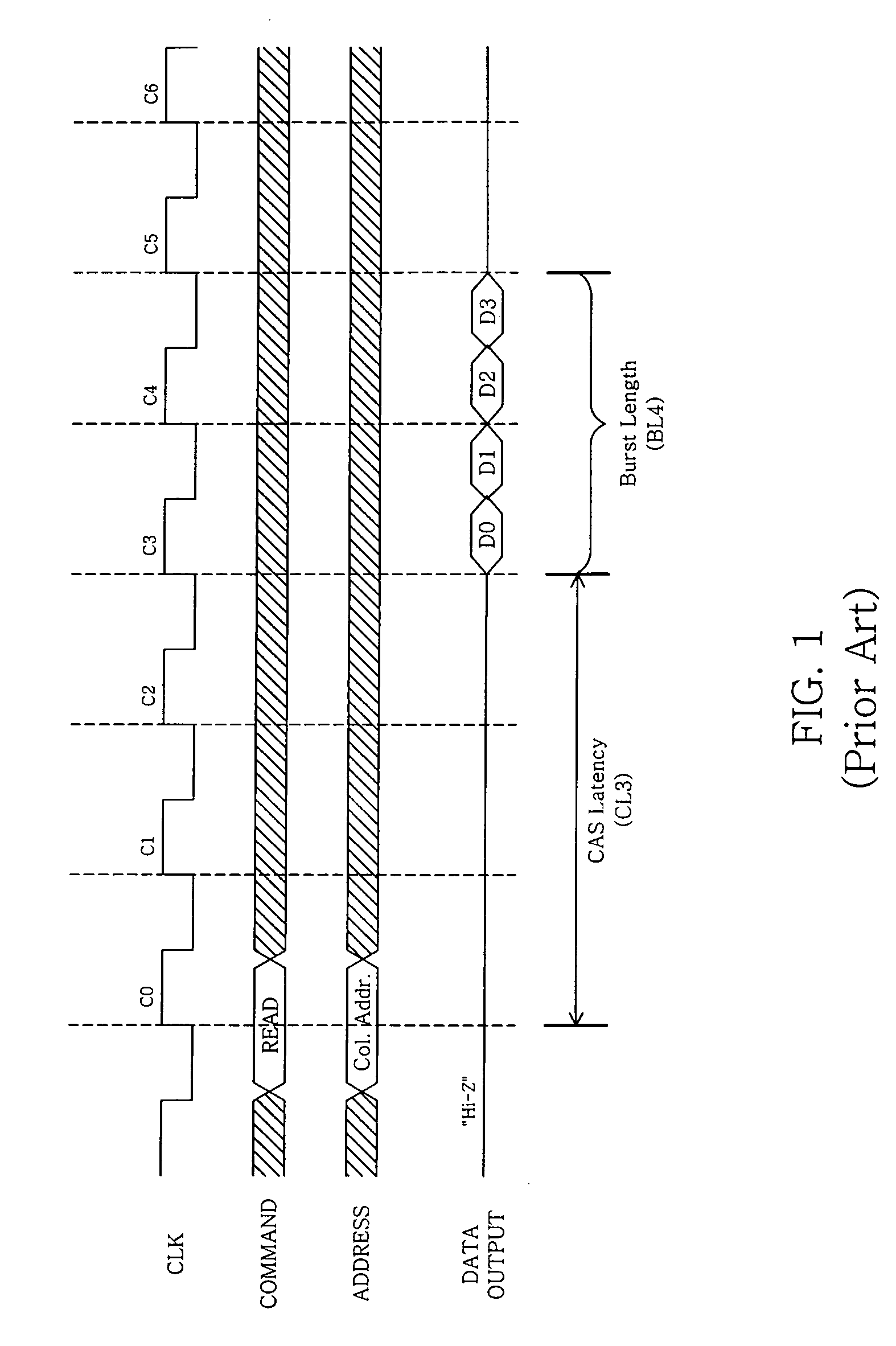

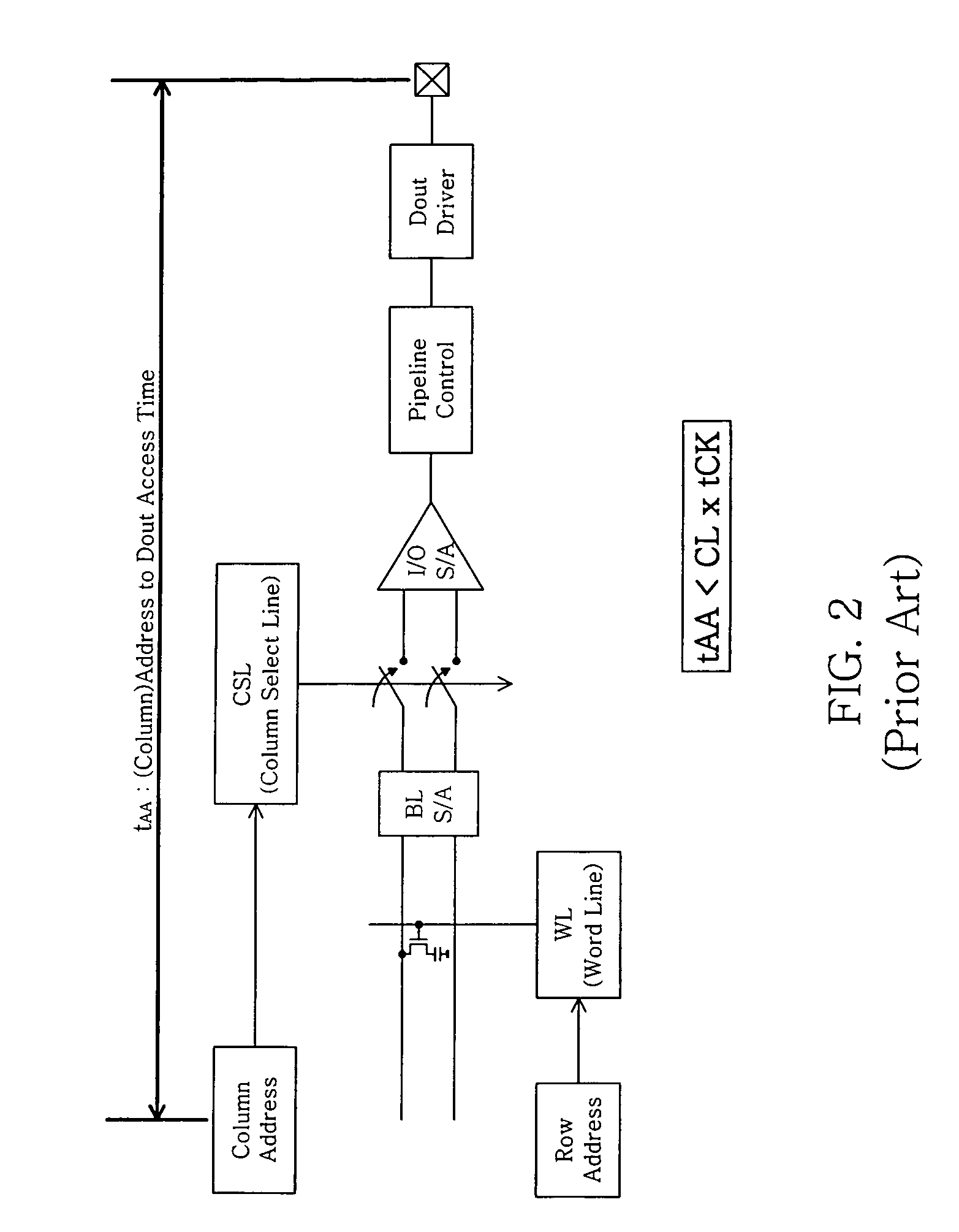

Semiconductor memories with block-dedicated programmable latency register

An apparatus and method to delay output of data from different regions of a memory device in response to a read enable signal, the delaying of the output of data is based on the location of the regions of the memory device with respect to an output circuit that receives the data, wherein the different regions of the memory device have different CAS latency values dedicated to each region to set the delay time of each region of the memory device.

Owner:SAMSUNG ELECTRONICS CO LTD

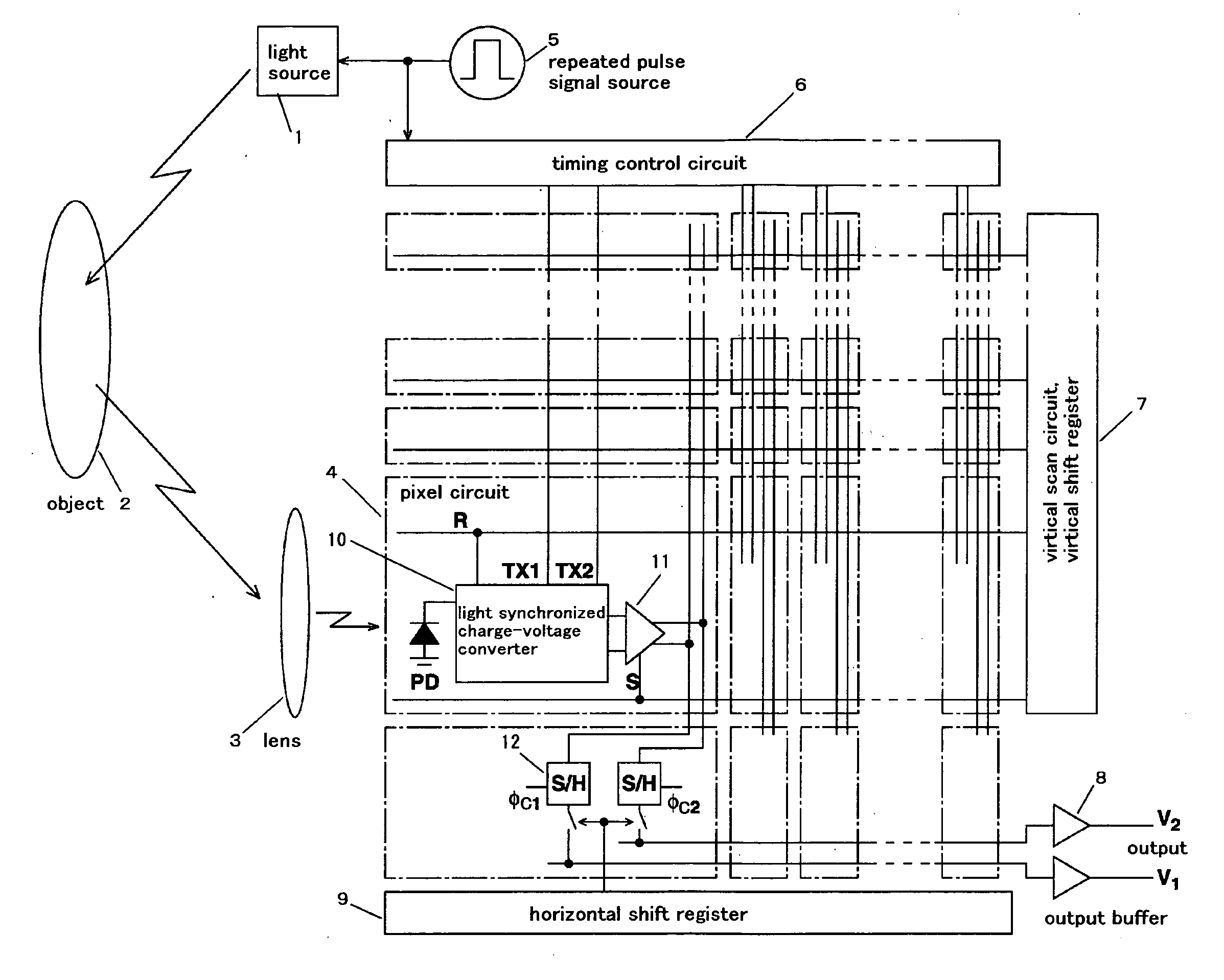

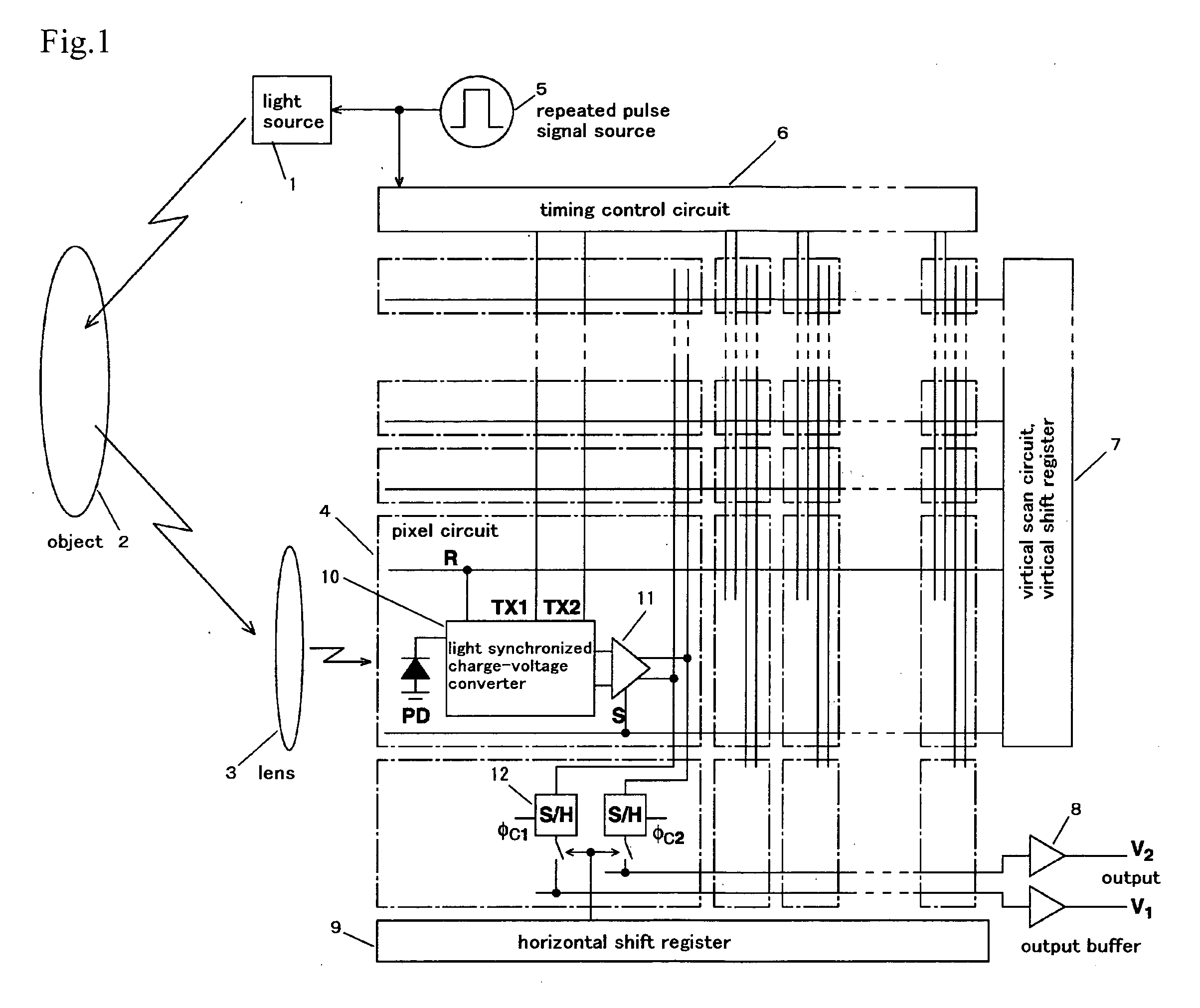

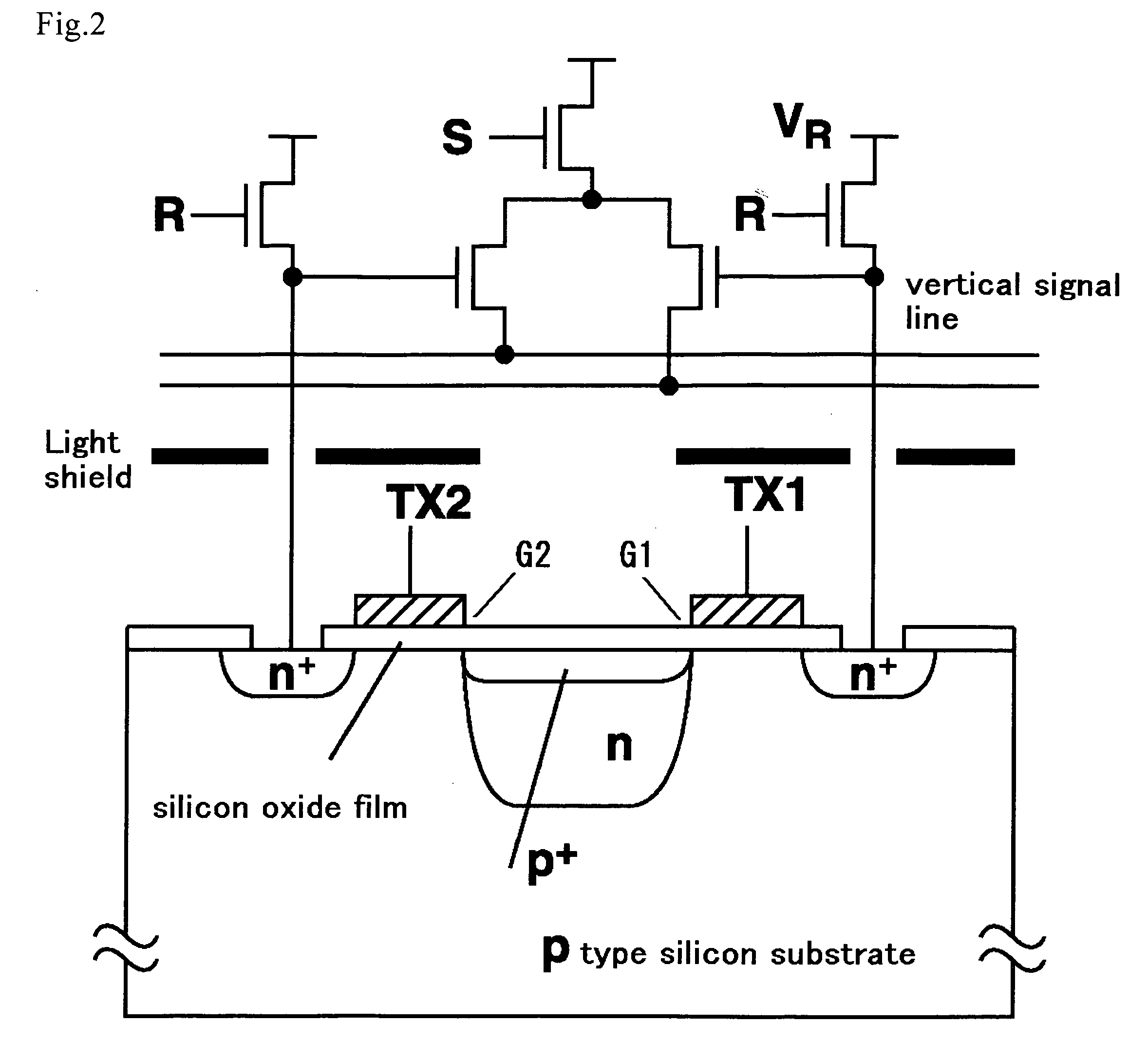

Distance image sensor

ActiveUS20060192938A1Advantage and disadvantageHigh sensitivityTelevision system detailsOptical rangefindersAudio power amplifierNegative feedback amplifier

A distance image sensor for removing the background light and improving the charge transfer efficiency in a device for measuring the distance to an object by measuring the time-of-flight of the light. In a distance image sensor for determining the signals of two charge storage nodes which depend on the delay time of the modulated light, a signal by the background light is received from the third charge storage node or the two charge storage nodes in a period when the modulated light does not exist, and is subtracted from the signal which depends on the delay time of the two charge storage nodes, so as to remove the influence of the background. Also by using a buried diode as a photo-detector, and using an MOS gate as gate means, the charge transfer efficiency improves. The charge transfer efficiency is also improved by using a negative feedback amplifier where a capacitor is disposed between the input and output.

Owner:NAT UNIV CORP SHIZUOKA UNIV

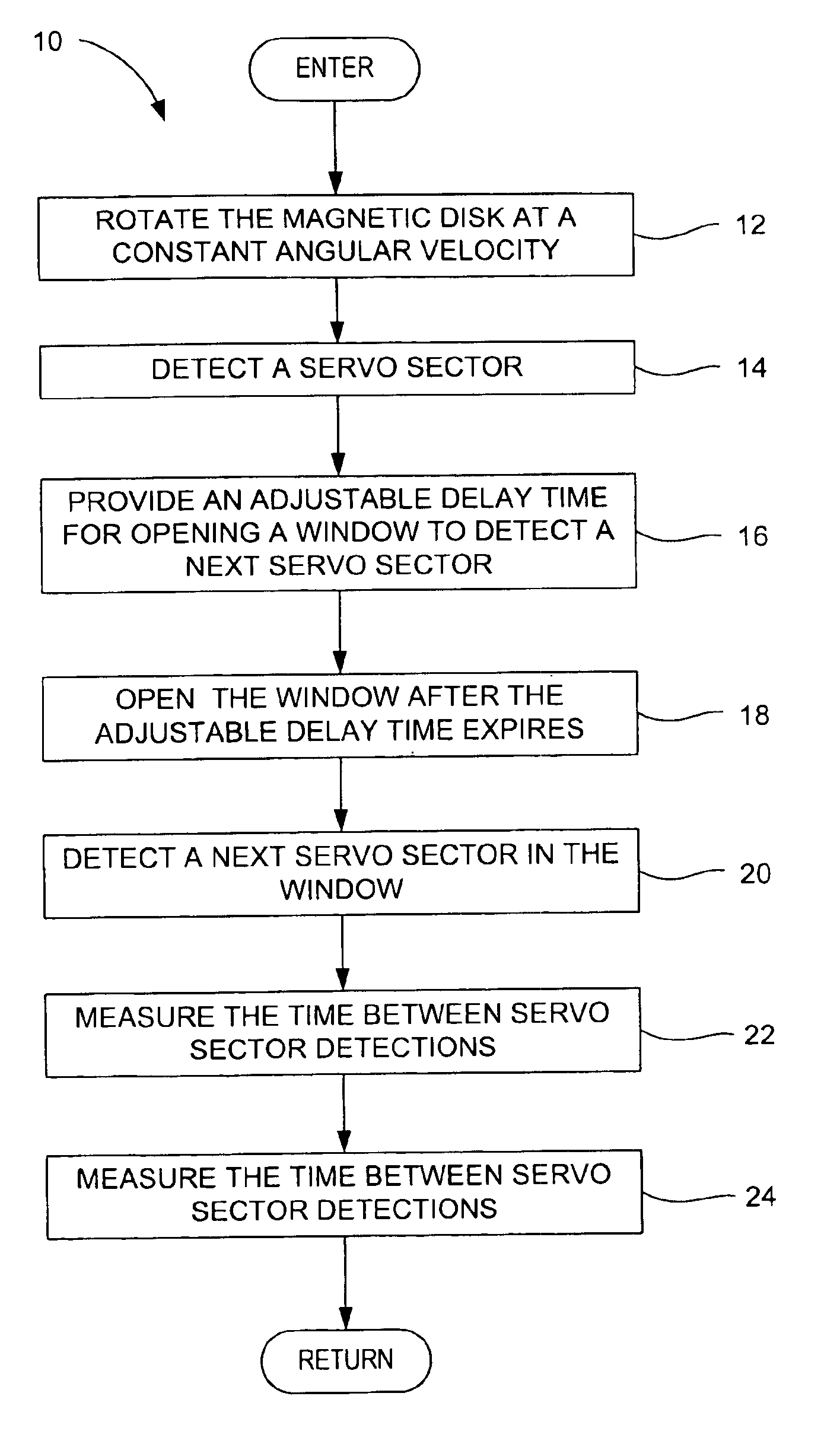

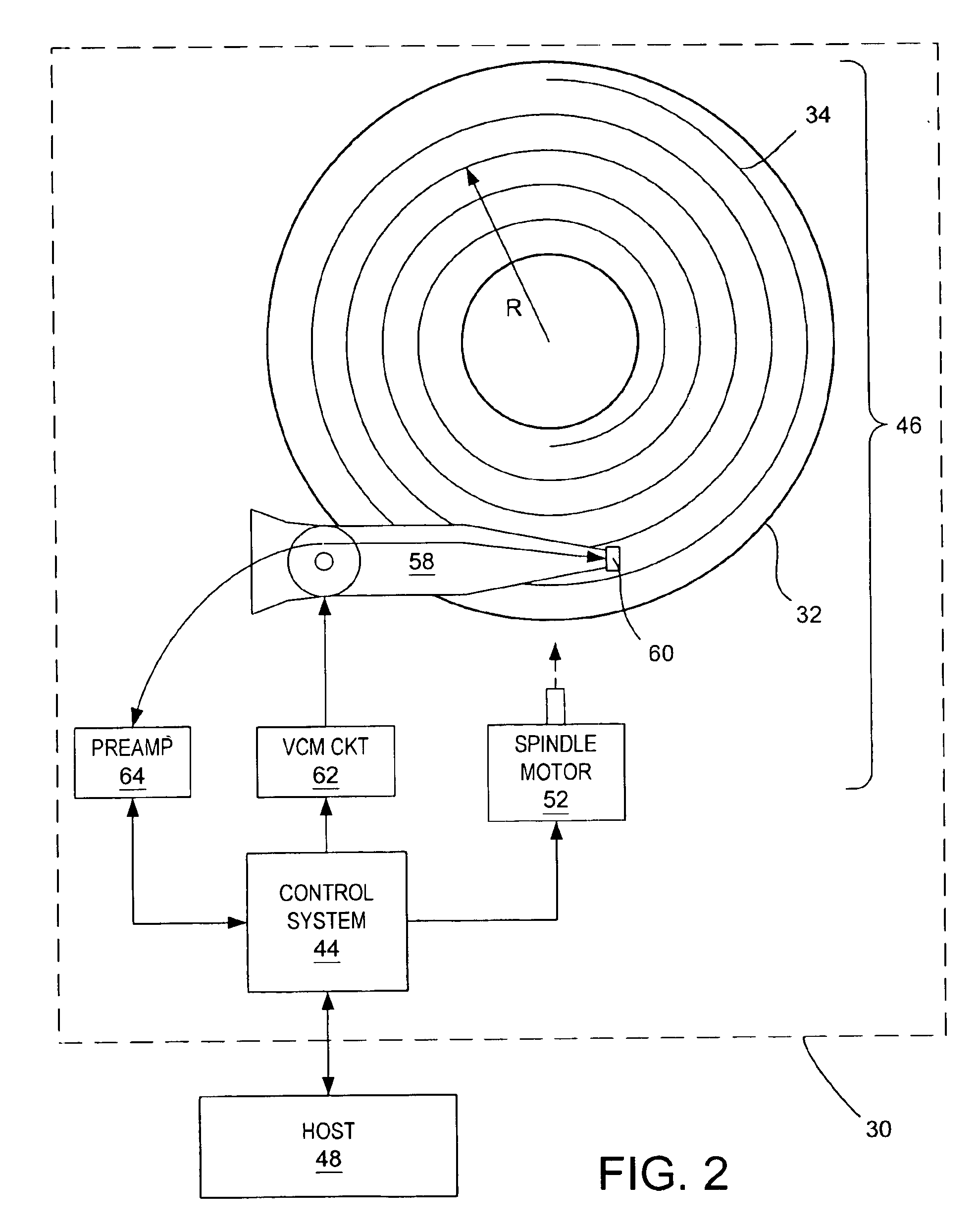

Method for adjusting a delay time for opening a servo sector detection window in a disk drive having a spiral track

InactiveUS6920004B1Disc-shaped record carriersRecord information storageLinear densityControl theory

The present invention may be embodied in a method for adjusting a servo sector detection delay time between detection windows in a disk drive. The disk drive includes a magnetic disk with a spiral track having contiguous storage segments. Each storage segment has a servo sector and a predetermined number of uniformly-sized data sectors. The storage segments are written at a relatively constant linear density along the spiral track. In the method, the magnetic disk is rotated at a constant angular velocity. A servo sector is detected. An adjustable delay time is provided for opening a window to detect a next servo sector. The window is opened after the adjustable delay time expires. A next servo sector is detected in the window. A time between the servo sector detections is measured and the adjustable delay time is adjusted based on the measured time.

Owner:WESTERN DIGITAL TECH INC

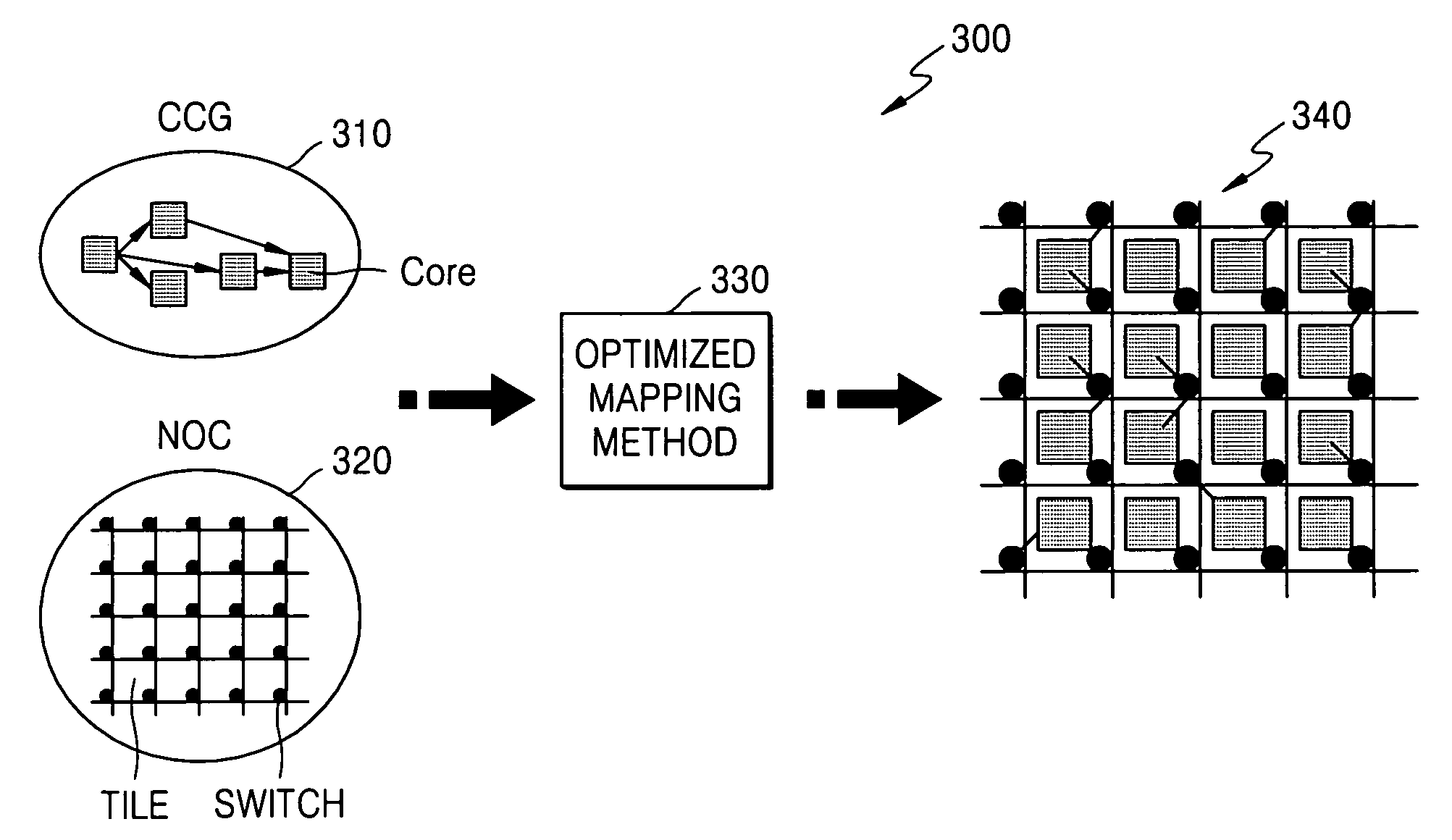

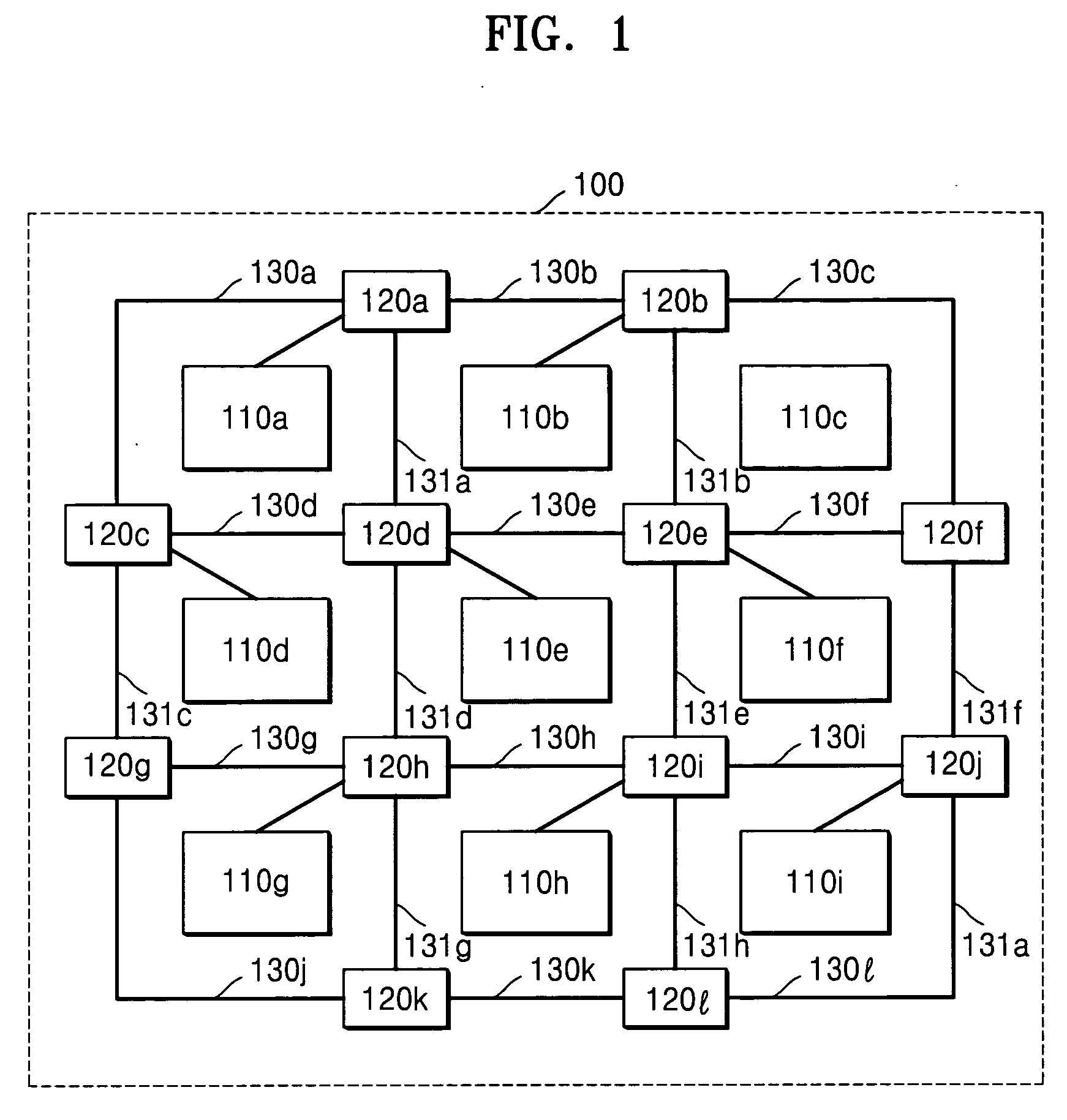

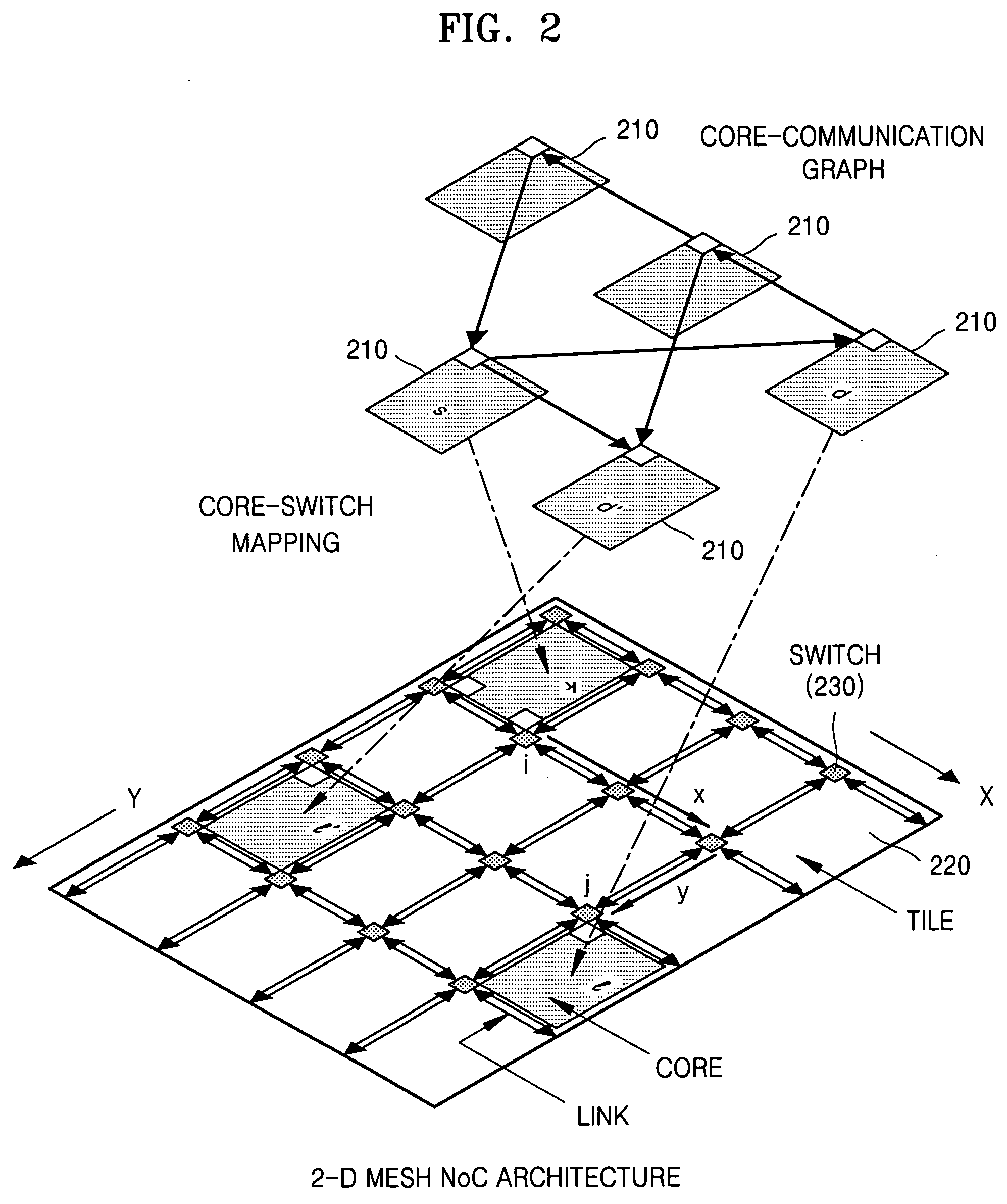

Method of creating core-tile-switch mapping architecture in on-chip bus and computer-readable medium for recording the method

There are provided a method of creating an optimized core-tile-switch mapping architecture in an on-chip bus and a computer-readable recording medium for recording the method. The core-tile-switch mapping architecture creating method includes: creating a core communication graph representing the connection relationship between arbitrary cores; creating a Network-on-chip (NOC) architecture including a plurality of switches, a plurality of tiles, and a plurality of links interconnecting the plurality of switches; and mapping the cores to the tiles using a predetermined optimized mapping method to thereby create the optimized core-tile-switch mapping architecture. The optimized mapping method includes first, second, and third calculating steps. According to the optimized core-tile-switch mapping architecture creating method and the computer-readable recording medium for recording the method, since the hop distance between cores is minimized, it is possible to minimize energy consumption and communication delay time in an on-chip bus. Furthermore, the optimized mapping architecture presents a standard for comparing the optimization of other mapping architectures.

Owner:SAMSUNG ELECTRONICS CO LTD

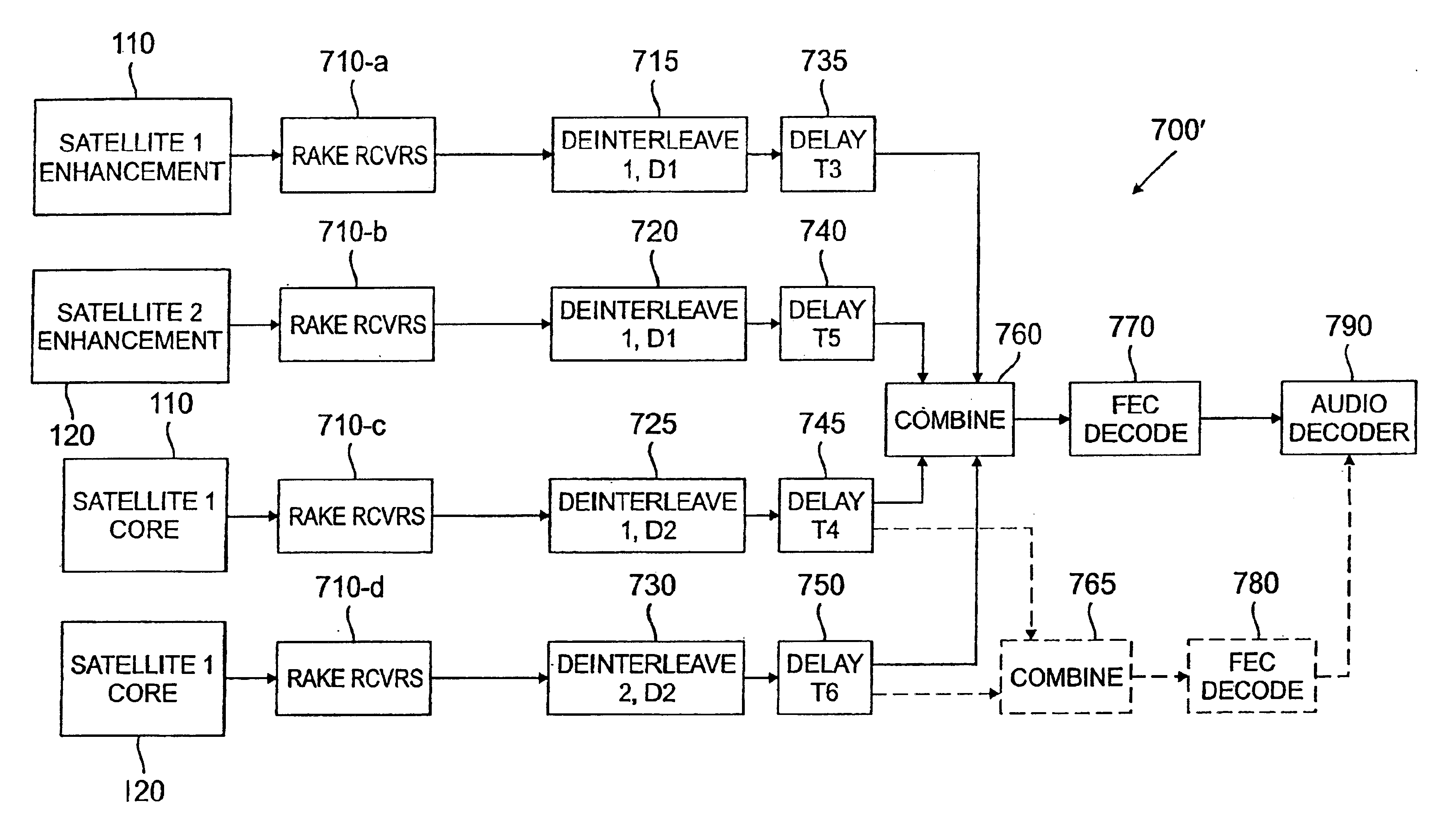

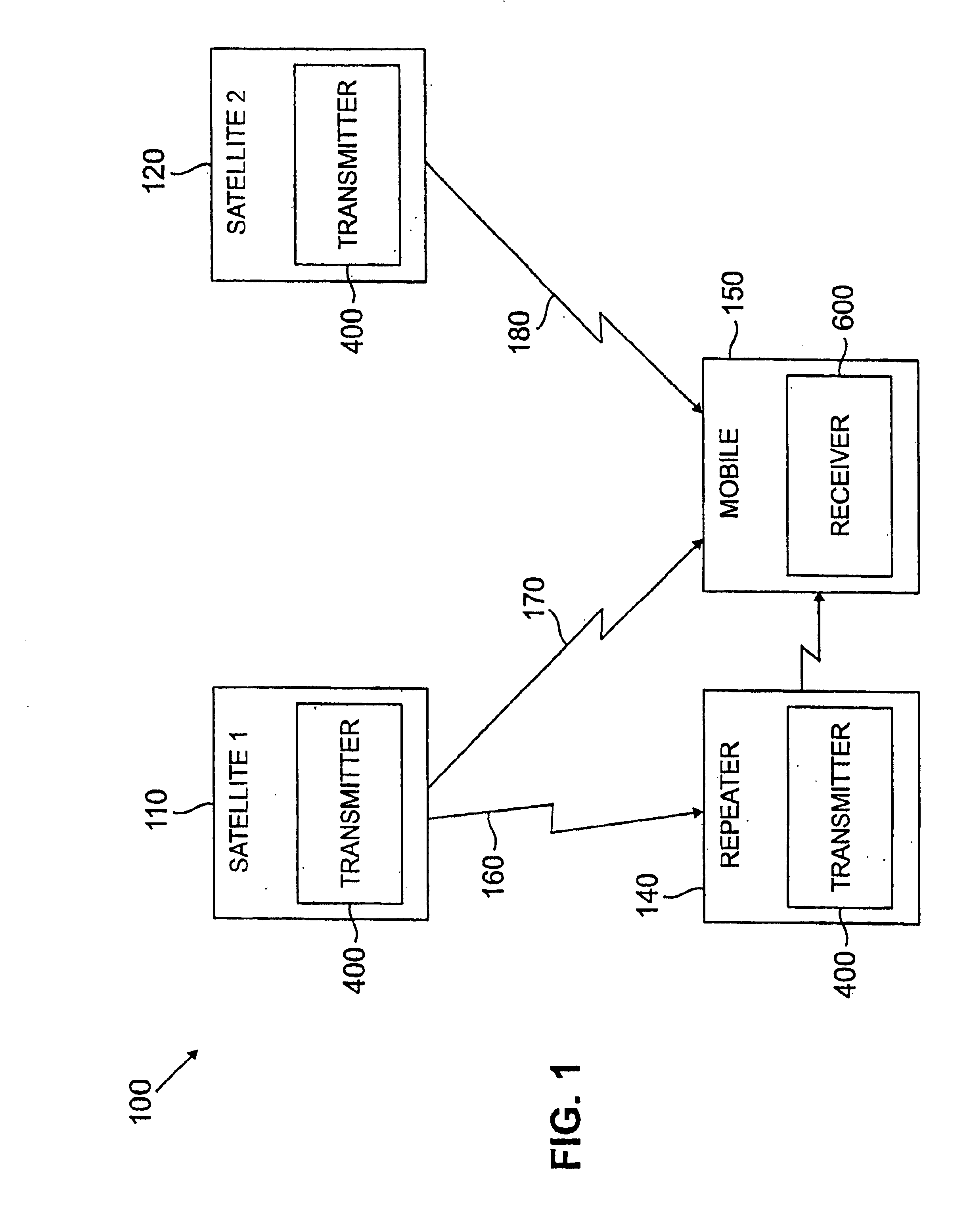

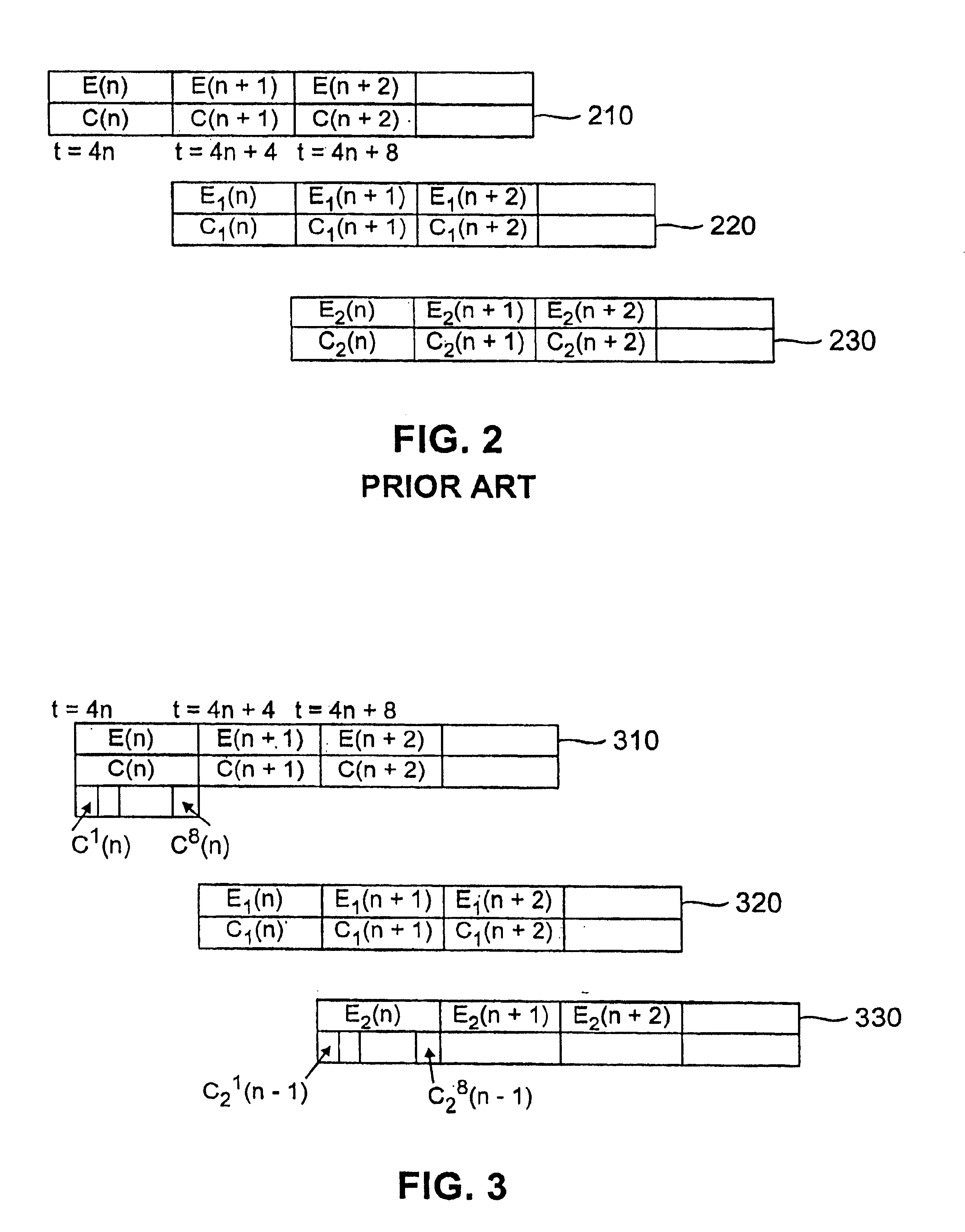

Tuning scheme for code division multiplex broadcasting system

InactiveUS6876623B1Reduce delaysSimple technologyGHz frequency transmissionBroadcast transmission systemsTransport systemCode division multiple access

A CDM satellite transmission system is disclosed that broadcasts programming content, such as audio and video information, using one or more geo-synchronous satellites based on Code Division Multiple Access technology. Forward error correction coding and interleaving are used prior to broadcasting the signals over the CDM channel to account for signal loss due to short-term fading. The CDM satellite transmission system provides a tuning channel corresponding to each program channel that reduces the delay when a mobile receiver is first tuned to a selected program channel. The tuning channel utilizes a shorter interleaver length, if any, than the corresponding primary program channel. The CDM satellite transmission system transmits a delayed version of a program signal with the on-time version of the audio output to accommodate uninterrupted reception in the event of such a blockage. In one implementation of the invention, the core layer, C(n), of the delayed version of the audio output of a scalable audio coding scheme is utilized as the tuning channel. The core layer, C1(n), and enhancement layers, E1(n), of the on-time signal and the enhancement layers, E2(n), of the delayed-time signal employ a representative block interleaver having a duration of four seconds. The tuning channel (C2(n), of the delayed-time signal) employs a representative block interleaver having a duration of 500 milliseconds.

Owner:AVAGO TECH INT SALES PTE LTD

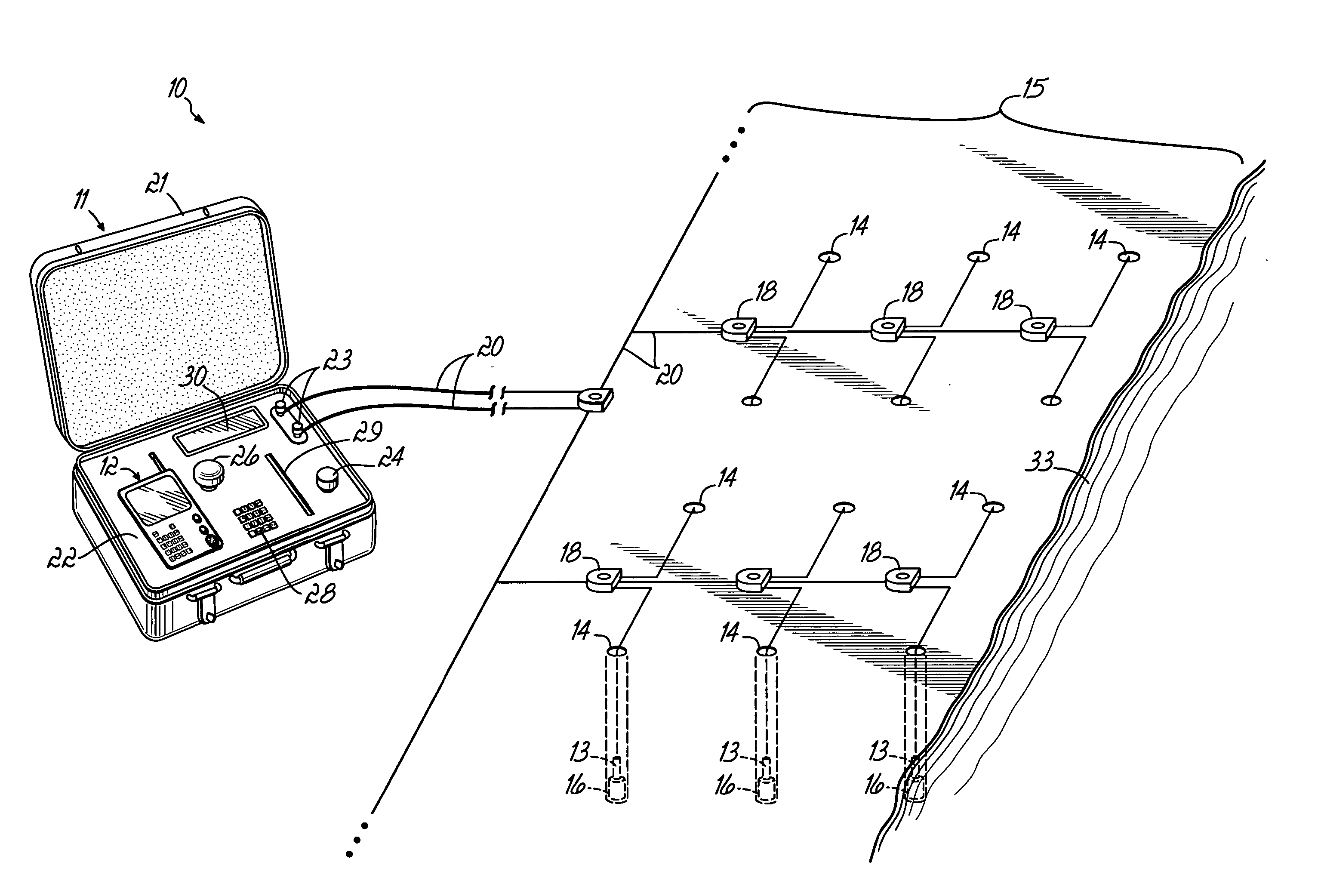

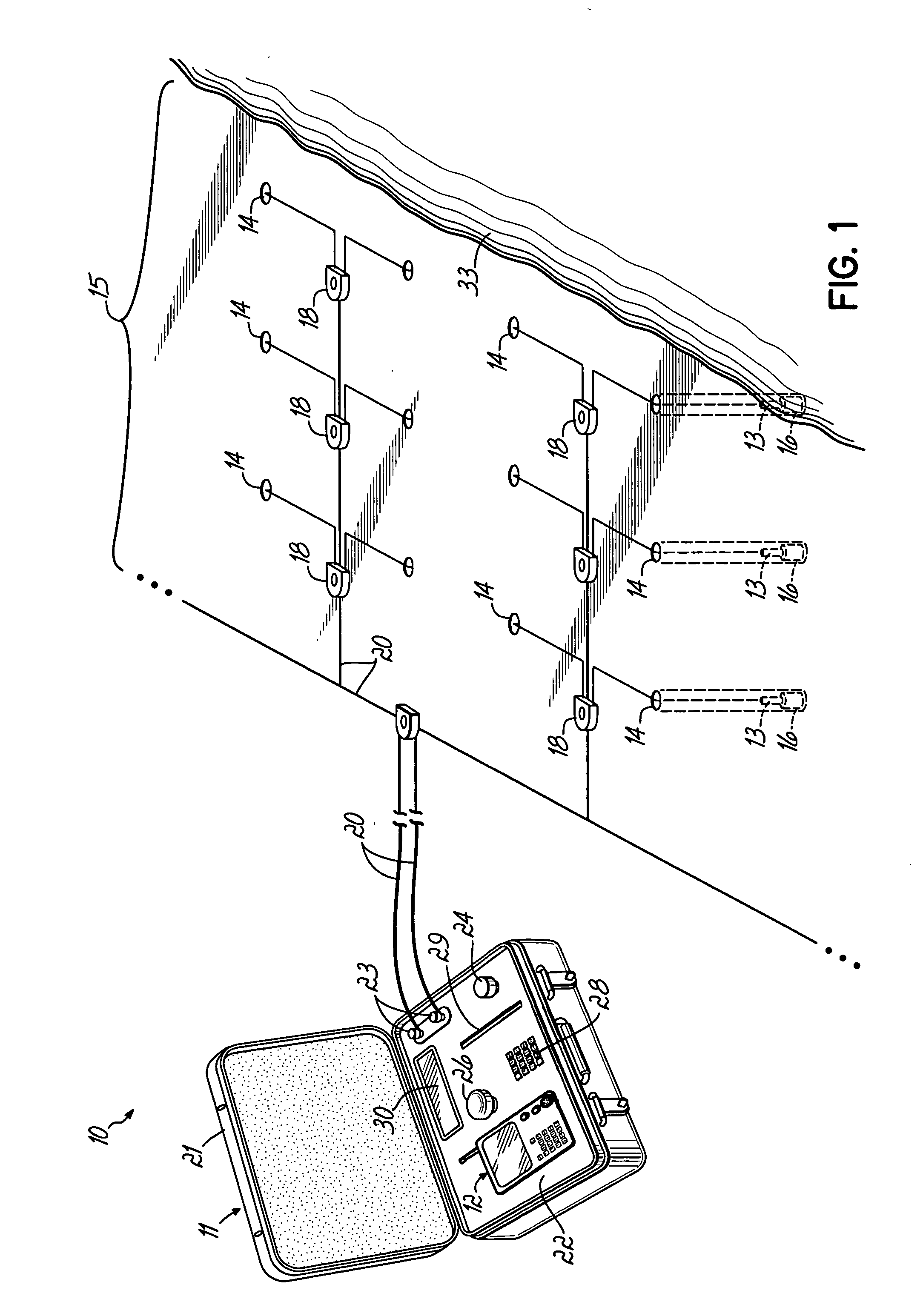

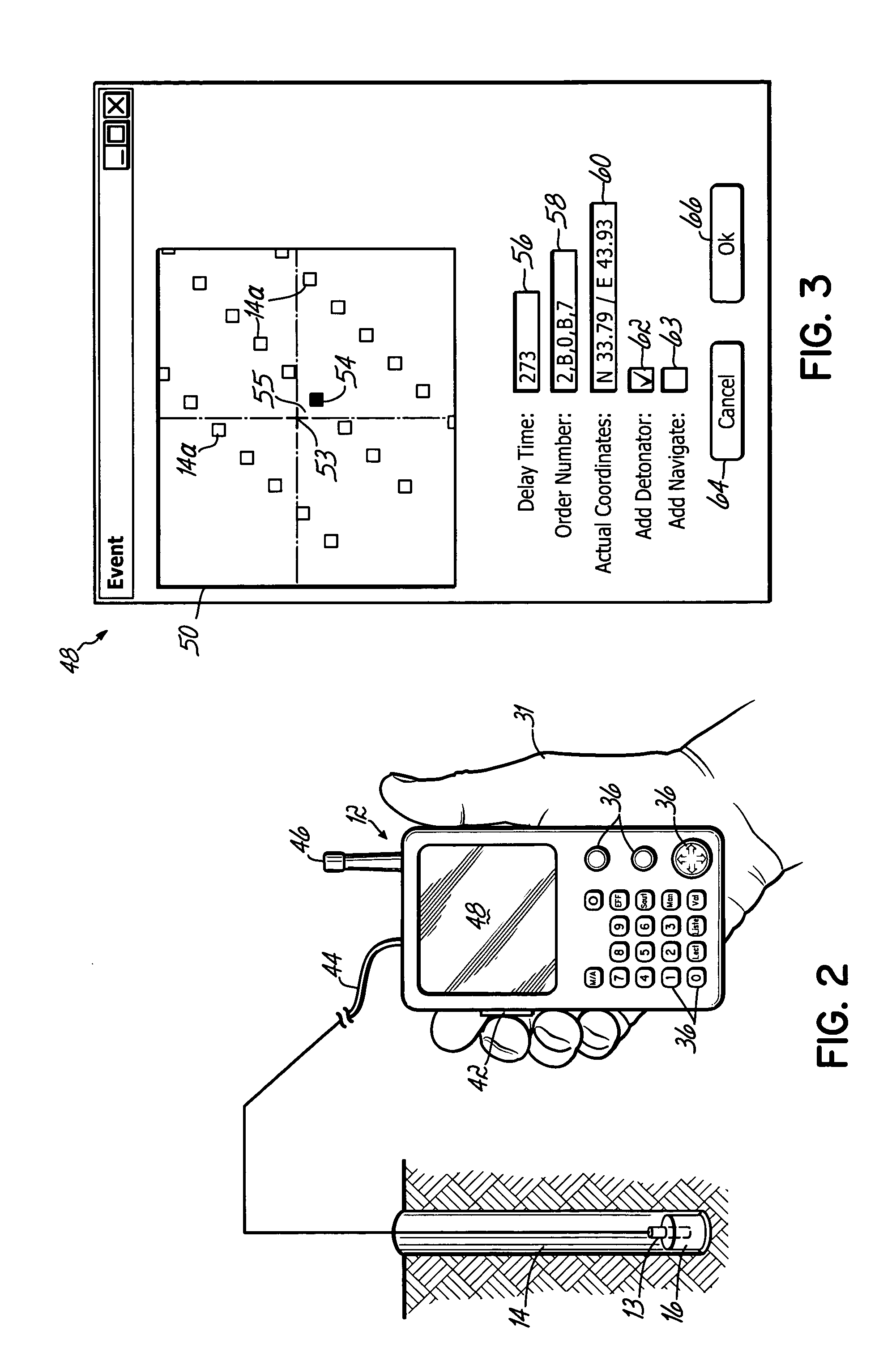

Positional blasting system

A blasting system facilitates the actuation of a plurality of programmable detonators according to a desired blasting pattern, to cause the discharge of a plurality of associated charges, by downloading to the detonators blasting information that can be automatically determined by a portable handheld unit that incorporates a positional detecting device, such as a GPS device. The blasting information for any given detonator can be determined by the handheld unit as a function of the distance and the direction of the movement of the unit to the detonator, and / or by the actual GPS location while at the site of the detonator. This automatic determination of blasting information, and particularly the delay times, based on the movement of the unit to the detonator, eliminates error prone human calculations of the delay times needed for multiple detonators at a blasting site. This simplifies the operations and procedures needed for achieving a desired blasting pattern, without sacrificing safety or quality.

Owner:DAVEY BICKFORD USA

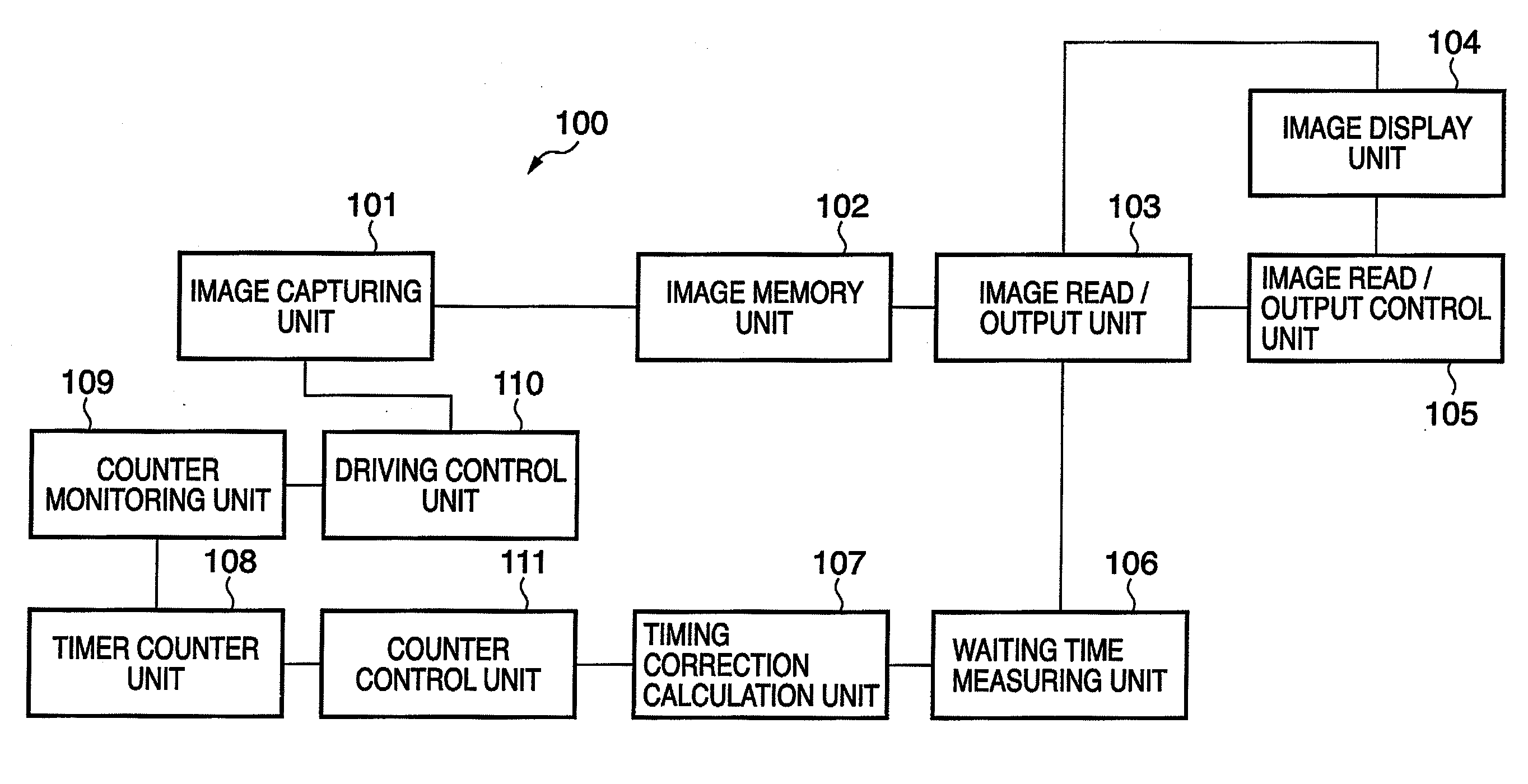

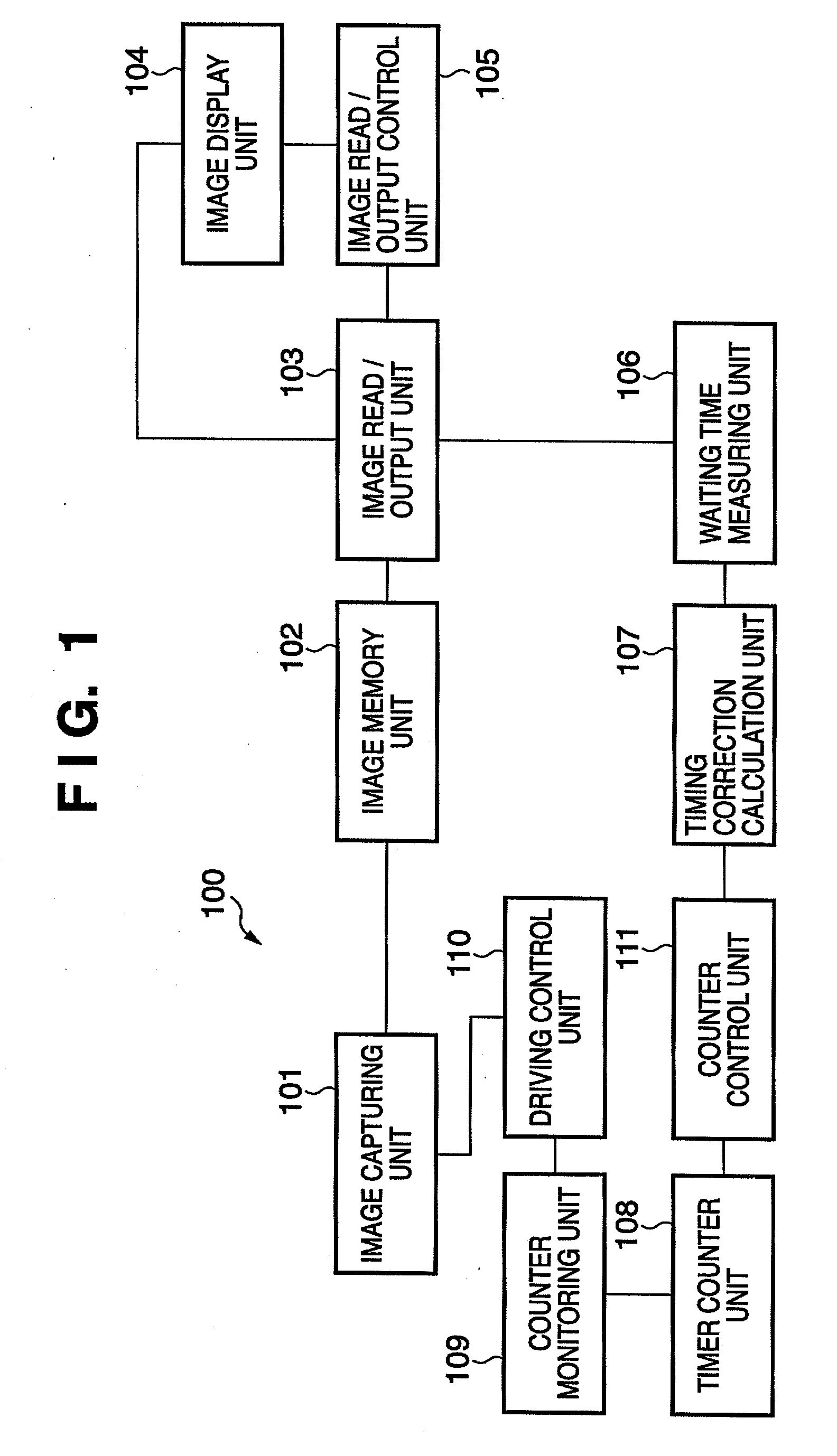

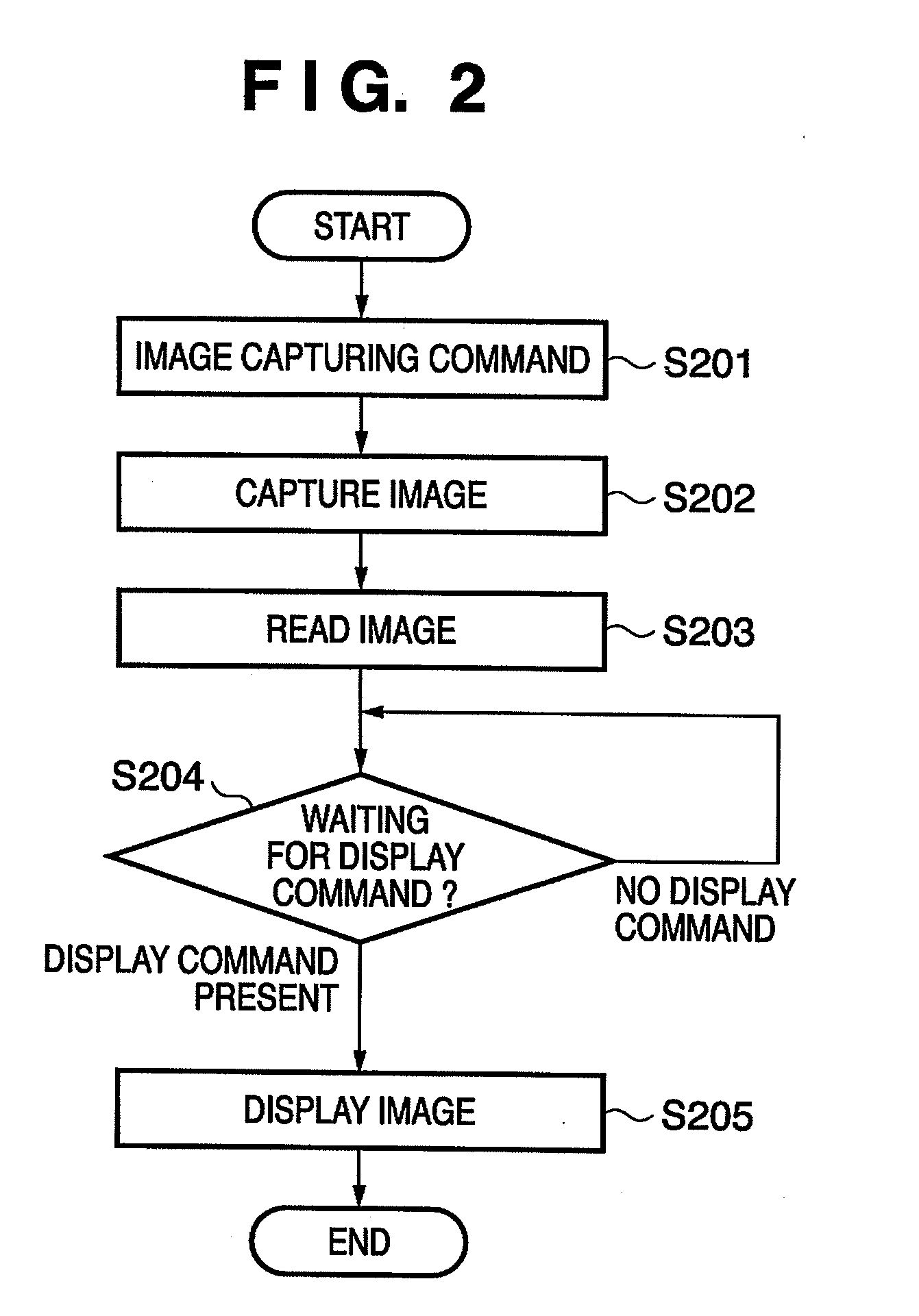

Image capture and display control apparatus, image capture and display control method, and image capture and display system

InactiveUS20080151070A1Easy to trackReduce latencyTelevision system detailsPicture signal generatorsImaging dataImage capture

The invention provides an image capture and display control apparatus that includes an imaging control unit that operates an image capturing unit at a first time interval so as to obtain a captured image with the image capturing unit and a display control unit that displays the captured image on a display unit, which operates at a second time interval. The apparatus changes at least one of an image capture start timing of the image capturing unit and a processing time from the start of image capturing by the image capturing unit until entering a standby state in which the captured image can be displayed by the display unit, so as to shorten a display delay time, which is caused by the second time interval, from the start of operation by the image capturing unit until display of the image data by the display unit.

Owner:CANON KK

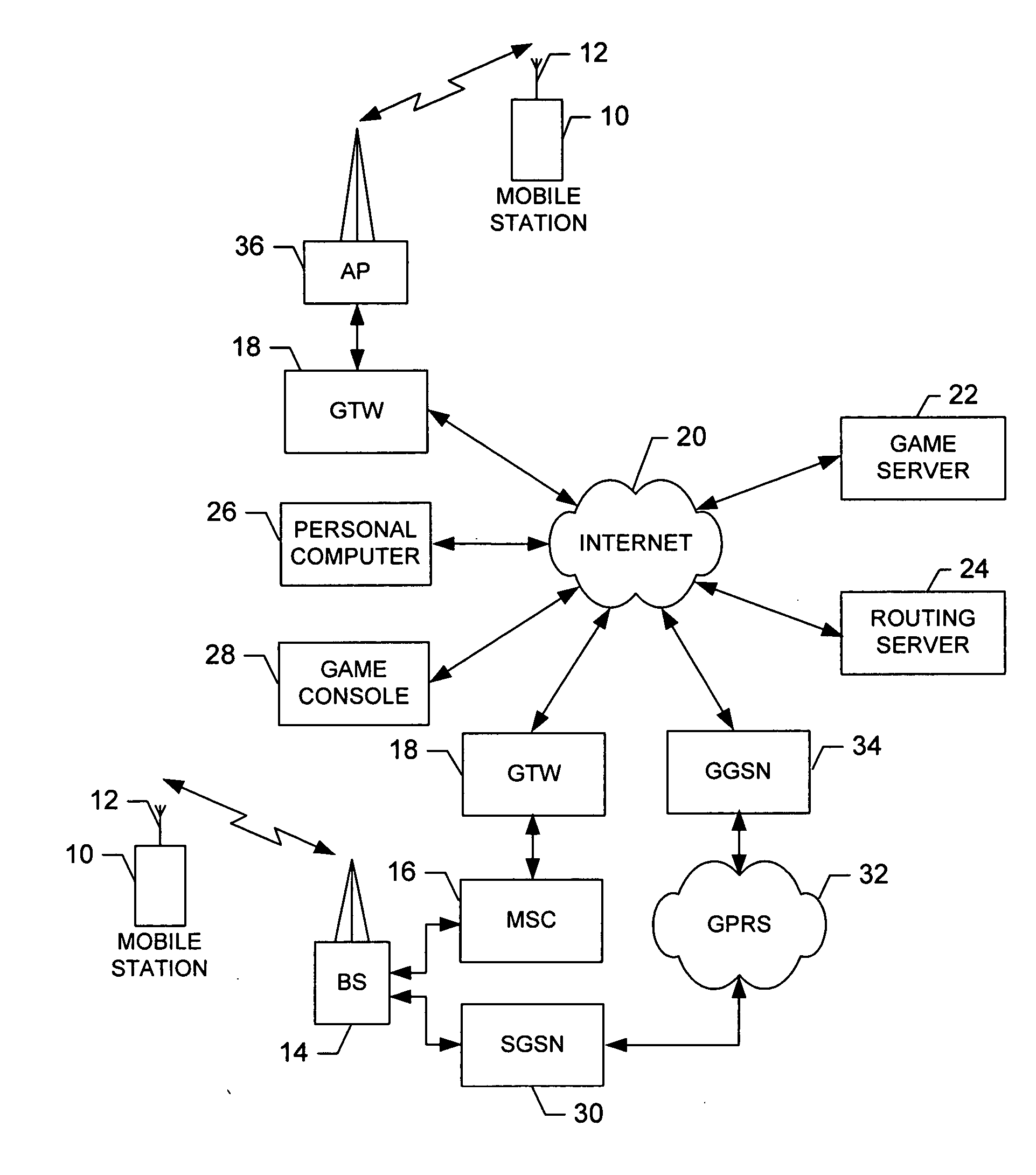

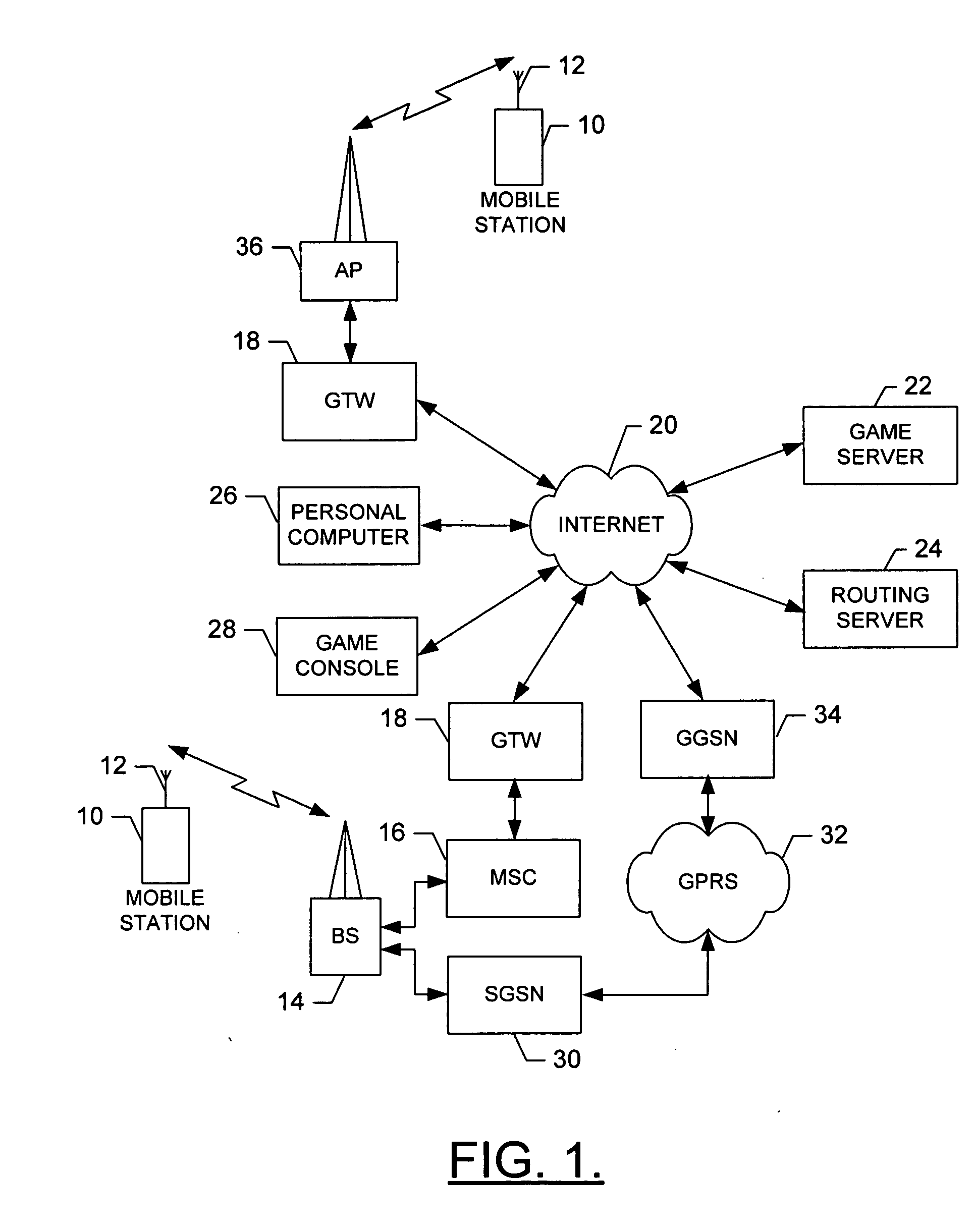

System, network entity, client and method for facilitating fairness in a multiplayer game

InactiveUS20060135258A1High network latencyPromotes fairnessApparatus for meter-controlled dispensingVideo gamesTime delaysMultiplayer game

A system for facilitating fairness in a multiplayer game includes a network entity (e.g., game server) capable of operating a game application that can operate a multiplayer game. A plurality of clients is associated with a network latency, and can communicate with the network entity across at least one network. The system further includes a time-delay module disposed between the clients and the game application. The time-delay module can receive a data packet associated with a particular client during play of the multiplayer game, and delaying the data packet for at least a portion of delay time associated with the particular client before passing the delayed packet to the game application or the particular client for processing. In this regard, the delay time is based upon the network latency of the first client and an effective network latency set based upon the network latencies of the plurality of clients.

Owner:NOKIA CORP

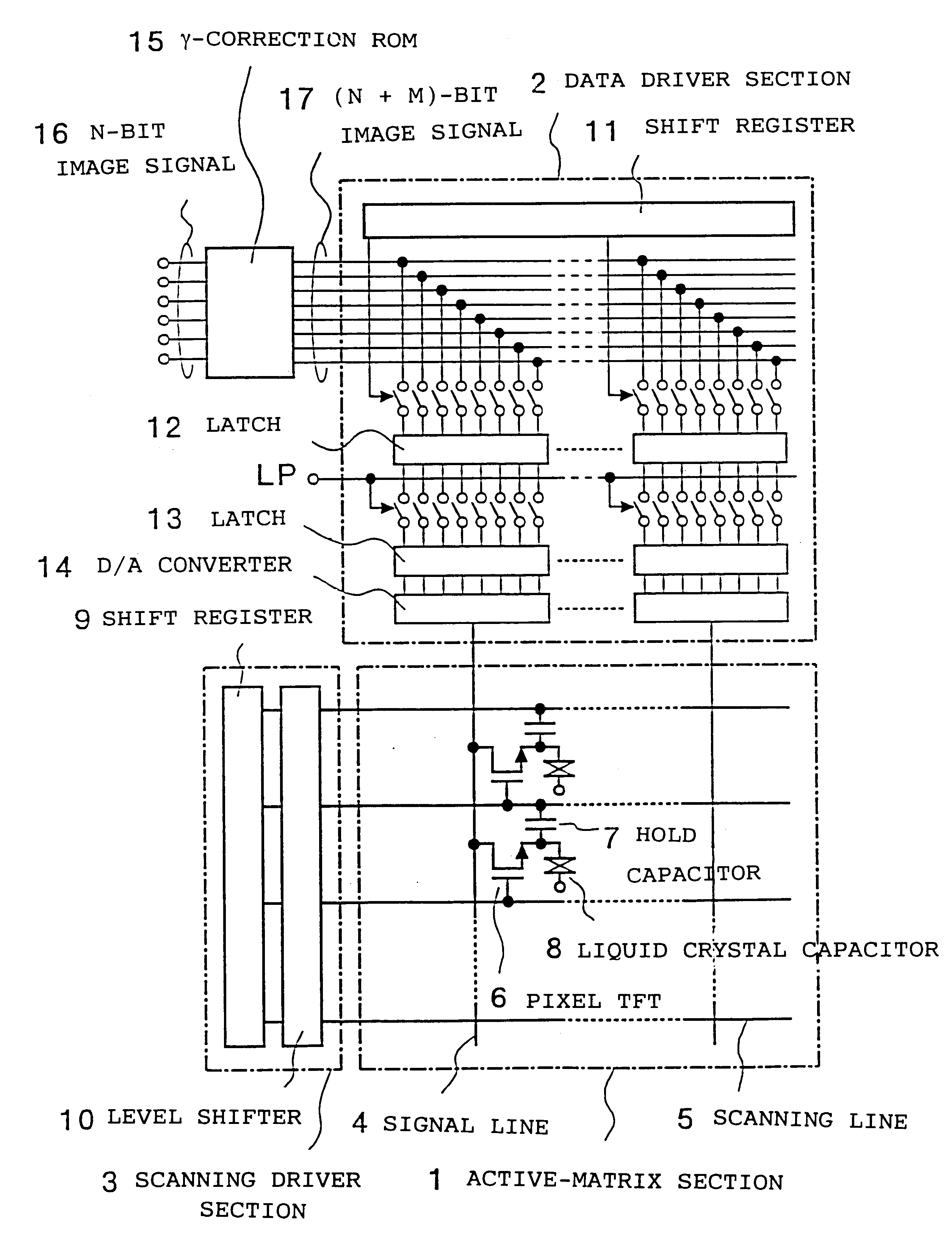

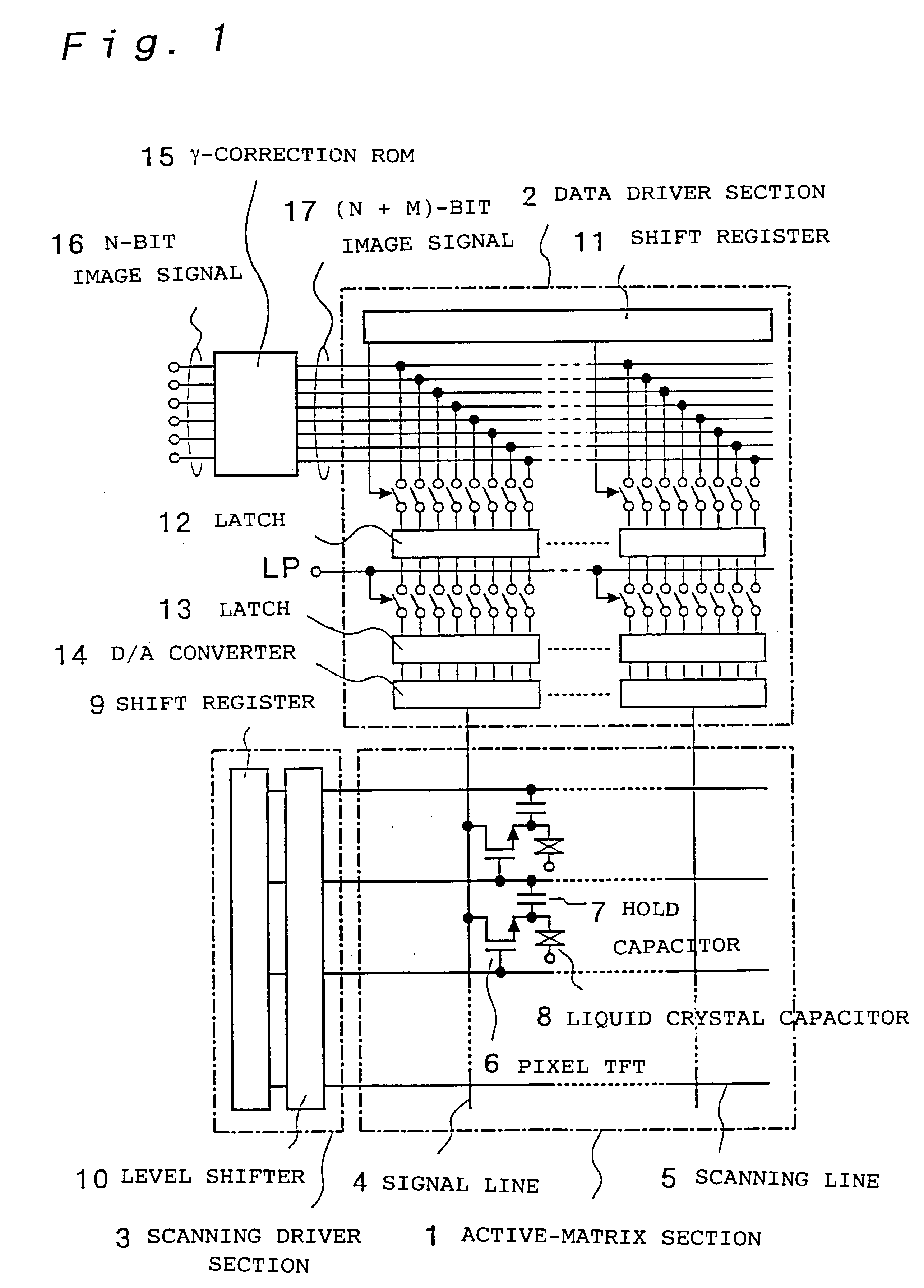

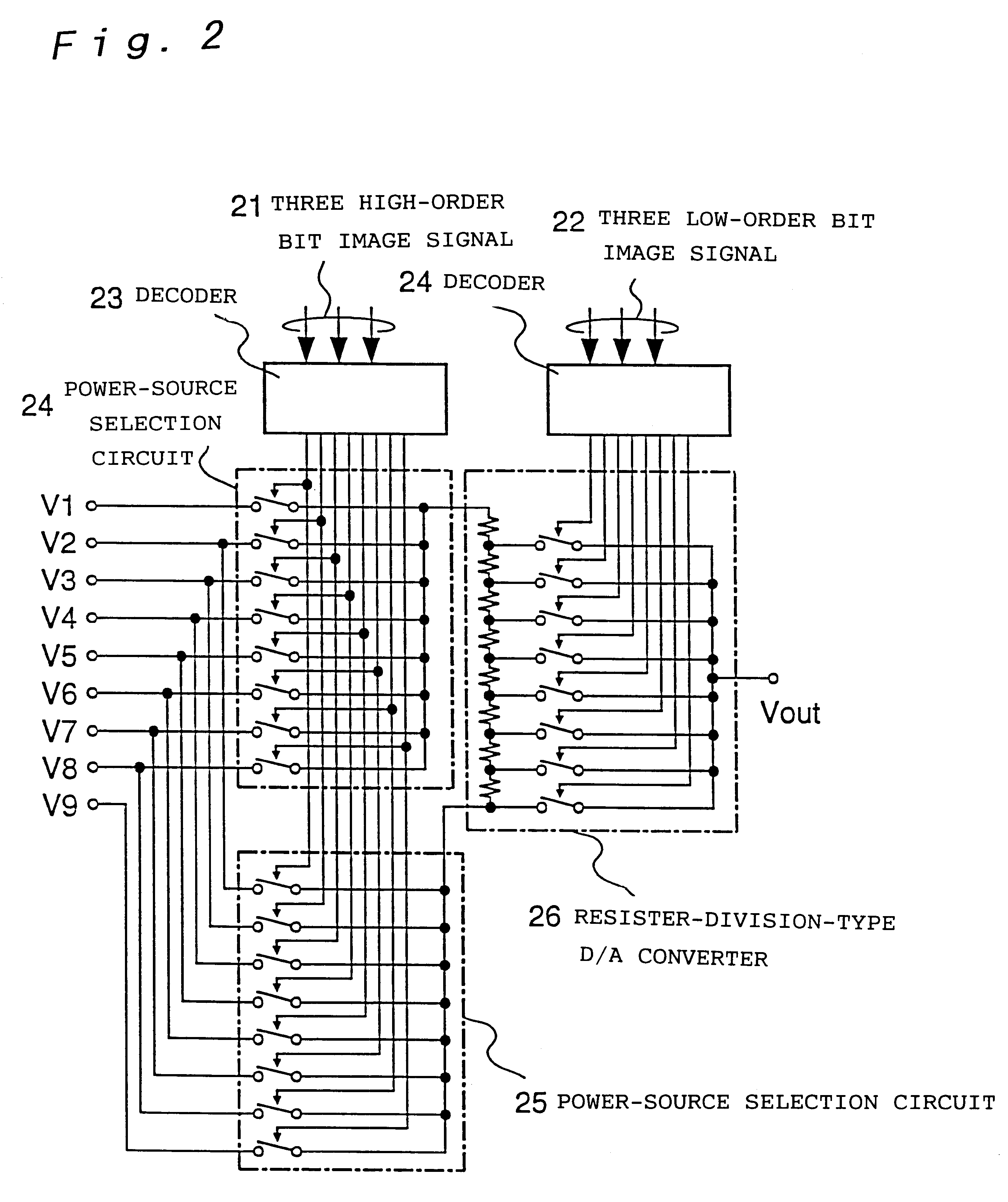

Liquid crystal display apparatus, driving method therefor, and display system

An n-bit digital image data is converted to (n+m)-bit data with a g-correction table, and displayed by the use of a (n+m)-bit D / A converter. A peripheral-driver logic section is driven with a low-voltage common power source and countermeasures to noise are taken. Data input to the D / A converter is not reversed and the power to the D / A converter is made alternating to apply an AC voltage to aligned crystal layer. A circuit is provided in order to compensate for a delay time in the driver. With this configuration, the image quality of a liquid crystal display apparatus in which the D / A converter is built is improved.

Owner:BOE TECH GRP CO LTD

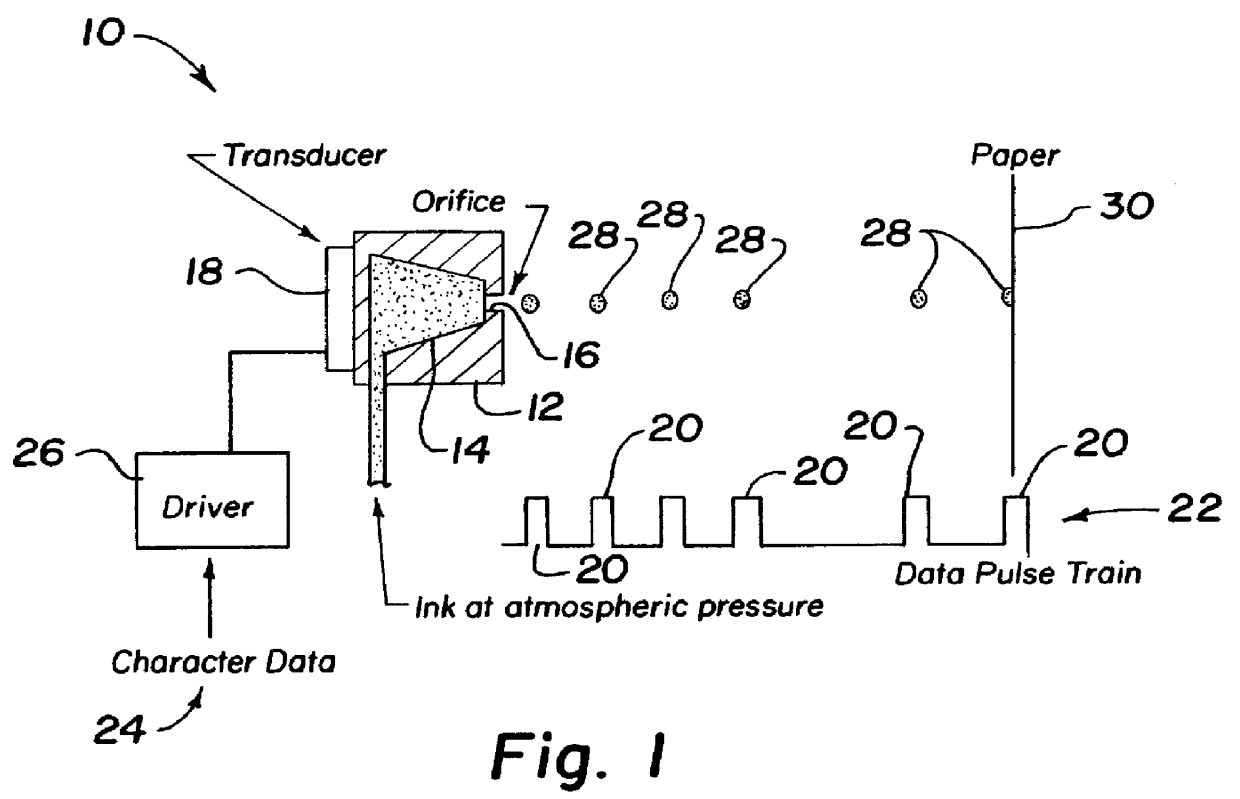

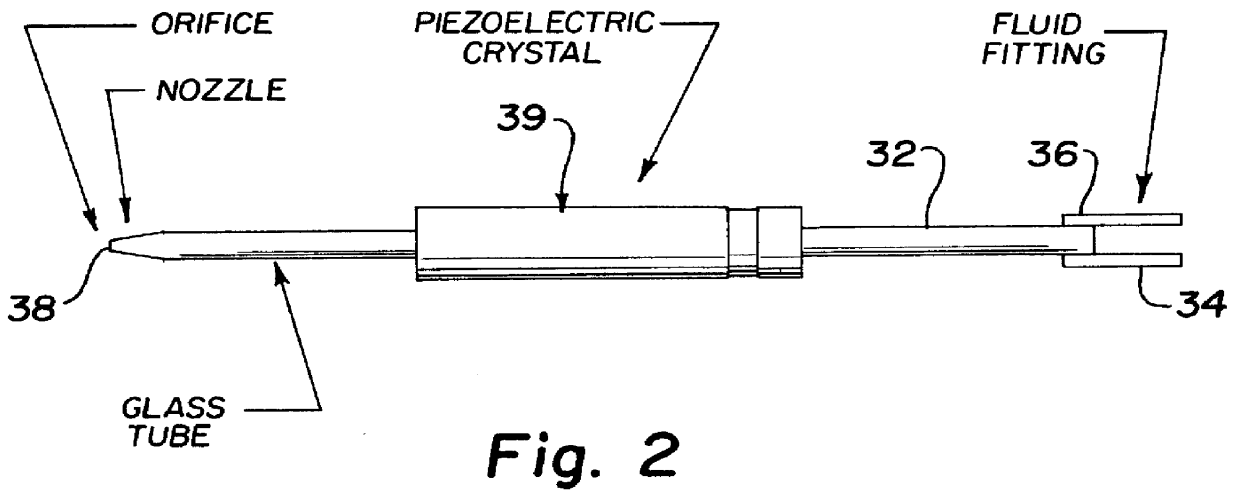

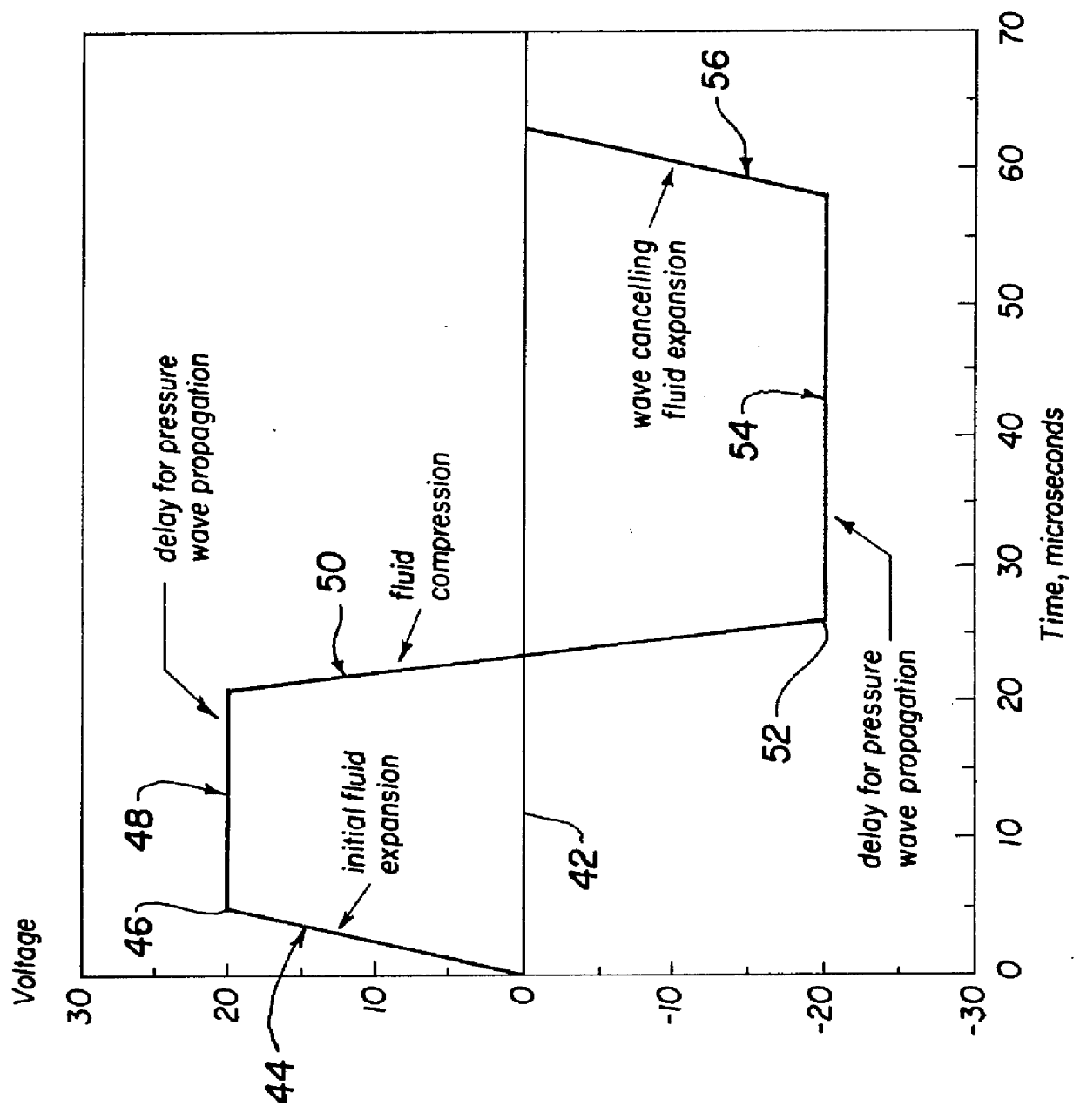

Method of drop size modulation with extended transition time waveform

The present invention uses a novel waveform to allow the droplet volume dispensed from a demand mode inkjet type device to be increased and selected according to easily controllable parameters. The current invention departs from the conventional drive method by significantly increasing the time for energy input in the initial instance as well is in all later application of the drive voltage to the device. In shape, the waveform is the same whether a unipolar or bipolar pulse is utilized; however, the transition times in the initial instance are up to three times the acoustic resonance and the delay times are of the same order. Droplet diameter can be varied from 1X the orifice diameter to 2X the orifice diameter resulting in an 8:1 range of droplet volume. Since the volume modulation results from changes in the waveform used to drive the solder jet device, the drop volume can be changed and altered in real time.

Owner:MICROFAB TECH

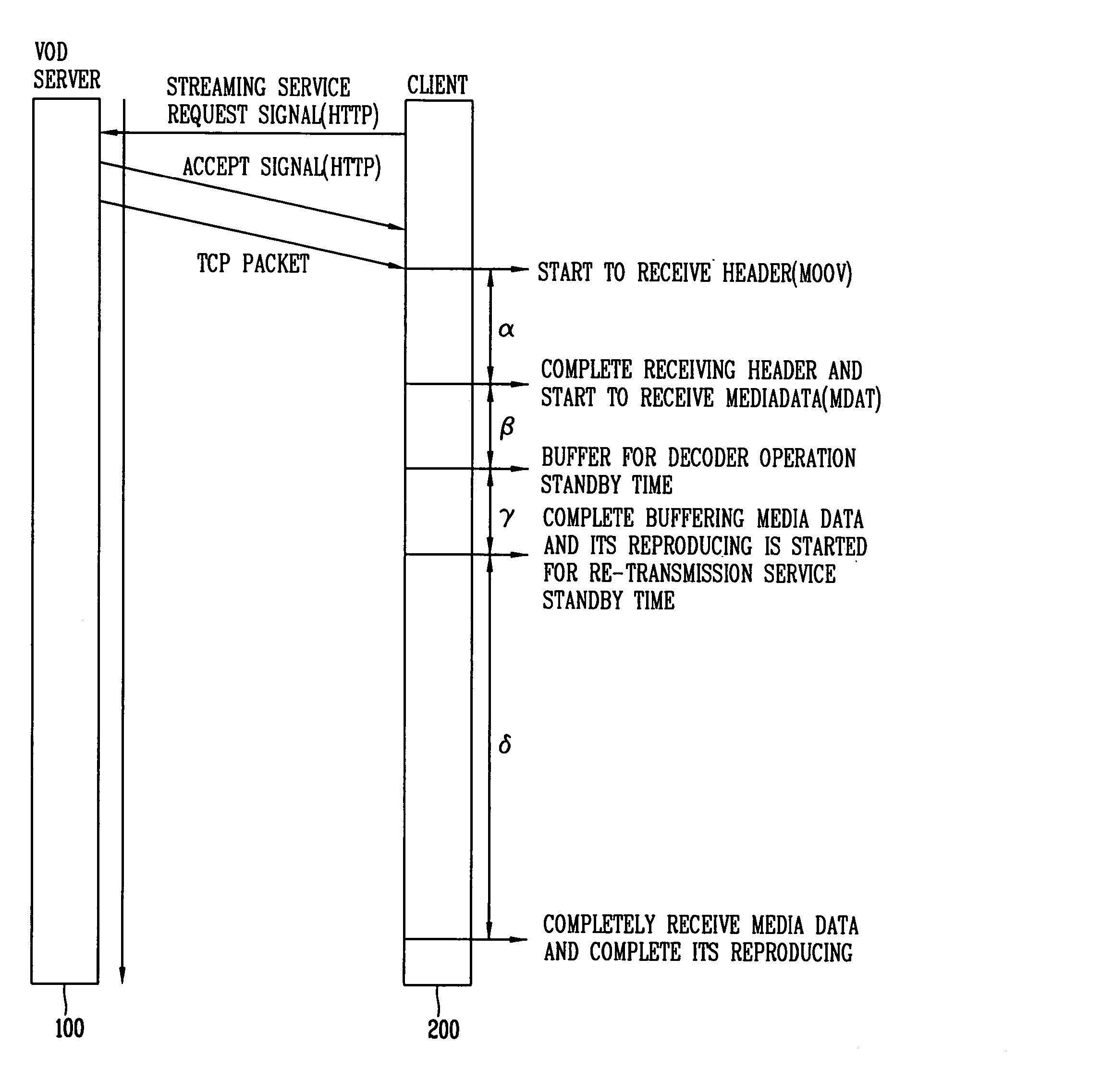

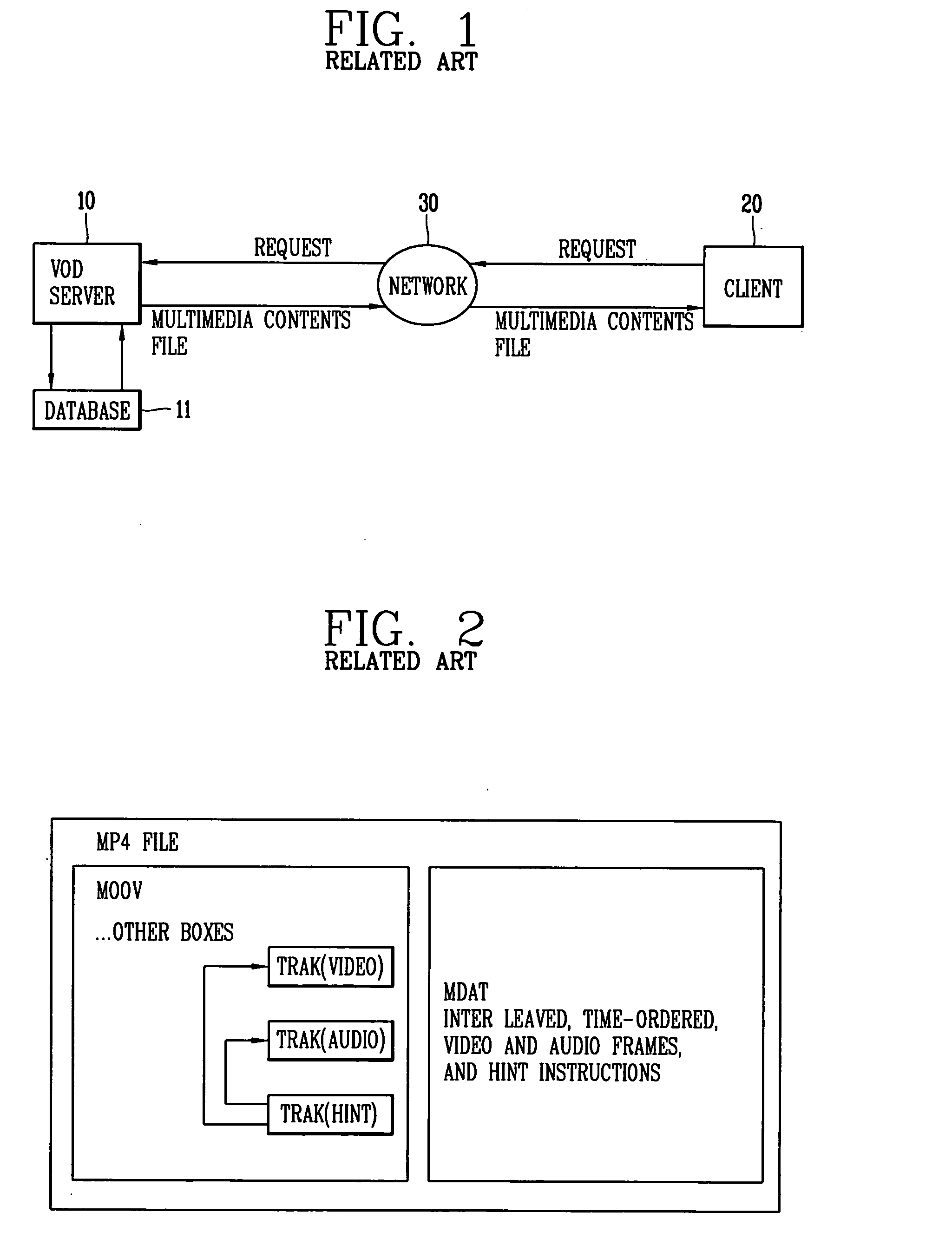

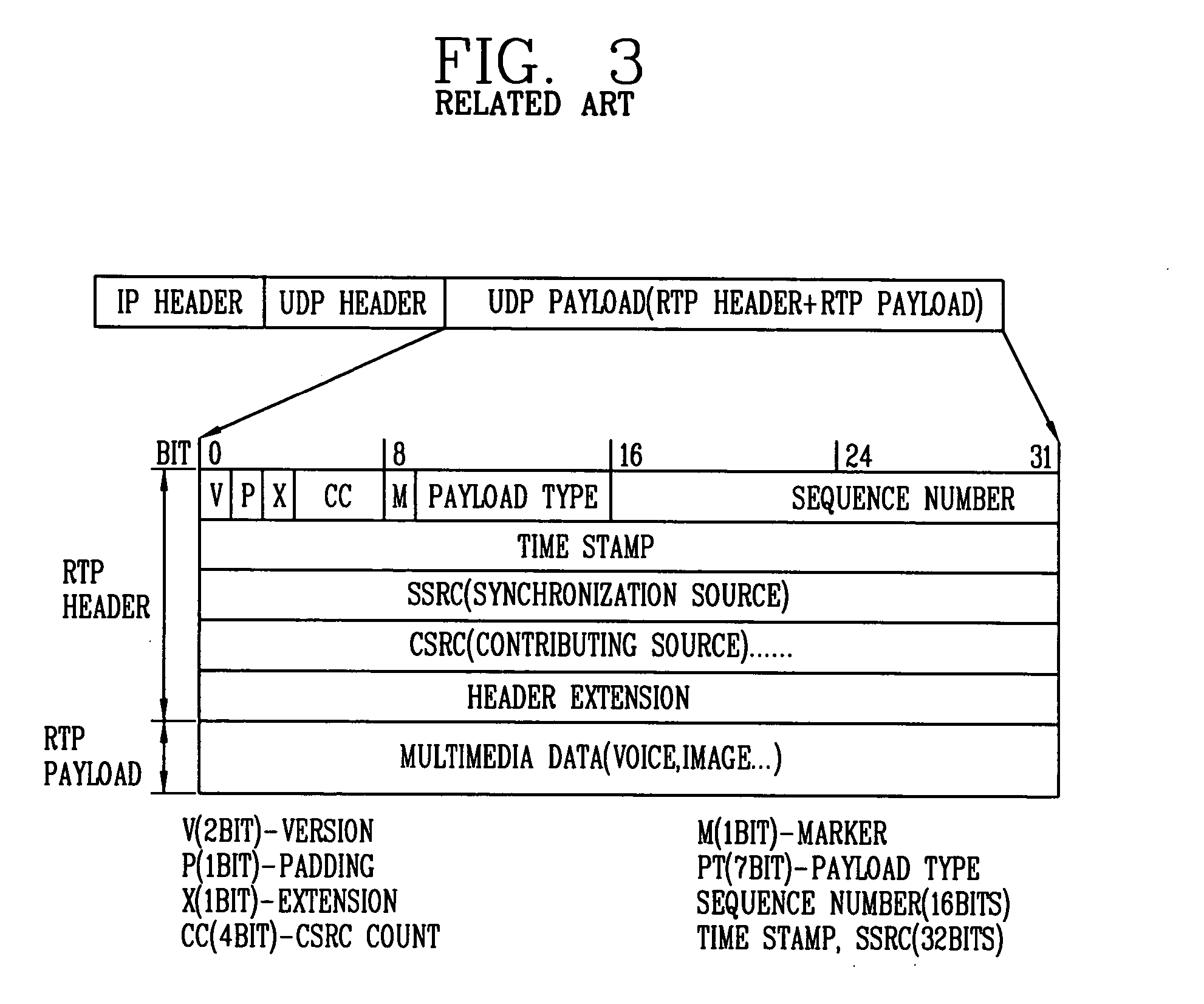

Multimedia streaming service system and method

InactiveUS20050071491A1Analogue secracy/subscription systemsMultiple digital computer combinationsClient-sideReal-time computing

A multimedia streaming service system is provided that includes a VOD server to sequentially transmit a header (moov) and media data (mdat) of MP4 contents in a TCP packet and a client to transmit a streaming service request signal in HTTP to the VOD server. The client may accumulate the media data (mdat) received from the VOD server in a decoder buffer for a predetermined time, and reproduce the data on a real time basis. A guaranteed rate of QoS may be enhanced as compared to an RTP / UDP-based streaming method. A service delay time may be reduced as compared with a TCP-based downloading method, thereby implementing contents on a real time basis.

Owner:LG ELECTRONICS INC

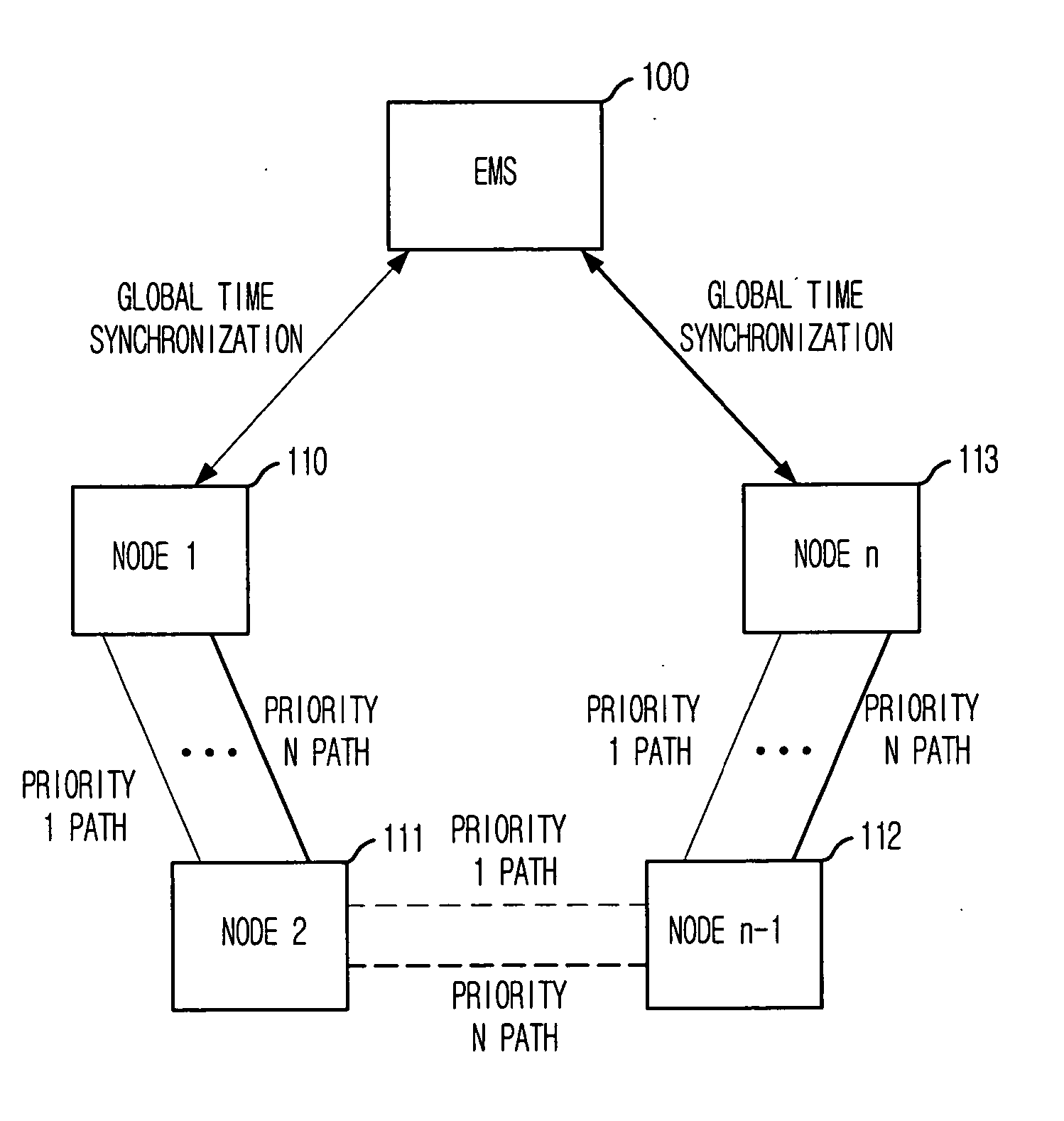

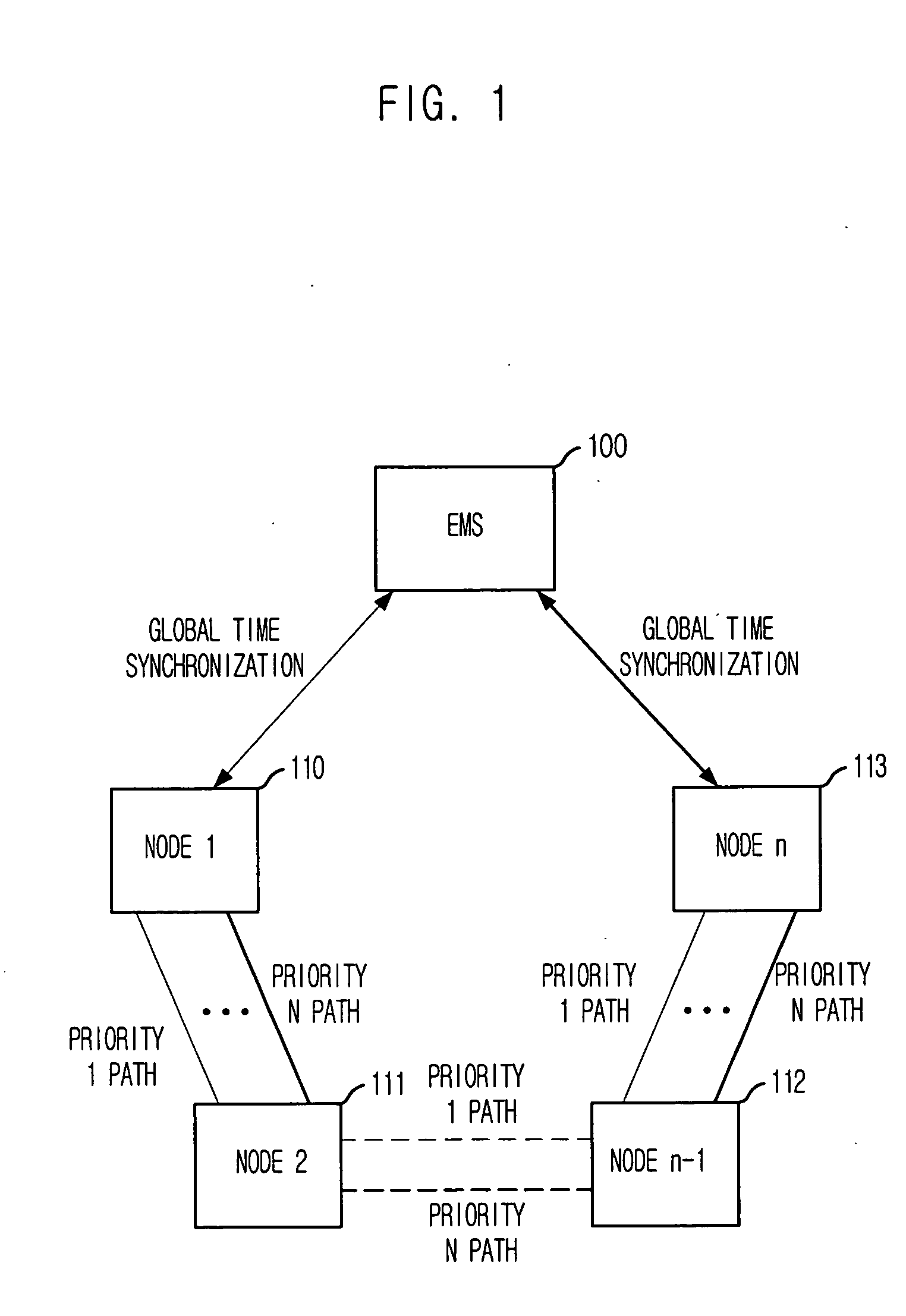

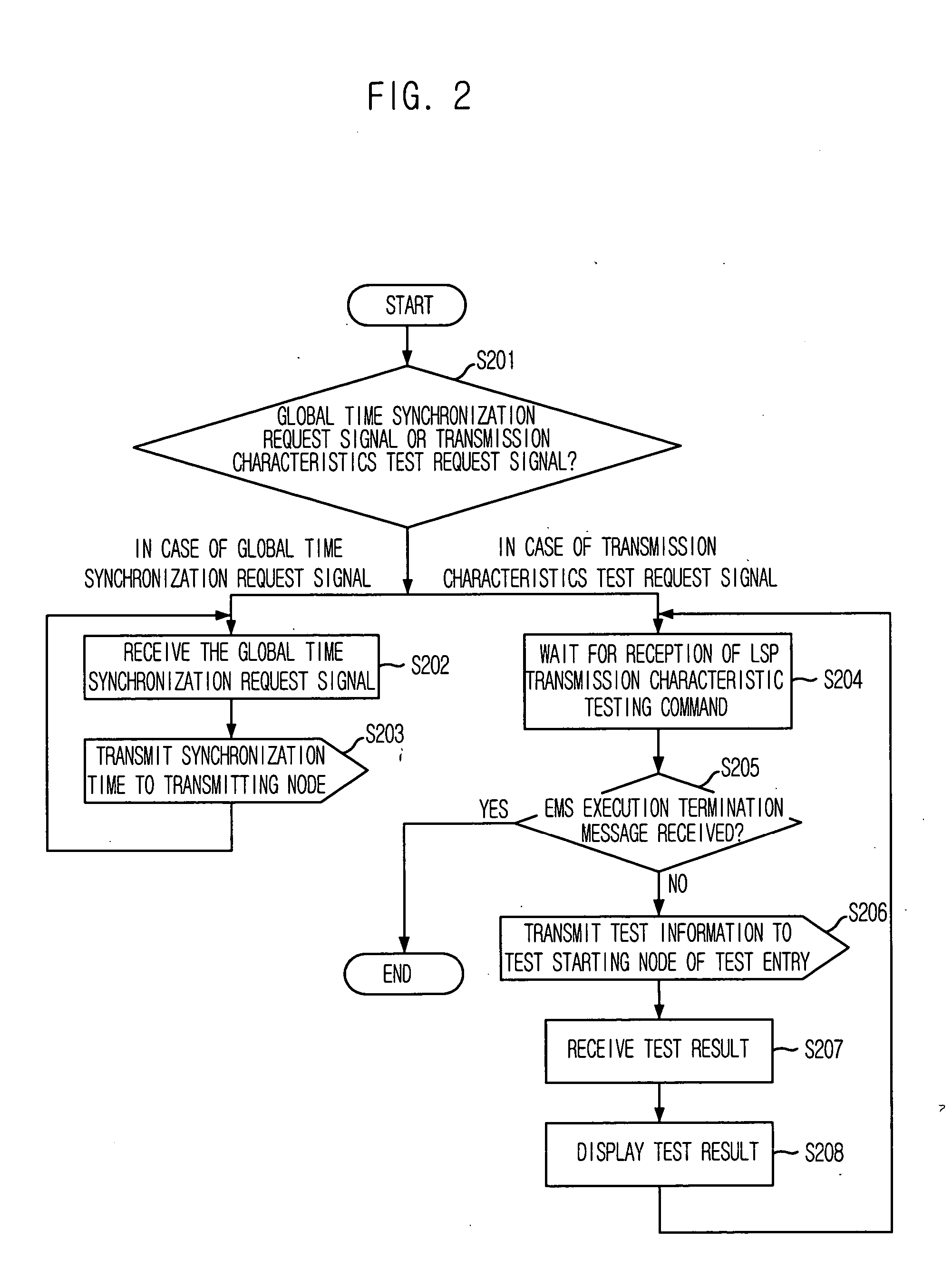

Method for measuring characteristics of path between nodes by using active testing packets based on priority

Provided are a method for measuring characteristics of a path between nodes by using active testing packets based on priority, i.e., an inter-node path characteristic measuring method, which can measure and provide characteristics of a generated node, when an inter-node data transmission path is generated based on Multi-Protocol Label Switching (MPLS) to provide a path with satisfactory transmission delay, jitter and packet loss that are required by a user, and to provide a computer-readable recording medium for recording a program that implement the method. The method includes the steps of: a) synchronizing system time of the nodes with a global standard time; b) forming each testing packet; c) registering frame sequence and the global standard time during transmission; and d) calculating transmission delay time, jitter and packet loss by using time stamp and packet sequence information of a frame received by the destination node and transmitting the result to the management system.

Owner:ELECTRONICS & TELECOMM RES INST

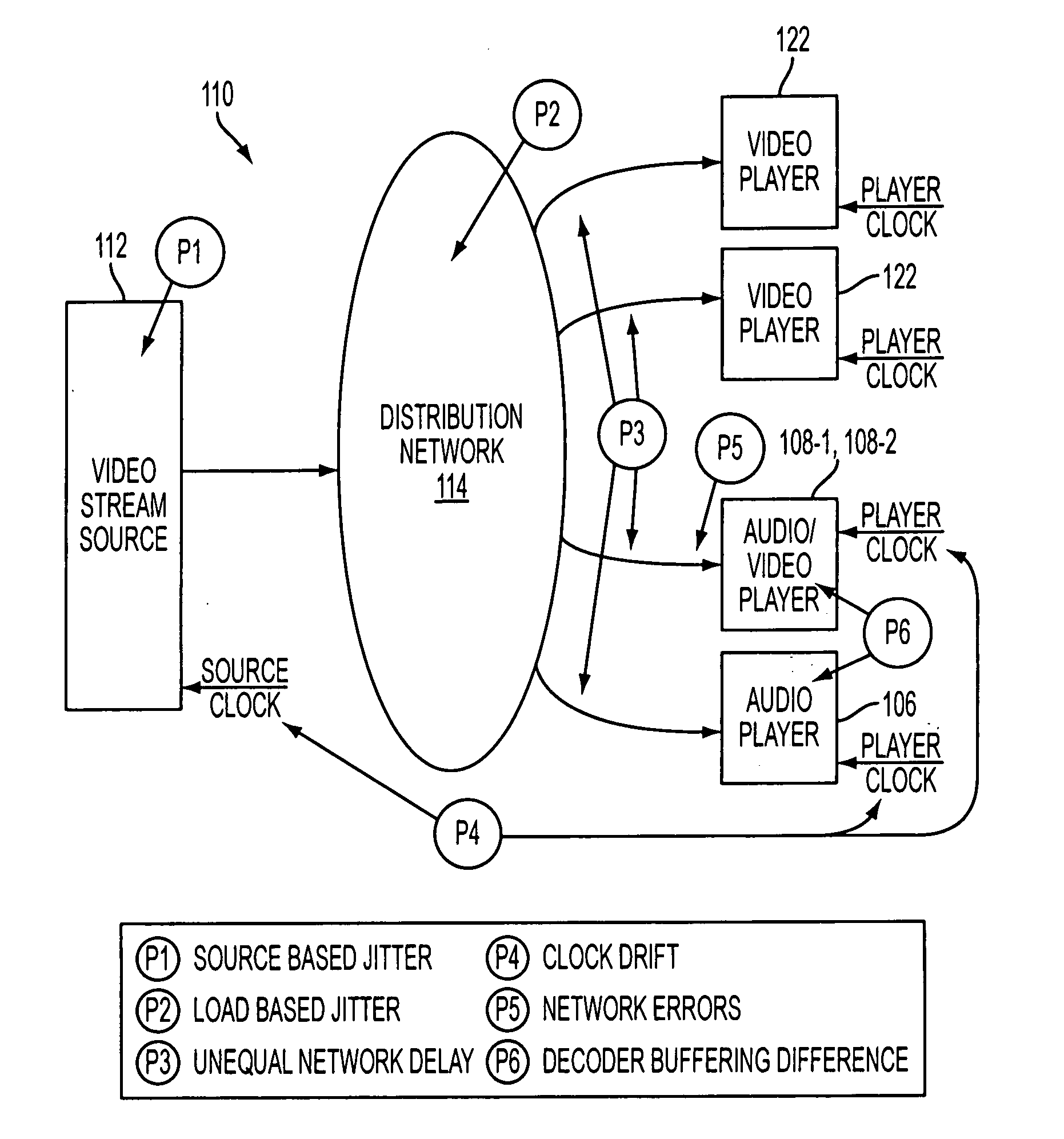

System and method for synchronizing playback of audio and video

ActiveUS20080187282A1Television system detailsPulse modulation television signal transmissionComputer hardwareVideo player

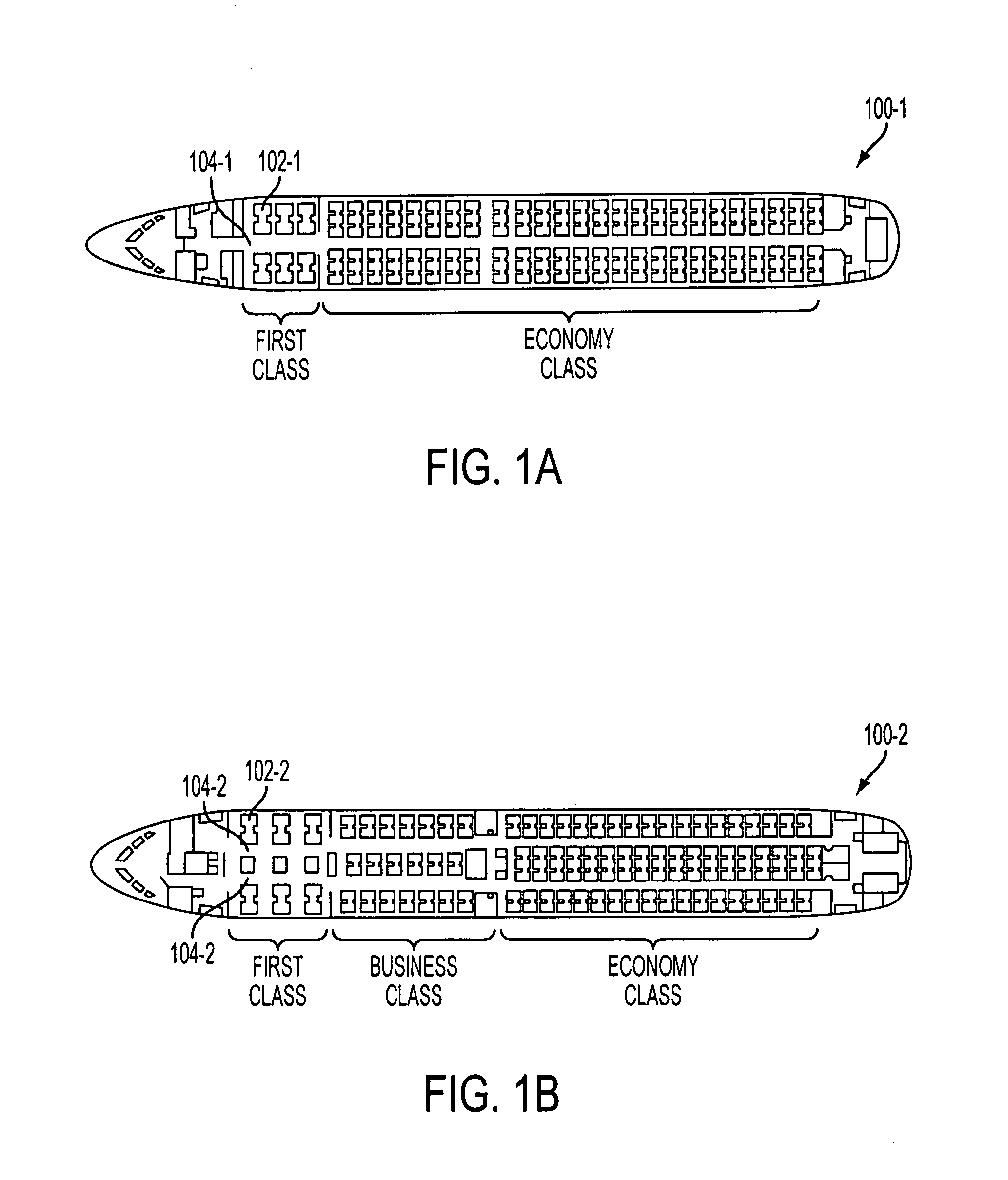

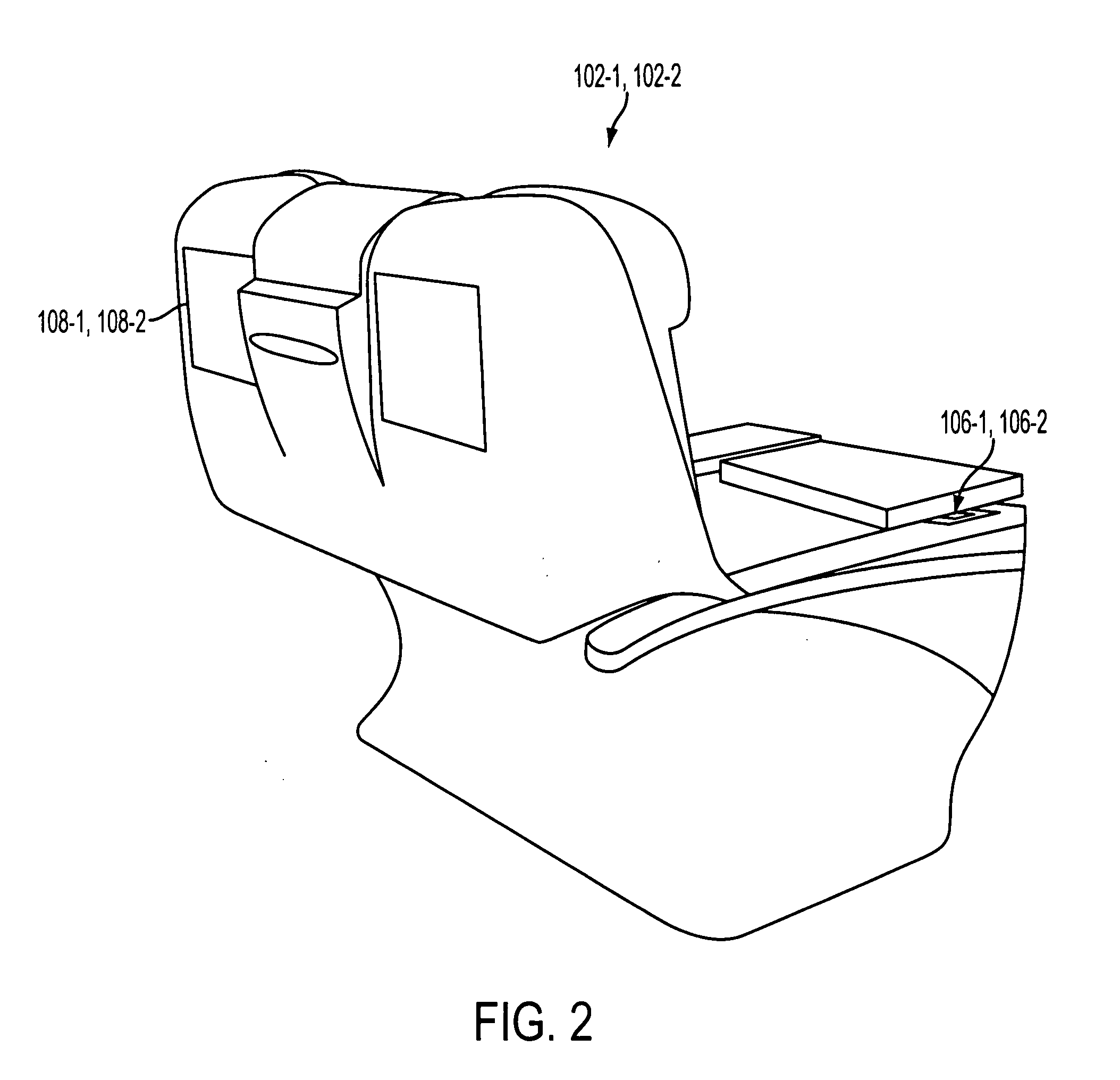

A system and method for providing a digital In-Flight Entertainment (IFE) system in a vehicle, such as an aircraft, that is capable of presenting a video program and associated audio in a synchronized manner to a large number of individual video monitors and speakers. The system and method employ processing operations in at least one decoder of the IFE system, to perform operations such as adjusting a local clock based on a master clock, setting a delay time in relation to a master clock, and adjusting video and audio playback based on the delay, to substantially synchronize playback of the audio and video data by the audio and video players, to thus eliminate or at least minimize the negative effects of source and load based jitter, network delays, clock drifts, network errors and decoder buffering differences, on synchronizing video and audio playback.

Owner:THALES AVIONICS INC

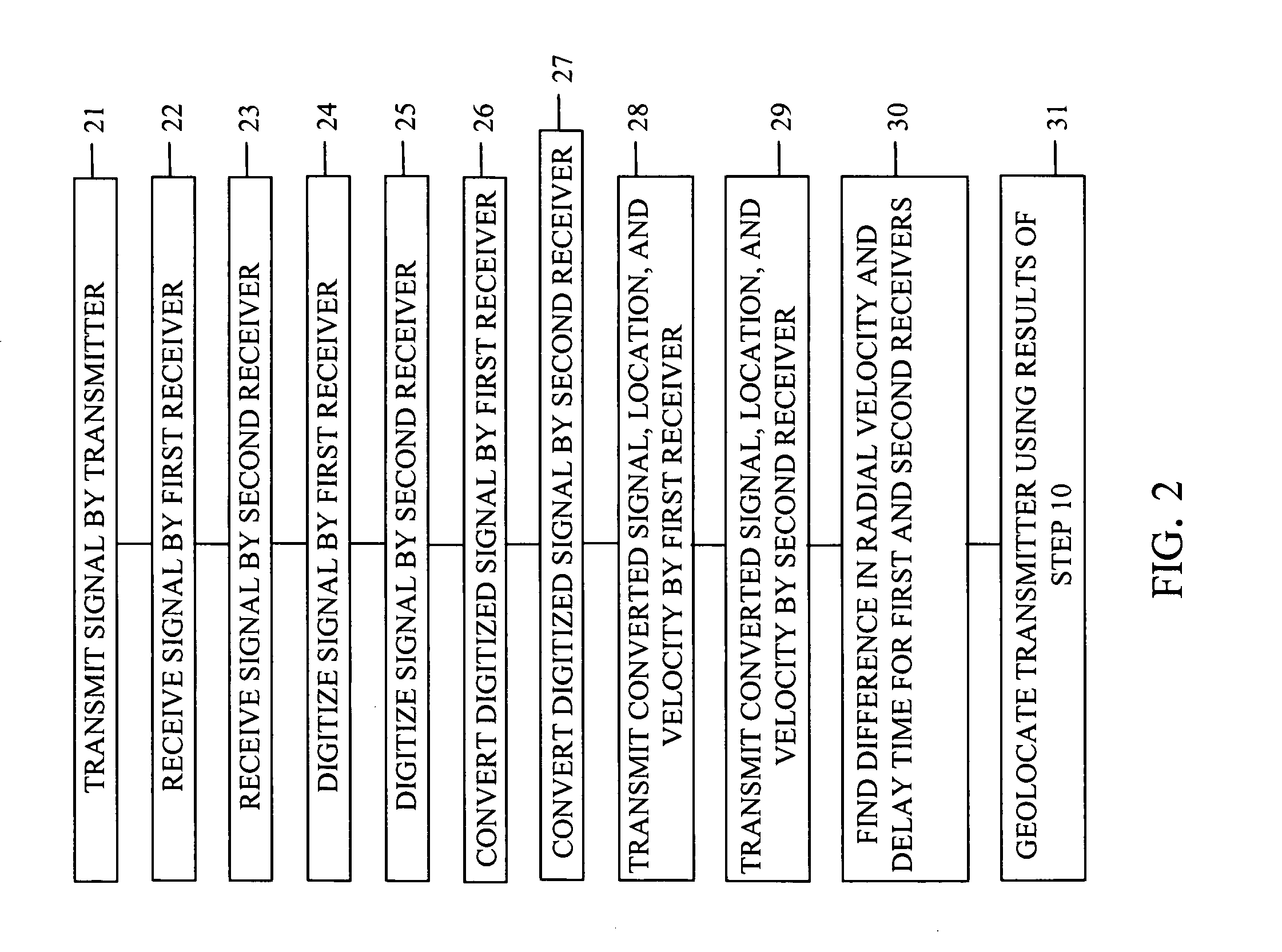

Device for and method of geolocation

ActiveUS7893875B1More precisionDirection finders using radio wavesPosition fixationGeolocationEngineering

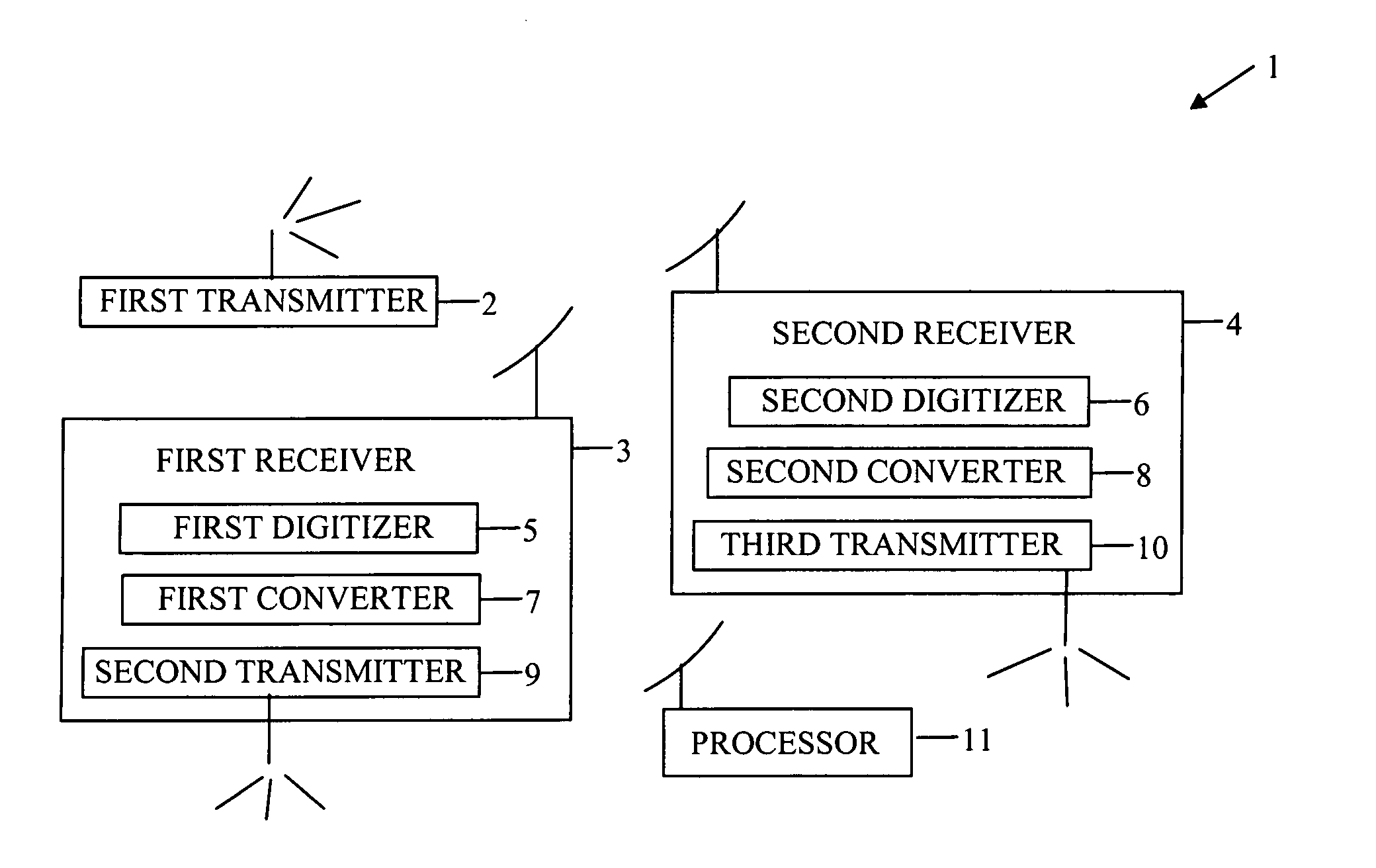

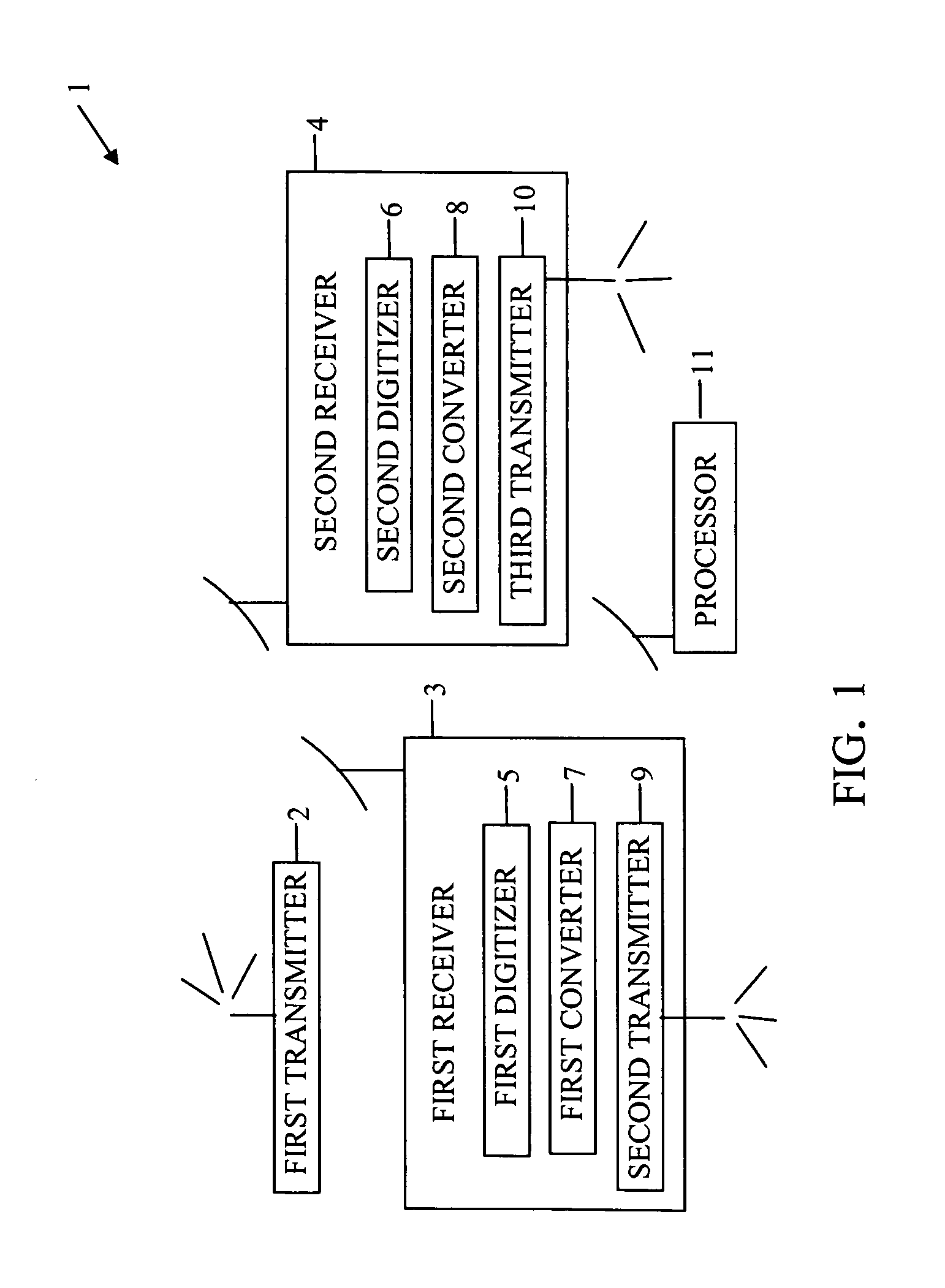

A device and method of geolocating a transmitter. First and second receivers, in motion, receive a signal from the transmitter. Digitizers in the receivers digitize the signal. Converters in the receivers for converting the digitized signals to complex-valued signals. Transmitters on the receivers transmit their digitized signals, locations, and velocities at the time the signal was received to a processor. A central processing unit on the processor determines a difference in radial velocities of the receivers relative to the transmitter. The difference in radial velocities and delay time between the signals received at the receivers are used to geolocate the transmitter.

Owner:NATIONAL SECURITY AGENCY

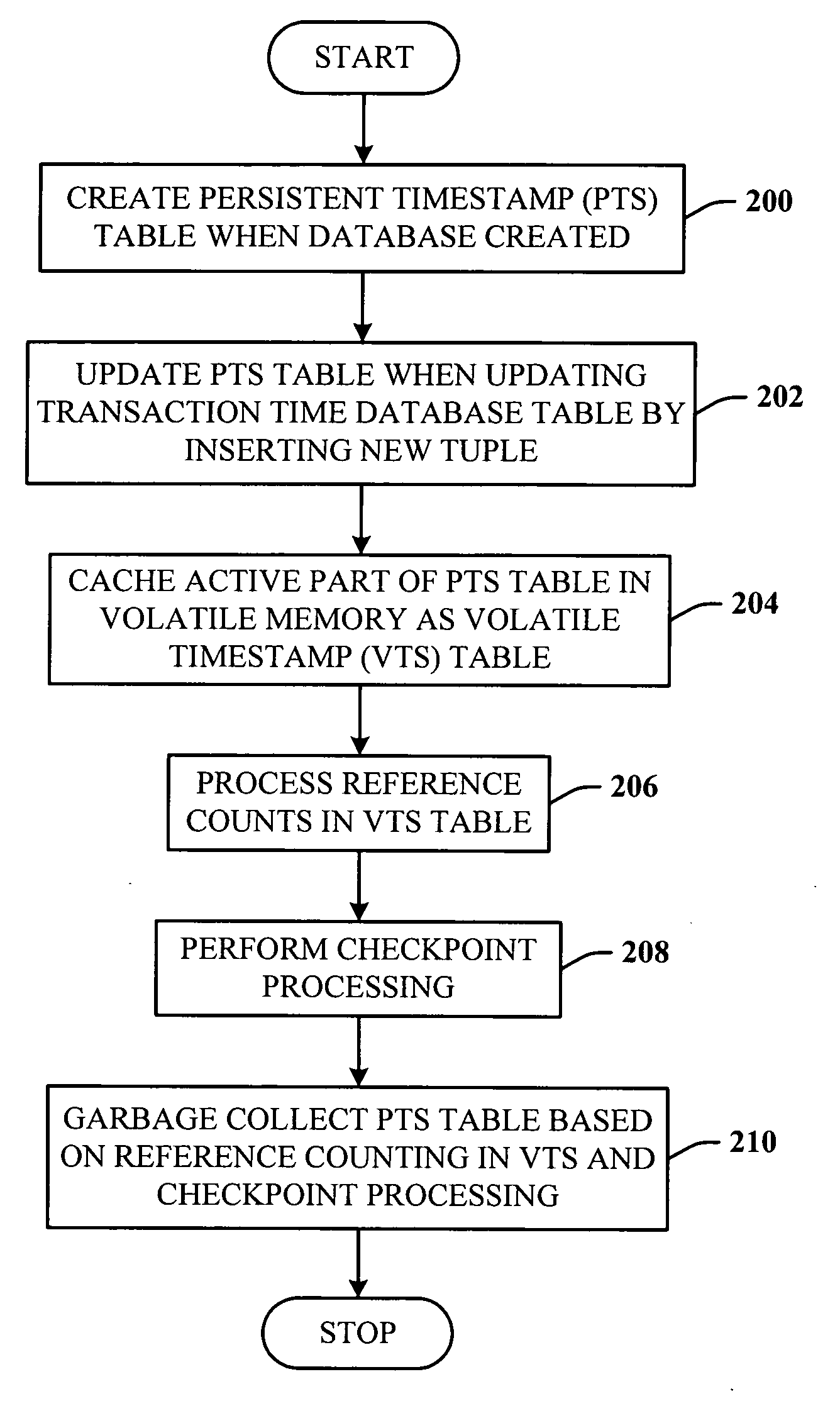

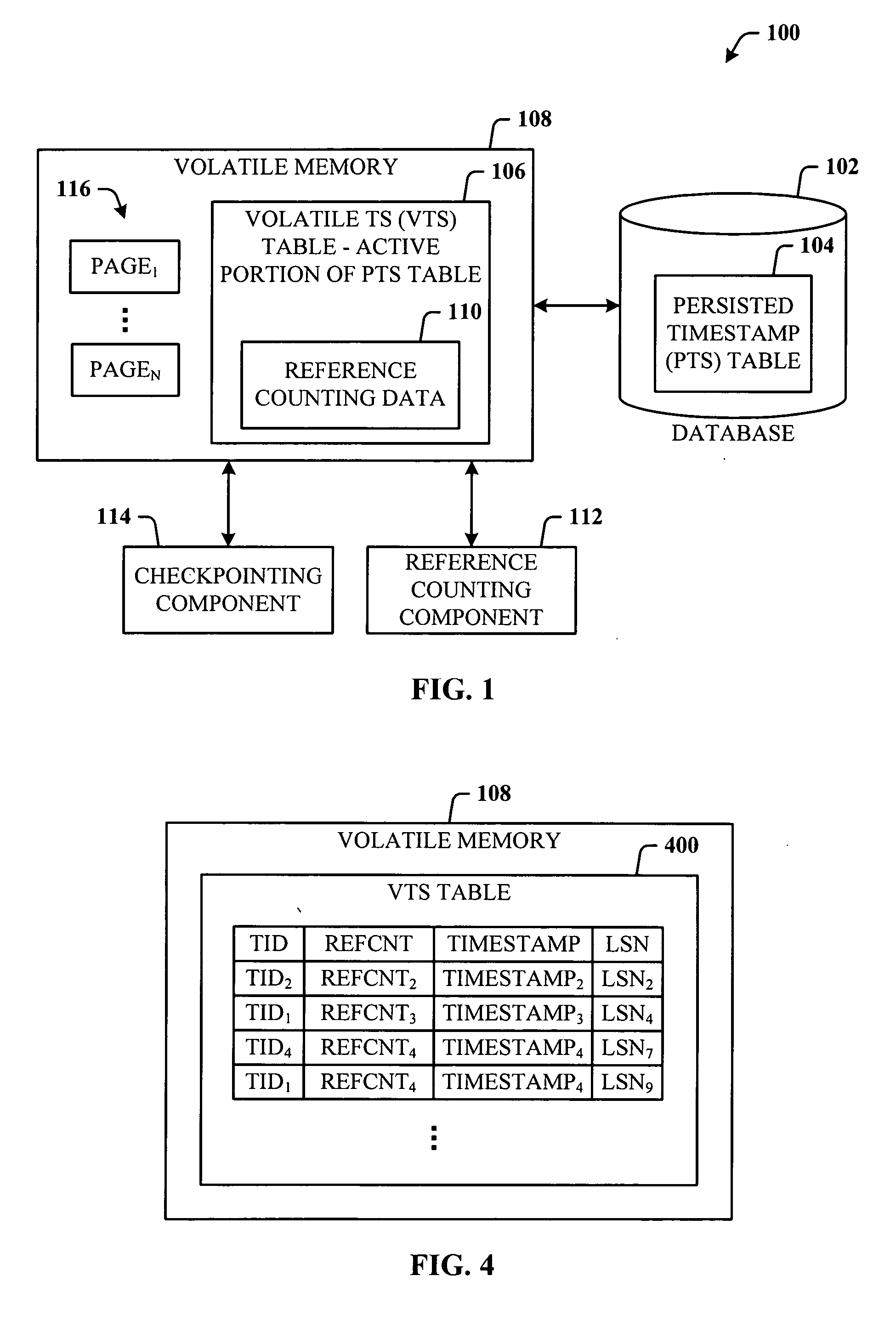

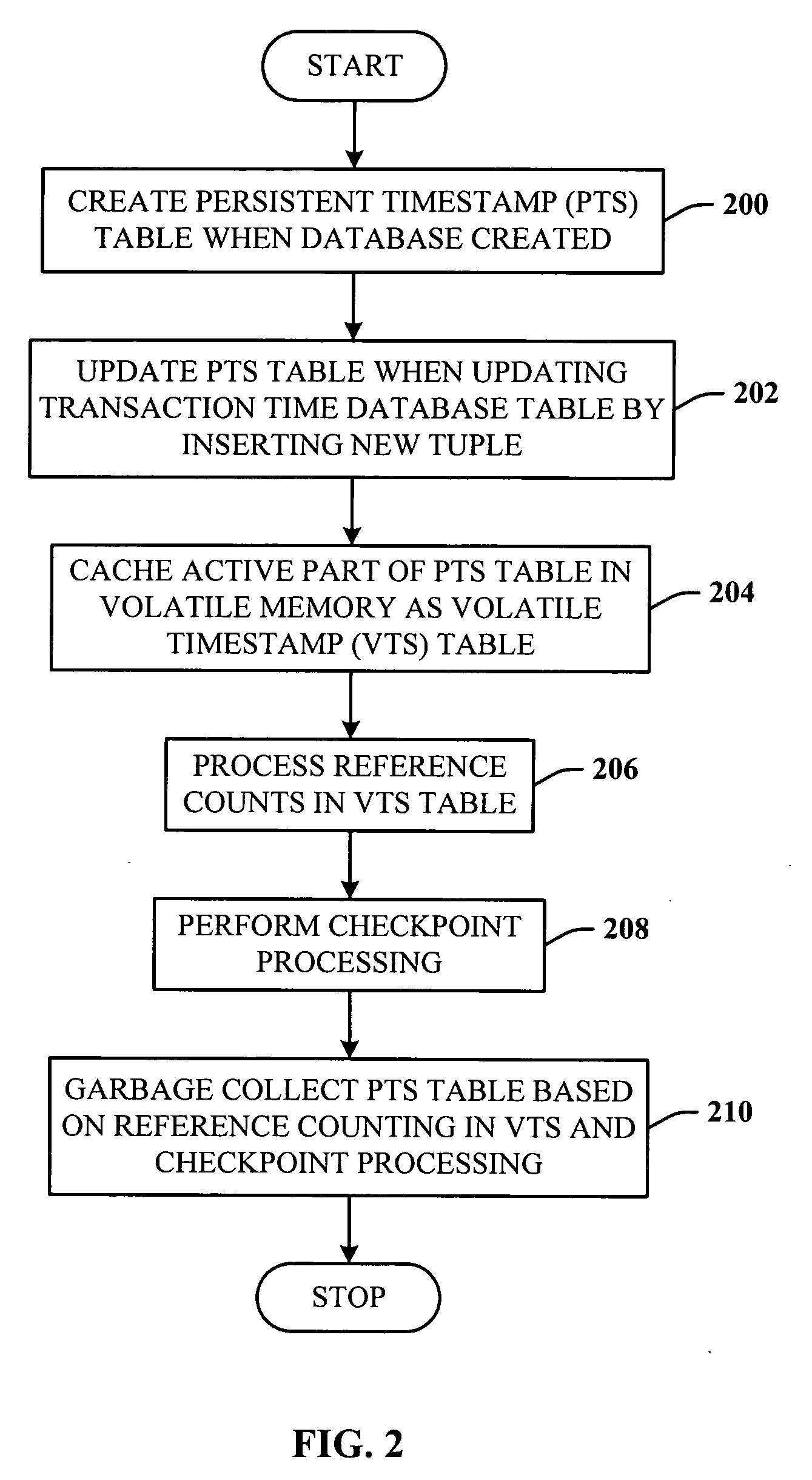

Lazy timestamping in transaction time database

InactiveUS20060167960A1Minimize accessEfficient record timestamping processData processing applicationsDigital data information retrievalTemporal databaseTimestamp

Lazy timestamping in a transaction time database is performed using volatile reference counting and checkpointing. Volatile reference counting is employed to provide a low cost way of garbage collecting persistent timestamp information about a transaction by identifying exactly when all record versions of a transaction are timestamped and the versions are persistent. A volatile timestamp (VTS) table is created in a volatile memory, and stores timestamp, reference count, transaction ID, and LSN information. Active portions of a persisted timestamp (PTS) table are stored in the VTS table to provide faster and more efficient timestamp processing via accesses to the VTS table information. The reference count information is stored only in the VTS table for faster access. When the reference count information decrements to zero, it is known that all record versions that were updates for a transaction were timestamped. A checkpointing component facilitates checkpoint processing for verifying that timestamped records have been written to the persistent database and that garbage collection of the PTS table can be performed for transaction entries with zero reference counts.

Owner:MICROSOFT TECH LICENSING LLC

Air conditioning and heating environmental control sensing system

InactiveUS6196468B1Avoid deactivationInhibit wearTemperature control using analogue comparing deviceSpace heating and ventilation safety systemsStopwatchThermostat

A device for controlling an HVAC system in which opening a door or window for more than a shutdown delay period causes the fan and compressor to be deactivated, but opening and closing the door or window for less than the shutdown delay period does not affect the fan and compressor. Reactivation of the compressor is delayed for a startup delay, in order to avoid overcycling of the compressor and the additional wear and tear and maintenance that would be caused thereby. Preferably, the door / window sensors are wireless for ease of installation and maintenance. Optionally, an occupancy sensor and occupancy timer are provided to turn off the system if the room is unoccupied for an unoccupied delay time. Optionally, a secondary thermostat with energy saving settings is provided so that if the room is unoccupied for the occupancy delay, then instead of being shut off, the HVAC system will be operated at energy saving settings.

Owner:YOUNG DENNIS GUY

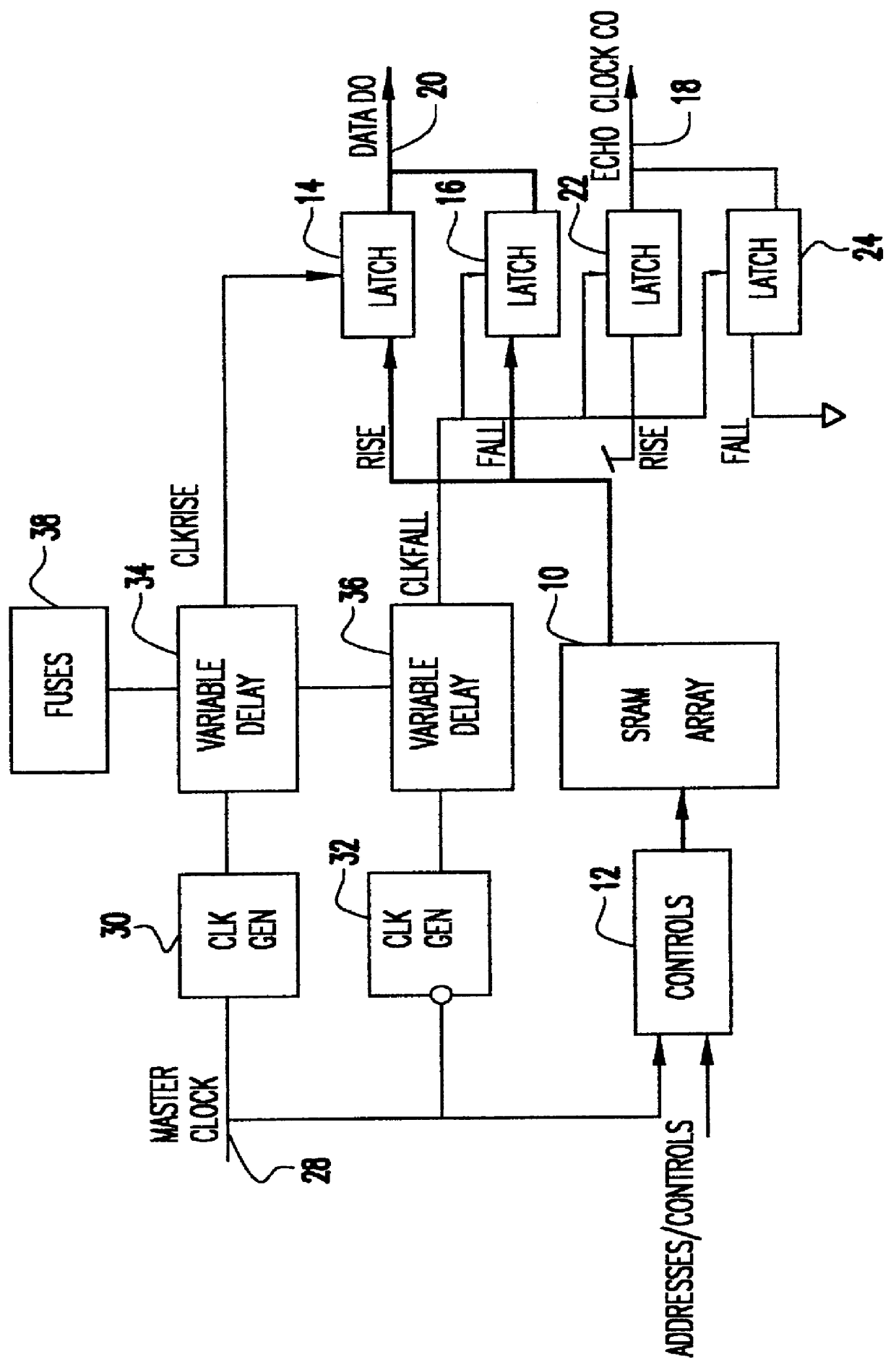

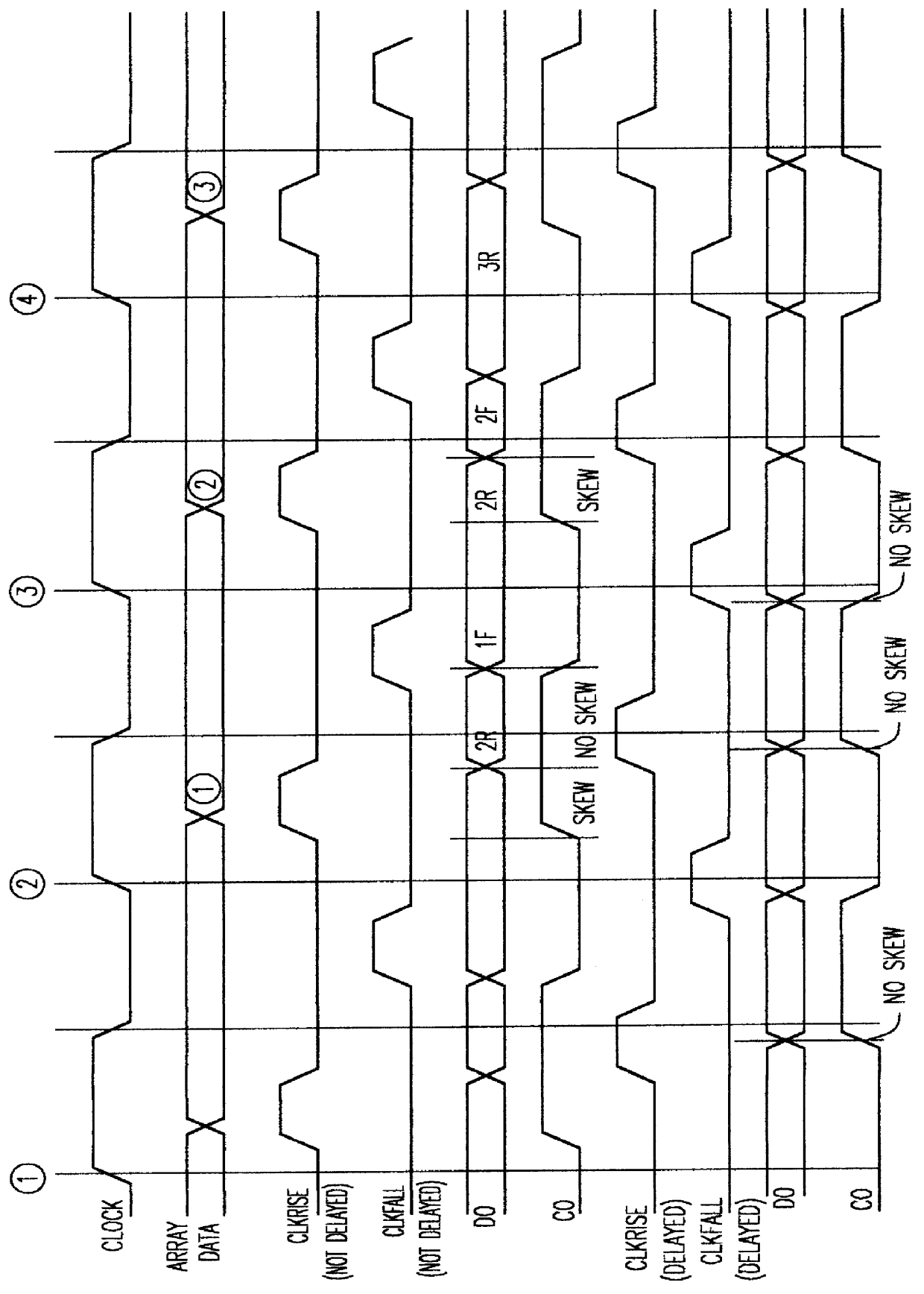

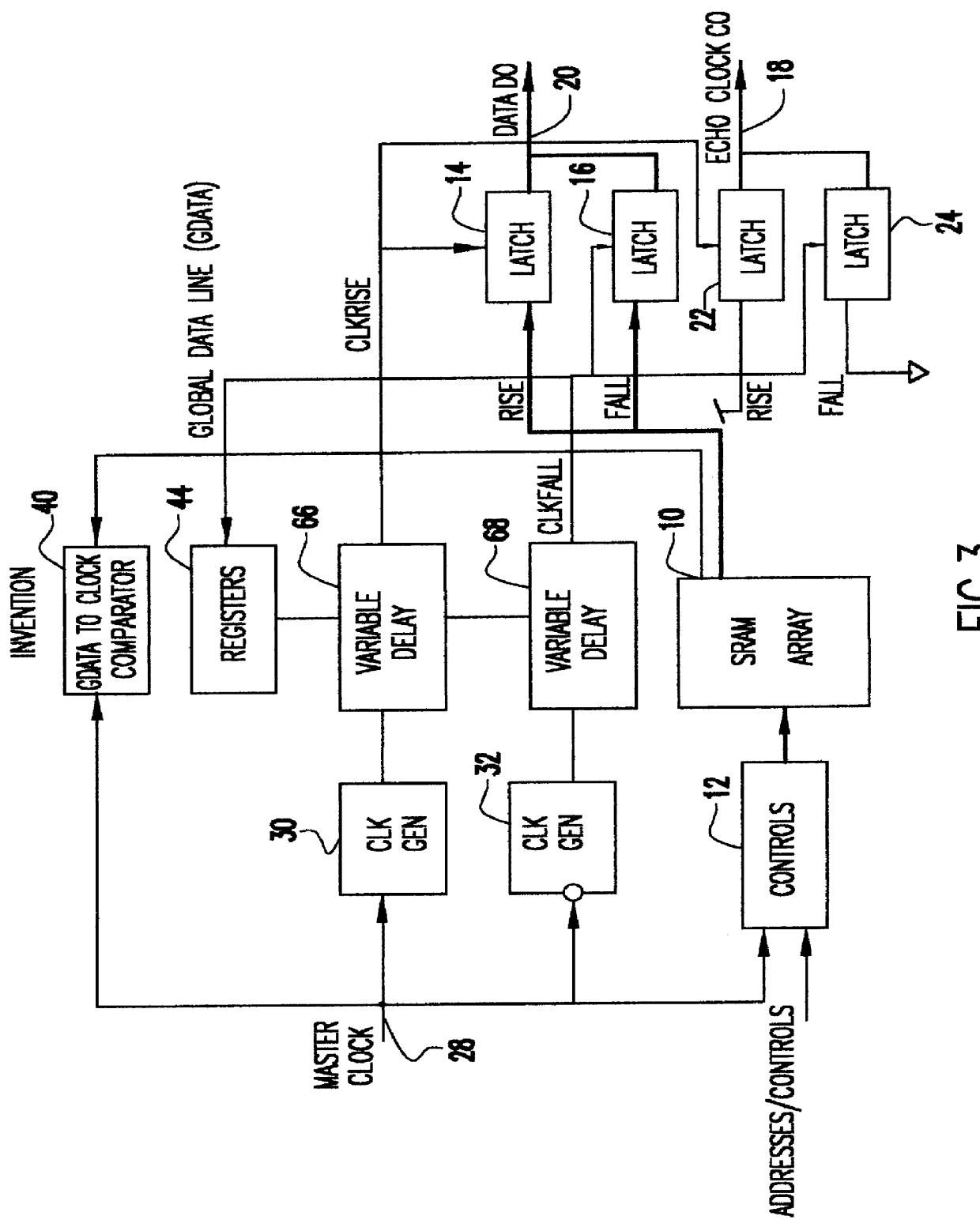

Cycle independent data to echo clock tracking circuit

InactiveUS6134182AAvoid dataDigital storageGenerating/distributing signalsDouble data rateData signal

A comparator and variable delay circuit are provided to maintain the tracking between data and echo clocks in a double data rate (DDR)RAM device. This is accomplished by providing a global data signal (dummy data signal) that tracks with the actual memory array data. This global data signal is compared to the timing of the RAM clock (CLOCK) to determine a delay time between the two by which the pipeline clocks (CLKRISE / CLKFALL) must be delayed. As a result, the pipeline clocks are pushed out as needed so that they always transition after the array data arrives at the output latch. Therefore, as cycle time decreases, both echo clocks and data are pushed out identically and maintain their required tracking.

Owner:IBM CORP

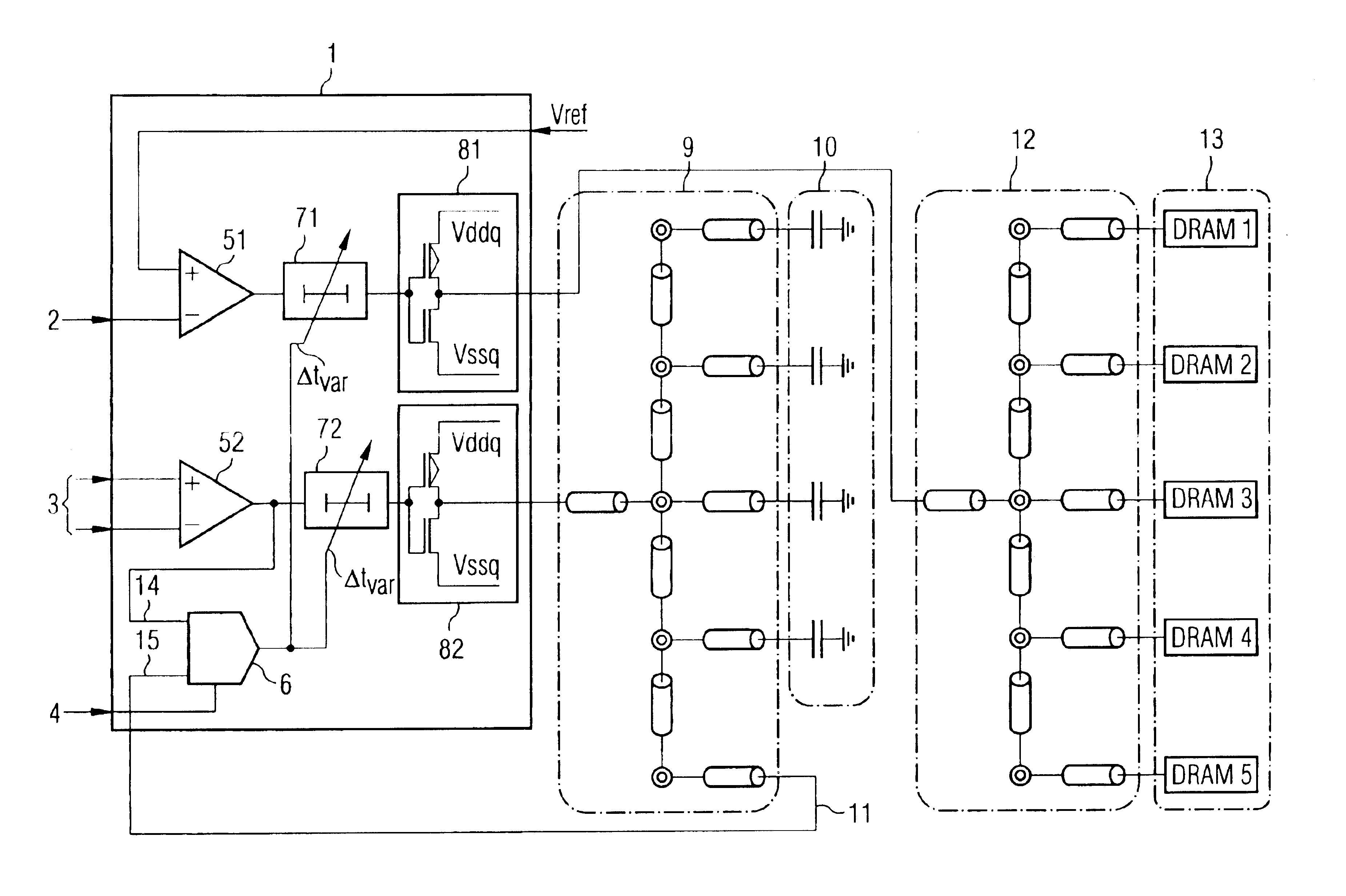

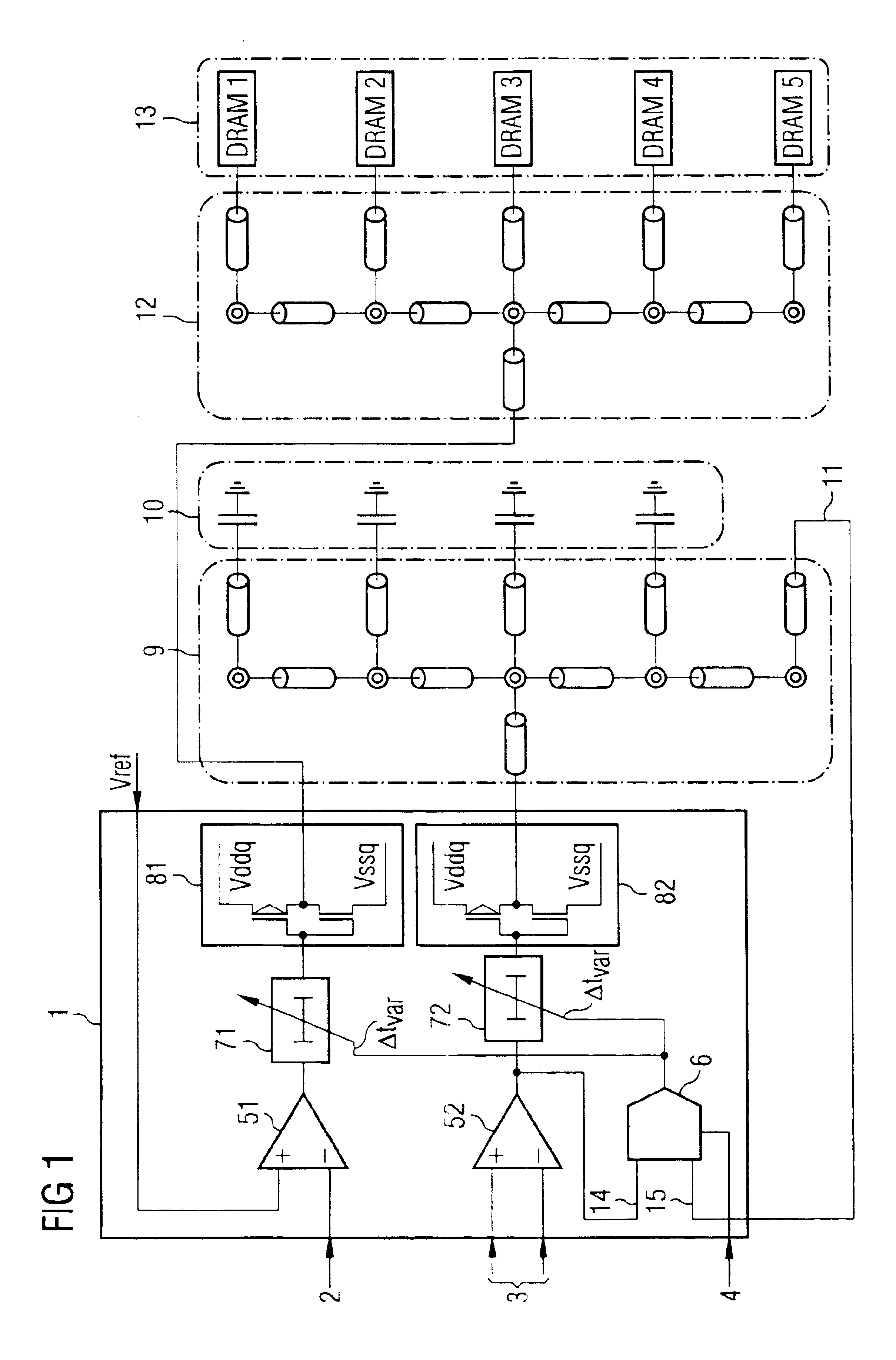

Buffer amplifier architecture for semiconductor memory circuits

A buffer amplifier architecture for buffering signals which are supplied in parallel to identical chips, particularly DRAM chips, on a semiconductor memory module, is disclosed. The architecture has adjustable delay circuits in each signal line and a delay detector circuit which receives a clock signal from the buffer amplifier architecture at the input and at the output of the buffer amplifier architecture, and takes the phase difference between the two signals to produce a control signal for setting the variable delay time of the delay circuits. To ensure that the delay time set by the delay detector circuit is independent of variations in parameters of the DRAM memory chips, the feedback path routed to the input of the delay detector circuit has a reference line network of the same structure and having the same electrical properties as capacitance elements which terminate the line network routed to the DRAM memory chips and the reference line network, and which have the same capacitances as the signal inputs on the DRAM memory chips.

Owner:POLARIS INNOVATIONS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com