Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

81results about How to "Long delay time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

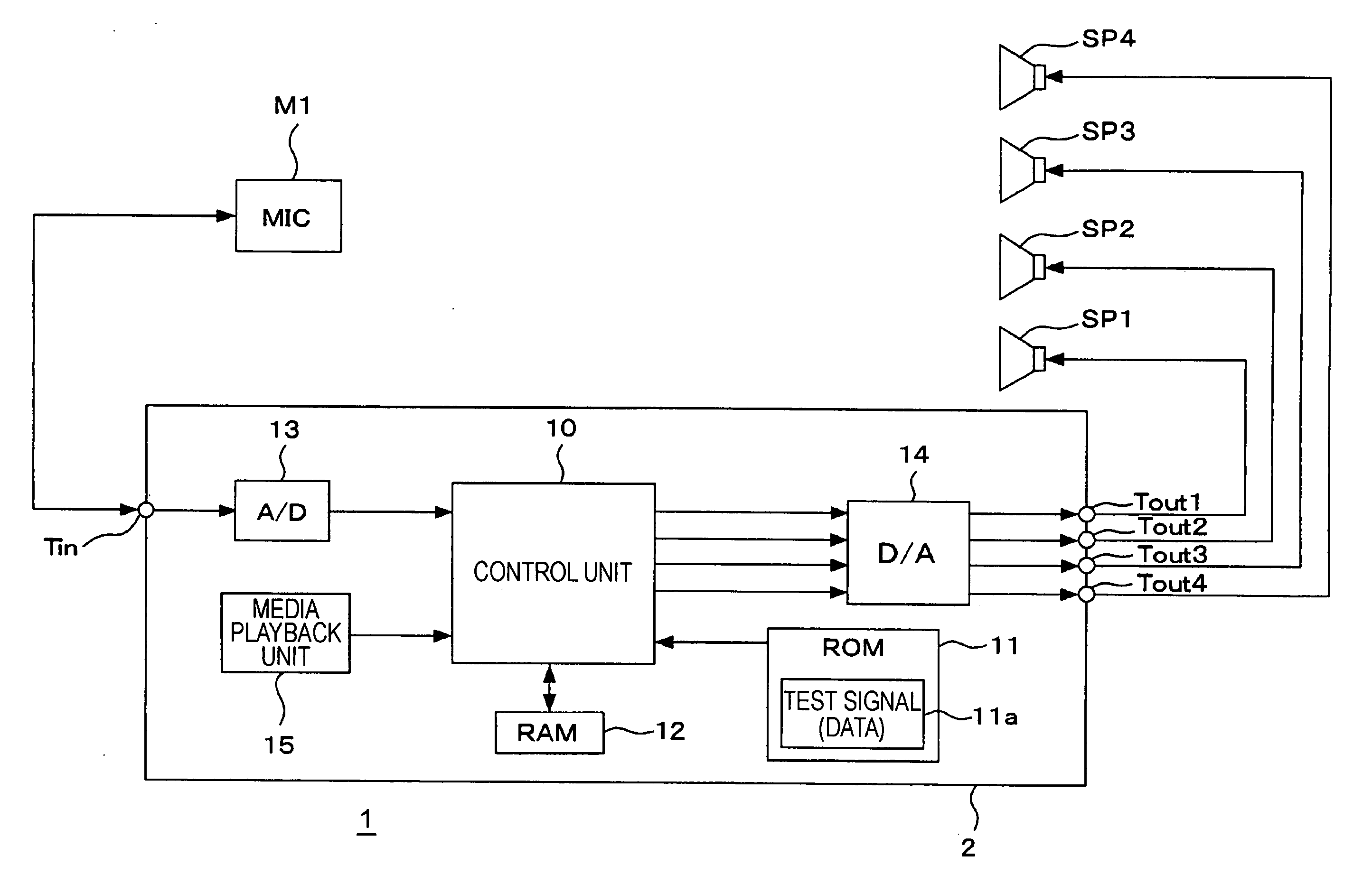

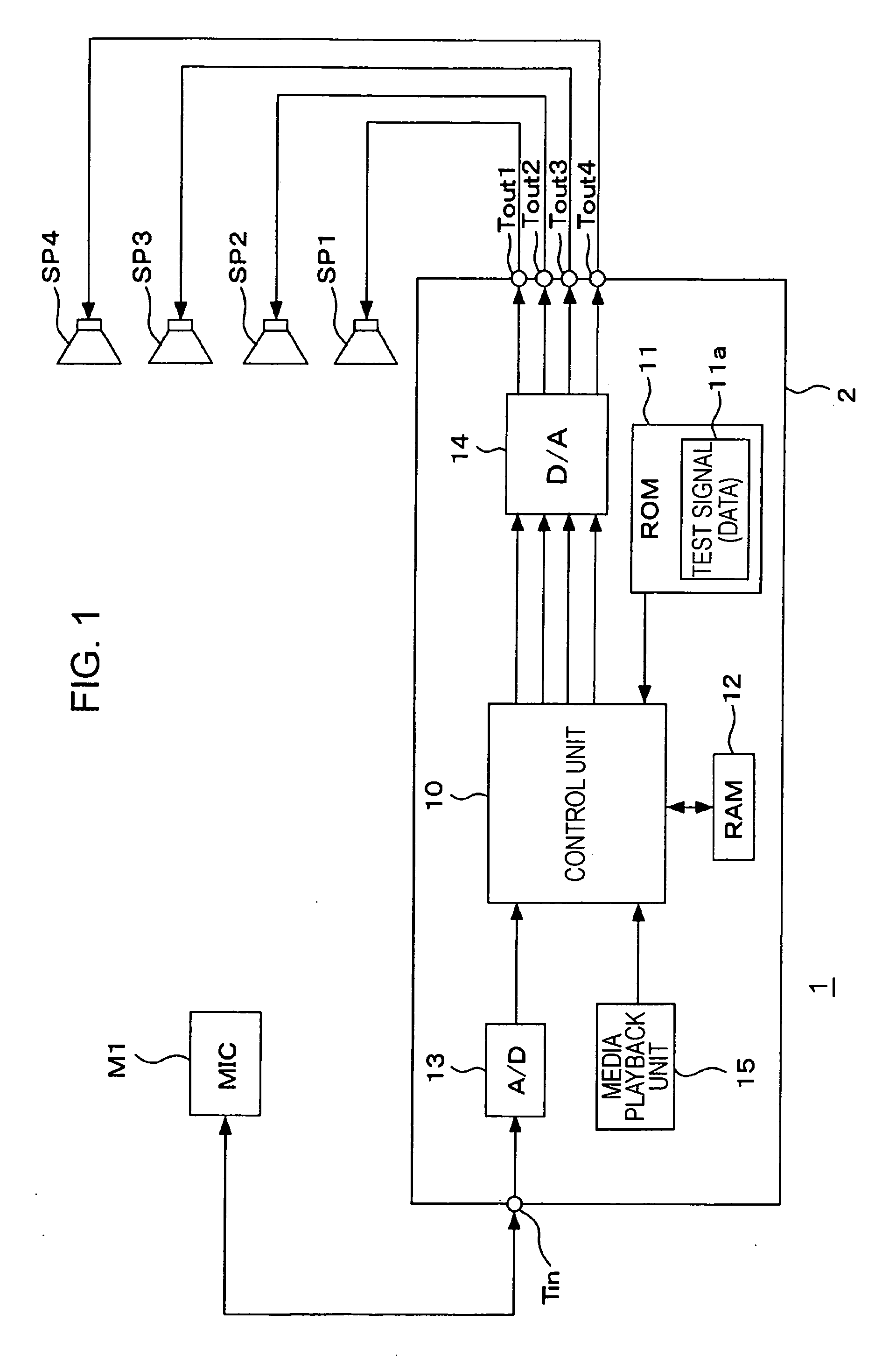

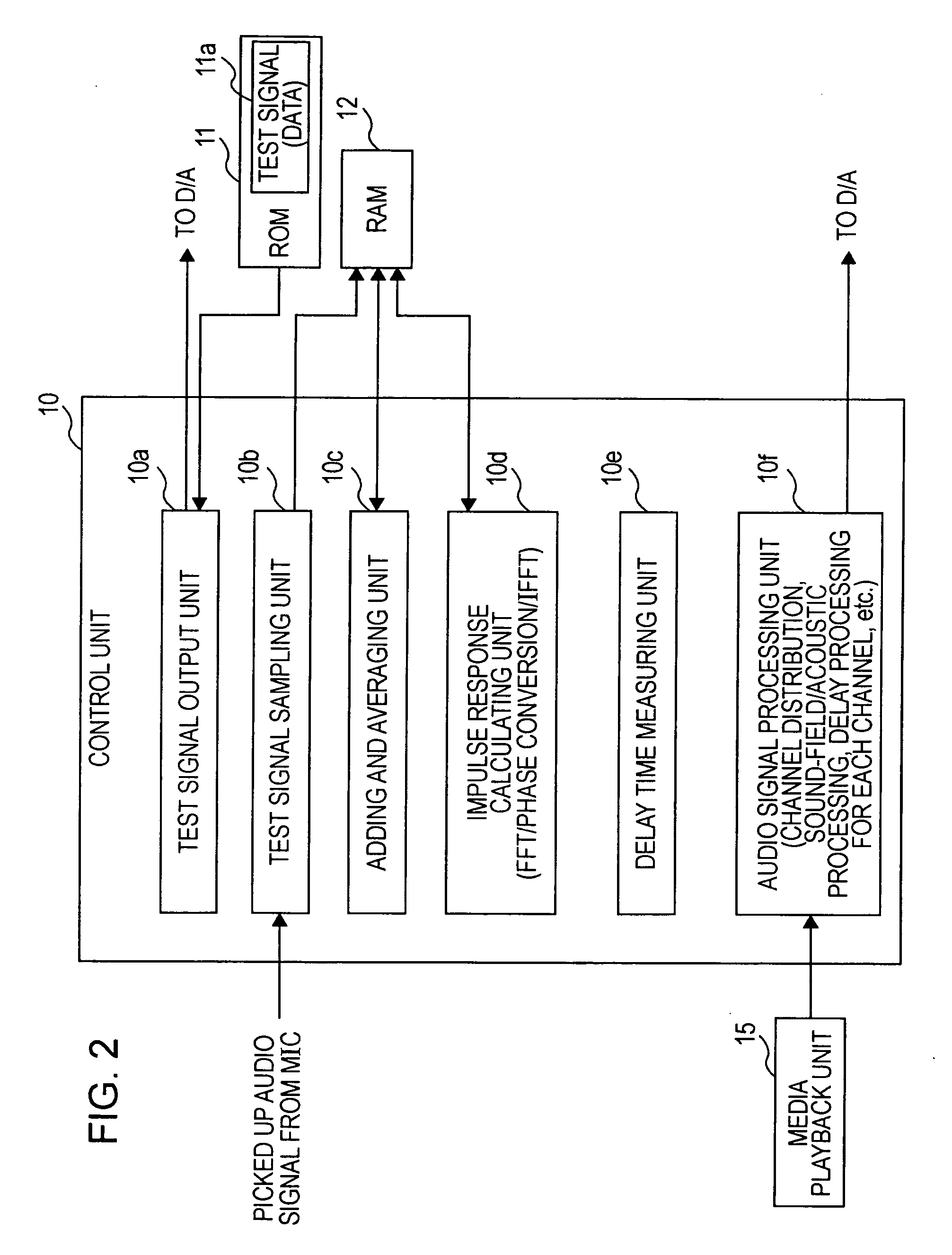

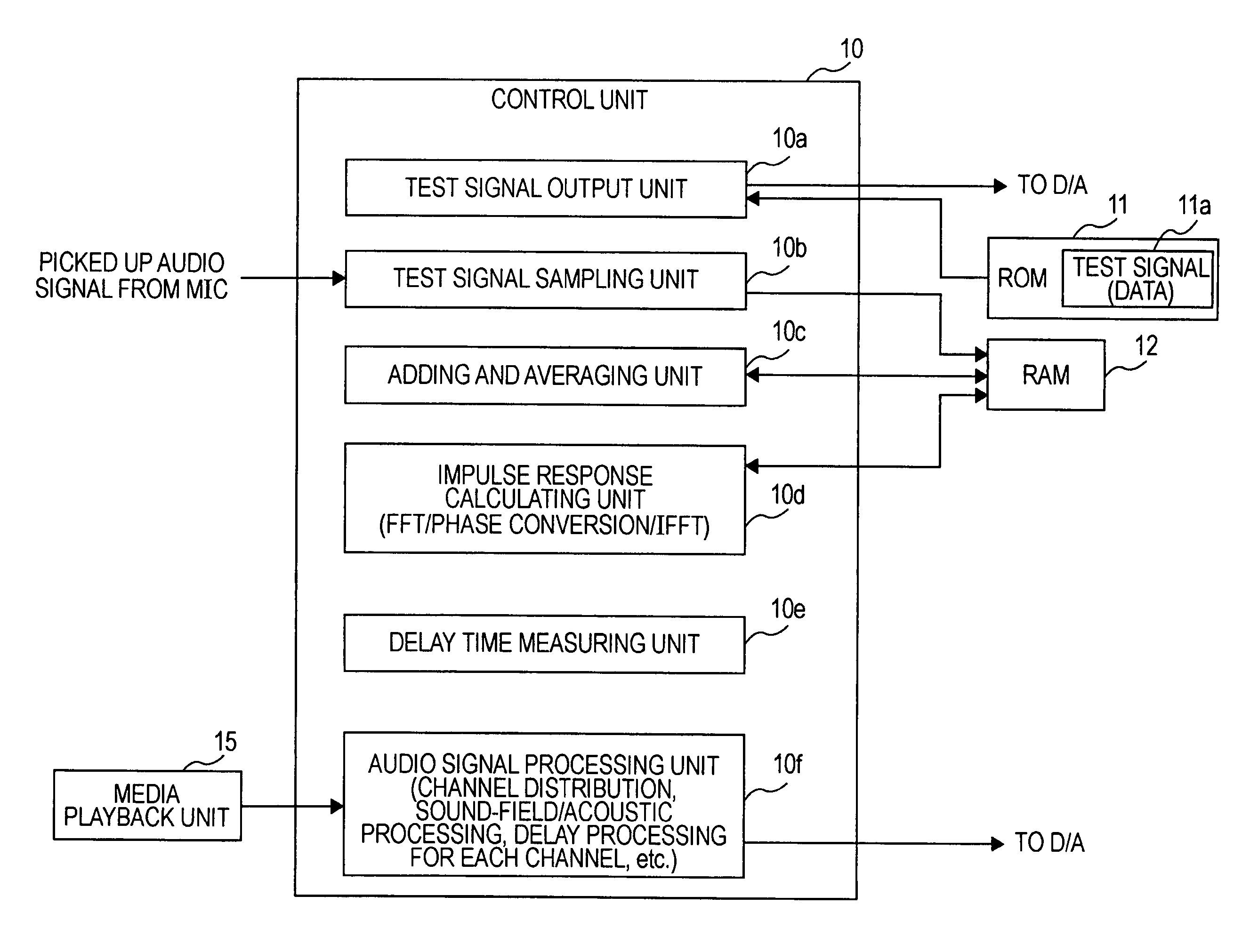

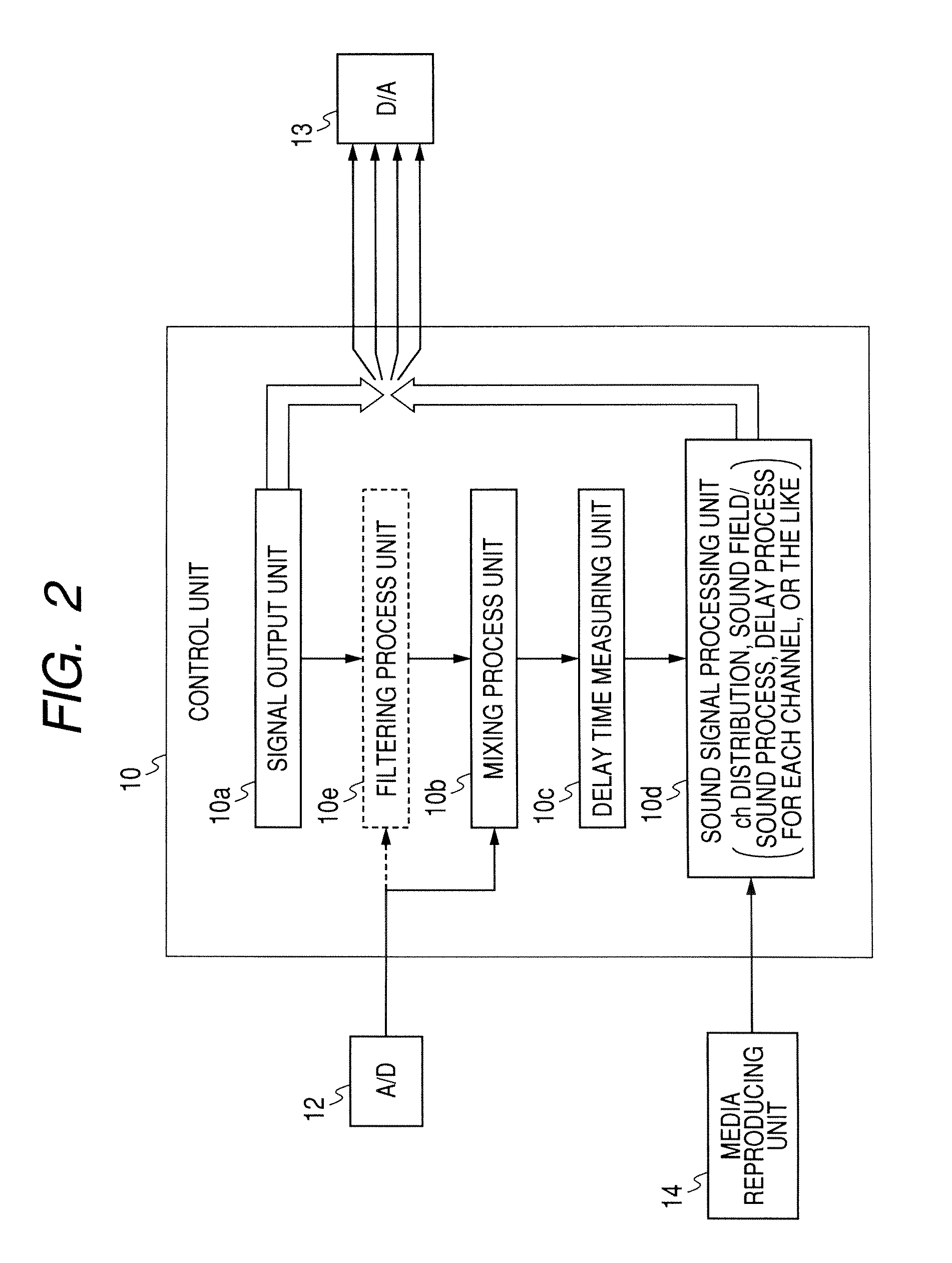

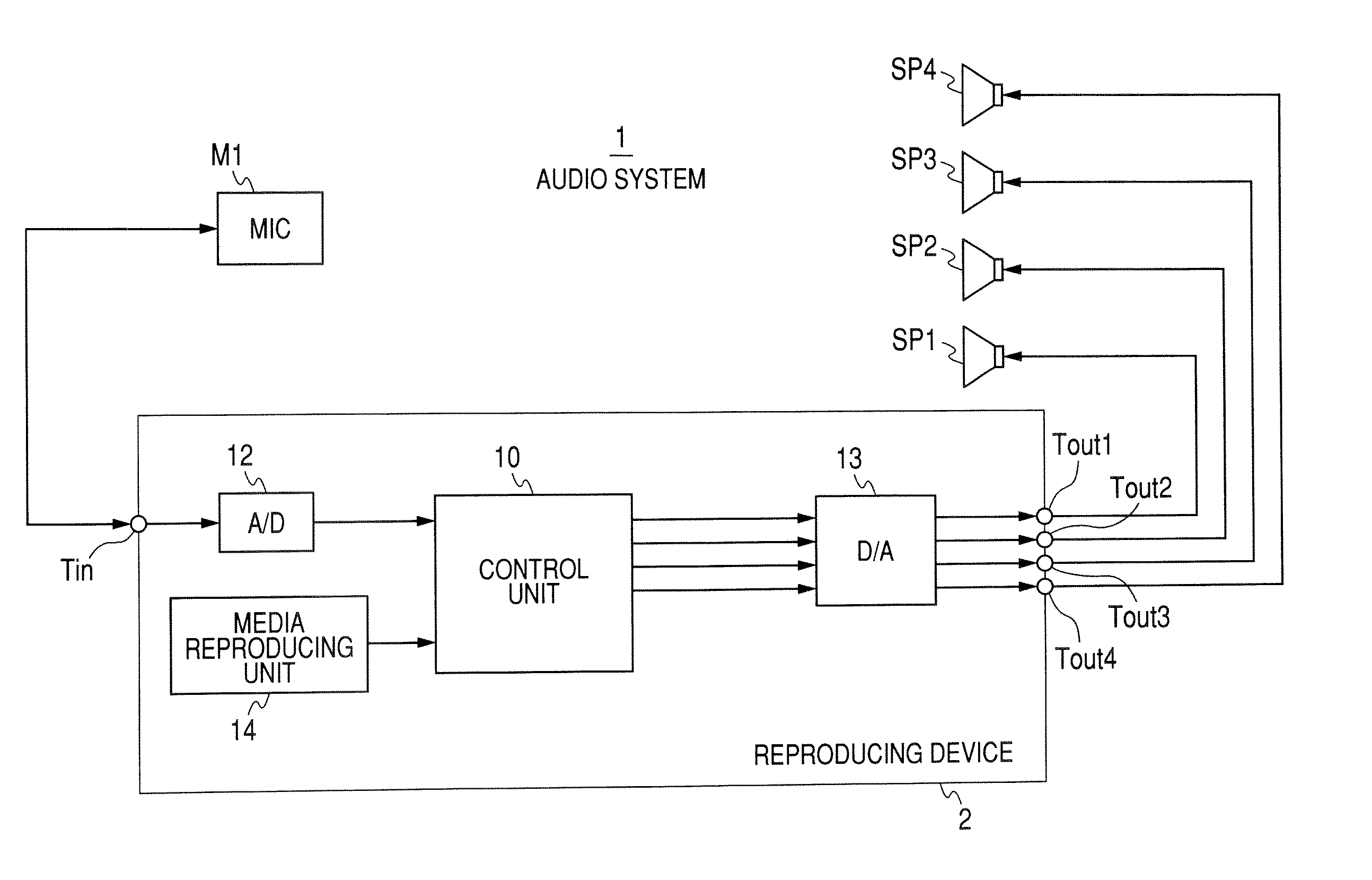

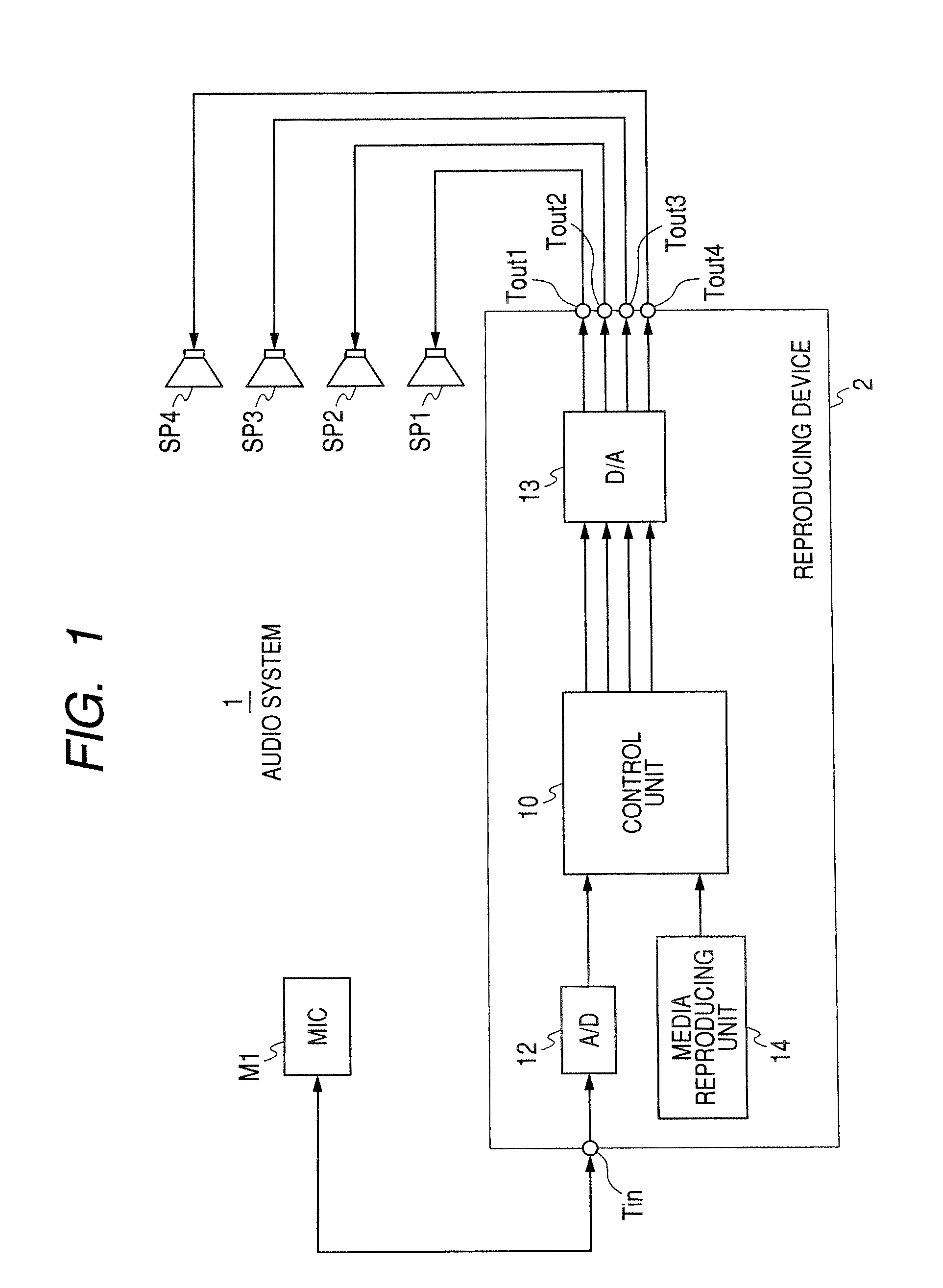

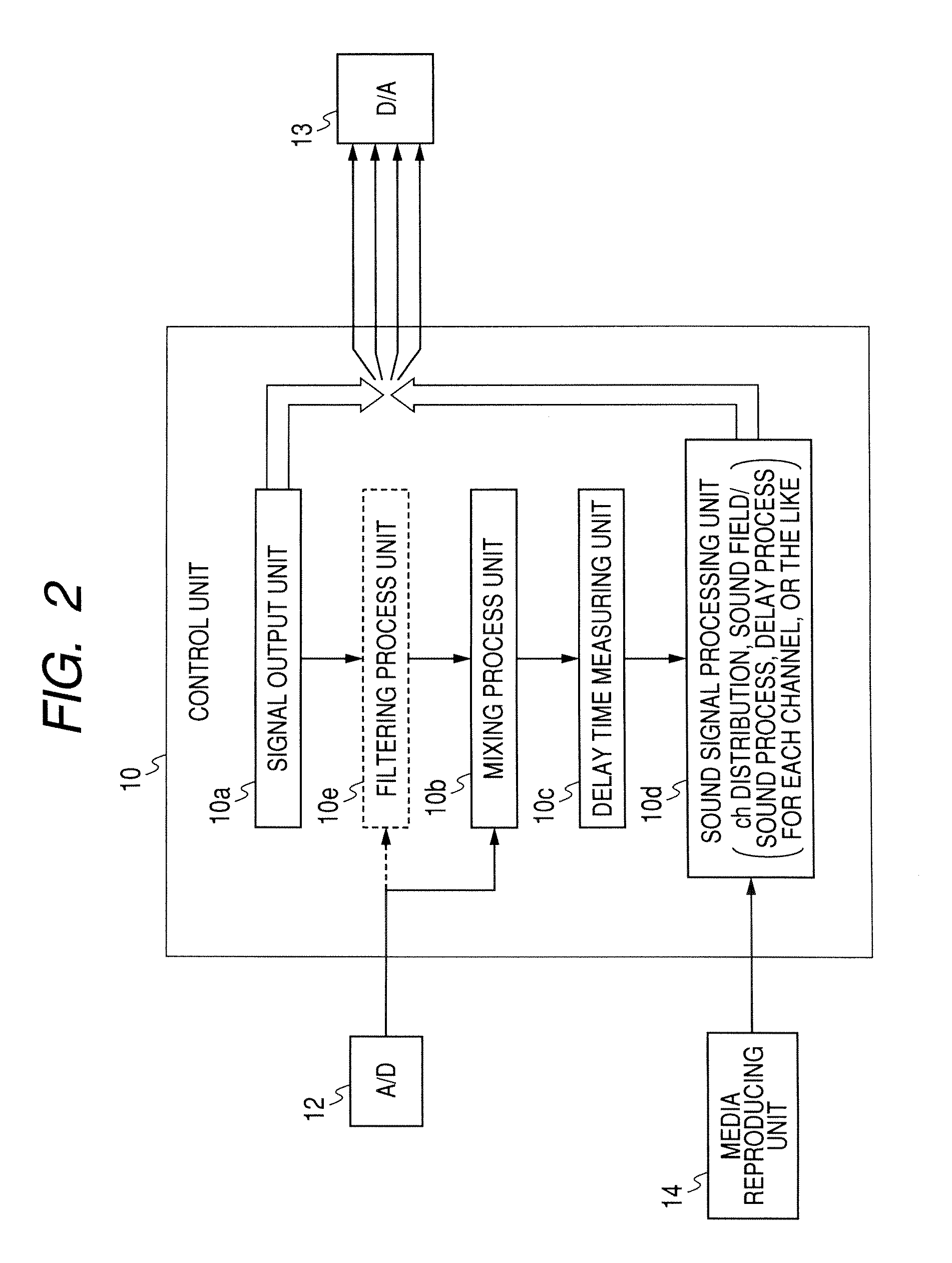

Sound measuring apparatus and method, and audio signal processing apparatus

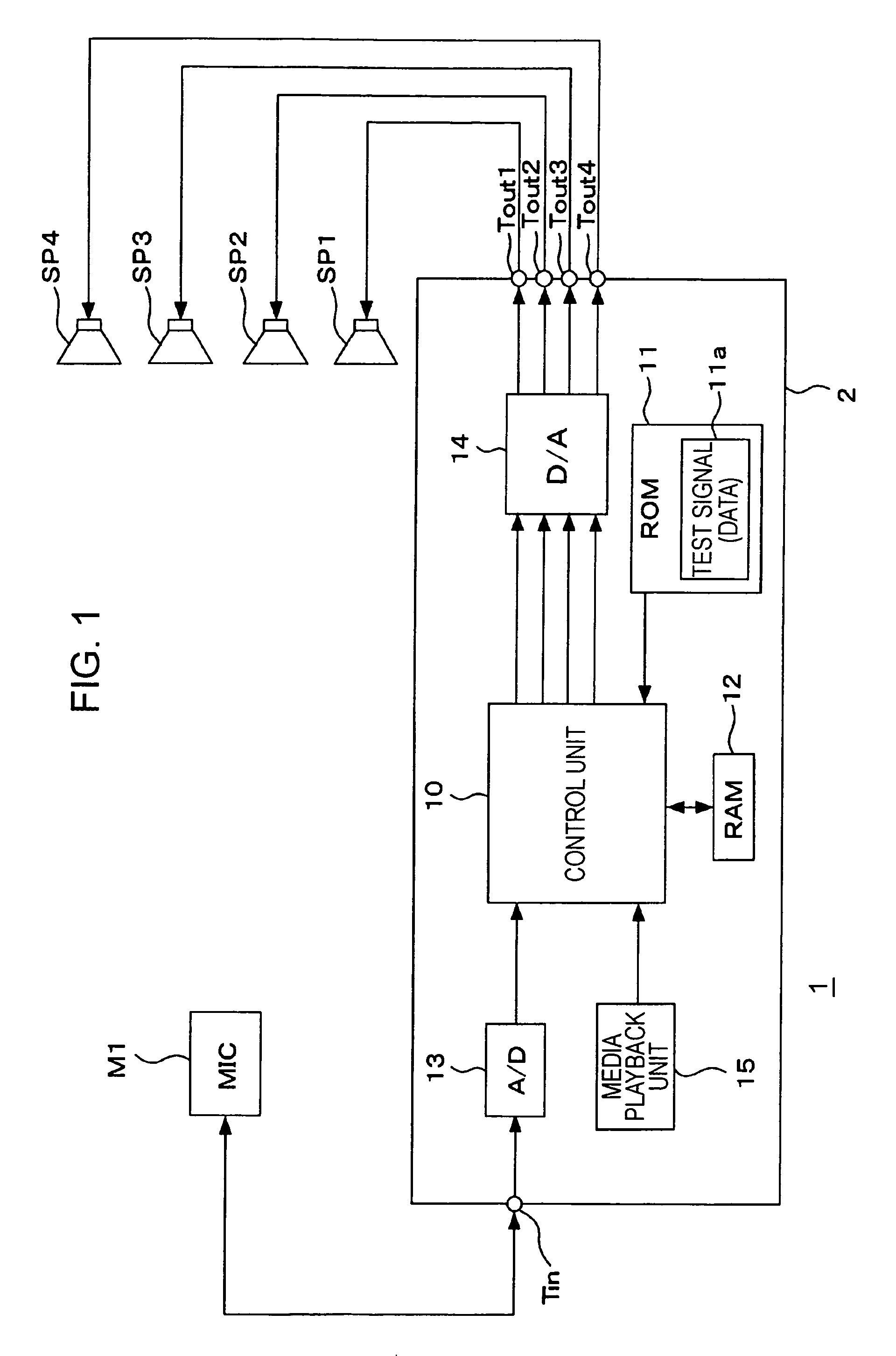

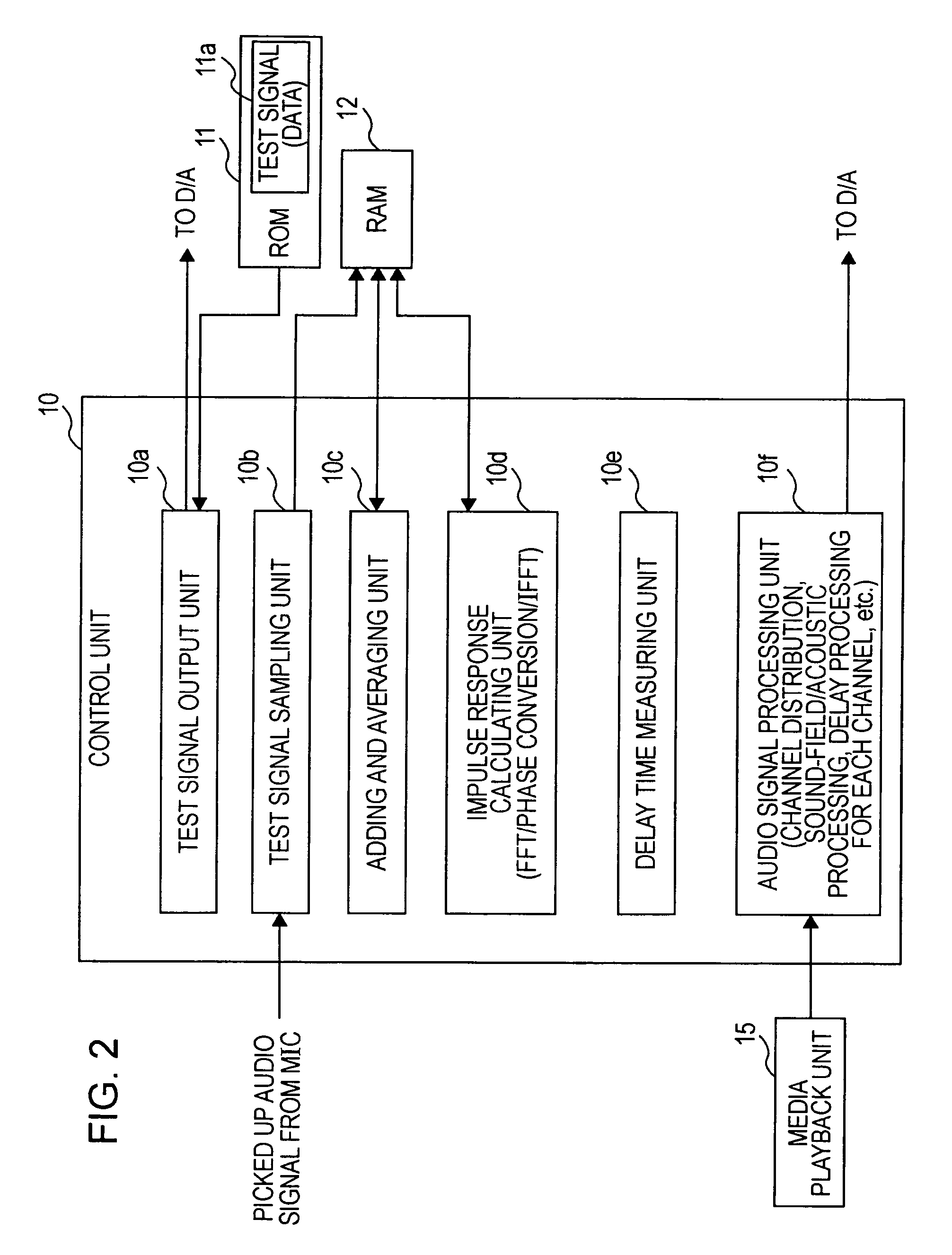

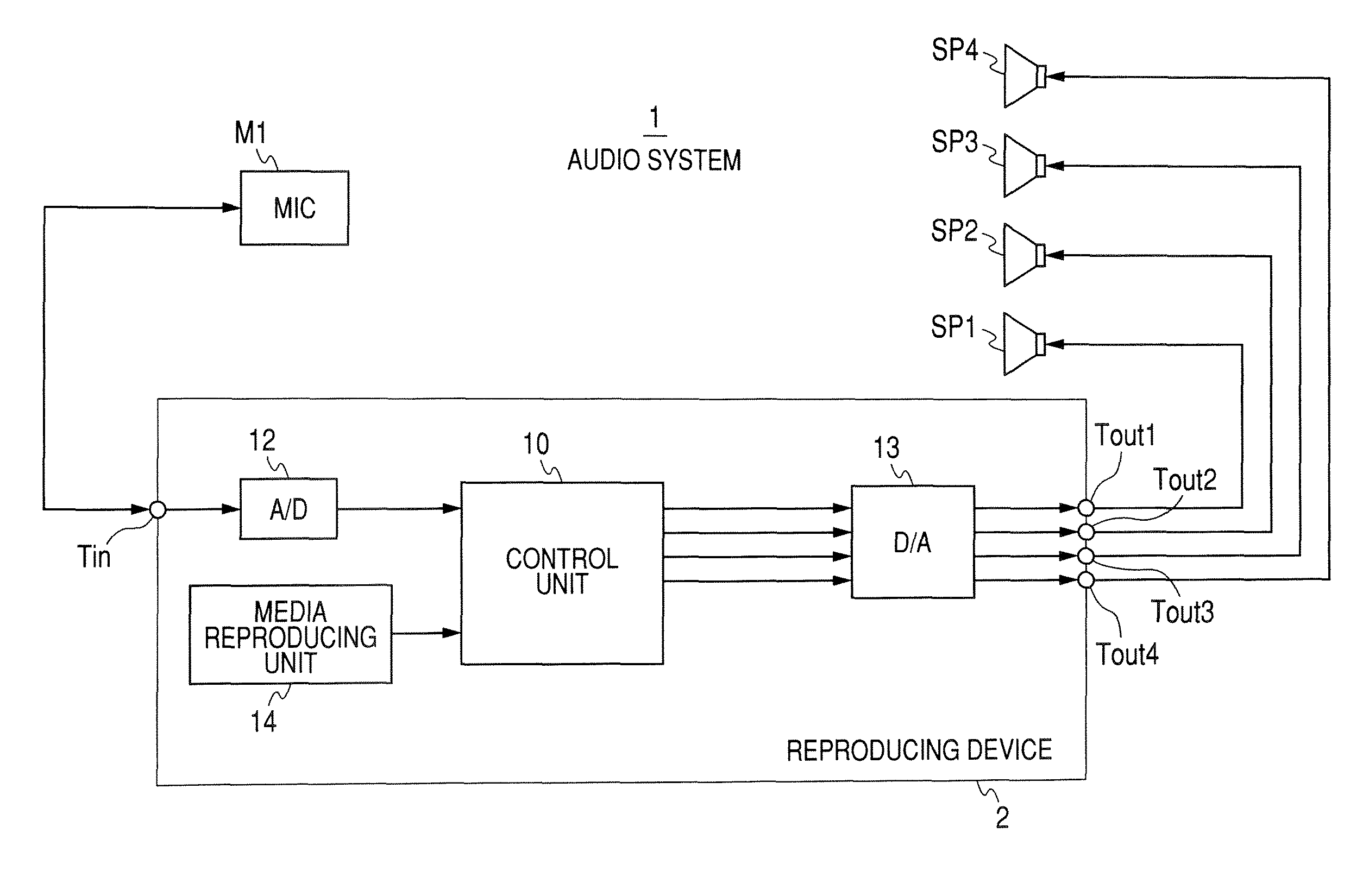

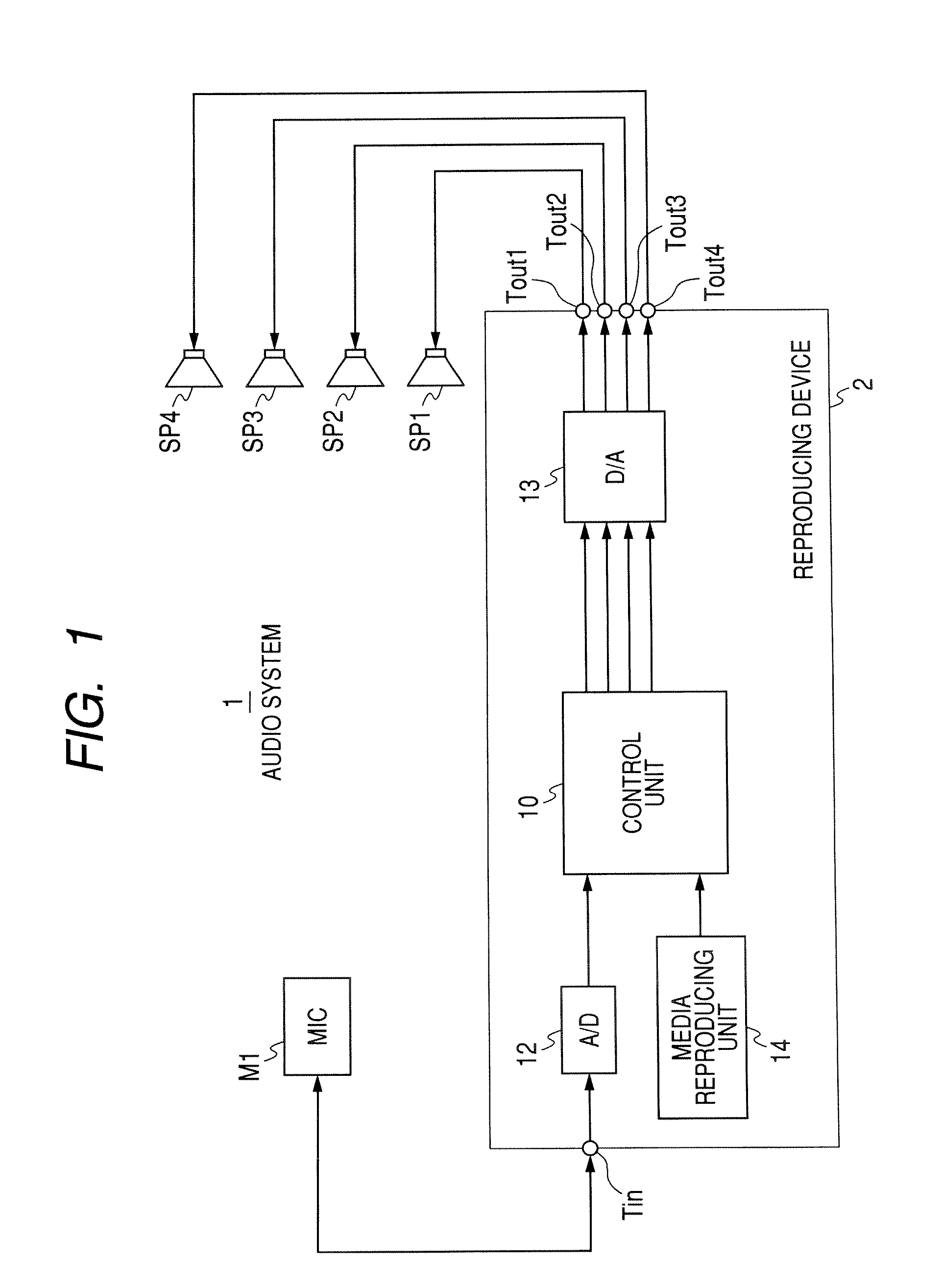

InactiveUS20070086597A1Increase sample sizeLong delay timeTwo-channel systemsSpecial data processing applicationsDelayed timeEngineering

A sound measuring apparatus for measuring a sound-arrival delay time from a speaker to a microphone on the basis of a result obtained by outputting a test signal from the speaker and picking up the test signal using the microphone includes the following elements. A control unit performs control so that the test signal is expanded in a time axis and is then output from the speaker. A delay time measuring unit measures an expansion-based measured delay time on the basis of a delay time that is measured on the basis of a time difference between the test signal expanded in the time axis and output from the speaker and a signal obtained from the microphone by picking up the output expanded test signal, and obtains the sound-arrival delay time as the expansion-based measured delay time.

Owner:SONY CORP

Sound measuring apparatus and method, and audio signal processing apparatus

InactiveUS7949140B2Increase sample sizeLong delay timeTwo-channel systemsSpecial data processing applicationsEngineeringLoudspeaker

A sound measuring apparatus for measuring a sound-arrival delay time from a speaker to a microphone on the basis of a result obtained by outputting a test signal from the speaker and picking up the test signal using the microphone includes the following elements. A control unit performs control so that the test signal is expanded in a time axis and is then output from the speaker. A delay time measuring unit measures an expansion-based measured delay time on the basis of a delay time that is measured on the basis of a time difference between the test signal expanded in the time axis and output from the speaker and a signal obtained from the microphone by picking up the output expanded test signal, and obtains the sound-arrival delay time as the expansion-based measured delay time.

Owner:SONY CORP

Measuring apparatus, measuring method, and sound signal processing apparatus

InactiveUS7961893B2Long delay timeEasy to operateLoudspeaker spatial/constructional arrangementsStereophonic systemsMeasurement deviceLoudspeaker

Owner:SONY CORP

Pharmaceutical composition for intranasal administration containing a CGRP antagonist

Owner:BOEHRINGER INGELHEIM PHARM KG

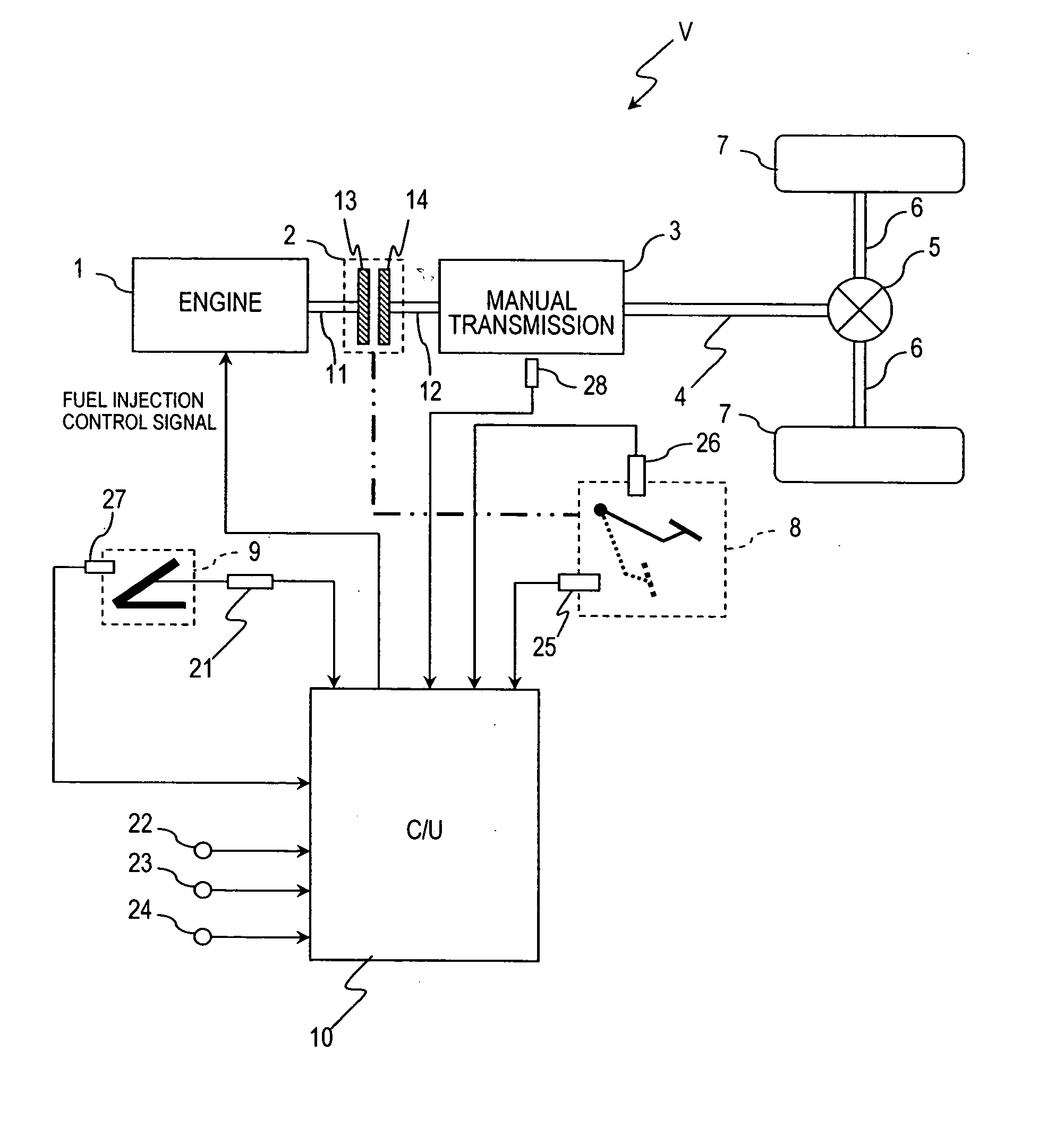

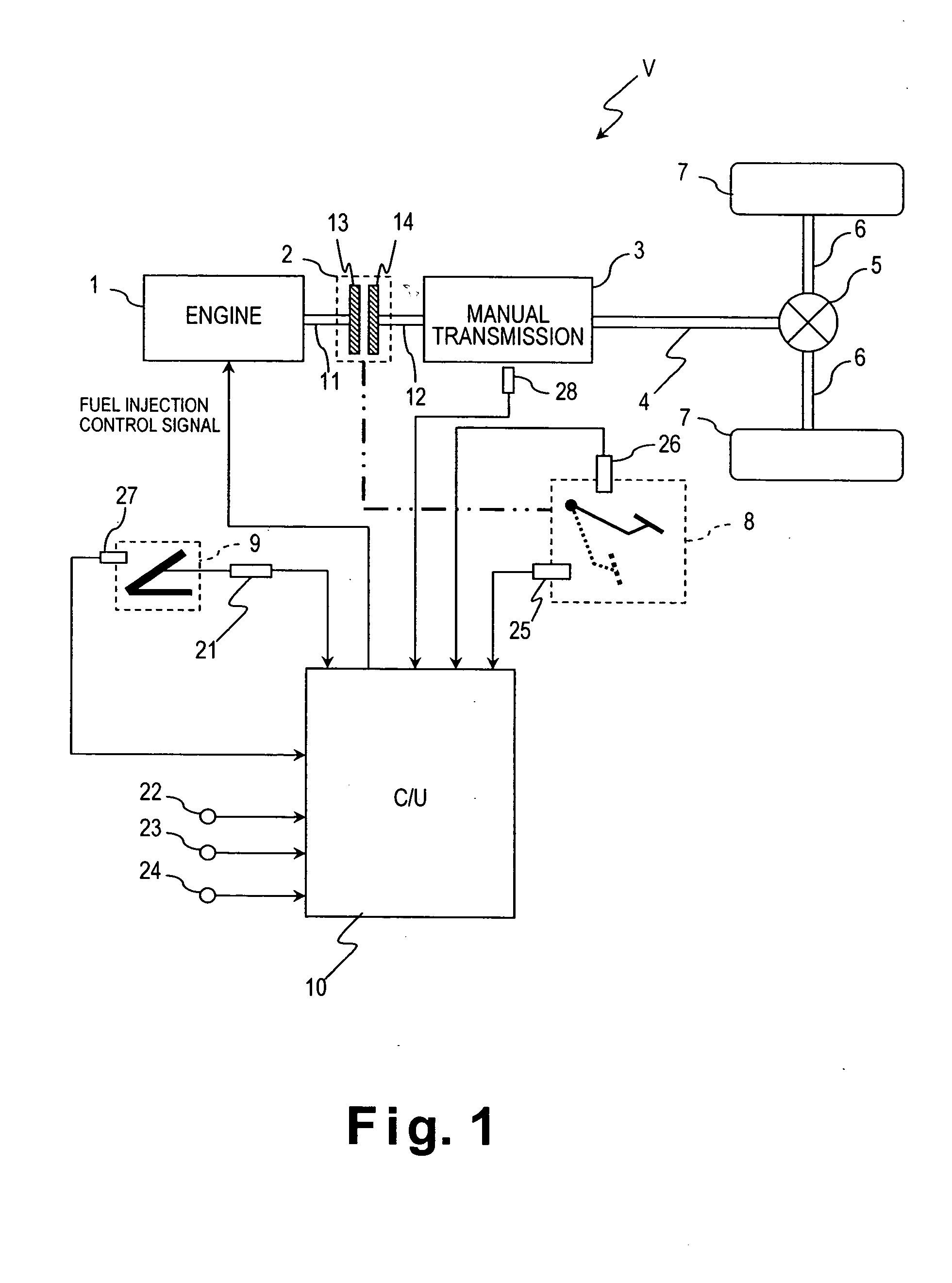

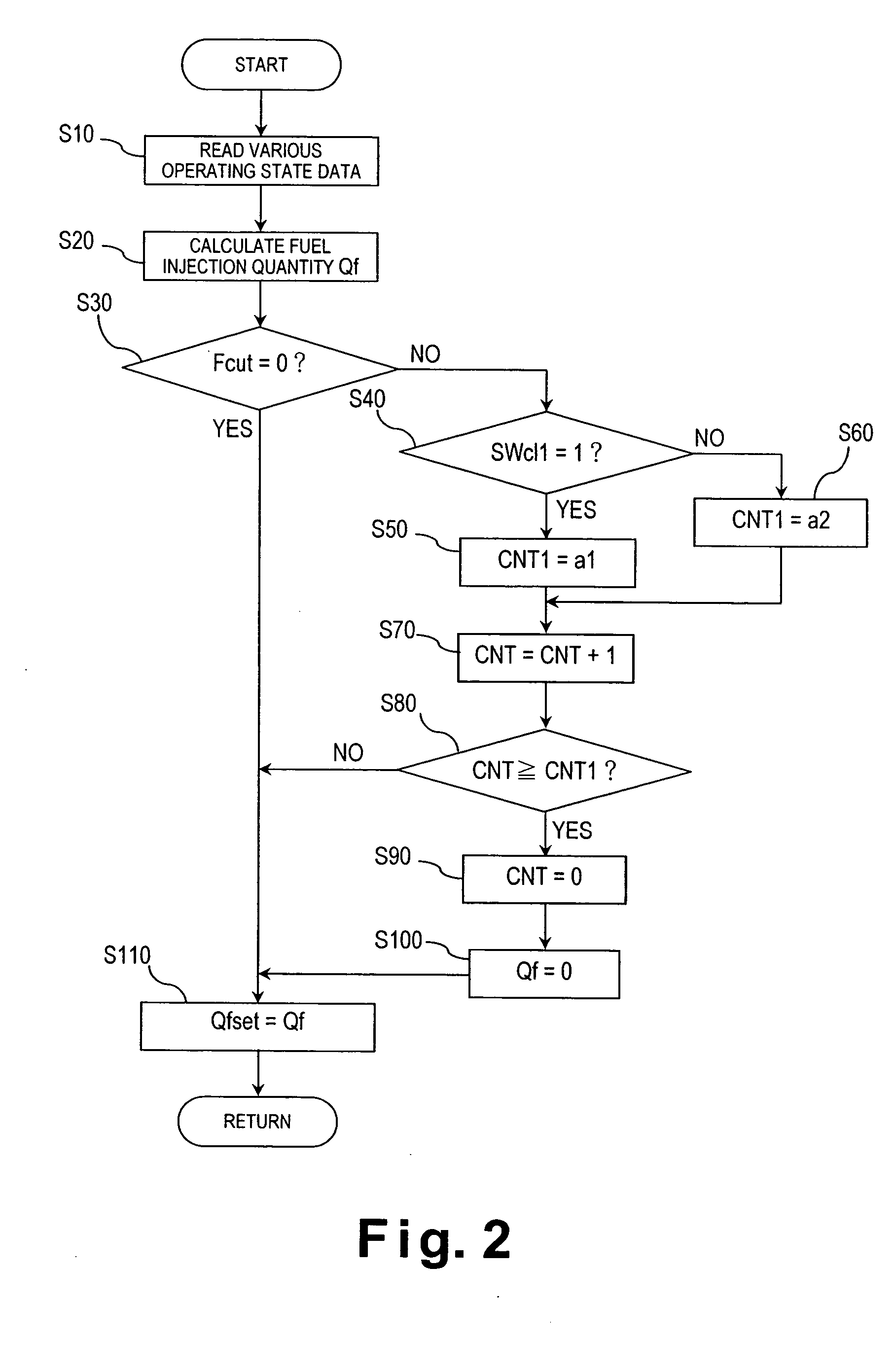

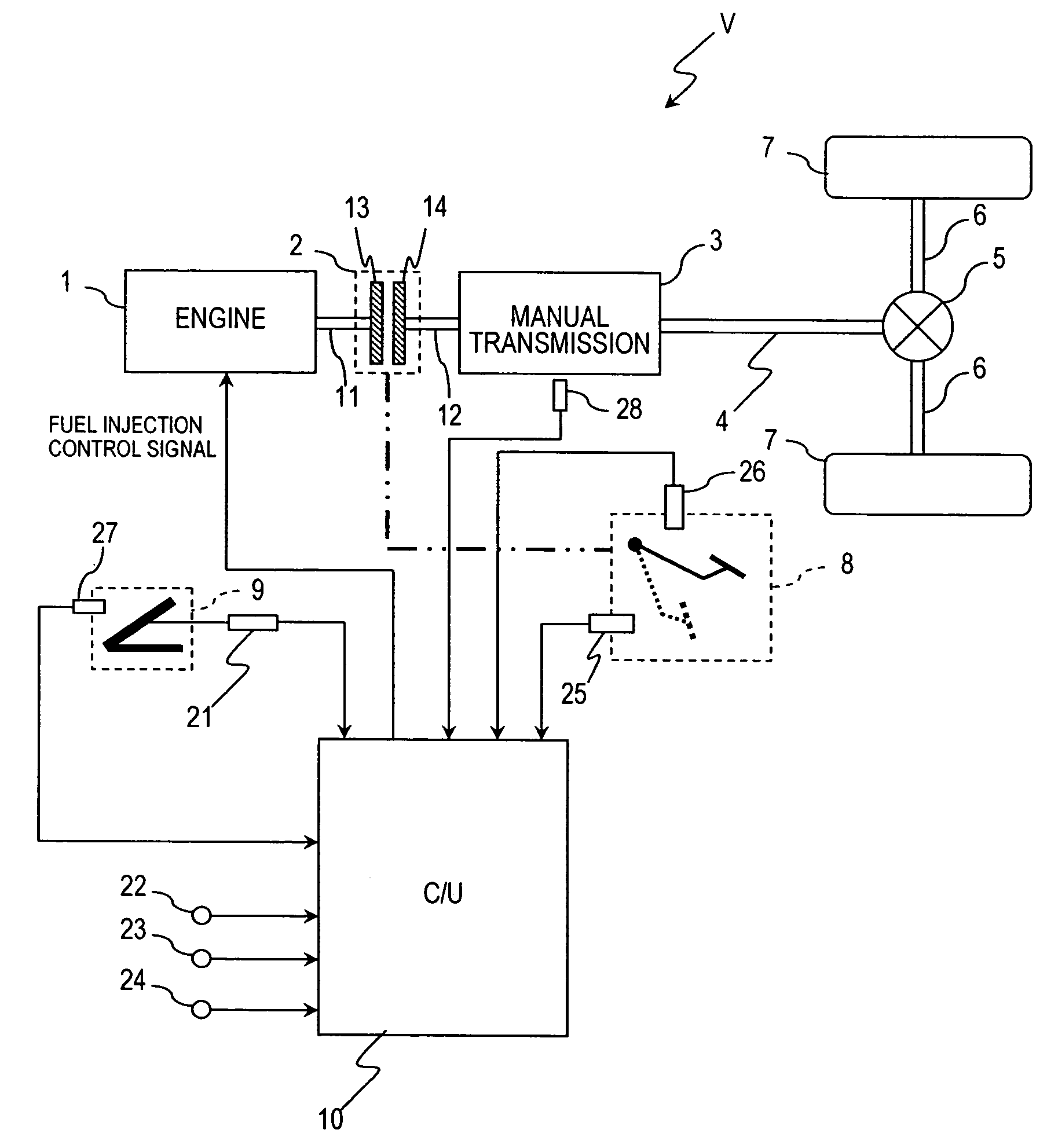

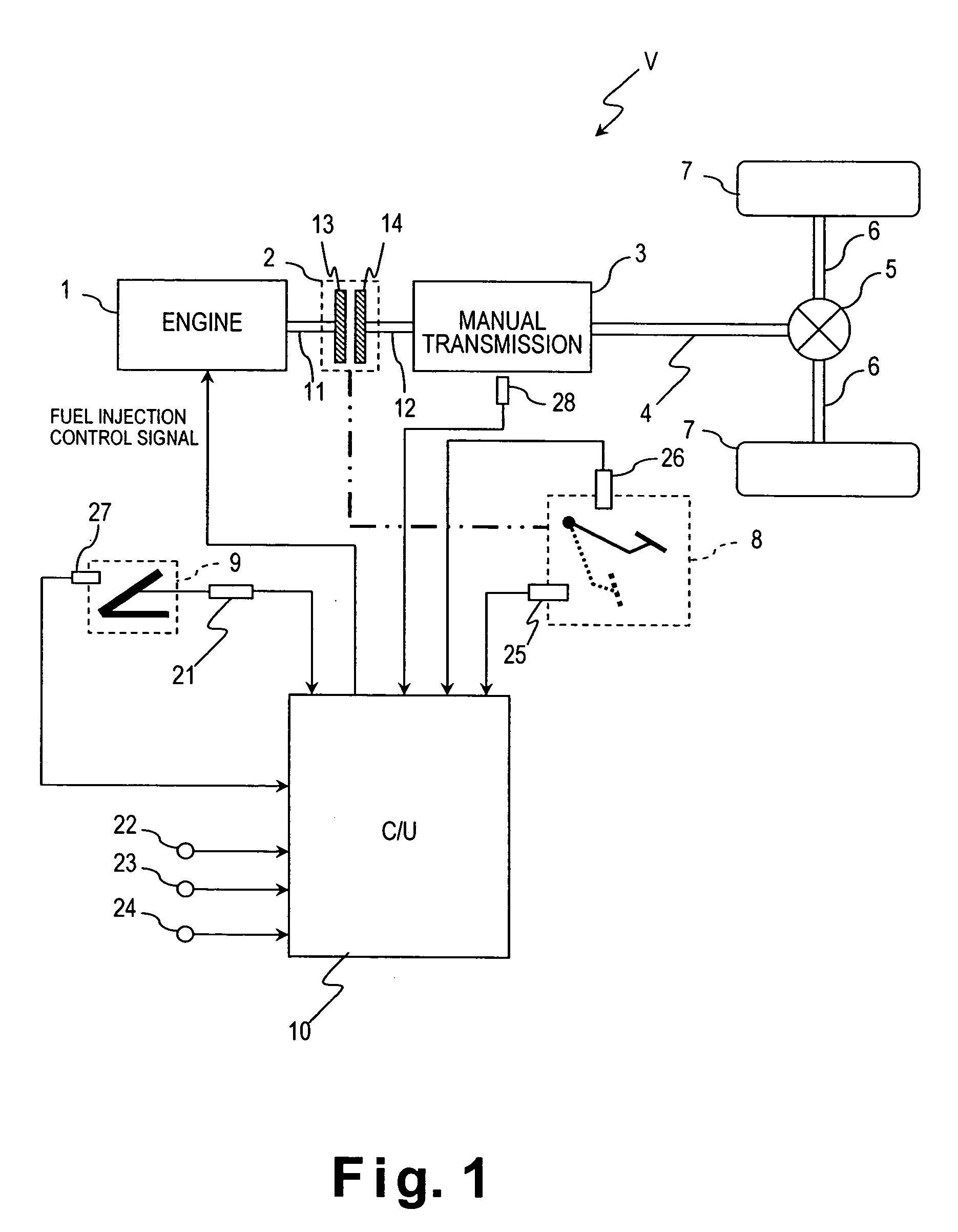

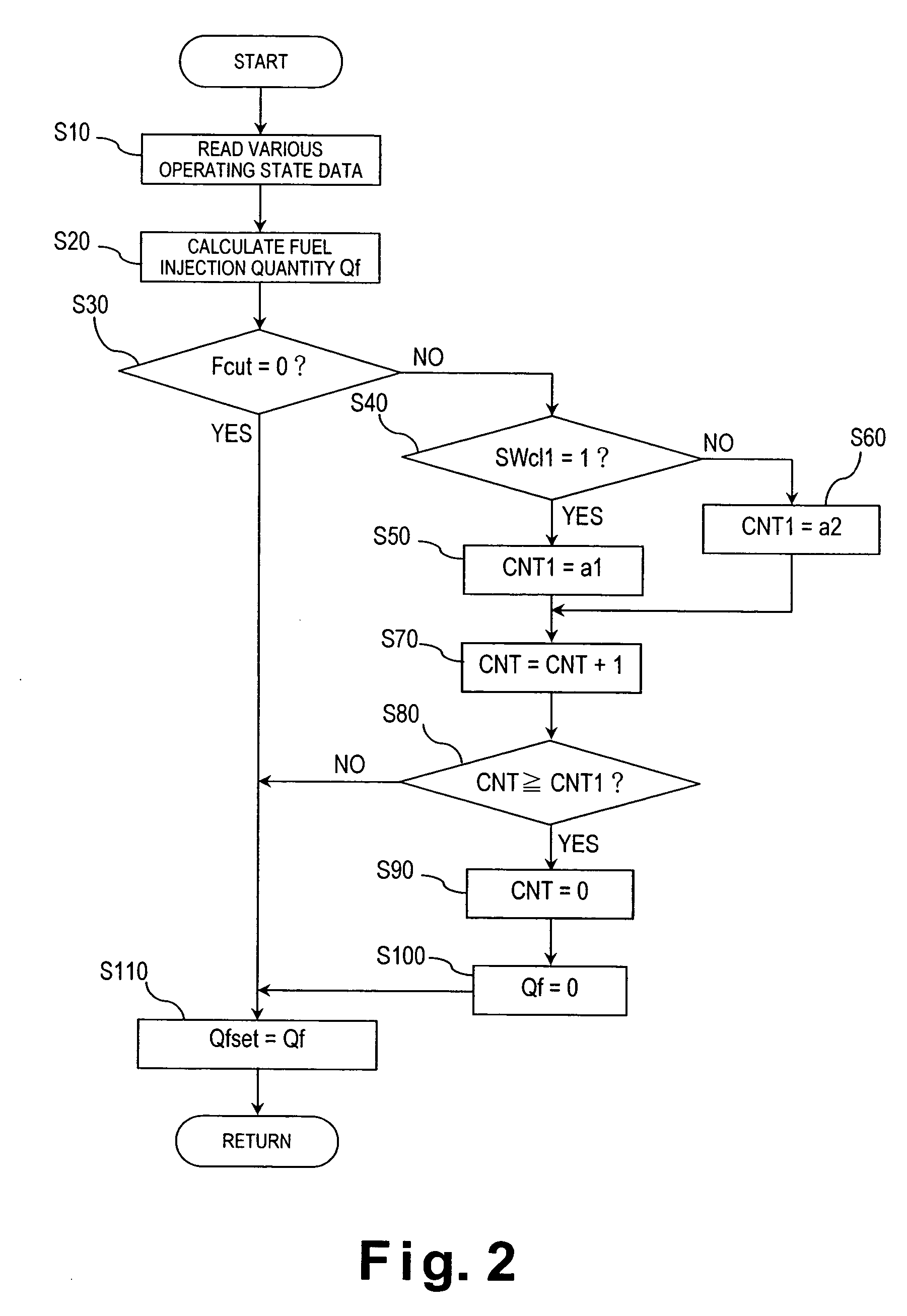

Engine fuel supply control device

InactiveUS20050124460A1Raise engine output and efficiencyLong delay timeElectrical controlConjoint controlClutchFuel supply

An engine fuel supply control device is configured to stop supplying fuel to an engine when specific fuel cut-off condition has been met. The timing of the fuel cut-off is delayed depending on an operating state of the vehicle. Preferably, the engine fuel supply control device has an operating state detection section that detects an operating condition (e.g., a clutch position or a shifting operation), and a fuel supply stoppage section that stops supplying fuel to the engine when a specific delay time has elapsed since the specific fuel cut-off condition was met. Preferably, the fuel supply stoppage section selectively sets the specific delay time to a different delay time depending upon the detected operating condition detection, e.g., a first delay time is set if either the clutch is detected as disengaged or a shifting operation is detected as being in progress, otherwise a different delay time is set.

Owner:NISSAN MOTOR CO LTD

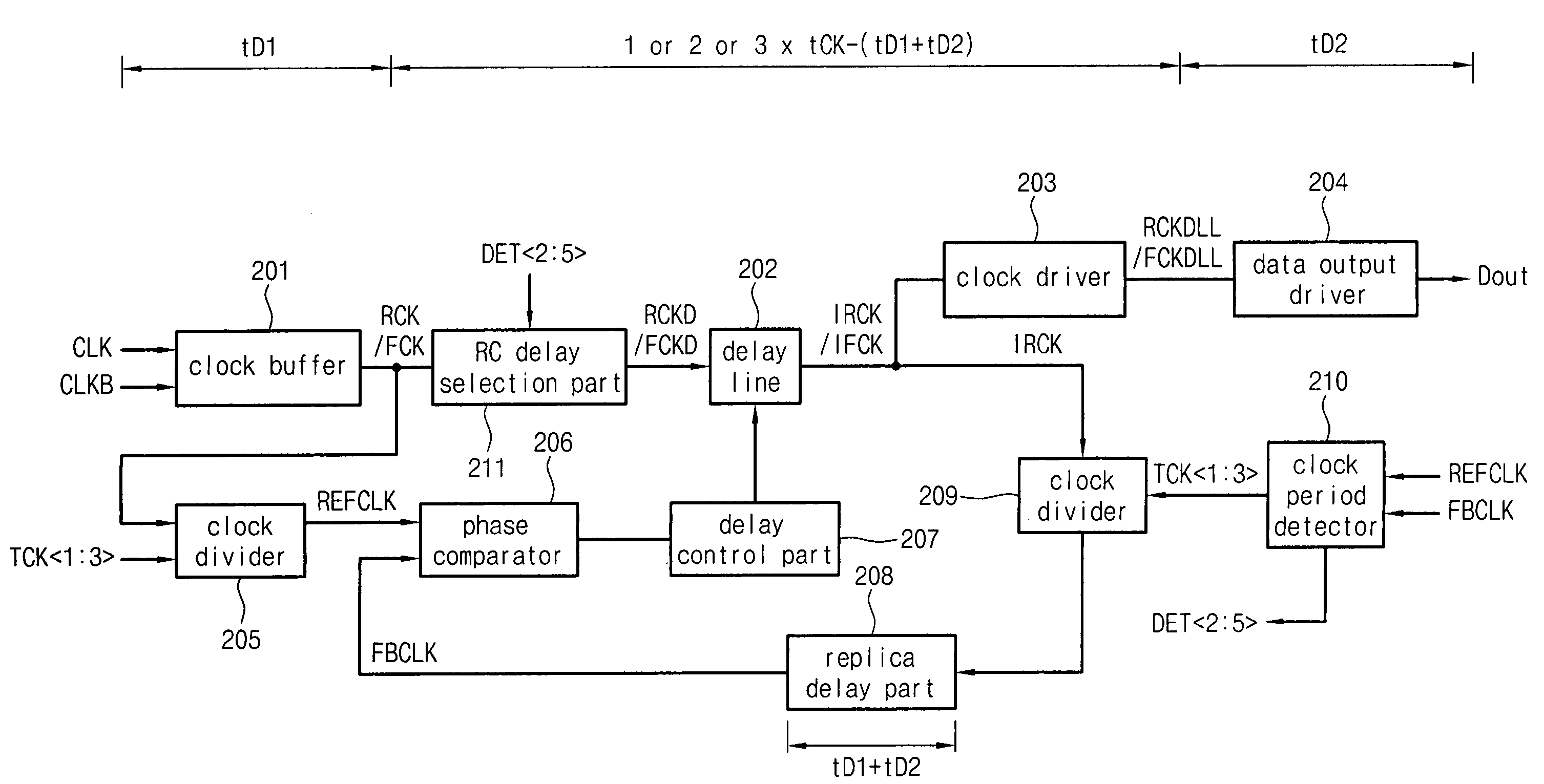

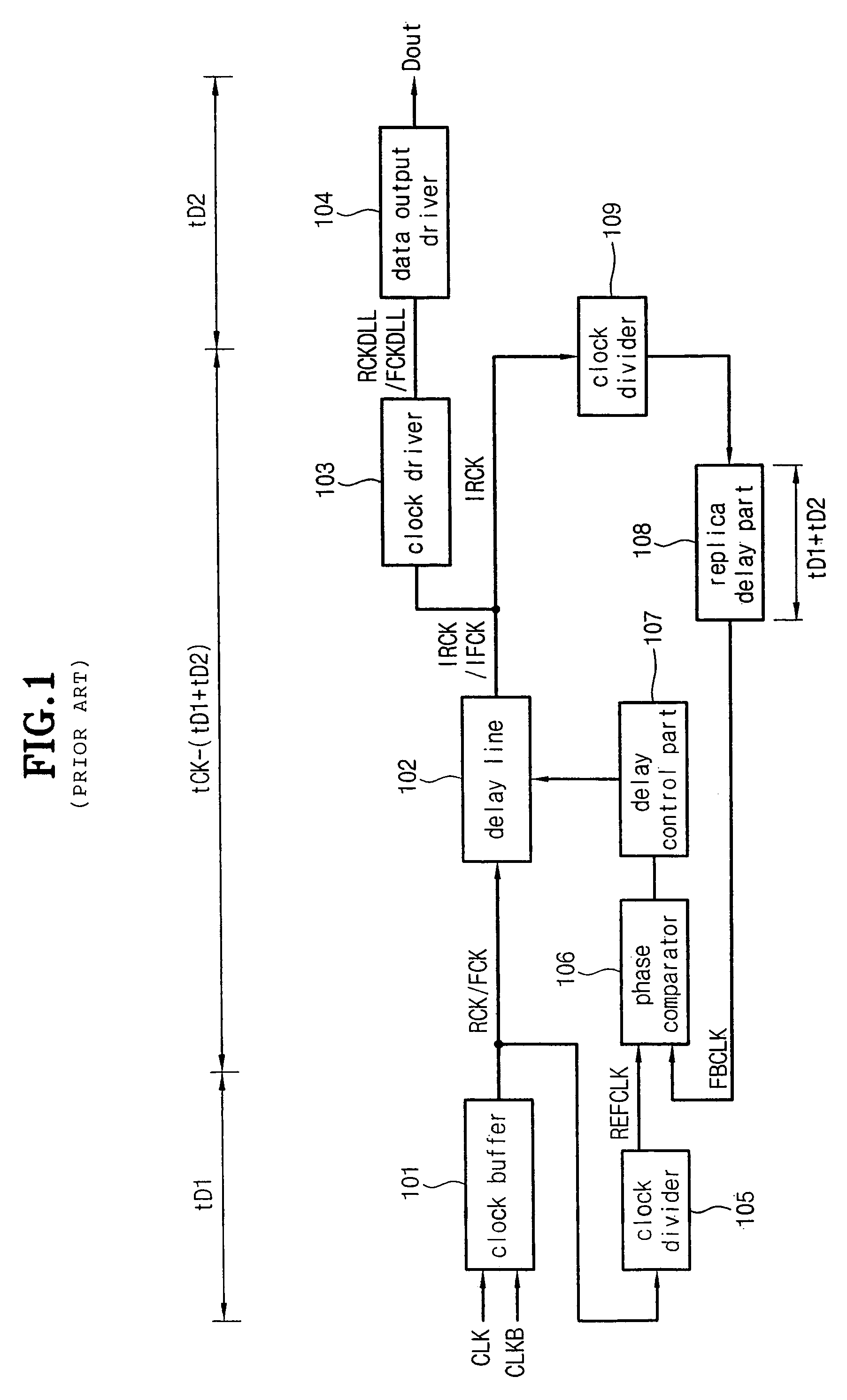

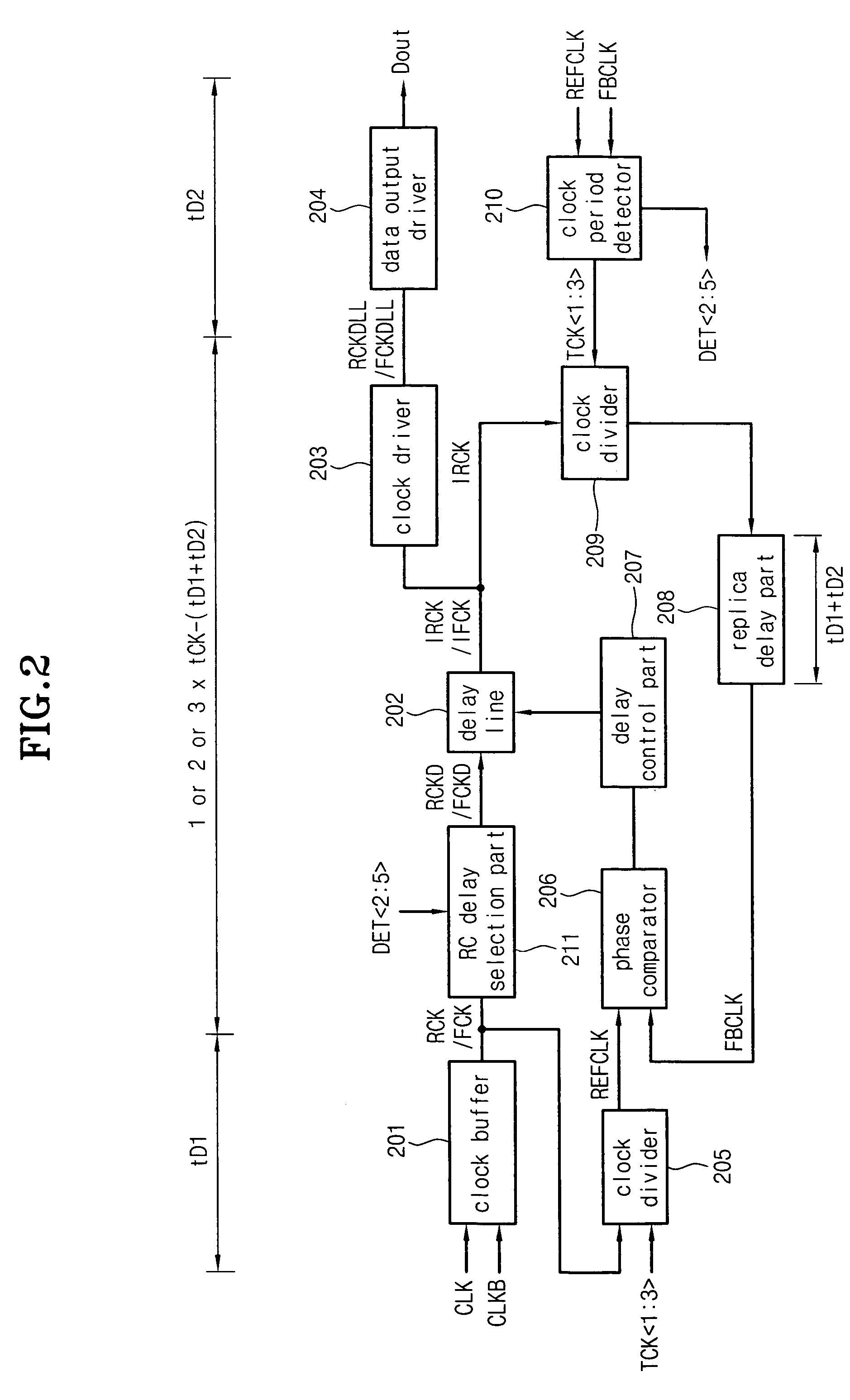

Delay locked loop circuit

ActiveUS7298189B2Quick functionDelay line areaPulse automatic controlSingle output arrangementsDelay-locked loopHigh frequency

The DLL circuit detects a frequency of an external clock signal and adjusts a coarse delay during a DLL circuit operation, thereby quickly terminating a feedback operation of the DLL circuit and having a reduced circuit area of a delay line. Therefore, the DLL circuit can be used for next generation high-integration and high-frequency memory devices such as DDR2 SDRAMs.

Owner:SK HYNIX INC

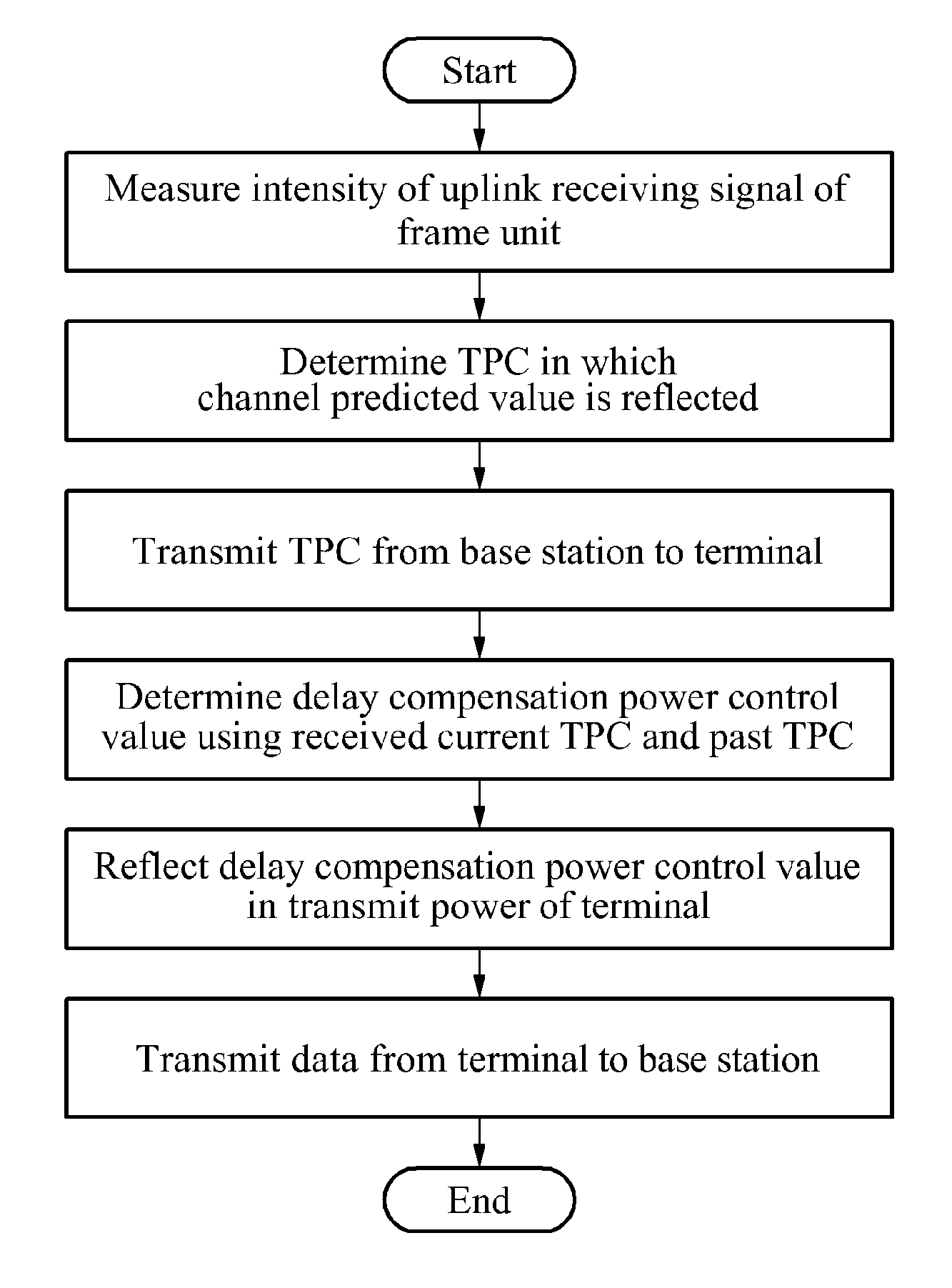

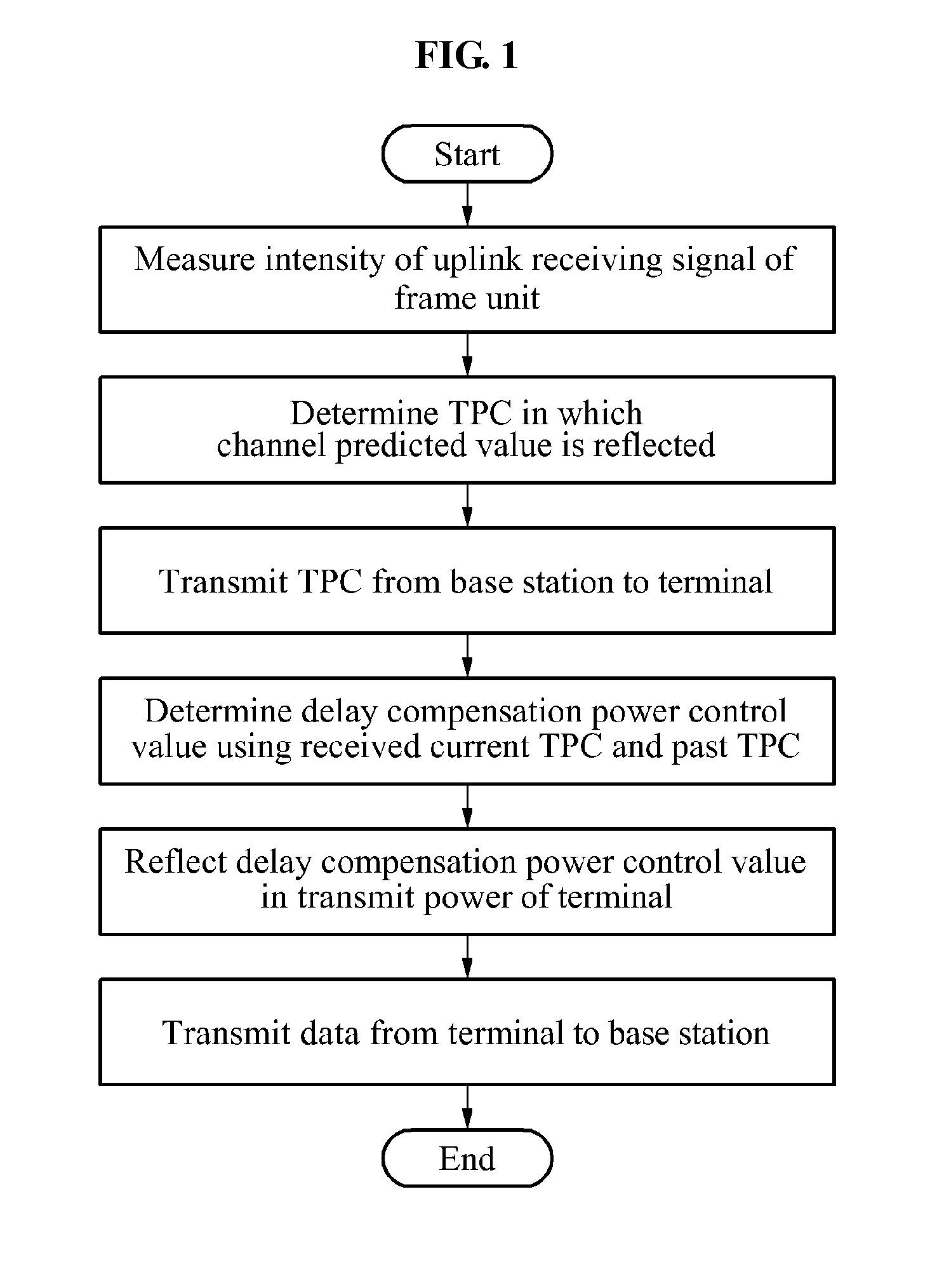

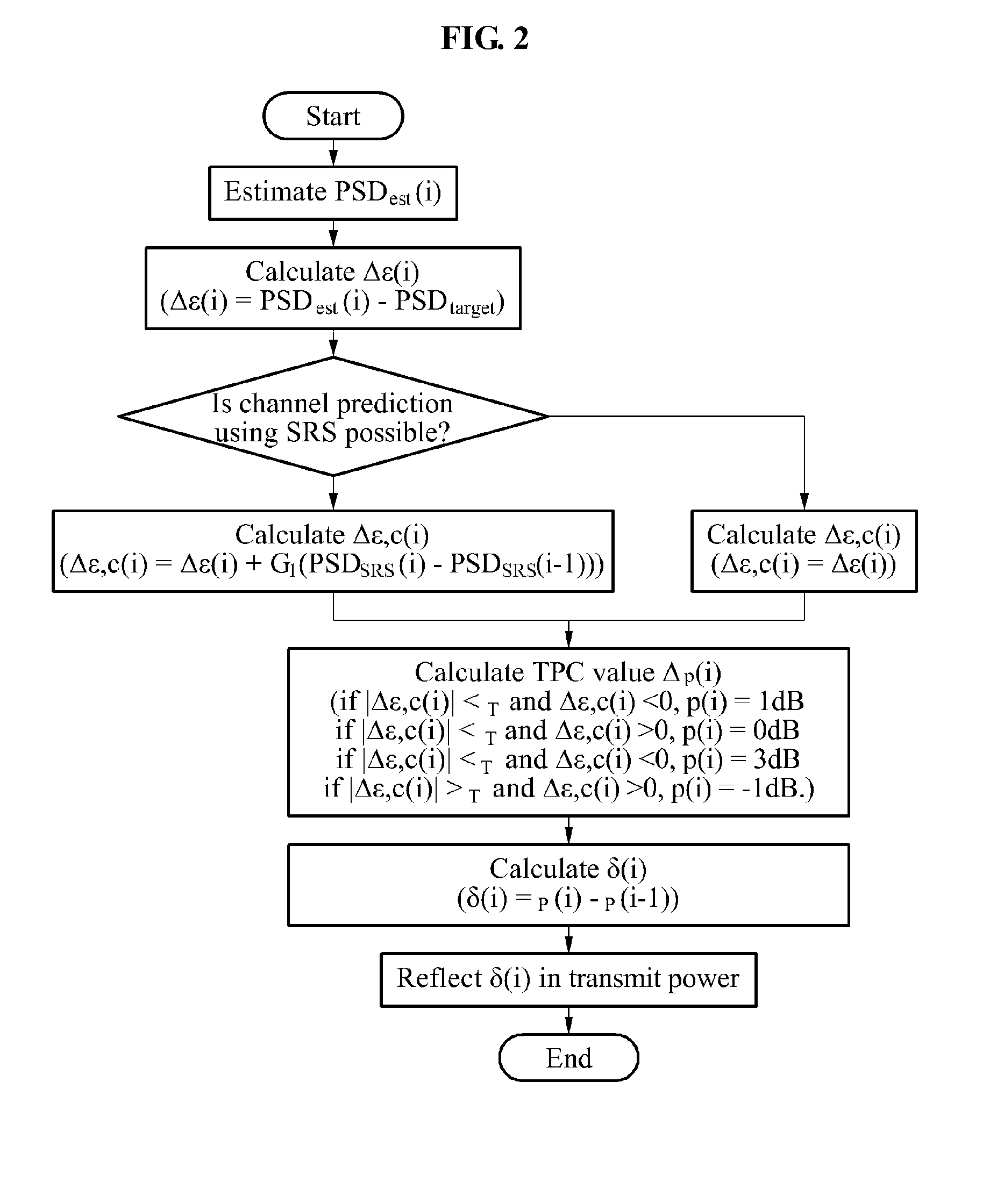

Methods for power control and link adapation in lte-based mobile communication system

InactiveUS20150126239A1Long delay timePower managementRadio transmissionTransmitted powerClosed loop

Provided is a power control and link adaptation method for compensating for a long round trip delay time and slow channel fading in a long term evolution (LTE)-based mobile communication system having a long round trip delay time, similar to a satellite mobile system, the method that may compensate for the long round trip delay time of the satellite mobile system in which a distance between a base station and a terminal is relatively long, when compared to a terrestrial LTE system, support a modulation and coding scheme (MCS) level requested by a terminal, by predicting a channel after the round trip delay time elapses, maintain compatibility within an existing LTE frame, by generating a transmit power control (TPC) instruction for an uplink closed-loop power control, on a frame by frame basis, and compensate for slow channel fading of the satellite mobile system.

Owner:ELECTRONICS & TELECOMM RES INST

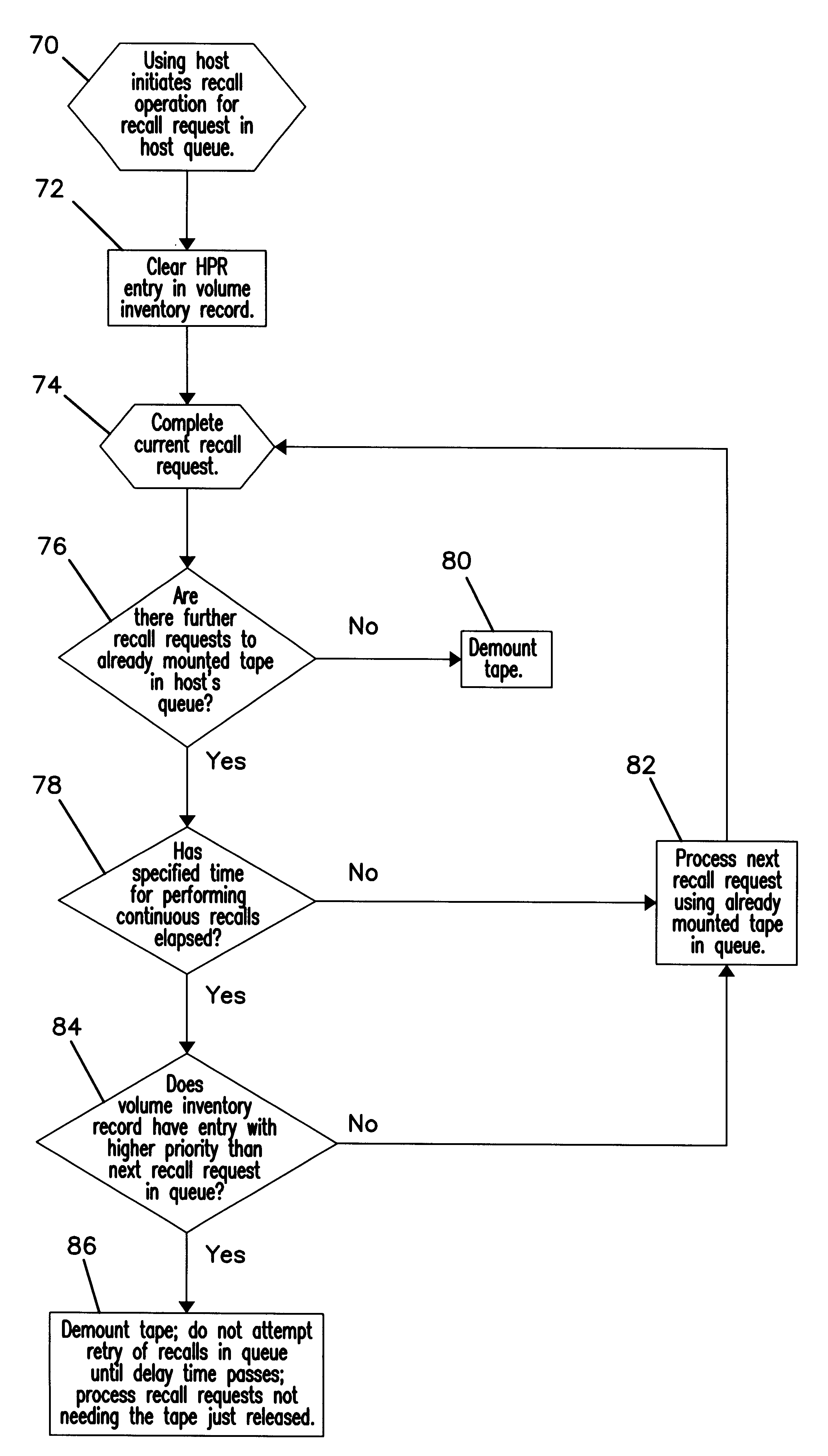

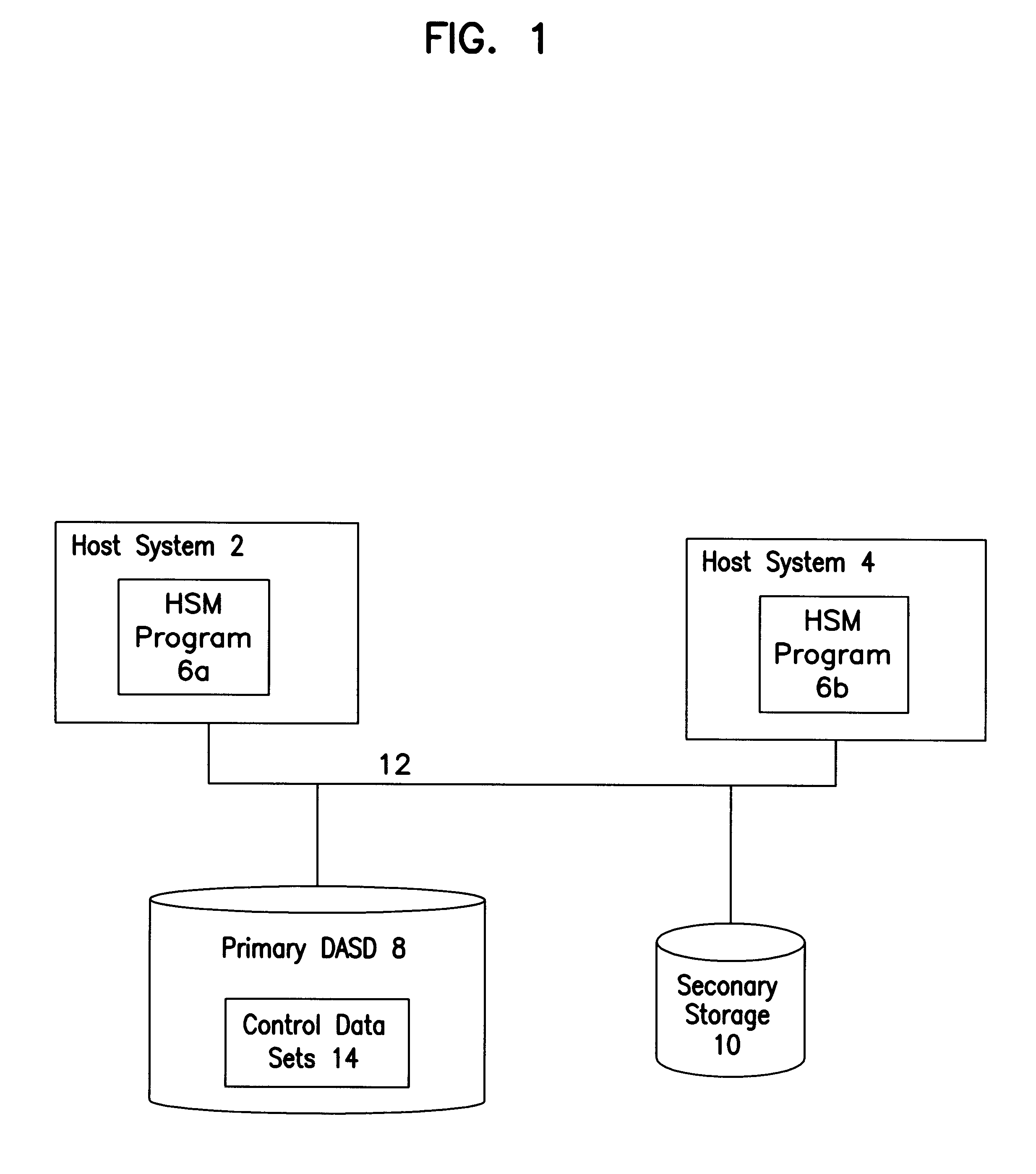

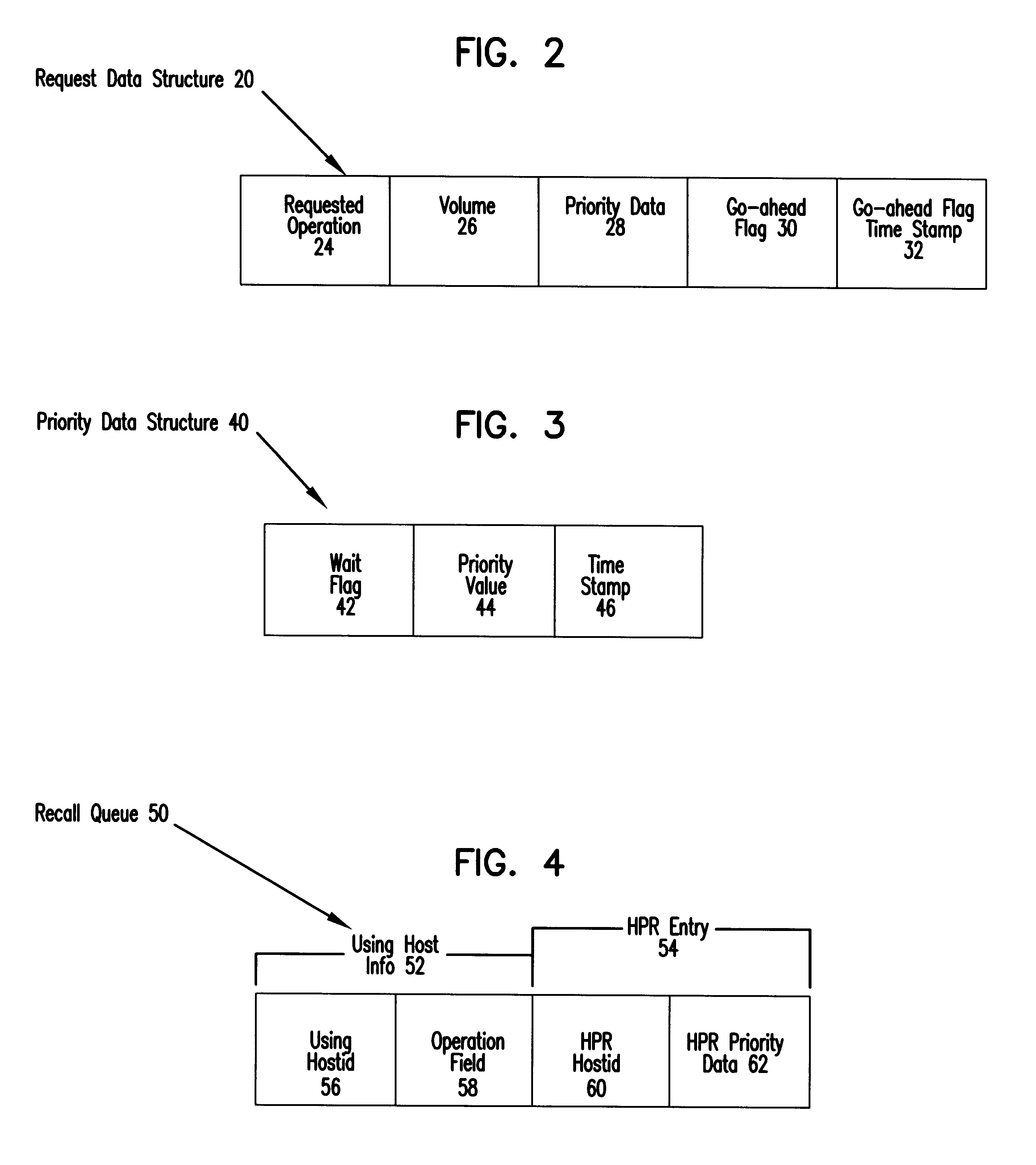

System using priority data of a host recall request to determine whether to release non-volatile storage with another host before processing further recall requests

InactiveUS6272605B1Raise priorityLong delay timeInput/output to record carriersDigital computer detailsMagnetic tapeSystem usage

Disclosed is a system for handling recall requests for data maintained in a storage device accessible to multiple systems. Initially, a storage device is allocated to the first host system to process recall requests in a recall queue including a plurality of recall requests. A second host recall request is initiated with the second host system to recall data from the storage device. The second host system determines whether the storage device is allocated to the first host system. If so, the second host systems stores priority data in a common or shared data structure indicating a priority of the second host recall request after determining that the storage device is allocated to the first host system. The first host system then conditionally releases the storage device before processing all the recall requests needing the subject tape in its queue to make the storage device available if the priority in the common data structure is higher than its own highest priority request. The second host system retries the second host recall request after the first host system releases the storage device. The second host system then determines whether the storage device is available and whether the highest priority second host recall request is greater than or equal to the priority data indicated in the data structure when retrying the second host recall request. The storage device is allocated to the second host system to process the second host recall request after determining that the storage device is available and that the priority of the second host recall request is greater than or equal to the priority data indicated in the data structure.

Owner:IBM CORP

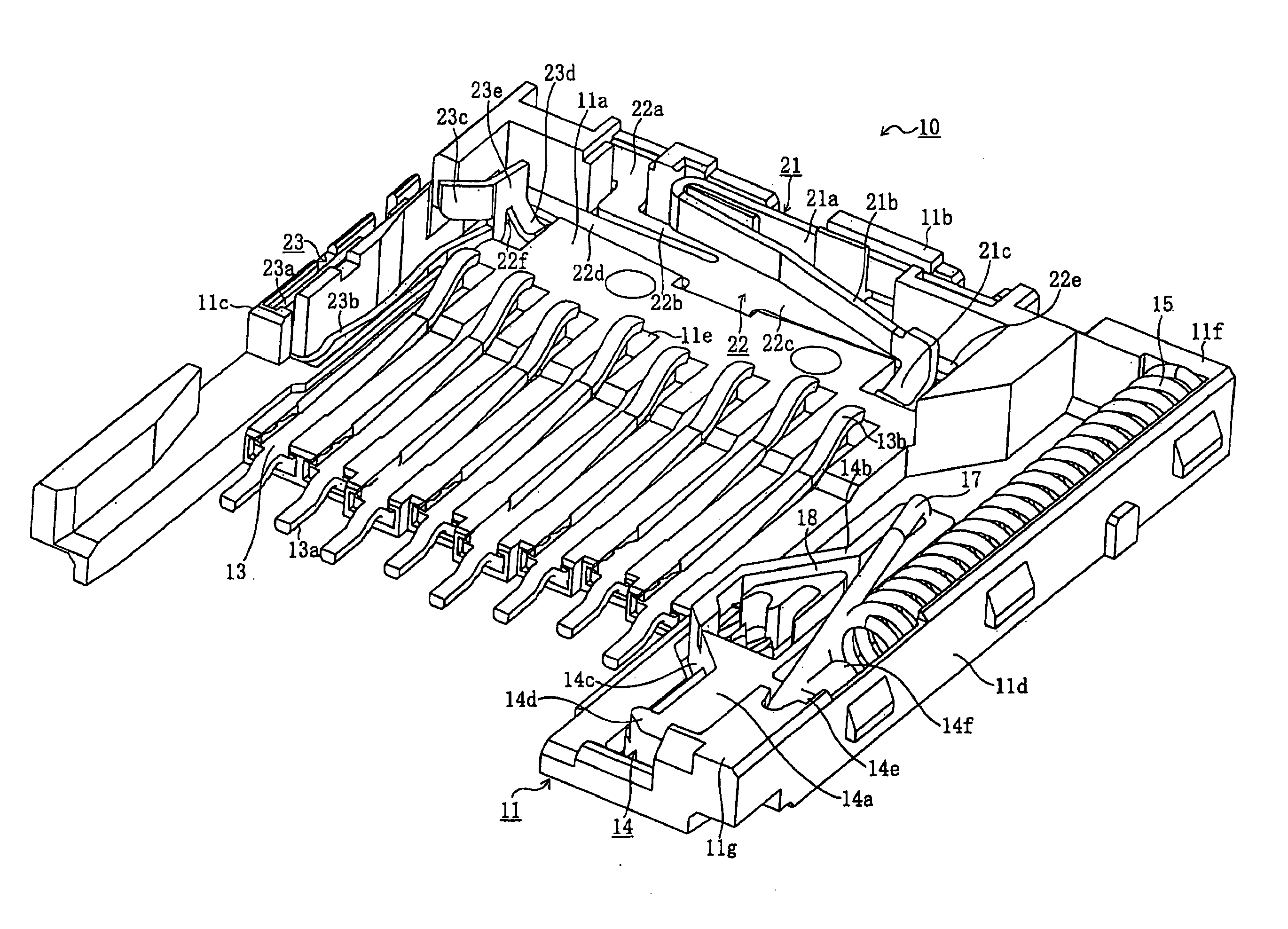

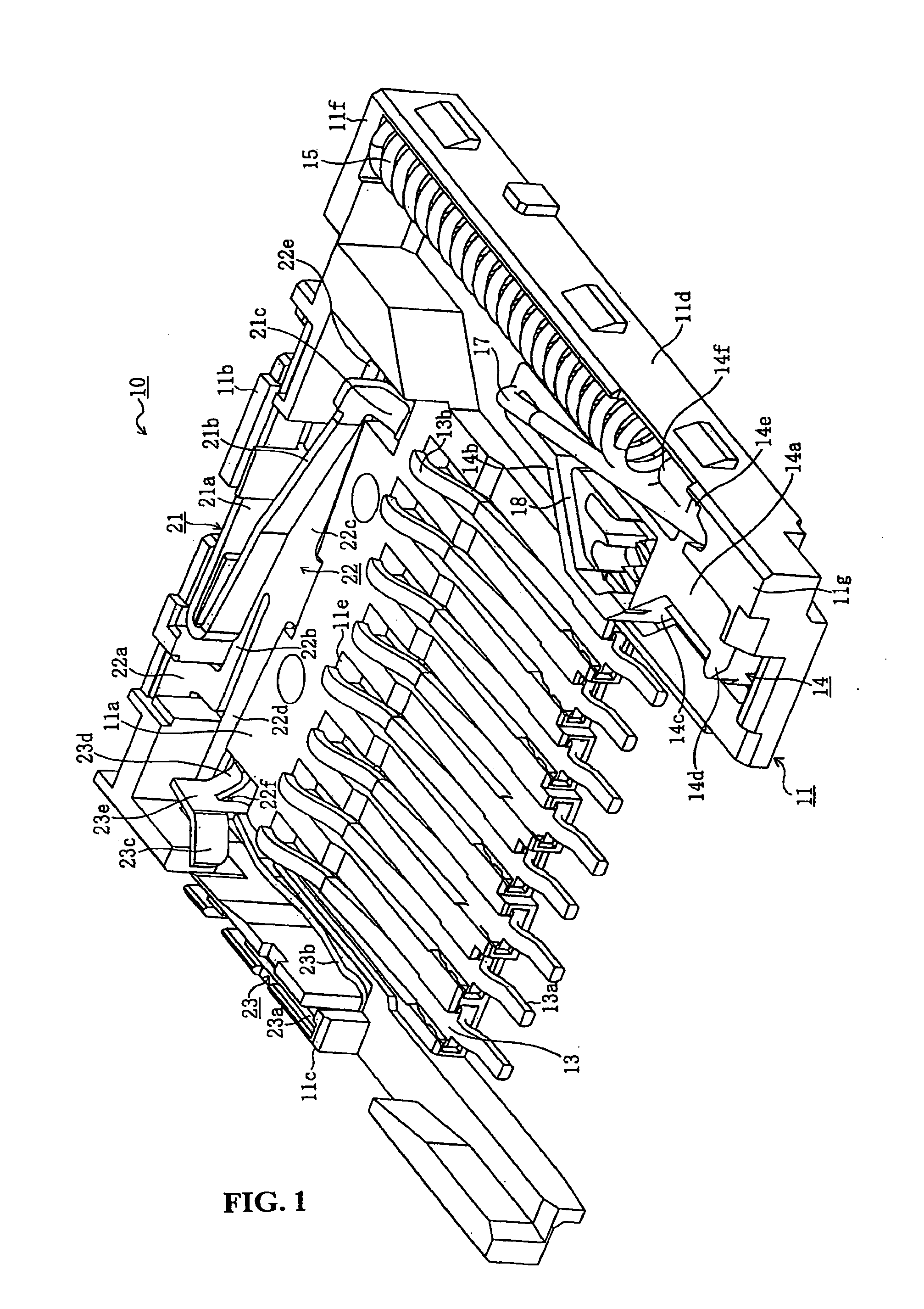

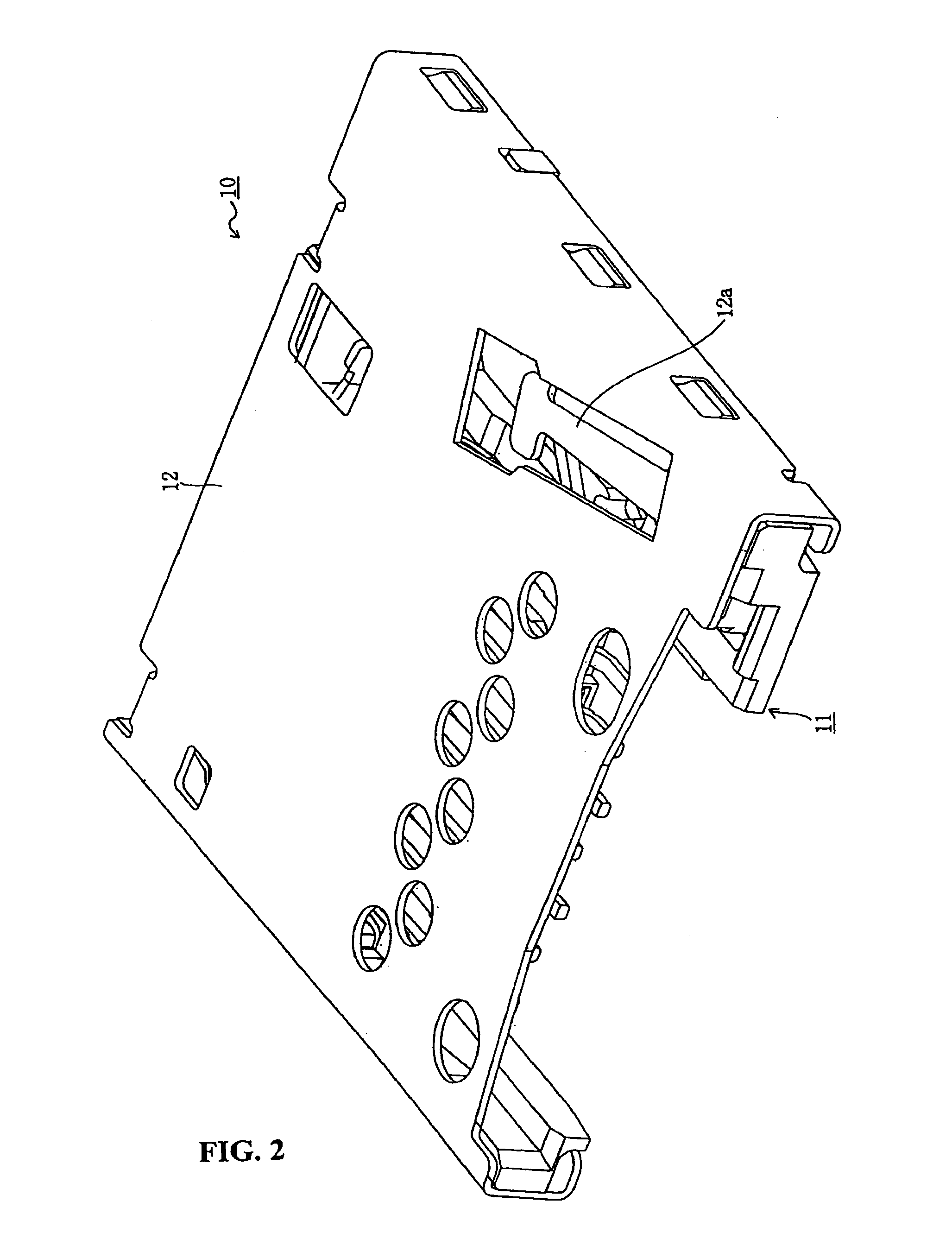

Card connector with double cam

InactiveUS20100159724A1Simple structureReduce manufacturing costEngagement/disengagement of coupling partsConveying record carriersEngineeringCam

A card connector includes a housing having a receptacle to receive therein a card in an insertion direction and the card has a terminal member. A connection terminal is secured to the housing and is configured to contact the terminal member of the card. A card ejecting action detecting switch is configured to detect when the card is ejected from the housing. A card guide mechanism is provided with an urging member for urging the card in a direction opposite the insertion direction. The card guide mechanism is configured to hold the card at a locked position to ensure that the terminal member of the card is in contact with the connection terminal and to permit movement of the card in the opposite direction by a pushing force exerted on the card in the insertion direction. The card guide mechanism ejects the card after performing a pushing action on the card a plurality of times.

Owner:MOLEX INC

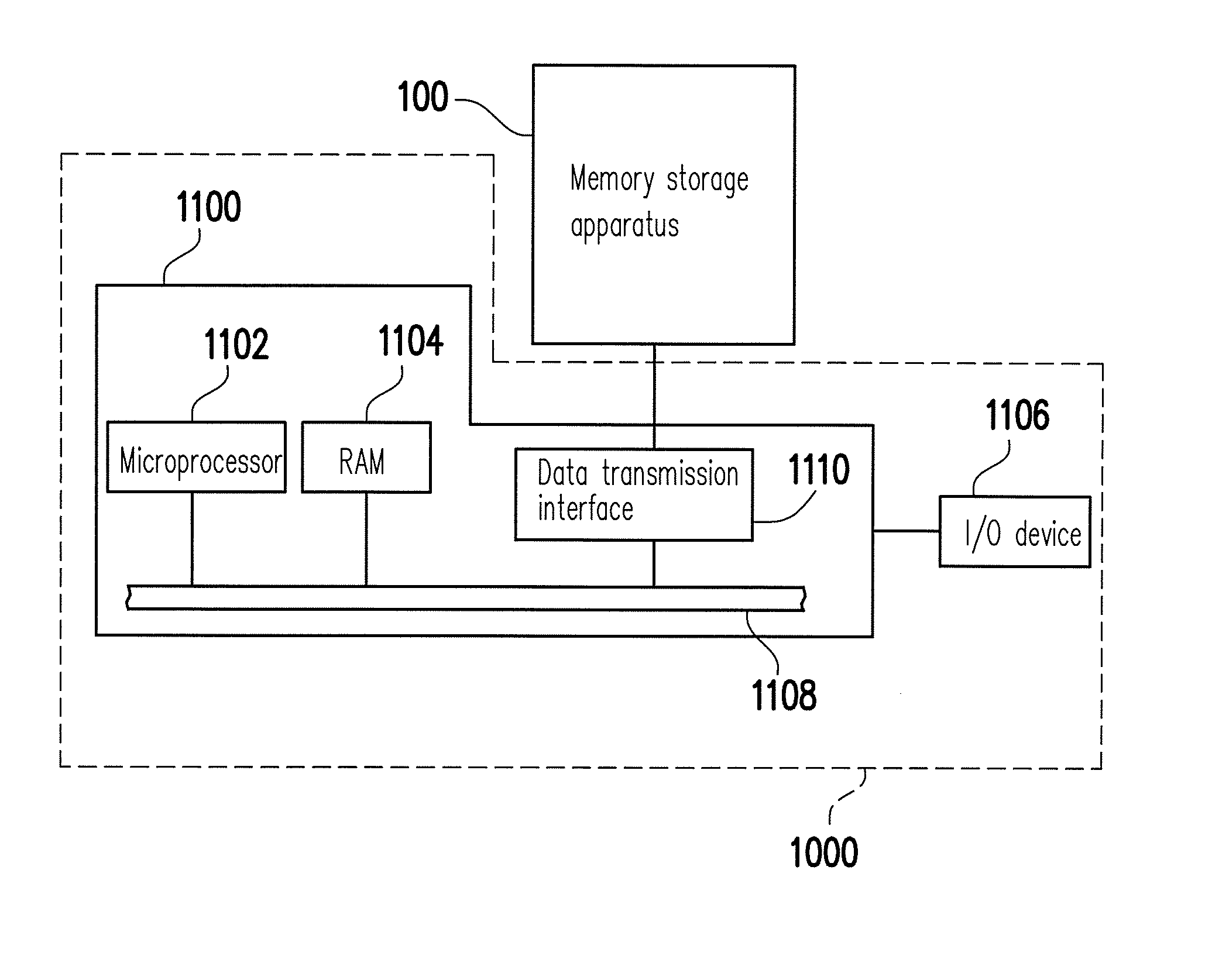

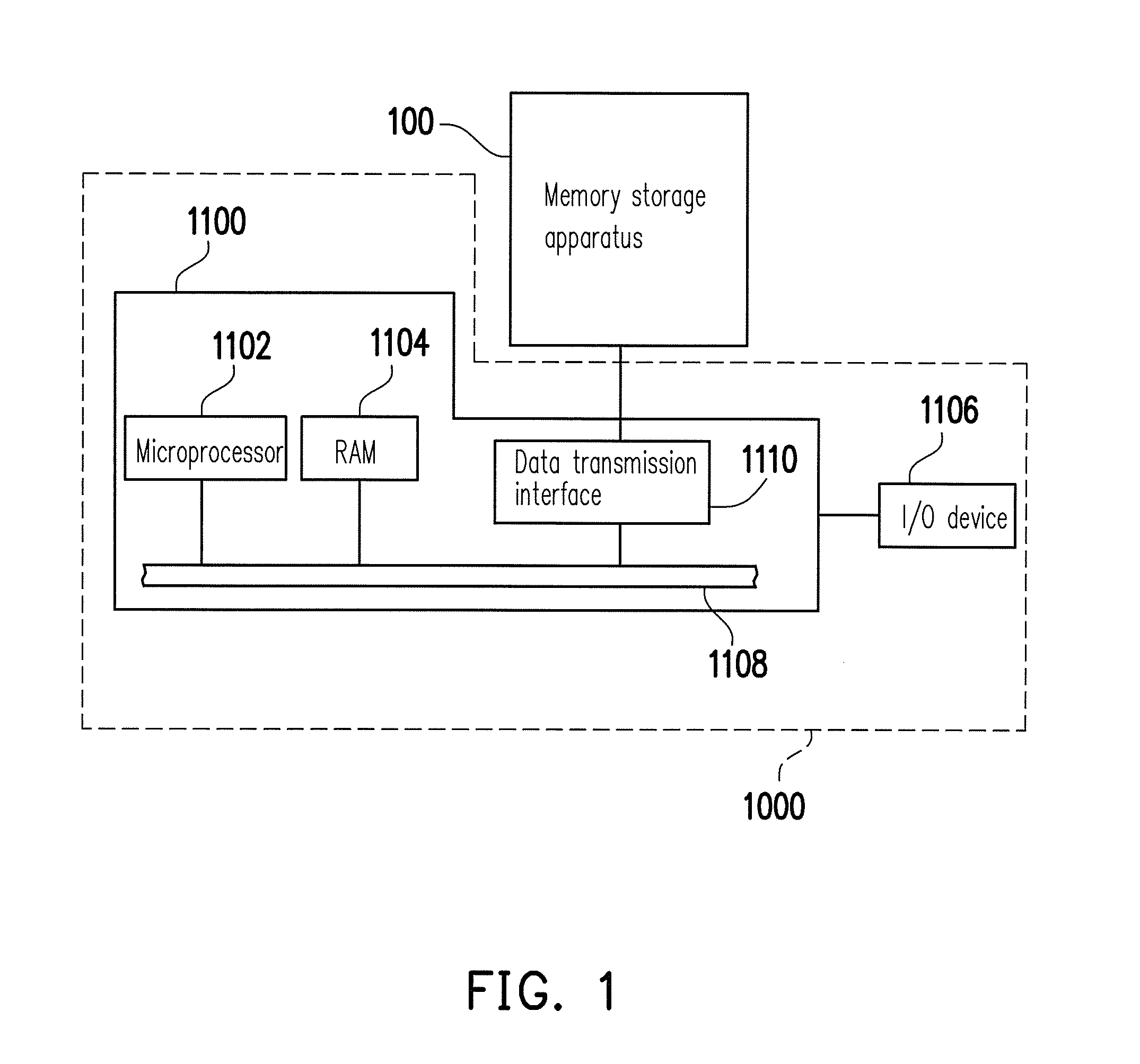

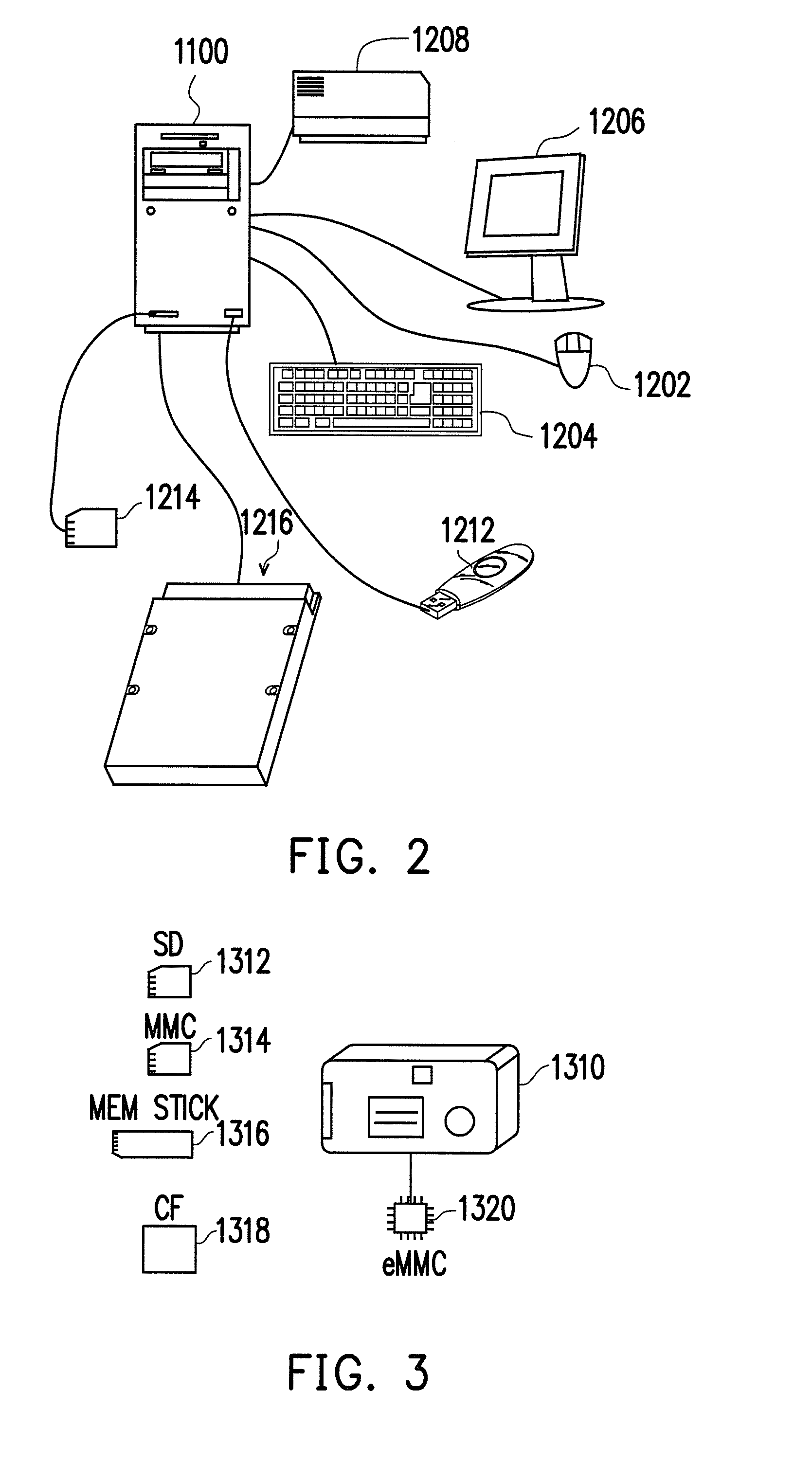

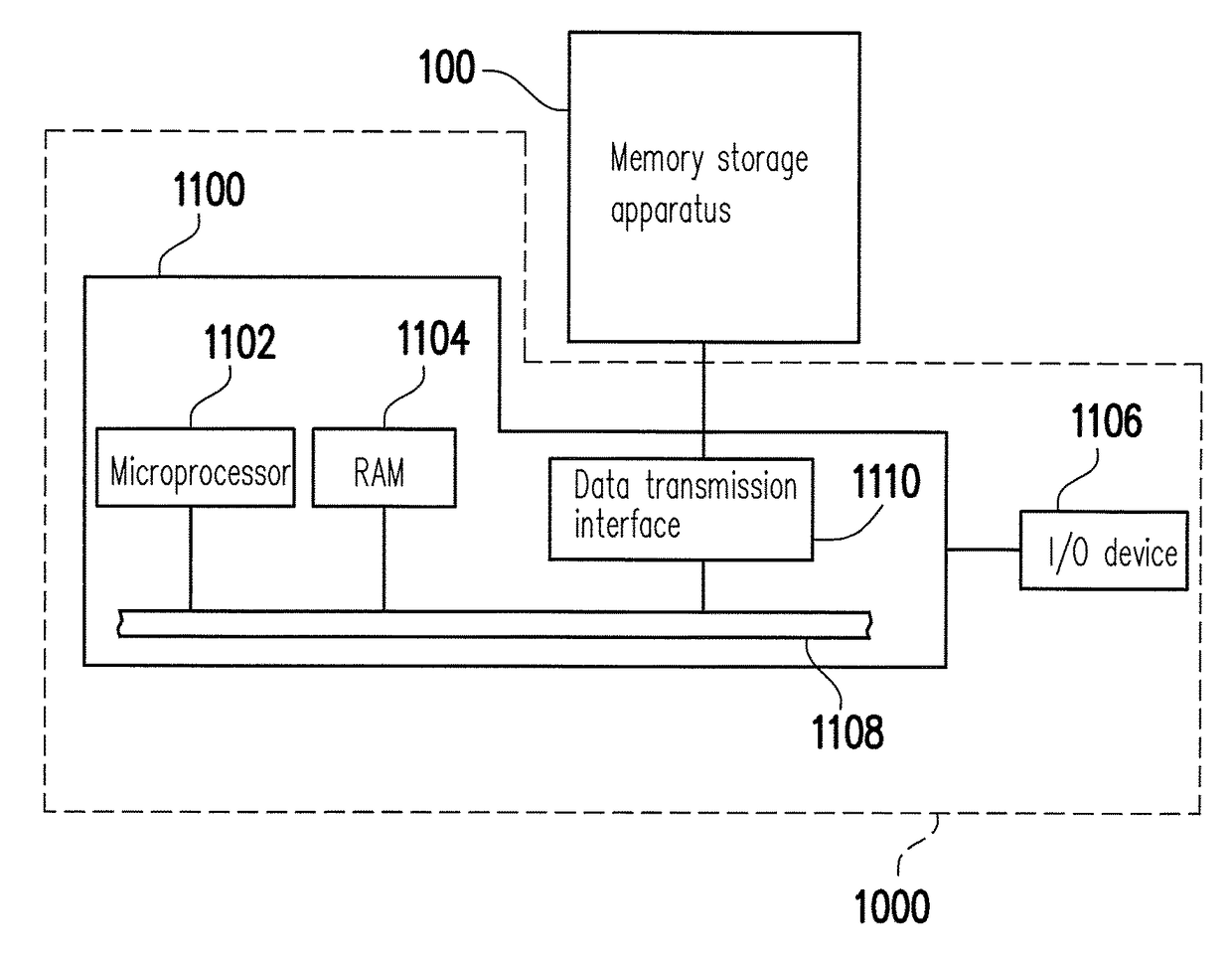

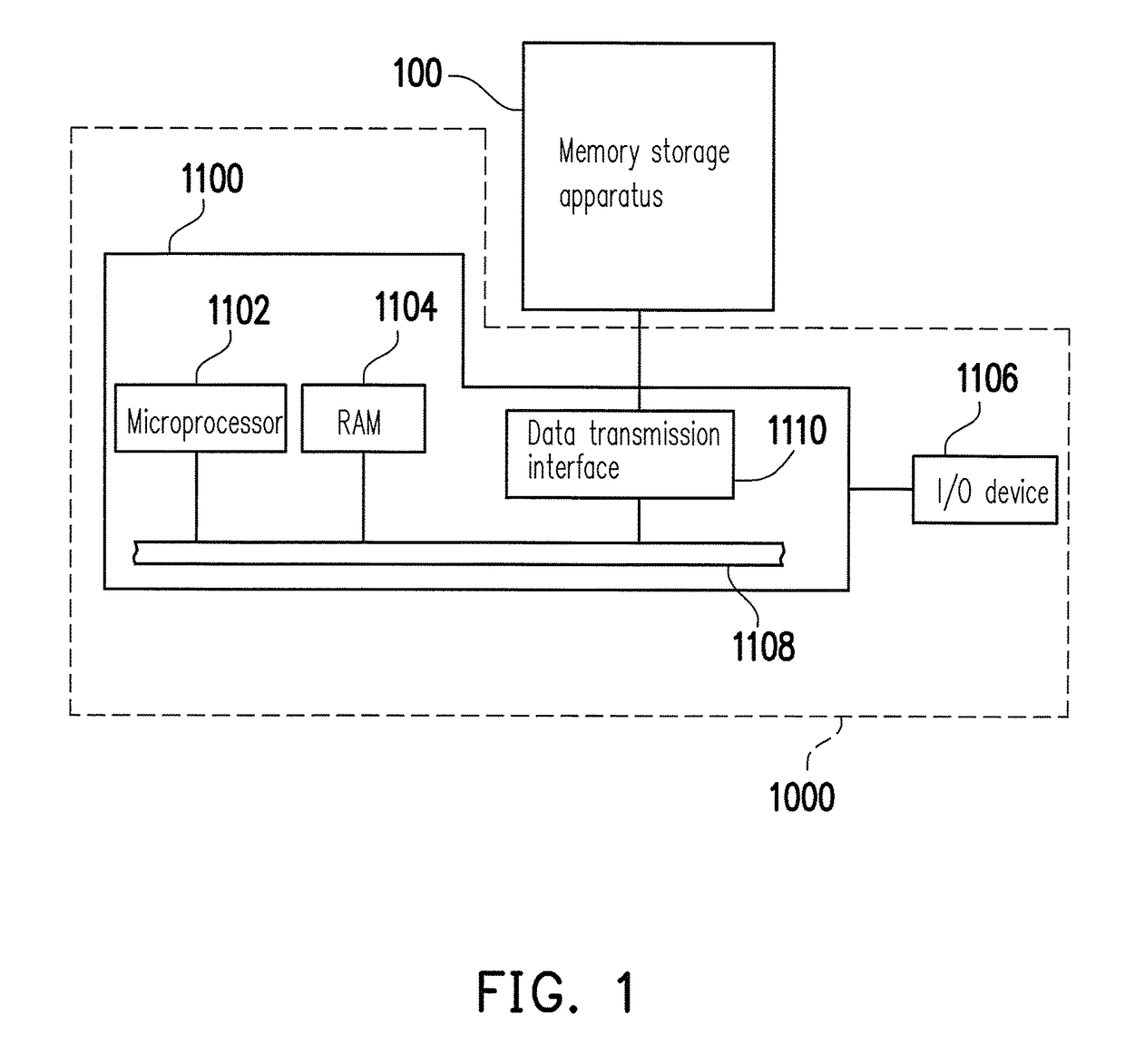

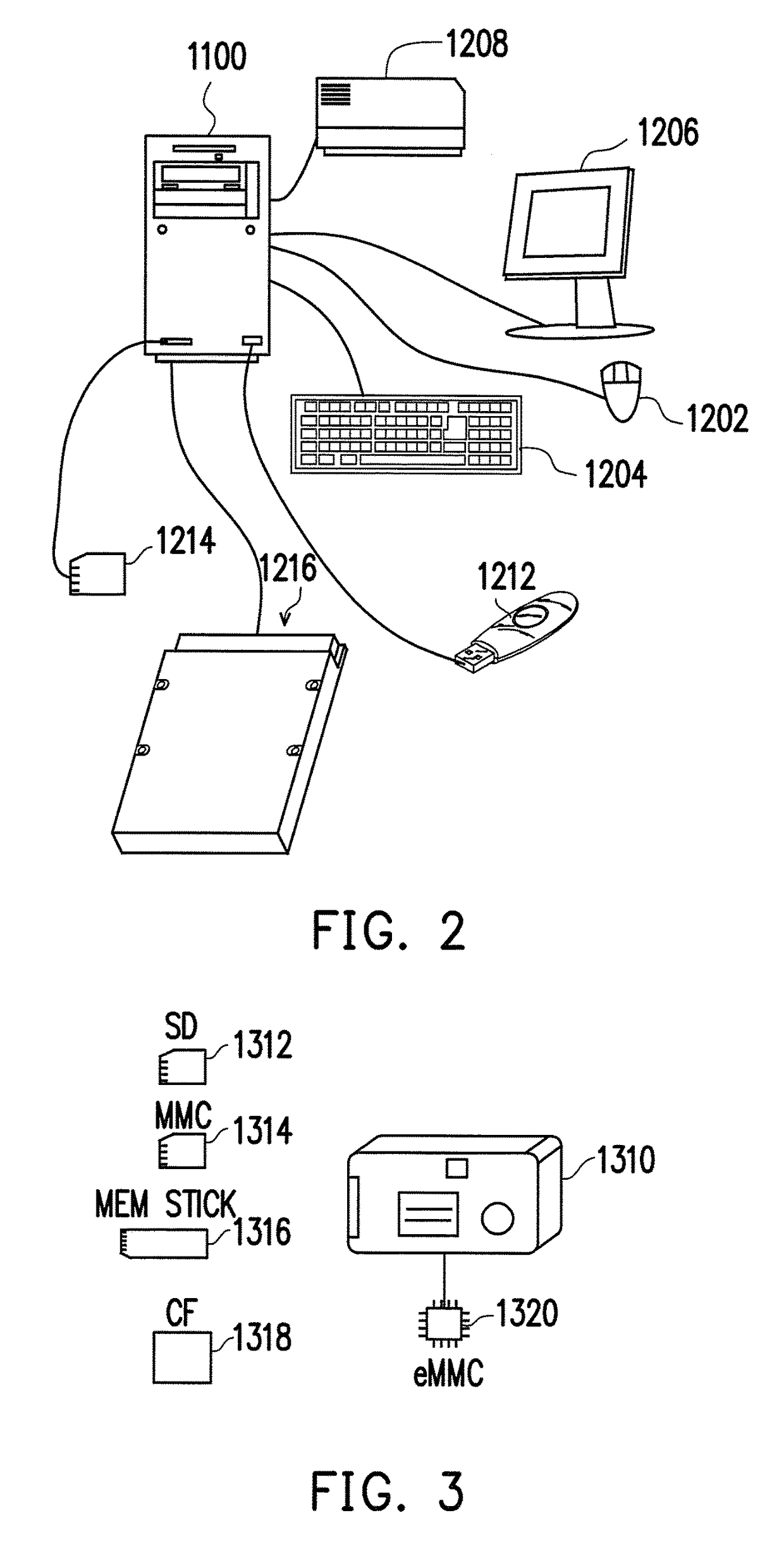

Valid data merging method, memory controller and memory storage apparatus

ActiveUS20170038977A1Reduce delaysEfficient solutionMemory architecture accessing/allocationInput/output to record carriersComputer hardwareMemory controller

A valid data merging method, a memory controller and a memory storage apparatus are provided. The method includes: selecting a first physical erasing unit, and loading a first logical address-physical address mapping table according to a physical address-logical address mapping table. The method also includes: updating the first logical address-physical address mapping table according to the physical address-logical address mapping table, and identifying valid data in the first physical erasing unit according to the physical address-logical address mapping table and the first logical address-physical address mapping table. The method further includes: storing the first logical address-physical address mapping table, copying the valid data to a second physical erasing unit, and performing an erasing operation for the first physical erasing unit.

Owner:PHISON ELECTRONICS

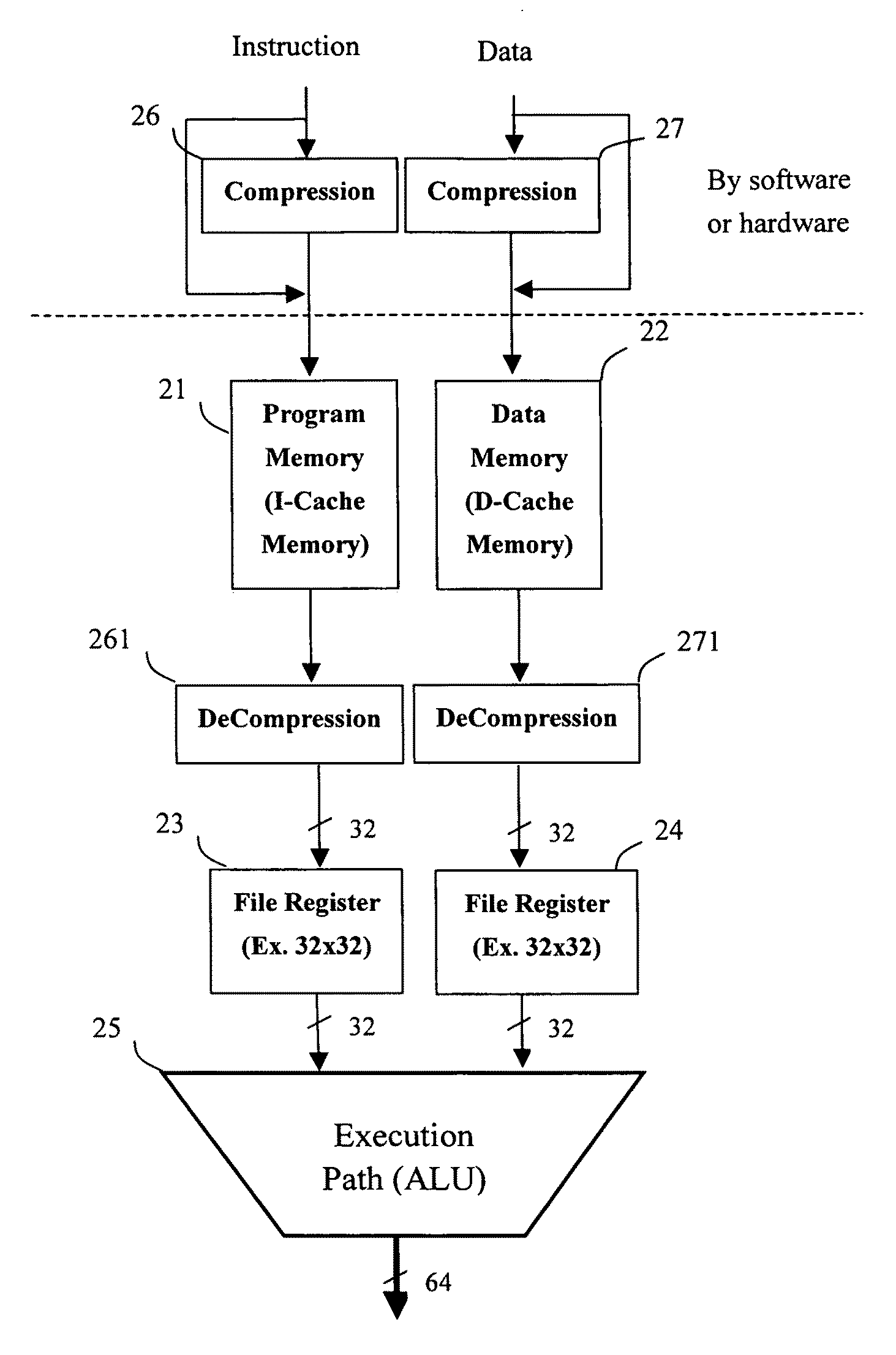

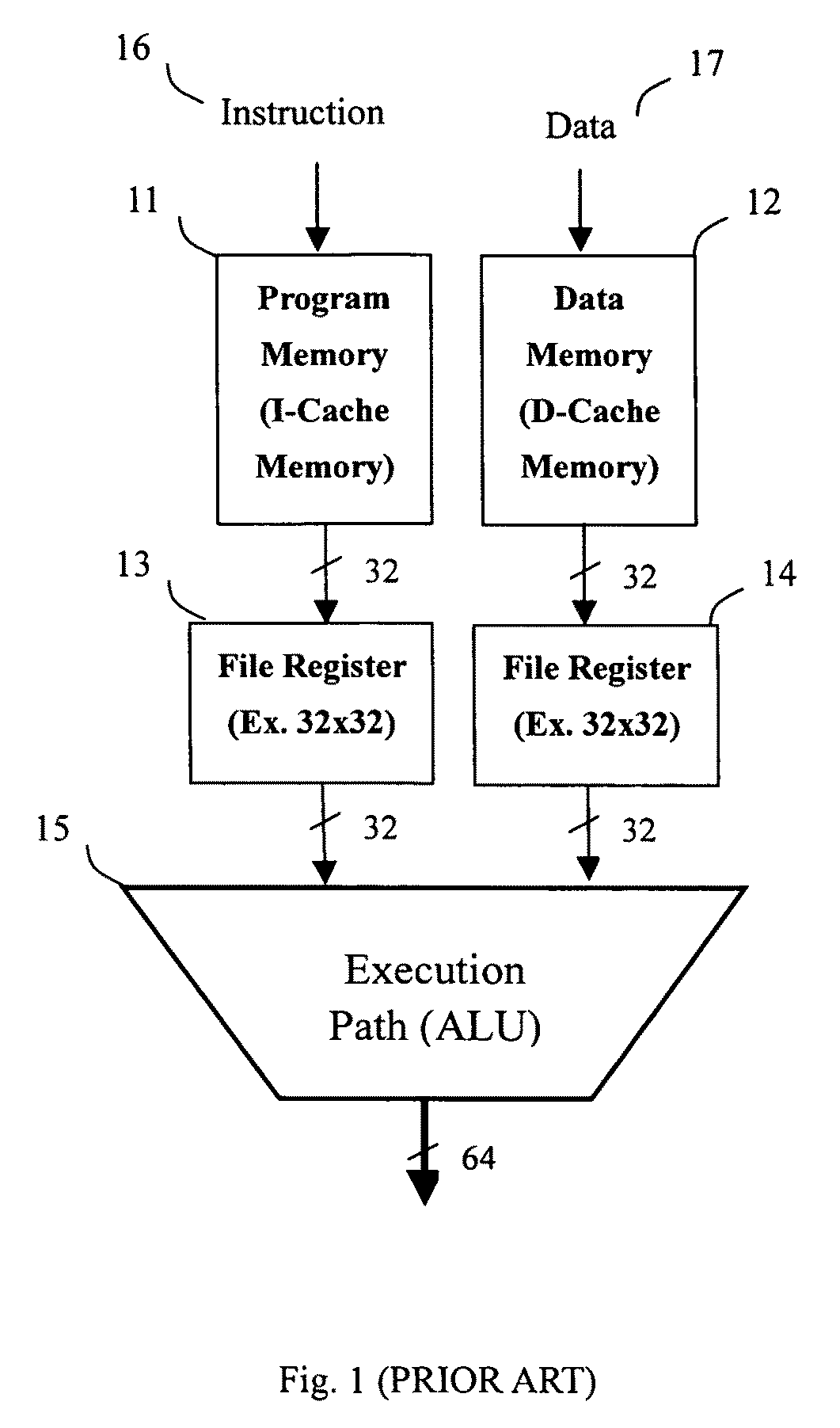

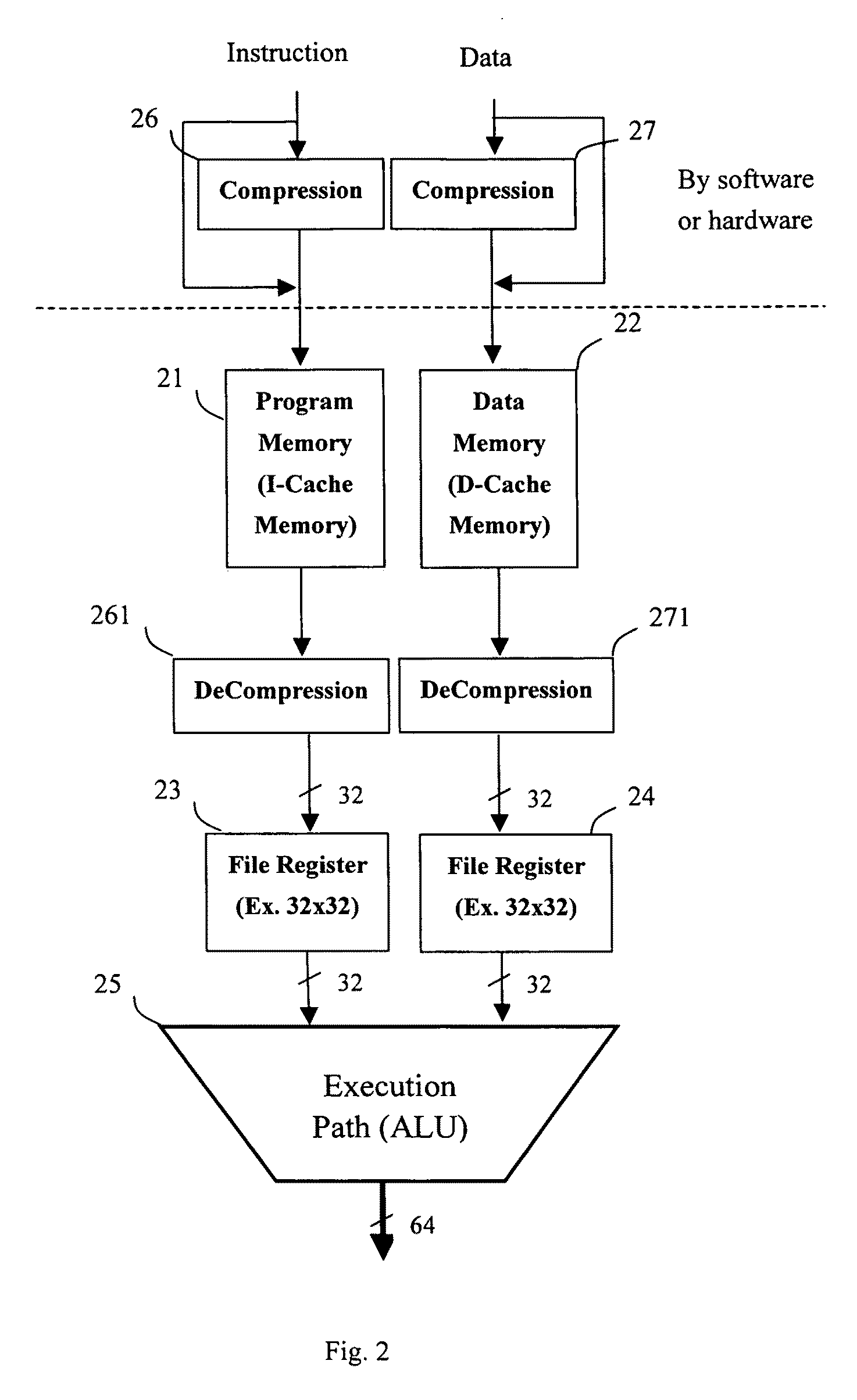

Method and apparatus of reducing CPU chip size

InactiveUS20110029761A1Improve efficiencyReduce dataDigital computer detailsSpecific program execution arrangementsChip sizeCompression method

A new compression method and apparatus compresses instructions embedded in a CPU chip which significantly reduces the density of storage device of storing the program. Multiple groups of instructions in the form of binary code are compressed separately by a mapping unit indicating the starting location of a group of instructions which helps quickly recovering the corresponding instructions. A mapping unit is applied to interpret the corresponding address of a group of data for quickly recovering the corresponding instructions for a CPU to execute smoothly.

Owner:TAIWAN IMAGINGTEK

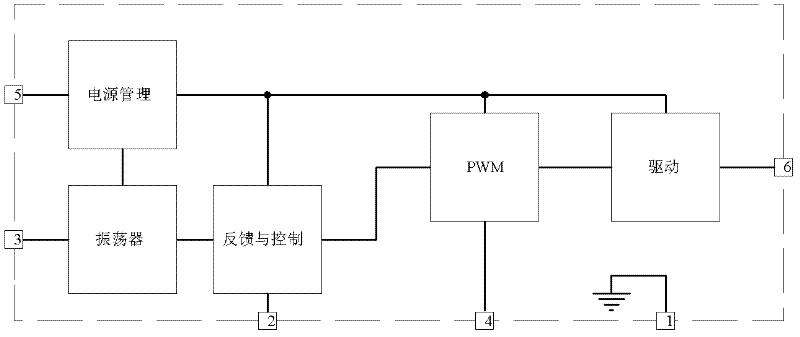

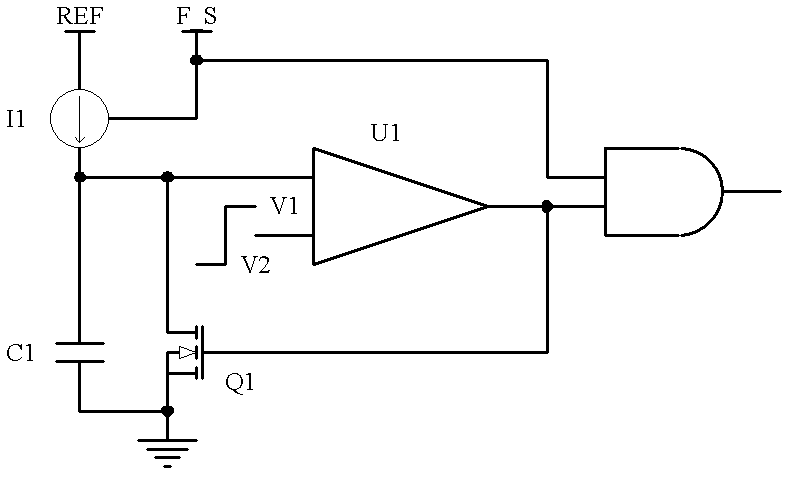

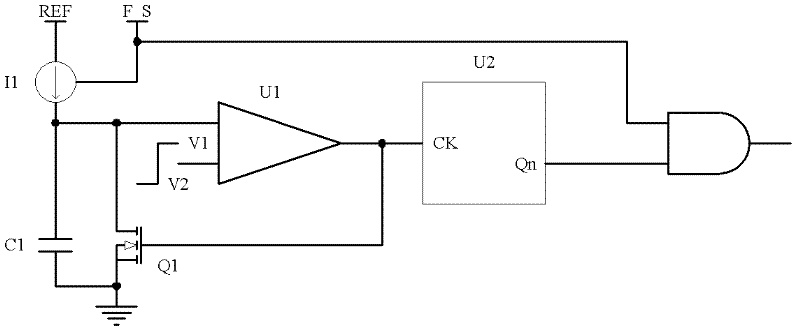

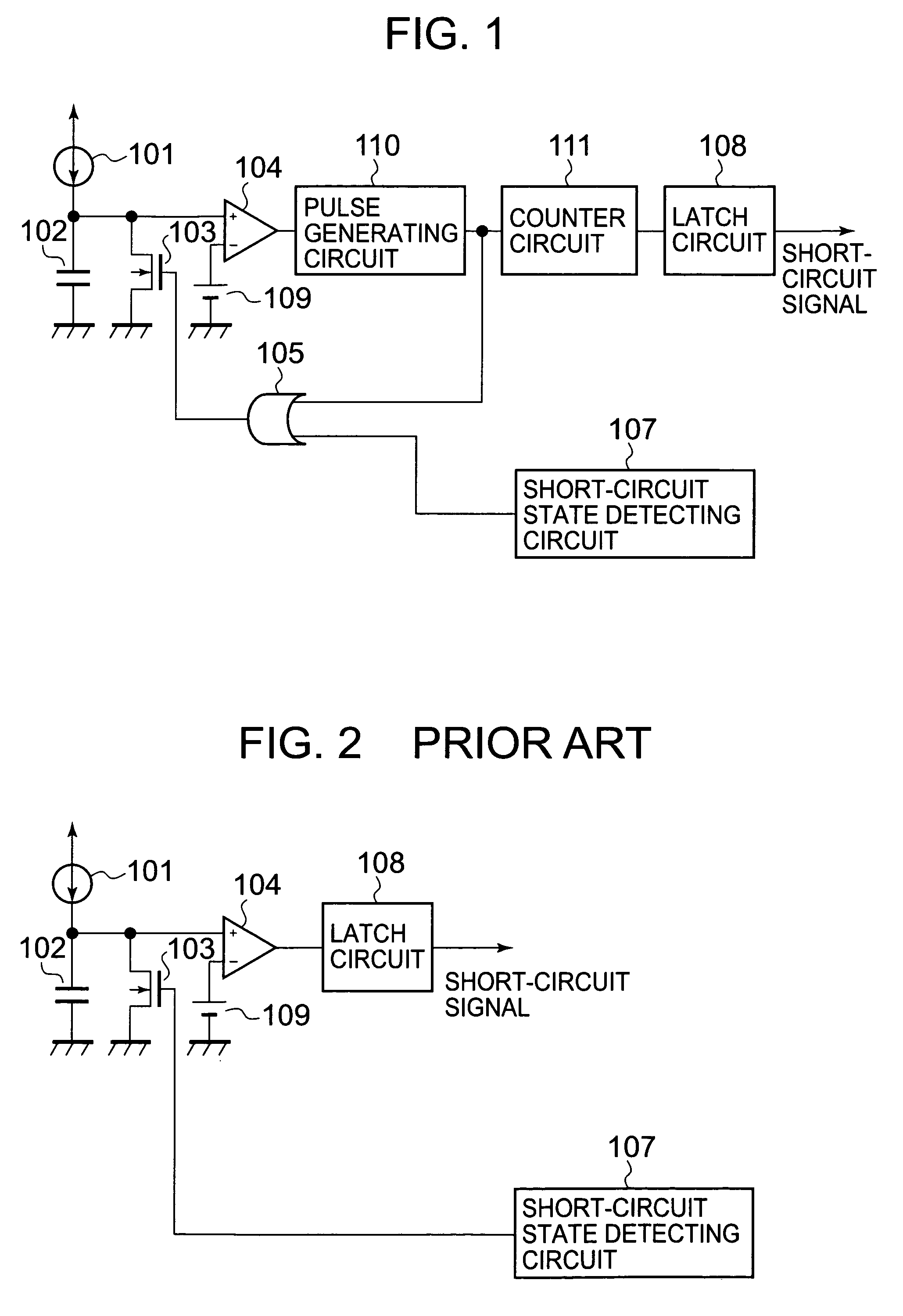

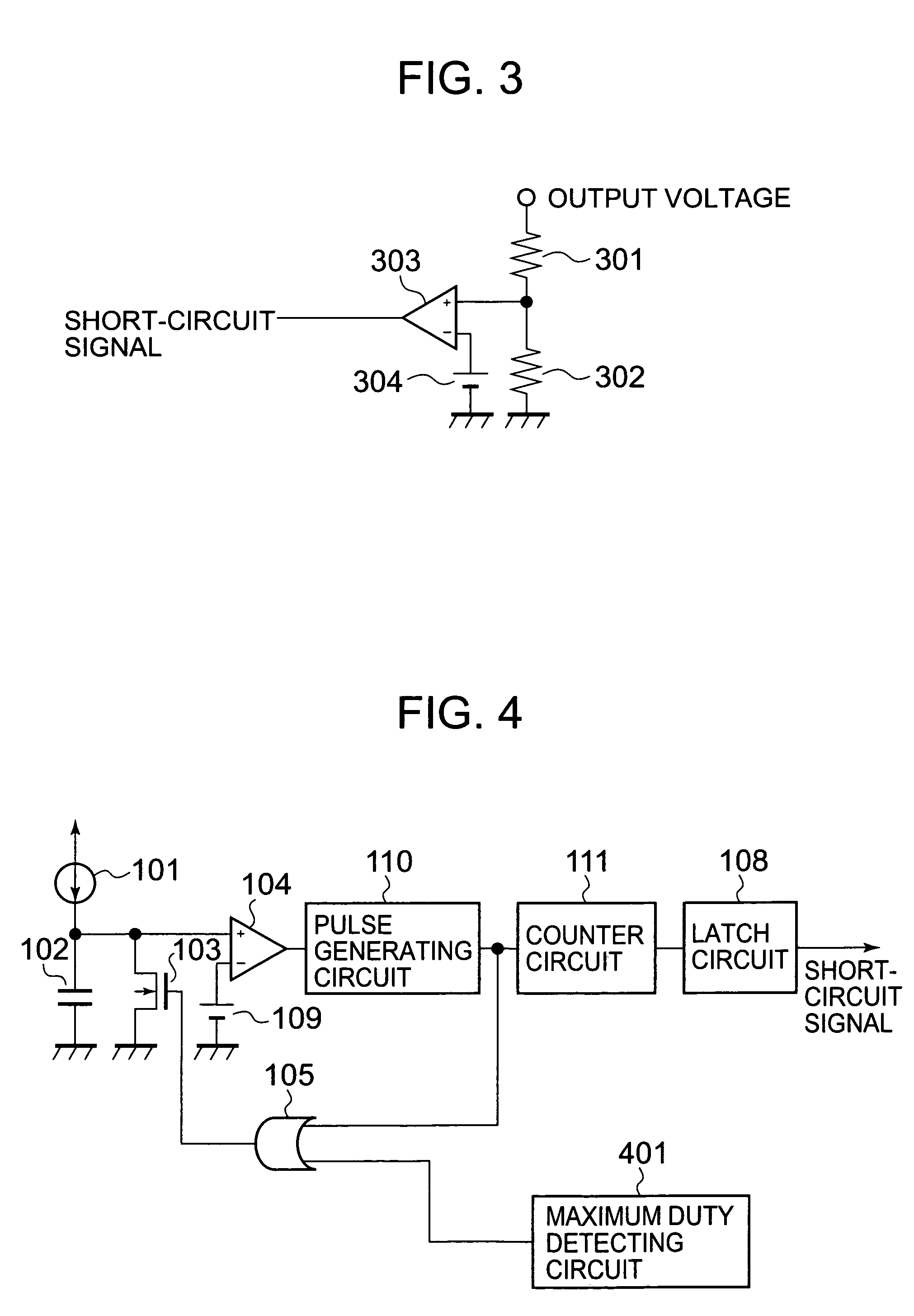

Delay circuit and switching power controller with delay circuit

The invention discloses a delay circuit and a switching power controller with the delay circuit. The delay circuit comprises a comparator, a delay setting unit and a counter, wherein the comparator comprises two input ends, one of which is connected with a set reference level; the delay setting unit is connected with the other input end of the comparator and comprises a first capacitor, a first current source and a discharge switch; the first current source is in matched connection with a charging capacitor, namely the first capacitor; the discharge switch is under the control of the output of the comparator; and the counter counts output pulses of the comparator. By the invention, the supportable delay time of the delay circuit can be greatly prolonged, and the functions of the switching power controller can be expanded with the minimum resources.

Owner:SHENZHEN LII SEMICON CO LTD

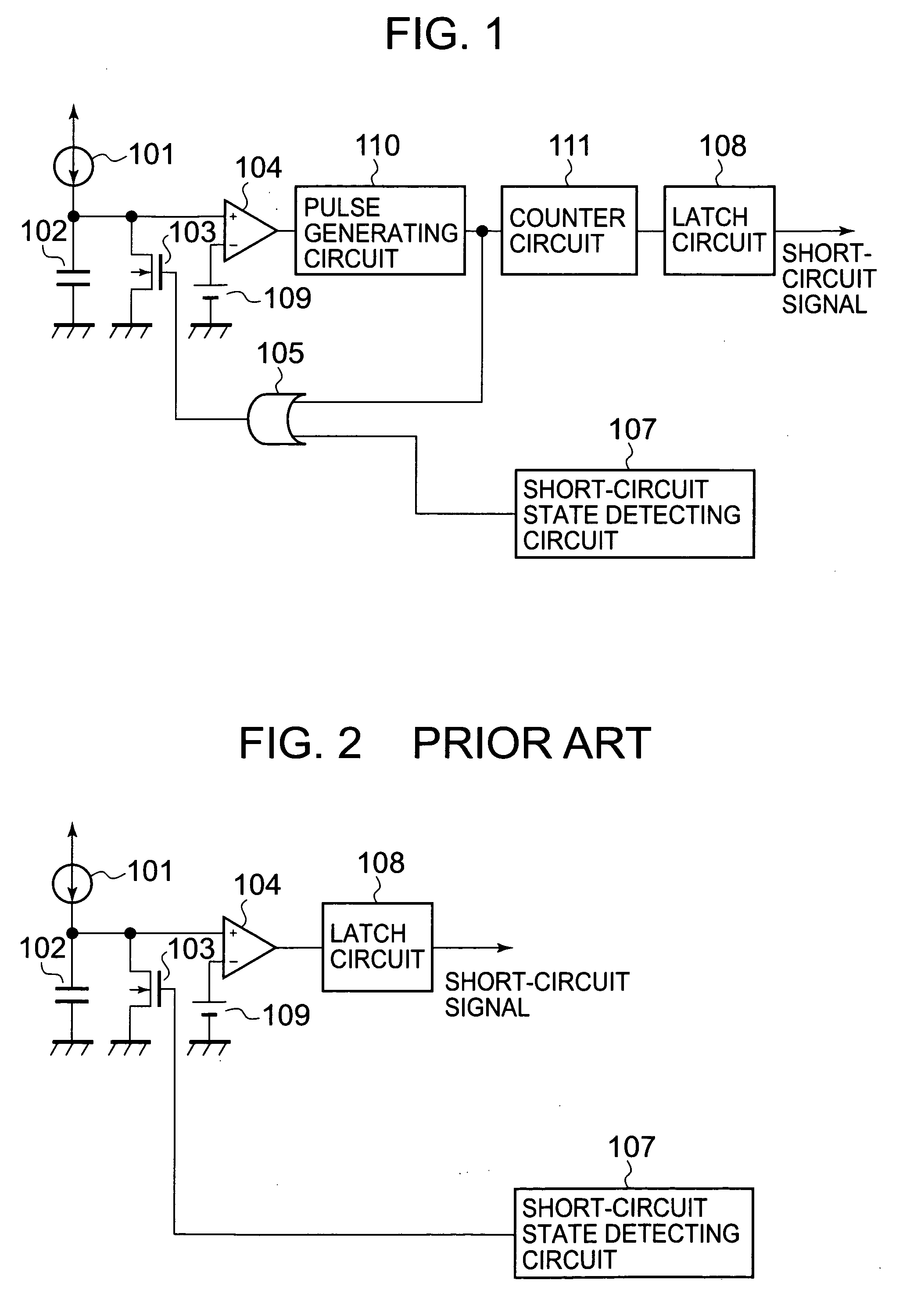

Switching regulator

ActiveUS20060076941A1Long delay timeMiniaturization possibleDc-dc conversionElectronic switchingWork periodDelayed time

The present invention provides a short-circuit protecting circuit of a switching regulator which does not require a capacitor having a large capacity in order to obtain a sufficient duty time. A pulse generating circuit for generating one clock with a short-circuit detection signal as a trigger signal is added, and a counter circuit for counting clock pulses of a clock signal is further inserted between a comparator and a latch circuit, whereby it becomes possible to produce a sufficient delay time based on a signal having a short period using a capacitor having a small capacity.

Owner:ABLIC INC

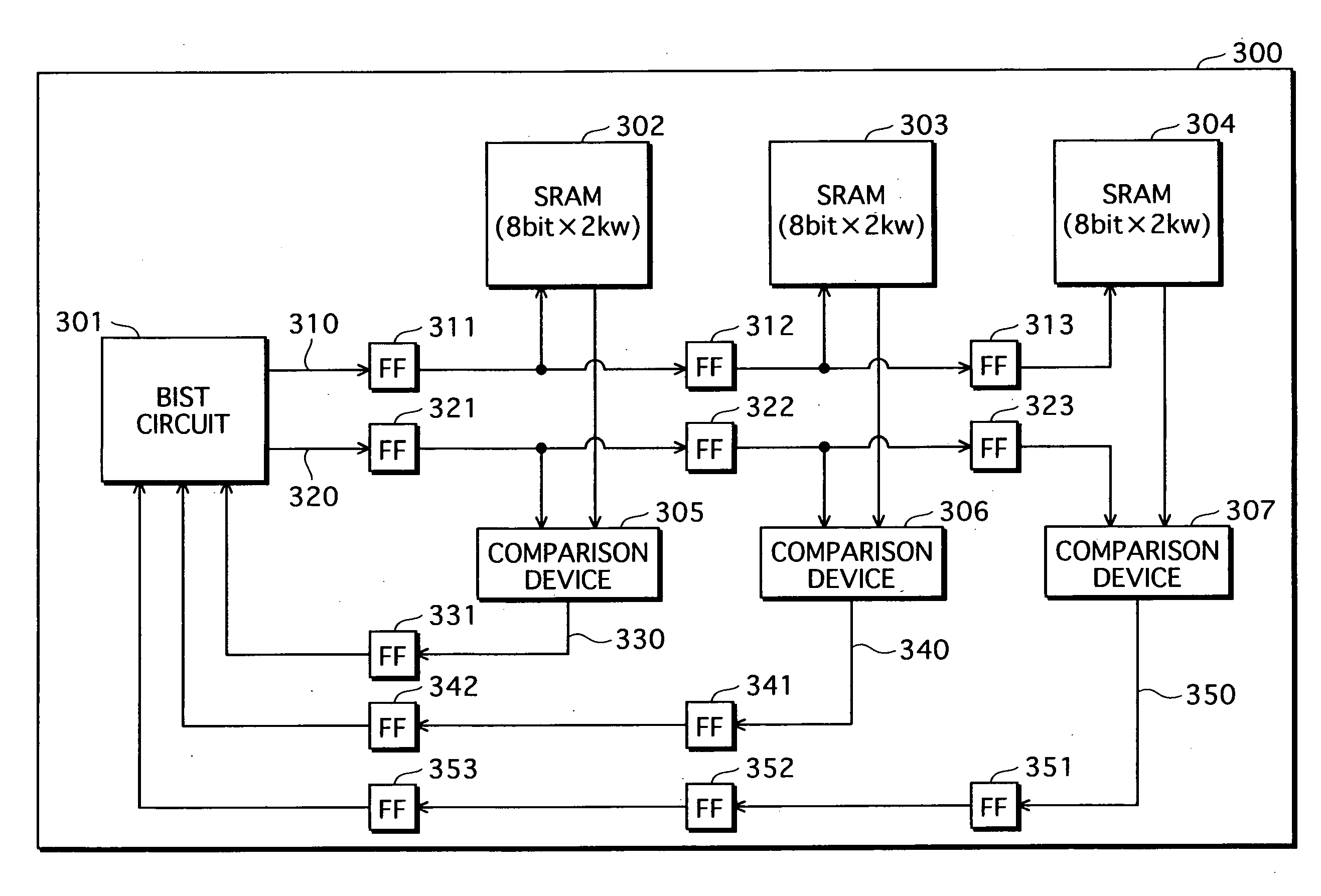

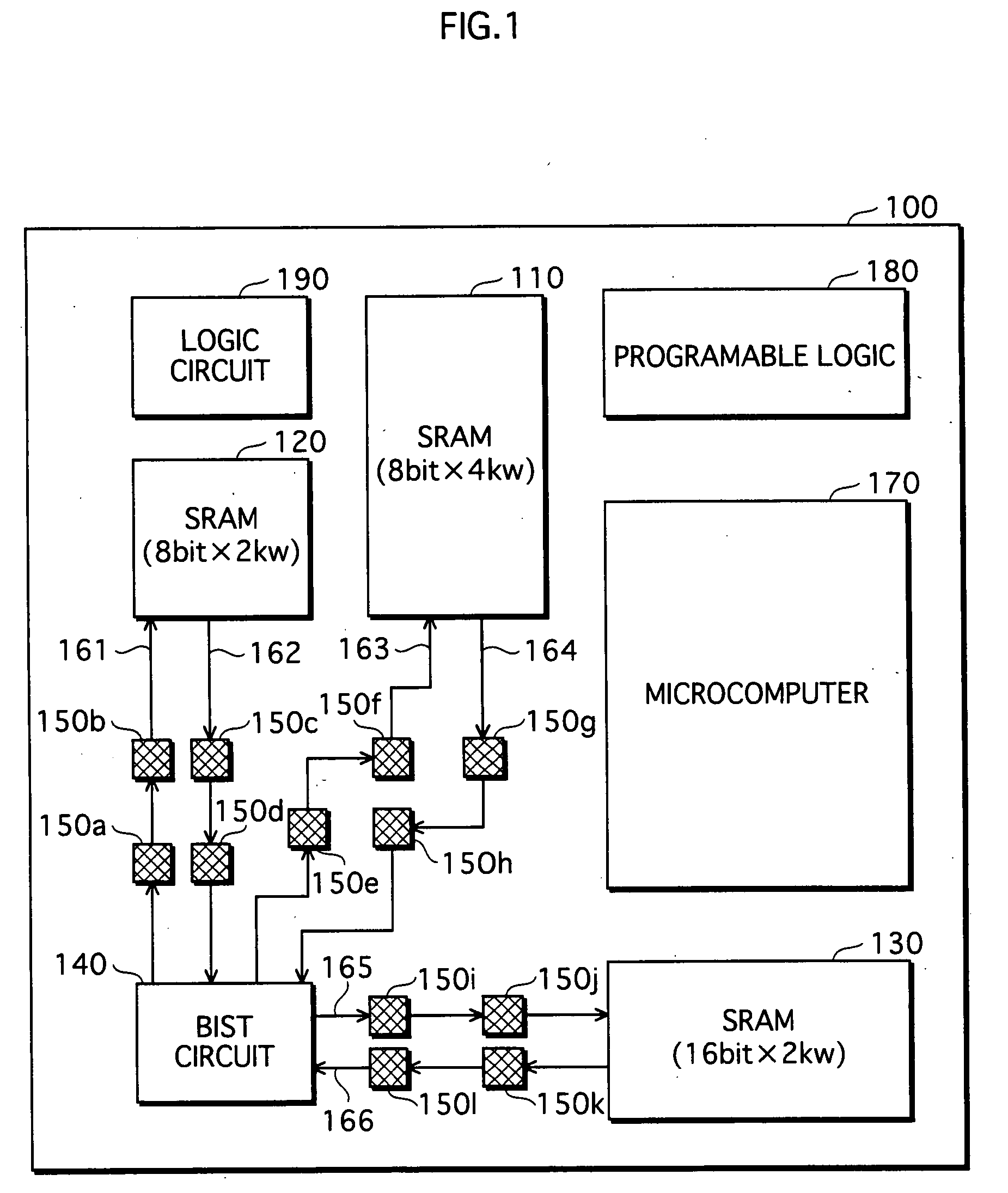

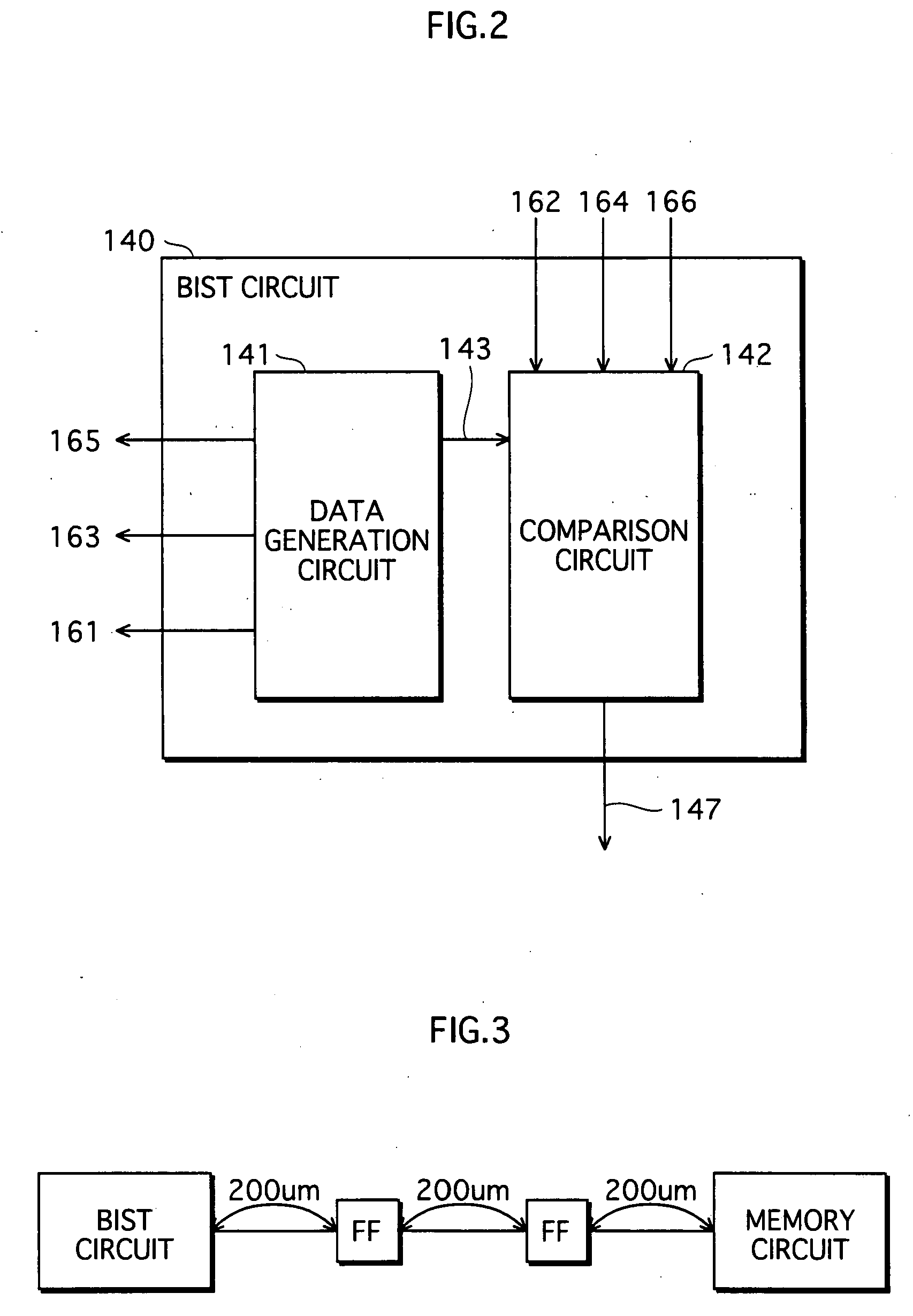

Semiconductor integrated circuit and bist circuit design method

InactiveUS20080040640A1Solve the slow test speedLong delay timeDigital circuit testingError detection/correctionProcessor registerEngineering

A semiconductor integrated circuit comprising a plurality of memory circuits; a BSIT circuit 140 operable to output test vectors; and one or more register circuit(s) 150 each allocated on a signal line that transmits test vectors output by the BIST circuit 140 to any of the memory circuits, and operable to sequentially transfer the test vectors to an adjoining macro cell in accordance with the clock signals.

Owner:PANASONIC CORP

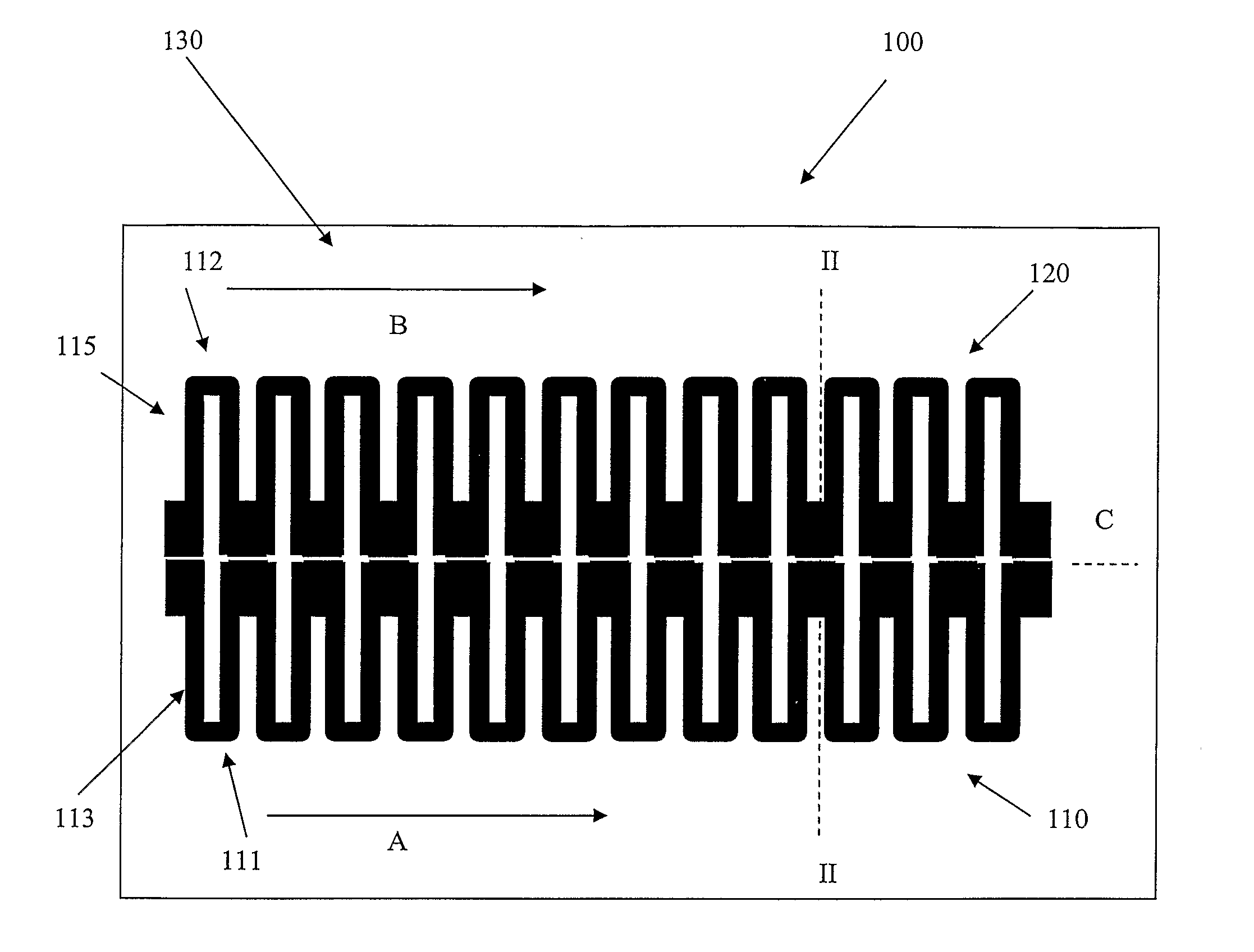

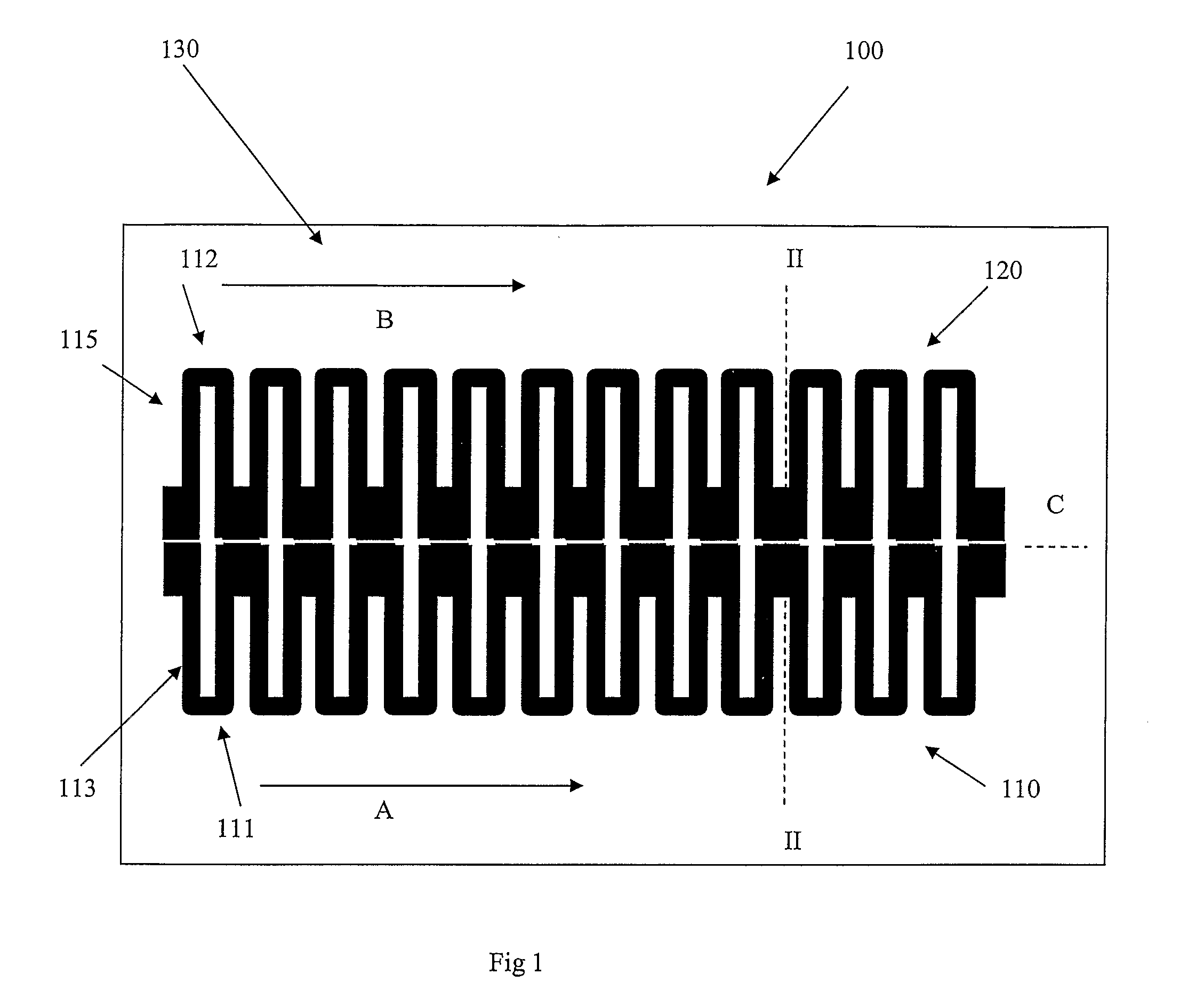

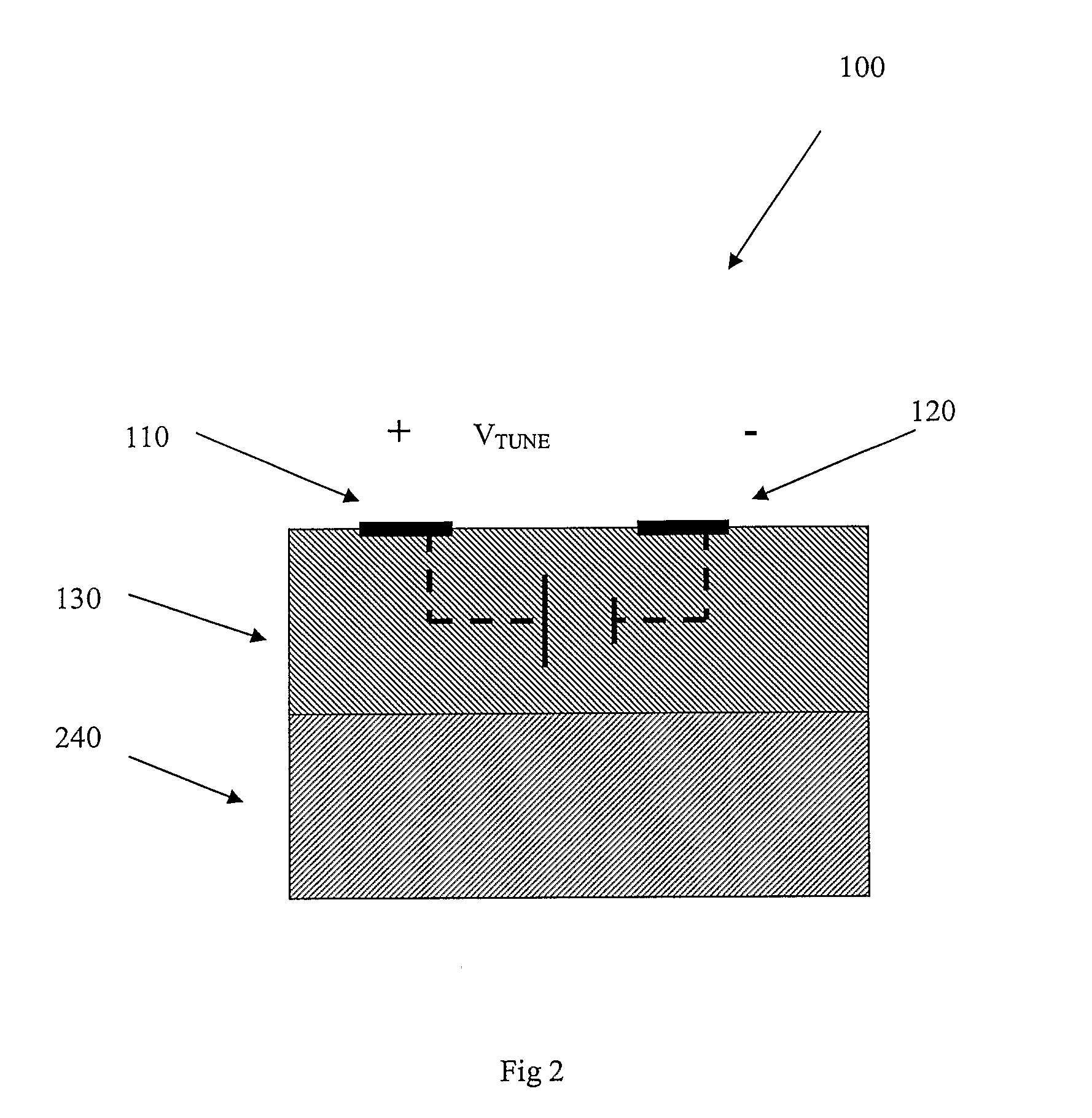

Tuneable delay line

InactiveUS20070159271A1Small sizeReduce power consumptionDelay linesWaveguidesElectrical conductorEngineering

A tunable electromagnetic delay line, comprising a first conductor with a first main direction of extension, said first conductor being arranged on top of a non-conducting substrate, characterized in that the delay line additionally comprises a layer of a ferroelectric material with first and second main surfaces, which layer separates the first conductor and the substrate, and in that the delay line also comprises a second conductor with a second main direction of extension, with the first and second main directions of extensions essentially coinciding with each other, and with the first and second conductors being each other's mirror image with respect to an imagined line in the center of the delay line along said first and second main directions of extension, said tuning being accomplished by applying a voltage between said first and second conductors.

Owner:HIGHBRIDGE PRINCIPAL STRATEGIES LLC AS COLLATERAL AGENT

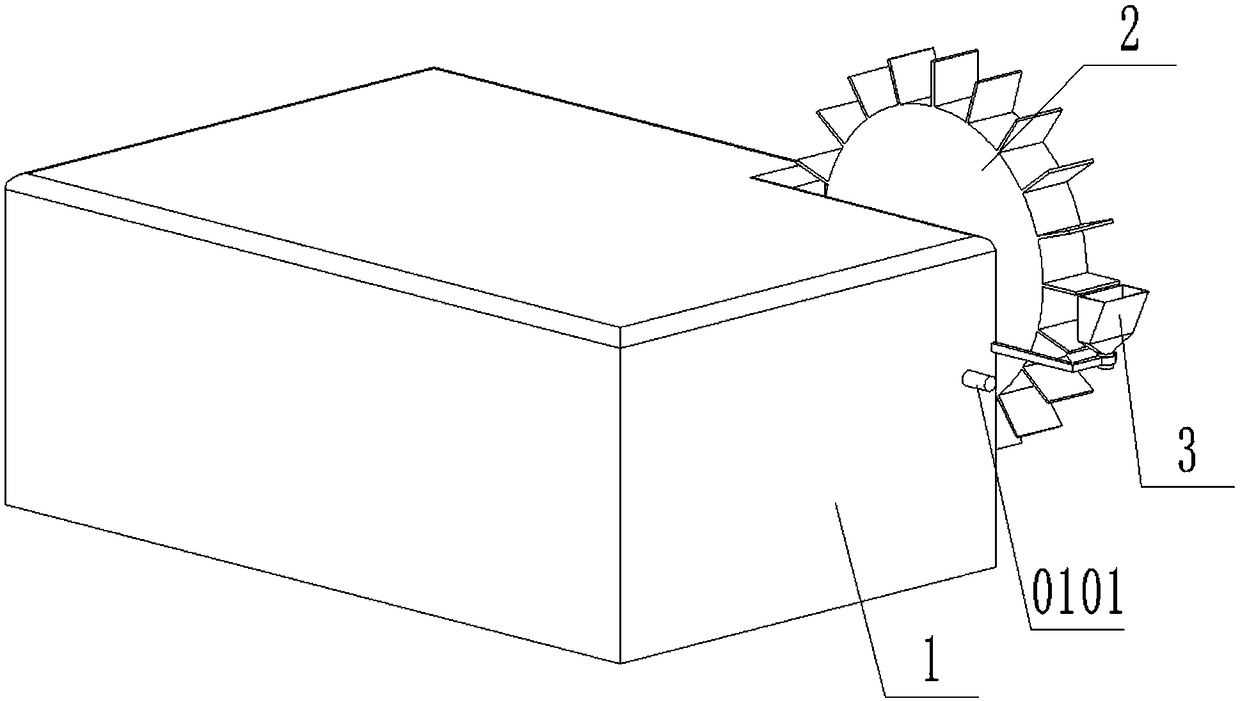

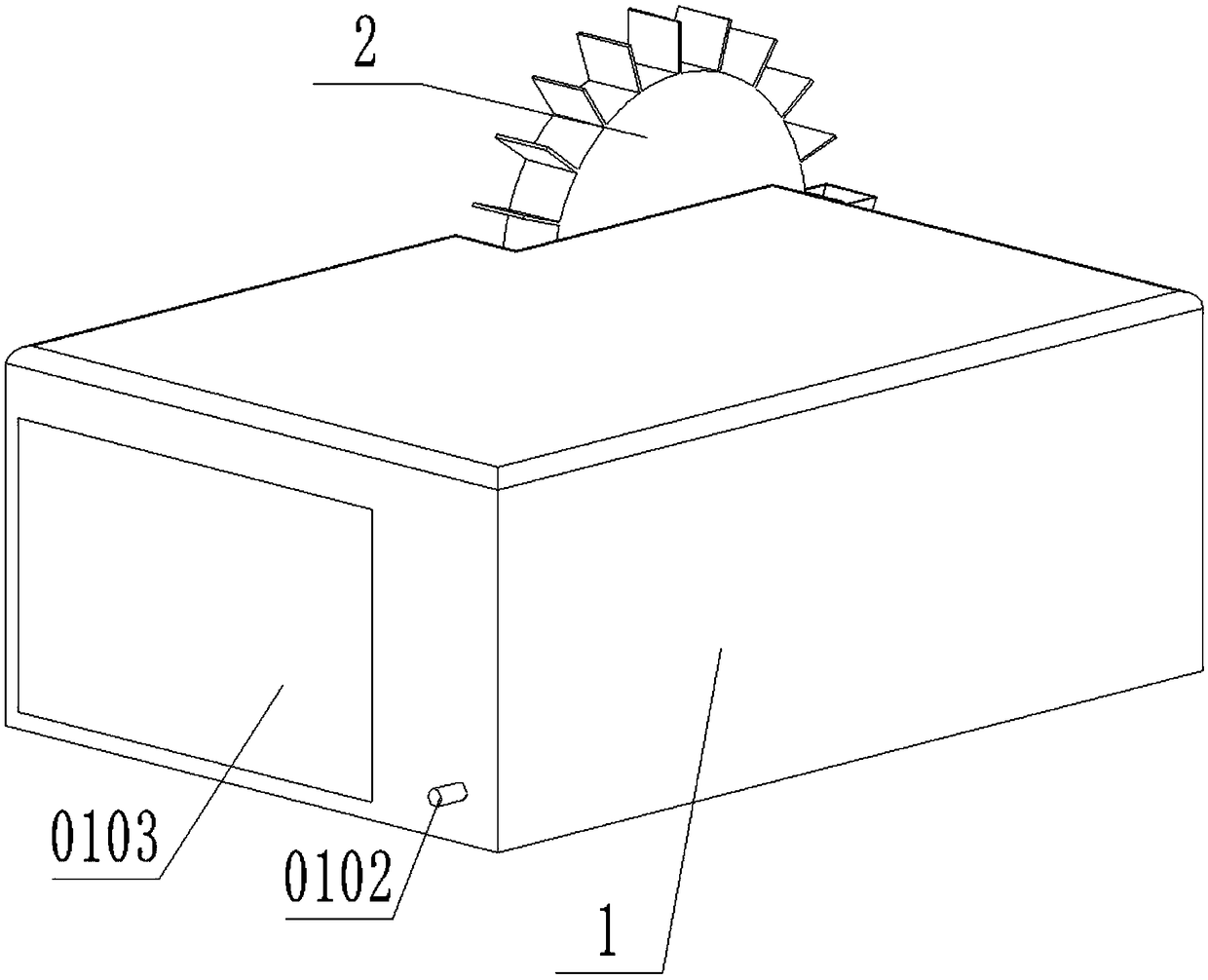

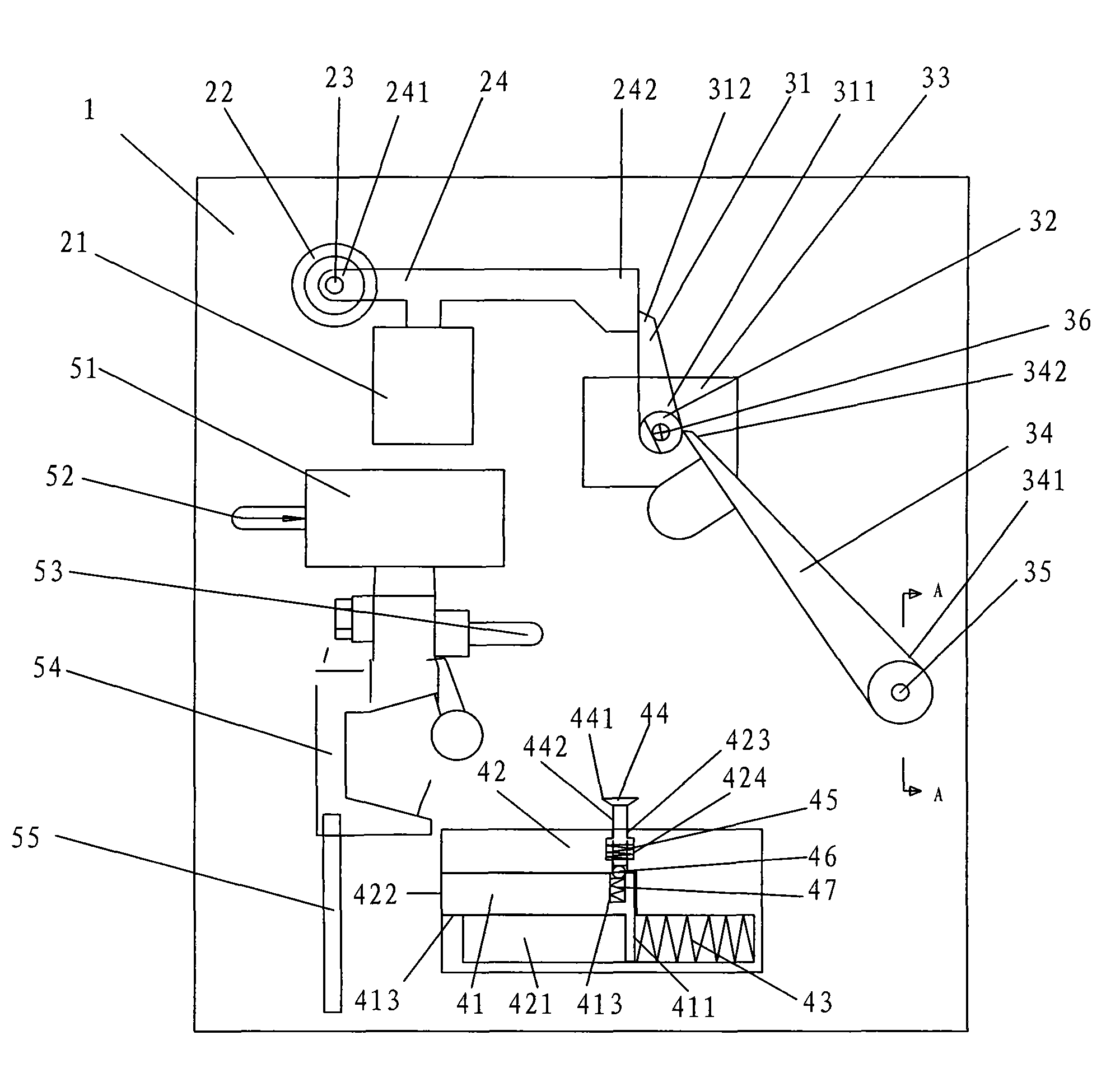

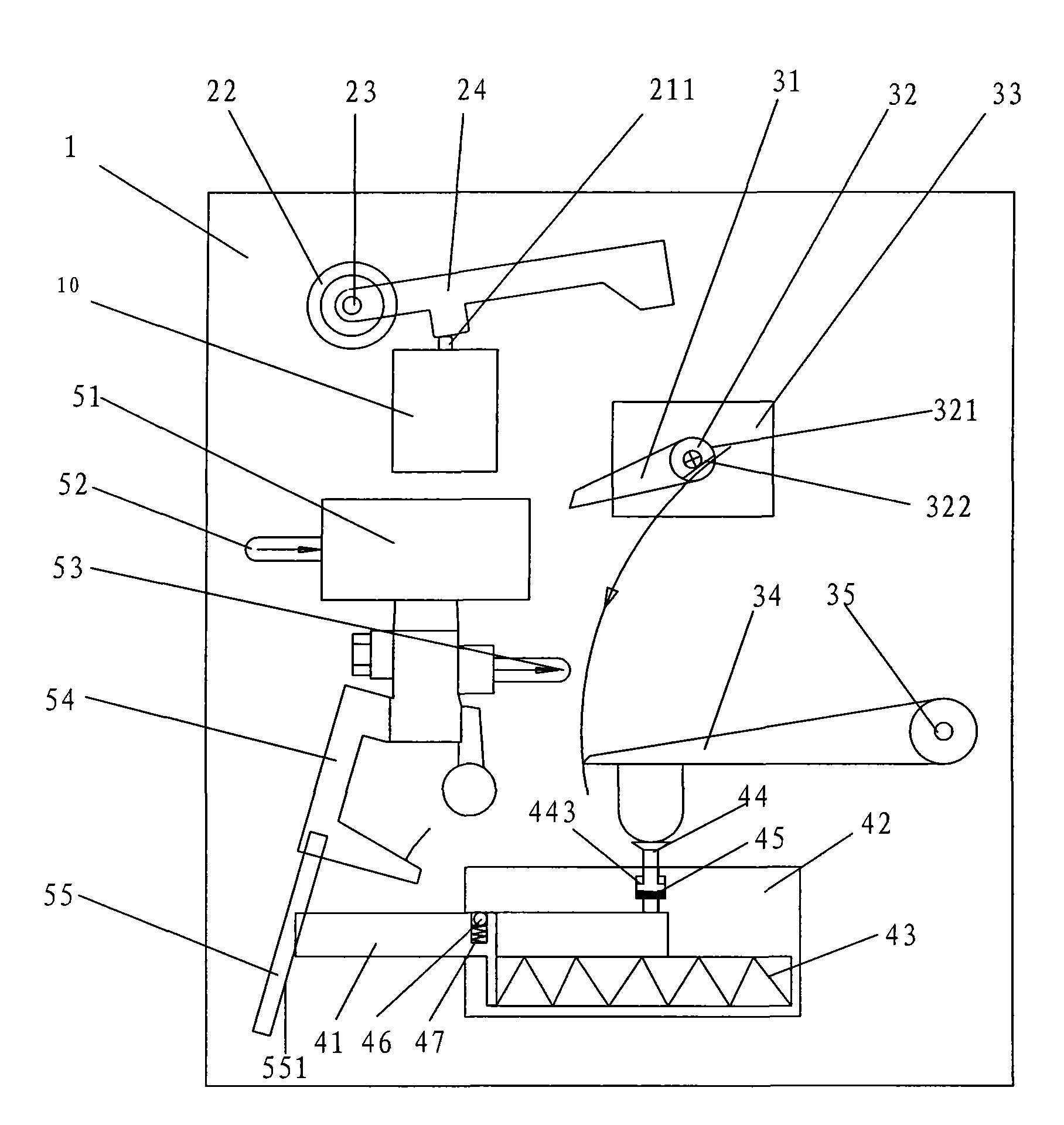

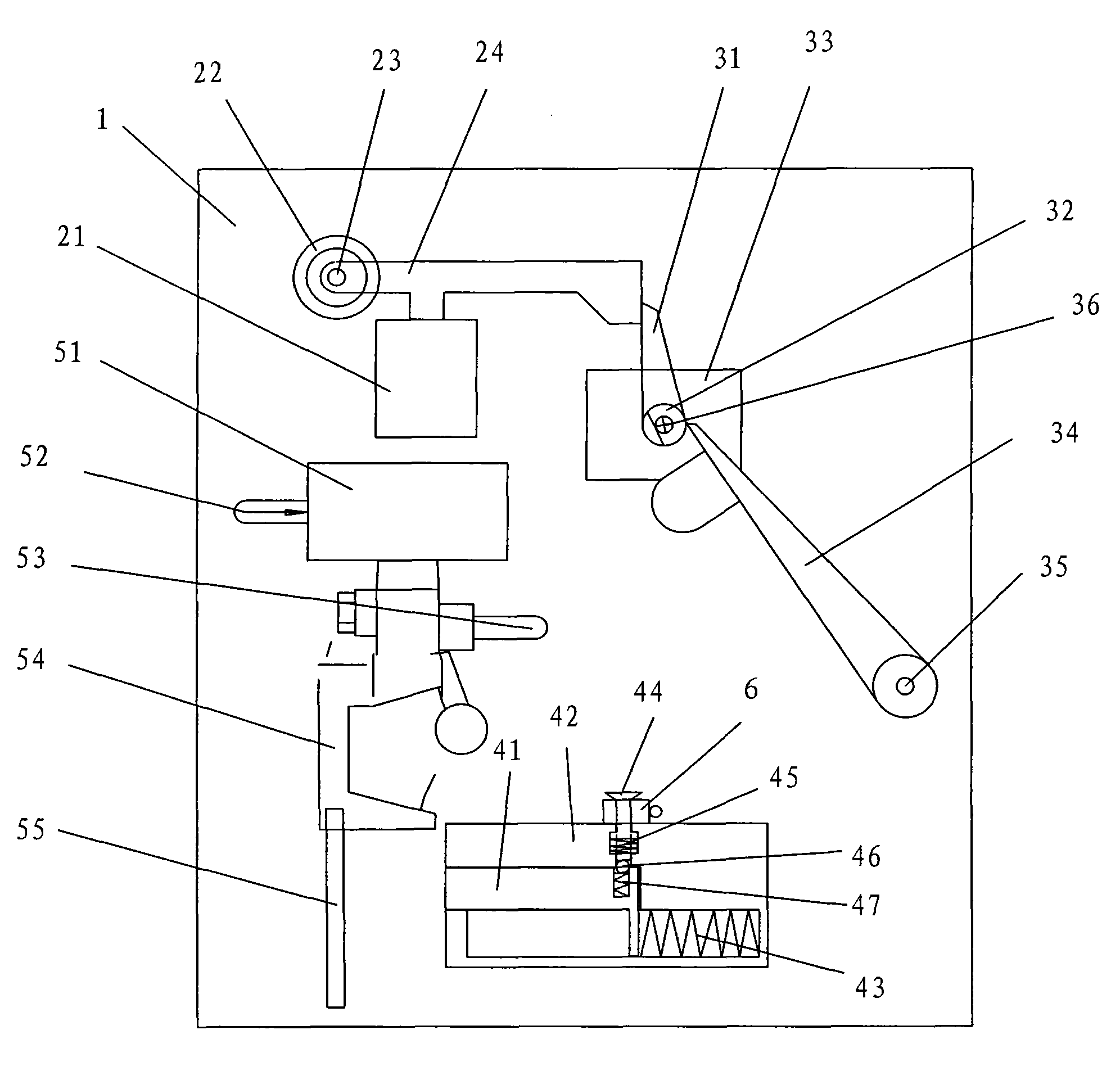

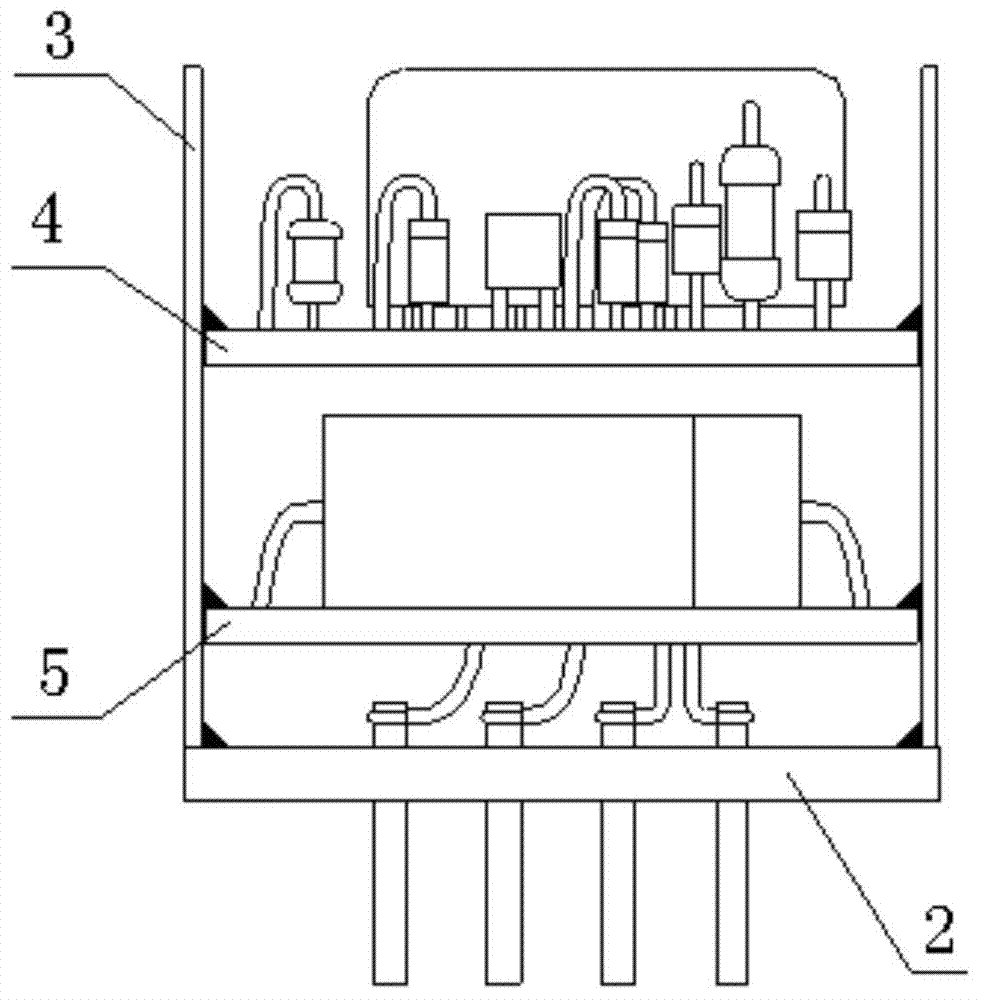

Automatic sampling device for monitoring water quality of water discharge port

ActiveCN108663237AReduce laborReduce consumptionWithdrawing sample devicesGearingWater wheelWater discharge

The invention provides an automatic sampling device for monitoring water quality of a water discharge port. The device comprises a casing, water inlet pipes and sample collection pipes, wherein a group of water wheels are axially connected with the right side of the rear end face of the casing; a group of stirring gears are coaxially and fixedly connected with bottoms of first-stage driven wheels;a reversing valve comprises a valve core, a valve body, a water inlet, a water outlet, a collecting port and a spring; sample collecting ports are connected with the water inlet pipes through water pipes; the water inlet is communicated with the water inlet pipes through water pipes; the water outlet is communicated with drain pipes through water pipes; a group of the sample collection pipes arefixedly connected to the collecting port; water outlets of the sample collection pipes face the group of the sample collection pipes. Power is provided by impact force of water in the water dischargeport, the device is energy-saving and environmentally friendly, regular quantitative automatic sampling can be realized through various mechanisms, and labor cost is saved.

Owner:郑州富铭科技股份有限公司

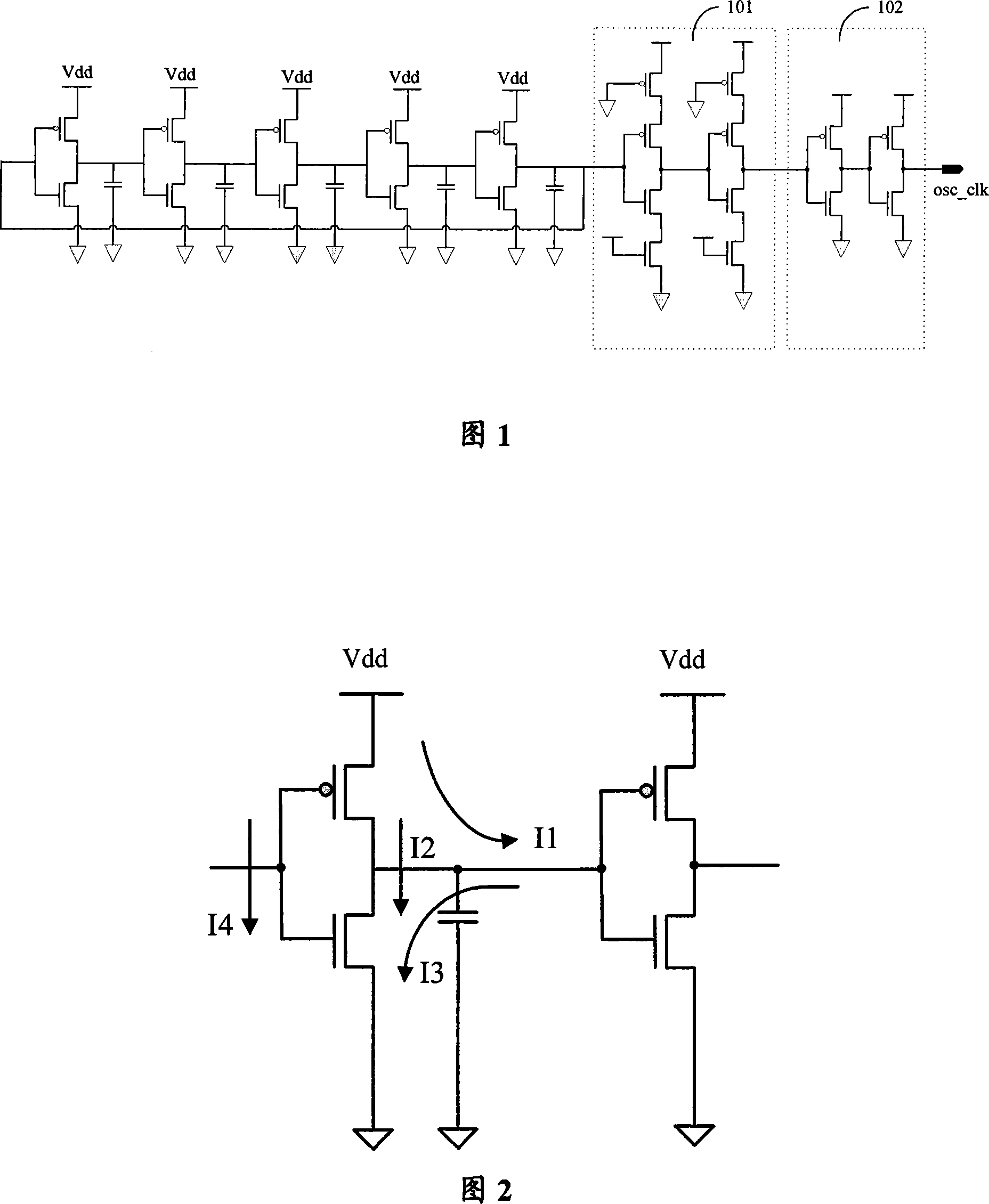

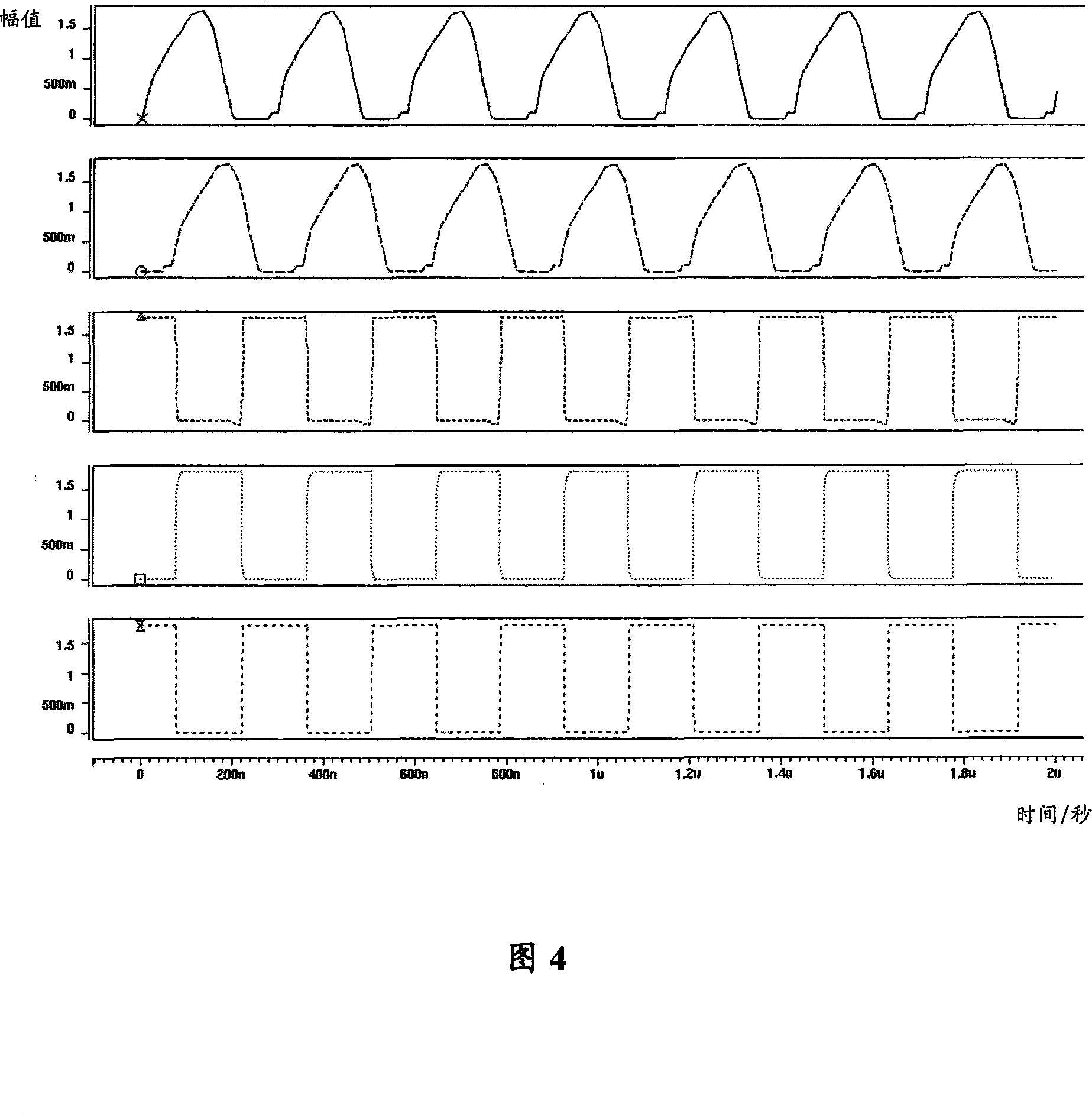

Oscillator and design method thereof

ActiveCN101202540ASimple designEfficient designLogic circuits characterised by logic functionSingle output arrangementsDc currentDelayed time

The invention discloses an oscillator and a design method thereof, comprising an offset module, a delaying module, a conversion module, a damping module and an output module; wherein, the offset module is used for generating an offset current according to an input signal; the delaying module is used for receiving the offset current which is generated by the offset module and generates the oscillation signals with scheduled periods according to the offset signal; the delaying module comprises a current source submodule, a variable resistance submodule and an inverter submodule; the maximum up-pulling current and the maximum down-pulling current of the delaying module are controlled by the power source submodule, thus controlling the power loss current of the delaying module; the delaying time of the delaying module is controlled by the variable resistance submodule; the gate capacitance of the delaying module is adjusted by the inverter submodule, thus controlling the power loss of the delaying module. The conversion module reduces the power loss of the oscillator by further reducing the DC current. The invention provides the oscillator which has simple structure, high efficiency, side application range and ultra-low power loss, and is especially suitable for low frequency application.

Owner:GIGADEVICE SEMICON (BEIJING) INC

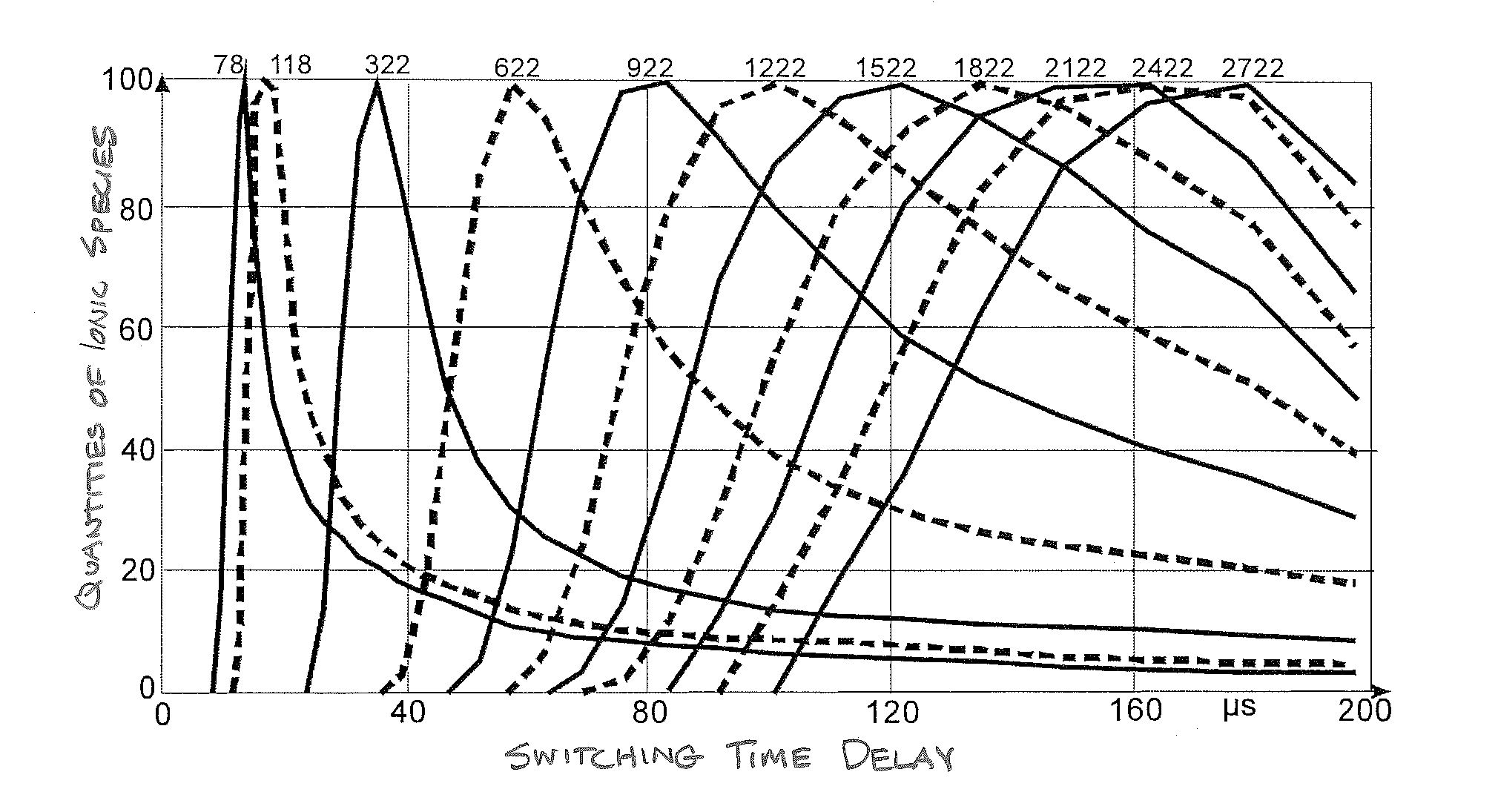

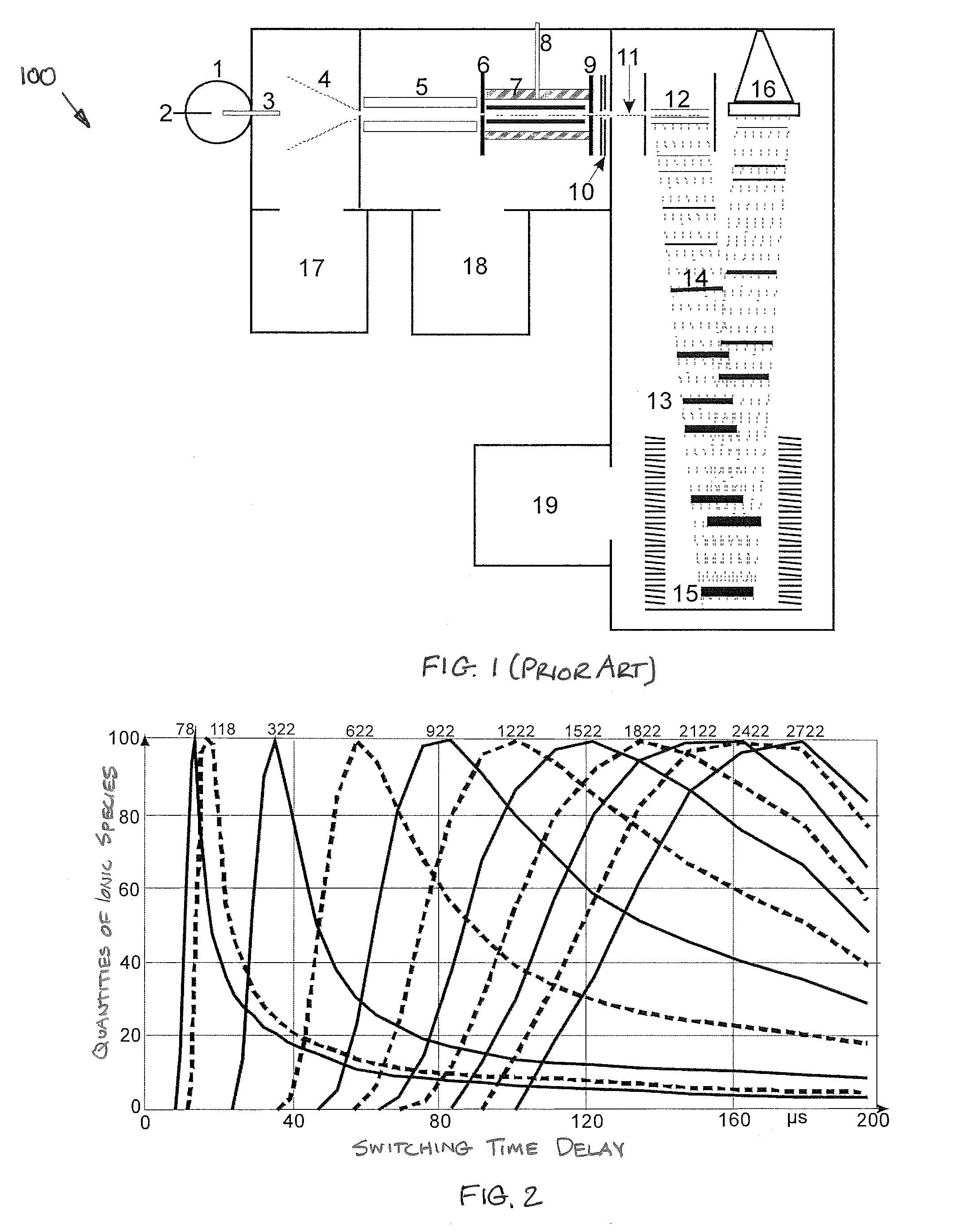

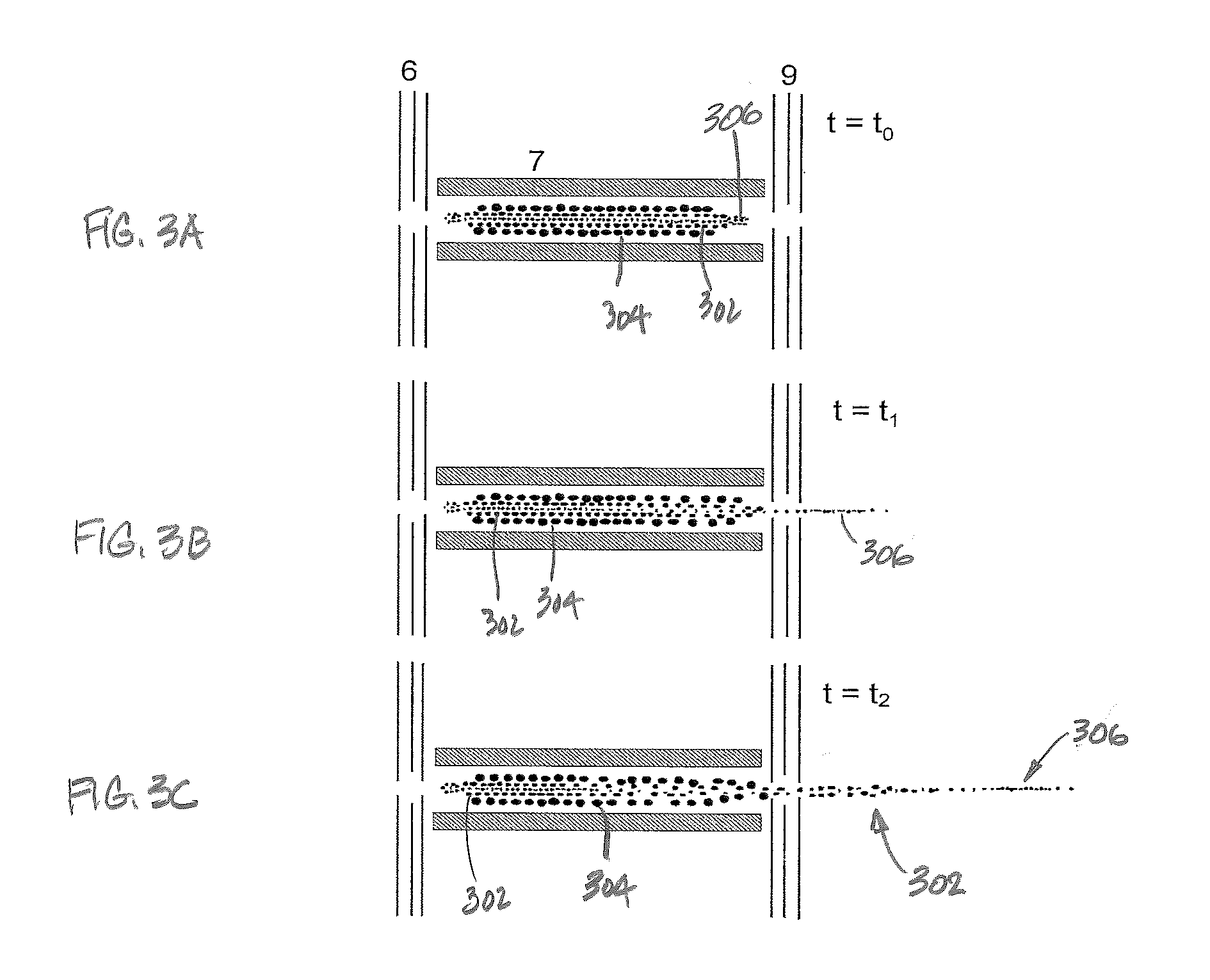

Method for operating a time-of-flight mass spectrometer with orthogonal ion pulsing

ActiveUS8927928B2Short delay timeLong delay timeTime-of-flight spectrometersIsotope separationTime-of-flight mass spectrometryMass analyzer

Methods are provided for acquiring sum spectra in a time-of-flight mass spectrometer with orthogonal pulsed acceleration, where each of the sum spectra is obtained from a plurality of summed individual spectra. The mass spectrometer has an ion storage device that collects the ions temporarily before they are transferred to an ion pulser, which pulses out the ions orthogonally. Acquisition conditions such as, for example, delay times between opening the ion storage device and the pulsed ejection in the ion pulser are varied for the individual spectra, which are added together to form the sum spectrum of ions with light masses and high masses.

Owner:BRUKER DALTONIK GMBH & CO KG

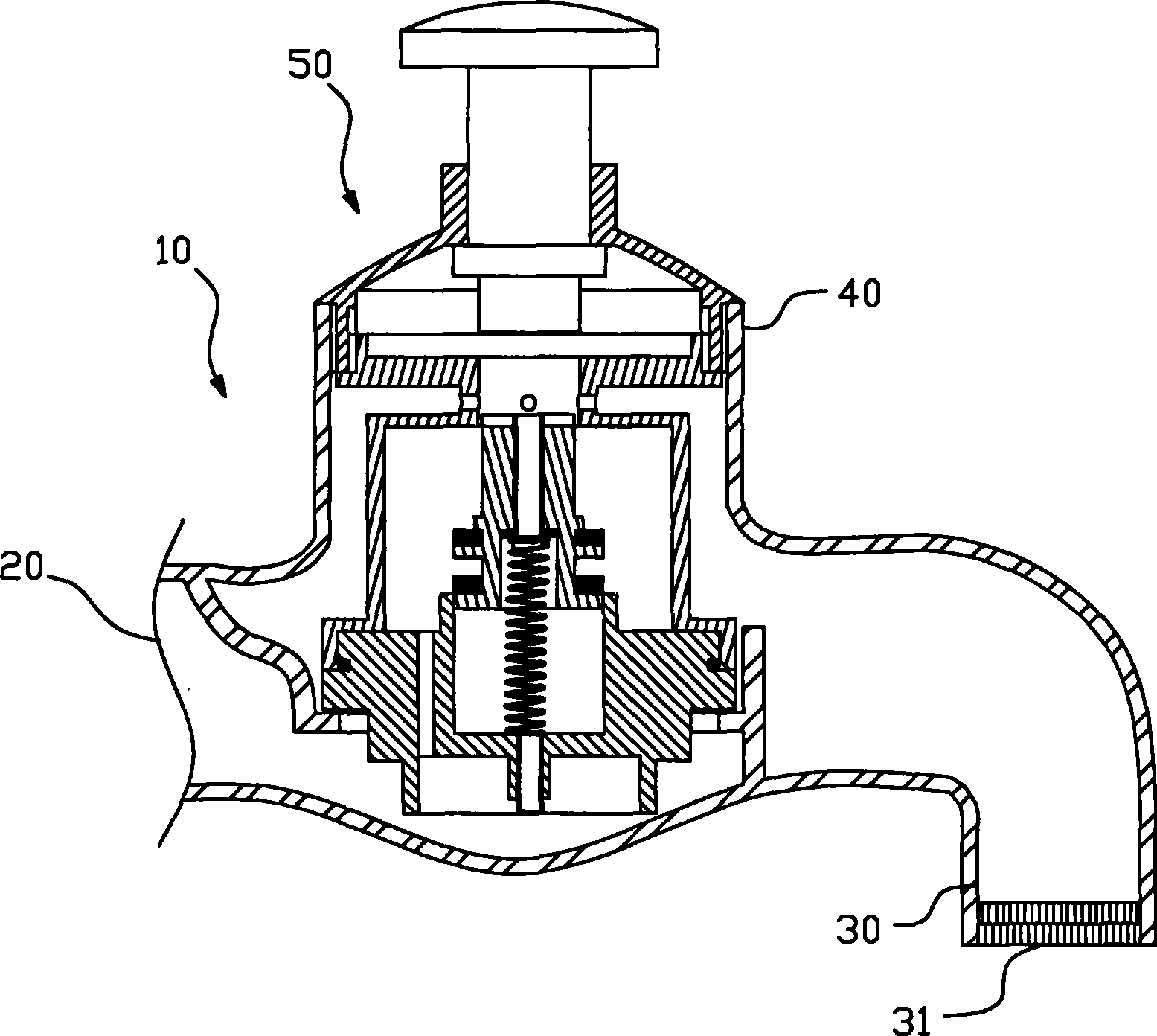

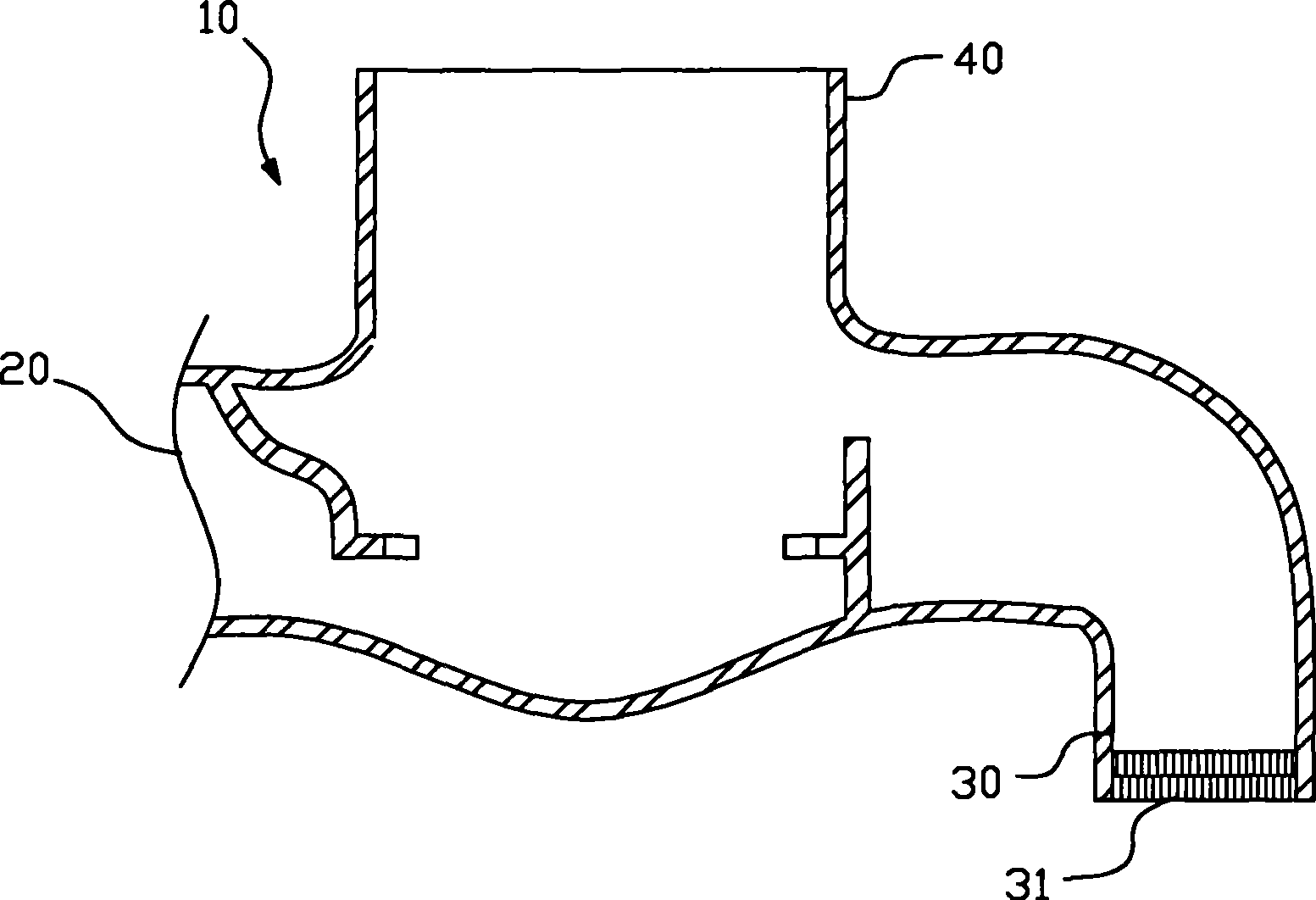

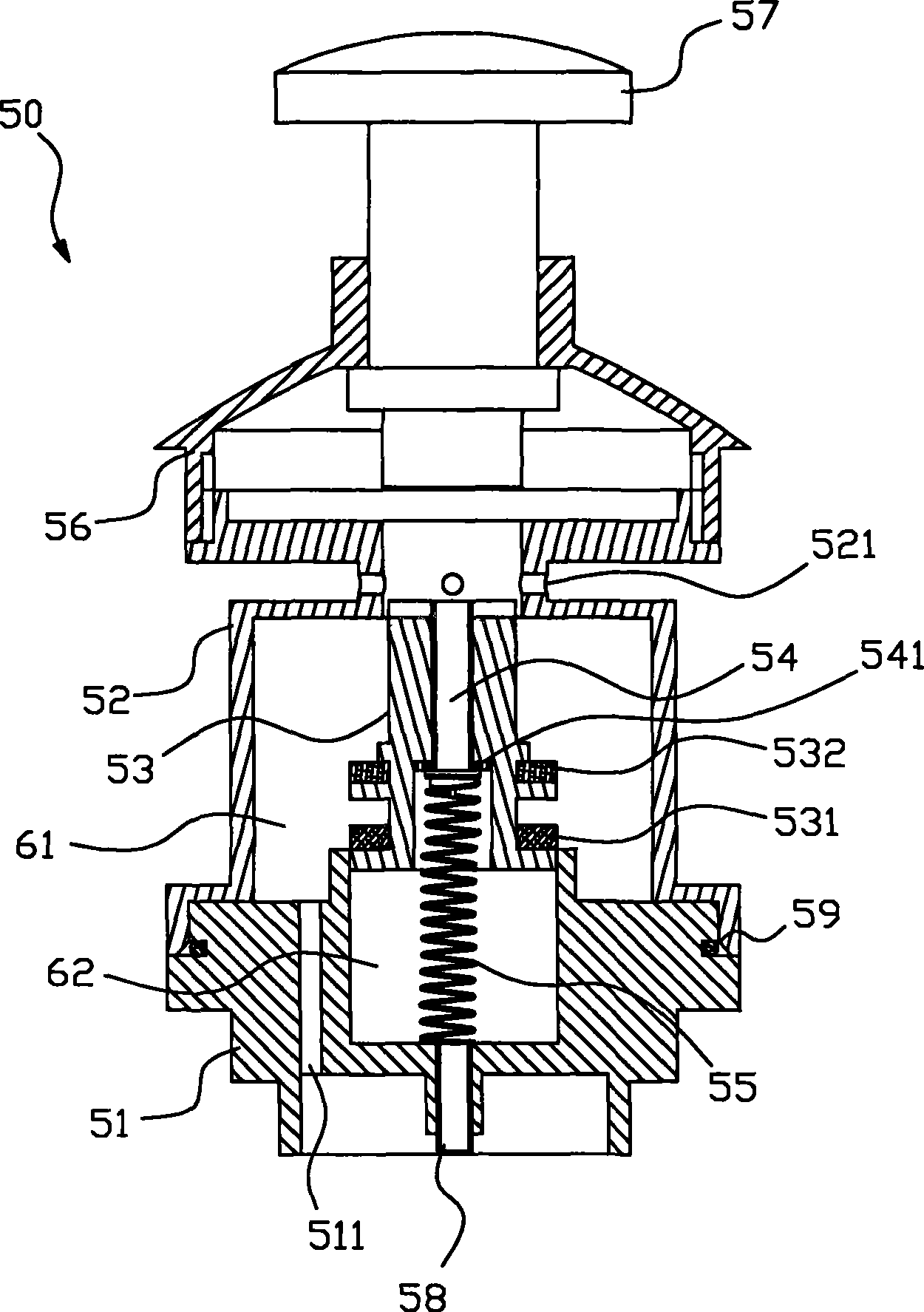

Mechanical time-delay trigger

InactiveCN102688576AReliable time for safe evacuationOpen reliableOperating means/releasing devices for valvesFire rescueEngineeringHigh pressure

The invention relates to a mechanical time-delay trigger which ensures reliable time delay by ingeniously using the reliability of a mechanical structure; when the trigger of the invention is at fault, the delay time is prolonged limitlessly without the probability of CO2 jetting in advance; therefore life safety of people possibly existing in a enclosed space is guaranteed, and reliable time for safe evacuation is provided. In addition, the invention is exquisite in structure, and all required parts are integrated on a whole substrate with an area of 300 mm*400 mm. The mechanical time-delay trigger of the invention is also an energy-storage trigger device with compact design; only small force is needed to trigger so as to release great force and realize a long stroke; thus a high pressure CO2 gas valve can be opened reliably, and CO2 gas is released at delayed time; the invention has low cost and high profits.

Owner:LUOYANG YUFO FIRE FIGHTING EQUIP

Measuring apparatus, measuring method, and sound signal processing apparatus

InactiveUS20070086596A1Measure long delay timeEasy to operateStereophonic systemsLoudspeaker spatial/constructional arrangementsMeasurement deviceDelayed time

A measuring apparatus that measures sound arrival delay time from a speaker to a microphone on the basis of a result obtained by collecting signals output from the speaker by means of the microphone includes: measuring means for measuring the sound arrival delay time that makes a control such that a first sine wave signal having a first frequency and a second sine wave signal having a second frequency different from the first frequency are output from the speaker, is input with the first sine wave signal and the second sine wave signal collected by the microphone and then mixes the first sine wave signal and the second sine wave signal so as to generate a third sine wave signal having a frequency corresponding to a difference between the first frequency and the second frequency, and measures the sound arrival delay time on the basis of the third sine wave signal.

Owner:SONY CORP

Finger pressing type tap

InactiveCN101509570AEasily pressLong delay timeOperating means/releasing devices for valvesFluid-delivery valvesEngineeringControl valves

The invention relates to a finger-pressing type water faucet provided with a control valve in a detachable way, the control valve comprises a valve seat, a valve core, a valve rod, an offsetting spring, an upper cover and a finger gland which is fixed on the upper cover in a movable way, the upper cover is connected with the valve seat in a detachable way, the valve core, the valve rod and the offsetting spring are arranged in the valve seat, the valve seat is of split type dual section structure and comprises a first valve seat and a second valve seat which are connected in a detachable way, a first time delay chamber is formed between the first valve seat and the second valve seat, a second time delay chamber is formed between the valve core and the first valve seat which is provided with a pressure regulation screw. The finger-pressing type water faucet can regulate the finger pressure, the time delay length and the water output amount by the pressure regulation screw and has wide applicability, thus having high marketing value.

Owner:洪崎峰

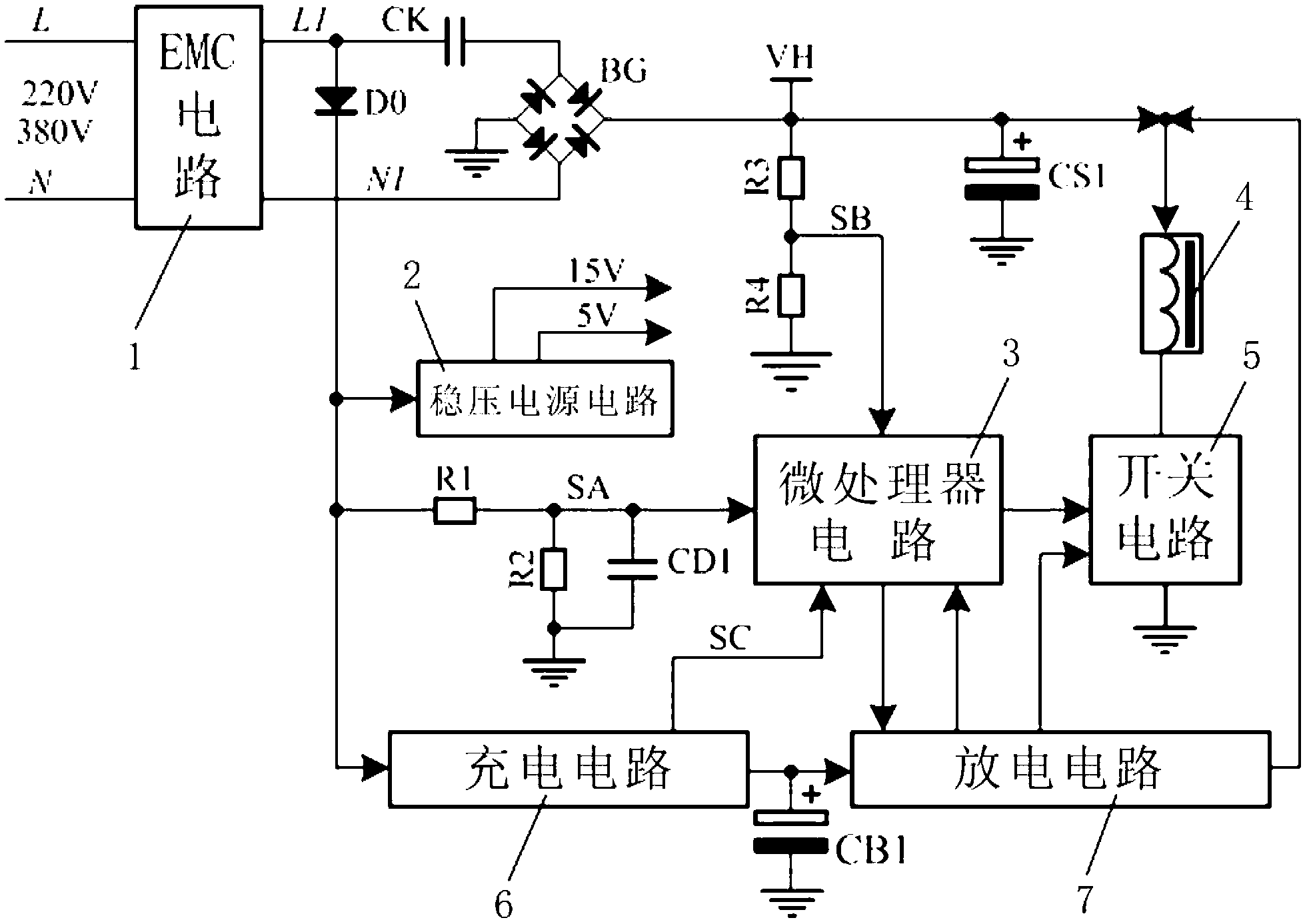

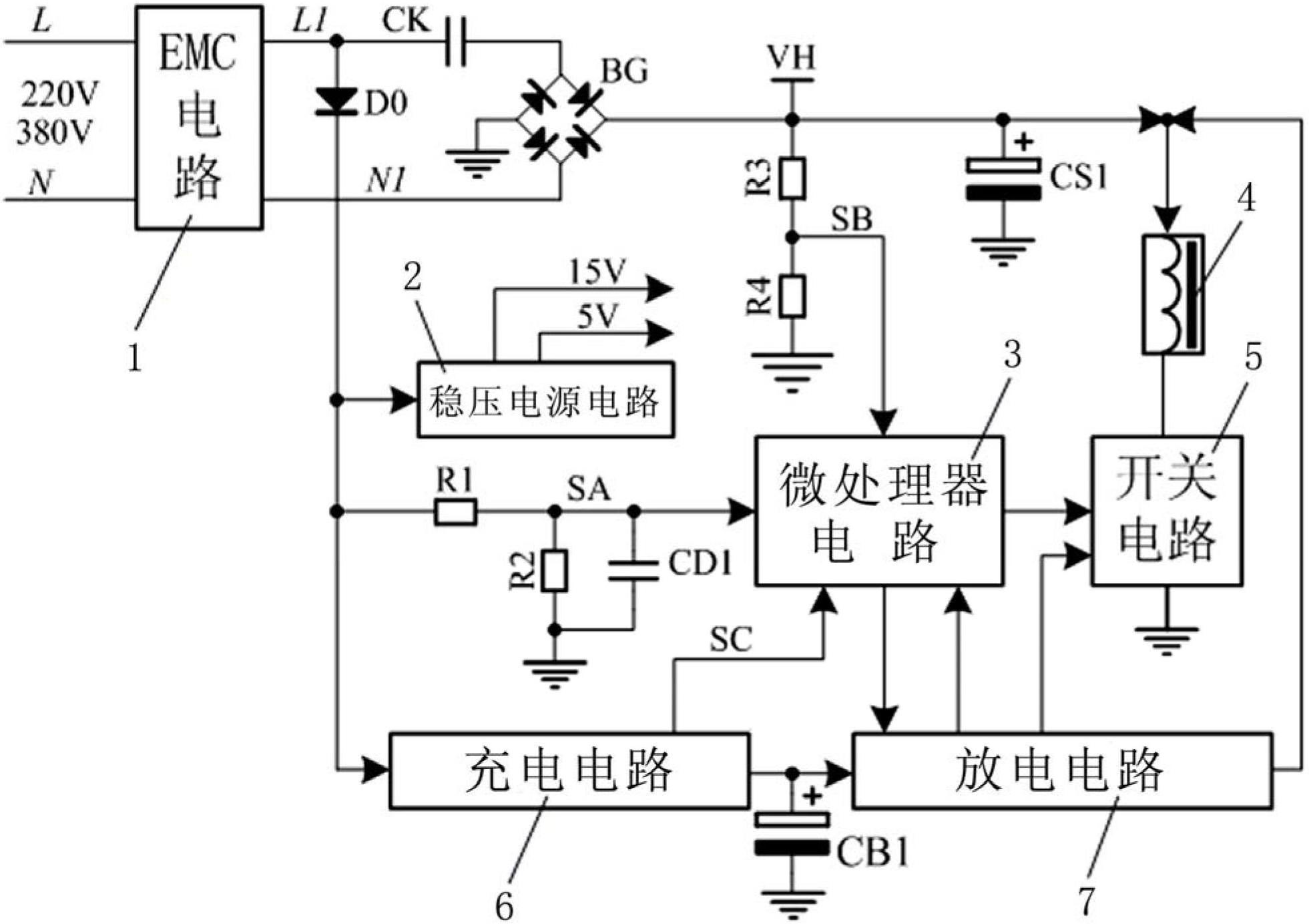

Zero-voltage delay release

ActiveCN102709876ALow calorific valueReduce power consumptionEmergency protective arrangements for automatic disconnectionPower gridPower circuits

The invention relates to the field of releases, in particular to a zero-voltage delay release, which comprises a filter circuit, a starting power circuit, an electromagnet for releasing control, a switching circuit, a delay circuit for controlling delay releasing, a control circuit for controlling the turn-on / off of the switching circuit, and a regulated power circuit for supplying power to the switching circuit and the control circuit, wherein the power input end of the filter circuit is connected with a power grid, and the power output end of the filter circuit is connected with the power input end of the starting power circuit; and the power output end of the starting power circuit, the switching circuit and a coil of the electromagnet form a series loop. The zero-voltage delay release is simple in circuit, high in starting torque, reliable in closing, low in coil heat and high in charging speed; and after zero voltage, the power of the coil (the retention of an armature) is maintained to be constant, and delay time is long.

Owner:JIANGSU GUOXING ELECTRIC EQUIP

Switching regulator

ActiveUS7088083B2Long delay timeMiniaturization possibleDc-dc conversionElectronic switchingWork periodDelayed time

Owner:ABLIC INC

Engine fuel supply control device

InactiveUS7285073B2Reduce latencyIncrease delay timeElectrical controlMachines/enginesDelayed timeOperant conditioning

An engine fuel supply control device is configured to stop supplying fuel to an engine when specific fuel cut-off condition has been met. The timing of the fuel cut-off is delayed depending on an operating state of the vehicle. Preferably, the engine fuel supply control device has an operating state detection section that detects an operating condition (e.g., a clutch position or a shifting operation), and a fuel supply stoppage section that stops supplying fuel to the engine when a specific delay time has elapsed since the specific fuel cut-off condition was met. Preferably, the fuel supply stoppage section selectively sets the specific delay time to a different delay time depending upon the detected operating condition detection, e.g., a first delay time is set if either the clutch is detected as disengaged or a shifting operation is detected as being in progress, otherwise a different delay time is set.

Owner:NISSAN MOTOR CO LTD

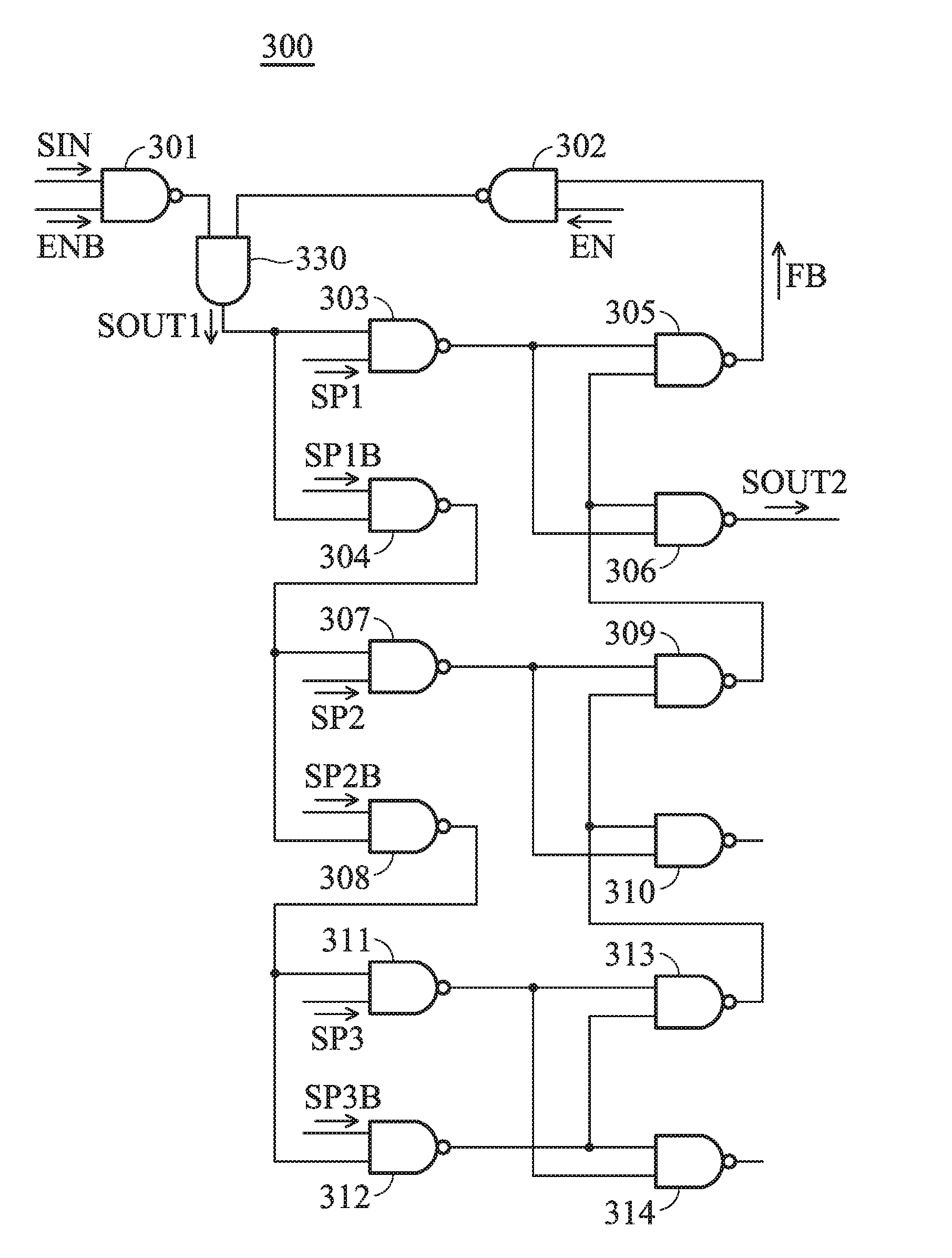

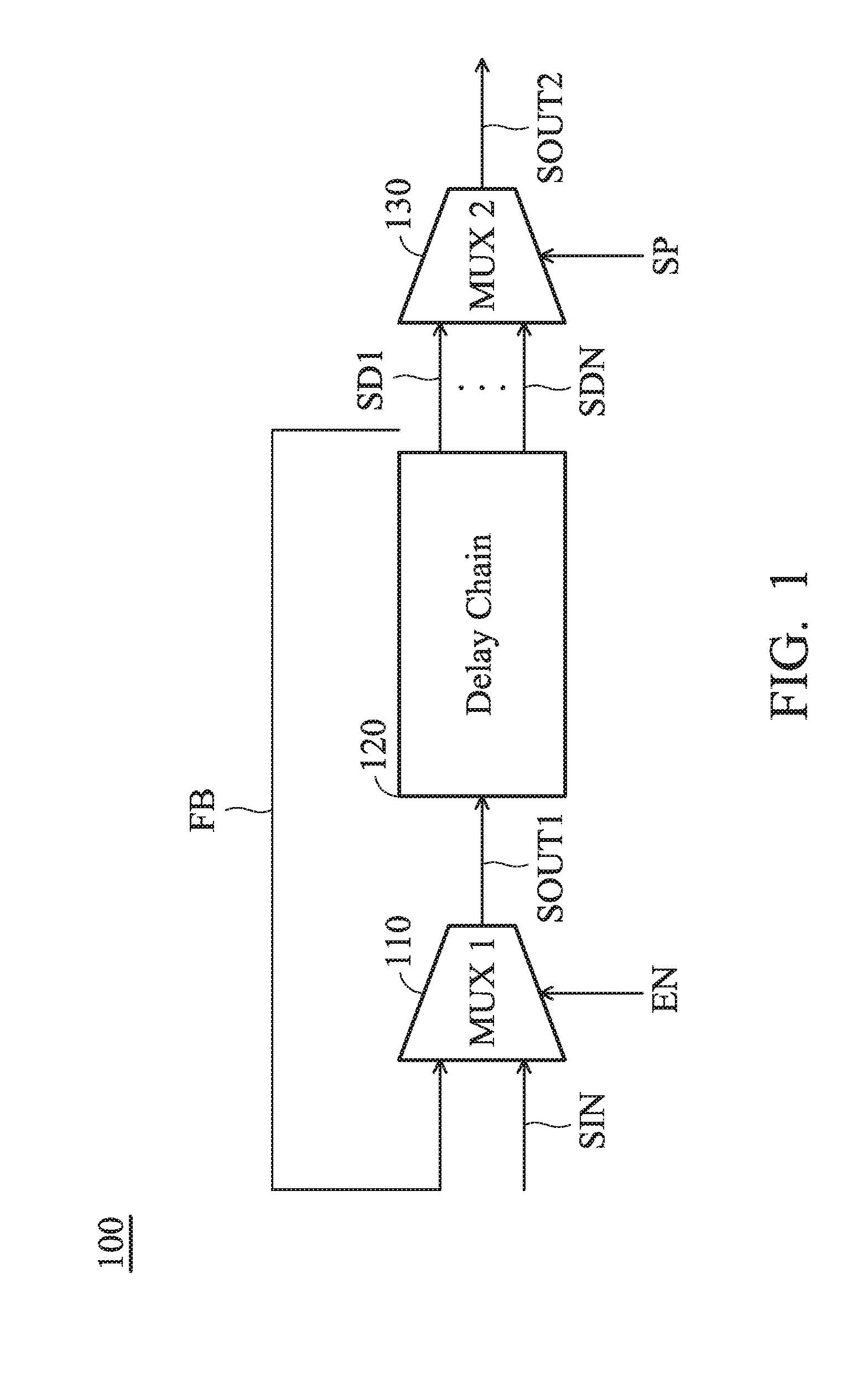

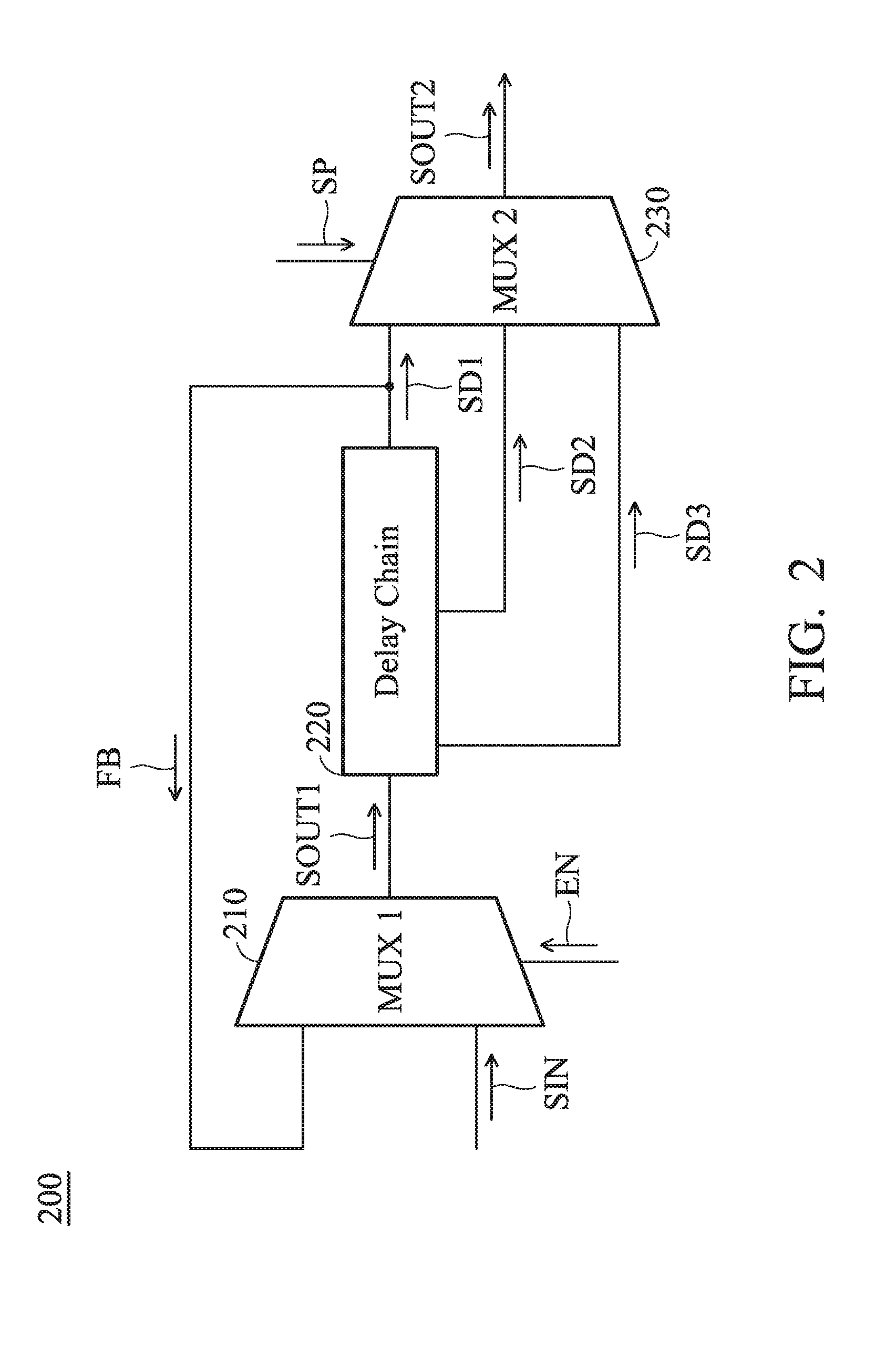

Tunable delay circuit and operating method thereof

ActiveUS20160211835A1Short delay timeShorten the timeLogic circuits characterised by logic functionSingle output arrangementsMultiplexerEngineering

A tunable delay circuit includes a first multiplexer, a delay chain, and a second multiplexer. The first multiplexer selects an input signal or a feedback signal as a first output signal according to an enable signal. The delay chain delays the first output signal for different time periods so as to generate a plurality of delay signals. One of the delay signals is used as the feedback signal. The second multiplexer selects one of the delay signals as a second output signal according to a pass signal.

Owner:MEDIATEK SINGAPORE PTE LTD SINGAPORE

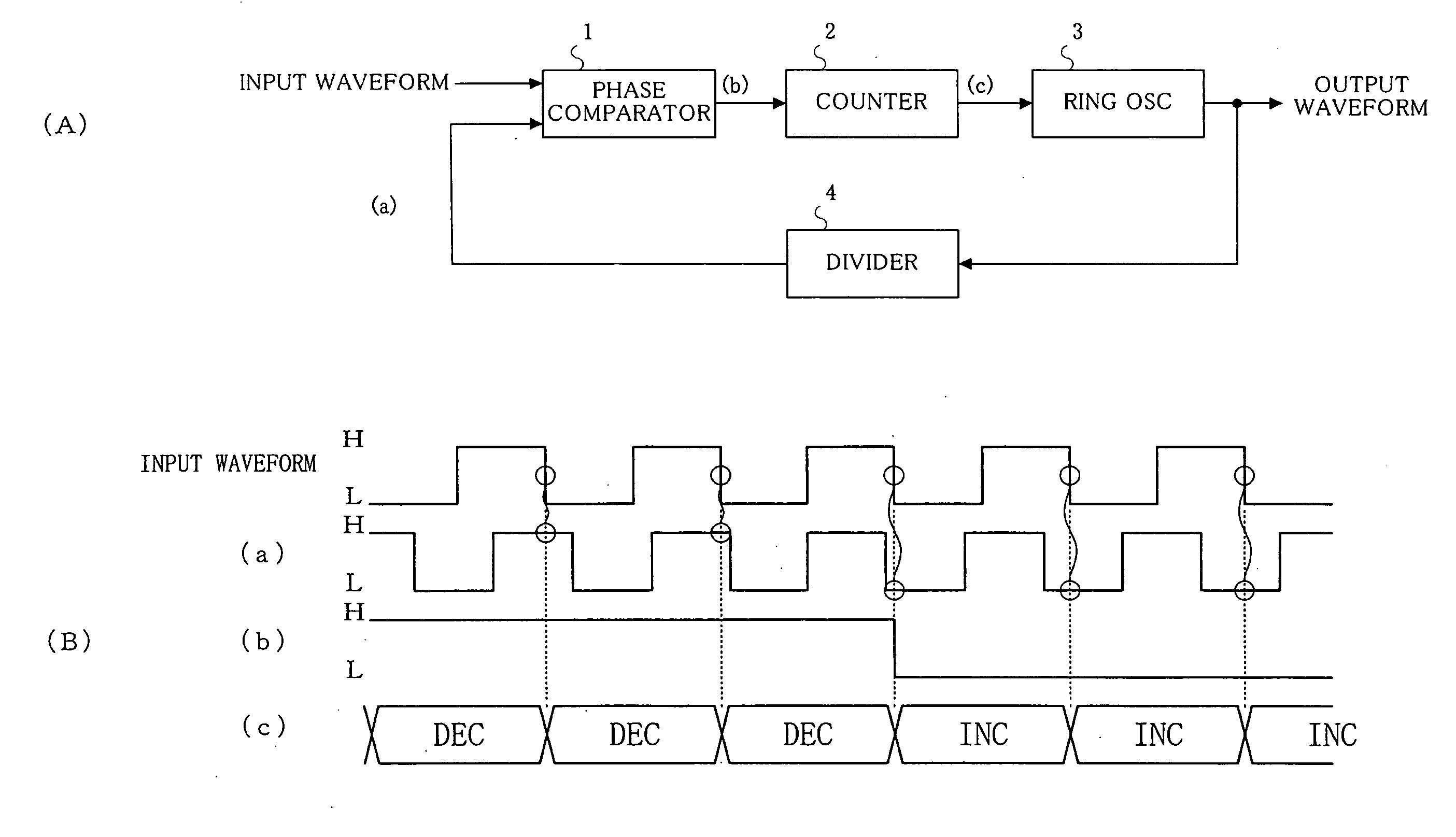

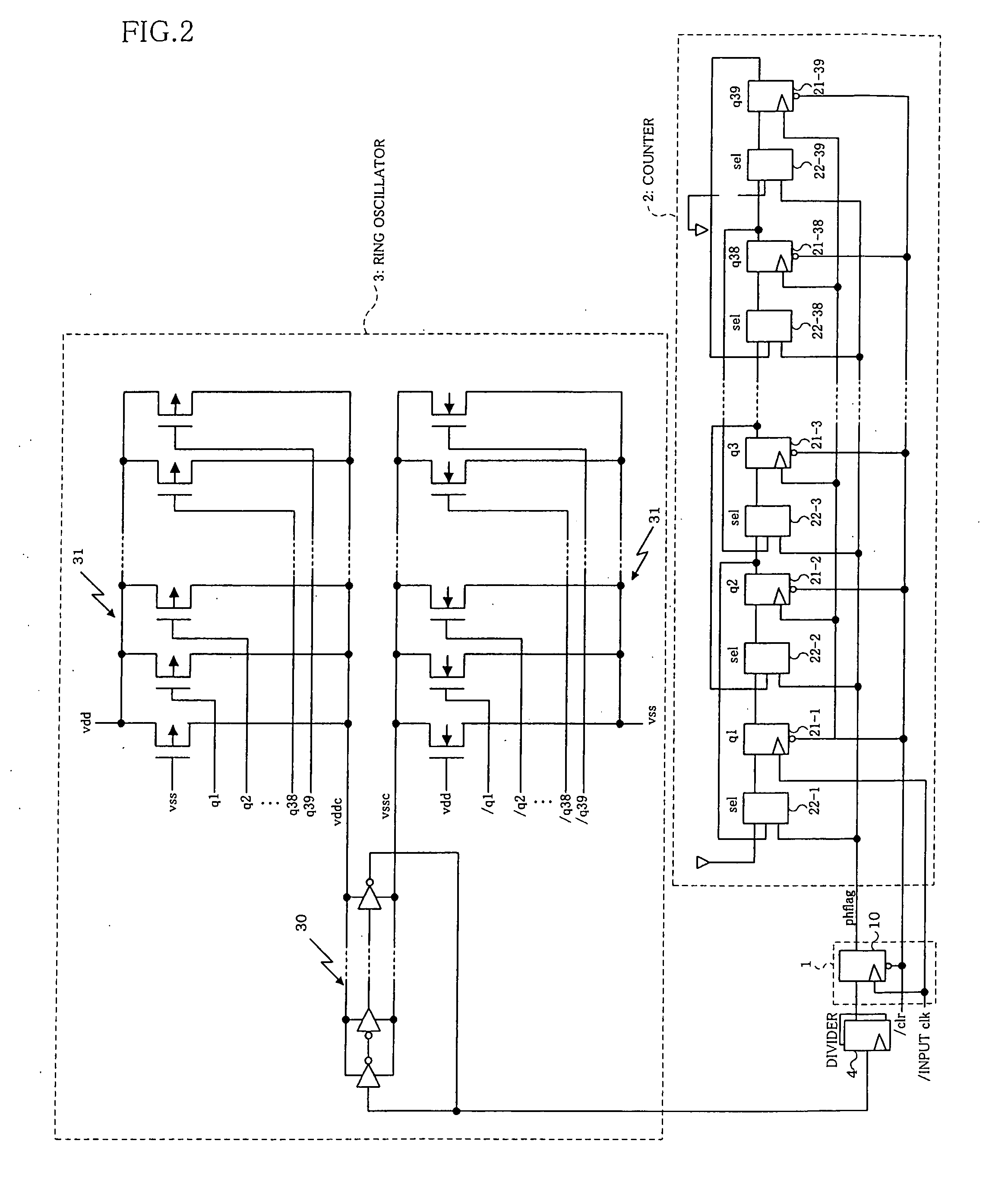

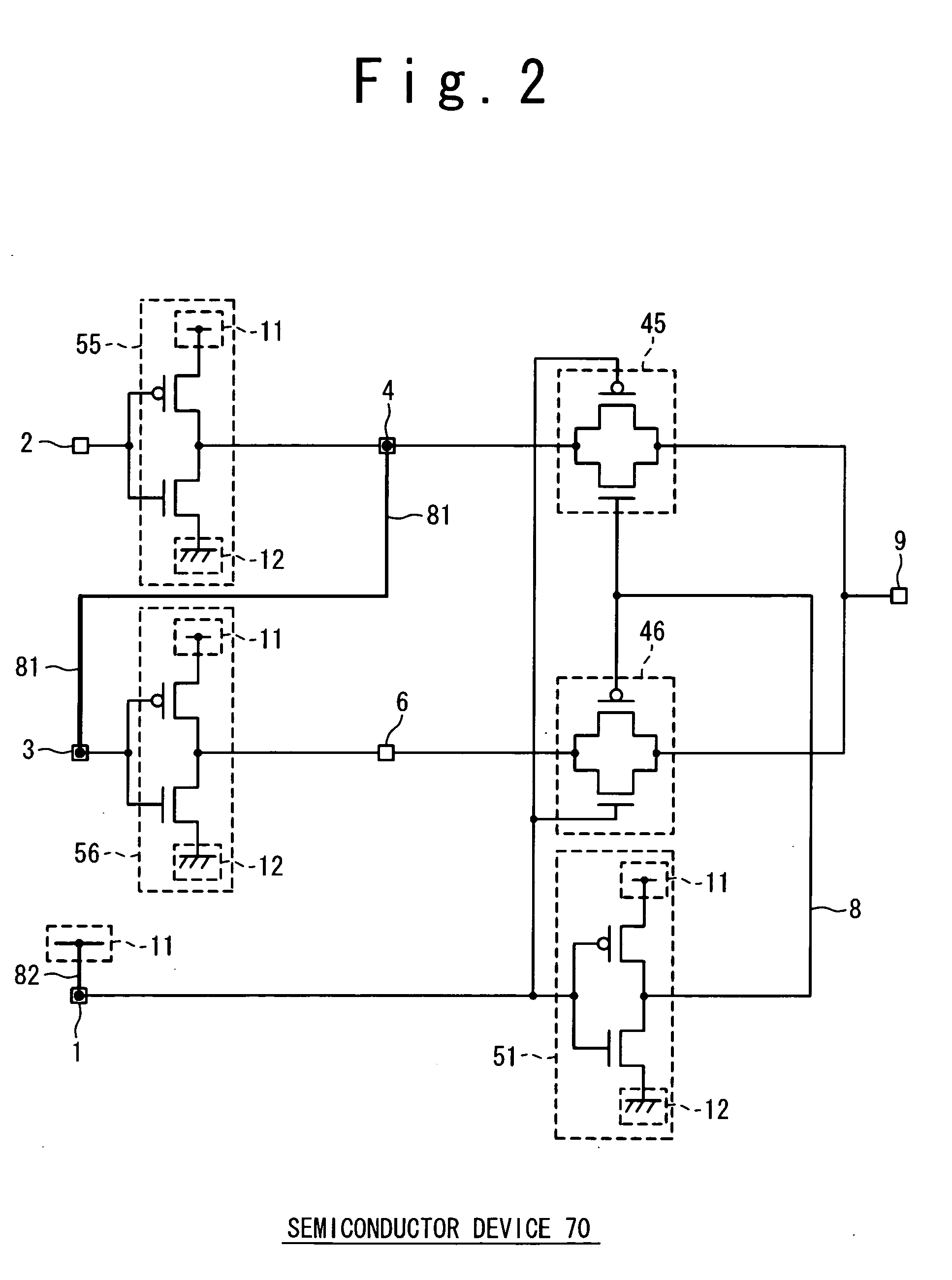

Phase-locked loop circuit, delay locked loop circuit, timing generator, semiconductor test instrument, and semiconductor integrated circuit

InactiveUS20080143399A1Improve reliabilityReduce errorsPulse automatic controlVoltage-current phase angleControl signalPhase locked loop circuit

A PLL and DLL are designed such that the power consumption can be reduced, the size can be easily reduced, the band of the locked loop can be a higher one, and the reliability can be improved. There are provided a phase comparator for measuring a feedback signal in synchronism with an input signal and outputting a phase signal representing the lead or lag of the phase of the feedback signal, a counter for increasing the number of bits representing “H” in a control signal when the phase signal represents the lead or decreasing the number of bits representing “H” in the control signal when the phase signal represents the lag, and a ring oscillator for increasing the oscillation period when the number of bits representing “H” increases or decreasing the oscillation period when the number of bits representing “H” decreases.

Owner:ADVANTEST CORP

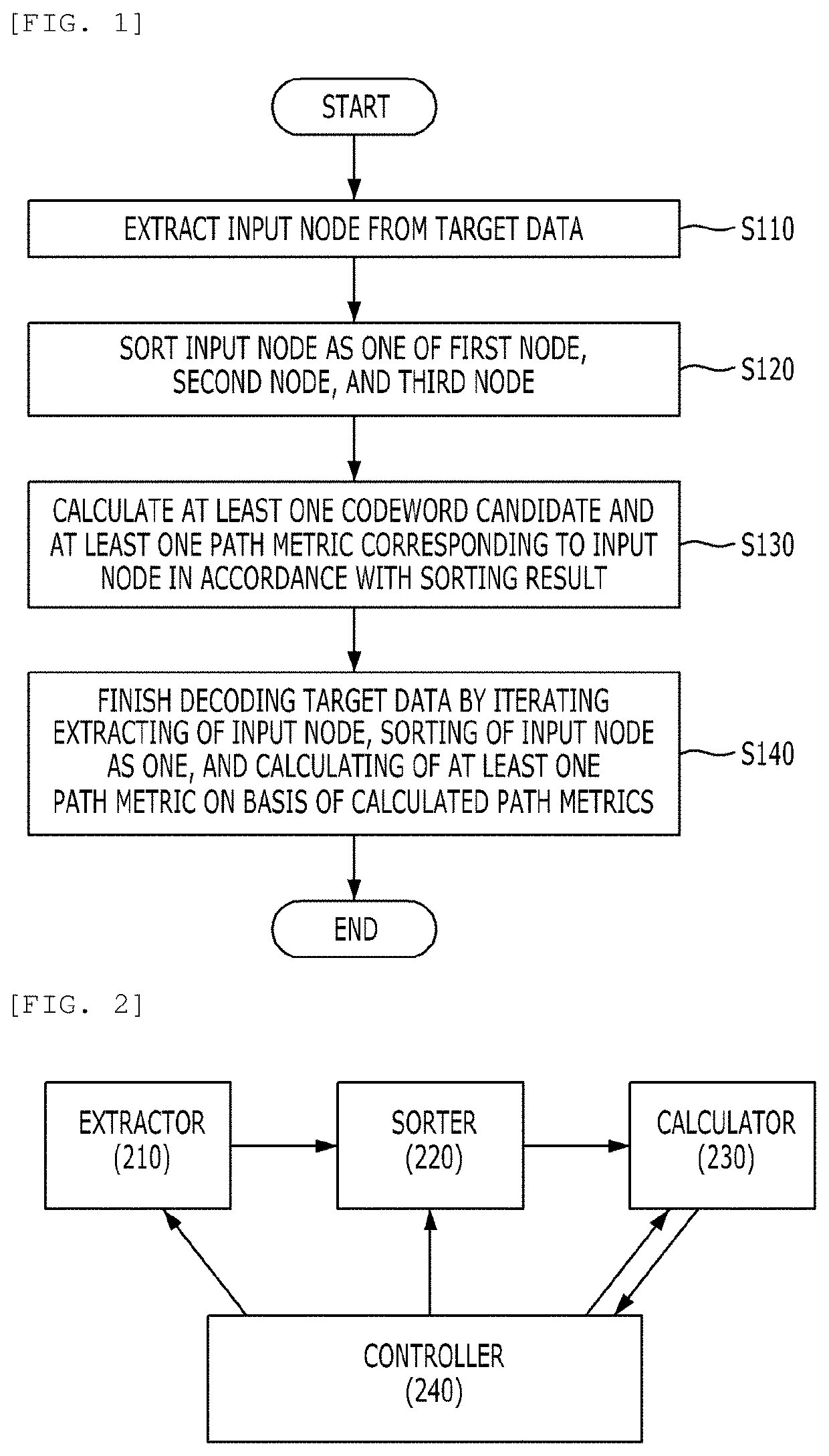

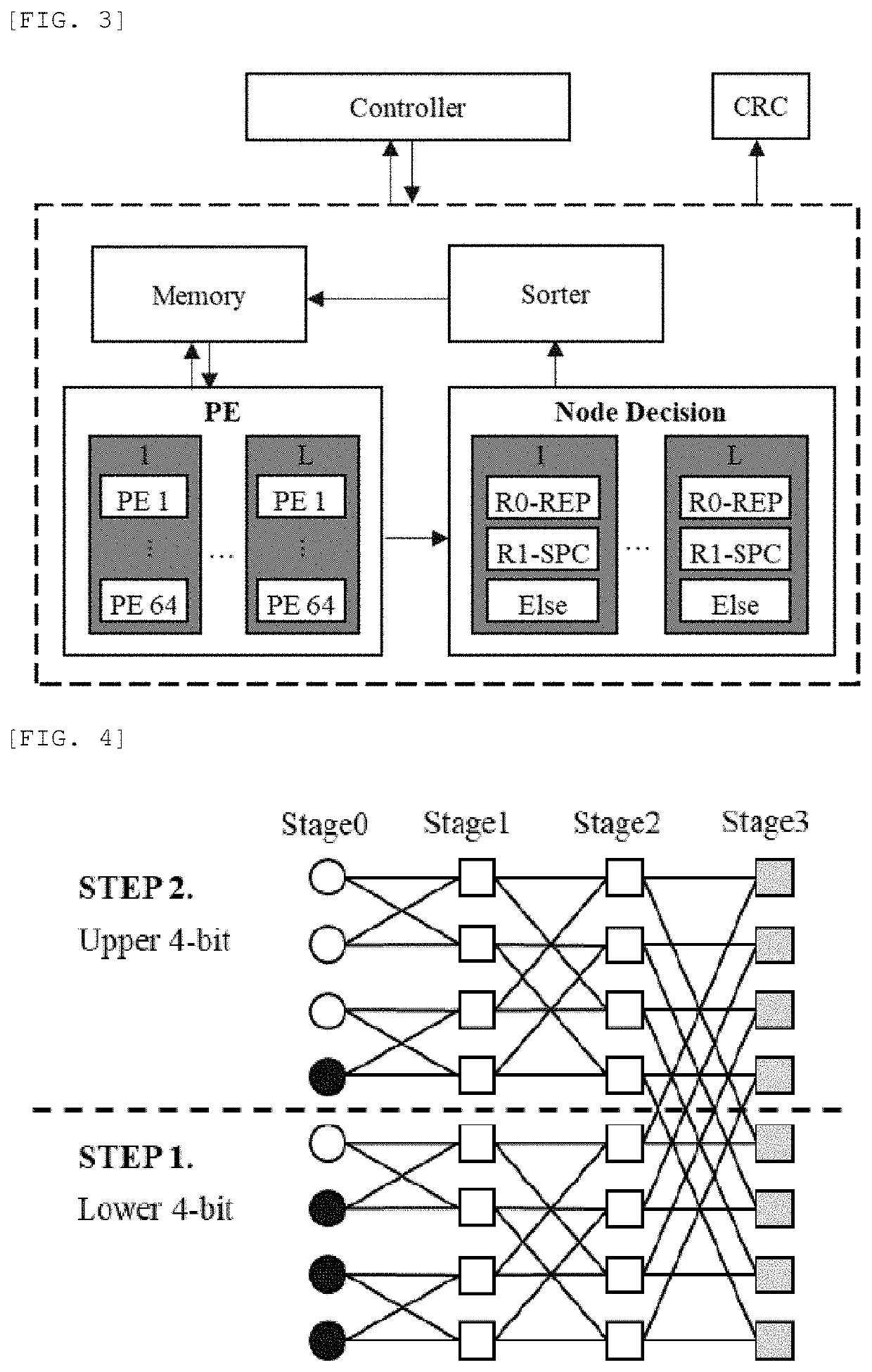

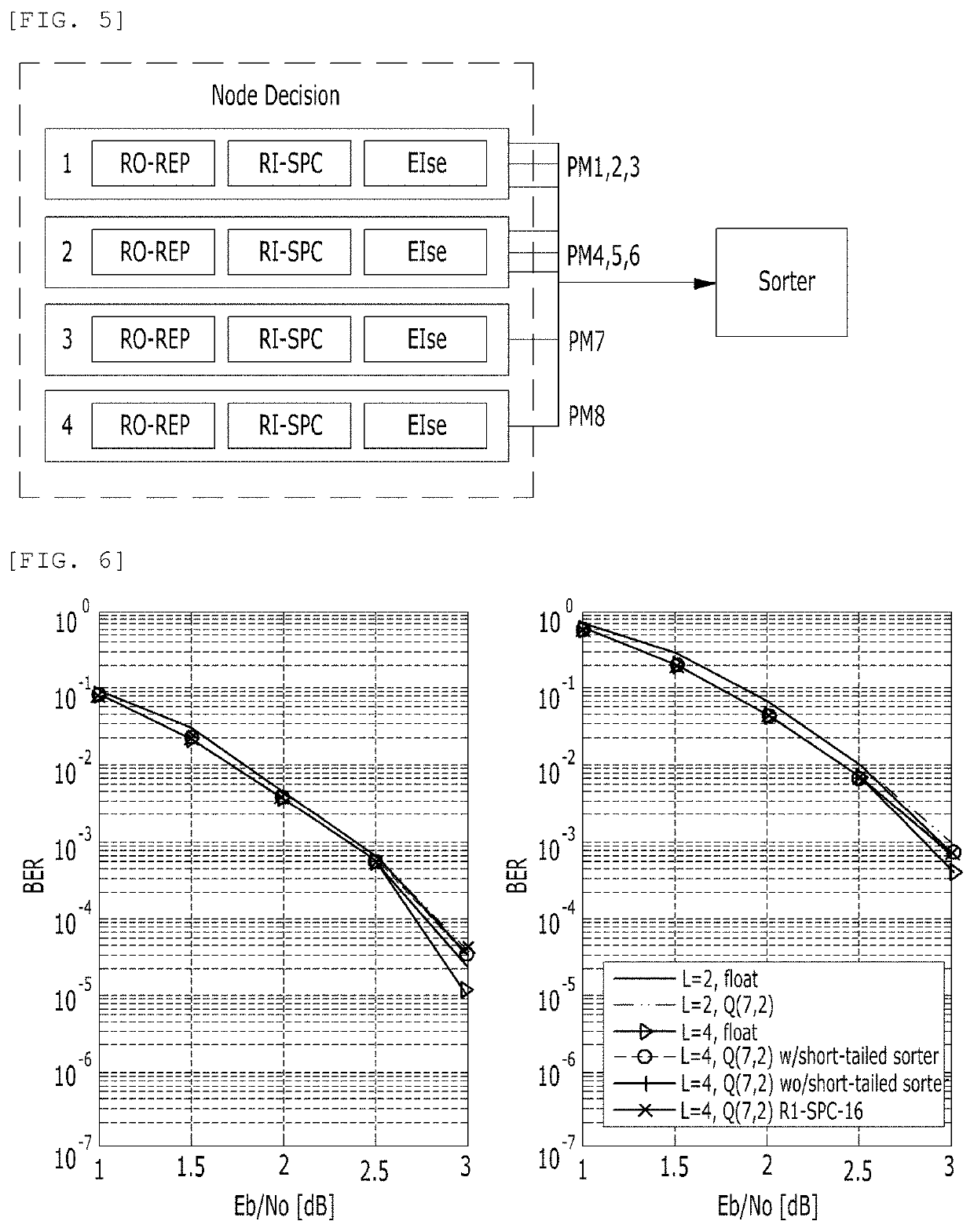

Method and apparatus for decoding polar codes based on shared node

ActiveUS20200266840A1Long delay timeShorten the timeOther decoding techniquesCode conversionPathPingAlgorithm

The present disclosure a method of decoding a polar code based on a shared node, the method includes extracting an input node from target data that are data to be decoded, by an extractor, sorting the input node as one of a first node of which the pattern of the frozen bit satisfies a predetermined first reference, a second node of which the pattern of the information bit satisfies a predetermined second reference, and a third node that is not the first node and the second node, by a sorter, calculating at least one codeword candidate and at least one path metric that correspond to the input node in accordance with the sorting result by a calculator, finishing decoding the target data by iterating the extracting, the sorting as one, and the calculating of at least one path metric by a controller.

Owner:AJOU UNIV IND ACADEMIC COOP FOUND

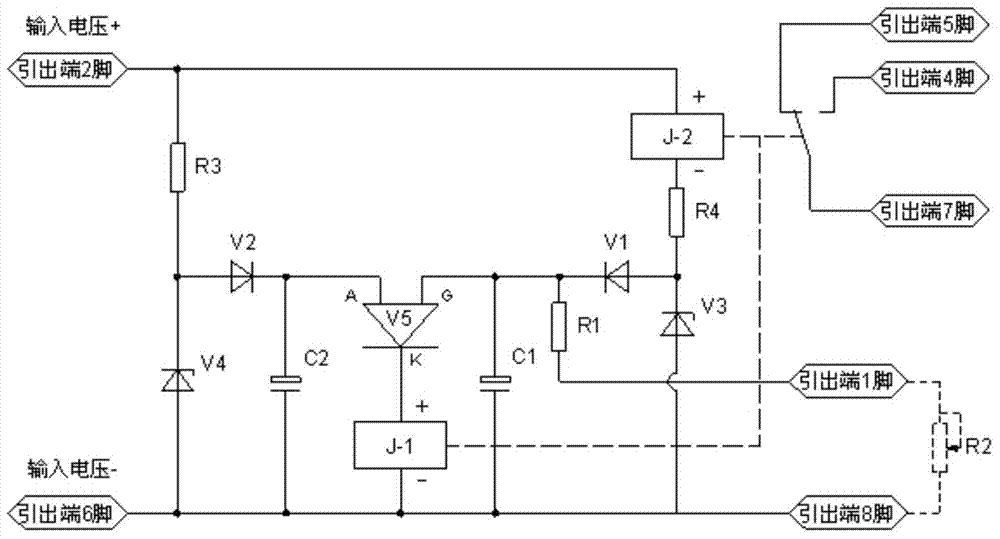

Small sealing release delay relay with long delay time

The invention relates to a small sealing release delay relay with long delay time. A programmable unijunction transistor V5 is taken as a potential comparison and drive element, a contact of a sealing magnetic latching relay J is taken as an output switching contact, and a three-layer structure design is adopted. The size is small, the environmental adaptation performance is good, the reliability is high, the delay time is up to 1200s, and the leakage rate is less than or equal to 1*10<-1>Pa.cm<3> / s.

Owner:SHAANXI QUNLI ELECTRIC

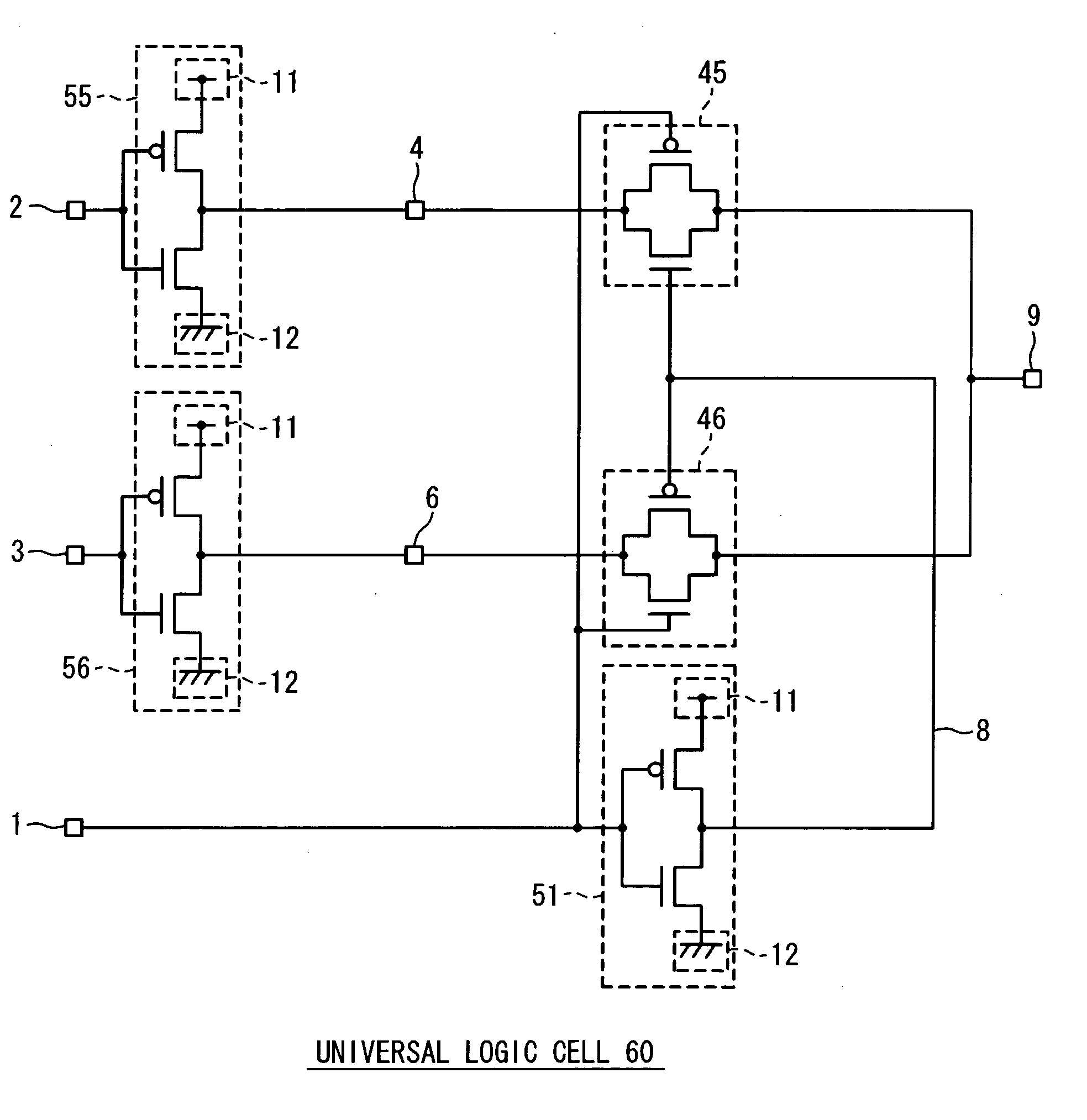

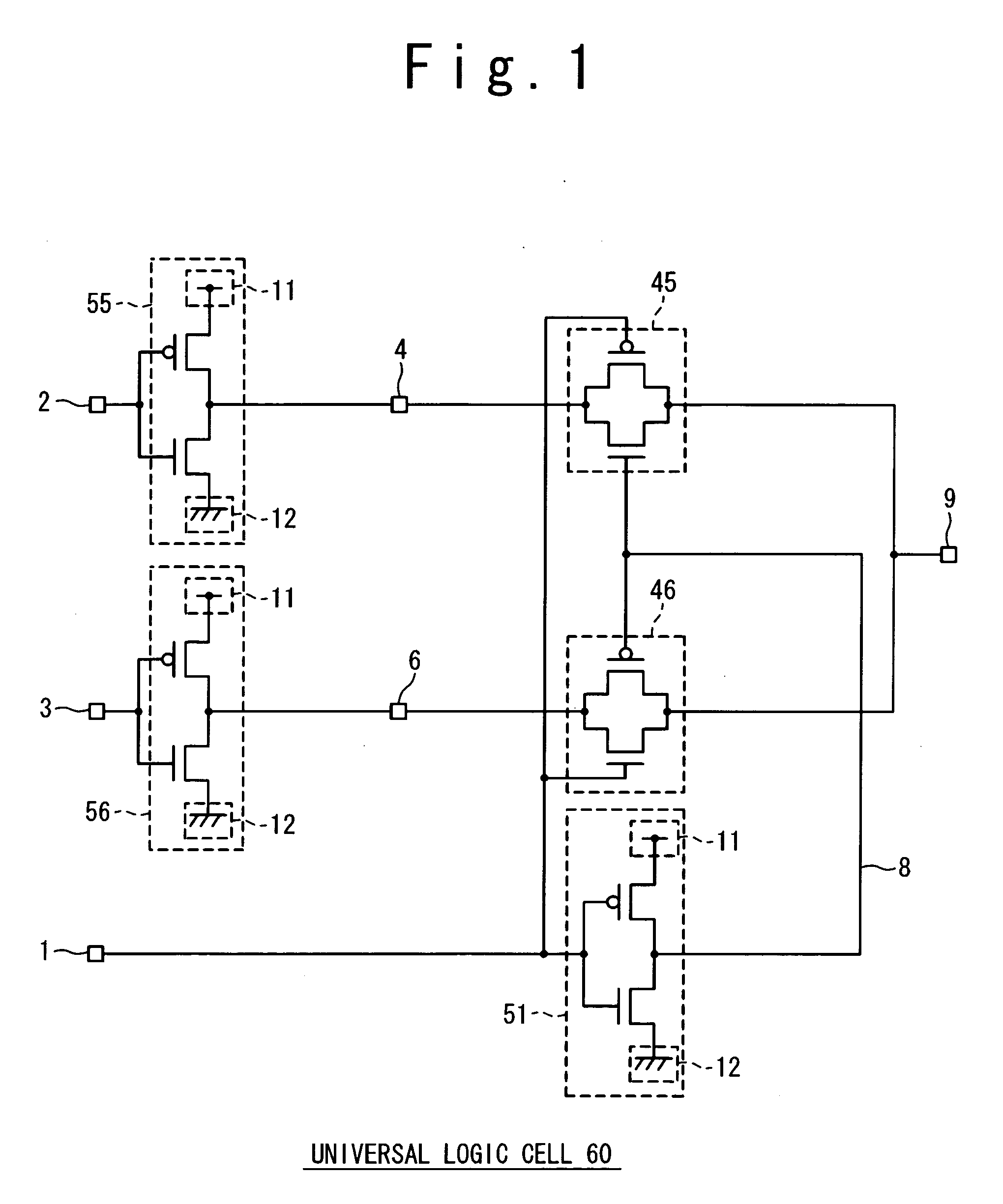

Semiconductor device and manufacturing method of the same

InactiveUS20060033526A1Efficient processReduce development costsLogic circuits characterised by logic functionSolid-state devicesLogic cellDevice material

A semiconductor device has a plurality of universal logic cells, a power supply line, a ground line, a first interconnection and a second interconnection. Each universal logic cell includes first to seventh nodes formed in a top layer of common interconnection layers which are allocated to the universal logic cells. The first interconnection connects the third node, the fourth node and the fifth node, and the second interconnection connects the power supply line and the first node. Or, the first interconnection connects the second node, the sixth node and the seventh node, and the second interconnection connects the ground line and the first node. The first and second interconnections are formed in a customize interconnection layer provided on the common interconnection layers.

Owner:RENESAS ELECTRONICS CORP

Valid data merging method, memory controller and memory storage apparatus

ActiveUS9880742B2Reduce delaysEfficient solutionMemory architecture accessing/allocationInput/output to record carriersComputer hardwareMemory controller

A valid data merging method, a memory controller and a memory storage apparatus are provided. The method includes: selecting a first physical erasing unit, and loading a first logical address-physical address mapping table according to a physical address-logical address mapping table. The method also includes: updating the first logical address-physical address mapping table according to the physical address-logical address mapping table, and identifying valid data in the first physical erasing unit according to the physical address-logical address mapping table and the first logical address-physical address mapping table. The method further includes: storing the first logical address-physical address mapping table, copying the valid data to a second physical erasing unit, and performing an erasing operation for the first physical erasing unit.

Owner:PHISON ELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com