Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

176results about How to "Increase delay time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

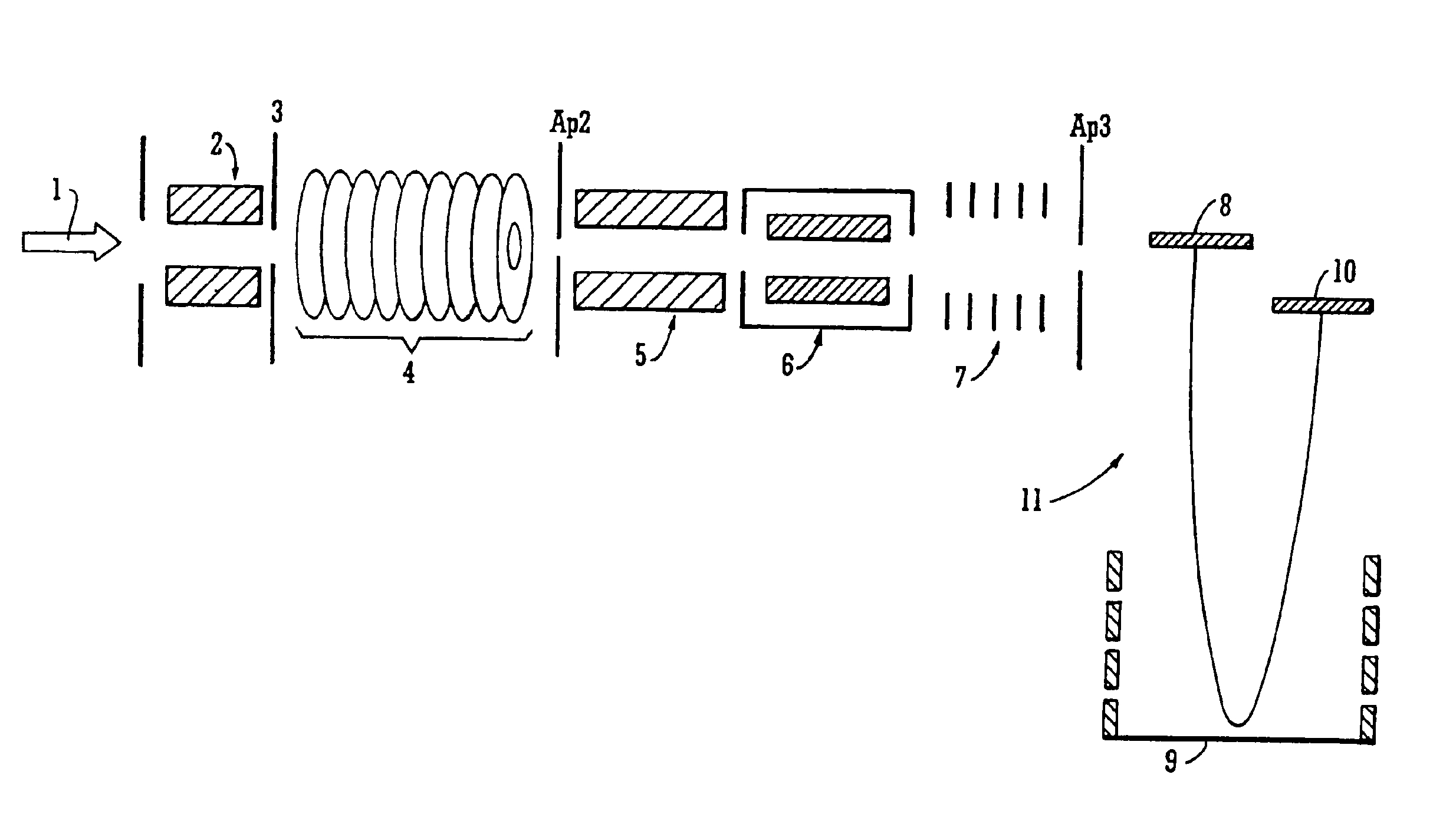

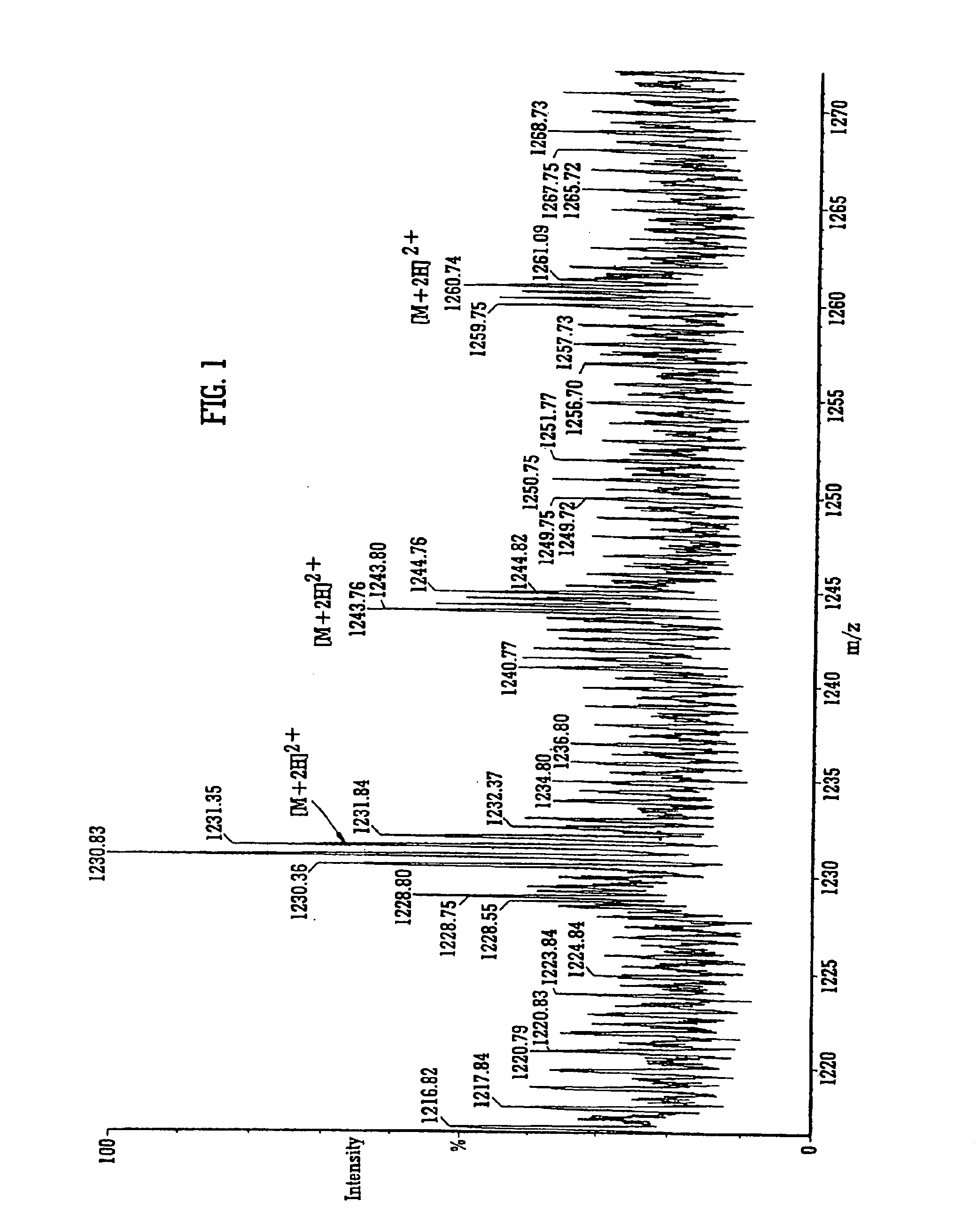

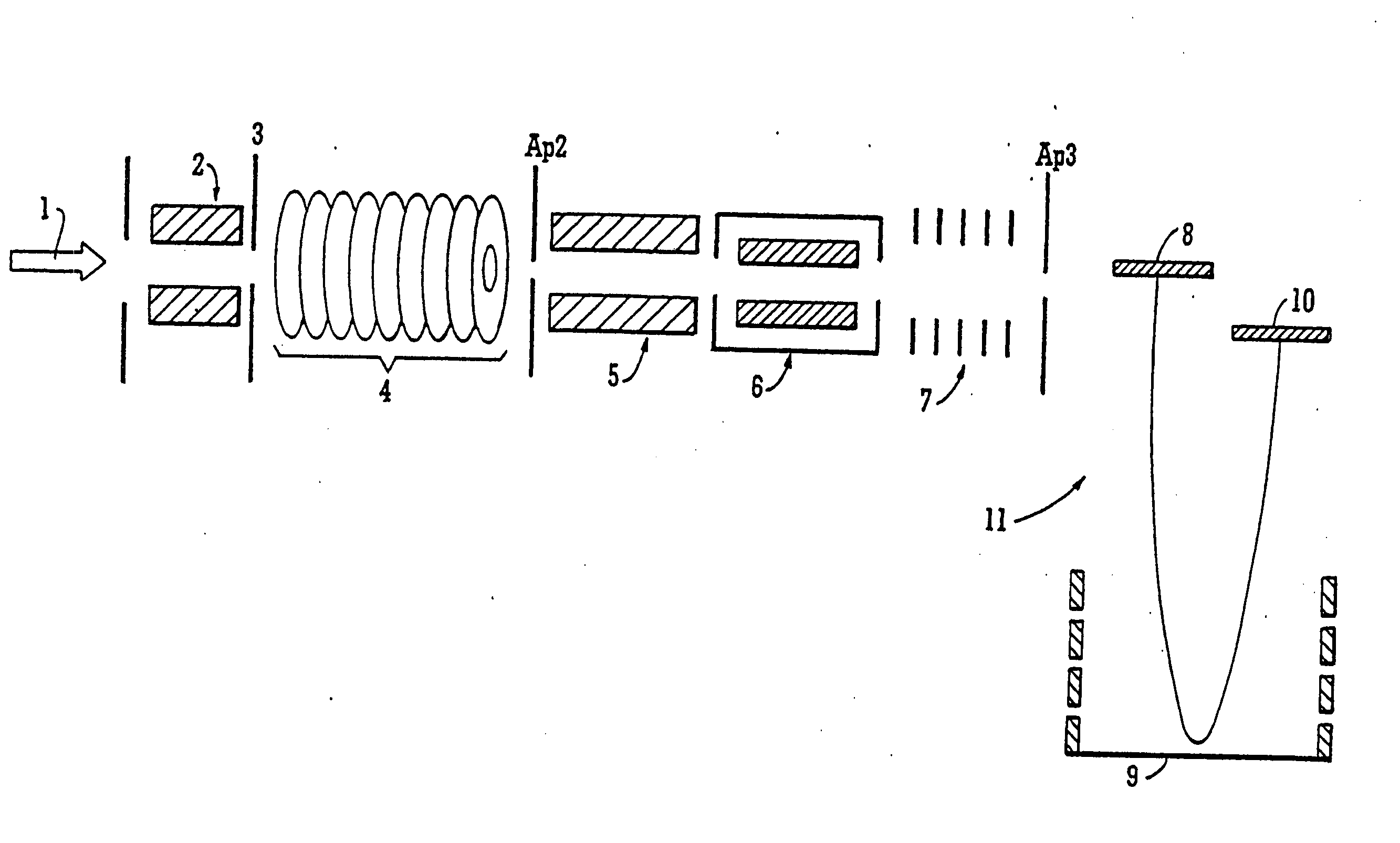

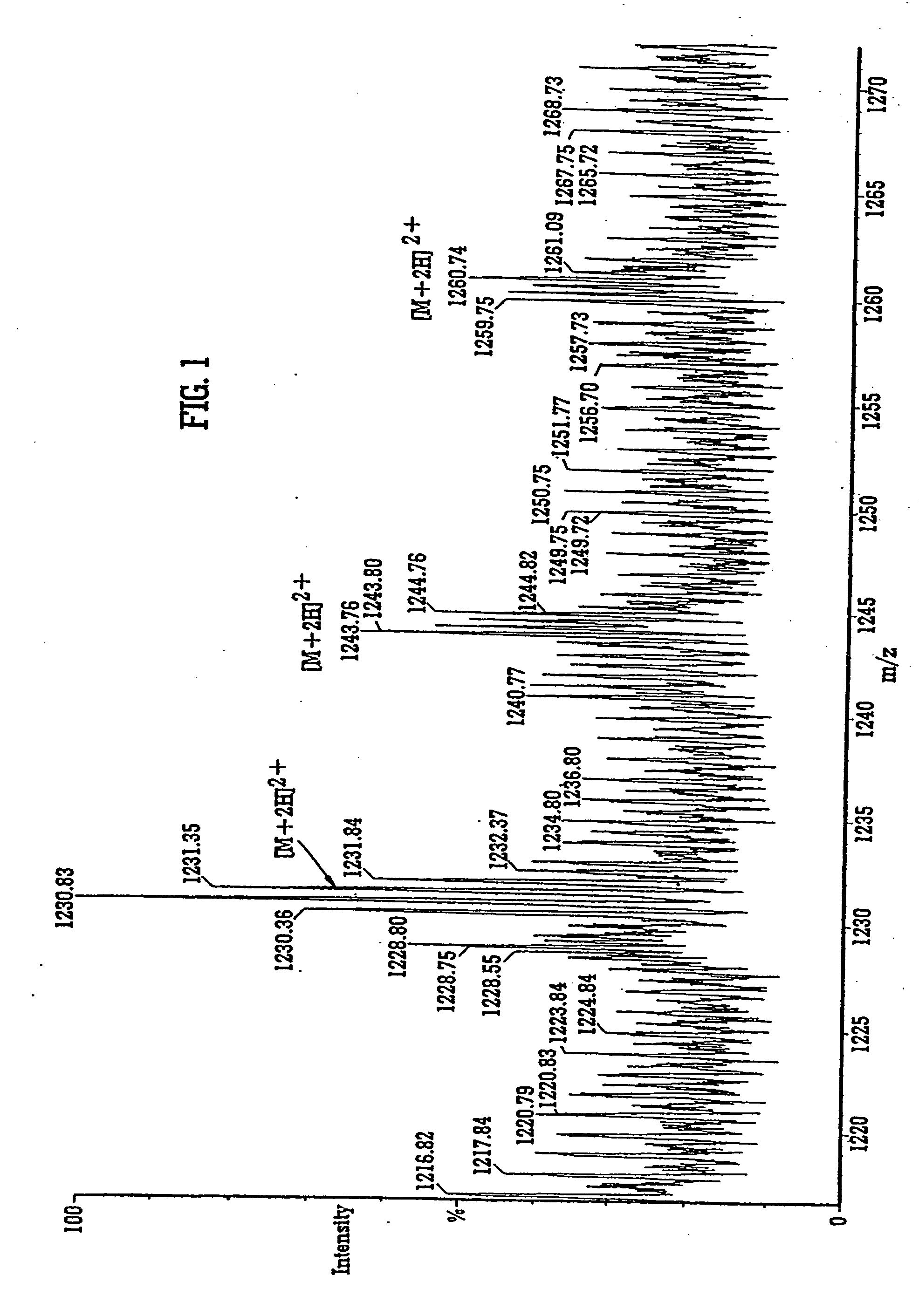

Mass spectrometer

InactiveUS6906319B2High sensitivityIncrease delay timeStability-of-path spectrometersTime-of-flight spectrometersIon trap mass spectrometryMass analyzer

A mass spectrometer is disclosed wherein ions having a particular desired charge state are selected by operating an ion mobility spectrometer in combination with a quadrupole mass filter. Precursor ions are fragmented or reacted to form product ions in a collision cell ion trap and sent back upstream to an upstream ion trap. The fragment or product ions are then passed through the ion mobility spectrometer wherein they become temporally separated according to their ion mobility. Fragment or product ions are then re-trapped in the collision cell ion trap before being released therefrom in packets. A pusher electrode of a time of flight mass analyzer is energized a predetermined period of time after a packet of ions is released from the collision cell ion trap. Accordingly, it is possible to select multiply charged precursor ions from a background of singly charged ions, fragment them, and mass analyze the fragment ions with a near 100% duty cycle across the whole mass range.

Owner:MICROMASS UK LTD

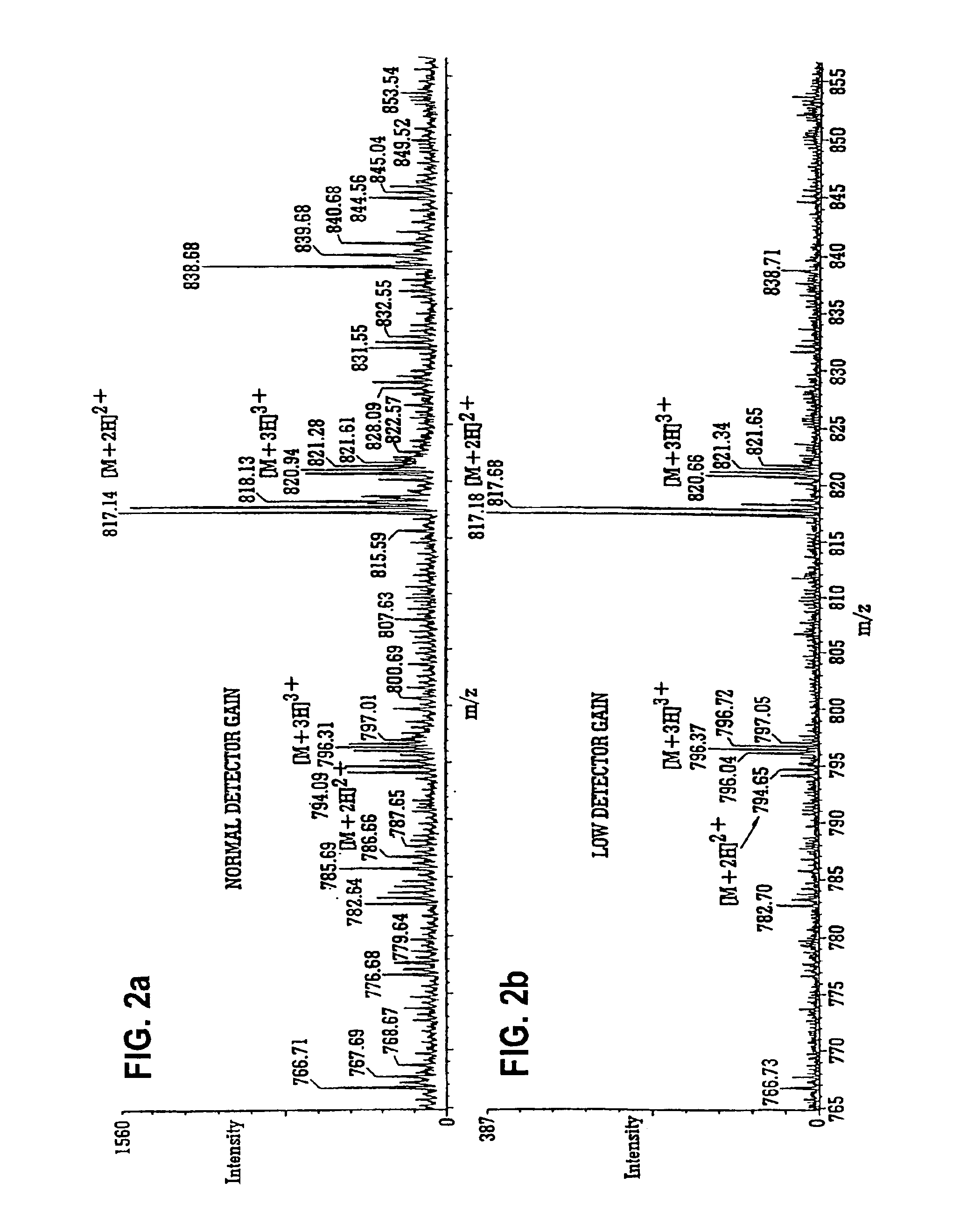

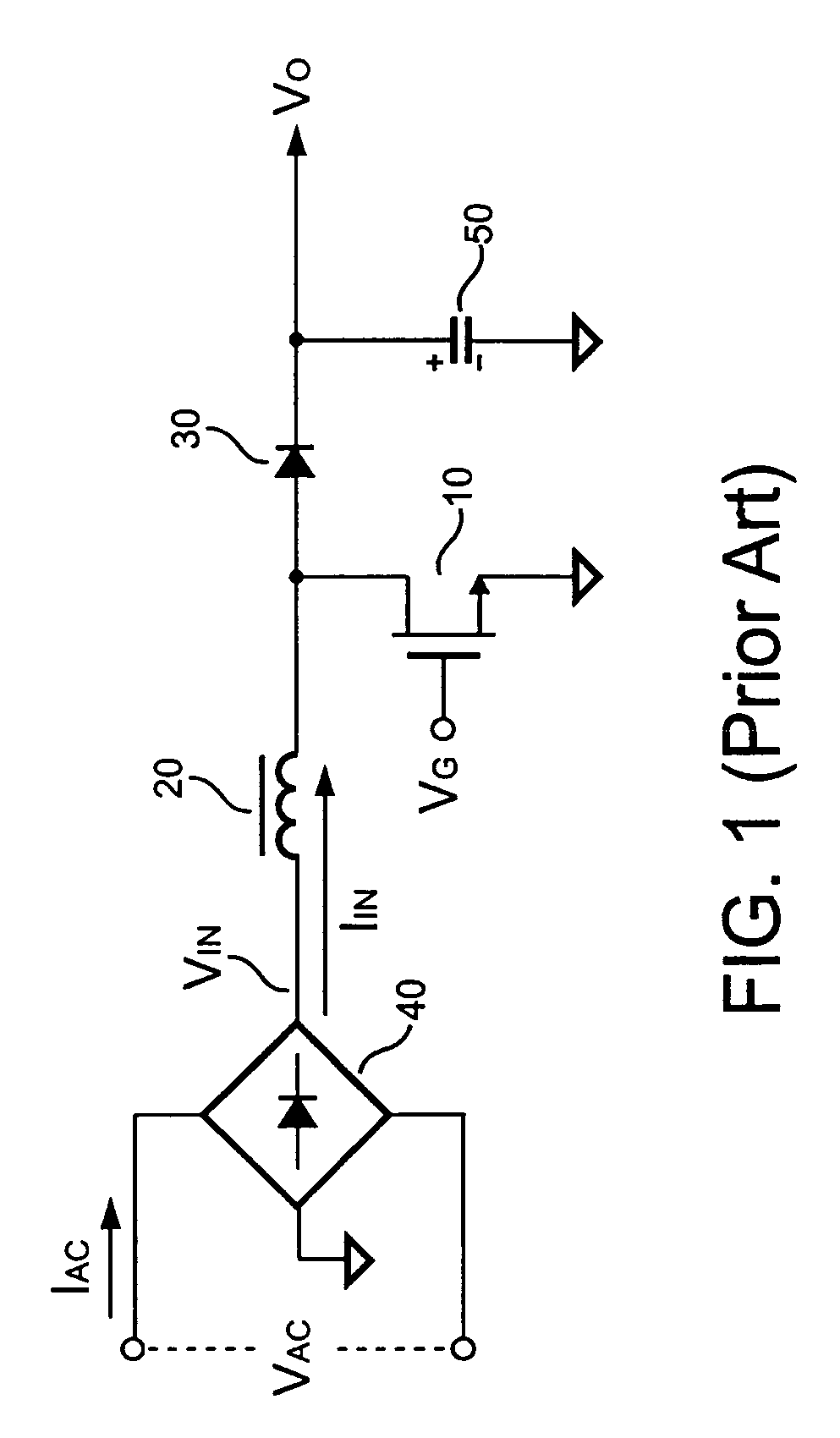

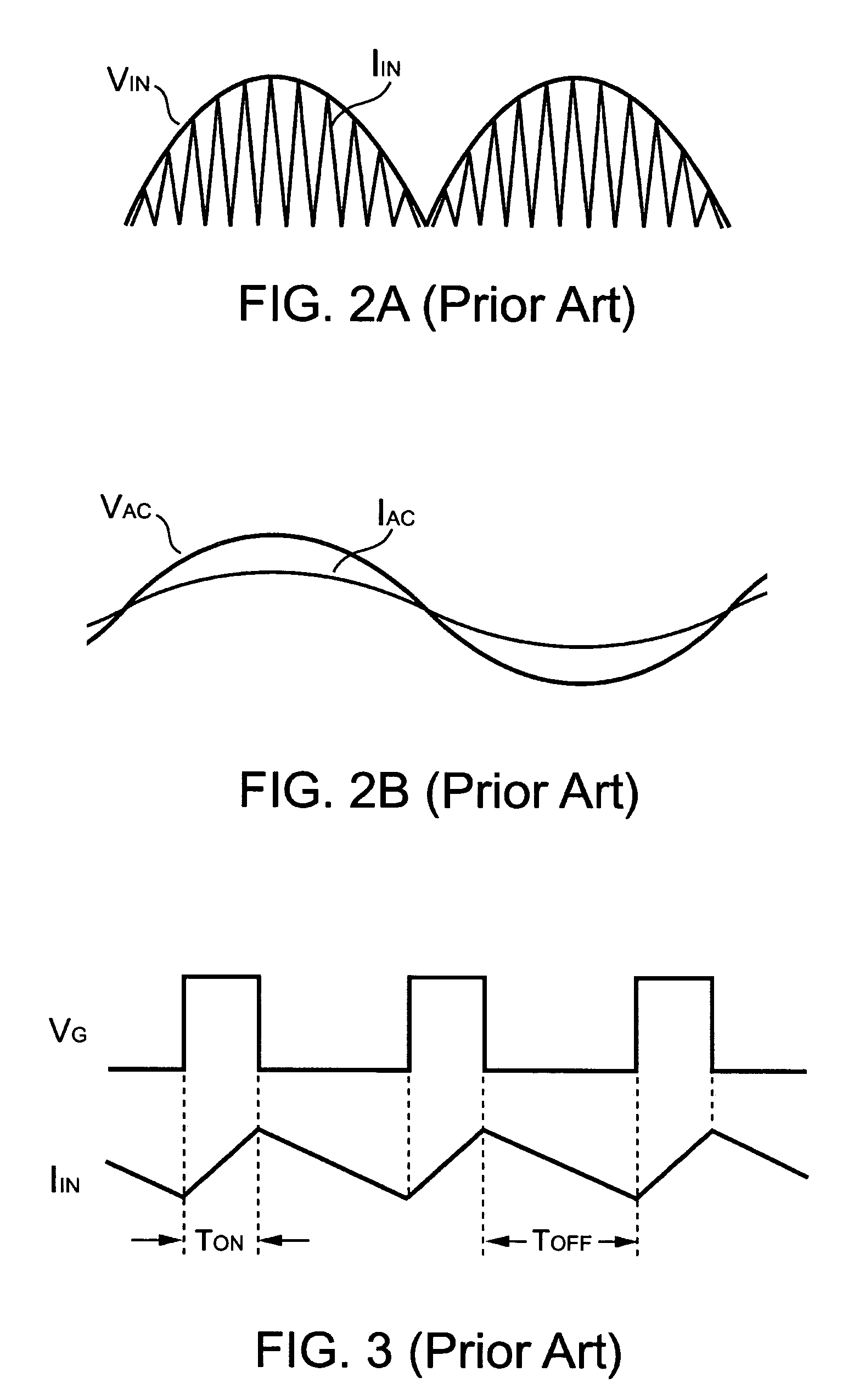

Switching control circuit for discontinuous mode PFC converters

ActiveUS7116090B1Reduce power consumptionDelay time increaseEfficient power electronics conversionElectric variable regulationInductorSlew rate

A switching control circuit having detection terminal, input terminal, ramp generator, program terminal, error amplifier, mix circuit, and delay circuit for power factor control is provided. The detection terminal generates a detection signal in response to the inductor discharge. An input terminal is connected for detecting a switching current signal. The program terminal determines the slew rate of the ramp signal and the maximum on-time of the switching signal. An error amplifier generates an error signal for regulating the output. A mix circuit generates a mixing signal proportional to ramp signal and the switching current signal. The switching signal is turned on in response to the detection signal, and is turned off based on the error signal. The slew rate of the mixing signal is increased in response to the increase of the input voltage. The on-time of the switching signal is increased inversely proportional to the input voltage.

Owner:SEMICON COMPONENTS IND LLC

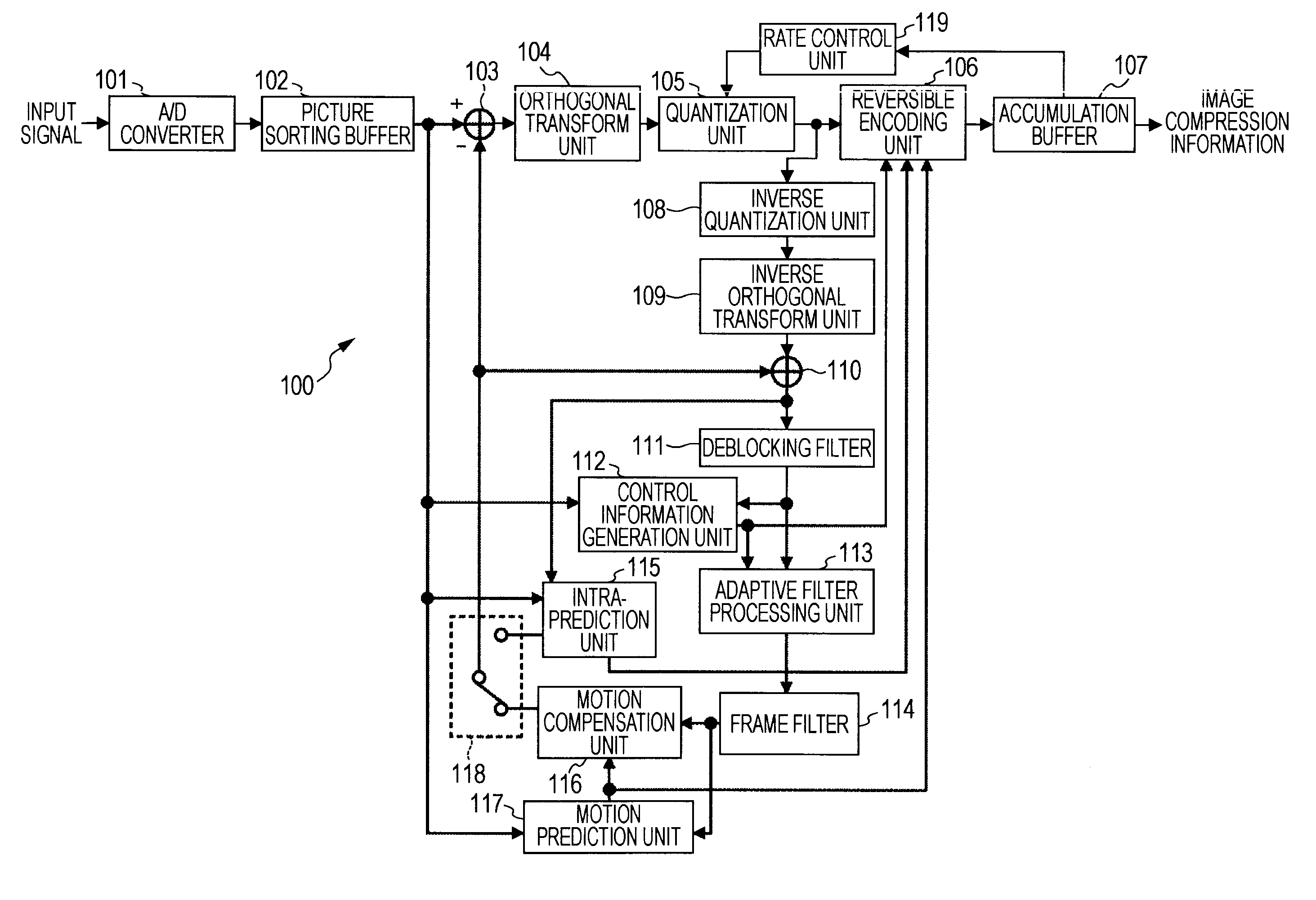

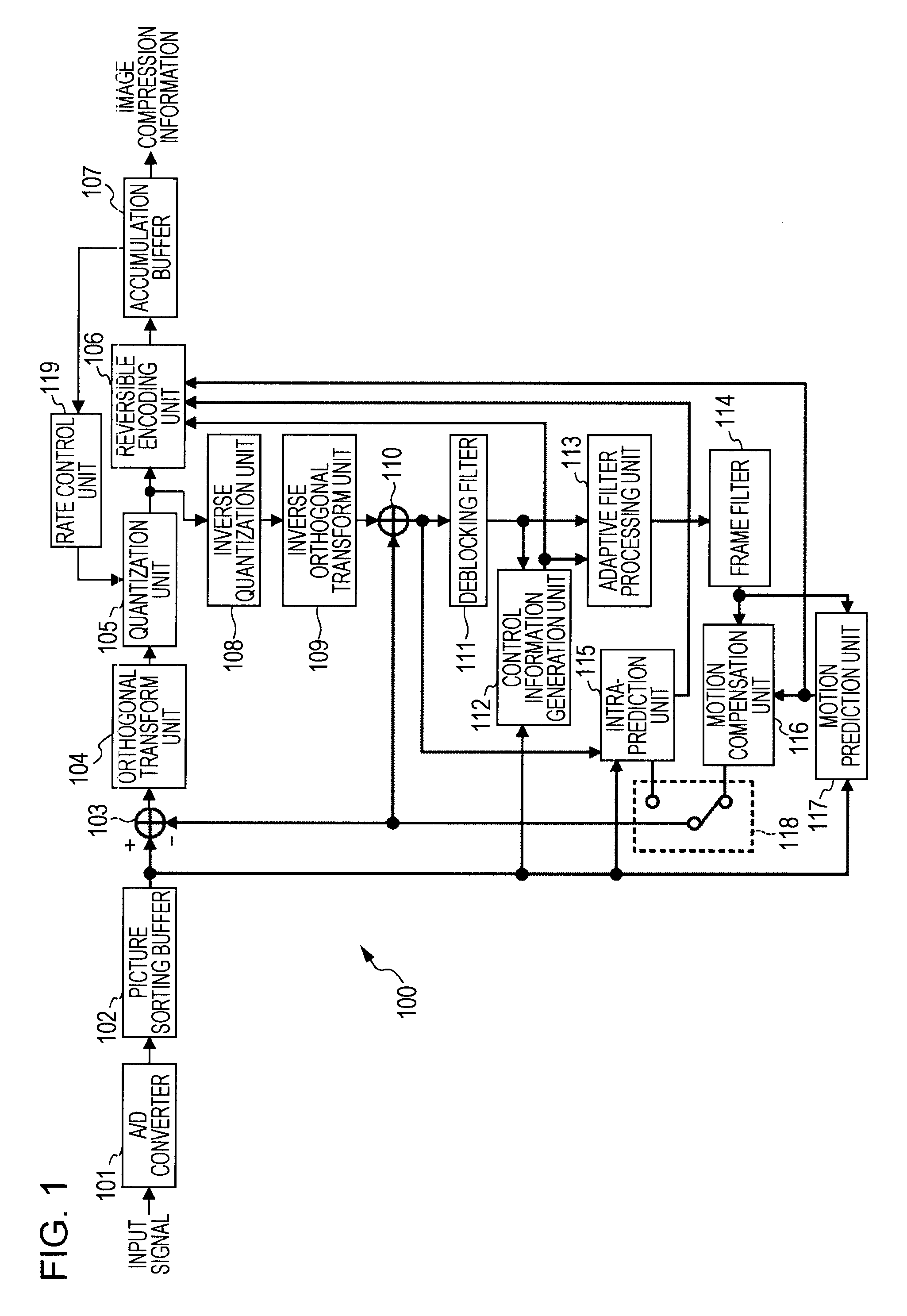

Image processing apparatus and method

ActiveUS20110026600A1Appropriate performanceReduce filter effectColor television with pulse code modulationColor television with bandwidth reductionImaging processingControl unit

Provided is an image processing apparatus which includes a setting unit assigning a control block, which is a control unit of a filter process that is locally performed with respect to an image, to an initial position of the image determined based on a predetermined reference point; a movement unit moving the control block, which has been assigned to the initial position of the image by the setting unit, a to a position in which the result of the filter process is improved; and a filter processing unit performing the filter process for the respective control blocks which has been moved by the movement unit.

Owner:SONY CORP

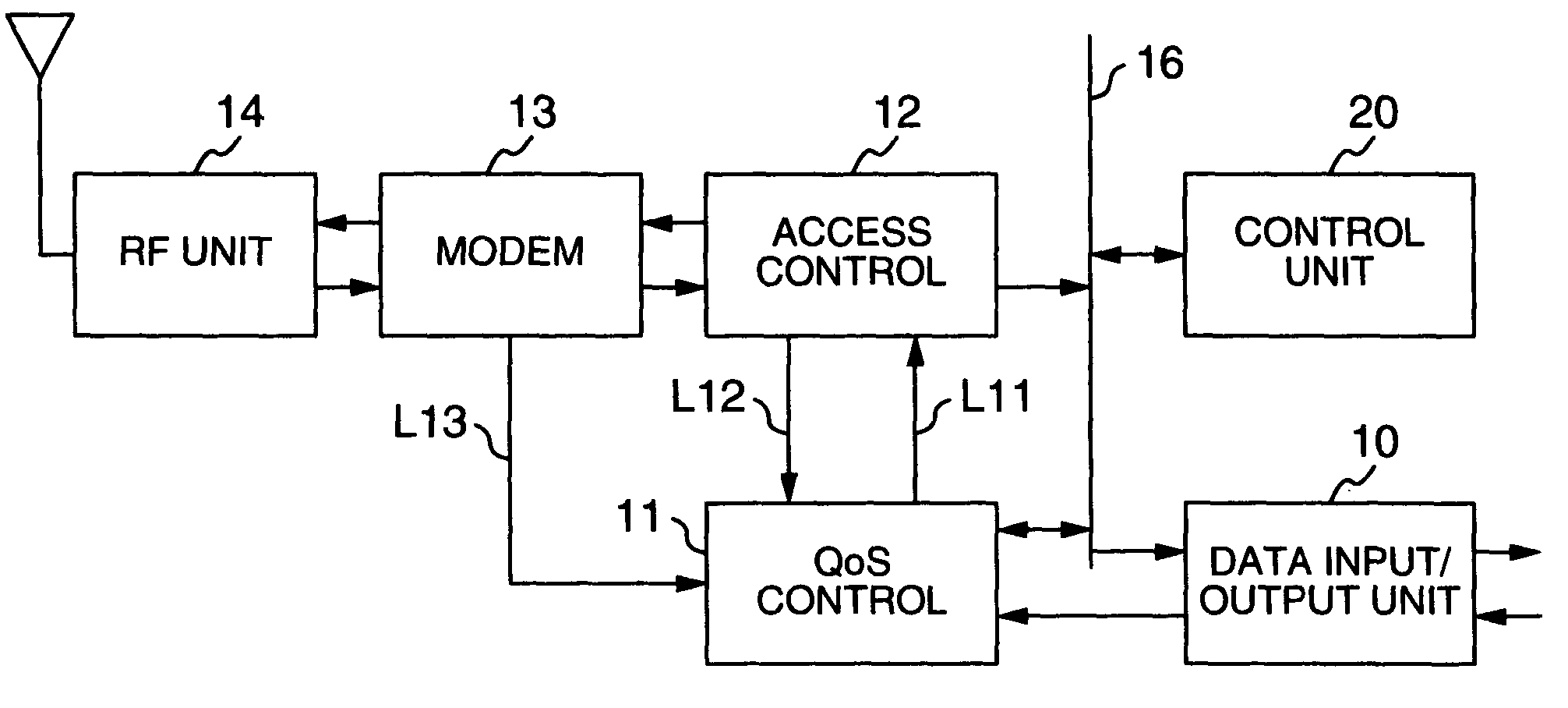

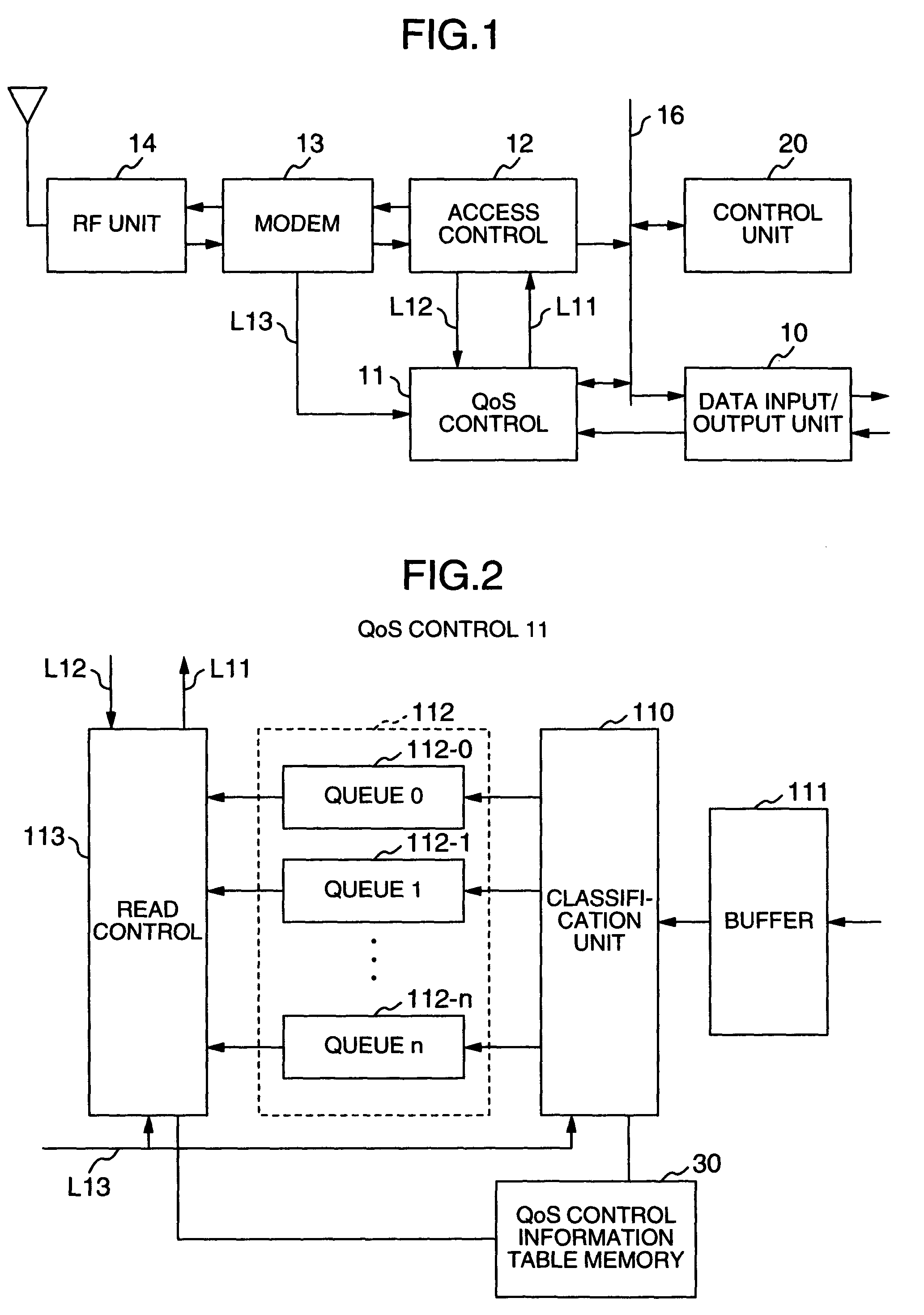

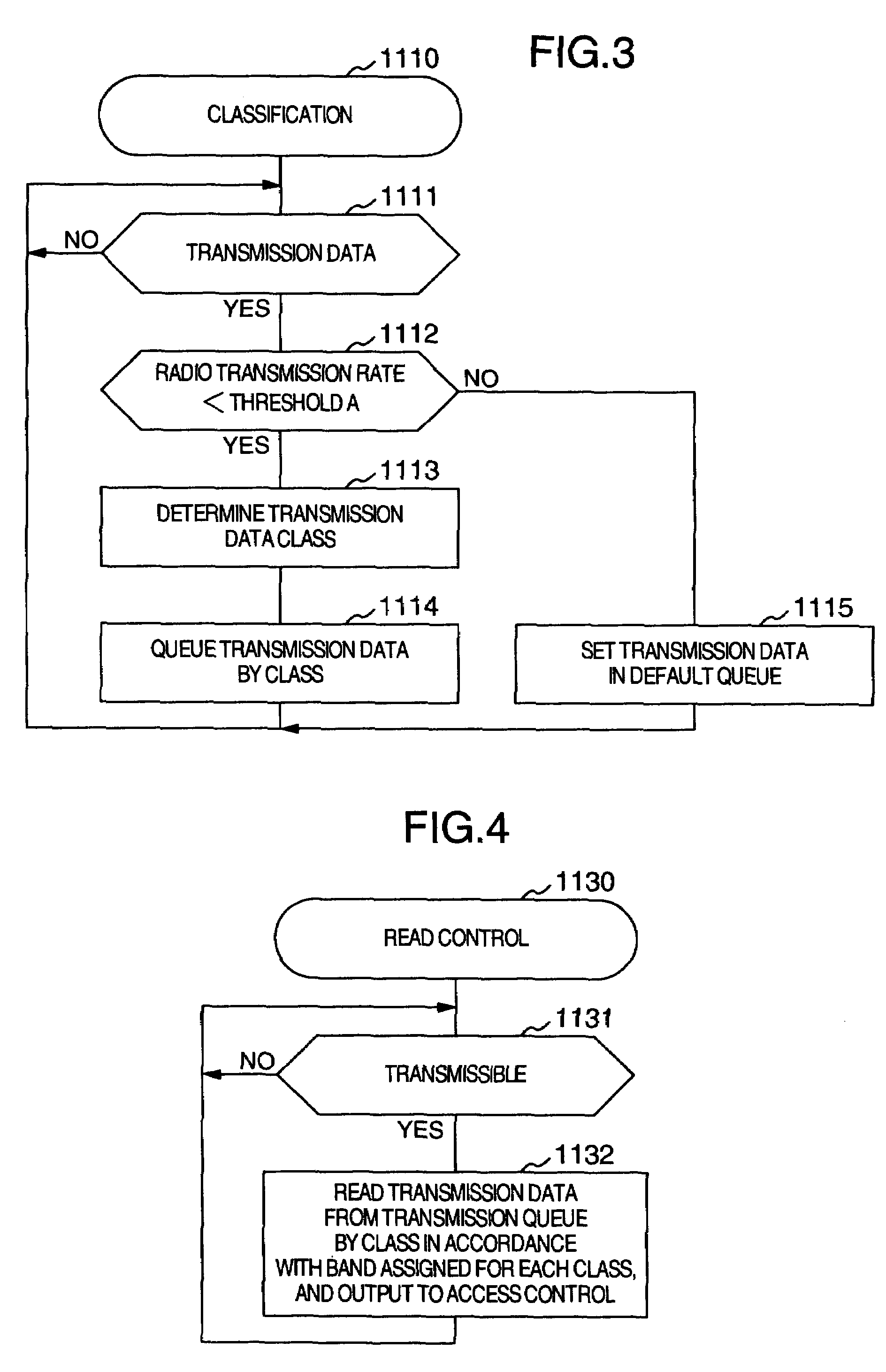

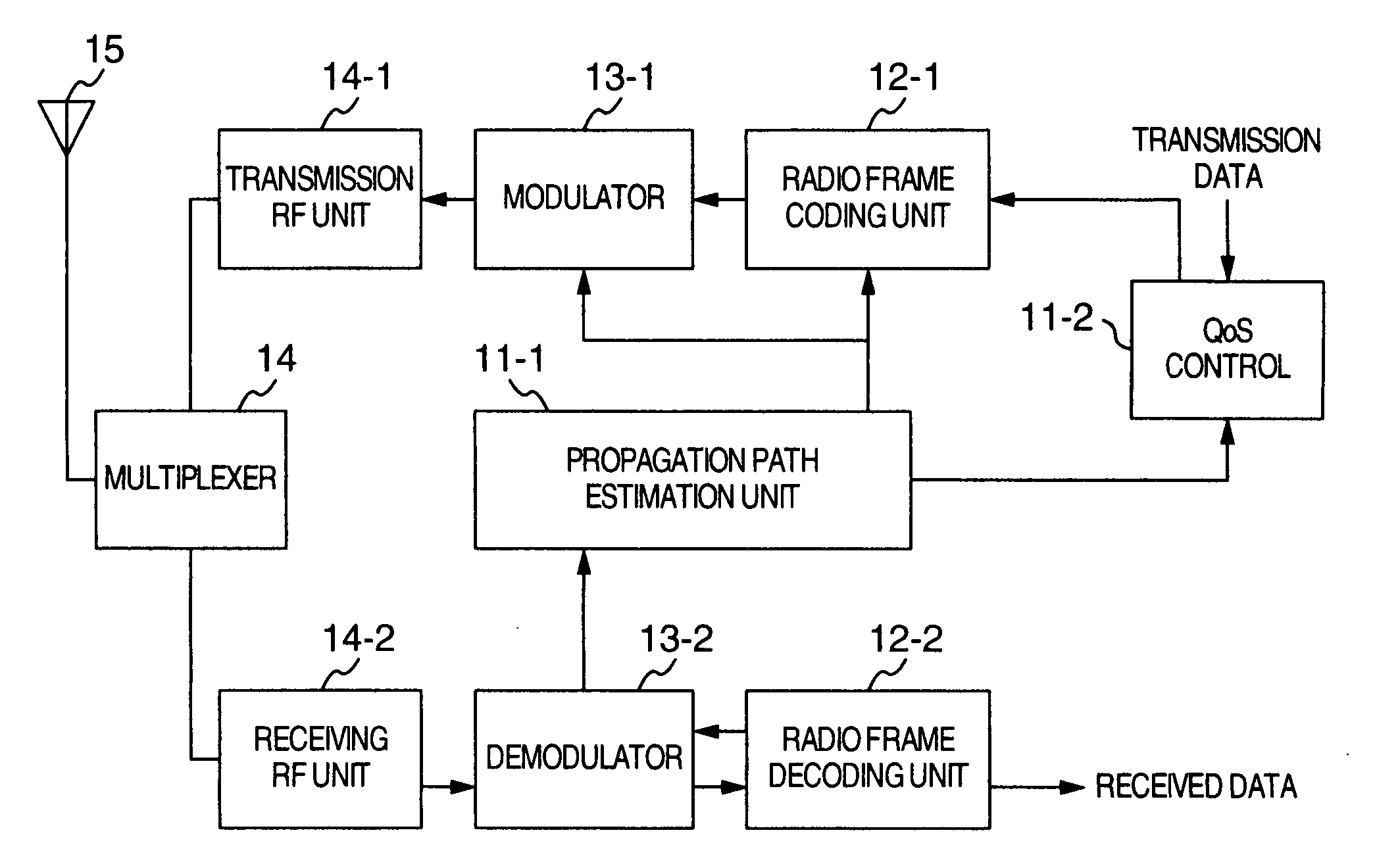

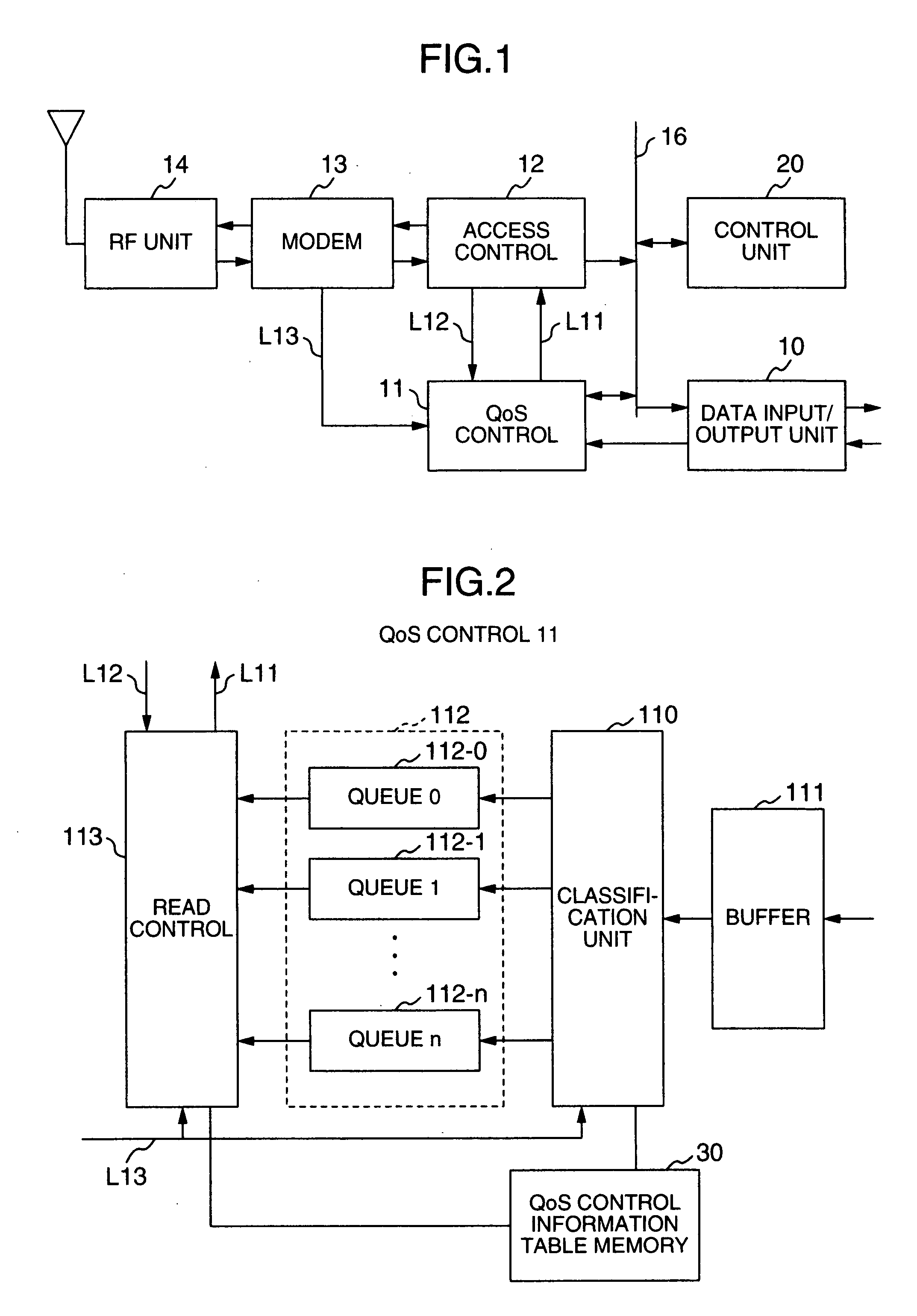

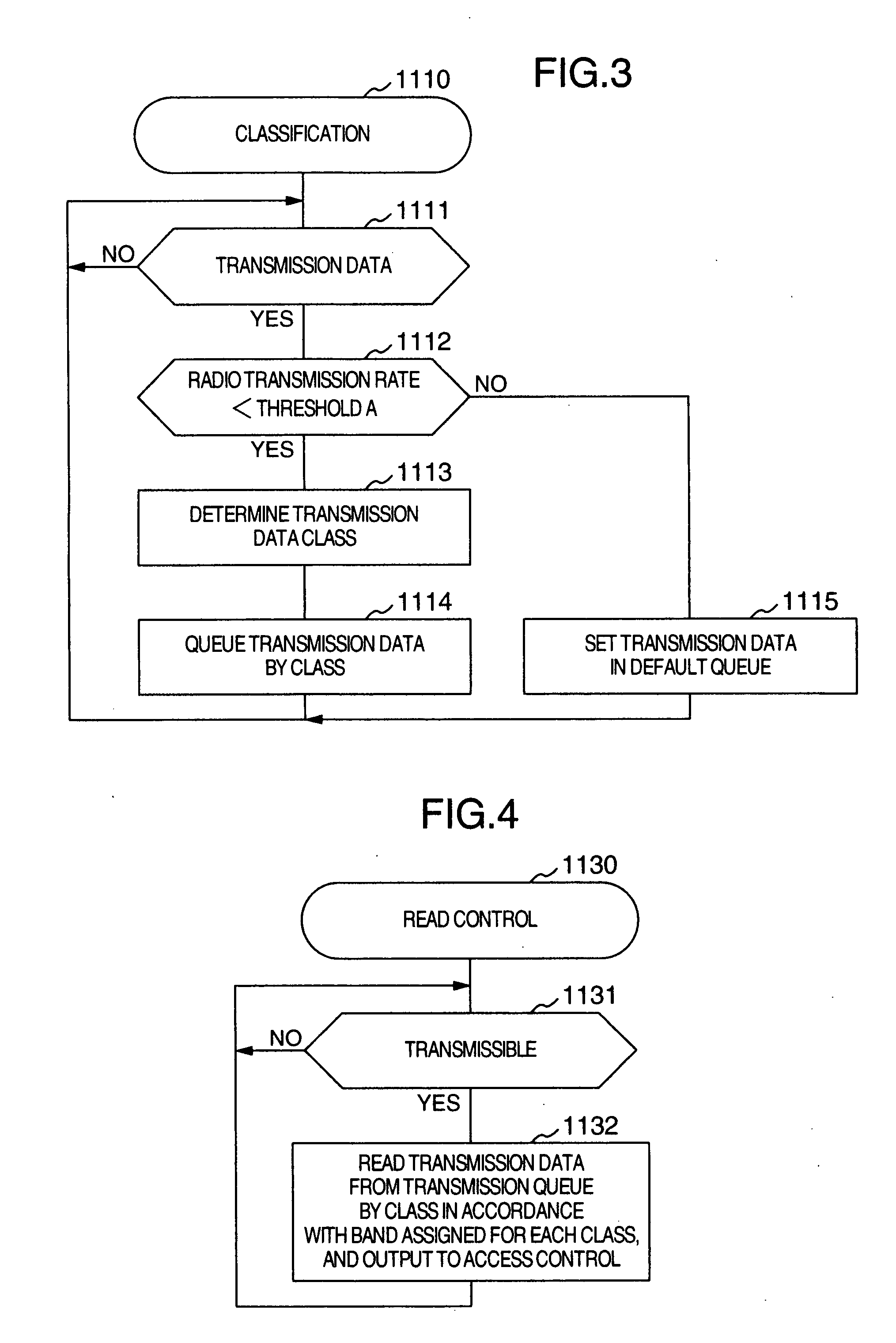

QoS control method for transmission data for radio transmitter and radio receiver using the method

InactiveUS7274730B2Considerable length of timeIncrease delay timeWireless commuication servicesAdaptation strategy characterisationRadio receiver designQuality of service

A radio transmitter / receiver having a QoS control unit for outputting the transmission data in order taking the quality of service (QoS) into consideration. In the case where the information transmission rate for a radio section is not lower than a threshold value, the QoS control operation of the transmission data is omitted, and the transmission data are output in the order of input. In the case where the information transmission rate for the radio section is lower than the threshold value, on the other hand, the QoS control mode is switched in accordance with the information transmission rate for the radio section.

Owner:KOKUSA ELECTRIC CO LTD

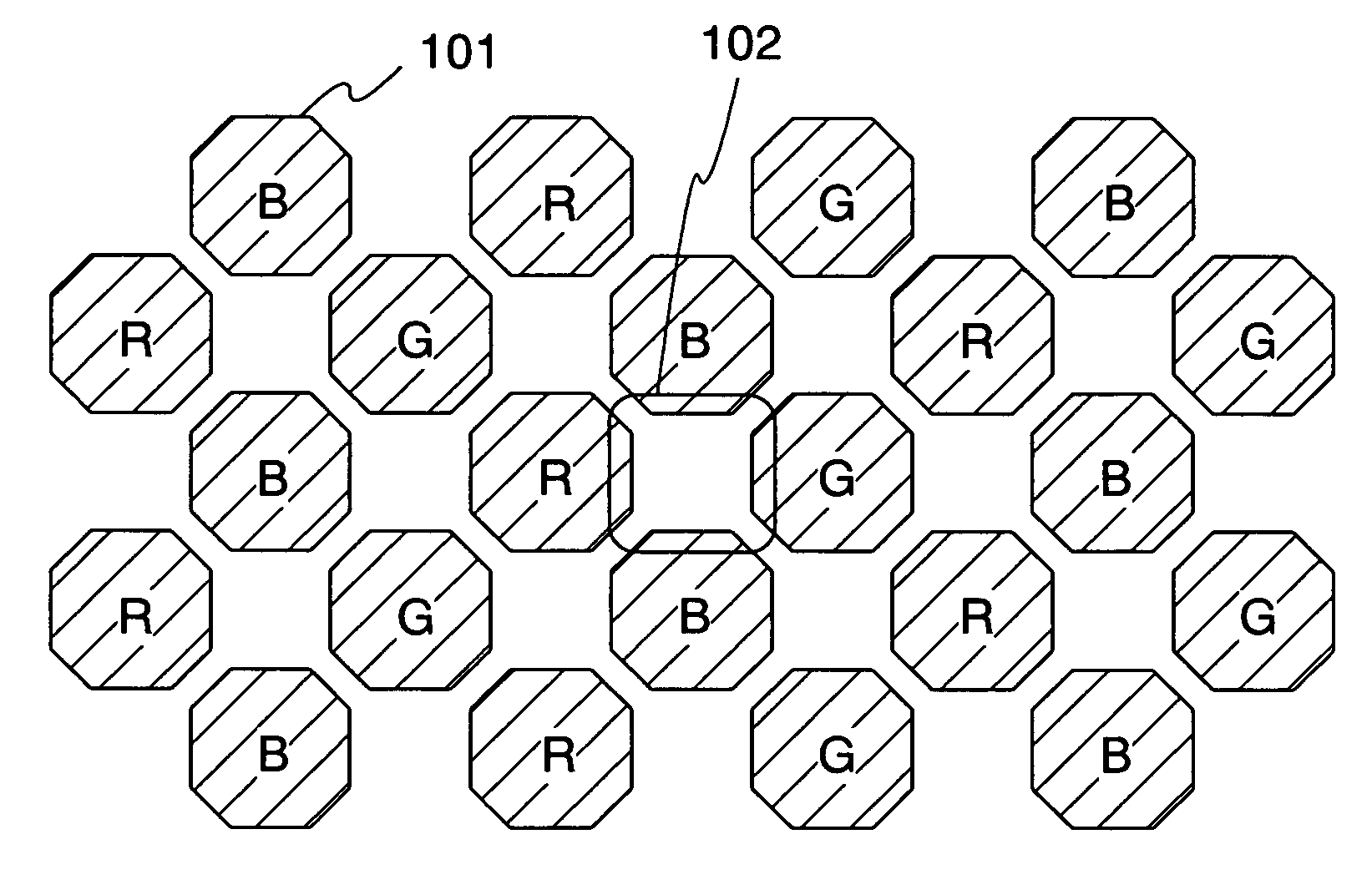

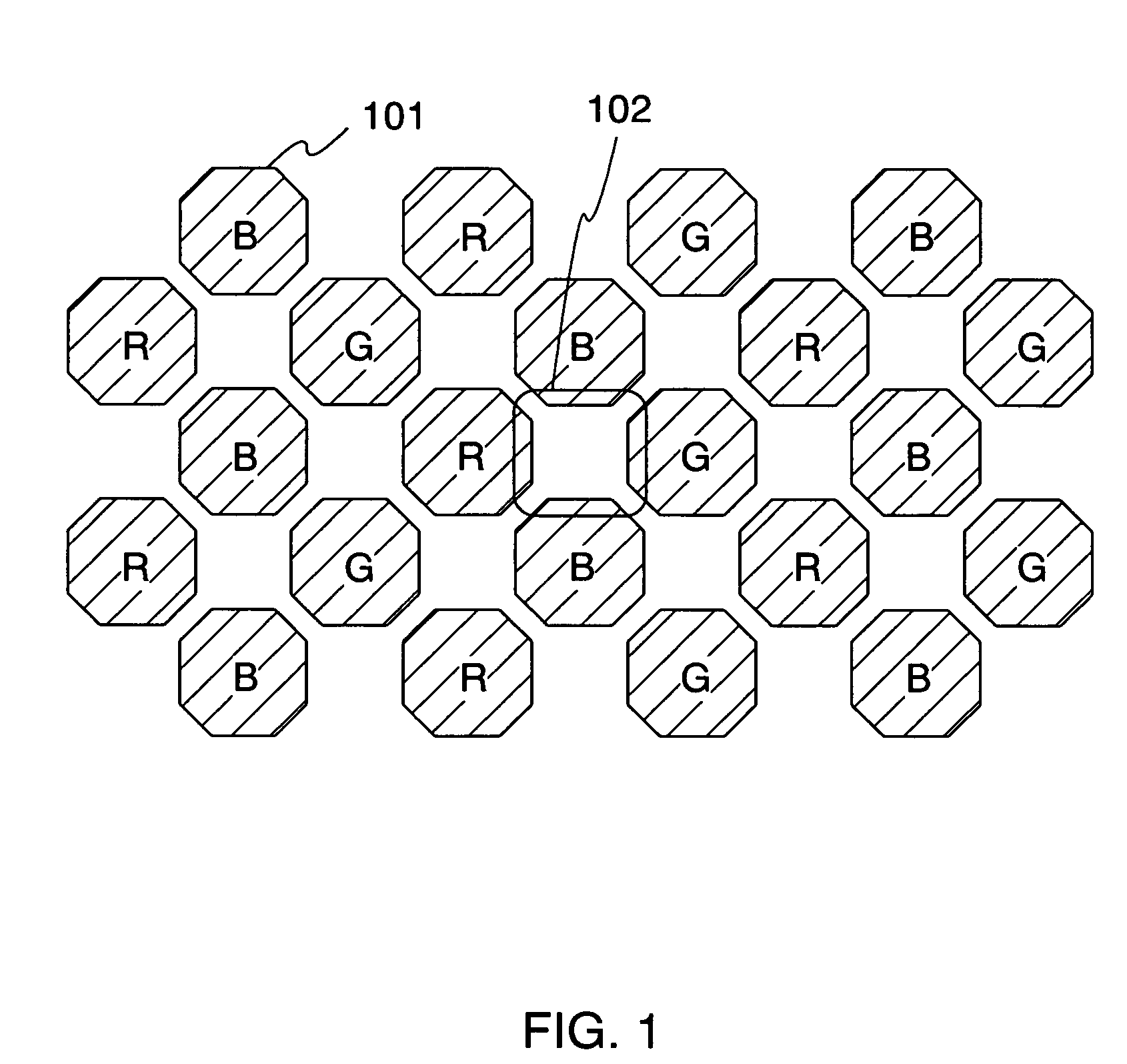

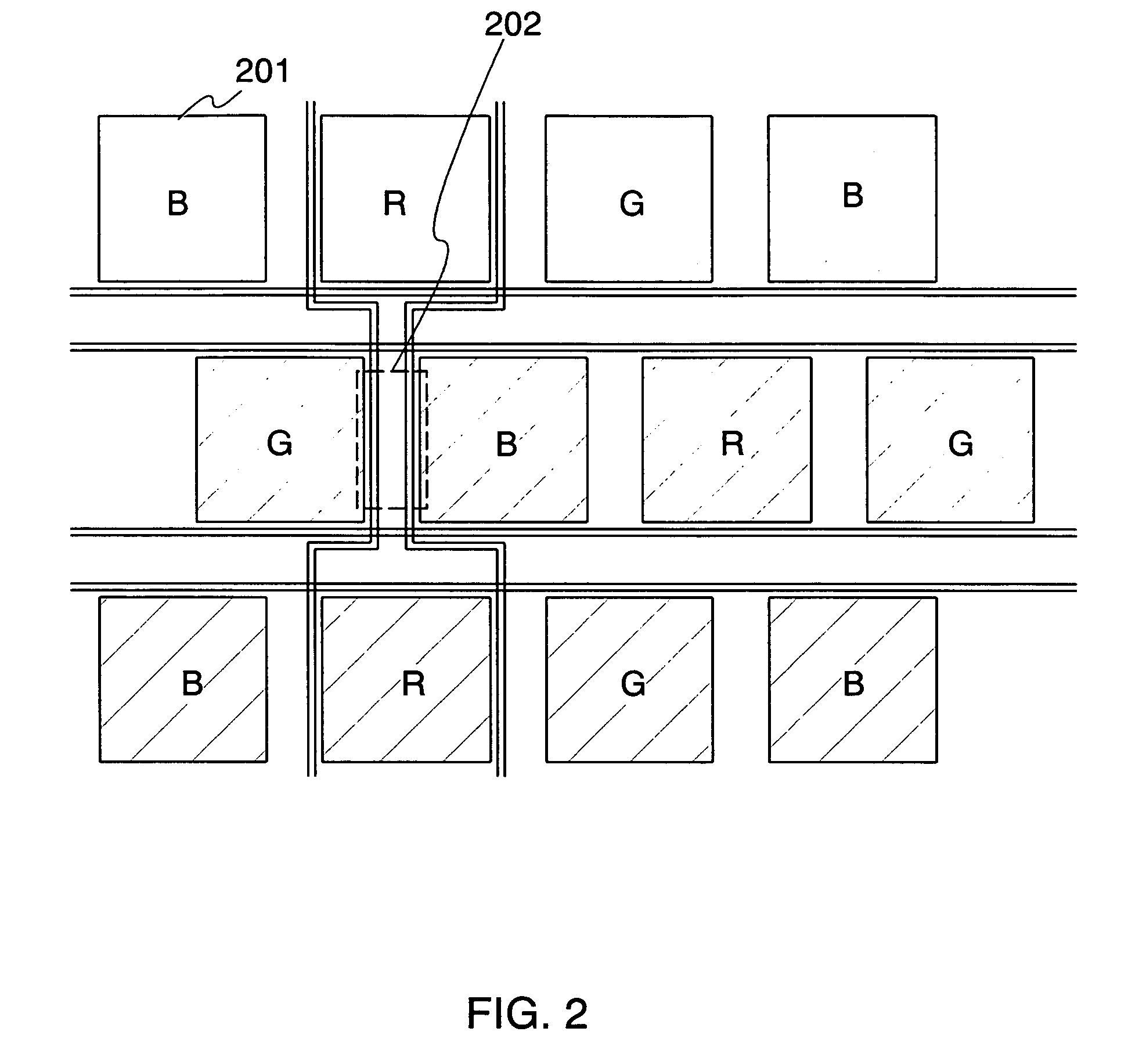

Display device, and computer, camera, portable information terminal device, image reproducing device, clock, mobile phone device and other electronic apparatuses using the display device

InactiveUS20060274090A1Reduce delay timeConvenient ArrangementElectrical apparatusElectroluminescent light sourcesDisplay deviceMobile phone

In a display device using a delta arrangement, in a case where a circuit of a large number of elements such as a static memory is arranged every pixel, a wire becomes complicated to cause wiring delay. A shape of a pixel electrode is formed polygonally to arrange in a case where the number of elements such as a static memory is large or in a case where an area of an element required to be included in a pixel is large in a delta arrangement. The shape of the pixel electrode is arranged in a polygon so that a wire along a pixel shape can be used. Even in a case of a pixel with a large number of elements, parasitic resistance of a wire and parasitic capacitance of a wire can be reduced so that wiring delay can be solved.

Owner:SEMICON ENERGY LAB CO LTD

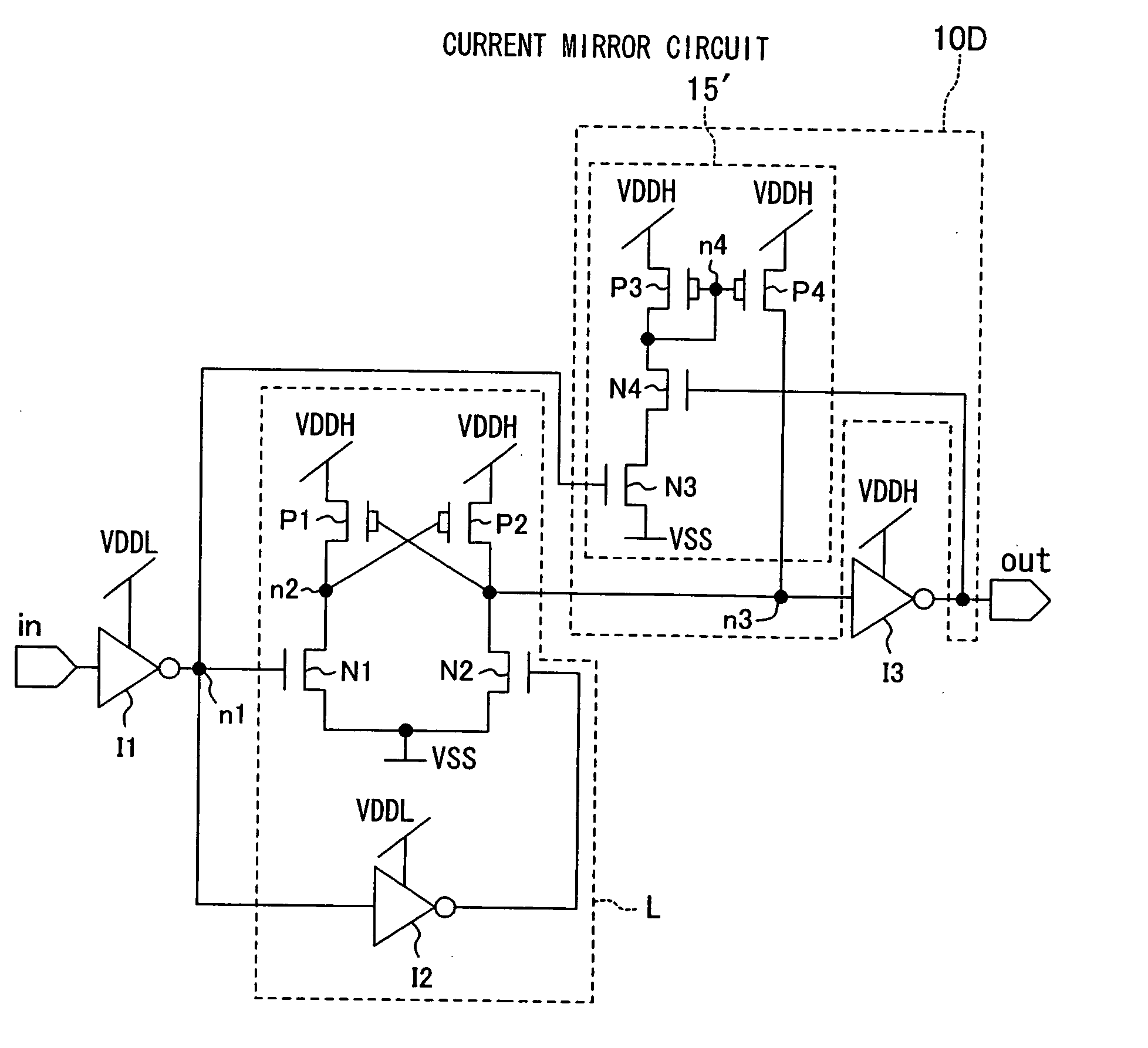

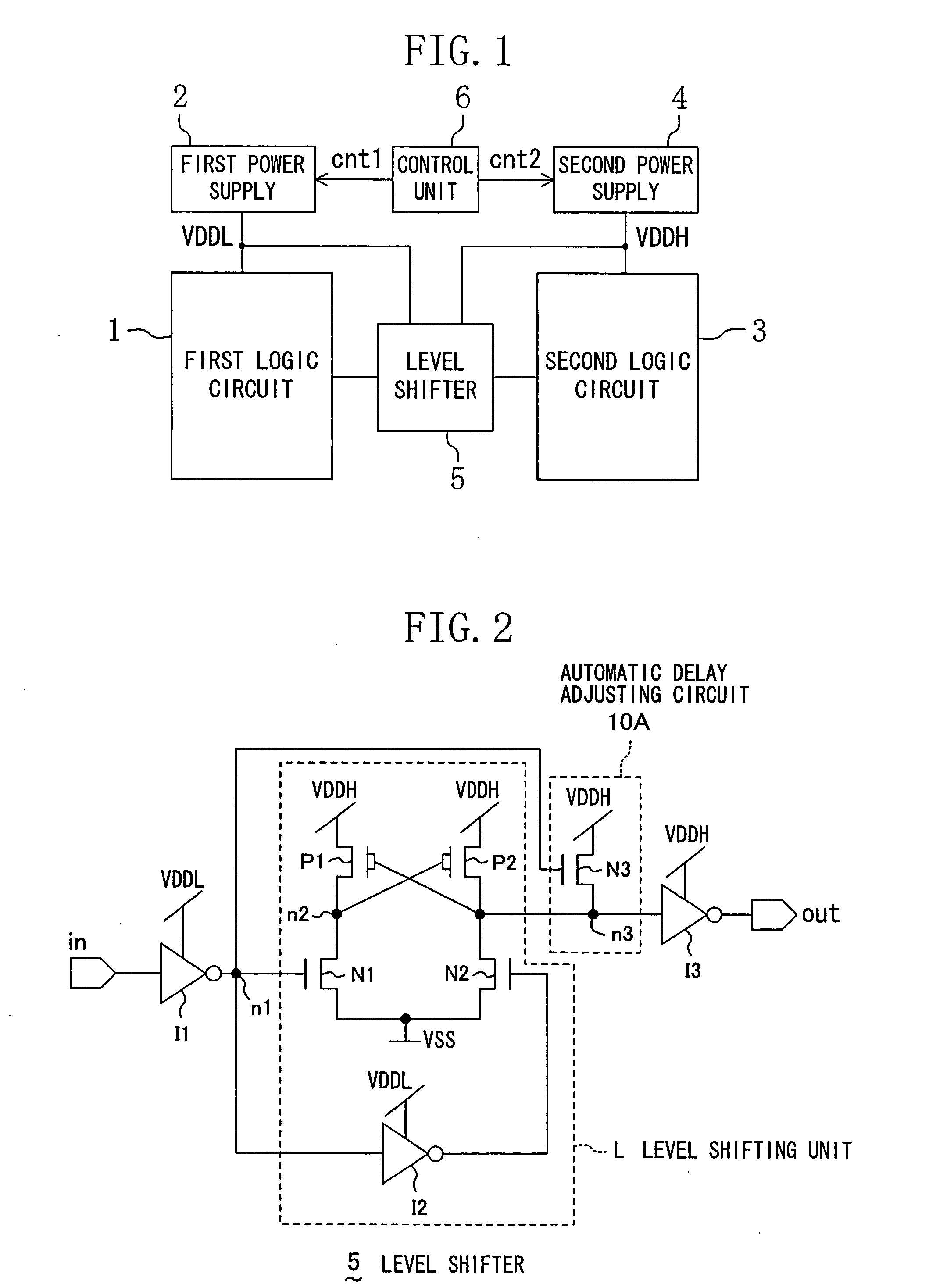

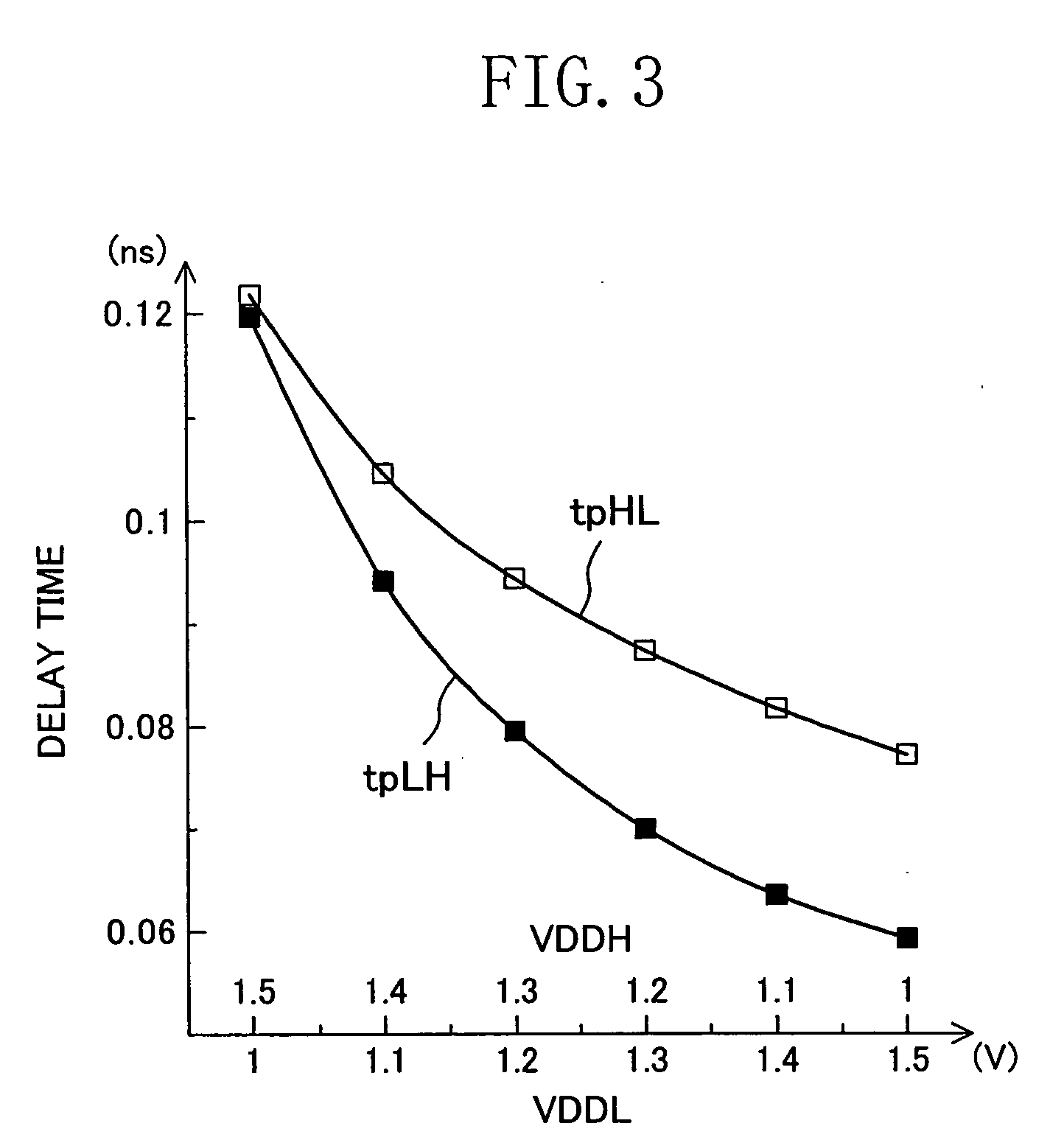

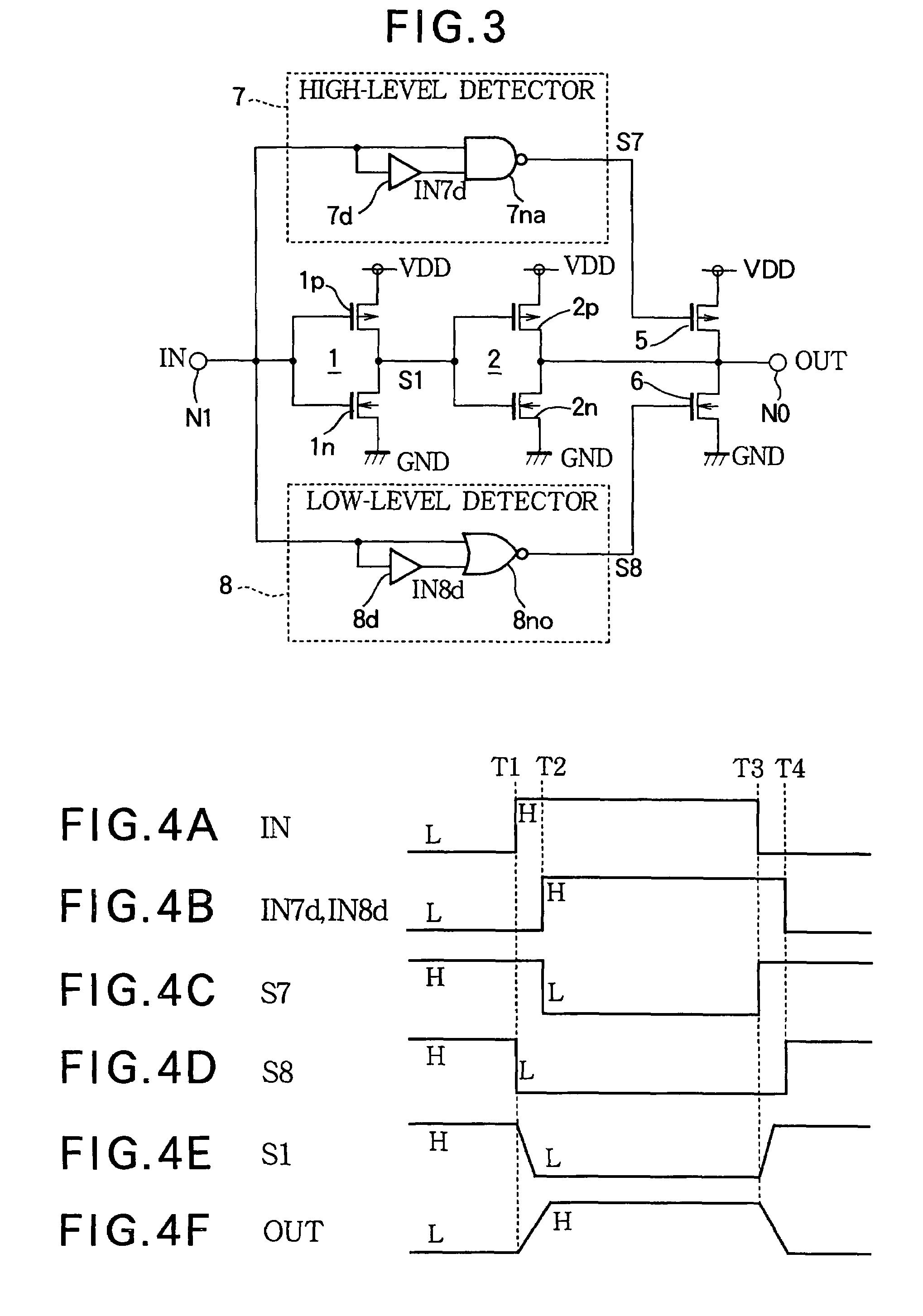

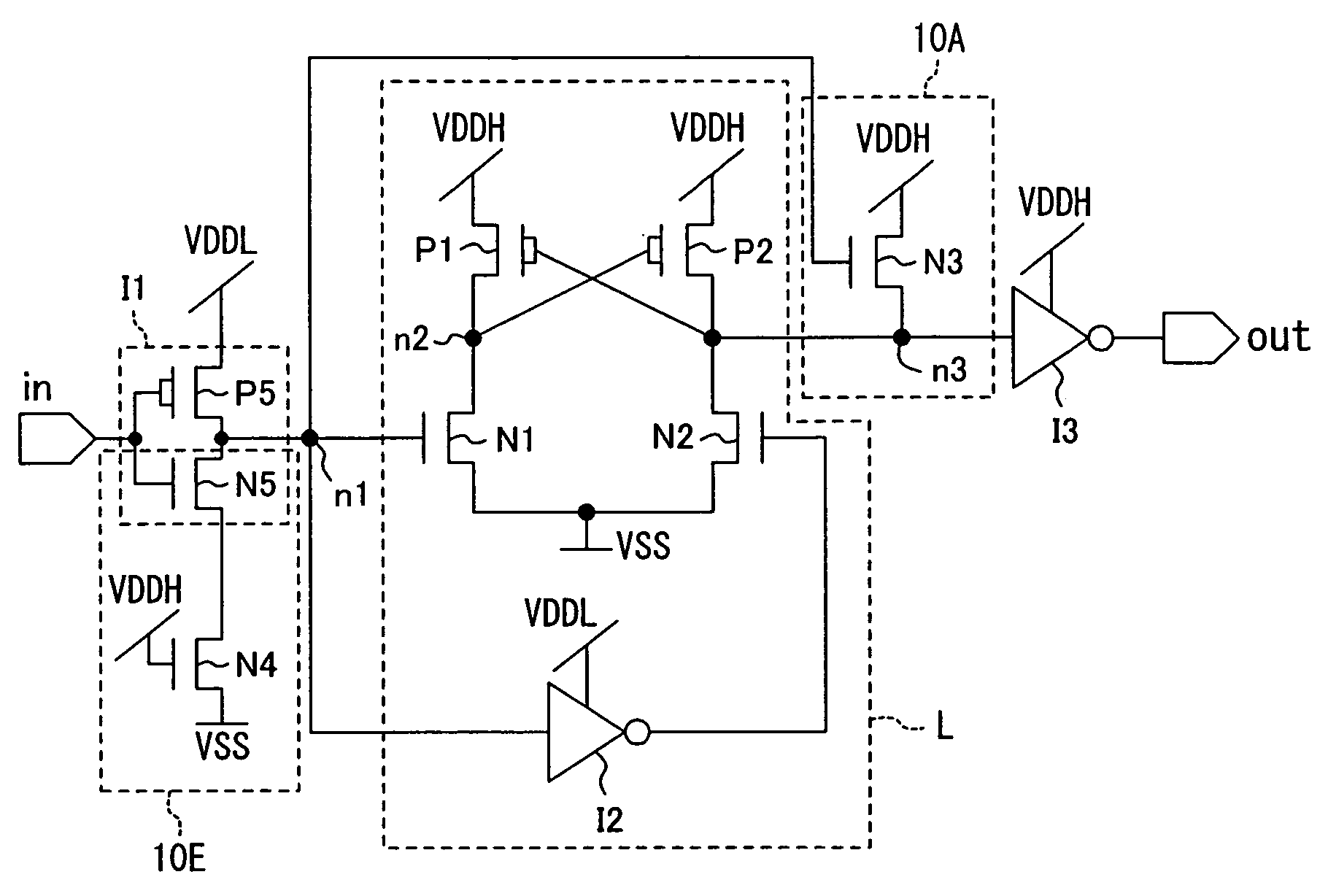

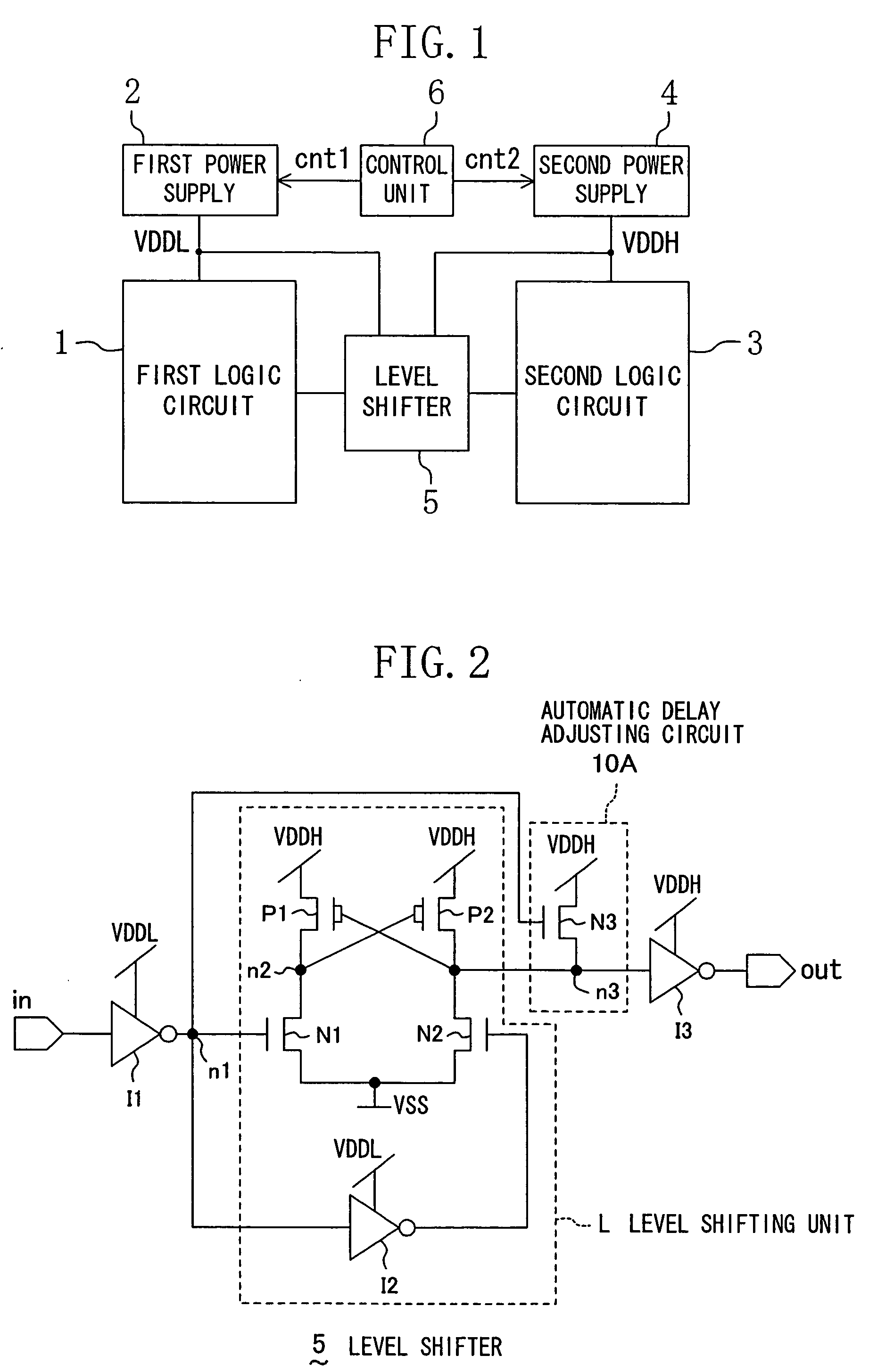

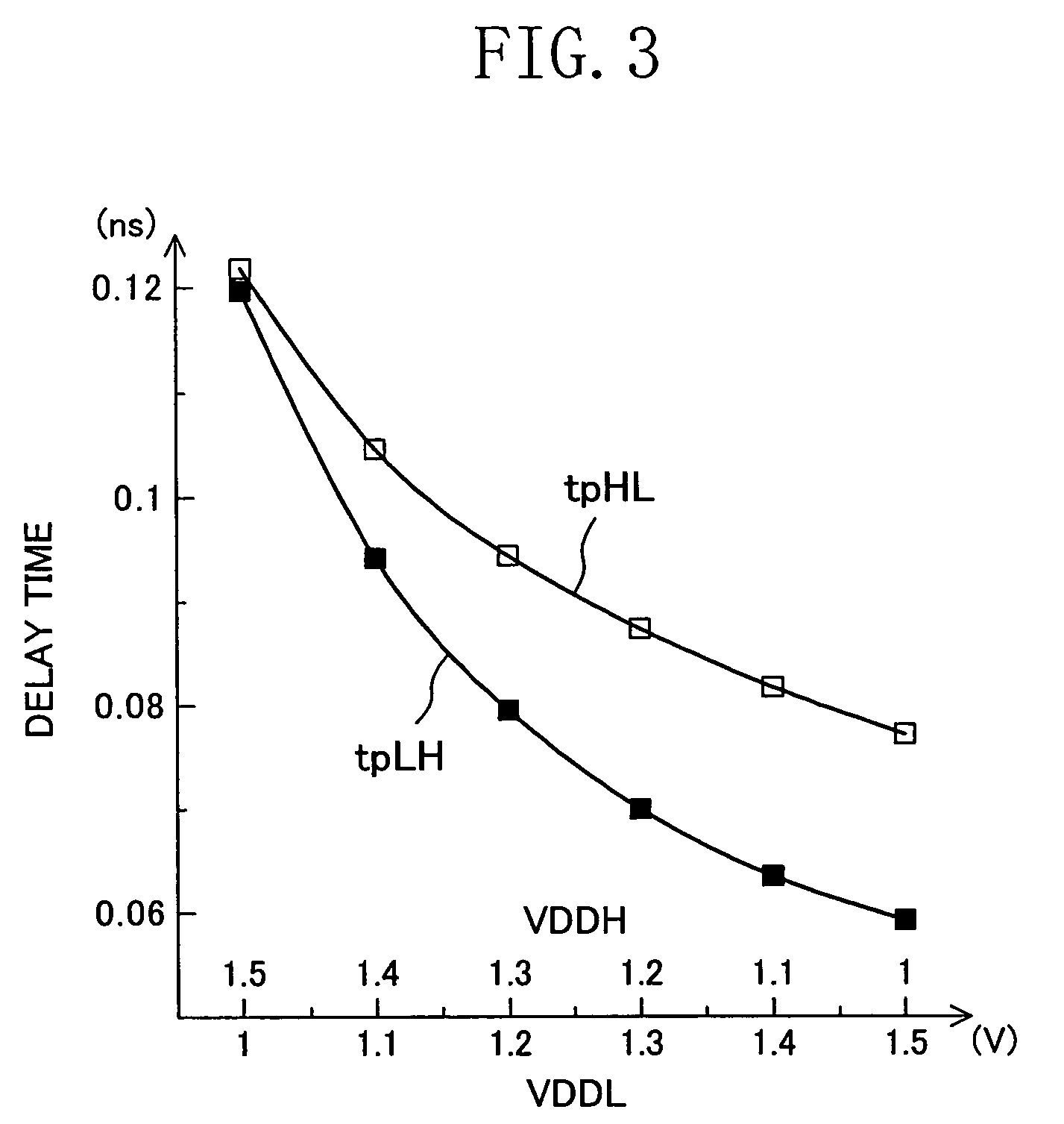

Level shifter having automatic delay adjusting function

InactiveUS20050258887A1Increase the number ofReduce decreasePulse automatic controlInstant pulse delivery arrangementsLevel shiftingDelayed time

In a level shifter, in the case where the amplitude voltage of an input signal (i.e., a first power voltage VDDL) input to an input terminal is changed to be higher and the amplitude voltage of an output signal (i.e., a second power voltage VDDH) output from an output terminal is changed to be lower, a fall delay time of the signal output from the output terminal tends to be longer than a rise delay time of the signal. However, an inverted input signal obtained by an inverter is input to a level shifting unit and also to the gate of an N-type transistor, and therefore, the N-type transistor is turned on at the fall of the input signal input to the input terminal, so as to supply a current based on the second power voltage VDDH to an output node of the level shifting unit for assisting the shift into H level performed in the level shifting unit. Accordingly, even when at least one of the amplitude voltage of the input signal and the amplitude voltage of the output signal is changed, balance between the fall delay time characteristic and the rise delay time characteristic of the output signal can be satisfactorily kept.

Owner:SOCIONEXT INC

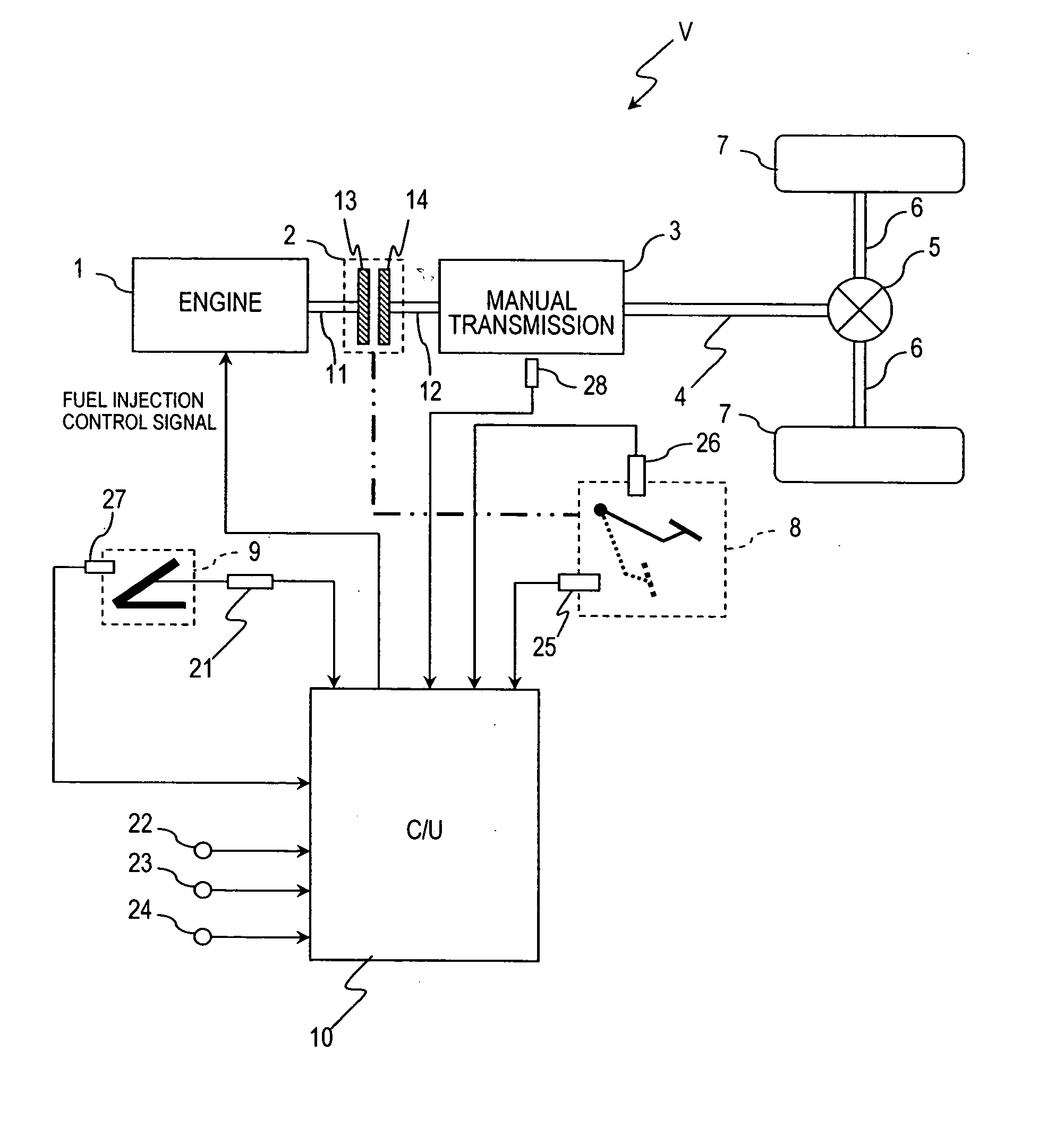

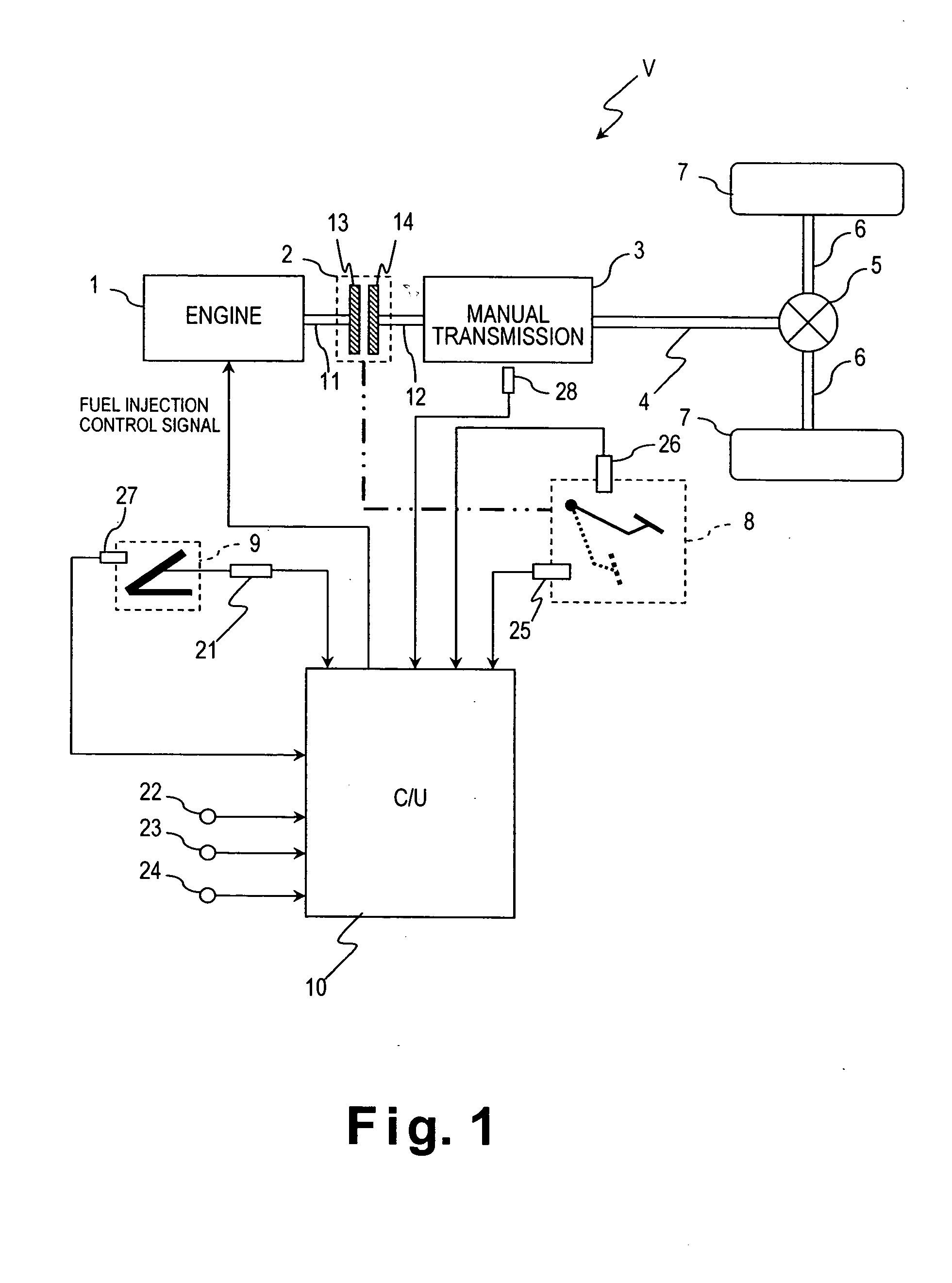

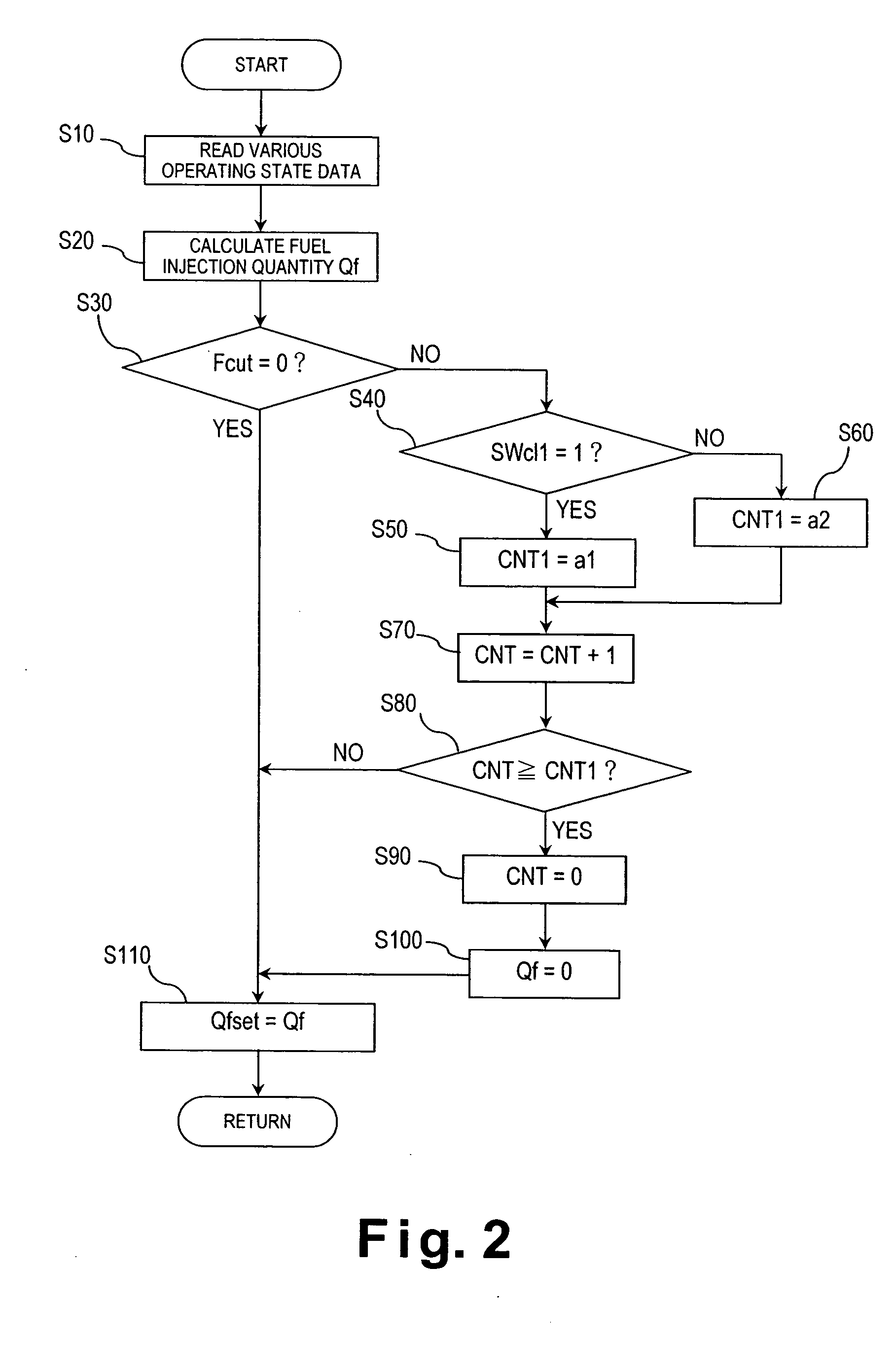

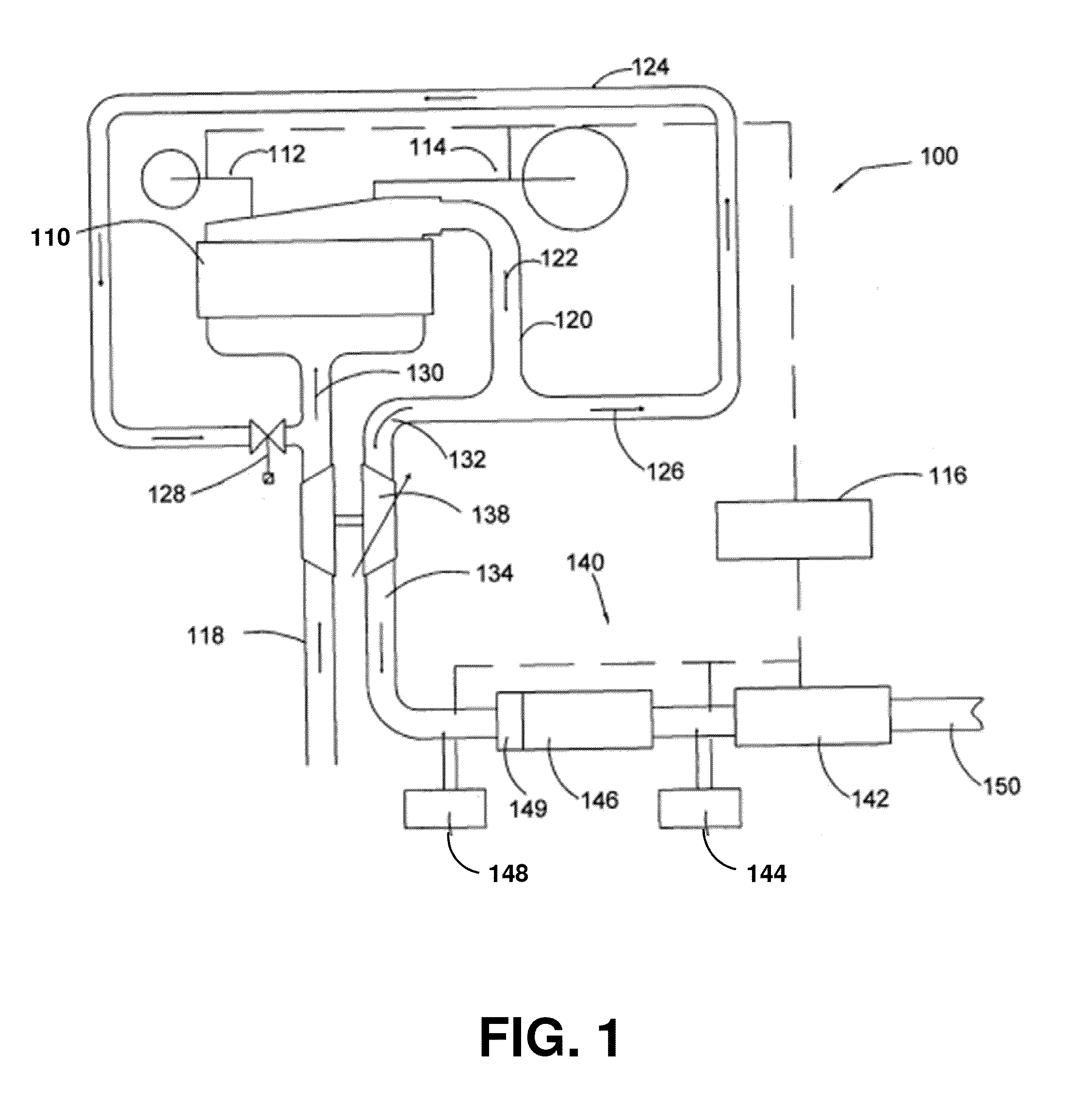

Engine fuel supply control device

InactiveUS20050124460A1Raise engine output and efficiencyLong delay timeElectrical controlConjoint controlClutchFuel supply

An engine fuel supply control device is configured to stop supplying fuel to an engine when specific fuel cut-off condition has been met. The timing of the fuel cut-off is delayed depending on an operating state of the vehicle. Preferably, the engine fuel supply control device has an operating state detection section that detects an operating condition (e.g., a clutch position or a shifting operation), and a fuel supply stoppage section that stops supplying fuel to the engine when a specific delay time has elapsed since the specific fuel cut-off condition was met. Preferably, the fuel supply stoppage section selectively sets the specific delay time to a different delay time depending upon the detected operating condition detection, e.g., a first delay time is set if either the clutch is detected as disengaged or a shifting operation is detected as being in progress, otherwise a different delay time is set.

Owner:NISSAN MOTOR CO LTD

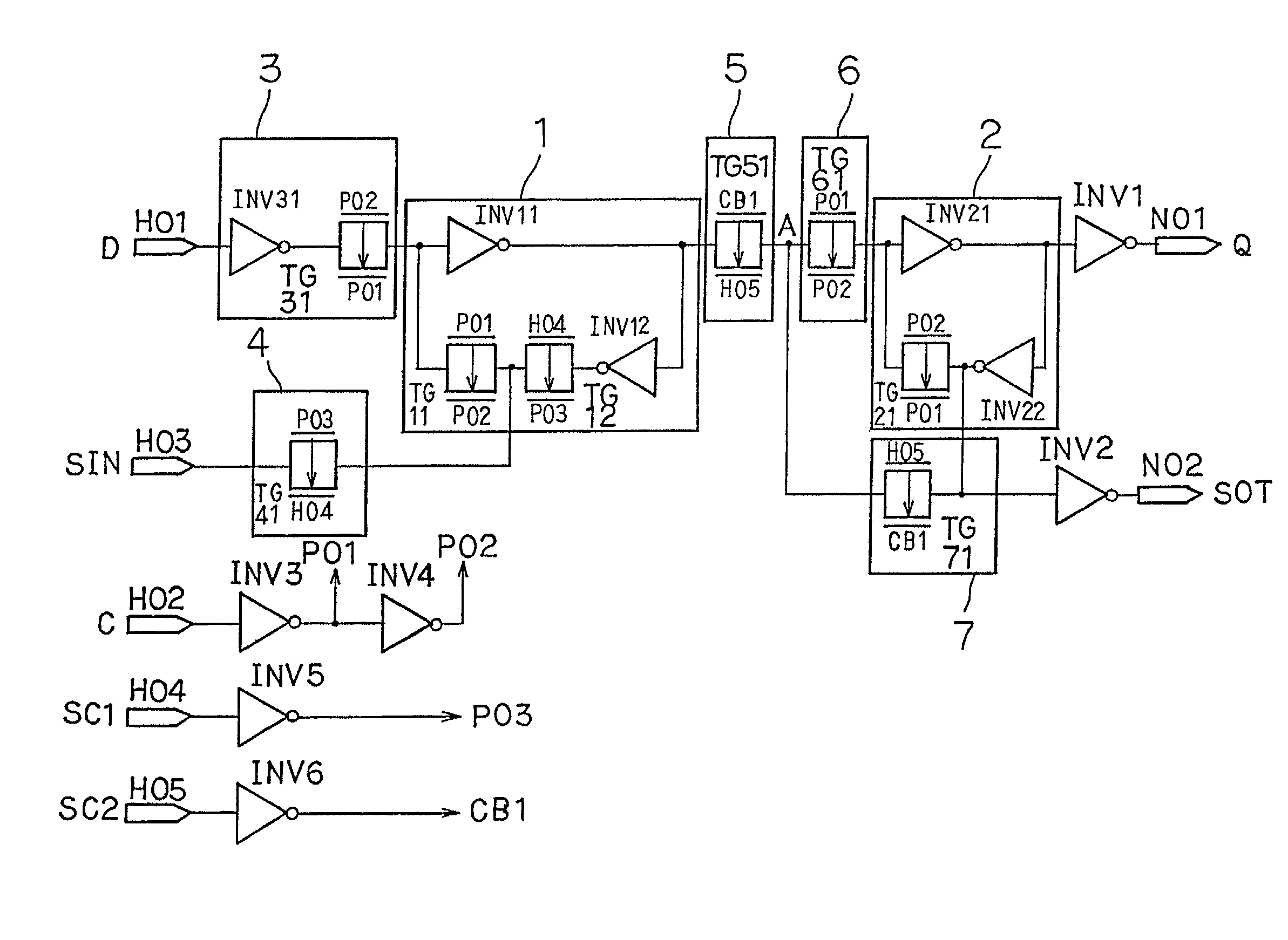

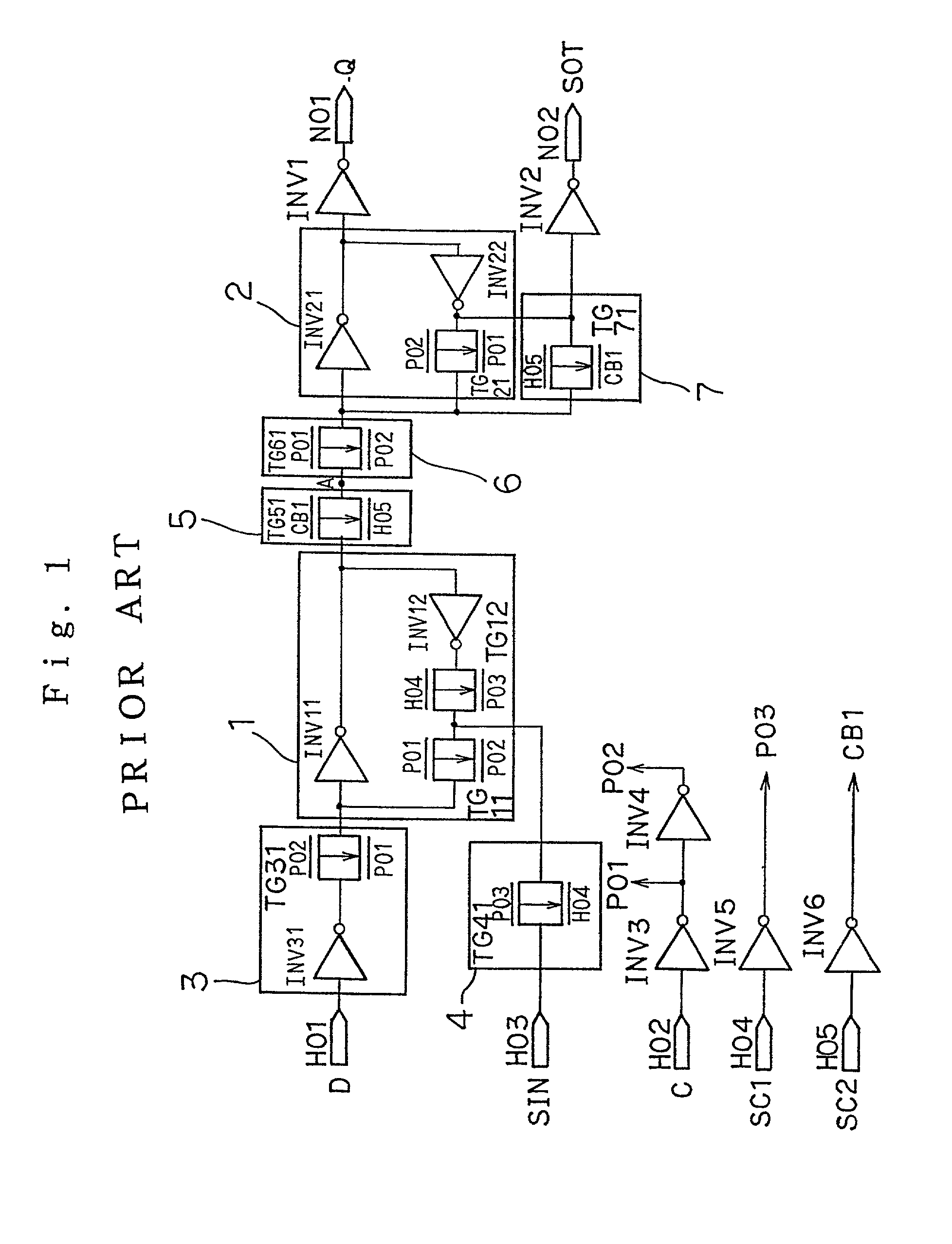

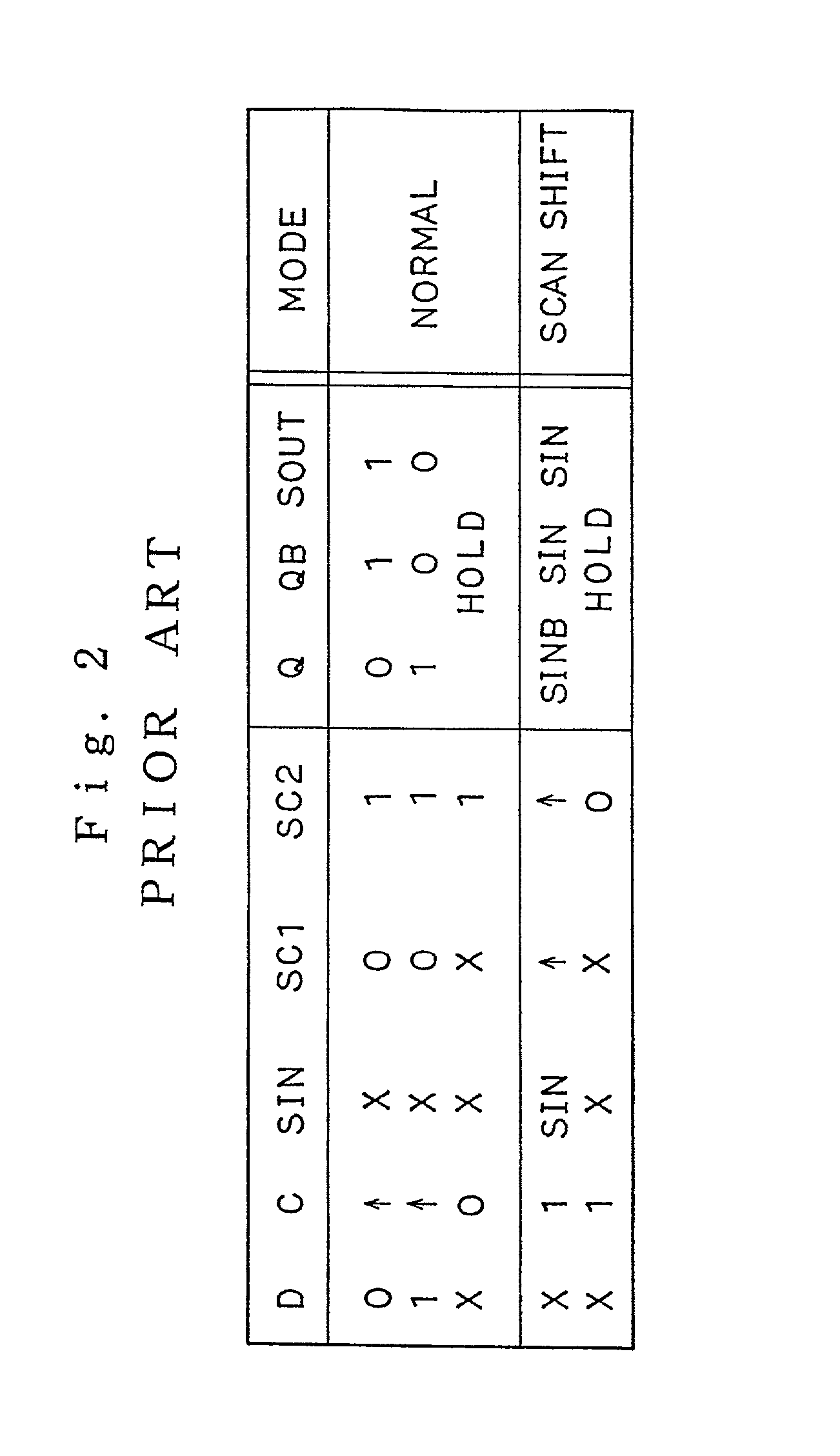

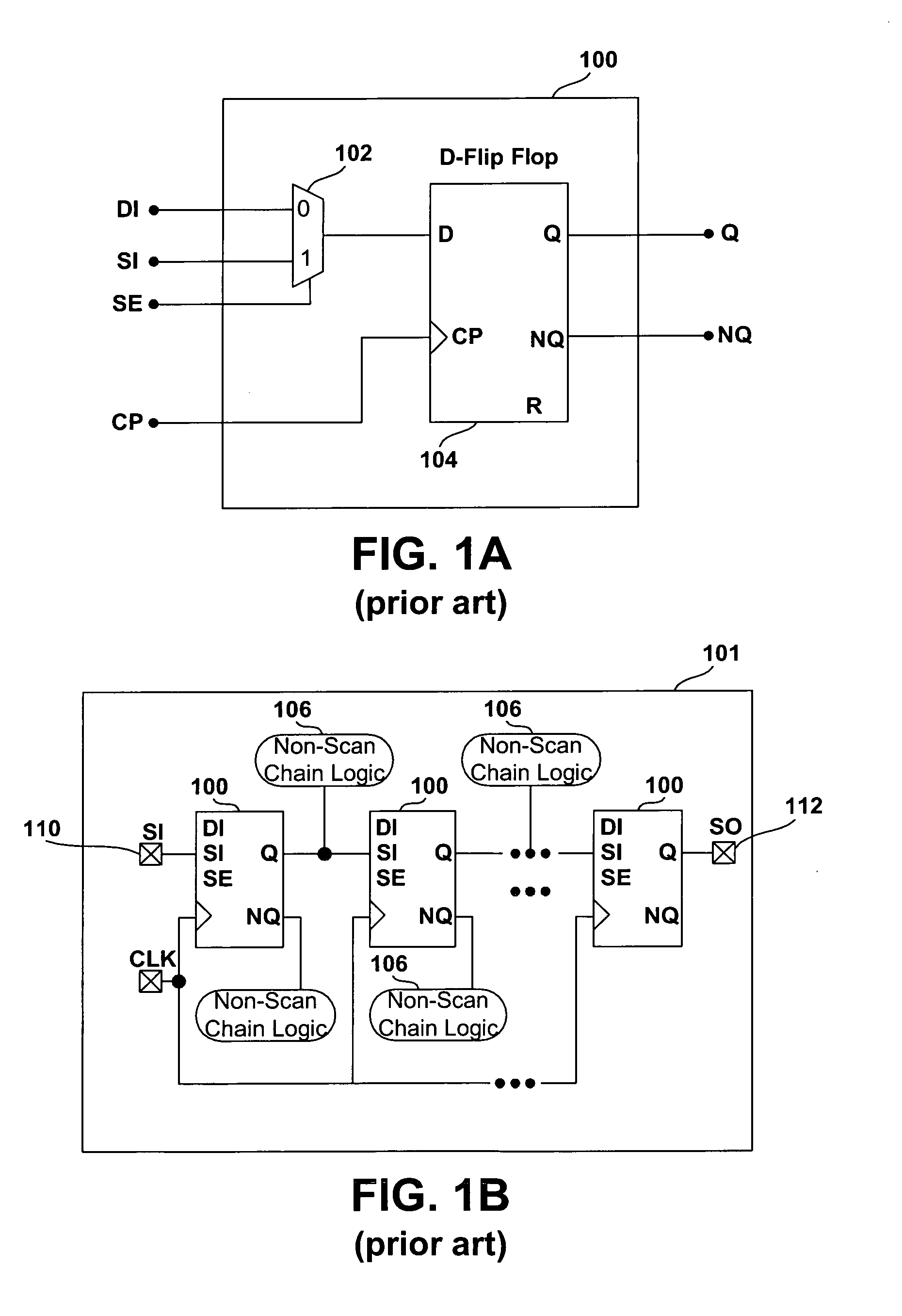

Master-slave-type scanning flip-flop circuit for high-speed operation with reduced load capacity of clock controller

InactiveUS6968486B2Increase speedIncrease delay timeElectronic circuit testingDigital storageNormal modeEngineering

A master-slave-type scanning flip-flop circuit is capable of operating at a higher speed by reducing a load capacity of a clock controller. The master-slave-type scanning flip-flop circuit is used to test a semiconductor integrated circuit device, and has a master latch and a slave latch each for temporarily holding an input signal, a first scan controller, a clock controller, and a second scan controller. The first scan controller receives an output signal from the master latch and outputs the received output signal in synchronism with a scan clock which is a clock for testing the semiconductor integrated circuit device, when the semiconductor integrated circuit device is tested. The clock controller receives an output signal from the first scan controller and outputs the received output signal to the slave unit in synchronism with a predetermined clock when in a normal mode of operation. The second scan controller has an input terminal connected to an output terminal of the first scan controller, and outputs a scan-out signal corresponding to a scan-in signal which is an input signal for testing the semiconductor integrated circuit device, in synchronism with the scan clock when the semiconductor integrated circuit device is tested.

Owner:NEC CORP

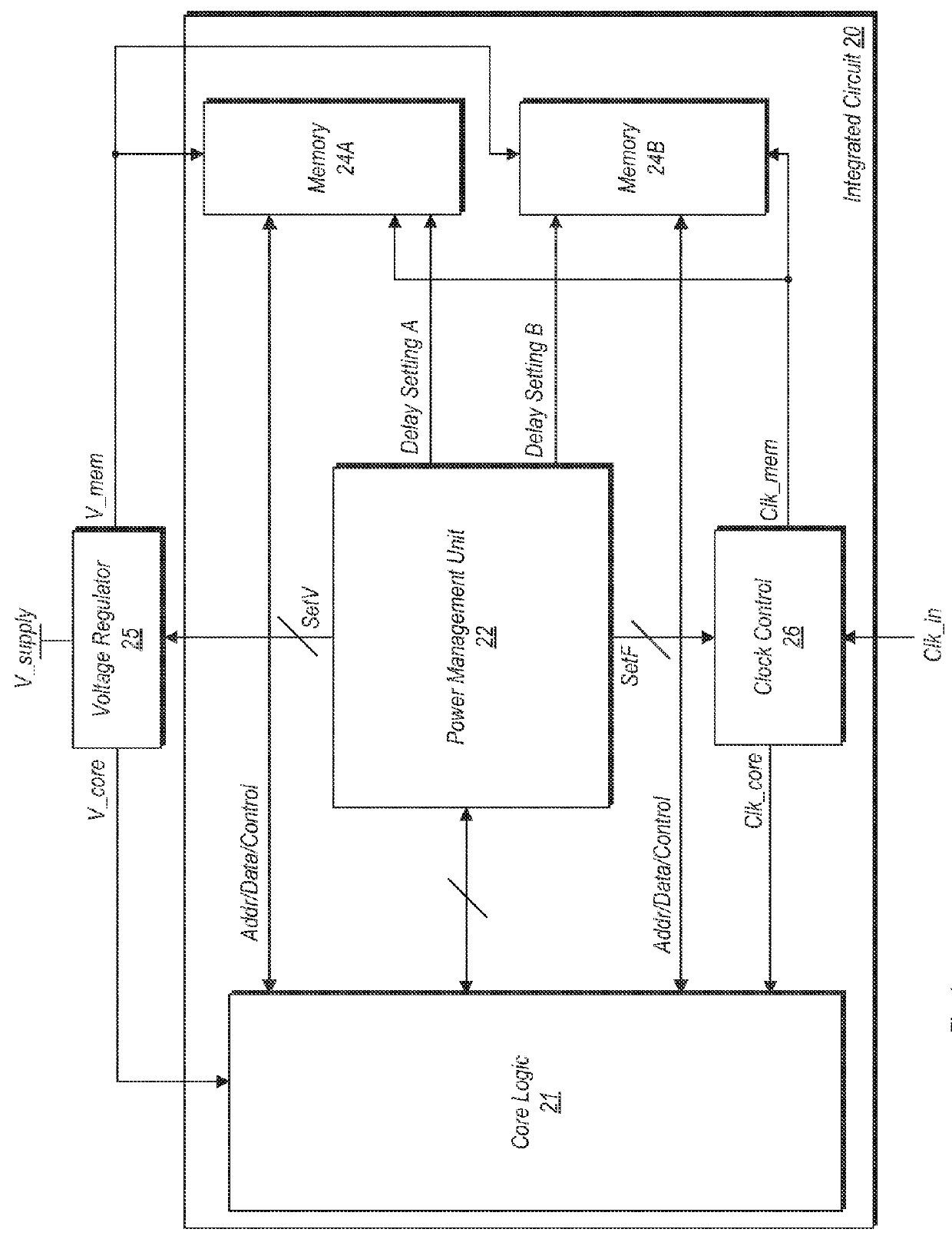

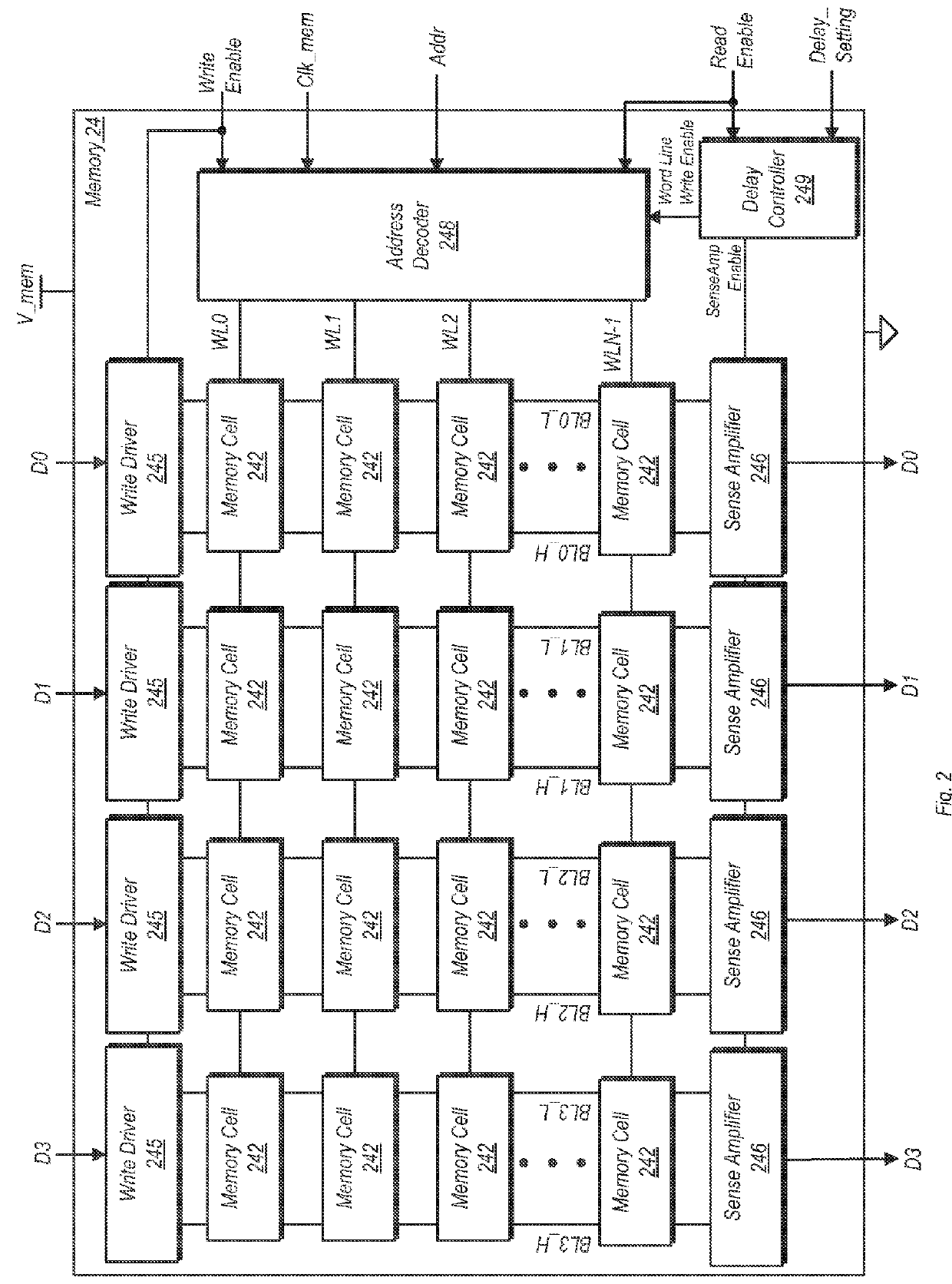

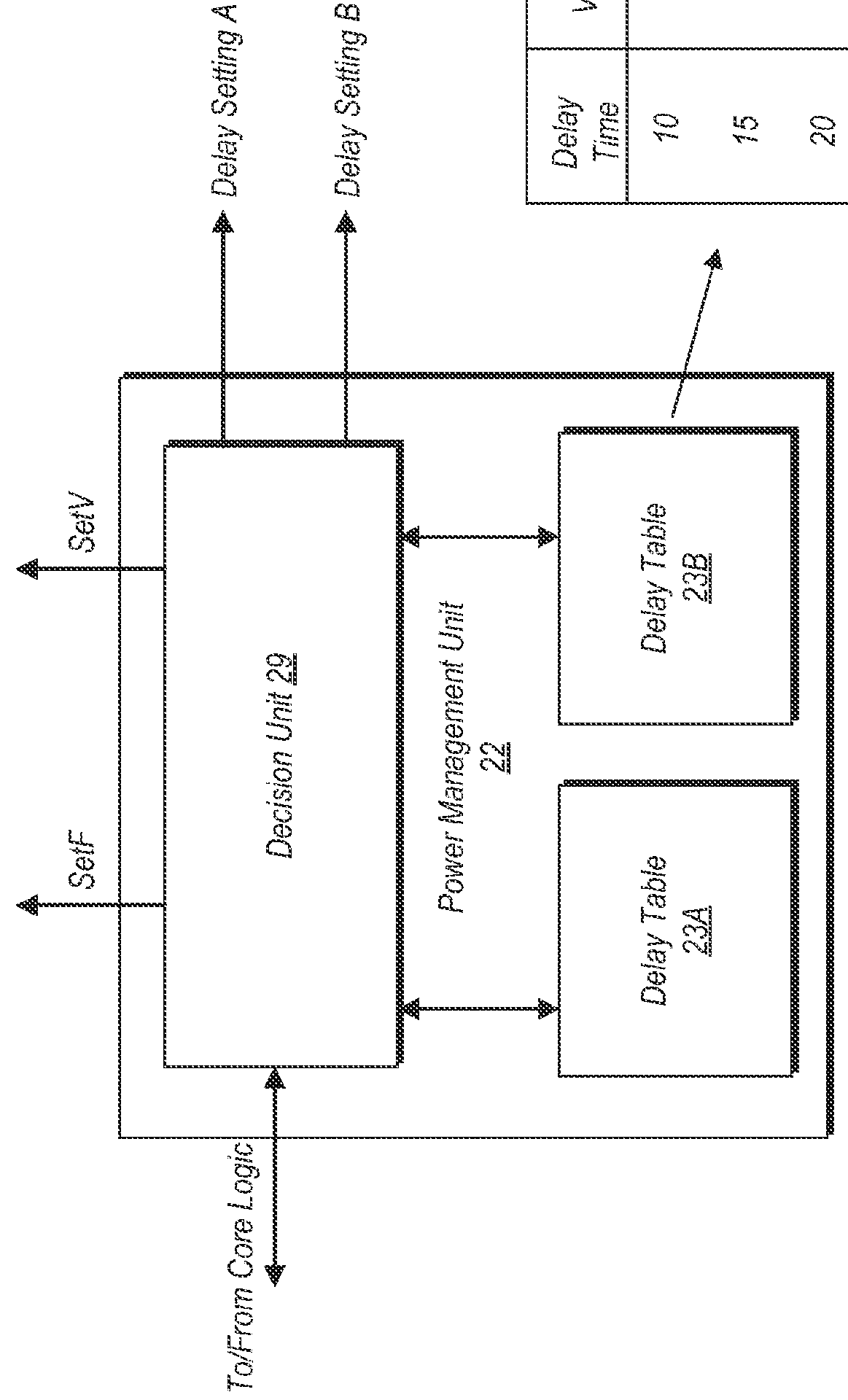

Memory Read Timing Margin Adjustment

ActiveUS20120117402A1Improve performanceReduce latencyEnergy efficient ICTVolume/mass flow measurementTiming marginOperating point

An apparatus and method for changing the extra margin adjustment (EMA) for a memory is disclosed. A control unit may access a table responsive to an indication of a change of operating point. The table includes a number of different delay times, each of which corresponds to a particular operating point. The control unit may select the delay time that corresponds to the new operating point to which the memory operation is being changed. The control unit may further convey an indication of the selected delay time to the memory, thereby causing the memory to operate according thereto.

Owner:APPLE INC

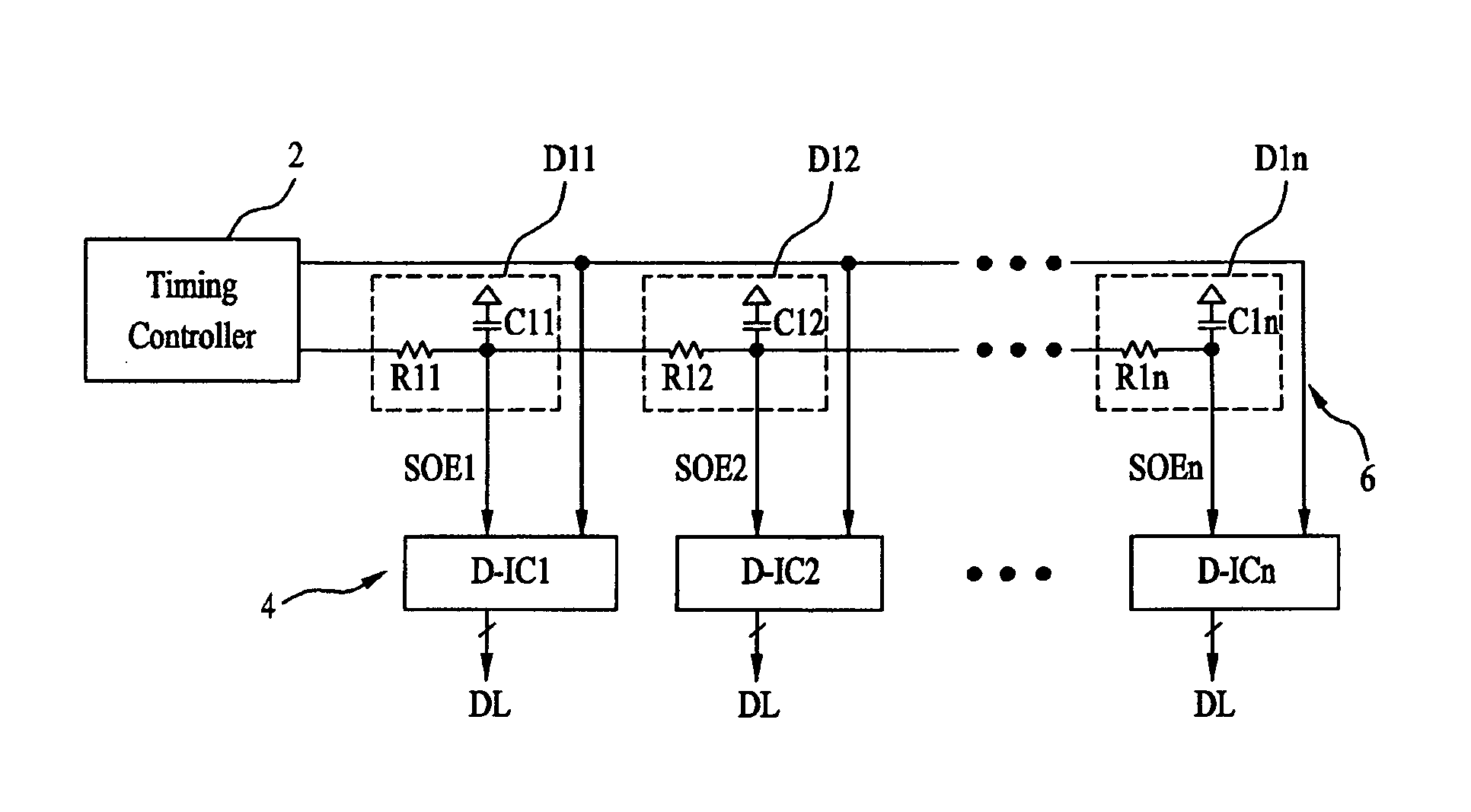

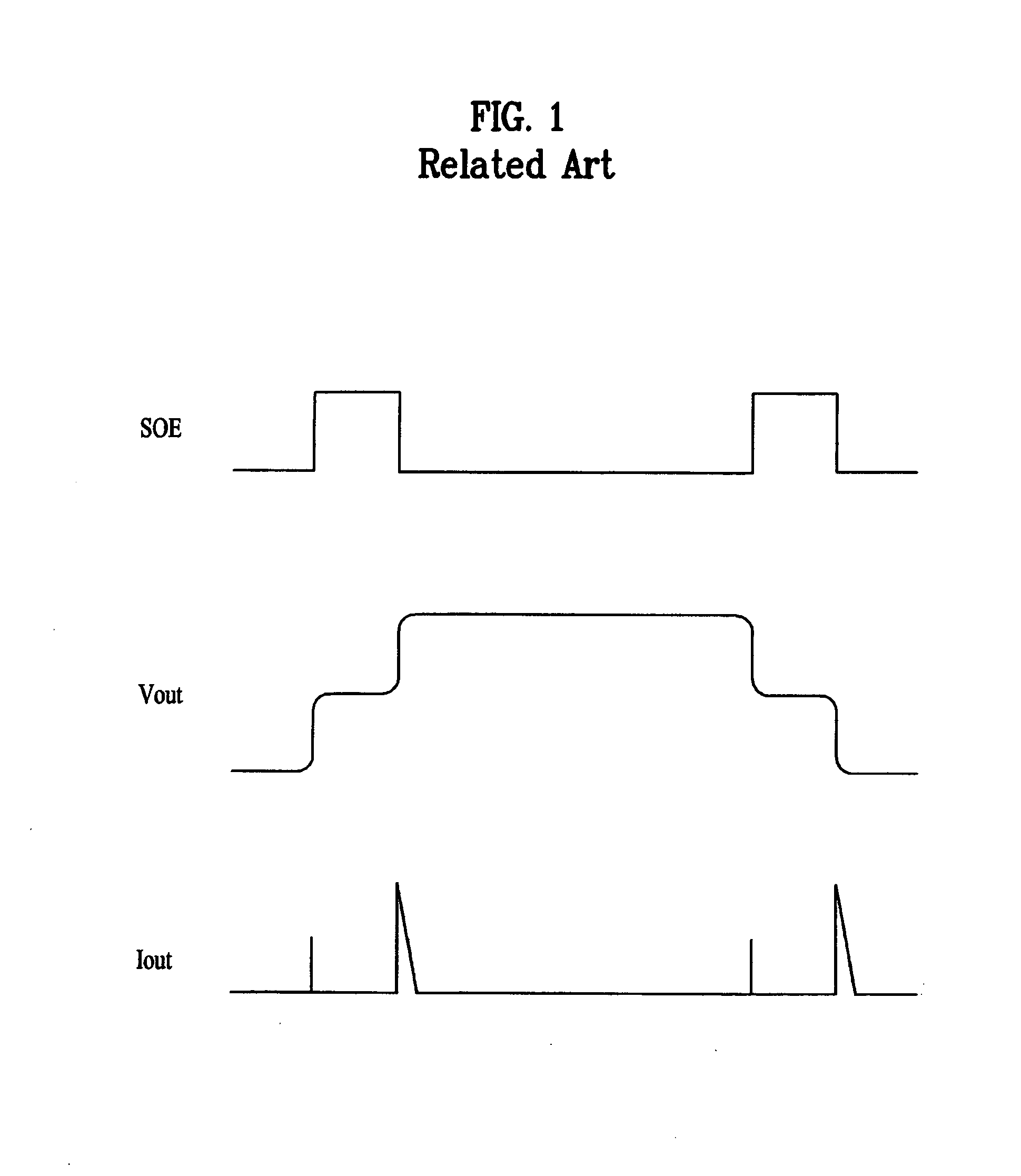

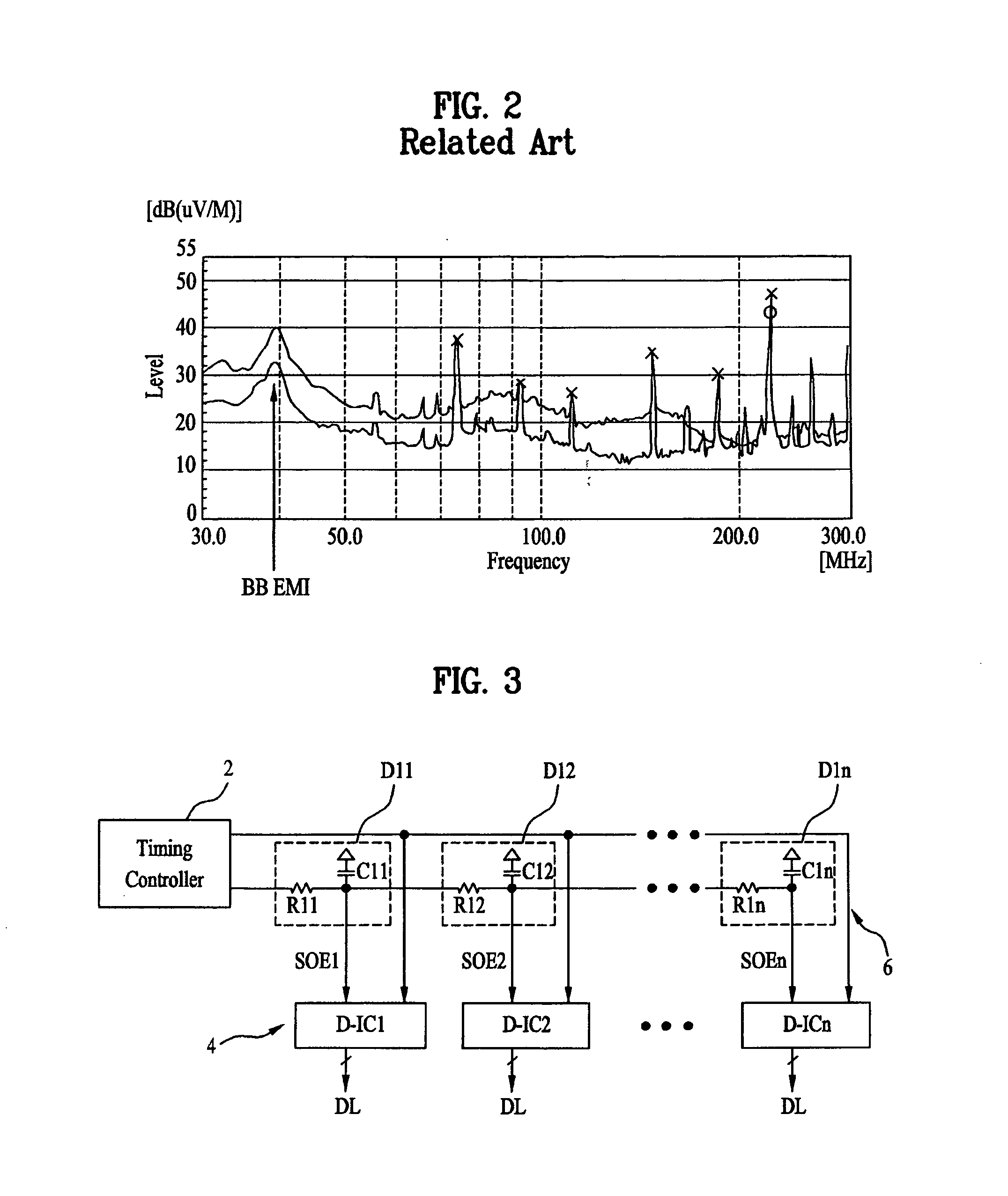

Apparatus and method of driving data of liquid crystal display device

InactiveUS20090058788A1Increase delay timeStatic indicating devicesNon-linear opticsLiquid-crystal displayLiquid crystal

An apparatus and method of driving data of a liquid crystal display device is disclosed, which can minimize an electromagnetic interference EMI noise by decreasing an output peak current of a data driver, the apparatus comprising a timing controller for supplying a reference source output enable signal; a delay circuit for delaying the reference source output enable signal and supplying a plurality of source output enable signals provided with the different delay times; and a data driver, including a plurality of data ICs to divide and drive data lines of a liquid crystal panel into a plurality of data blocks, for dispersing data output timing of the plurality of data ICs in response to the plurality of source output enable signals.

Owner:LG DISPLAY CO LTD

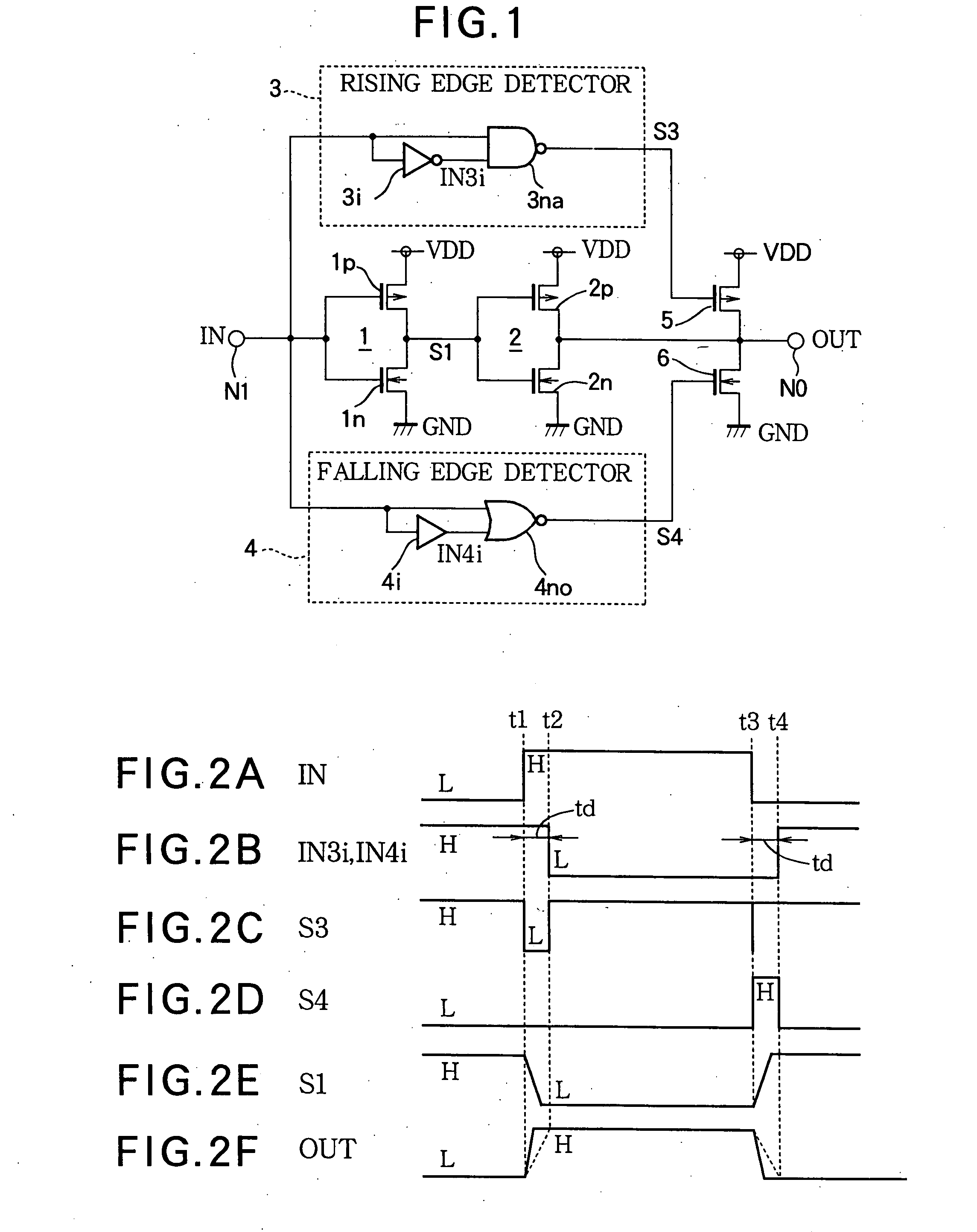

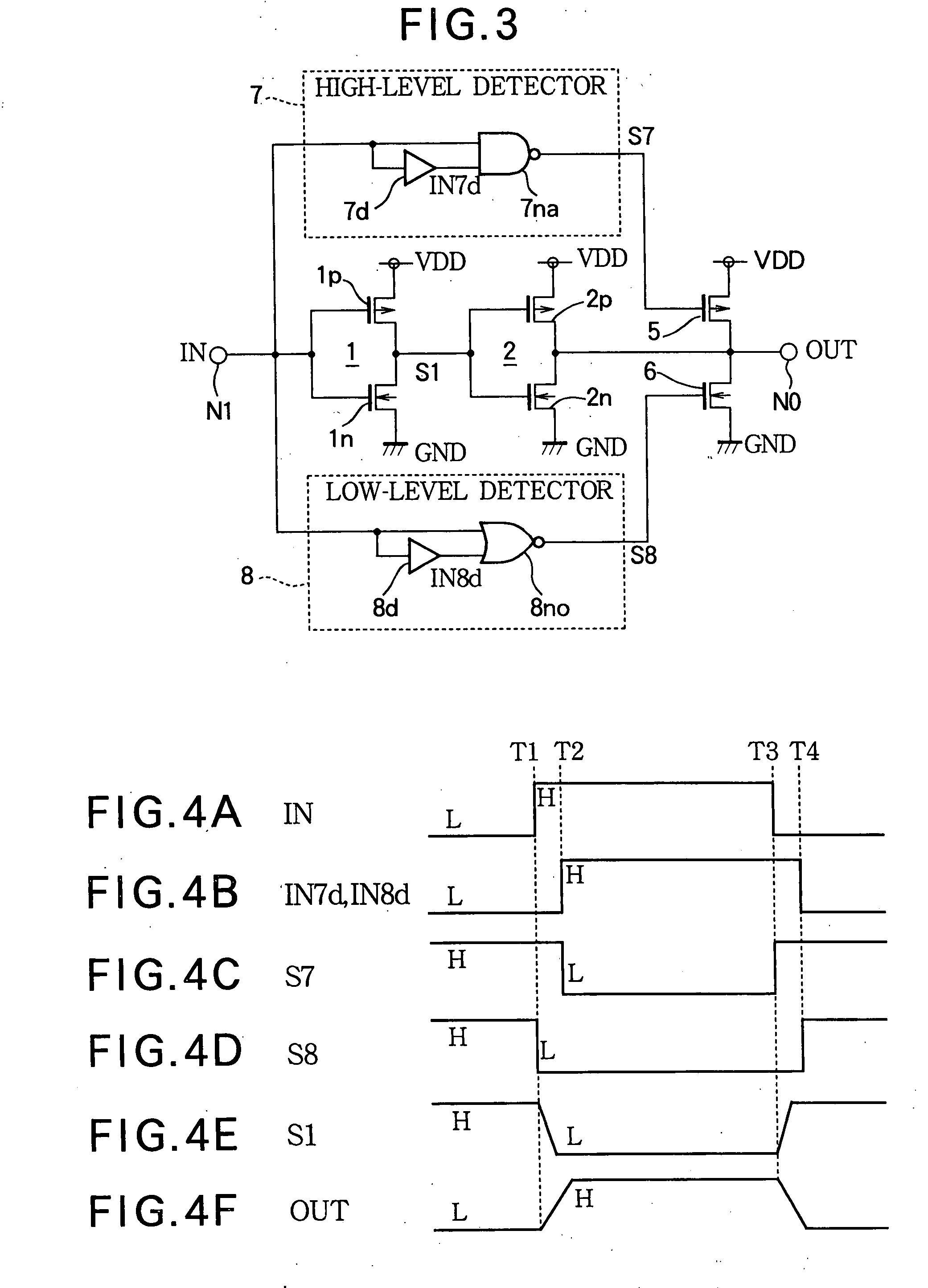

Driving circuit that eliminates effects of ambient temperature variations and increases driving capacity

ActiveUS7508242B2Eliminate the effects ofIncrease delay timeTransistorSwitching accelaration modificationsCMOSDriving circuit

In addition to two-stage CMOS inverters inverting and amplifying the input signal, a rising edge detector detects the rising edge of the input signal, and outputs a rising edge detection signal having a pulse width corresponding to ambient temperature, a PMOS drives the output node to the power supply potential according to the rising edge detection signal, a falling edge detector detects the falling edge of the input signal and outputs a falling edge detection signal having a pulse width corresponding to ambient temperature, and an NMOS drives the output node to ground potential according to the falling edge detection signal. When ambient temperature rises, and delay time of the inverters are thereby increased, pulse widths of the rising and falling edge detection signals are increased. The additional driving restrains delay time variation in a driving circuit due to ambient temperature change.

Owner:LAPIS SEMICON CO LTD

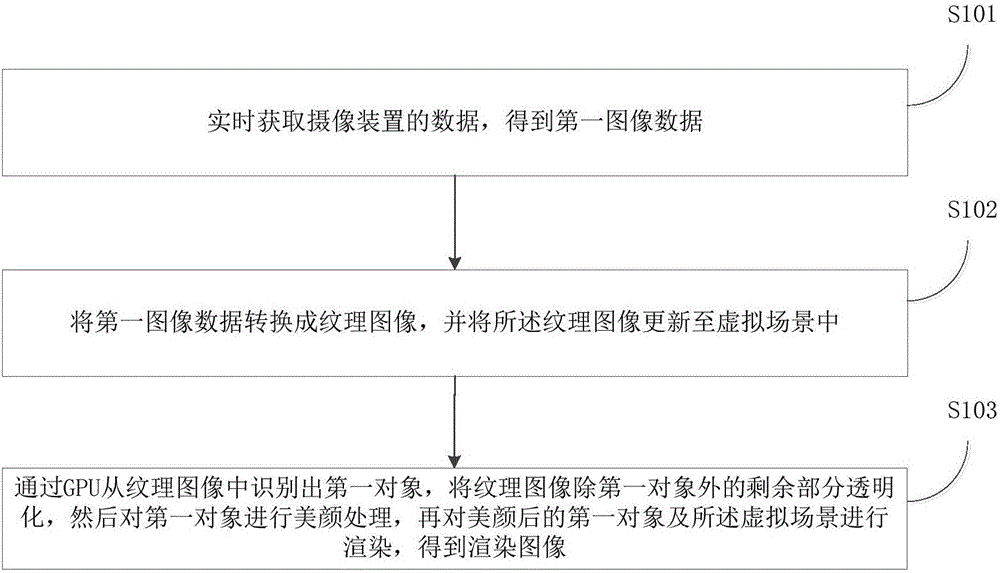

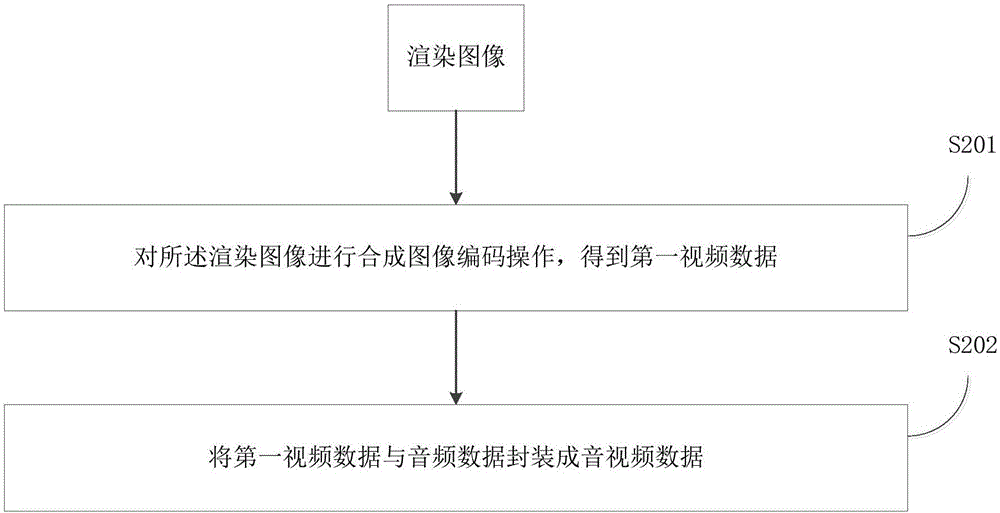

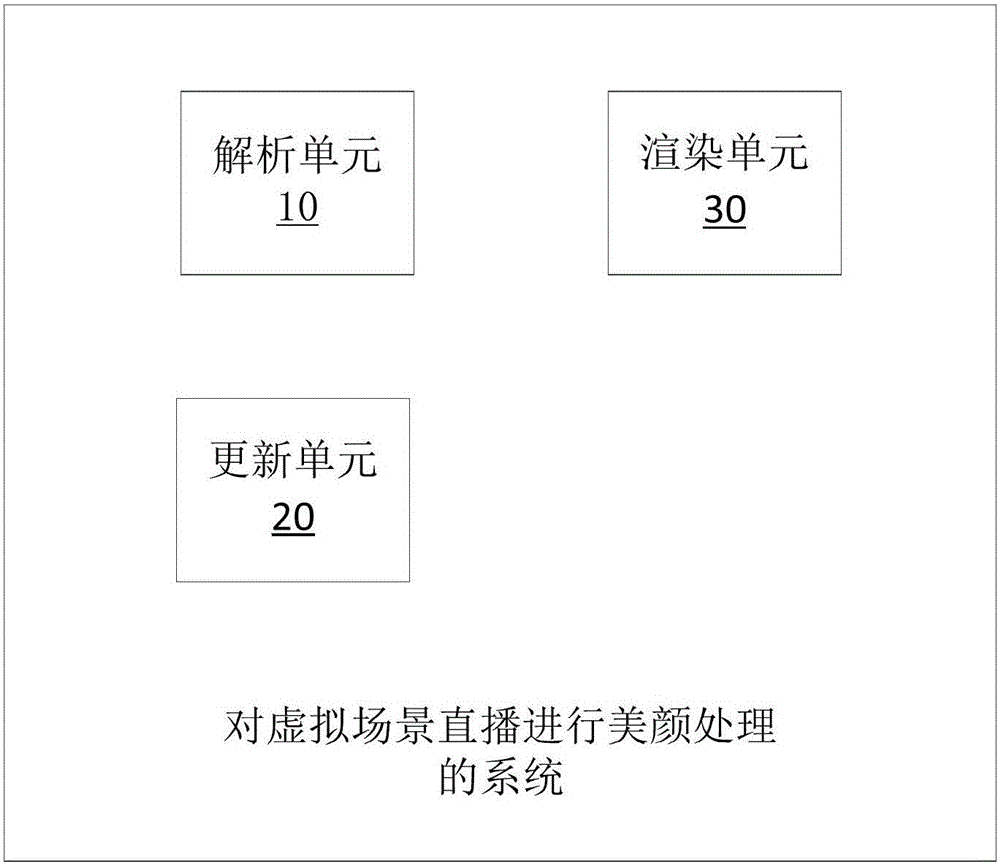

Beautifying method and system for virtual scene live

InactiveCN106713988AIncrease delay timeReduce latencySelective content distributionComputer graphics (images)Computer science

The invention relates to the field of multimedia data processing, and discloses a beautifying method and system for virtual scene live. The method comprising the steps that the data of a camera device are acquired in real time to acquire first image data; the first image data are converted into a texture image, and the texture image is updated to a virtual scene; a first object is extracted from the virtual scene through a GPU; and the first object is beautified and the virtual scene is rendered to acquire a render image. According to the technical scheme, the data of the camera device are converted into the texture image; the texture image is updated to the virtual scene; at the rendering stage of the virtual scene, the first object is extracted through the GPU; the first object is beautified to acquire the render image; rendering and beautifying are carried out in parallel; and the delay time of beautifying in virtual scene live is greatly reduced.

Owner:FUJIAN STAR NET EVIDEO INFORMATION SYST CO LTD

Mass spectrometer

InactiveUS20050092911A1High sensitivityIncrease delay timeStability-of-path spectrometersTime-of-flight spectrometersIon trap mass spectrometryMass spectrometric

A mass spectrometer is disclosed wherein ions having a particular desired charge state are selected by operating an ion mobility spectrometer in combination with a quadrupole mass filter. Precursor ions are fragmented or reacted to form product ions in a collision cell ion trap and sent back upstream to an upstream ion trap. The fragment or product ions are then passed through the ion mobility spectrometer wherein they become temporally separated according to their ion mobility. Fragment or product ions are then re-trapped in the collision cell ion trap before being released therefrom in packets. A pusher electrode of a time of flight mass analyser is energised a predetermined period of time after a packet of ions is released from the collision cell ion trap. Accordingly, it is possible to select multiply charged precursor ions from a background of singly charged ions, fragment them, and mass analyse the fragment ions with a near 100% duty cycle across the whole mass range.

Owner:MICROMASS UK LTD

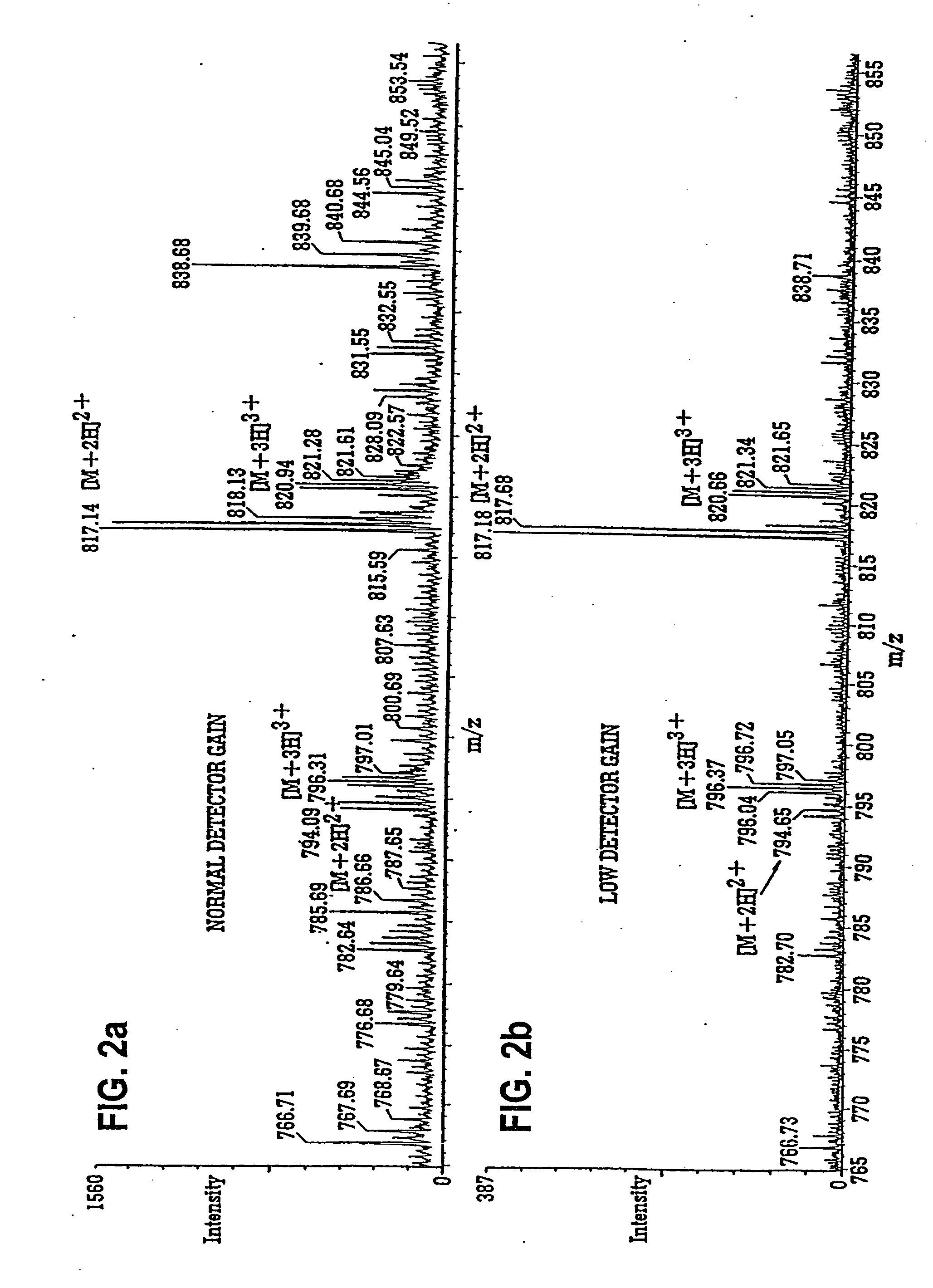

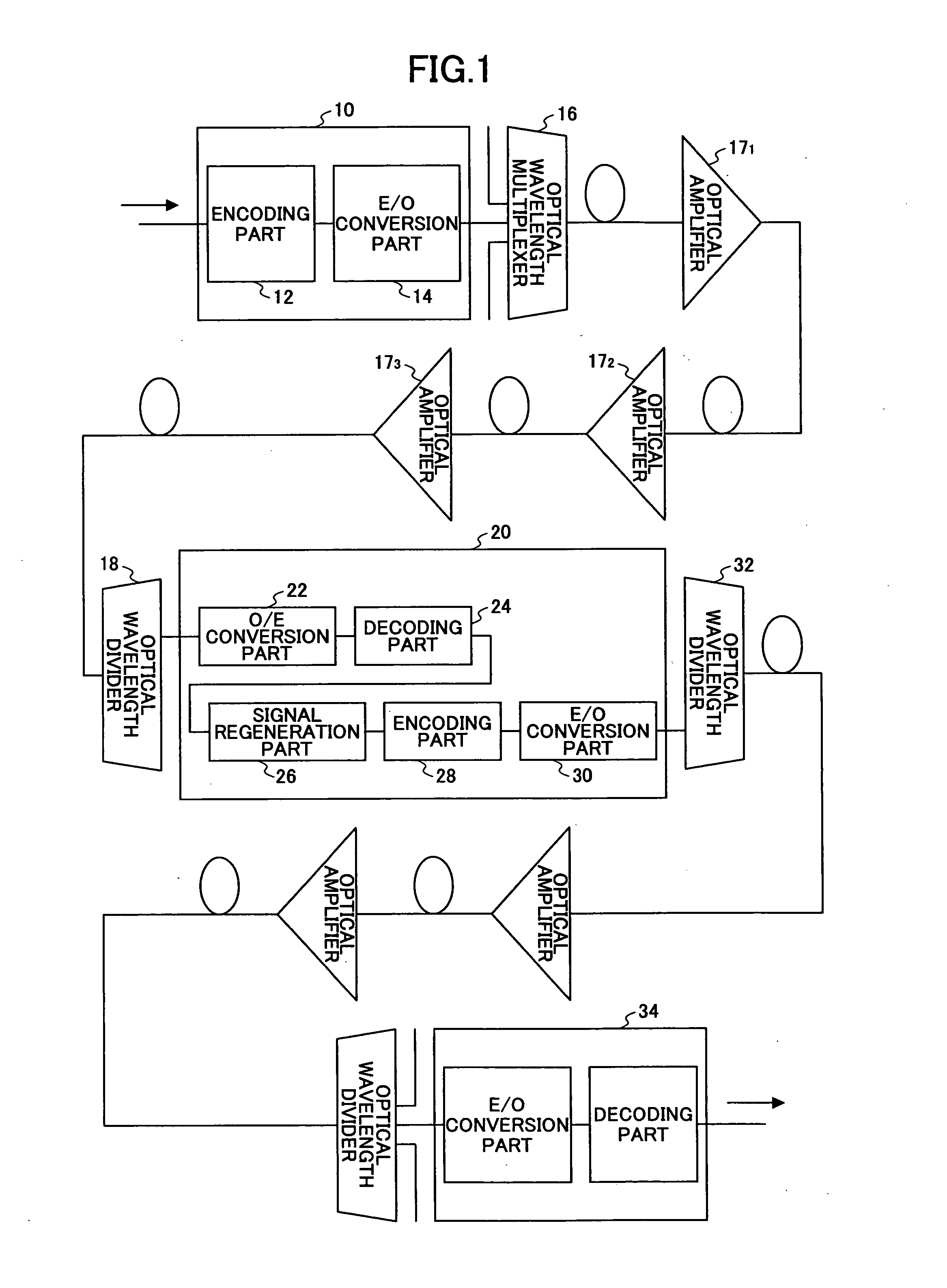

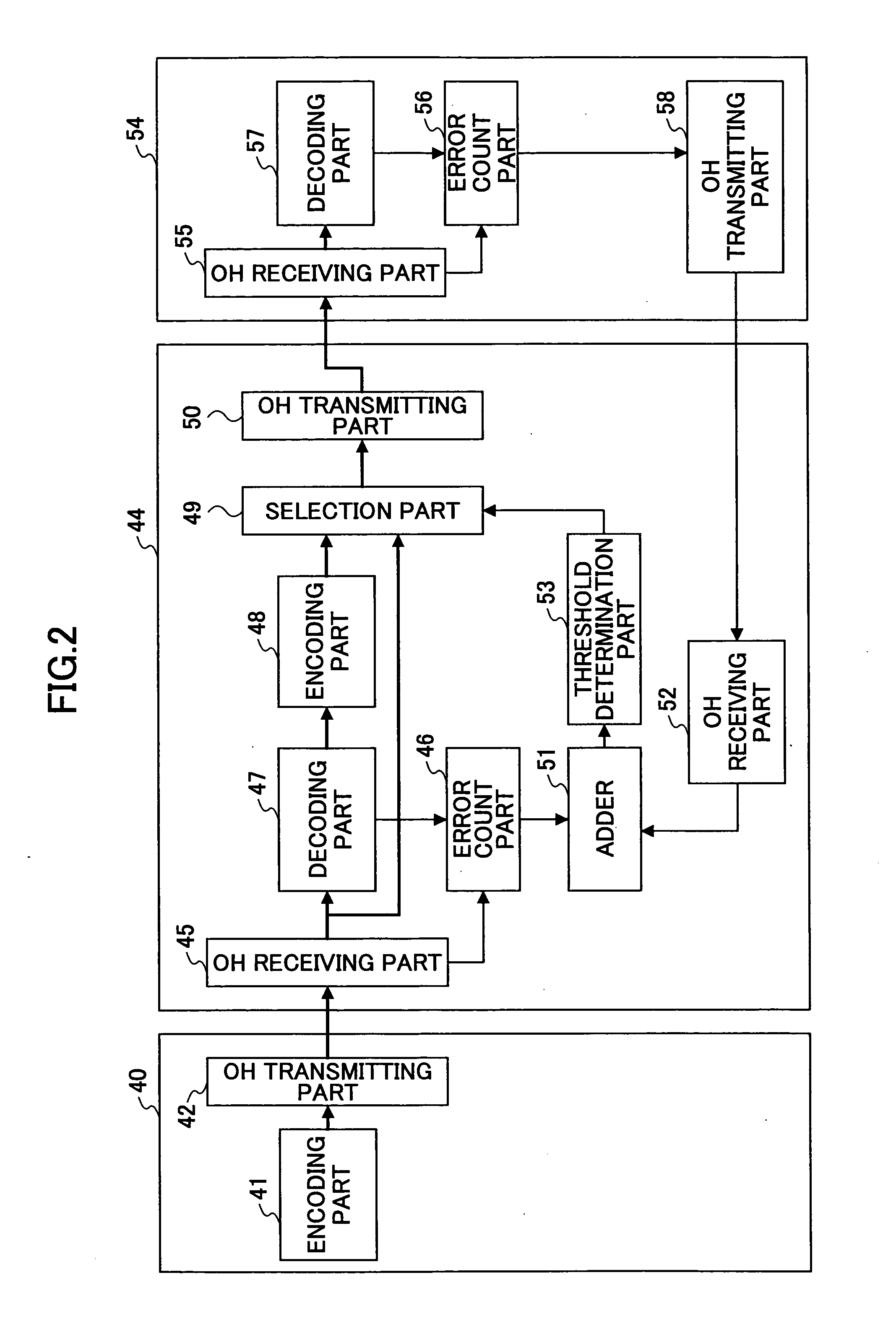

Regenerative relay system and regenerative relay apparatus

InactiveUS20060080581A1Increase delay timeImprove transmission qualityError detection/prevention using signal quality detectorOther decoding techniquesComputer hardwareCorrection code

A regenerative relay method includes the steps of: i) calculating an error rate of a transmission path between the first half apparatus and a main apparatus; ii) calculating an error rate of a transmission path between the main apparatus and the latter apparatus; iii) adding the error rates; iv) selecting the error correction code and data before the error is corrected in the main apparatus so as to be supplied to the latter apparatus if the added error rates are lower than a designated error correction threshold; and v) selecting data after the error is corrected in the main apparatus and the other error correction code generated from the data so as to be supplied to the latter apparatus if the added error rates are higher than the designated error correction threshold.

Owner:FUJITSU LTD

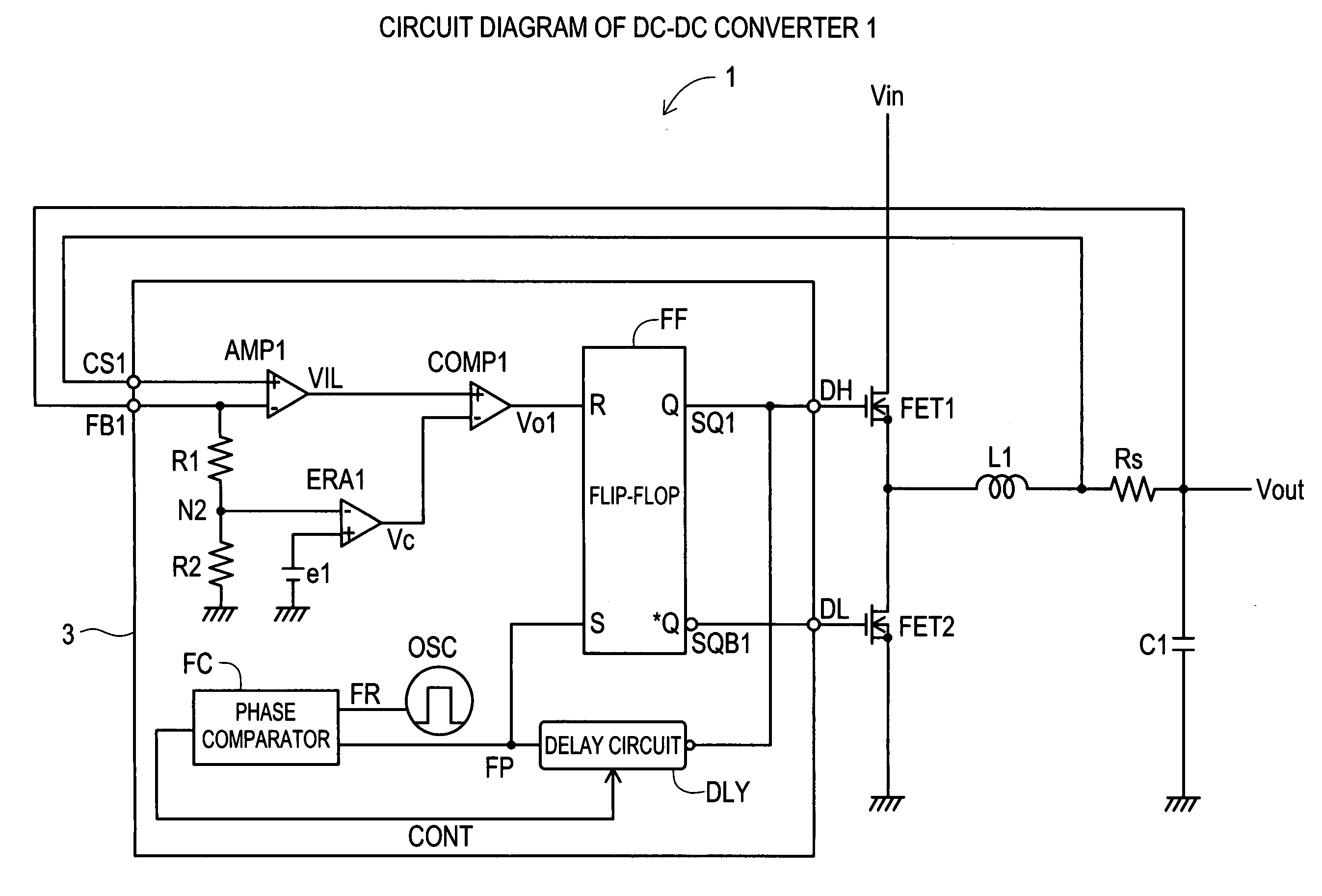

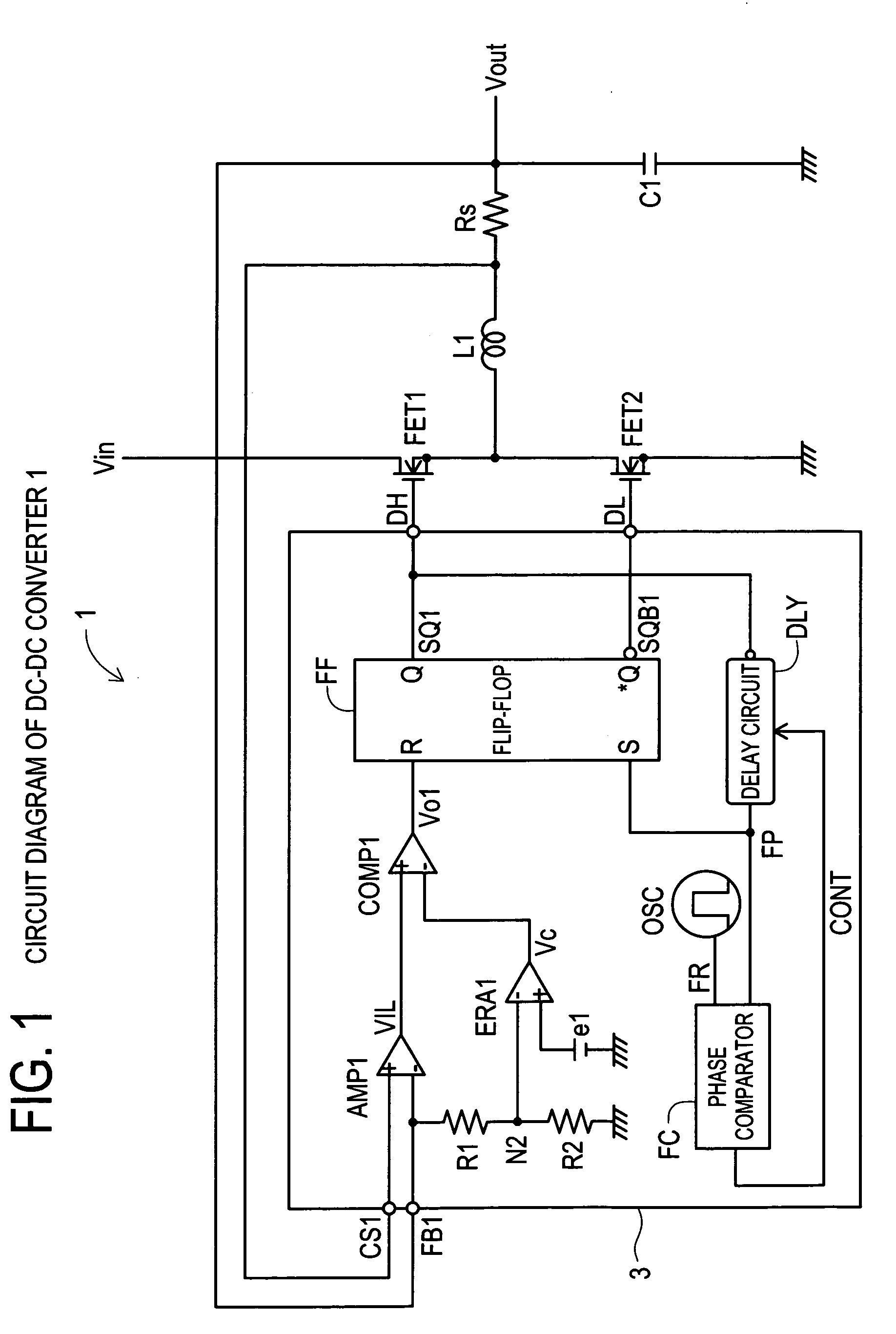

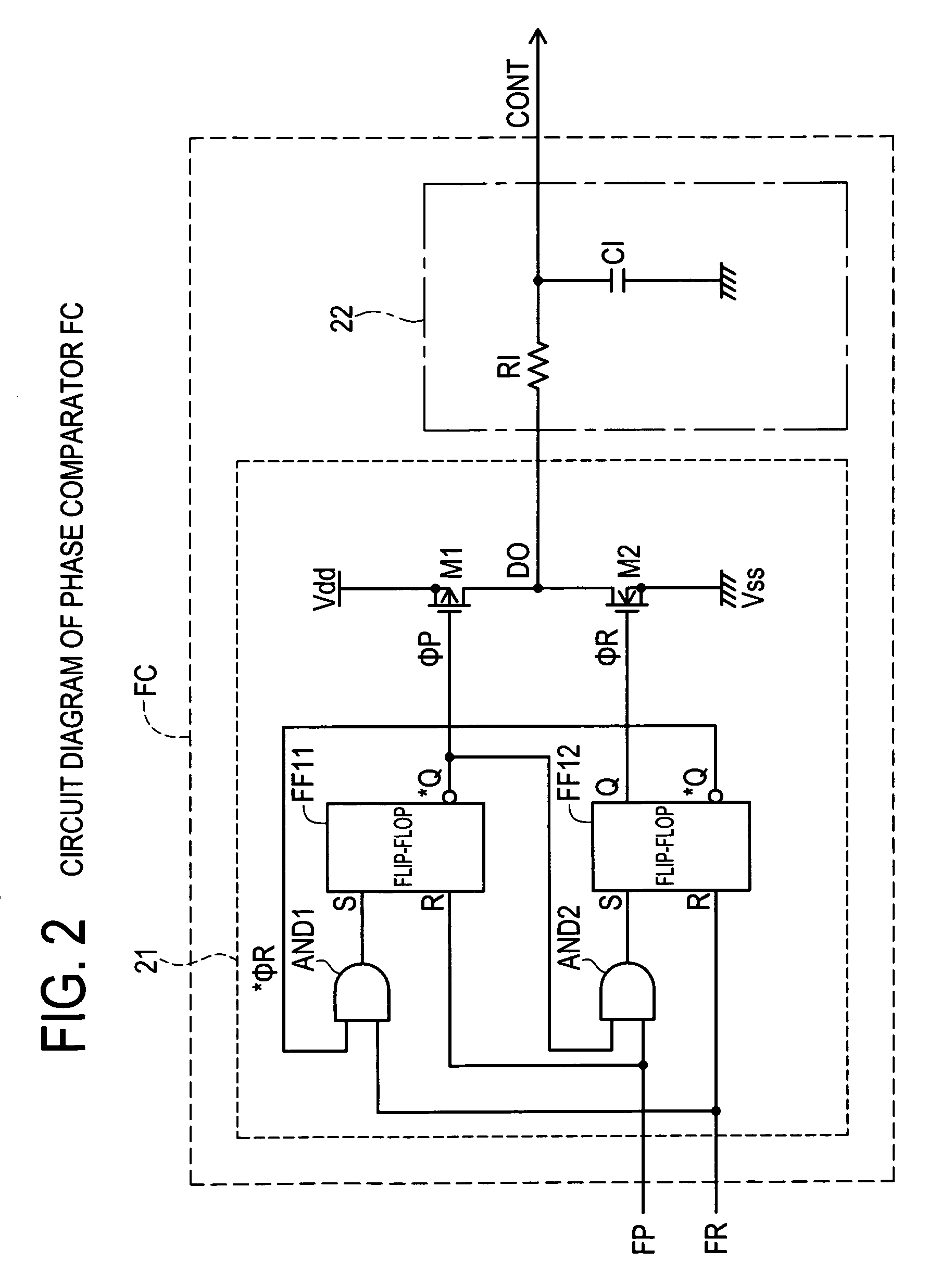

Control circuit and control method for DC-DC converter

ActiveUS7193401B1Avoid disturbancePrevent fluctuationEfficient power electronics conversionDc-dc conversionSubharmonic oscillationDc converter

It is an object of the present invention to provide a control circuit and a control method for a current mode control type DC—DC converter capable of preventing a subharmonic oscillation even if an on-duty is not less than 50% and capable of preventing a switching frequency from fluctuating depending on an input voltage. When a high-level output signal Vo1 is inputted to a reset input terminal R of a flip-flop FF, a transistor FET1 is turned off. A phase comparator FC outputs a comparison result signal CONT in accordance with a phase difference between a delay signal FP and a reference signal FR. A delay circuit DLY outputs a high-level delay signal FP after the passage of a delay time DT adjusted in accordance with the comparison result signal CONT from the turn-off of the transistor FET1. The transistor FET1 is turned on in accordance with an input of the high-level delay signal FP.

Owner:CYPRESS SEMICON CORP

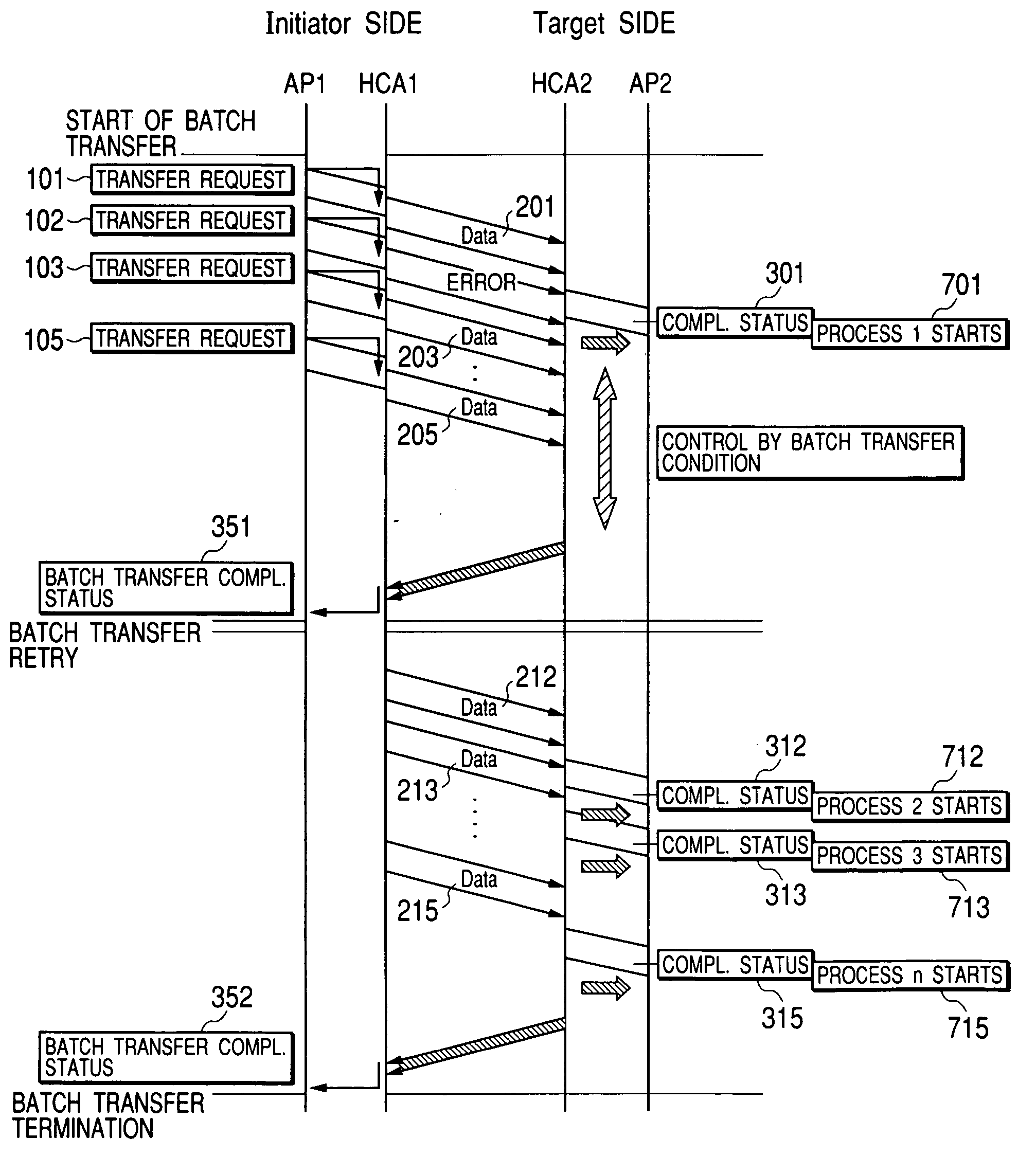

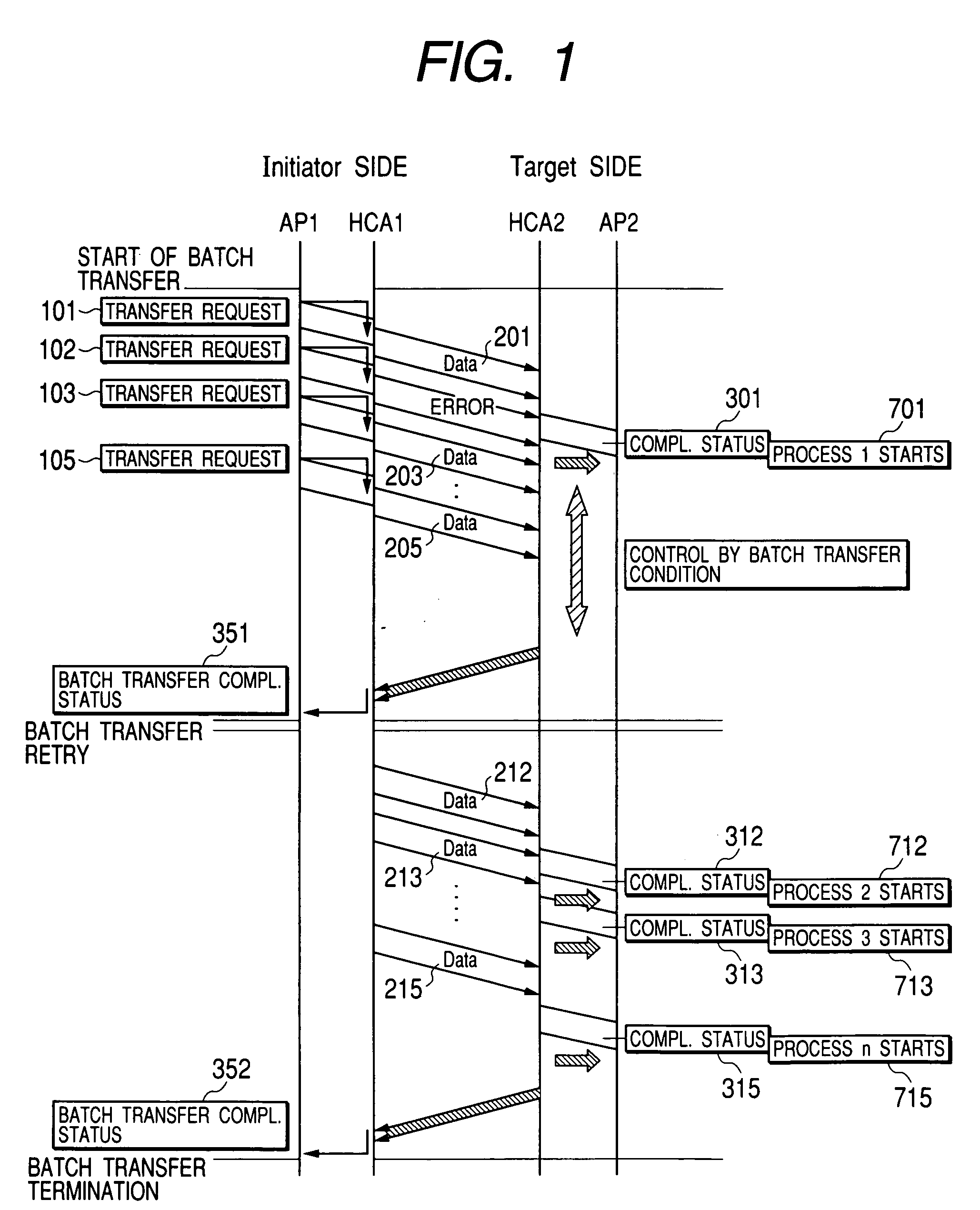

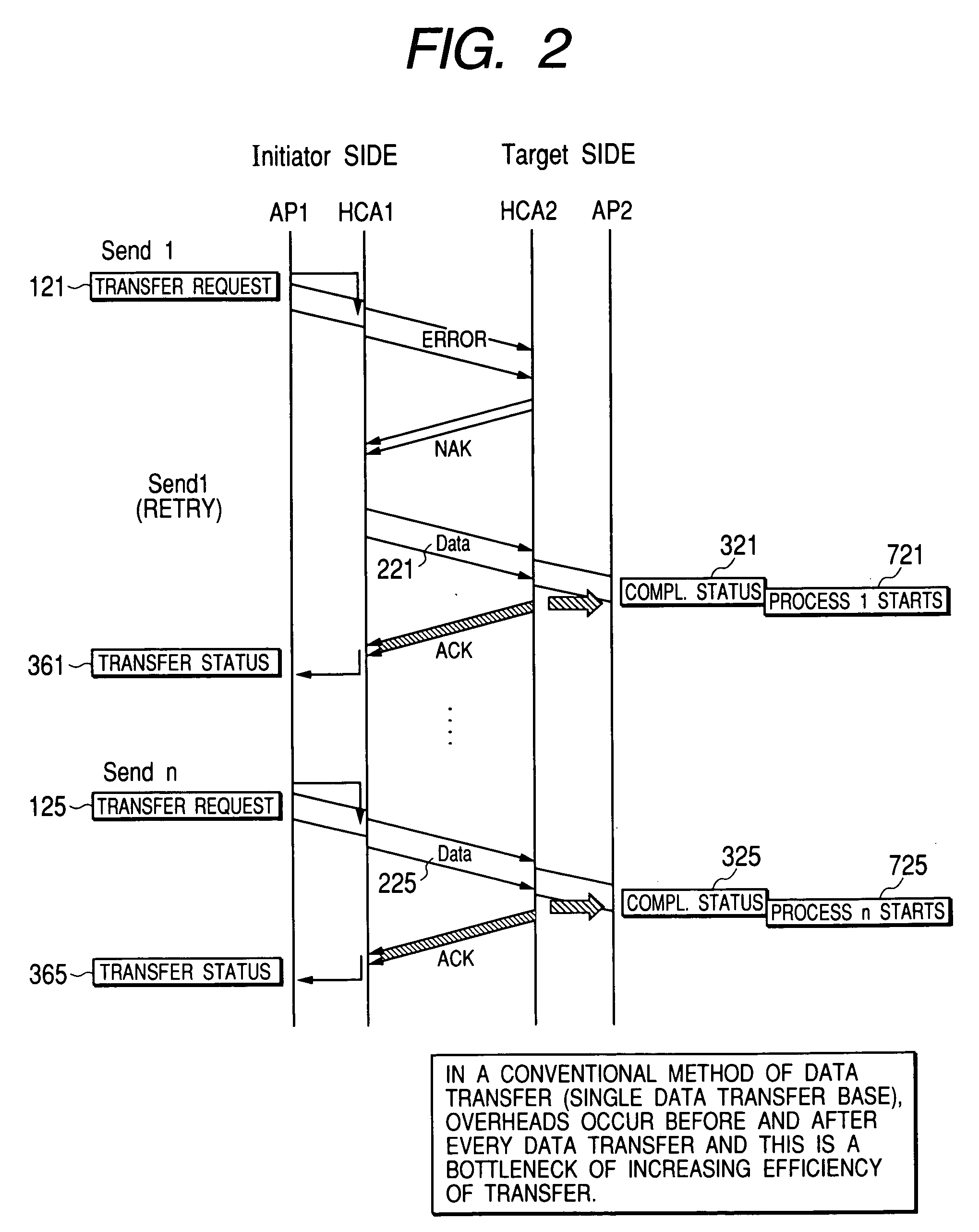

Data transfer method and disk control unit using it

ActiveUS20050080946A1Improve transmission efficiencyAccelerate the application processInput/output to record carriersError checkCompletion Status

The present invention provides a reliable and high-speed data transfer method that achieves a high transfer efficiency and a high application processing efficiency concurrently and a disk control unit (disk controller) using such a method. In reliable data transfer in which, when data is transferred from an initiator to a target, the data received by the target is checked for validity by using an error check code attached to the data, a transfer status indicating whether the data is valid is returned from the target to the initiator, and, if a transfer error occurring during the data transfer is detected by the transfer status, the initiator retries to transfer the data to the target, a data transfer method for logical records that are units of data transfer between the initiator and the target is disclosed. This method is characterized in that: when each logical record transferred by a transfer request issued by the initiator arrives correctly on the target, the target posts a completion status corresponding to the transfer request for the logical record to a completion queue existing in the target; a plurality of logical records in a block are batch transferred; the initiator confirms the transfer status at every batch transfer; and, for each logical record that meets a predetermined batch transfer condition, the target posts a completion status corresponding to the transfer request for the logical record to the completion queue existing in the target upon correct reception of the logical record.

Owner:GOOGLE LLC

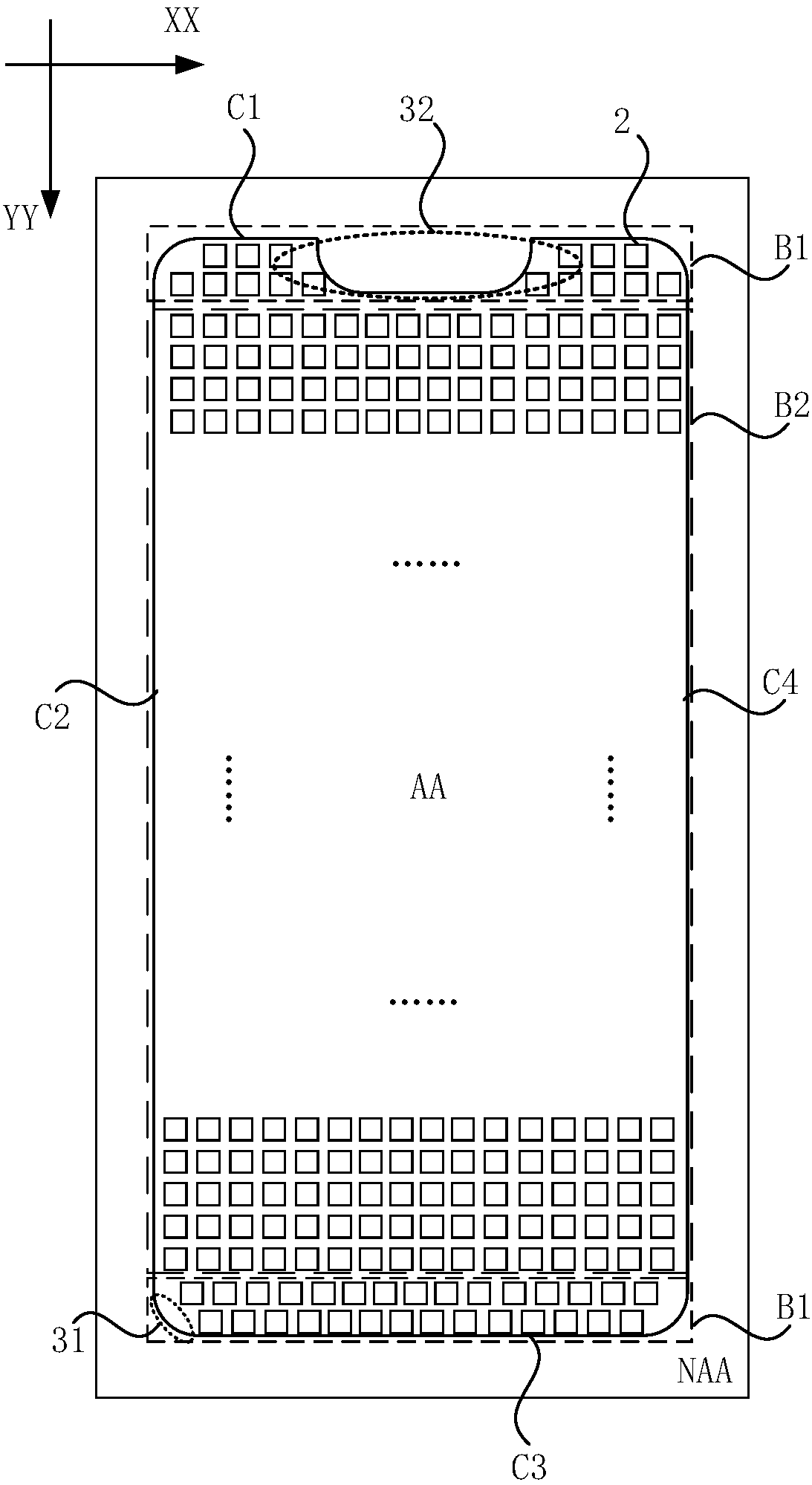

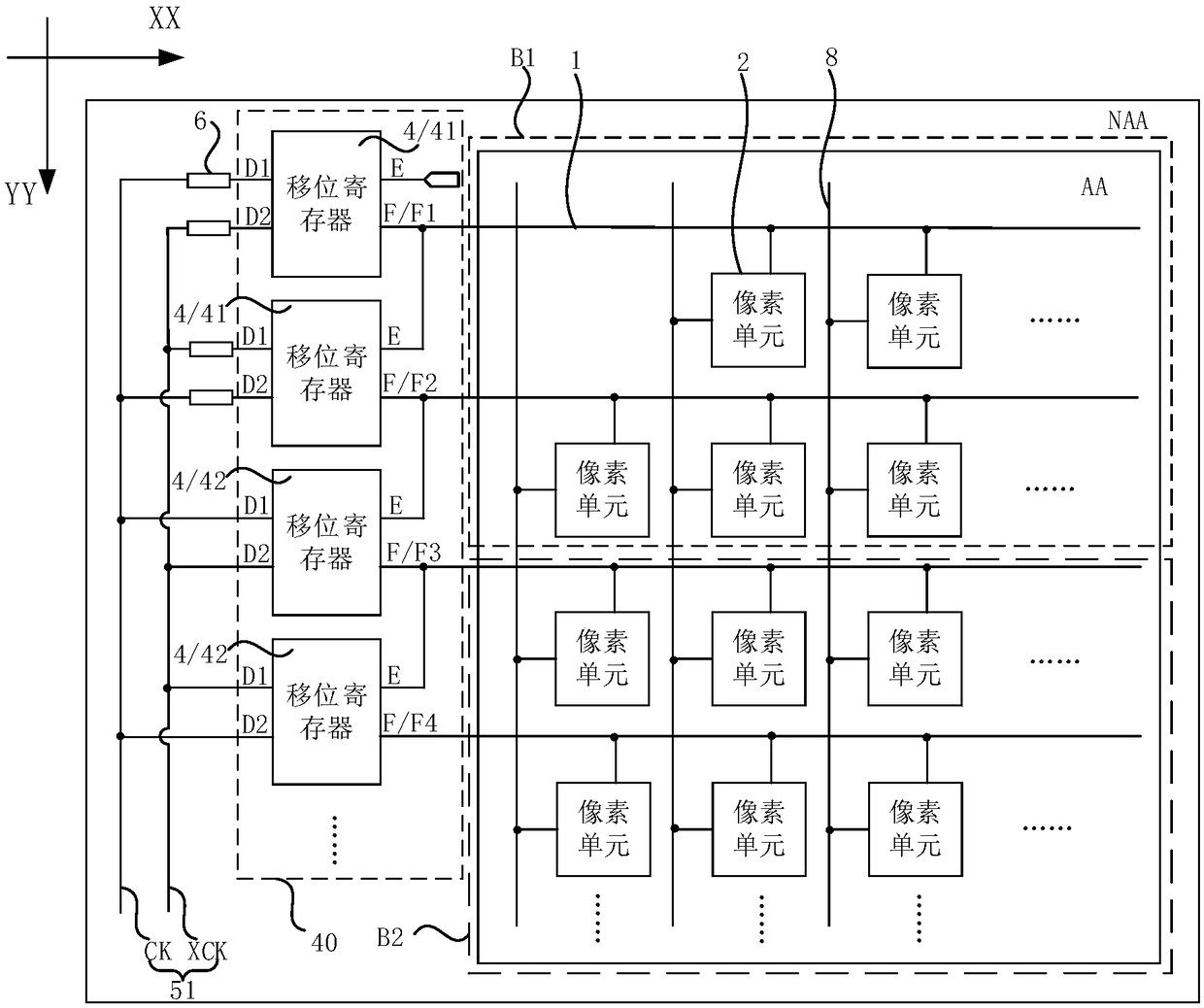

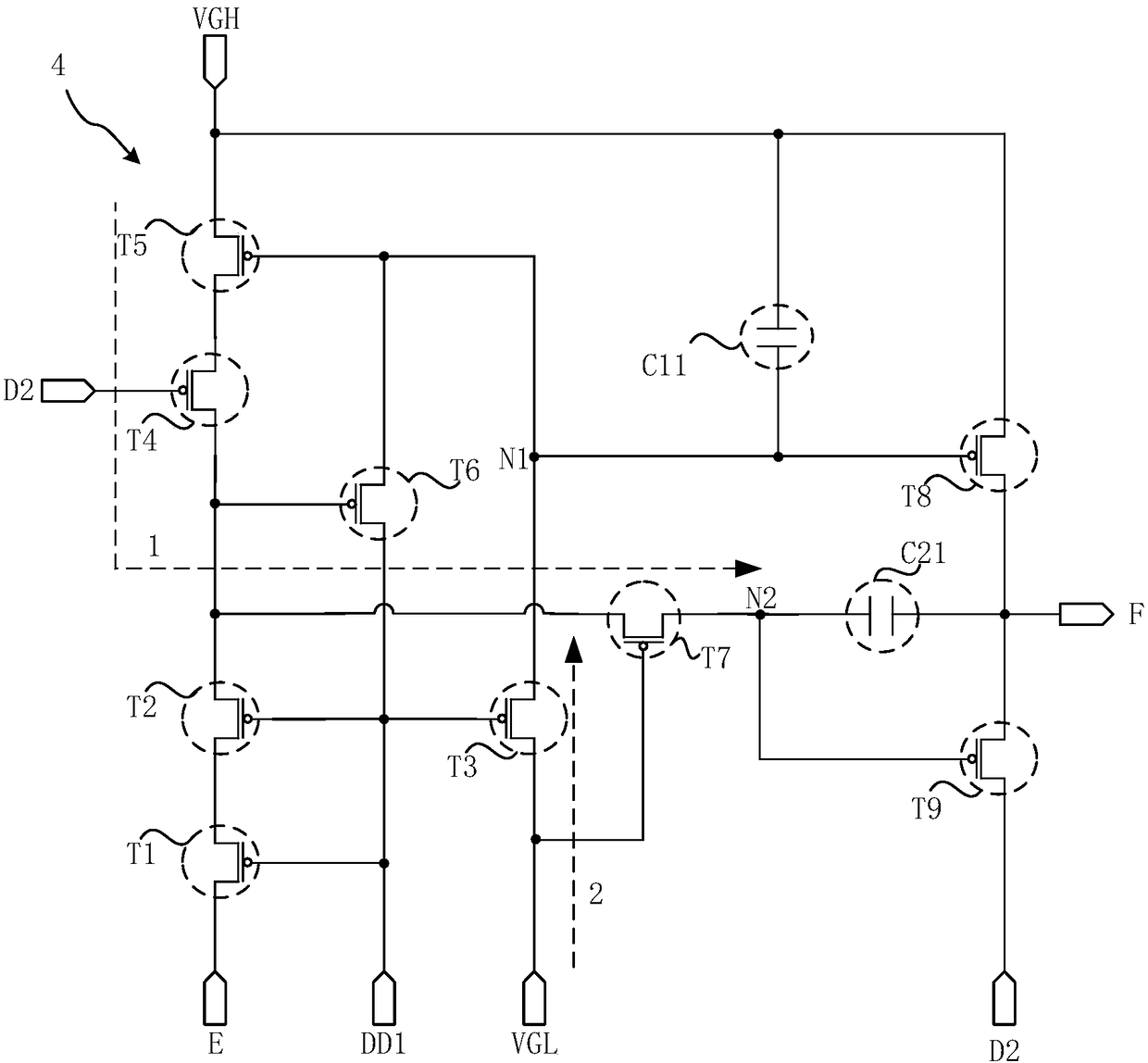

Display panel and display device

PendingCN108564916AImprove display brightness varianceImprove display uniformityStatic indicating devicesDigital storageElectricityShift register

The invention discloses a display panel and a display device. Display areas of the display panel comprise a first area and a second area, wherein the quantity of pixel units in each row in the first area is smaller than the quantity of pixel units in each row in the second area; a scanning line in electrical connection with a first shifting register is positioned in the first area, and a scanningline in electrical connection with a second shifting register is positioned in the second area; the first shifting register and the second shifting register are electrically connected with a first clock signal line; the first shifting register is electrically connected with the first clock signal line by using a resistance compensation unit; or the first shifting register is electrically connectedwith a second clock signal line; the second shifting register is electrically connected with a third clock signal line; an effective signal duty ratio of the second clock signal line is greater thanan effective signal duty ratio of the third clock signal line. According to the technical scheme in the invention, delay time of enabling the first shifting register to output a scanning drive signalto the scanning line positioned in the first area is prolonged, and display uniformity of the display panel is improved.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

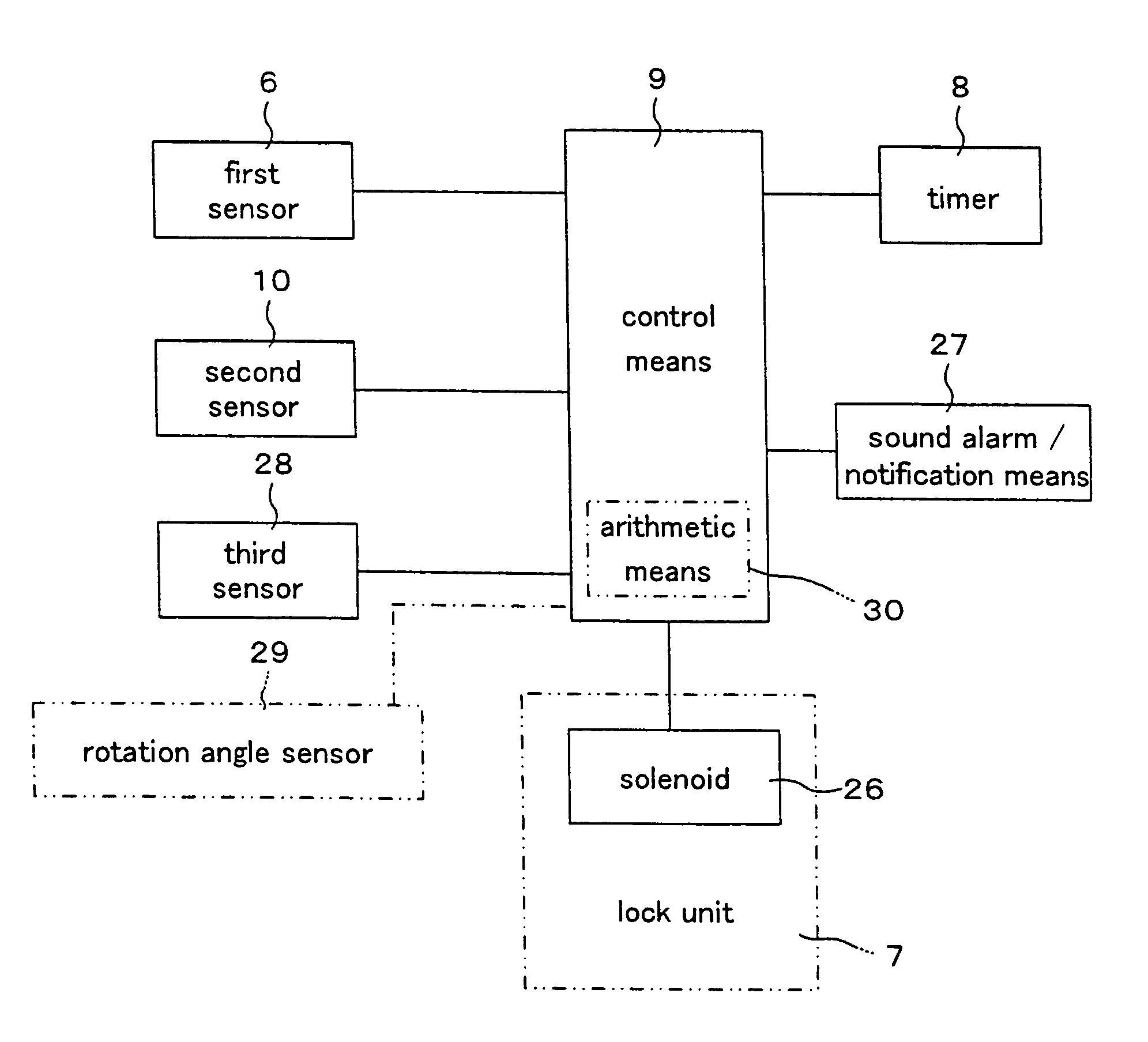

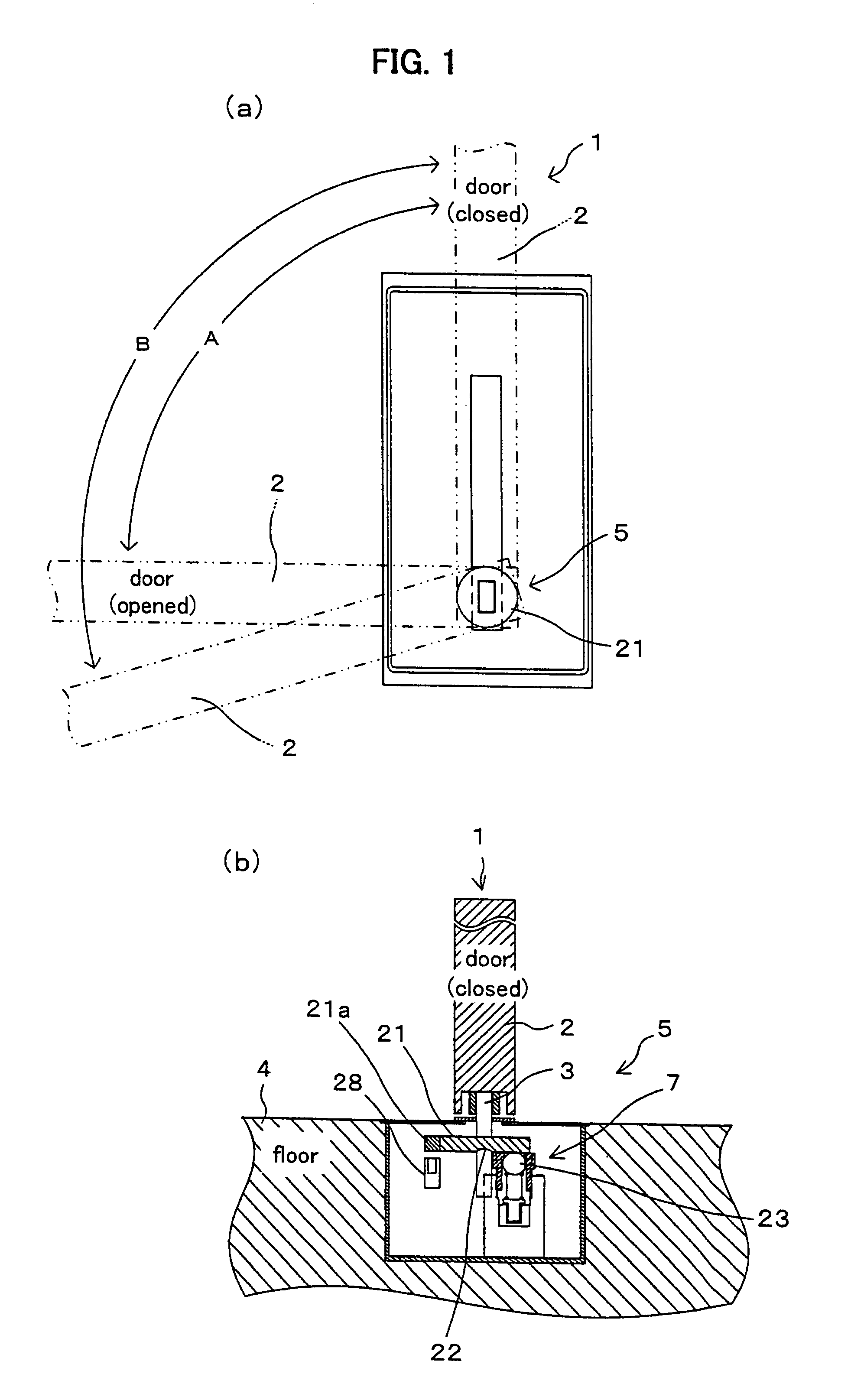

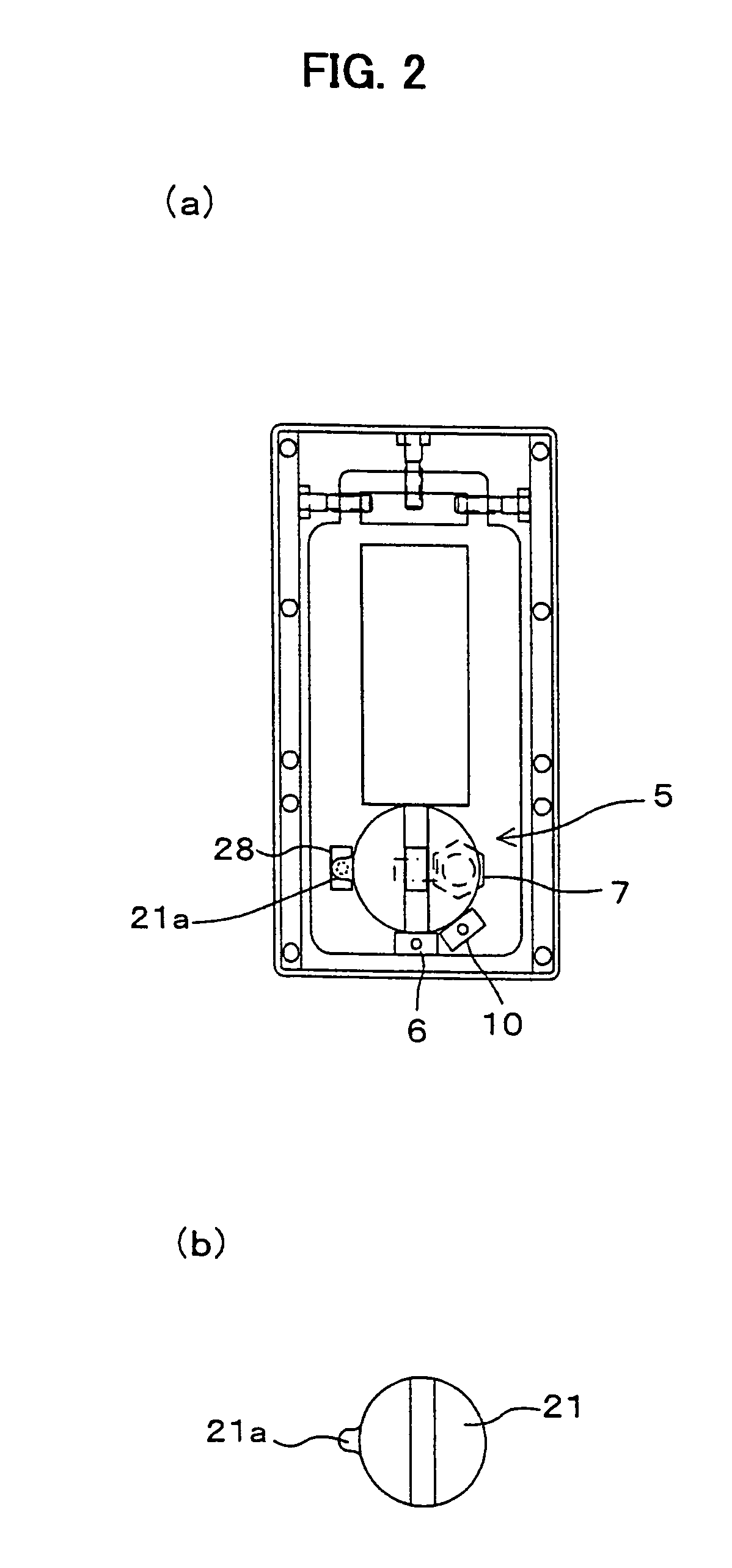

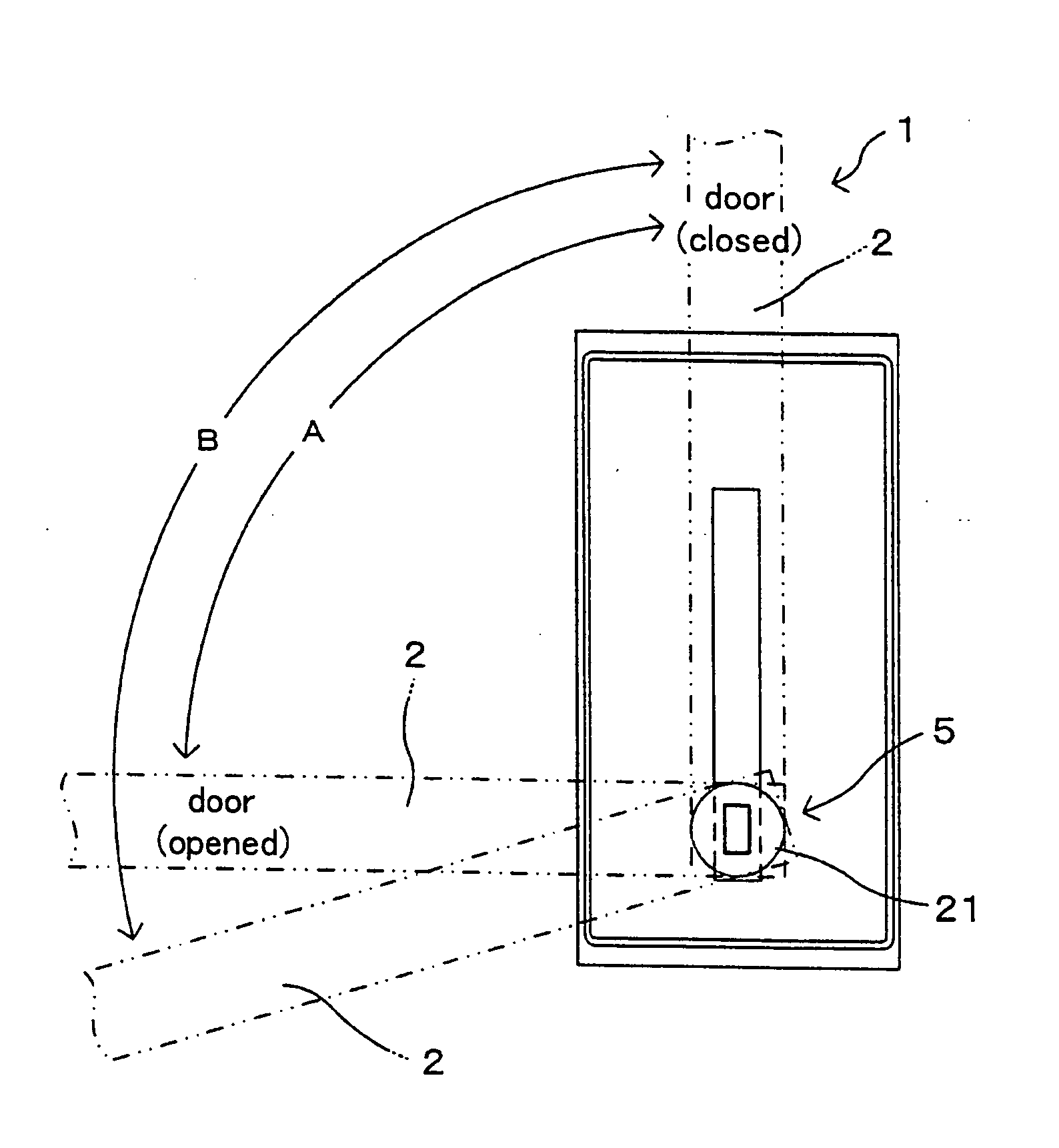

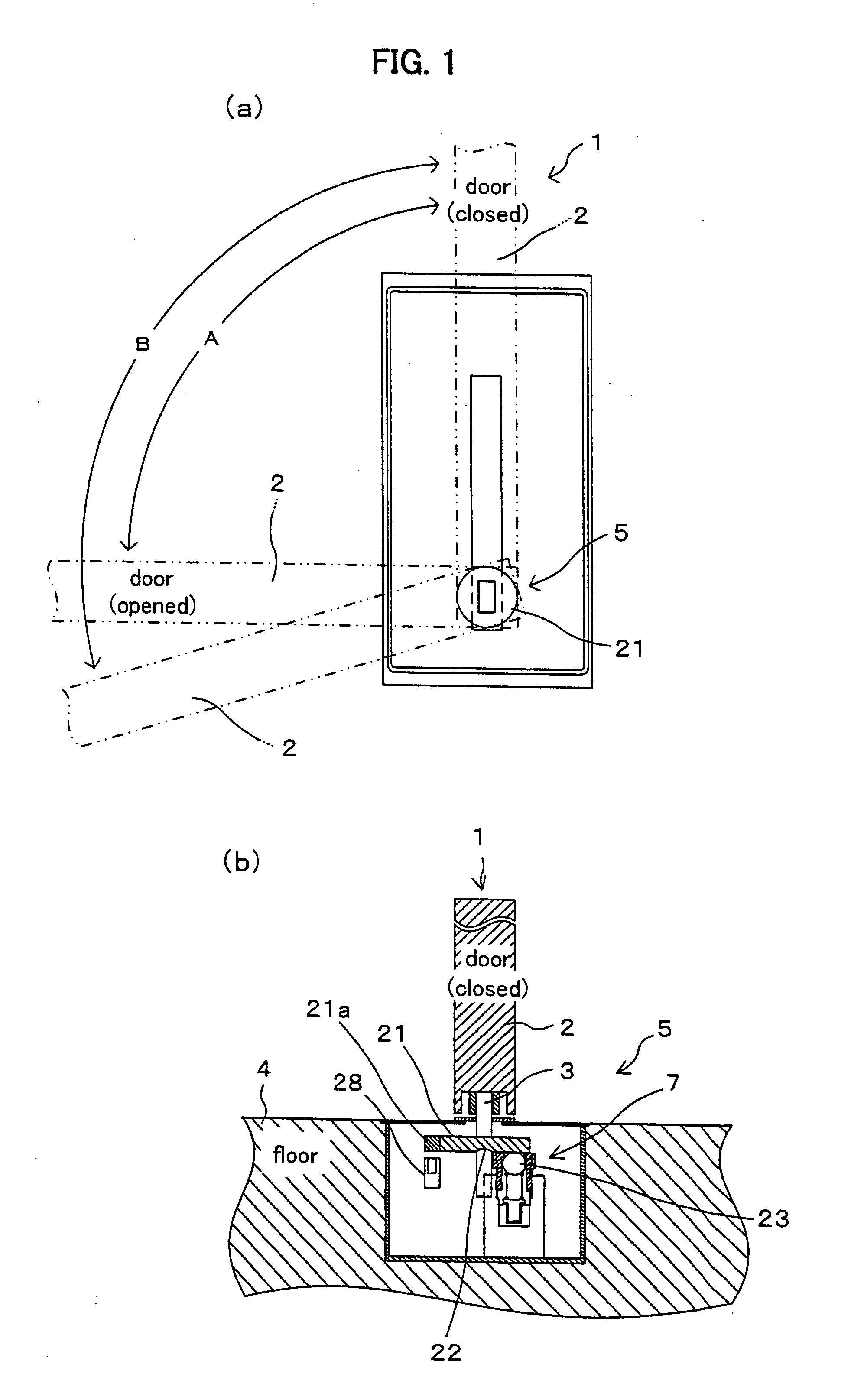

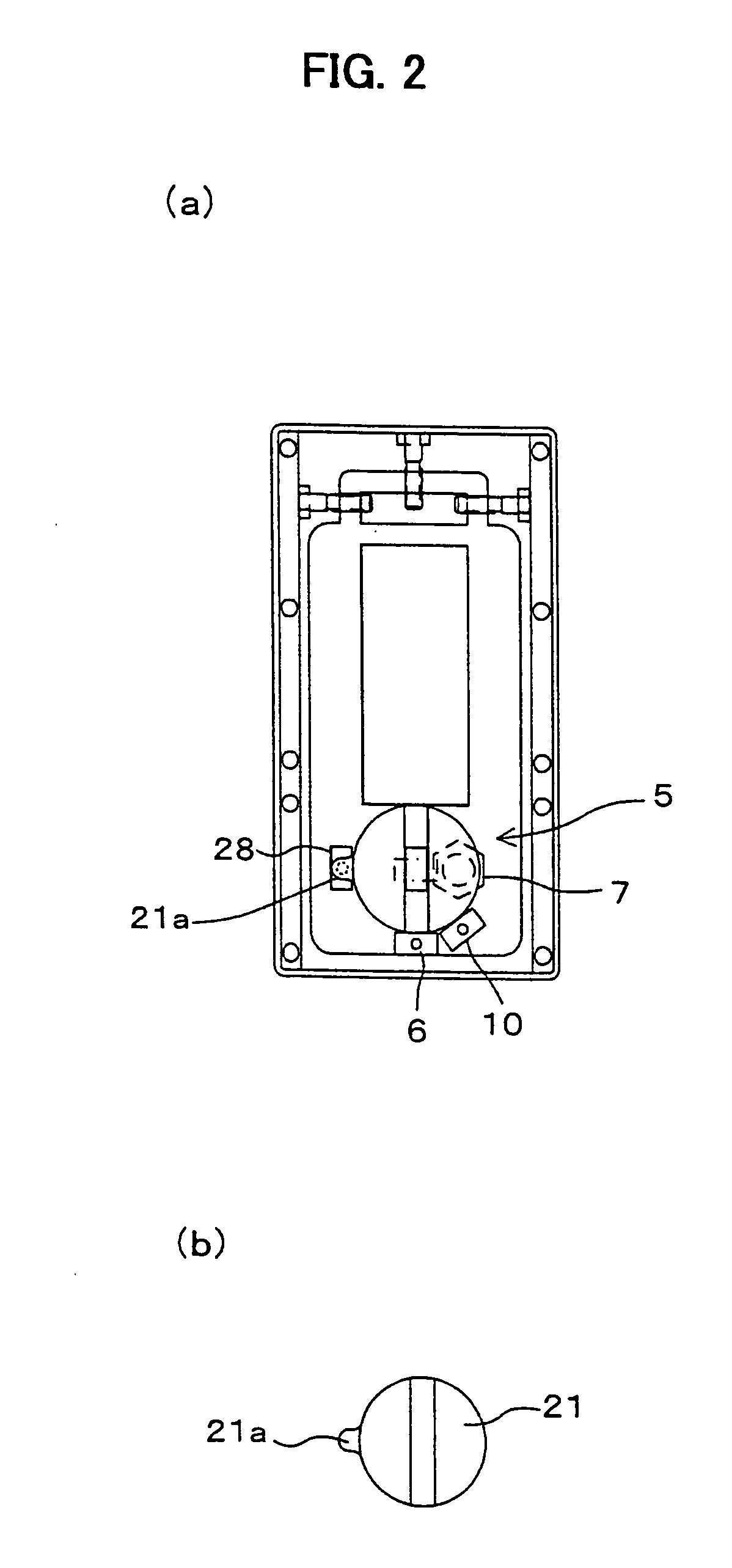

Delay unit for door with a door closer, door closer with a delay unit, and door with a door closer having a delay unit

InactiveUS7859203B2Increase delay timeEasy to set upDC motor speed/torque controlBuilding braking devicesTimerKymograph

The Objective of the present invention is to provide a delay unit for door with a door closer, which is capable of automatically closing the door after the elapse of a certain time since the door was opened and can be installed in case that the door closer is embedded inside the building and thereby being not exposed.The objective is solved by providing a delay unit 5 for door with a door closer comprising: a first sensor for detecting the door 2 opened to the first angle A, a lock unit 7 for electrically lock / unlock of the rotation of the rotation axis 3 of the door 2, a timer, a first sensor, and a control means, with which the first sensor, lock unit 7, and timer is connected, for controlling the lock unit 7 based on the signals from the first sensor and timer.

Owner:DT ENG

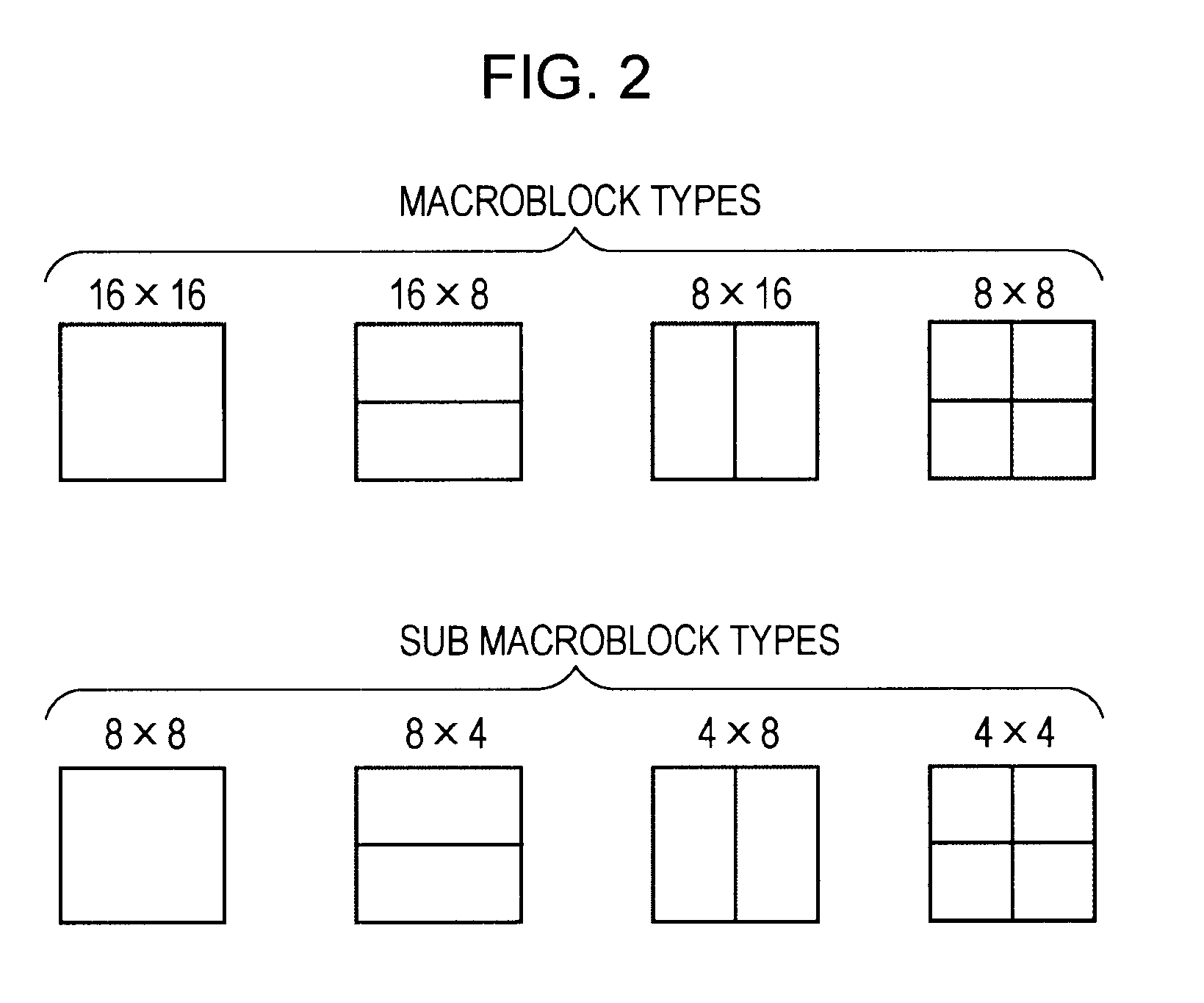

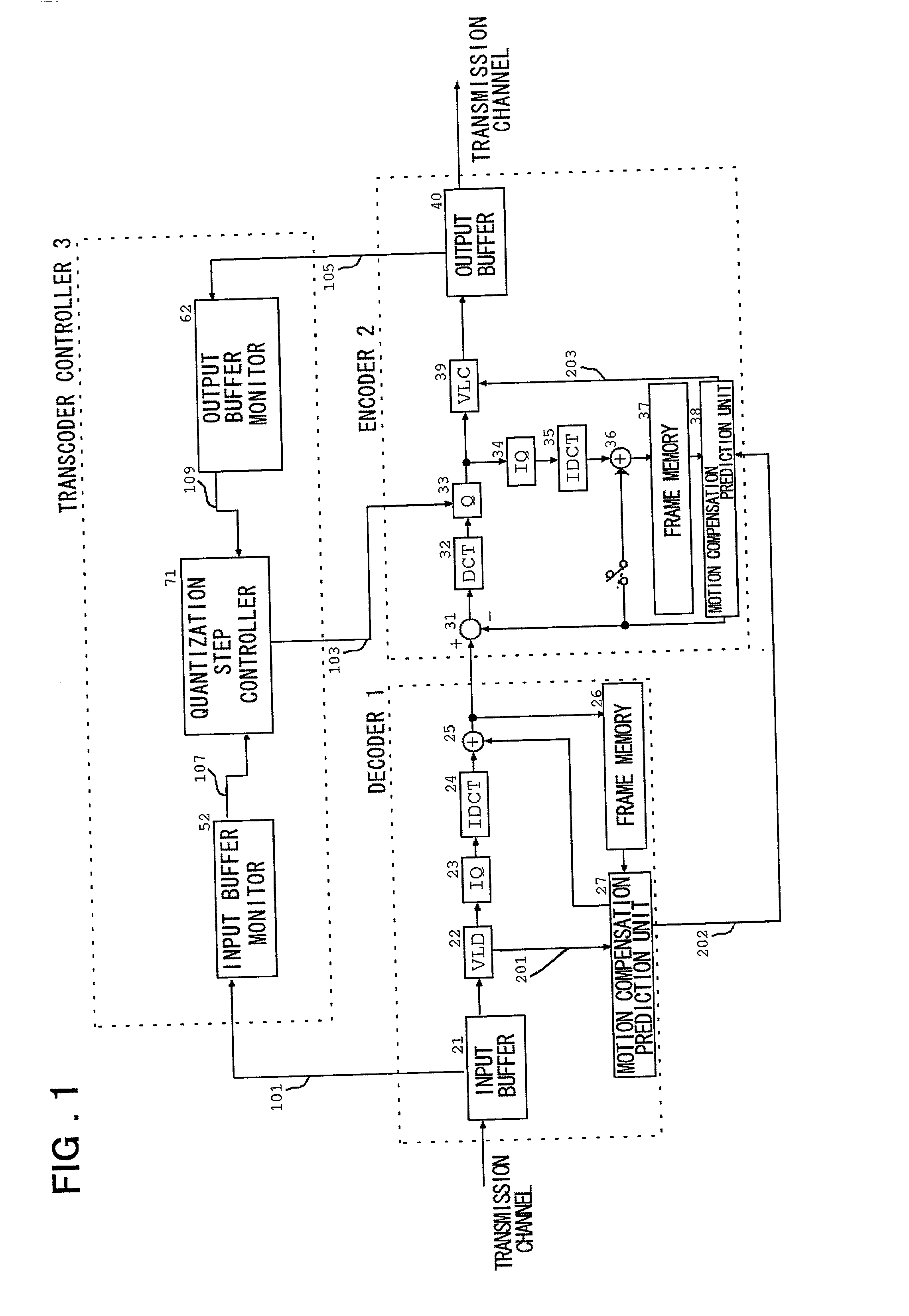

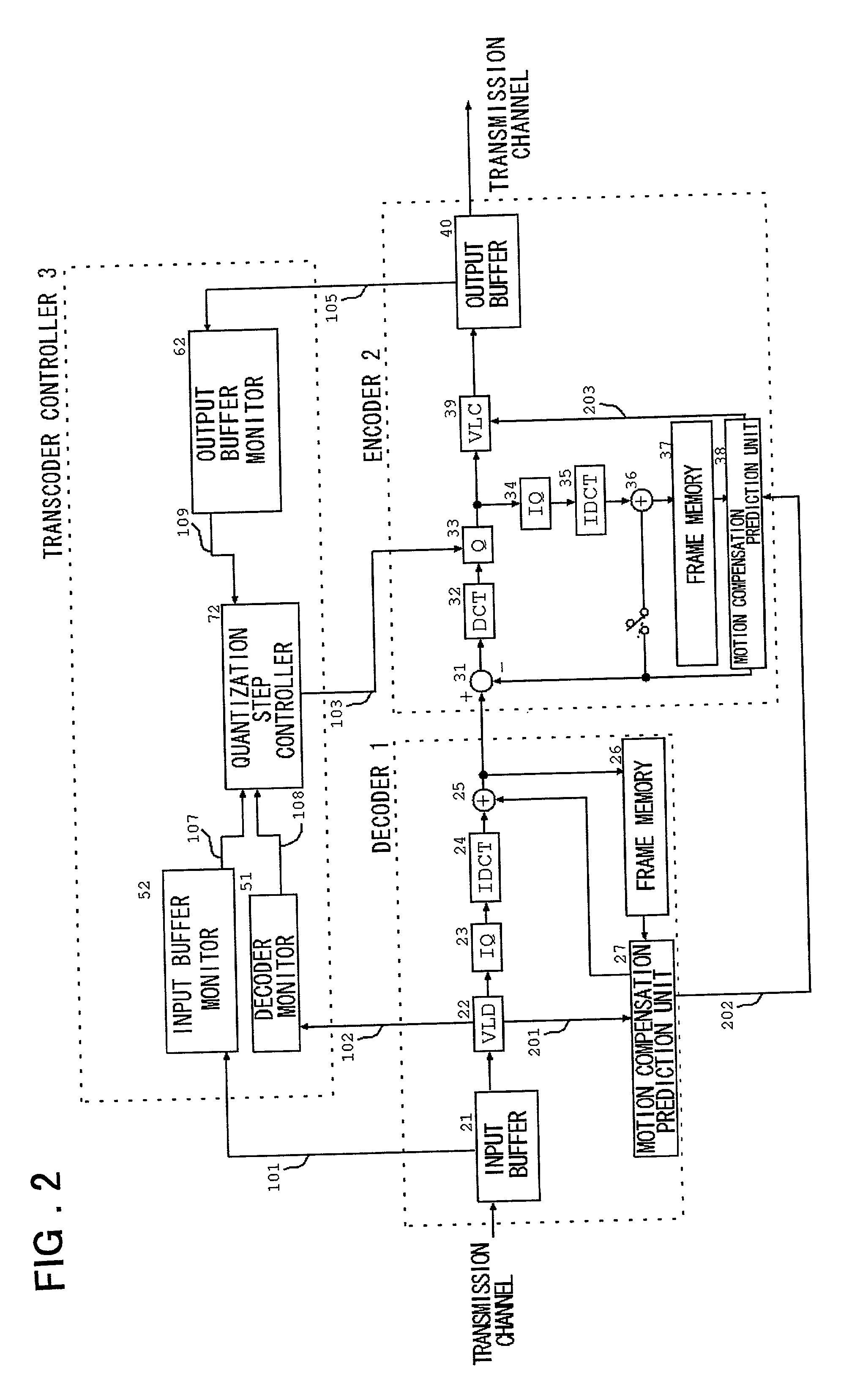

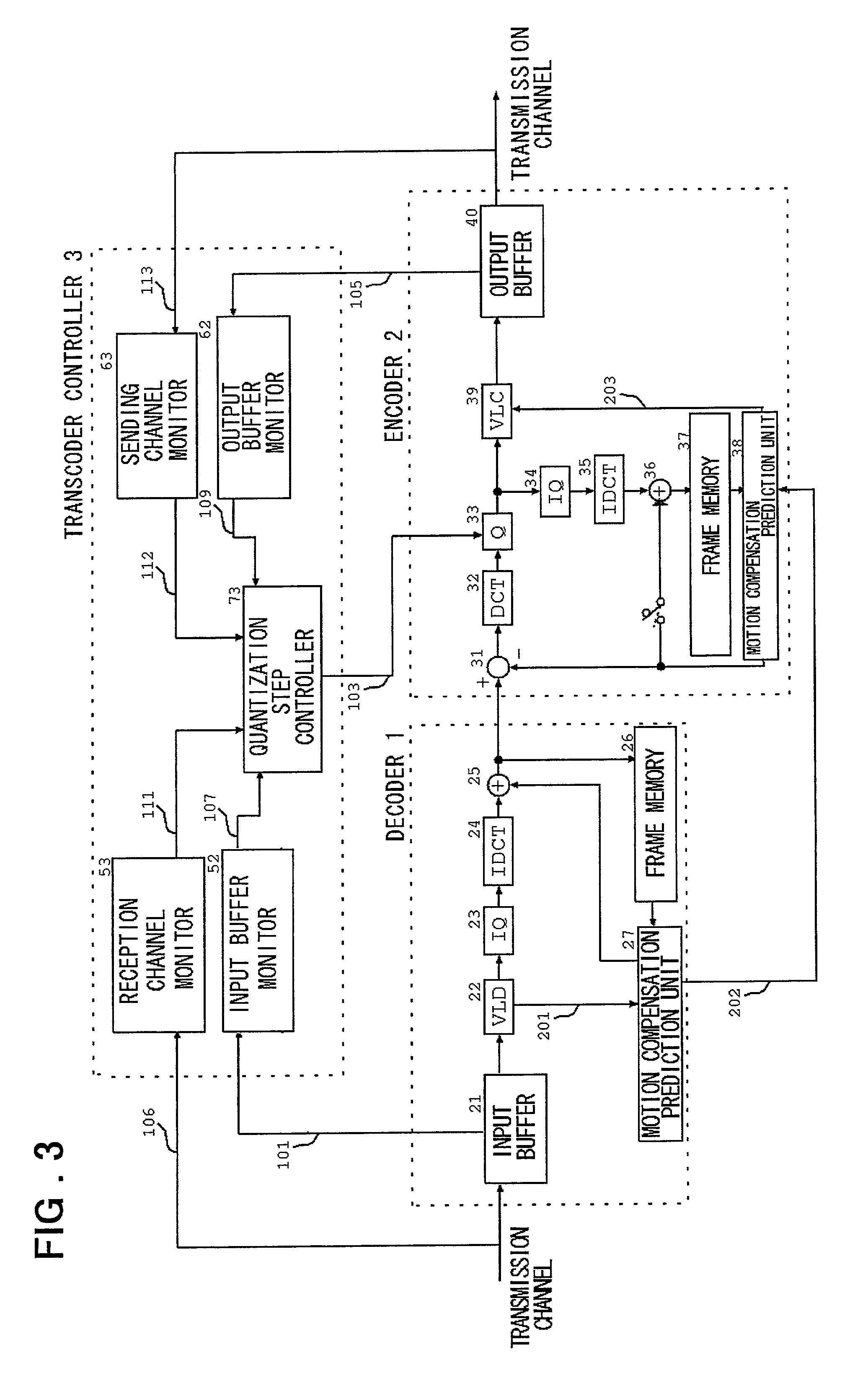

Picture encoding system conversion device and encoding rate conversion device

InactiveUS20010008544A1Lower quality of serviceIncrease delay timePulse modulation television signal transmissionPicture reproducers using cathode ray tubesTransmission channelComputer science

A picture encoding system conversion device and a code rate conversion device for realizing the conversion taking into account both time delay and picture quality using the information on the code volume of the encoding parameters, input and output buffers and an input bitstream. There are provided a decoder 1 including an input buffer 21, a VLD unit 22, an inverse quantizer 23, an IDCT unit 24, an adder 35, a frame memory 26 and a motion compensation prediction unit 27; an encoder 2 including an adder 31, a DCT unit 32, a quantizer 33, an inverse quantizer 34, an IDCT unit 35, an adder 36, a frame memory unit 37, a motion compensation prediction unit 38, a VLD unit 39 and an output buffer 40; and a transcoder controller 3 including a decoder monitor unit 51, an input buffer monitor unit 52, a reception transmission channel monitor 53, a sending transmission channel monitor 63, an output buffer monitor unit 62 and a quantization step controller 74. The quantization step controller 74 modifies the quantization step of the encoder based on the information from the input buffer monitor, output buffer monitor, decoder monitor, reception transmission channel monitor and sending transmission channel monitor.

Owner:NEC CORP

Level shifter having automatic delay adjusting function

InactiveUS7148735B2Increase the number ofReduce decreasePulse automatic controlInstant pulse delivery arrangementsLevel shiftingDelayed time

In a level shifter, in the case where the amplitude voltage of an input signal (i.e., a first power voltage VDDL) input to an input terminal is changed to be higher and the amplitude voltage of an output signal (i.e., a second power voltage VDDH) output from an output terminal is changed to be lower, a fall delay time of the signal output from the output terminal tends to be longer than a rise delay time of the signal. However, an inverted input signal obtained by an inverter is input to a level shifting unit and also to the gate of an N-type transistor, and therefore, the N-type transistor is turned on at the fall of the input signal input to the input terminal, so as to supply a current based on the second power voltage VDDH to an output node of the level shifting unit for assisting the shift into H level performed in the level shifting unit. Accordingly, even when at least one of the amplitude voltage of the input signal and the amplitude voltage of the output signal is changed, balance between the fall delay time characteristic and the rise delay time characteristic of the output signal can be satisfactorily kept.

Owner:SOCIONEXT INC

Delay unit for door with a door closer, door closer with a delay unit, and door with a door closer having a delay unit

InactiveUS20070214725A1Fabricate compactlySave electric powerDC motor speed/torque controlBuilding braking devicesEngineeringTimer

The Objective of the present invention is to provide a delay unit for door with a door closer, which is capable of automatically closing the door after the elapse of a certain time since the door was opened and can be installed in case that the door closer is embedded inside the building and thereby being not exposed. The objective is solved by providing a delay unit 5 for door with a door closer comprising: a first sensor for detecting the door 2 opened to the first angle A, a lock unit 7 for electrically lock / unlock of the rotation of the rotation axis 3 of the door 2, a timer, a first sensor, and a control means, with which the first sensor, lock unit 7, and timer is connected, for controlling the lock unit 7 based on the signals from the first sensor and timer.

Owner:DT ENG

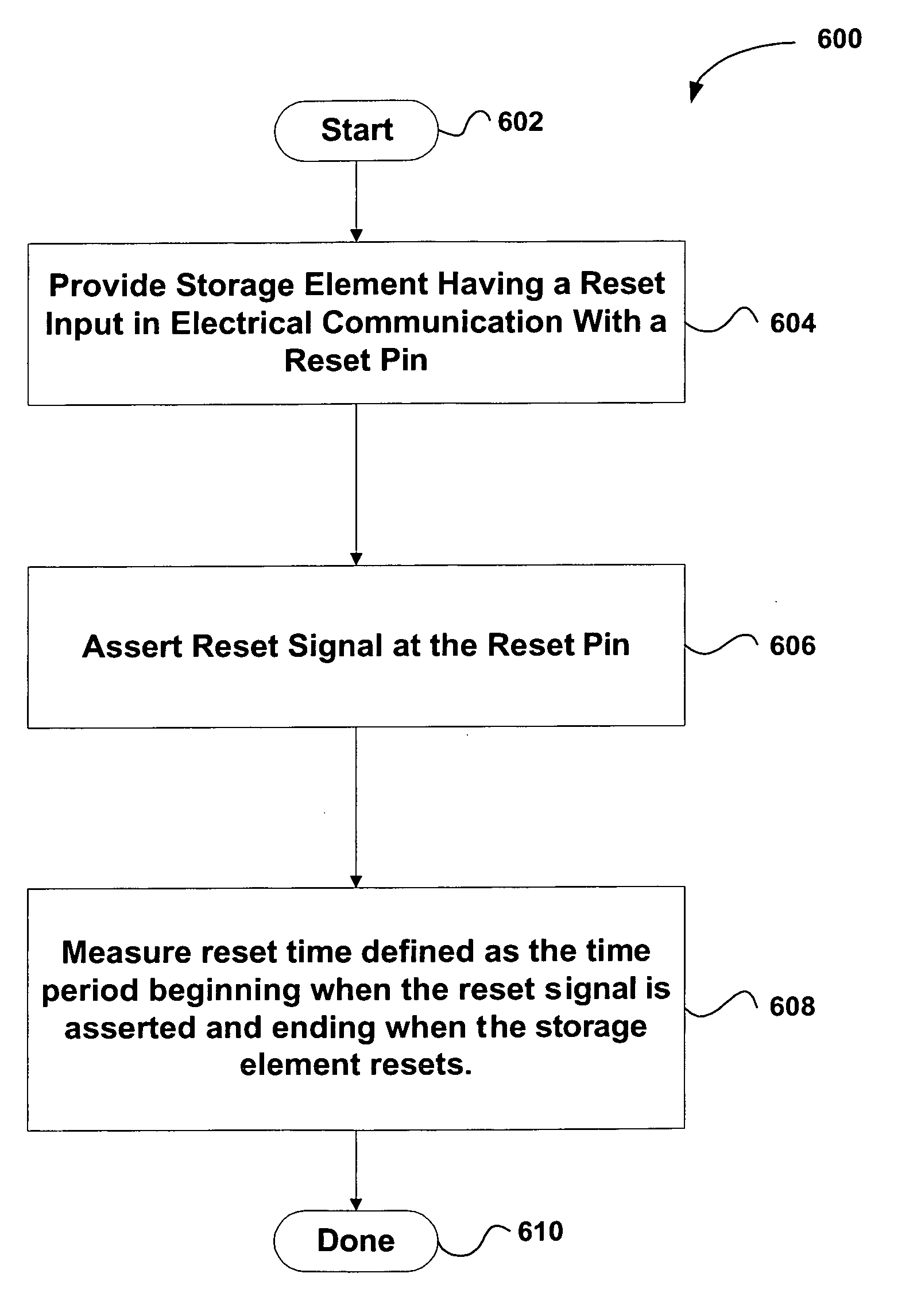

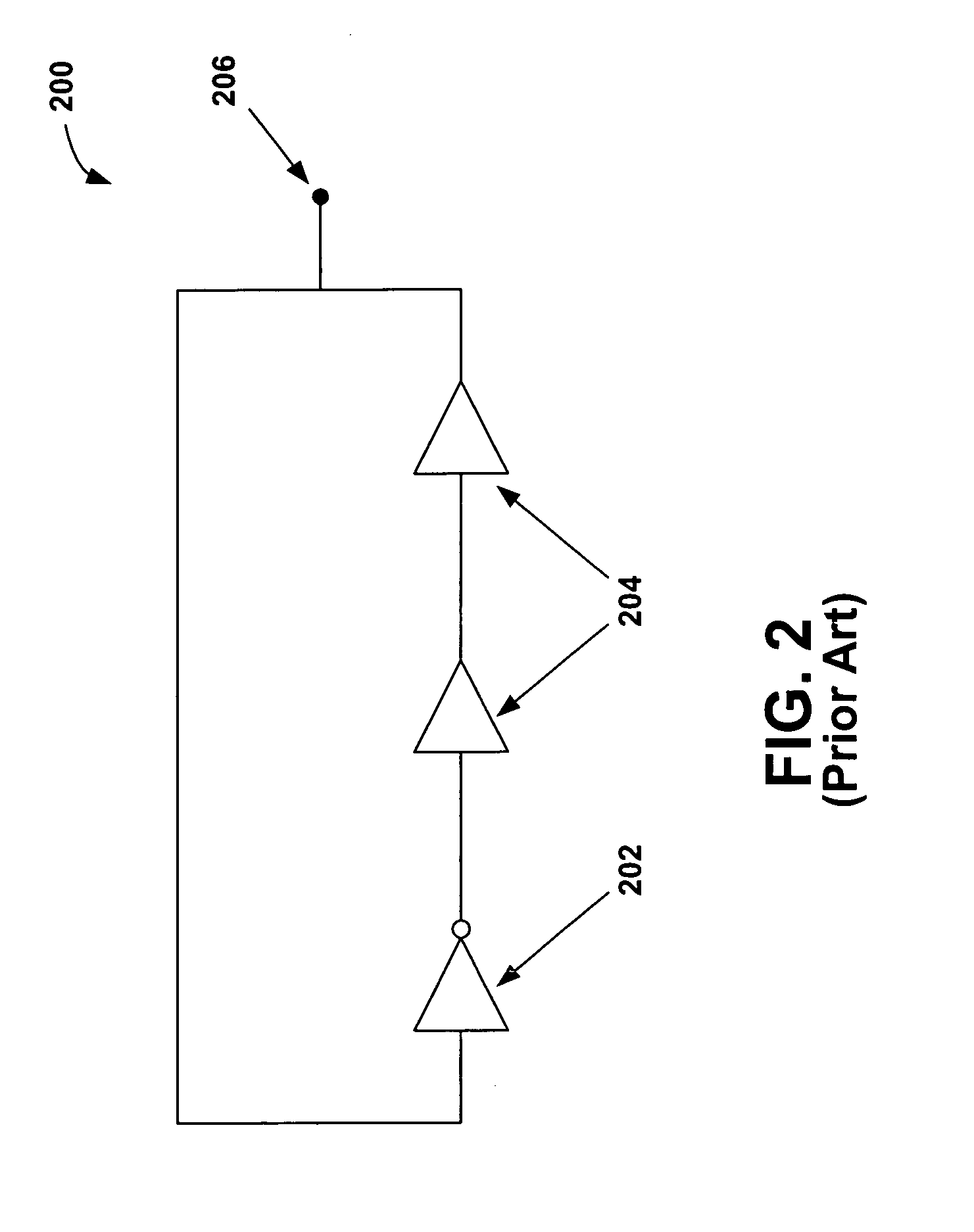

System and method for determining integrated circuit logic speed

InactiveUS6966022B1Increase delay timeEasy to measurePulse automatic controlError detection/correctionElectricityTime segment

An invention is disclosed for determining integrated circuit (IC) logic speed. A storage element is provided that includes a reset input in electrical communication with a reset pin. A reset signal is then asserted at the reset pin, and a reset time is measured. The reset time is defined as the time period beginning when the reset signal is asserted and ending when the storage element resets. In this manner, the reset time can be used to determine a speed of the IC logic relative to a process. In one aspect, delay logic is provided that is in electrical communication with the reset pin and in electrical communication with the storage element. In this aspect, the delay logic delays the reset signal for a predetermined time period. Optionally, the reset time can be compared to a predetermined fast corner reset time and a predetermined slow corner reset time. Further, the IC logic speed can be correlated to a simulation using the embodiments of the present invention.

Owner:ADAPTEC +1

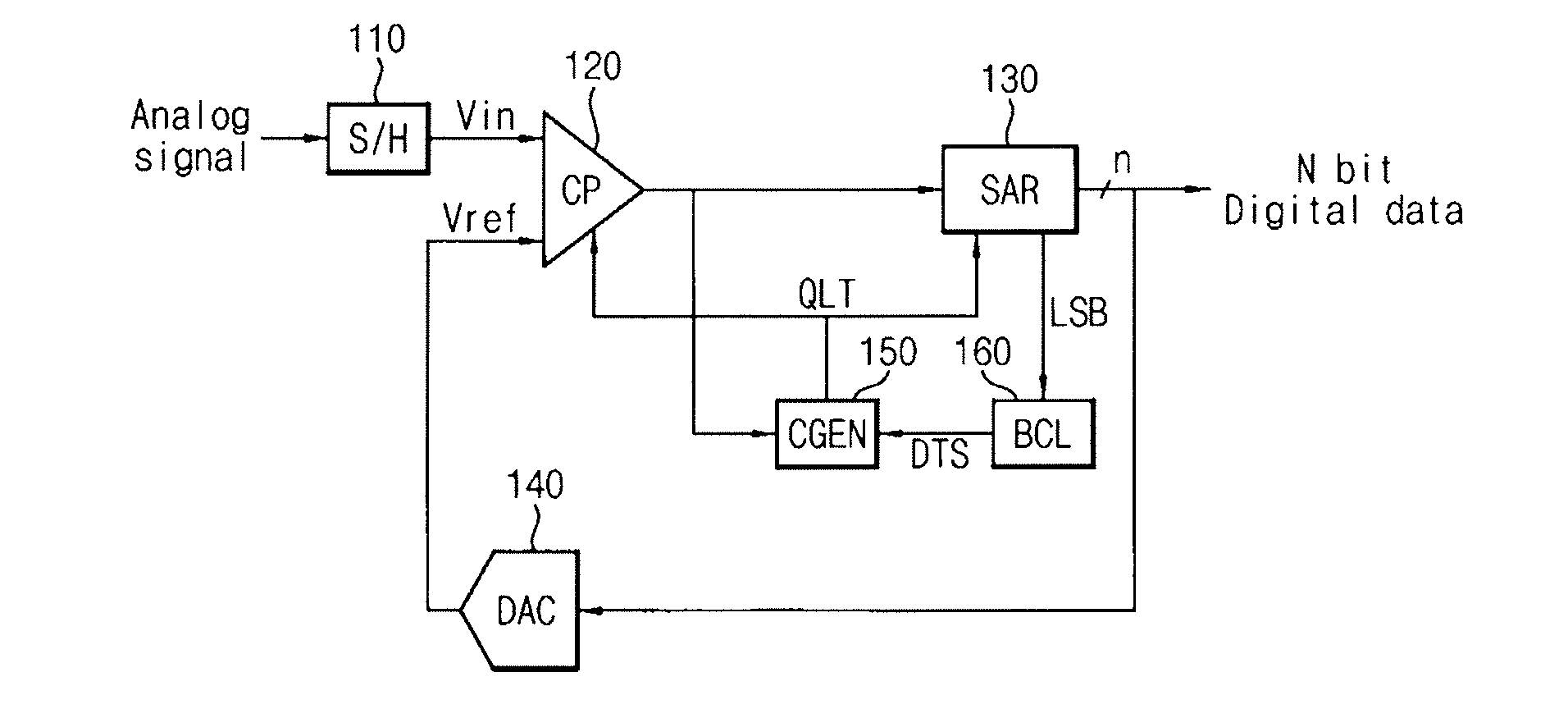

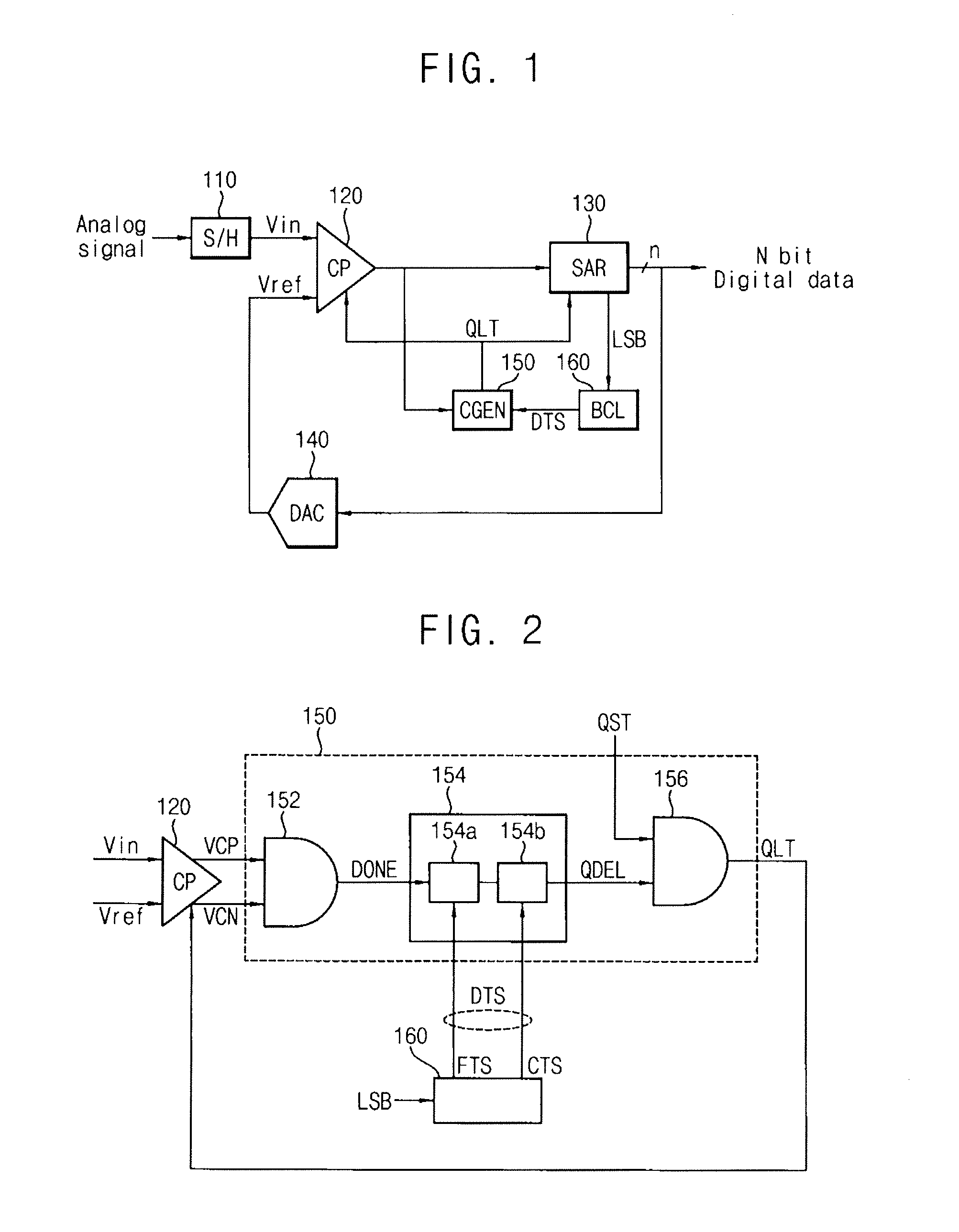

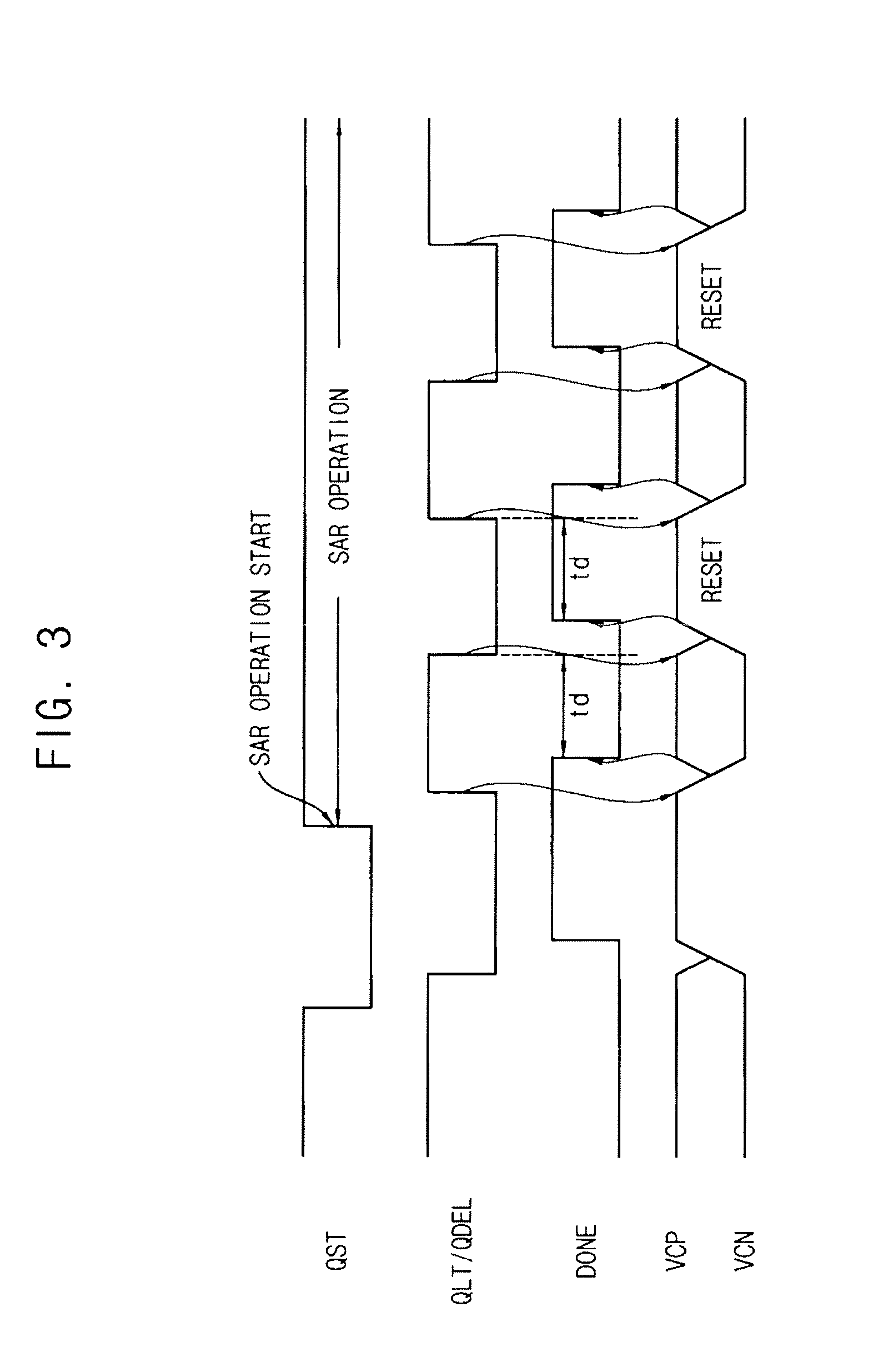

Apparatus and methods for converting analog signal to n-bit digital data

ActiveUS20140184436A1Follow exactlyReduce latencyElectric signal transmission systemsAnalogue-digital convertersDigital dataAnalog signal

An apparatus includes a sample holding circuit, a comparator, a digital-to-analog converter, a clock generator, a successive approximation logic circuit, and a background calibration circuit. The apparatus converts an analog signal into digital data based on an asynchronous clock signal. The clock signal follows the number of clocks in a converting operation section through a background calibration scheme.

Owner:SAMSUNG ELECTRONICS CO LTD

QoS control method for transmission data for radio transmitter and radio receiver using the method

InactiveUS20070153921A1Minimized transmission delayImprove data throughputWireless commuication servicesAdaptation strategy characterisationQuality of serviceInformation transmission

A radio transmitter / receiver having a QoS control unit for outputting the transmission data in order taking the quality of service (QoS) into consideration. In the case where the information transmission rate for a radio section is not lower than a threshold value, the QoS control operation of the transmission data is omitted, and the transmission data are output in the order of input. In the case where the information transmission rate for the radio section is lower than the threshold value, on the other hand, the QoS control mode is switched in accordance with the information transmission rate for the radio section.

Owner:KOKUSA ELECTRIC CO LTD

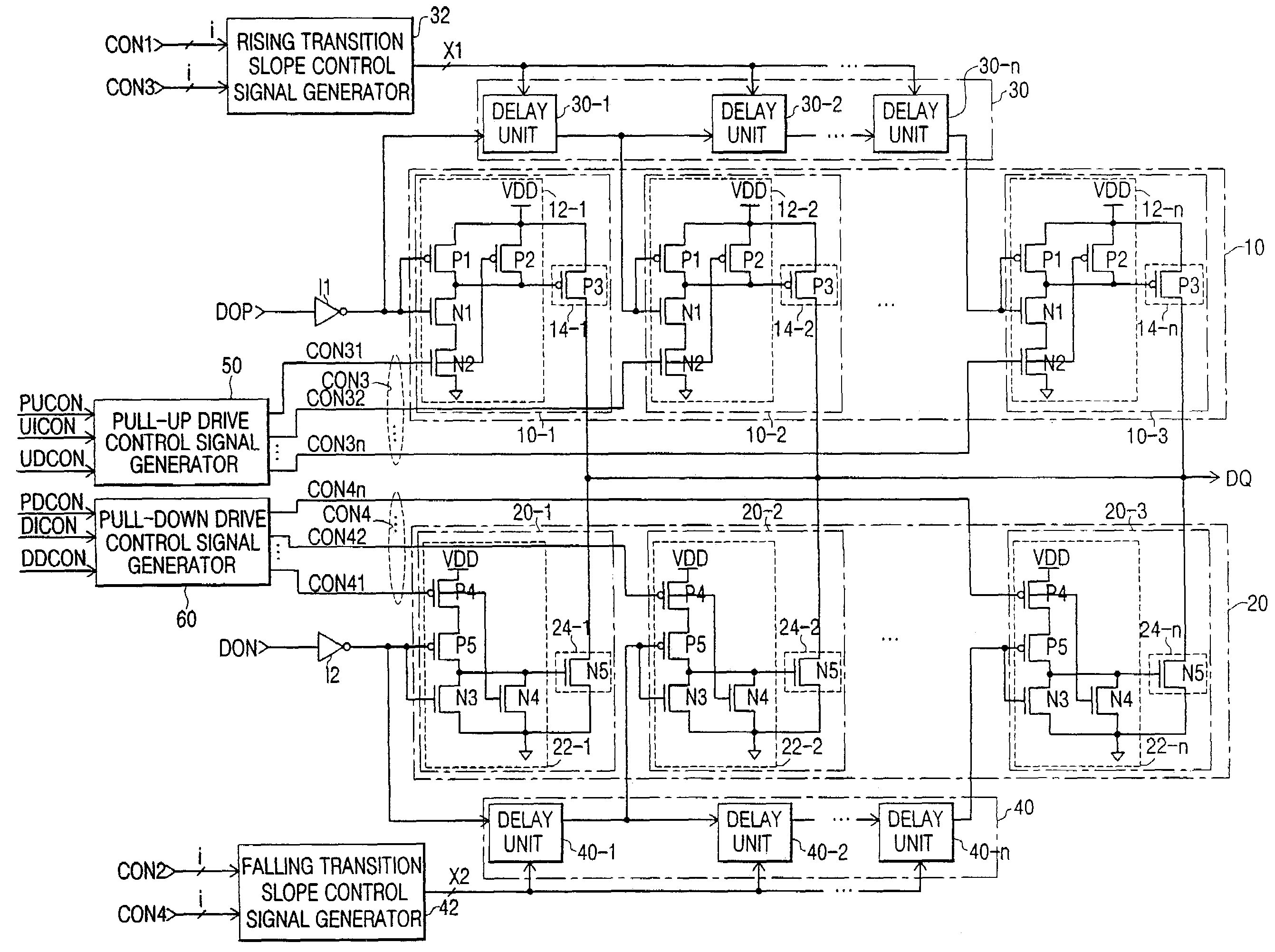

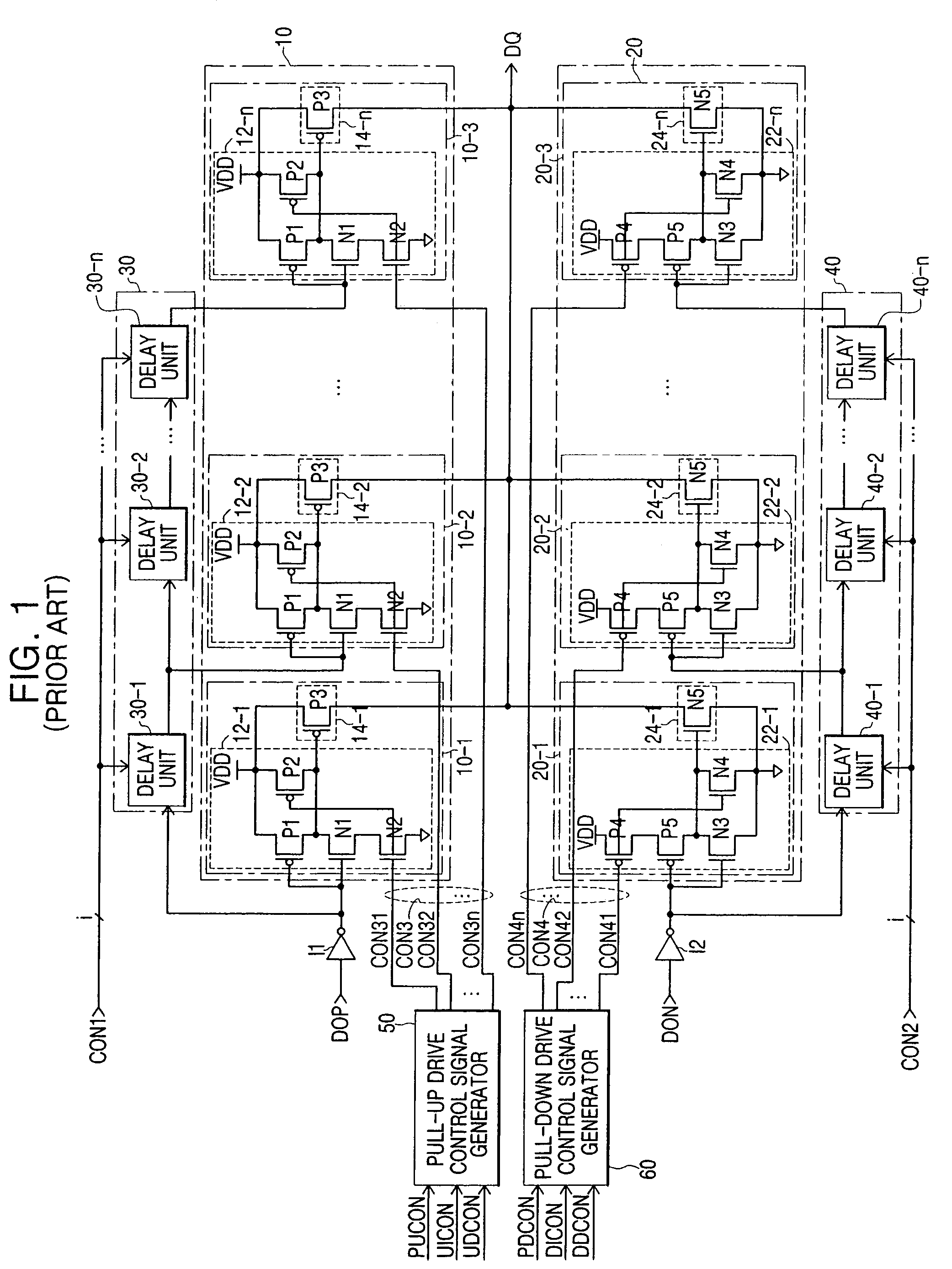

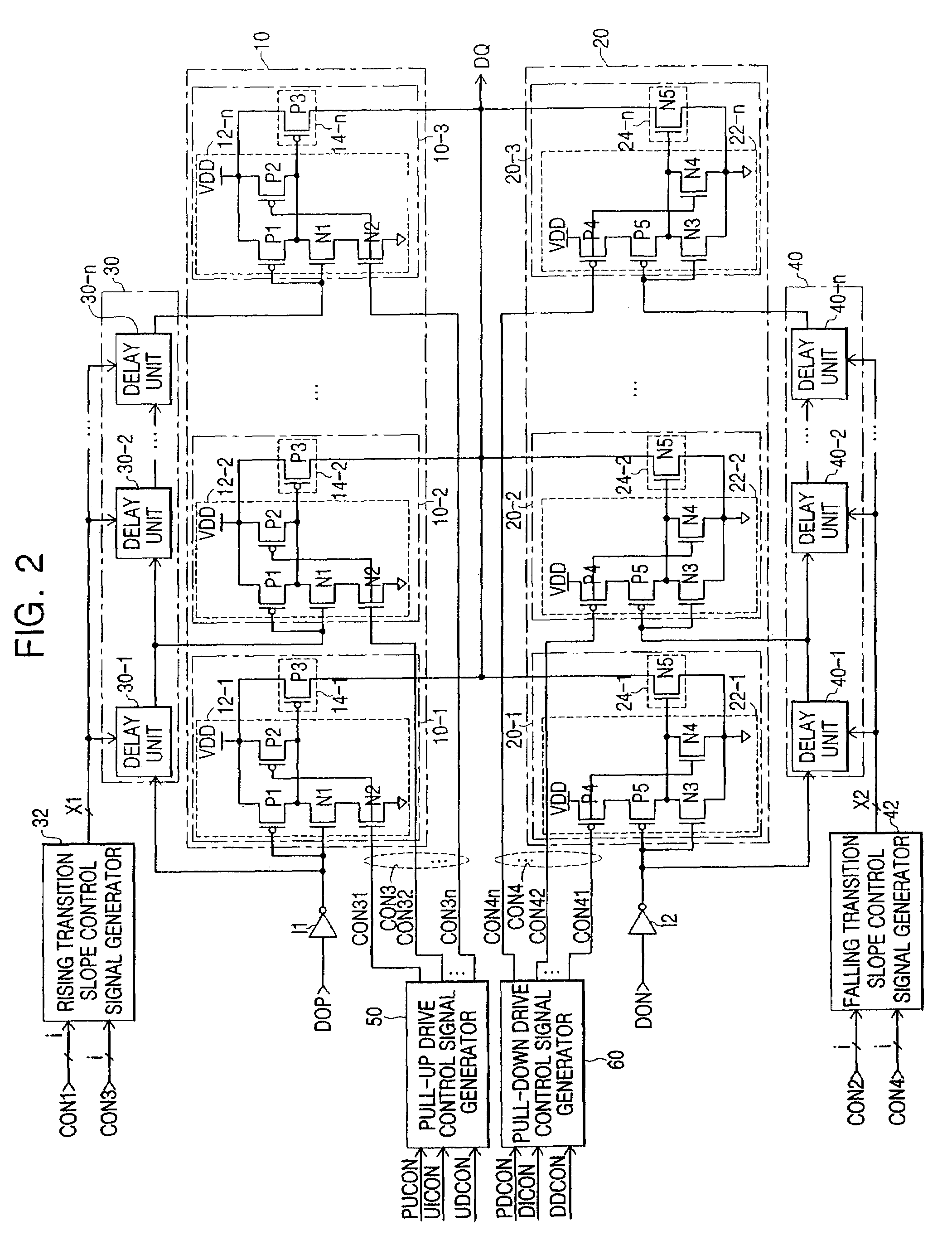

Data output driver and semiconductor memory device having the same

InactiveUS7282968B2Increase delay timeReduce latencyInput/output impedence modificationReliability increasing modificationsSignal responseControl signal

A data output driver and a semiconductor memory device having the same are disclosed. This data output driver includes: a rising transition slope adjuster including a plurality of first delay units cascade-connected to each other and receiving data and generating delayed data, each of the first delay units having a delay time which varies in response to a first control signal; a falling transition slope adjuster including a plurality of second delay units cascade-connected to each other and receiving inverted data and generating delayed inverted data, each of the second delay units having a delay time which varies in response to a second control signal; a pull-up driver including a plurality of pull-up circuits, the driving capabilities of the pull-up circuits being adjustable in response to a third control signal, each pull-up circuit pulling-up output data in response to each of the data and the delayed data; and a pull-down driver including a plurality of pull-down circuits, the driving capabilities of the pull-down circuits being adjustable in response to a fourth control signal, each pull-down circuit pulling-down output data in response to each of the inverted data and the delayed inverted data, wherein the first control signal varies in response to the third control signal, and wherein the second control signal varies in response to the fourth control signal. Accordingly, the rising and falling transition slopes of the output data can be constant even when the driving capability is varied, so that output data having desired characteristics can be produced.

Owner:SAMSUNG ELECTRONICS CO LTD

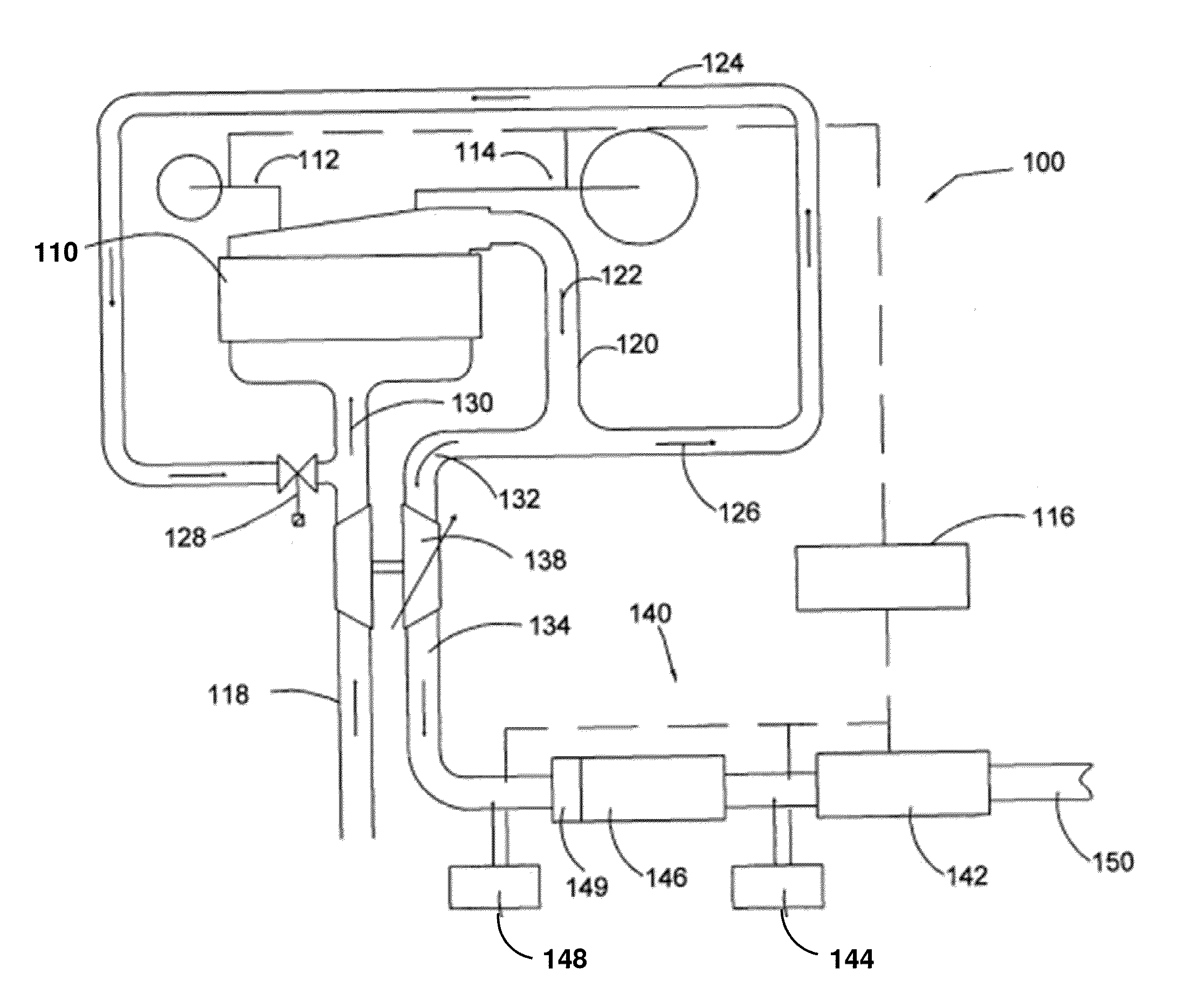

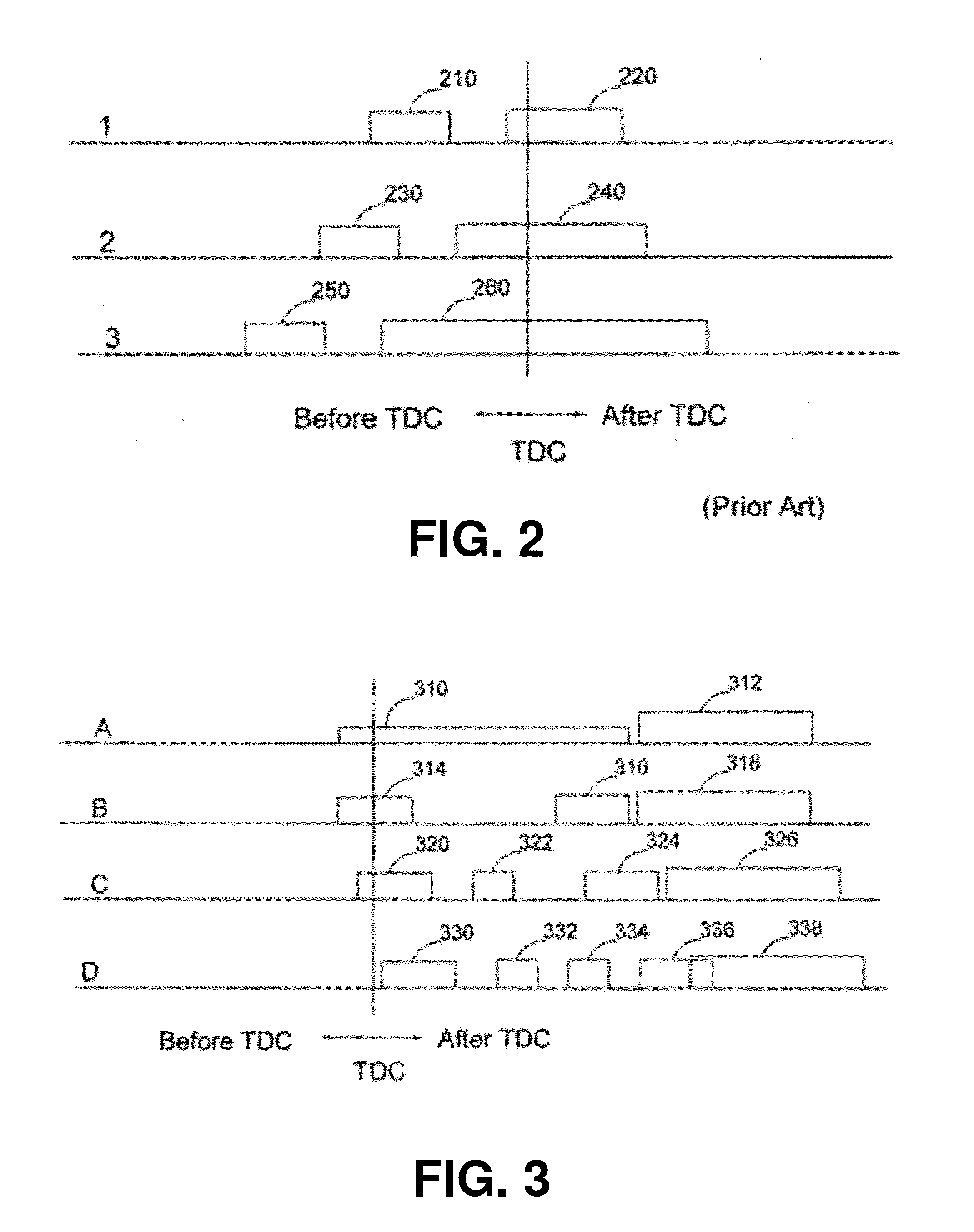

Method Of Controlling A Direct-Injection Gaseous-Fuelled Internal Combustion Engine System With A Selective Catalytic Reduction Converter

ActiveUS20130019588A1Transfer of heatIncrease exhaust temperatureElectrical controlNon-fuel substance addition to fuelExhaust gasTop dead center

A method controls a direct-injection gaseous-fuelled internal combustion engine system to improve the conversion efficiency of an SCR converter that is operative to reduce levels of NOx. The method comprises detecting when the internal combustion engine is idling and timing the injection of a first quantity of fuel to begin injection when the engine's piston is near top dead center; and controlling the temperature of exhaust gas to be above a predetermined temperature that is defined by an operating temperature range that achieves a desired conversion efficiency for the selective catalytic reduction converter, by: (a) timing injection of the gaseous fuel to begin after timing for injection the first quantity of fuel, and (b) increasing exhaust gas temperature by increasing a delay in timing for injecting the gaseous fuel, while limiting the delay to keep concentration of unburned fuel exiting the combustion chamber below a predetermined concentration.

Owner:WESTPORT FUEL SYST CANADA INC

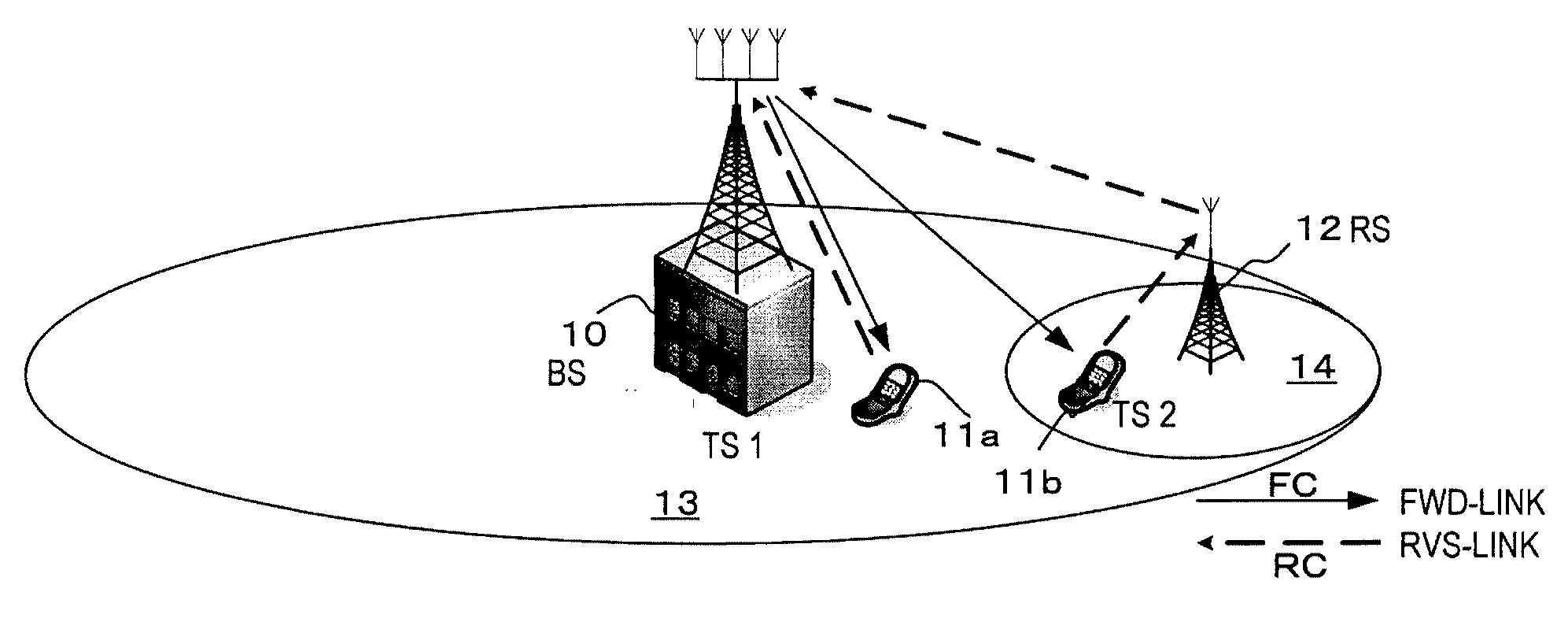

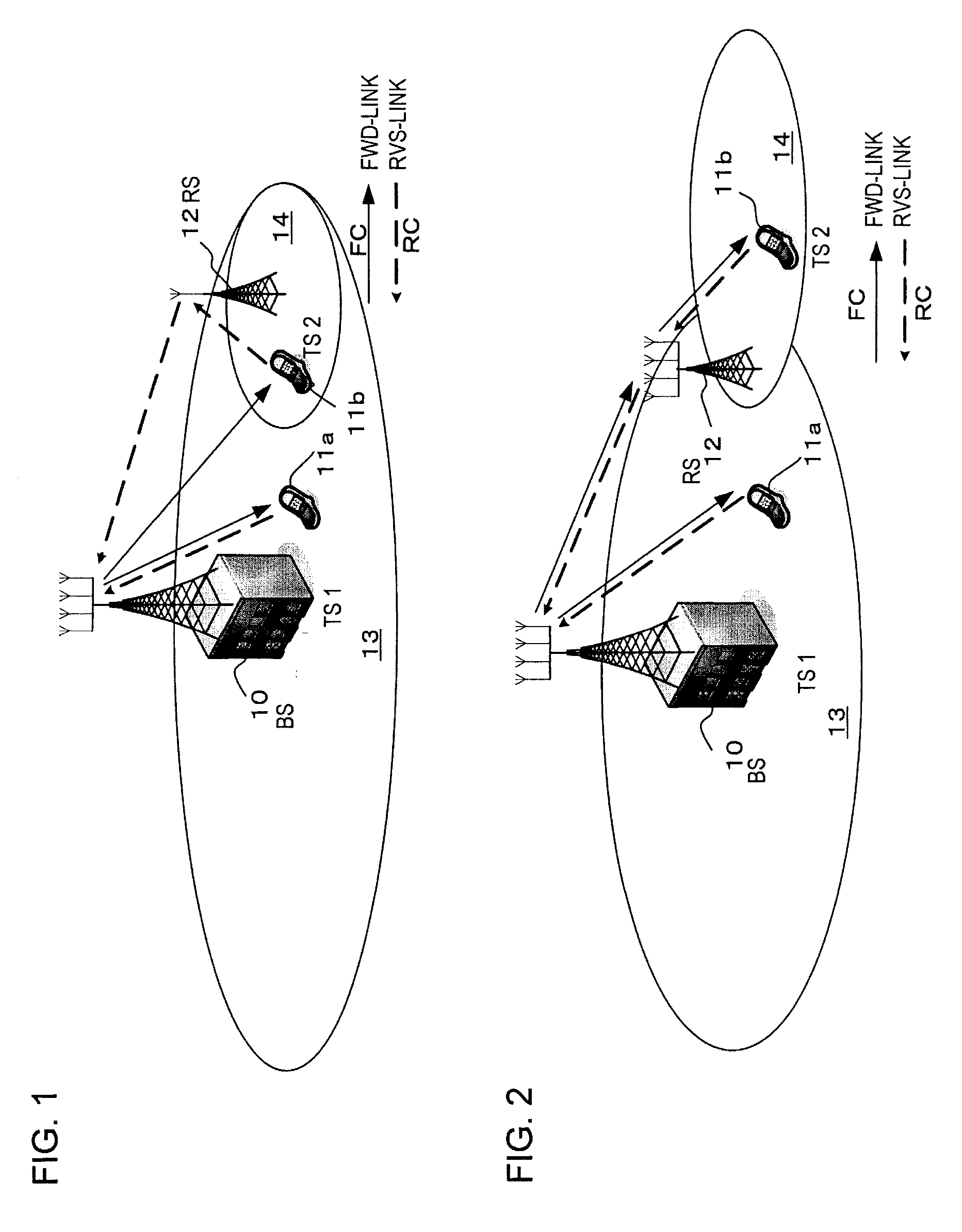

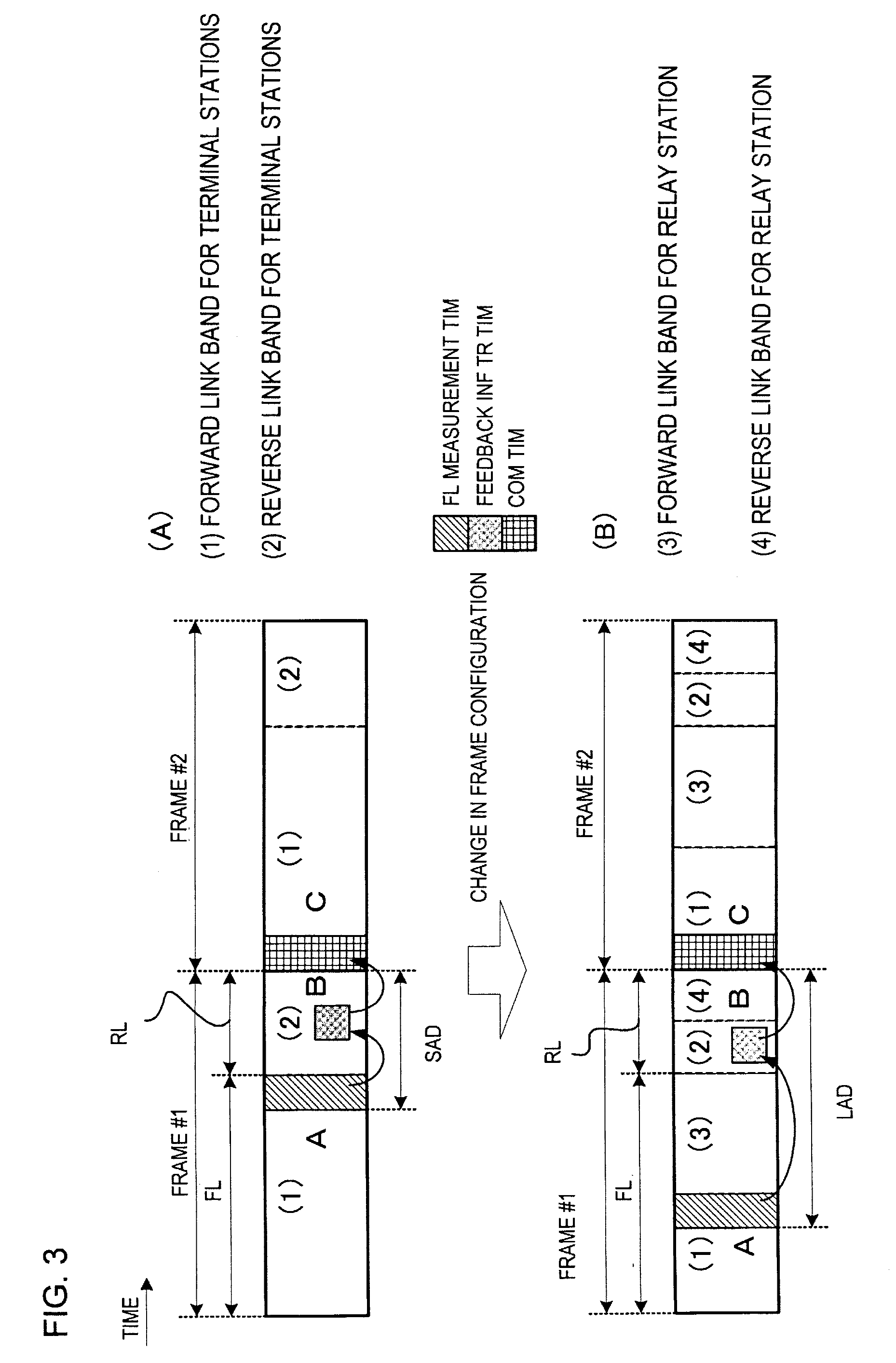

Mobile Communication System Using Adaptive Multi-Antenna

InactiveUS20100222051A1Easy to receiveEffective band utilizationSubstation equipmentWireless commuication servicesDelayed timeRadio relay

A mobile communication system using an adaptive multiantenna realizes improvement of reception characteristics, effective use of the band, and optimization of the throughput in comparison with a system in which application of the same multiantenna communication method is continued irrespective of a variation of the number of radio relay stations. The mobile communication system comprises a radio base station, a radio relay station, and mobile terminal stations for communicating with the radio base station through a radio relay station. The radio base station has a multiantenna and is characterized in that the radio base station judges if there is any variation of the number of radio relay stations when the radio base station carries out transmission through a radio relay station, and the radio base station communicates with the mobile terminal station by switching the multiantenna communication method using the multiantenna depending on the delay time of the feedback signal from the mobile terminal station if there is a variation of the number of radio relay stations.

Owner:FUJITSU LTD

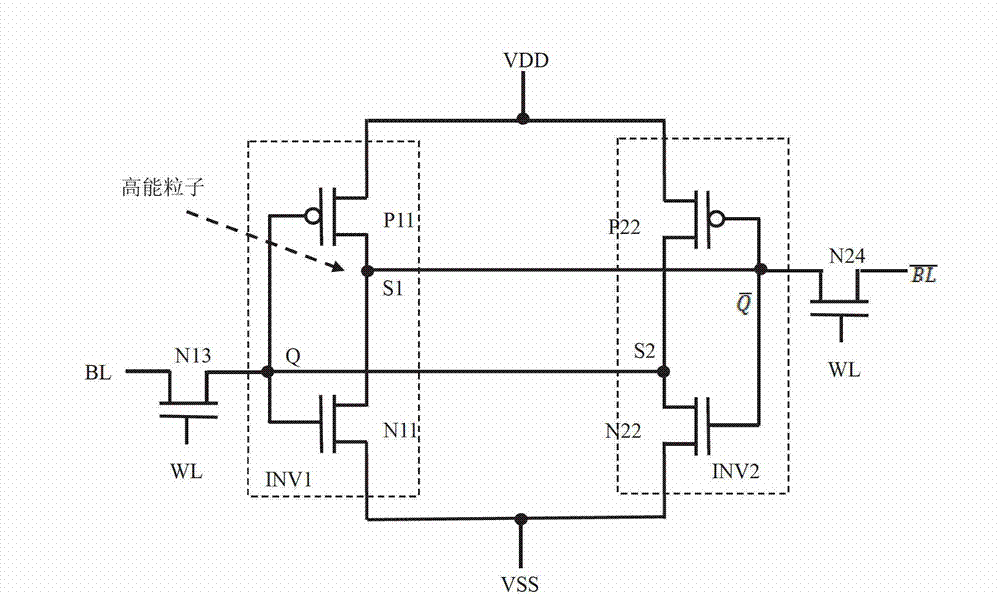

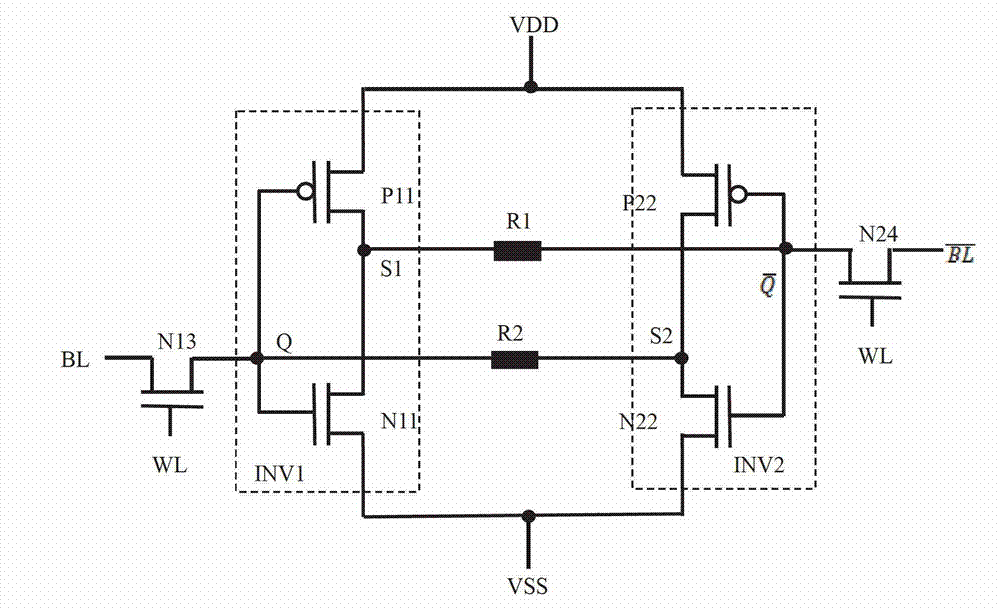

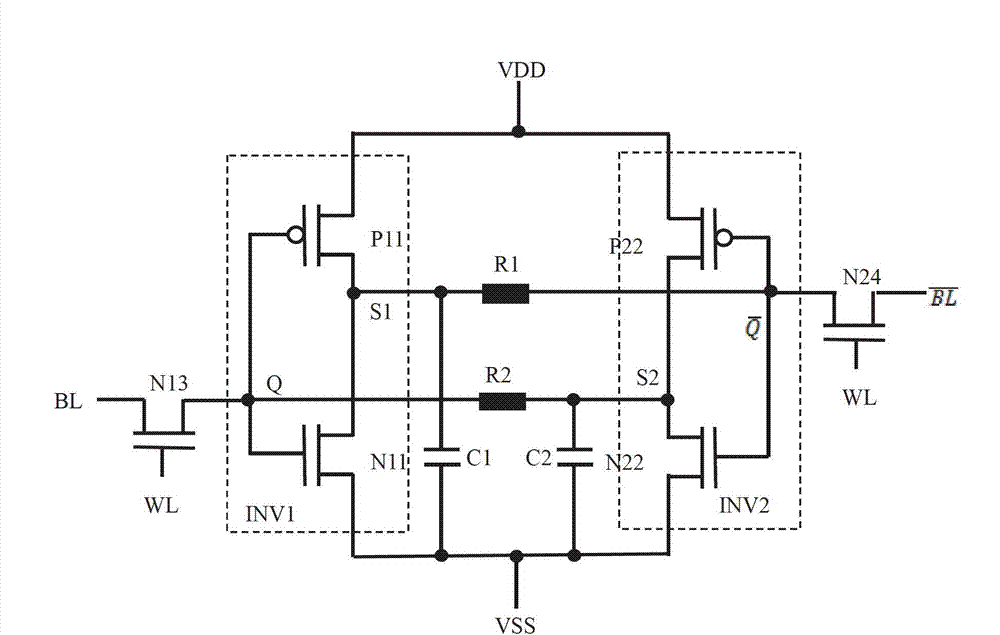

Static random memory unit

InactiveCN102903386AIncrease delay timeImprove read and write speedDigital storageEngineeringSingle event upset

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

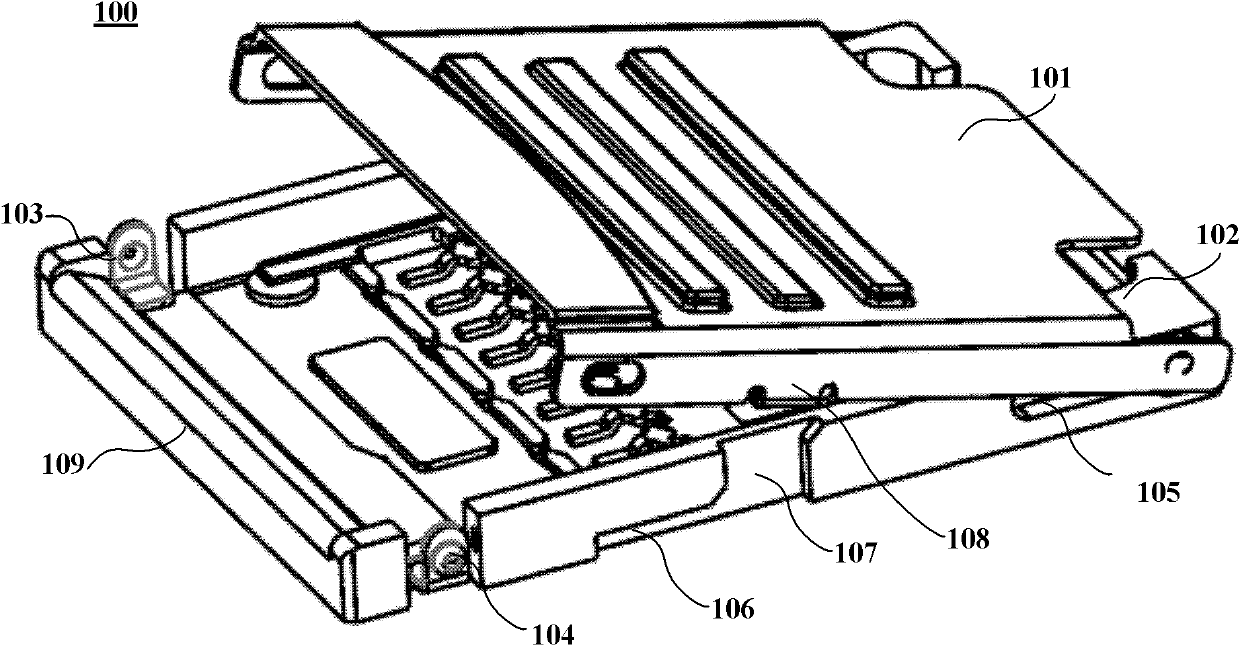

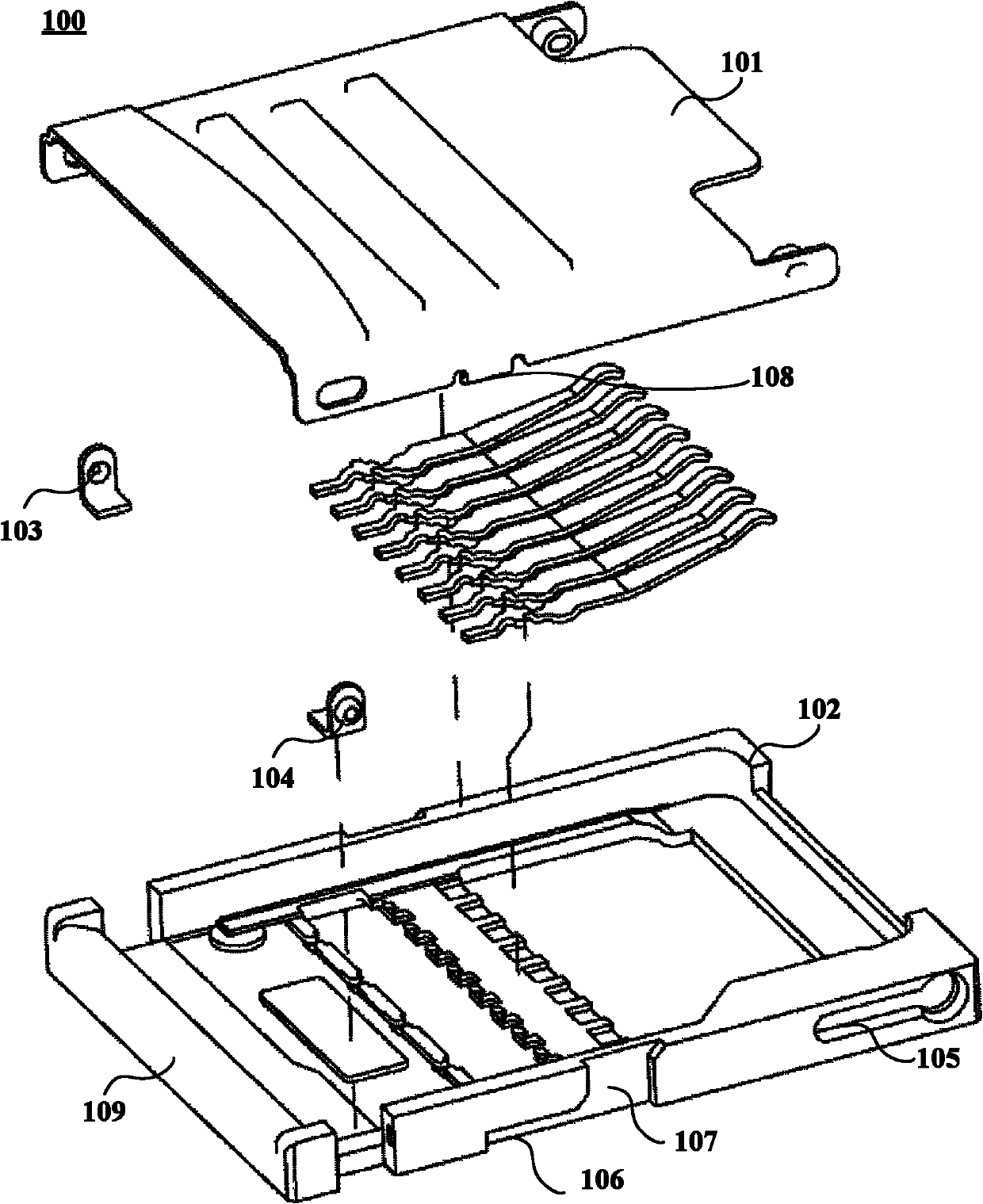

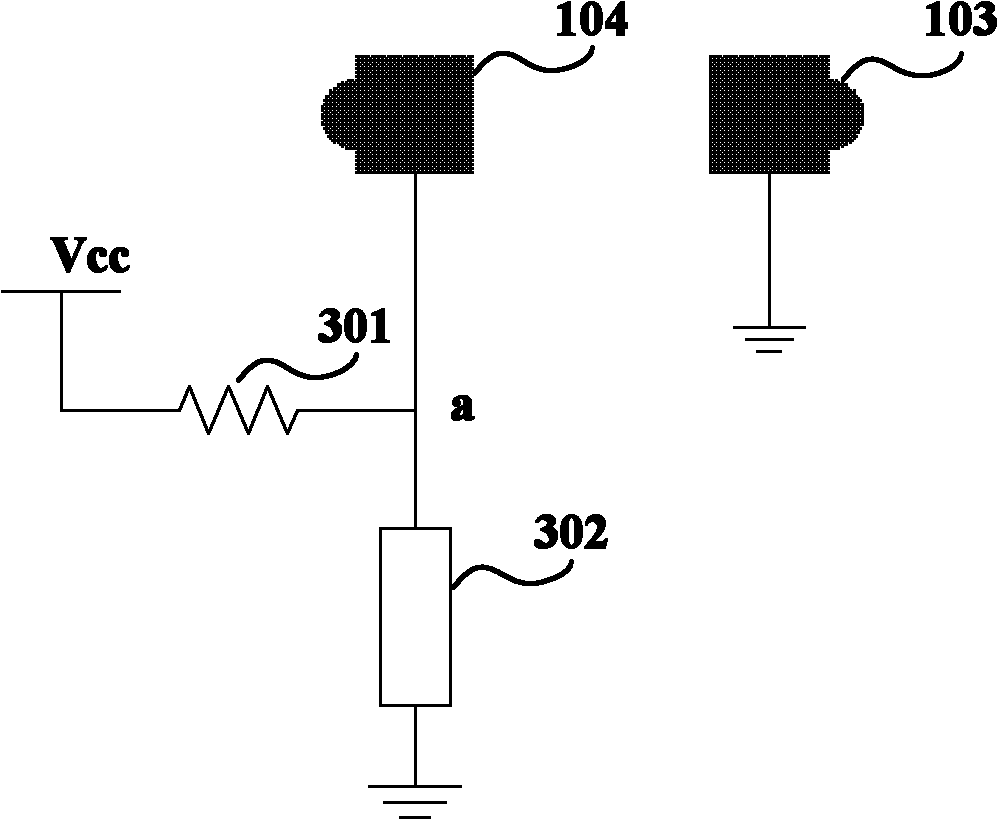

Storage card base, mobile terminal and method for protecting storage card

InactiveCN102738618ATimely protectionReduce repair rateLine/current collector detailsConveying record carriersElectricityWrite protection

An embodiment of the invention provides a storage card base, a mobile terminal and a method for protecting a storage card. The storage card base comprises a first contact point, a second contact point, a guide groove, and a junction embedded guide groove. The first contact point is disposed on a foundation of the storage card base. The second contact point is disposed on the foundation of the storage card base and is electrically connected with the first contact point when an upper cover of the storage card base is closed. The guide groove is disposed on the foundation of the storage card base and is located on a side of a junction which connects the foundation and the upper cover. The storage card base enables increase of delay time of stopping read-write protection. The storage card is protected timely, and repair rate of the storage card is reduced.

Owner:SONY ERICSSON MOBILE COMM AB

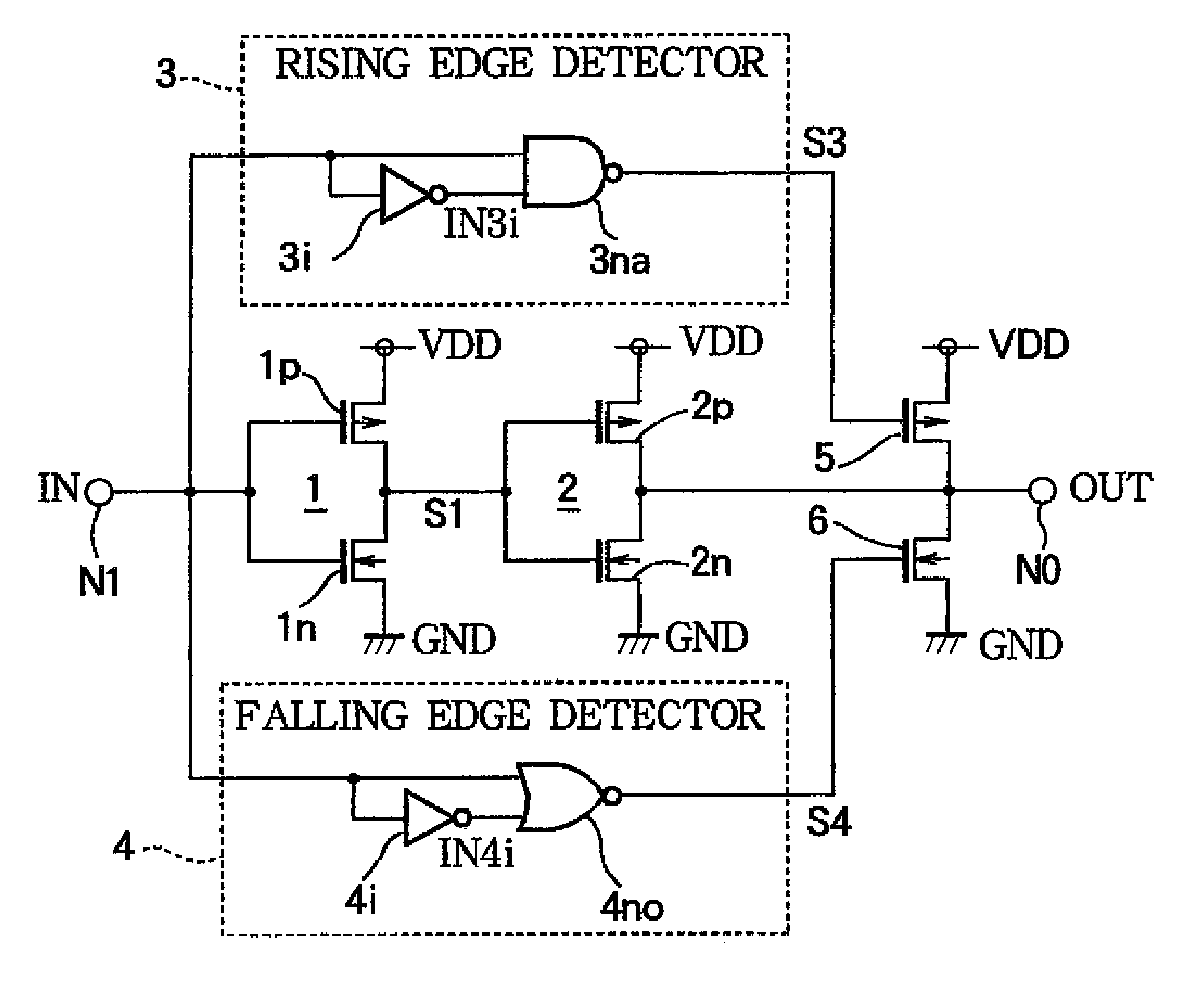

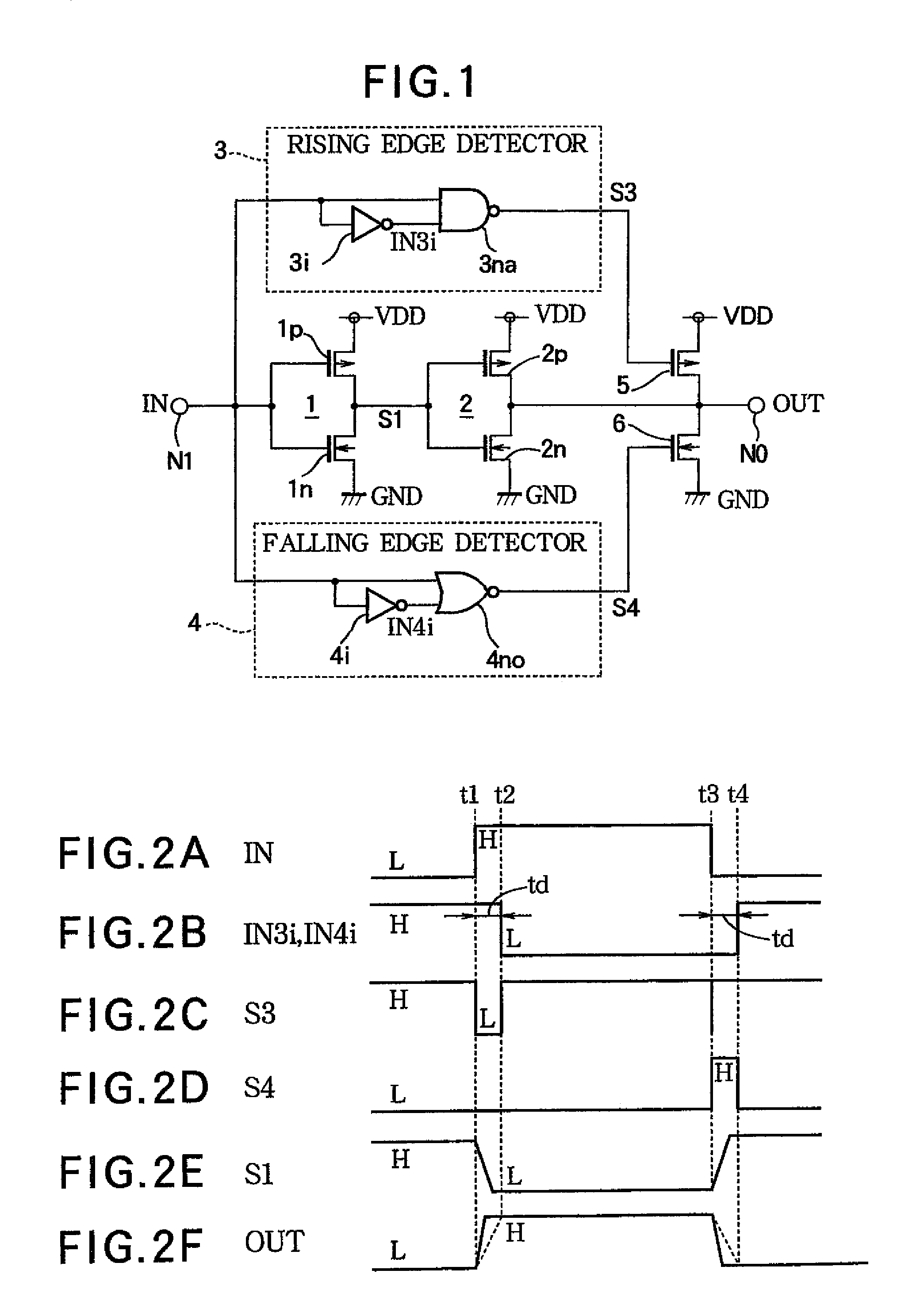

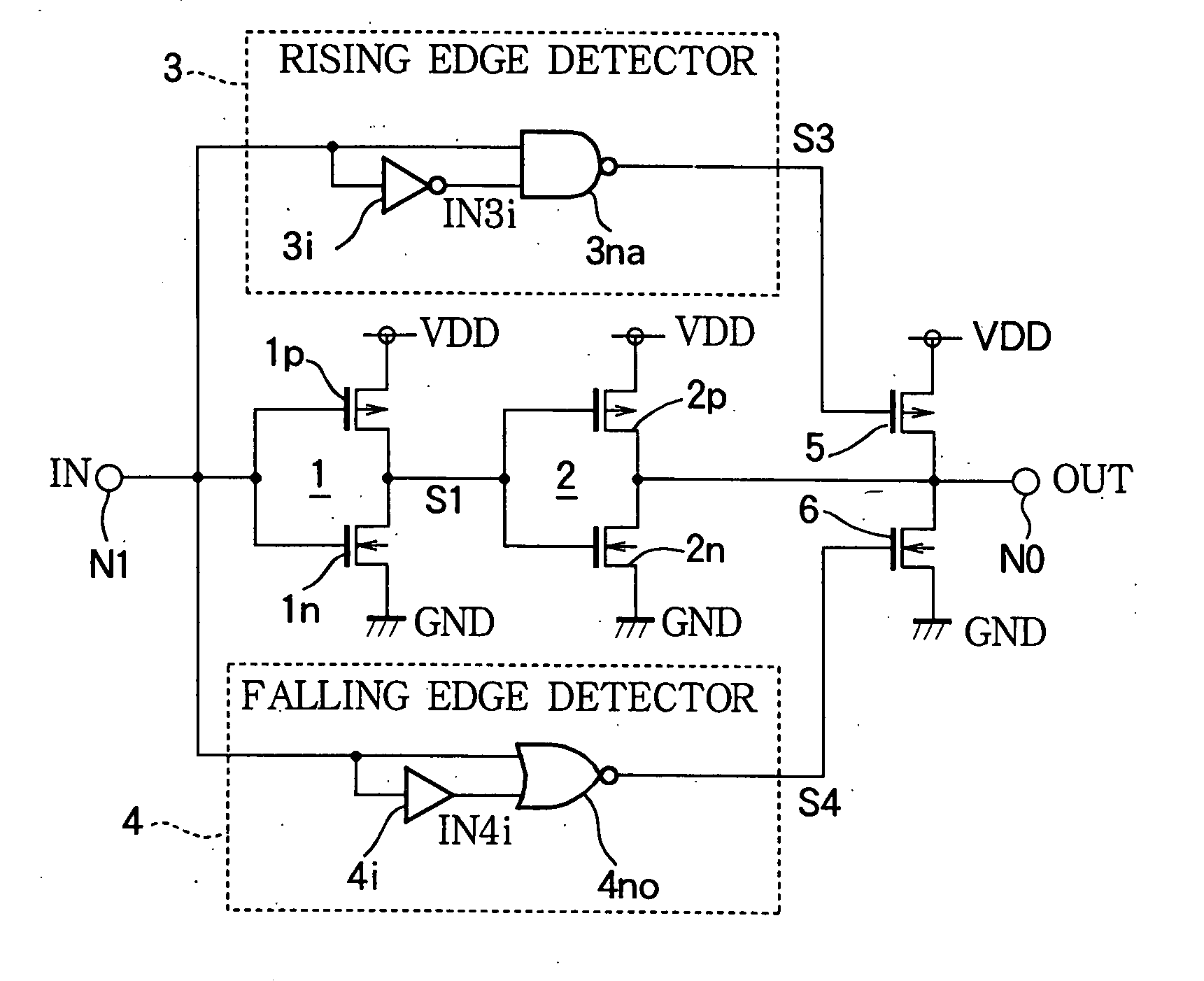

Driving circuit

ActiveUS20070229124A1Increase drive capacityEliminate the effects ofTransistorSwitching accelaration modificationsCMOSEdge detector

In addition to two-stage CMOS inverters for inverting and amplifying the input signal IN, a rising edge detector 3 for detecting the rising edge of the input signal IN, and outputting a rising edge detection signal S3 having a pulse width corresponding to the ambient temperature, and a PMOS 5 for driving the output node NO to the power supply potential VDD according to the rising edge detection signal S3, and the falling edge detector 4 for detecting the falling edge of the input signal IN and outputting a falling edge detection signal S4 having a pulse width corresponding to the ambient temperature, and an NMOS 6 driving the output node NO to the ground potential GND according to the falling edge detection signal S4. When the ambient temperature rises, and the delay time of the CMOS inverters 1, 2 are thereby increased, the pulse widths of the rising edge detection signal S3, and the falling edge detection signal S4 are also increased, and because of the additional driving by means of the PMOS 5 and the NMOS 6, the delay time is reduced. Thus, the variation in the delay time in the driving circuit in an LSI, due to the ambient temperature change can be restrained.

Owner:LAPIS SEMICON CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com