Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

136 results about "Transfer error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

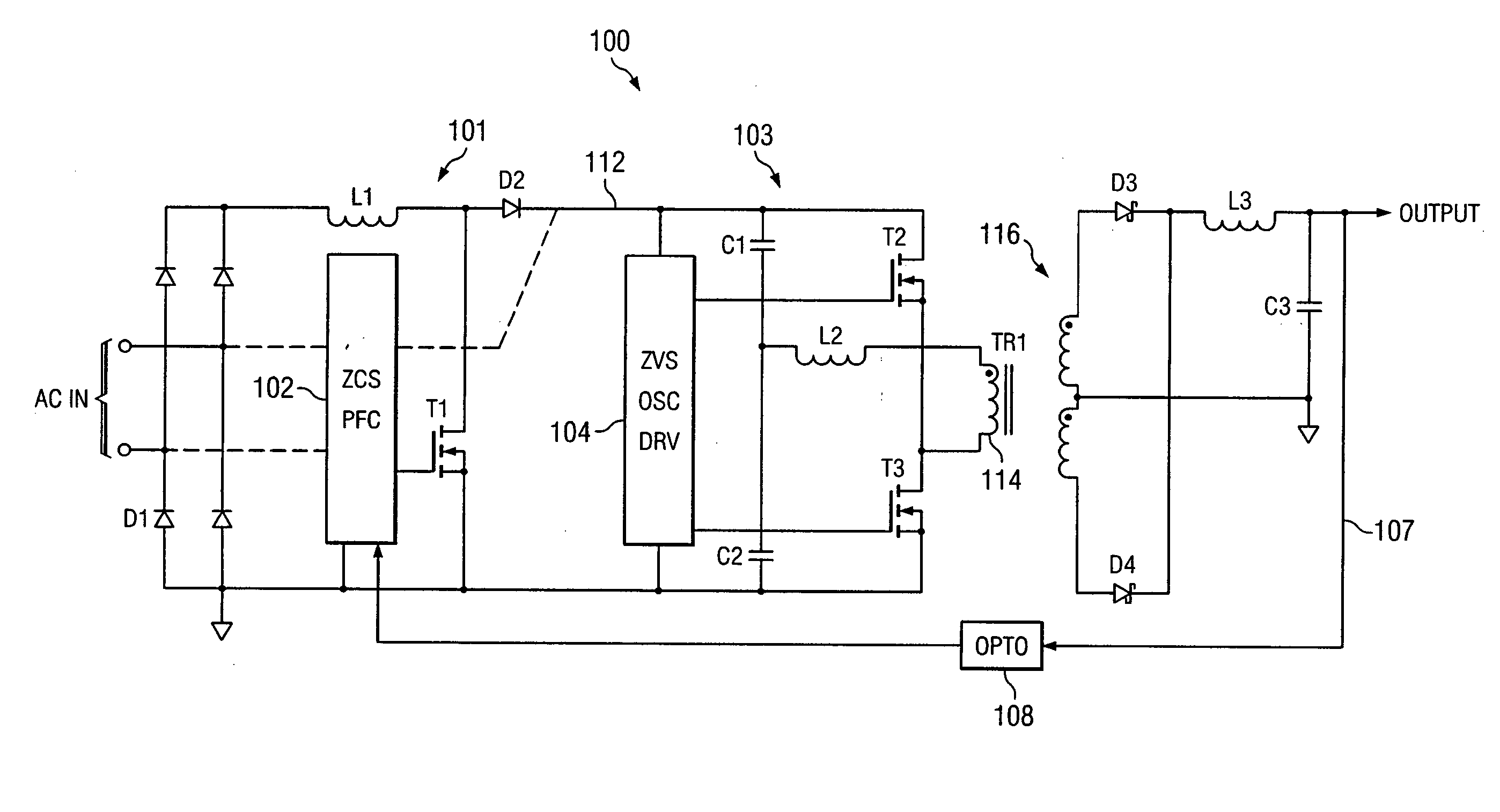

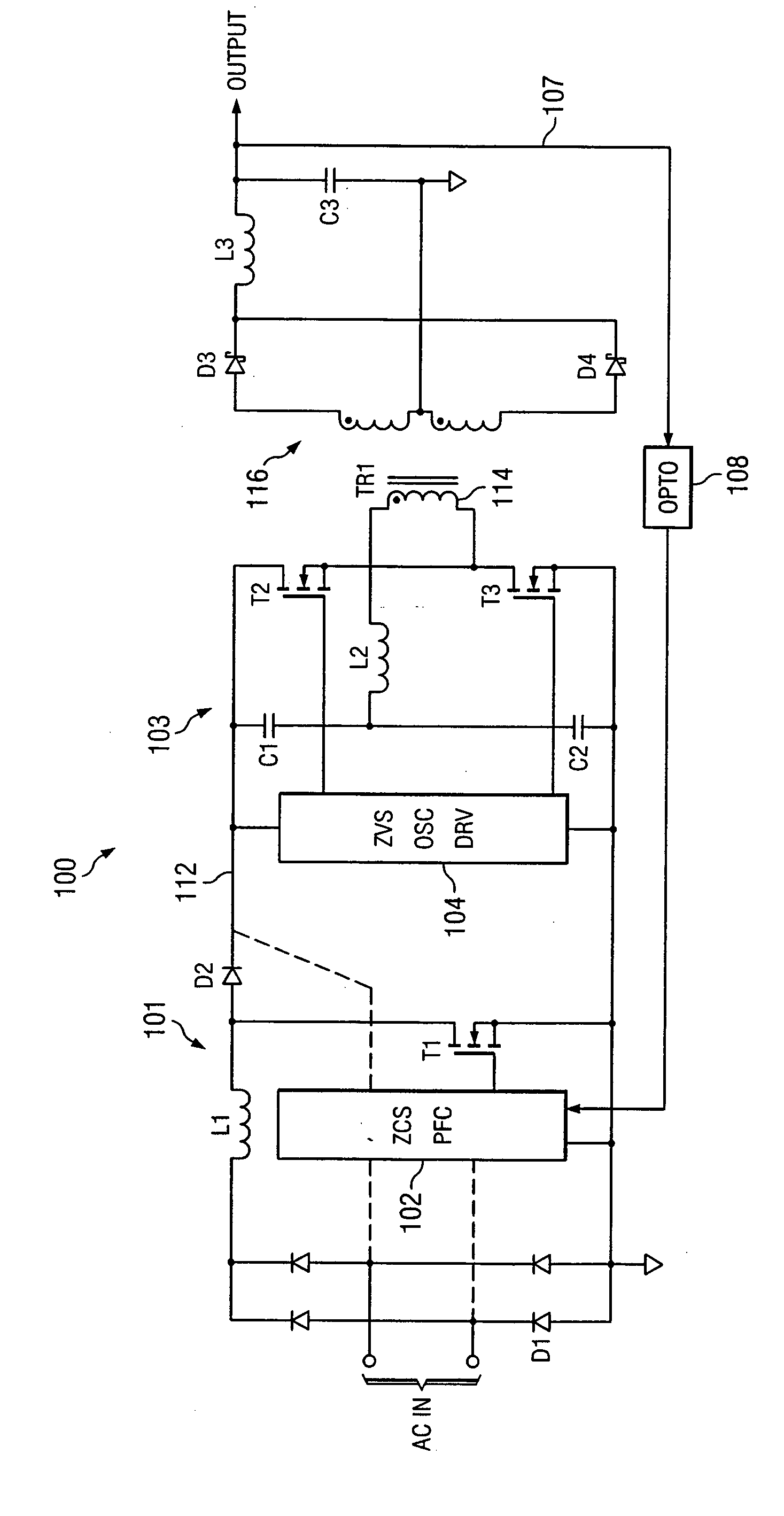

Highly efficient isolated AC/DC power conversion technique

ActiveUS20070081364A1Reduce circuit sizeReduce complexityAc-dc conversion without reversalEfficient power electronics conversionTransformerEngineering

An AC-to-DC power converter that is capable of generating a regulated, isolated DC voltage output from a power factor corrected AC voltage input with improved efficiency. The AC-to-DC power converter is a two-stage power converter including a PFC stage connected in series to a power conversion stage. The PFC stage performs power factor correction using a zero current switching technique, and the power conversion stage includes a zero voltage switched half-bridge converter. The power conversion stage includes a transformer for providing the isolated DC voltage output. The AC-to-DC power converter includes a single feedback control loop for transferring error information from the DC voltage output to the PFC stage, thereby obtaining regulation of the DC voltage output.

Owner:TEXAS INSTR INC

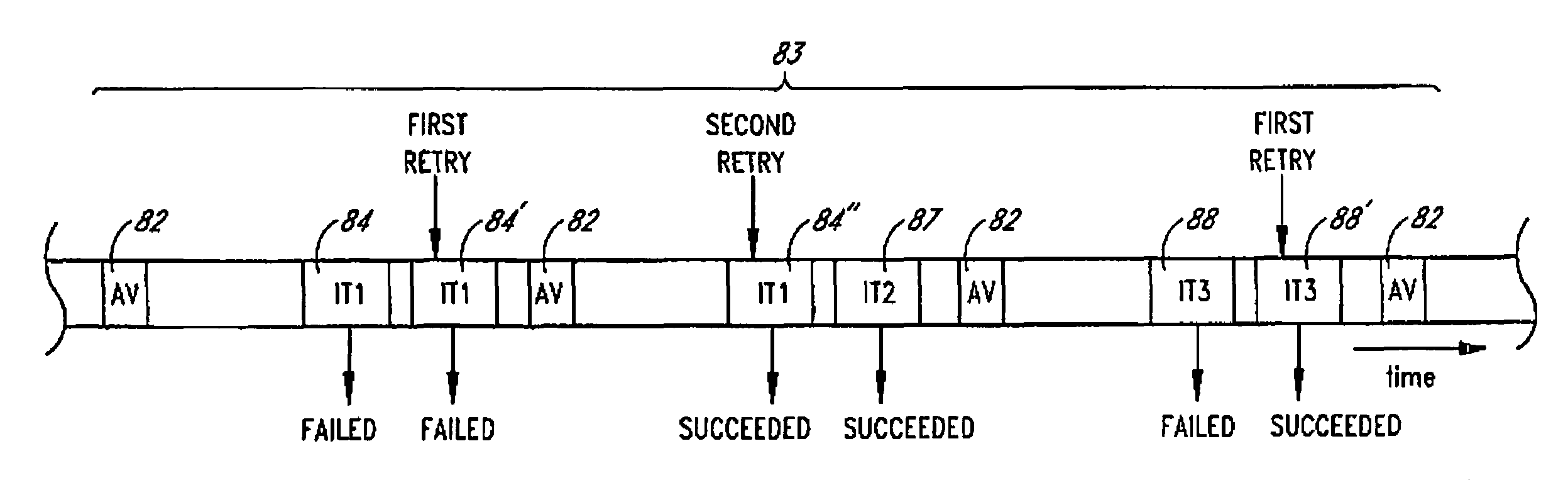

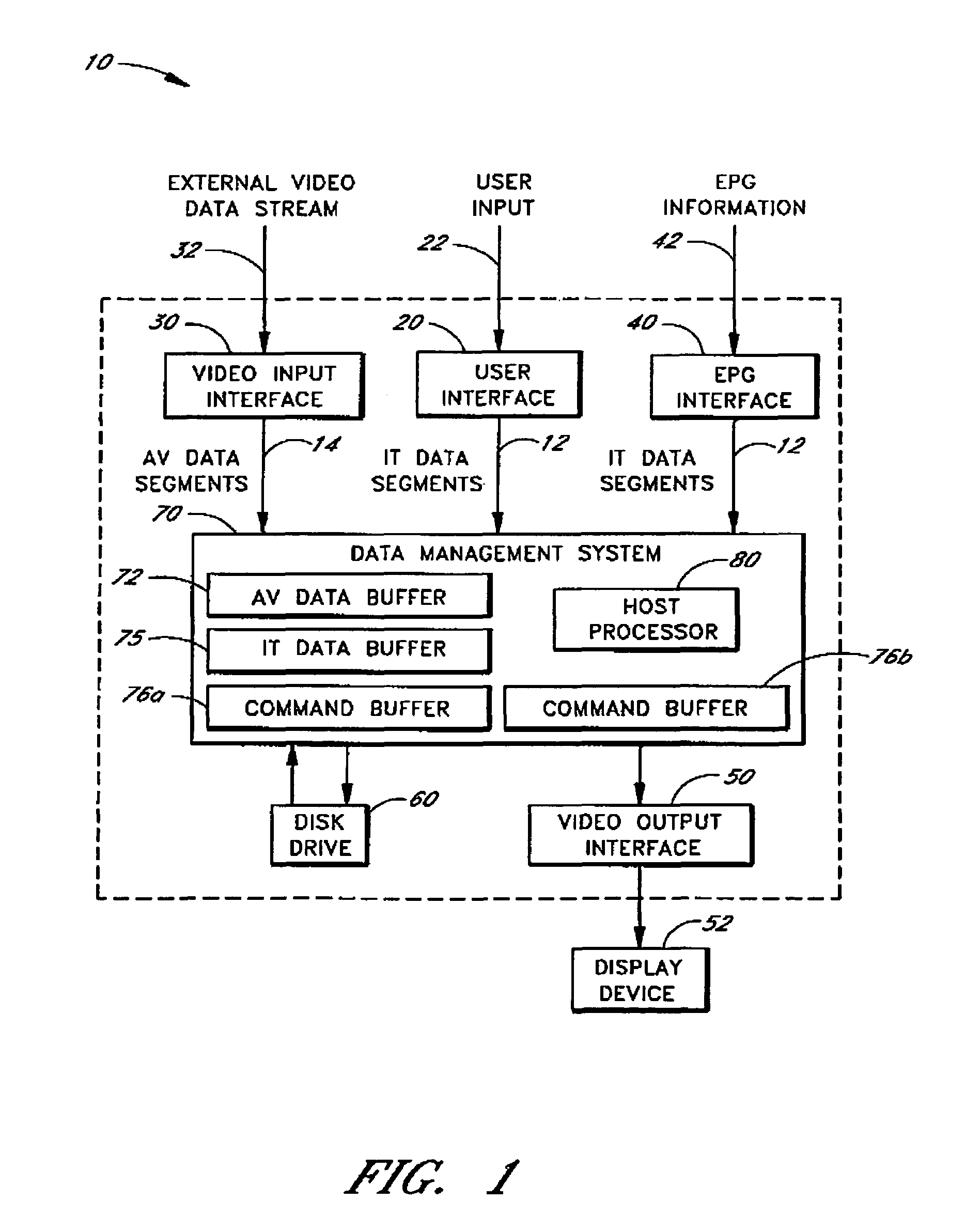

Video recording system utilizing storage redundancy to transfer non-time-critical, error-intolerant data segments while transferring time-critical, error-tolerant streaming data segments at a required data transfer rate

InactiveUS7133600B1Maintaining data transfer bandwidthEasy transferTelevision system detailsRecording carrier detailsStreaming dataData segment

The present invention may be regarded as a video recording system and method of transferring a non-time-critical, error-intolerant data segment stored on a disk drive, which is responsive to a set of data transfer commands generated by a host processor and which is operating in a mode optimized for transferring time-critical, error-tolerant streaming data segments stored or to be stored on the disk drive. The method includes sending a sequence of data transfer commands generated by the host processor to the disk drive to transfer a respective sequence of time-critical, error-tolerant streaming data segments at a required data transfer rate. The method further includes selectively interposing a first data transfer command into the sequence of data transfer commands, the first data transfer command initiating a first transfer of the non-time-critical, error-intolerant data segment from a first storage location. The method further includes transmitting a data transfer error signal generated by the disk drive to the host processor, the data transfer error signal having a state that indicates whether any data transfer errors have occurred with respect to the first transfer of the non-time-critical, error-intolerant data segment. The method further includes selectively interposing a second data transfer command into the sequence of data transfer commands, the second data transfer command initiating a second transfer of the non-time-critical, error-intolerant data segment from a second storage location, thereby utilizing storage redundancy to achieve an accuracy required for the non-time-critical, error-intolerant data segment while maintaining the required data transfer rate of the sequence of time-critical, error-tolerant data segments.

Owner:KEEN PERSONAL MEDIA +1

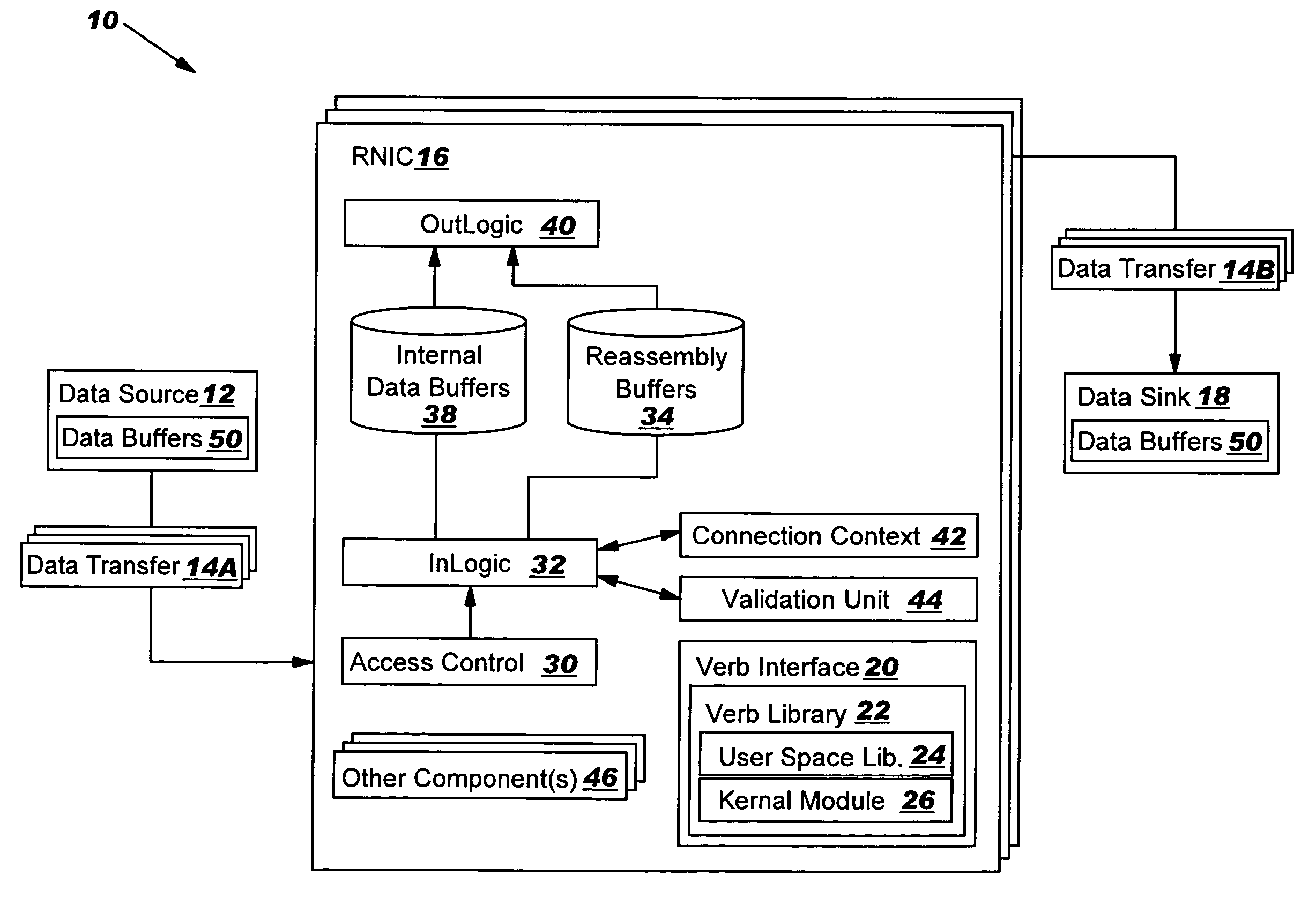

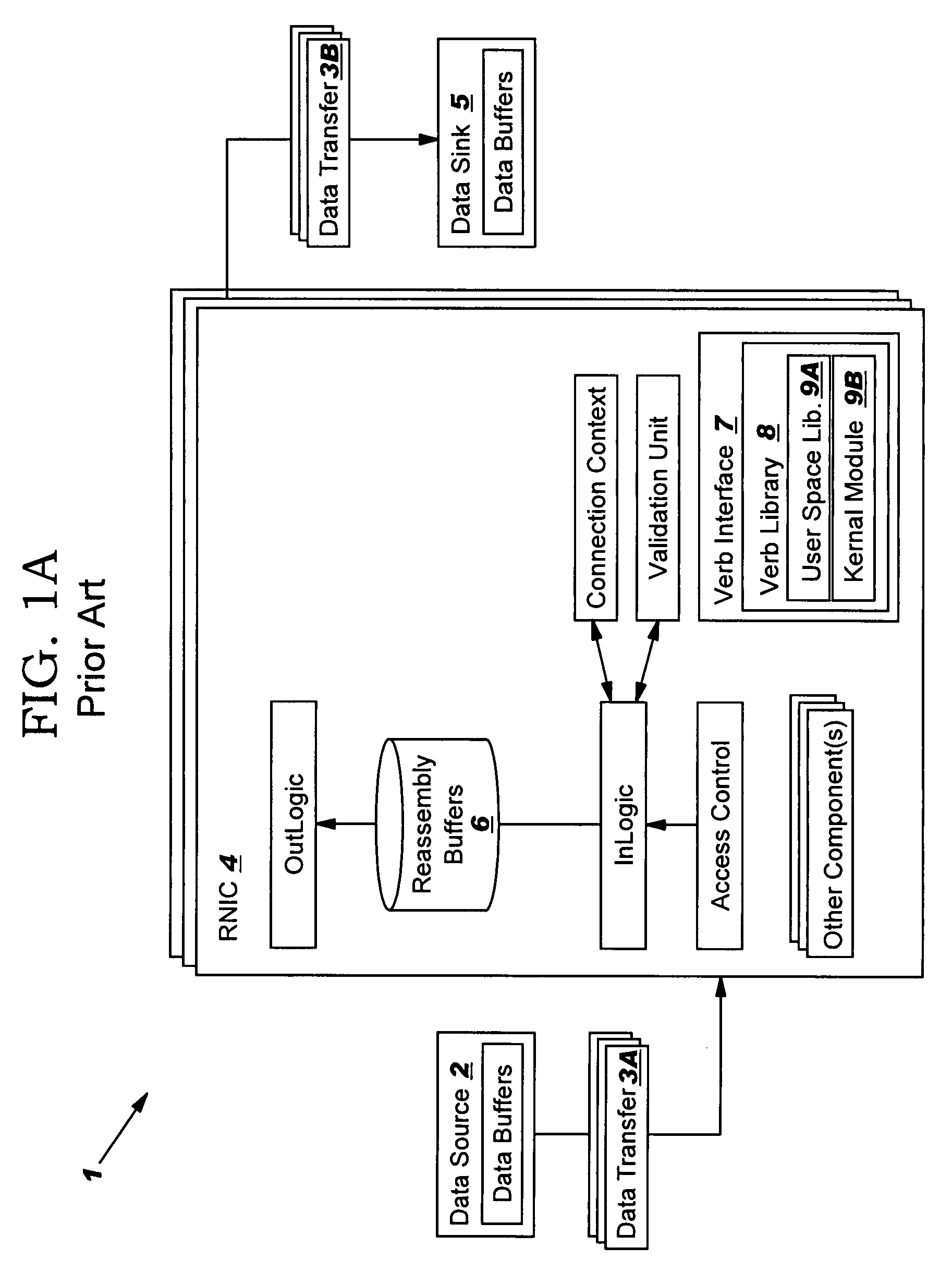

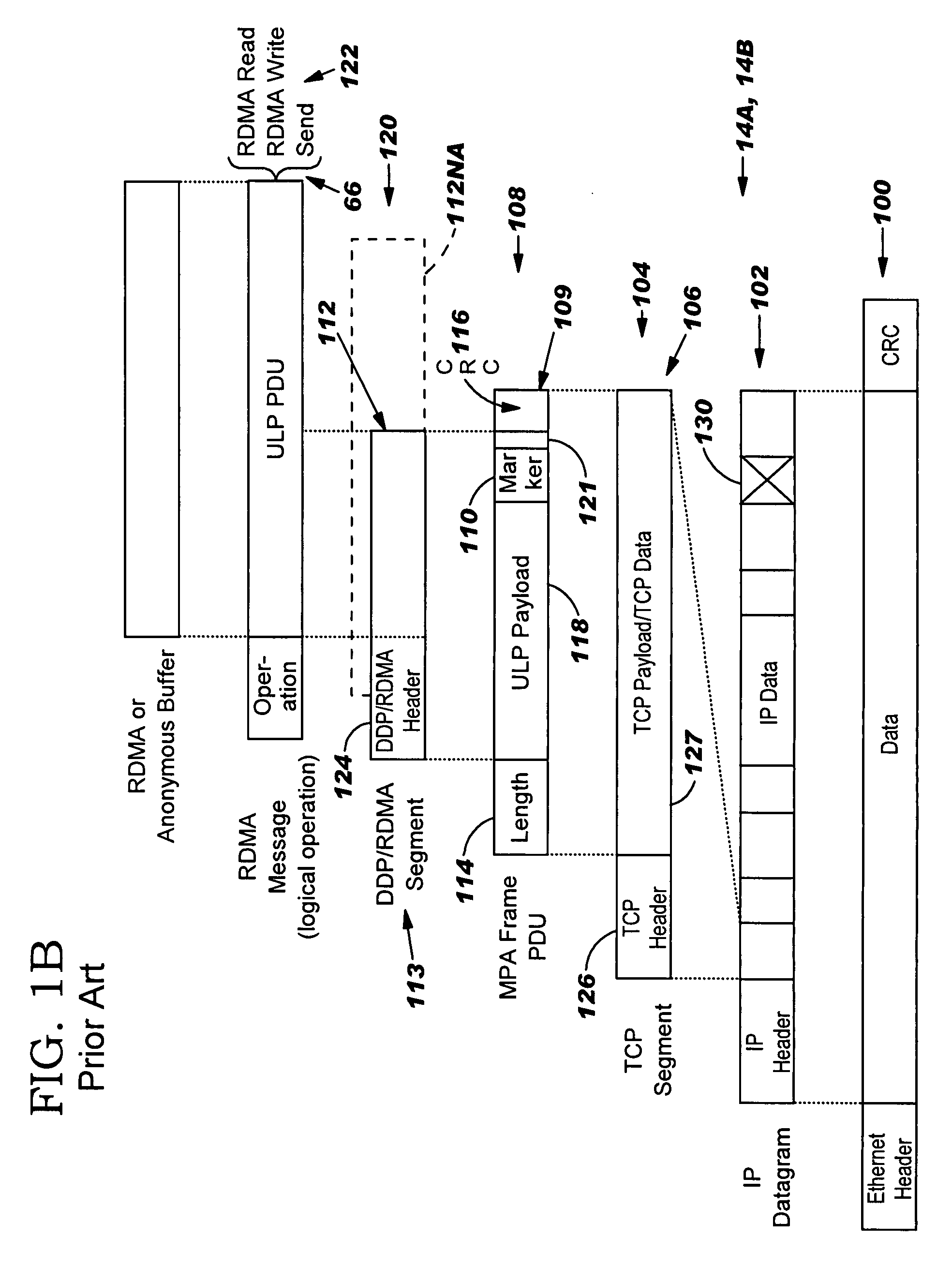

Data transfer error checking

InactiveUS20050149817A1Reduce memory bandwidthReduce latencyCode conversionError detection onlyConnection typeData placement

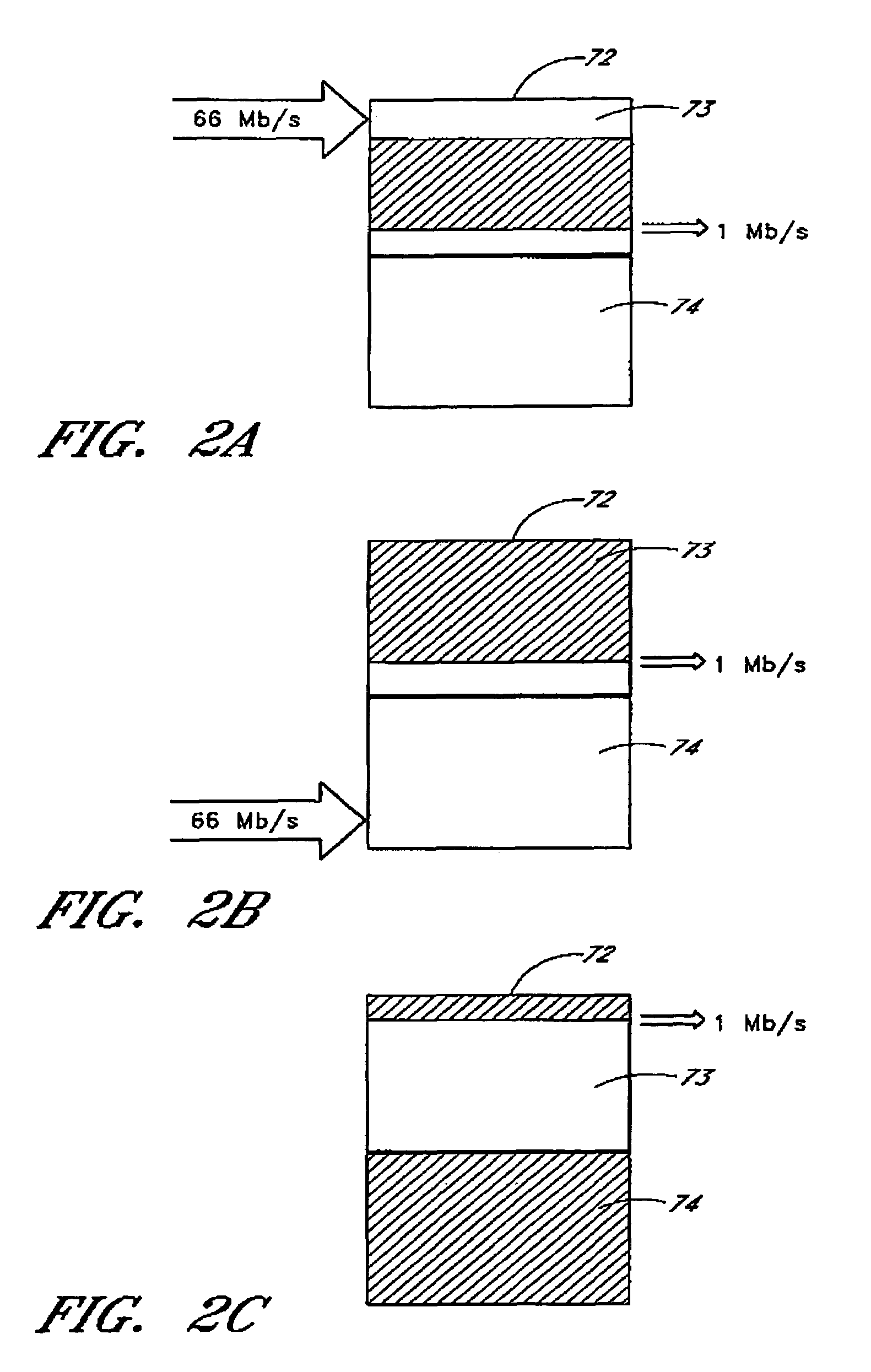

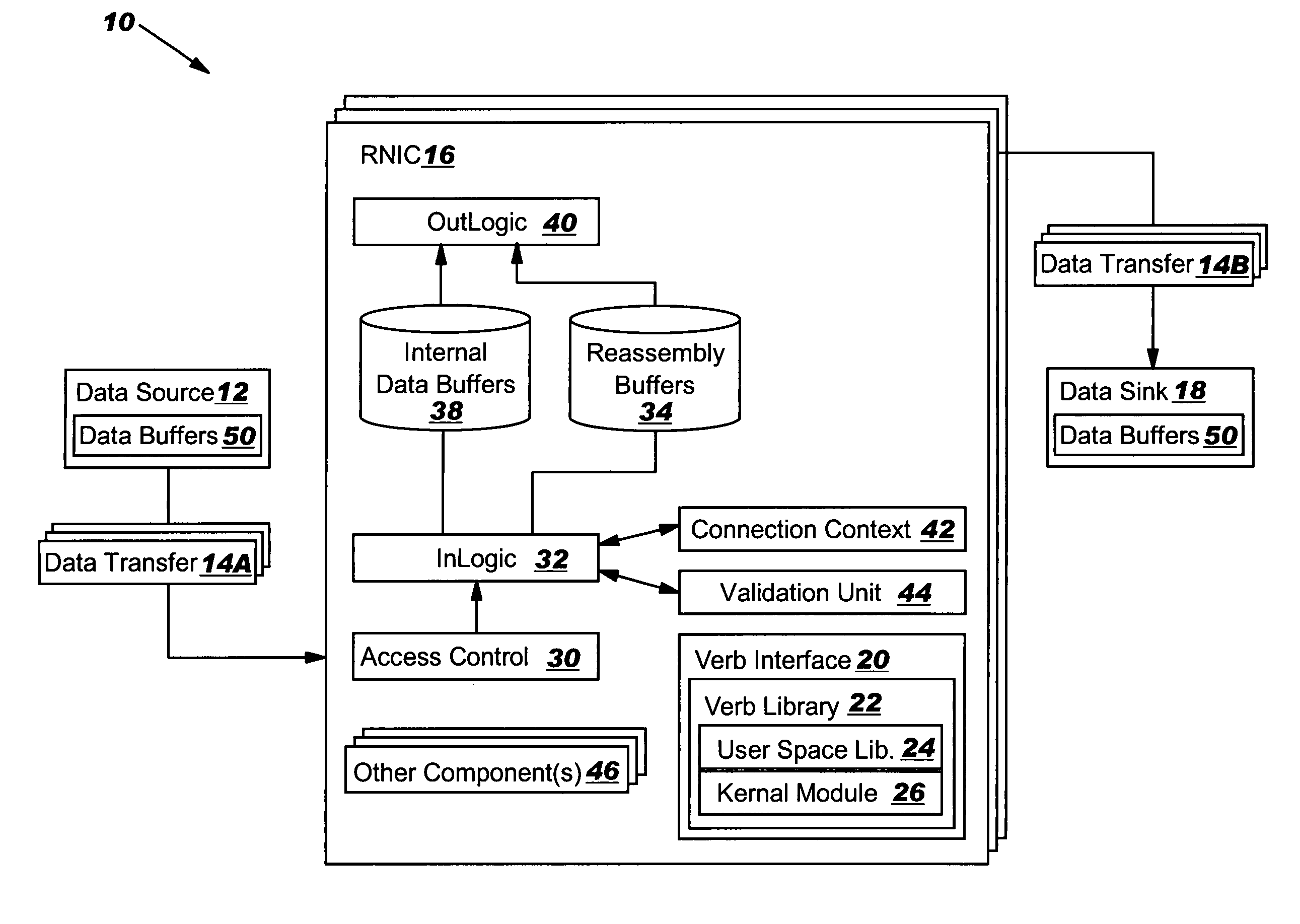

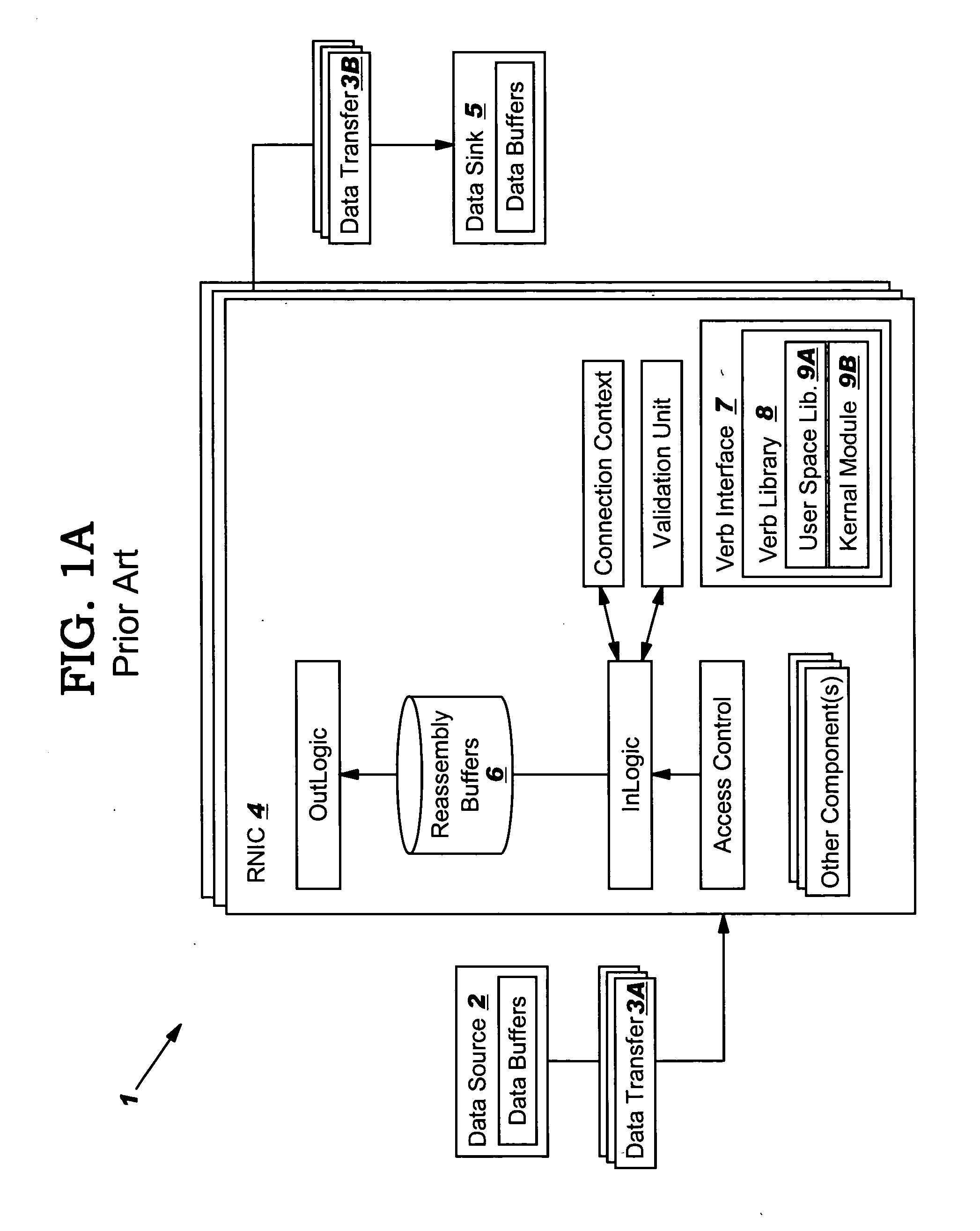

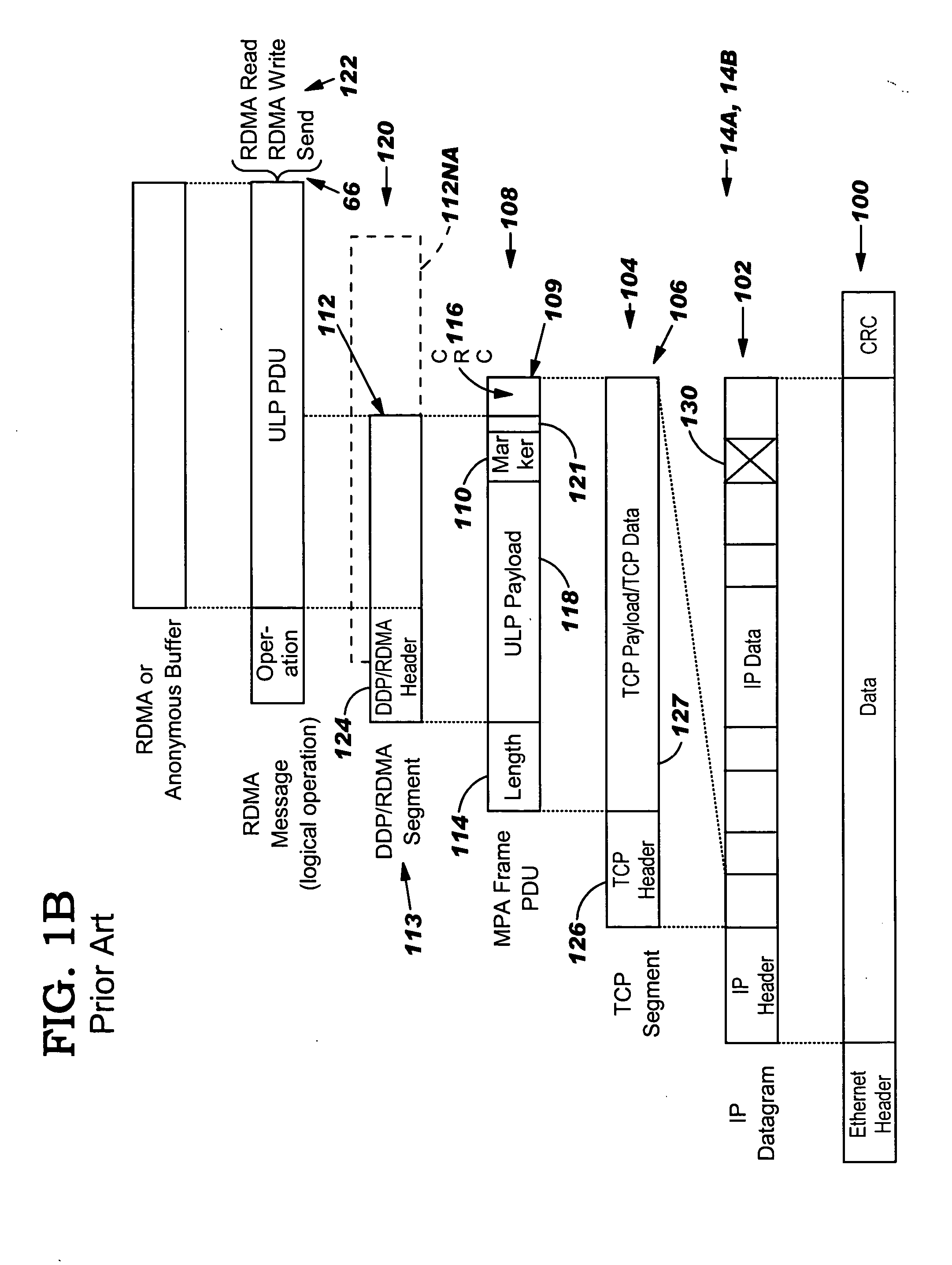

An RNIC implementation that performs direct data placement to memory where all segments of a particular connection are aligned, or moves data through reassembly buffers where all segments of a particular connection are non-aligned. The type of connection that cuts-through without accessing the reassembly buffers is referred to as a “Fast” connection because it is highly likely to be aligned, while the other type is referred to as a “Slow” connection. When a consumer establishes a connection, it specifies a connection type. The connection type can change from Fast to Slow and back. The invention reduces memory bandwidth, latency, error recovery using TCP retransmit and provides for a “graceful recovery” from an empty receive queue. The implementation also may conduct CRC validation for a majority of inbound DDP segments in the Fast connection before sending a TCP acknowledgement (Ack) confirming segment reception.

Owner:IBM CORP

Highly efficient isolated AC/DC power conversion technique

ActiveUS7375994B2Improve efficiencyReduced Power RequirementsAc-dc conversion without reversalEfficient power electronics conversionTransformerEngineering

An AC-to-DC power converter that is capable of generating a regulated, isolated DC voltage output from a power factor corrected AC voltage input with improved efficiency. The AC-to-DC power converter is a two-stage power converter including a PFC stage connected in series to a power conversion stage. The PFC stage performs power factor correction using a zero current switching technique, and the power conversion stage includes a zero voltage switched half-bridge converter. The power conversion stage includes a transformer for providing the isolated DC voltage output. The AC-to-DC power converter includes a single feedback control loop for transferring error information from the DC voltage output to the PFC stage, thereby obtaining regulation of the DC voltage output.

Owner:TEXAS INSTR INC

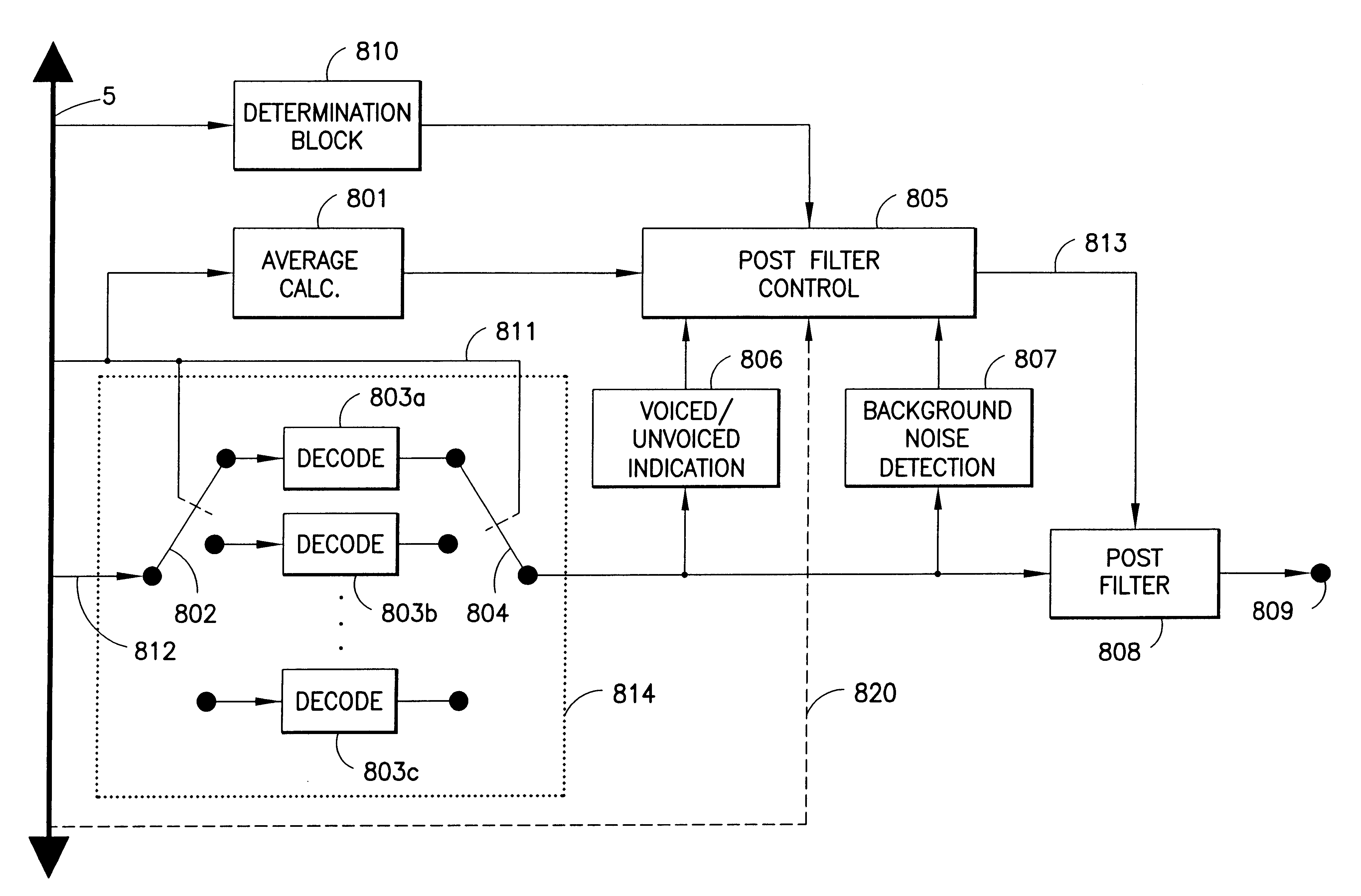

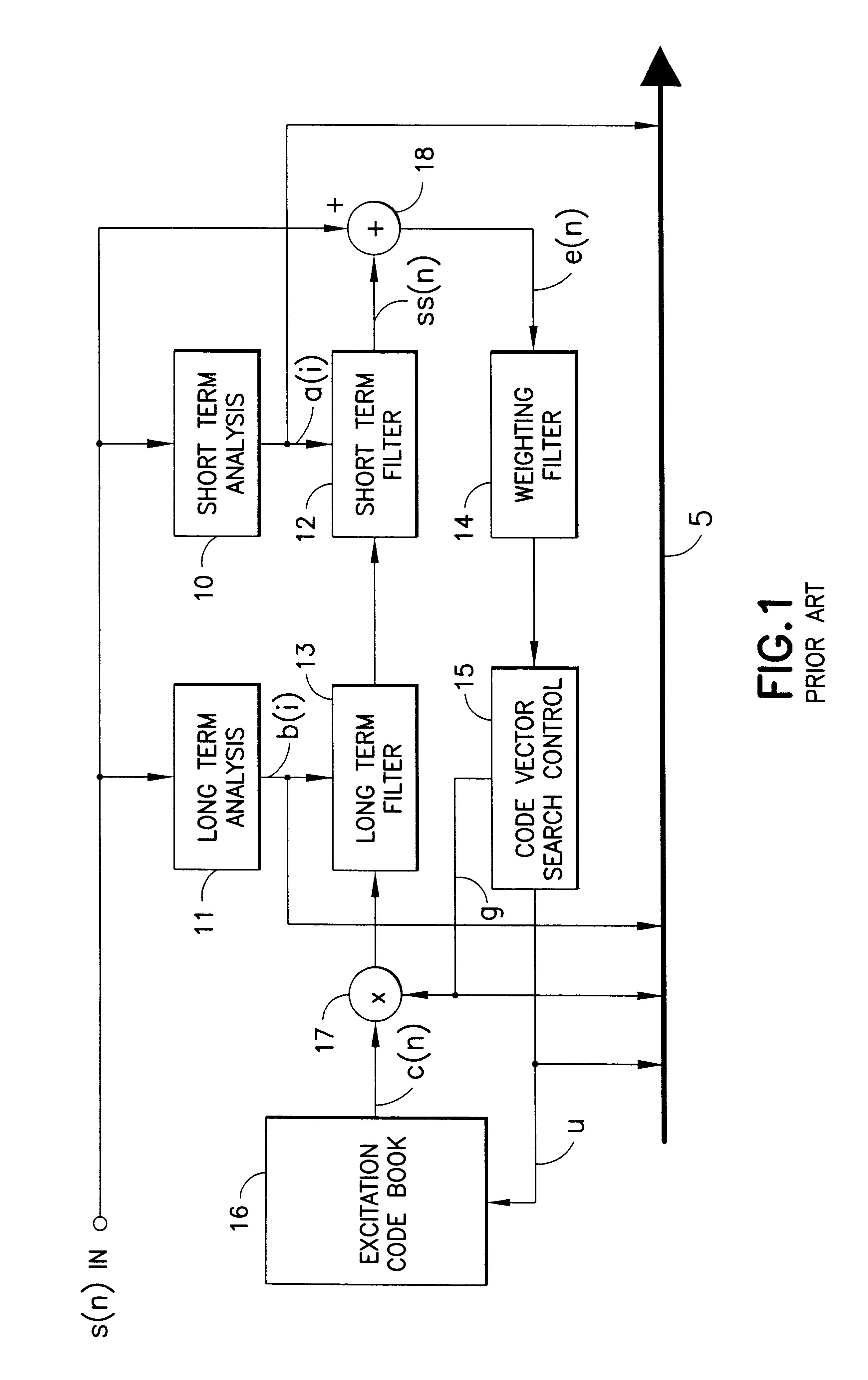

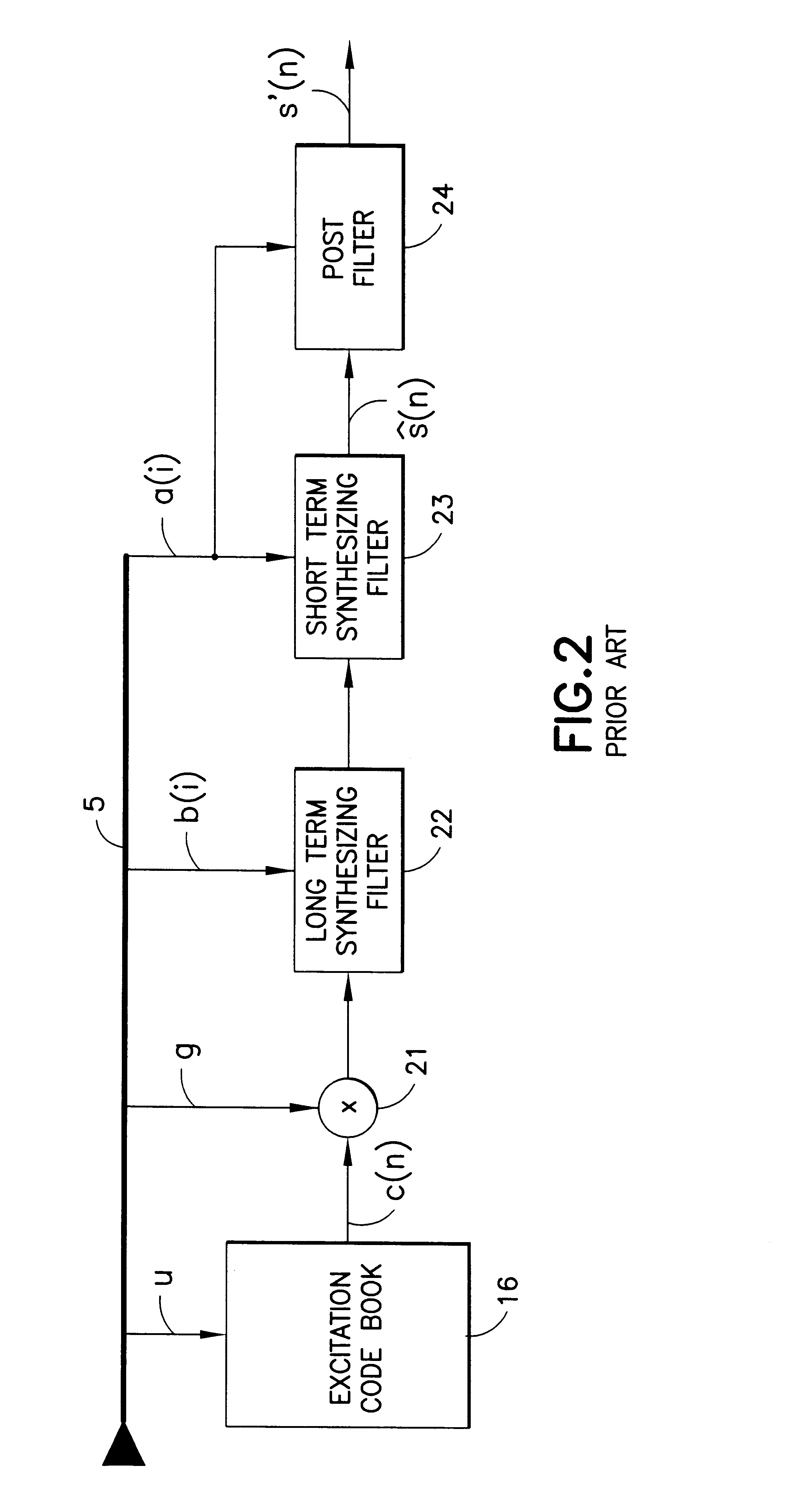

Adaptive postfilter

InactiveUS6584441B1Easy data transferQuality improvementAdaptive networkDigital technique networkSignal qualityTransfer error

The invention relates to the coding of speech at a variable bit rate, whereby the bit rates can vary from frame to frame, and more specifically to the methods and filters used for improving the quality of the decoded speech. In the solution according to the invention the weighting factors of the postfilter are not adapted on the basis of the momentary bit rate or the bit rate used in the coding of each frame, but the weighting factors are adapted according to the average bit rate calculated on the basis of a predetermined length of time. In addition to this, the weighting factors of the postfilter are also adjusted on the basis of whether the frame in question contains a voiced speech signal, an unvoiced speech signal or background noise. At frames containing an unvoiced speech signal or background noise, postfiltering is weakened so as to avoid the distortion of the signal tone because the postfiltering is adapted to a voiced signal. The weighting factors of the postfilter can also be adapted on the basis of the error rate or other parameter describing the quality of the signal or the data transfer channel. For example, postfiltering can conveniently be adjusted so that when the channel error rate and the amount of coding error increase, postfiltering is increased, whereby the effect of data transfer errors on the decoded speech signal is reduced and the tolerance of the system with regard to data transfer errors increases.

Owner:NOKIA MOBILE PHONES LTD +1

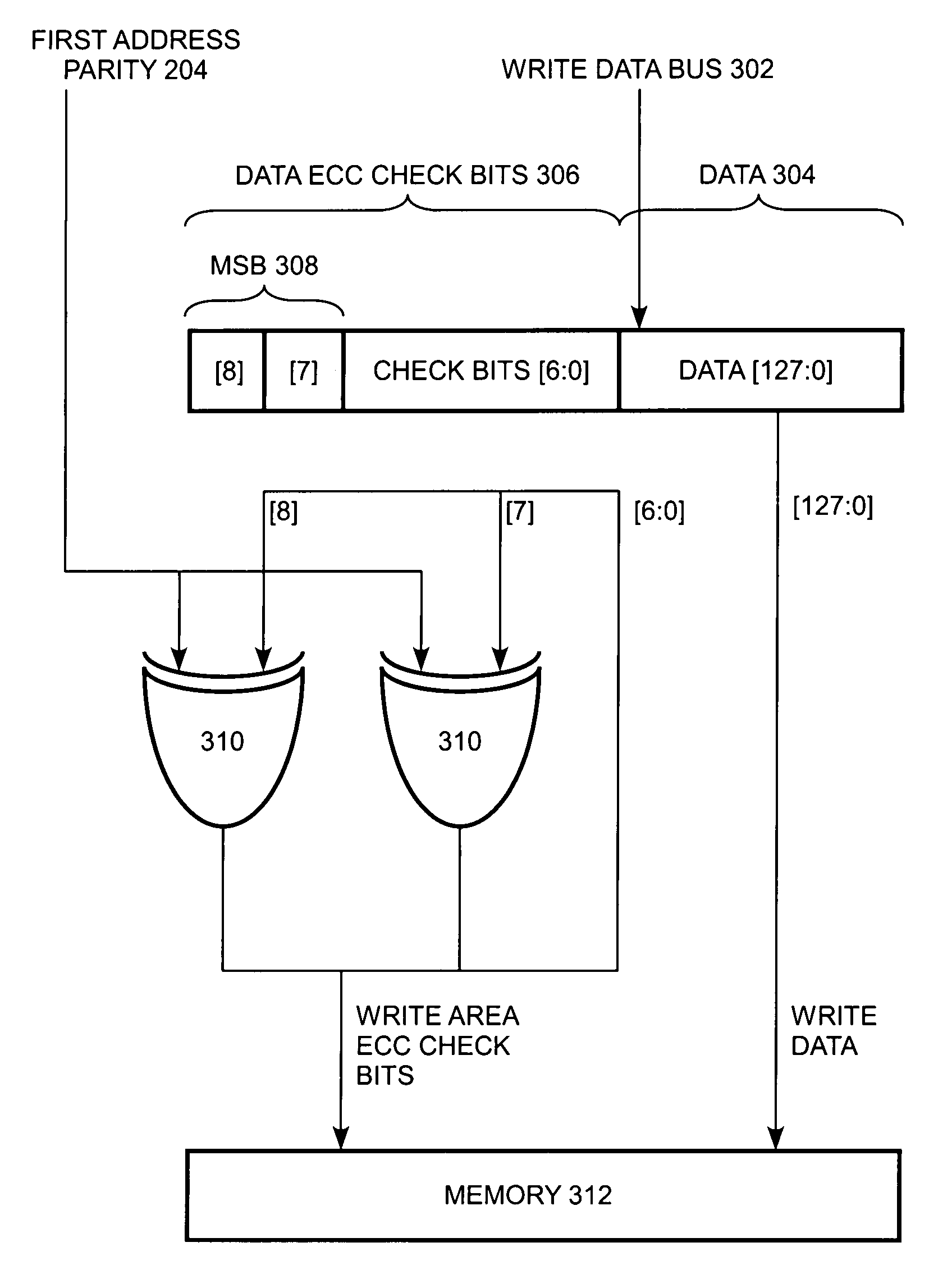

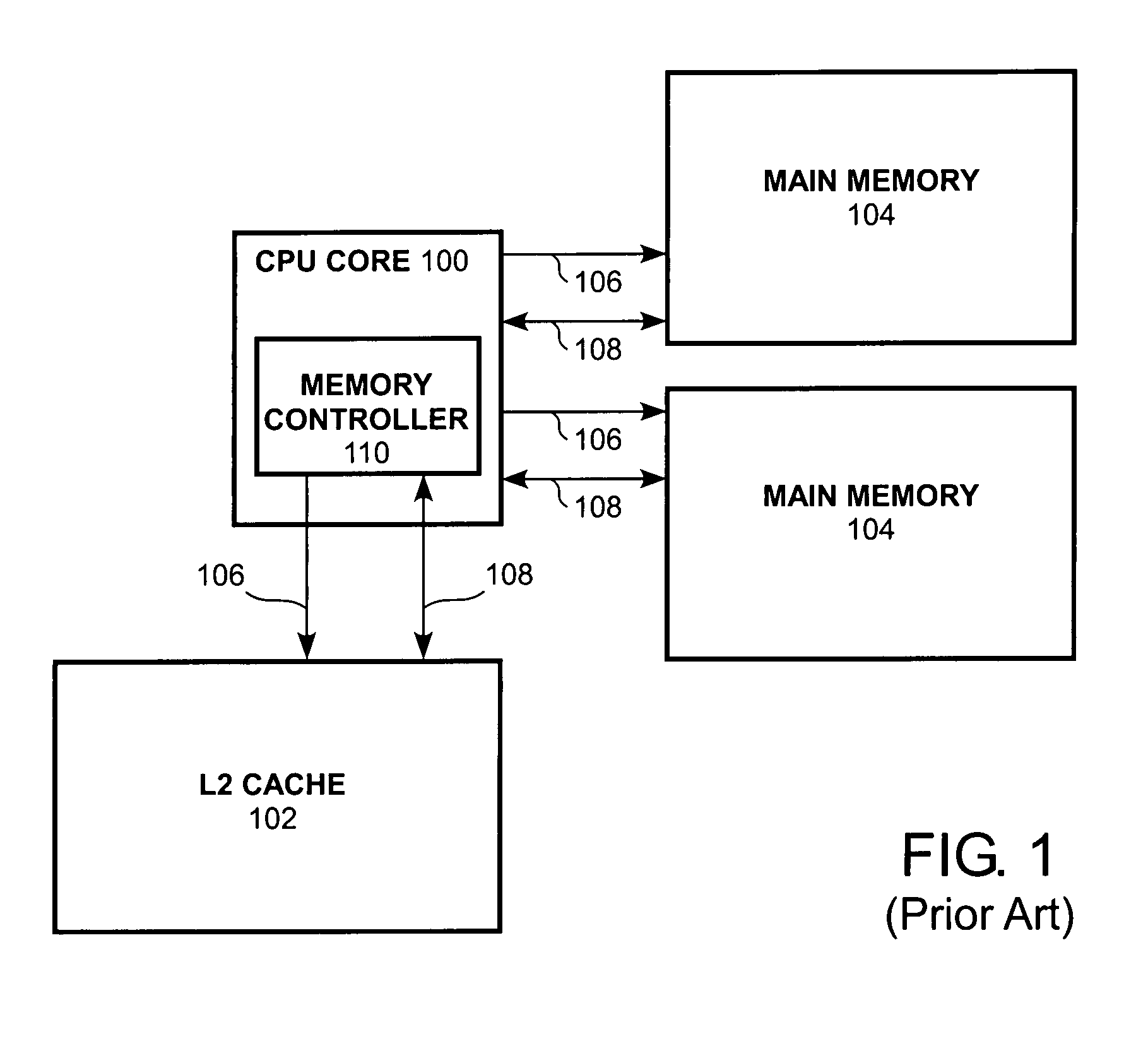

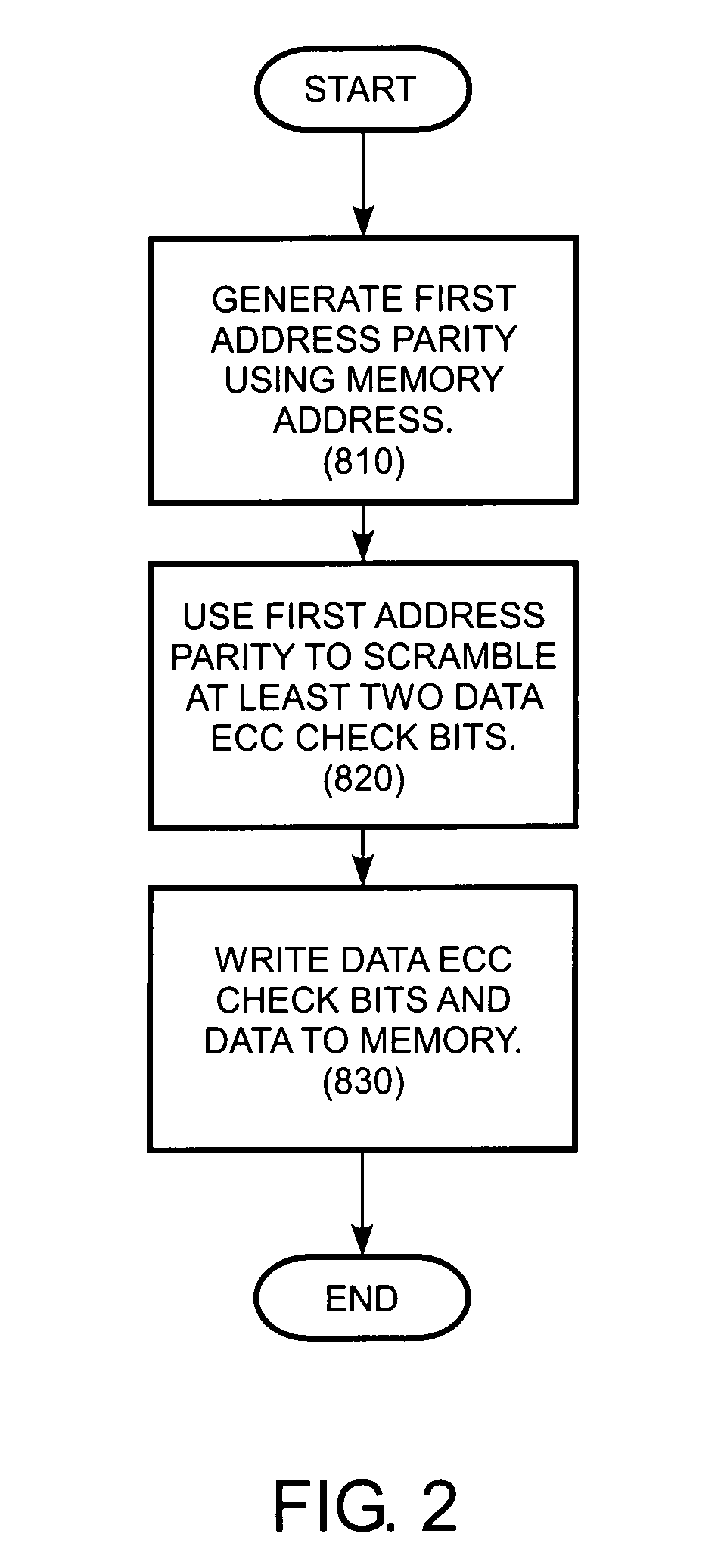

Methods and systems for detecting memory address transfer errors in an address bus

ActiveUS7293221B1Enabling detectionError detection/correctionStatic storageMemory addressAddress bus

A method for detecting transfer errors in an address bus is provided. In this method, a first address parity is generated using a memory address. Next, at least two data error-correction-code (ECC) check bits are scrambled using the first address parity. Subsequently, the data ECC check bits are written to a memory and the data ECC check bits enable detection of transfer errors in the address bus. A system for detecting transfer errors in an address bus is also described.

Owner:ORACLE INT CORP

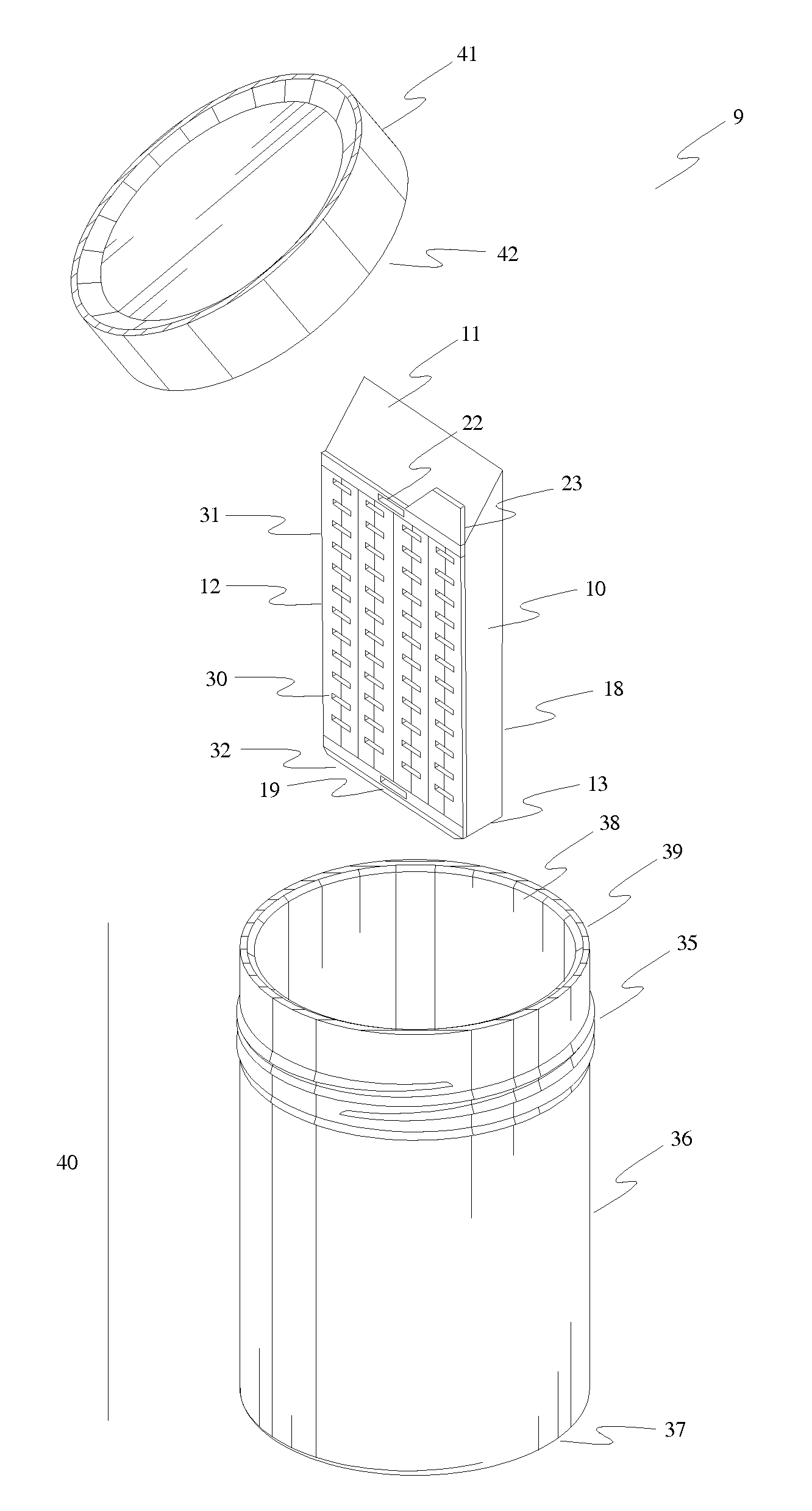

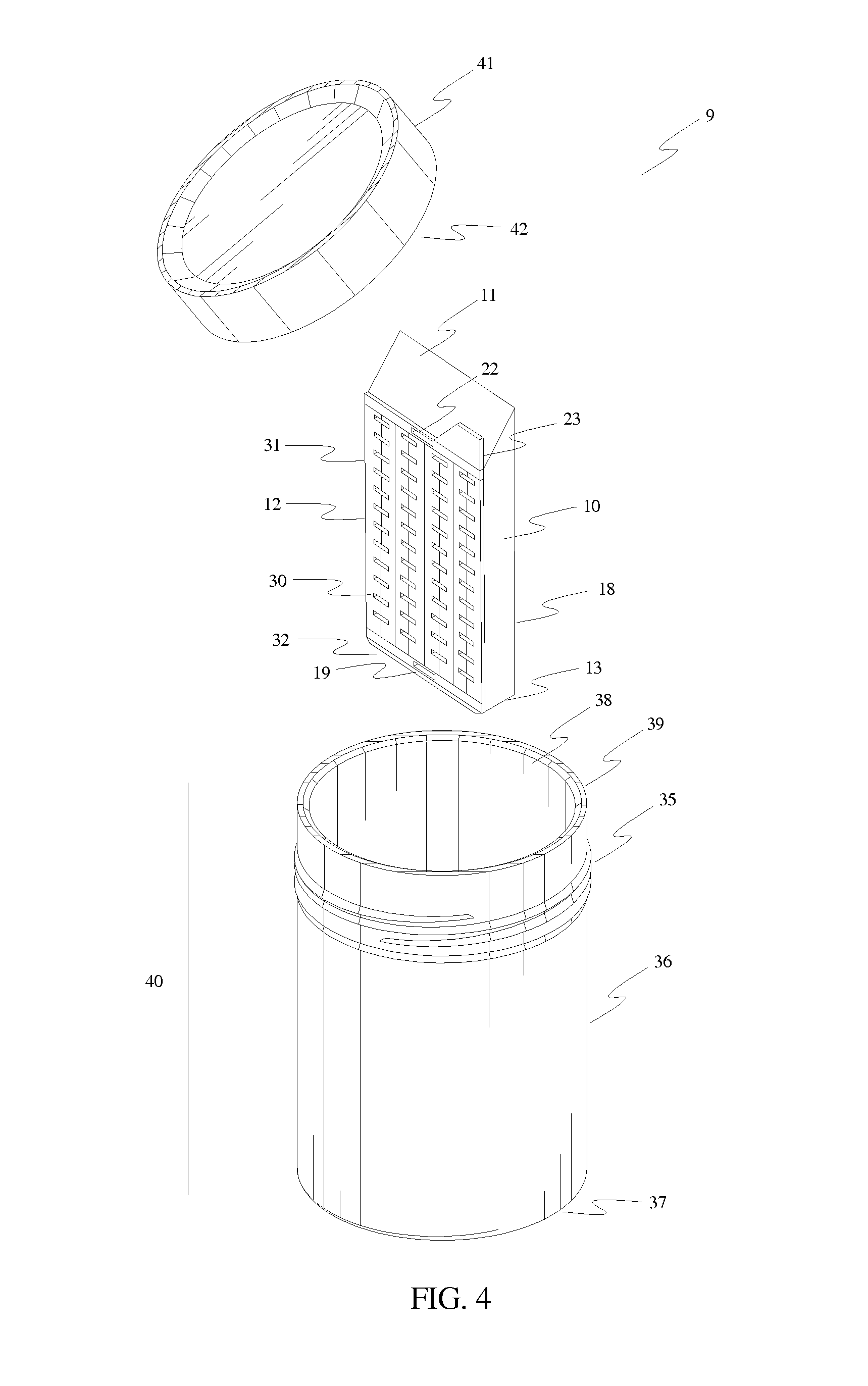

Reusable Tissue Biopsy Kit with Padded Cassette

InactiveUS20100075410A1Promote resultsBig errorBioreactor/fermenter combinationsAnalysis using chemical indicatorsTissue biopsySample integrity

An improved biopsy kit for the collection, storage, transportation, and processing of biopsy tissue samples is disclosed. The disclosed biopsy kit consists of a typical specimen container and an improved tissue cassette with adhesively attached polyvinyl alcohol foam pads on both the base and lid portions. An excised tissue sample is sandwiched between the pads upon cassette closure, simultaneously isolating and securing the sample in its original orientation. Superior wicking, absorbency, and moisture retention rate of these polyvinyl alcohol pads allows maximum tissue fixation as well as maintains sample integrity. Once the tissue is placed by the physician at the patient's side, it remains there until the tissue is ready to be processed. This eliminates transfer errors as well as tissue loss.

Owner:DESAI VIRENDRA +1

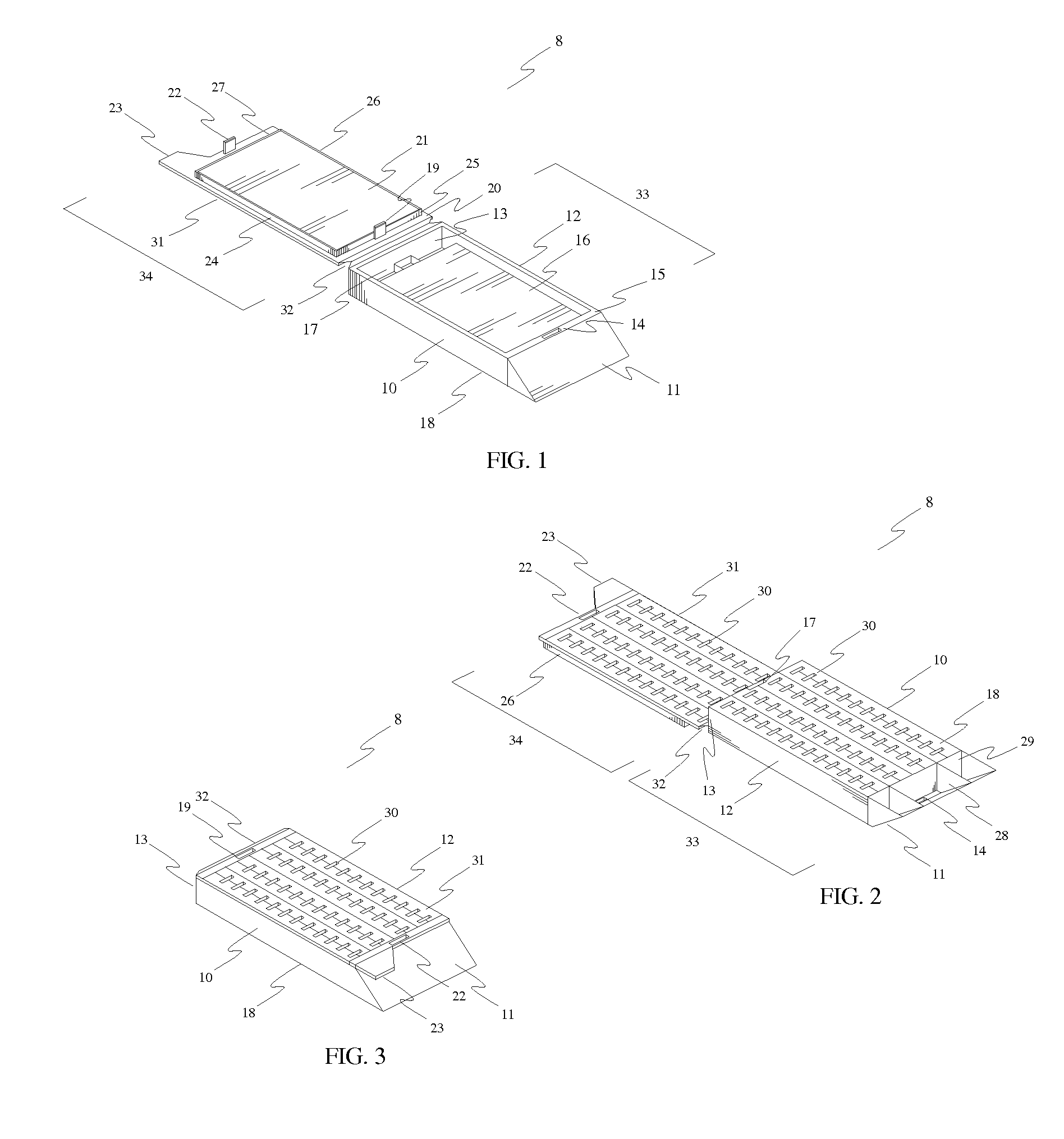

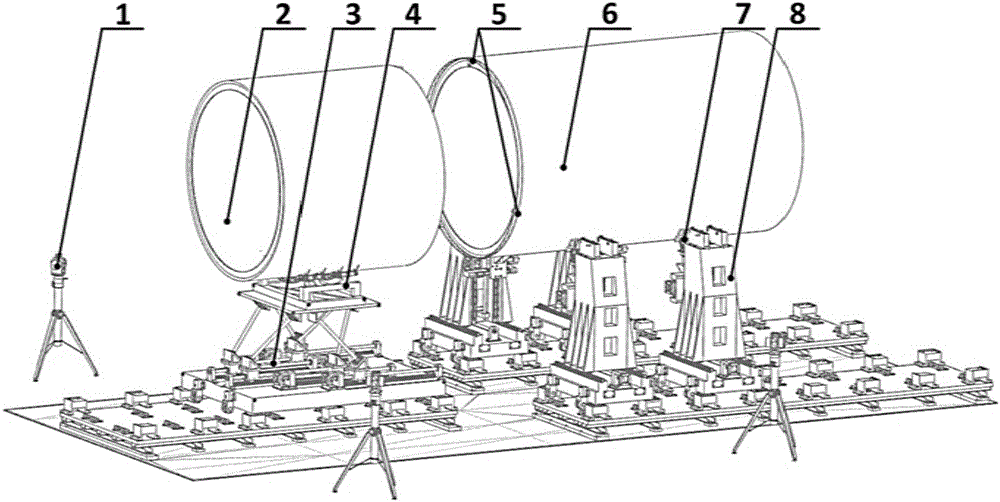

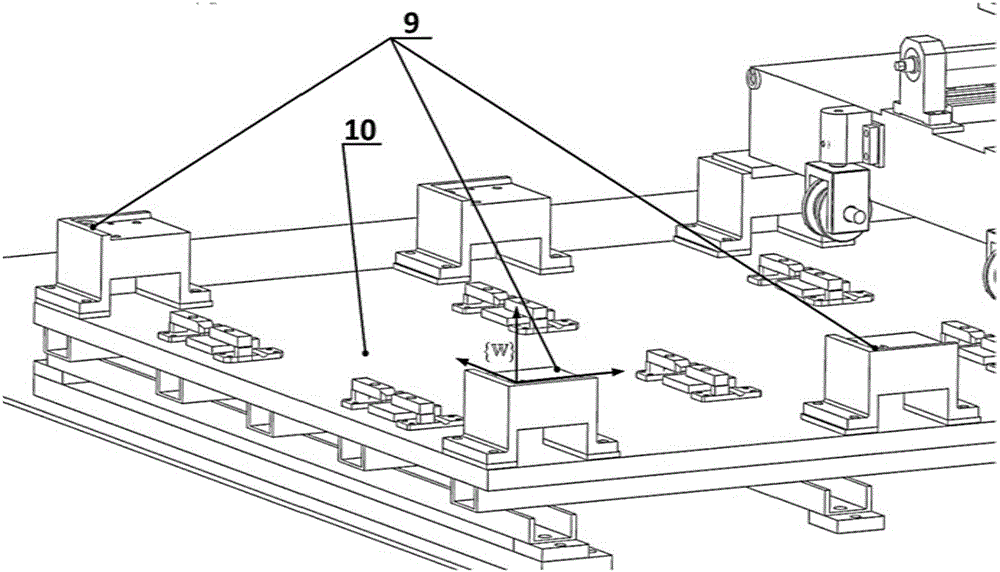

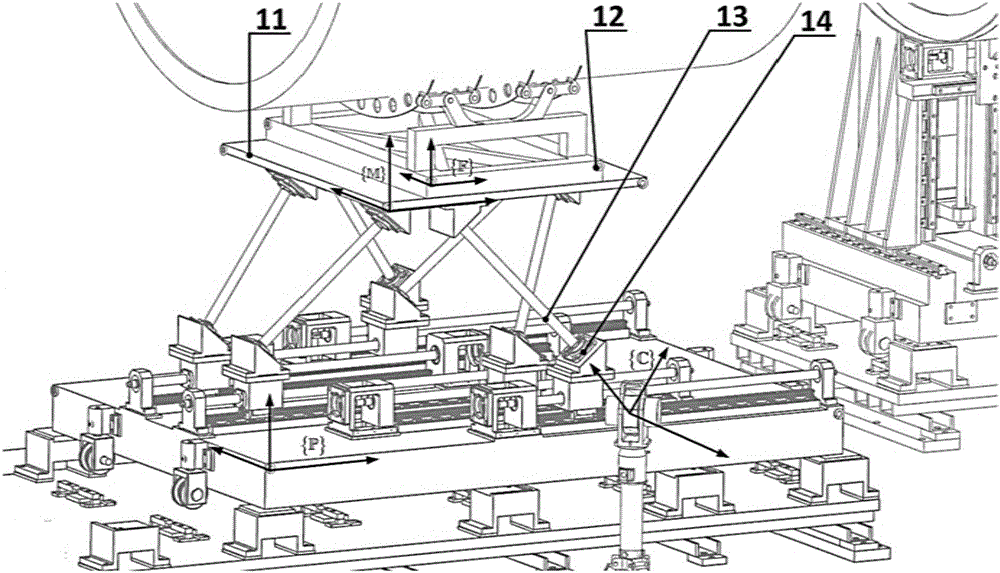

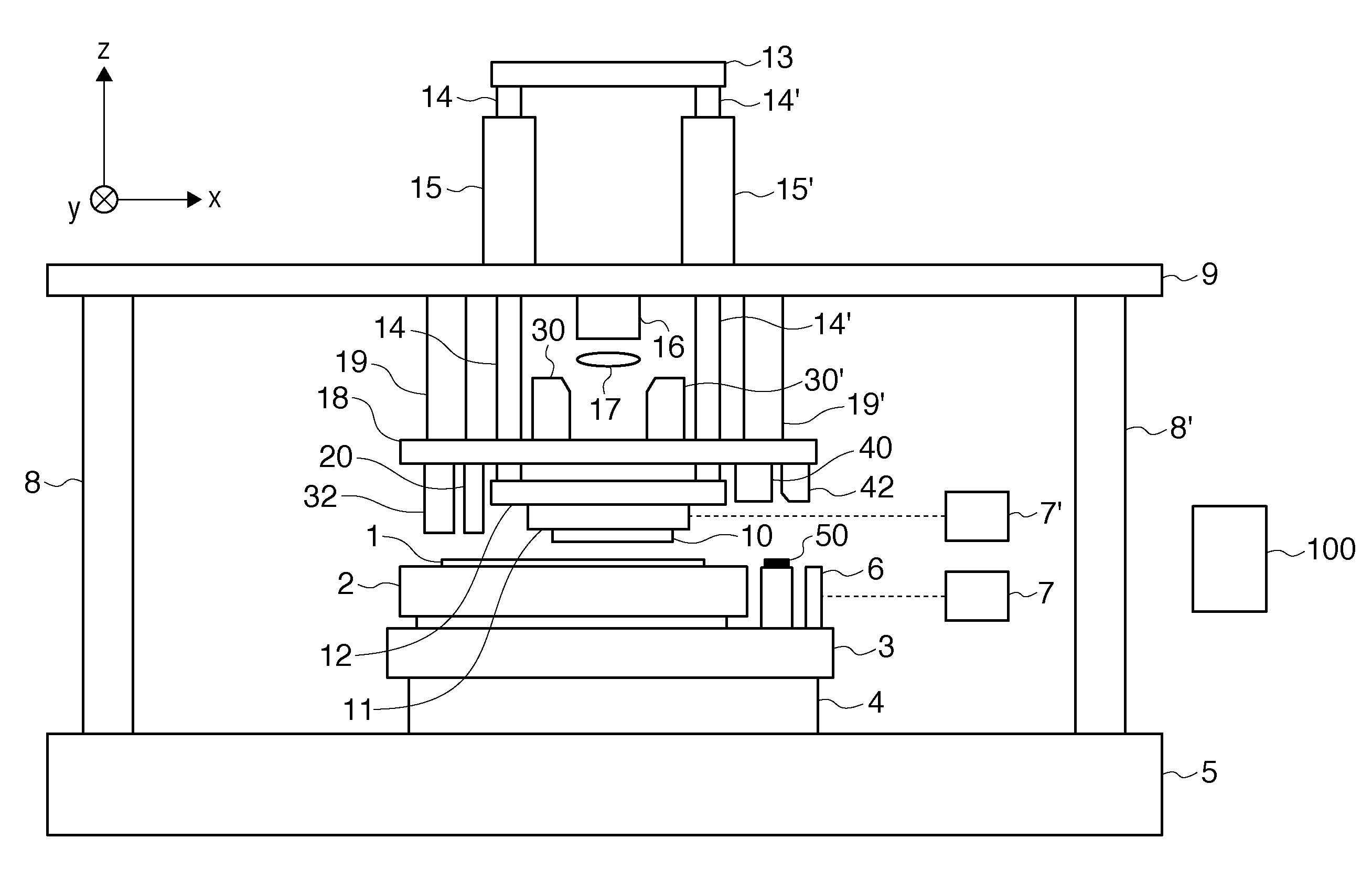

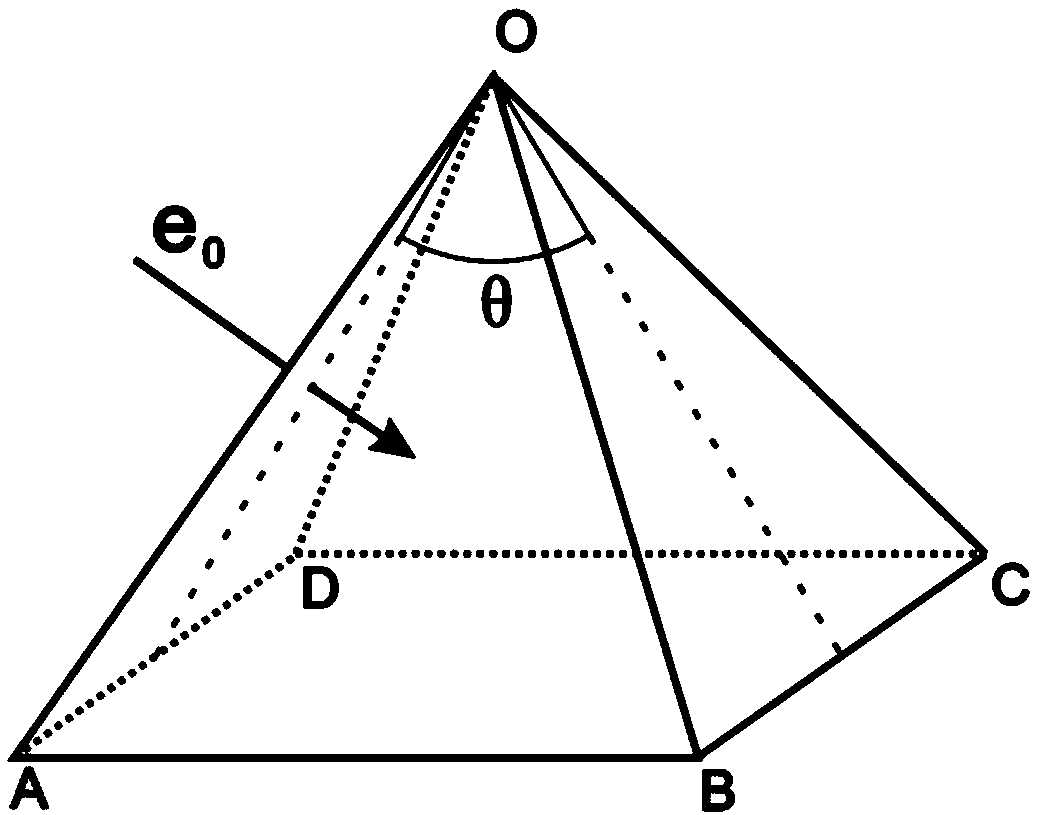

Automatic butt assembling method for large part as well as system

ActiveCN105787200AReduce the impactReduce transmission errorGeometric CADAssembly machinesKinematicsMathematical model

The invention discloses an automatic butt assembling method for a large part as well as a system. The method comprises steps as follows: kinematic parameters of a servo posture adjusting positioner under the loading condition are calibrated firstly, an actual mathematical model of a butt part is established according to measurement data of the butt part, the butt part is corrected or reworked through comparison of the actual mathematical model and an ideal mathematical model of the butt part, then the relative position between a butt feature point of the butt part and a support measurement point arranged on a support device is calibrated, the butt part is mounted on the servo posture adjusting positioner, the position of the butt part in an overall reference coordinate system is determined, then a path of the butt part is planned with the optimum matching algorithm, the driving amount of each shaft of the servo posture adjusting positioner is obtained through inverse solution, finally, the butt part is moved by the servo posture adjusting positioner, and butt assembly of the butt part is completed. According to the automatic butt assembling method for the large part as well as the system, transfer errors are reduced, and errors caused by utilization of the ideal mathematical model or non-measurable property of the butt feature point are avoided, so that the quality and the success rate of automatic assembly are guaranteed.

Owner:SHANGHAI JIAO TONG UNIV

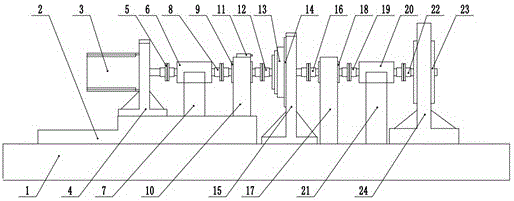

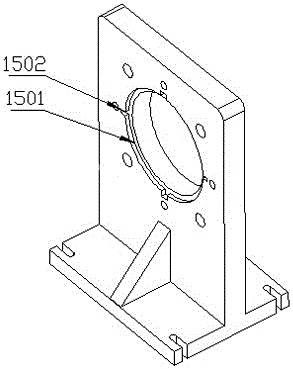

RV reducer comprehensive test bench

InactiveCN106053062AGuaranteed positioning accuracyHigh precisionMachine gearing/transmission testingReduction driveEngineering

The invention discloses an RV reducer comprehensive test bench, which can test multiple performance parameters such as the angle transfer error, the return difference, the torsional rigidity, the service life, the temperature rise, the efficiency and the torque of the high-precision RV reducer. The RV reducer comprehensive test bench comprises a base, and a servo motor, a linear motor, a first torque sensor, a first high-precision angle encoder, a to-be-tested RV reducer bracket, a mounting flange disc, a temperature sensor, a second torque sensor, a second high-precision angle encoder, a diaphragm coupling and a brake arranged above the base. The mounting flange disc can be replaced, and thus, test on reducers of multiple types can be realized. compared with other test instruments, the RV reducer comprehensive test bench of the invention has the advantages that the test efficiency and the test precision are greatly enhanced; the performance is reliable; the test repetition is good; the operation for replacing a tested object is simple; the mounting and positioning precision is high; and the cost is low.

Owner:NANJING INST OF TECH

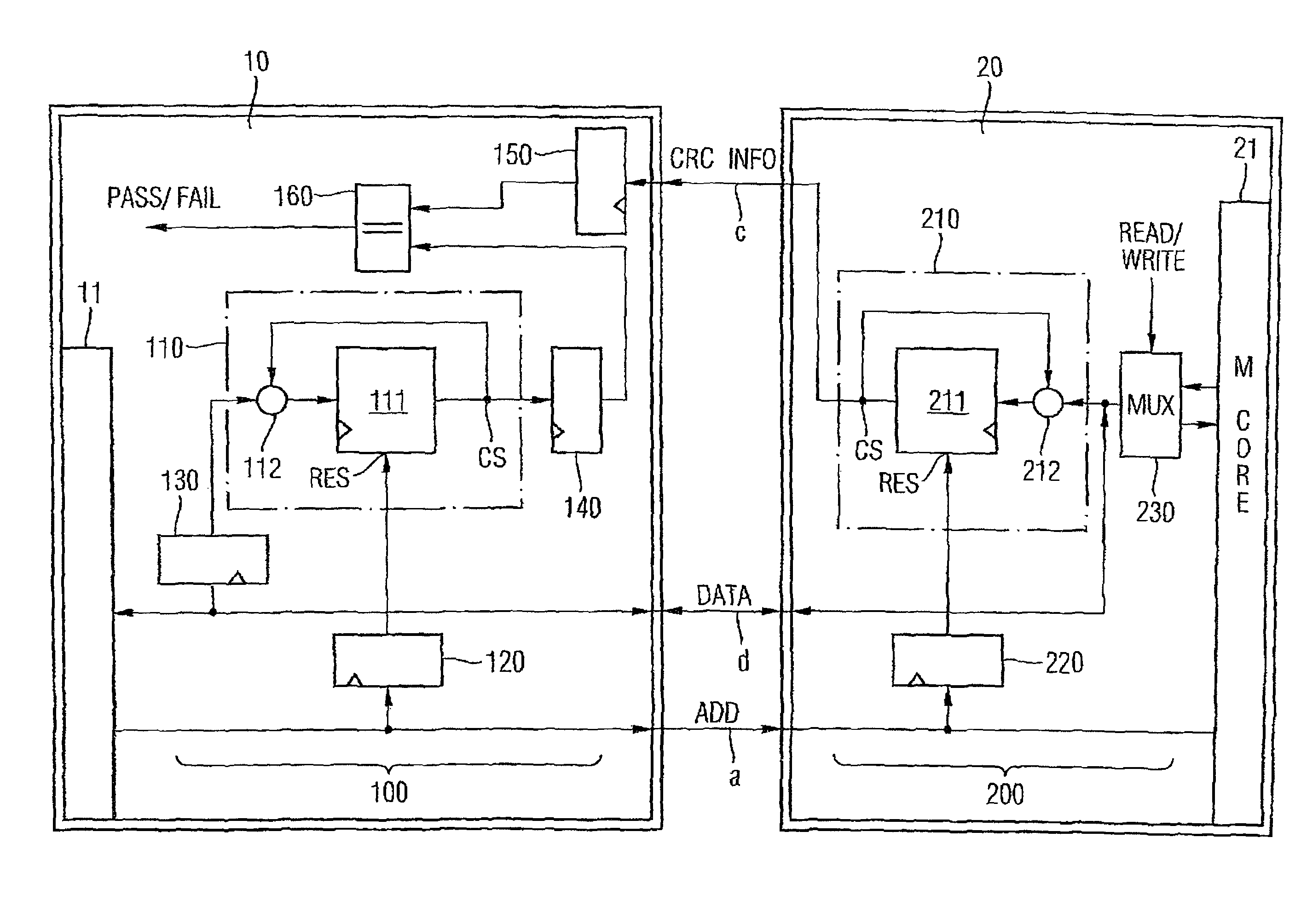

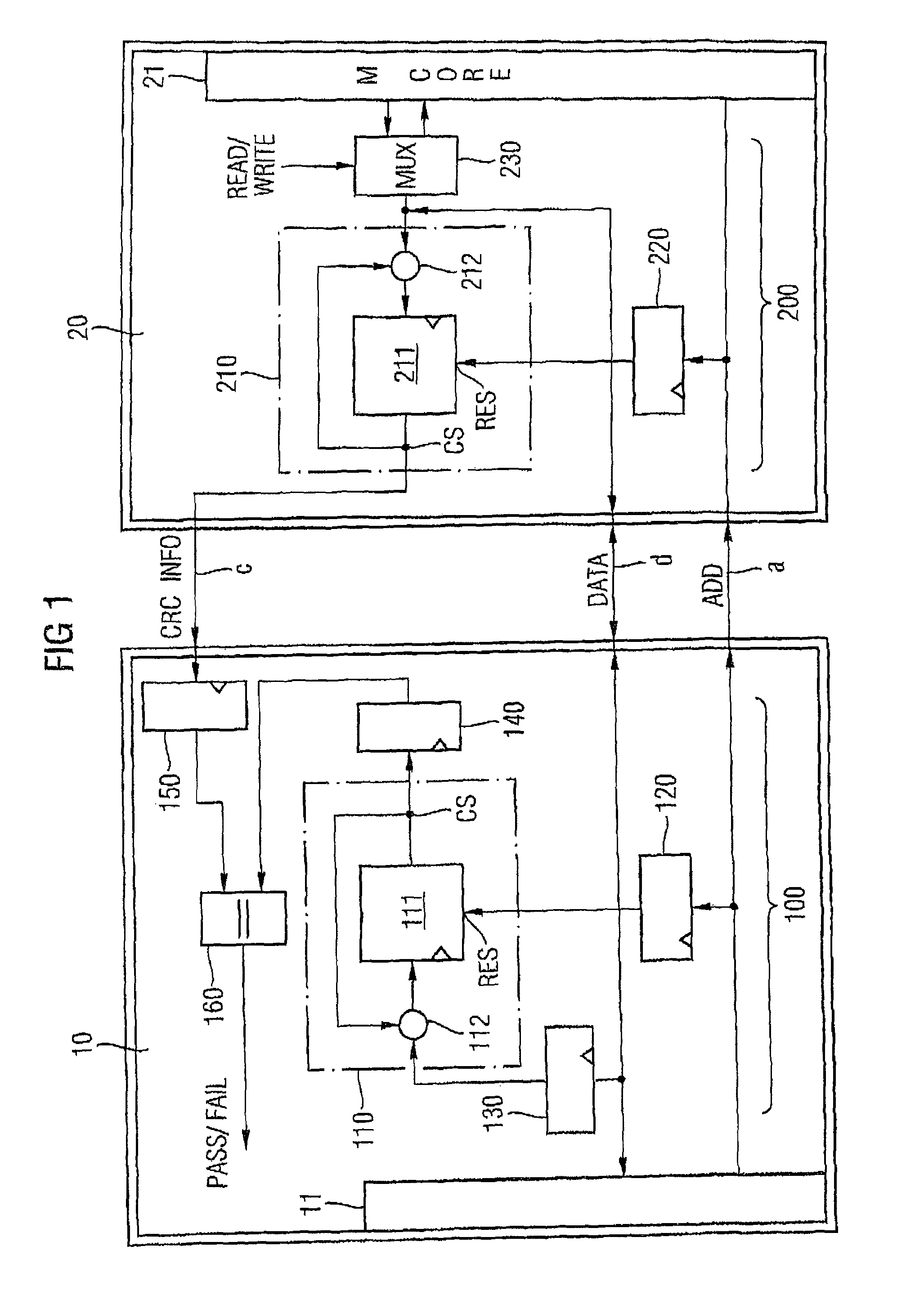

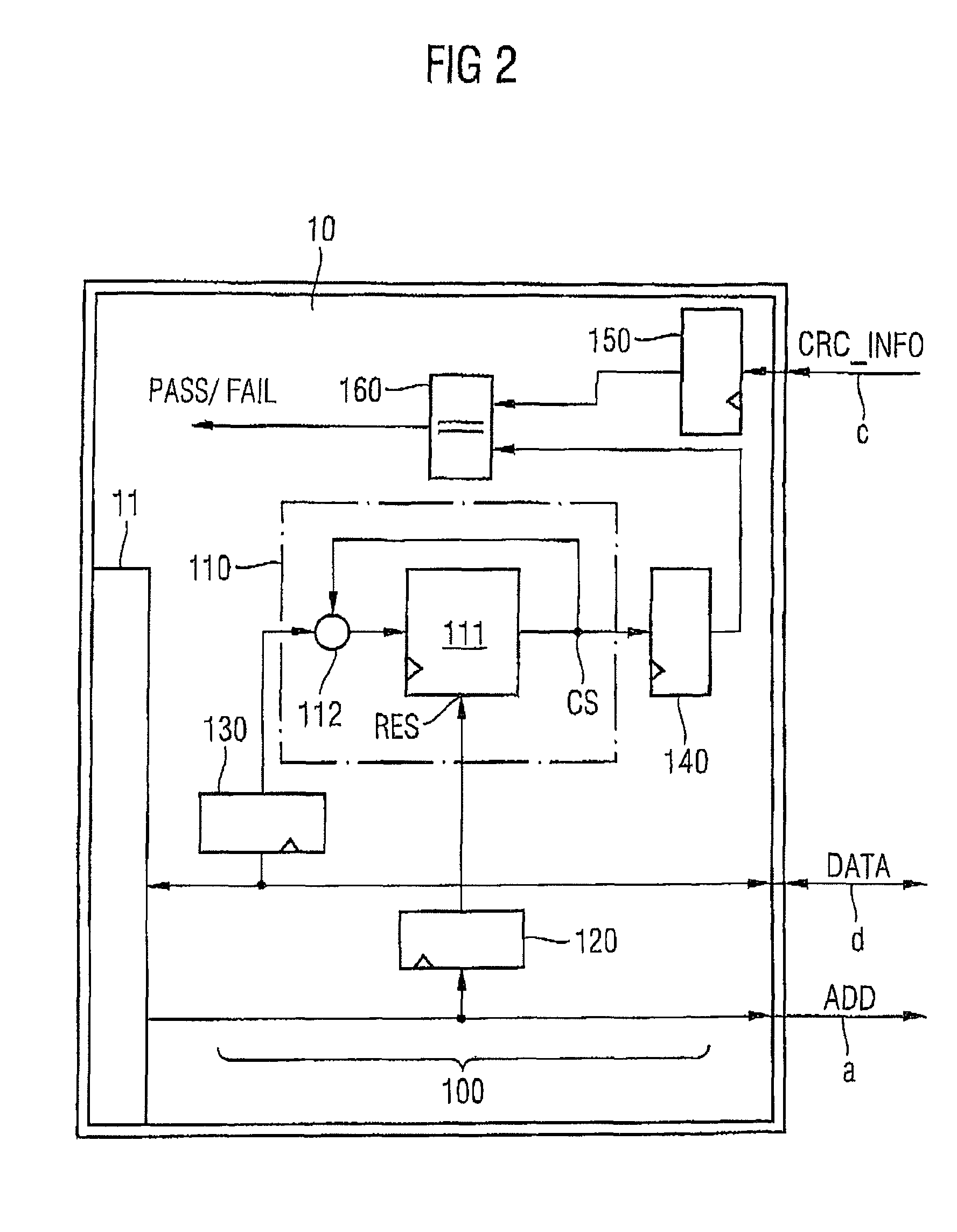

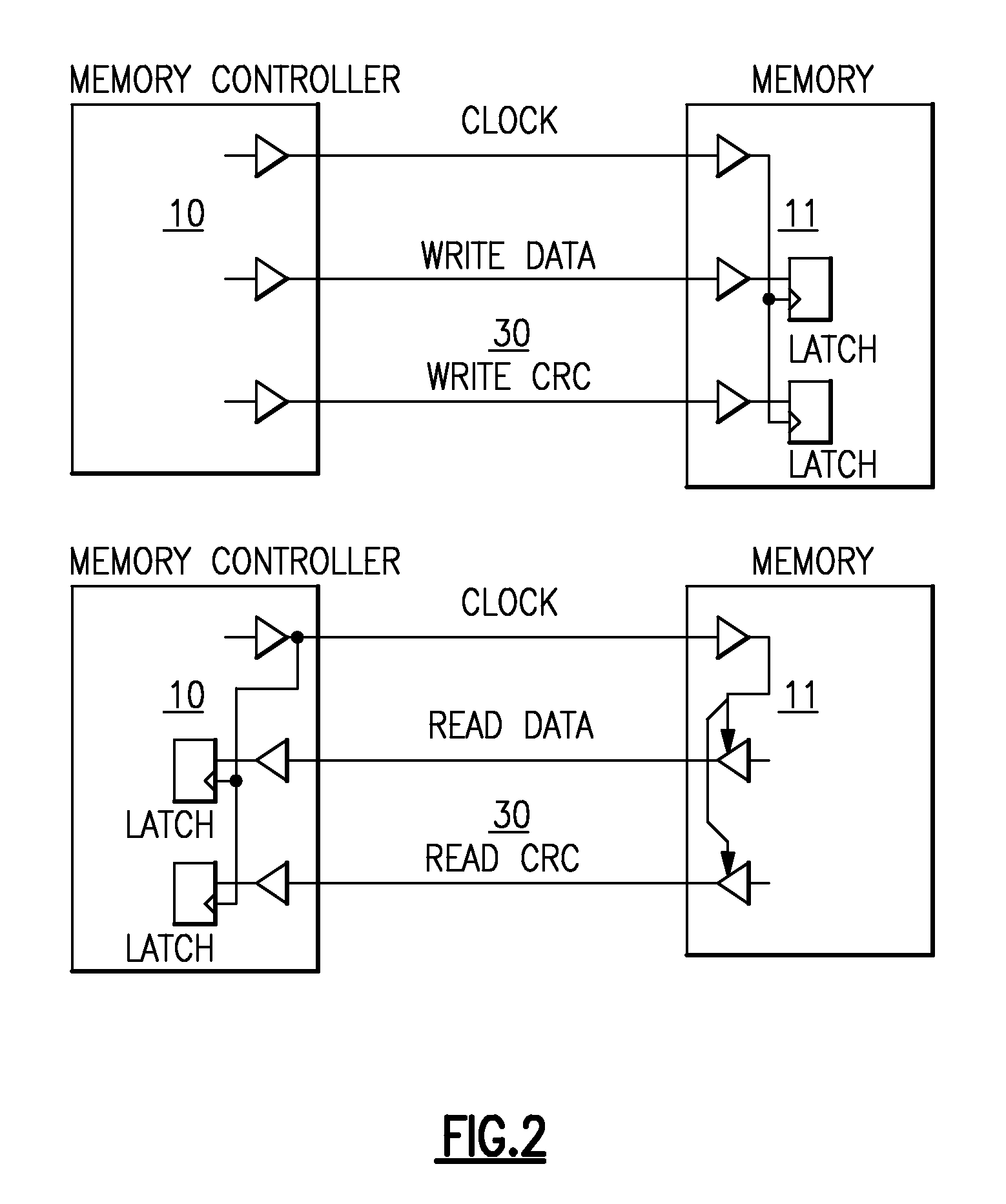

Memory system with cyclic redundancy check

A memory system, with a memory controller and a memory module, is configured to transfer error securing data and address signals within signal frames between the memory controller and the memory module. The memory system includes: an address register configured to pre-store an address signal associated with at least one block of data signals to be transferred, and at least one cyclic redundancy checksum calculator included in one of the memory controller and the memory module, the calculators being configured to calculate a cyclic redundancy checksum for the at least one data signal block, wherein the pre-stored address signal is used as an initial value for the calculation of the cyclic redundancy checksum and the at least one block of data and address signals are transferred together with the calculated cyclic redundancy checksum.

Owner:POLARIS INNOVATIONS LTD

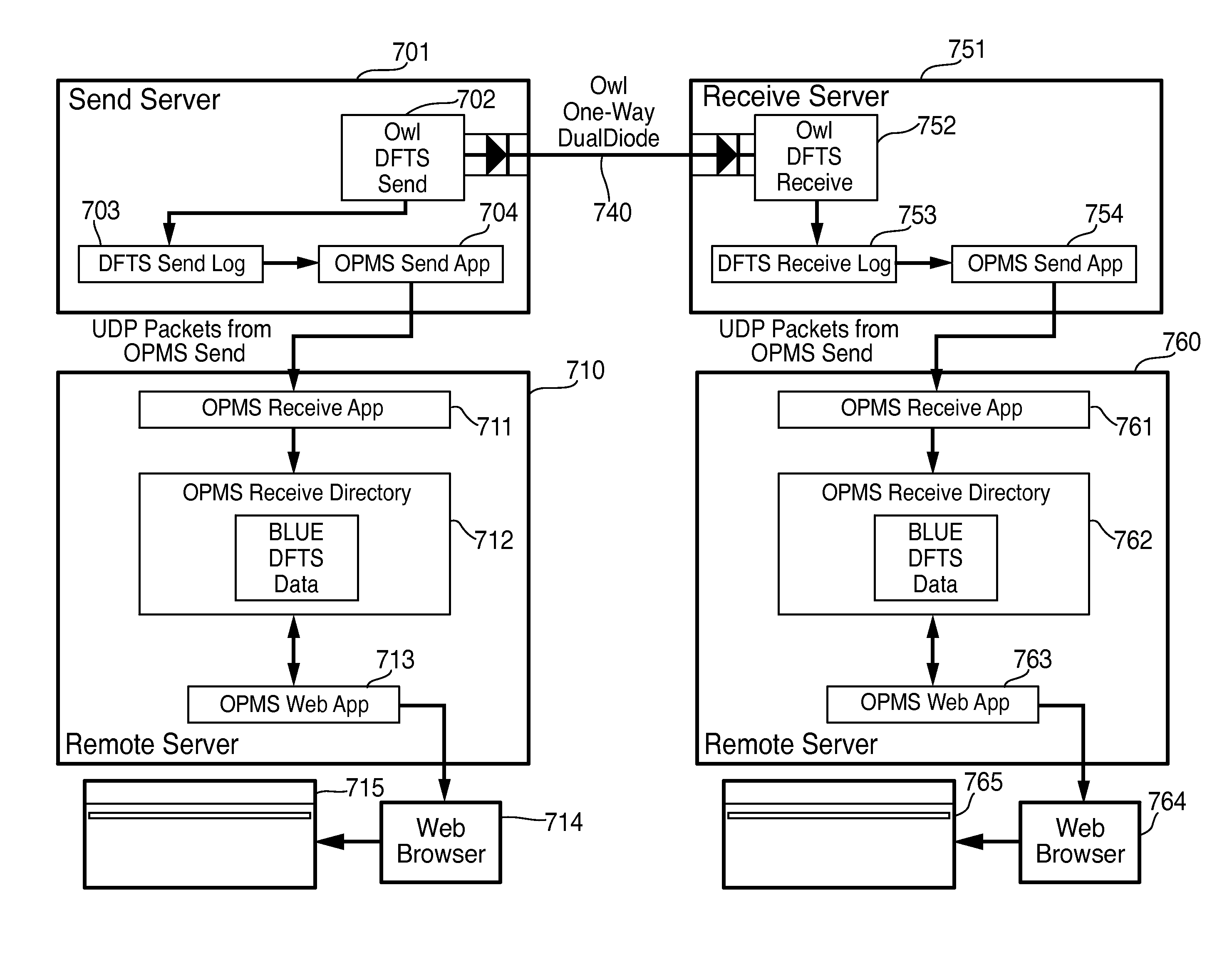

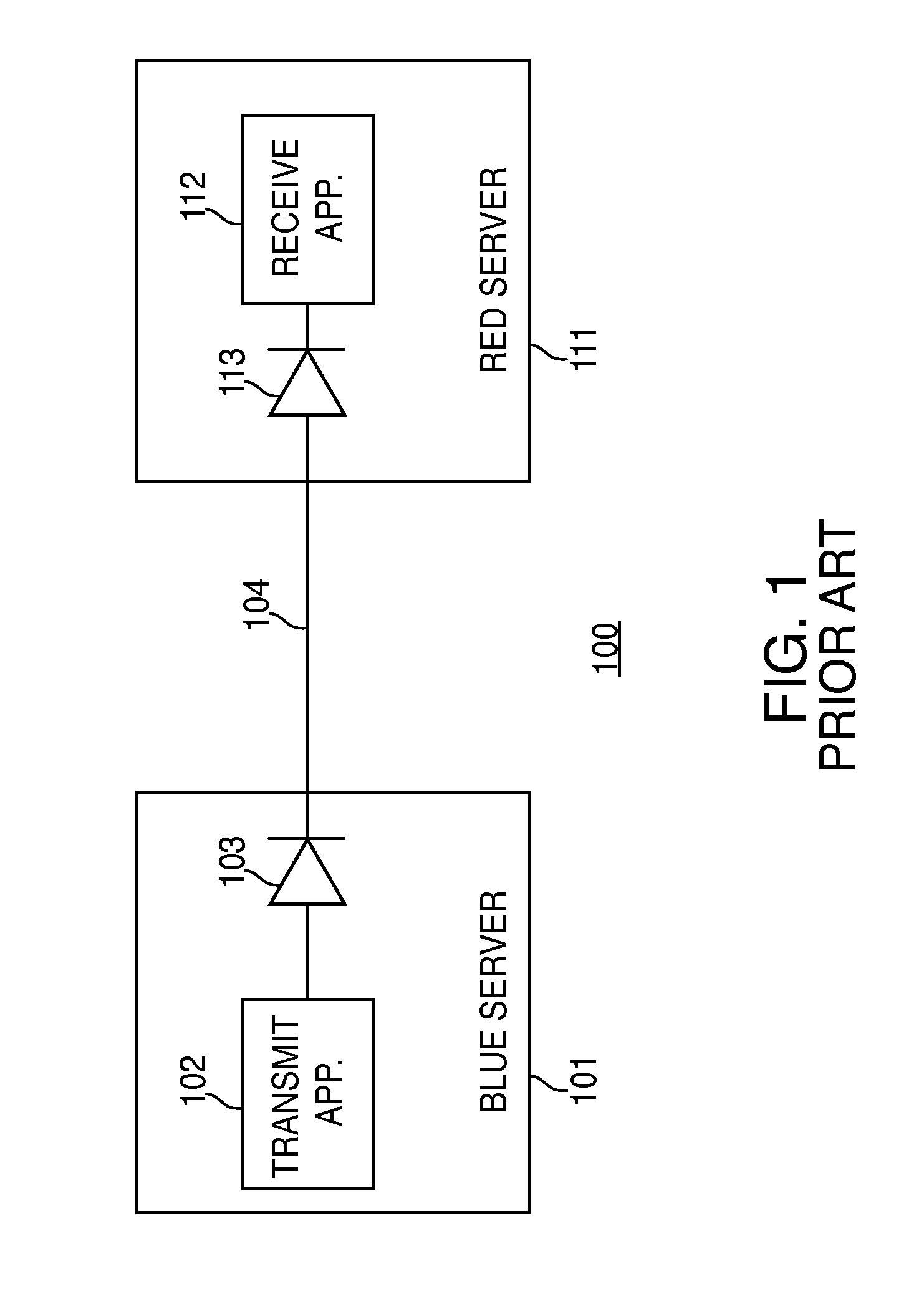

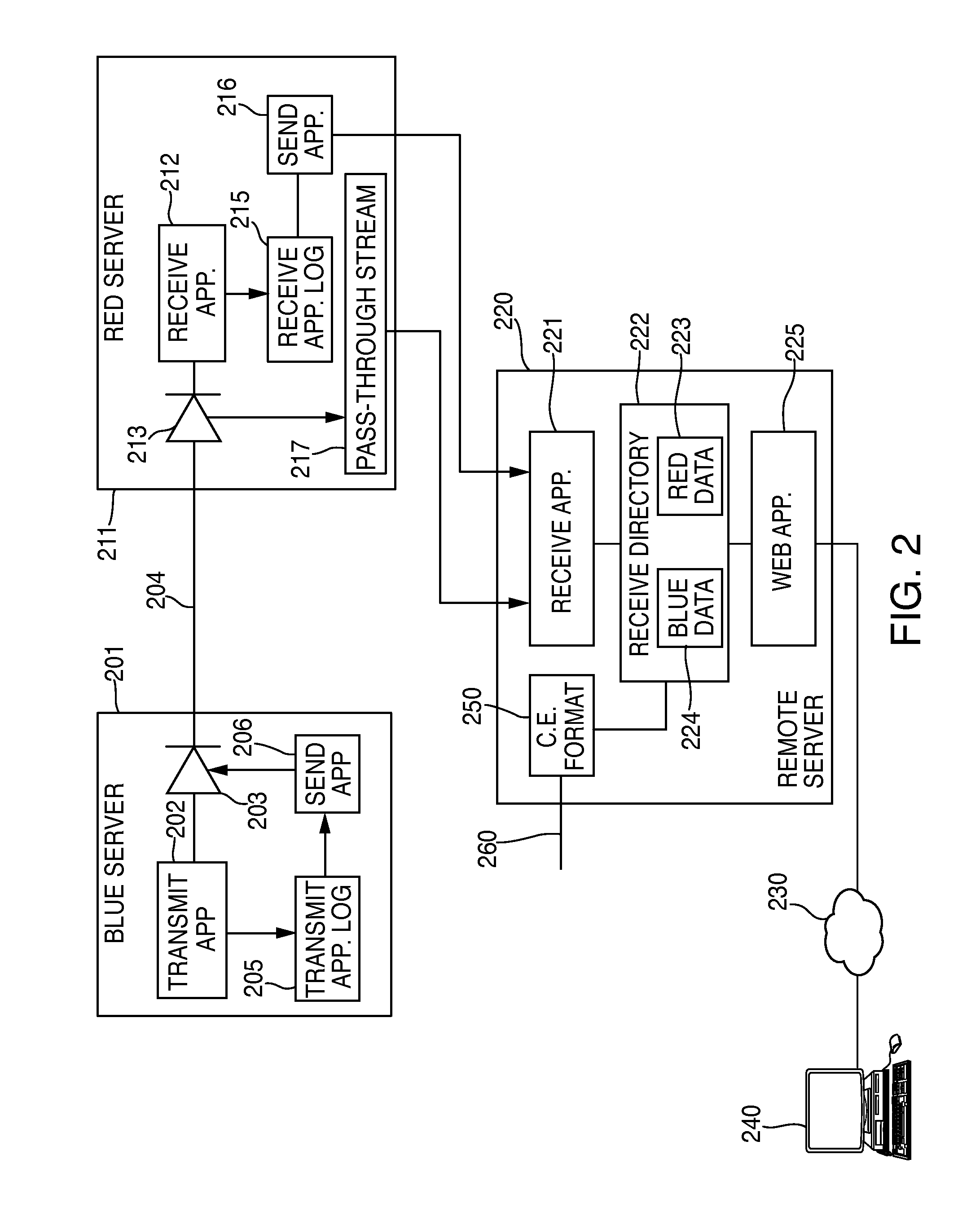

Method and apparatus for data transfer reconciliation

A method and system for monitoring data transfers over a one-way data link from a send node to a receive node. A send log file monitoring and transmitting module associated with the send node on a first server outputs a send log file containing information about data sent by the send node. A receive log file monitoring and transmitting module associated with the receive node on a second server outputs a receive log file containing information about data received by the receive node. A reconciliation module on a third server receives the send log file and the receive log file and identifies any data transfer errors by comparing the send log file with the receive log file. A web server is coupled to the reconciliation module to provide user access to the identified data transfer errors.

Owner:OWL CYBER DEFENSE SOLUTIONS LLC

Data transfer error checking

InactiveUS20070288828A1Increase probabilityAttenuation bandwidthCode conversionError detection onlyConnection typeData placement

An RNIC implementation that performs direct data placement to memory where all segments of a particular connection are aligned, or moves data through reassembly buffers where all segments of a particular connection are non-aligned. The type of connection that cuts-through without accessing the reassembly buffers is referred to as a “Fast” connection because it is highly likely to be aligned, while the other type is referred to as a “Slow” connection. When a consumer establishes a connection, it specifies a connection type. The connection type can change from Fast to Slow and back. The invention reduces memory bandwidth, latency, error recovery using TCP retransmit and provides for a “graceful recovery” from an empty receive queue. The implementation also may conduct CRC validation for a majority of inbound DDP segments in the Fast connection before sending a TCP acknowledgement (Ack) confirming segment reception.

Owner:IBM CORP

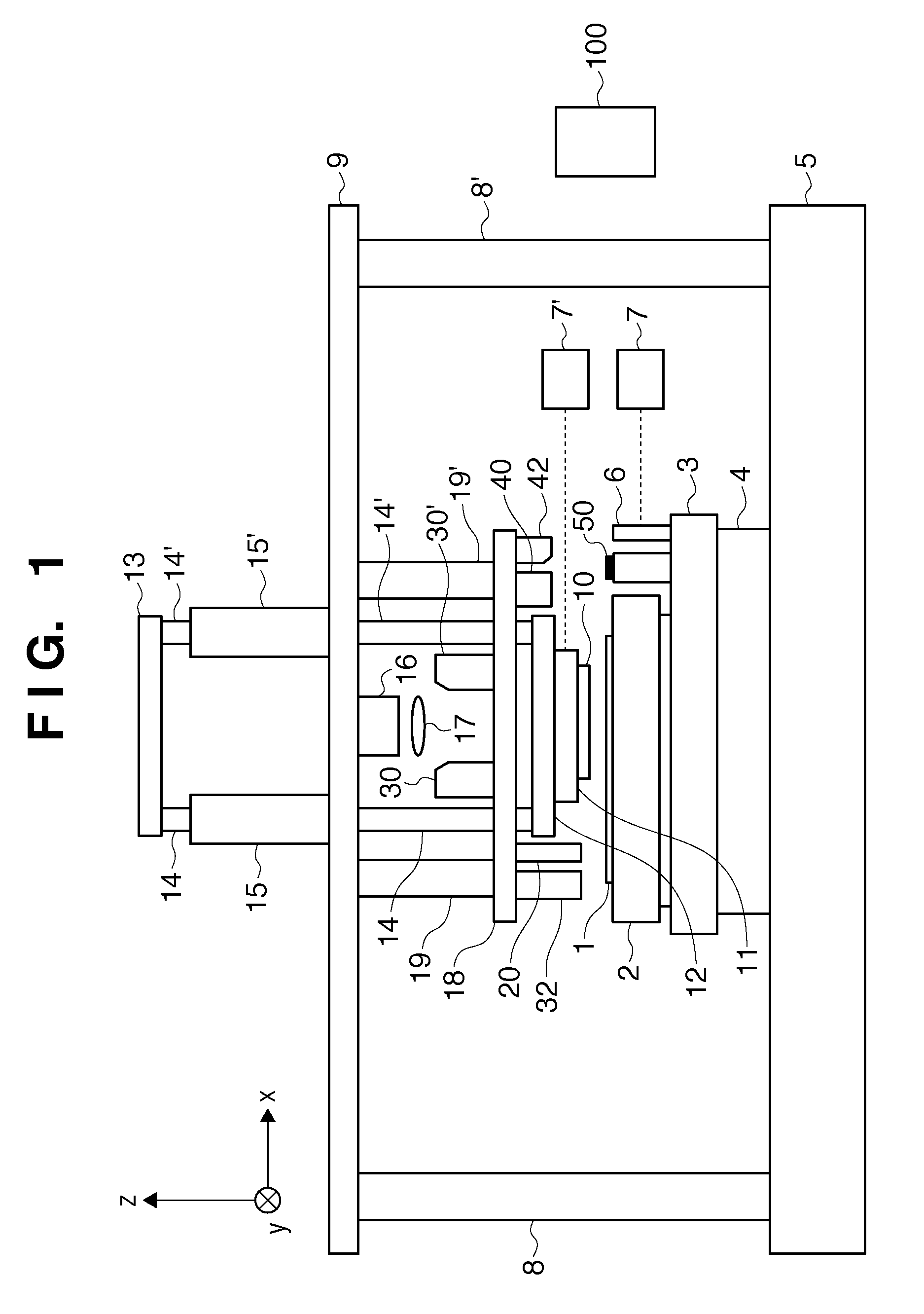

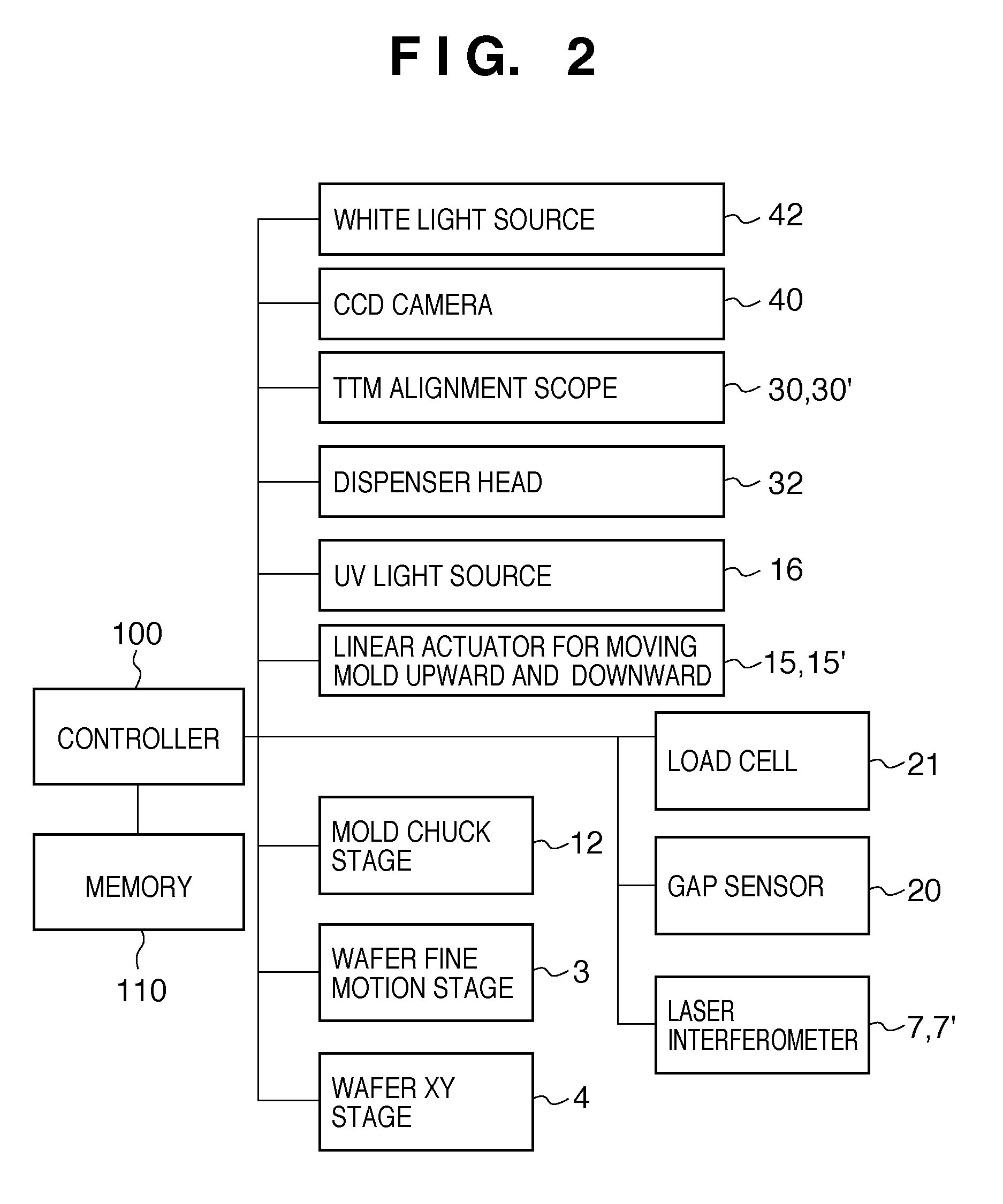

Imprint apparatus and method of manufacturing article

An imprint apparatus, which performs an imprint process for forming a pattern of a mold on a resin coated on a substrate, includes an imaging unit configured to image the resin on which the pattern is formed, and a controller configured to control the imprint process. When the pattern is continuously formed on the substrate, the controller compares an image of at least a partial area imaged by the imaging unit and an image of a reference state, which is obtained in advance, and when patterns each having a difference, which falls outside an allowable range, between the images are continuously formed, it determines a transfer error.

Owner:CANON KK

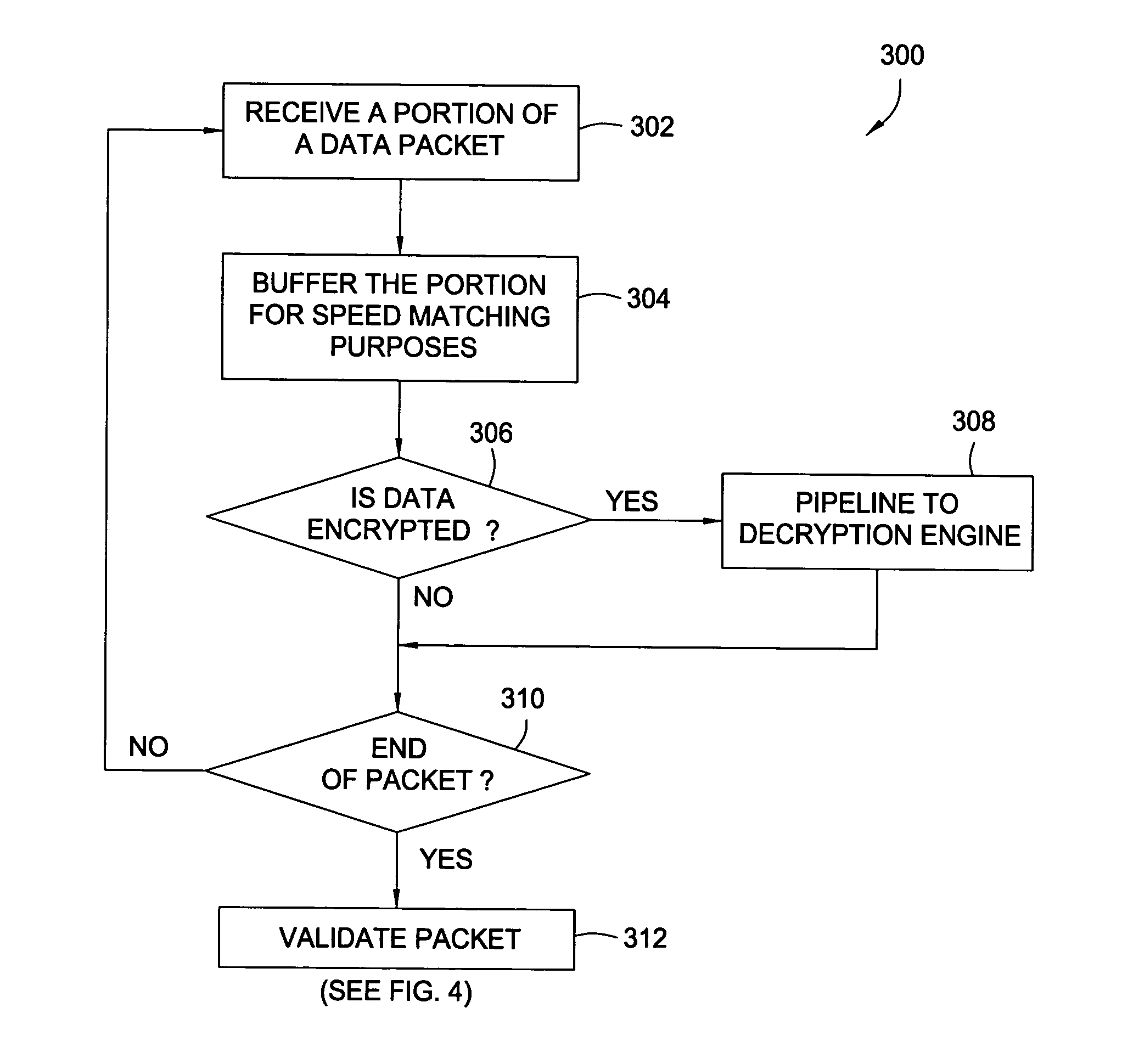

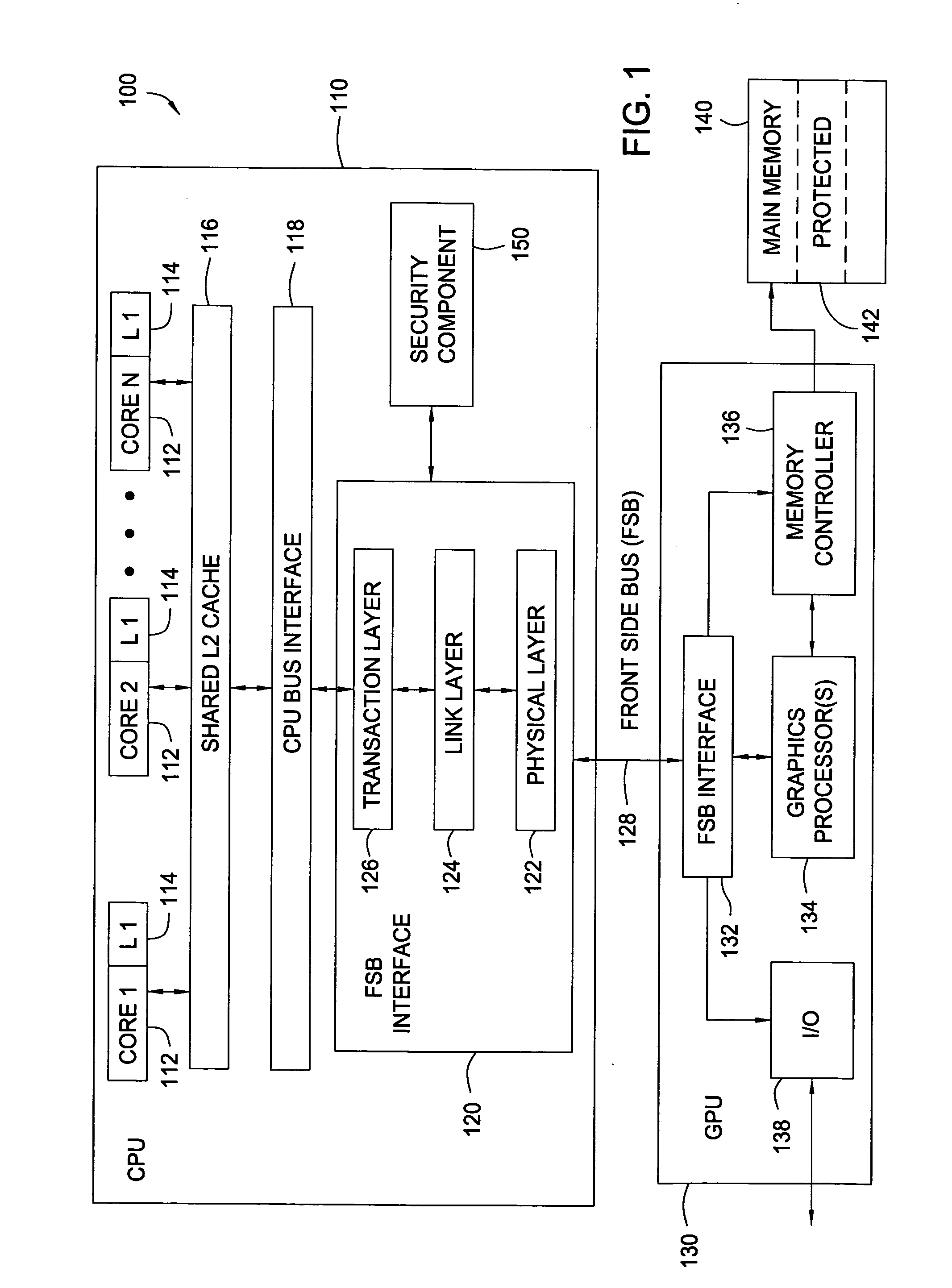

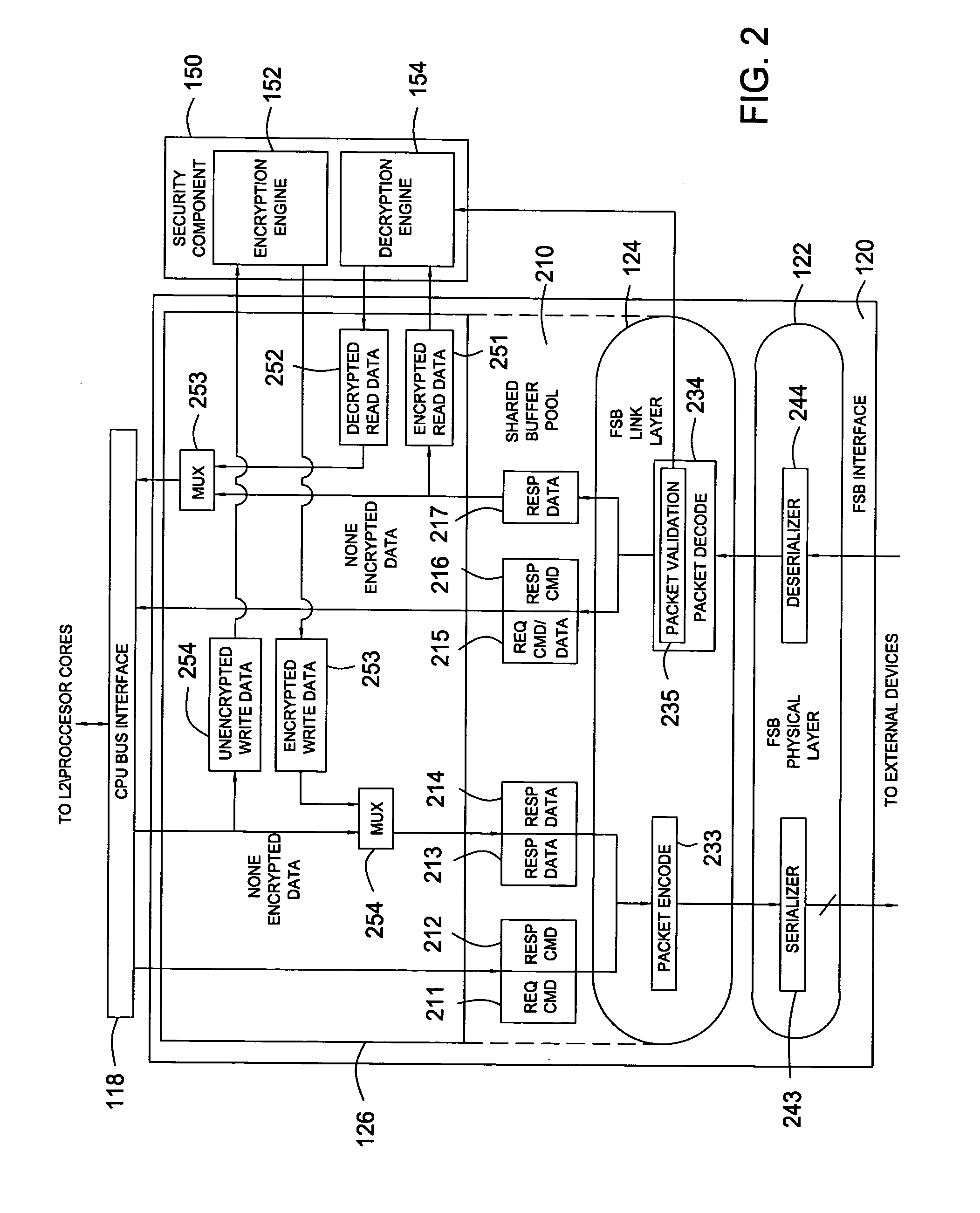

Low-latency data decryption interface

ActiveUS20060047953A1Reduce the amount requiredLower latencyEncryption apparatus with shift registers/memoriesUser identity/authority verificationComputer hardwareLatency (engineering)

Methods and apparatus for reducing the impact of latency associated with decrypting encrypted data are provided. Rather than wait until an entire packet of encrypted data is validated (e.g., by checking for data transfer errors), the encrypted data may be pipelined to a decryption engine as it is received, thus allowing decryption to begin prior to validation. In some cases, the decryption engine may be notified of data transfer errors detected during the validation process, in order to prevent reporting false security violations.

Owner:IBM CORP

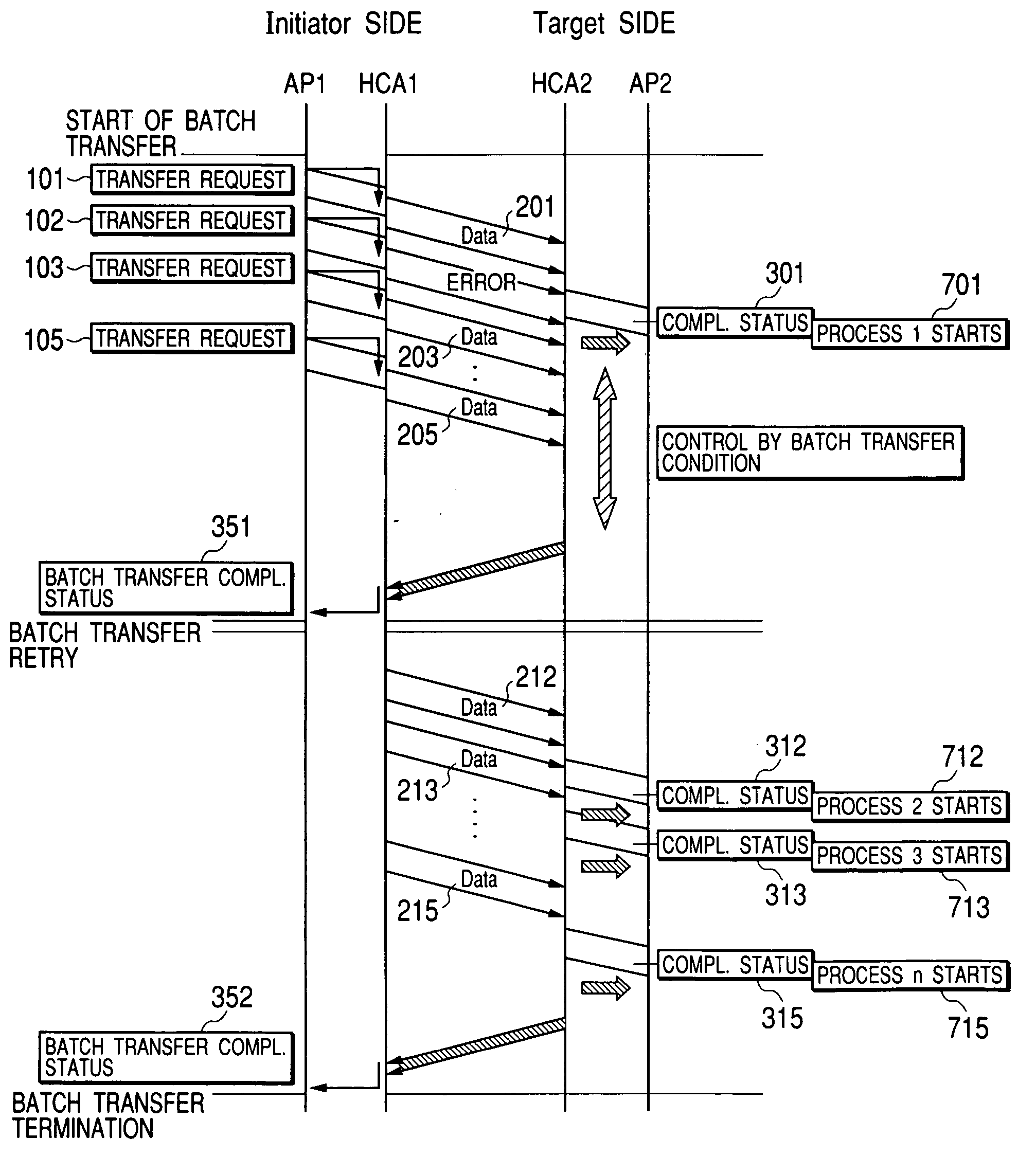

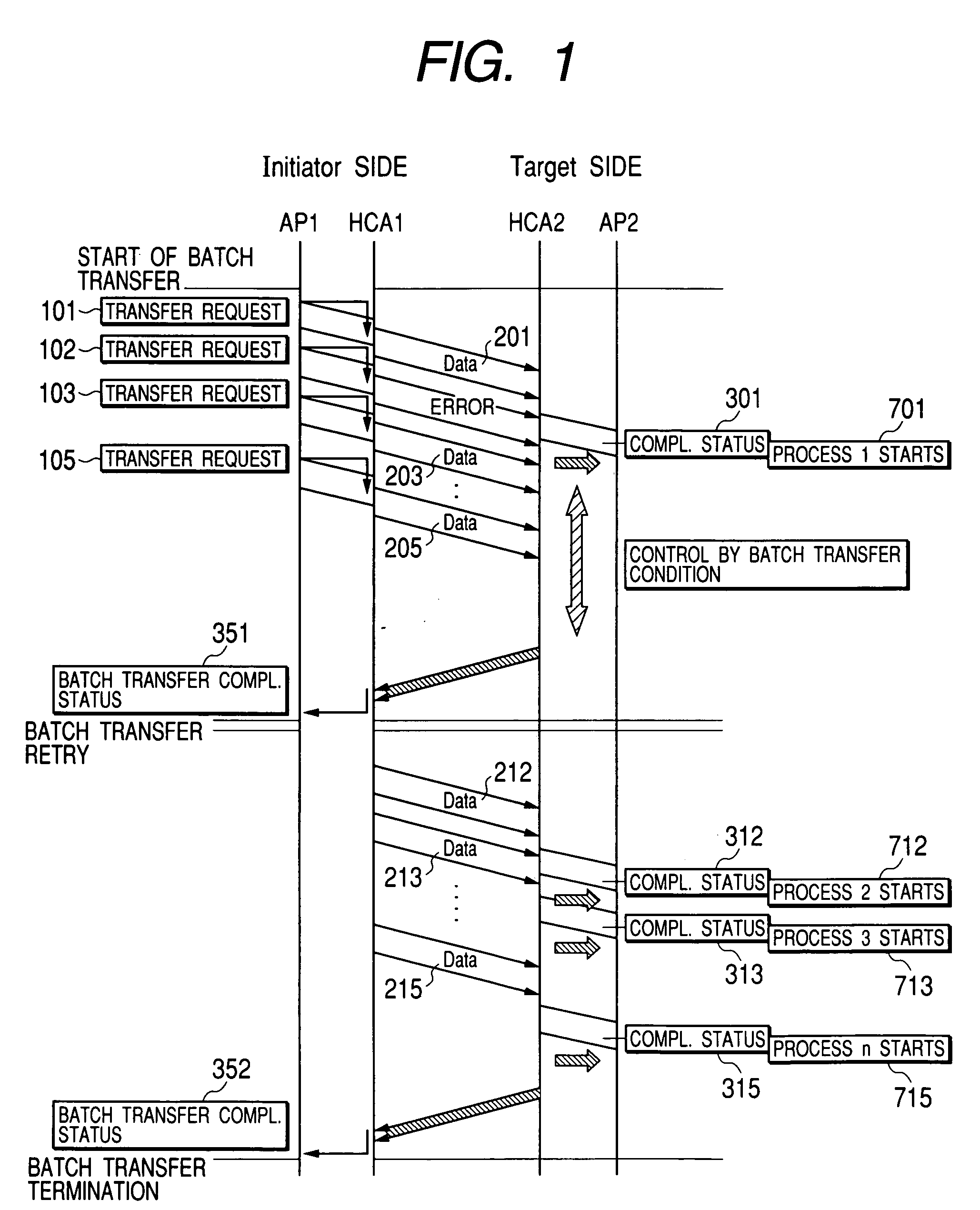

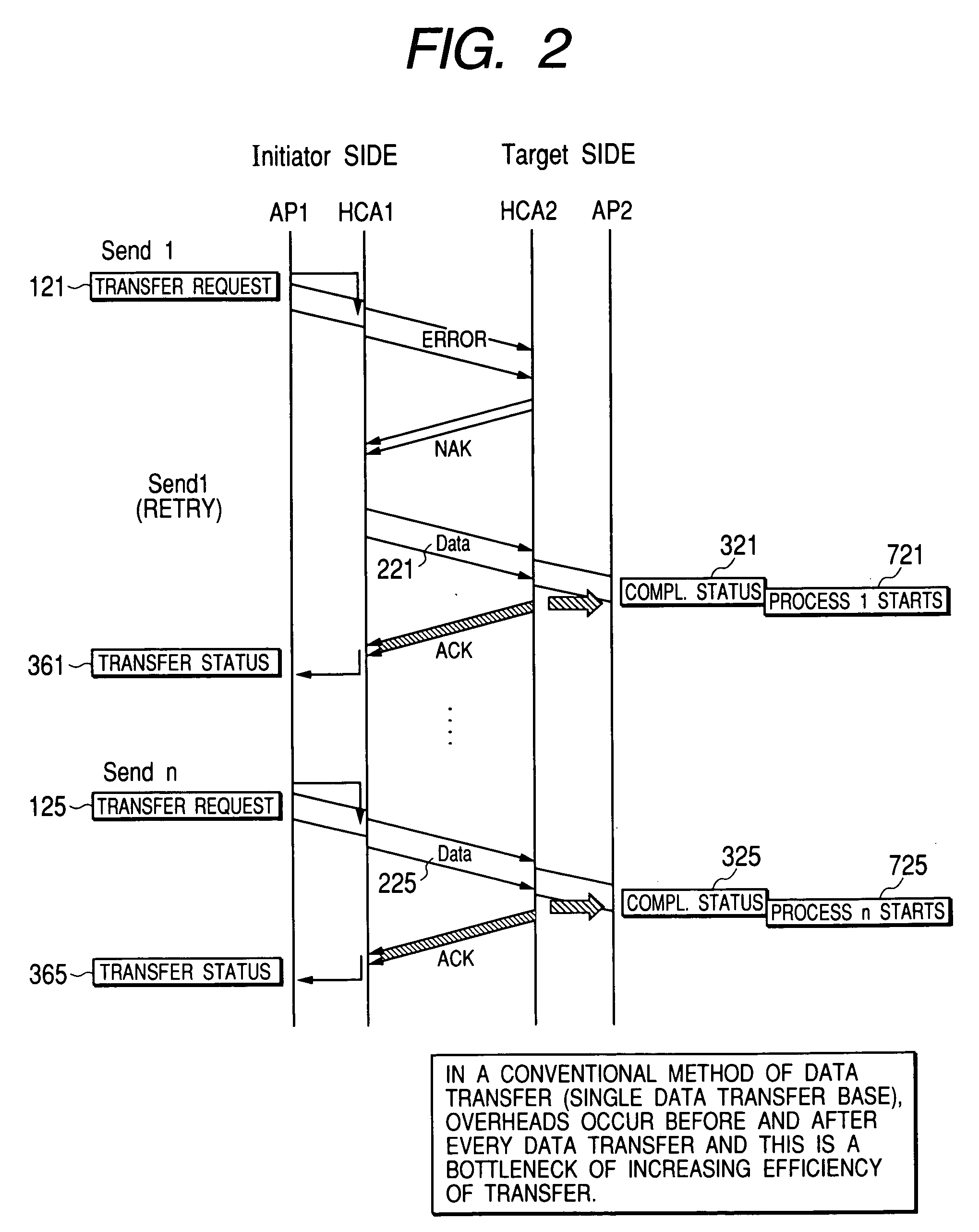

Data transfer method and disk control unit using it

ActiveUS20050080946A1Improve transmission efficiencyAccelerate the application processInput/output to record carriersError checkCompletion Status

The present invention provides a reliable and high-speed data transfer method that achieves a high transfer efficiency and a high application processing efficiency concurrently and a disk control unit (disk controller) using such a method. In reliable data transfer in which, when data is transferred from an initiator to a target, the data received by the target is checked for validity by using an error check code attached to the data, a transfer status indicating whether the data is valid is returned from the target to the initiator, and, if a transfer error occurring during the data transfer is detected by the transfer status, the initiator retries to transfer the data to the target, a data transfer method for logical records that are units of data transfer between the initiator and the target is disclosed. This method is characterized in that: when each logical record transferred by a transfer request issued by the initiator arrives correctly on the target, the target posts a completion status corresponding to the transfer request for the logical record to a completion queue existing in the target; a plurality of logical records in a block are batch transferred; the initiator confirms the transfer status at every batch transfer; and, for each logical record that meets a predetermined batch transfer condition, the target posts a completion status corresponding to the transfer request for the logical record to the completion queue existing in the target upon correct reception of the logical record.

Owner:GOOGLE LLC

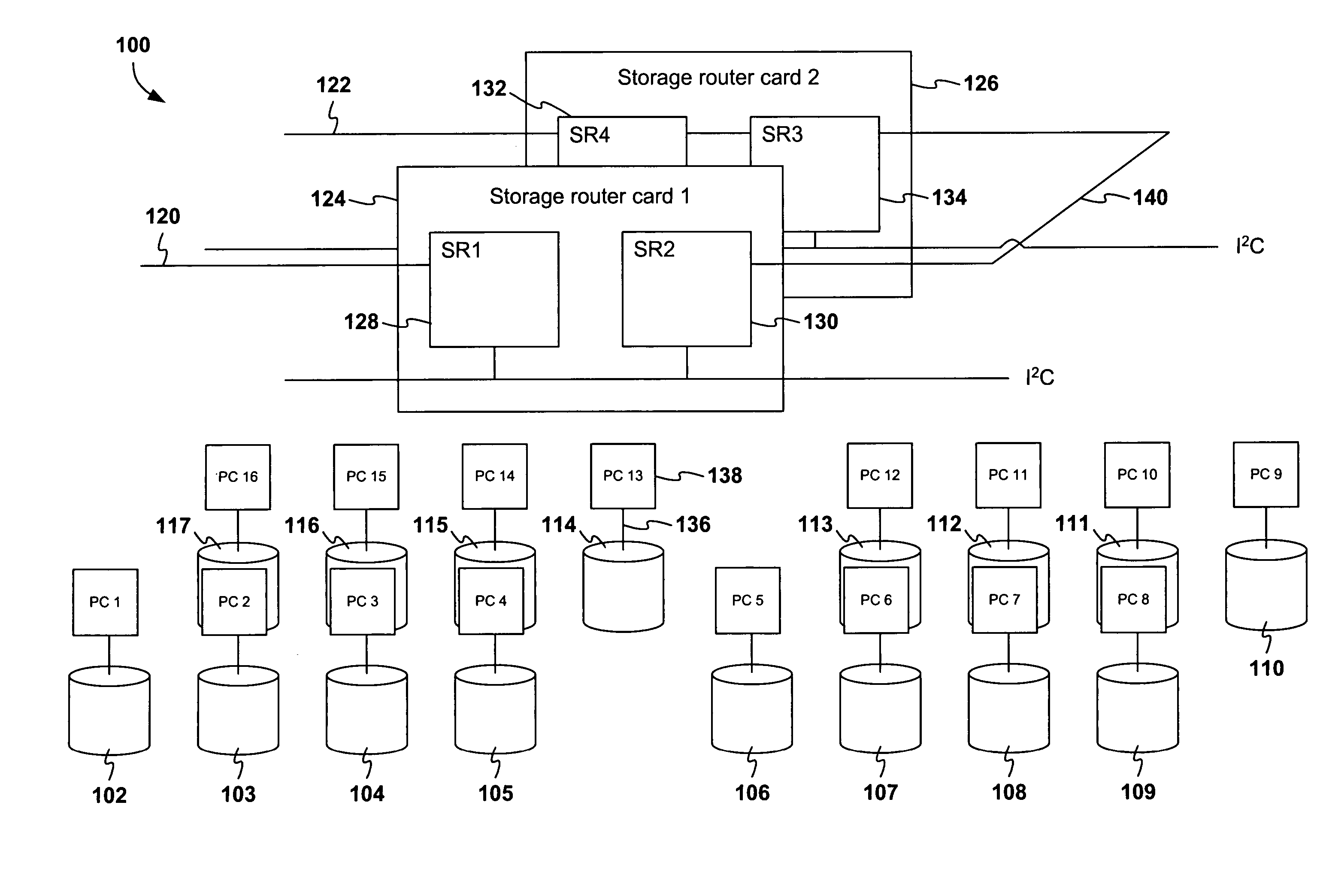

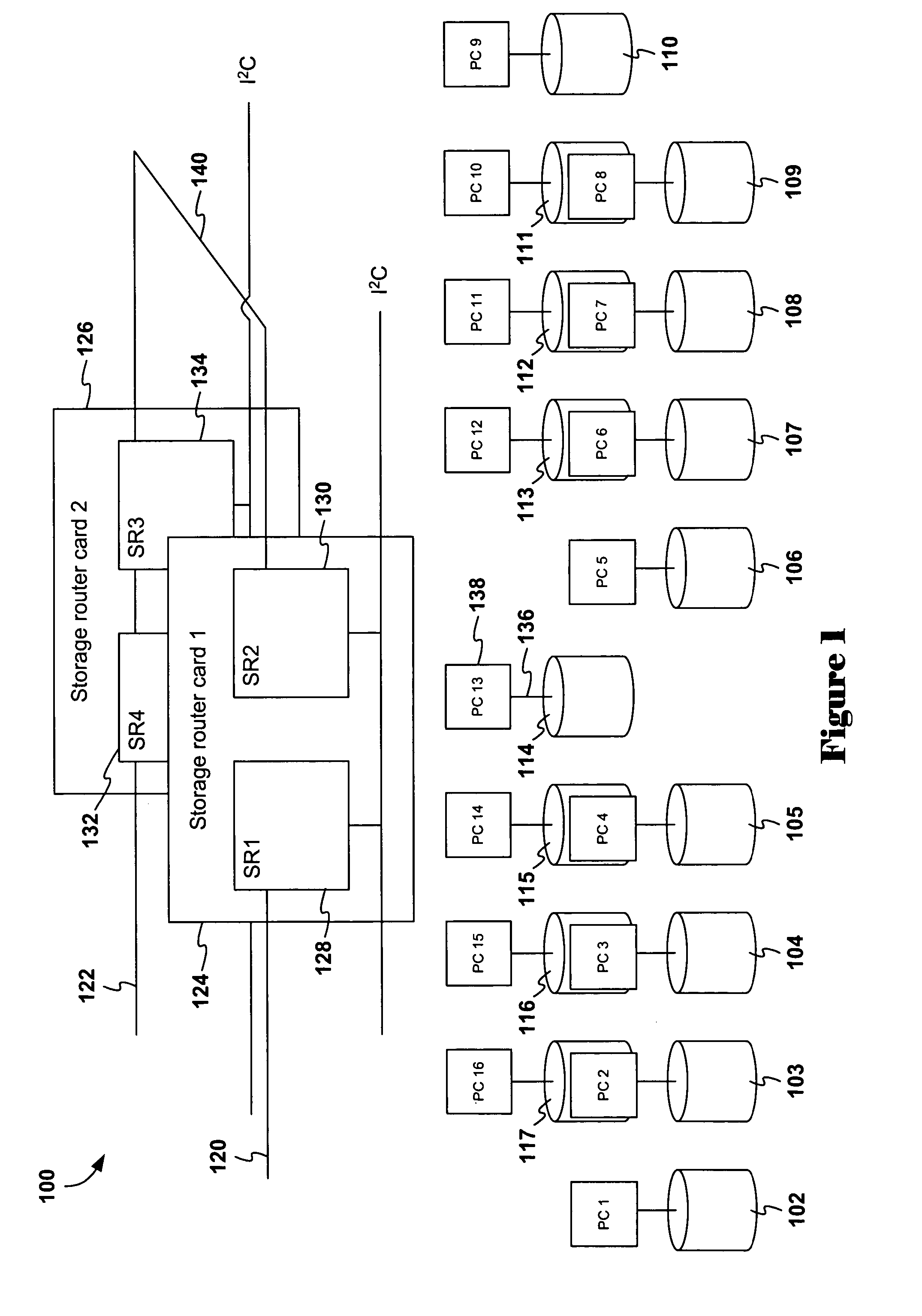

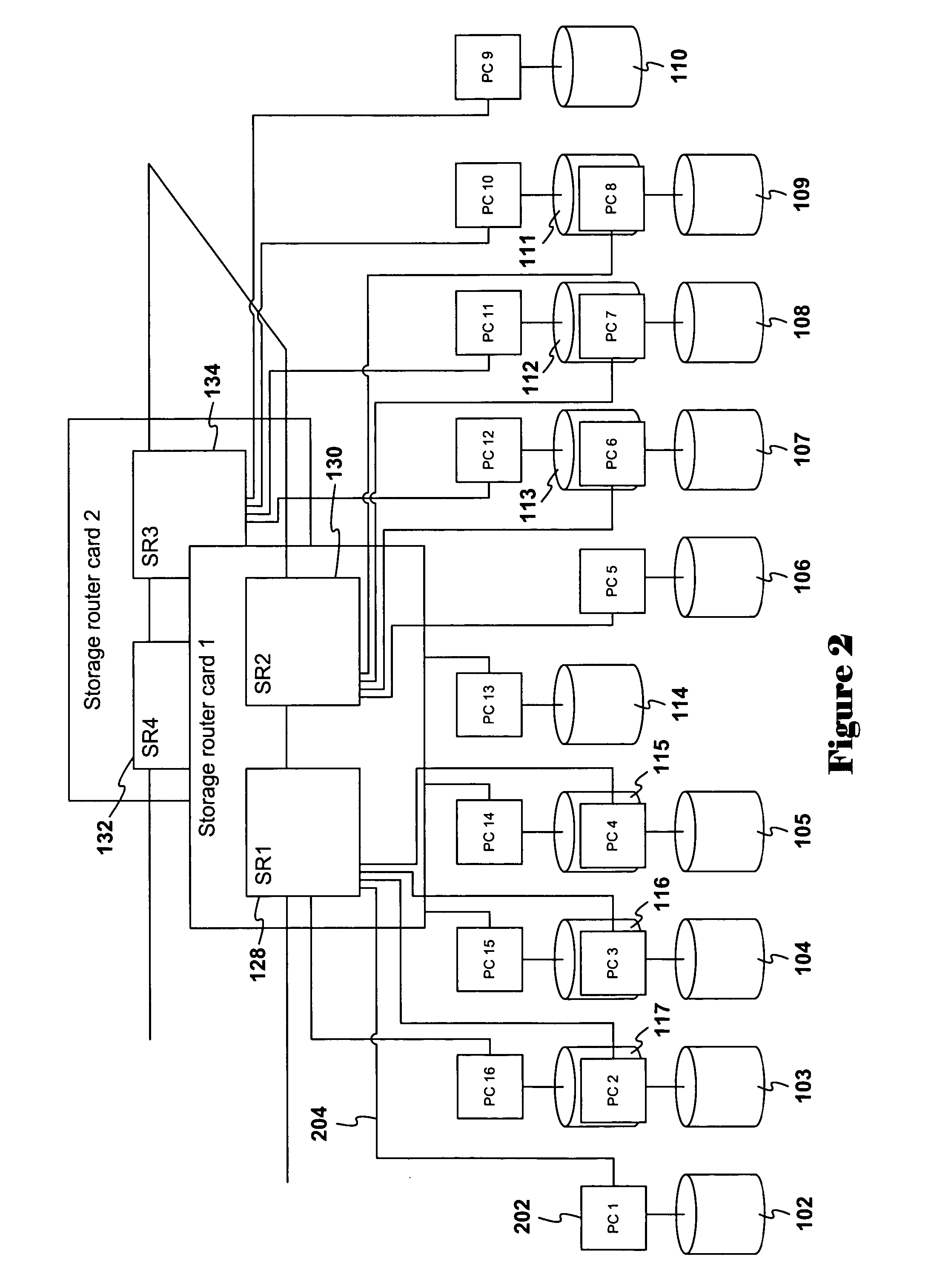

Management of error conditions in high-availability mass-storage-device shelves by storage-shelf routers

ActiveUS20050022064A1Ameliorate error conditionError preventionFrequency-division multiplex detailsHigh availabilityTransfer error

Embodiments of the present invention include a storage-shelf-router-to-disk-drive interconnection method within a high-availability storage shelf amenable to dynamic reorganization in order to ameliorate error conditions that arise within the high-availability storage shelf. In one embodiment, each path-controller card within the storage shelf is interconnected to two storage-shelf routers on separate storage-shelf-router cards via two serial management links and two serial data links. Different types of errors that may arise within the storage shelf are carefully classified with respect to a number of different error-handling techniques, including local path failovers, single path failovers, error reporting and logging, and other types of error handling techniques. In many implementations, particular error handling methods are conifigurably associated with particular errors, in order to adapt error behavior in a storage shelf to the needs and requirements of a system that includes the storage shelf. Additional embodiments of the present invention concern detection and diagnosis of errors, in addition to handling errors that arise within a storage shelf.

Owner:SIERRA LOGIC

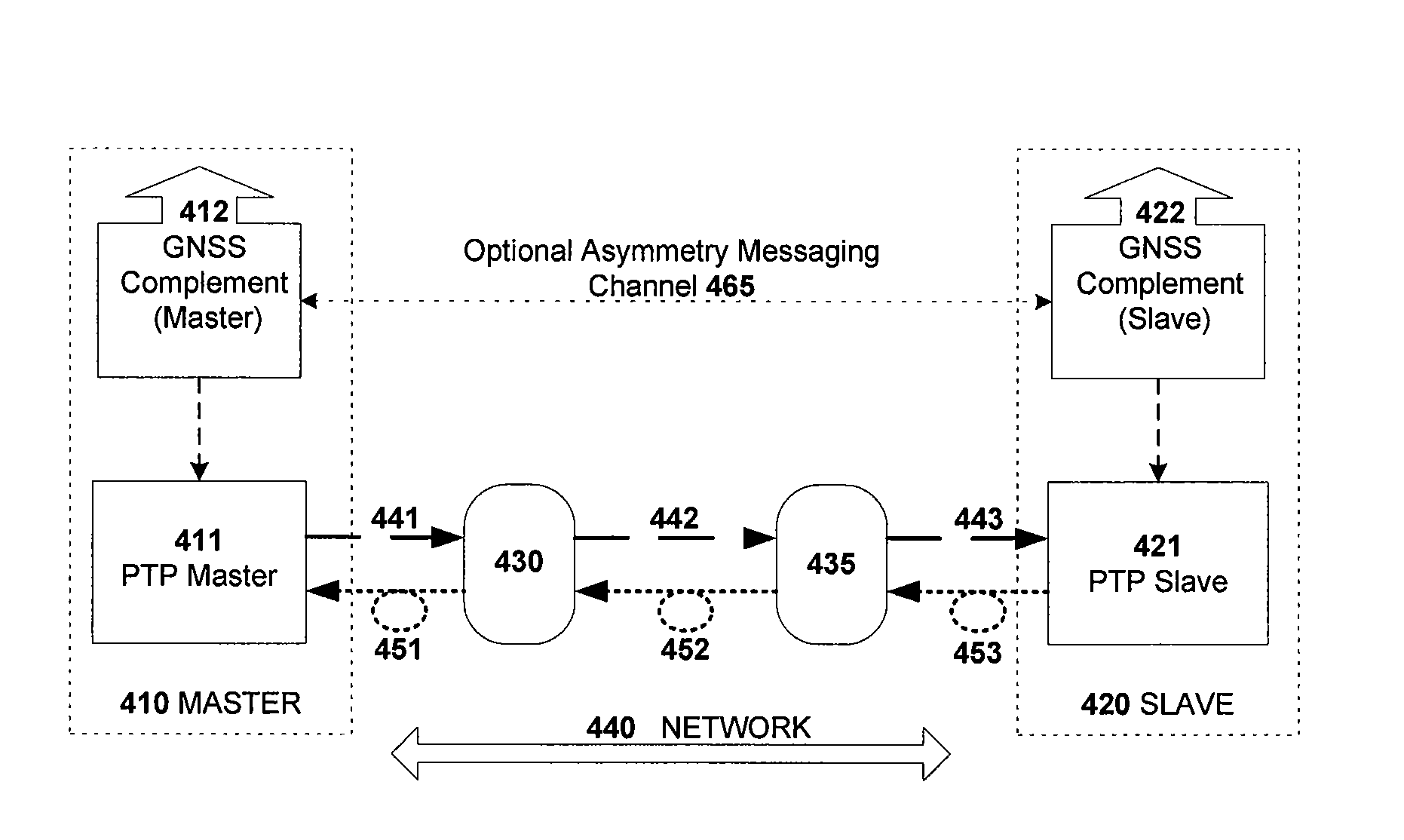

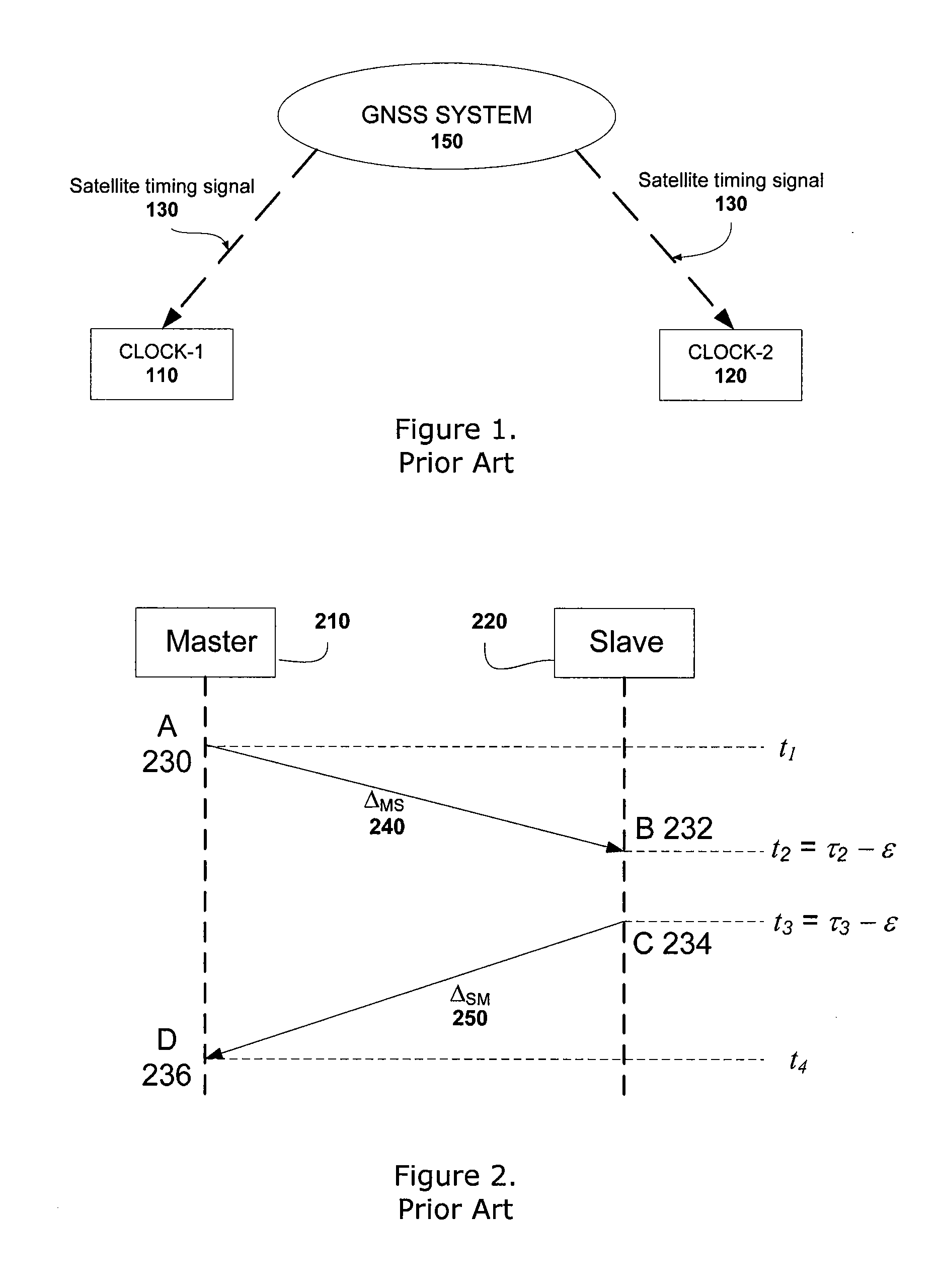

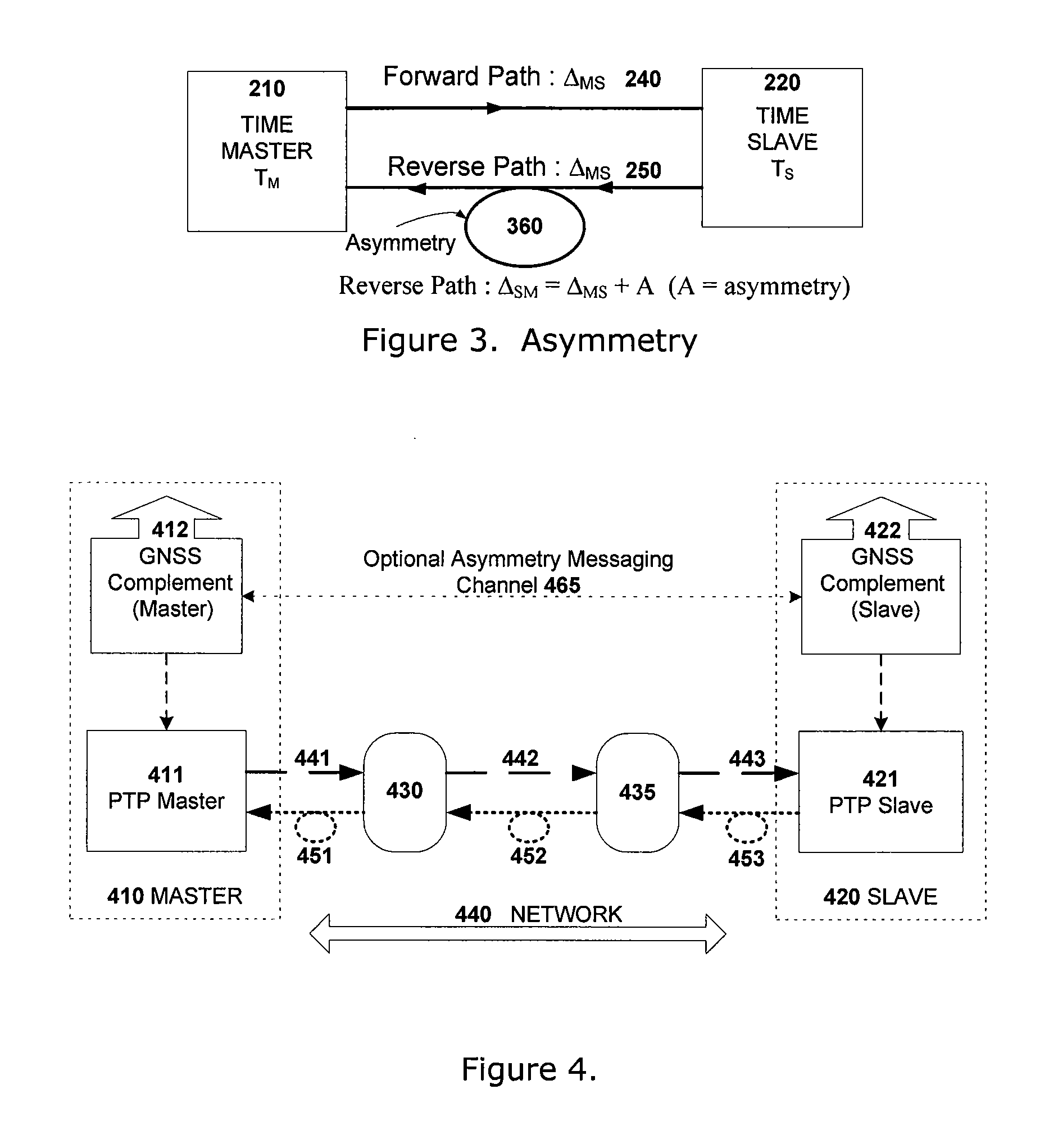

Universal asymmetry compensation for packet timing protocols

ActiveUS20140192826A1Time accuracy be improveImprove accuracy of synchronizationTime-division multiplexTransmission monitoring/testing/fault-measurement systemsNetwork elementTransmission medium

The notion of a “PTP aware” path is one current proposed approach to reduce asymmetry effects. In a fully PTP aware path there is the notion of on-path support mechanisms such as boundary clocks and transparent clocks at every switching or routing node. However, on-path support methods only address time-transfer errors introduced inside network elements and any asymmetry in the transmission medium, such as, for example, the fiber strands for the two directions of transmission, cannot be compensated for by on-path support mechanisms. Furthermore, in a real operational network, which may traverse different operational domains administered by different entities, full on-path support is a difficult challenge. In certain managed network scenarios full on-path support can be contemplated. Nevertheless, the universal asymmetry compensation method described herein mitigates the asymmetry in a network path, without requiring on-path support mechanisms such as transparent clocks and boundary clocks.

Owner:MICROSEMI +1

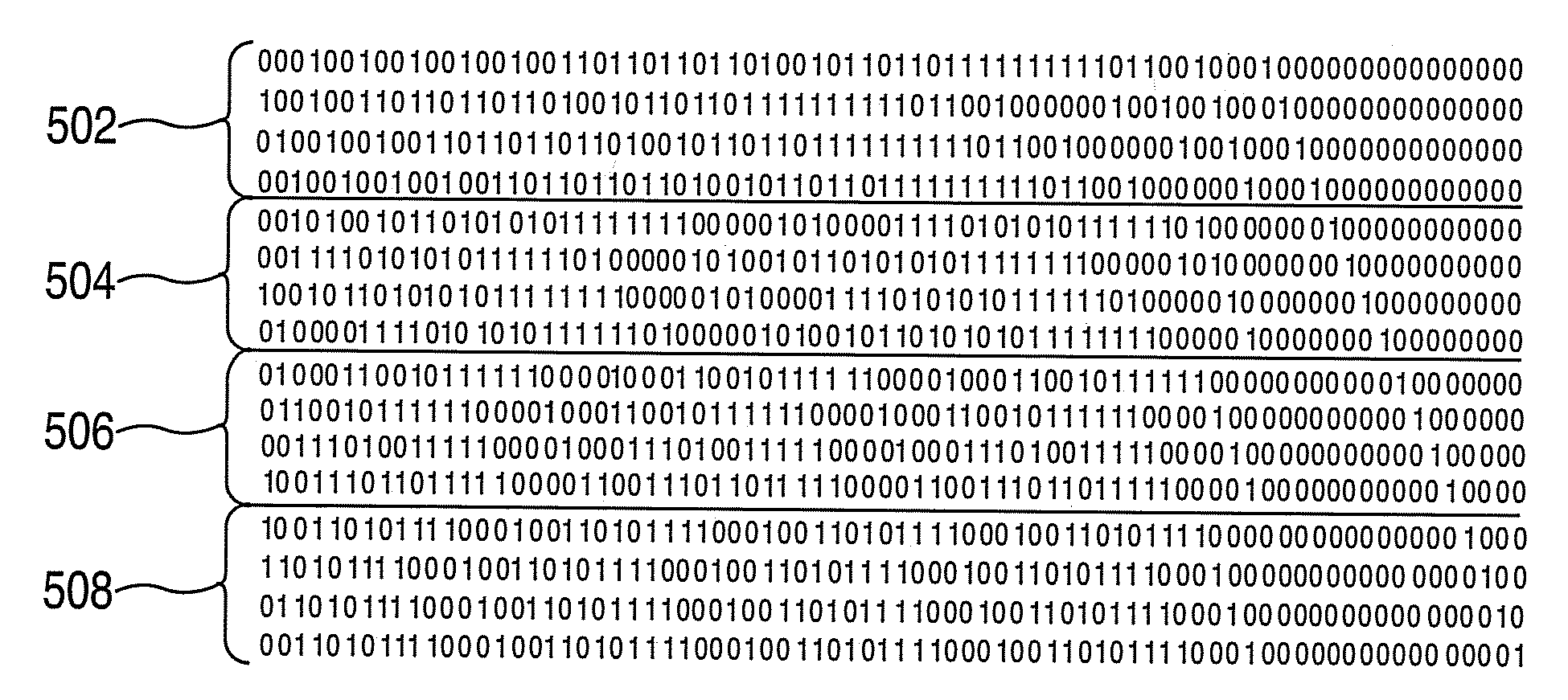

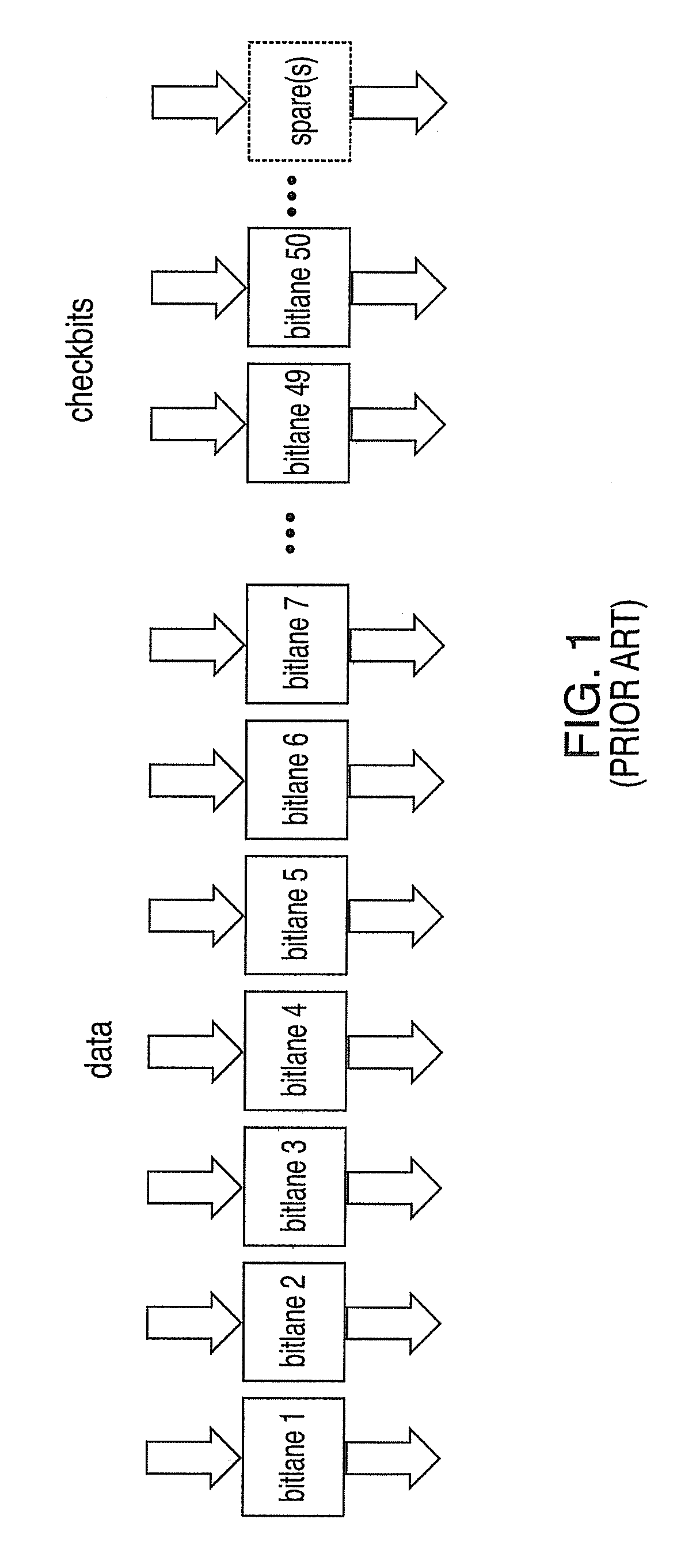

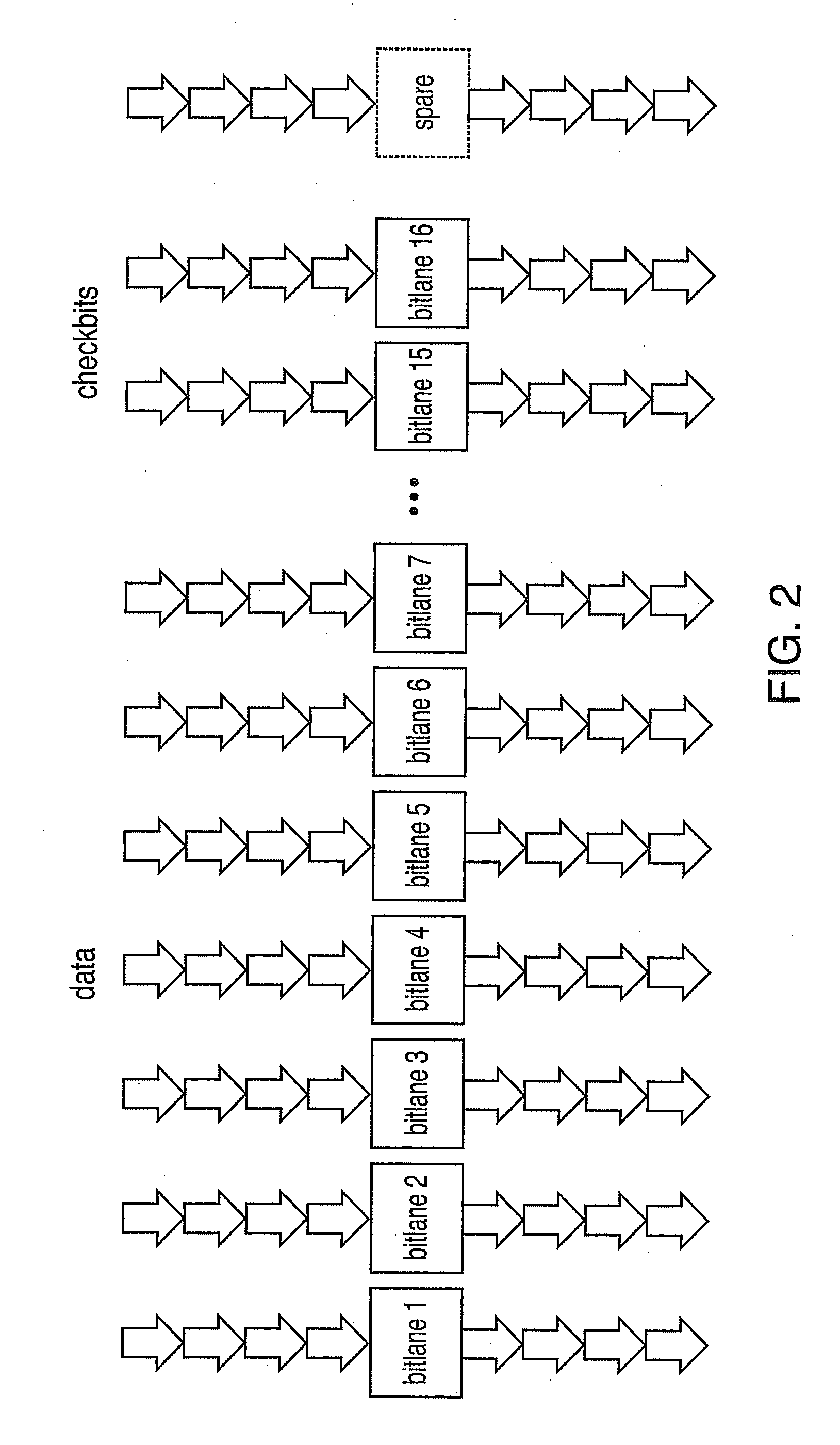

Systems, methods and computer program products for utilizing a spare lane for additional checkbits

ActiveUS20080005644A1Detection errorPrecise functionError preventionFrequency-division multiplex detailsBit lineCommunications system

Systems, method, and computer program products for utilizing a spare lane for additional checkbits. Systems include computer, storage or communications systems with bitlanes for transferring error correcting code (ECC) words in packets over a bus in multiple cycles, a spare bitlane available to the bus, a spared mode and an initial mode. The spared mode is executed when the spare bitlane has been deployed as a replacement bitlane for carrying data for one of the other bitlanes. The initial mode is executed when the spare bitlane has not been deployed as a replacement bitlane. The initial mode includes utilizing the spare bitlane for carrying one or more additional ECC checkbits. The initial mode provides at least one of a more robust error detecting function for the bus than the spared mode and a more robust error correcting function for the bus than the spared mode.

Owner:IBM CORP

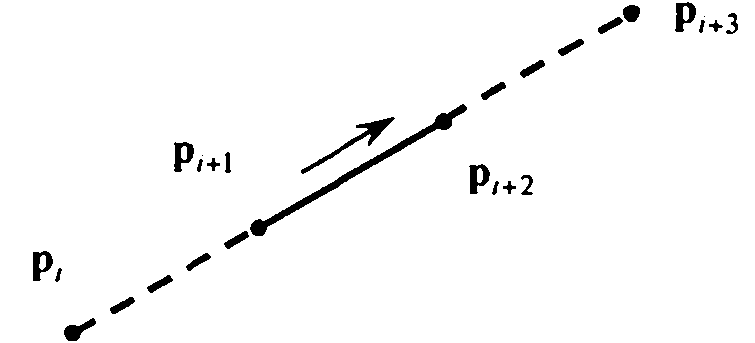

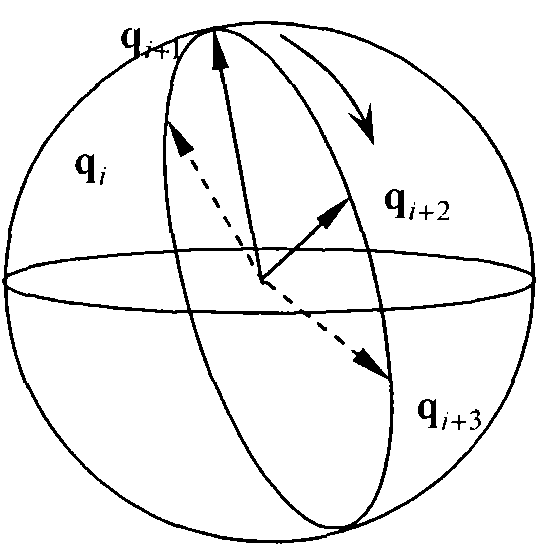

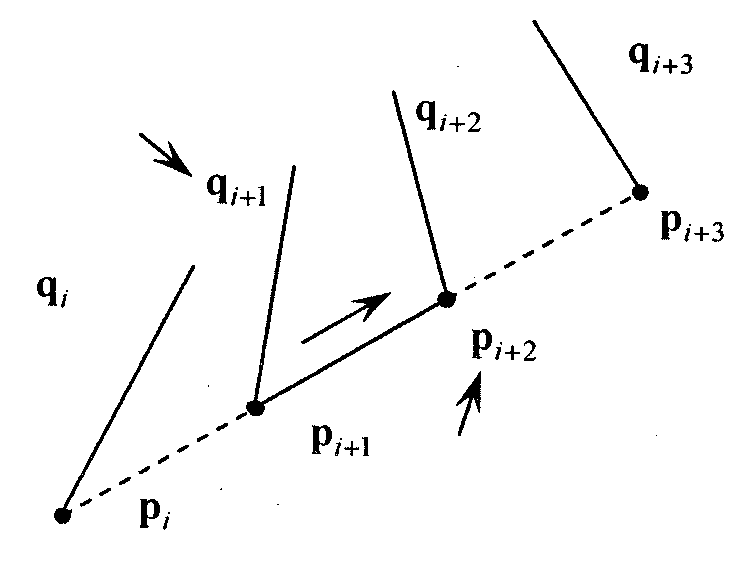

Quaternion-based five-coordinate spline interpolation control method

InactiveCN101738984ASolve the fitting problemSmooth feed rateNumerical controlQuaternionInverse dynamics

The invention discloses a quaternion-based five-coordinate spline interpolation control method, and relates to a numerical control system. In order to solve the problems that the transfer error between a CAD / CAM system and CNC, the discontinuity between segments destroys the track precision, and the movement speed becomes nonuniform and discontinuous, the quaternion-based five-coordinate spline interpolation control method comprises the following implementing processes: 1, CAM software reads track data on a curve of a parts design drawing, and establishes a CAM tool path; 2, the CAM tool path is converted into a numerical control code format of the five-coordinate spline interpolation, wherein the numerical control code format of the five-coordinate spline interpolation is divided into three formats: a linear-translation numerical control code format of the five-coordinate spline interpolation, a linear-rotation numerical control code format of the five-coordinate spline interpolation, and a universal numerical control code format of the five-coordinate spline interpolation; 3, converting the three numerical control code formats of the five-coordinate spline interpolation into a joint movement program through an inverse dynamics transformation formula; and 4, finishing processing parts. The quaternion-based five-coordinate spline interpolation control method is widely applied to the field of numerical control systems.

Owner:HARBIN INST OF TECH

Method for processing sheet material

InactiveUS6955263B2Avoid mix-upAvoid misallocationsCoin/currency accepting devicesSortingProcess engineeringTransfer error

A method for processing sheet material, in particular papers of value such as bank notes, checks, etc., wherein different groups of sheet material are processed one after the other, the different groups of sheet material being separated for processing. A container for each group of sheet material is used for separating and processing each group of sheet material. The separating means or container thus delimits the individual groups of sheet material clearly from each other. Designing the separating means as a container obtains reliable separation of the individual groups of sheet material. Since the different groups of sheet material are already clearly separated and grouped before actual processing, one can avoid mixups, misallocations and transfer errors as can occur with later, simultaneous grouping of the different groups of sheet material.

Owner:GIESECKE & DEVRIENT GMBH

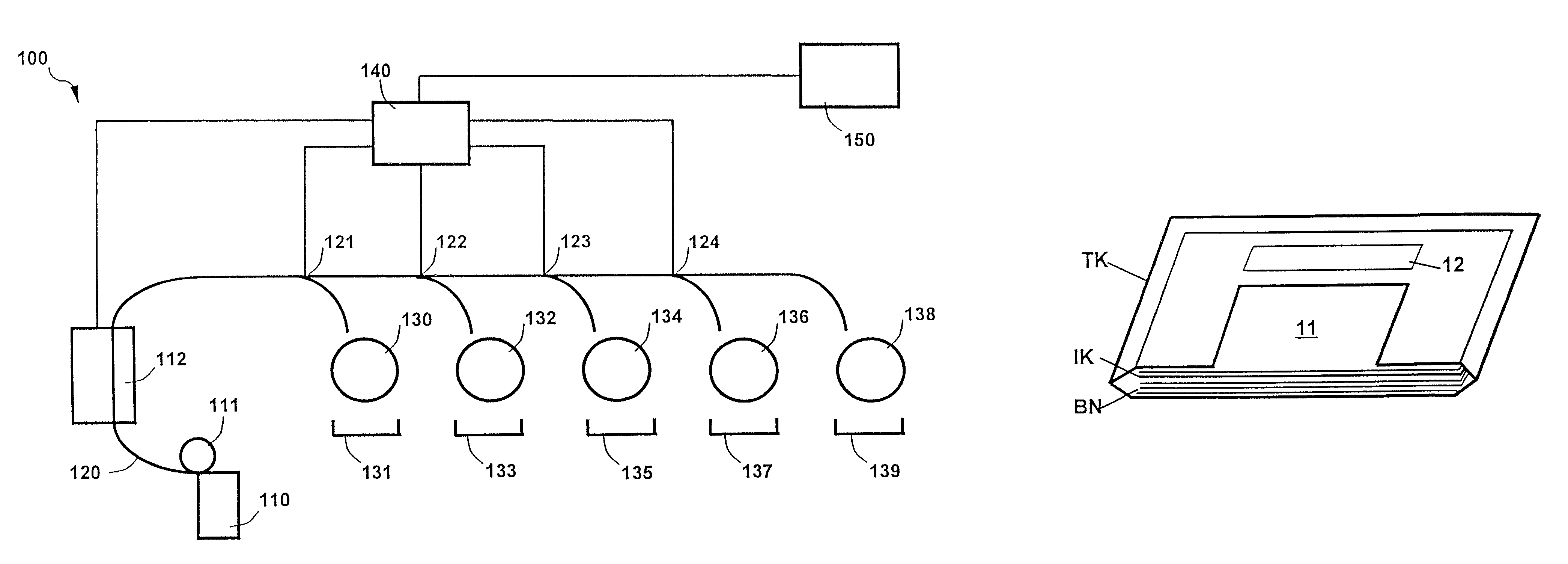

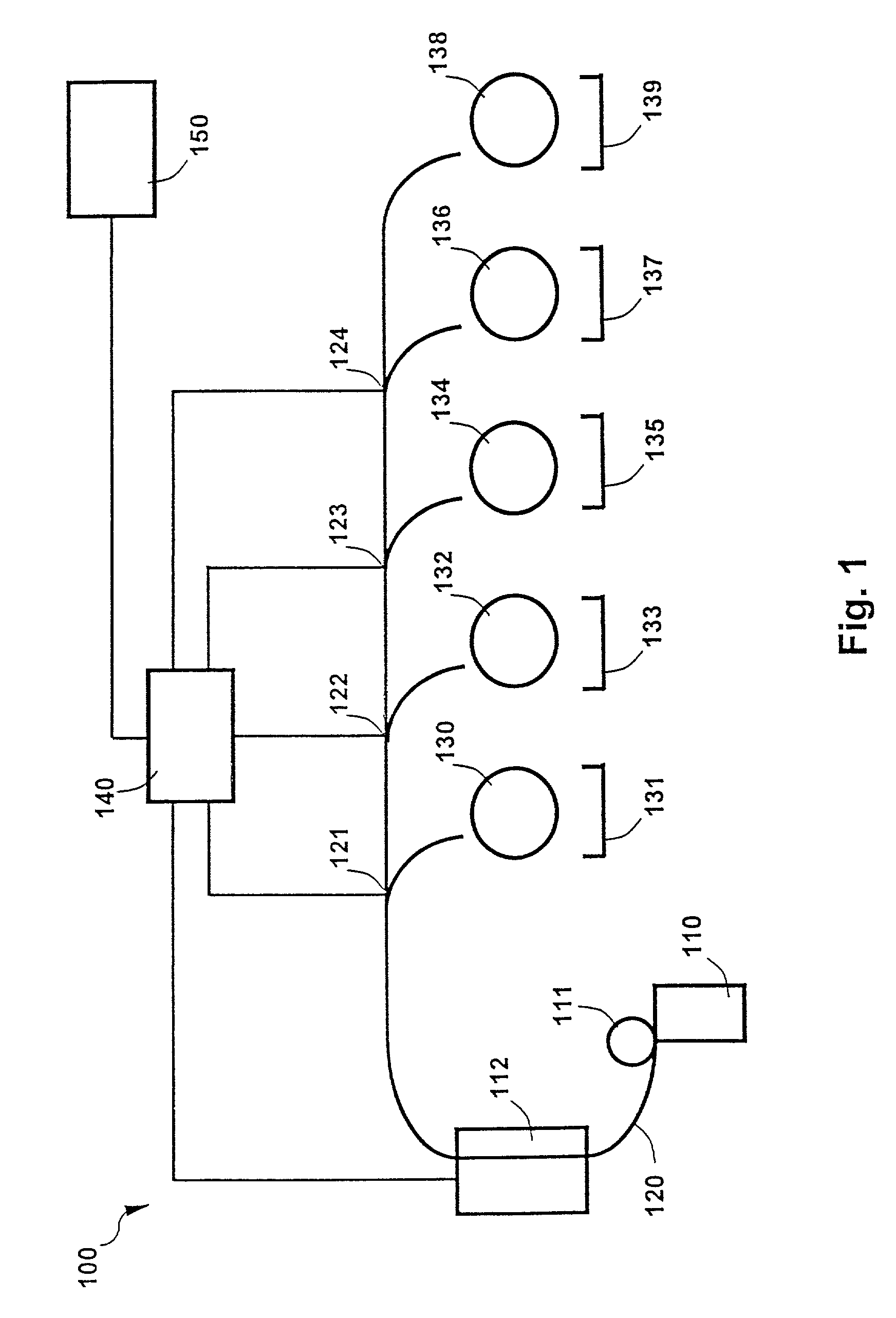

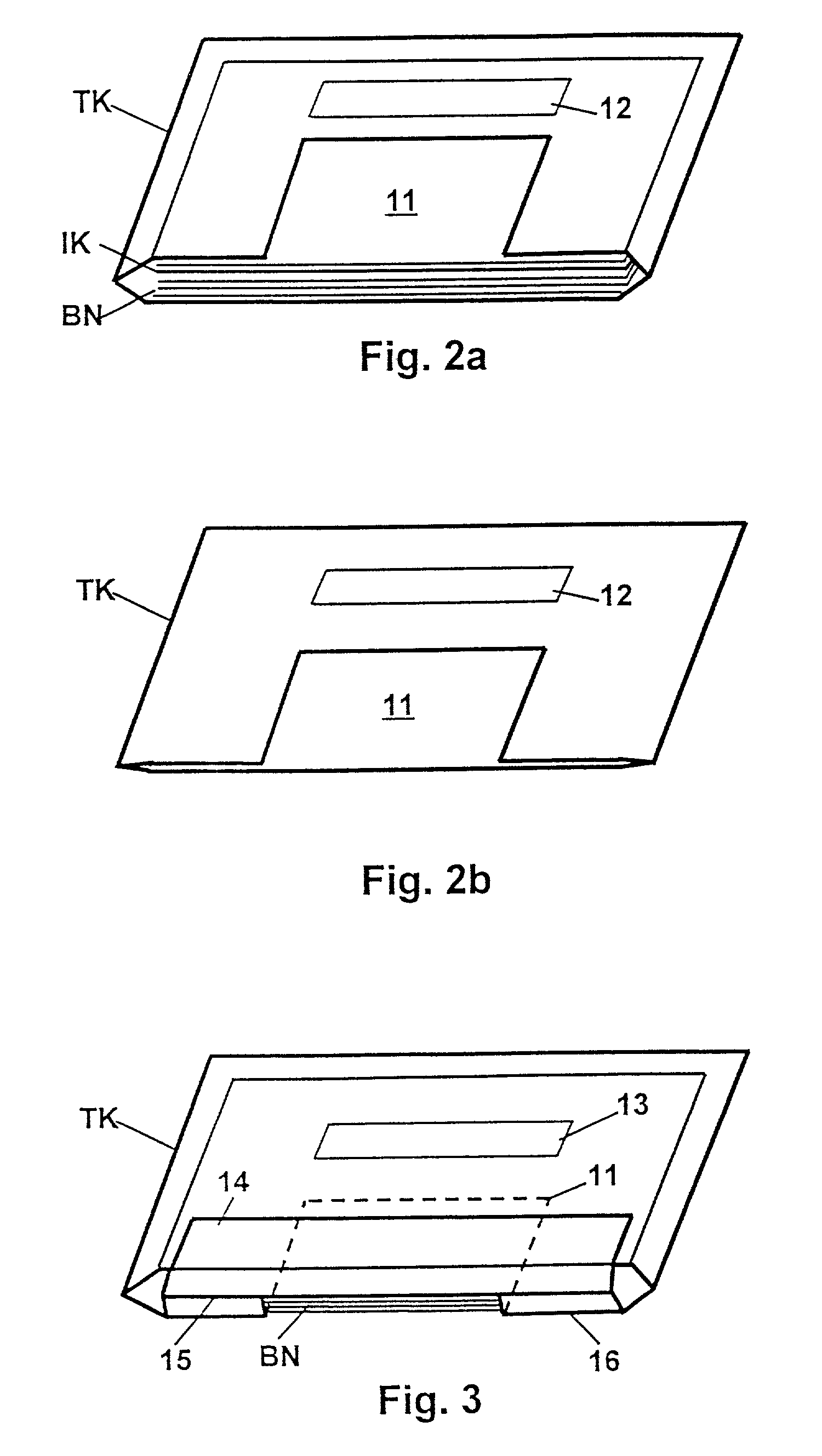

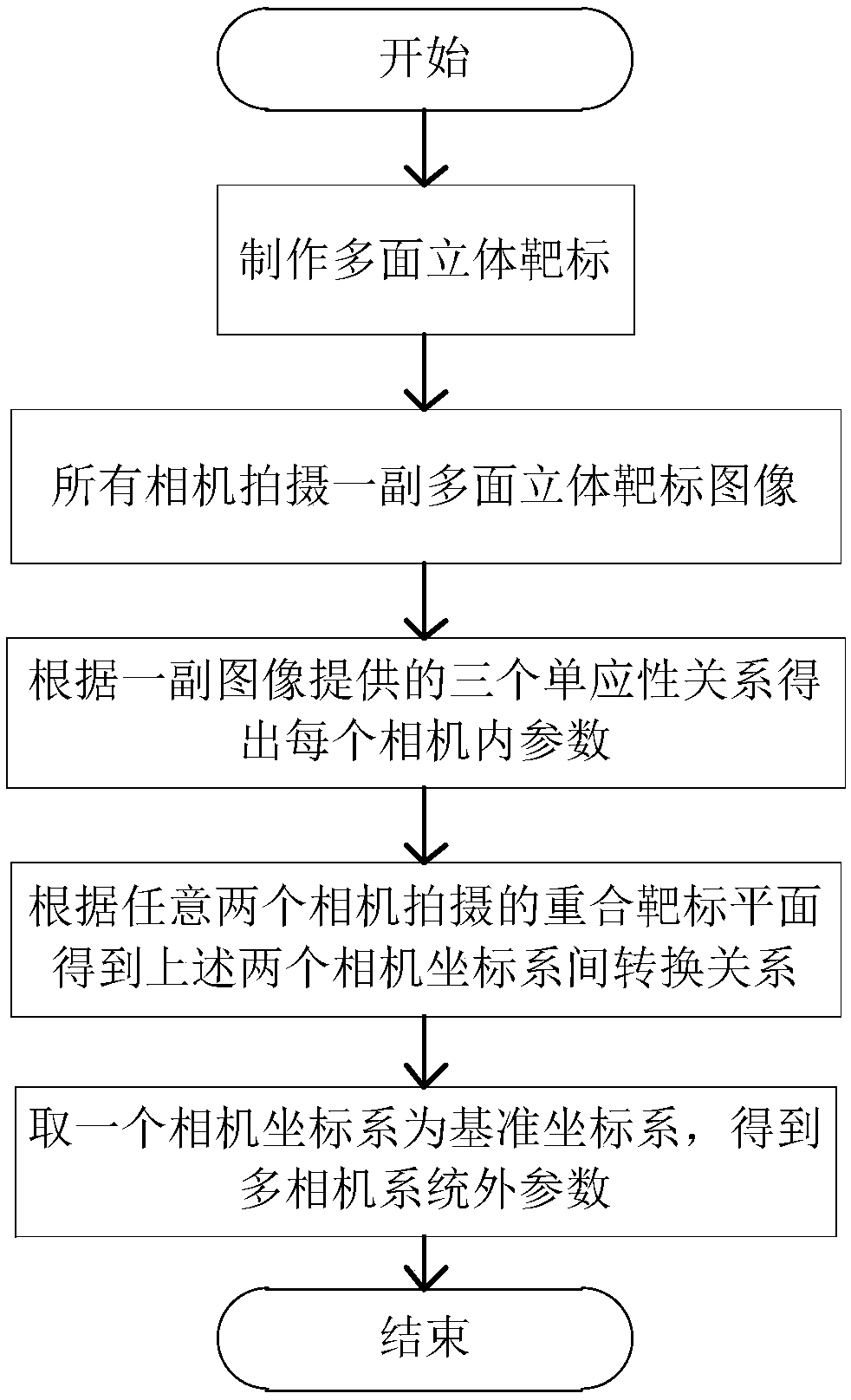

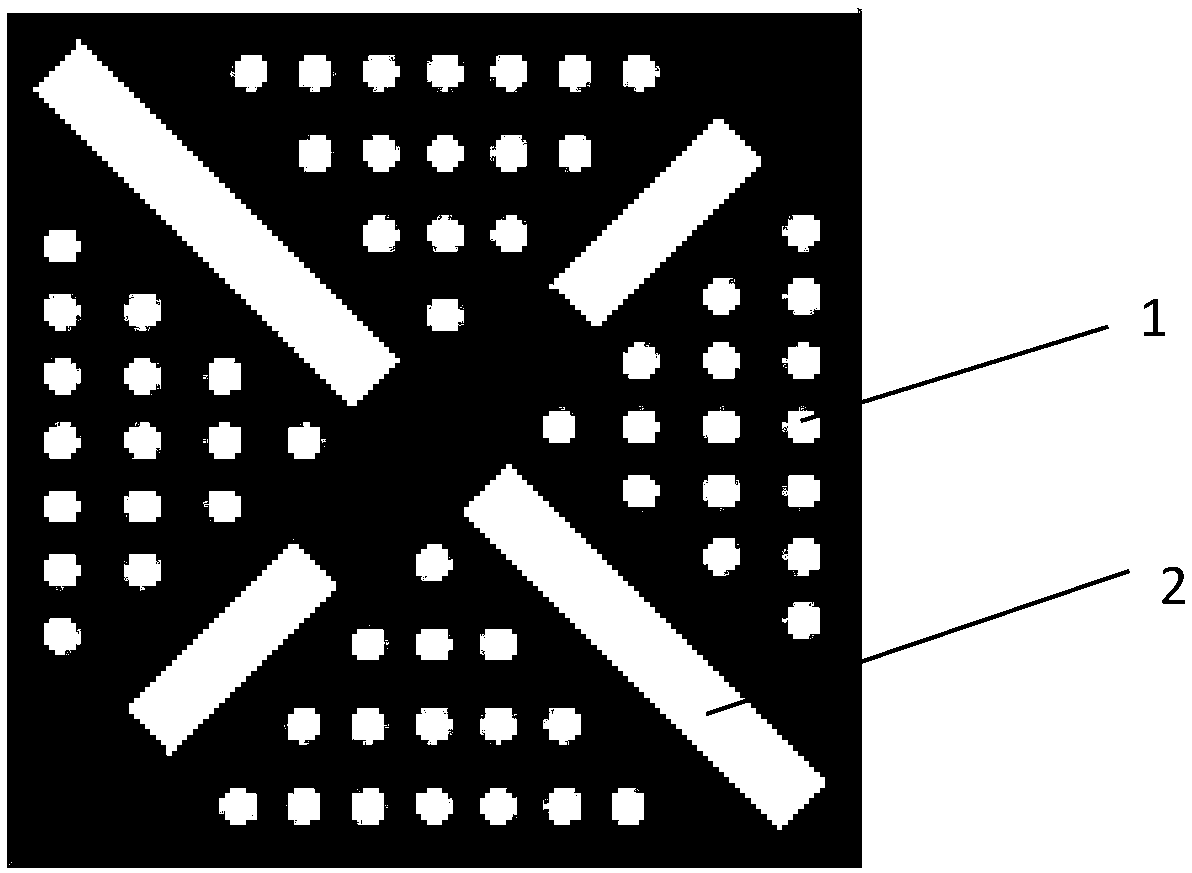

Calibration method of multi-camera system based on multi-planar stereo target

The invention discloses a multi-camera system calibration method based on a multi-plane stereoscopic target. The multi-plane stereoscopic target is manufactured. At least three target planes of the multi-plane stereoscopic target are photographed by different cameras at the same time, and at least two target planes photographed by any two cameras coincide. The homography between the target plane and the photographed image plane is used to calculate the intrinsic parameters of the camera. The conversion relationship between each camera coordinate system and the world coordinate system corresponding to the coincident target plane is solved, and the conversion relationship between camera coordinate systems of each camera is solved, and the external parameters of the multi-camera system is determined. The calibration process of the invention is fast and simple, and the calibration result has high precision. Only one image needs to be photographed, and there is no transfer error; The process of target processing is simple. Feature circle contour and rectangular pattern can be easily detected.

Owner:HEFEI UNIV OF TECH

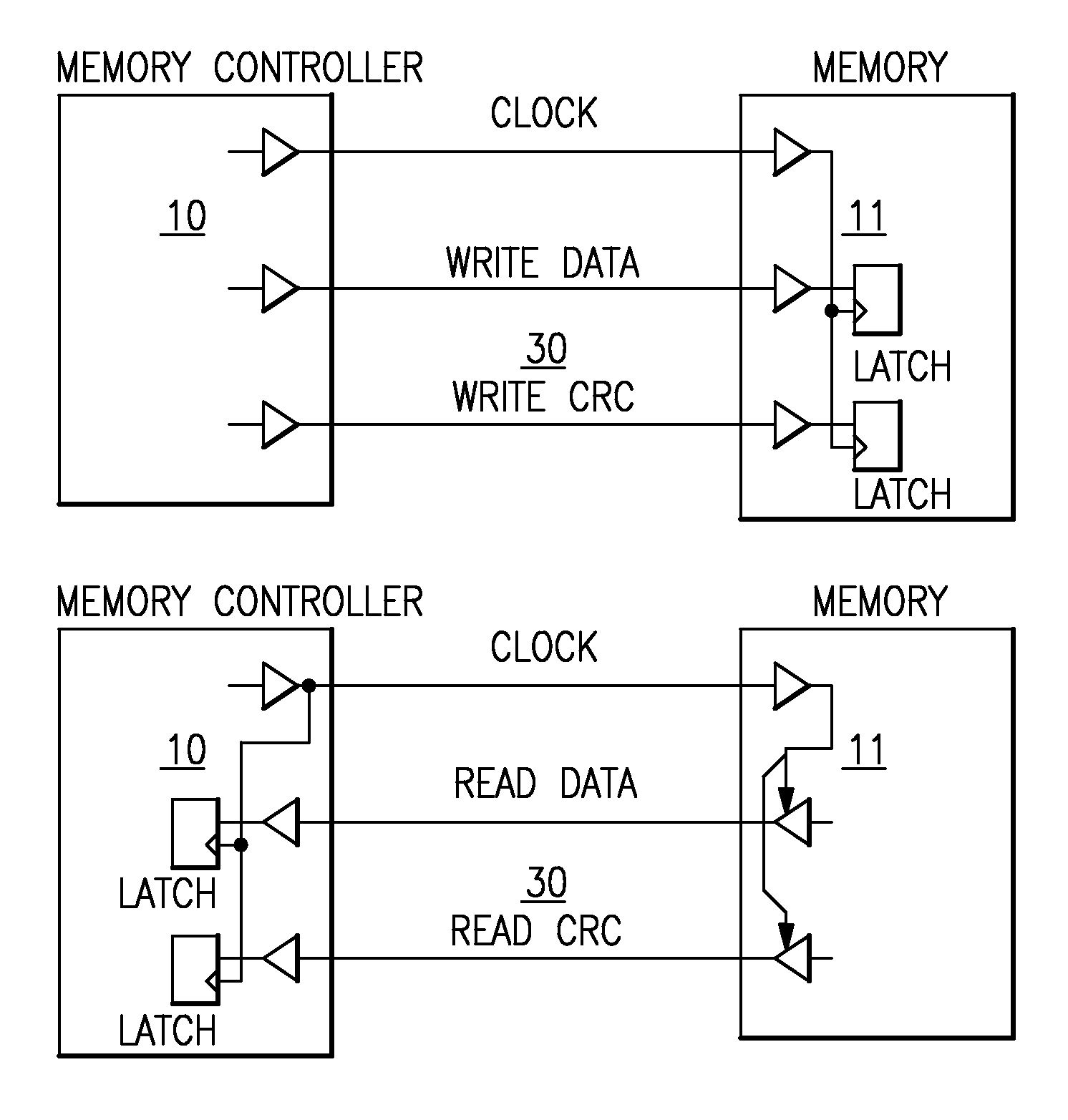

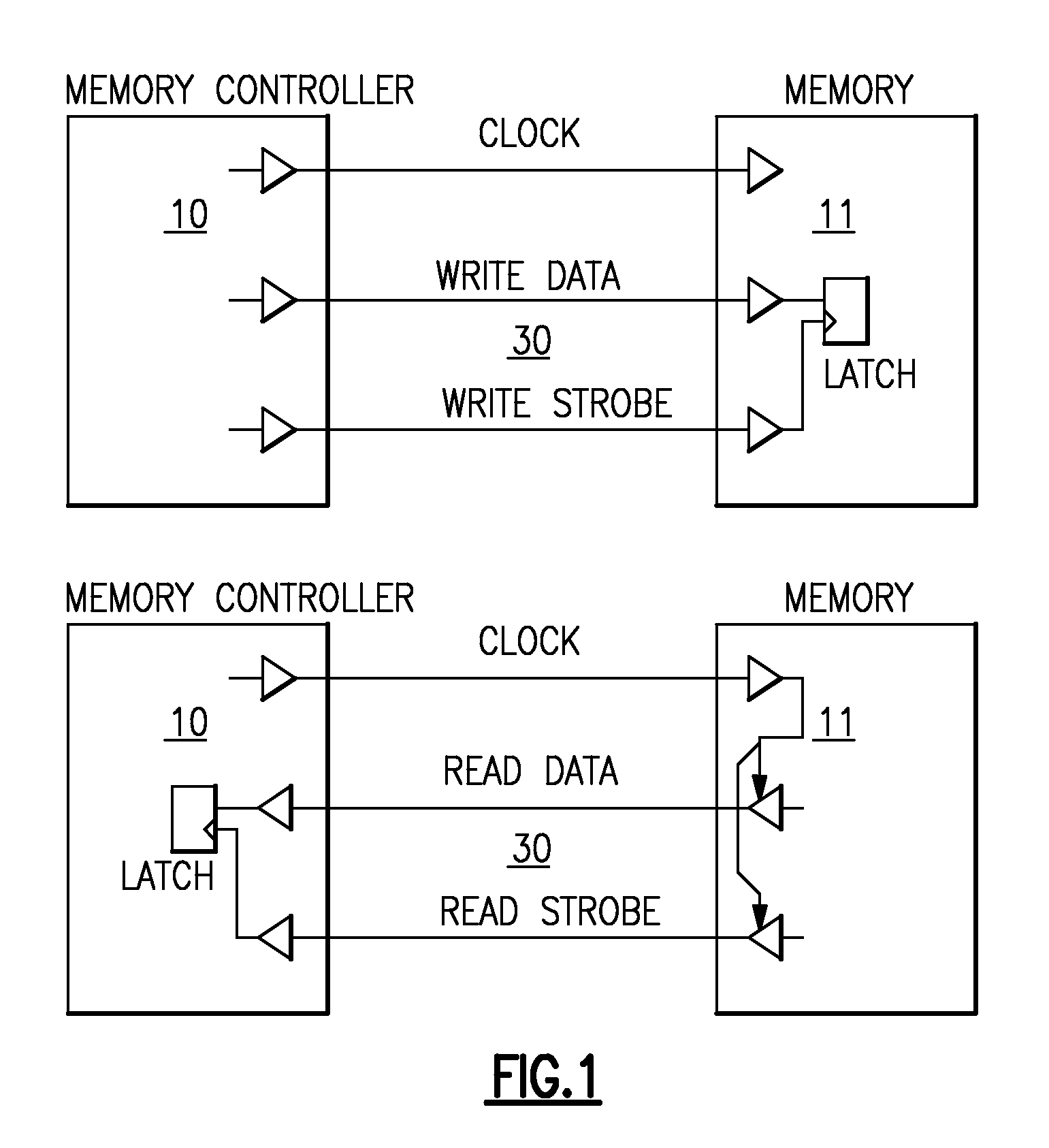

Synchronous memory having shared CRC and strobe pin

A memory system having a memory element chip (DRAM) and a memory controller chips having a plurality of drivers and receivers and latches for transferred data. For writes clocks, write data and write for CRC (cyclic redundancy checks) is transferred to the DRAM from the memory controller and latched for error checking. The reads are clocked and the read data is received and transferred to a read data latch with also receives a clocked read strobe for verification of data integrity from DRAM. Each chip has a bi-functional pin that acts as a shared CRC pin during write and acts as a shared strobe pin during READ. Data transfers with the CRC signal and DQS signal are transferred across two paths CRC0 / DQS and CRC1 / DQS1. One could also transfer the CRC signal across one path with only the CRC0 / DQS signal. Read operations have no CRC, and have no need for CRC because transfer errors during read can be detected by memory error correction coding (ECC). Write data provides source synchronous I / O data to said memory element chip needed for modem high speed memory communications.

Owner:IBM CORP

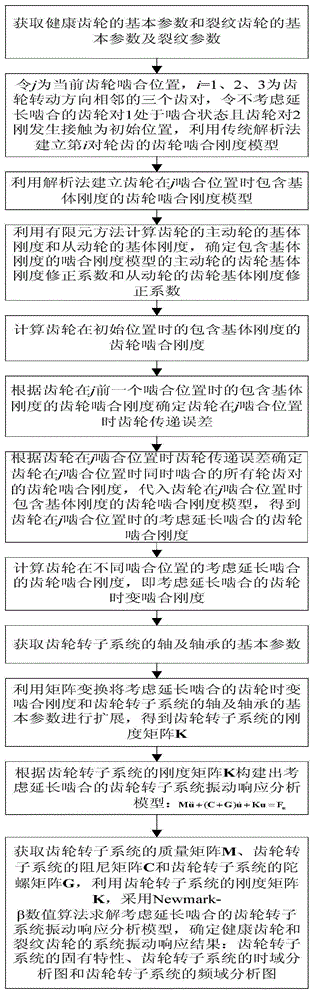

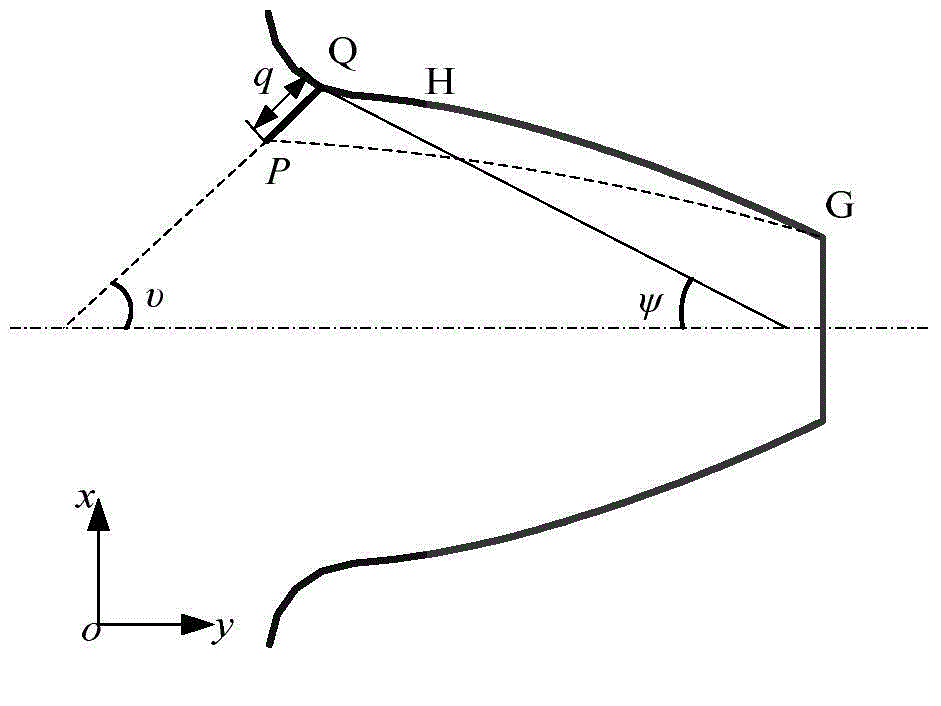

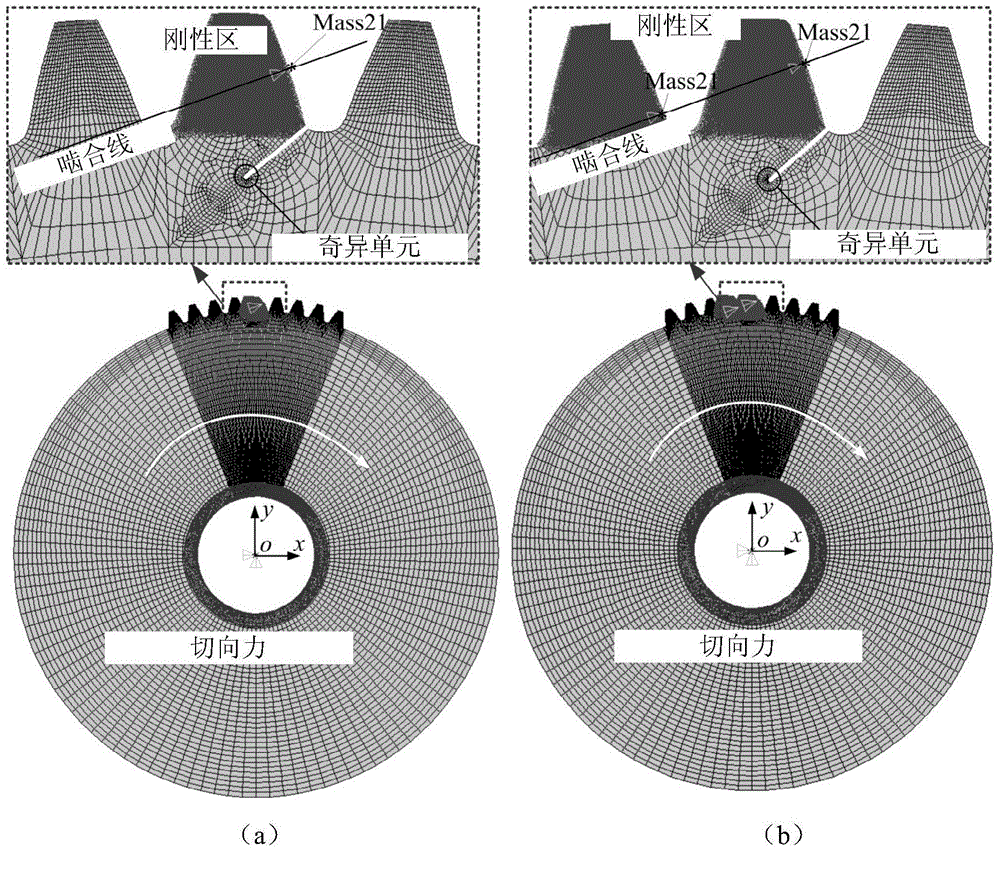

Kinetic parameter determination method of extended tooth contact considered crack gear rotor system

ActiveCN104820756AFix the problem of repeated calculation of stiffnessCalculation method is simpleSpecial data processing applicationsDrive wheelEngineering

The invention relates to a kinetic parameter determination method of an extended tooth contact considered crack gear rotor system. The method comprises the following steps: obtaining a basic parameter of a healthy gear and a basic parameter and a crack parameter of a crack gear; establishing a gear meshing rigidity model, which comprises matrix rigidity, of the gear; calculating the matrix rigidity of a driving wheel of the gear and the matrix rigidity of a driven wheel of the gear by a finite element method; determining a gear matrix rigidity correction coefficient of the meshing rigidity model which comprises the matrix rigidity; determining the gear tooth deformation of the gear by a method that a gear transferring error is solved to obtain extended tooth contact considered gear time varying meshing rigidity; obtaining the basic parameters of a shaft and a bearing of a gear rotor system; obtaining a rigidity matrix K of the gear rotor system; and according to the rigidity matrix K of the gear rotor system, constructing an extended tooth contact considered rotor system vibration response analysis model, and determining a system vibration response result of the healthy gear and the crack gear.

Owner:NORTHEASTERN UNIV

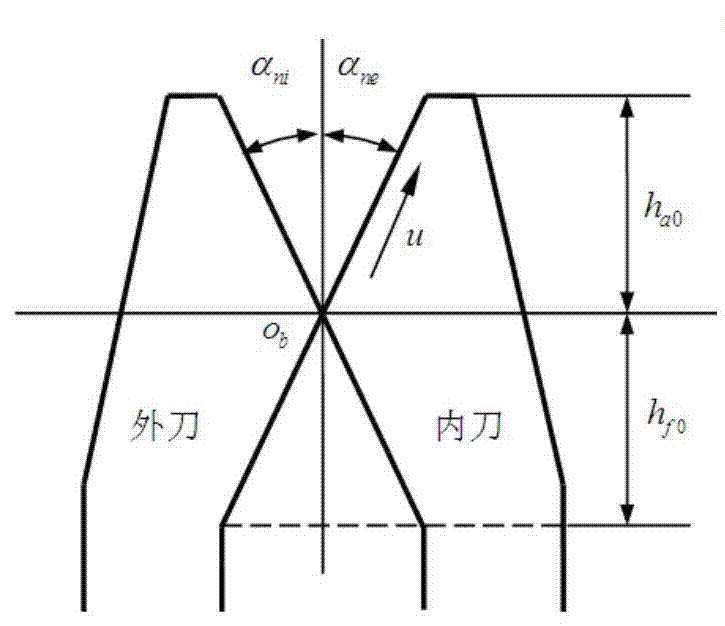

Machining method of cycloidal-tooth bevel gear

The invention discloses a machining method of a cycloidal-tooth bevel gear. The machining method comprises the following steps: (1) determining basic parameters of a generating wheel; (2) determining the movement for forming a tooth surface of the generating wheel; (3) determining the movement for expanding the generating wheel into the gear; (4) correcting the movement for expanding the generating wheel into the gear; and (5) finishing expansion of the machined gear. Compared with the Klingelnberg method, the machining method disclosed by the invention has the advantages that the structure of a tool disc is greatly simplified, a cross-shaped sliding block mechanism is not needed and the rigidity is improved; compared with the Oerlikon method, the machining method disclosed by the invention has the advantages that a tool inclining mechanism is not needed, so that the structure of a machine tool is greatly simplified and the rigidity is improved; the cycloidal-tooth bevel gear and a quasi-hyperbolic gear are processed on a bevel gear milling machine without a tool inclining and swinging disc; the correction of the tooth surface does not cause additional adjustment of the machine tool and the tool; second-order precontrol of the position, the size and the shape of contact spots of the tooth surface can be realized; second-order precontrol of required transfer errors can be realized; and a cycloidal-teeth bevel gear pair conjugate completely on theory also can be machined.

Owner:TIANJIN TEEK TRANSMISSION

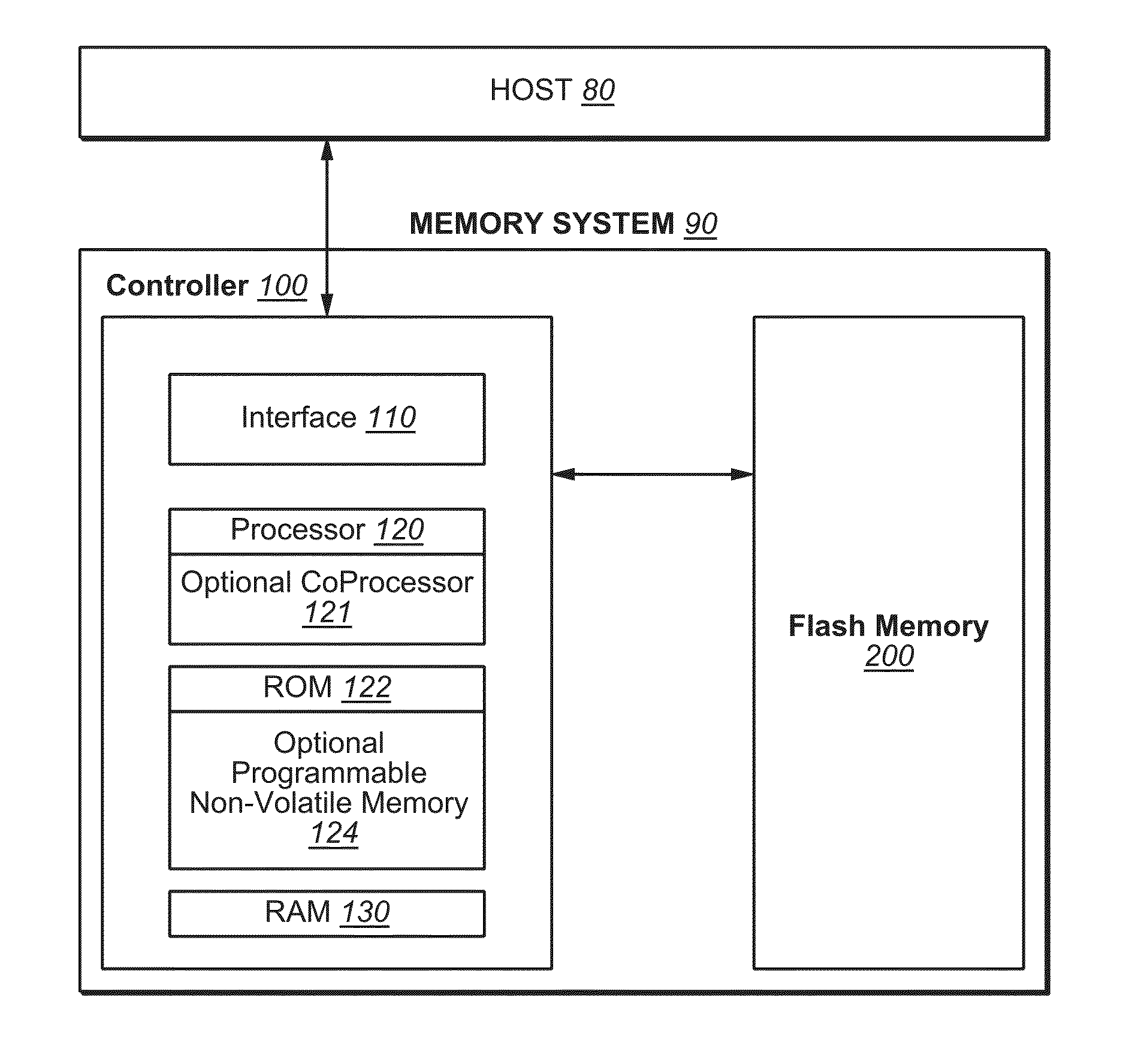

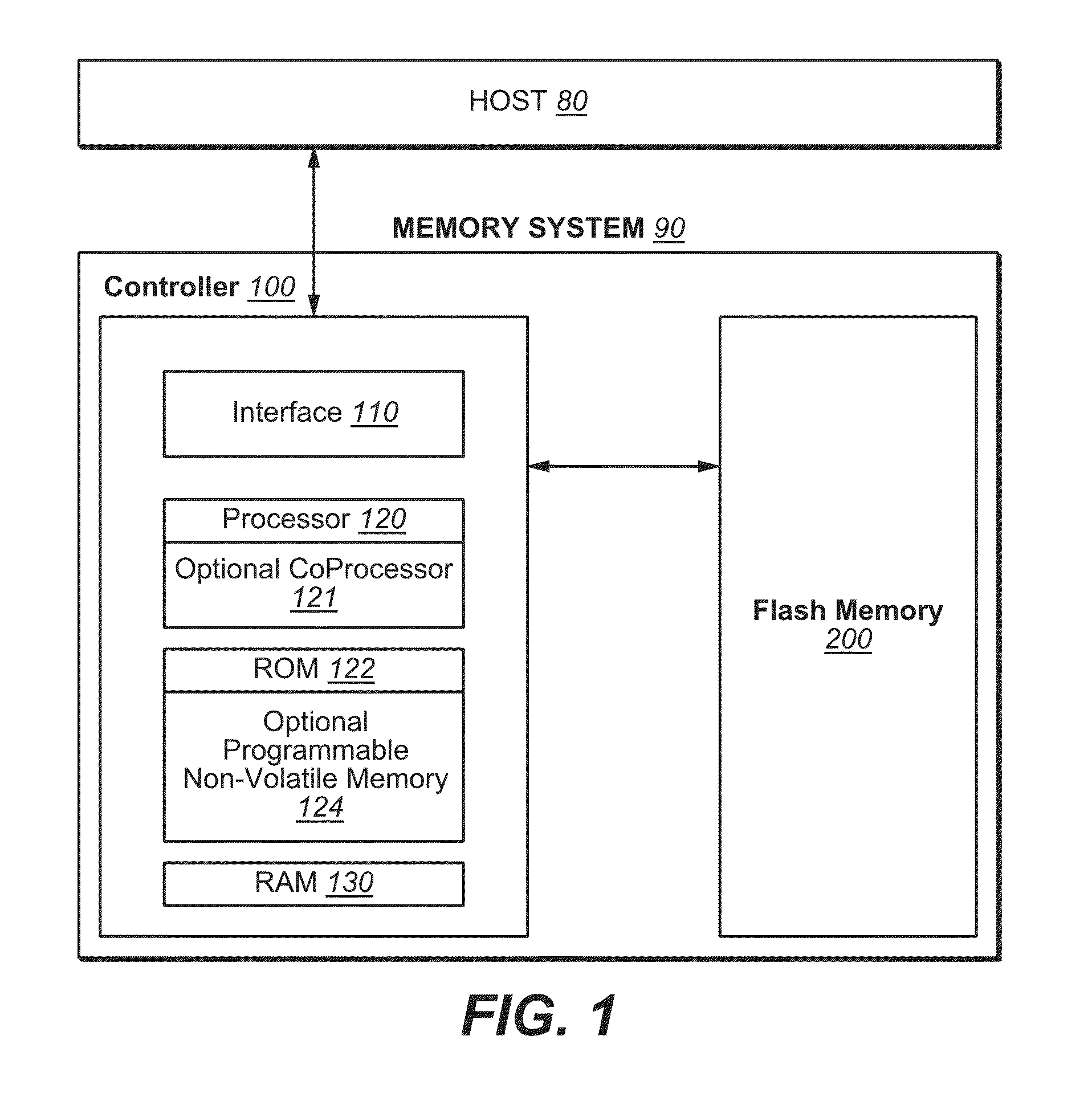

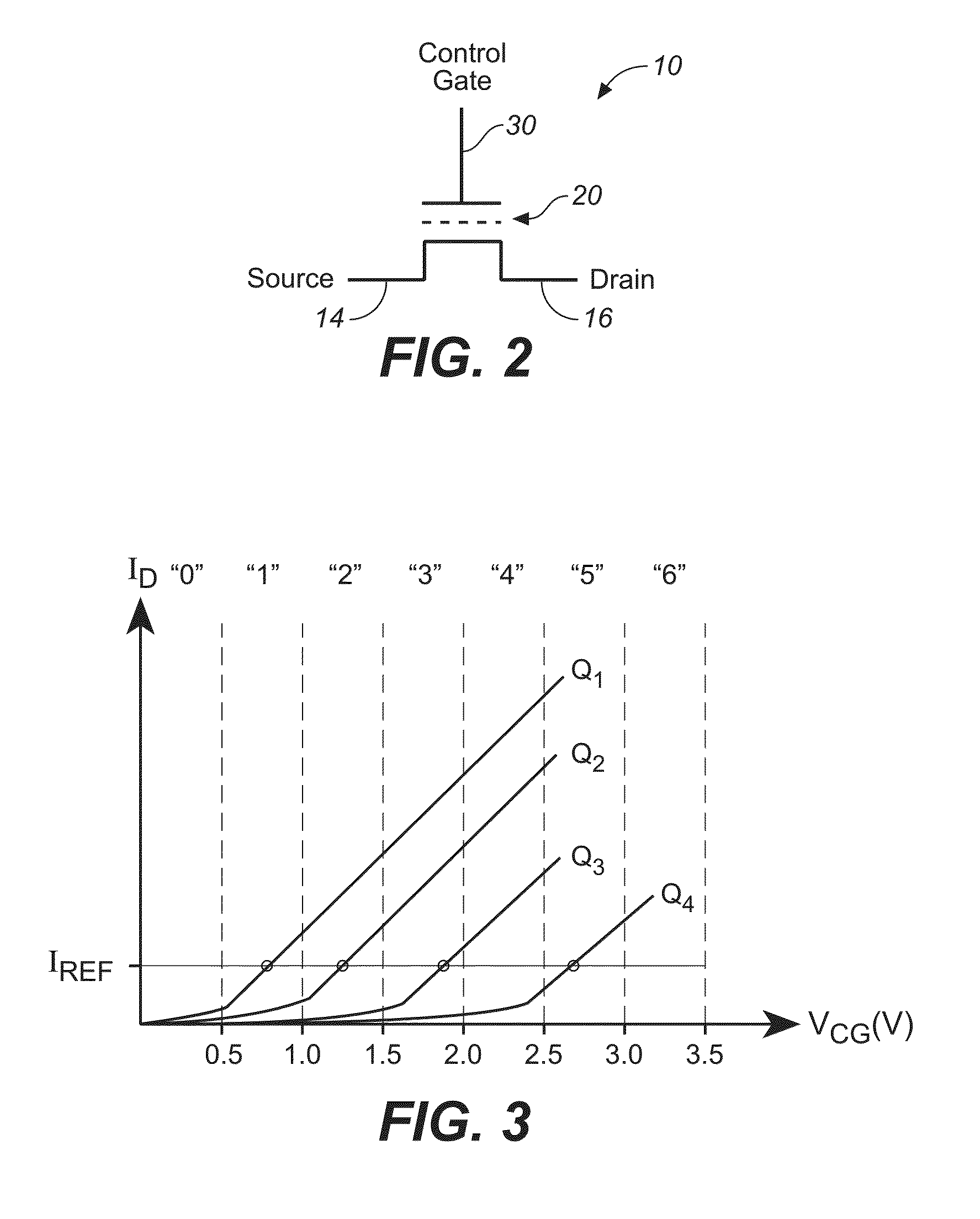

Multi-Level Redundancy Code for Non-Volatile Memory Controller

ActiveUS20150301933A1Memory architecture accessing/allocationMemory adressing/allocation/relocationData setTransfer error

In the controller circuit of a non-volatile memory system, data is protected by CRC (cyclic redundancy code) between functional blocks of the controller: Before a data set is transmitted from one functional block (such the host interface) to another functional block (such as data encryption or ECC), corresponding CRC is generated and transferred with the data. At the second block, the data set can be checked with the CRC at the second block before it operates on the data. This allows the controller to check for internal transfer errors early, allow for corrupted data to be re-requested, such as from a host when this process is applied to a data write operation. After the second block finishes with the data, a new CRC can then be generated to protect the data on its next internal transfer. This arrangement can particularly useful for functional blocks that transform the data set.

Owner:SANDISK TECH LLC

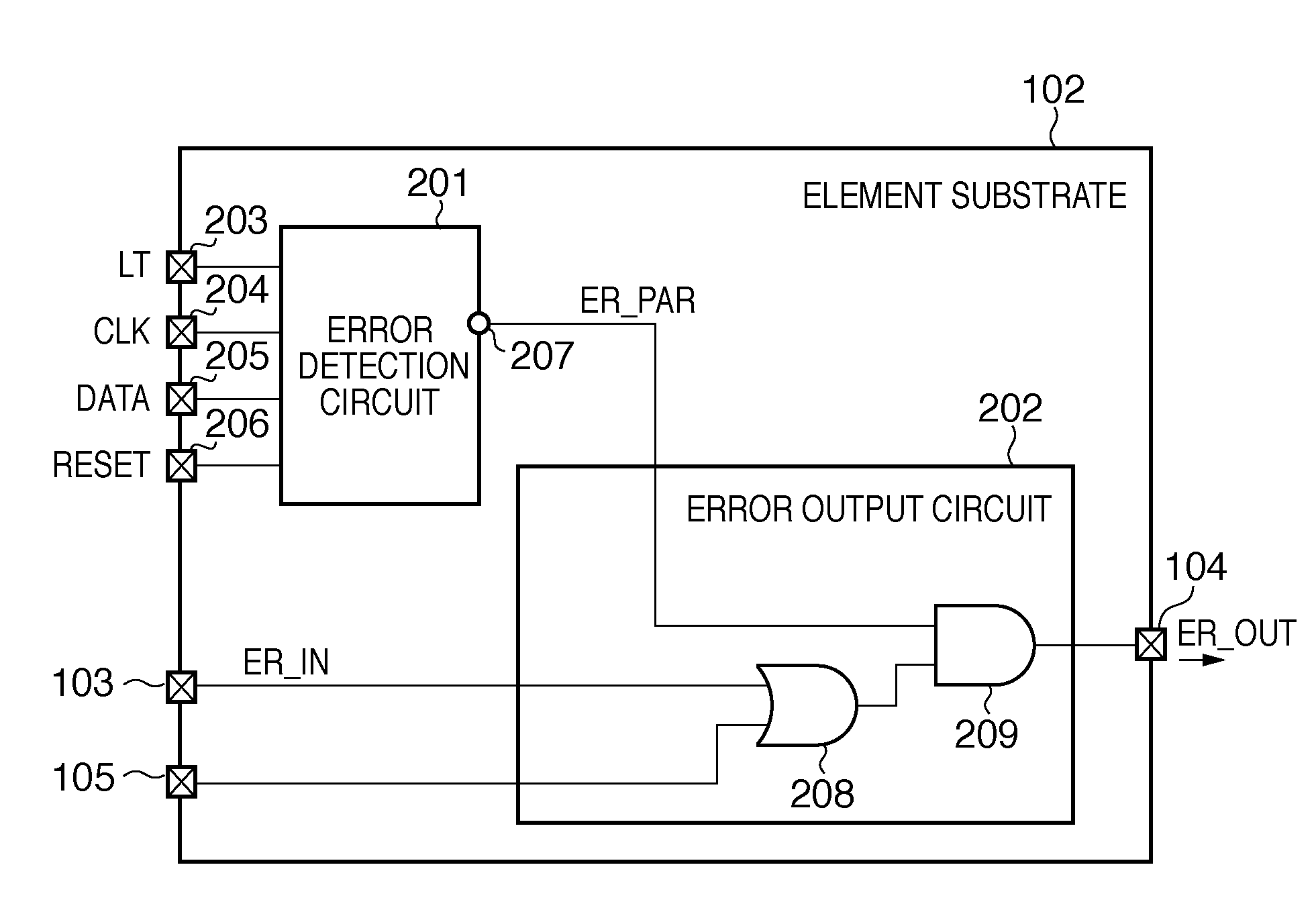

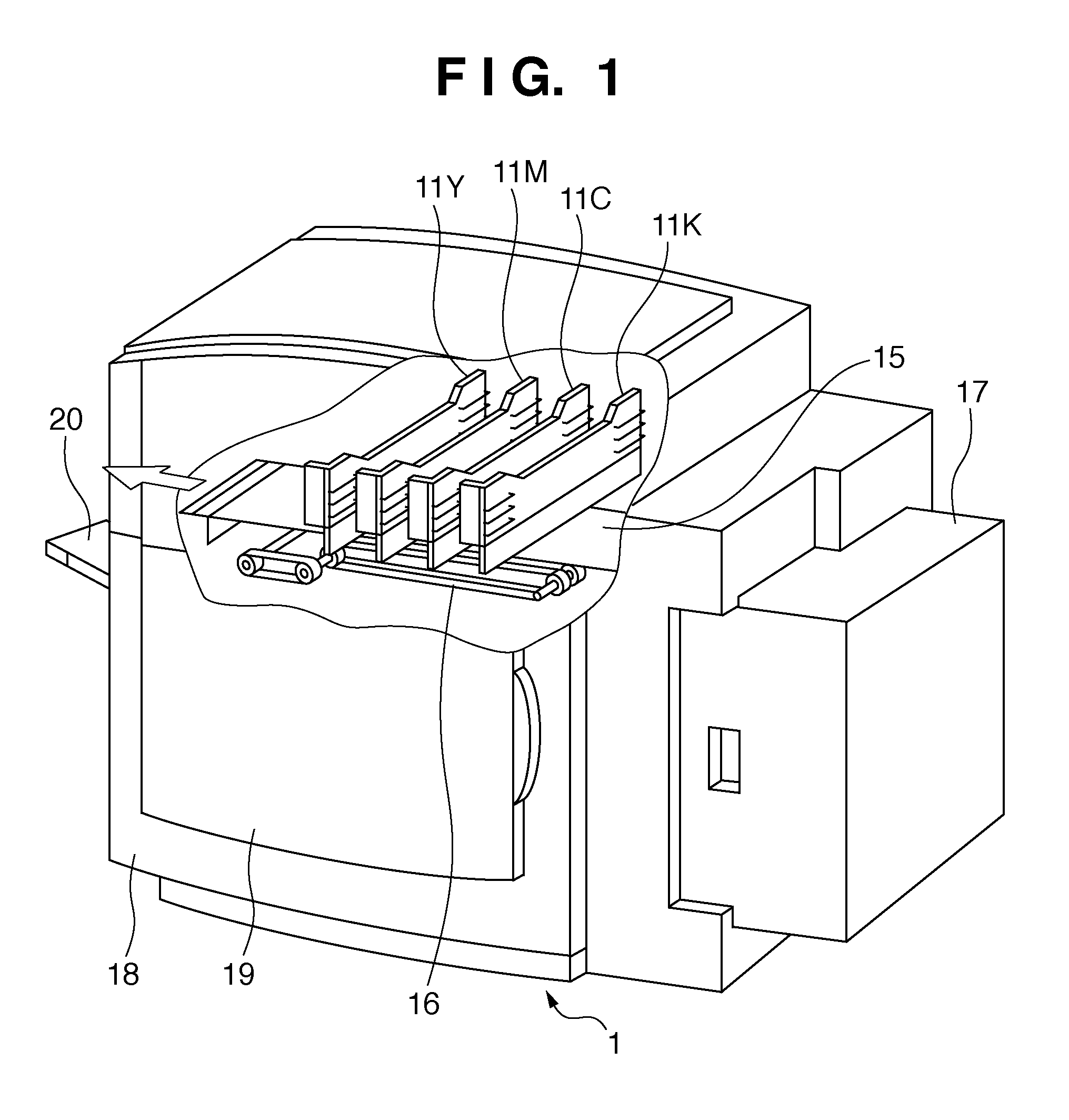

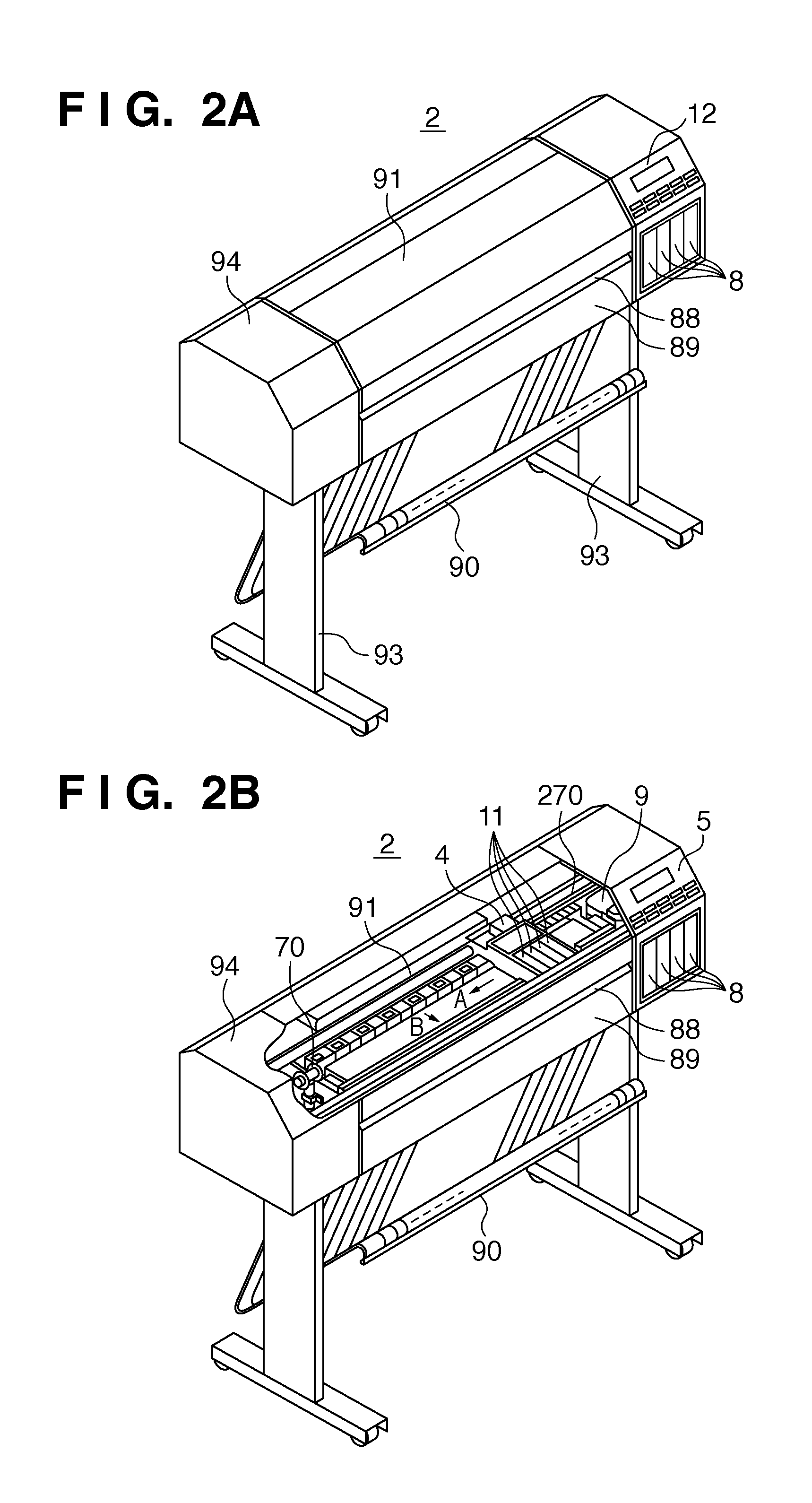

Printhead and printing apparatus

ActiveUS20110273507A1Improve reliabilityInking apparatusOther printing apparatusData signalTransfer error

This invention is directed to real time detection of occurrence of a transfer error and feedback of the detection result to a printing apparatus in consideration of a possible risk that a signal transfer error occurs on a transfer path that becomes longer as the printhead is elongated. To accomplish this, in a printhead configured by cascade-connecting a plurality of element substrates, information of a transfer error detected in real time in each element substrate during transfer of a print data signal is output to an element substrate on the next stage by taking account of information input from an element substrate on the preceding stage. Information containing pieces of information from all element substrates is output from an element substrate on the final stage.

Owner:CANON KK

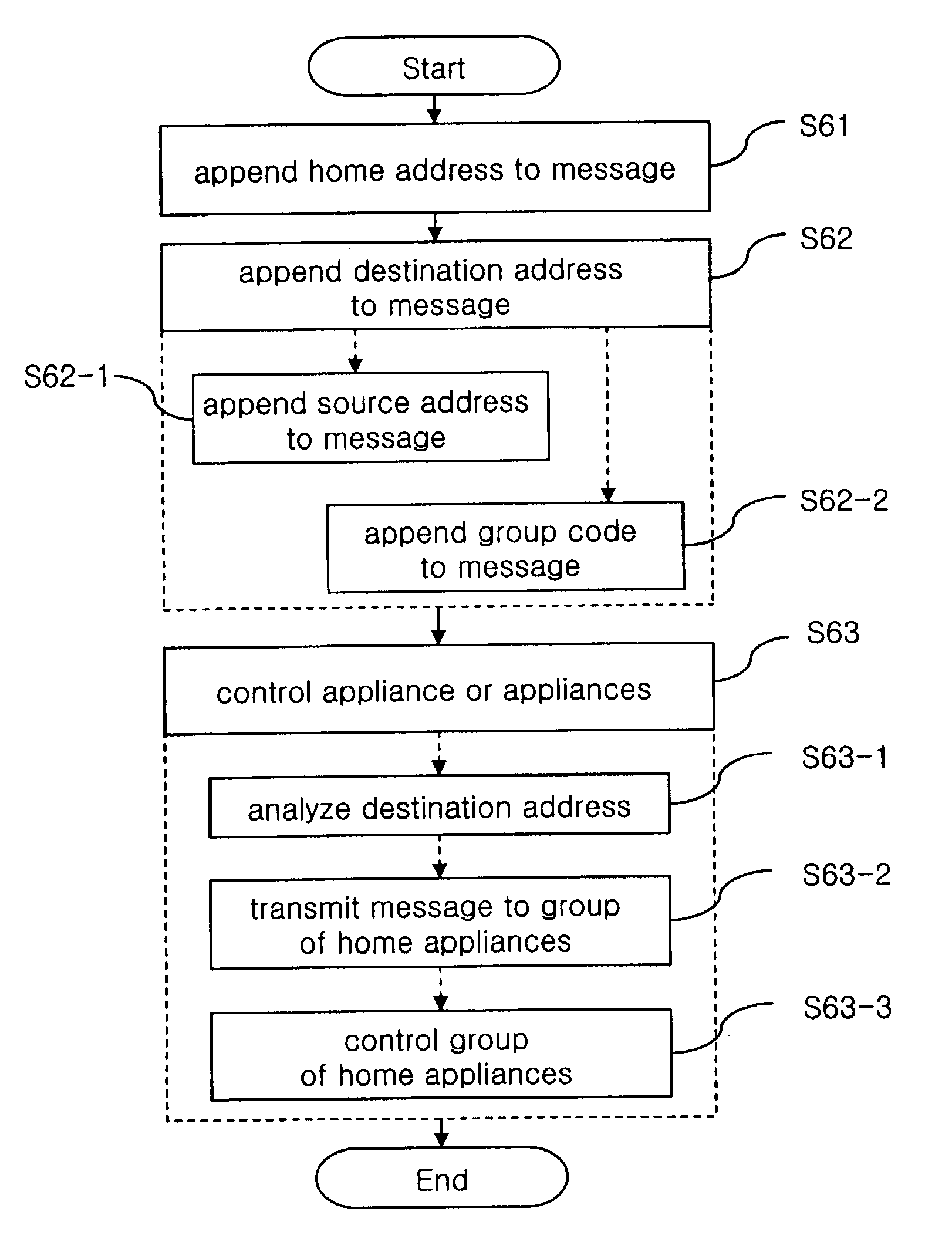

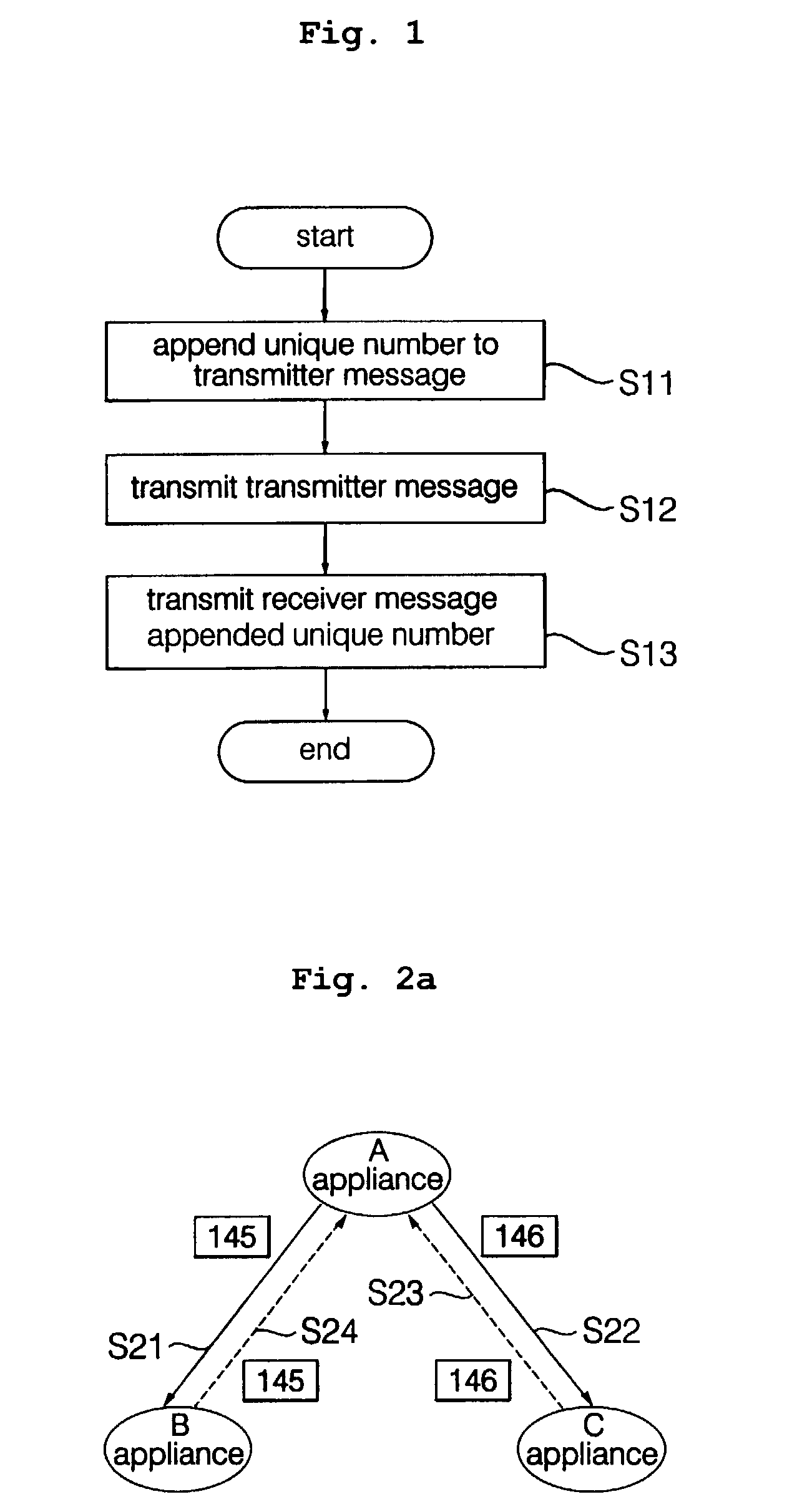

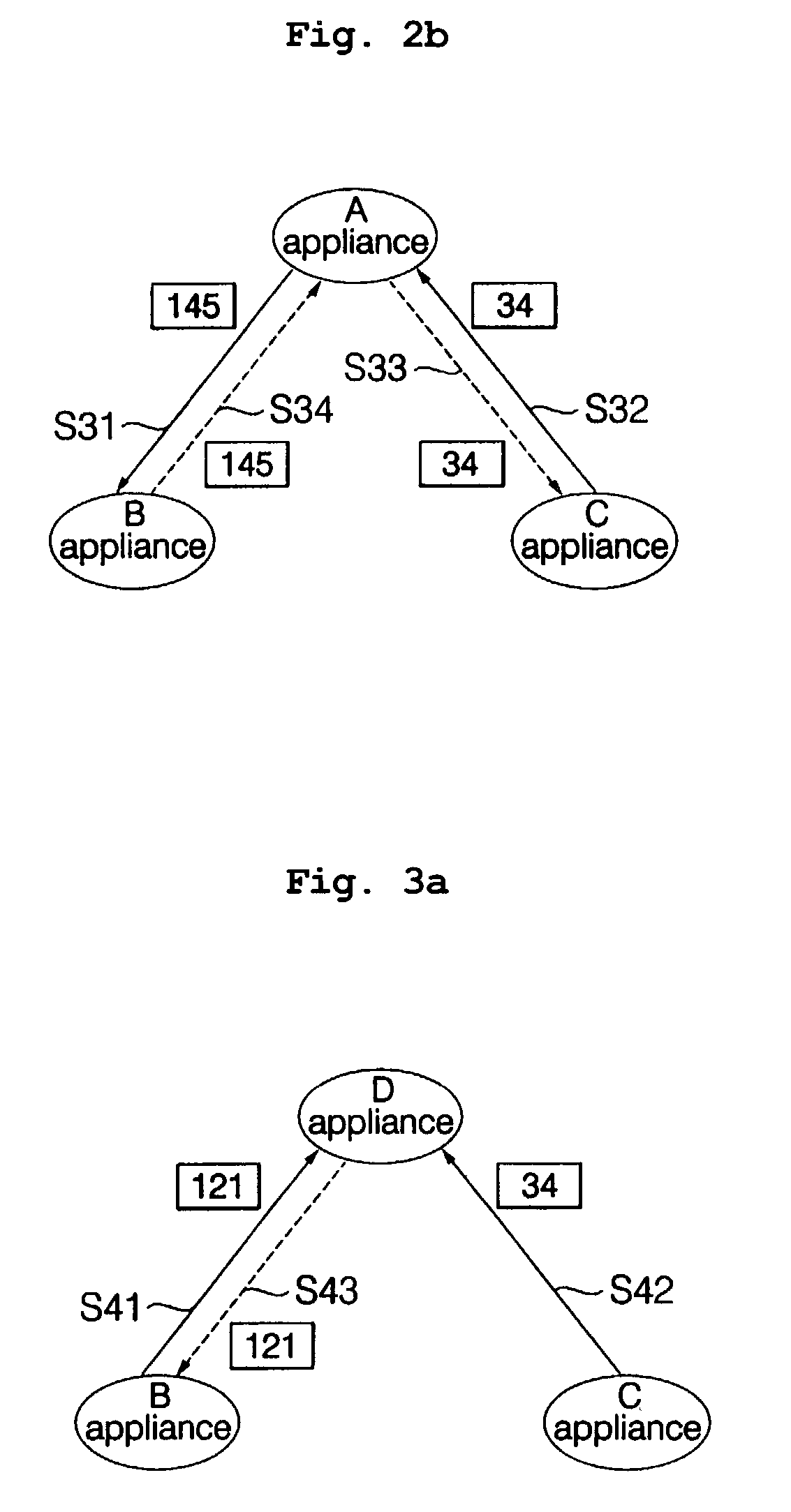

Method for transmitting and receiving messages in home appliance networking system

InactiveUS7026949B2Reduce transmission errorsComputer controlCircuit arrangementsHome applianceTransfer error

A method for transmitting and receiving messages in a home appliance networking system, wherein a first home appliance connected to a network appends a unique message identification number to a header of a message and transmits the resulting message to a second home appliance connected to the network. Messages transmitted and received among a plurality of home appliances can be distinguished from one another, resulting in a reduction in message transfer errors. Moreover, as needed, a group code corresponding to a specific group of home appliances may be appended to a transmitter message for control of the specific group so that the home appliances can be conveniently and efficiently controlled at one time.

Owner:LG ELECTRONICS INC

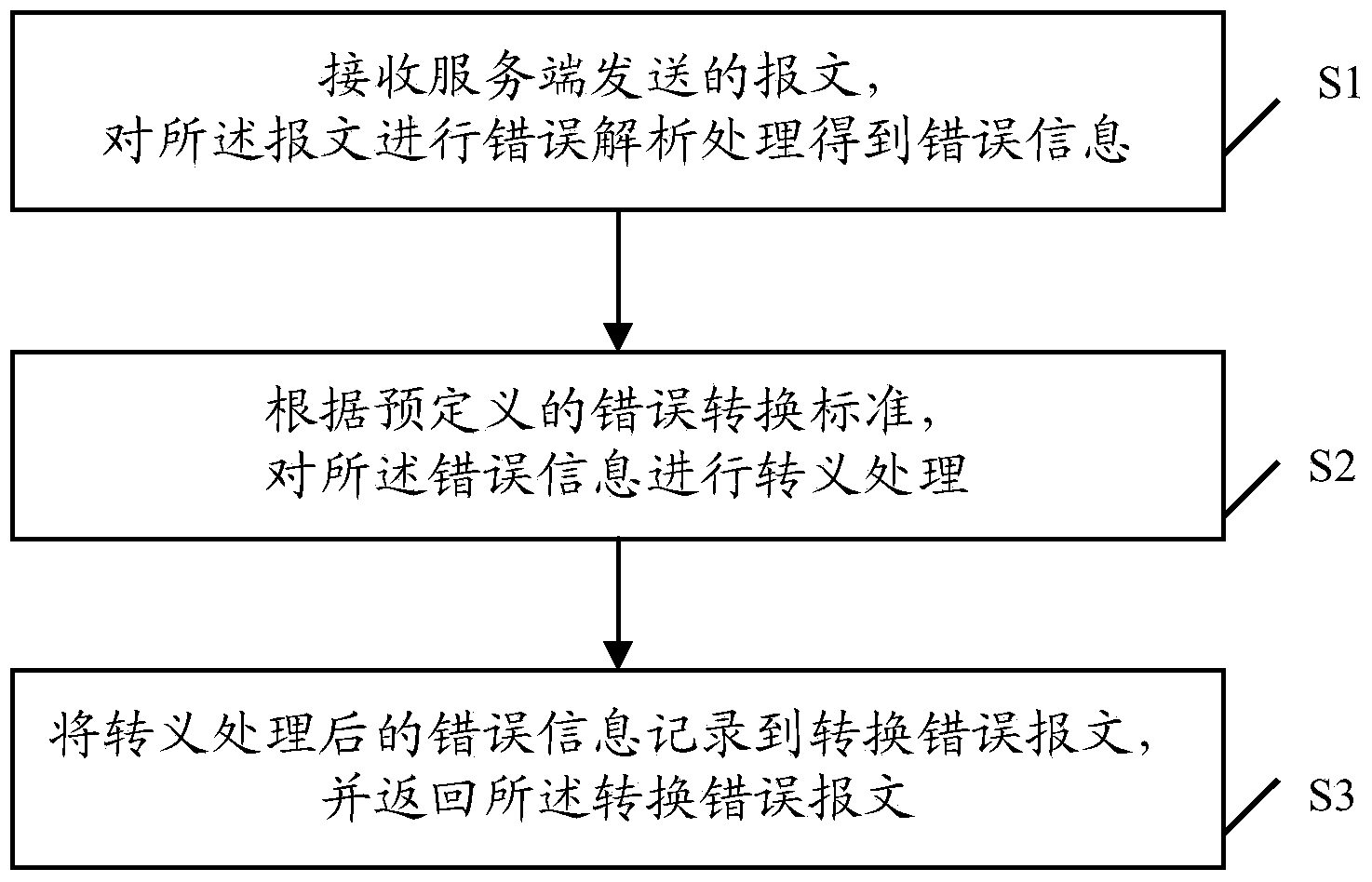

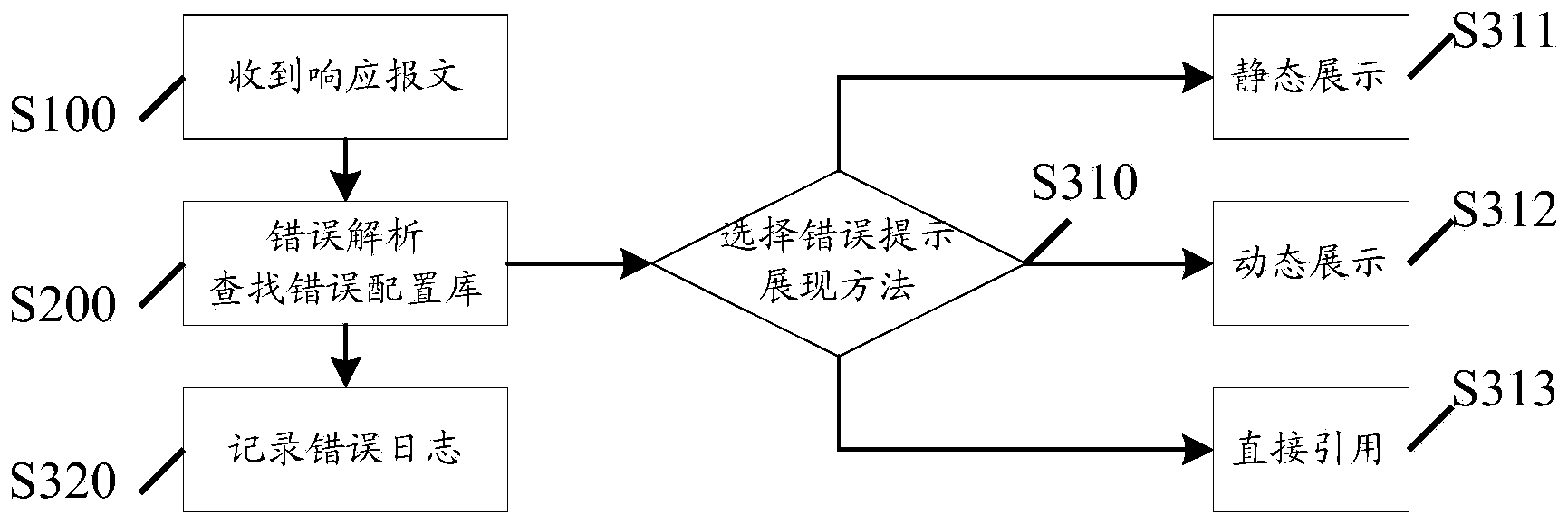

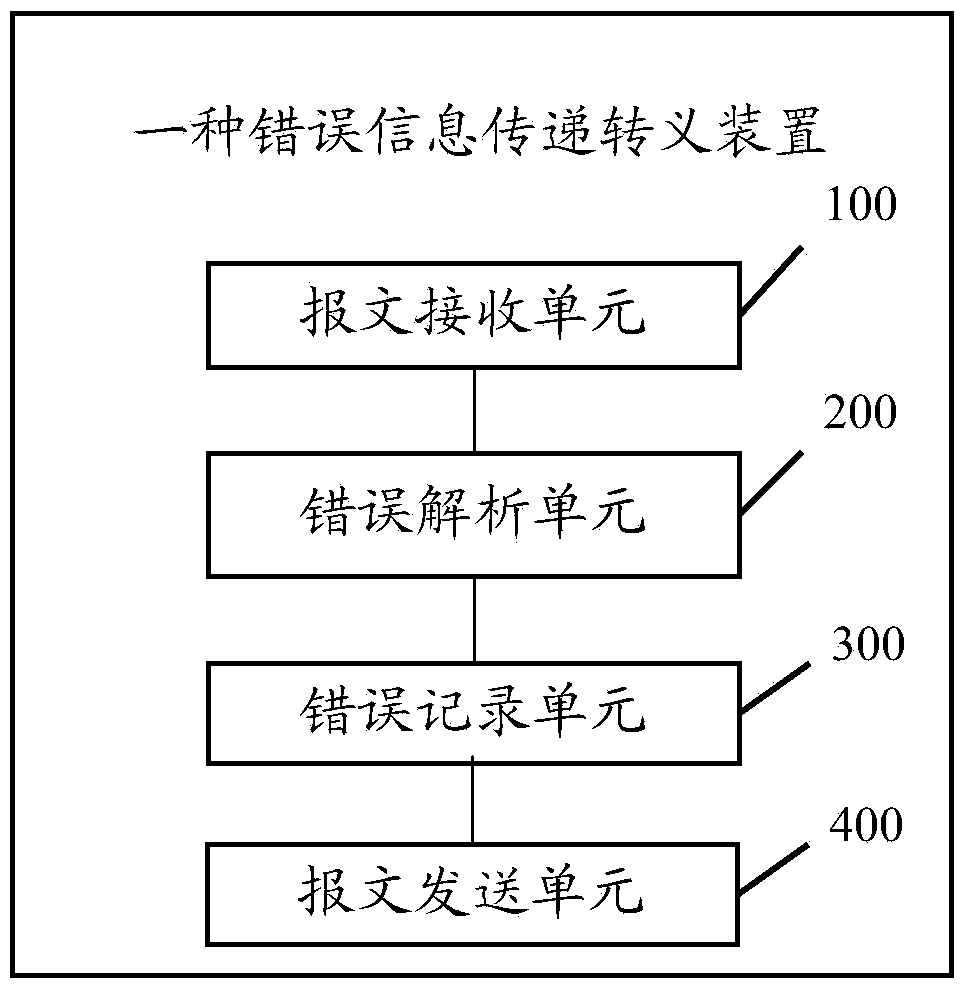

Error information transfer and escape method, error information transfer and escape device and error information transfer and escape system

ActiveCN104363072APrecise deliveryOptimization definitionTransmitted data organisation to avoid errorsTransfer systemTransfer error

The invention provides an error information transfer and escape method, an error information transfer and escape device and an error information transfer and escape system. The method includes: receiving a message sent by a server side and subjecting the message to error parsing so as to obtain error information; subjecting the error information to escaping according to a predefined error conversion standard; recording the error information subjected to escaping to a conversion error message and returning the conversion error message. The error information transfer and escape method, the error information transfer and escape device and the error information transfer and escape system have the advantages that the problem in the prior art that error codes are difficult to transfer and apply is solved, and defining and transferring error information in large-scale enterprise-level IT (information technology) systems are facilitated, so that the purposes that the error information is parsed correctly and transferred accurately are achieved, and better customer experience and a more perfect error code transfer system are provided.

Owner:CHINA CONSTRUCTION BANK

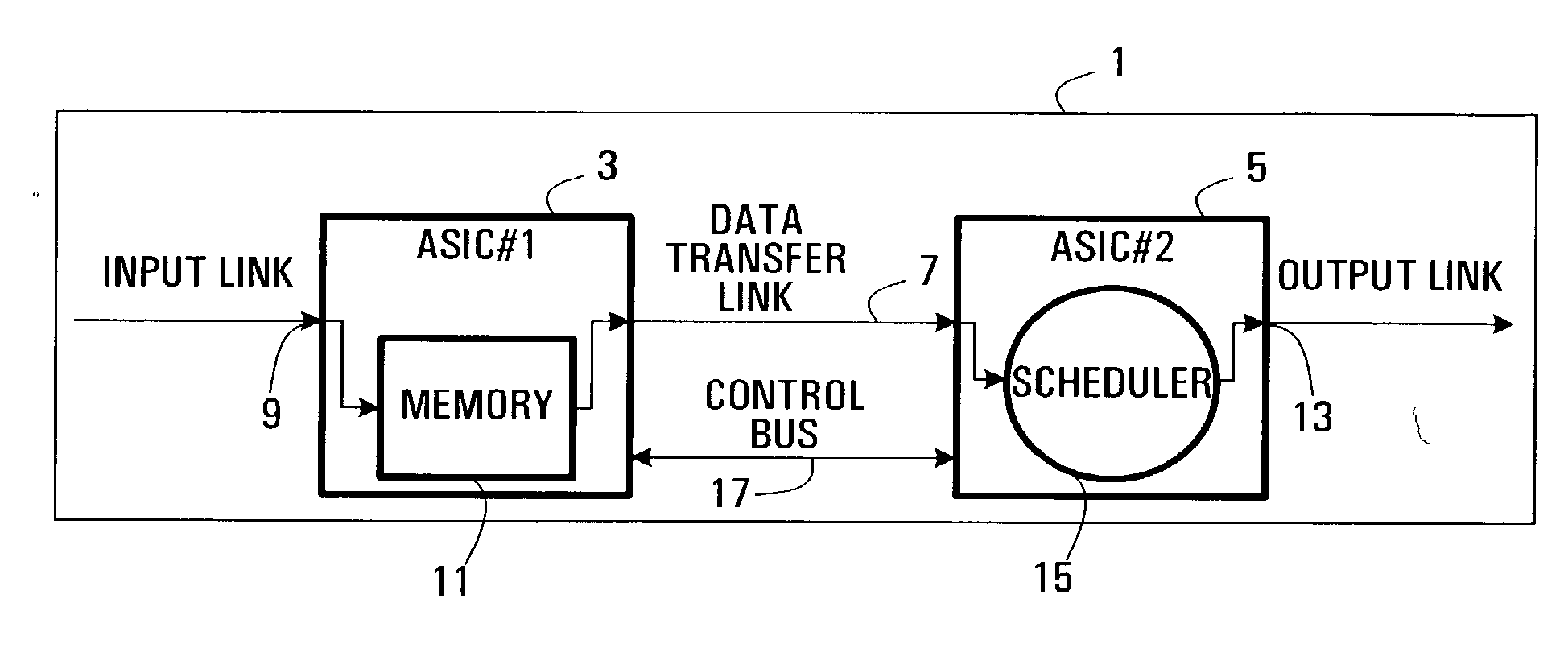

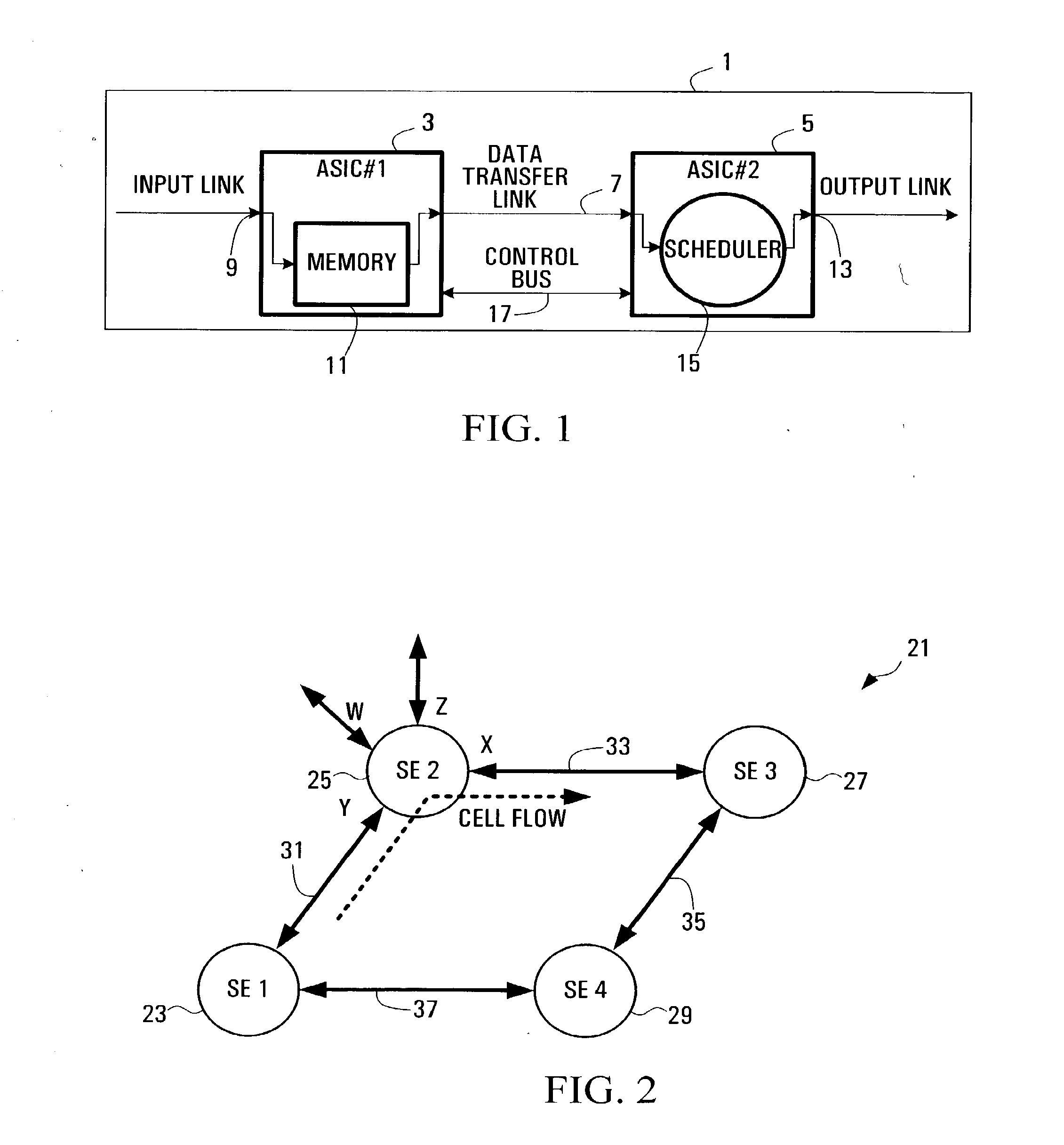

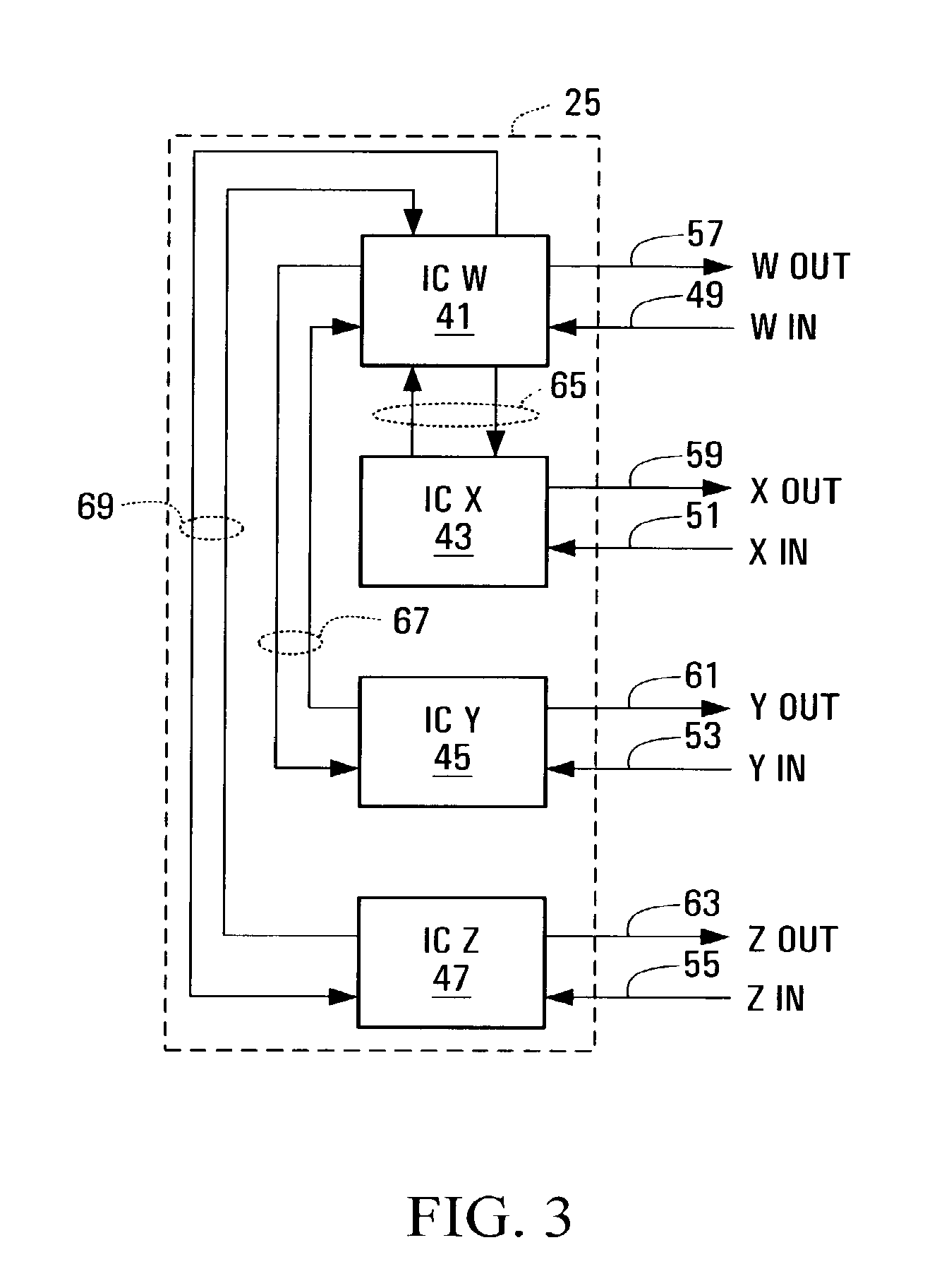

Apparatus and method for controlling data transmission

ActiveUS20100155493A1Simple methodPromote disseminationParallel/series conversionError detection/correctionControl signalControl data

An interface for controlling the transmission of data between integrated circuit (IC) chips. The interface comprises a data bus for transmitting data from a first integrated circuit chip to a second integrated circuit chip, and a control bus for transmitting control signals between the first and second integrated circuits. The first IC has a memory for receiving data for transmission to the second IC, and the second IC has a scheduler and a data output port, the scheduler being arranged to control the transfer of data from the memory of the first IC to the data output port of the second IC via the data bus. The interface is capable of stopping and reinitiating data transmission on detection of errors in transmitted data, and the interface may include a code transfer bus for transferring error detection code separately from associated data.

Owner:ALCATEL LUCENT CANADA +1

Method and System for Charged-Particle Beam Lithography

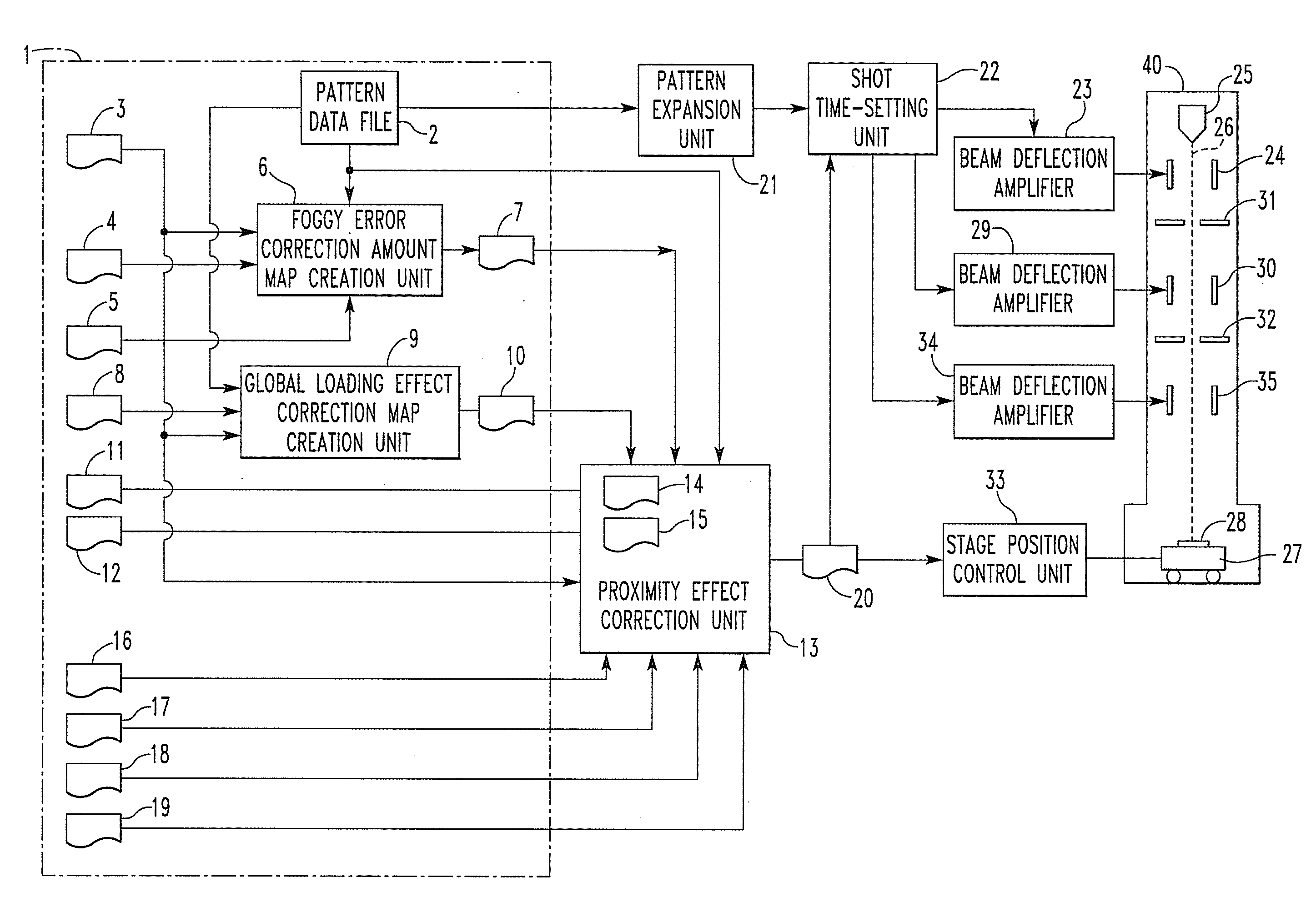

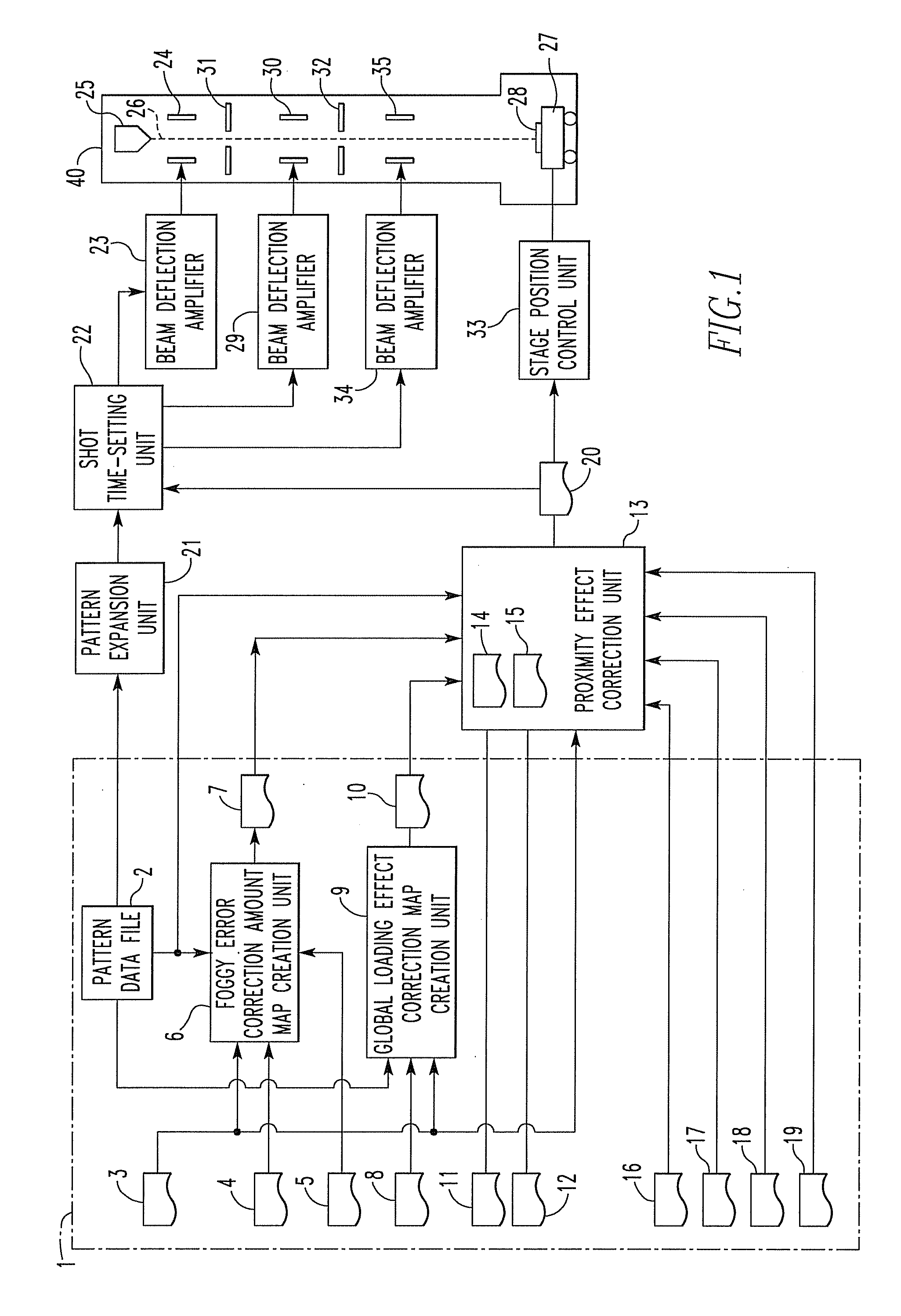

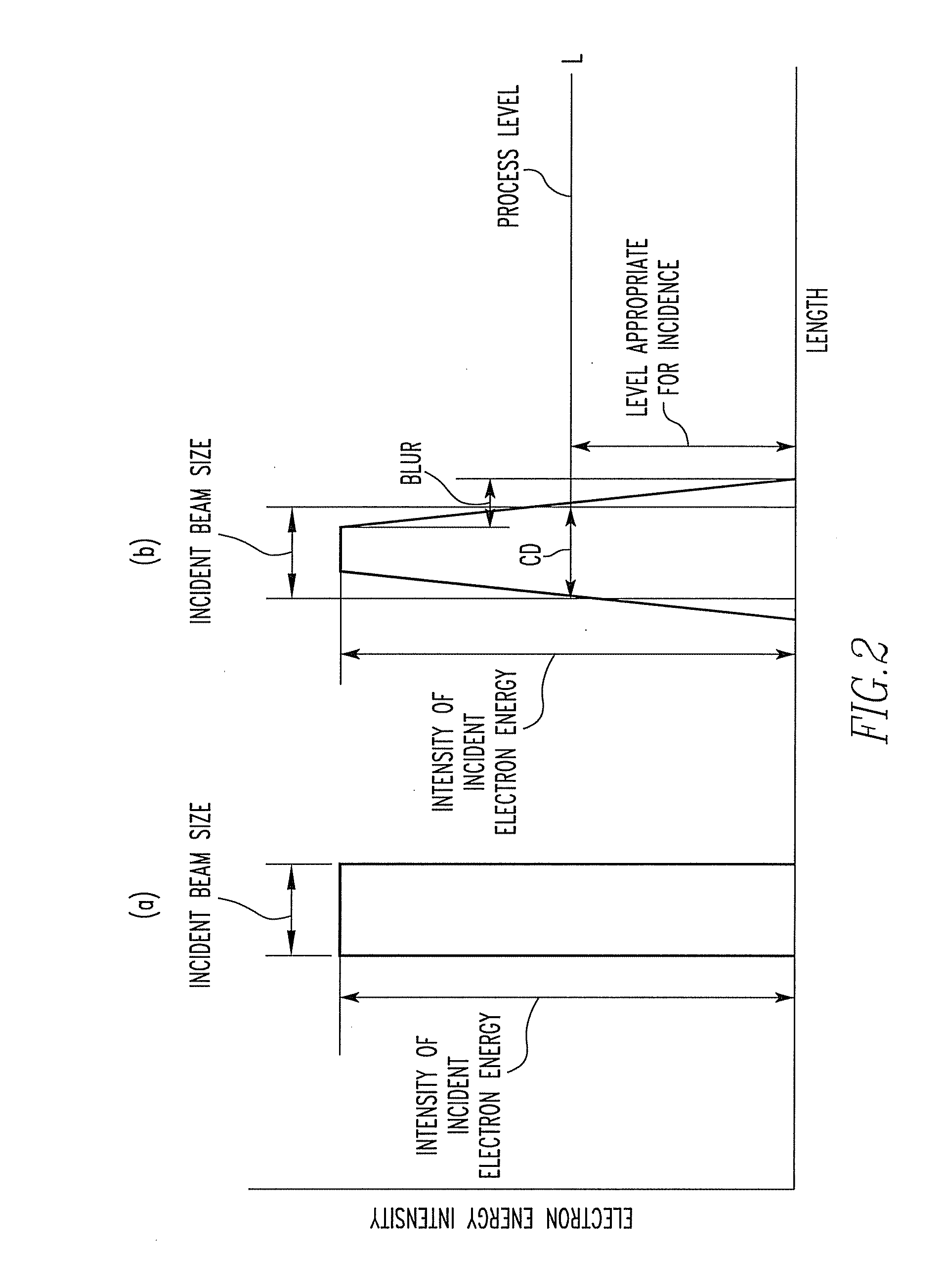

InactiveUS20090032739A1Improve accuracySimple processElectric discharge tubesNanoinformaticsLithographic artistProcess error

Charged-particle beam lithography method and system. The lithography system has a map creation unit and a lithographic data creation unit. The map creation unit creates a proximity effect correction amount map from pattern data supplied from a pattern data file, pattern layout information, a foggy error correction amount map, loading effect correction amount maps, a process error correction amount map, a transfer error correction amount map, proximity effect correction parameters, and a proximity effect correction map. The lithographic data creation unit creates lithographic data based on the pattern data from the pattern data file, creates shot time data based on the proximity effect correction amount map from the map creation unit, and attaches the created shot time data to the lithographic data.

Owner:JEOL LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com