Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

767 results about "Error checking" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Error checking tests assess a candidate’s ability to identify errors in data sets and assess the correctness of information. They are also known as Data checking tests. Candidates are required to complete error checking tests under timed test conditions.

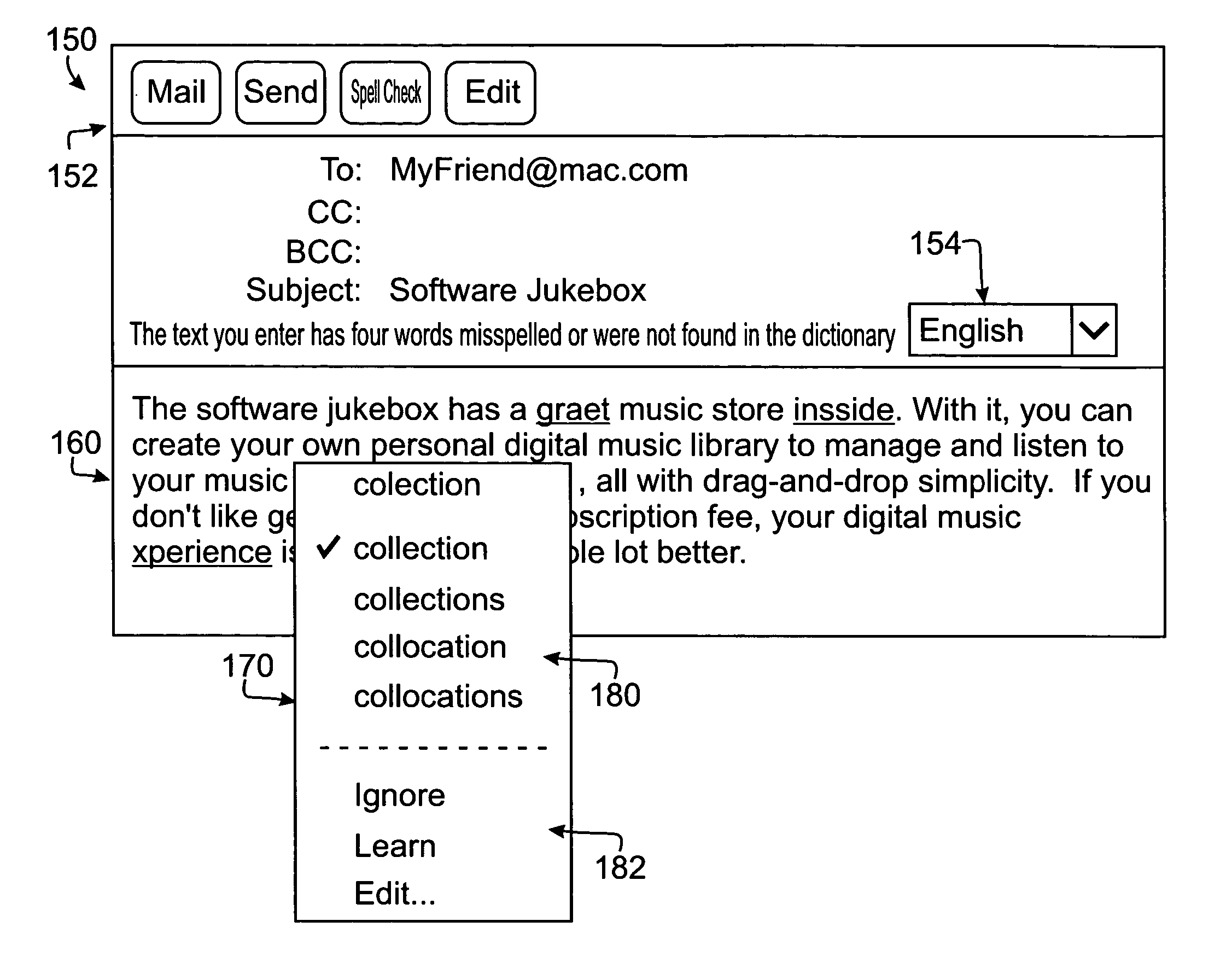

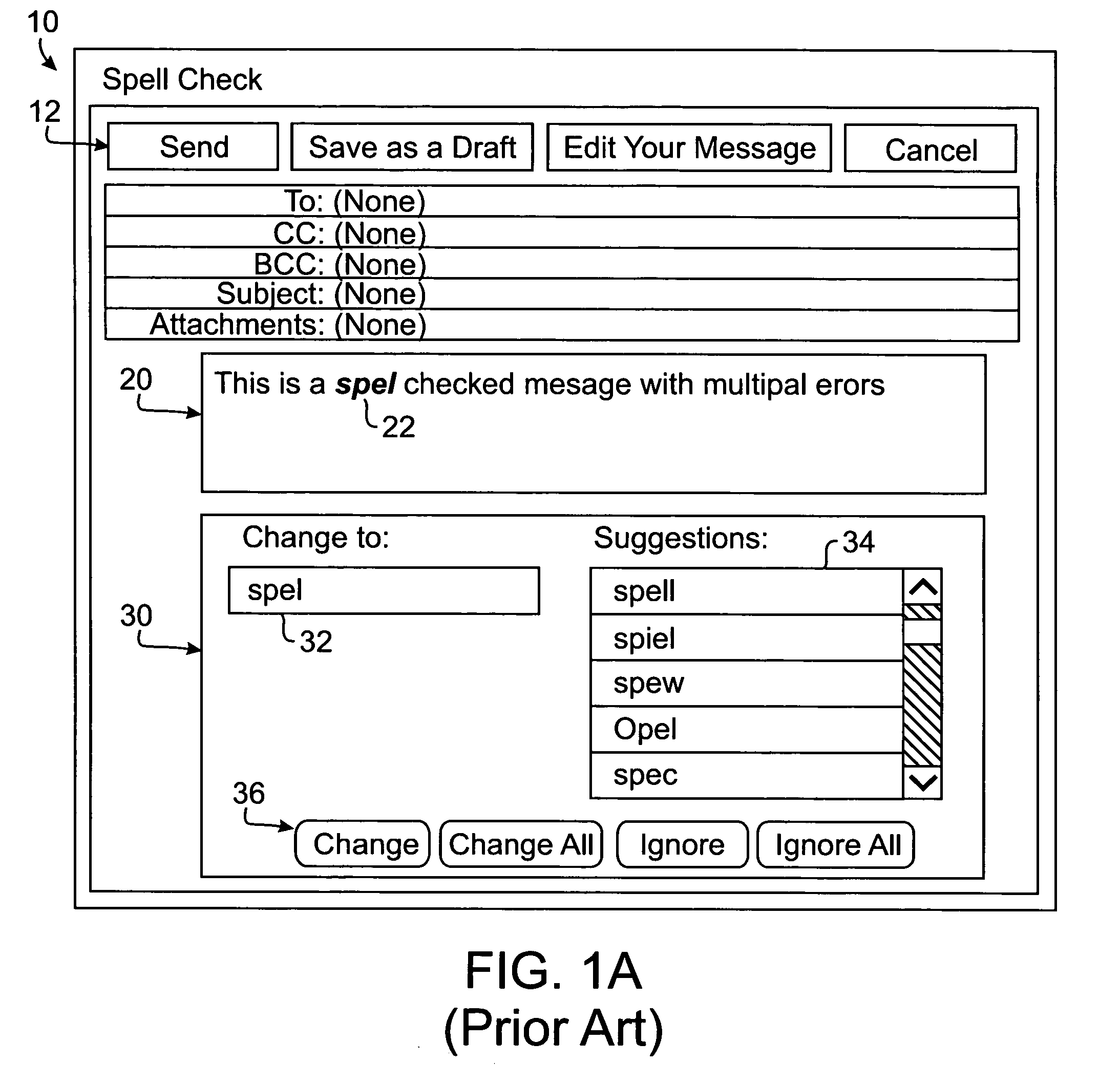

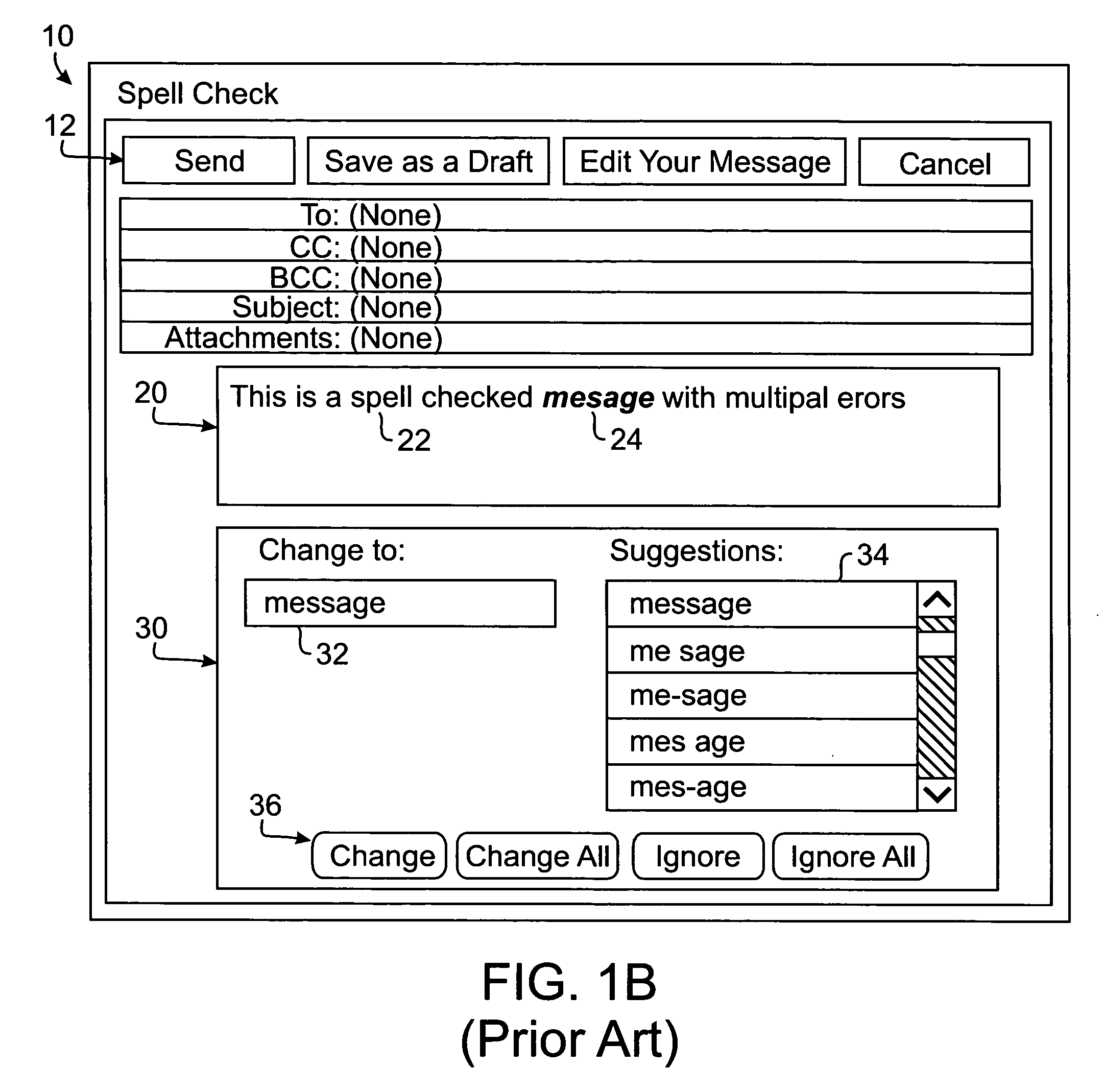

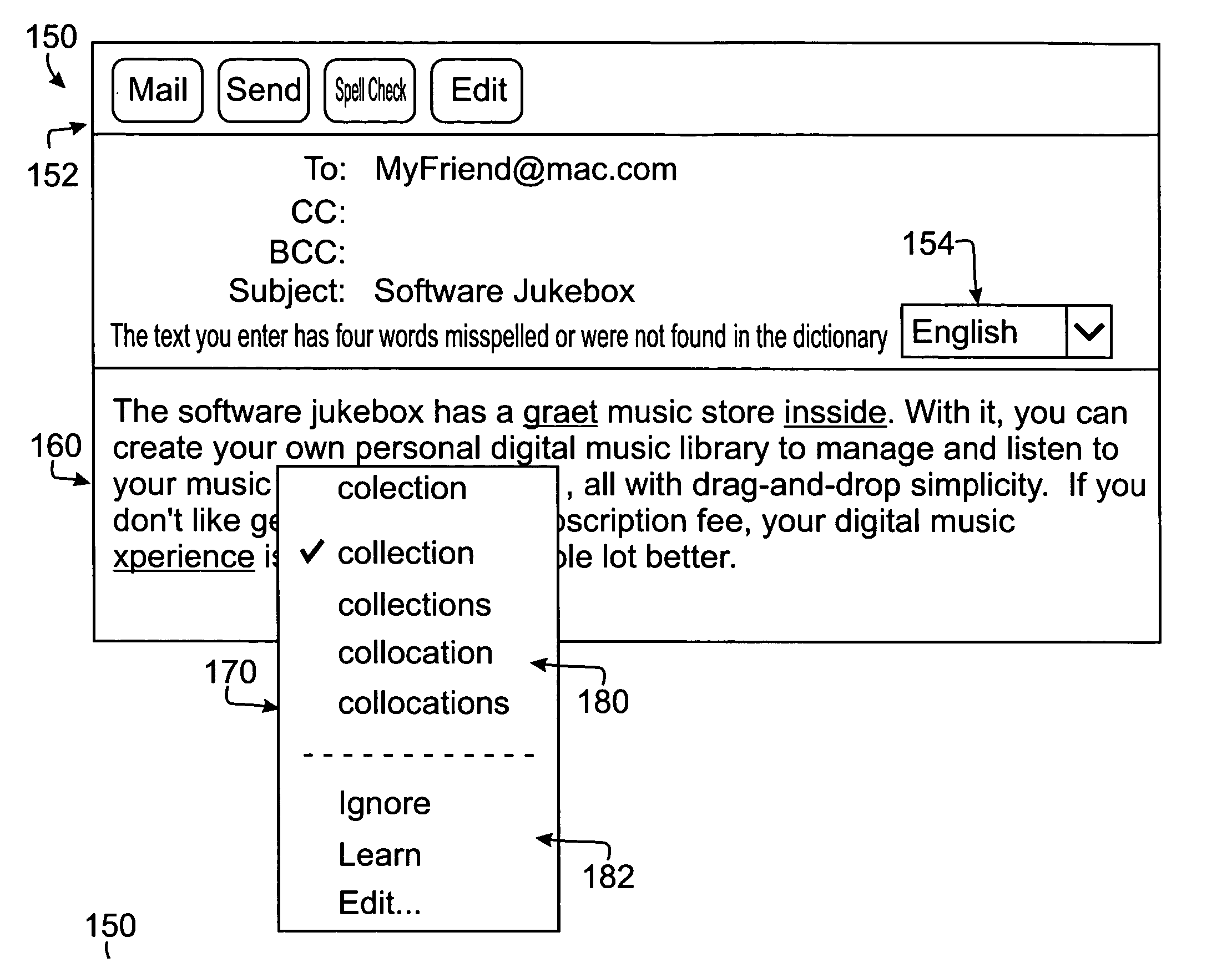

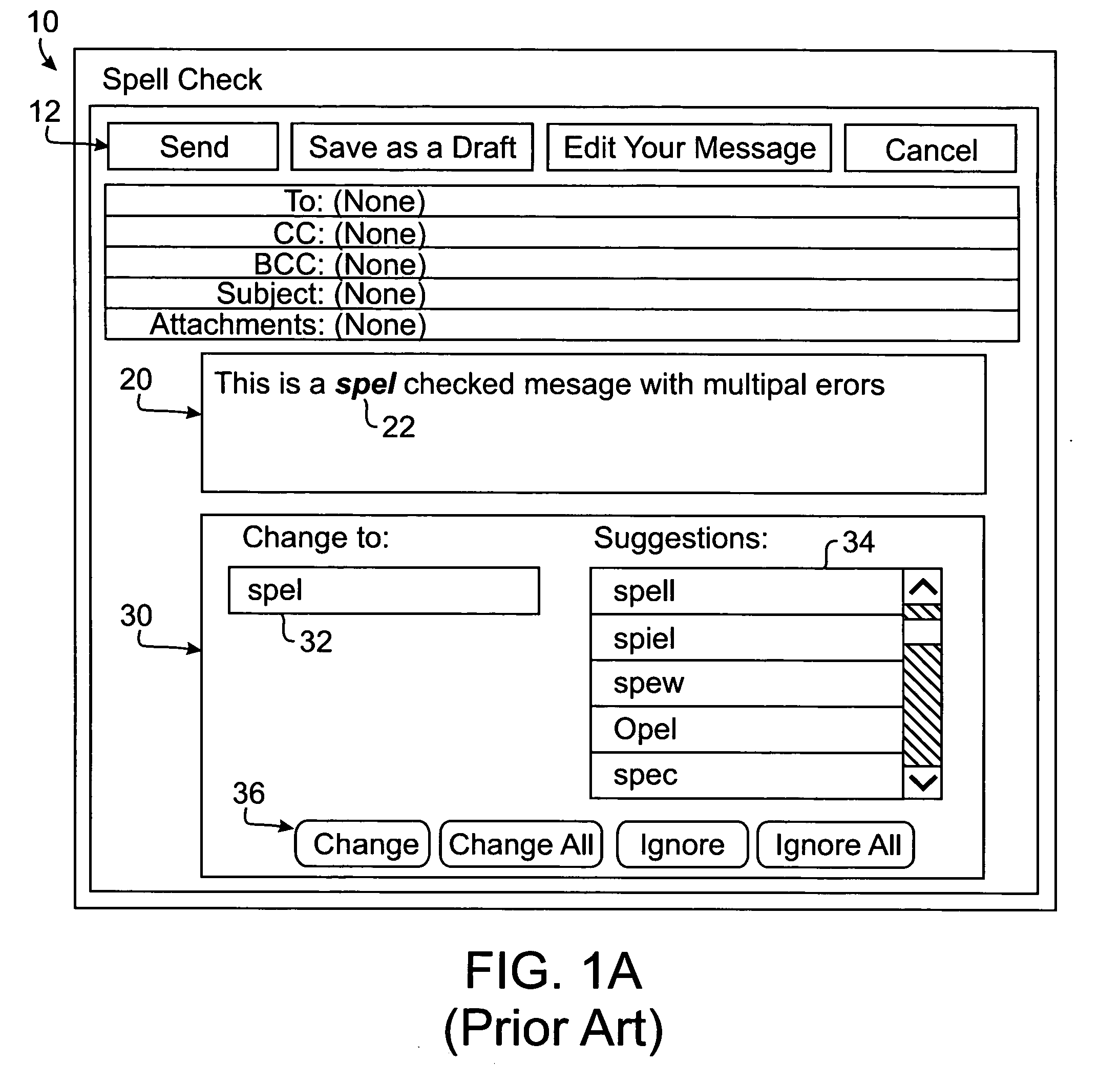

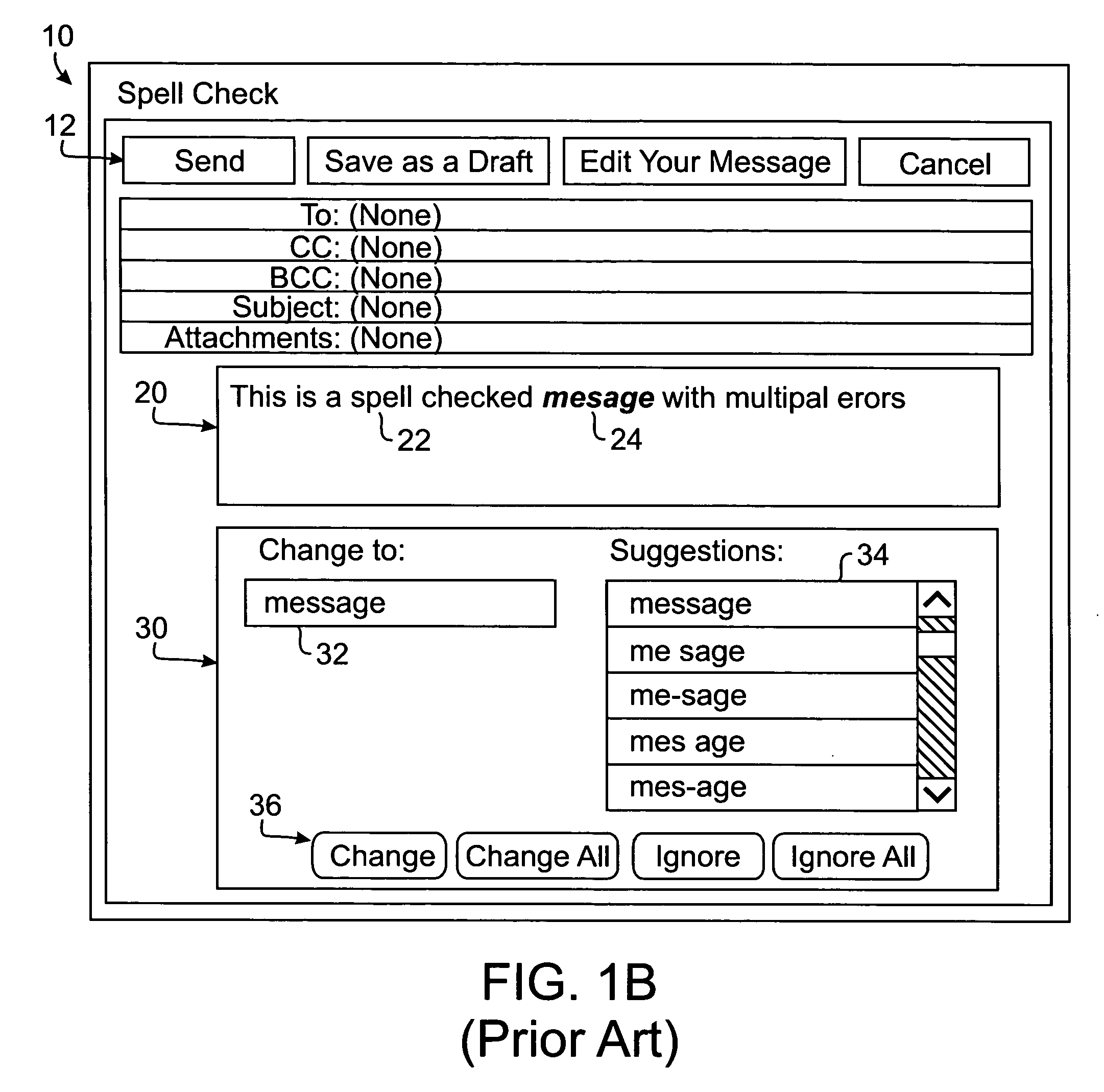

Routine and interface for correcting electronic text

ActiveUS8321786B2Easy to correctNatural language data processingSpecial data processing applicationsError checkingApplication software

Error checking and correction techniques for web based applications use an error checking routine on a server or a client station to find errors in electronic text of an E-mail message. The disclosed error checking routine detects errors such as spelling errors in the electronic text and creates a correction file of the electronic text containing tags, markers and other information allowing errors to be displayed and corrected using the user's graphical interface. The graphical interface allows the user to review all the errors concurrently in the correction file and to correct the errors in any order. In a preferred embodiment, correction is facilitated in response to the user moving a mouse pointer over an error of interest, which provides correction options to be displayed in-line with the original text. The user can then select a suitable correction to correct the error.

Owner:APPLE INC

Routine and interface for correcting electronic text

ActiveUS20050283726A1Easy to correctNatural language data processingSpecial data processing applicationsError checkingCorrection technique

Error checking and correction techniques for web based applications use an error checking routine on a server or a client station to find errors in electronic text of an E-mail message. The disclosed error checking routine detects errors such as spelling errors in the electronic text and creates a correction file of the electronic text containing tags, markers and other information allowing errors to be displayed and corrected using the user's graphical interface. The graphical interface allows the user to review all the errors concurrently in the correction file and to correct the errors in any order. In a preferred embodiment, correction is facilitated in response to the user moving a mouse pointer over an error of interest, which provides correction options to be displayed in-line with the original text. The user can then select a suitable correction to correct the error.

Owner:APPLE INC

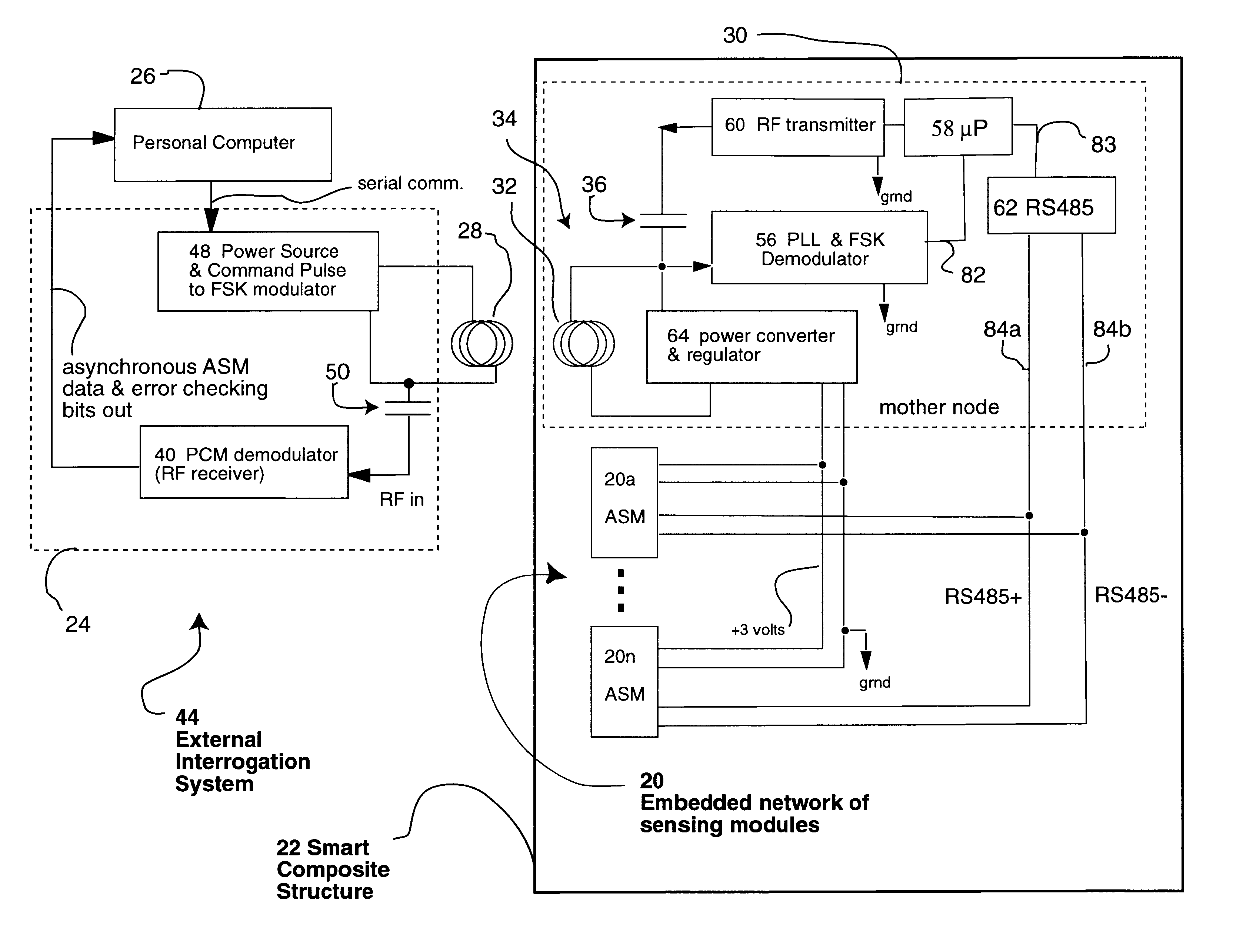

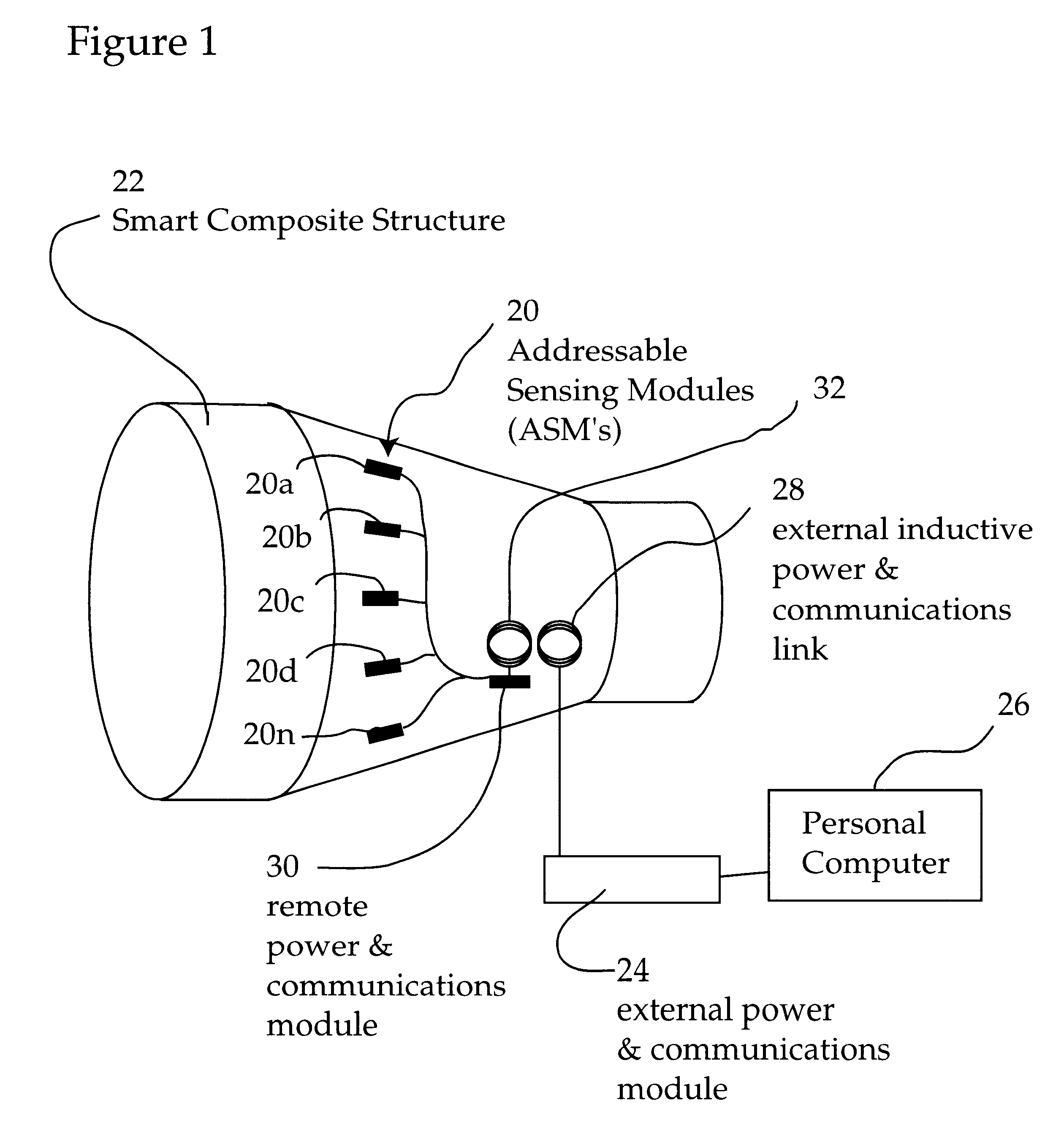

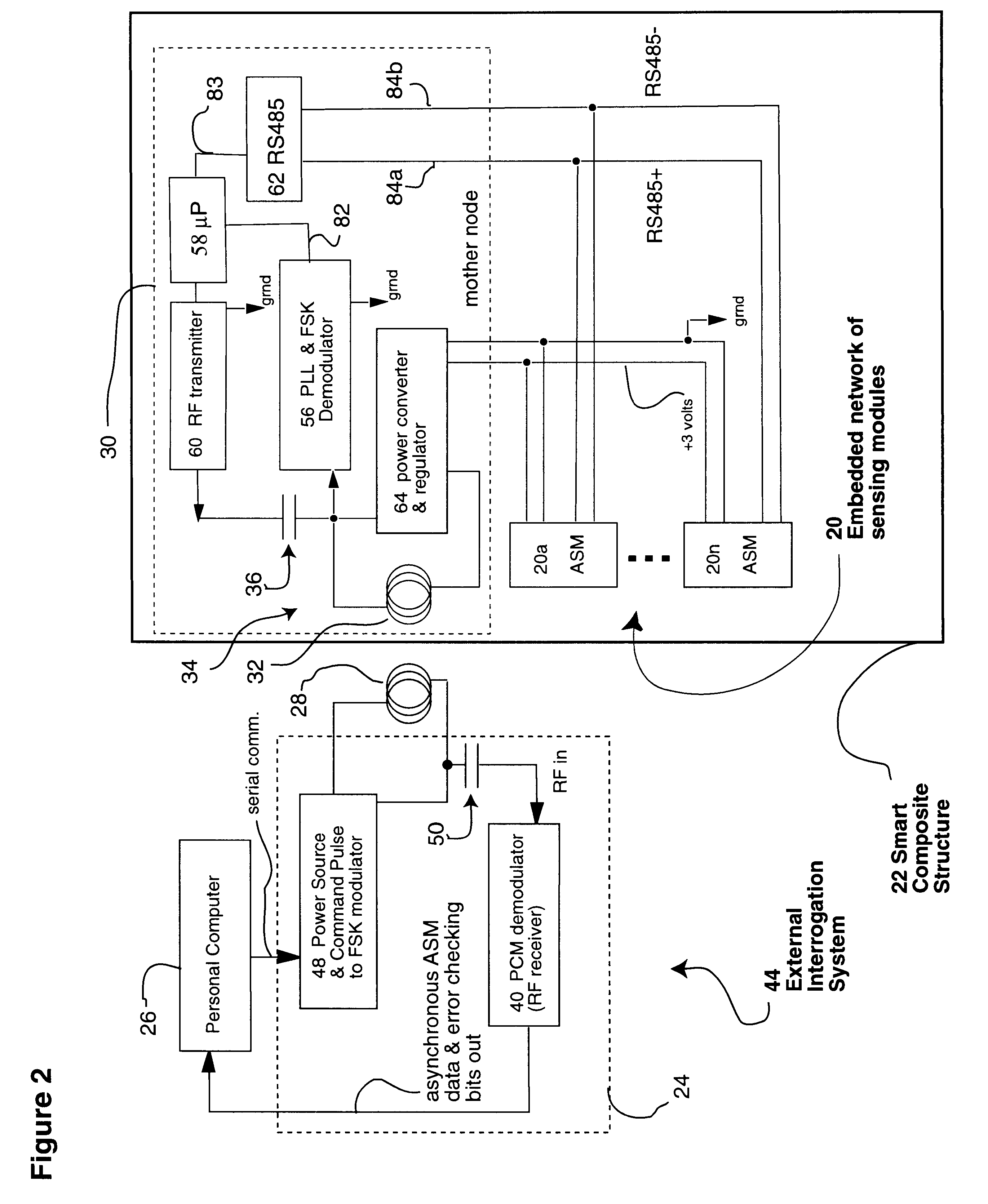

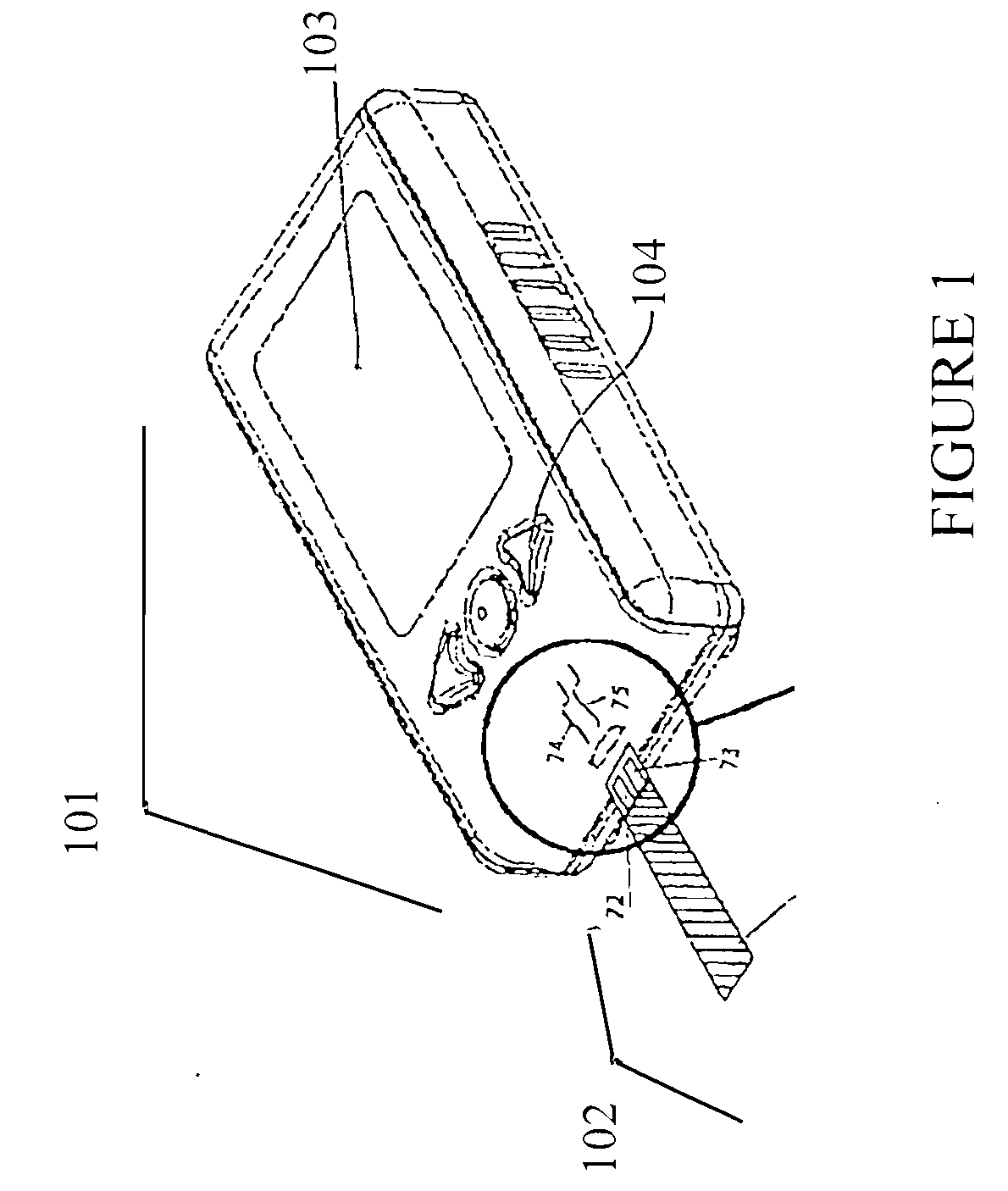

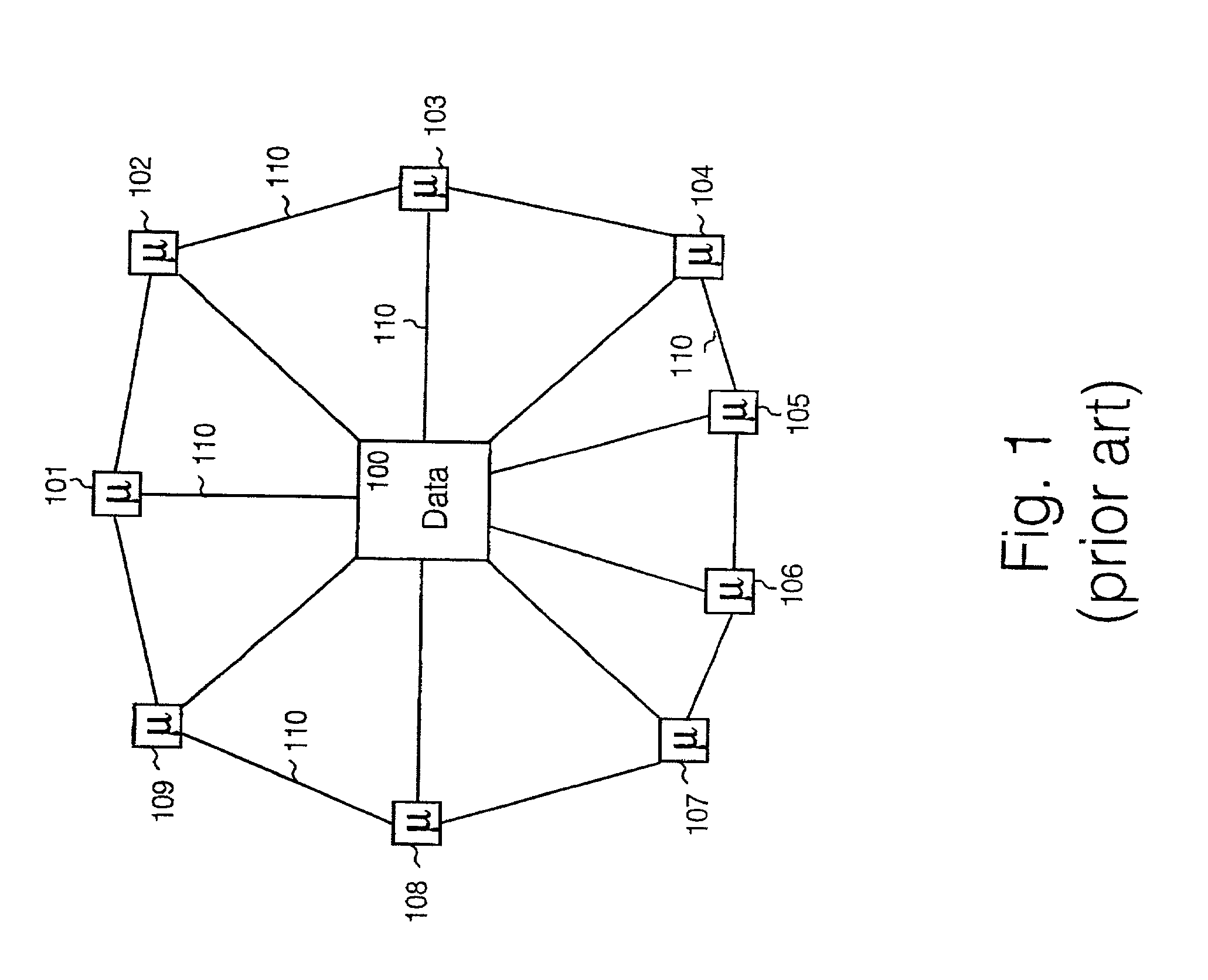

System for remote powering and communication with a network of addressable, multichannel sensing modules

InactiveUS6529127B2Low costElectric signal transmission systemsDigital data processing detailsError checkingInstrumentation amplifier

A multidrop network of multichannel, addressable sensing modules (ASM's), to be embedded within a composite structure, remotely powered, and interrogated by a personal computer through a non-contacting inductive link. Each ASM contains a microprocessor with non-volatile memory, multiplexer, programmable gain and filter instrumentation amplifier, and sigma delta analog to digital converter (all housed in two thin surface mount packages). An embedded mothernode includes circuitry for power and data reception (into the structure), and data transmission (back out of the structure). The external interrogation system communicates into the network of ASM's by modulating the AC waveform that delivers power to the embedded electronics. Once addressed, each ASM powers up its programmable (gain & filter) sensing channels (3 full differential or 5 pseudo differential) and data conversion elements. Sensed data are pulse code modulated, including error checking, which serially modulate an RF carrier for wireless transmission out of the composite to the interrogating computer. These advanced, micro-miniature sensing networks may be applied to a wide variety of military, medical, & civil structures.

Owner:LORD CORP

Distortion resistant double-data correcting color transition barcode and method of generating and using same

InactiveUS6070805AEliminate useDigitally marking record carriersRecord carriers used with machinesError checkingLinear growth

A color barcode symbology is disclosed that can be accurately decoded despite severe distortions, misreads or altered symbols. This disclosed barcode is a color transition barcode having linear growth properties designed to resist the single or combined effects of: scaling distortions, perspective distortions, shear distortions, and wave distortions of both the uniform and non-uniform type distributed across the barcode's vertical or horizontal axis. This color barcode symbology is also resistant to missing symbols and altered symbols while offering, high security, error checking, and double error correcting capability.

Owner:ZEBRA TECH CORP

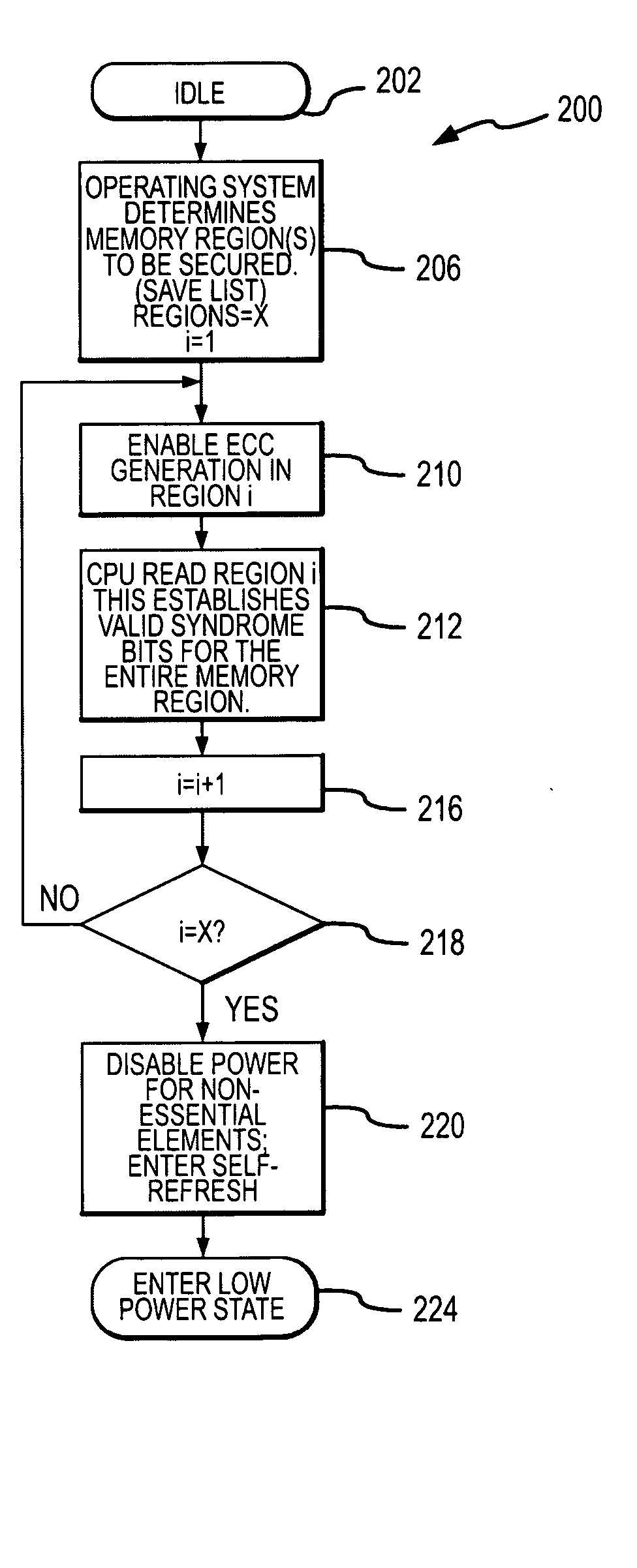

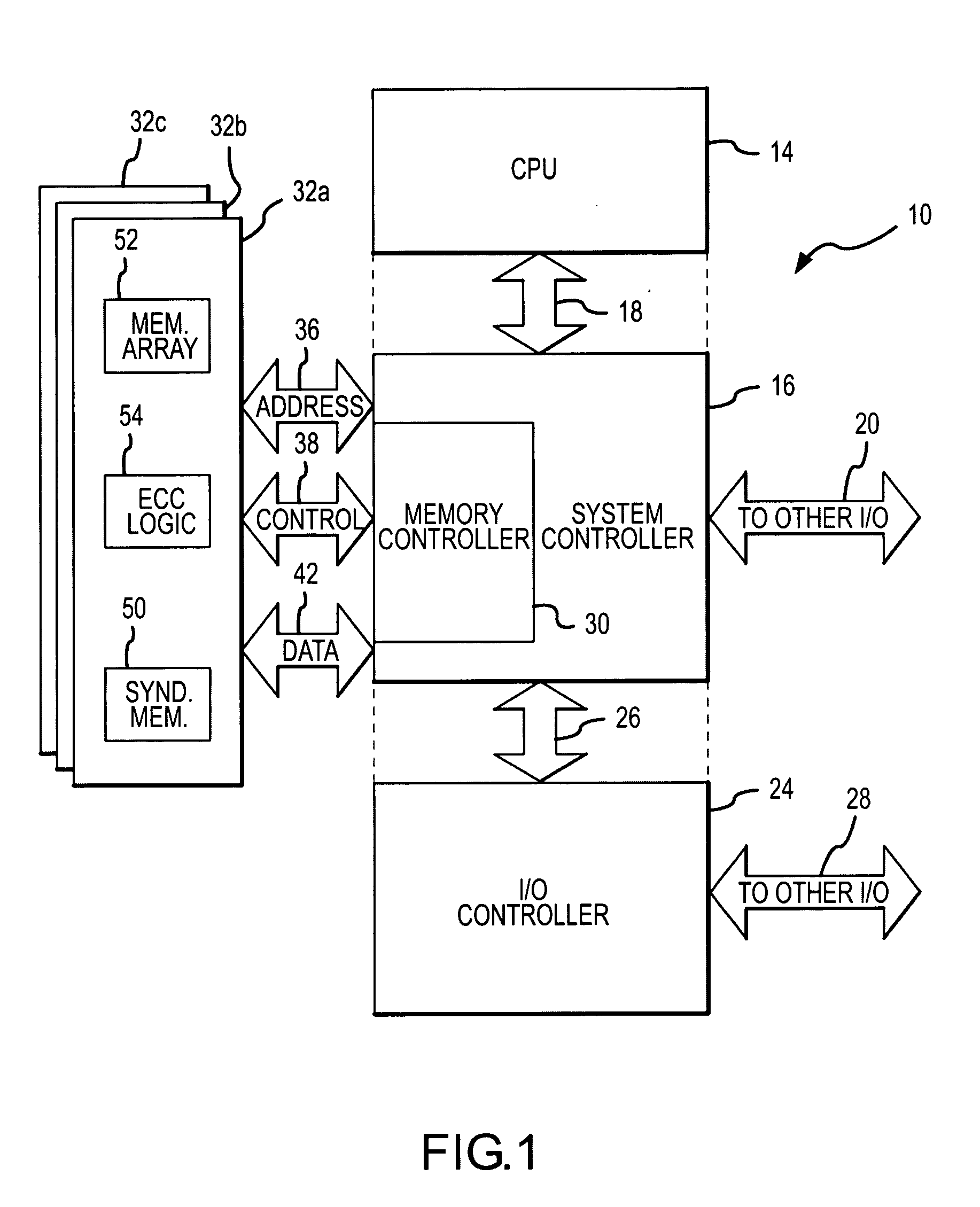

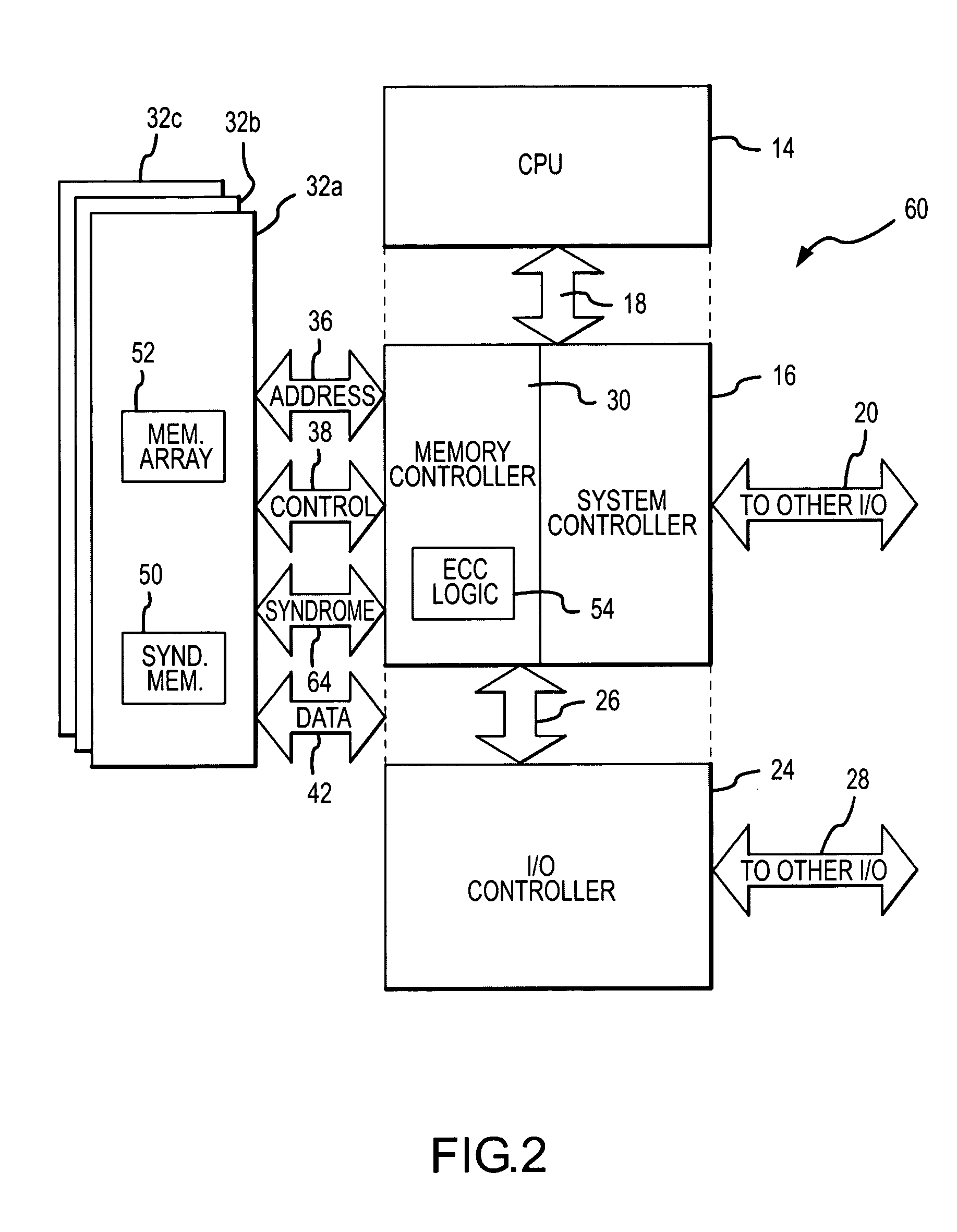

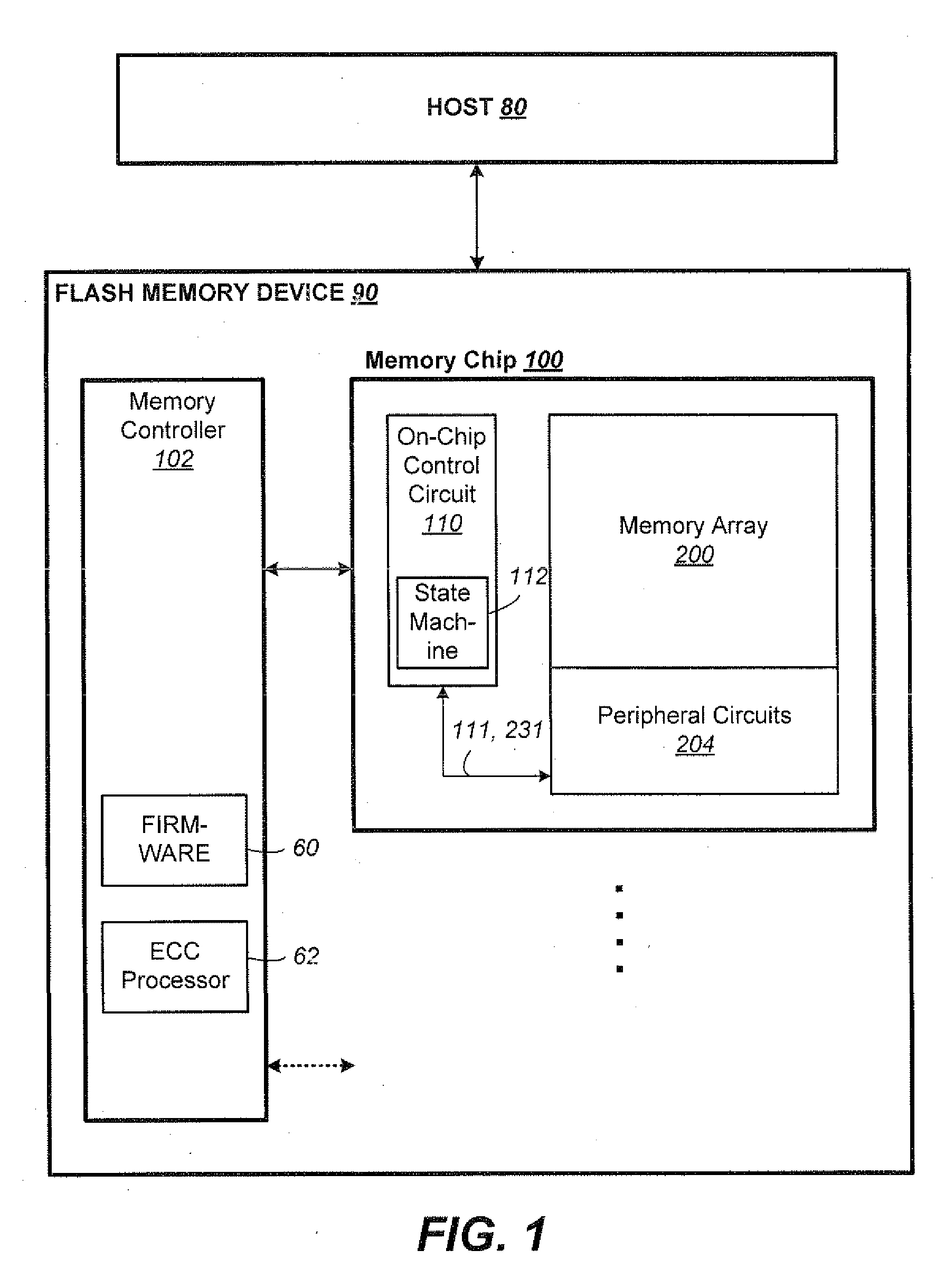

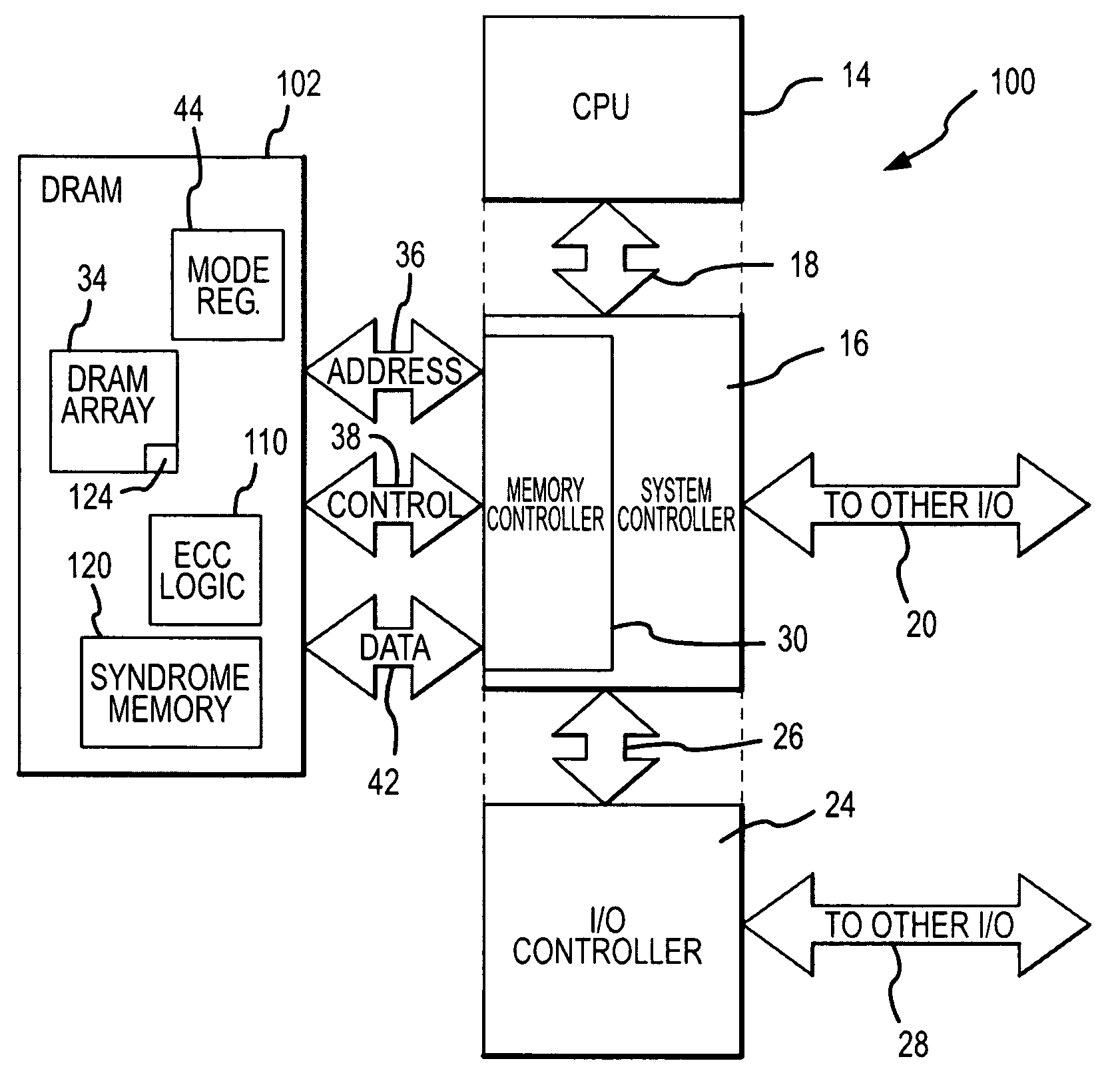

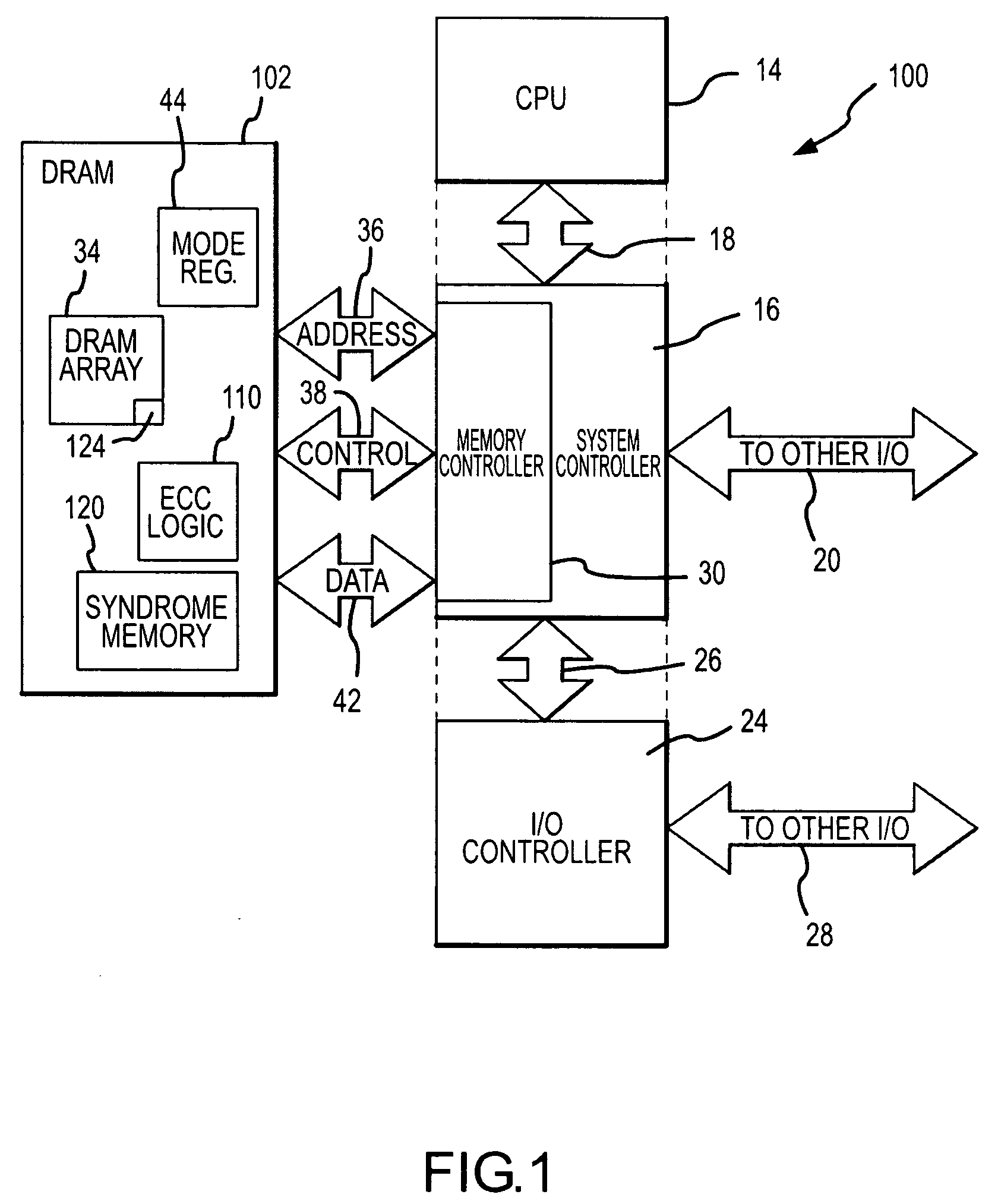

Memory system and method having selective ECC during low power refresh

InactiveUS20060010339A1Reduced power ratingMemory loss protectionError avoidanceError checkingMemory controller

A computer system includes a processor coupled to a DRAM through a memory controller. The processor switches the DRAM to a low power refresh mode in which DRAM cells are refreshed at a sufficiently low rate that data retention errors may occur. Prior to switching the DRAM to the low power refresh mode, the processor identifies a region of an array of DRAM cells that contains essential data that needs to be protected from such data retention errors. The processor then reads data from the identified region, and either the DRAM or the memory controller generates error checking and correcting syndromes from the read data. The syndromes are stored in the DRAM, and the low power refresh mode is then entered. Upon exiting the low power refresh mode, the processor again reads the data from the identified region, and the read data is checked and corrected using the syndromes.

Owner:MICRON TECH INC

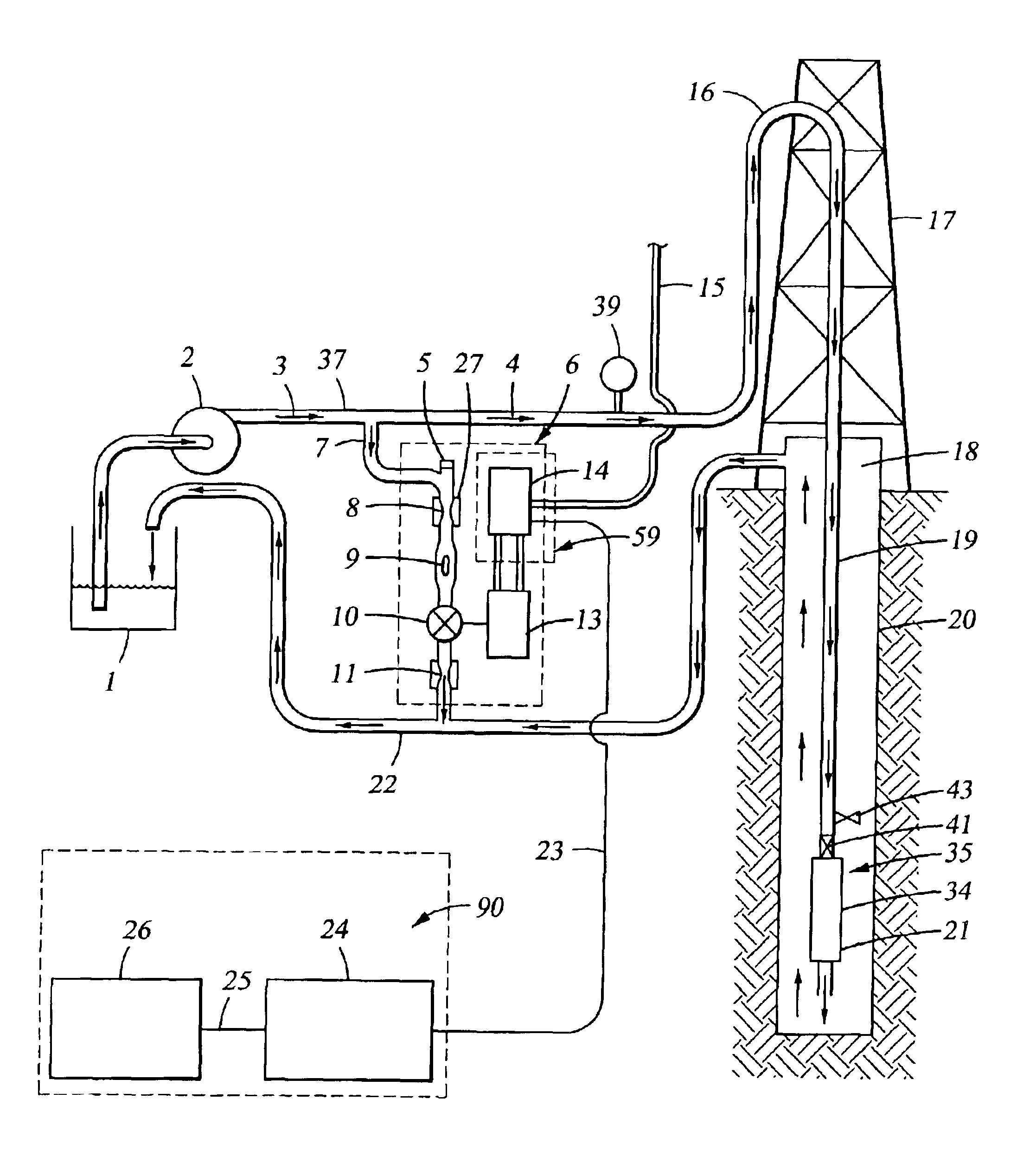

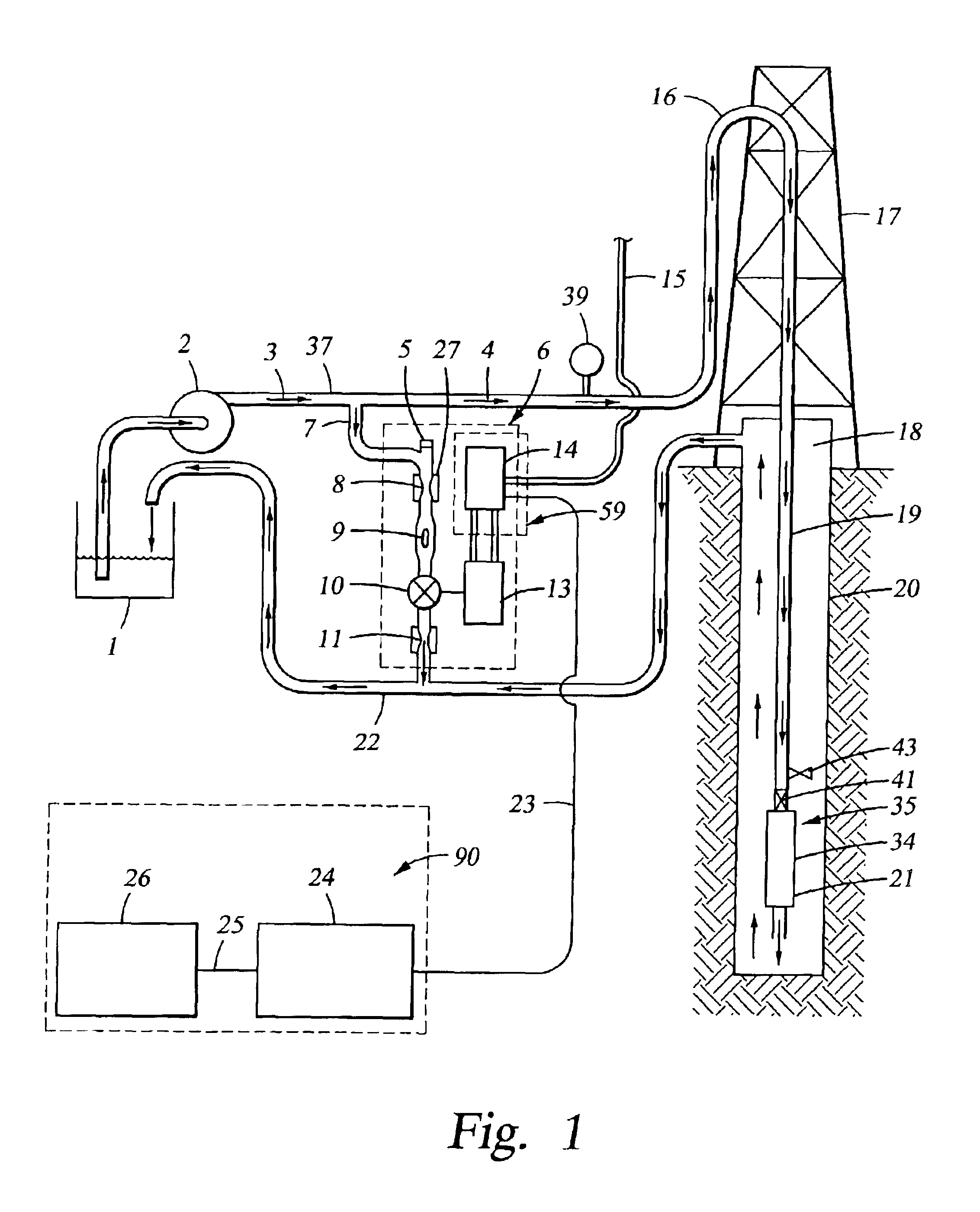

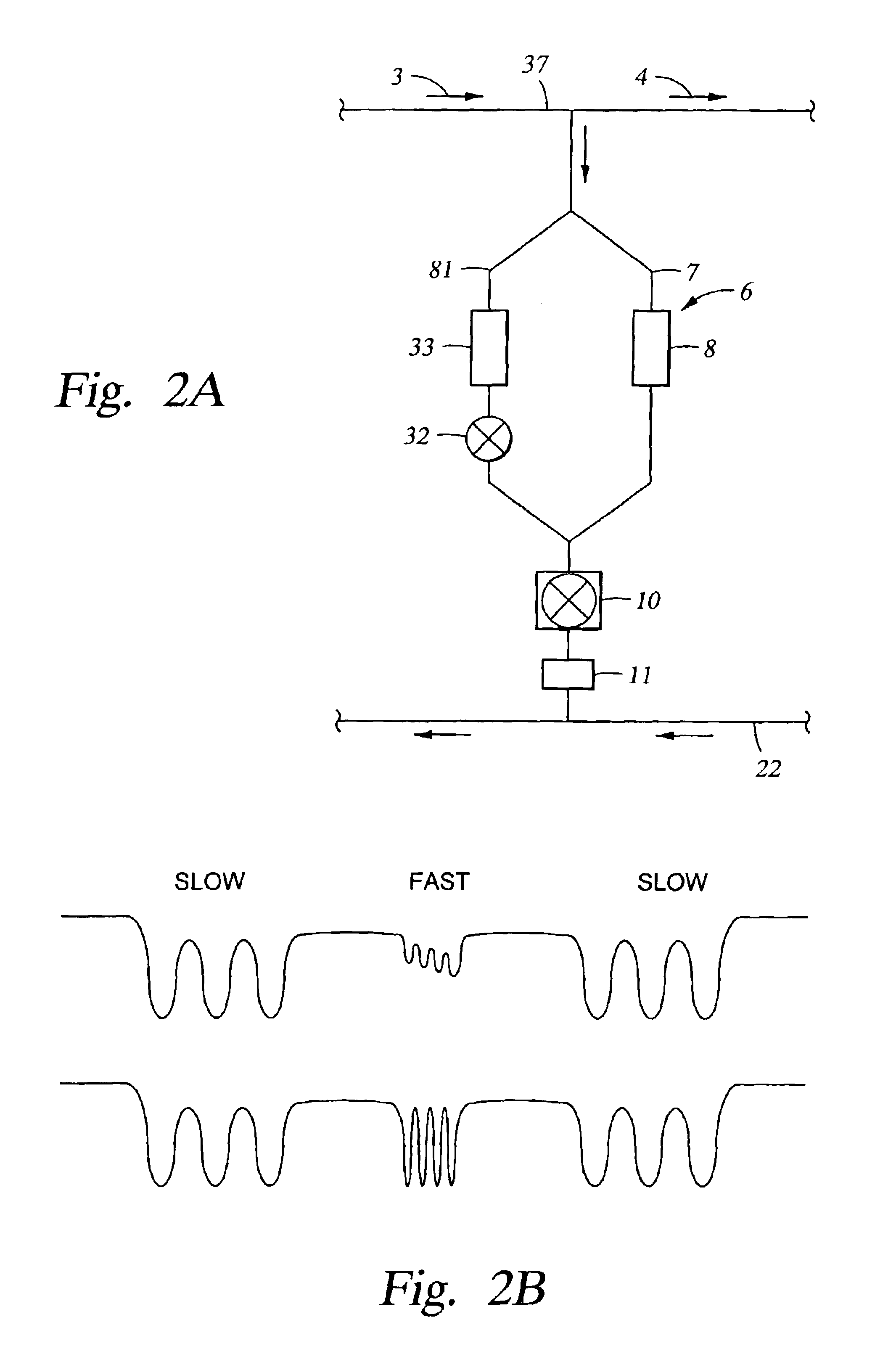

Downlink telemetry system

InactiveUS6920085B2Shorten the timeGuaranteed accuracySurveyConstructionsError checkingControl system

A downlink telemetry system providing improved apparatus and methods for communicating instructions via pressure pulses from surface equipment to a downhole assembly. The apparatus comprises a surface transmitter for generating pressure pulses, a control system, and a downhole receiver for receiving and decoding pulses.In operation, a bypass valve is opened and closed to create a series of pressure pulses received and decoded by a downhole receiver. The method significantly reduces the time required for downlink communication without interrupting drilling and without interrupting uplink communications such that simultaneous, bi-directional communication is achievable if the uplink and downlink signals are sent at different frequencies.The telemetry scheme and algorithm provide an inventive method for filtering and decoding the downlink signals. The algorithm determines the time intervals between pulse peaks and decodes the intervals into an instruction. The algorithm also includes error checking for verifying that the instruction was properly received downhole.

Owner:HALLIBURTON ENERGY SERVICES INC

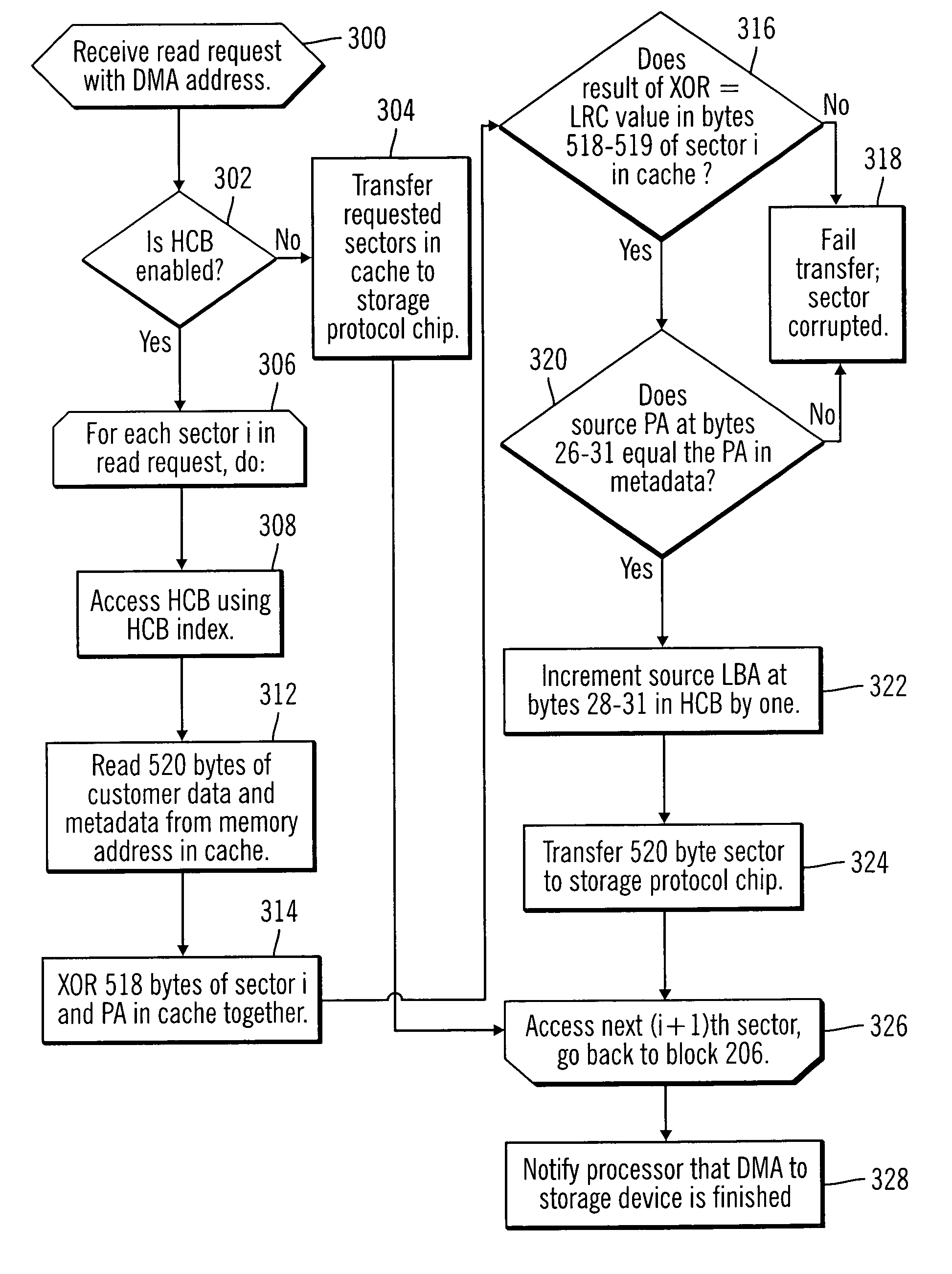

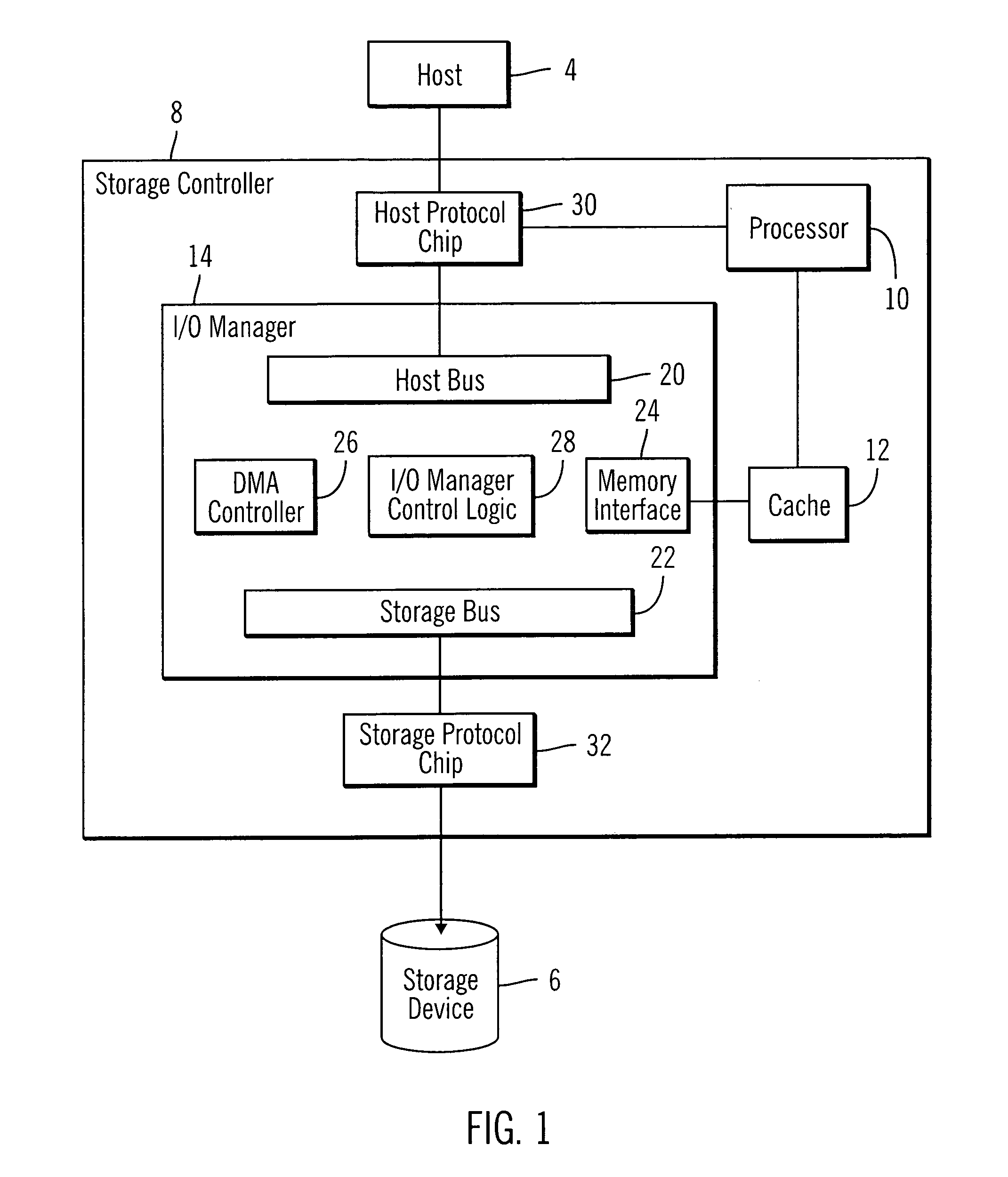

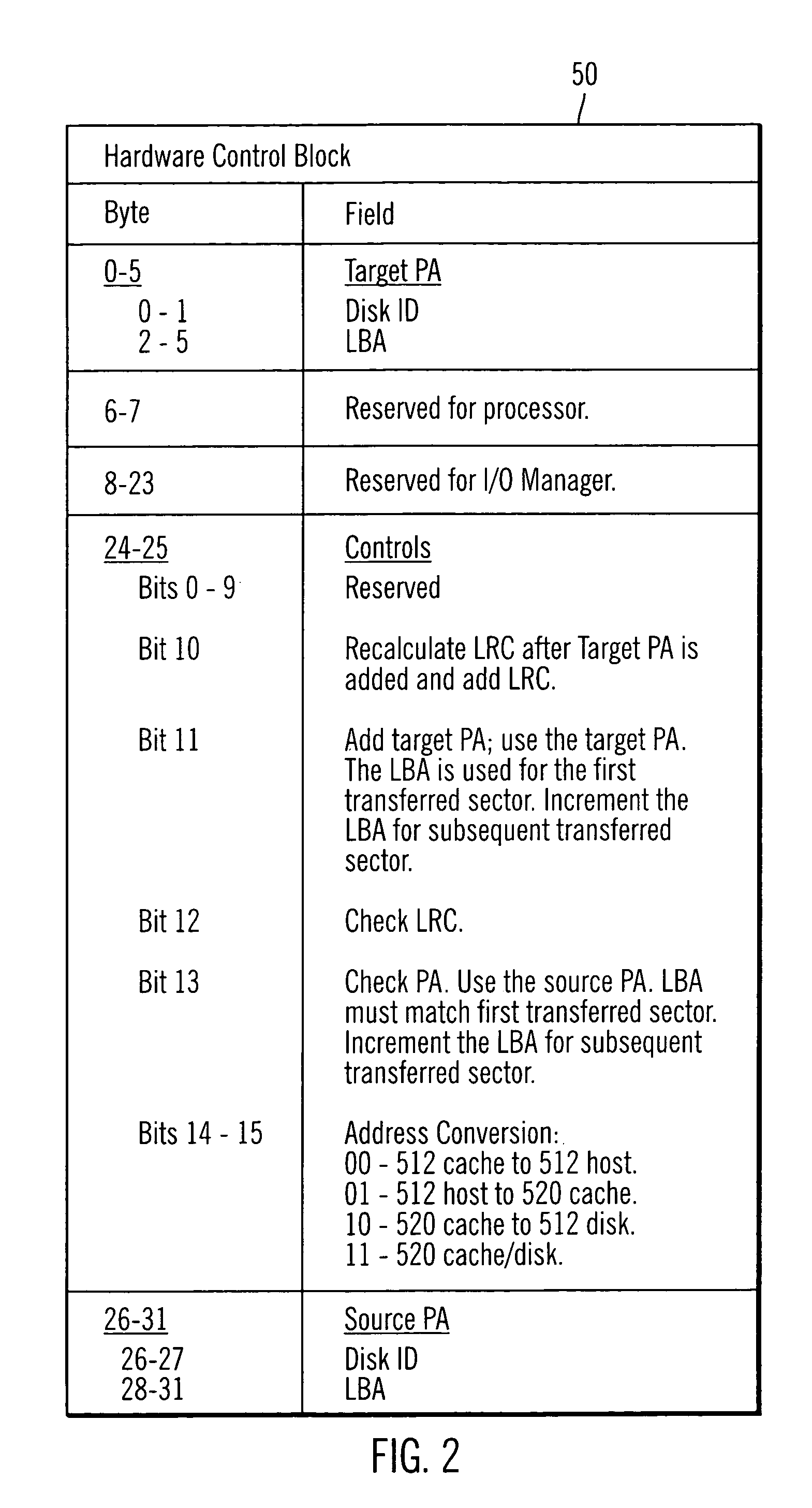

Method, system, and data structures for using metadata in updating data in a storage device

InactiveUS6928521B1RelievingRelieving the storage controller main processorMemory adressing/allocation/relocationError checkingMetadata

Disclosed is a method, system, and data structures for updating data in a storage device. An update to one or more blocks of customer data at addresses in the storage device is received. For each block of data to update, metadata is generated indicating the address of the block in the storage device and an error checking code that is capable of being used to determine whether the customer data in the block has changed. For each block of data to update, the block of data to update and the metadata for the block are written to cache. Further, for each block of data to update, the block of data and the metadata are transferred for the block from the cache to the storage device. The metadata may be used during power loss and recovery.

Owner:IBM CORP

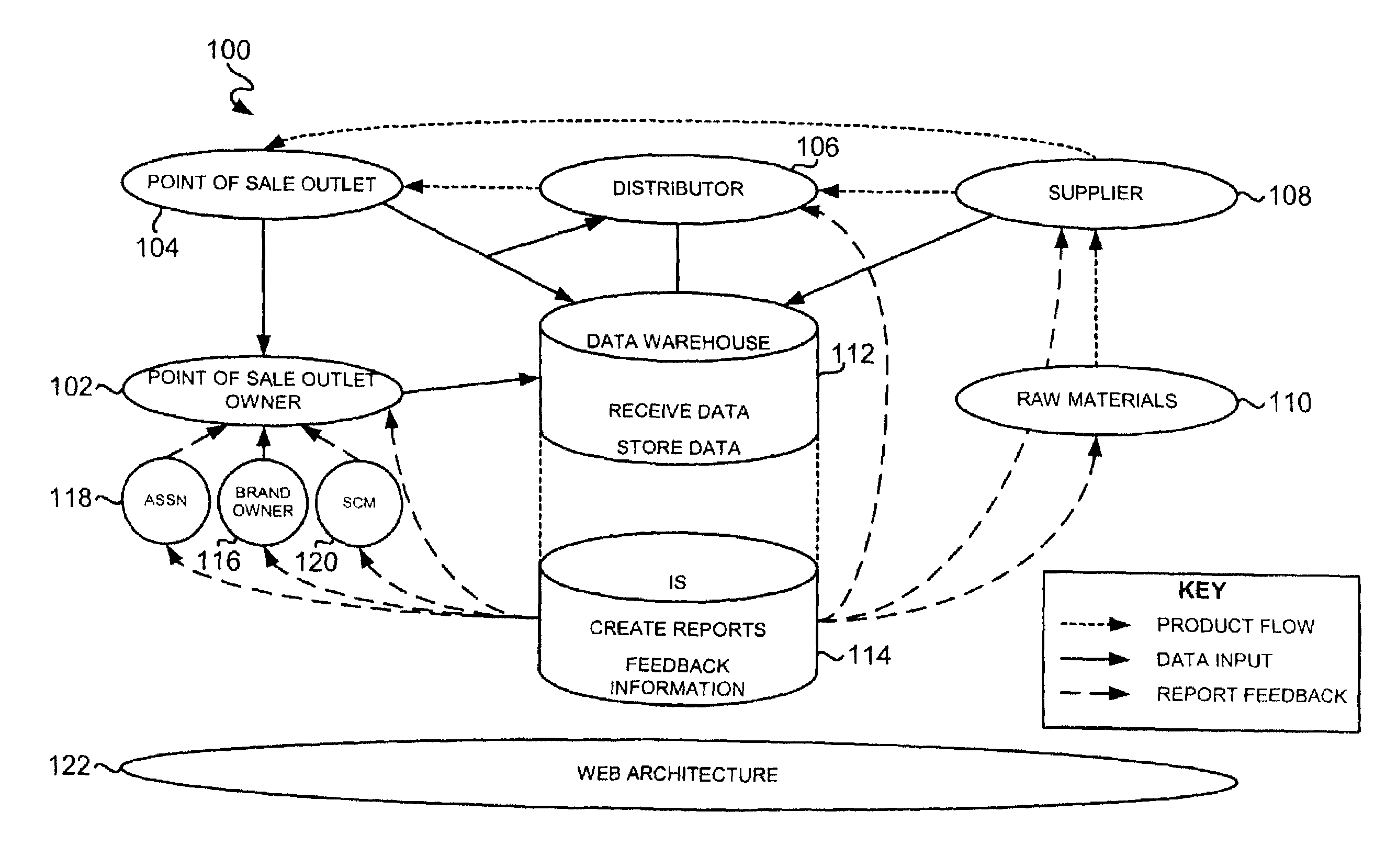

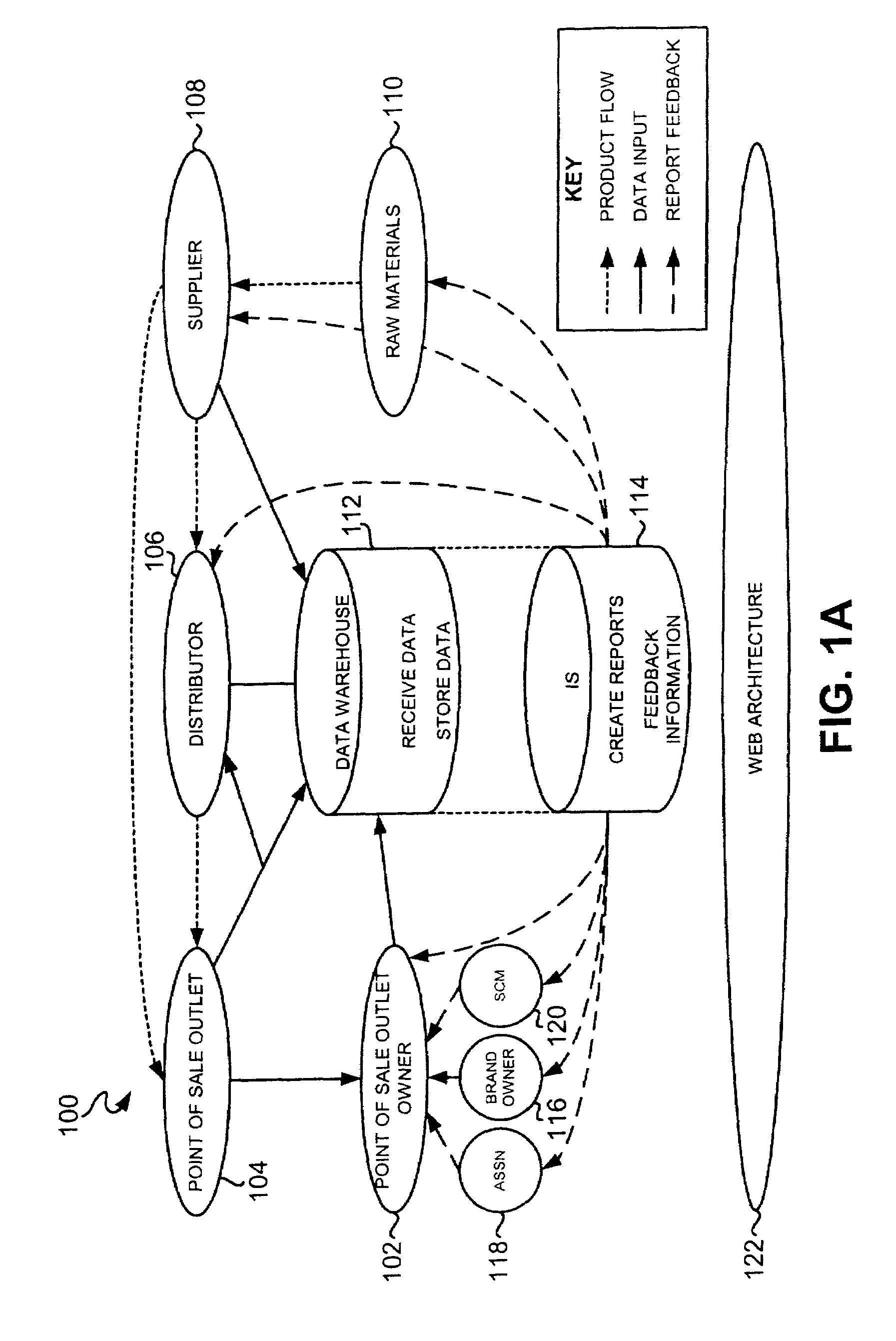

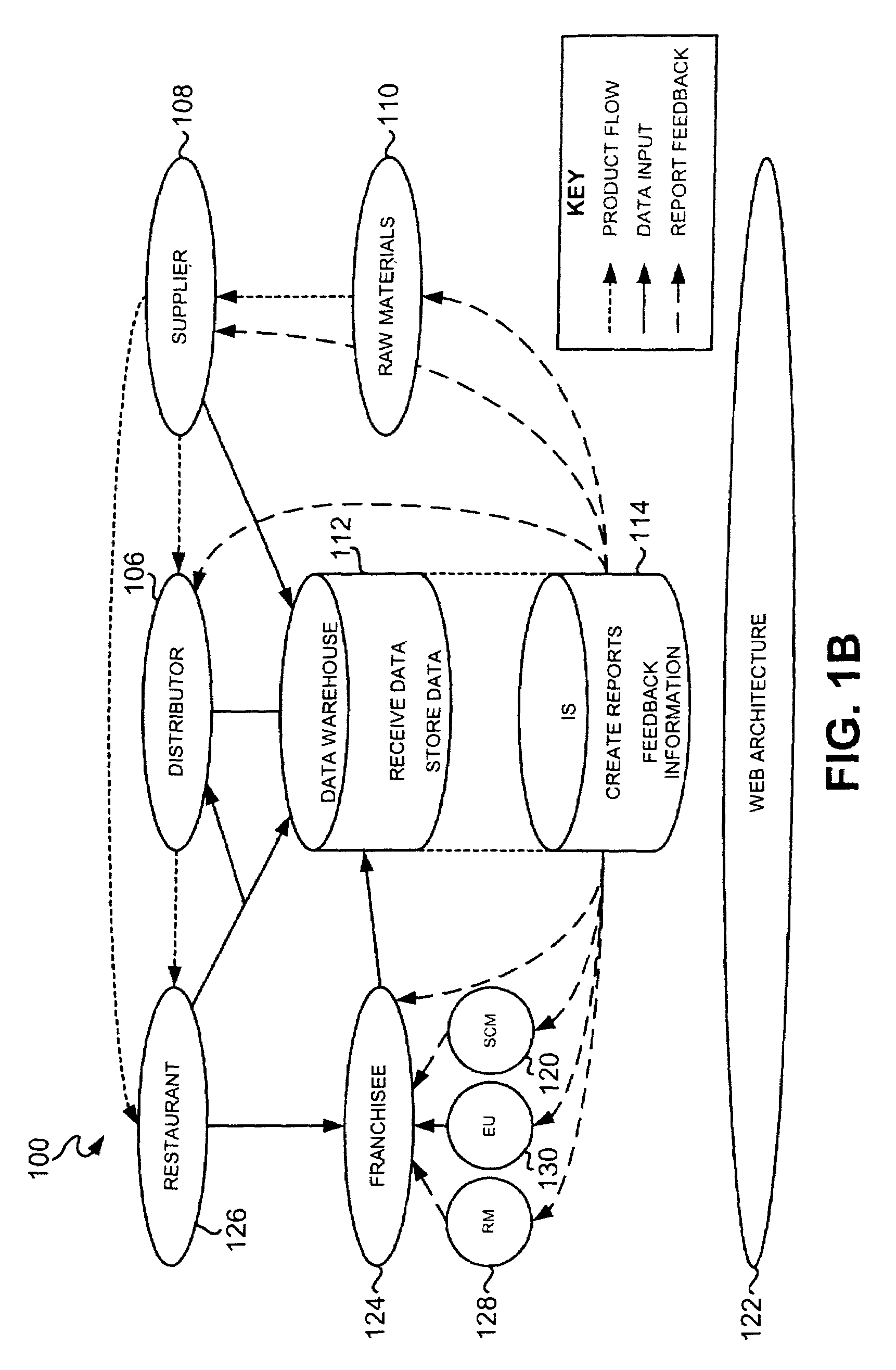

System, method and computer program product for error checking in a supply chain management framework

InactiveUS7072843B2Market predictionsHand manipulated computer devicesError checkingComputer science

A system, method and computer program product are disclosed for forecasting the sale of goods. Data is received utilizing a network from a plurality of point of sale outlets of a supply chain where the data relates to an amount of goods sold by the point of sale outlets. The data is checked for errors. Each detected error is identified as either a point of sale set-up error, a point of sale entry error, a back office error, a polling error, or a menu item mapping error so that the data can be corrected using the identification.

Owner:RESTAURANT SERVICES

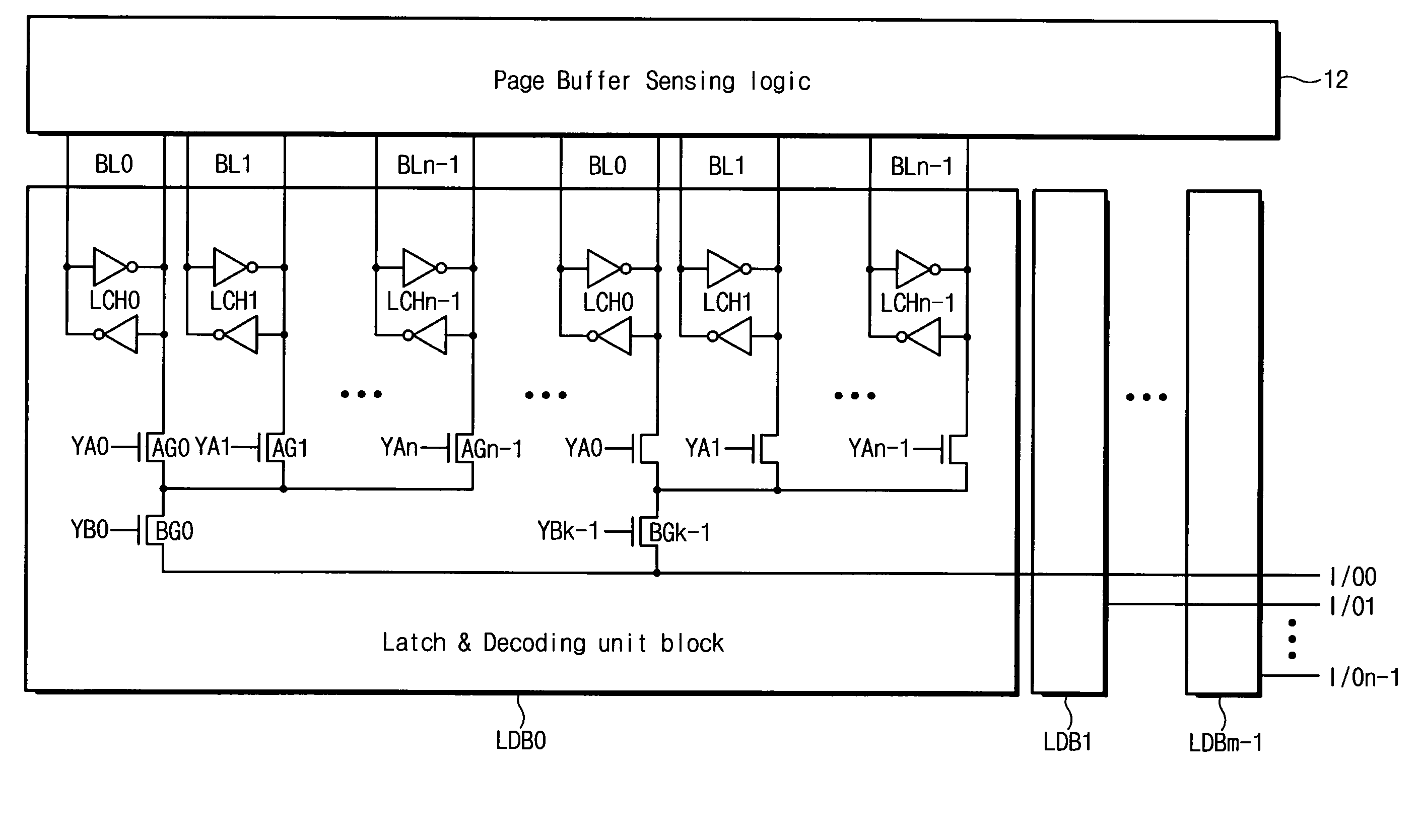

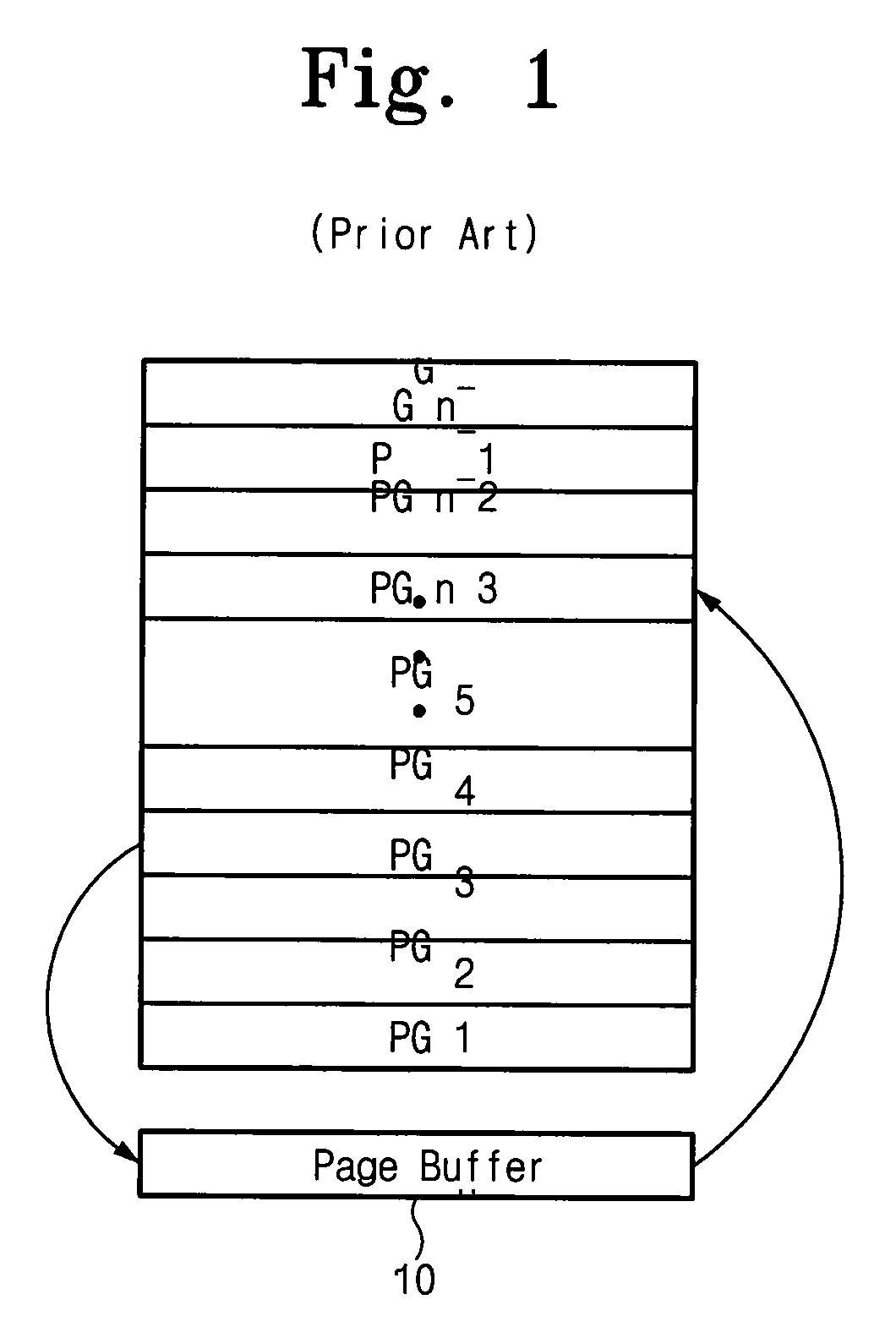

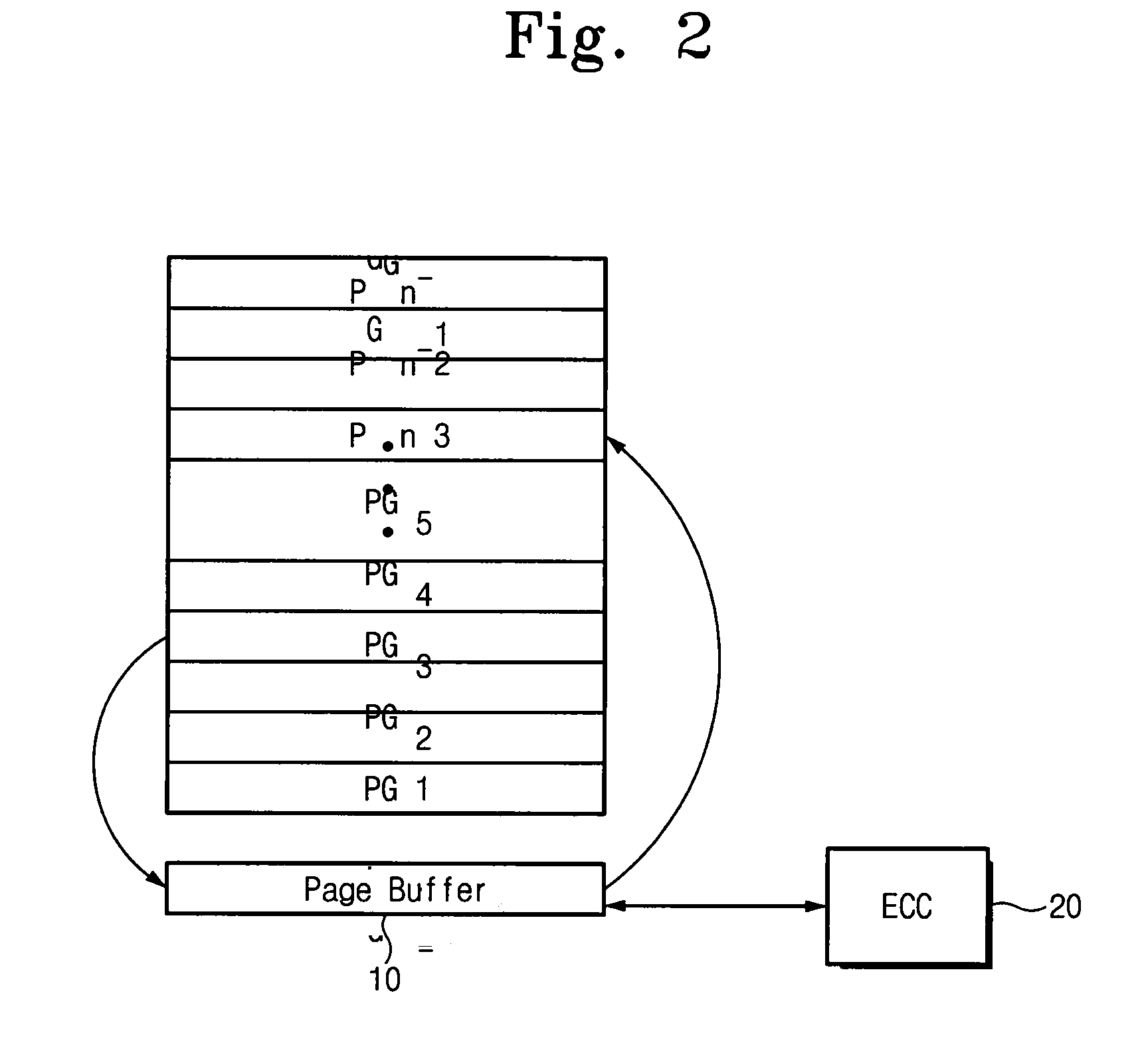

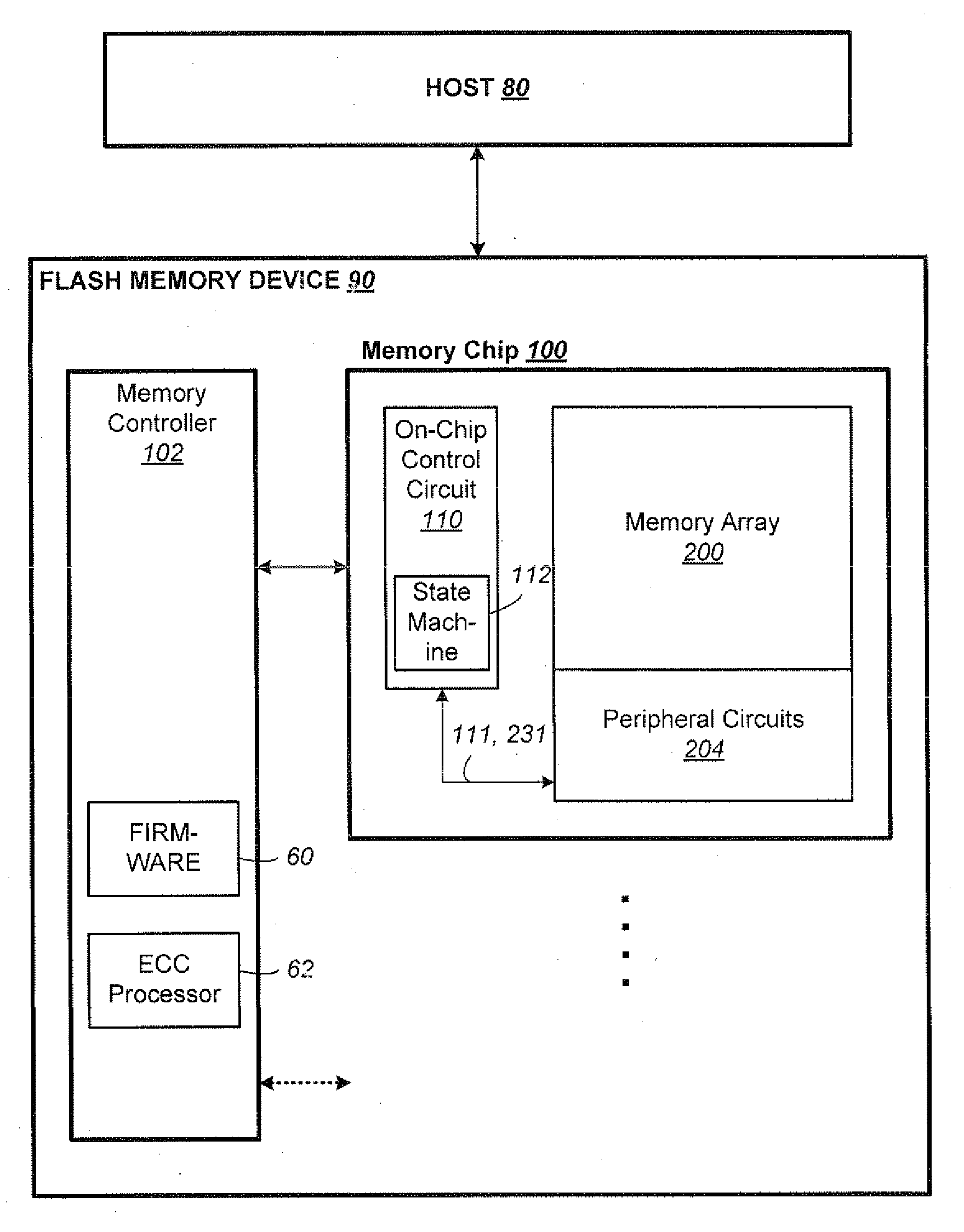

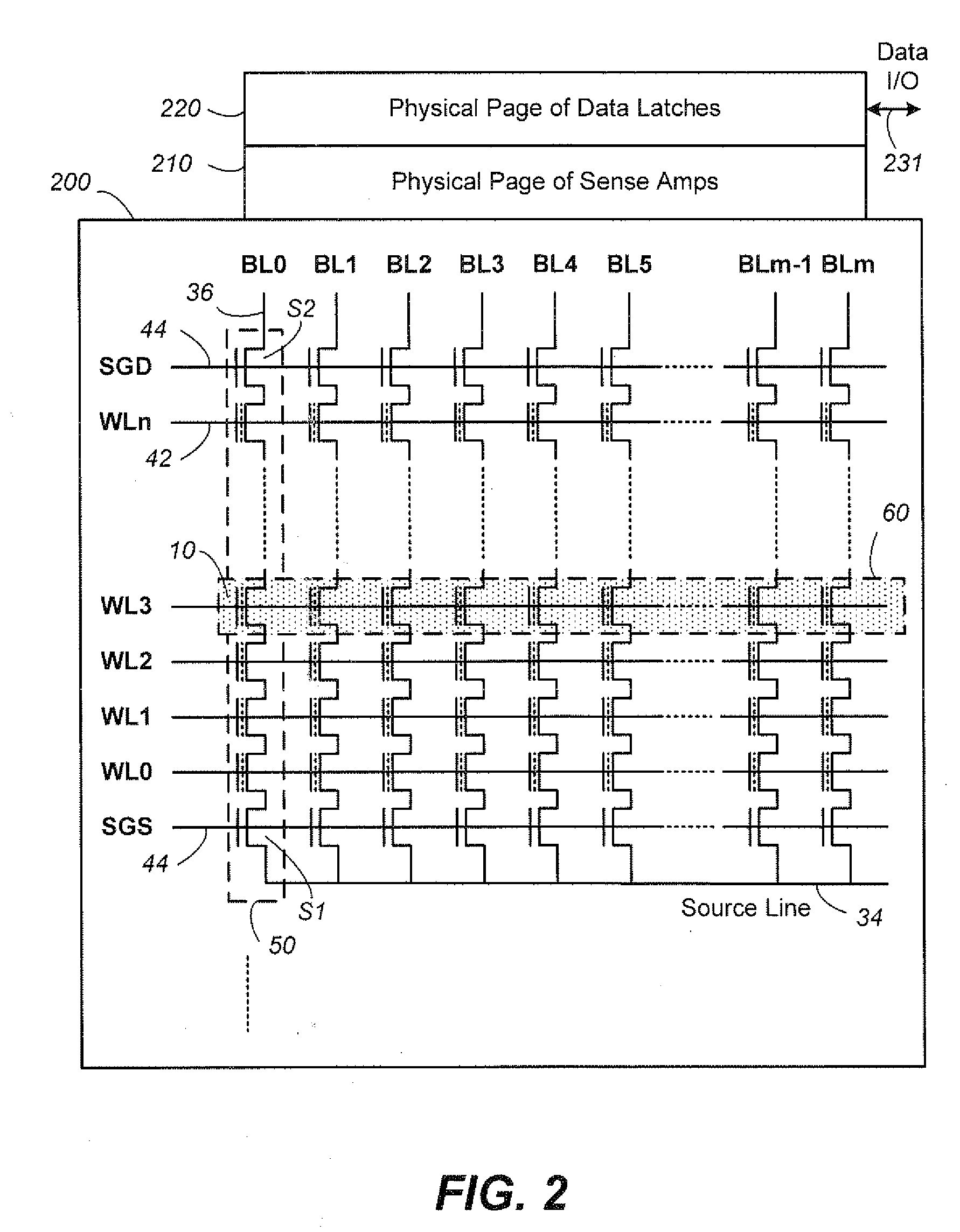

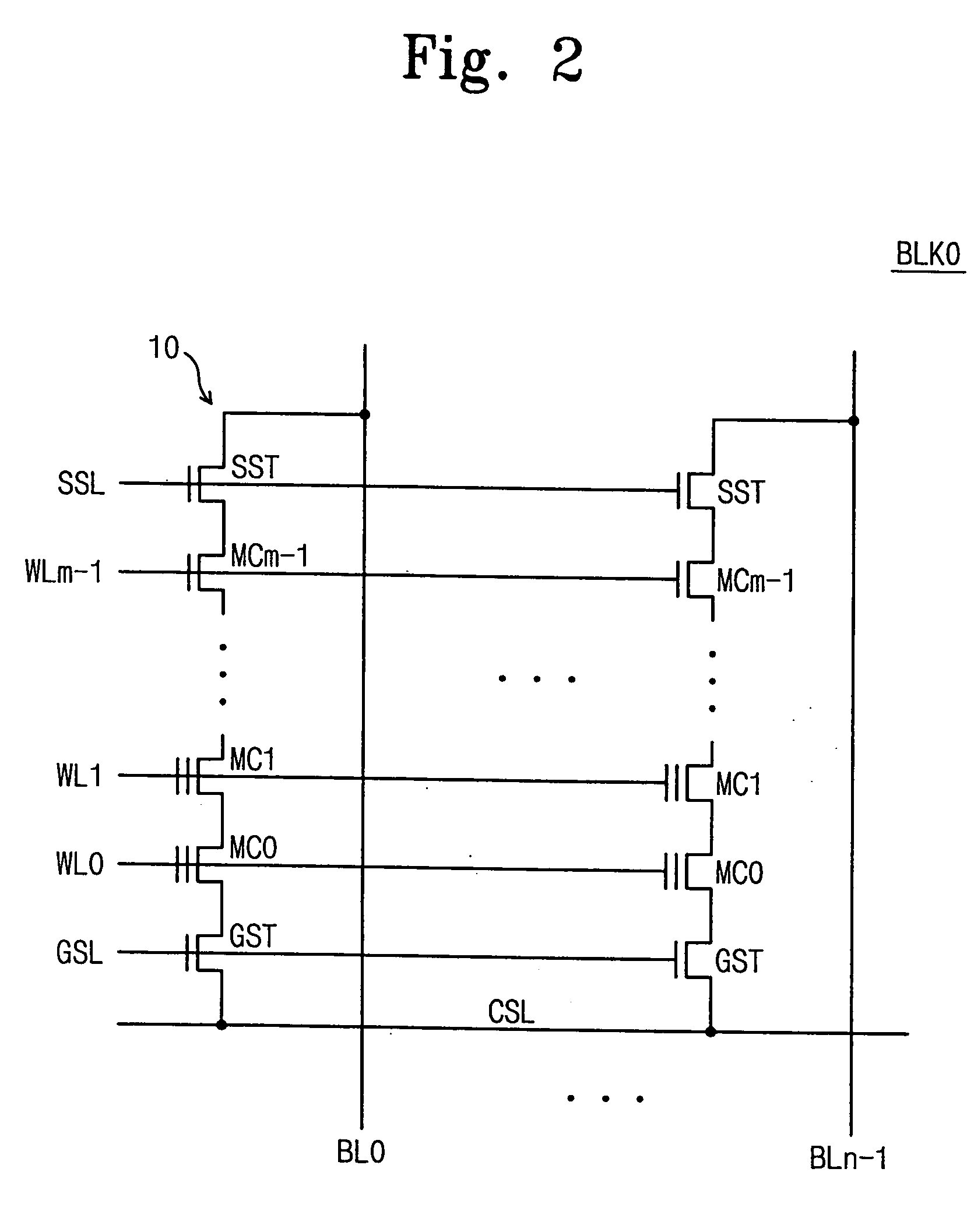

Nonvolatile memory with error correction for page copy operation and method thereof

InactiveUS20080163030A1Transcription errorMaintain integrityMemory loss protectionMemory adressing/allocation/relocationError checkingData storing

The disclosure is a NAND flash memory with the function of error checking and correction during a page copy operation. The NAND flash memory is able to prohibit transcription of erroneous bits to a duplicate page from a source page. Embodiments of the inventive flash memory include a correction circuit for correcting bit errors of source data stored in a page buffer, a circuit configured to provide the source data to the correction circuit and to provide correction data to the page buffer, and a copy circuit configured to copy the source data to the page buffer, and to store the correction data in the other page from the page buffer.

Owner:SAMSUNG ELECTRONICS CO LTD

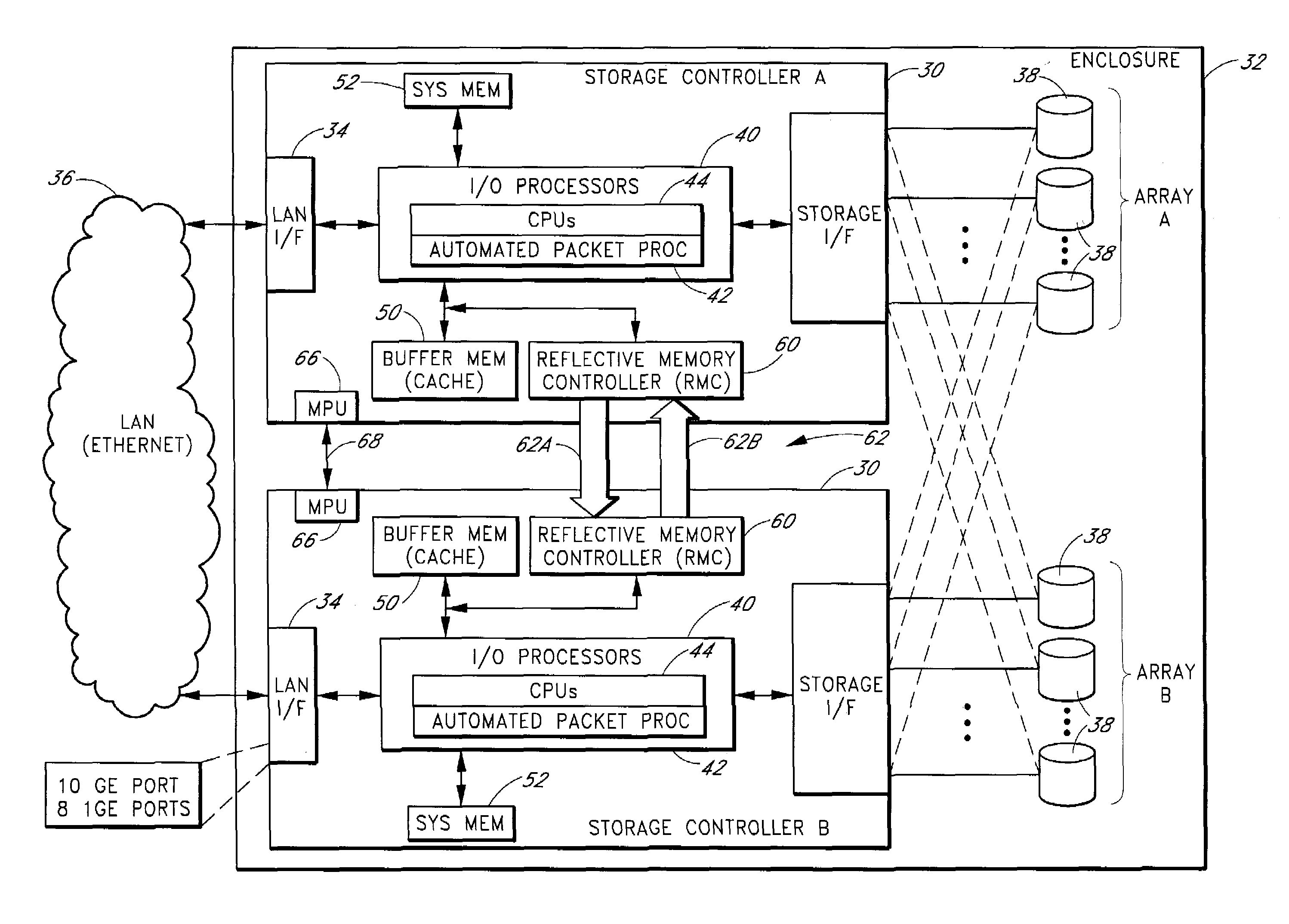

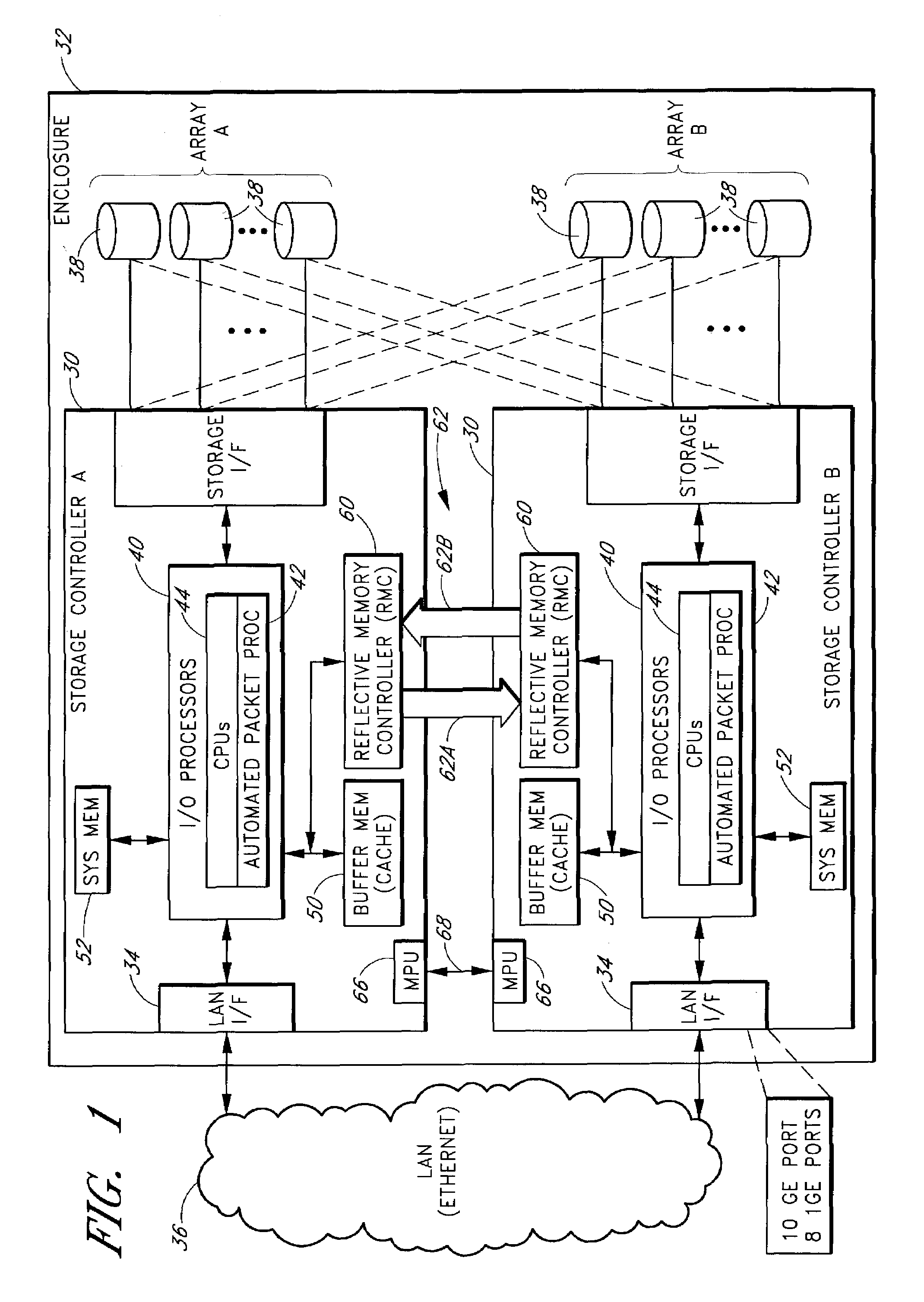

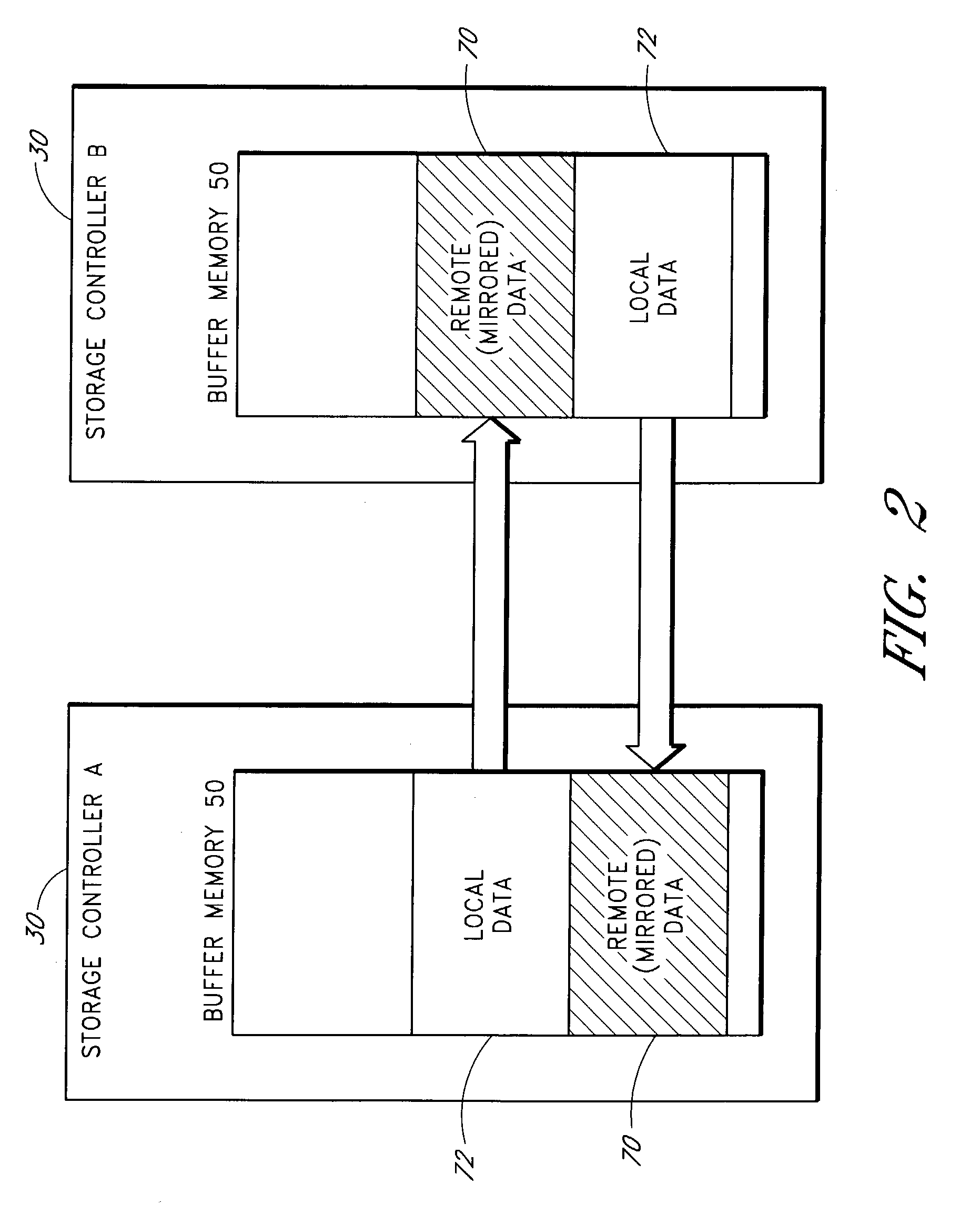

Storage controller redundancy using bi-directional reflective memory channel

InactiveUS6941396B1Reduce protocol overheadRapid generation of packet CRC valuesInput/output to record carriersData processing applicationsError checkingFailover

A bi-directional reflective memory channel between a pair of storage controllers is used to maintain a mirrored copy of each storage controller's native buffer contents within the buffer of the other storage controller. To maintain such mirrored copies, buffer write operations that fall within a reflective memory segment of one storage controller are automatically reflected across this channel to the other storage controller for execution, and vice versa. The write operations are preferably transmitted across the reflective memory channel using a protocol that provides for error checking, acknowledgements, and retransmissions. This protocol is preferably implemented entirely in automated circuitry, so that the mirrored copies are maintained without any CPU intervention during error-free operation. When a failover occurs, the surviving storage controller uses the mirrored copy of the failed storage controller's native buffer contents to assume control over the failed storage controller's disk drives.

Owner:SUPRO STORTEK CO LTD

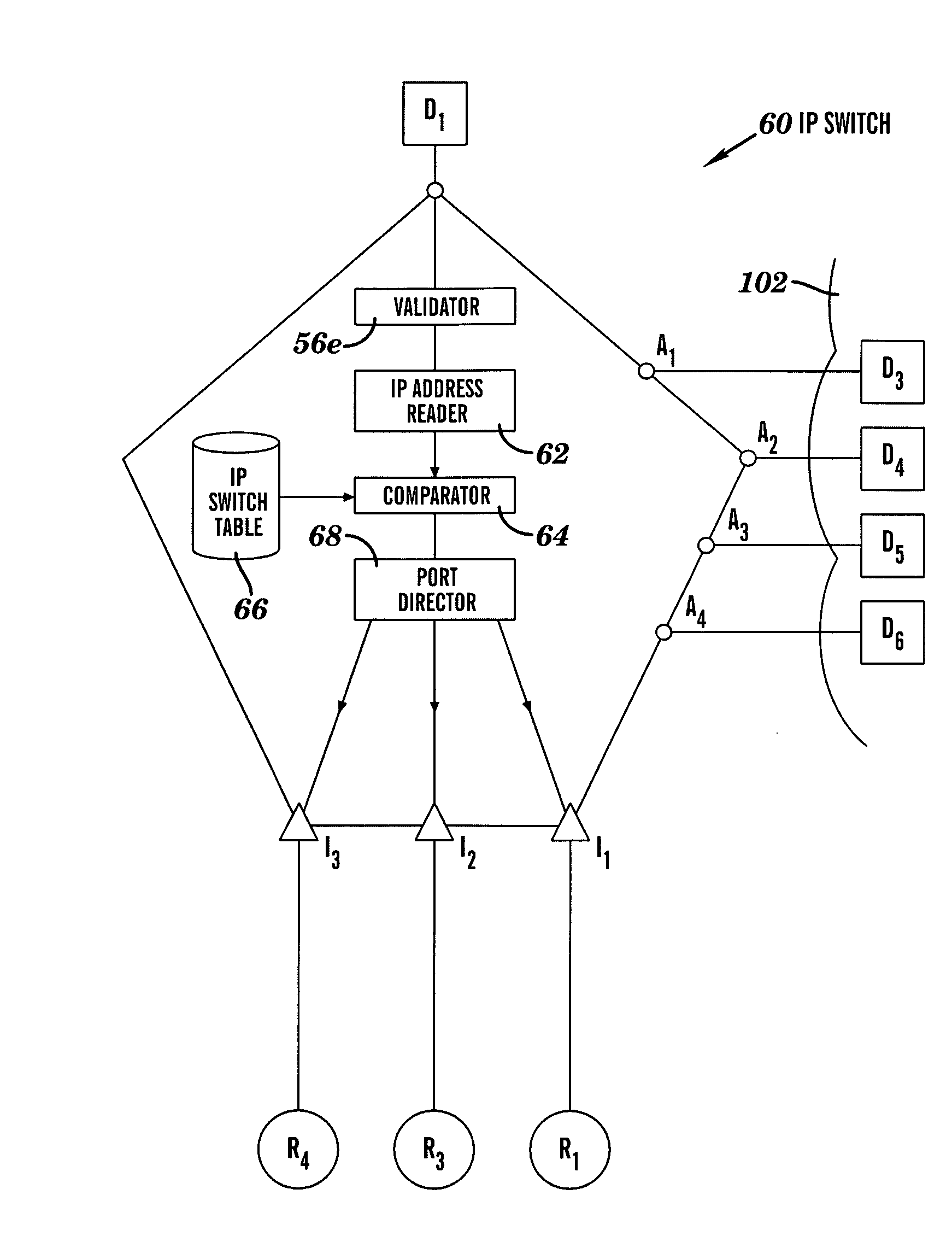

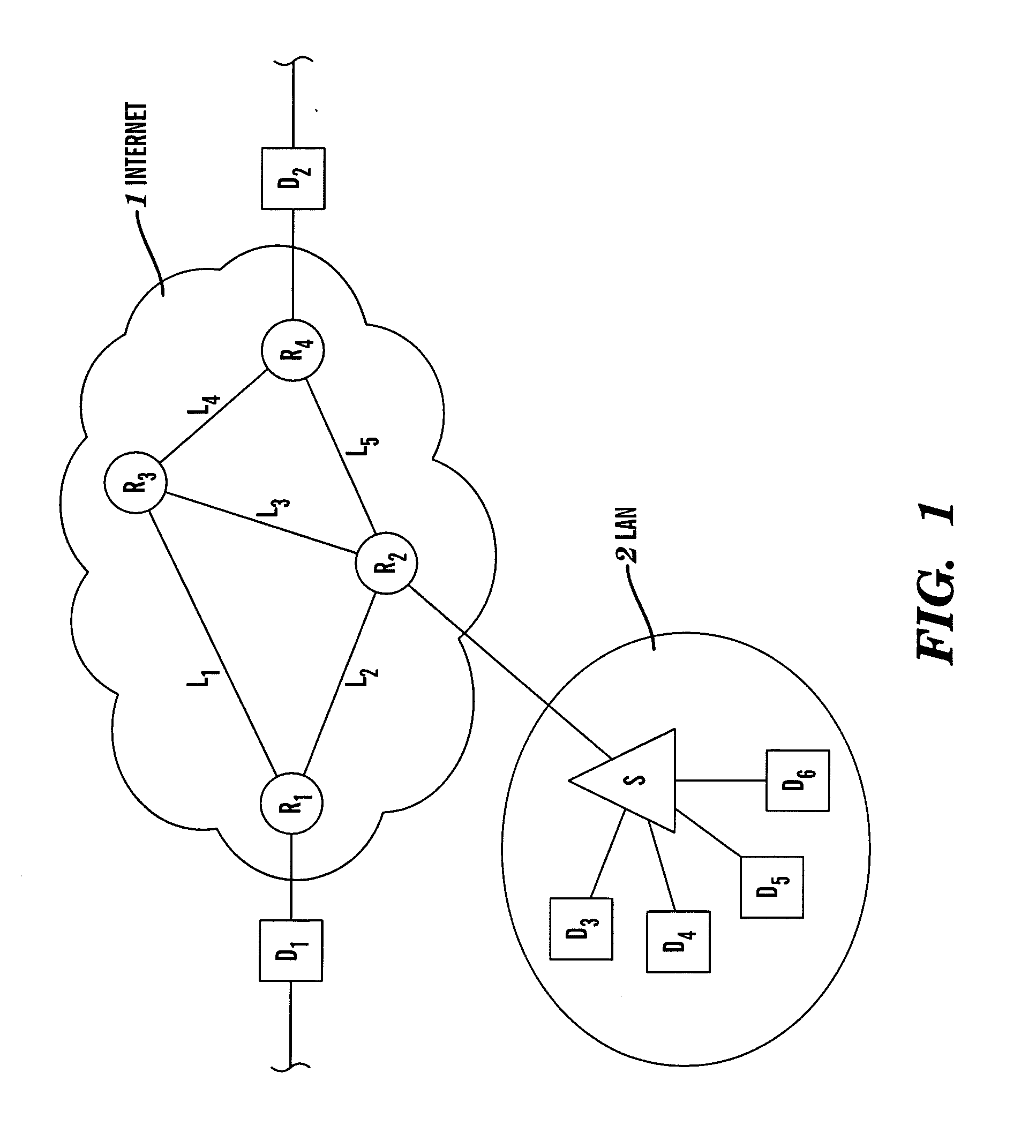

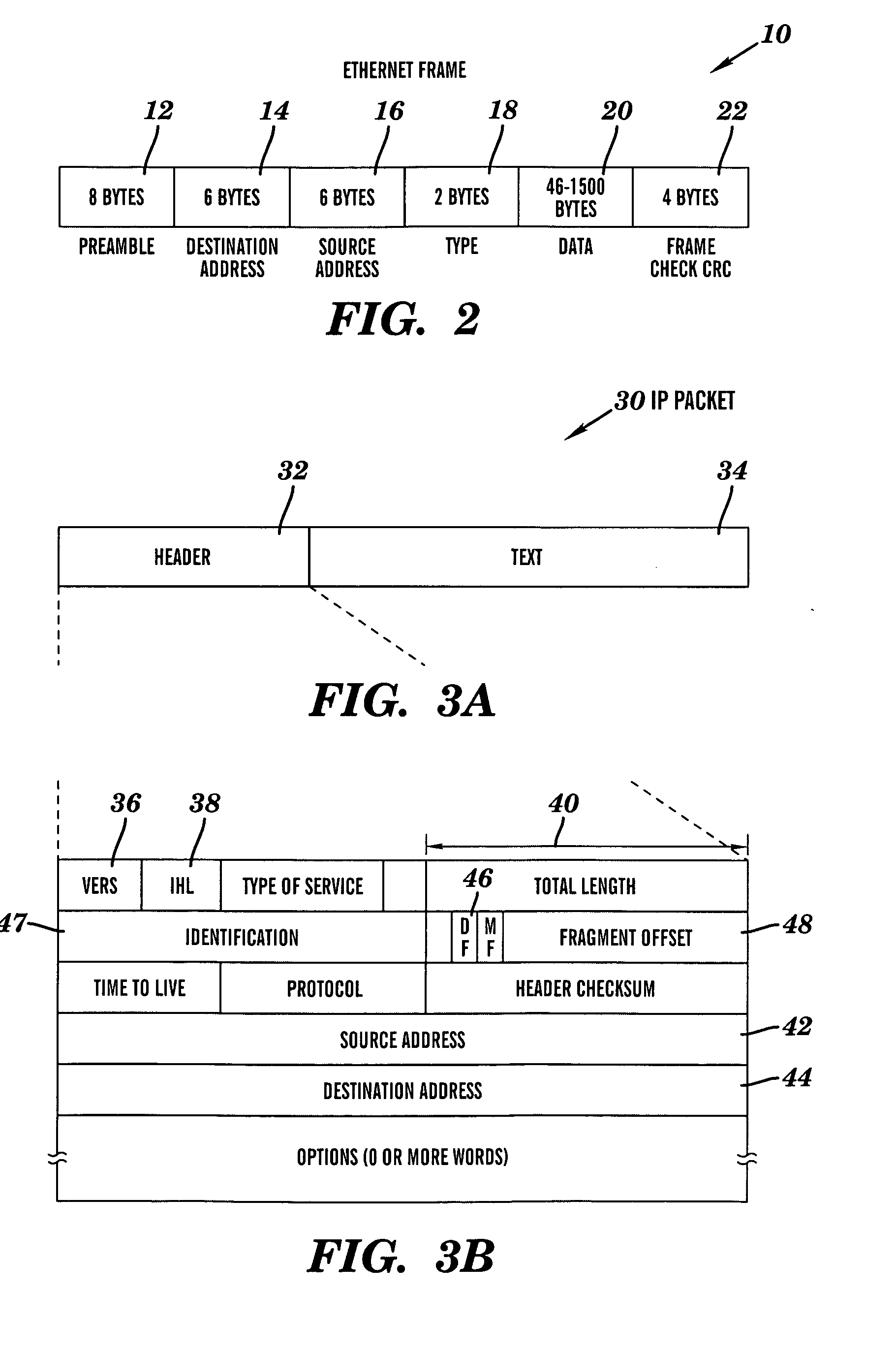

Method, system and computer processing an IP packet, routing a structured data carrier, preventing broadcast storms, load-balancing and converting a full broadcast IP packet

InactiveUS20080247396A1Data switching by path configurationNetwork connectionsError checkingBroadcast radiation

Method for processing content of an Internet Protocol (IP) packet and method for processing a full broadcast IP packet. Processing content of an IP packet includes: extracting IP source and destination addresses and payload from the IP packet; and generating an IP frame encapsulating the IP source and destination addresses and the payload between a preamble field and an error checking field. Processing a full broadcast IP packet includes: receiving the full broadcast IP packet including an IP source address and a full broadcast IP destination address; ascertaining a closest matching IP address and a subnet thereof in a switching table of an IP switch; replacing the full broadcast IP destination address in the IP packet with a subnetted source address generated by applying the subnet mask to the IP source address; transmitting the IP packet to all IP addresses in the switching table within the subnetted source address.

Owner:IBM CORP

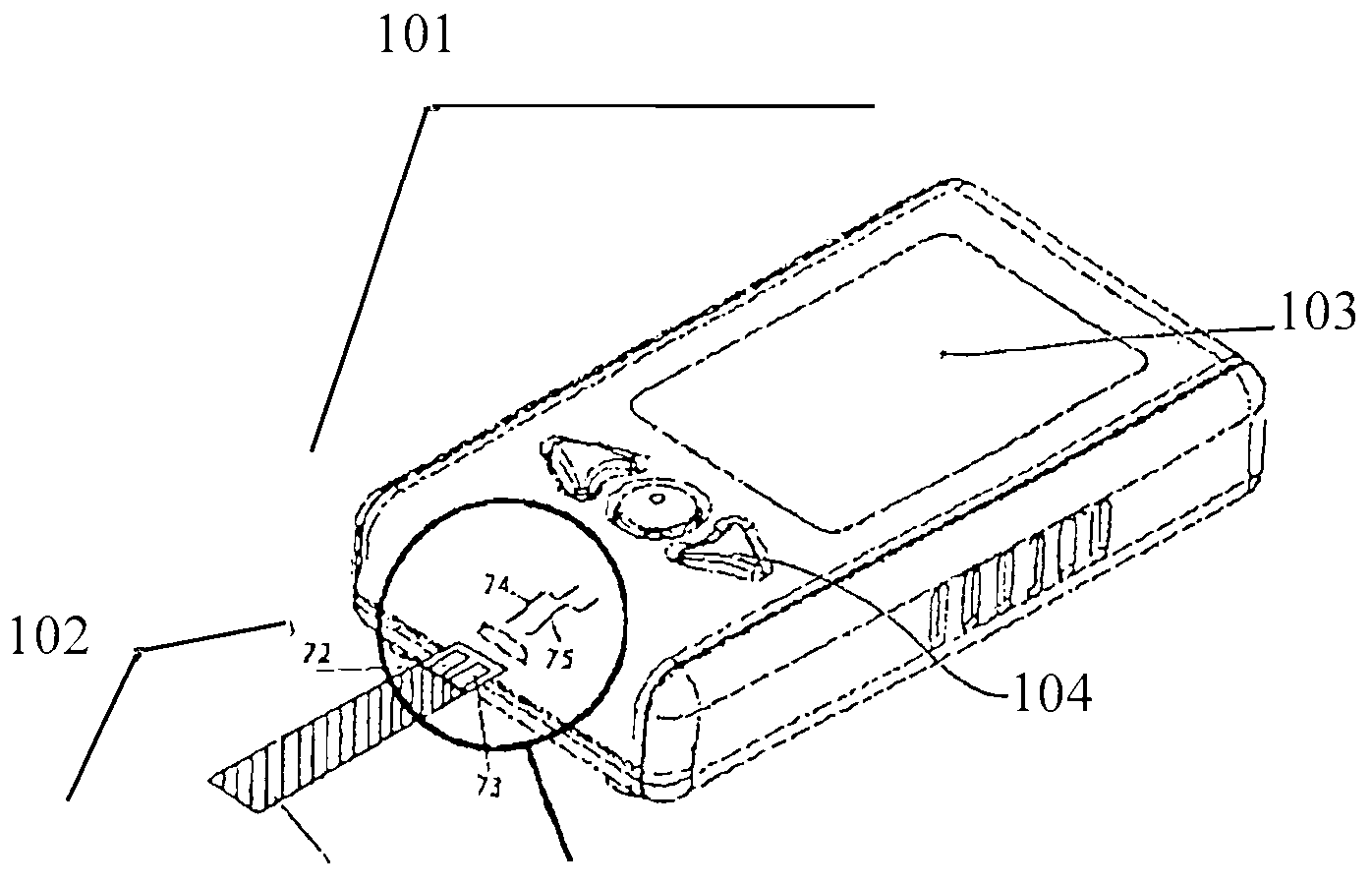

Method and apparatus for providing a stable voltage to an analytical system

ActiveUS20080093228A1Weather/light/corrosion resistanceVolume/mass flow measurementError checkingAnalyte

A method and apparatus for provide a stable voltage to an electrochemical cell used for measurement of an analyte such as glucose in a liquid sample. The apparatus uses a circuit in which multiple switching positions provide both calibration information for use in calibration of electronic components in the circuit and error checking functionality.

Owner:AGAMATRIX INC

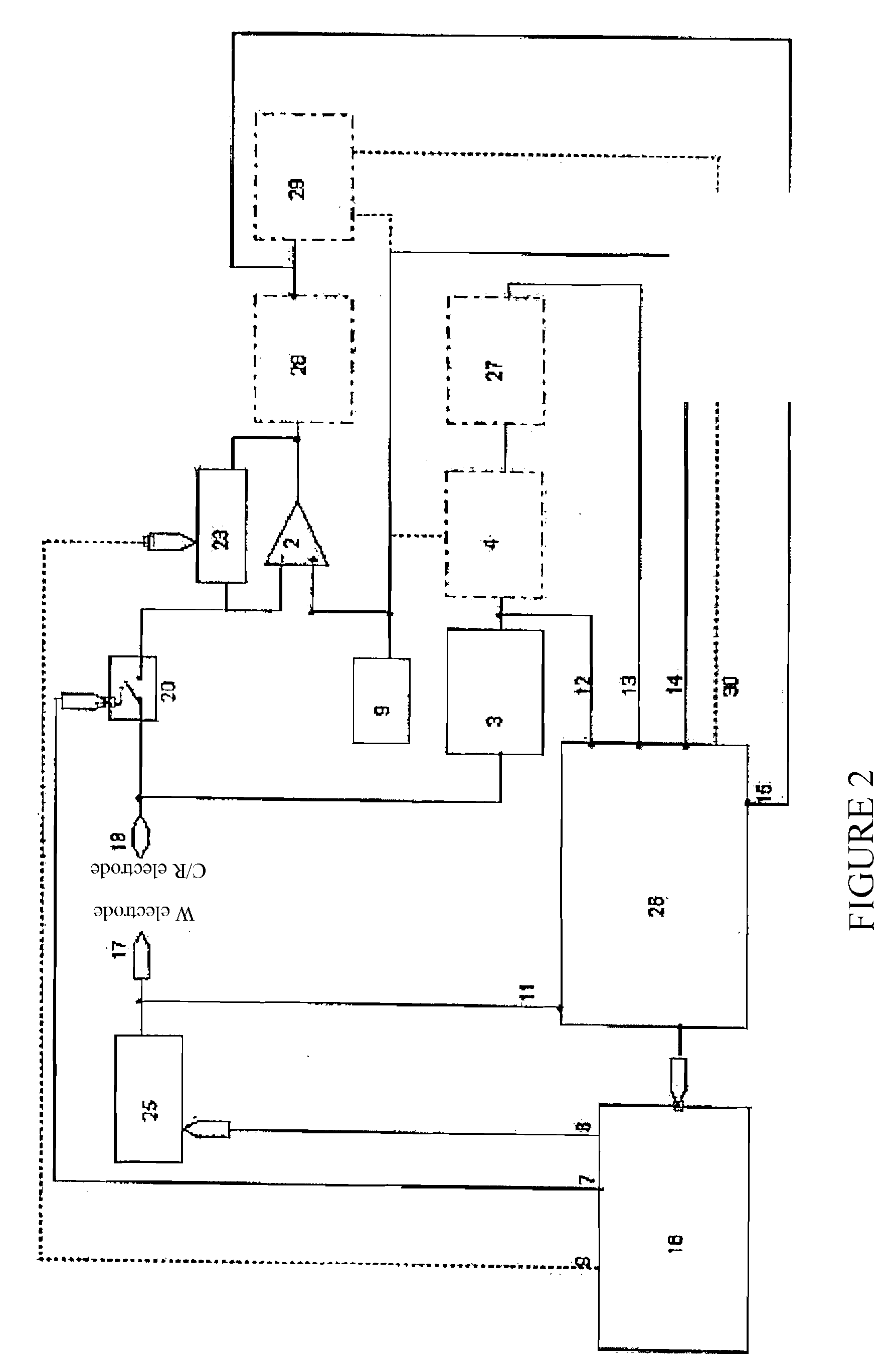

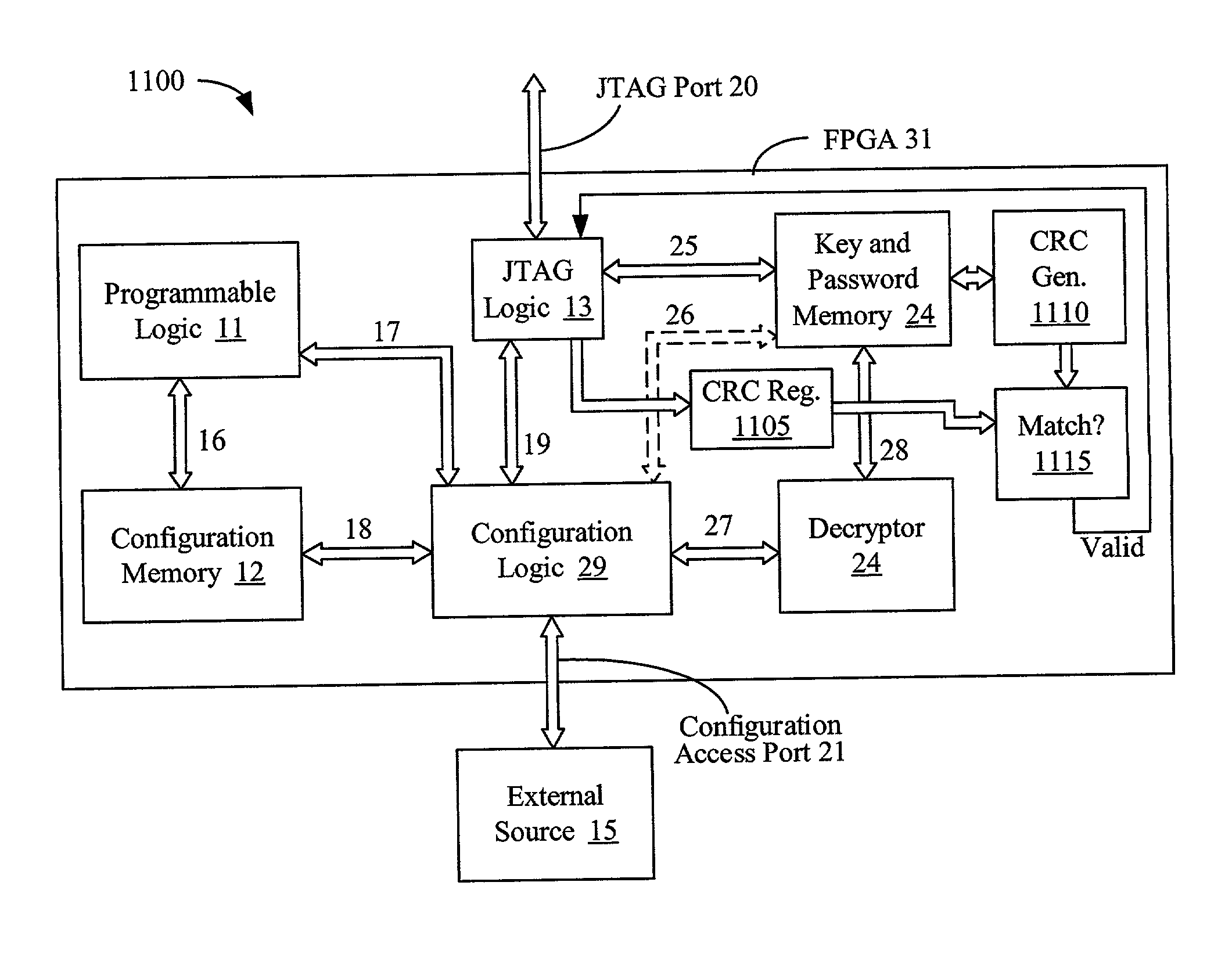

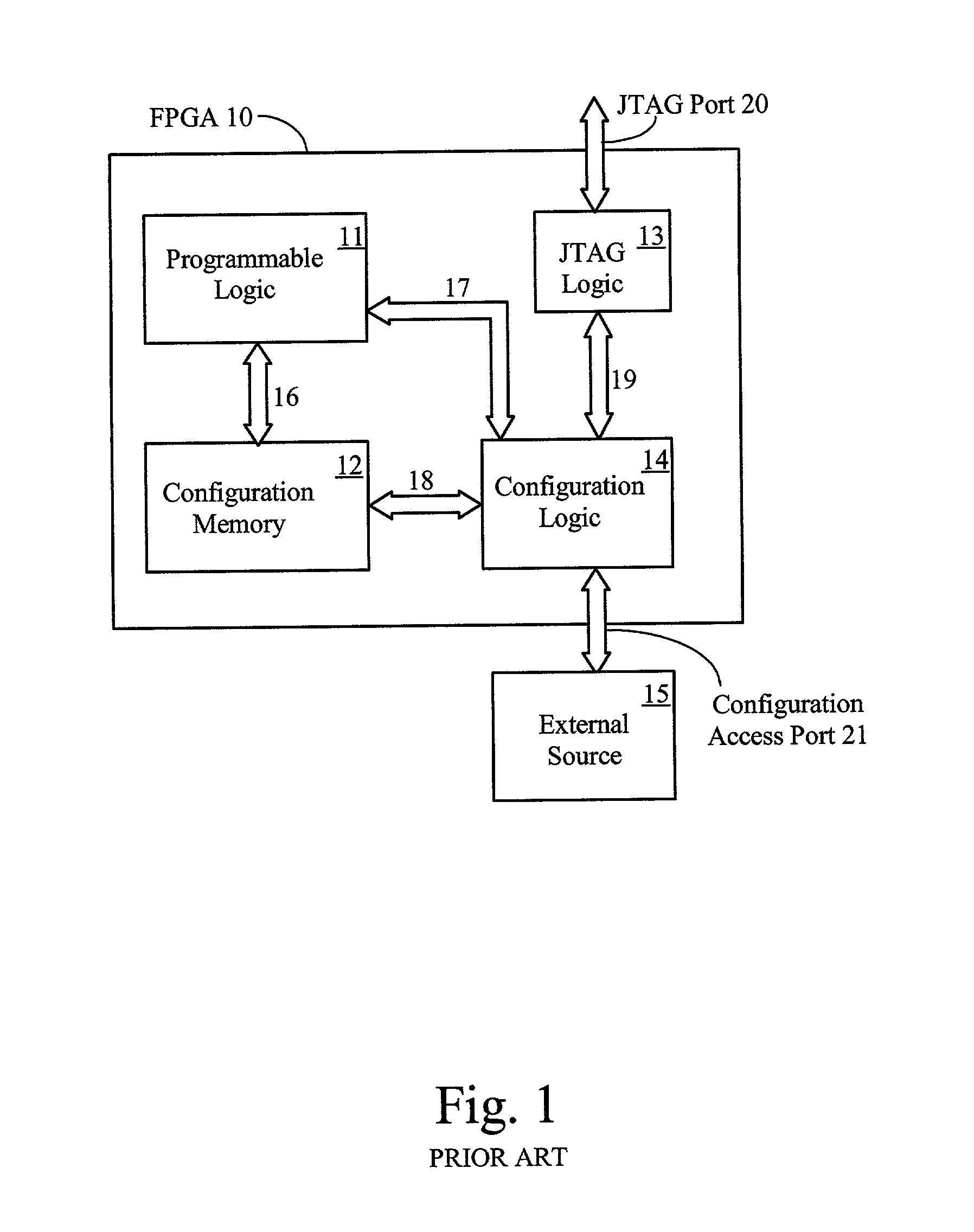

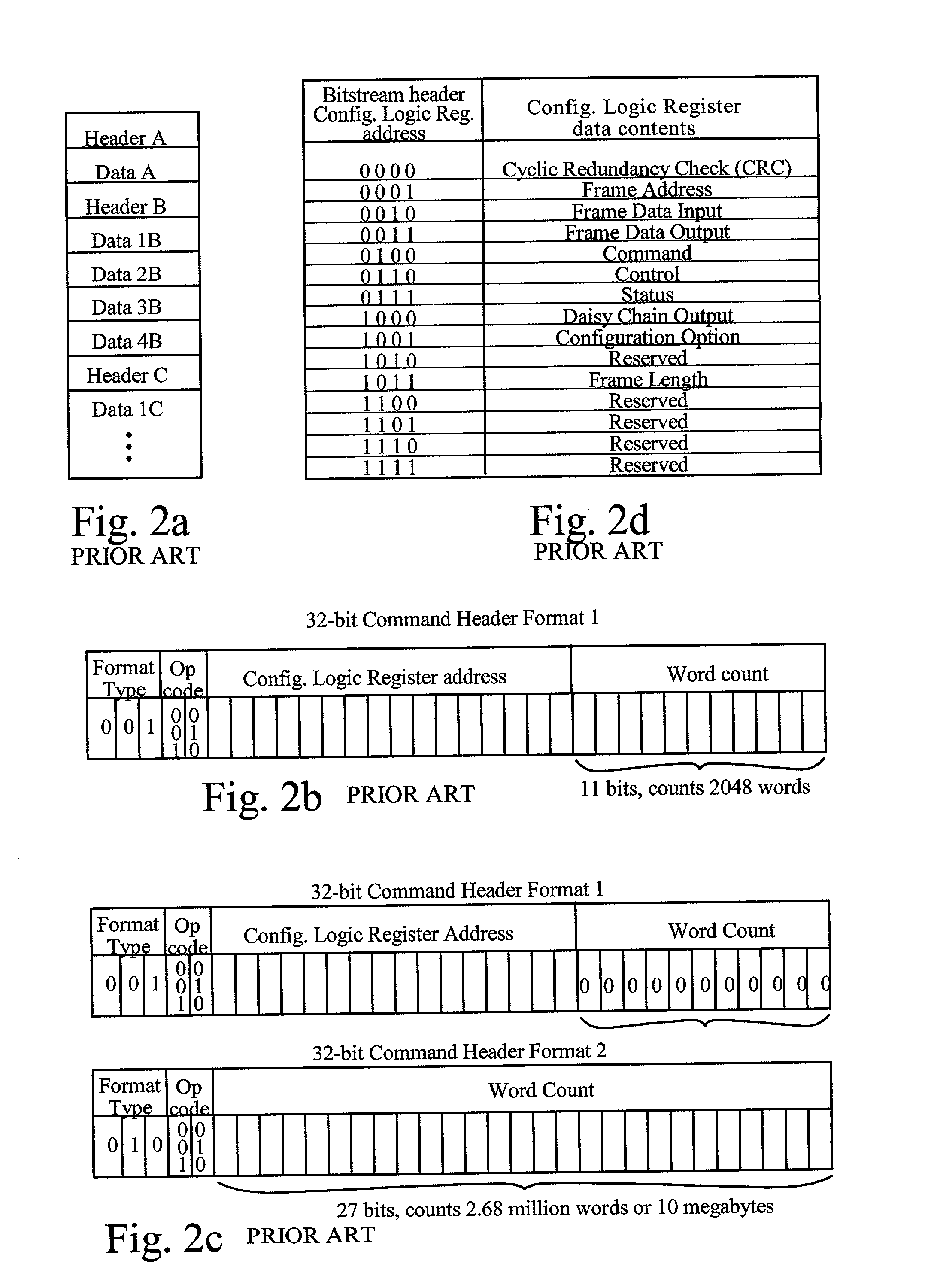

Error-checking and correcting decryption-key memory for programmable logic devices

ActiveUS7200235B1Reduce riskPreventing the overwriting of framesReliability increasing modificationsError preventionError checkingProgrammable logic device

Described are circuits that detect and correct for decryption key errors. In one example, a programmable logic device includes a decryption key memory with a number of decryption-key fields and, for each key field, an associated error-correction-code (ECC) field. The PLD additionally includes error-correction circuitry that receives each key and associated ECC and performs an error correction before conveying the resulting error-corrected key to a decryptor.

Owner:XILINX INC

Aggregation of multiple headless computer entities into a single computer entity group

InactiveUS20020129128A1Multiple digital computer combinationsProgram controlError checkingDisplay device

A group of headless computer entities is formed via a local area network connection by means of an aggregation service application, operated on a headless computer entity selected as a master entity, which propagates configuration settings for time zone, application settings, security settings and the like across individual slave computer entities within the group. A human operator can change configuration settings globally at group level via a user interface display on a conventional computer having a user console, which interacts with the master headless computer entity via a web administration interface. Addition and subtraction of computer entities from a group are handled by an aggregation service application, and interlocks and error checking is applied throughout the group to ensure that no changes to a slave computer entity are made, unless those changes conform to global configuration settings enforced by the master headless computer entity.

Owner:HEWLETT PACKARD DEV CO LP

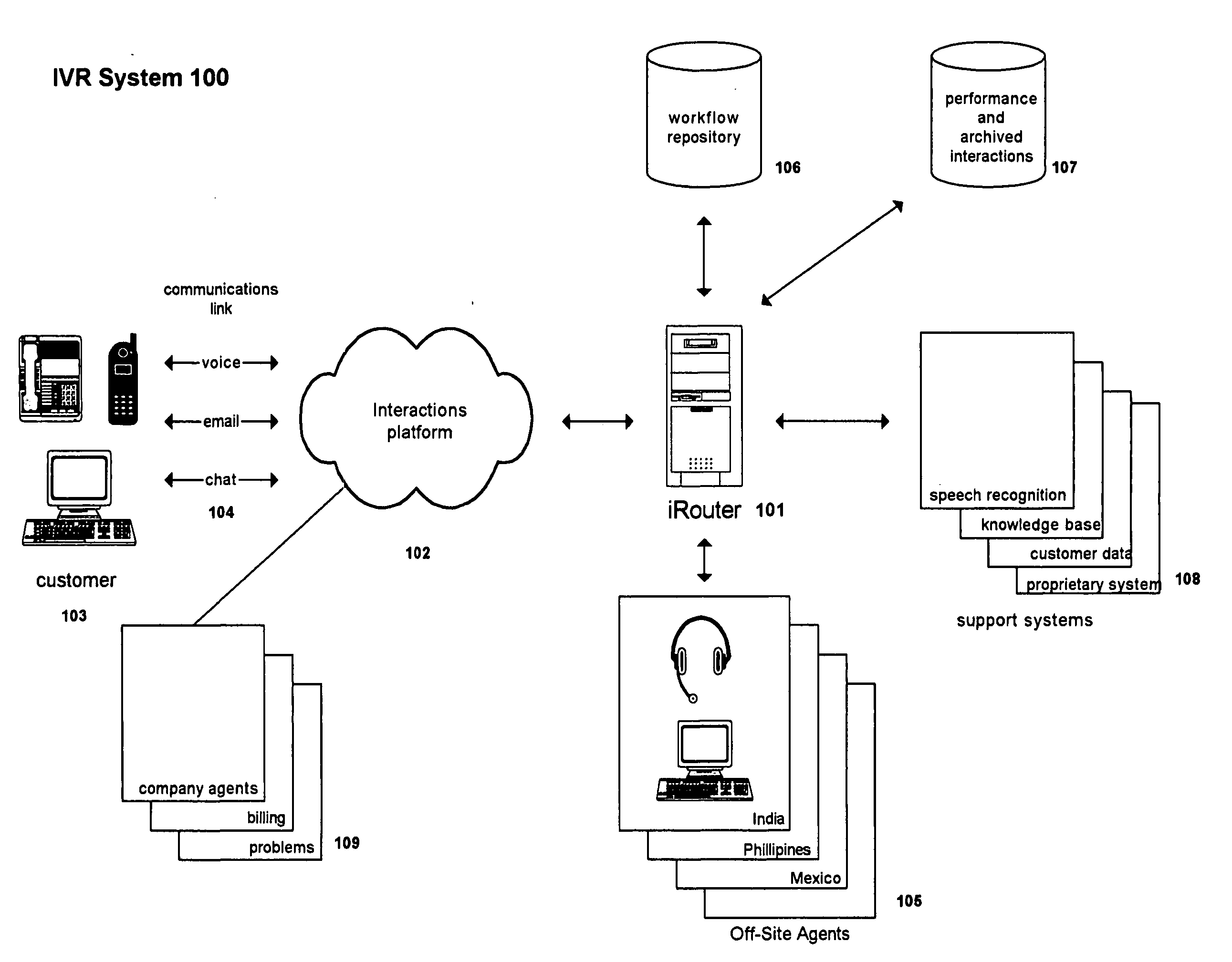

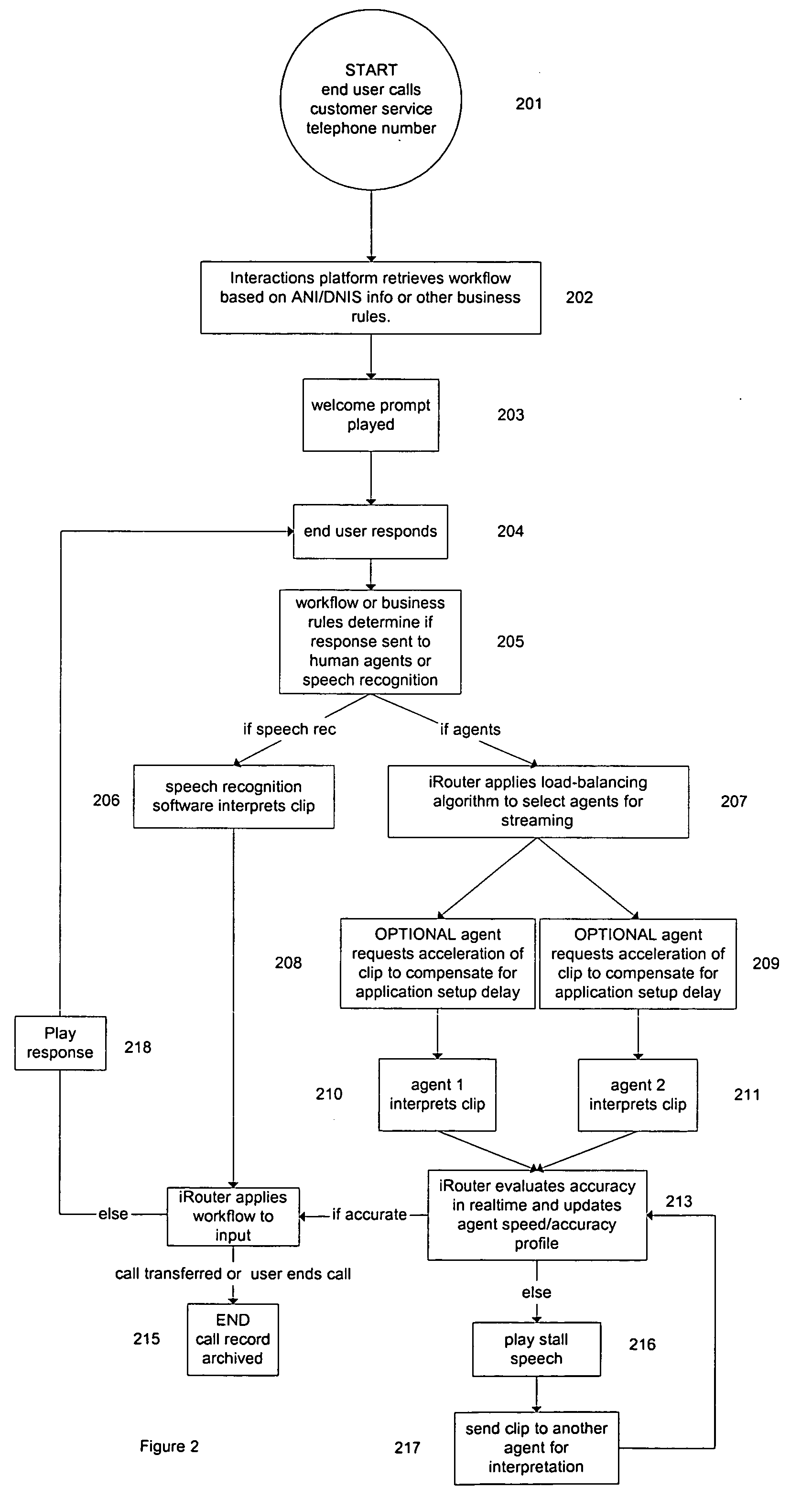

Apparatus and method for processing service interactions

ActiveUS7606718B2Accurately determineImprove accuracyCredit schemesSupervisory/monitoring/testing arrangementsError checkingHuman agent

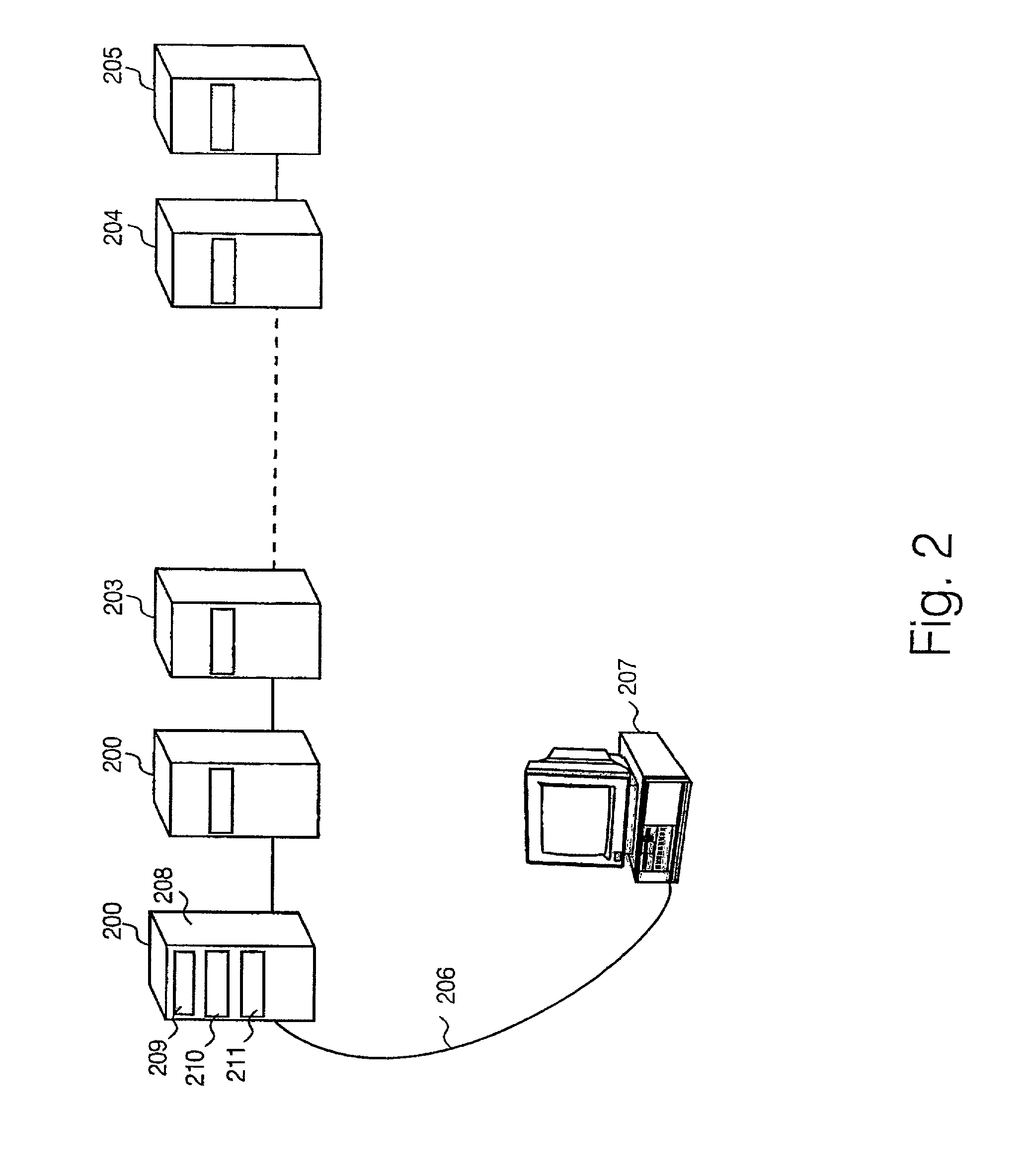

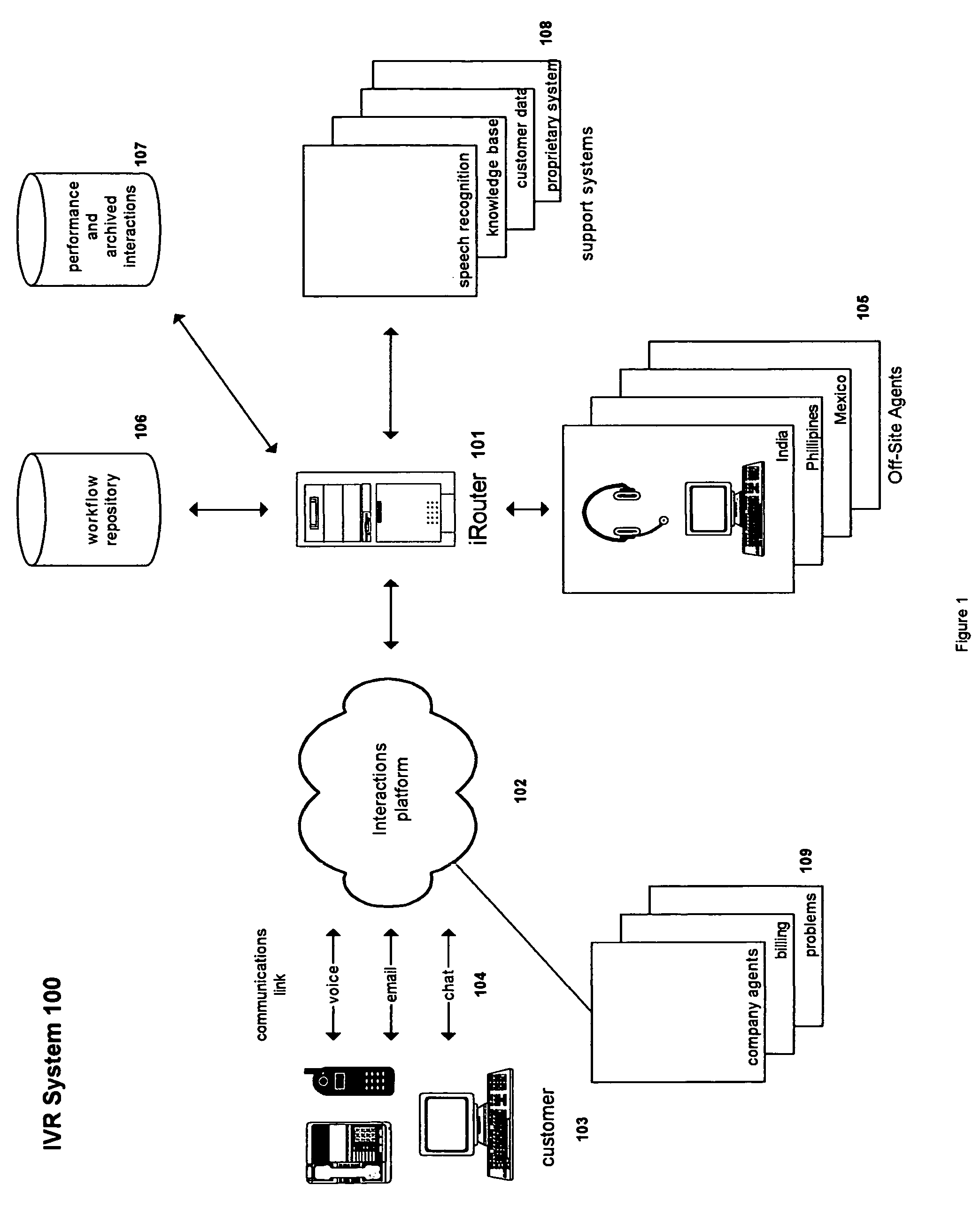

An interactive voice and data response system that directs input to a voice, text, and web-capable software-based router, which is able to intelligently respond to the input by drawing on a combination of human agents, advanced speech recognition and expert systems, connected to the router via a TCP / IP network. The digitized input is broken down into components so that the customer interaction is managed as a series of small tasks rather than one ongoing conversation. The router manages the interactions and keeps pace with a real-time conversation. The system utilizes both speech recognition and human intelligence for purposes of interpreting customer utterance or customer text. The system may use more than one human agent, or both human agents and speech recognition software, to interpret simultaneously the same component for error-checking and interpretation accuracy.

Owner:ARES VENTURE FINANCE

Non-Volatile Memory and Method Having Efficient On-Chip Block-Copying with Controlled Error Rate

A non-volatile memory chip having SLC blocks acting as a write cache for MLC blocks for high density storage requires constant copying or folding of SLC blocks into MLC blocks. To avoid the time-consuming toggling out and in of the pages of the entire SLC block for ECC checking by a controller chip, only a small sample is checked. An optimal read point for reading the memory cells in the sample of the SLC block is dynamically determined by trying different read points so that the data is read within an error budget. Once the optimal read point is determined, it is used to read the entire SLC block without further error checking. Then the SLC block can be copied (blind folded) to the MLC block with the confidence of being within the error budget.

Owner:SANDISK TECH LLC

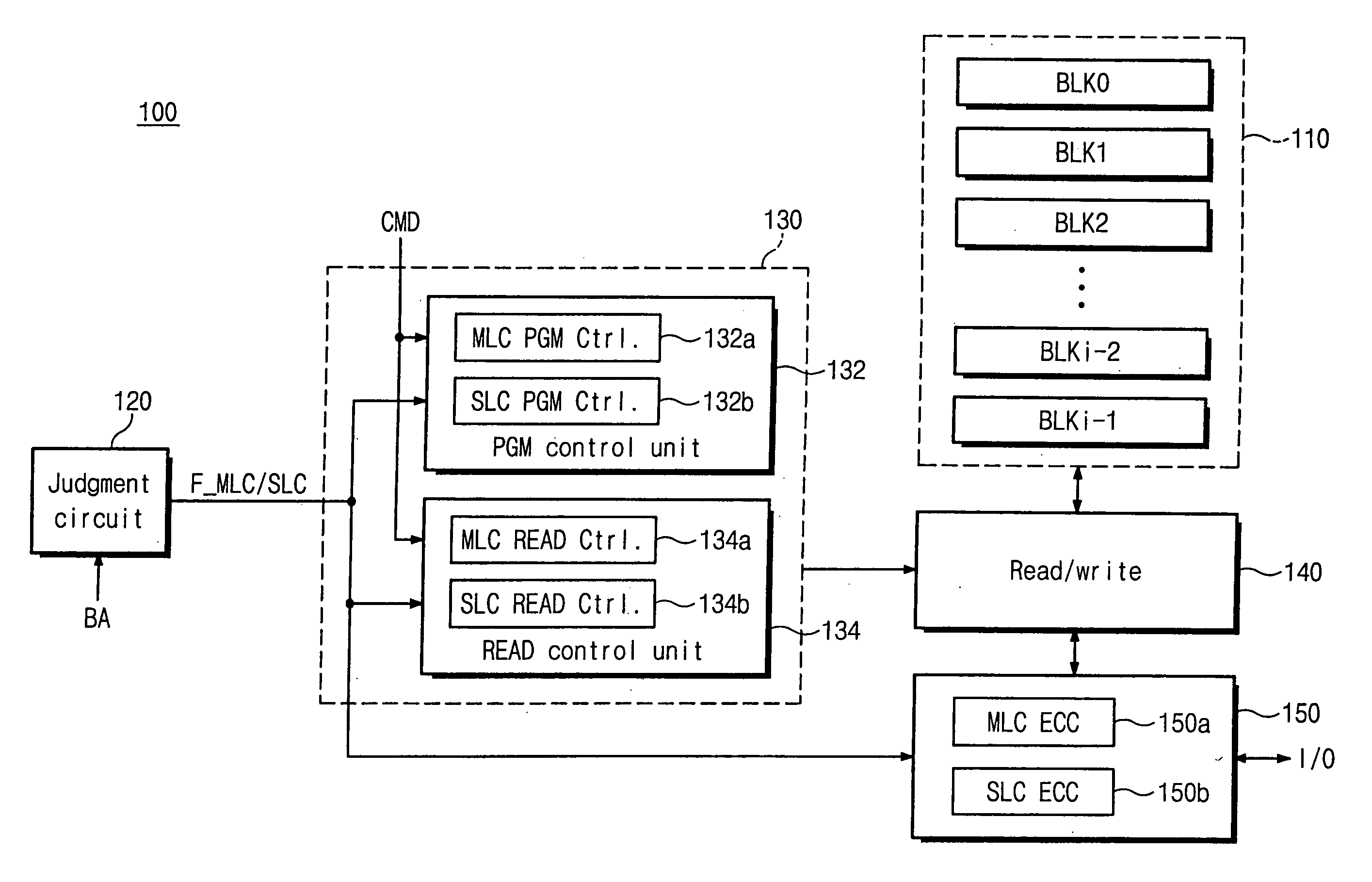

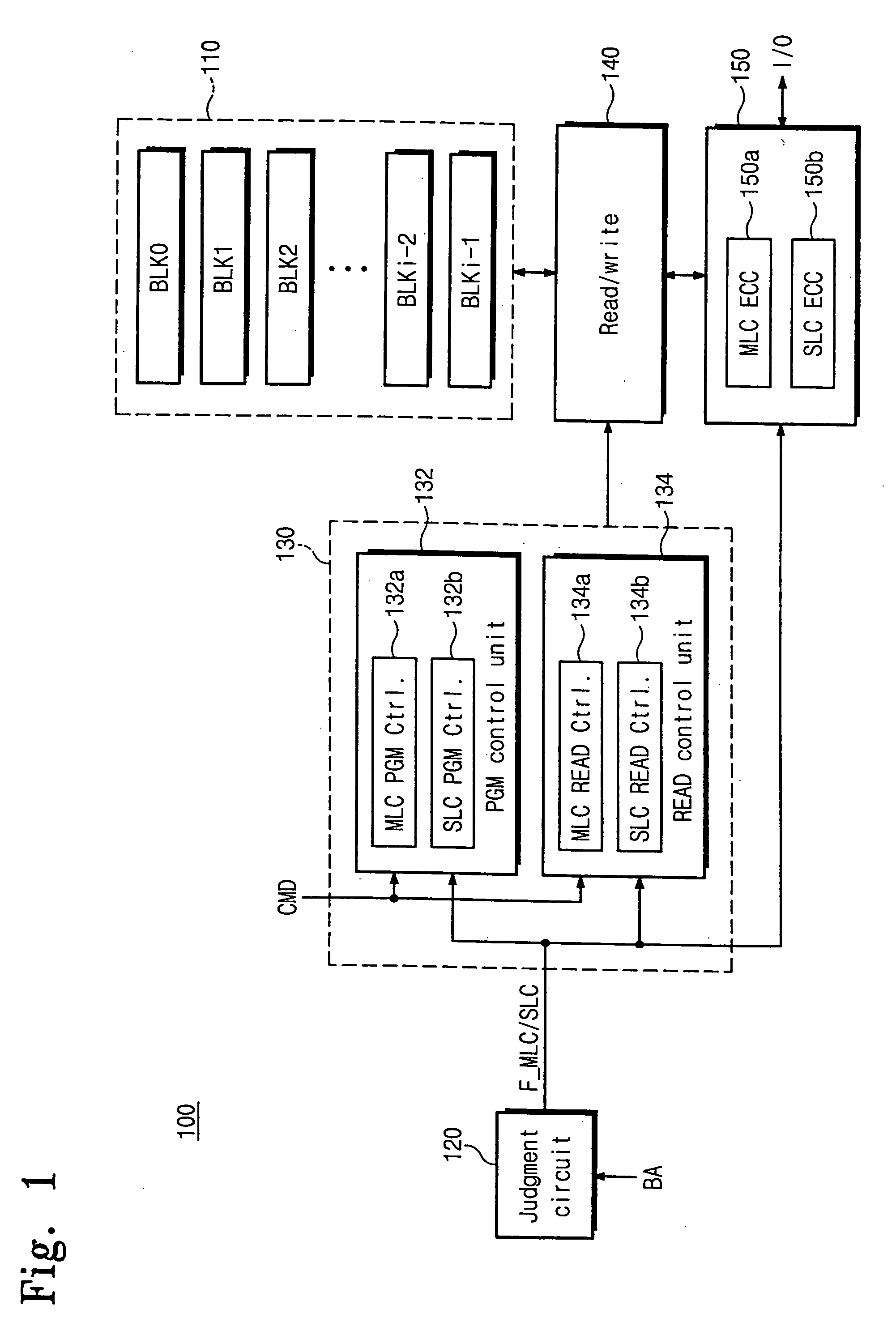

Flash memory device capable of storing multi-bit data and single-bit data

There is provided a flash memory device capable of manipulating multi-bit and single-bit data. The flash memory device can include a memory cell array with a plurality of memory blocks. The flash memory device can also include a judgment circuit for storing multi-bit / single-bit information indicating whether each of the memory blocks is a multi-bit memory block or not, determining whether or not a memory block of an inputted block address is a multi-bit memory block according to the stored multi-bit / single-bit information and outputting an appropriate flag signal. A read / write circuit for selectively performing multi-bit and single-bit read / program operations of the memory block corresponding to the block address is also included, as well as control logic for controlling the read / write circuit such that the read / write circuit can perform multi-bit or single-bit read / program operations based on the flag signal. An error checking and correction (ECC) circuit including a multi-bit ECC unit and a single-bit ECC unit for checking and correcting an error in a data of the read / write circuit can also be included.

Owner:SAMSUNG ELECTRONICS CO LTD

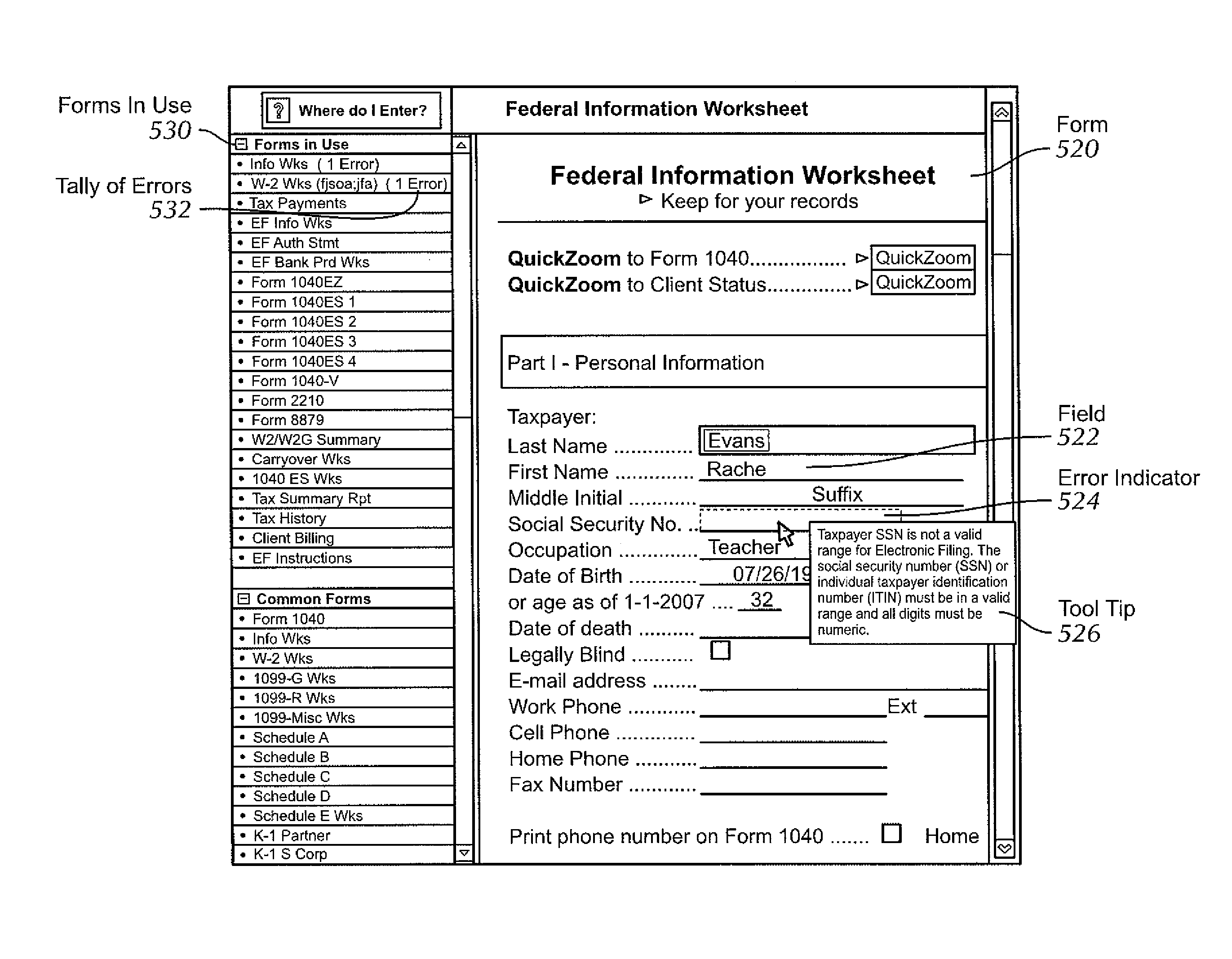

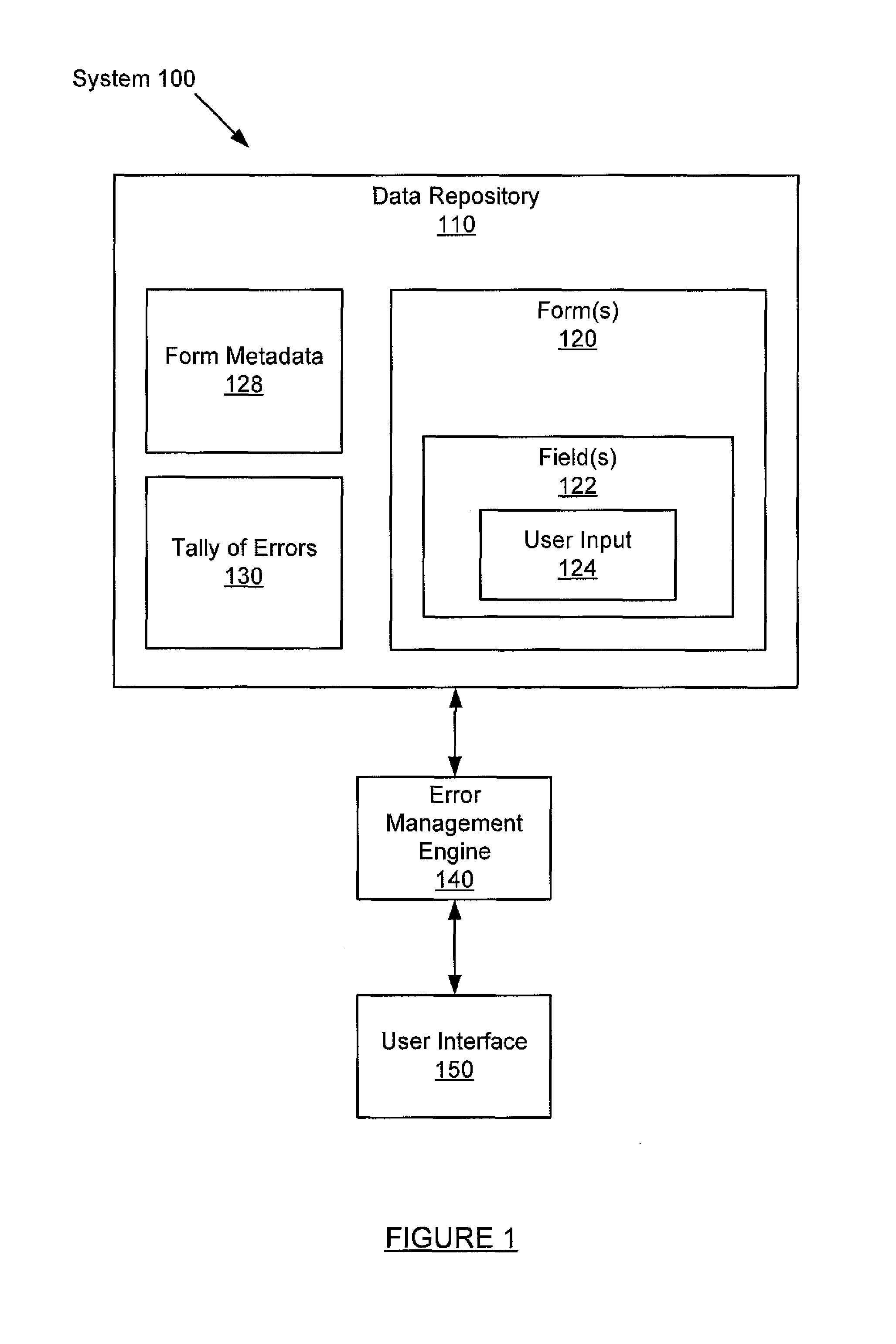

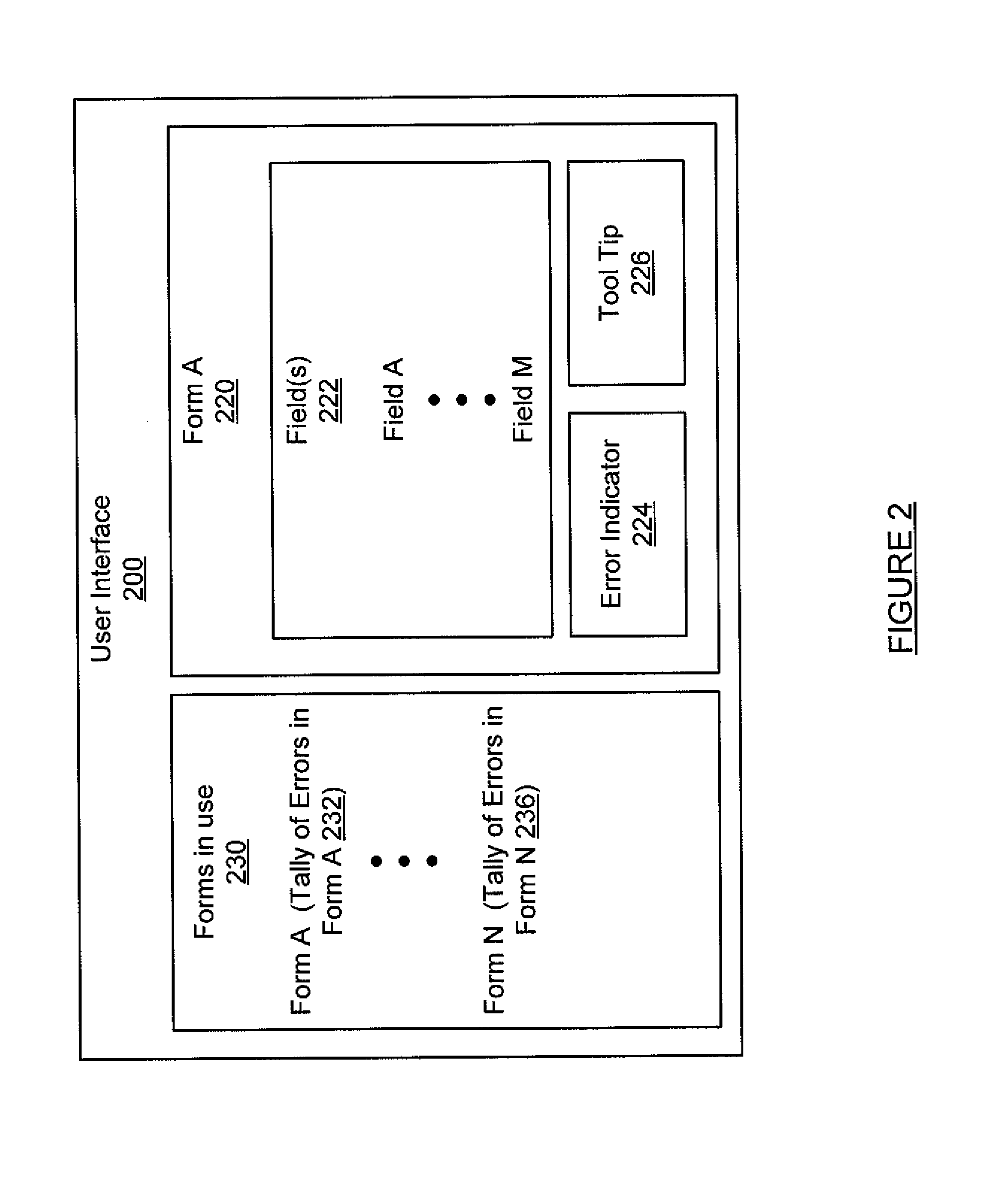

Error checking for data entry

ActiveUS8234562B1Natural language data processingSpecial data processing applicationsError checkingReal-time computing

Owner:INTUIT INC

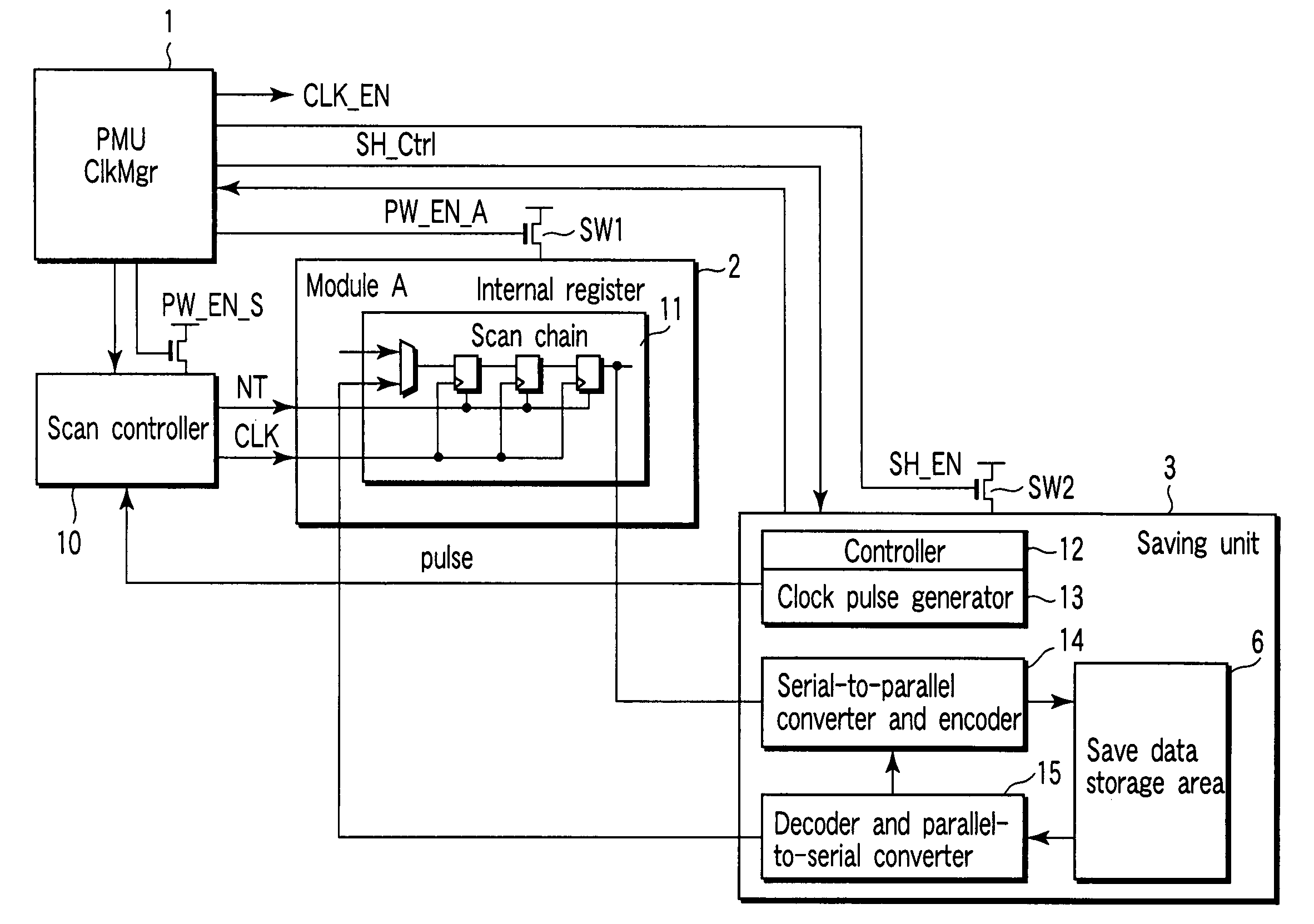

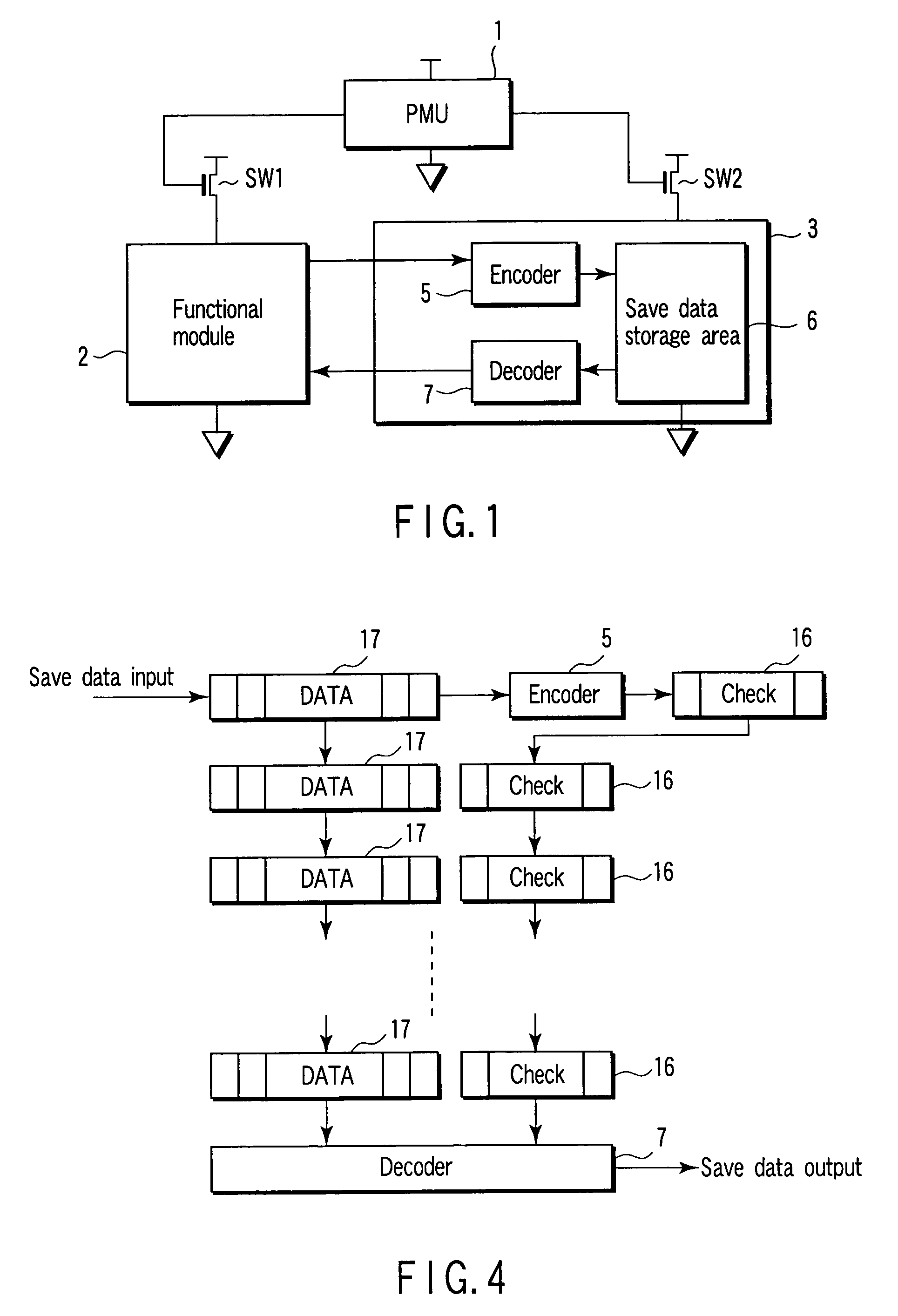

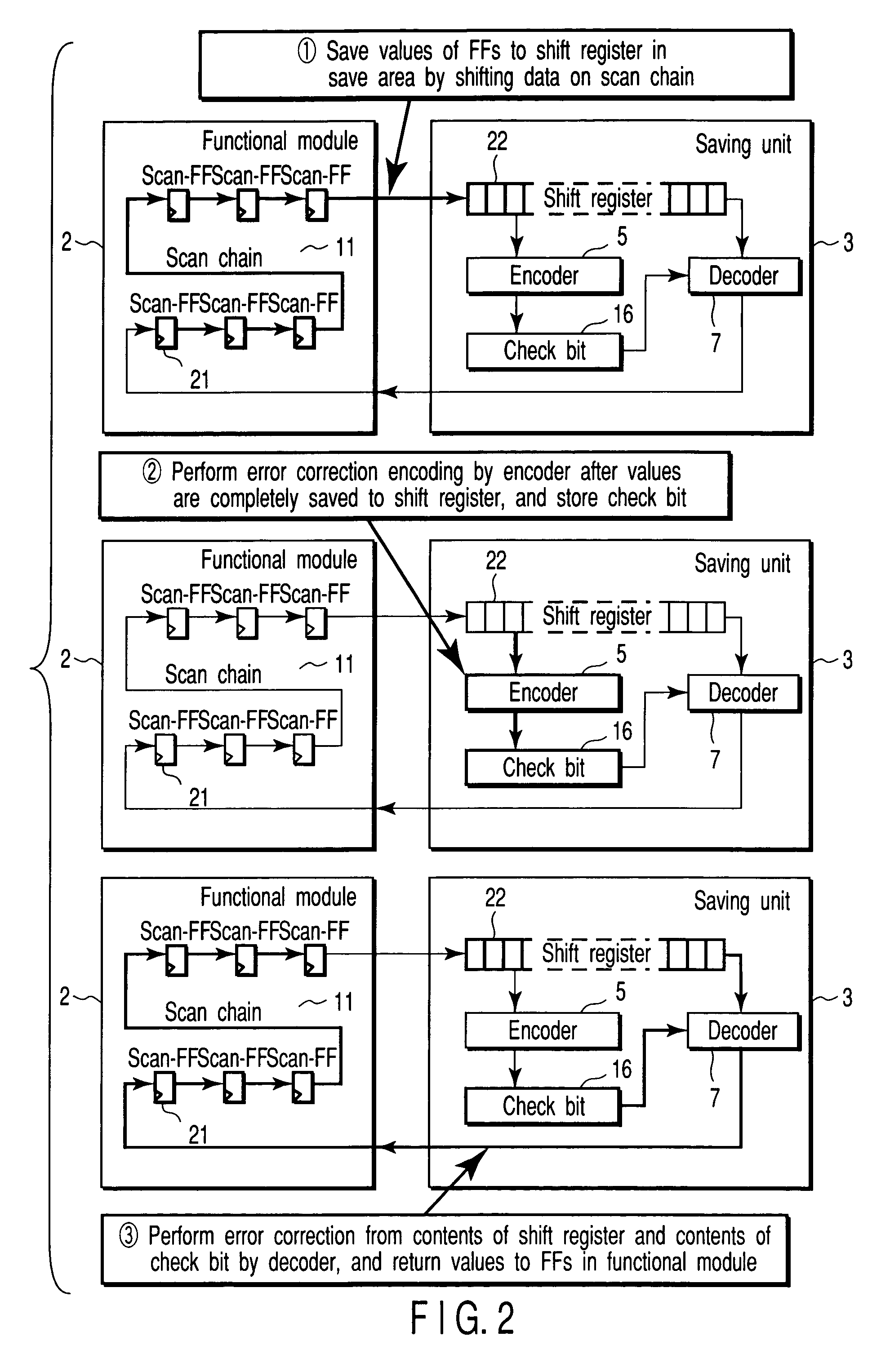

Power management for circuits with inactive state data save and restore scan chain

An integrated circuit device includes at least one functional module which outputs save data in synchronism with a saving clock signal, a power supply control unit which selects one of the functional modules, and controls stop and resumption of power supply to the selected functional module, a save data storage unit which stores save data output from a functional module selected by the power supply control unit, and an error checking and correction unit which performs error checking and correction for the save data stored in the save data storage unit when the save data is to be restored to the functional module in synchronism with a restoration clock signal.

Owner:SOCIONEXT INC

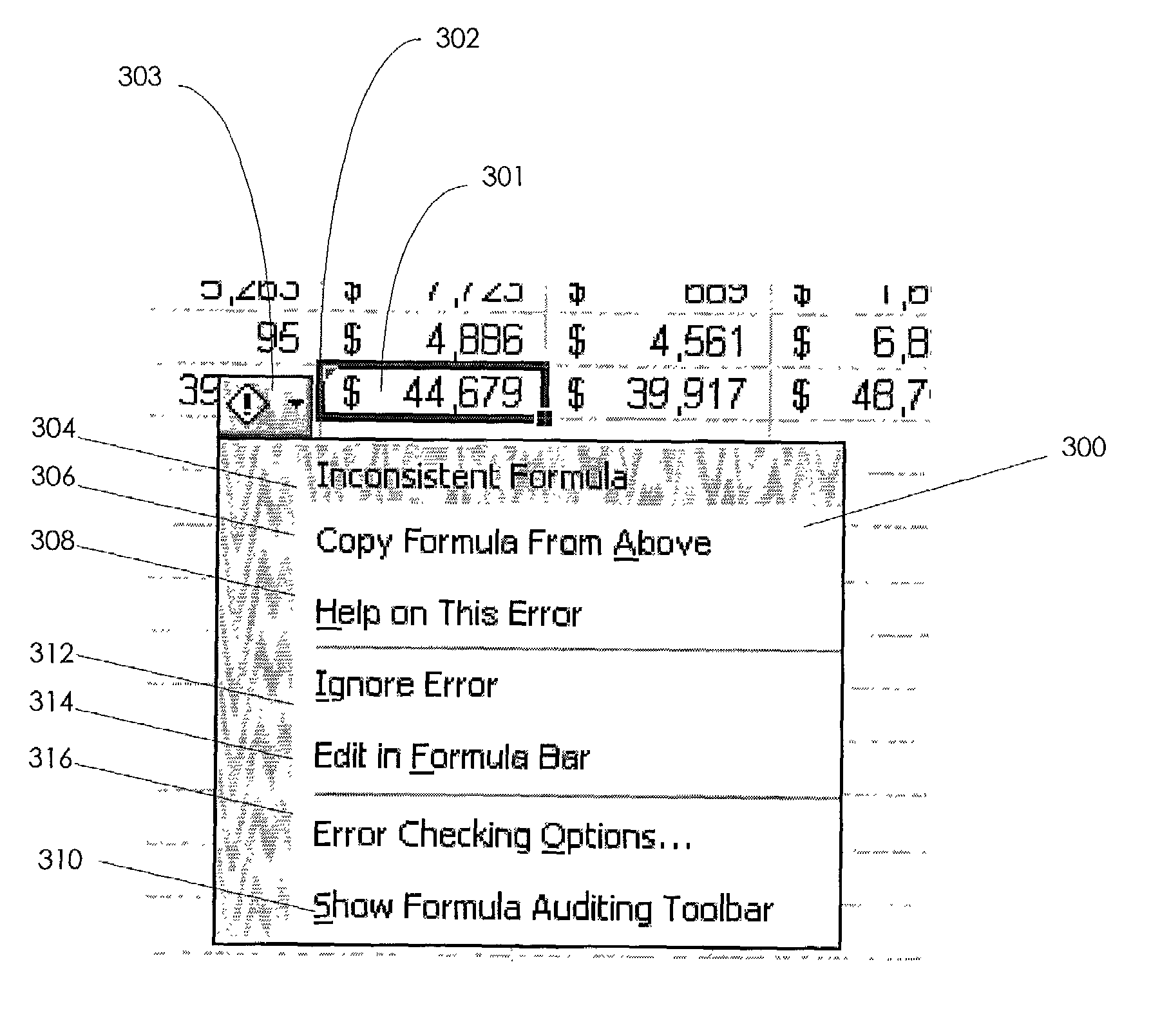

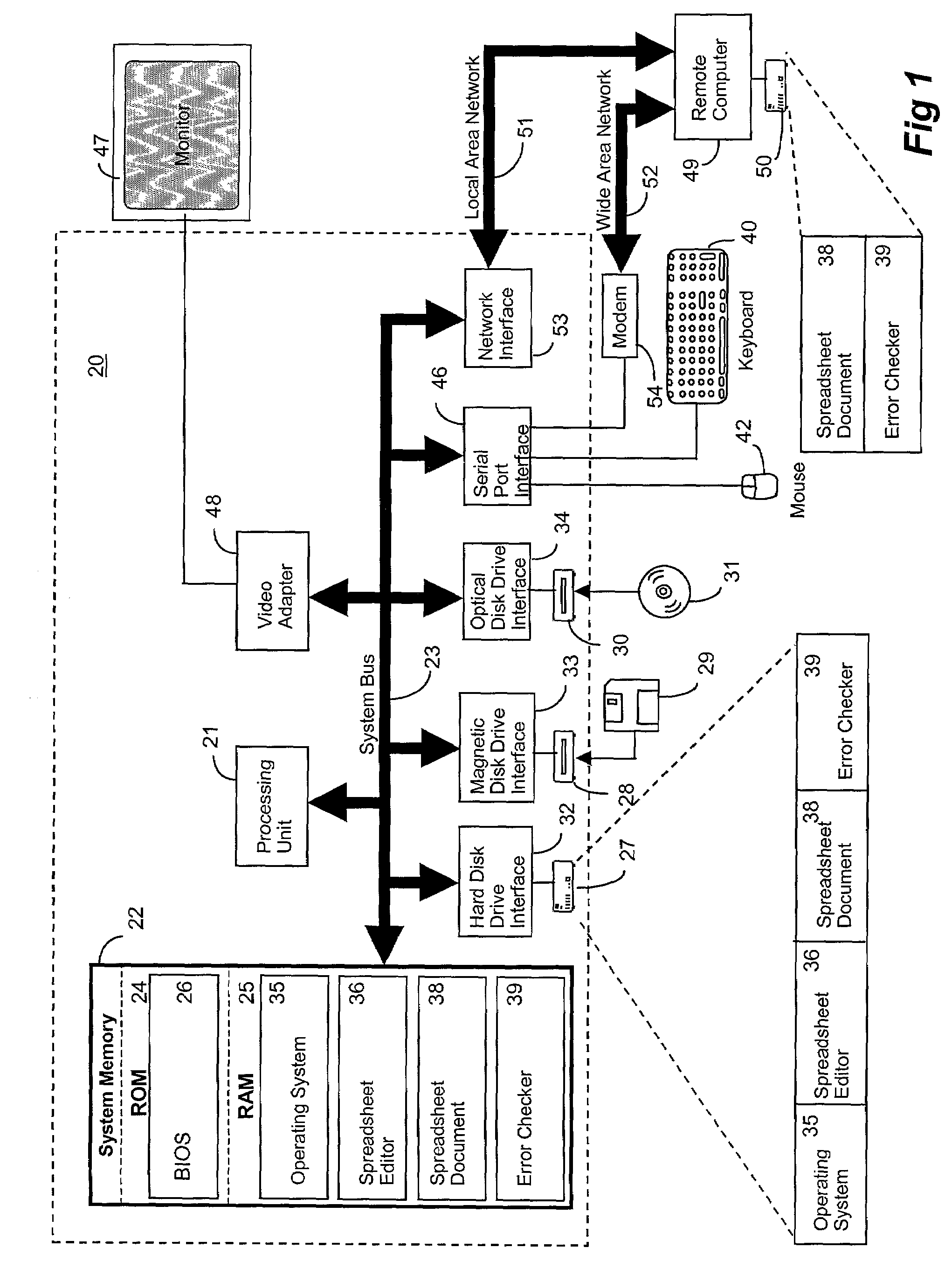

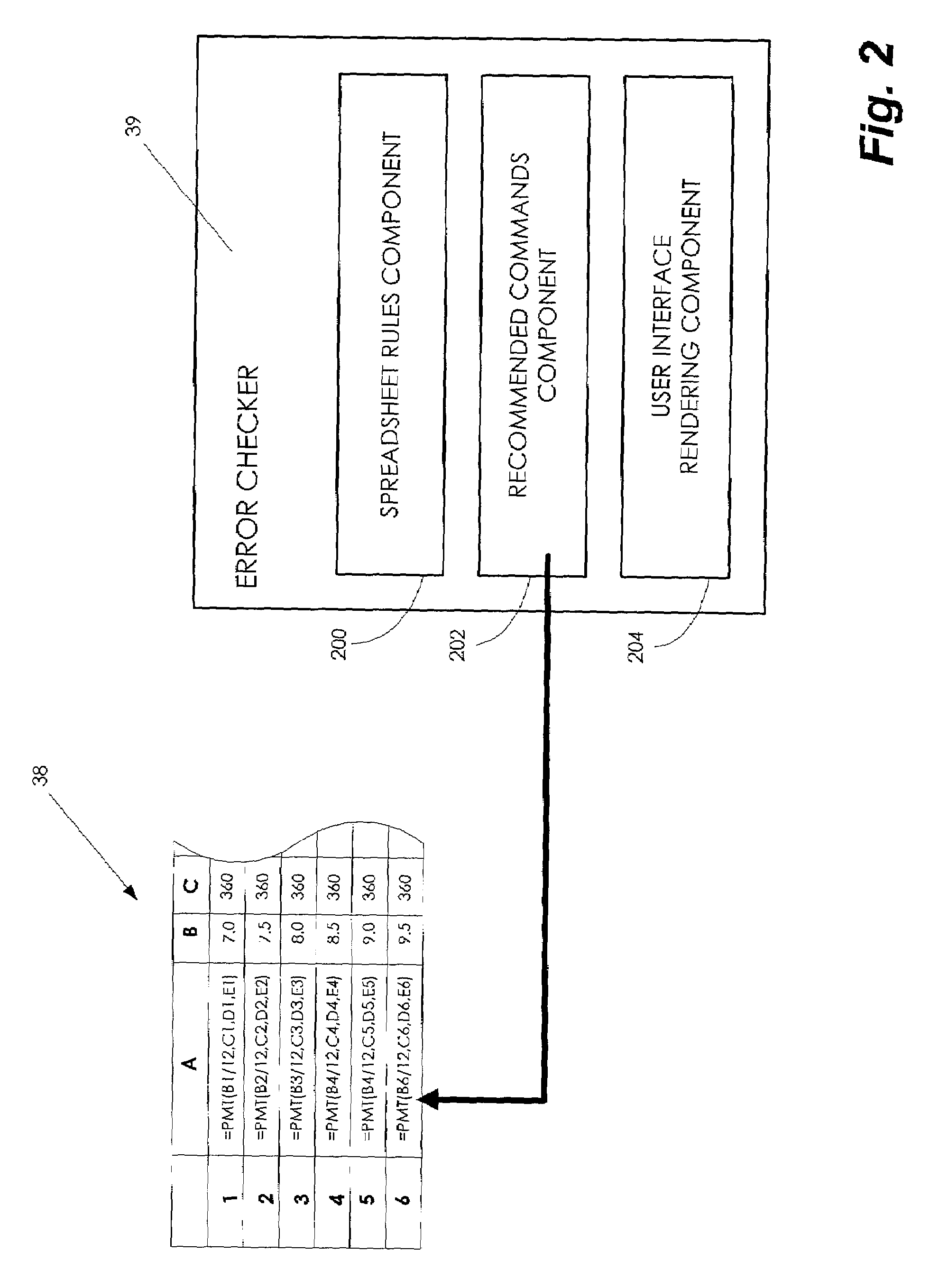

Spreadsheet error checker

An error checker identifies spreadsheet errors by traversing a spreadsheet cell-by-cell and comparing each cell's contents to a list of error rules. When a cell's contents satisfy an error rules, then the cell is identified as containing a potential spreadsheet error. The error checker identifies potential spreadsheet errors and marks the cells containing the potential errors with an error indicator. A drop-down menu is provided that includes an element identifying the error rule that was invoked by the cell's contents and may include one or more recommended actions to resolve the identified error.

Owner:MICROSOFT TECH LICENSING LLC

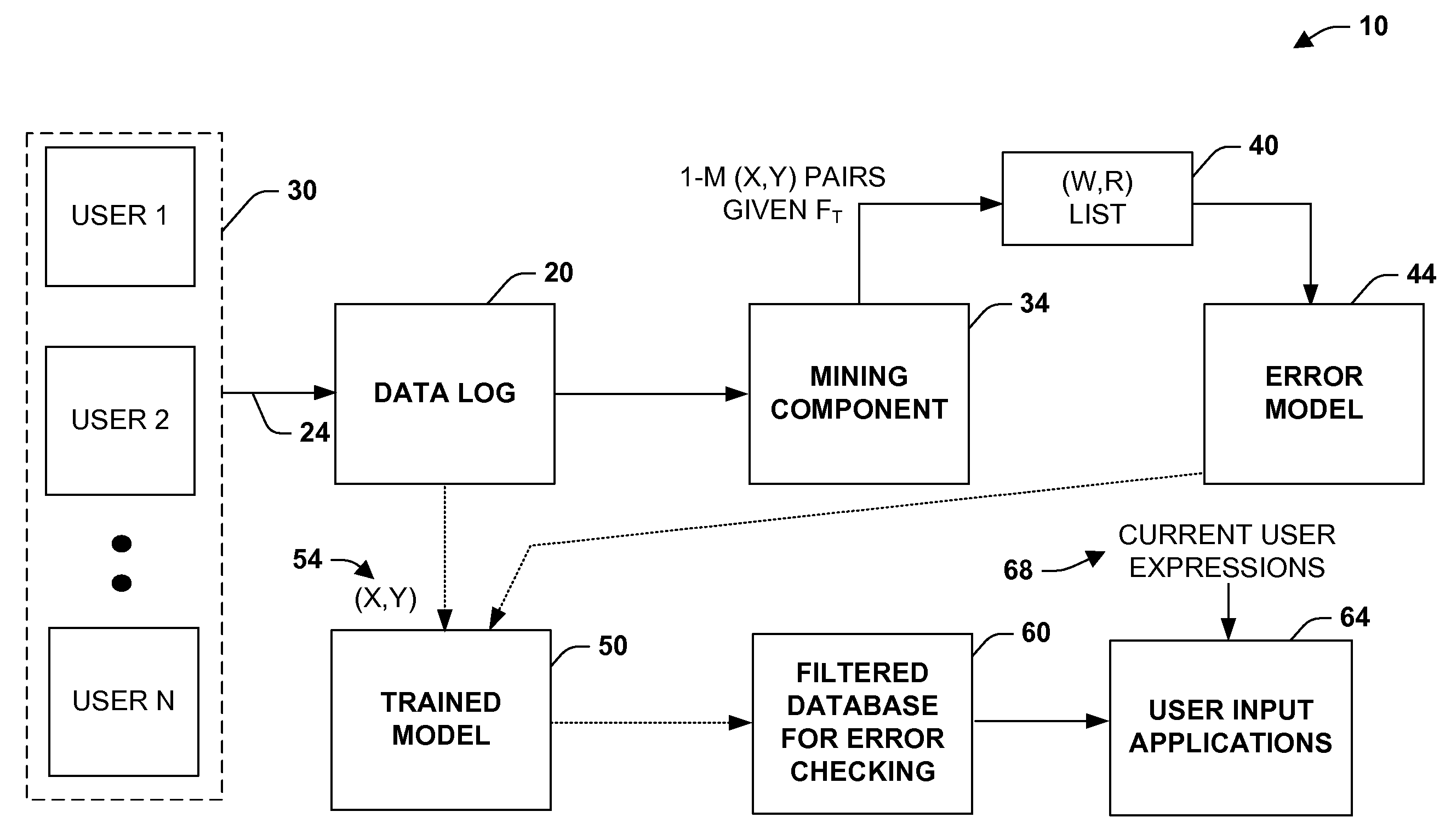

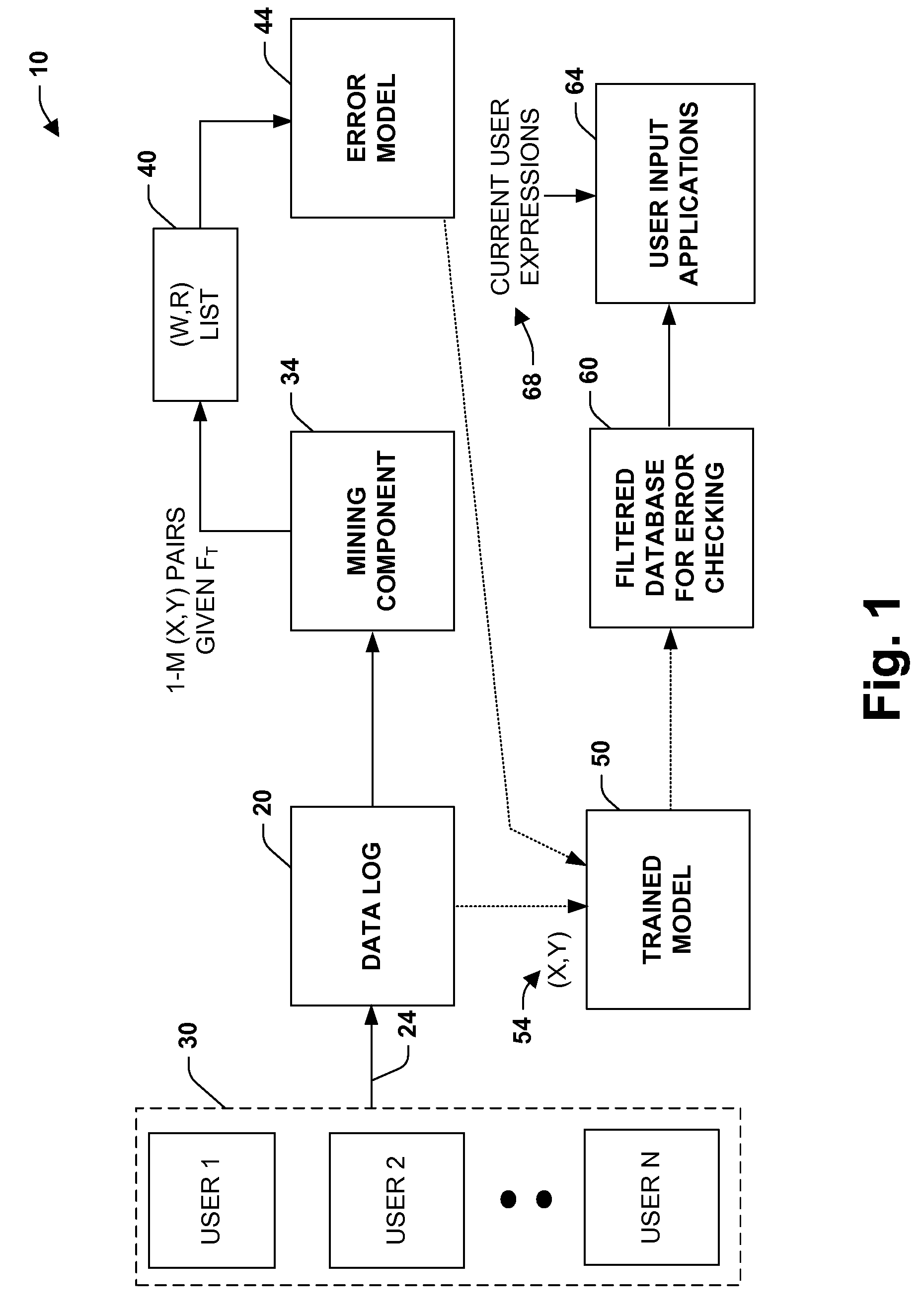

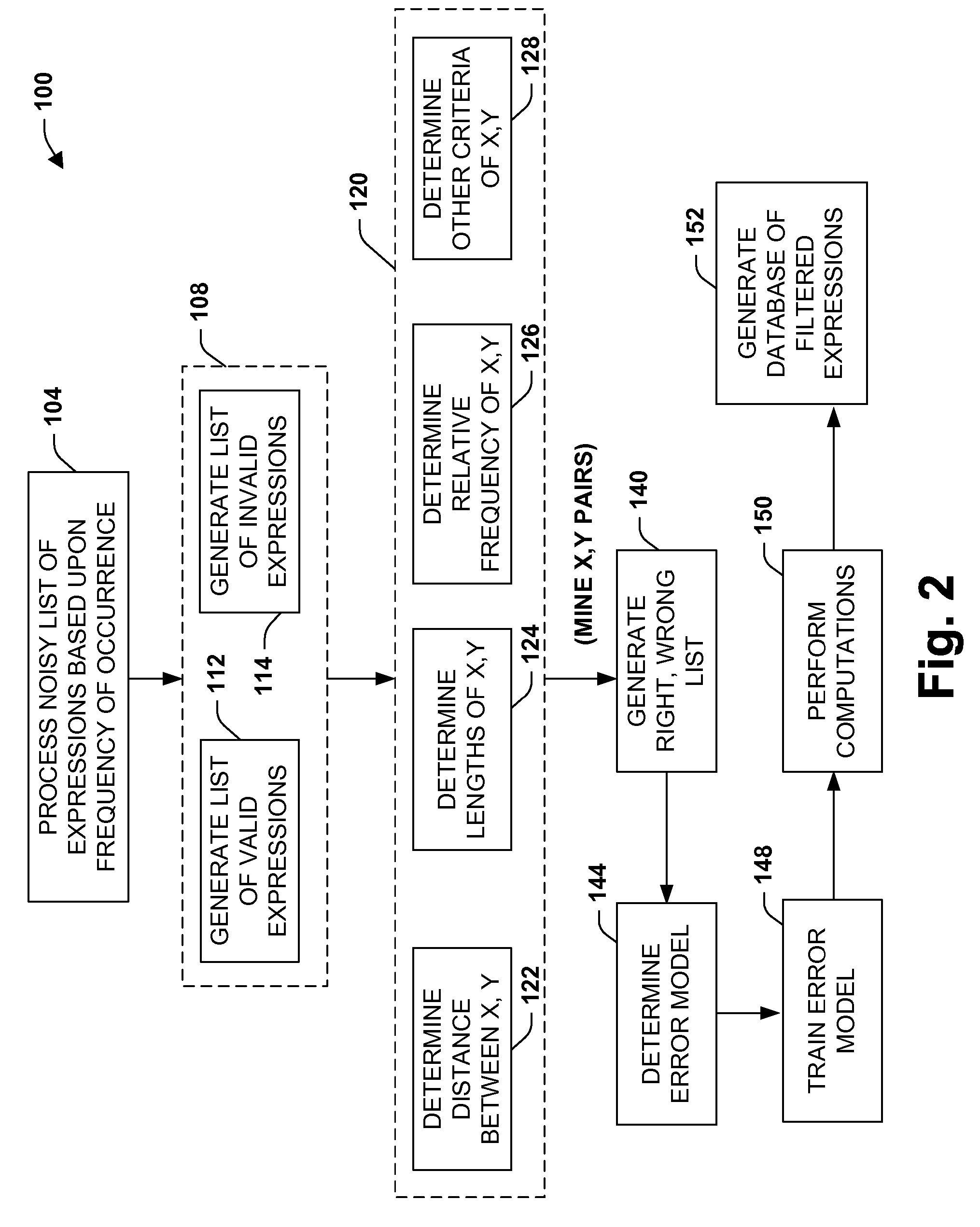

Automated error checking system and method

InactiveUS20070016616A1Facilitate automated error correctionFacilitate error checkingData processing applicationsNatural language data processingError checkingSpoken language

The present invention relates to a system and methodology to facilitate automated error correction of user input data via an analysis of the input data in accordance with an automatically generated and filtered database of processed structural groupings or formulations selected and filtered from past user activities. The filtered database provides a relevant foundation of potential phrases, topics, symbols, speech and / or colloquial structures of interest to users—which are automatically determined from previous user activity, and employed to facilitate automated error checking in accordance with the user's current input, command and / or request for information.

Owner:MICROSOFT TECH LICENSING LLC

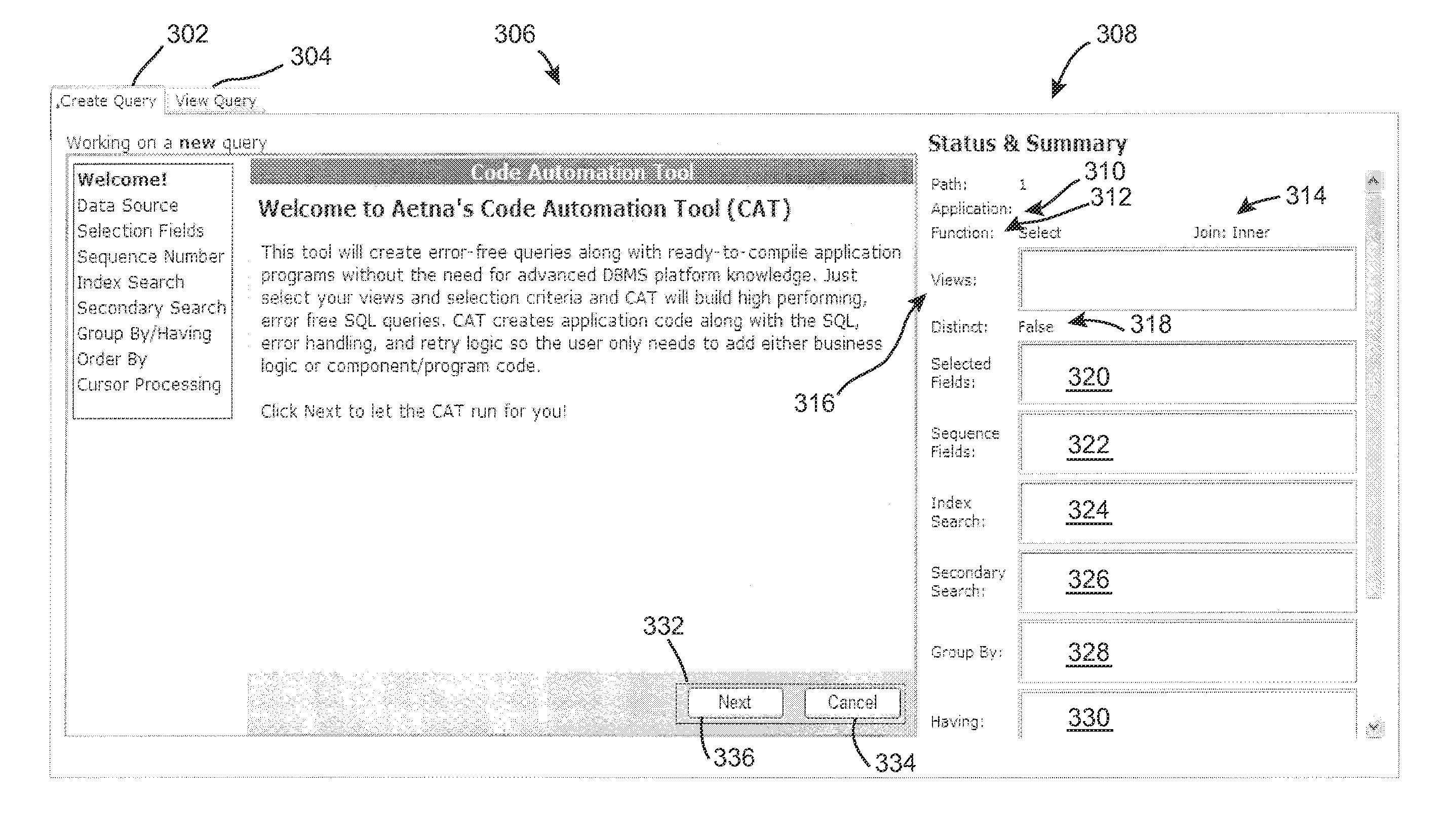

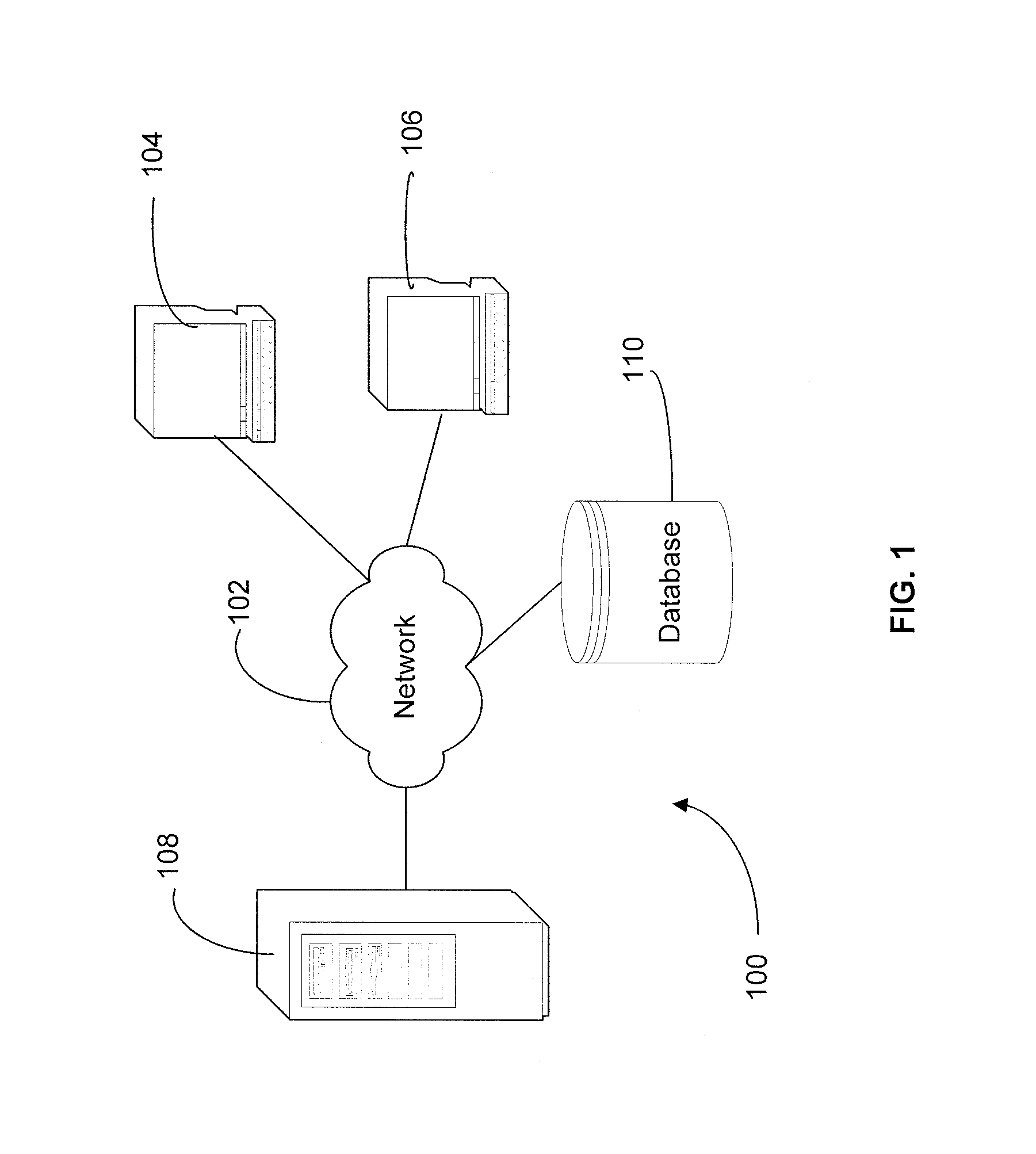

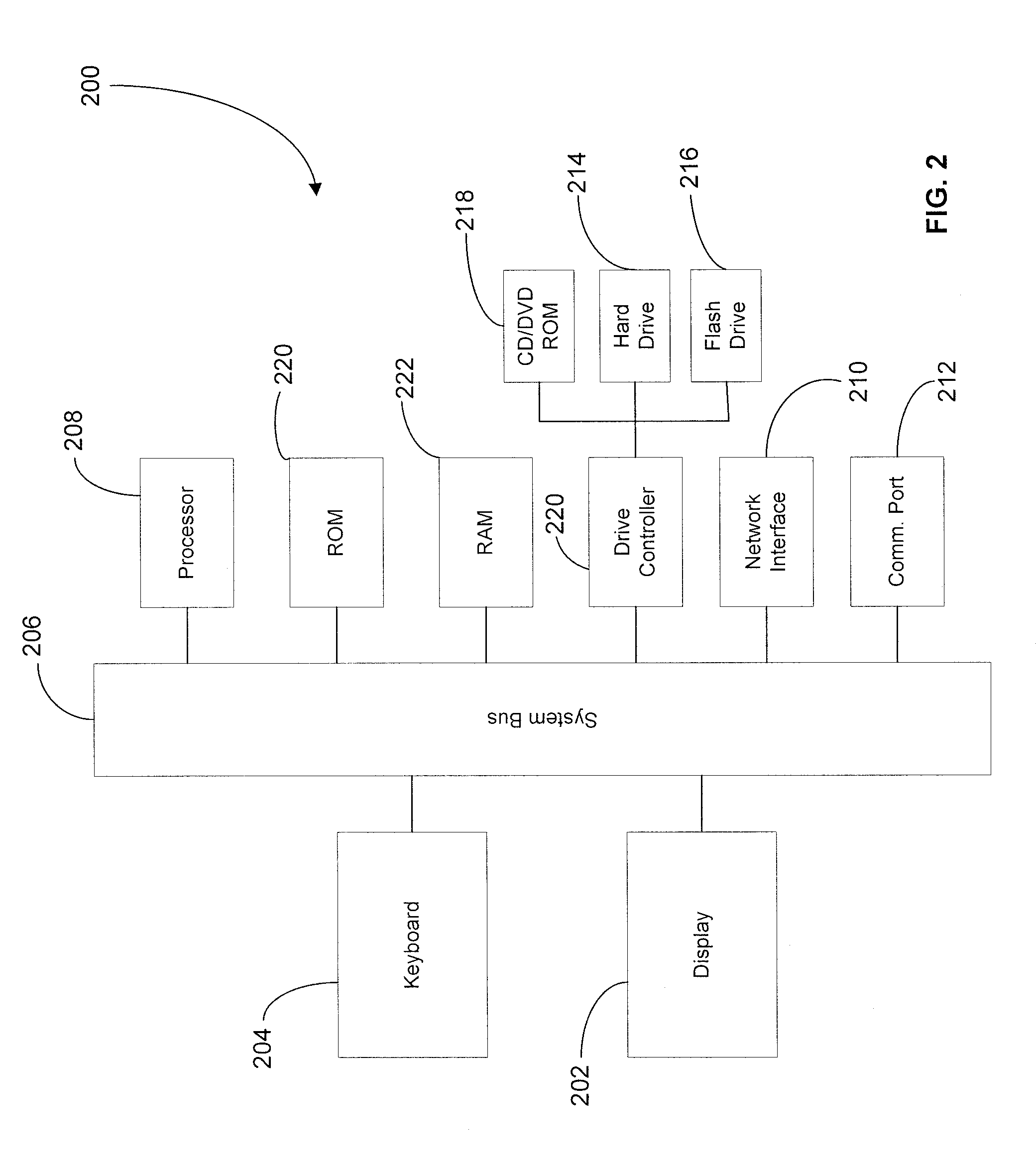

System and method for code automation

ActiveUS8555263B2Reduces the percentage of SQL codeIncrease speedSoftware designProgram controlError checkingUser input

A system is provided for computer application code automation comprising a code automation computer server configured for presenting an electronic user interface for receiving user input for generating a Structured Query Language (SQL) query, the user input comprising a plurality of SQL tokens, a processor, associated with the code automation computer server, for receiving the plurality of SQL tokens, the processor retrieving from memory and executing computer executable instructions for at least one of: (a) optimizing performance of the SQL query while receiving the user input, and (b) error checking the SQL query while receiving the user input, wherein the processor is adapted for automatically incorporating the generated SQL query into the computer application code and storing the computer application code in a non-transitory computer readable medium.

Owner:AETNA

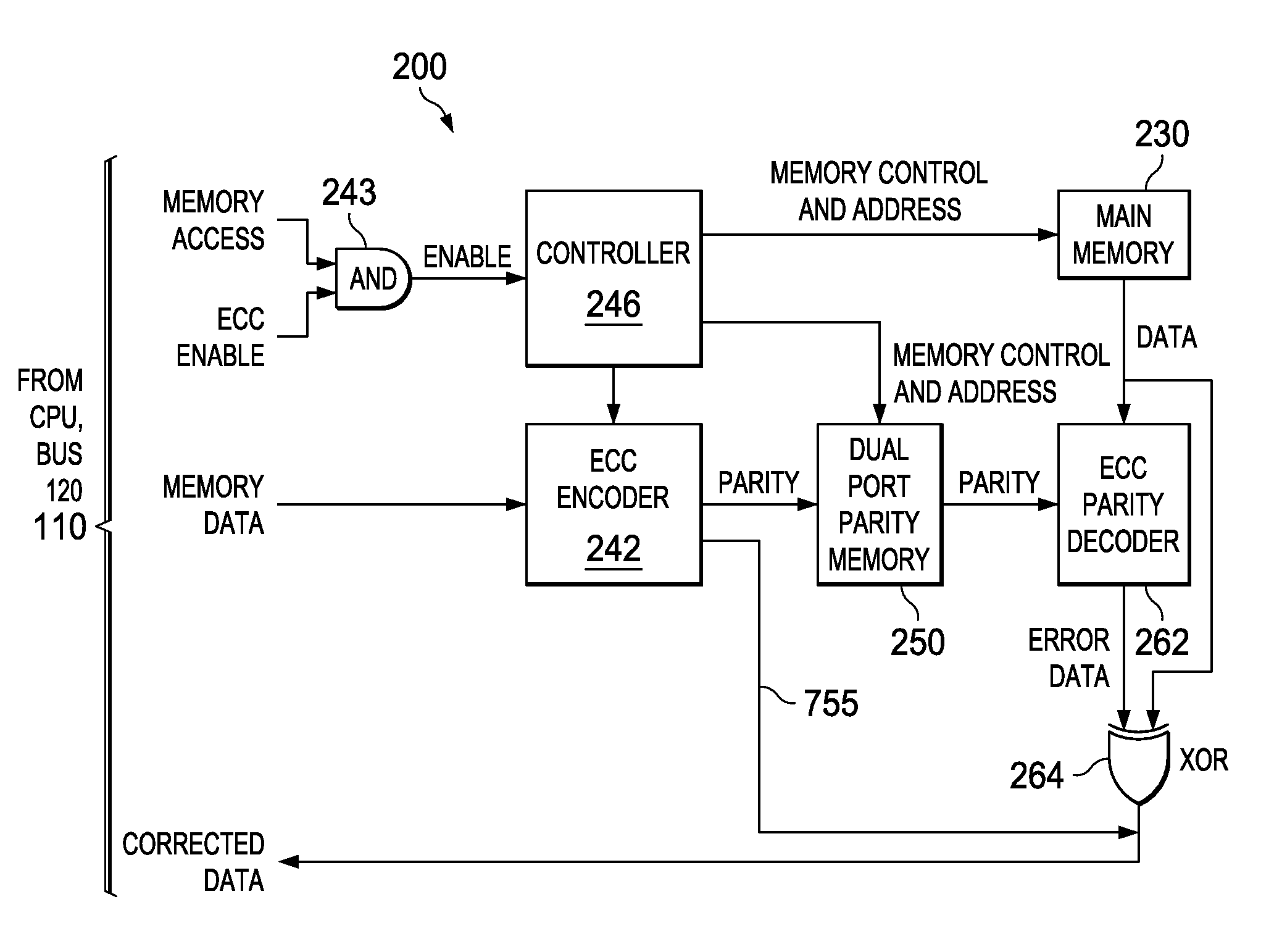

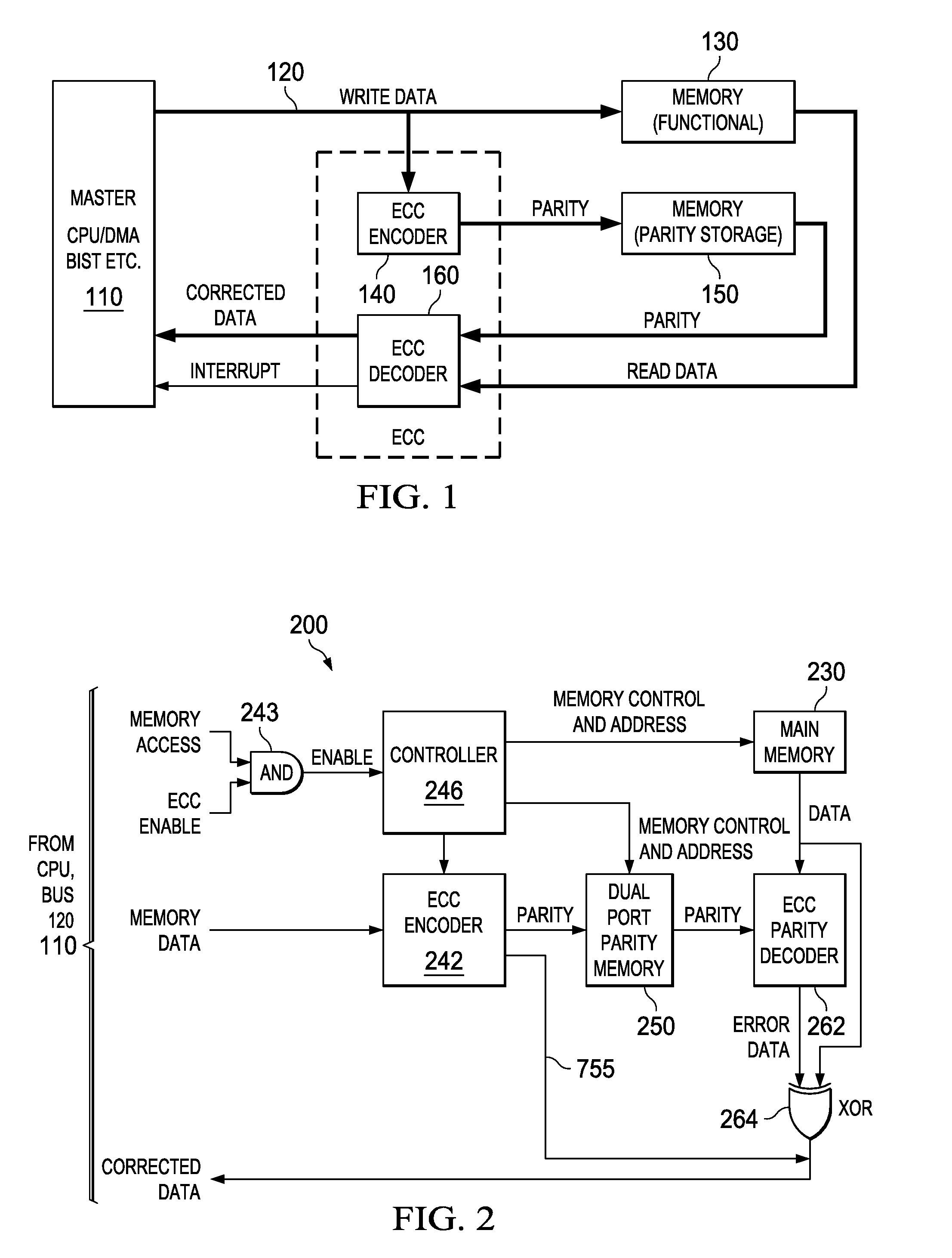

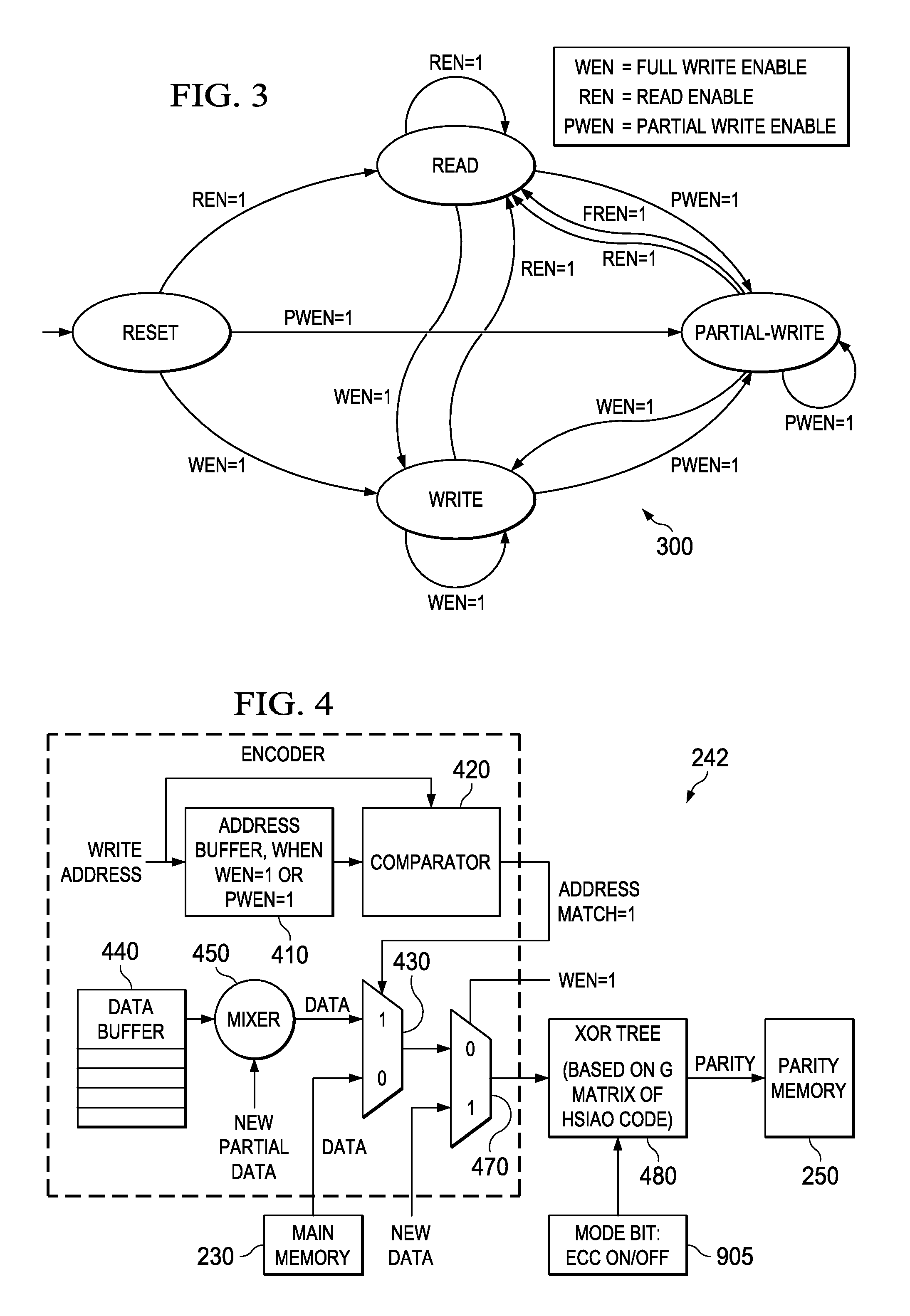

Low overhead and timing improved architecture for performing error checking and correction for memories and buses in system-on-chips, and other circuits, systems and processes

An electronic circuit (200) for use with an accessing circuit (110) that supplies a given address and a partial write data portion and also has dummy cycles. The electronic circuit (200) includes a memory circuit (230) accessible at addresses, an address buffer (410), a data buffer (440) coupled to the memory circuit (230), and a control circuit (246) operable in the dummy cycles to read data from the memory circuit (230) to the data buffer (440) from a next address location in the memory circuit (230) and to store that next address in the address buffer (410). The electronic circuit further includes a multiplexer (430), a comparing circuit (420) responsive to the given address and a stored address in the address buffer (410), to operate the multiplexer (430) to pass data from the data buffer (440) or to pass data from the memory circuit (230) instead; and a mixer circuit (450) operable to put the partial write data portion into the data taken from the selected one of the data buffer (440) or memory circuit (230). Other circuits, devices, systems, processes of operation and processes of manufacture are also disclosed.

Owner:TEXAS INSTR INC

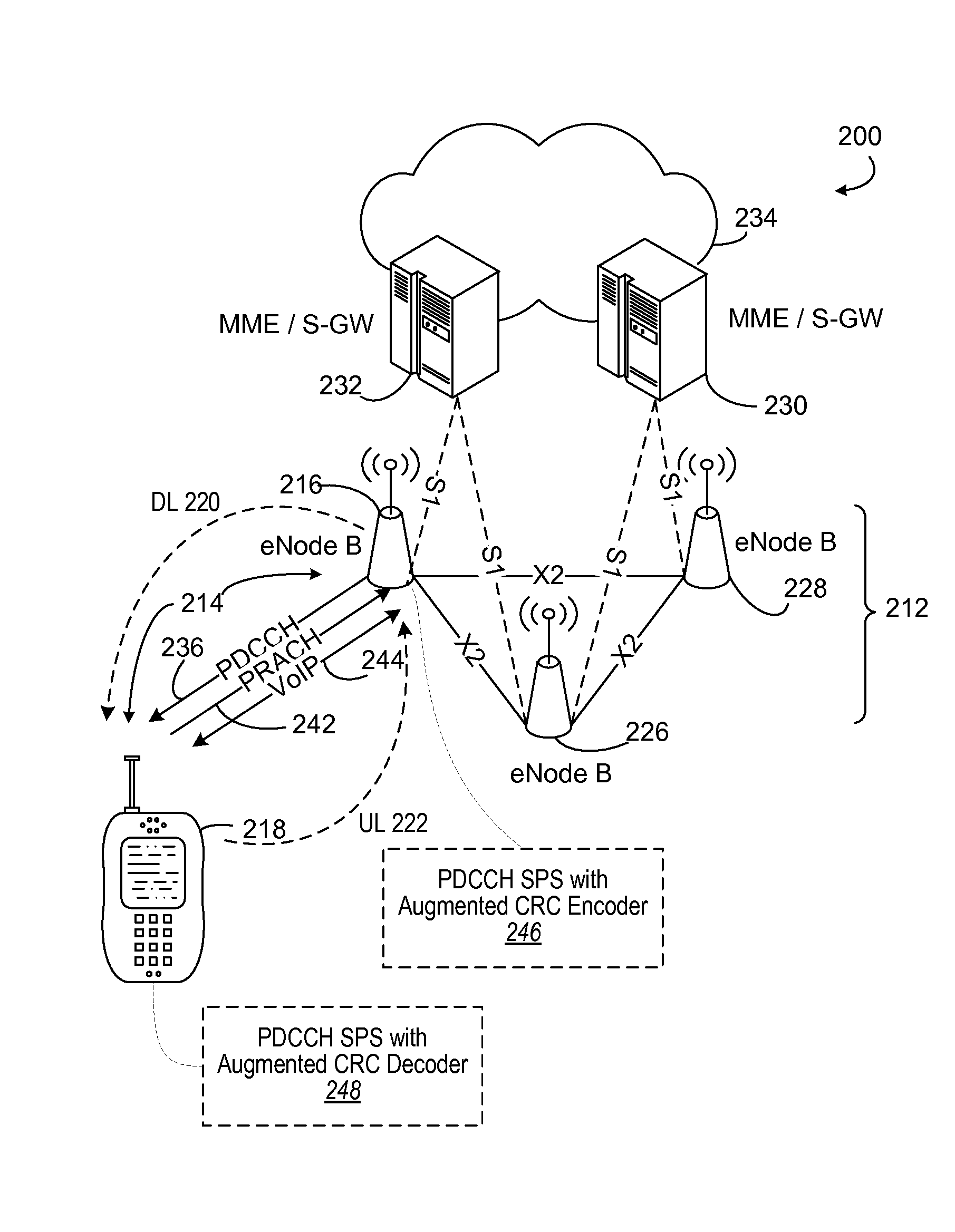

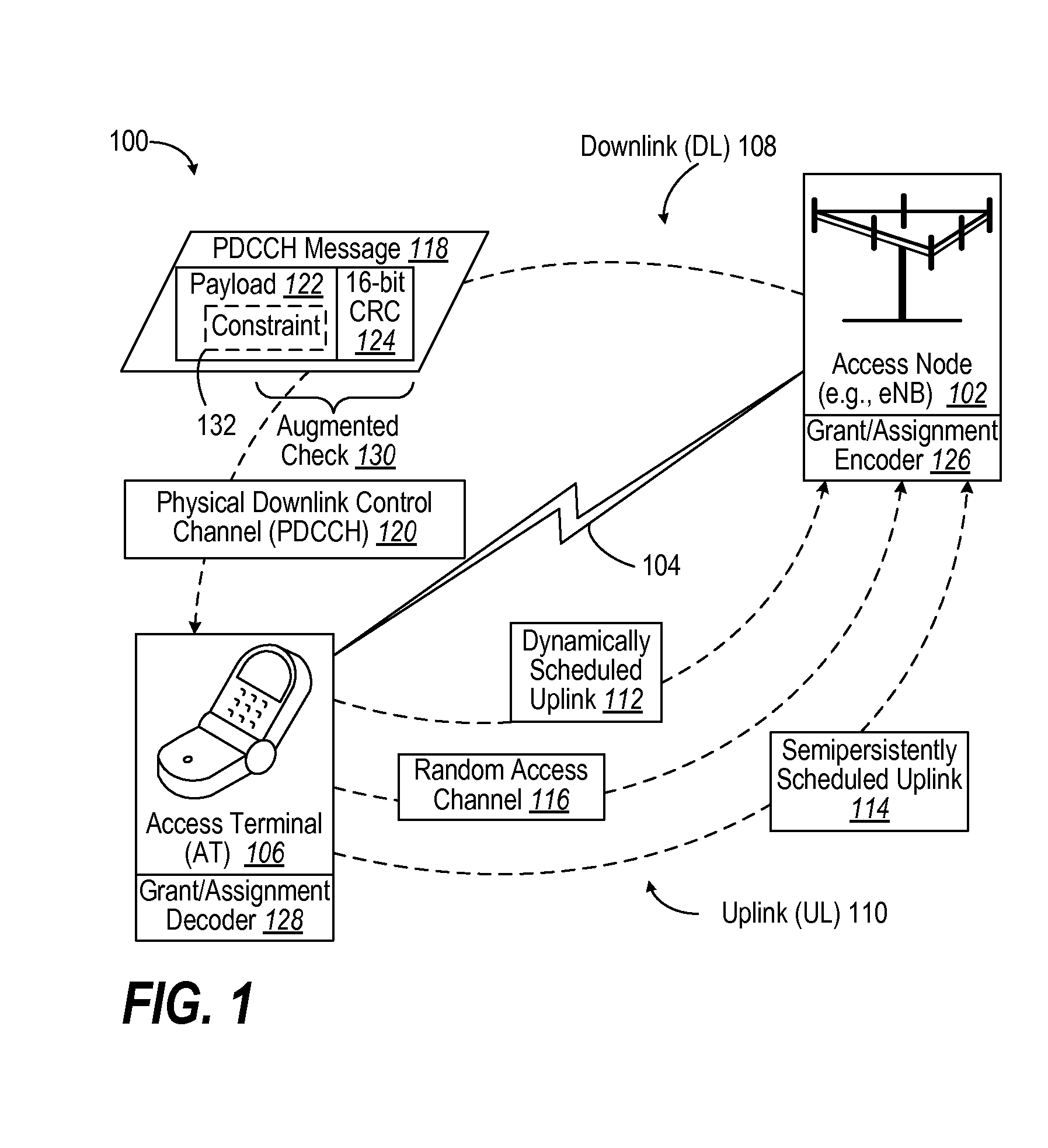

Filtering semi-persistent scheduling false alarms

ActiveUS20090257385A1Network traffic/resource managementForward error control useError checkingCommunications system

A scheduled data communication system of an access node and terminal supports recurring communications of small data amounts such as Voice over IP (VoIP). In order to make error checking more robust in a random access response (RAR), such as for semi-persistent scheduling (SPS) for VoIP, a portion of a grant or assignment payload has a constraint imposed that can be verified as a condition precedent to determining a valid grant or assignment rather than only relying upon a validity check field, such as a cyclic redundancy check (CRC). Thereby, incorrect validation of a grant or assignment is avoided for dynamic scheduling or for semi-persistent scheduling, the latter causing a persistent error.

Owner:QUALCOMM INC

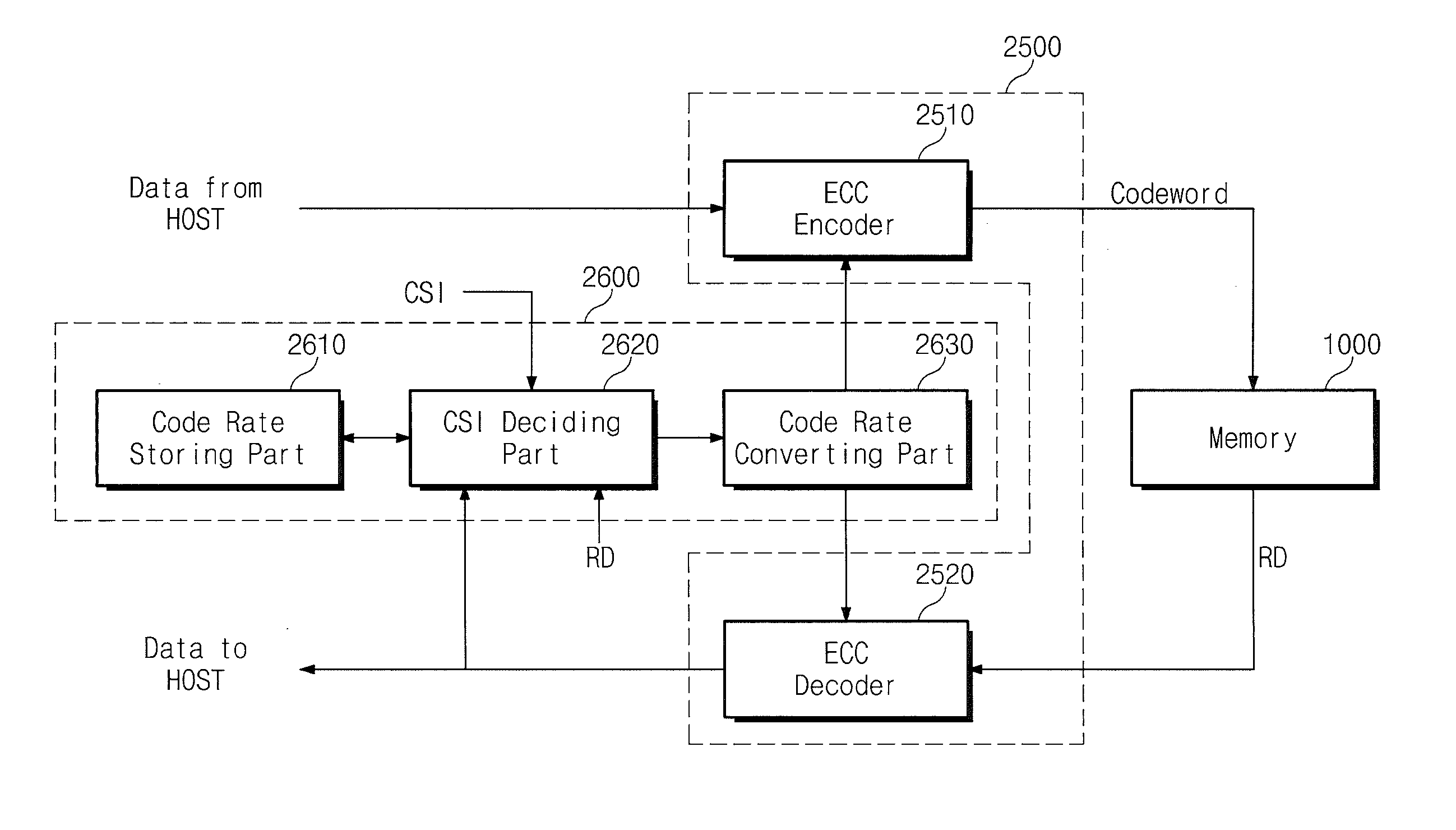

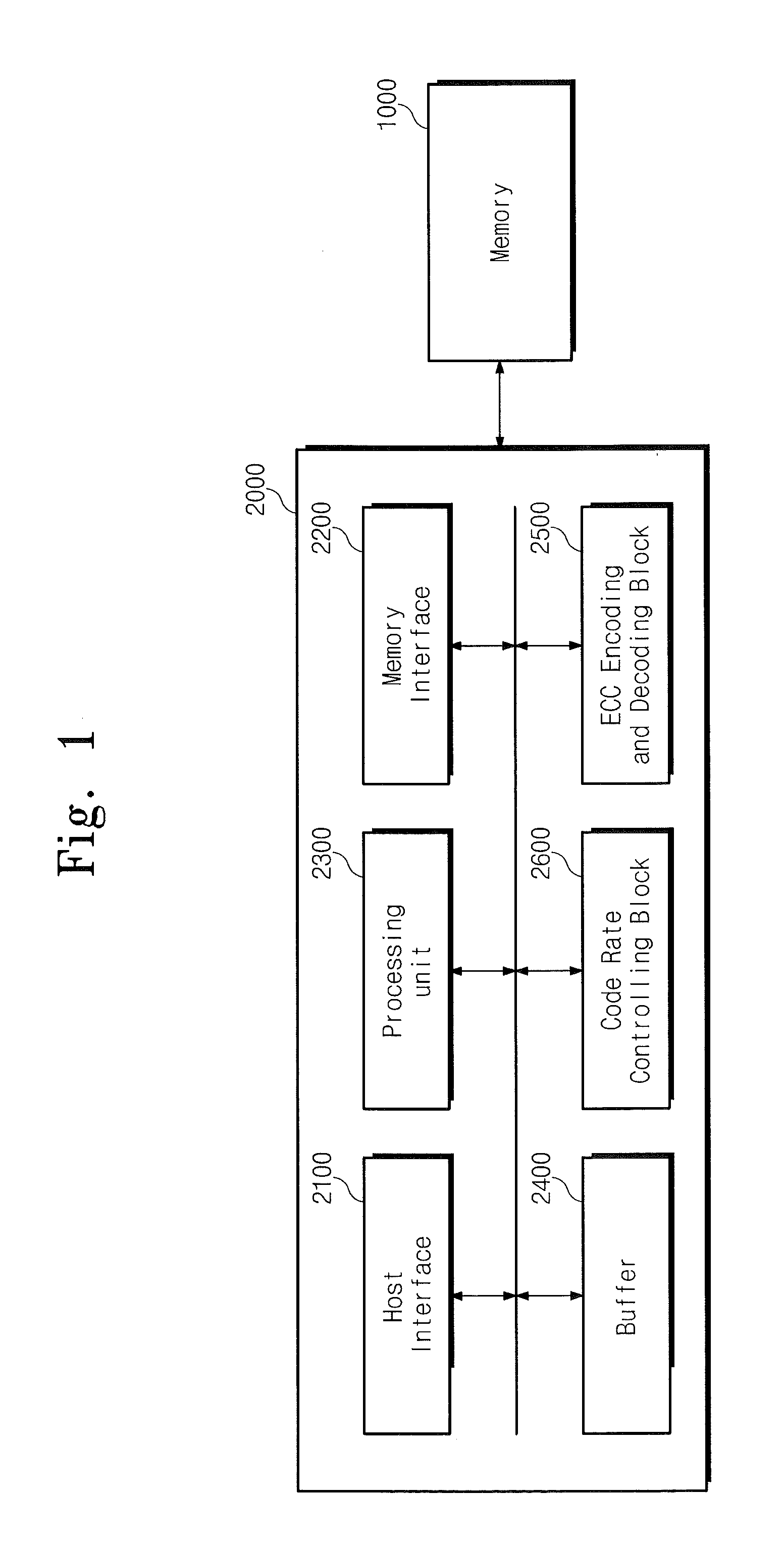

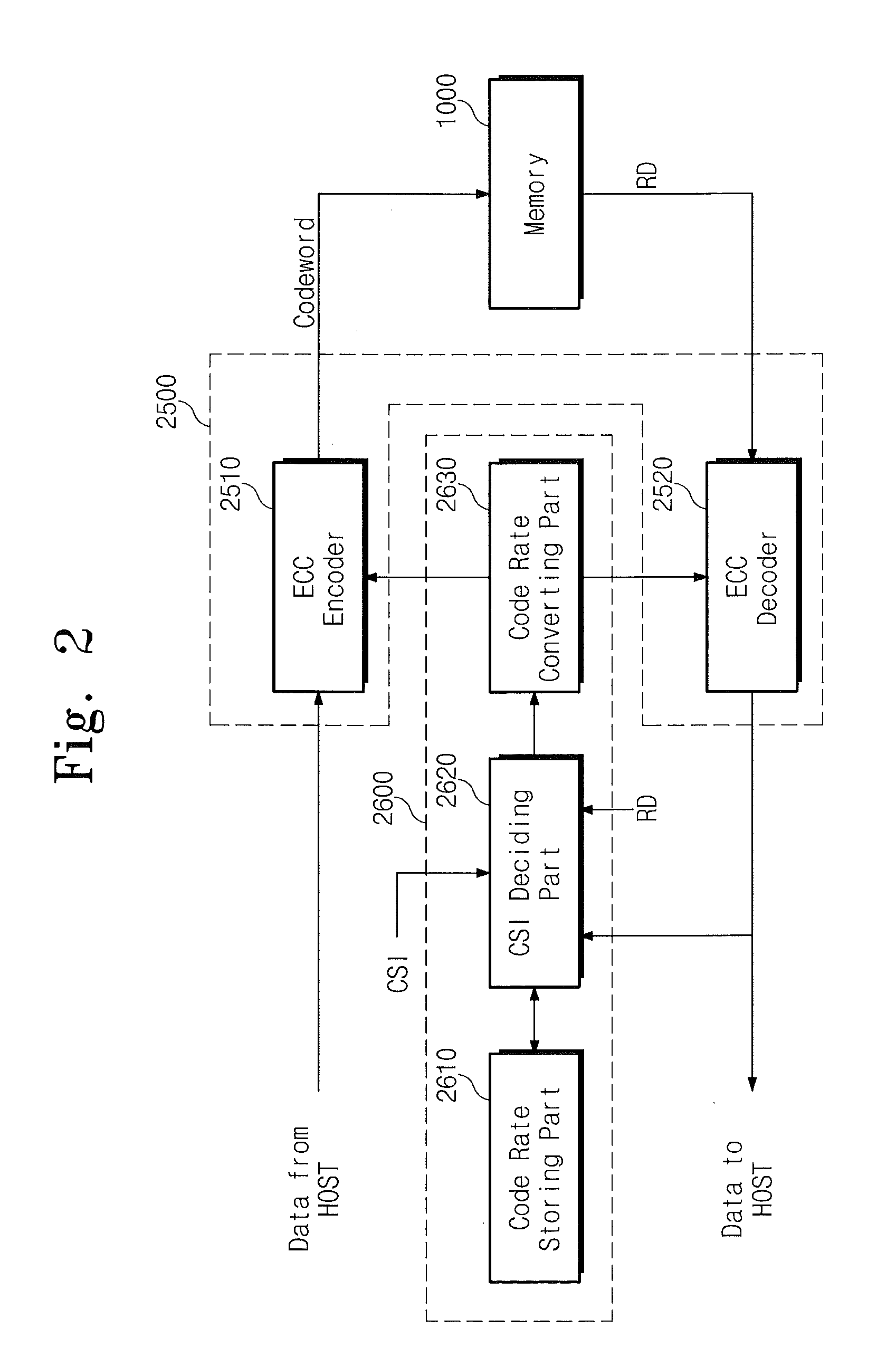

Data Processing System Having ECC Encoding and Decoding Circuits Therein with Code Rate Selection Based on Bit Error Rate Detection

InactiveUS20100241928A1Code conversionError correction/detection using linear codesError checkingData processing system

A data processing system includes an error checking and correction (ECC) encoding circuit, an integrated circuit memory and a code rate control circuit. The ECC encoding circuit is configured to selectively apply a plurality of unique ECC code rates to write data received by the data processing system during an operation to convert the write data into encoded data, in response to a code rate selection signal. The integrated circuit memory includes a plurality of storage regions therein. These storage regions are configured to receive respective portions of the encoded data from the ECC encoding circuit. The code rate control circuit is configured to generate the code rate selection signal. This code rate selection signal has a value that specifies the corresponding ECC code rate to be applied to respective portions of the write data.

Owner:SAMSUNG ELECTRONICS CO LTD

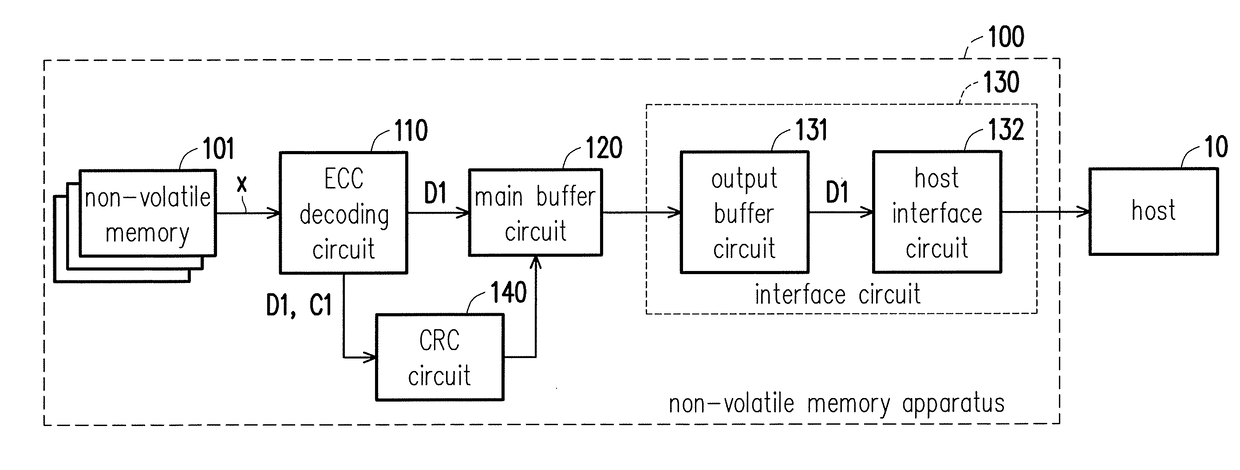

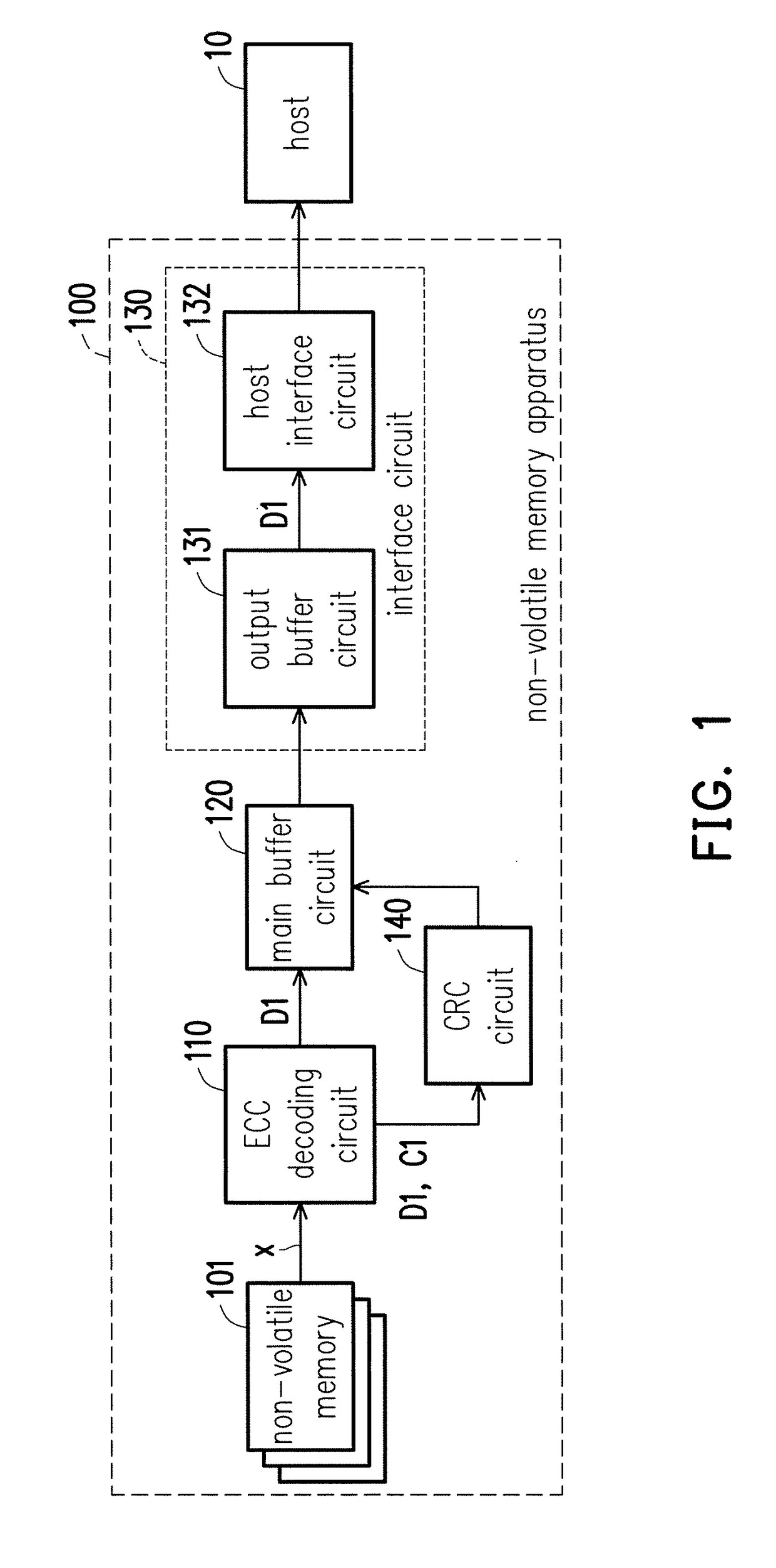

Non-volatile memory apparatus and reading method thereof

ActiveUS20180329776A1Reducing the pipeline stagesAccelerate the non-sequential read rateCode conversionError correction/detection by combining multiple code structuresError checkingMultiplexer

A non-volatile memory apparatus includes an error checking and correcting (ECC) decoding circuit, a main buffer circuit, a multiplexer, and an interface circuit. The ECC decoding circuit decodes an original codeword to obtain a decoded codeword. The main buffer circuit is coupled to the ECC decoding circuit for receiving and storing a first data portion of the decoded codeword. The multiplexer's first input end is coupled to the output end of the main buffer circuit. The second input end of the multiplexer is coupled to the output end of the ECC decoding circuit. The interface circuit is coupled to the output end of the multiplexer and receives the first data portion from the multiplexer to provide the first data portion to a host.

Owner:VIA TECH INC

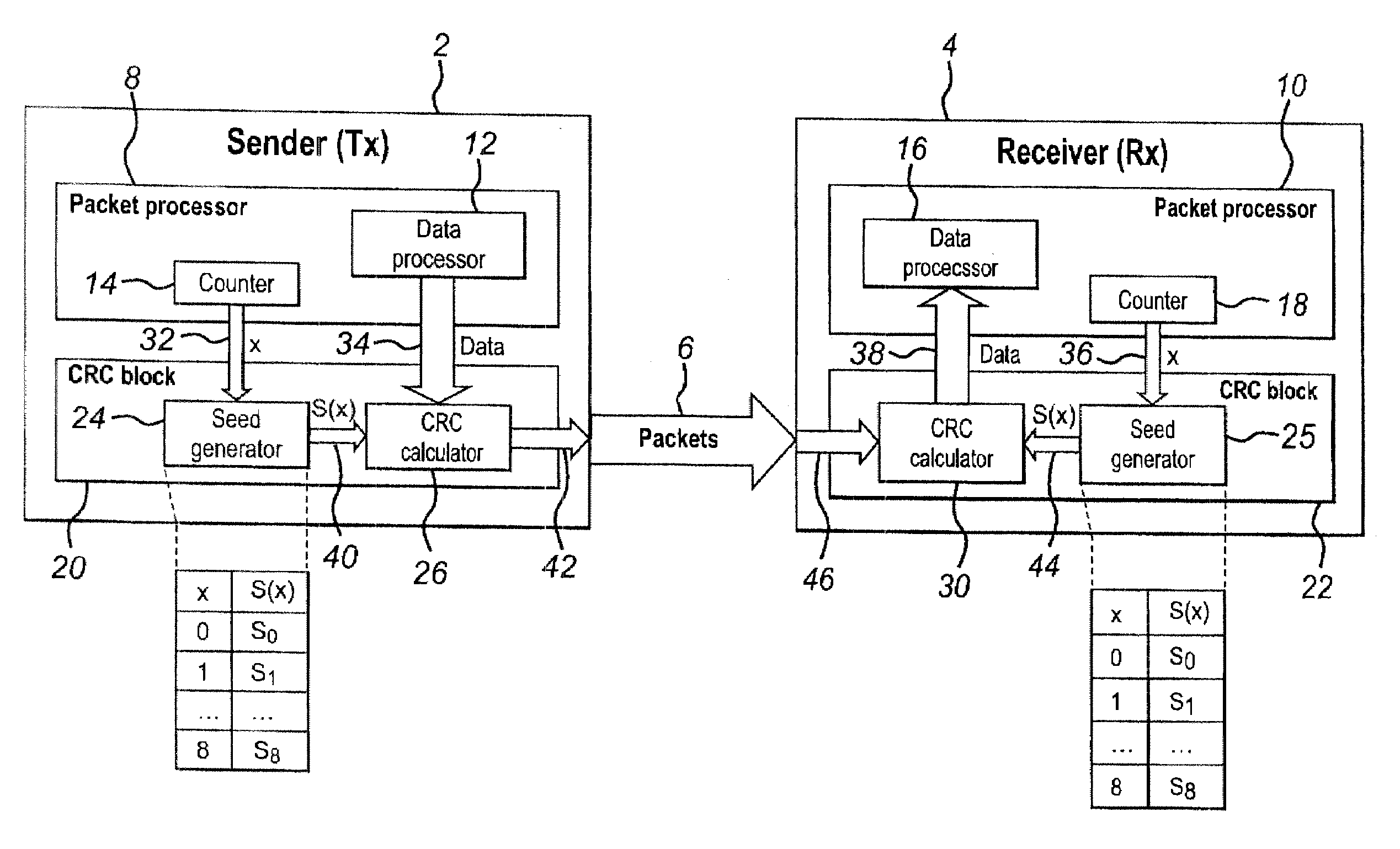

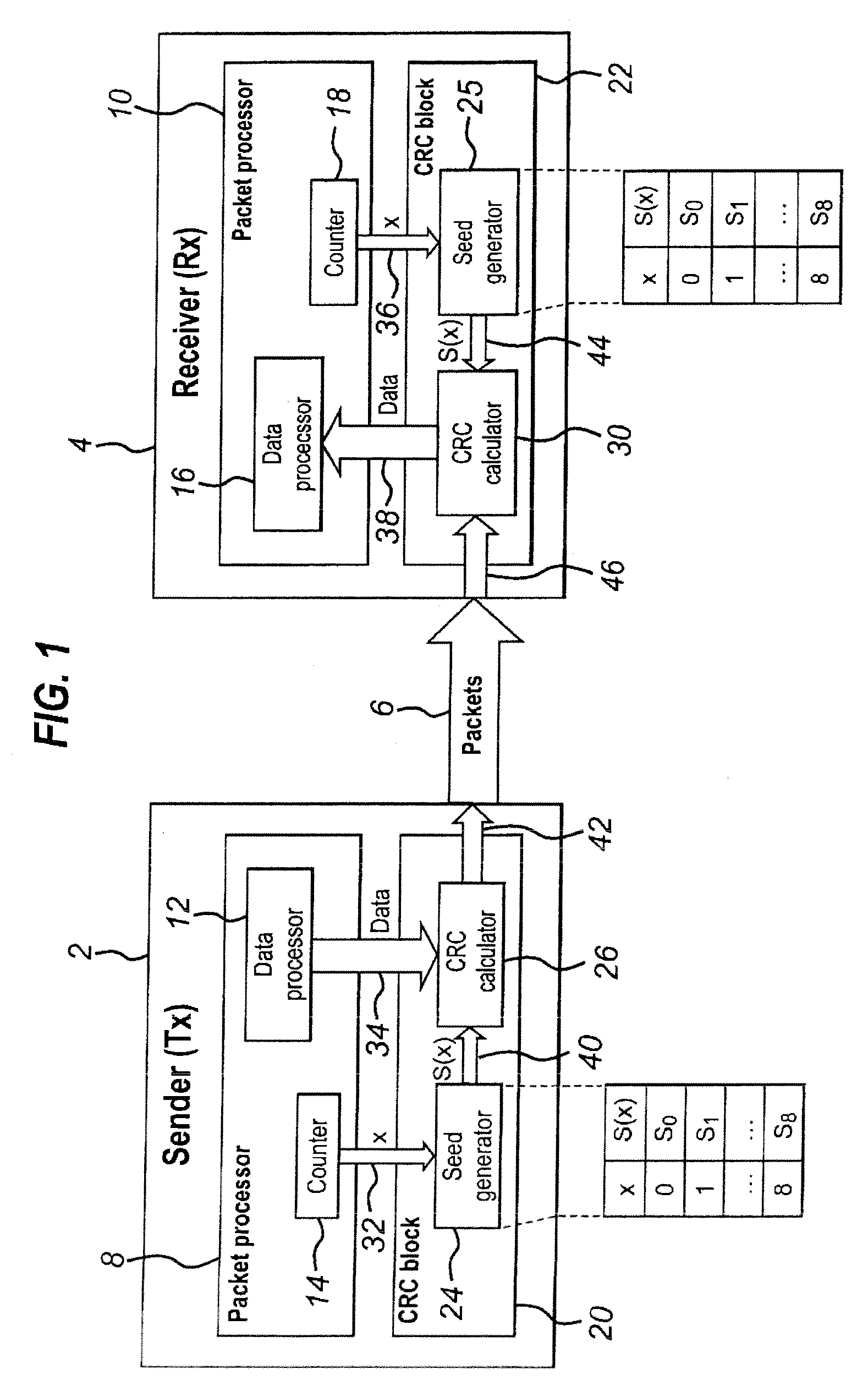

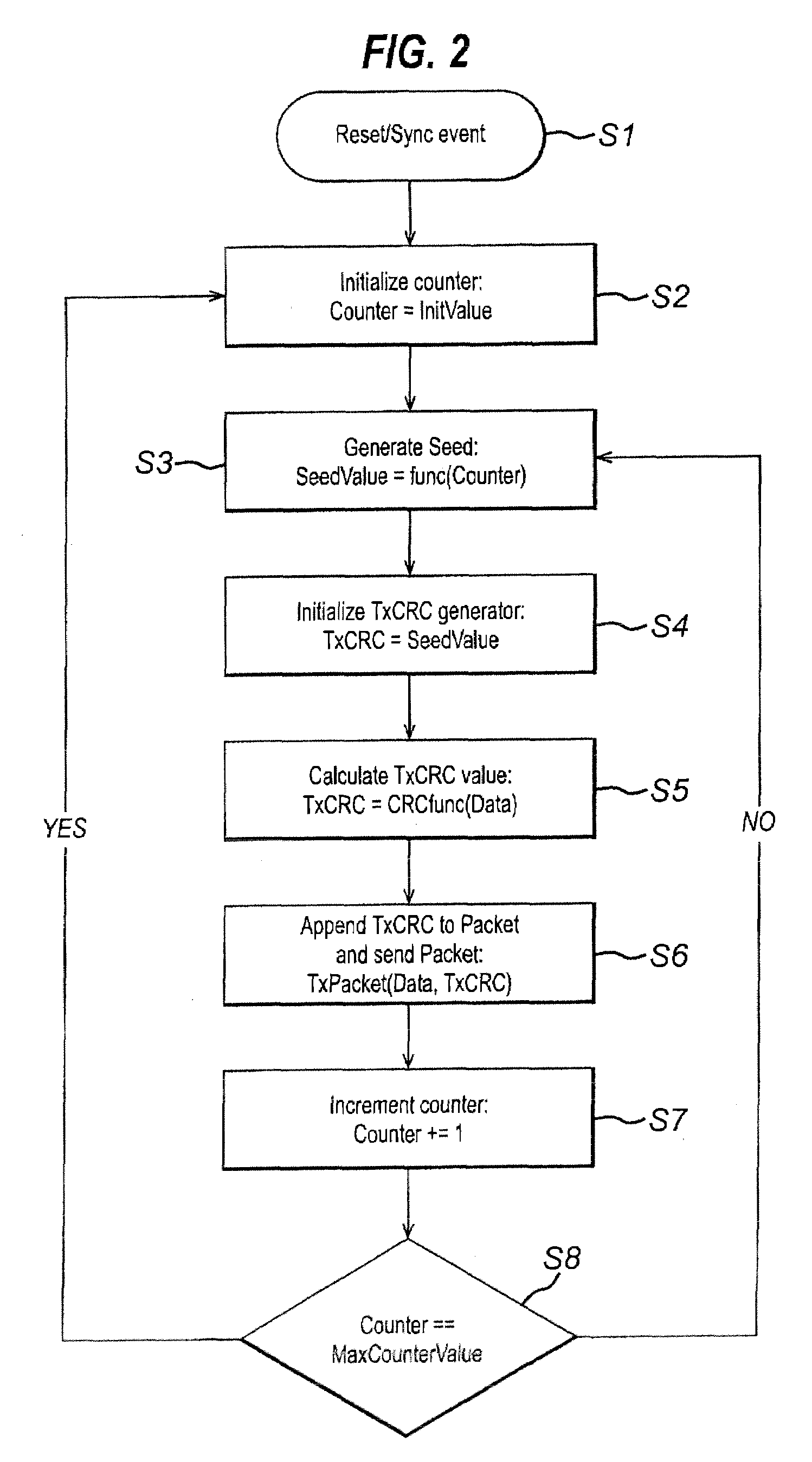

Method of communicatoin

A sending node comprising a processor configured to generate an error checking message, said error checking message being generated from data, said error checking message providing order information; and a transmitter configured to transmit said error checking message and said data.

Owner:NOKIA CORP

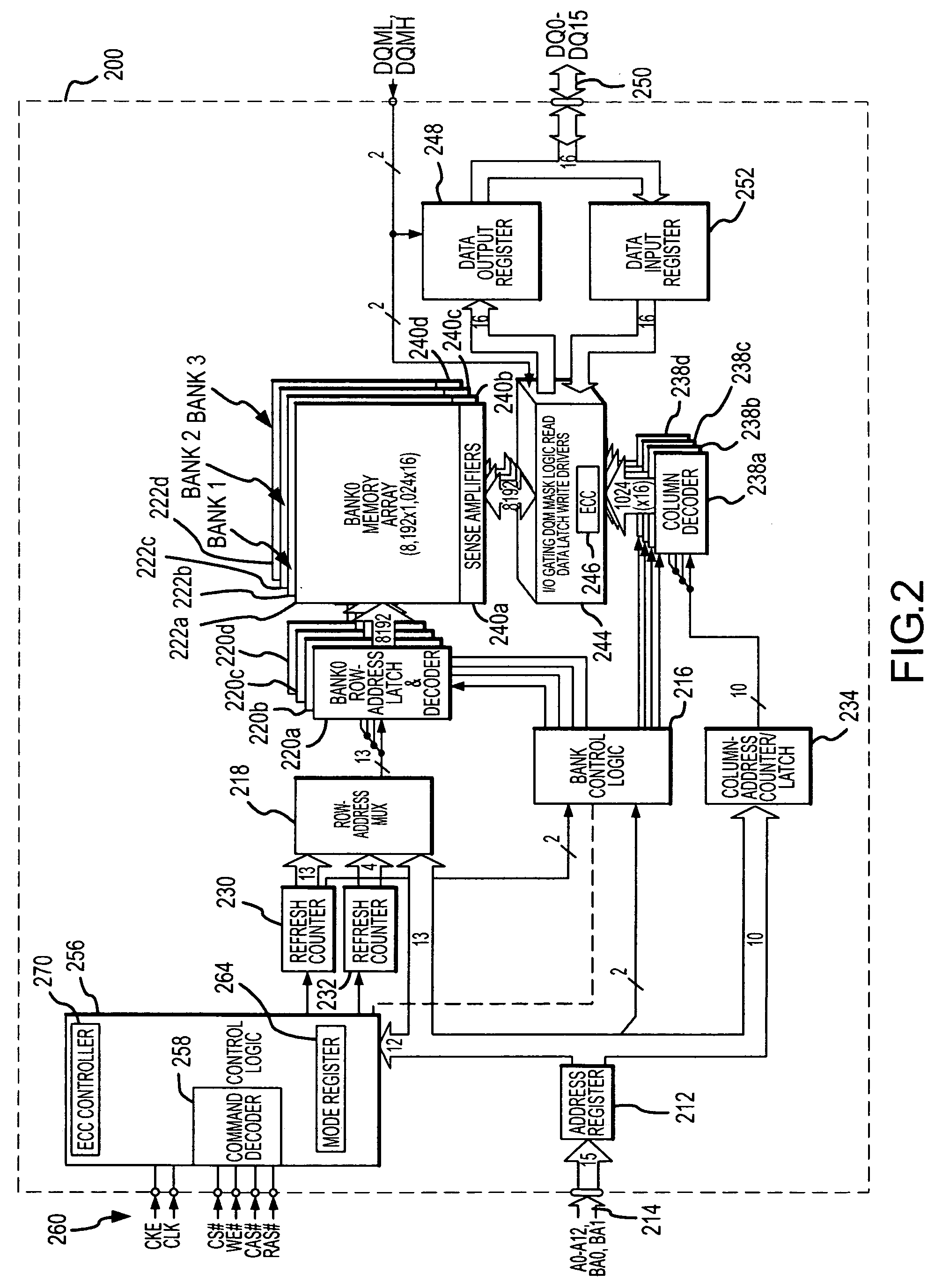

Memory system and method using partial ECC to achieve low power refresh and fast access to data

ActiveUS20080092016A1Reduced power refreshReduce power consumptionError detection/correctionCode conversionError checkingDram memory

A DRAM memory device includes several banks of memory cells each of which are divided into first and second sets of memory cells. The memory cells in the first set can be refreshed at a relatively slow rate to reduce the power consumed by the DRAM device. Error checking and correcting circuitry in the DRAM device corrects any data retention errors in the first set of memory cells caused by the relatively slow refresh rate. The memory cells in the second set are refreshed at a normal rate, which is fast enough that data retention errors do not occur. A mode register in the DRAM device may be programmed to select the size of the second set of memory cells.

Owner:MICRON TECH INC

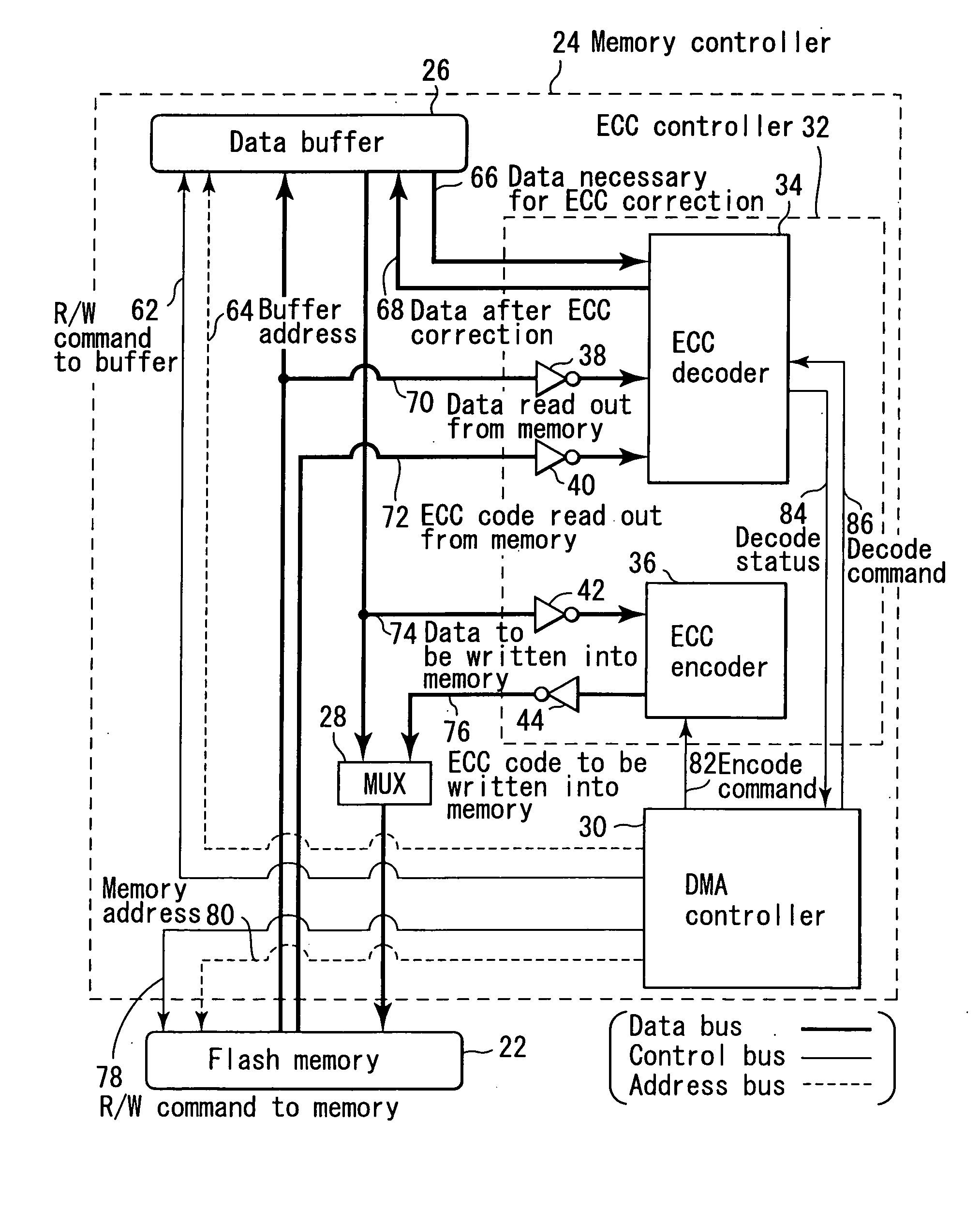

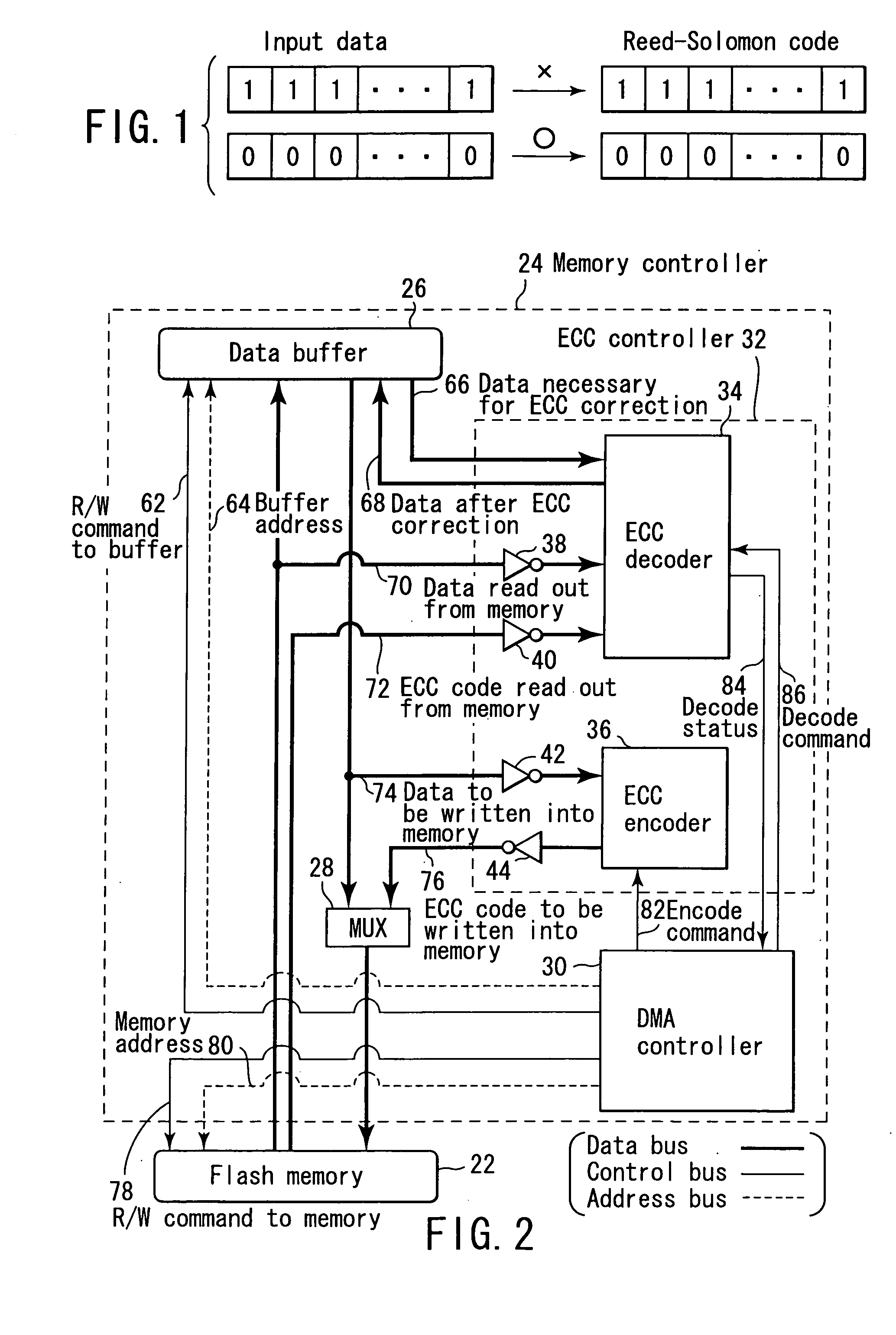

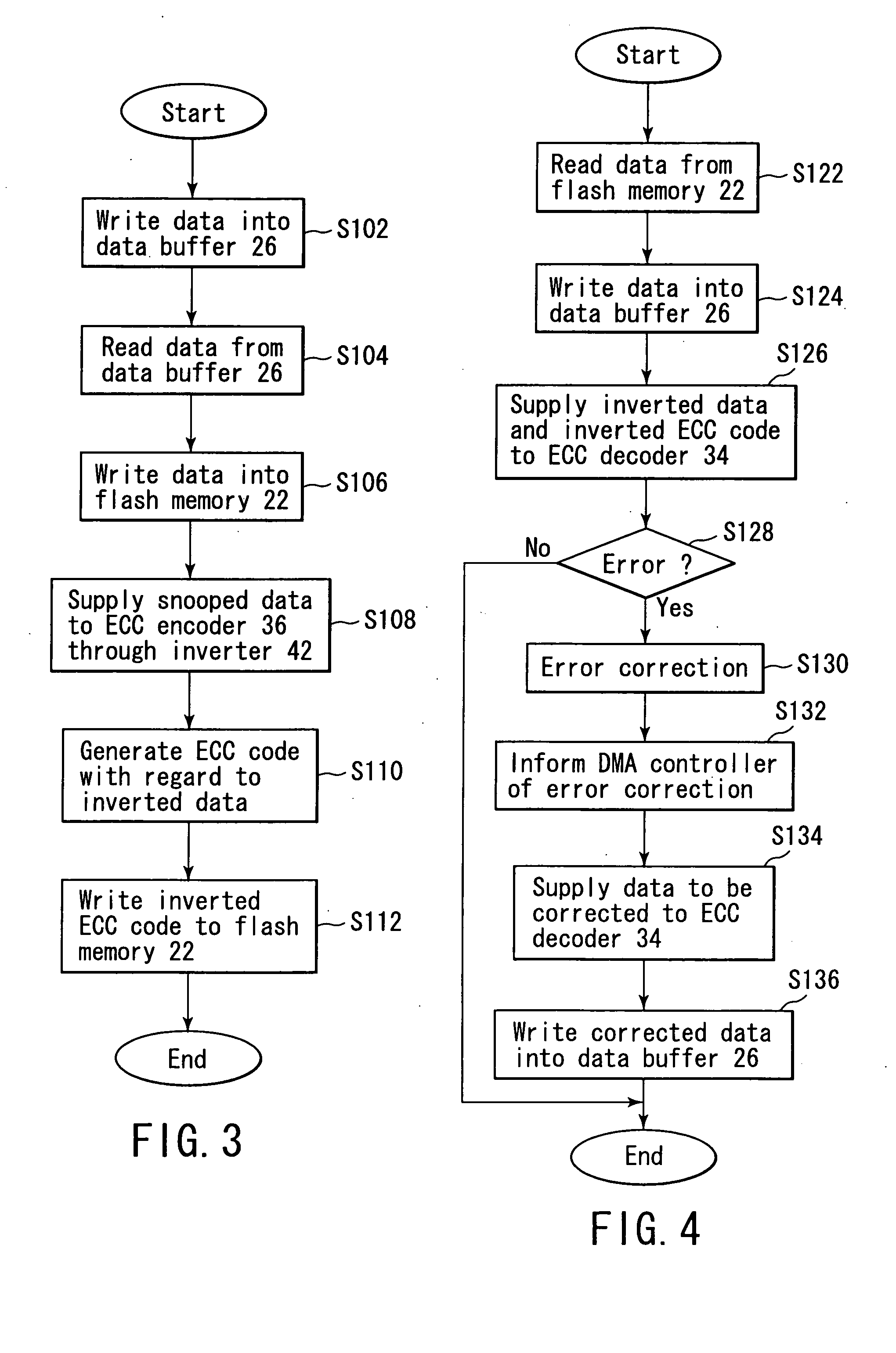

Control circuit for error checking and correction and memory controller

A control circuit for a memory device, comprises an inverter which inverts all bits of data read out from the memory device, and a decoder which executes error correction and decoding for an output of the inverter.

Owner:KK TOSHIBA

Apparatus and method for processing service interactions

ActiveUS20050002502A1Accurately determineImprove accuracyCredit schemesAutomatic exchangesError checkingHuman agent

An interactive voice and data response system then directs input to a voice, text, and web-capable software-based router, which is able to intelligently respond to the input by drawing on a combination of human agents, advanced speech recognition and expert systems, connected to the router via a TCP / IP network. The digitized input is broken down into components so that the customer interaction is managed as a series of small tasks rather than one ongoing conversation. The router manages the interactions and keeps pace with a real-time conversation. The system utilizes both speech recognition and human intelligence for purposes of interpreting customer utterance or customer text. The system may use more than one human agent, or both human agents and speech recognition software, to interpret simultaneously the same component for error-checking and interpretation accuracy.

Owner:ARES VENTURE FINANCE

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com