Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

106results about How to "Improves latch-up resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

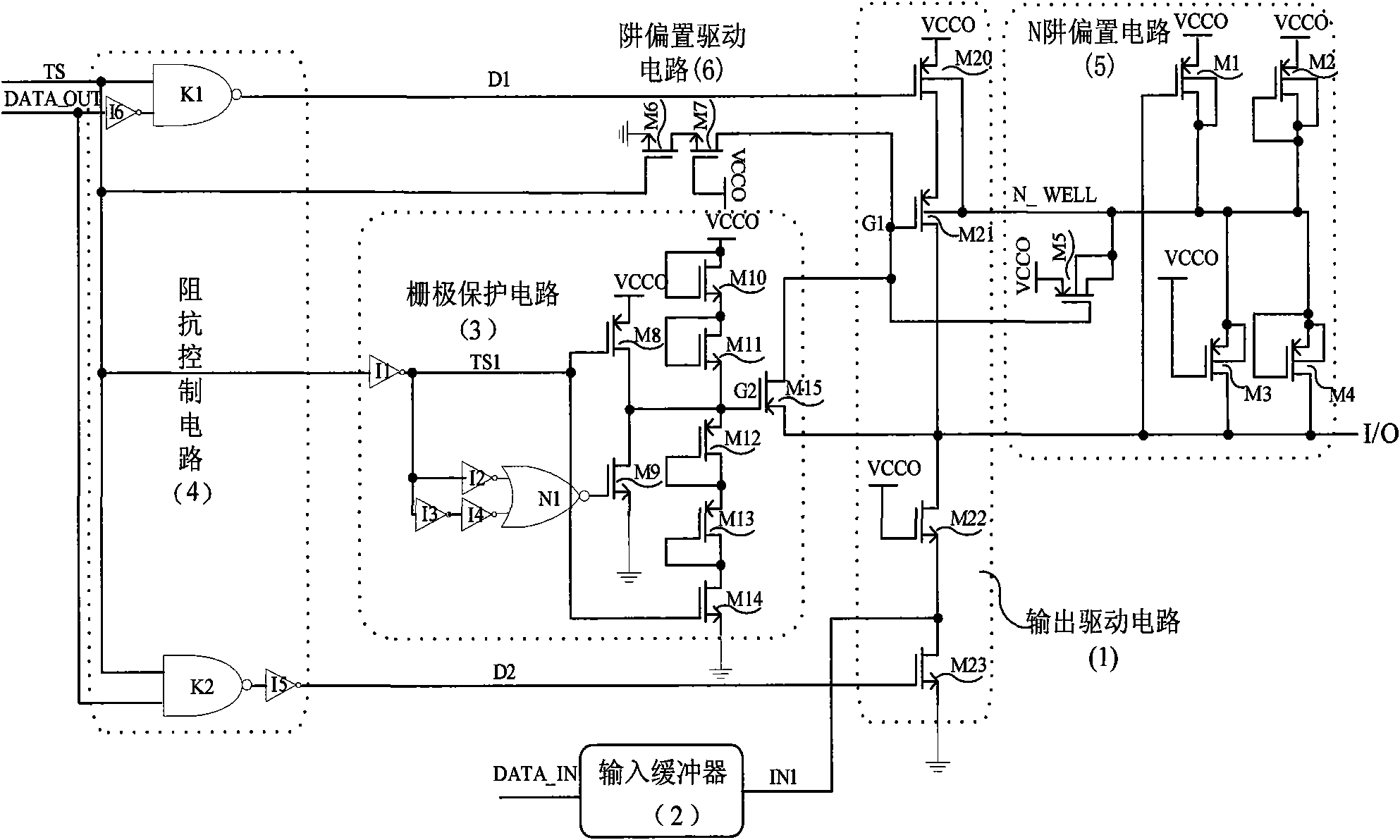

An interface circuit capable of tolerating high voltage input

InactiveCN101552605ASolve pressureReduce manufacturing costLogic circuits coupling/interface using field-effect transistorsElectric pulse generator circuitsDriver circuitTransfer mode

An interface circuit capable of tolerating high voltage input, I / O pin connecting external, a pull-up / pull-down structure provides high / low power level of output to the I / O pin. An impedance control circuit shuts the pull-up / pull-down structure in receiving mode, and activates the pull-up / pull-down structure in transmission mode. A pull-up / pull-down protection structure protects the pull-up / pull-down structure in receiving mode. A gate protection circuit provides protection voltage to the pull-up protection structure in receiving mode. A N-well bias circuit provides a bias voltage that equaling to internal power supply for the pull-up structure and the N-well where the PMOS located in of the pull-up protection structure in transmission mode; and in a receiving mode, if voltage of the I / O pin is higher than voltage of the internal power supply, providing a bias voltage that approaching to voltage of the I / O pin to the pull-up structure and the N-well where the PMOS located in of the pull-up protection structure, otherwise, providing a bias voltage that equaling to internal power supply. Well bias drive circuit provides driving signal to the N-well bias circuit in transmission mode.

Owner:BEIJING MXTRONICS CORP +1

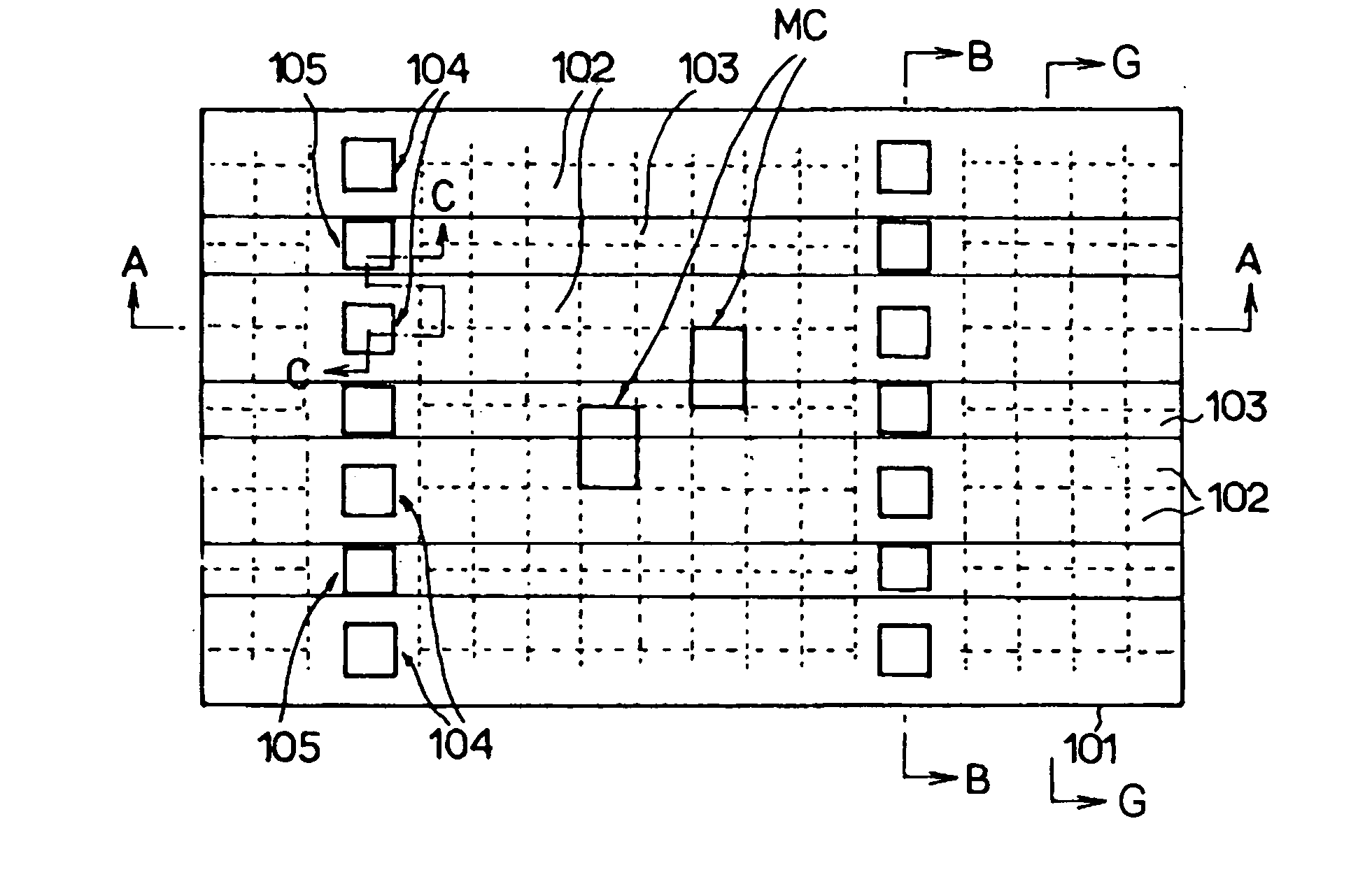

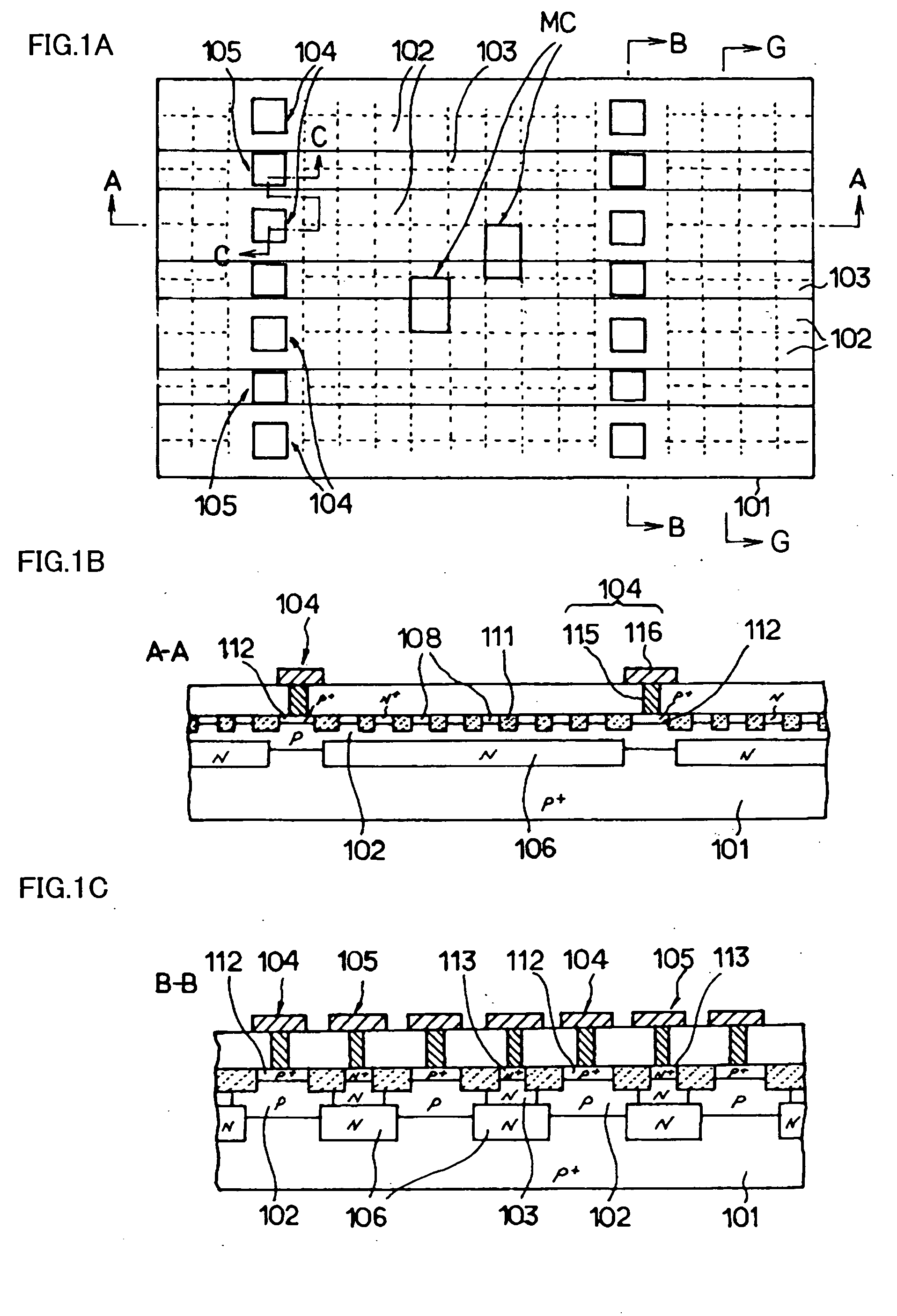

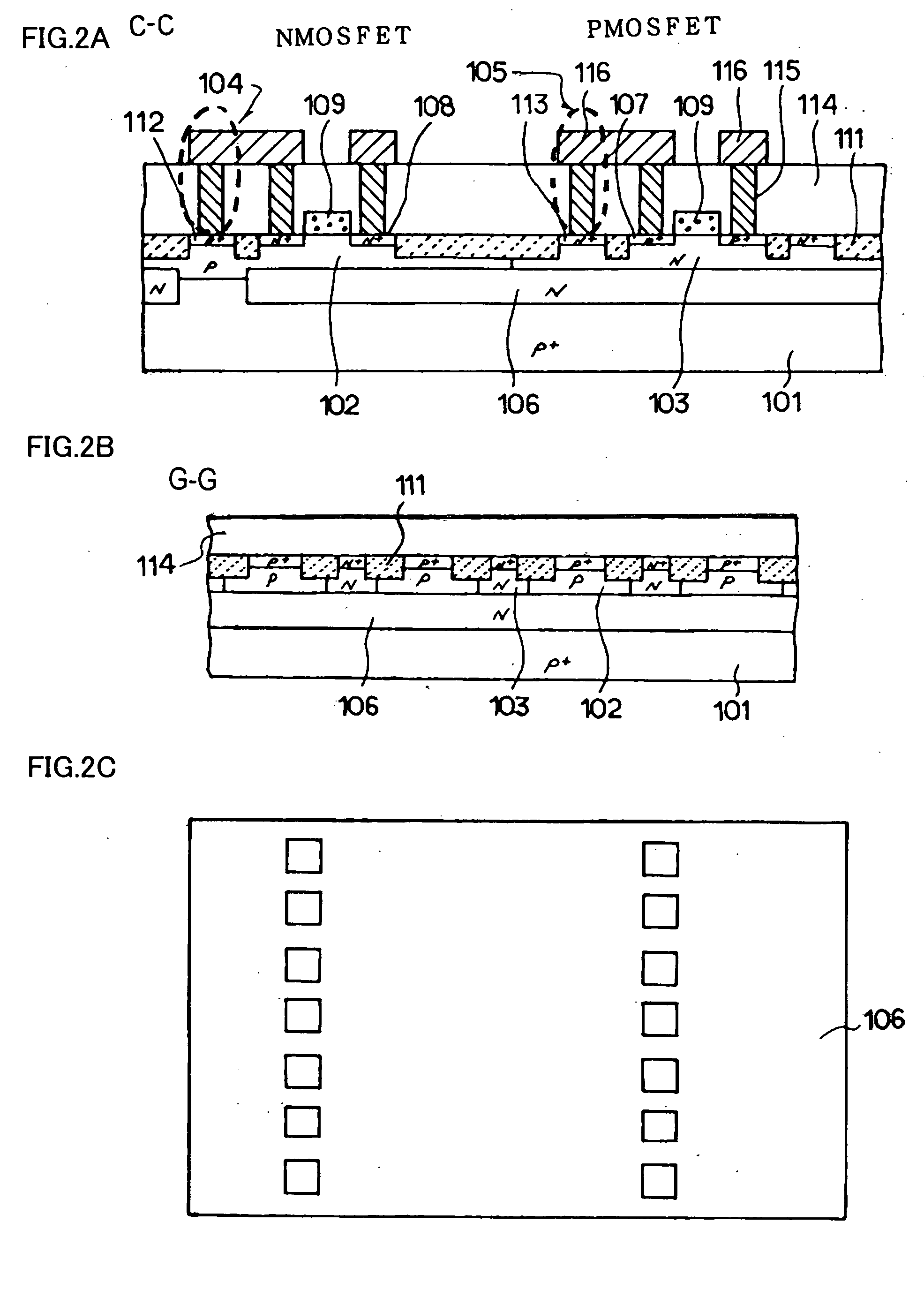

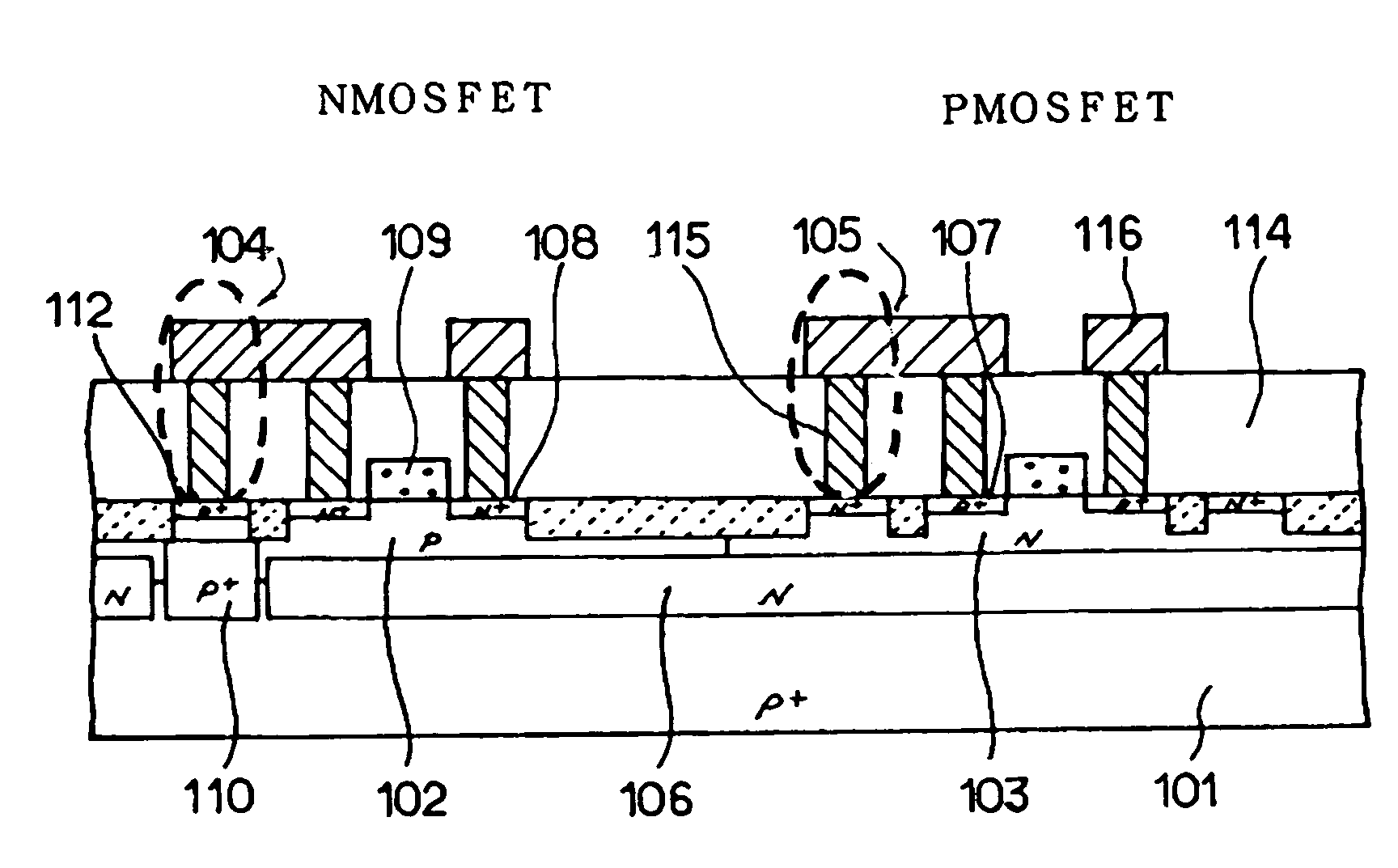

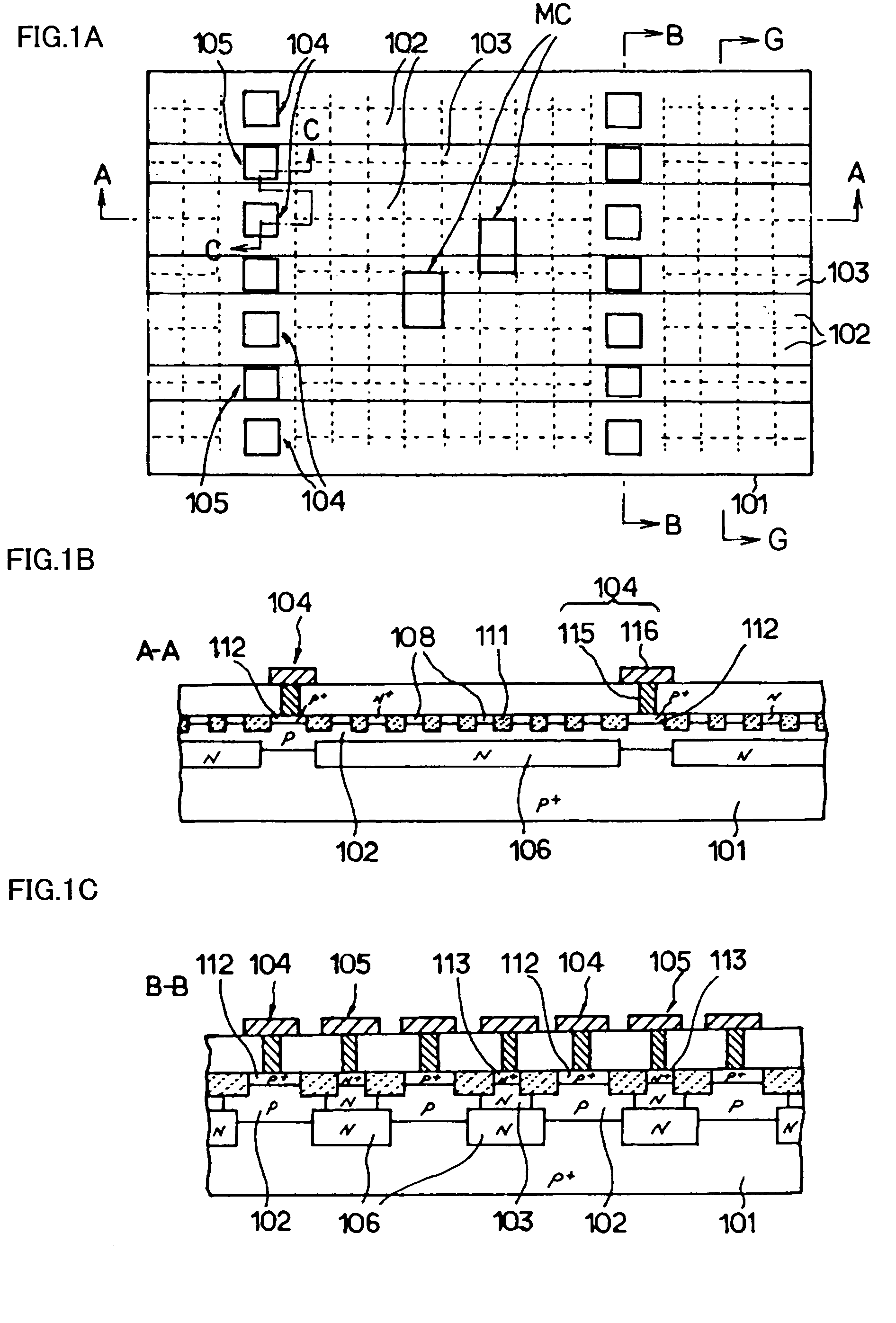

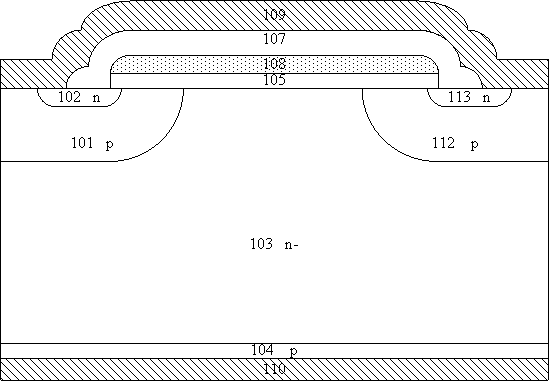

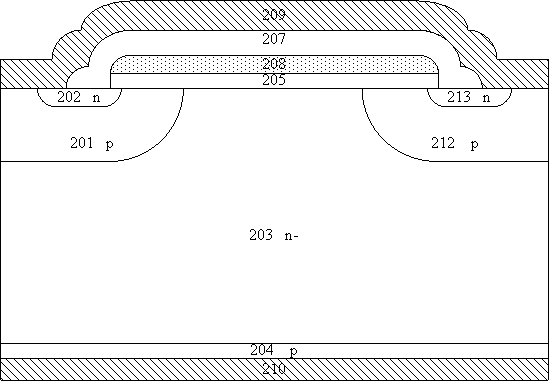

Semiconductor device and semiconductor integrated circuit device

InactiveUS20050098835A1Improves latch-up resistanceGood of latch-upTransistorSolid-state devicesElectrical resistance and conductanceHigh density

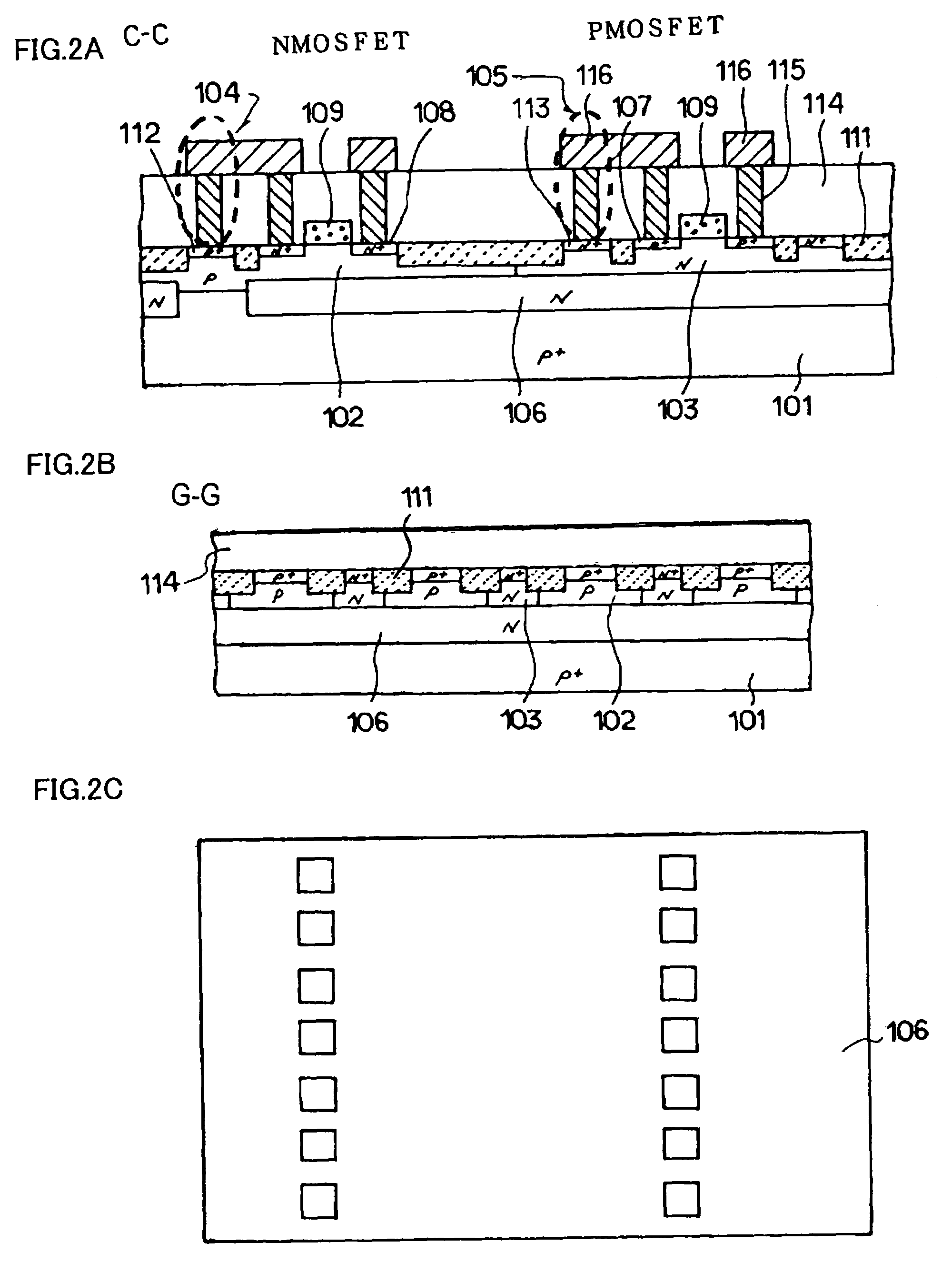

Soft-error resistance and latch up resistance are simultaneously improved for LSI involving miniaturization and reducing operating voltage. Pwells andN wells are formedin a higher density substrate (P on P+ substrate), and buried N wells are formed on a layer underlying thereof. A PMOSFET is formed in the N well and a NMOSFET is formed in the P well. A P well electric potential junction for coupling P well electric potential of the P well to predetermined electric potential is provided, and a region directly under the P well electric potential junction is provided with a region where the aforementioned buried N well is not disposed. The soft-error resistance is improved by having the buried N well therein, and the latch up resistance is improved by coupling the P well to the substrate.

Owner:RENESAS ELECTRONICS CORP

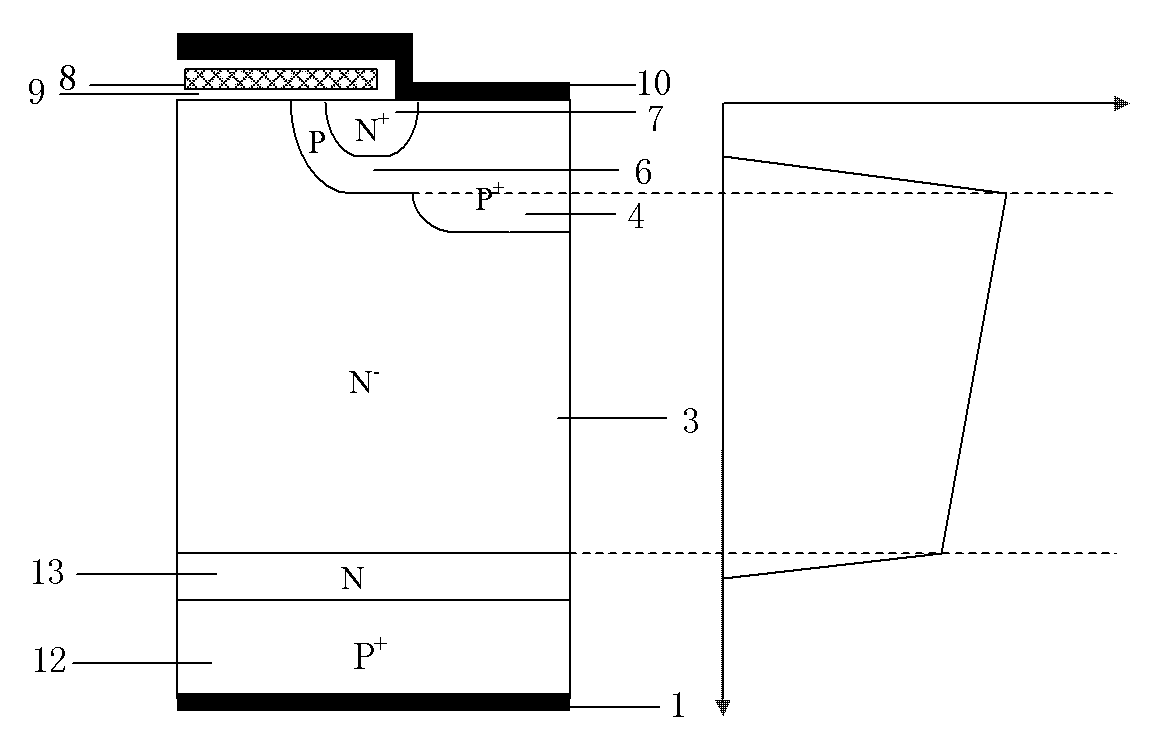

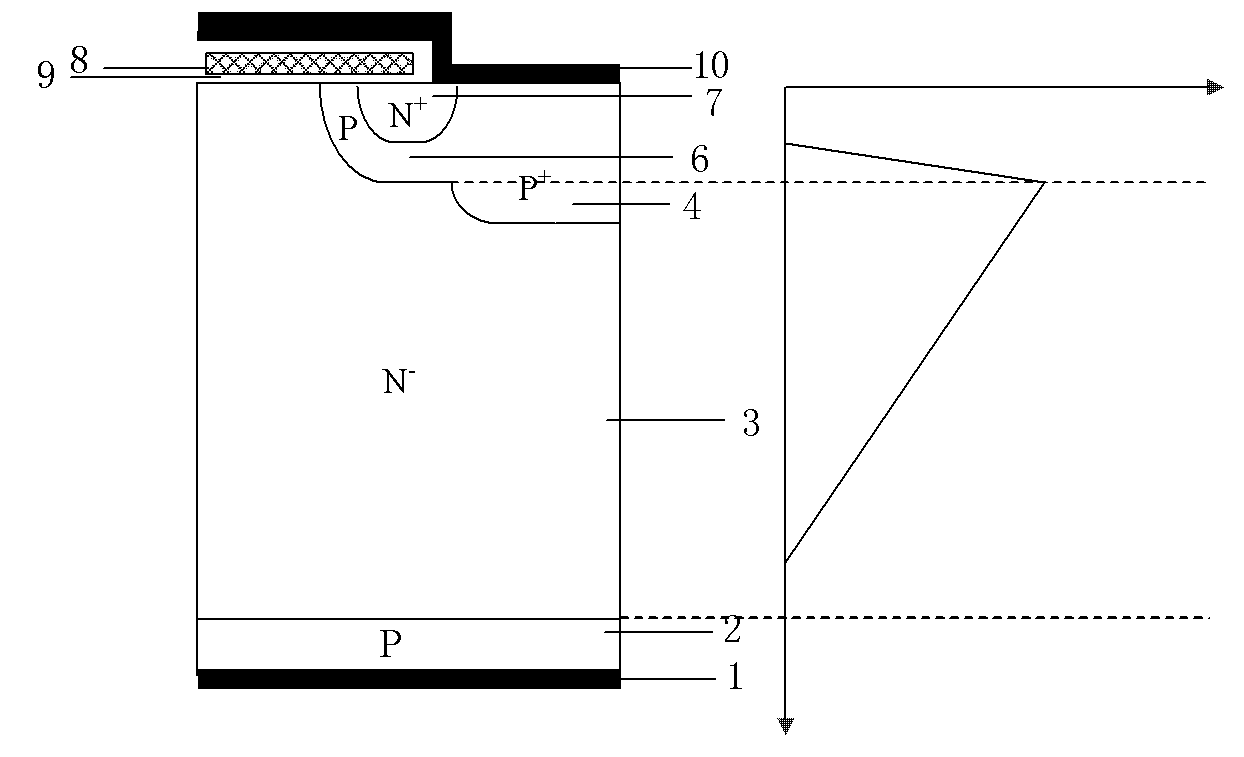

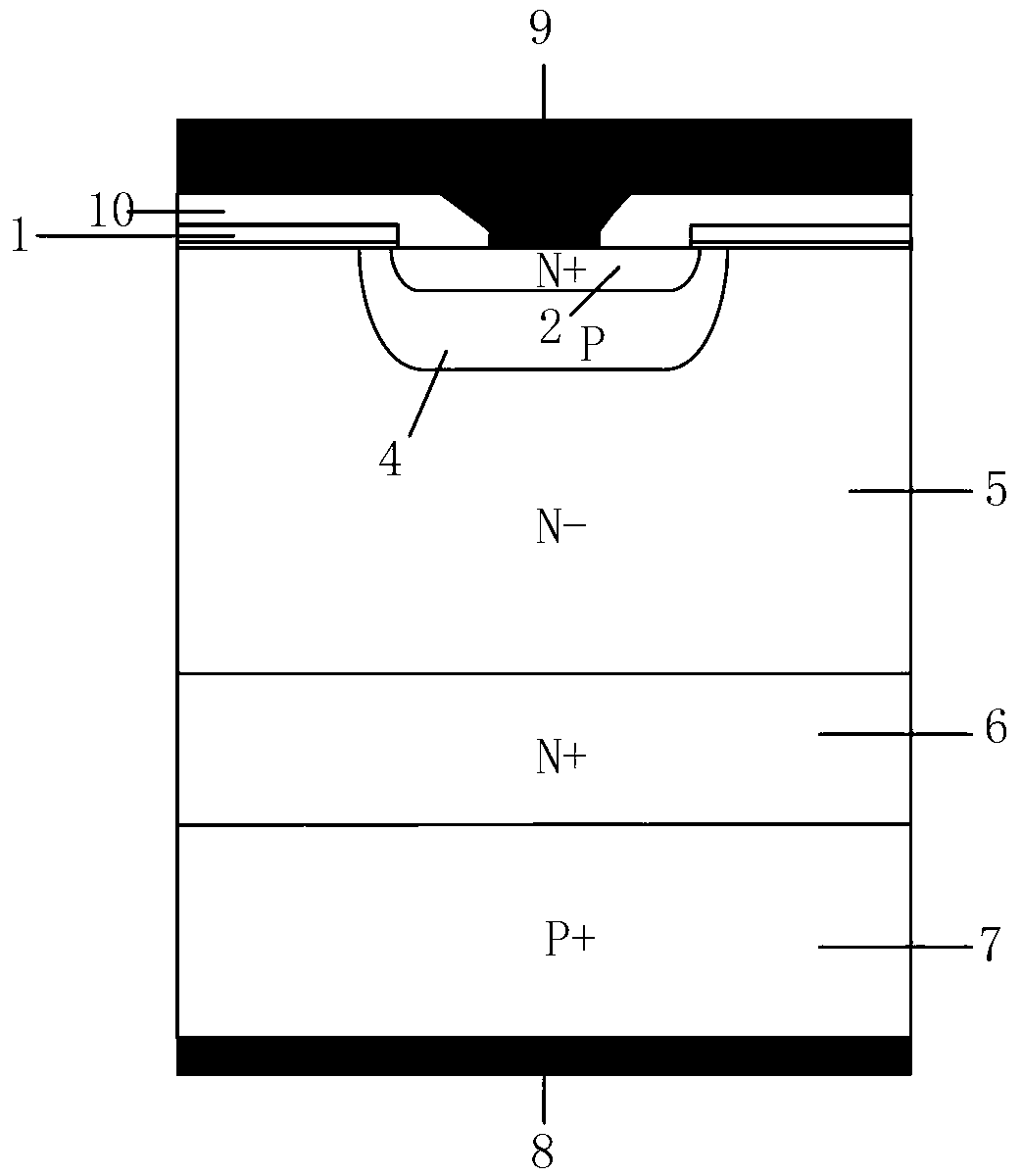

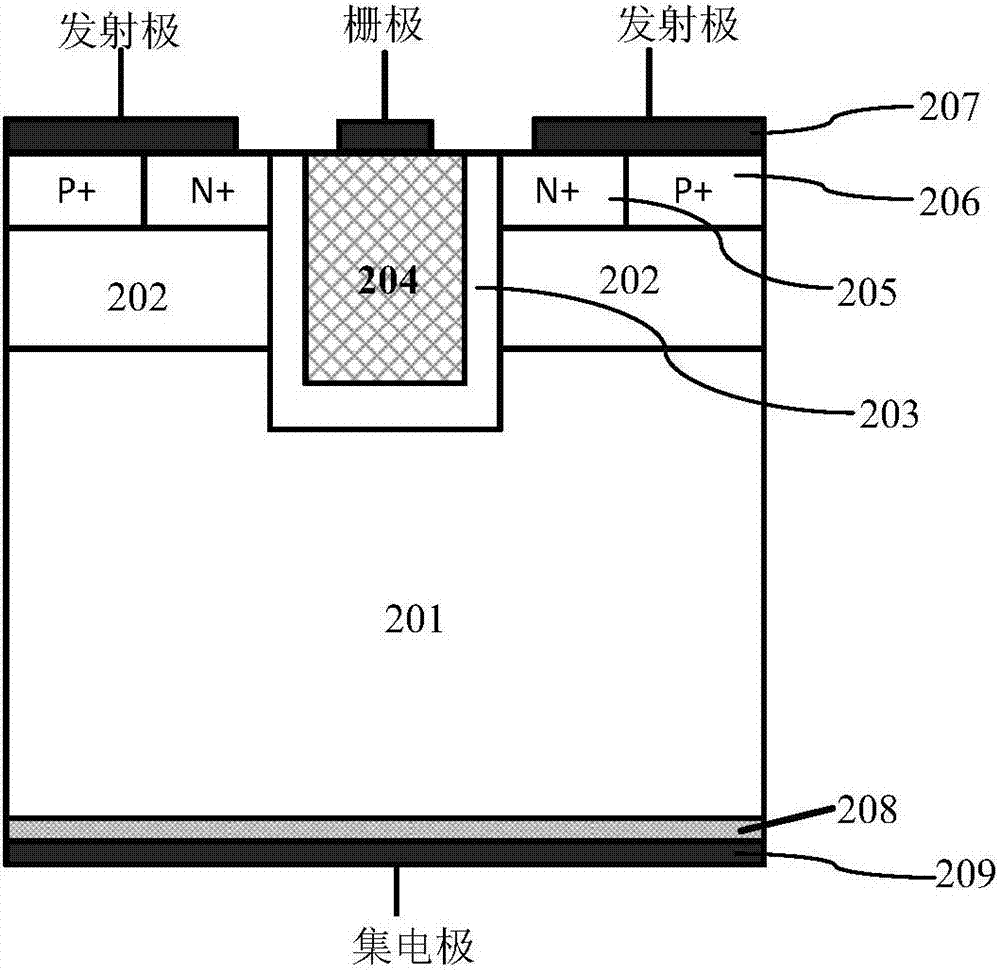

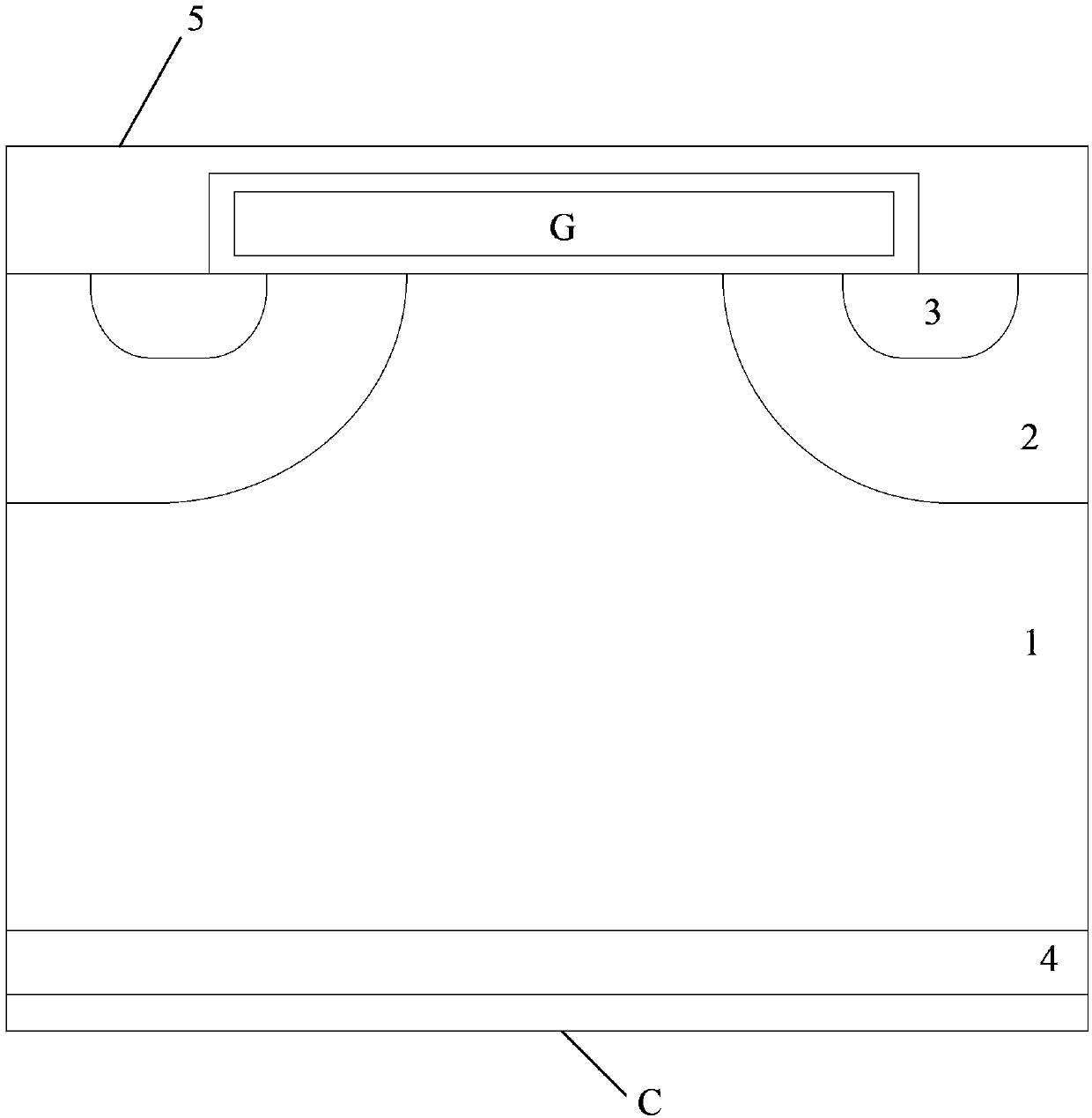

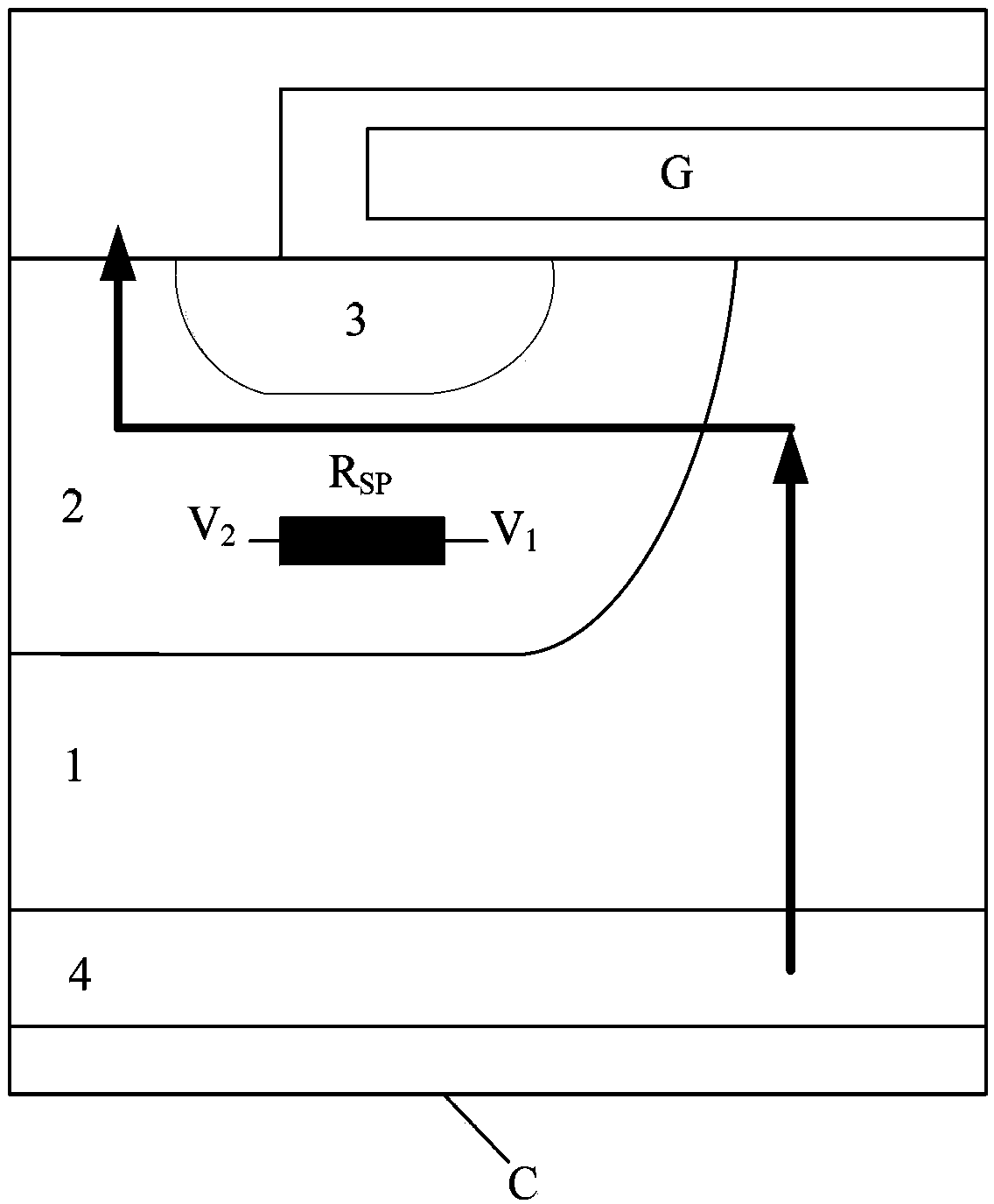

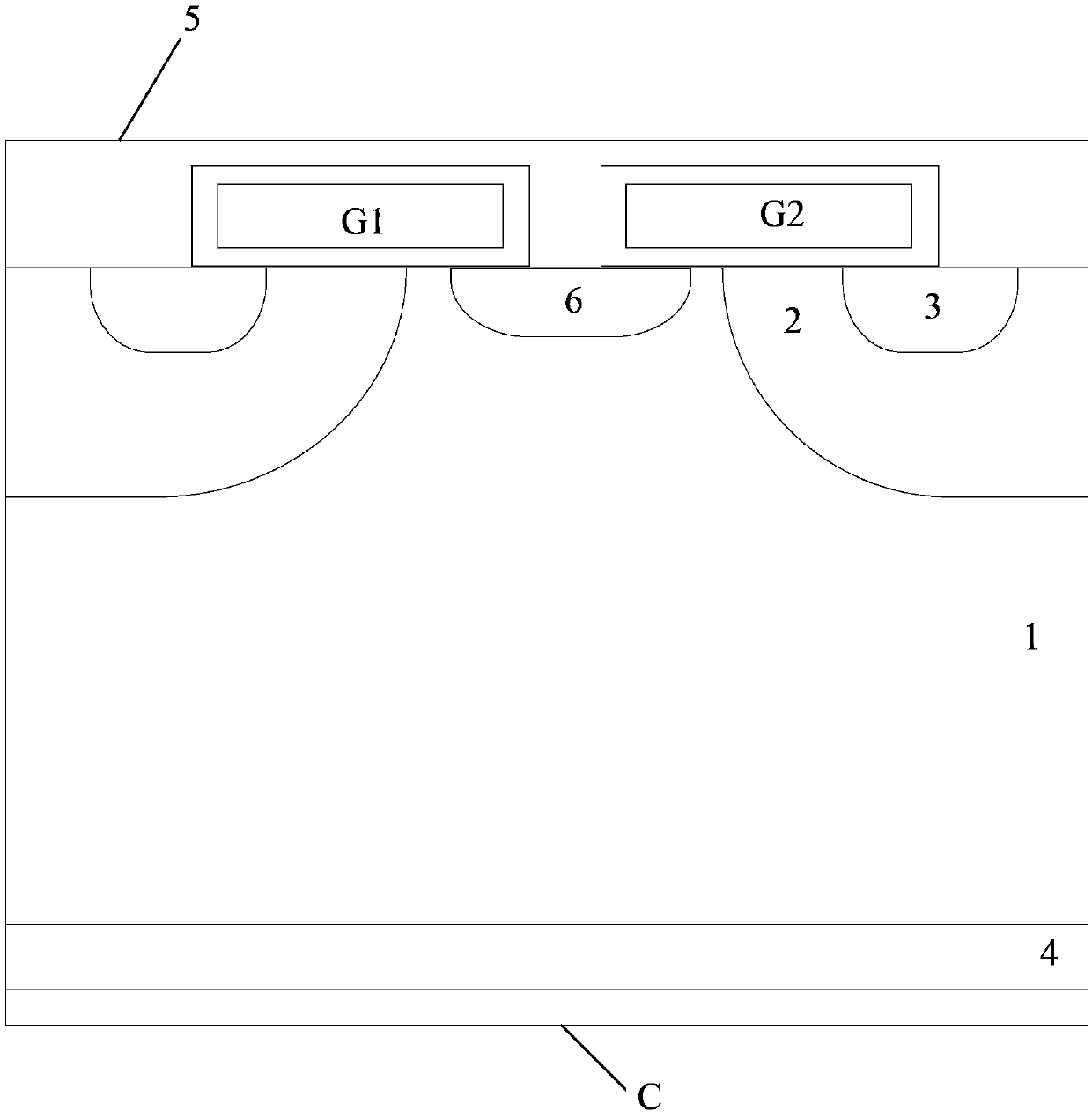

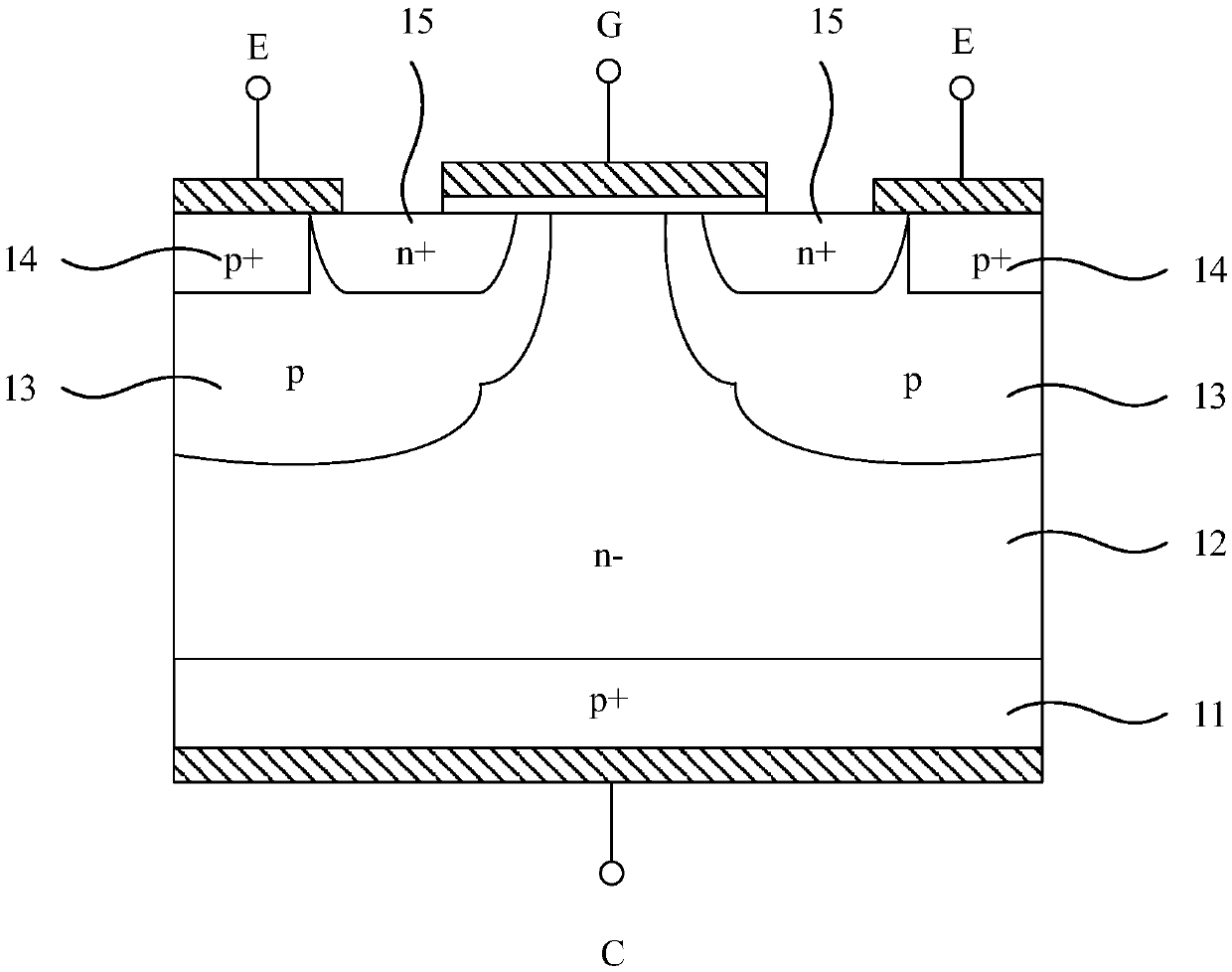

IGBT with current carrier storage layer and additional hole passage

InactiveCN102157551AIncrease the minority carrier concentrationPrevent openingSemiconductor devicesCharge carrierConductivity modulation

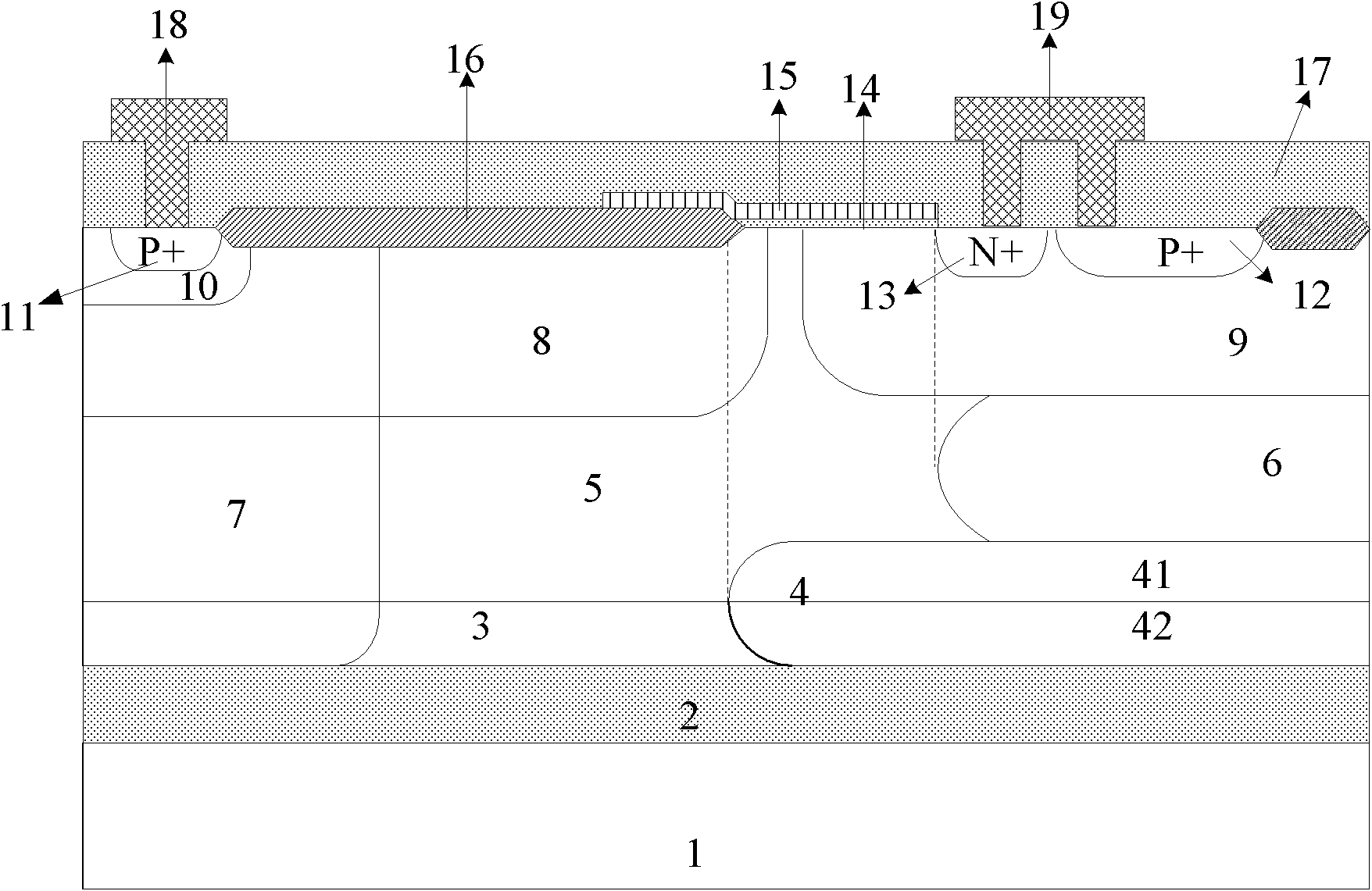

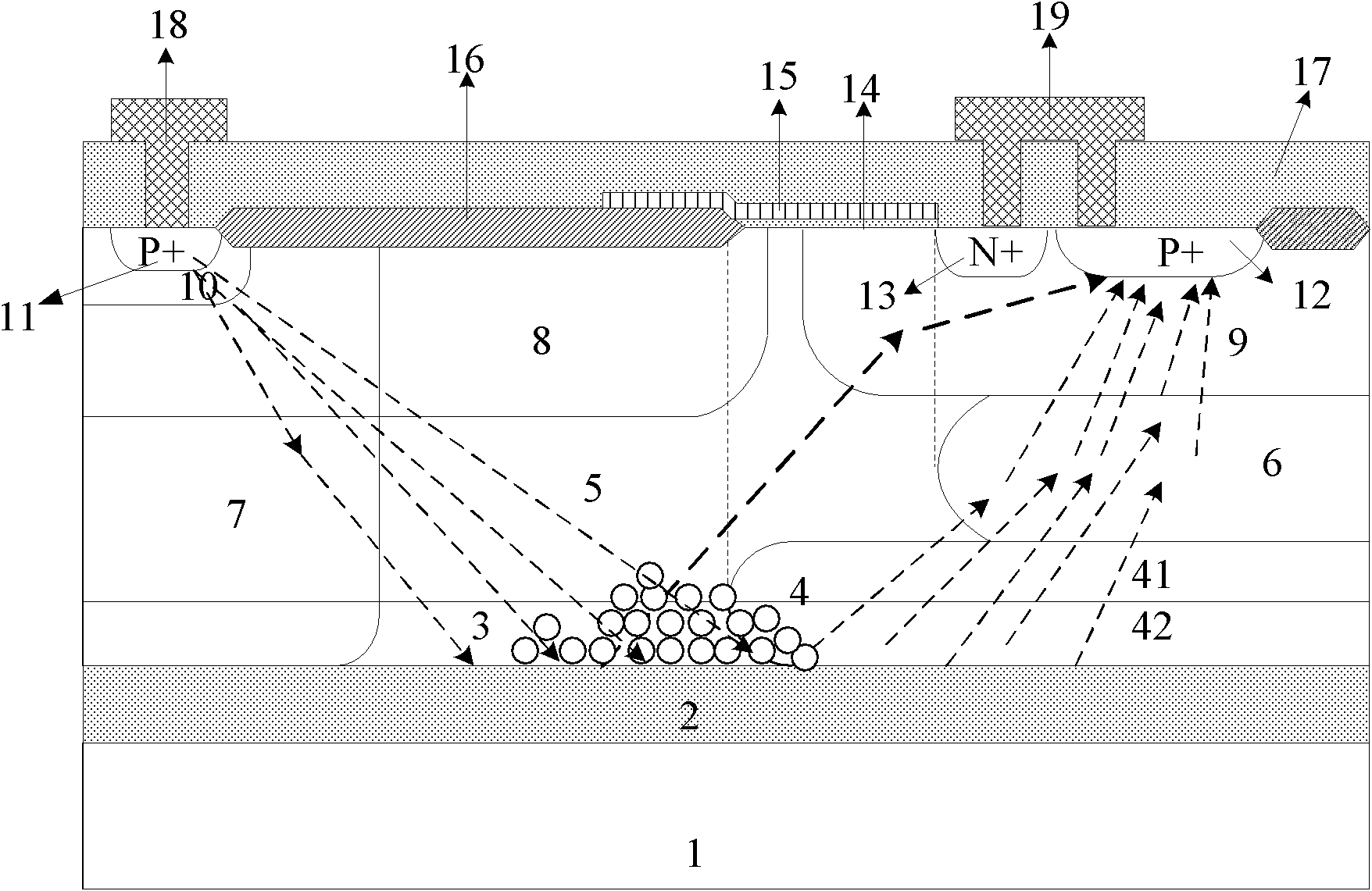

The invention discloses an insulate gate bipolar transistor (IGBT) with a current carrier storage layer and an additional hole passage, and belongs to the technical field of semiconductor power devices. In the IGBT, an N-type current carrier storage layer (5) and a large P<+> tagma (4) structure are introduced on the basis of a conventional planar non-pouch-through IGBT. The N-type current carrier storage layer (5) improves a conductivity modulation effect close to an emitter and the large P<+> tagma (4) structure plays a role in providing an additional passage for a hole so that the latch-up resistance is improved. Due to the design of the N-type current carrier storage layer (5) and the large P<+> tagma (4), the flow path of a hole current of the conventional IGBT is optimized, so that a safety operation area of a device is enlarged and the sensitivity of latch current density to a temperature is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

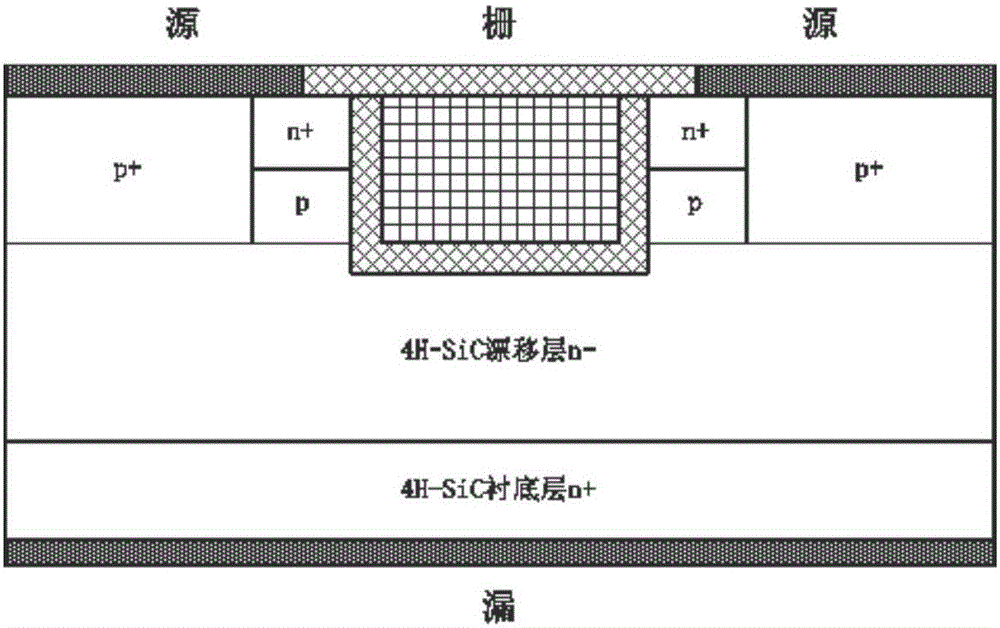

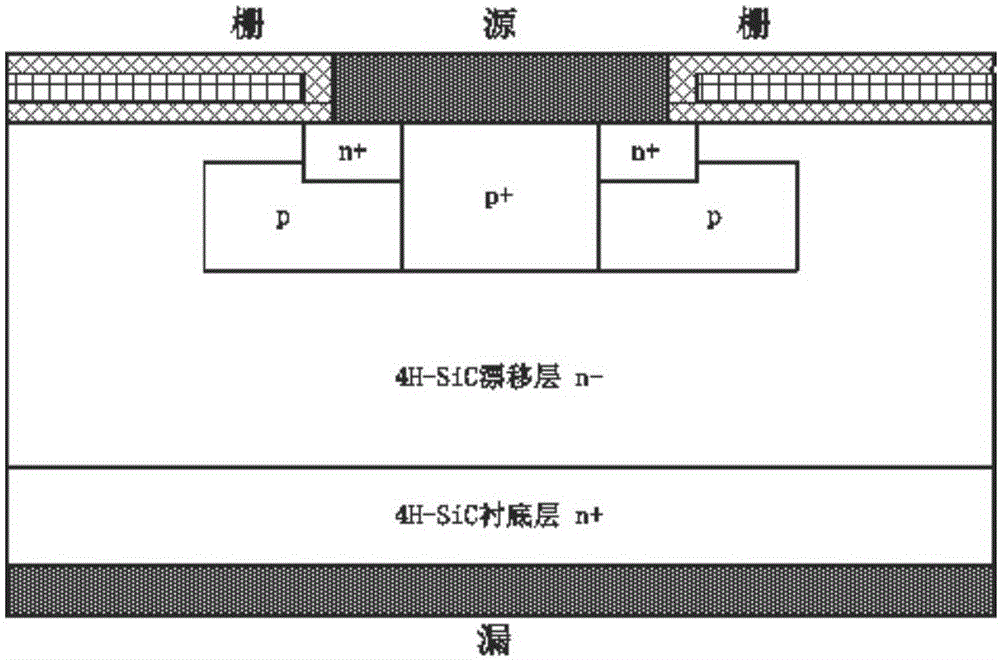

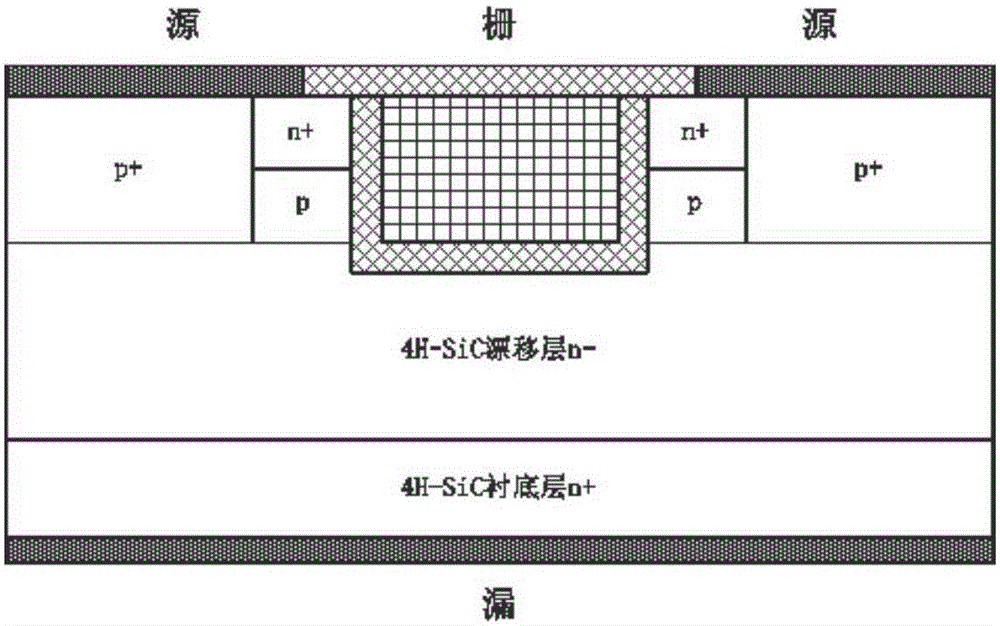

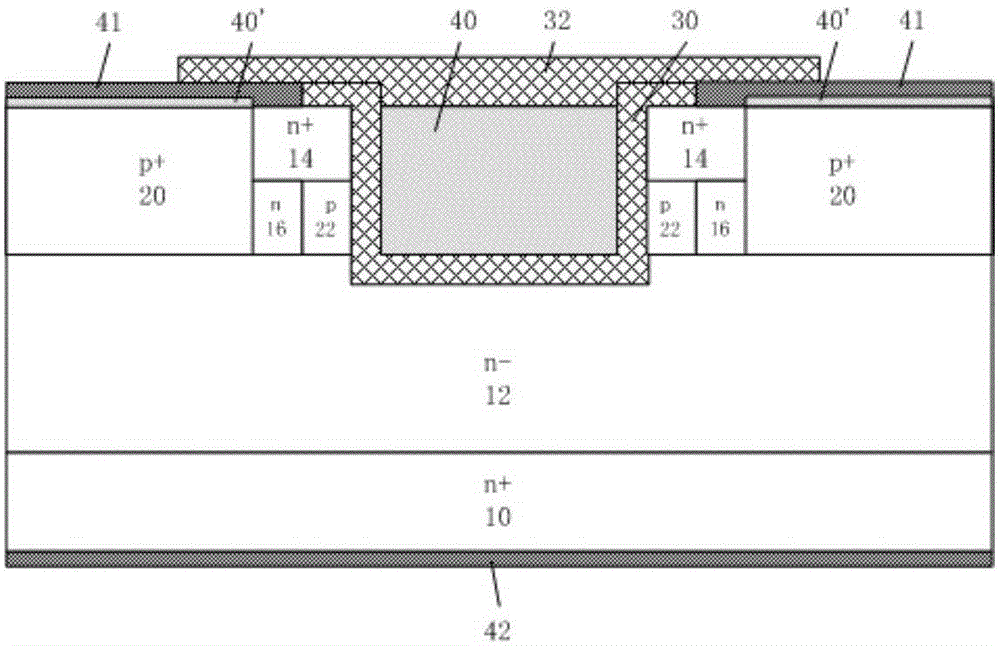

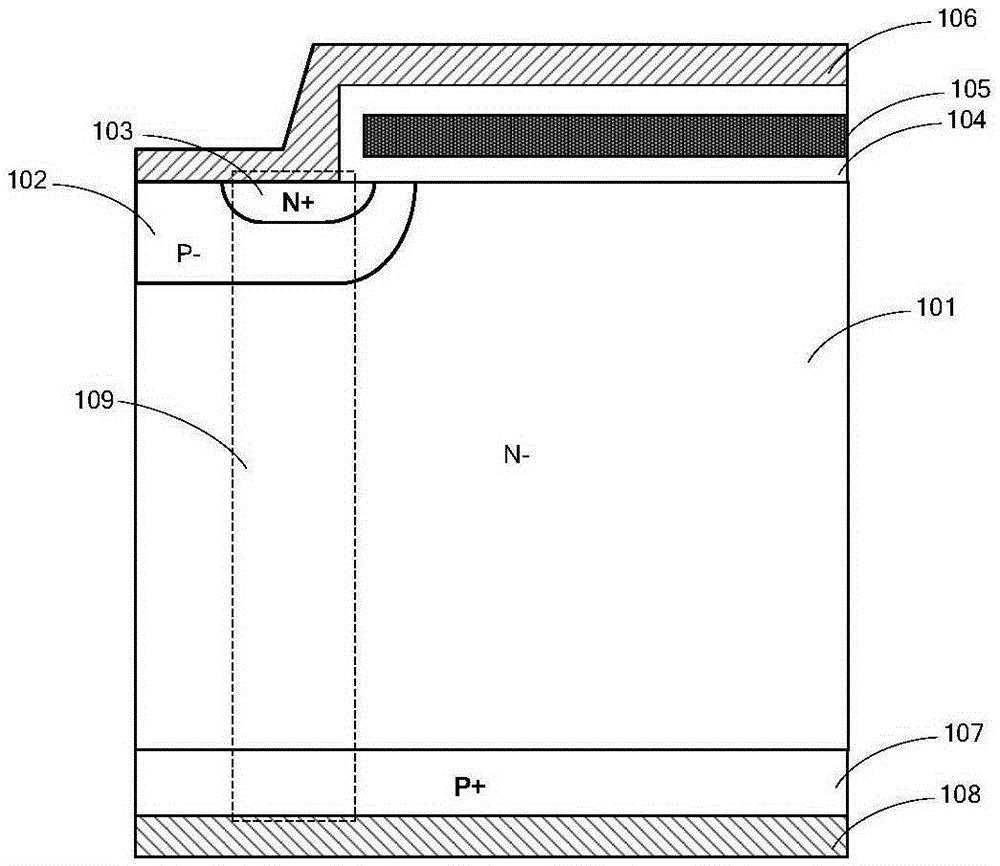

Silicon carbide trench gate power metal-oxide-semiconductor field effect transistors (MOSFETs) device and manufacturing method thereof

InactiveCN105047721AReduced effective mobilityAvoid High Threshold VoltageSemiconductor/solid-state device manufacturingSemiconductor devicesHigh energyP type silicon

The invention provides a silicon carbide trench gate power metal-oxide-semiconductor field effect transistors (MOSFETs) device and a manufacturing method thereof. The device comprises an n-type silicon carbide substrate, an n-type trench, a trench gate medium, a gate contact, a source contact and a drain contact, wherein an n-type silicon carbide drift layer is arranged on the substrate, and comprises p-type silicon carbide regions with intervals; an n+ silicon carbide source region is formed between the p-type silicon carbide regions; and the n-type trench is located between the p-type silicon carbide regions and is arranged in the n-type silicon carbide drift layer below the n+ silicon carbide source region. On the basis of a vertical double-injection MOSFET structure, the surface of the trench is counter-doped with an n-type doped impurity, so that a surface accumulation layer is realized; reduction of the effective electron mobility of the surface accumulation layer of the trench caused by high-energy and large-dose ion injection and high-temperature annealing is avoided; performance degradation of the device is reduced; the anti-latch-up capacity is improved; the manufacturing method of the silicon carbide MOSFET device is simplified; and the silicon carbide trench gate power MOSFETs device is suitable for industrial production.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

Semiconductor device and semiconductor integrated circuit device

InactiveUS7214989B2Good balance of soft-error resistance and latch-up resistanceResistance of the first region of the single conductivity type is apt to be increasedTransistorSolid-state devicesElectrical resistance and conductanceHigh density

Soft-error resistance and latch up resistance are simultaneously improved for LSI involving miniaturization and reducing operating voltage. P wells and N wells are formed in a higher density substrate (P on P+ substrate), and buried N wells are formed on a layer underlying thereof. A PMOSFET is formed in the N well and a NMOSFET is formed in the P well. A P well electric potential junction for coupling P well electric potential of the P well to predetermined electric potential is provided, and a region directly under the P well electric potential junction is provided with a region where the aforementioned buried N well is not disposed. The soft-error resistance is improved by having the buried N well therein, and the latch up resistance is improved by coupling the P well to the substrate.

Owner:RENESAS ELECTRONICS CORP

Silicon-on-insulator N-type transverse insulated gate bipolar transistor and preparation method thereof

InactiveCN102130153ARaise the trigger threshold conditionRaise the threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsPolycrystalline silicon

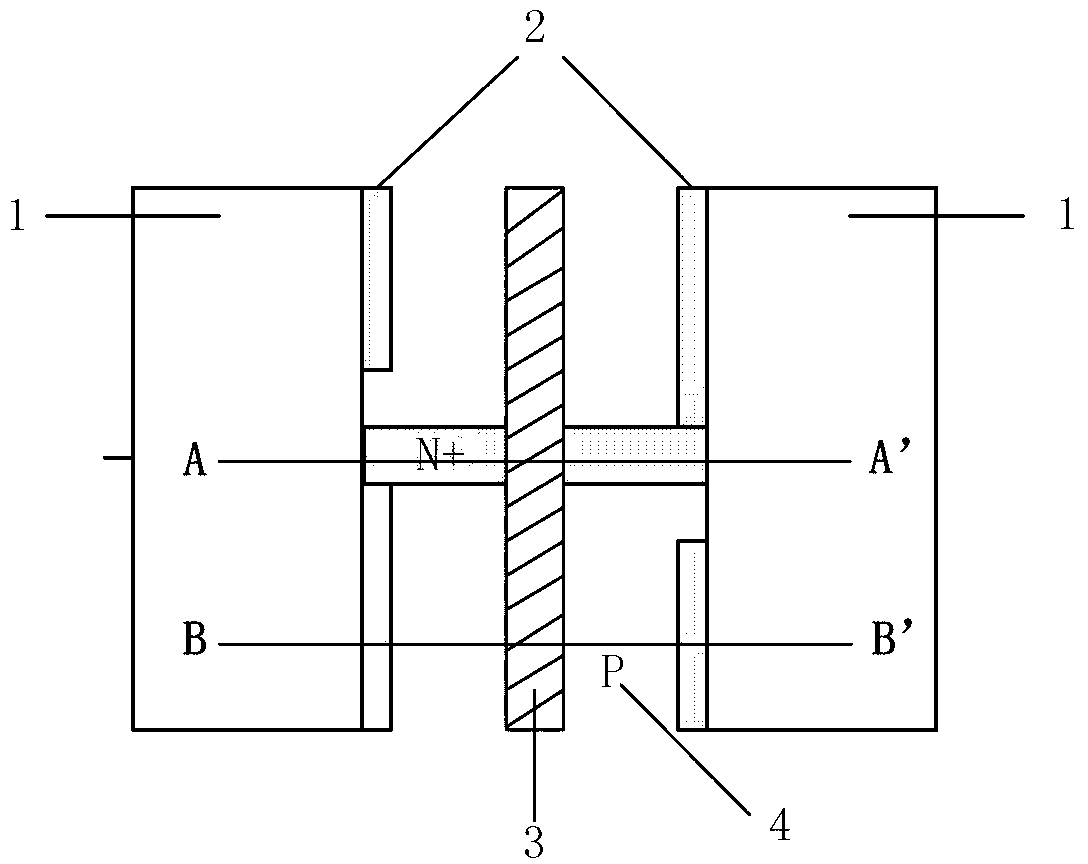

The invention relates to a silicon-on-insulator N-type transverse insulated gate bipolar transistor and a preparation method thereof. The silicon-on-insulator N-type transverse insulated gate bipolar transistor comprises a P-type silicon-on-insulator silicon wafer, wherein the right region of a first P-type epitaxial layer is provided with a P-type buried layer; a second P-type epitaxial layer is arranged above the first P-type epitaxial layer; a P-type high-energy ion-implantation layer and a P-type channel region are arranged in the second P-type epitaxial layer; the left side is provided with an N-type deep well and an N-type drift region; an N-type buffer layer and a P-type anode contact region are arranged in the N-type drift region; an N-type cathode contact region and a P-type body contact region are arranged in the P-type channel region; a first field oxide layer and a gate oxide layer are arranged above the N-type drift region; the gate oxide layer extends rightwards to above the P-type channel region; and polycrystalline silicon is arranged above the gate oxide layer and used as a gate. The preparation method comprises the following steps: carrying out implantation onto the right region of the first P-type epitaxial layer to form the P-type buried layer, and carrying out implantation onto the right region of the second P-type epitaxial layer to form the P-type high-energy ion-implantation layer which is communicated with the P-type buried layer, so that the concentration gradually increases from bottom to top so as to form an electrically conductive path which can effectively inhibit the latch effect.

Owner:SOUTHEAST UNIV

Current enhanced type lateral insulated gate bipolar transistor

ActiveCN104916674AStrong on-current capabilityImprove the conduction current capabilitySemiconductor devicesHigh current densityParasitic bipolar transistor

A current enhanced type lateral insulated gate bipolar transistor improves current density and the turn-off speed on the premise that a latching ability is maintained to be unchanged. The semiconductor is provided with buried oxide disposed on a P-type substrate and an N-drift region disposed on the buried oxide, a P-body region and an N-buffer region are disposed on the N-drift region, a P-type collecting electrode region is disposed in the N-buffer region, an anode metal is connected to the P-type collecting electrode region, a field oxide layer is disposed on the N-drift region, a P-well region is disposed in the P-body region, a P-type emitting electrode region and an emitting electrode region are disposed in the P-well region, the inner-side boundaries of the four regions, i.e., the P-body region, the P-well region, the P-type emitting electrode region and the emitting electrode region are synchronously recessed inwardly to form a square groove, the emitting electrode region surrounding the groove is successively defined as a first P-type emitting electrode region, second, third and fourth N-type emitting electrode regions and a fifth P-type emitting electrode region, the N-drift region protrudes outwardly and fills the square groove, a surface of the P-body region is provided with a gate oxide layer, a surface of the gate oxide layer is provided with a polysilicon layer, and a gate metal is connected to the polysilicon layer.

Owner:SOUTHEAST UNIV +1

Standard cell design method resistant to single-particle latch-up effect

ActiveCN103886158AReduce the impactImprove radiation resistanceSpecial data processing applicationsEngineeringDesign methods

A standard cell design method resistant to the single-particle latch-up effect comprises the steps that (1) trap contact protecting regions are arranged in a standard cell layout, namely areas in contact connection with traps in the standard cell layout and stretch to two sides of a transistor active area are arranged into the protecting regions, and multiple contact holes are formed in the trap contact protecting regions; (2) separation distances of the trap contact protecting regions are reduced, and the biggest separation distance (dWC) of the trap contact protecting regions is not more than 4 microns; (3) the separation distance between an NMOS and a PMOS active area is increased, and the separation distance between the NMOS and the PMOS active area is not less than 0.69 micron; (4) the distance between each trap contact protecting region and an MOS transistor source electrode is reduced, the width of a first metal layer, the width of a second metal layer and the width of a third metal layer are respectively 0.4 micron according to the design rule of the SMIC013MMRF technology, and the height of an adopted unit is 4.0 microns equivalent to the pitch widths of 10 metal layers. The method achieves reinforcing of resistance to the single-particle latch-up effect, and is low in cost, easy to implement and high in reliability.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

Insulated gate bipolar transistor (IGBT) device with positive temperature coefficient emitter ballast resistance

InactiveCN103258848AImprove short circuit performanceImproves latch-up resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCompensation effectEngineering

The invention discloses an insulated gate bipolar transistor (IGBT) device with positive temperature coefficient emitter ballast resistance (EBR), and belongs to the technical field of power semiconductor devices. In a conventional IGBT device of an EBR structure, the EBR is composed of a strip-shaped N<+> emitter region strip, the resistance value of the EBR generally represents a negative-temperature coefficient, namely, the higher the temperature is, the smaller the resistance value is, saturation current of the IGBT is increased, and the short-circuit capacity of the IGBT device with the positive temperature coefficient EBR will be remarkably reduced in high-temperature environments. According to the IGBT device with the positive temperature coefficient EBR, deep energy level acceptor impurities, including In or Ti or Co or Ni, are doped into the N<+> emitter region, holes produced after ionization of the deep energy level acceptor impurities have a certain compensation effect on N-type impurities, positive temperature coefficient EBR is achieved, thus the resistance value of the EBR is increased along with rise of the temperature of the IGBT device, and the short circuit capacity and latch resistant capacity of the IGBT are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

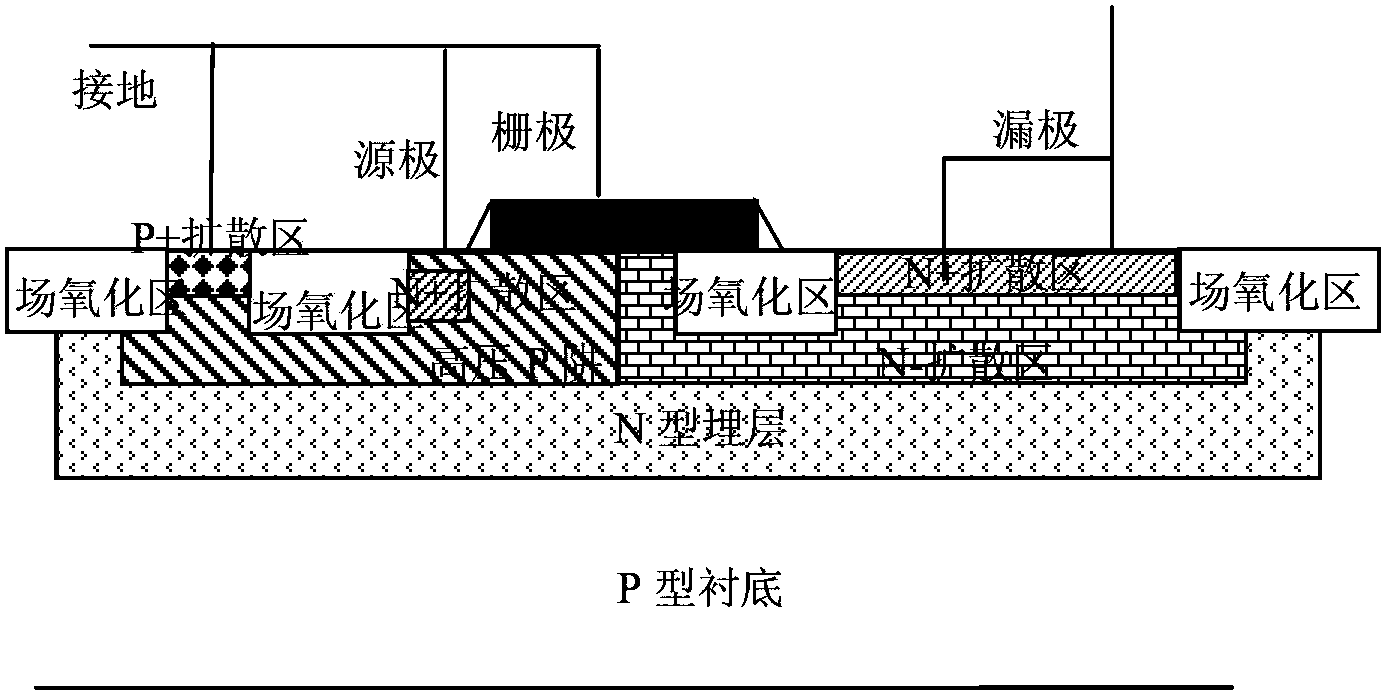

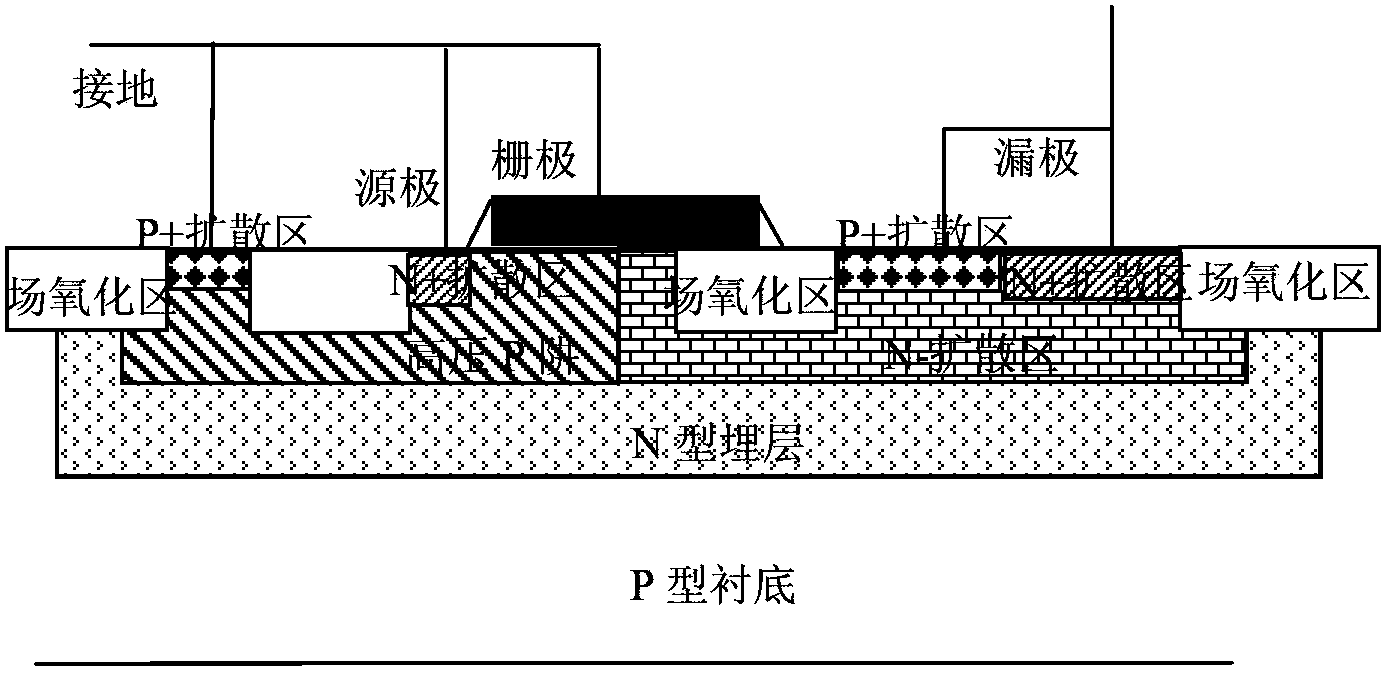

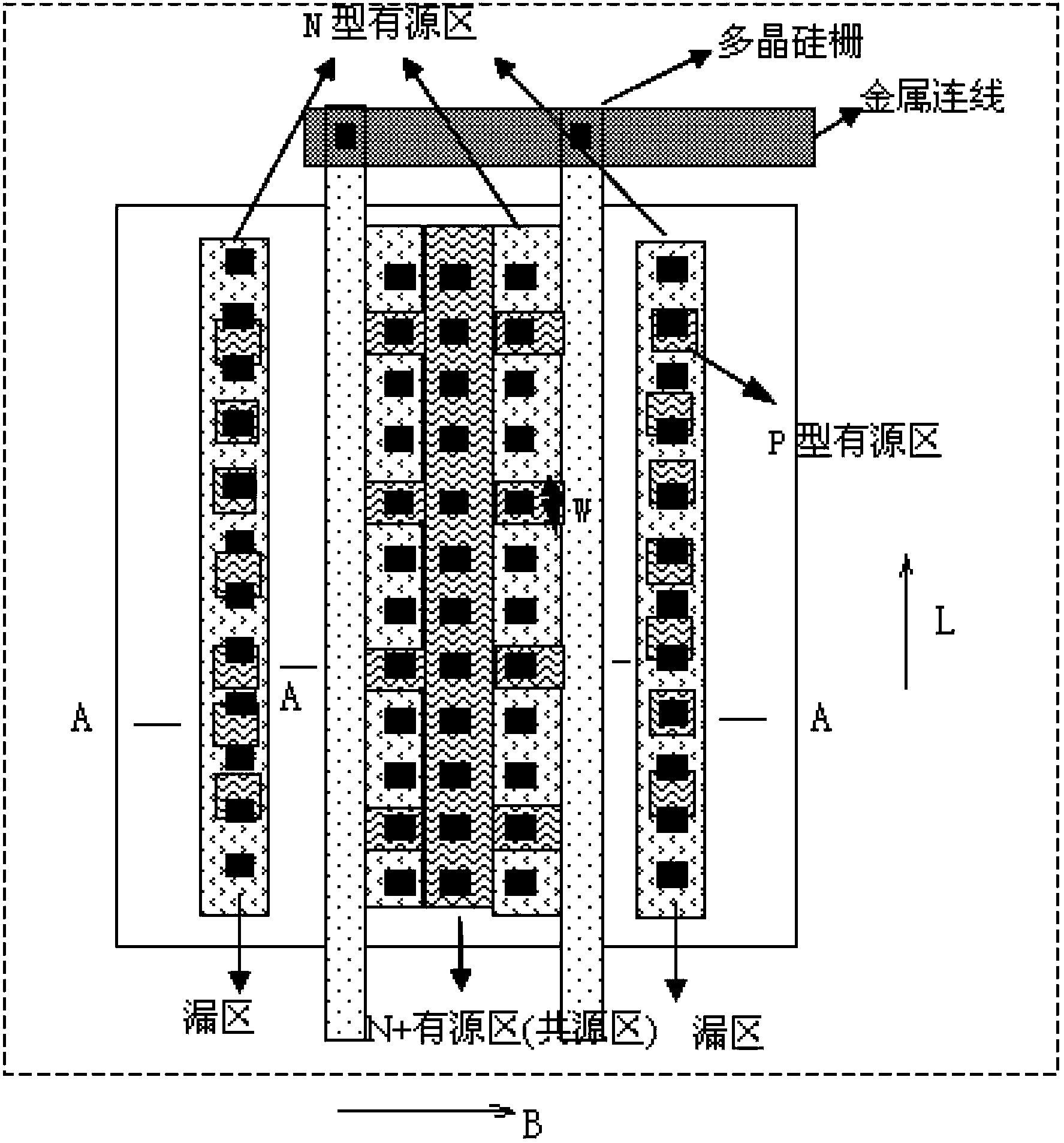

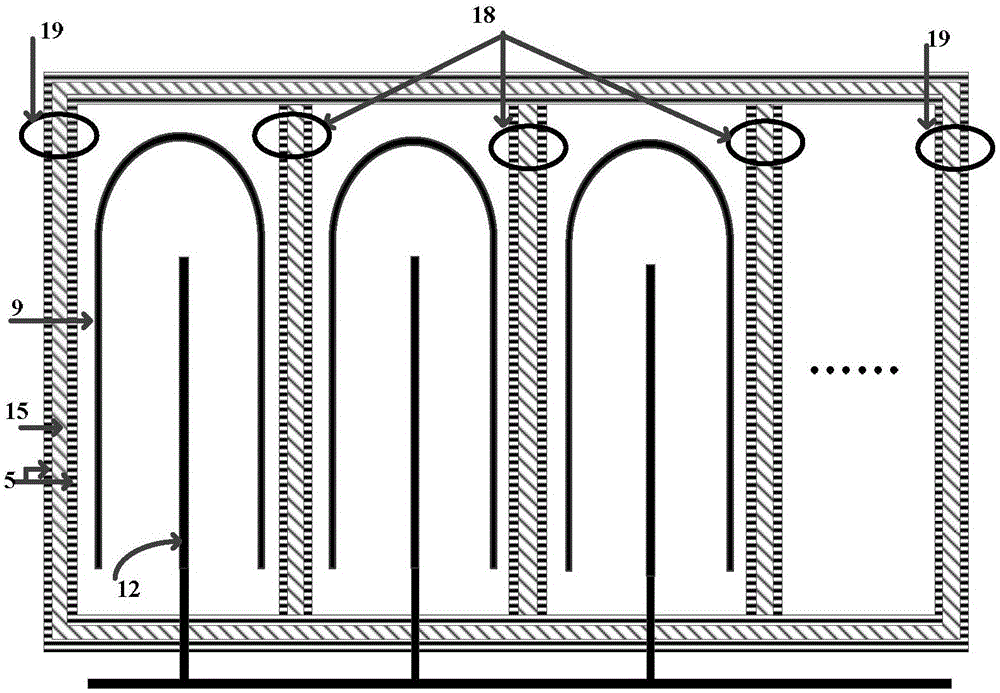

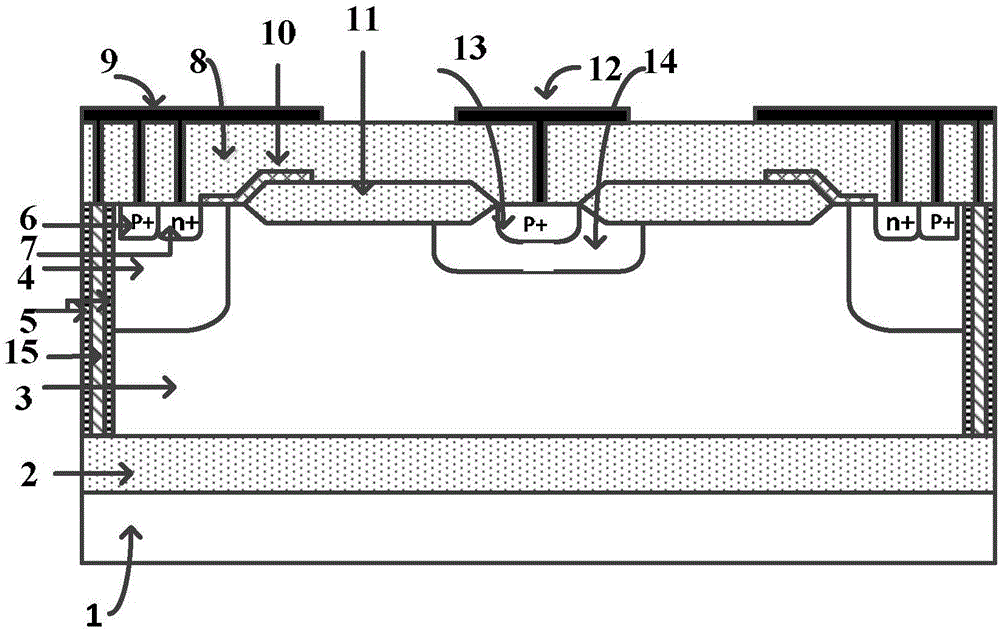

High-voltage NLDMOS (N-type laterally diffused metal oxide semiconductor) structure for electrostatic protection

The invention discloses a high-voltage NLDMOS (N-type laterally diffused metal oxide semiconductor) structure for electrostatic protection. The high-voltage NLDMOS structure comprises an NLDMOS formed in an N-type buried layer above a silicon substrate. The NLDMOS is arranged to be a multi-finger structure. A source region between two drain regions is a joint source region. N-type active regions and P-type active regions are arranged at intervals along the length direction in active regions of the drain regions. The P-type active regions are inserted into the joint source region and embedded in the N-type active regions. The N-type active regions in the source region are separated respectively by the P-type active regions. The P-type active regions and the N-type active regions are arranged at intervals along the length direction. All drain electrodes are connected to an ESD (electro-static discharge) access end. All source electrodes are connected to the ground. All grid electrodes are connected to a signal end. By changing the width of a diffused region P+, close to the grid electrodes, on the source region, the high-voltage NLDMOS structure can effectively adjust trigger current and snapback voltage. By the high-voltage NLDMOS structure applied to high-voltage electrostatic protection, locking-resisting capability of an LDMOS (laterally diffused metal oxide semiconductor) can be effectively improved, and electrostatic protection capability of the LDMOS can be ensured not to be affected.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

High-speed and low-loss multi-trench gate high-voltage power device

ActiveCN110504308AImprove injection efficiencyImproves latch-up resistanceSemiconductor devicesChannel densityCharge carrier

The invention belongs to the technical field of power semiconductors and particularly relates to a high-speed and low-loss multi-trench gate high-voltage power device. Compared with a traditional structure, the structure of the high-speed and low-loss multi-trench gate high-voltage power device has the advantage that a plurality of trench gate structures are introduced into an emitter terminal anda collector terminal. Channels in side walls of trench gates at the collector terminal are turned off and a connection path of an N+ collector region and an N-type buffer layer is blocked during forward conduction, so that the voltage foldback effect can be eliminated. A trench gate structure at the emitter terminal can increase the channel density to reduce the resistance of a channel region, and a barrier trench gate and a carrier storage layer can effectively improve the carrier concentration of a drift region, so that the novel device can obtain lower forward conduction voltage drop. In the turn-off process, the channels in the side walls of the trench gates at the collector terminal are opened along with voltage rise of a collector, so that the N+ collector region communicates with the N-type buffer layer to form a rapid electron extraction path and turn-off of the device is accelerated to reduce the turn-off loss. Therefore, the high-speed and low-loss multi-trench gate high-voltage power device has lower forward conduction voltage drop and smaller turn-off loss and does not have the voltage foldback effect.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

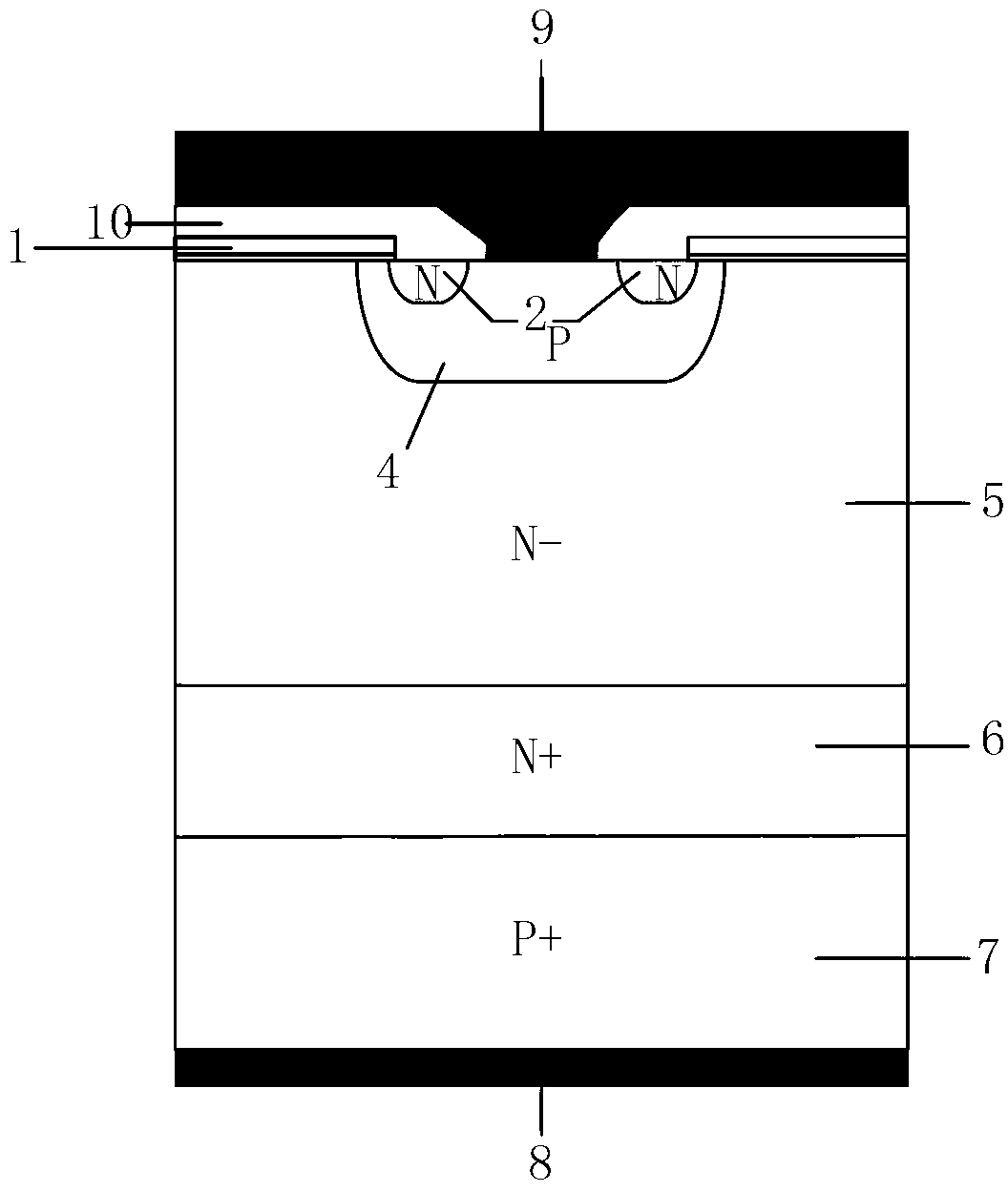

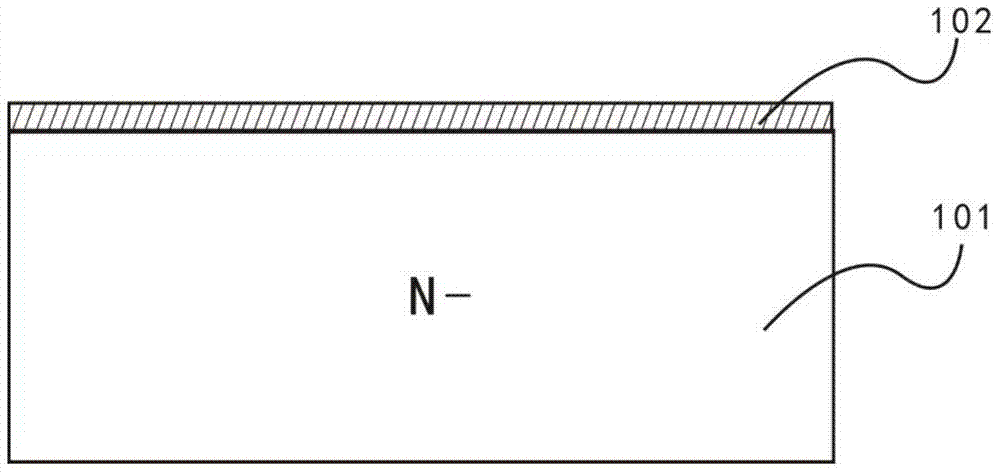

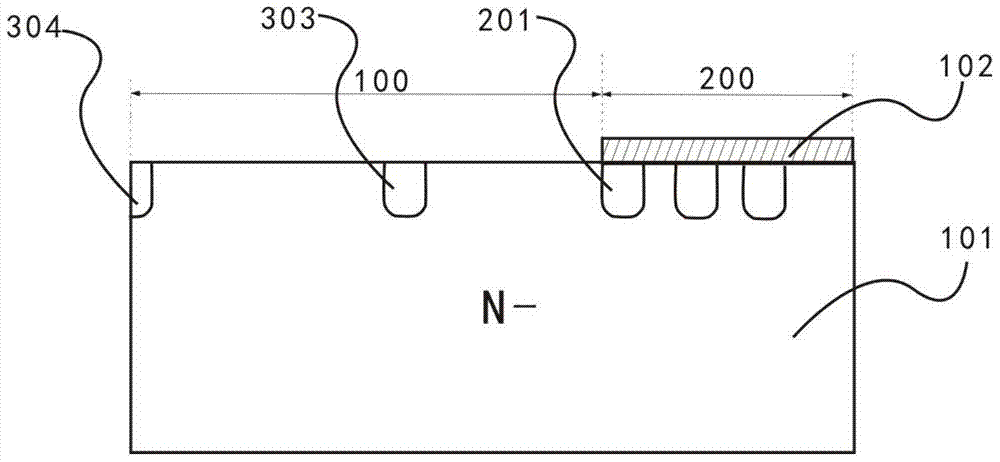

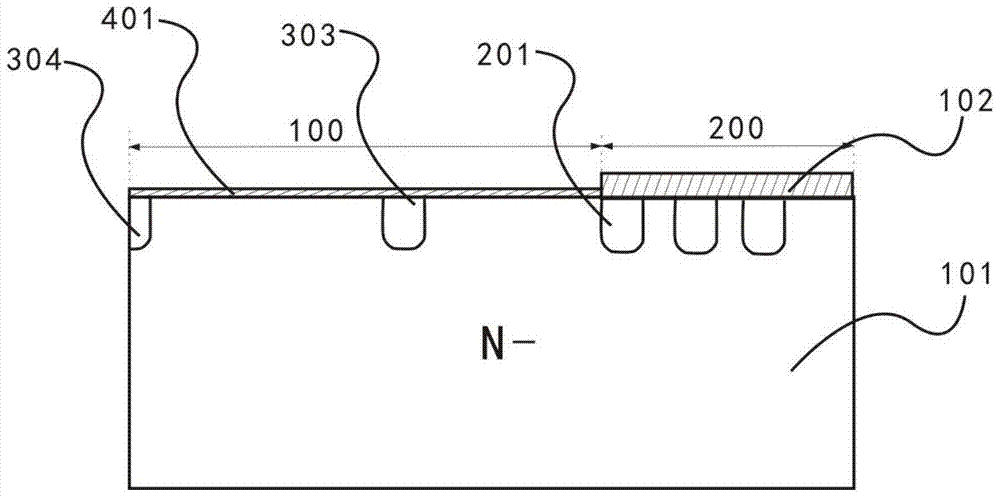

Method for manufacturing insulated gate bipolar transistor

ActiveCN104517837AImproves latch-up resistanceImprove application reliabilityTransistorSemiconductor/solid-state device manufacturingInsulated-gate bipolar transistorEngineering

The invention discloses a method for manufacturing an insulated gate bipolar transistor, comprising the following steps: providing a semiconductor substrate of a first conductivity type, selectively forming a deep well region of a second conductivity type at a first main surface side of an active region of the semiconductor substrate, and selectively forming a protection terminal of the second conductivity type in a terminal protection region around the active region; implanting ions of the first conductivity type at the first main surface side of the active region of the semiconductor substrate of the first conductivity type; selectively photoetching and etching a gate oxide layer and a polycrystalline silicon layer to form a polycrystalline silicon gate and a window; and continuing to implant ions of the second conductivity type in the position of the deep well region at the first main surface side of the active region of the semiconductor substrate based on the window and activating the ions to form a base region of the second conductivity type. On the premise of not increasing the thermal process or even reducing the thermal process, the well junction depth is expanded largely, the anti-latch-up capability is improved, and the application reliability of products is improved.

Owner:CSMC TECH FAB2 CO LTD

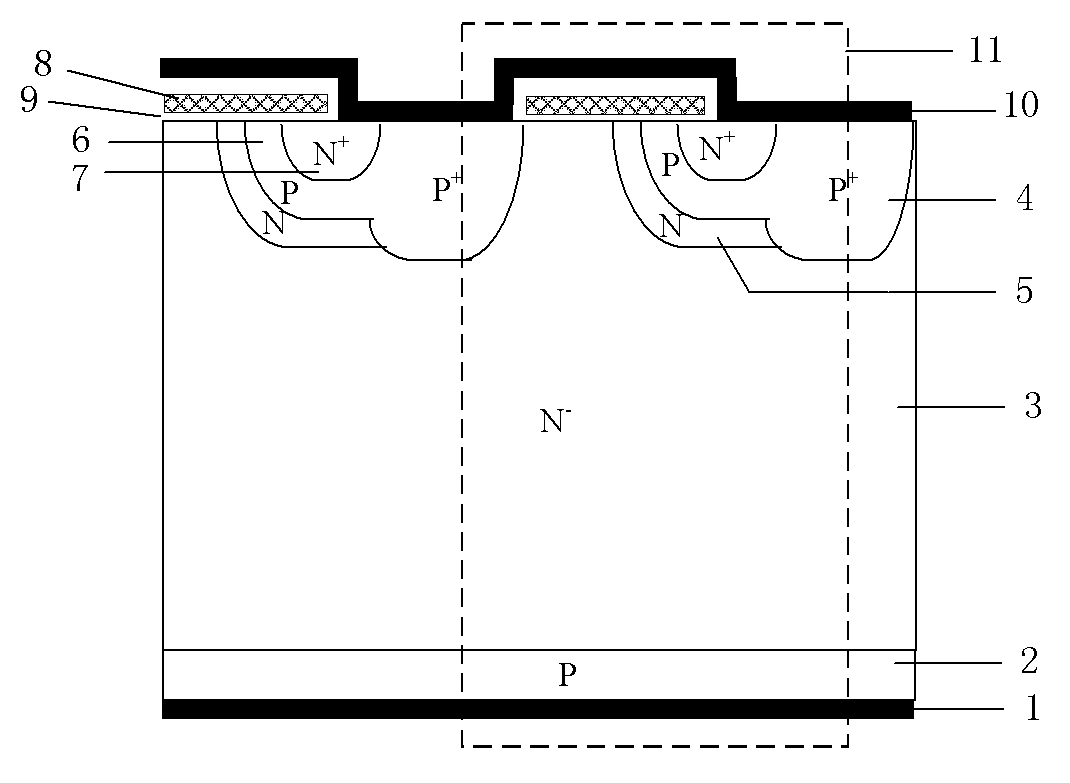

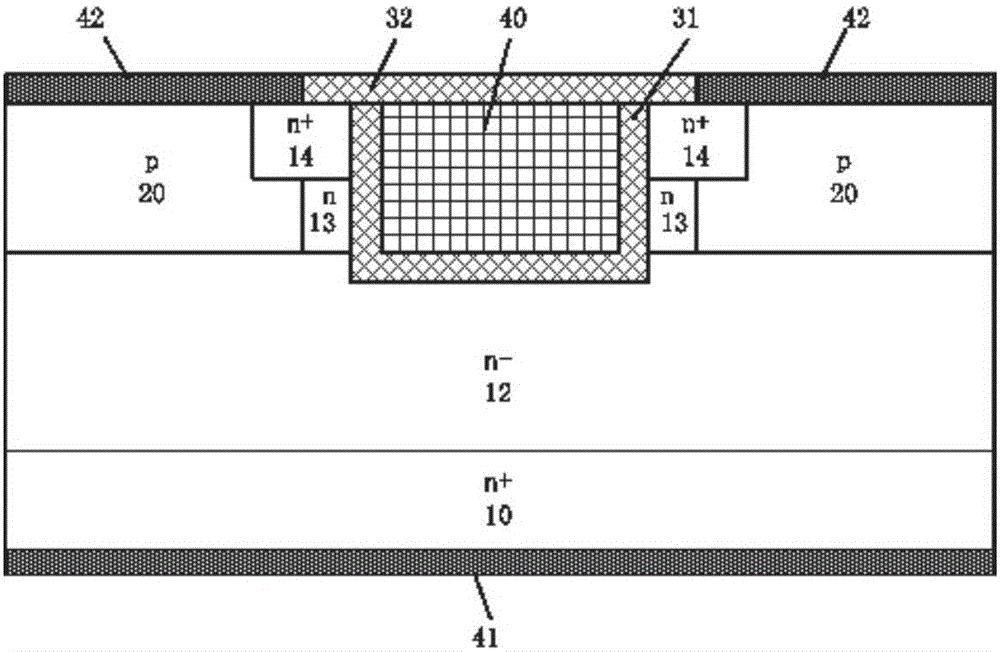

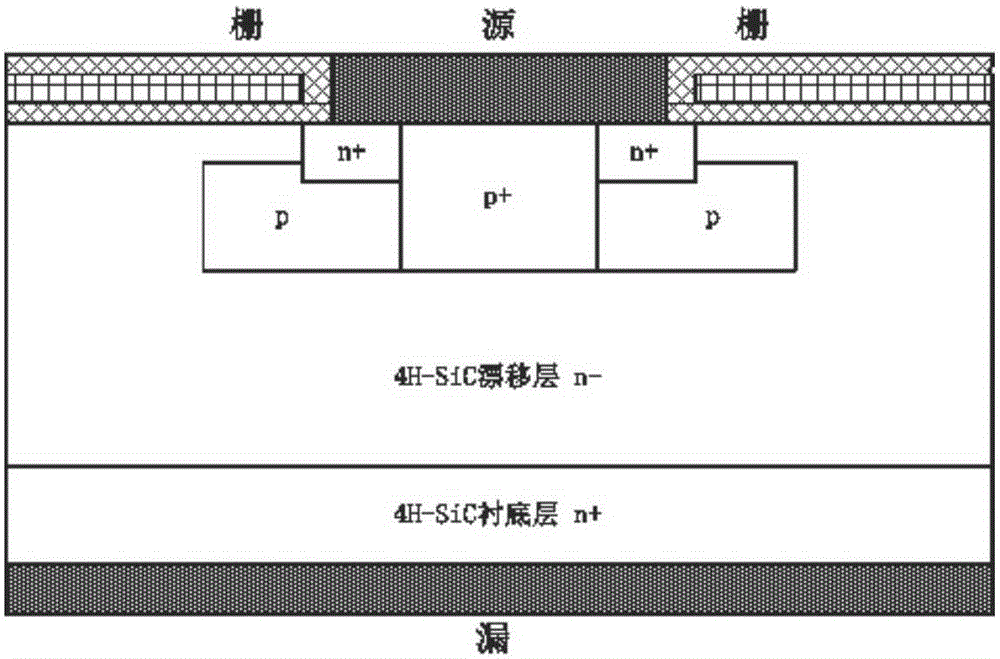

Buried-channel SiC trench gate metal oxide semiconductor field effect transistors (MOSFETs) device and fabrication method thereof

ActiveCN105185833AAvoid effectivenessImprove effective mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEngineering

The invention provides a buried-channel SiC trench gate metal oxide semiconductor field effect transistors (MOSFETs) device and a fabrication method thereof. The device comprises an n-type SiC substrate, n-type buried channels, p-type SiC regions, a trench medium, a gate contact, base region contacts, source contacts and a drain contact, wherein an n-type SiC drift layer is arranged on the substrate and internally comprises p<+>-type SiC regions at intervals, and n<+>-type SiC regions are arranged between the p<+>-type SiC regions; the n-type buried channels are arranged between the p<+>-type SiC regions and arranged in the n-type SiC drift layers under the n<+>-type SiC source regions; and the p-type SiC regions are arranged under the n<+>-type SiC source regions, are arranged in the n-type buried channels, and are opposite to the p<+>-type SiC regions. On the basis of a trench gate MOSFET structure, the buried channels provided for source and drain conductive passages are achieved by reversely doping a part of p well regions, the problems of low effective mobility of surface electrons and high threshold voltage are prevented, and a normally-closed device is achieved.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

Trench gate IGBT and manufacturing method

InactiveCN106876453AReduce contact widthReduce parasitic resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricZone melting

The invention discloses a trench gate IGBT, including a drift region, a collection zone and P-type body regions. The trench gate IGBT also comprises a gate trench, wherein a gate dielectric layer is formed on the surface and the side surface of the bottom of the gate trench, and a polysilicon gate fills the gate trench. The top surface of the polysilicon gate is lower than the top surface of zone melting silicon, and source regions are formed in the zone melting silicon at two sides of the gate trench on the top of the polysilicon gate by self-aligning ion implantation with an inclination angle. The trench gate IGBT also comprises P+ contact regions formed on the surface of the P-type body regions. The P+ contact regions and the source regions are connected to an emitter electrode through contact holes. The invention also discloses a manufacturing method of the trench gate IGBT. The width of the source regions can be reduced by self-aligning ion implantation, so that the parasitic resistance of the P-type body regions is reduced, and the anti-latching capability of the device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

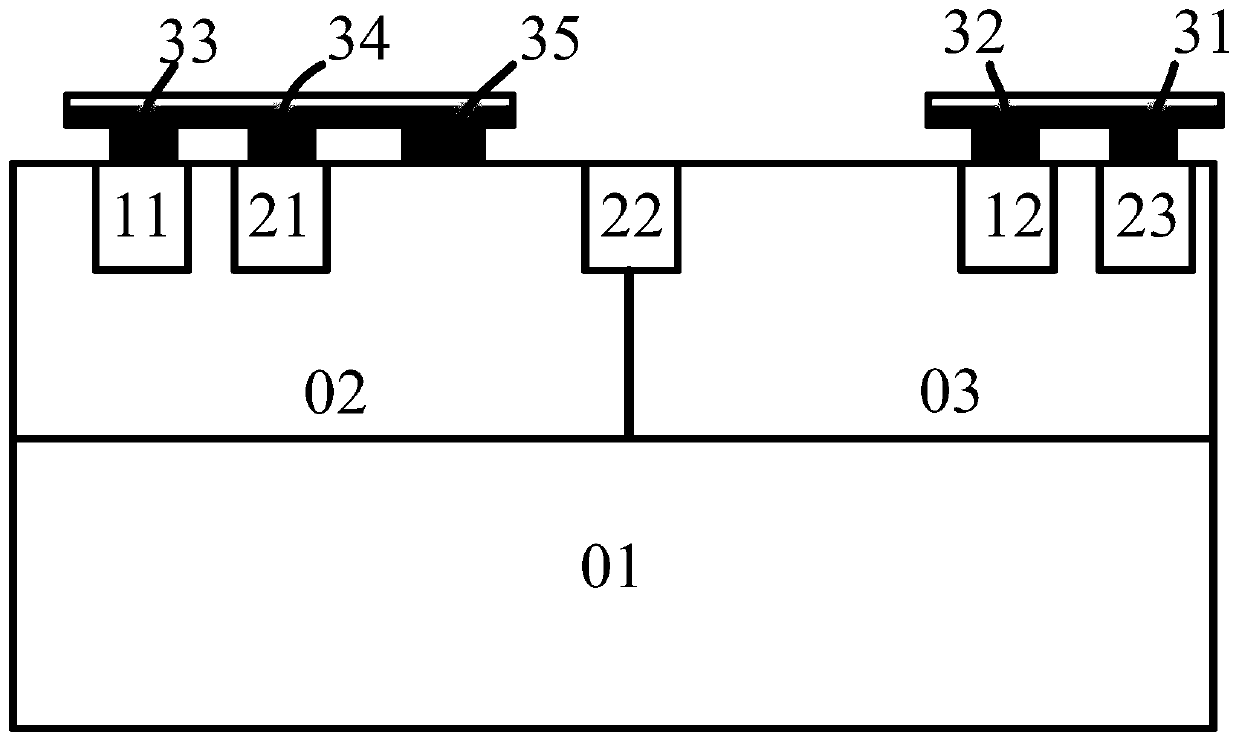

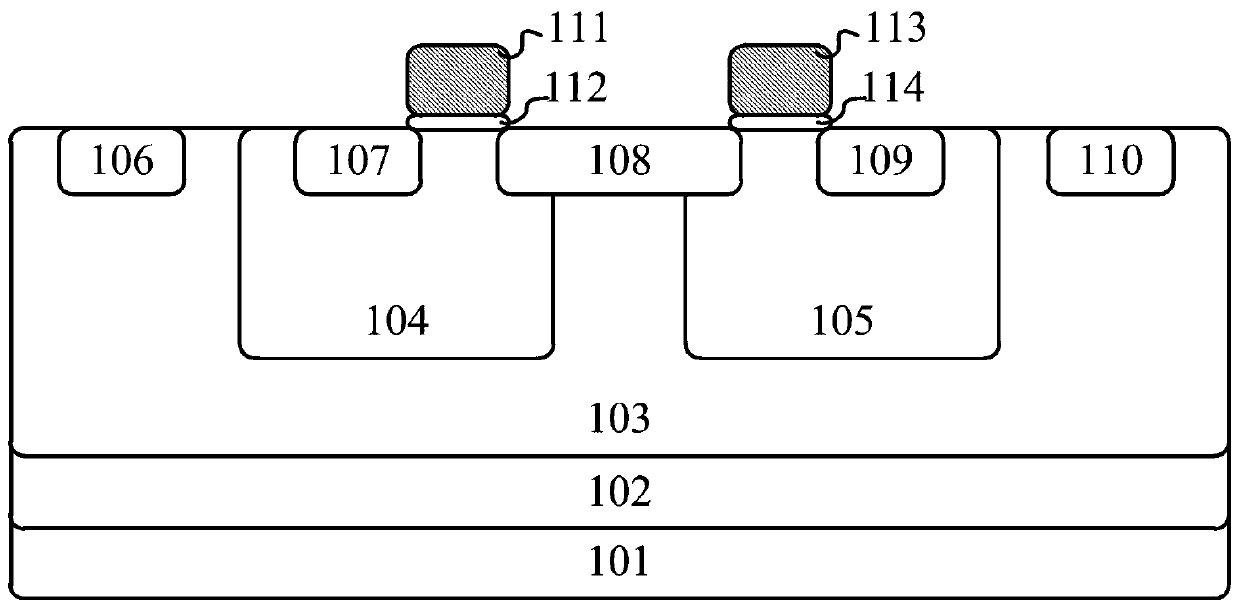

Method for improving high-low voltage ESD protection performance by employing well segmentation technology

ActiveCN108109997AReduce parasitic capacitanceMeet protection needsSolid-state devicesDiodeLow voltageParasitic capacitance

A method for improving high-low voltage ESD protection performance by employing a well segmentation technology concretely comprises a well segmentation technology and a special metal wiring method toimprove the reliability of on-chip IC low-voltage ESD protection. A device 1 in one embodiment of the invention is mainly formed by a P substrate, a first N well, a first P well, a second P well, a second N well, a third P well, a third N well, a fourth P well, a fourth N well, a fourth P+ injection region and a fifth N+ injection region. Under an ESD stress effect, the well segmentation technology is employed so as to obtain a low-voltage ESD protection device of an SCR triggered by a diode, avoid generation of an avalanche breakdown effect at the internal portion of the device and reduce a triggering voltage of the device and so as to greatly reduce stray capacitance of the device and meet ESD protection demands of a radio frequency IC. Besides, the positions of the N+ injection region and the P+ injection region at the internal portion of the device are regulated to change the ESD current discharge path of the SCR structure, and the method provided by the invention combines the metal wiring design to regulate a maintenance voltage of the device.

Owner:JIANGNAN UNIV

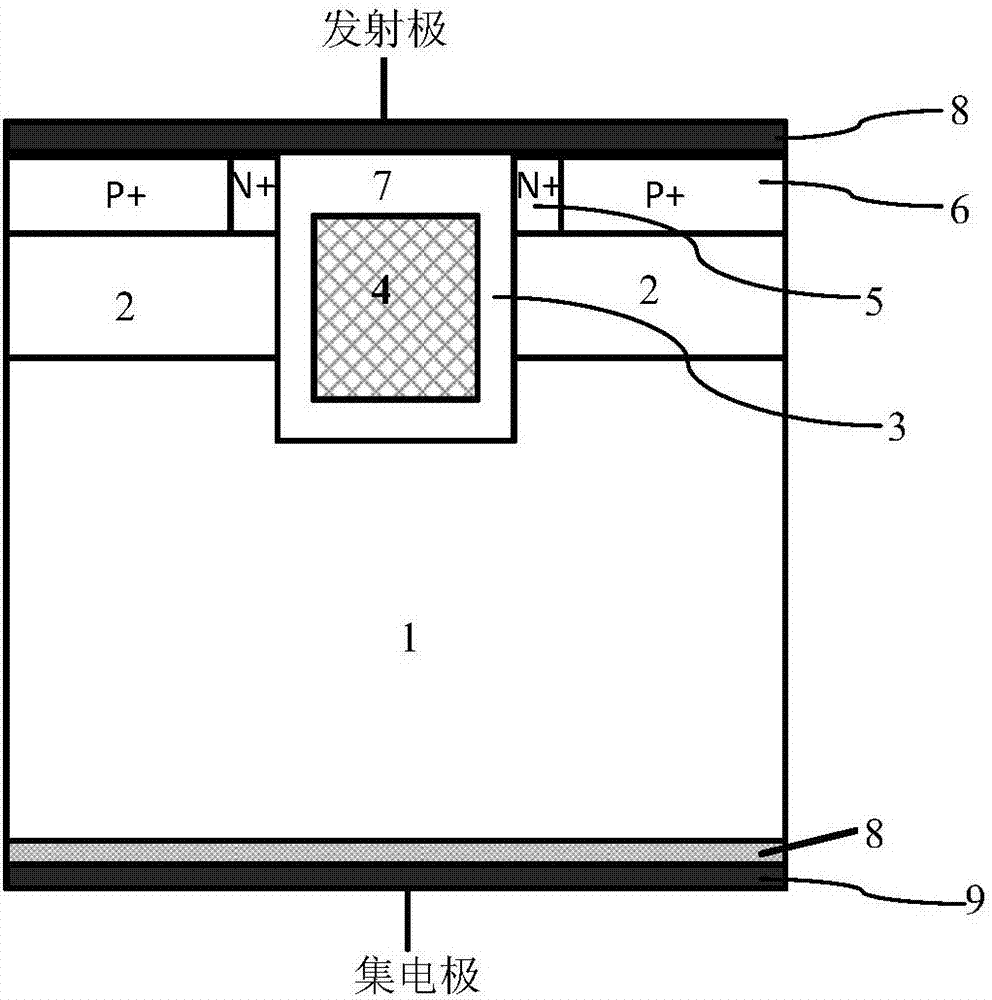

IGBT and manufacturing method thereof

InactiveCN103872111AIncreased latch-up currentImproves latch-up resistanceTransistorSemiconductor/solid-state device manufacturingCurrent channelEngineering

The invention discloses an IGBT and a manufacturing method thereof. The IGBT includes: a gate structure located on an upper surface of a semiconductor substrate; a well region, a source region and a shallow well region located inside the upper surface of the semiconductor substrate, the well region being internally provided with the source region, upper surfaces of the well region, the source region and the shallow well region being flush with the upper surface of the semiconductor substrate, and the well region and the shallow well region being not in contact and the same in doping type; a source electrode located on surfaces of the well region, the shallow well region and the source region; and a reverse side structure located on a lower surface of a semiconductor, and the reverse side structure including a collector region. When the IGBT works, a part of a hole current can pass the collector region, a drift region and the well region, and flow into the source electrode, and a part of the hole currents can pass the collector region, the drift region and the shallow region, and flow into the source electrode. Thus, the shallow well region provides an extra current channel for the IGBT to shunt the hole current, thereby improving a latching current of the IGBT, and enhancing an anti-latching capability of the IGBT.

Owner:SHANGHAI LIANXING ELECTRONICS +2

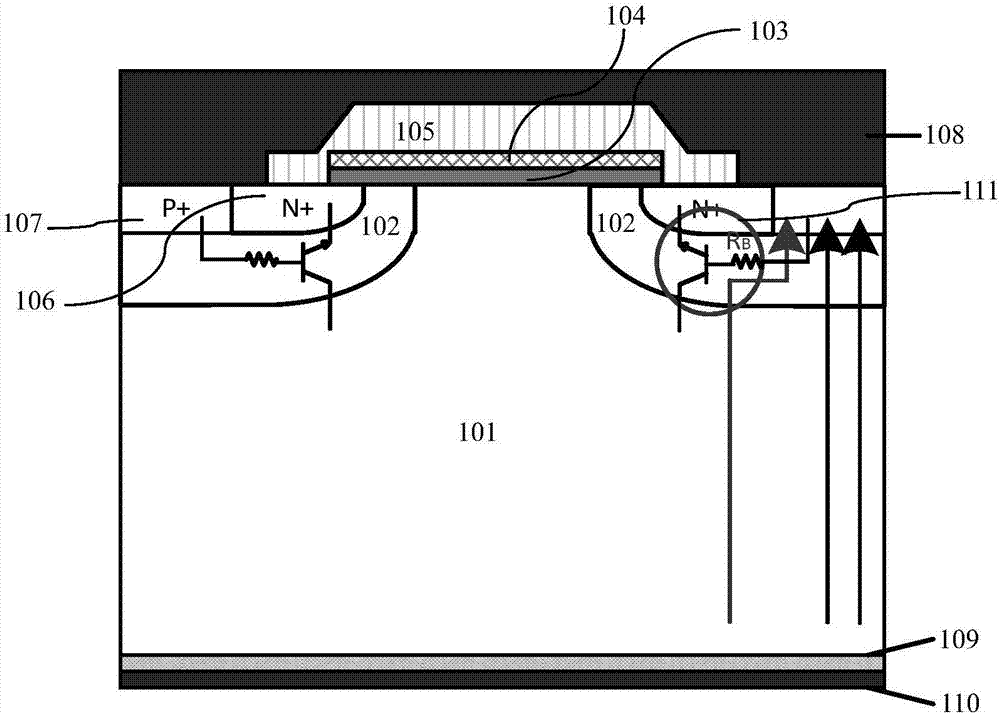

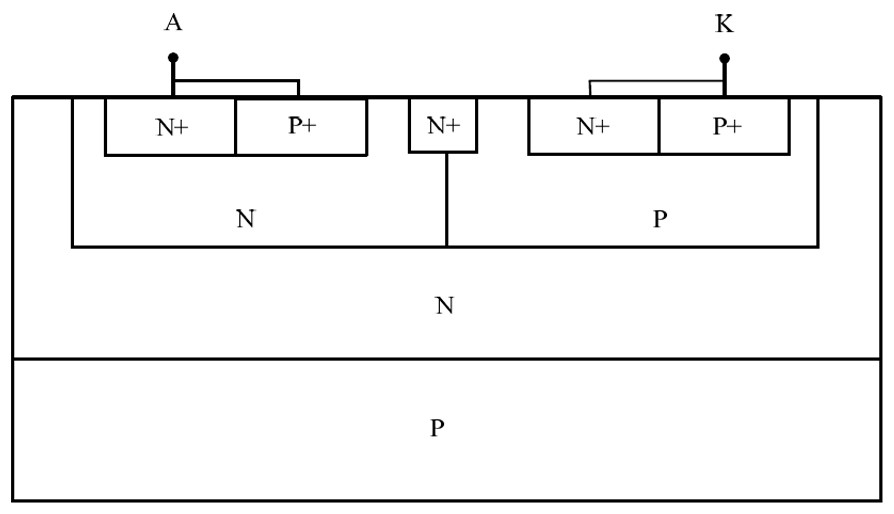

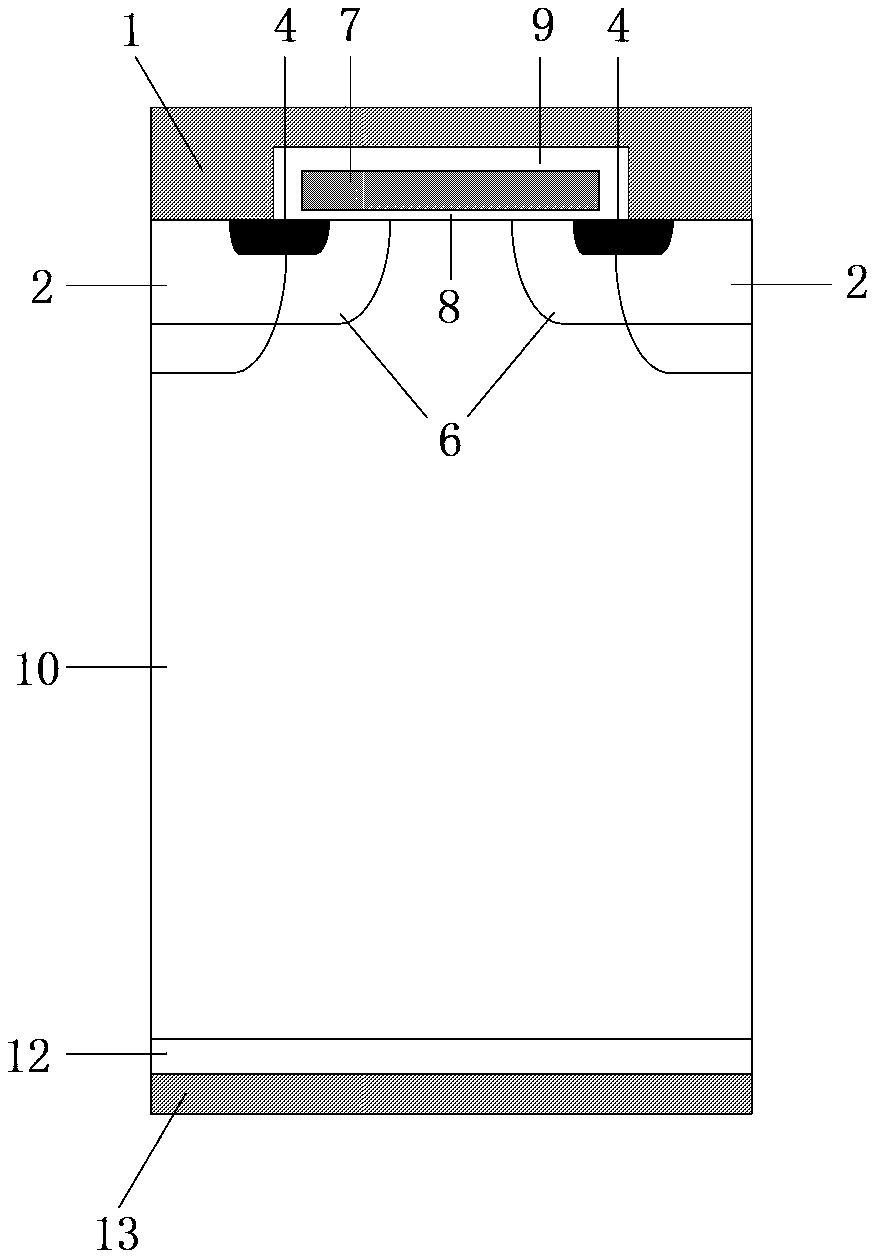

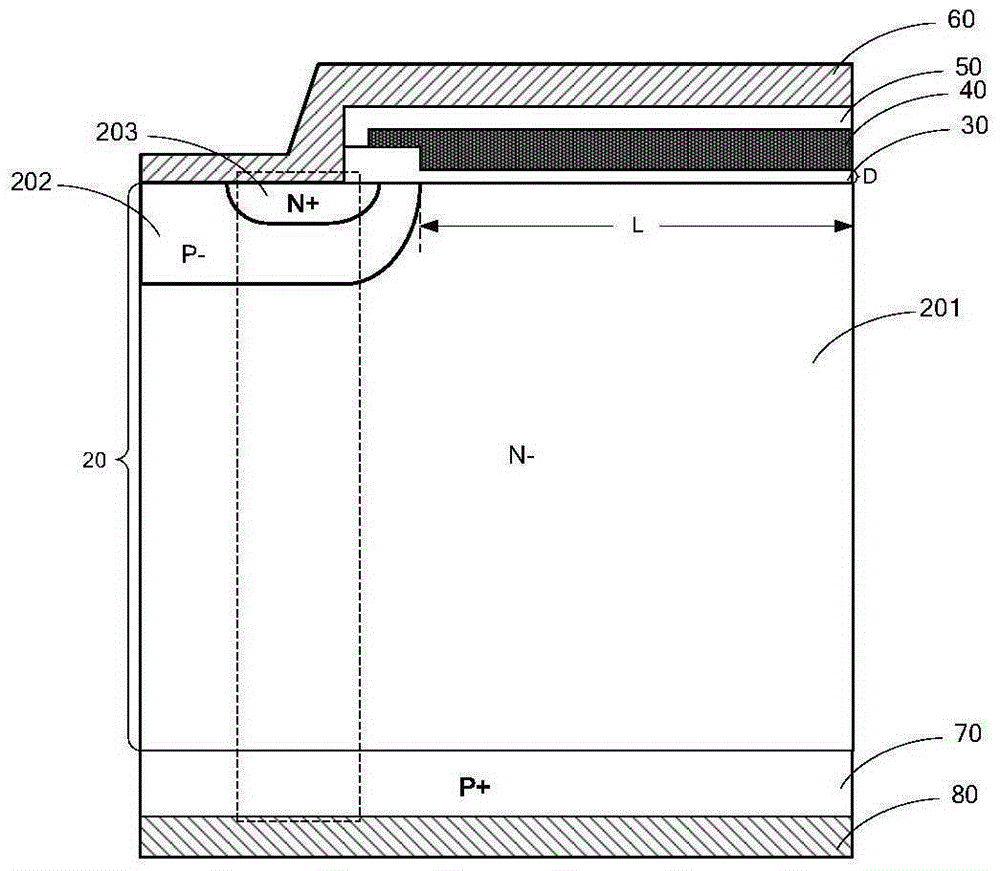

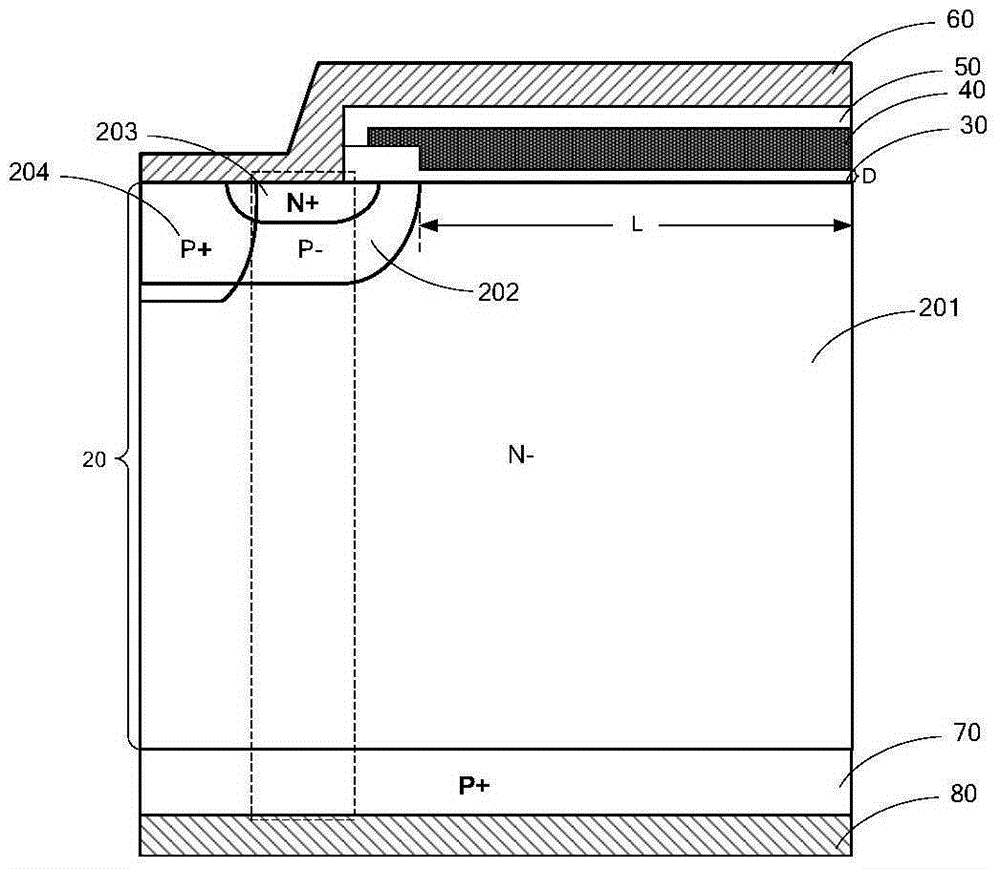

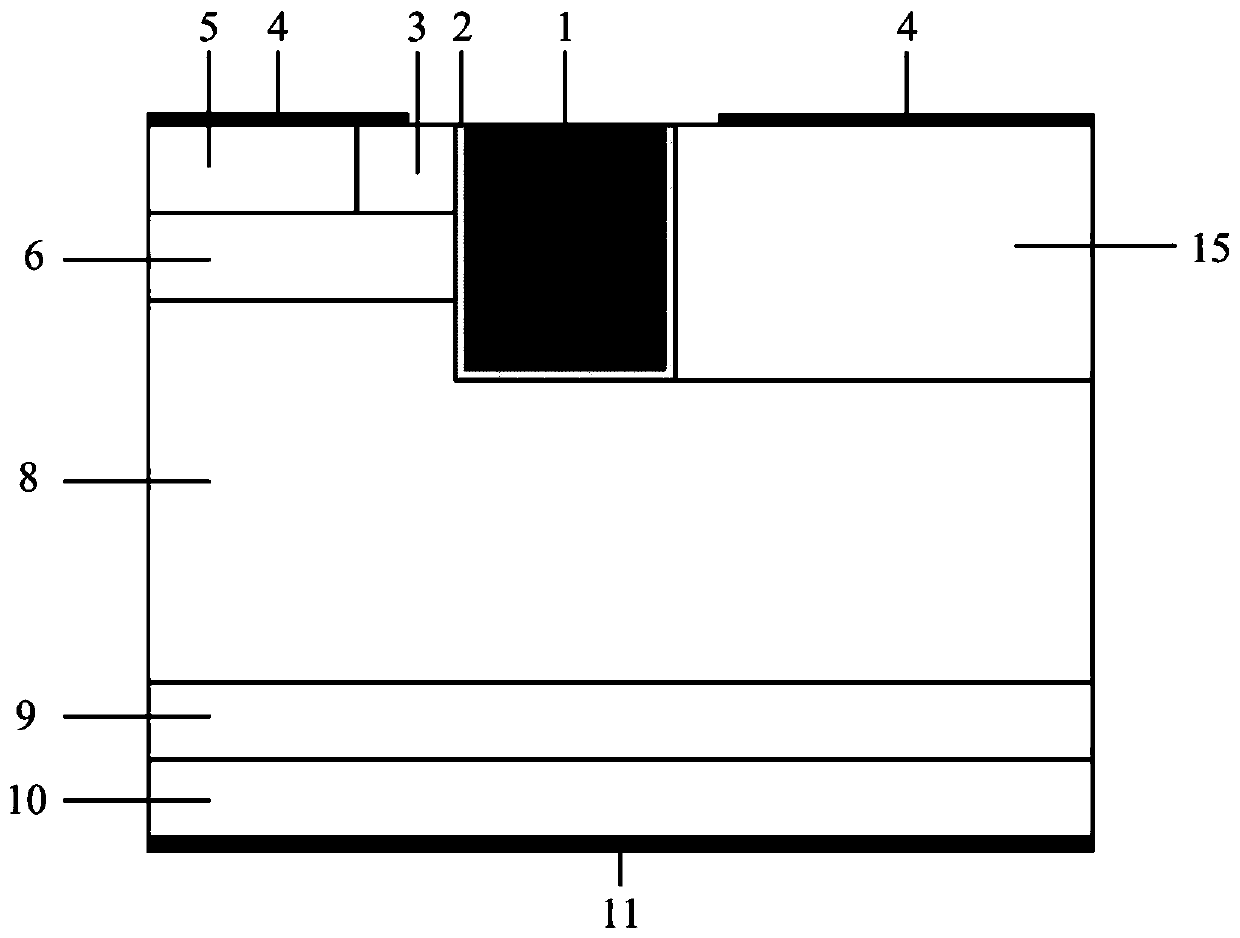

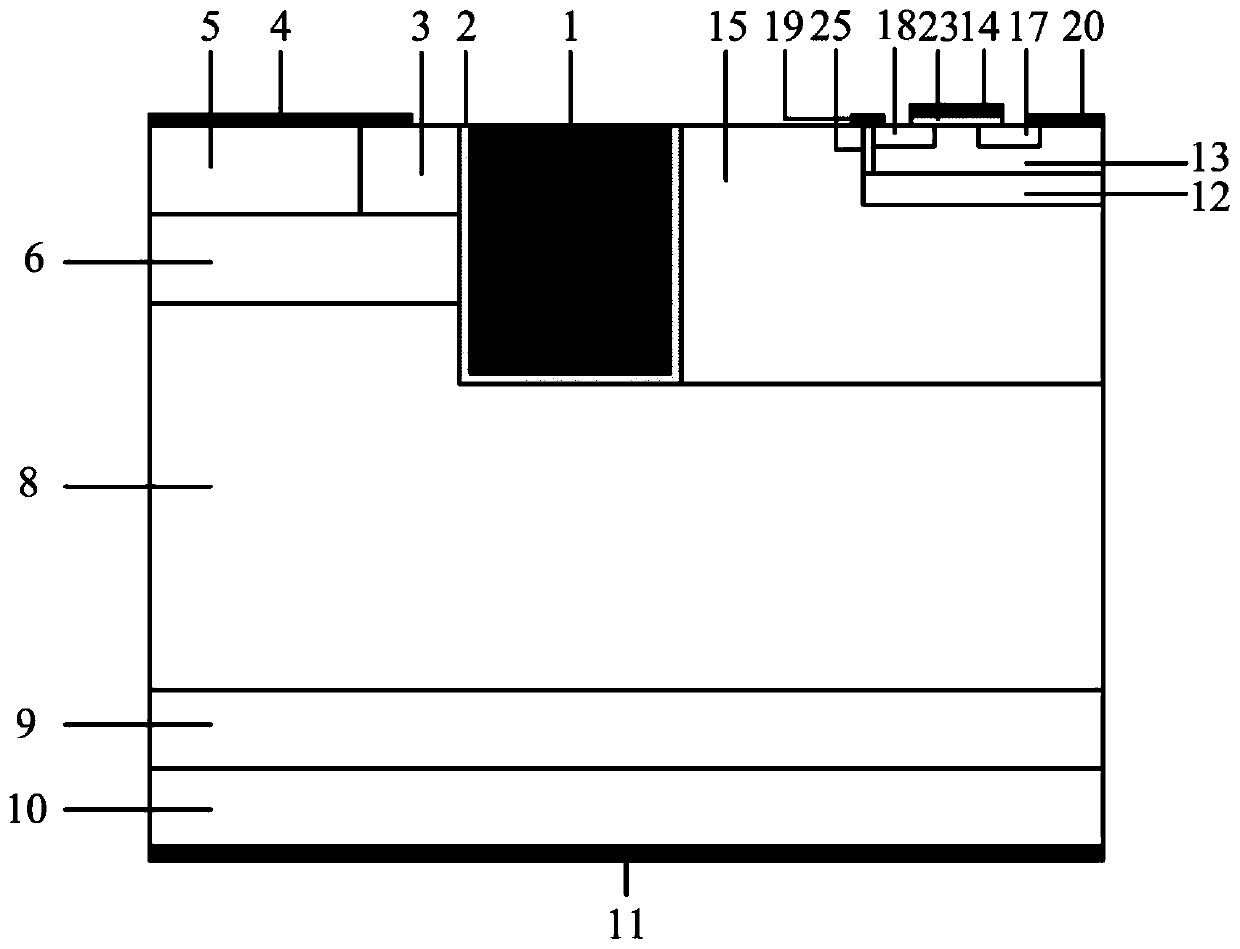

Thick-film SOI-LIGBT device and method for improving latch-up resistance thereof

ActiveCN106252400AImproves latch-up resistanceSmall pressure dropSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsBody region

The invention provides a thick-film SOI-LIGBT device and a method for improving latch-up resistance thereof. The device comprises a P-type substrate. A buried oxide layer is arranged on the P-type substrate. An N-type drift region is arranged above the buried oxide layer. A P-type body region and an N-type buffer region are arranged inside the N-type drift region. A P-type cathode contact region and an n-type cathode contact region are provided on the surface of the P-type body region. The contact region is connected with the cathode contact metal layer. A P-type anode contact region is arranged on the surface of the N-type buffer region. The contact region is connected with the anode contact metal layer. A field oxide layer and a conductive polysilicon gate are arranged on the surface of the N-type drift region. Passivation layers are arranged on the surface of the cathode contact region, the anode contact region, the field oxide layer and the conductive polysilicon gate. The device is characterized in that an isolation trench is arranged on the outside of the cathode of the device; and conductive polysilicon in the isolation trench is shorted to the cathode contact region and the cathode metal layer. According to the method, the potential difference between the conductive polysilicon in the isolation trench and the N-type drift region is increased; hole current flowing through a lateral channel in the P-type body region is reduced; and the latch-up resistance is improved.

Owner:SOUTHEAST UNIV

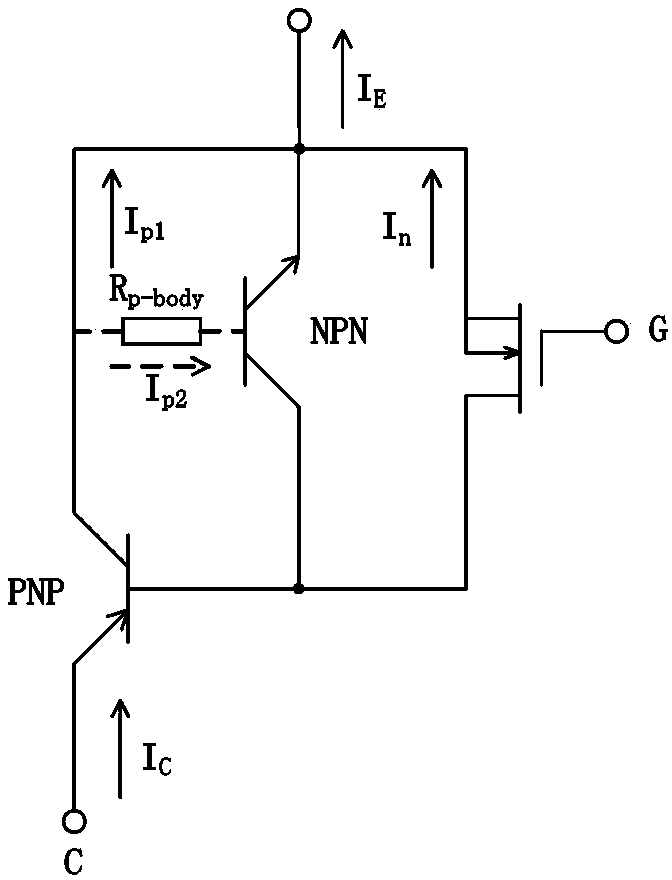

IGBT device with high latching resisting capability

ActiveCN105762182AReduce flow throughReduce or even prevent flow throughSemiconductor devicesDielectric cylinderVoltage drop

The invention relates to an IGBT device with a high latching resisting capability.Each active cell of the IGBT device comprises a second conduction type base region and a first conduction type source electrode region.Barrier rings are arranged in the second conduction type base regions.On the section of the IGBT device, each barrier ring comprises a first conduction type buried layer and an insulating dielectric cylinder, wherein the upper end of the insulating dielectric cylinder makes contact with source electrode metal, the end, located under the corresponding first conduction type source electrode region, of the first conduction type buried layer makes contact with the insulating dielectric cylinder, the other end of the first conduction type buried layer makes contact with the side wall of a conducting channel, the length of the part, under the corresponding first conduction type source electrode region, of the first conduction type buried layer is not smaller than the length of the part, in the corresponding second conduction type base region, of the corresponding first conduction type source electrode region, and the first conduction type buried layer is insulated from the source electrode metal.The IGBT device is compact in structure, compatible with the existing process, safe, reliable and capable of effectively reducing the latching risk and providing a basis for reducing the on-state voltage drop.

Owner:JIANGSU CAS IGBT TECHNOLOGY CO LTD +1

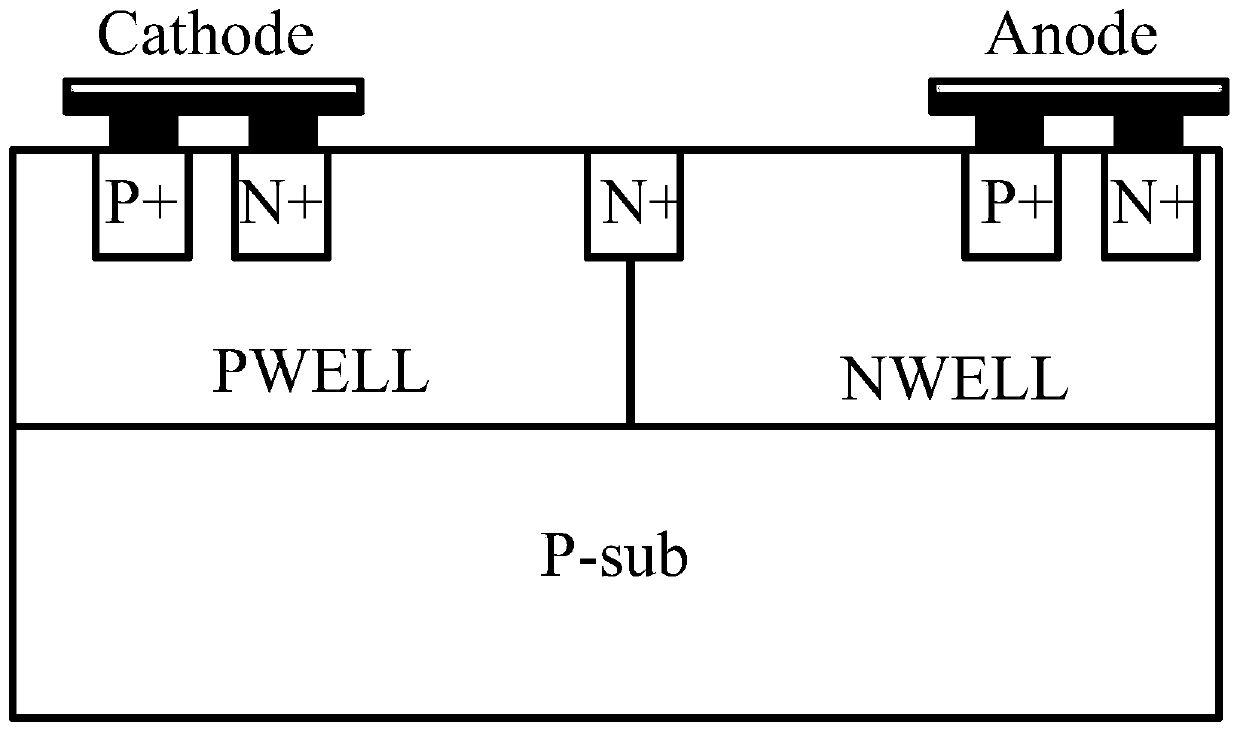

Schottky clamped SCR device for ESD protection

ActiveCN109698194AImproves latch-up resistanceCurrent positive feedback weakensTransistorSolid-state devicesSchottky diodePositive feedback

The invention provides a Schottky clamped SCR device for ESD protection, including a P-type substrate, a p-well region and an n-well region, a first n+ injection layer and a first p+ injection layer in the p-well region, a third n+ injection layer and a second p+ injection layer in the n-well region, and a second n+ injection layer cross-connected between the n-well region and the p-well region toreduce the breakdown voltage. A first metal hole is in contact with the third n+ injection layer. A second metal hole is in contact with the second p+ injection layer. A third metal hole is in contact with the first p+ injection layer. A fourth metal hole is in contact with the first n+ injection layer. A fifth metal hole is directly connected with the p-well region to form Schottky contact, so as to form a Schottky diode. The positive feedback process inside the SCR structure is weakened by the additional Schottky diode, so that the positive feedback of current of the SCR is weakened. Therefore, the maintaining voltage of the SCR rises, and the anti-latch ability of the device is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

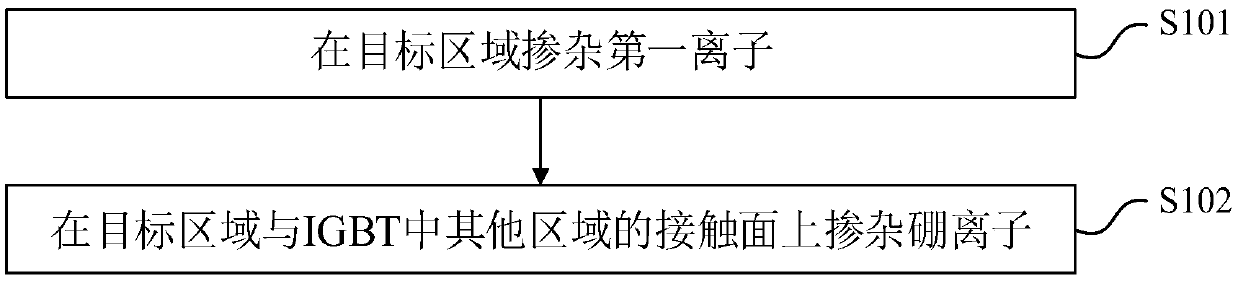

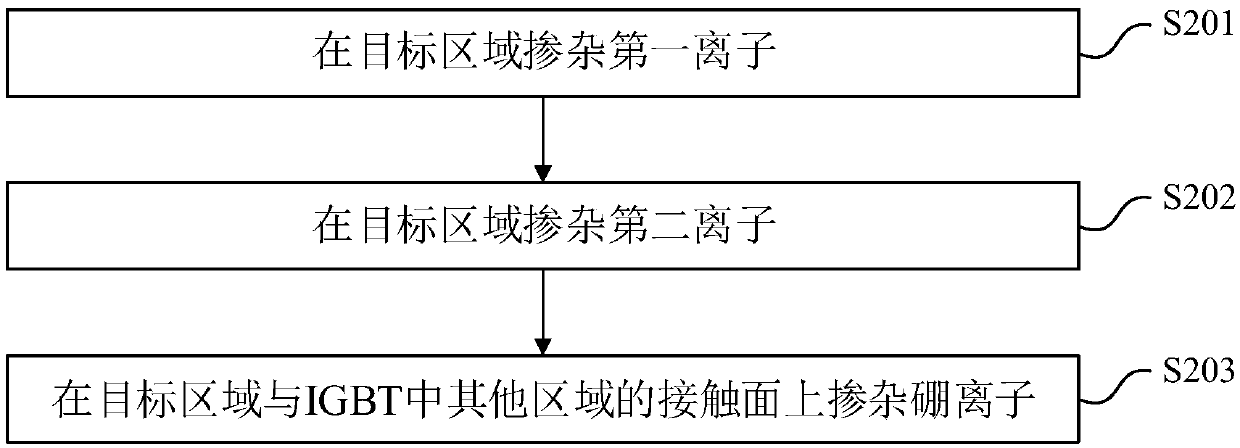

IGBT and manufacturing method thereof

ActiveCN110858609AImprove performanceIncrease the diffusion coefficientTransistorChemical physicsImpurity diffusion

The invention discloses an IGBT and a manufacturing method thereof. A target region in the IGBT is doped with first ions, the target region comprises at least one of a P-type substrate, a P-type wellregion and a P-type source region, and the diffusion coefficient of the first ions is greater than that of boron ions. The diffusion coefficient of the first ions doped in the IGBT target region is greater than the diffusion coefficient of boron ions. Unlike the prior art of adopting boron ions as doping impurities, the distribution morphology of the impurities formed under the same condition is thus more gradually changed, that is, the formed PN junctions are gradually-changed junctions, so that the breakdown voltage is improved, the turn-off time is shortened, the latch-up resistance is improved, and the performance of the IGBT is further improved. Besides, the impurity diffusion coefficient is large, so that a wider and deeper PN junction can be formed at a lower temperature in a shorter time, and a certain cost advantage is achieved.

Owner:ADVANCED SEMICON MFG CO LTD

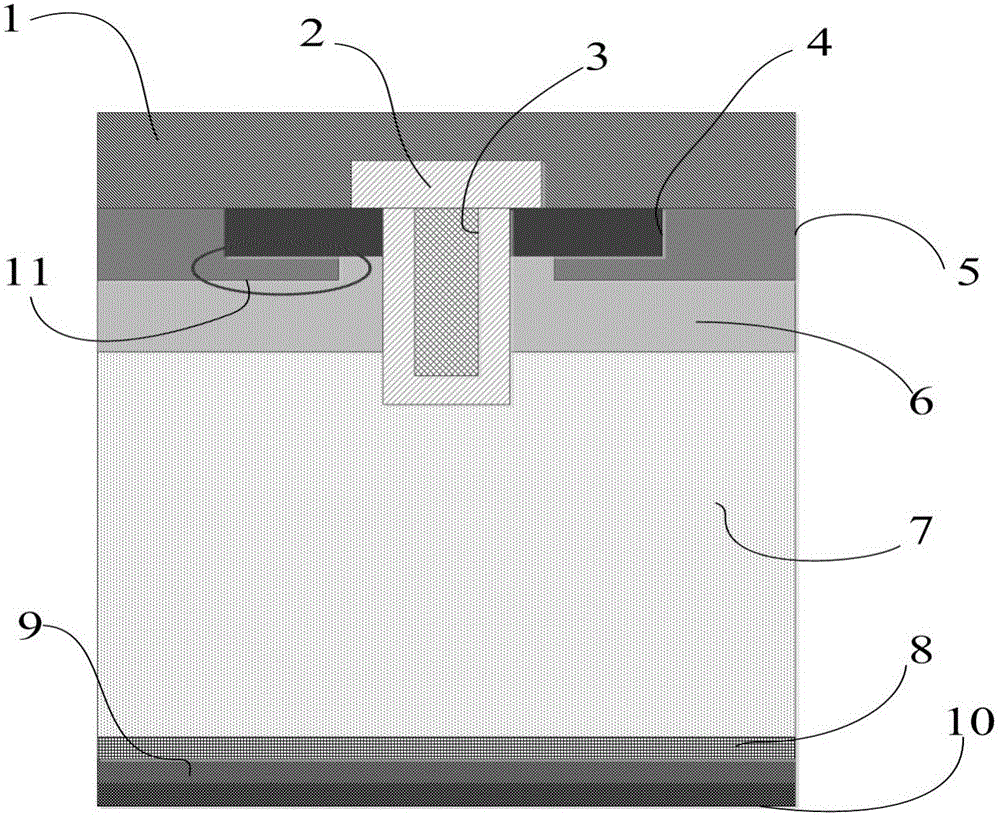

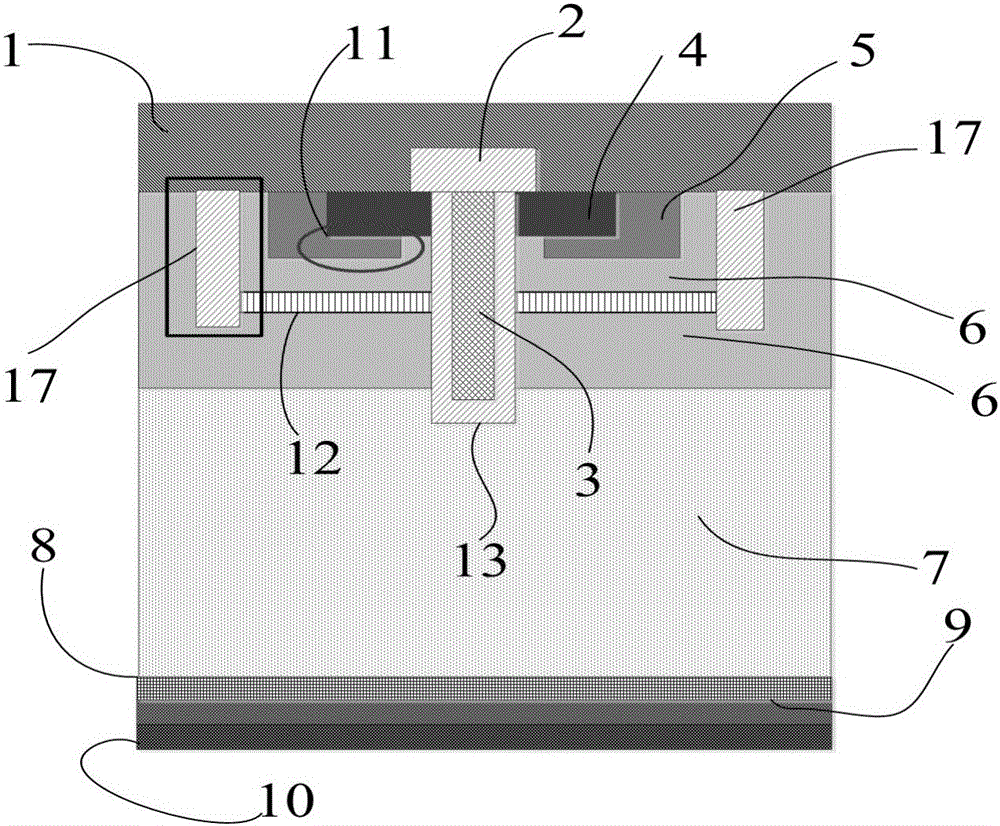

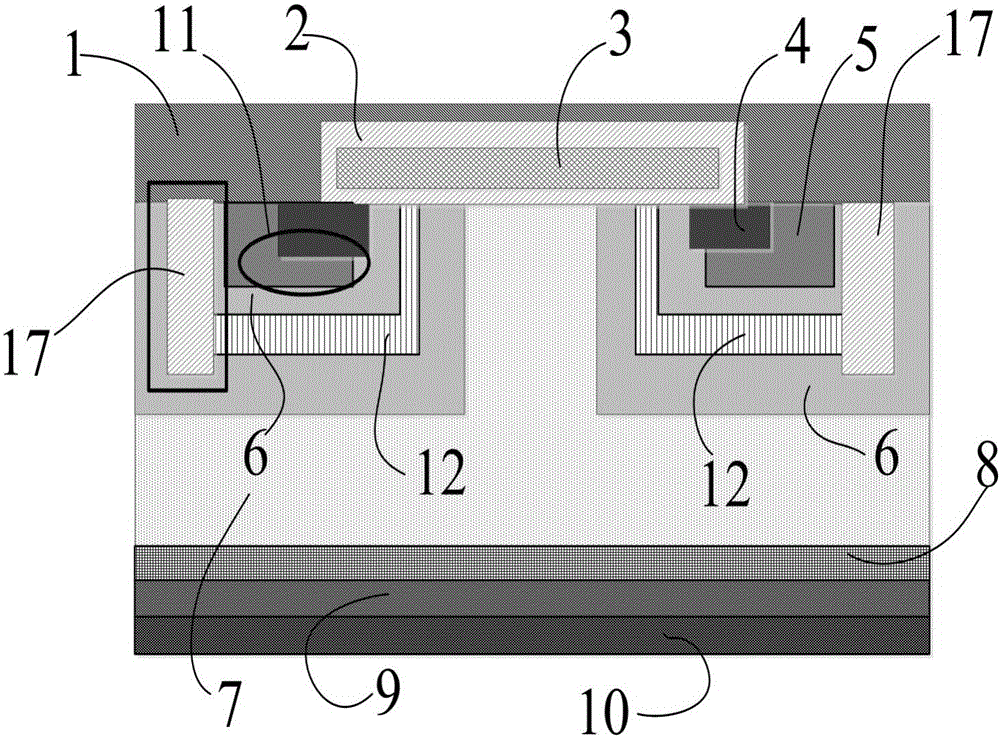

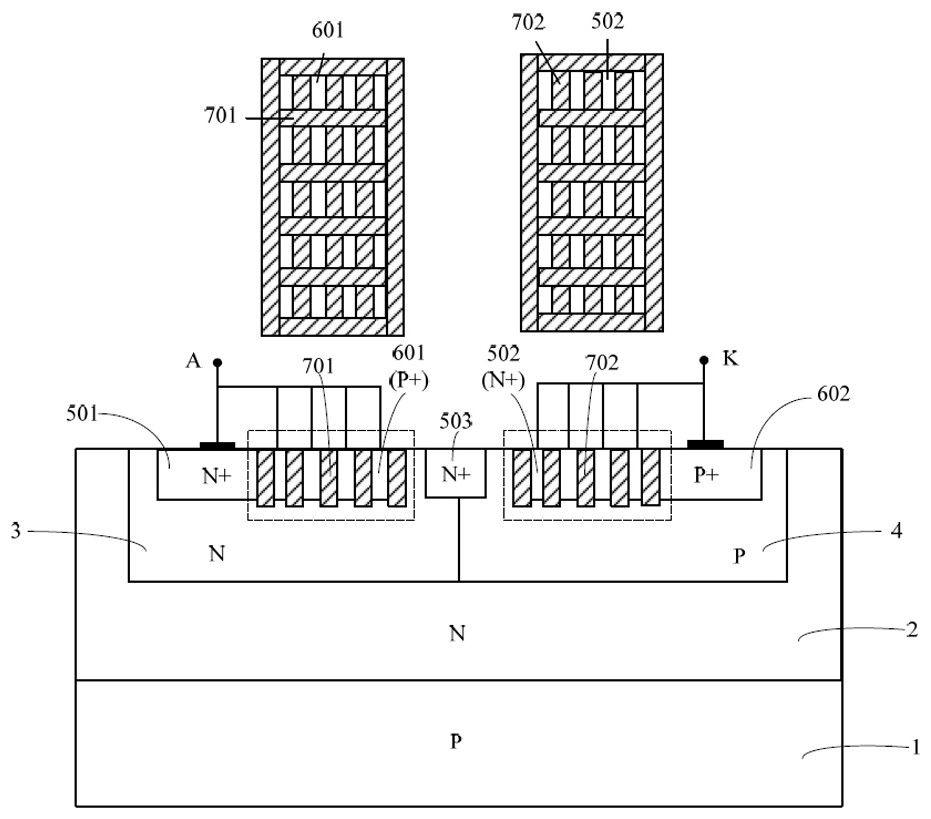

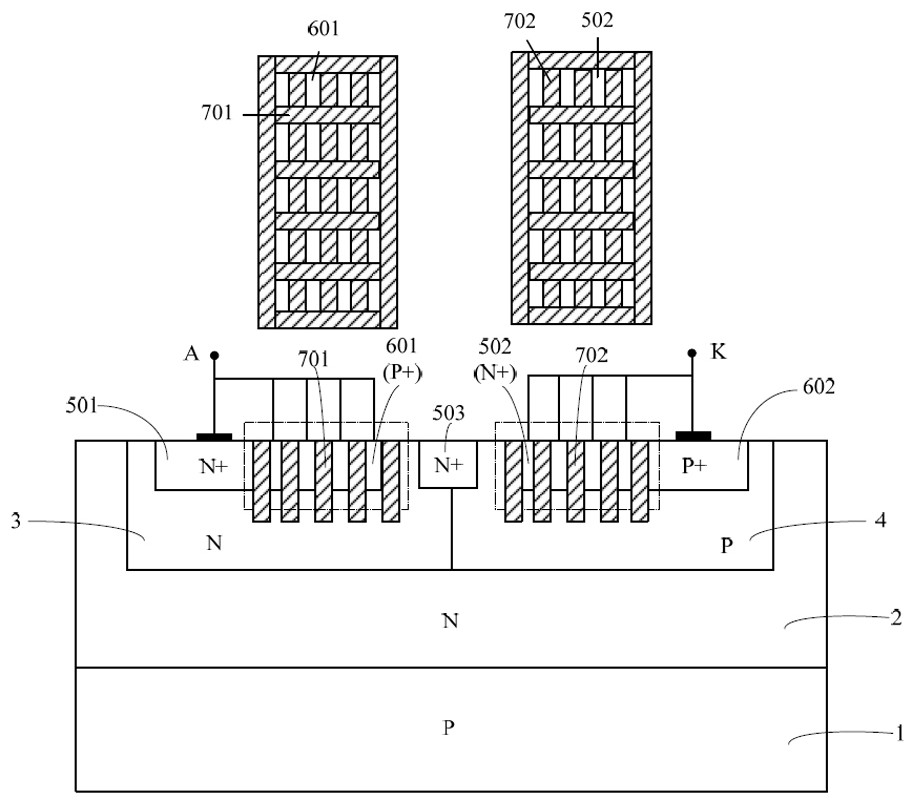

Transient voltage suppression protection device with latticed cathode and anode groove structures

ActiveCN113488464AIncreased current capabilitySustain voltage Vh risesTransistorSolid-state devicesChemical physicsCurrent distribution

The invention provides a transient voltage suppression protection device with a latticed cathode and anode groove structure. The device comprises a P-type substrate. An N-type epitaxy is grown on the P-type substrate; an N-type well region is manufactured on the left side of the upper part of the N-type epitaxy, and a P-type well region tangent to the N-type well region is manufactured on the right side of the upper part of the N-type epitaxy; a first N + region is manufactured on the inner left side below the surface of the N-type well region, and a first P + region tangent to the right side of the first N + region is manufactured on the right side; a second N + region is manufactured on the inner left side below the surface of the P-type well region, and a second P + region tangent to the right side of the second N + region is manufactured on the right side; a third N + region is manufactured at the junction of the N-type well region and the P-type well region and is used for forming a trigger region; a latticed first groove structure is arranged in the first P + region to divide the first P + region into a plurality of grids; and a latticed second groove structure is arranged in the second N + region to divide the second N + region into a plurality of grids. On one hand, the maintaining voltage Vh of the device can be improved to avoid latch-up, and on the other hand, the current distribution of the device is more uniform, and the current capability of the device is improved.

Owner:江苏应能微电子股份有限公司

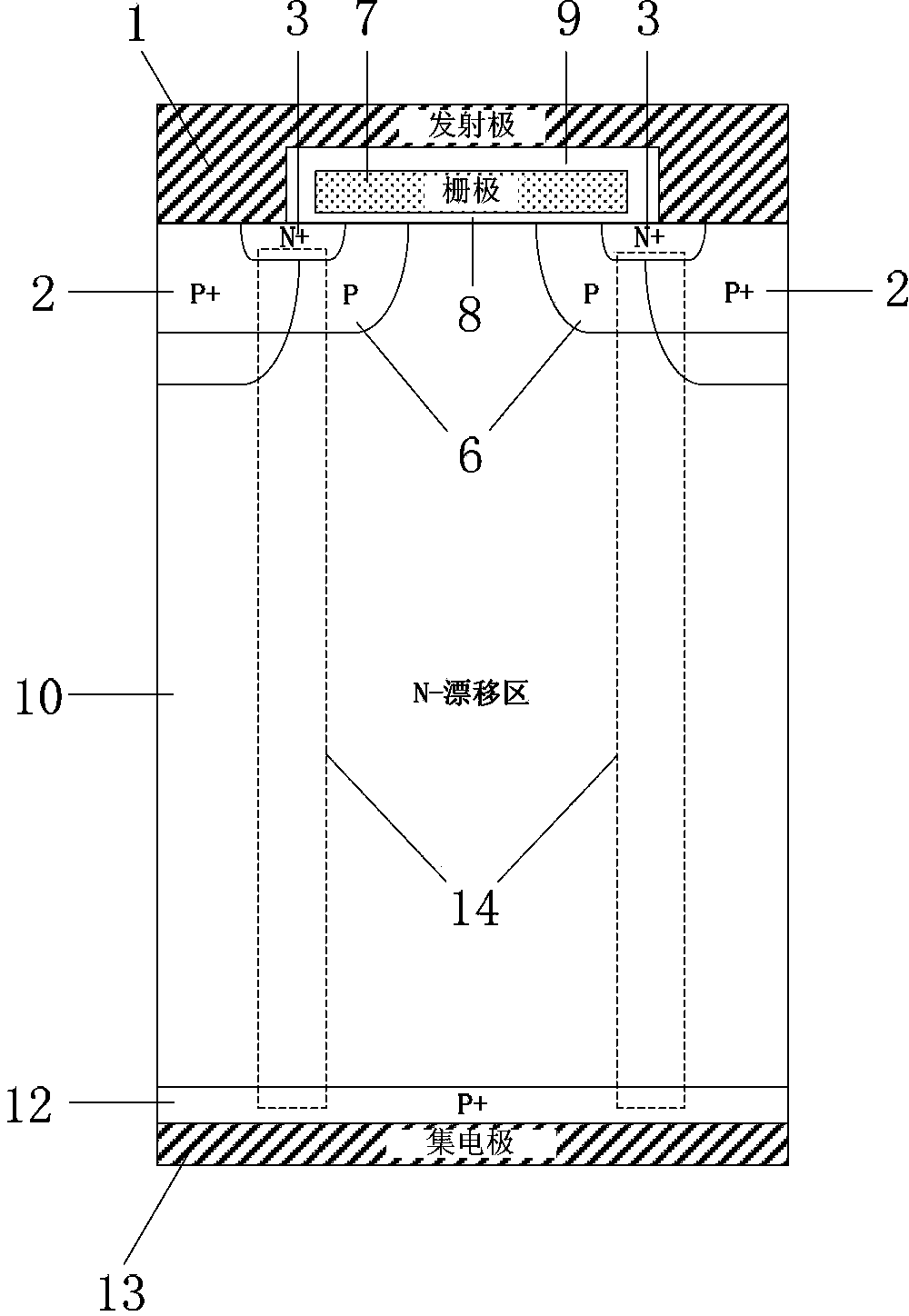

Latch-up prevention IGBT with mixed crystal emission area with variable components

InactiveCN103441143ADoes not affect normal operating characteristicsImproves latch-up resistanceSemiconductor devicesElectronic band structureDiffusion current

The invention discloses a latch-up prevention IGBT with a mixed crystal emission area with variable components and belongs to the technical field of power semiconductor devices. The latch-up prevention IGBT is based on a conventional IGBT structure, pure silicon materials in the emission area are changed into a mixed crystal with the variable components, and therefore a emission area energy band structure with an energy gap changed gradually is formed. The energy band structure forms an accelerating field of an emission area carrier in the emission area under the precondition that built-in potential of a PN junction formed by the emission area and a base area is not reduced, therefore, carrier diffusion current density in the emission area is increased, and injection on the emission area by the base area is enhanced; on the other hand, injection on the base area by the emission area remains unchanged. Therefore, injection efficiency of an emitter junction of a parasitic transistor formed by the emission area, the base area and a drifting area is reduced, current amplification factors are lowered, the parasitic transistor in the IGBT can not achieve the latch-up condition, consequently, critical latch-up current of the IGBT is improved, safe work areas of the IGBT are increased, and reliability of the IGBT is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

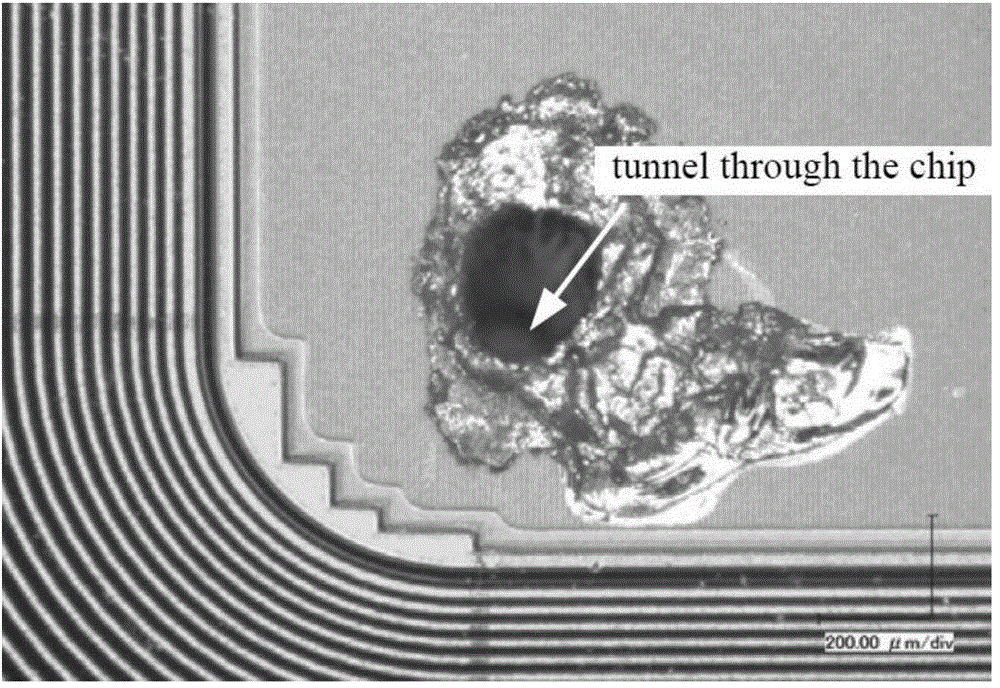

Manufacturing technology method for anti-latch-up groove type insulated gate bipolar transistor

InactiveCN104701169AGood latch-up resistanceGood consistency of anti-latch-up abilityTransistorSemiconductor/solid-state device manufacturingManufacturing technologyField-effect transistor

The invention discloses a manufacturing technology method for an anti-latch-up groove type insulated gate bipolar transistor. A side wall technology is used for the groove type insulated gate bipolar field effect transistor, polycrystalline silicon which remains on the top of a groove and is exposed out of a silicon surface serves as a step, an oxide layer is deposited and is carved by a dry method to form a side wall, a base resistance adjusting region injection window is manufactured, base resistance between a channel and a source electrode is reduced, a reverse safe working region is optimized to a great degree, and consistency of the base resistance between different cellular structures is improved. Moreover, a special photomask for adjusting the base resistance is saved, and the technology is simplified.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Semiconductor device

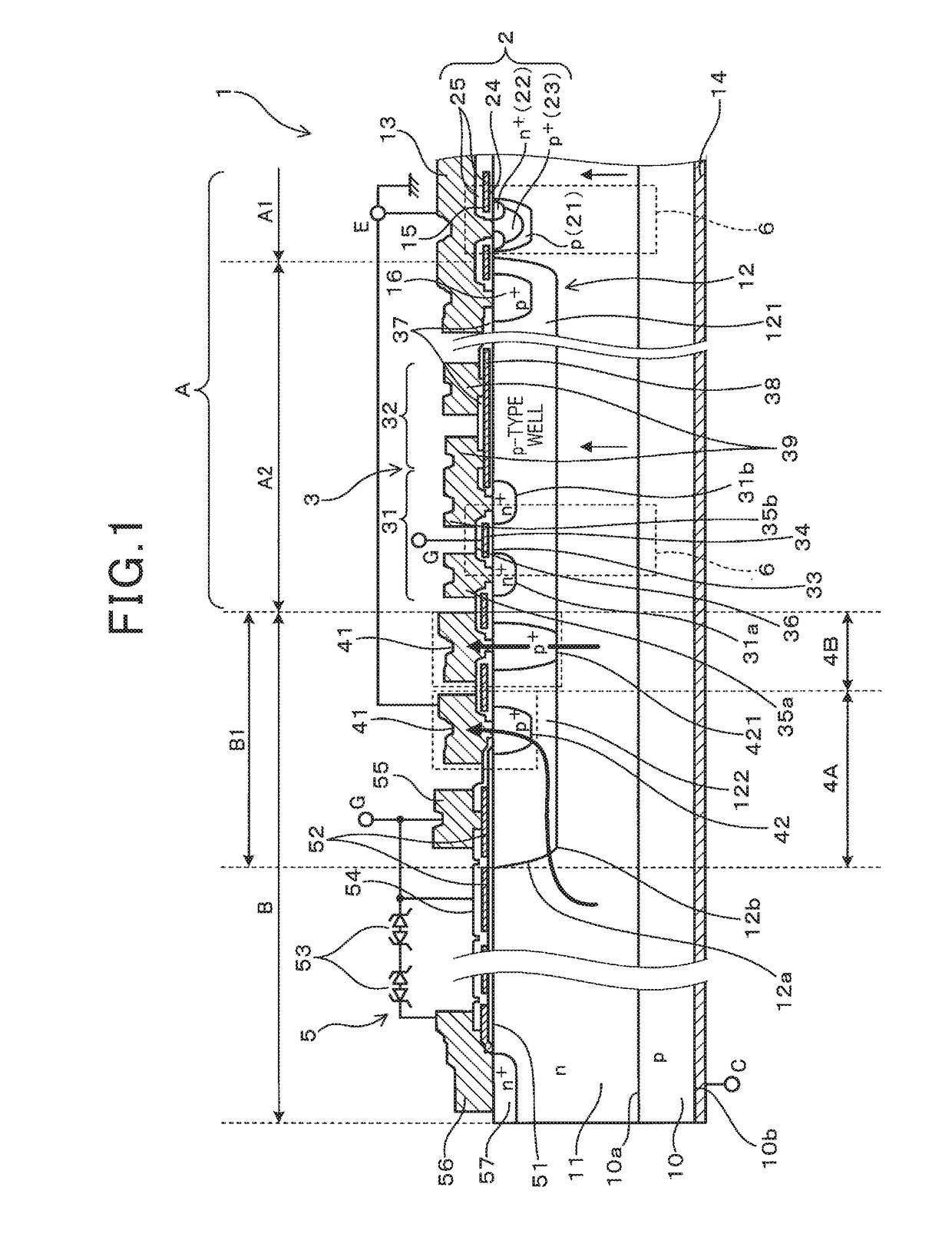

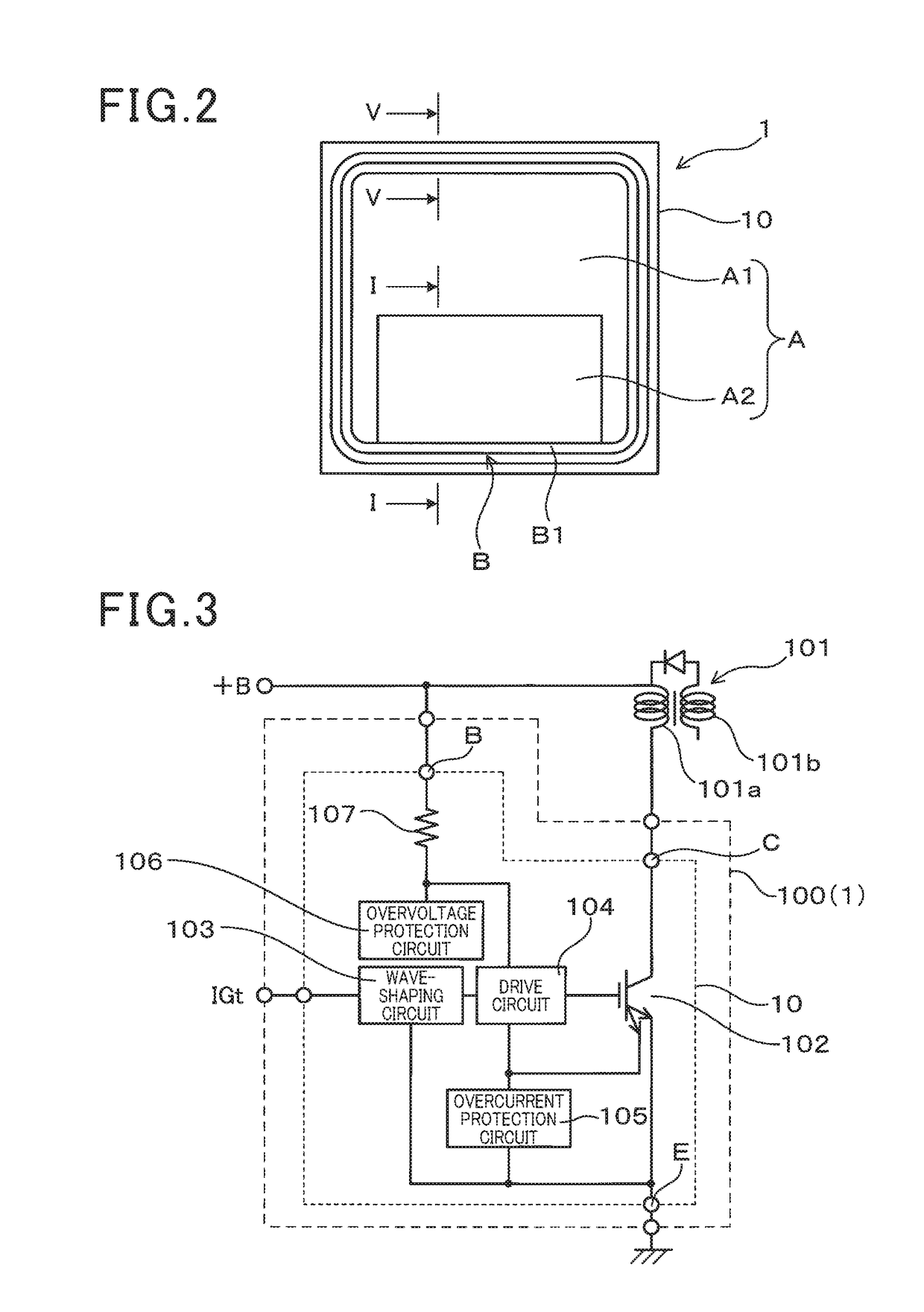

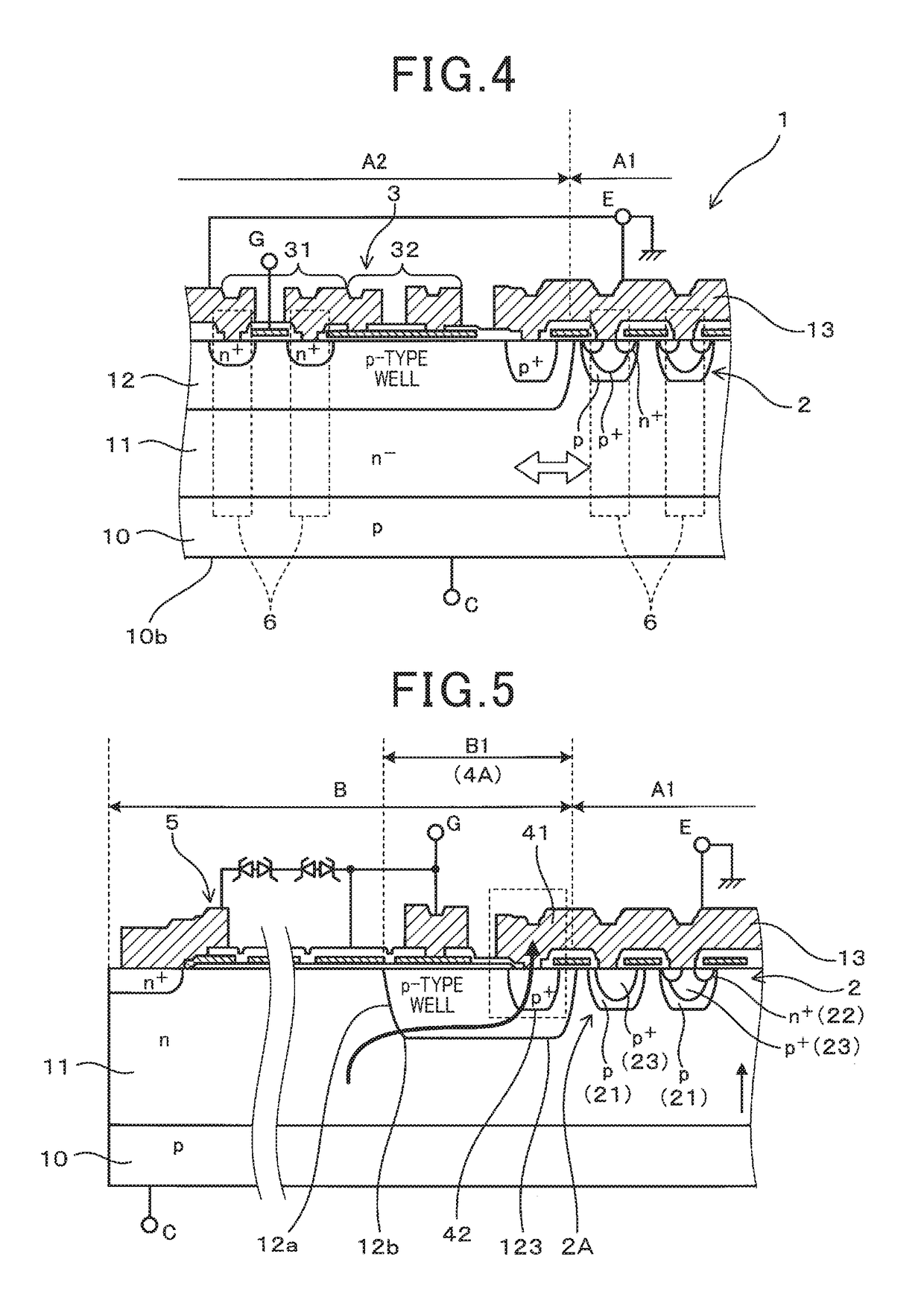

ActiveUS20190088736A1Small sizeSuppress surge currentTransistorSemiconductor/solid-state device manufacturingCell regionBoundary region

A semiconductor device includes a semiconductor substrate having a major surface and both an element-forming region and an outer peripheral voltage-withstanding region that are provided on the major surface side of the semiconductor substrate. The element-forming region includes both a cell region for forming a power element and a circuit element region for forming at least one circuit element. The circuit element region is interposed between the outer peripheral voltage-withstanding region and the cell region. The outer peripheral voltage-withstanding region includes a boundary region that adjoins the element-forming region. In the boundary region, there is provided one or more voltage-withstanding regions. At least one of the one or more voltage-withstanding regions has a withstand voltage lower than both the withstand voltages of the cell region and the circuit element region.

Owner:DENSO CORP

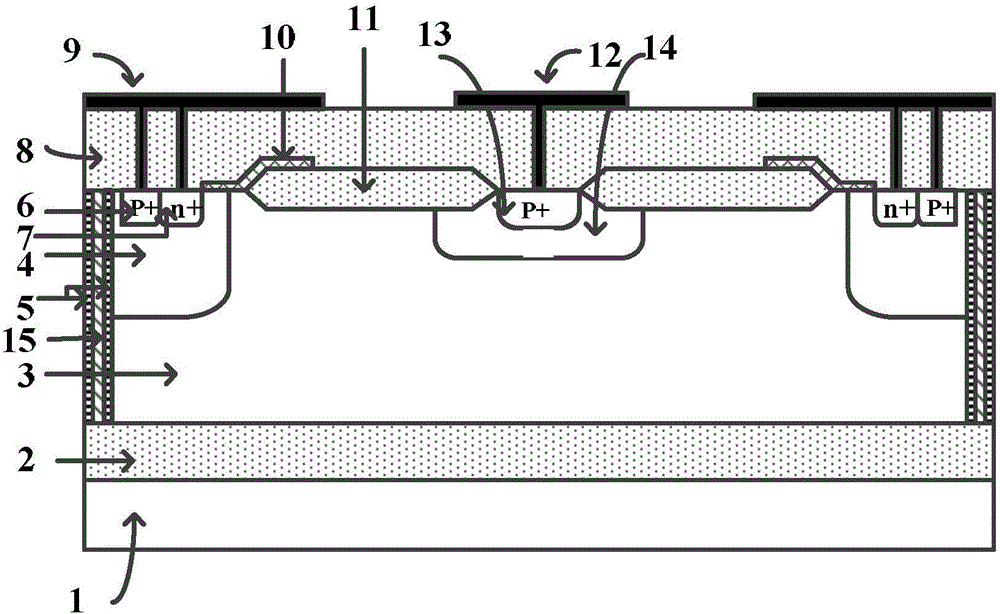

IGBT device and manufacturing method thereof

ActiveCN106711204AImproves latch-up resistanceReduce spacingSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceDielectric layer

The invention provides an IGBT device and a manufacturing method thereof. The IGBT device comprises a substrate, a first dielectric layer, a grid electrode, a second dielectric layer and an emitter electrode; the substrate comprises a body layer and well and source regions positioned in the surface of the body layer; the first dielectric layer is positioned in the front side of the substrate; the grid electrode is positioned in the surface of the first dielectric layer; the thickness of the first dielectric layer between the grid electrode and the body layer ranges from 1nm to 100nm; the second dielectric layer is positioned in the surface of the grid electrode; and the emitter electrode is positioned in the front side of the second dielectric layer and the substrate. Due to the thickness of the first dielectric layer between the grid electrode and the body layer is limited in the range from 1nm to 100nm, the distance of Miller capacitance between the grid electrode and a collector electrode at the back side of the substrate is reduced, the Miller capacitance is increased, the voltage change rate born by the IGBT in the ON / OFF process is reduced, and the anti-latch-up capability of the IGBT device is improved.

Owner:JIANGSU CAS IGBT TECHNOLOGY CO LTD

Semiconductor power device

ActiveCN102760752AImproves latch-up resistanceSemiconductor devicesElectrical conductorSemiconductor

The invention relates to a power device, in particular to a semiconductor power device. The semiconductor power device comprises a first conducting type first semiconductor layer, a second conducting type well region arranged in the first semiconductor layer, a first conducting type source region arranged in the second conducting type well region, a first insulating layer which is arranged on the first semiconductor layer and covers the well region and the source region, a polysilicon layer positioned on the first insulating layer, a second insulating layer which is arranged on the polysilicon layer and covers the source region and the drain region, a first metal layer which covers the second insulating layer and is connected with the well region and the source region, a second conducting type second semiconductor layer positioned on the back surface of the first semiconductor layer and a second metal layer connected with the second semiconductor layer, wherein the forbidden band width of the well region is larger than the forbidden band width of the source region. The semiconductor disclosed by the invention has the advantages of improving the anti-latching capability of the semiconductor power device and increasing the breakover power consumption of the semiconductor power device.

Owner:BYD SEMICON CO LTD

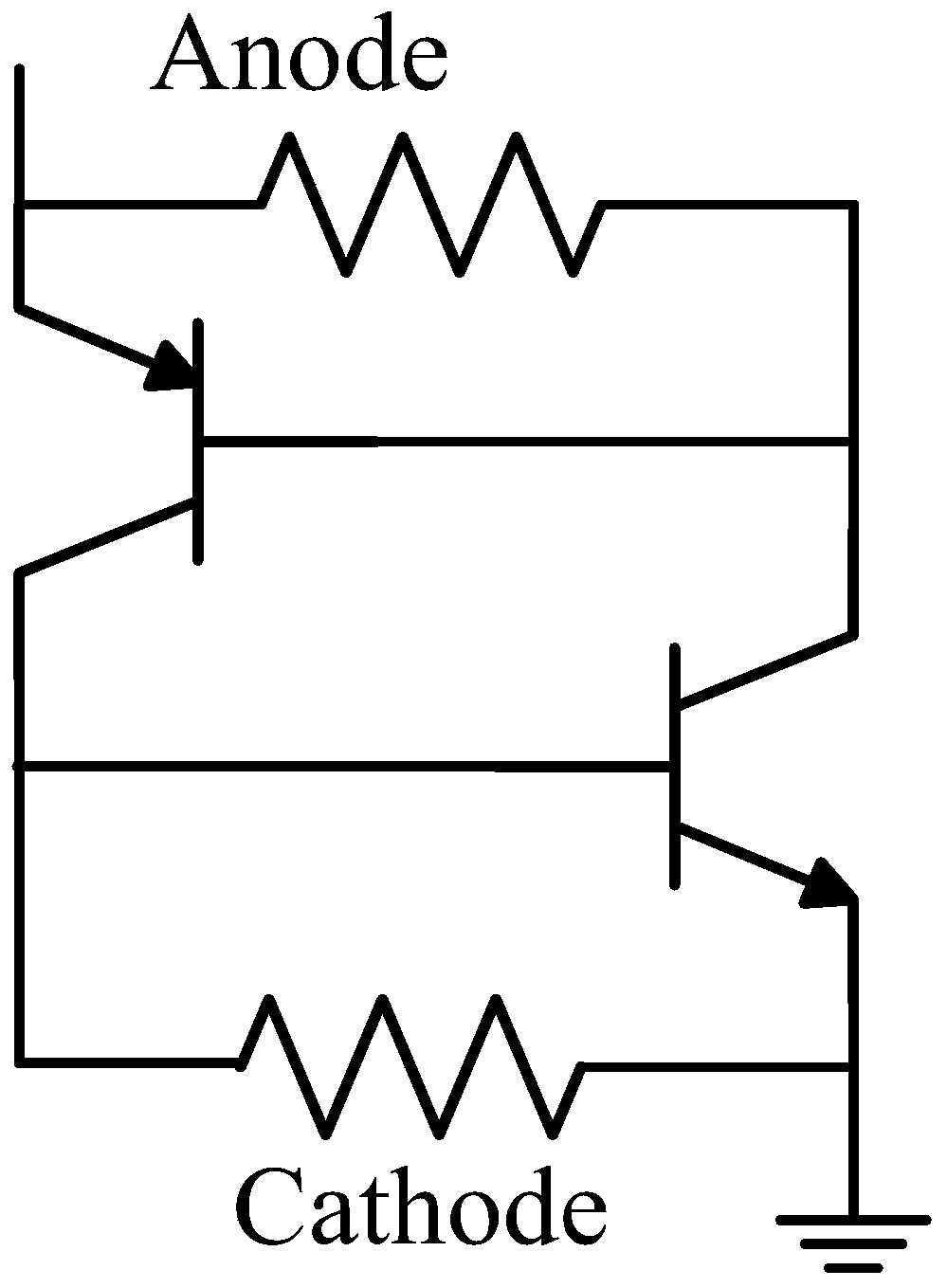

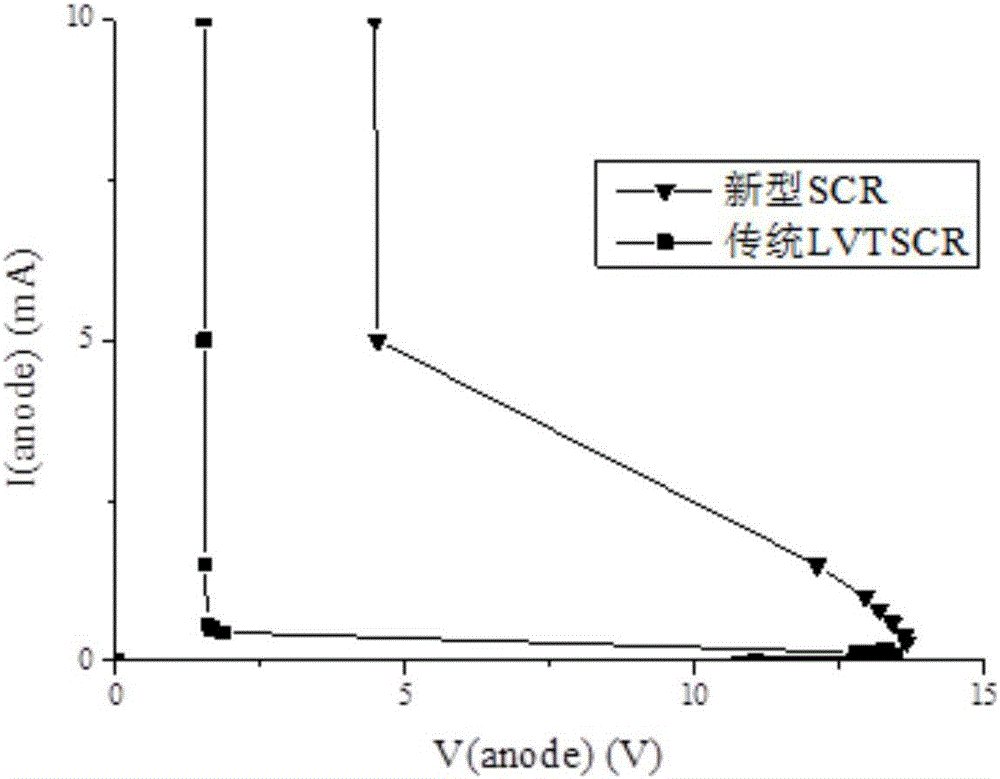

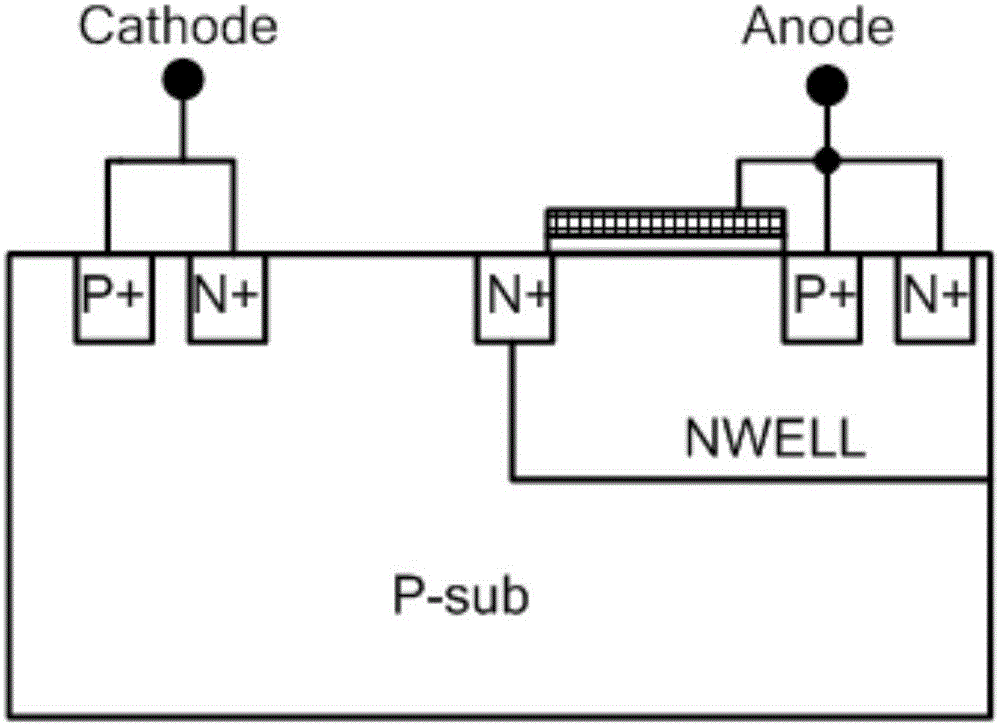

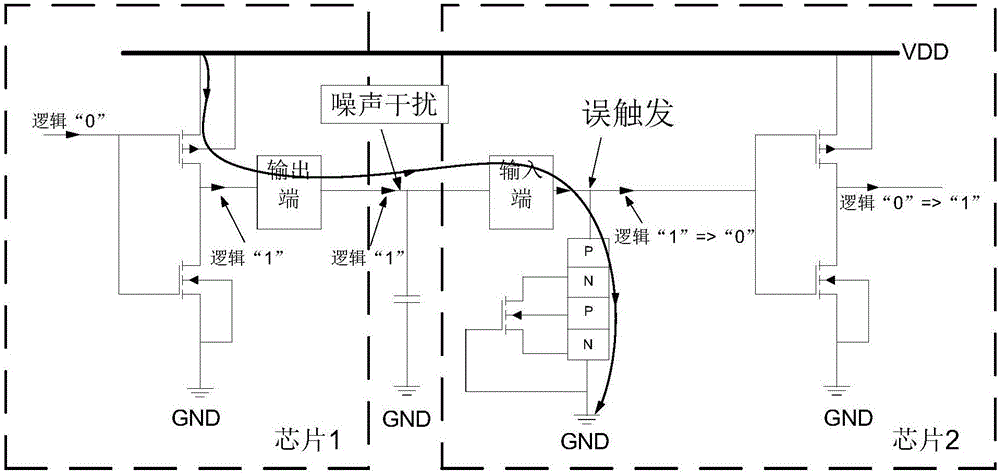

SCR (Semiconductor Control Rectifier) with high maintaining voltage for ESD (Electro-Static Discharge) protection

ActiveCN106449604AImproves latch-up resistanceGuaranteed normal potentialSemiconductor/solid-state device detailsSolid-state devicesPositive feedbackLow stress

The invention belongs to the technical field of electronic science and technology, is mainly used for a static discharge protection technology and specifically relates to an SCR (Semiconductor Control Rectifier) with a high maintaining voltage for ESD (Electro-Static Discharge) protection. An SCR device provided by the invention is used for ESD protection of a low voltage 5V technology, an additional NPN transistor is utilized to weaken a positive feedback process in the SCR structure, and then the current positive feedback of the SCR has a weakening trend, so that the SCR can maintain voltage boosting and can increase the anti-latch capacity of the device. Besides, even if the noise interference is generated by a chip and the SCR is mistakenly started by the noise voltage, the structure still can ensure the normal potential and normal transmission of the signal.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

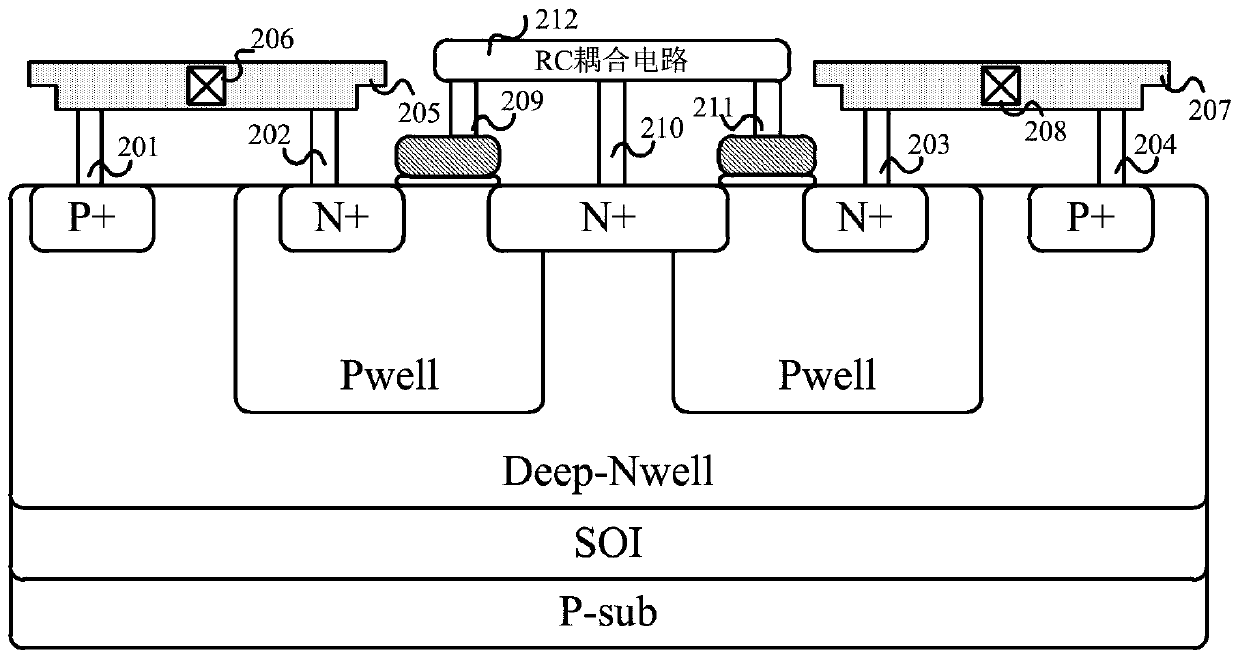

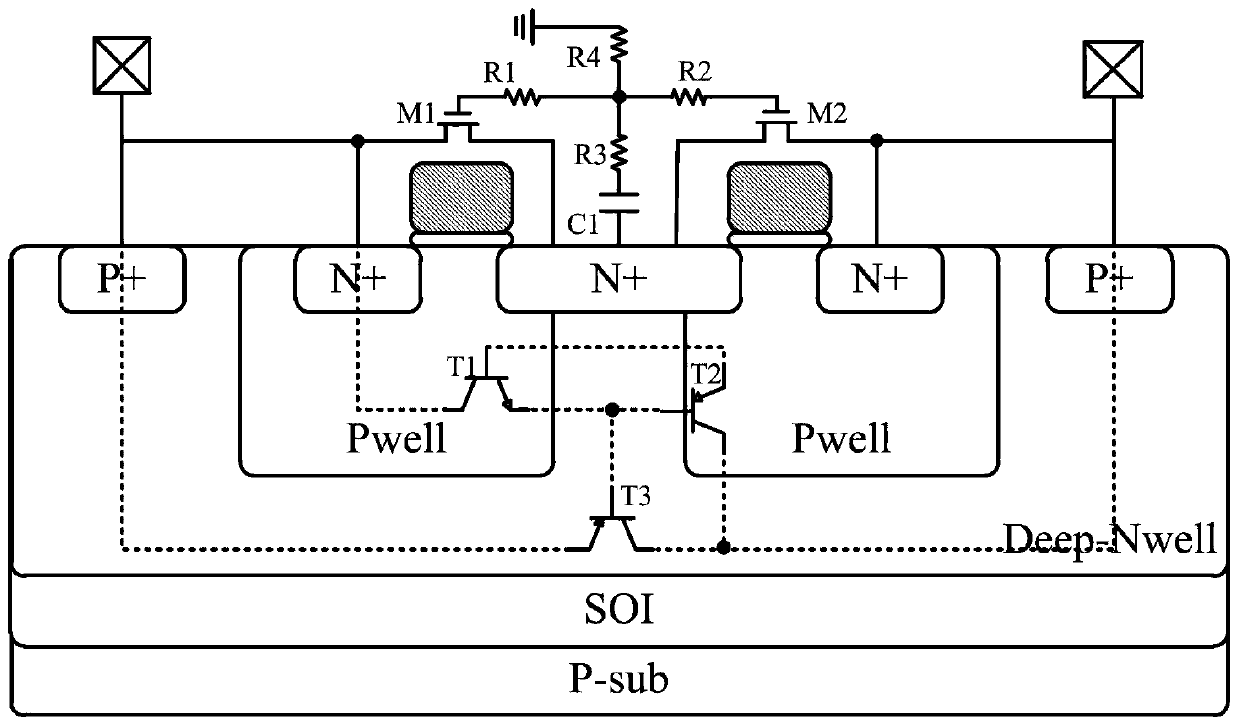

RC coupling triggering bidirectional transient voltage suppressor based on SOI process

ActiveCN110047828AAdd release pathReduce voltage hysteresisTransistorSolid-state devicesTransient voltage suppressorRadiation resistance

The invention discloses an RC coupling triggering bidirectional transient voltage suppressor based on an SOI process, belonging to the technical field of integrated circuits. According to the invention, a trigger voltage is reduced by fully utilizing the principle that a RC coupling circuit and a high-doping injection region have low reverse breakdown voltage, and the advantage of strong ESD robustness of a SCR structure is combined, so that the positive feedback of the SCR is weakened, a maintaining voltage is improved, and the ESD robustness is enhanced by introducing a transverse PNP type BJT. By utilizing the advantages of small parasitic parameters, low power consumption, radiation resistance and the like of the SOI layer, the performance of the device is further improved. In addition, the full symmetry is realized by designing the structure of the device, and the device can form an SCR current discharge path with the same electrical characteristics under the action of the positive and reverse ESD stress, so that the chip area of the ESD device can be reduced, and the bidirectional protection of the ESD pulse can be realized.

Owner:58TH RES INST OF CETC

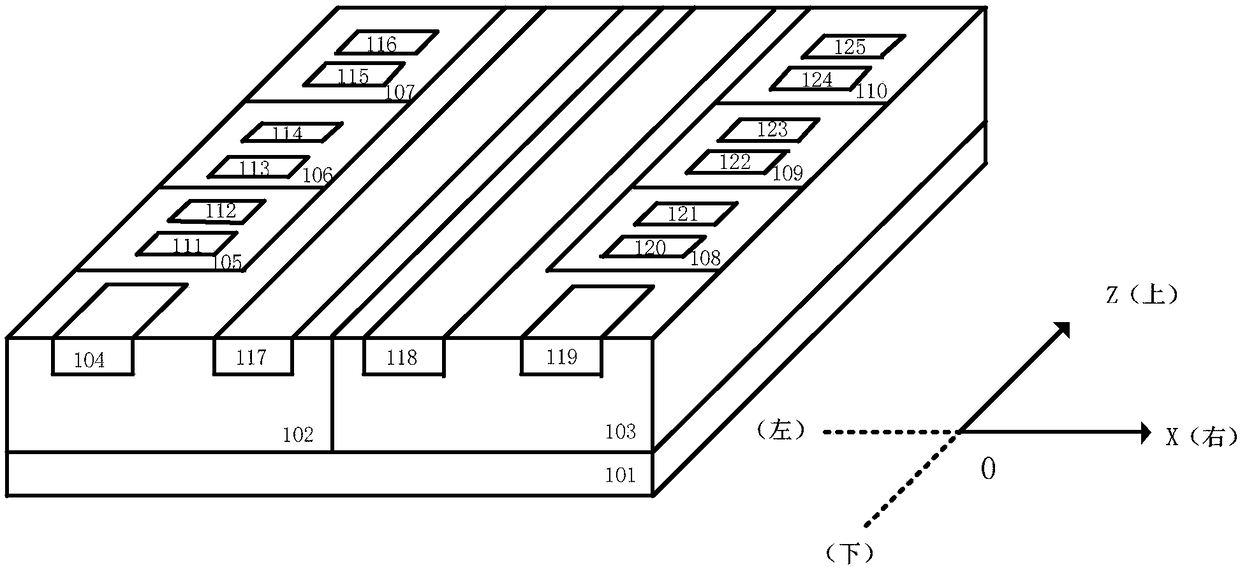

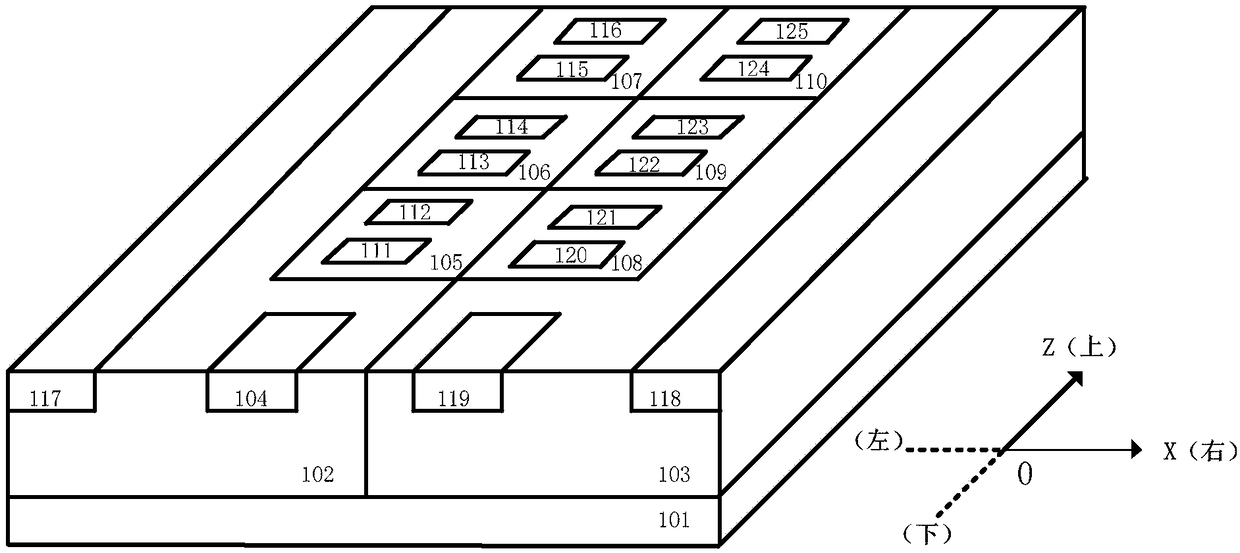

Insulated gate bipolar transistor

The invention discloses an insulated gate bipolar transistor comprising a substrate, gate structures, emitters and a collector. The gate structures, the emitters and the collector are arranged at the substrate; and the collector and the emitters are arranged at the two ends of the substrate. Each gate structure consists of a narrow part, a first widening part, and a second widening part; the narrow part is arranged between two emitters; the second widening part is arranged at one side, approaching the collector, of the gate structure; and the first widening part is connected between the narrow part and the second widening part. The first widening part is wider than the narrow part and thus areas that are connected with the emitter and are arranged in first directions of the emitters are filled, thereby suppressing starting of parasitic transistors at the edges of the emitters; and the second widening part is wider than the first widening part. Therefore, a technical problem of weak anti-latching capability of the existing PNM-IGBT device in the prior art can be solved; and thus a technical effect that the anti-latching capability is improved obviously while the parameter performance of the device is guaranteed is realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Trench type insulated gate bipolar transistor and preparation method thereof

ActiveCN110504314AImprove the conduction voltage dropIncrease lossSemiconductor/solid-state device manufacturingSemiconductor devicesElectron flowParasitic bipolar transistor

The invention relates to a trench type insulated gate bipolar transistor and a preparation method thereof, belonging to the technical field of power semiconductors. A first conductive trench MOSFET isintroduced in a second conductive floating zone of a trench type insulated gate bipolar transistor, a gate electrode of the MOSFET is in short circuit with current conversion metal, so that when thedevice is conducted forwardly, the MOSFET turns off due to low electric potential of the floating zone, electronic current converted by the conversion metal cannot flow out of a leakage electrode through MOSFET, so as not to increase voltage drop of forward conducting; when the device is turned off, MOSFET surface trench electron inverses so as to form an electron flow path due to very high electric potential of the floating zone, so that electron current converted from hole current by the conversion metal can flow out of the leakage electrode through MOSFET, surplus carriers are extracted atfaster speed, off time is shortened and off loss is reduced, and forward conducting and off loss are further balanced. The invention further relates to a preparation method for the trench type insulated gate bipolar transistor.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com