An interface circuit capable of tolerating high voltage input

An interface circuit and high-voltage technology, applied in the field of interface circuits, can solve problems such as occupying chip area and complicated circuit control, and achieve the effects of solving leakage problems, speeding up transformation, and improving anti-noise and anti-latch-up capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

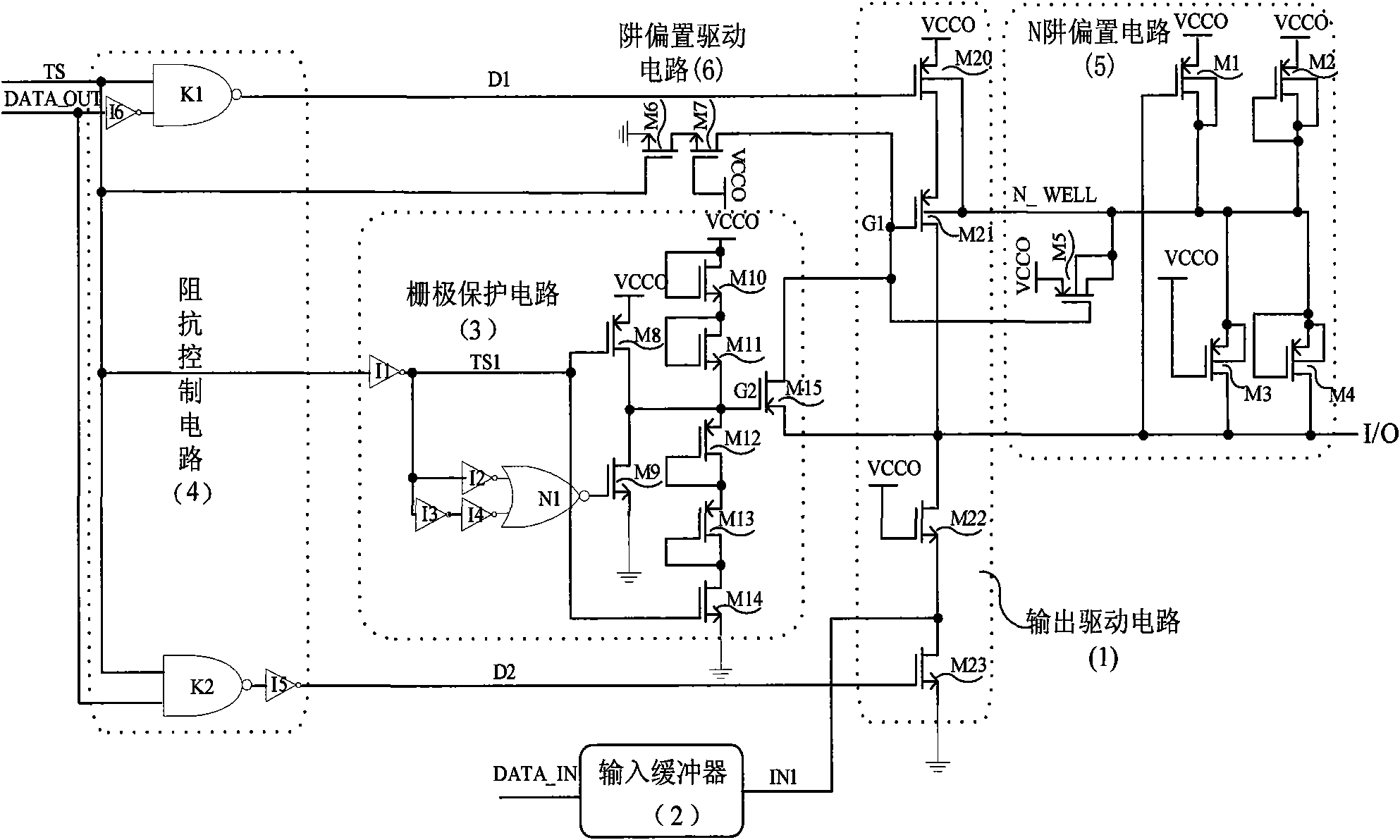

[0021] Such as figure 1 As shown, it is a functional block diagram of an interface circuit that can withstand high voltage input in the present invention, including an output drive circuit 1, an input buffer 2, a gate protection circuit 3, an impedance control circuit 4, an N well bias circuit 5 and a well bias circuit Set the drive circuit 6. Under the control of the mode control signal TS, the interface circuit can be in the transmission mode (that is, the I / O pin is used as an output pin), or in the reception mode (that is, the I / O pin is used as an input pin). When the circuit is in transfer mode, the DATA_OUT signal is the data output signal. When the circuit is in the receiving mode, the DATA_IN signal receives external signals and inputs them into the interface circuit.

[0022]If the mode control signal TS sets the interface circuit to the transmission mode, the impedance control circuit 4 receives the data output signal DATA_OUT generated by the configurable logic m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com