Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

575results about How to "Reduce parasitic resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

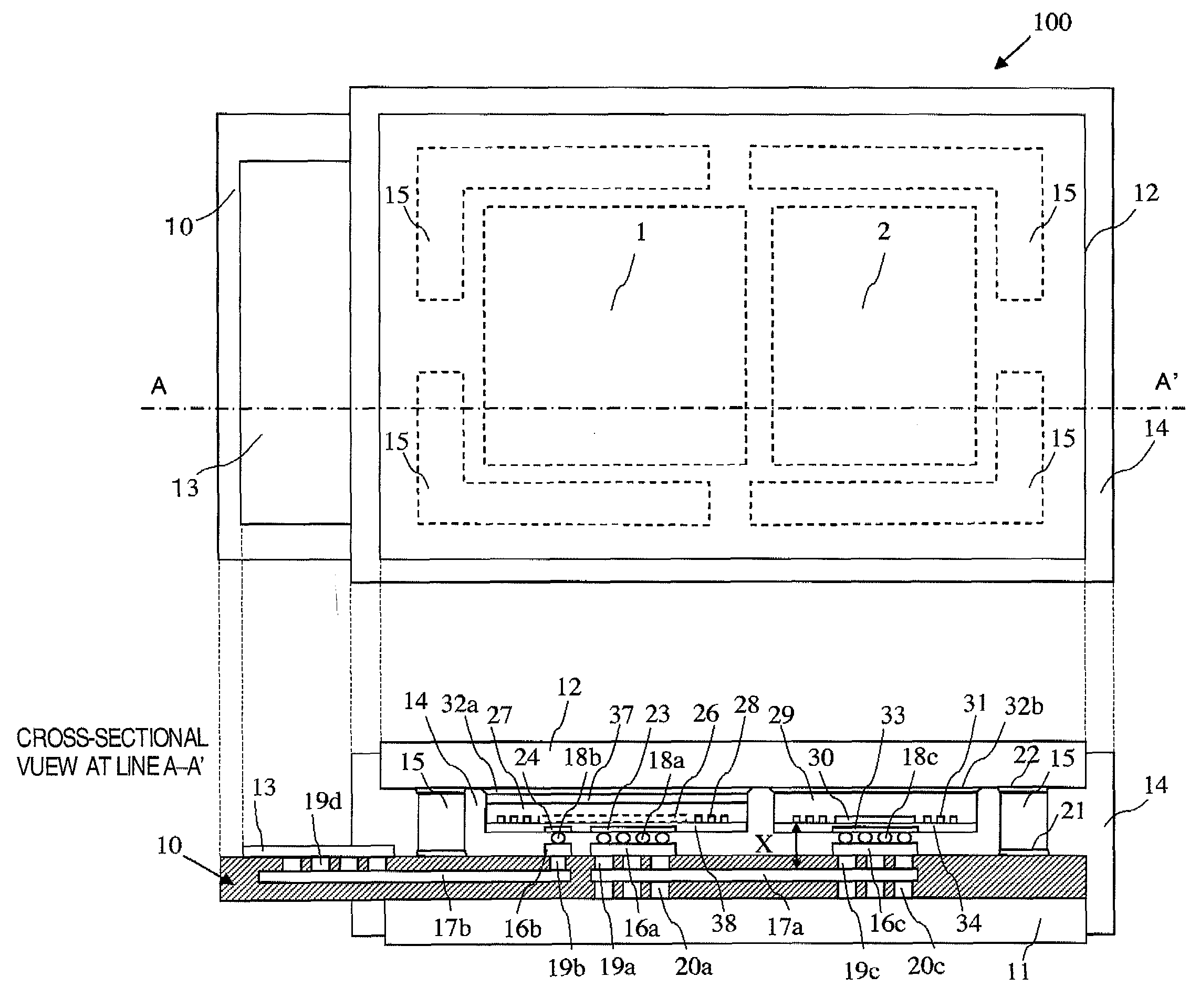

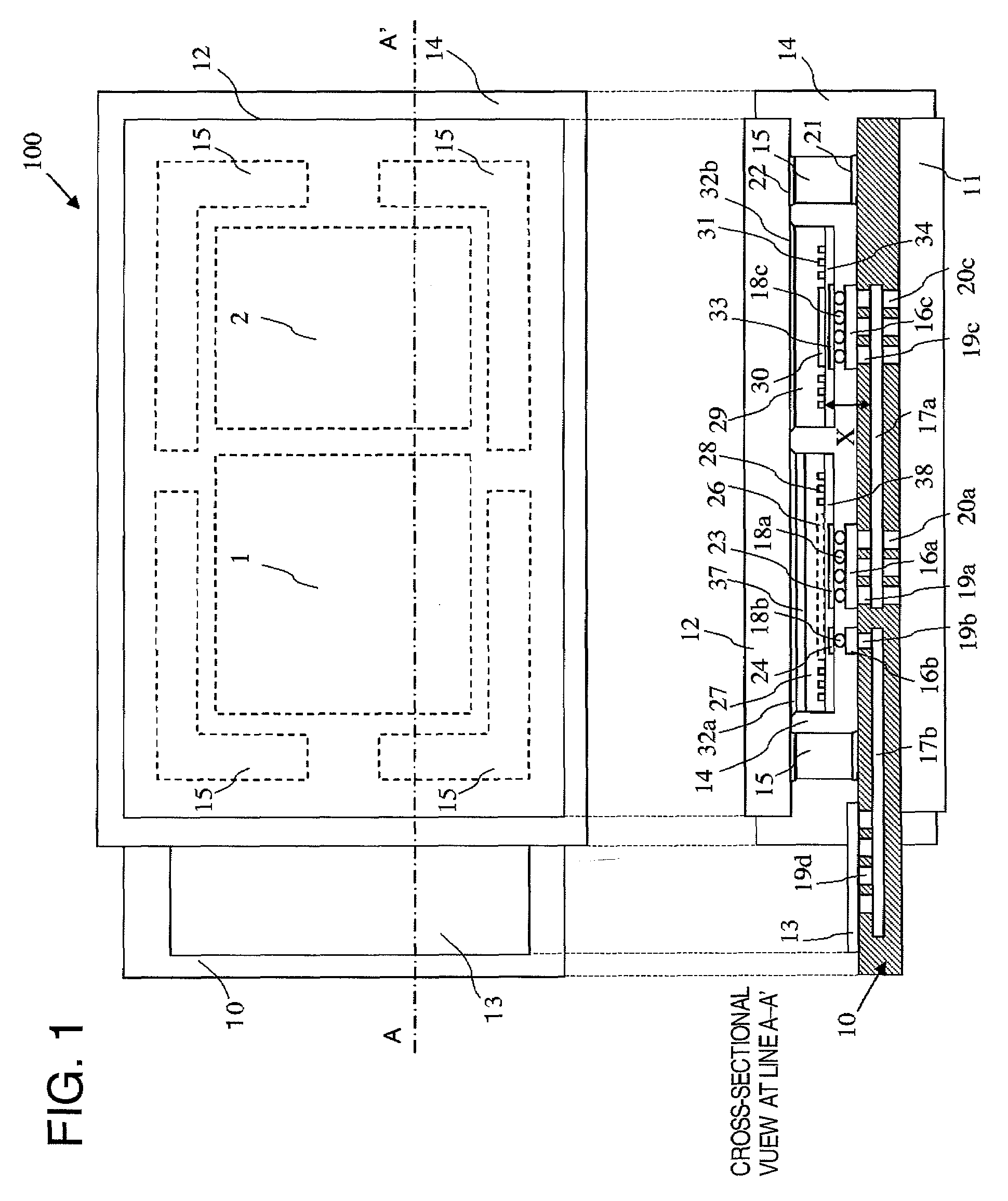

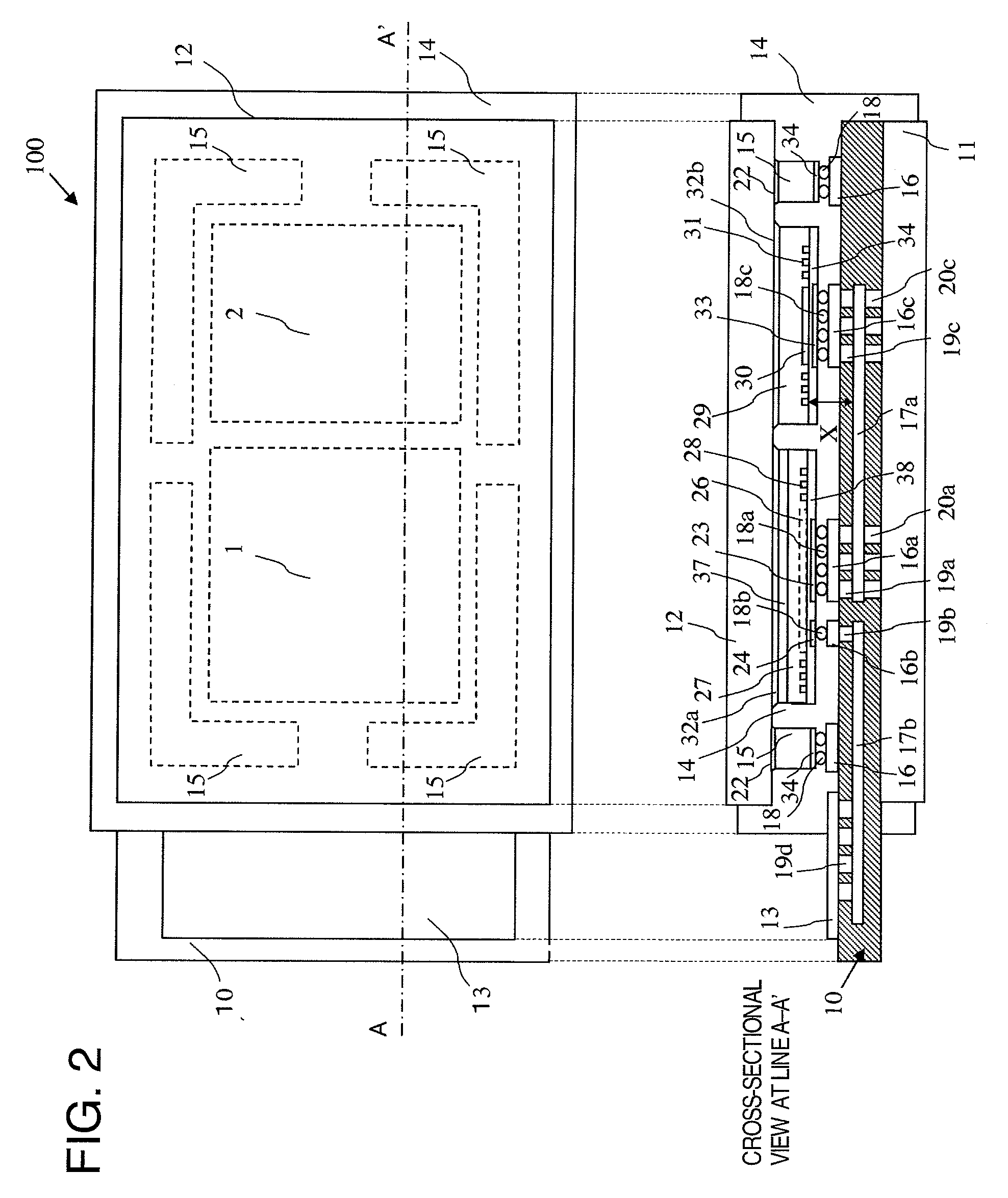

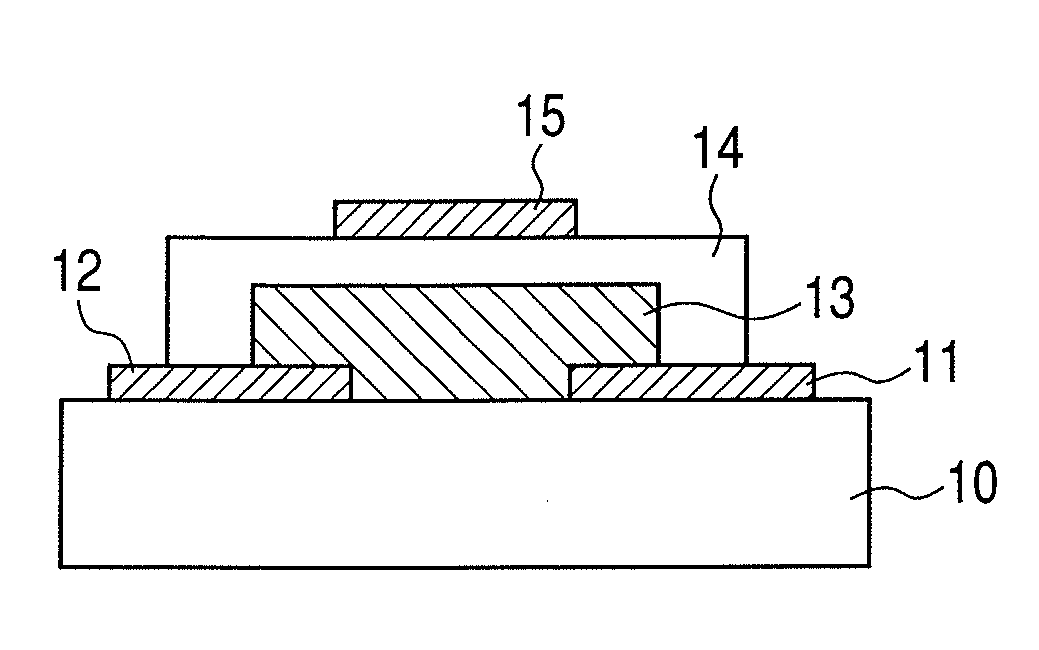

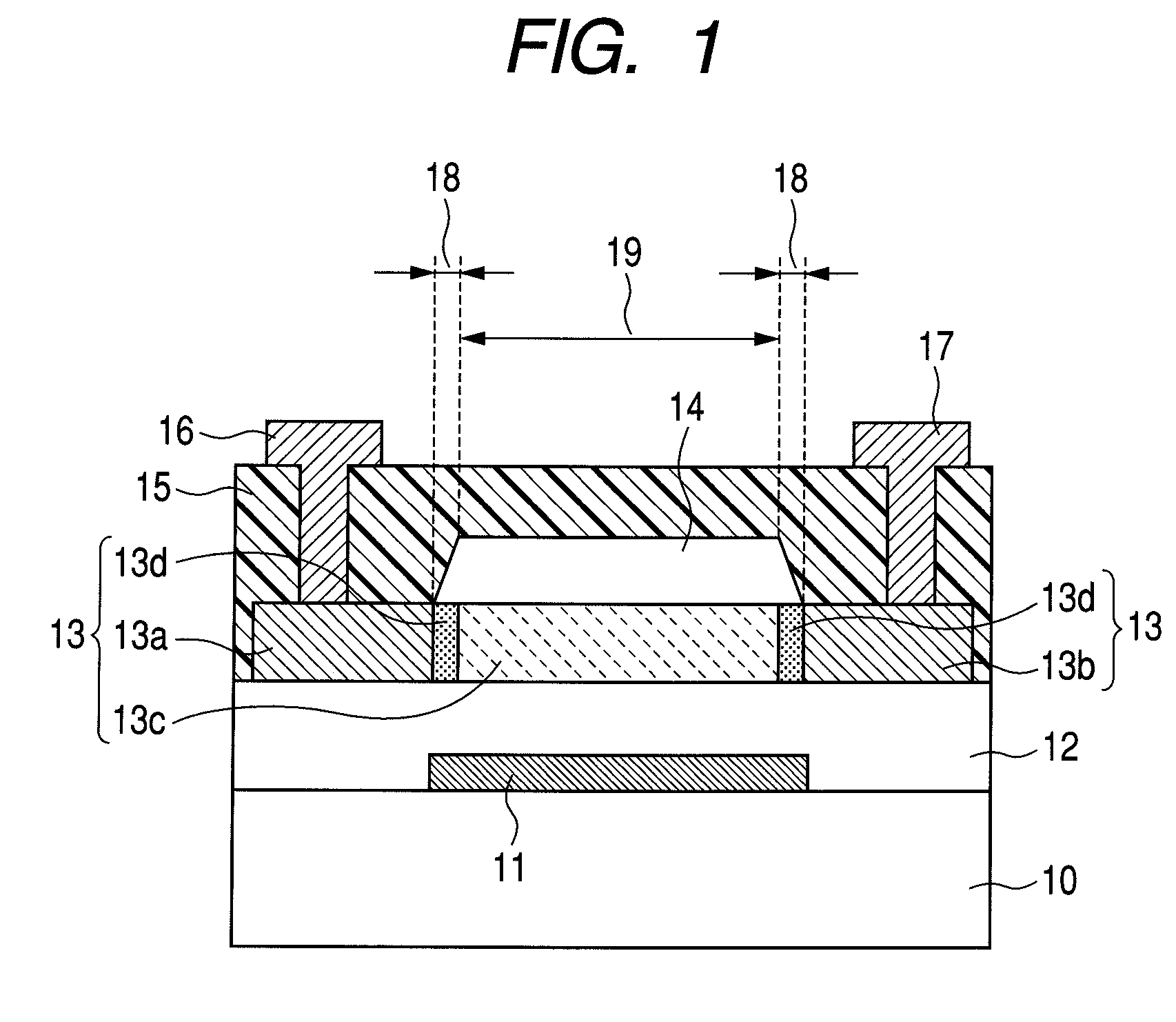

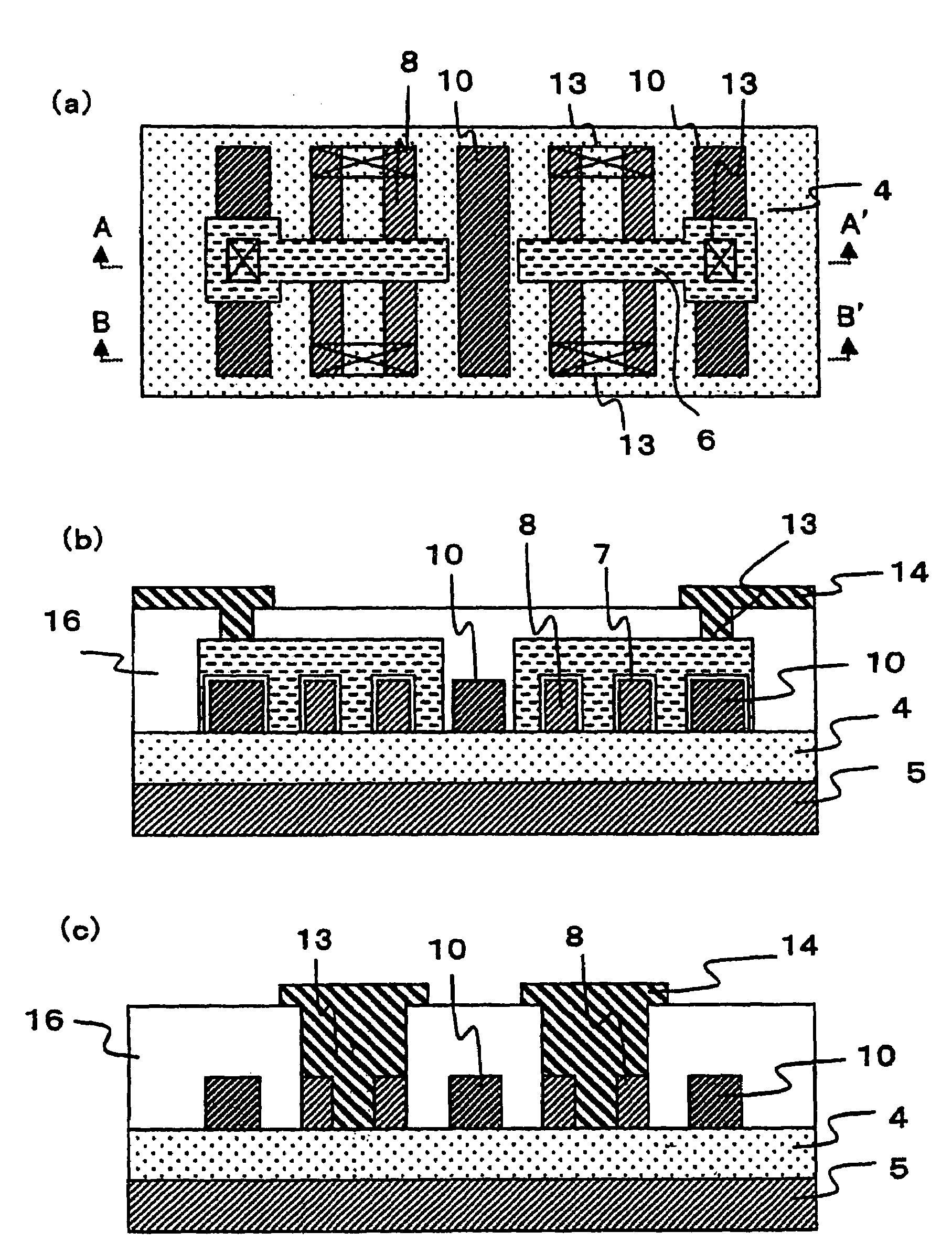

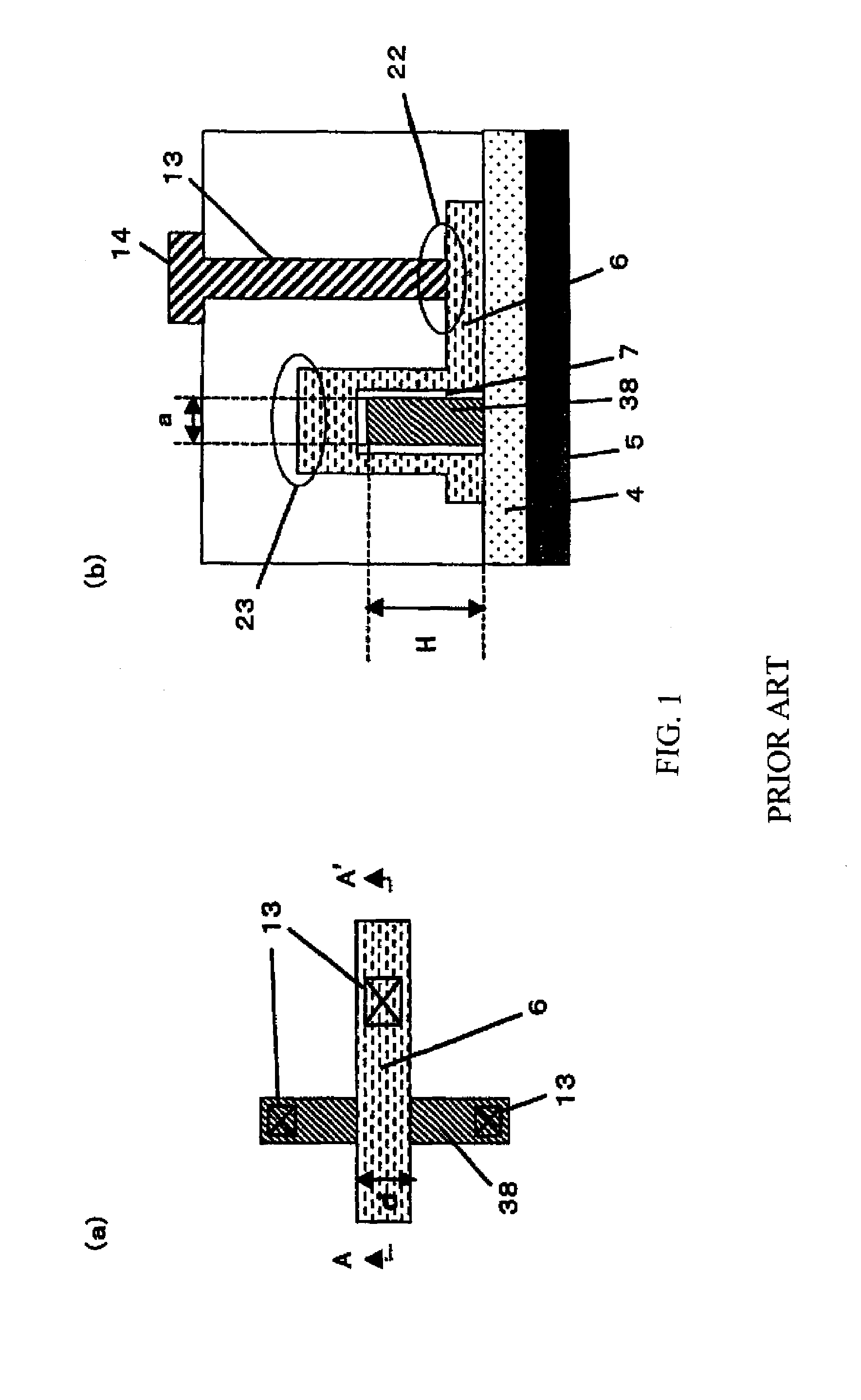

Power semiconductor device

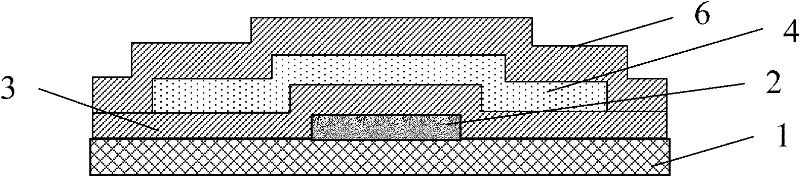

ActiveUS20070215903A1High blocking voltageLow thermal resistanceSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceEngineering

A power semiconductor device, having a first semiconductor region, and a second semiconductor region; mounted with a first electrode pad on a semiconductor substrate main surface at the inside surrounded by the third semiconductor region, mounted in the second semiconductor region, and a multilayer substrate having first and second wiring layers, to take out an electrode of the semiconductor chip; joining the first wiring layer part for the first electrode, mounted on the multilayer substrate, in a region opposing to the semiconductor substrate main surface at the inside surrounded by the third semiconductor region, and the first electrode pad, by a conductive material; joining the first wiring layer part for the first electrode, and the second wiring layer at a conductive part; and extending the second wiring layer to the outside of a region opposing the semiconductor substrate main surface at the inside surrounded by the third semiconductor region.

Owner:HITACHI LTD

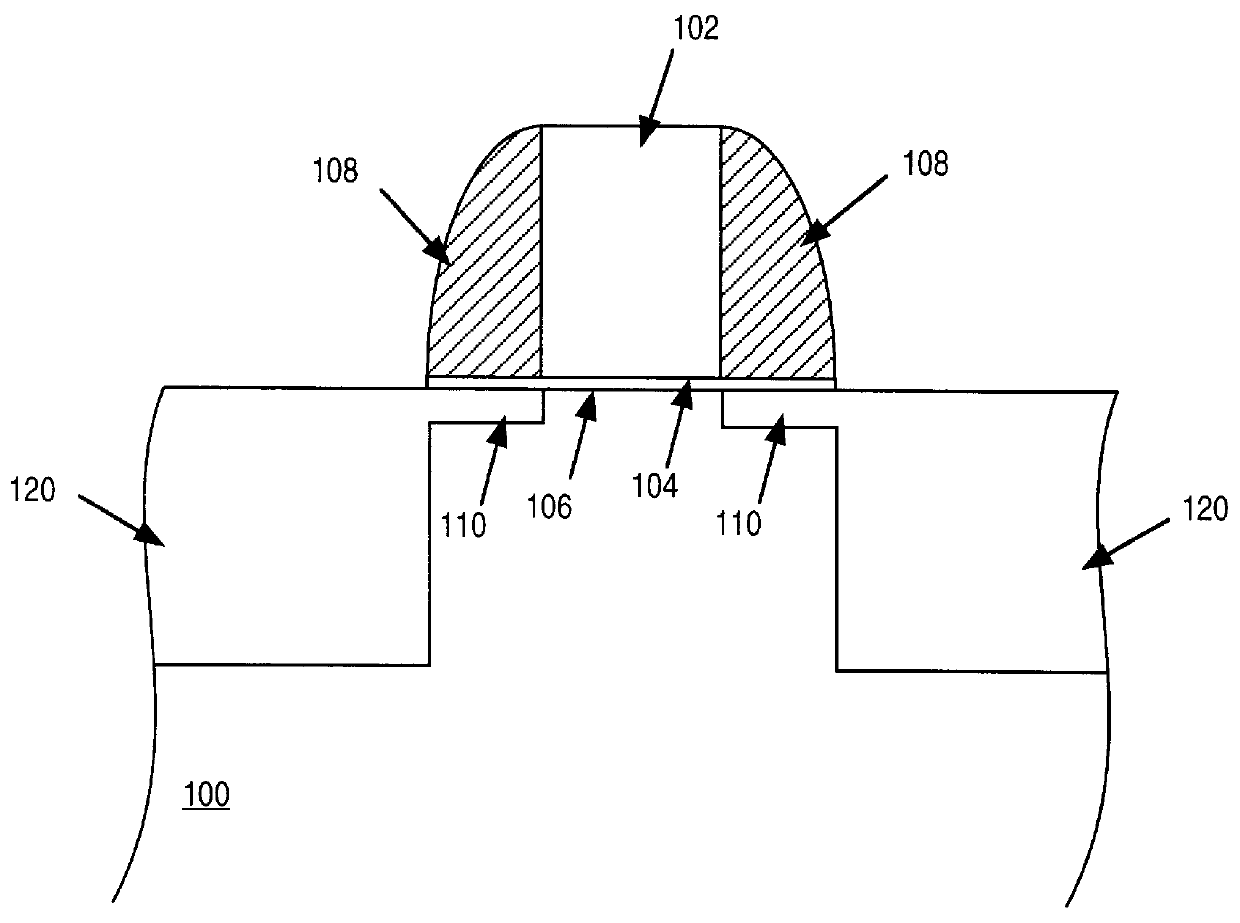

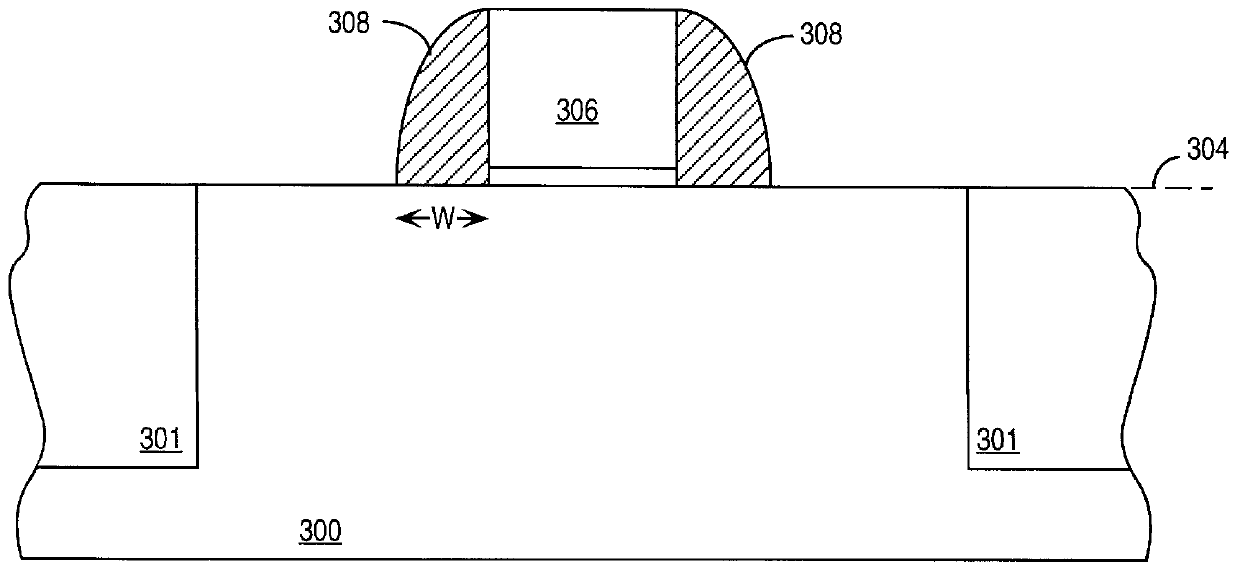

Method of fabricating a MOS transistor with a raised source/drain extension

InactiveUS6121100AReduce parasitic resistanceImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantSemiconductor materials

A method of forming a MOS transistor. According to the method of the present invention, a pair of source / drain contact regions are formed on opposite sides of a gate electrode. After forming the pair of source / drain contact regions, semiconductor material is deposited onto opposite sides of the gate electrode. Dopants are then diffused from the semiconductor material into the substrate beneath the gate electrode to form a pair of source / drain extensions.

Owner:INTEL CORP

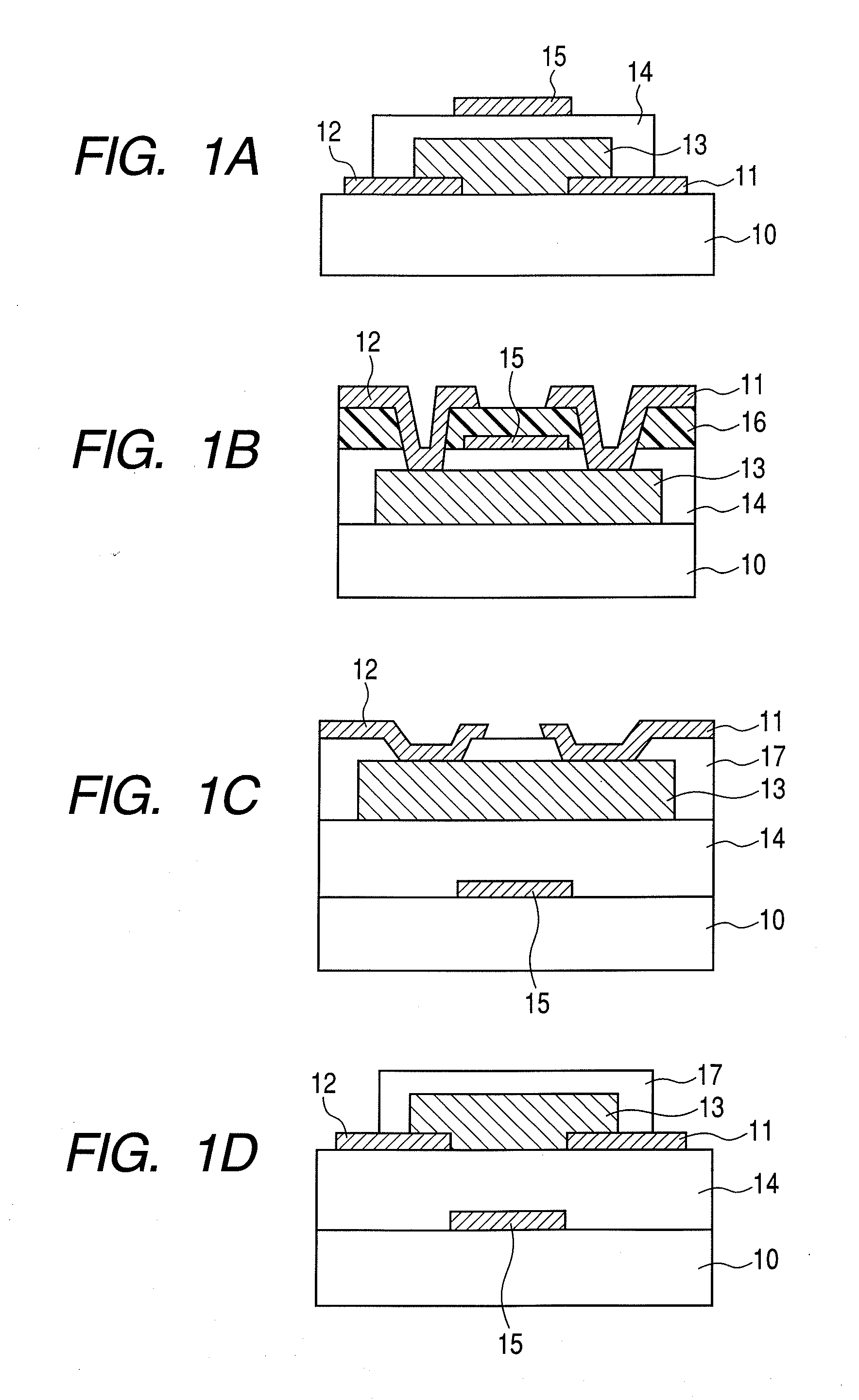

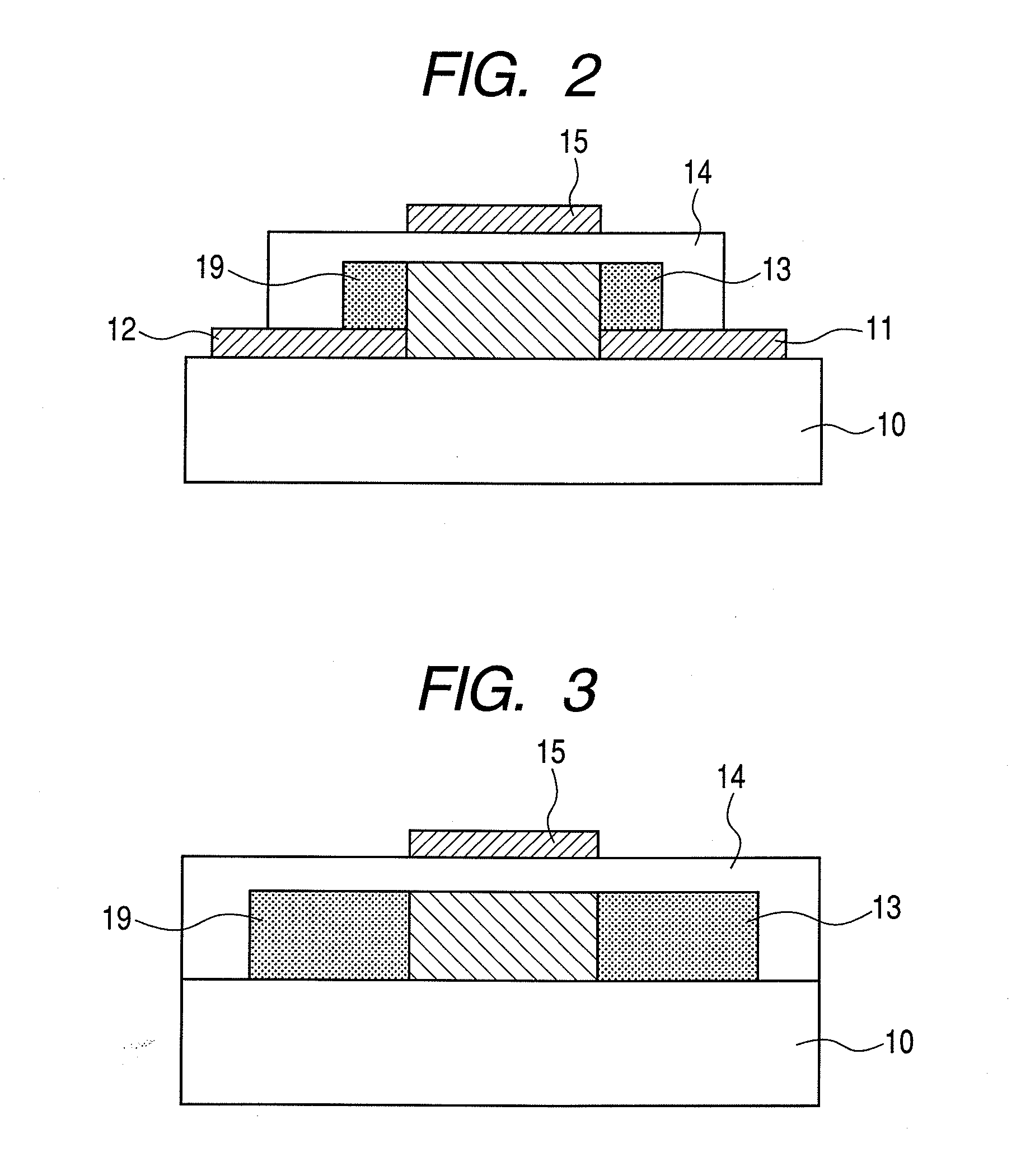

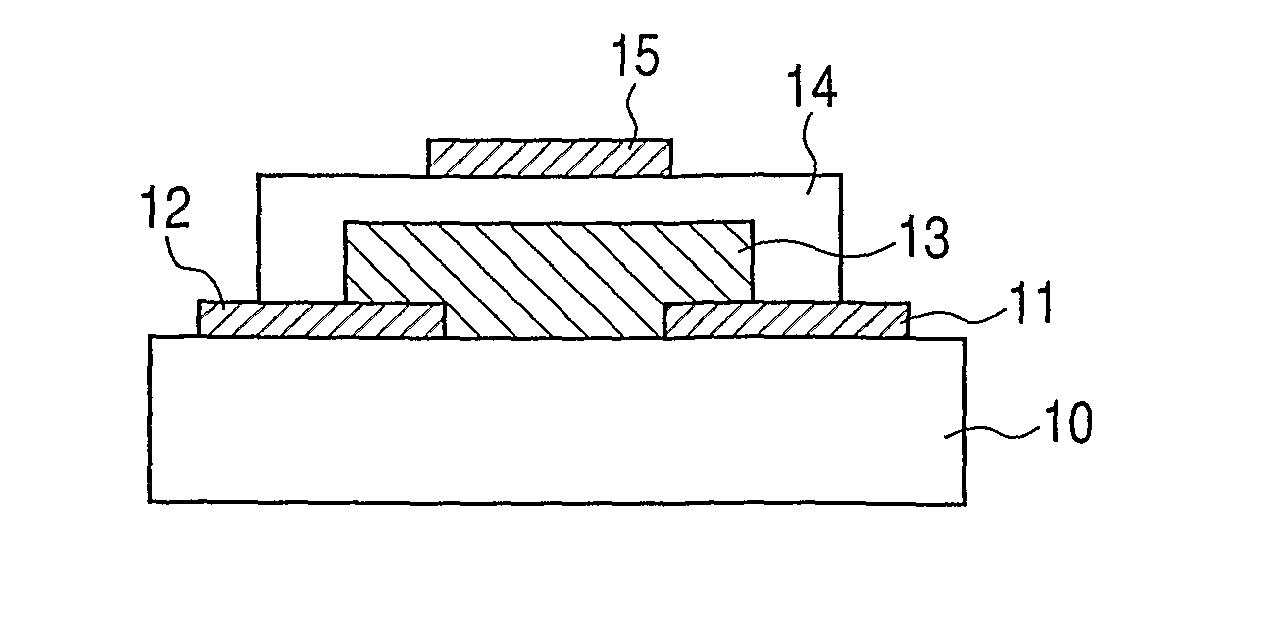

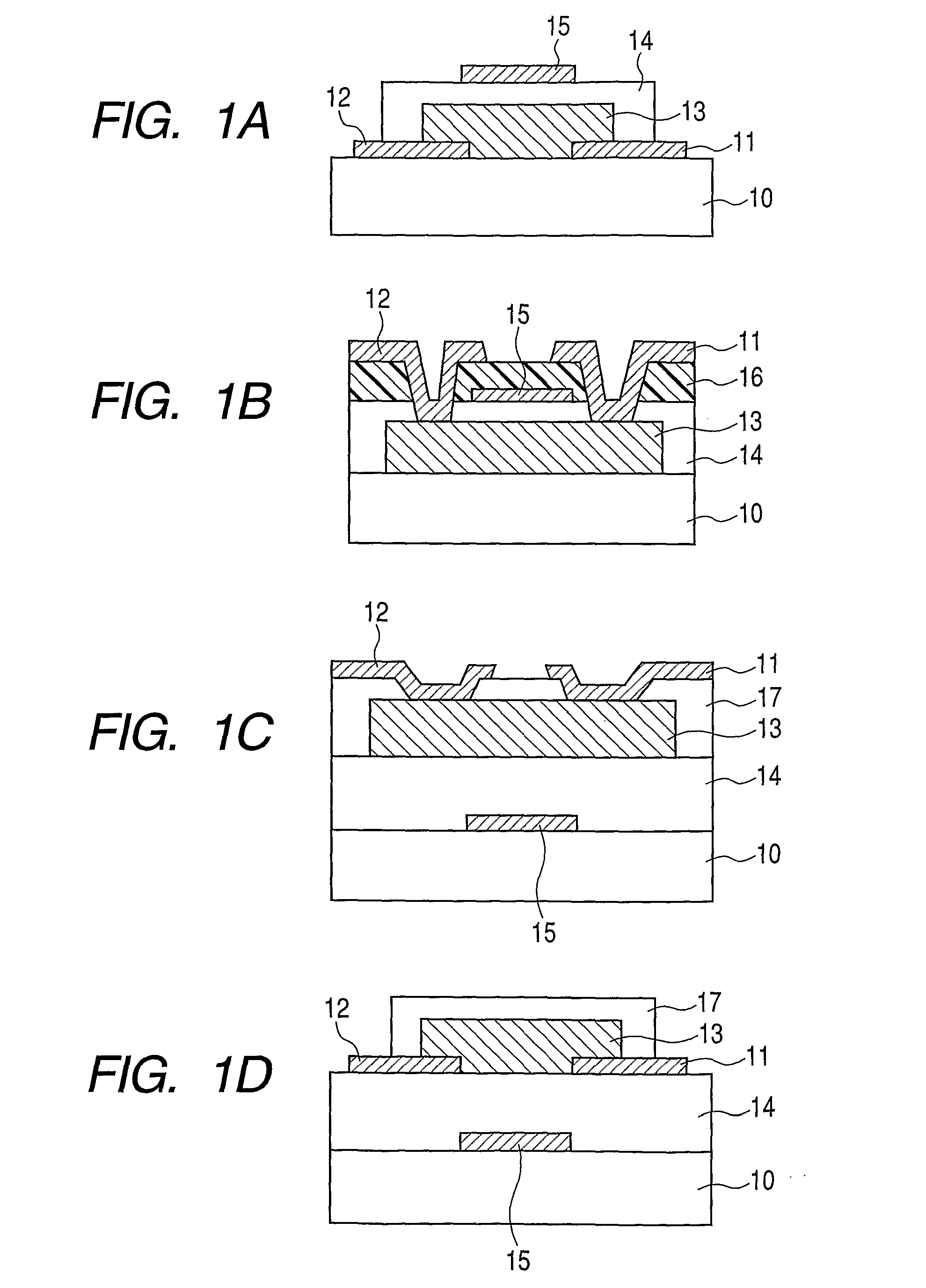

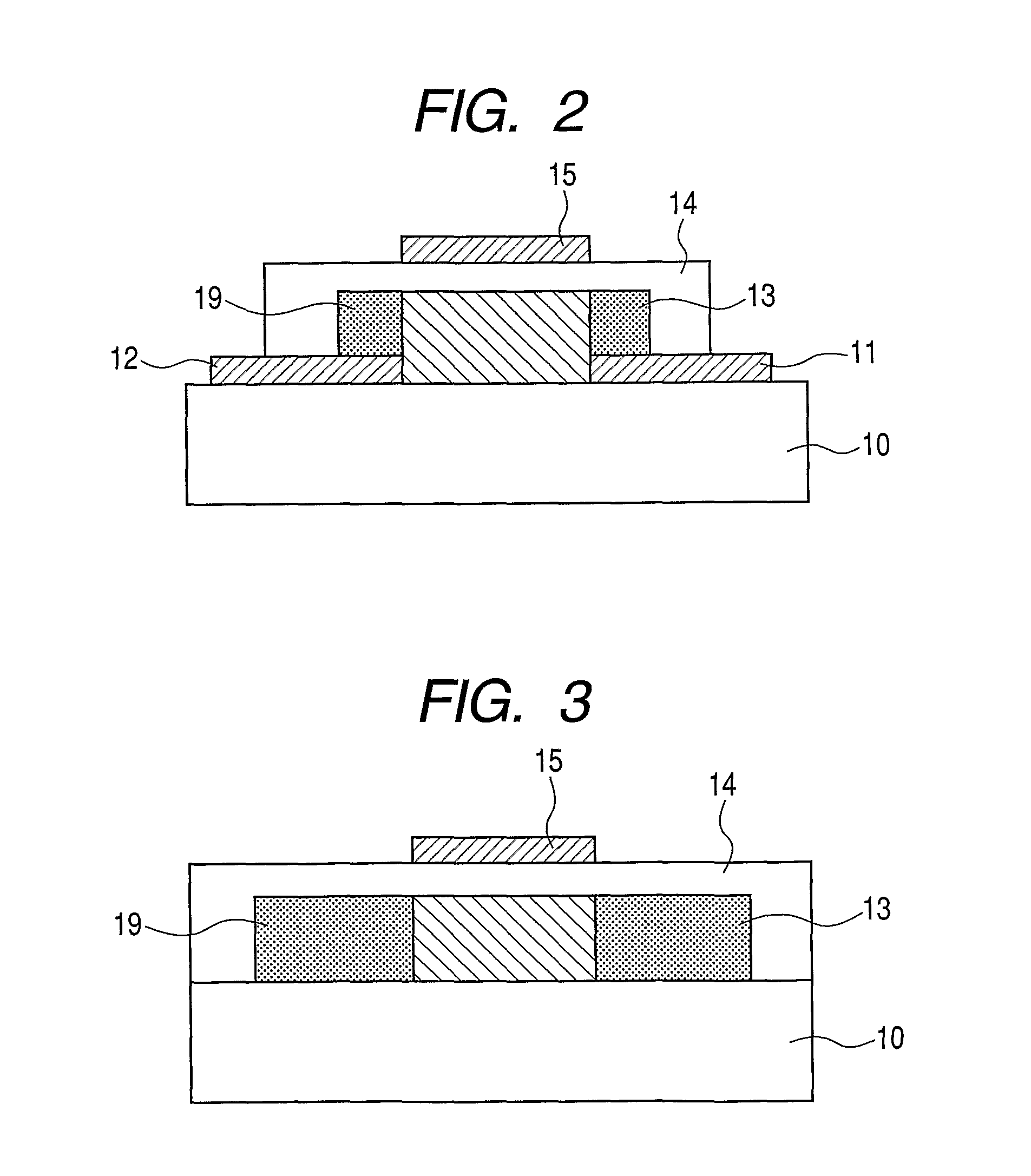

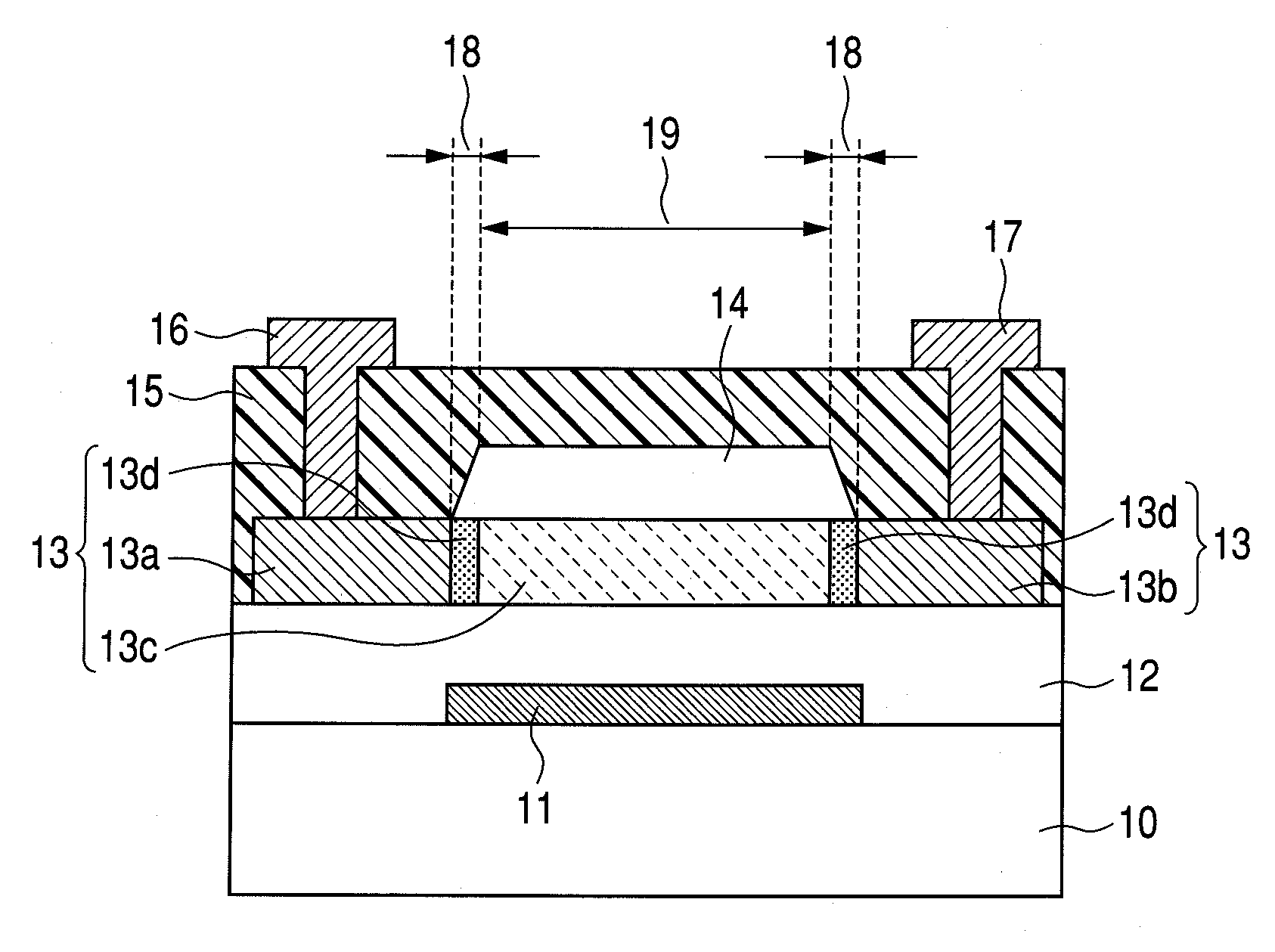

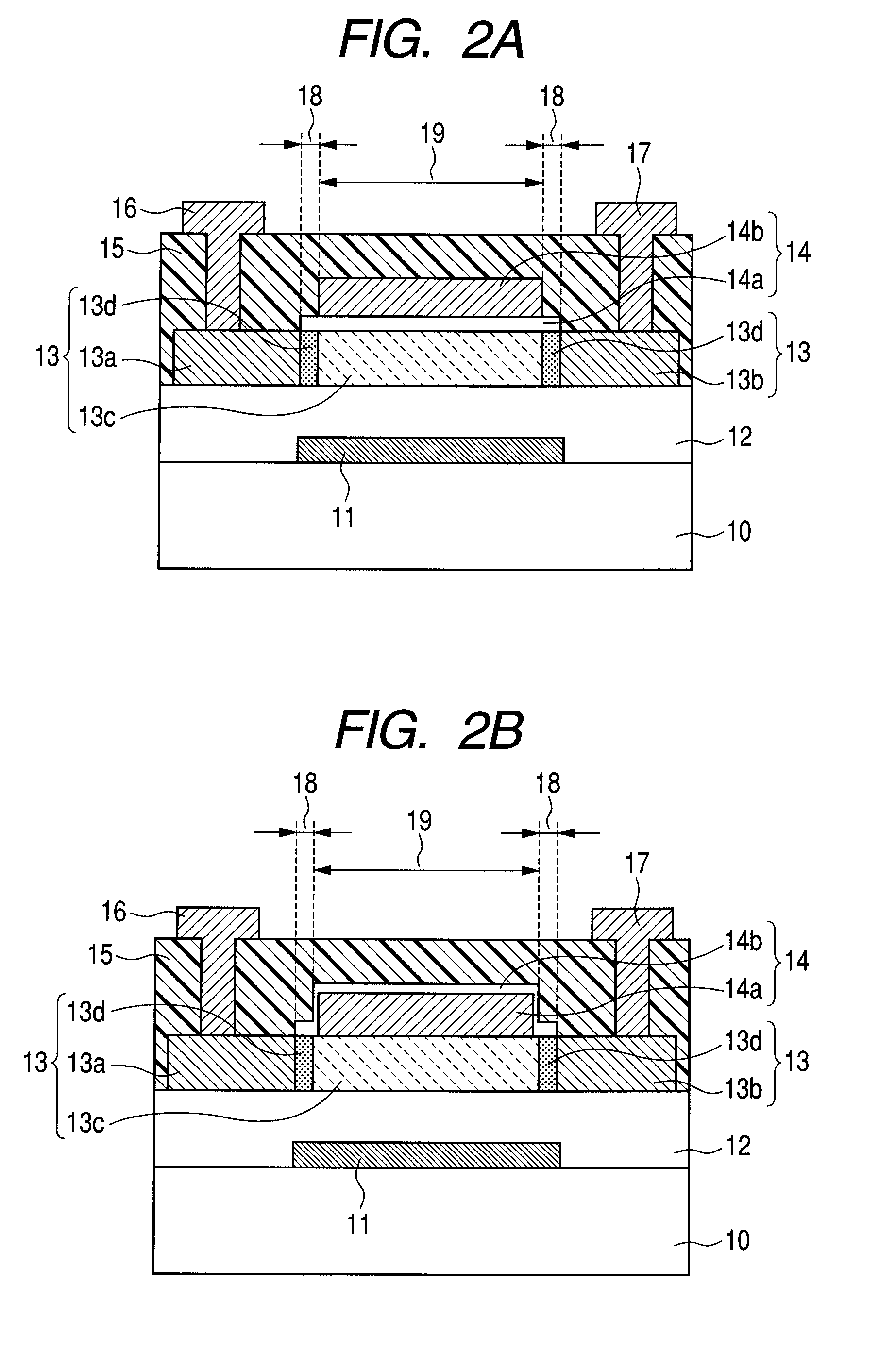

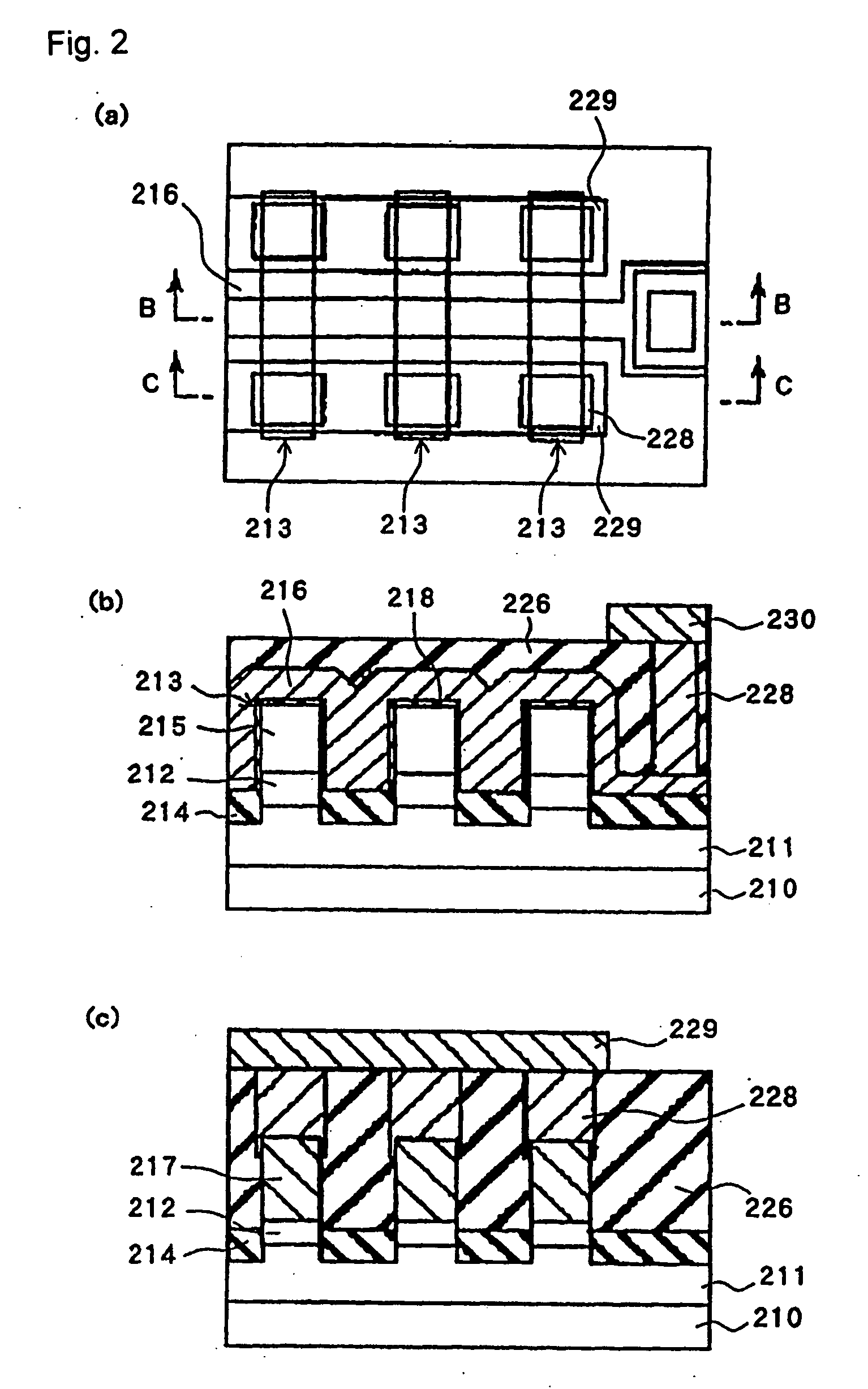

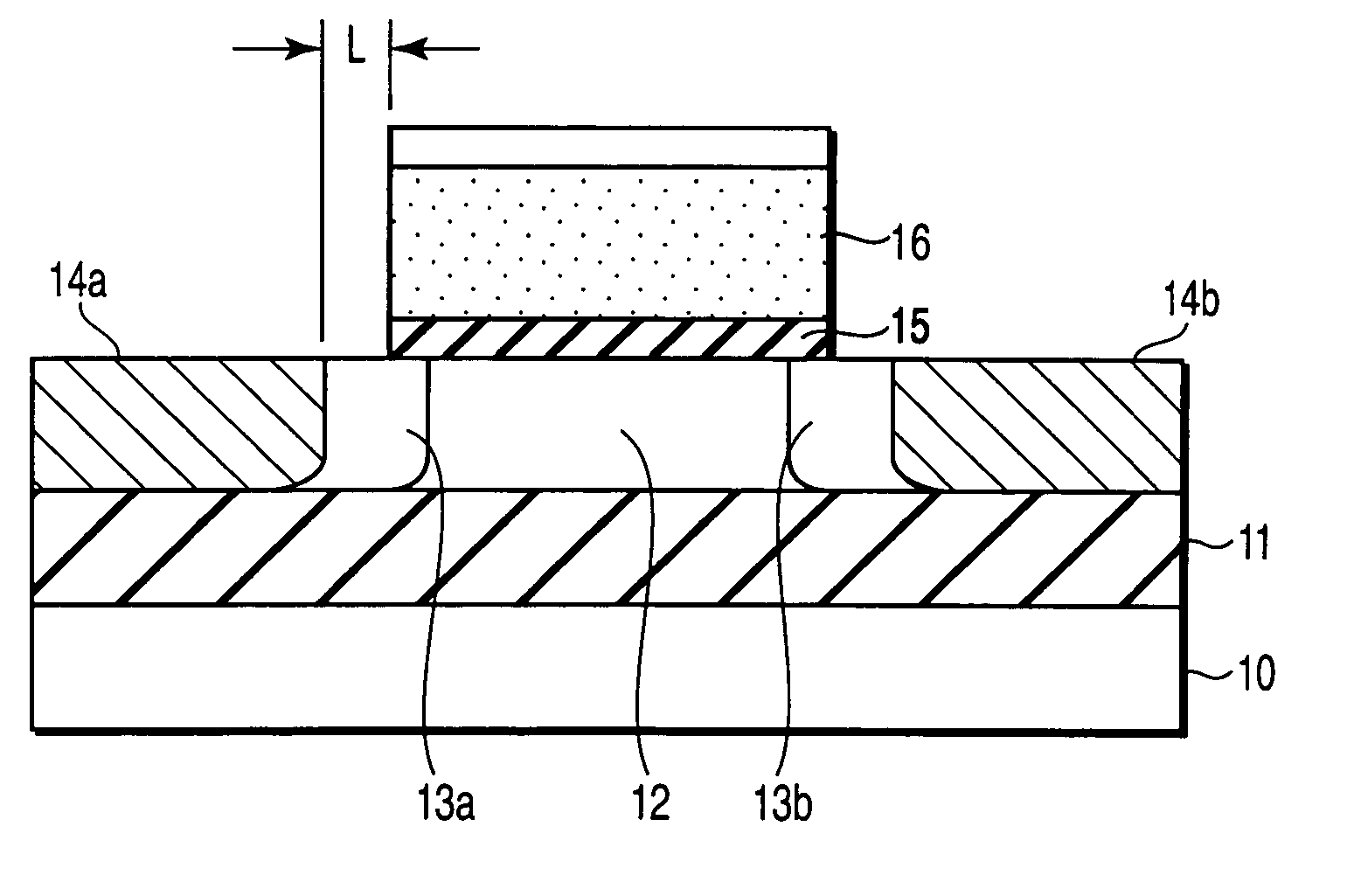

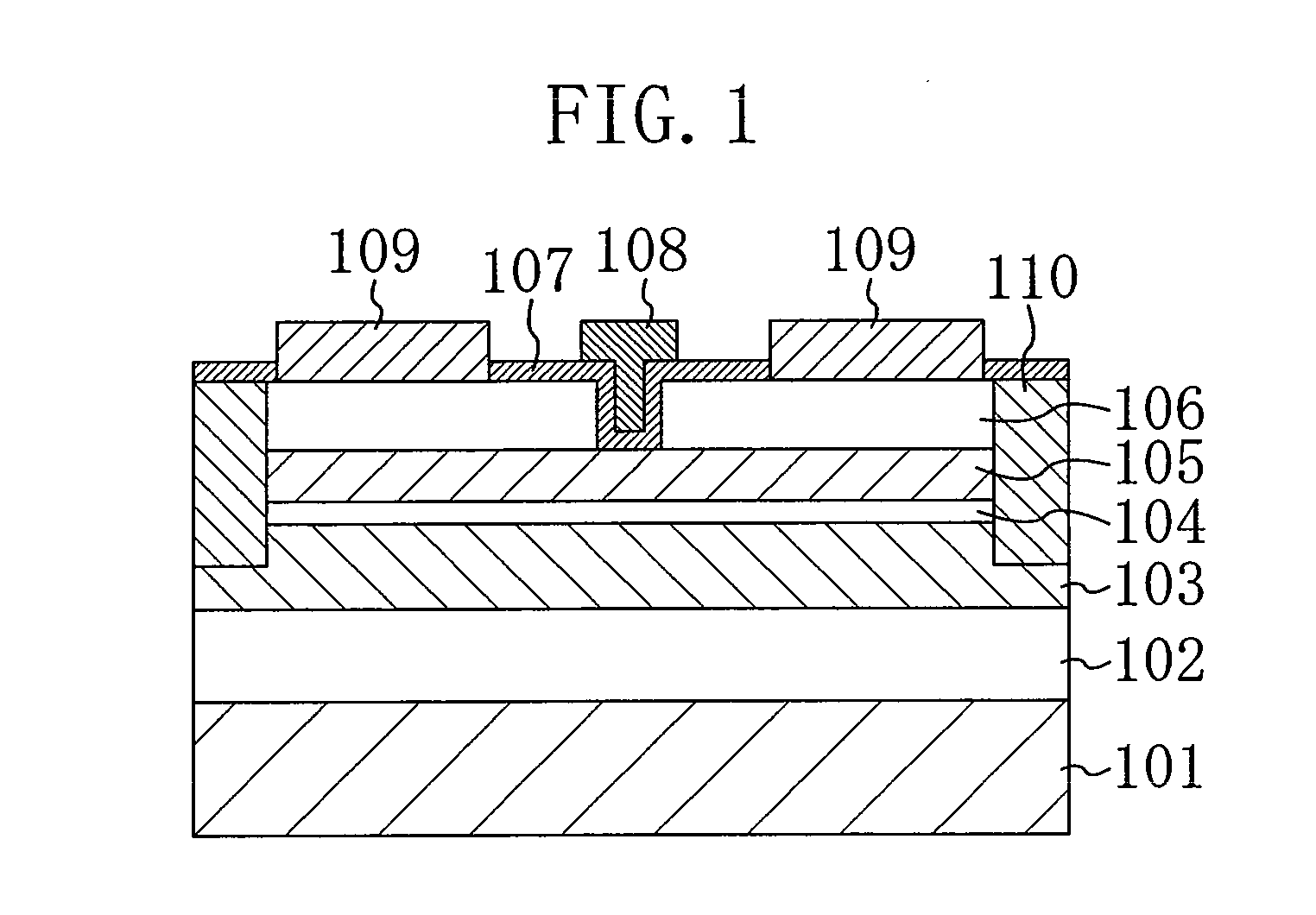

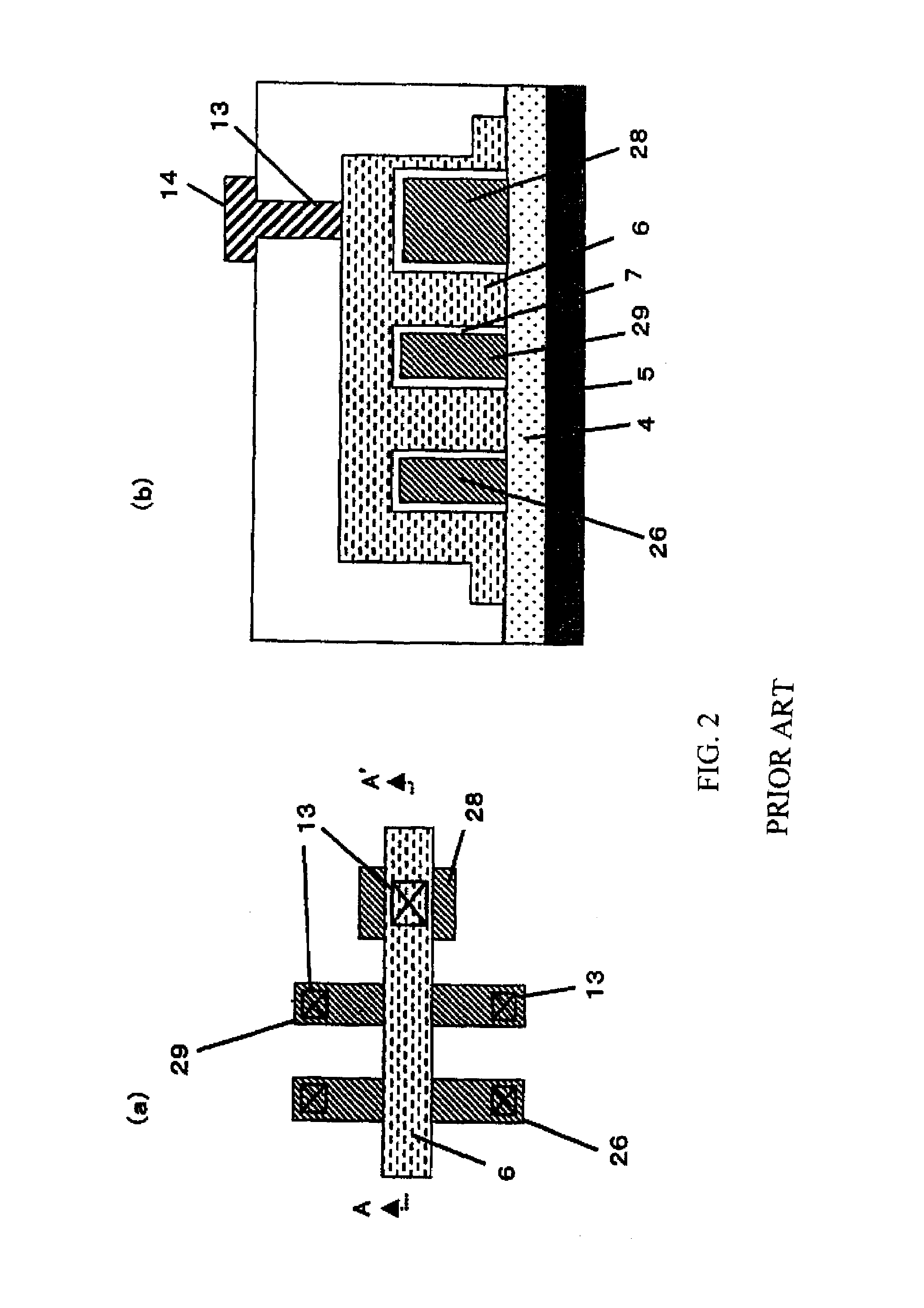

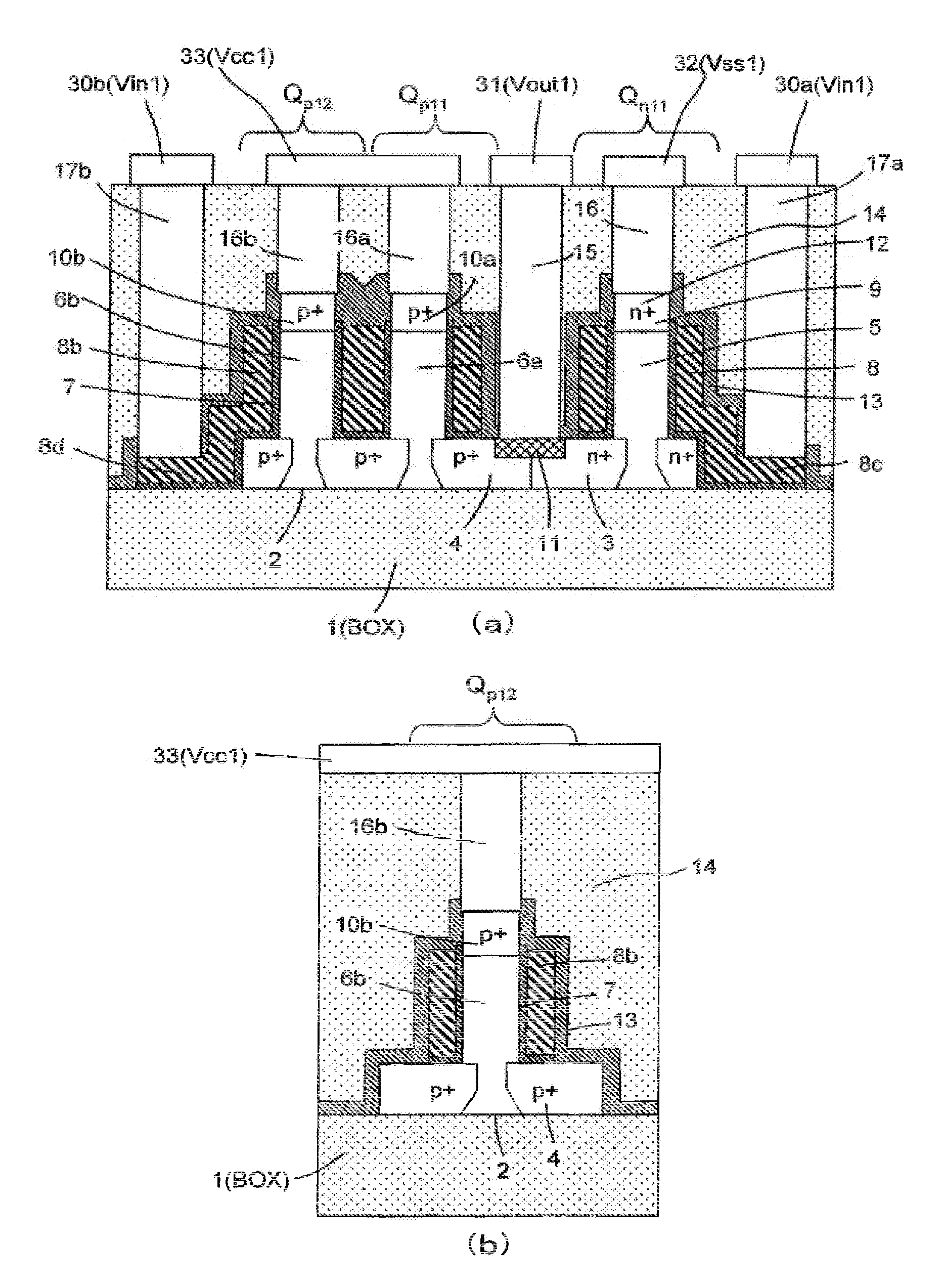

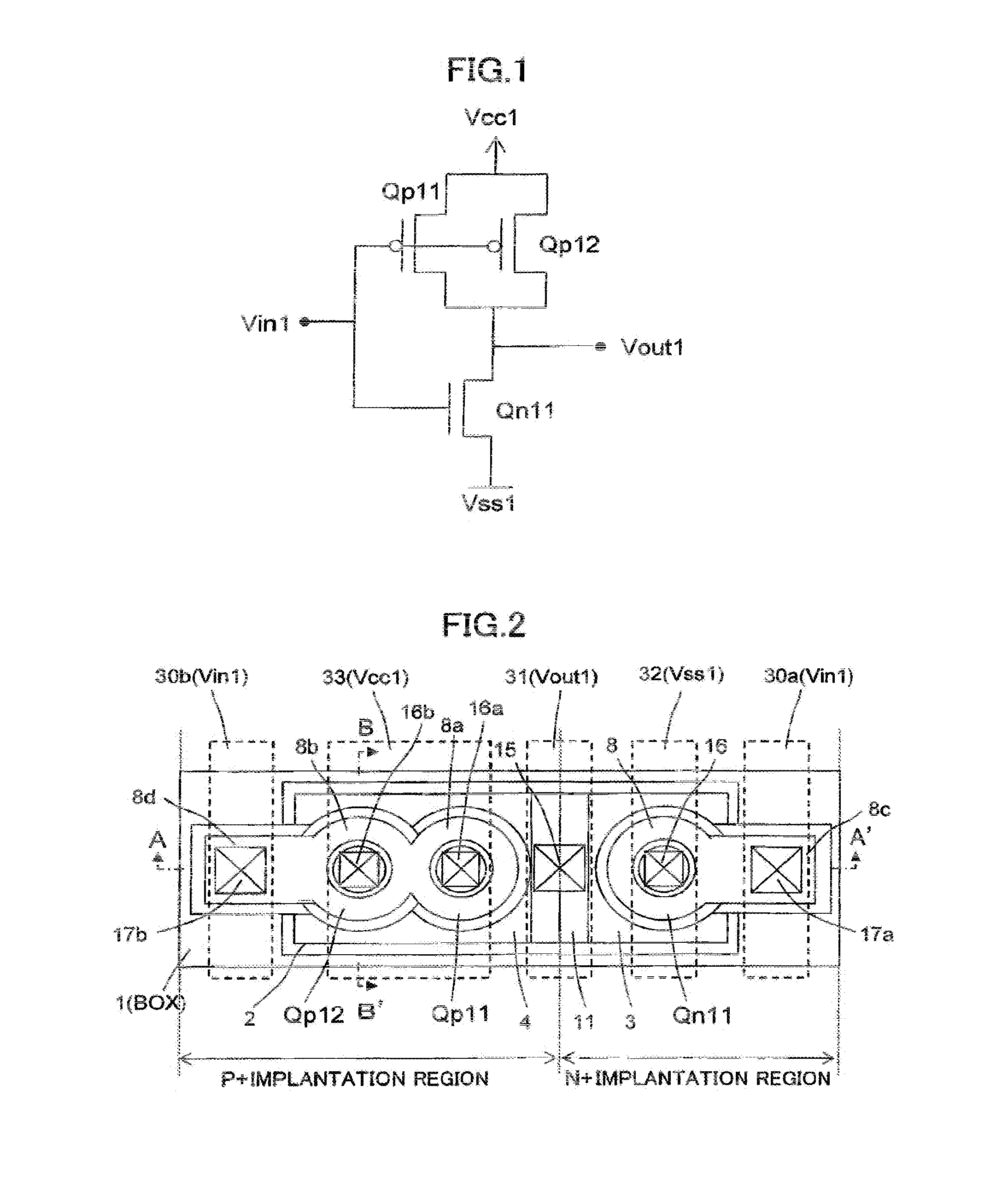

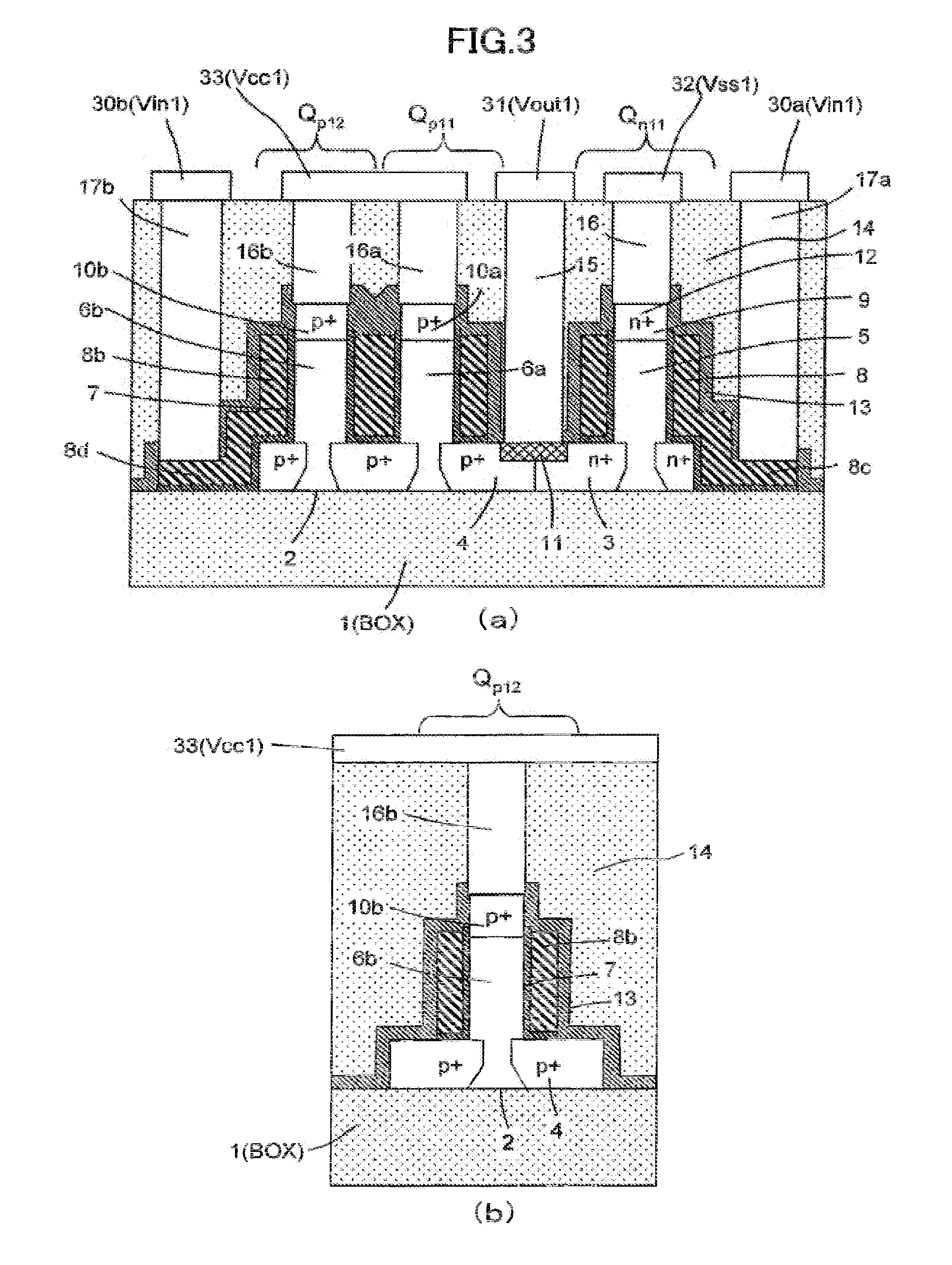

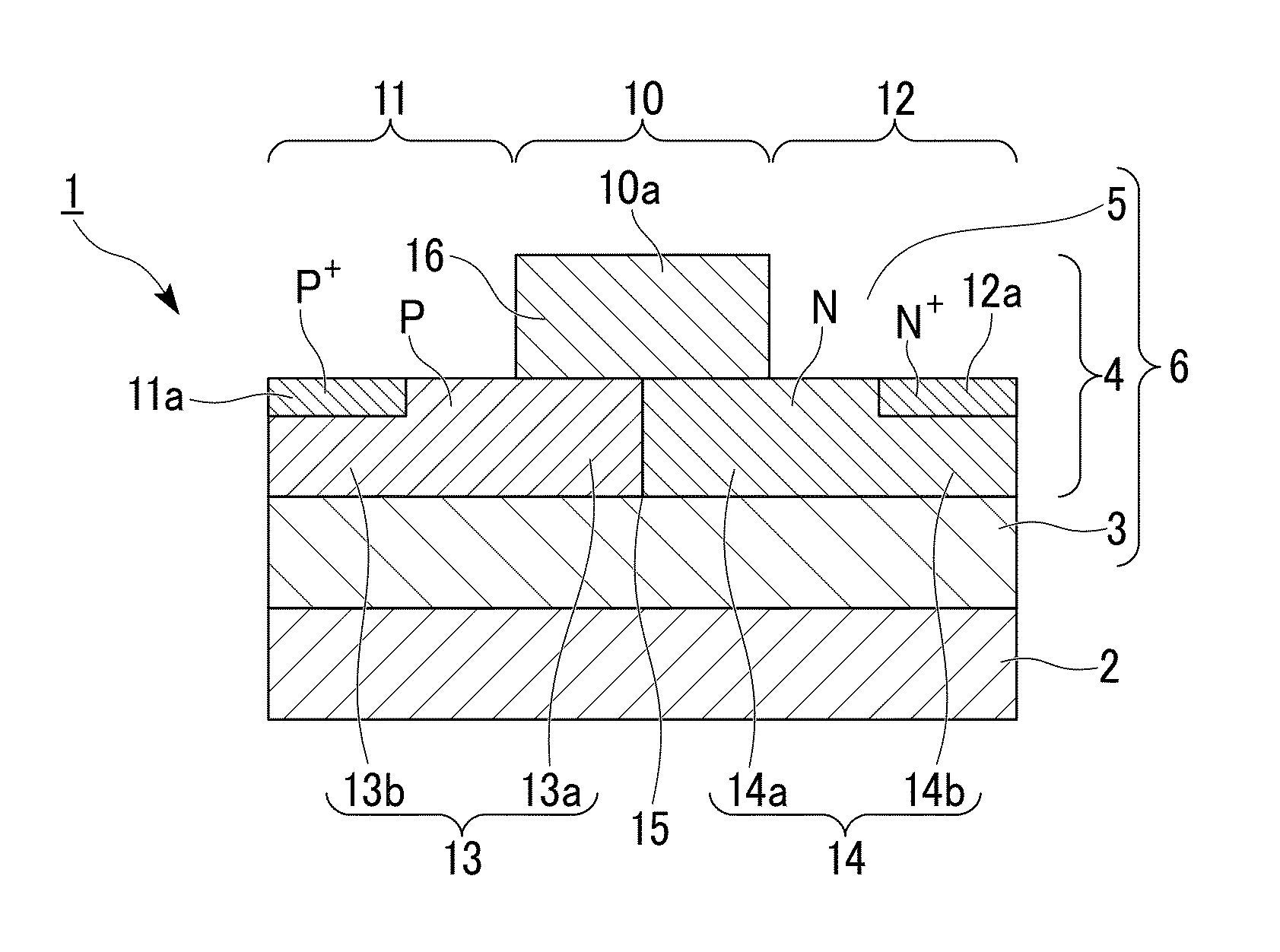

Field effect transistor and manufacturing method thereof

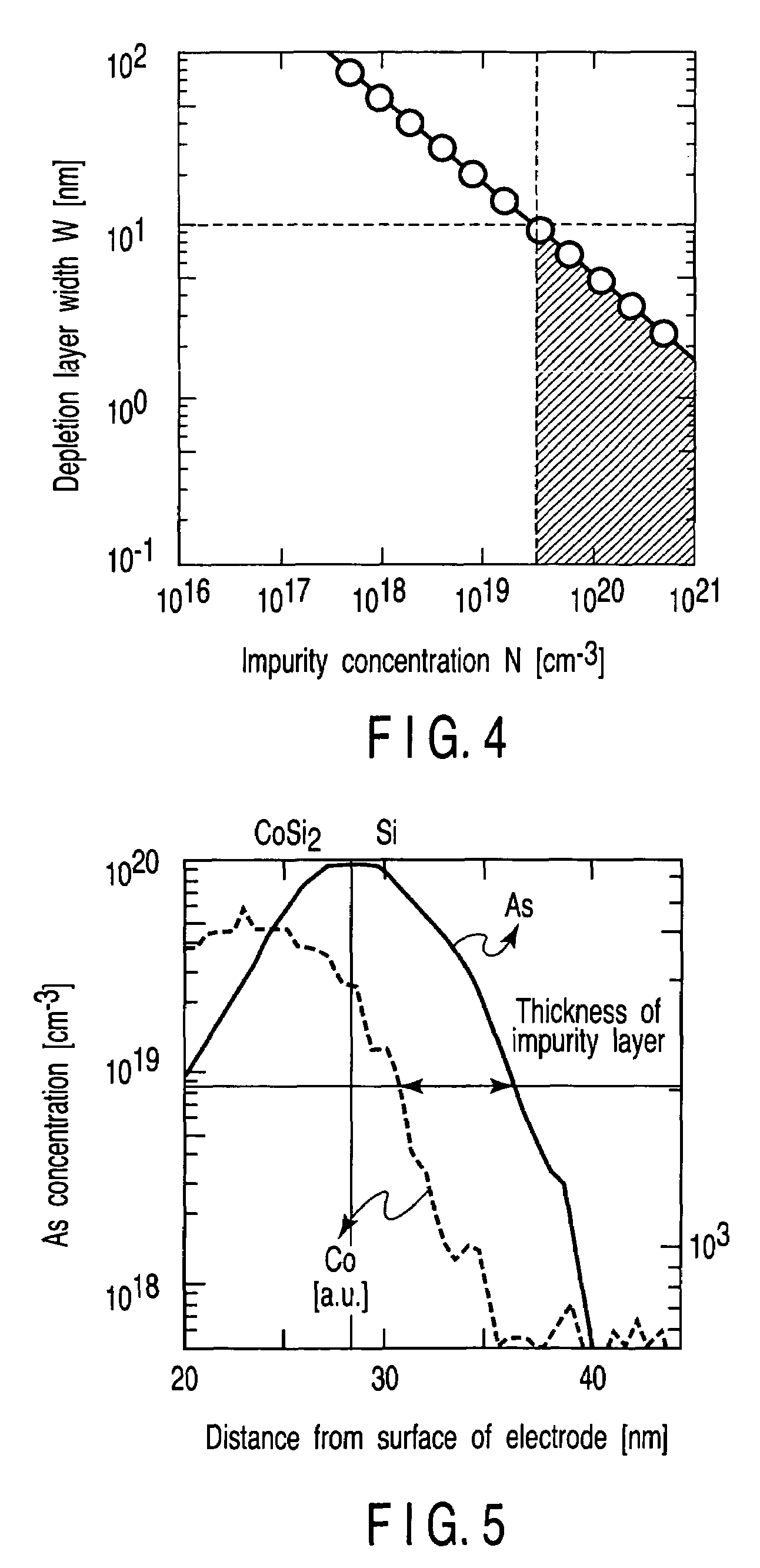

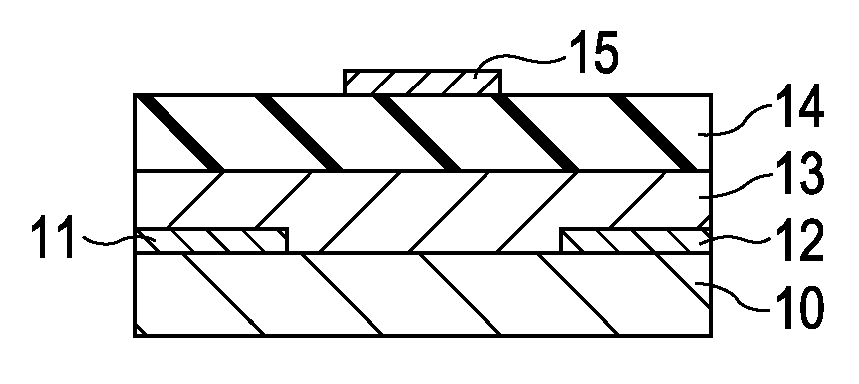

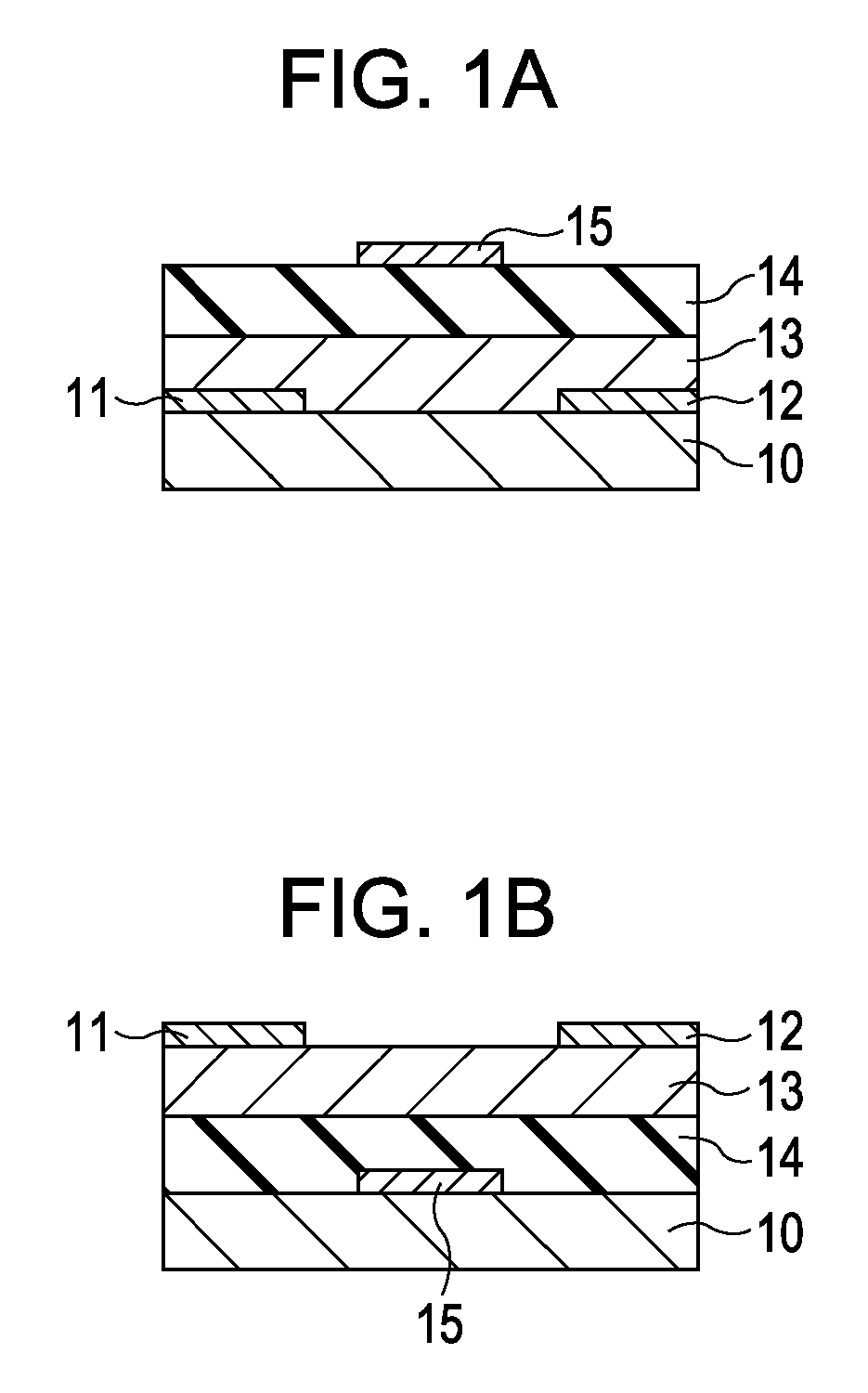

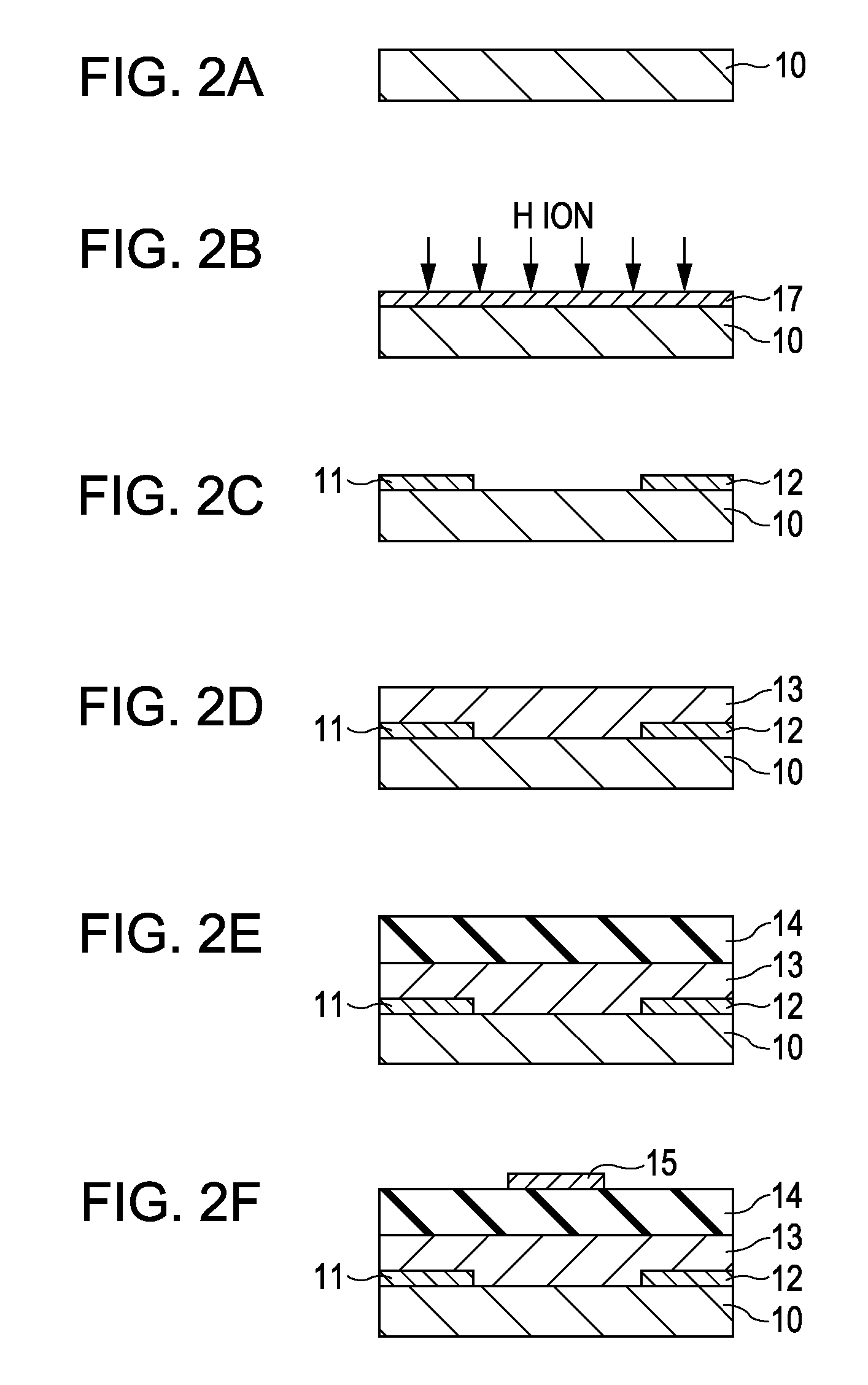

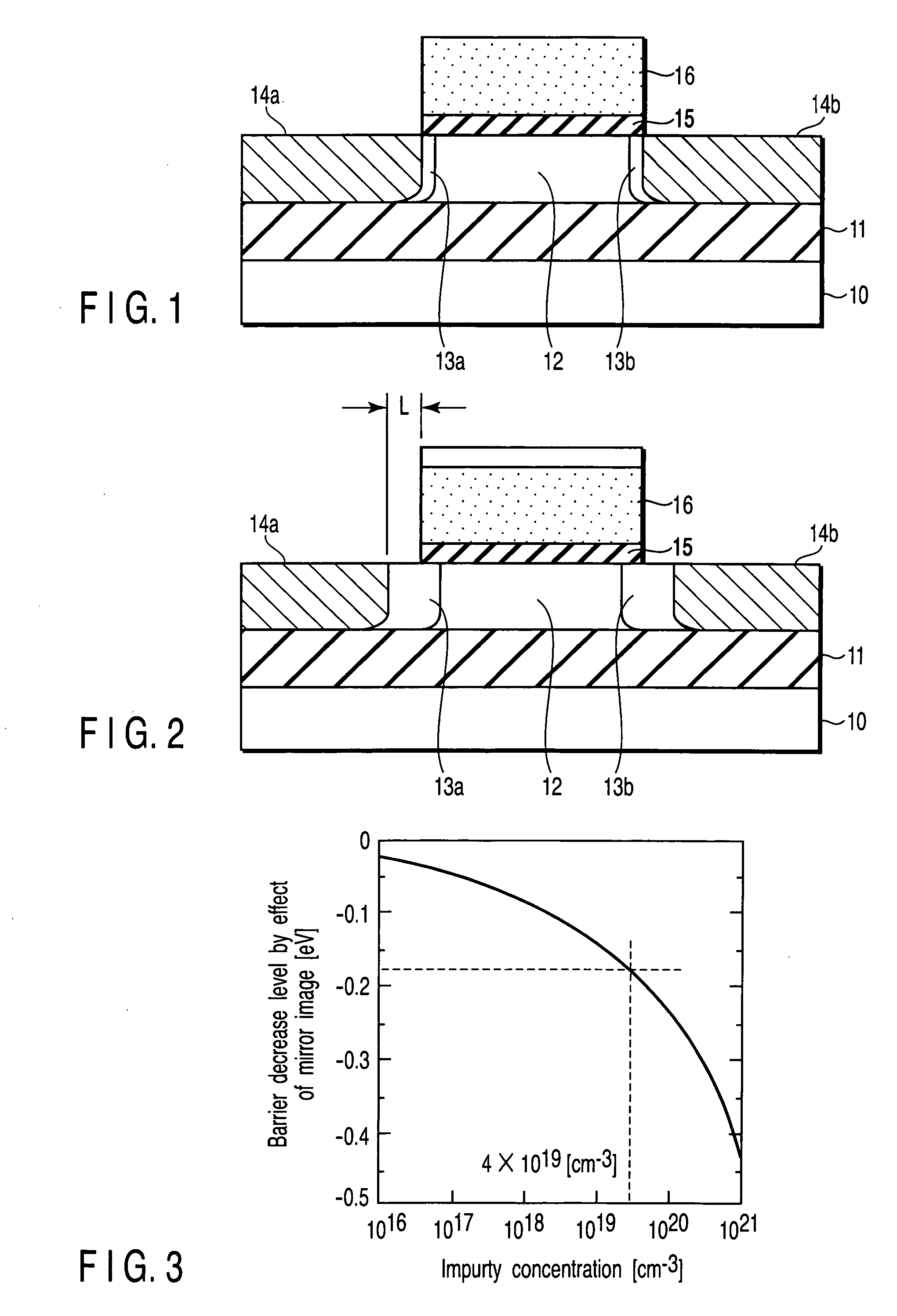

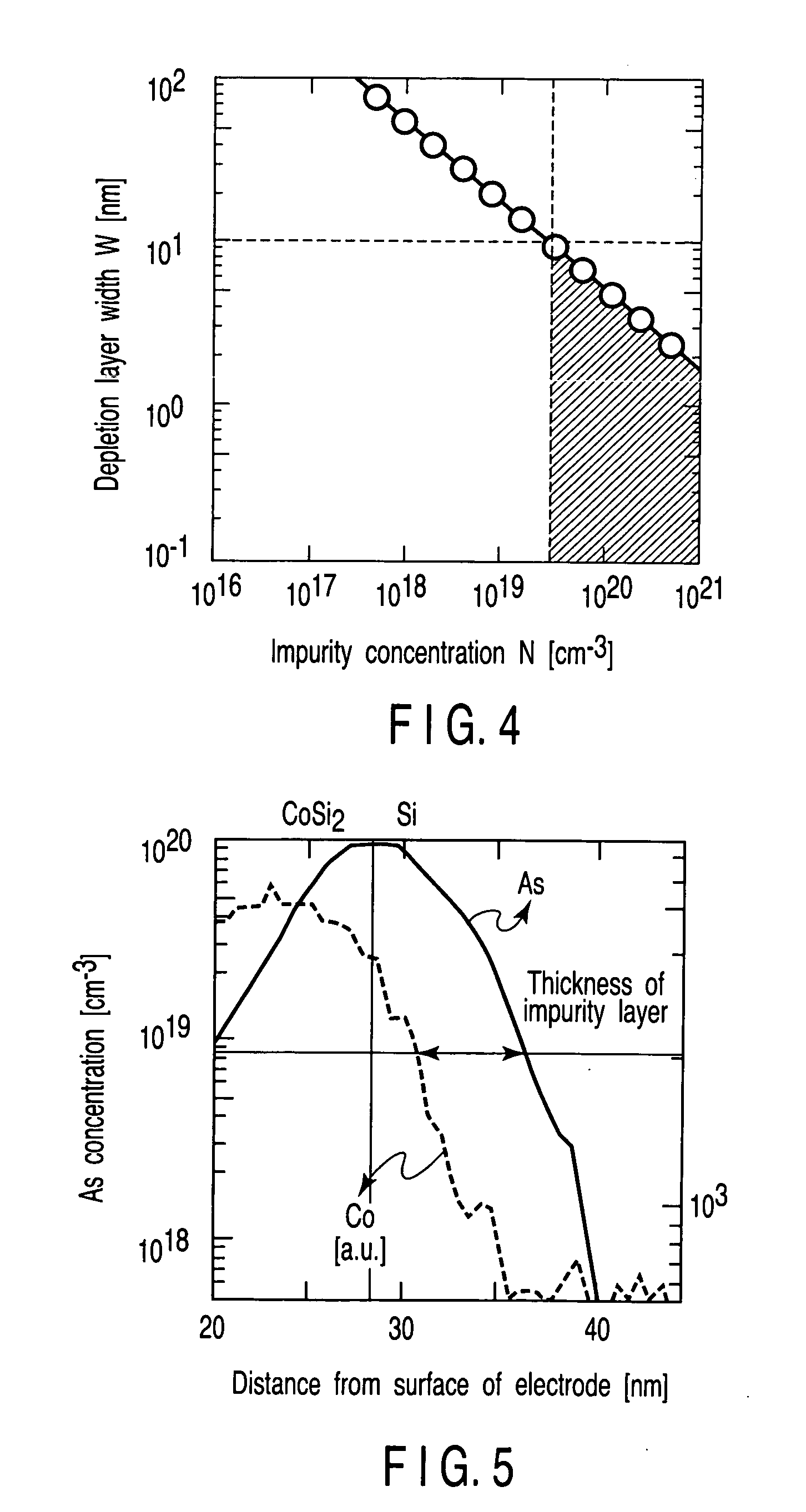

InactiveUS7119402B2High concentrationReduce parasitic resistanceTransistorSolid-state devicesEngineeringField-effect transistor

A field effect transistor includes a first semiconductor region forming a channel region, a gate electrode insulatively disposed above the first semiconductor region, source and drain electrodes formed to sandwich the first semiconductor region in a channel lengthwise direction, and second semiconductor regions formed between the first semiconductor region and the source and drain electrodes and having impurity concentration higher than the first semiconductor region. The thickness of the second semiconductor region in the channel lengthwise direction is set to a value equal to or less than depletion layer width determined by the impurity concentration so that the second semiconductor region is depleted in a no-voltage application state.

Owner:KK TOSHIBA

Field-effect transistor and method for manufacturing the same

InactiveUS20080067508A1Reduce parasitic resistanceIncrease concentrationSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorOxide

A method for manufacturing a field-effect transistor includes the steps of forming a source electrode and a drain electrode each containing hydrogen or deuterium; forming an oxide semiconductor layer in which the electrical resistance is decreased if hydrogen or deuterium is added; and, causing hydrogen or deuterium to diffuse from the source electrode and the drain electrode to the oxide semiconductor layer.

Owner:CANON KK

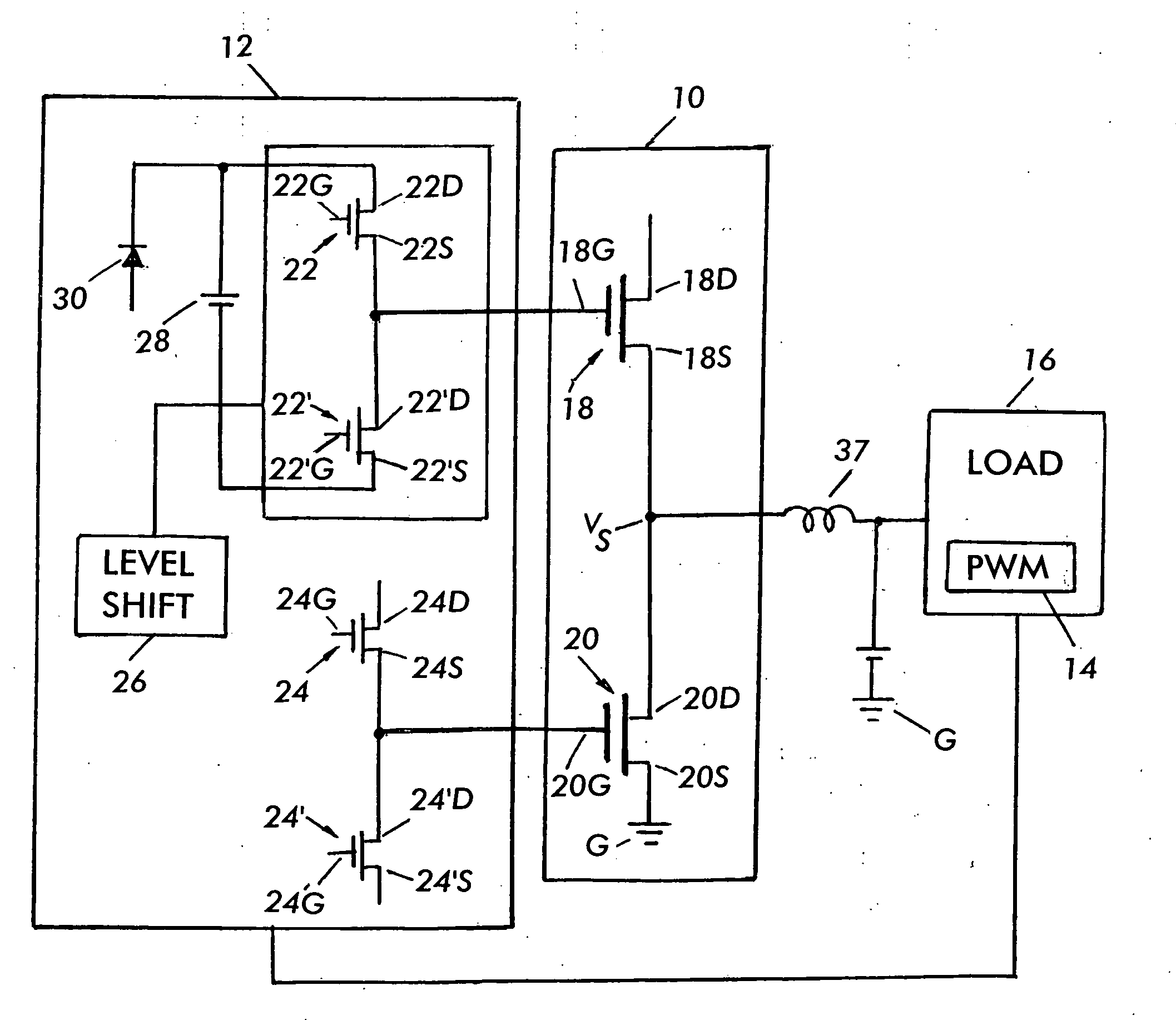

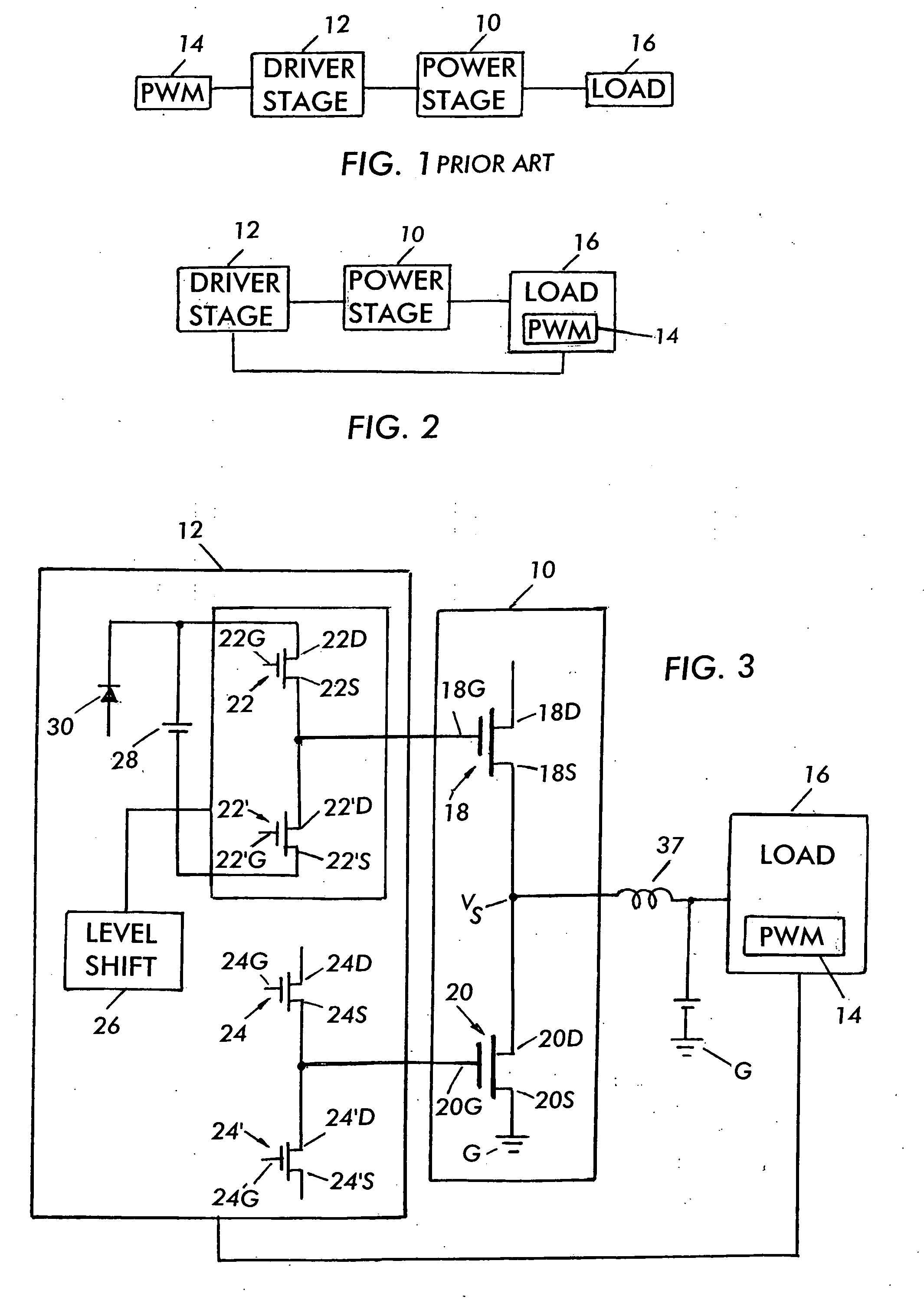

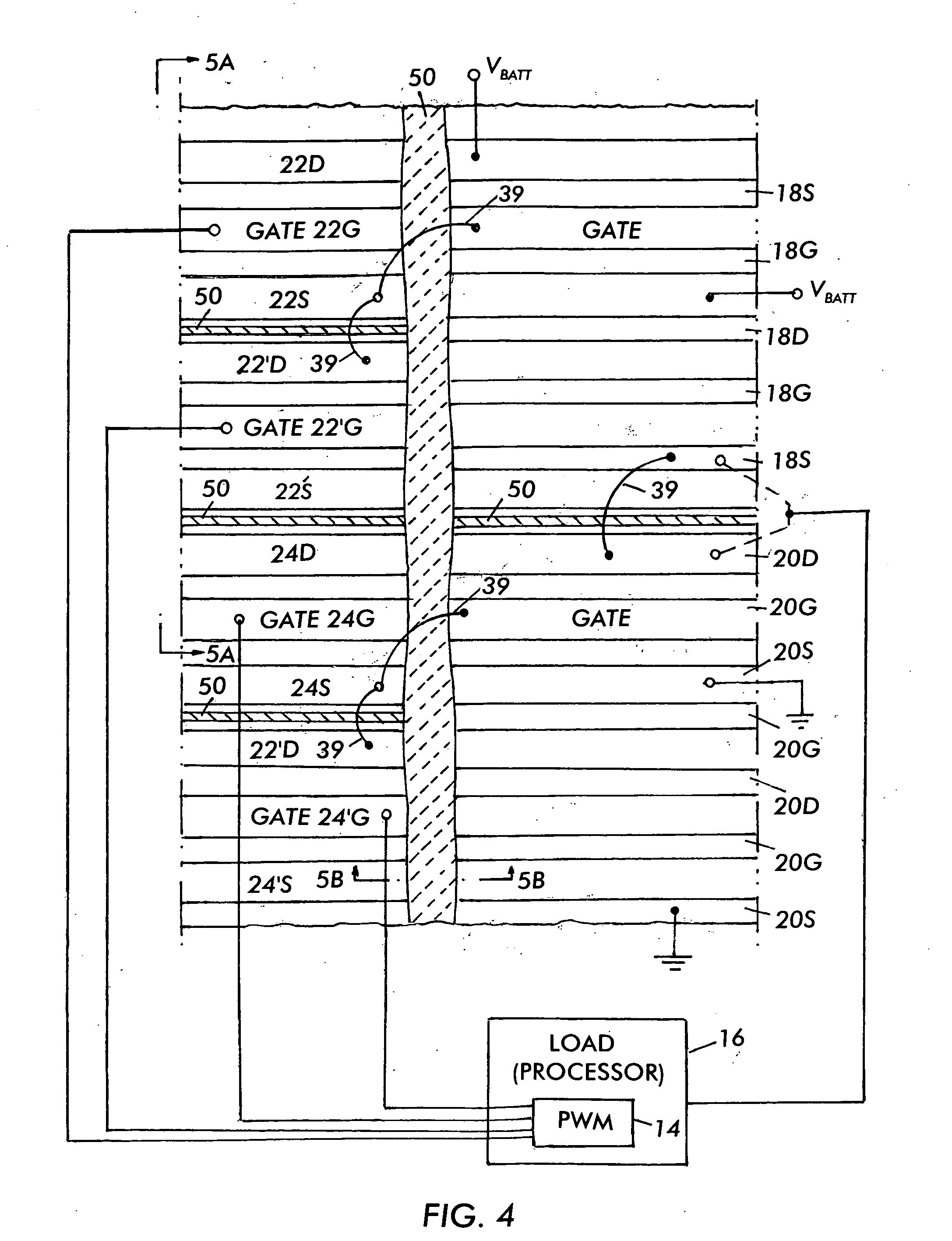

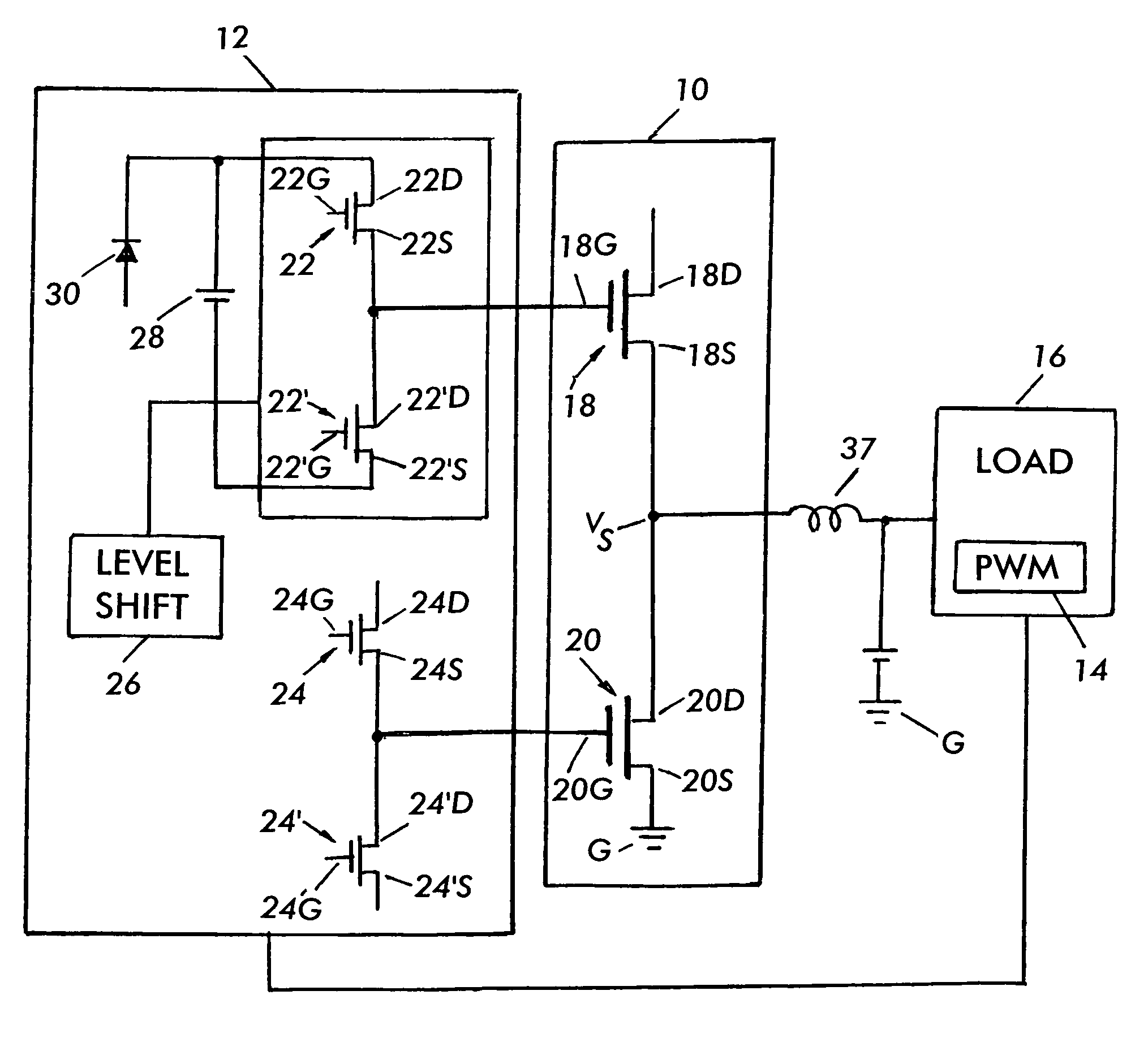

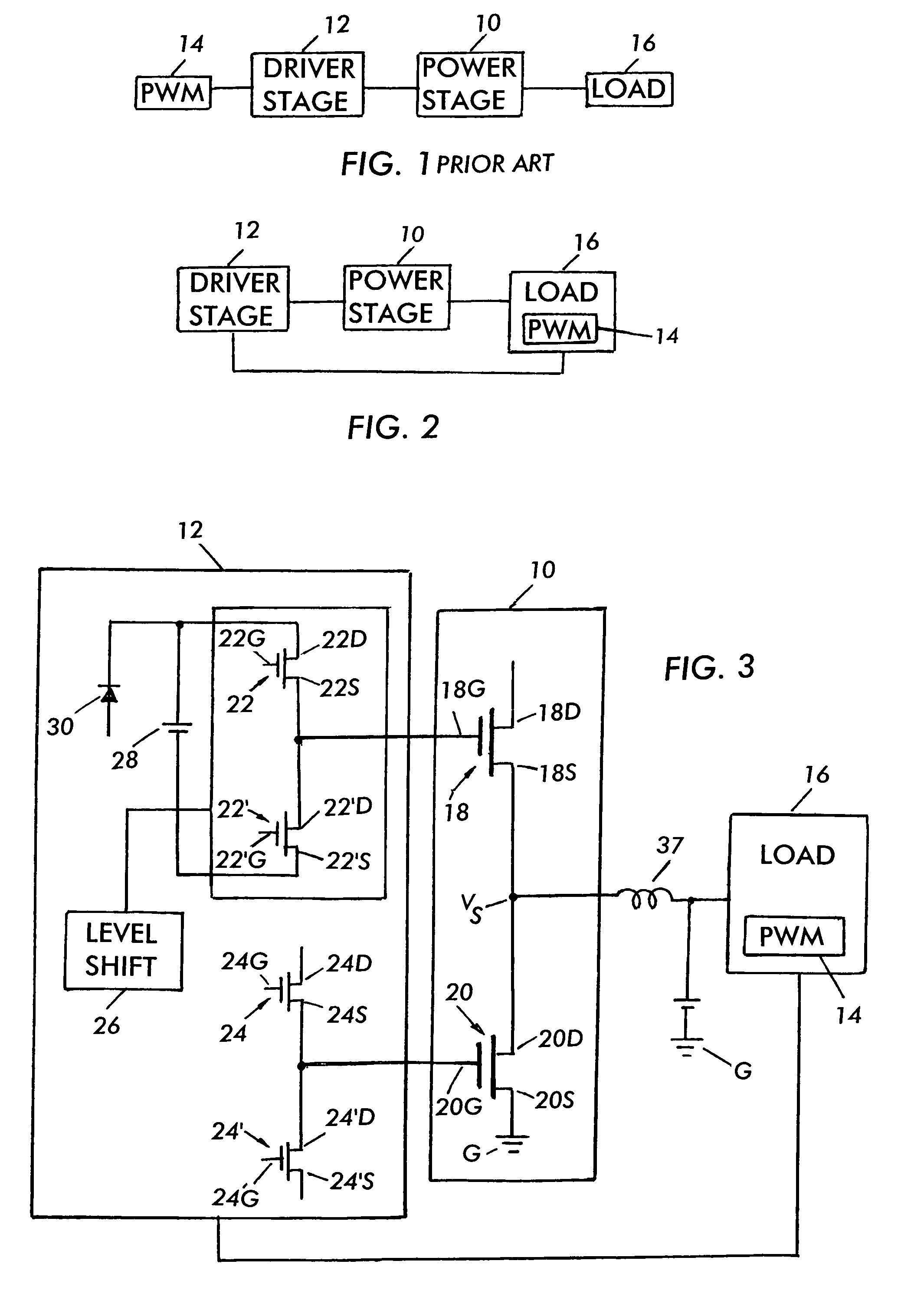

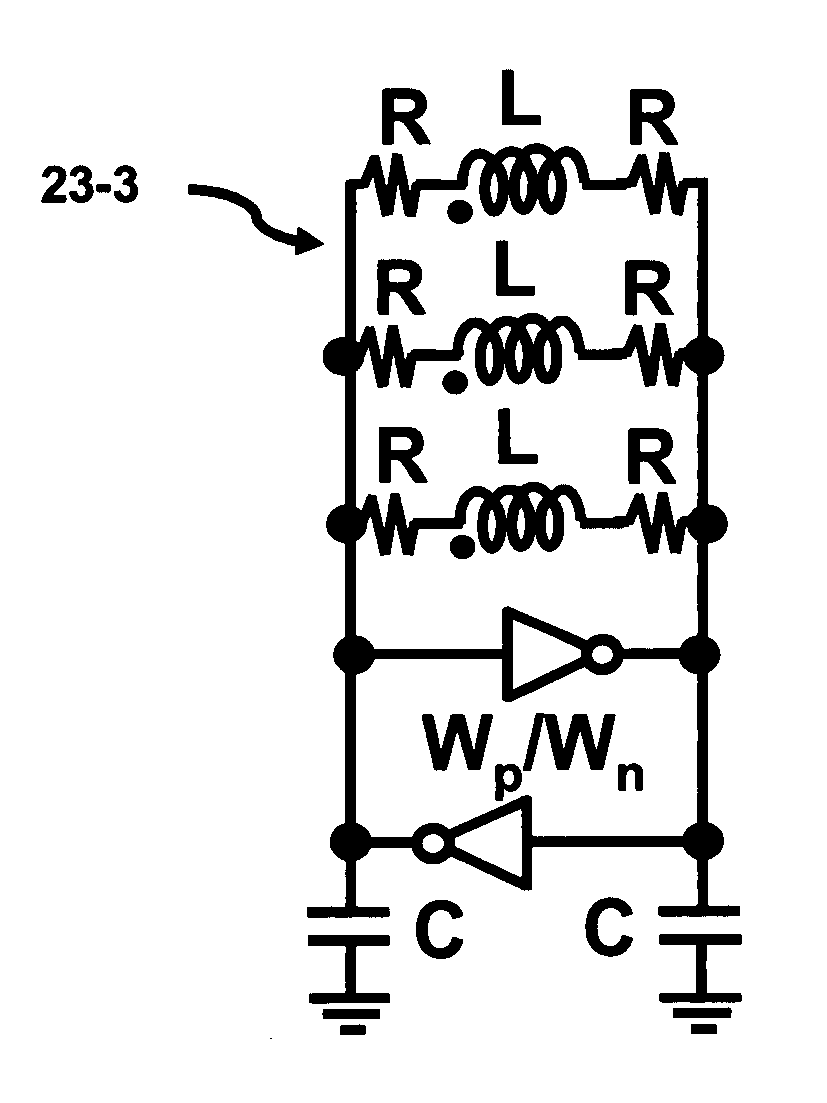

Monolithically integrated III-nitride power converter

ActiveUS20080136390A1Improve performanceReduces parasitic inductancesEfficient power electronics conversionSolid-state devicesEngineeringNitride

Owner:INFINEON TECH AMERICAS CORP

Method for manufacturing field-effect transistor

ActiveUS20100203673A1Improve conductivityImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesSteam pressureMetallurgy

A method for manufacturing a field-effect transistor is provided. The field-effect transistor includes on a substrate a source electrode, a drain electrode, an oxide semiconductor layer, an insulating layer and a gate electrode. The method includes, after forming the insulating layer on the oxide semiconductor layer, an annealing step of increasing the electrical conductivity of the oxide semiconductor layers by annealing in an atmosphere containing moisture. The steam pressure at the annealing step is higher than the saturated vapor pressure in the atmosphere at the annealing temperature.

Owner:CANON KK

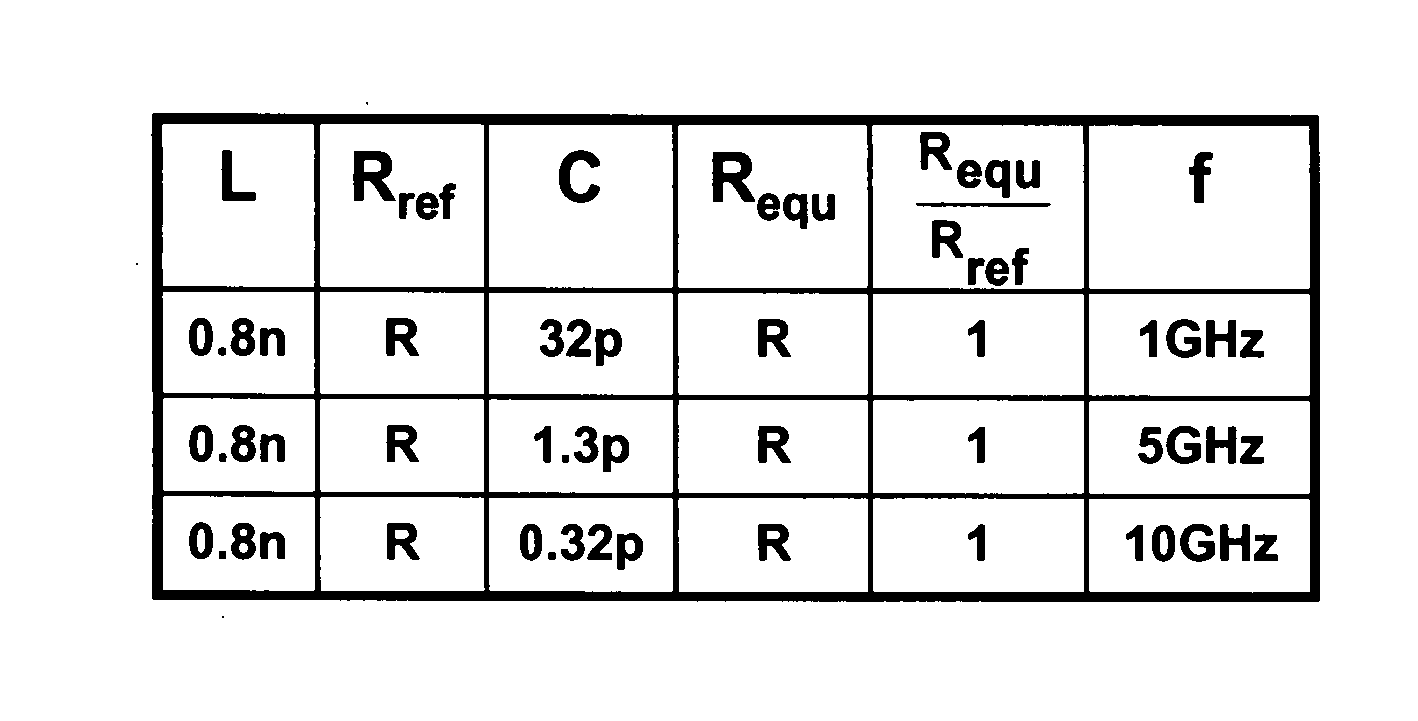

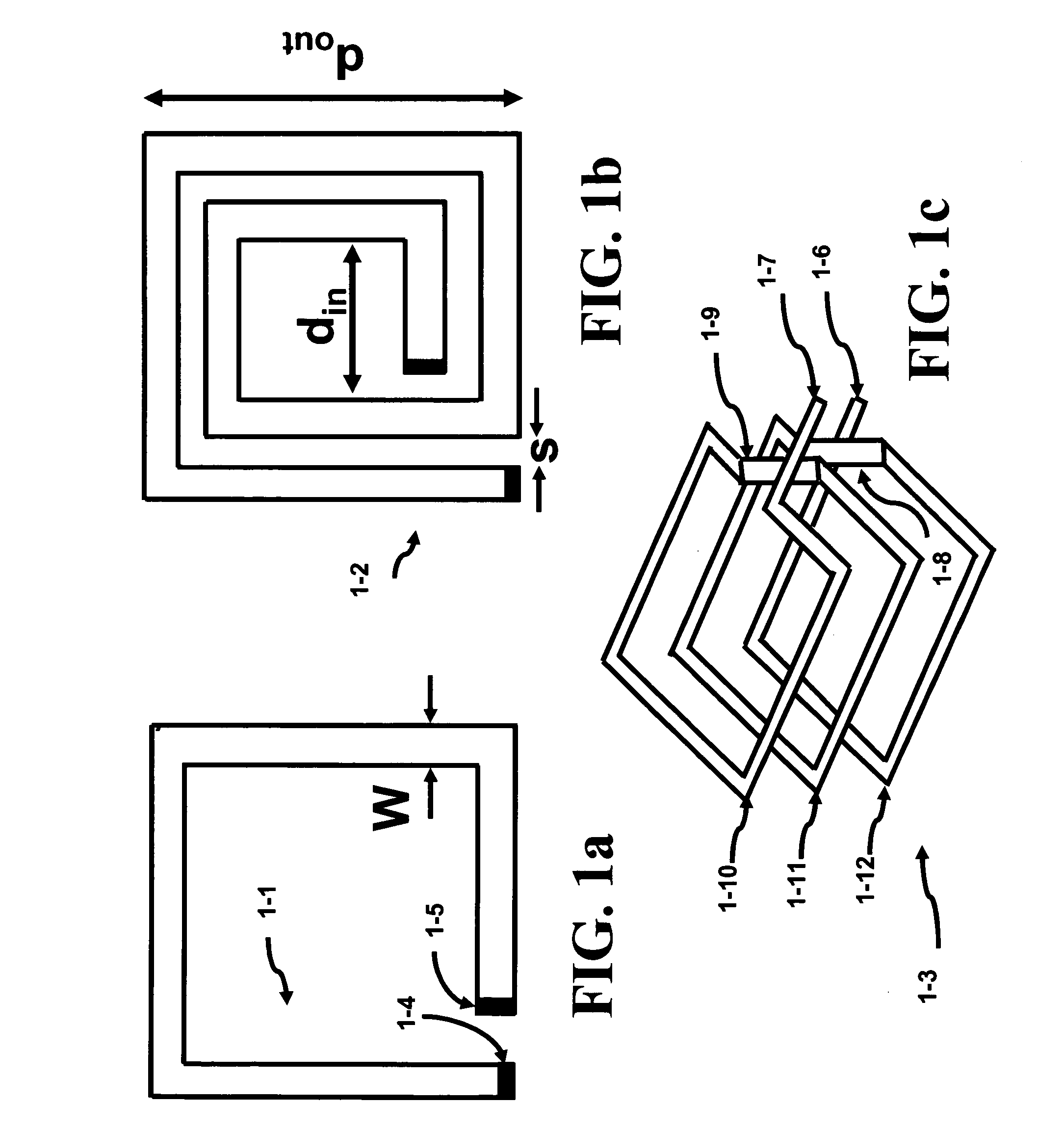

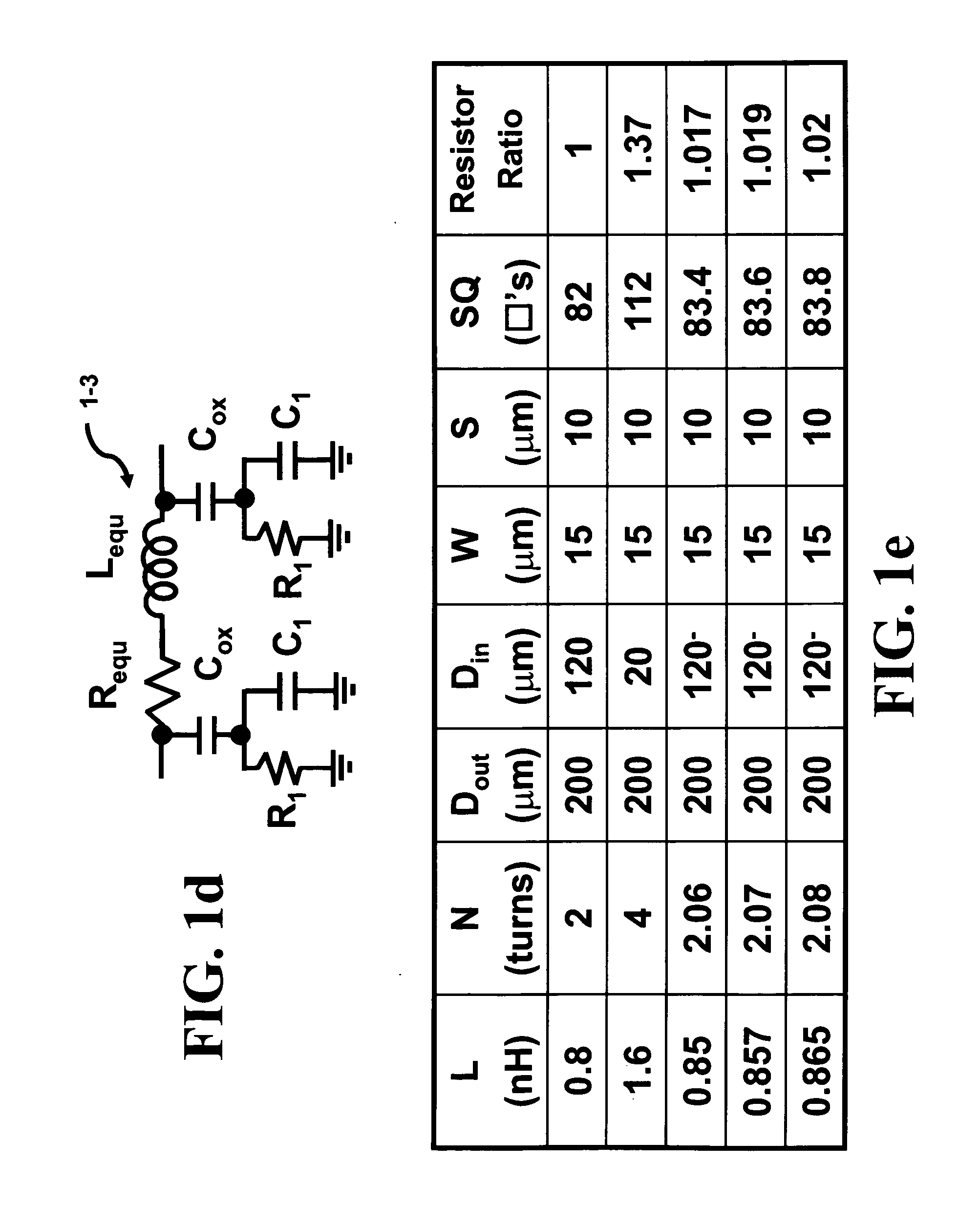

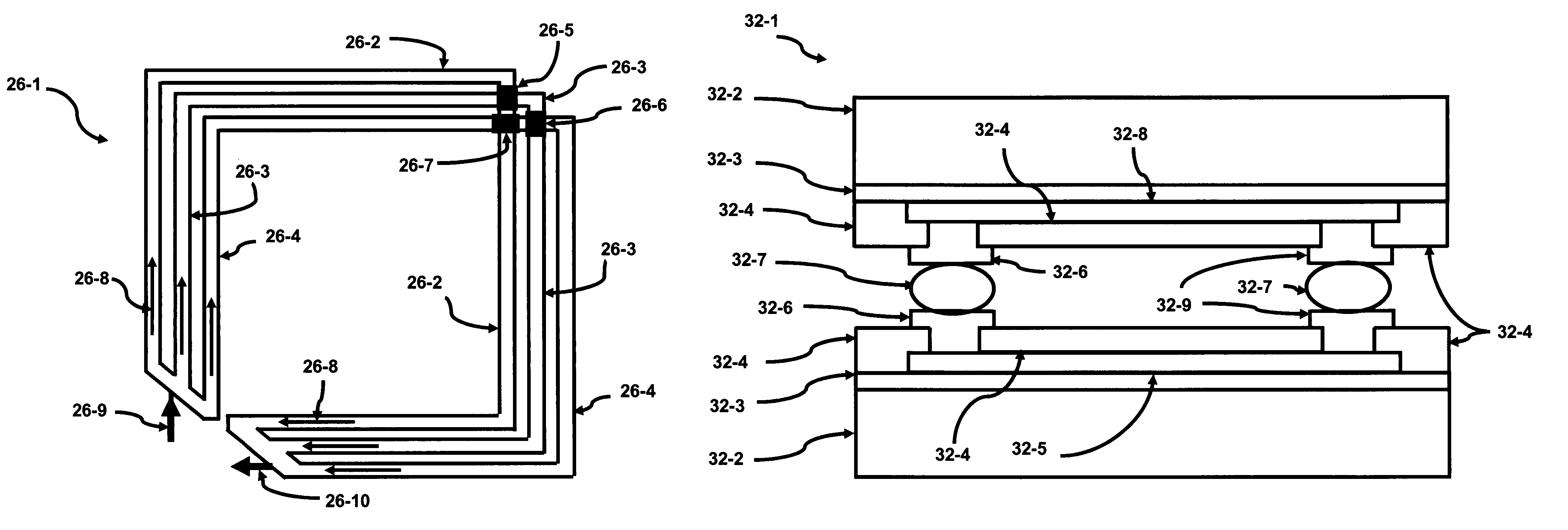

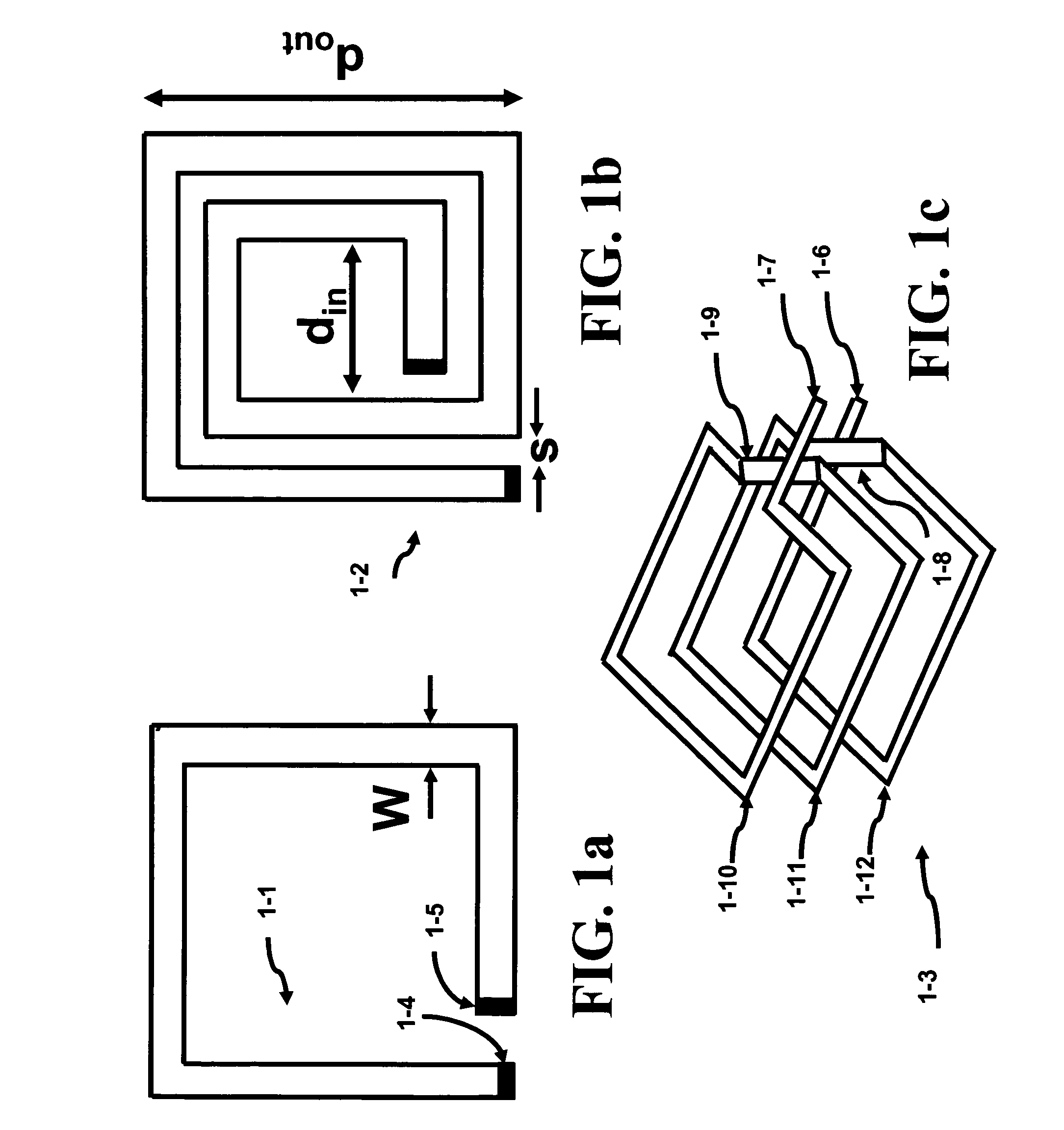

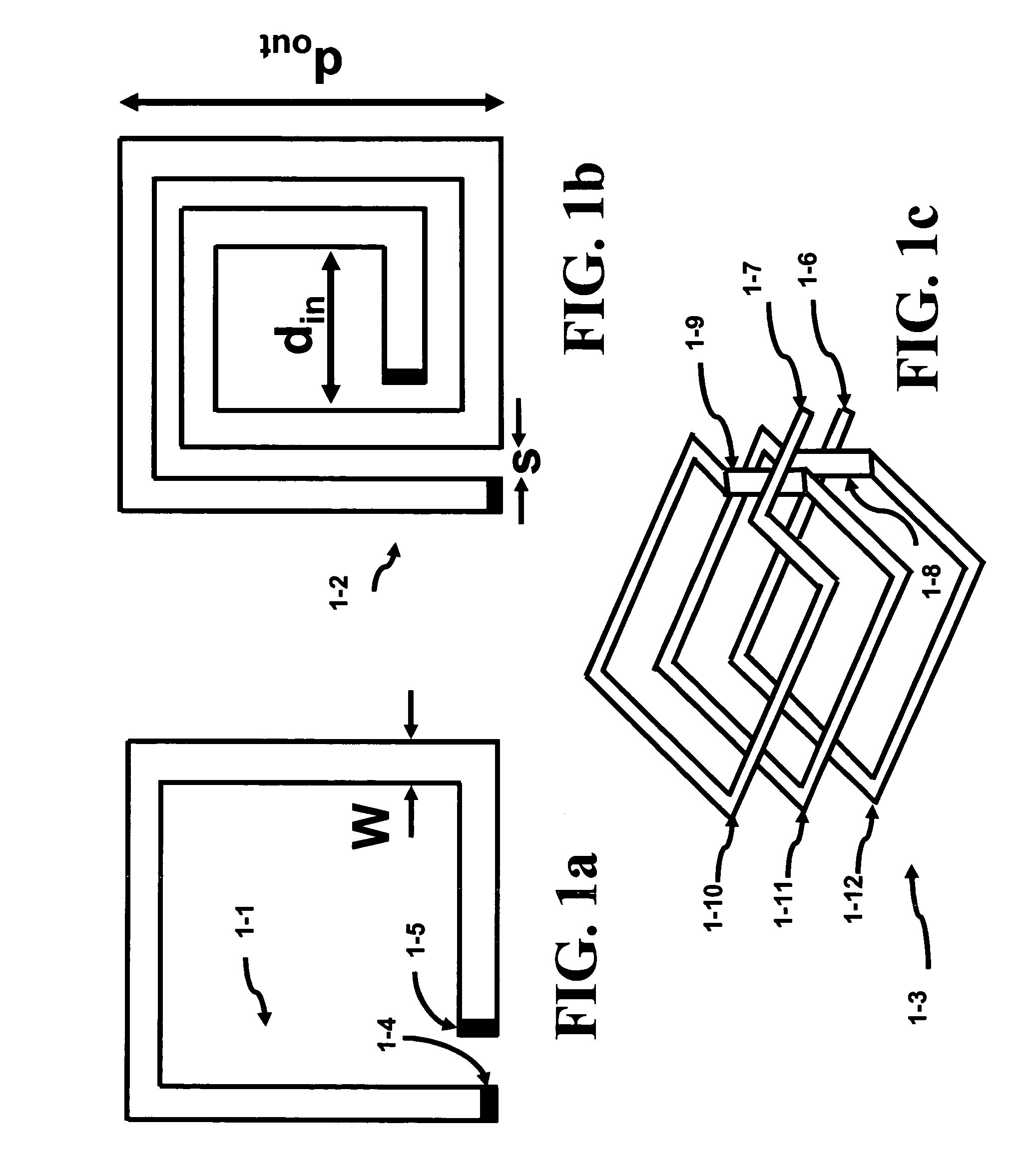

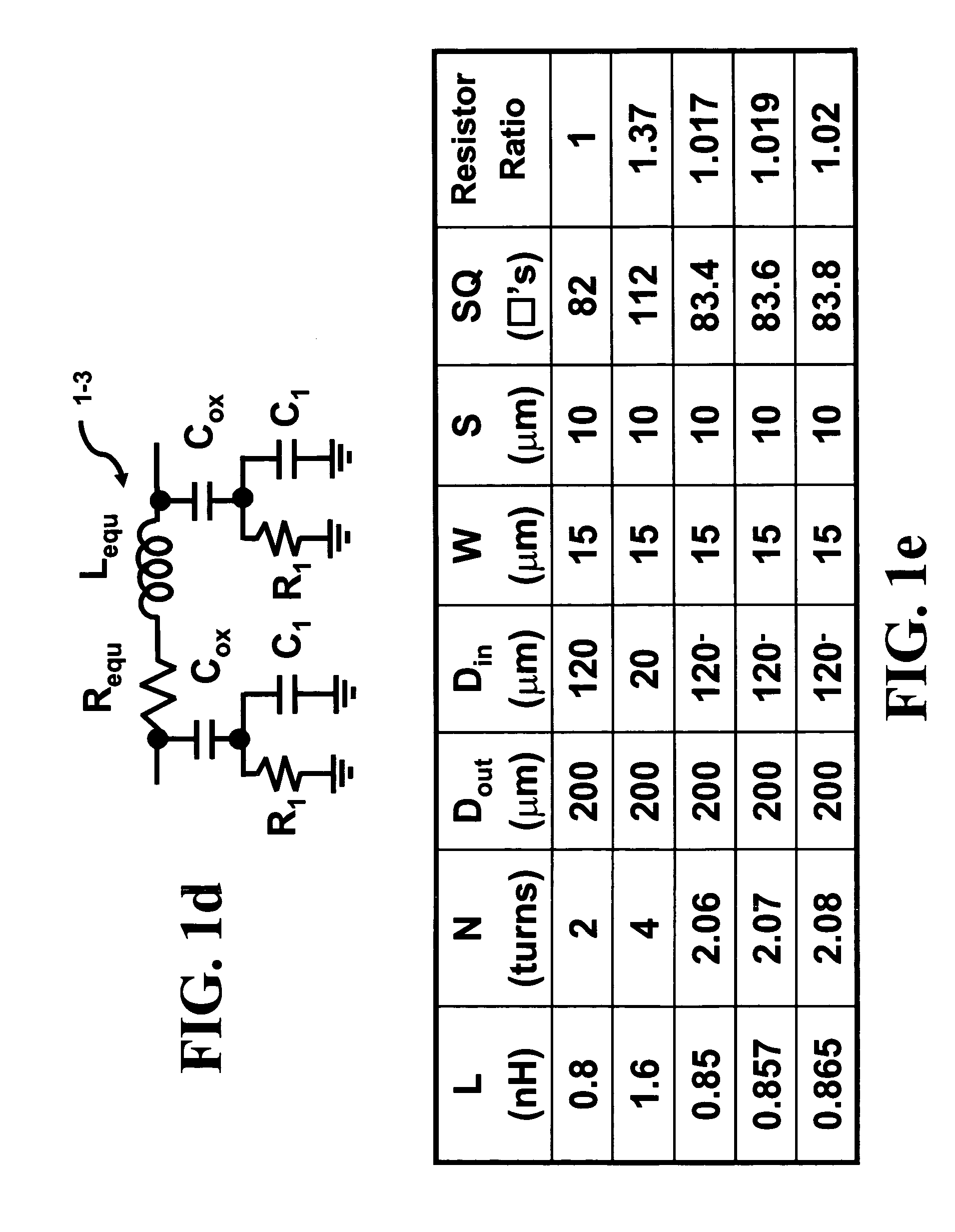

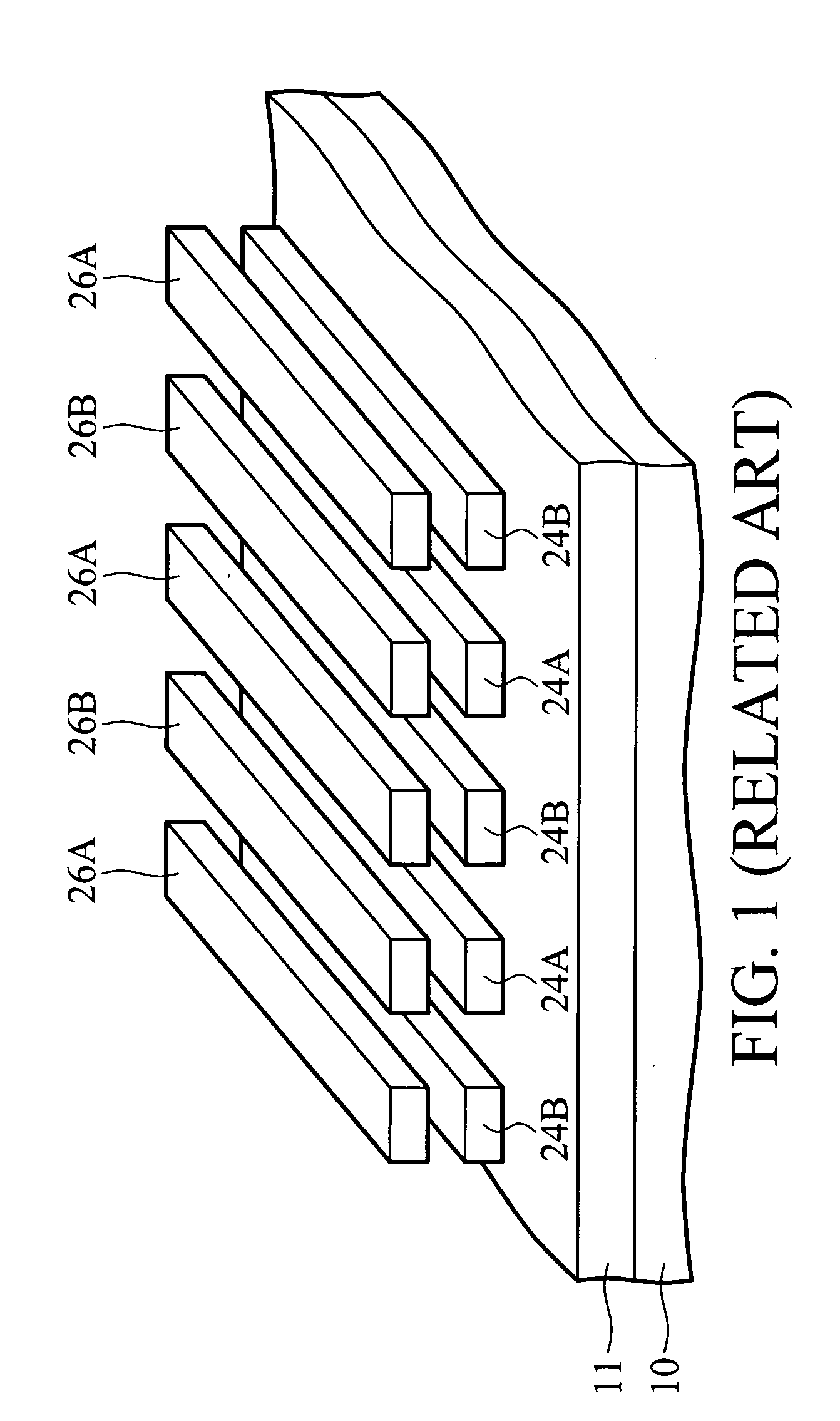

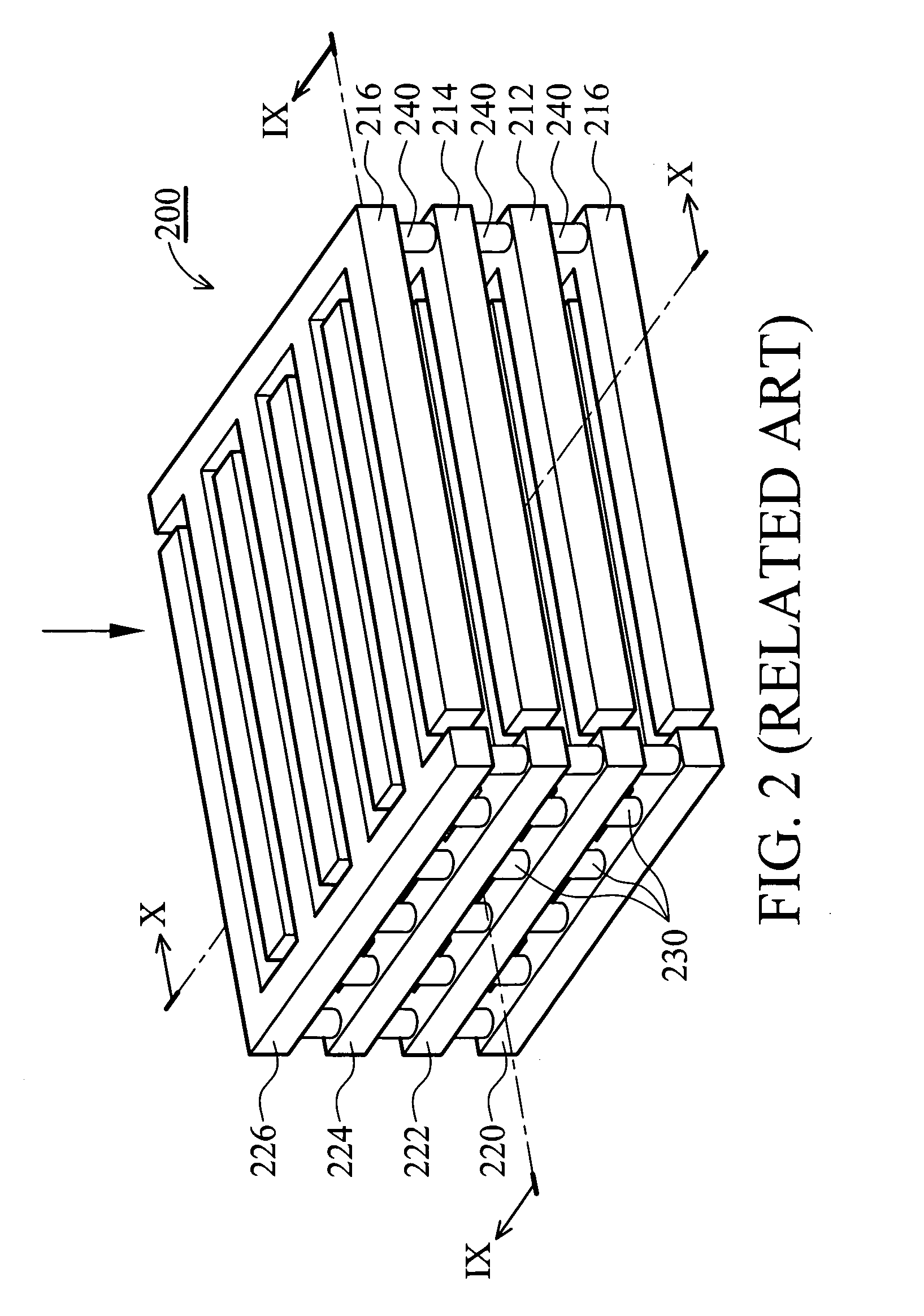

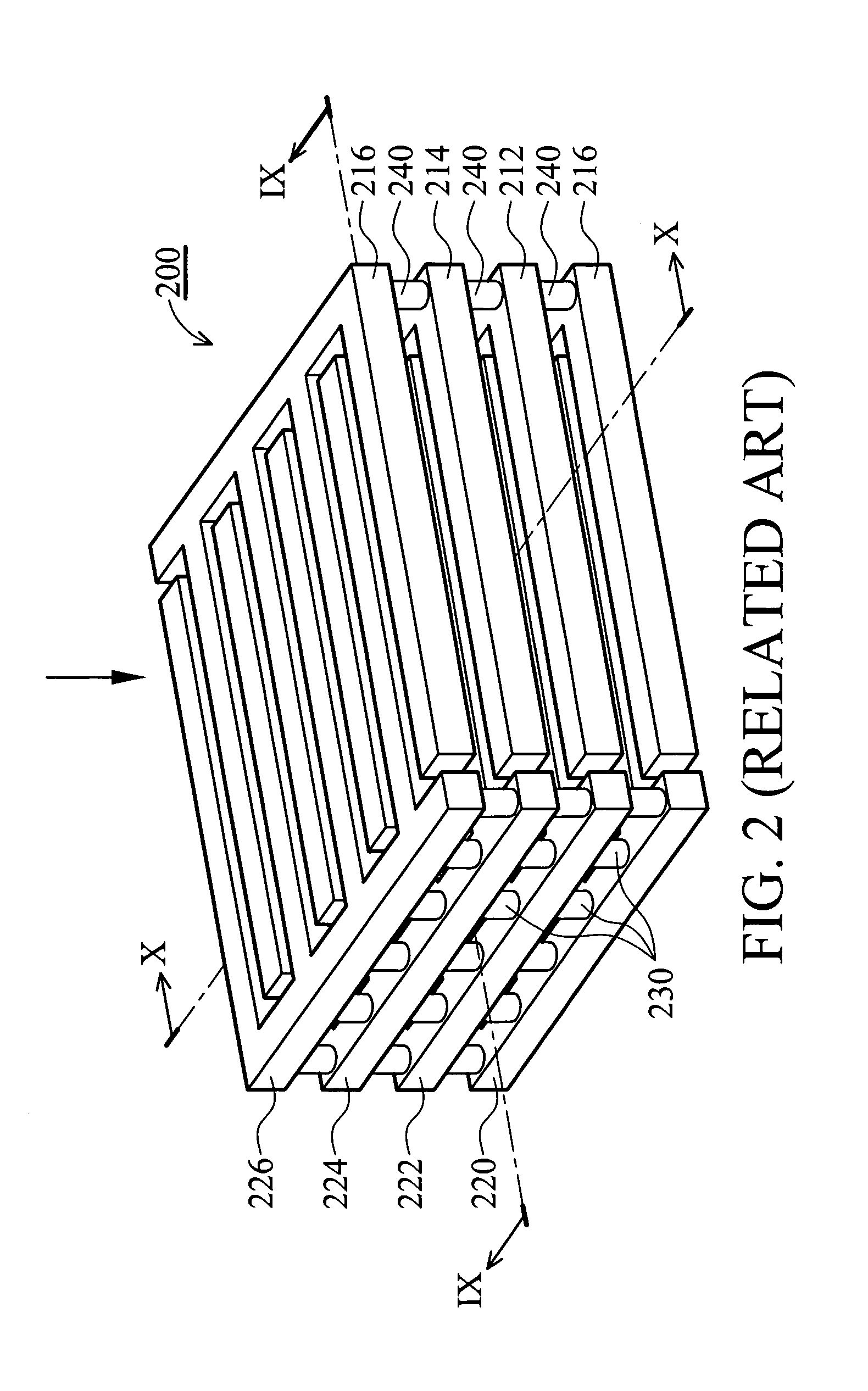

Fabrication of inductors in transformer based tank circuitry

ActiveUS20070018767A1Reduce the valueReduce energy lossSolid-state devicesPrinted inductancesElectrical resistance and conductanceTransformer

Placing inductors or resistors in parallel causes the combined value of inductance or resistance to decrease according to the parallel combination rule. This invention decreases the parasitic resistance of an inductor by placing several inductors in parallel. Furthermore, by careful placement of these inductors, the mutual inductance between these inductors can be used to increase the equivalent inductance value to a value near that of the original inductance value of a single inductor. Thus, it is possible to create an inductance with a much lower value of parasitic resistance. This invention allows the formation of high Q inductors and would be beneficial in any circuit design requiring inductances. Another aspect of this invention is that the coils can be partitioned to minimize eddy current losses. This invention can easily be implemented in a planar technology. Simulations of several tank circuits indicate that the power dissipation can be reduced 3 to 4 times when compared to conventional techniques.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

Method for manufacturing field-effect transistor

ActiveUS8110436B2Improve conductivityImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesSteam pressureAtmospheric air

A method for manufacturing a field-effect transistor is provided. The field-effect transistor includes on a substrate a source electrode, a drain electrode, an oxide semiconductor layer, an insulating layer and a gate electrode. The method includes, after forming the insulating layer on the oxide semiconductor layer, an annealing step of increasing the electrical conductivity of the oxide semiconductor layers by annealing in an atmosphere containing moisture. The steam pressure at the annealing step is higher than the saturated vapor pressure in the atmosphere at the annealing temperature.

Owner:CANON KK

Fabrication of inductors in transformer based tank circuitry

ActiveUS7786836B2Reduce the valueReduce parasitic resistanceSolid-state devicesPrinted inductancesElectrical resistance and conductanceTransformer

Placing inductors or resistors in parallel causes the combined value of inductance or resistance to decrease according to the parallel combination rule. This invention decreases the parasitic resistance of an inductor by placing several inductors in parallel. Furthermore, by careful placement of these inductors, the mutual inductance between these inductors can be used to increase the equivalent inductance value to a value near that of the original inductance value of a single inductor. Thus, it is possible to create an inductance with a much lower value of parasitic resistance. This invention allows the formation of high Q inductors and would be beneficial in any circuit design requiring inductances. Another aspect of this invention is that the coils can be partitioned to minimize eddy current losses. This invention can easily be implemented in a planar technology. Simulations of several tank circuits indicate that the power dissipation can be reduced 3 to 4 times when compared to conventional techniques.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

Thin film transistor and method of manufacturing the same

ActiveUS8445902B2Parasitic resistanceAvoid controlSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenEngineering

Provided are a coplanar structure thin film transistor that allows a threshold voltage to change only a little under electric stress, and a method of manufacturing the same. The thin film transistor includes on a substrate at least: a gate electrode; a gate insulating layer; an oxide semiconductor layer including a source electrode, a drain electrode, and a channel region; a channel protection layer; and an interlayer insulating layer. The channel protection layer includes one or more layers, the layer in contact with the oxide semiconductor layer among the one or more layers being made of an insulating material containing oxygen, ends of the channel protection layer are thinner than a central part of the channel protection layer, the interlayer insulating layer contains hydrogen, and regions of the oxide semiconductor layer that are in direct contact with the interlayer insulating layer form the source electrode and the drain electrode.

Owner:CANON KK

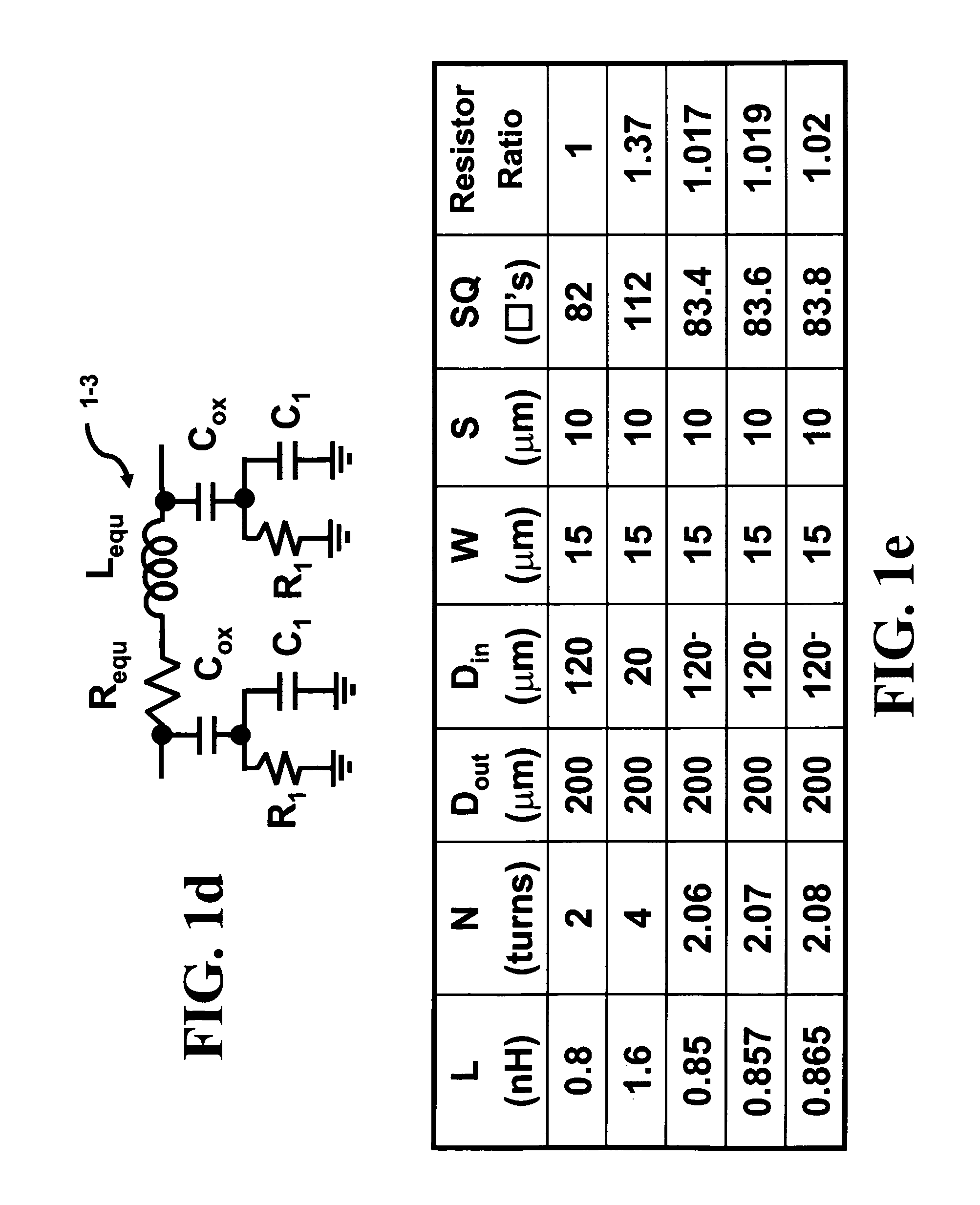

Semiconductor device and manufacturing process therefor

InactiveUS20070075372A1Easy alignmentReduce contact resistanceTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

There is provided a semiconductor device wherein at least the largest width of a source / drain region is larger than the width of a semiconductor region and the source / drain region has a slope having a width continuously increasing from the uppermost side to the substrate side, and a silicide film is formed in the surface of the slope.

Owner:NEC CORP

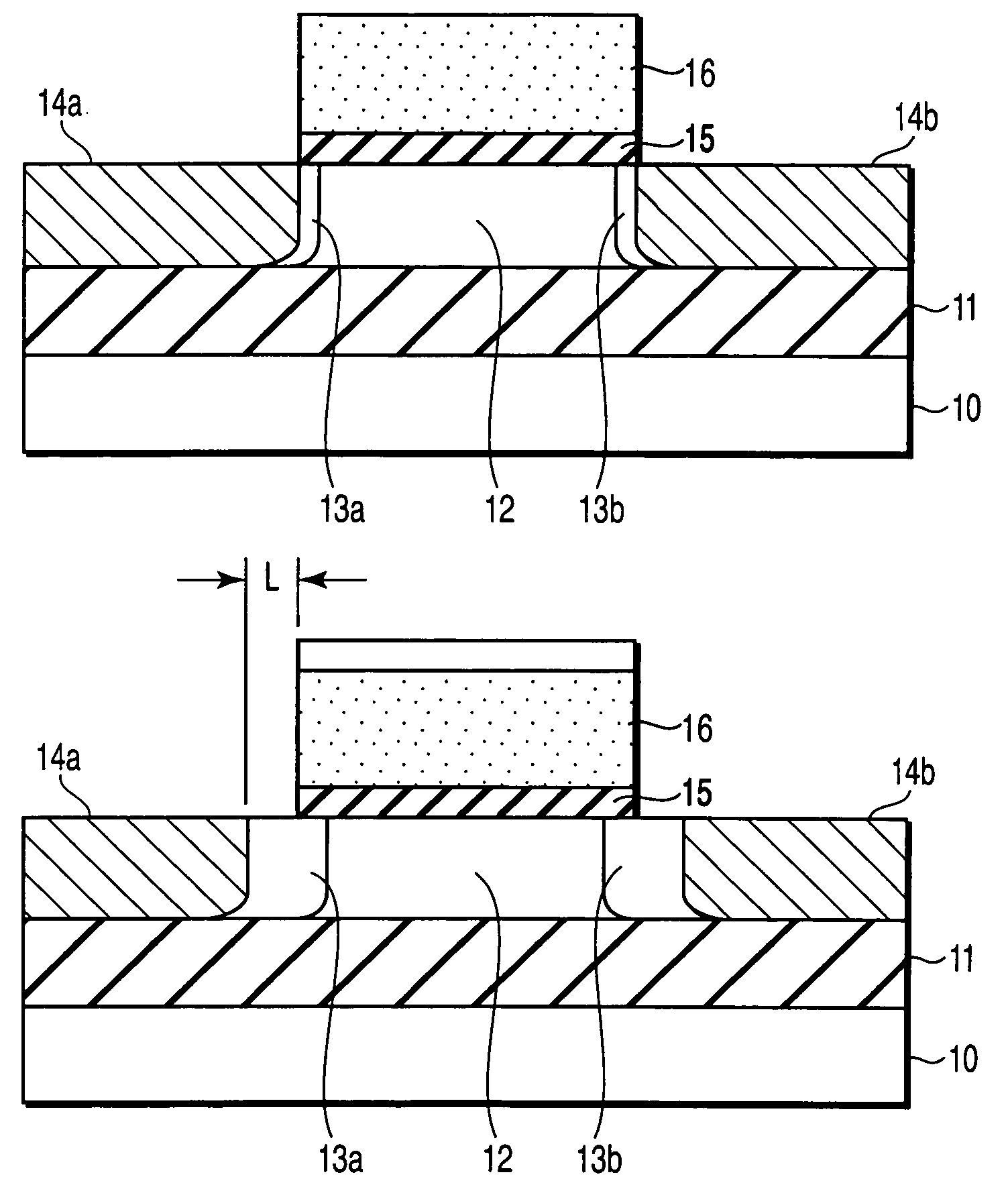

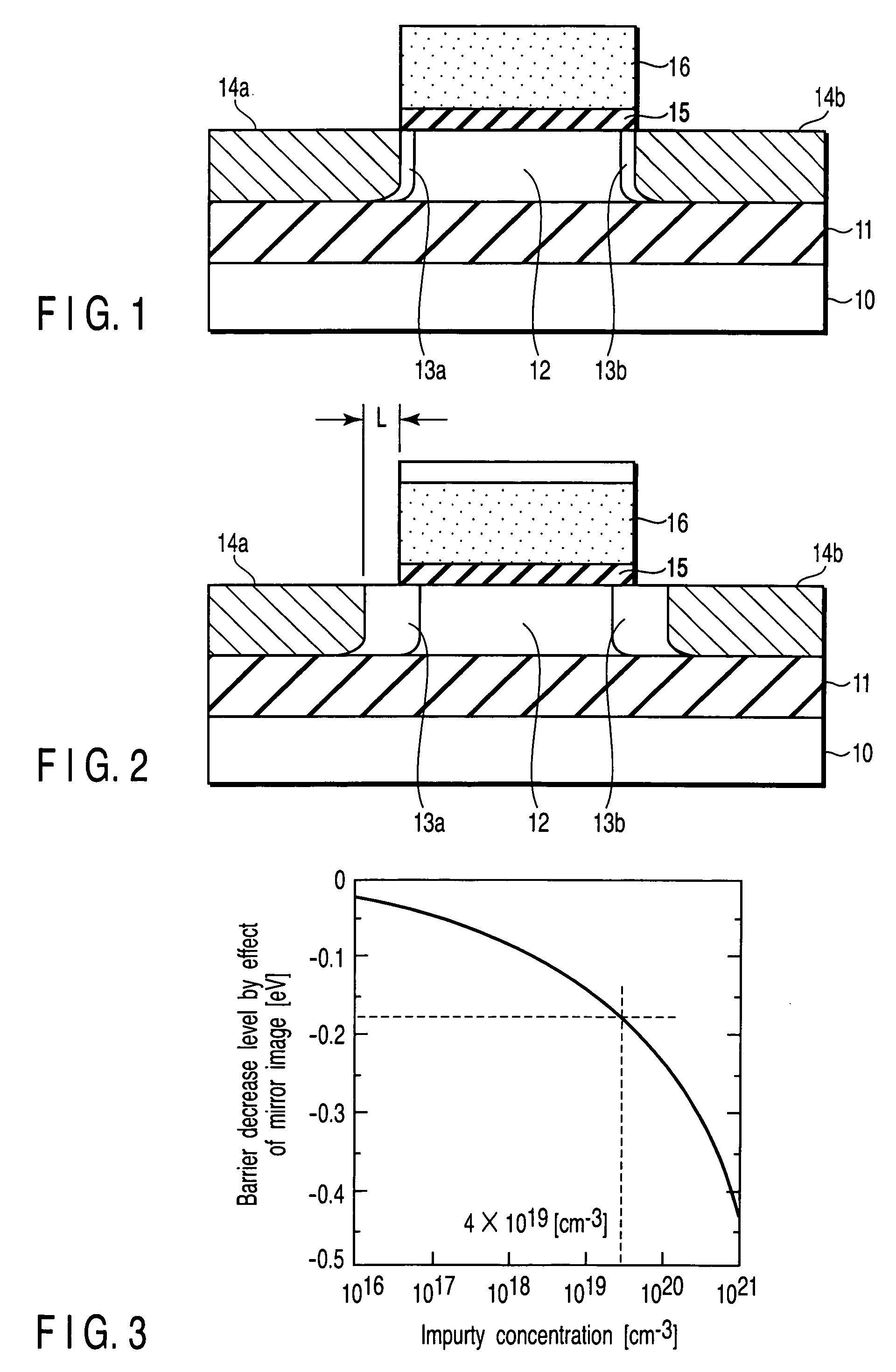

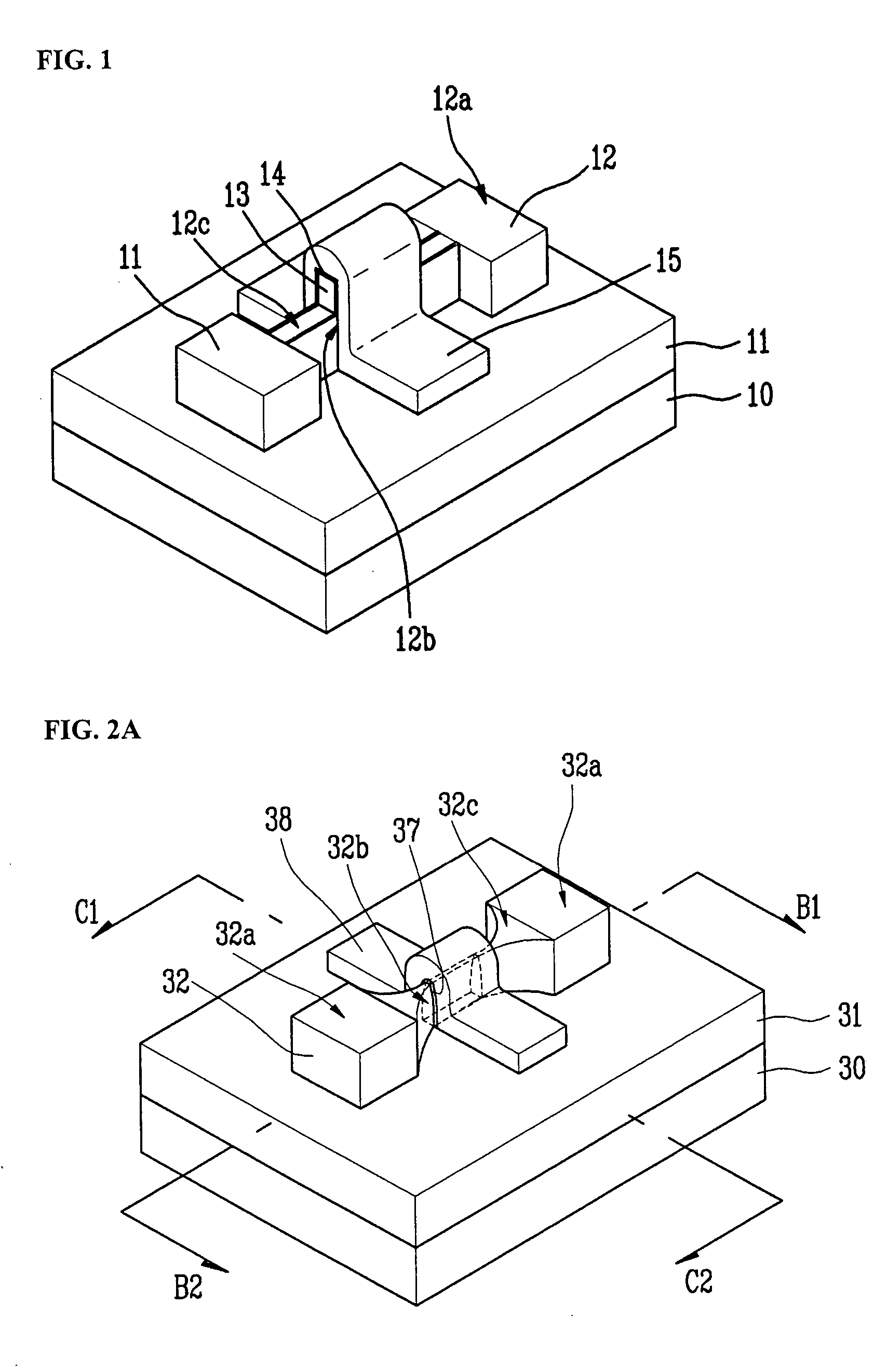

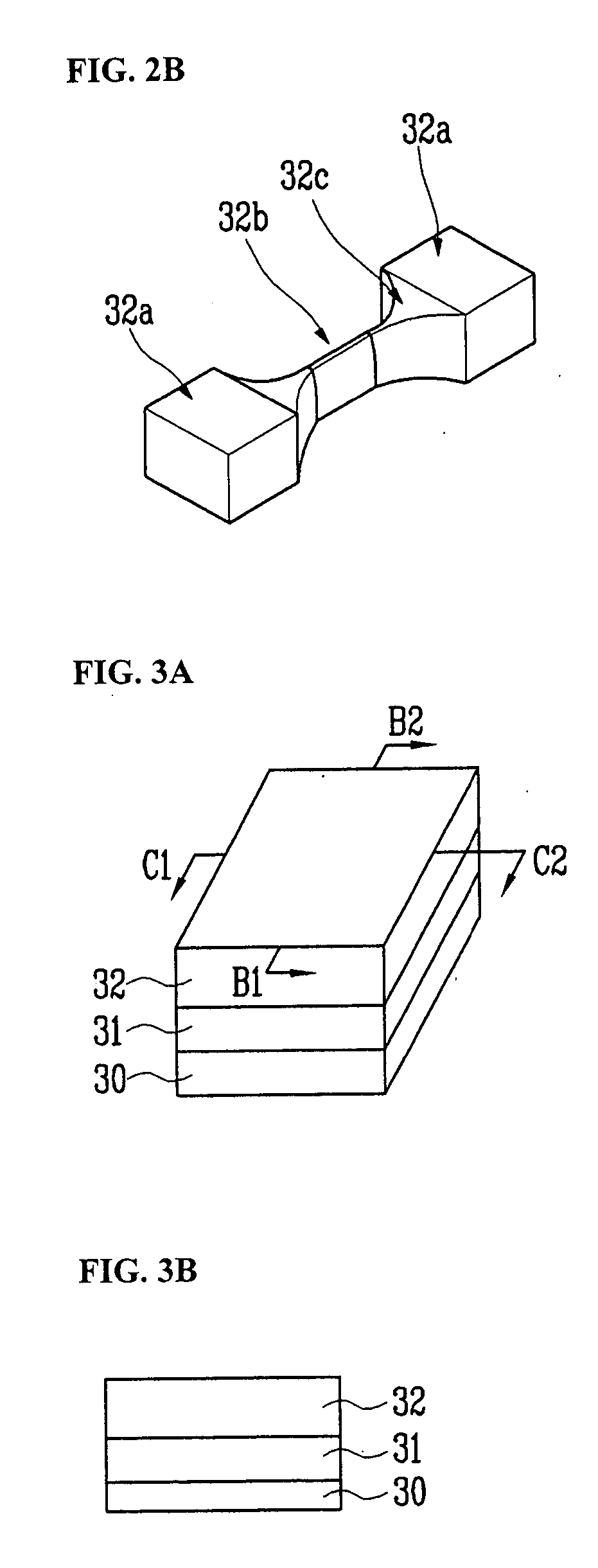

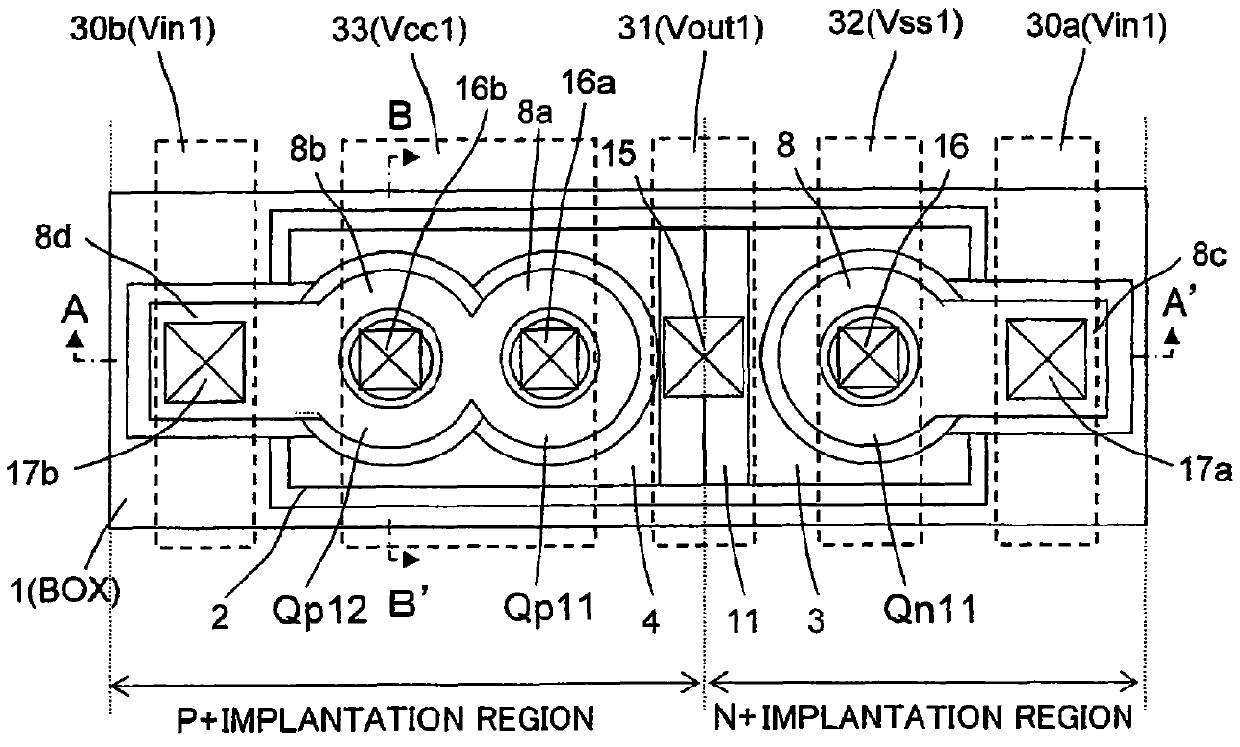

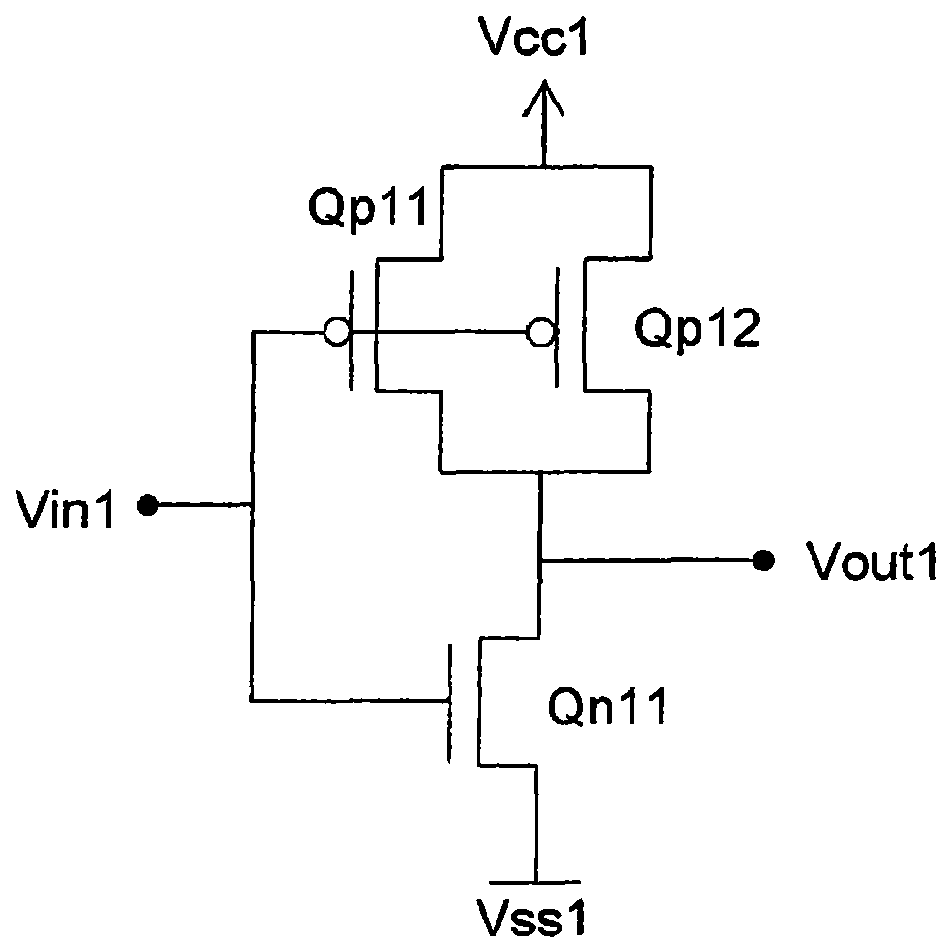

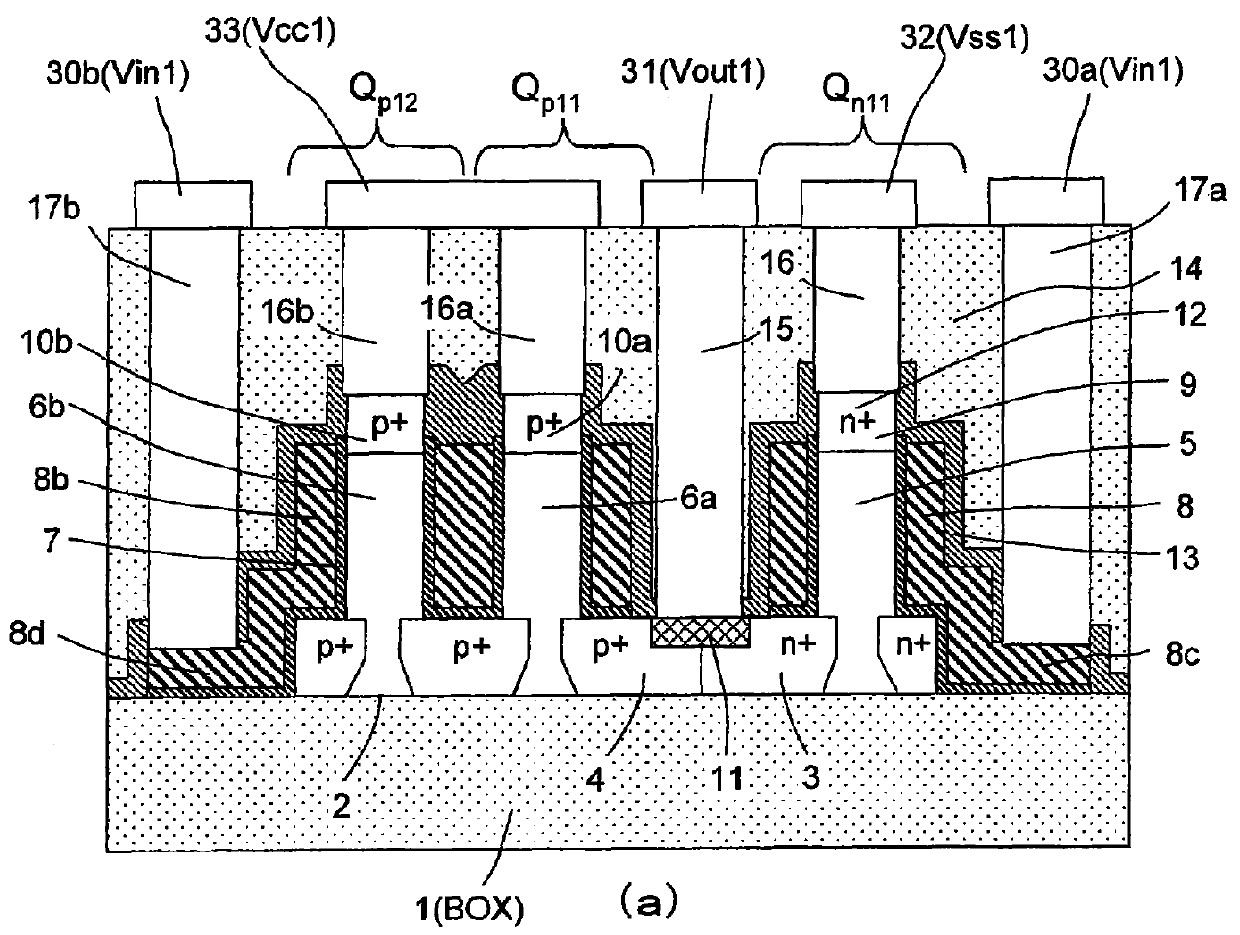

Field effect transistor and manufacturing method thereof

InactiveUS20050093033A1High impurity concentrationHigh concentrationTransistorSolid-state devicesEngineeringField-effect transistor

A field effect transistor includes a first semiconductor region forming a channel region, a gate electrode insulatively disposed above the first semiconductor region, source and drain electrodes formed to sandwich the first semiconductor region in a channel lengthwise direction, and second semiconductor regions formed between the first semiconductor region and the source and drain electrodes and having impurity concentration higher than the first semiconductor region. The thickness of the second semiconductor region in the channel lengthwise direction is set to a value equal to or less than depletion layer width determined by the impurity concentration so that the second semiconductor region is depleted in a no-voltage application state.

Owner:KK TOSHIBA

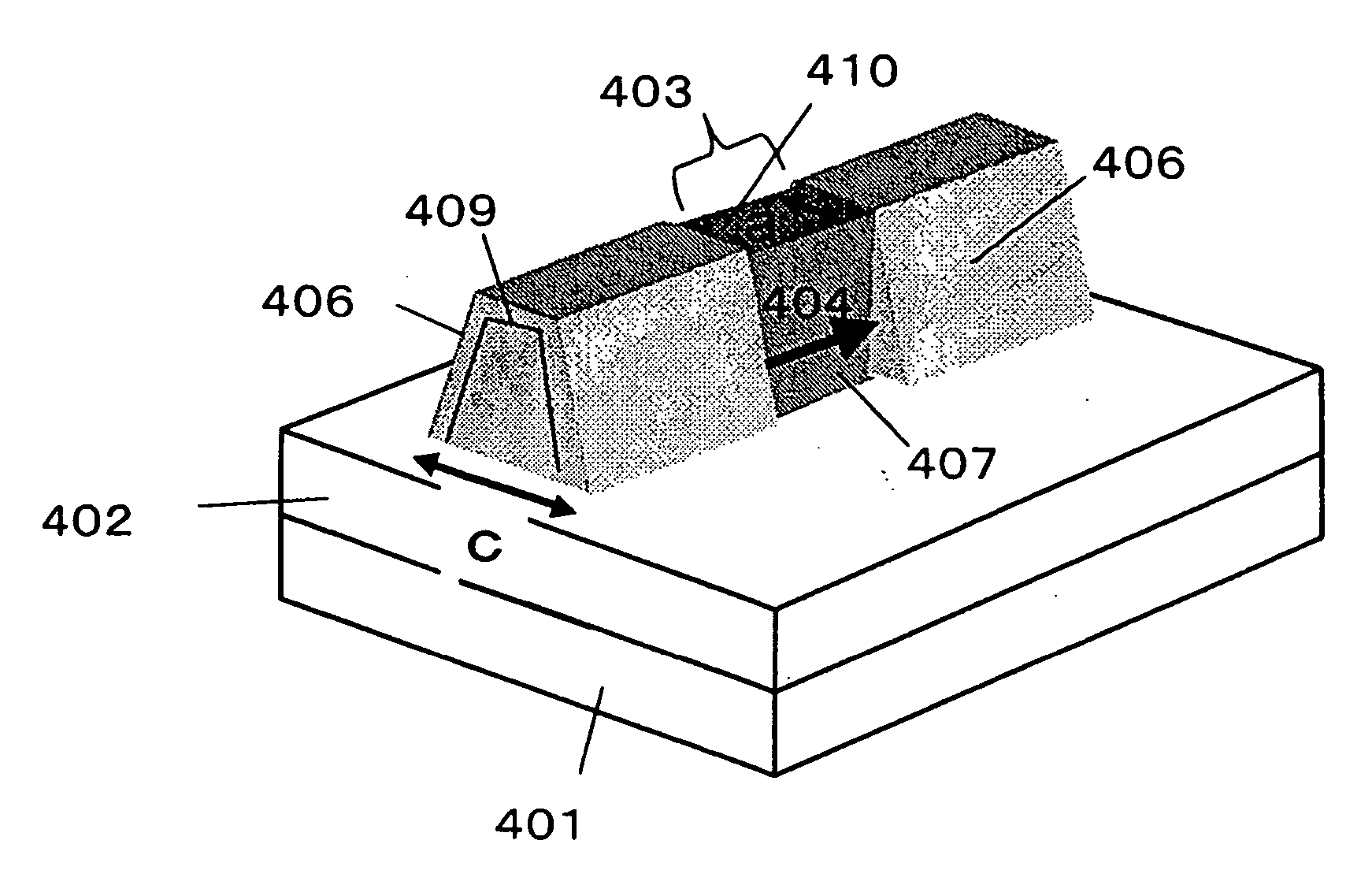

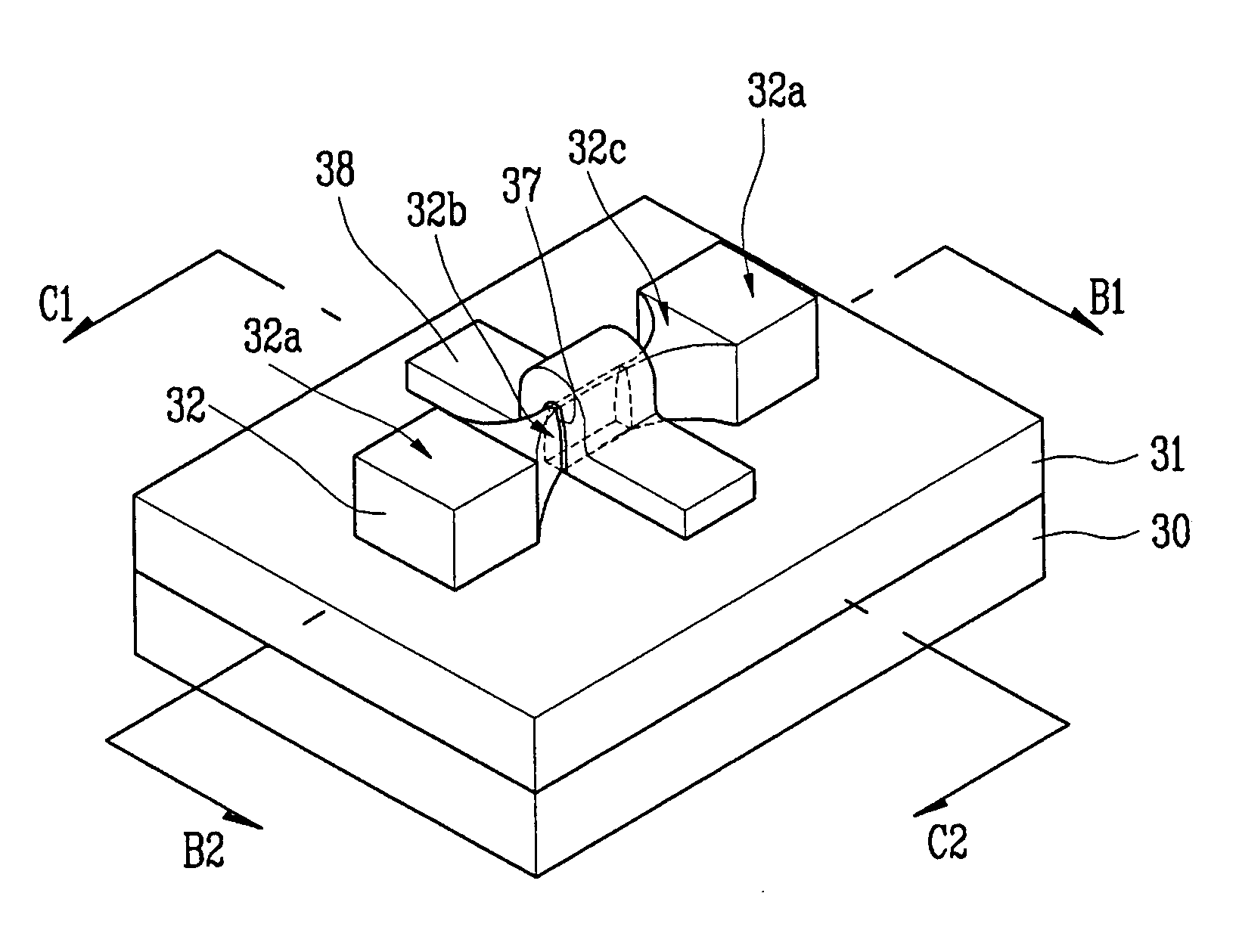

Multiple-gate MOS transistor and a method of manufacturing the same

InactiveUS20050263821A1Improve reliabilityImprove rendering capabilitiesTransistorGrinding drivesCrystal orientationGate voltage

Provided is a multiple-gate metal oxide semiconductor (MOS) transistor and a method for manufacturing the same, in which a channel is implemented in a streamline shape, an expansion region is implemented in a gradually increased form, and source and drain regions is implemented in an elevated structure by using a difference of a thermal oxidation rate depending on a crystal orientation of silicon and a geographical shape of the single-crystal silicon pattern. As the channel is formed in a streamline shape, it is possible to prevent the degradation of reliability due to concentration of an electric field and current driving capability by the gate voltage is improved because the upper portion and both sides of the channel are surrounded by the gate electrodes. In addition, a current crowding effect is prevented due to the expansion region increased in size and source and drain series resistance is reduced by elevated source and drain structures, thereby increasing the current driving capability.

Owner:III HLDG 2

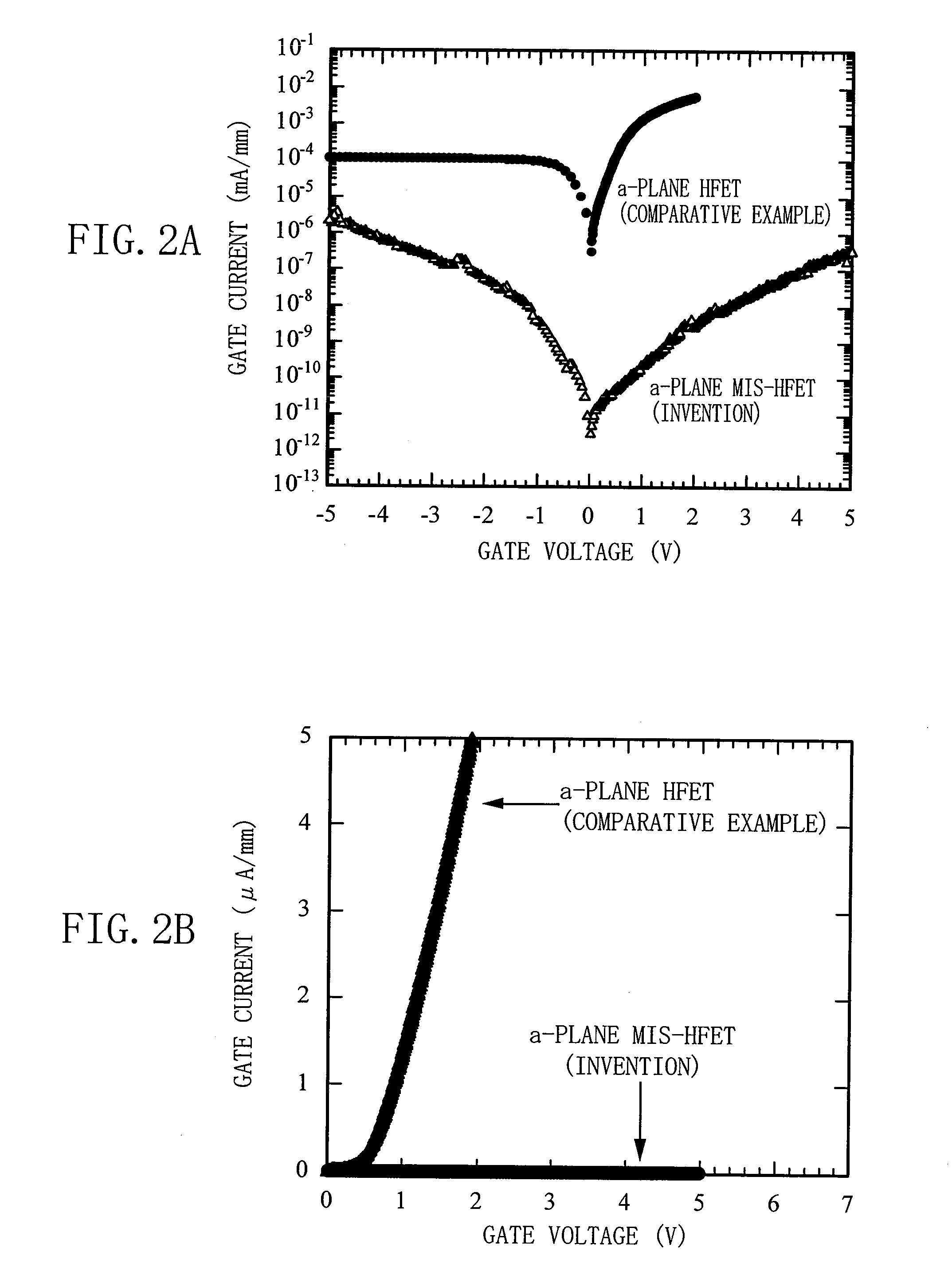

Field effect transistor

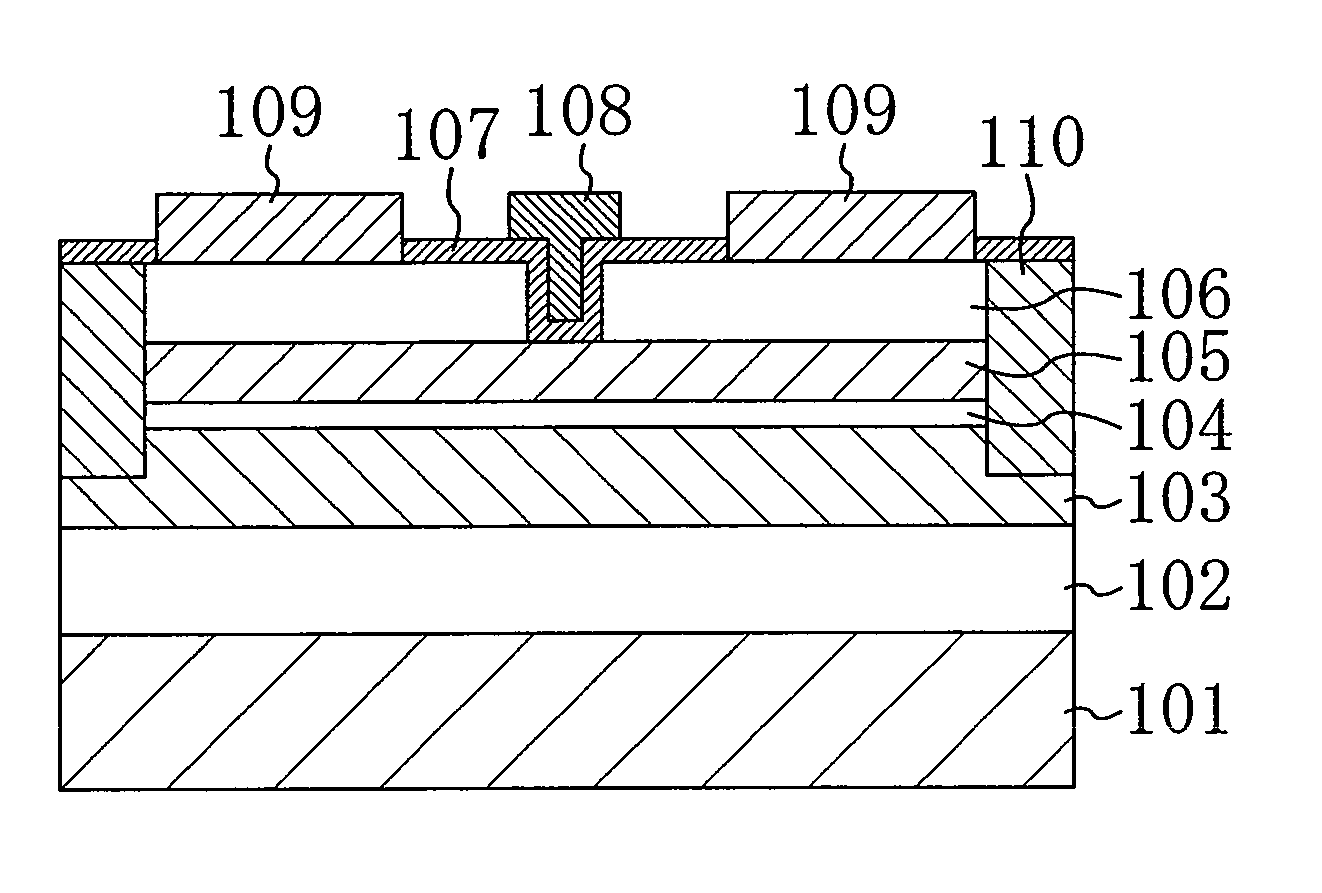

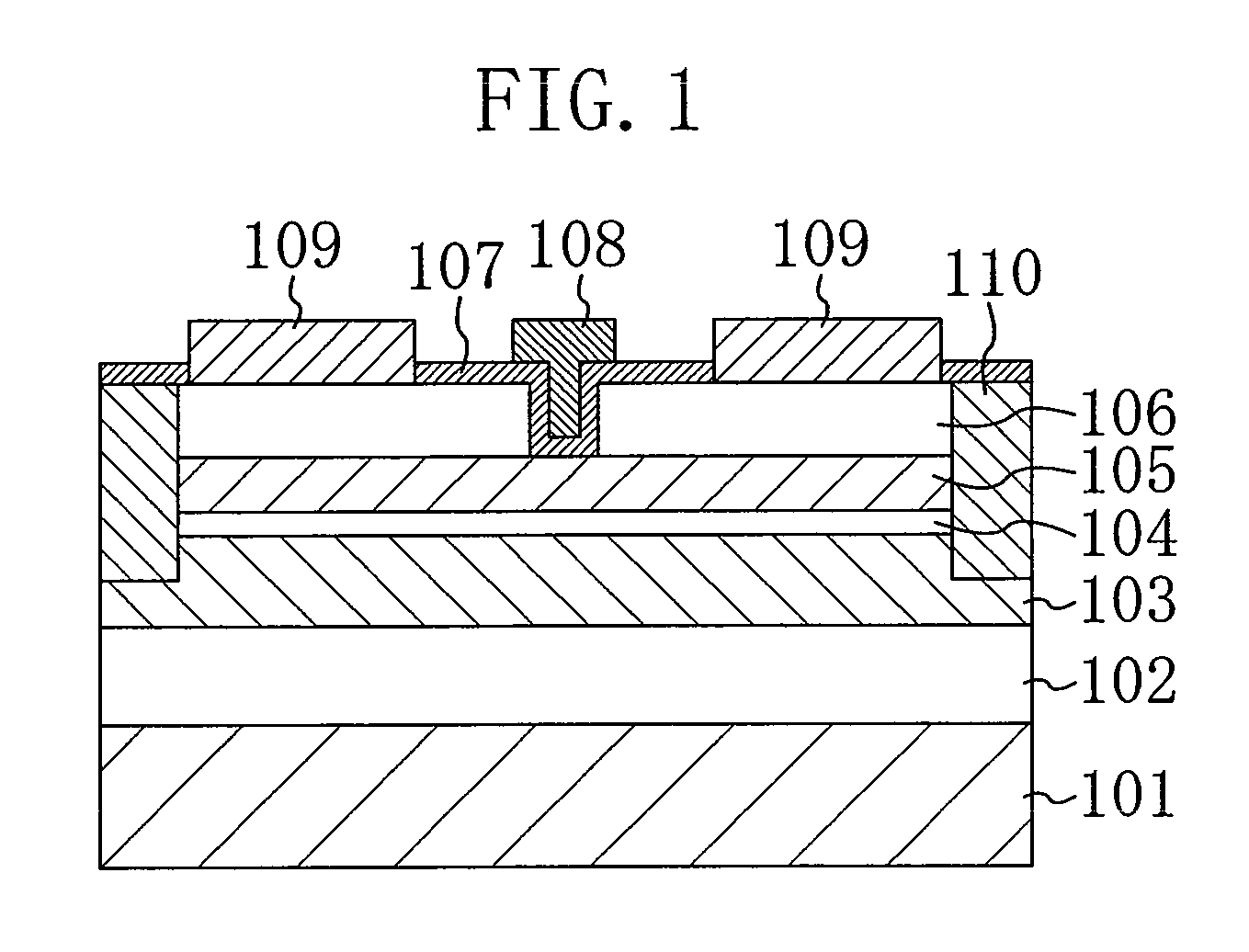

ActiveUS20080258243A1Suppress generationReduced series resistanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringField effect

A field effect transistor includes: a first nitride semiconductor layer having a plane perpendicular to a (0001) plane or a plane tilted with respect to the (0001) plane as a main surface; a second nitride semiconductor layer formed on the first nitride semiconductor layer and having a wider bandgap than the first nitride semiconductor layer; a third nitride semiconductor layer formed on the second nitride semiconductor layer; and a source electrode and a drain electrode formed so as to contact at least a part of the second nitride semiconductor layer or the third nitride semiconductor layer. A recess that exposes a part of the second nitride semiconductor layer is formed between the source electrode and the drain electrode in the third nitride semiconductor layer. A gate electrode is formed in the recess and an insulating film is formed between the third nitride semiconductor layer and the gate electrode.

Owner:PANASONIC CORP

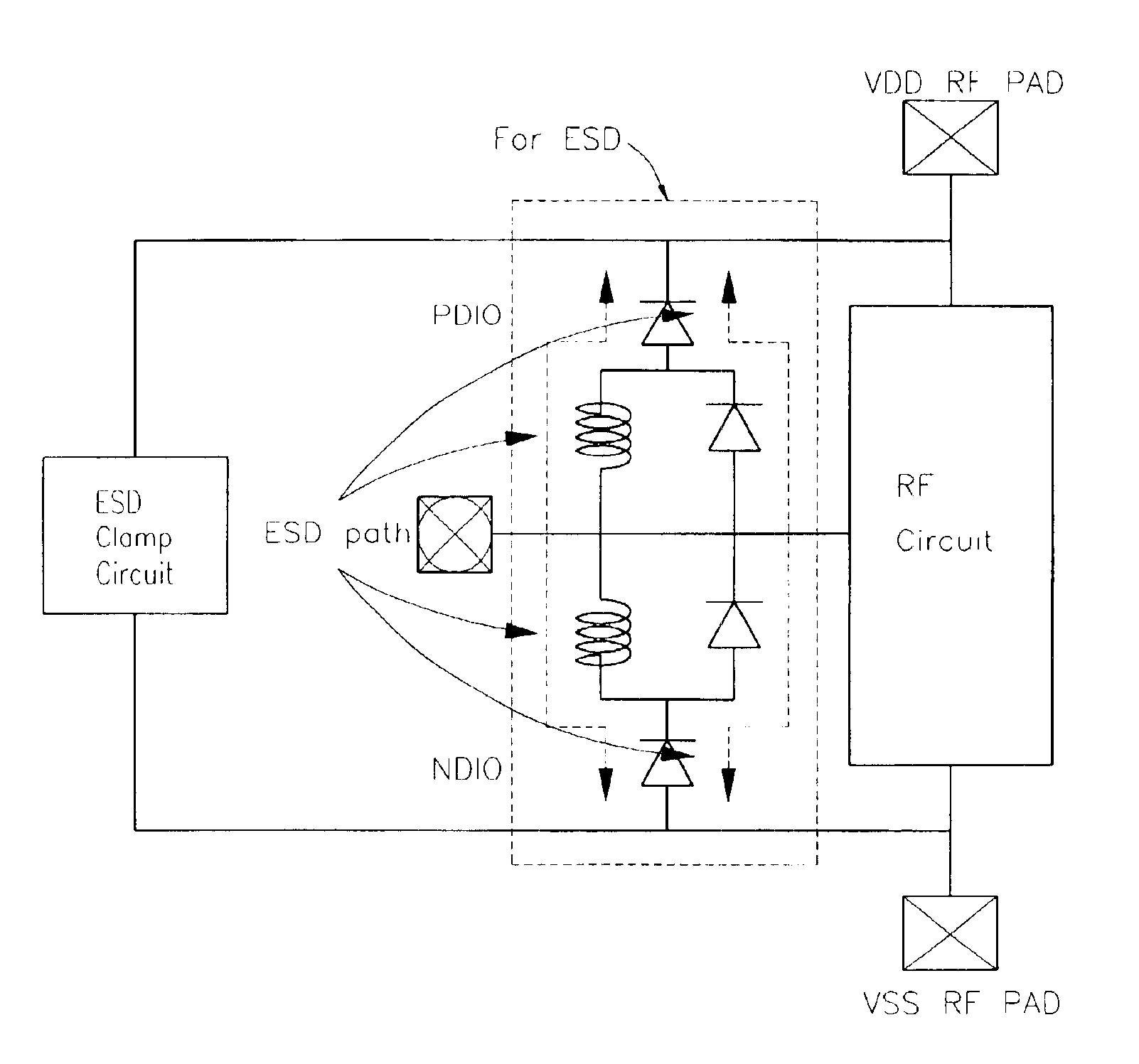

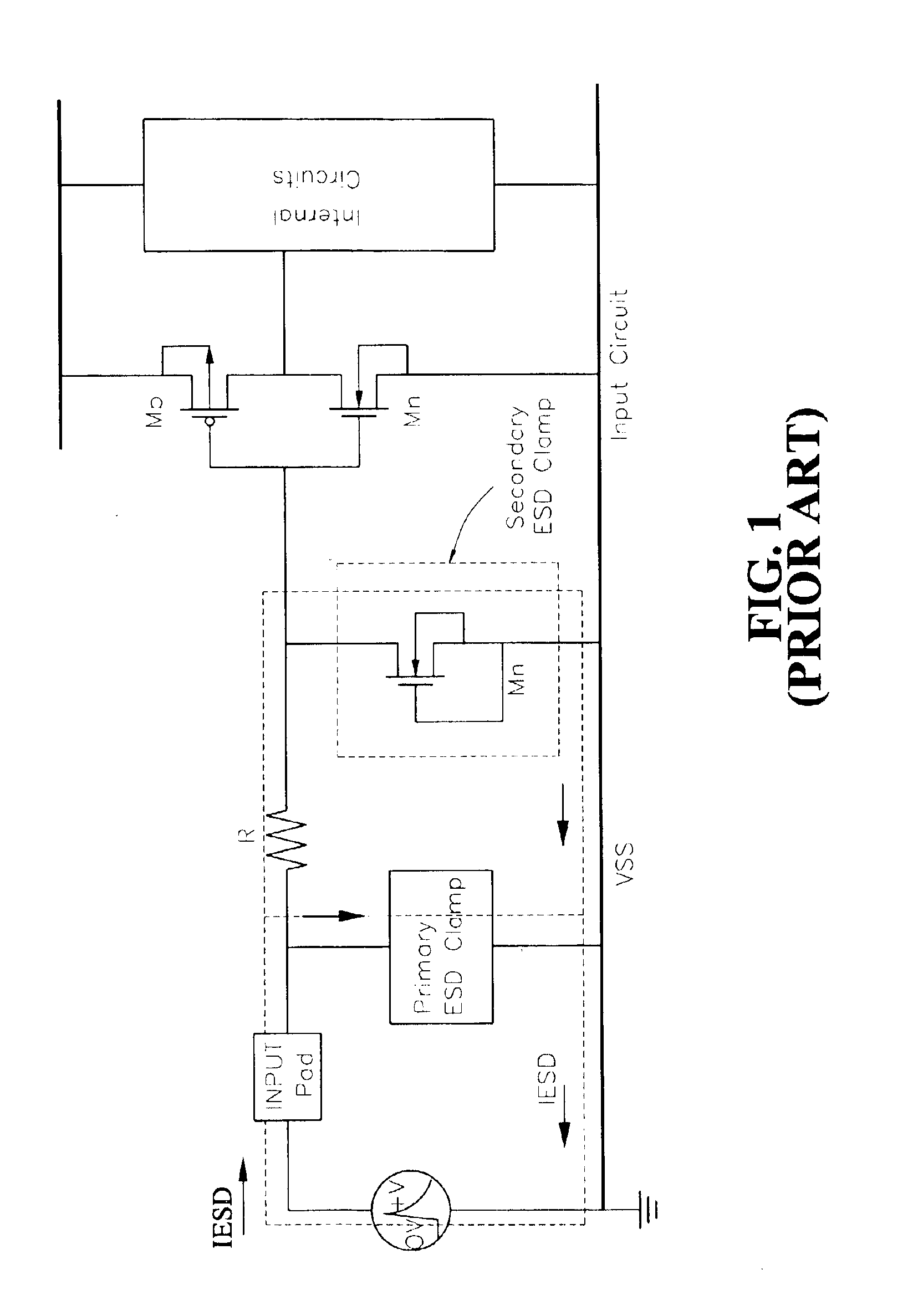

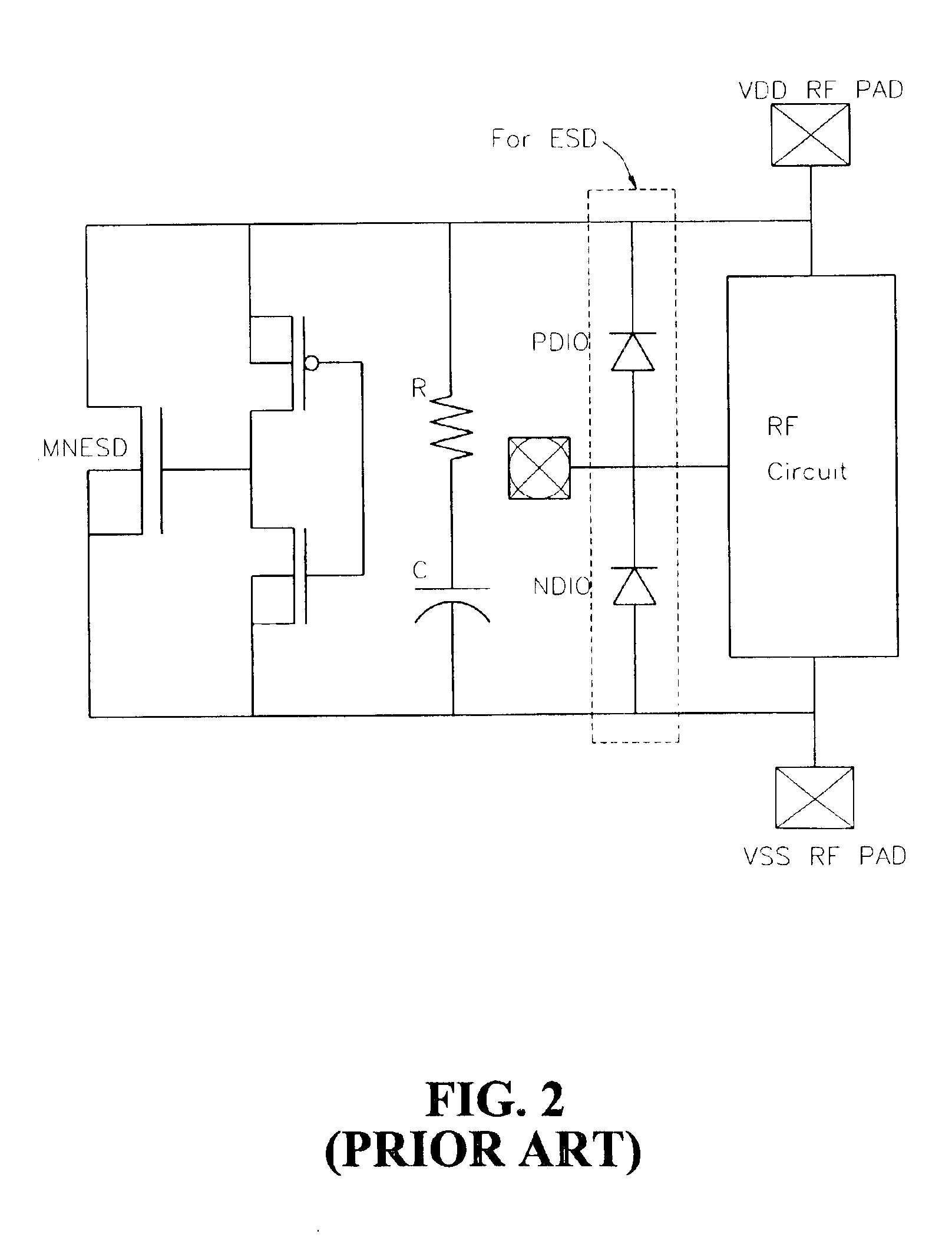

Electrostatic discharge protection device for giga-hertz radio frequency integrated circuits with varactor-LC tanks

InactiveUS6885534B2Solution value is not highHigh ESD levelSolid-state devicesEmergency protective arrangement detailsImpedance matchingEngineering

The present invention relates to a device for protecting high frequency RF integrated circuits from ESD damage. The device comprises at least one varactor-LC circuit tank stacked to avoid the power gain loss by the parasitic capacitance of ESD circuit. The varactor-LC tank could be designed to resonate at the RF operating frequency to avoid the power gain loss from the parasitic capacitance of ESD circuit. Multiple LC-tanks could be stacked for further reduction in the power gain loss. A reverse-biased diode is used as the varactor for both purposes of impedance matching and effective ESD current discharging. Because the inductor is made of metal, both the inductor and the varactor can discharge ESD current when ESD condition happens. It has a high enough ESD level to prevent ESD discharge.

Owner:LIBERTY PATENTS LLC

Semiconductor device and production method therefor

ActiveUS8188537B2Easy to integrateImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingCondensed matter physicsSemiconductor

It is intended to provide a semiconductor device including a MOS transistor, comprising: a semiconductor pillar; one of a drain region and a source region formed in contact with a lower part of the semiconductor pillar; a first gate formed around a sidewall of the semiconductor pillar through a first dielectric film therebetween; and an epitaxial semiconductor layer formed on a top surface of the semiconductor pillar, wherein the other of the source region and the drain region is formed so as to be at least partially in the epitaxial semiconductor layer, and wherein: the other of the source region and the drain region has a top surface having an area greater than that of the top surface of the semiconductor pillar.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

Monolithically integrated III-nitride power converter

ActiveUS7863877B2Improve performanceReduces parasitic inductancesEfficient power electronics conversionSolid-state devicesEngineeringNitride

Owner:INFINEON TECH AMERICAS CORP

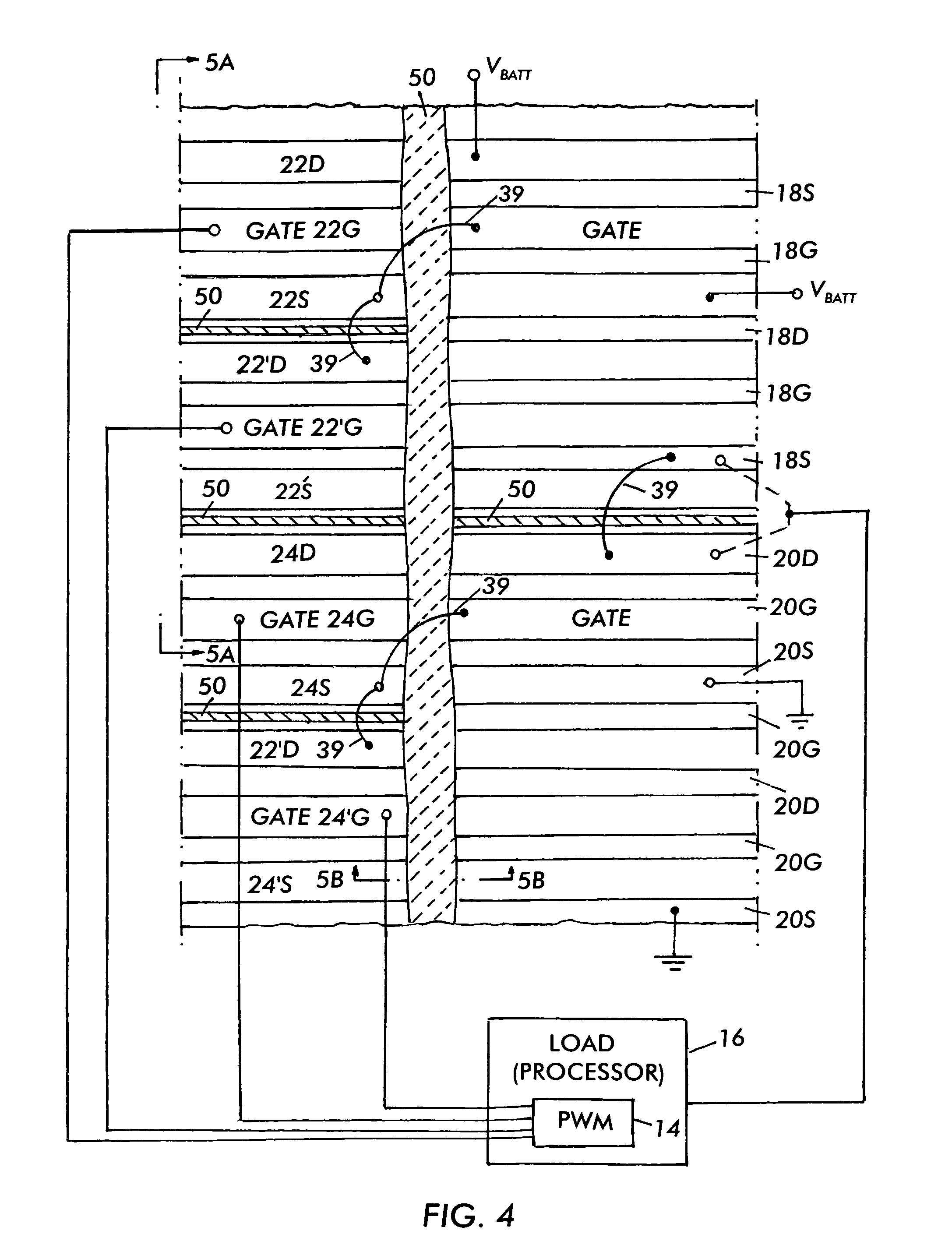

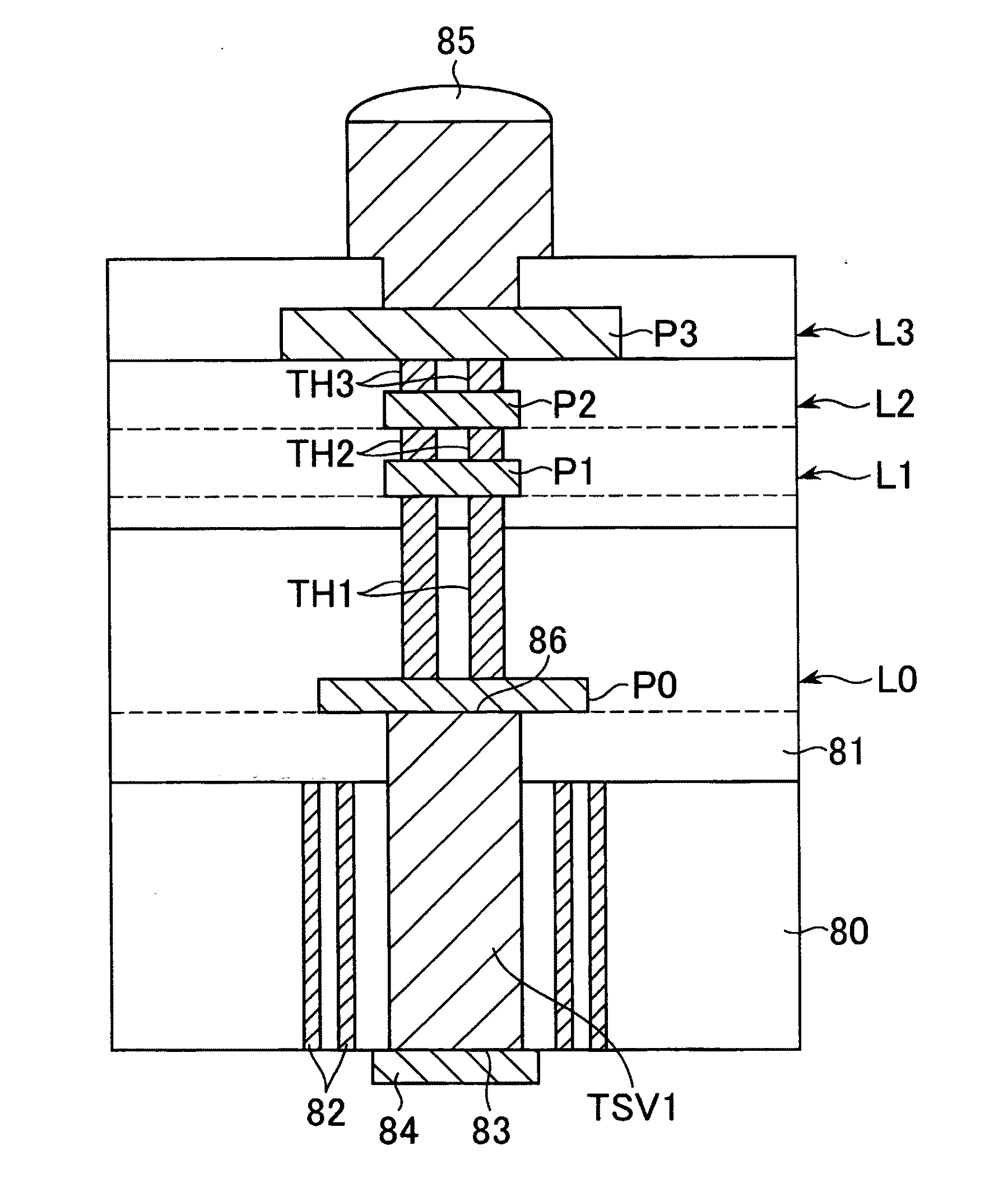

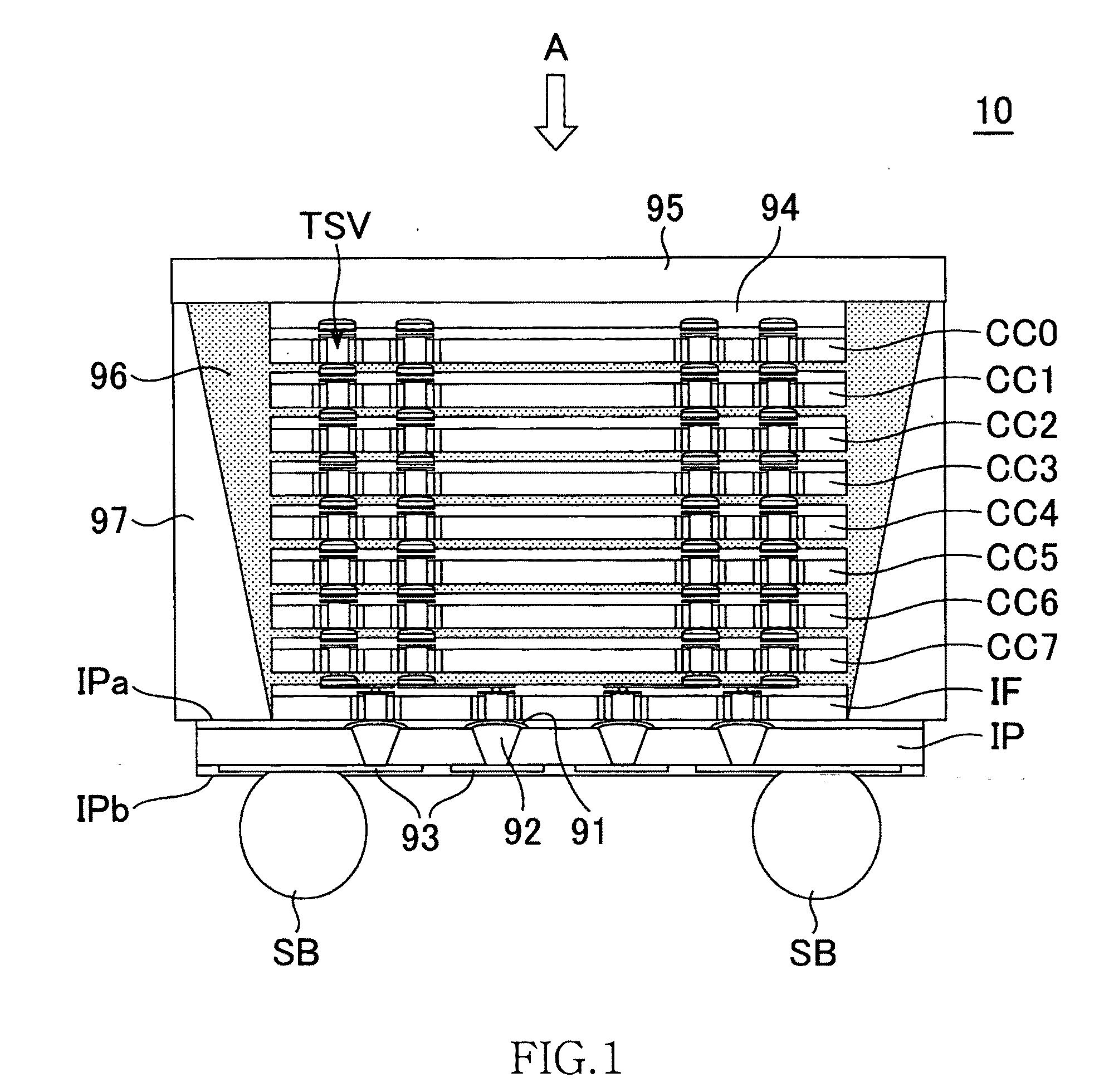

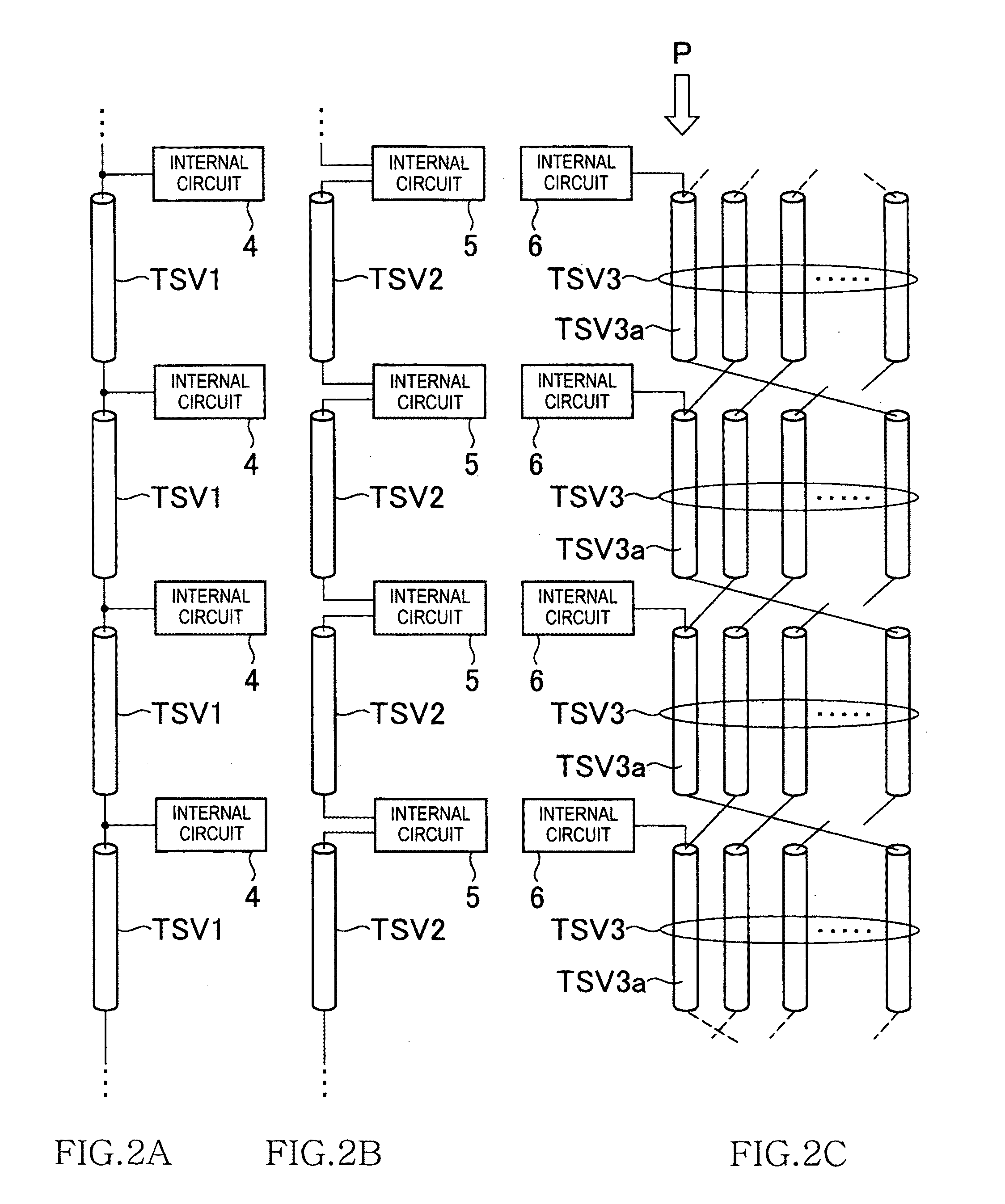

Semiconductor device and information processing system including the same

ActiveUS20110084385A1Large capacitance componentImprove signal qualitySemiconductor/solid-state device detailsPrinted electric component incorporationInformation processingParasitic capacitance

A semiconductor device includes a plurality of core chips and an interface chip that controls the core chips. Each of the core chips and the interface chip includes plural through silicon vias that penetrate a semiconductor substrate and plural pads respectively connected to the through silicon vias. The through silicon vias include a through silicon via of a power source system to which a power source potential or a ground potential is supplied, and a through silicon via of a signal system to which various signals are supplied. Among the pads, at least an size of a pad connected to the through silicon via of the power source system is larger than a size of a pad connected to the through silicon via of the signal system. Therefore, a larger parasitic capacitance can be secured.

Owner:LONGITUDE LICENSING LTD

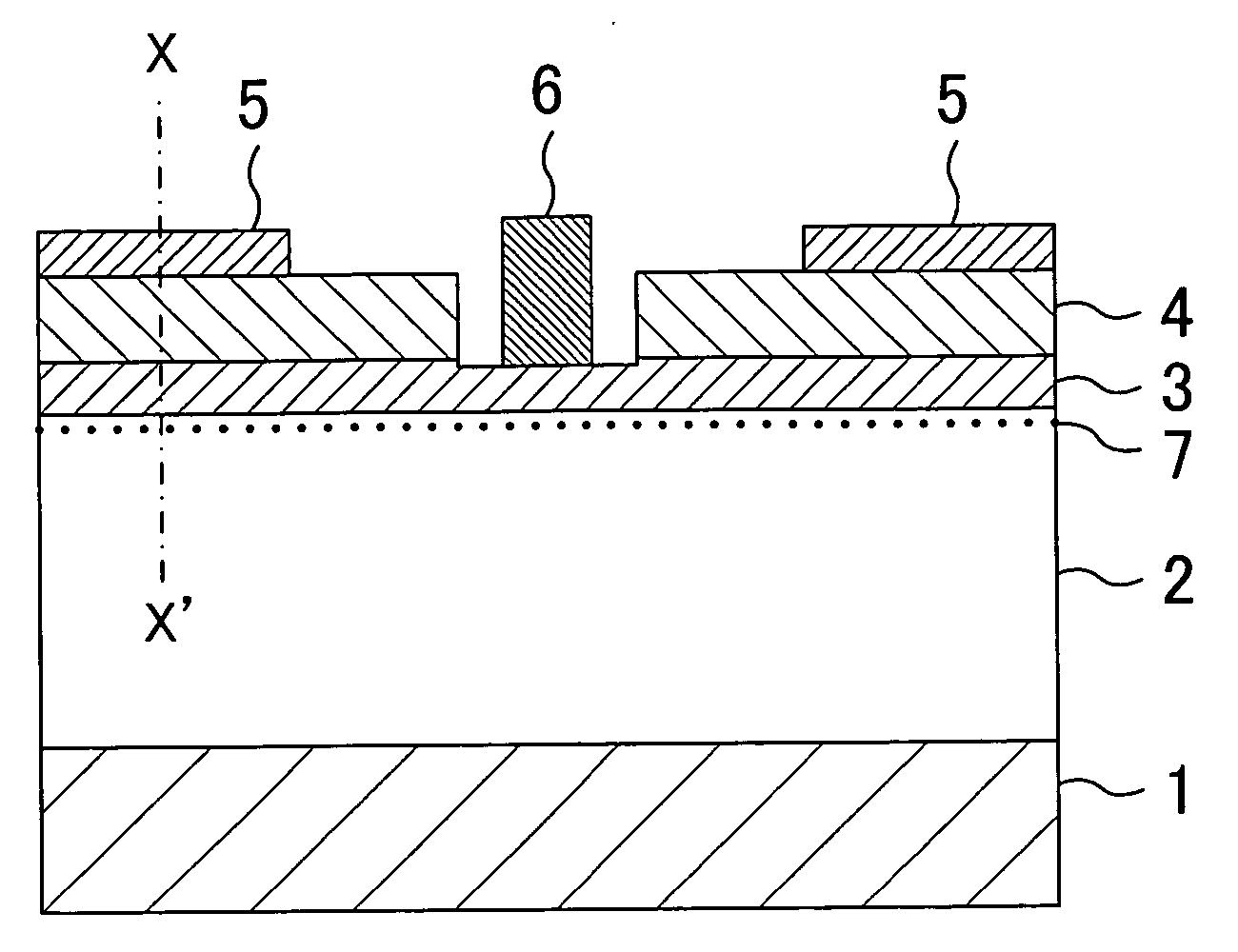

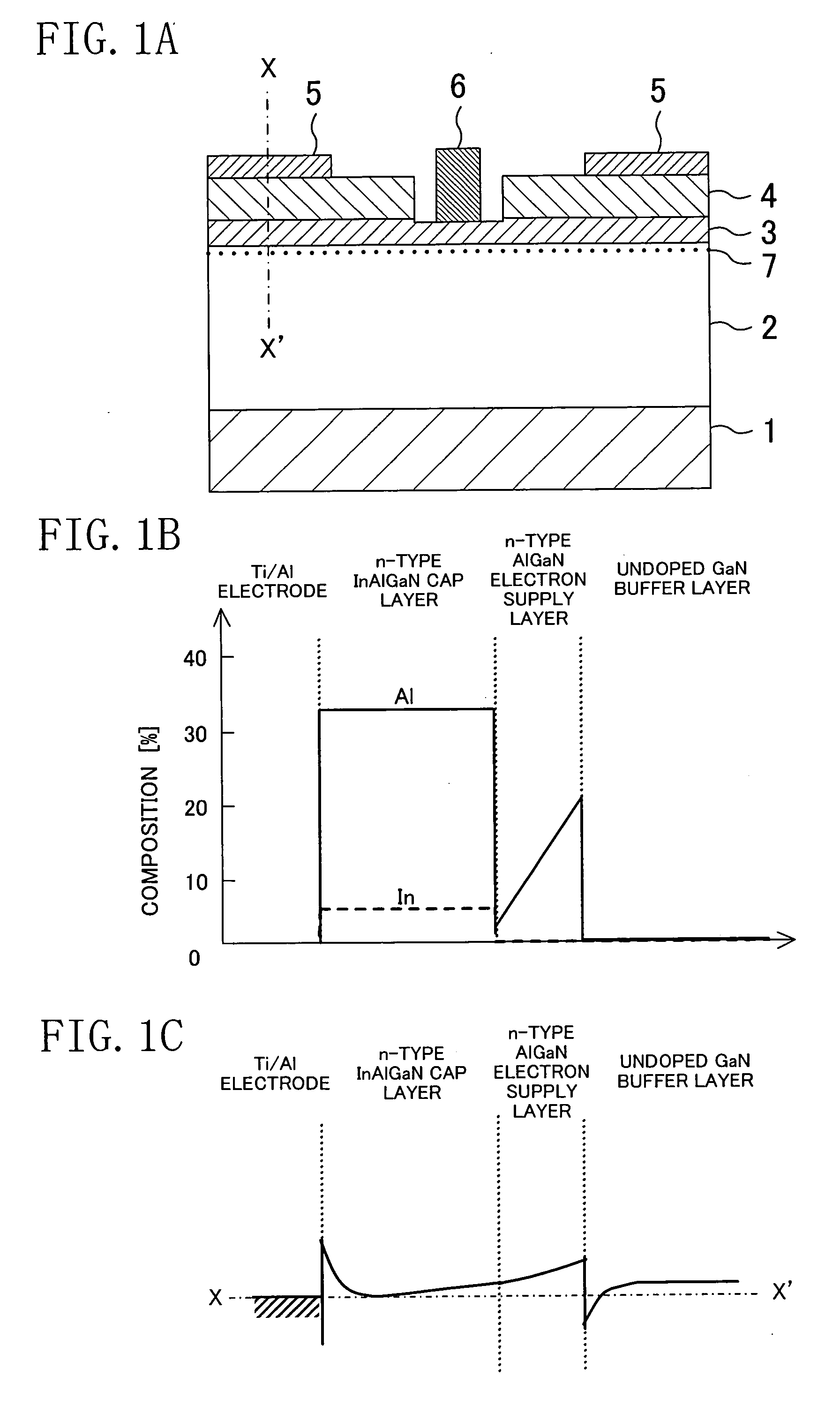

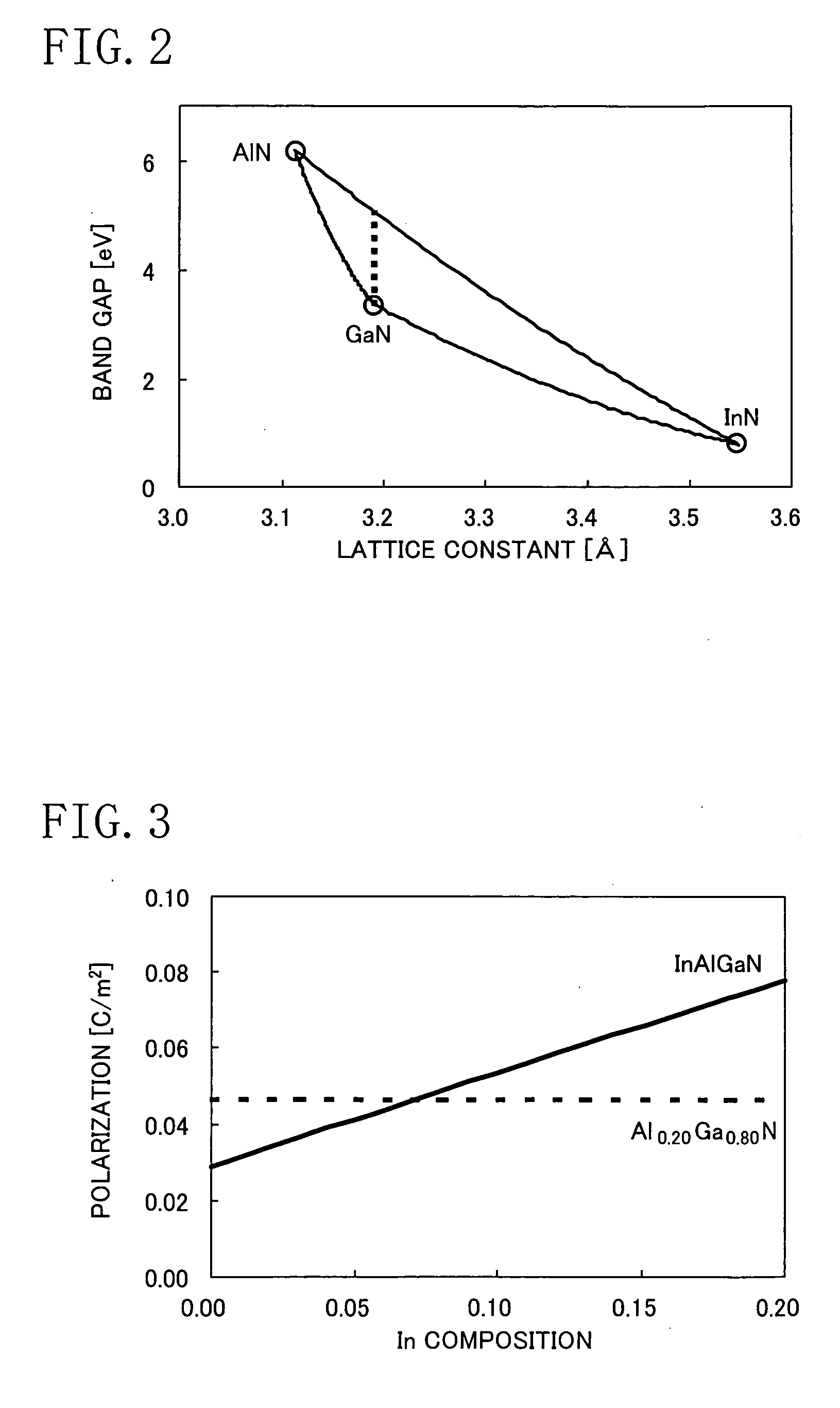

Field effect transistor and method for fabricating the same

ActiveUS20060180831A1High crystallinityIncrease parasitic resistanceSemiconductor devicesConduction bandField-effect transistor

A field effect transistor includes a nitride semiconductor layer; an InxAlyGa1-x-yN layer (wherein 0<x<1, 0<y<1 and 0<x+y<1) formed on the nitride semiconductor layer; and a source electrode and a drain electrode formed on and in contact with the InxAlyGa1-x-yN layer. The lower ends of the conduction bands of the nitride semiconductor layer and the InxAlyGa1-x-yN layer are substantially continuous on the interface therebetween.

Owner:PANASONIC CORP

Mutual inductance in transformer based tank circuitry

ActiveUS7250826B2Reduce the valueReduce parasitic resistanceAngle modulation by variable impedencePulse automatic controlElectrical resistance and conductanceTransformer

Placing inductors or resistors in parallel causes the combined value of inductance or resistance to decrease according to the parallel combination rule. This invention decreases the parasitic resistance of an inductor by placing several inductors in parallel. Furthermore, by careful placement of these inductors, the mutual inductance between these inductors can be used to increase the equivalent inductance value to a value near that of the original inductance value of a single inductor. Thus, it is possible to create an inductance with a much lower value of parasitic resistance. This invention allows the formation of high Q inductors and would be beneficial in any circuit design requiring inductances. Another aspect of this invention is that the coils can be partitioned to minimize eddy current losses. This invention can easily be implemented in a planar technology. Simulations of several tank circuits indicate that the power dissipation can be reduced 3 to 4 times when compared to conventional techniques.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

Field effect transistor

ActiveUS7956383B2Suppress generationInhibition formationSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField effect

A field effect transistor includes: a first nitride semiconductor layer having a plane perpendicular to a (0001) plane or a plane tilted with respect to the (0001) plane as a main surface; a second nitride semiconductor layer formed on the first nitride semiconductor layer and having a wider bandgap than the first nitride semiconductor layer; a third nitride semiconductor layer formed on the second nitride semiconductor layer; and a source electrode and a drain electrode formed so as to contact at least a part of the second nitride semiconductor layer or the third nitride semiconductor layer. A recess that exposes a part of the second nitride semiconductor layer is formed between the source electrode and the drain electrode in the third nitride semiconductor layer. A gate electrode is formed in the recess and an insulating film is formed between the third nitride semiconductor layer and the gate electrode.

Owner:PANASONIC CORP

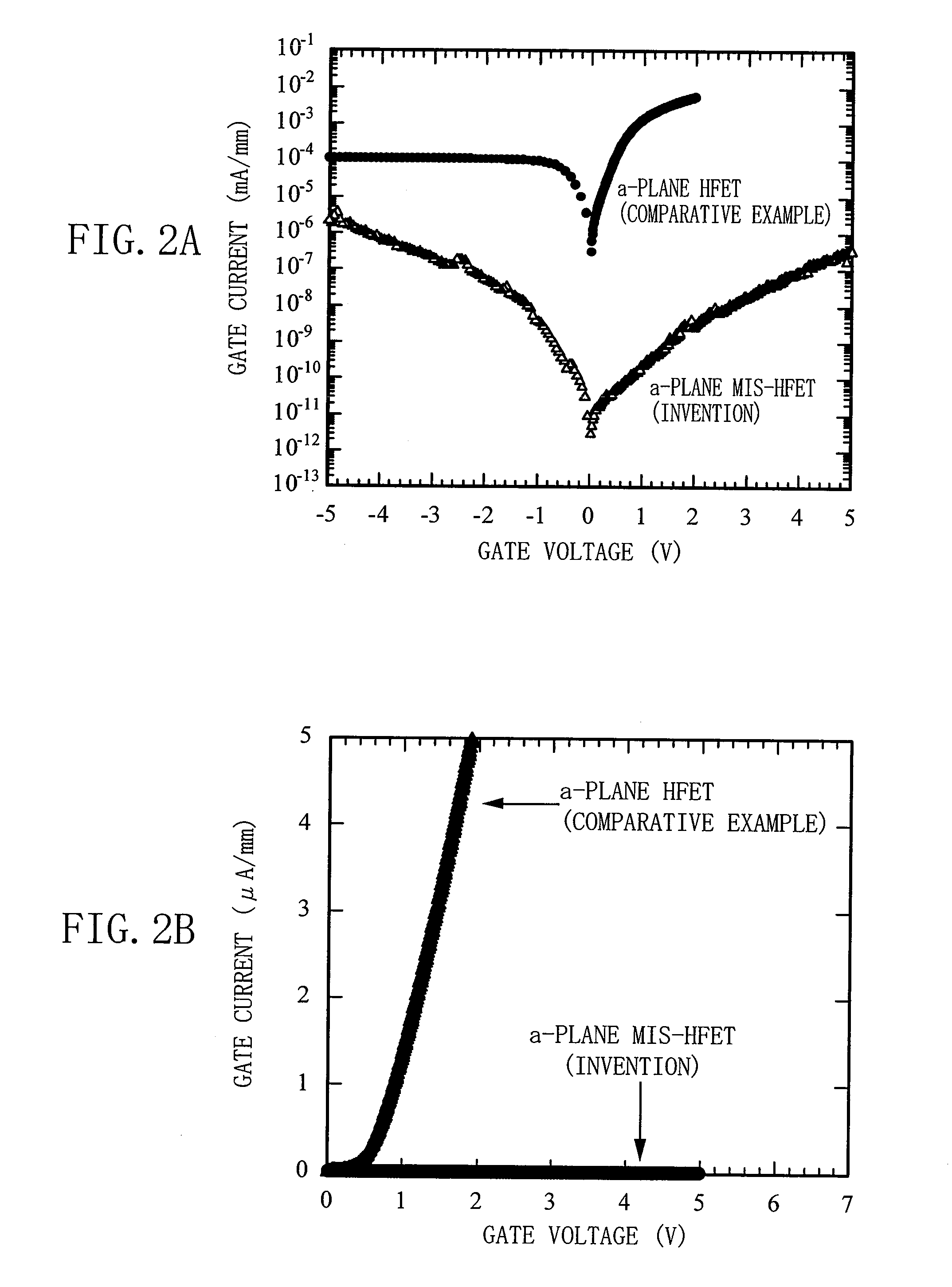

Nitride semiconductor device and manufacturing method thereof

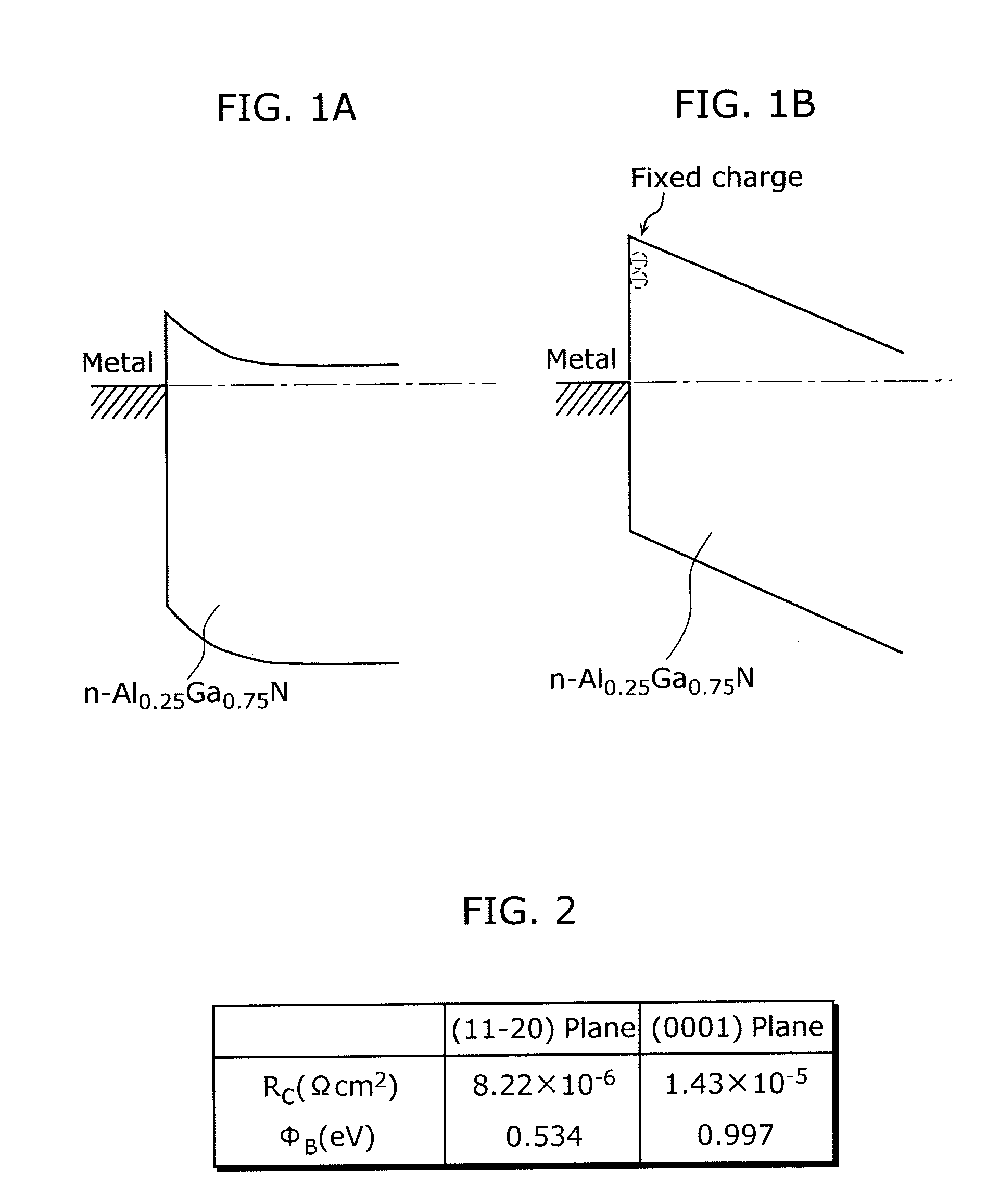

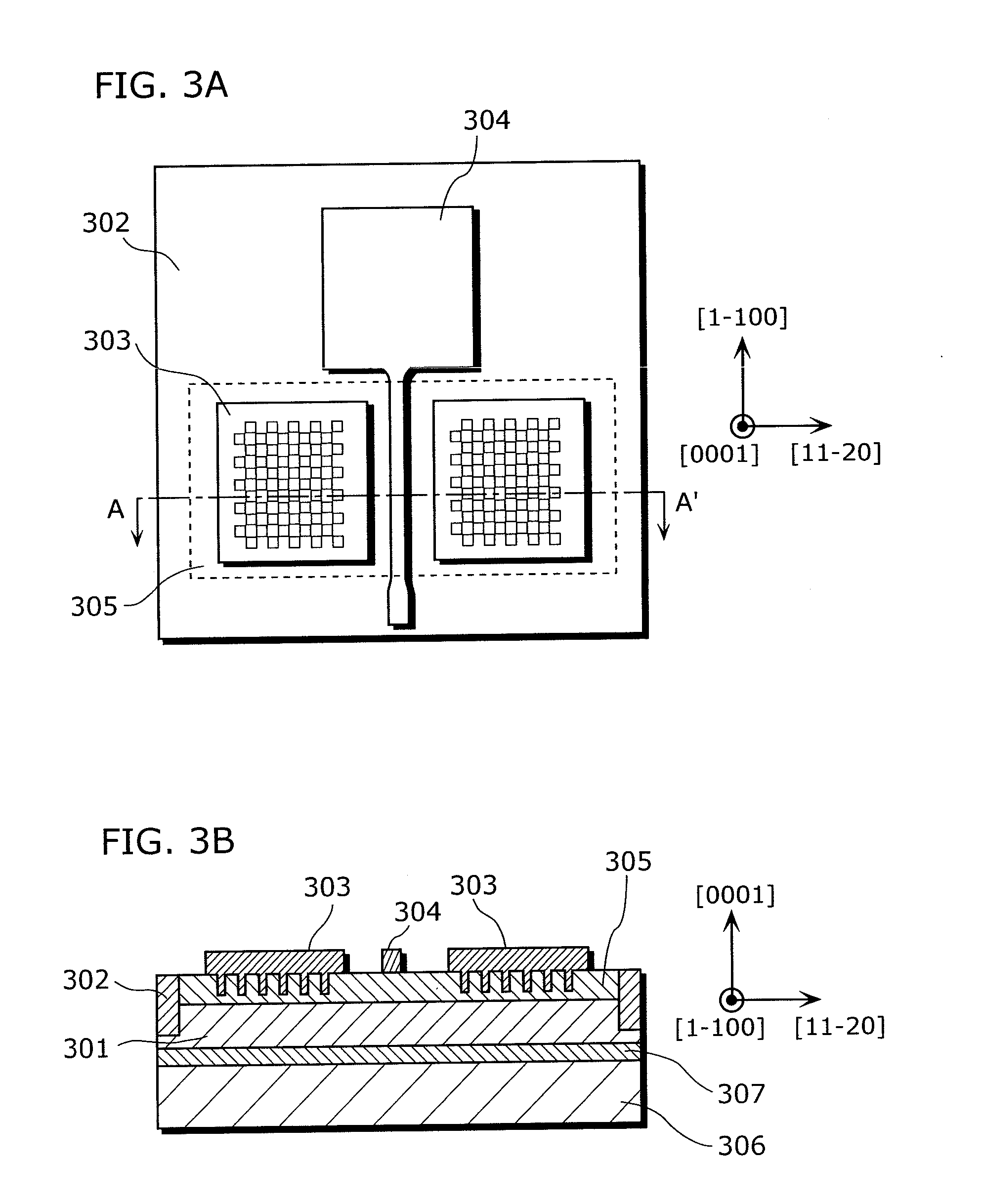

ActiveUS20080217625A1Reduce parasitic resistanceLower barrier heightSemiconductor/solid-state device manufacturingSemiconductor devicesCheckerboard patternIsolation layer

It is an object of the present invention to provide a nitride semiconductor device with low parasitic resistance by lowering barrier height to reduce contact resistance at an interface of semiconductor and metal. The nitride semiconductor device includes a GaN layer, a device isolation layer, an ohmic electrode, an n-type Al0.25Ga0.75N layer, a sapphire substrate, and a buffer layer. A main surface of the n-type Al0.25Ga0.75N layer is on (0001) plane as a main surface, and concaves are arranged in a checkerboard pattern on the surface. The ohmic electrode contacts the sides of the concaves of the n-type Al0.25Ga0.75N layer, and the sides of the concaves are on non-polar surfaces such as (11-20) plane or (1-100) plane.

Owner:PANASONIC CORP

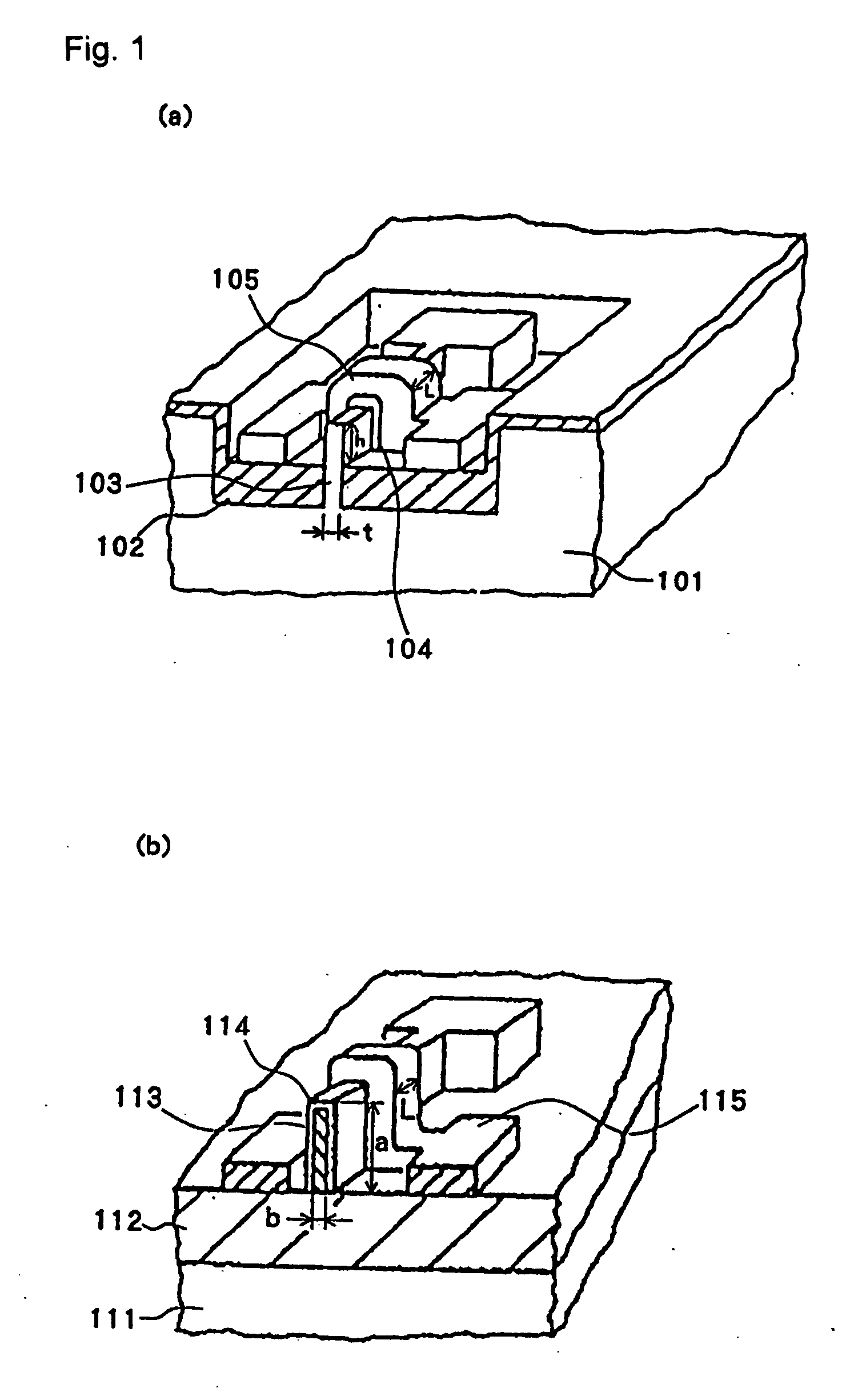

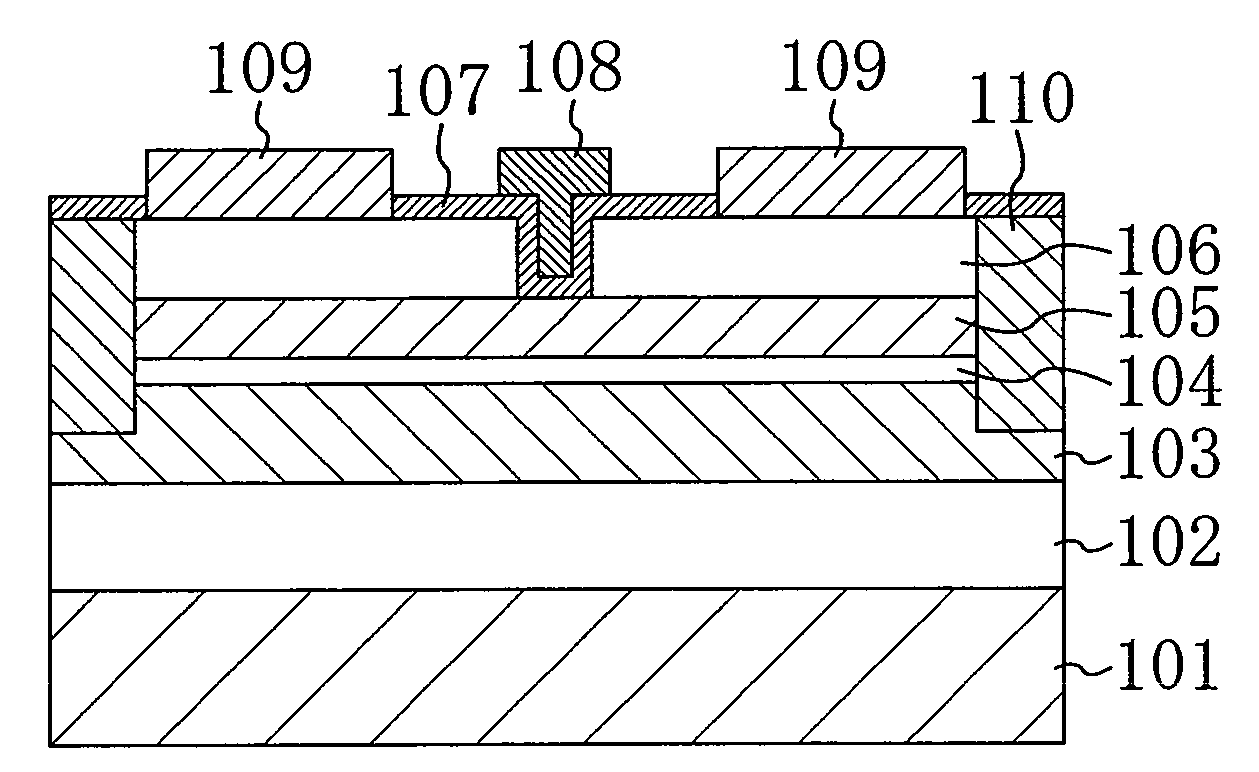

Semiconductor device and method for manufacturing same

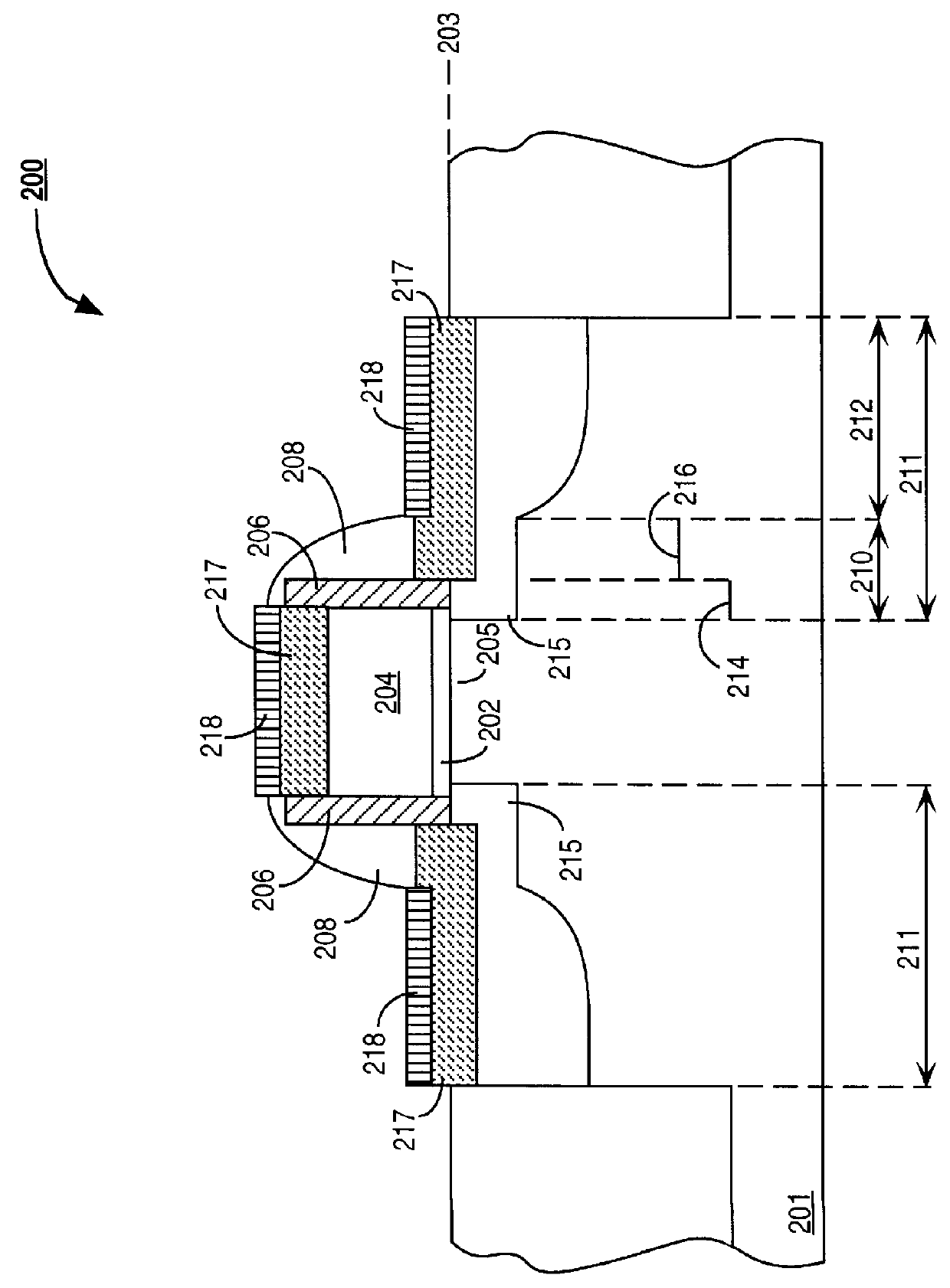

ActiveUS7701018B2Easy alignmentImprove running stabilityTransistorSolid-state devicesEngineeringField-effect transistor

A semiconductor device comprising a first semiconductor region and a second semiconductor region,(a) wherein a field effect transistor is comprised of the first semiconductor region comprising at least one semiconductor layer(s) protruding upward from a substrate, a gate electrode(s) formed via an insulating film such that the gate electrode(s) strides over the semiconductor layer(s) and source / drain regions provided in the semiconductor layer(s) on both sides of the gate electrode(s), whereby a channel region is formed in at least both sides of the semiconductor layer(s),(b) wherein the second semiconductor region comprises semiconductor layers protruding upward from the substrate and placed, at least opposing the first semiconductor region at both ends in the direction perpendicular to a channel current direction and the side surface of the semiconductor layers facing the first semiconductor region is parallel to the channel current direction.

Owner:GK BRIDGE 1

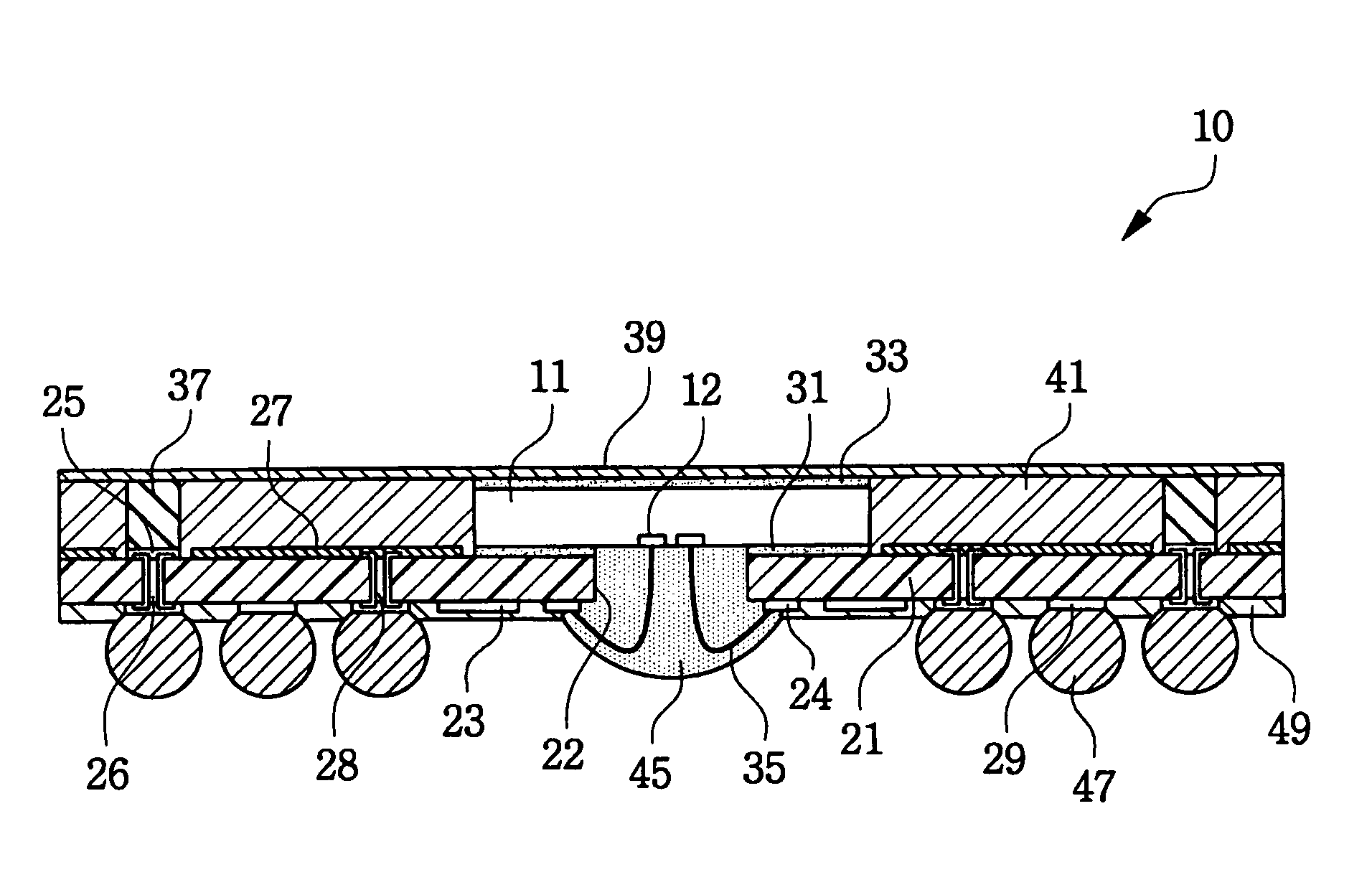

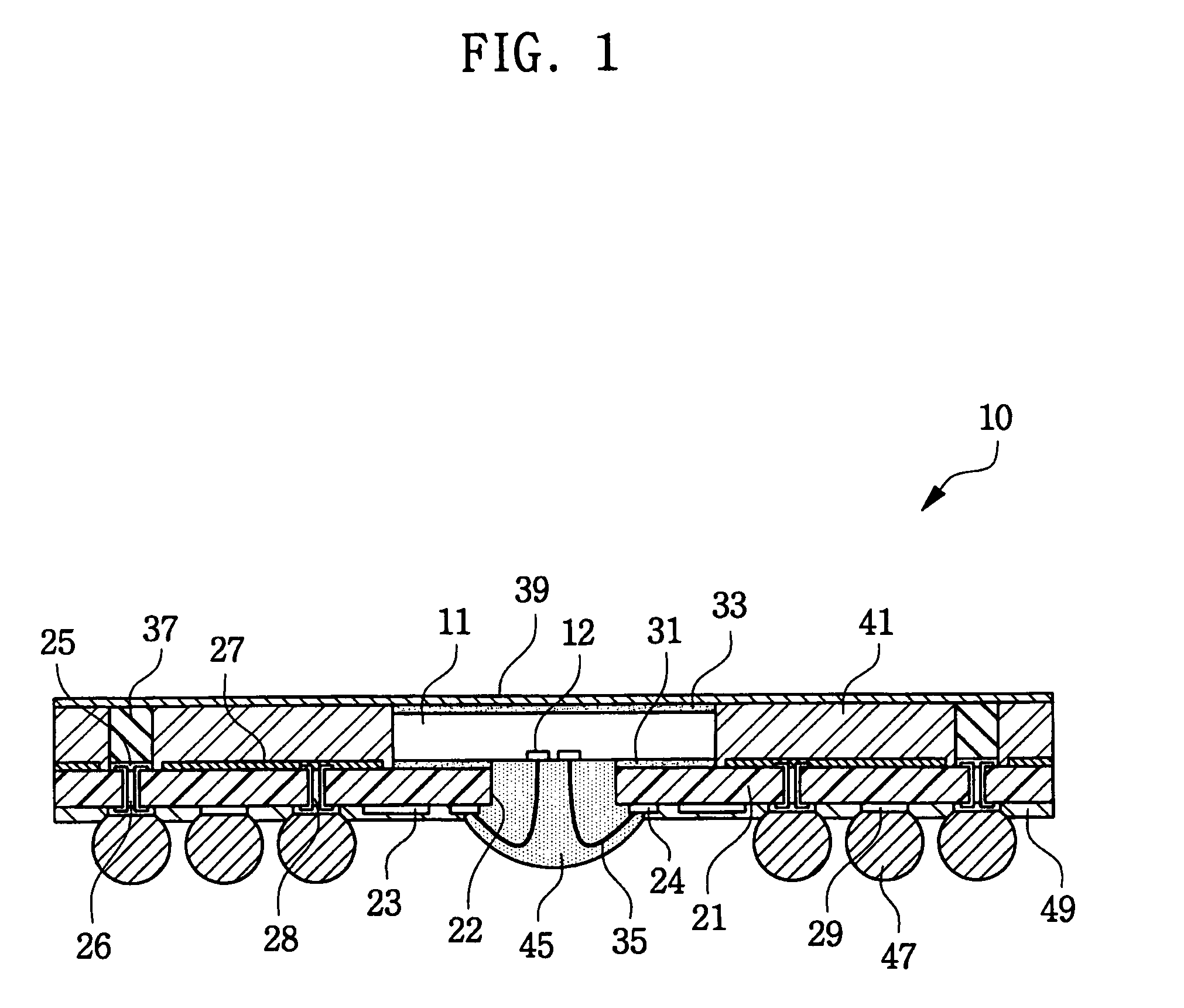

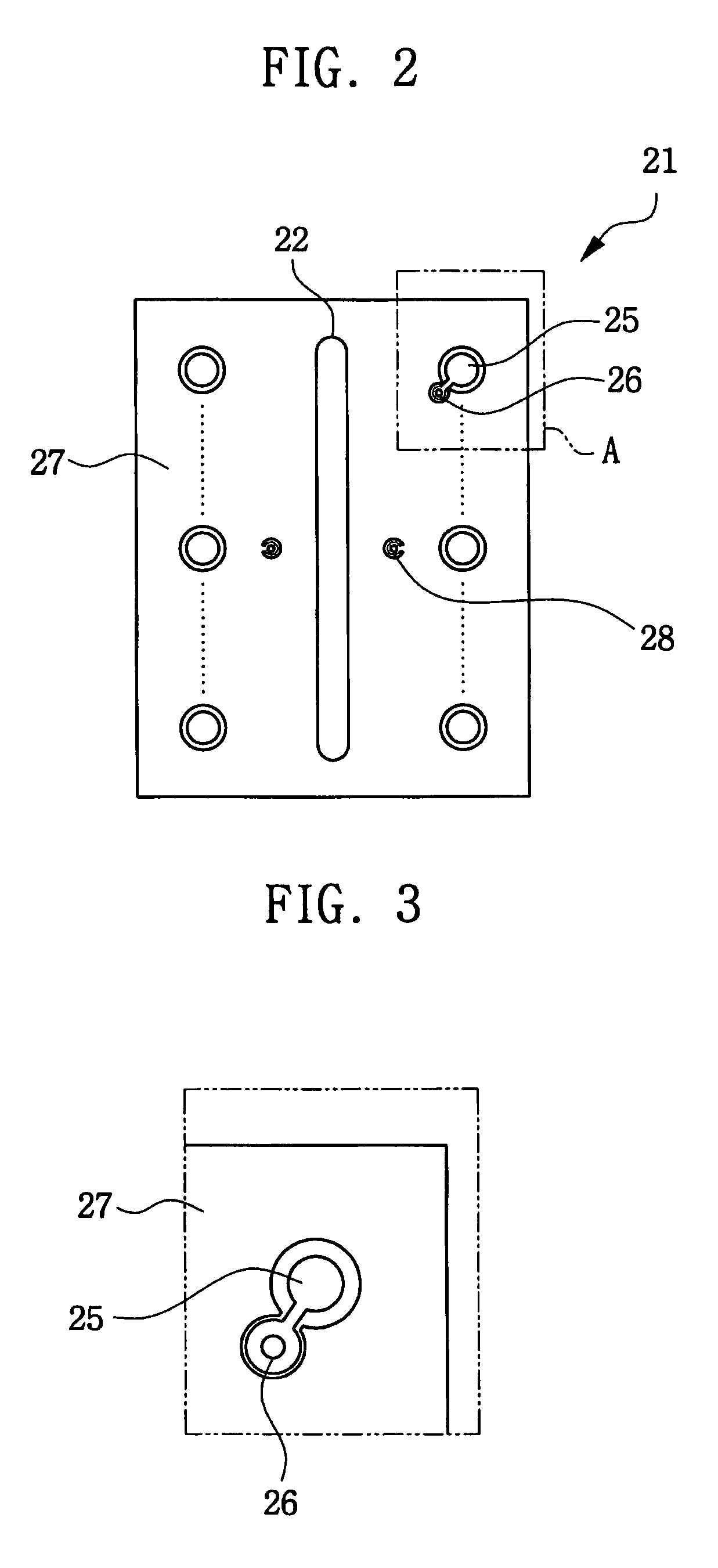

Semiconductor chip package having decoupling capacitor and manufacturing method thereof

ActiveUS7129571B2Short pathImproved decoupling capacitorSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

A semiconductor chip package has a substrate that includes circuit lines provided on first and / or second surfaces, a power plane provided on the second surface, bump lands provided on the second surface and coupled to the circuit lines, and ball lands provided on the first surface. The package further has a semiconductor chip attached to the second surface of the substrate and electrically coupled to the circuit lines, and a dielectric layer provided on the second surface of the substrate. The dielectric layer surrounds laterally the chip, covers the power plane, and exposes the bump lands. The package further has a ground plane provided on both the chip and the dielectric layer, vertical connection bumps provided within the dielectric layer and on the bump lands and electrically coupled to the ground plane, and solder balls provided on the ball lands.

Owner:SAMSUNG ELECTRONICS CO LTD

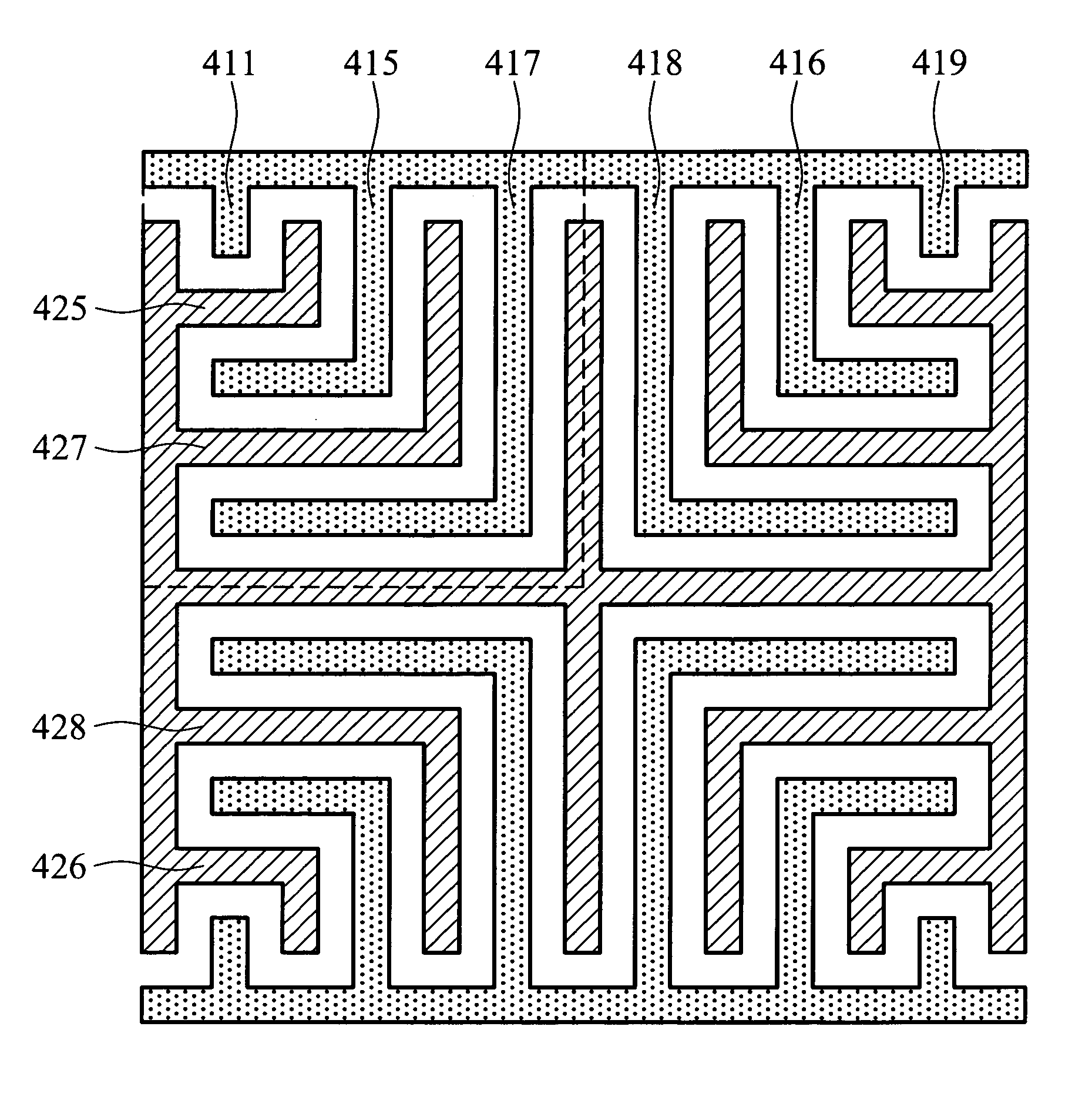

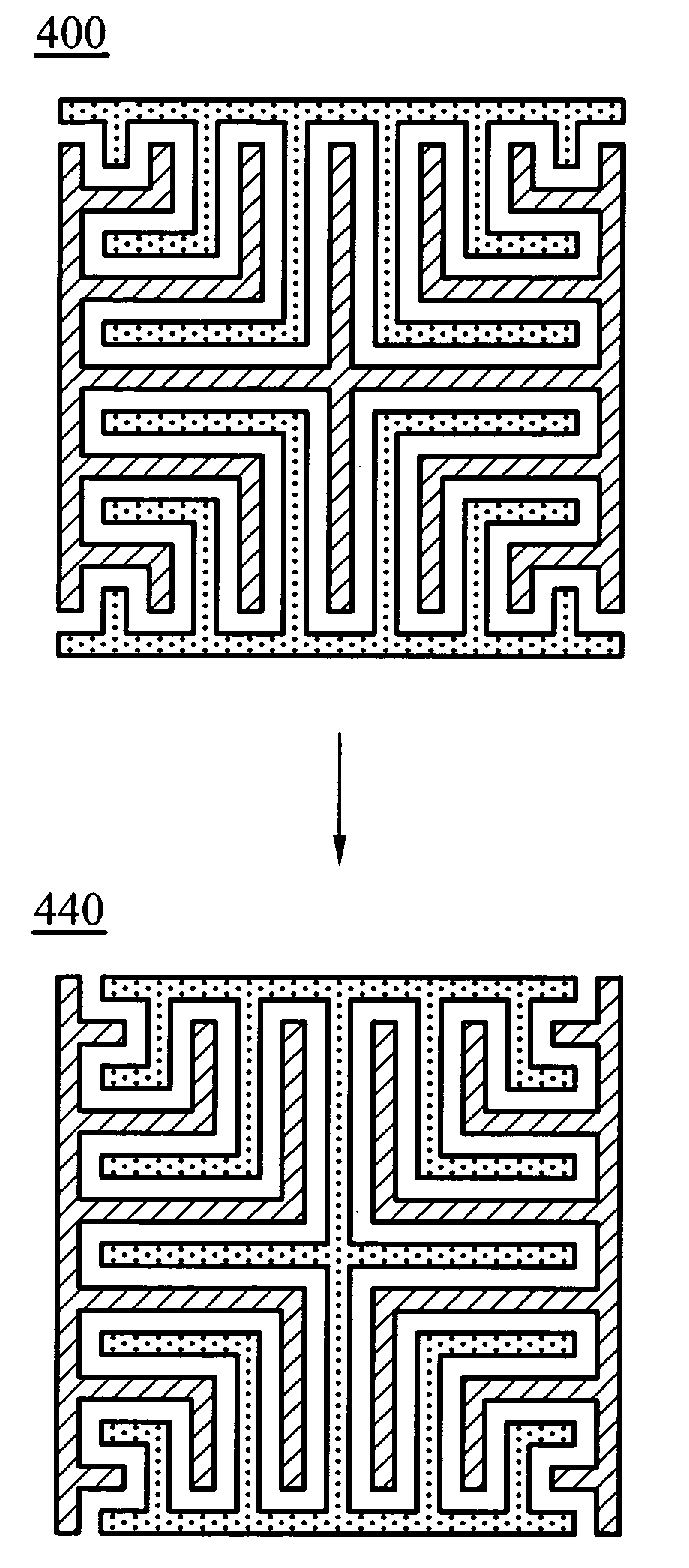

Interdigitized capacitor

ActiveUS20070126078A1Series parasitic resistanceQuality improvementTransistorSemiconductor/solid-state device detailsCapacitorAtomic physics

An interdigitized capacitor comprising first and second electrodes. The first electrode comprises two combs symmetrical to a first mirror plane. The fingers of the combs extend toward the first mirror plane. The second electrode comprises two combs and a linear plate. The combs are symmetrical to a second mirror plane and the fingers thereof extend toward the second mirror plane. The linear plate is located at the second mirror plane and connected to one finger of the combs of the second electrode. The first and second mirror planes are orthogonal. The fingers of the combs of the first and second electrodes are interdigitized.

Owner:NUVOTON

Interdigitized capacitor

ActiveUS7485914B2Series parasitic resistanceQuality improvementTransistorSemiconductor/solid-state device detailsCapacitorAtomic physics

An interdigitized capacitor comprising first and second electrodes. The first electrode comprises two combs symmetrical to a first mirror plane. The fingers of the combs extend toward the first mirror plane. The second electrode comprises two combs and a linear plate. The combs are symmetrical to a second mirror plane and the fingers thereof extend toward the second mirror plane. The linear plate is located at the second mirror plane and connected to one finger of the combs of the second electrode. The first and second mirror planes are orthogonal. The fingers of the combs of the first and second electrodes are interdigitized.

Owner:NUVOTON

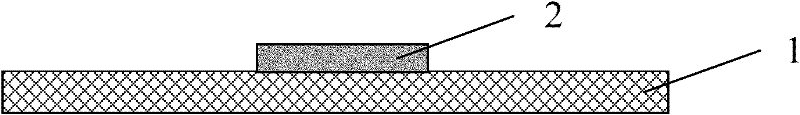

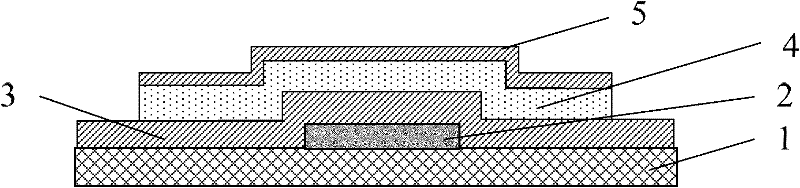

Manufacturing method of transistor

ActiveCN102130009AHas light transmission propertiesReduce generationSemiconductor/solid-state device manufacturingPhotomechanical coating apparatusBottom gateDouble gate

The invention discloses a manufacturing method of a thin film transistor with a double gate structure. An active region of the transistor and a top gate electrode are made of a transparent thin film material. The manufacturing method comprises the following steps of: during photoetching coating, coating photoresist on the surface of a transparent conductive thin film of the top gate electrode; during photoetching exposure, carrying out exposure from the back surface of a substrate; after photoetching development, forming a photoetching diagram over against a bottom gate electrode on the surface of the conductive thin film; and etching the conductive thin film to form the top gate electrode over against the bottom gate electrode according to the photoetching diagram. The double gate thin film transistor formed by adopting the method adopts the bottom gate electrode as a natural mask plate, saves the manufacturing cost of the transistor, improves the alignment precision of the top gate electrode and the bottom gate electrode and enhances the performance of the double gate structure thin film transistor.

Owner:BOE TECH GRP CO LTD

Semiconductor device and production method therefor

ActiveUS20120196415A1Easy to integrateImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering physics

A method of producing a semiconductor device including a MOS transistor, includes the steps of forming, on a top surface of at least one of semiconductor pillars, an epitaxial layer having a top surface larger in area than the top surface of the at least one of the semiconductor pillars and forming a source region or a drain region so as to be at least partially in the epitaxial layer.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

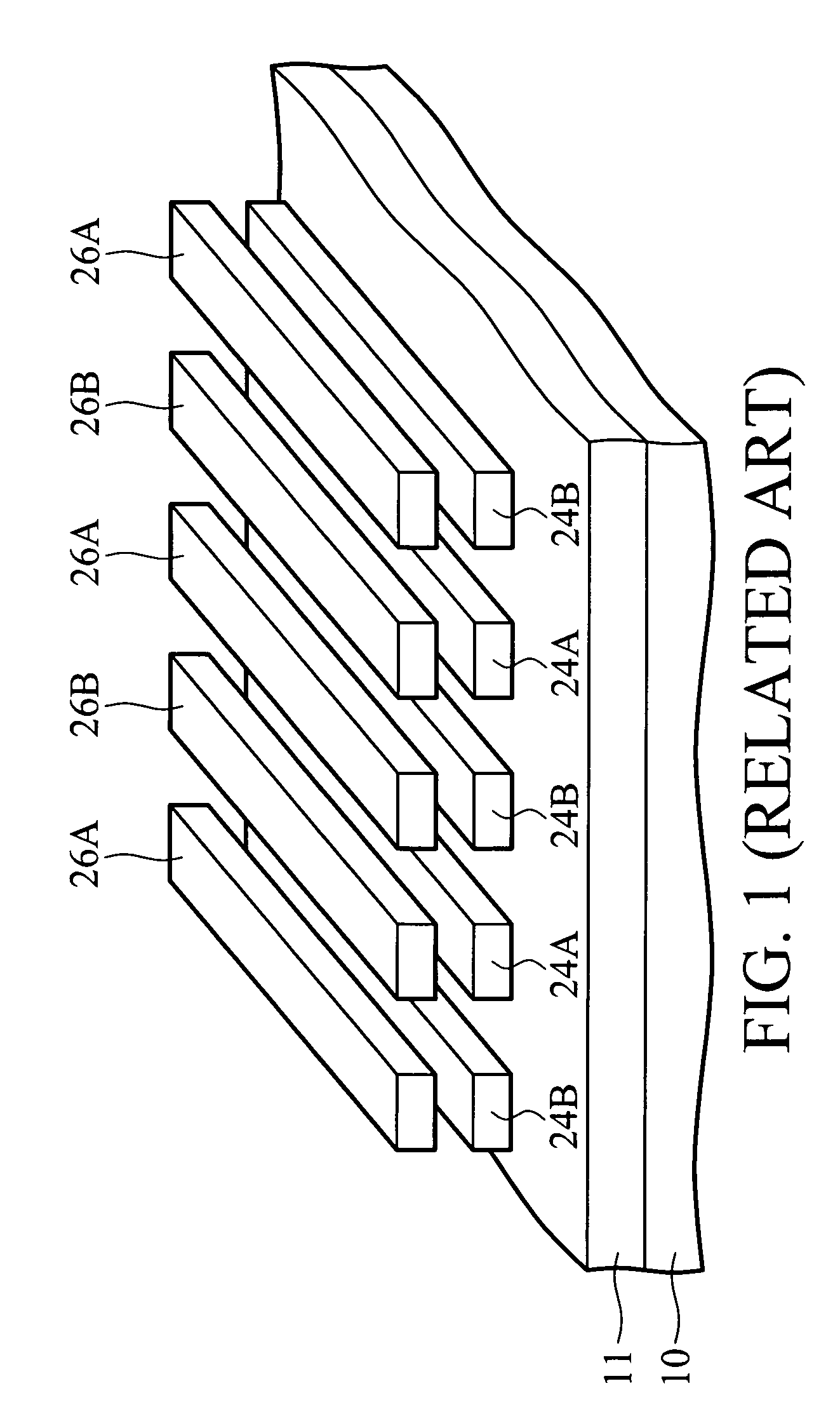

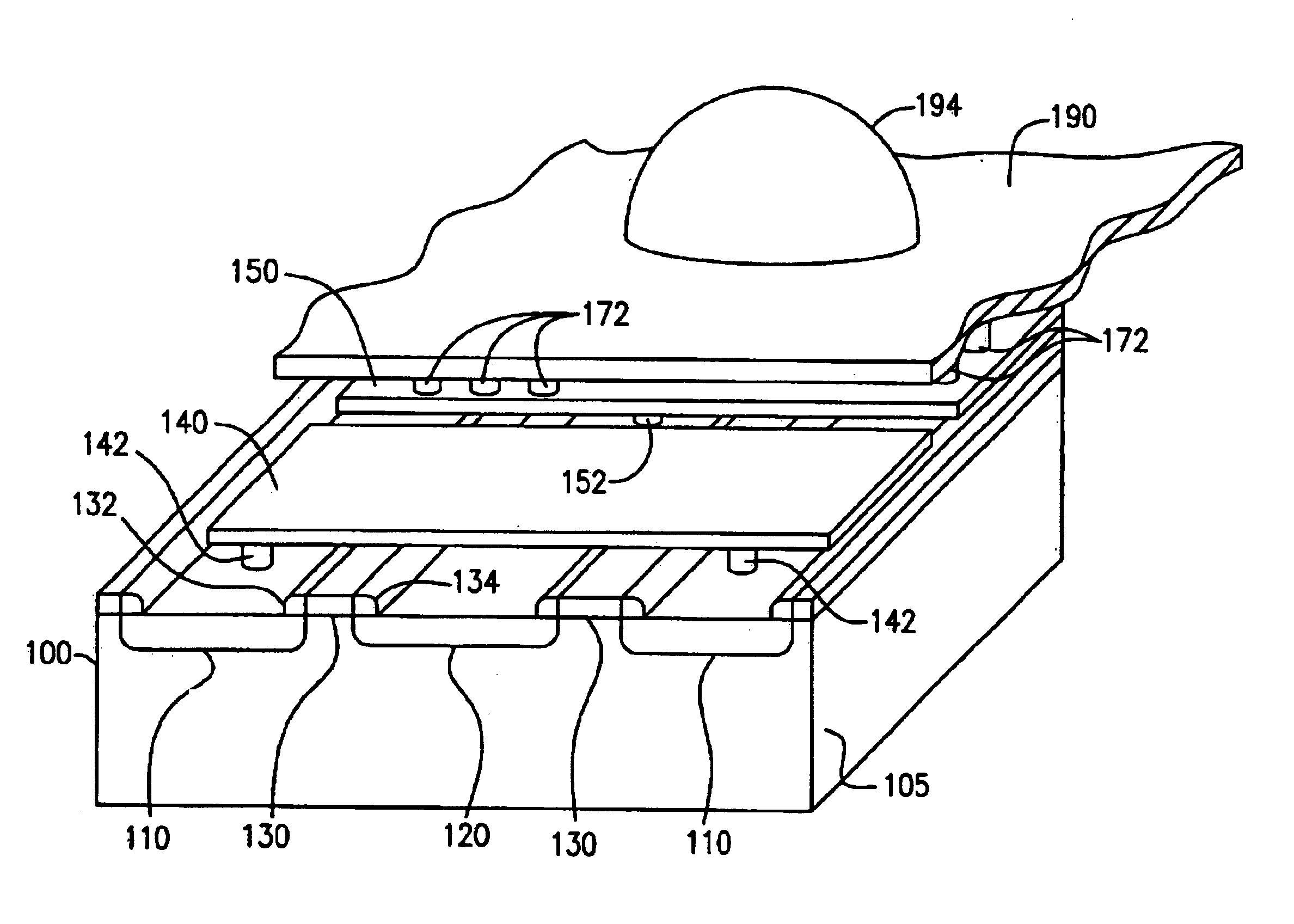

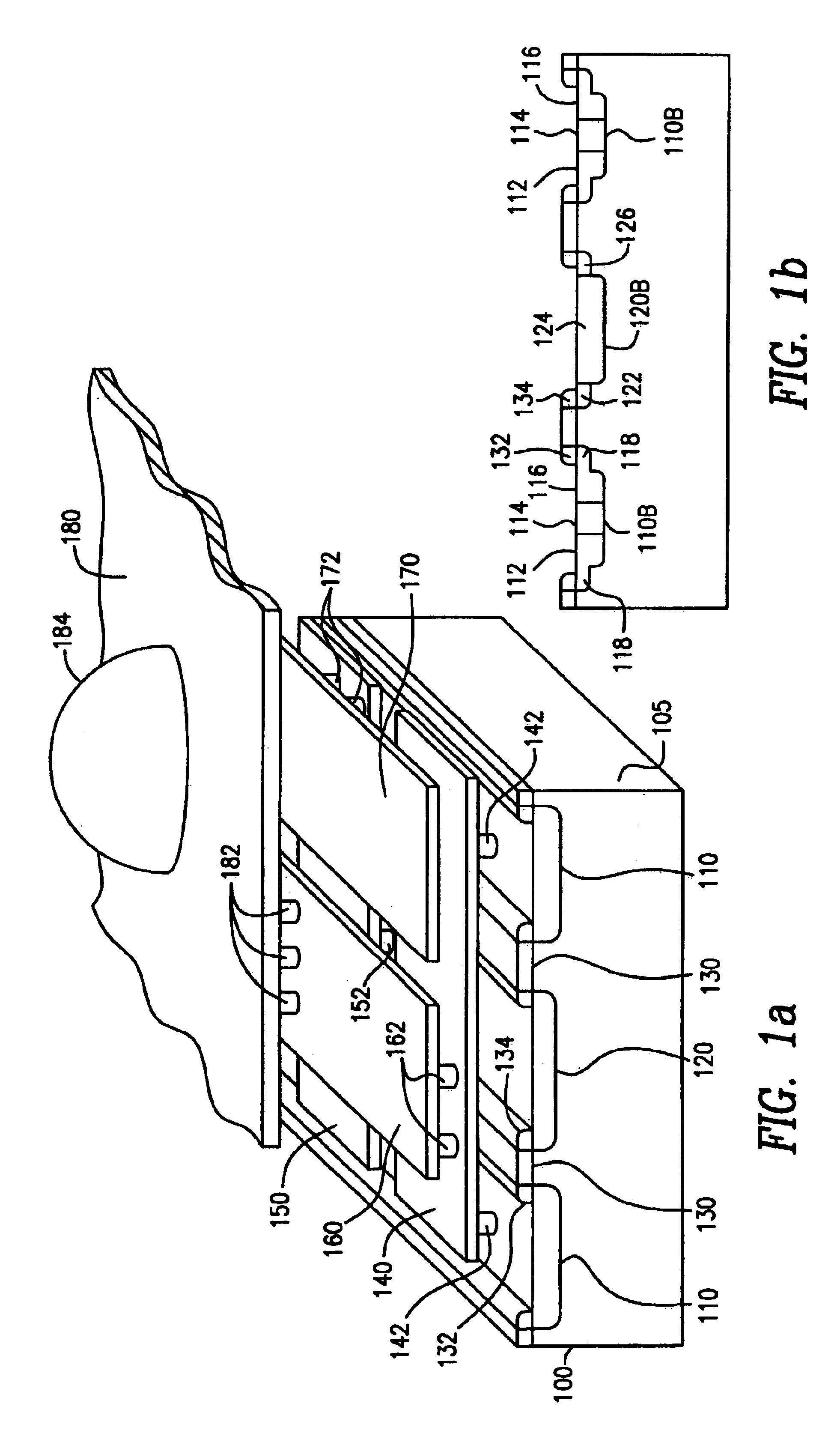

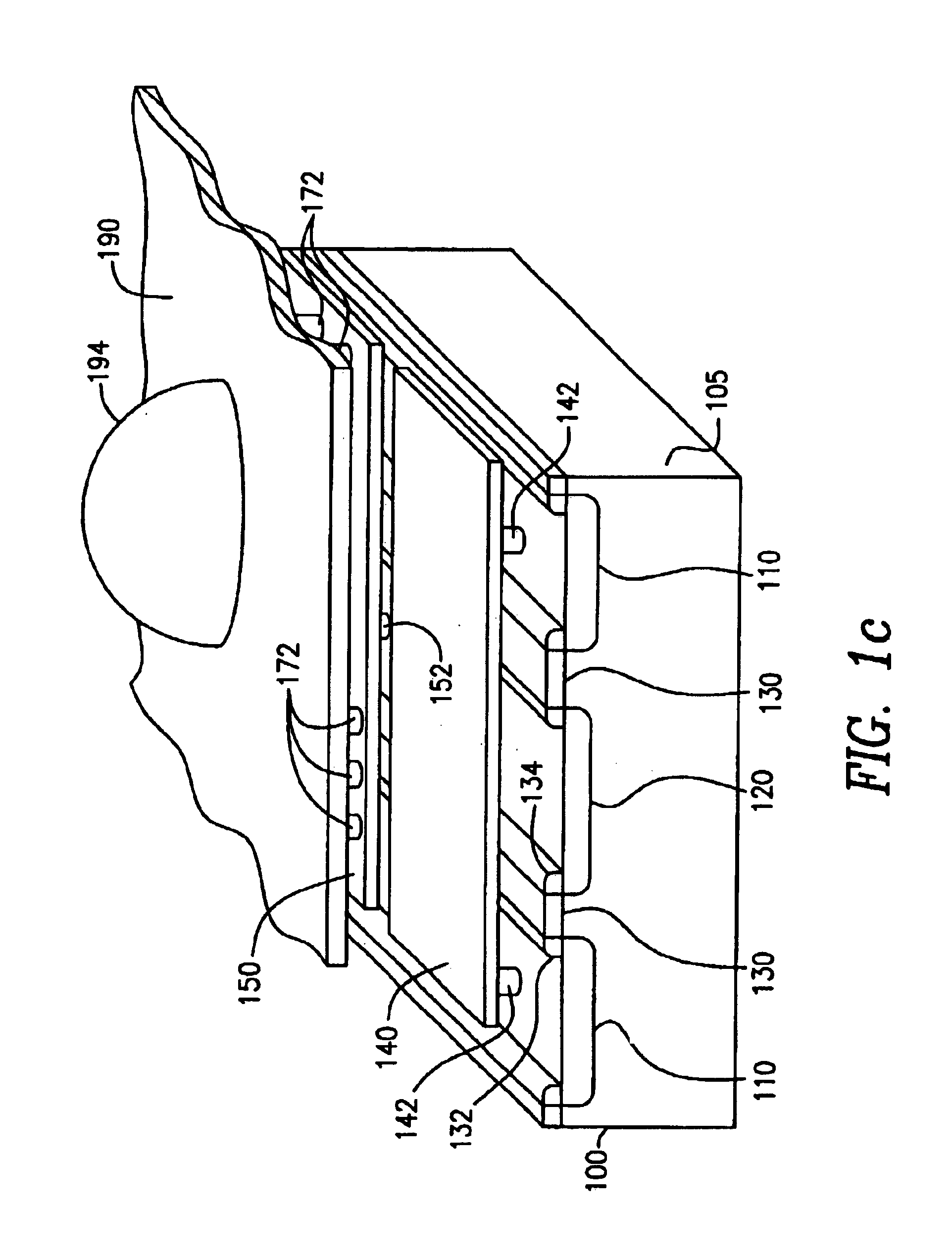

Power MOSFET

InactiveUS6972464B2Reduce parasitic resistanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

Owner:GREAT WALL SEMICON CORP

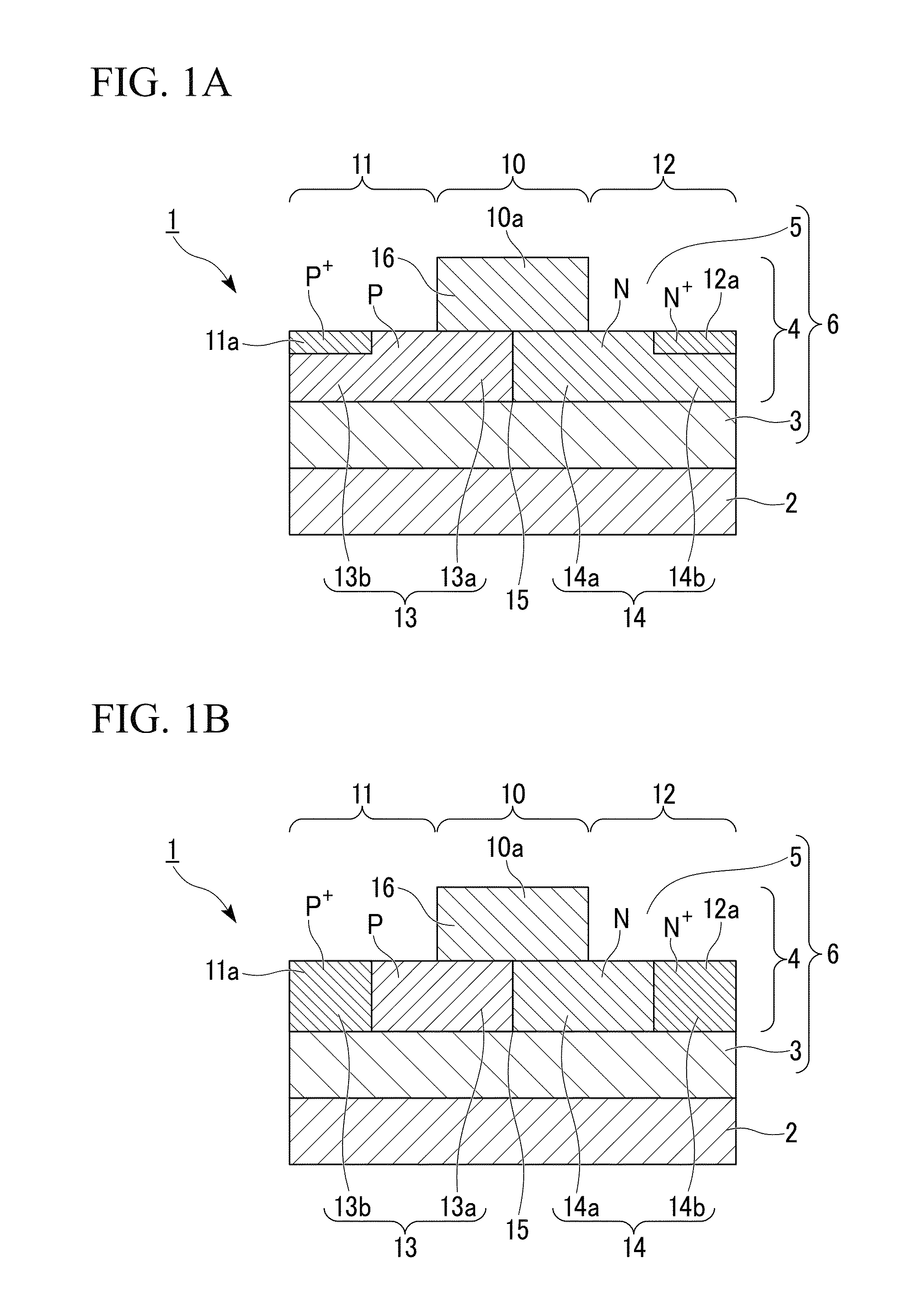

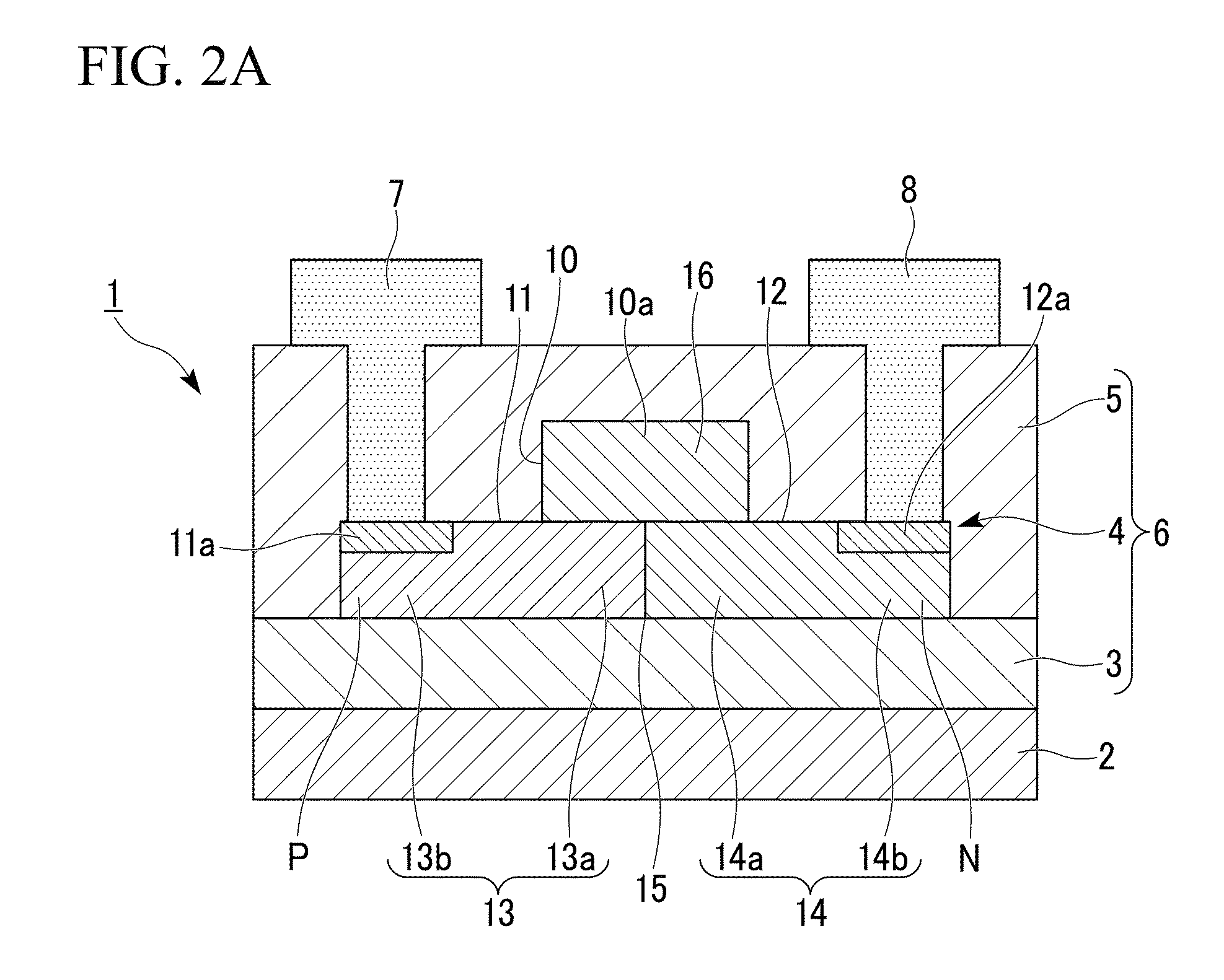

Optical element and mach-zehnder optical waveguide element

ActiveUS20140233878A1Increase changeEnlarge regionOptical waveguide light guideNon-linear opticsEngineeringWaveguide

Provided is an optical element including an optical waveguide including a core formed from: a rib part; and a first and second slab parts sandwiching the rib part. The first slab part includes a P-type region, the second slab part includes an N-type region, the rib part includes a P-type region which is in contact with the P-type region provided in the first slab part, and an N-type region which is in contact with the N-type region provided in the second slab part. The rib part includes a top portion which is located above the first and second slab parts and includes an undoped region formed from at least one of an intrinsic region and a low-concentration doping region which is doped at a dopant concentration 1 / 10 or less of a dopant concentration in at least one of the adjacent P-type region and the adjacent N-type region.

Owner:THE FUJIKURA CABLE WORKS LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com